Patents

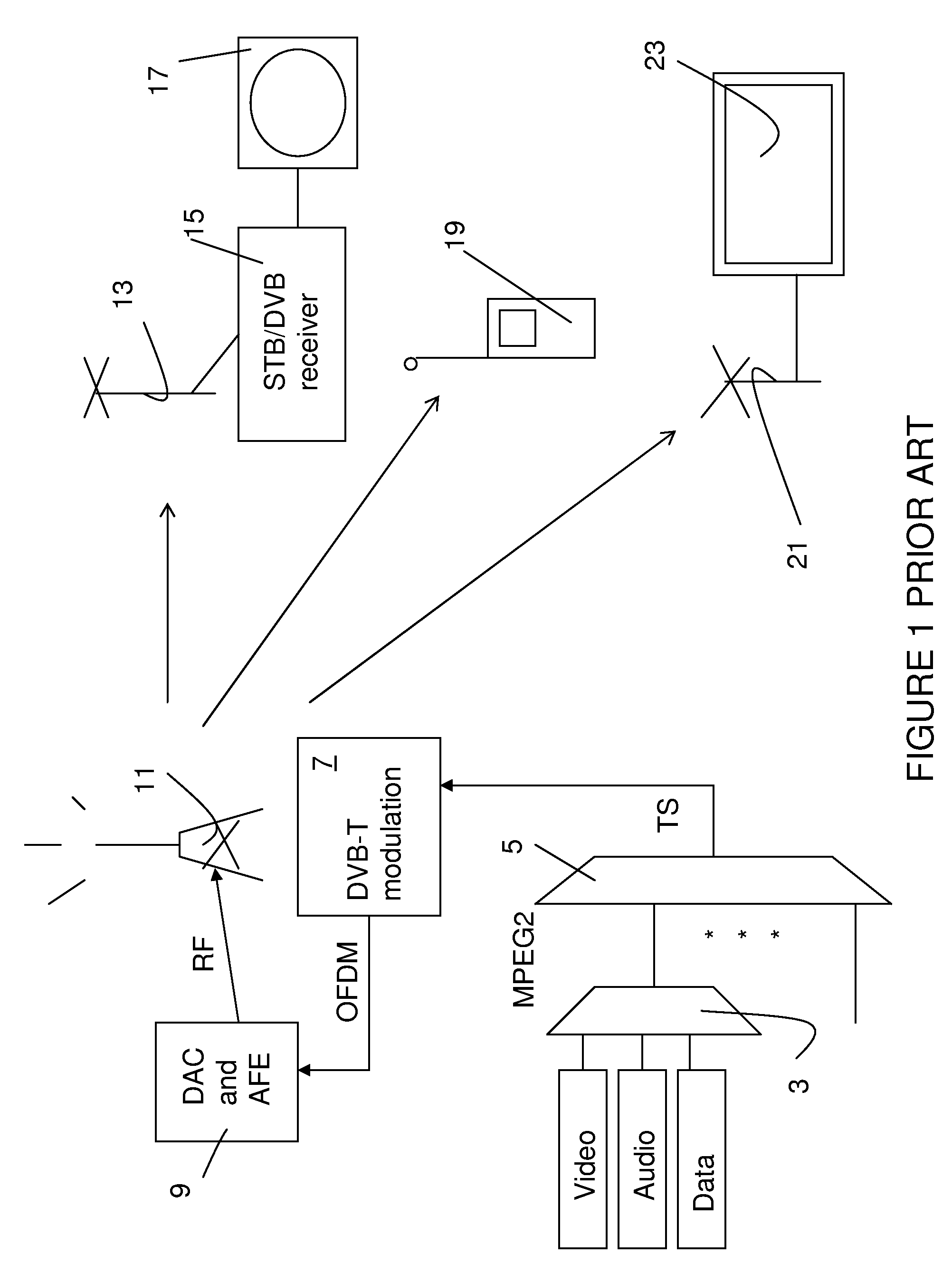

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3110 results about "Phase error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

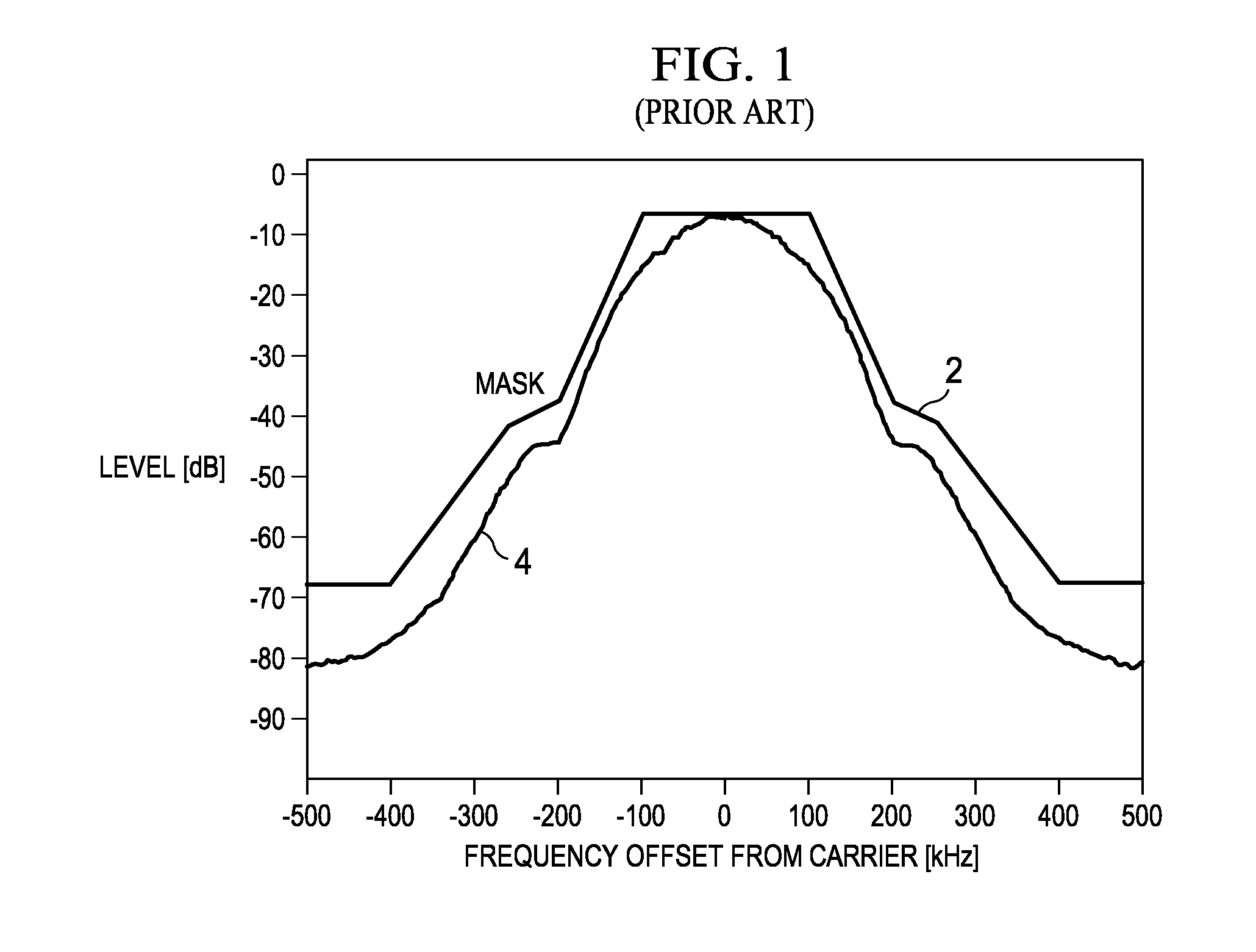

The frequency error is the difference in frequency, after adjustment for the effect of the modulation and phase error, between the RF transmission from the mobile station and the test set. The phase error is the difference in phase, after adjustment for the effect of the frequency error, between the mobile station and the theoretical "ideal" transmission.

Compensating filters

InactiveUS6760451B1Eliminate phase distortionAdaptive networkAutomatic tone/bandwidth controlDigital signal processingAmplitude response

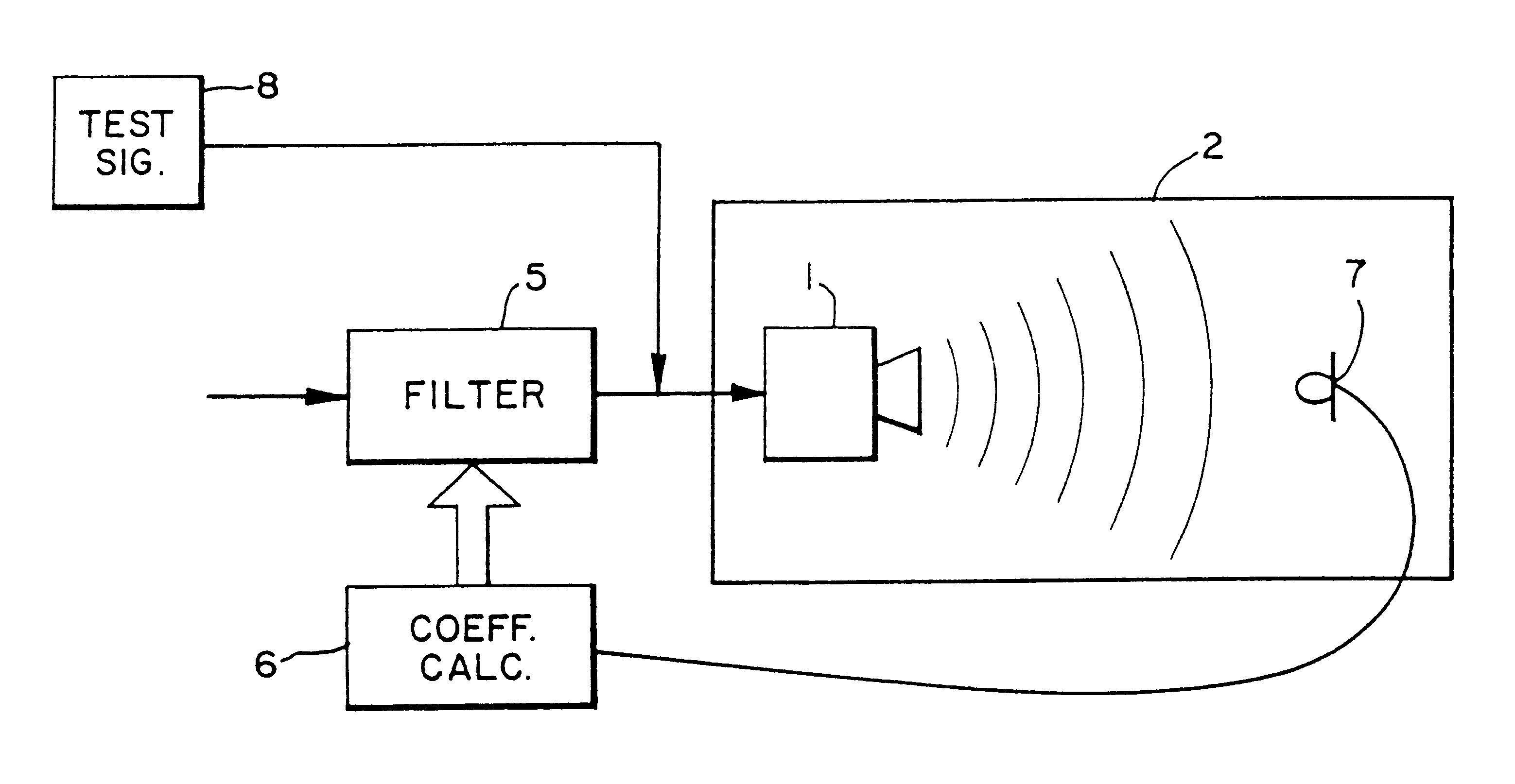

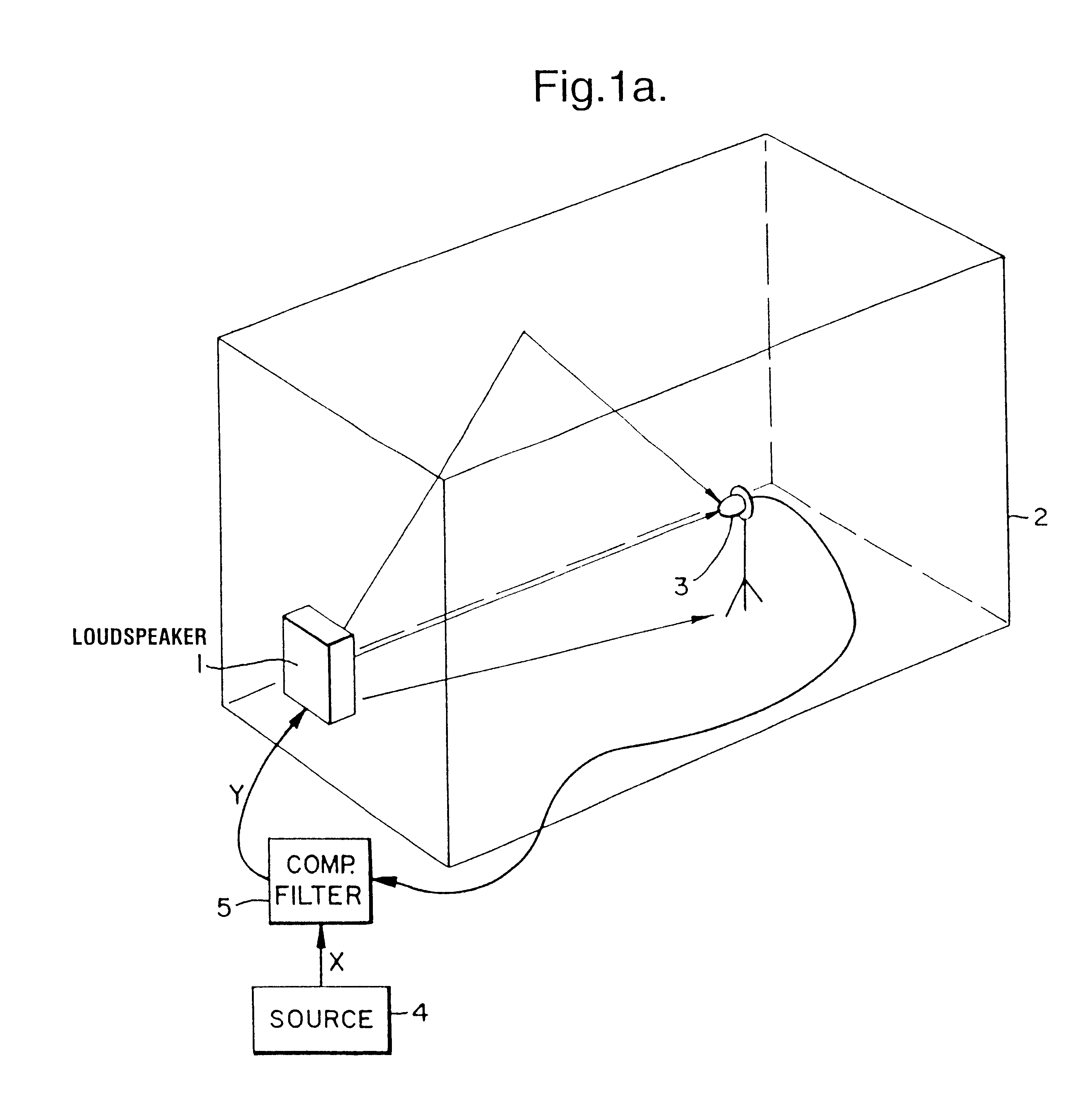

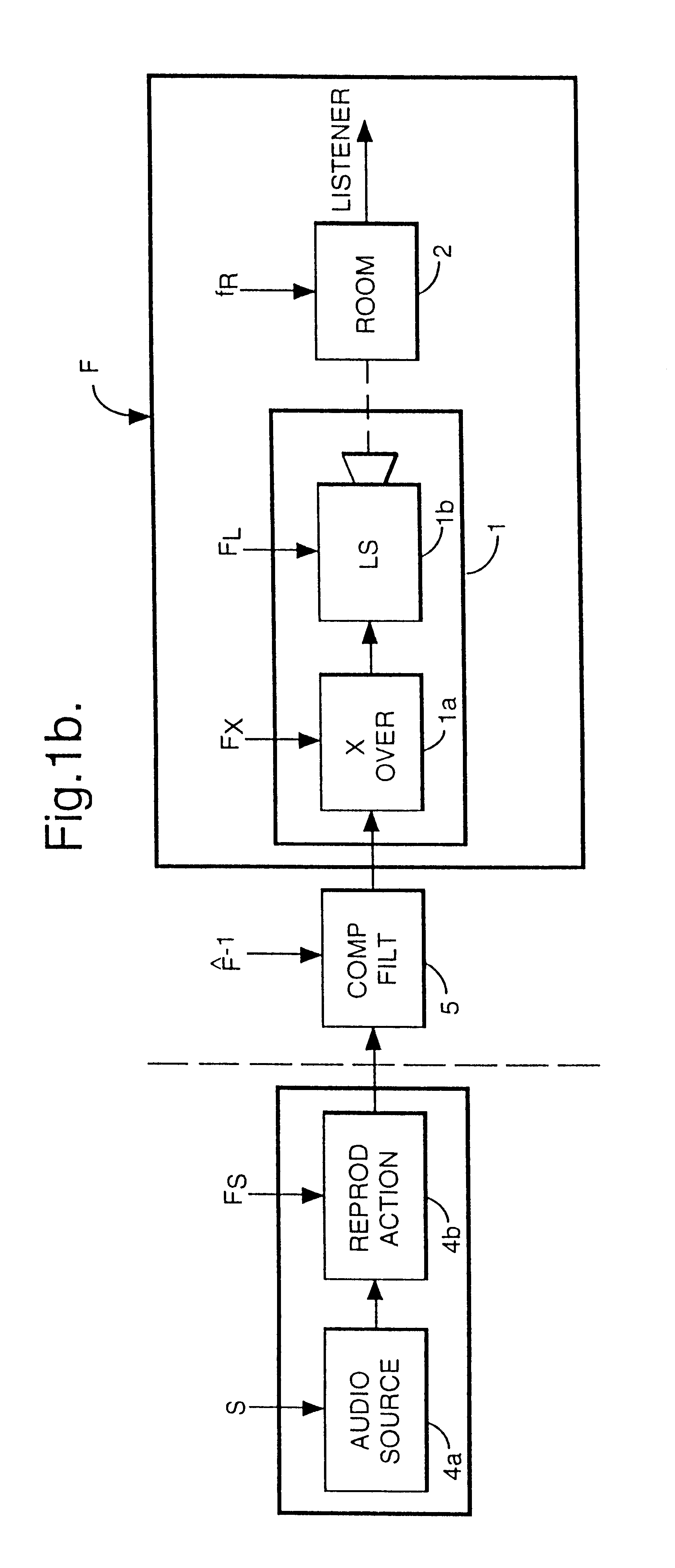

A prefilter (5) for an audio system comprising a loudspeaker (1) in a room (2), which corrects both amplitude and phase errors due to the loudspeaker (1) by a linear phase correction filter response and corrects the amplitude response of the room (2) whilst introducing the minimum possible amount of extra phase distortion by employing a minimum phase correction filter stage. A test signal generator (8) generates a signal comprising a periodic frequency sweep with a greater phase repetition period than the frequency repetition period. A microphone (7) positioned at various points in the room (2) measures the audio signal processed by the room (2) and loudspeaker (1), and a coefficient calculator (6) (e.g. a digital signal processor device) derives the signal response of the room and thereby a requisite minimum phase correction to be cascaded with the linear phase correction already calculated for the loudspeaker (1). Filter (5) may comprise the same digital signal processor as the coefficient calculator (6). Applications in high fidelity audio reproduction, and in car stereo reproduction.

Owner:CRAVEN PETER GRAHAM +1

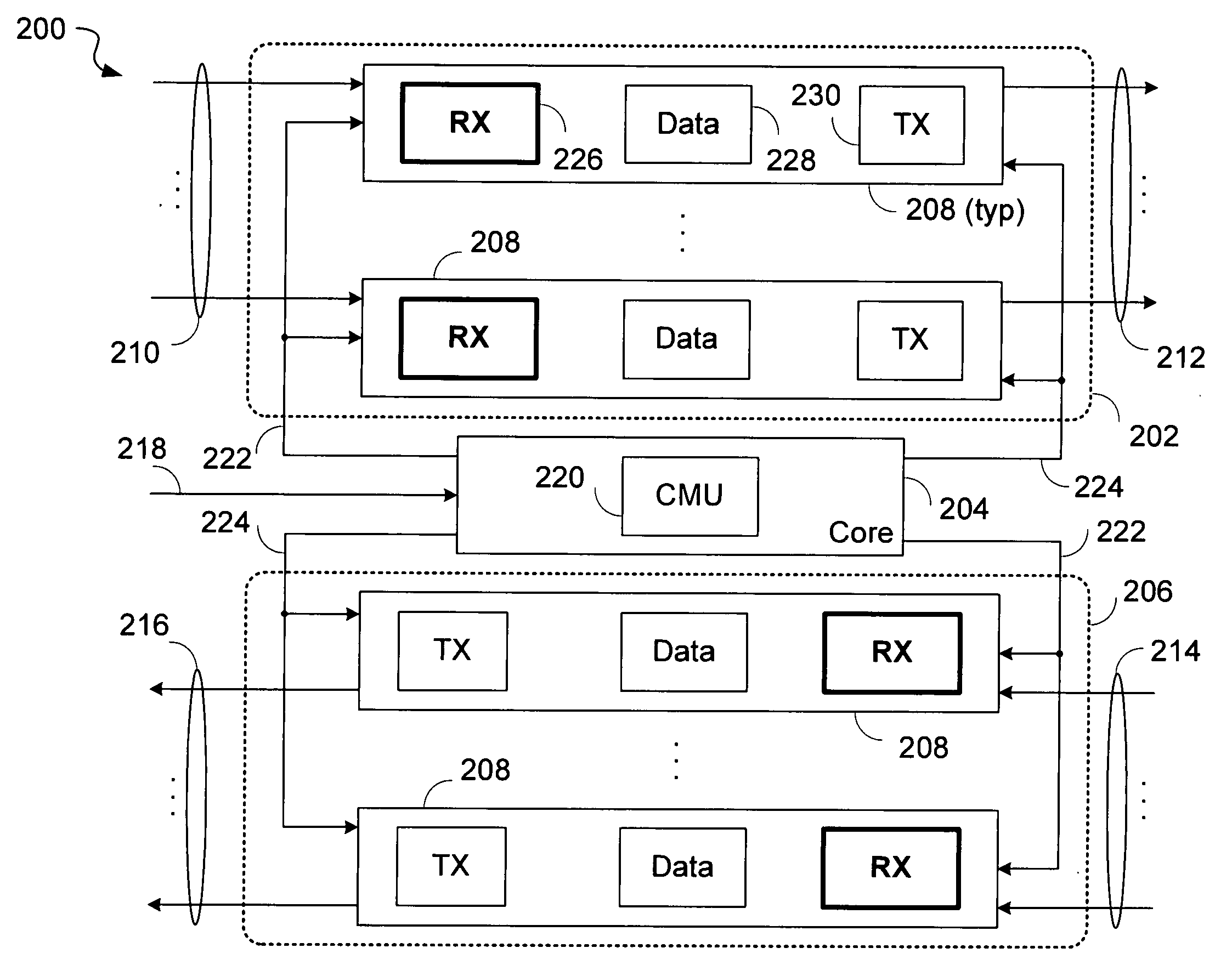

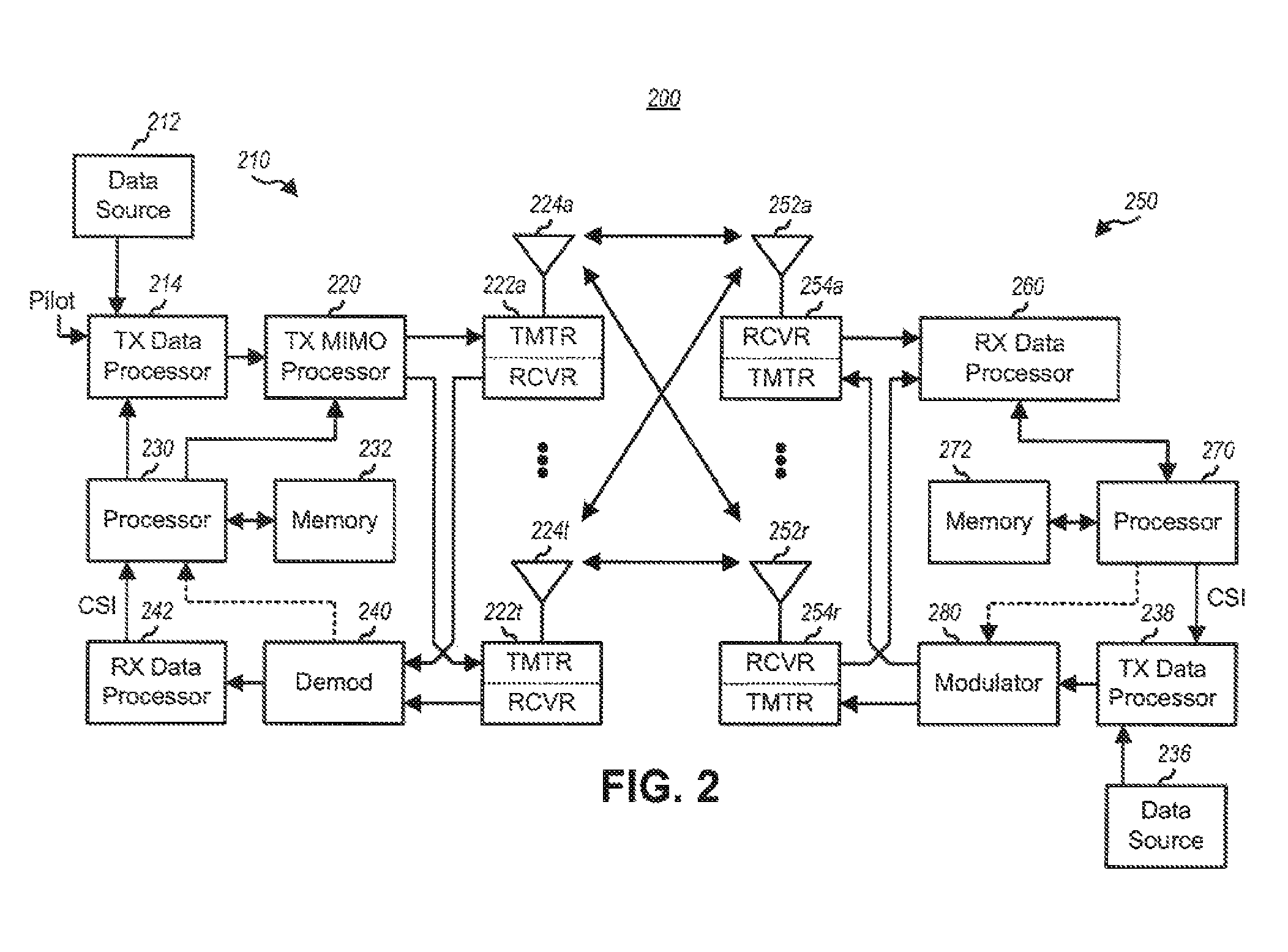

Method and system for multiple channel wireless transmitter and receiver phase and amplitude calibration

InactiveUS6862440B2Low costTransmitters monitoringReceivers monitoringTransmission channelEngineering

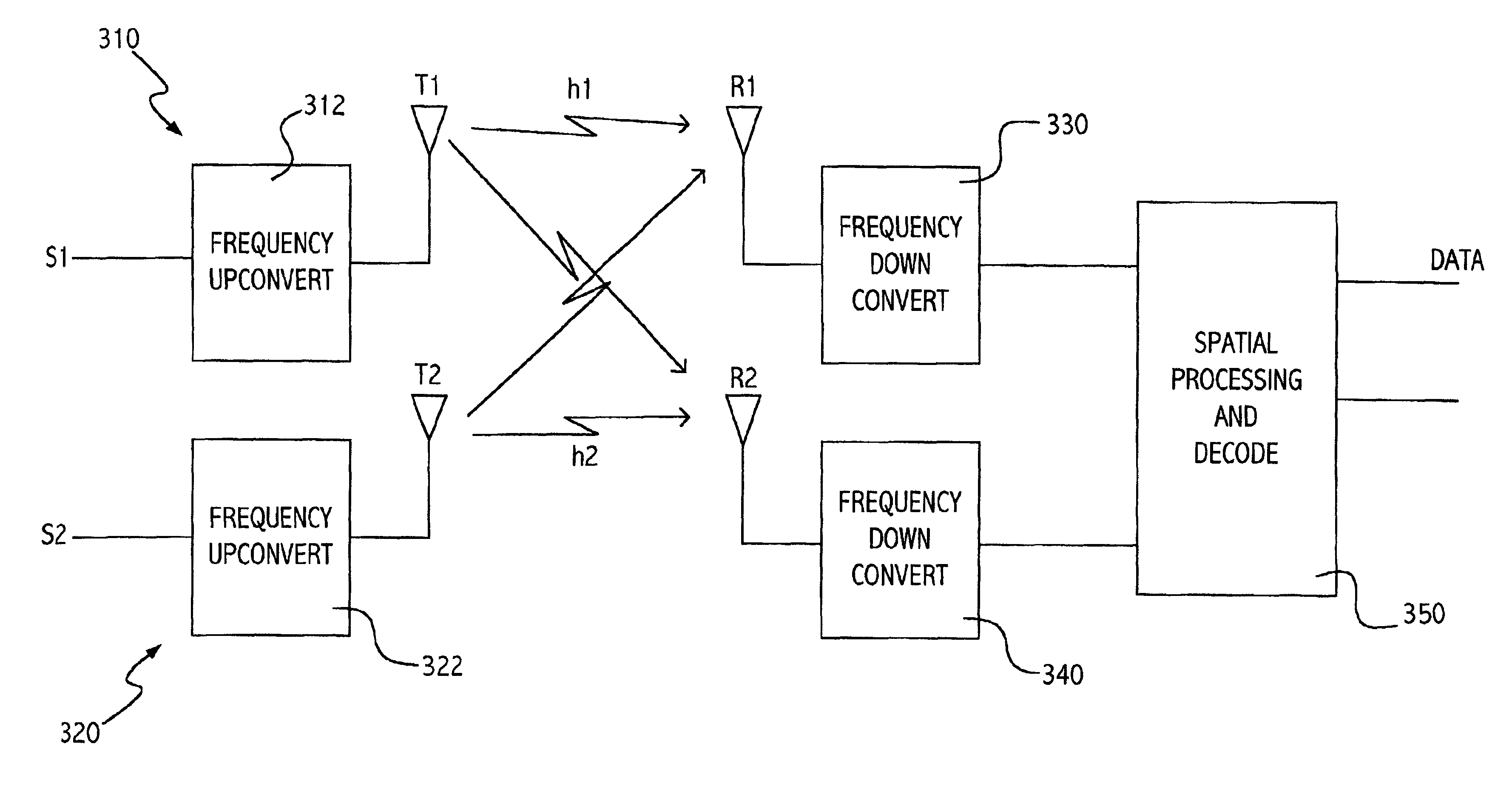

The present invention provides a method and system for estimating common amplitude and phase errors of a multiple channel wireless system. The multiple channel wireless system includes a plurality of transmission channels formed between a plurality of transmission antennas and a plurality of receiver antennas. The method includes estimating transmission channel elements between each transmission antenna and receiver antenna pair of the multiple channel wireless system. Calibration symbols are transmitted from each transmit antenna. Signals are received that correspond to the calibration symbols having traveled through the transmission channels. Received calibration symbols are estimated based upon spatial processing of the received signals and the estimated transmission channel elements. Common amplitude and phase errors are estimated for each transmit and receive antenna pair by comparing the transmitted calibration symbols with the received calibration symbols.

Owner:TAHOE RES LTD

Systems and methods for compensating for transmission phasing errors in a communications system using a receive signal

Owner:HARRIS CORP

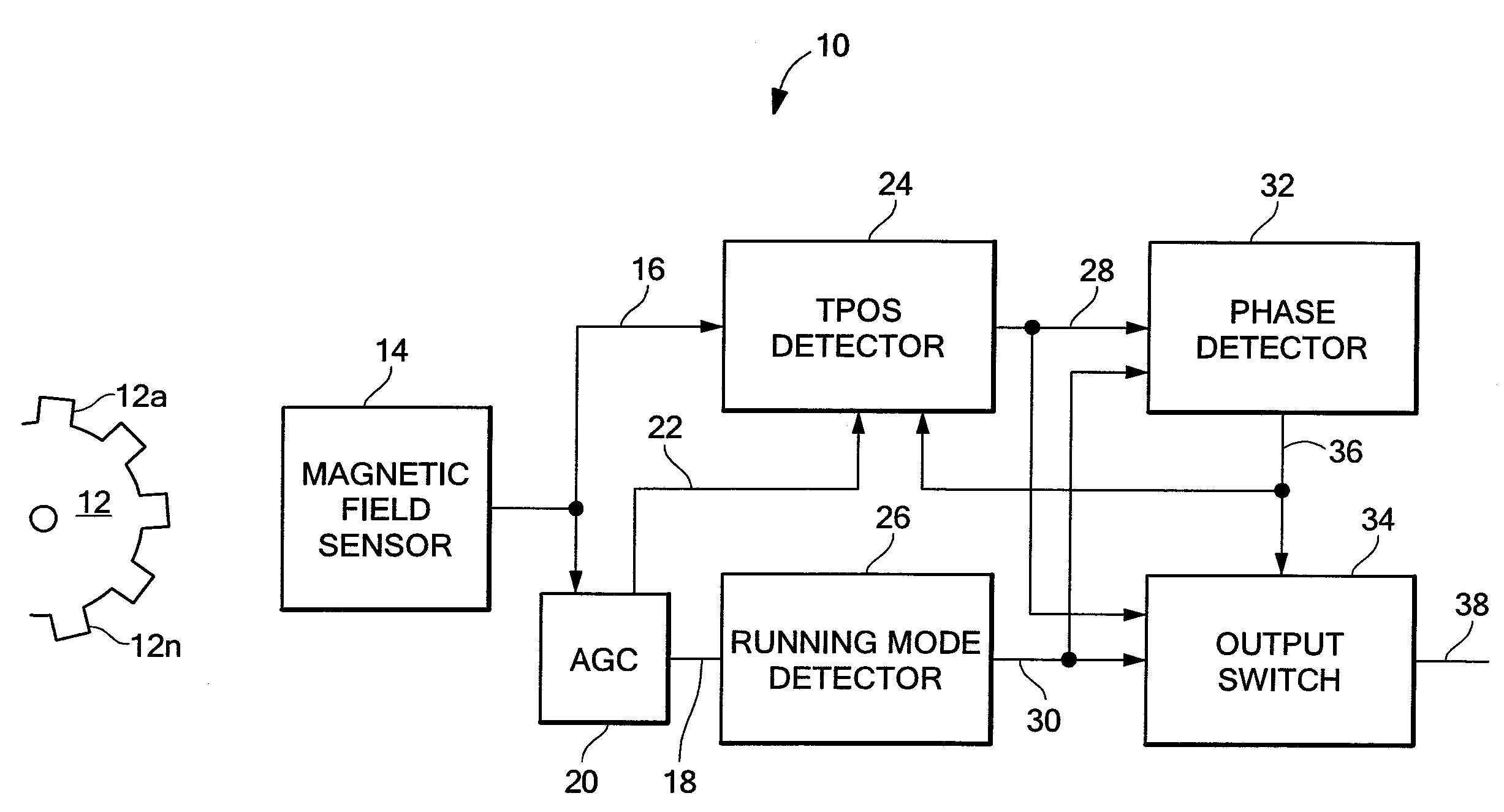

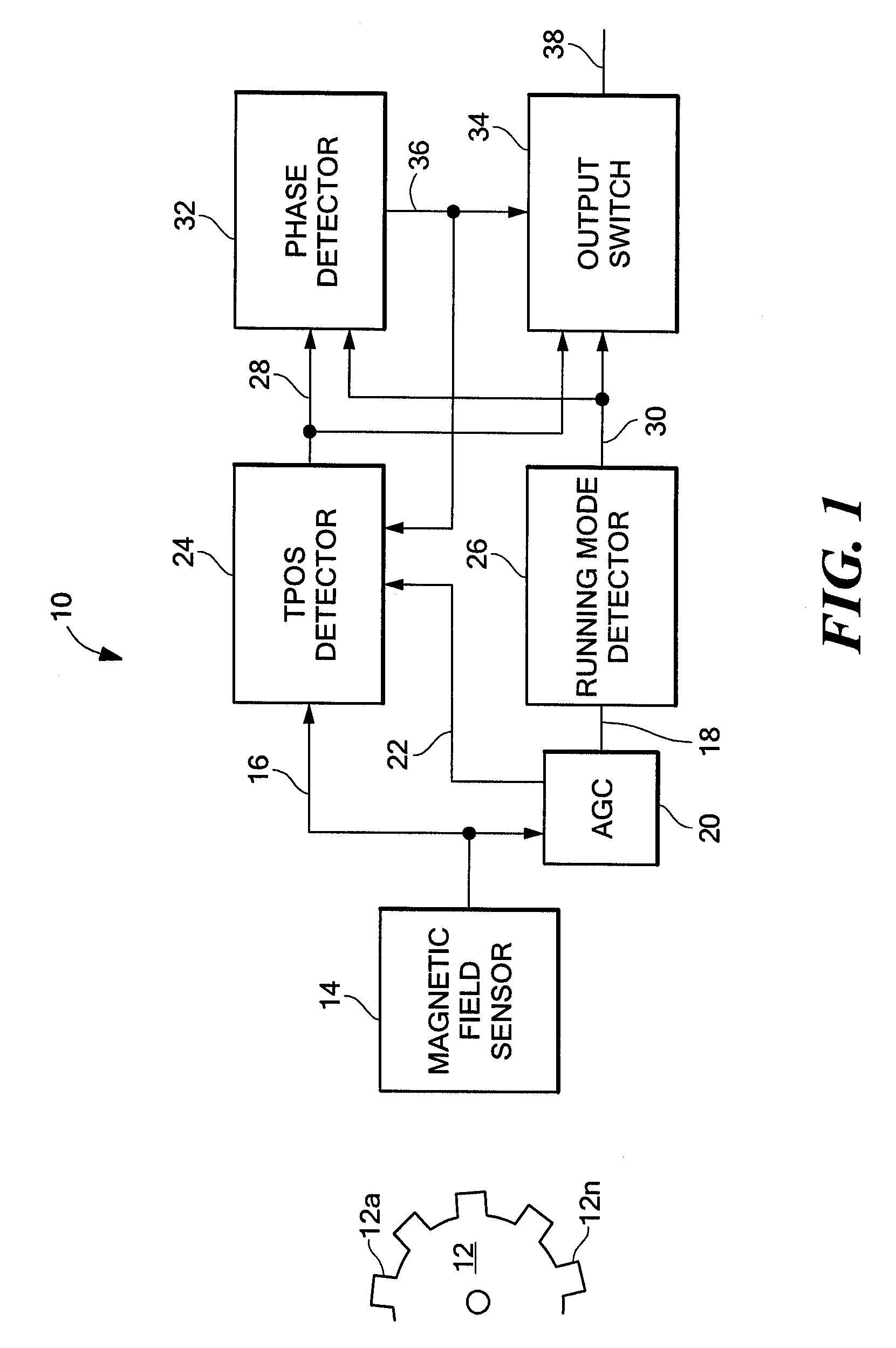

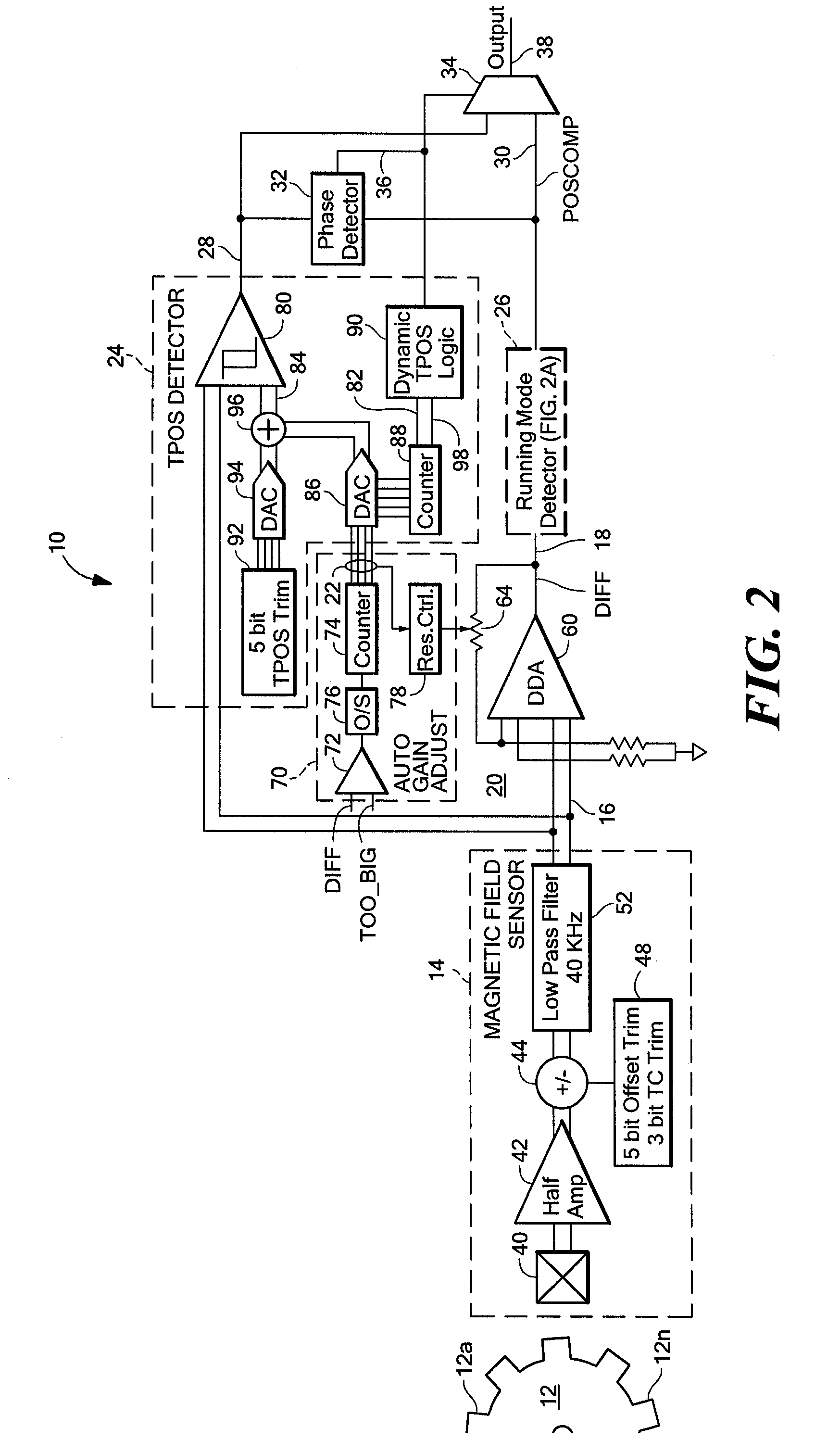

Methods and apparatus for magnetic article detection

ActiveUS7362094B2Reduce errorsUsing electrical meansDevices using electric/magnetic meansControl signalAutomatic gain control

Apparatus and methods for detecting passing magnetic articles using a first, True Power On State (TPOS) detector during a first time interval and transitioning to a second, running mode detector after the first time interval, when the output of the second detector is accurate. A phase comparator is responsive to the output signal of the first and second detectors and provides a control signal indicative of a change in the phase relationship between the two output signals. An output switch controlled by the phase comparator provides, as the detector output signal, the first detector output signal during the first time interval and the second detector output signal thereafter. A threshold signal associated with the TPOS detector is at a fixed level during a first portion of the first time interval and is adjusted during a second portion of the first time interval in response to an automatic gain control circuit in order to reduce the phase error associated with transitioning from the TPOS detector to the running mode detector. Also described are apparatus and methods for updating a running mode threshold signal that is a percentage of the peak-to-peak magnetic field sensor signal, so that unnecessary update events are reduced.

Owner:ALLEGRO MICROSYSTEMS INC

Digital Phase Locked Loop with Integer Channel Mitigation

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal with a plurality of phases. A switch is coupled to receive the RF clock, and is operative to select one of the plurality of phases. A phase detection circuit is coupled to the switch and is operable to receive a selected phase and to provide digital phase error samples indicative of a time difference between the reference clock and the selected phase.

Owner:TEXAS INSTR INC

Clock alignment circuit having a self regulating voltage supply

InactiveUS6928128B1Wide range of operationsReduce power consumptionPulse automatic controlDigital data processing detailsAudio power amplifierEngineering

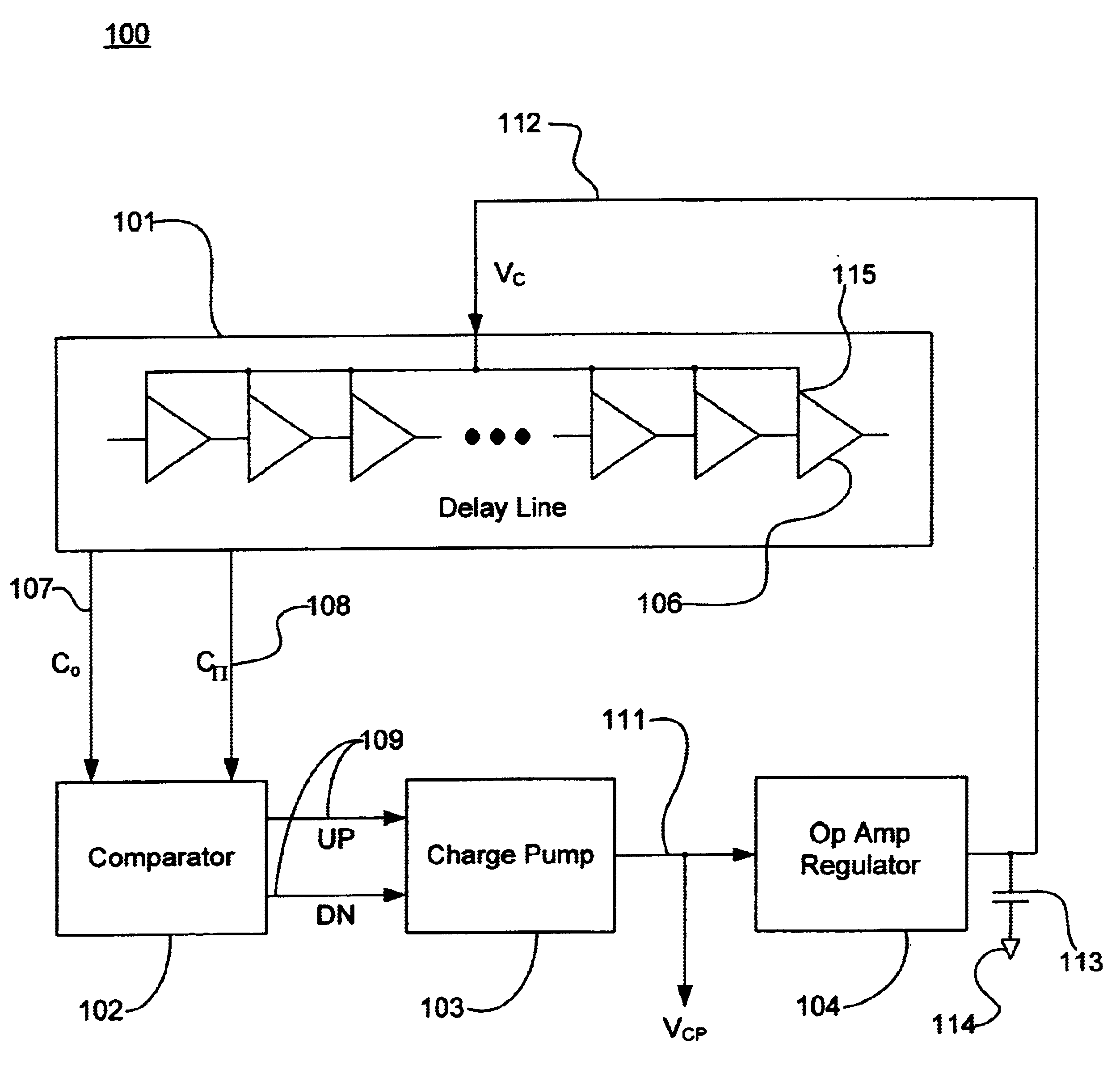

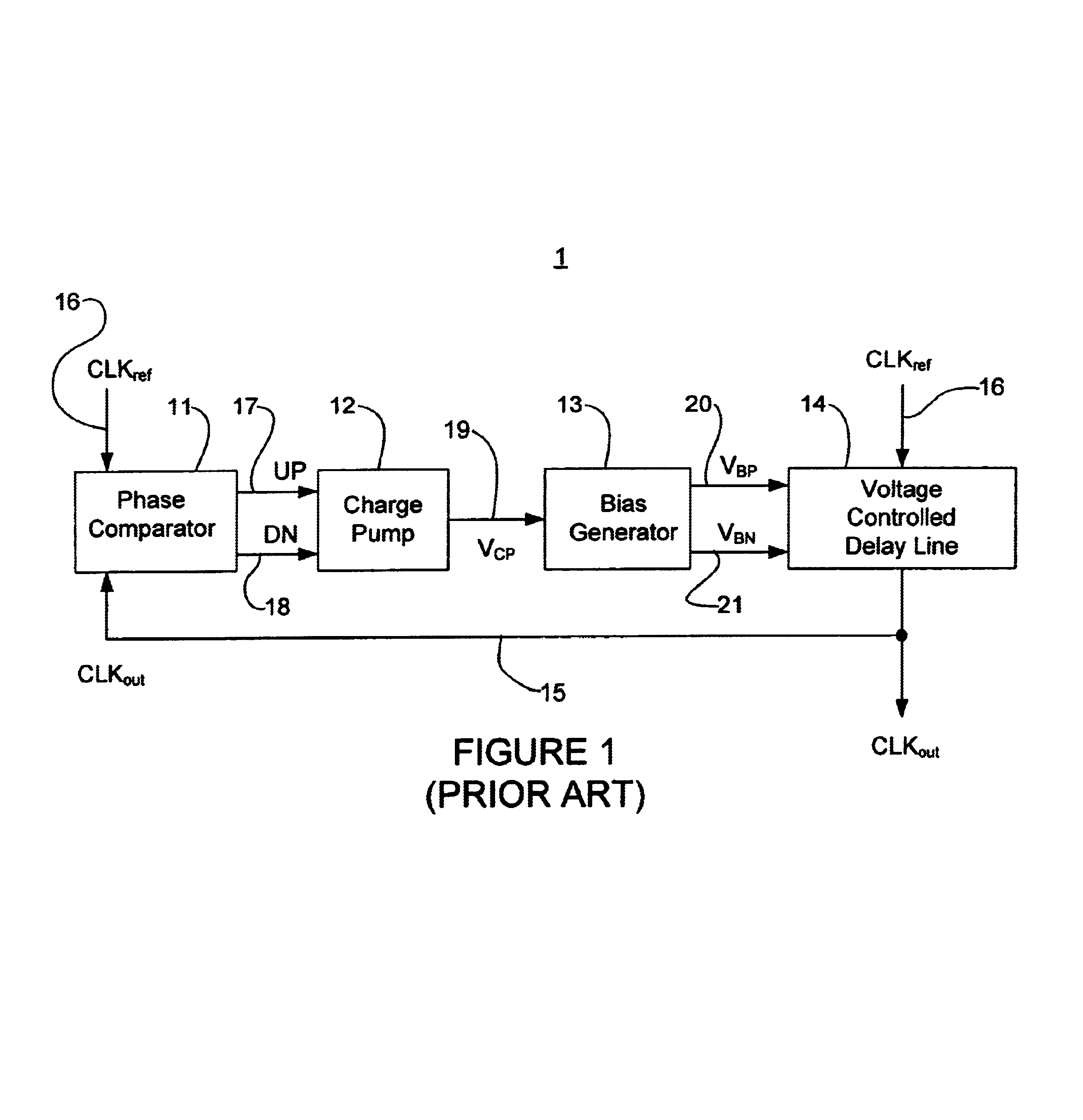

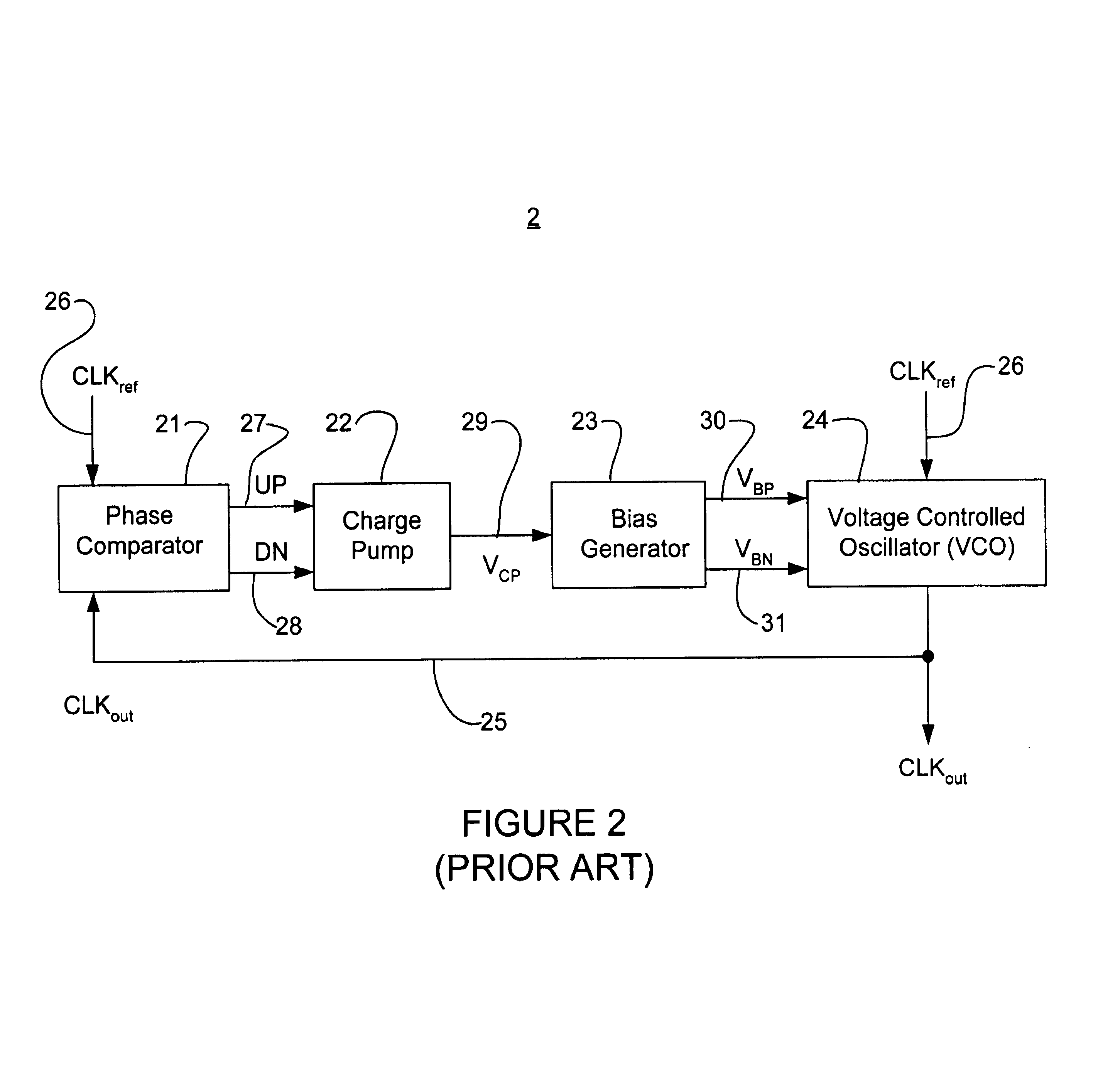

Clock alignment circuits and techniques for reducing power dissipation, increasing power supply noise immunity, decreasing process and temperature variation sensitivity, and providing a wide operating range. A power supply generator generates an isolated supply voltage for a delay line used in a clock alignment circuit. The delay line generates a delayed clock from a reference clock. A comparator detects a correction information (i.e., delay or phase error) between the delayed clock and the reference clock and generates error information representative of the correction information. A charge pump circuit converts the error information into a voltage signal, wherein the voltage signal is a scaled representation of the error information. The power supply generator includes an amplifier having a first input coupled to the voltage signal and an output to provide the supply voltage and a capacitor coupled between the supply voltage and a ground voltage, wherein the amplifier tracks the voltage signal level to regulate the supply voltage.

Owner:RAMBUS INC

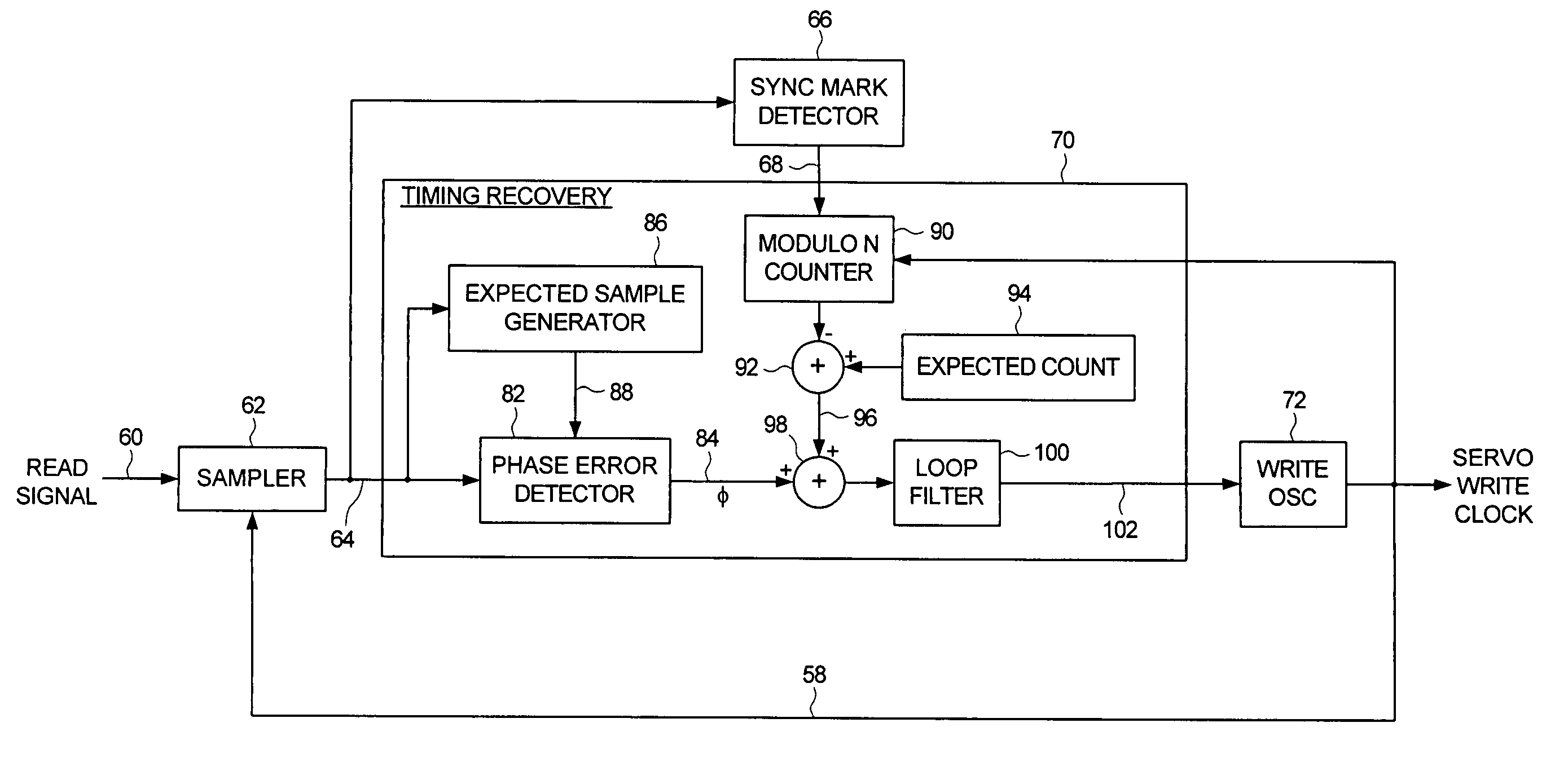

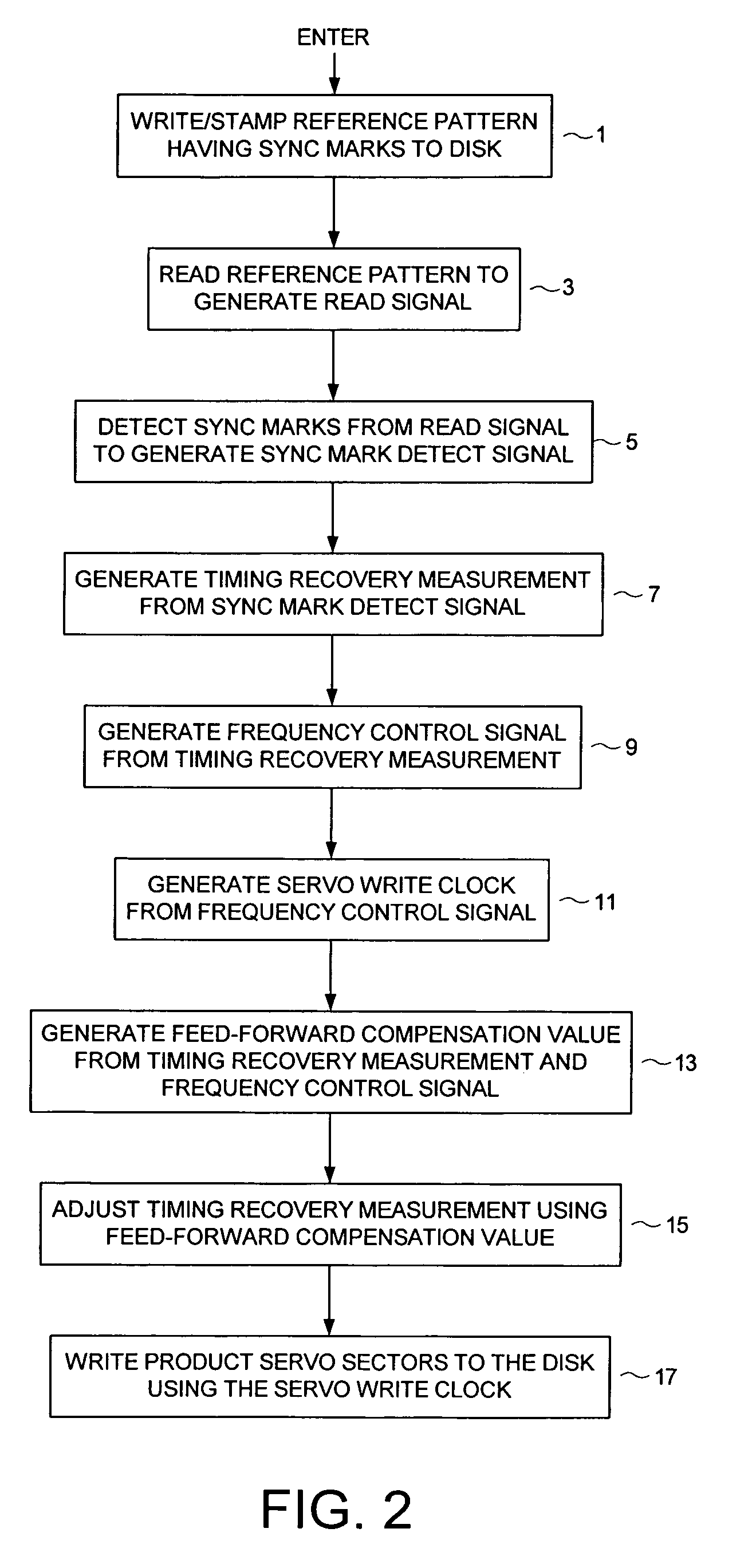

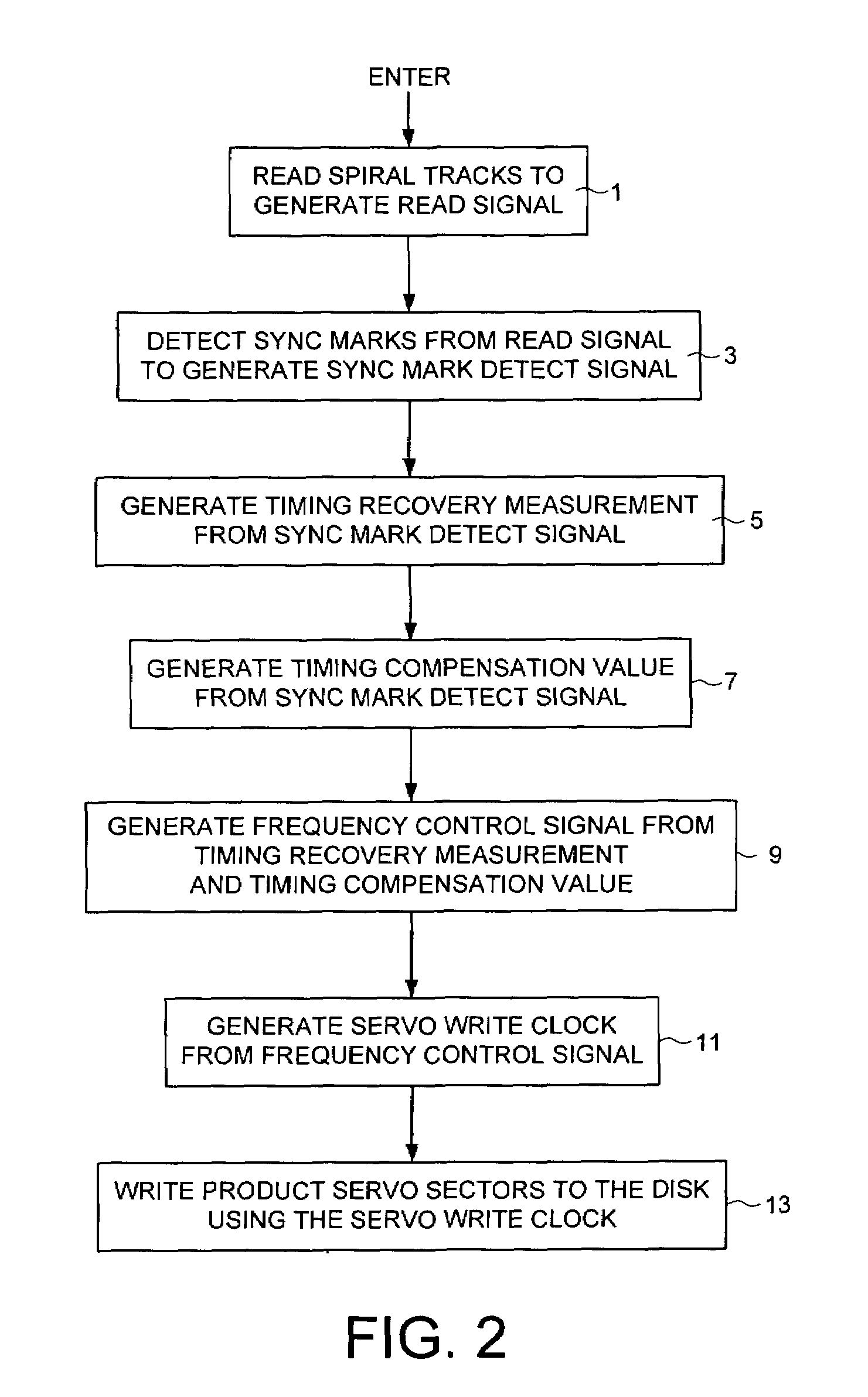

Servo writing a disk drive by synchronizing a servo write clock to a reference pattern on the disk and compensating for repeatable phase error

InactiveUS7333280B1Compensating for such errorDriving/moving recording headsRecord information storageControl signalReference patterns

A method of writing product servo sectors on a disk of a disk drive is disclosed. The disk comprises a reference pattern having a plurality of sync marks written around the disk. The sync marks are detected to generate a sync mark detect signal, and a timing recovery measurement is generated in response to the sync mark detect signal. A frequency control signal is generated in response to the timing recovery measurement, and a servo write clock is generated in response to the frequency control signal. A feed-forward compensation value is generated in response to the timing recovery measurement and the frequency control signal, and the timing recovery measurement is adjusted in response to the feed-forward compensation value to compensate for a repeatable phase error in the timing recovery measurement. The servo write clock and the head internal to the disk drive are used to write the product servo sectors to the disk.

Owner:WESTERN DIGITAL TECH INC

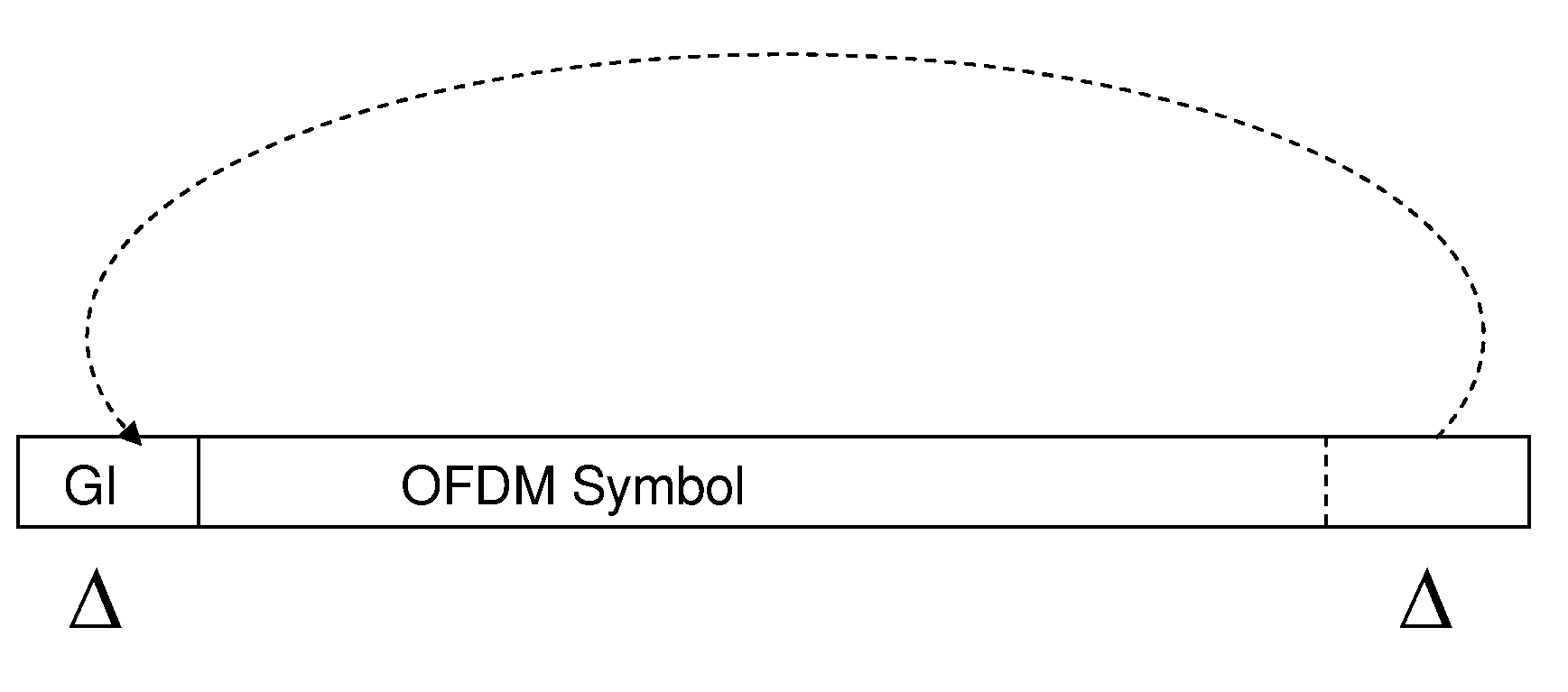

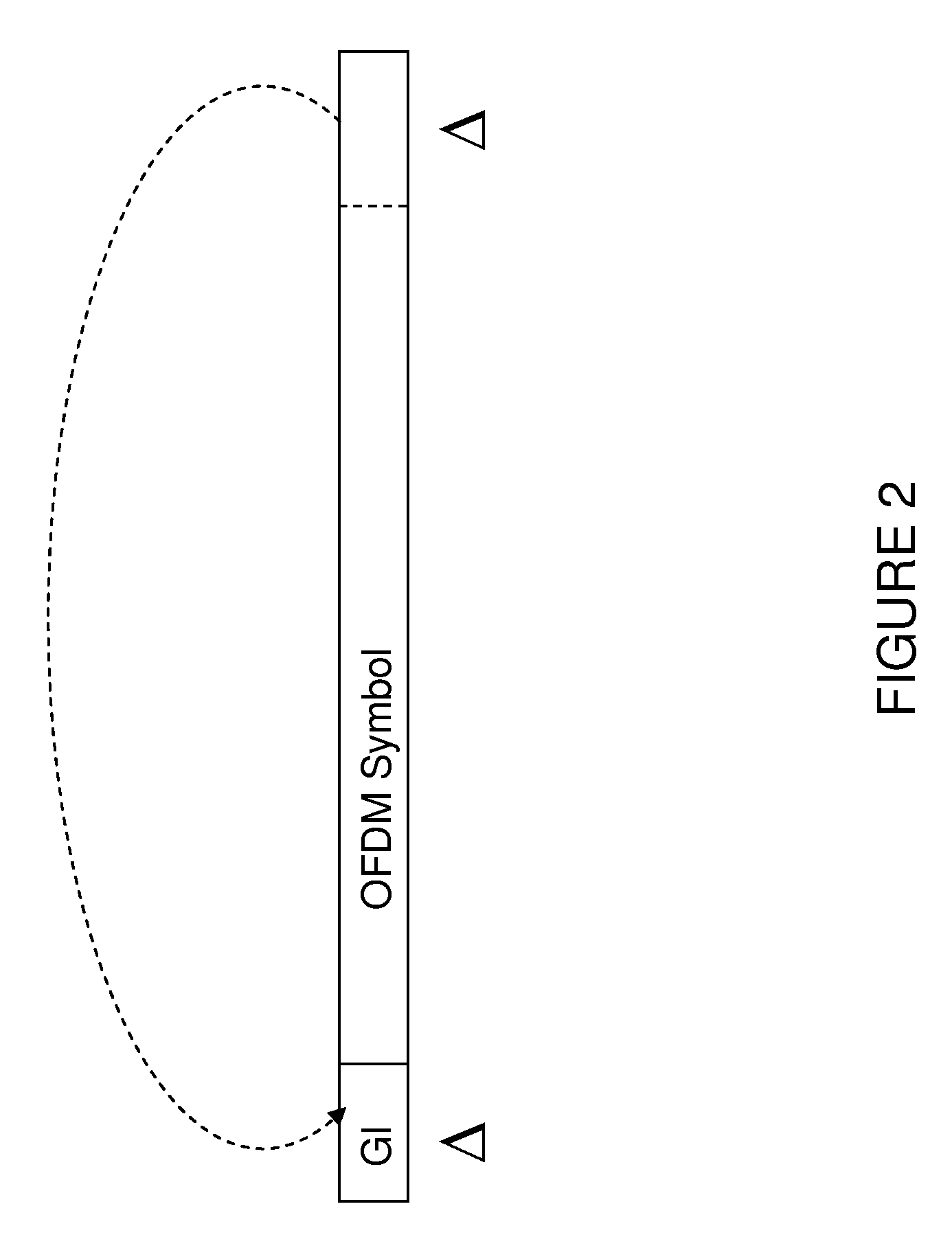

System and Methods for Receiving OFDM Symbols Having Timing and Frequency Offsets

InactiveUS20090225822A1Improve understandingEfficient algorithmNetwork traffic/resource managementCarrier regulationTime domainEngineering

Systems and methods for receiving an OFDM preamble without knowledge of channel characteristics are provided. An OFDM preamble signal with frequency shifted cyclic extensions is received. Taken together the cyclic extensions form a frequency shifted version of the OFDM preamble signal. Frequency offsets and timing offsets are estimated and corrected in an efficient manner using a simple concatenation approach in the time domain, followed by a summation of the OFDM preamble signal and the concatenation after a transformation of the OFDM preamble and the concatenation into the frequency domain. Phase errors in the frequency domain are estimated and corrected after FFT transformations of the received signals. A valid preamble is detected and additional parameters for receiving subsequently transmitted OFDM symbols in a channel are extracted from the OFDM preamble. The methods are computationally efficient and robust. Receiver implementations for performing the methods in a DVB receiver are disclosed.

Owner:NOKIA TECHNOLOGLES OY

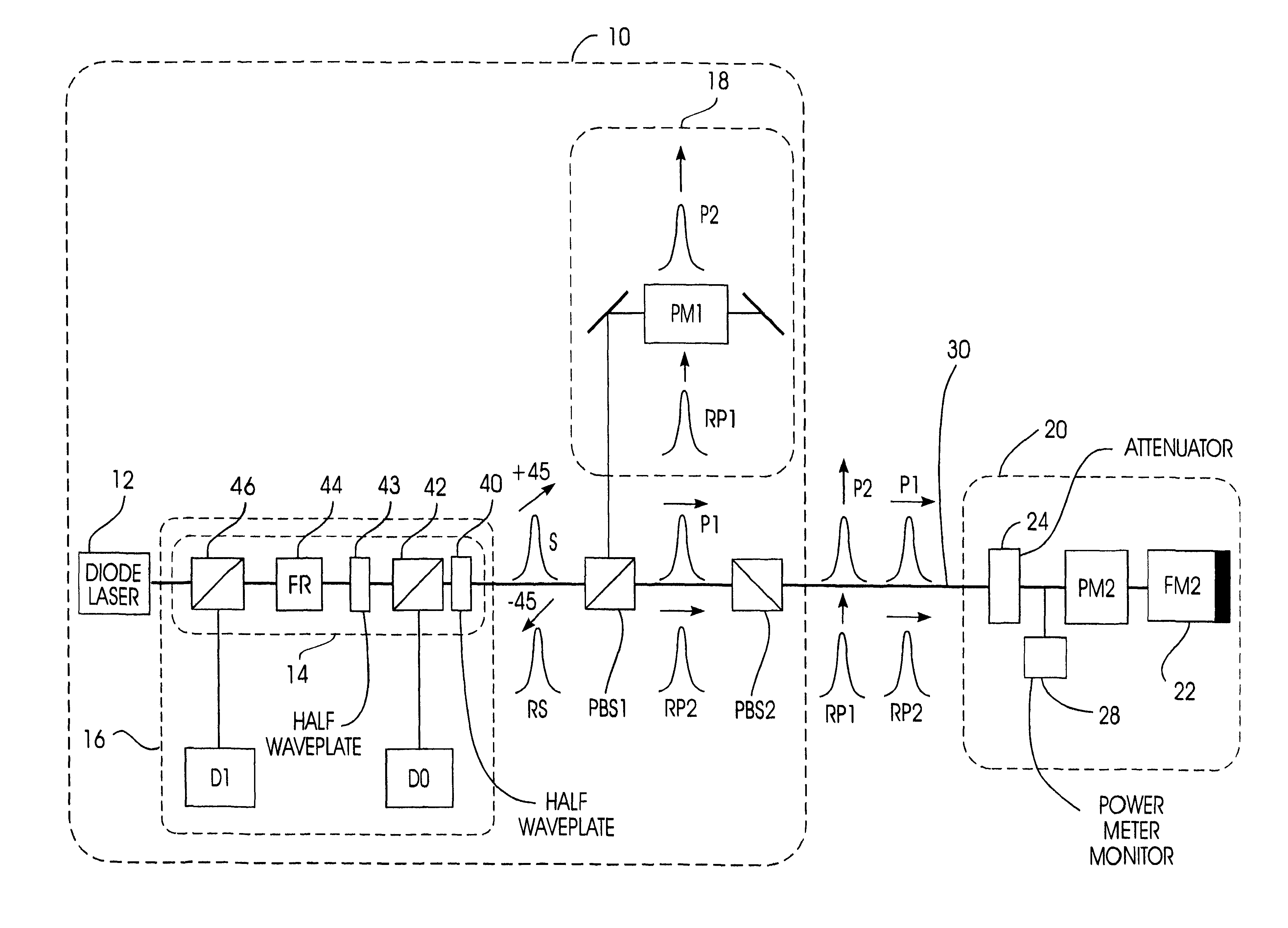

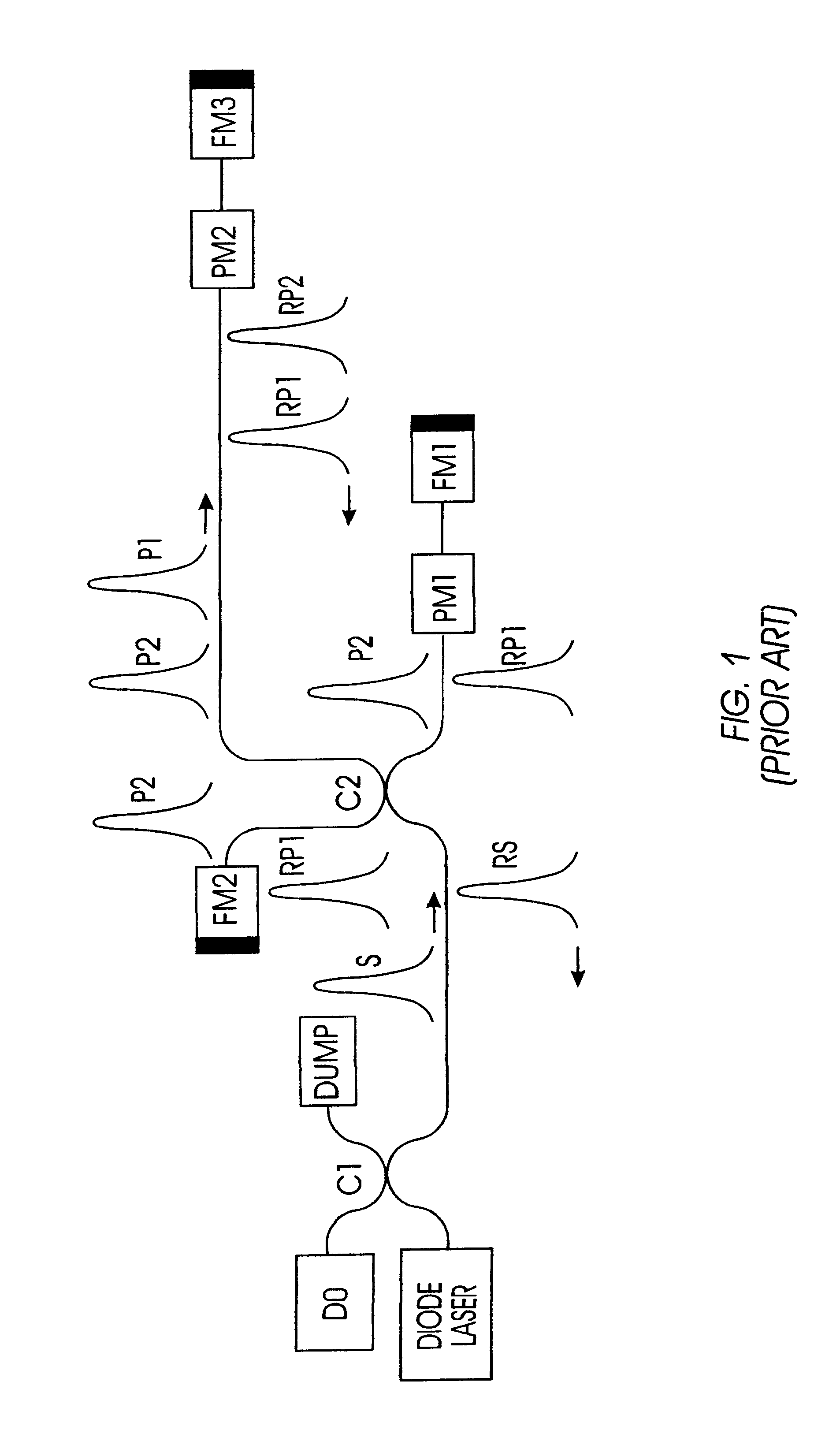

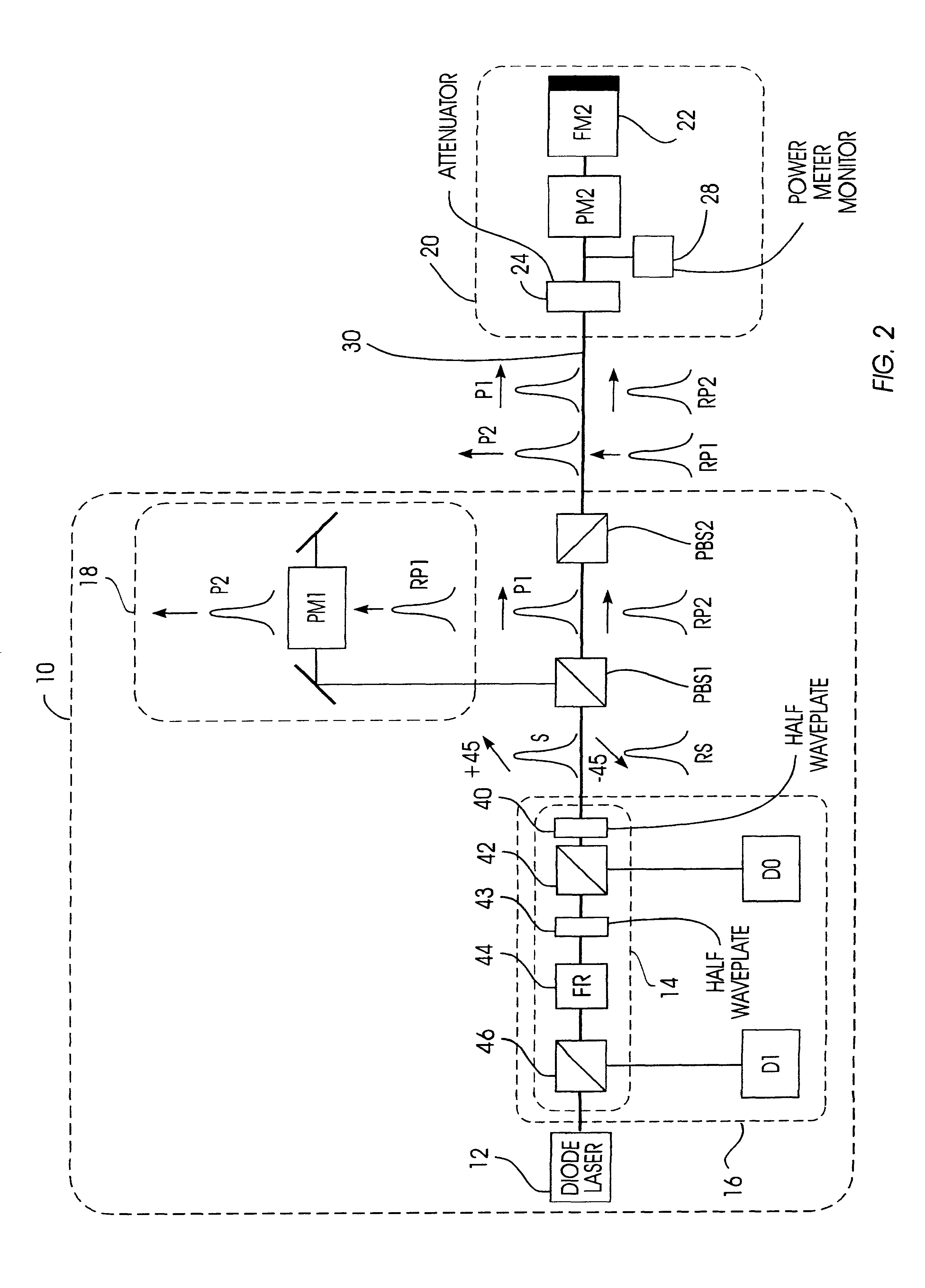

Autocompensating quantum cryptographic key distribution system based on polarization splitting of light

A quantum cryptographic key distribution (QKD) system splits discrete light signals from a laser source into a pair of light pulses that are orthogonally polarized with respect to each other, imparts a phase shift to one or both of these separate pulses during their round trip from the sender to the receiver and back, assures that the return pulses from the receiver are attenuated to single-photon pulses, recombines the phase-shifted pulses at the sender, and then detects from the recombined signal its polarization state, which is representative of the net phase shift imparted by the sender and receiver. The phase modulator at the receiver transmits only one polarization (e.g., vertical), but is used in a manner that permits it to equally modulate both polarization components of an arriving pulse. In this arrangement, when both components of a pulse reach the phase modulator at the receiver, they are both entirely vertically polarized and a phase shift is imparted at that time. This has the advantage that the effect of any time variation or phase errors in the phase modulator will be the same on both components. The key information is decoded at a detection stage at the sender that uses two detectors, one of which detects a first polarization state corresponding to the phase difference between the two phase shifts being 0 and the other of which detects a second polarization state corresponding to the phase difference between the two phase shifts being pi.

Owner:IBM CORP

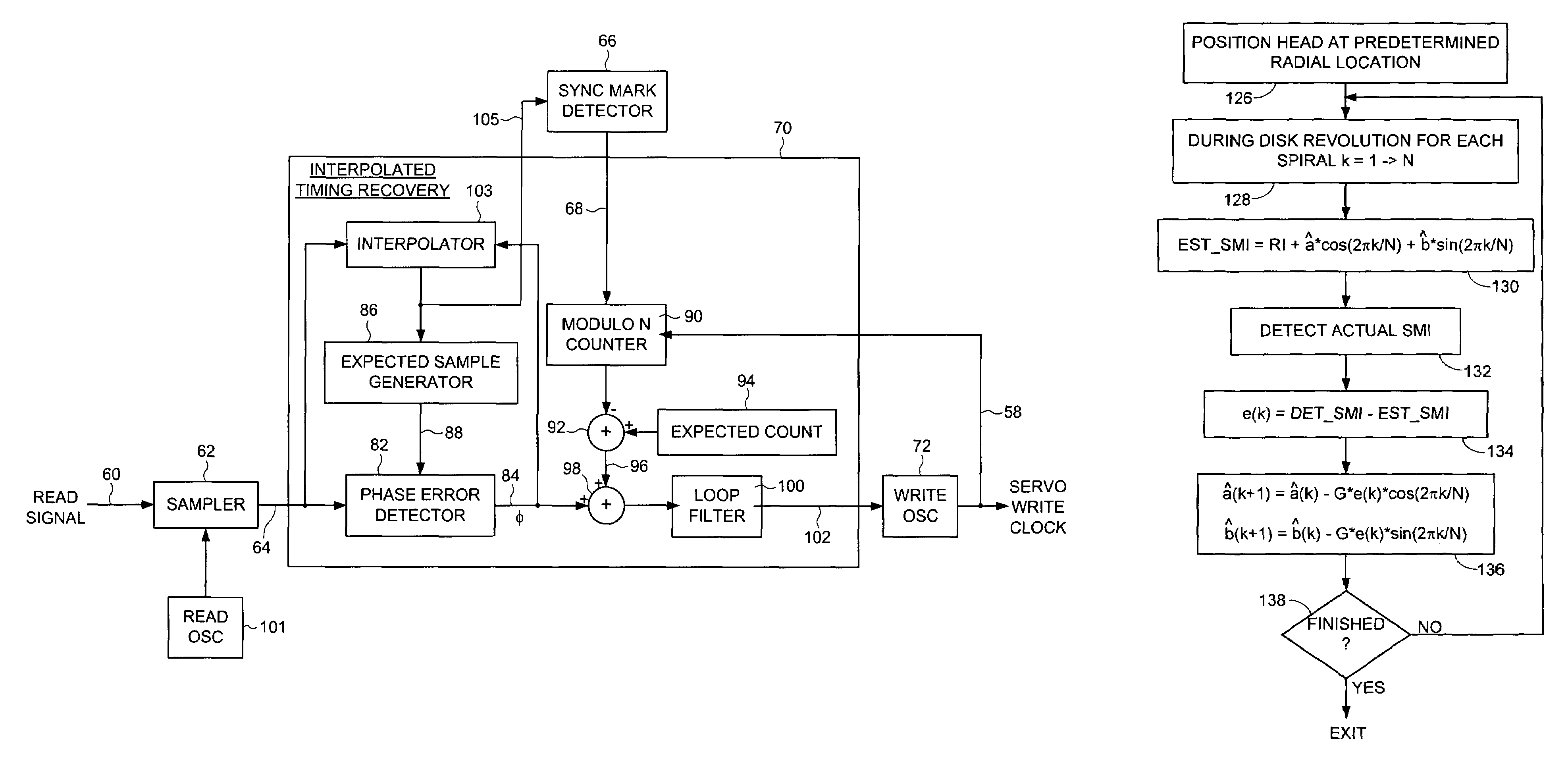

Compensating for repeatable phase error when servo writing a disk drive from spiral tracks

InactiveUS7391584B1Driving/moving recording headsRecord information storageControl signalEngineering

A method of servo writing a disk of a disk drive is disclosed. The disk comprises a plurality of spiral tracks, wherein each spiral track comprises a high frequency signal interrupted periodically by a sync mark. A timing recovery measurement is generated in response to the sync marks, wherein the timing recovery measurement comprises a sinusoidal component. A timing compensation value is generated in response to the sync marks which estimates the sinusoidal component in the timing recovery measurement. A frequency control signal is generated in response to the timing recovery measurement and the timing compensation value, a servo write clock is generated in response to the frequency control signal, and the servo write clock and the head internal to the disk drive are used to write the product servo sectors to the disk.

Owner:WESTERN DIGITAL TECH INC

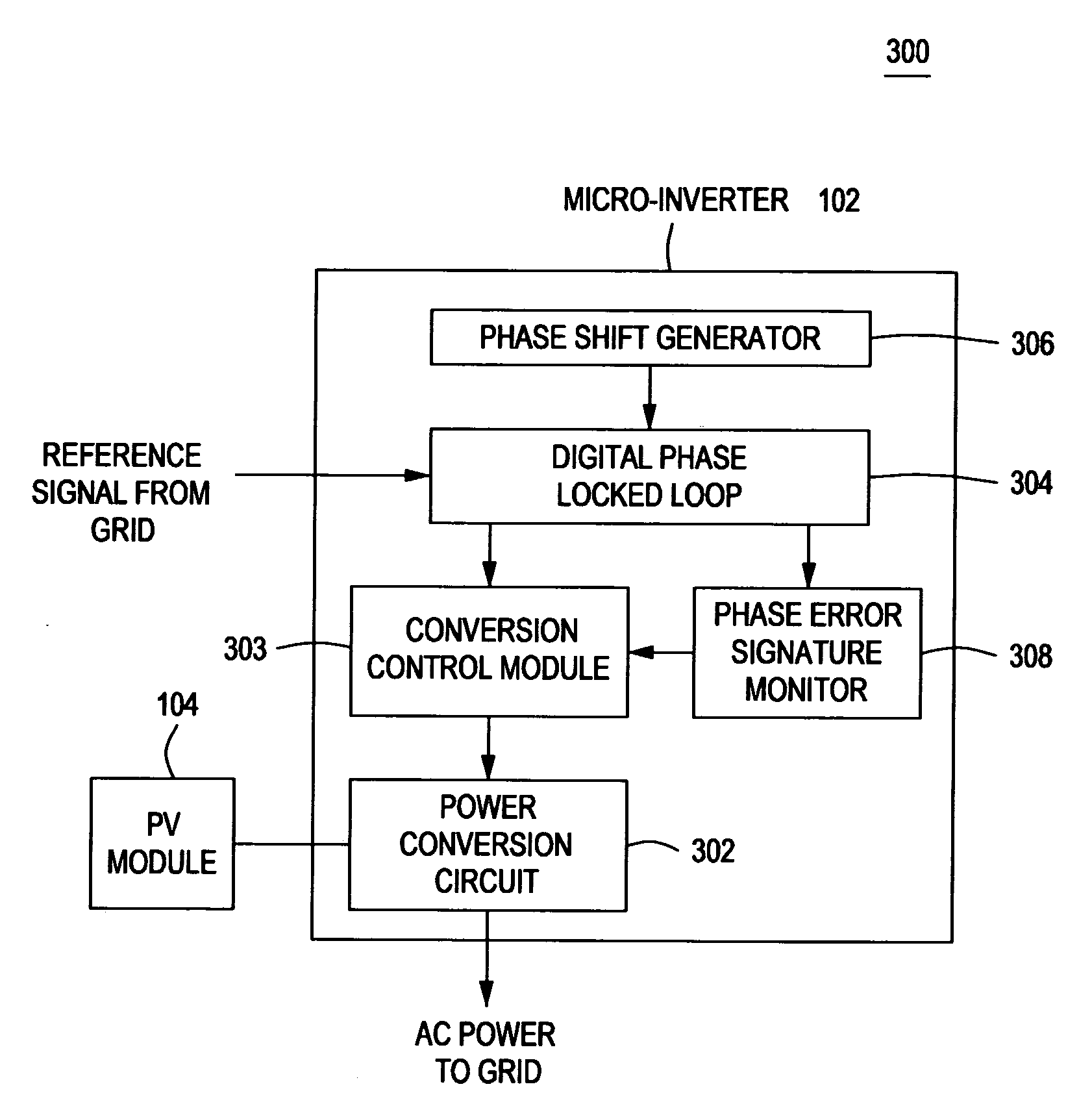

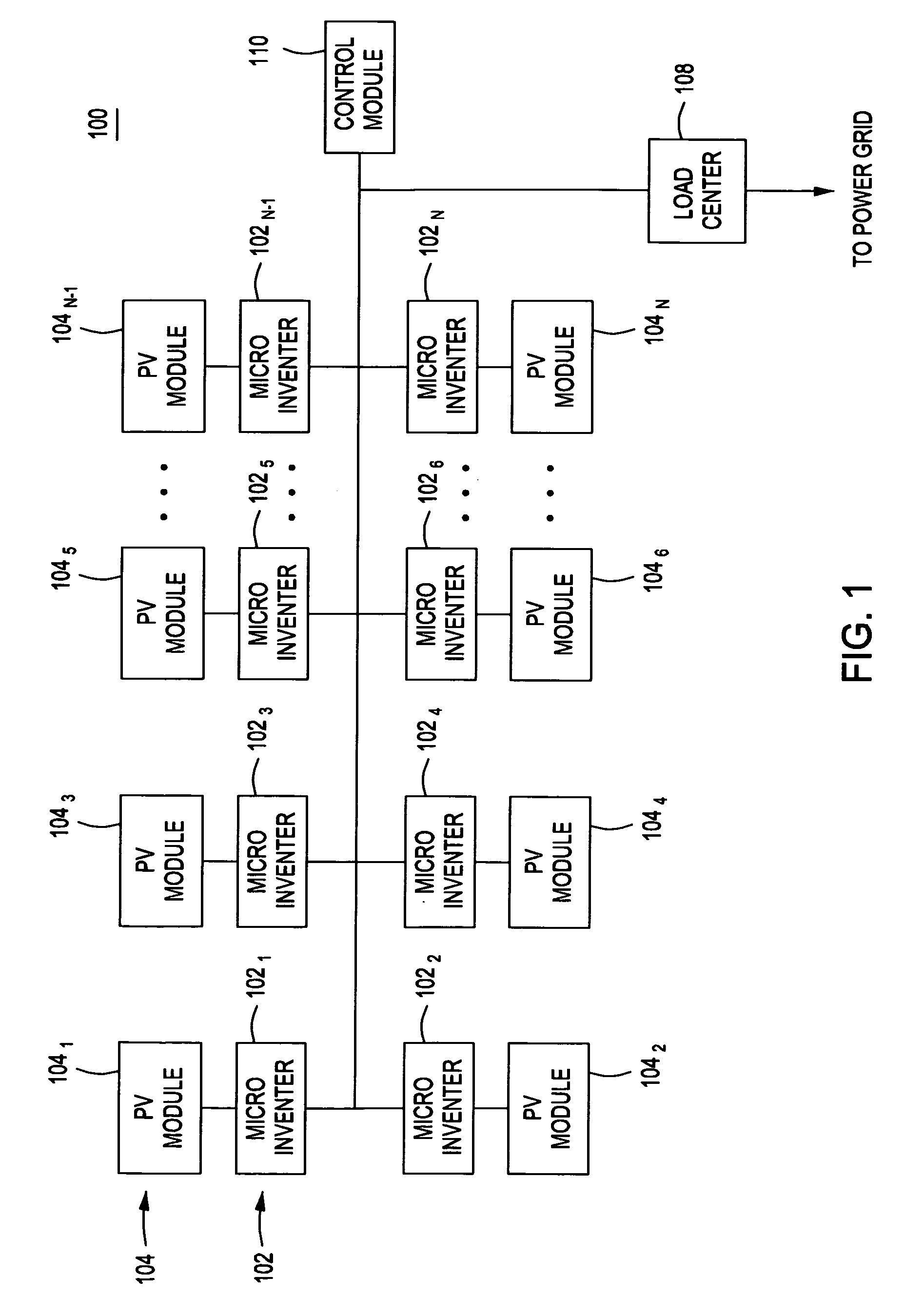

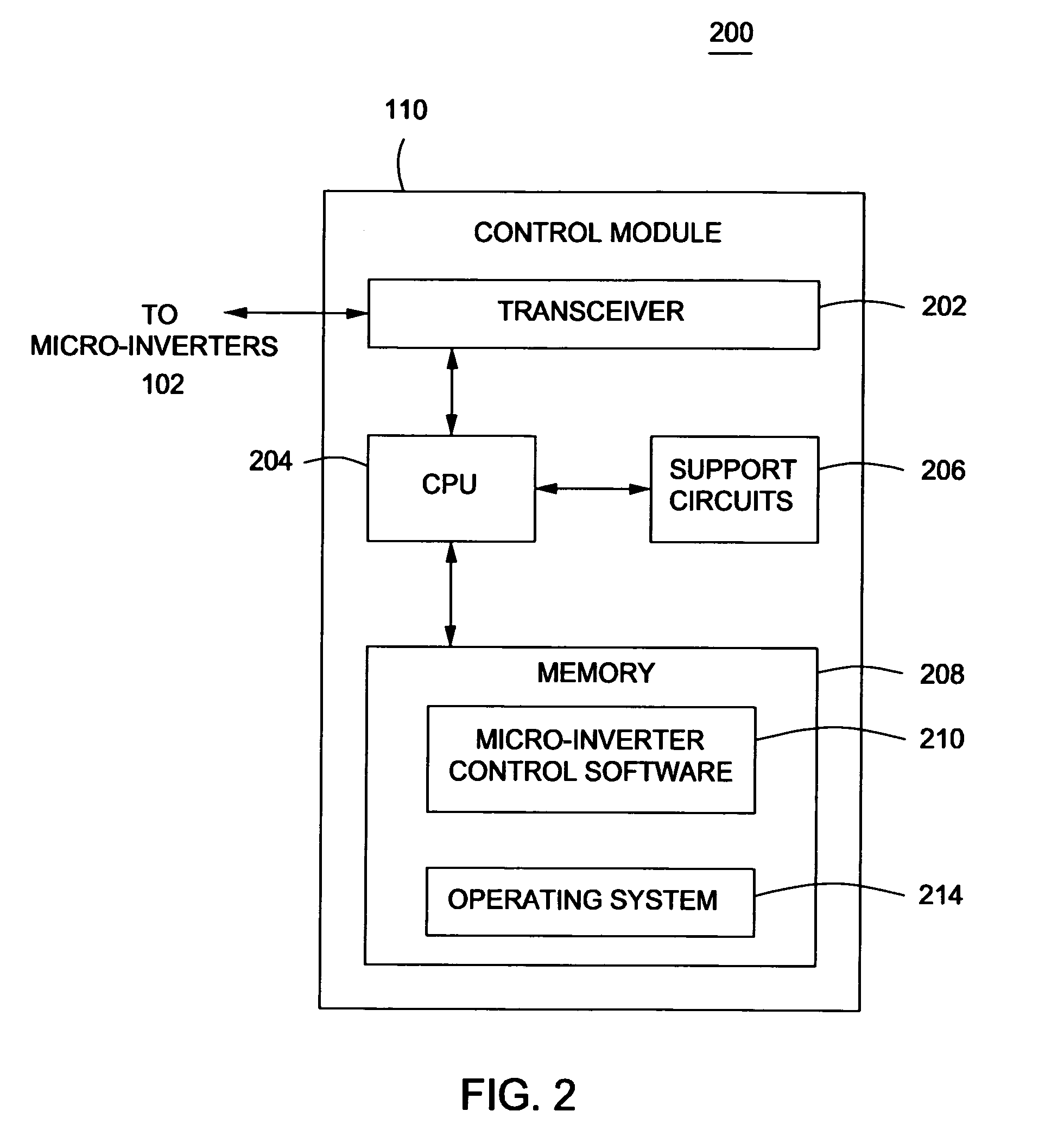

Method and apparatus for anti-islanding of distributed power generation systems

InactiveUS20090021877A1Noise figure or signal-to-noise ratio measurementApparatus with intermediate ac conversionIslandingPhase shifted

A method and apparatus for anti-islanding of distributed power generation systems having an inverter comprising a phase locked loop (PLL), a phase shift generator for injecting a phase shift into the PLL during at least one sample period, and a phase error signature monitor for monitoring at least one phase error response of the PLL during the at least one sample period.

Owner:ENPHASE ENERGY

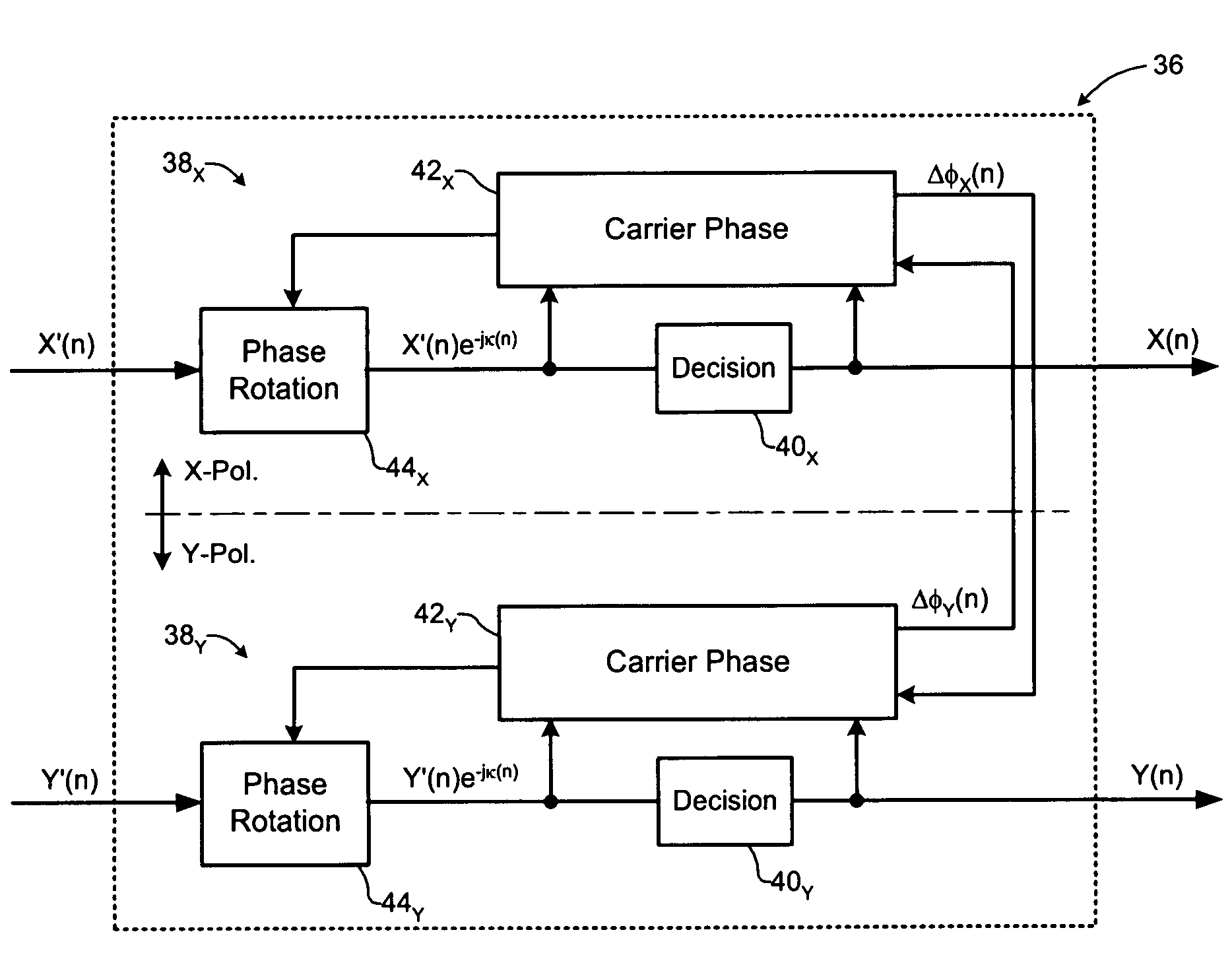

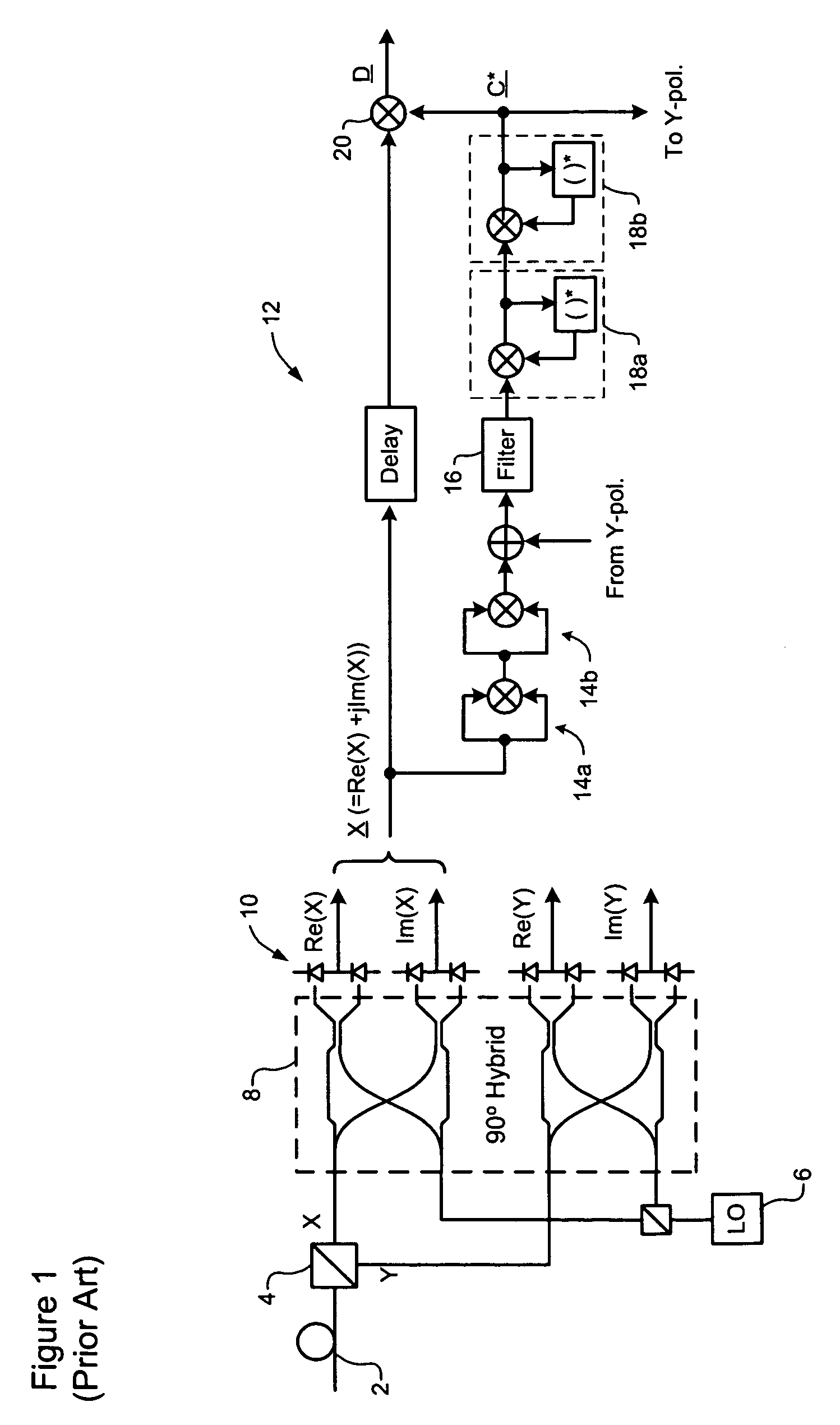

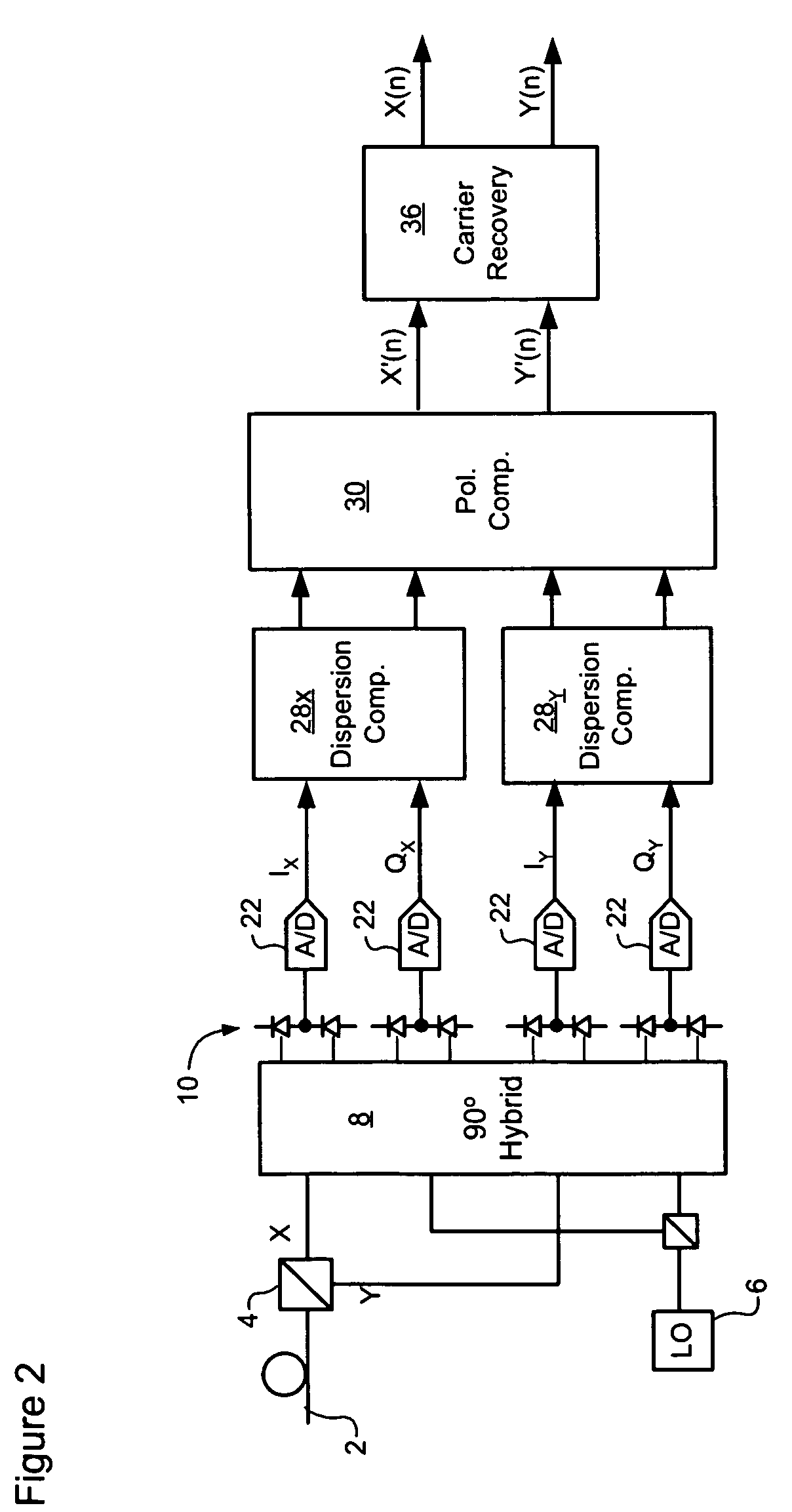

Carrier recovery in a coherent optical receiver

ActiveUS7606498B1Receiver initialisationSynchronisation by photonic/optical meansCarrier recoveryOptical receivers

A method of carrier recovery from a high speed optical signal received through an optical communications network. A stream of multi-bit digital samples of the optical signal is processed to generate a multi-bit estimate X′(n) of each one of a plurality of transmitted symbols. A phase of each symbol estimate X′(n) is rotated, and a respective symbol phase error Δφ(n) of the rotated symbol estimate determined.

Owner:CIENA

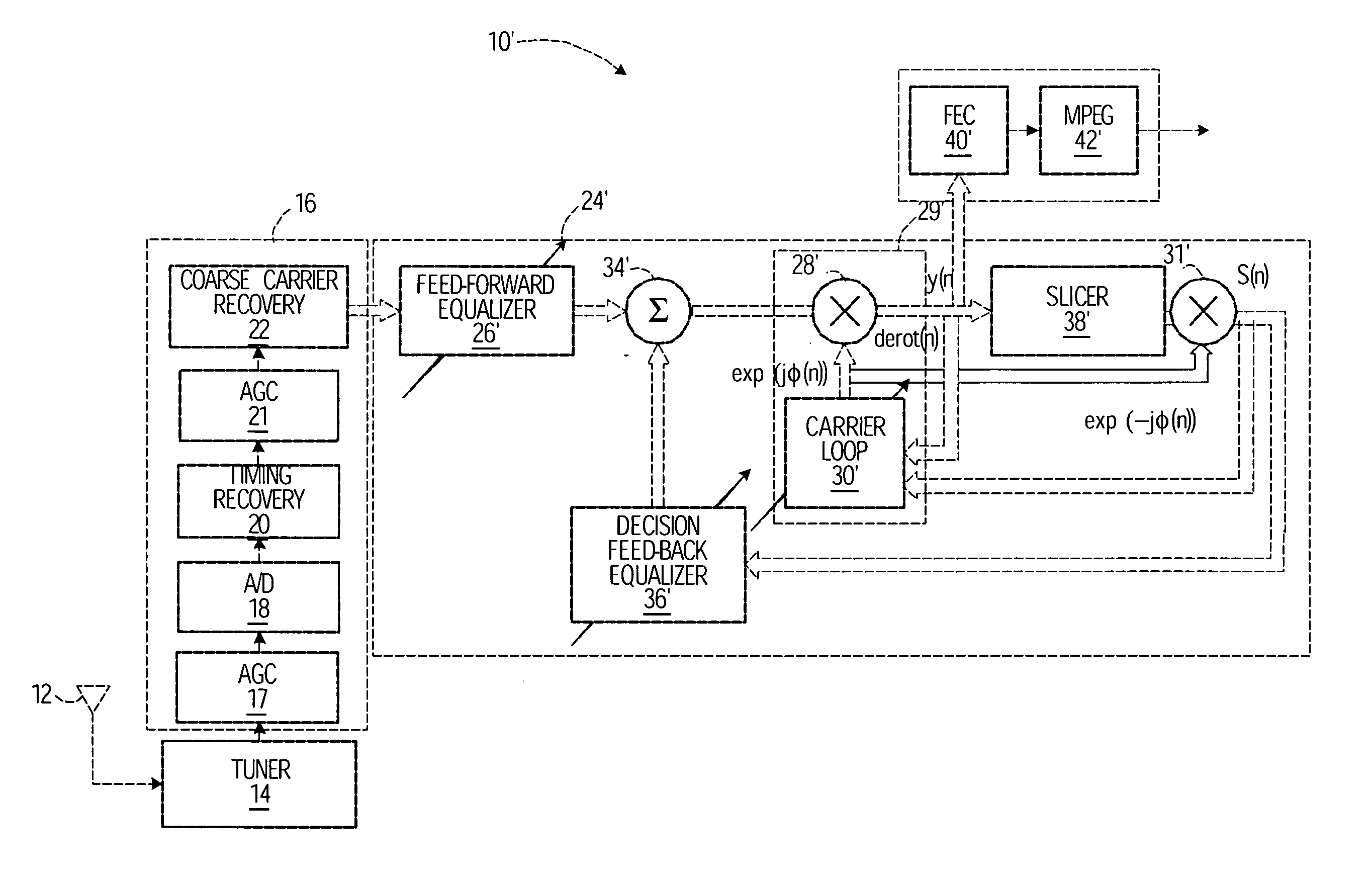

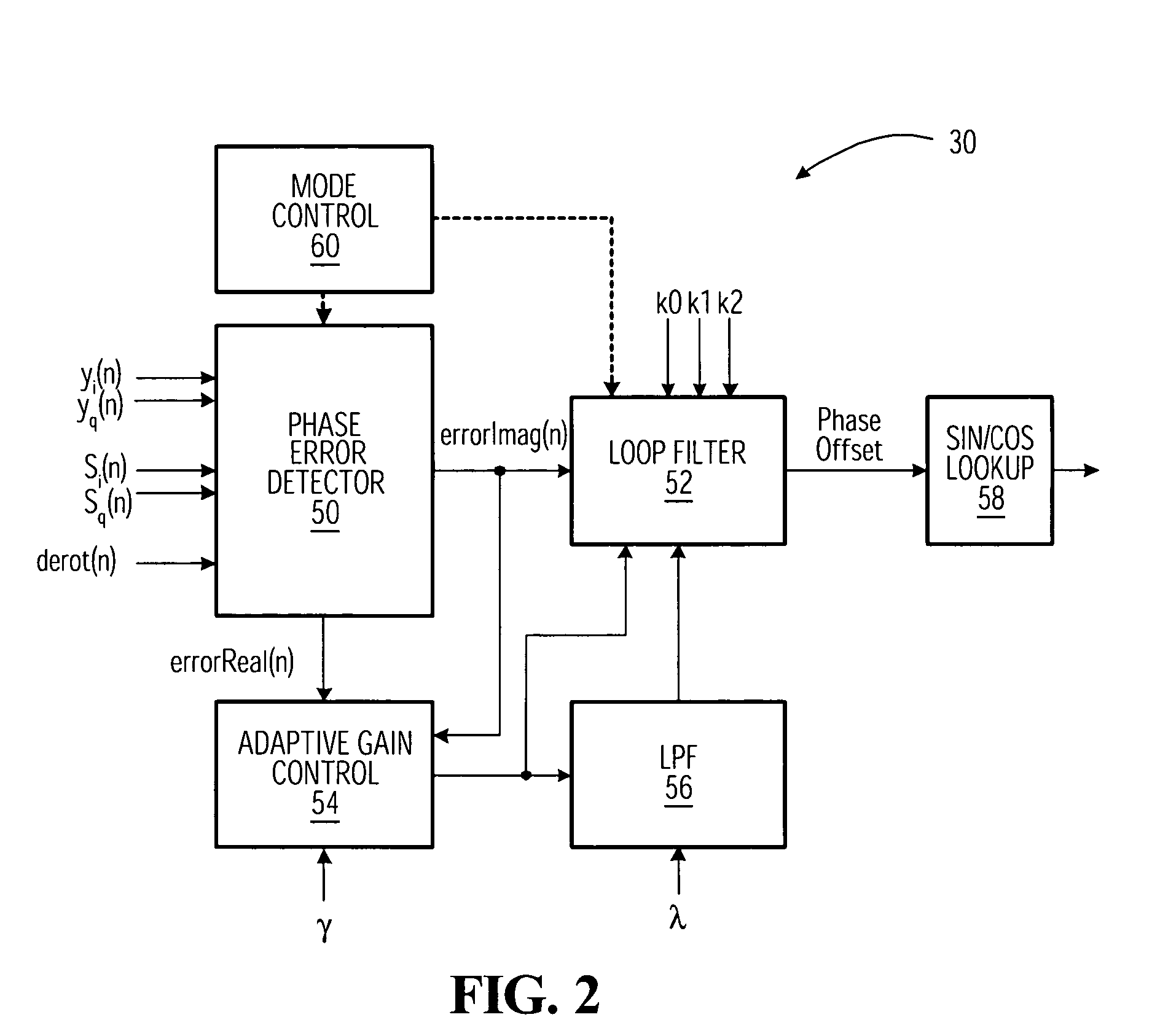

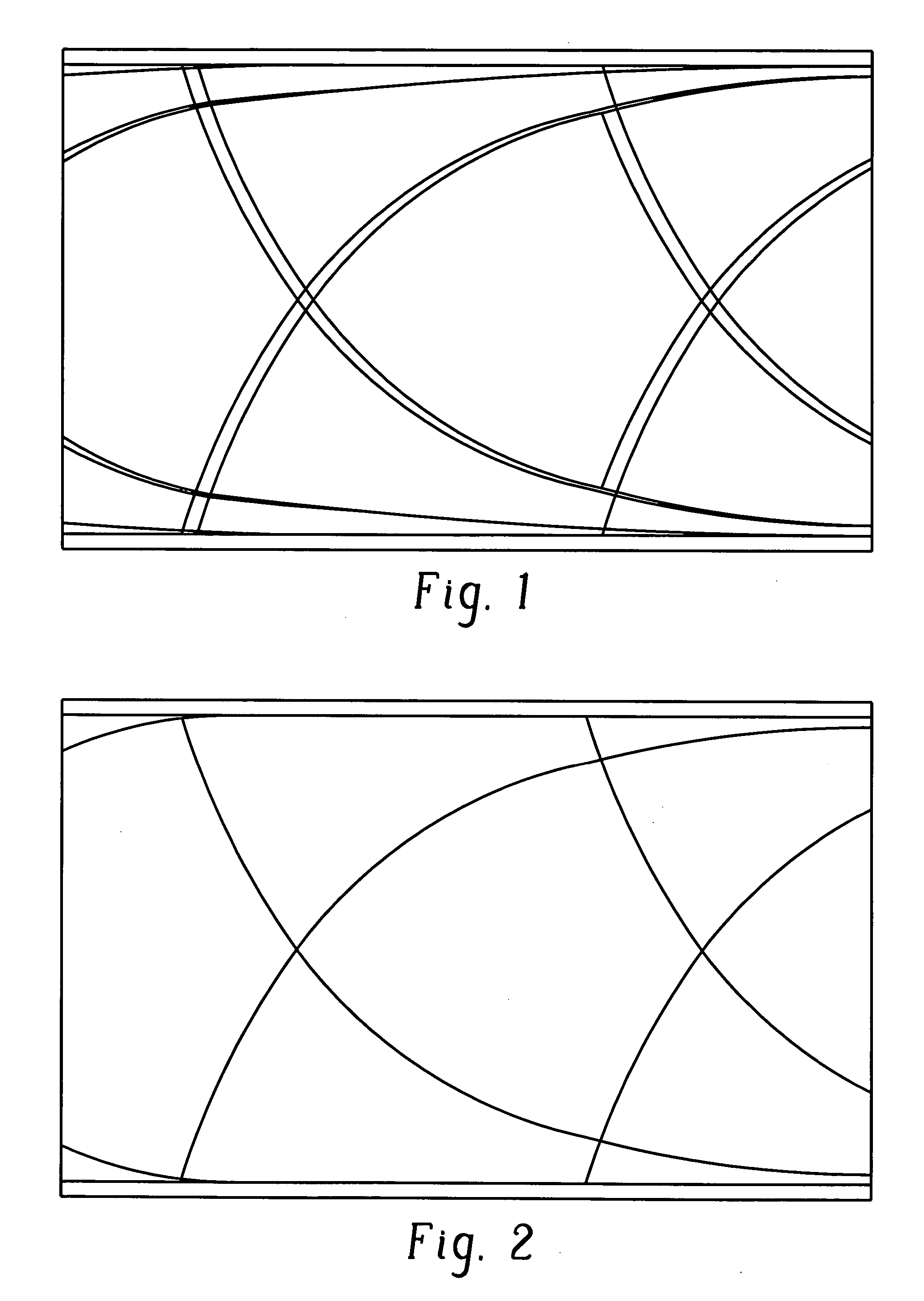

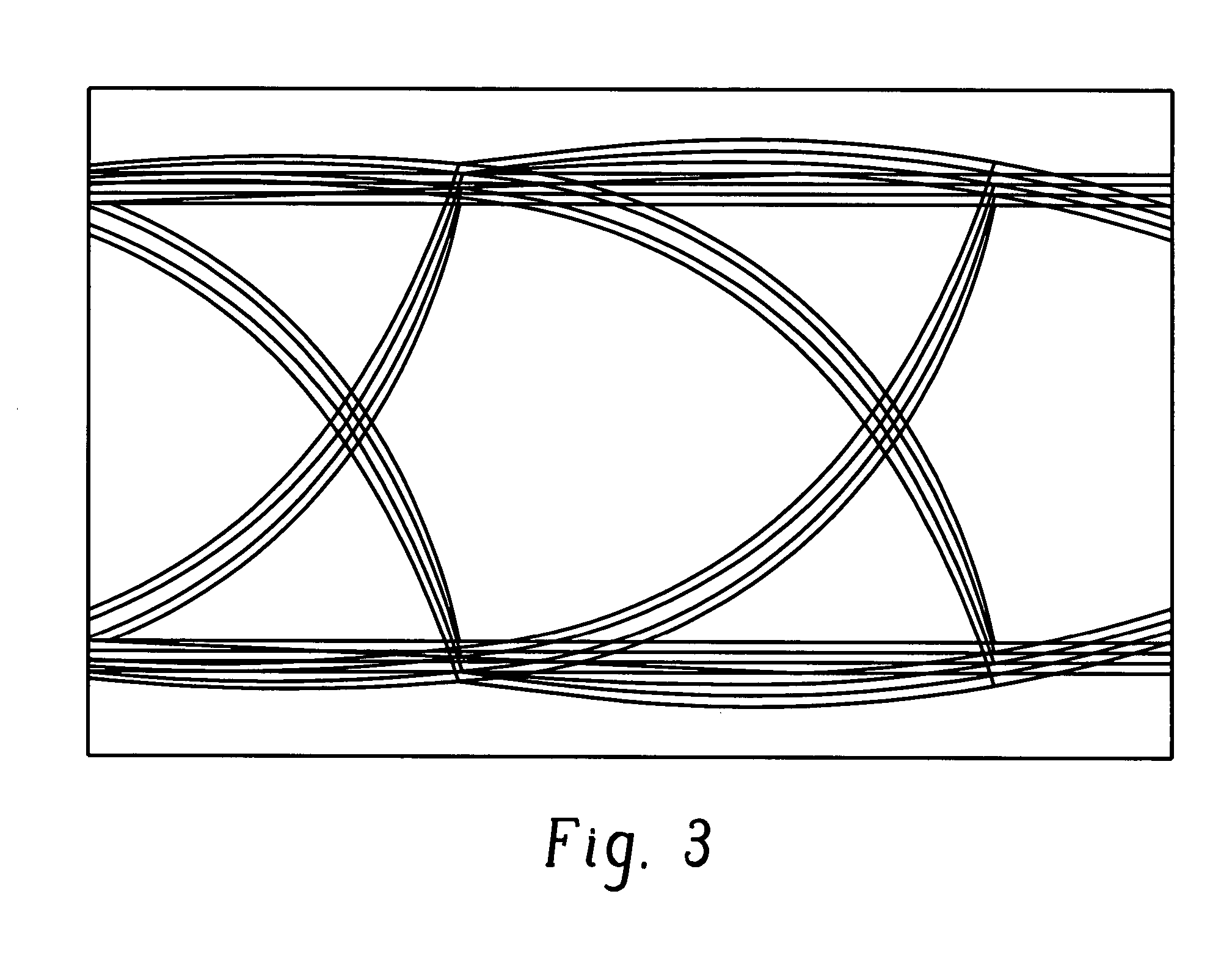

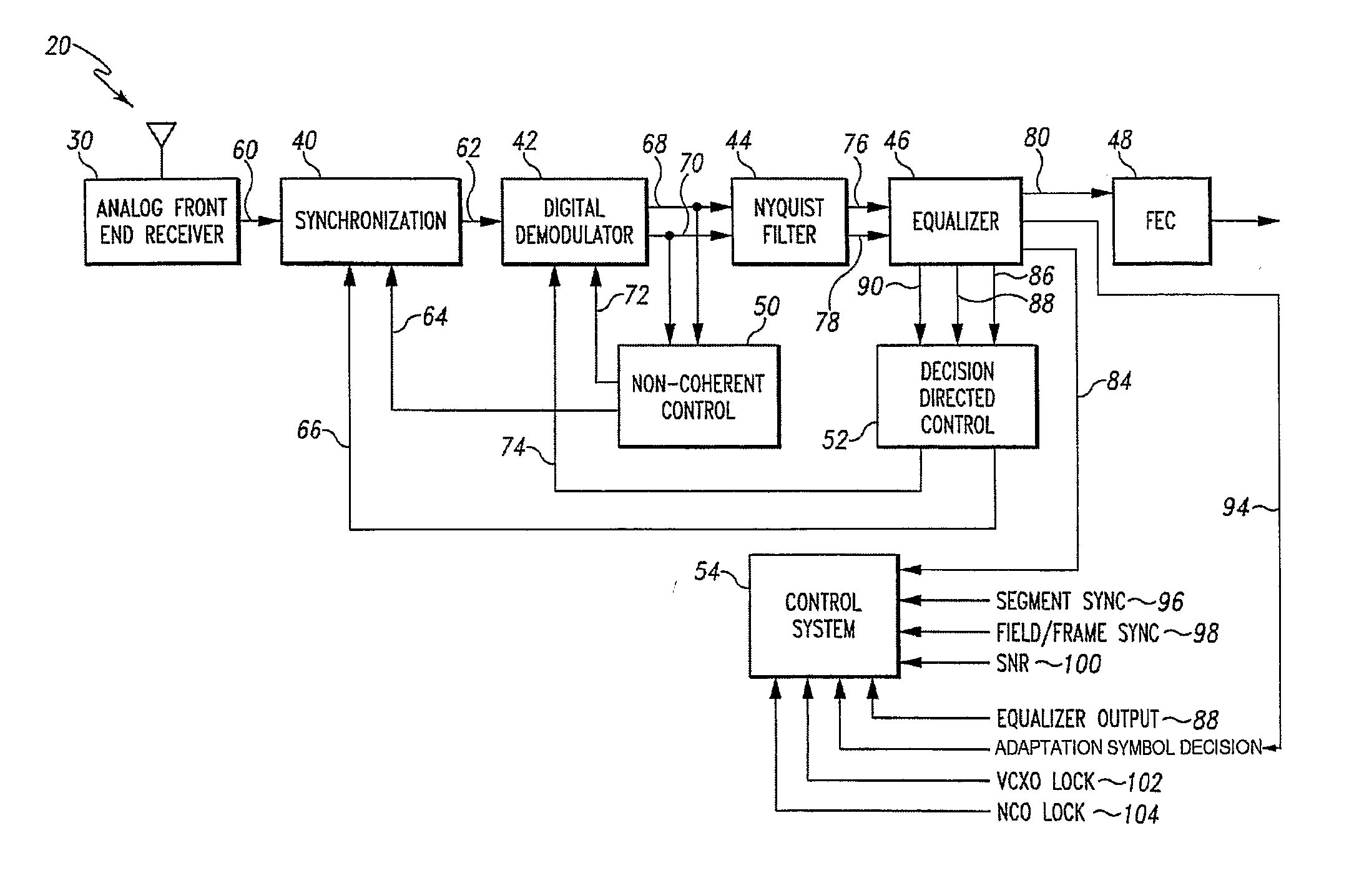

Digital receiver having adaptive carrier recovery circuit

InactiveUS20050157820A1Reduce instabilityCompensation deviationMultiple-port networksDelay line applicationsInstabilityEngineering

A digital receiver, that may be used to receive VSB / QAM digital television signals, includes an adaptive fine carrier recovery circuit that compensates for deviations in the carrier frequency or phase. The carrier recovery circuit de-rotates a signal including phase errors. Estimations of phase errors are filtered using a filter whose gain and bandwidth are adjusted adaptively. This allows the carrier recovery circuit to track phase / frequency offset without introducing significant jitter. In one embodiment, the receiver includes a DFE, and the adaptive carrier recovery circuit mitigates instability that might be associated with the DFE.

Owner:AVAGO TECH INT SALES PTE LTD

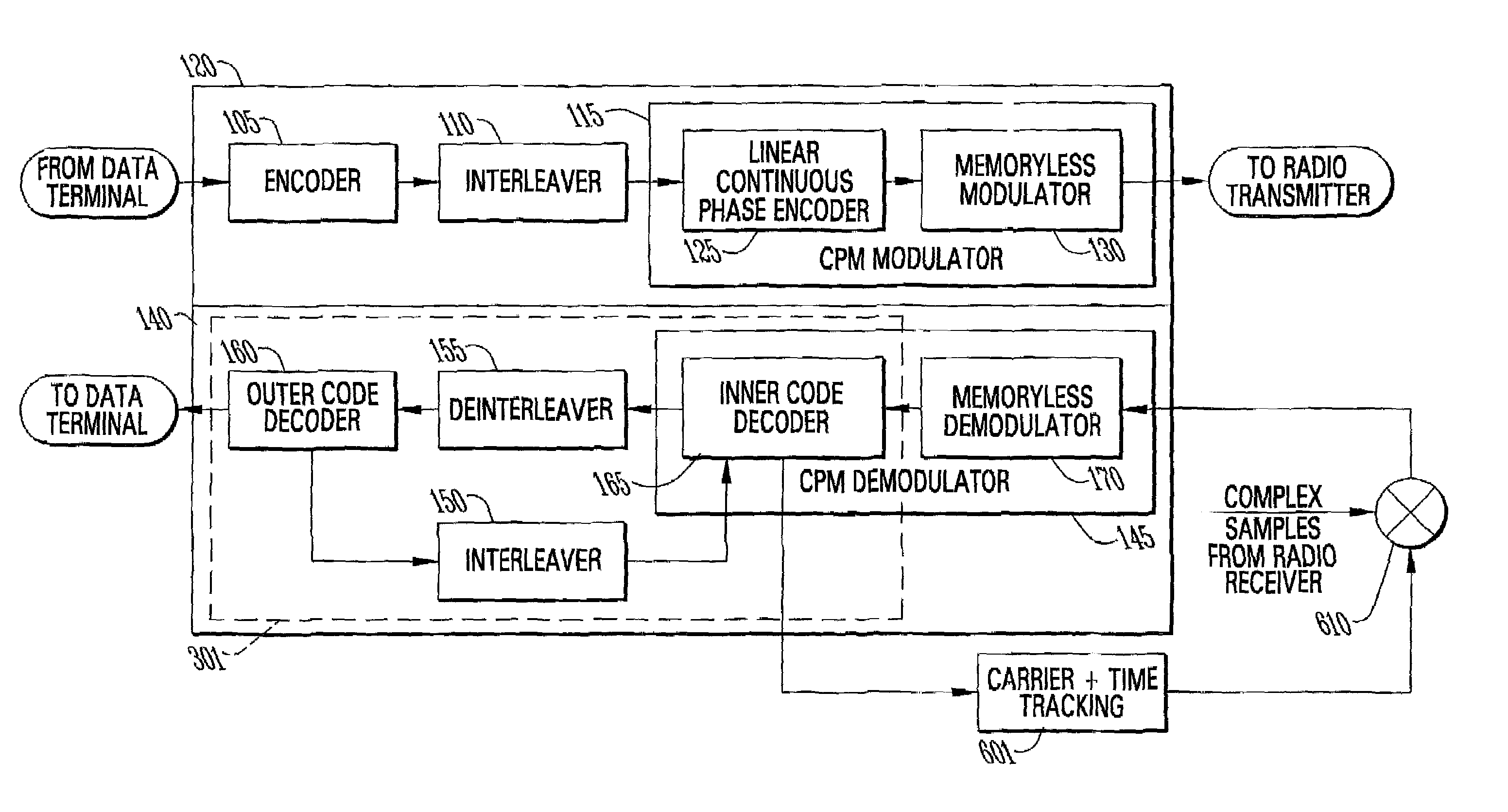

Synchronization method and apparatus for modems based on jointly iterative turbo demodulation and decoding

ActiveUS6968021B1Reliable decisionLow signal noiseTransmission systemsError detection/correctionData streamModem device

A bandwidth efficient advanced modulation waveform modem using concatenated iterative turbo coding and continuous phase modulation is disclosed. A demodulator in the modem has a turbo decoder and a decision feedback carrier and time tracking algorithm to track a carrier and adjust timing. The decision feedback carrier and time tracking algorithm may use an APP decoder as a decision device to provide symbol decisions at a high error rate and low latency for a coded input data stream. A symbol phase estimator produces a symbol phase error estimate from the symbol decisions. An erasure decision function decides which symbol decisions are correct and which symbol decisions are erasures. A carrier tracking function receives the symbol phase error estimates when the symbol decisions are correct and receives erasure inputs when the symbol decisions are erasures to maintain carrier tracking.

Owner:ROCKWELL COLLINS INC

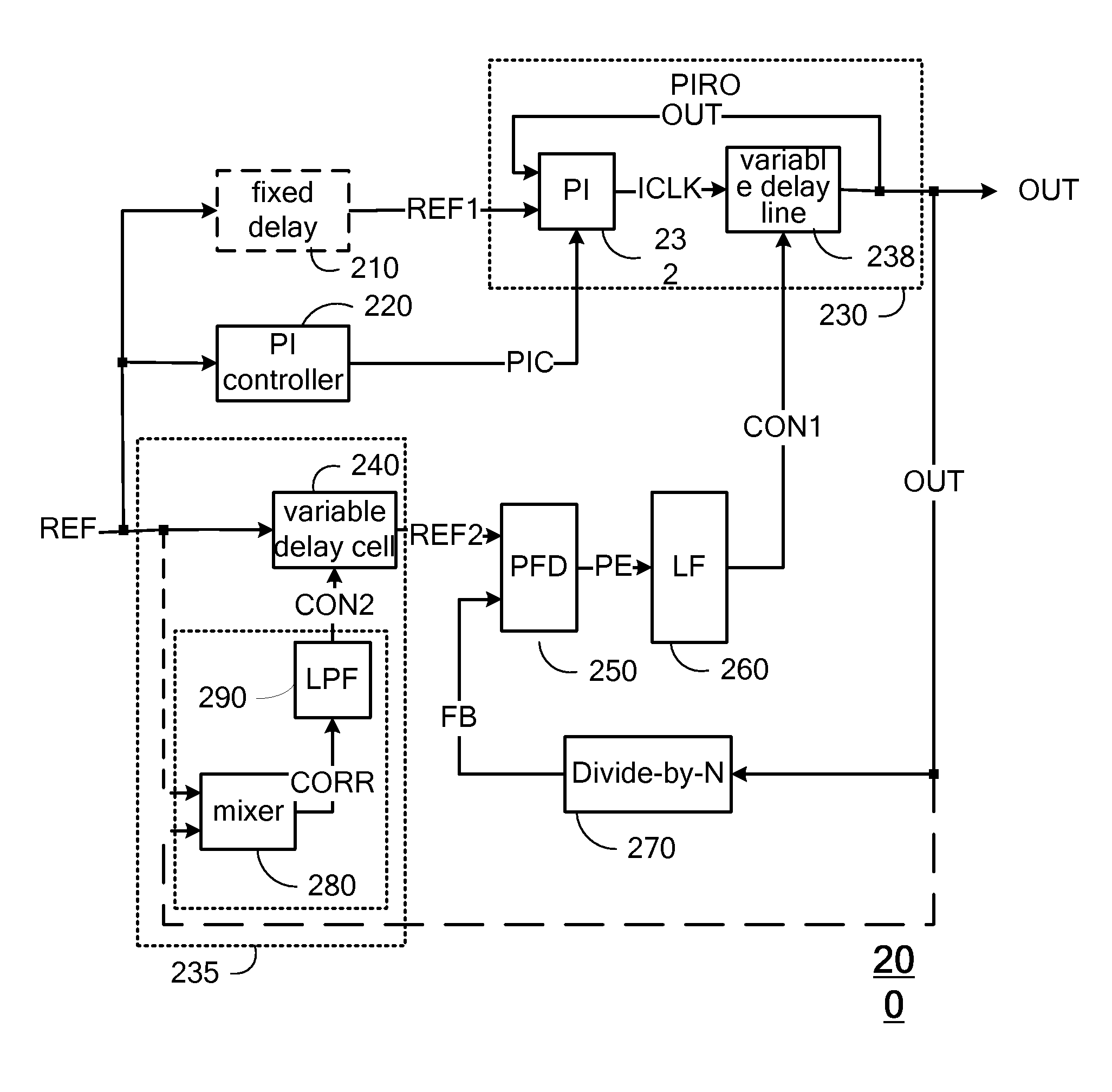

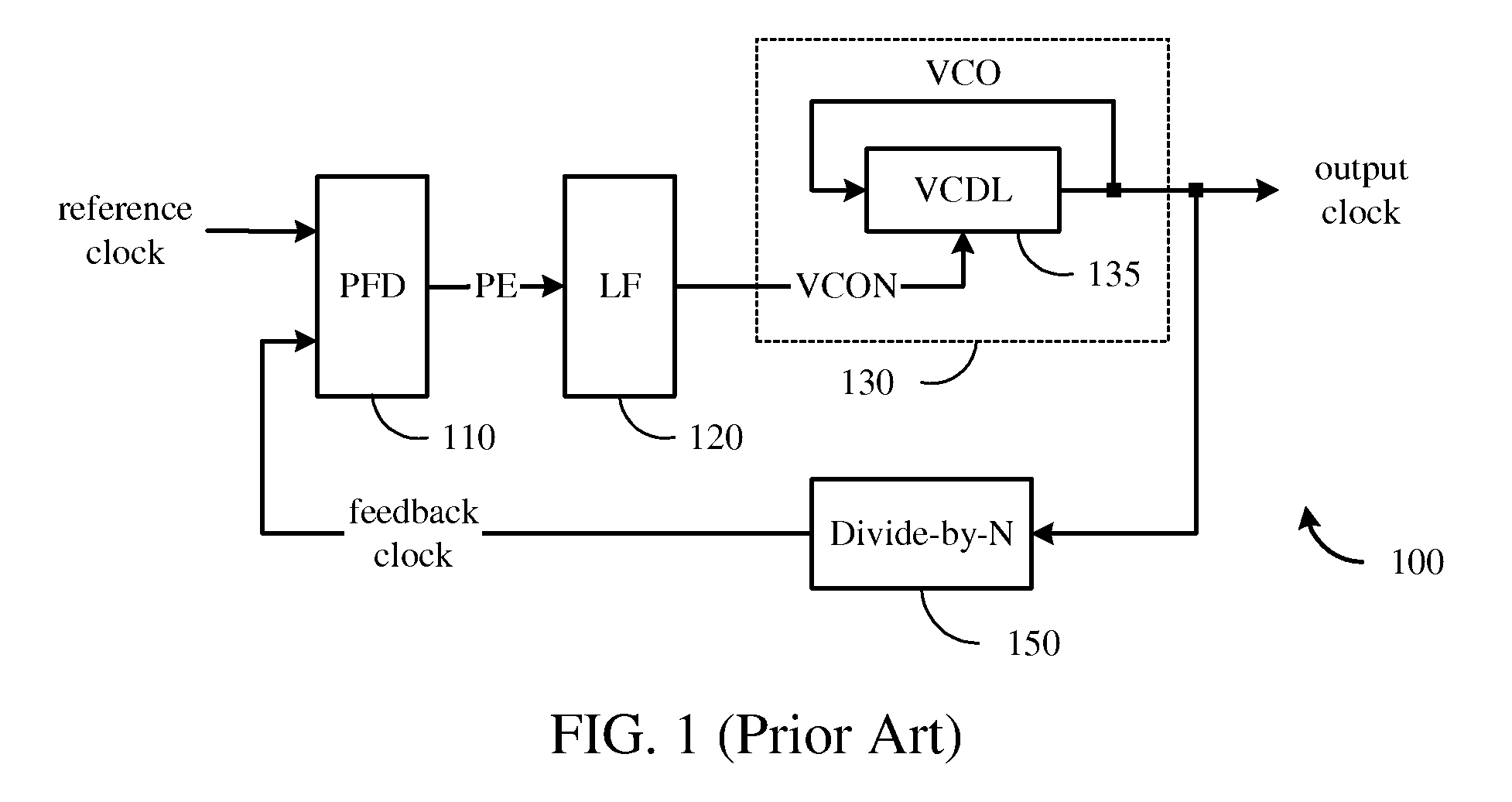

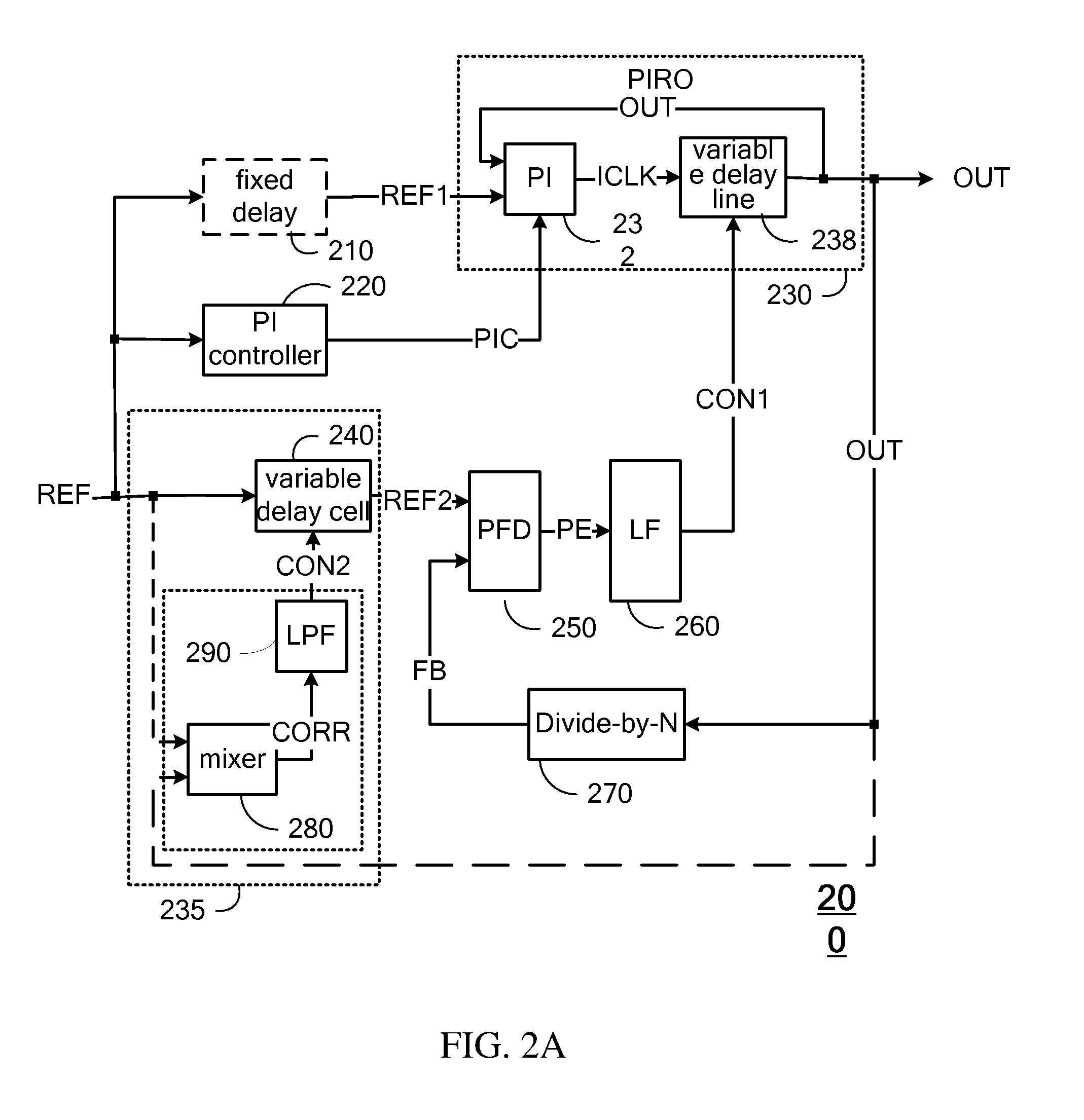

Phase lock loop with phase interpolation by reference clock and method for the same

The present invention relates to a PLL that utilizes a phase interpolation by a reference clock. The PLL includes a phase-interpolated controller for generating a phase-interpolation control signal; a phase / frequency detector for detecting a phase difference between a second reference clock and a feedback clock and outputting a phase error signal to represent the phase difference; a loop filter for filtering the phase error signal to generate a first control signal; a phase-interpolated oscillator for generating an output clock under a control by the phase-interpolation control signal and the first control signal; and a divide-by-N circuit for dividing down the output clock by a factor of N to generate the feedback clock, where N is an integer.

Owner:REALTEK SEMICON CORP

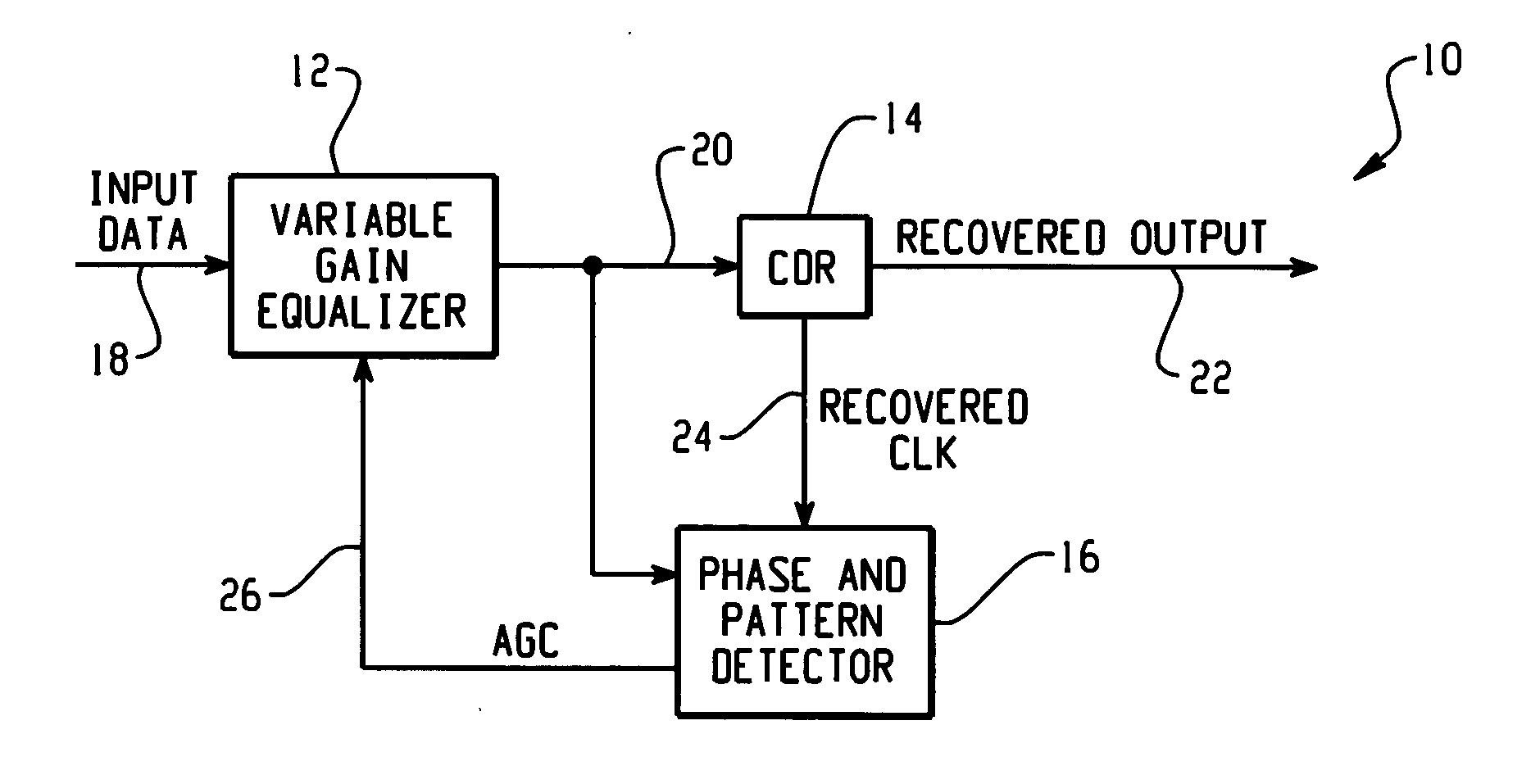

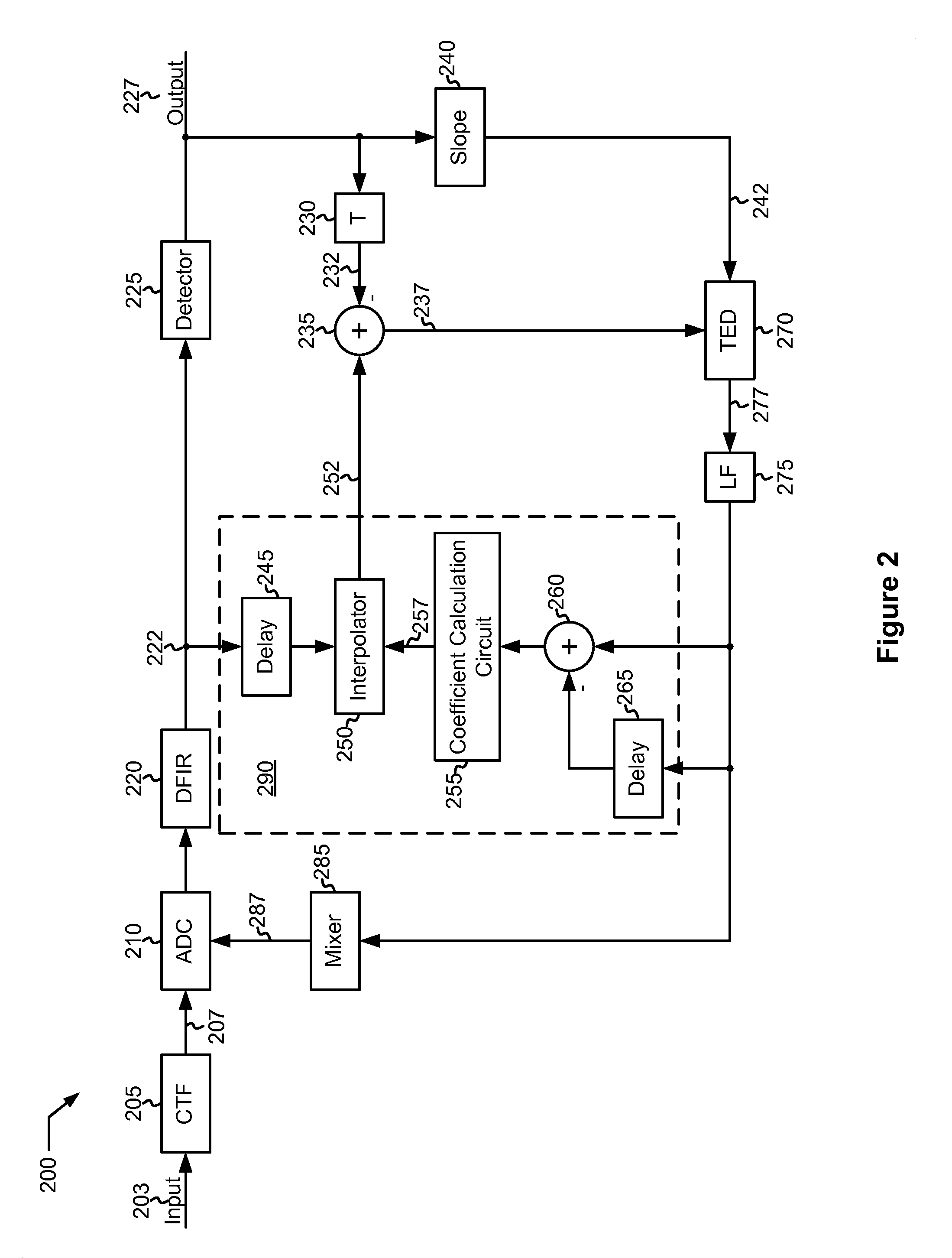

Precision adaptive equalizer

InactiveUS20050047500A1Multiple-port networksAdaptive networkDetector circuitsAutomatic gain control

In accordance with the teachings described herein, systems and methods are provided for a precision adaptive equalizer. A variable gain equalizer may be used to apply a variable gain to an input signal to generate an equalized output signal. A phase and pattern detector circuit may be coupled in a feedback loop with the variable gain equalizer. The phase and pattern detector circuit may be used to identify a high frequency data pattern in the equalized output signal and compare the high frequency data pattern with a clock signal to detect a high frequency phase error. The phase and pattern detector circuit may be further operable to generate an automatic gain control signal as a function of the high frequency phase error, the automatic gain control signal being fed back to the variable gain equalizer to control the variable gain applied to the input signal.

Owner:SEMTECH CANADA

Apparatus For And Method Of Controlling A Feedforward Filter Of An Equalizer

InactiveUS20070201544A1Multiple-port networksDelay line applicationsPhase correctionComplex representation

A method of controlling a feedforward filter of an equalizer includes the steps of generating a complex representation of an output of the feedforward filter and generating a representation of a decision from an output of the equalizer. The complex representation and the decision representation are correlated to obtain a phase error estimate. A phase correction value is generated based on the phase error estimate and used to adjust the phase of the output of the feedforward filter.

Owner:ENTROPIC COMM INC

Linear phase interpolator and phase detector

ActiveUS20090103675A1Pulse automatic controlAngle demodulation by phase difference detectionPhase detectorOperating point

A novel interpolating phase detector for use in a multiphase PLL is described comprising an array of individual phase comparators, all operating at essentially the same operating point which permits the circuits to be designed simultaneously for high speed and for low power consumption. Two adjacent phase outputs of a multi-phase VCO may be selected and interpolated in between, by selectively attaching a variable number of phase comparators to each phase output and summing their phase error outputs. By varying the number of phase comparators attached to each phase output, interpolation can be achieved with high linearity.

Owner:RAMBUS INC

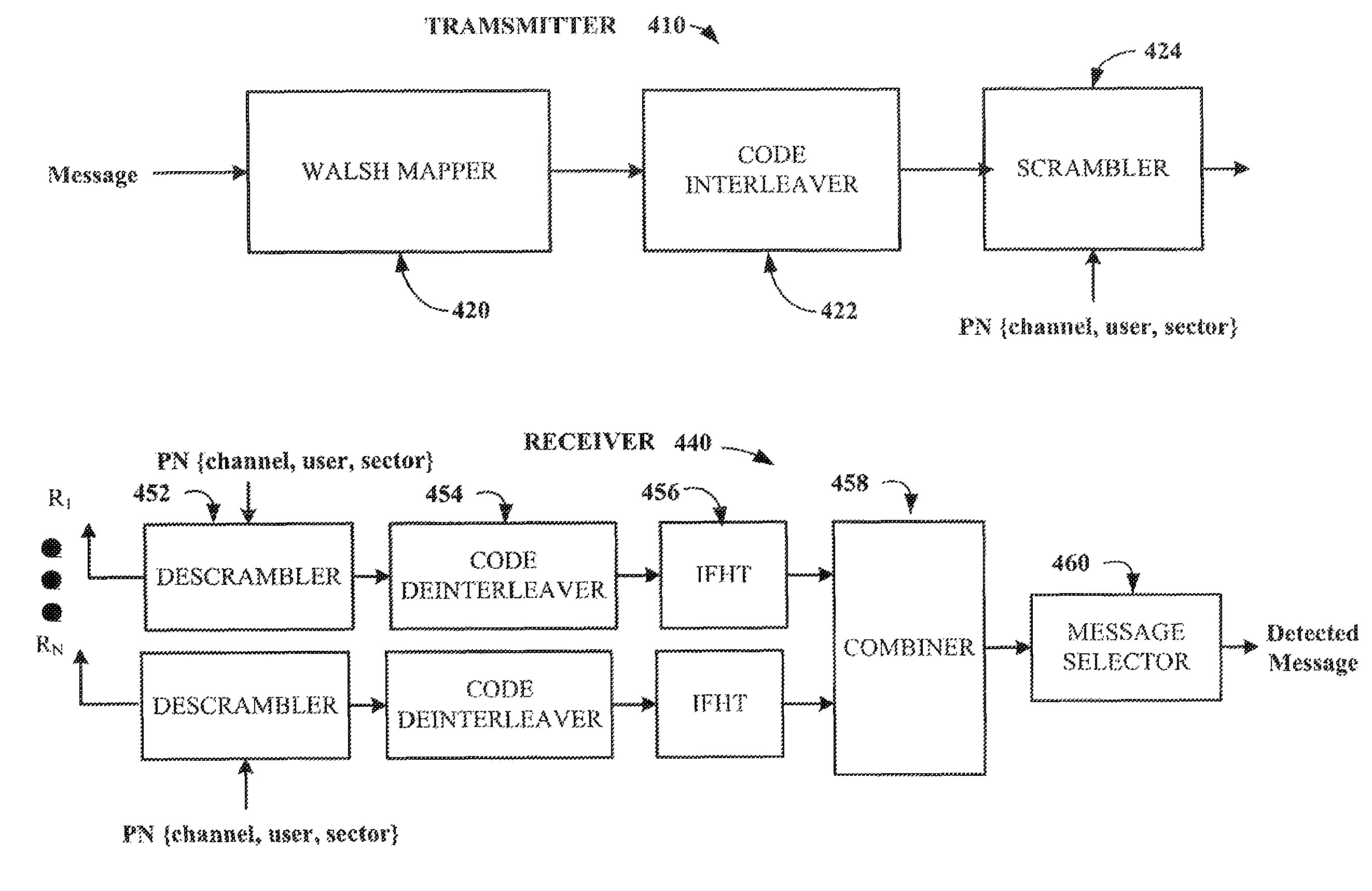

Code interleaving for a structured code

ActiveUS8295250B2Higher false alarmsRadio transmissionError correction/detection using interleaving techniquesComputer hardwareCommunications system

Communication systems and methods that mitigate false alarms due to Doppler shift are disclosed. Received message data is mapped to orthogonal Walsh codes, interleaved and scrambled with appropriate PN sequence prior to transmission. The transmitted message data is descrambled and deinterleaved upon reception. The energies associated with each of the Walsh code from various antennas and / or signal paths are combined to obtain a total energy for each Walsh code. If the total energy of the Walsh code exceeds a certain threshold it is declared as the received message else an erasure is indicated. As the data is interleaved prior to transmission, any phase ramp introduced due to Doppler is transformed into random phase errors upon deinterleaving at the receiver thereby mitigating false alarms.

Owner:QUALCOMM INC

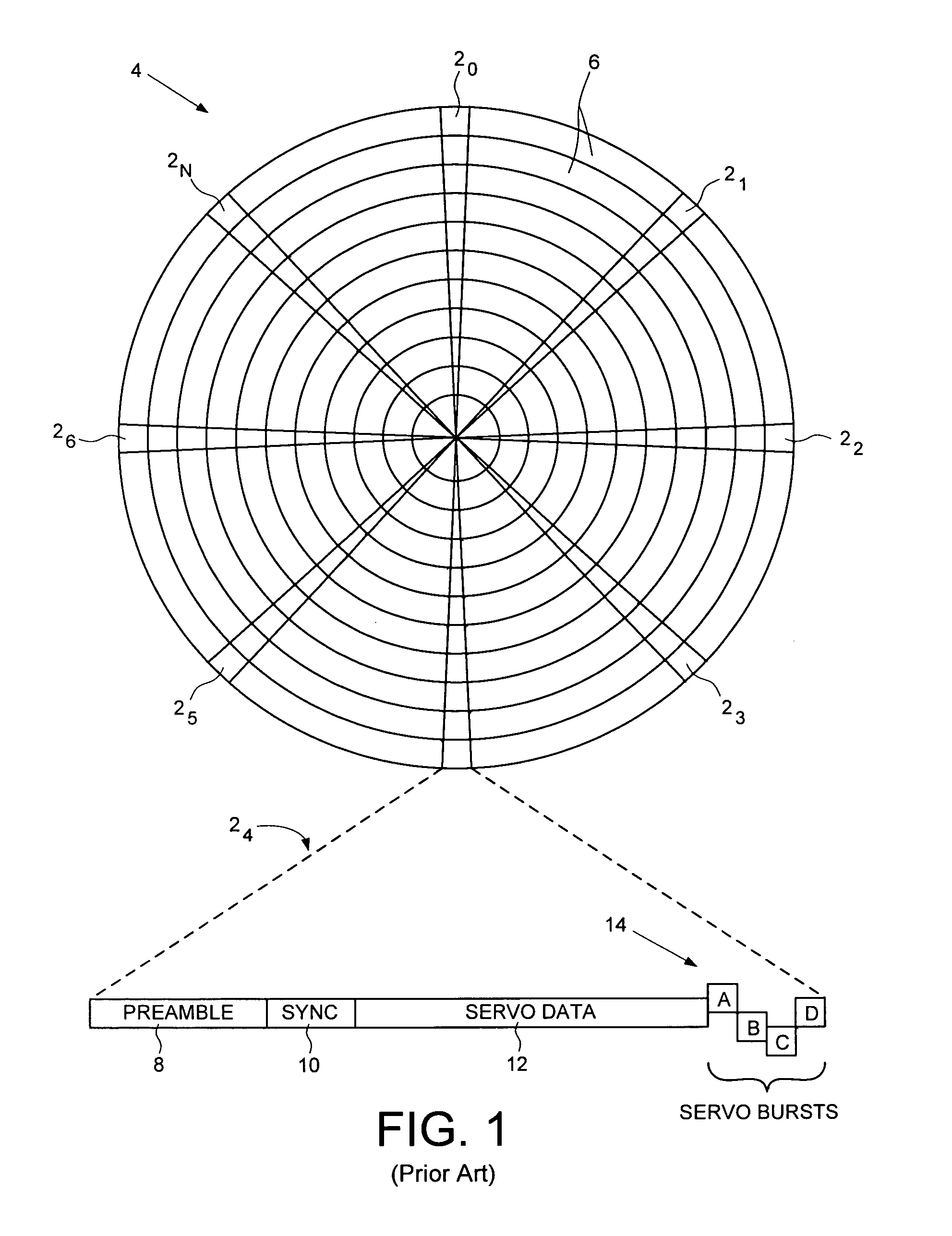

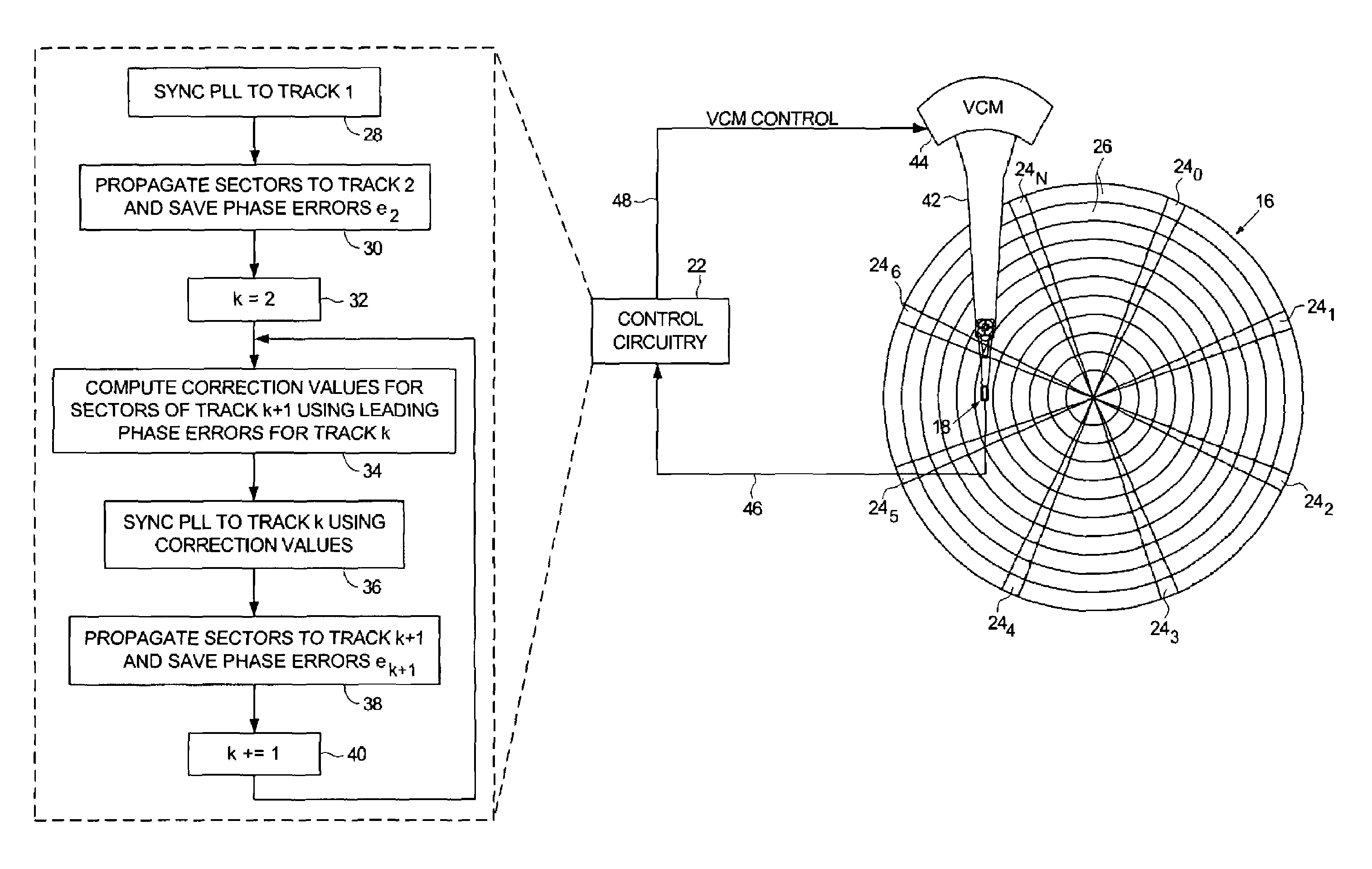

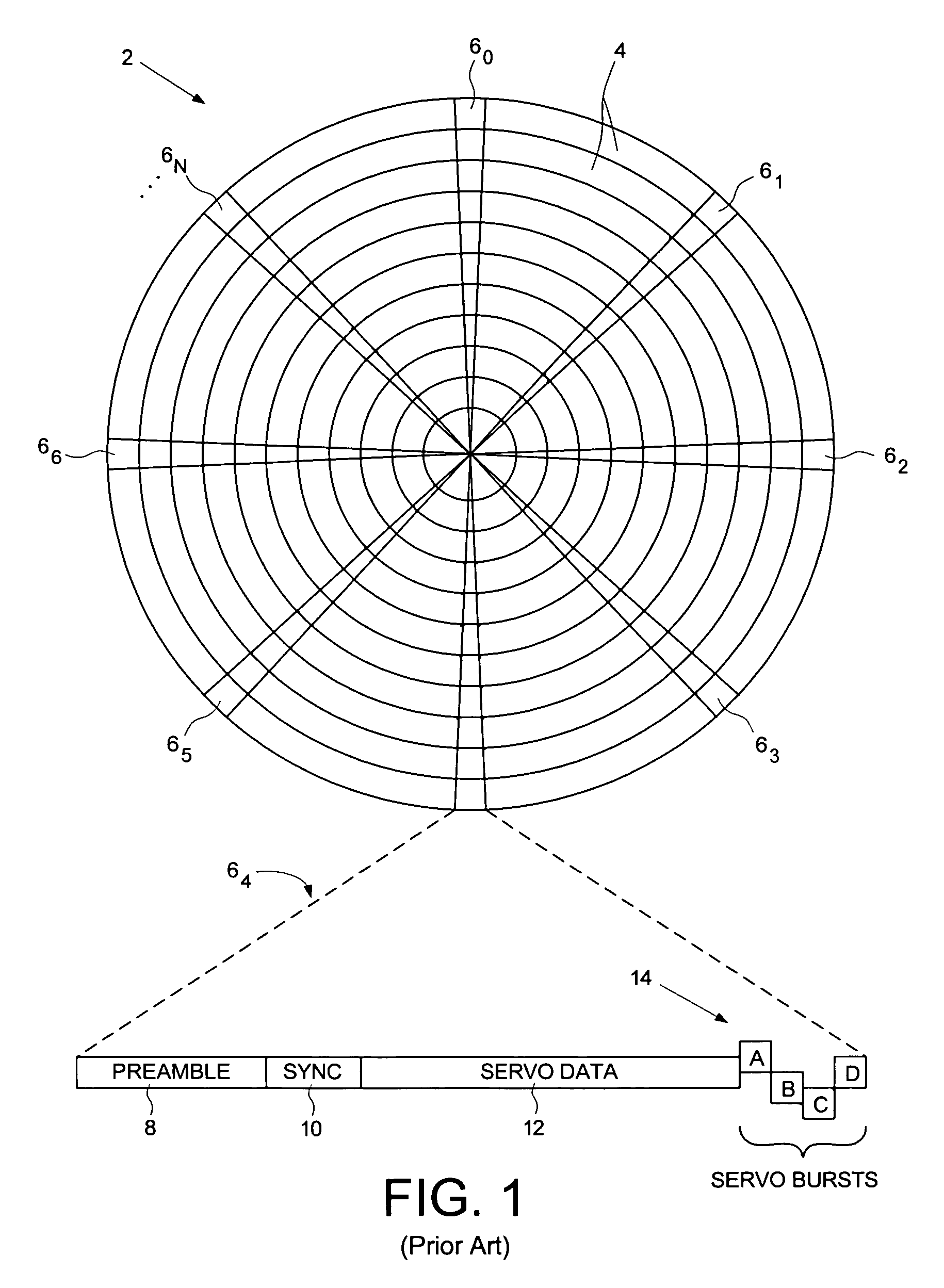

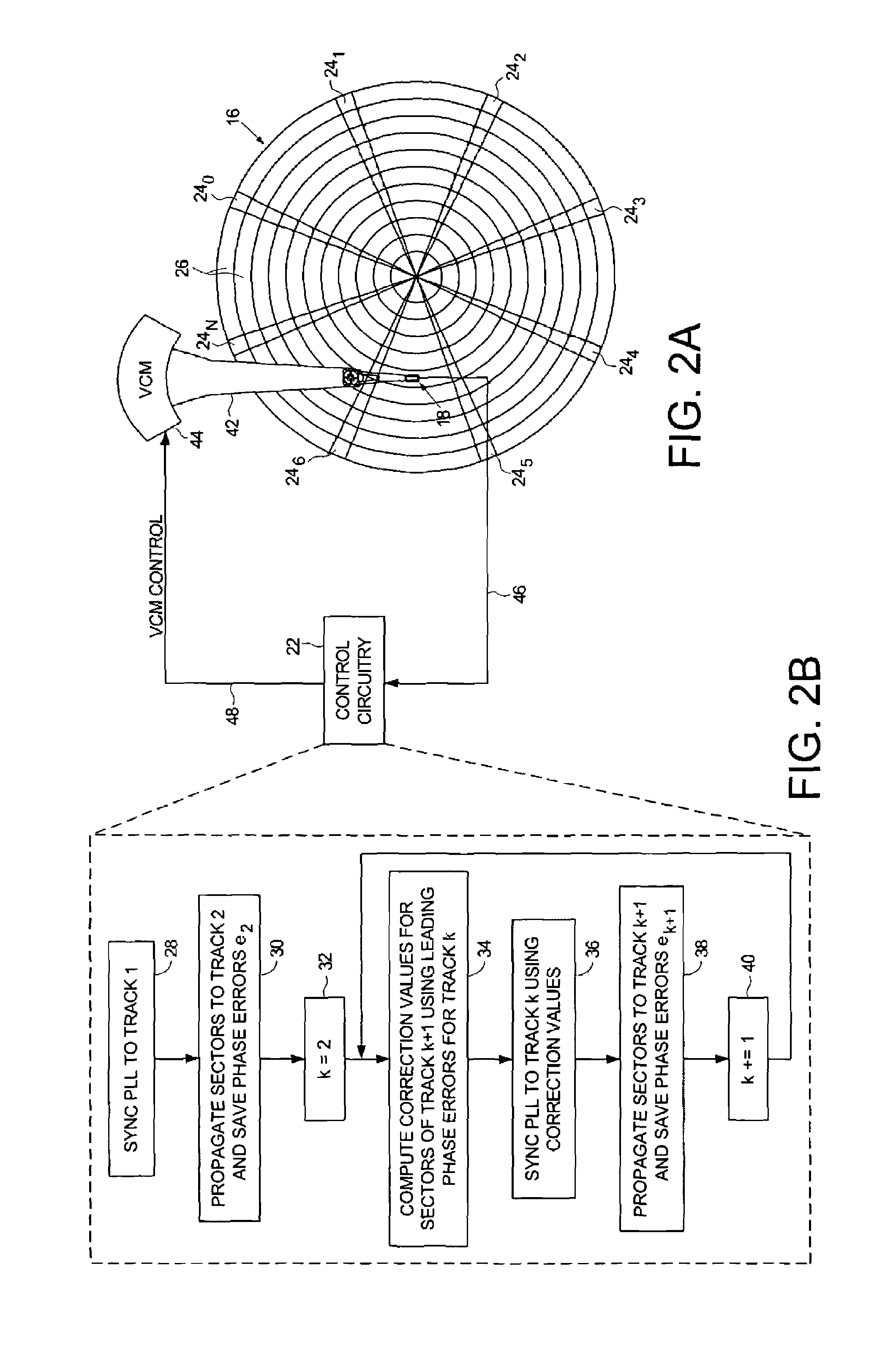

Servo writing a disk drive using correction values that attenuate phase error propagation

InactiveUS7298574B1Filamentary/web carriers operation controlDriving/moving recording headsPhase-locked loopPhase error

Servo writing a disk of a disk drive is disclosed. A phase locked loop (PLL) is synchronized to first sectors previously written on a first track, and second sectors are written to a second track using the PLL, wherein a plurality of phase errors corresponding to the second sectors are saved. A correction value is computed corresponding to a selected one of the second sectors, wherein the correction value is computed in response to a plurality of the phase errors generated for a plurality of the second sectors leading the selected sector. The PLL is synchronized to the second sectors using the correction value, a third sector is written to a third track using the PLL, and a phase error is saved corresponding to the third sector.

Owner:WESTERN DIGITAL TECH INC

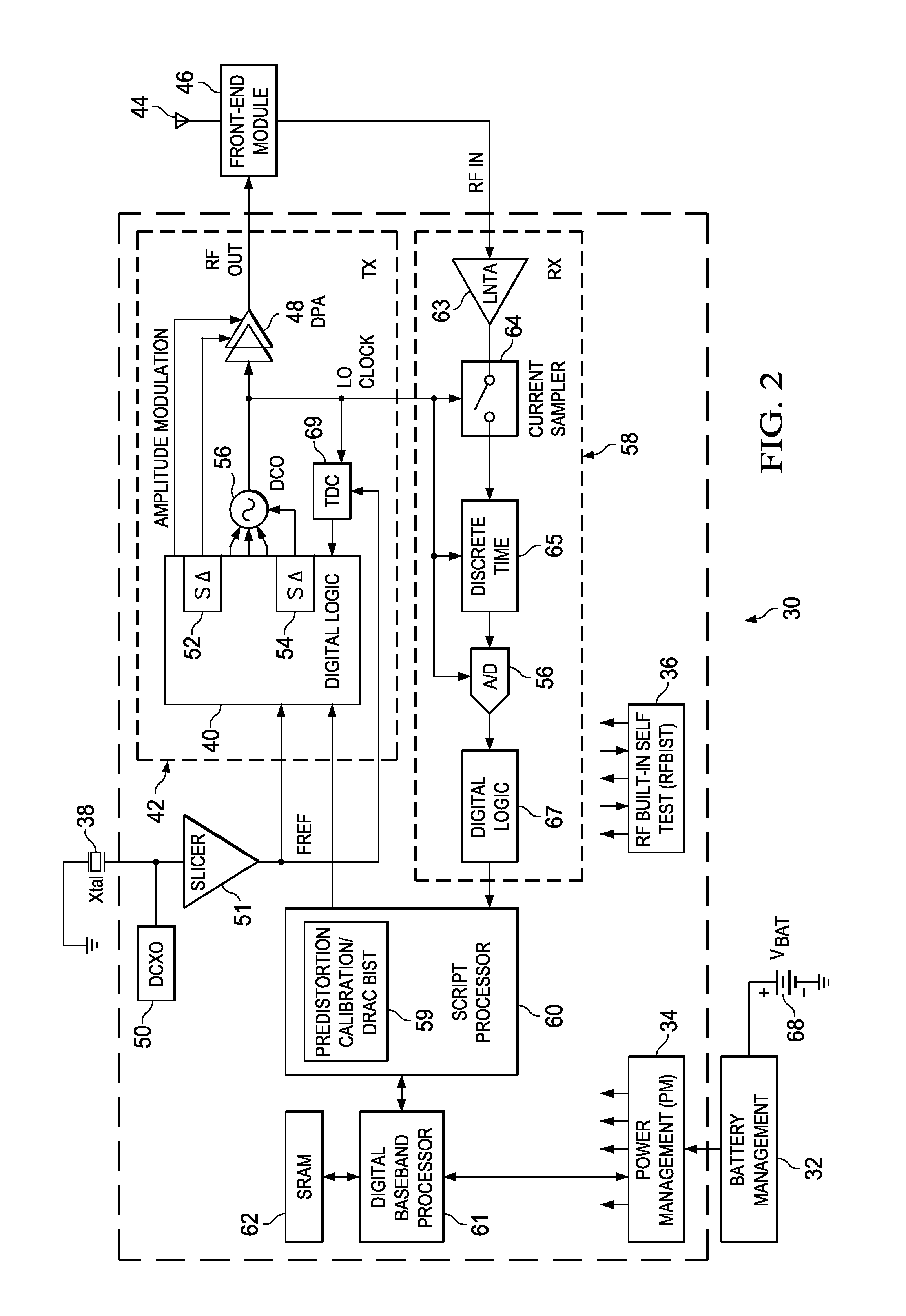

Predistortion calibration and built in self testing of a radio frequency power amplifier using subharmonic mixing

ActiveUS20120252382A1No significant hardware overheadStrain is placedTransmitters monitoringPower amplifiersHarmonicTested time

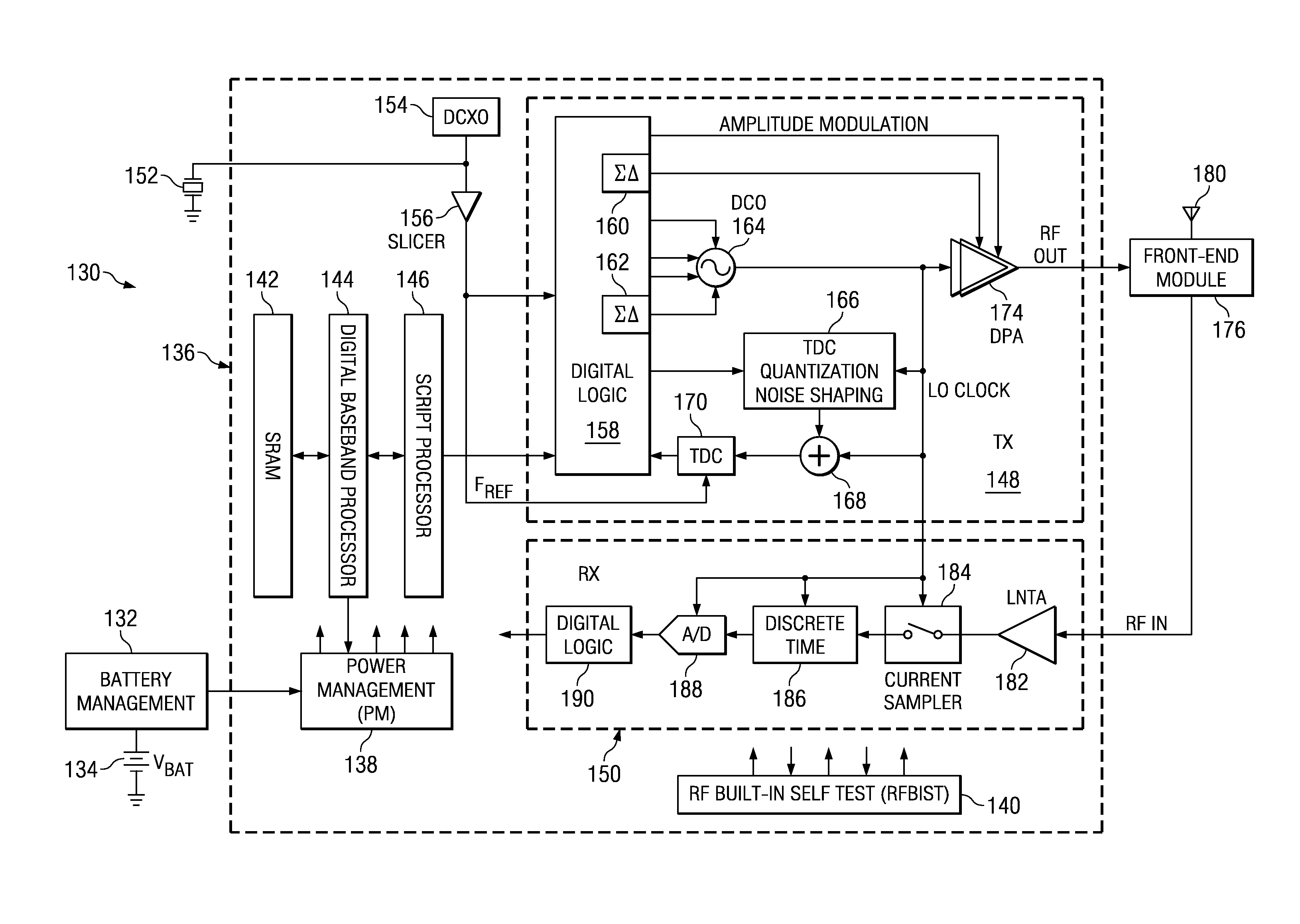

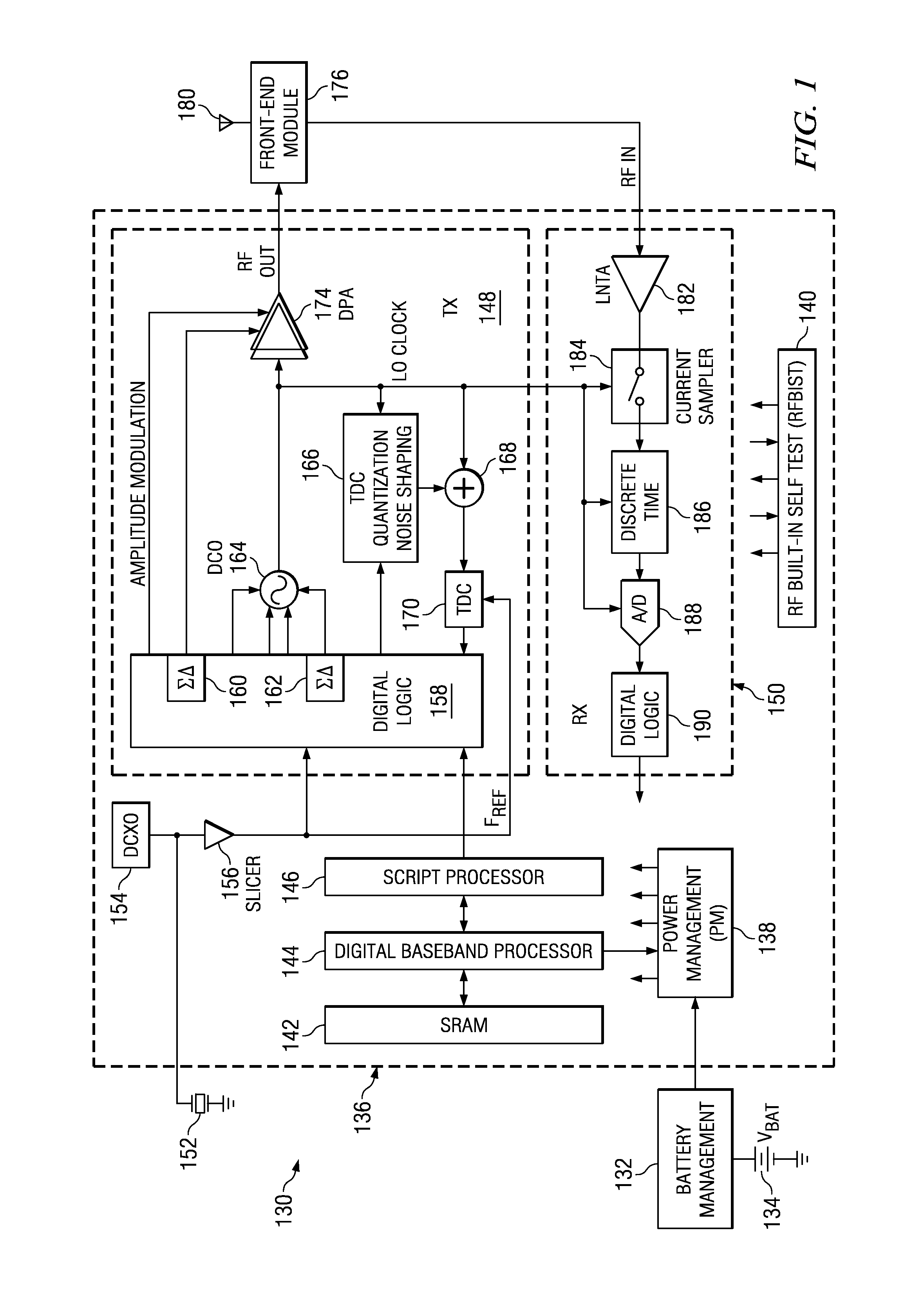

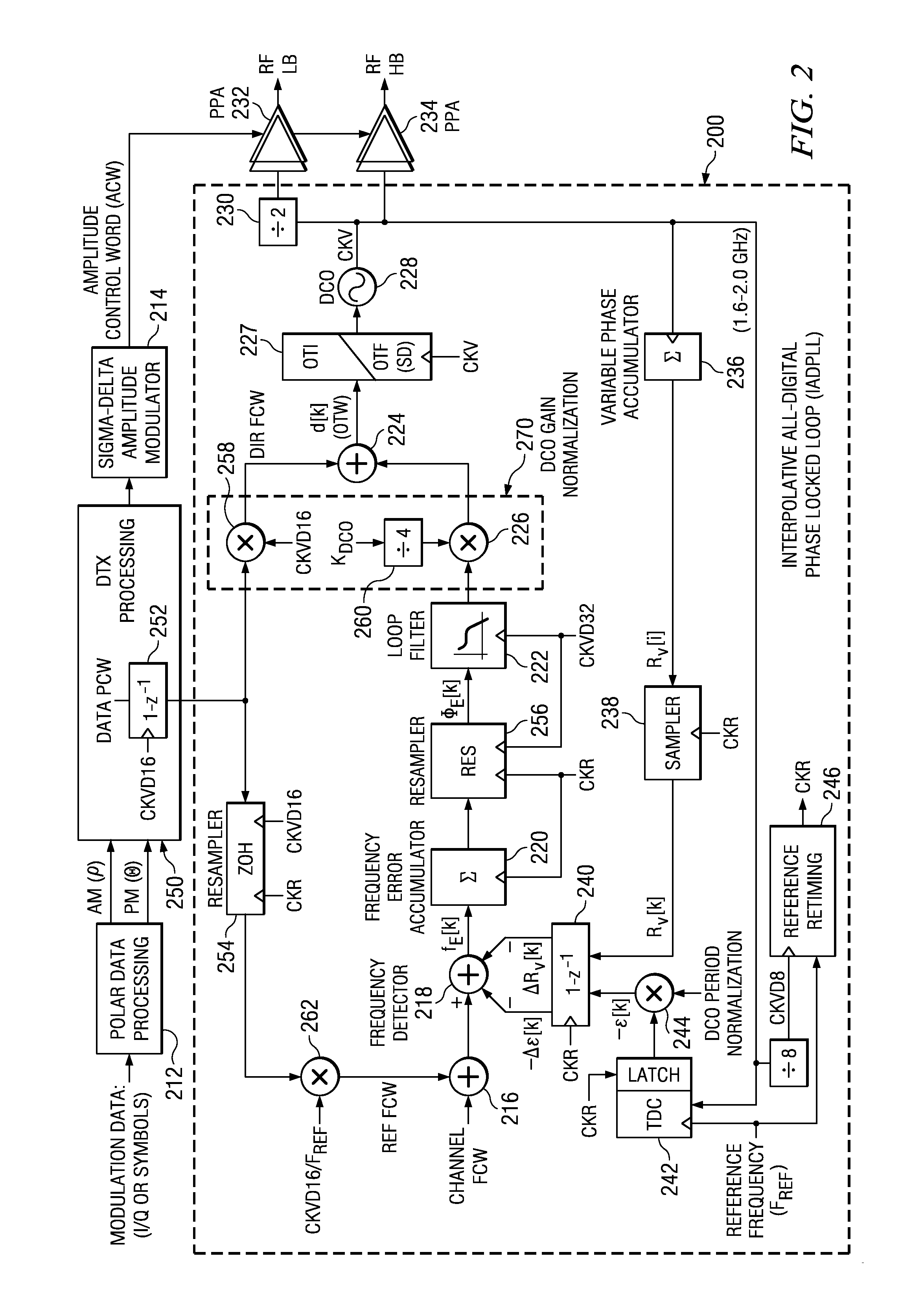

A novel and useful apparatus for and method of predistortion calibration and built-in self testing (BIST) of a nonlinear digitally-controlled radio frequency (RF) power amplifier (DPA) using subharmonic mixing. The RF power amplifier output is temporarily coupled into the frequency reference (FREF) input and the phase error samples generated in the phase locked loop (PLL) are then observed and analyzed. The digital predistortion and BIST mechanisms process the phase error samples to calibrate and test the DPA in the transmitter of the Digital RF Processor (DRP). The invention enables the characterization of nonlinearities, the configuration of internal predistortion, as well as the testing of the transmitter's analog / RF circuitry, thereby eliminating commonly employed RF performance testing using high-cost test equipment and associated extended test times.

Owner:TEXAS INSTR INC

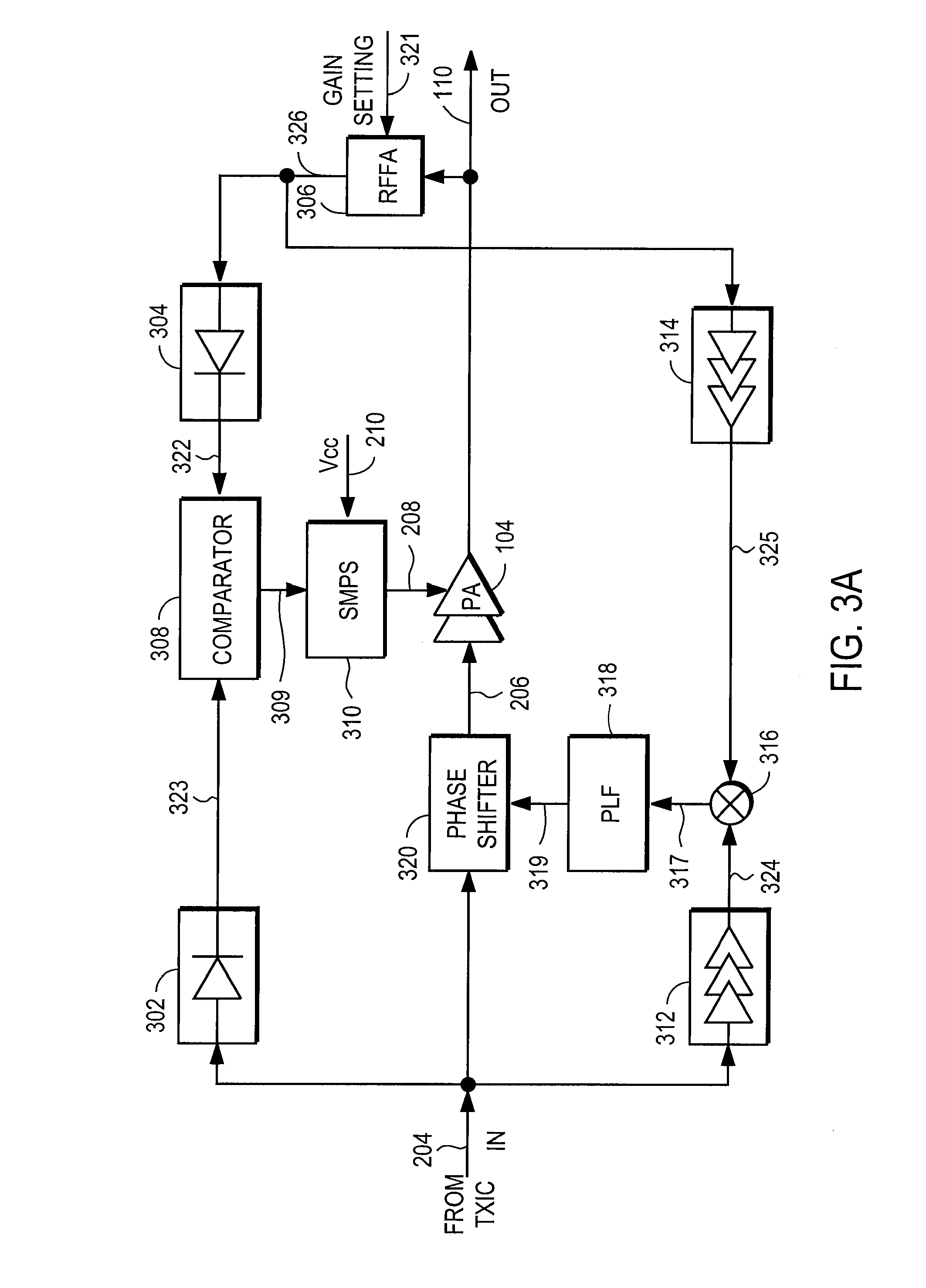

RF Power Amplifier Controller Circuit Including Calibrated Phase Control Loop

ActiveUS20070184794A1Reduce phase distortionNarrow bandwidthResonant long antennasPower amplifiersAudio power amplifierPhase difference

An RF power amplifier system comprises an amplitude control loop and a phase control loop. The amplitude control loop adjusts the supply voltage to the power amplifier based upon the amplitude correction signal indicating the amplitude difference between the amplitude of the input signal and an attenuated amplitude of the output signal. The phase control loop adjusts the phase of the input signal based upon a phase error signal indicating a phase difference between phases of the input signal and the output signal. The phase control loop may comprise one or more variable phase delays introducing a relative phase delay to allow the phase differences between the input and output signals of the PA circuit to be within a range compatible with a phase comparator generating the phase error signal, and a low frequency blocking module that removes the larger extent, lower frequency components of the phase error signal.

Owner:QUANTANCE

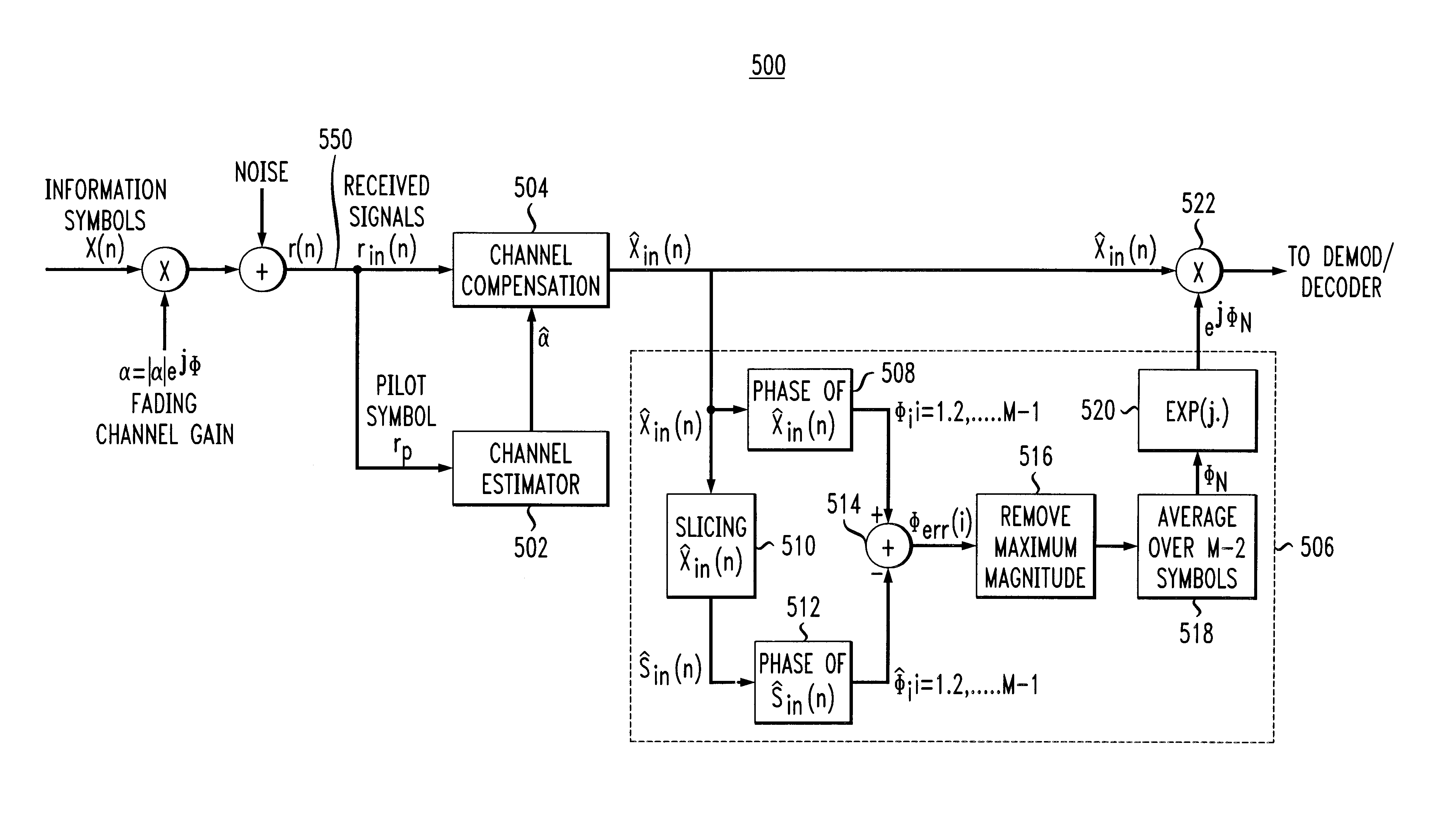

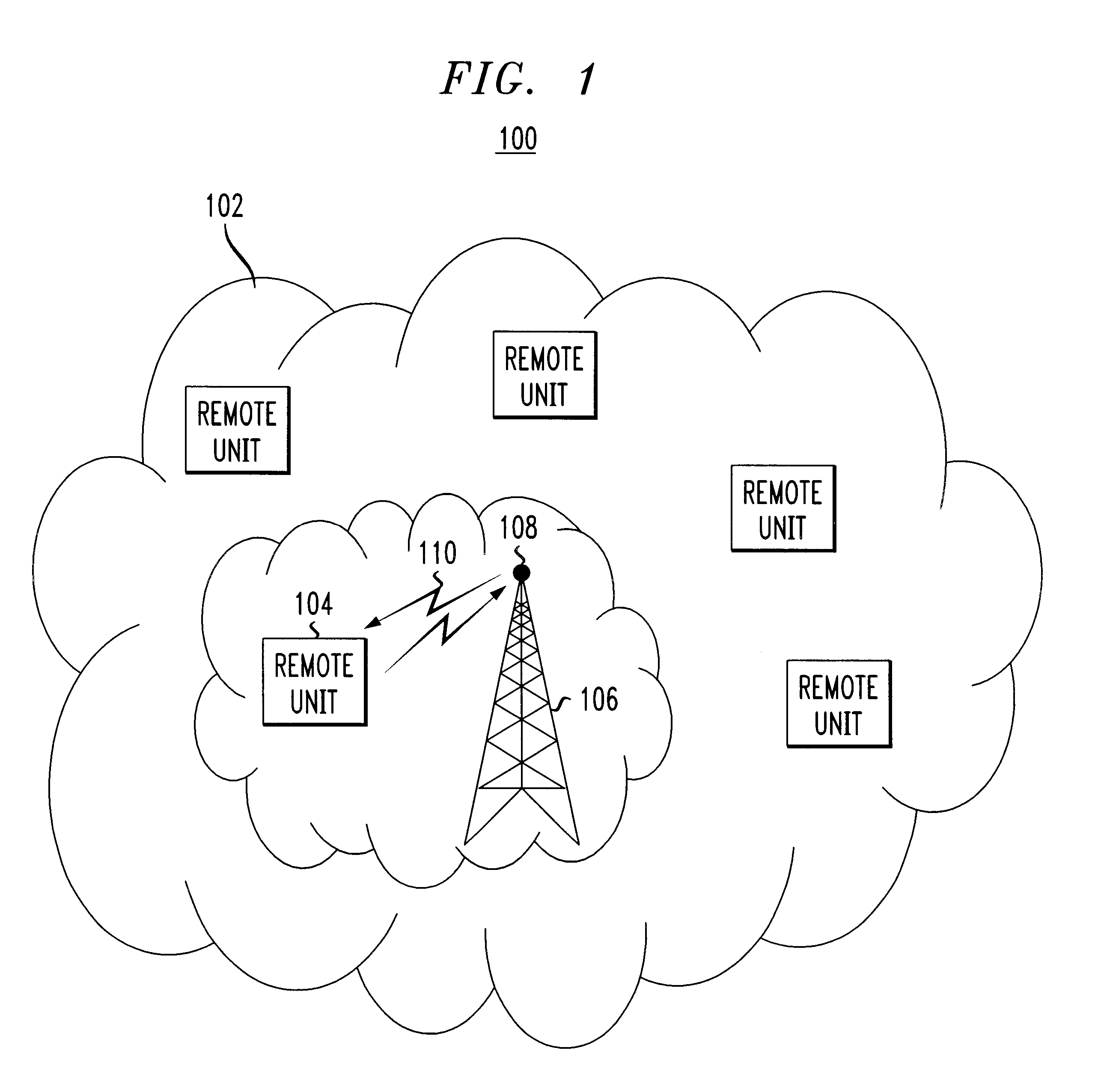

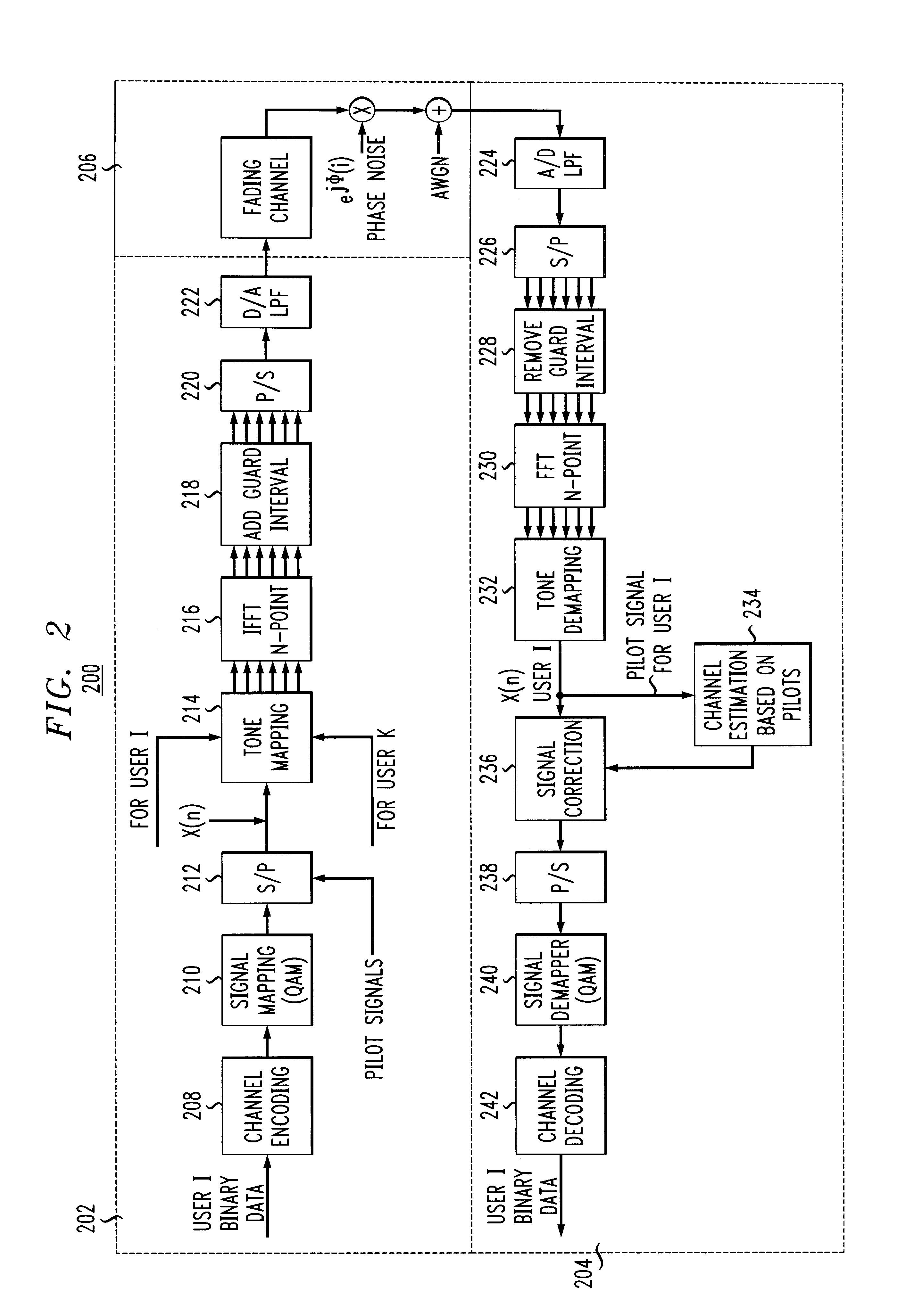

Methods and apparatus for use in reducing residual phase error in OFDM communication signals

InactiveUS6928120B1Reduce errorsPolarisation/directional diversityTime-division multiplexRelevant informationPhase difference

Methods and apparatus for use in reducing residual phase error (RPE) in orthogonal frequency division multiplexed (OFDM) communication signals are described. One method includes the steps of calculating a phase of each one of a plurality of channel-compensated data symbols to generate a plurality of data symbol phases; performing a hard-decision on each one of the plurality of channel-compensated data symbols to estimate a plurality of information symbols; calculating a phase of each one of the plurality of information symbols to generate a plurality of information symbol phases; calculating a phase difference between each data symbol phase and its associated information symbol phase to generate a plurality of phase differences; and determining a residual phase error based on the plurality of phase differences.

Owner:AT&T WIRELESS SERVICES

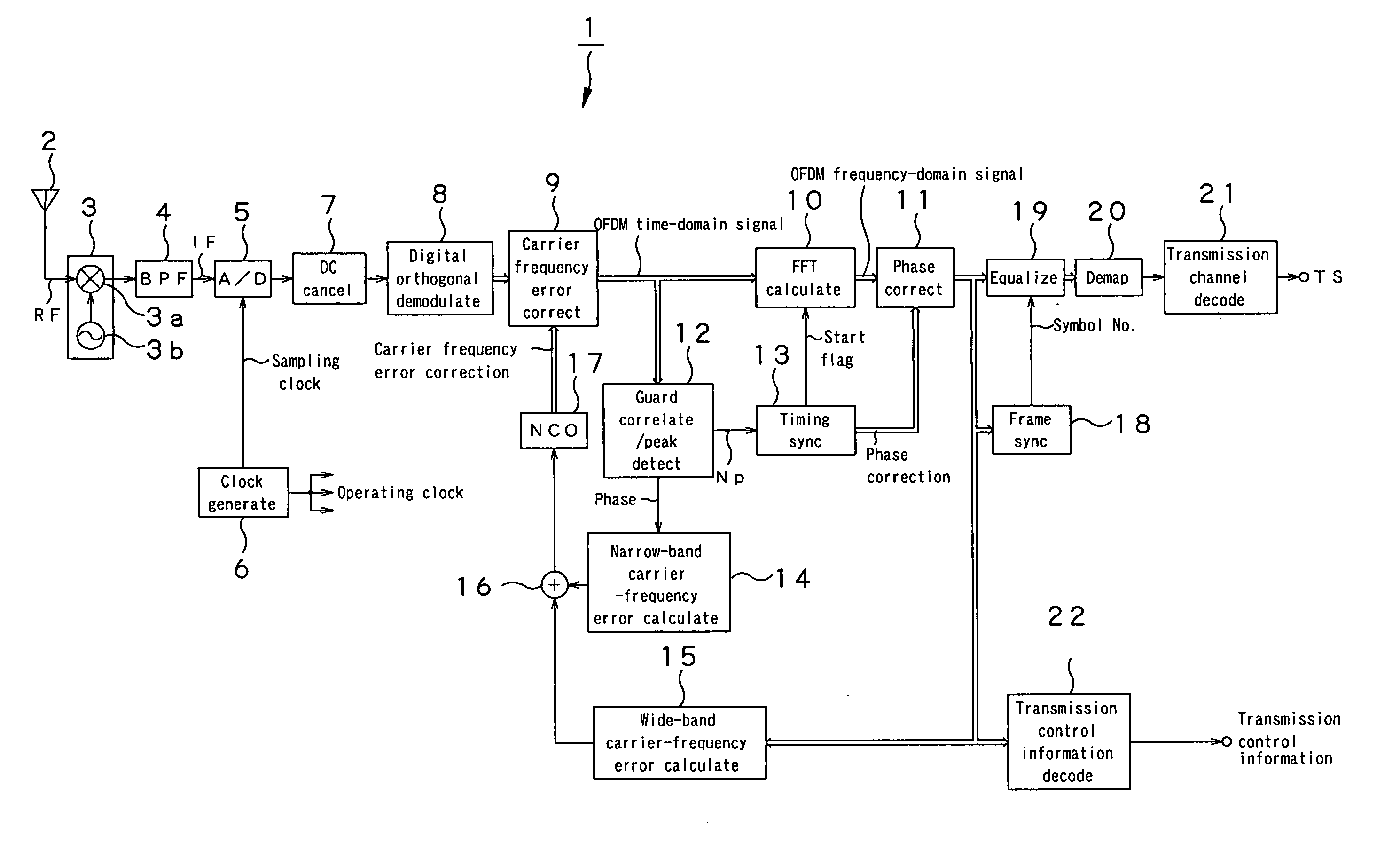

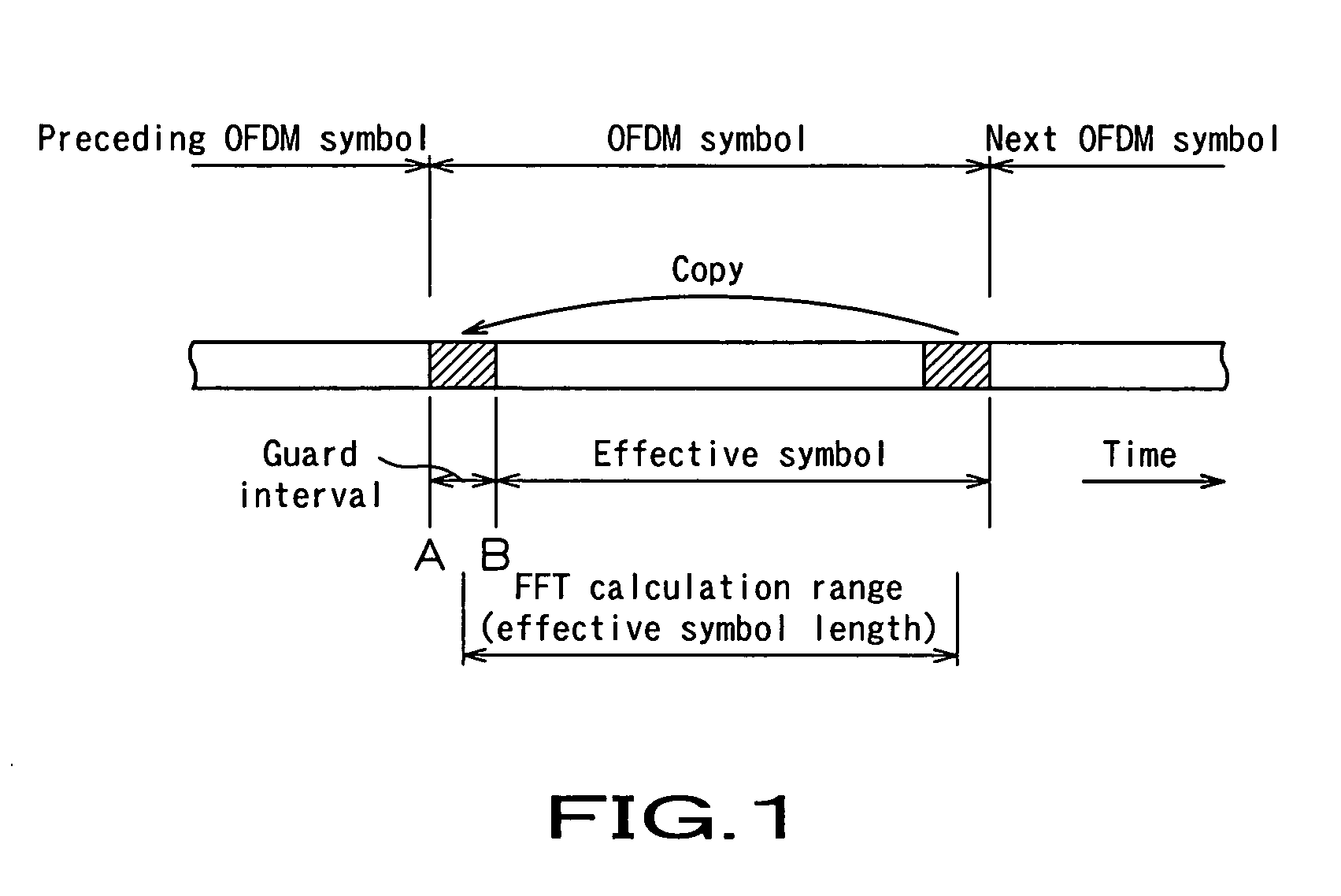

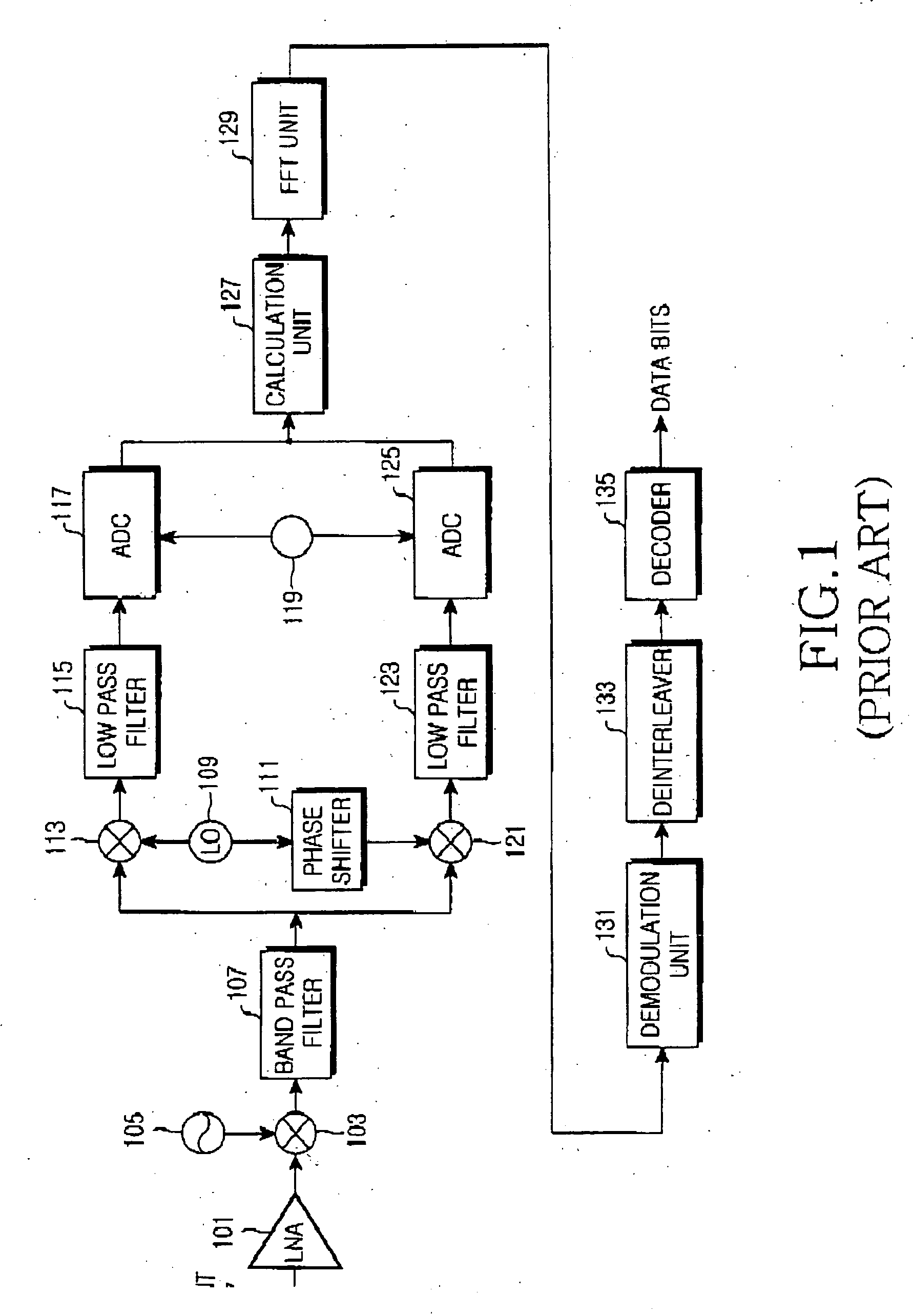

Ofdm demodulation apparatus

InactiveUS20050147186A1Improve accuracySynchronisation signal speed/phase controlFrequency-modulated carrier systemsGuard intervalDelay-locked loop

An OFDM demodulation (1) is provided which includes a guard correlation / peak time detection circuit (12) to generate a peak timing Np of a guard interval correlation value, and a timing synchronization circuit (13) to estimate a symbol-boundary time Nx from the peak timing Np. The timing synchronization circuit (13) calculates the symbol-boundary time Nx by filtering the peak time Np by a DLL (delay locked loop) filter (43). Further, the DLL filter (43) includes a limiter (52) to limit the range of phase-error component and an asymmetric gain circuit (53) to change the magnitude of the gain correspondingly to the polarity of the phase error to prevent the timing from being pulled out due to a fading or multipath.

Owner:SONY CORP

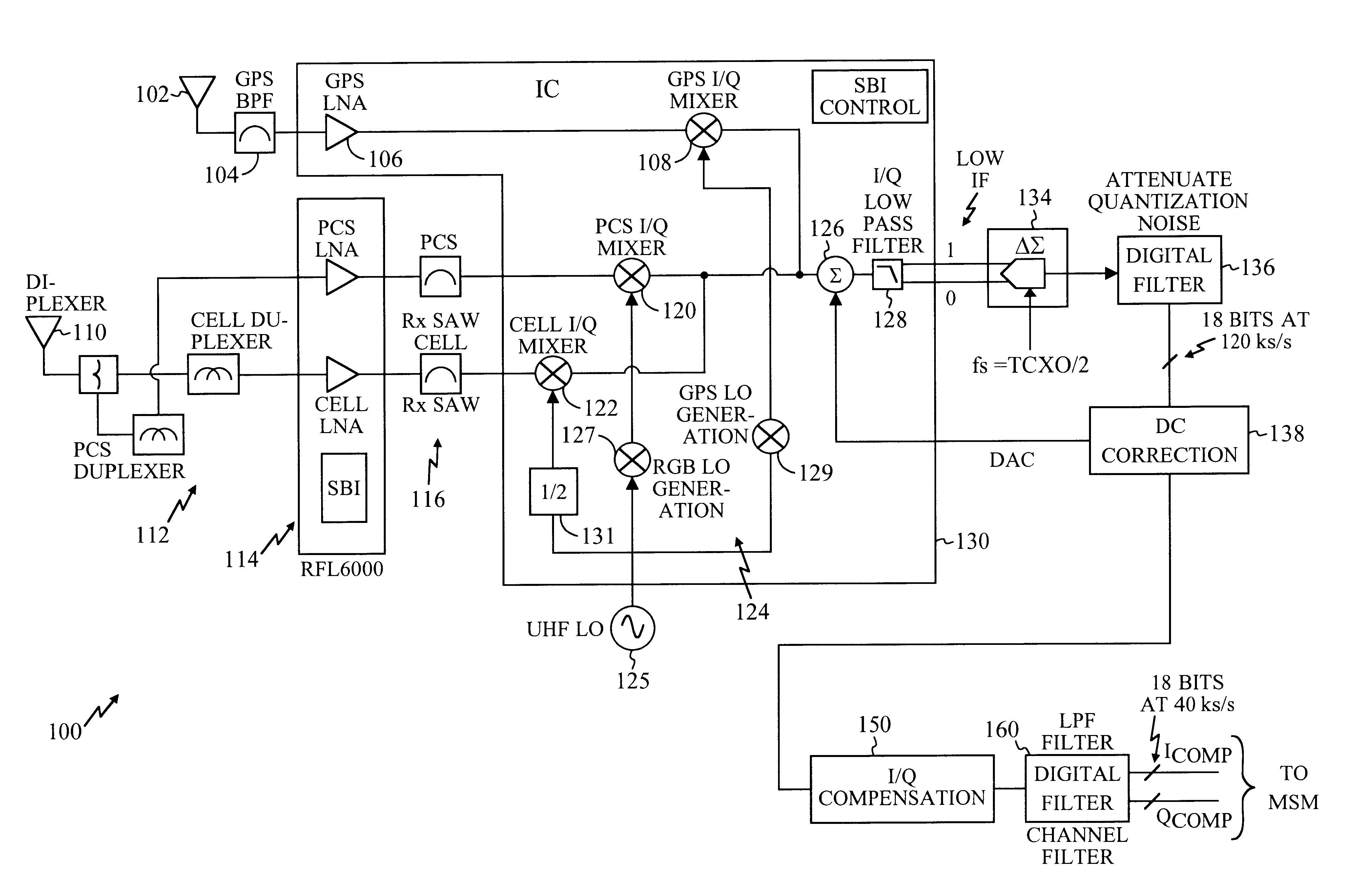

System and method for I-Q mismatch compensation in a low IF or zero IF receiver

InactiveUS6785529B2Modulated-carrier systemsAngle demodulation by oscillations conversionLocal oscillator signalFrequency mixer

Owner:QUALCOMM INC

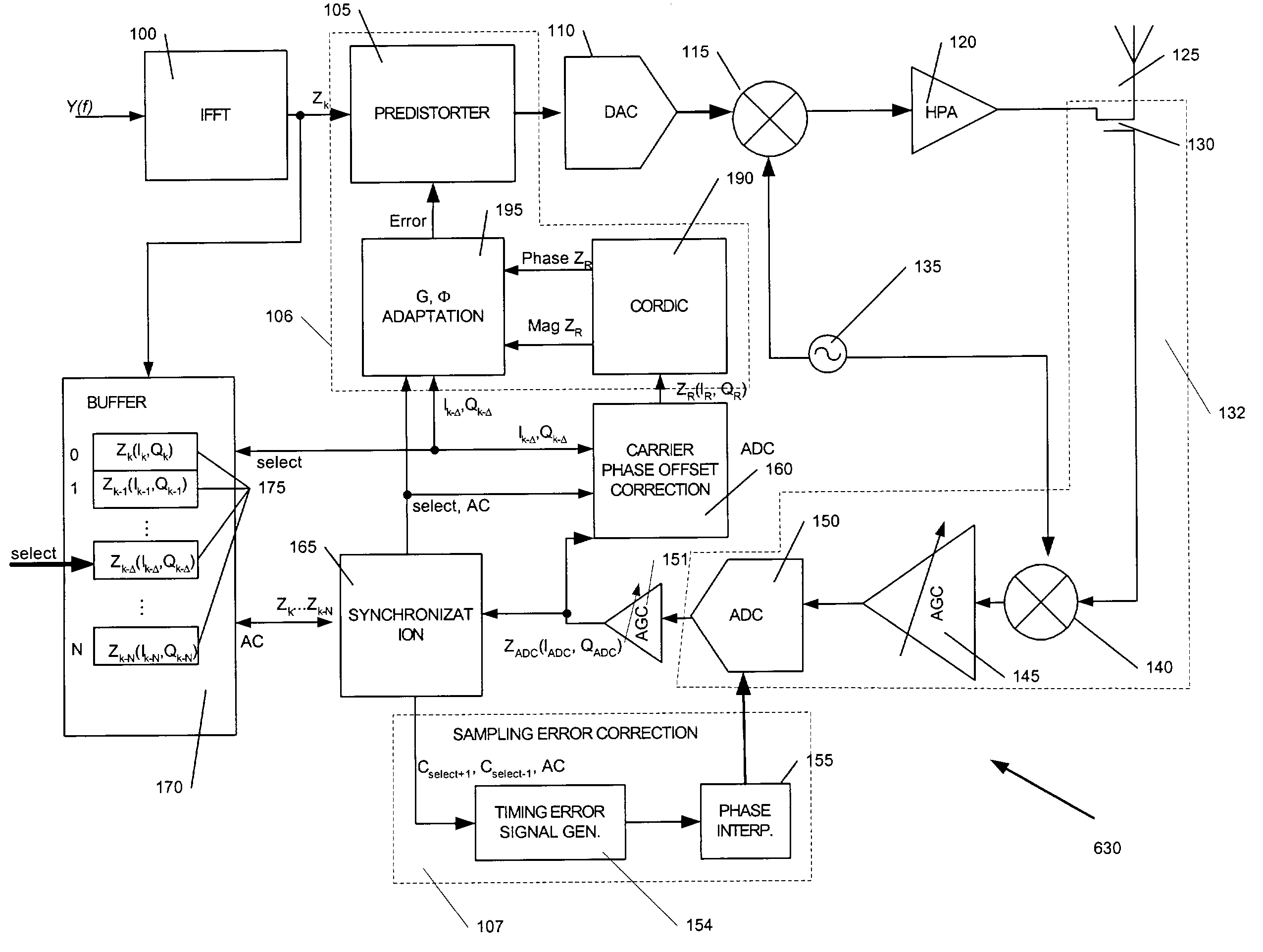

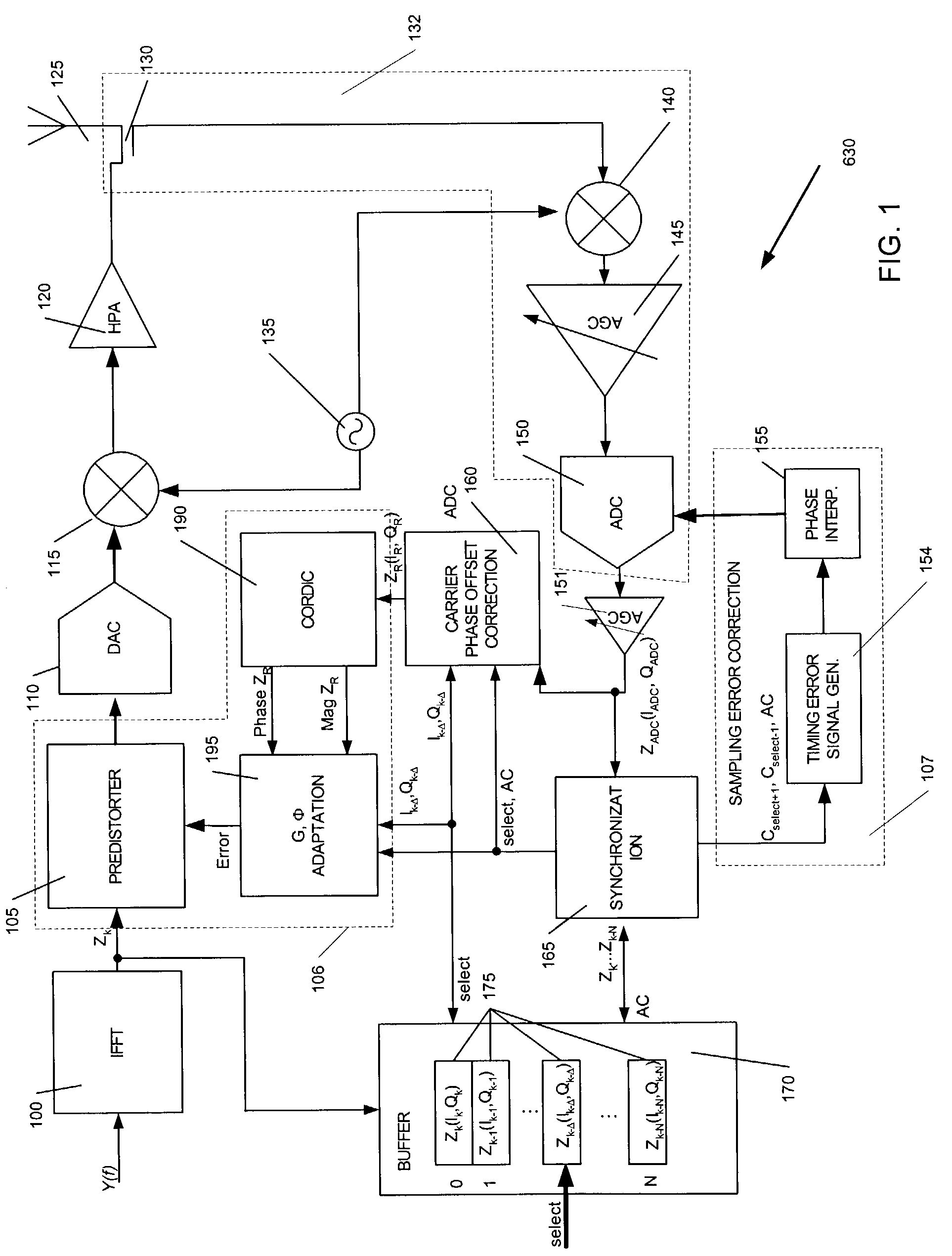

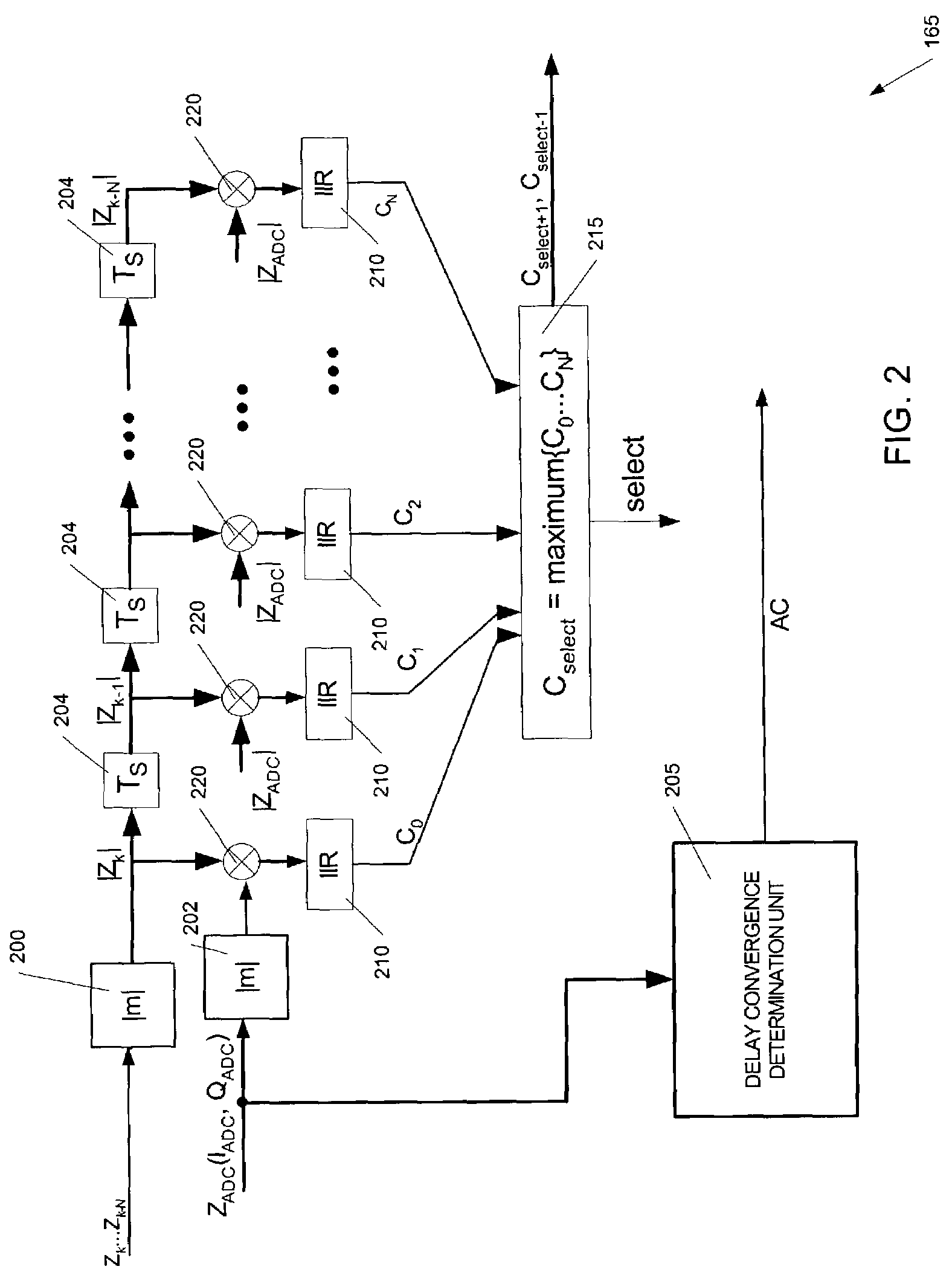

Method and apparatus for amplifier linearization using adaptive predistortion

ActiveUS7085330B1Accurate measurementPrecise and aggressive adaptive predistortionResonant long antennasModulated-carrier systemsAudio power amplifierEngineering

A signal processing method and apparatus capable of correcting signal distortion introduced by an RF power amplifier is disclosed, which includes the use of a buffer to store a plurality of samples representing at least a portion of an input signal intended for amplification by the RF power amplifier, the use of a self-receiver to receive an output signal generated by the RF power amplifier, the use of a synchronization unit to determine, as a matching input sample, which of the stored plurality of samples corresponds most closely to the output signal, and the use of a predistortion unit to selectively apply a distortion correction function to the input signal prior to amplification by the RF power amplifier in which the distortion correction function being derived from a relationship between the matching input sample and the output signal. This permits more precise and updateable determination of the delays involved in the RF modulation and amplification stages of the amplifier and the self-receiver, thus allowing for more precise and aggressive adaptive predistortion to be used. A phase offset correction is optionally provided to correct a phase offset in the realized sample of the output signal relative to the matching input symbol. Additionally, a sampling phase error correction unit may be provided to generate sampling alteration information to an analog-to-digital converter to cause such analog-to-digital converter to selectively alter sampling of the output signal.

Owner:MARVELL ASIA PTE LTD

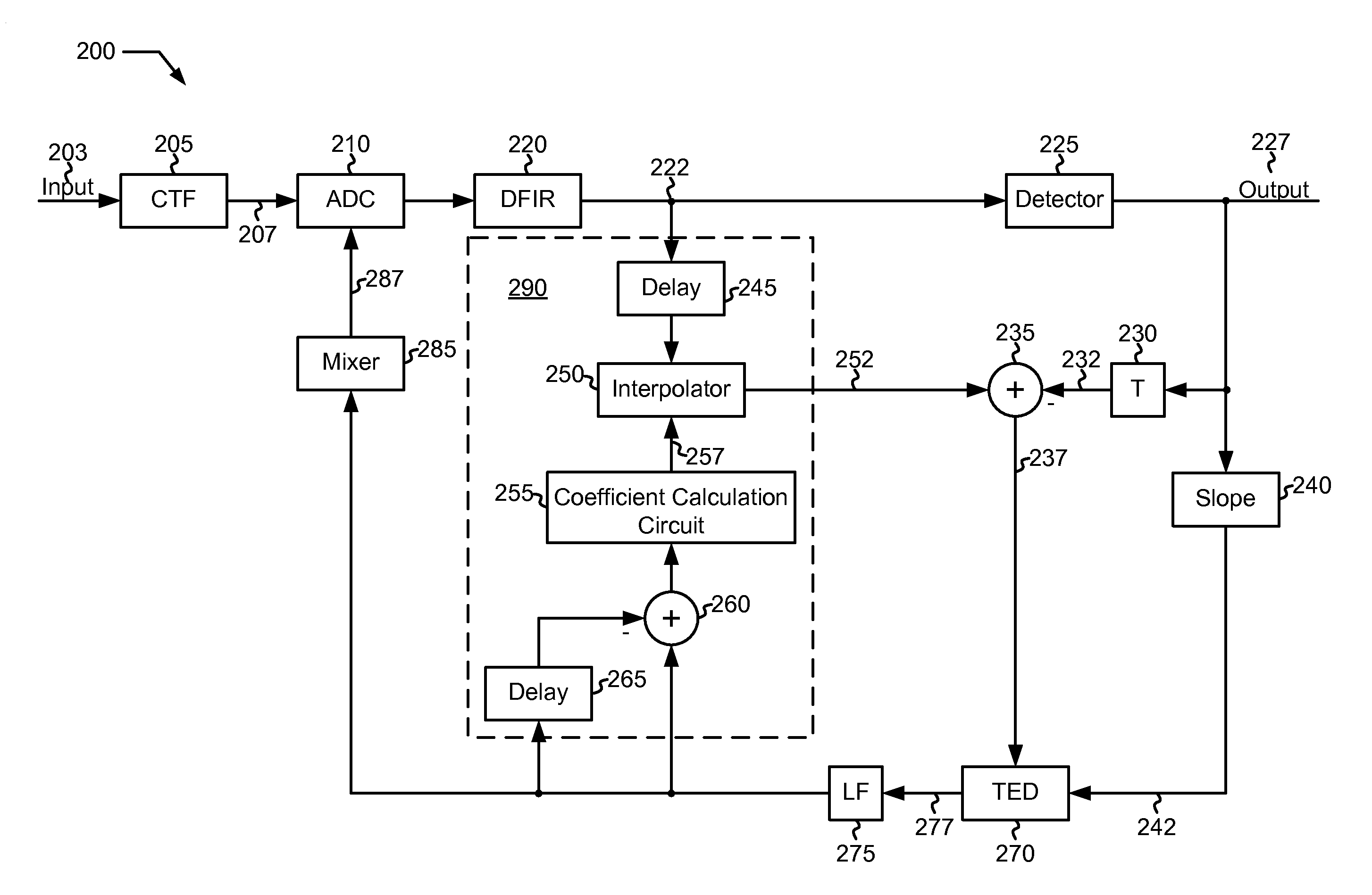

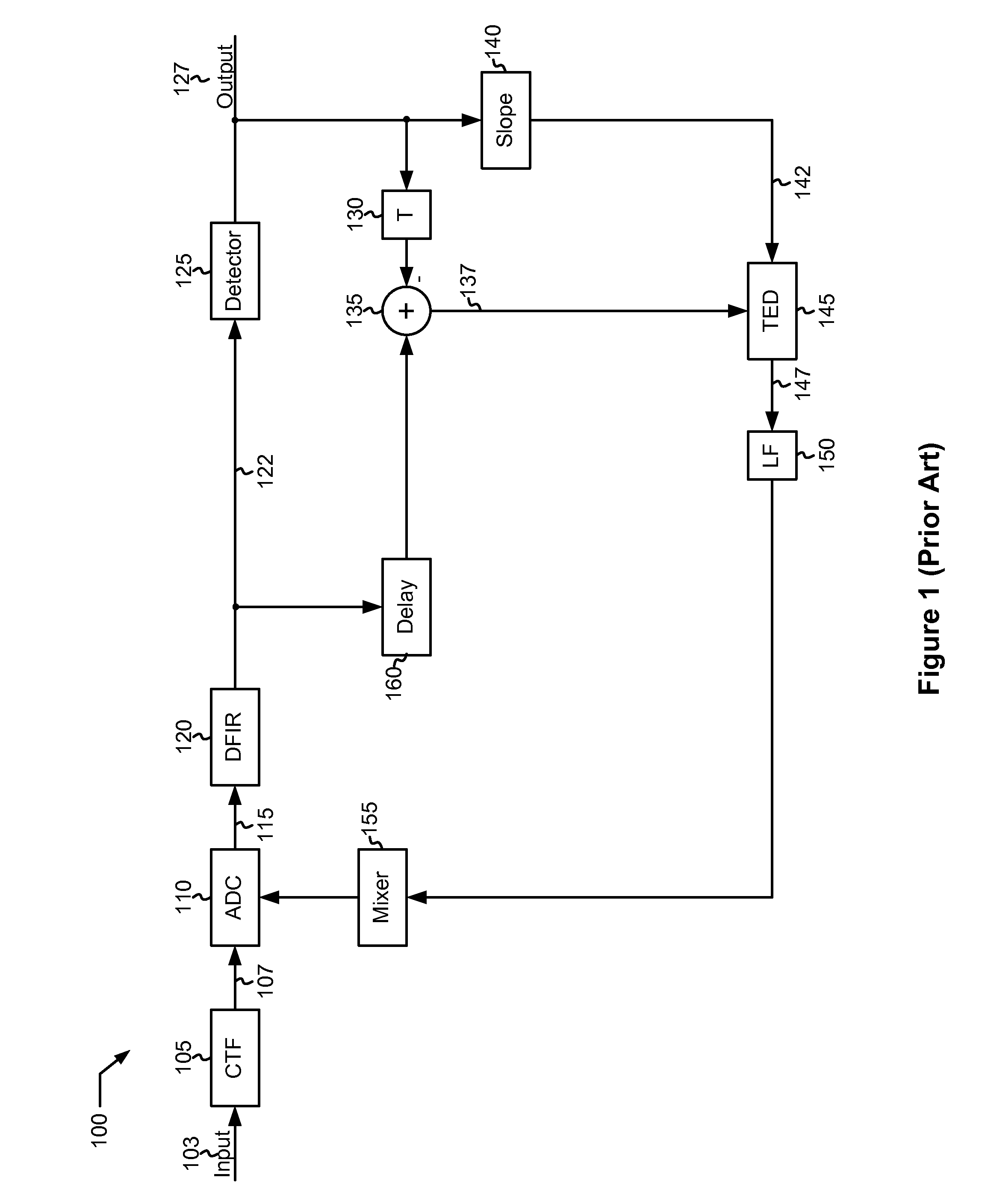

Systems and methods for mitigating latency in a data detector feedback loop

InactiveUS8018360B2Reduce latency impactLower latencyModification of read/write signalsElectric signal transmission systemsSampling instantData retrieval

Methods and systems for mitigating latency in a data detector feedback loop are included. For example, a method for reducing latency in an error corrected data retrieval system is included. The method includes performing an analog to digital conversion at a sampling instant to create a digital sample, and performing a data detection on the digital sample to create a detected output. The detected output is compared with the digital sample to determine a phase error. During an interim period, the digital sample is adjusted to reflect the phase error to create an adjusted digital sample. After the interim period, the sampling instant is adjusted to reflect the phase error.

Owner:LSI CORP +1

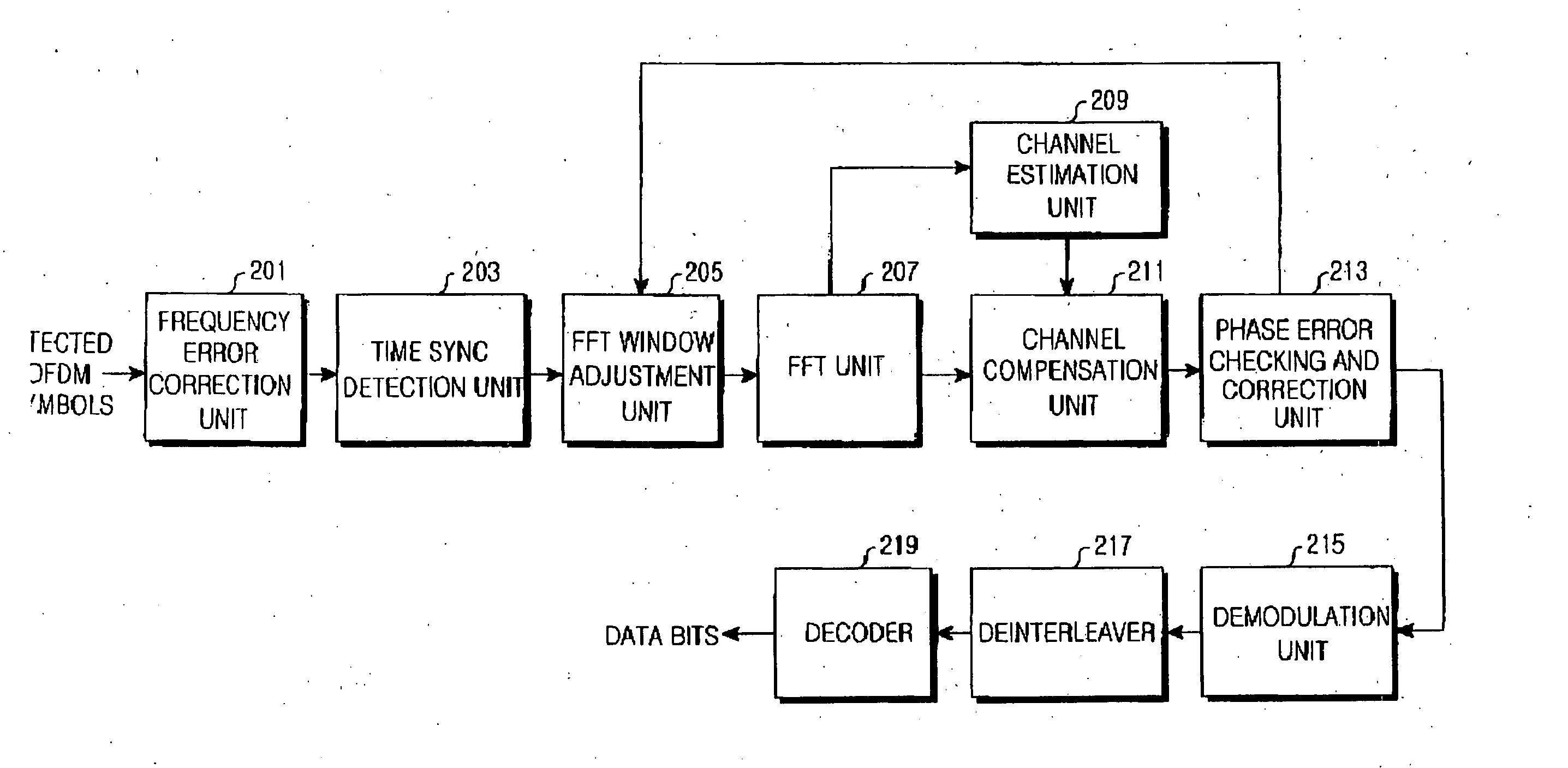

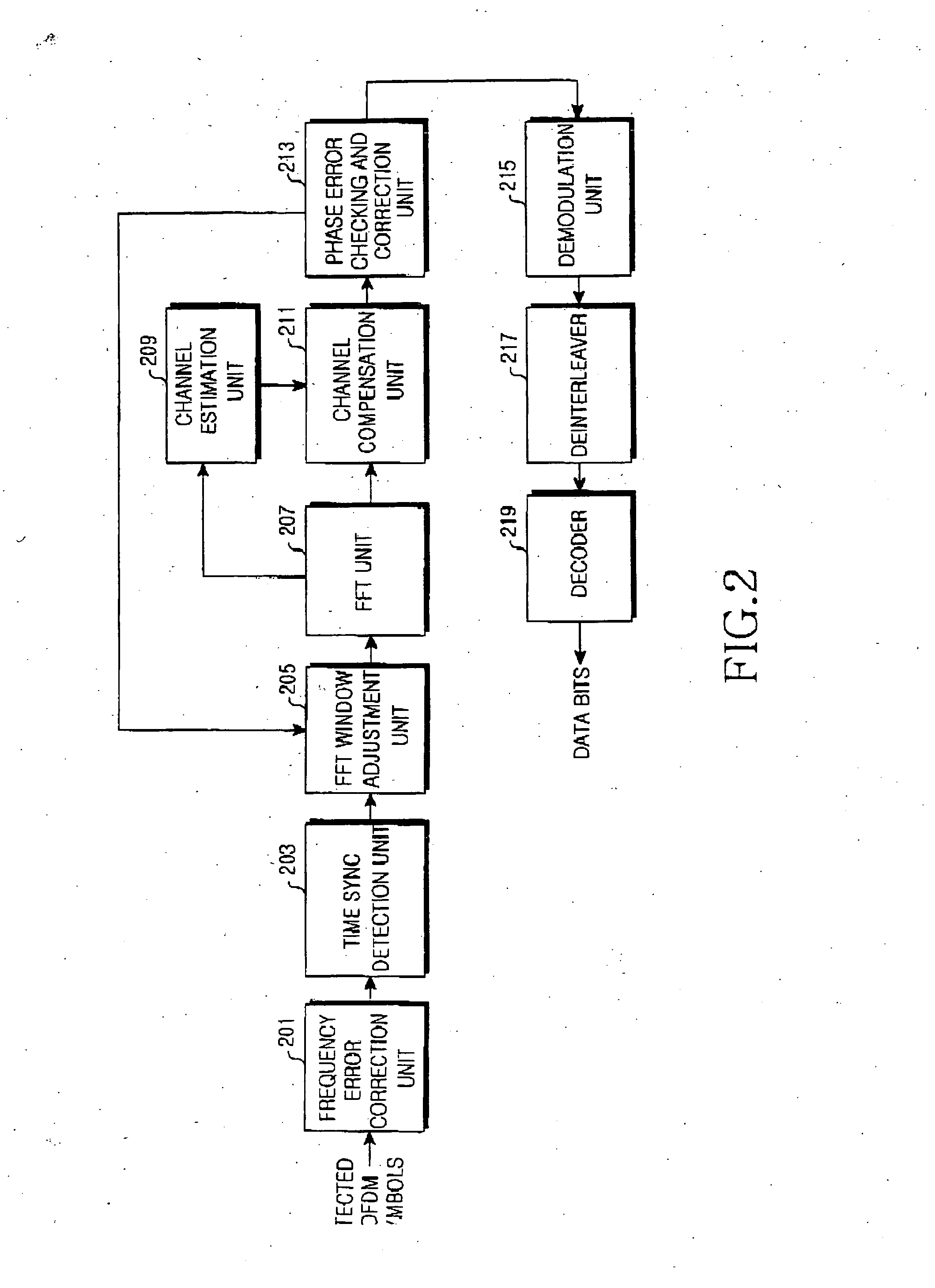

Apparatus and method for compensating for frequency offset in wireless communication system

InactiveUS20060176802A1Modulated-carrier systemsConstructions elementsTime domainSampling frequency offset

Disclosed is an apparatus and method for compensating for frequency offset in a wireless communication system using an OFDM system which can compensate for phase change due to carrier frequency offset and sampling frequency offset of data carried on subcarriers. The apparatus includes an FFT window adjustment unit for receiving sampling data when a packet is received, setting a start point of a FFT window at a start point of long training symbols and adjusting a position of the FFT window according to an input window adjustment value, an FFT unit for receiving an output of the FFT window adjustment unit, transforming time-domain symbols into frequency-domain symbols and calculating FFT coefficients, a channel estimation unit for receiving the coefficients from the FFT unit, estimating a channel state and outputting a value for compensating for an estimated value, a channel compensation unit for compensating for the frequency-domain symbols using the output of the channel estimation unit and a phase error tracking and correction unit for receiving an output of the channel compensation unit, detecting a sampling frequency offset and a phase change of a carrier signal and outputting the window adjustment value to the FFT window adjustment unit.

Owner:SAMSUNG ELECTRONICS CO LTD

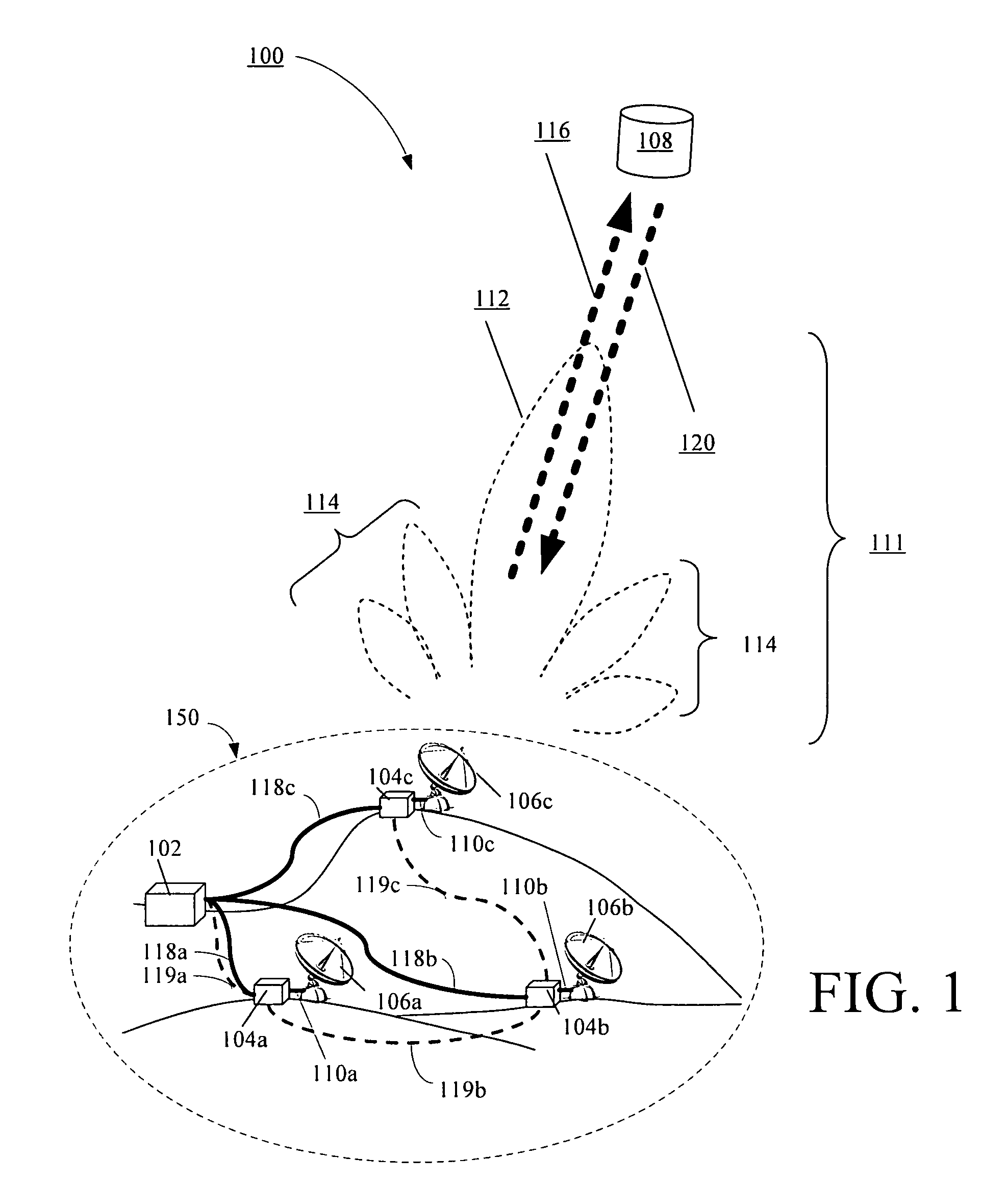

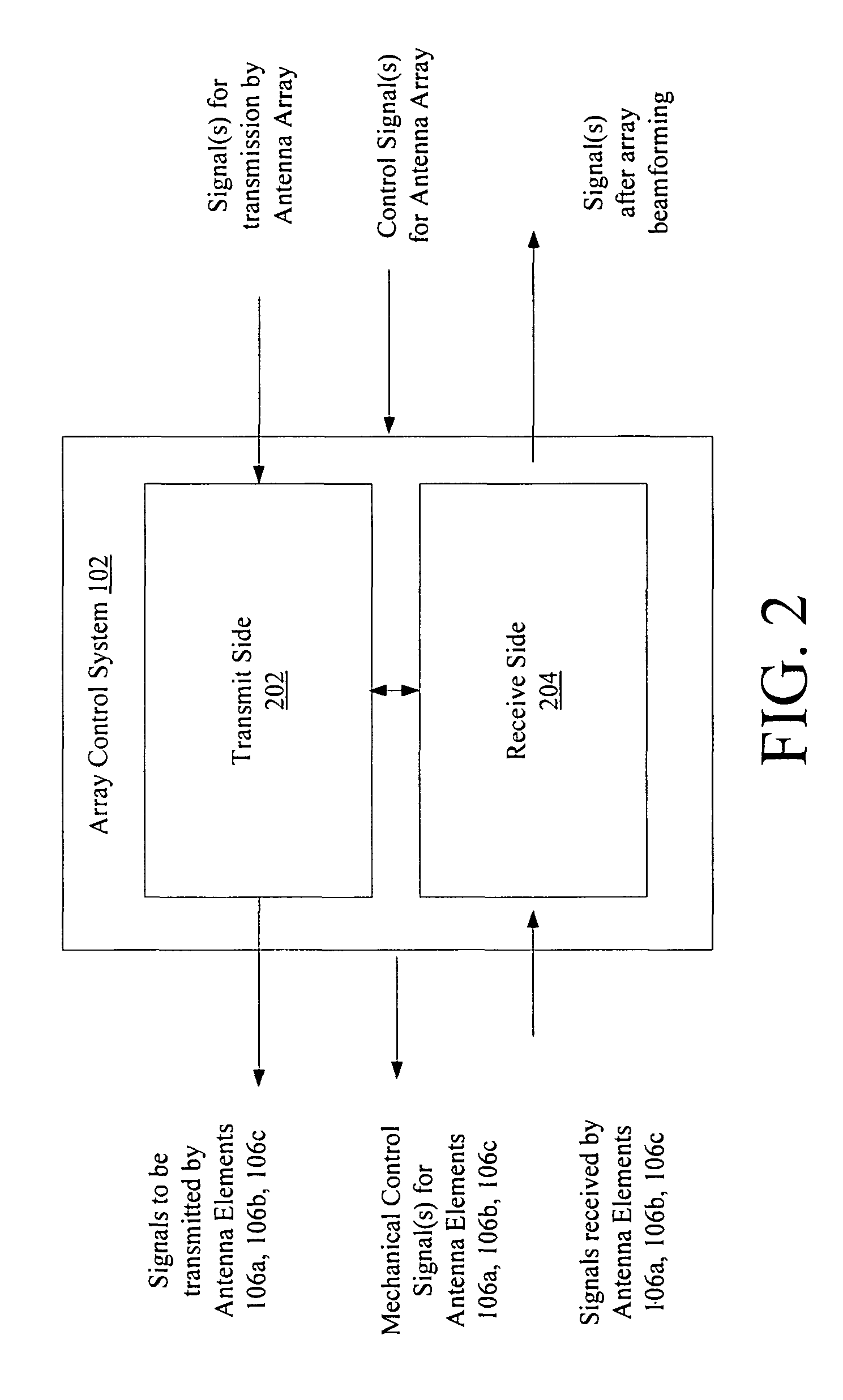

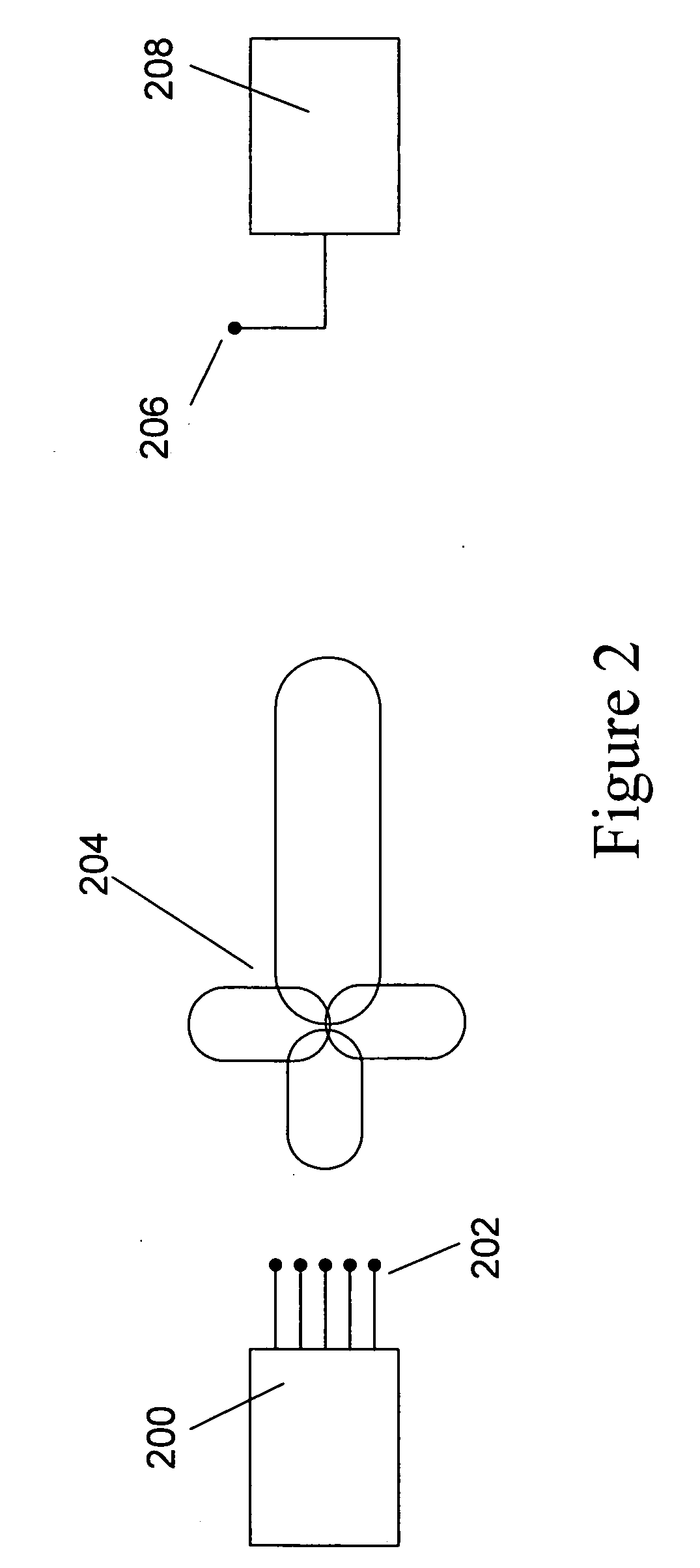

Systems and methods for calibrating transmission of an antenna array

Disclosed herein are various embodiments of methods, systems, and apparatuses for sending and receiving signals in a digital communication system. In one embodiment performs steps of transmitting a signal from a device with a first antenna array and calibrating the signal with a phase shift of the signal. In one exemplary method embodiment, a signal is transmitted from a beam-forming transmitter to an assisting receiver in an IEEE 802.11 wireless transmission. A return calibration signal from the assisting receiver with information regarding the phase error of signal is received by the beam-forming transceiver. The beam-forming transmitter introduces a calibration phase error to cancel the phase error as reported by the assisting receiver.

Owner:CONEXANT SYST INC

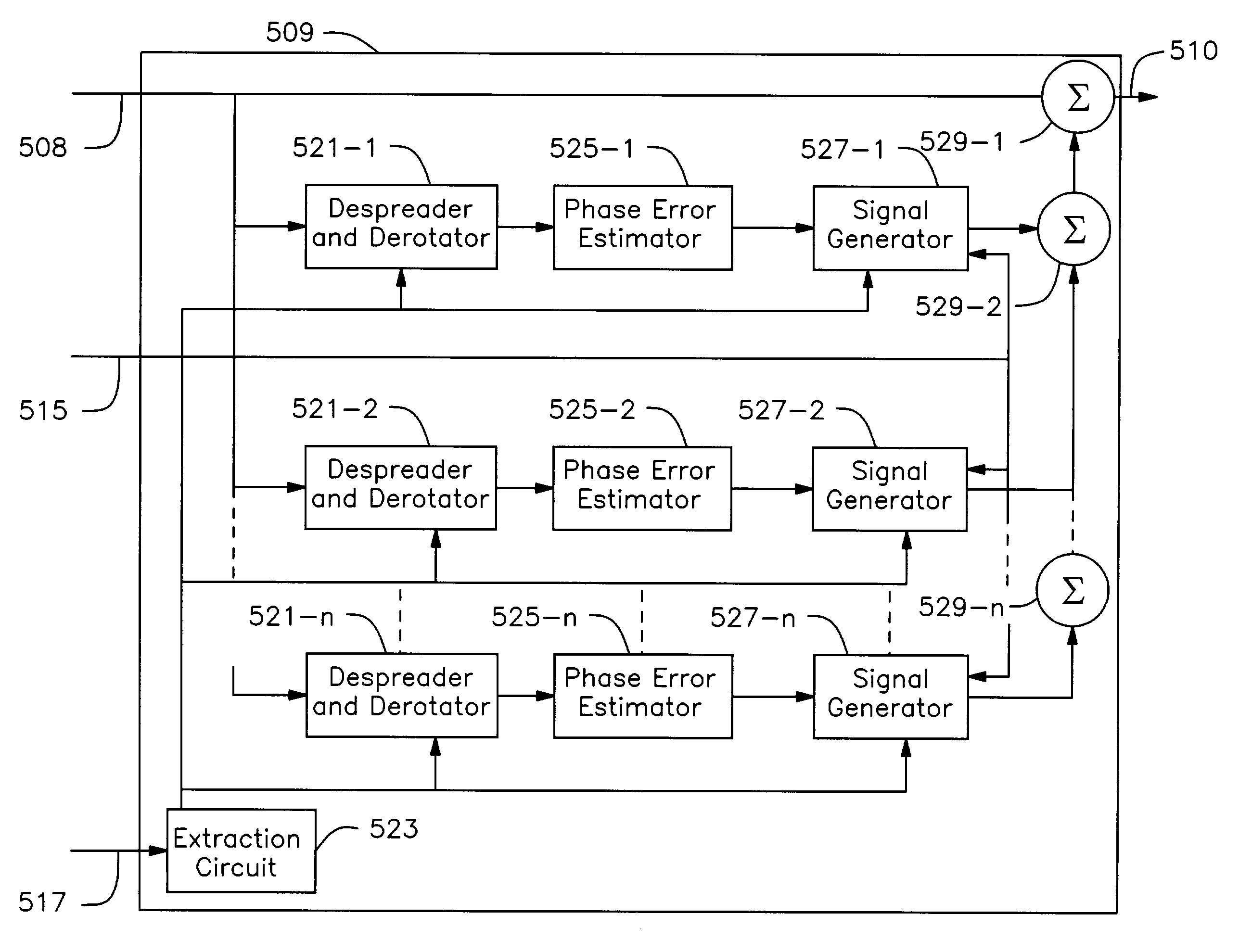

External correction of errors between traffic and training in a wireless communications system

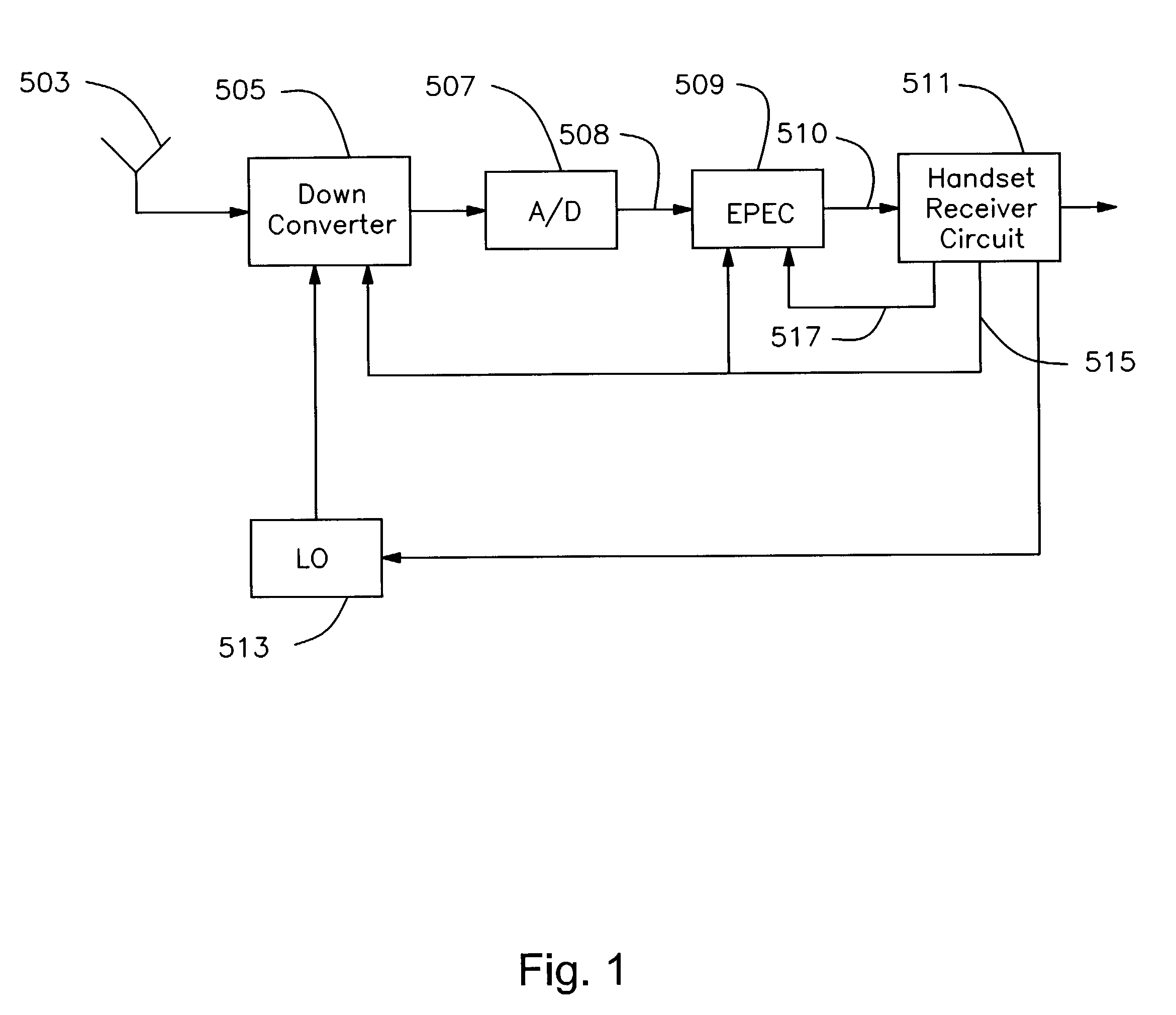

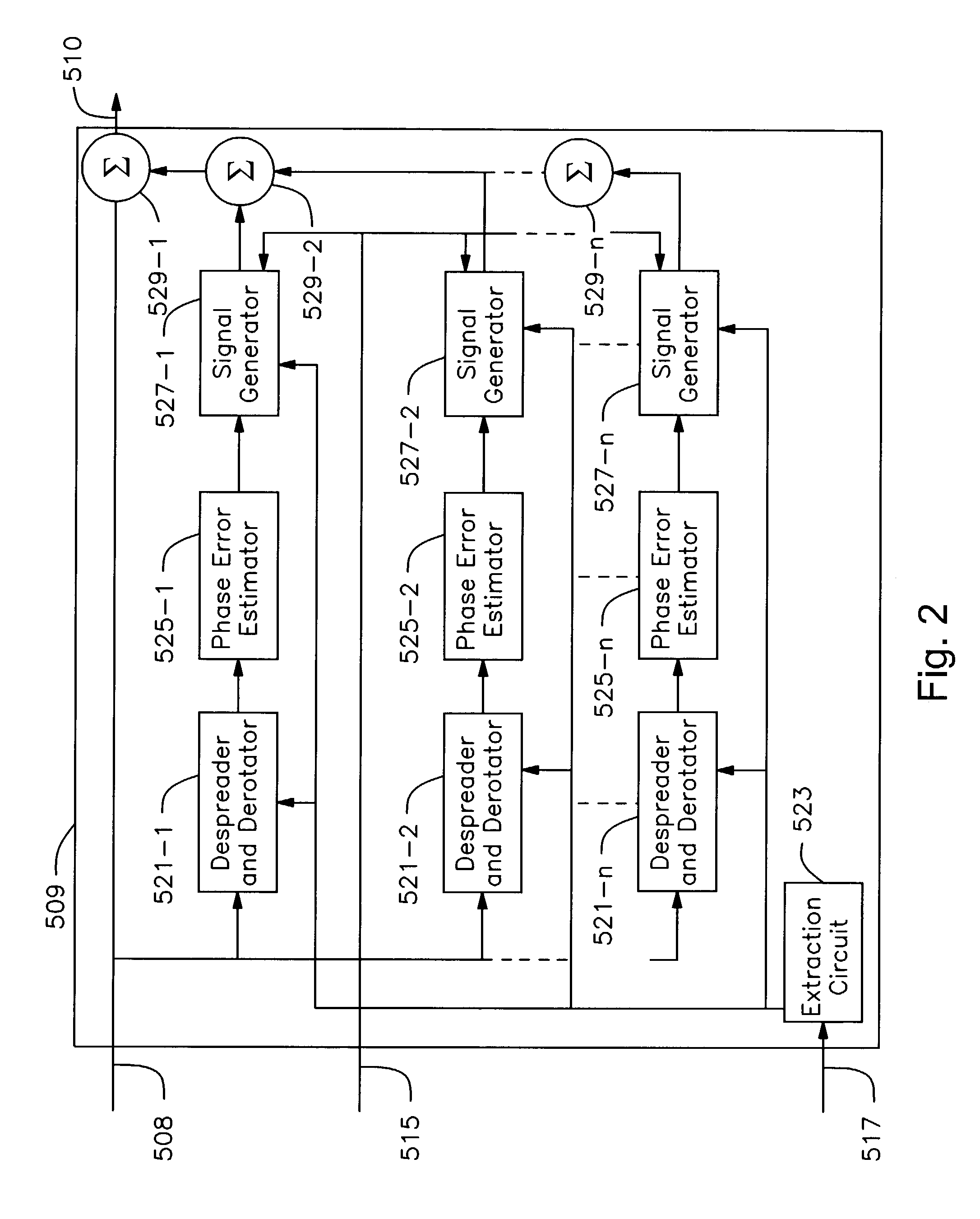

InactiveUS7221699B1Compensating for such errorTime-division multiplexAmplitude-modulated carrier systemsPhase correctionTraffic capacity

A method and apparatus are provided that allows a training and traffic signal to be compensated for phase errors without modifying a receiver. In one embodiment, the invention encompasses an external error correction circuit having a signal input to receive training and traffic channel signals from a receive chain, a signal processing circuit to compute phase corrections to at least one of the training and traffic channel signals, and a signal generator to supply a compensation signal to effect the computed correction.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com