Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

604results about How to "Reduce circuit area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

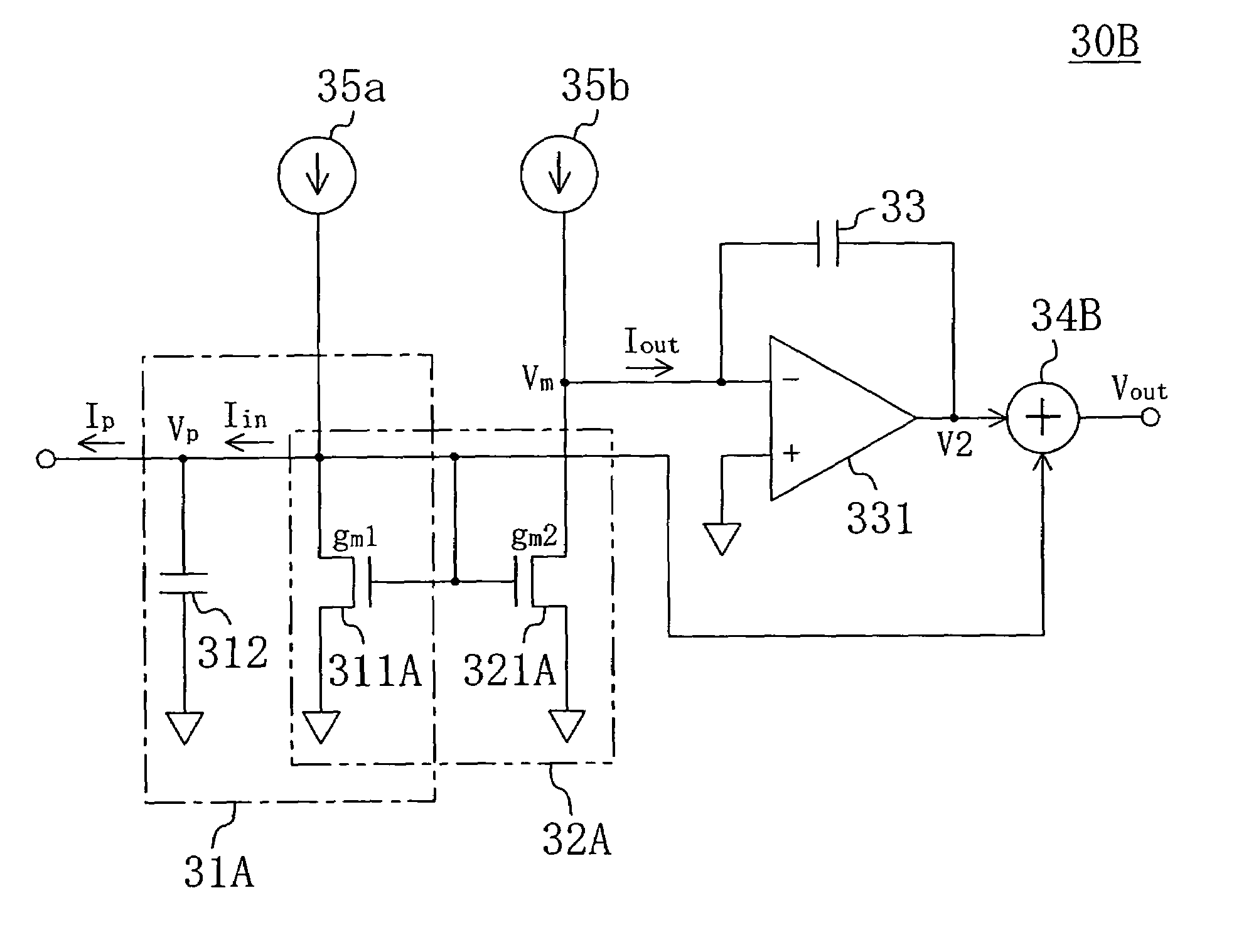

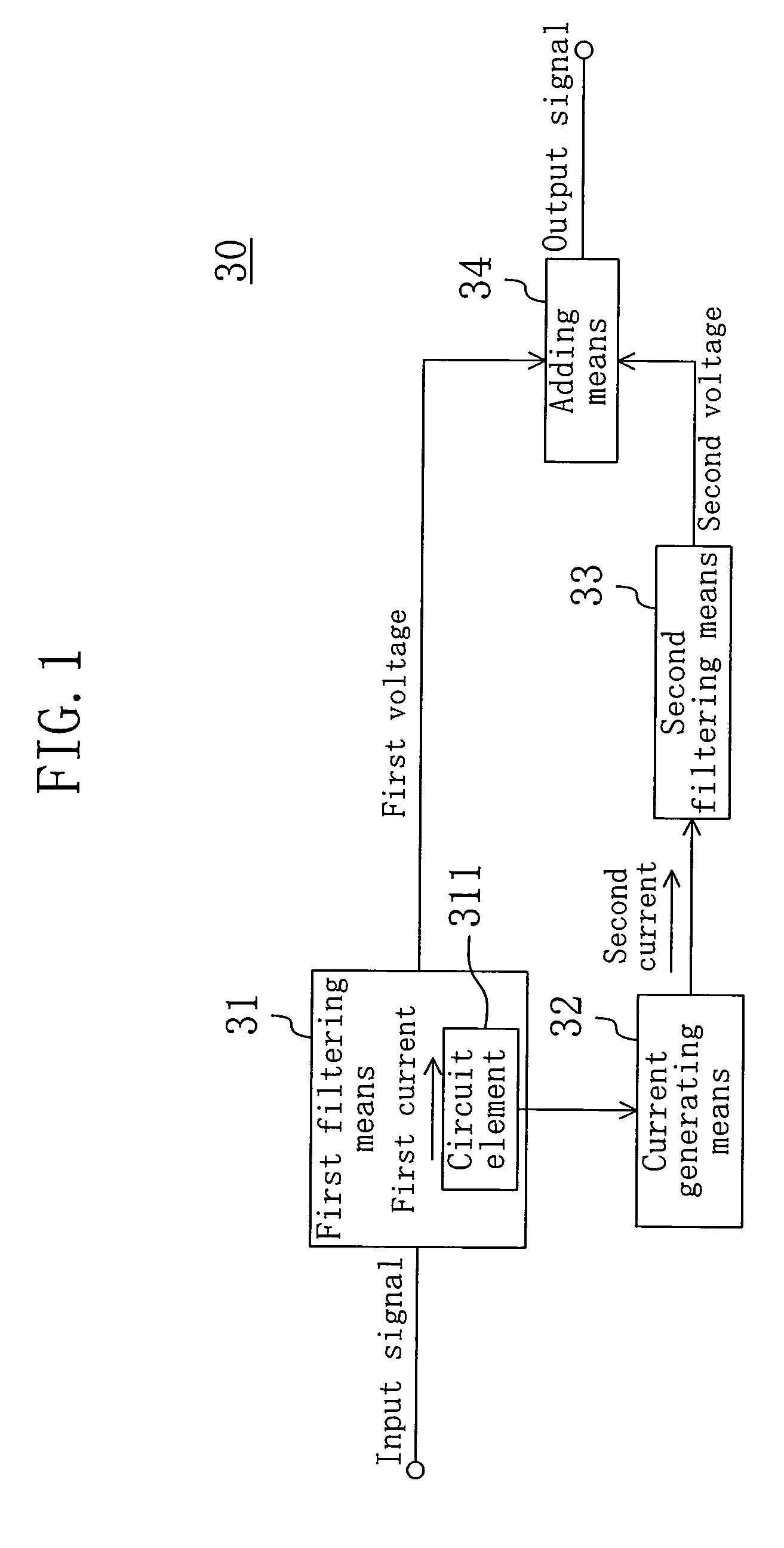

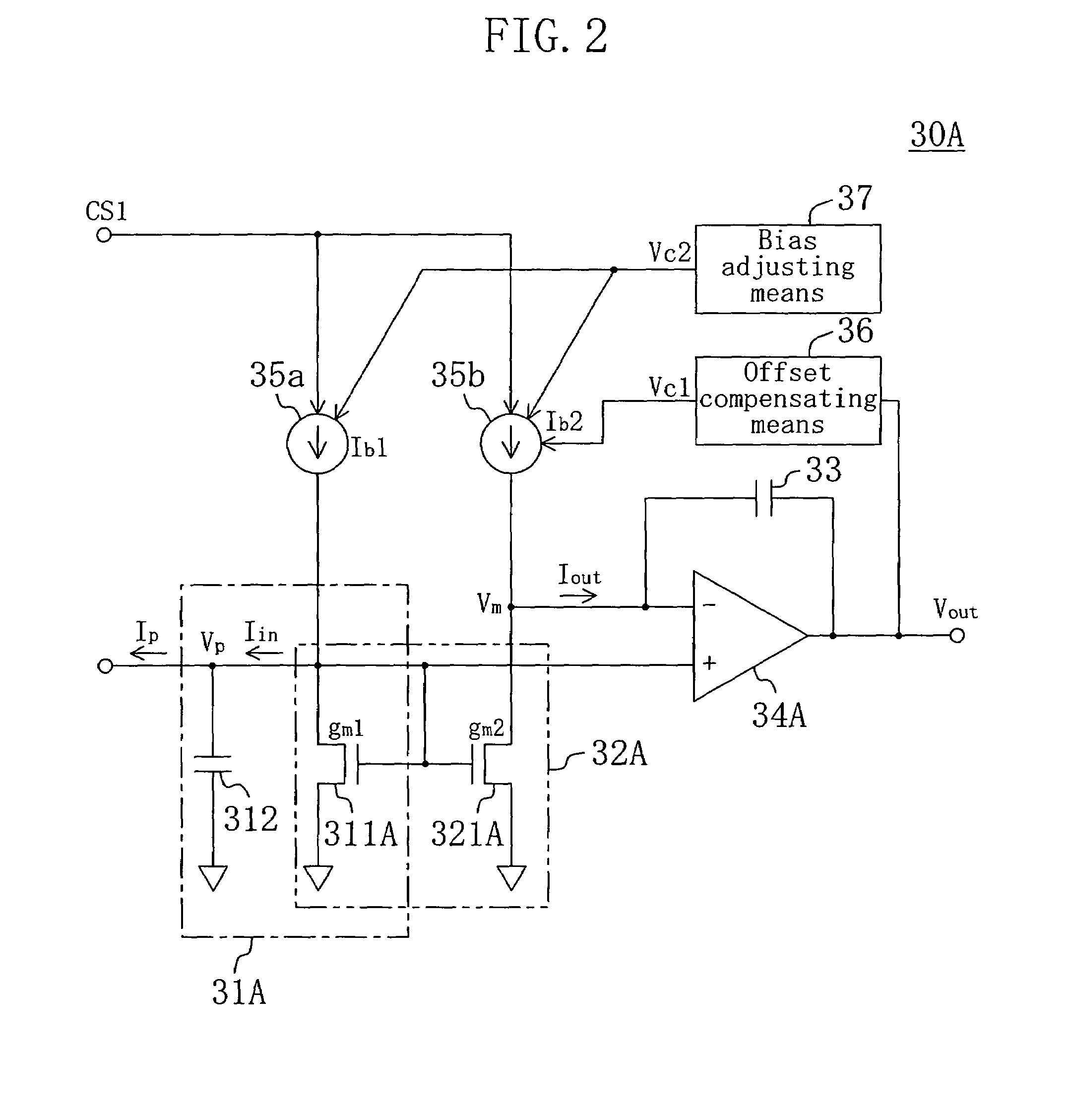

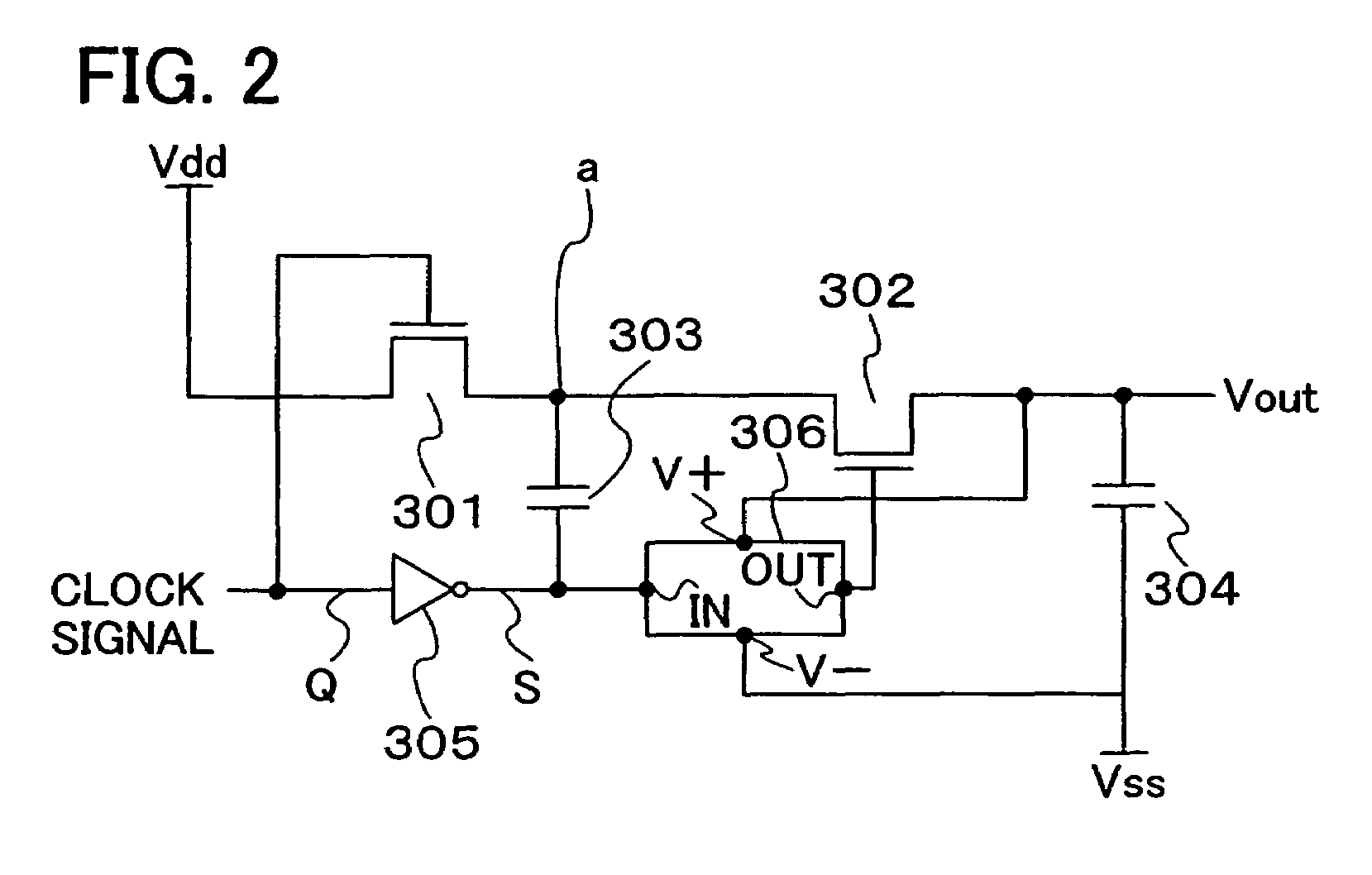

Low-pass filter for a PLL, phase-locked loop and semiconductor integrated circuit

InactiveUS7030688B2Reduce circuit sizeReduce circuit areaPulse automatic controlOscillations generatorsLoop filterBand-pass filter

The invention provides a low-pass filter suitably used as a loop filter for a PLL or a DLL that has a filtering characteristic equivalent to that of a conventional one and can be realized in a smaller circuit area. The low-pass filter includes first filtering means (31) for accepting, as an input, an input signal to the low-pass filter and outputting a first voltage; a circuit element (311) included in the first filtering means (31) for allowing a first current to flow in accordance with the first voltage; current generating means (32) for generating a second current at a given rate to the first current; second filtering means (33) for accepting, as an input, the second current and outputting a second voltage; and adding means (34) for adding the first voltage and the second voltage and outputting an output signal of the low-pass filter, in which the second current is set to be smaller than the first current.

Owner:PANASONIC CORP

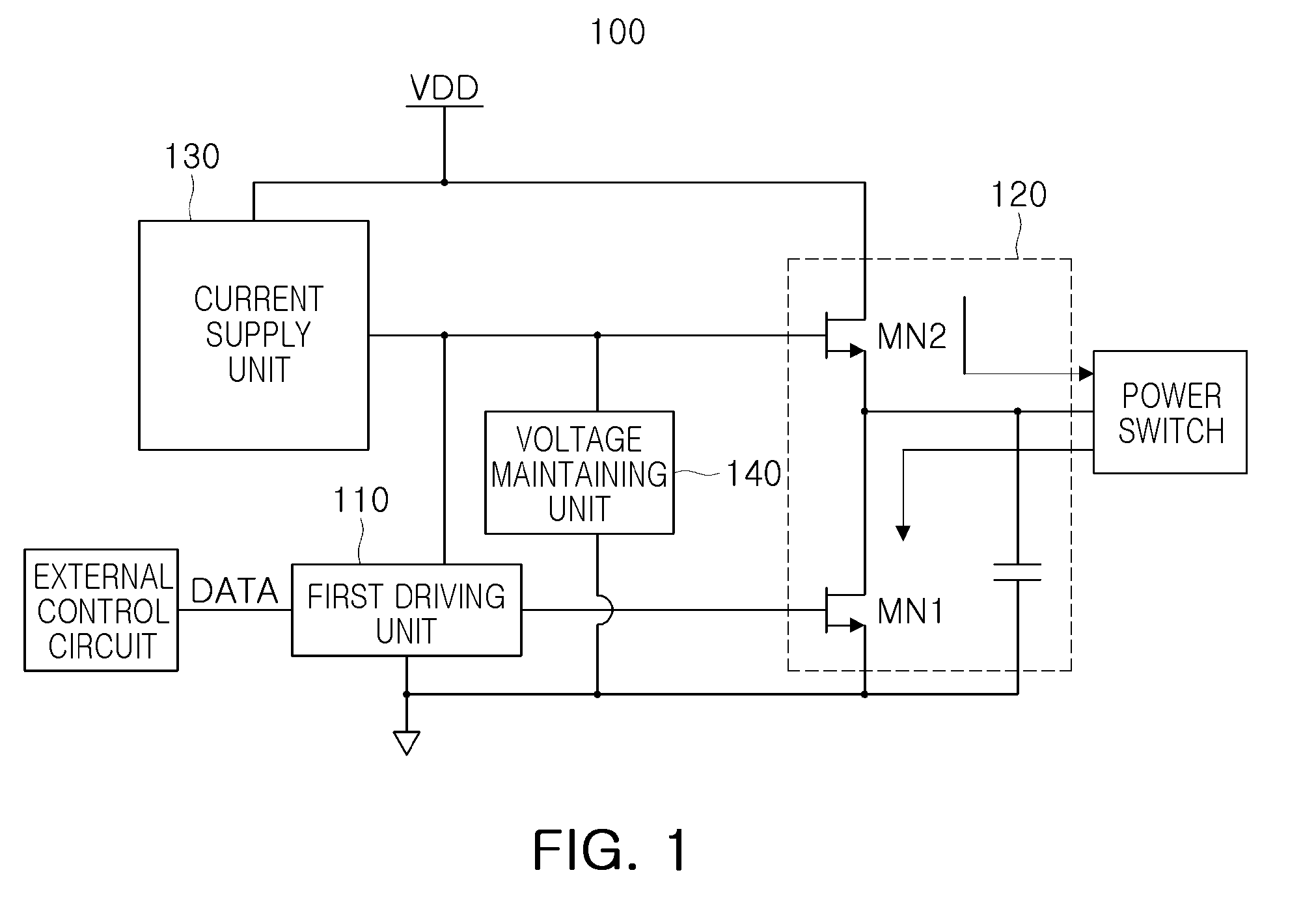

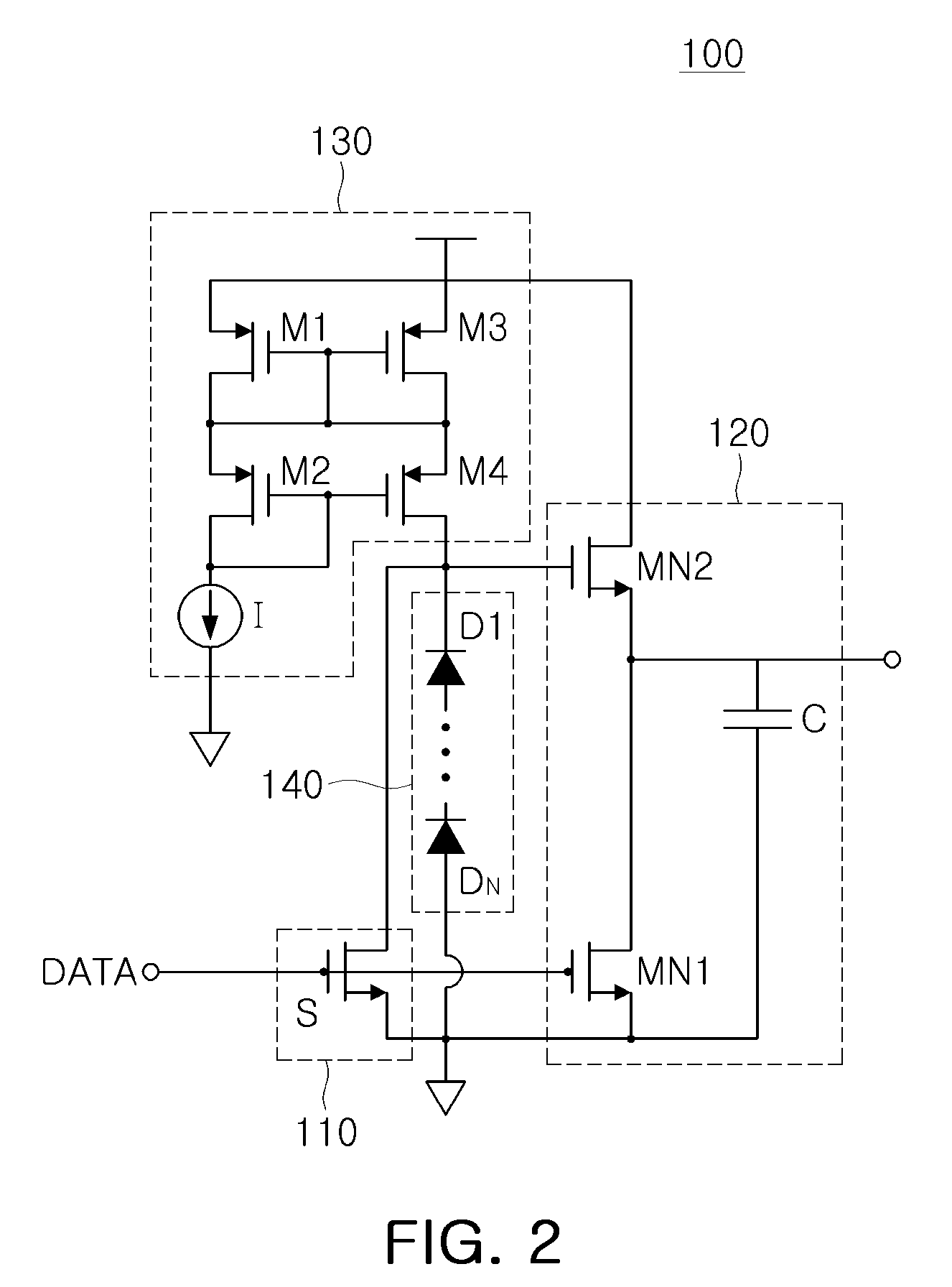

Power switching driving apparatus, and power factor correction device and power supply device having the same

InactiveUS20130163289A1Reduce circuit areaIncrease driving speedEfficient power electronics conversionEnergy industryControl signalPower switching

There are provided a power switching driving apparatus able to reduce a circuit area and increase a driving speed, and a power factor correction device and a power supply device having the same. The power switching driving apparatus includes: a first driving unit providing a switching signal in response to a control signal from the outside; a second driving unit including first and second NMOS FETs cascode-connected between an operational power source terminal supplying pre-set operation power and a ground, and performing switching complimentarily in response to the switching signal to provide a switching control signal controlling power switching; a current supply unit supplying a current for driving the second driving unit; and a voltage maintaining unit maintaining a voltage for driving the second driving unit.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

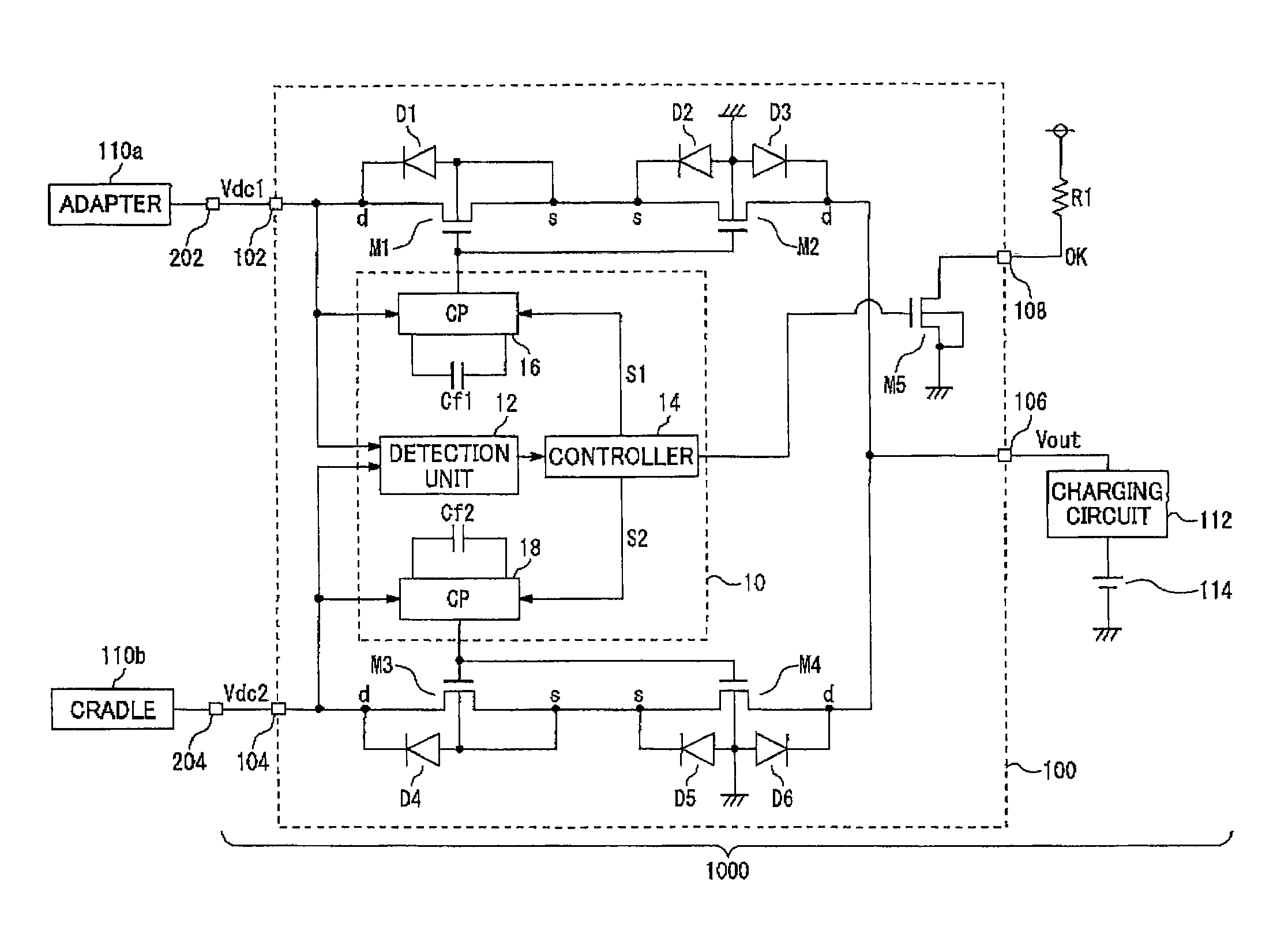

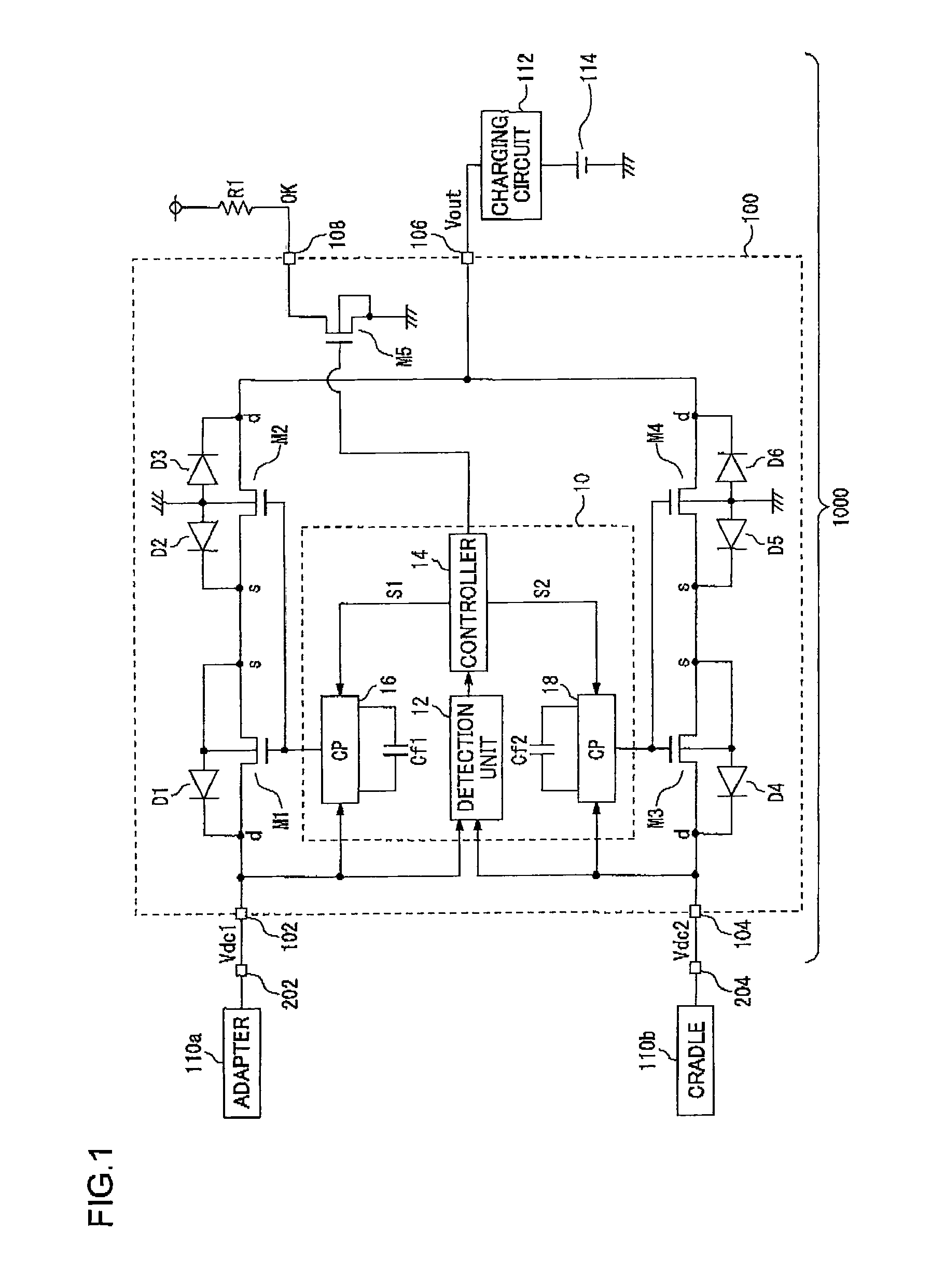

Selector circuit

ActiveUS8044639B2Prevent backflowReduce circuit areaElectric signal transmission systemsDc source parallel operationEngineeringTransistor

A selector circuit outputs one of a first input voltage or a second input voltage via an output terminal. A first transistor and a second transistor are provided in series between a first input terminal and the output terminal. A third transistor and a fourth transistor are provided in series between a second input terminal and the output terminal. A control unit controls the ON / OFF operations of the first transistor through the fourth transistor. The back gates of the first transistor and the second transistor are connected such that at least one body diode of the first transistor M1 and at least one body diode of the second transistor are arranged in opposing directions. The back gates of the third transistor and the fourth transistor are connected in the same way.

Owner:ROHM CO LTD

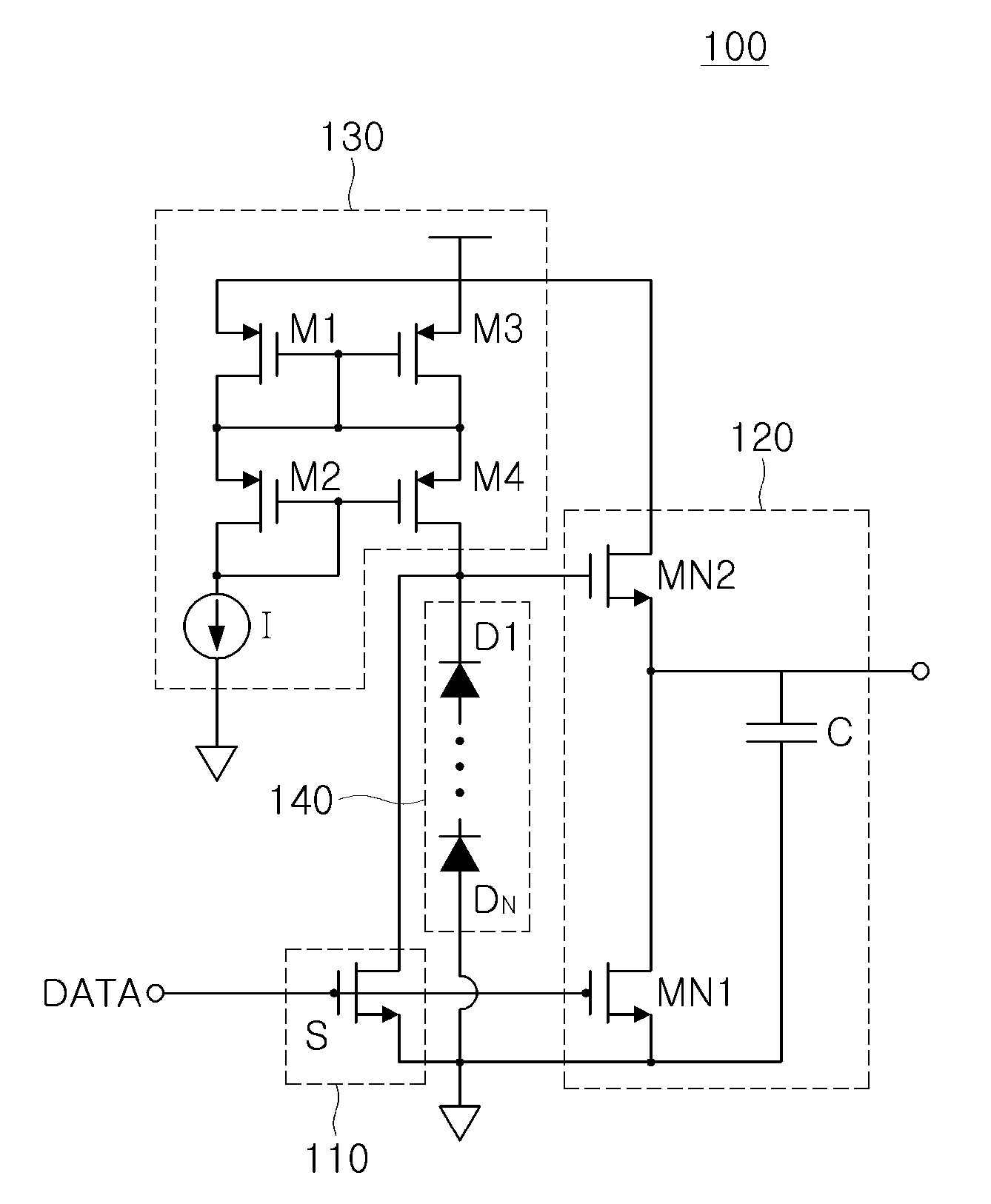

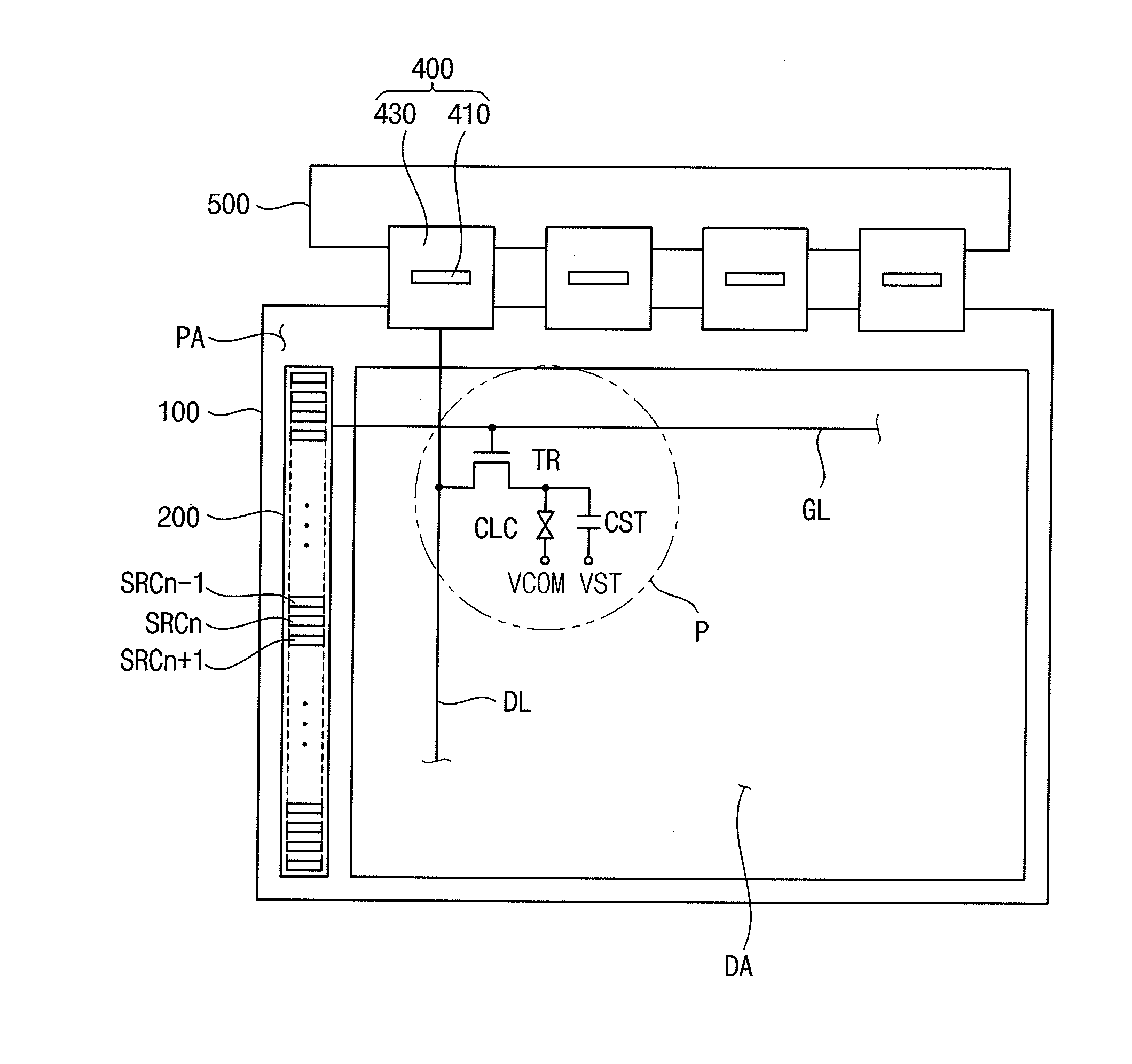

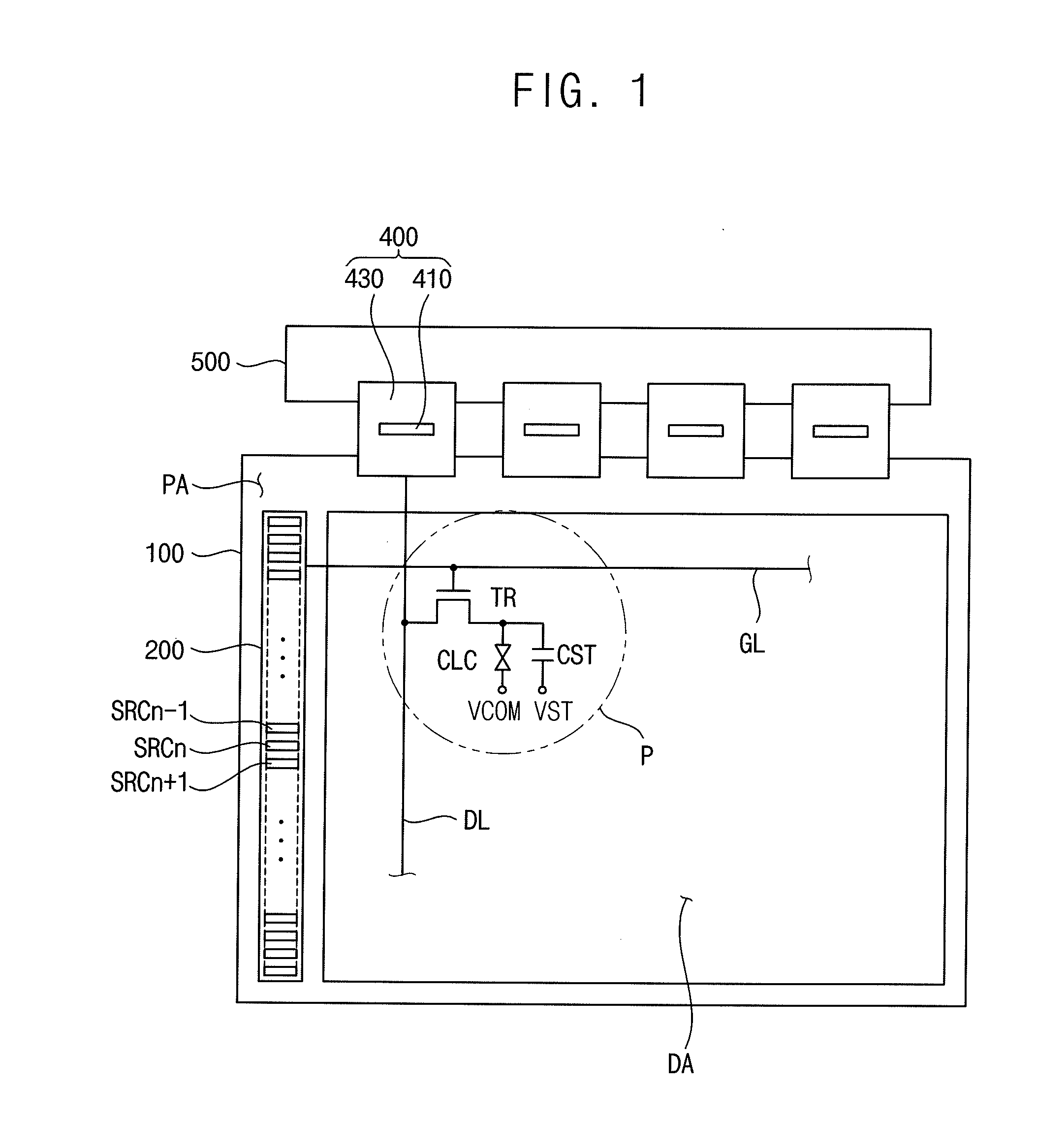

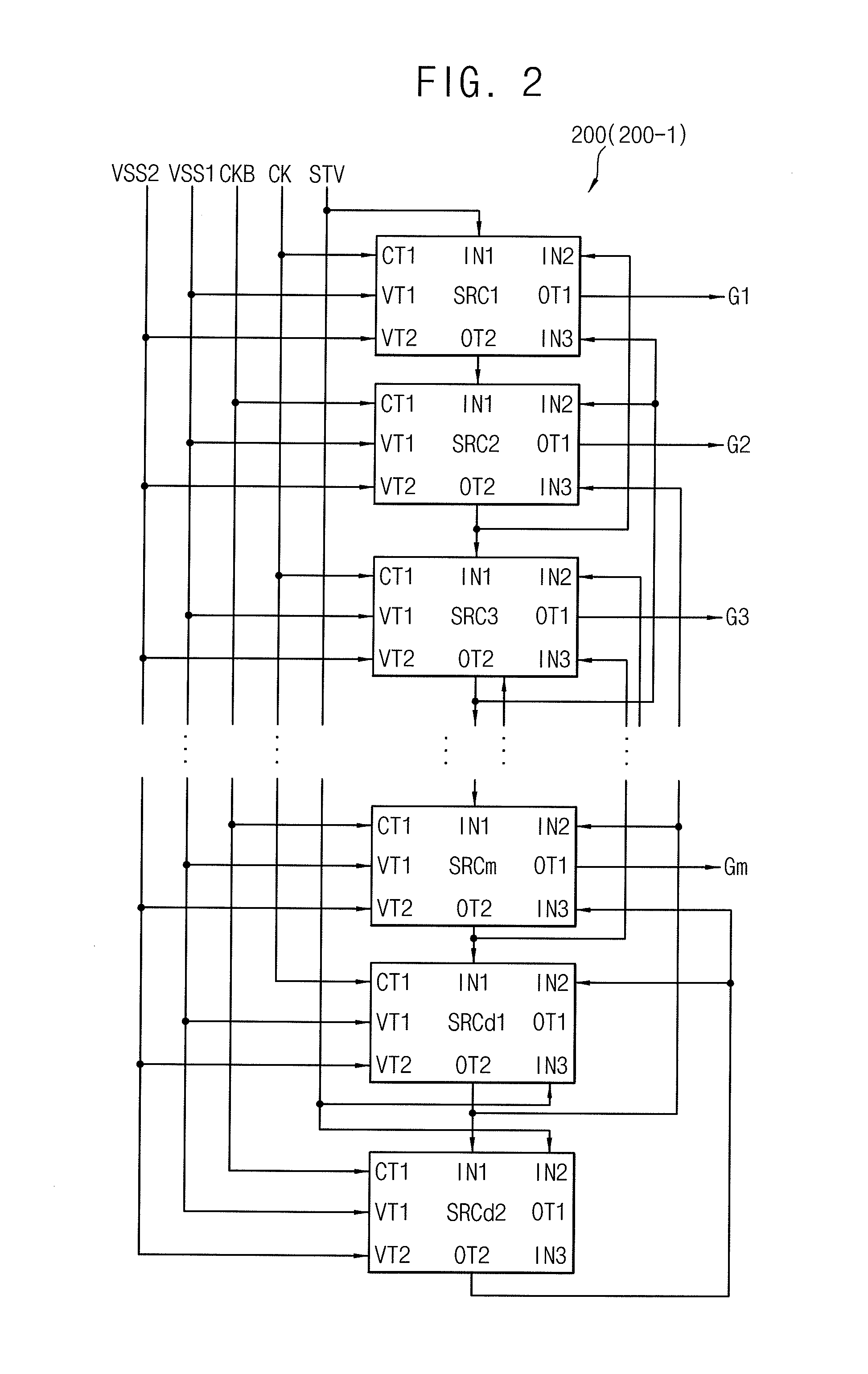

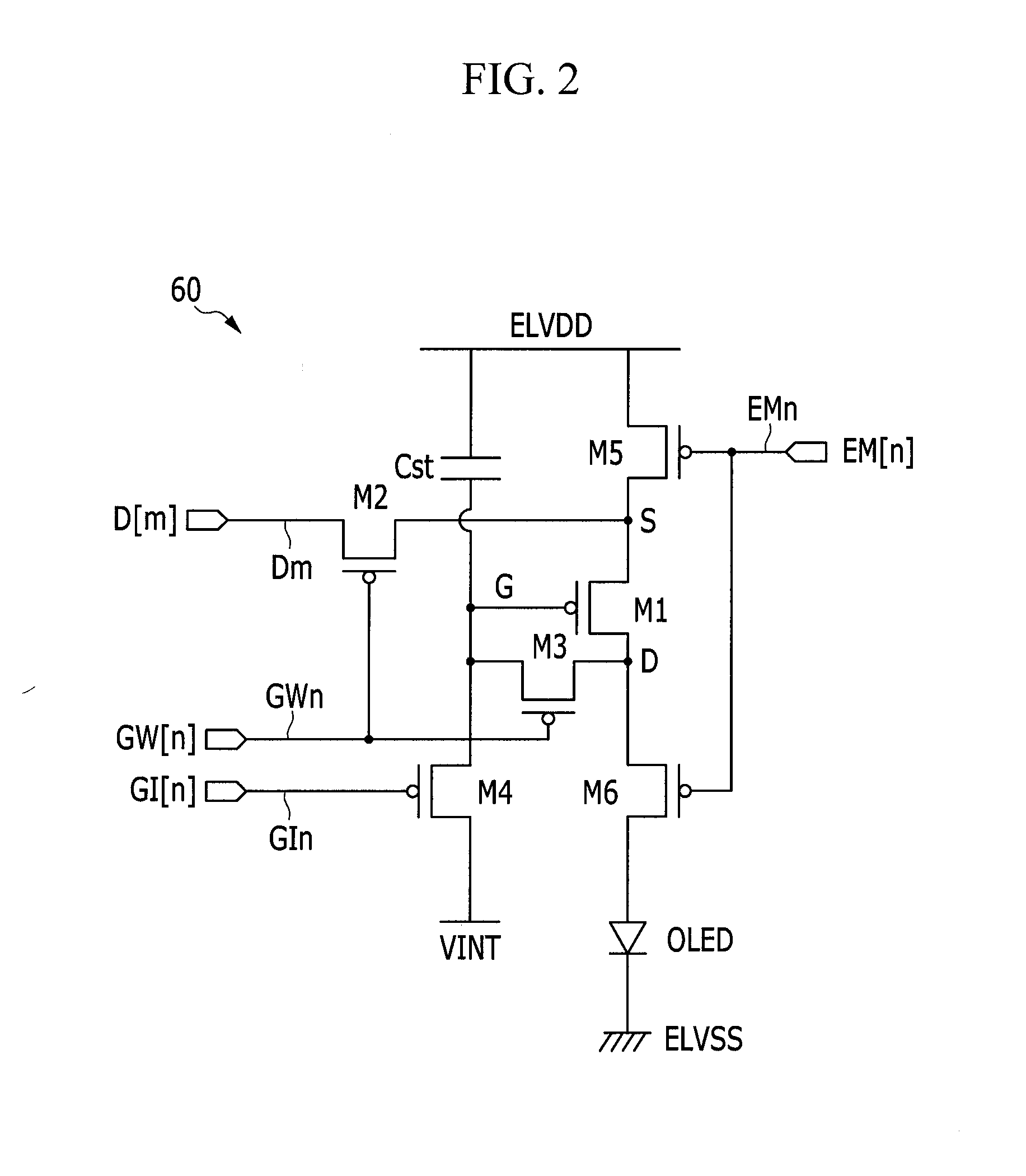

Gate drive circuit and display apparatus having the same

ActiveUS20120139883A1Gate area is reducedReduce power consumptionCathode-ray tube indicatorsDigital storageShift registerLow voltage

A gate drive circuit includes a shift register in which plural stages are cascade-connected to each other. In an n-th stage, a pull-up part outputs a high voltage of a clock signal to an output node as a high voltage of an n-th gate signal in response to a high voltage on a first node. A pull-down part pulls the high voltage of the n-th gate signal down to a first low voltage in response to an (n+1)th carry signal. A discharging part discharges the first node to a second low voltage level lower than the first low voltage level in response to the (n+1)th carry signal. A carry part outputs the high voltage of the clock signal as an n-th carry signal (mirroring the n-th gate signal) in response to a high voltage on the first node.

Owner:SAMSUNG DISPLAY CO LTD

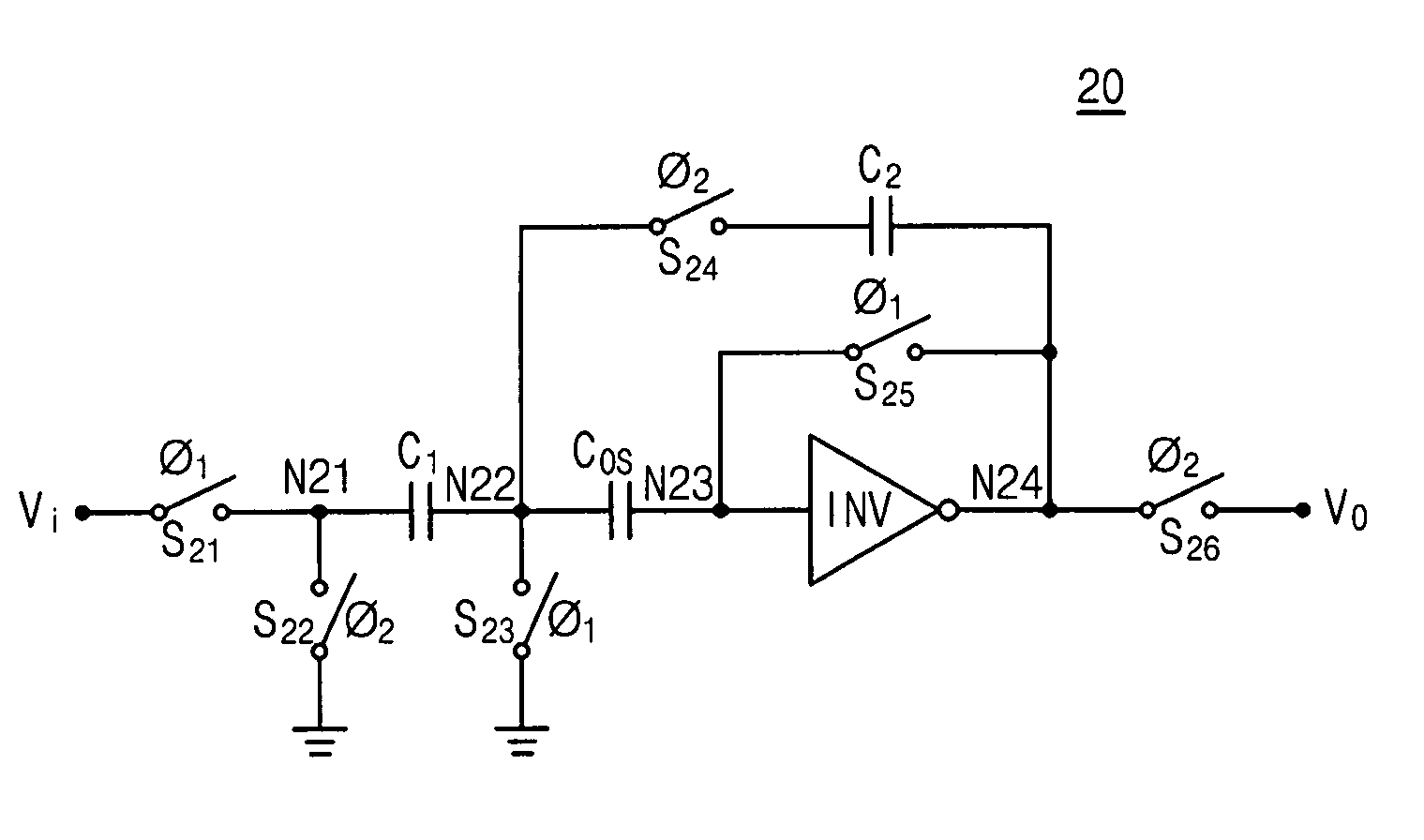

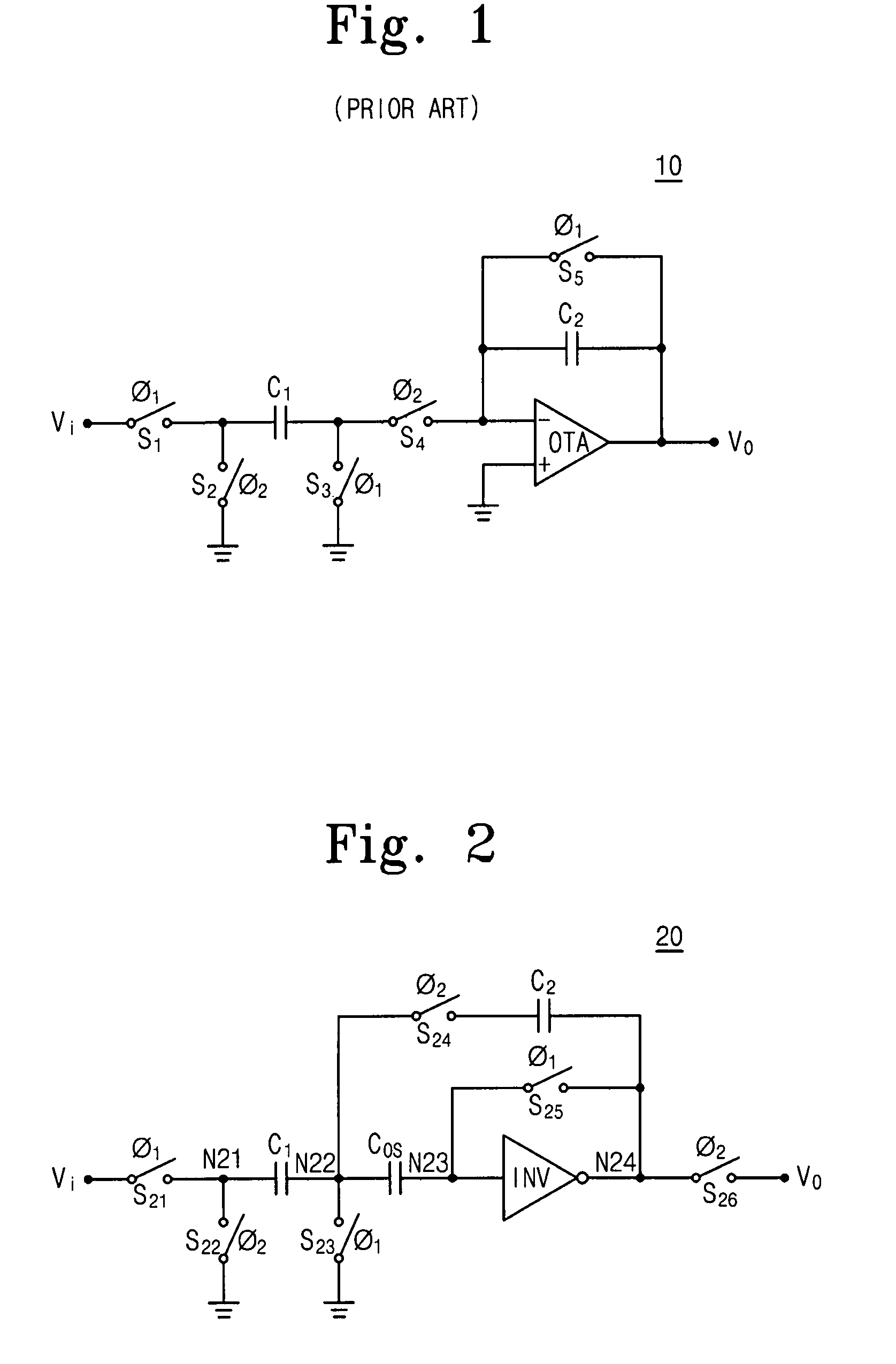

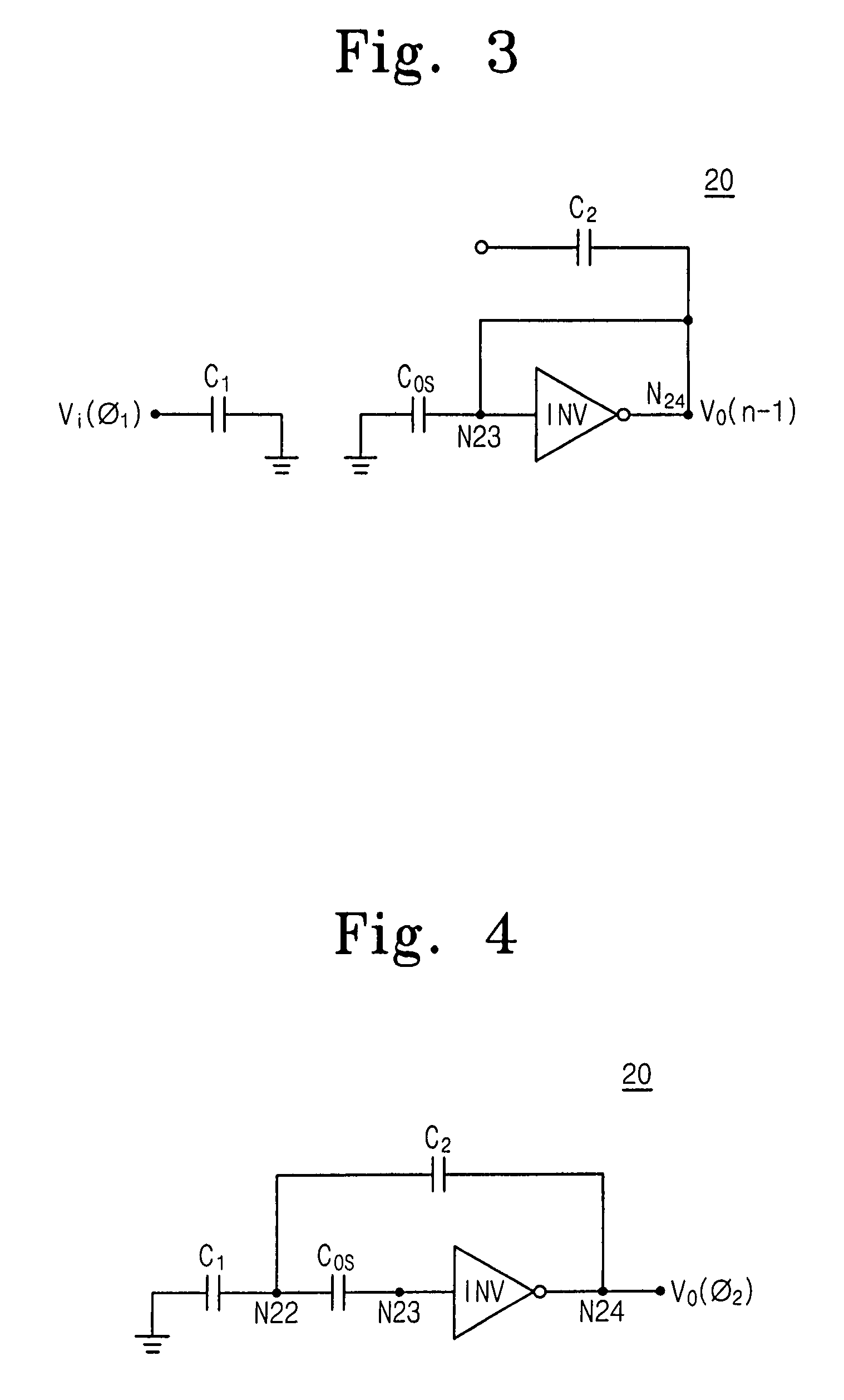

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS7800427B2Reduce power consumptionReduce circuit areaAmplifier modifications to reduce non-linear distortionComputing operations for integral formationCapacitanceAudio power amplifier

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

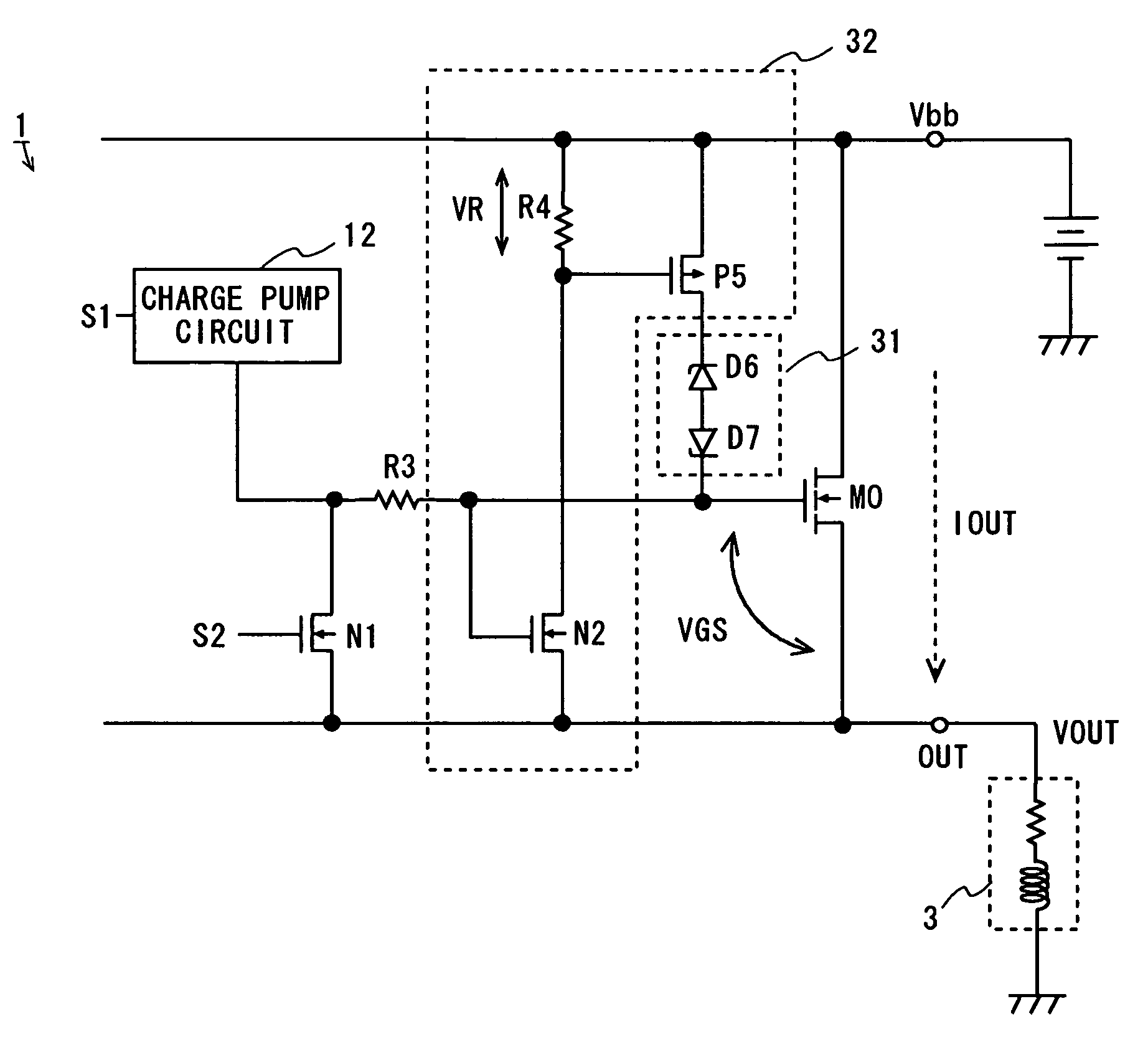

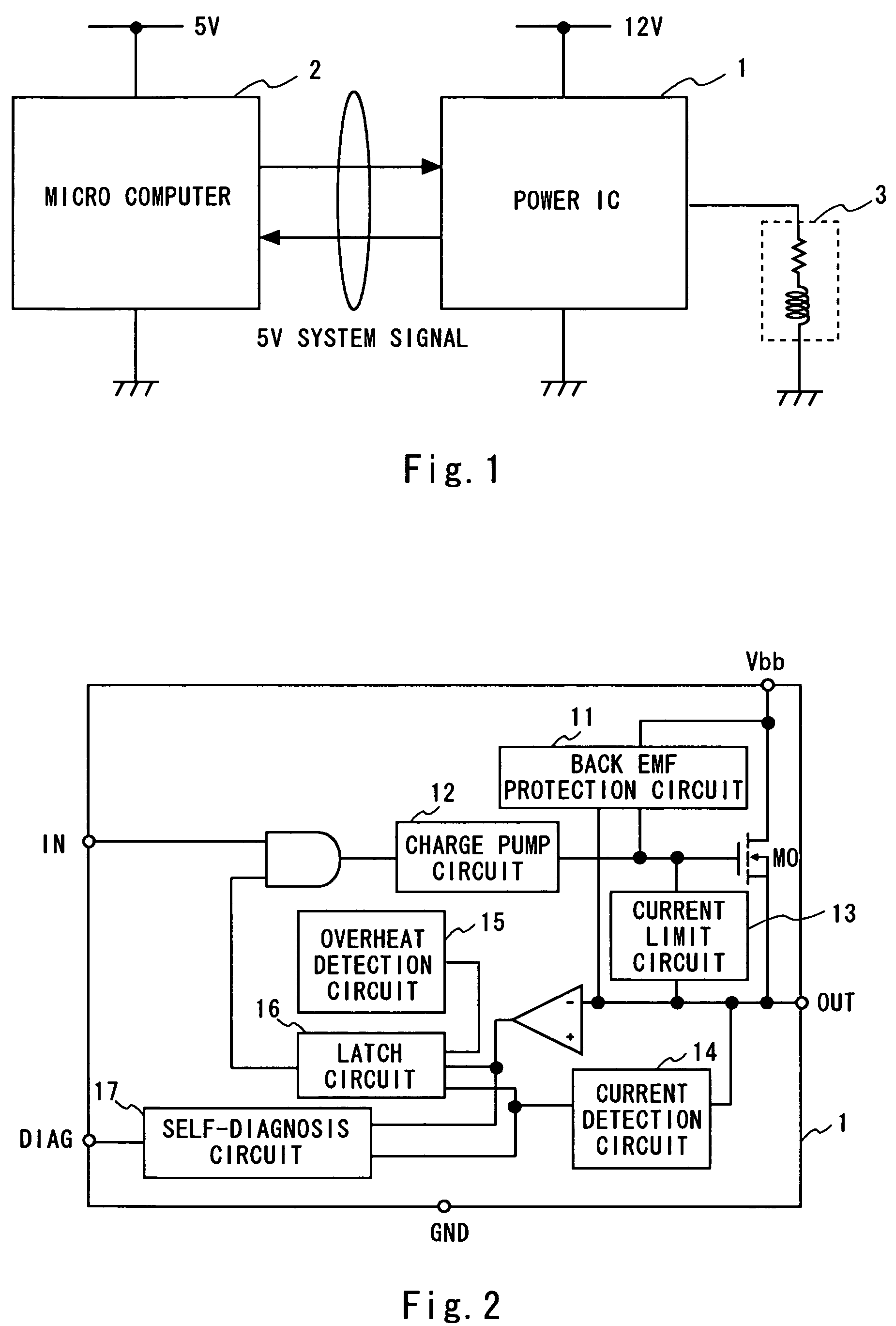

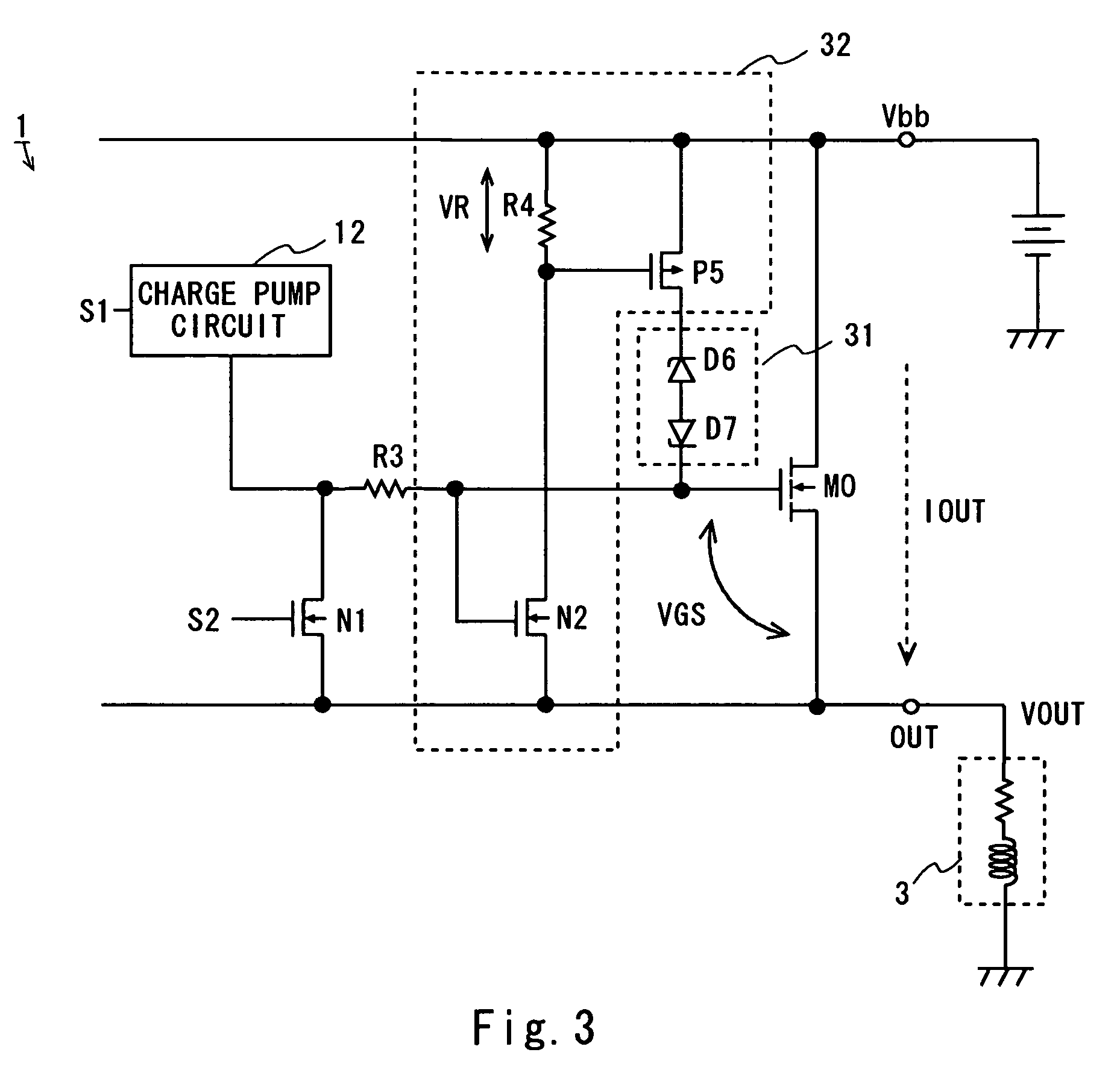

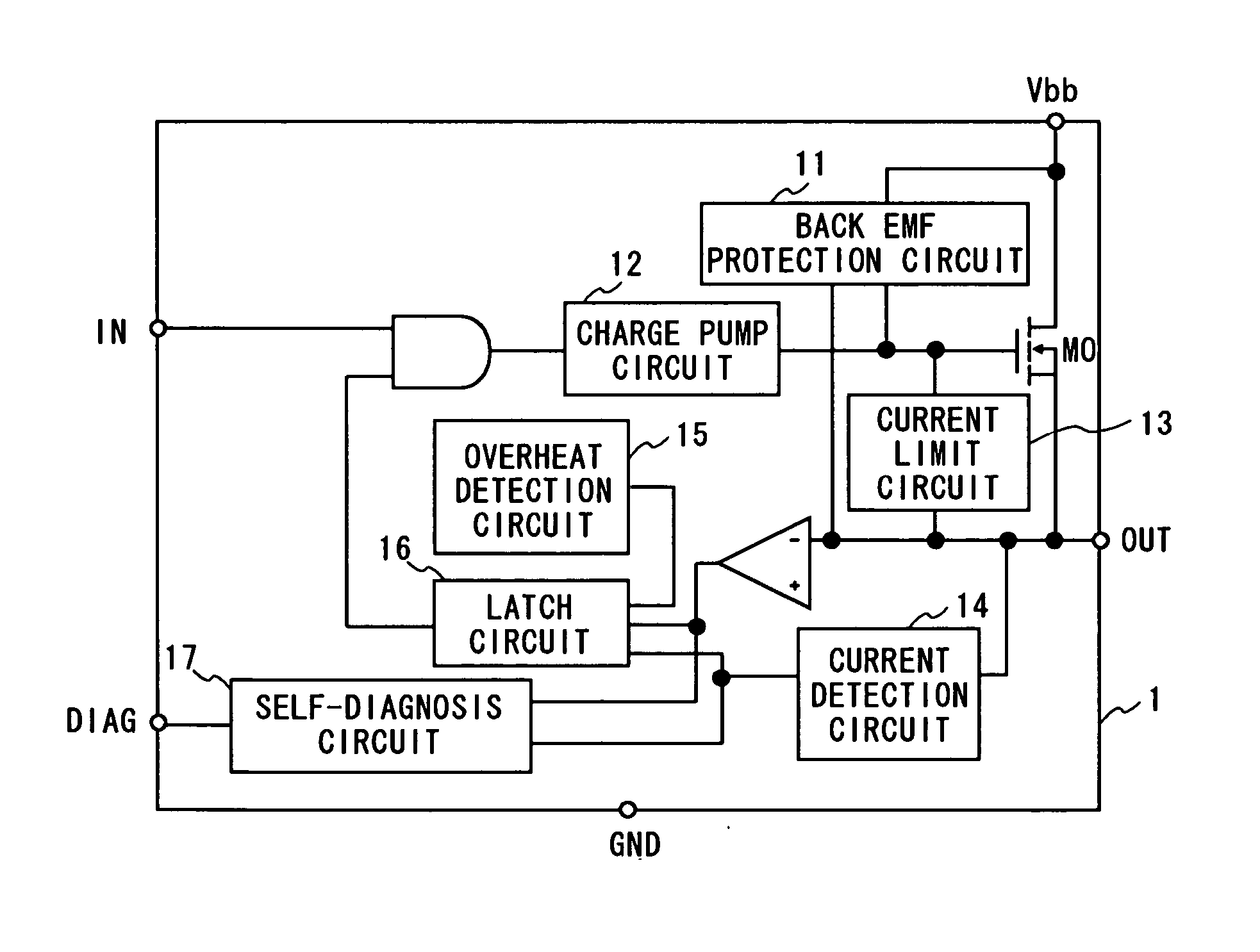

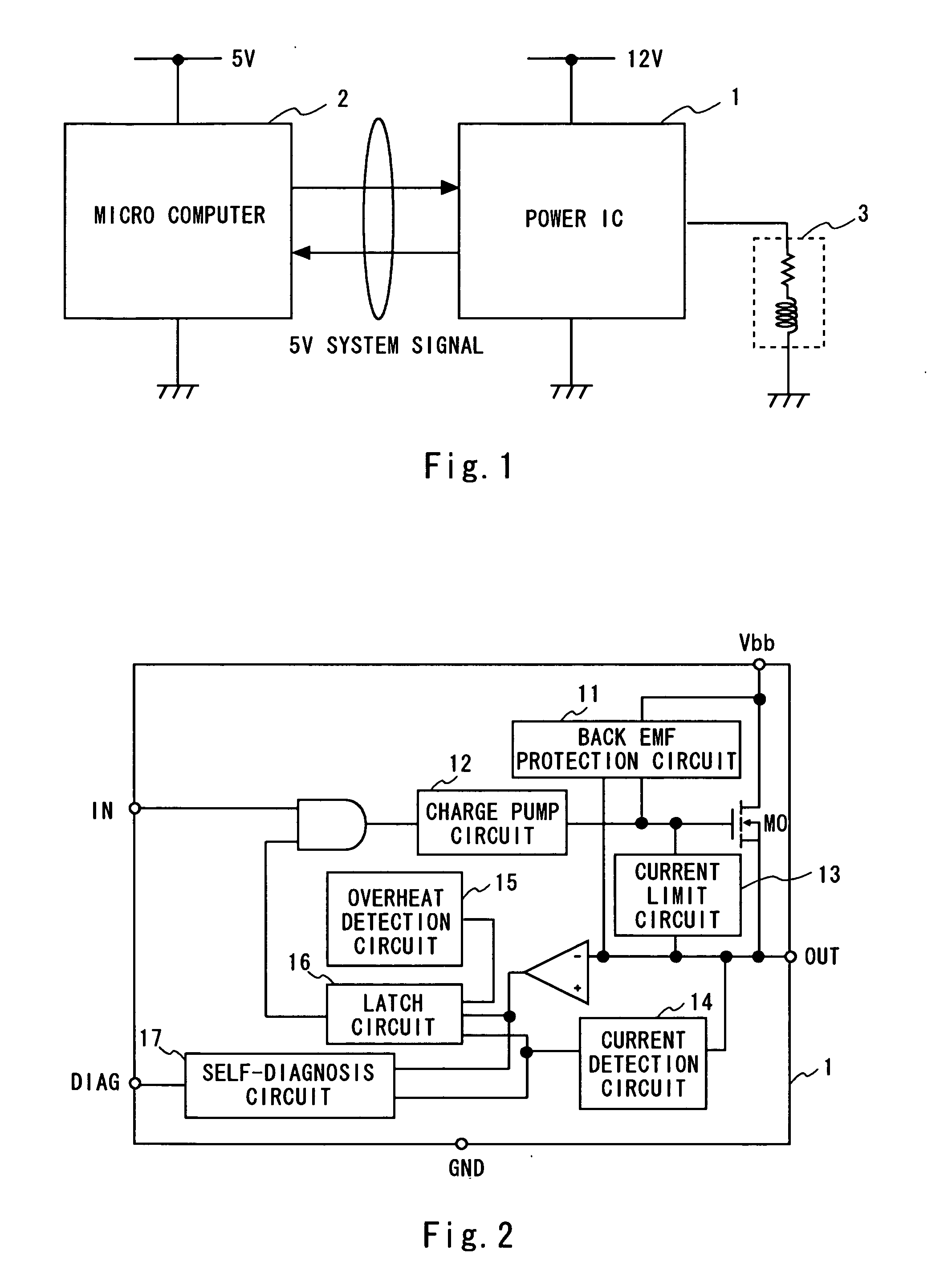

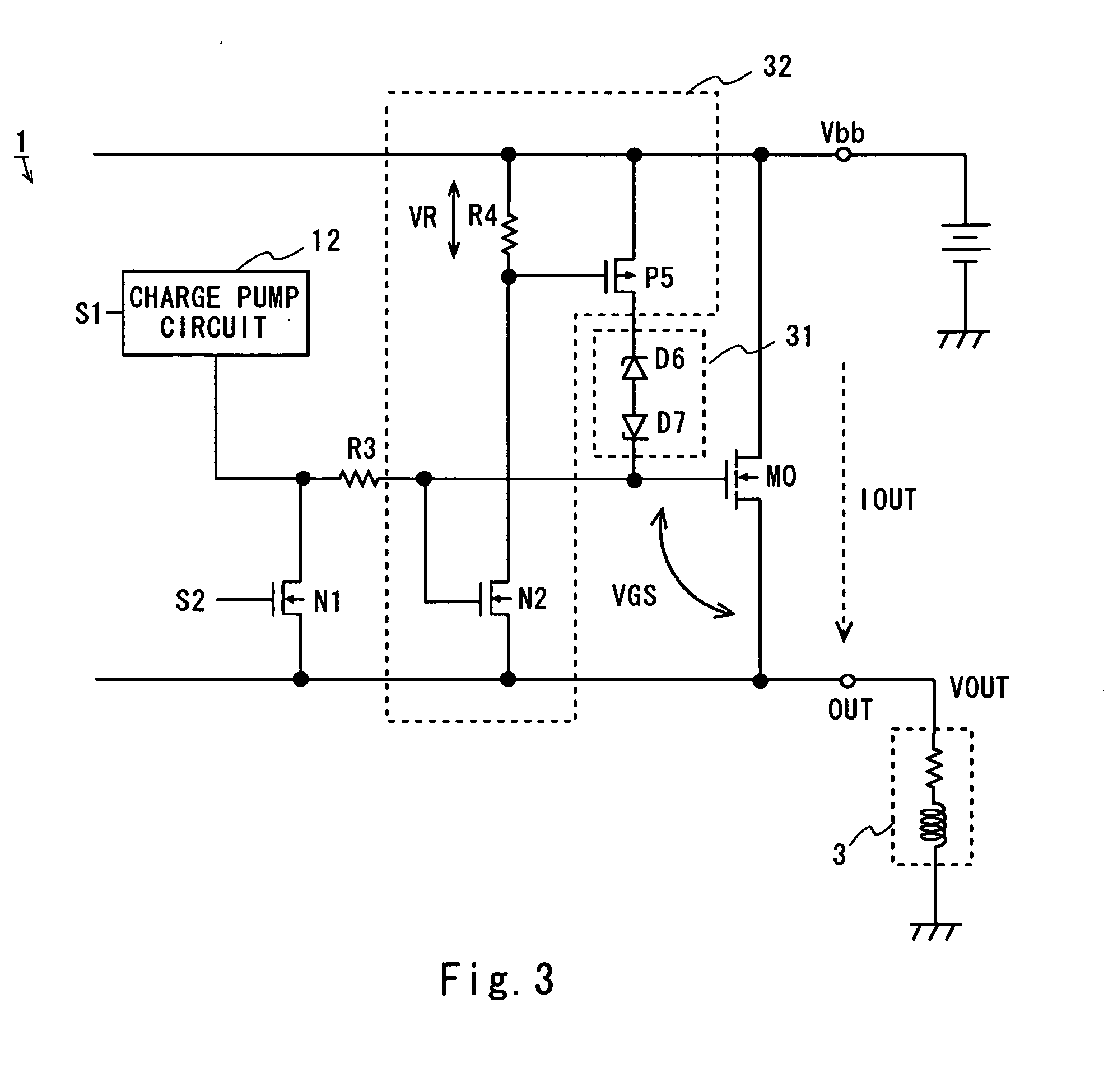

Integrated circuit including an overvoltage protection circuit

InactiveUS7129759B2Reduce circuit areaLow setTransistorPulse automatic controlOvervoltageEngineering

The power IC includes an output transistor M0 which controls a current flowing into an L load, a dynamic clamp circuit which clamps an overvoltage, and a clamp control circuit which controls the operation of the dynamic clamp circuit. The clamp control circuit activates the dynamic clamp circuit, which is normally inactive, upon detection of a back EMF by the L load.

Owner:RENESAS ELECTRONICS CORP

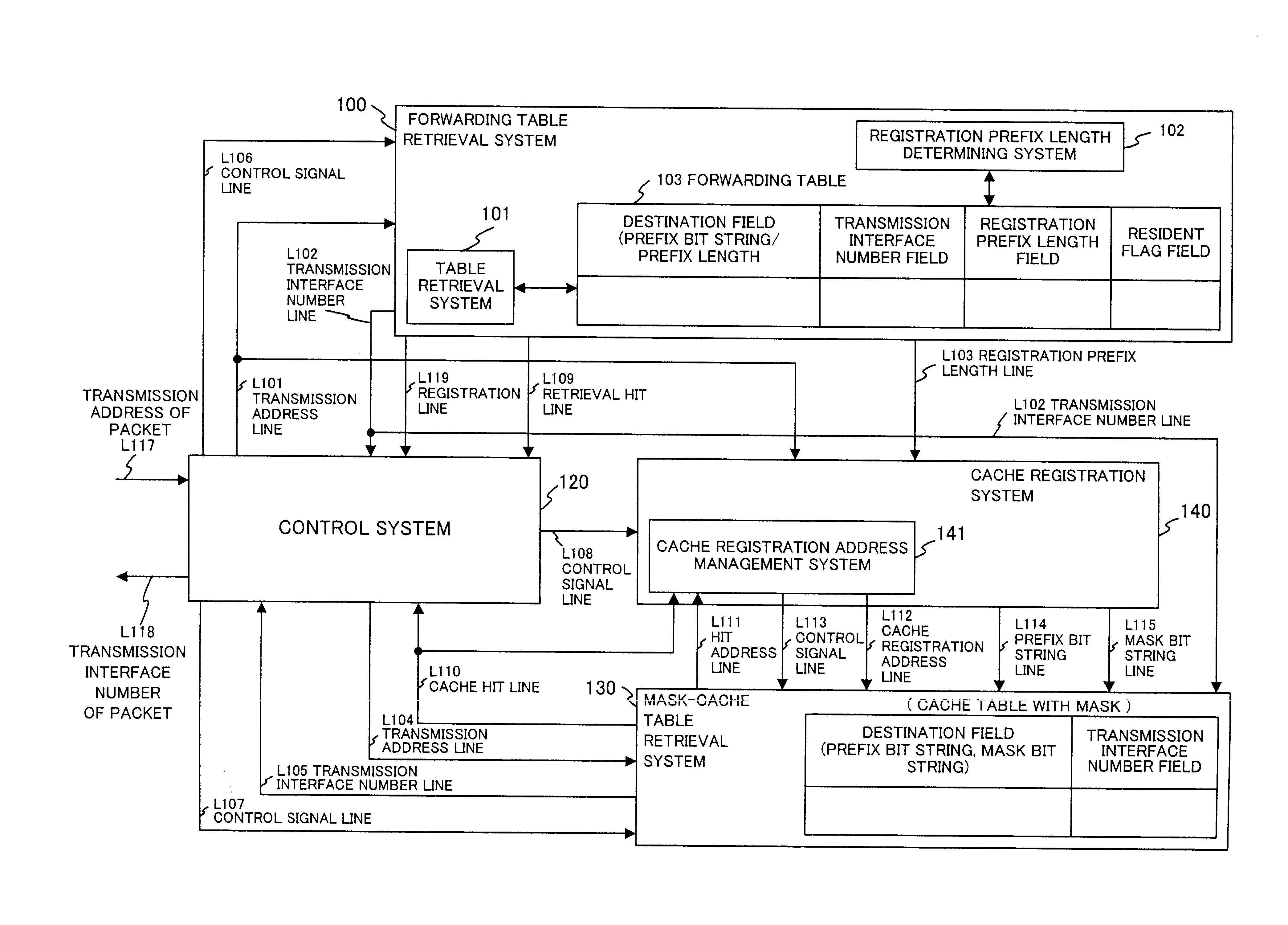

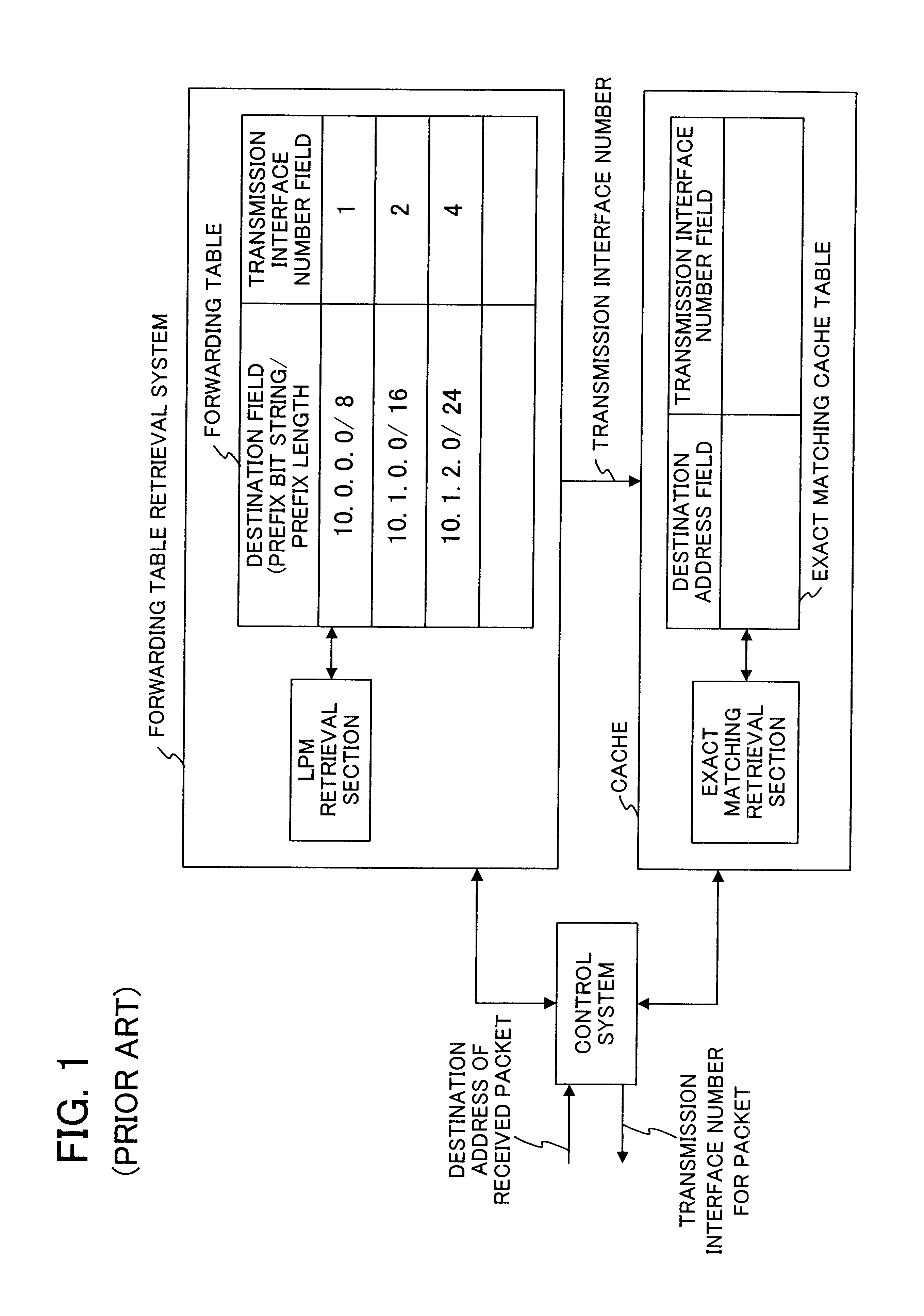

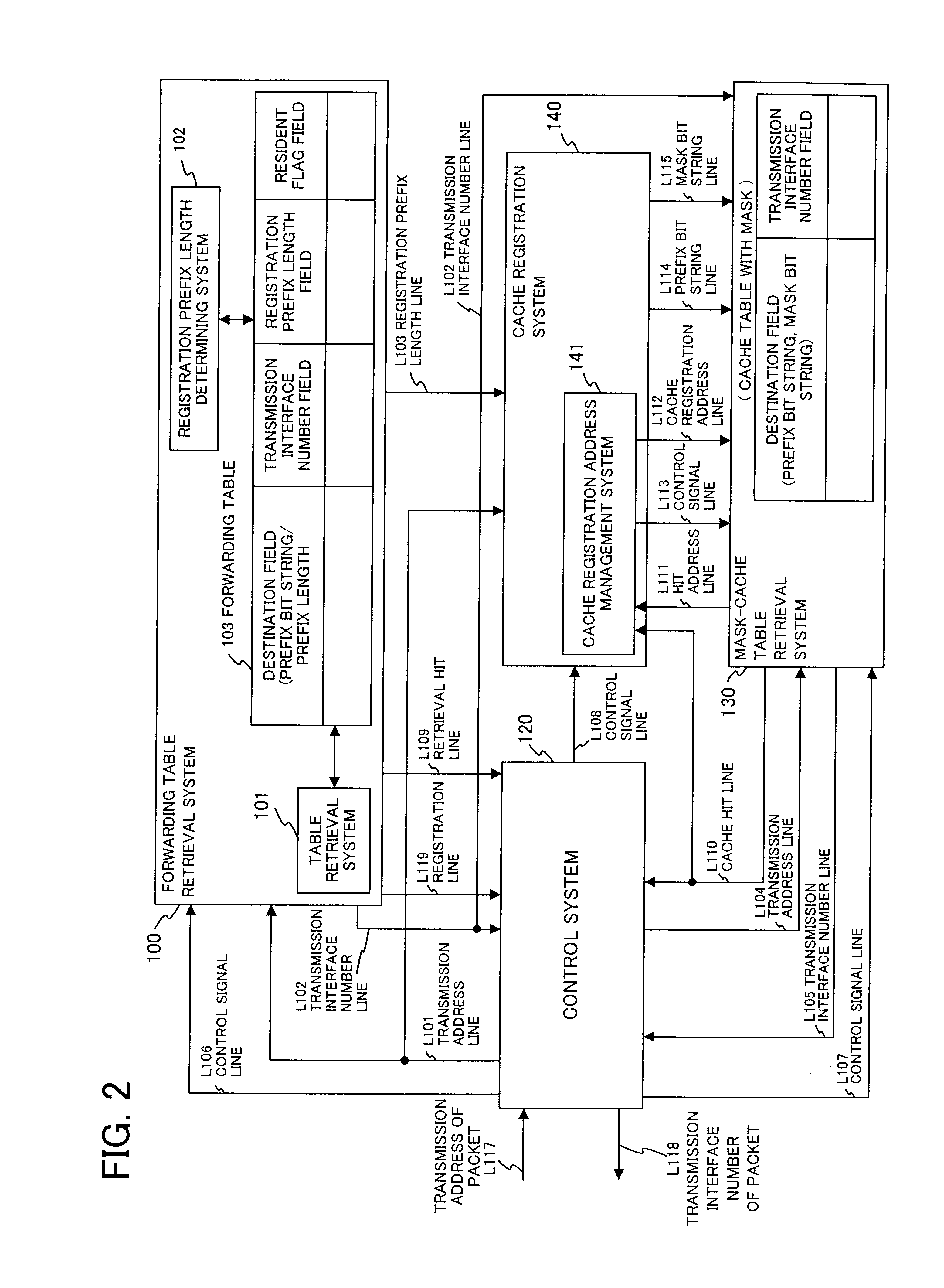

Router with a cache having a high hit probability

InactiveUS6768739B1Reduce cache capacityReduce circuit areaData switching by path configurationMemory systemsLongest prefix matchParallel computing

A router allowing the entry hit probability of the cache to be increased is disclosed. The cache is searched using a different mask for each cache entry. A maximum or optimum cache prefix length is determined as a length of upper bits of the destination address of the received packet which are not masked by a corresponding mask. Alternatively, the cache is searched using longest prefix match (LFM). A cache entry allowing a plurality of destination addresses to be hit can be registered in the cache, resulting in increased cache hit probability.

Owner:NEC CORP

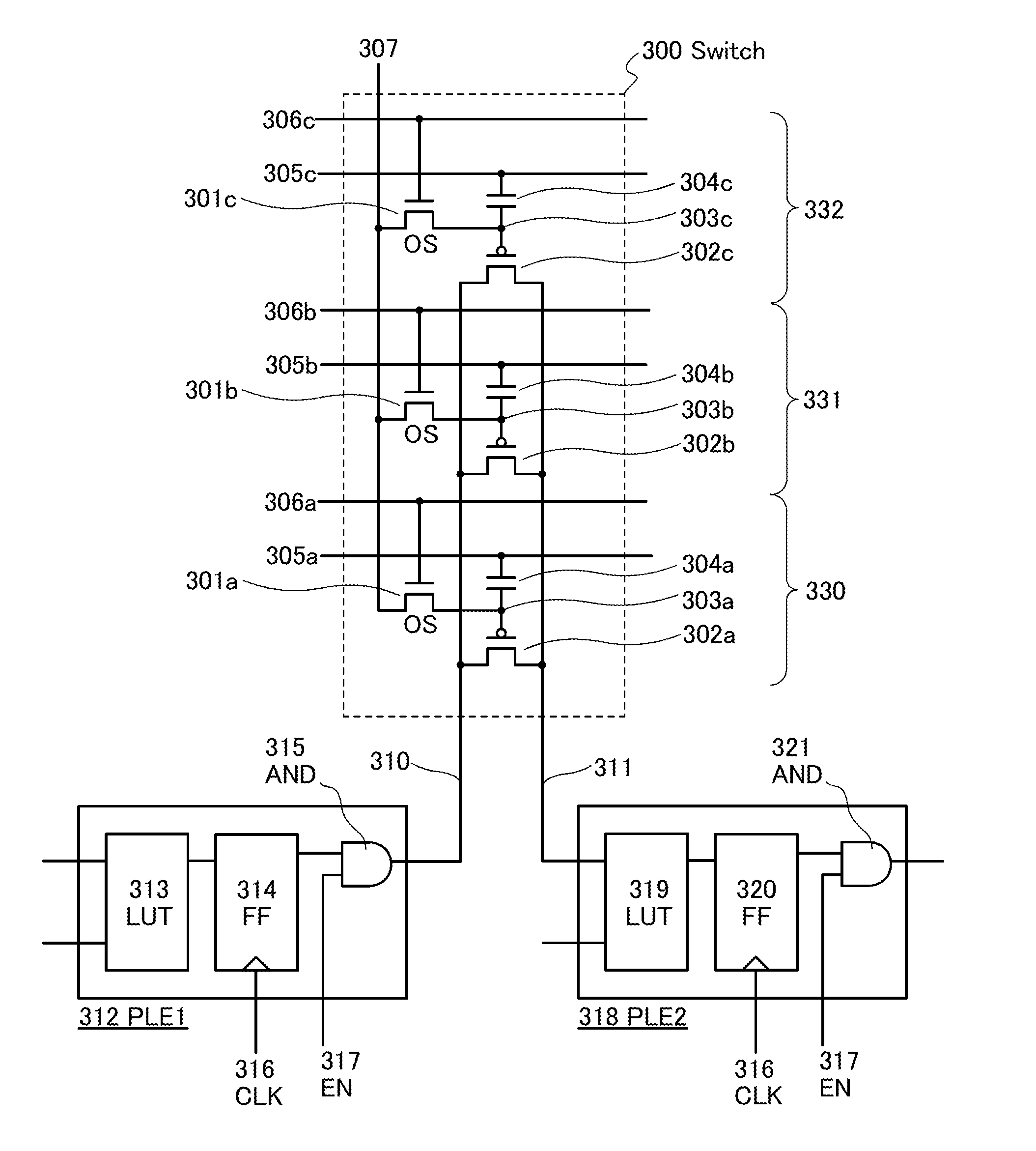

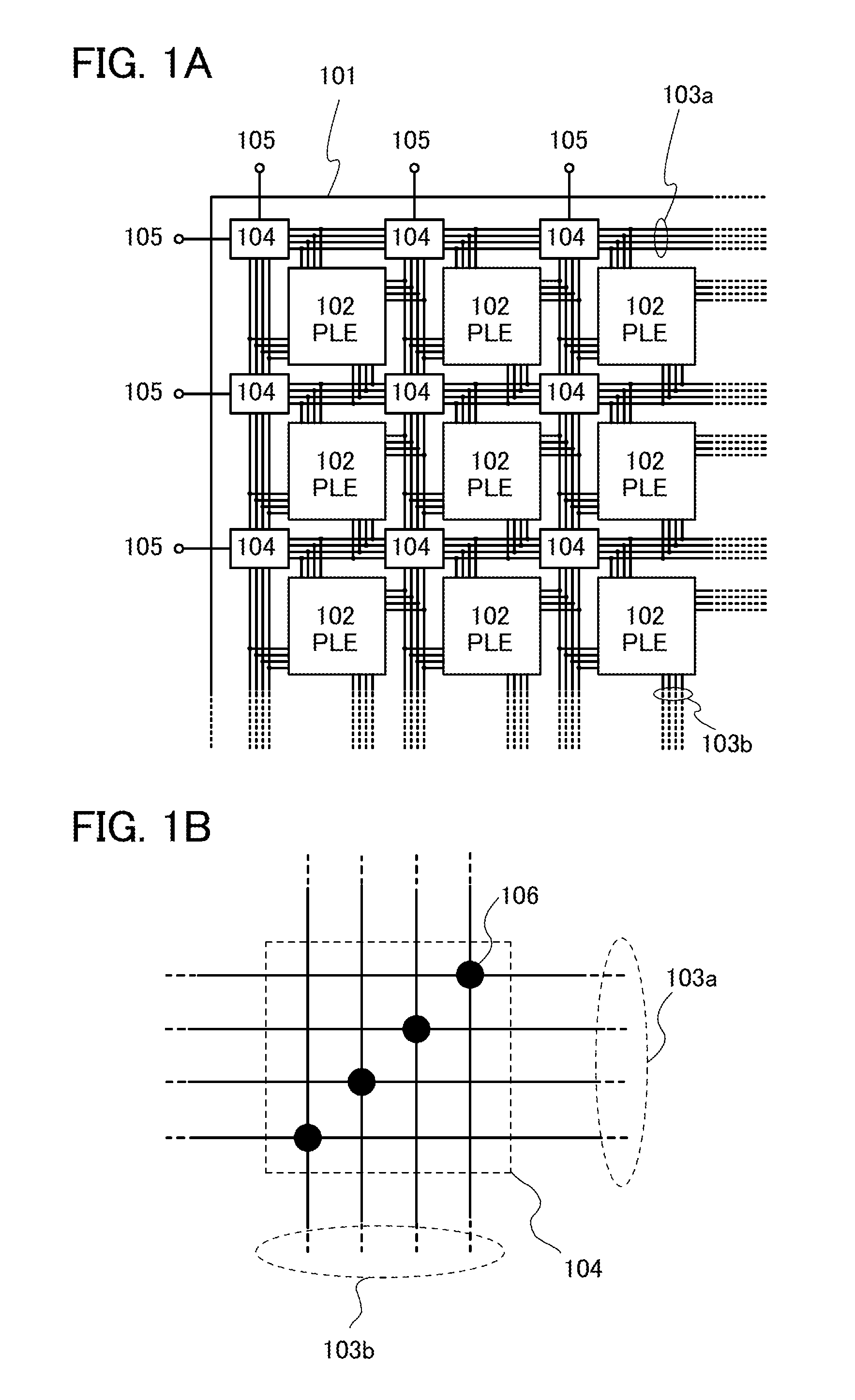

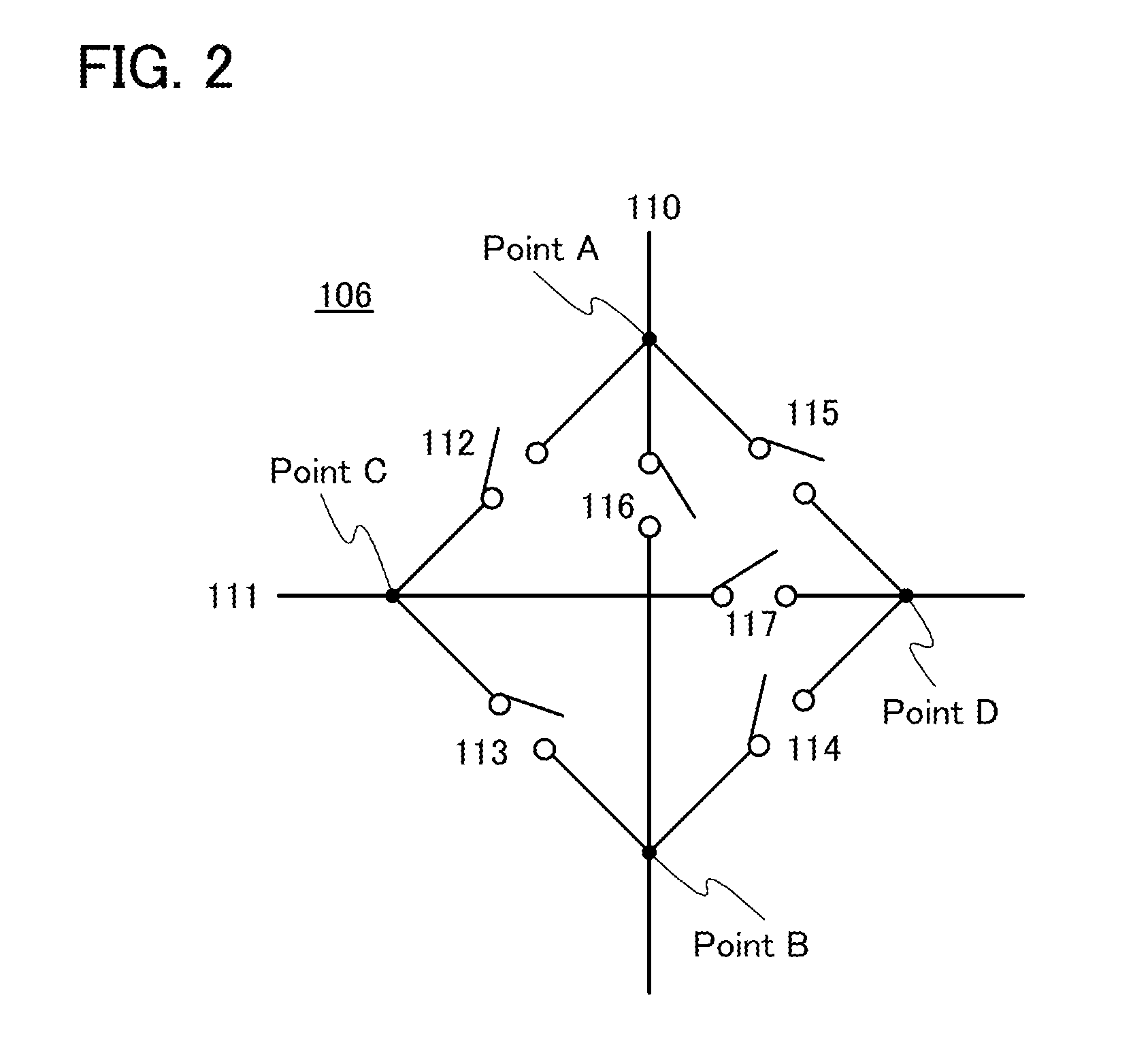

Programmable logic device

InactiveUS20130293263A1Reduce power consumptionShort startup timePower reduction in field effect transistorsSolid-state devicesProgrammable logic deviceSoftware engineering

Disclosed is a programmable logic device (PLD) which can undergo dynamic configuration at a high speed. The PLD includes a plurality of programmable logic elements (PLEs) and a switch for selecting electrical connection between the PLEs. The switch includes a plurality of circuit groups each of which includes first and second transistors. The second transistors of the circuit groups are electrically connected in parallel with one another. In each of the circuit groups, the electrical conduction between a source and a drain of the second transistor is determined based on configuration data held at a node between the gate of the second transistor and a drain of the first transistor, which allows the selection of the electrical connection and disconnection between the programmable logic elements by the selection of one of the circuit groups.

Owner:SEMICON ENERGY LAB CO LTD

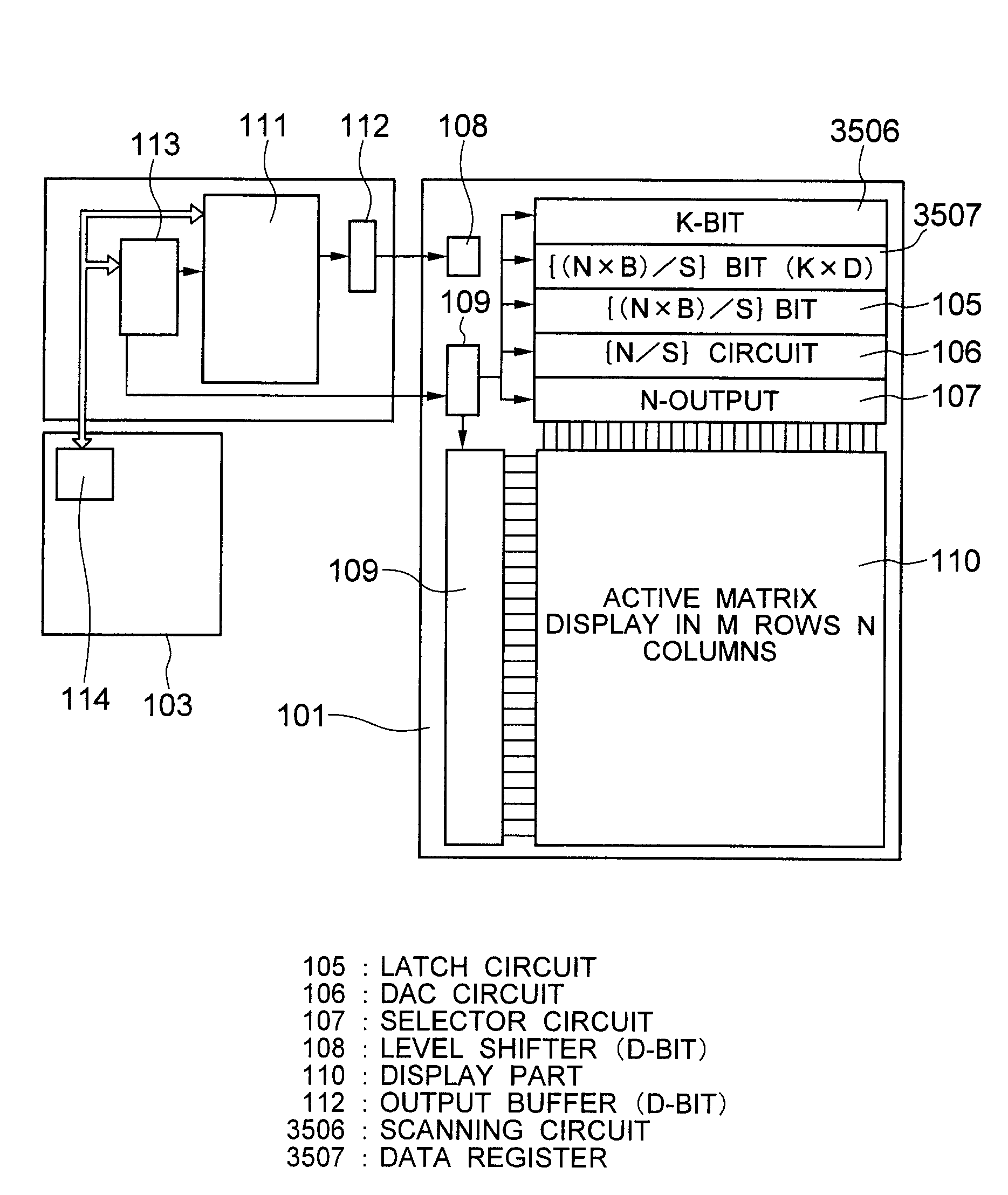

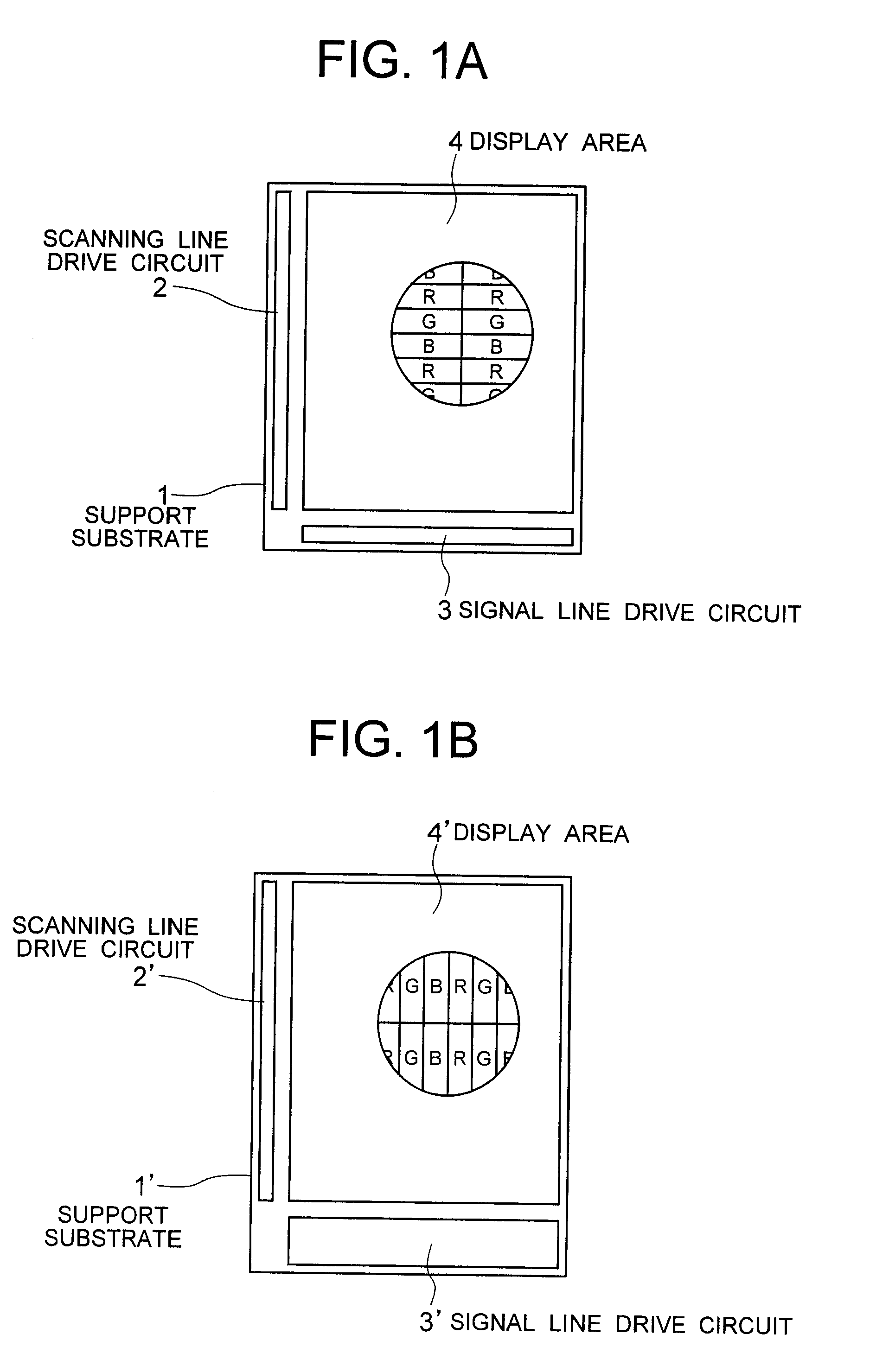

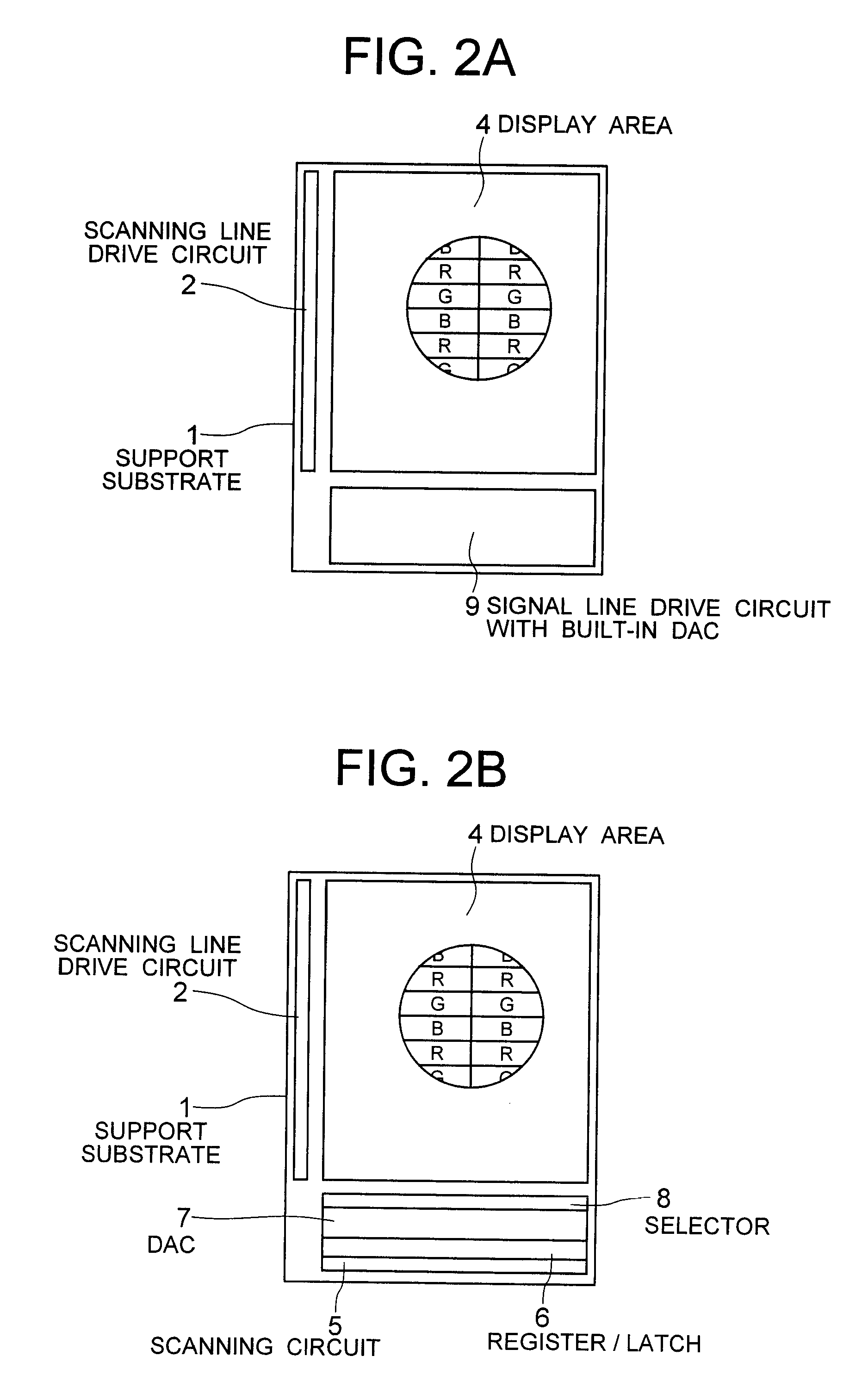

Display apparatus

ActiveUS20070205976A1Simple calculationReduce circuit sizeCathode-ray tube indicatorsInput/output processes for data processingEngineeringDriving circuit

Provided is a display apparatus capable of reducing the scale of a drive circuit and decreasing the frame. A display area in which pixels are provided in matrix, a scanning line drive circuit for driving scanning lines, and a signal line drive circuit for driving signal lines are provided on a support substrate. The pixel within the display area is constituted with a plurality of dots. Each dot corresponds to a color filter of a certain color. The dot is in a laterally long shape, i.e. in a shape extending in a direction along the scanning lines. In other words, each dot is in a shape extending in parallel with the longitudinal direction of the signal line drive circuit. The color filters are of lateral stripe type, for example.

Owner:HANNSTAR DISPLAY CORPORATION

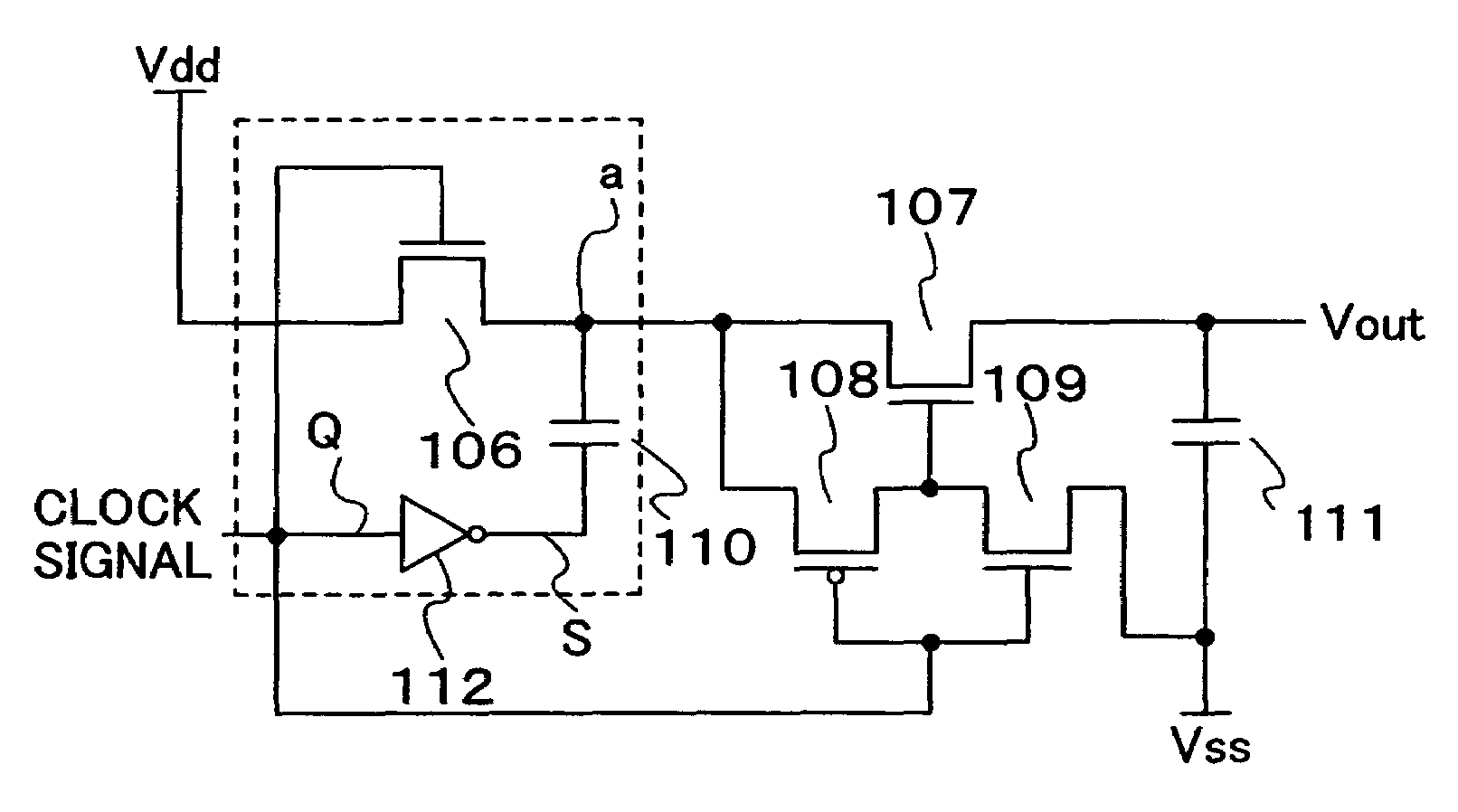

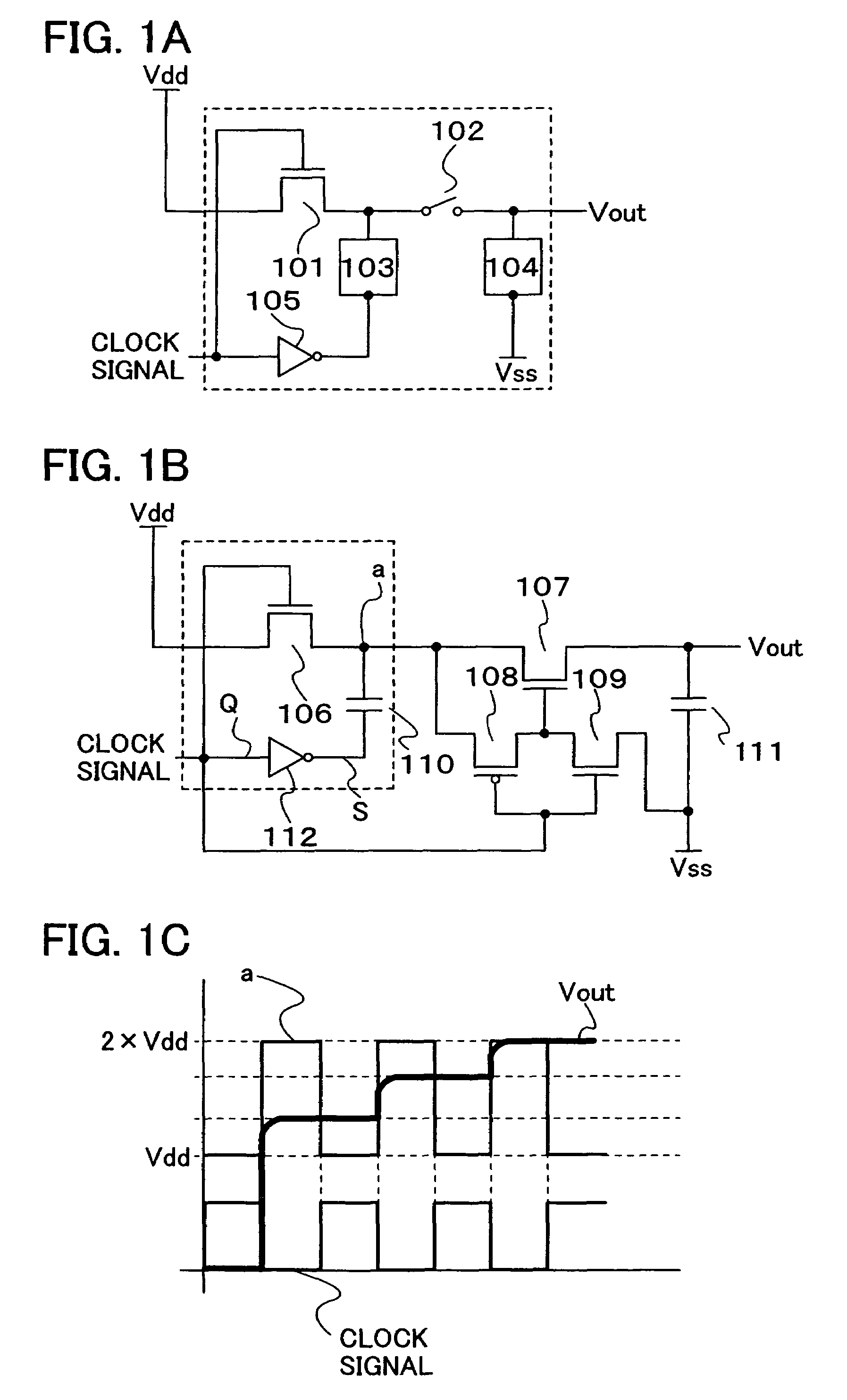

Charge pump circuit and semiconductor device having the same

InactiveUS7495501B2Reduce power consumptionIncrease currentAc-dc conversionApparatus without intermediate ac conversionEngineeringSemiconductor

A conventional charge pump circuit requires a step-up circuit or the like for turning on or off a transistor. Therefore, it has a problem of an increase in circuit scale, which leads to increases in circuit area and power consumption. One feature is to provide a charge pump circuit including a first transistor, a switch, a first capacitor, a second capacitor, and an inverter, in which one electrode of the first transistor is connected to a first potential, an output side of the inverter is connected to the other electrode of the first transistor and one side of the switch through the first capacitor, the other side of the switch is connected to a second potential through the second capacitor.

Owner:SEMICON ENERGY LAB CO LTD

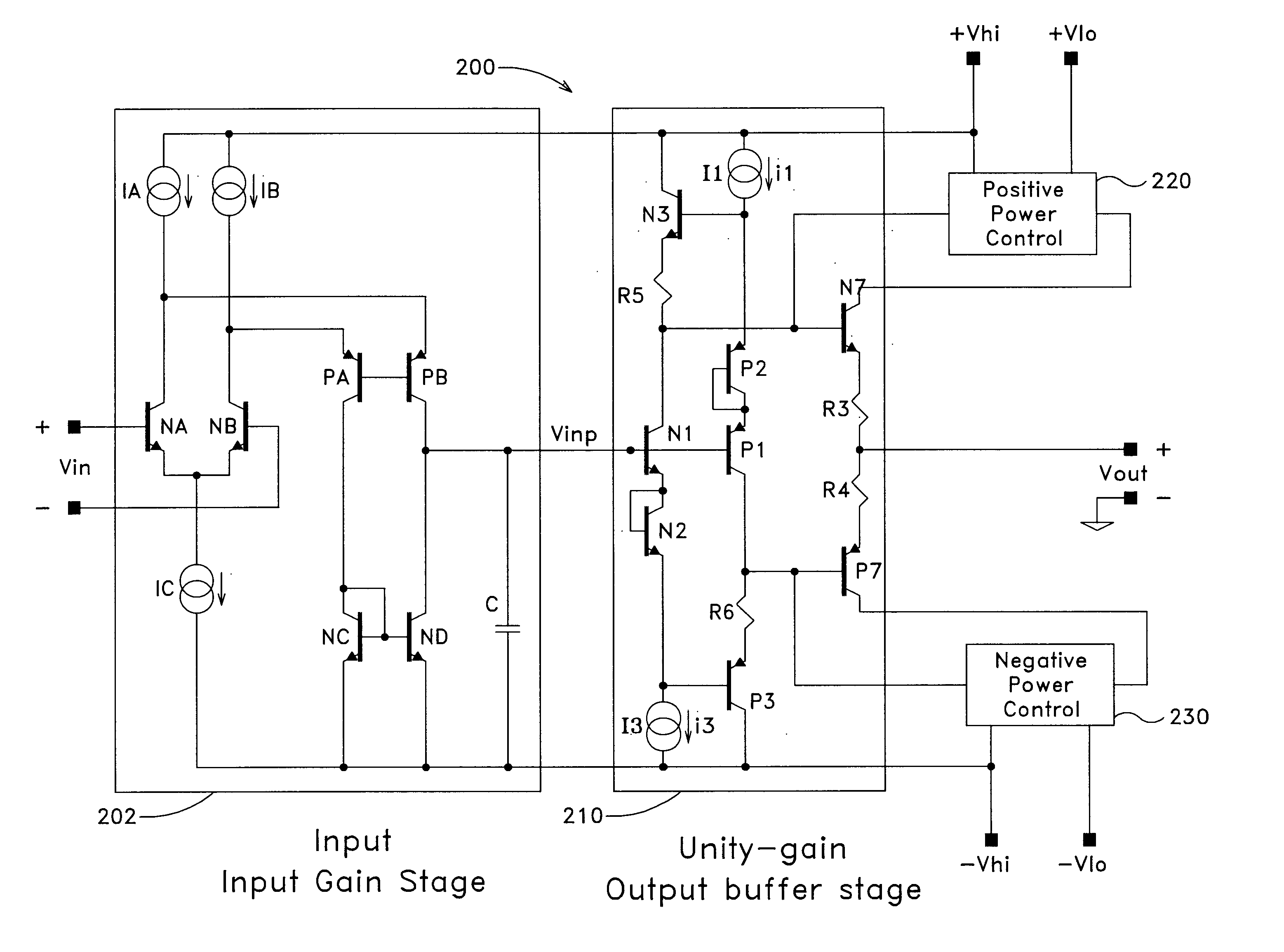

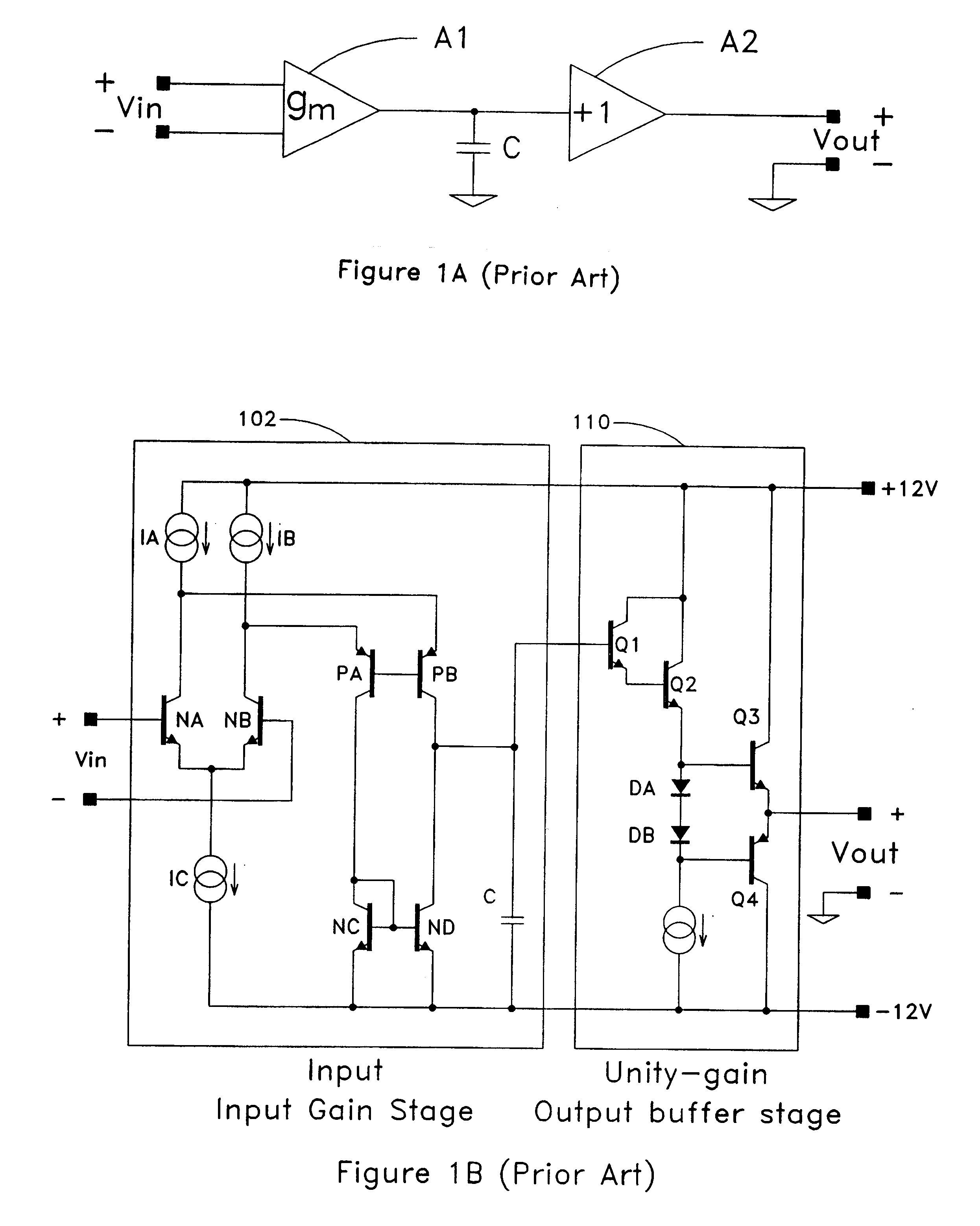

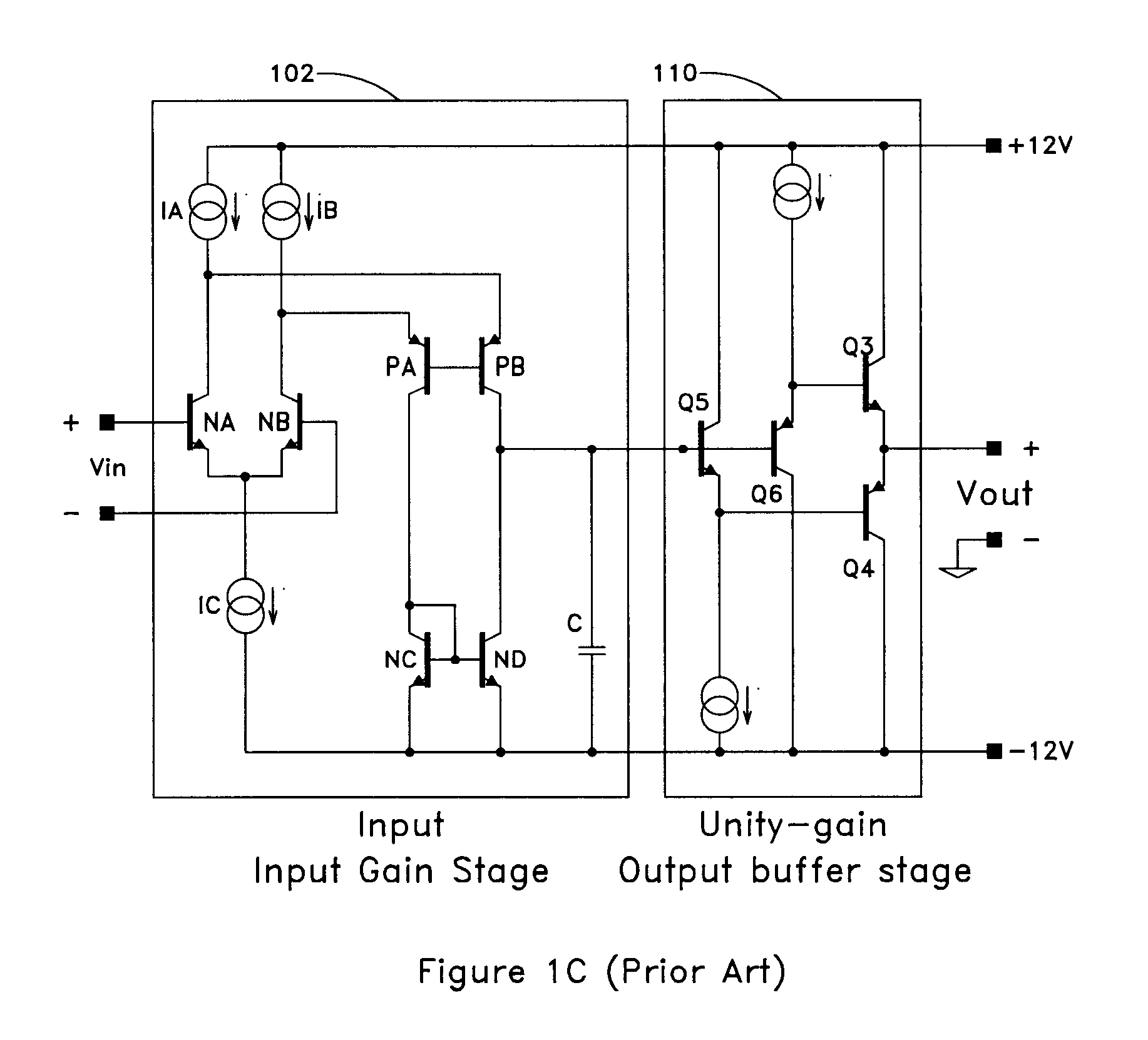

Multiple-voltage supply power amplifier with dynamic headroom control

InactiveUS6417736B1Reduce circuit areaHigh voltagePush-pull amplifiersPhase-splittersAudio power amplifierVoltage source

A monolithic integrated circuit amplifier has a gain stage and a buffer stage. The buffer stage includes an output stage and two separate voltage supplies, the second of which has a greater magnitude than the first. Switching circuitry is included that is connected to the output stage via a regulator bus. When an output demand voltage is less than a switch-over threshold, current to the output stage is provided substantially from the first voltage supply; when the output demand voltage is greater than the switch-over threshold, current to the output stage is provided substantially from the second voltage supply. Collector voltage at the output stage is dynamically controlled to be greater than the emitter voltage by a difference voltage that increases proportionally as output voltage increases above the switch-over threshold. This difference voltage is commonly referred to as "headroom." The dynamic headroom control circuitry preferably includes means for predictably setting and controlling the headroom voltage at switch-over and smoothly increasing the headroom voltage up to maximum output voltage.

Owner:LEWYN CONSULTING

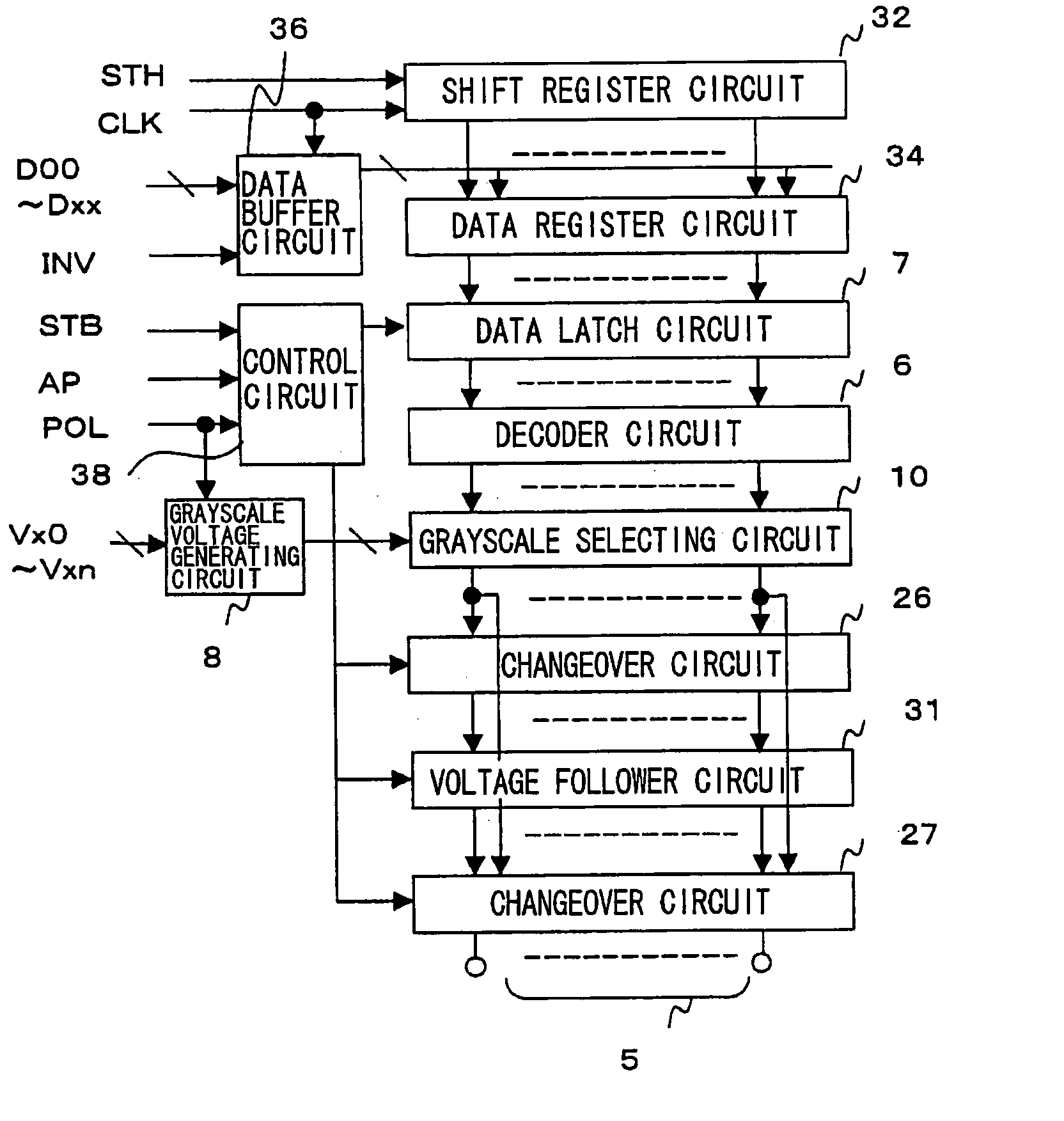

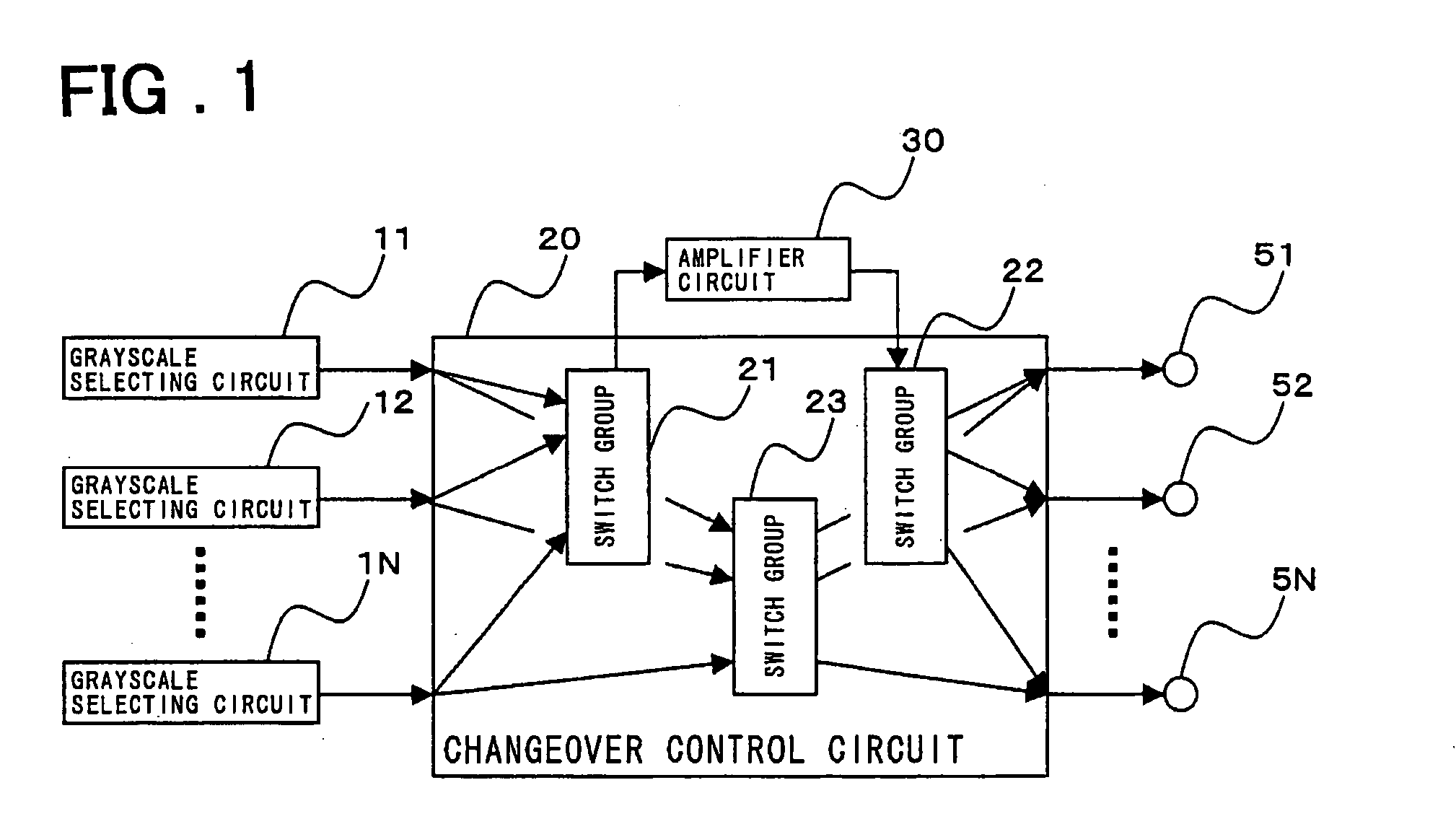

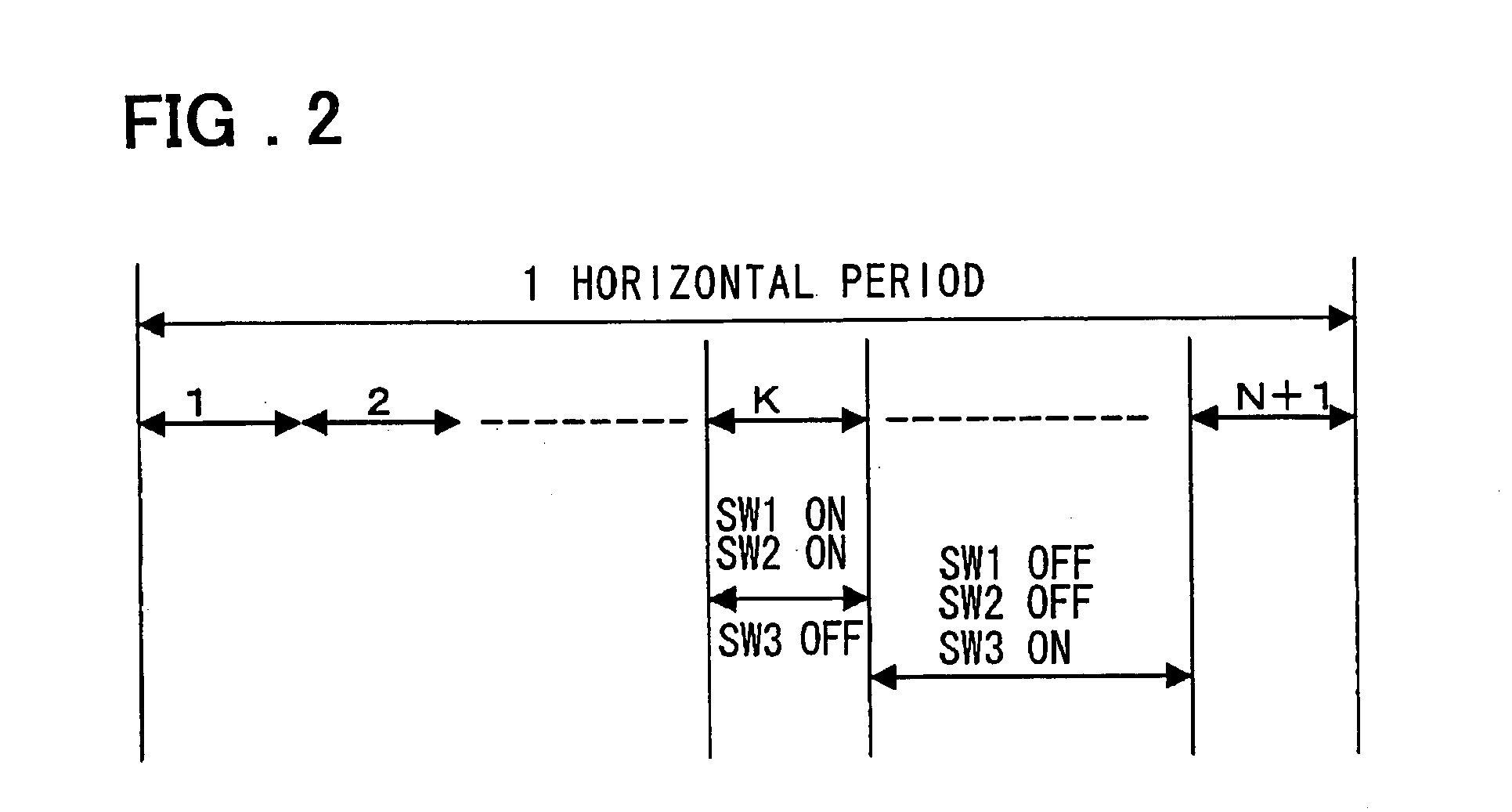

Display device, driver circuit therefor, and method of driving same

ActiveUS20050122303A1High quality displayEliminate display unevennessCathode-ray tube indicatorsInput/output processes for data processingDriver circuitDisplay device

Disclosed is a driver circuit for driving a display device. The driver circuit includes N-number (where N is a natural number) of grayscale selecting circuits, which correspond to N-number of data electrodes, each for selecting one grayscale voltage from among a plurality of grayscale voltages in accordance with an image signal; one voltage follower circuit for subjecting the grayscale voltages, which have been selected by the grayscale selecting circuits, to an impedance conversion to thereby drive the data electrodes; and a changeover control circuit for exercising control so as to divide one horizontal interval into at least (N+1)-number of intervals, drive a Kth data electrode by the output of the amplifier circuit by inputting only an output of a Kth grayscale selecting circuit to the amplifier circuit in a Kth (K=1 to N) interval, and drive the Kth data electrode by the output of the Kth grayscale selecting circuit in at least some intervals other than the Kth interval.

Owner:RENESAS ELECTRONICS CORP

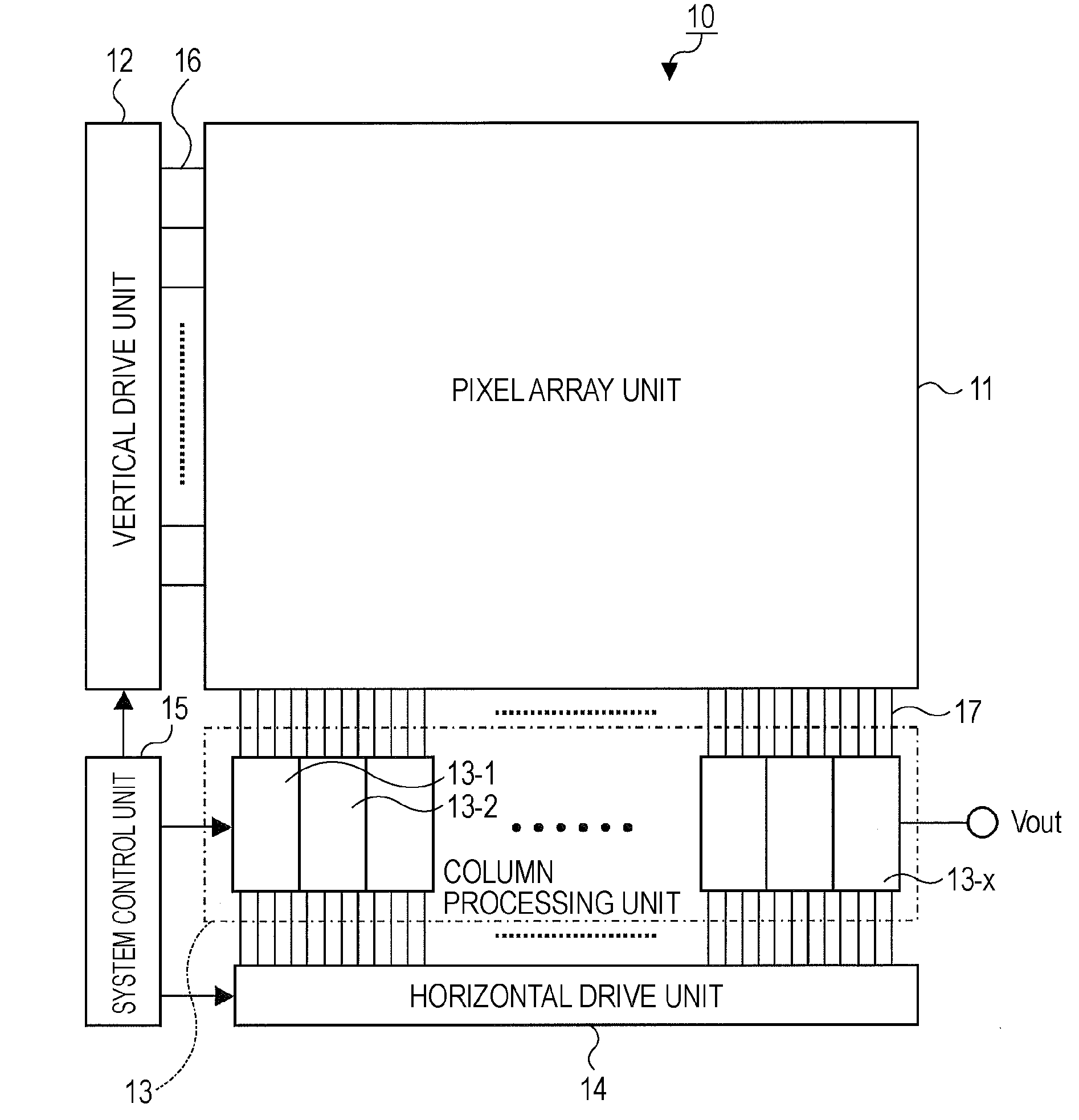

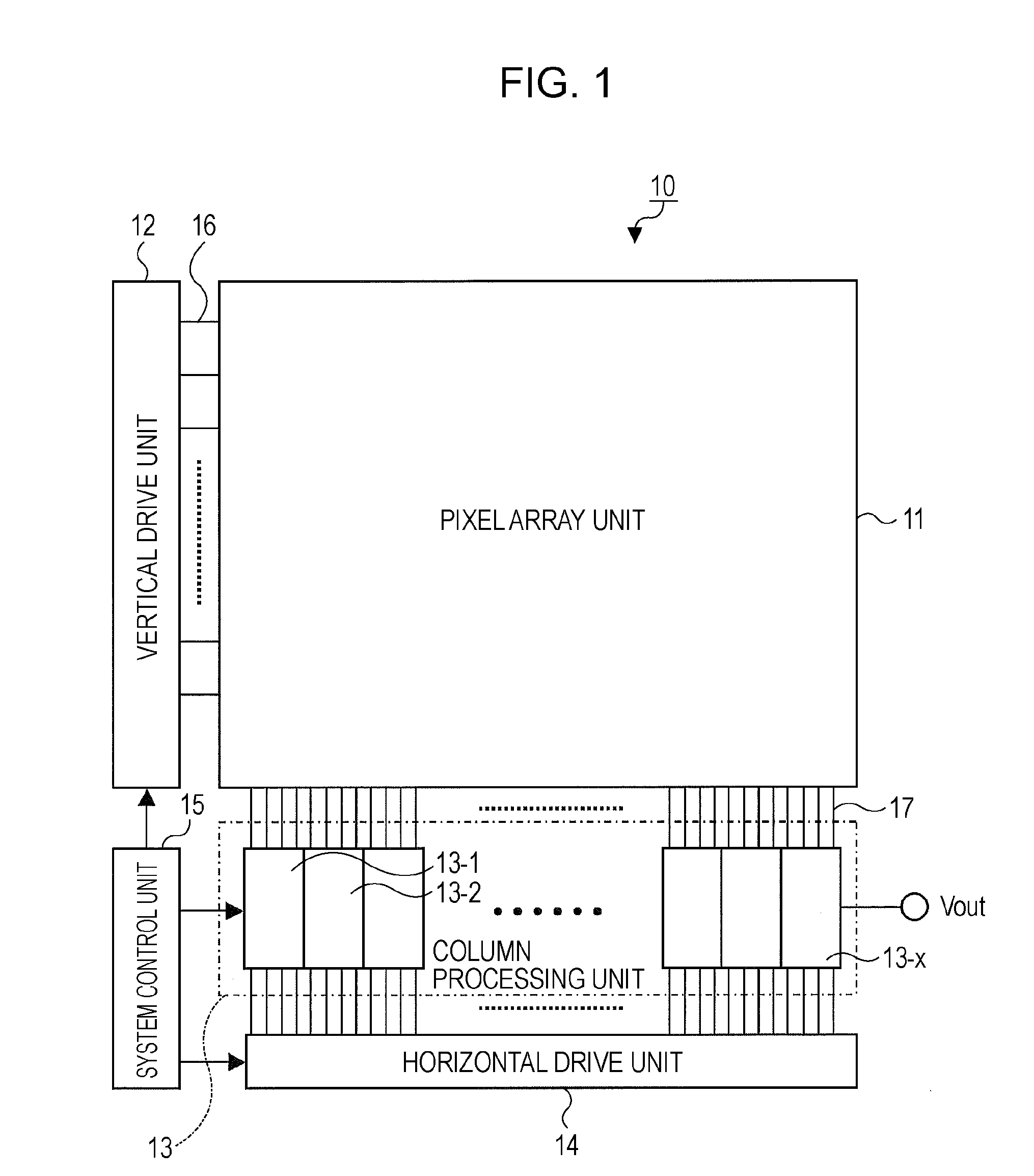

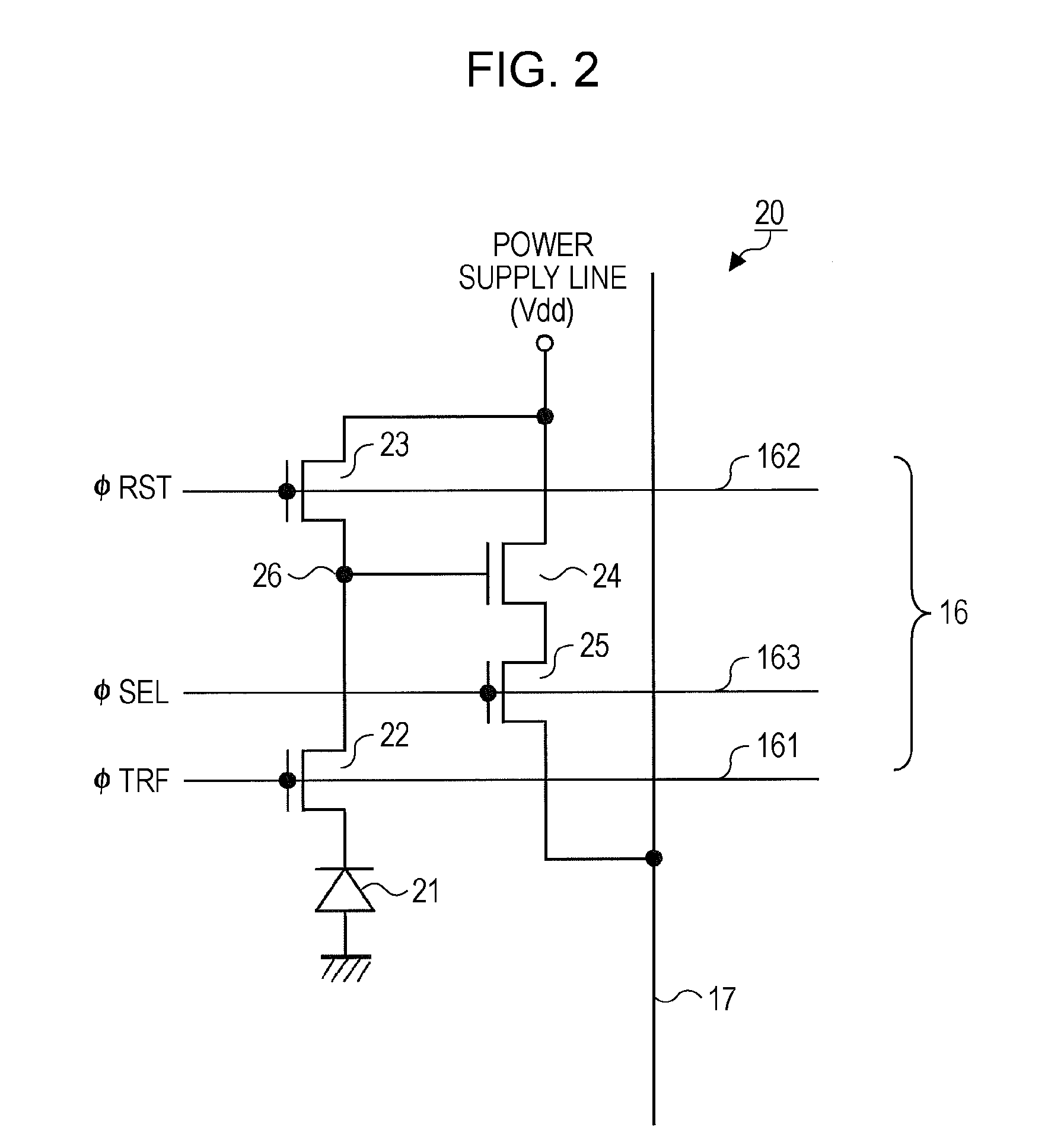

Solid-state image sensing device, method for reading signal of solid-state image sensing device, and image pickup apparatus

ActiveUS20090190018A1Reduce circuit areaReduce chip sizeTelevision system detailsTelevision system scanning detailsCapacitanceAudio power amplifier

An image sensor includes a pixel array having vertical signal lines, each interconnected to one of columns of the pixel array, and a column processor including a unit readout circuit provided for each of sets of a predetermined number of columns. The unit readout circuit includes input switches, each connected to a corresponding one of the vertical signal lines and being sequentially turned on and off, an input capacitor having one end commonly connected to the input switches, a reference switch for selectively providing a reference voltage to the input capacitor, an operational amplifier connected to the other end of the input capacitor, a reset switch for selectively providing a short-circuit between input and output ends of the operational amplifier, and a feedback circuit provided for each of the columns and including a feedback switch and a feedback capacitor connected in series between the two ends of the operational amplifier.

Owner:SONY CORP

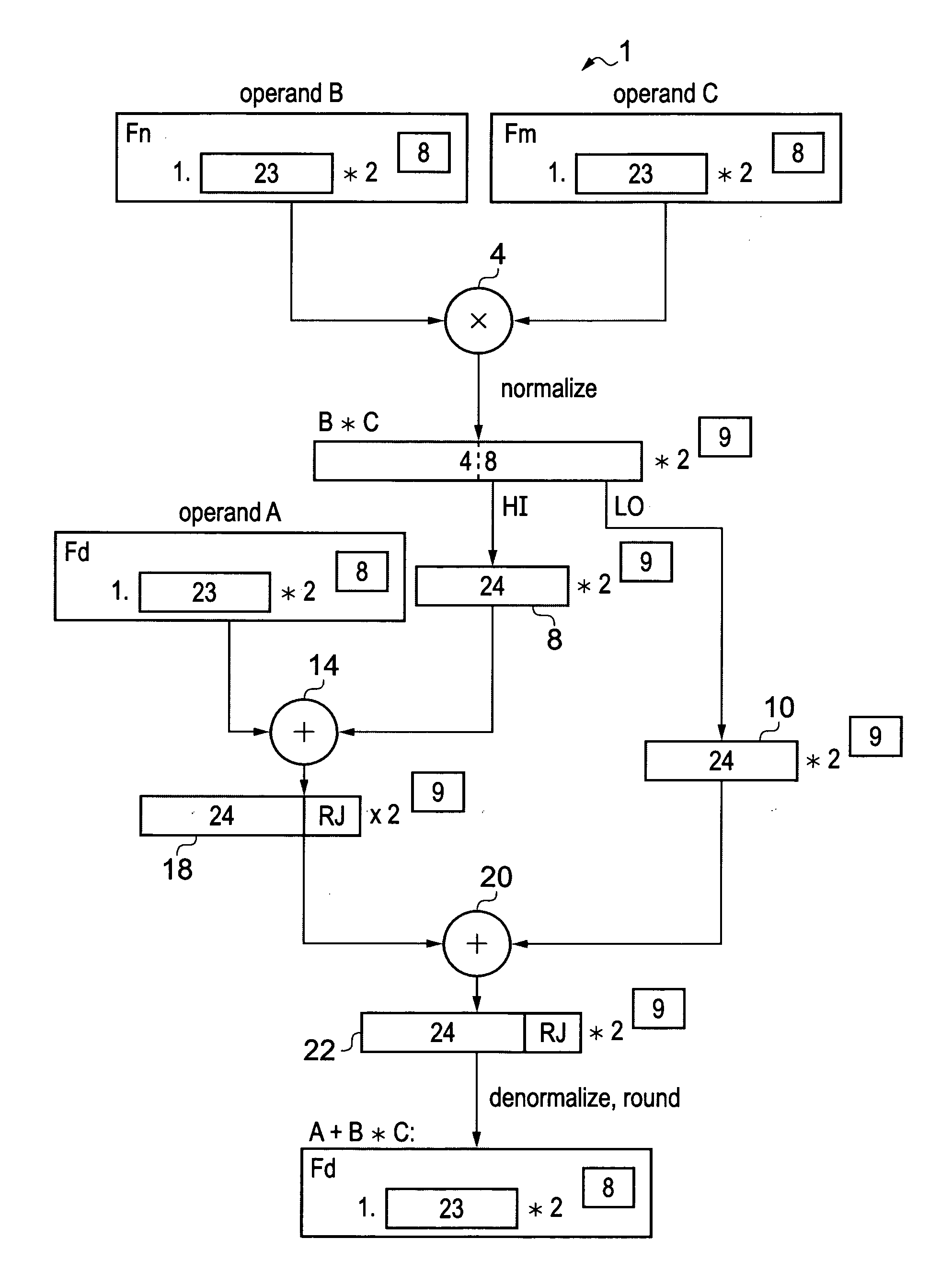

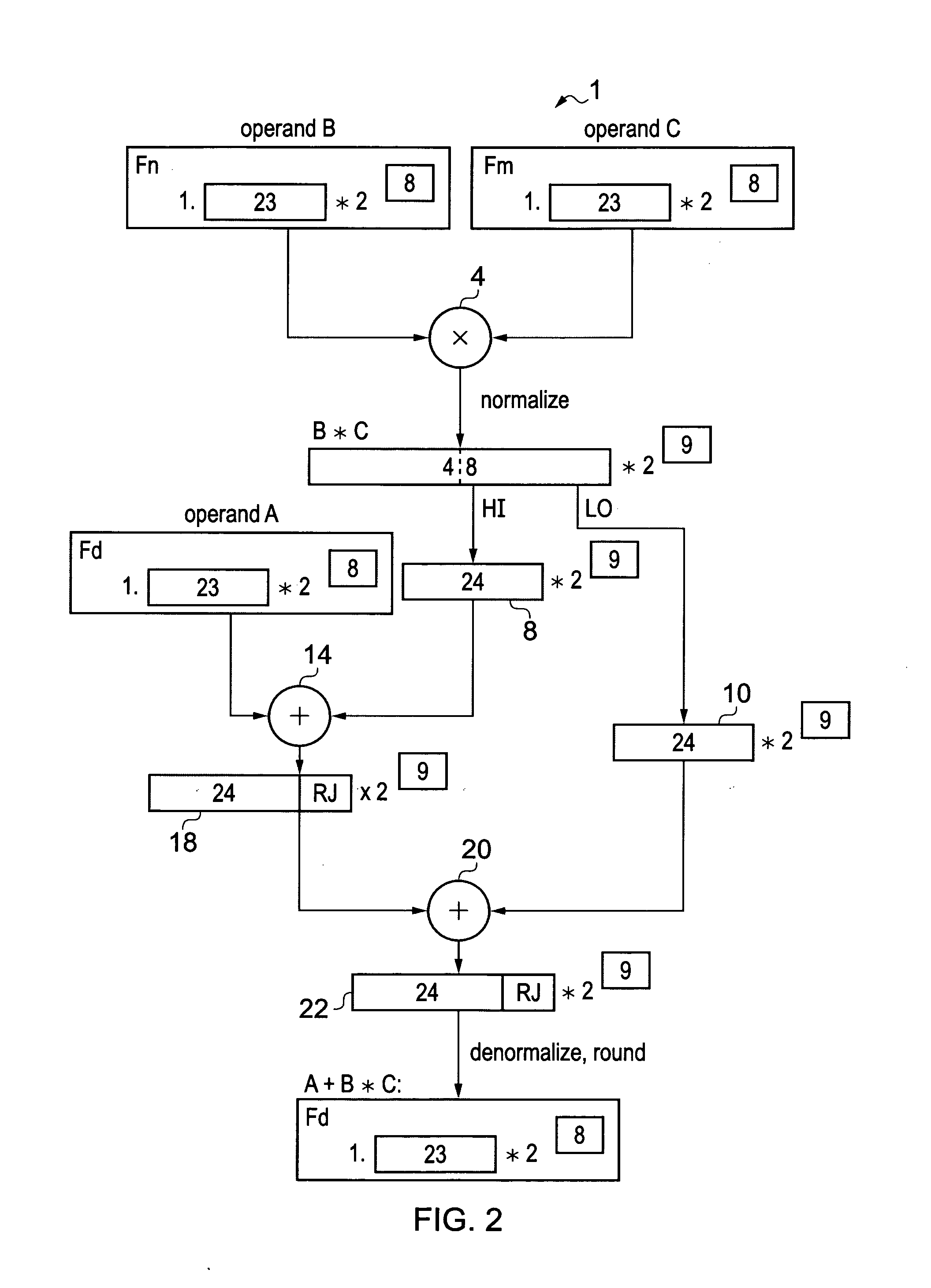

Apparatus and method for performing fused multiply add floating point operation

ActiveUS20110040815A1Reduce the amount requiredReduce the amount of processingDigital computer detailsComputation using denominational number representationFloating pointOperand

A data processing apparatus is arranged to perform a fused multiply add operation. The apparatus 100 has multiplying circuitry 110 configured to multiply operands B and C to generate a product B*C having a high order portion 160 and a low order portion 170. The apparatus has adding circuitry 130 configured to: (i) add an operand A to one of the high order portion 160 and the low order portion 170 to generate an intermediate sum value; and (ii) add the intermediate sum value to a remaining one of the high order portion 160 and the low order portion 170 to generate a result A+B*C.

Owner:ARM LTD

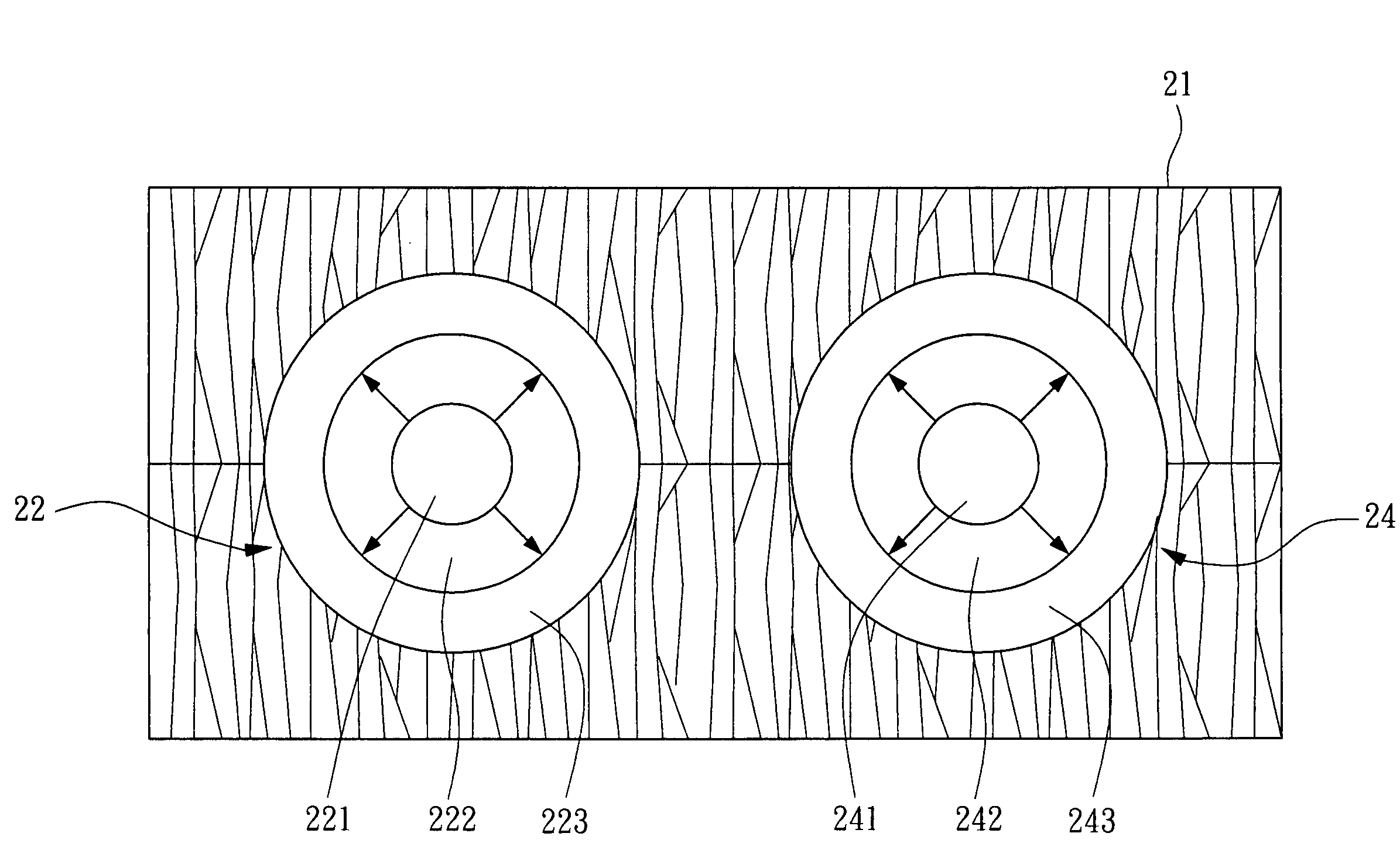

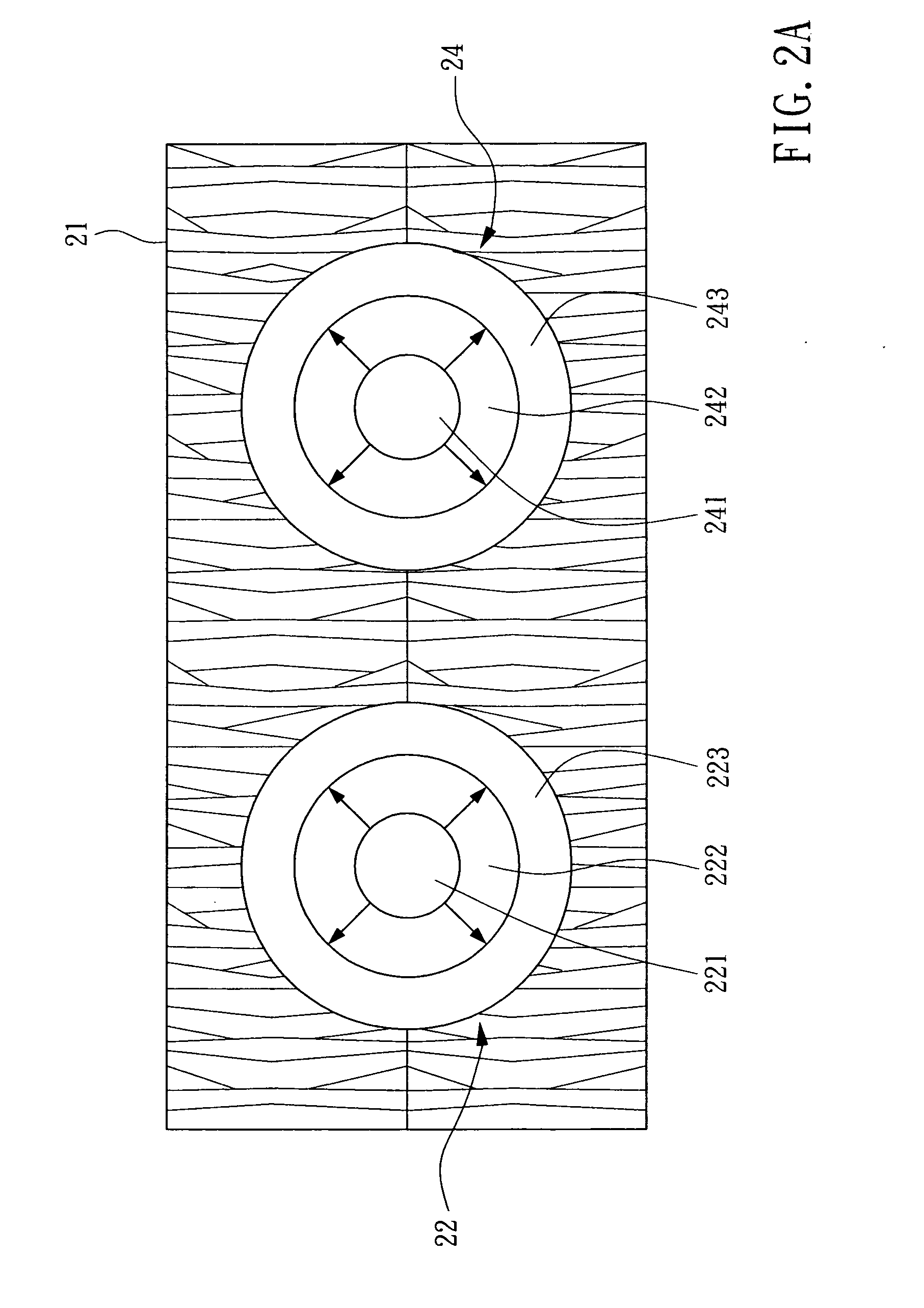

Thin film transistor device with high symmetry

InactiveUS20070215942A1High symmetryIncreased complexitySolid-state devicesSemiconductor/solid-state device manufacturingGrain boundaryCircuit design

A thin film transistor device with high symmetry is disclosed, in which the symmetrical structure of transistor is utilized to enable currents flowing in the channels of each transistor formed on a polysilicon film of a specific crystallization direction to pass the same amount of grain boundaries, thereby improving the uniformity of electrical characteristics of the device. By the thin film transistor device of the invention, not only the freedom of circuit design is increased, but also the circuit area of a TFT device occupied is reduced.

Owner:IND TECH RES INST

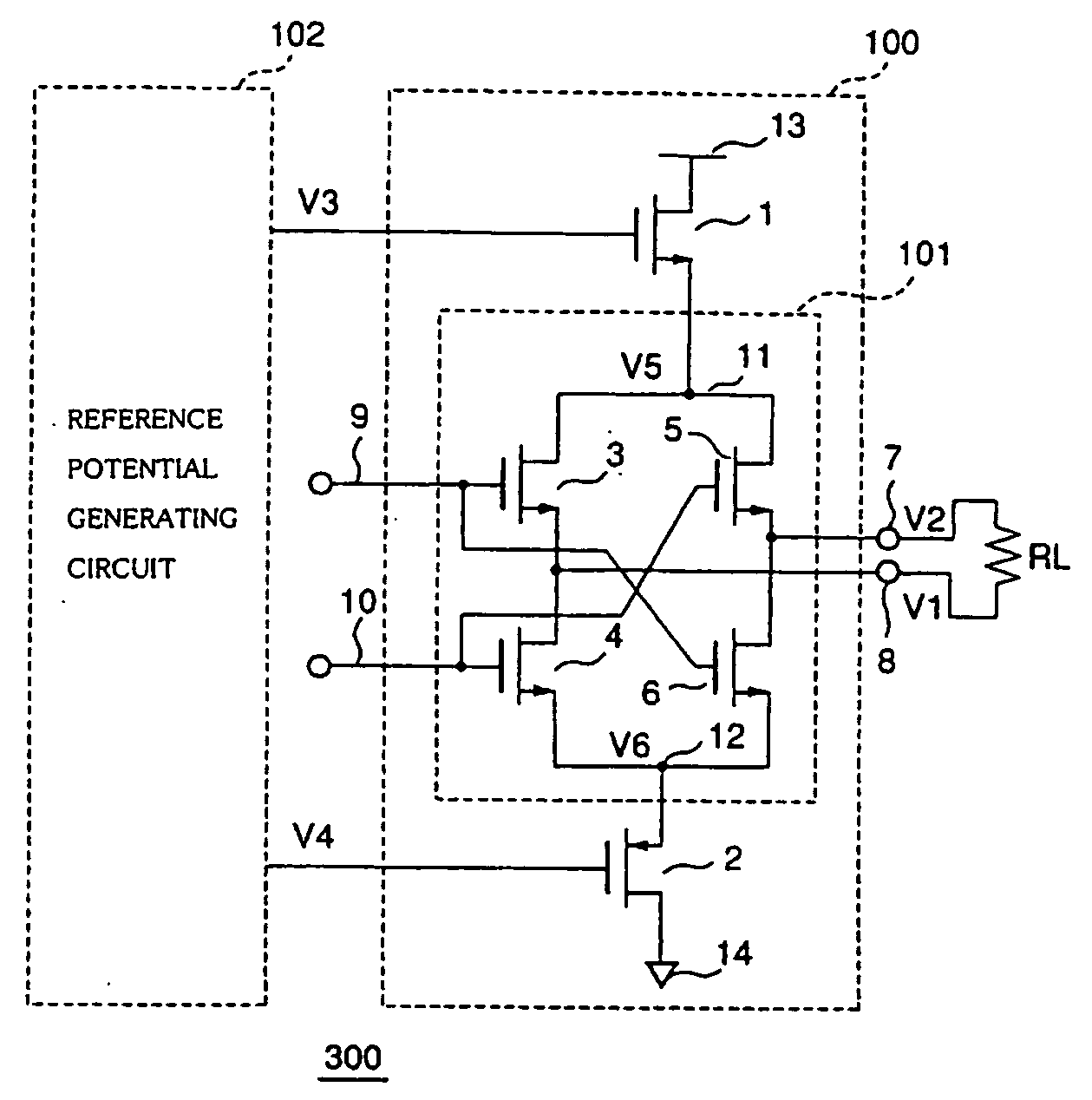

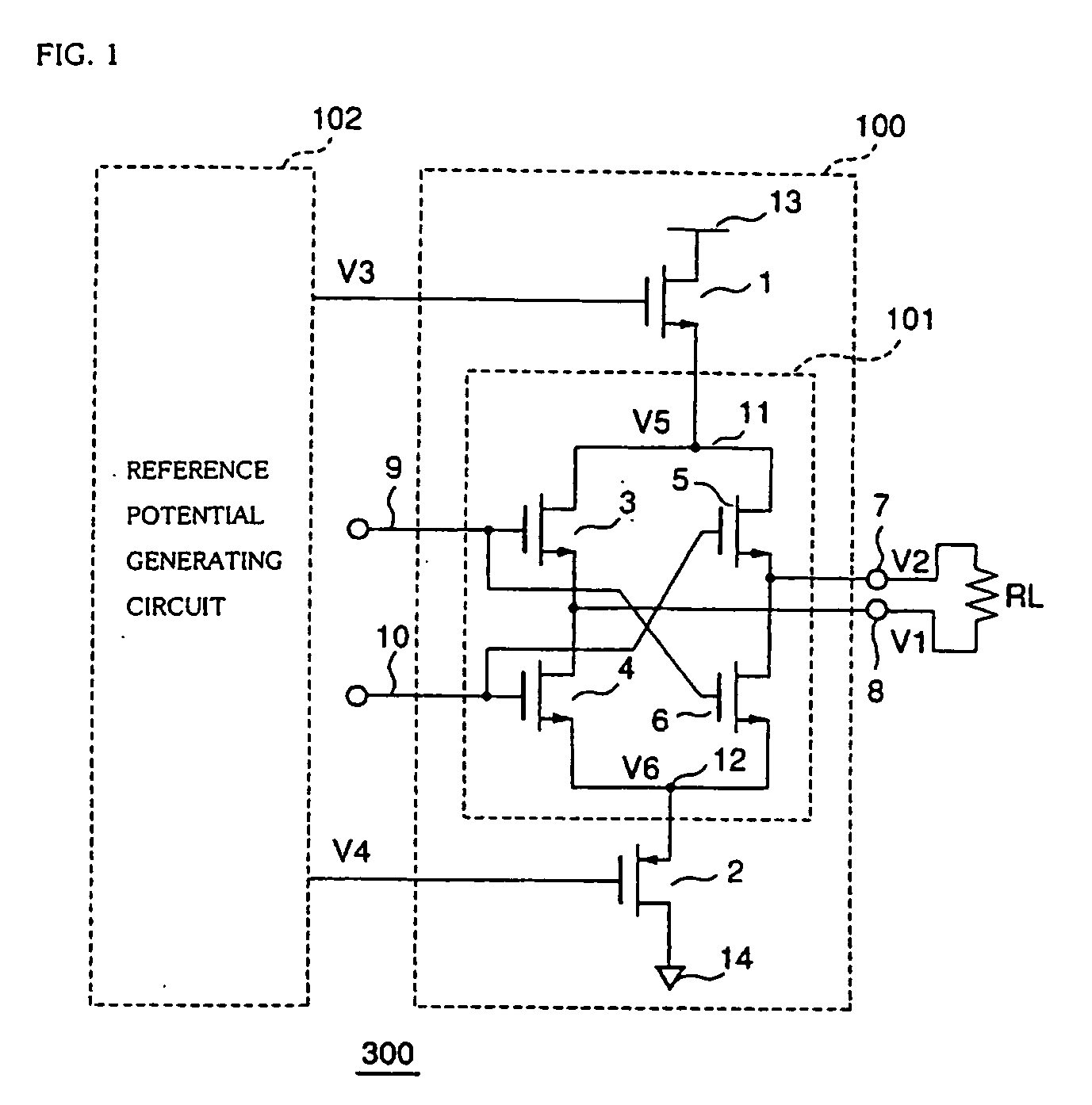

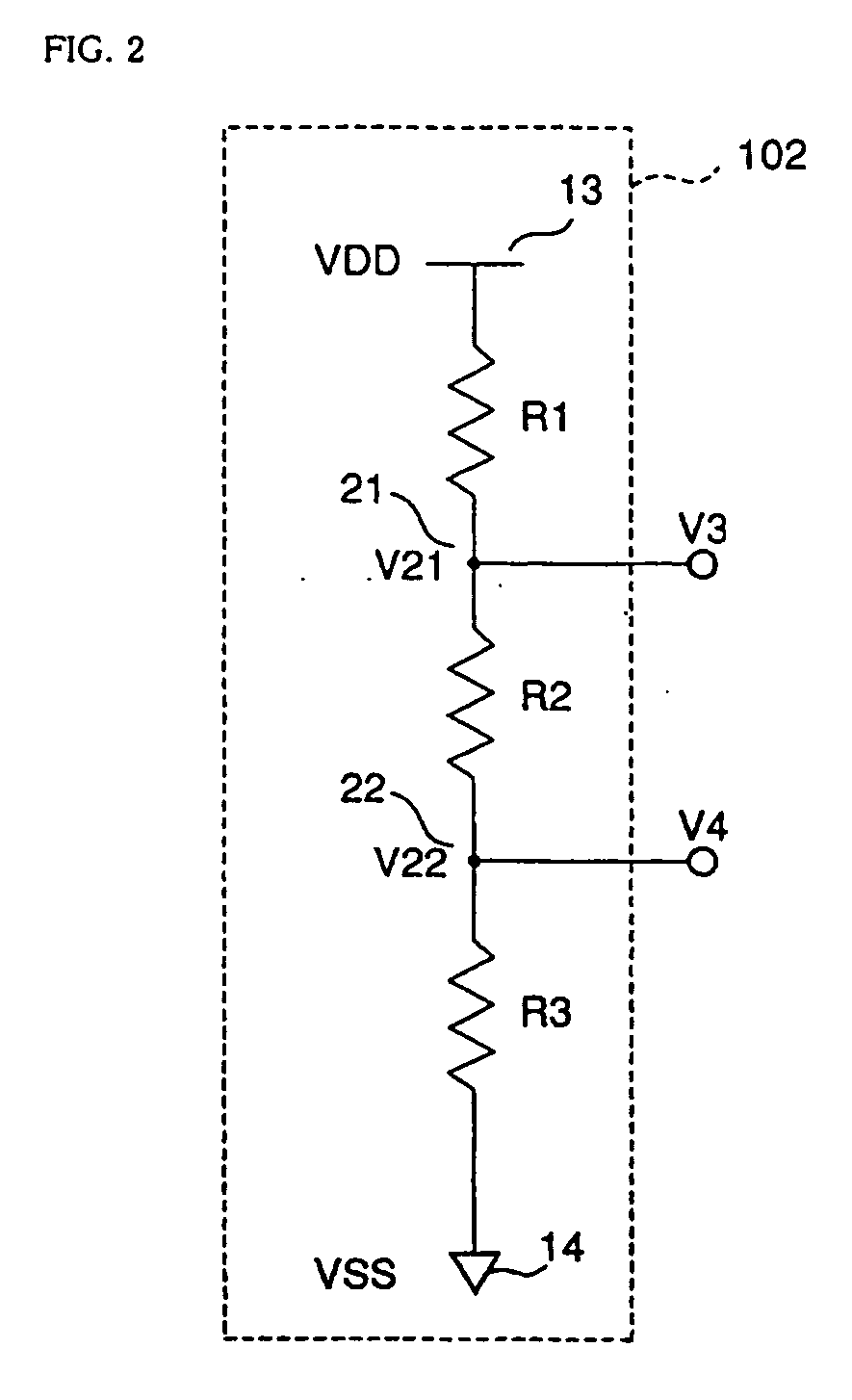

Differential Drive Circuit and Electronic Apparatus Incorporating the Same

InactiveUS20080246511A1Reduce troubleHigh driving capabilityAmplifier with semiconductor-devices/discharge-tubesElectric pulse generatorDifferential amplifierHigh potential

A differential driving circuit used for low voltage differential signals and an electronic device incorporating the same are provided wherein no differential amplifiers are used or the number of differential amplifiers are reduced, thereby reducing the circuit area and the current consumption and further solving the problem of oscillation caused by noise, while a high driving performance is achieved. There are included a switch circuit an output circuit and a reference potential generating circuit. The switch circuit, which comprises MOS transistors, receives differential signals and outputs current signals. The output circuit comprises an NMOS transistor, an end of which is connected to the power supply potential of a higher potential side, the other end of which is connected to a node of the switch circuit and which acts as a source follower, and an PMOS transistor, an end of which is connected to the power supply potential of a lower potential side, the other end of which is connected to the other node of the switch circuit and which acts as a source follower. The reference potential generating circuit supplies reference potentials to the respective gates of the PMOS and NMOS transistors. The reference potential generating circuit includes a potential varying means that varies the differential potentials with an offset potential kept constant. Further, there is included an emphasis circuit for the output circuit.

Owner:THINE ELECTRONICS

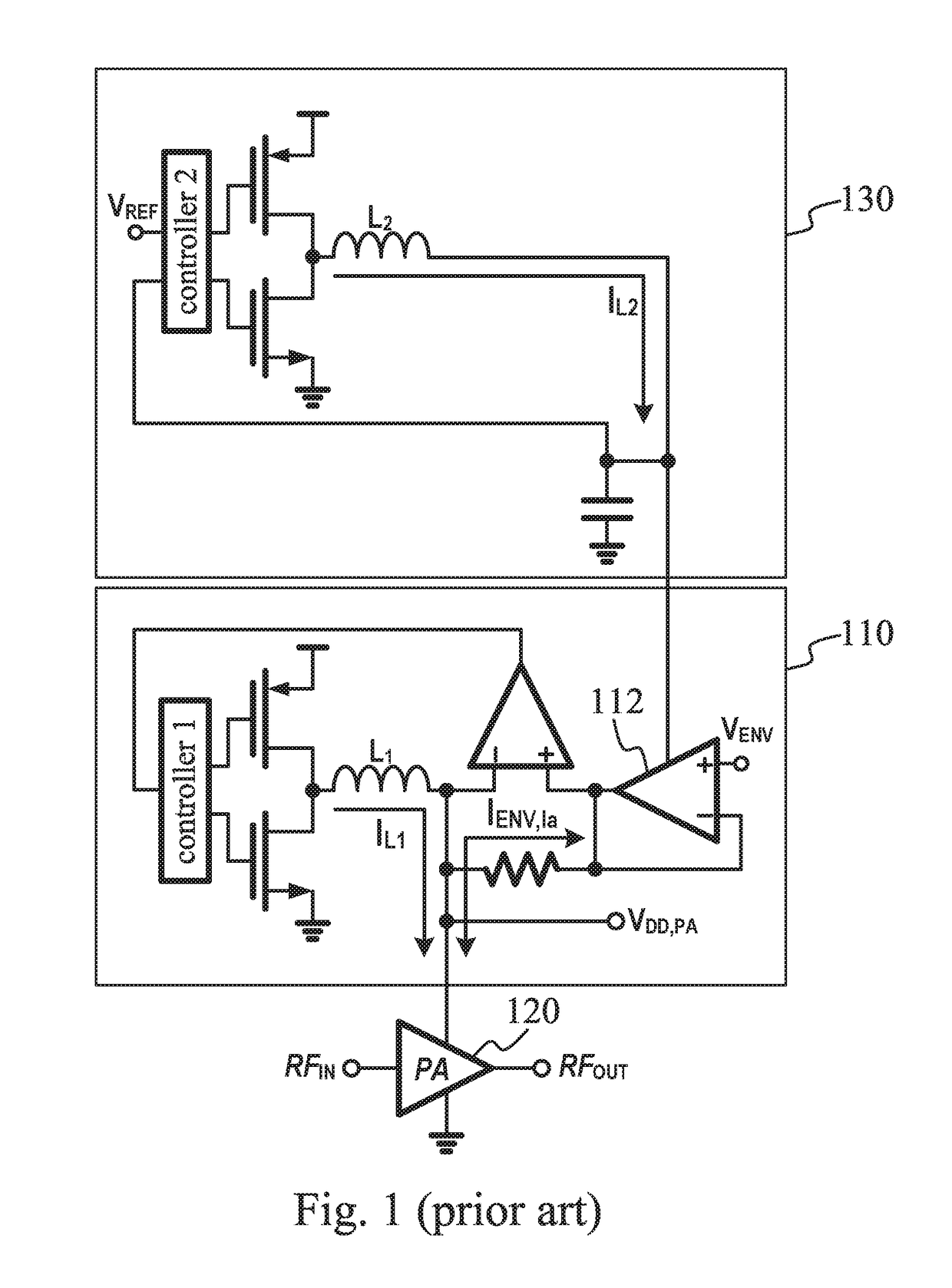

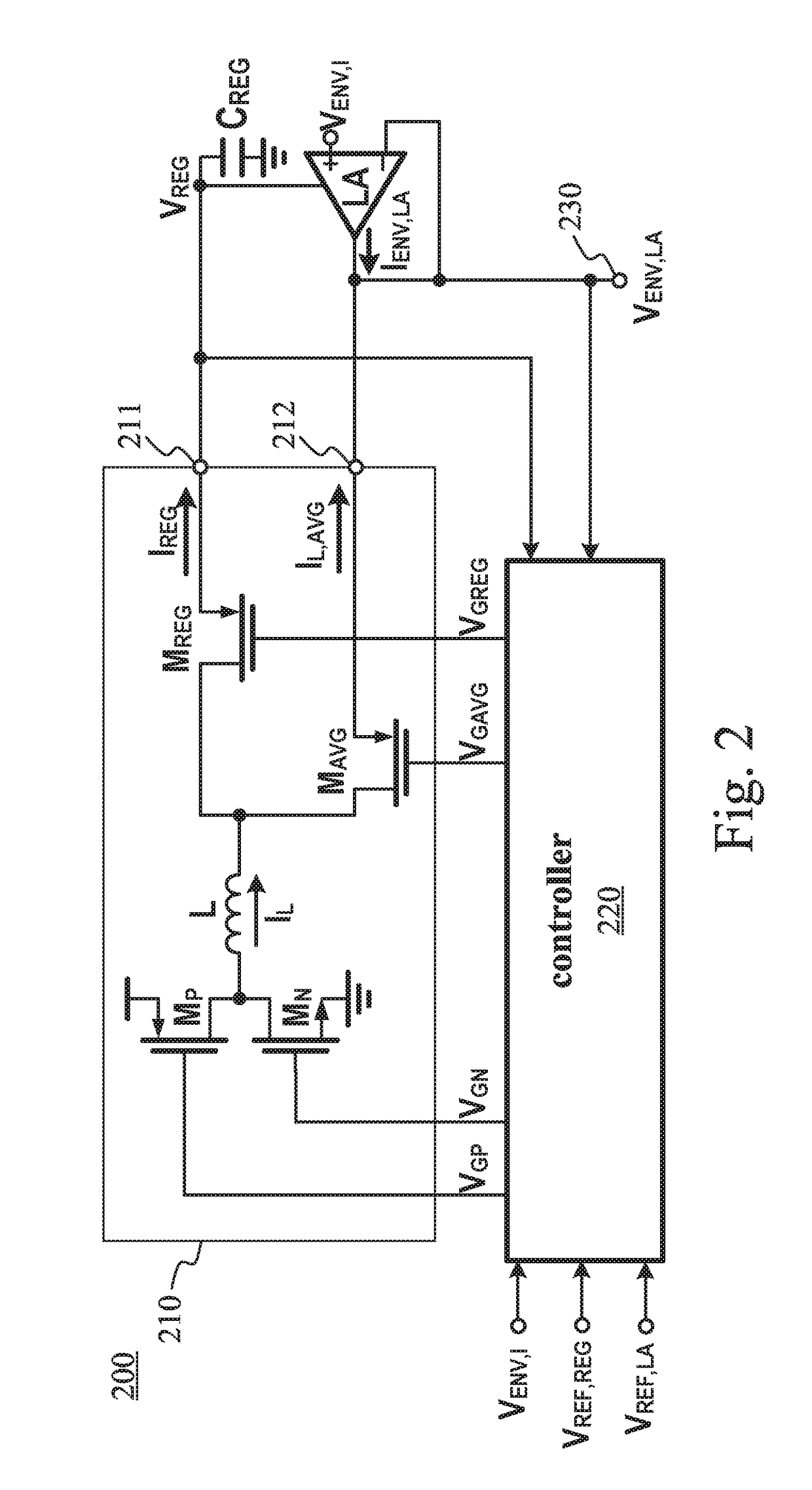

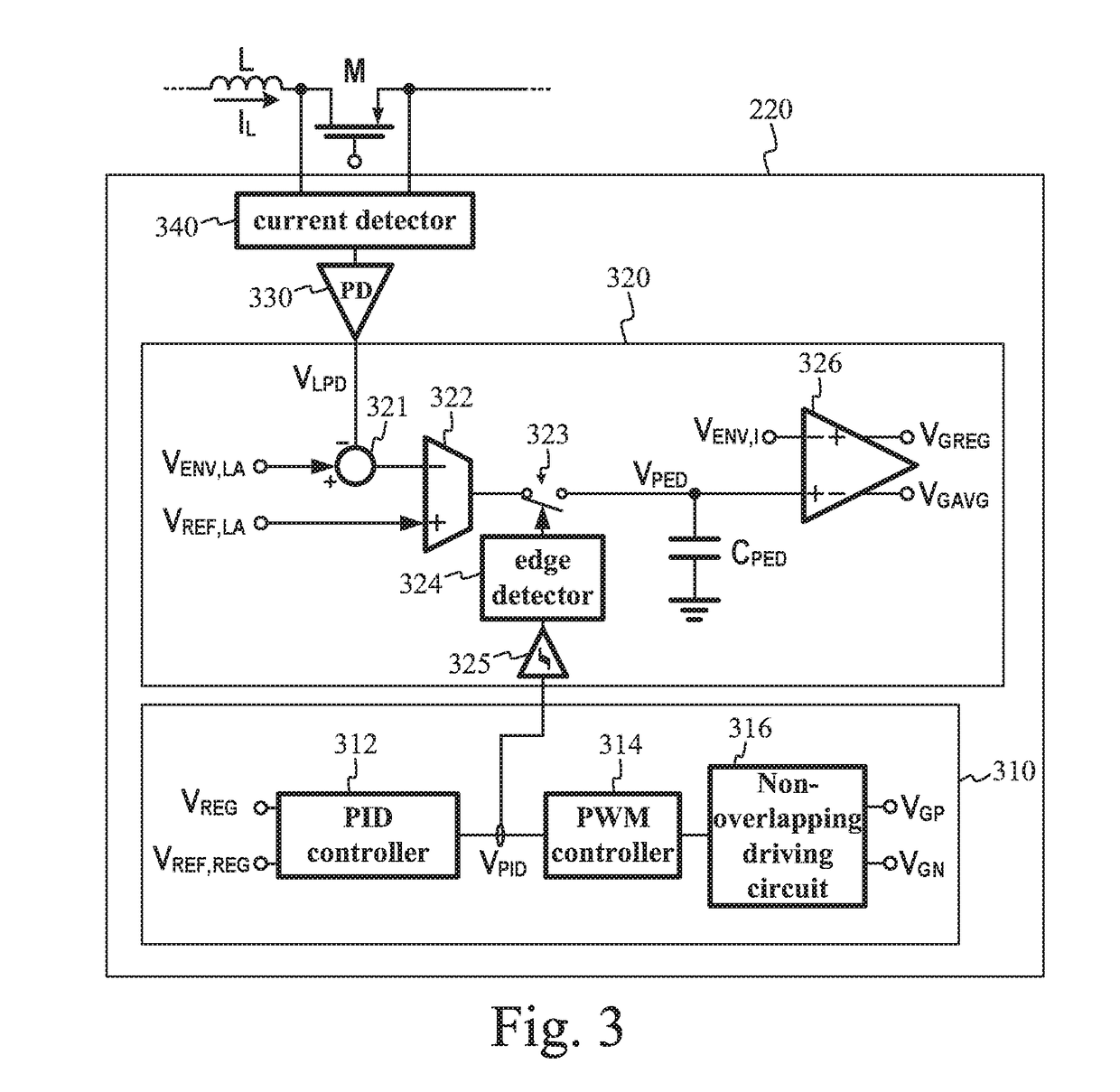

Envelope-tracking power supply modulator

ActiveUS20180367101A1Reduce hardware costsAvoid energy wasteHigh frequency amplifiersPower amplifiersAudio power amplifierEngineering

An envelope-tracking power supply modulator (ETSM) supplies power to a radio frequency power amplifier (RFPA) of a radio frequency (RF) circuit according to a baseband envelope signal. The ETSM includes a linear amplifier, a capacitor, a single inductor multiple output (SIMO) switch-mode converter, and a controller. The linear amplifier receives the baseband envelope signal, and has its output terminal coupled to a power input of the RFPA. One terminal of the capacitor is coupled to a reference voltage, and the other terminal is coupled to a power input of the linear amplifier. The SIMO switch-mode converter includes two output terminals. One of the output terminals is coupled to the capacitor and the power input of the linear amplifier, and the other of the output terminals is coupled to the output terminal of the linear amplifier and the power input of the RFPA. The controller controls the SUMO switch-mode converter.

Owner:REALTEK SEMICON CORP

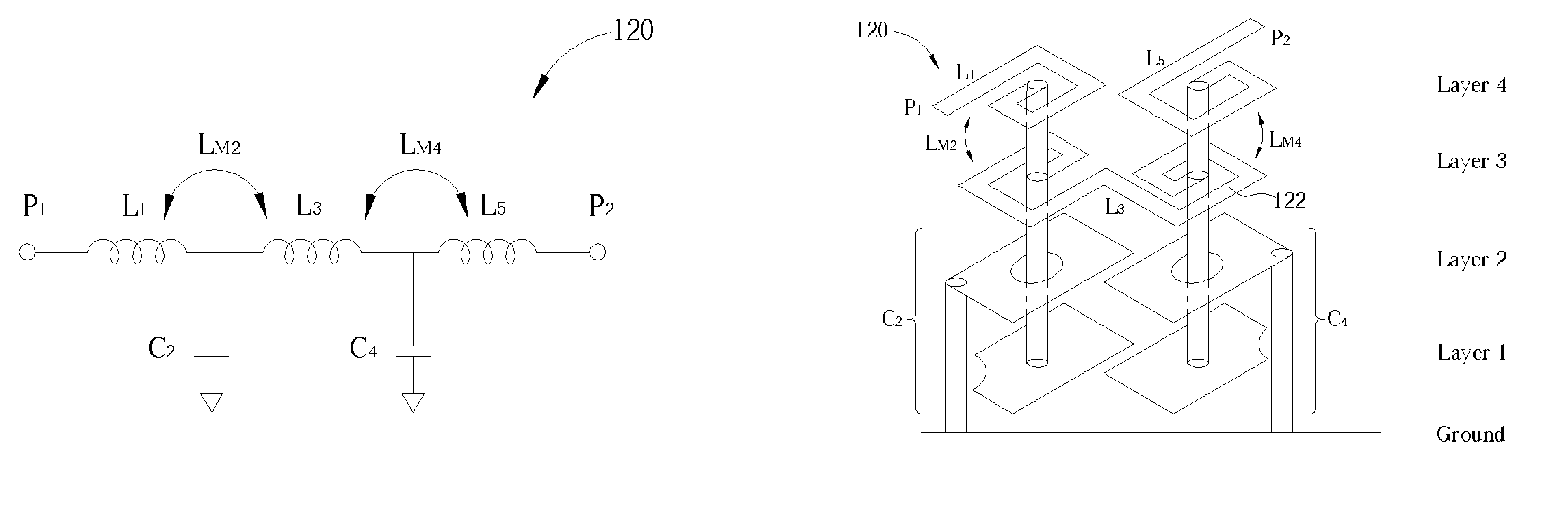

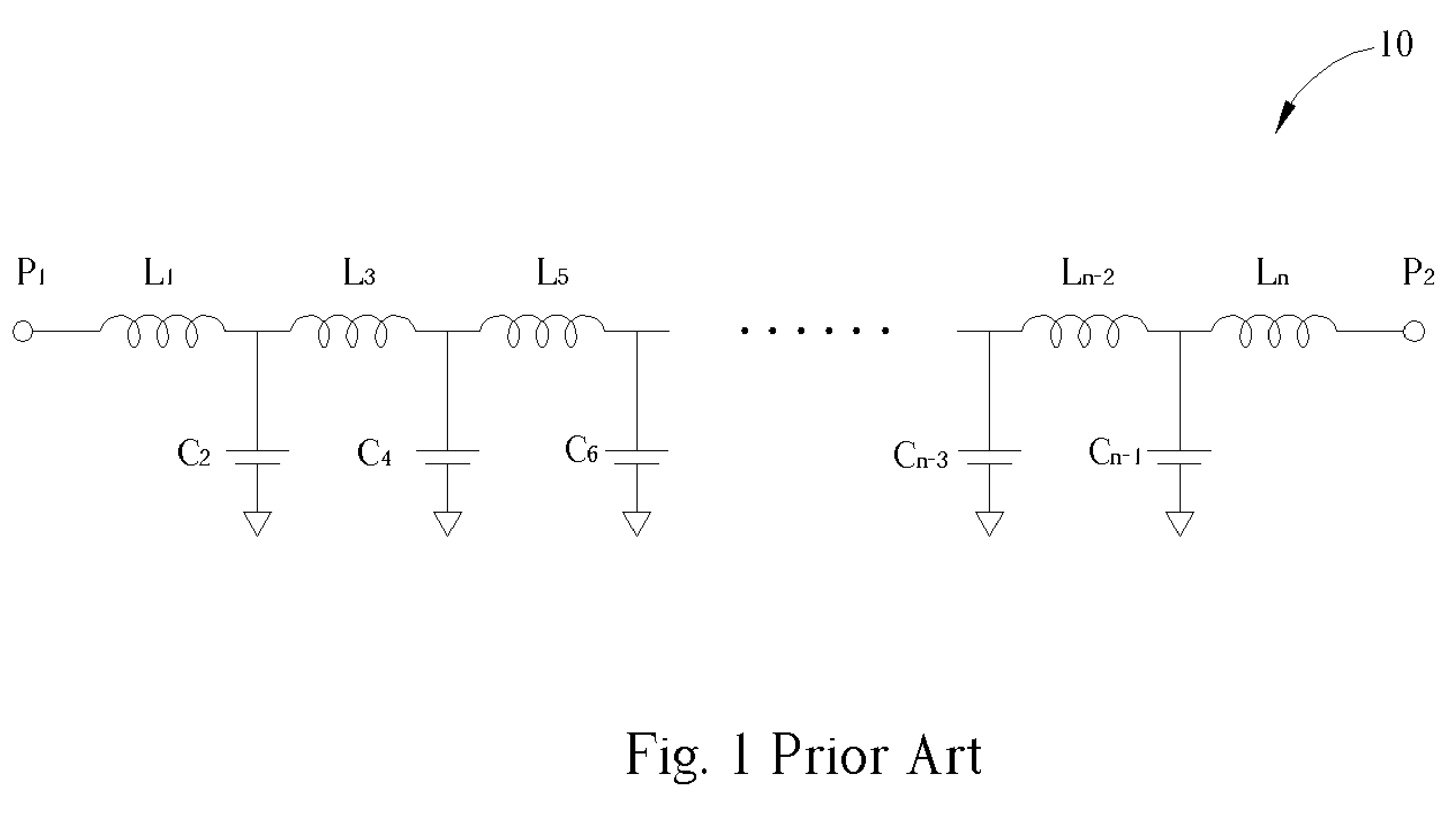

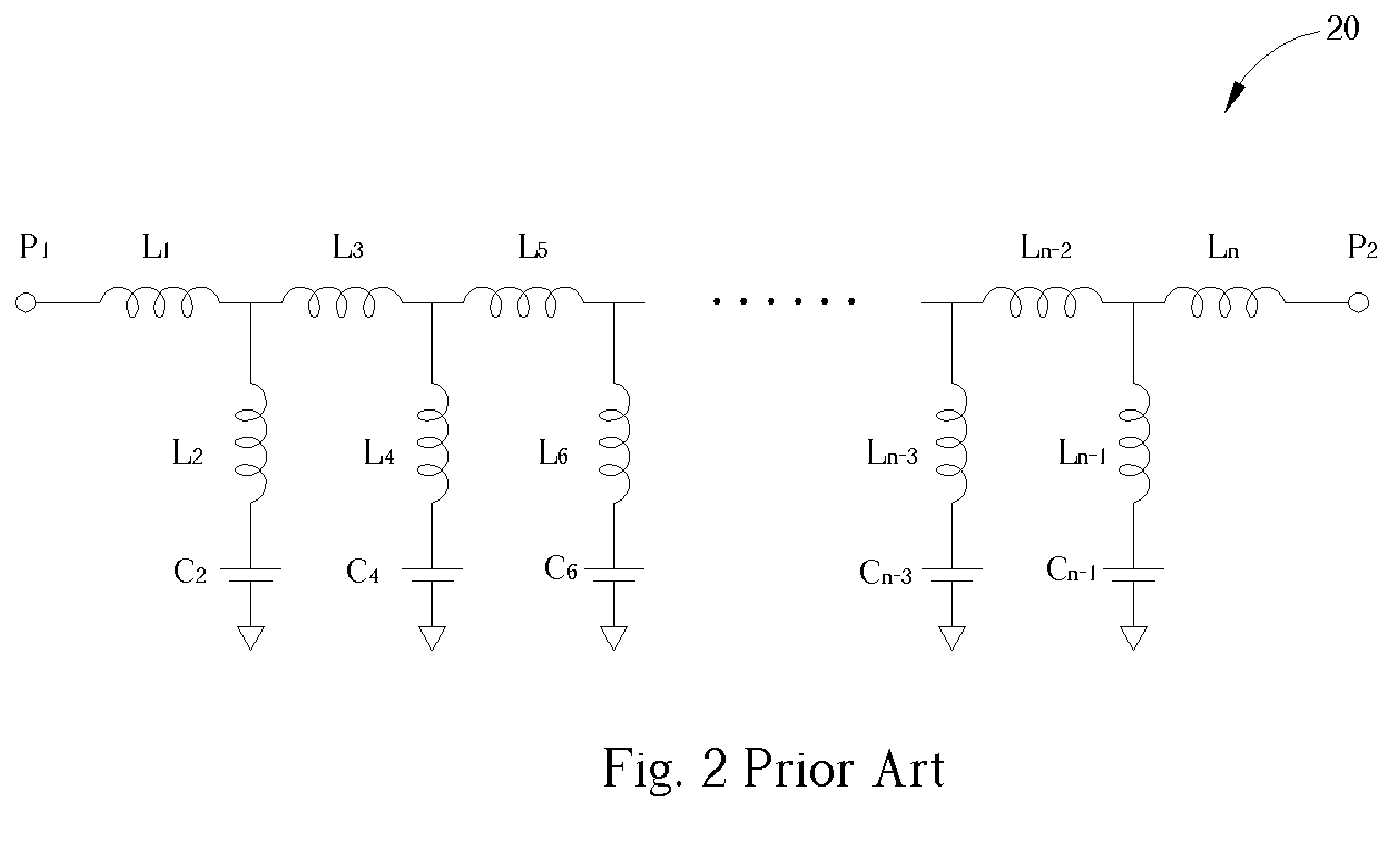

Lowpass filter formed in a multi-layer ceramic

InactiveUS6970057B2Reduce areaIncreased rejectMultiple-port networksPrinted capacitor incorporationLow-pass filterInductor

A lowpass filter formed in a multi-layered substrate includes a first capacitor formed on at least one layer of the multi-layered substrate and being electrically connected to a first node, a first inductor being electrically connected to the first capacitor at the first node, and a second inductor being electrically connected to the first inductor and the first capacitor at the first node. In the lowpass filter, negative mutual inductance exists between the first inductor and the second inductor.

Owner:CHI MEI COMM SYST INC

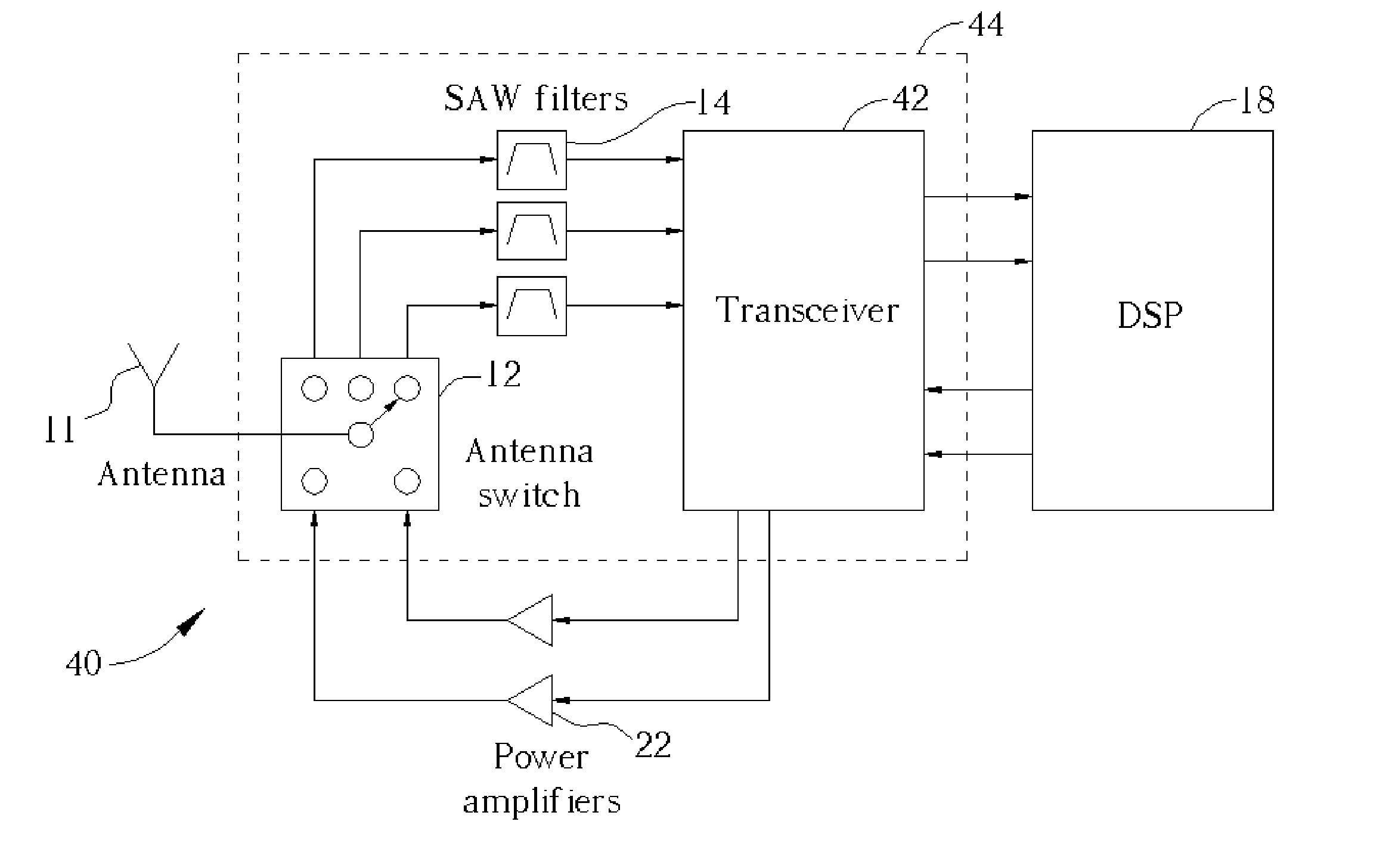

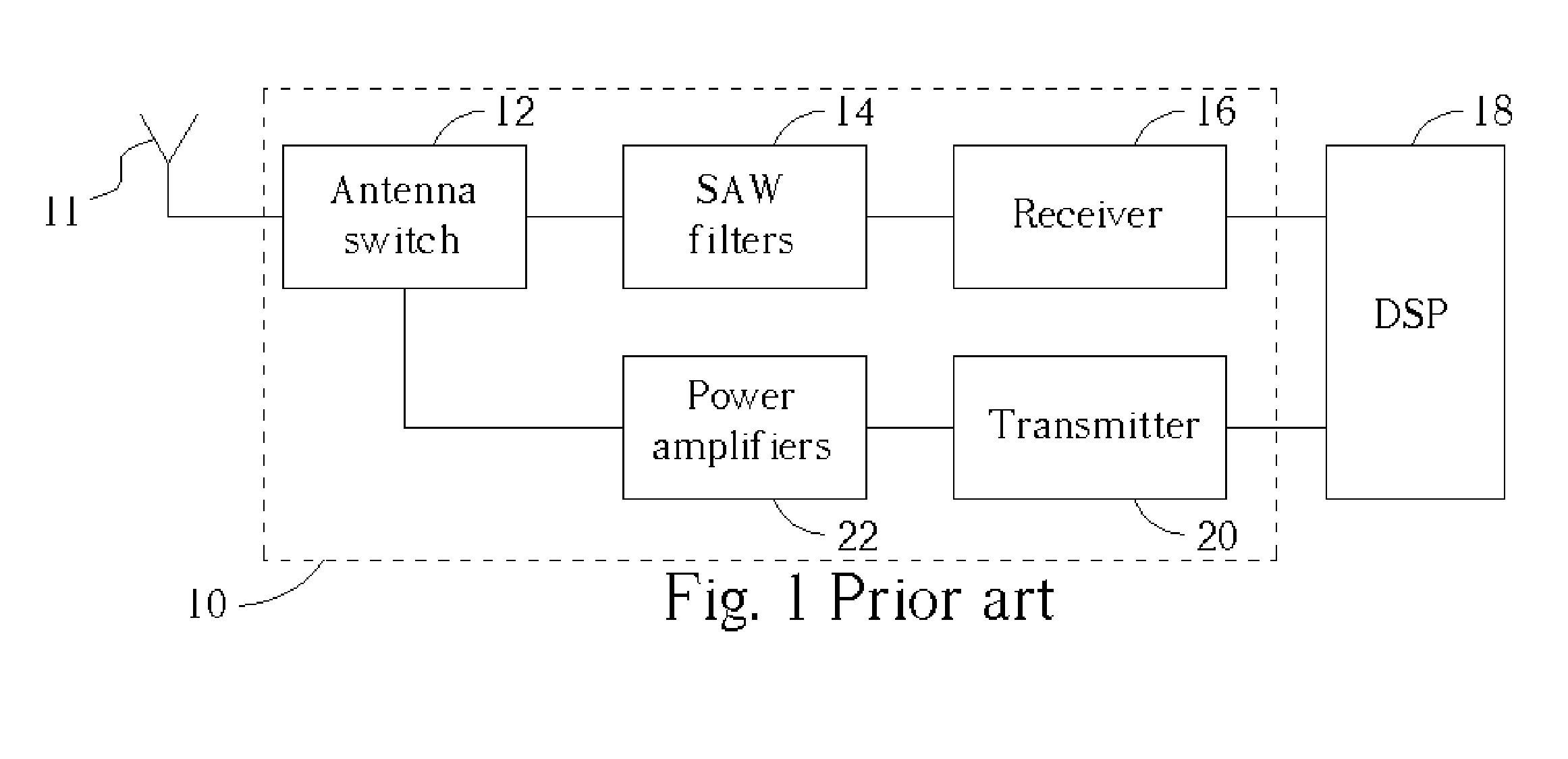

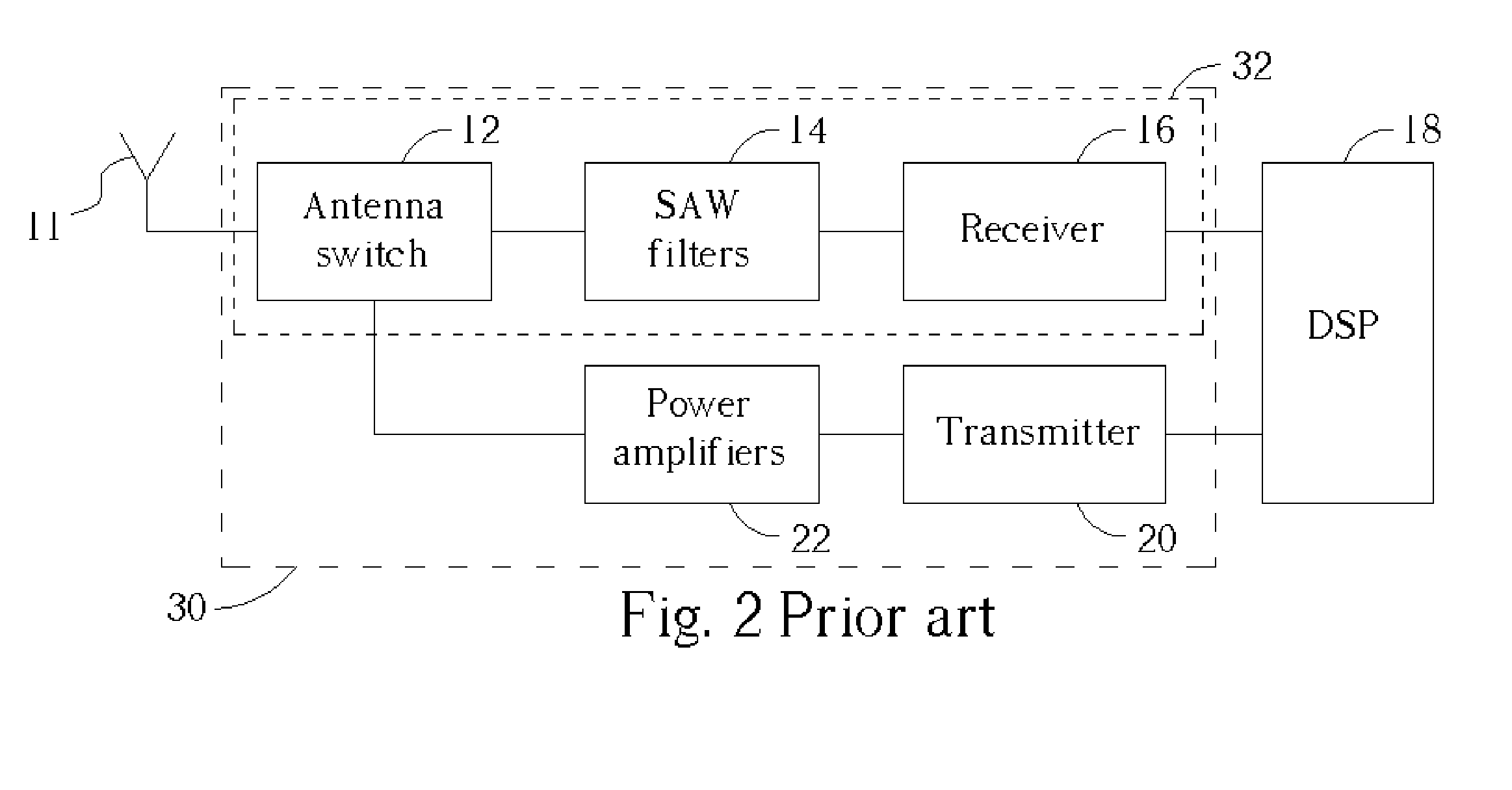

RF transceiver module formed in multi-layered ceramic

InactiveUS20050026647A1Reduce circuit areaReduce the number of partsResonant long antennasModulation with suppressed carrierTransceiverAudio power amplifier

An RF transceiver module for wireless communication devices includes a multi-layered substrate, an RF transceiver IC mounted on the multi-layered substrate for receiving and transmitting voice or data signals, at least one band selection filter mounted on the multi-layered substrate for filtering received RF signals, an antenna switch integrated in the multi-layered substrate which can be switched to transmit RF signals generated by the power amplifiers to the external antenna or to receive RF signals from an external antenna to the RF transceiver IC through the band selection filter, a plurality of passive devices embedded in the multi-layered substrate, and wiring embedded in the multi-layered substrate for electrically connecting the passive devices, the RF transceiver IC, and the band selection filter.

Owner:CHI MEI COMM SYST INC

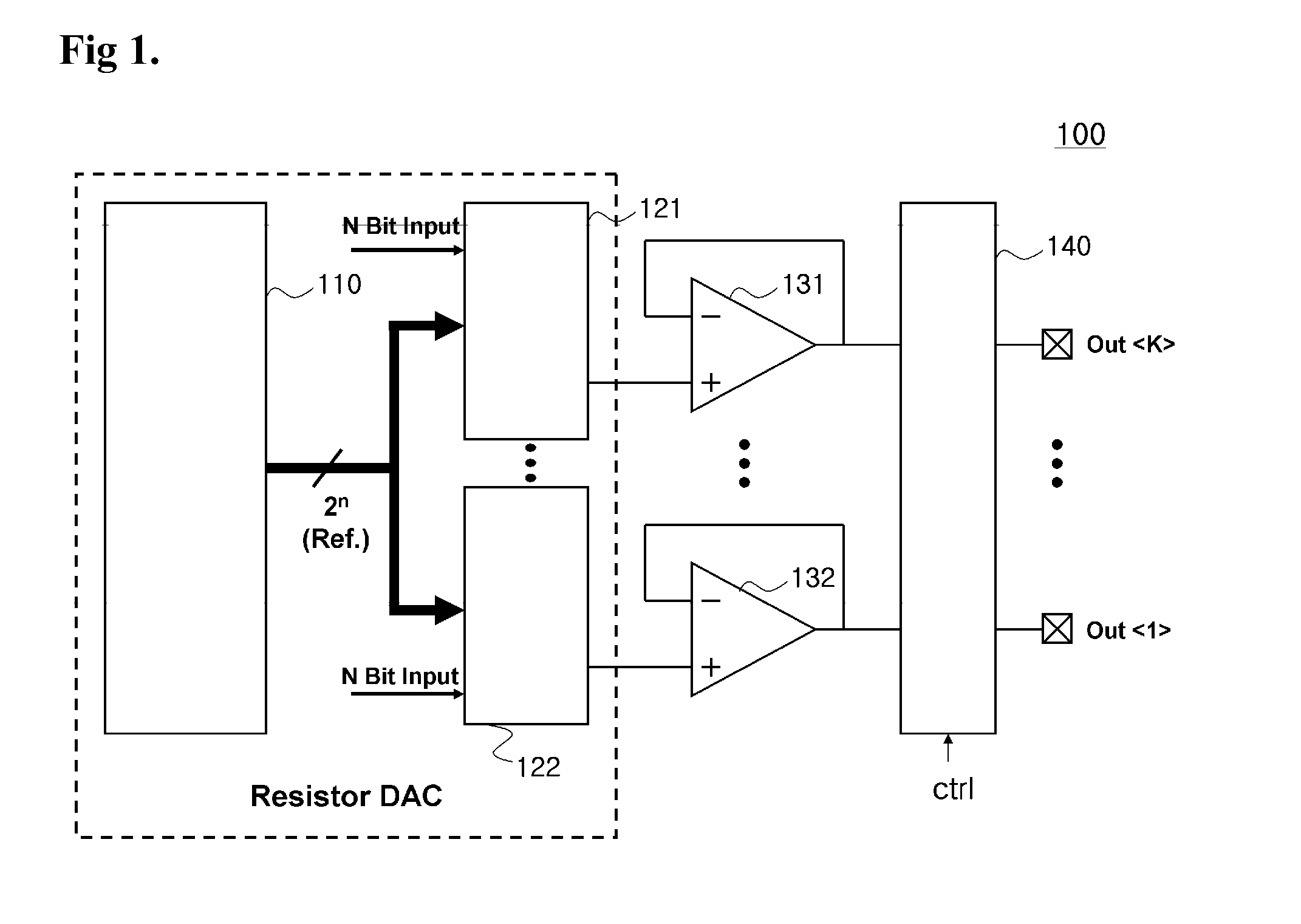

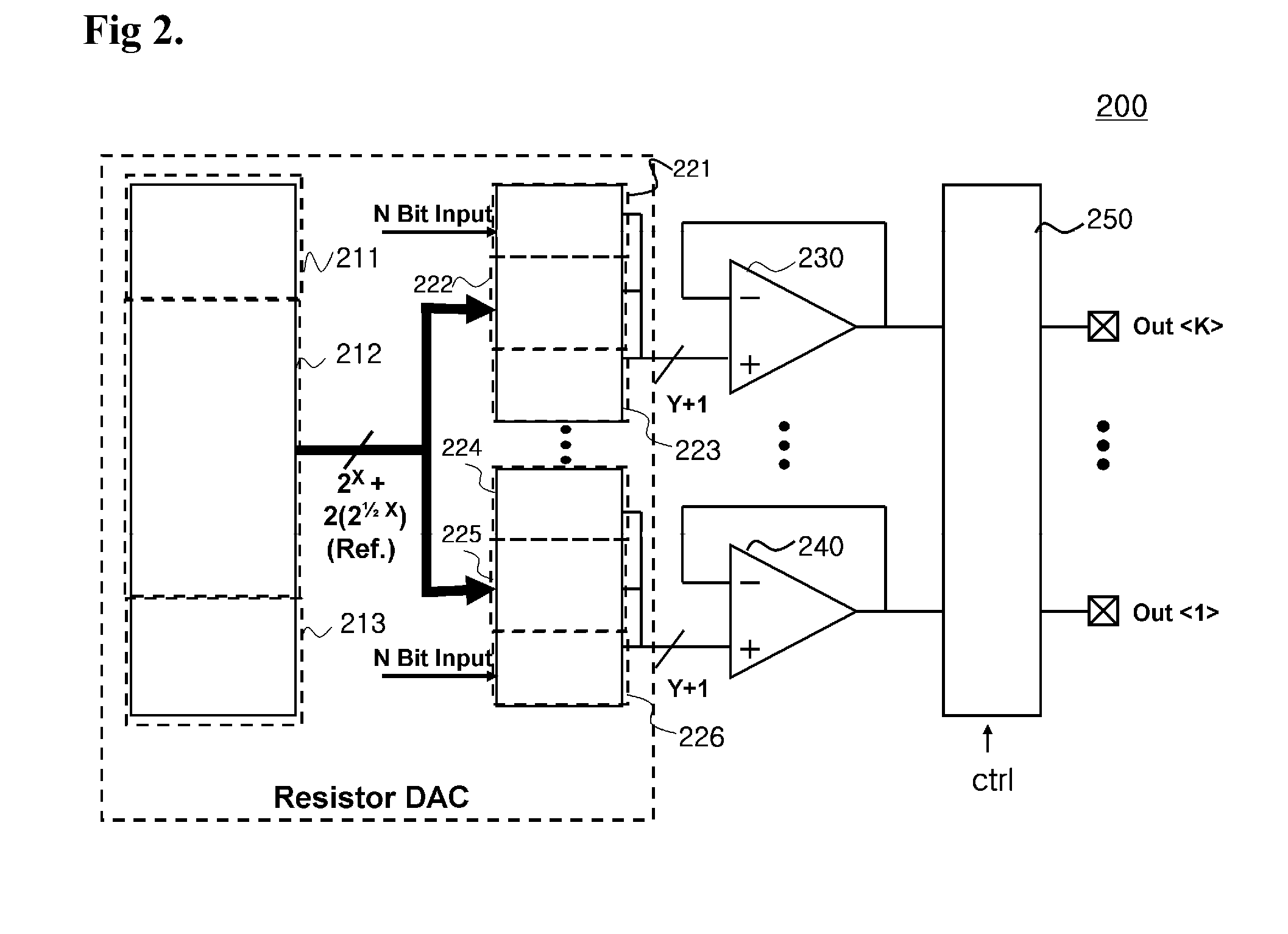

Liquid crystal display panel driving circuit

ActiveUS20110096054A1Reduce circuit areaCathode-ray tube indicatorsInput/output processes for data processingDigital dataElectrical resistance and conductance

Disclosed is a liquid crystal display panel driving circuit for driving a liquid crystal display panel with a resolution of N bits. N-bit digital data including upper X bits and lower Y bits is inputted. The liquid crystal display panel driving circuit includes a resistor string unit according to areas, a DAC converter switching unit according to areas, and an interpolation amplifier. The resistor string unit outputs analog reference voltages at different ratios according to three areas. The DAC converter switching unit receives the N-bit digital data, selects (Y+1) analog voltages from the analog reference voltages based on the upper X bits, outputs the (Y+1) analog voltages, and outputs the (Y+1) analog voltages of different combinations based on the lower Y bits. The interpolation amplifier receives the (Y+1) analog voltages and generates an interpolated output voltage by setting weights for the (Y+1) analog voltages by using multi-factors.

Owner:SILICON WORKS CO LTD

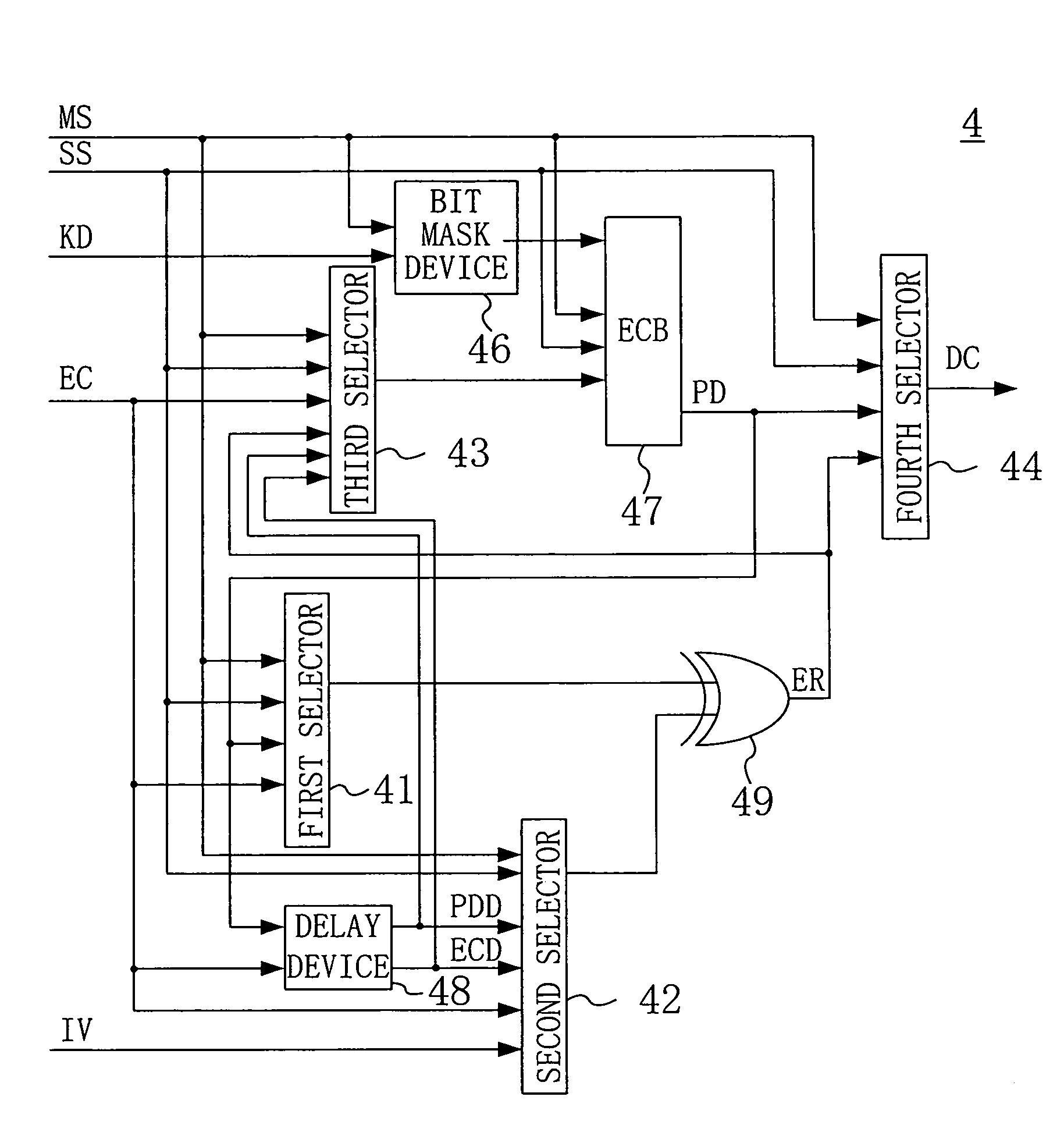

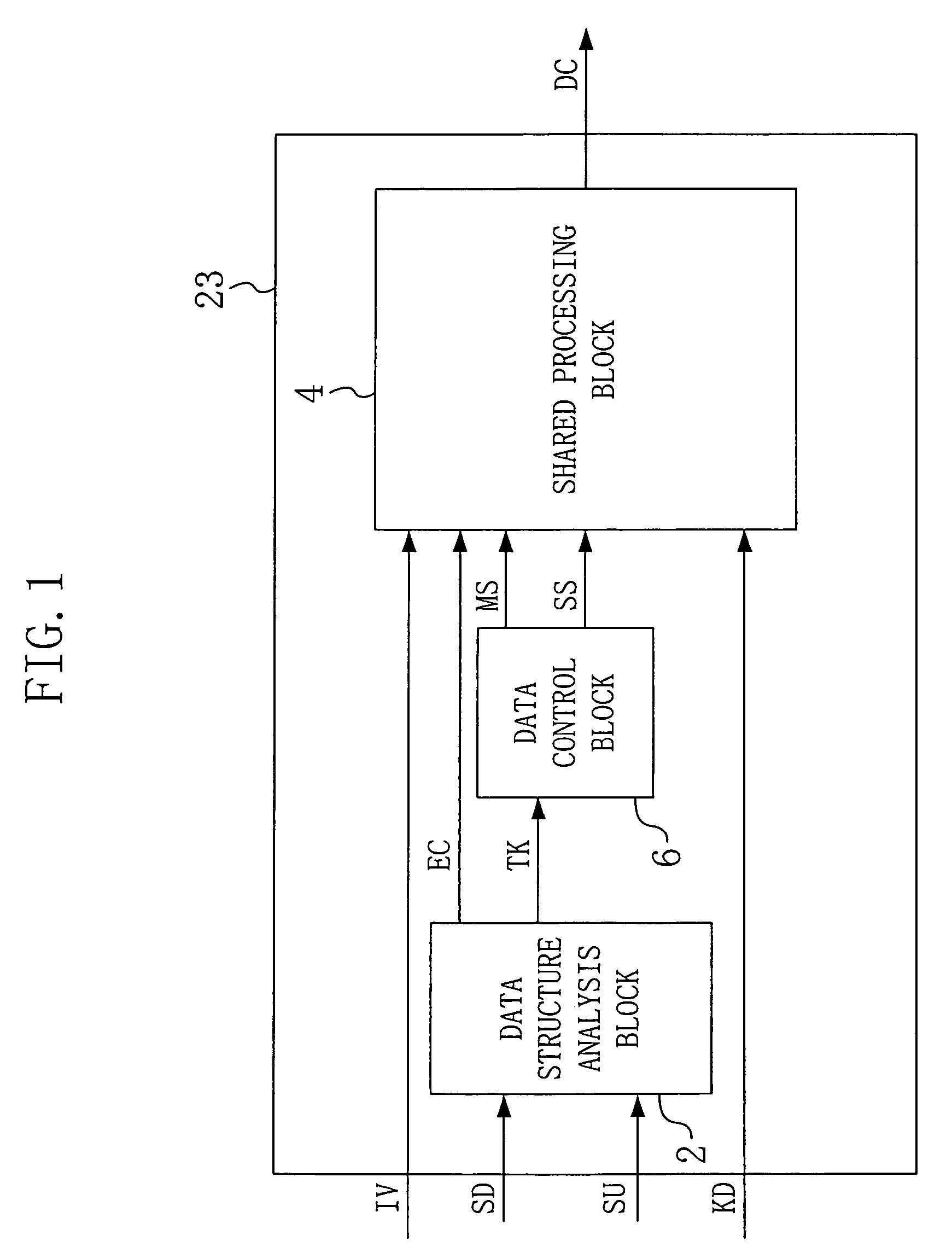

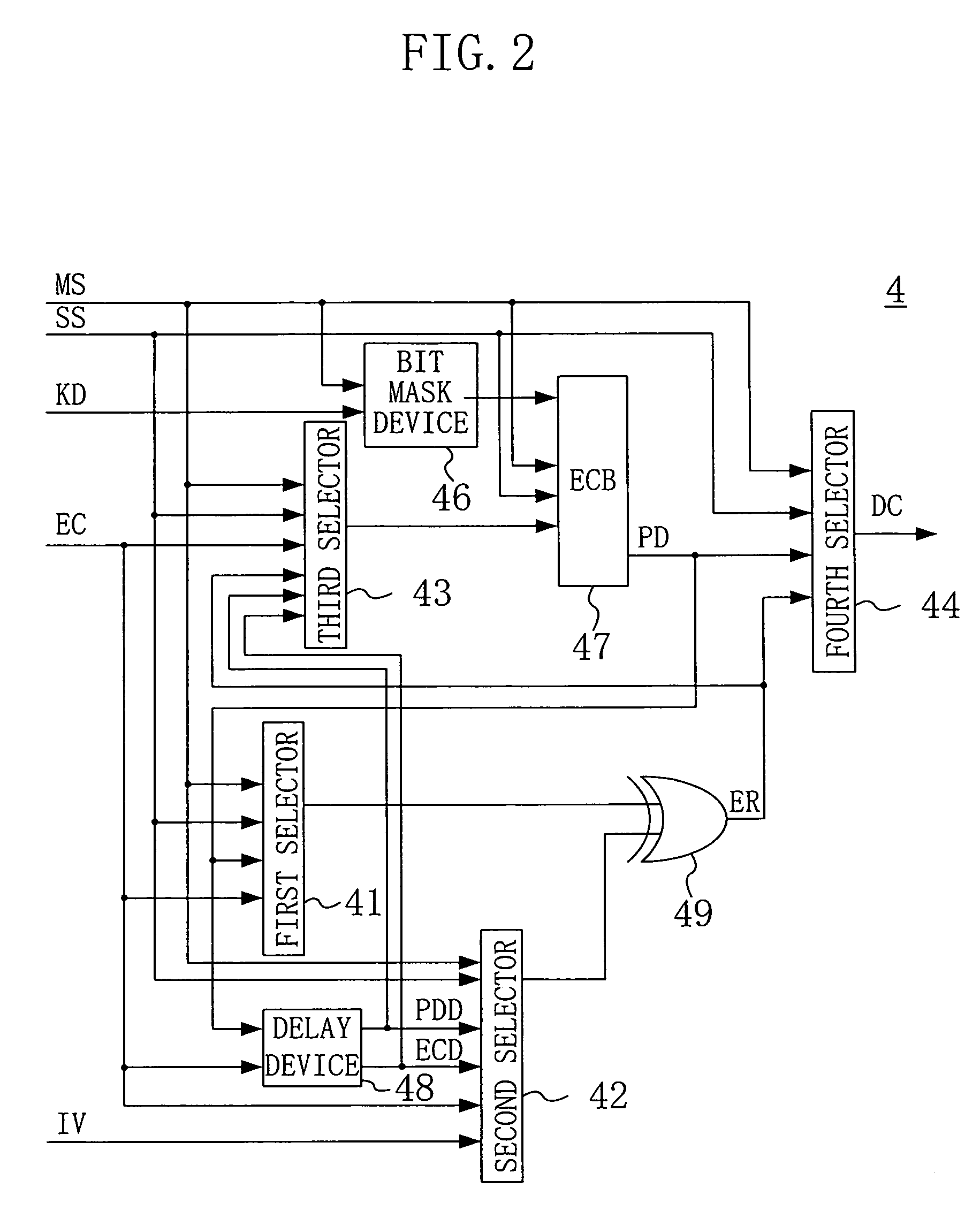

Encryption/decryption device and method, encryption device and method, decryption device and method, and transmission/reception apparatus

InactiveUS7532726B2Reduce circuit areaLow costEncryption apparatus with shift registers/memoriesUnauthorized memory use protectionData controlControl data

Owner:PANASONIC CORP

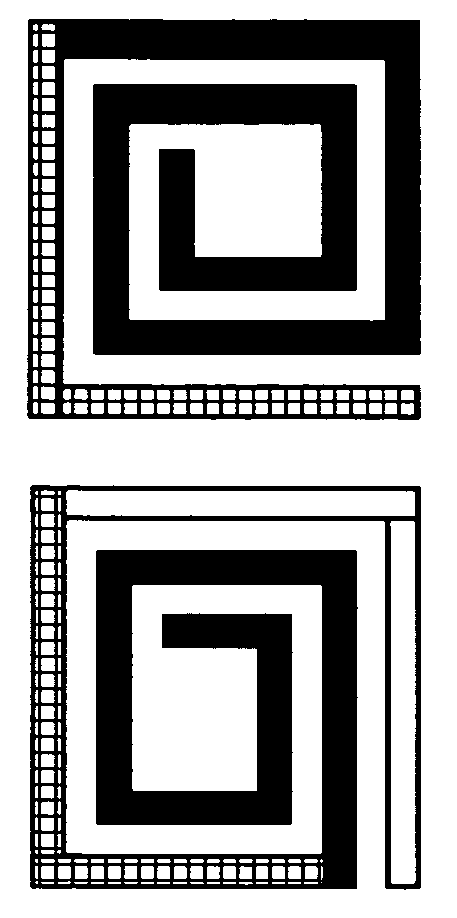

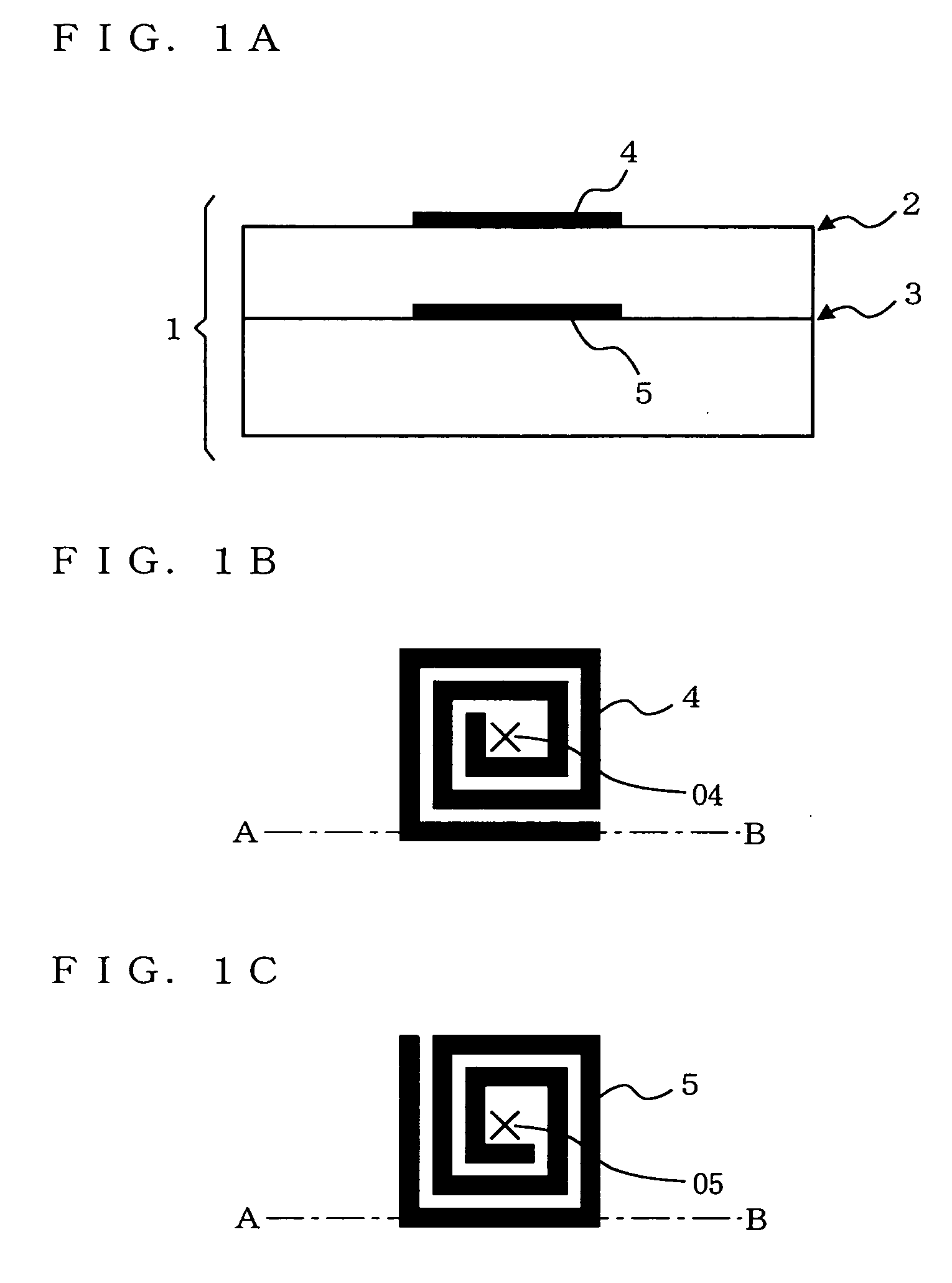

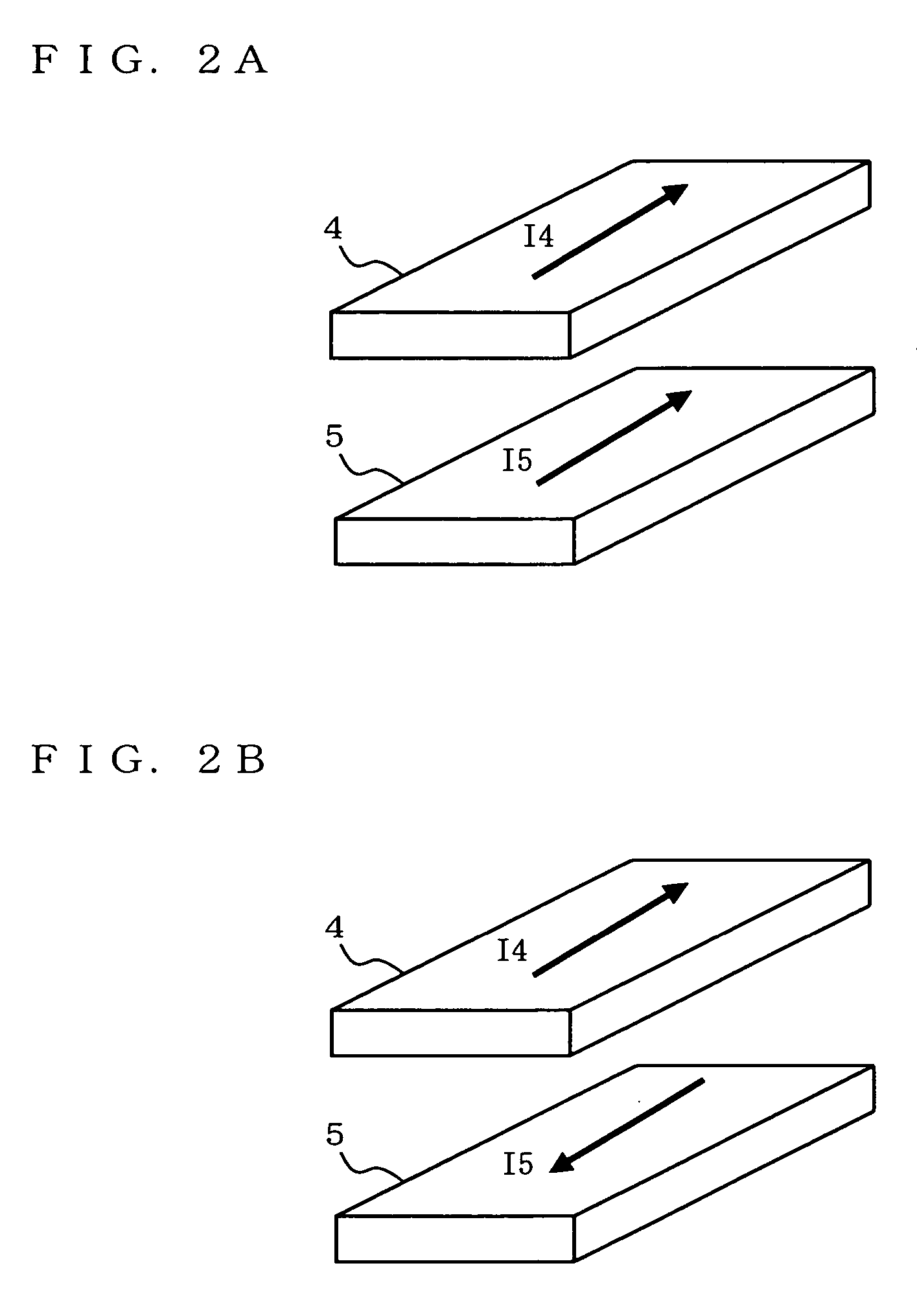

High-frequency circuit

ActiveUS20050077993A1Broad-band filter characteristicEnergy efficiencyTransformers/inductances coils/windings/connectionsResonatorsDielectric substrateEngineering

A high-frequency circuit is formed on a multilayered dielectric substrate 1 having at least two conductive circuit layers. The high-frequency circuit includes: a first spiral conductive strip 4 formed in the first conductive circuit layer, the first spiral conductive strip having at least one turn; and a second spiral conductive strip 5 formed in a second conductive circuit layer which is different from the first conductive circuit layer, the second spiral conductive strip having at least one turn and not being in electrical conduction with the first spiral conductive strip. The first spiral conductive strip and the second spiral conductive strip, located at different levels, overlap each other. The first spiral conductive strip has a rotating direction opposite to a rotating direction of the second spiral conductive strip.

Owner:PANASONIC CORP

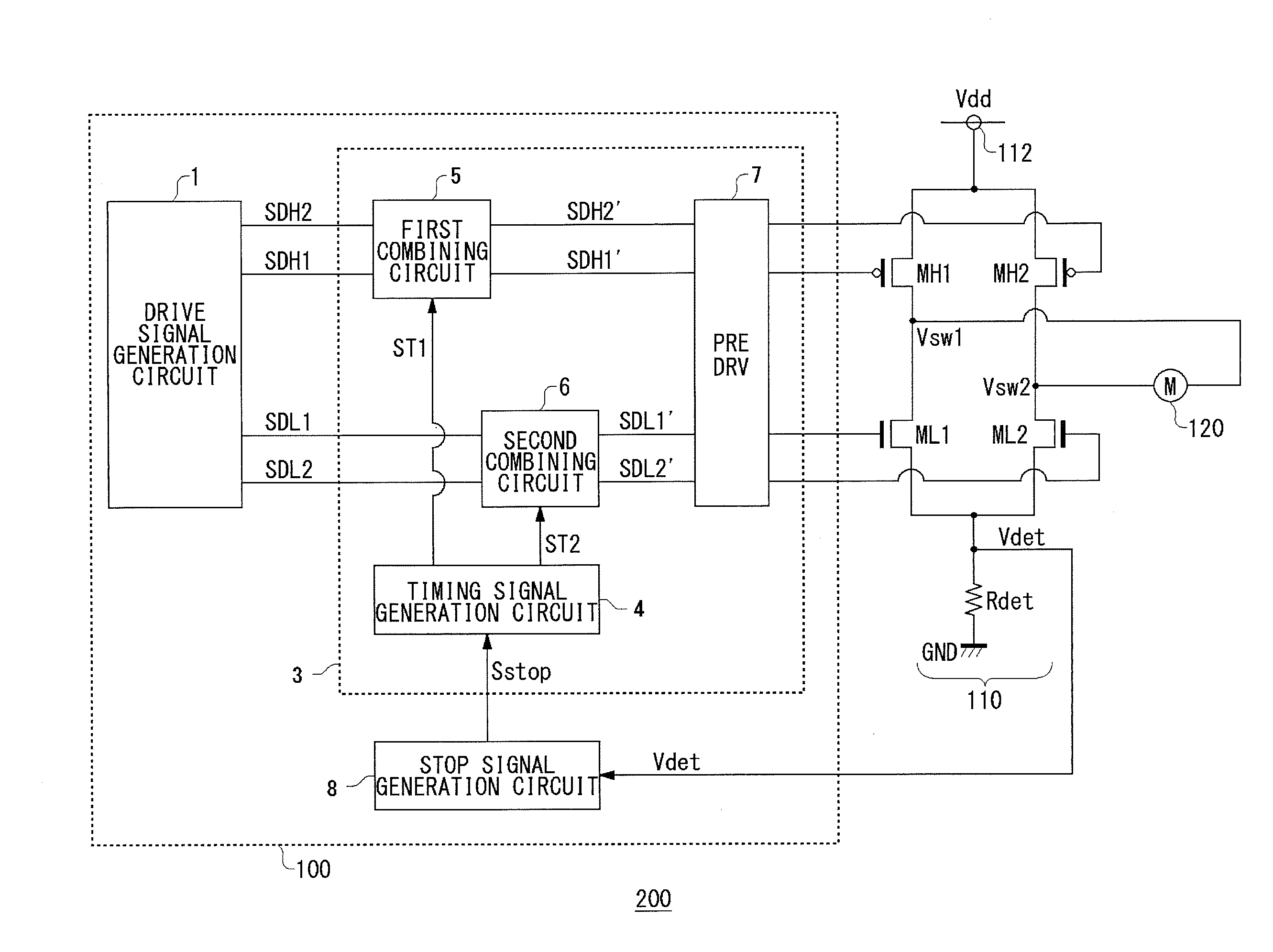

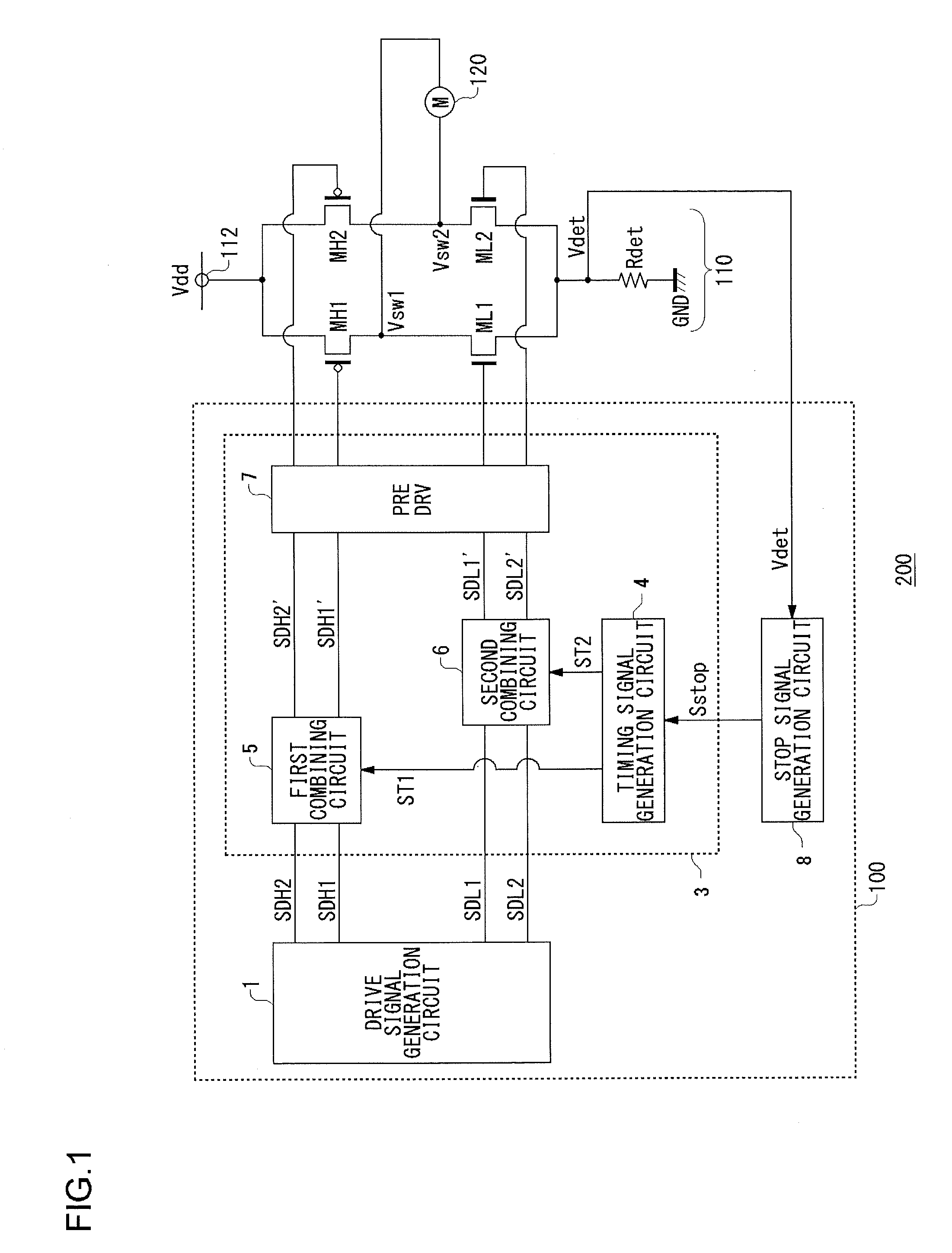

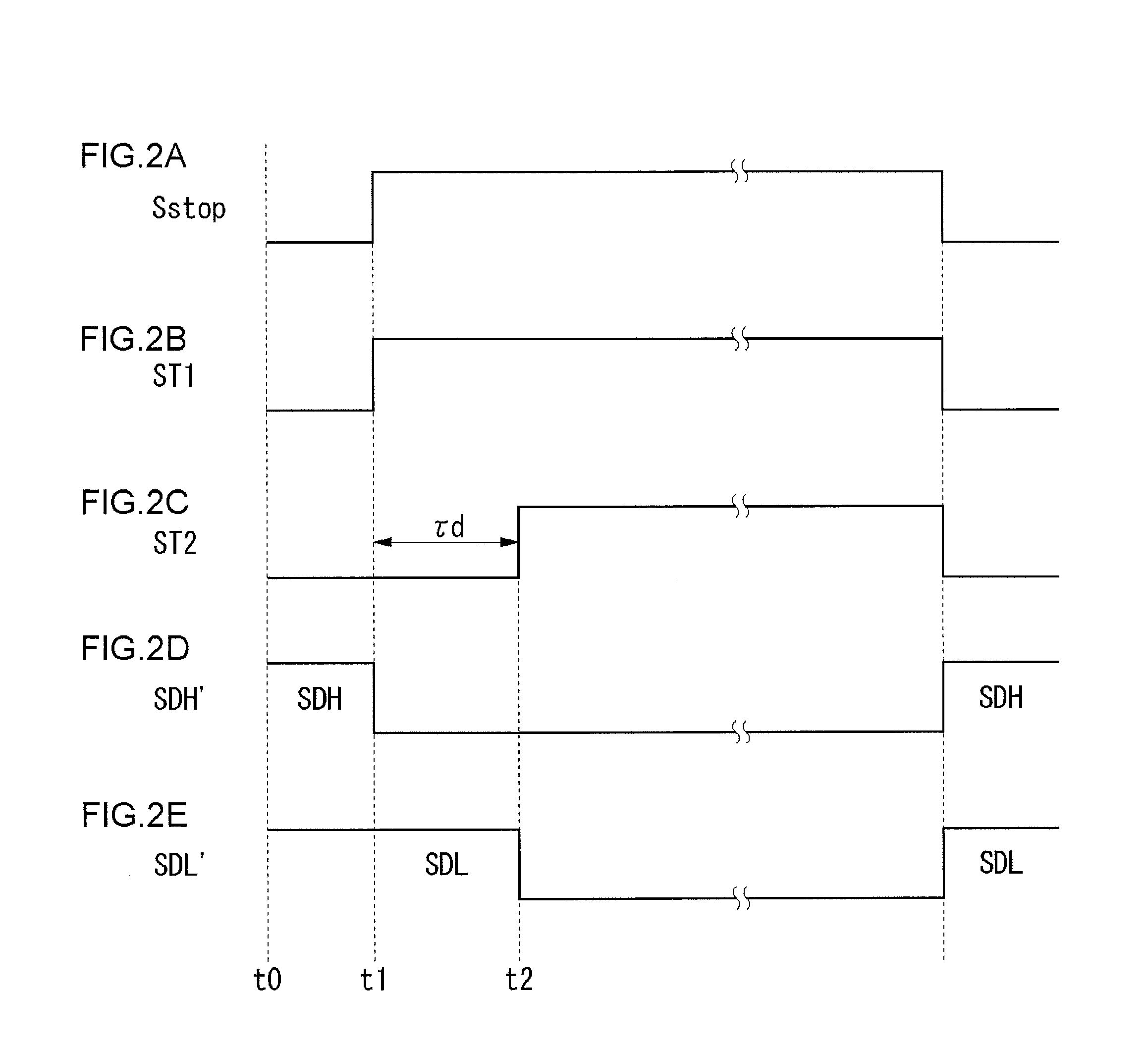

Motor drive circuit, method, and cooling device using the same

ActiveUS20090045762A1Increase freedomLower resistanceSynchronous motors startersAC motor controlDriver circuitMotor drive

A drive signal generation circuit generates drive signals that control ON and OFF states of transistors of a H-bridge circuit, in accordance with a target value of torque. A driver circuit alternatively turns ON and OFF high side transistors, and low side transistors of the H-bridge circuit, based on the drive signals outputted from the drive signal generation circuit. The driver circuit immediately turns OFF the high side transistors, when an instruction is issued to stop a motor, and after a predetermined delay time τd has elapsed, turns OFF the low side transistors.

Owner:ROHM CO LTD

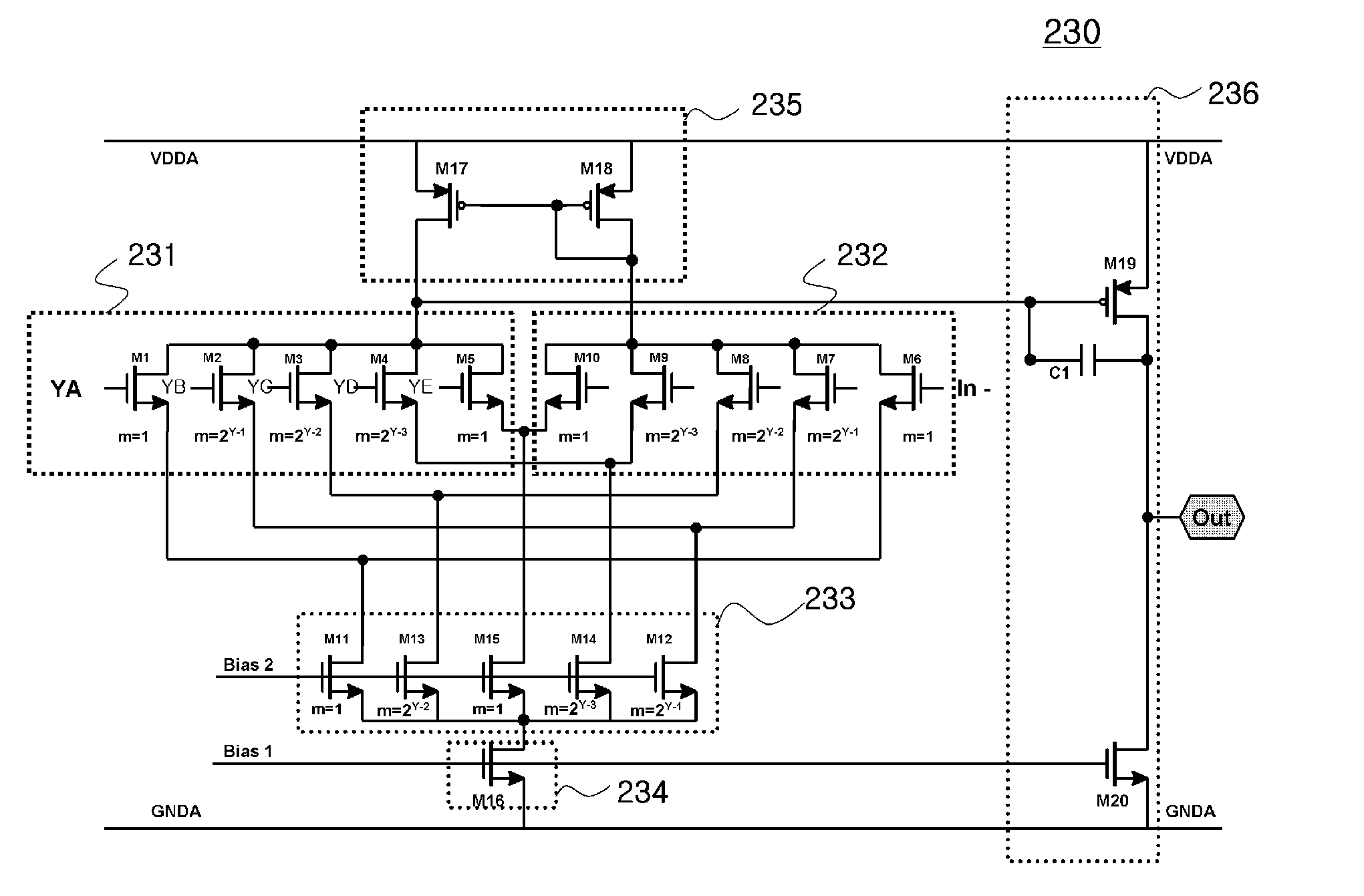

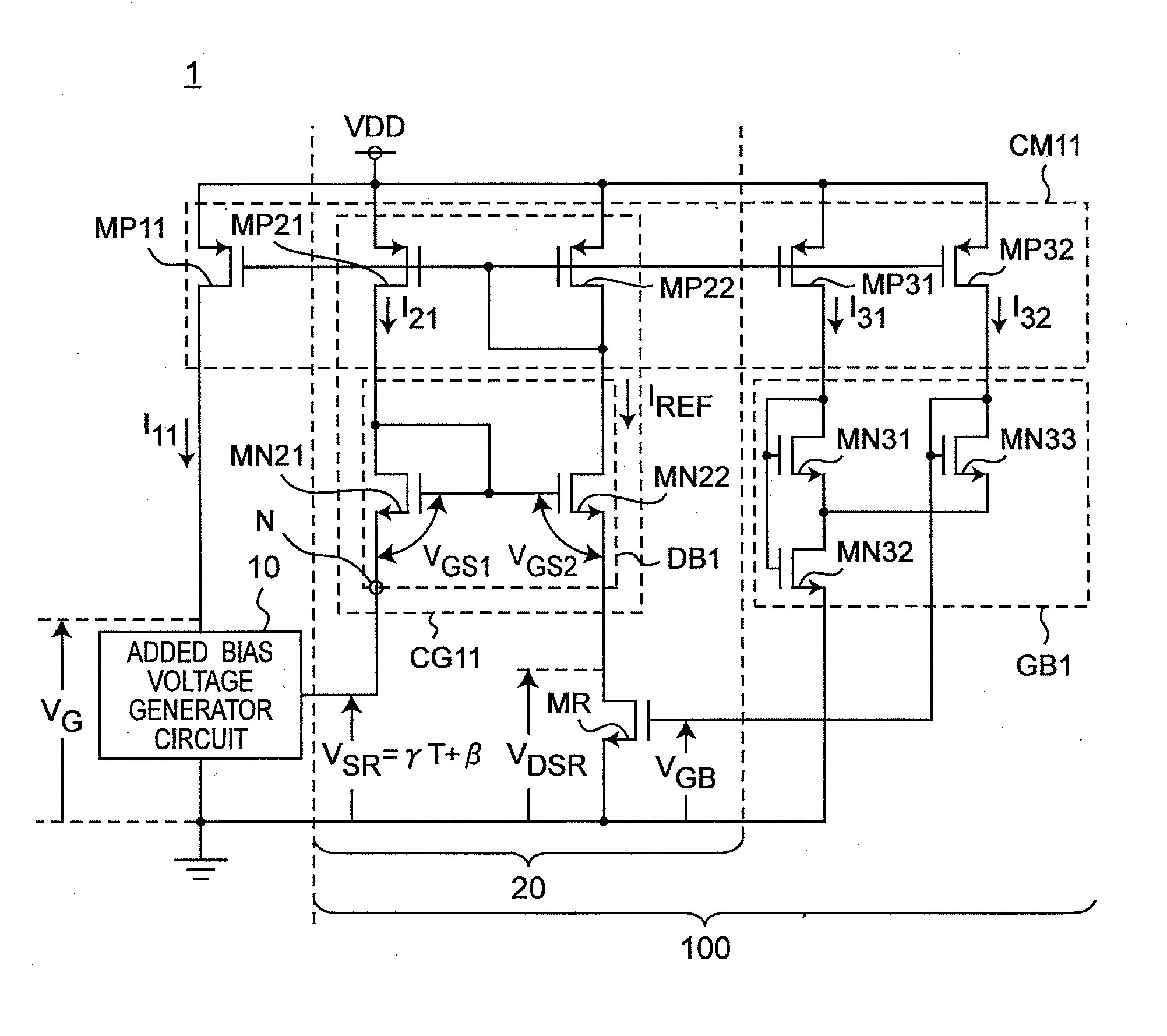

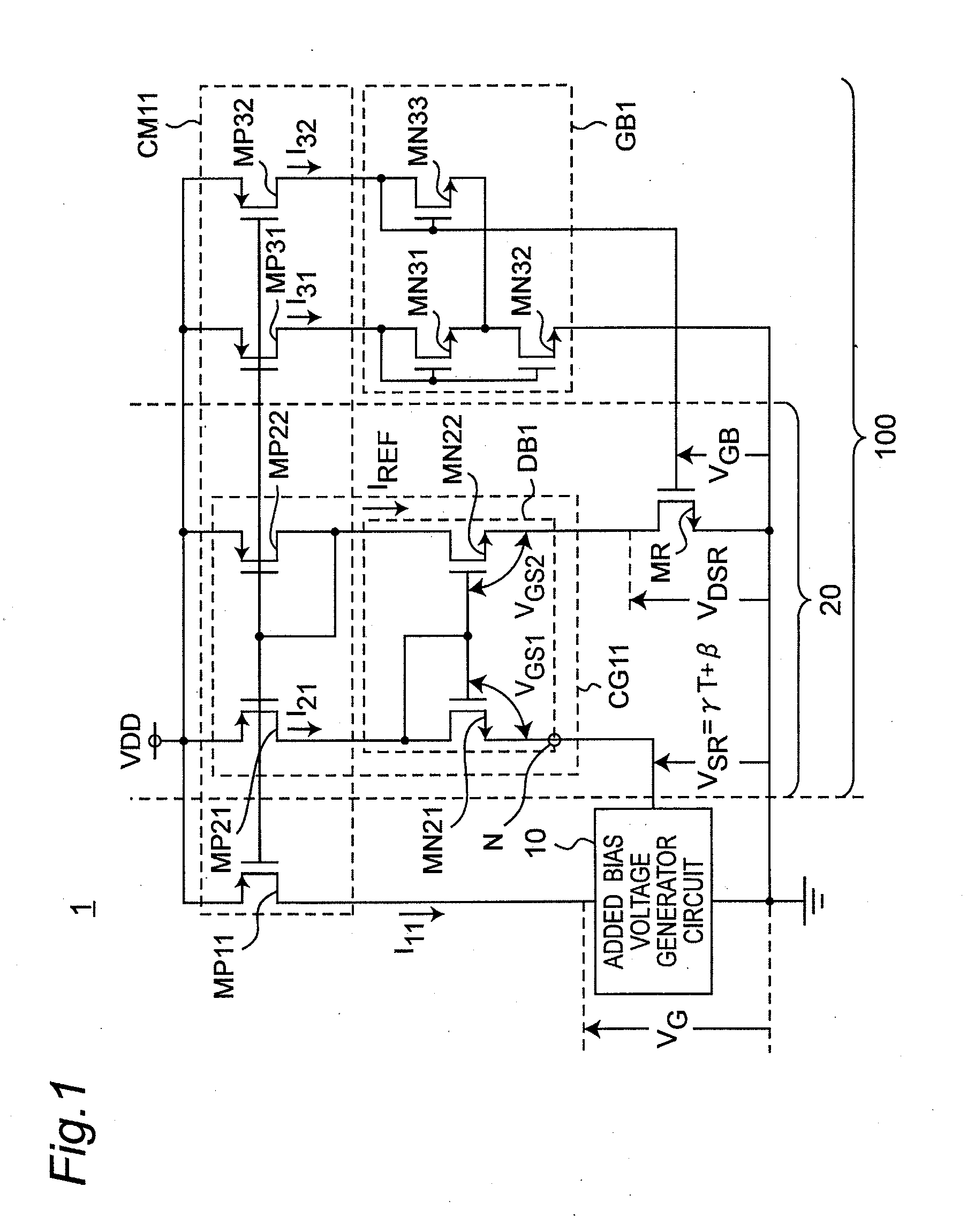

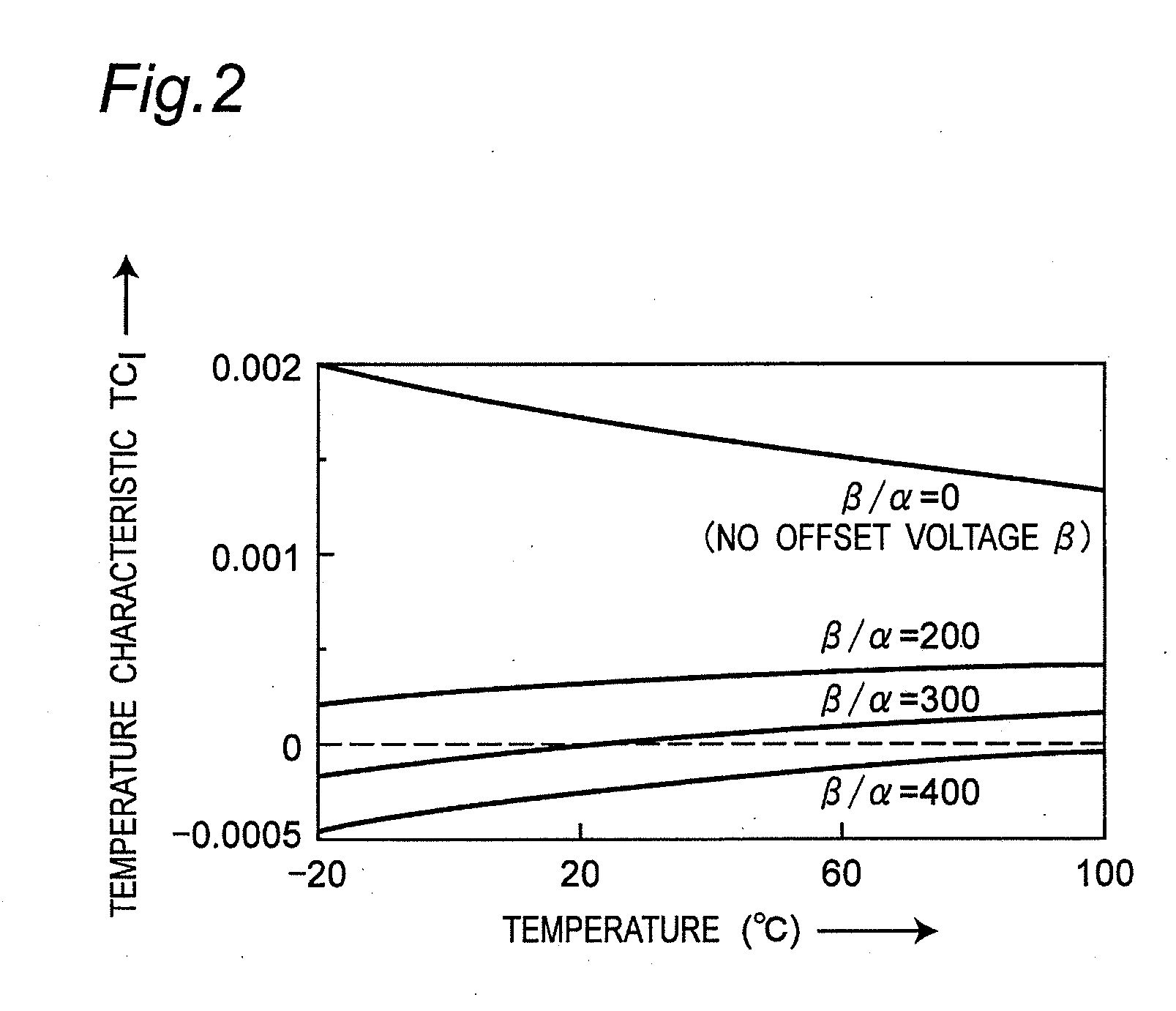

Reference current source circuit including added bias voltage generator circuit

InactiveUS20120025801A1Reduce circuit areaSuppress inclinationElectric variable regulationVoltage generatorLinear region

A MOS resistor generates an output current based on a voltage induced across a drain and a source thereof. A gate bias voltage generator circuit generates a gate bias voltage so as to operate the MOS resistor in a strong-inversion linear region, and applies the gate bias voltage to a gate of the MOS resistor. A drain bias voltage generator circuit generates a drain bias voltage, and applies the drain bias voltage to the drain of the MOS resistor. An added bias voltage generator circuit generates an added bias voltage, which has a predetermined temperature coefficient and includes a predetermined offset voltage, so that the output current becomes constant against temperature changes. The drain bias voltage generator circuit adds the added bias voltage to the drain bias voltage, and applies a voltage of adding results to the drain of the MOS resistor as the drain bias voltage.

Owner:SEMICON TECH ACADEMIC RES CENT

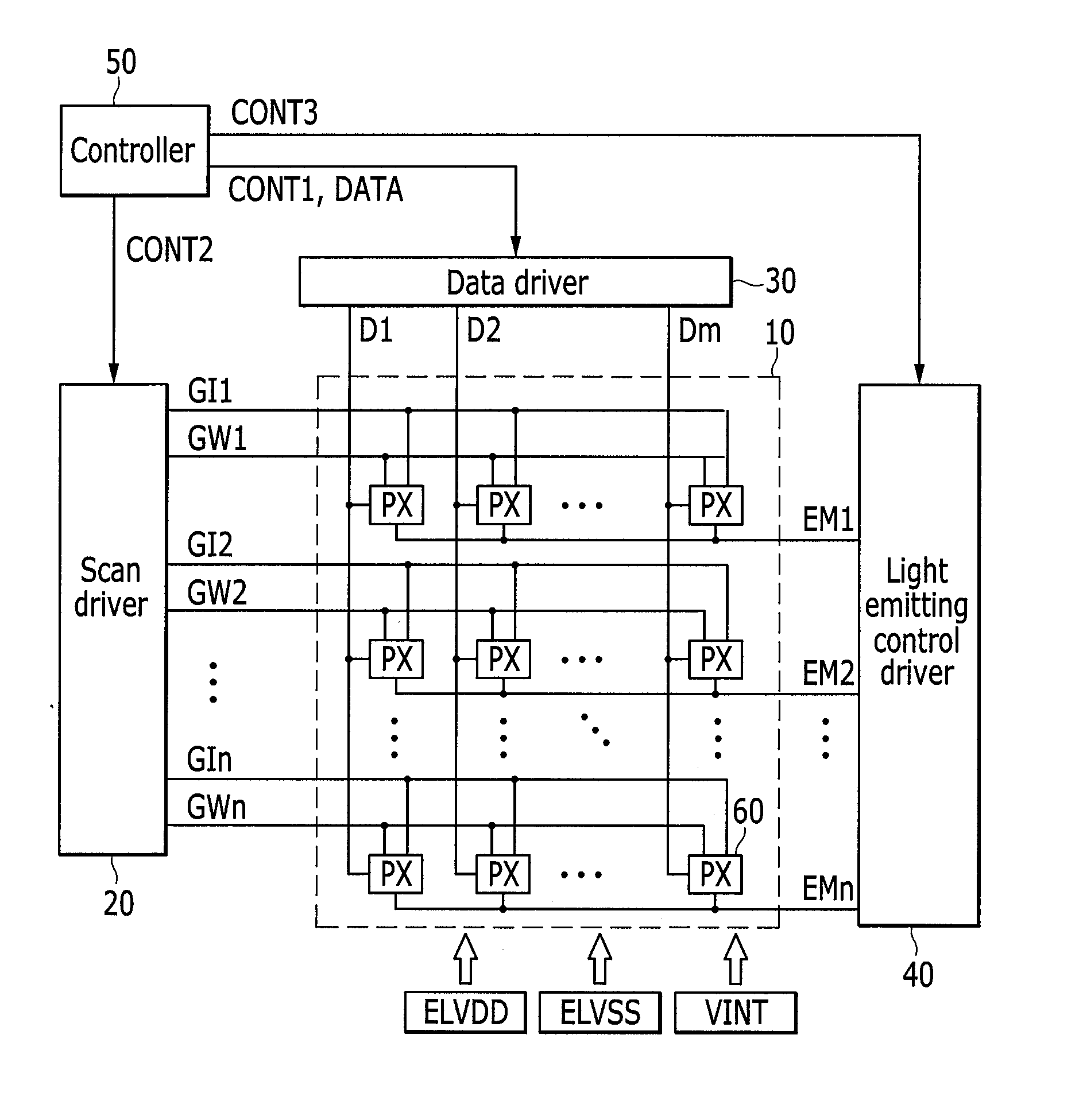

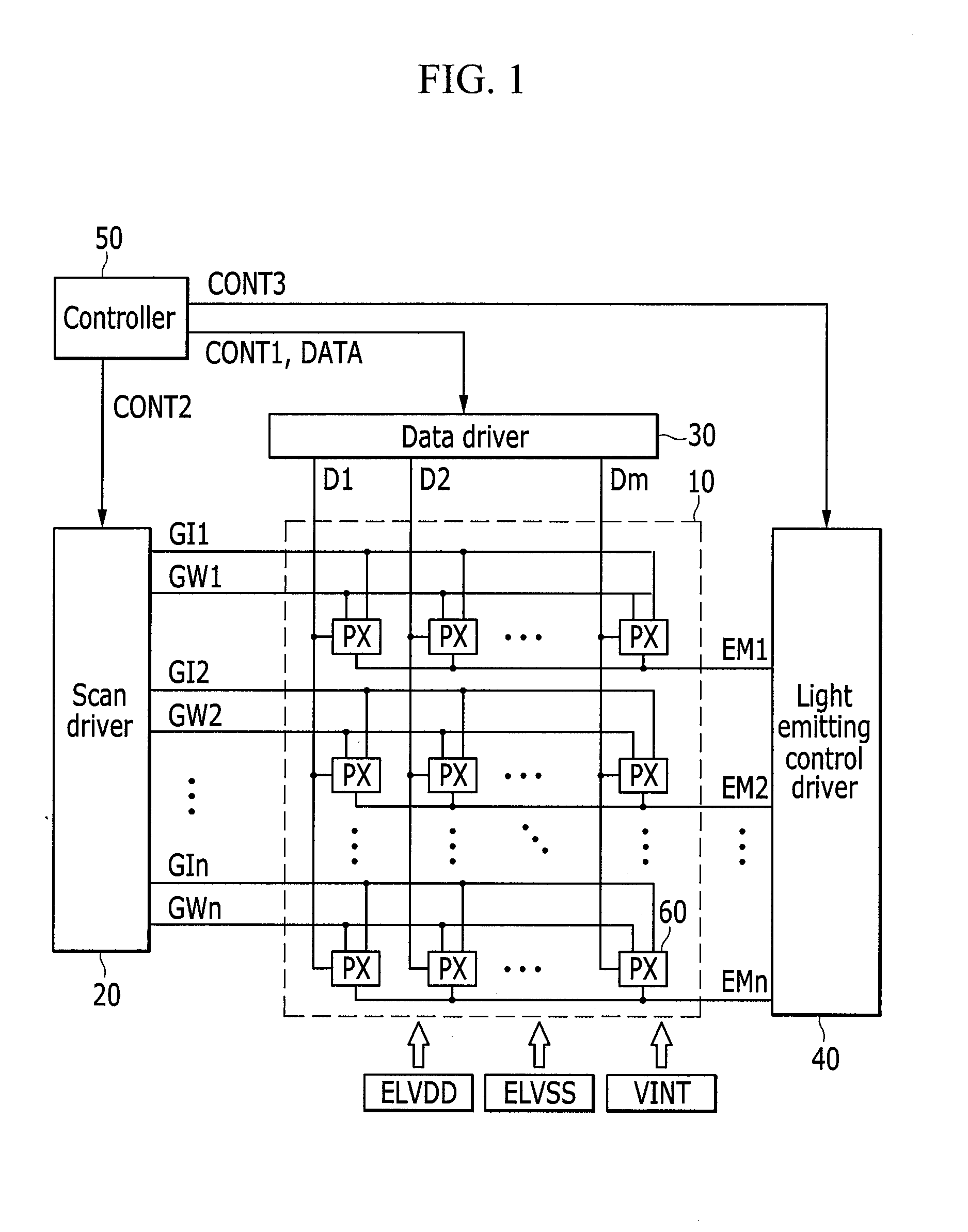

Scan driver and display device including the same

InactiveUS20140111490A1Reduce circuit areaImprove production yieldCathode-ray tube indicatorsDigital storageDisplay deviceEngineering

A scan driver and a display device including the scan driver are provided. The scan driver is configured to drive a plurality of pixels with a plurality of gate signals and includes a plurality of stages, each of the stages including one or more regions, each of the regions including: a plurality of sub-drivers configured to generate ones of the gate signals and to transmit the ones of the gate signals to ones of the pixels; and a driver commonly coupled to the sub-drivers and configured to concurrently supply a common signal to each of the sub-drivers, the driver of one of the one or more regions being configured to receive the common signal of one of the one or more regions of a previous one of the stages during forward direction driving or of a next one of the stages during reverse direction driving.

Owner:SAMSUNG DISPLAY CO LTD

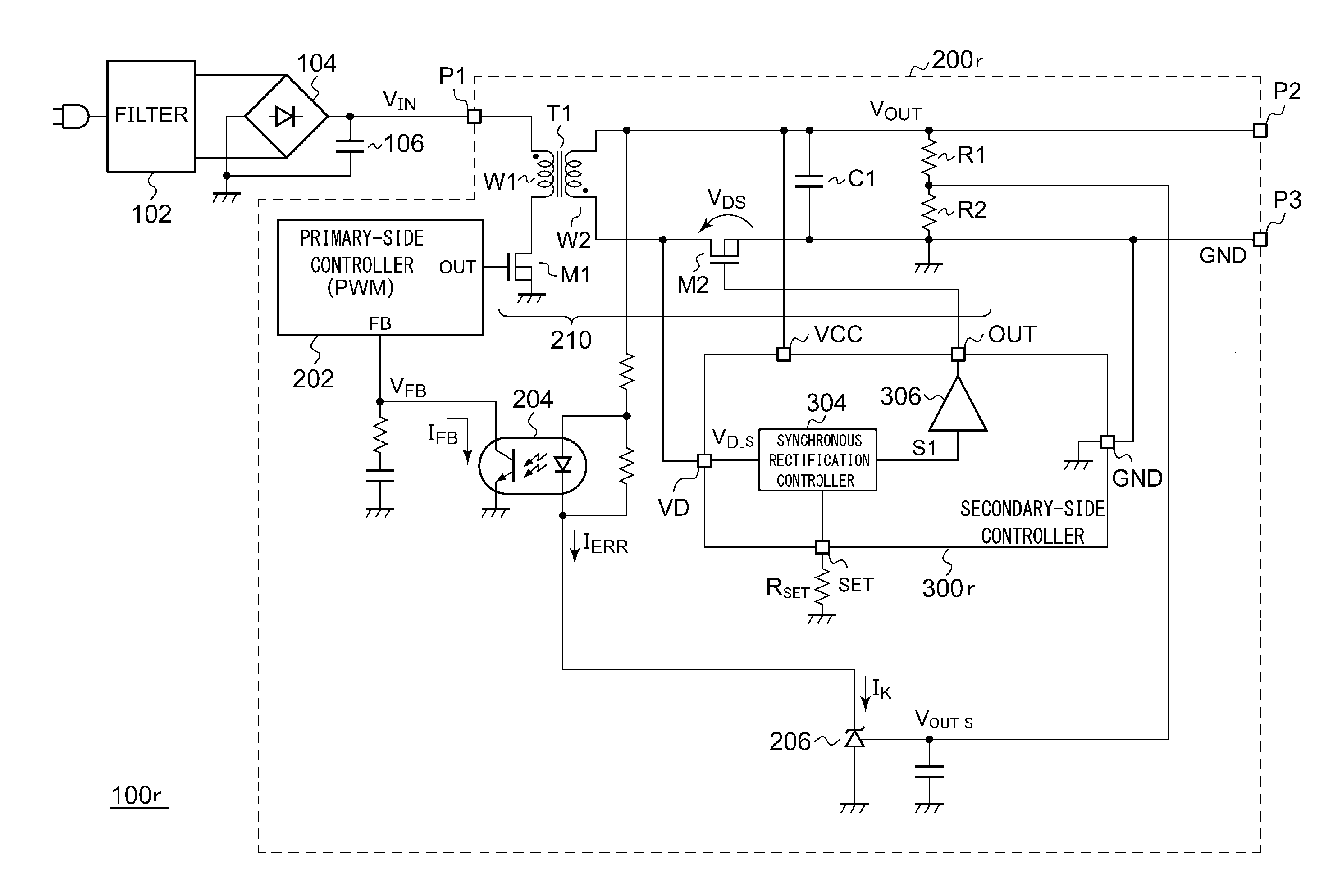

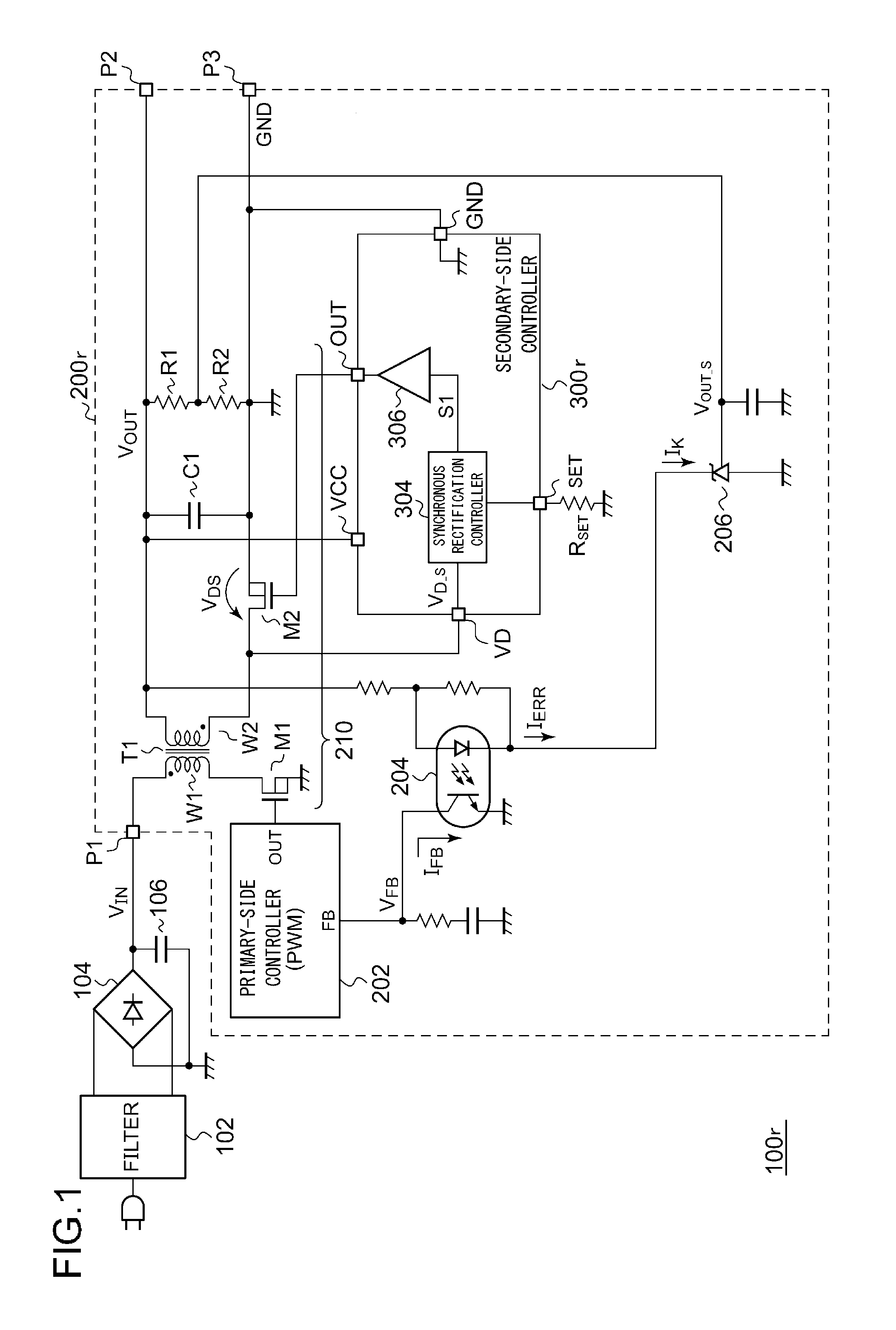

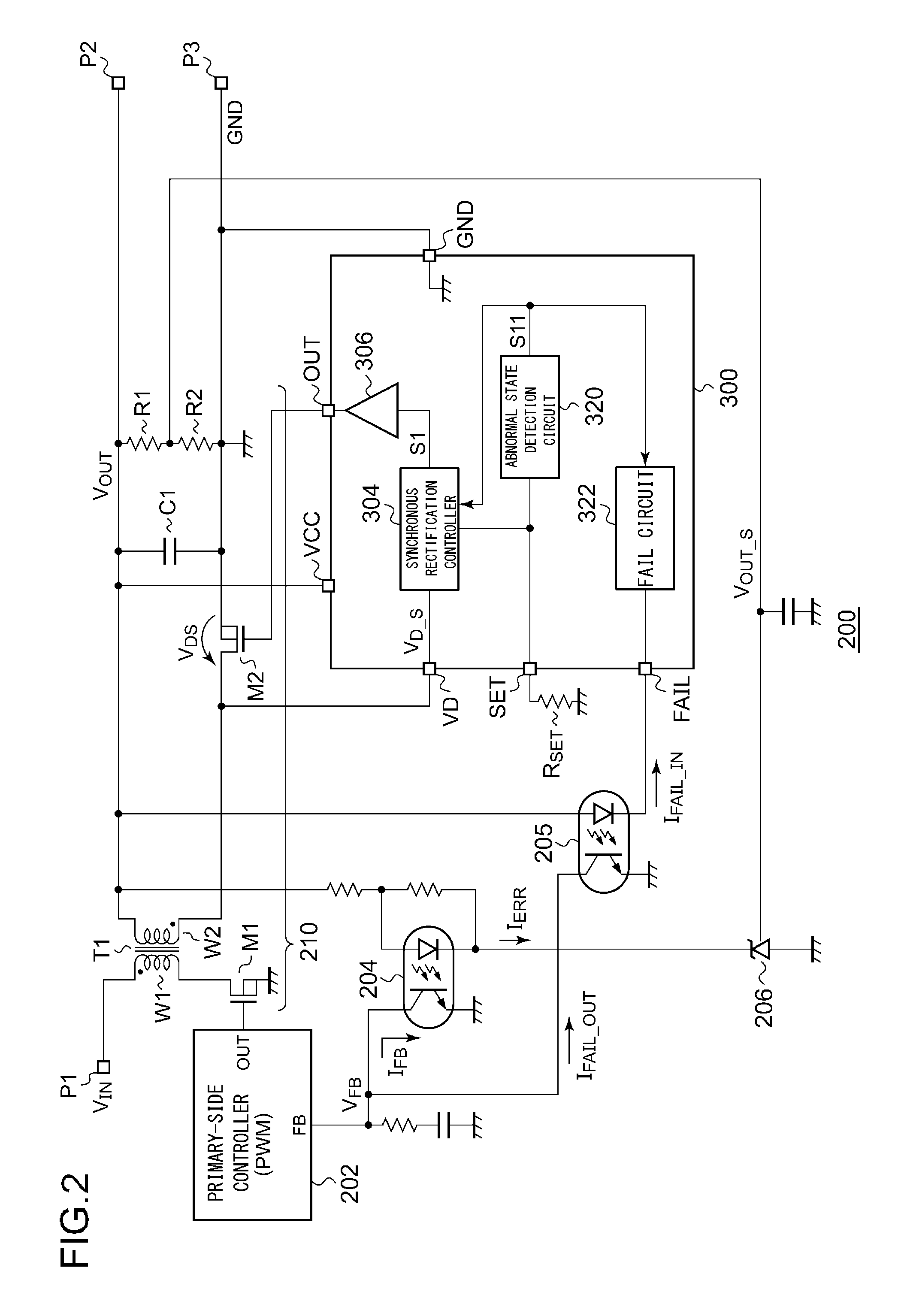

Insulated synchronous rectification dc/dc converter

ActiveUS20160261204A1Uniform characteristicsReduce circuit areaEfficient power electronics conversionDc-dc conversionEngineeringExternal circuit

An external circuit element RSET is connected in use to an SET terminal. A synchronous rectification controller generates a pulse signal S1 based on a control time determined according to the state of the SET terminal. A driver switches on and off the synchronous rectification transistor according to the pulse signal S1. An abnormal state detection circuit is capable of detecting an open-circuit state and / or a short-circuit state that can occur in the SET terminal. When the abnormal state detection circuit detects such an open-circuit state and / or short-circuit state, the abnormal state detection circuit asserts a detection signal S11. When the detection signal S11 is asserted, a primary-side controller arranged on the primary side of the DC / DC converter is instructed to suspend the switching operation of a switching transistor.

Owner:ROHM CO LTD

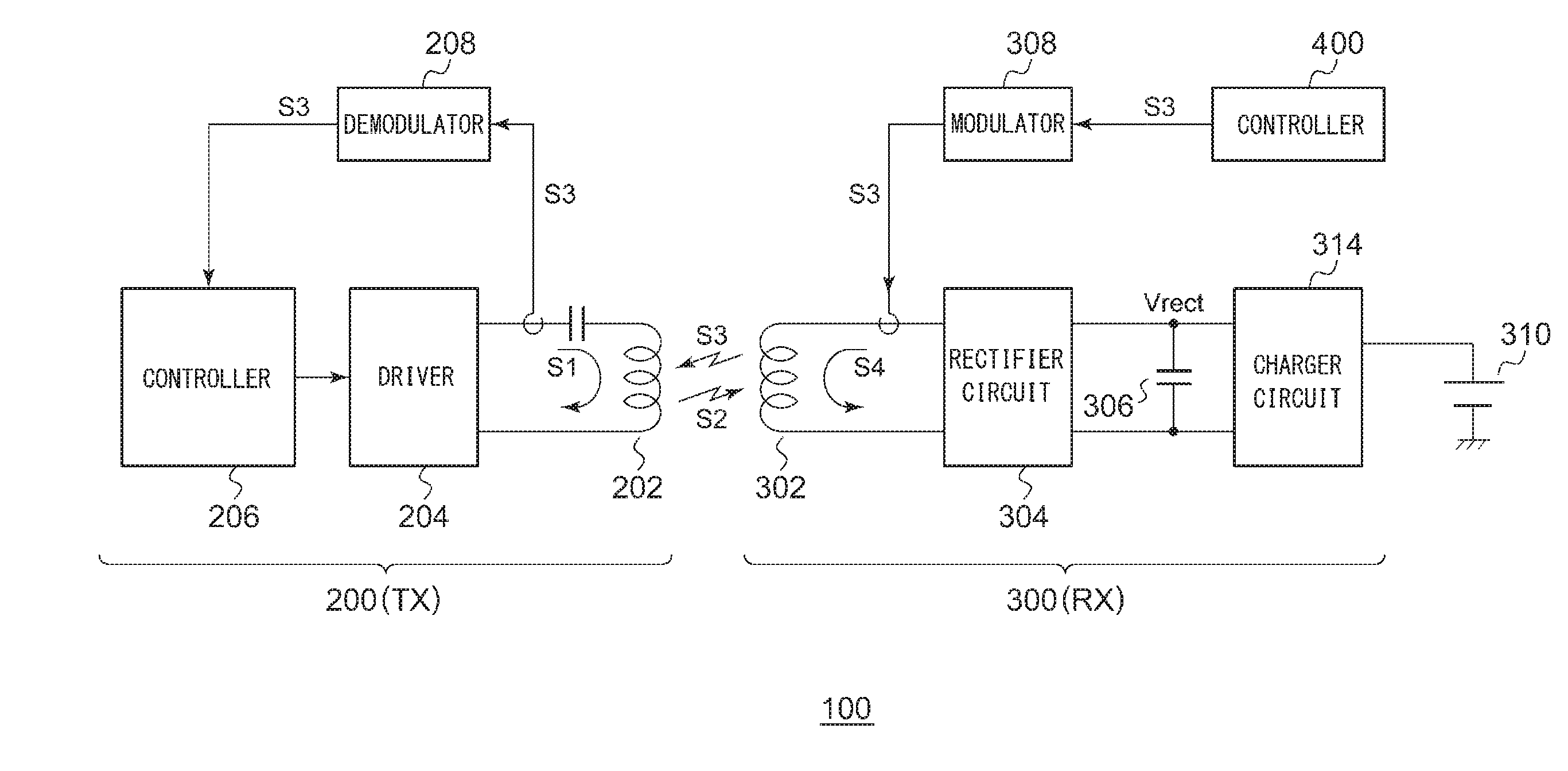

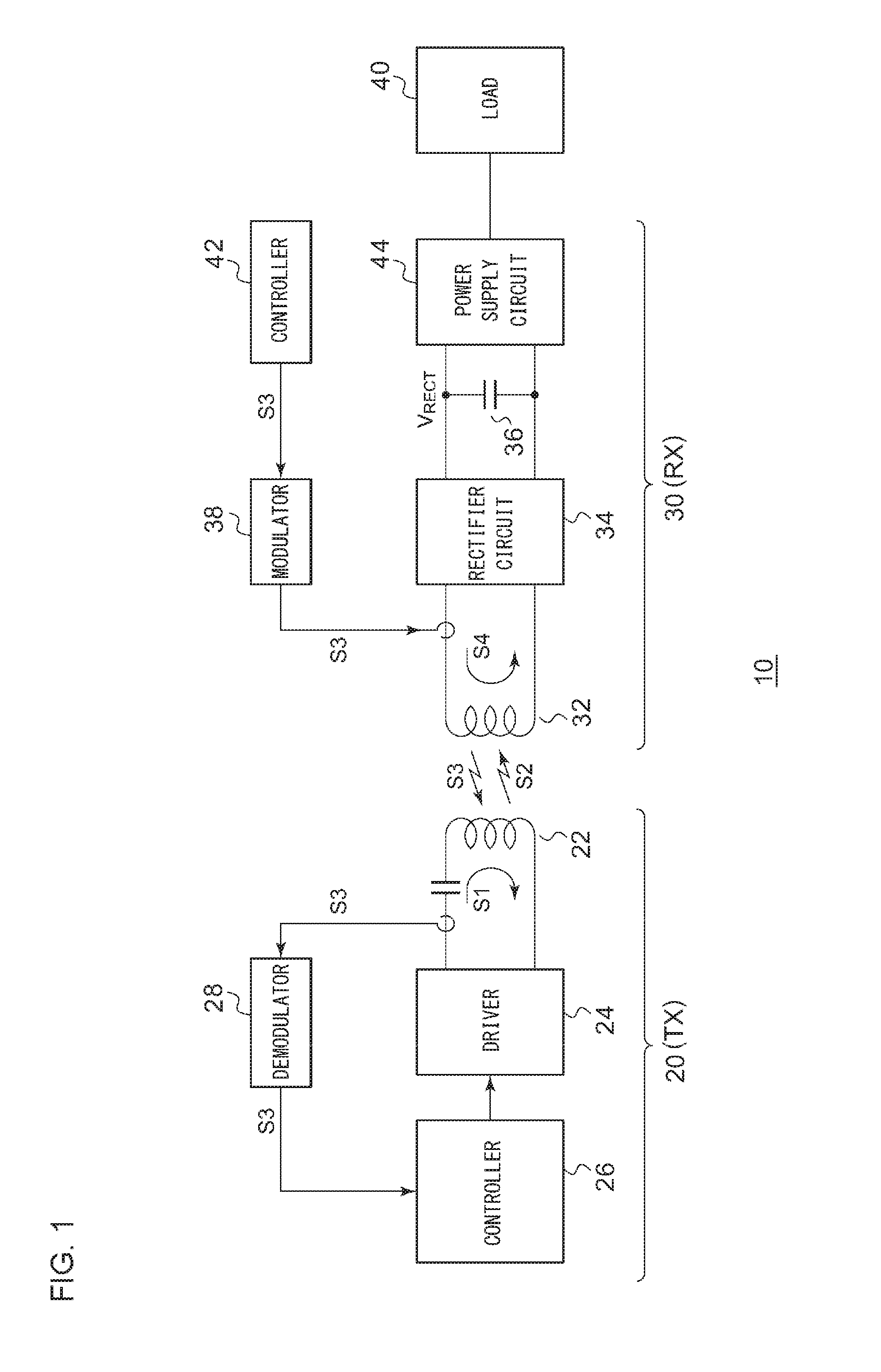

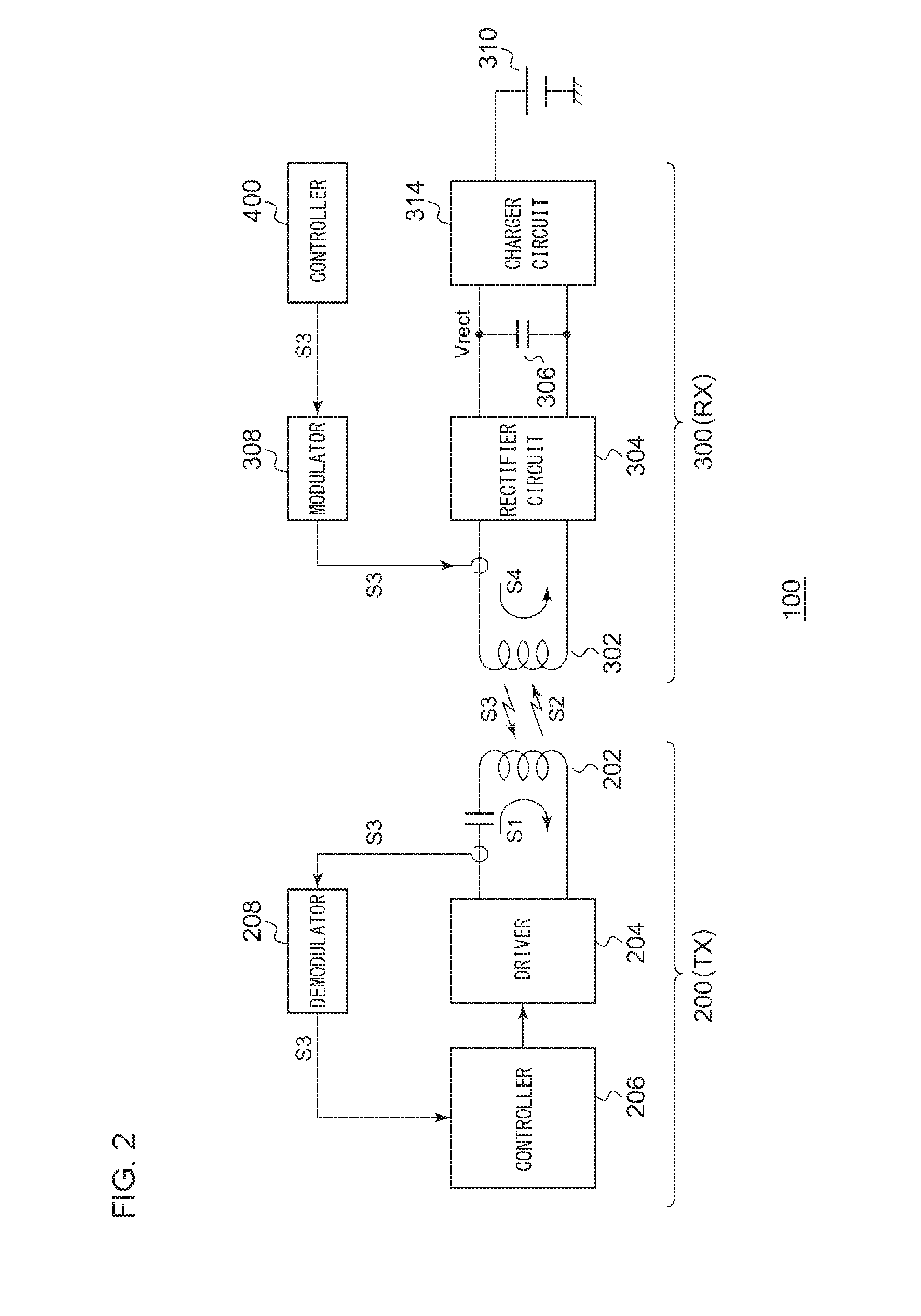

Wireless power receiving apparatus

ActiveUS20160352155A1Reduce circuit areaUniform characteristicElectric powerExchanging data chargerElectric power transmissionEngineering

A control circuit is employed for controlling a wireless power receiving apparatus that receives an electric power signal from a wireless power transmission apparatus. An electric power detection unit detects the received electric power PRX received by the wireless power receiving apparatus. A control unit generates a control signal CE for controlling the electric power PTX to be transmitted by the wireless power transmission apparatus. When the received electric power PRX detected by the electric power detection unit falls despite the control signal CE not indicating an instruction to lower the electric power PTX to be transmitted, an abnormal state judgment unit judges that an abnormal state has occurred.

Owner:ROHM CO LTD

Integrated circuit

InactiveUS20050168264A1Reduce circuit areaLow setTransistorPulse automatic controlOvervoltageEngineering

The power IC includes an output transistor MO which controls a current flowing into an L load, a dynamic clamp circuit which clamps an overvoltage, and a clamp control circuit which controls the operation of the dynamic clamp circuit. The clamp control circuit activates the dynamic clamp circuit, which is normally inactive, upon detection of a back EMF by the L load.

Owner:RENESAS ELECTRONICS CORP

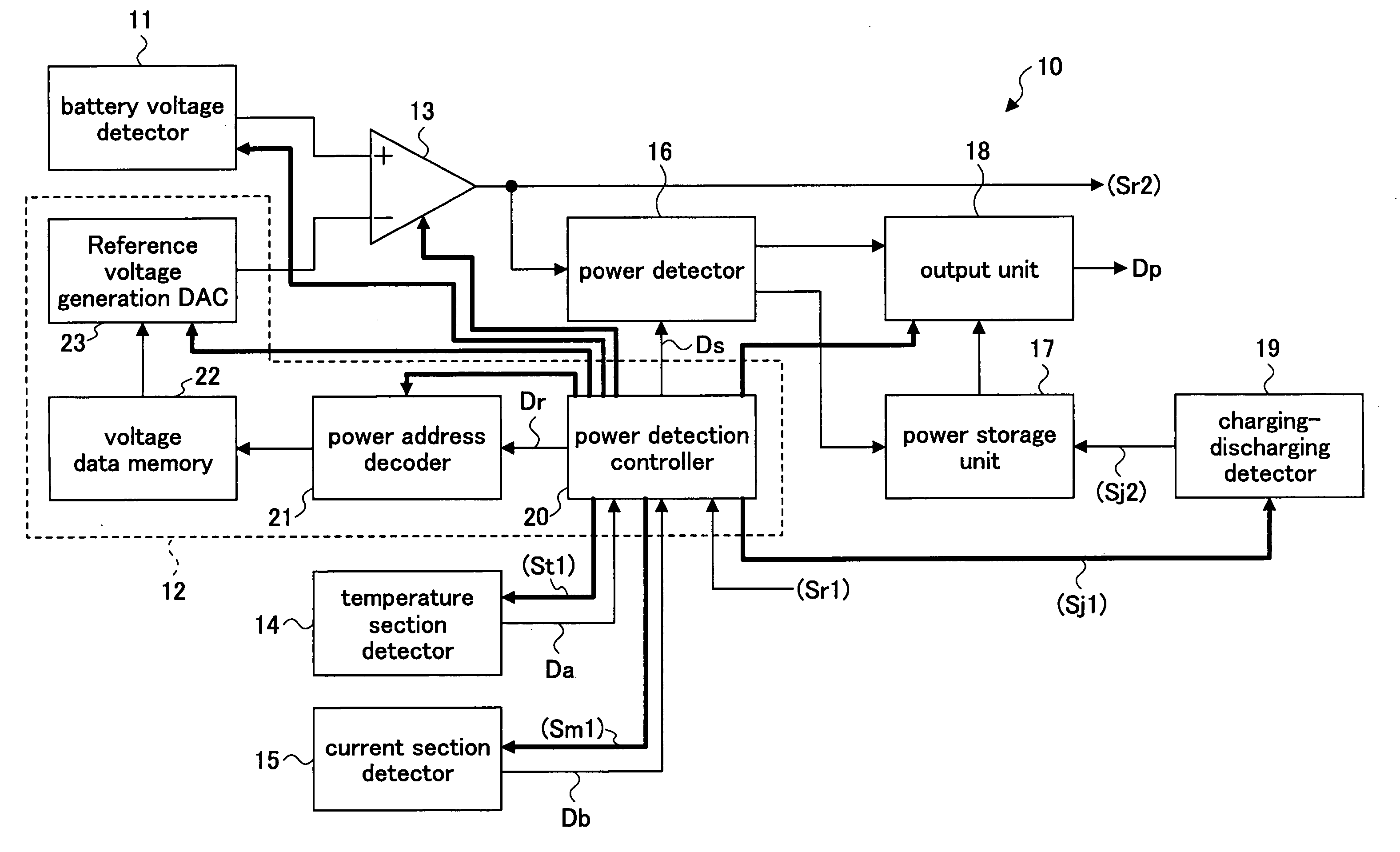

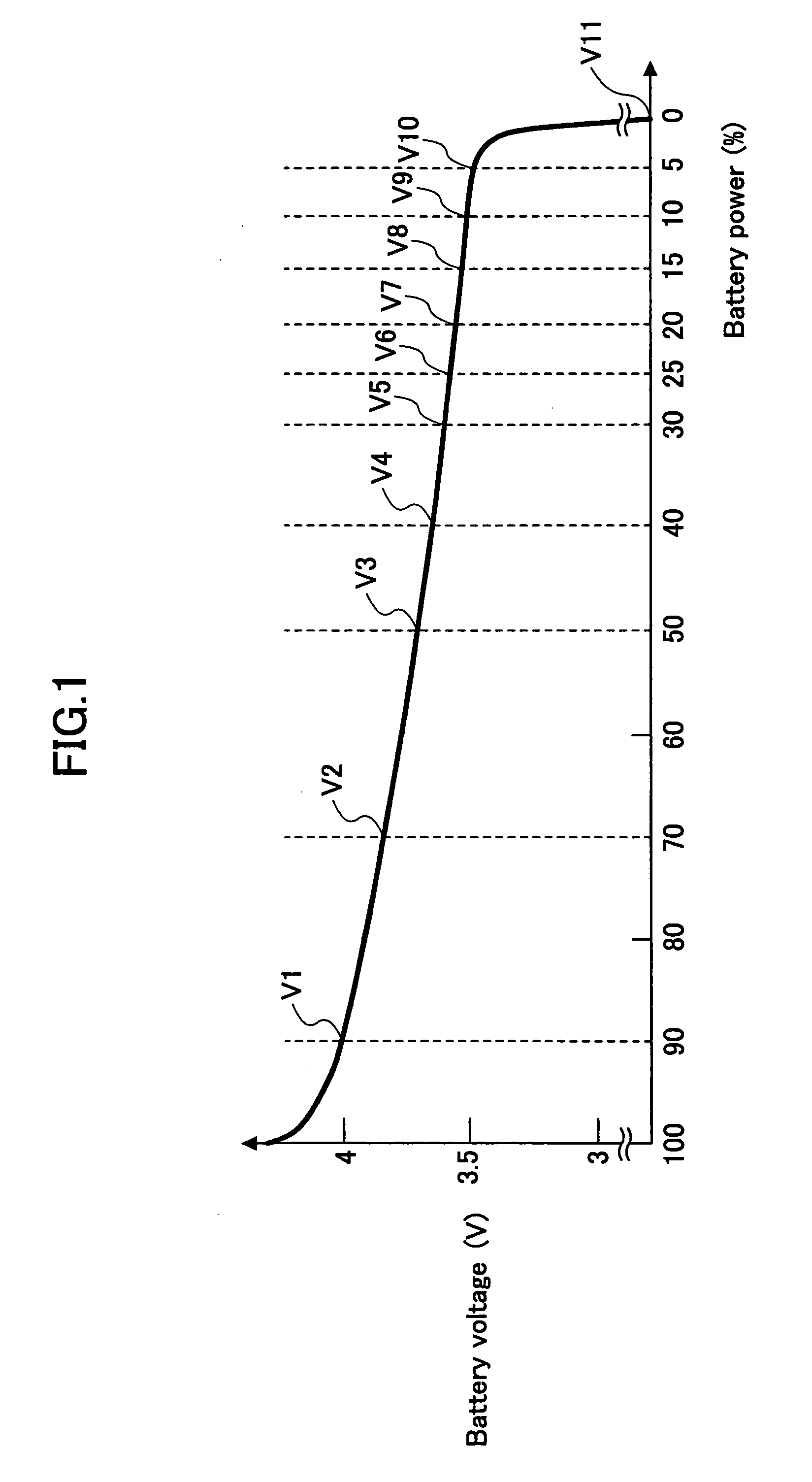

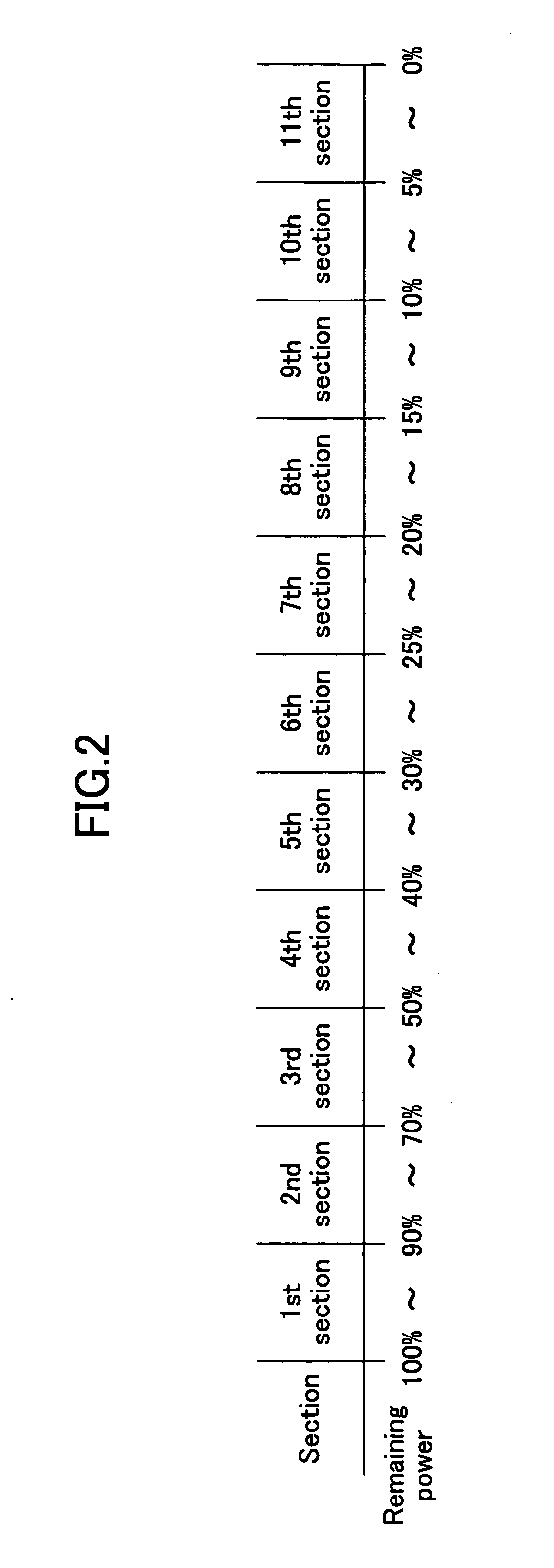

Battery power detection device

InactiveUS20060117194A1Reduce circuit areaSufficient high detection accuracyBatteries circuit arrangementsVolume/mass flow measurementElectrical batteryEngineering

A battery power detection device is disclosed that has a reduced circuit area and is able to achieve sufficiently high detection accuracy. The battery power detection device includes a temperature section detection unit that detects a temperature of the battery and detects one of plural predetermined temperature sections including the detected temperature, a current section detection unit that detects a current output from the battery and detects one of plural predetermined current sections including the detected current; and a power section detection unit that has plural voltage-power data tables including data indicating the relation between the voltage output from the battery and the remaining power sections of the battery. The power section detection unit selects one of the voltage-power data tables according to the detected temperature section and the detected current section, and detects one of the remaining power sections associated with a given voltage of the battery.

Owner:RICOH KK

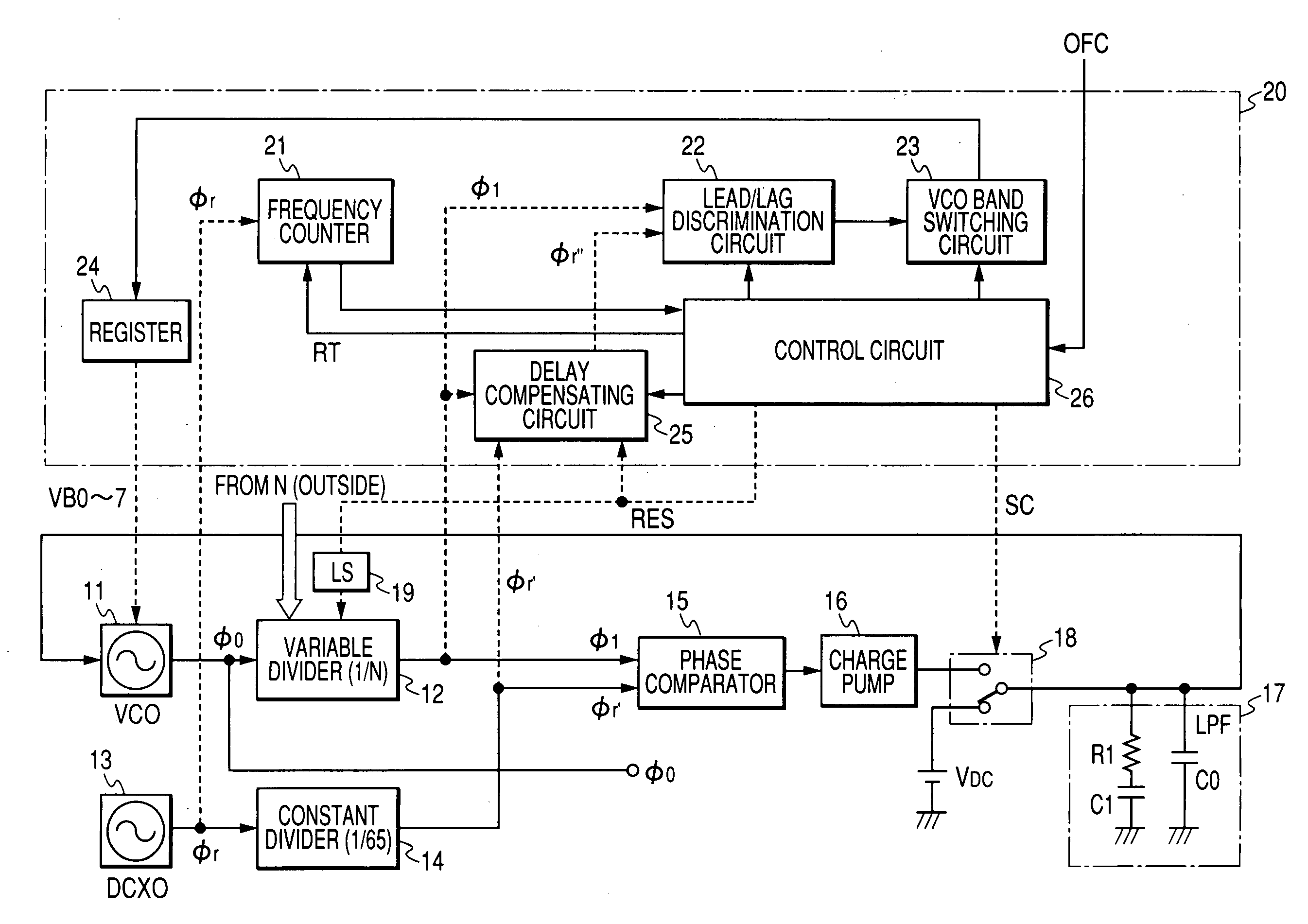

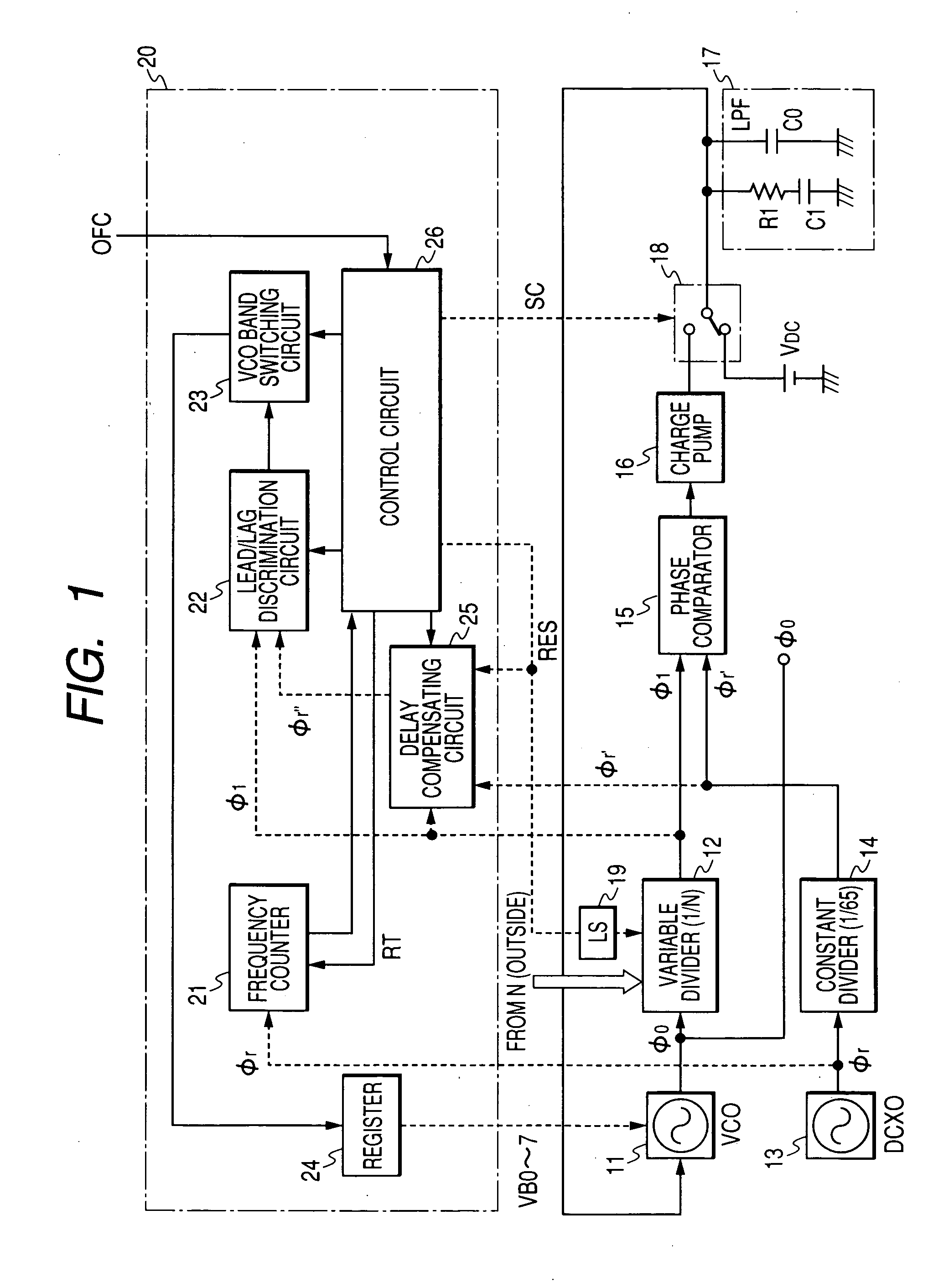

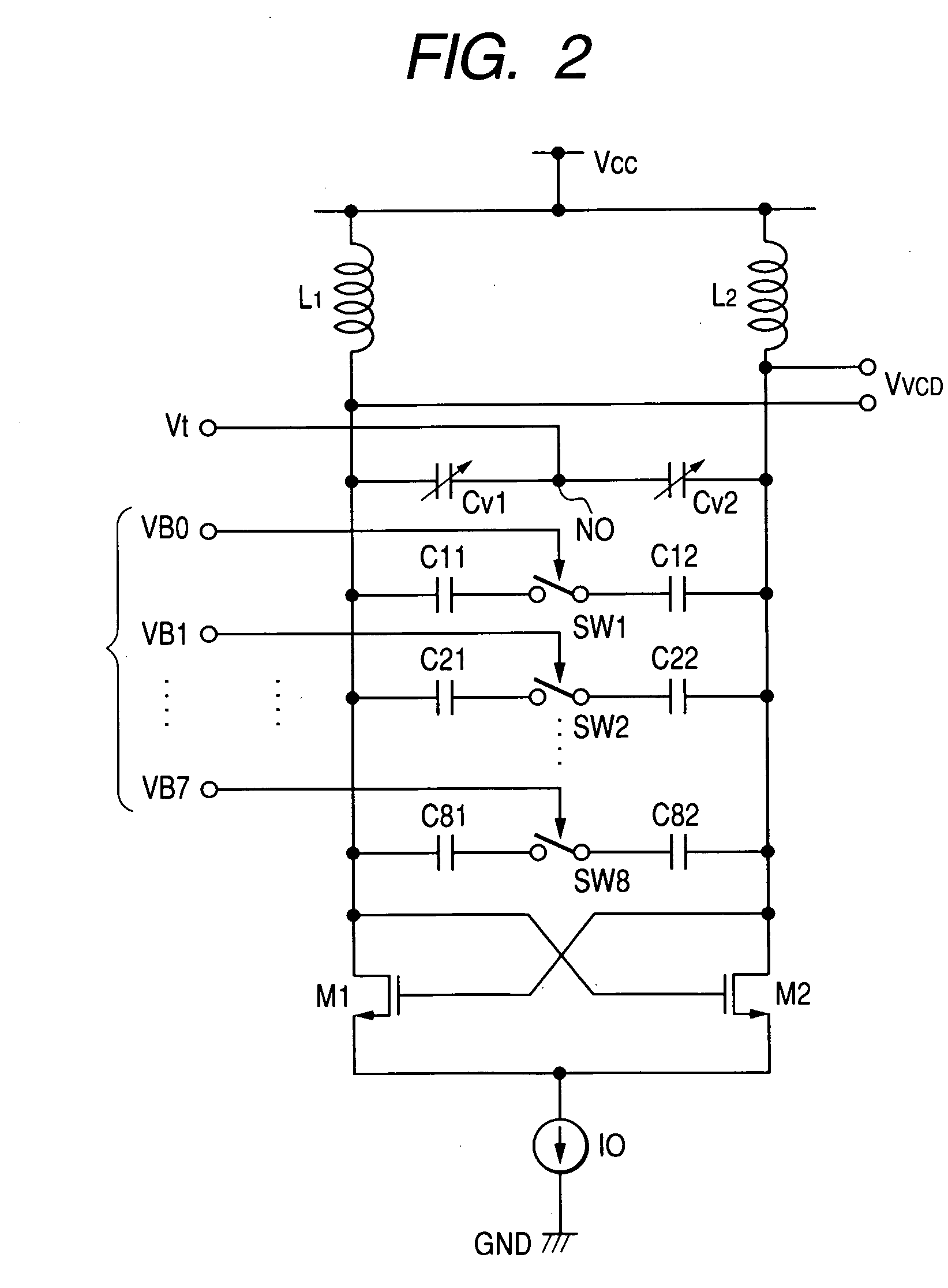

Semiconductor integrated circuit for wireless communication

InactiveUS20060014510A1Reduce circuit areaReduce occupied areaPulse automatic controlRadio transmissionFrequency bandPhase lead

A semiconductor integrated circuit with a PLL (Phase Locked Loop) built therein is used in a semiconductor integrated circuit for wireless communication. The PLL circuit generates an oscillation signal having a predetermined frequency, which is combined with a receive signal or a transmit signal for wireless communication. The PLL circuit includes a VCO capable of switching an oscillation frequency band, a variable divider, a loop filter and a phase comparator. An oscillation frequency of the VCO is controlled according to the difference in phase between a signal obtained by dividing the output of the VCO and a reference signal, and a discrimination circuit makes a decision as to a lead or delay of the phase of an output of the variable divider with respect to a reference signal having a predetermined frequency. An auto band selection circuit generates a signal for selecting a frequency band for the VCO.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com