Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1735results about "Printed capacitor incorporation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High density chip carrier with integrated passive devices

InactiveUS6962872B2Reduce inductanceEasy accessSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityEngineering

Owner:GLOBALFOUNDRIES U S INC

High reliability multlayer circuit substrates and methods for their formation

InactiveUS20040061234A1Semiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

A multilayer circuit substrate for multi-chip modules or hybrid circuits includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by shadow mask techniques. Substrates formed in this manner enable significant increases in interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC

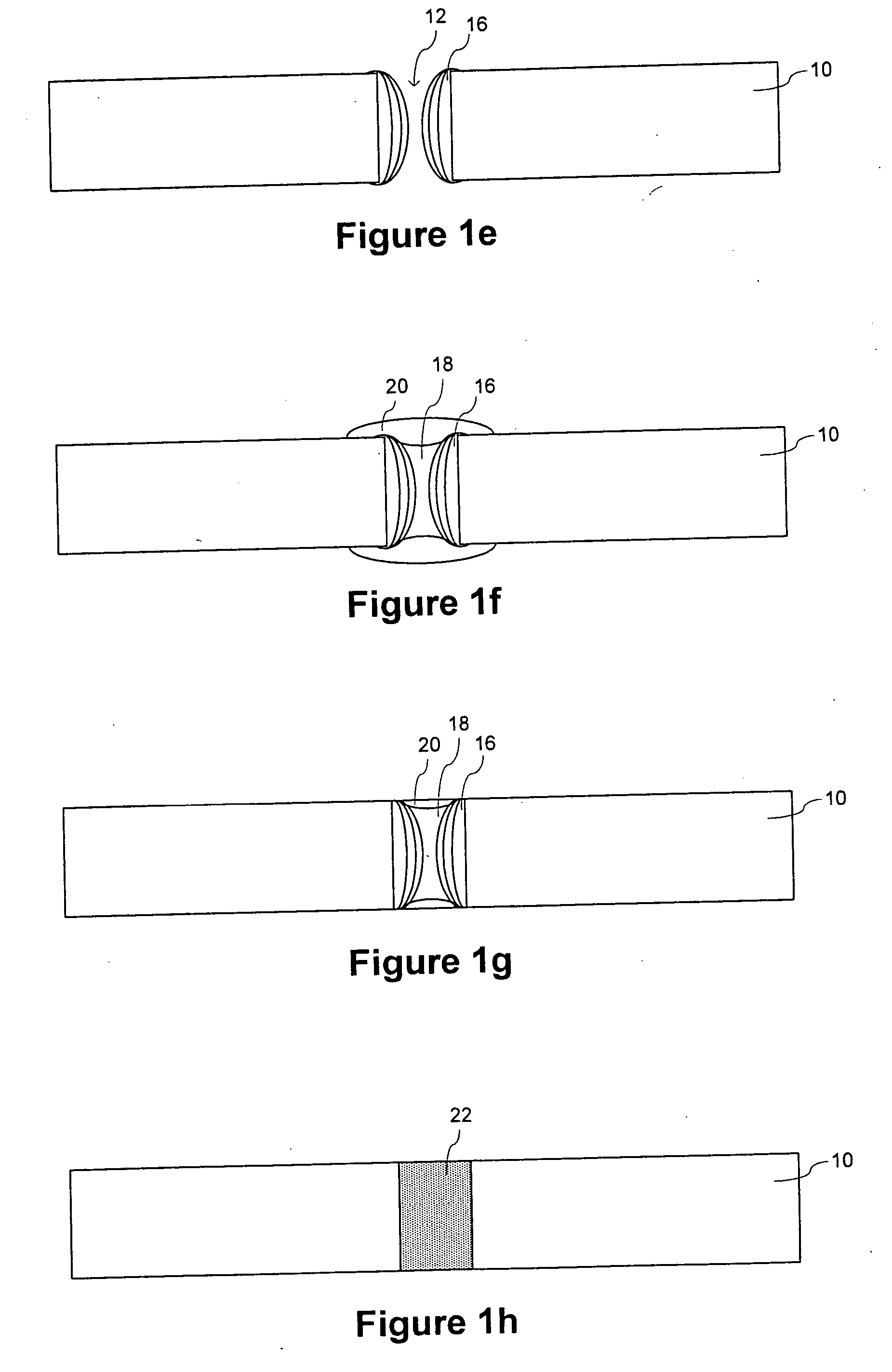

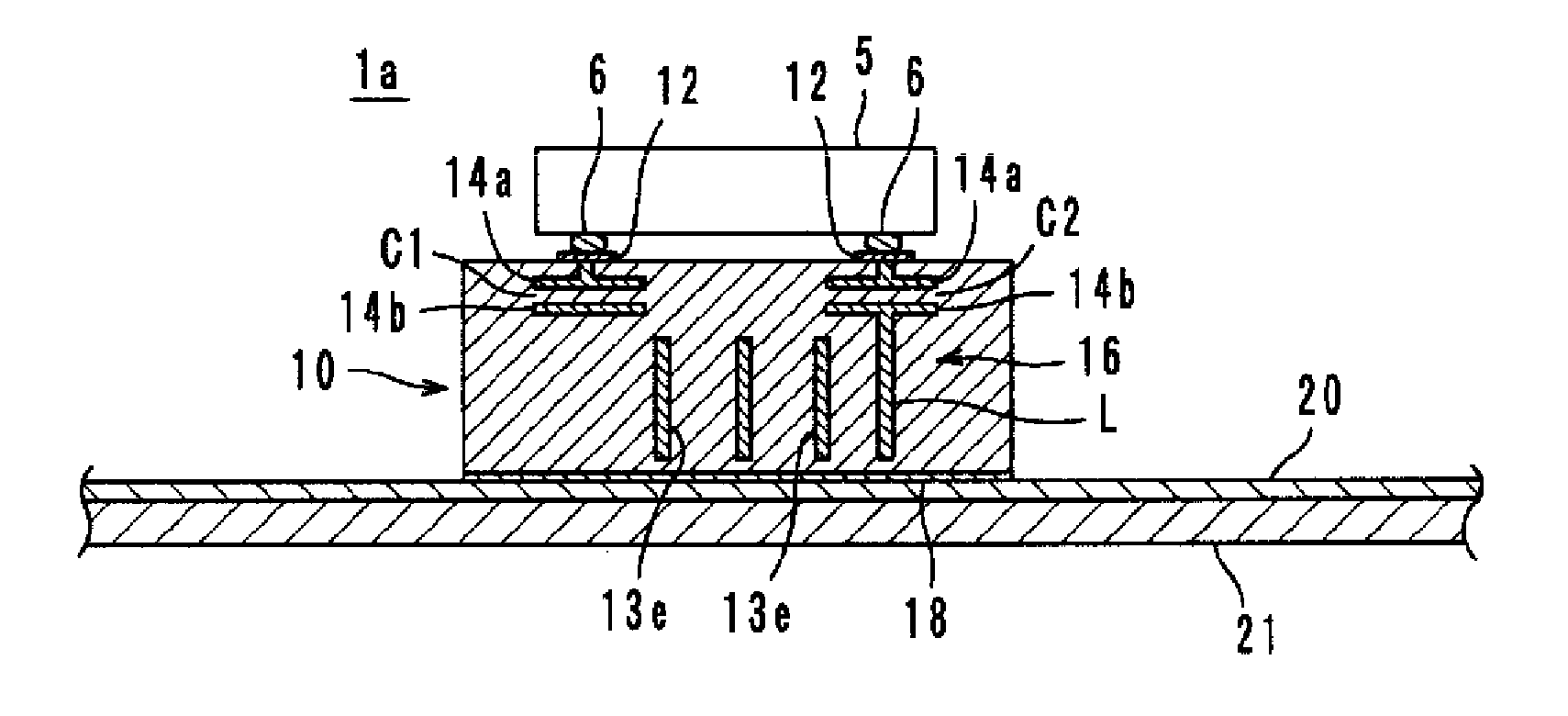

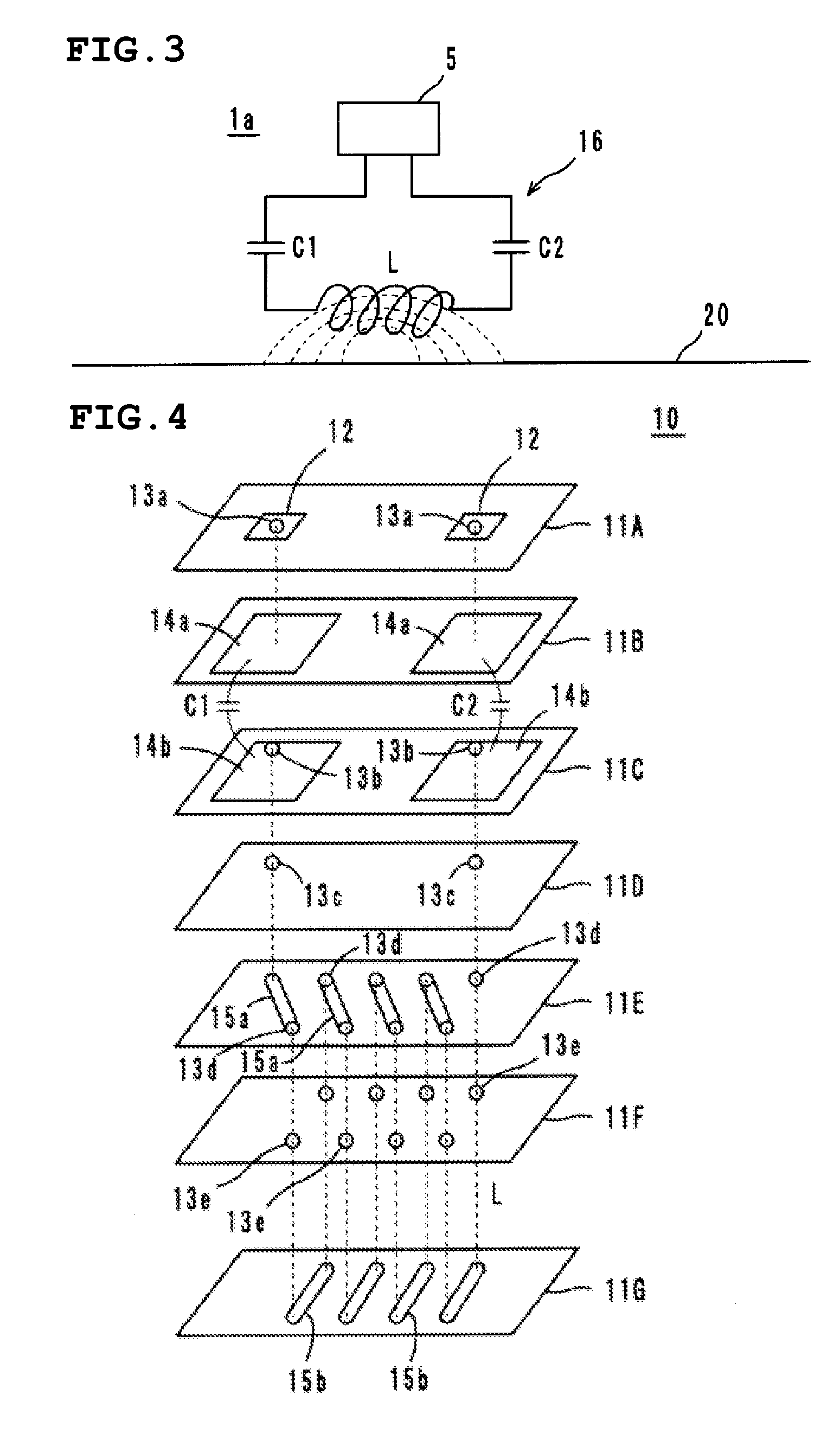

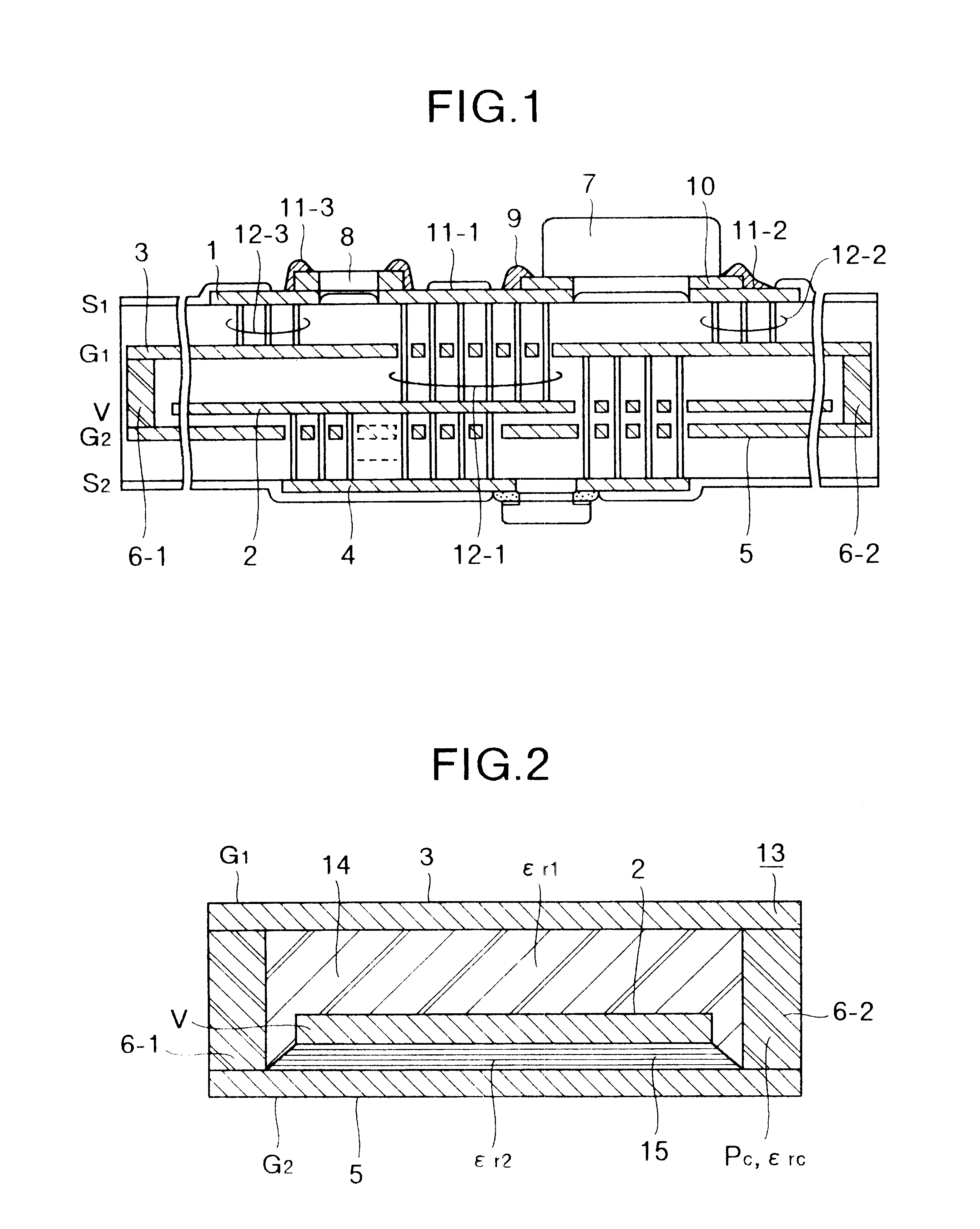

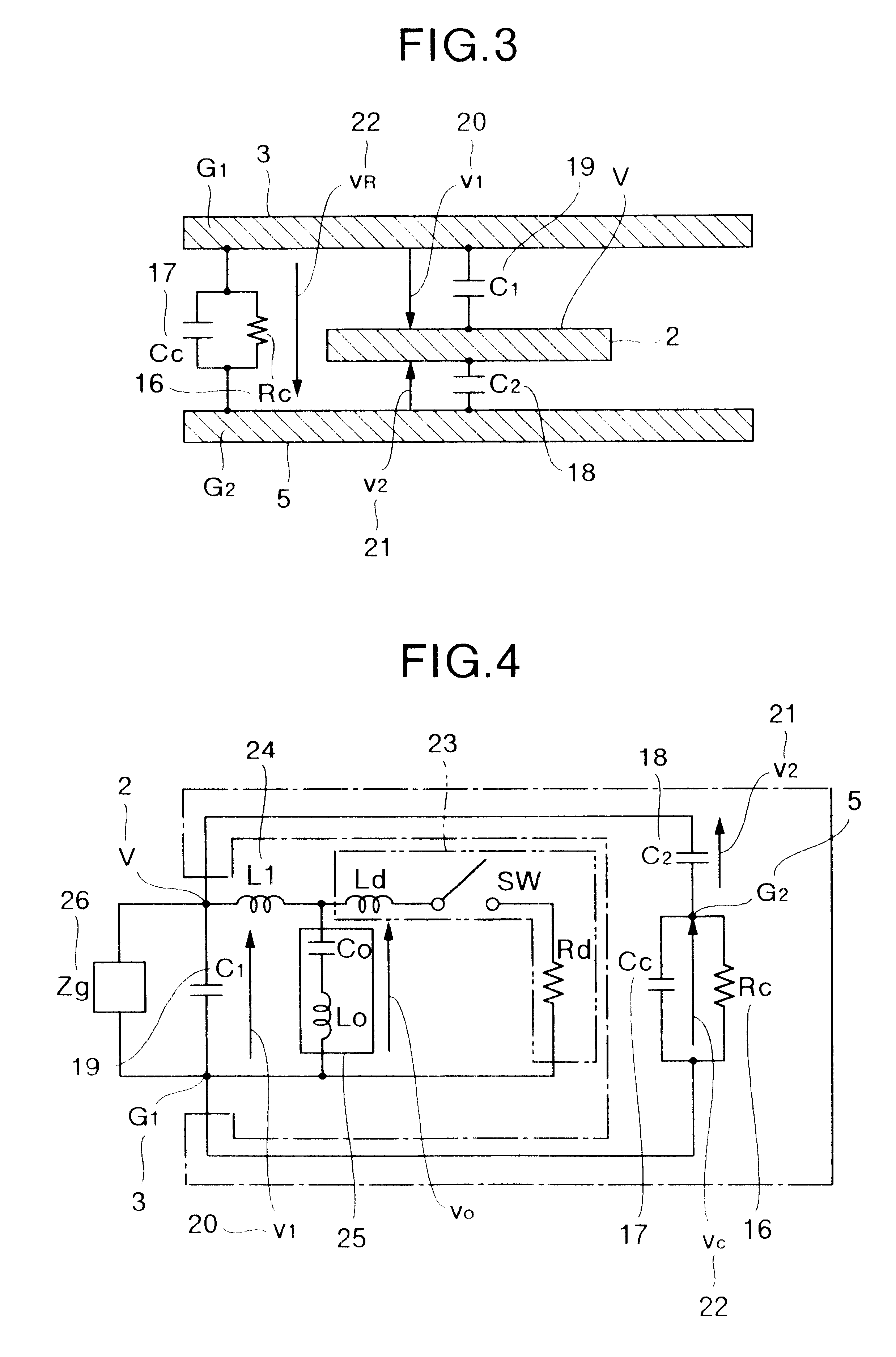

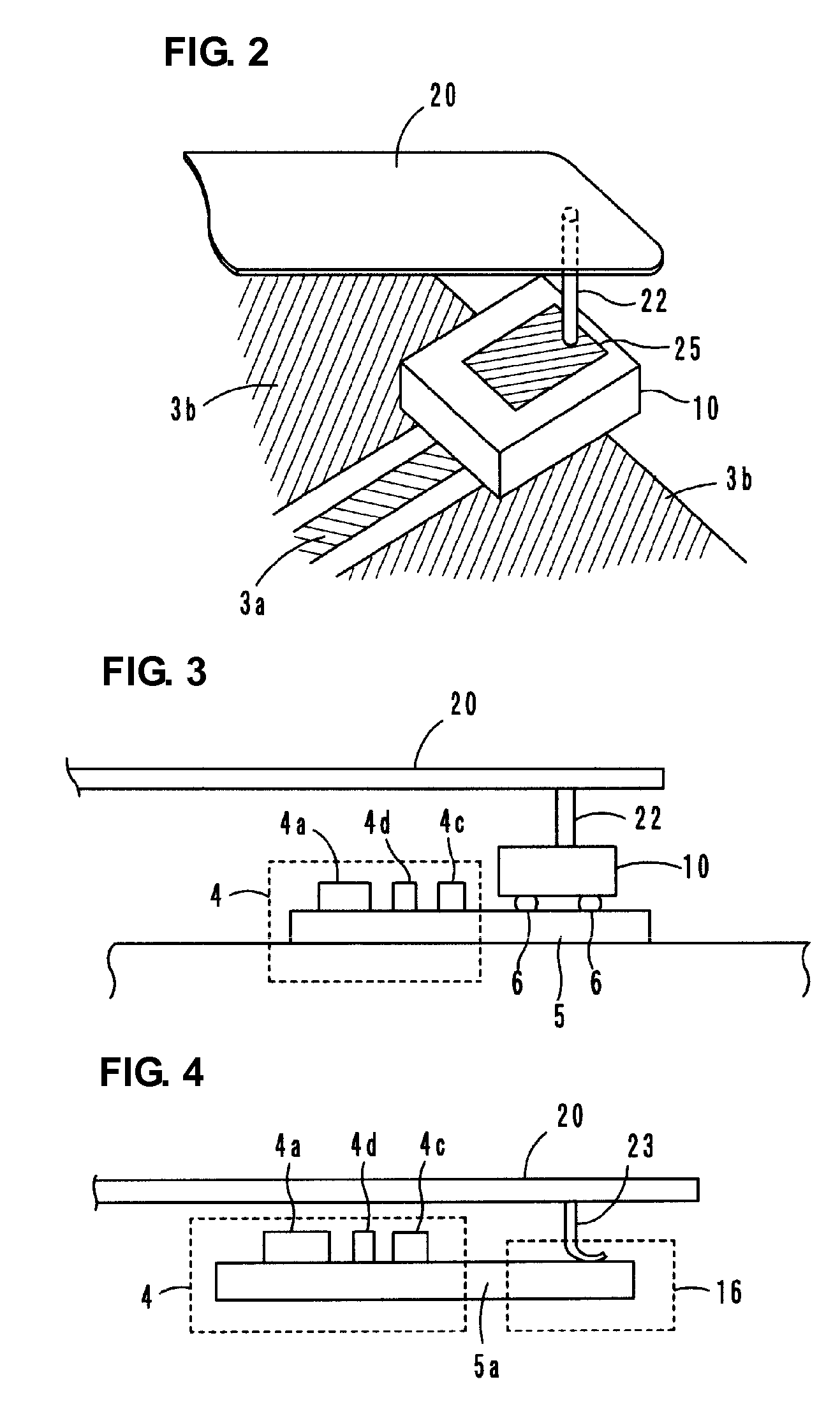

Wireless IC device and component for wireless IC device

ActiveUS20070164414A1Maintain stable propertiesPrevent electromagnetic leakageNear-field transmissionSemiconductor/solid-state device detailsCapacitanceCapacitive coupling

A wireless IC device includes a wireless IC chip, a power supply circuit board upon which the wireless IC chip is mounted, and in which a power supply circuit is provided, the power supply circuit includes a resonant circuit having a predetermined resonant frequency, and a radiation pattern, which is adhered to the underside of the power supply circuit board, for radiating a transmission signal supplied from the power supply circuit, and for receiving a reception signal to supply this to the power supply circuit. The resonant circuit is an LC resonant circuit including an inductance device and capacitance devices. The power supply circuit board is a multilayer rigid board or a single-layer rigid board, and between the wireless IC chip and the radiation pattern is connected by DC connection, magnetic coupling, or capacitive coupling.

Owner:MURATA MFG CO LTD

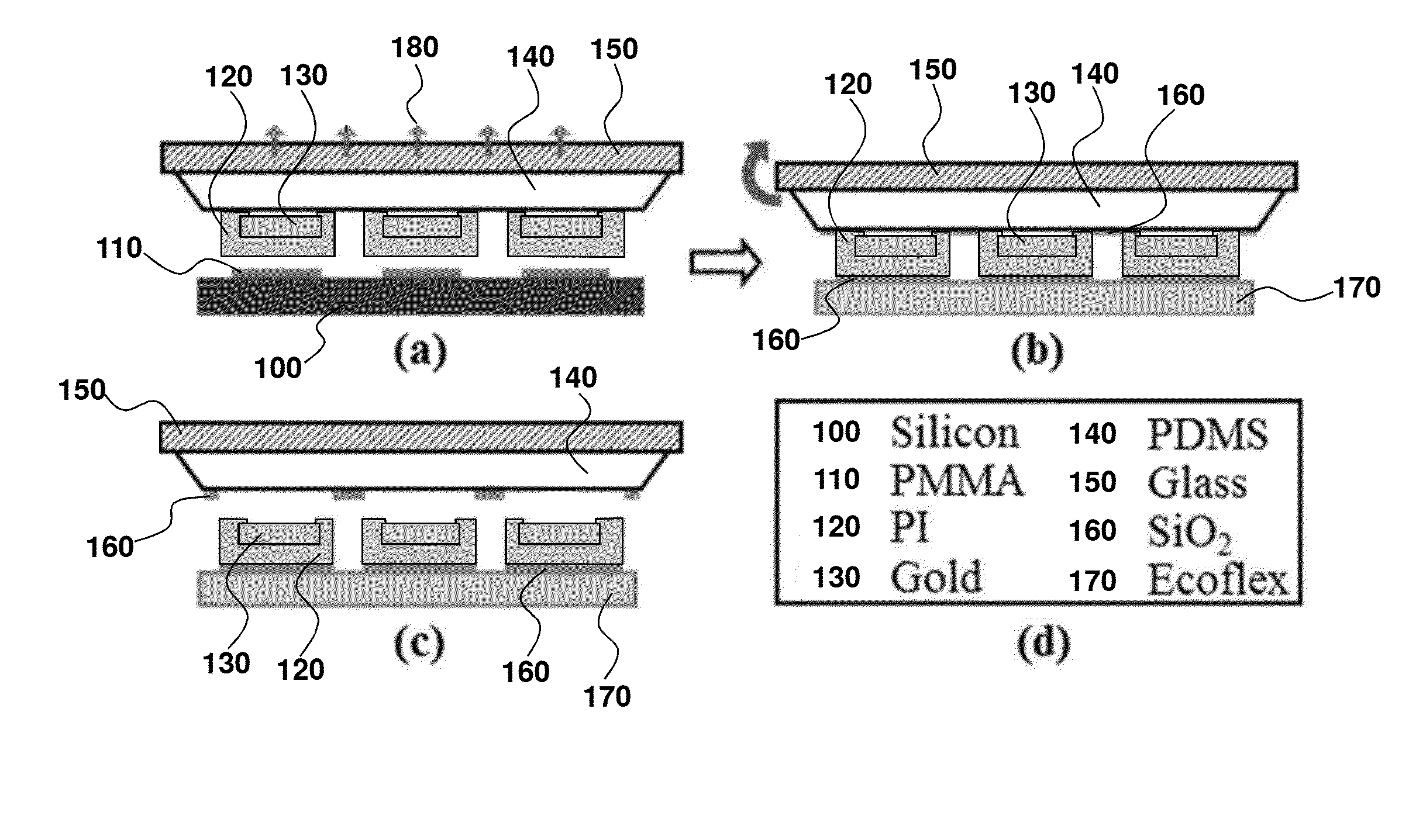

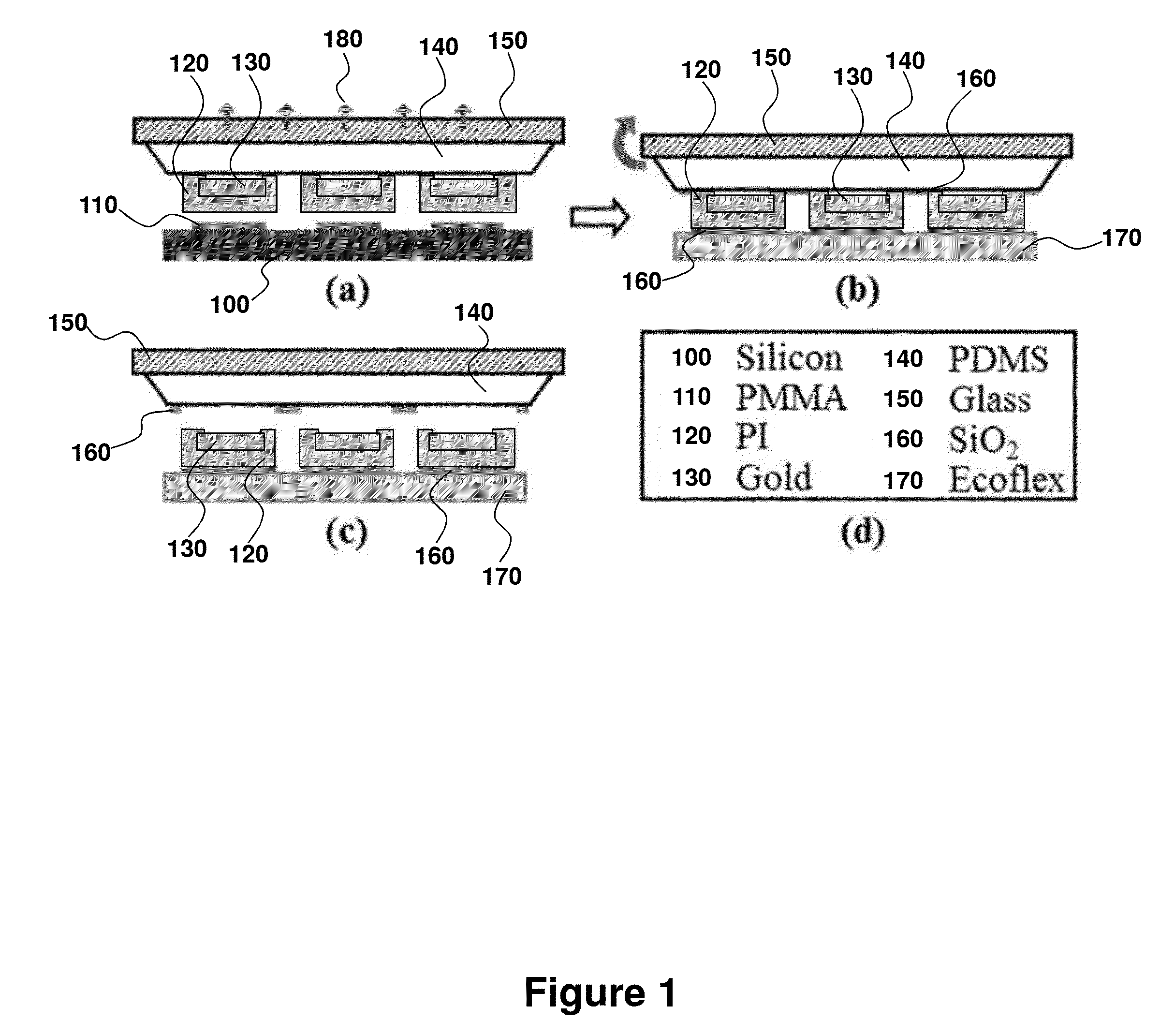

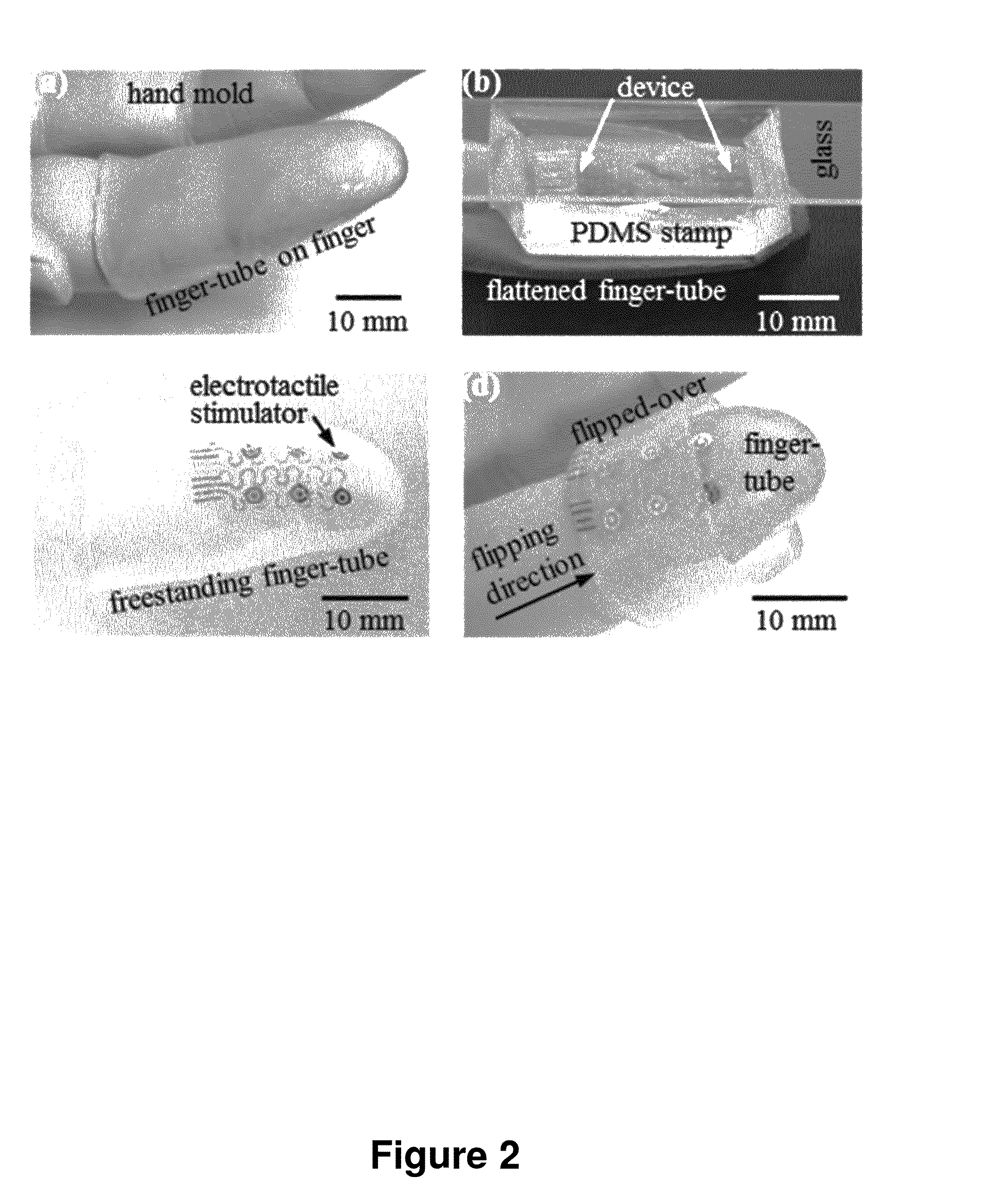

Appendage Mountable Electronic Devices COnformable to Surfaces

ActiveUS20130333094A1Lower the volumeReduce the overall diameterDigital data processing detailsSolid-state devicesSensor arrayElectronic systems

Disclosed are appendage mountable electronic systems and related methods for covering and conforming to an appendage surface. A flexible or stretchable substrate has an inner surface for receiving an appendage, including an appendage having a curved surface, and an opposed outer surface that is accessible to external surfaces. A stretchable or flexible electronic device is supported by the substrate inner and / or outer surface, depending on the application of interest. The electronic device in combination with the substrate provides a net bending stiffness to facilitate conformal contact between the inner surface and a surface of the appendage provided within the enclosure. In an aspect, the system is capable of surface flipping without adversely impacting electronic device functionality, such as electronic devices comprising arrays of sensors, actuators, or both sensors and actuators.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

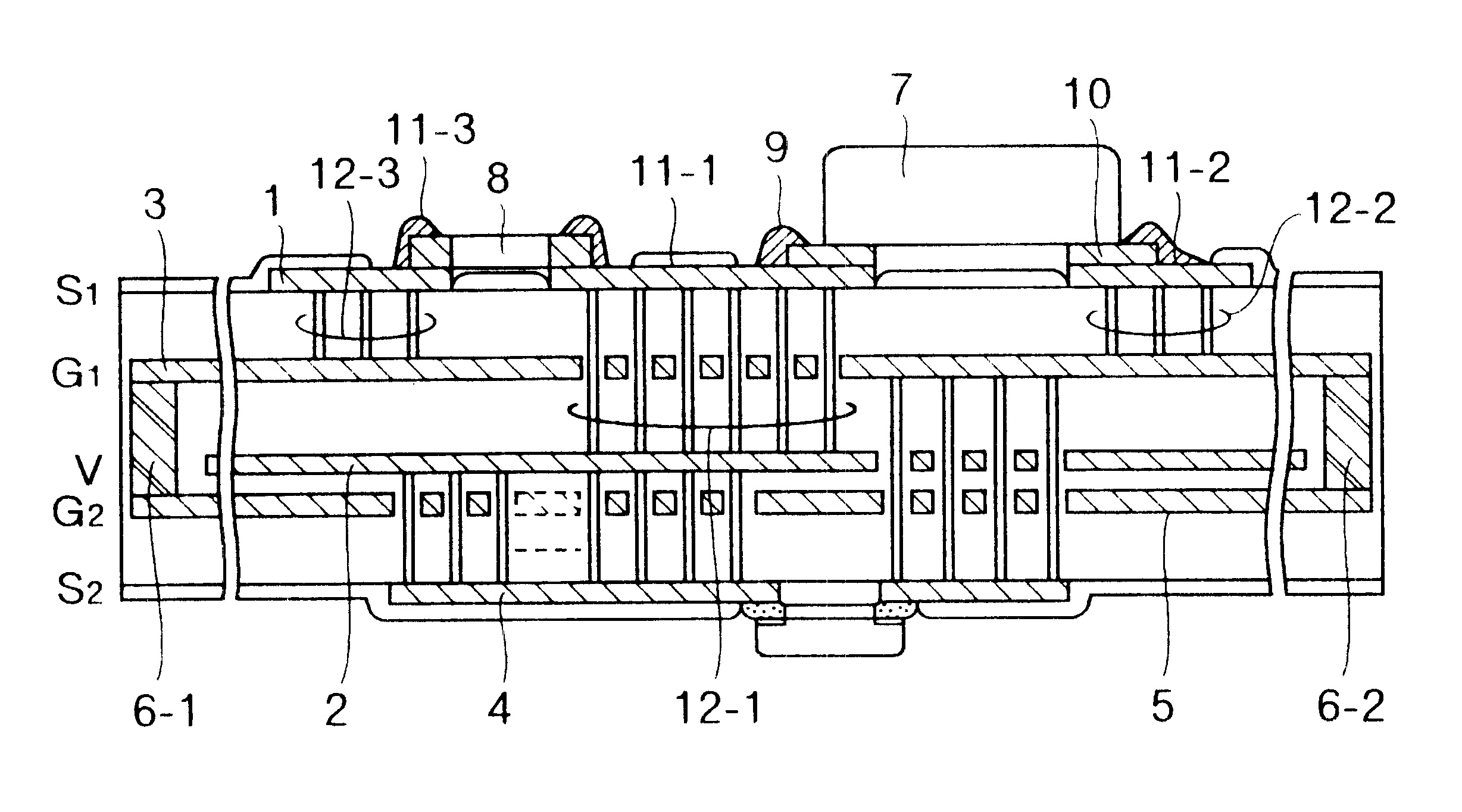

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

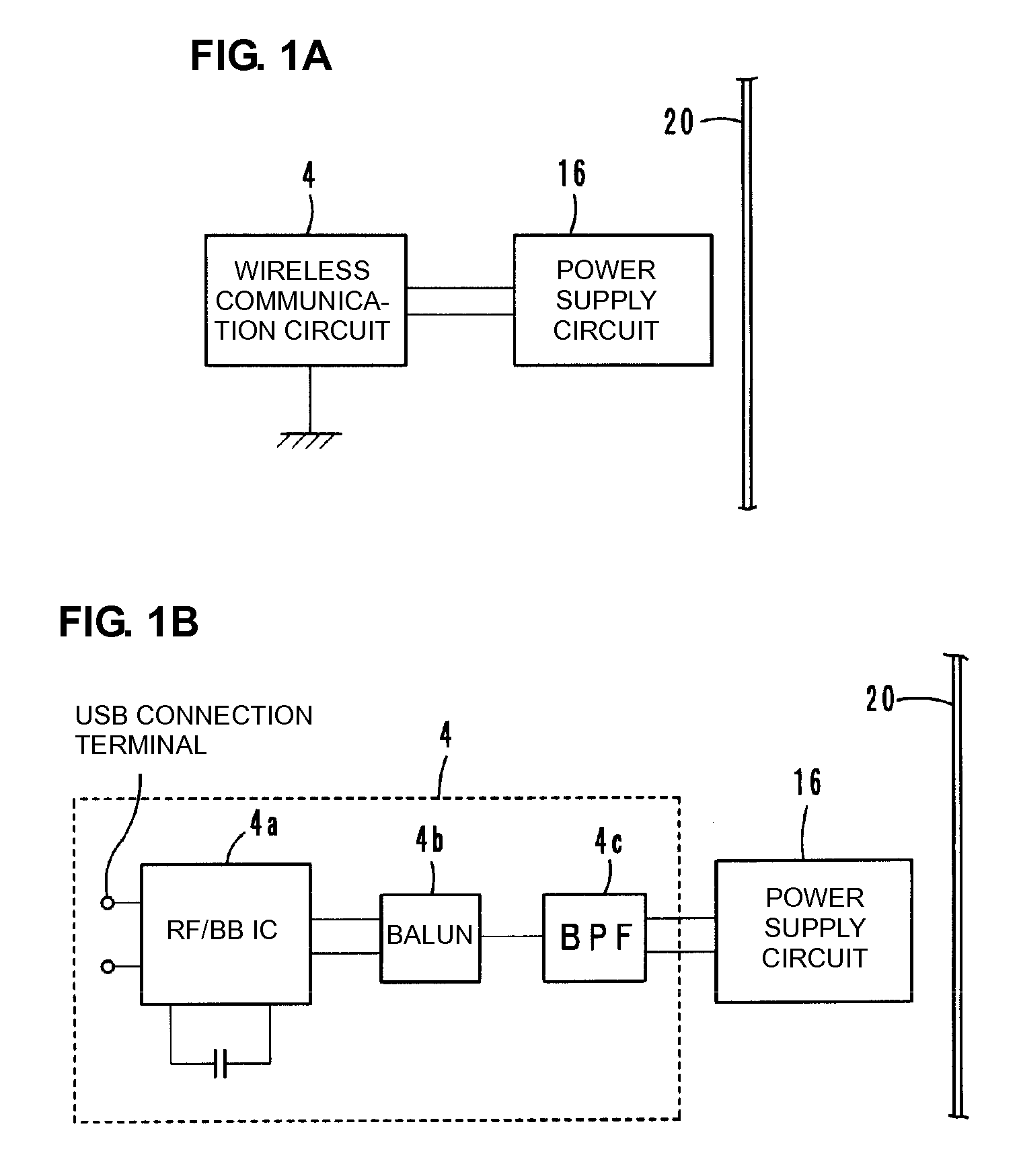

Product including power supply circuit board

ActiveUS20090009007A1Frequency stabilityEnhanced signalAntenna supports/mountingsSolid-state devicesElectricityElectromagnetic field coupling

A product includes a power supply circuit board, which includes a power supply circuit having a stable frequency characteristic which enables communication among various products to be obtained. The product includes a power supply circuit board including a power supply circuit arranged thereon having an inductance element, and a wireless communication circuit board electrically connected to the power supply circuit. The wireless communication circuit board is mounted on the power supply circuit board. The product further includes a radiation plate which emits a transmission signal which is supplied from the power supply circuit through electromagnetic field coupling and which has a frequency substantially determined in accordance with a resonant frequency of the power supply circuit, and which is used to supply a reception signal to the power supply circuit through electromagnetic field coupling.

Owner:MURATA MFG CO LTD

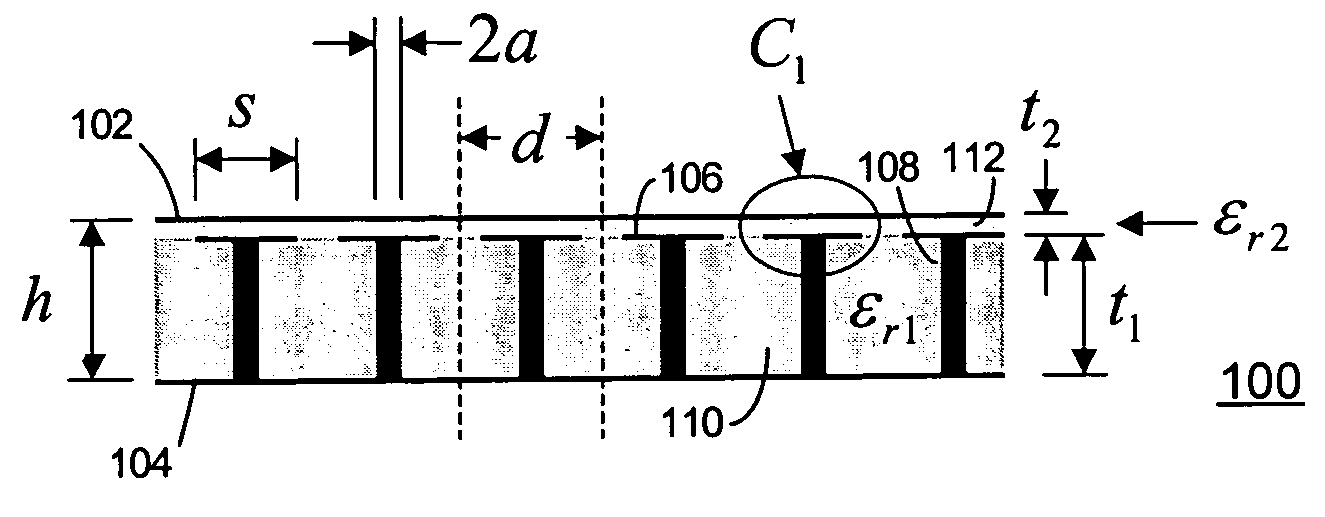

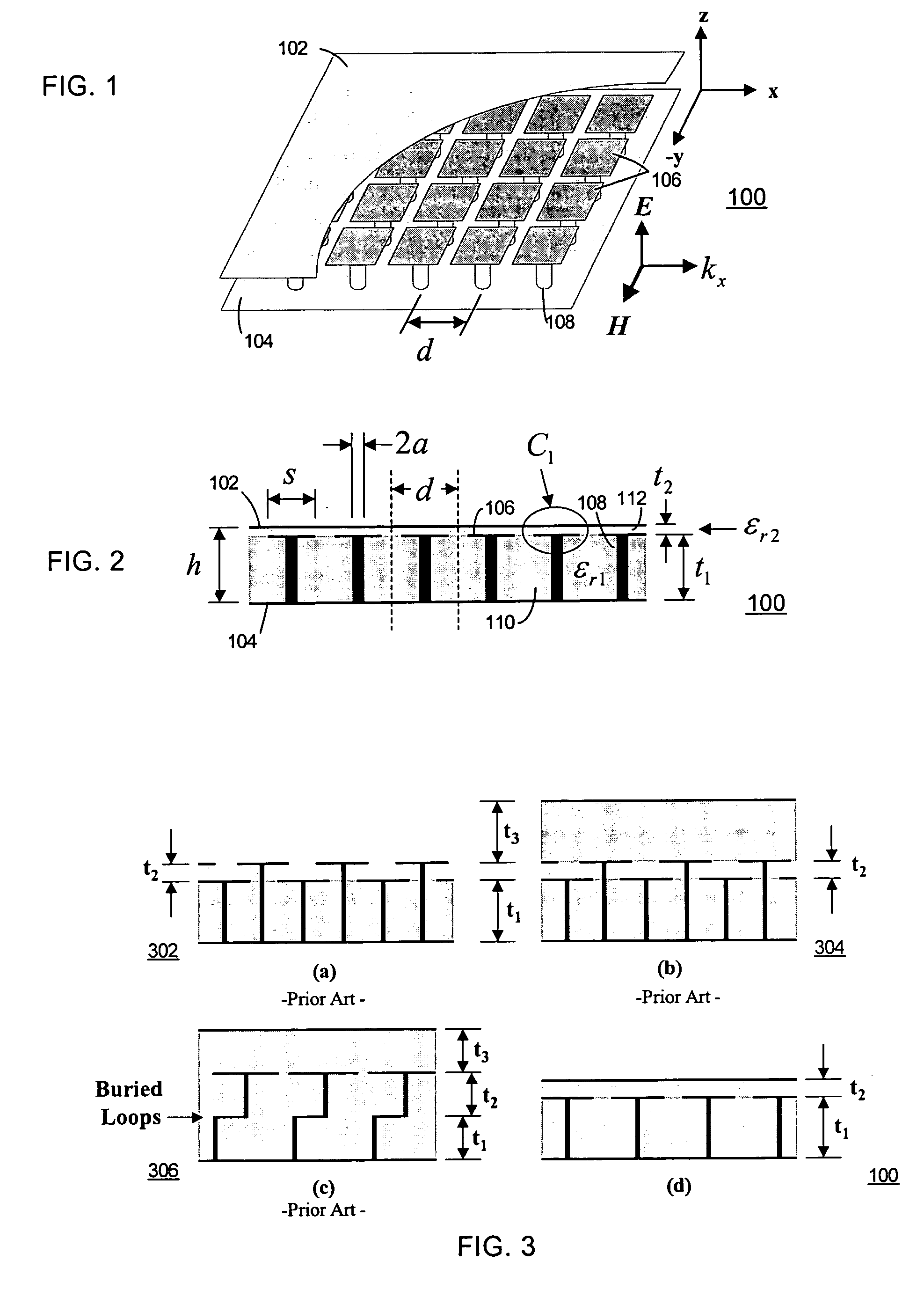

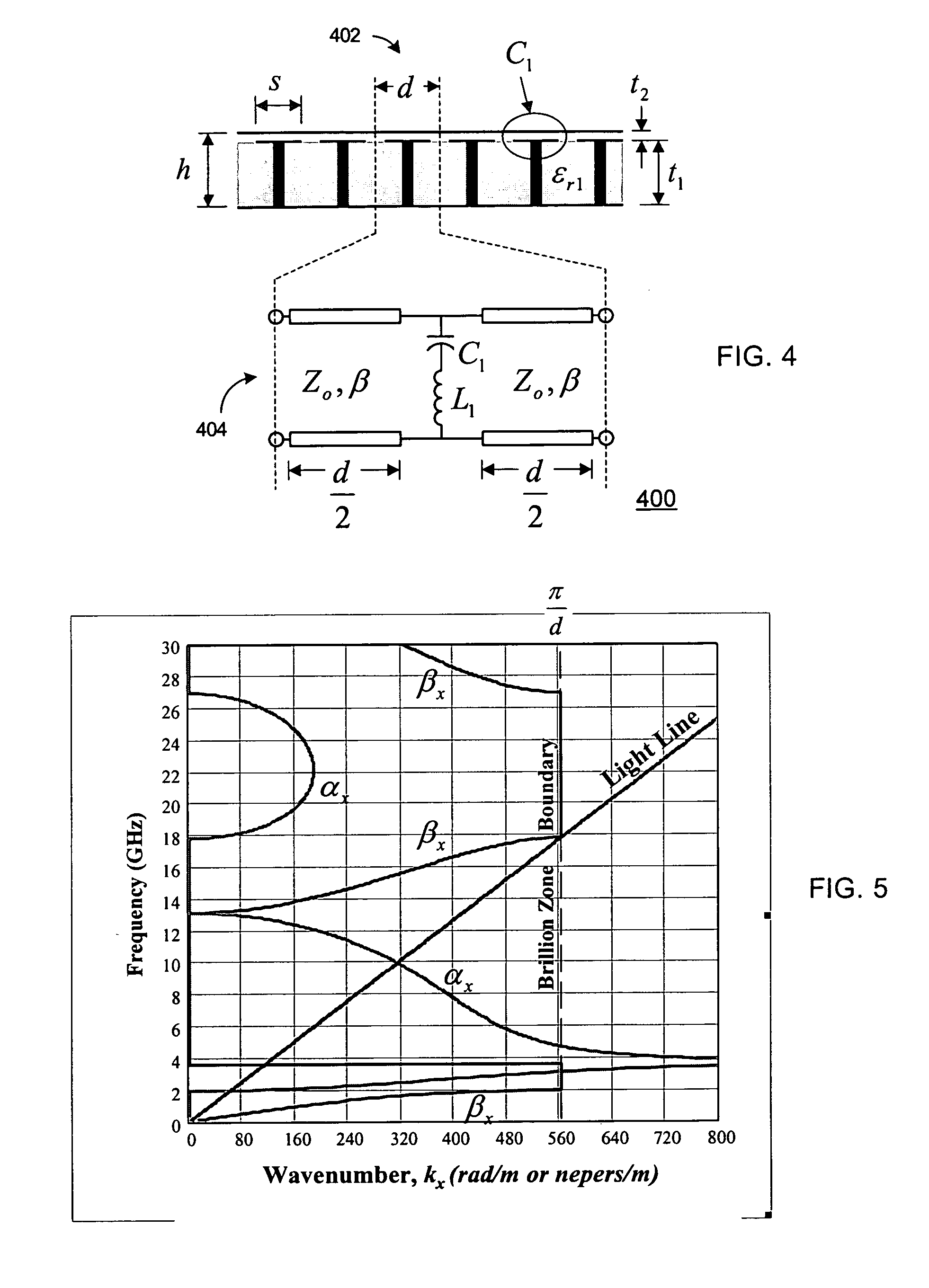

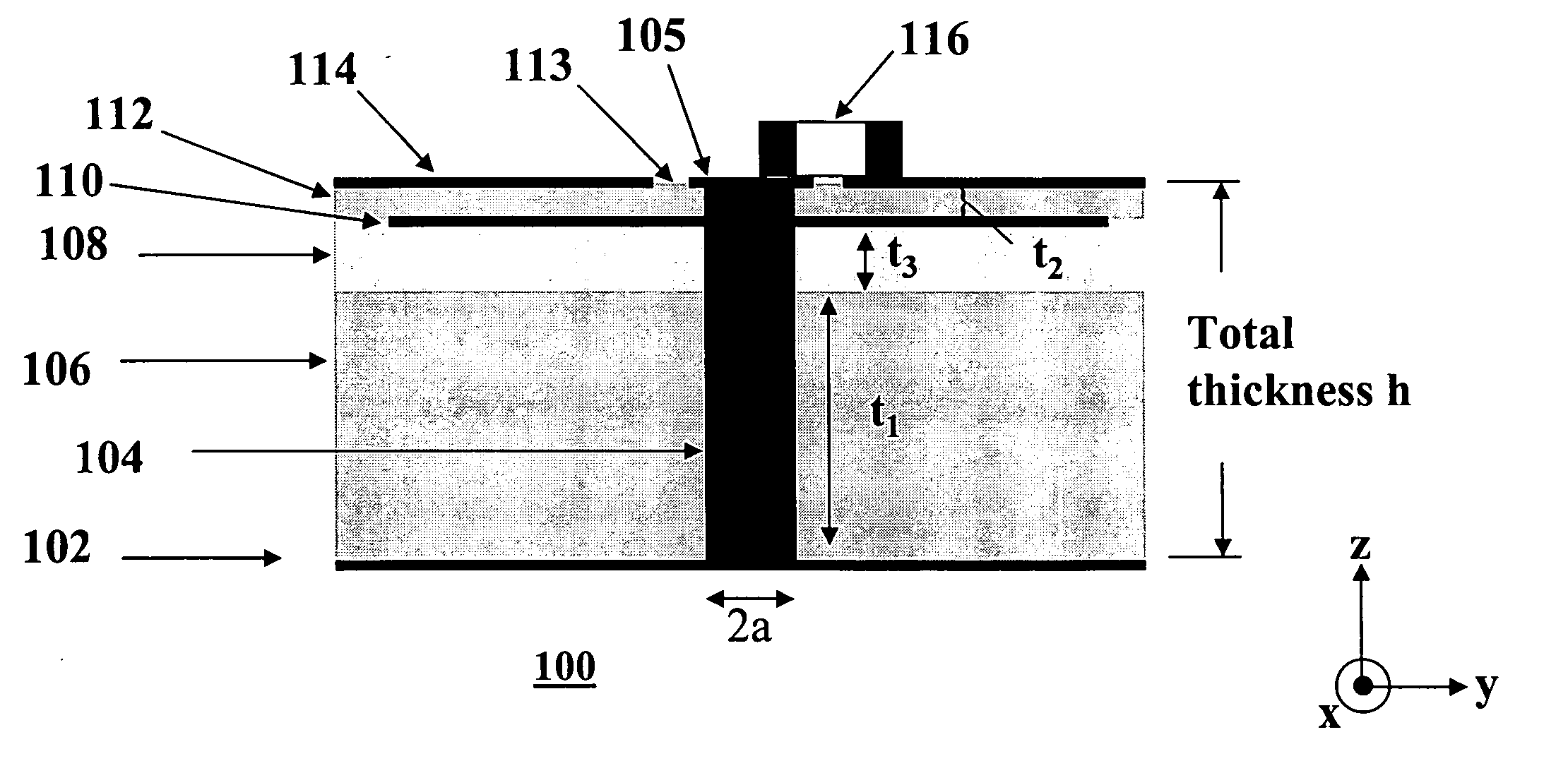

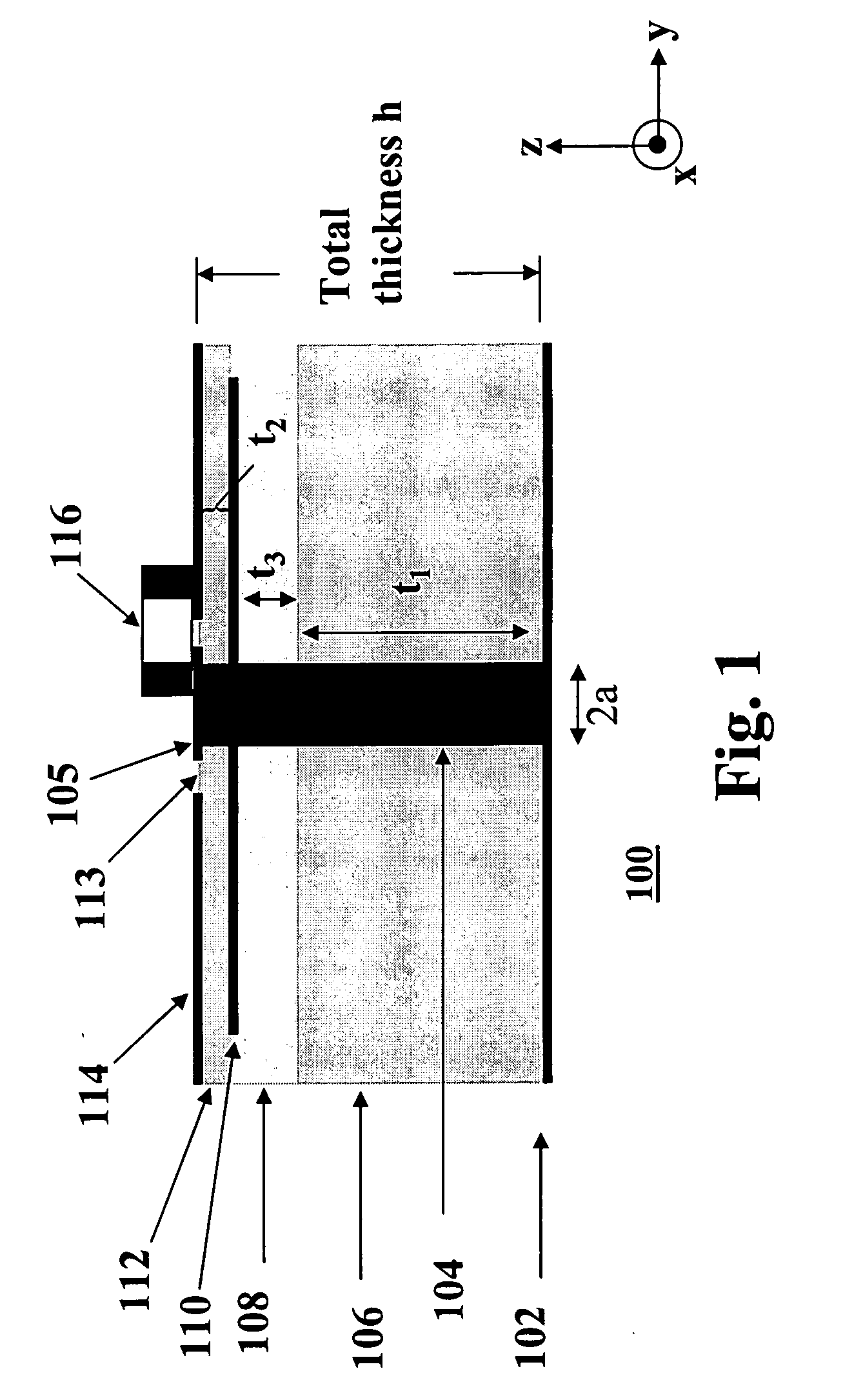

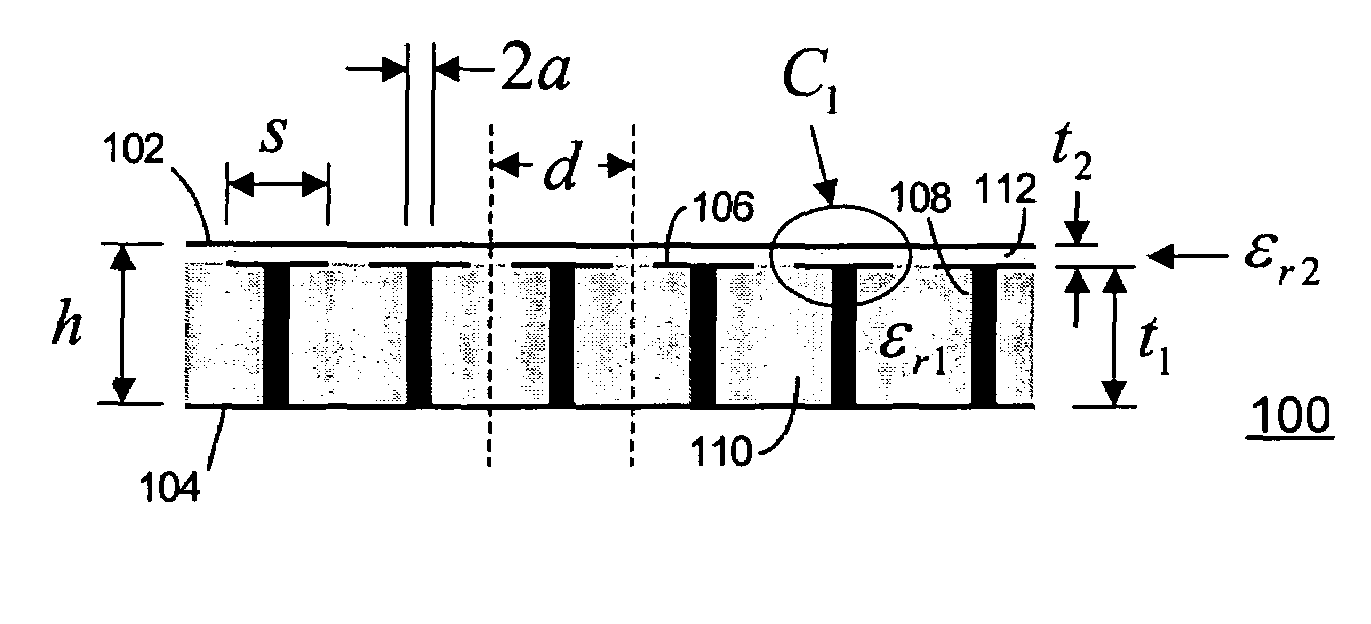

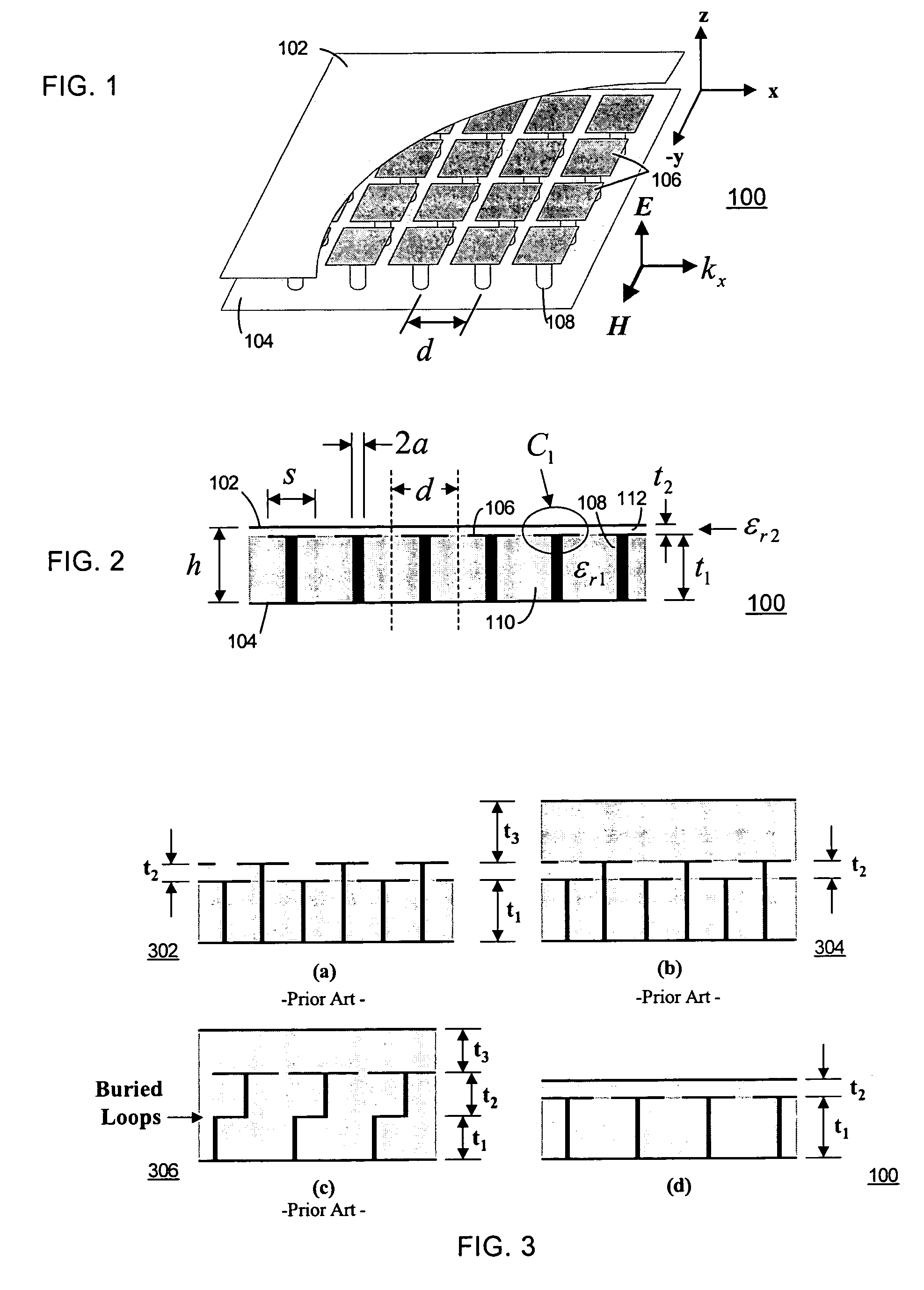

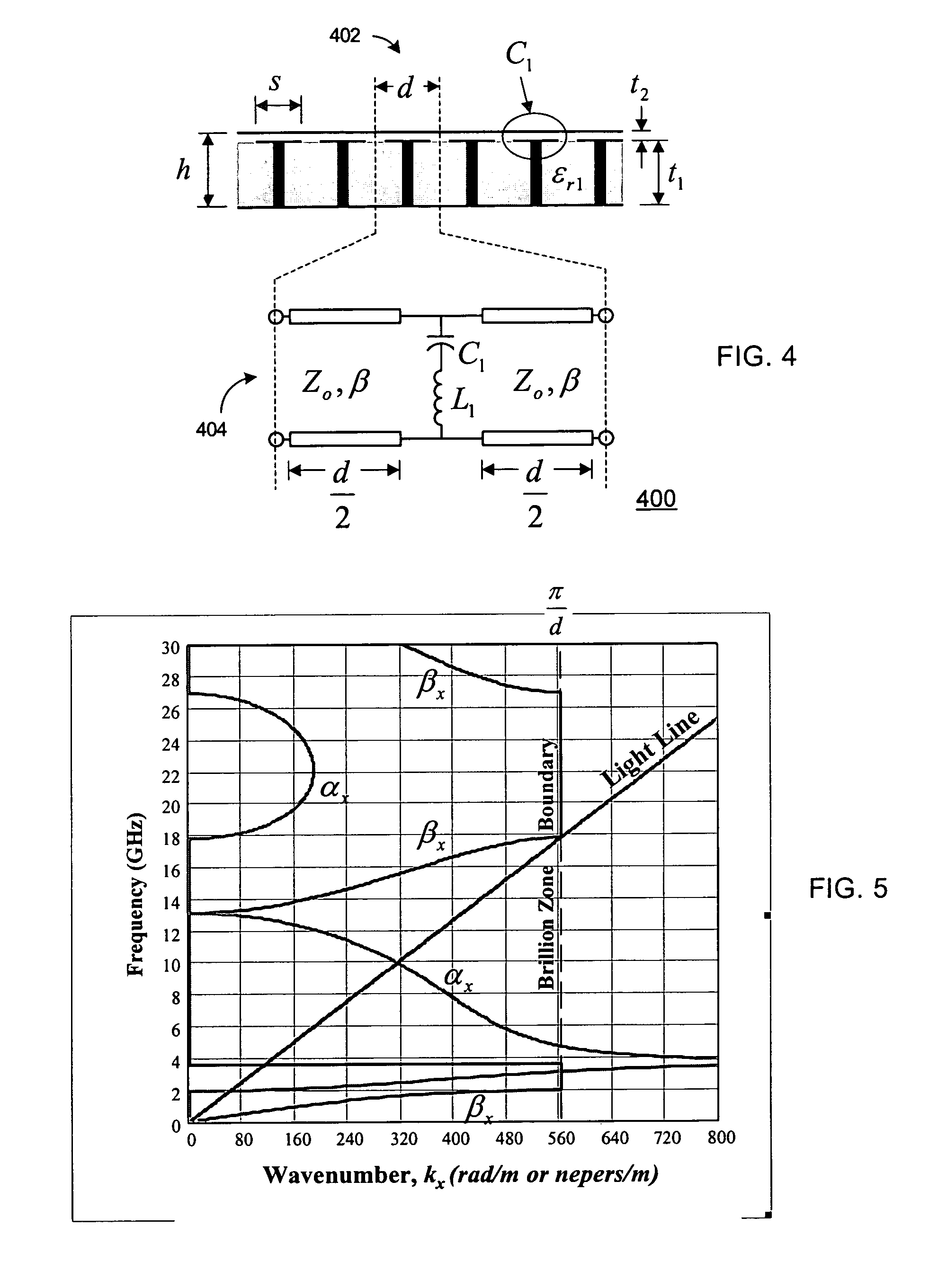

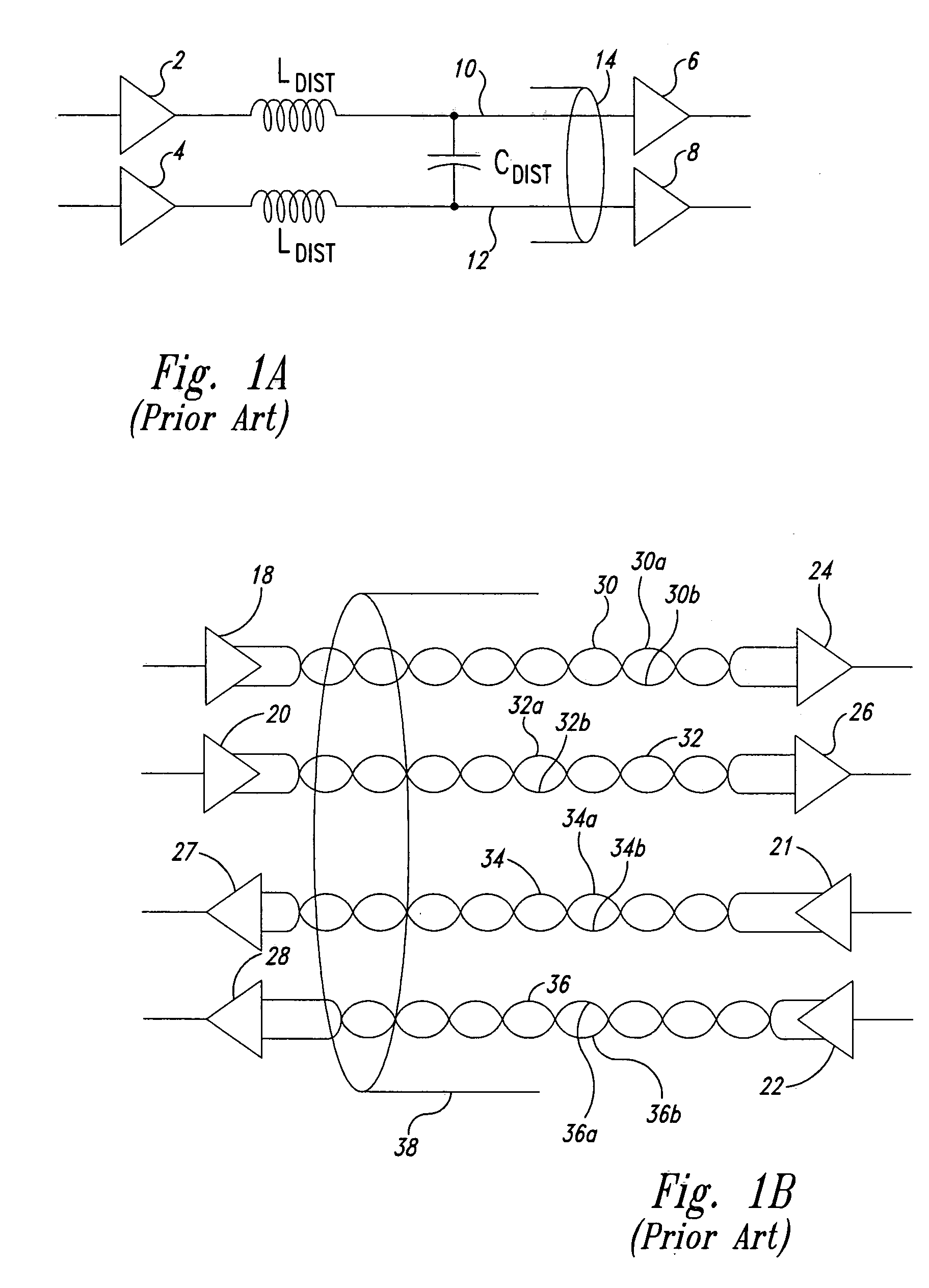

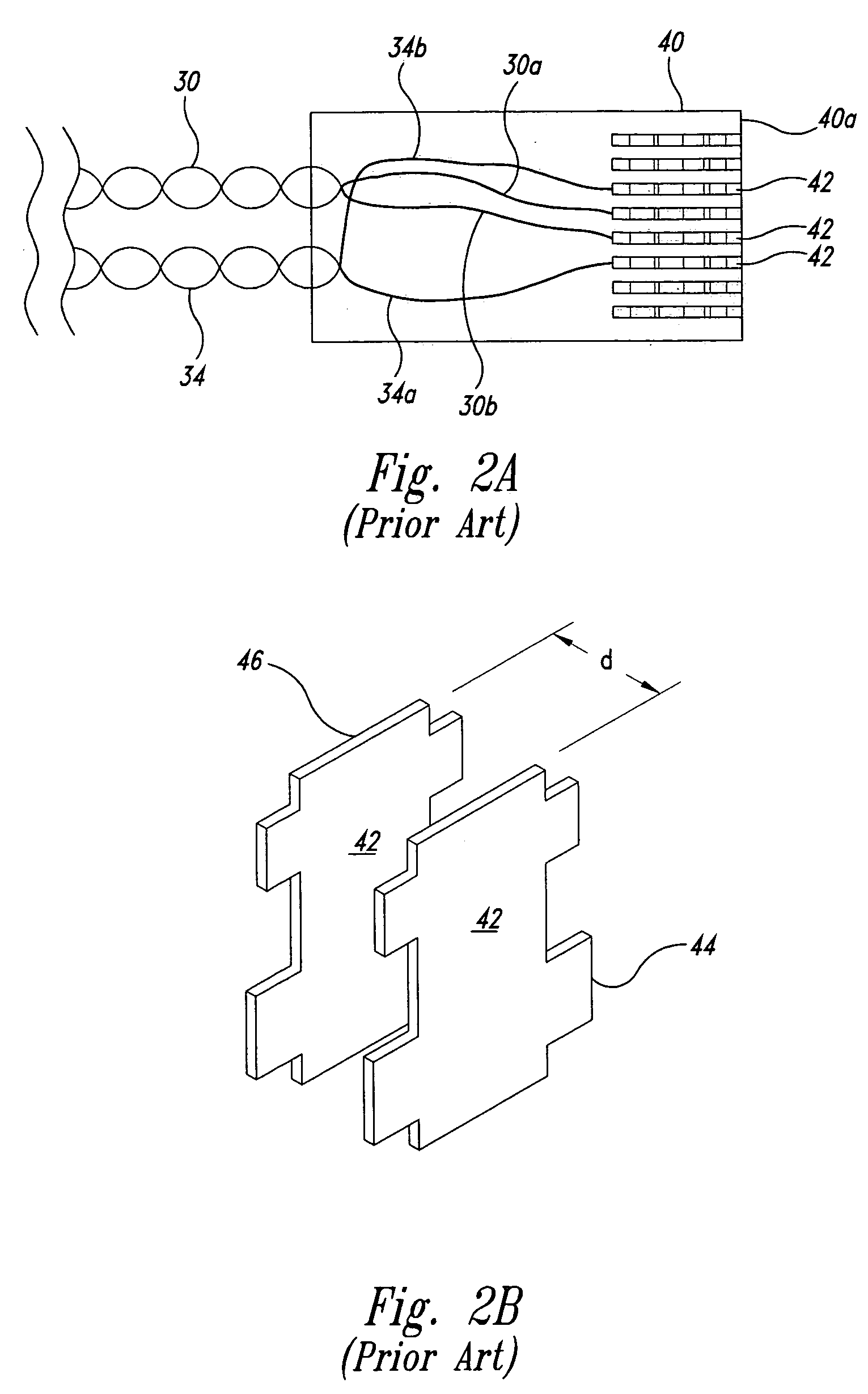

Circuit and method for suppression of electromagnetic coupling and switching noise in multilayer printed circuit boards

InactiveUS20050029632A1Eliminate power plane resonanceSuppress powerTransmission control/equlisationSemiconductor/solid-state device detailsCapacitanceElectromagnetic coupling

Apparatus for suppressing noise and electromagnetic coupling in the printed circuit board of an electronic device includes an upper conductive plate and an array of conductive coplanar patches positioned a distance t2 from the upper conductive plate. The distance t2 is chosen to optimize capacitance between the conductive coplanar patches and the upper conductive plate for suppression of noise or electromagnetic coupling. The apparatus further includes a lower conductive plate a distance t1 from the array of conductive coplanar patches and conductive rods extending from respective patches to the lower conductive plate.

Owner:WEMTEC

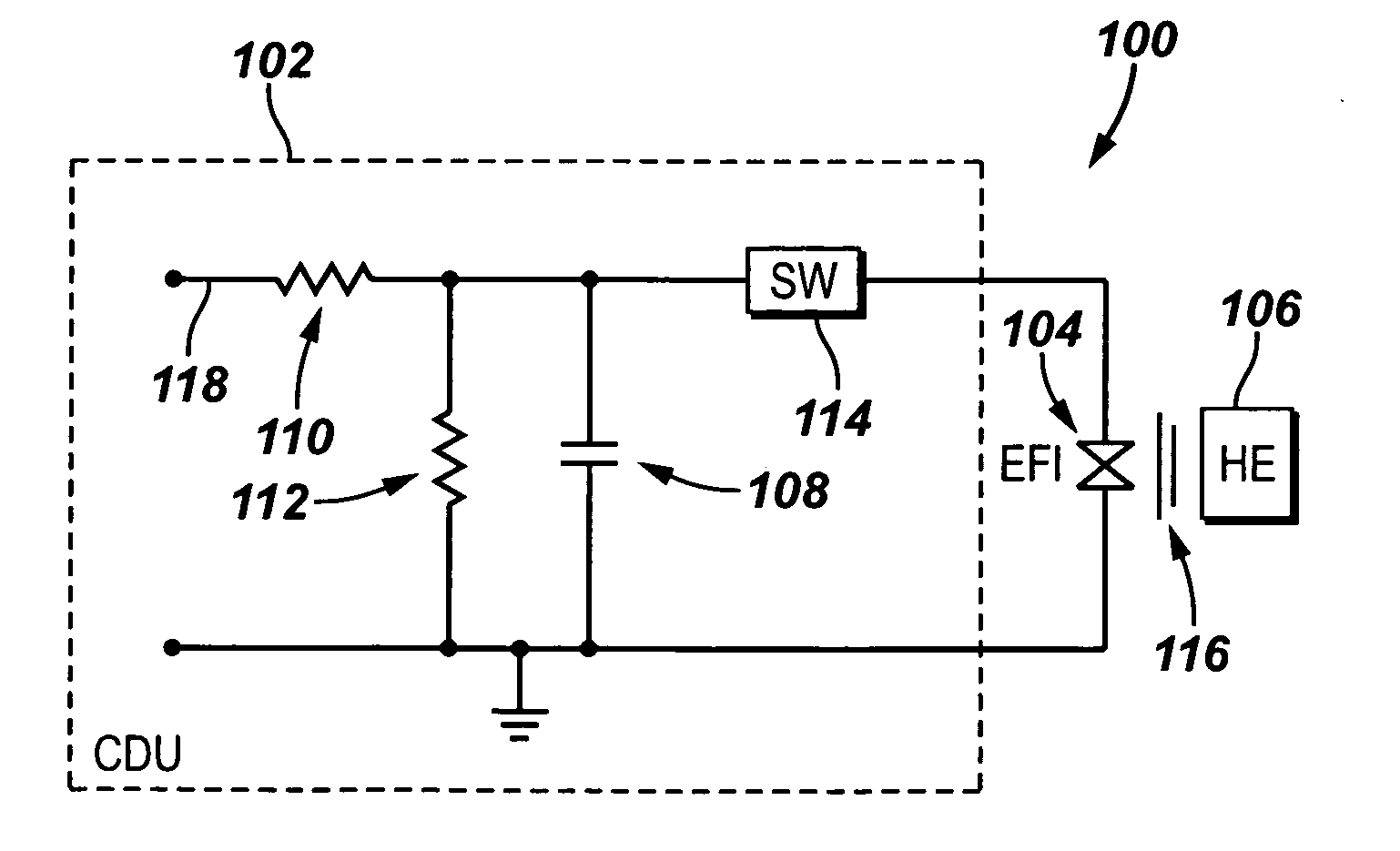

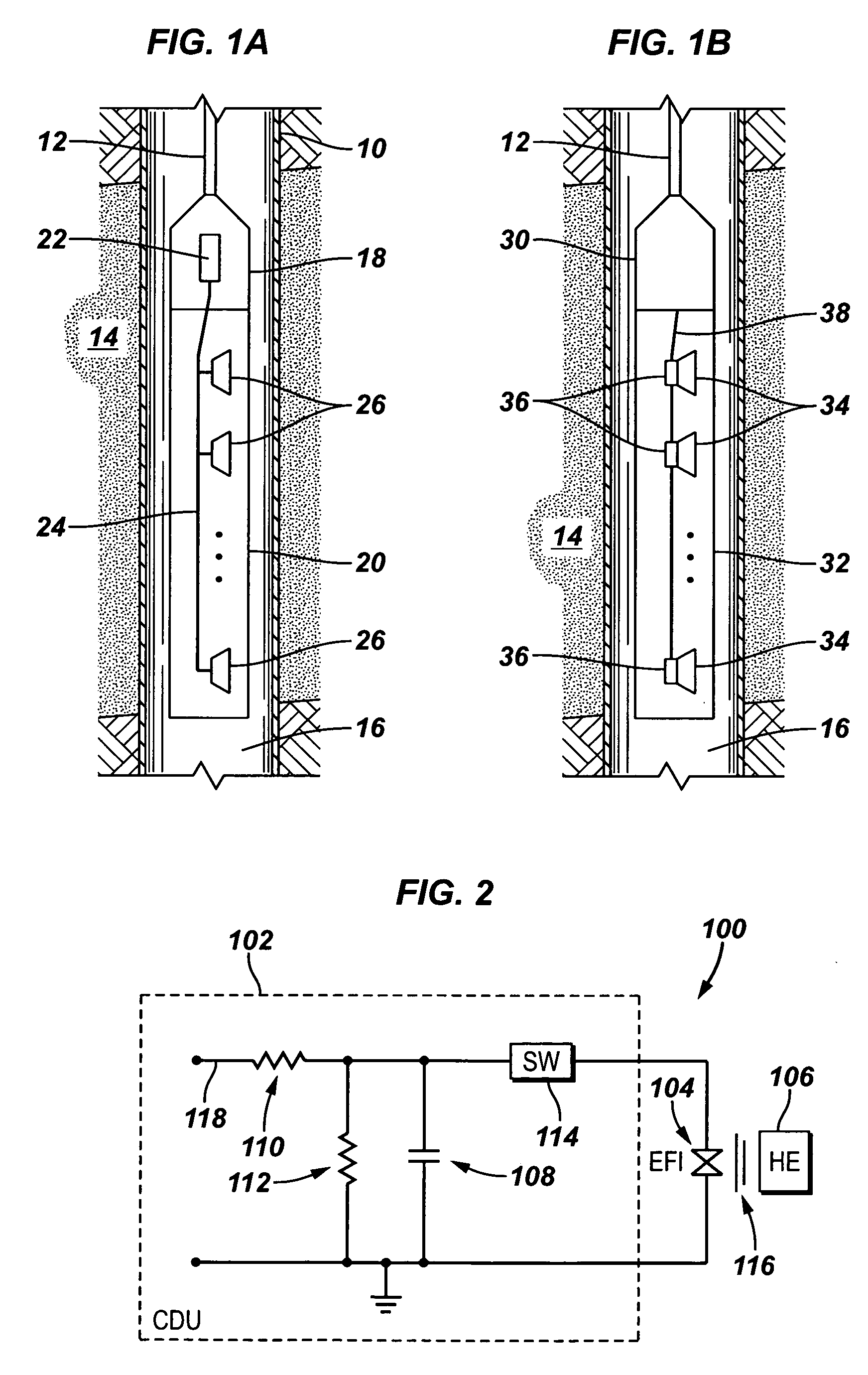

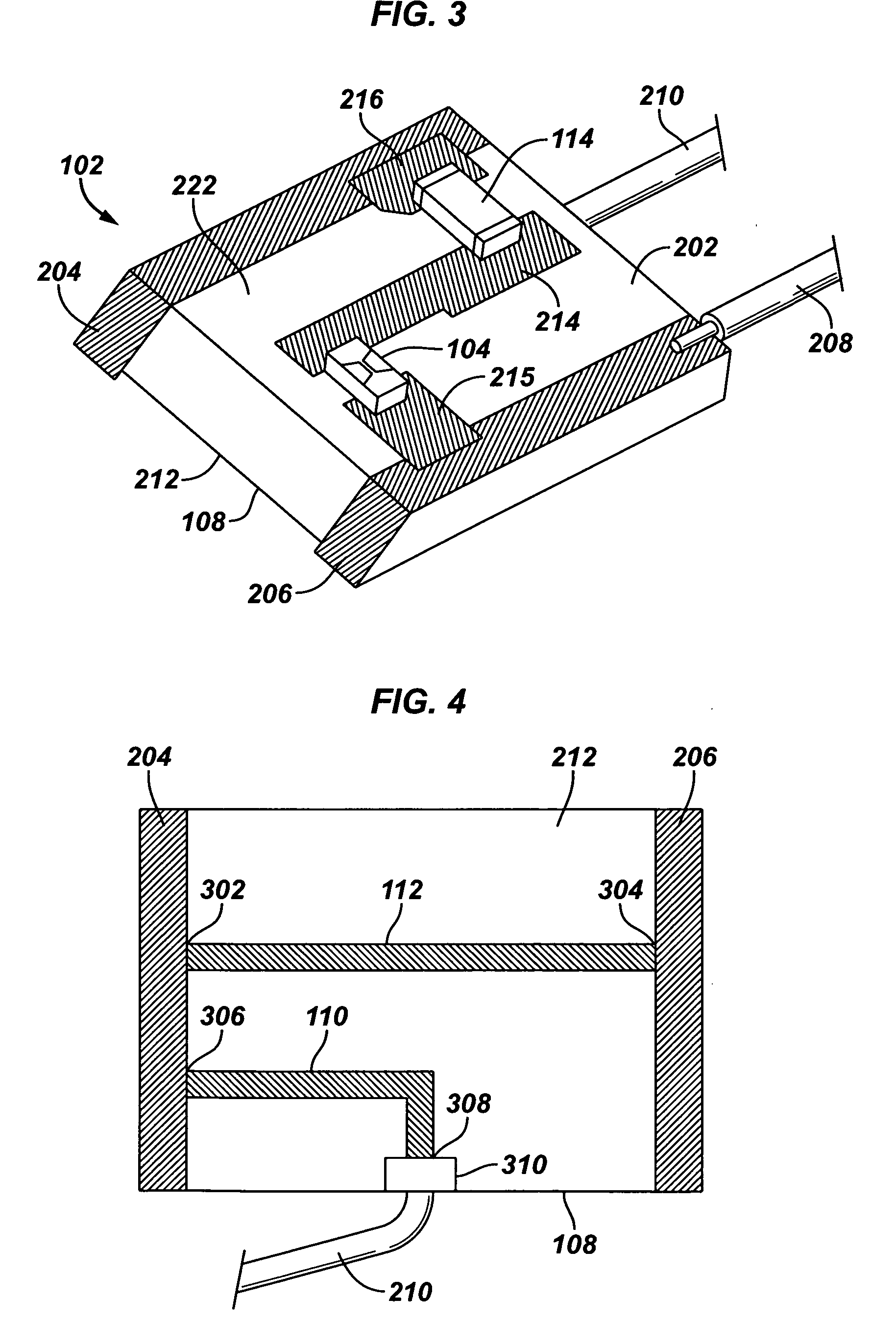

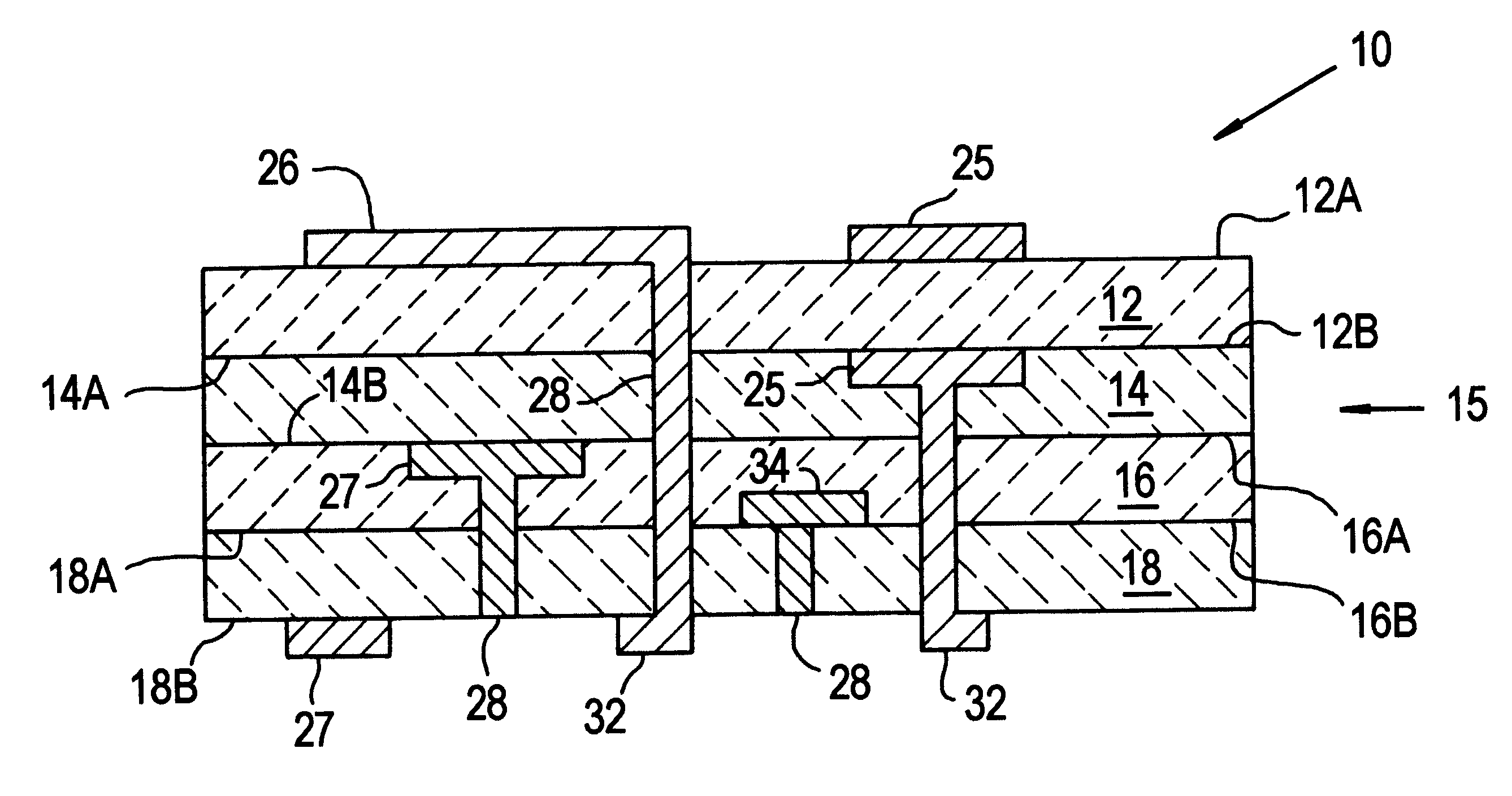

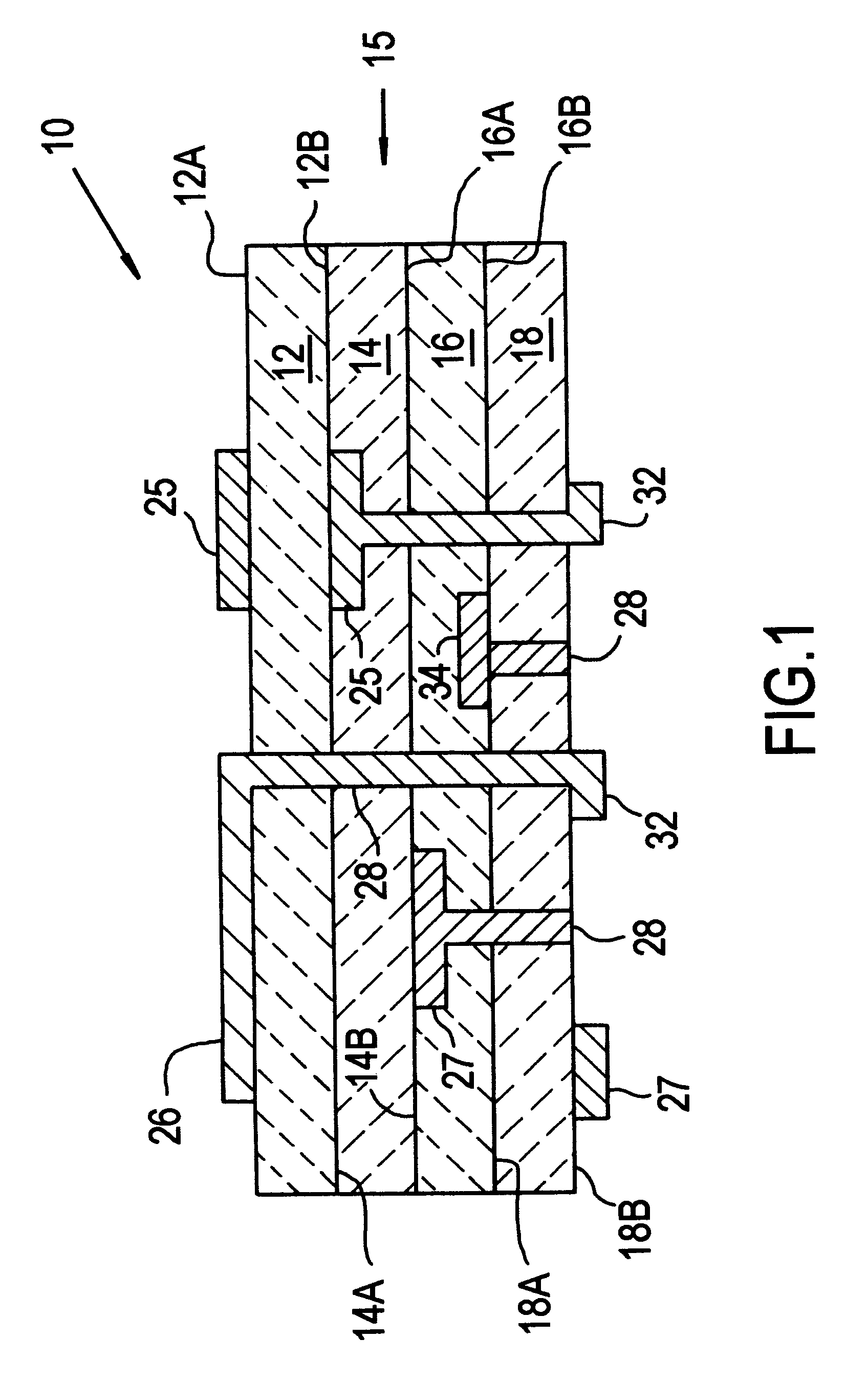

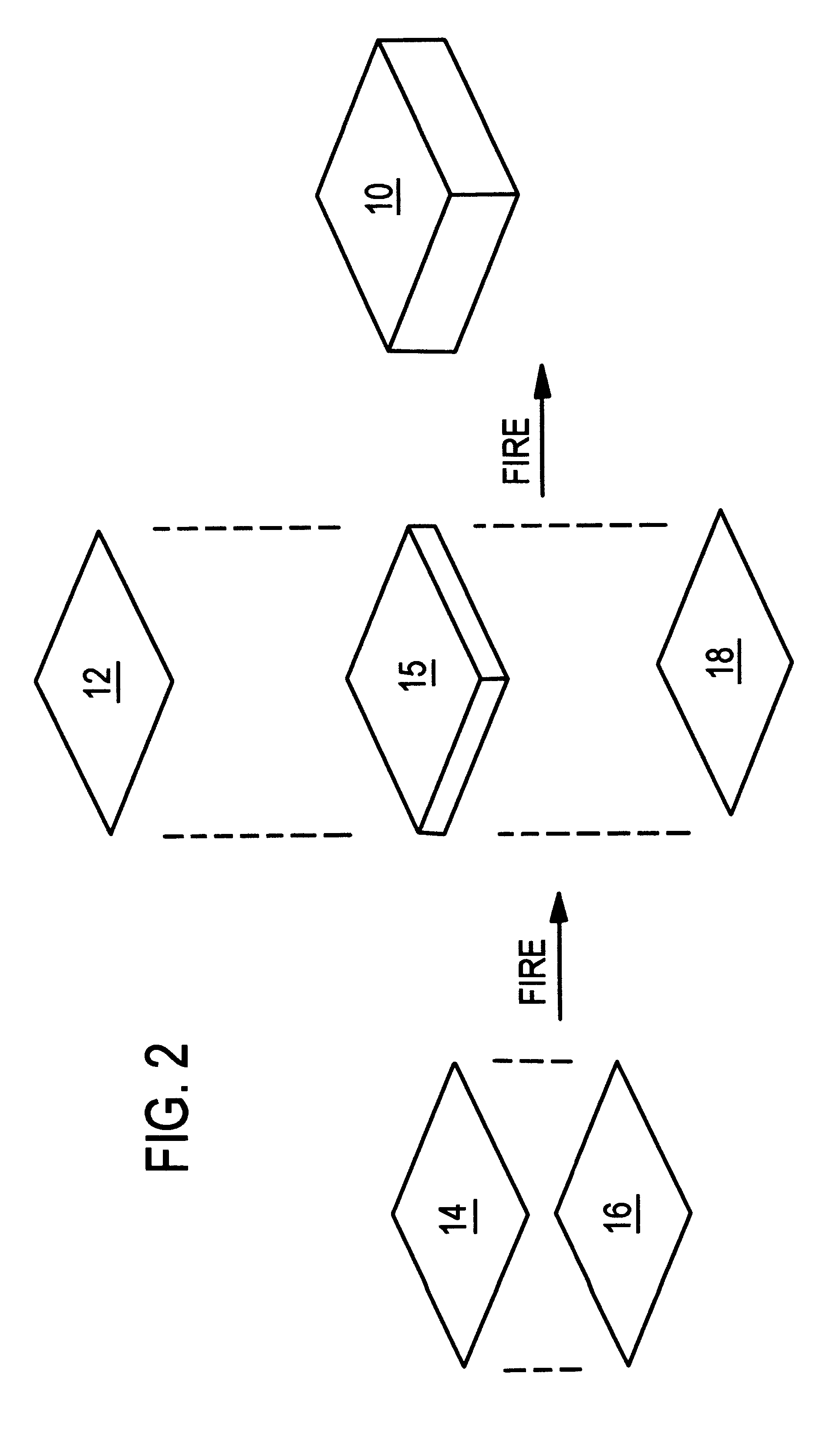

Integrated detonators for use with explosive devices

A detonator assembly is provided for use in oilfield operations to detonate an explosive downhole including a capacitor discharge unit and initiator electrically connected together to form a single unit. It is emphasized that this abstract is provided to comply with the rules requiring an abstract, which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:SCHLUMBERGER TECH CORP

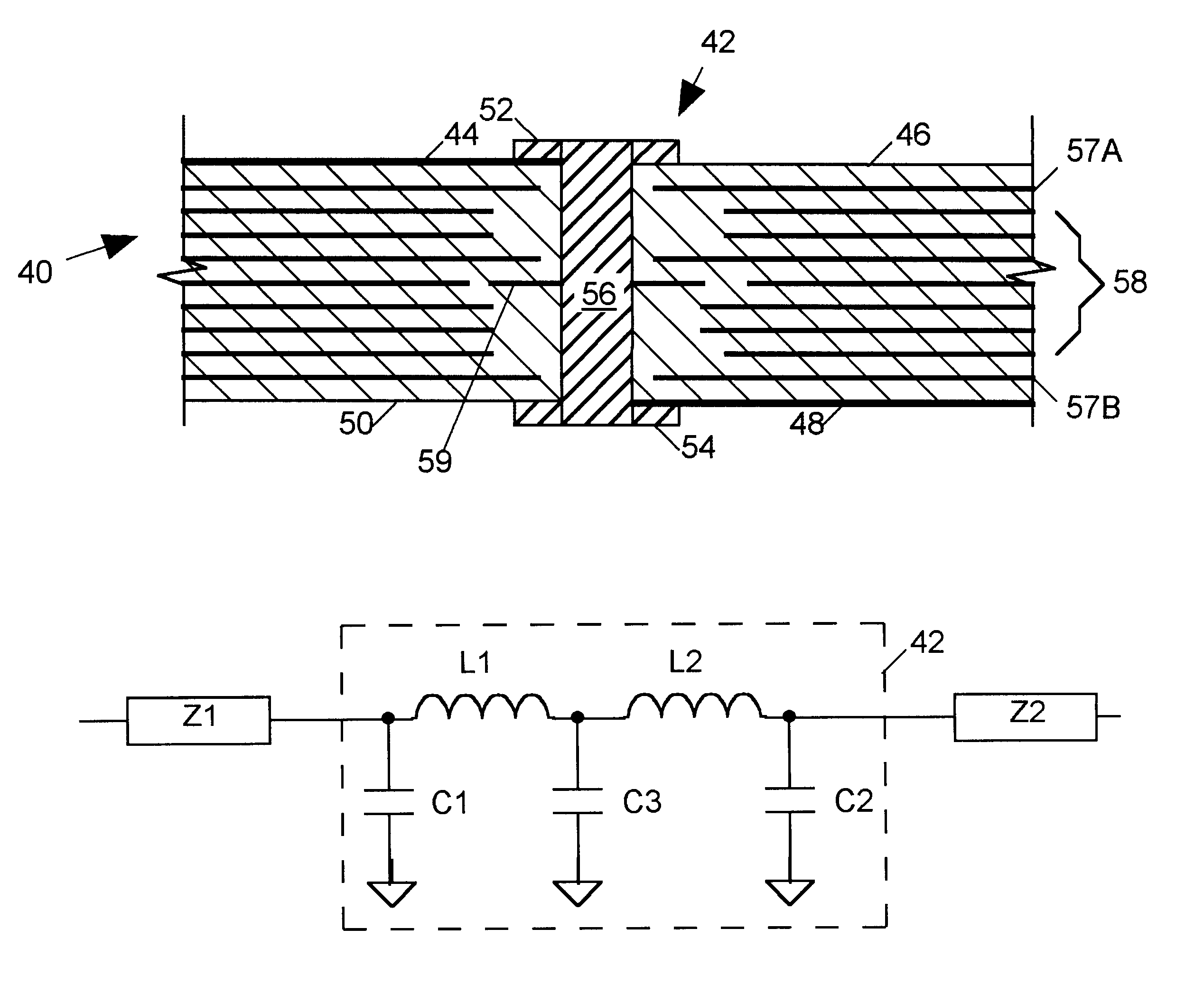

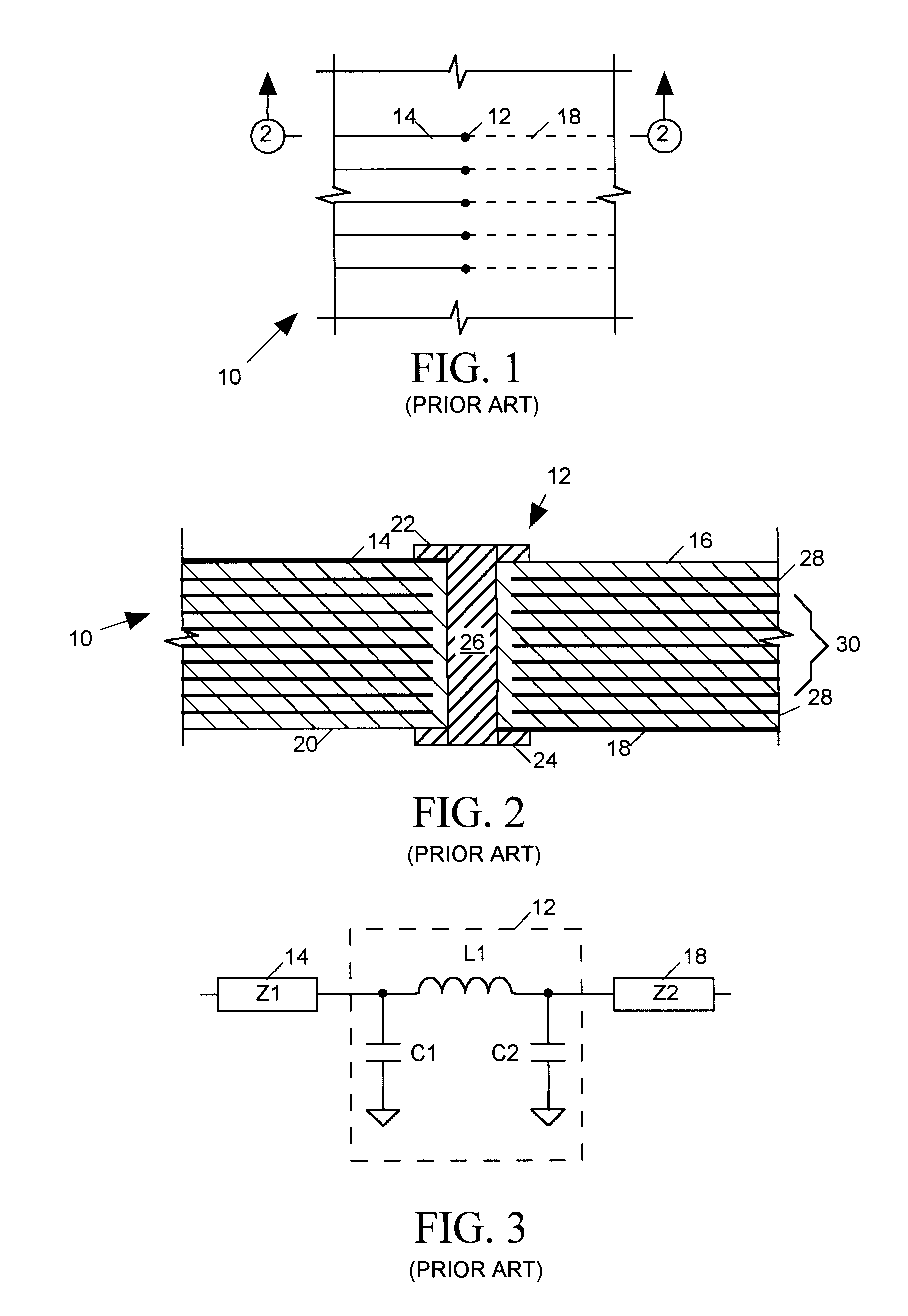

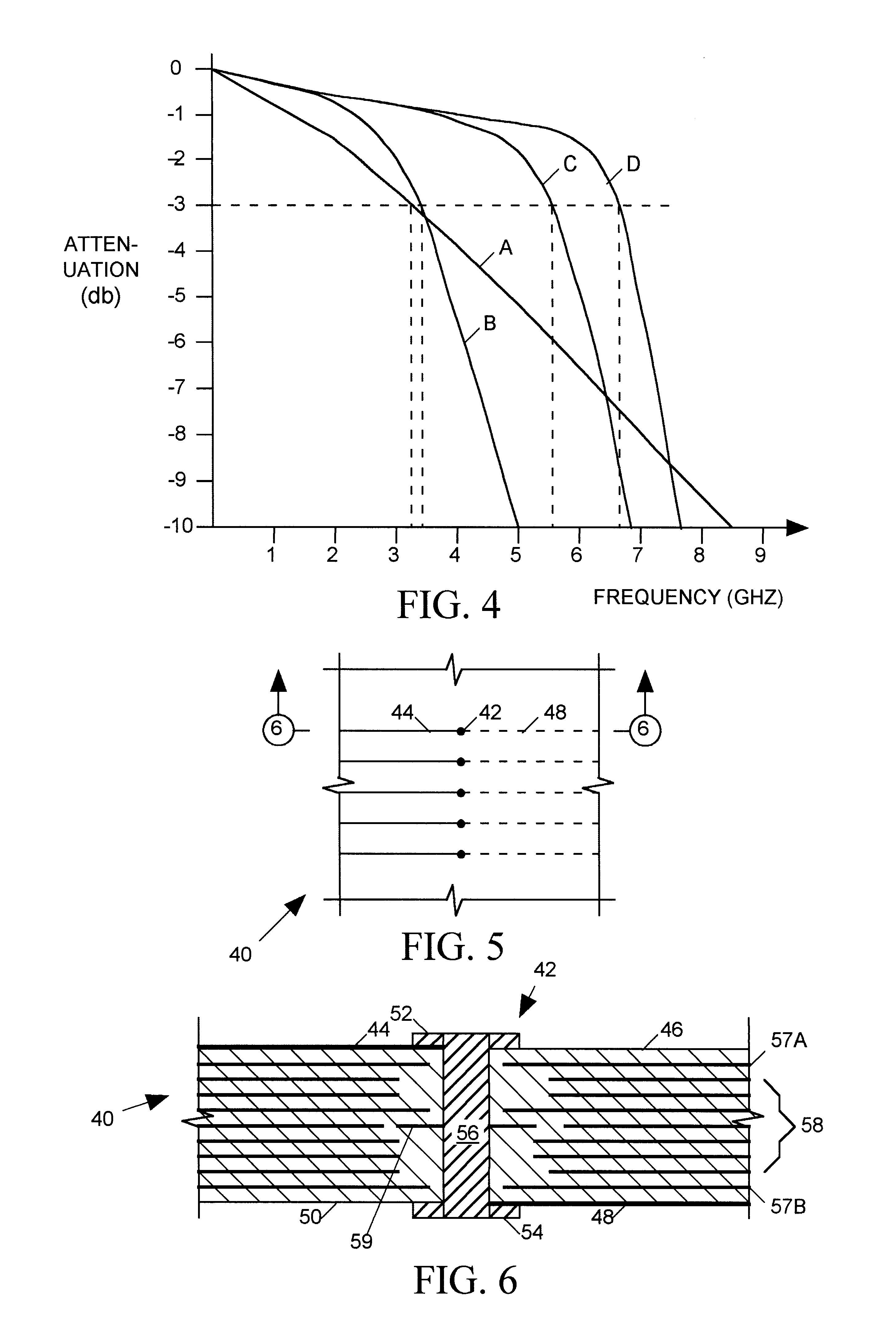

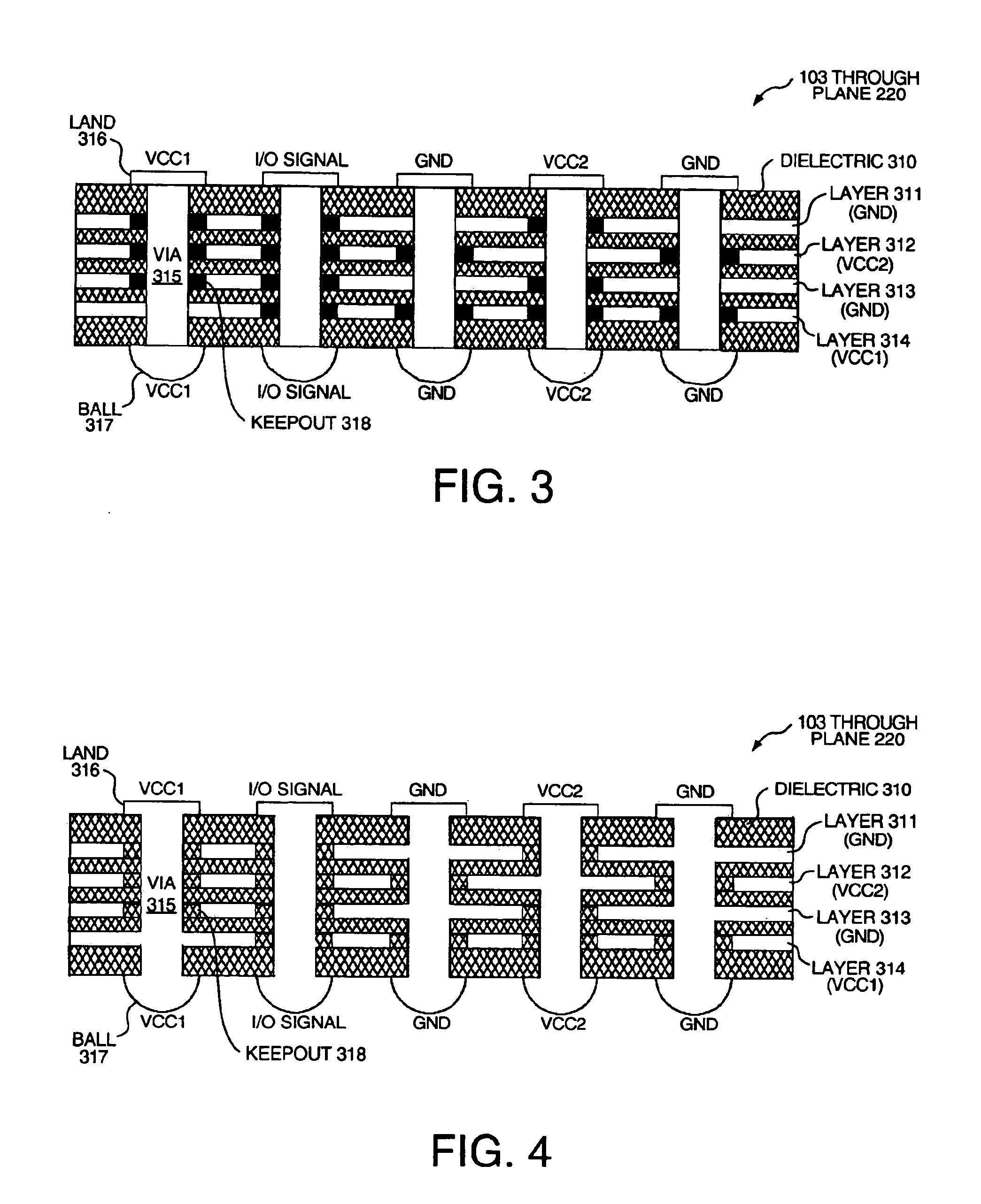

High frequency printed circuit board via

A printed circuit board (PCB) via, providing a conductor extending vertically between microstrip or stripline conductors formed on separate layers of a PCB, includes a conductive pad surrounding the conductor and embedded within the PCB between those PCB layers. The pad's shunt capacitance and the magnitudes of capacitances of other portions of the via are sized relative to the conductor's inherent inductance to optimize frequency response characteristics of the via.

Owner:FORMFACTOR INC

Resin composition, cured resin, sheet-like cured resin, laminated body, prepreg, electronic parts and multilayer boards

InactiveUS20050003199A1Maintain electrical propertiesHigh dielectric constantSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsEpoxyDielectric loss

The invention provides electronic parts which comprise a composite dielectric layer composed of an organic insulating material and a dielectric ceramic powder having a larger relative dielectric constant than the organic insulating material, and which also comprise conductive element sections forming inductor elements, etc., wherein the organic insulating material comprises a cured resin obtained by curing reaction of an epoxy resin with an active ester compound obtained by reaction between a compound with two or more carboxyl groups and a compound with a phenolic hydroxyl group. The dielectric ceramic powders of the described electronic parts have larger relative dielectric constants than the organic insulating materials, and the organic insulating materials have low dielectric loss tangents. It is possible to adequately reduce time-dependent dielectric constant changes in the high-frequency range of 100 MHz and above even with prolonged use at high temperatures of 100° C. and higher, while it is also possible to satisfactorily prevent deformation and other damage to the electronic parts during their handling.

Owner:TDK CORPARATION

High temperature, conductive thin film diffusion barrier for ceramic/metal systems

A multilayer ceramic substrate having a thin film structure containing capacitor connected thereto is provided as an interposer capacitor, the capacitor employing platinum as the bottom electrode of the capacitor. In a preferred capacitor, a dielectric material such as barium titanate is used as the dielectric material between the capacitor electrodes. The fabrication of the interposer capacitor requires an in-situ or post deposition high temperature anneal and the use of such dielectrics requires heating of the capacitor structure in a non-reducing atmosphere. A layer of a high temperature, thin film diffusion barrier such as TaSiN on the lower platinum electrode between the electrode and underlying multilayer ceramic substrate prevents or minimizes oxidization of the metallization of the multilayer ceramic substrate to which the thin film structure is connected during the fabrication process. A method is also provided for fabricating an interposer capacitor with a multilayer ceramic substrate base and a thin film multilayer structure having at least one capacitor comprising at least one bottom platinum electrode.

Owner:IBM CORP

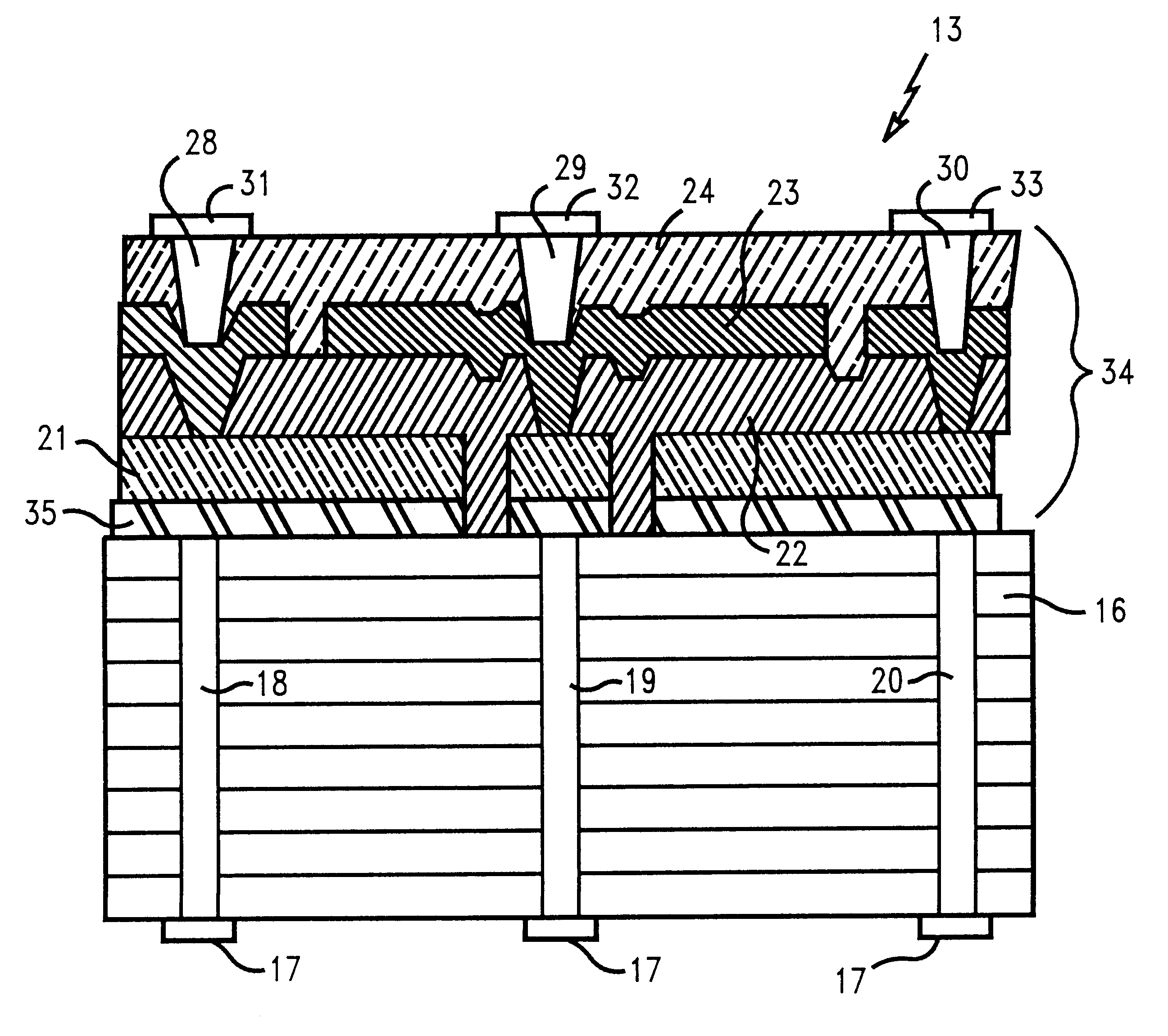

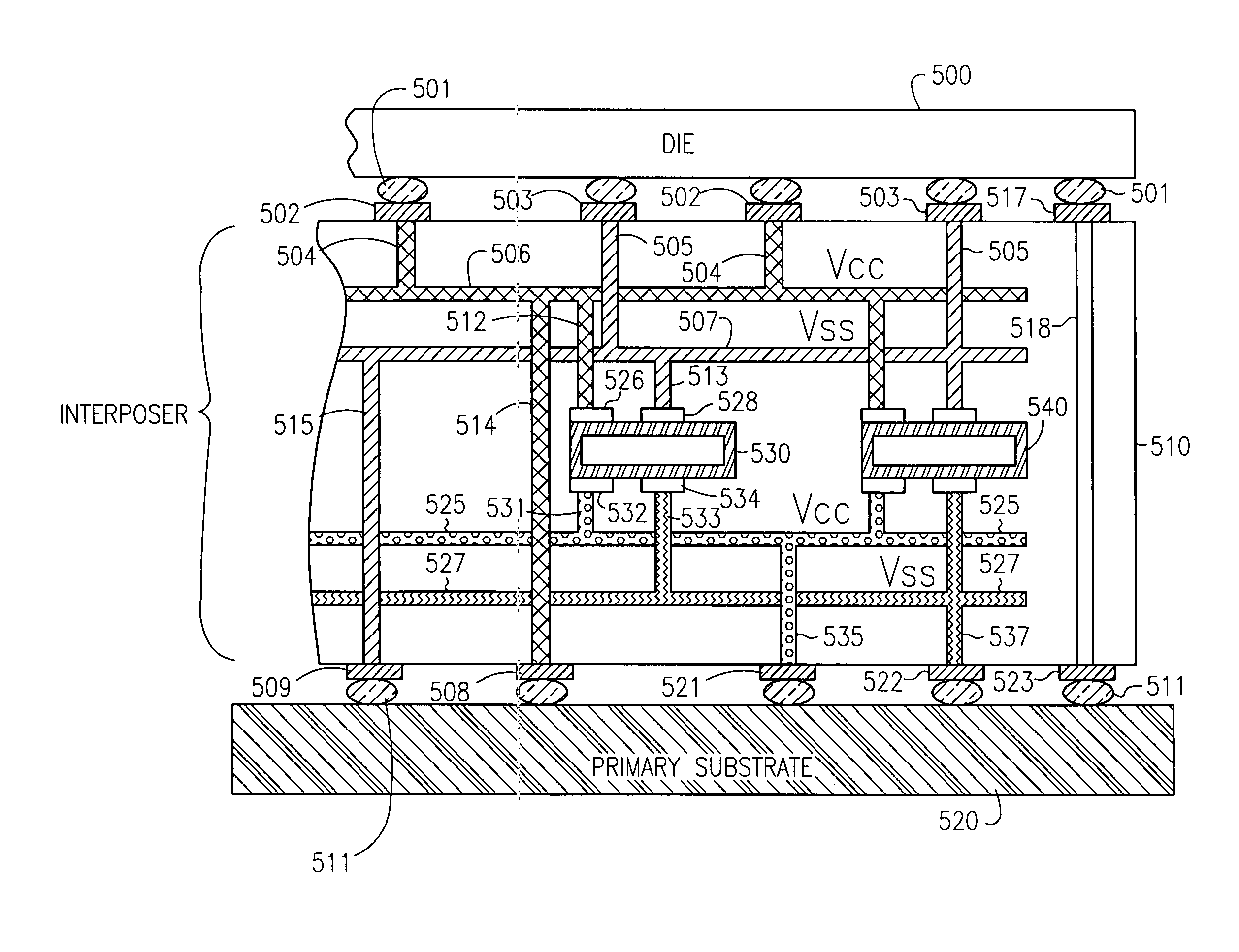

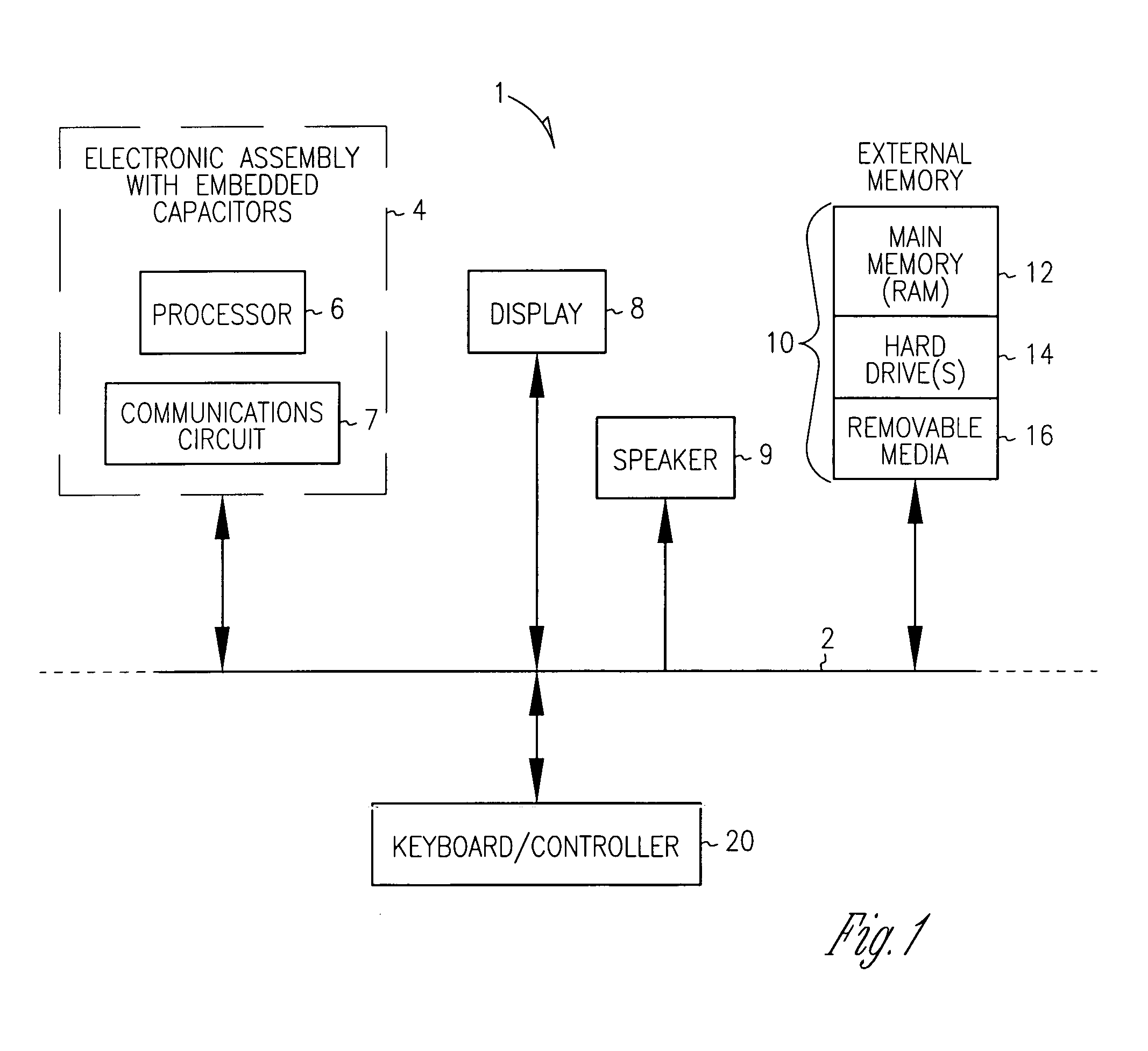

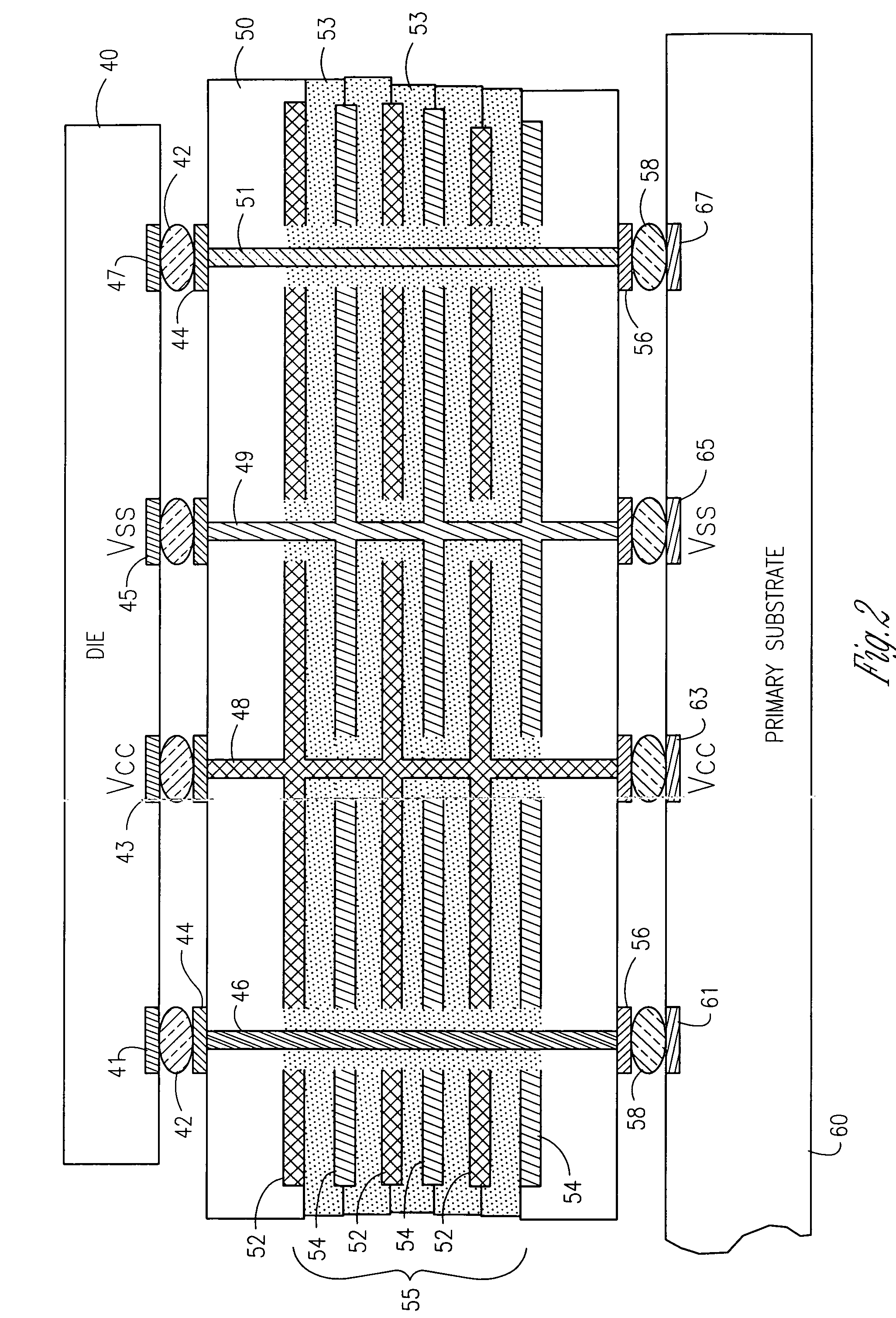

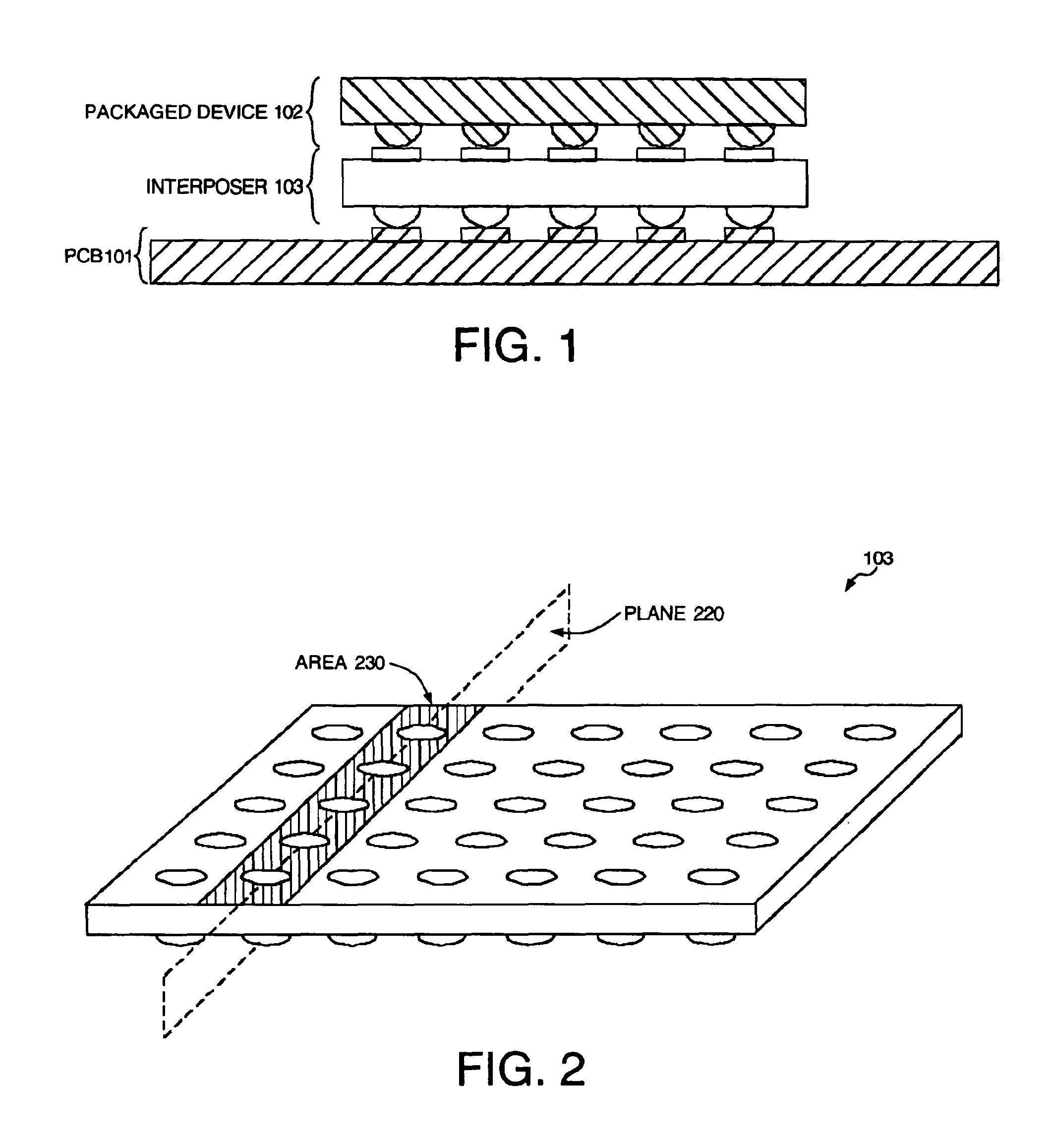

Electronic assemblies and systems comprising interposer with embedded capacitors

InactiveUS20060012966A1Semiconductor/solid-state device detailsSolid-state devicesData processing systemElectrical conductor

To reduce switching noise, the power supply terminals of an integrated circuit die are coupled to the respective terminals of at least one capacitor embedded in an interposer that lies between the die and a substrate. In an embodiment, the interposer is a multilayer ceramic structure that couples power and signal conductors on the die to corresponding conductors on the substrate. The capacitor is formed of at least one high permittivity layer and in an embodiment comprises several high permittivity layers interleaved with conductive layers. Alternatively, the capacitor can comprise at least one embedded discrete capacitor. Also described are an electronic system, a data processing system, and various methods of manufacture.

Owner:INTEL CORP

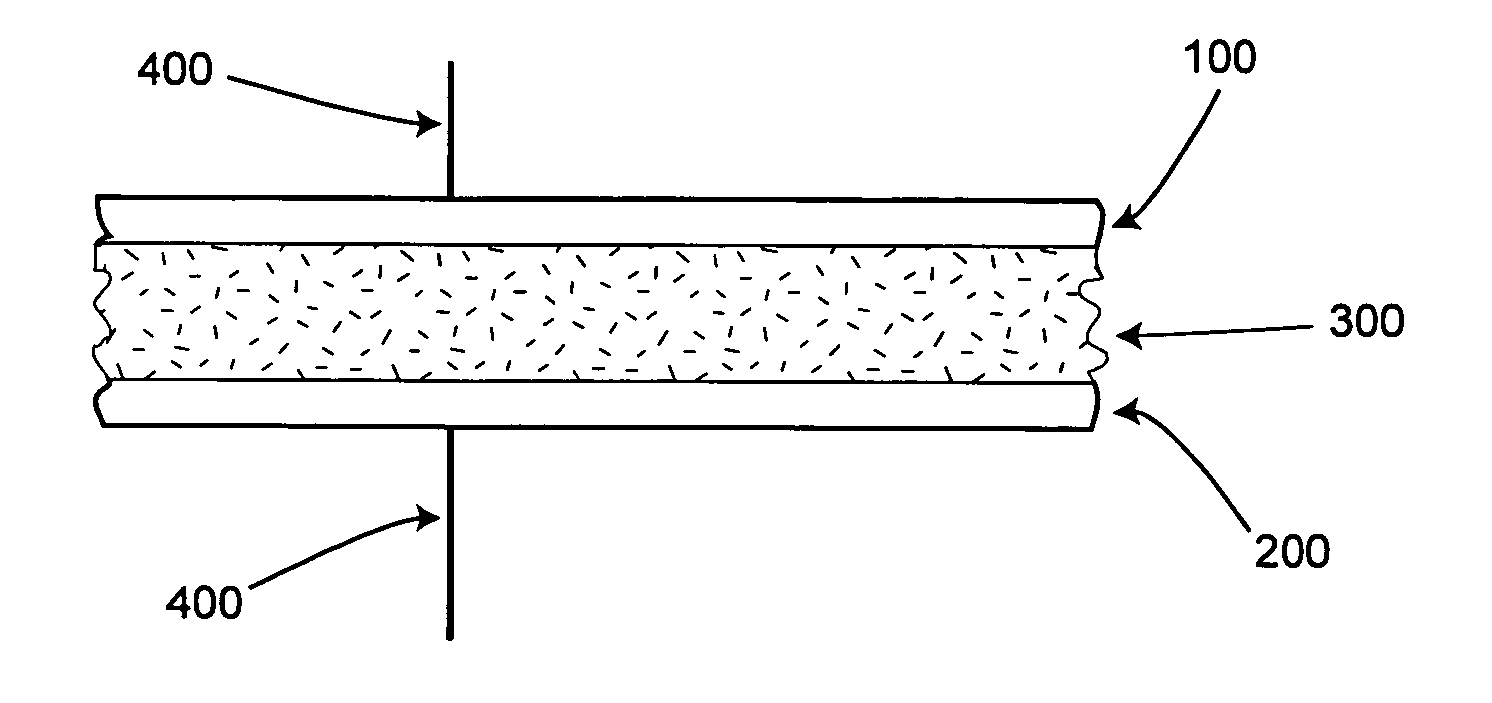

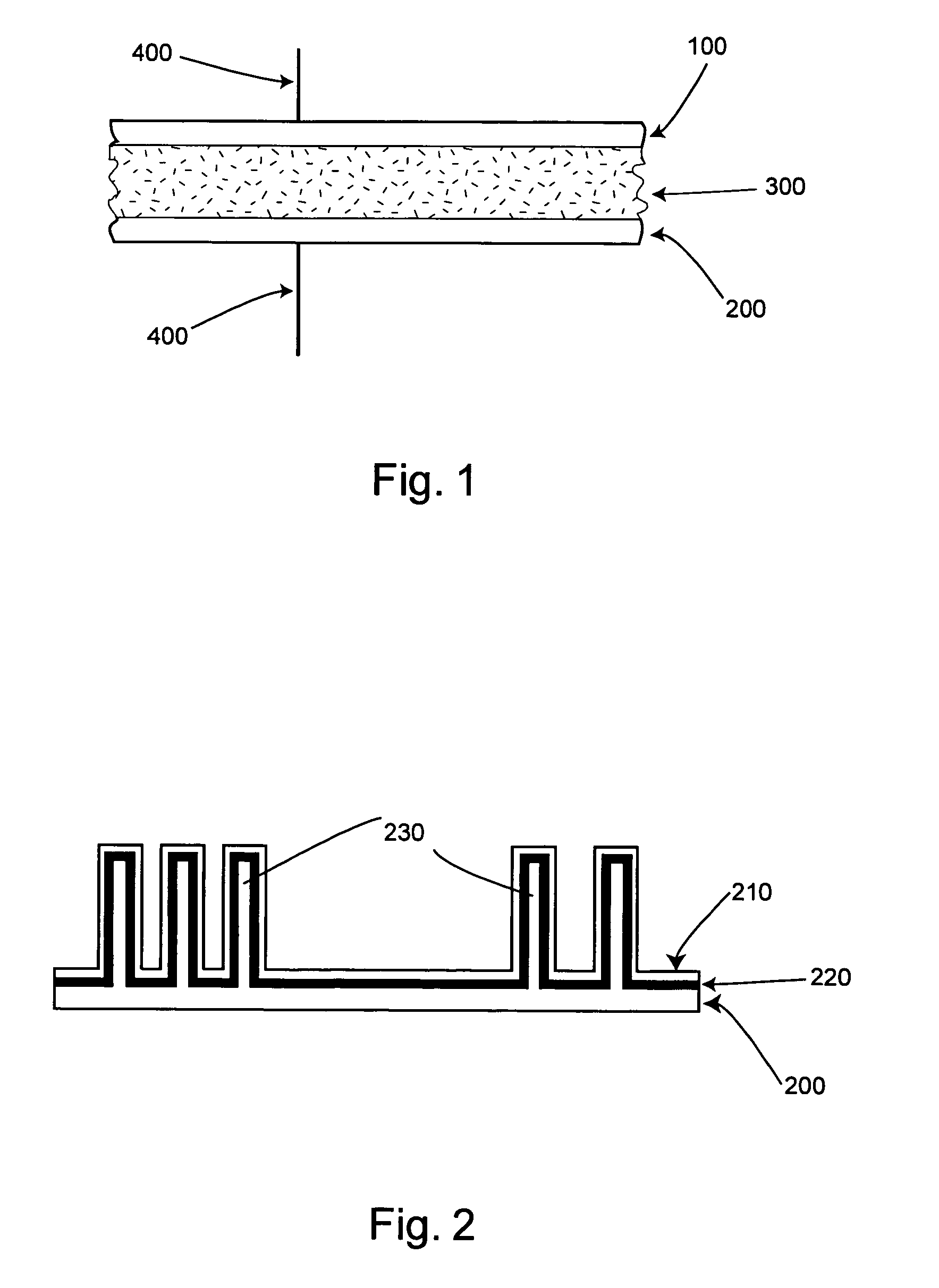

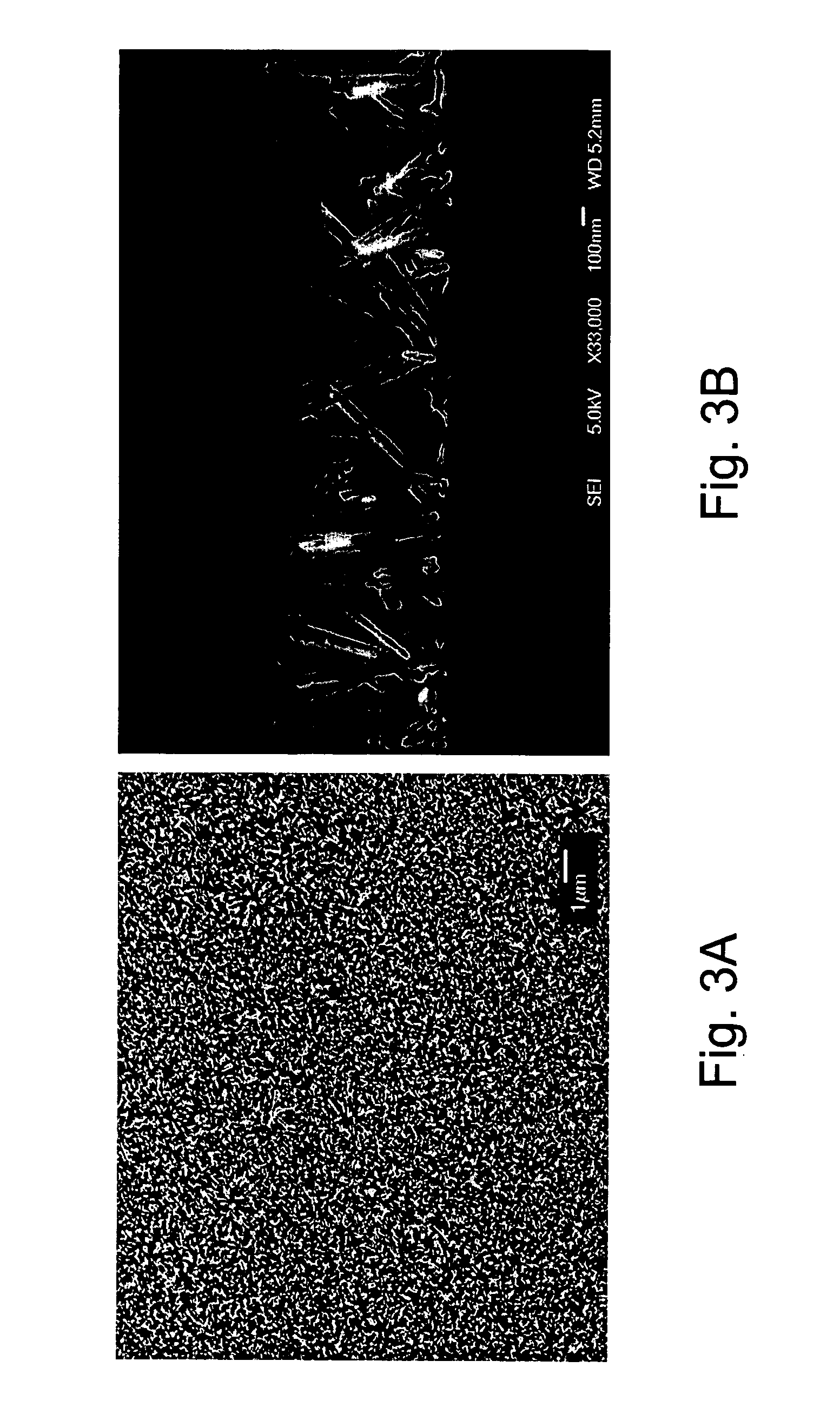

Nanofiber surface based capacitors

ActiveUS7057881B2Increase surface areaFixed capacitor electrodesThin/thick film capacitorNanofiberEngineering

This invention provides novel capacitors comprising nanofiber enhanced surface area substrates and structures comprising such capacitors, as well as methods and uses for such capacitors.

Owner:ONED MATERIAL INC

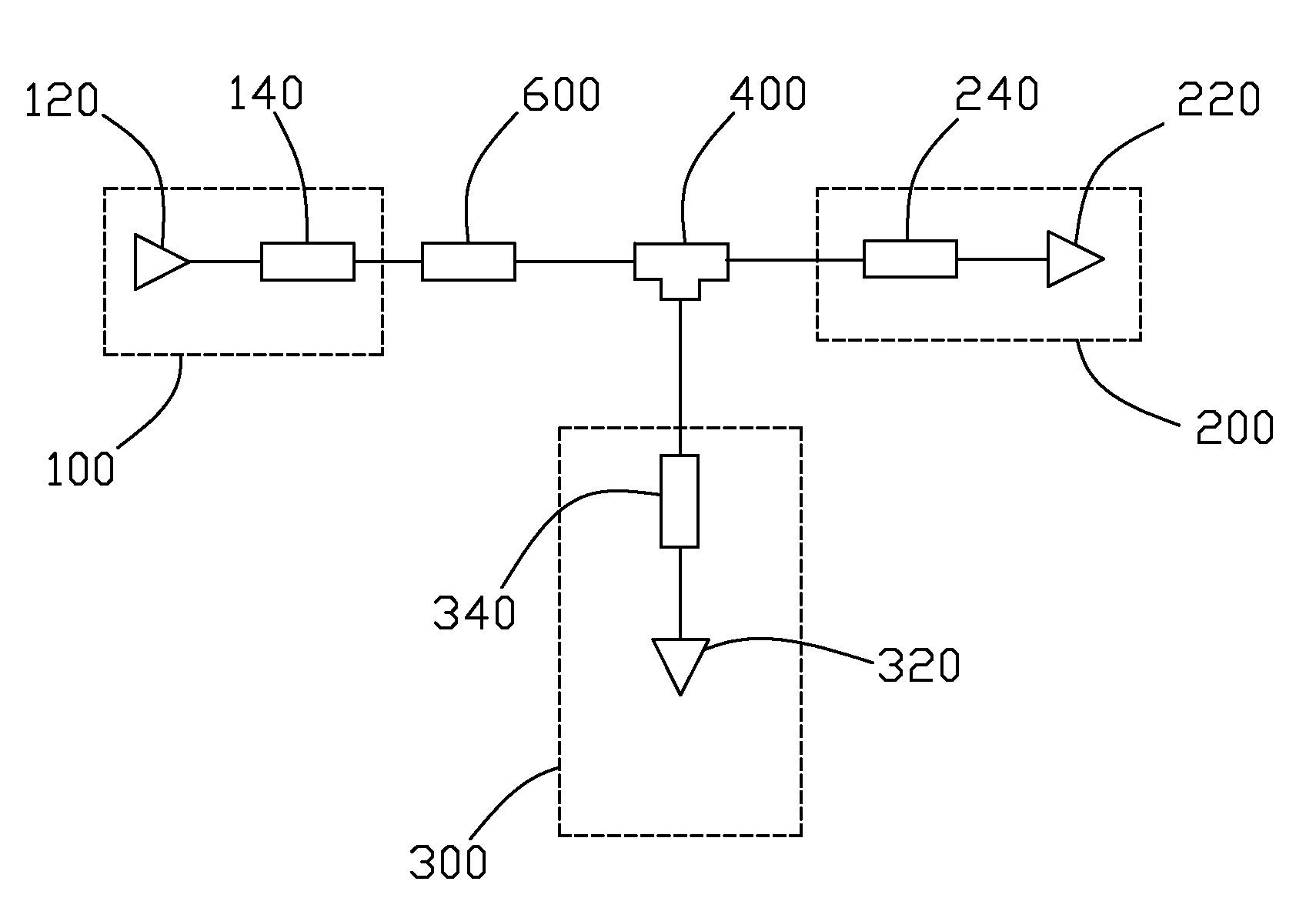

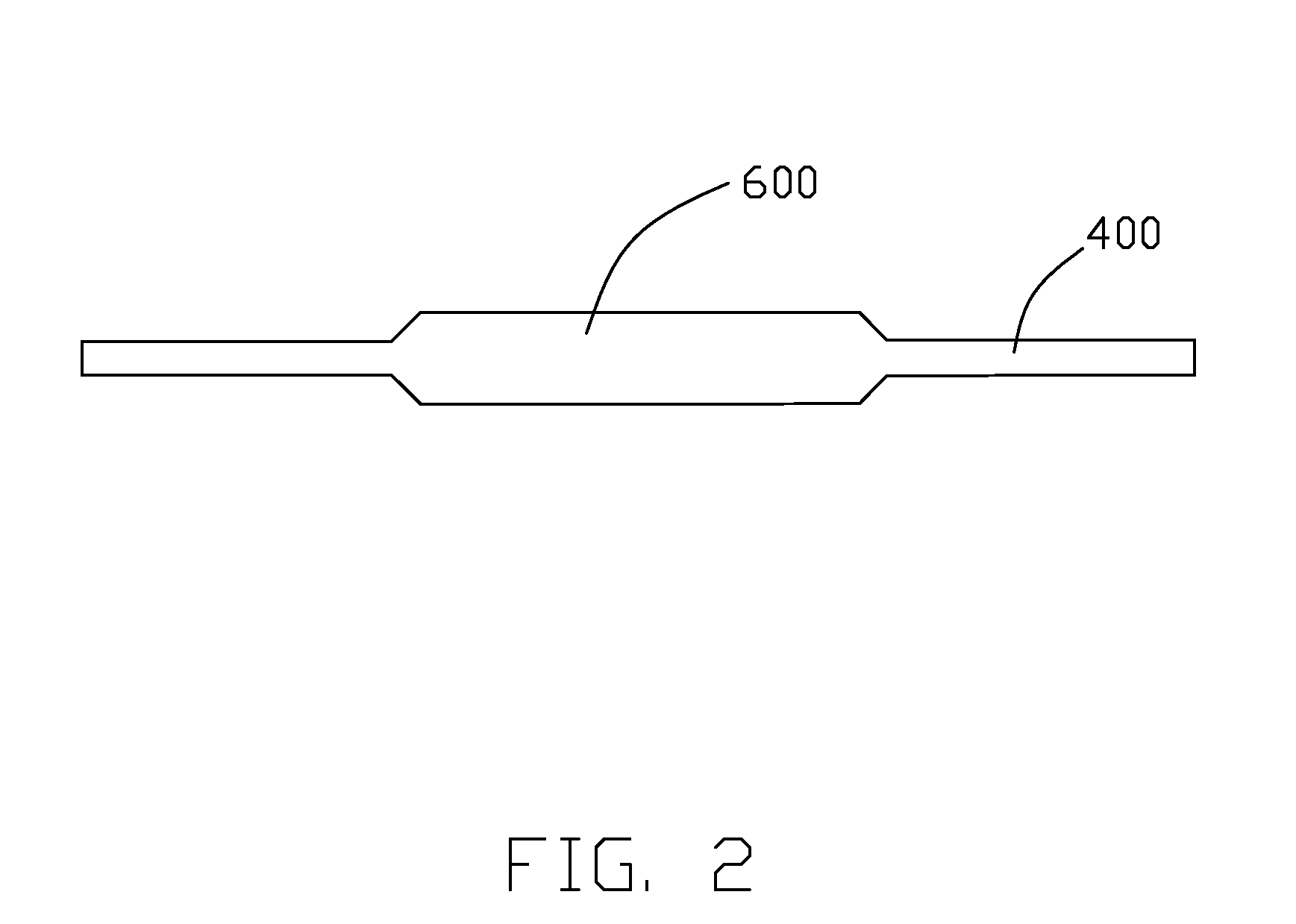

High speed signal transmission structure

InactiveUS20070229184A1Easy to manufactureSuitable for mass productionPrinted circuit aspectsPrinted capacitor incorporationEngineeringCopper

A signal transmission structure includes a driving circuit block, a receiving circuit block, a main transmission line, and a copper patch. The main transmission line connects the driving circuit block to the receiving circuit block for transmitting signals therebetween. The copper patch is arranged at the main transmission line, and has a rectangular shape. The copper patch can reduce switching rates when the signal state of the driving circuit changes rapidly. The copper patch serves as a compensation capacitor, to reduce a rate of switching of the signal, and to reduce or even eliminate the problems of crosstalk and overshooting and undershooting of signals. It is of advantage that the copper patch is simple to manufacture and very suitable for mass production.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

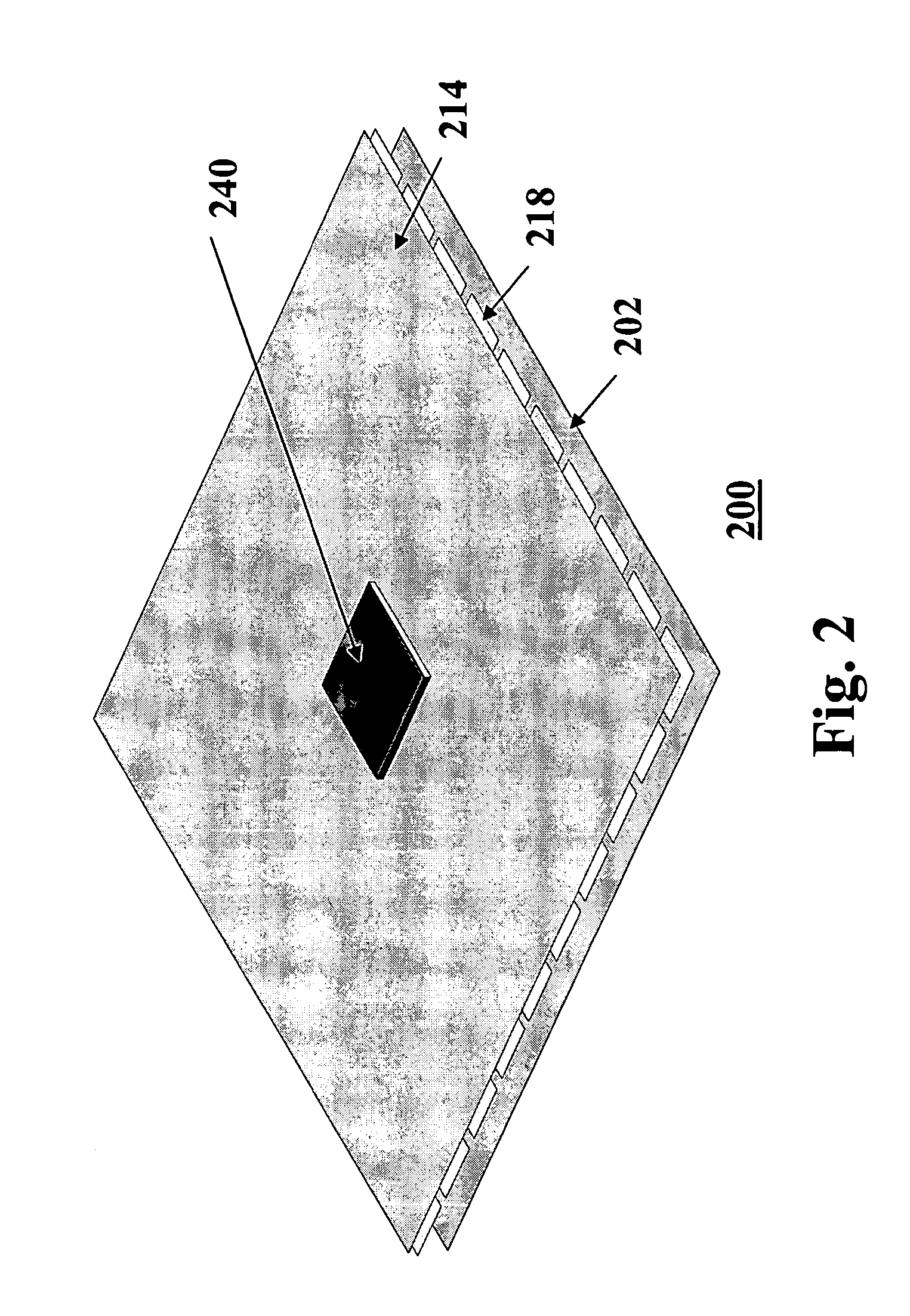

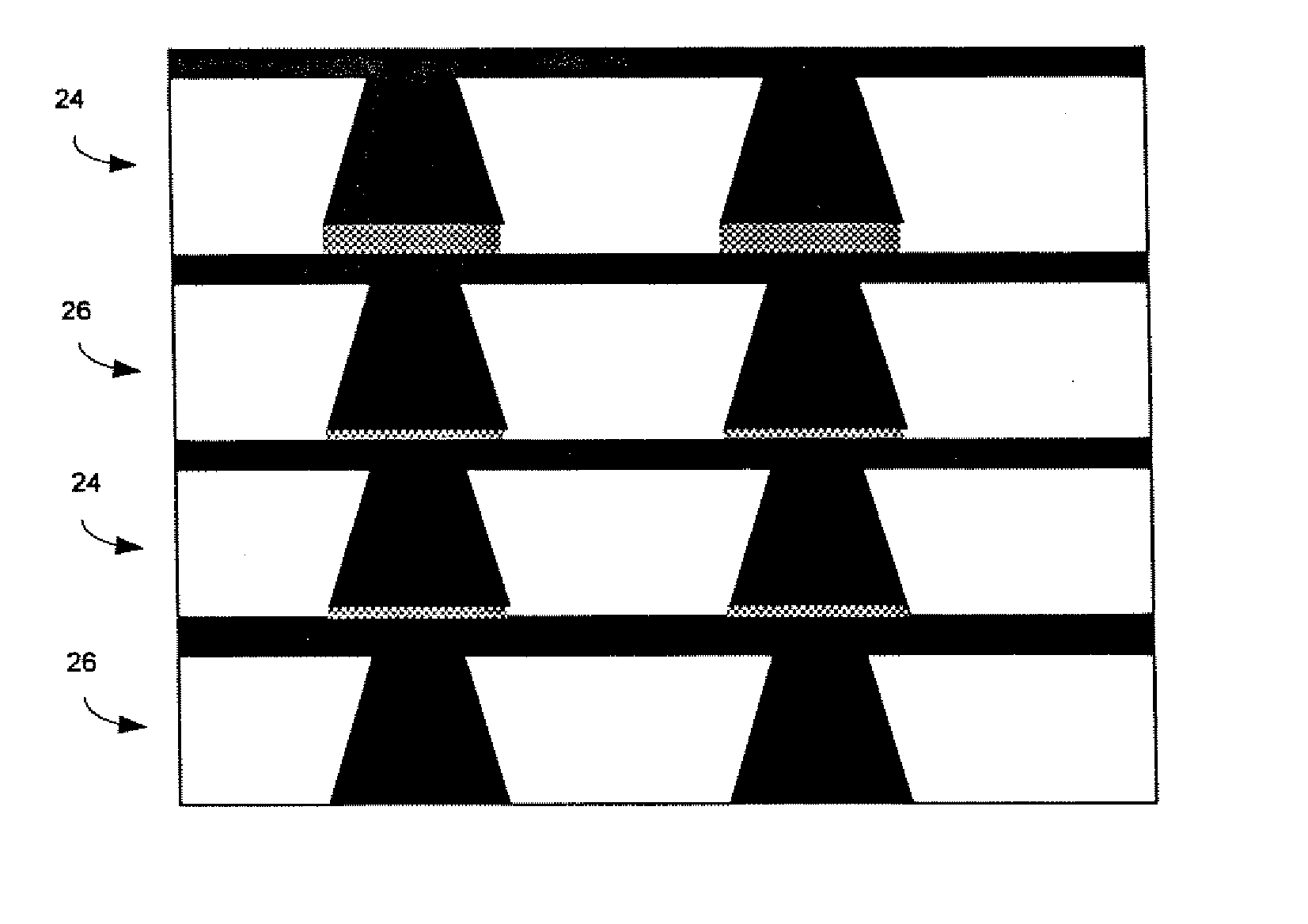

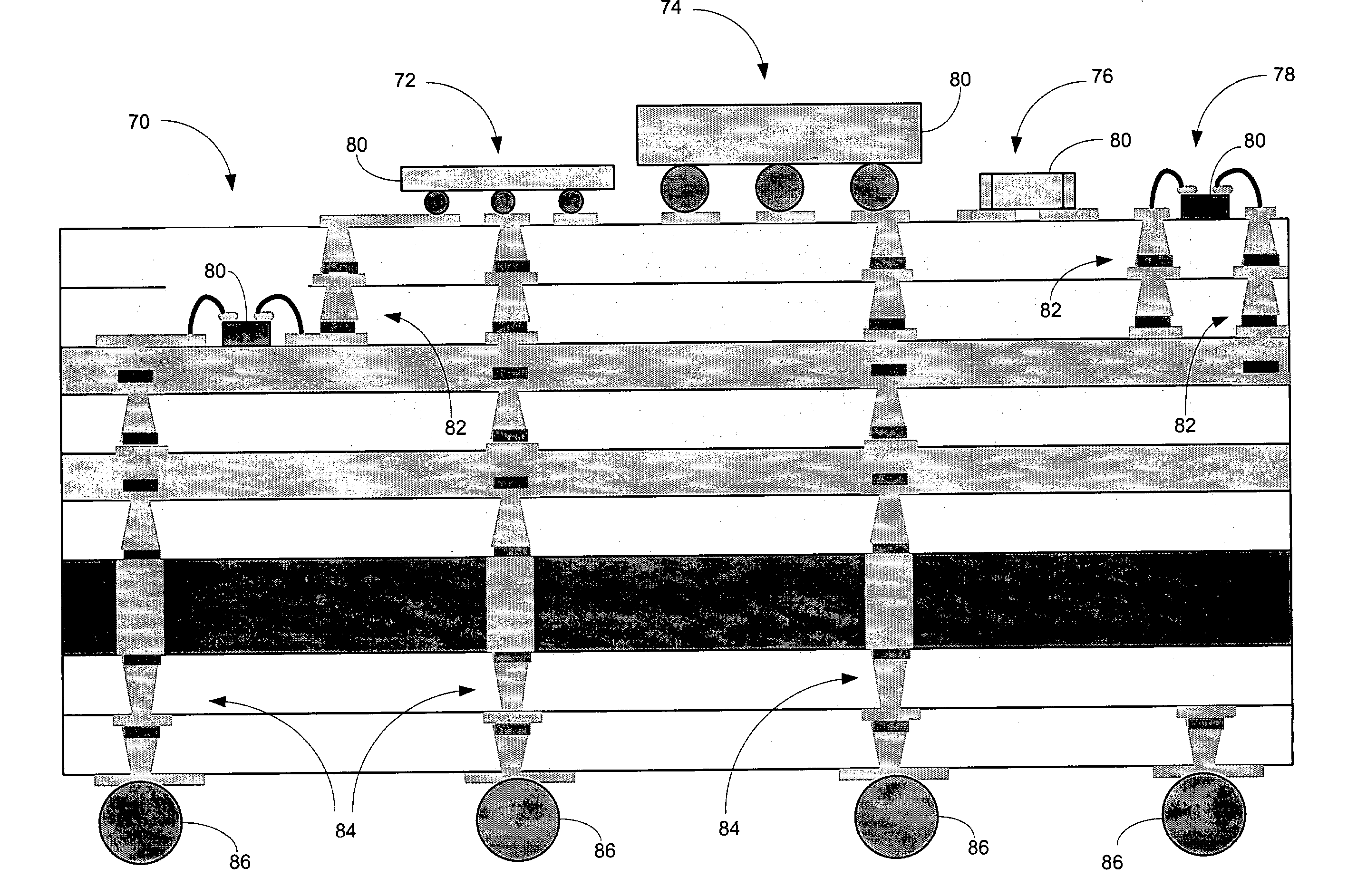

Circuit and method for broadband switching noise suppression in multilayer printed circuit boards using localized lattice structures

InactiveUS20050205292A1Eliminate power plane resonanceImproved RF isolationMagnetic/electric field screeningCross-talk/noise/interference reductionBroadbandNoise suppression

An apparatus for suppressing noise in an electronic device includes a multiple layer structure in which localized arrays of chip capacitors and / or patches around sources of electromagnetic waves are used. The PCB includes multiple conductive layers at different potentials, dielectric layers separating the conductive layers, conductive rods extending between at least two of the conductive layers, and a layer of patches disposed adjacent or on one or more of the conductive layers. The conductive rods are connected to one of the conductive layers and chip capacitors connect the conductive rods to another of the conductive layers. A particular location can be effectively isolated from noise using a few unit cells of an array of patches / capacitors partially or completely surrounding the particular location.

Owner:ETENNA

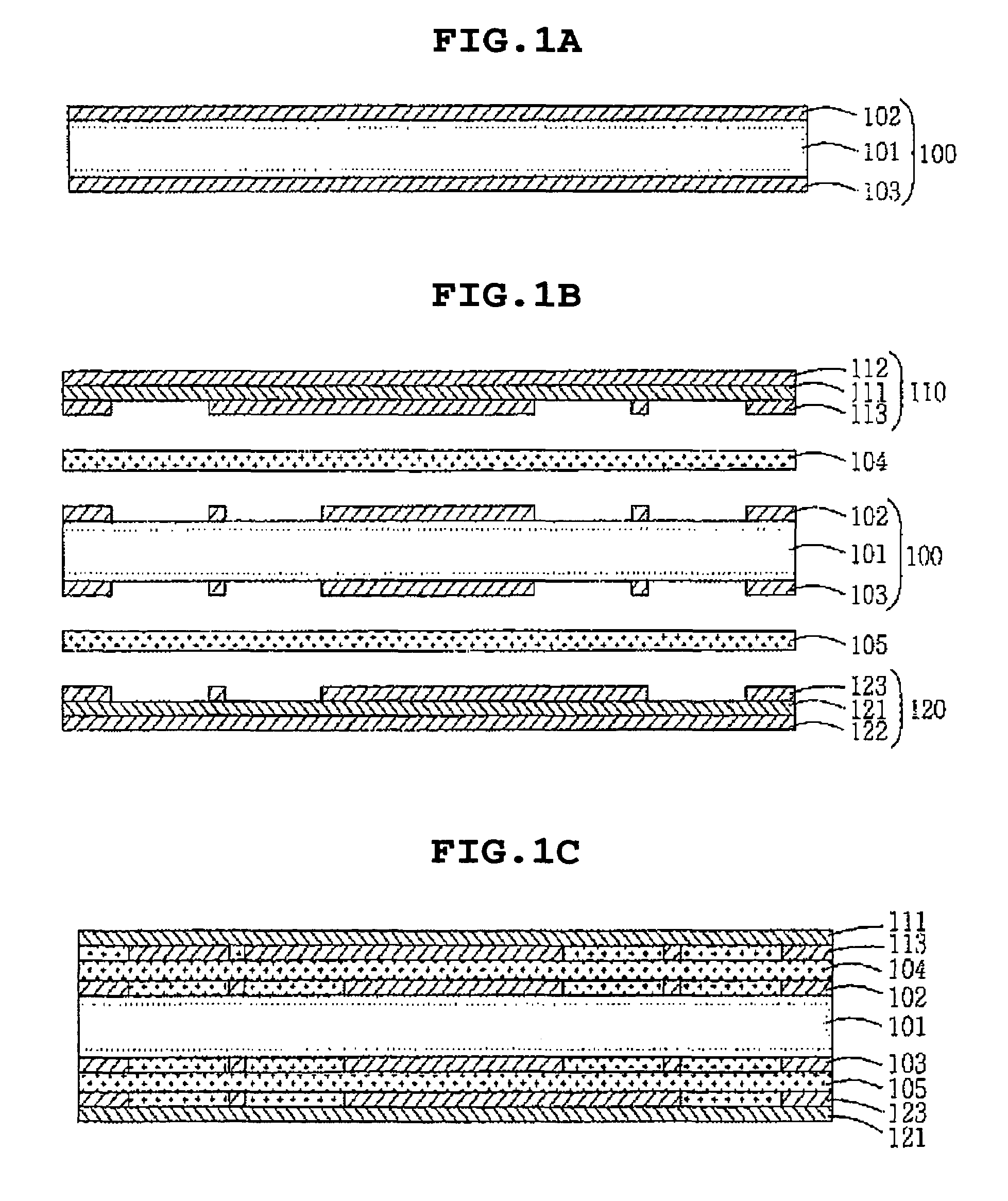

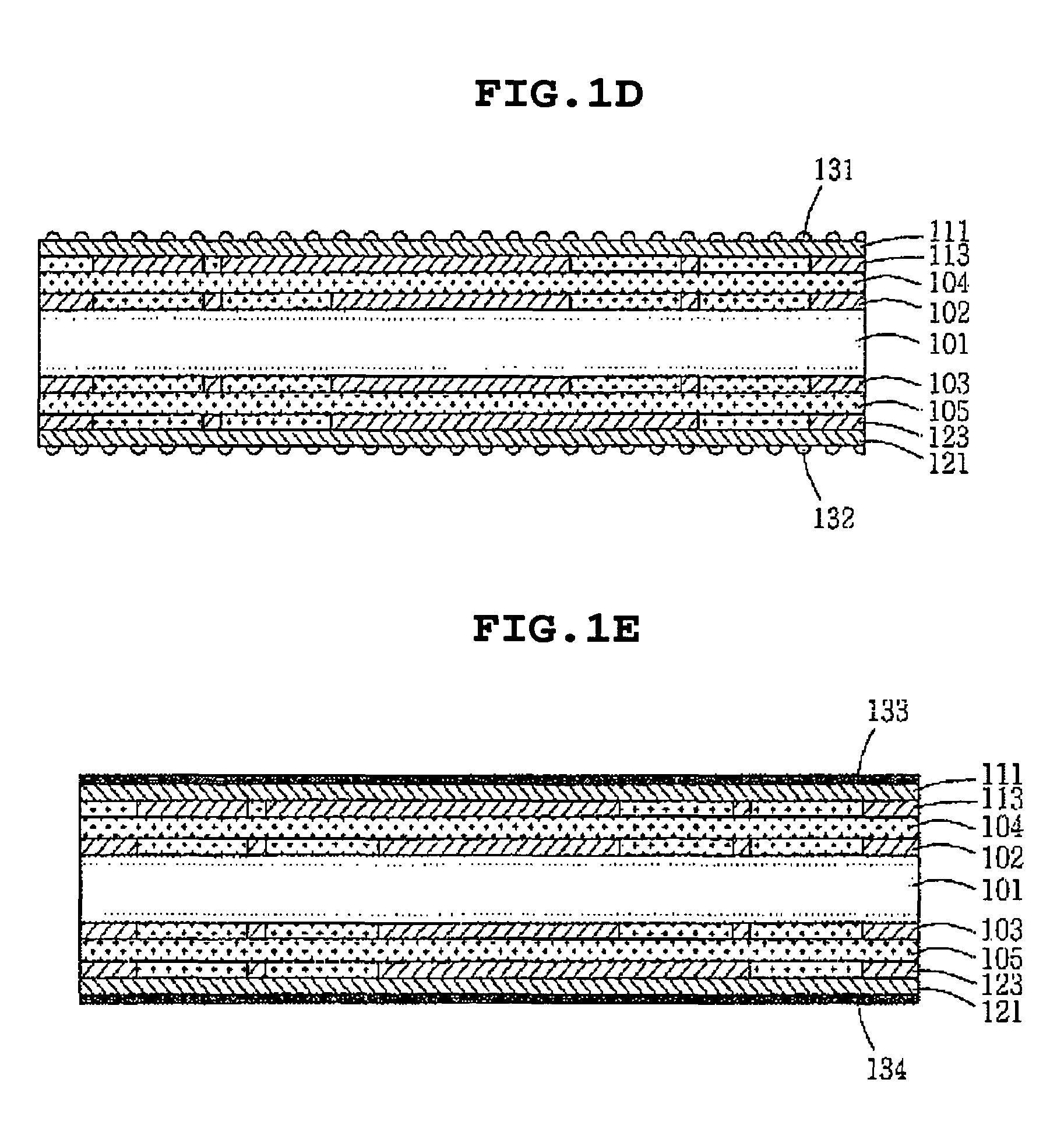

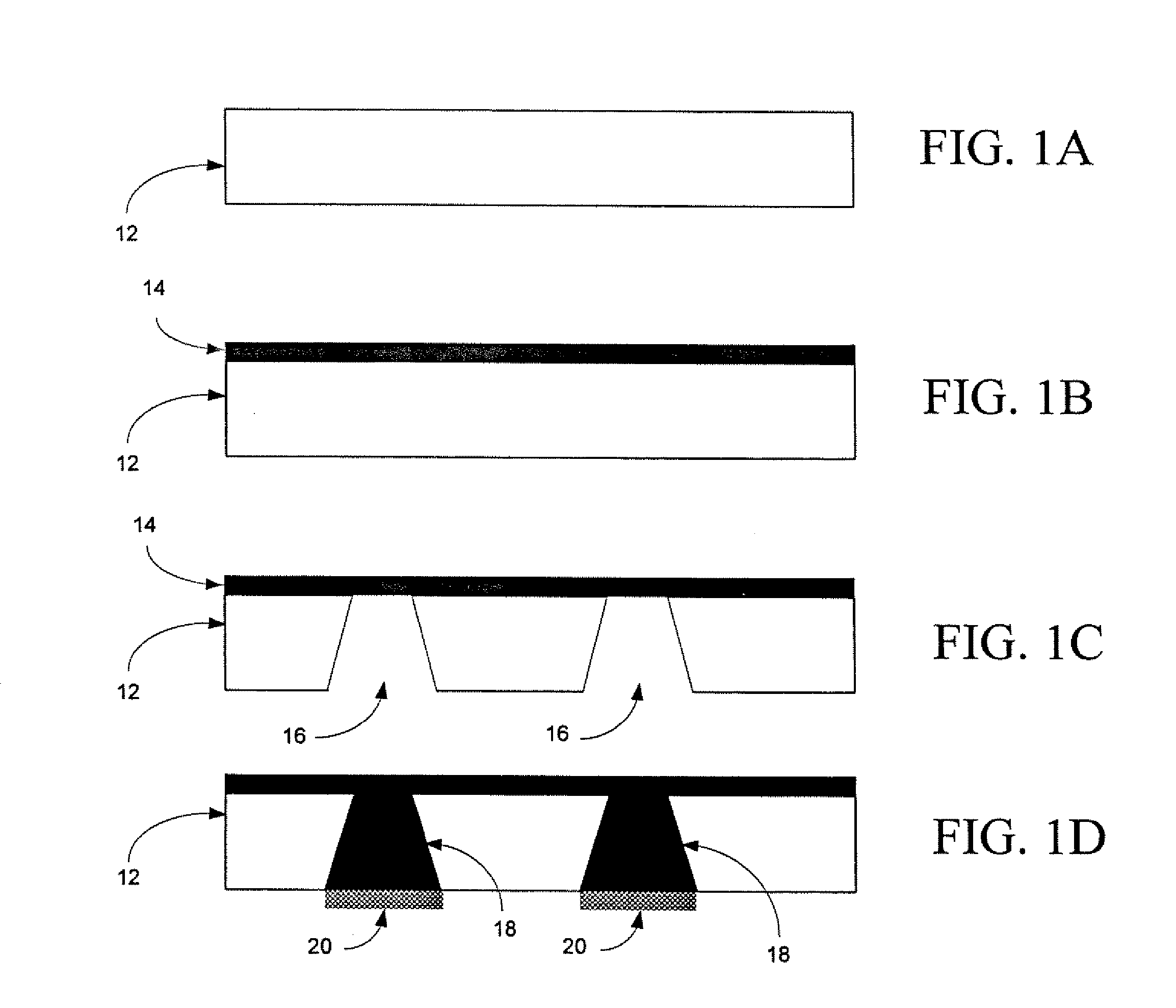

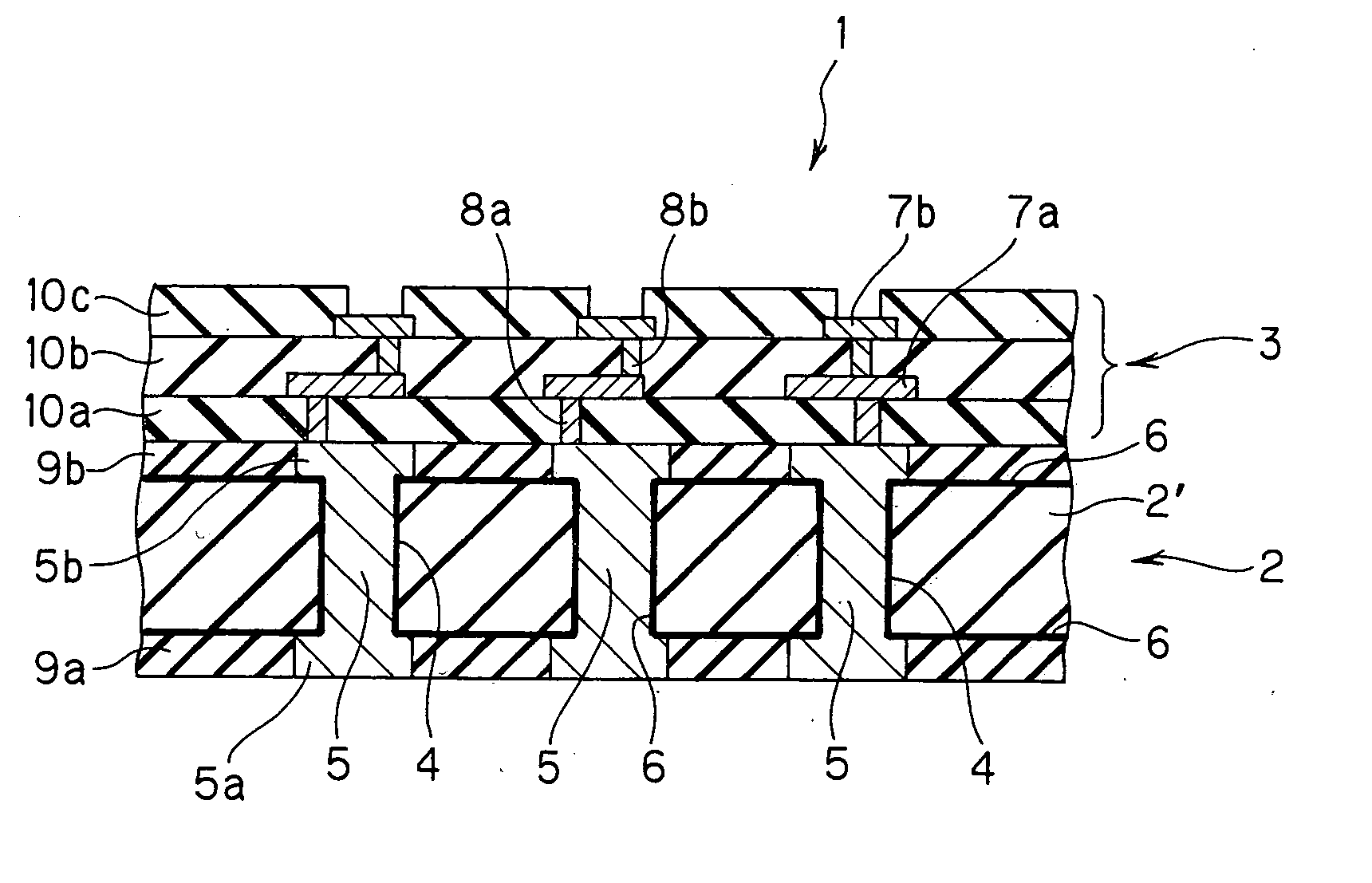

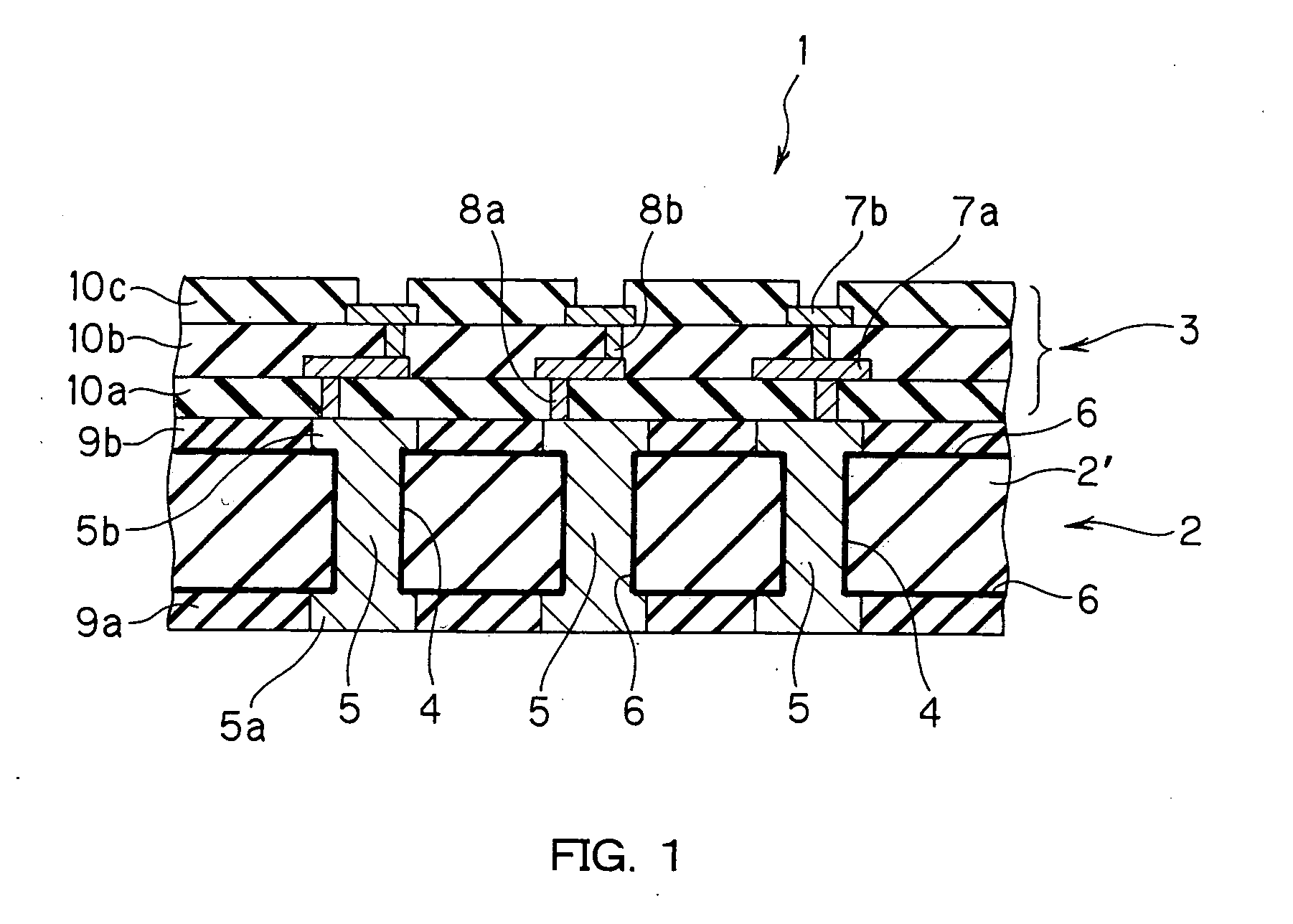

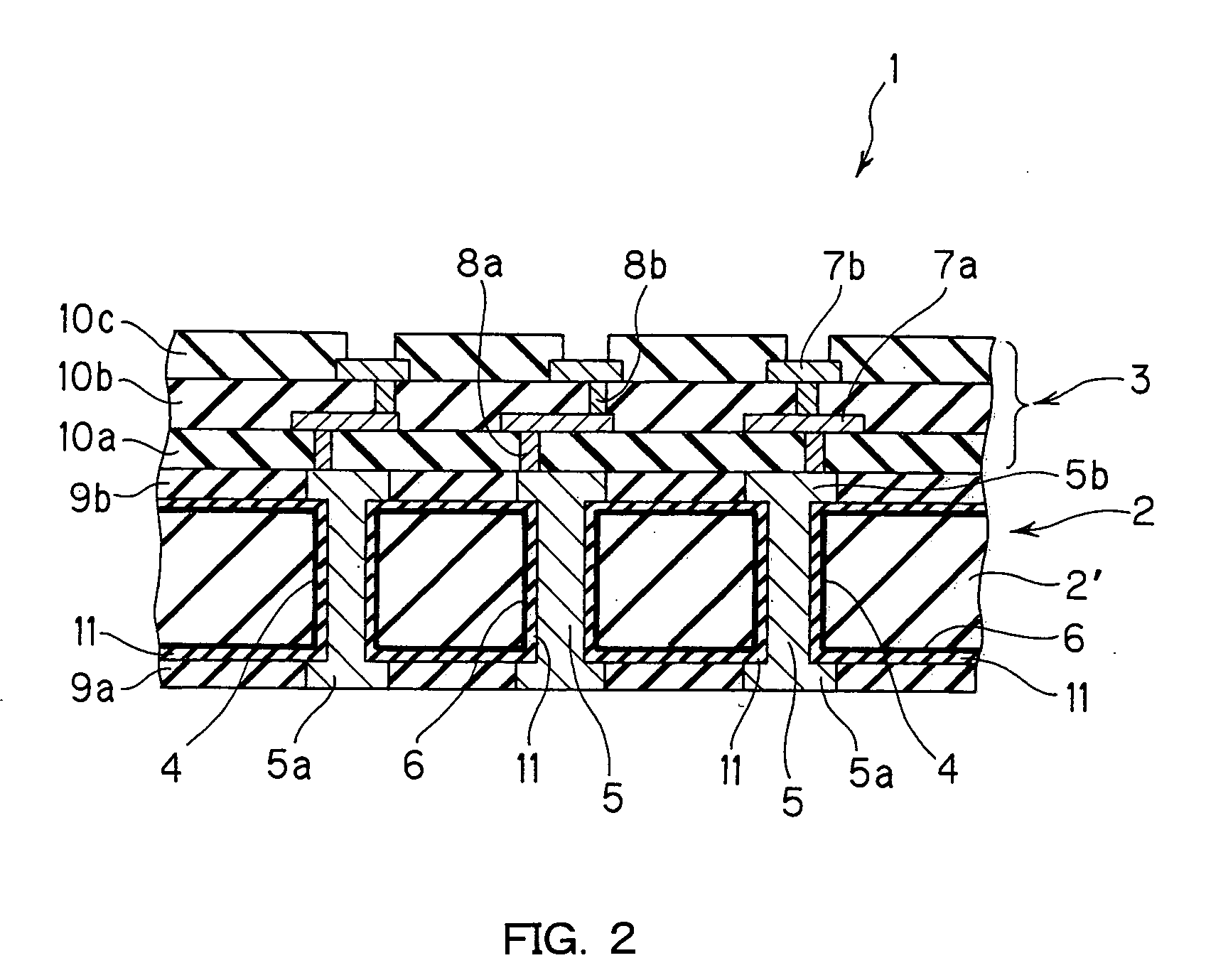

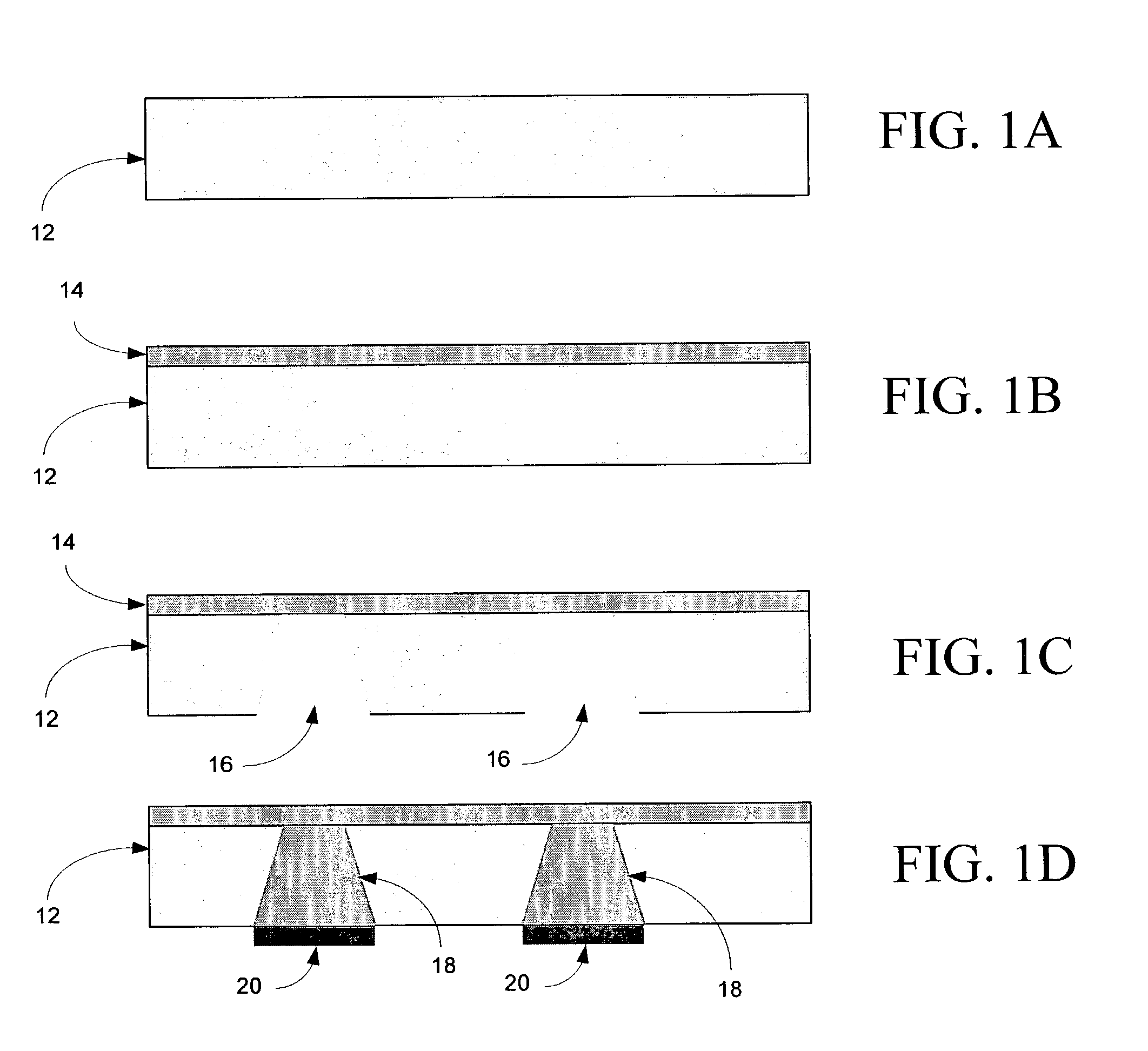

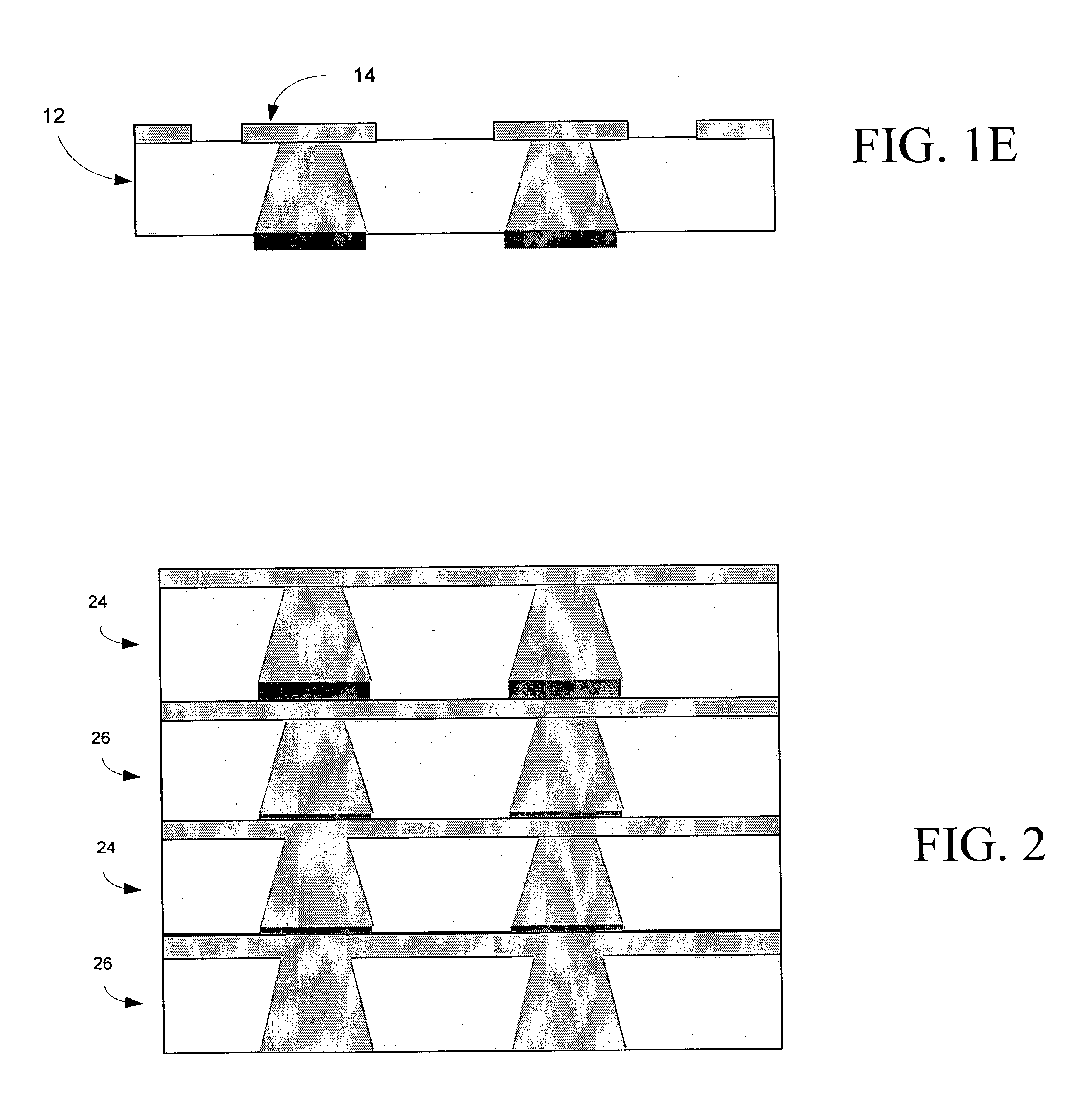

Method of fabricating printed circuit board having embedded multi-layer passive devices

InactiveUS7293356B2Increase capacitancePrinted circuit assemblingPrinted circuit aspectsCapacitancePrinted circuit board

The present invention relates to a method of fabricating a printed circuit board having embedded multi-layer passive devices, and particularly, to a method of fabricating a printed circuit board having an embedded multi-layer capacitor, in which a capacitor is formed to have multiple layers in the PCB to increase capacitance.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Circuit and method for suppression of electromagnetic coupling and switching noise in multilayer printed circuit boards

InactiveUS7215007B2Suppress powerRemoval of powerTransmission control/equlisationSemiconductor/solid-state device detailsElectromagnetic couplingCapacitance

Apparatus for suppressing noise and electromagnetic coupling in the printed circuit board of an electronic device includes an upper conductive plate and an array of conductive coplanar patches positioned a distance t2 from the upper conductive plate. The distance t2 is chosen to optimize capacitance between the conductive coplanar patches and the upper conductive plate for suppression of noise or electromagnetic coupling. The apparatus further includes a lower conductive plate a distance t1 from the array of conductive coplanar patches and conductive rods extending from respective patches to the lower conductive plate.

Owner:WEMTEC

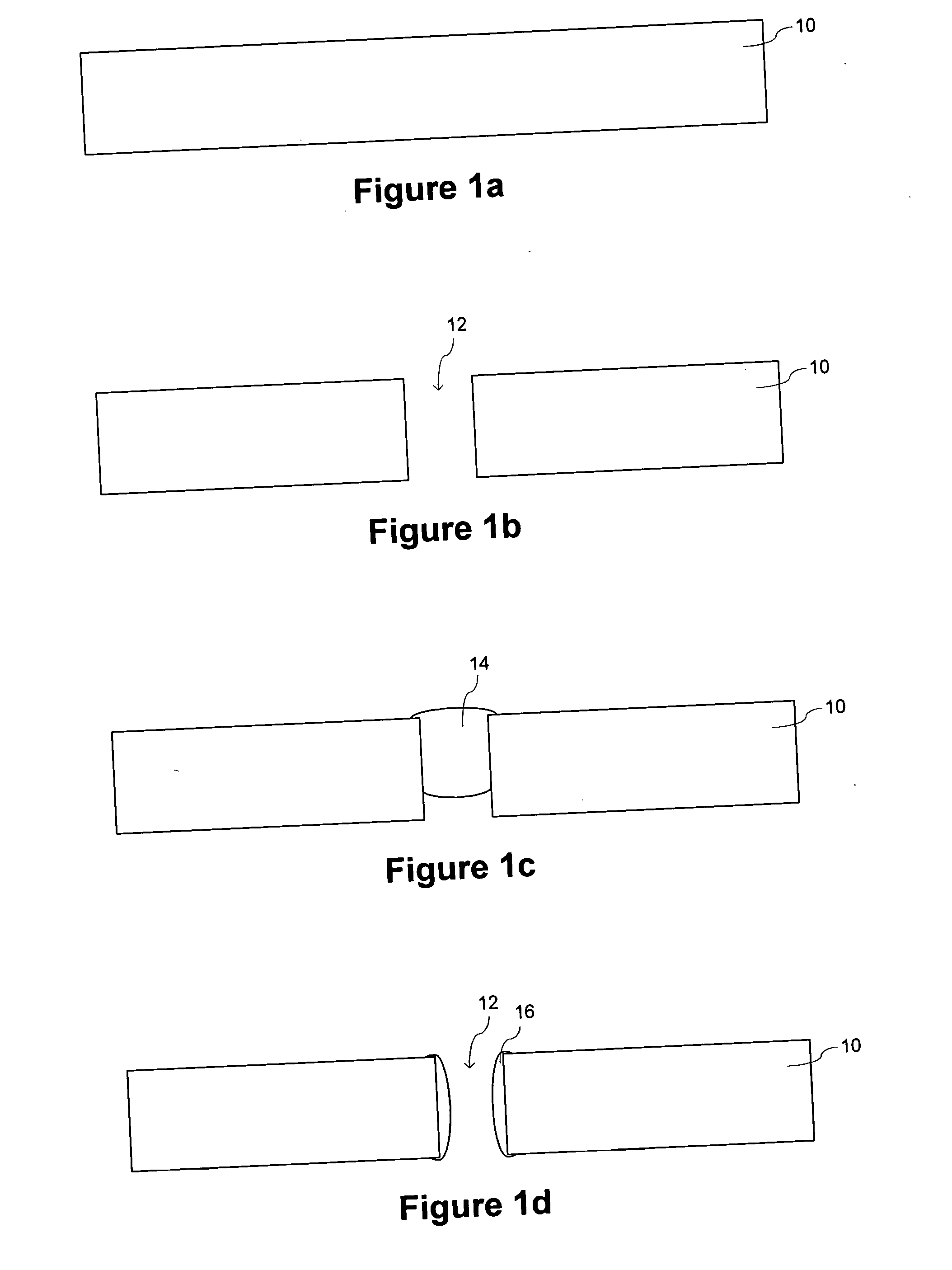

Methods for Fabricating Three-Dimensional All Organic Interconnect Structures

InactiveUS20070267138A1High frequency and high bandwidth applicationsSemiconductor/solid-state device detailsSolid-state devicesLiquid crystallineMaterials science

The present invention includes methods for making liquid crystalline polymer (LCP) interconnect structures using a high temperature and low temperature single sided LCP, where both the high and low temperature LCP are provided with a z-axis connection. The single sided conductive layer is a bus layer to form z-axis conductive stud within the high and low temperature LCP. High and low temperature LCP layers are etched or built up to form circuit patterns and subsequently bonded together to form final multilayer circuit pattern where the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond.

Owner:GEORGIA TECH RES CORP

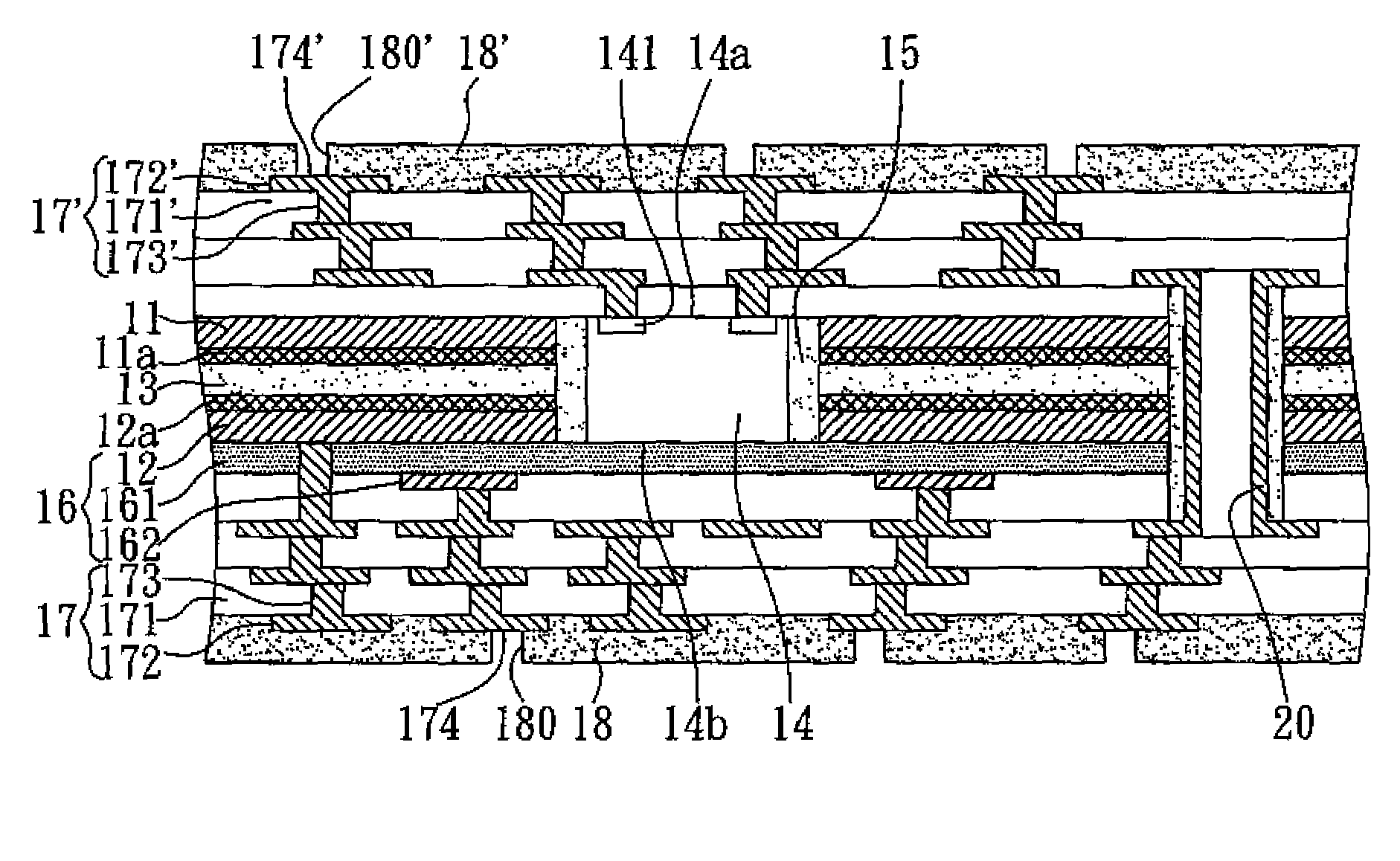

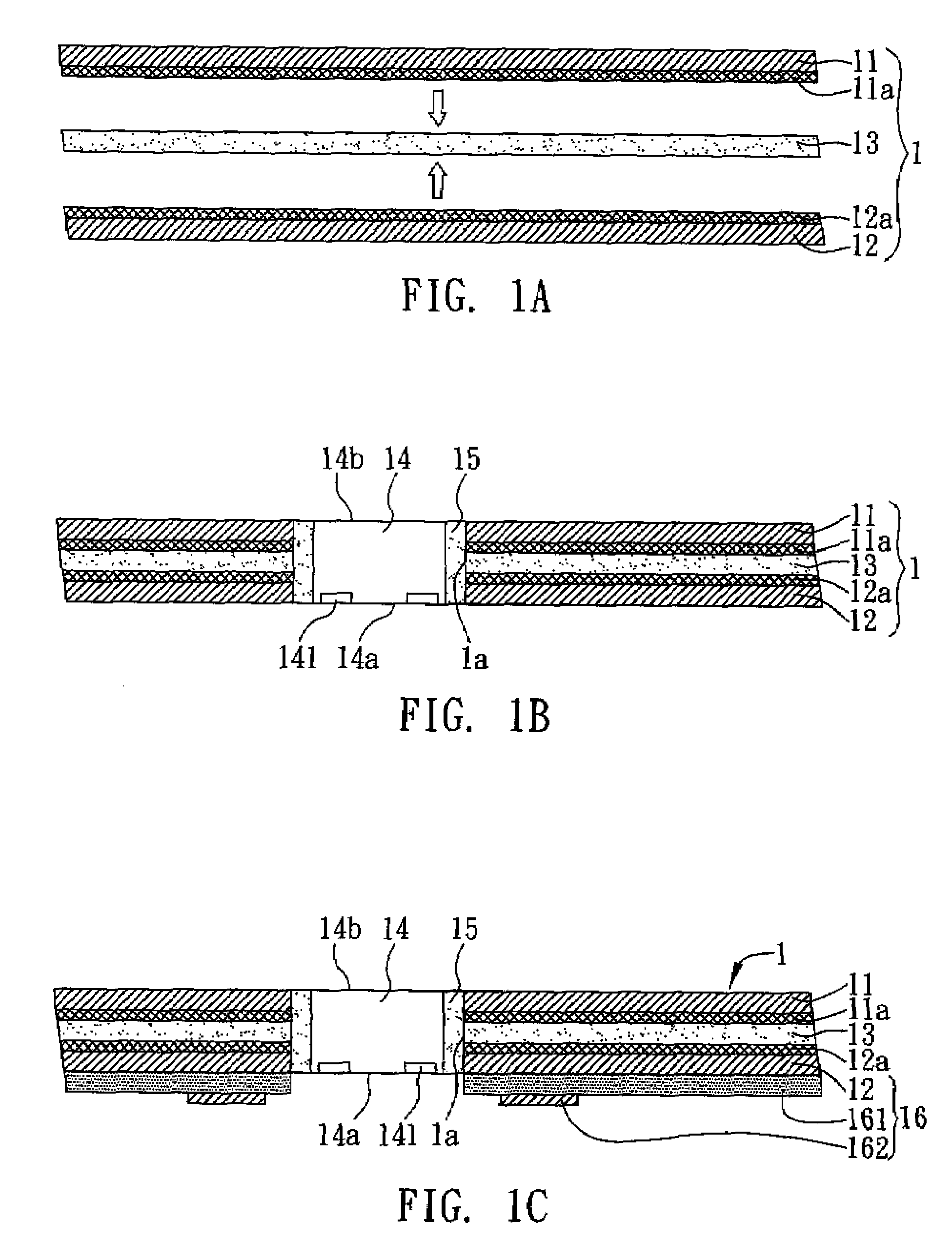

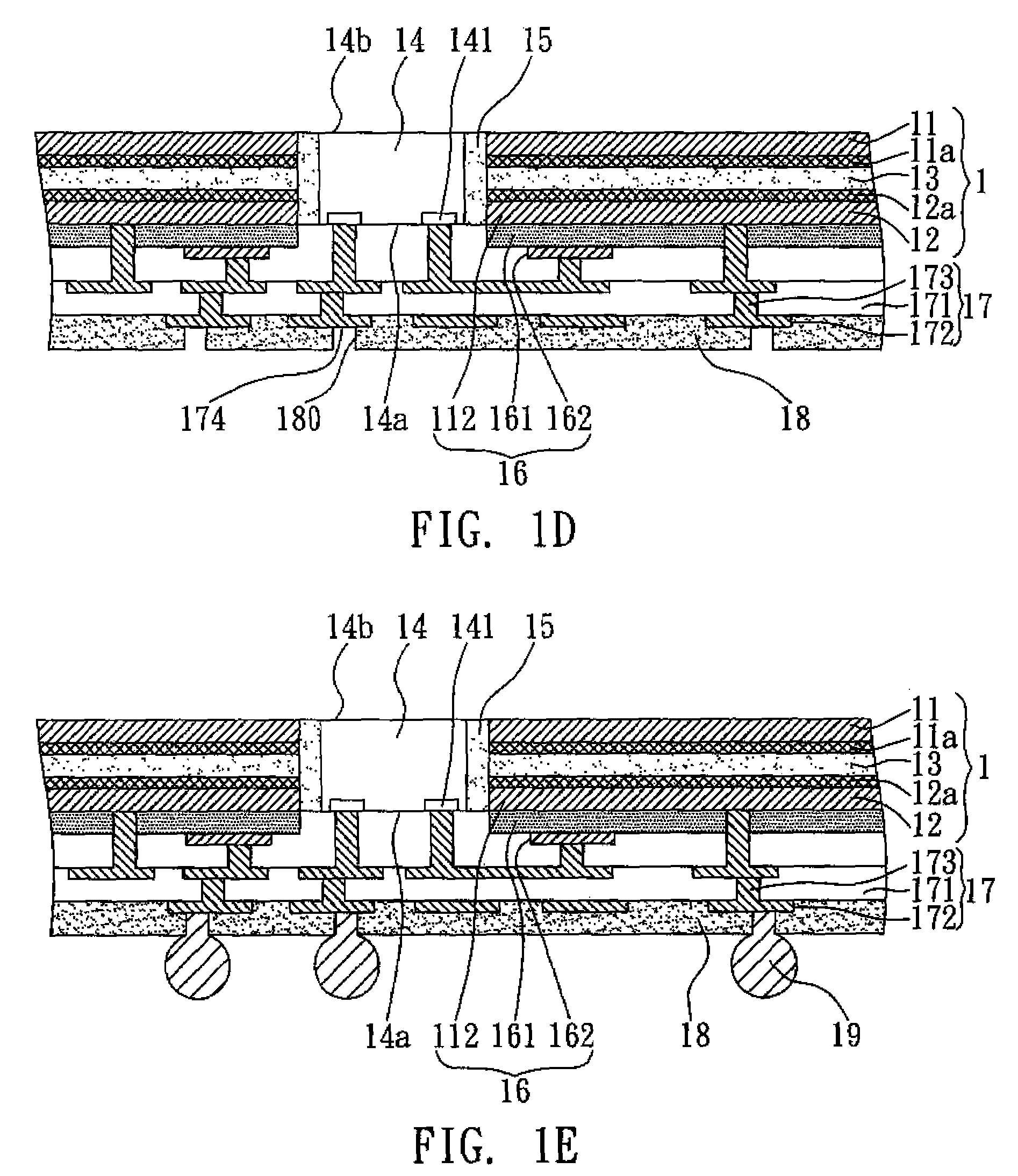

Circuit board structure with embedded electronic components

ActiveUS7639473B2Improve bending strengthSimple structureElectric spark ignitersFixed capacitor dielectricCapacitanceSemiconductor chip

A circuit board structure with embedded electronic components includes: a carrier board having an adhesive layer with two surfaces formed with first and second metal oxide layers covered by first and second metal layers and having at least one through hole; at least one semiconductor chip received in the through hole of the carrier board; an adhesive material filling a gap between the through hole and the semiconductor chip so as to secure the semiconductor chip in position to the through hole; a high dielectric material layer formed outwardly on the second metal layer; and at least one electrode board formed outwardly on the high dielectric material layer such that a capacitance component is formed with the second metal layer, high dielectric material layer, and electrode board. Accordingly, the capacitance component is integrated into the circuit board structure.

Owner:PHOENIX PRECISION TECH CORP

Low temperature co-fired ceramic with improved registration

InactiveUS6205032B1Semiconductor/solid-state device detailsSolid-state devicesHigh densityMetallurgy

A low temperature co-fired ceramic assembly (LTCC) with a constraining core to minimize shrinkage of outer ceramic layers during firing. The outer ceramic layers have high density circuit features. A ceramic core includes several ceramic layers. Several via holes are located in the first and second ceramic layers. Several low density circuit features are located on the ceramic layers that make up the core. Outer ceramic layers are placed top and bottom of the ceramic core. The outer ceramic layers have via holes and high density circuit features. The circuit features patterned on the ceramic layers include resistors, capacitors, circuit lines, vias, inductors, or bond pads. The ceramic core is fired first in a furnace. The outer layers are then laminated to the ceramic core and fired. The ceramic core controls the shrinkage rate of the outer ceramic layers during firing allowing higher density circuit features on the outer layers.

Owner:CTS CORP ELKHART

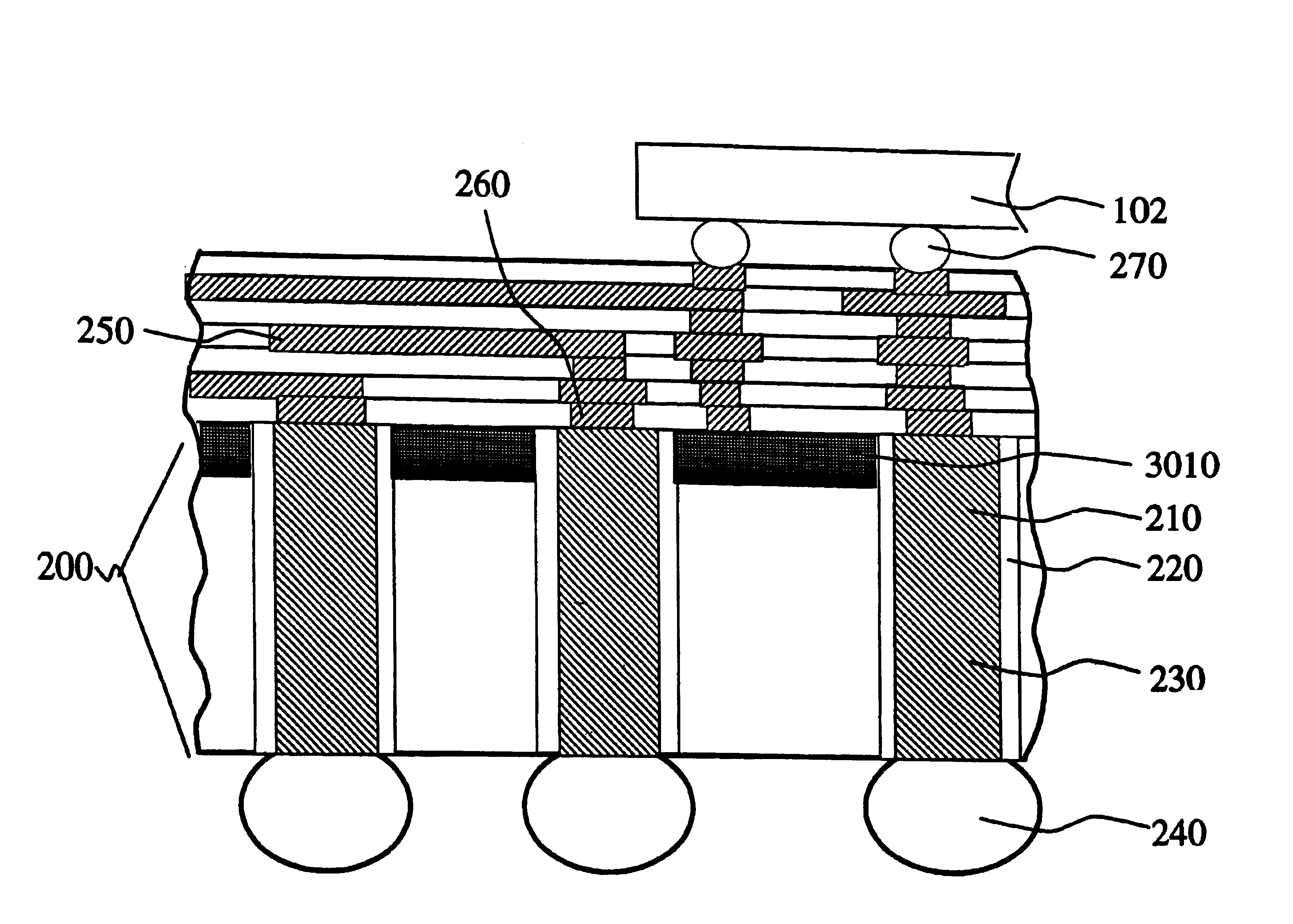

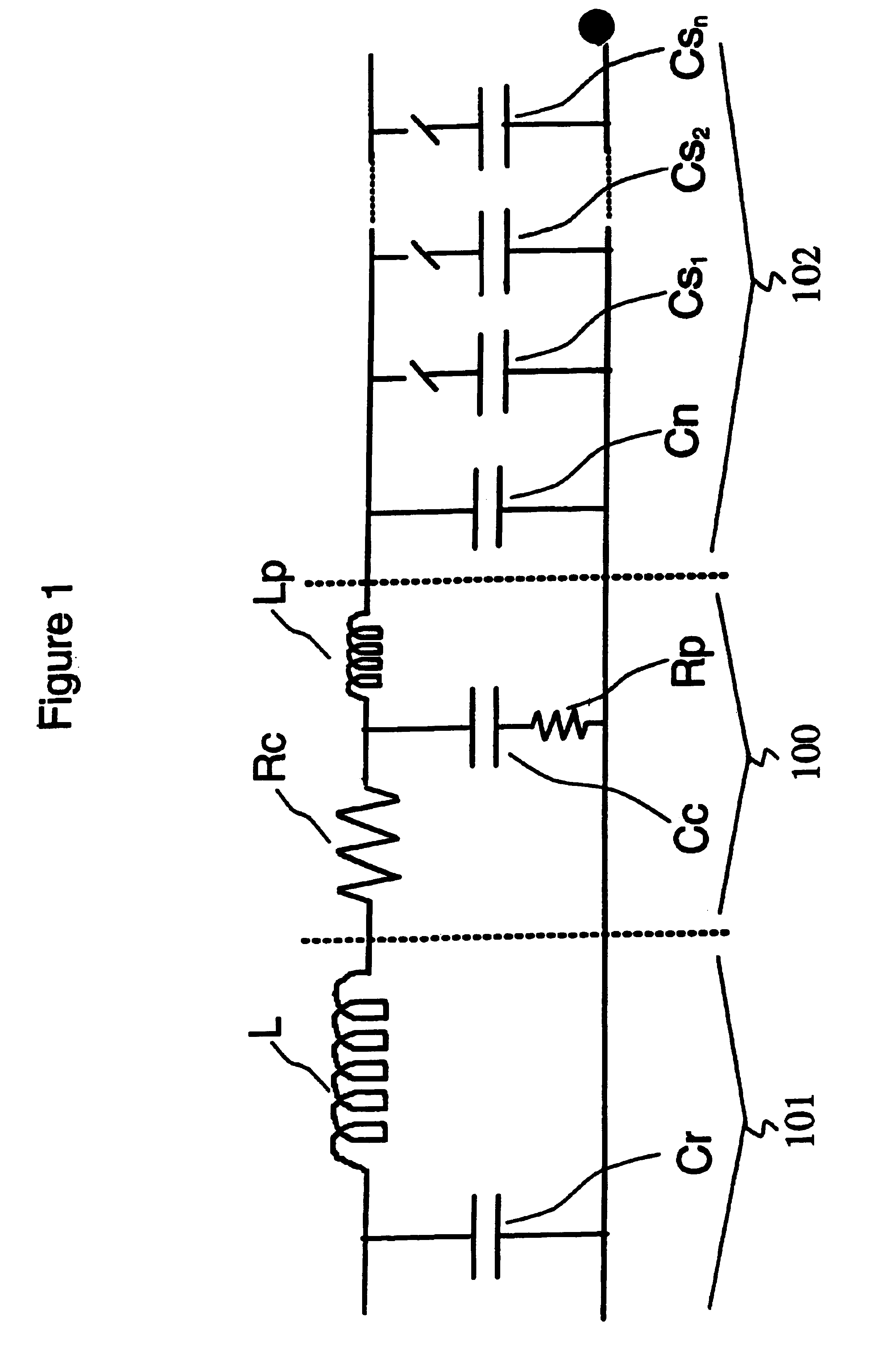

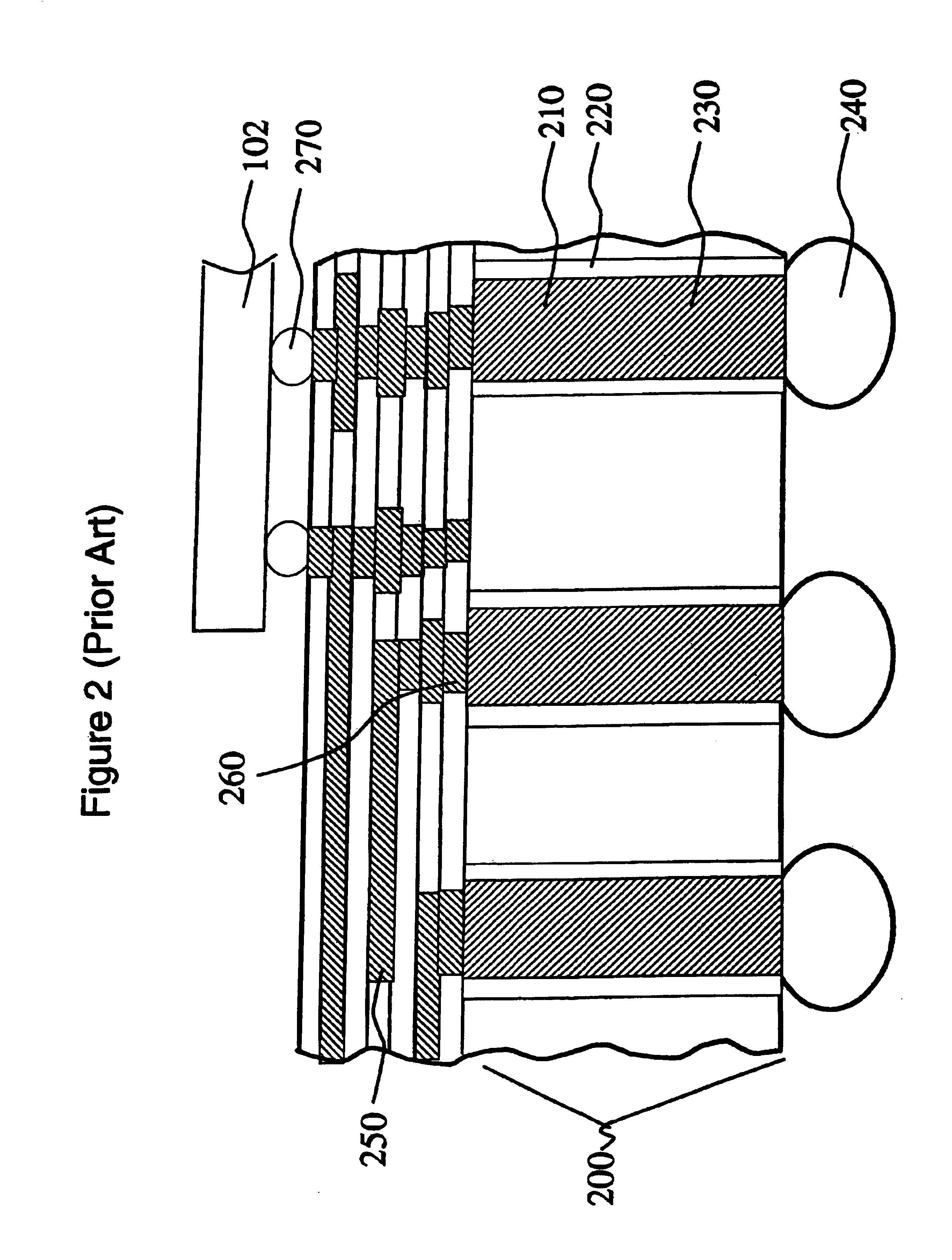

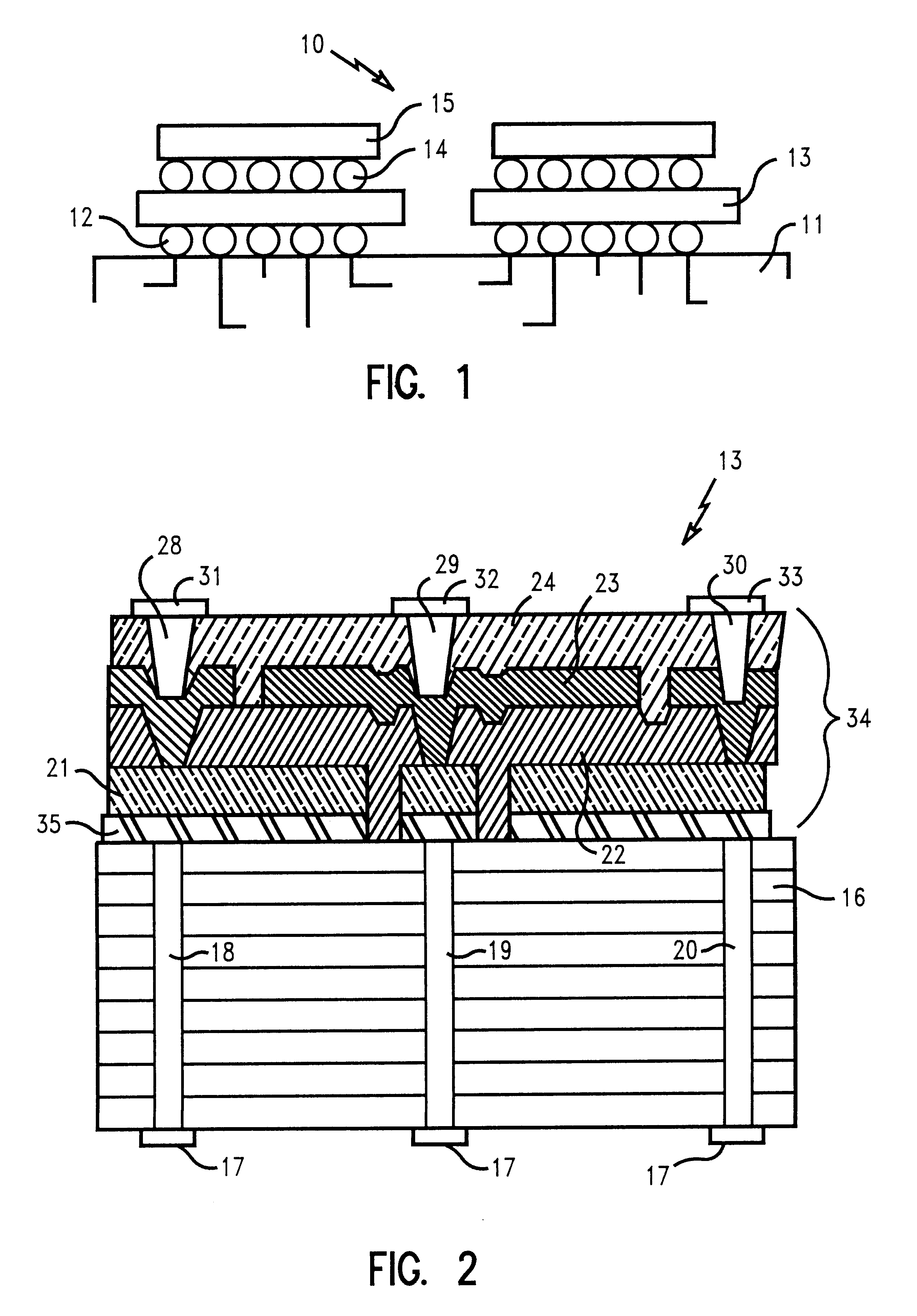

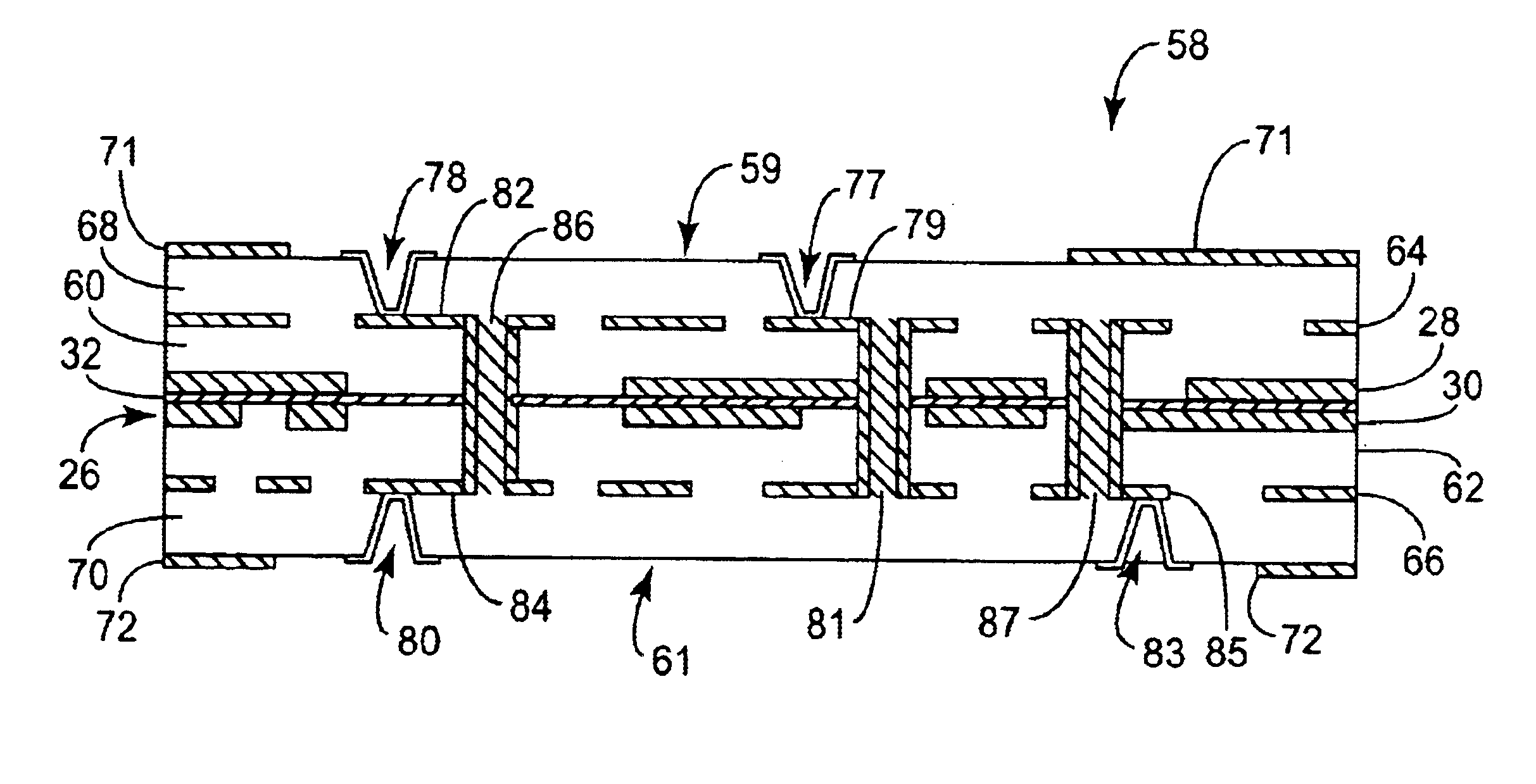

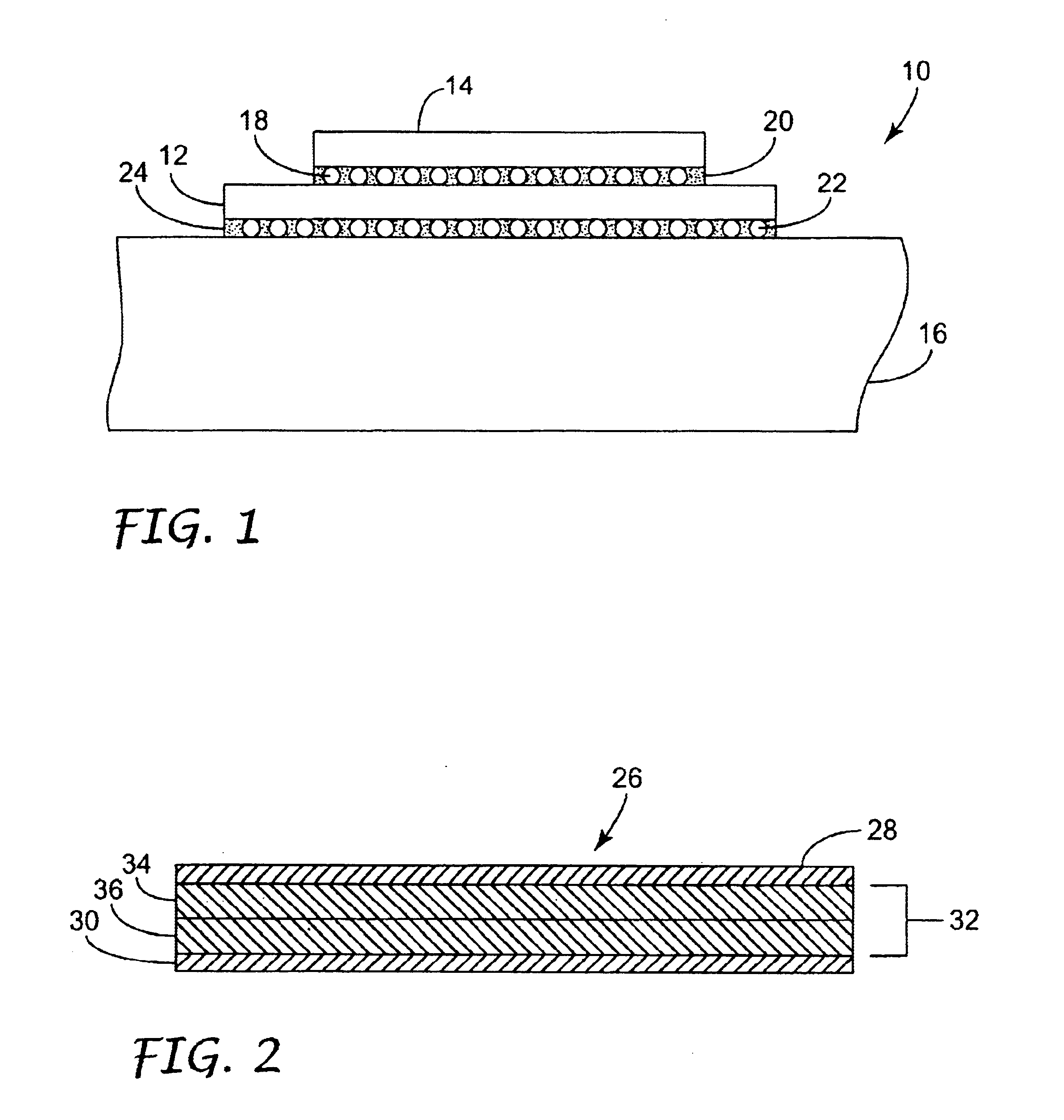

Interconnect module with reduced power distribution impedance

InactiveUS6847527B2Reduced impedance powerReduced ground distributionLight absorption dielectricsSemiconductor/solid-state device detailsSolder ballOperating frequency

An interconnect module for an integrated circuit chip incorporates a thin, high dielectric constant embedded capacitor structure to provide reduced power distribution impedance, and thereby promote higher frequency operation. The interconnect module is capable of reliably attaching an integrated circuit chip to a printed wiring board via solder ball connections, while providing reduced power distribution impedance of less than or equal to approximately 0.60 ohms at operating frequencies in excess of 1.0 gigahertz.

Owner:3M INNOVATIVE PROPERTIES CO

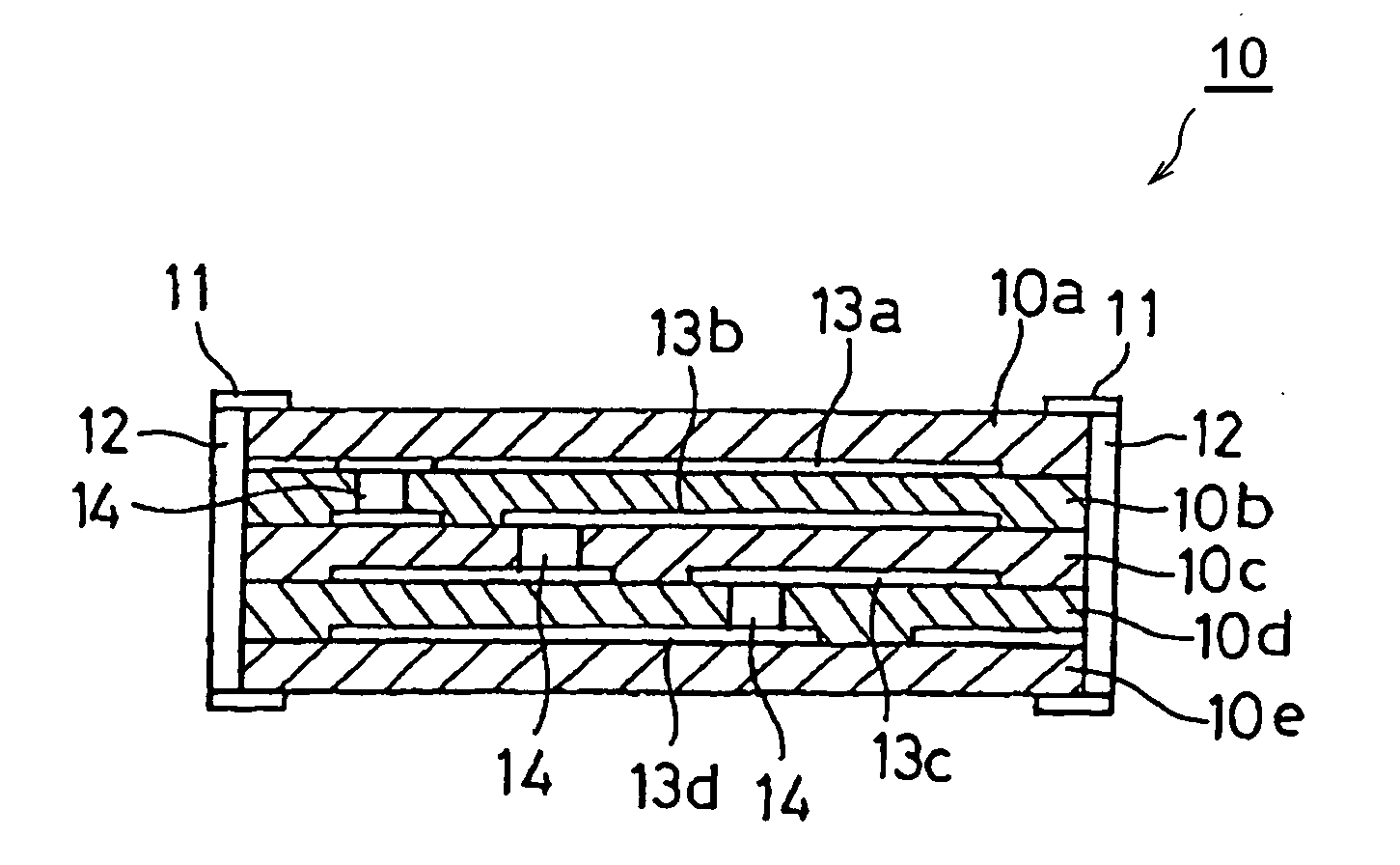

Multilayer wiring board and manufacture method thereof

ActiveUS20050012217A1Improve electrical performanceBroaden your optionsInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringThermal expansion

In a multilayer wiring board comprising a core board, and a wiring layer and an electrically insulating layer that are stacked on one surface of said core board, a thermal expansion coefficient of said core board in XY directions falls within a range of 2 to 20 ppm, a core member for said core board is a core member selected from silicon, ceramics, glass, a glass-epoxy composite, and metal, said core board is provided with a plurality of through holes that are made conductive between the front and the back by a conductive material, and a capacitor is provided on one surface of said core board, wherein said capacitor comprises an upper electrode being the conductive material in said through hole, and a lower electrode disposed so as to confront said upper electrode via a dielectric layer.

Owner:DAI NIPPON PRINTING CO LTD

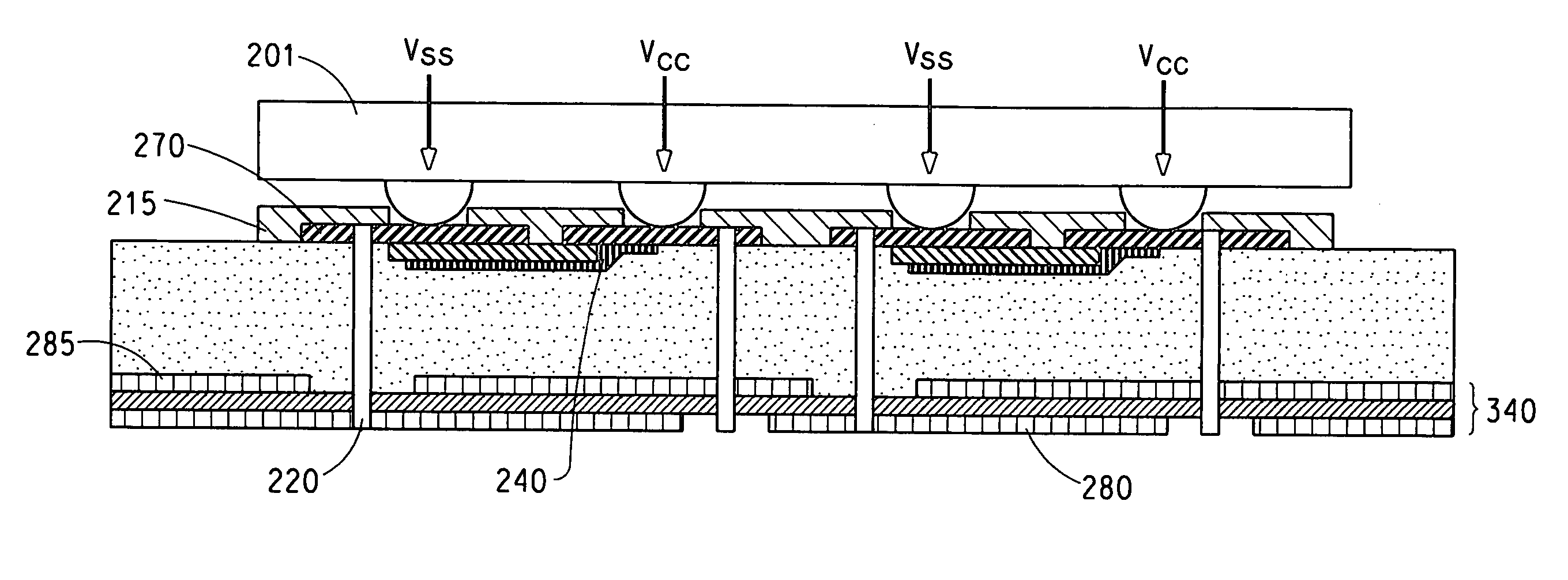

Power core devices and methods of making thereof

ActiveUS20070090511A1Semiconductor/solid-state device detailsPrinted circuit aspectsEngineeringCapacitor

A device comprising a power core wherein said power core comprises: at least one embedded singulated capacitor layer containing at least one embedded singulated capacitor wherein said embedded singulated capacitor comprises at least a first electrode and a second electrode and wherein said embedded singulated capacitor is positioned on the outer layer of the power core with both first and second electrodes of the capacitor on the outer layer of the power core so that at least one Vcc (power) terminal and at least one Vss (ground) terminal of a semiconductor device can be directly connected to at least one first and at least one second electrode, respectively.

Owner:CHEMTRON RES

Printing of electronic circuits and components

InactiveUS6855378B1Reduce the content of particulate matterCell electrodesFinal product manufactureParticulatesHigh concentration

Methods are disclosed for printing (2-7) multilayer electronic components, and circuits on a surface (2), where at least one of the layers is formed by a redox reaction (6) occurring in a deposited solution (4, 5). Electronic components may comprise semiconductors such as in transistors or diode, or metal oxide or electrolyte such as in batteries or fuel cells, or are capacitors, inductors, and resistors. Preferably, the oxidizer of the redox reaction is a strong oxidizer, and the reducer is a strong reducer (3). Reactions are preferably sufficiently exothermic that they can be initiated (6), rather than driven to completion, by microwave or other suitable energy sources, and may yield substantially pure metal or metal oxide layers. The solution being deposited (5) may have either high concentrations of particulates, such as 60-80 wt. % of dry weight, or low concentrations of particulates, such as ≦5 wt. % or ≦2 wt. %. Low particulate content provides printing of structures having lateral resolution of ≦10 μm, ≦5 μm, or ≦1 μm.

Owner:SRI INTERNATIONAL

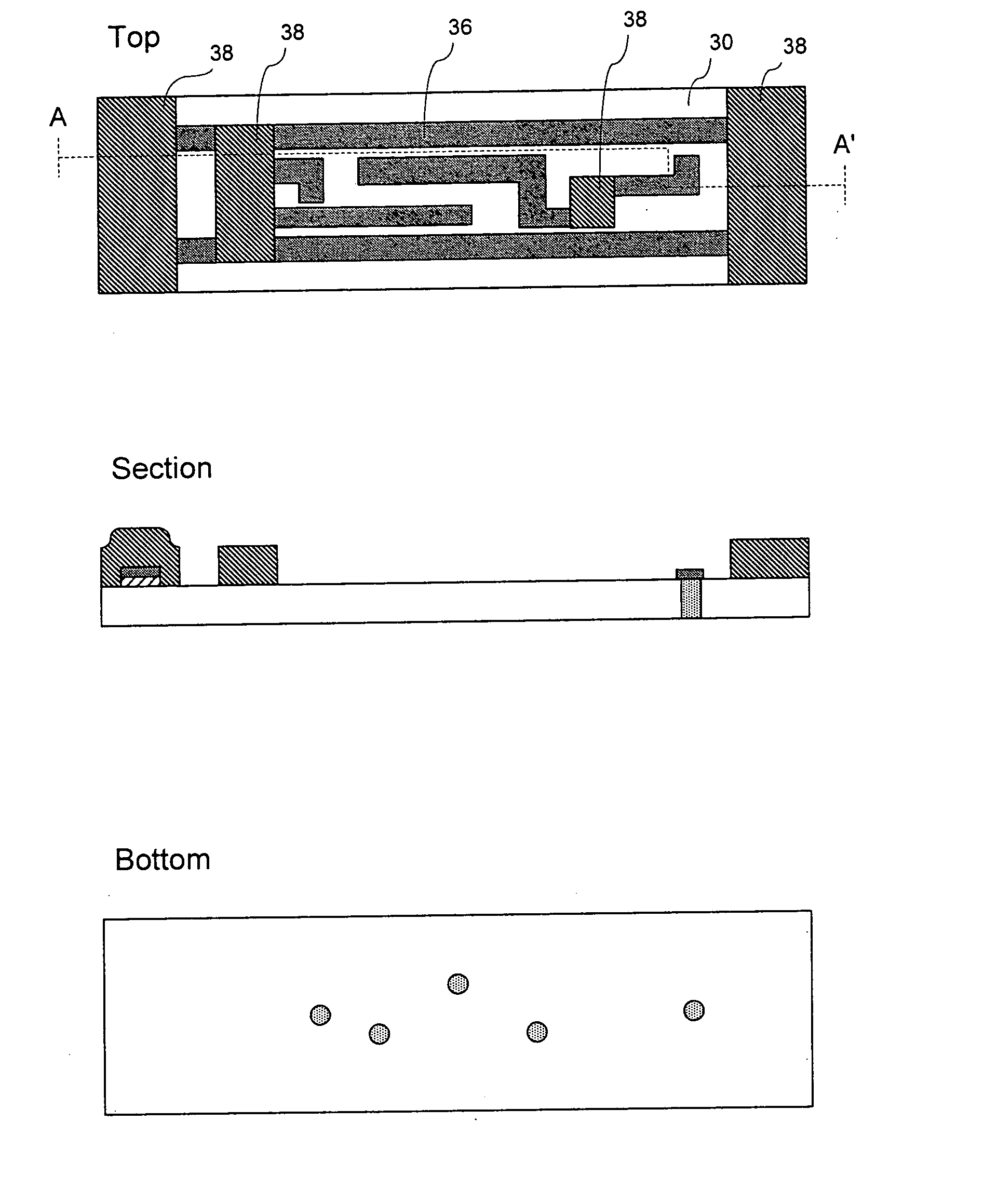

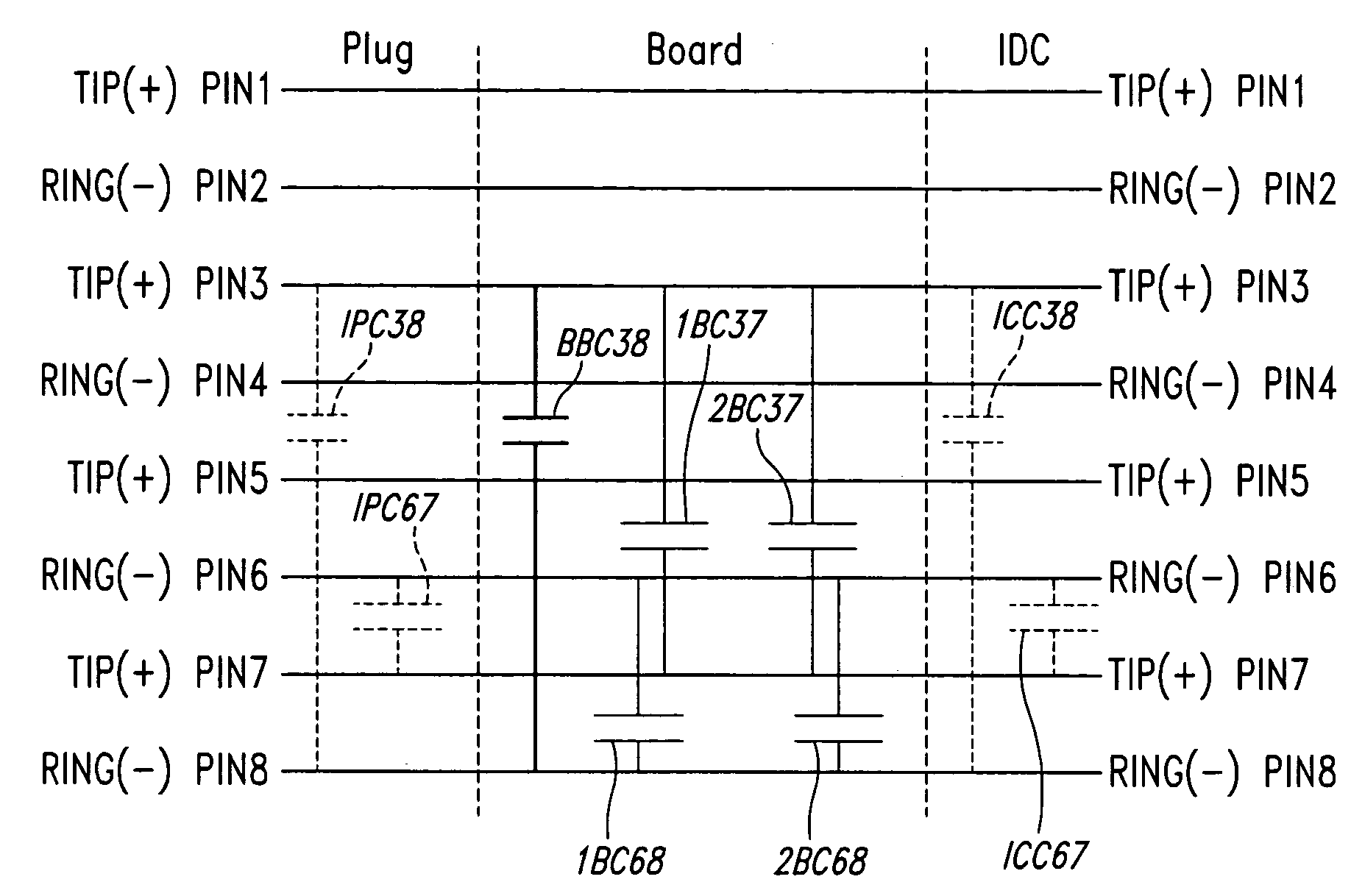

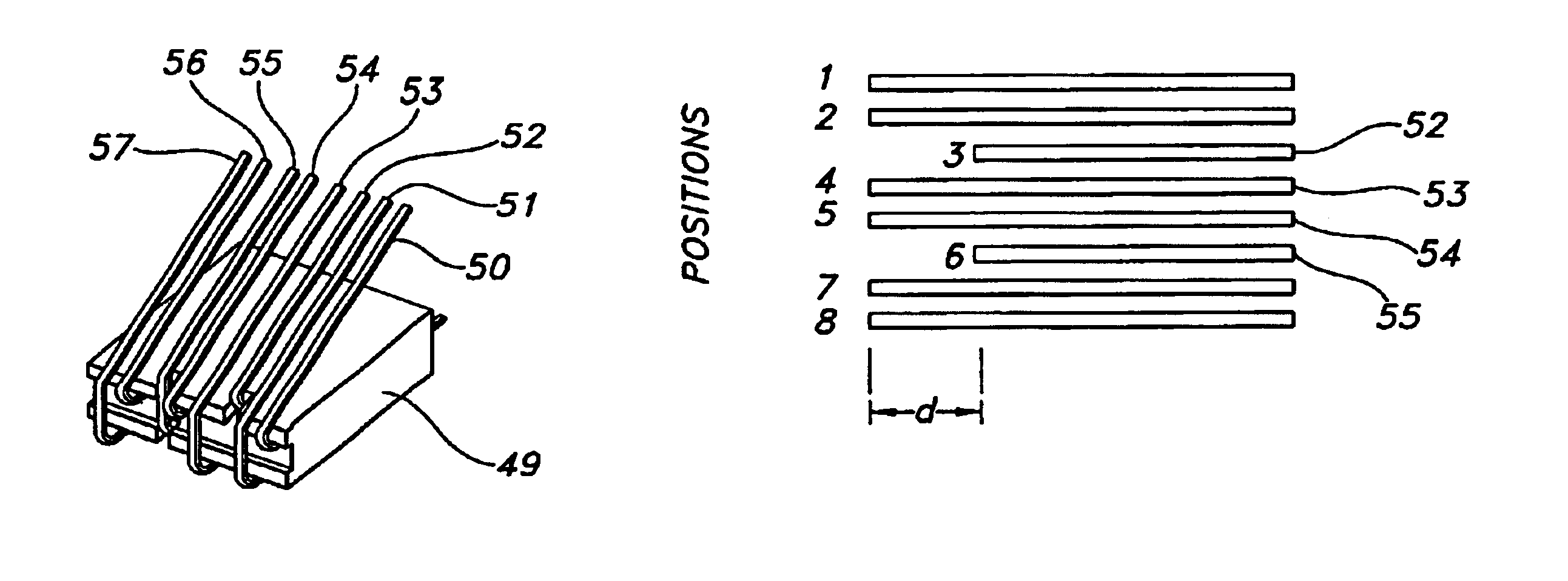

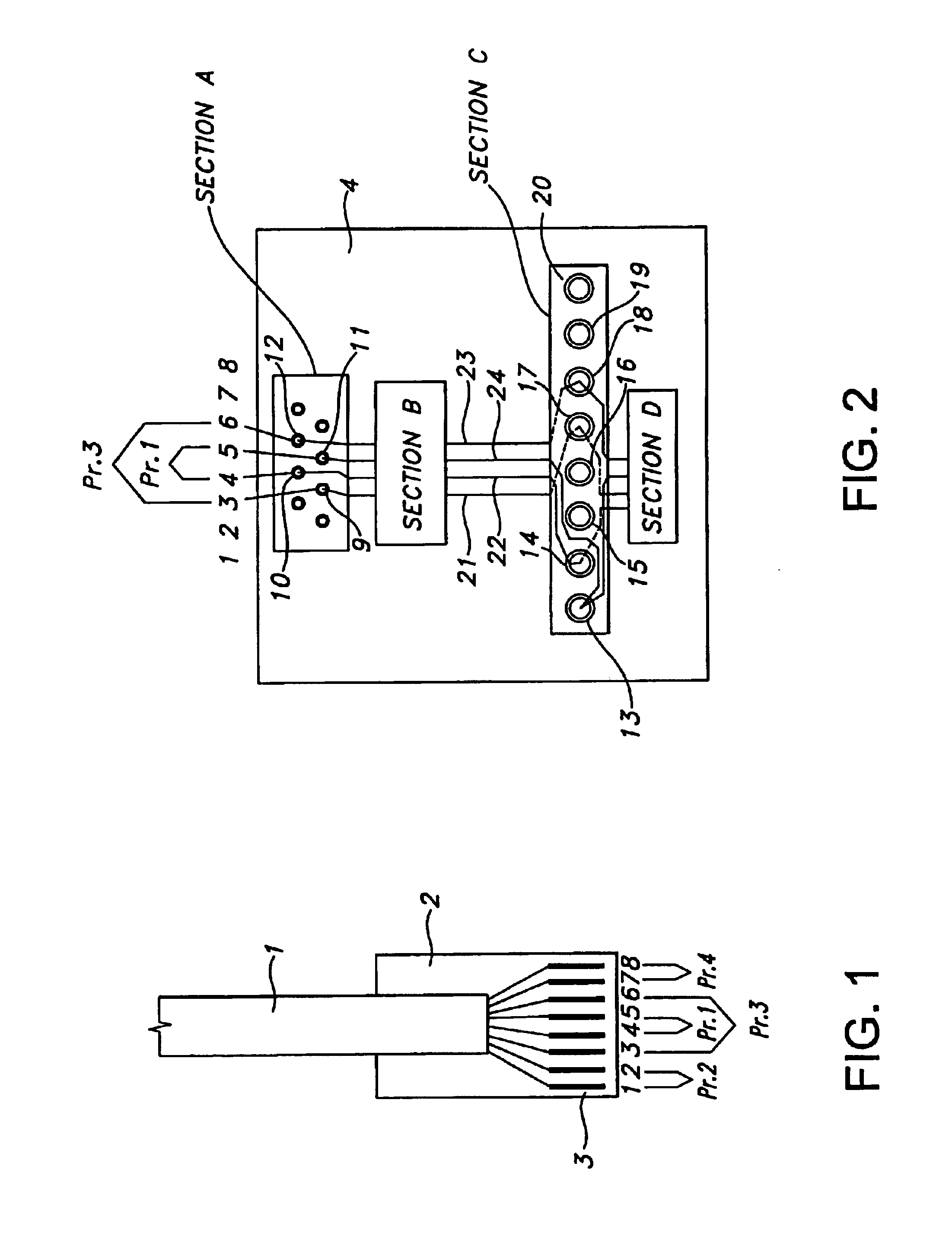

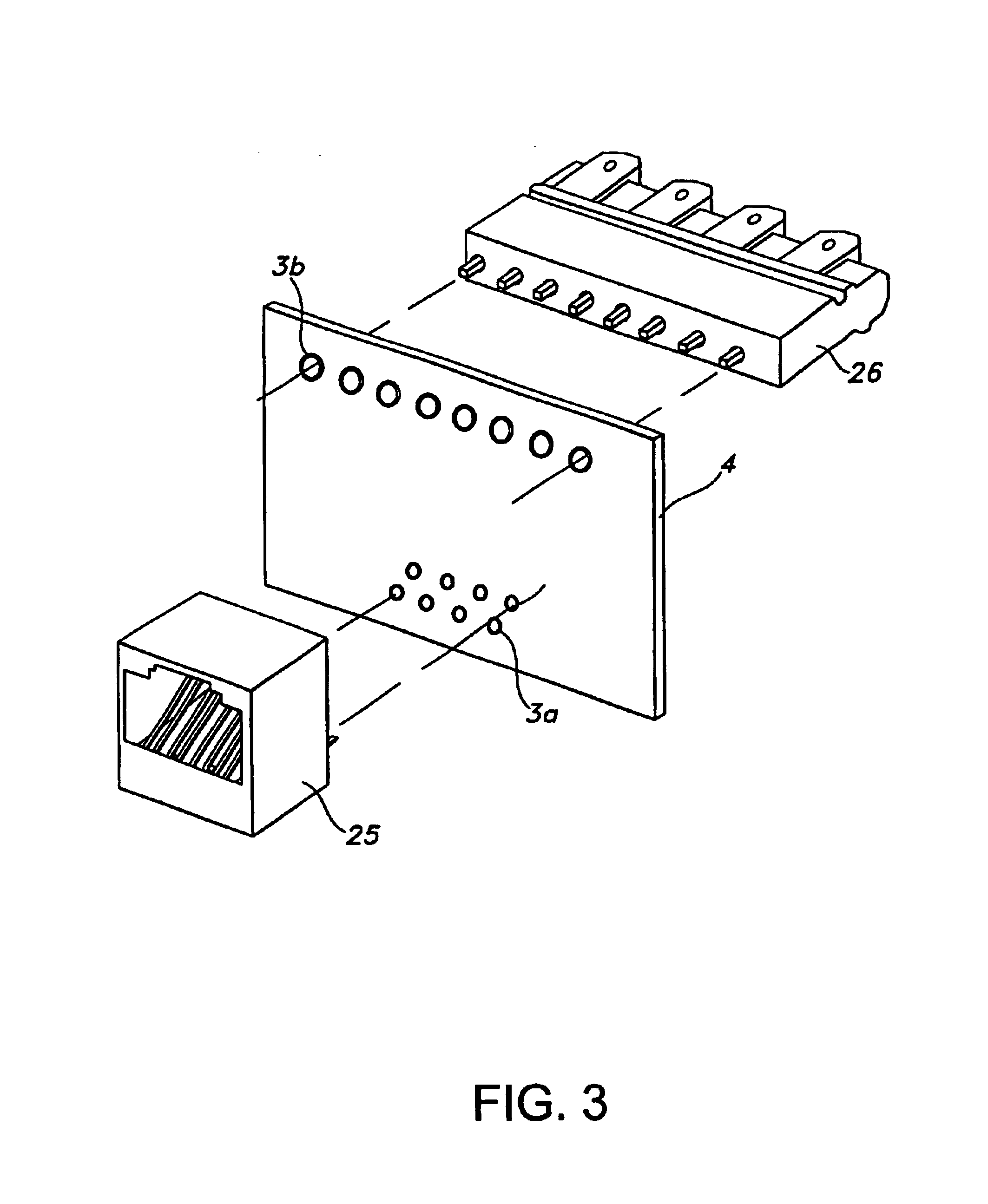

Crosstalk compensation with balancing capacitance system and method

ActiveUS20050253662A1Reduce crosstalkMultiple-port networksCoupling device detailsPatch panelCapacitance

A insulation displacement connector (IDC) patch panel includes a circuit (PC) board with interdigitated capacitance for balancing out inherent capacitance found within IDCs of the panel and conventional plug connectors coupled to the panel. Unwanted cross-talk signals are reduced as a consequence.

Owner:LEVITON MFG

Power core devices

ActiveUS7701052B2Semiconductor/solid-state device detailsPrinted circuit aspectsCapacitorSemiconductor

A device comprising a power core wherein said power core comprises: at least one embedded singulated capacitor layer containing at least one embedded singulated capacitor wherein said embedded singulated capacitor comprises at least a first electrode and a second electrode and wherein said embedded singulated capacitor is positioned on the outer layer of the power core with both first and second electrodes of the capacitor on the outer layer of the power core so that at least one Vcc (power) terminal and at least one Vss (ground) terminal of a semiconductor device can be directly connected to at least one first and at least one second electrode, respectively.

Owner:CHEMTRON RES

Methods and compositions for the formation of recessed electrical features on a substrate

InactiveUS20070122932A1Reduce settlementGood dispersionPrinted circuit aspectsConductive materialElectrical conductorMechanical property

Precursor compositions having a low conversion temperature and methods for the fabrication of recessed electrical features from the precursor compositions. The electrical features can be conductors, resistors and dielectric features. The precursor compositions are deposited into recessed features, such as trenches, formed in a substrate and are reacted at a low temperature to form electrical features having good electrical and mechanical properties. The substrate can be a low temperature substrate, such as an organic substrate.

Owner:CABOT CORP

Bi-directional balance low noise communication interface

InactiveUS6840816B2Reduce crosstalkSimple and inexpensive to manufacturePrinted circuit detailsCoupling device detailsLow noiseCommunication interface

The present invention relates to RJ45 modular inserts that are connected to a printed circuit board used to transfer high speed signals for telecommunication interface media connections. The printed circuit board is configured to reduce near-end cross-talk (“NEXT”) without compromising impedance. NEXT is substantially reduced by utilizing a low reactance dielectric insert with a two-stage combination positive and negative compensation removal technique. By utilizing this method, the pair-to-pair NEXT is substantially reduced and differential pair impedance are controlled in a simple and cost effective manner.

Owner:ORTRONICS INC

Methods for fabricating three-dimensional all organic interconnect structures

InactiveUS20040000425A1Semiconductor/solid-state device detailsSolid-state devicesLiquid crystallineAdhesive

The present invention comprises methods for making three-dimensional (3-D) liquid crystalline polymer (LCP) interconnect structures using a high temperature singe sided liquid crystalline polymer, and low temperature single sided liquid crystalline polymer, whereas both the high temperature LCP and the low temperature LCP are drilled using a laser or mechanical drill or mechanically punch to form a z-axis connection. The single sided Conductive layer is used as a bus layer to form z axis conductive stud conductive stud within the high temperature and low temperature LCP, followed by deposition of a metallic capping layer of the stud that serves as the bonding metal between the conductive interconnects to form the z-axis electrical connection. High temperature and low temperature LCP circuit layers are etched or built up to form circuit patterns and subsequently bonded together to form final 3-D multilayer circuit pattern whereas the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond, whereas, metal to metal bonding occurs with high temperature metal capping layer bonding to conductive metal layer. The resultant structure is then packaged using two metallized organic cores that are laminated onto either side of the device using a low temperature adhesive with similar electrical properties and subsequently metallized to form the input output terminals and EM shielding.

Owner:GEORGIA TECH RES CORP

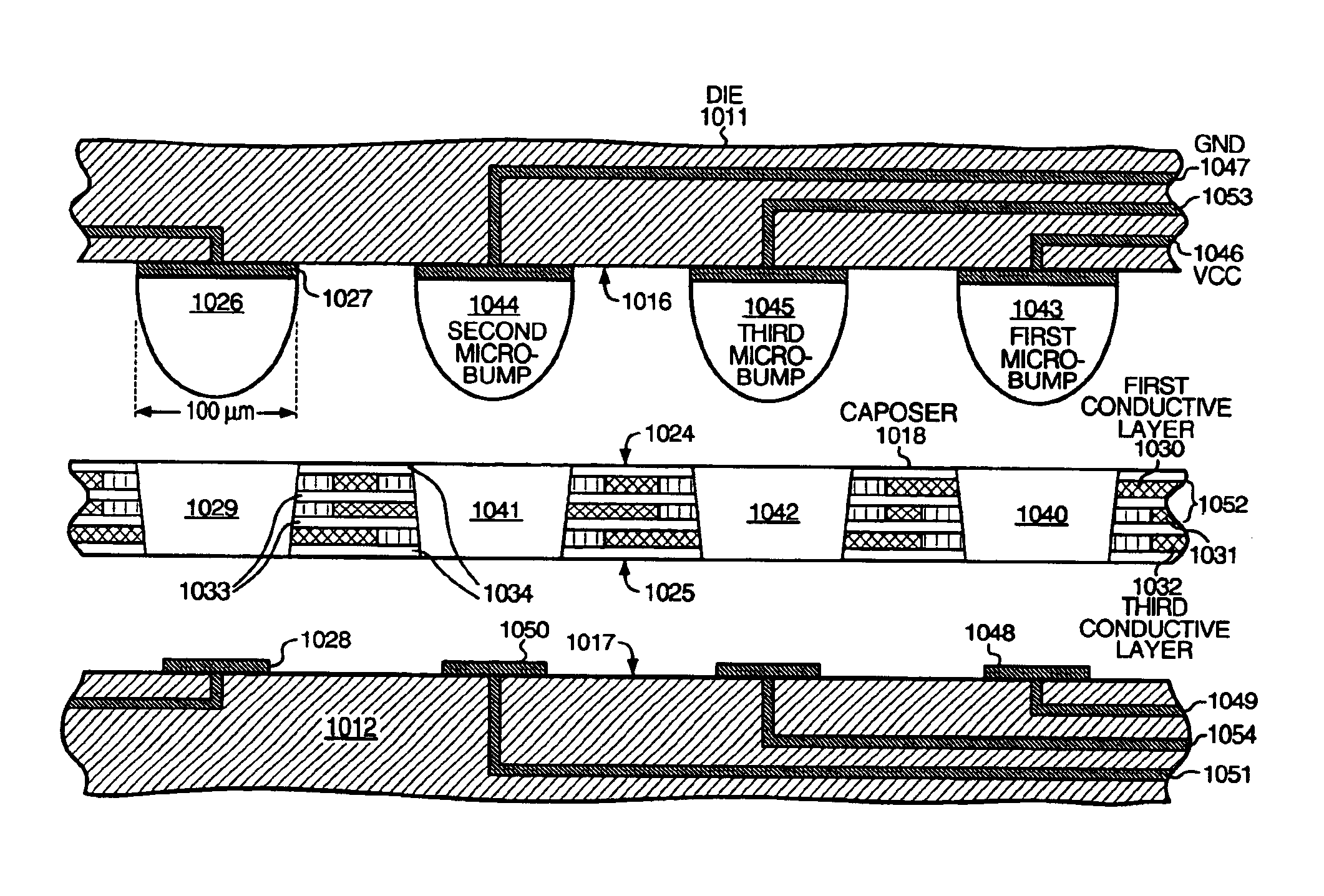

Capacitive interposer

ActiveUS6875921B1Thick structureReduce Impedance DiscontinuitiesSemiconductor/solid-state device detailsCross-talk/noise/interference reductionCapacitanceInterposer

A capacitive interposer (caposer) is disposed inside an integrated circuit package between a die and an inside surface of the package. Conductive layers within the caposer constitute a bypass capacitor. In a through-hole caposer, micro-bumps on the die pass through through-holes in the caposer and contact corresponding landing pads on the package. As they pass through the caposer, power and ground micro-bumps make contact with the plates of the bypass capacitor. In a via caposer, power and ground micro-bumps on the die are coupled to power and ground landing pads on the package as well as to the plates of the bypass capacitor by power and ground vias that extend through the caposer.

Owner:XILINX INC

Popular searches

Semiconductor/solid-state device manufacturing Printed resistor incorporation Multilayer circuit manufacture Semiconductor devices Conductive material mechanical removal Printed element electric connection formation High frequency circuit adaptations Radio transmission Printed inductor incorporation Record carriers used with machines

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com