Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4382 results about "Solder ball" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

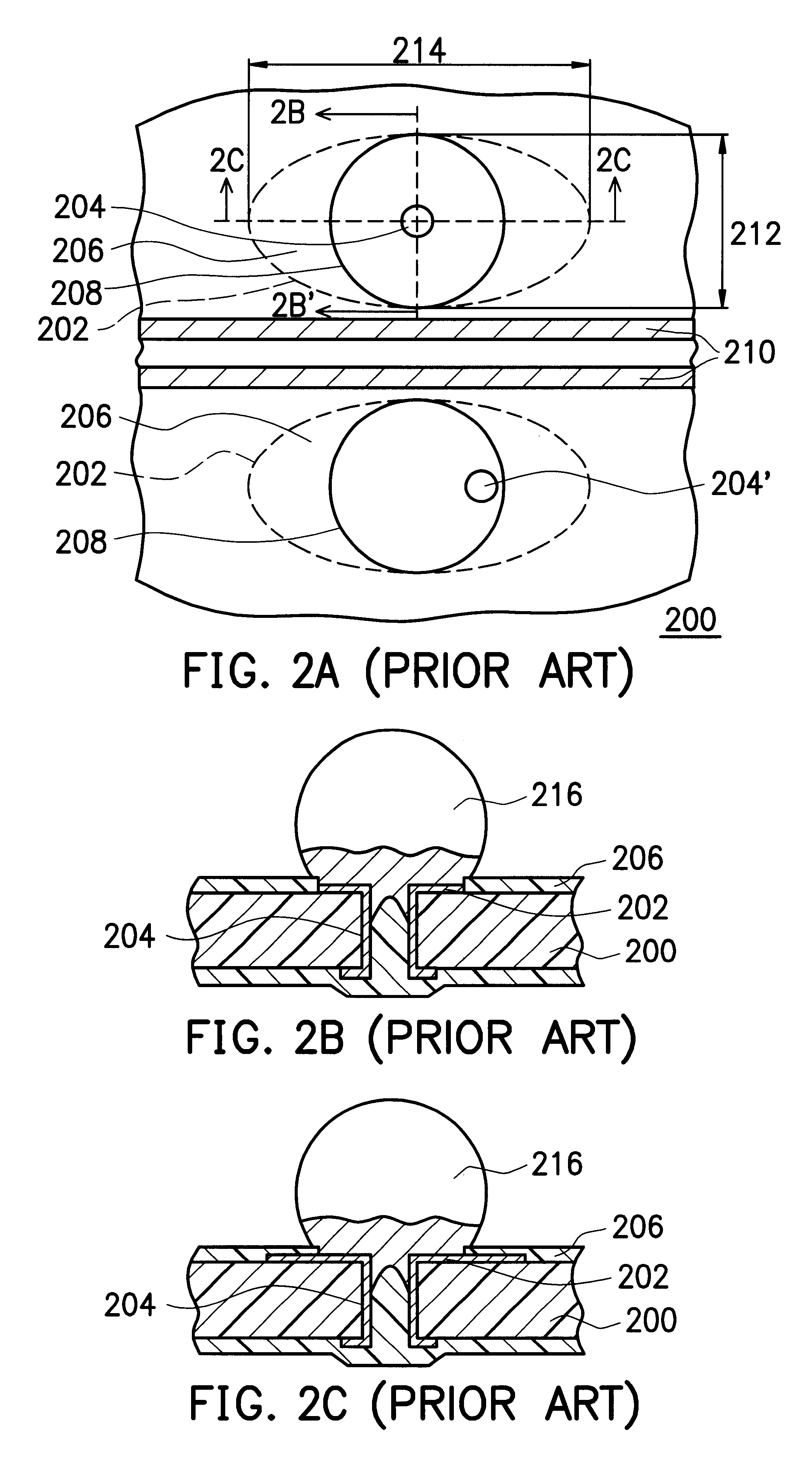

In integrated circuit packaging, a solder ball, also a solder bump (ofter referred to simply as "ball" or "bumps") is a ball of solder that provides the contact between the chip package and the printed circuit board, as well as between stacked packages in multichip modules; in the latter case, they may be referred to as microbumps (μbumps, ubumps), since they are usually significantly smaller than the former. The solder balls can be placed manually or by automated equipment, and are held in place with a tacky flux.

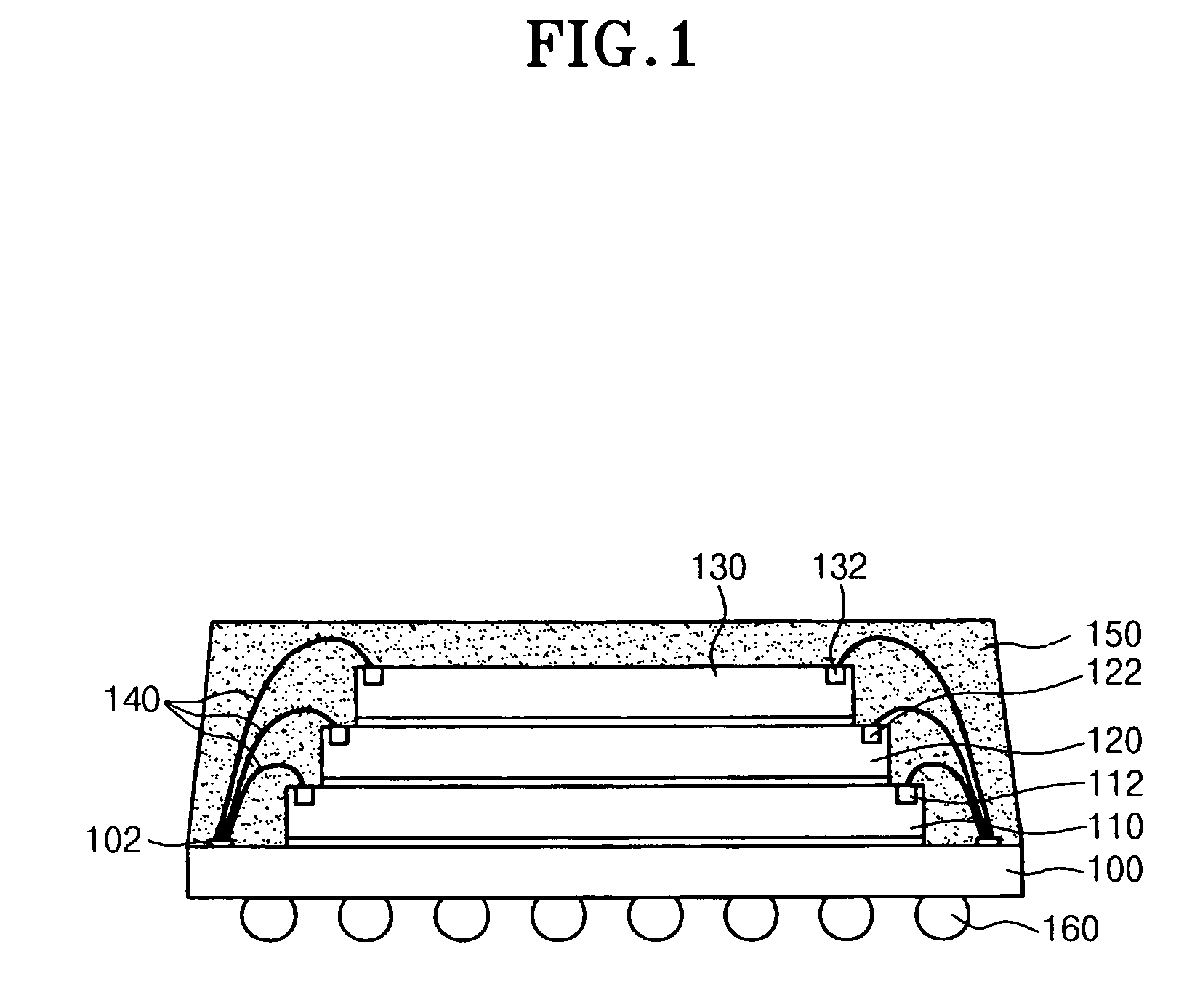

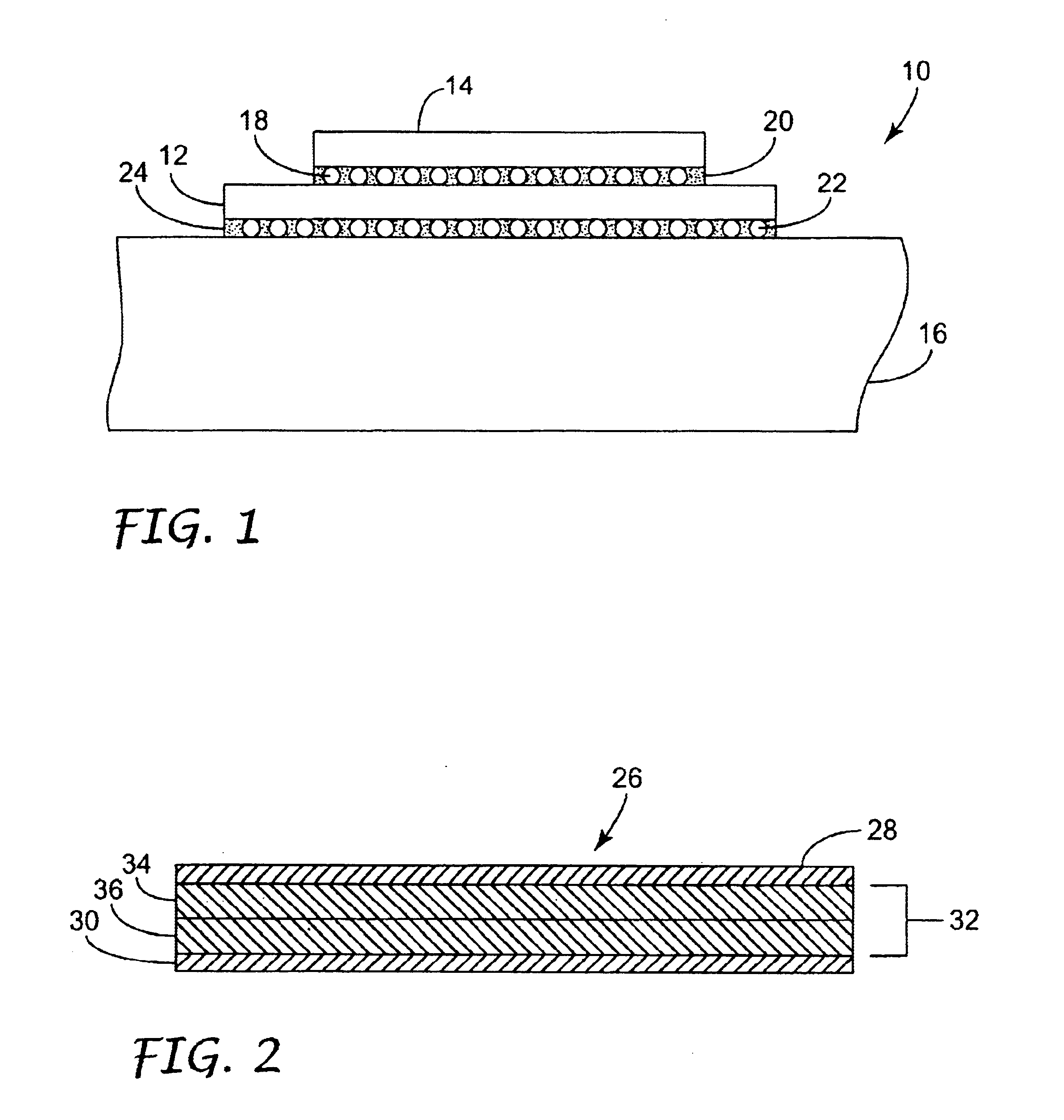

Integrated circuit (IC) package stacking and IC packages formed by same

ActiveUS20070290376A1Semiconductor/solid-state device detailsSolid-state devicesContact padSolder ball

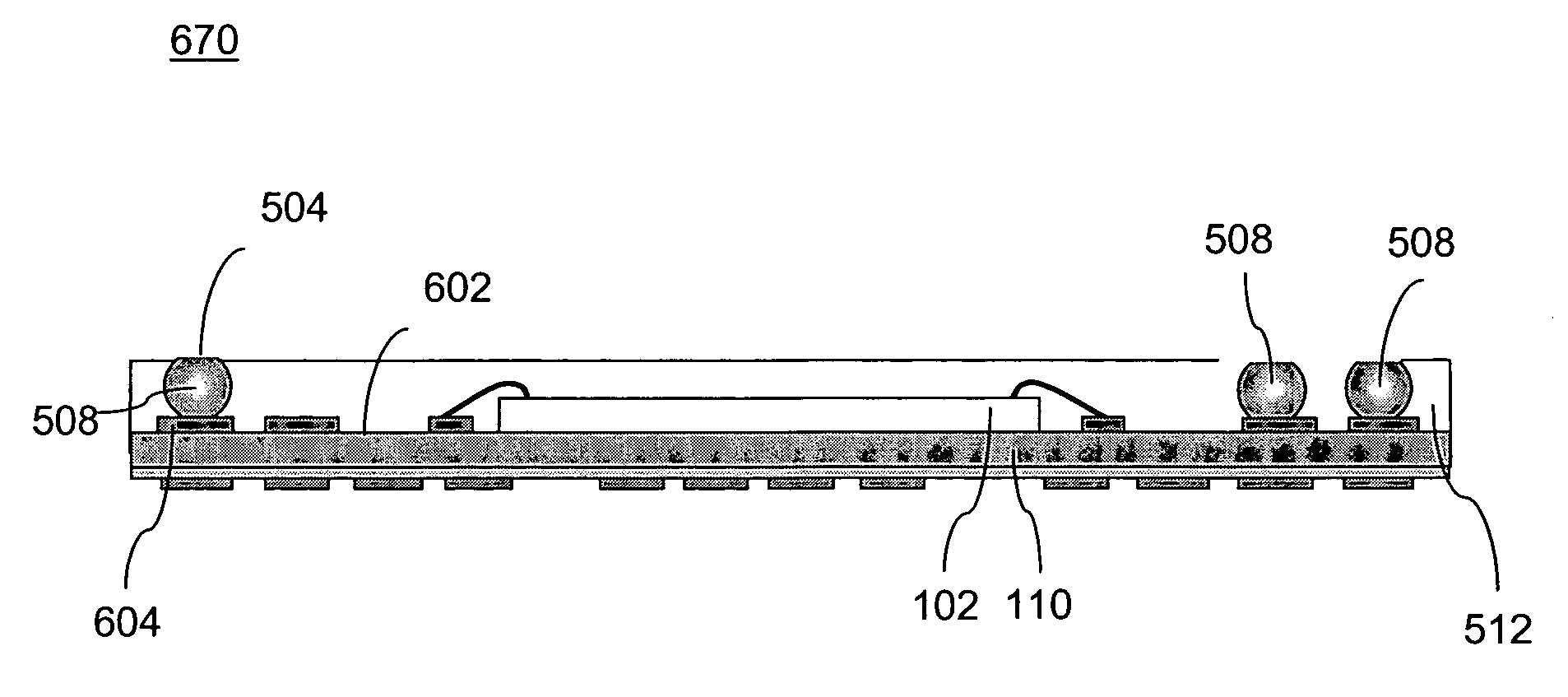

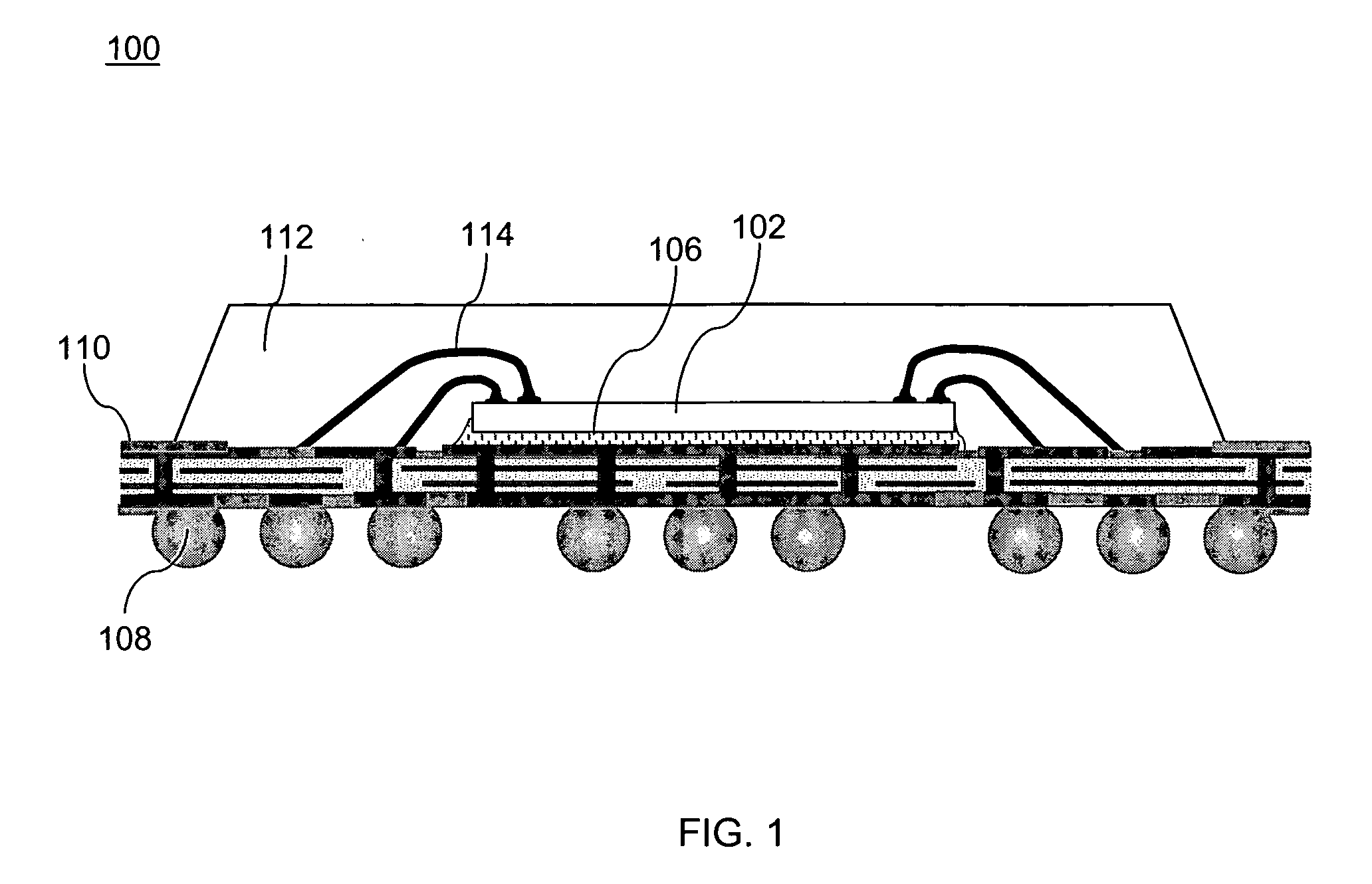

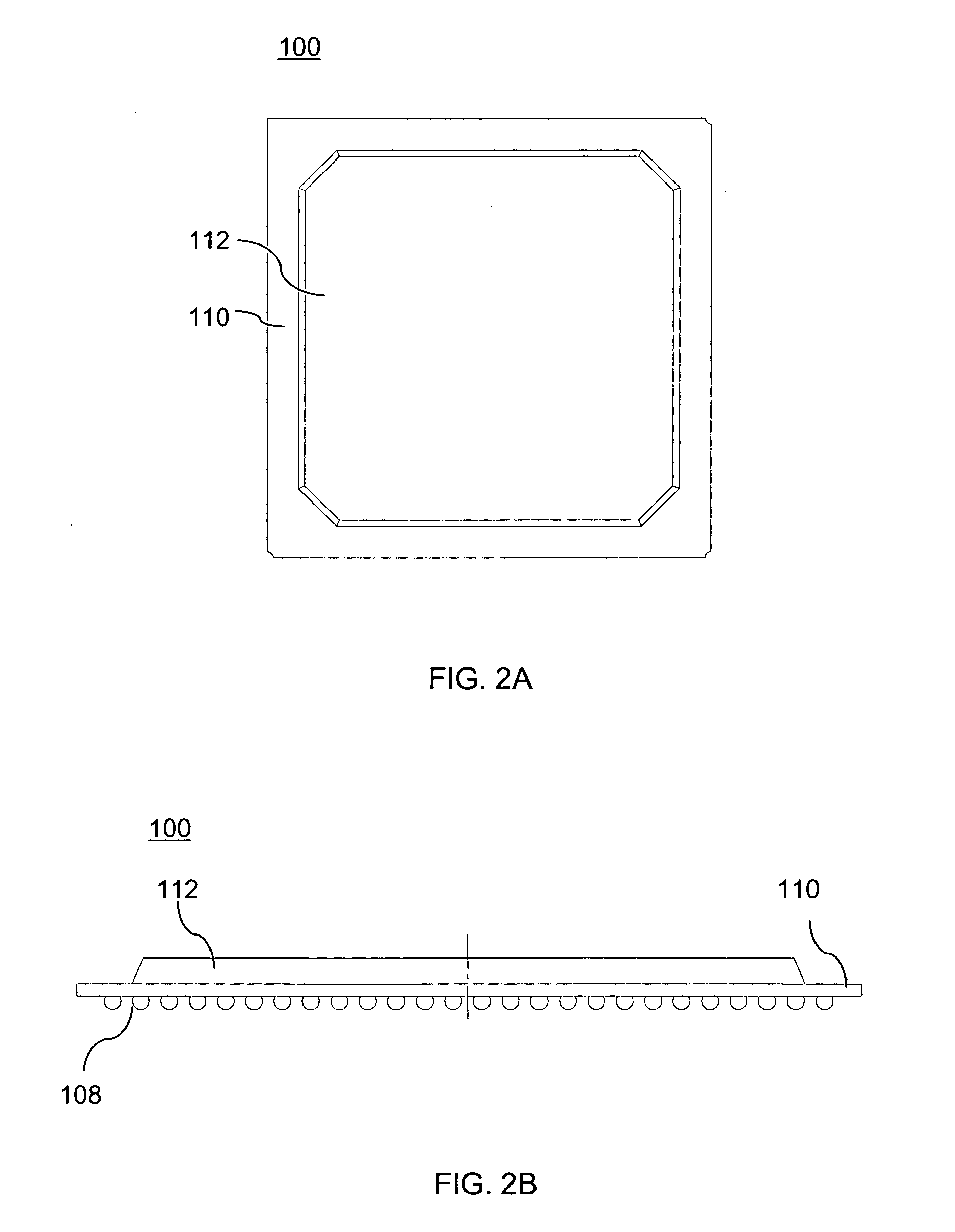

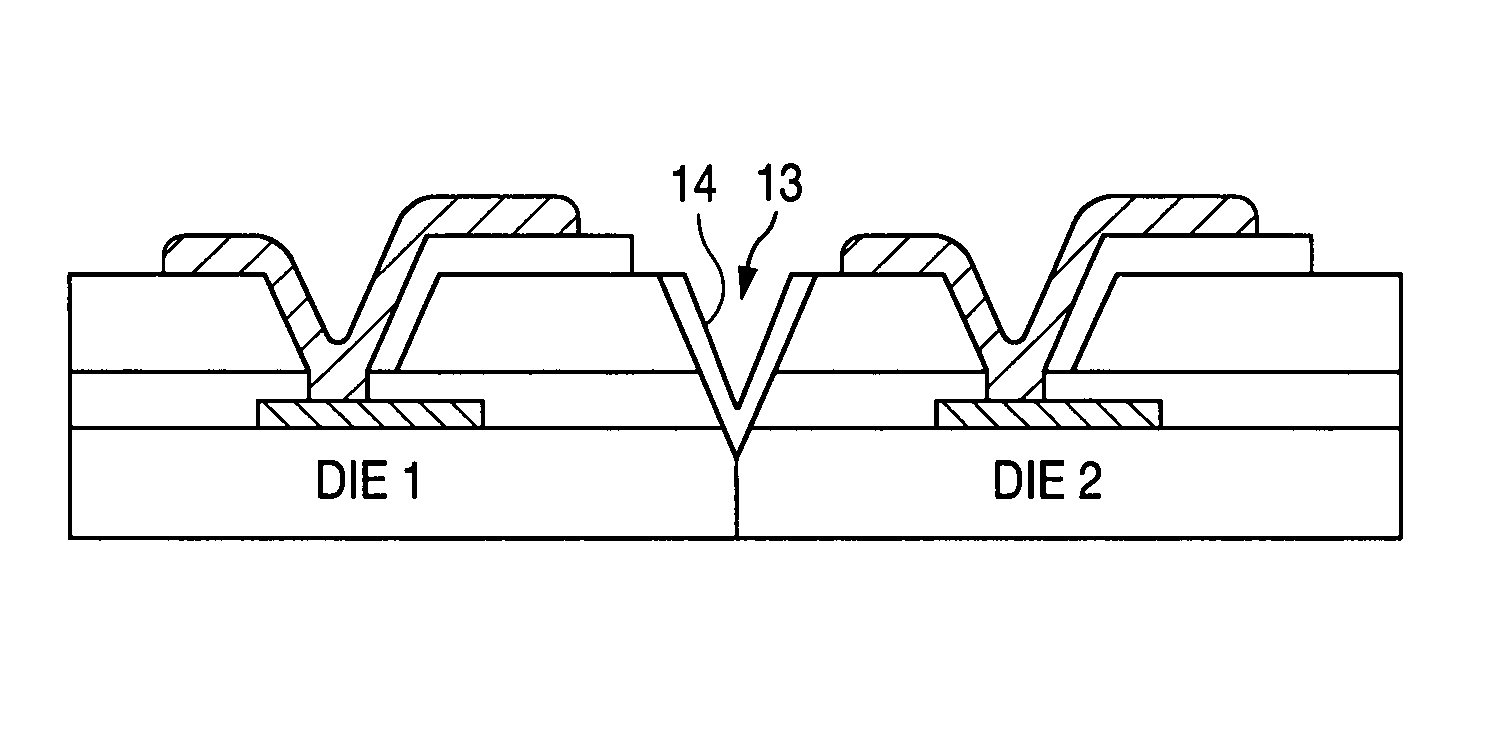

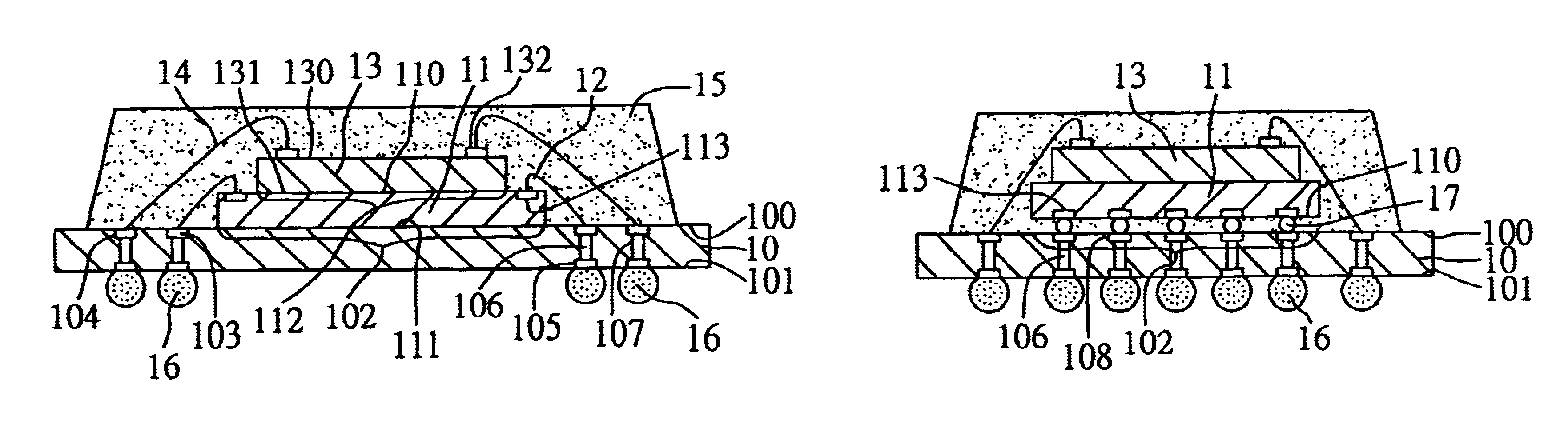

Methods, systems, and apparatuses for integrated circuit (IC) package vertical interconnection are described herein. In an aspect of the invention, an IC package includes an IC die with contact pads. The IC package also includes interconnect members which are coupled to the die at the contact pads. An encapsulating material encapsulates the IC die and the interconnect members such that a contact surface of each interconnect member is accessible at a surface of the encapsulating material. A second IC package is coupled to the first IC package through the plurality of interconnect members of the first IC package. In an example, solder balls attached to a bottom of the second IC package are coupled to the contact surfaces of the interconnect members to couple the first IC package and the second IC package.

Owner:AVAGO TECH INT SALES PTE LTD

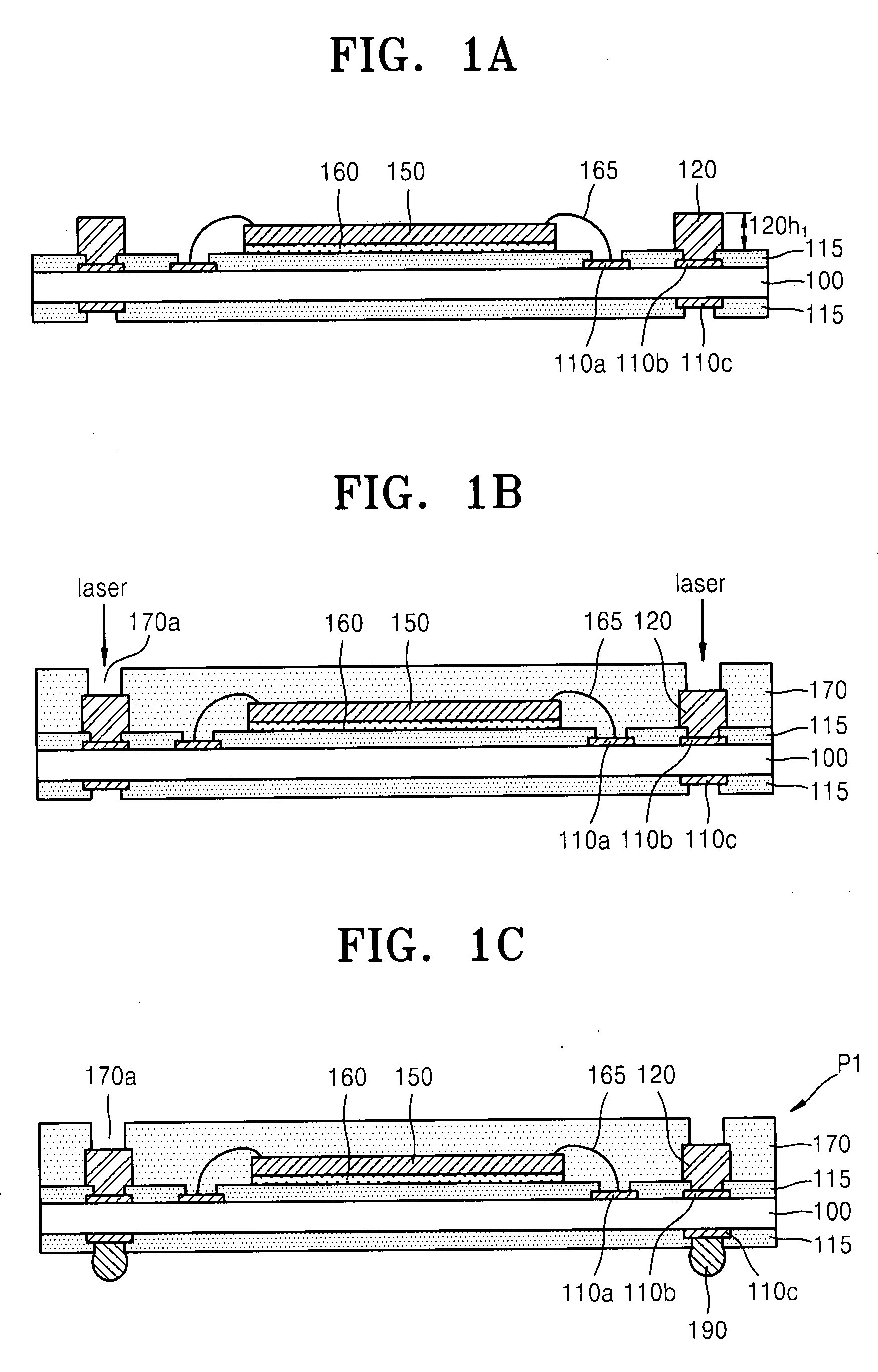

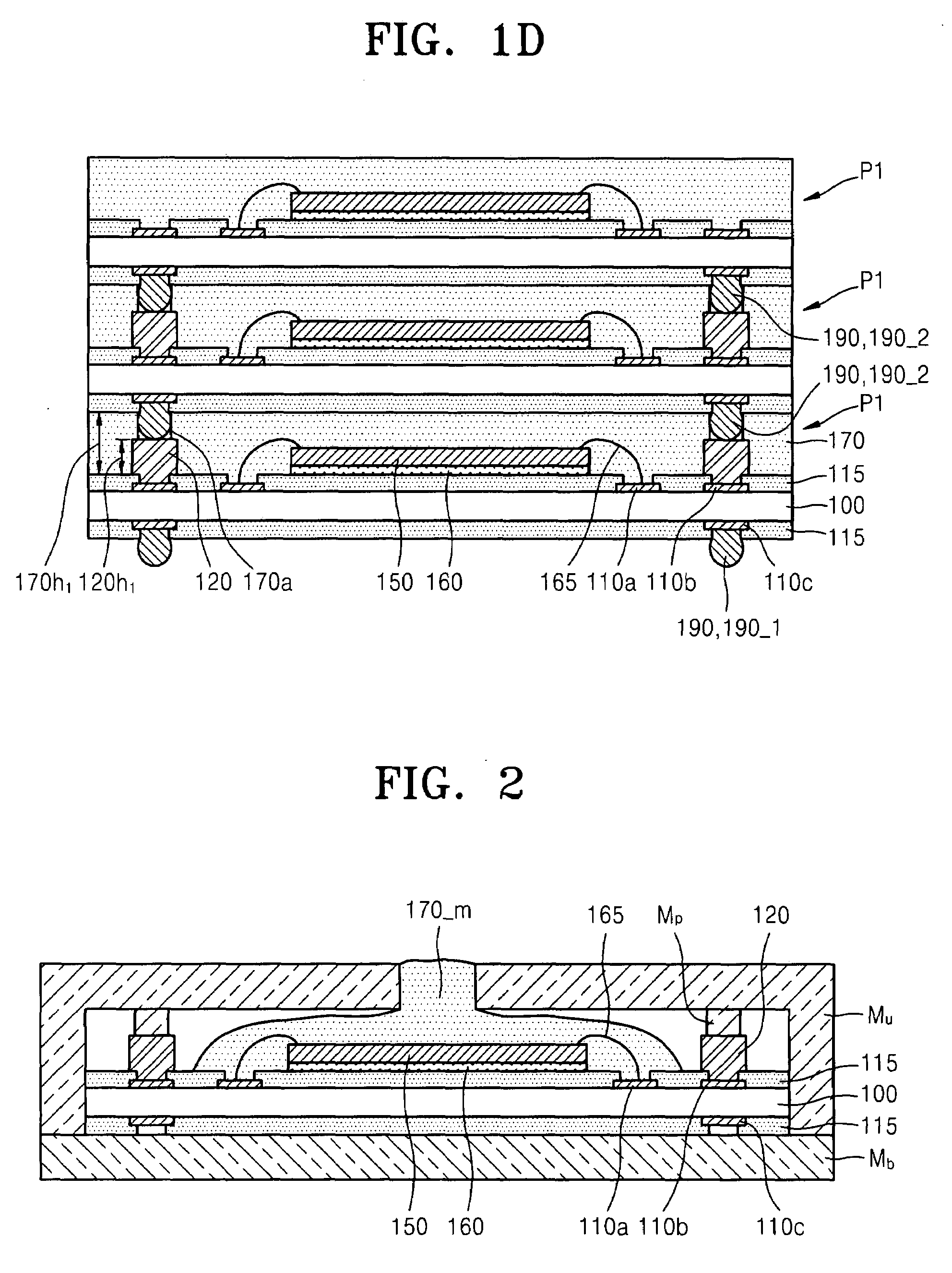

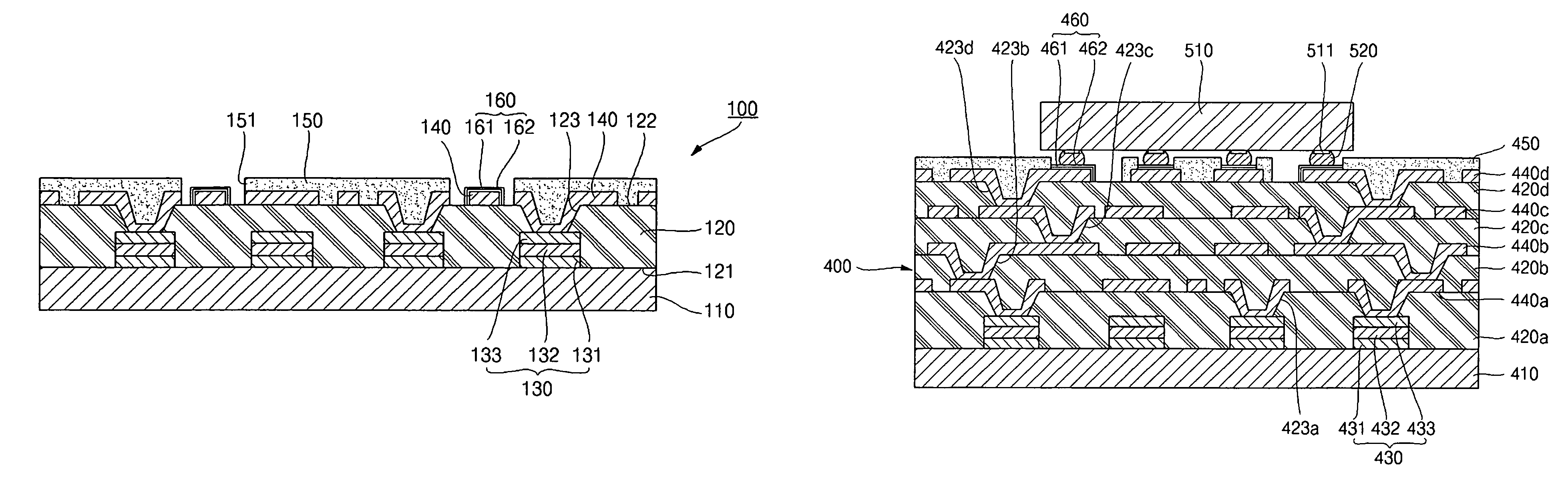

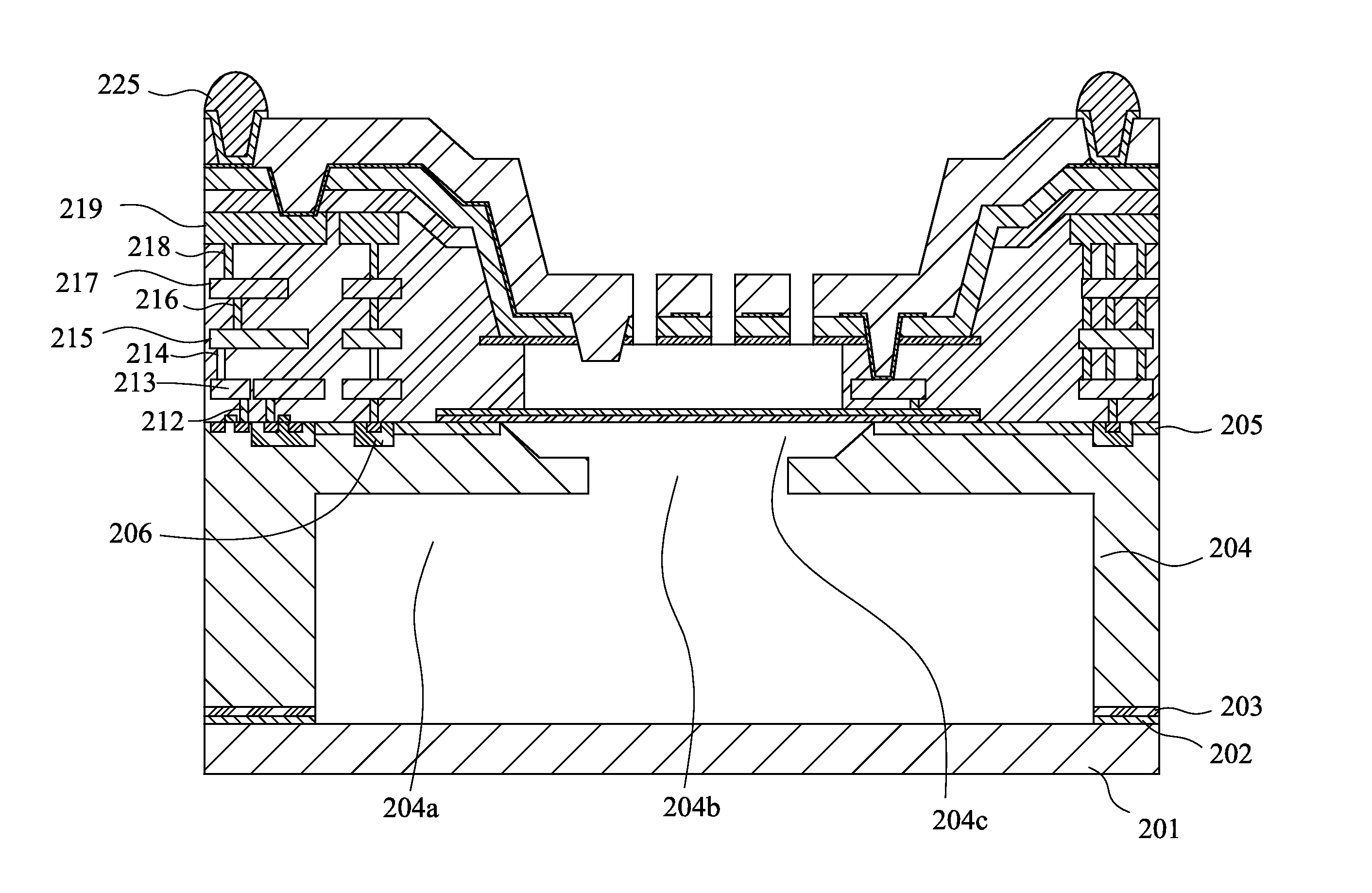

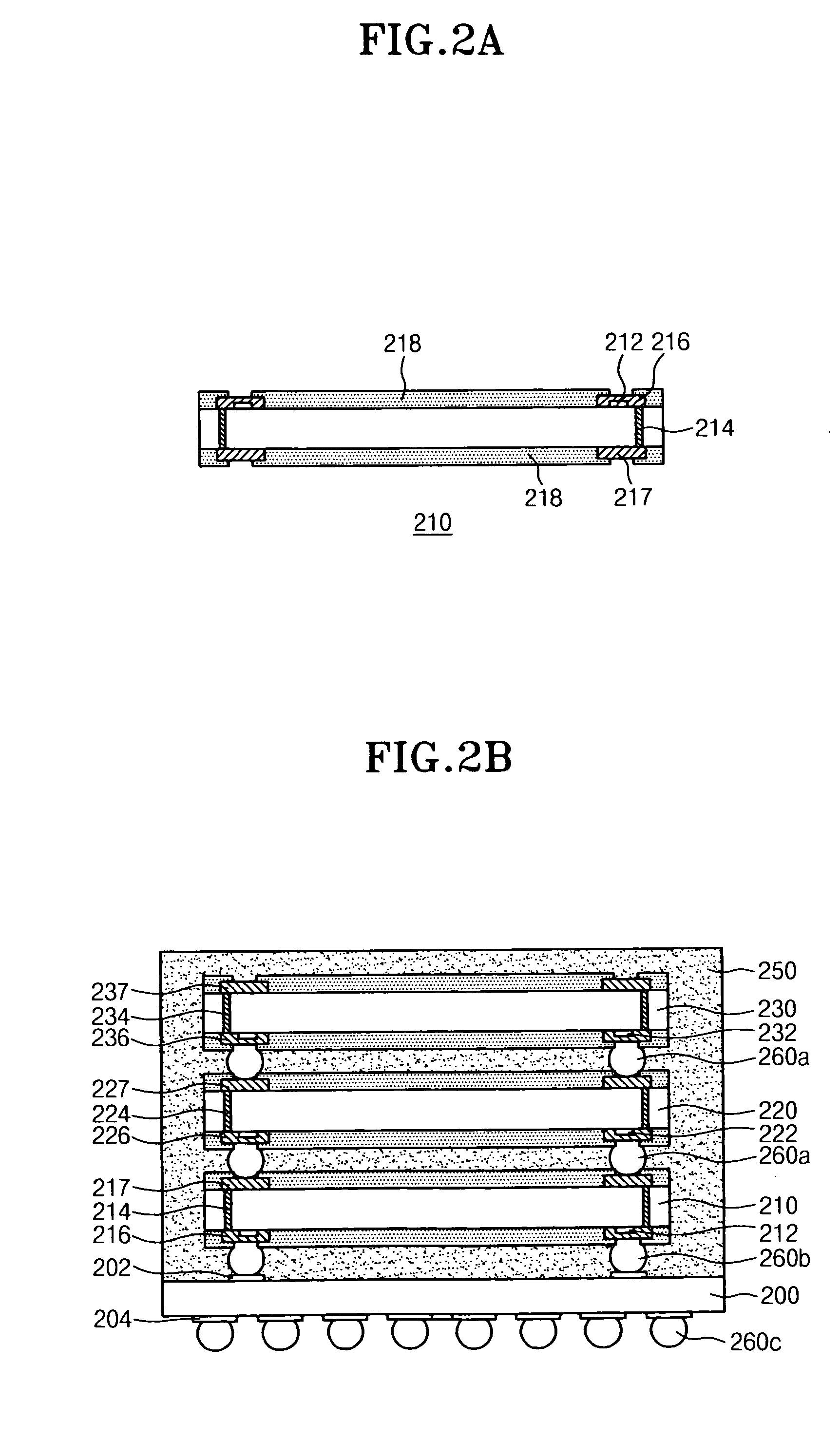

Stack type semiconductor package and method of fabricating the same

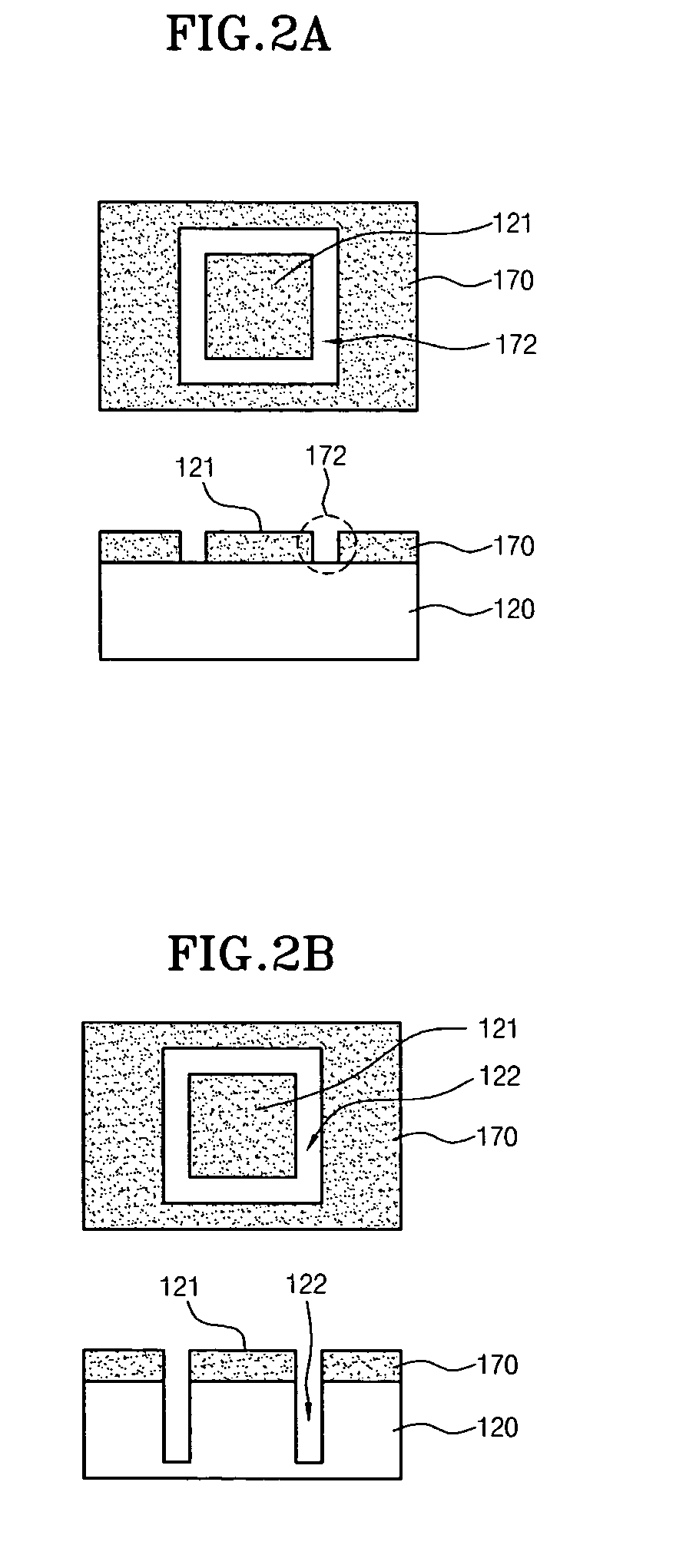

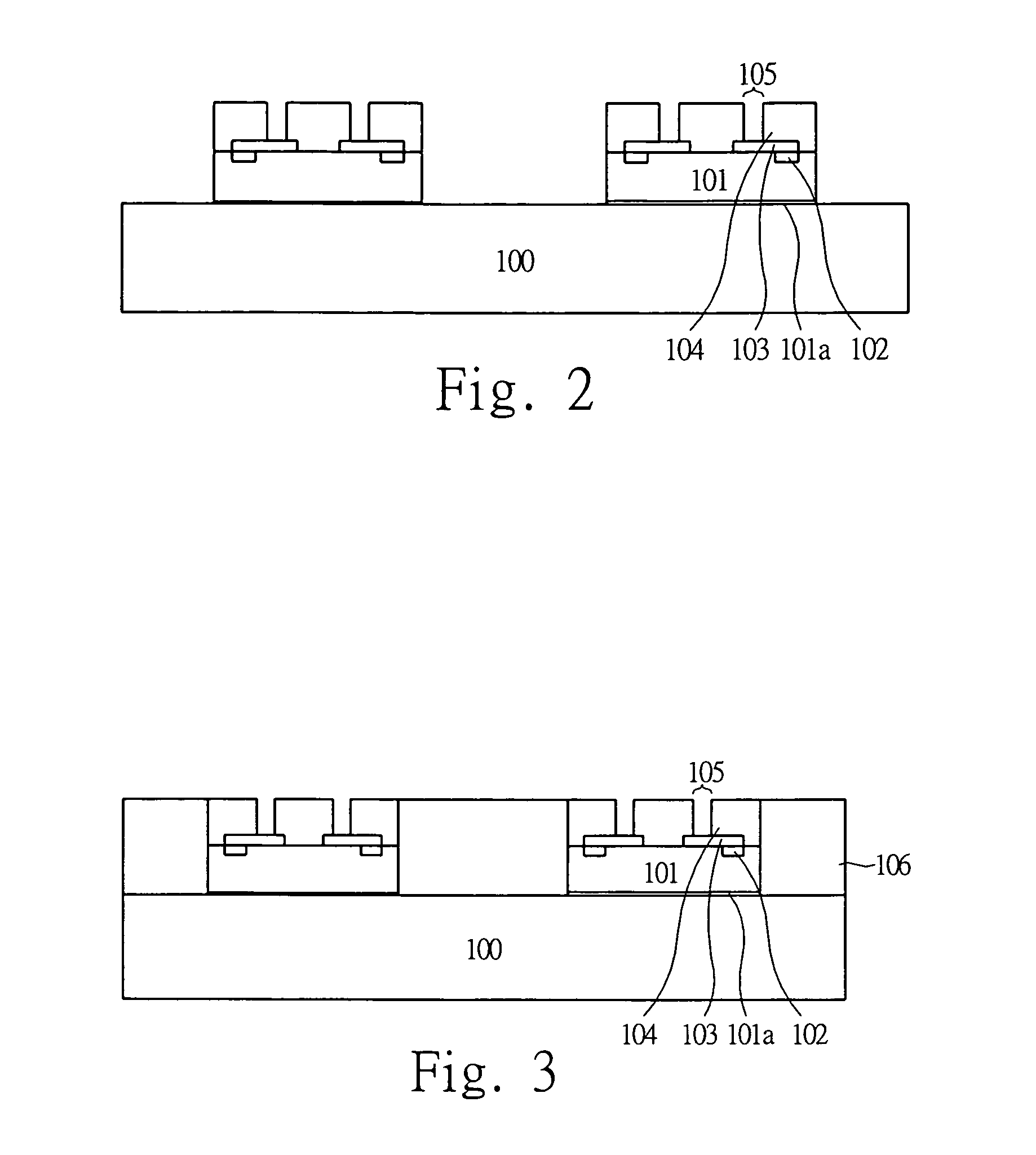

InactiveUS20080017968A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

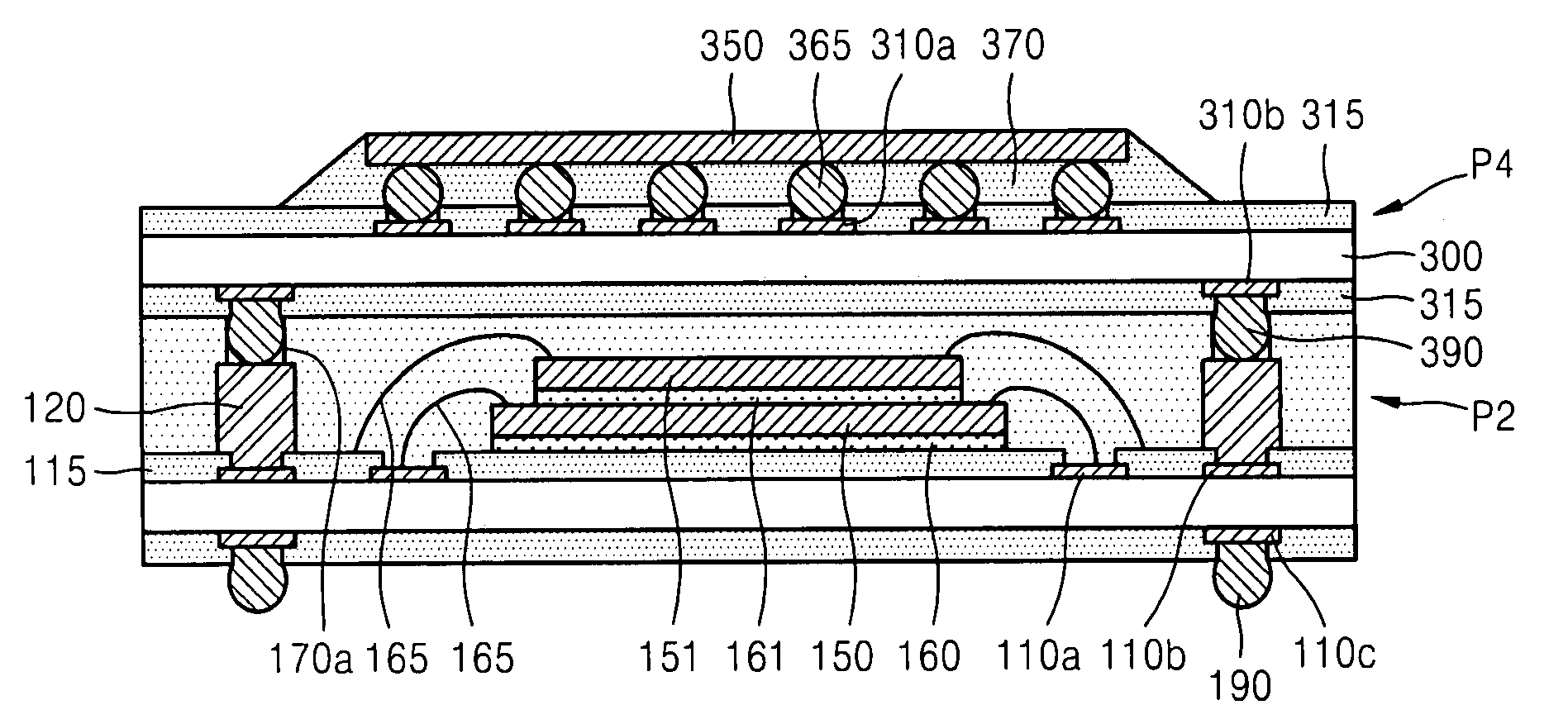

A stack type semiconductor package, and a method of fabricating the same are provided. The stack type semiconductor package may include a lower unit package and an upper unit package. The lower unit package may include a substrate, and a semiconductor chip on an upper surface of the substrate. A bump may be on an upper surface of the substrate, and a protecting layer, covering the semiconductor chip, may be formed. The protecting layer may include a via hole partially exposing the bump. The upper unit package may be on the protecting layer, and may include an internal connection solder ball on a lower surface of the upper unit package. The internal connection solder ball may be inserted into the via hole and connected to the bump.

Owner:SAMSUNG ELECTRONICS CO LTD

Stack package having guard ring which insulates through-via interconnection plug and method for manufacturing the same

ActiveUS7525186B2Avoid crackingAvoid disconnectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A stack package comprises a substrate having a circuit pattern; at least two semiconductor chips stacked on the substrate, having a plurality of through-via interconnection plugs and a plurality of guard rings which surround the respective through-via interconnection plugs, and connected with each other by the medium of the through-via interconnection plugs; a molding material for molding an upper surface of the substrate including the stacked semiconductor chips; and solder balls mounted to a lower surface of the substrate.

Owner:SK HYNIX INC

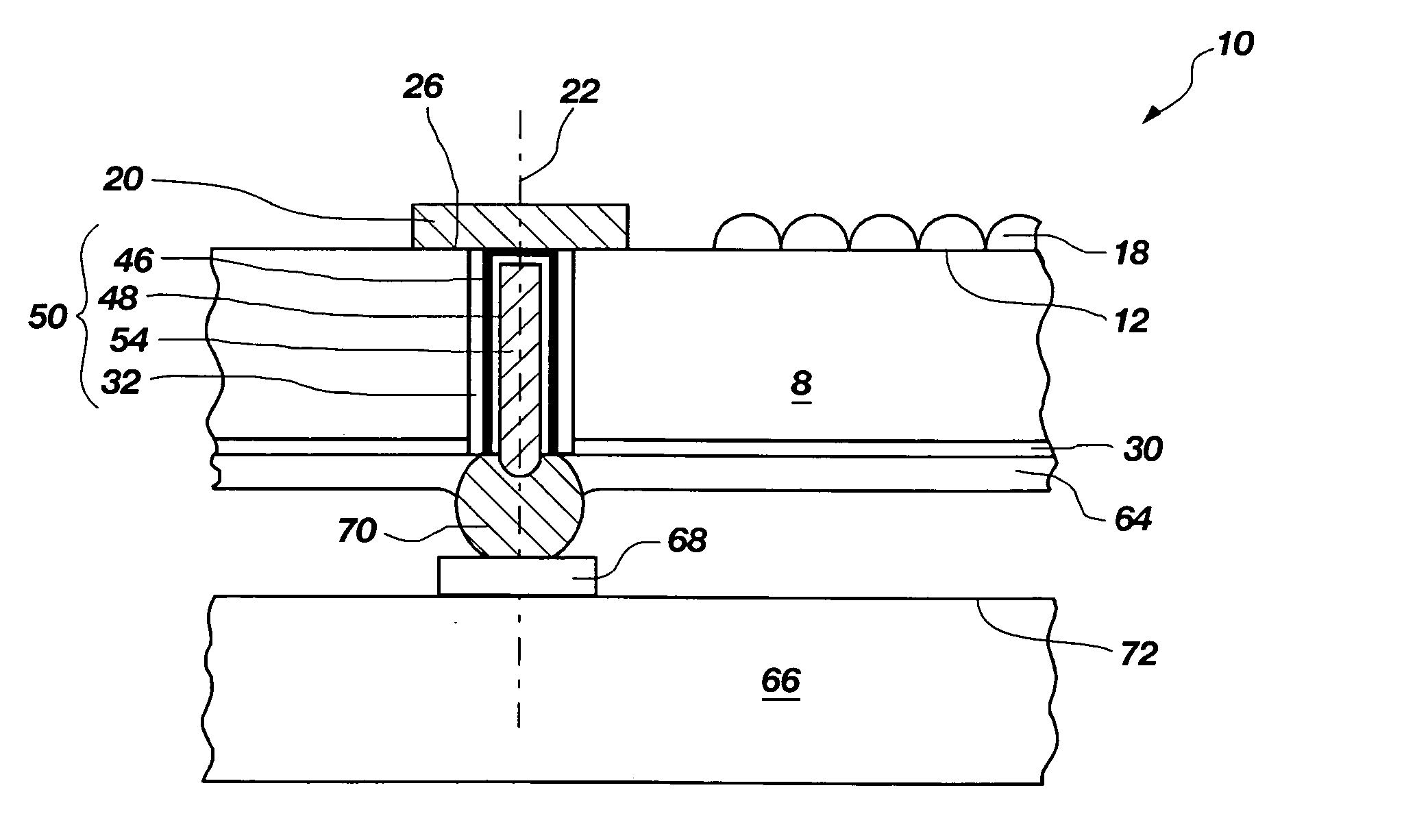

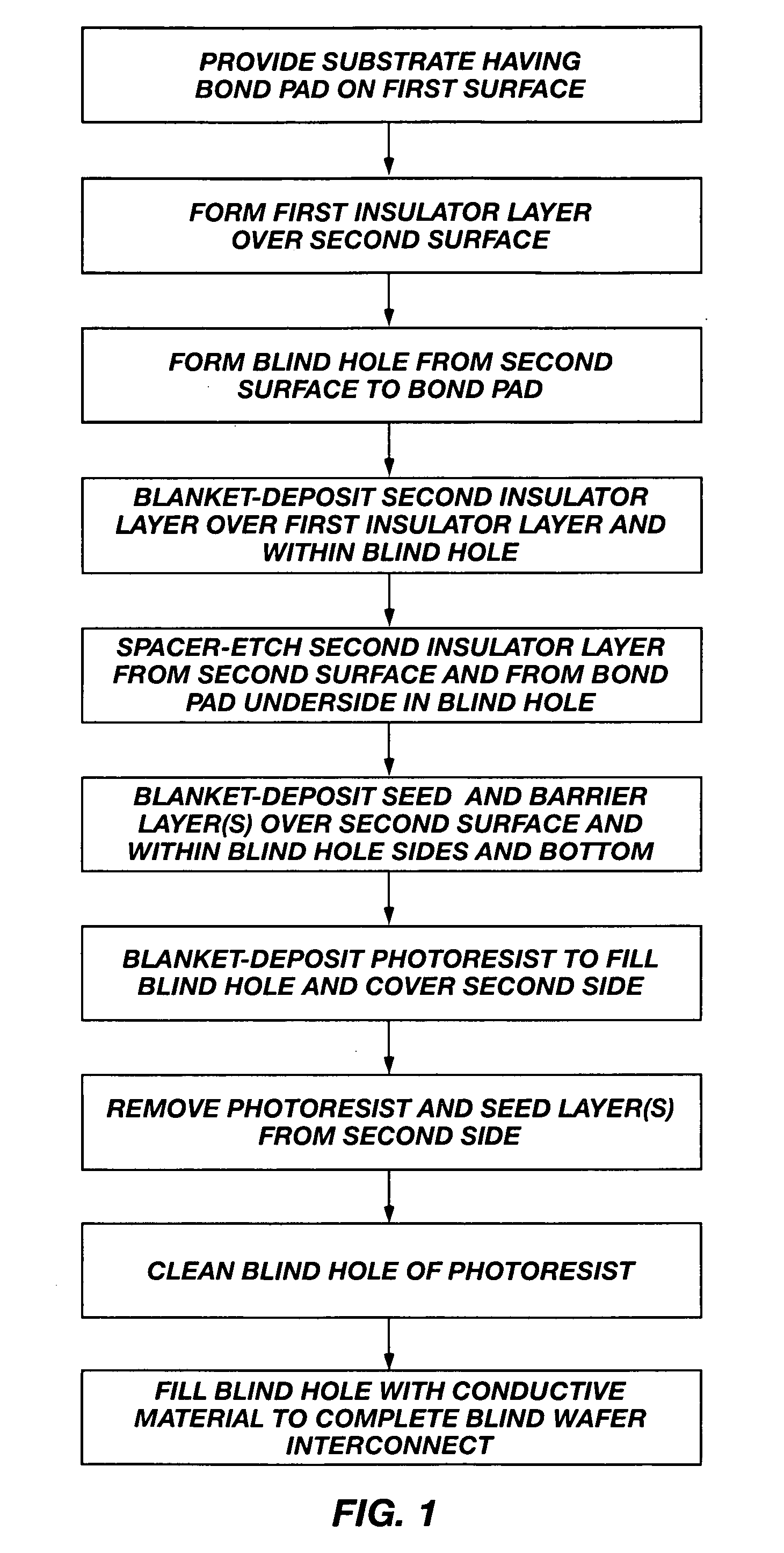

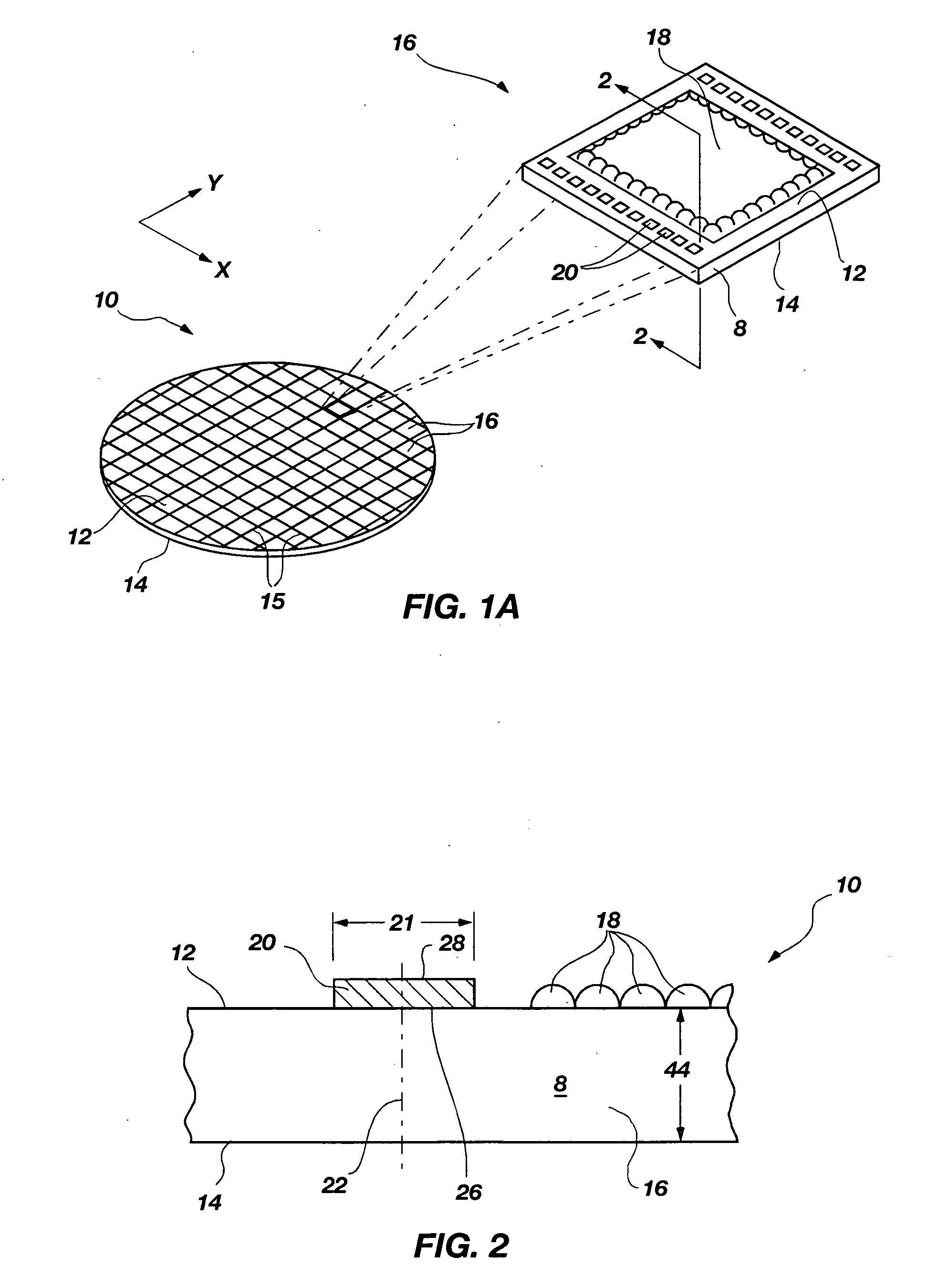

Methods of forming blind wafer interconnects, and related structures and assemblies

InactiveUS20070045780A1Reduce expensesReduce processing timeSemiconductor/solid-state device detailsSolid-state devicesResistSolder ball

Methods for forming blind wafer interconnects (BWIs) from the back side of a previously thinned substrate structure such as a semiconductor wafer to the underside of a bond pad on its active surface includes the formation of a blind hole from the back side, application of a passivating layer therein, anisotropically etching to remove passivation material from the blind hole bottom, blanket-depositing at least one conductive layer within the blind hole and over the back side, blanket-depositing a resist in the blind hole and over the back side, planarizing the back side to remove resist and the at least one conductive layer, removing resist from the blind hole, and filling the blind hole with solder or other conductive material or a dielectric material. Variations in the methods include formation of a conductive pad adjacent the back side surface, disposition of a solder ball or other conductive structure on the BWI, or forming an end thereof in the form of an extended slug protruding from the back side (for ball-less attachment) as the outer terminus of the BWI.

Owner:ROUND ROCK RES LLC

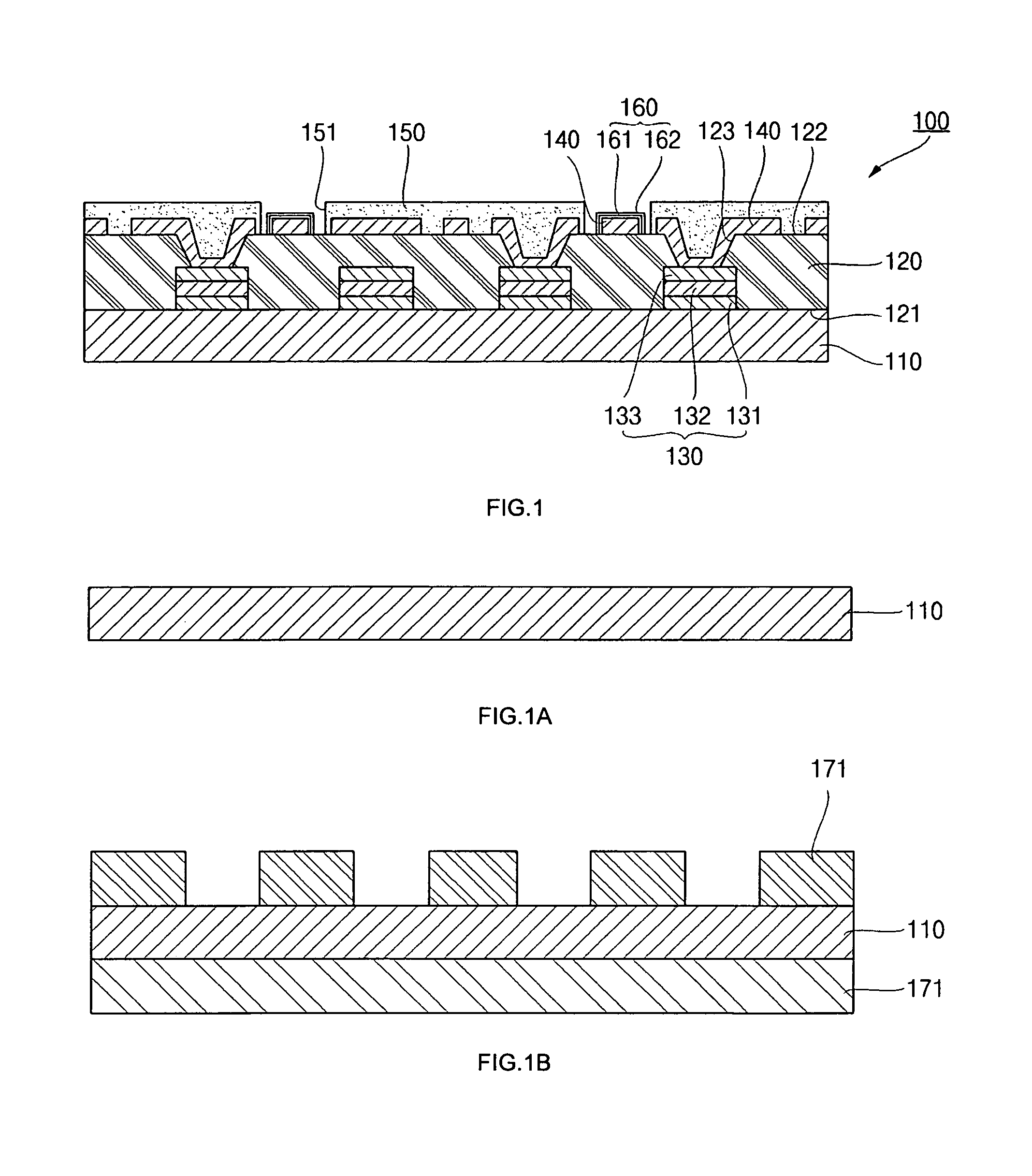

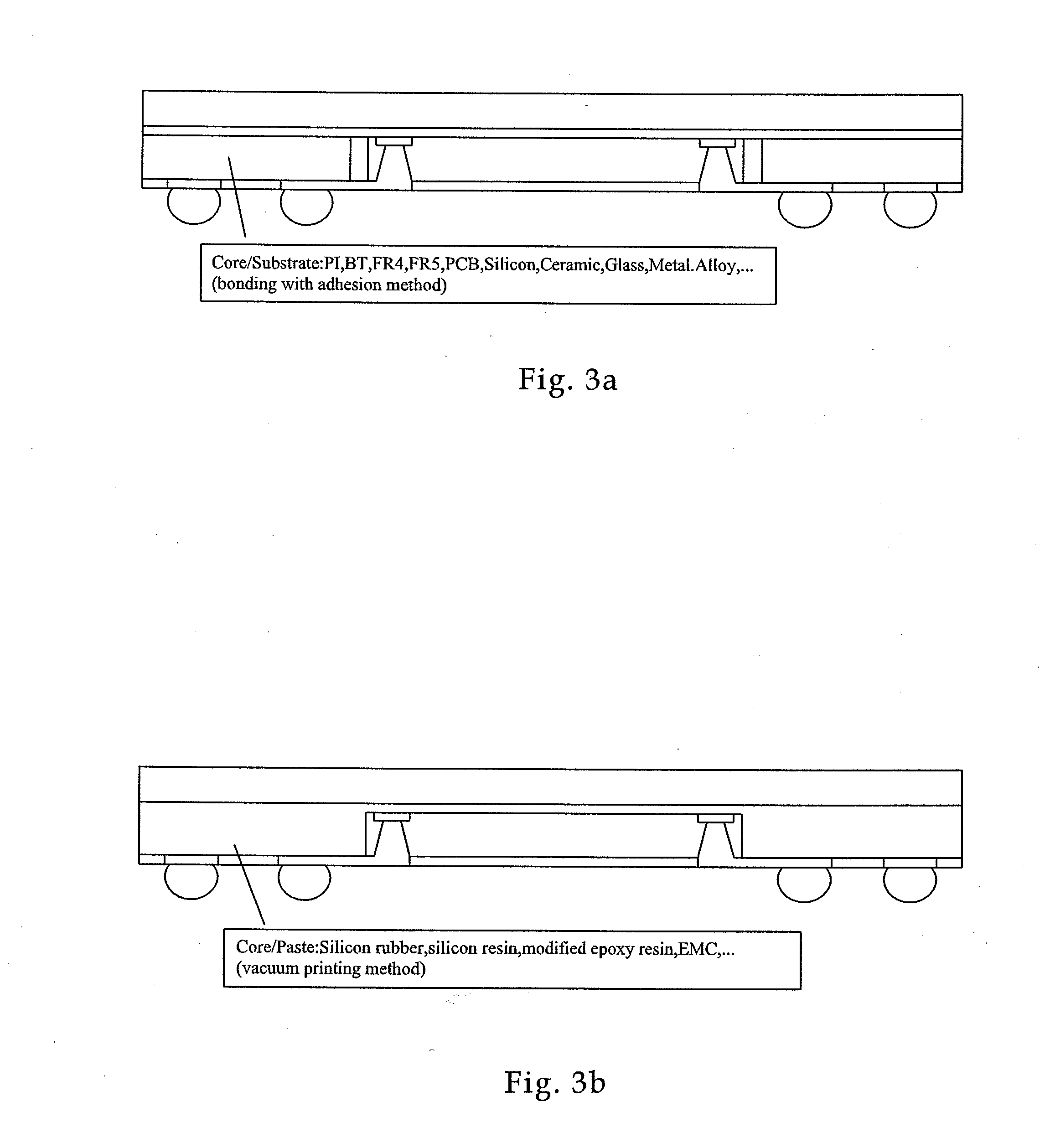

Substrate for semiconductor device and manufacturing method thereof

ActiveUS7902660B1Thin thicknessAvoid warpingSemiconductor/solid-state device detailsSolid-state devicesElectricitySolder ball

A substrate for a semiconductor device and a manufacturing thereof, and a semiconductor device using the same and a manufacturing method thereof are disclosed. For example, in the substrate according to the present invention, a core is eliminated, so that the substrate has a very thin thickness, as well, the length of electrically conductive patterns becomes shorter, whereby the electrical efficiency thereof is improved. Moreover, since a carrier having a stiffness of a predetermined strength is bonded on the substrate, it can prevent a warpage phenomenon during the manufacturing process of the semiconductor device. Furthermore, the carrier is removed from the substrate, whereby a solder ball fusing process or an electrical connecting process of the semiconductor die can be easily performed.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

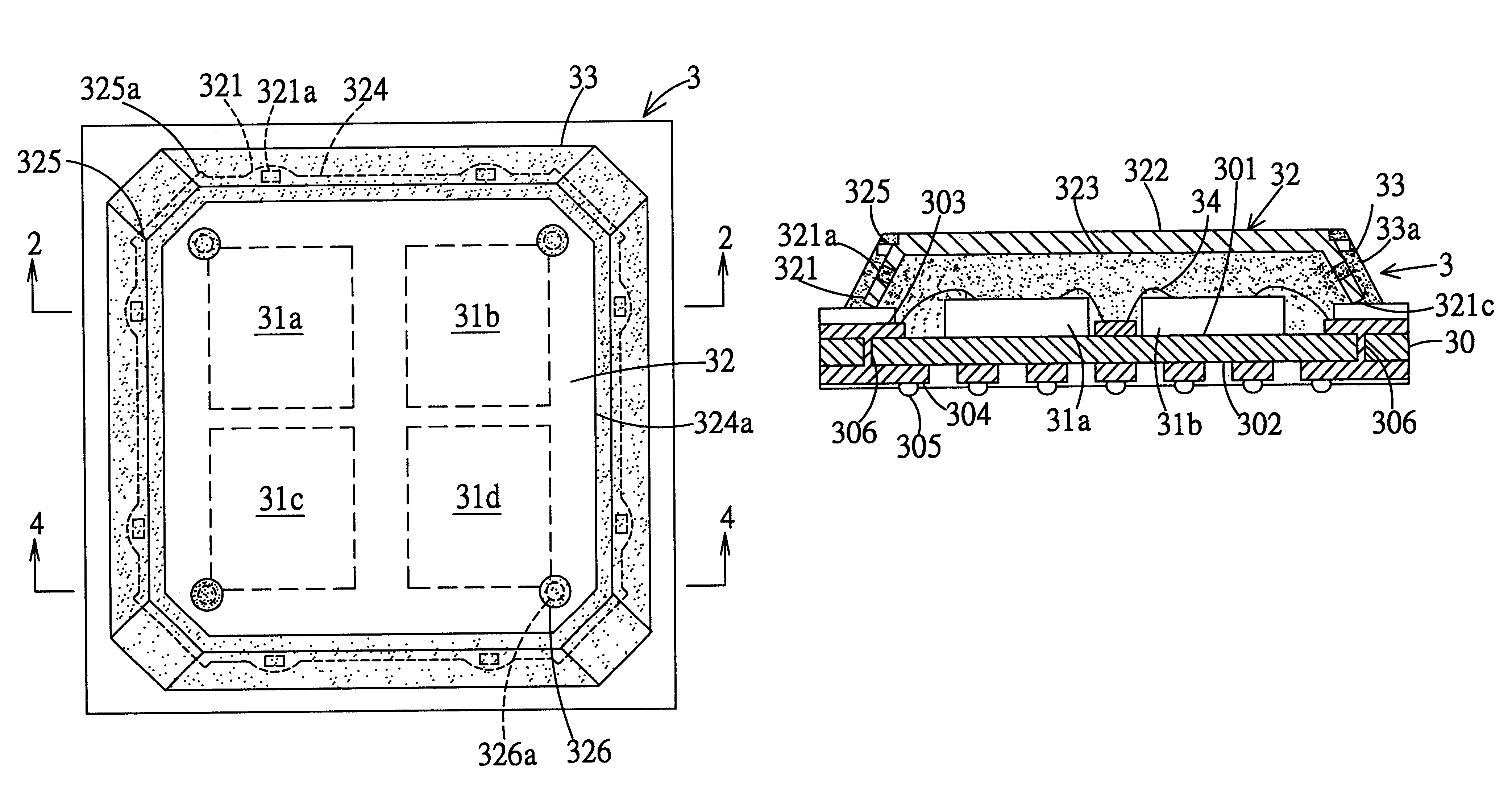

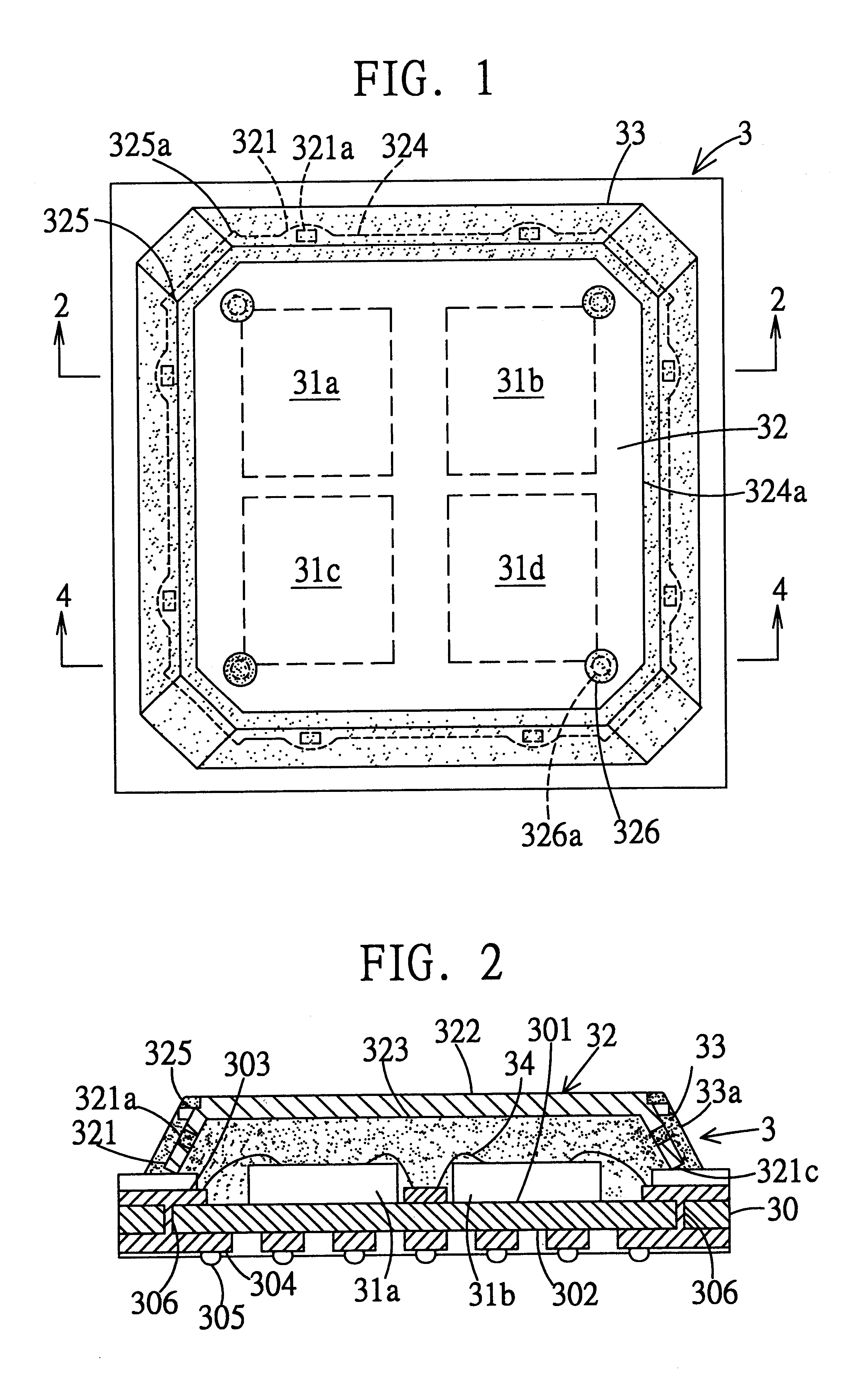

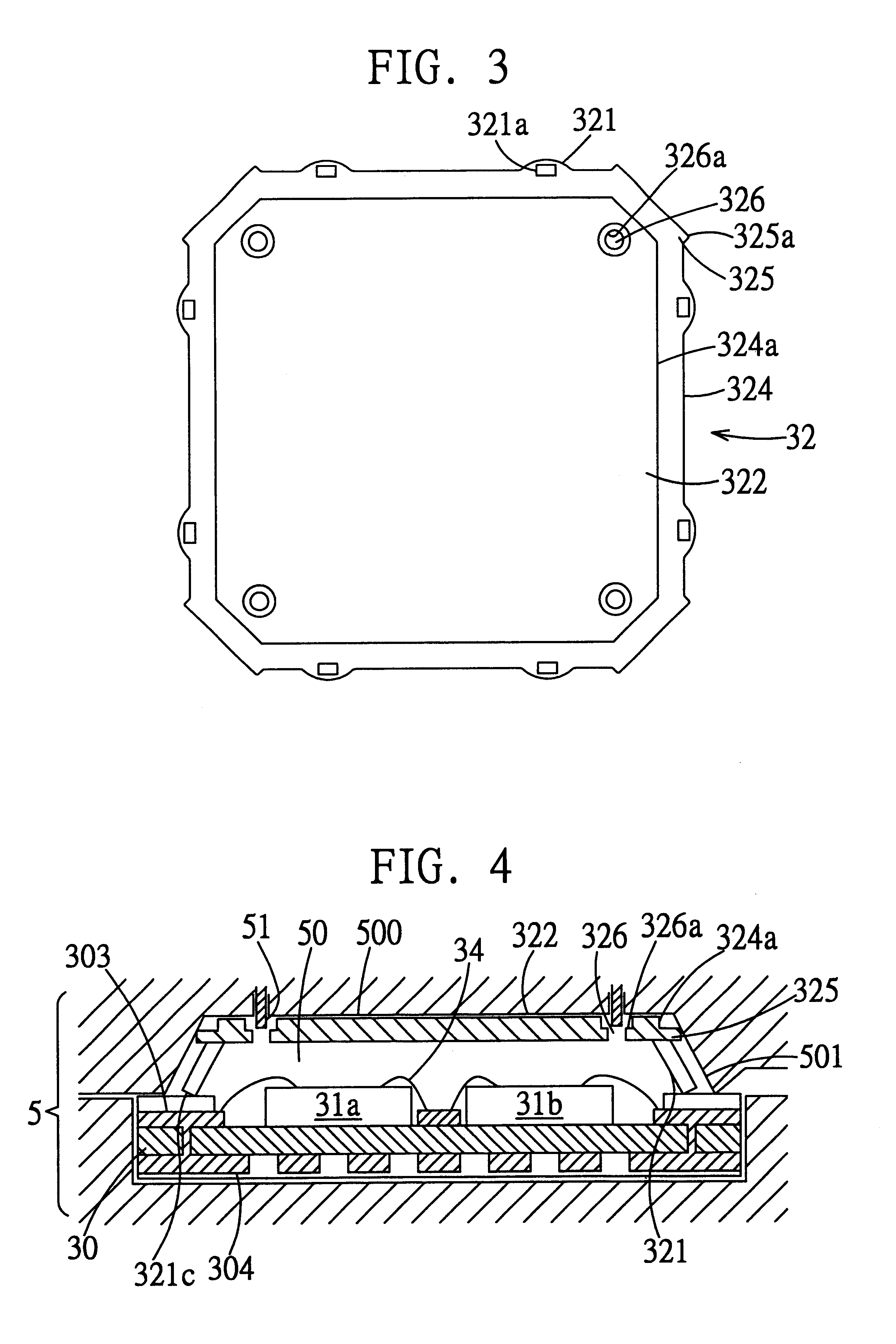

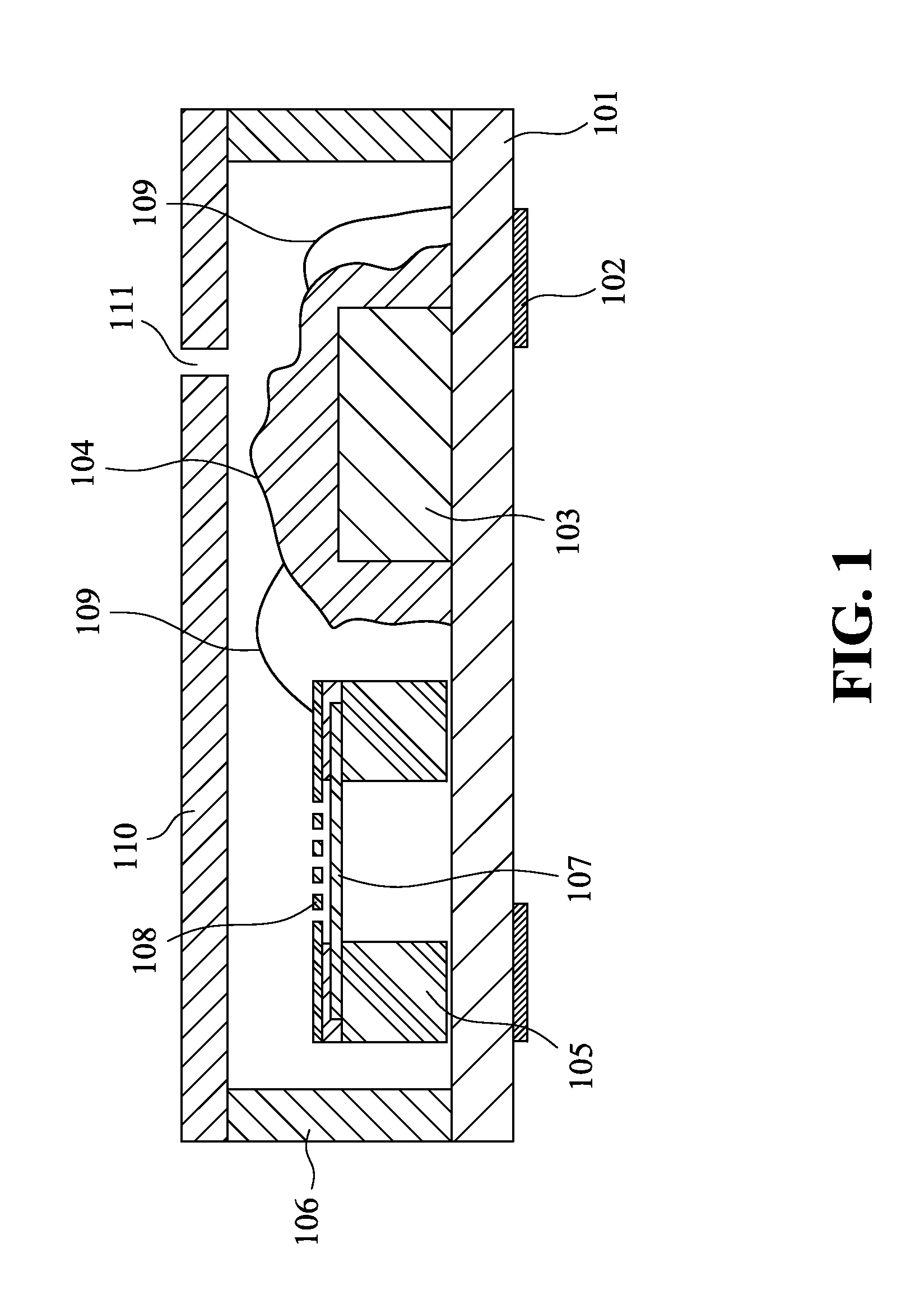

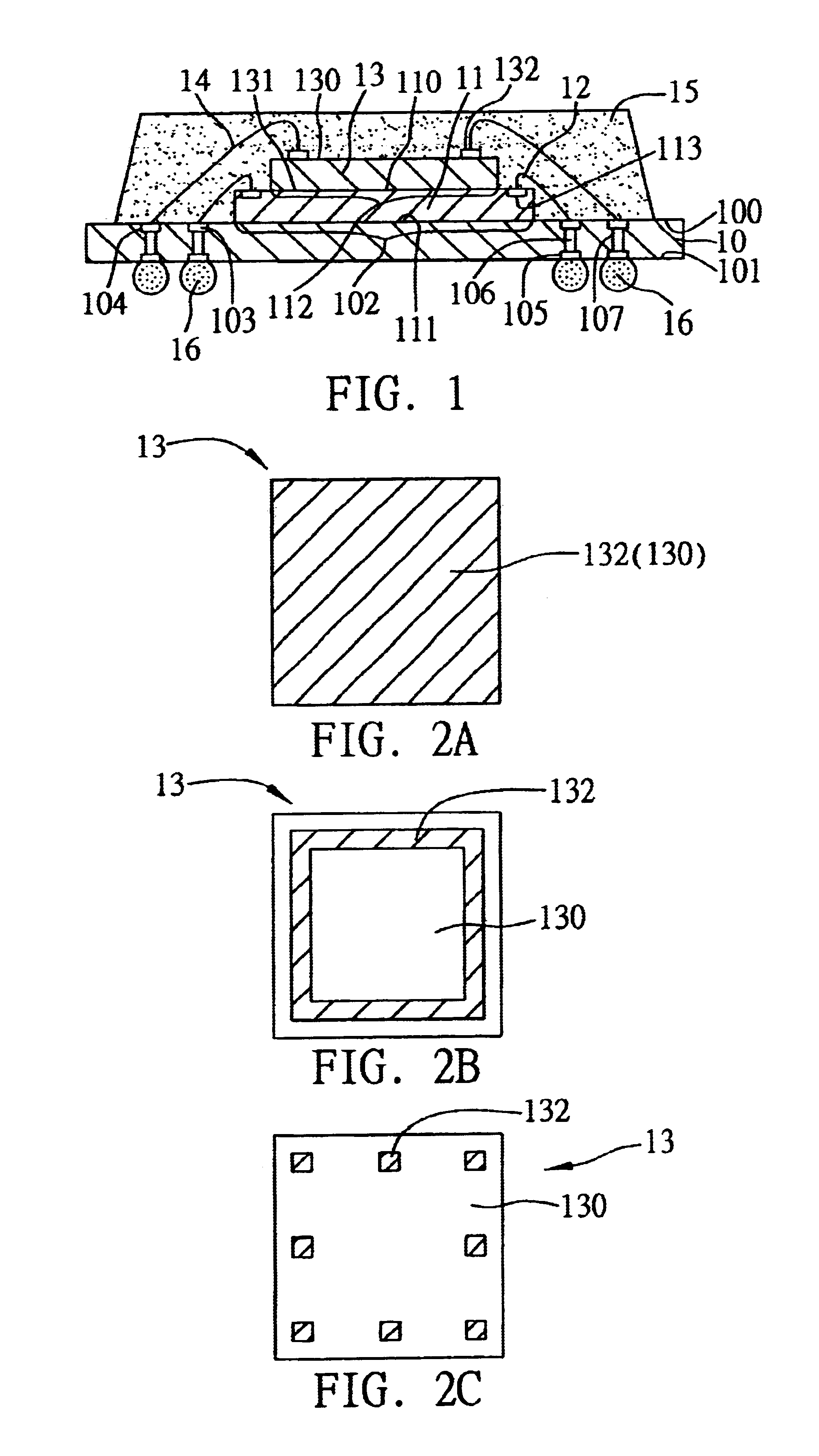

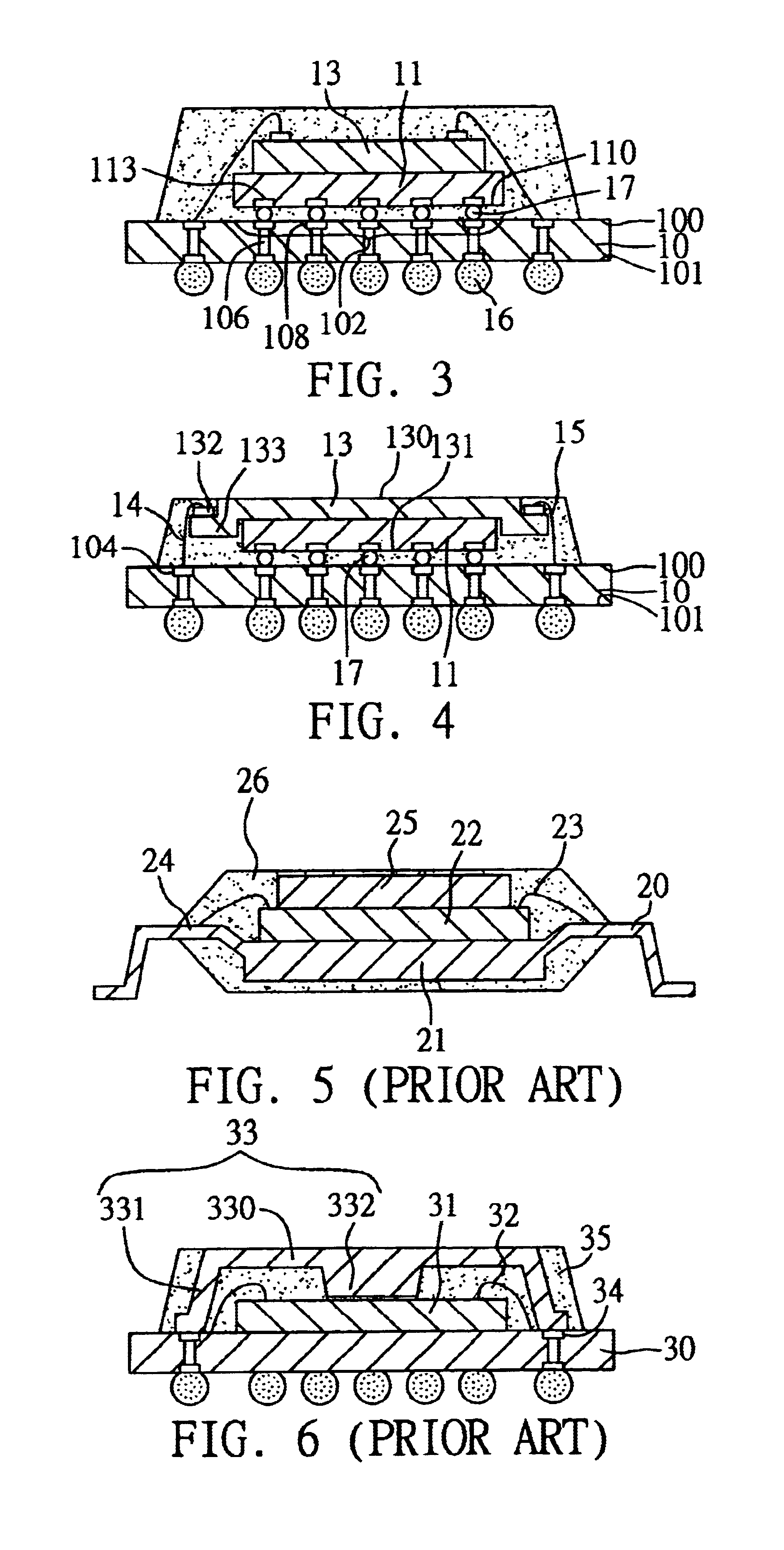

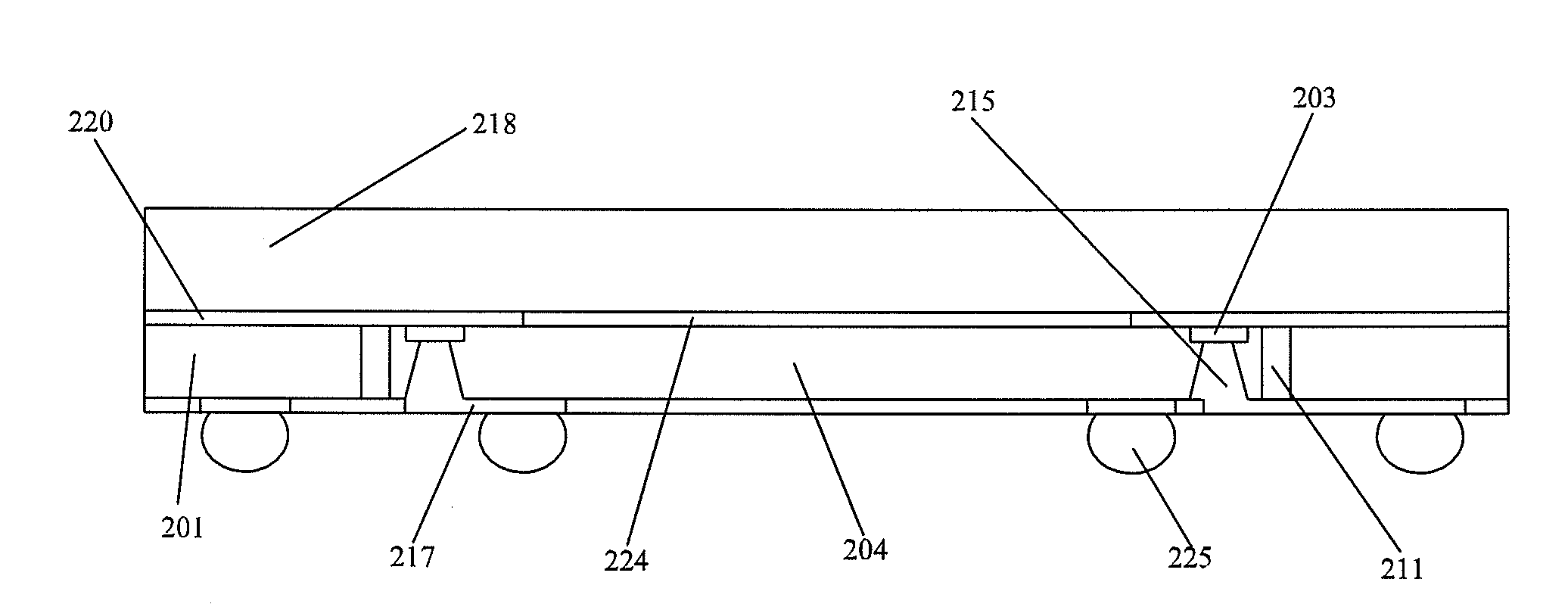

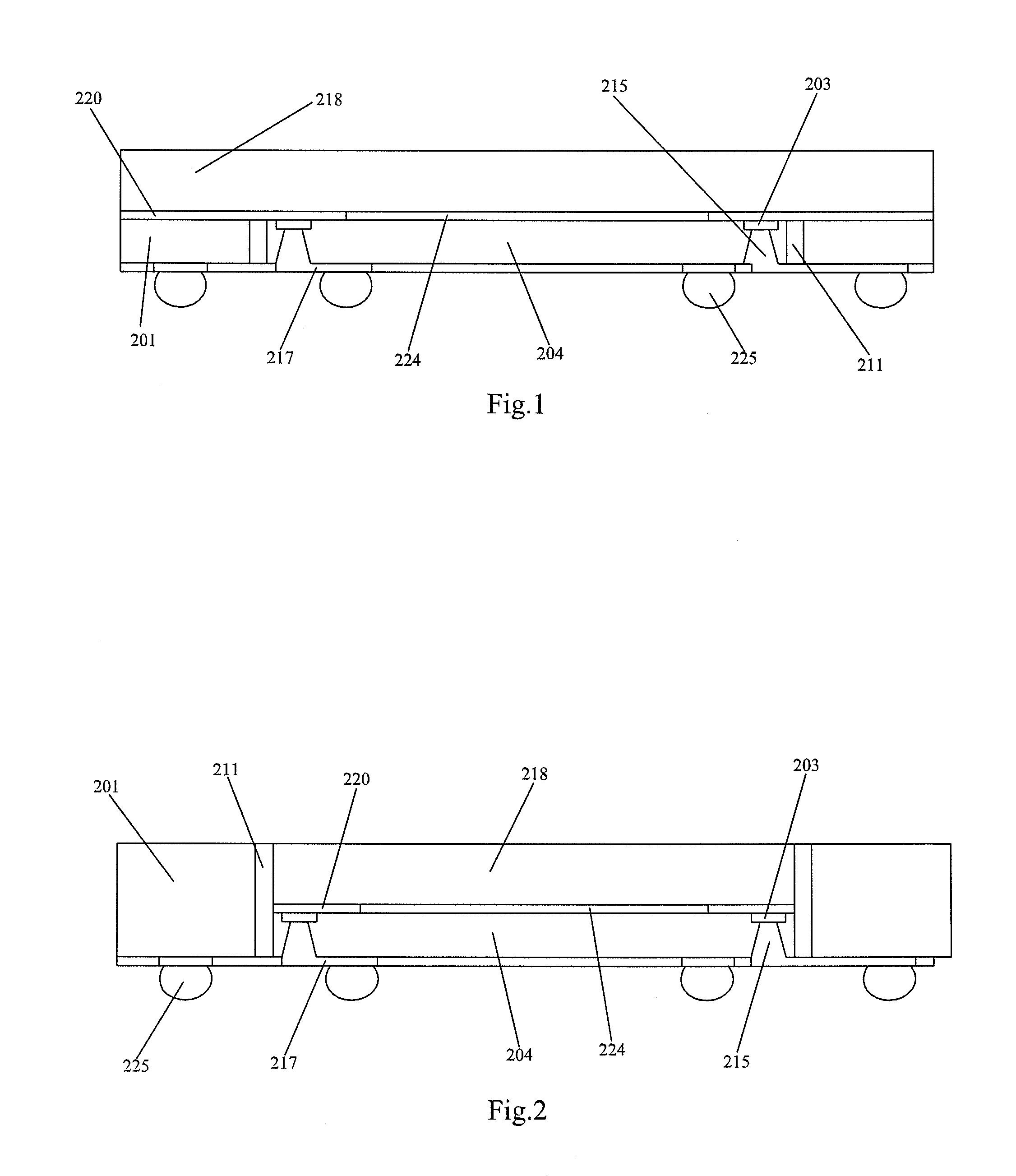

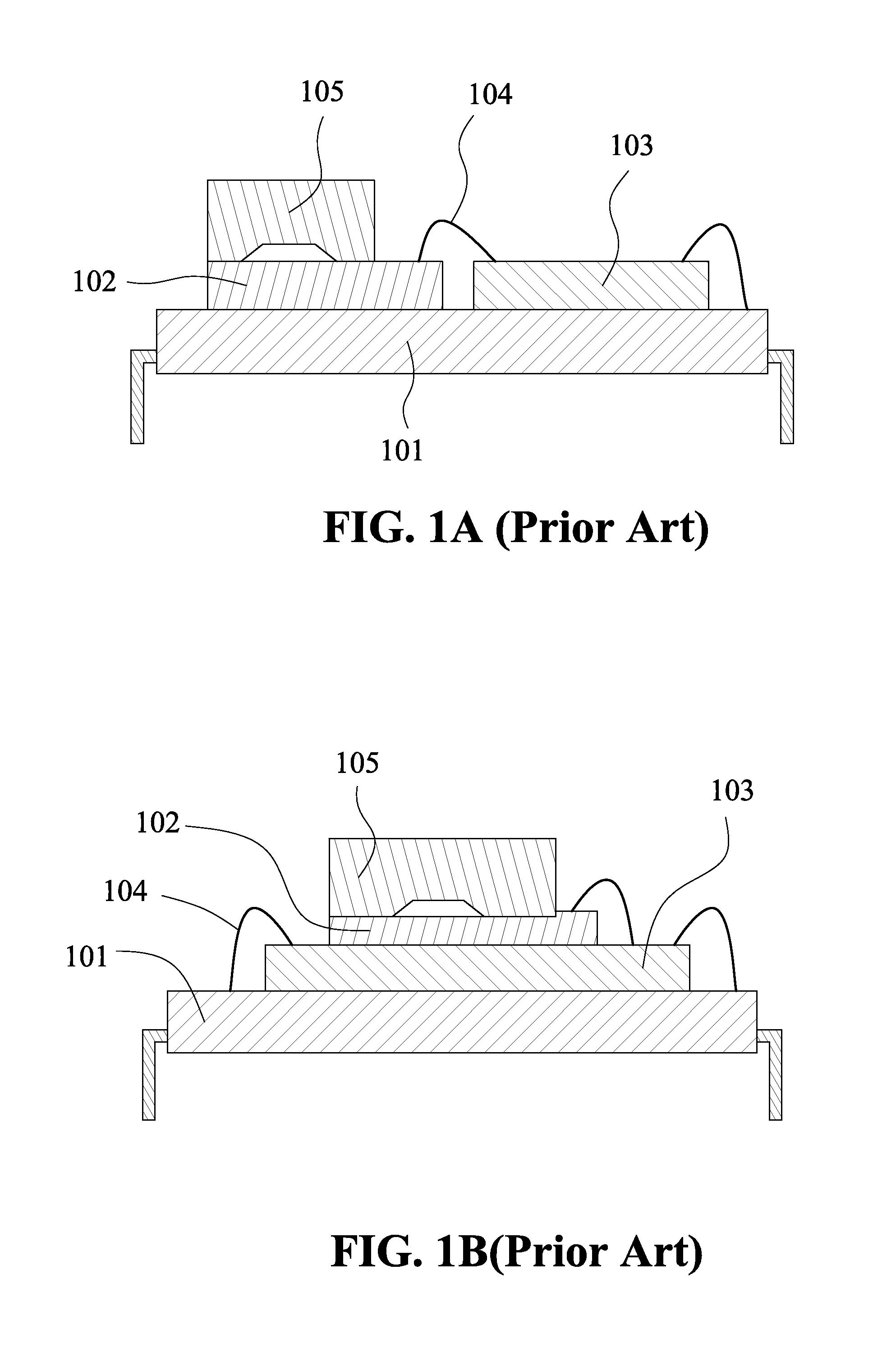

Semiconductor package having a heat sink with an exposed surface

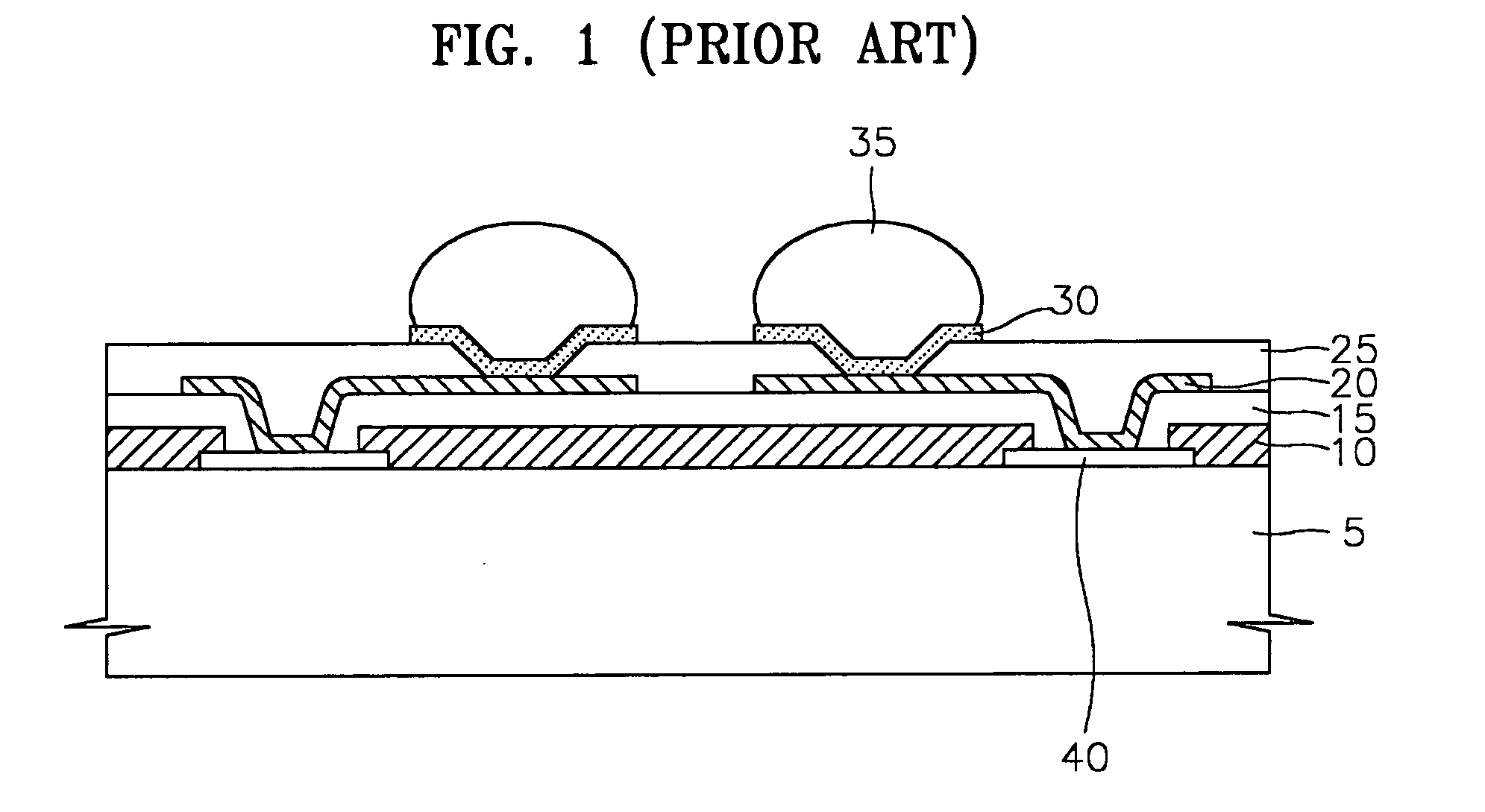

InactiveUS6246115B1Precise positioningAvoid flashSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor package

An integrated circuit package with a fully-exposed heat sink is provided. The integrated circuit package includes a substrate having a first side being formed with first conductive traces and a second side being formed with second conductive traces. At least one chip is mounted on the substrate and electrically connected to the first conductive traces. A plurality of solder balls are provided at the terminal ends of the second conductive traces to allow external connection of the chip. The fully-exposed heat sink is mounted on the substrate. The heat sink is formed with a plurality of supportive legs arranged in such a manner as to allow a bottom surface of the heat sink to be separated from the chip and a top surface of the heat sink to be tightly attached to a cavity in a mold used to form an encapsulant for enclosing the chip. A plurality of positioning tongues are formed on the heat sink for securing the heat sink in position when performing a molding process for forming the encapsulant. With this integrated circuit package, no jig is required in the assembly of the integrated circuit package. Moreover, since there is no need to use adhesives to adhere the supportive legs onto the substrate, the integrated circuit package would not suffer from delamination as in the case of the prior art. The fully-exposed heat sink allows an increased heat-dissipating efficient as compared to the prior art.

Owner:SILICONWARE PRECISION IND CO LTD

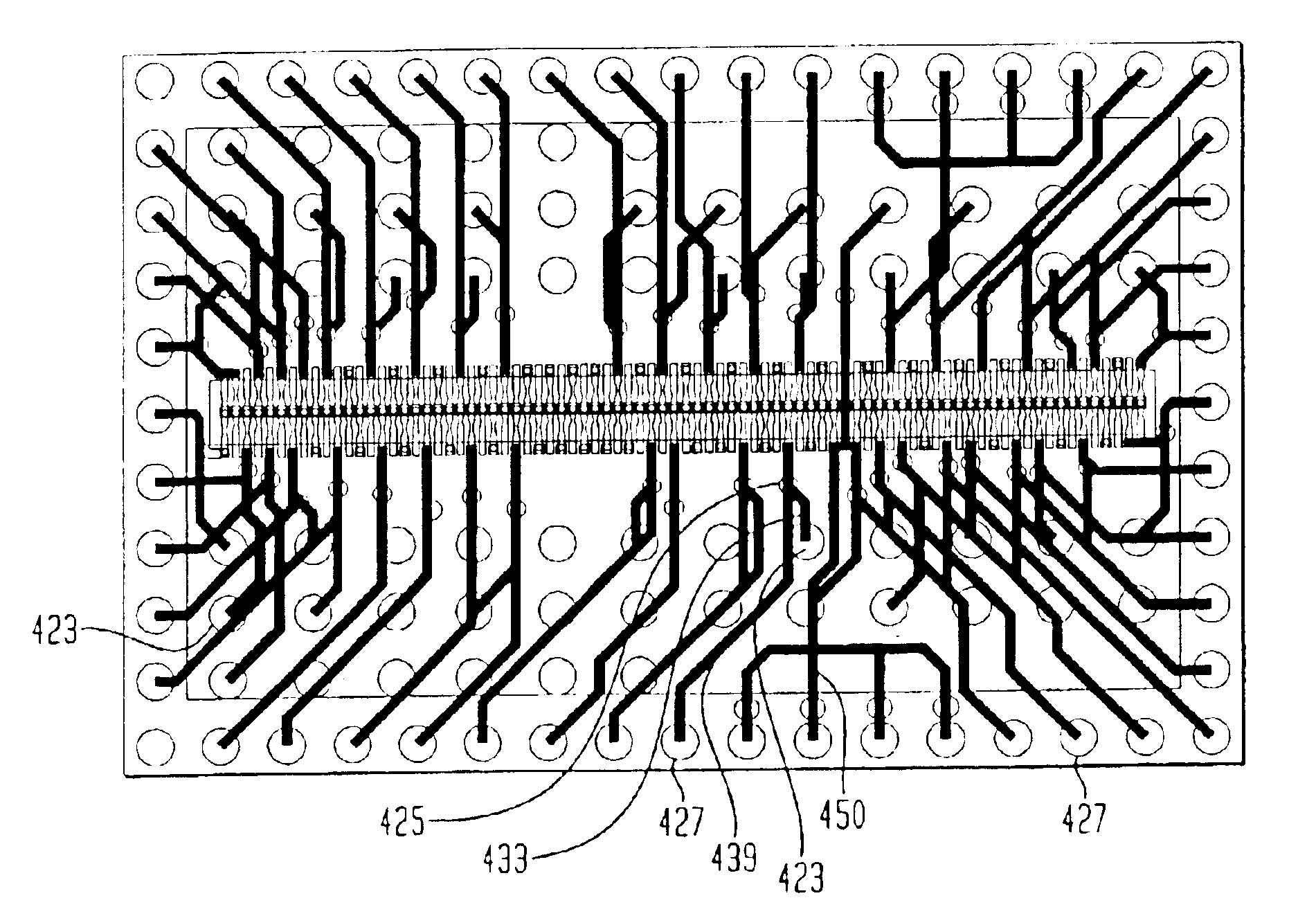

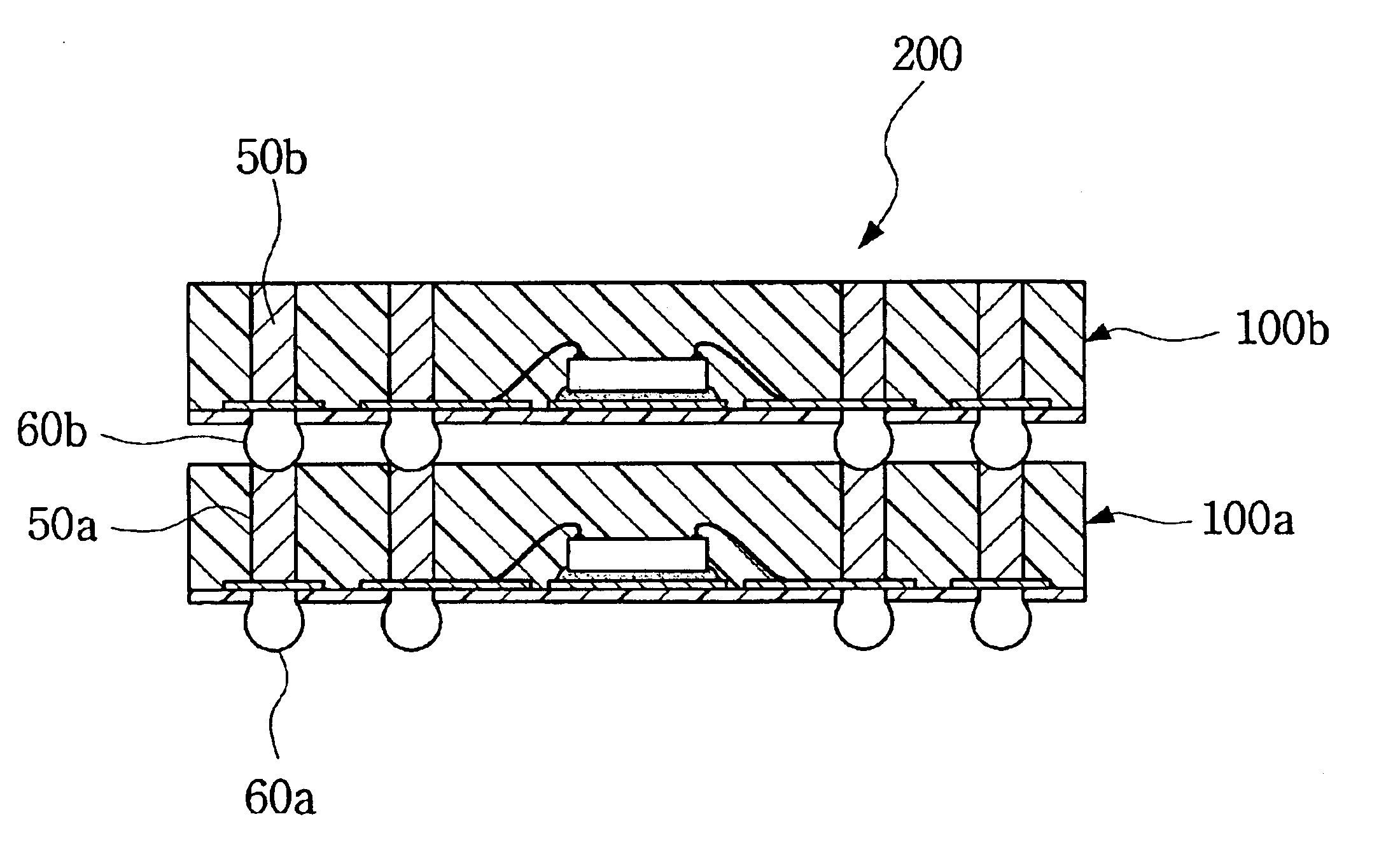

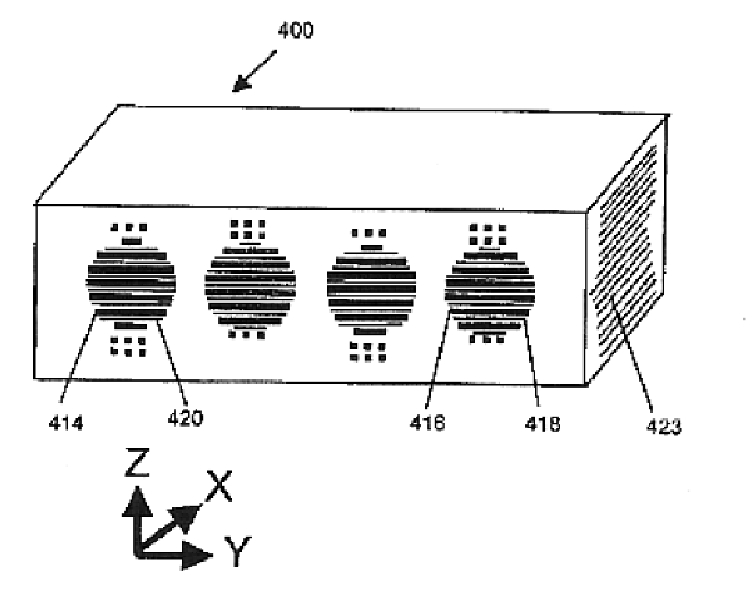

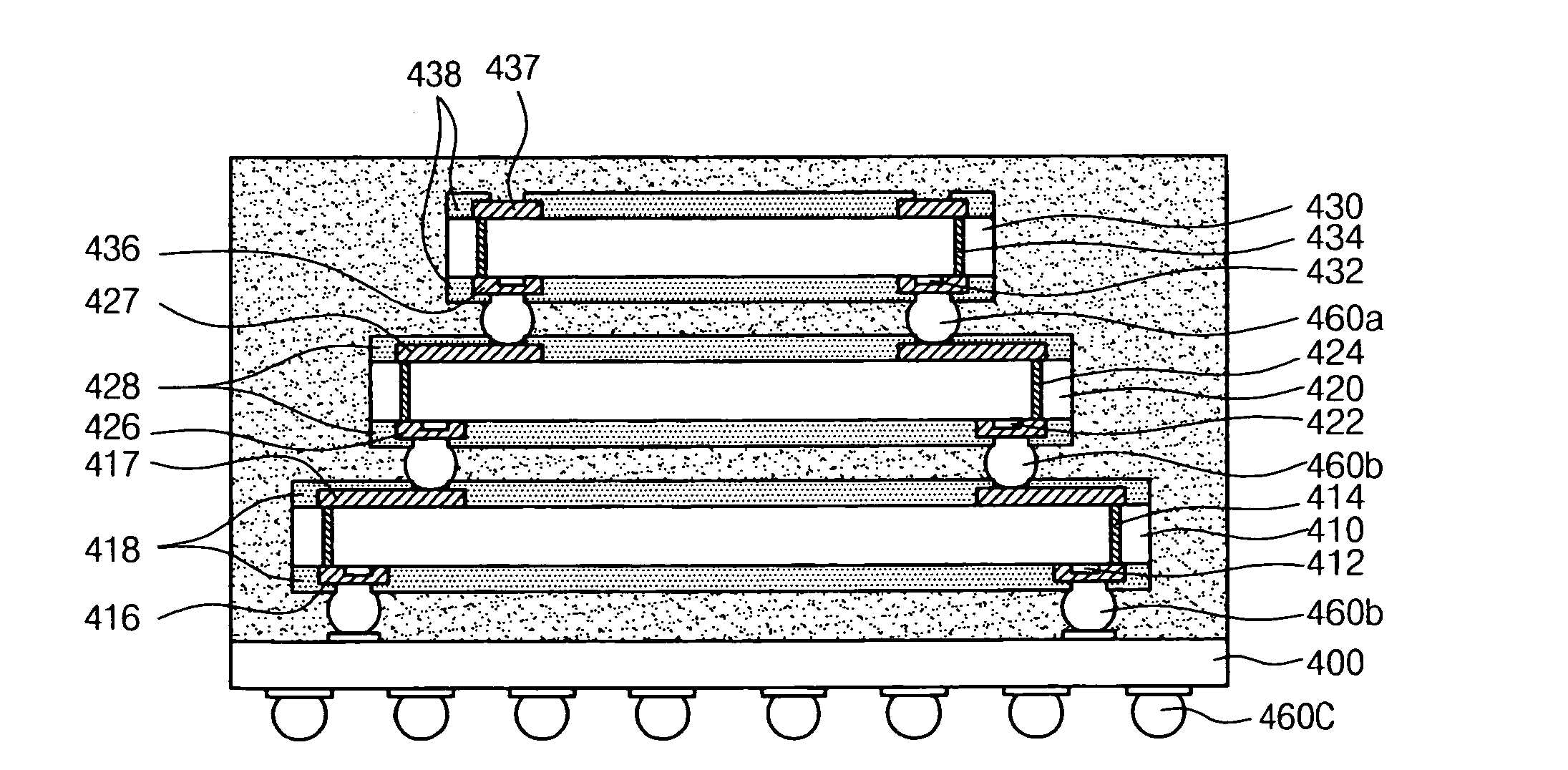

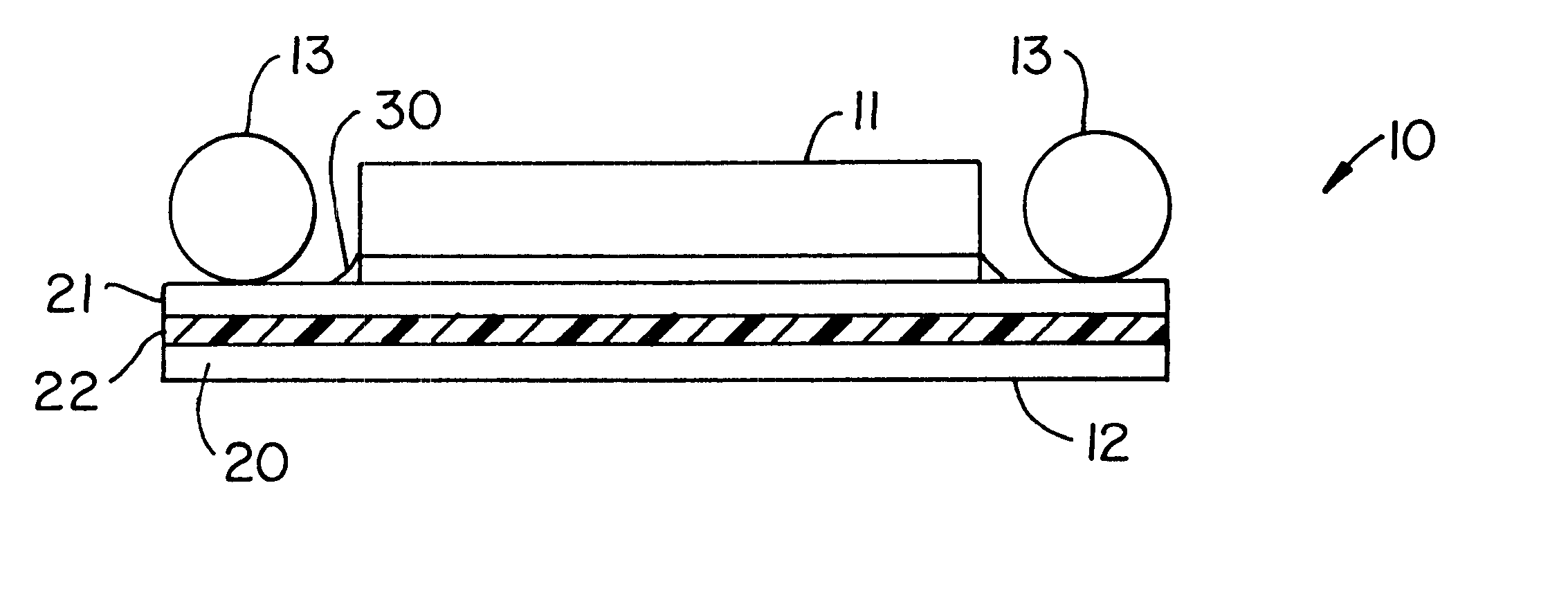

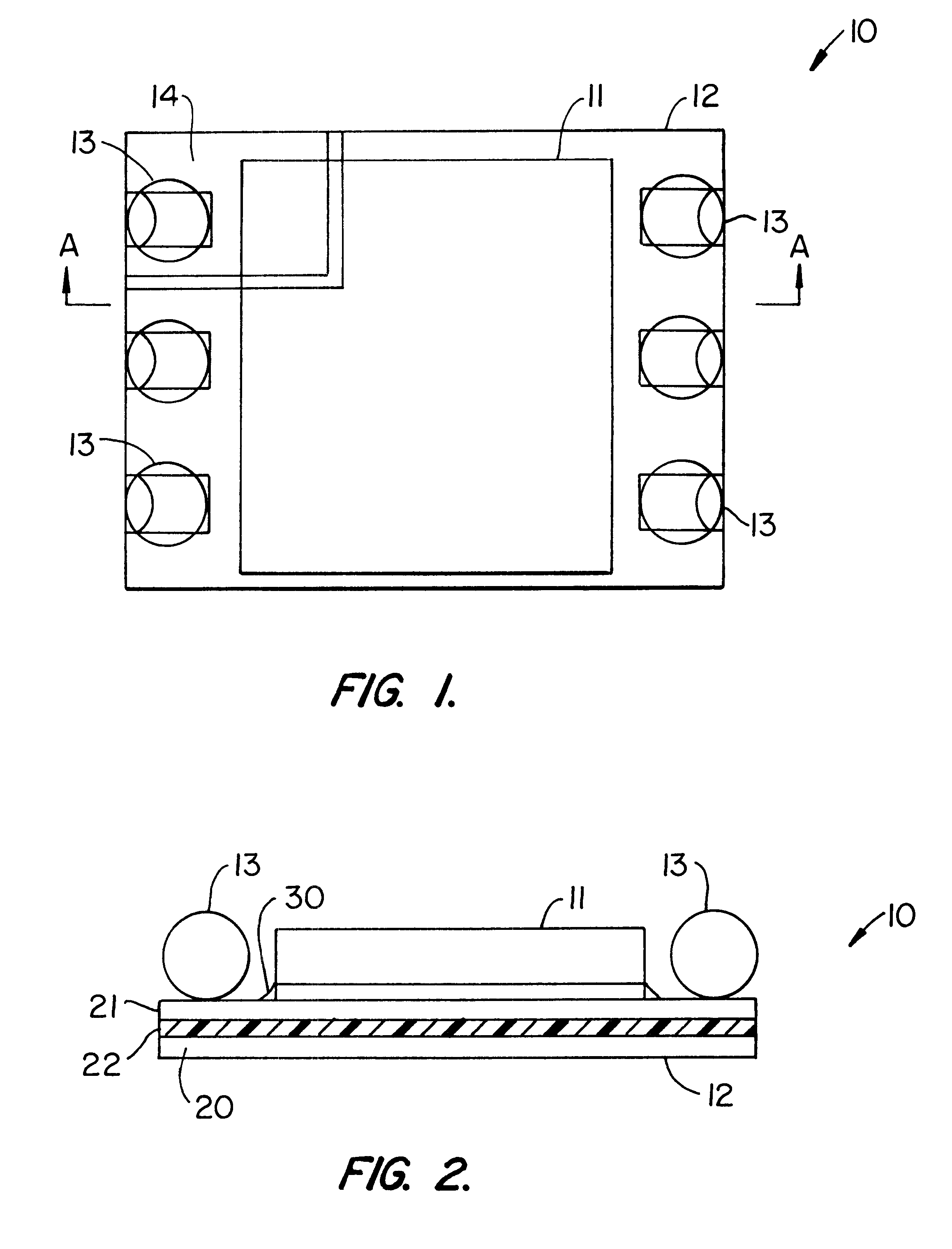

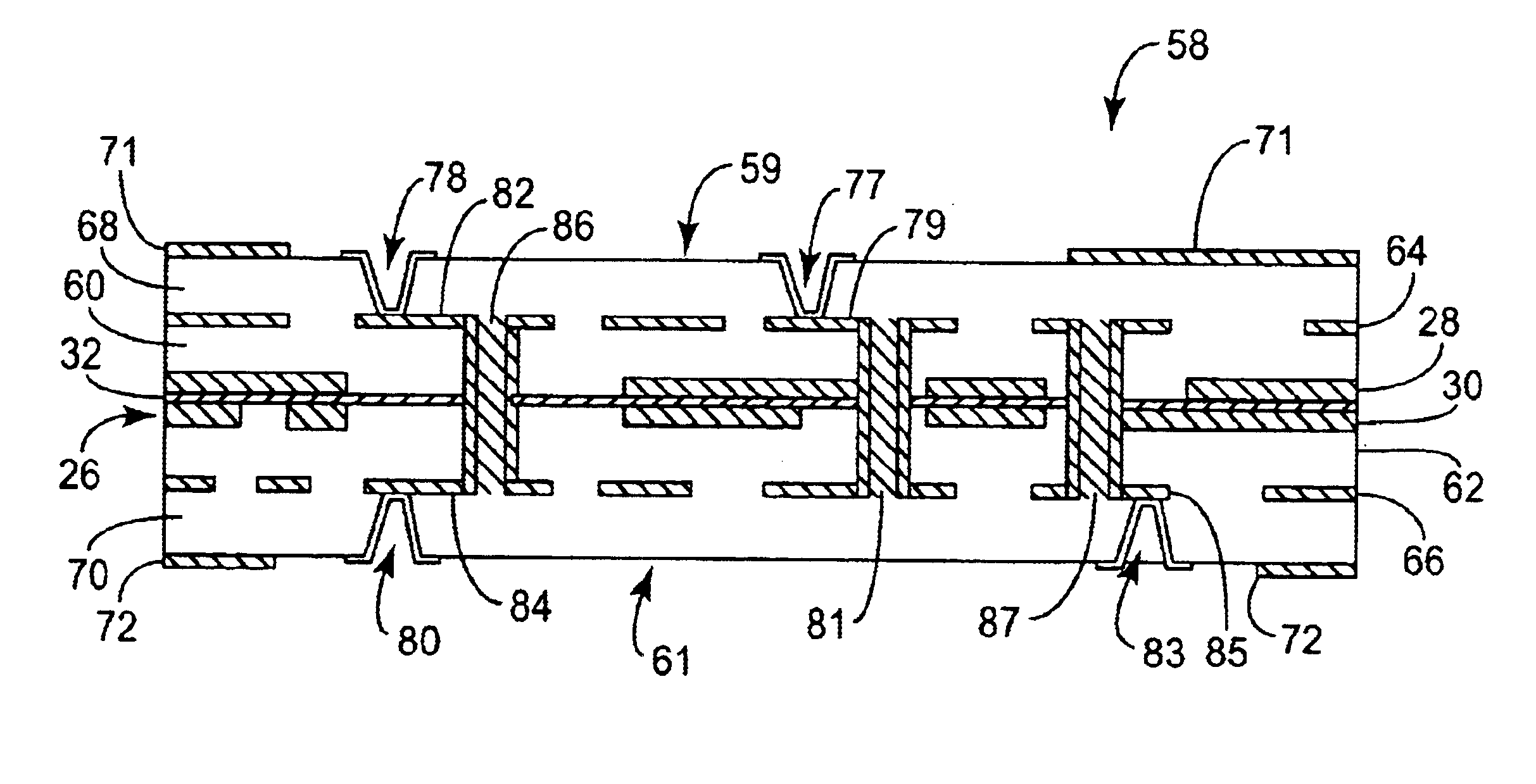

Stacked packages

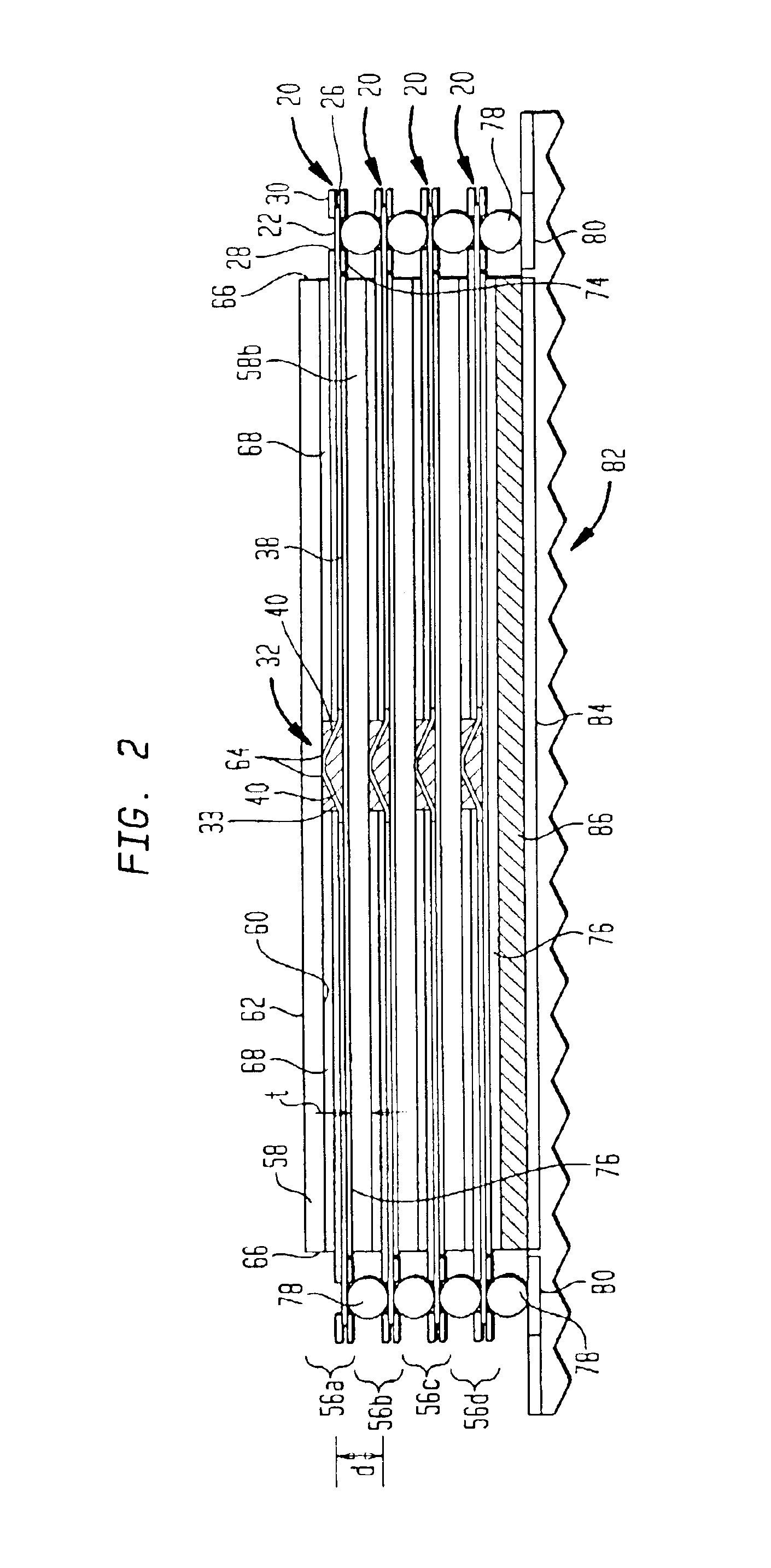

InactiveUS6977440B2Well formedSimplifying handling and stockingPrinted circuit detailsFinal product manufactureSolder ballChip select

A stacked chip assembly includes individual units having chips mounted on dielectric layers and traces on the dielectric layers interconnecting the contacts of the chips with terminals disposed in peripheral regions of the dielectric layers. At least some of the traces are multi-branched traces which connect chip select contacts to chip select terminals. The units are stacked one above the other with corresponding terminals of the different units being connected to one another by solder balls or other conductive elements so as to form vertical buses. Prior to stacking, the multi-branched traces of the individual units are selectively connected, as by forming solder bridges, so as to leave chip select contacts of chips in different units connected to different chip select terminals and thereby connect these chips to different vertical buses. The individual units desirably are thin and directly abut one another so as to provide a low-height assembly with good heat transfer from chips within the stack.

Owner:TESSERA INC

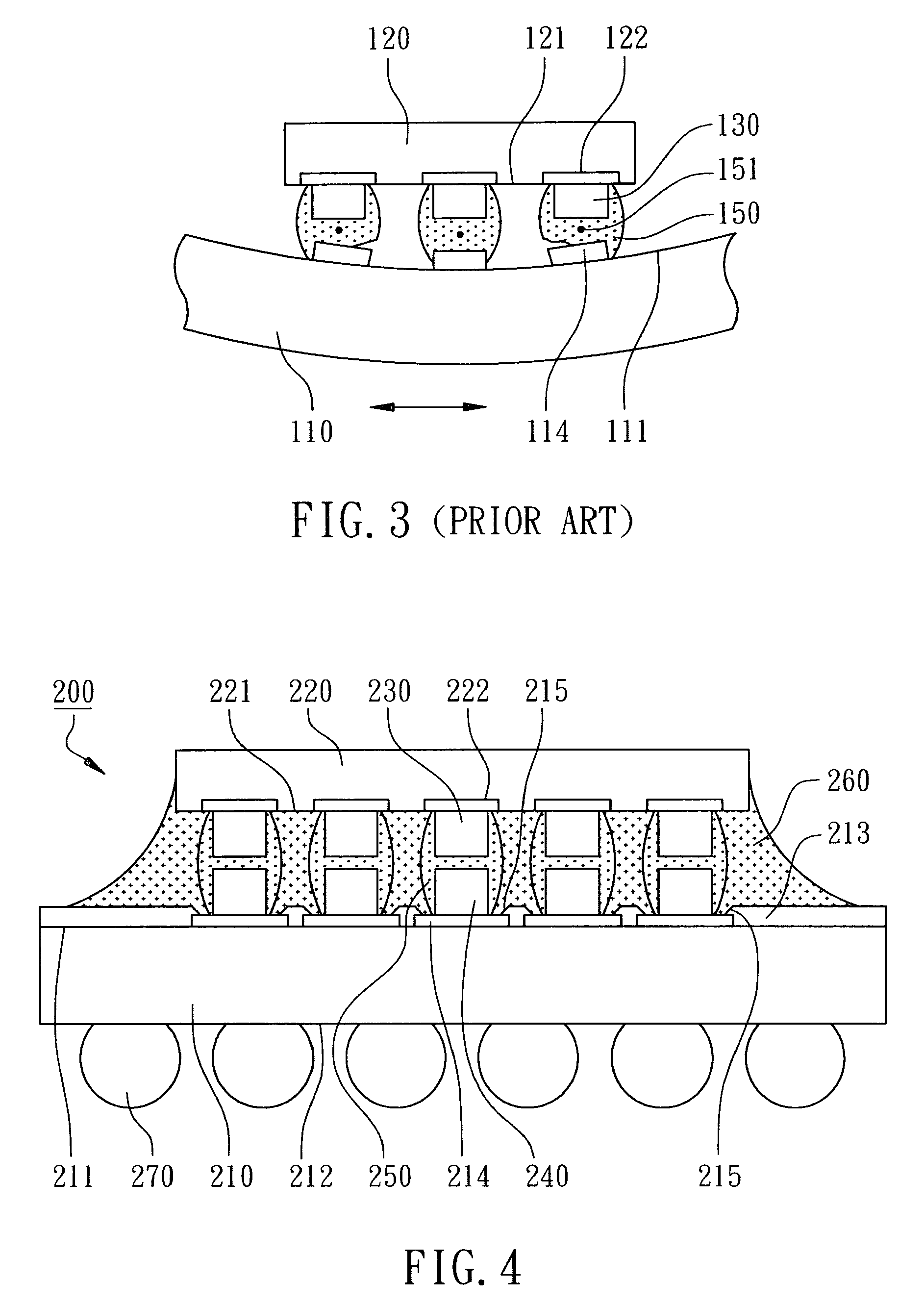

Ball grid array package with multiple interposers

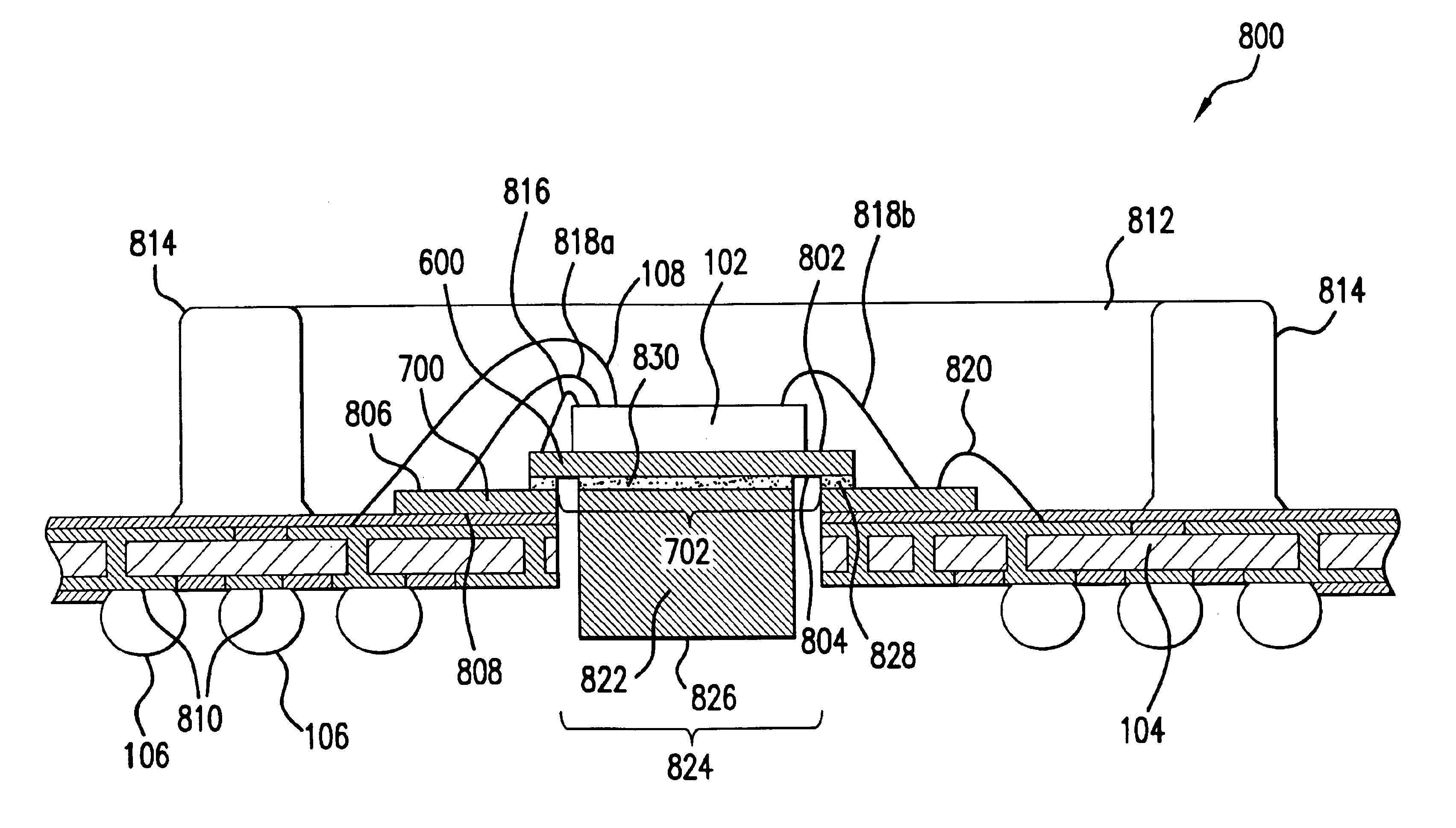

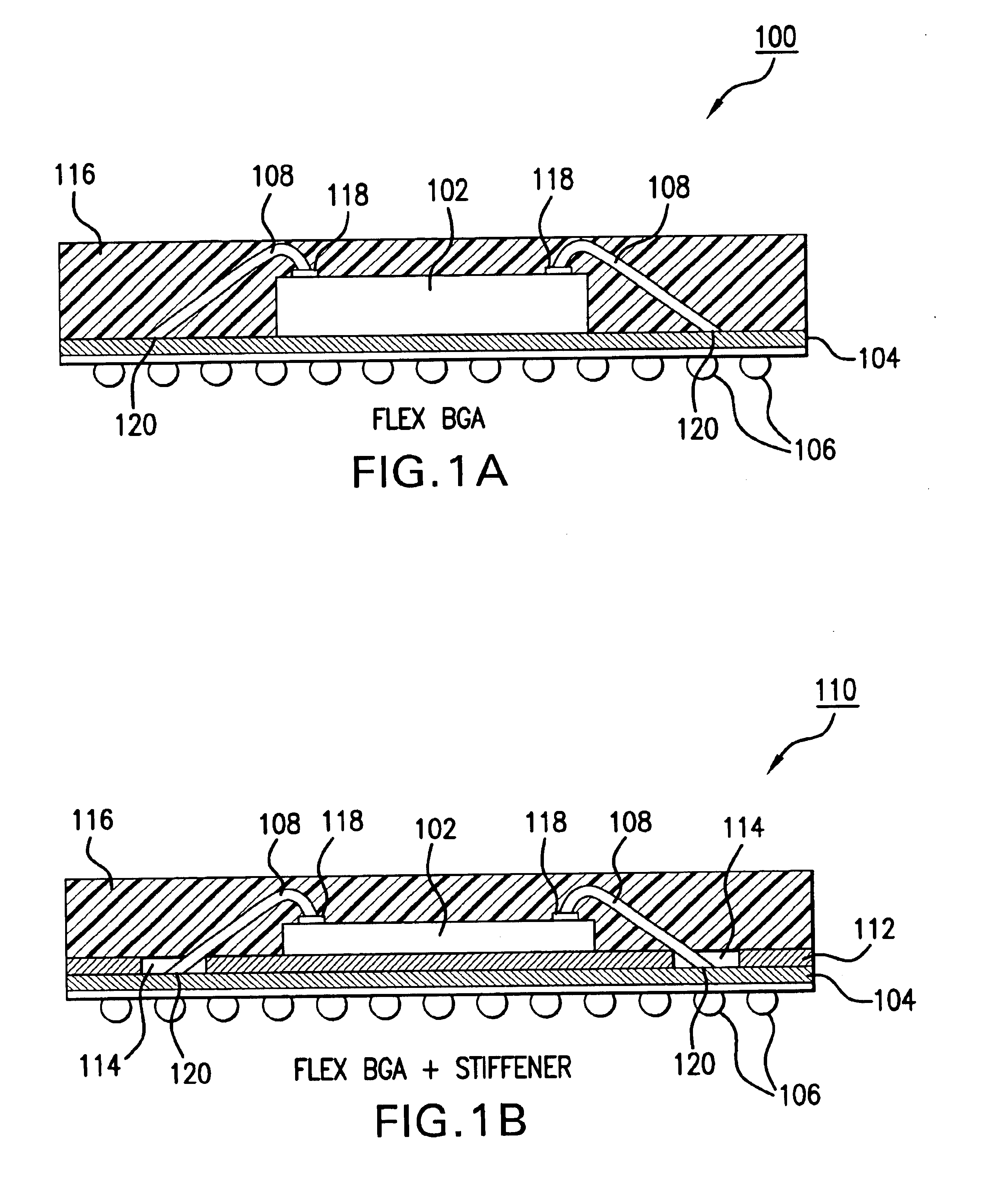

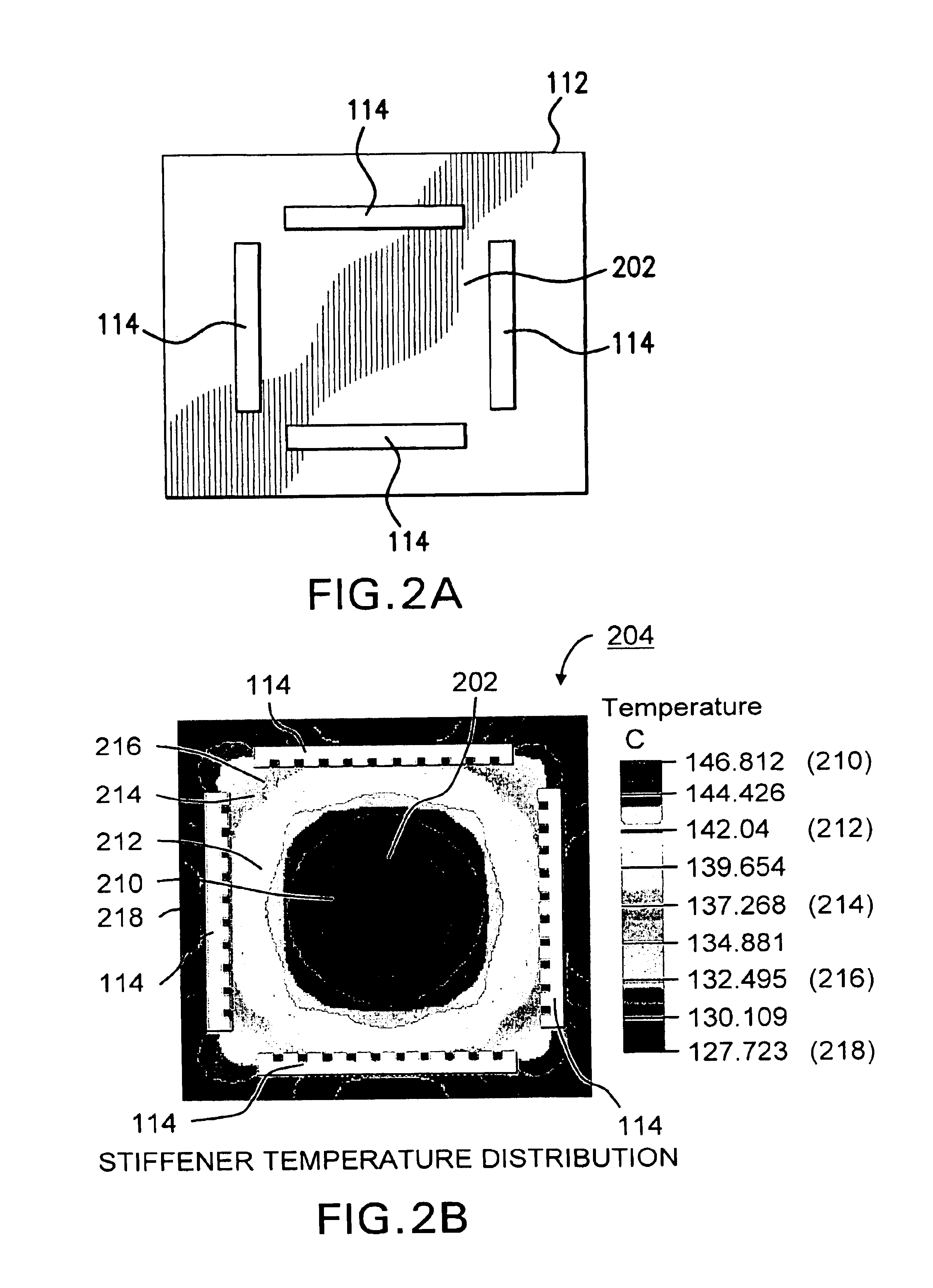

InactiveUS6861750B2Increase stiffness/rigidityImprove heat transfer performanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContact padPlanar substrate

Electrically, thermally and mechanically enhanced ball grid array (BGA) packages are described. An IC die is mounted to a first surface of a first stiffener. A peripheral edge portion of a second surface of the first stiffener is attached to a first surface of a second stiffener to cover an opening through the second stiffener that is open at the first surface and a second surface of the second stiffener. The second surface of the second stiffener is attached to a first surface of a substantially planar substrate that has a plurality of contact pads on the first surface of the substrate. The plurality of contact pads are electrically connected through the substrate to a plurality of solder ball pads on a second surface of the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

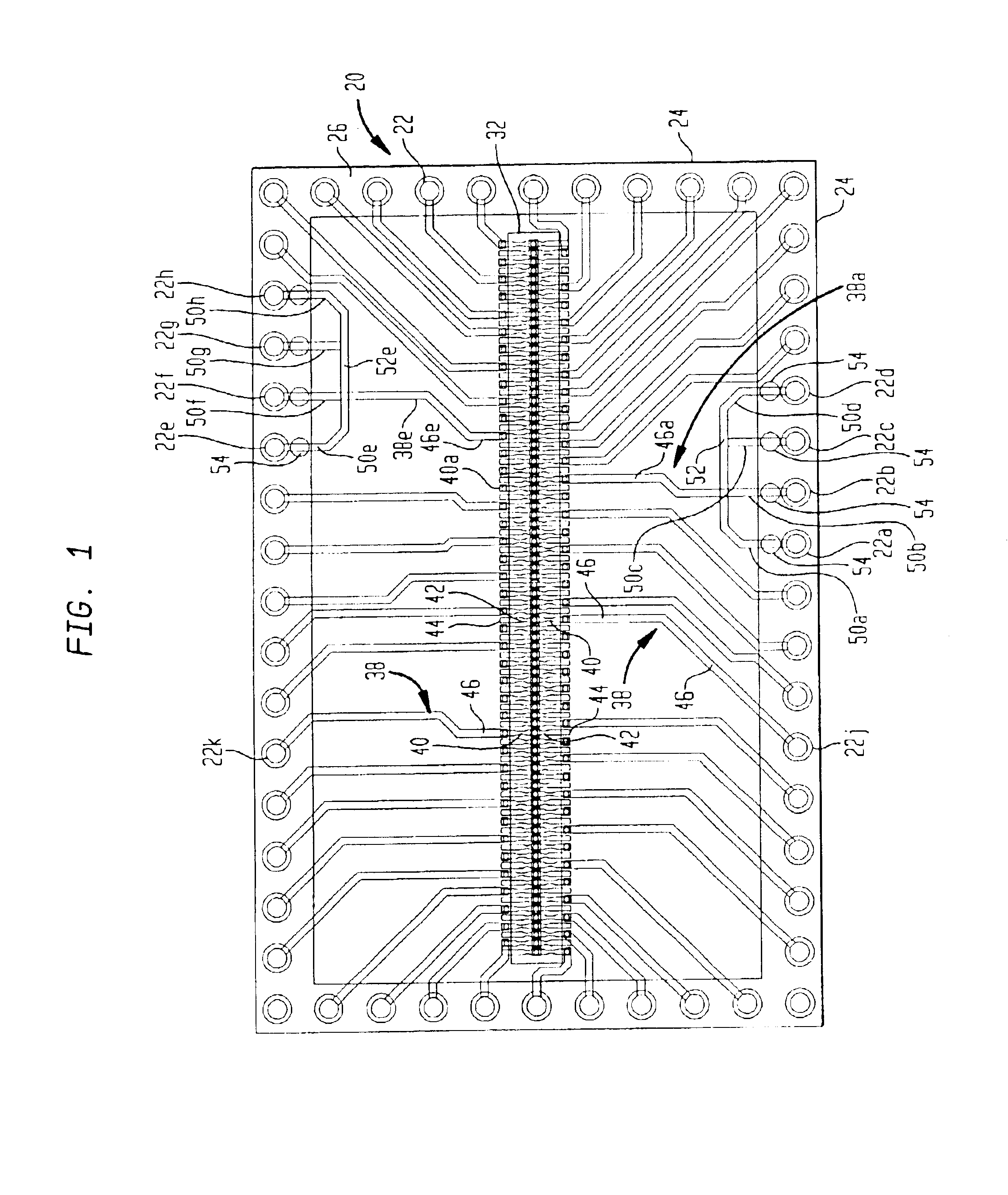

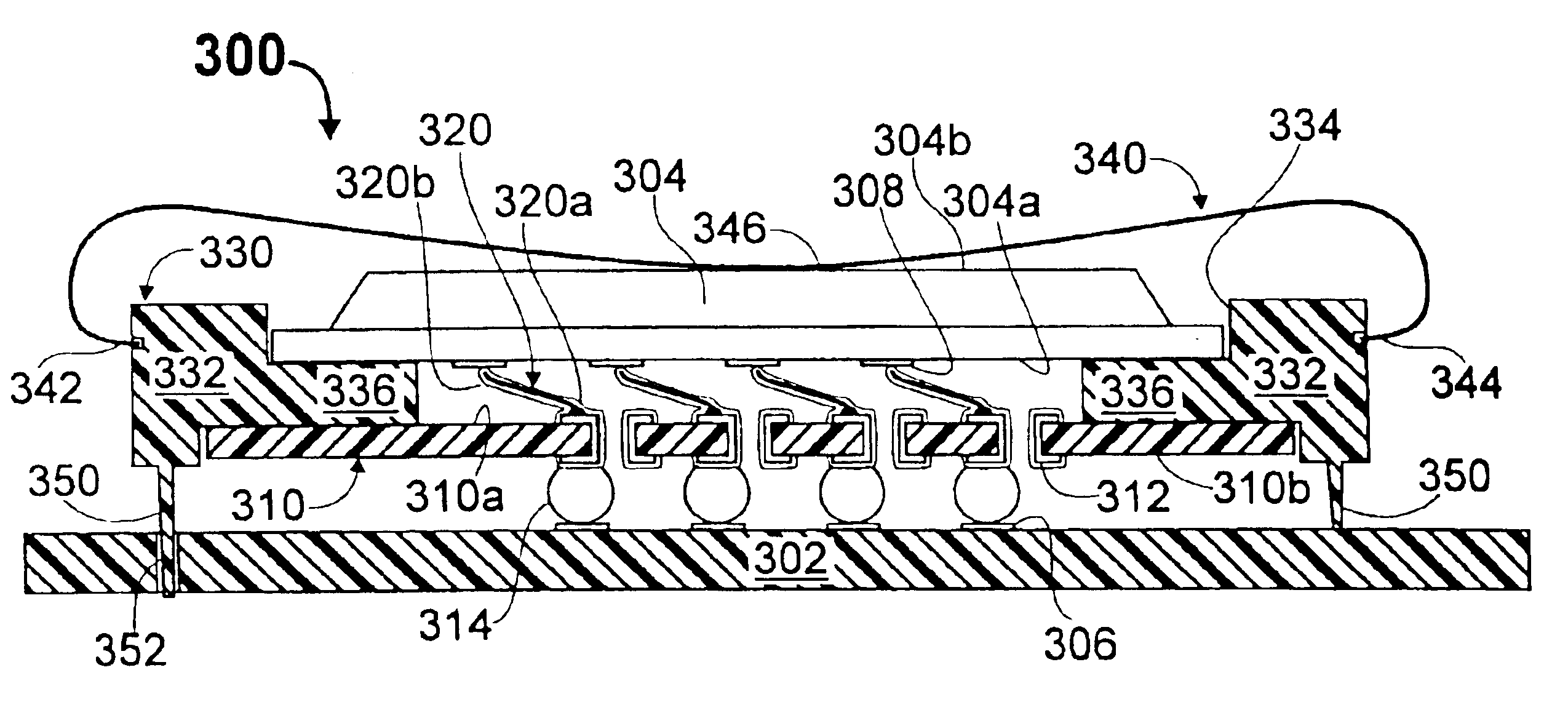

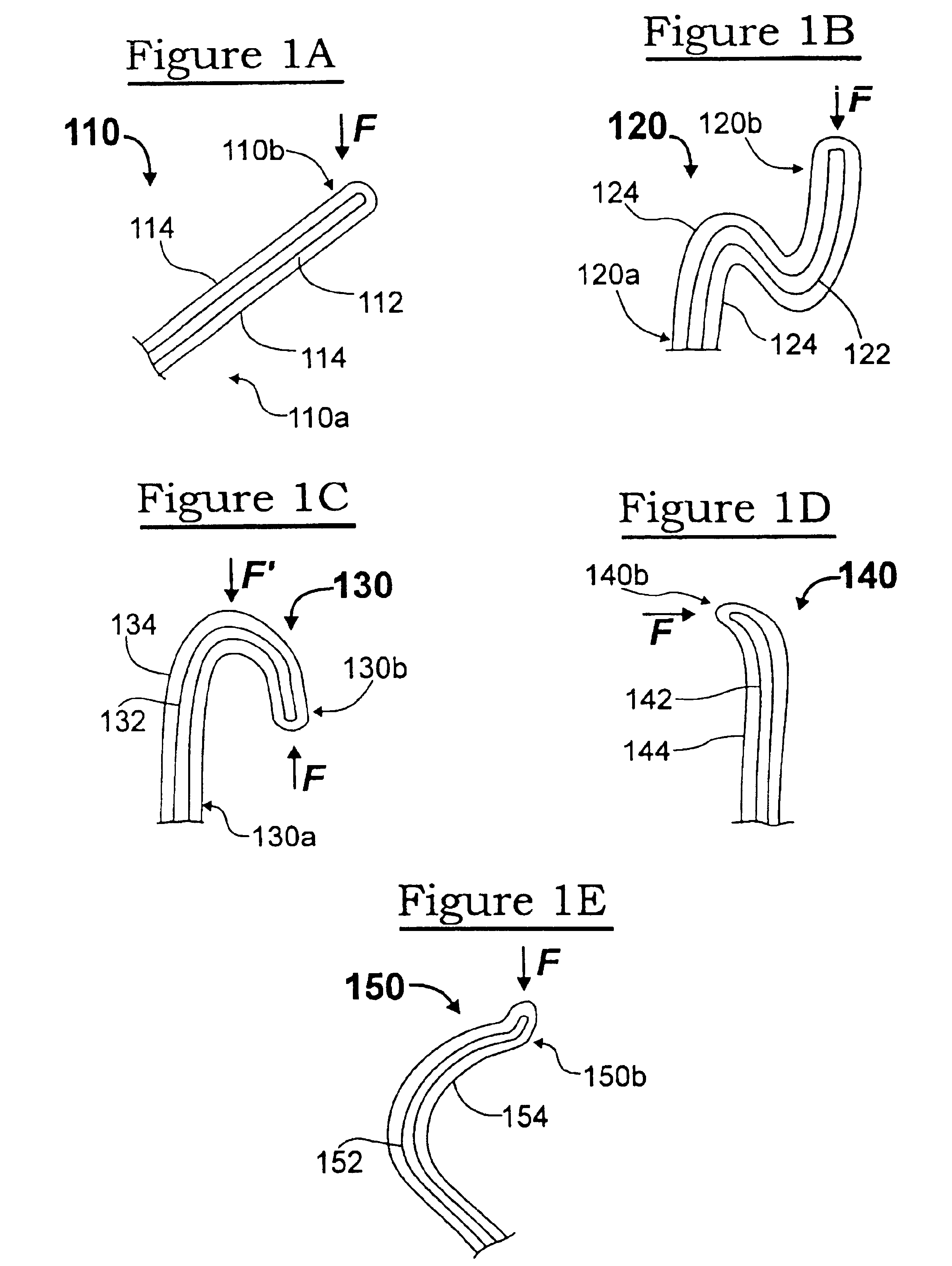

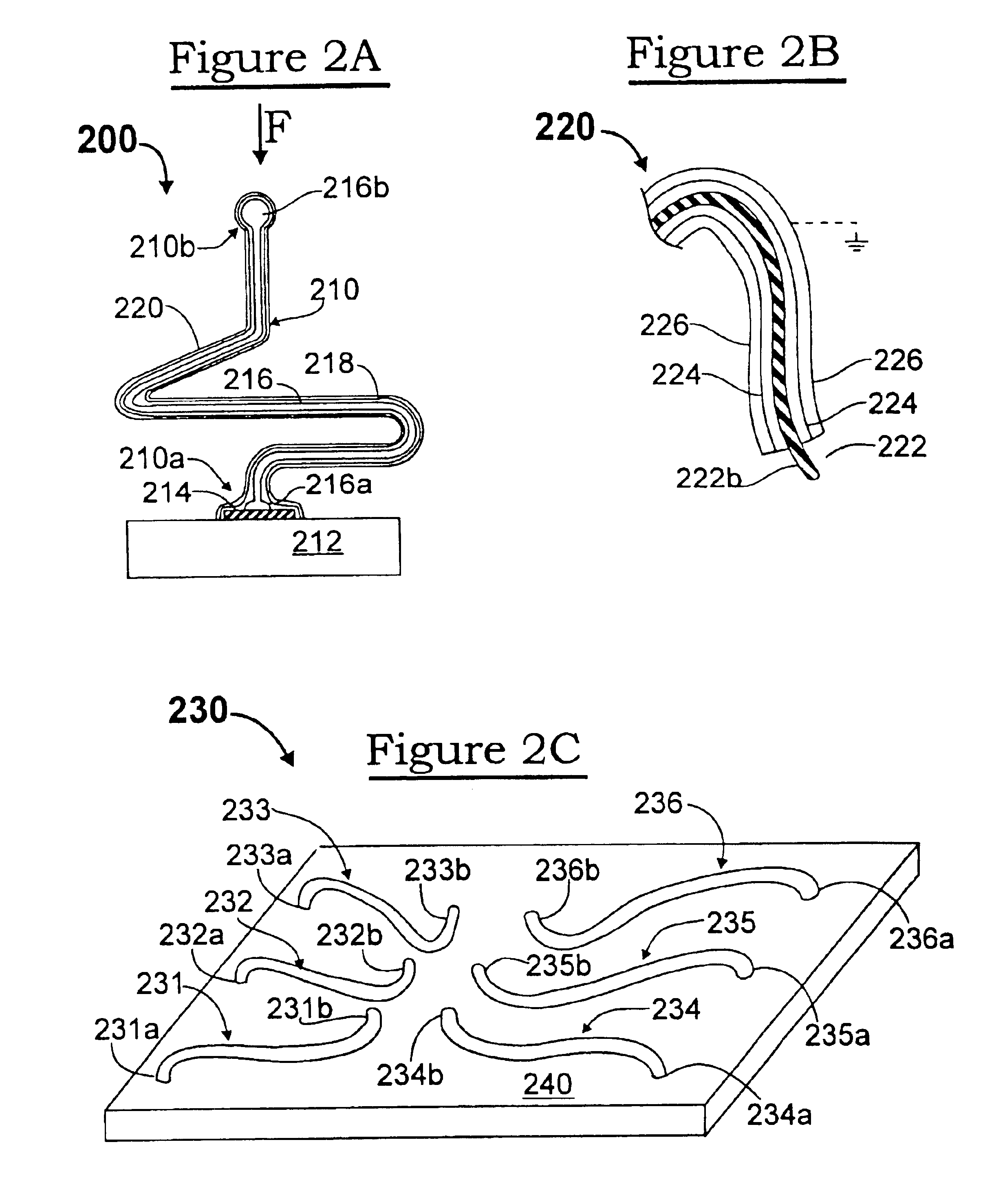

Methods of removably mounting electronic components to a circuit board, and sockets formed by the methods

InactiveUS6913468B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureSurface mountingSolder ball

Surface-mount, solder-down sockets are described which permit electronic components such as semiconductor packages to be releasably mounted to a circuit board. Generally, the socket includes resilient contact structures extending from a top surface of a support substrate, and solder-ball (or other suitable) contact structures disposed on a bottom surface of the support substrate. Composite interconnection elements are described for use as the resilient contact structures disposed atop the support substrate. In use, the support substrate is soldered down onto the circuit board, the contact structures on the bottom surface of the support substrate contacting corresponding contact areas on the circuit board. In any suitable manner, selected ones of the resilient contact structures atop the support substrate are connected, via the support substrate, to corresponding ones of the contact structures on the bottom surface of the support substrate.

Owner:FORMFACTOR INC

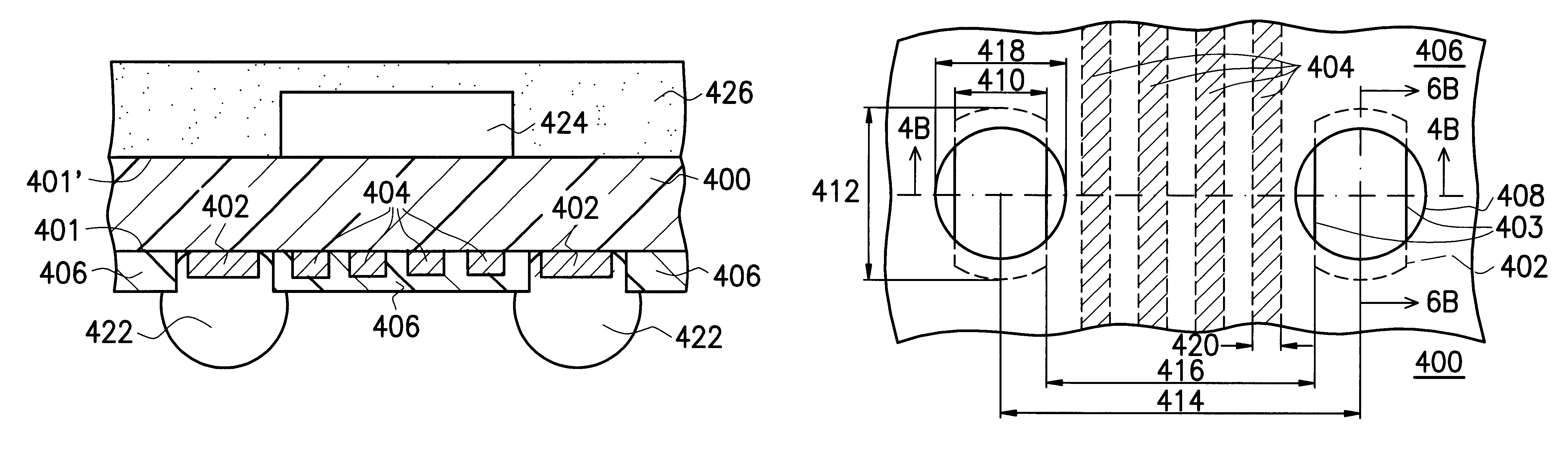

Substrate with reinforced contact pad structure

ActiveUS7005750B2Improve positional stabilitySimple structurePrinted circuit assemblingFinal product manufactureSolder maskContact pad

A substrate with reinforced contact pad structure includes a metal wiring layer and a solder mask formed over its surface. The metal wiring layer includes at least a NSMD (Non-Solder Mask Defined) type contact pad, a trace and an extension. The extension connects the contact pad and the trace, and has an upper surface which is covered by the solder mask so as to enhance the connecting strength between the trace and the contact pad and to improve the position stability of the NSMD type contact pad on the substrate. In an embodiment, the contact pad is circular for bonding a bump or a solder ball. The first extension is fan-shaped. The extension also has a sidewall exposed out of the solder mask.

Owner:ASE SHANGHAI

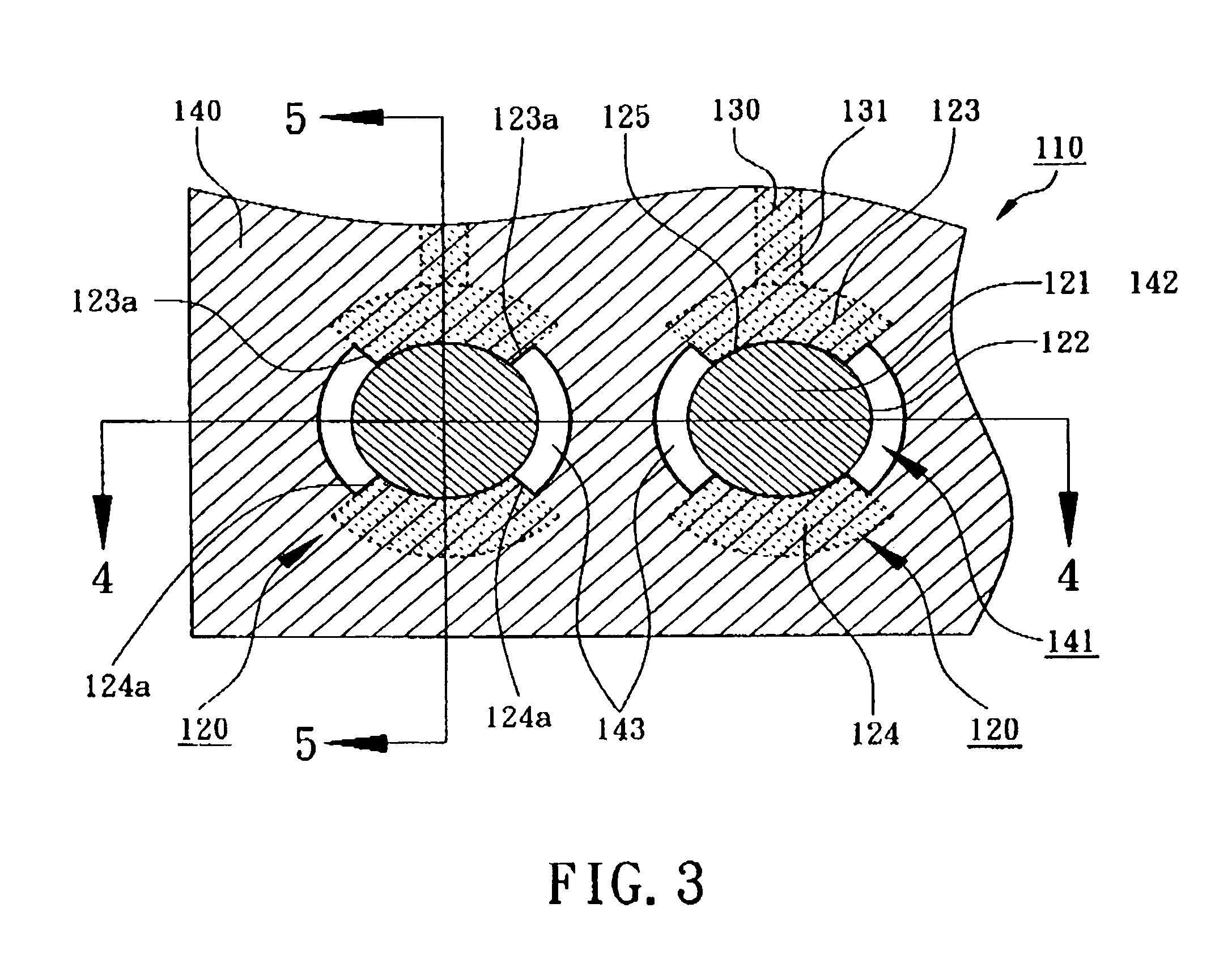

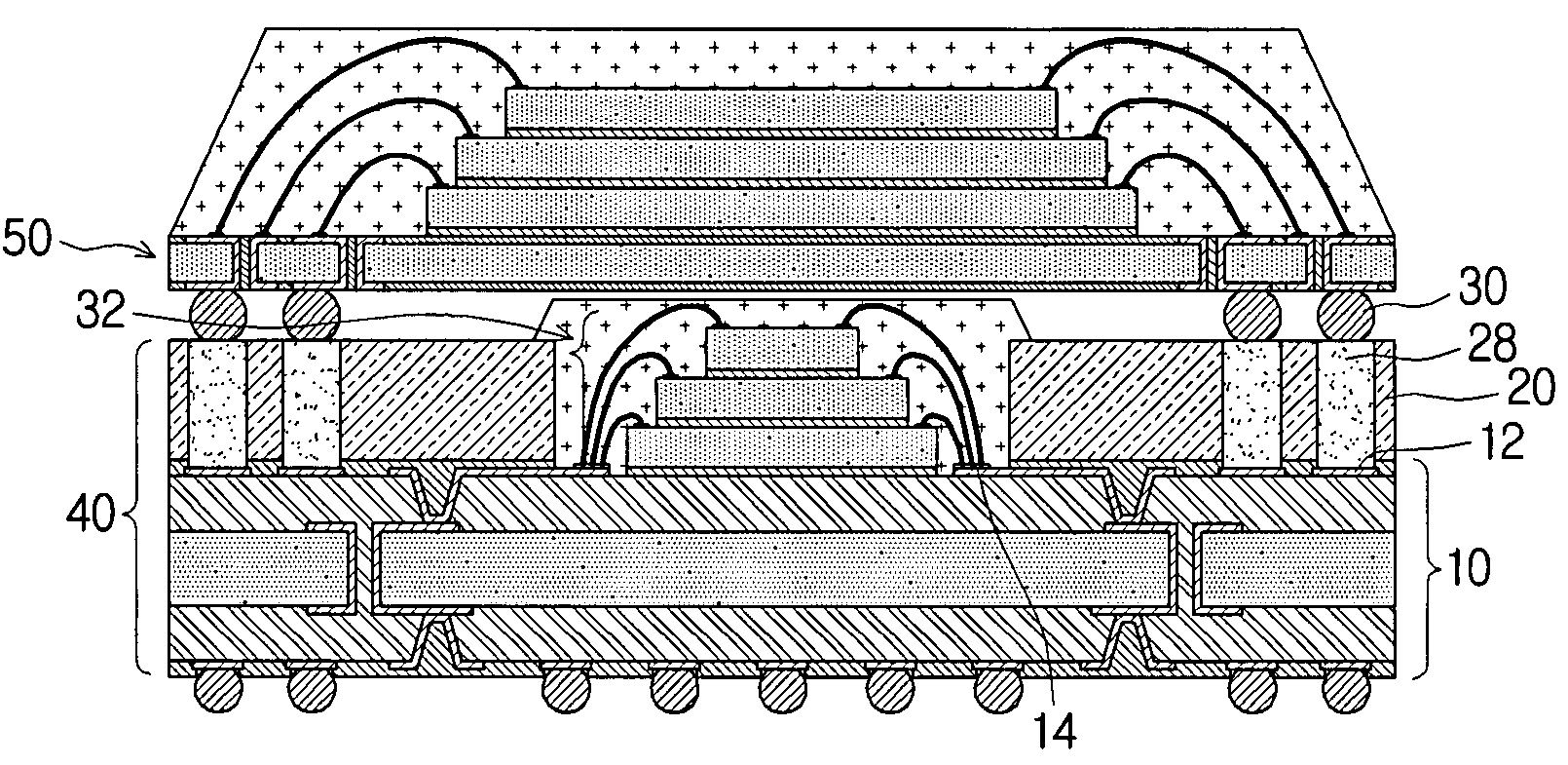

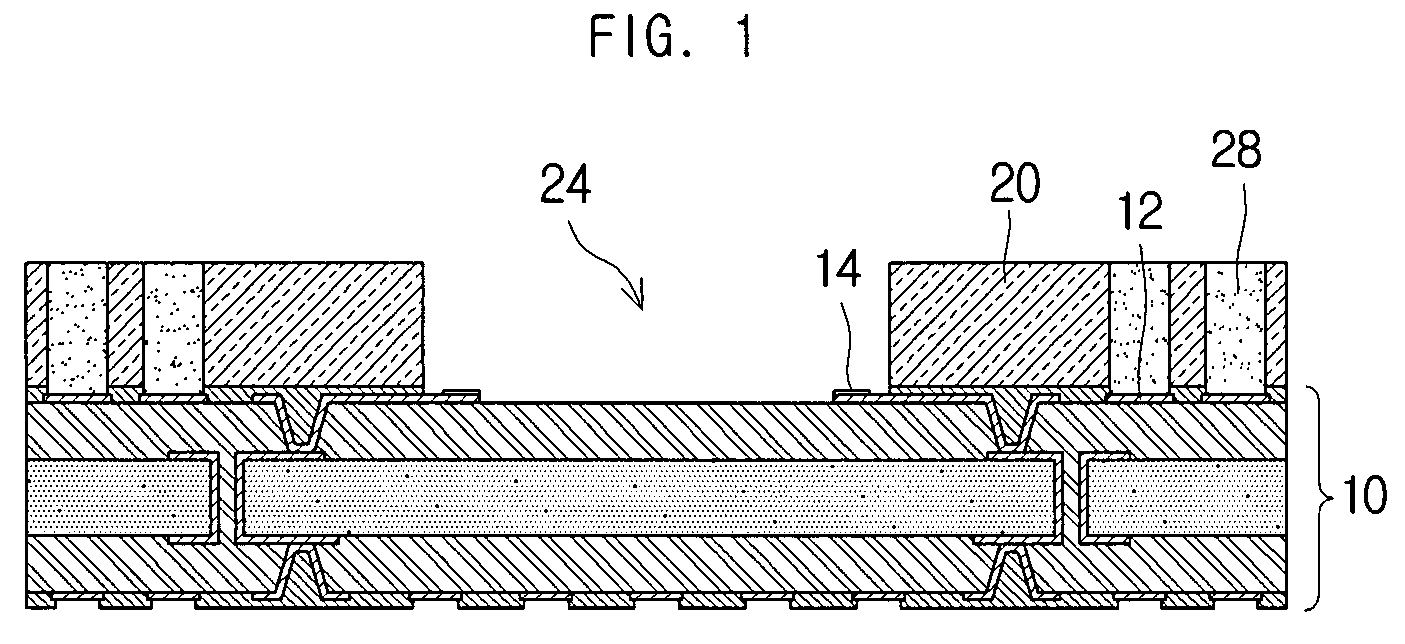

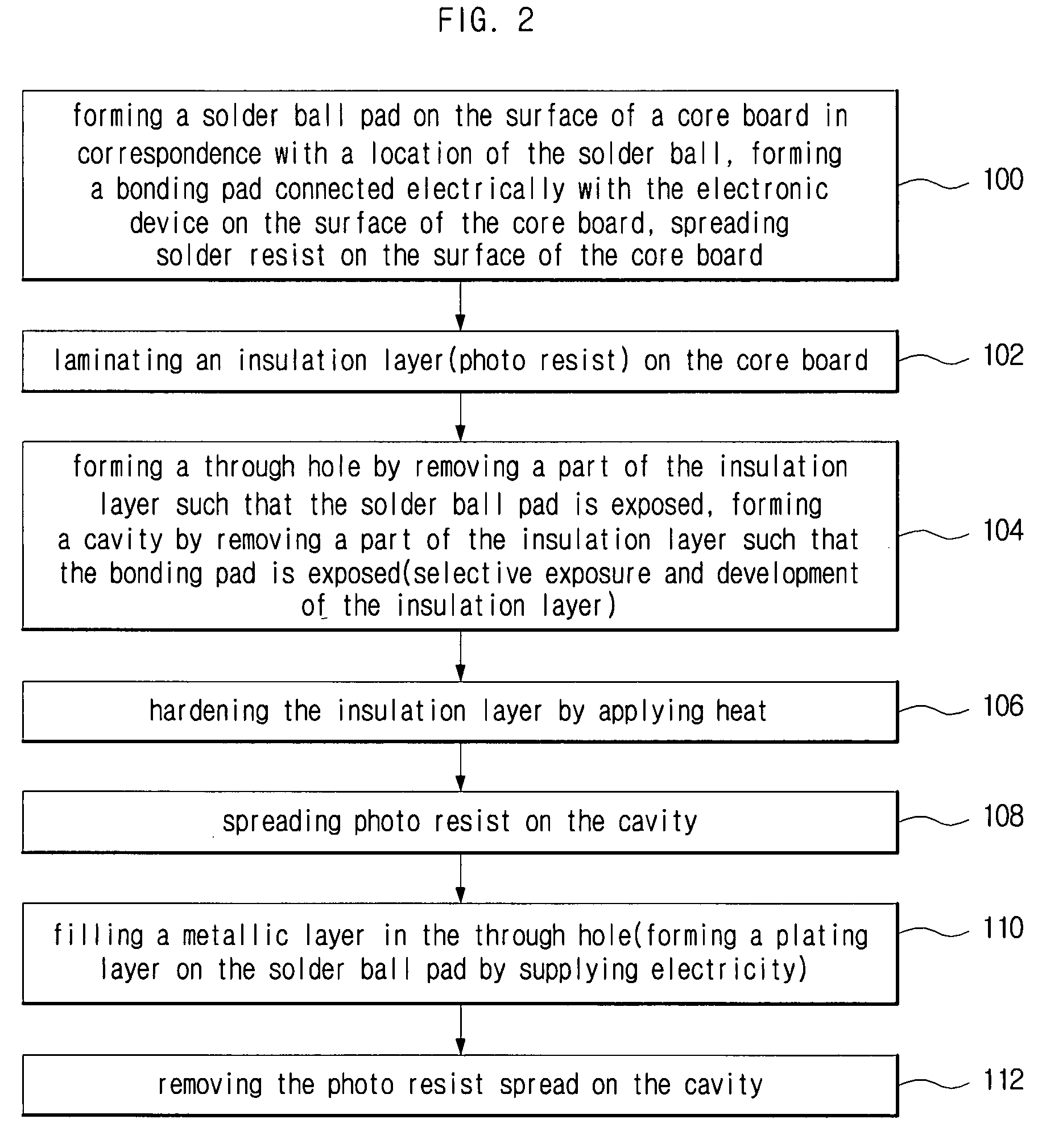

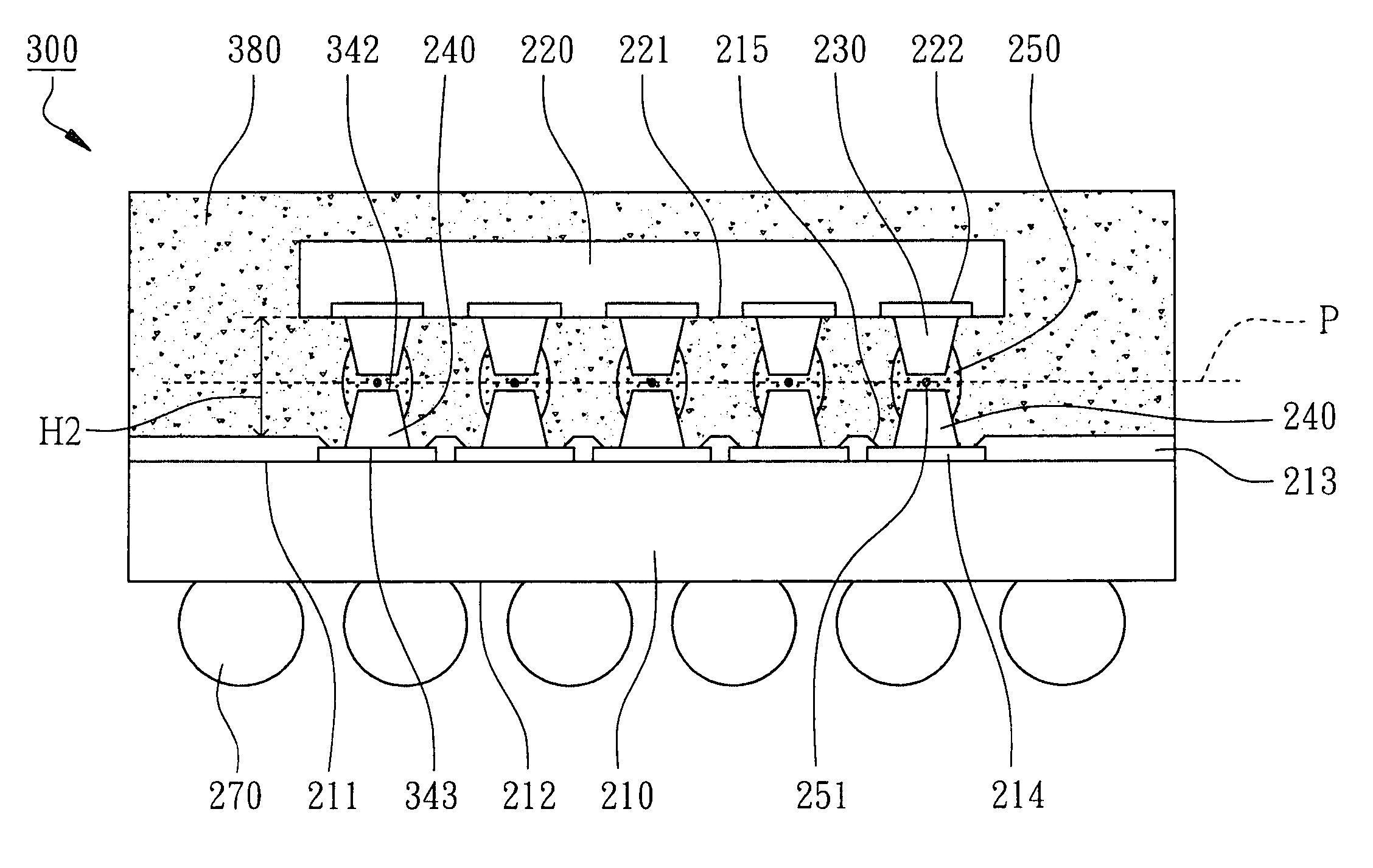

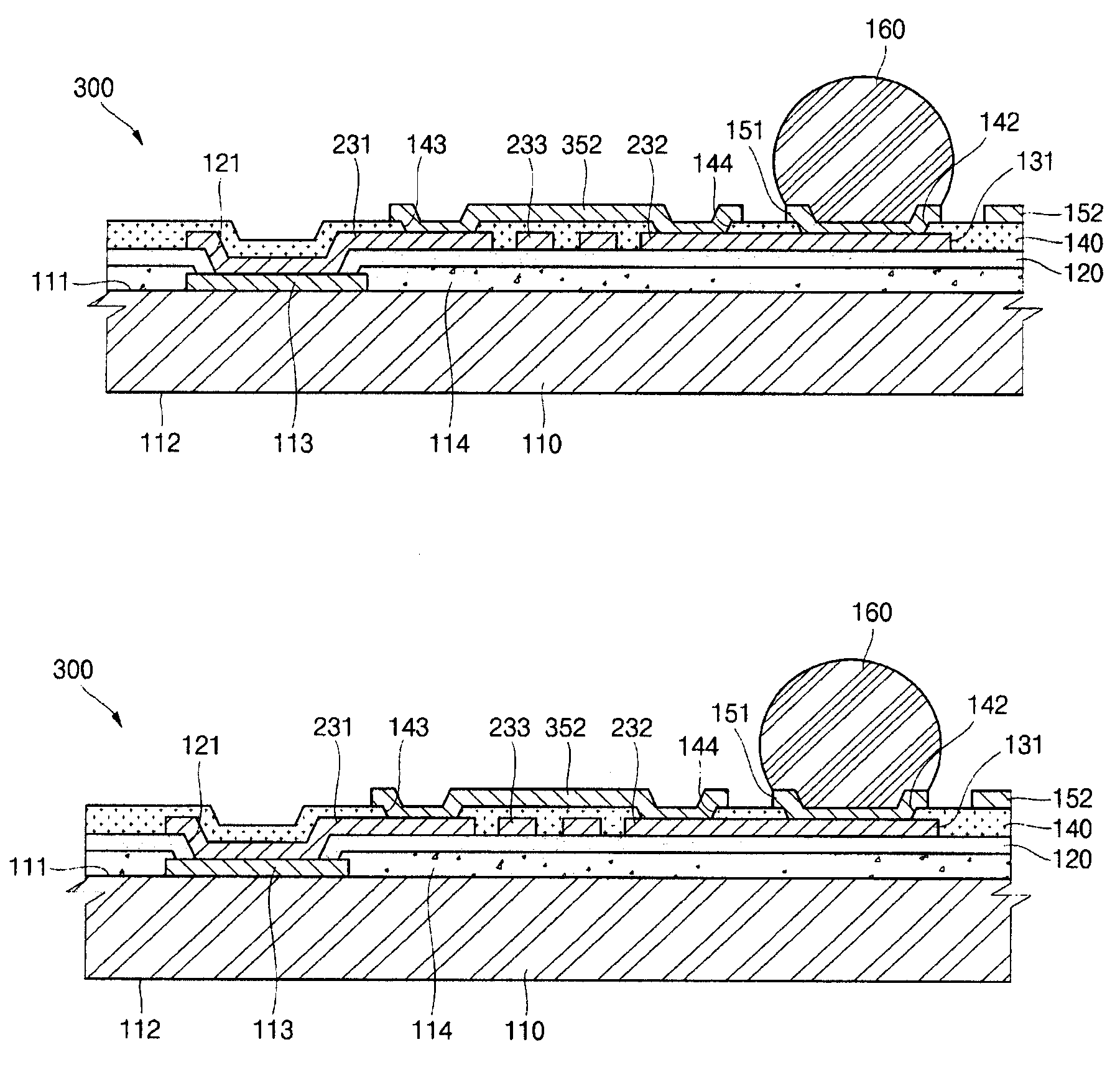

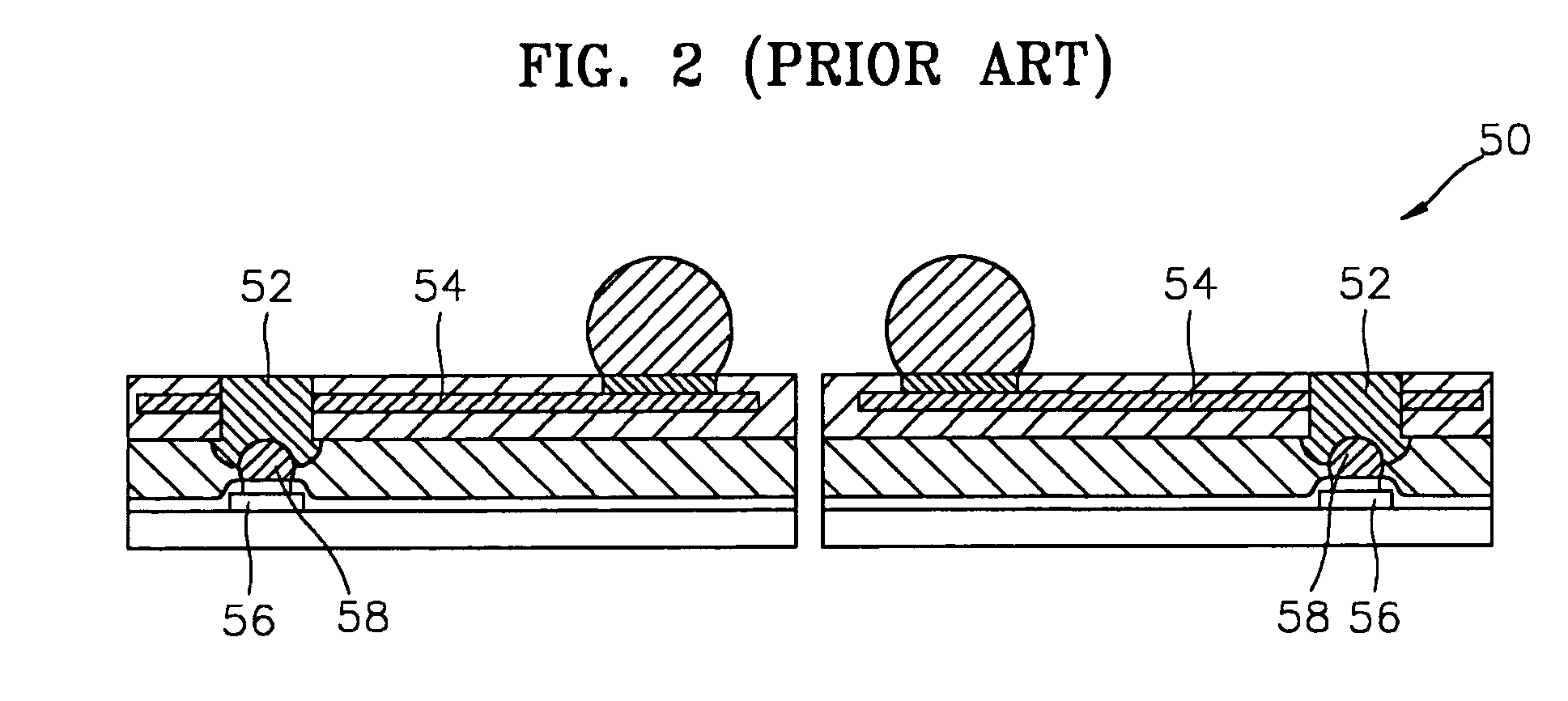

Bottom substrate of package on package and manufacturing method thereof

InactiveUS20080006942A1Increasing the thicknessSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSolder ball

A bottom substrate of package on package and manufacturing method thereof is disclosed. A bottom substrate of a package on package electrically connected to a top substrate by means of a solder ball, including a core board, a solder ball pad formed on a surface of the core board in correspondence with a location of the solder ball, an insulation layer laminated on the core board, a through hole formed by removing a part of the insulation layer such that the solder ball pad is exposed, and a metallic layer filled in the through hole and connected electrically with the solder ball, allows the number of ICs mounted on a bottom substrate to be increased without increasing the size of a solder ball, and allows the size and pitch of the solder balls to be made smaller by controlling the thickness of the insulation layer laminated on the bottom substrate, whereby more signal transmission is possible between a top substrate and a bottom substrate.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

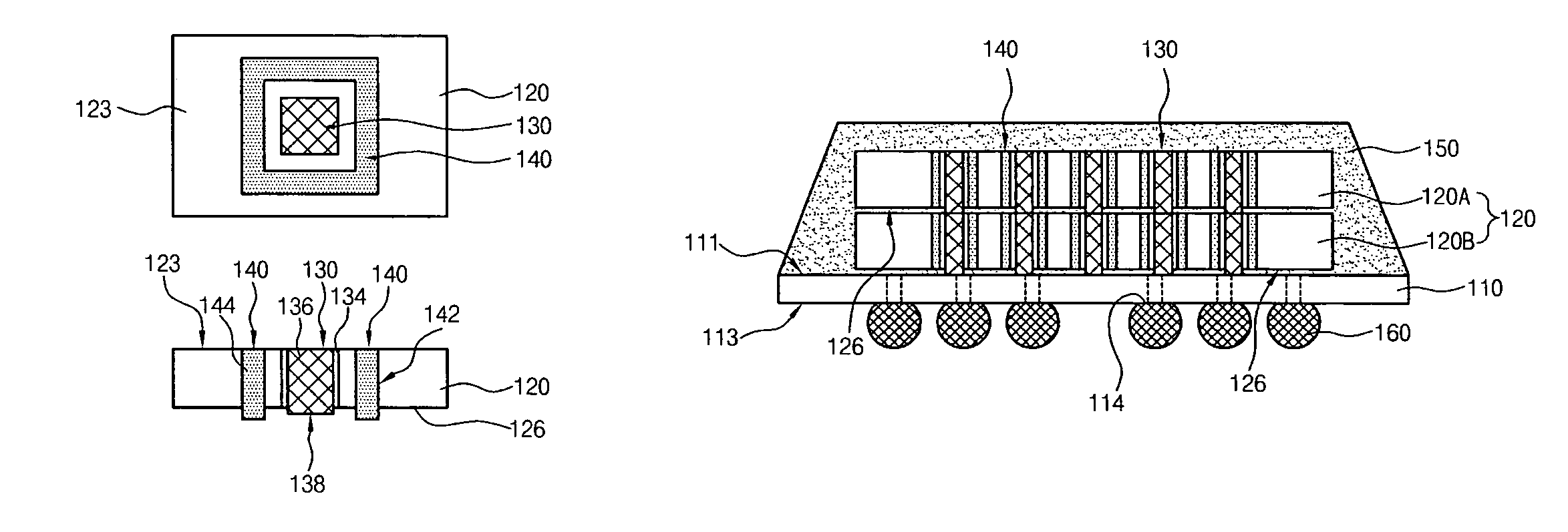

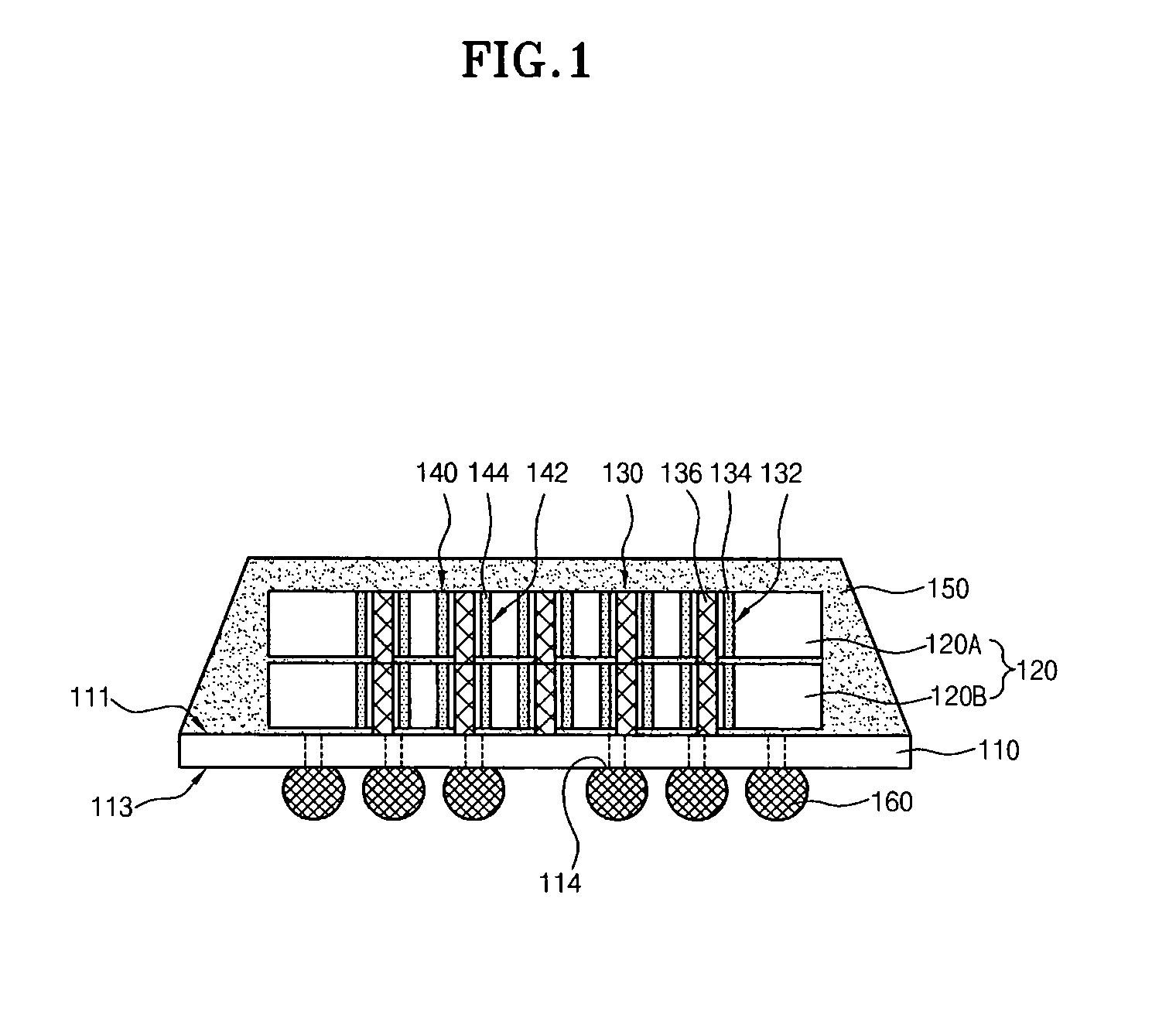

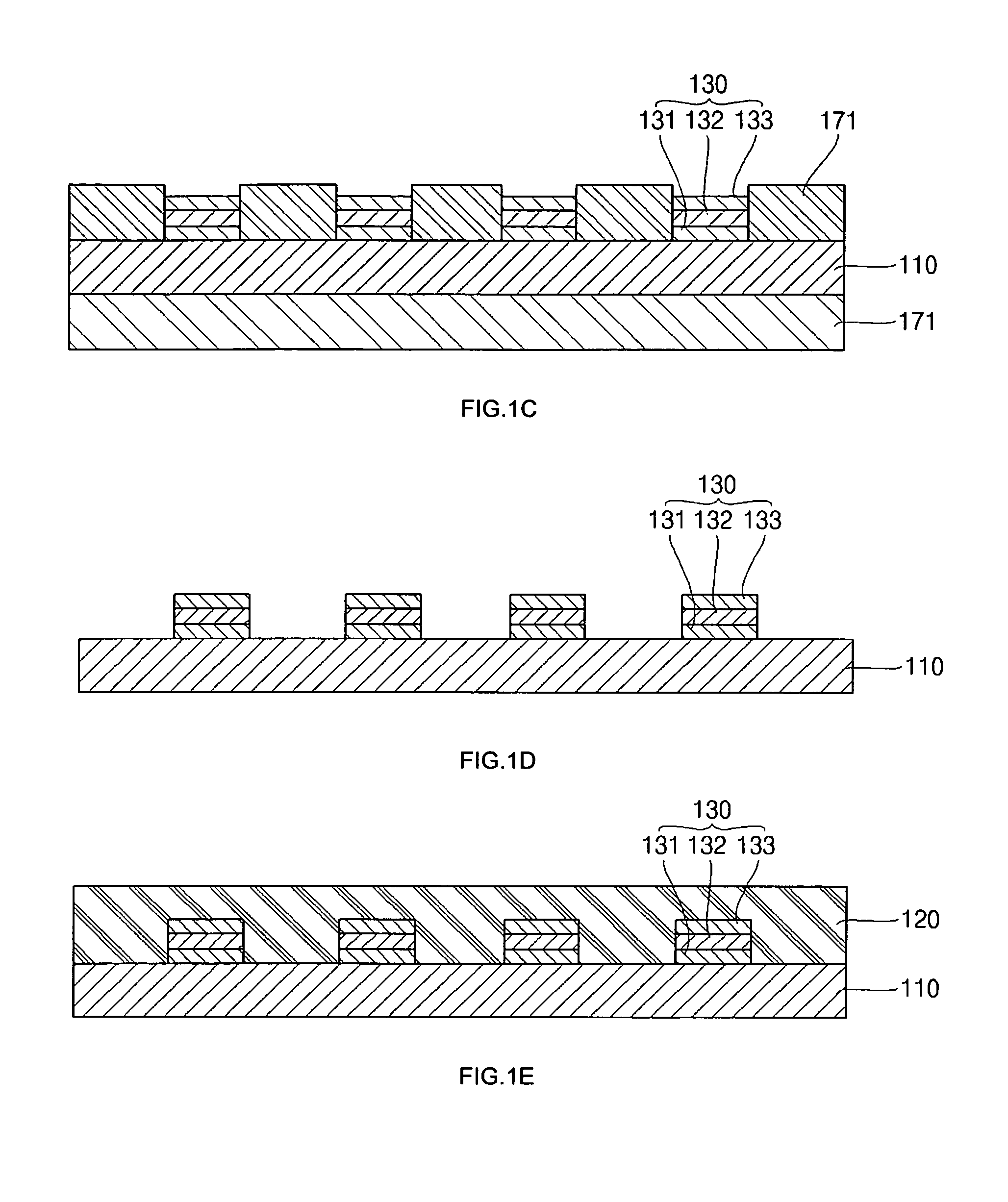

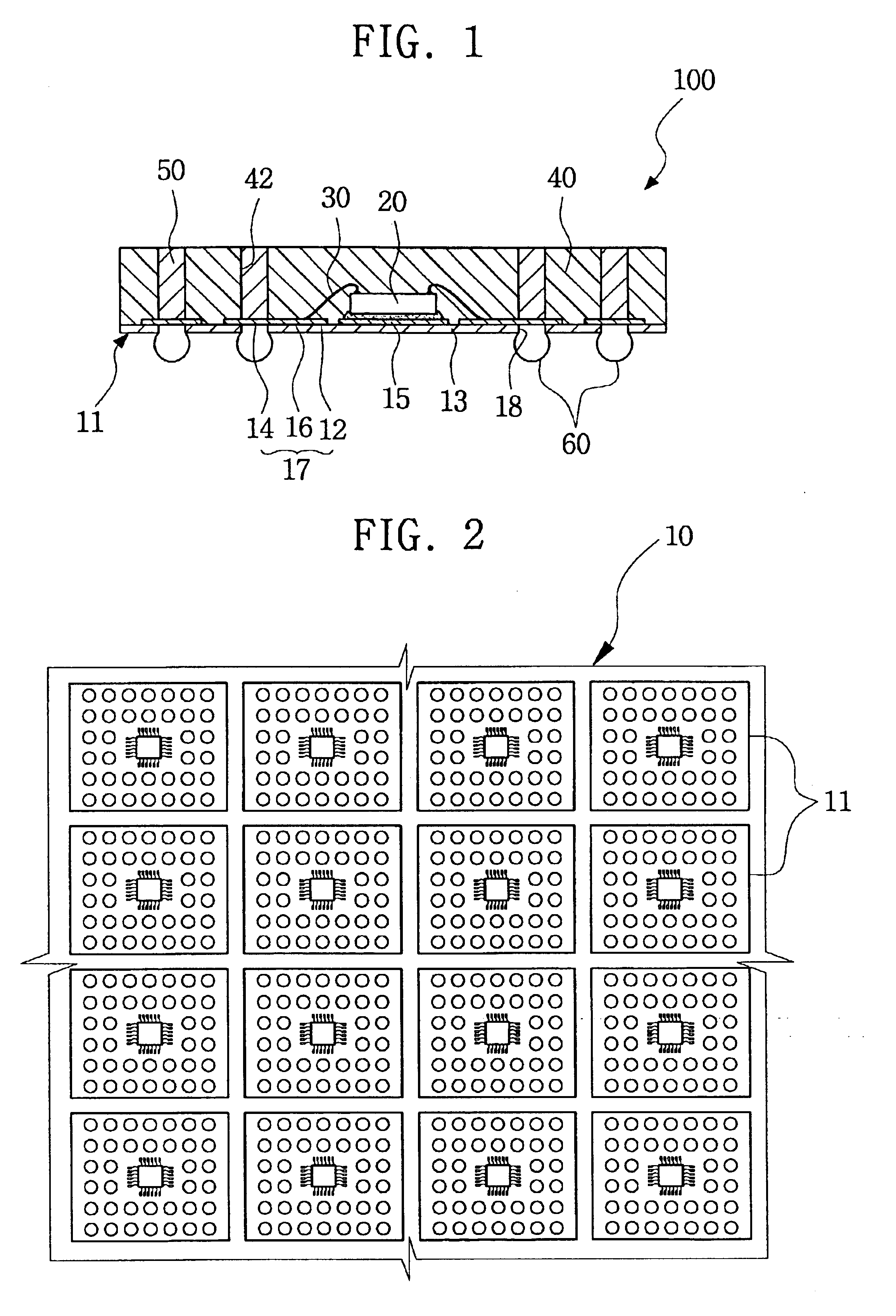

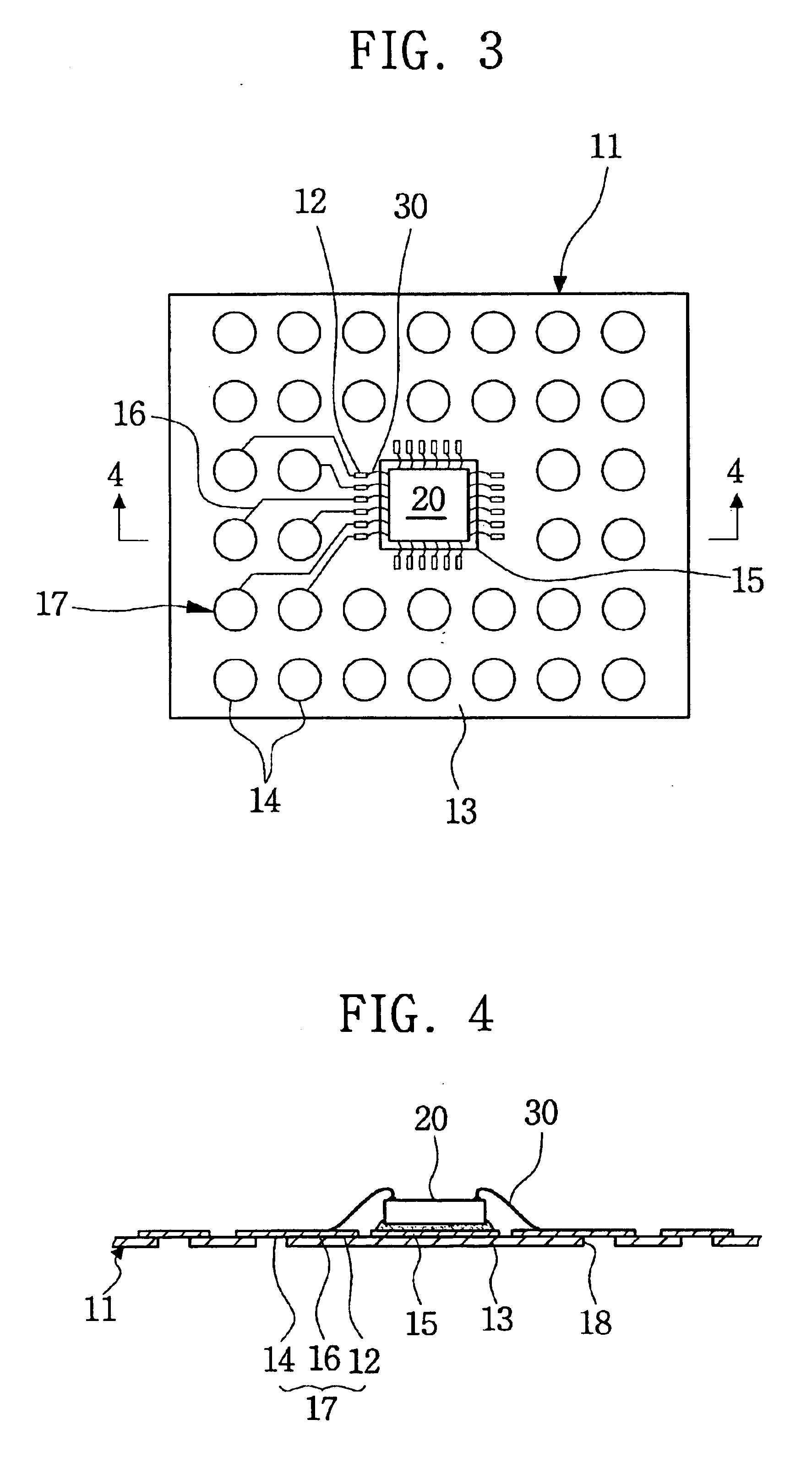

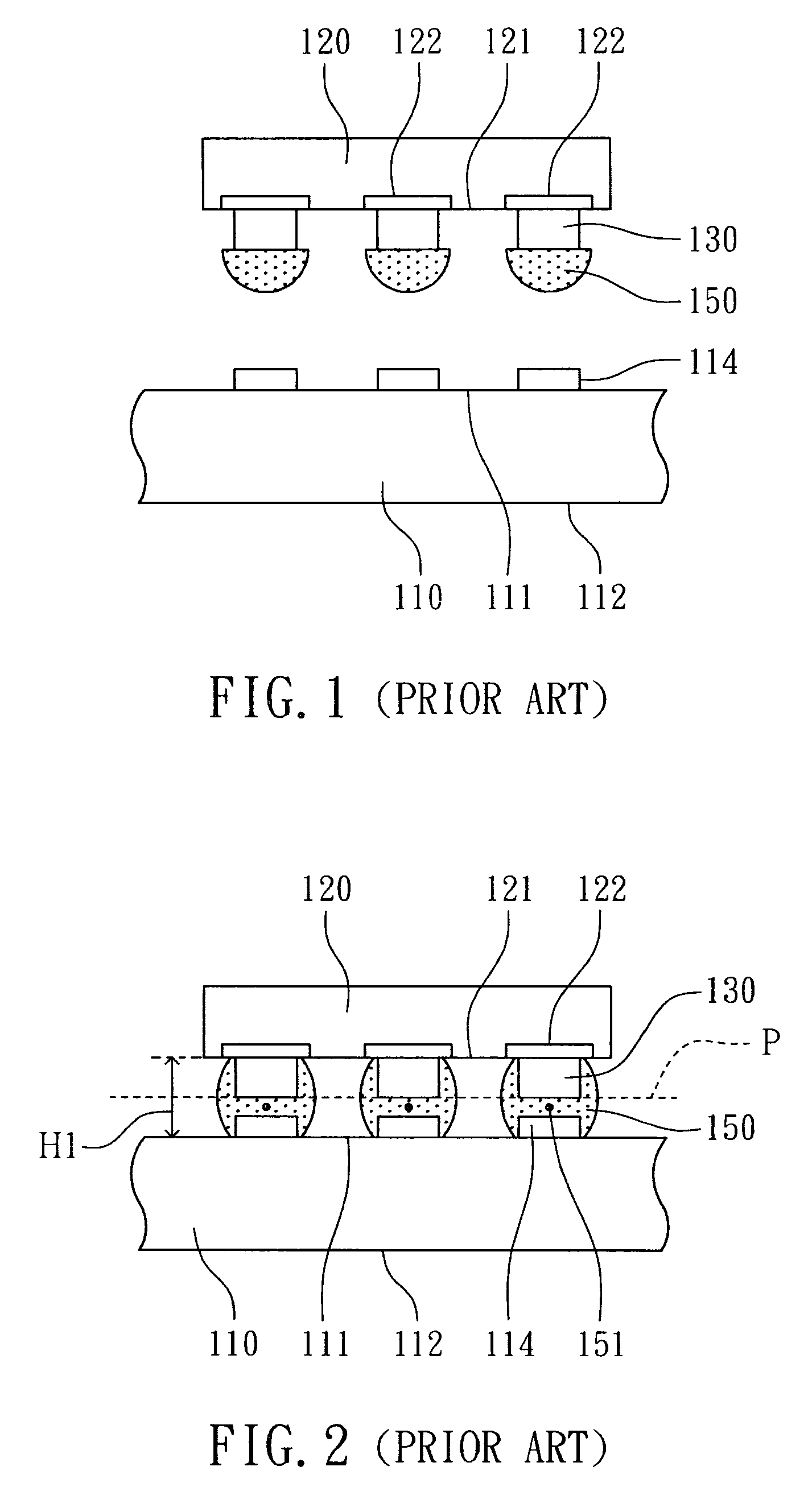

Area array semiconductor package and 3-dimensional stack thereof

InactiveUS6847109B2Semiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

An area array type semiconductor package suitable for use in the formation of a 3-dimensional stack of the area array type packages. The area array type semiconductor package includes a circuit board, typically a tape circuit board, a semiconductor chip, bonding wires, an encapsulation body, solder posts, and solder balls. A plurality of the area array type semiconductor packages can be electrically connected through the corresponding solder balls and solder posts on adjacent packages to form semiconductor stack packages.

Owner:SAMSUNG ELECTRONICS CO LTD

Pillar-to-pillar flip-chip assembly

ActiveUS7569935B1Reduce thermal stressPrevent peelingFinal product manufactureSemiconductor/solid-state device detailsSolder maskSolder ball

A pillar-to-pillar flip-chip assembly primarily comprises a substrate, a chip disposed on the substrate, a plurality of first copper pillars on the bonding pads of the chip, a plurality of second copper pillars on the bump pads of the substrate, and a soldering material. A first height of the first copper pillars protruding from the active surface of the chip is the same as a second height of the second copper pillars from the solder mask on the substrate. When the soldering material electrically and mechanically connects the first copper pillars to the second copper pillars, a plurality of central points of the soldering material are formed on an equal-dividing plane between the chip and the substrate to reduce the direct stresses exerted at the soldering material to avoid peeling or breaks from the bump pads. Moreover, each of conventional solder balls is replaced with two soldered copper pillars to meet the lead-free requirements with higher reliability and lower costs.

Owner:POWERTECH TECHNOLOGY

Ball grid array package

InactiveUS6396707B1Printed circuit assemblingSemiconductor/solid-state device detailsSolder maskSolder ball

A ball grid array package comprises a substrate having a first surface and a second surface, a chip, an insulating material, and a solder ball. The surface of the substrate comprises ball pads, conducting traces, and solder masks wherein the conducting traces are disposed in between the adjacent ball pads, and are covered by the solder mask, in addition, a portion of each of the ball pads is also covered by the solder mask. The solder mask includes an opening positioned in the area corresponding to the ball pads wherein the opening exposes a portion of the surface the ball pad and a portion of the side wall of the ball pad. The chip is disposed on the second surface of the substrate, and is sealed and encapsulated by the insulated material. The solder balls are disposed on the first surface of the substrate, and are positioned at the openings of the ball pads. Additionally, the solder balls are electrically connected to a portion of the surface of the ball pads and a portion of the side wall of the ball pads disposed at the ball pad openings.

Owner:SILICONWARE PRECISION IND CO LTD

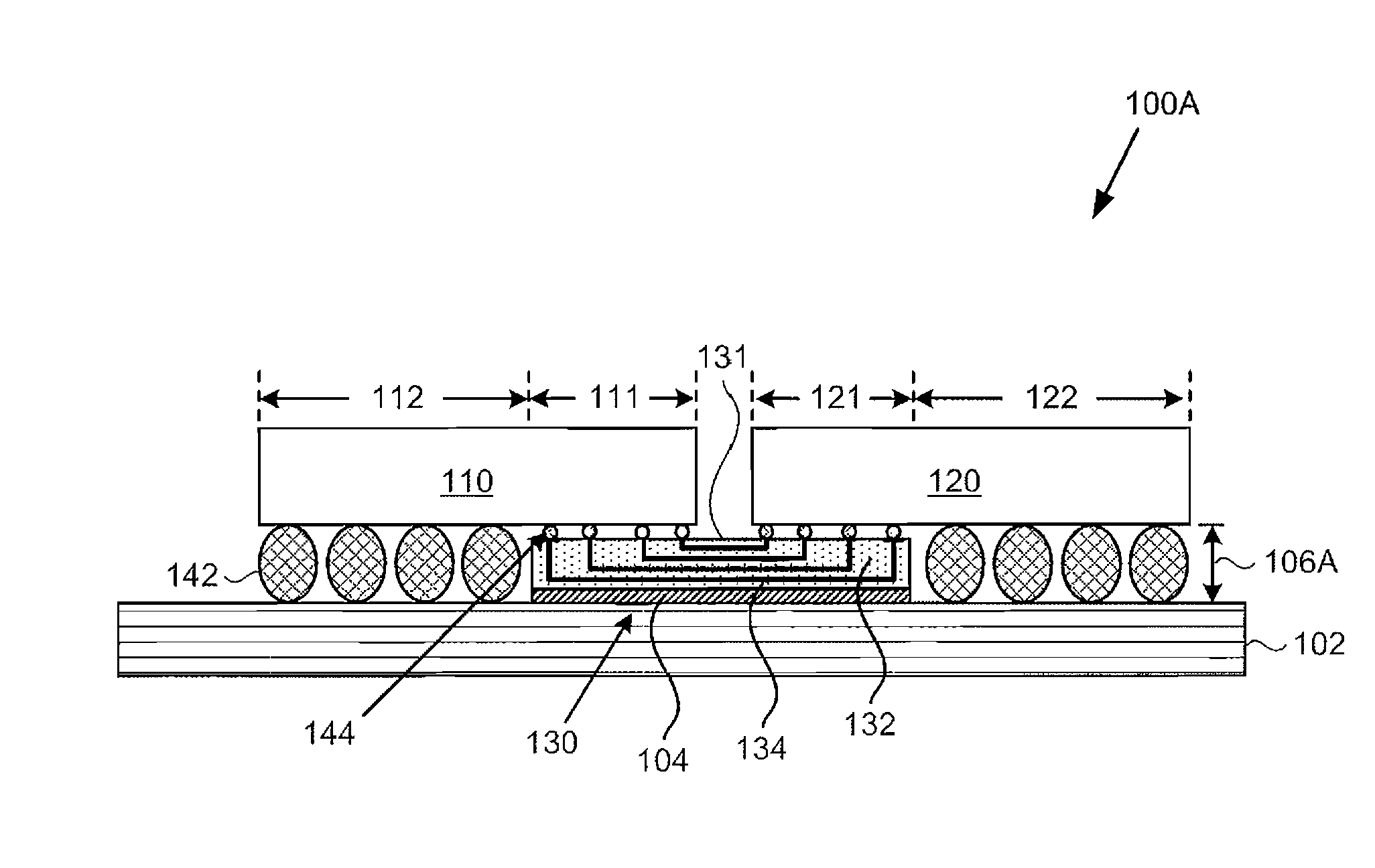

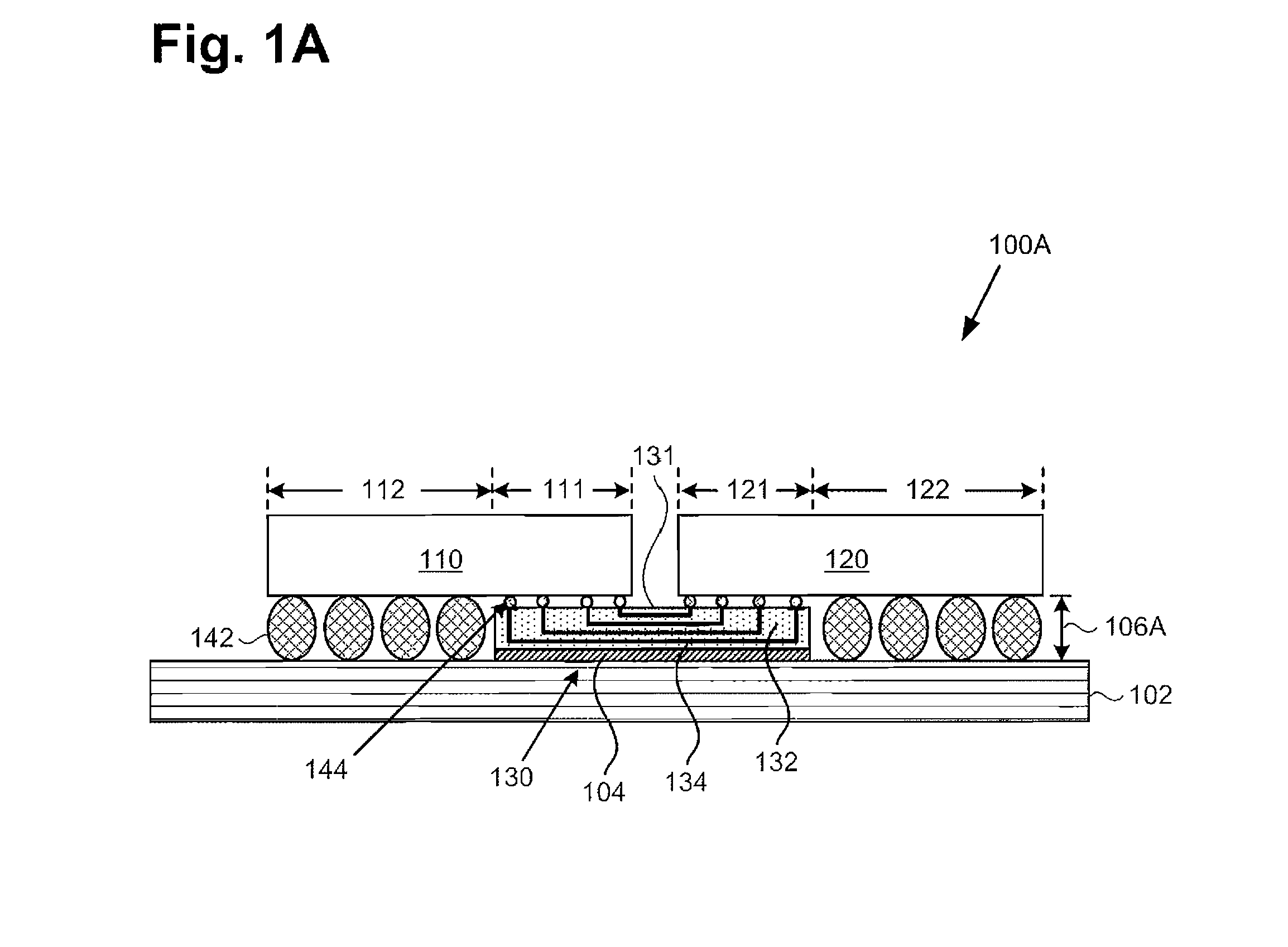

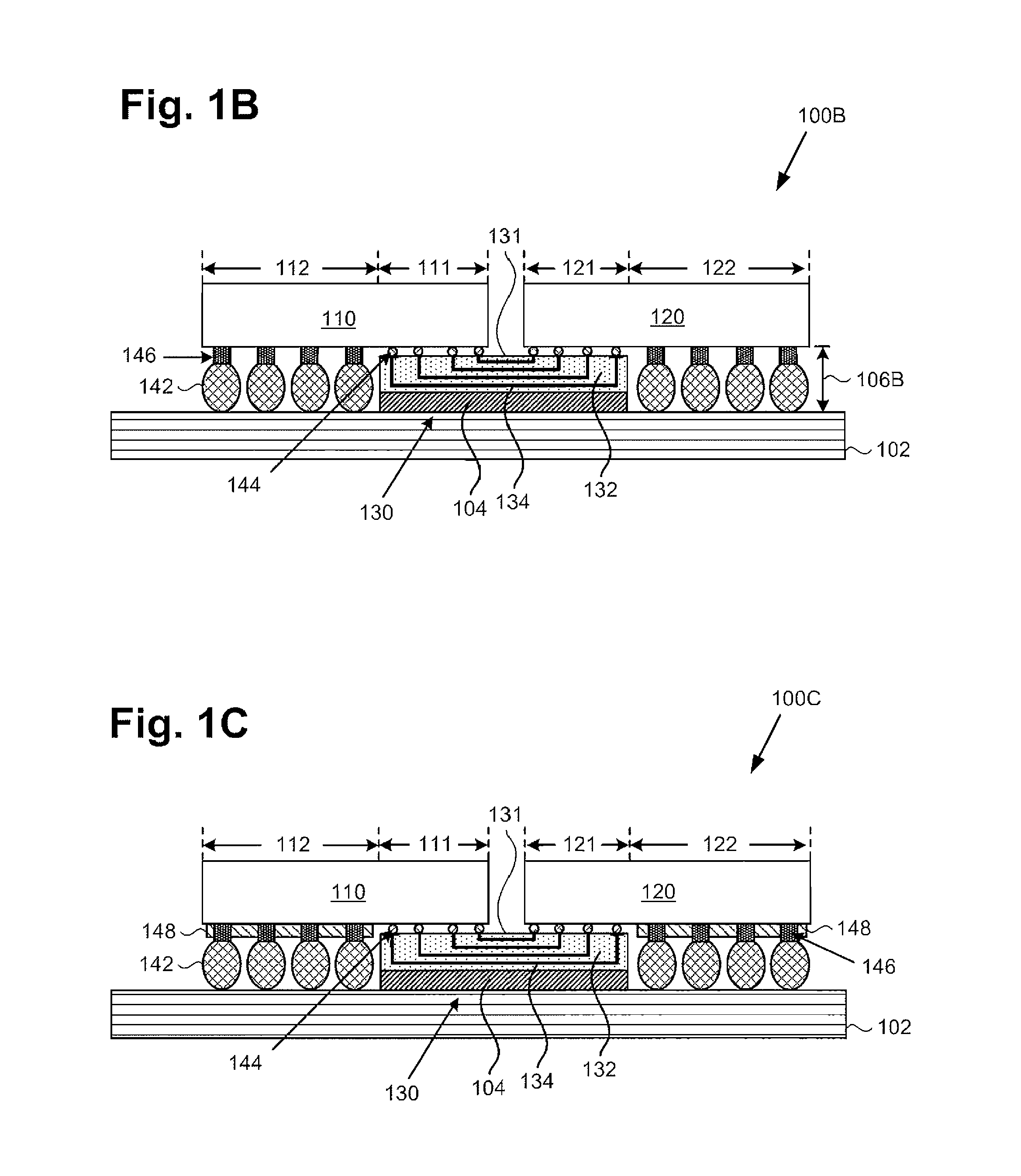

Semiconductor Package with a Bridge Interposer

ActiveUS20130168854A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSolder ball

There are disclosed herein various implementations of semiconductor packages including a bridge interposer. One exemplary implementation includes a first active die having a first portion situated over the bridge interposer, and a second portion not situated over the bridge interposer. The semiconductor package also includes a second active die having a first portion situated over the bridge interposer, and a second portion not situated over the bridge interposer. The second portion of the first active die and the second portion of the second active die include solder balls mounted on a package substrate, and are configured to communicate electrical signals to the package substrate utilizing the solder balls and without utilizing through-semiconductor vias (TSVs).

Owner:AVAGO TECH INT SALES PTE LTD

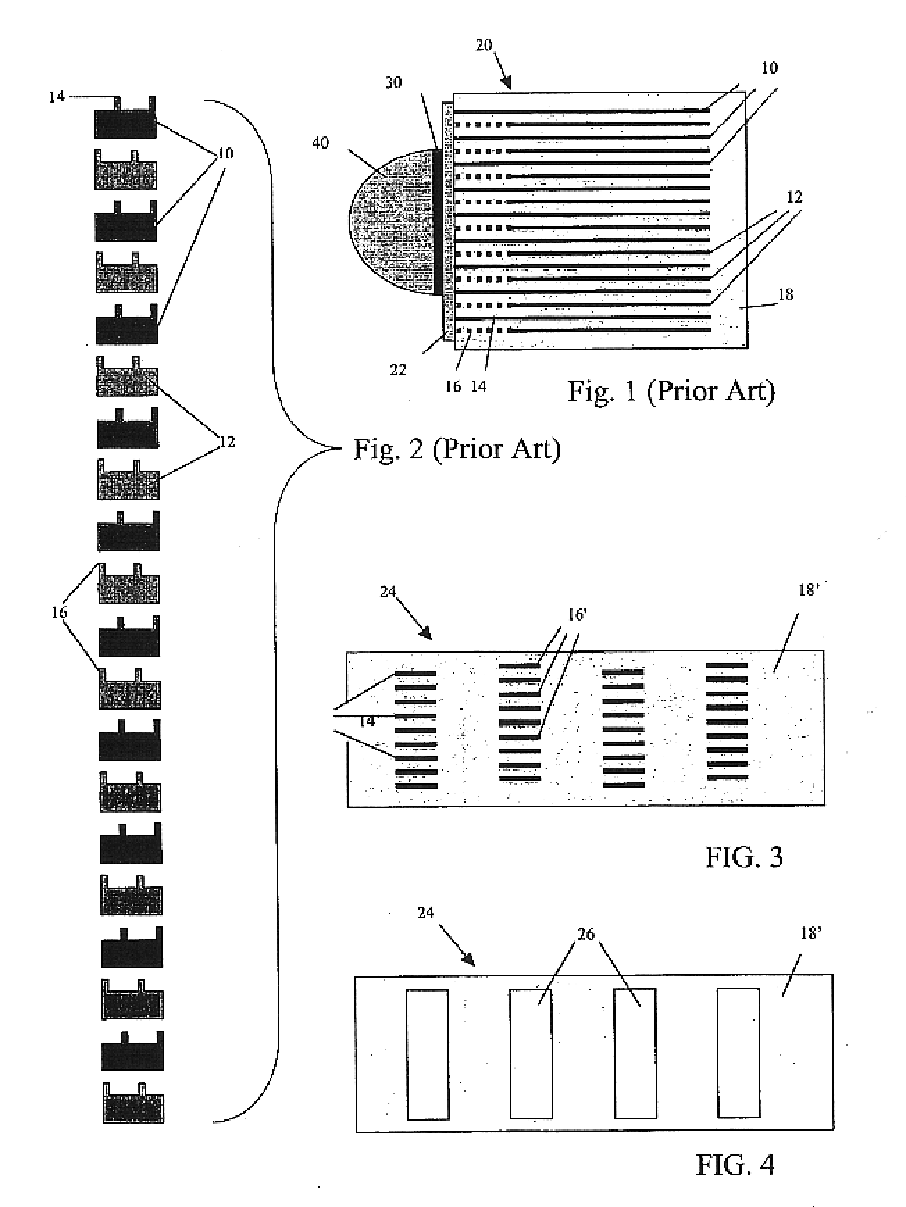

Component formation via plating technology

InactiveUS6982863B2Improved termination featureEliminate or greatly simplify thick-film stripesStacked capacitorsWound capacitorsTermination problemSolder ball

Improved terminations, interconnection techniques, and inductive element features for multilayer electronic components are formed in accordance with disclosed plating techniques. Monolithic components are provided with plated terminations whereby the need for typical thick-film termination stripes is eliminated or greatly simplified. Such plated termination technology eliminates many typical termination problems and enables a higher number of terminations with finer pitch, which may be especially beneficial on smaller electronic components. The subject plated terminations are guided and anchored by exposed varying width internal electrode tabs and additional anchor tab portions. Such anchor tabs may be positioned internally or externally relative to a chip structure to nucleate additional metallized plating material. The combination of electrode tabs and anchor tabs may be exposed in respective arrangements to form generally discoidal portions of plated material. Such plated material may ultimately form generally round portions of ball limiting metallurgy (BLM) to which solder balls may be reflowed. The disclosed technology may be utilized with a plurality of monolithic multilayer components, including interdigitated capacitors, multilayer capacitor arrays, and integrated passive components. A variety of different plating techniques and materials may be employed in the formation of the subject self-determining plated terminations and inductive components.

Owner:KYOCERA AVX COMPONENTS CORP

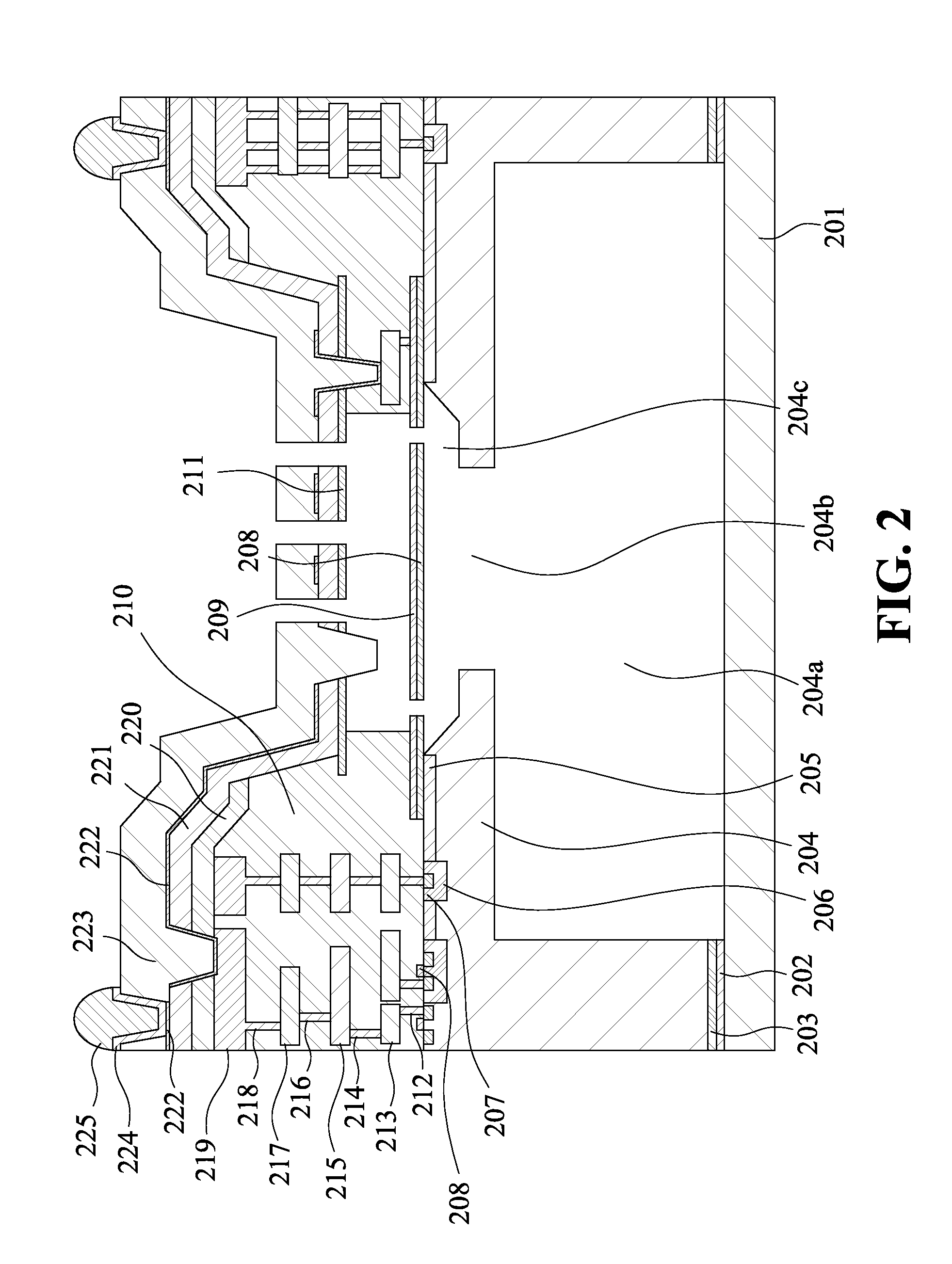

Integrated MEMS device

InactiveUS20130161702A1Improve reliabilityReduce manufacturing costMicrophonesLoudspeakersCMOSControl layer

An integrated MEMS device is provided, including, from bottom up, a bonding wafer layer, a bonding layer, an aluminum layer, a CMOS substrate layer defining a large back chamber area (LBCA), a small back chamber area (SBCA) and a sound damping path (SDP), a set of CMOS wells, a field oxide (FOX) layer, a set of CMOS transistor sources / drains, a first polysilicon layer forming CMOS transistor gates, a second polysilicon layer, said CMOS wells, said CMOS transistor sources / drains and said CMOS gates forming CMOS transistors, an oxide layer embedded with a plurality of metal layers interleaved with a plurality of via hole layers, and a gap control layer, an oxide layer, a first Nitride deposition layer, a metal deposition layer, a second Nitride deposition layer, an under bump metal (UBM) layer made of preferably Al / NiV / Cu and a plurality of solder spheres.

Owner:WINDTOP TECH CORP

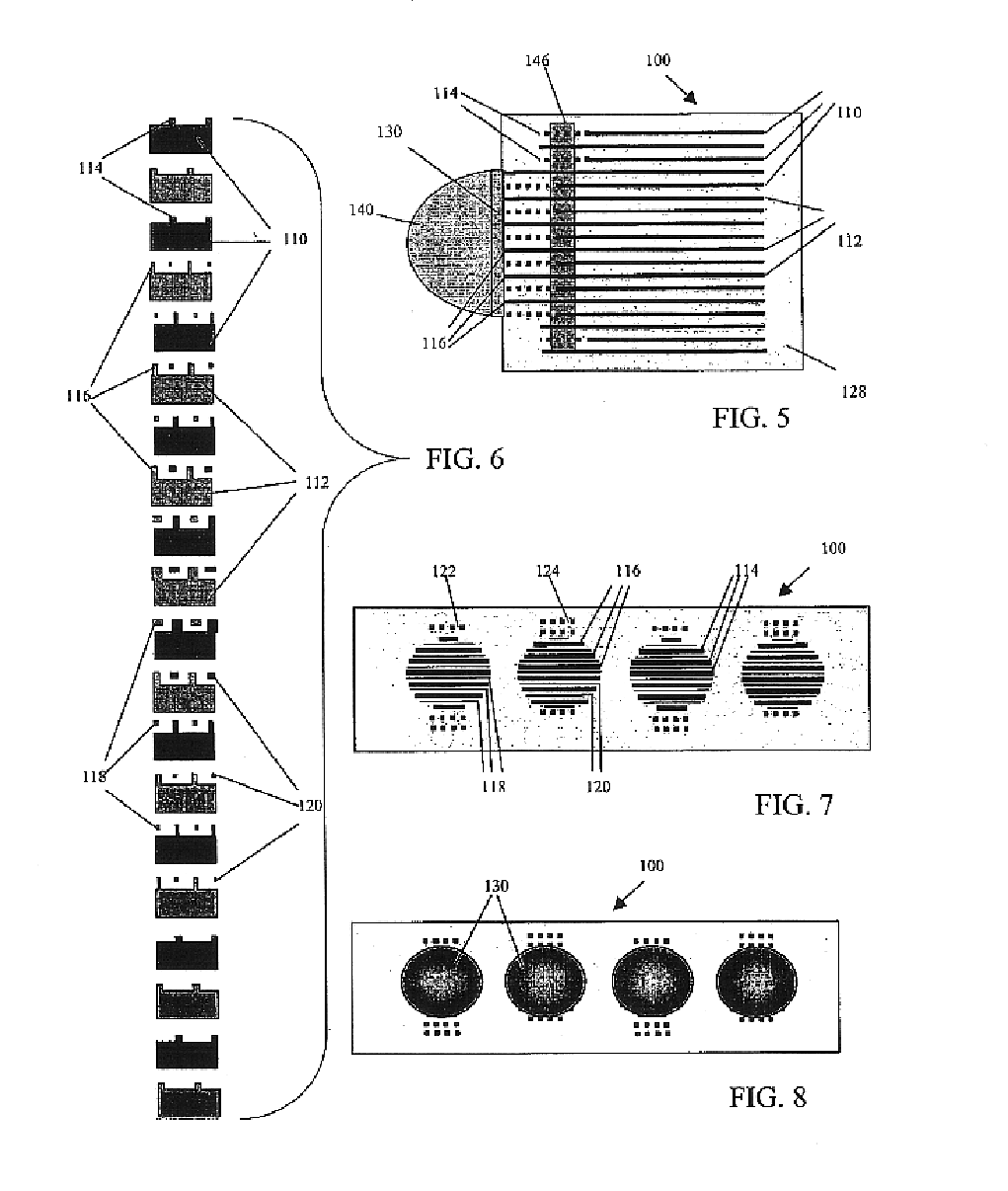

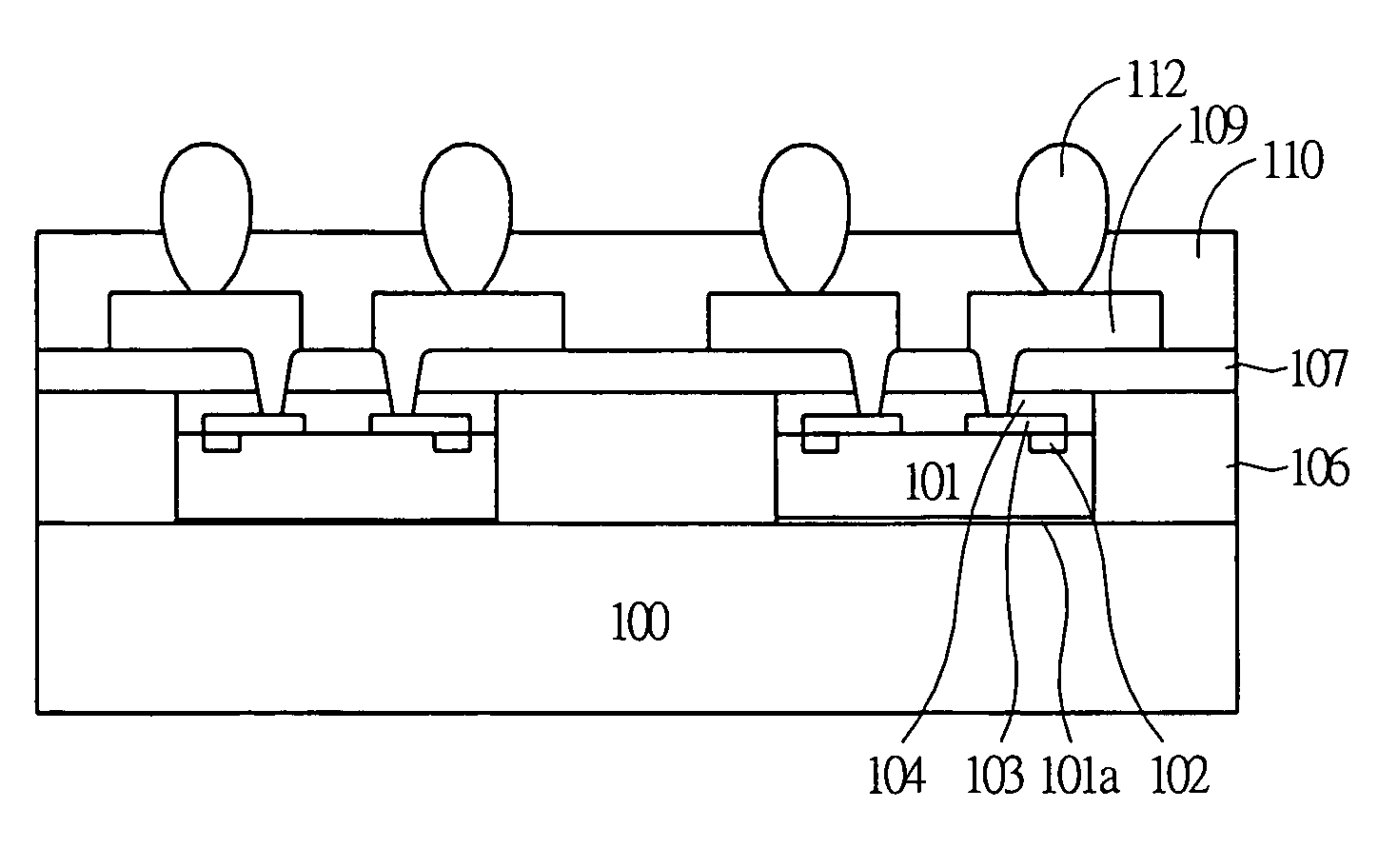

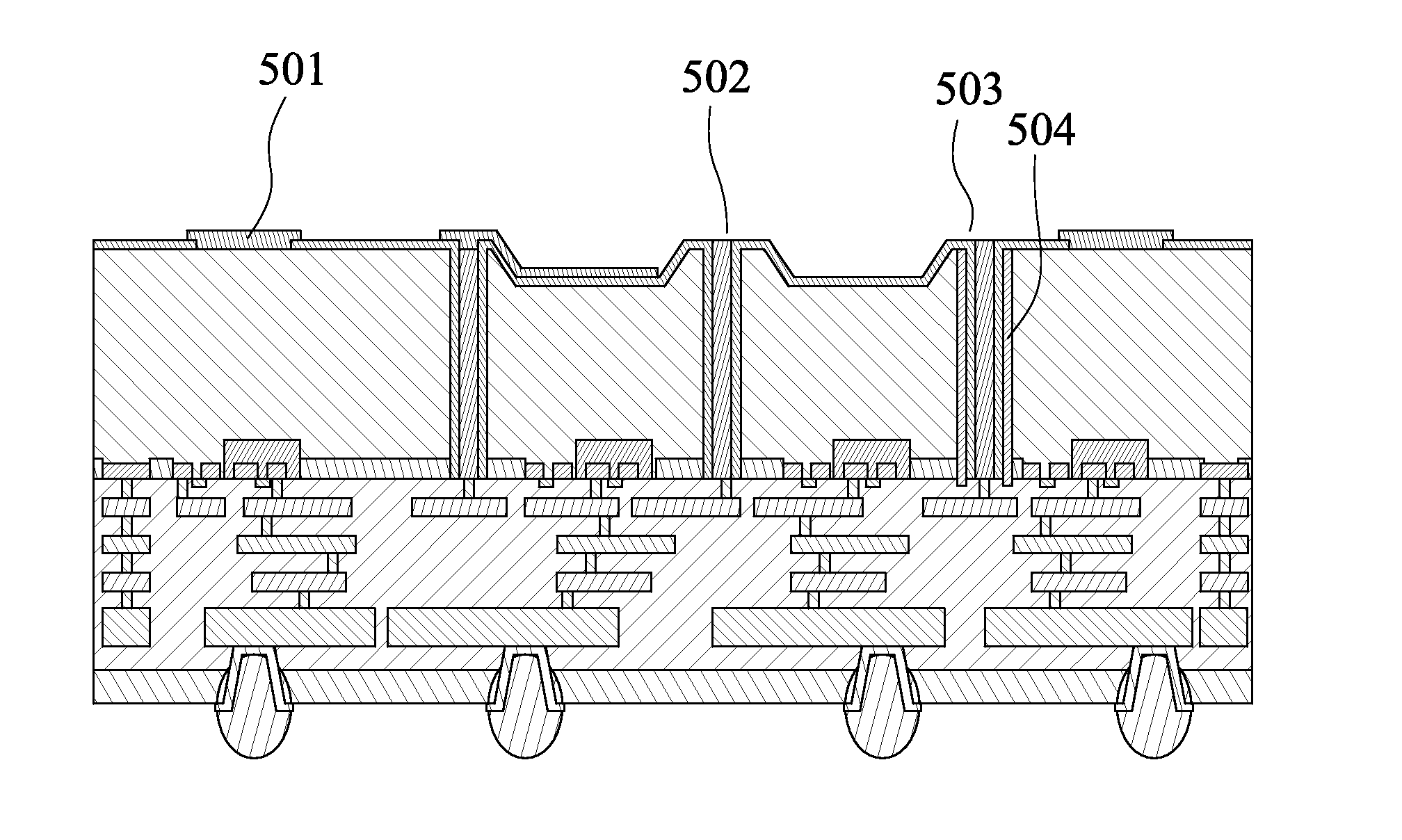

Stack package utilizing through vias and re-distribution lines

ActiveUS20070222050A1Easily applied to high-speed productSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A stack package includes a printed circuit board; at least two semiconductor chips stacked on the printed circuit board, each having first re-distribution lines formed on the upper surface thereof and connected to bonding pads, through silicon vias which are formed therethrough and connected to the first re-distribution lines, and second re-distribution lines formed on the lower surface thereof and connected to the through silicon vias; first and second solder balls interposed between the first and second re-distribution lines which face each other and between the first re-distribution lines of the lowermost semiconductor chip and electrode terminals of the printed circuit board; a molding material for molding the upper surface of the printed circuit board including the stacked semiconductor chips; and third solder balls attached to ball lands formed on the lower surface of the printed circuit board.

Owner:SK HYNIX INC

Unmolded package for a semiconductor device

InactiveUS6469384B2Printed circuit assemblingSemiconductor/solid-state device detailsMOSFETDevice material

A semiconductor device that does not include a molded body or package. The semiconductor device includes a substrate and a die coupled to the substrate. The die is coupled to the substrate such that the source and gate regions of the die, assuming a MOSFET-type device, are coupled to the substrate. Solder balls are provided adjacent to the die such that when the semiconductor device is coupled to a printed circuit board, the exposed surface of the serves as the drain connections while the solder balls serve as the source and gate connections.

Owner:SEMICON COMPONENTS IND LLC

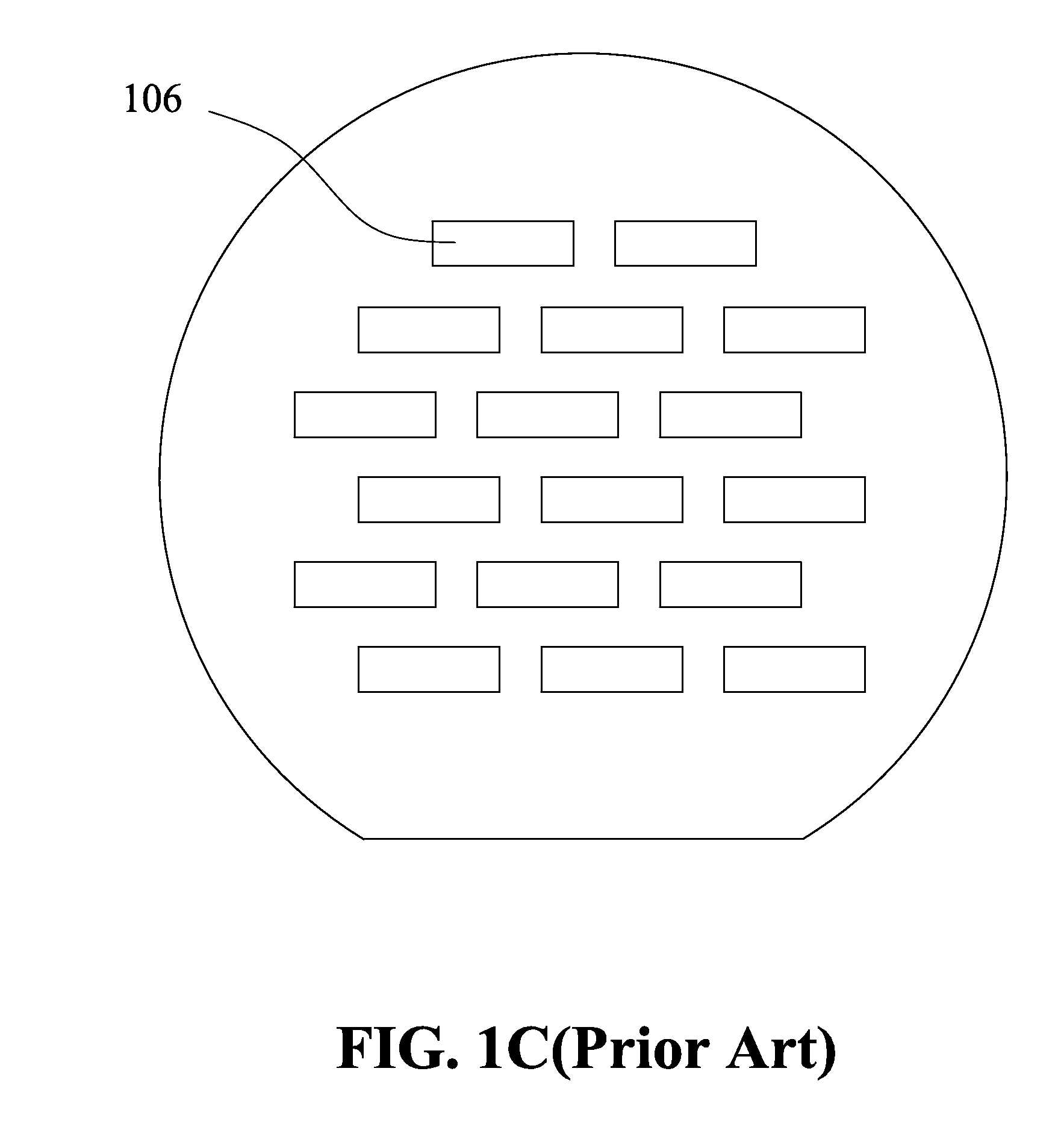

Hermetic wafer scale integrated circuit structure

InactiveUS6982475B1Prevent surfaceDamaged and destroyedSemiconductor/solid-state device detailsSolid-state devicesScale structureHermetic seal

A wafer scale semiconductor integrated circuit packaging technique provides a hermetic seal for the individual integrated circuit die formed as part of the wafer scale structure. A semiconductor wafer is manufactured to include a number of individual semiconductor die. Each individual die formed on the wafer includes a number of bond pads that are exposed on the die surface in various locations to provide electrical connections to the circuitry created on the die. The wafer further includes a planar glass sheet that is substantially the same size as the wafer, the glass sheet being adhered to the wafer using a suitable adhesive. The glass sheet has a number of pre-formed holes in it, the arrangement of the pre-formed holes corresponding to the location of the bond pads at each of the individual semiconductor die formed as part of the wafer structure. Following adherence of the glass sheet to the semiconductor wafer utilizing the intermediate adhesive material, metal connections are made between pads formed on the glass sheet and the bond pads formed on the integrated circuit die. Solder balls are then attached to the pads on the glass sheet to provide a conductive flow between the solder balls and the bond pads. After the solder balls are attached, trenches are cut around each of the individual die on the wafer. The trenches are cut at an angle and extend through the glass sheet and the intermediate adhesive material and into the semiconductor substrate in which the integrated circuits are formed. After the trenches are cut around each individual semiconductor die, a noble metal is deposited on the sidewalls of the trench to extend over the interface between the glass sheet, the adhesive material and the semiconductor die. The wafer is then cut along the noble metal lined trenches to provide individual, hermetically sealed packaged integrated circuit die.

Owner:MICRO CHIP SCALE PACKAGING

Thermally enhanced semiconductor package with EMI shielding

InactiveUS6865084B2Reduce thermal stressSimple structureMagnetic/electric field screeningSemiconductor/solid-state device detailsSolder ballElectromagnetic interference

A thermally enhanced semiconductor package with EMI (electric and magnetic interference) shielding is provided in which a chip is mounted on and electrically connected to a surface of a substrate, and a thermally conductive member is stacked on the chip and electrically coupled to the surface of the substrate by bonding wires. An encapsulant is formed and encapsulates the chip, thermally conductive member, and bonding wires. A plurality of solder balls are implanted on an opposite surface of the substrate. The thermally conductive member is grounded via the bonding wires, substrate, and solder balls, and provides an EMI shielding effect for the chip to protect the chip against external electric and magnetic interference. The thermally conductive member has a coefficient of thermal expansion similar to that of the chip, and reduces thermal stress exerted on the chip and enhances mechanical strength of the chip to thereby prevent chip cracks.

Owner:SILICONWARE PRECISION IND CO LTD

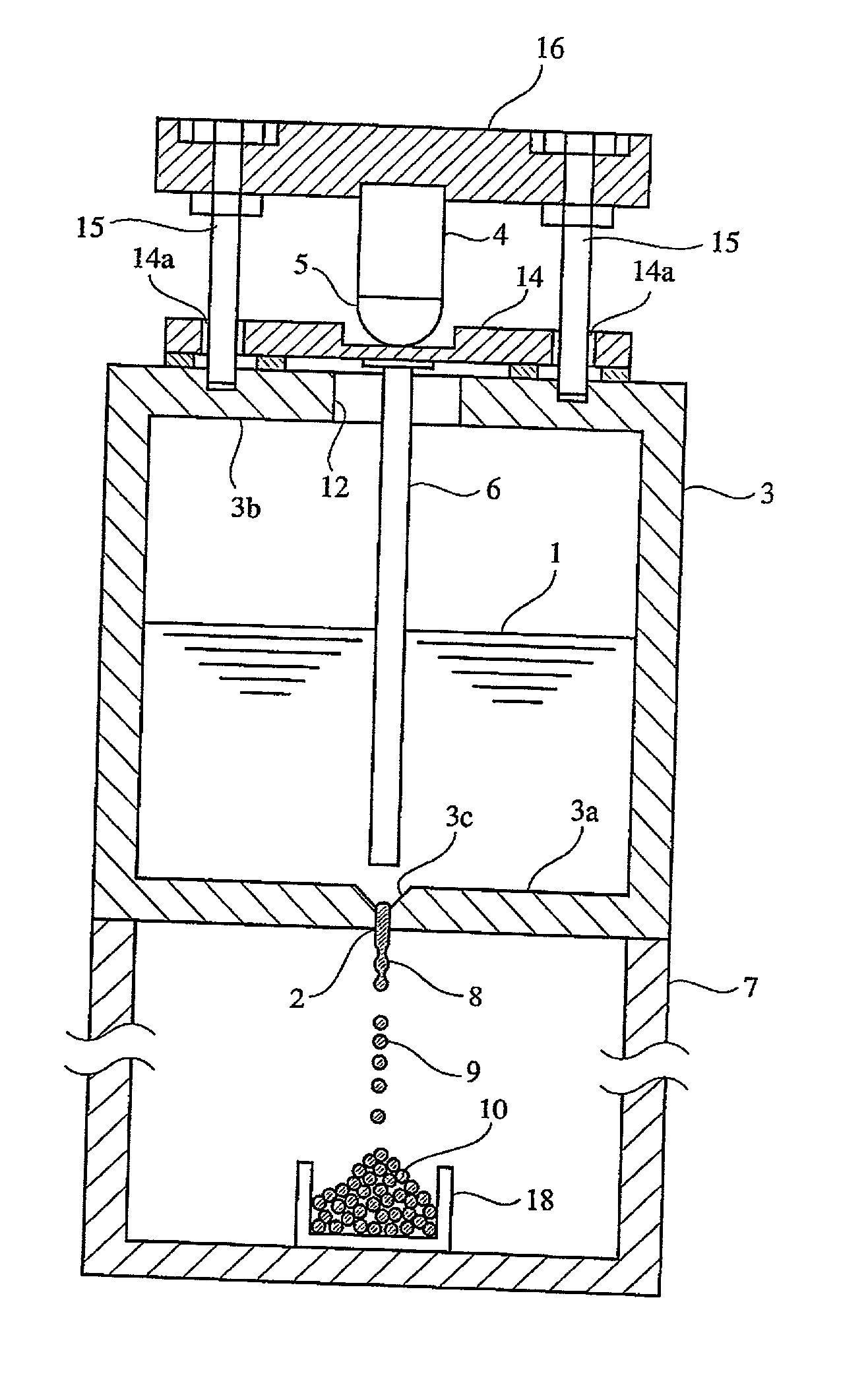

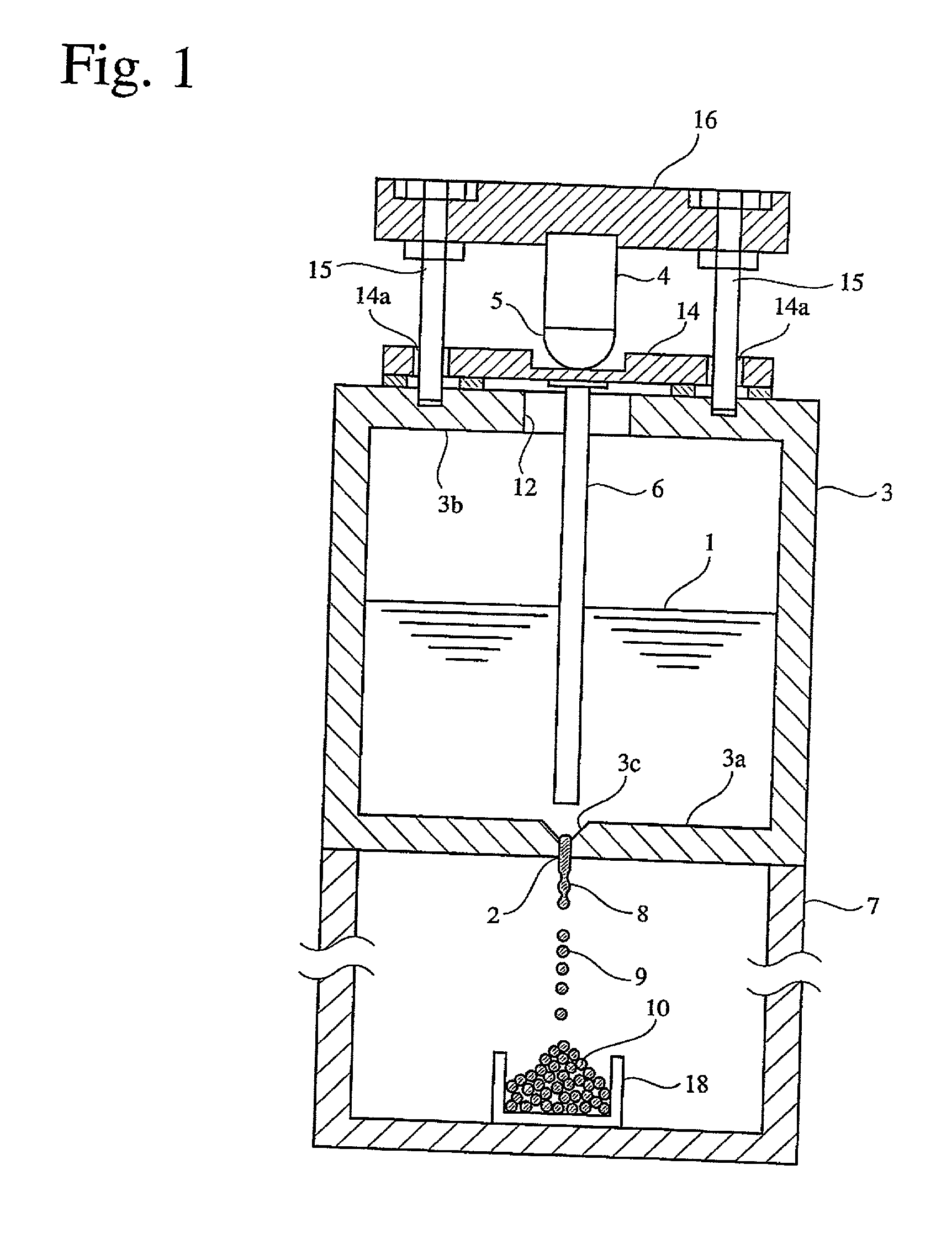

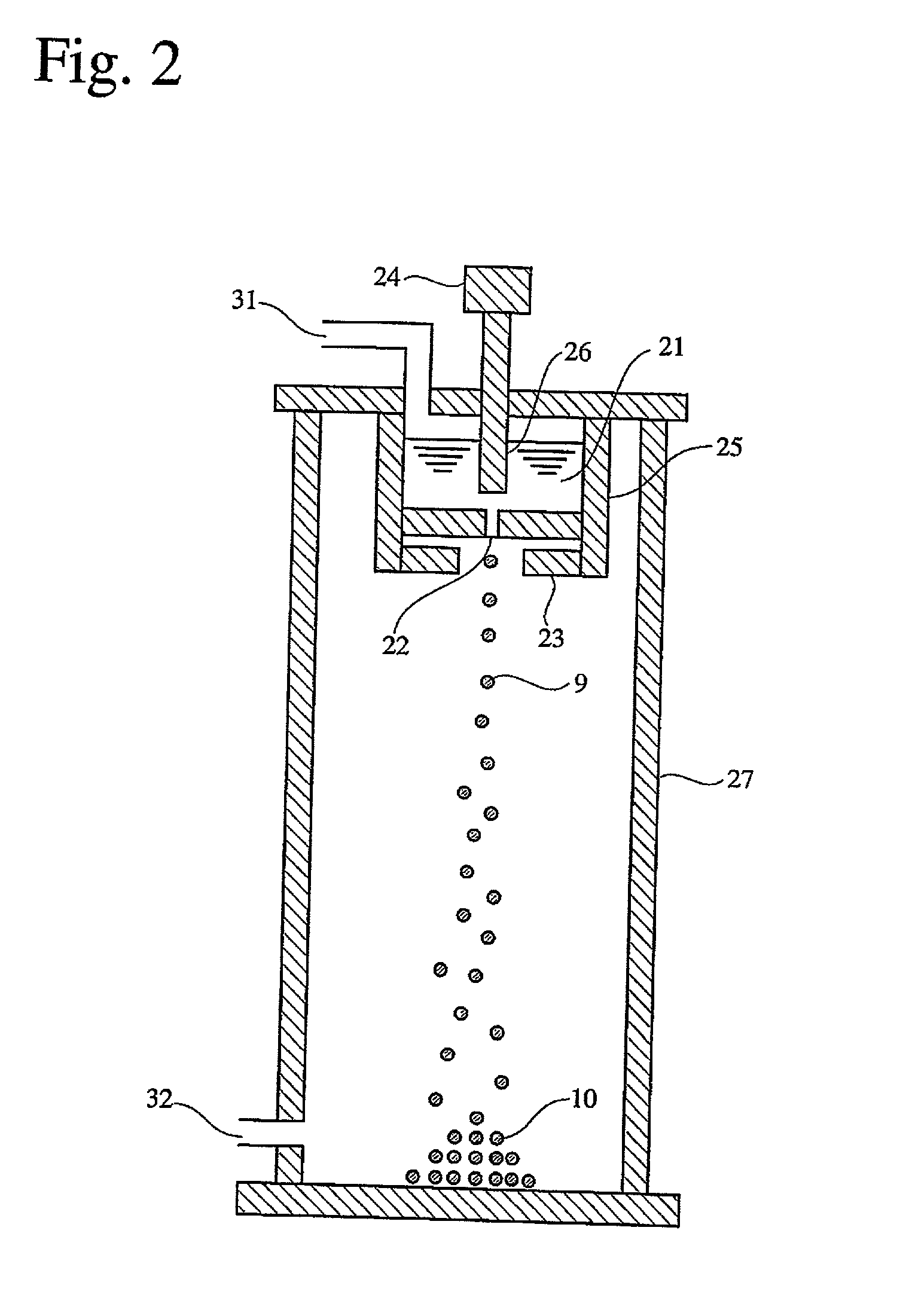

Solder ball and method for producing same

InactiveUS20020051728A1High degree of sphericityNarrow dimension distributionPrinted circuit assemblingTransportation and packagingCrucibleSolder ball

A solder ball having a diameter of 1.2 mm or less, a dispersion of a diameter distribution of 5% or less and sphericity of 0.95 or more, an area ratio of the maximum dendrite being 80% or less of a cross section including a center of the solder ball, comprises a first additional element of 0.5-8 mass% of Ag and / or 0.1-3 mass % of Cu, and 0.006-10 mass %, in total, of at least one second additional element selected from the group consisting of Bi, Ge, Ni, P, Mn, Au, Pd, Pt, S, In and Sb, the balance being substantially Sn. The solder ball is produced by a uniform droplet-spraying method comprising the steps of vibrating a melt of a solder alloy in a crucible under pressure to force the melt to drop through orifices of the crucible; permitting the melt dropping through the orifices to become spherical droplets in a non-oxidizing gas atmosphere; and rapidly solidifying them.

Owner:DUKSAN HI METAL

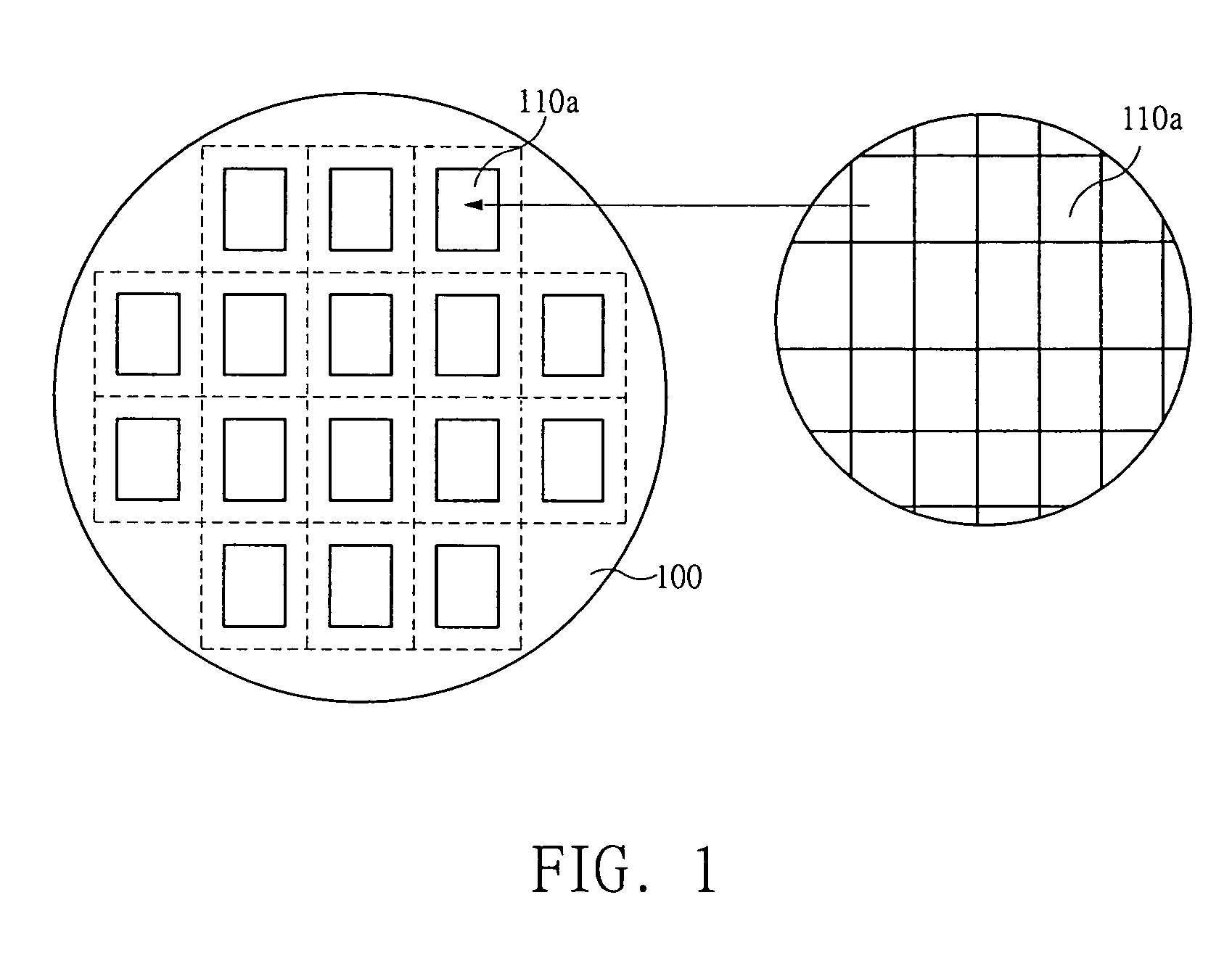

Wafer level chip size package having redistribution layers

ActiveUS7977783B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A wafer level chip size package (WLCSP) and a method of manufacturing the same are disclosed. Lands are formed at the ends of redistribution layers. The redistribution layers excluding the lands and a first dielectric layer are covered with a second dielectric layer. After forming a first under bump metallurgy (UBM) layer on the land, a solder ball is reflowed to the first UBM layer. A second UBM layer is widely formed on the entire second dielectric layer that is the outer circumference of the first UBM layer and is connected to the redistribution layer through a via-hole. Therefore, the second UBM layer having a large area can be used as a ground plane or a power plane. In addition, the second UBM layer can electrically connect the redistribution layers physically separated from each other. Therefore, the plurality of redistribution layers can cross each other without being electrically shorted with each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Interconnect module with reduced power distribution impedance

InactiveUS6847527B2Reduced impedance powerReduced ground distributionLight absorption dielectricsSemiconductor/solid-state device detailsSolder ballOperating frequency

An interconnect module for an integrated circuit chip incorporates a thin, high dielectric constant embedded capacitor structure to provide reduced power distribution impedance, and thereby promote higher frequency operation. The interconnect module is capable of reliably attaching an integrated circuit chip to a printed wiring board via solder ball connections, while providing reduced power distribution impedance of less than or equal to approximately 0.60 ohms at operating frequencies in excess of 1.0 gigahertz.

Owner:3M INNOVATIVE PROPERTIES CO

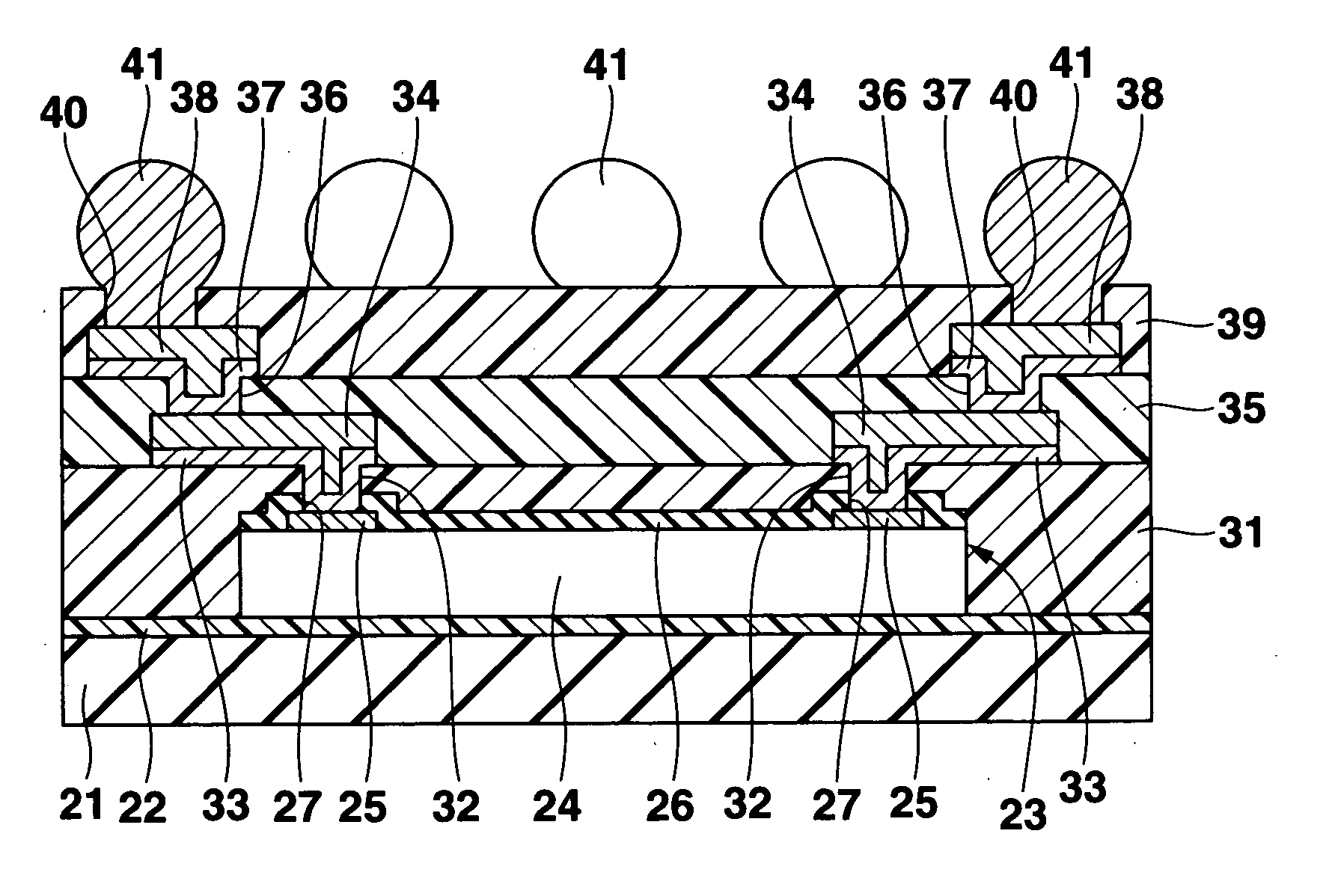

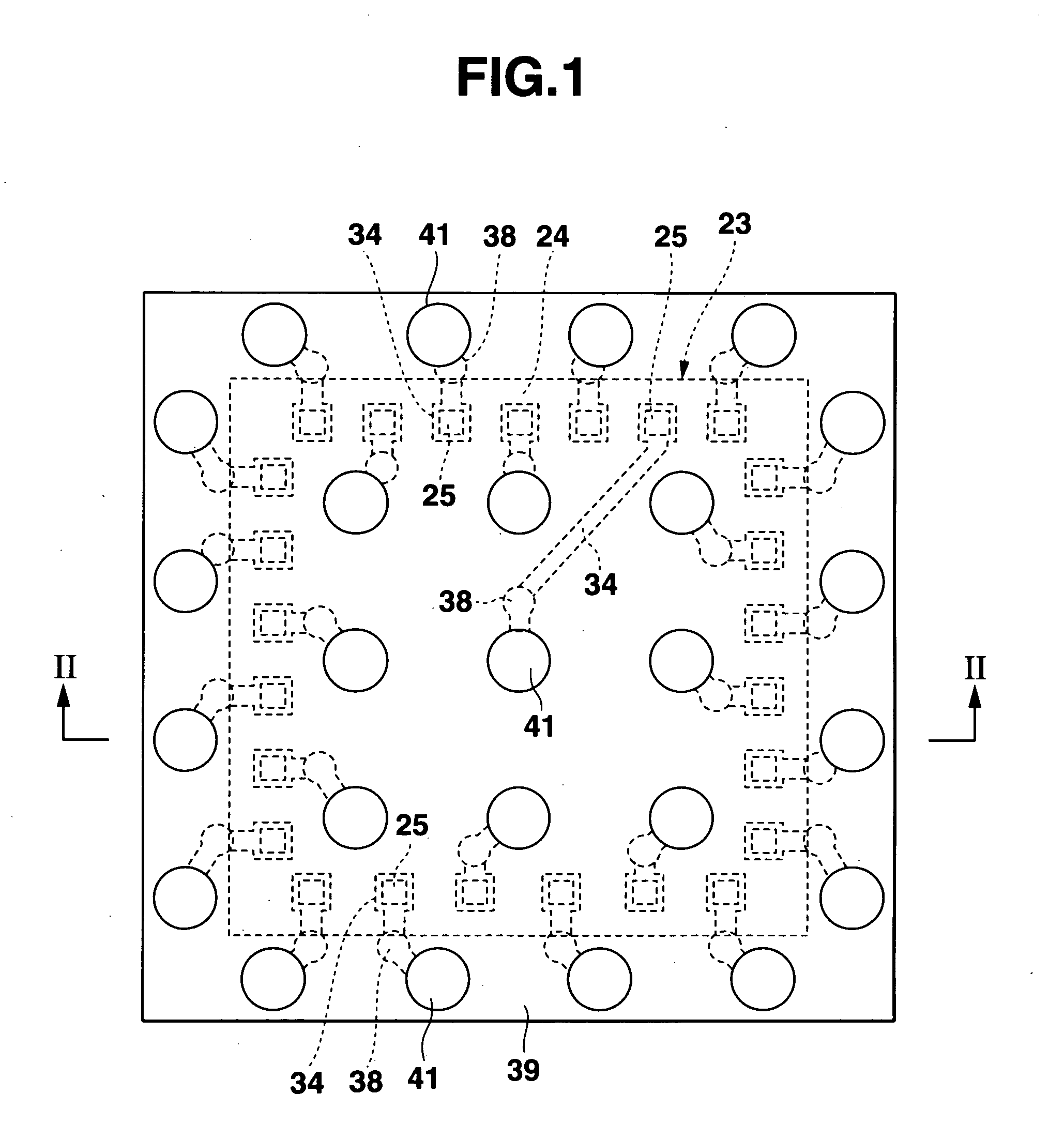

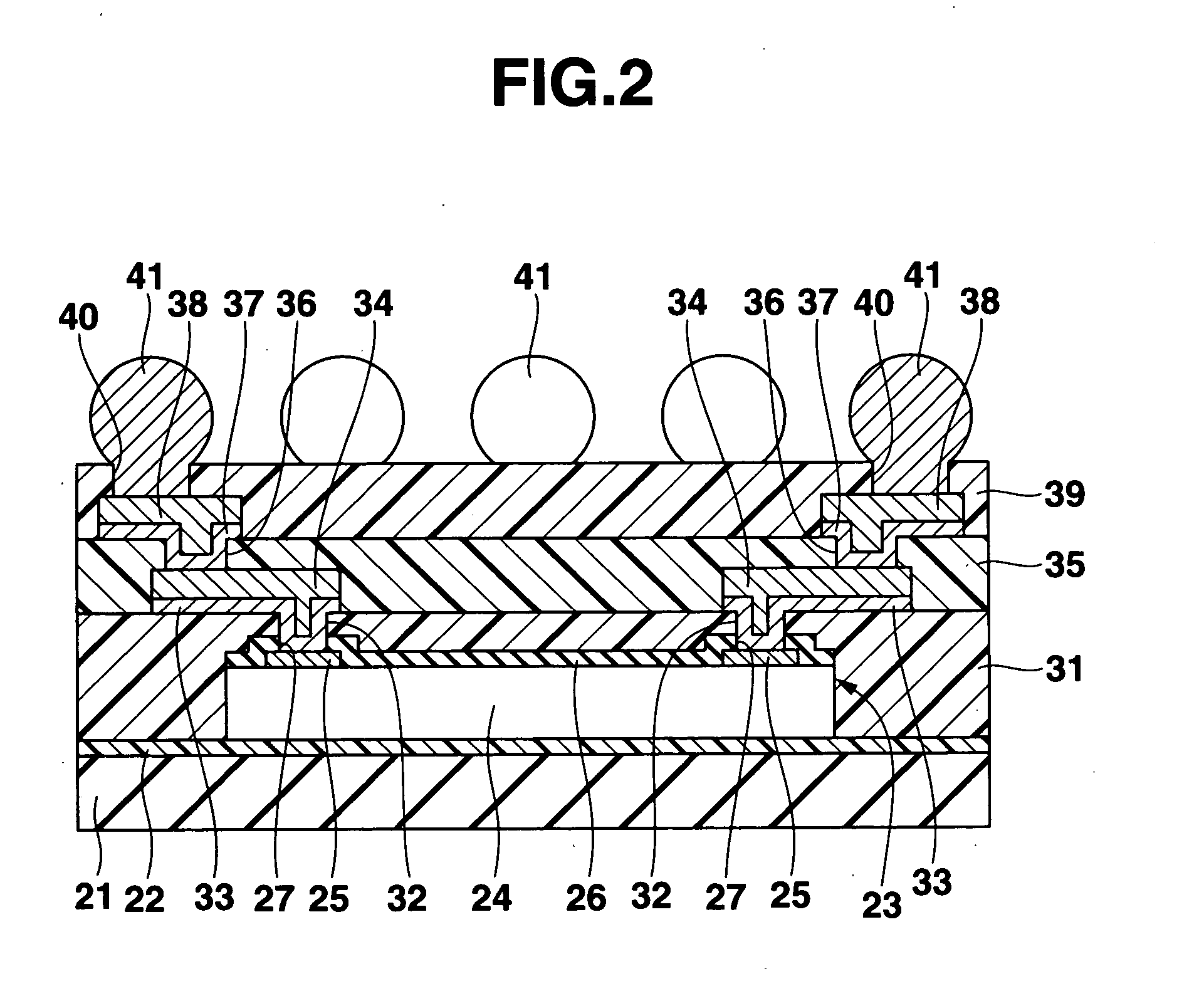

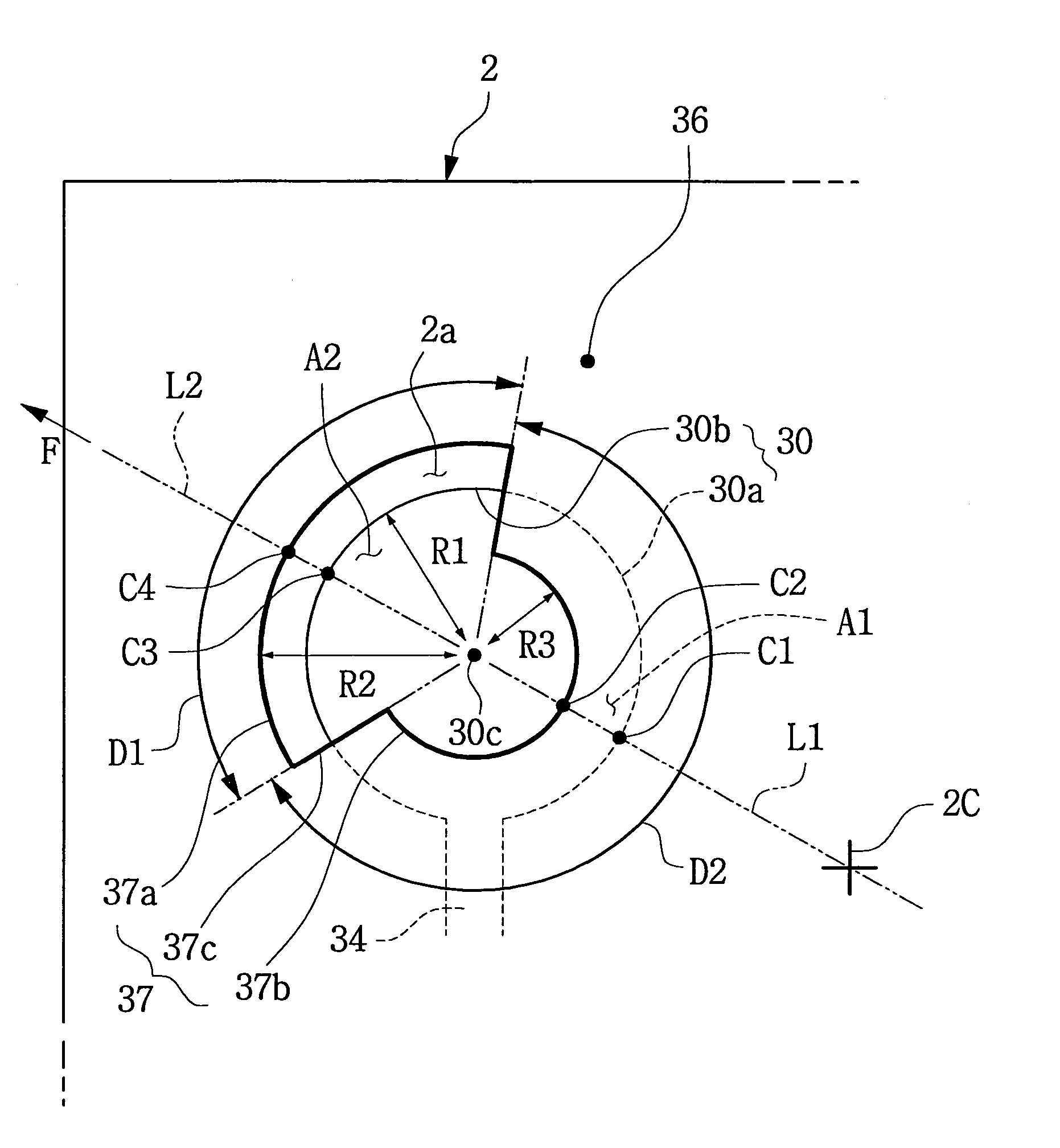

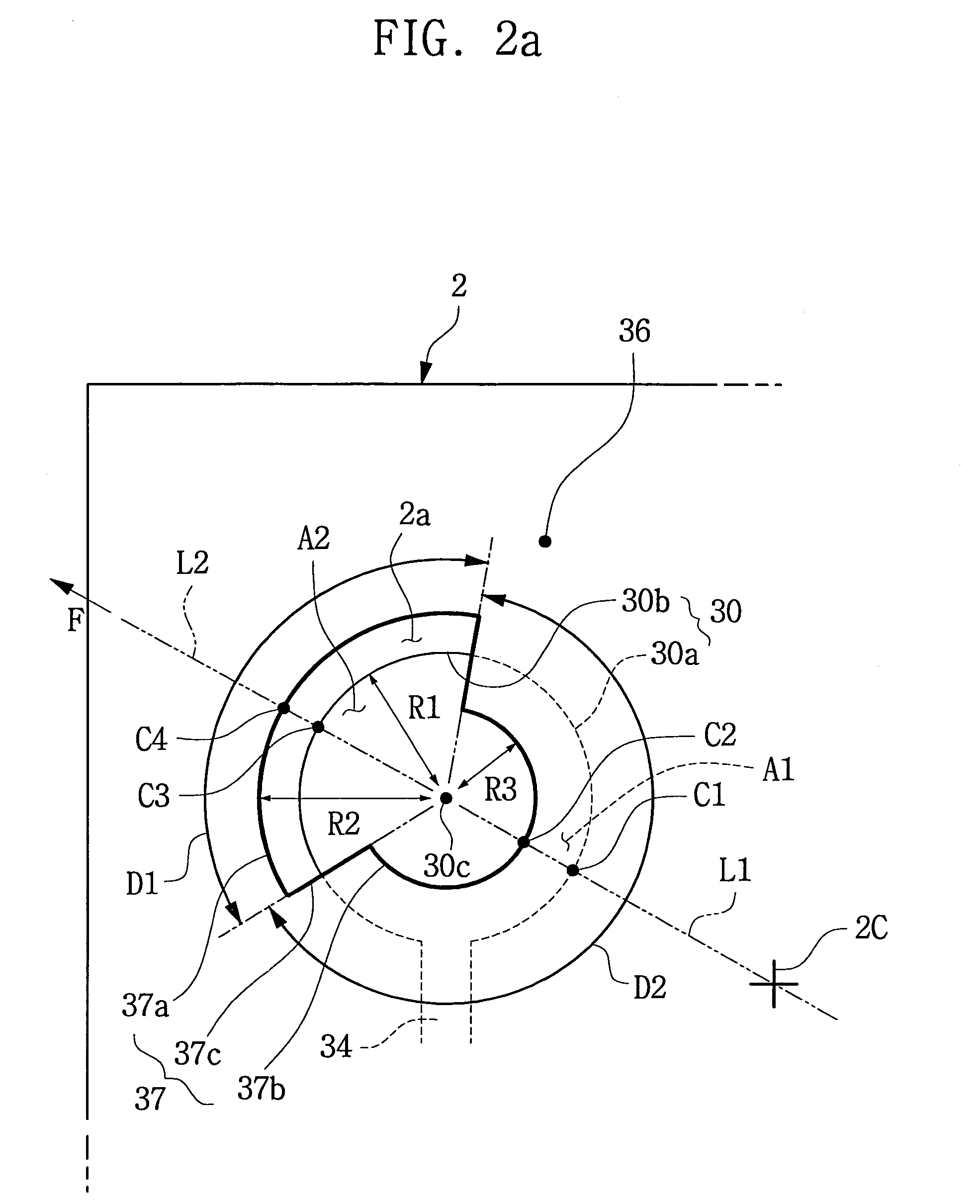

Semiconductor device and method of manufacturing the same

InactiveUS20050098891A1Semiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

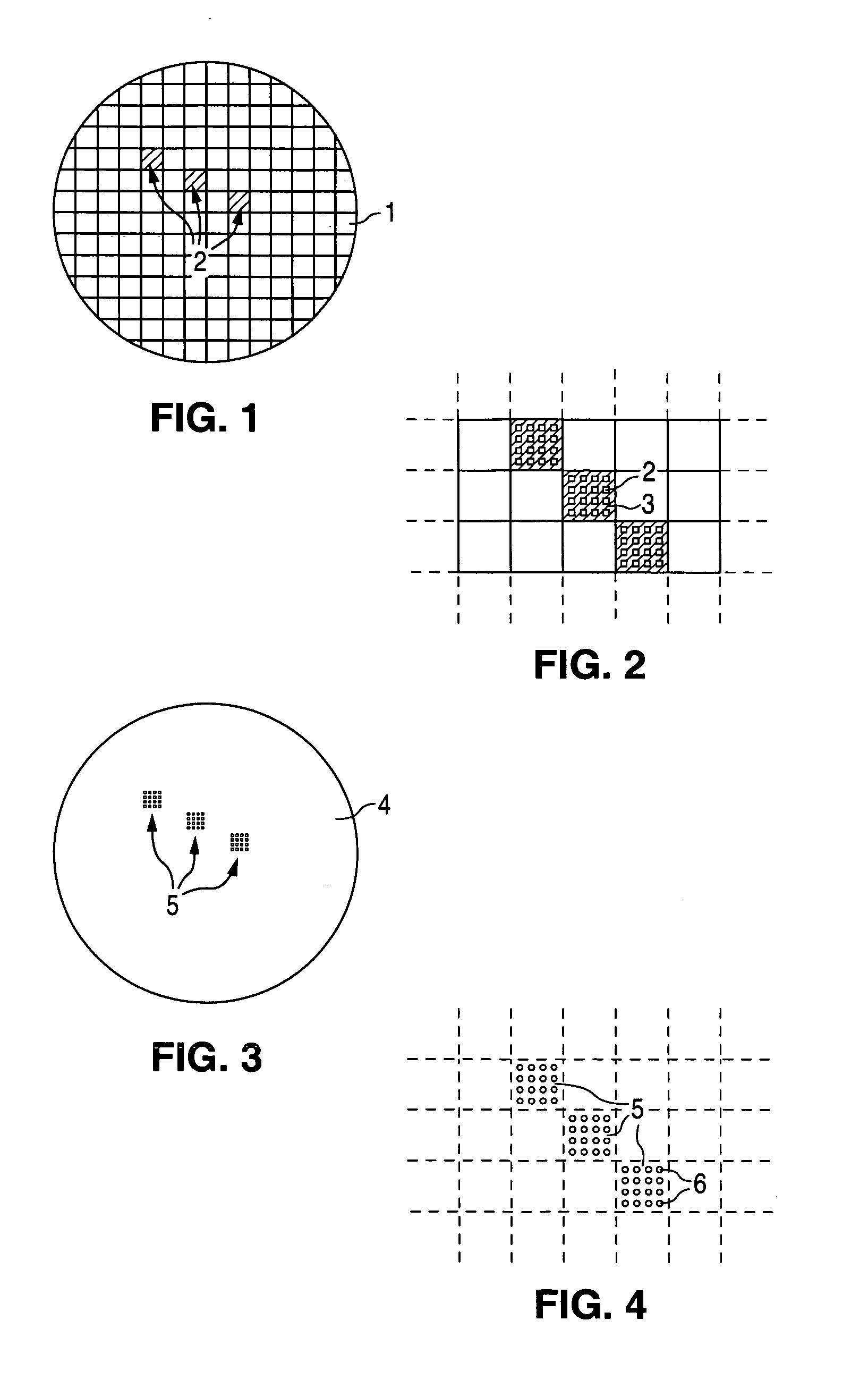

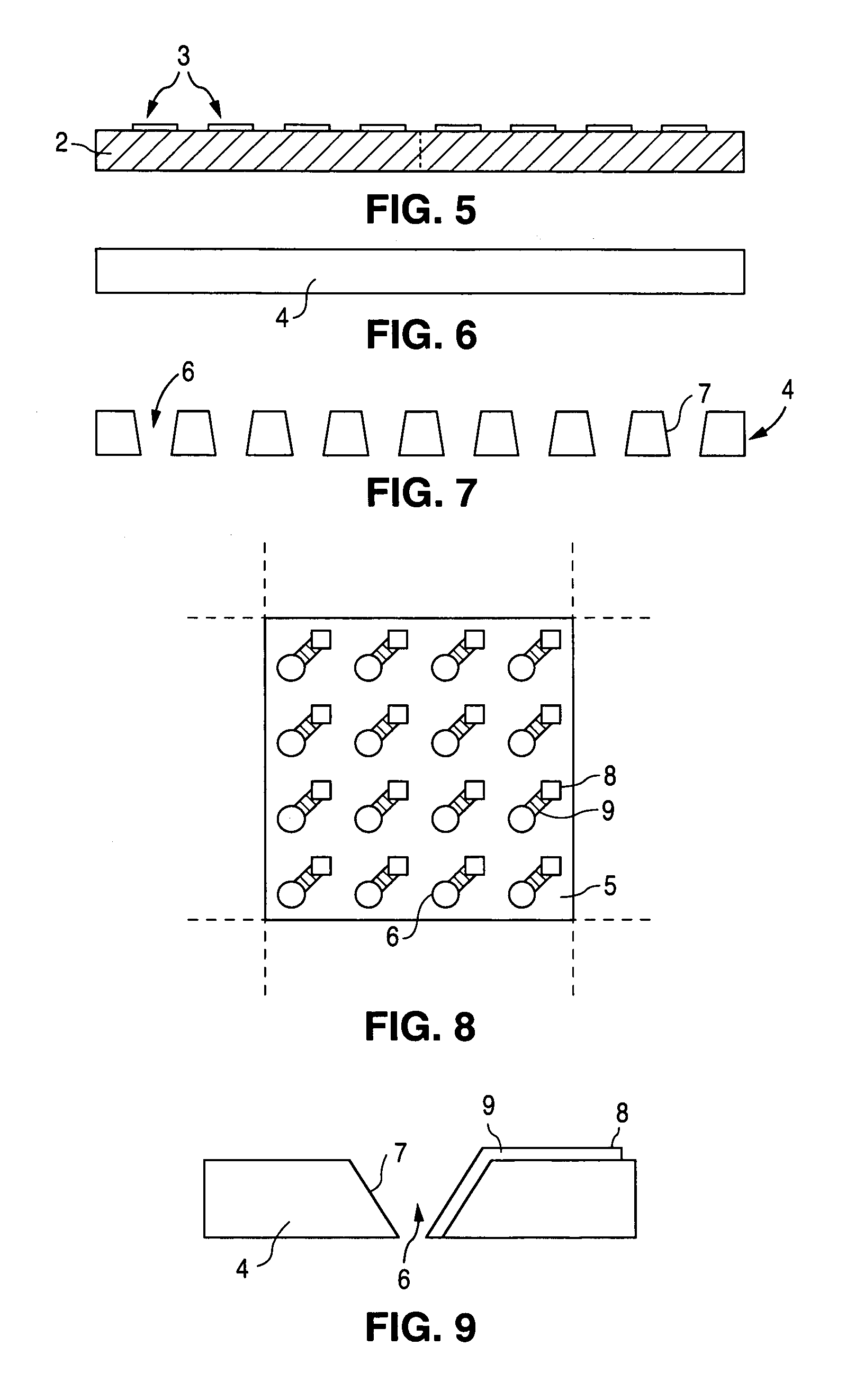

A plurality of semiconductor chips (23) are bonded to an adhesive layer (22) formed on a base plate (21). Then, first to third insulating films (31, 35, 39), first and second underlying metal layers (33, 37), first and second re-wirings (34, 38), and a solder ball (41) are collectively formed for the plural semiconductor chips (23). In this case, the first and second underlying metal layers (33, 37) are formed by a sputtering method, and the first and second re-wirings (34, 38) are formed by an electroplating method. Then, a laminate structure consisting of the three insulating films (39, 35, 31), the adhesive layer (22), and the base plate (21) is cut in a region positioned between the adjacent semiconductor chips (23).

Owner:AOI ELECTRONICS CO LTD

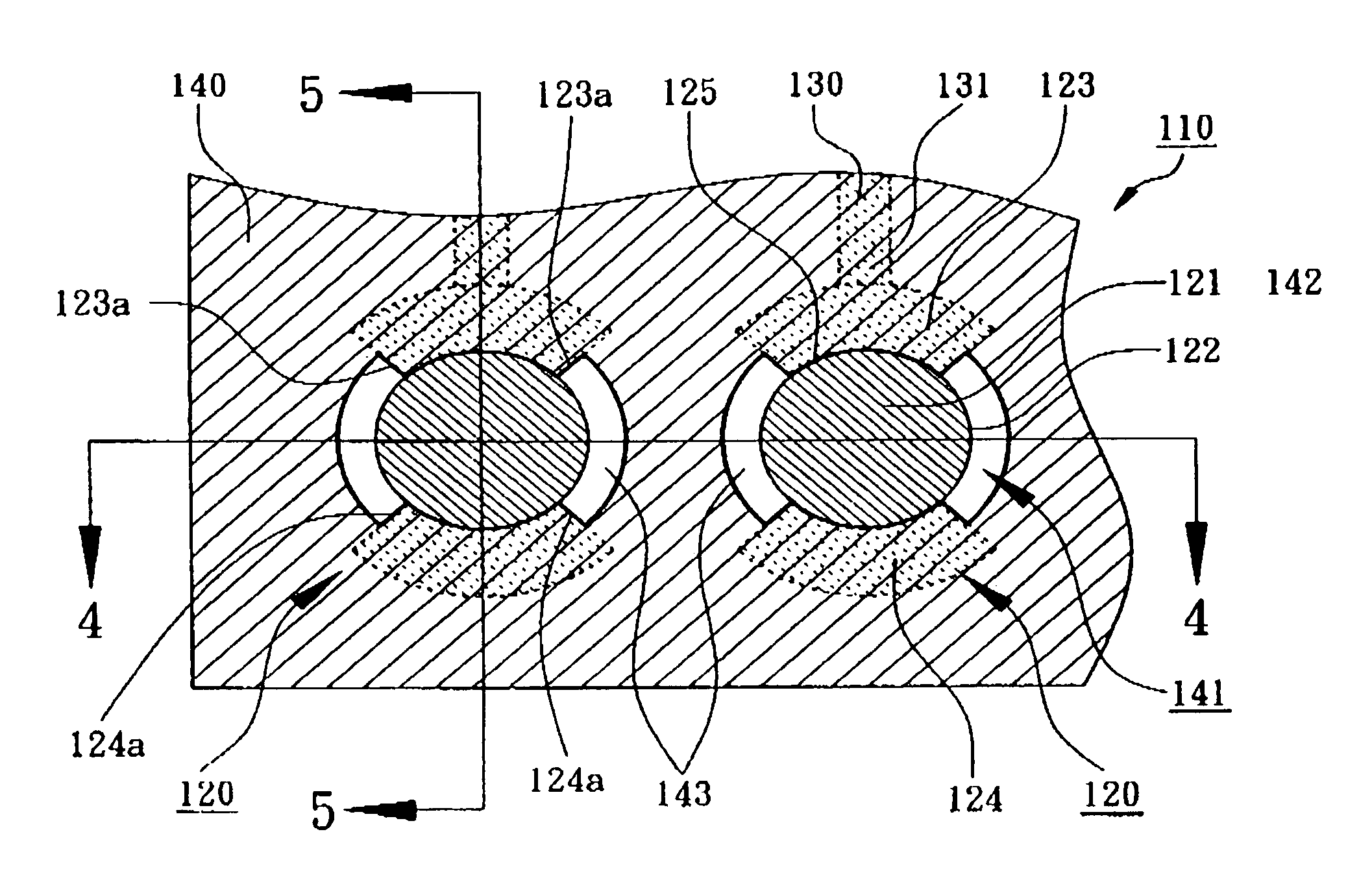

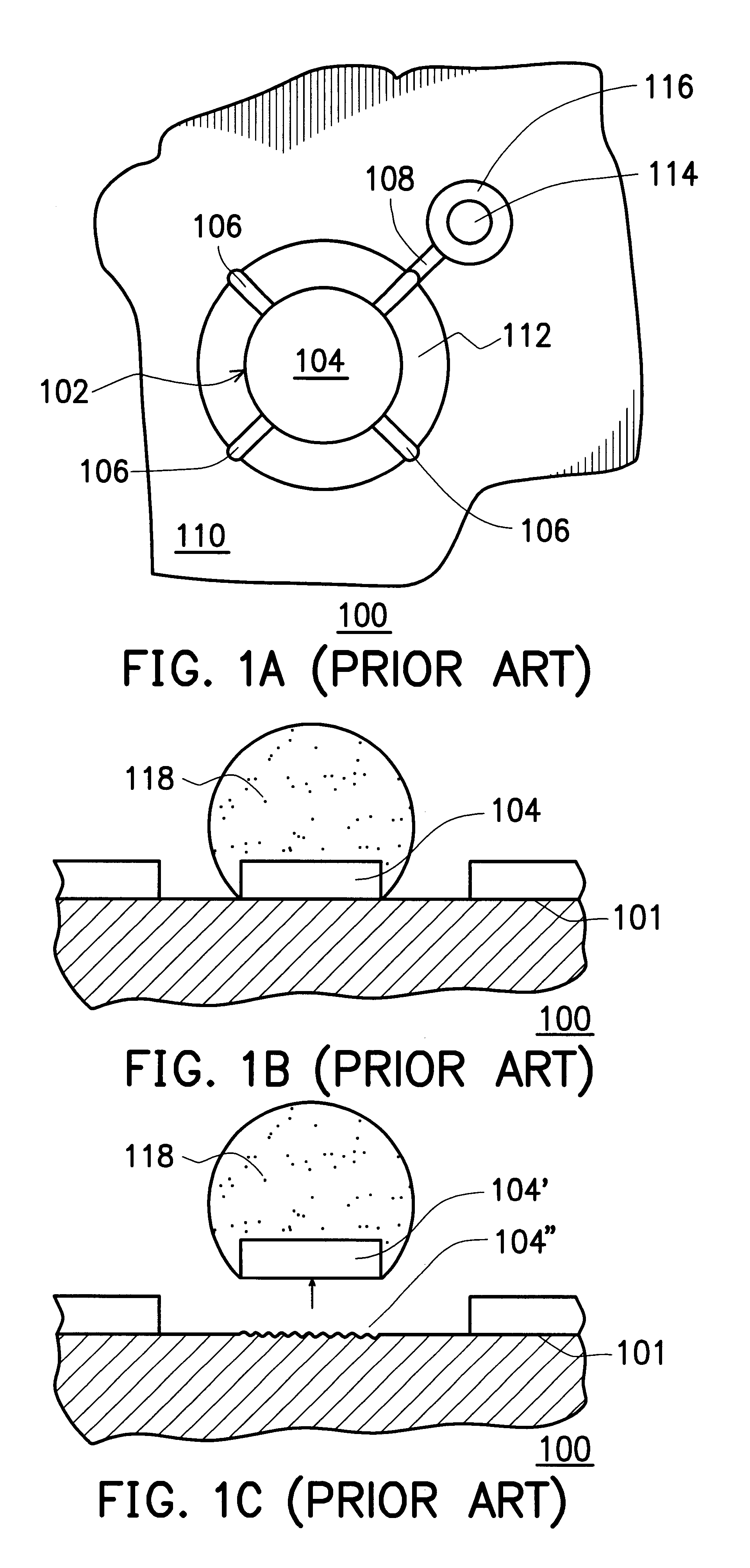

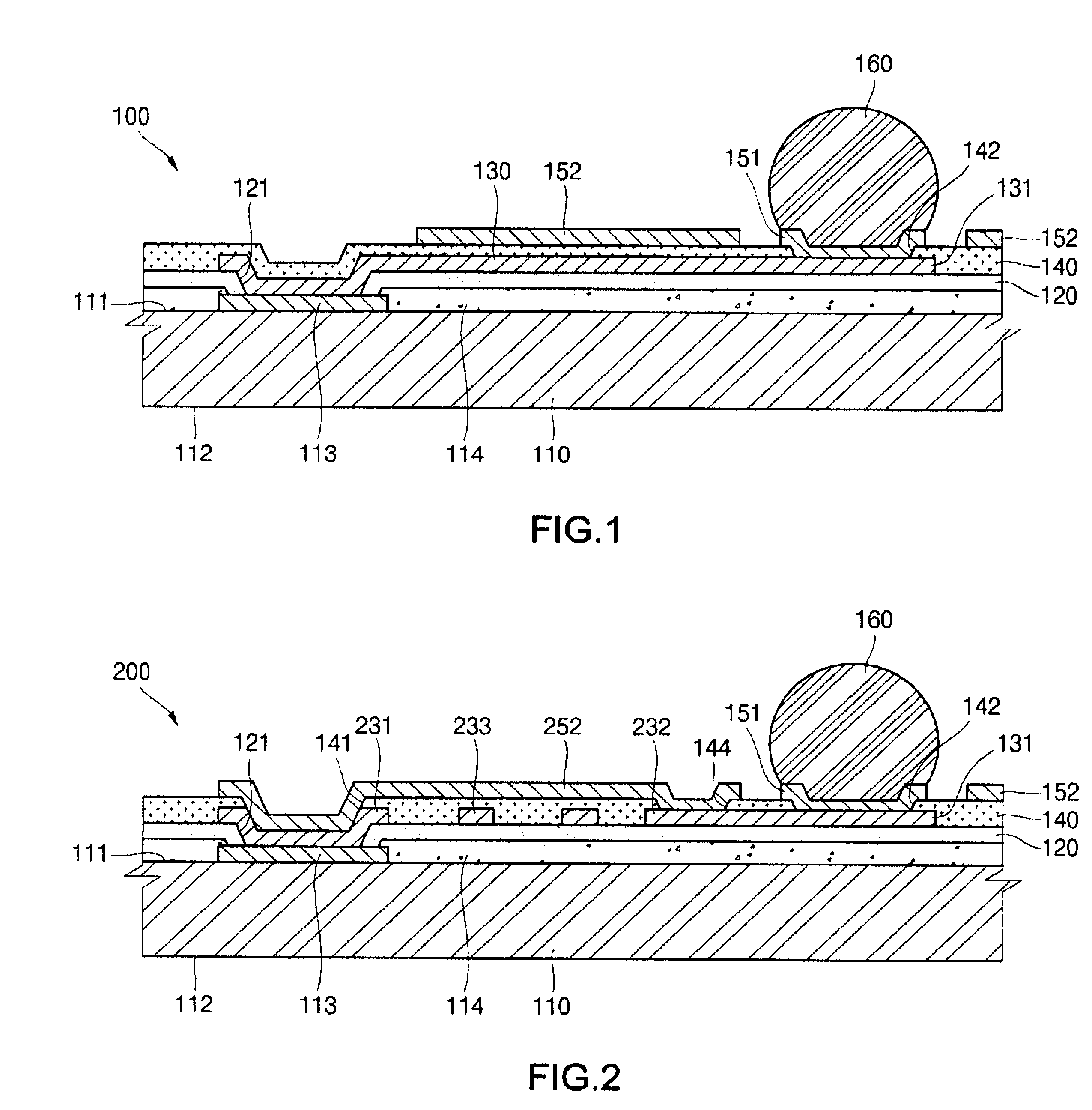

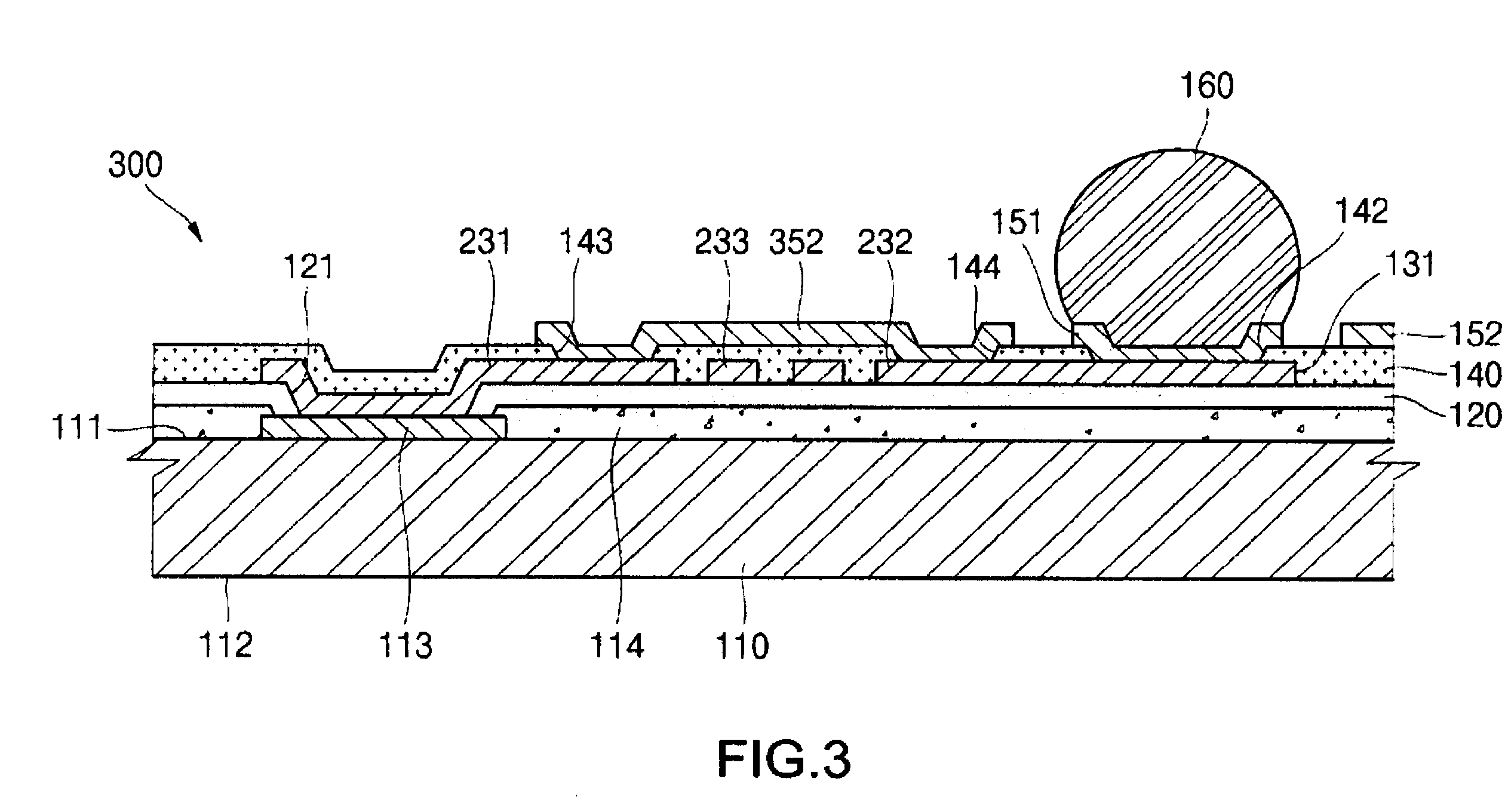

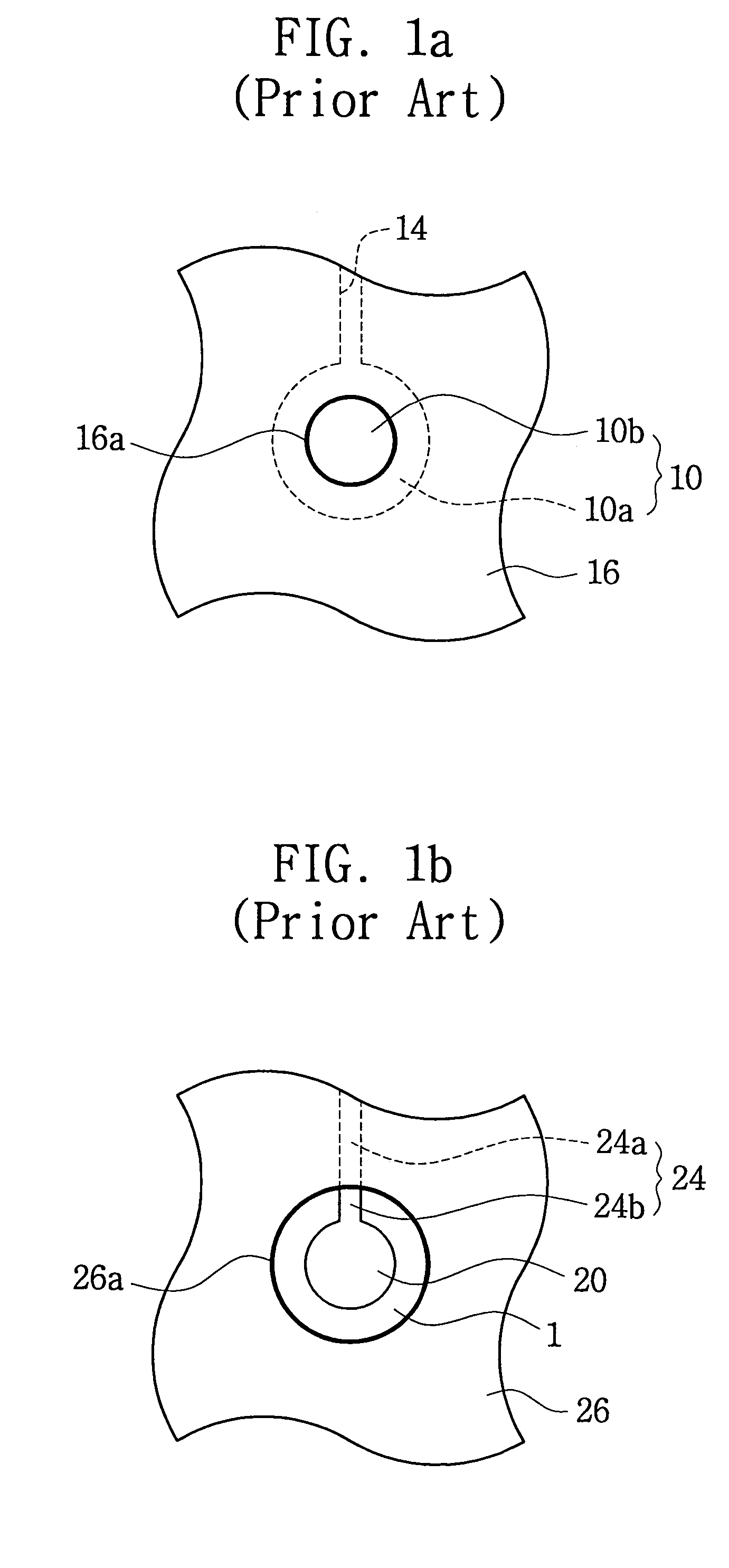

Semiconductor package with improved ball land structure

ActiveUS7064435B2Improved ball land structureSmooth connectionPrinted circuit assemblingFinal product manufactureSolder ballSemiconductor package

A semiconductor package has ball lands each configured to have a composite structure of SMD type and NSMD type. One peripheral portion of the ball land is covered with a mask layer, thus forming the SMD type, whereas the other peripheral portion is exposed through an opening area of the mask layer, thus forming the NSMD type. In one embodiment, the first peripheral portion is disposed to face a central point of a ball-mounting surface of a substrate, and the second peripheral portion is disposed to face the opposite direction to the central point. The composite structure of the ball lands provides more stable and enhanced connections between connection balls, such as solder balls, and the ball-mounting surface.

Owner:SAMSUNG ELECTRONICS CO LTD

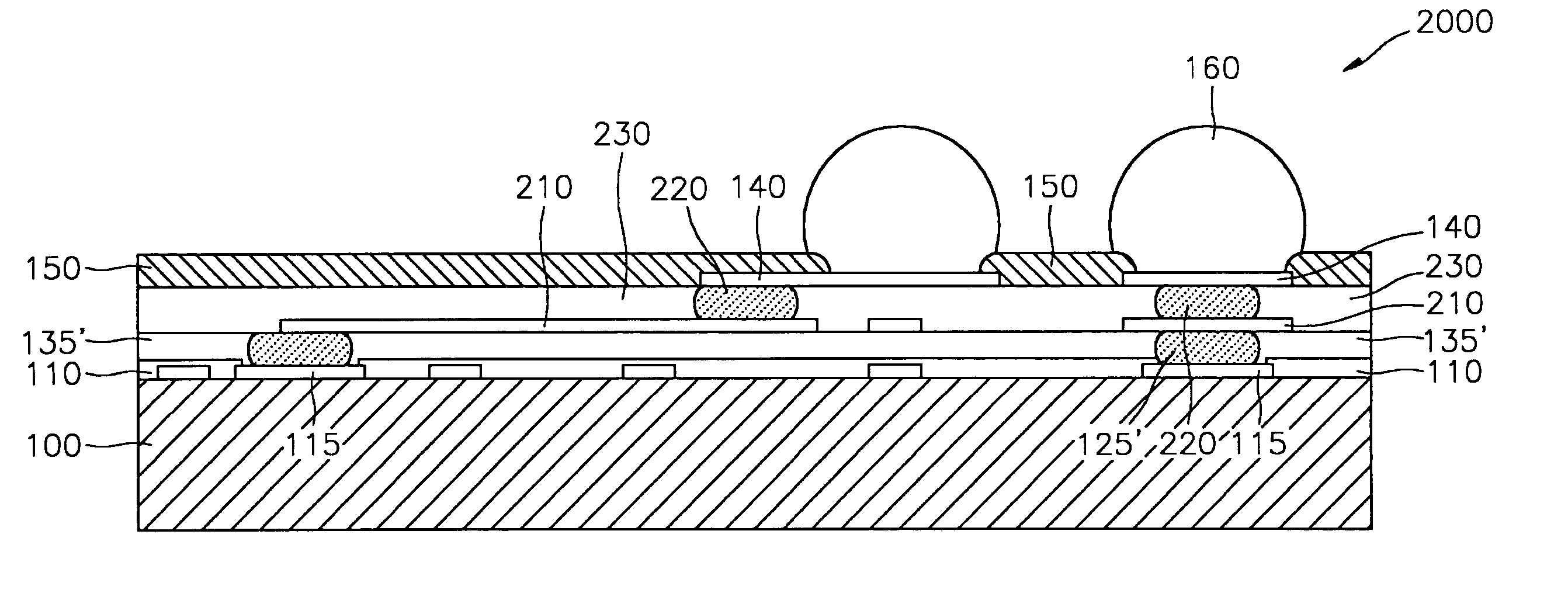

Inter-connecting structure for semiconductor device package and method of the same

InactiveUS20090166873A1Low costImprove performanceSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor package

The interconnecting structure for a semiconductor die includes a die having bonding pads on an active surface; a core attached the side wall (edge) of the die by adhesion material; an isolating base adhered on the active surface of the die by adhesion glue; a through silicon via (TSV) open from the back side of the die to expose the bonding pads; a build up layer coupled between the bonding pads to terminal metal pads by the through silicon via; solder balls melted on terminal pads, wherein the terminal pads located on the core and / or the die.

Owner:ADVANCED CHIP ENG TECH

Wafer-level chip scale package and method for fabricating and using the same

InactiveUS20050012225A1Address rising pricesSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A packaged semiconductor device (a wafer-level chip scale package) containing a conductive adhesive material as an electrical interconnect route between the semiconductor die and a patterned conductive substrate is described. The patterned conductive substrate acts not only as a substrate, but also as a redistribution layer that converts the dense pad layout of the die to a larger array configuration of the solder balls in the circuit board. Using the invention allows the formation of a lower priced chip scale package that also overcomes the restriction of the die size used in die-sized chip packages and the input-output pattern that can be required by the printed circuit board. Thus, the invention can provide a familiar pitch (i.e.,interface) to the printed circuit board for any small die.

Owner:SEMICON COMPONENTS IND LLC

Chip-size package structure and method of the same

ActiveUS7238602B2Reduce contact resistanceLow costSemiconductor/solid-state device detailsSolid-state devicesChip sizeSolder ball

Owner:ADL ENERGY CORP

Integrated compact MEMS device with deep trench contacts

InactiveUS20130168740A1High aspect ratioIncrease contactSolid-state devicesSpeed/acceleration/shock instrument detailsCMOSSolder ball

A compact MEMS motion sensor device is provided, including a CMOS substrate layer, with plural anchor posts having an isolation oxide layer surrounding a conductive layer. On one side of CMOS substrate layer, the device further includes a field oxide (FOX) layer, a first set and a second set of implant doped silicon areas, a first polysilicon layer, an oxide layer embedded with plural metal layers interleaved with via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. On the other side of CMOS substrate layer, the present invention further includes a backside interconnect isolation oxide layer, a first MEMS bonding layer, a first metal compound layer, a second MEMS bonding layer, a MEMS layer, a first MEMS eutectic bonding layer, a second metal compound layer, a second MEMS eutectic bonding layer, and a MEMS cap layer.

Owner:WINDTOP TECH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com