Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6510 results about "External connection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An external connection represents a link between a workbook and a particular external data source. It contains properties about the way that the application establishes the connection to the data source and retrieves the data, such as the type of data provider ( OLE DB , ODBC , and other data providers), a server name , security information,...

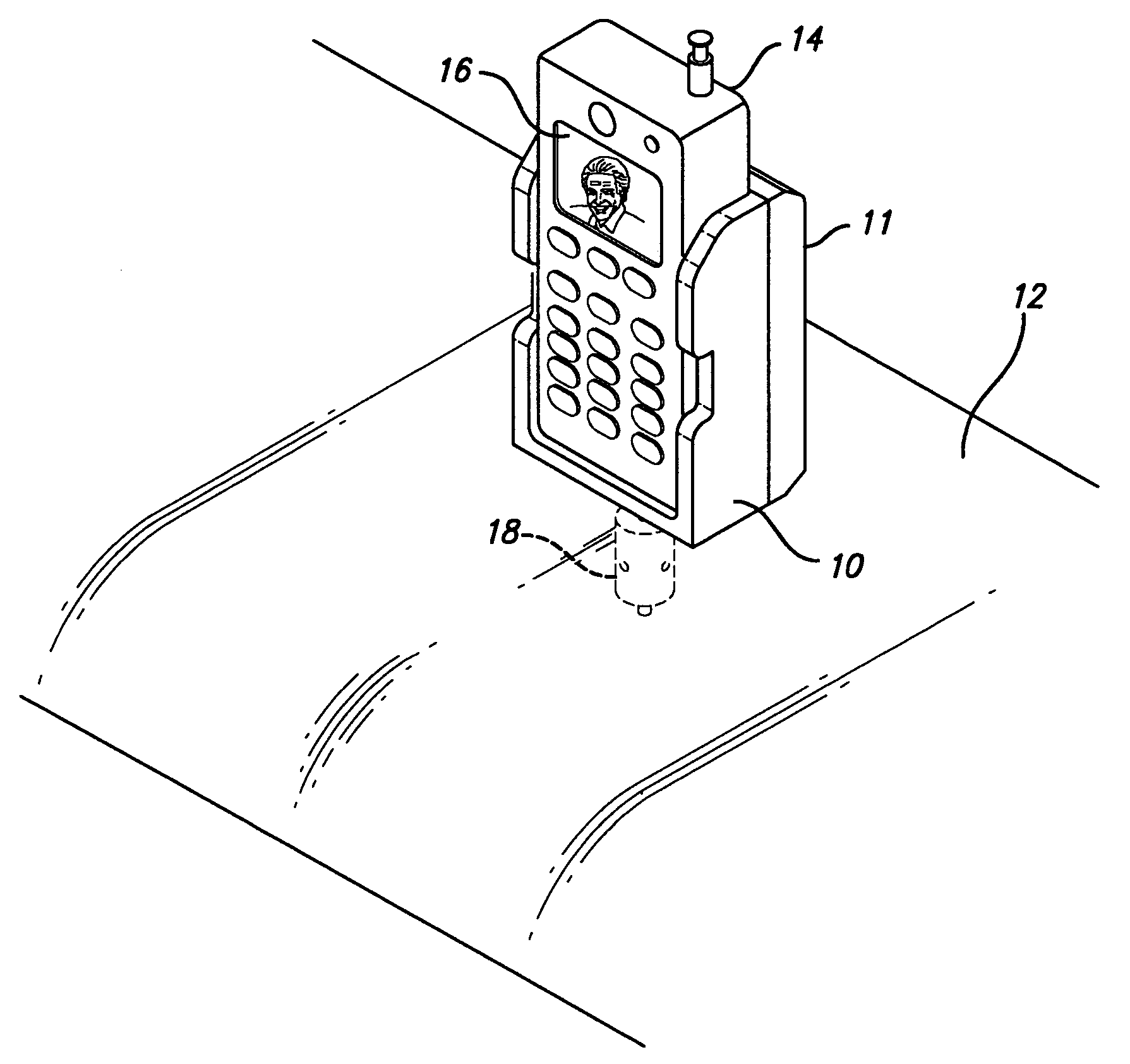

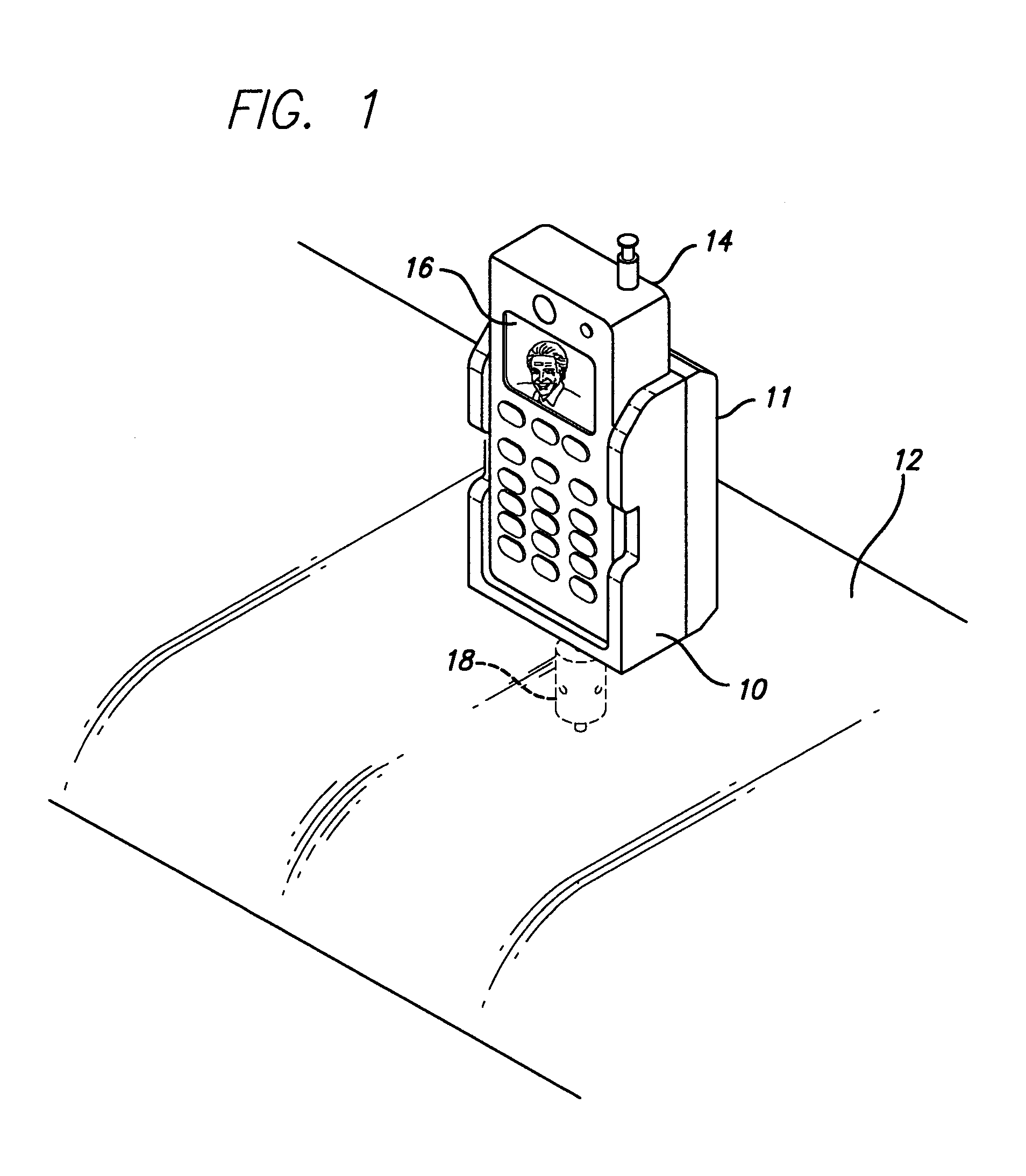

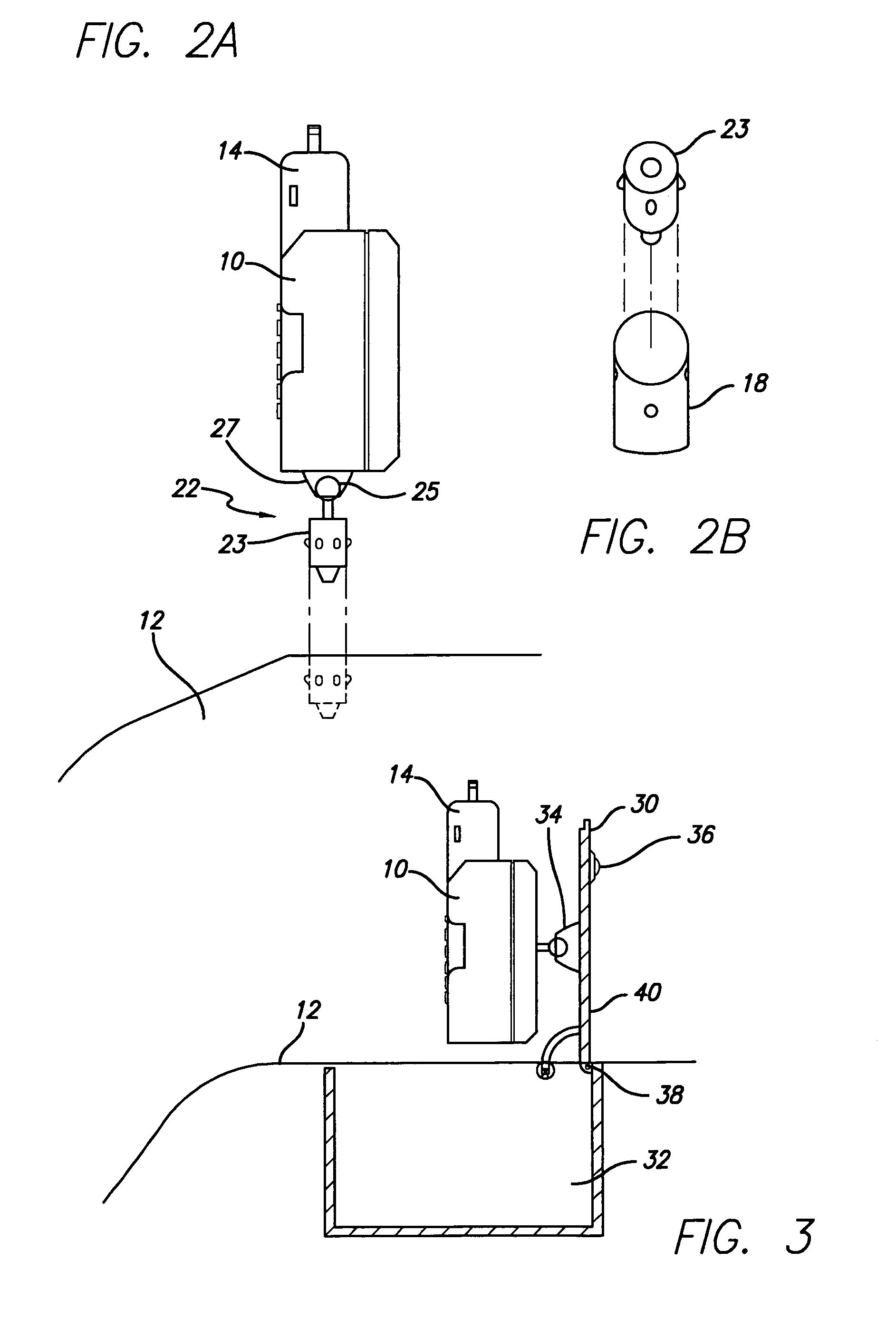

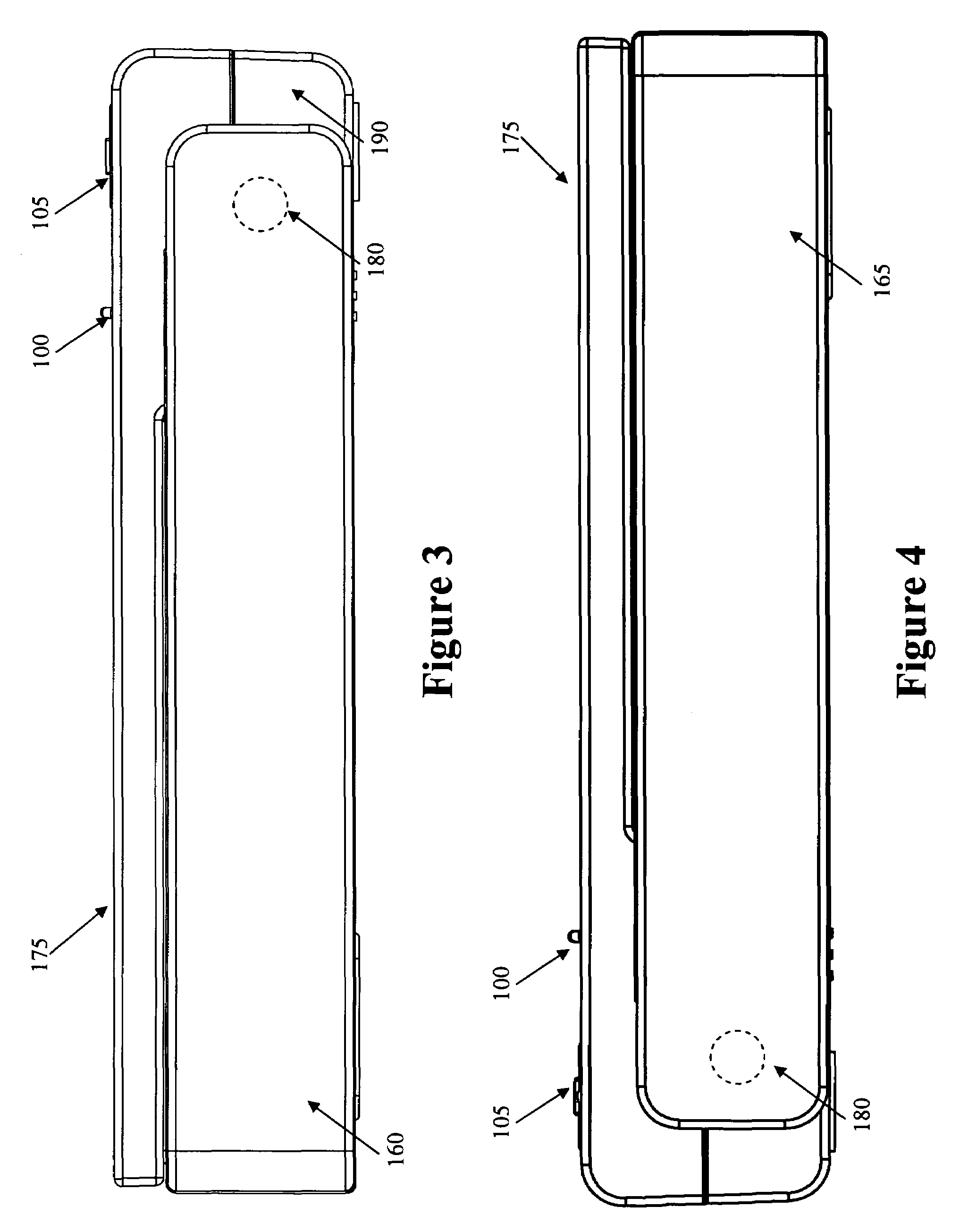

Cellular phone holder with charger mounted to vehicle dashboard

In a vehicle, means of mounting a cell phone on the vehicle dashboard with minimal wiring and external connections, using manufacturer power connections made available on the dashboard. The mounting means is either an after market accessory addition to the vehicle or a option available at the time of purchase to render easy and convenient mounting of the cell phone without loose wires and providing proper positioning of a video camera built into the cell phone. The cell phone is positioned for viewing either through the windshield or backward onto the occupants enabling monitoring accidents between vehicles, the result of an accident on the occupants of the vehicle or for security monitoring of the trespassers within the vehicle. This is accomplished by mounting the camera at the dashboard. Another advantage is to improve the power output of the cell phone by positioning the antenna (part of the hand held cell phone device) near the windshield.

Owner:KIM KI IL

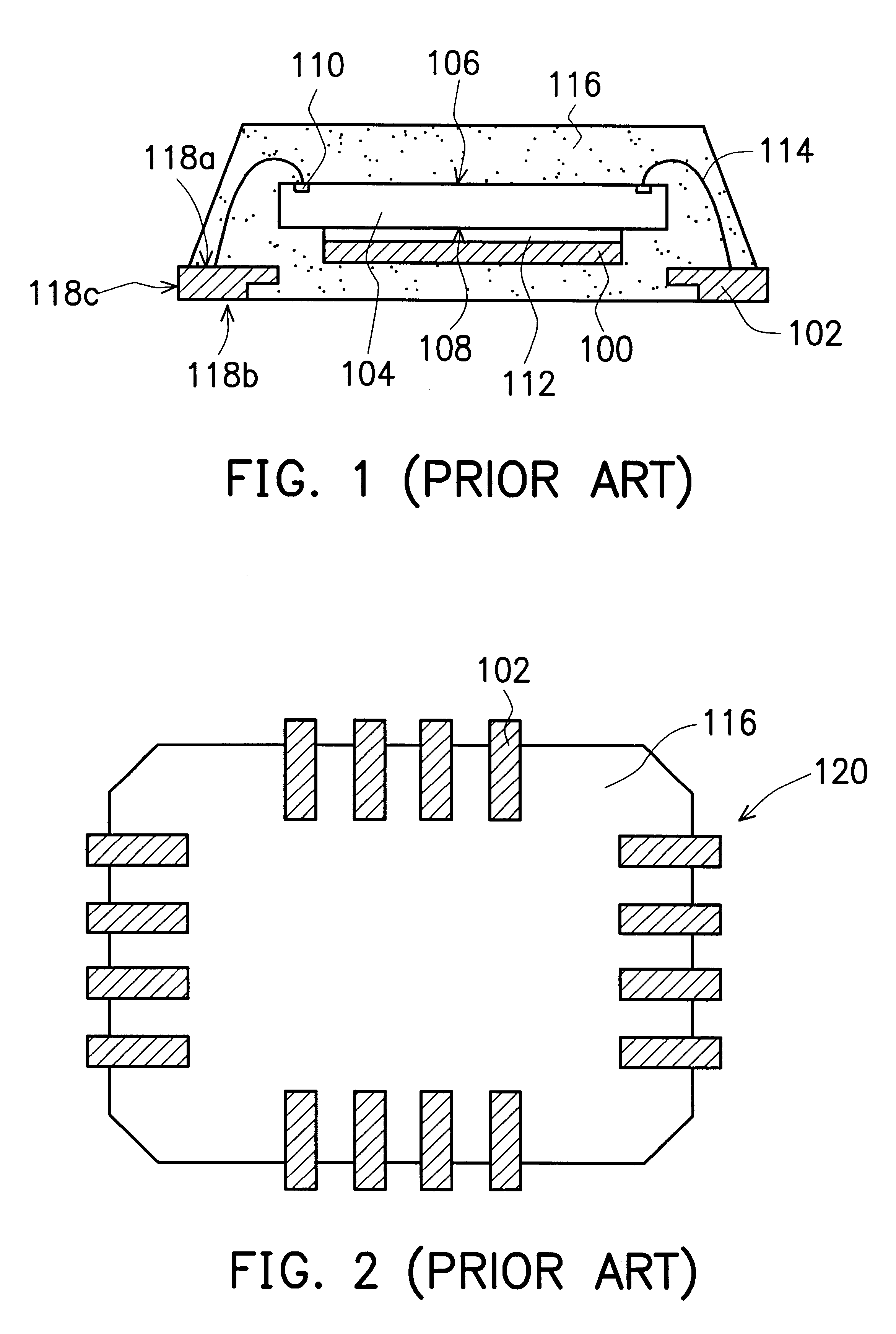

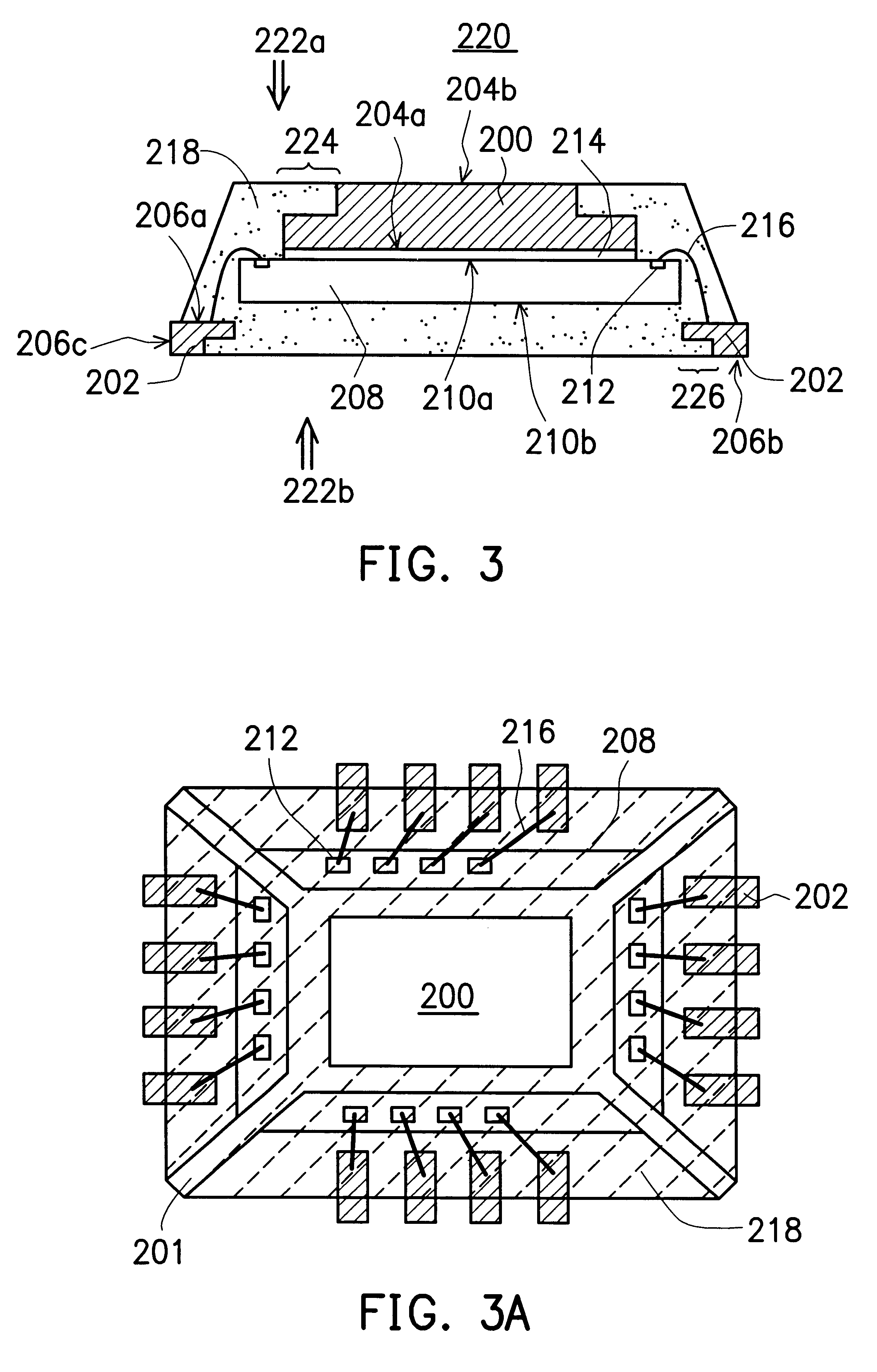

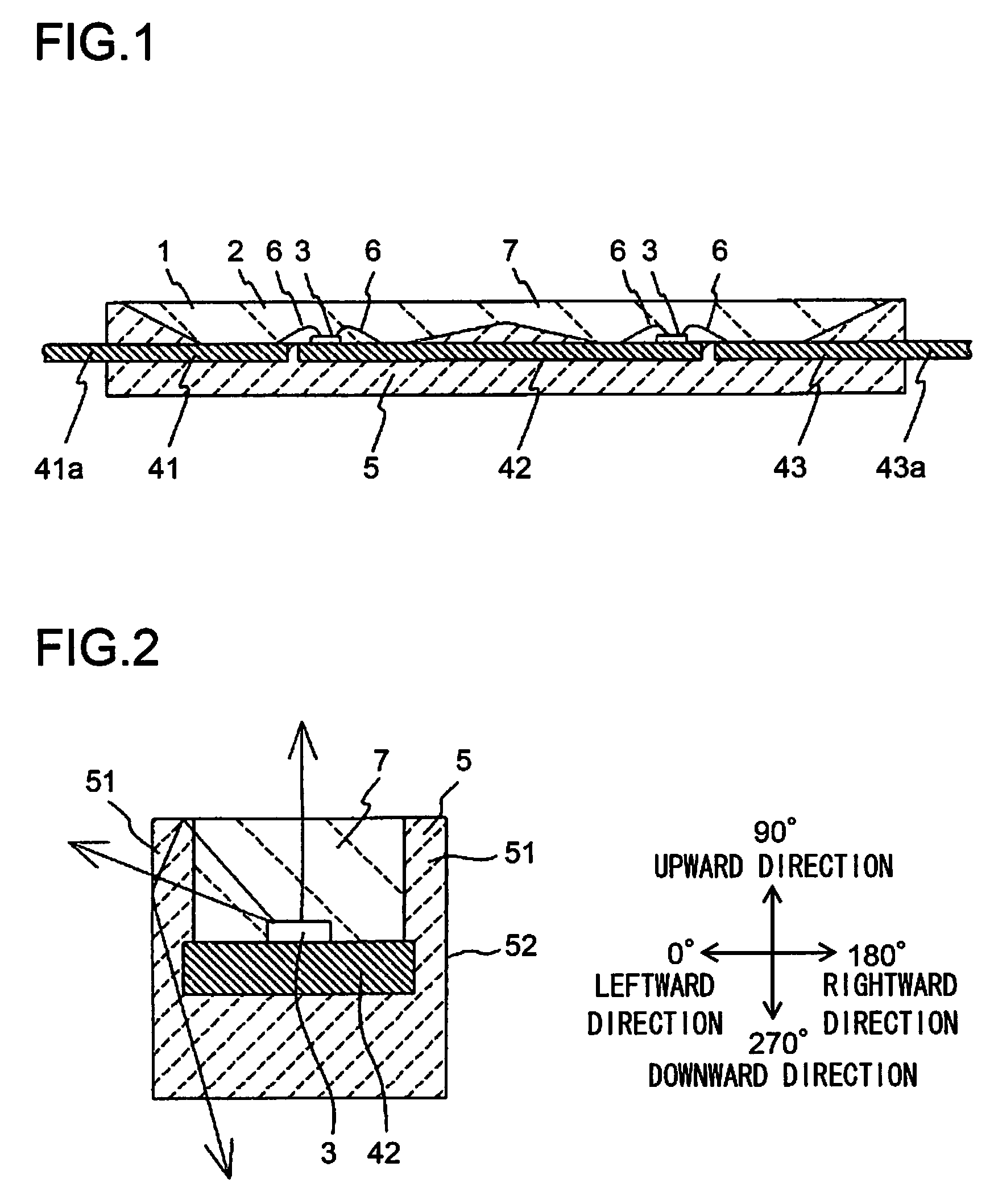

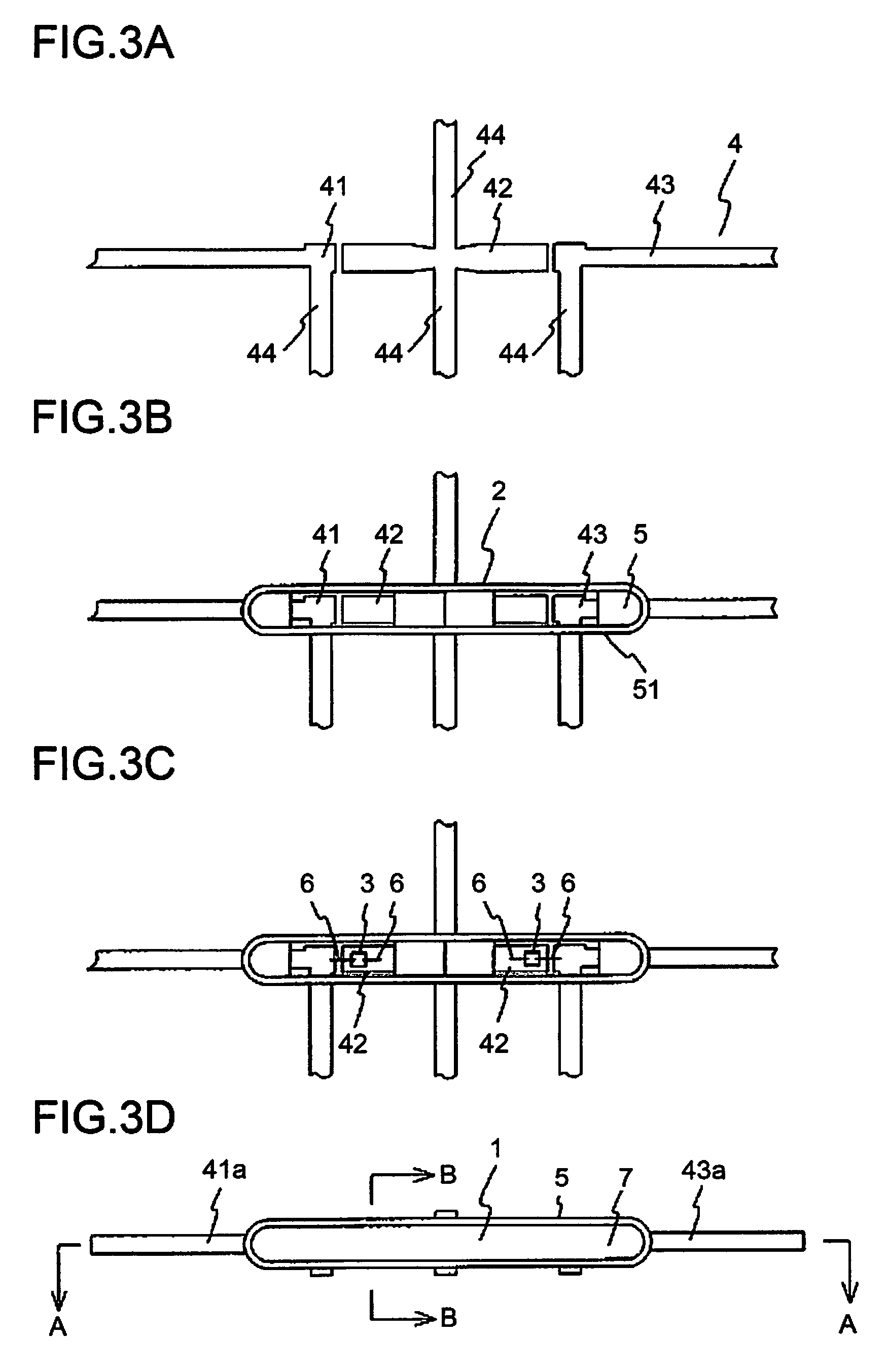

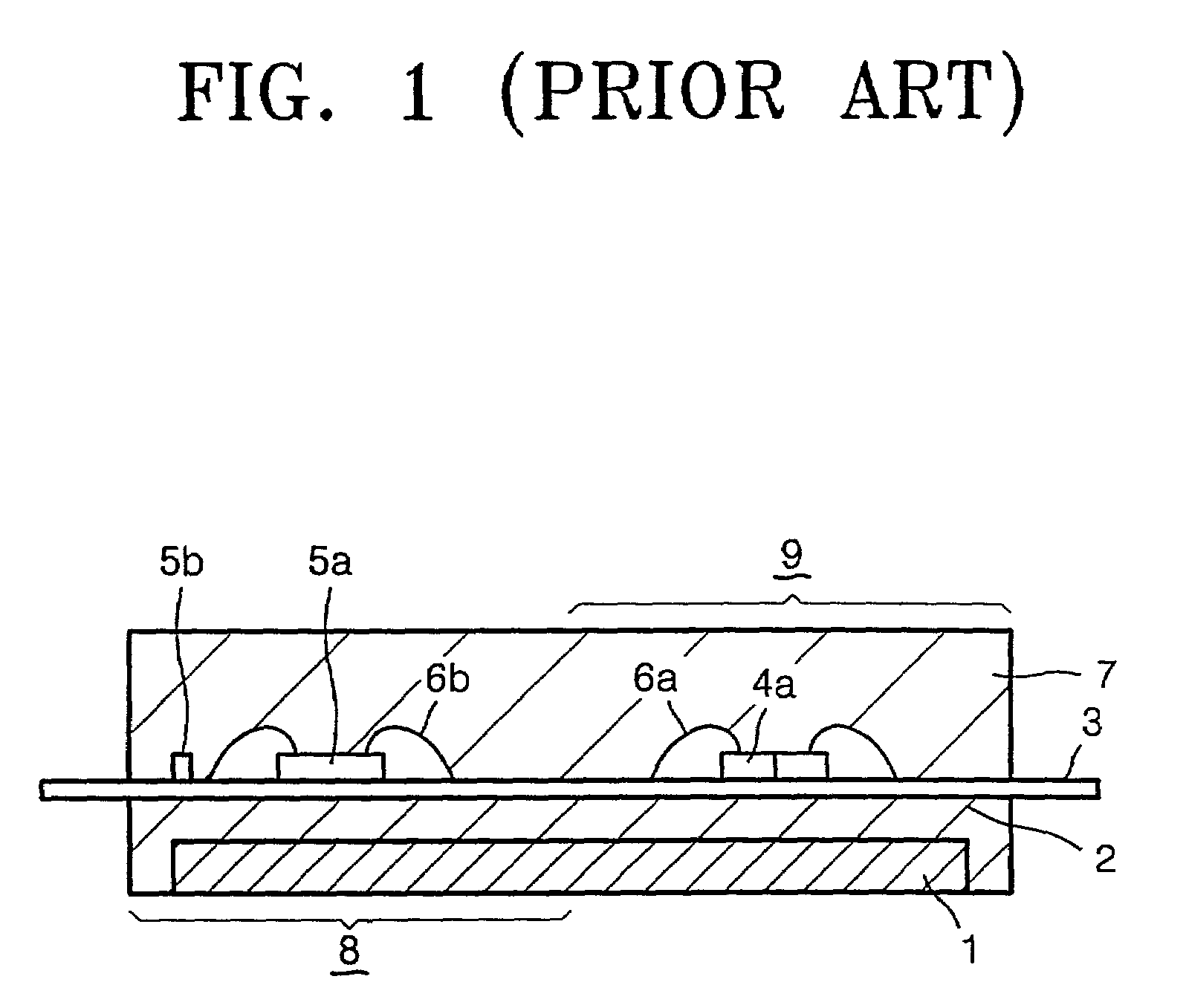

Quad flat non-lead package of semiconductor

InactiveUS6414385B1Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

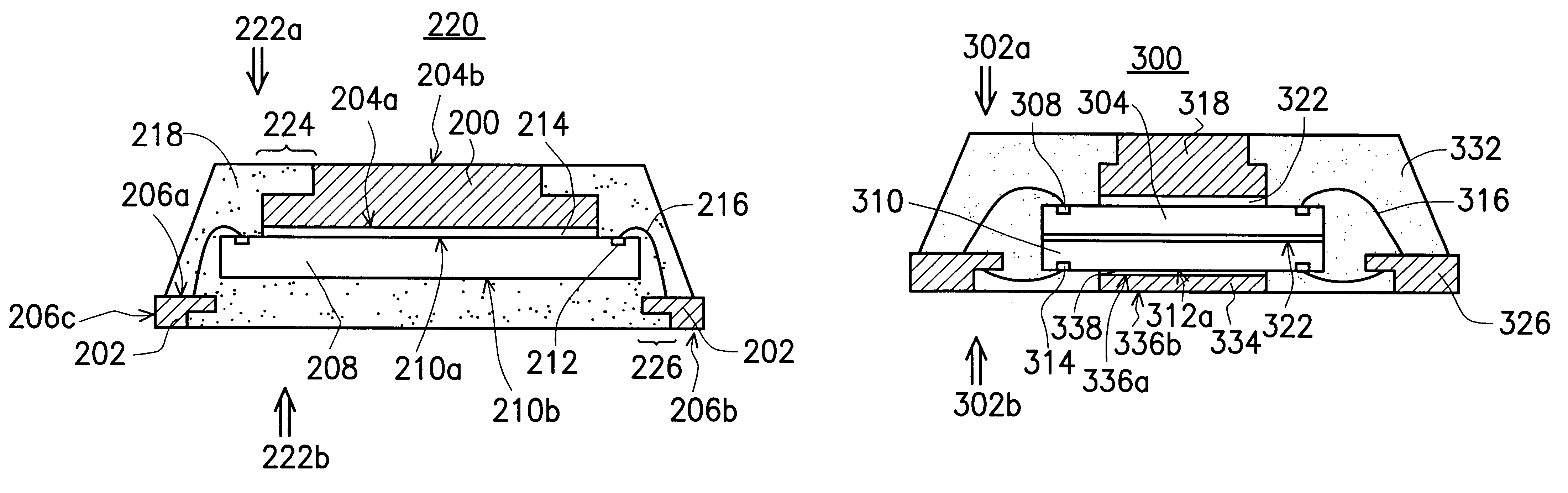

A Quad Flat Non-Lead package of semiconductor comprises a chip, a plurality of leads, and a molding compound. The chip has its active surface bonded to the die pad, and the area of the die pad is smaller than that of the chip in order to expose the bonding pad on the active surface of the chip. The leads are disposed at the periphery of the die pad. A plurality of bonding wires is used to electrically connect the top surface of the leads to the bonding pads. The molding compound encapsulates the chip, the die pad, the bonding wires, and a portion of the surface of the leads. In this way, the encapsulating process make the side surface of the lead, and the portion excluding the wire-bonding protruded zone of the bottom surface of the lead exposed in order to make the leads become the external connections of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

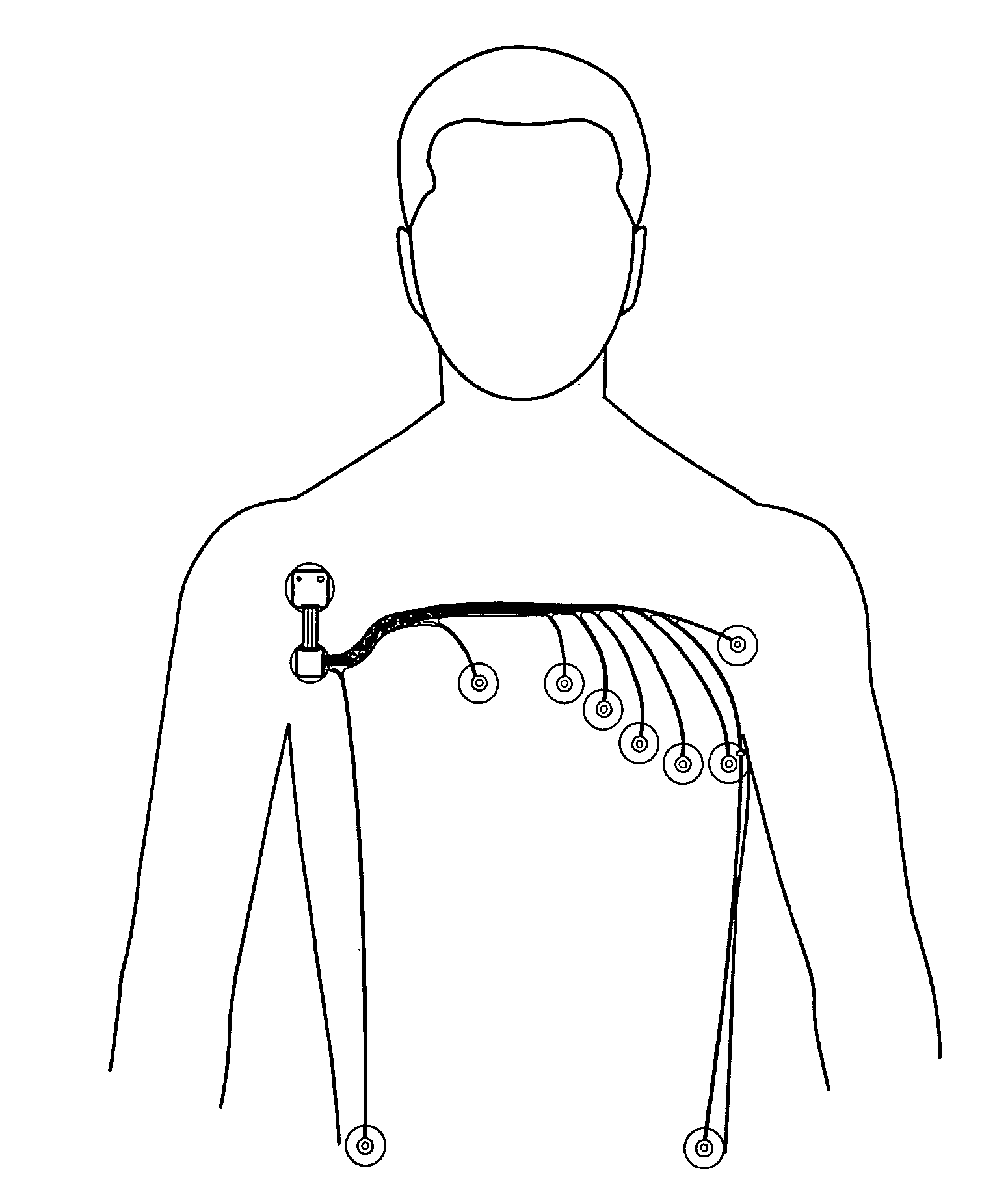

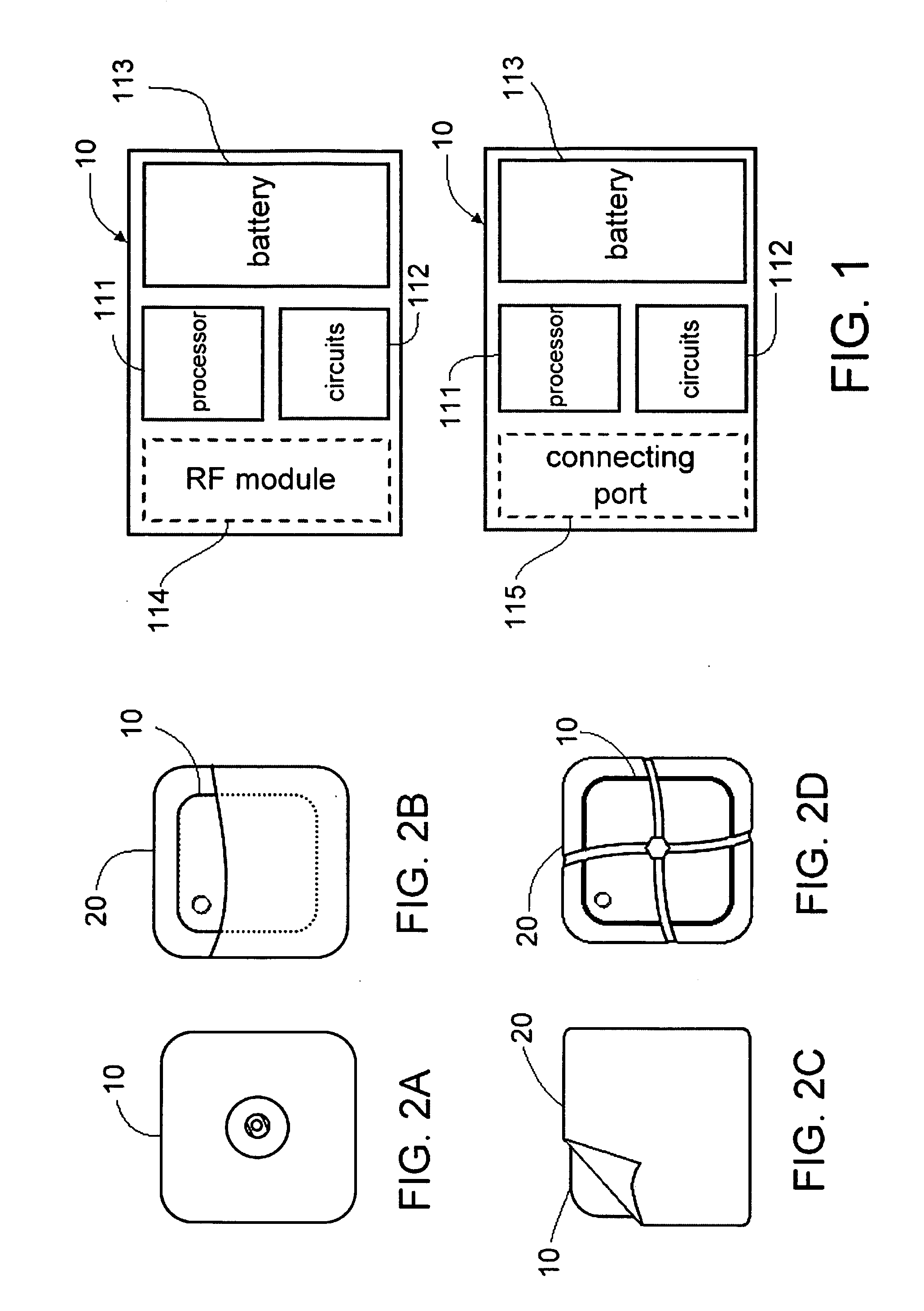

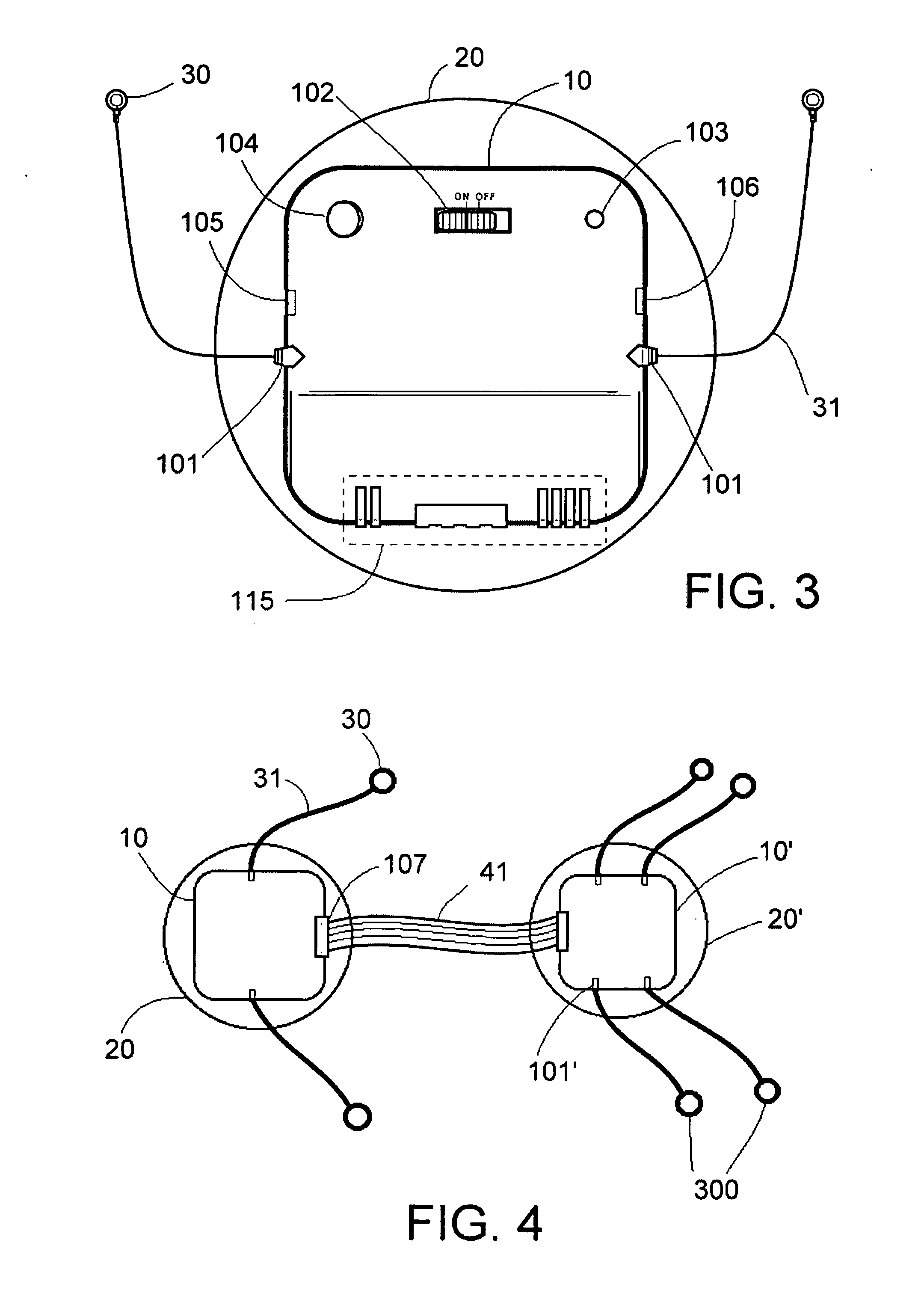

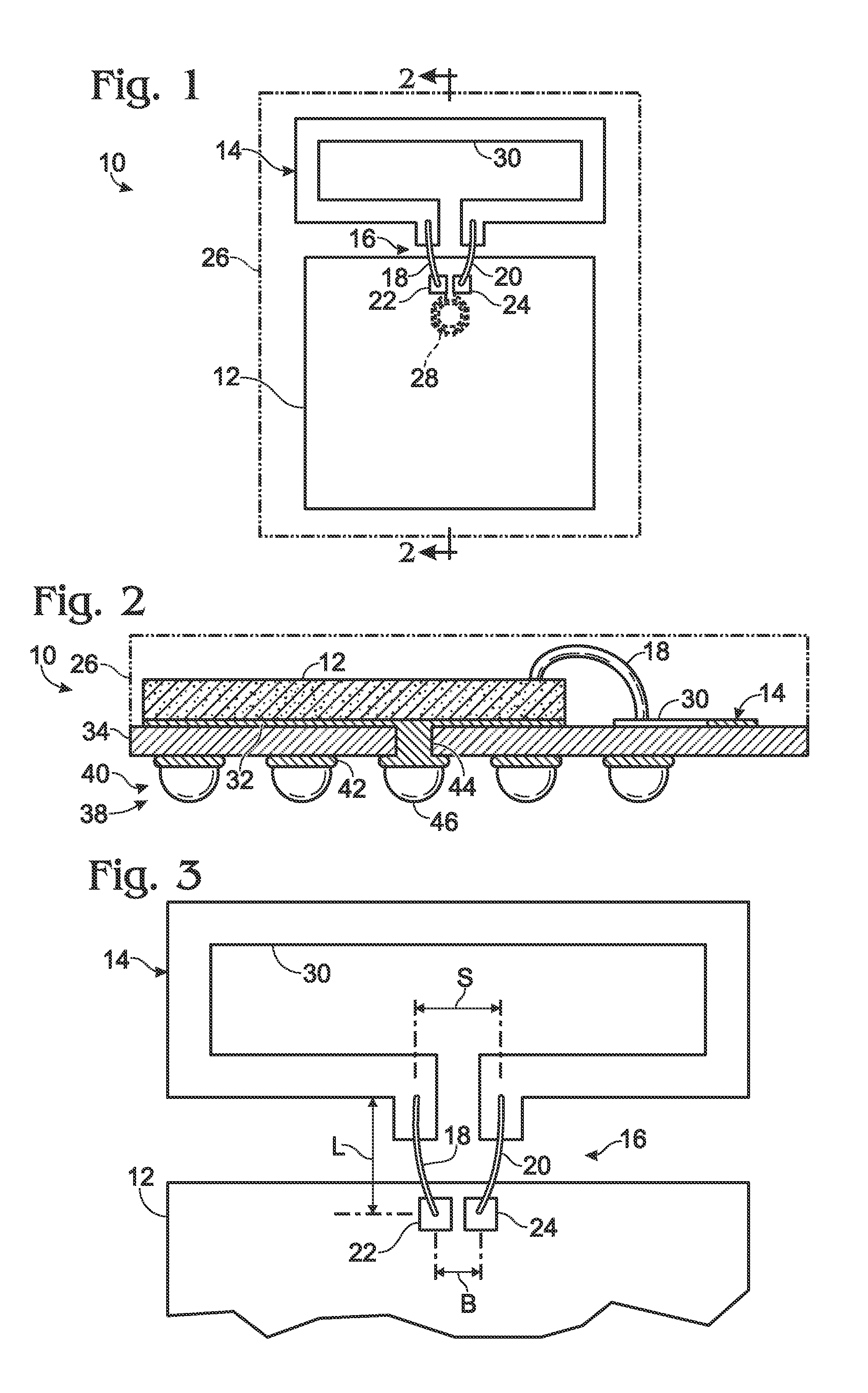

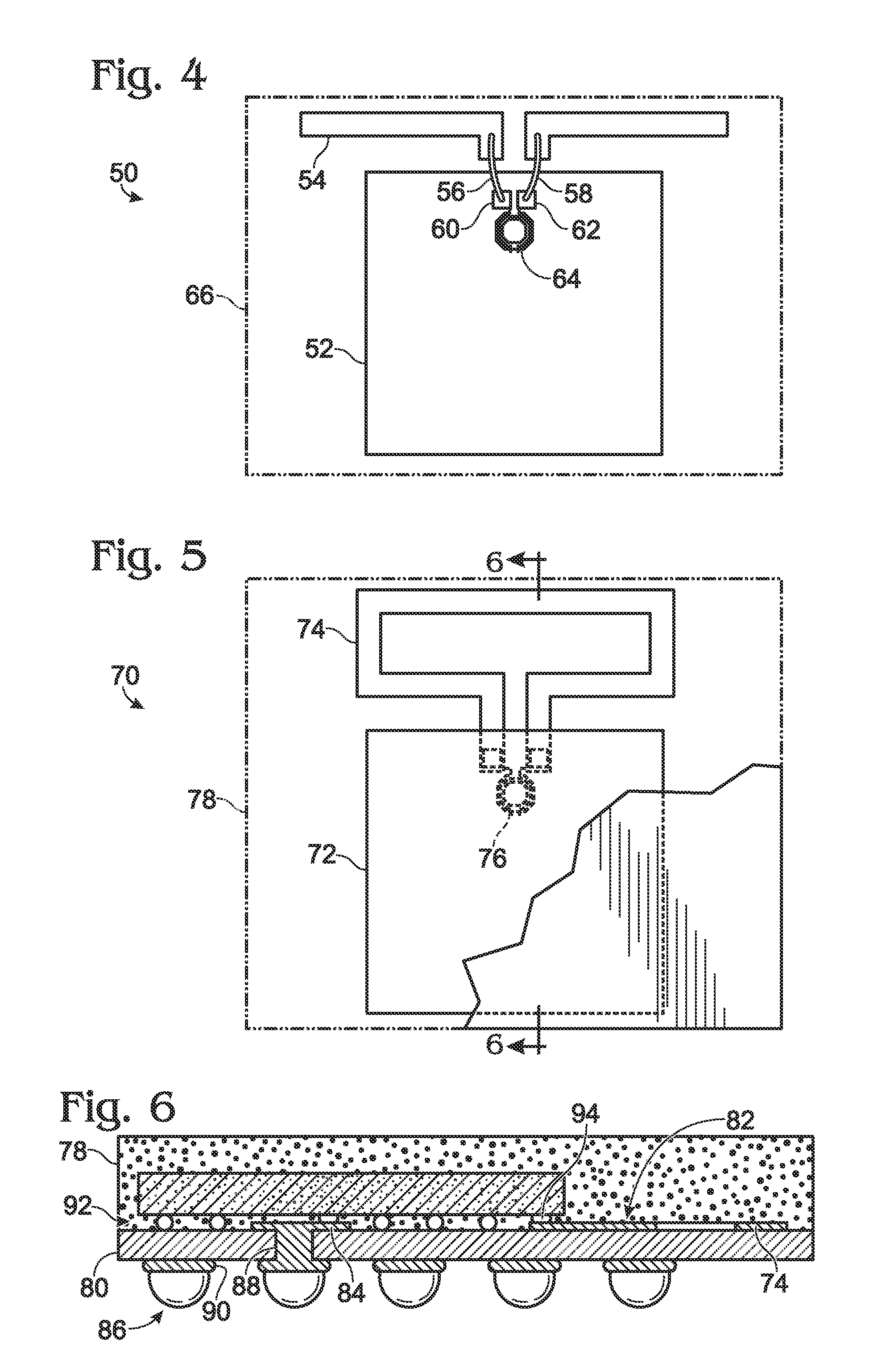

Patch-type physiological monitoring apparatus, system and network

InactiveUS20070027388A1Signal interferenceBioelectric signal measurementSensorsPatch electrodePhysiological monitoring

Patch-type physiological monitoring apparatus, system and network are disclosed. The patch-type physiological monitoring apparatus includes at least a node, and at least a patch for attaching to a skin surface of a user and for supporting the node on the skin surface through joining therewith, wherein the node includes at least a signal I / O port for externally connecting to at least a sensor or electrode through a connecting wire so as to acquire a physiological signal, and a RF module for transmitting and receiving signal. The apparatus according to the present invention is of light weight and compact size and easily attached to human body through adhesive patches. Through a RF module, the system can wirelessly communicate with corresponding devices without additional wiring. Further, the system can utilize conventional electrodes, patch electrodes and electrode wiring to avoid extra cost for facilities' renewal and replacement.

Owner:CHOU

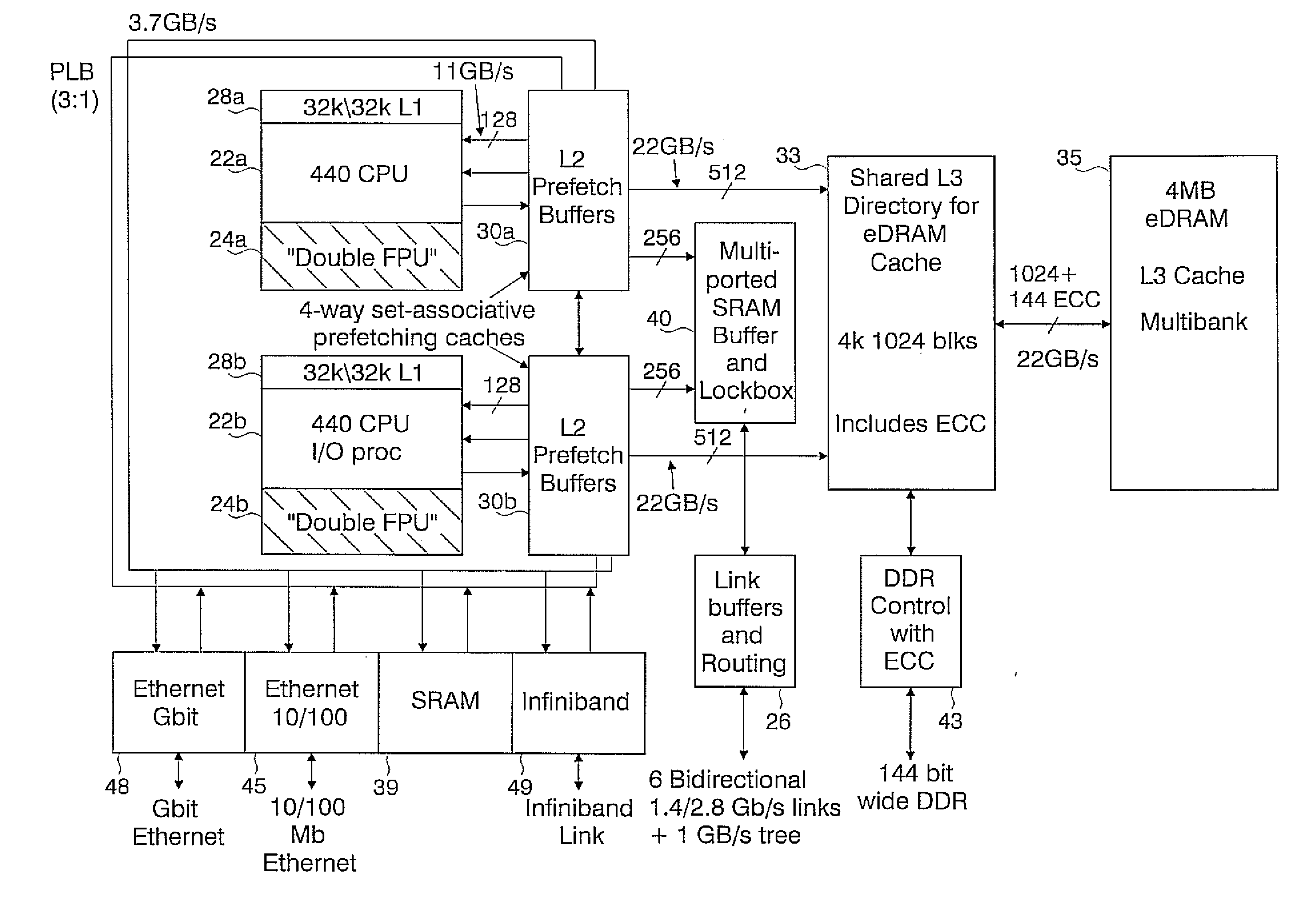

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

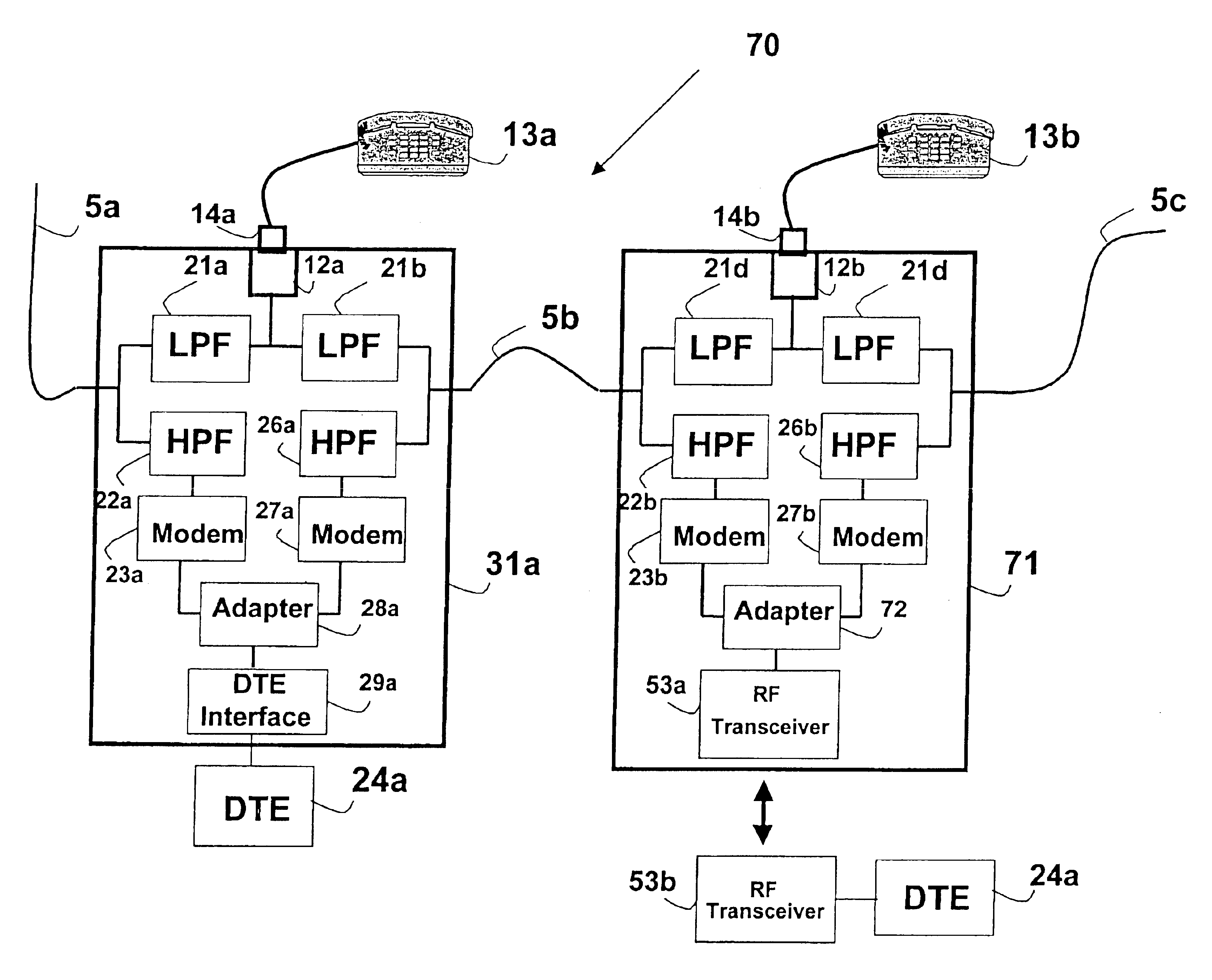

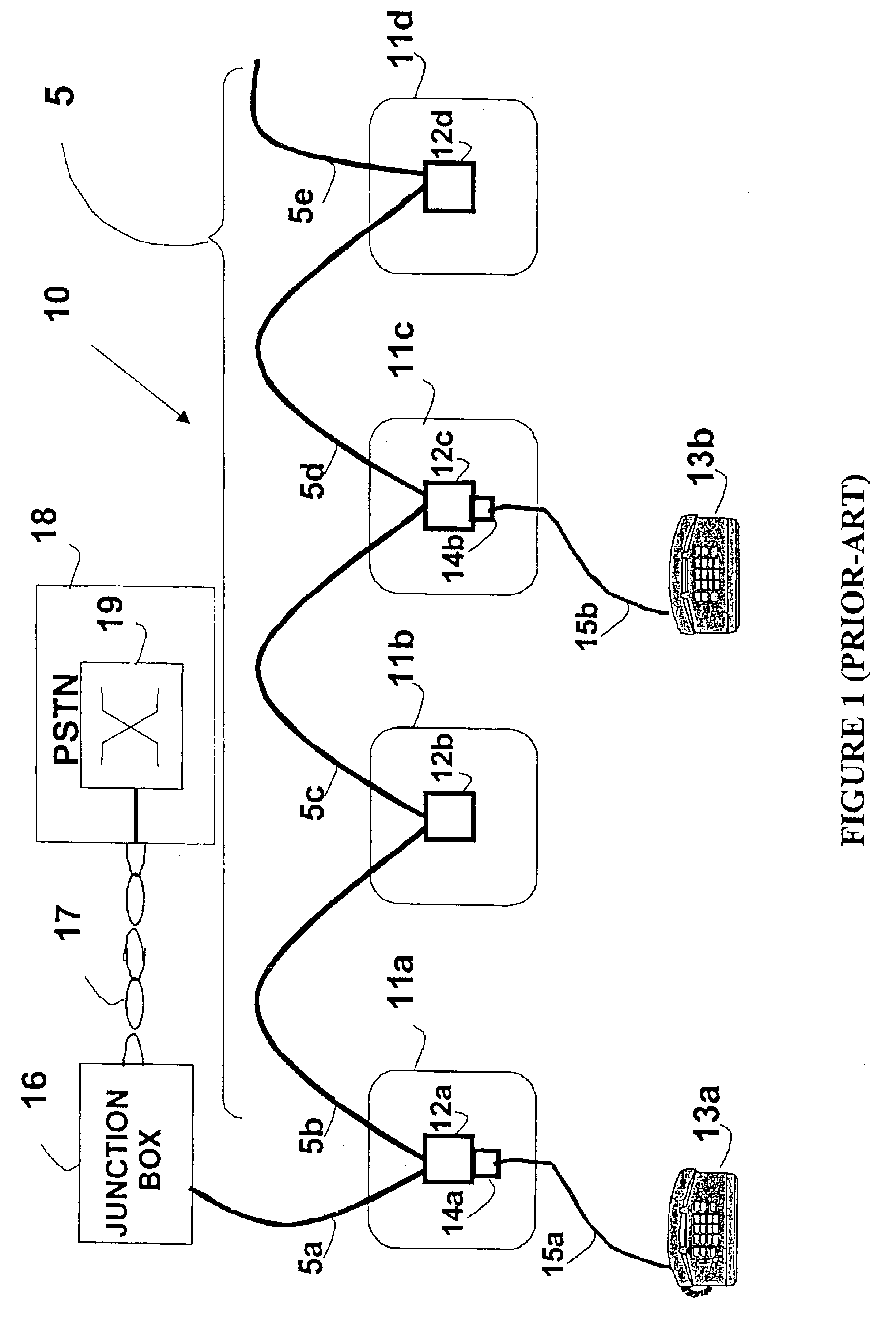

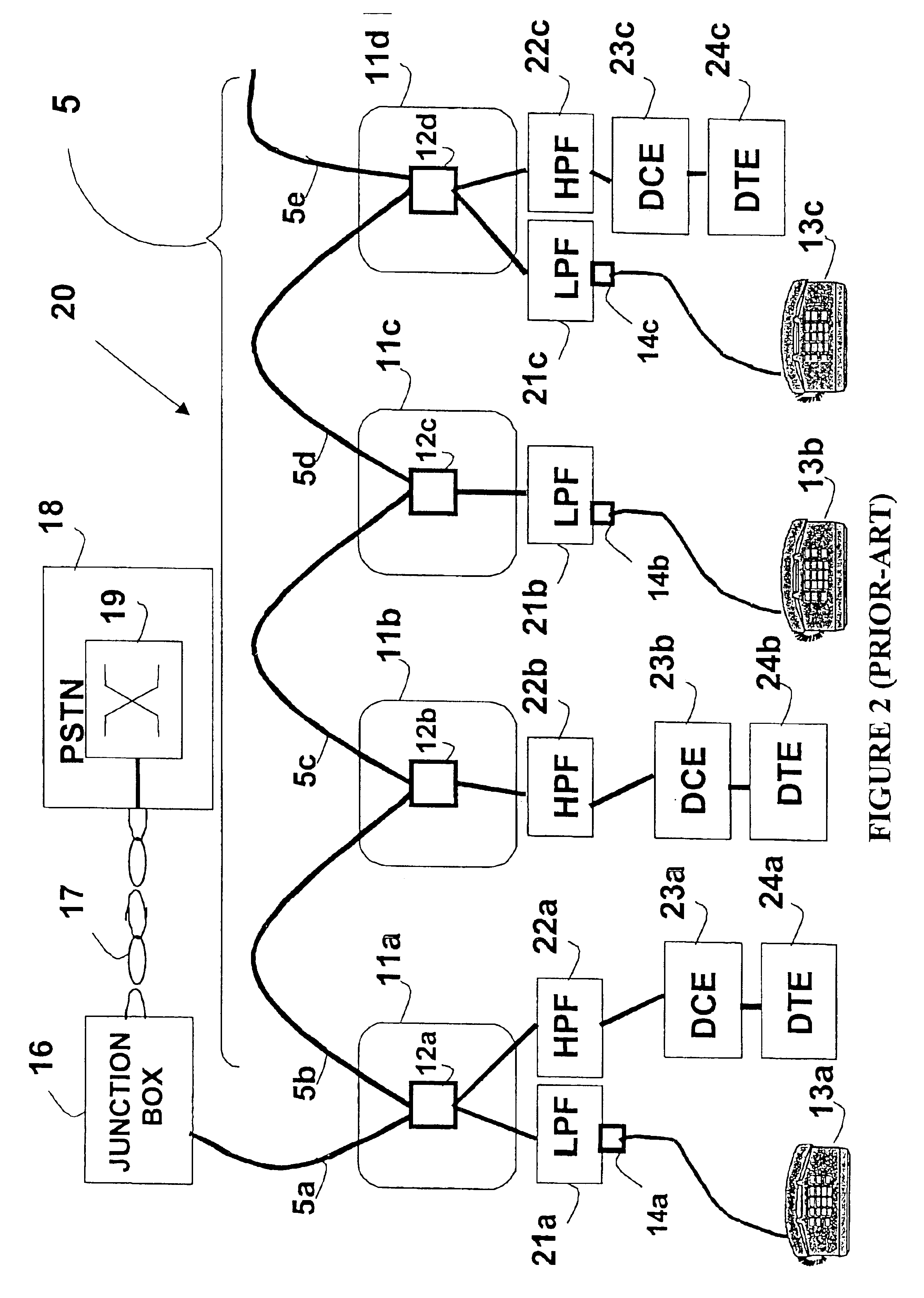

Network combining wired and non-wired segments

InactiveUS6842459B1Substations coupling interface circuitsFrequency-division multiplexResidenceOperating energy

A local area network within a residence or other building, including both wired and non-wired segments. The wired segments are based on new or existing wires in the building, wherein access to the wires is provided by means of outlets, such as a telephone system, electrical power distribution system, or cable television wiring system. The non-wired segments are based on communication using propagated waves such as radio, sound, or light (e.g. infrared). The wired and non-wired segments interface in the outlet, using a module which serves as mediator between the segments. The module can be integrated into the outlet, partially housed in the outlet, or attached externally to the outlet. Such a network allows for integrated communication of data units connected by wires and data units connected without wires.

Owner:CONVERSANT INTPROP MANAGEMENT INC

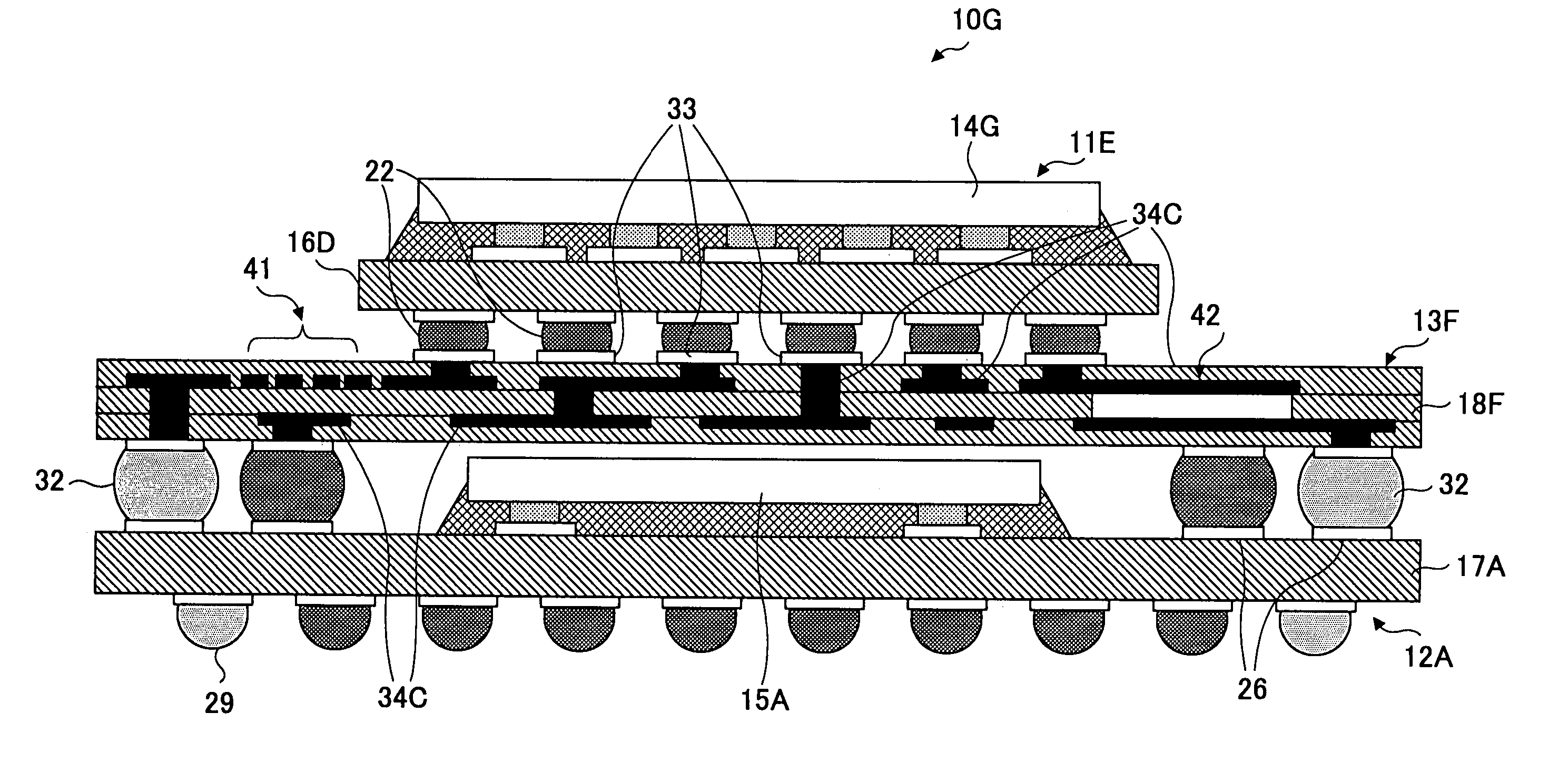

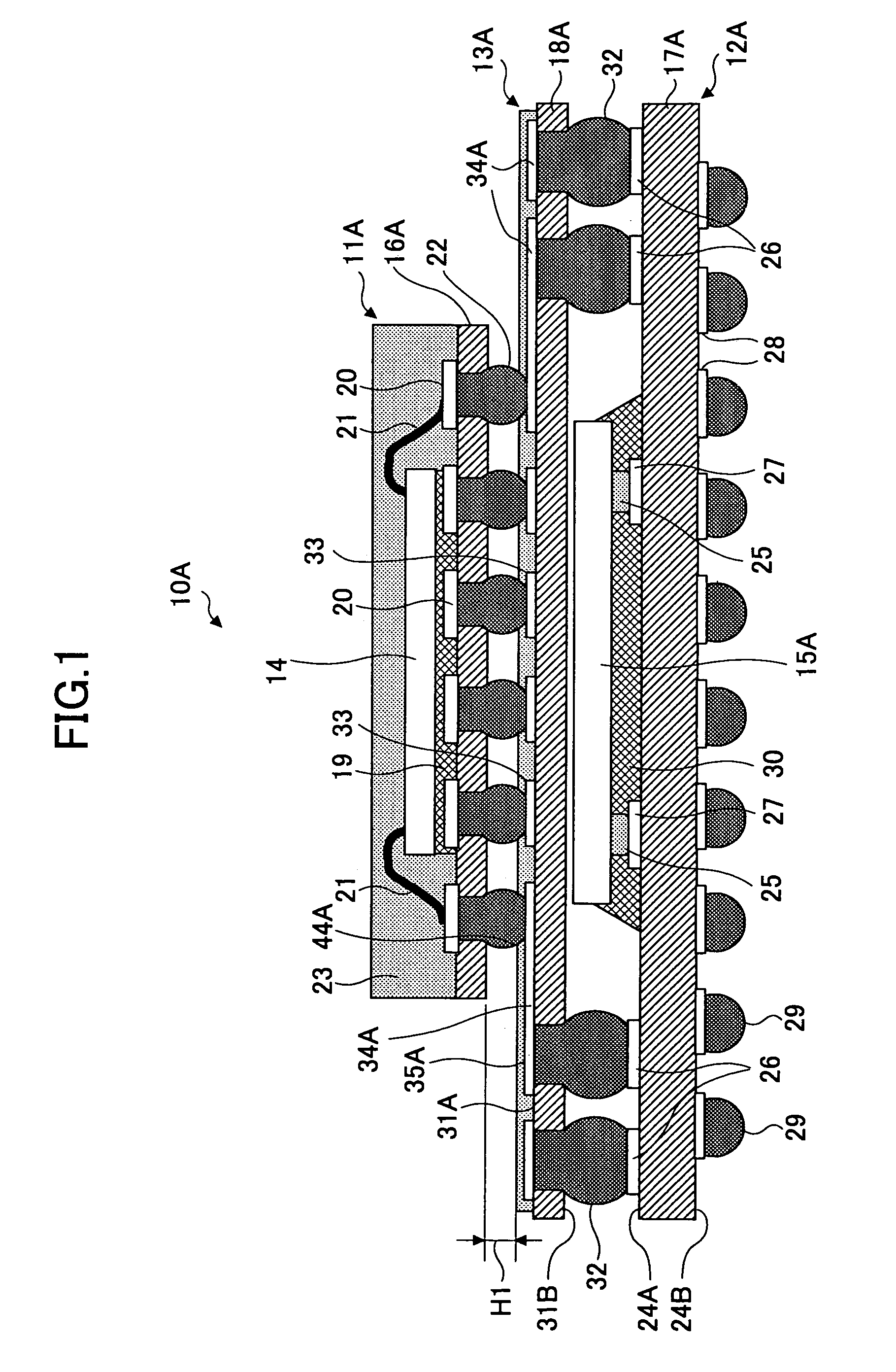

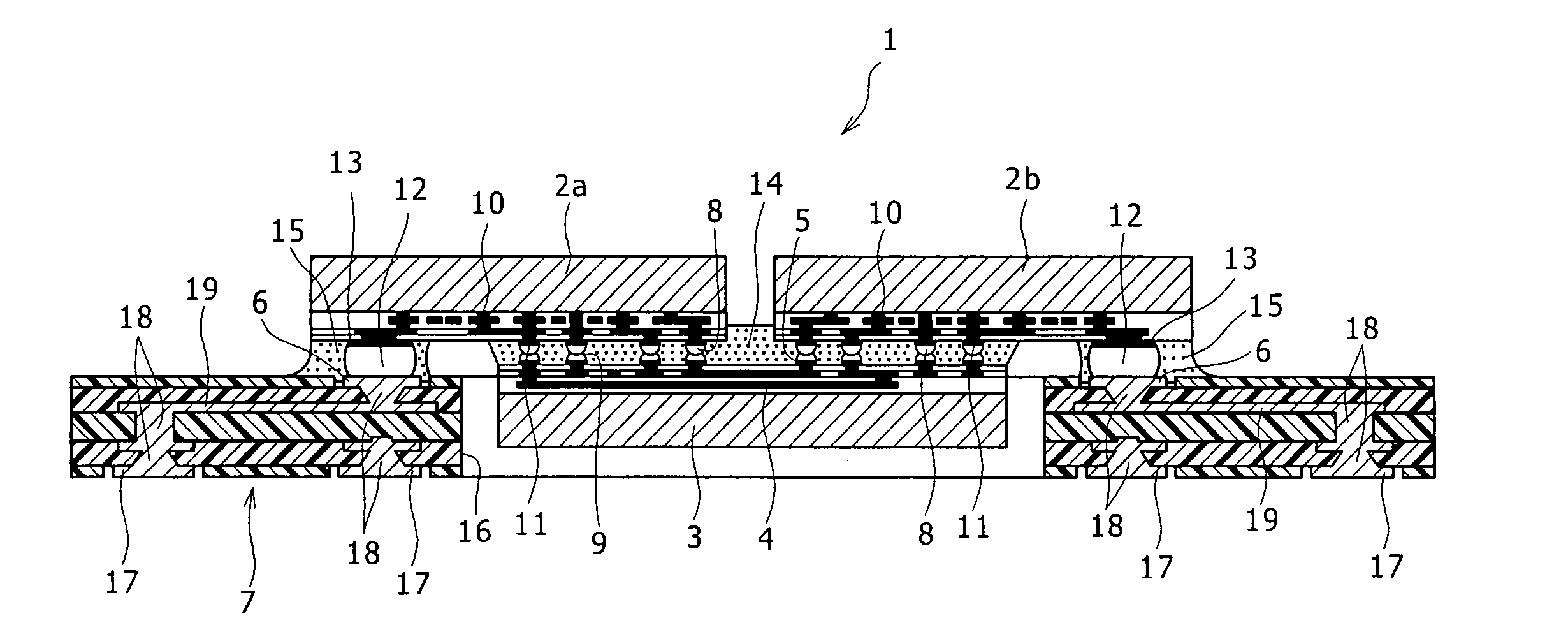

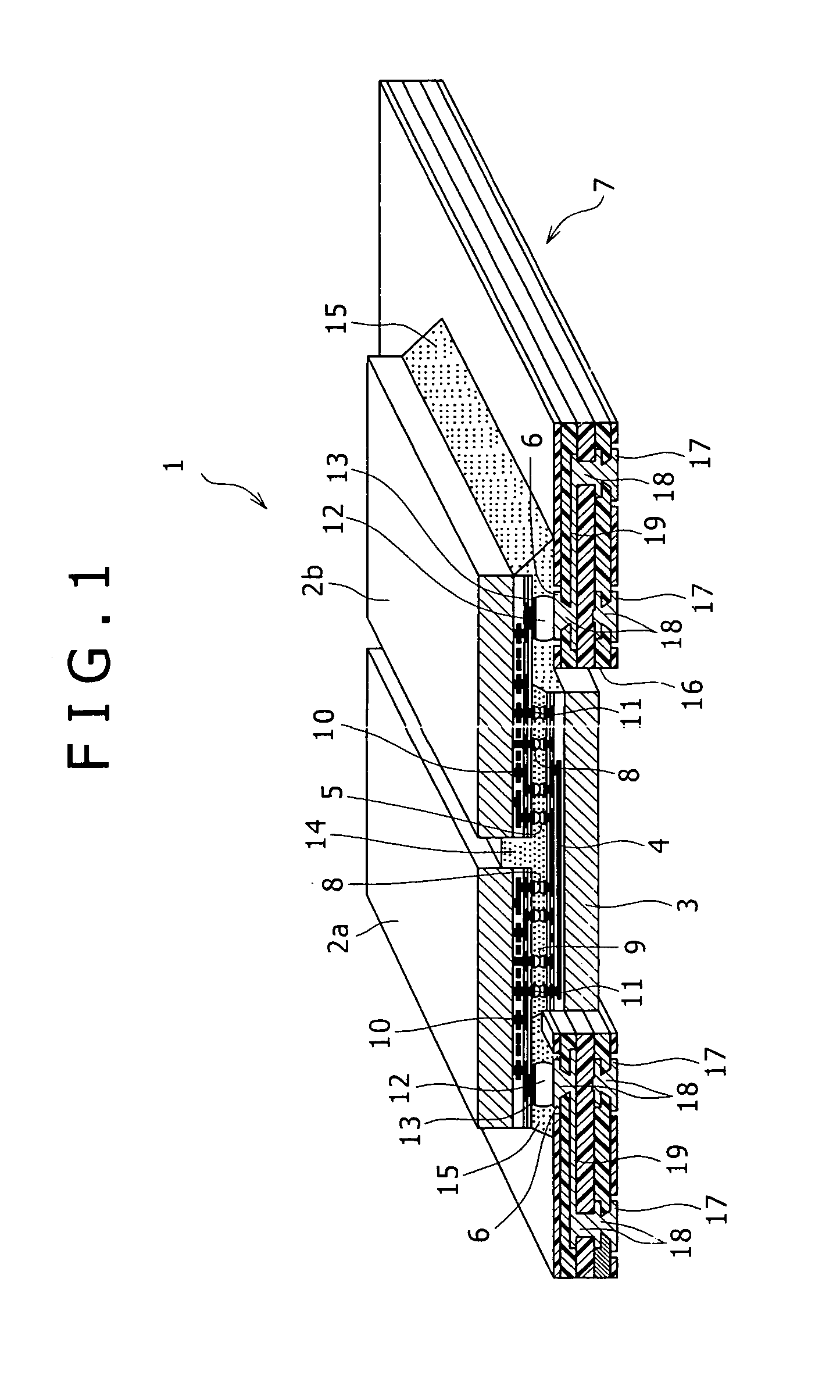

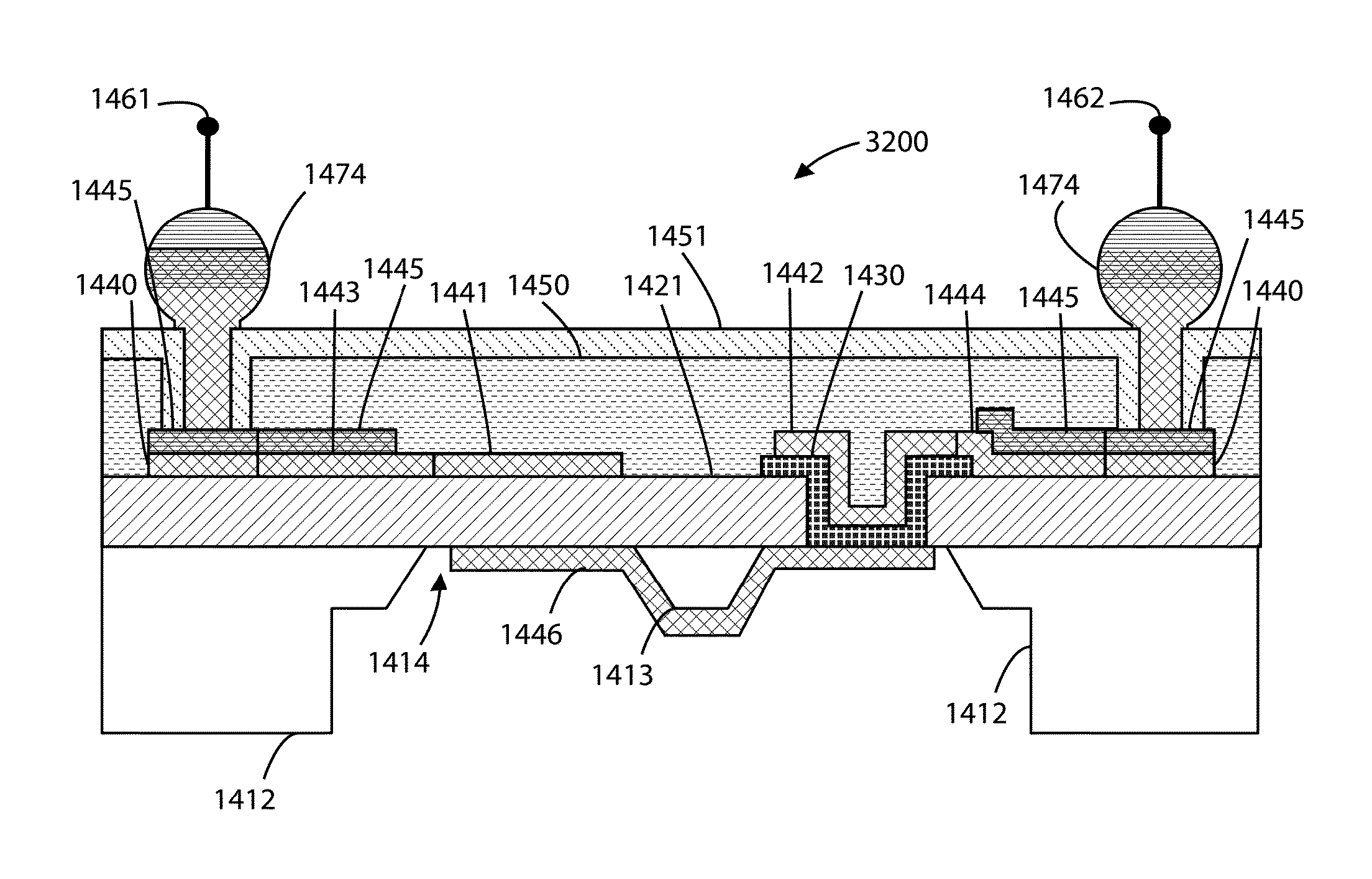

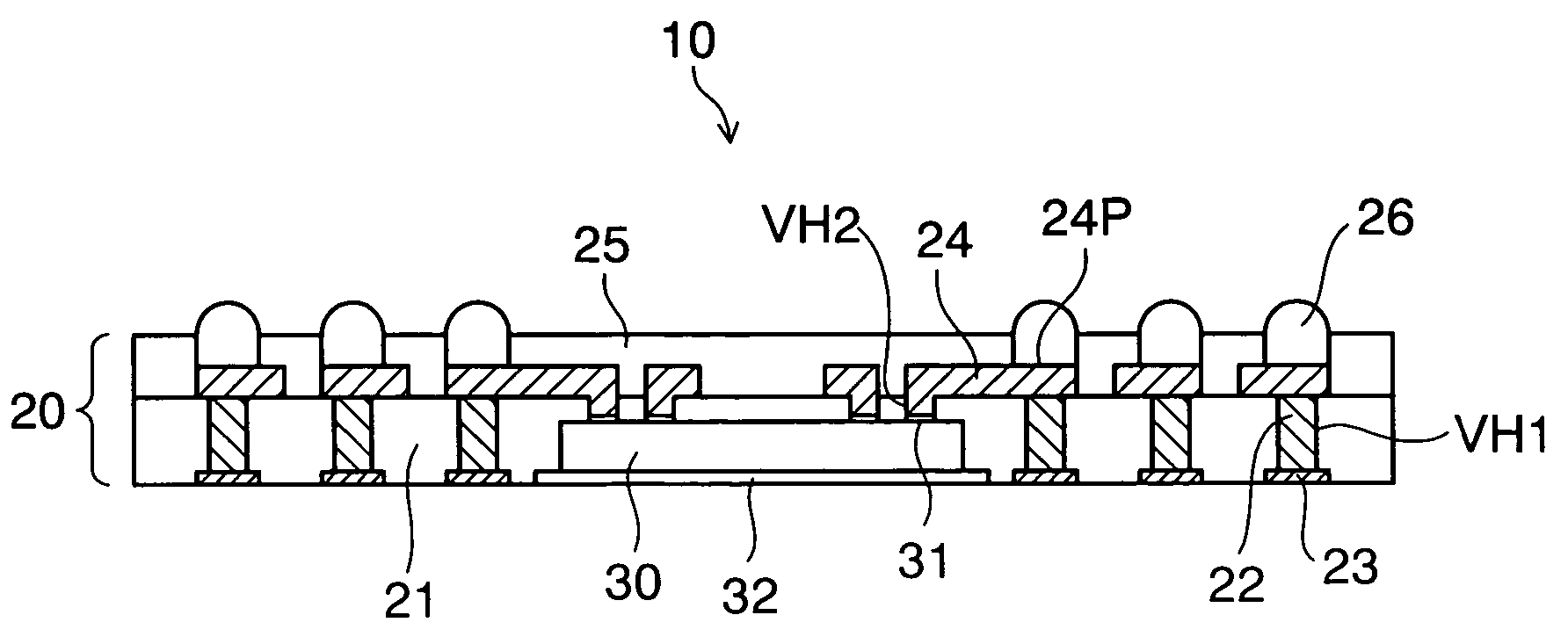

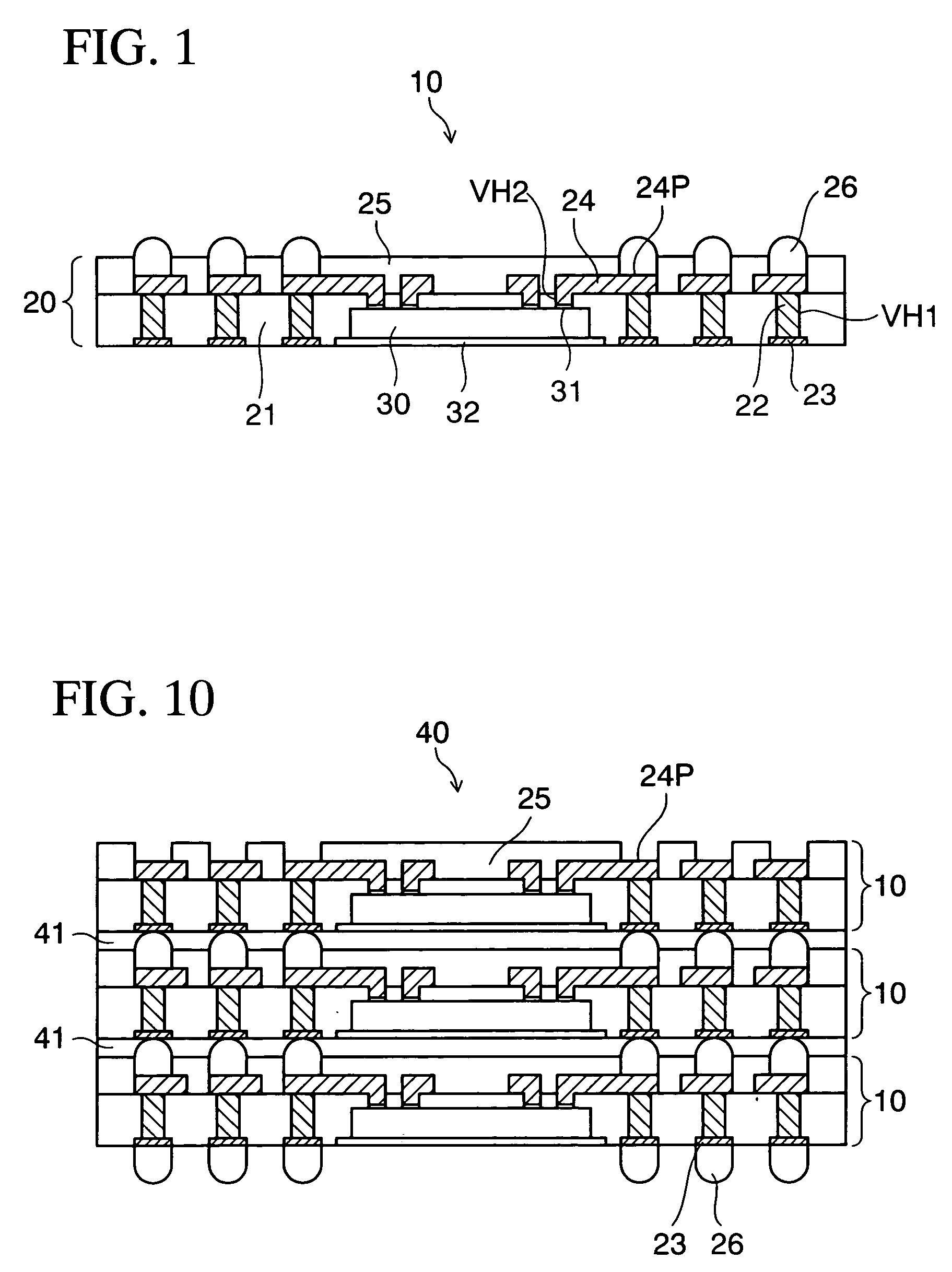

Stacked semiconductor device

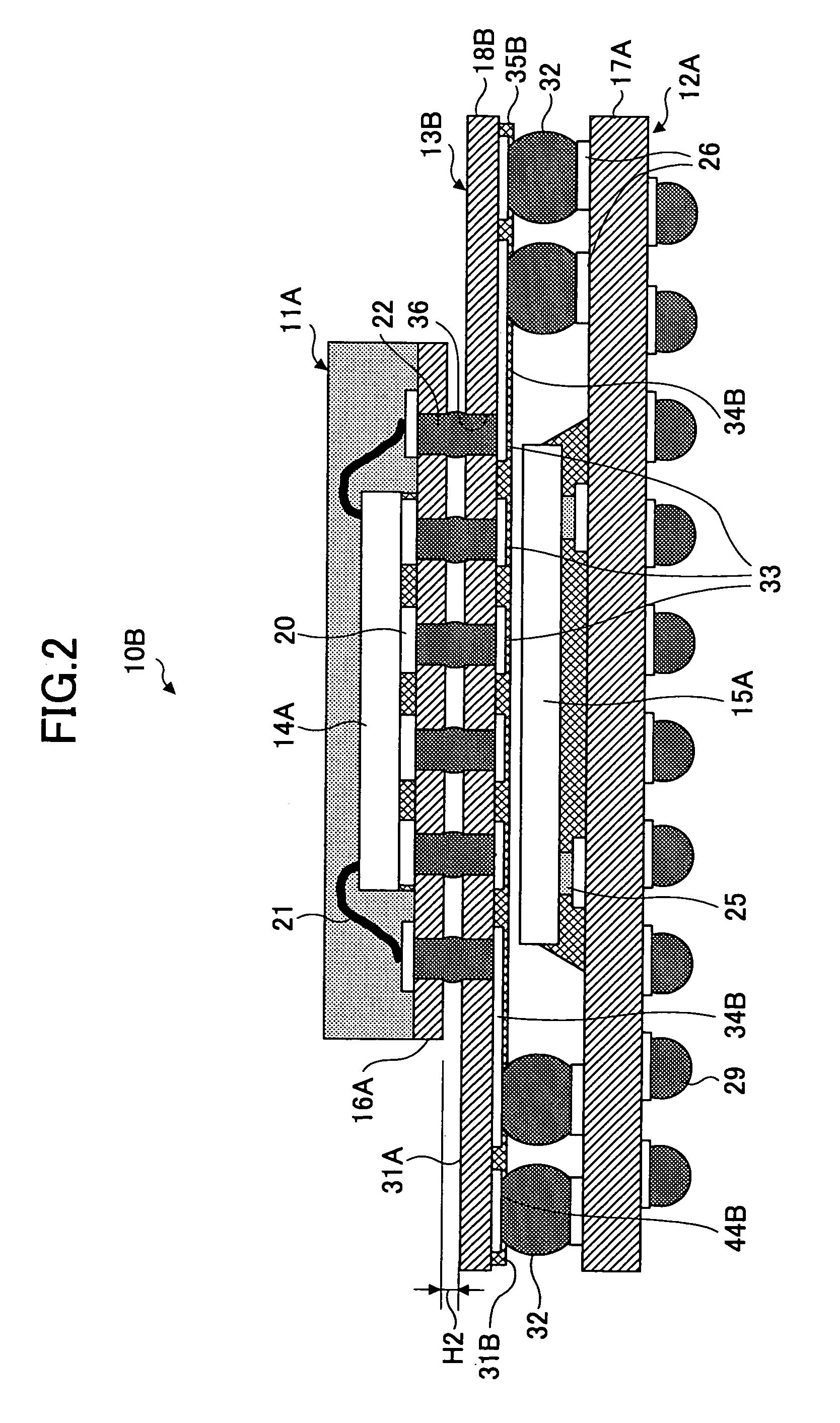

ActiveUS7049692B2Eliminate the problemPrinted circuit assemblingSemiconductor/solid-state device detailsGeneral purposeEngineering

A stacked semiconductor device is disclosed that has a three-dimensional structure using general-purpose semiconductor device units (semiconductor devices) that are stacked with an interposer substrate being provided between an upper device unit and a lower device unit. The upper device unit includes a semiconductor device, a first wiring substrate, and an external connection terminal. The lower device unit includes a semiconductor device, a second wiring substrate, and a connection electrode that is prepared on the upper surface of the second wiring substrate. The interposer substrate includes a circuit board, a first conductive material connecting to the connection electrode, a second conductive material formed in a form position of the external connection terminal that is electrically connected to the second conductive material, and a third conductive material for electrically connecting the first conductive material and the second conductive material.

Owner:SOCIONEXT INC

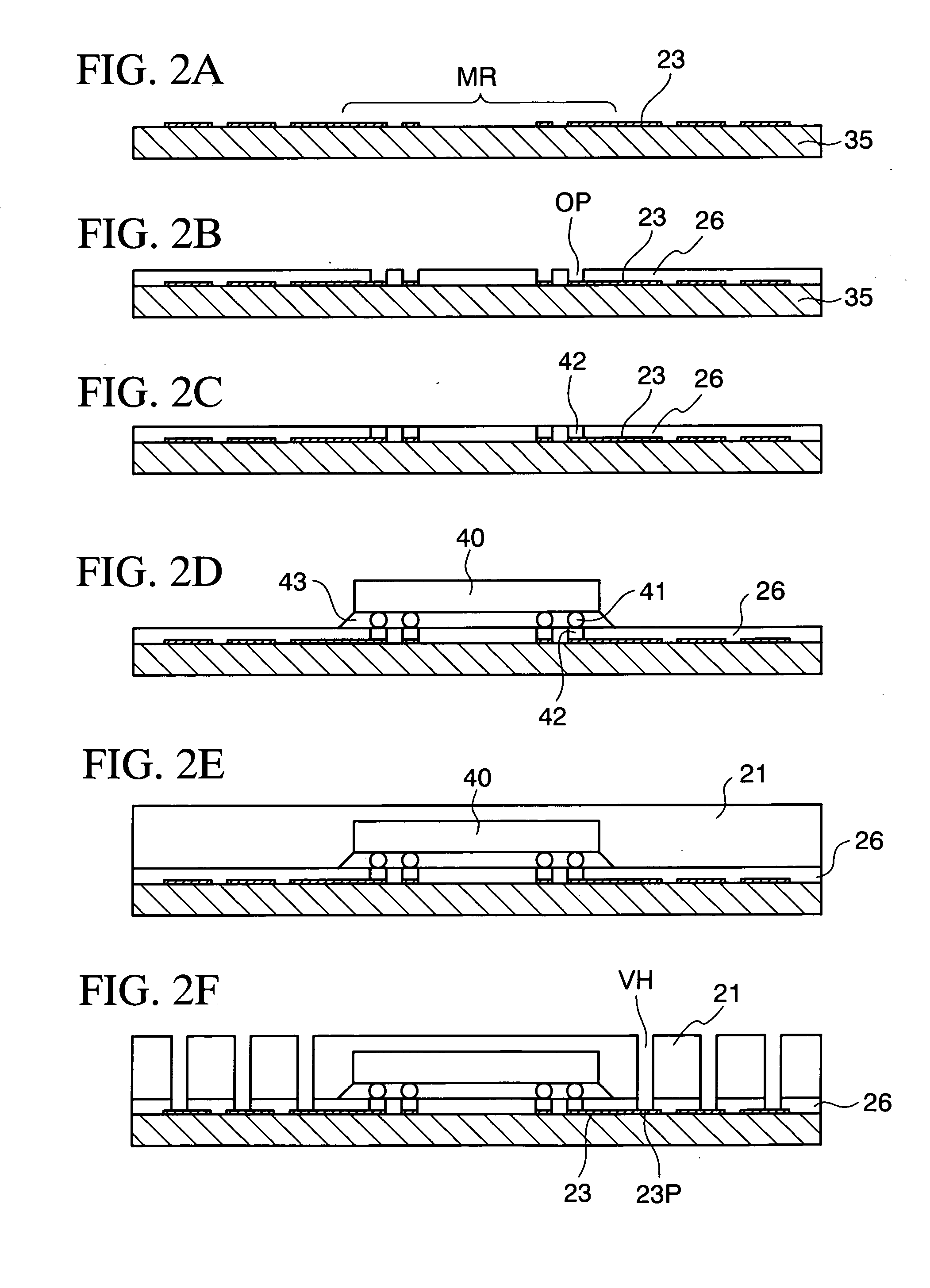

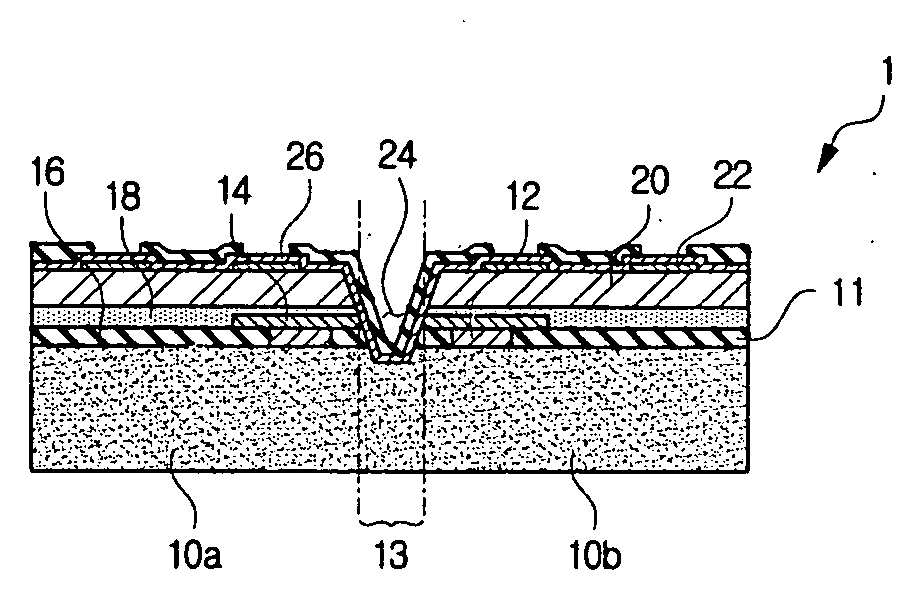

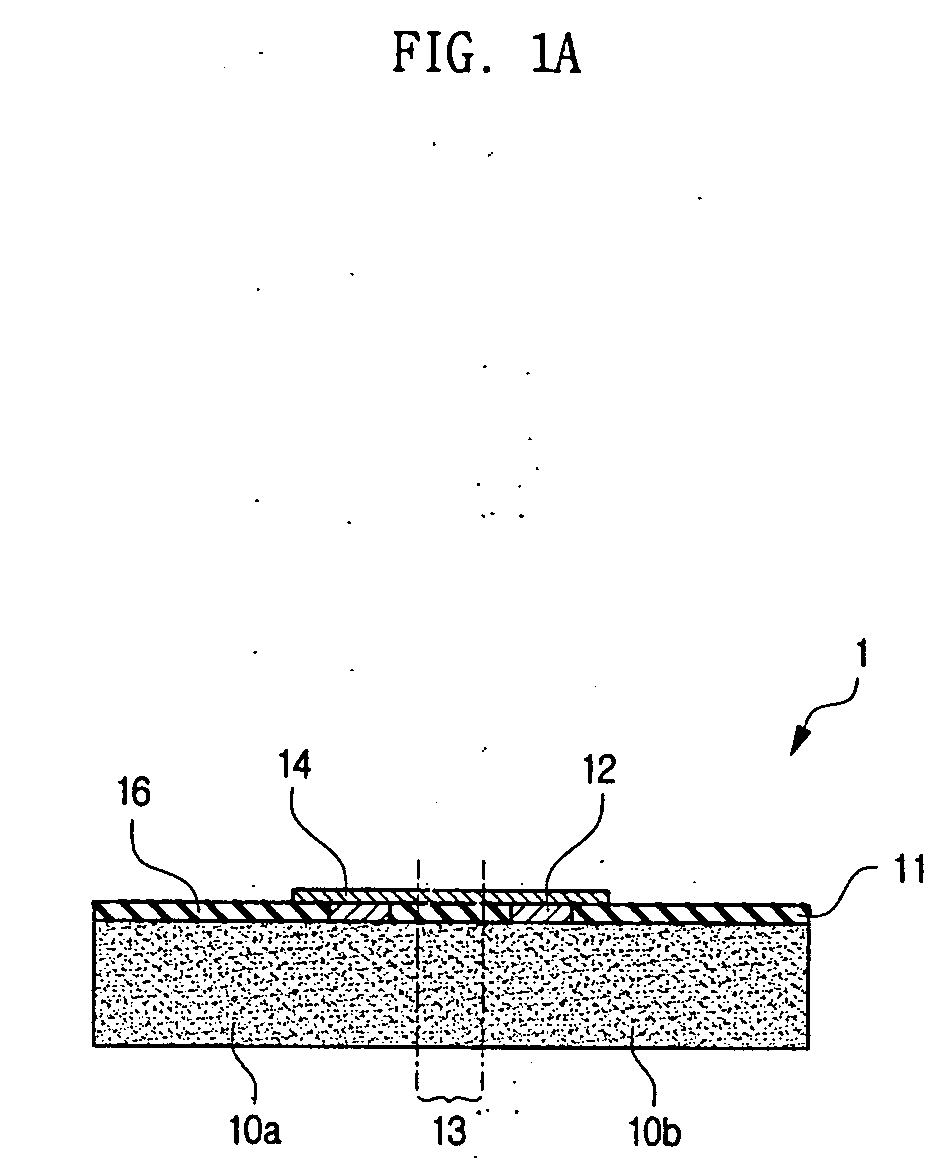

Semiconductor device and method of manufacturing the same

InactiveUS20050184377A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, and conductor layers are respectively formed to be connected to one end and another end of the conductor filled in the individual via hole. Portions (pad portions) of the conductor layers which correspond to the conductors are exposed from protective films, or external connection terminals are bonded to the pad portions. The chip is mounted with flip-chip technology so that at least some of electrode terminals thereof are electrically connected to the conductor layers.

Owner:SHINKO ELECTRIC IND CO LTD

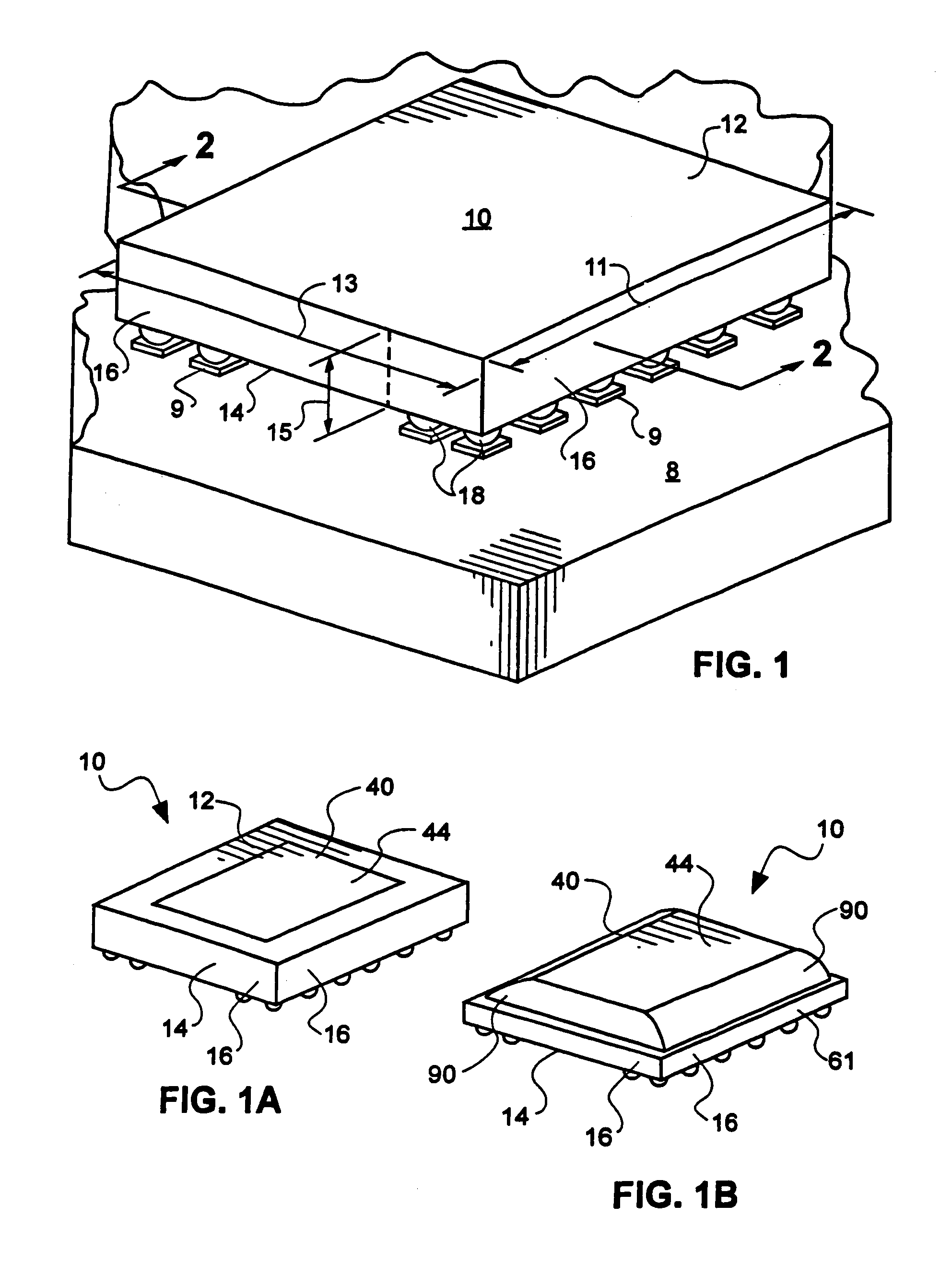

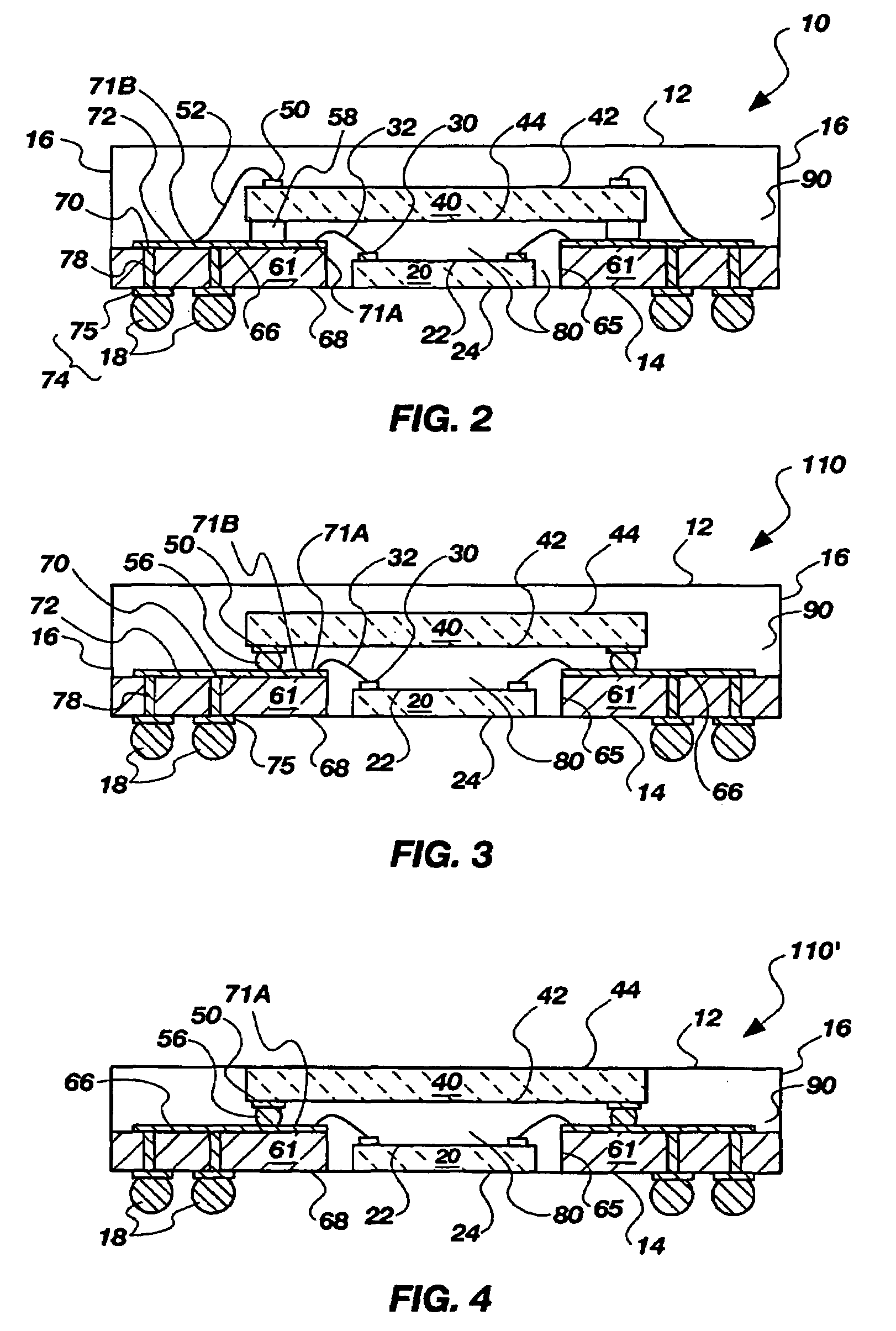

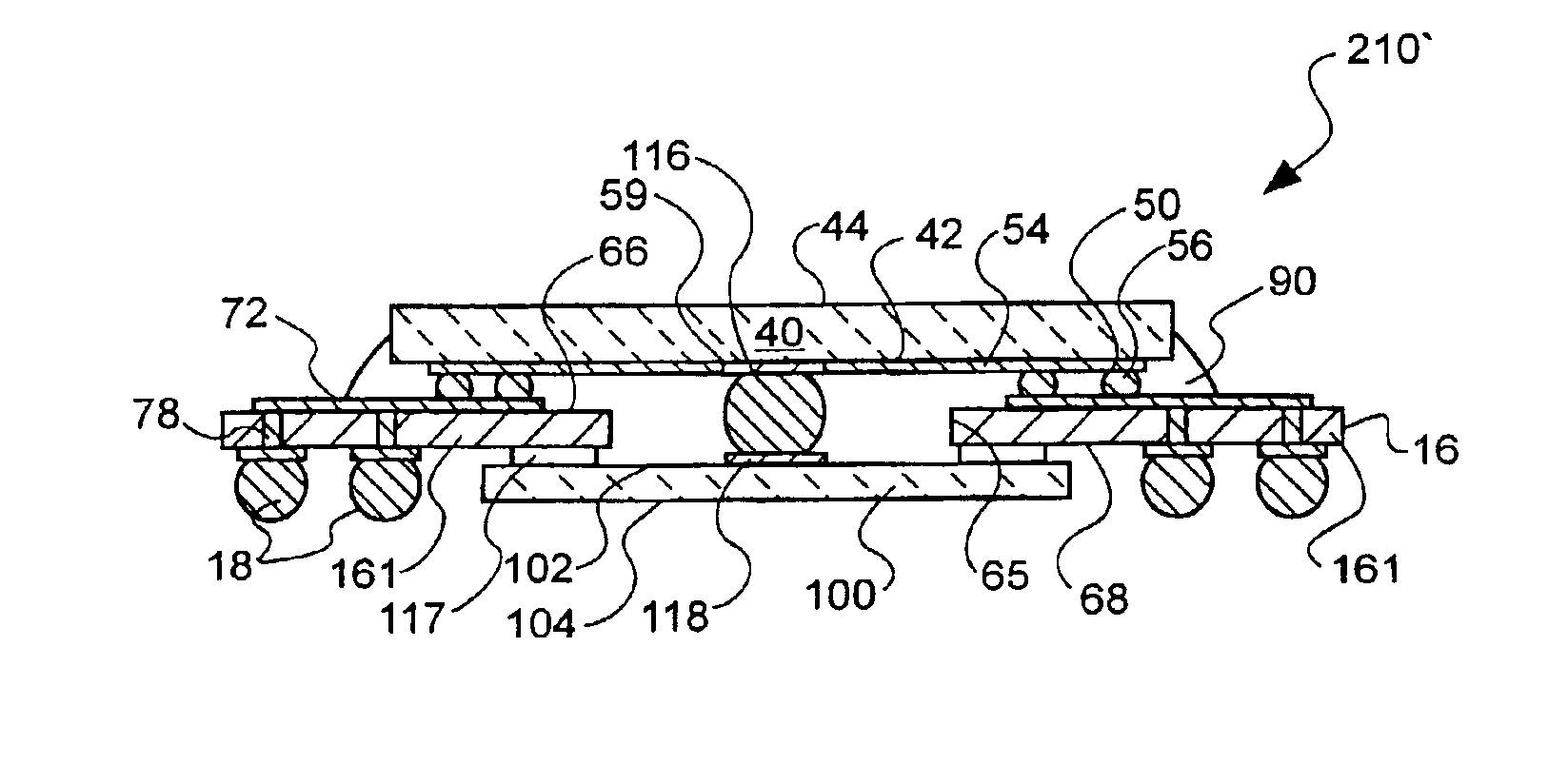

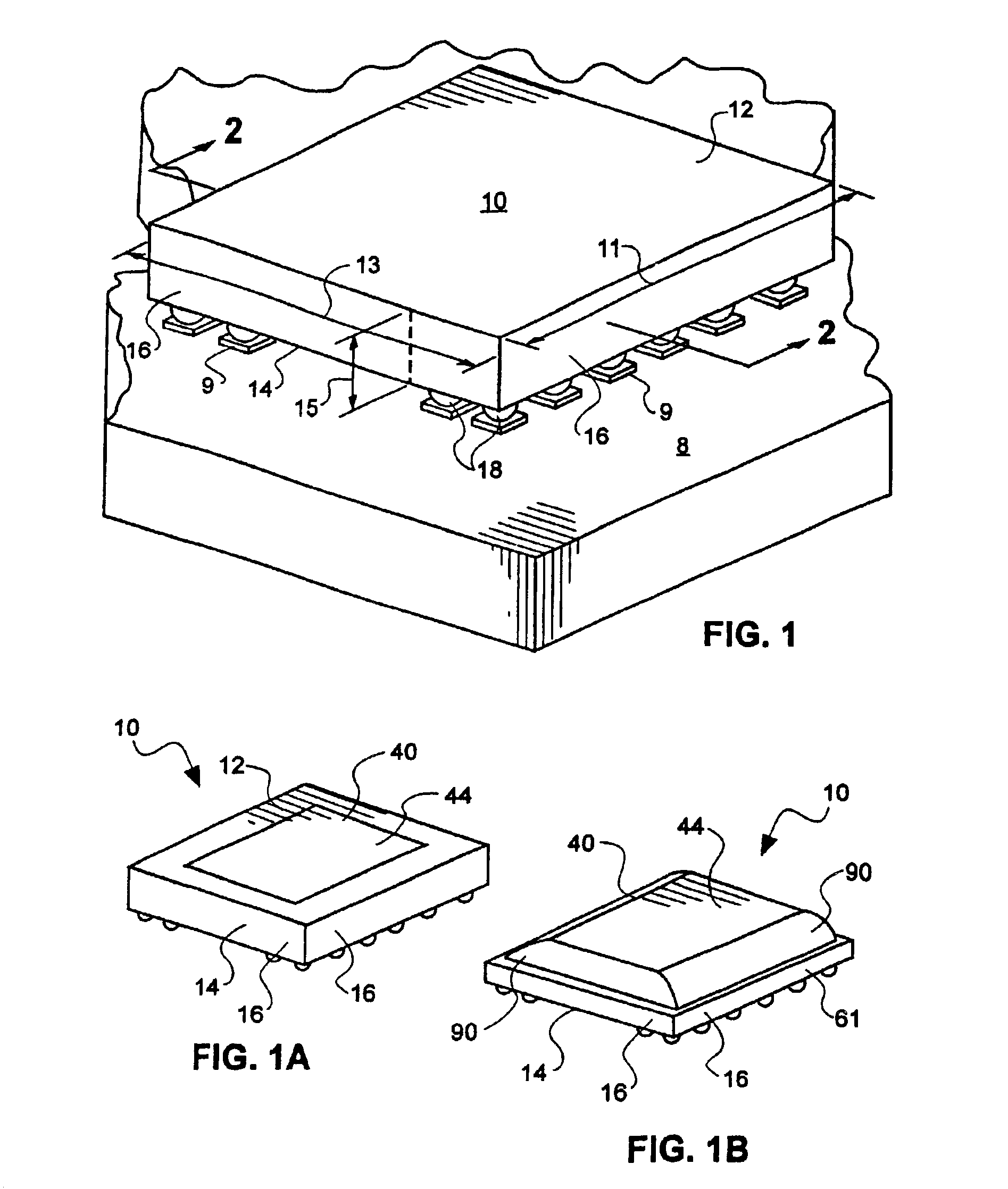

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

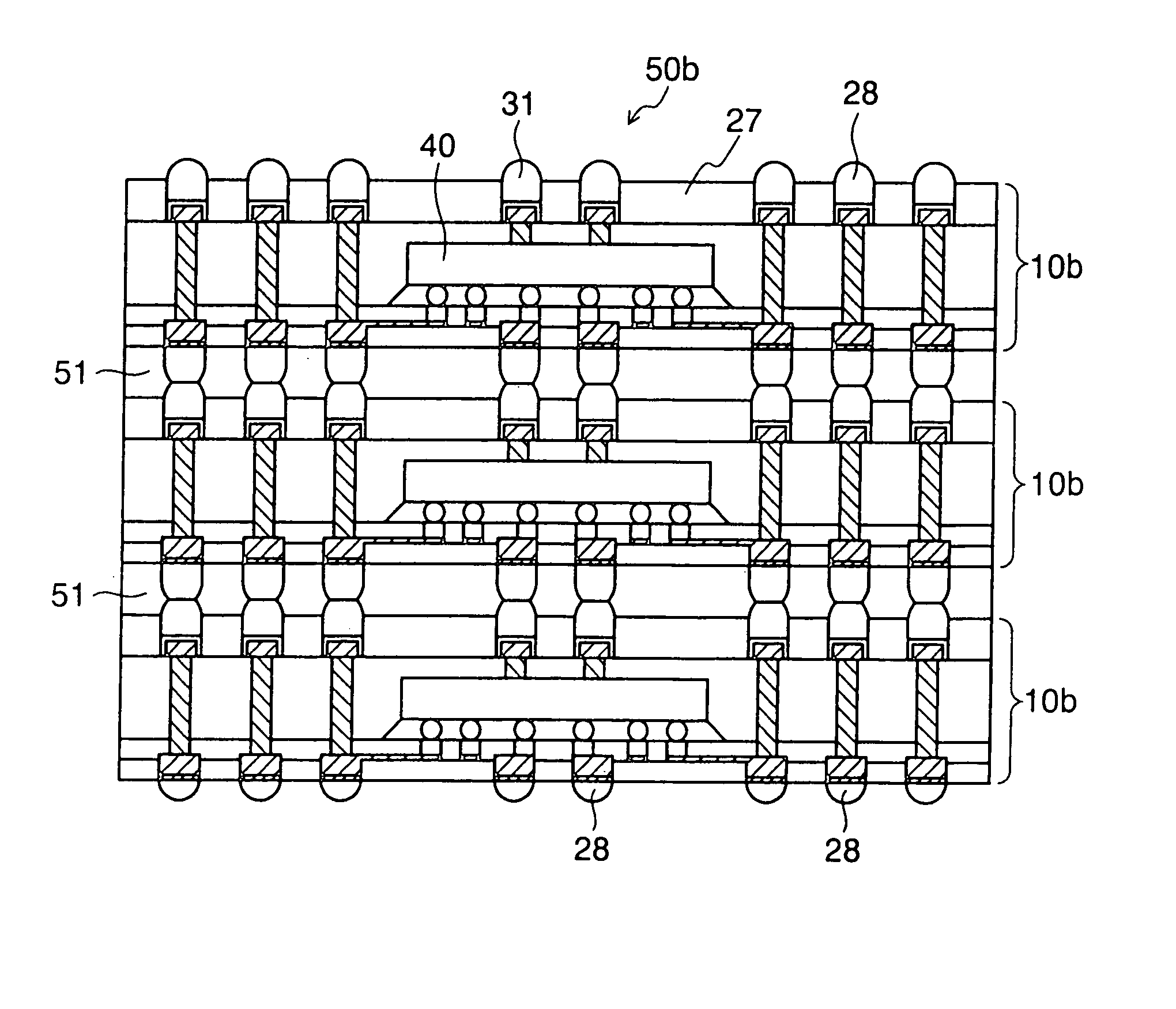

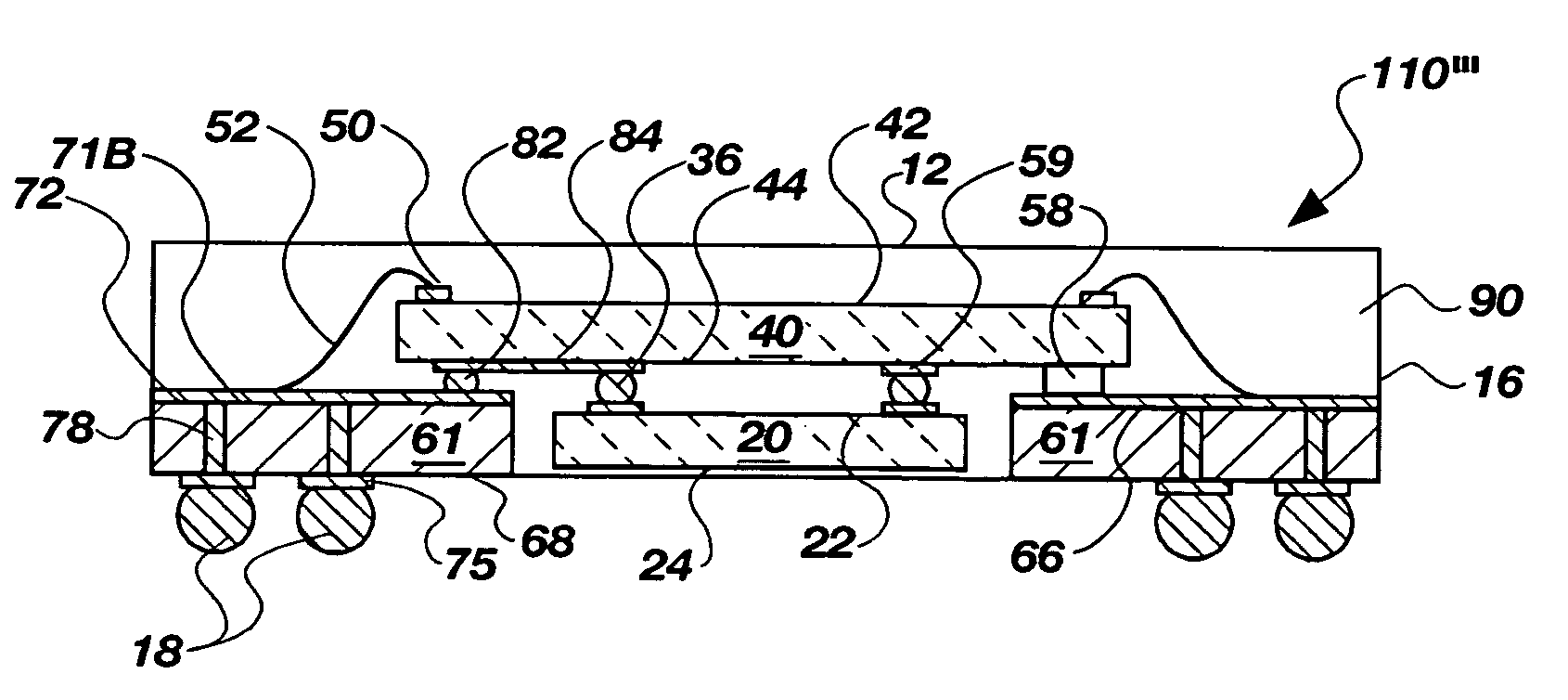

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

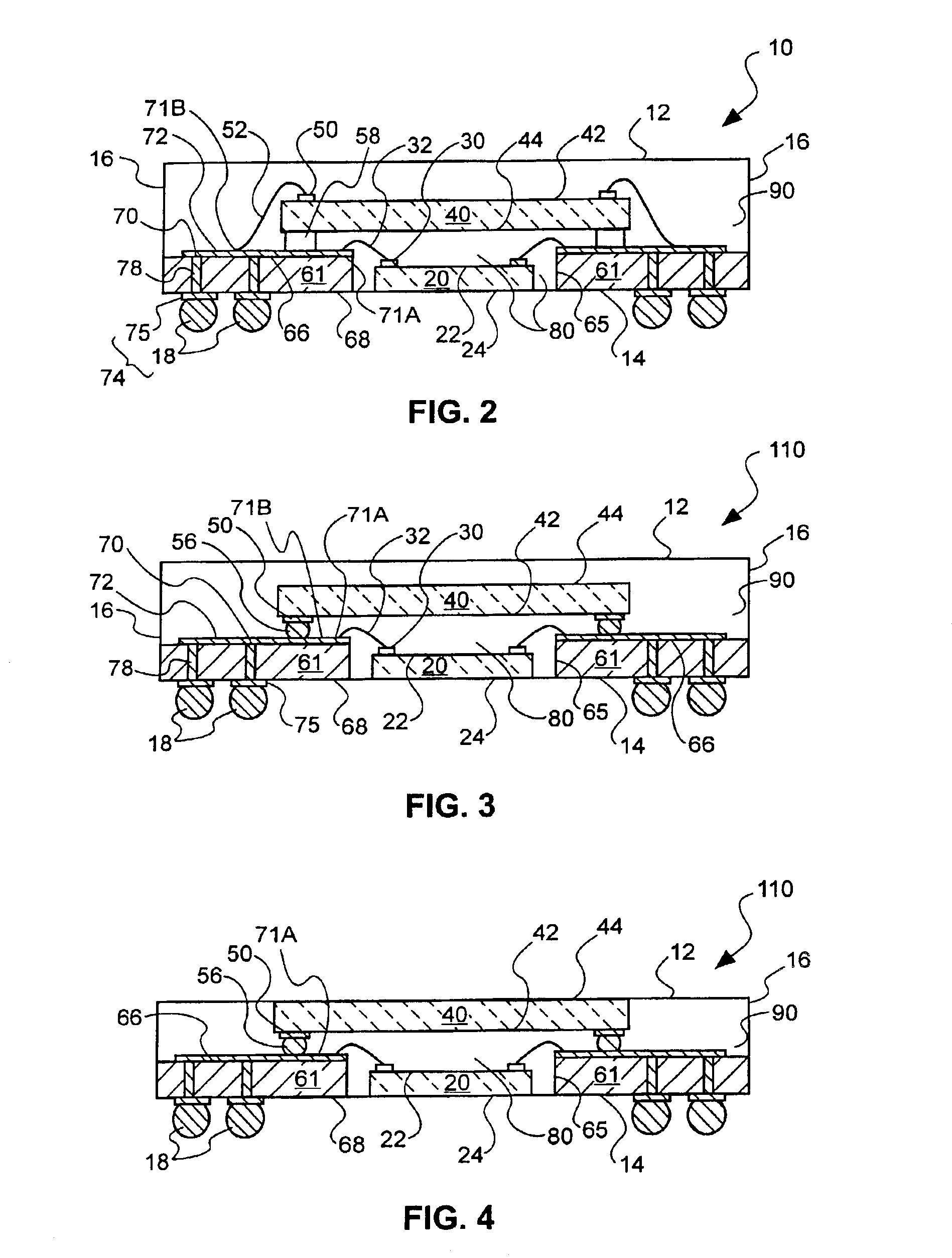

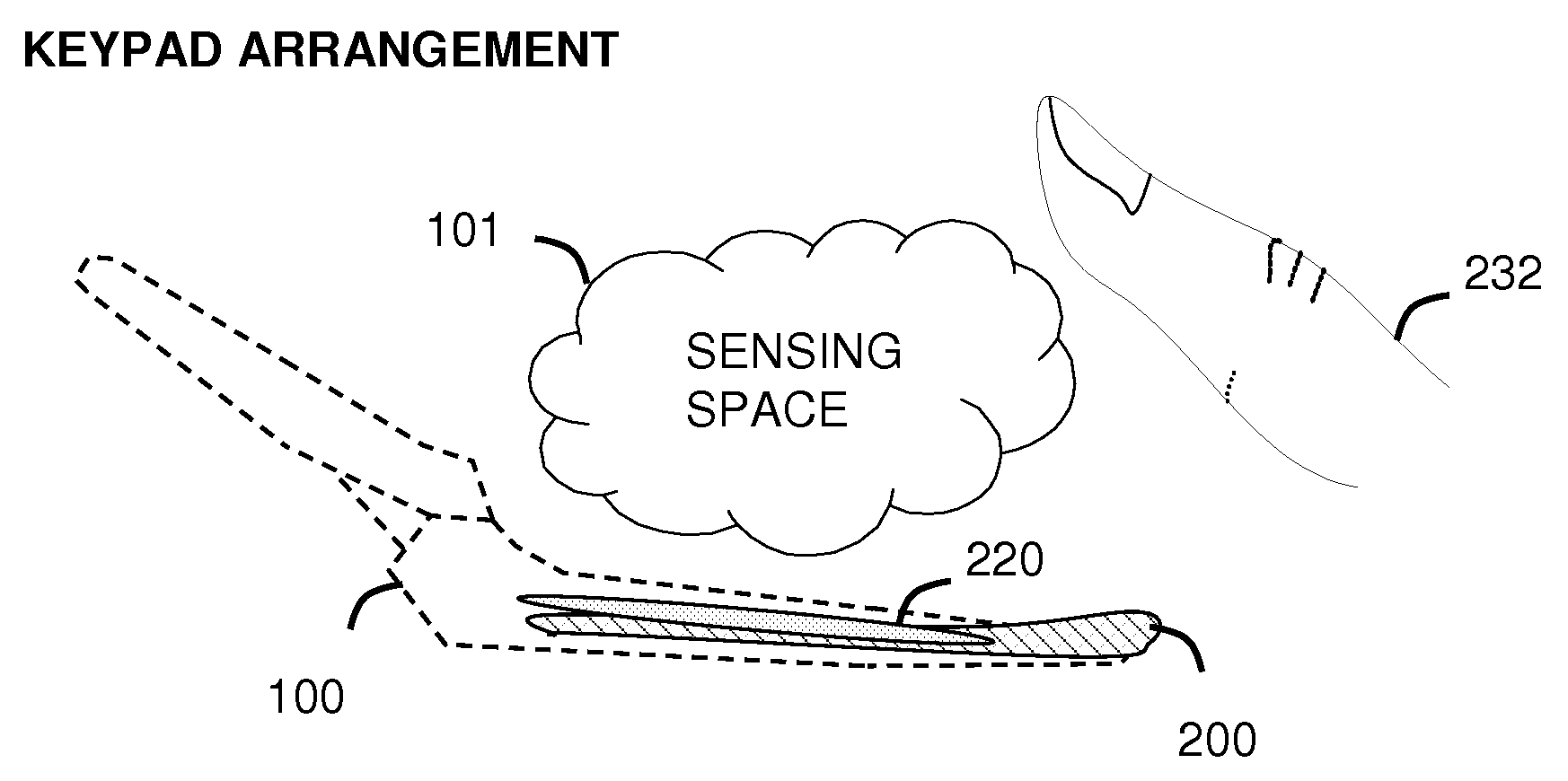

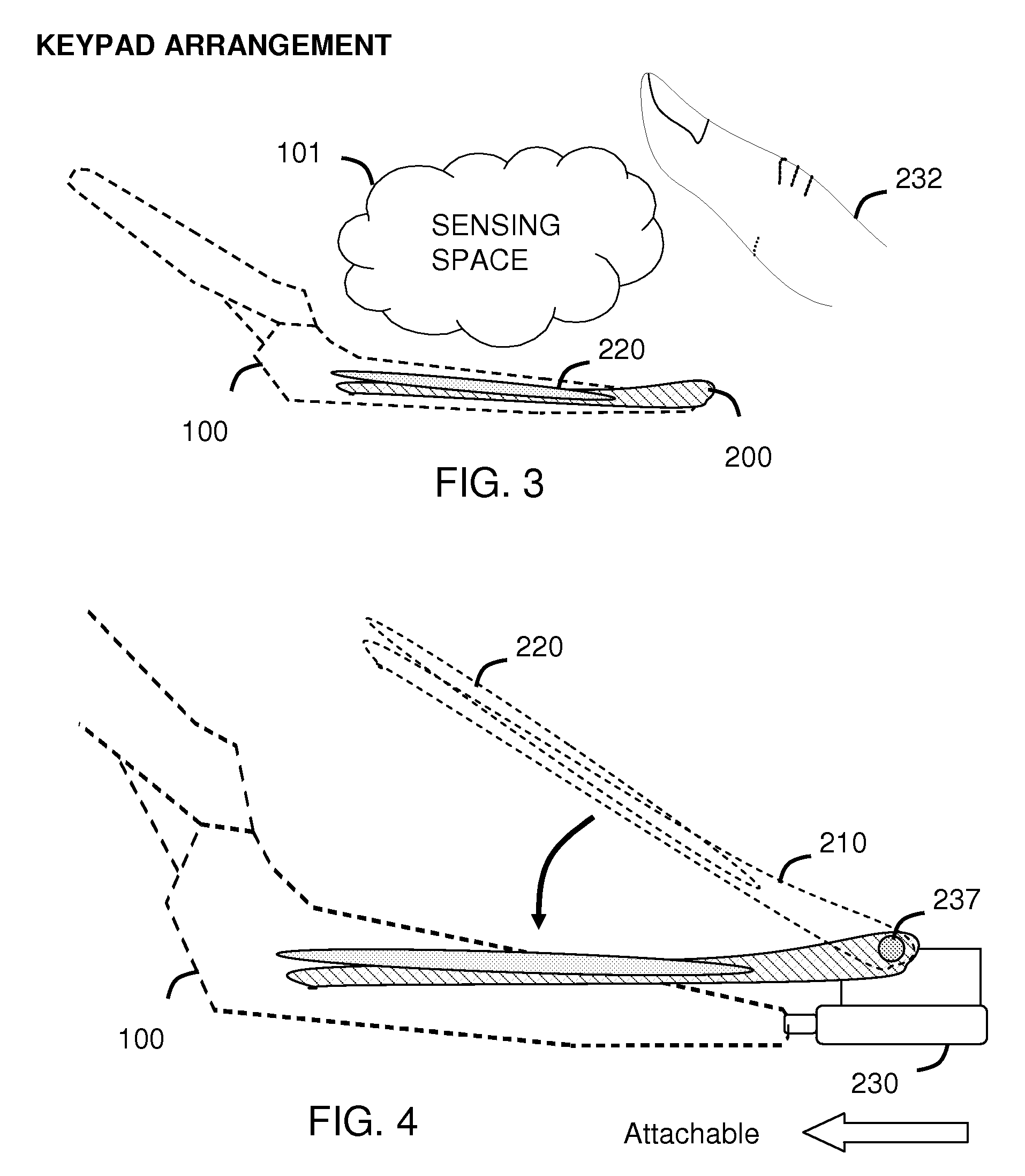

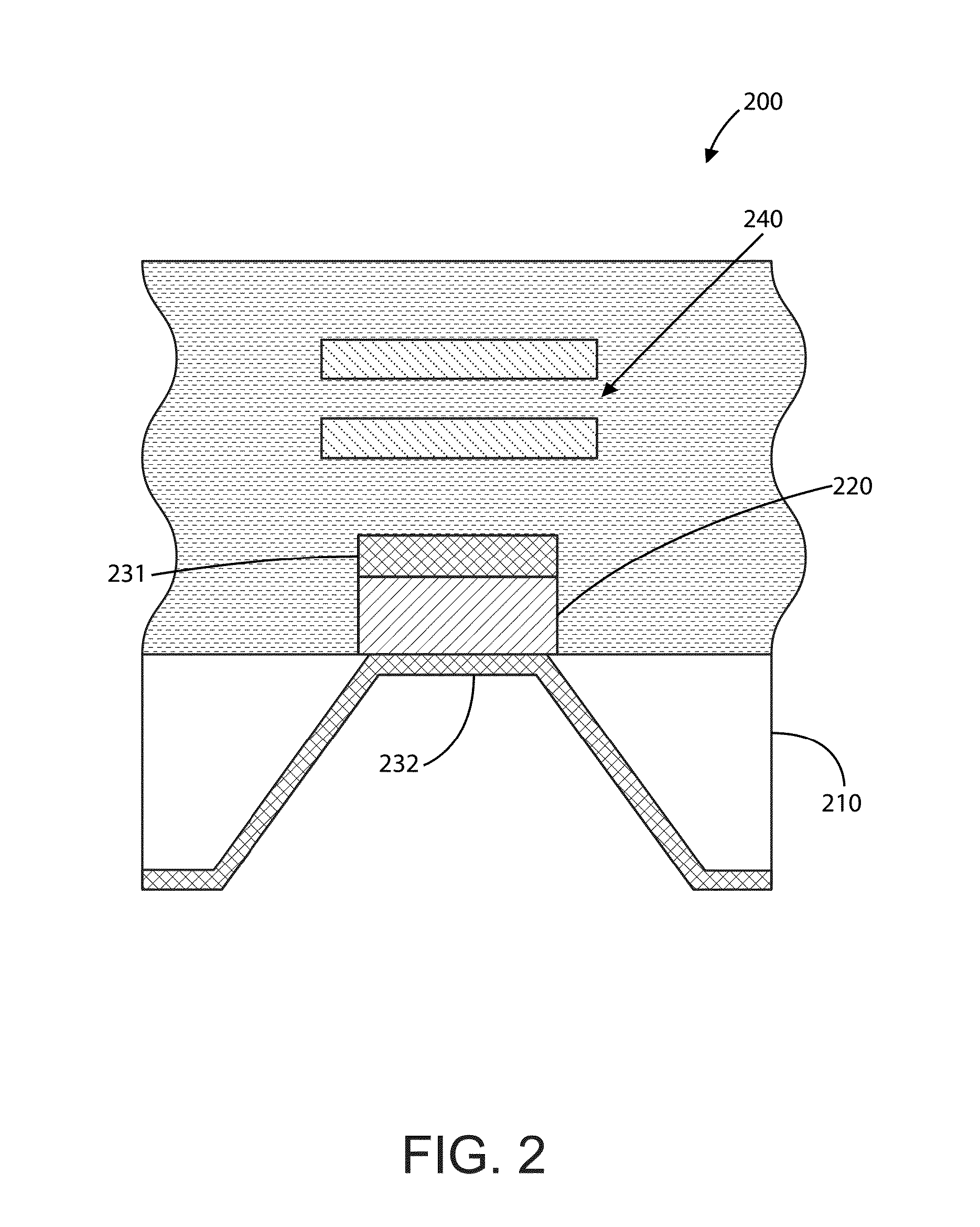

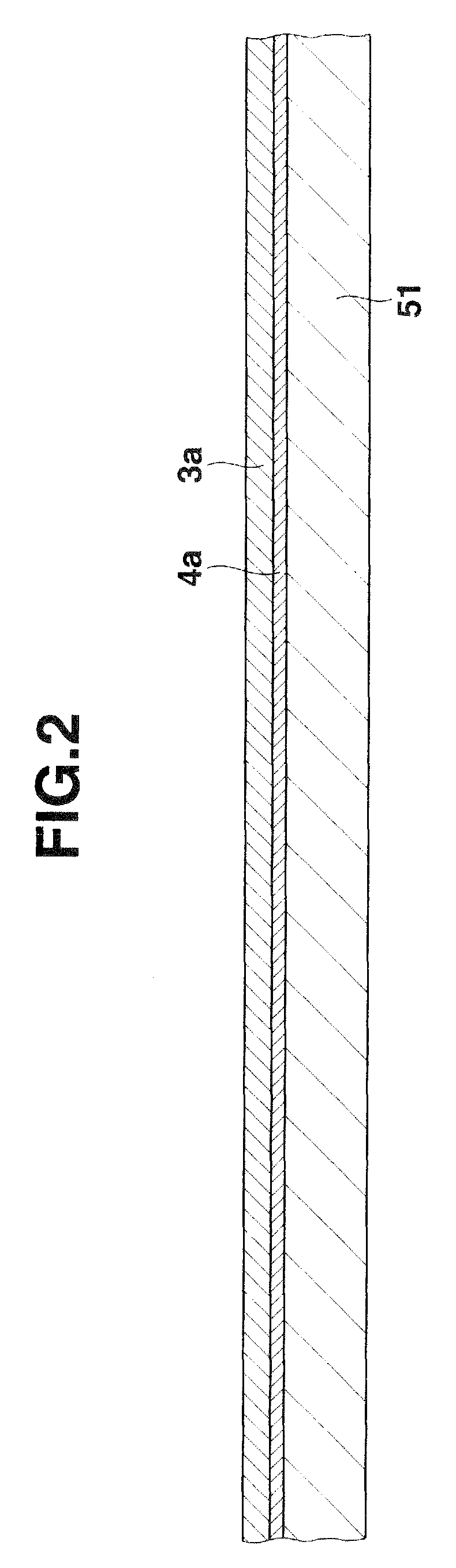

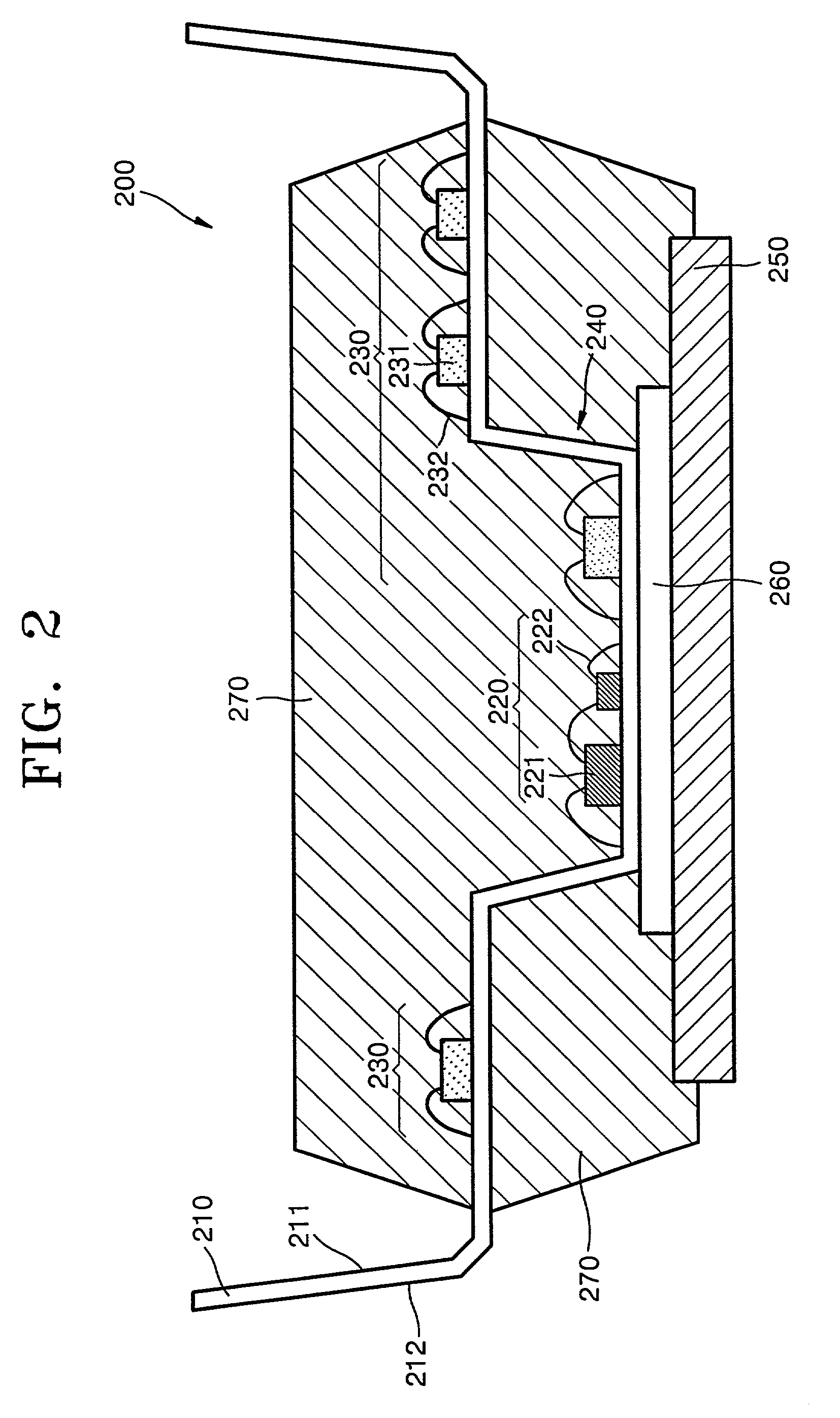

Touchless User Interface for a Mobile Device

InactiveUS20080100572A1Digital data processing detailsCathode-ray tube indicatorsDisplay deviceHuman–computer interaction

A sensory device (200) for providing a touchless user interface to a mobile device (100) is provided. The sensory device can include at least one appendage (210) having at least one sensor (220) that senses a finger (232) within a touchless sensing space (101), and a connector (230) for communicating sensory signals received by the at least one sensor to the mobile device. The sensory device can attach external to the mobile device. A controller (240) can trace a movement of the finger, recognize a pattern from the movement, and send the pattern to the mobile device. The controller can recognize finger gestures and send control commands associated with the finger gestures to the mobile device. A user can perform touchless acquire and select actions on or above a display or removable face plate to interact with the mobile device.

Owner:NAVISENSE

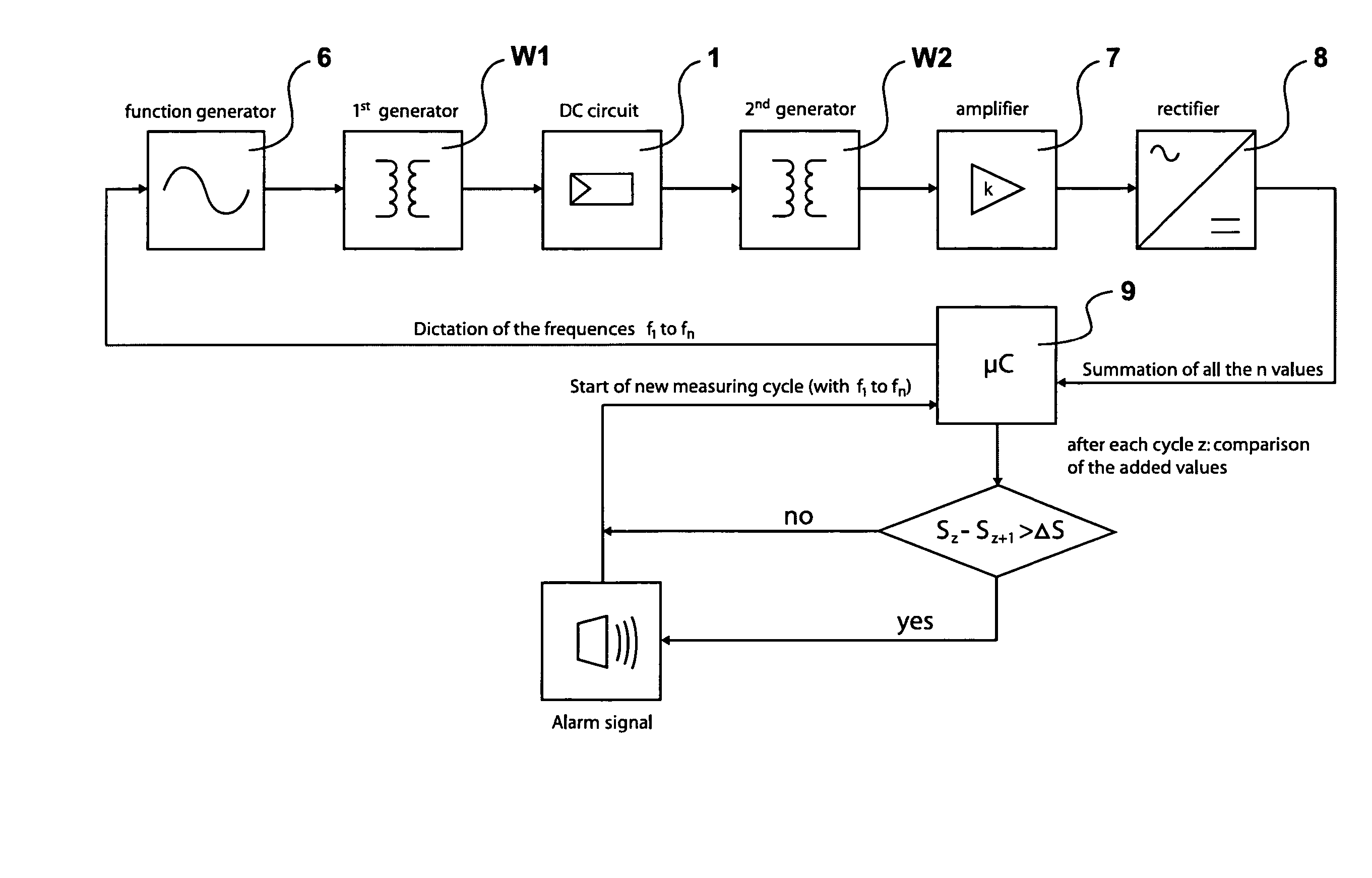

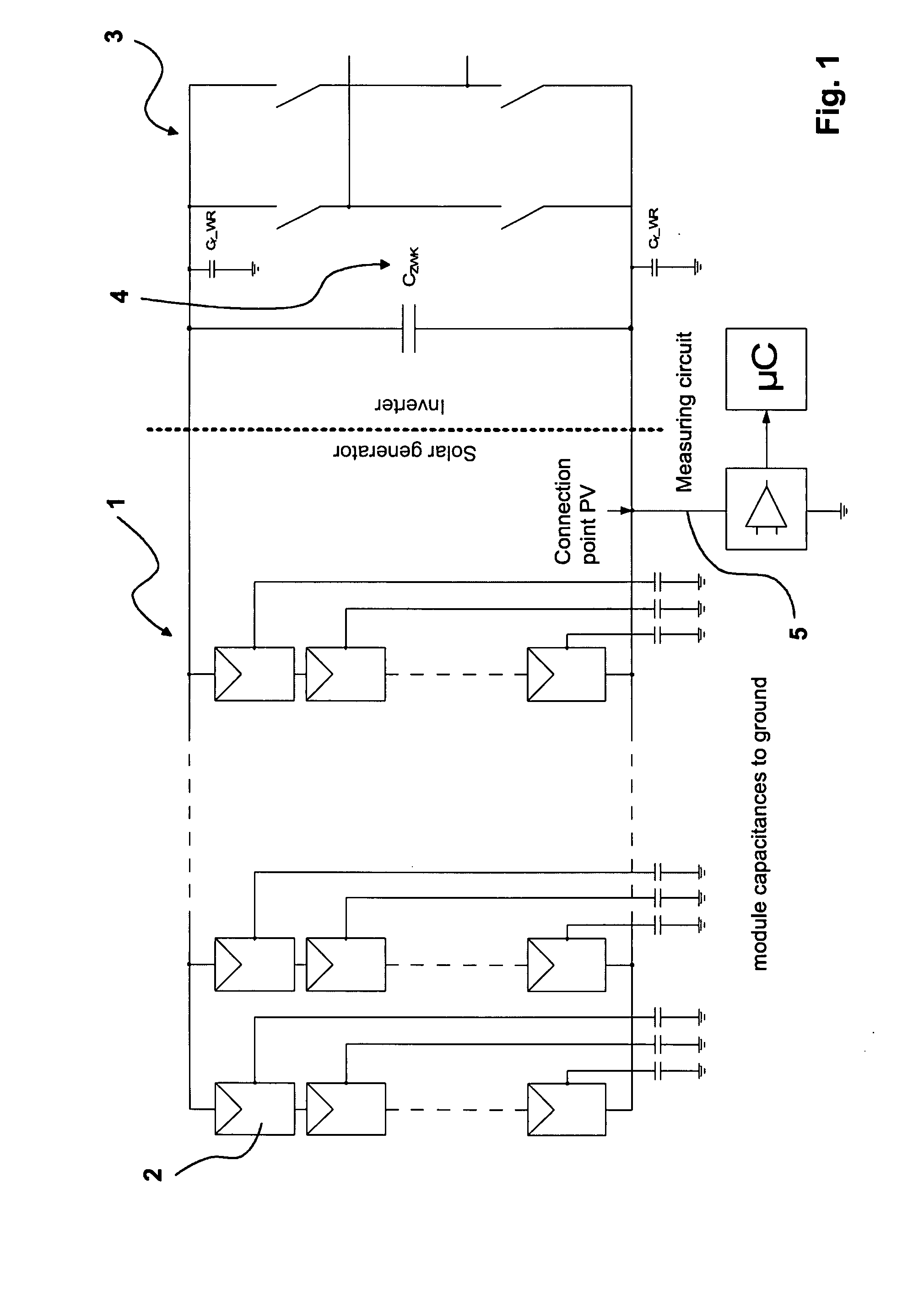

Method of monitoring a photvoltaic generator

ActiveUS20080106250A1Cost advantageOptimal theft securityPhotovoltaic monitoringPV power plantsFrequency spectrumElectrical battery

The subject matter of the present invention is a method for monitoring a photovoltaic generator (1) for generating current with a number of solar cells connected between two external connections by repeated feeding of a current with a frequency spectrum into the generator current circuit, detecting thereby a respective frequency response in the frequency spectrum with the supplied current as the input variable and an electric variable of the generator as the output variable, and detecting a change in the frequency response for monitoring the photovoltaic generator (1) in the event of a change during repeated feeding.

Owner:SMA SOLAR TECH AG

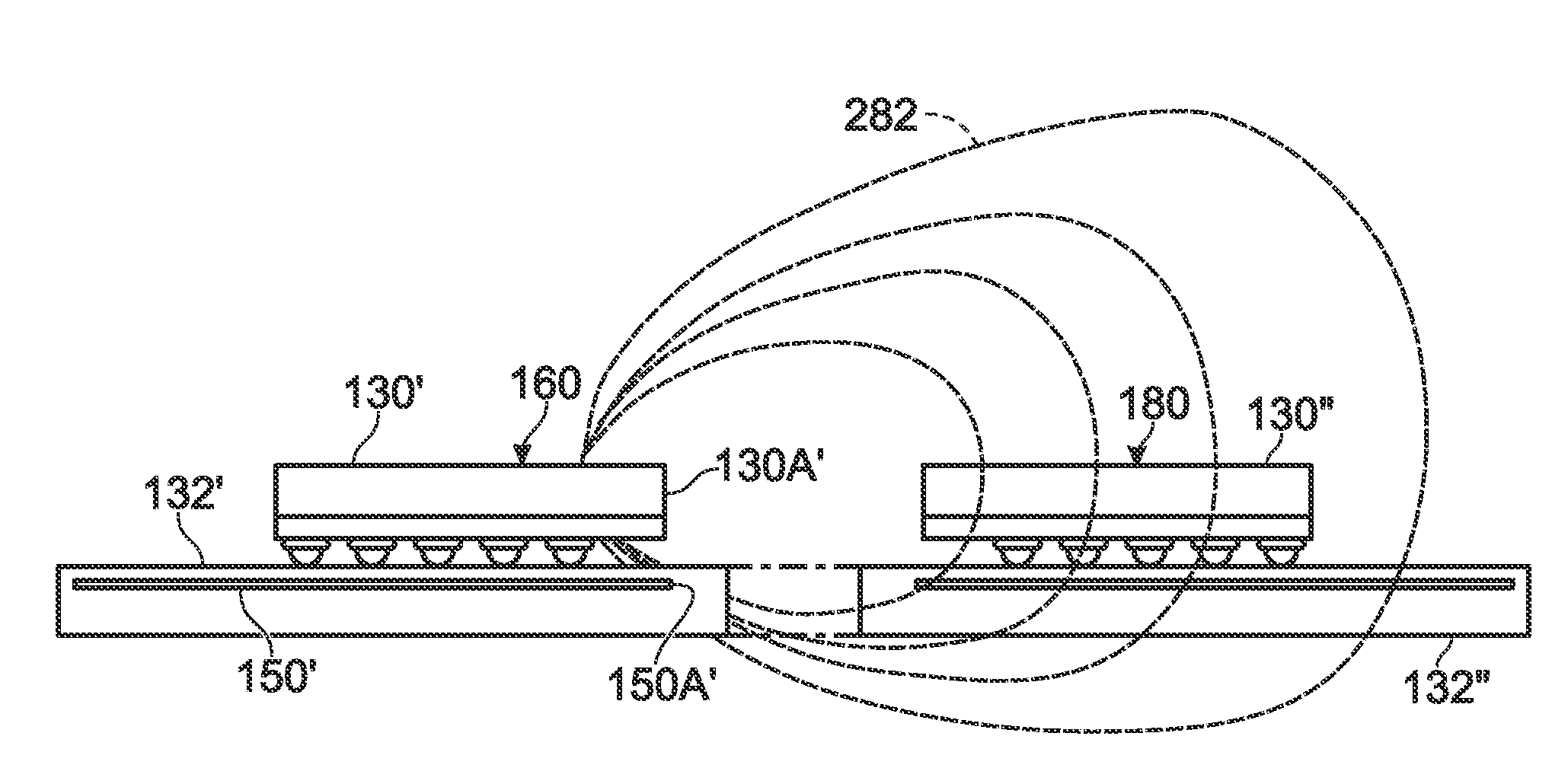

Integrated circuit with electromagnetic communication

ActiveUS20120263244A1Baseband system detailsModulated-carrier systemsElement spaceElectrical conductor

A system for transmitting or receiving signals may include an integrated circuit (IC), a transducer operatively coupled to the IC for converting between electrical signals and electromagnetic signals; and insulating material that fixes the locations of the transducer and IC in spaced relationship relative to each other. The system may further include a lead frame providing external connections to conductors on the IC. An electromagnetic-energy directing assembly may be mounted relative to the transducer for directing electromagnetic energy in a region including the transducer and in a direction away from the IC. The directing assembly may include the lead frame, a printed circuit board ground plane, or external conductive elements spaced from the transducer. In a receiver, a signal-detector circuit may be responsive to a monitor signal representative of a received first radio-frequency electrical signal for generating a control signal that enables or disables an output from the receiver.

Owner:MOLEX INC

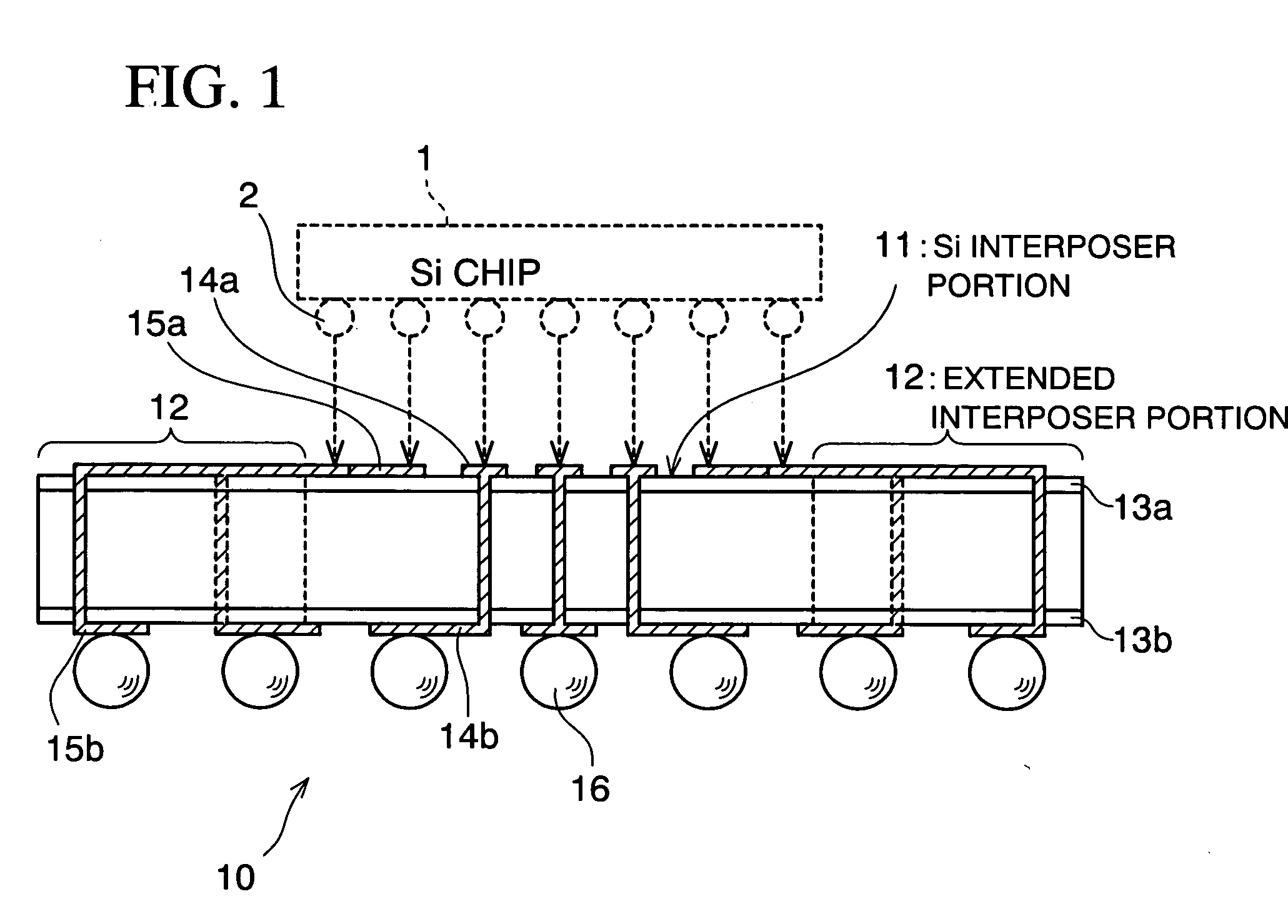

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20060226527A1Low costSmall sizeSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

The present invention provides a semiconductor device that is inexpensive and can suppress signal transmission delay, and a manufacturing method thereof. The semiconductor device includes: a plurality of semiconductor chips; a semiconductor substrate that has, on the same surface thereof, a chip-to-chip interconnection for electrically connecting the plurality of semiconductor chips to each other, and a plurality of chip-connection pads connected to the chip-to-chip interconnection; and a wiring board that has a plurality of lands of which pitch is larger than a pitch of the chip-connection pads, wherein a major surface of each of the plurality of semiconductor chips is connected to the chip-connection pads via a first connector so that the plurality of semiconductor chips are mounted on the semiconductor substrate, and an external-connection pad is formed on the major surface other than a region facing the semiconductor substrate, and is connected to the land on the wiring board via a second connector.

Owner:SONY CORP

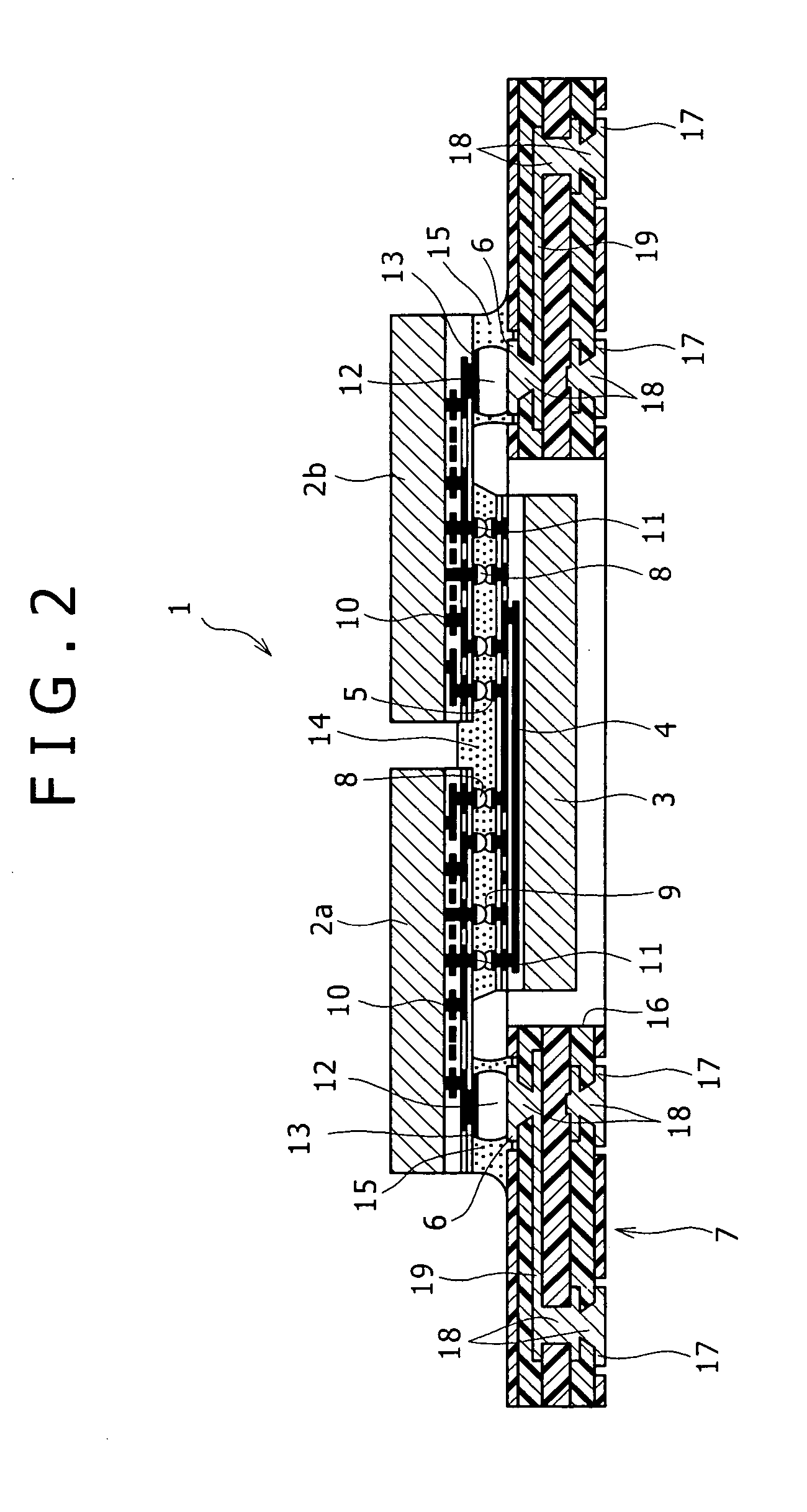

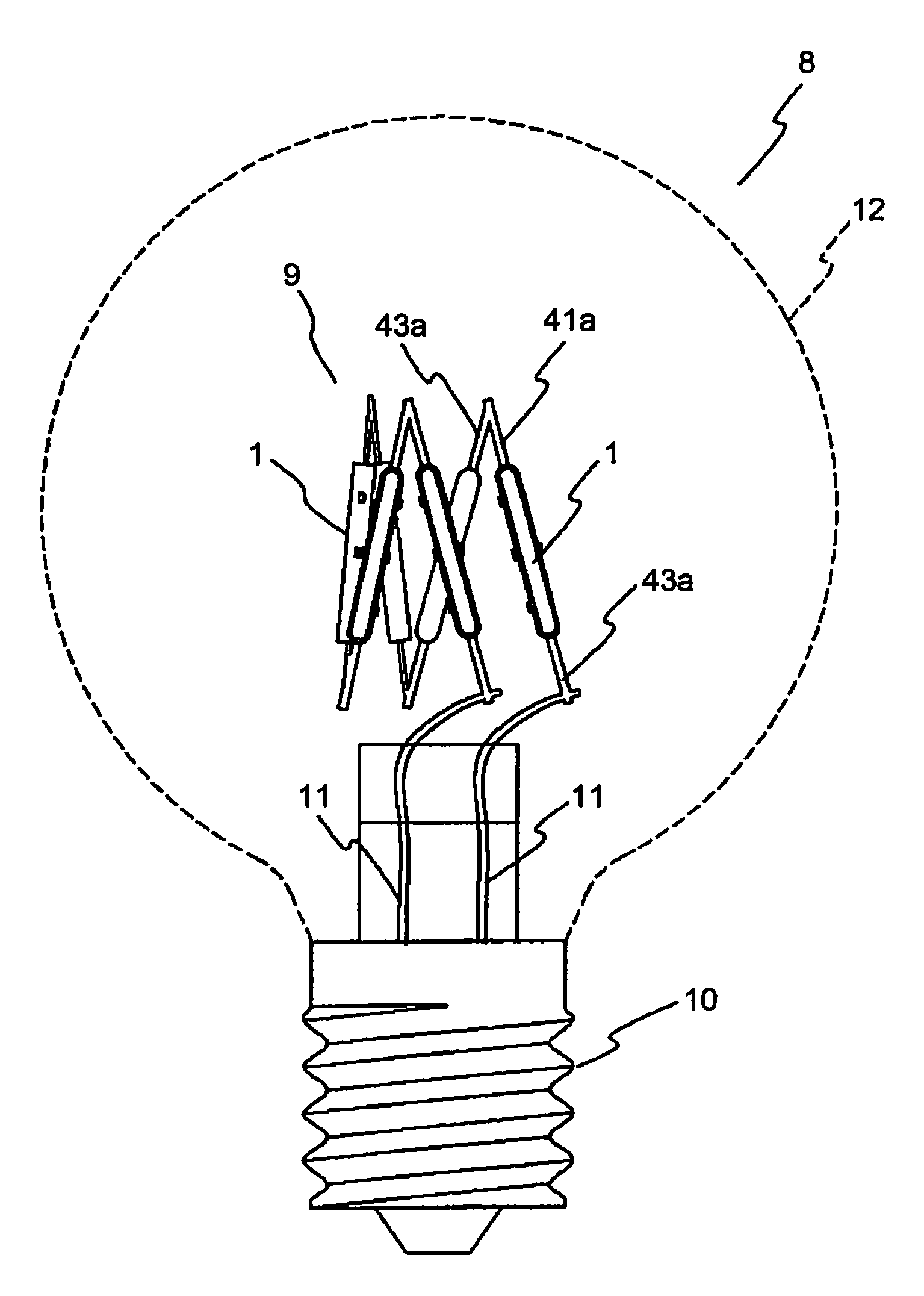

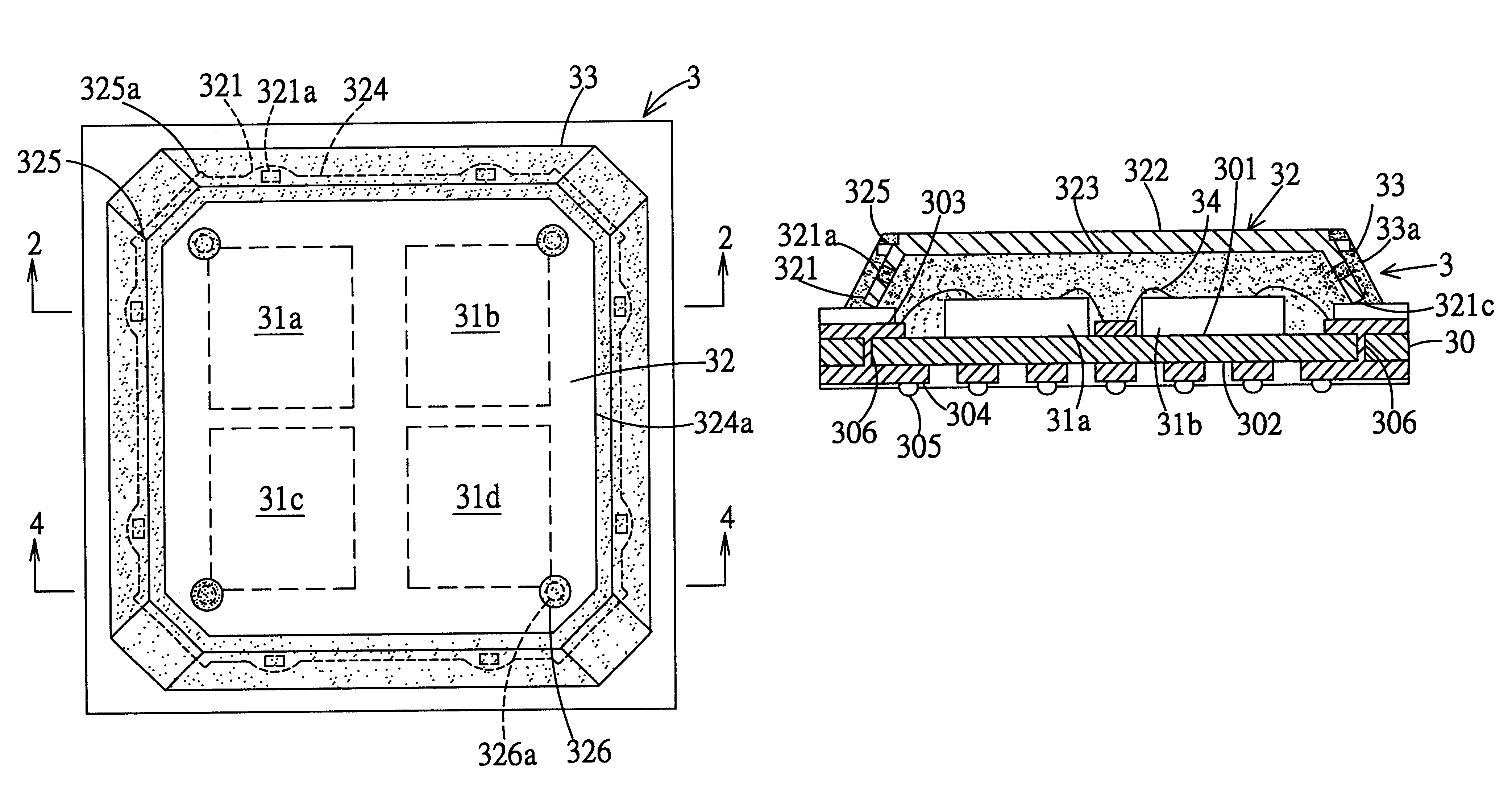

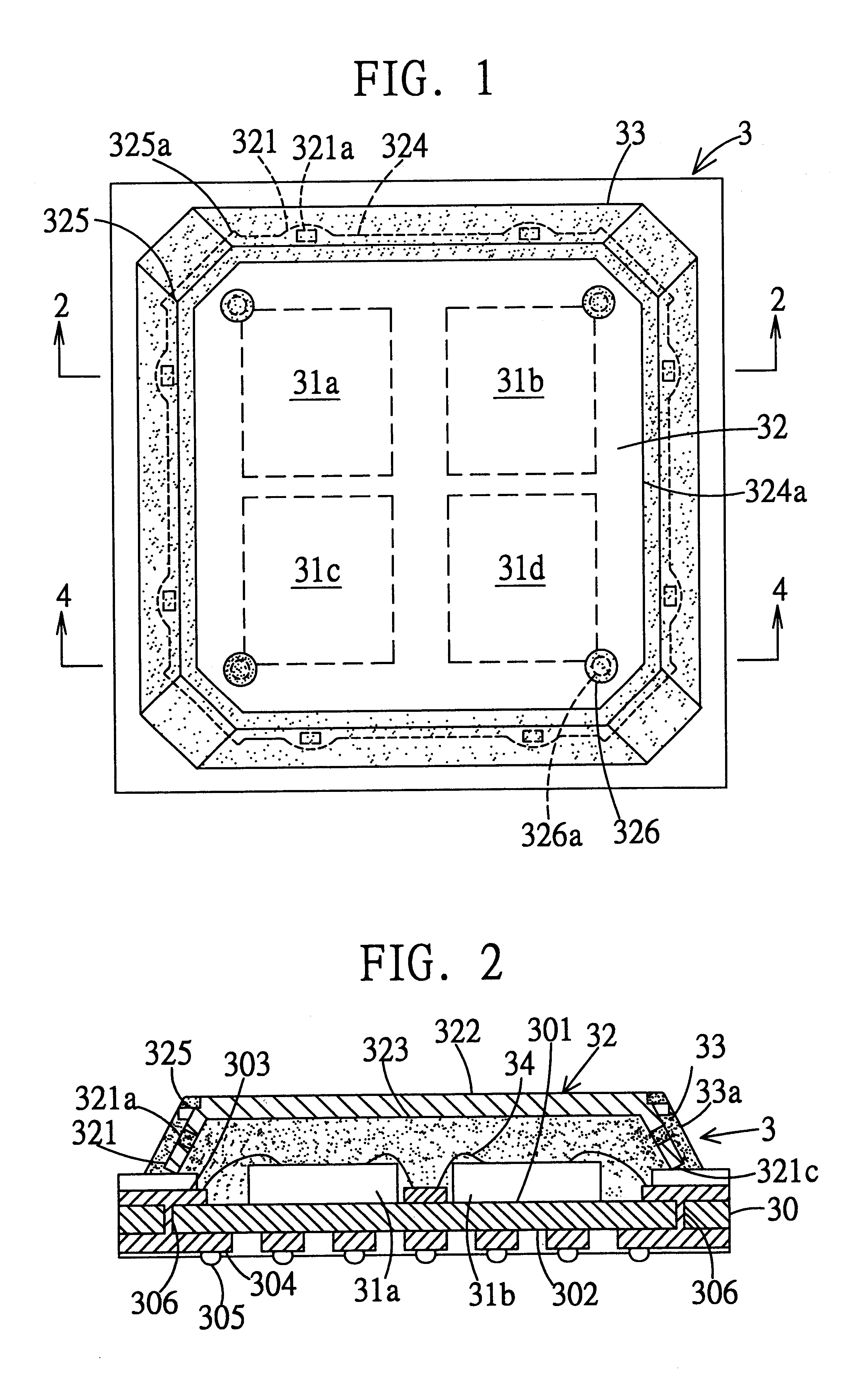

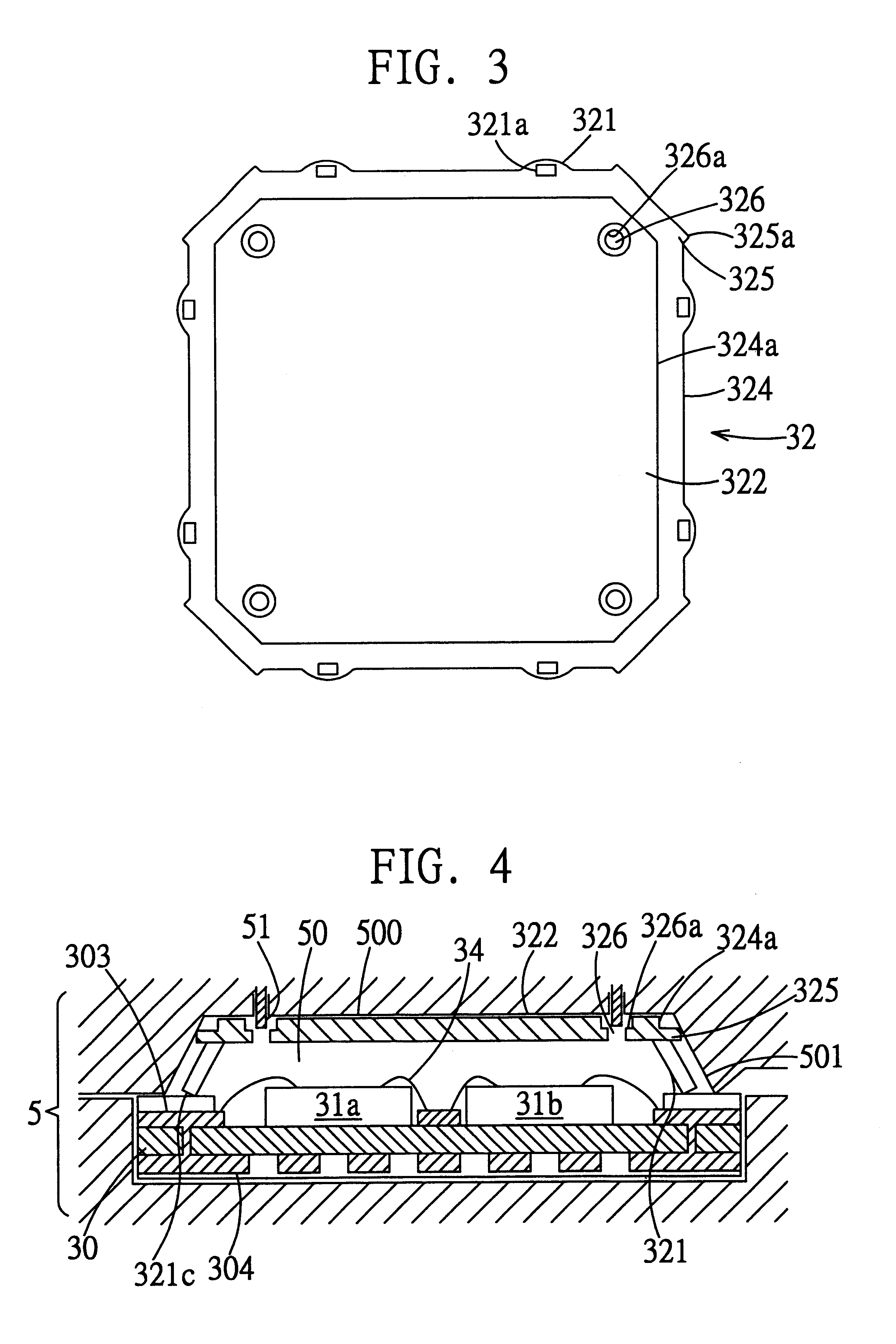

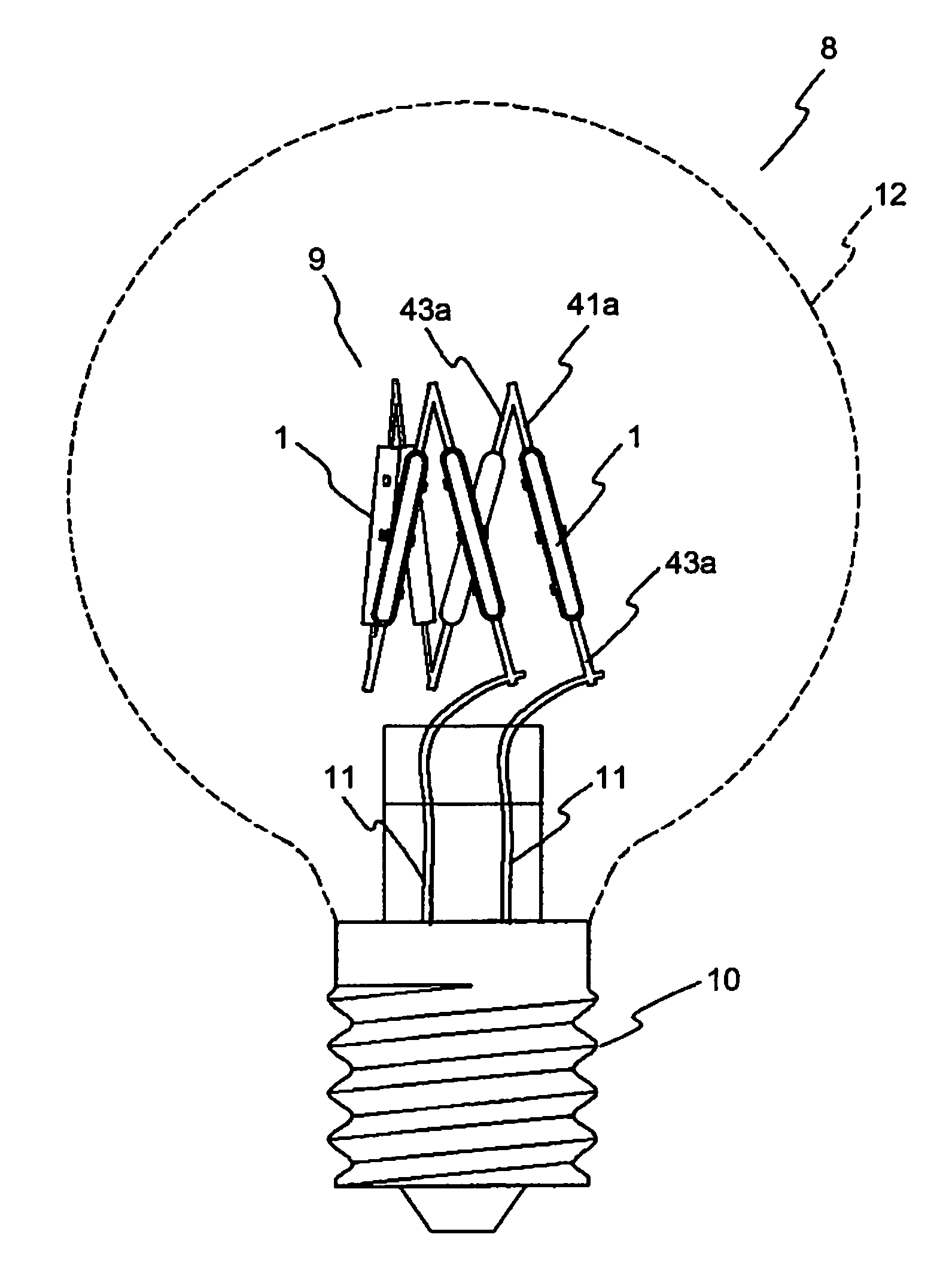

Light-emitting device and lighting apparatus incorporating same

ActiveUS20090184618A1Wide range of fieldsWide directivityDischarge tube luminescnet screensPoint-like light sourceLight equipmentEngineering

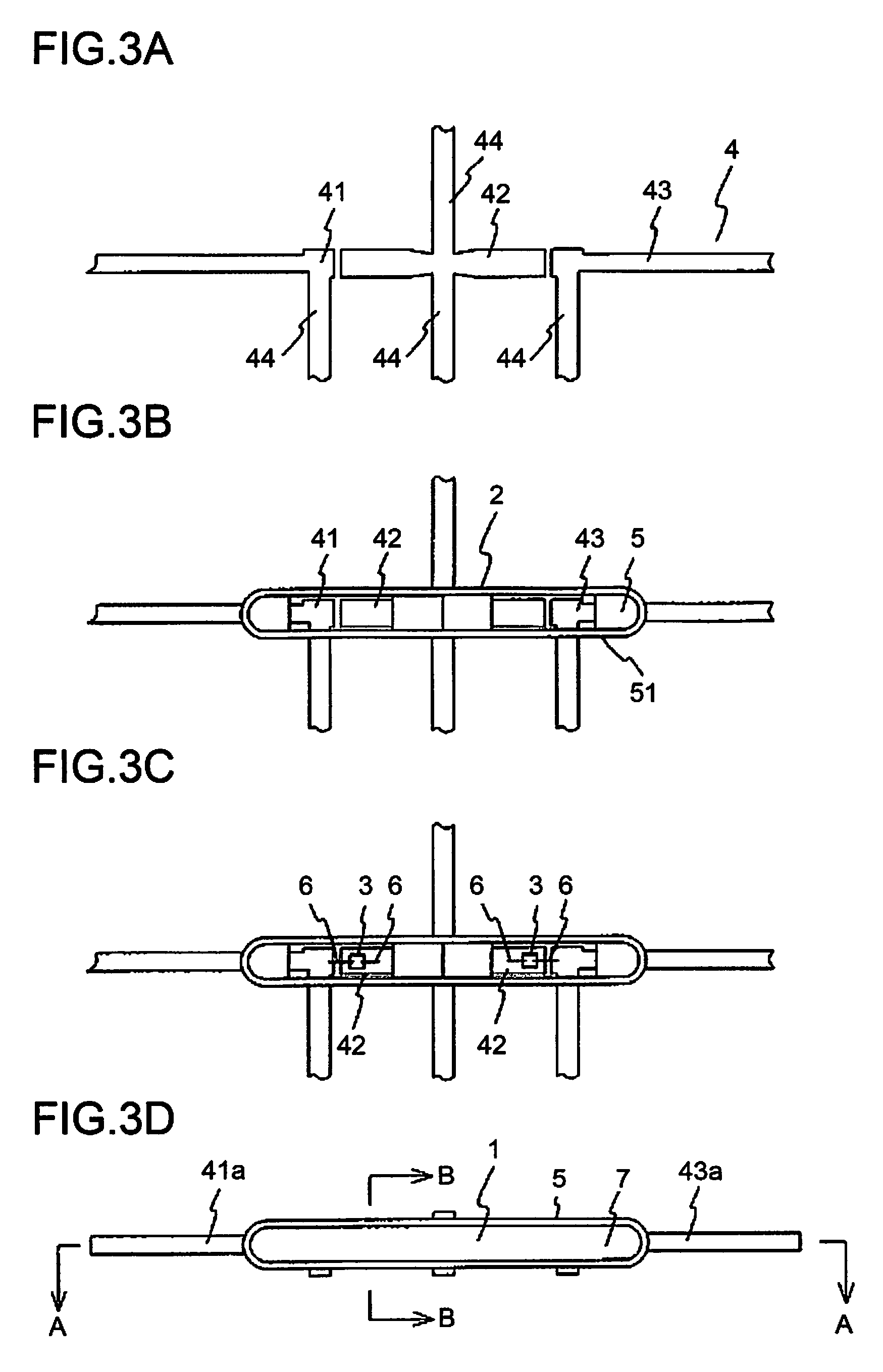

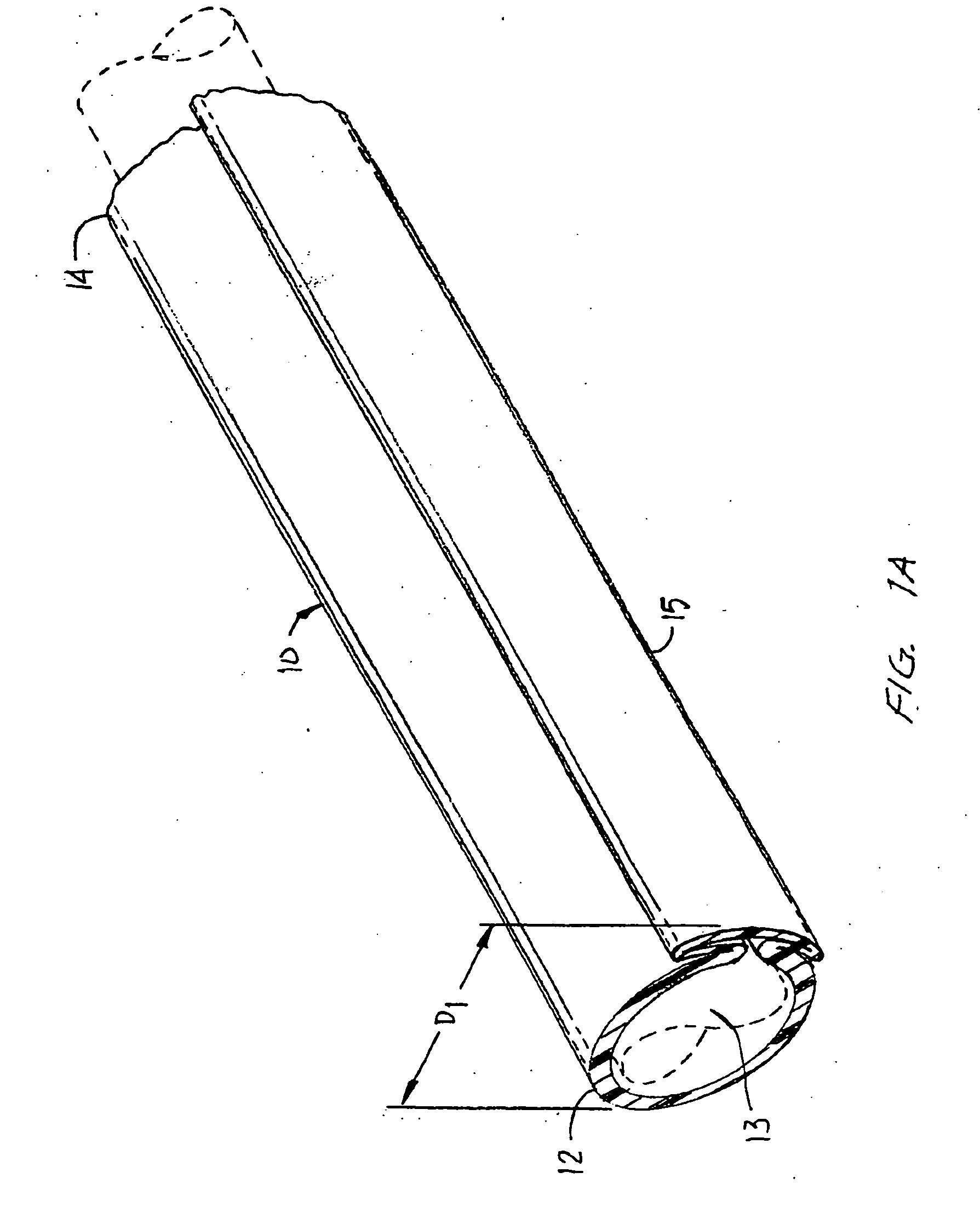

A light-emitting device is provided that can extract light in all directions and that has wide directivity. This light-emitting device includes: an elongated bar-shaped package extending sideways, the package being formed such that a plurality of leads are formed integrally with a first resin with part of the leads exposed; a light-emitting element that is fixed onto at least one of the leads and that is electrically connected to at least one of the leads; and a second resin sealing the light-emitting element. In the light-emitting device, the first resin and the second resin are formed of optically transparent resin, and the leads have outer lead portions used for external connection and protruding sideways from both left and right ends of the package.

Owner:USHIO DENKI KK

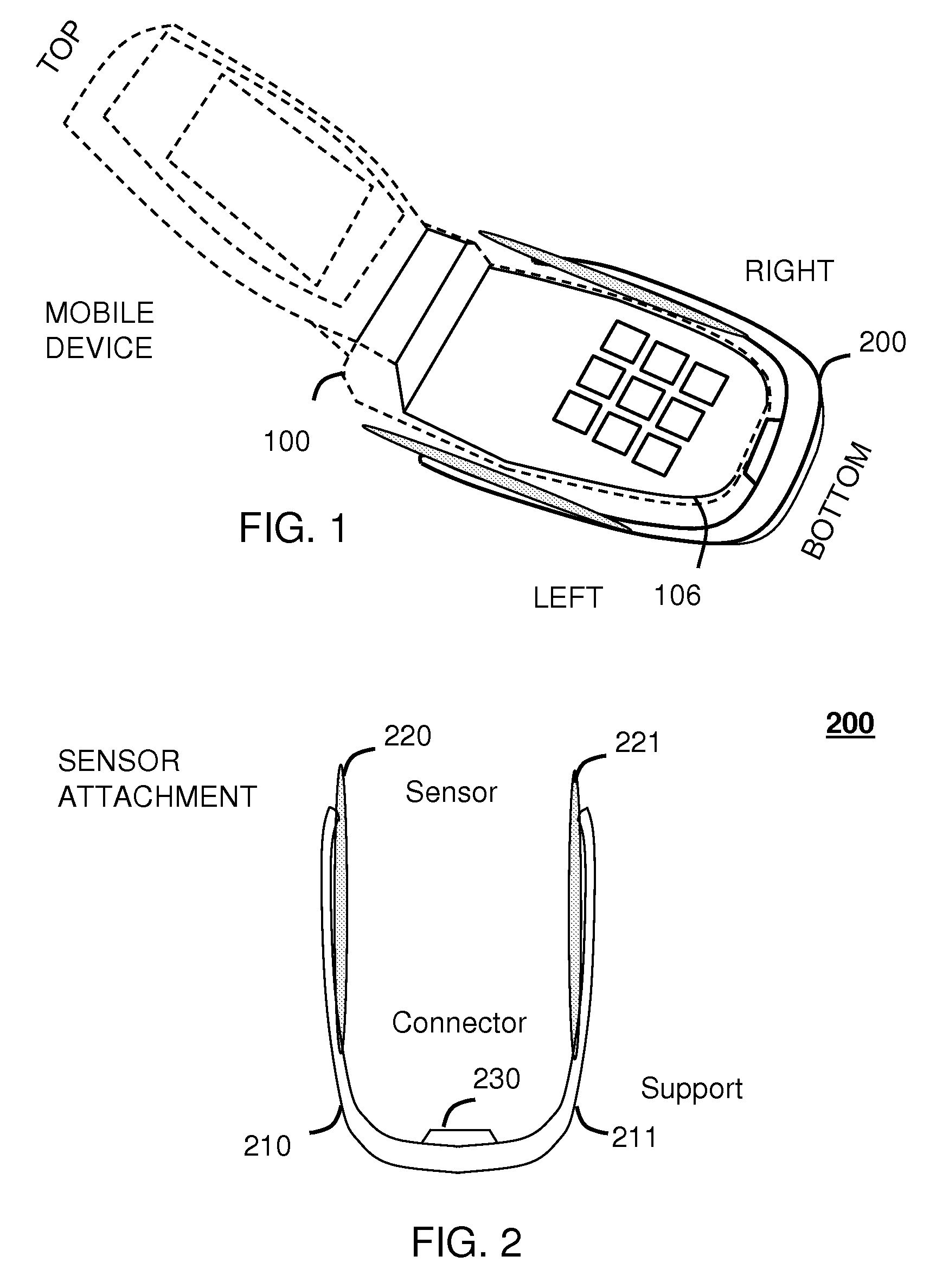

Semiconductor package having a heat sink with an exposed surface

InactiveUS6246115B1Precise positioningAvoid flashSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor package

An integrated circuit package with a fully-exposed heat sink is provided. The integrated circuit package includes a substrate having a first side being formed with first conductive traces and a second side being formed with second conductive traces. At least one chip is mounted on the substrate and electrically connected to the first conductive traces. A plurality of solder balls are provided at the terminal ends of the second conductive traces to allow external connection of the chip. The fully-exposed heat sink is mounted on the substrate. The heat sink is formed with a plurality of supportive legs arranged in such a manner as to allow a bottom surface of the heat sink to be separated from the chip and a top surface of the heat sink to be tightly attached to a cavity in a mold used to form an encapsulant for enclosing the chip. A plurality of positioning tongues are formed on the heat sink for securing the heat sink in position when performing a molding process for forming the encapsulant. With this integrated circuit package, no jig is required in the assembly of the integrated circuit package. Moreover, since there is no need to use adhesives to adhere the supportive legs onto the substrate, the integrated circuit package would not suffer from delamination as in the case of the prior art. The fully-exposed heat sink allows an increased heat-dissipating efficient as compared to the prior art.

Owner:SILICONWARE PRECISION IND CO LTD

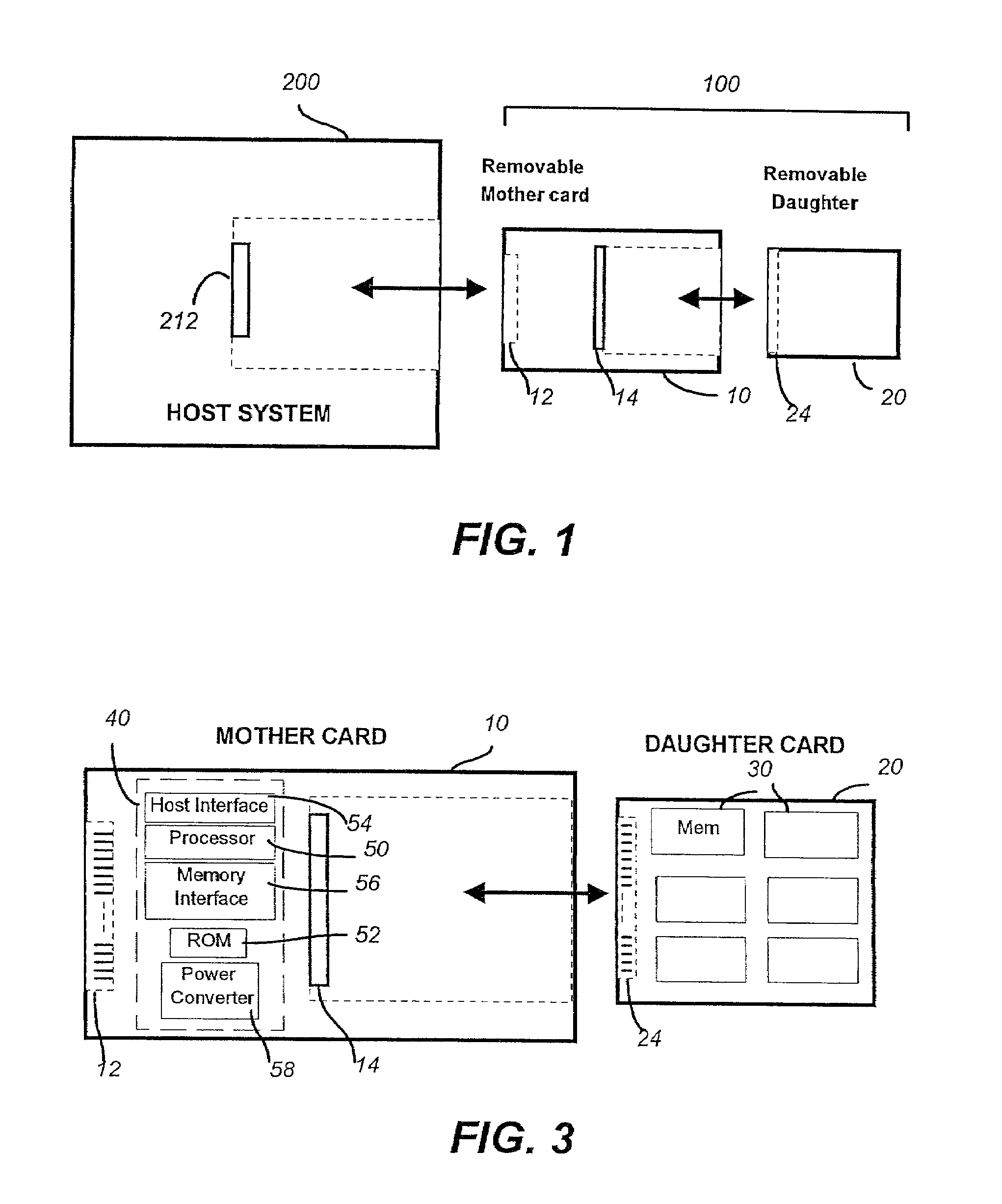

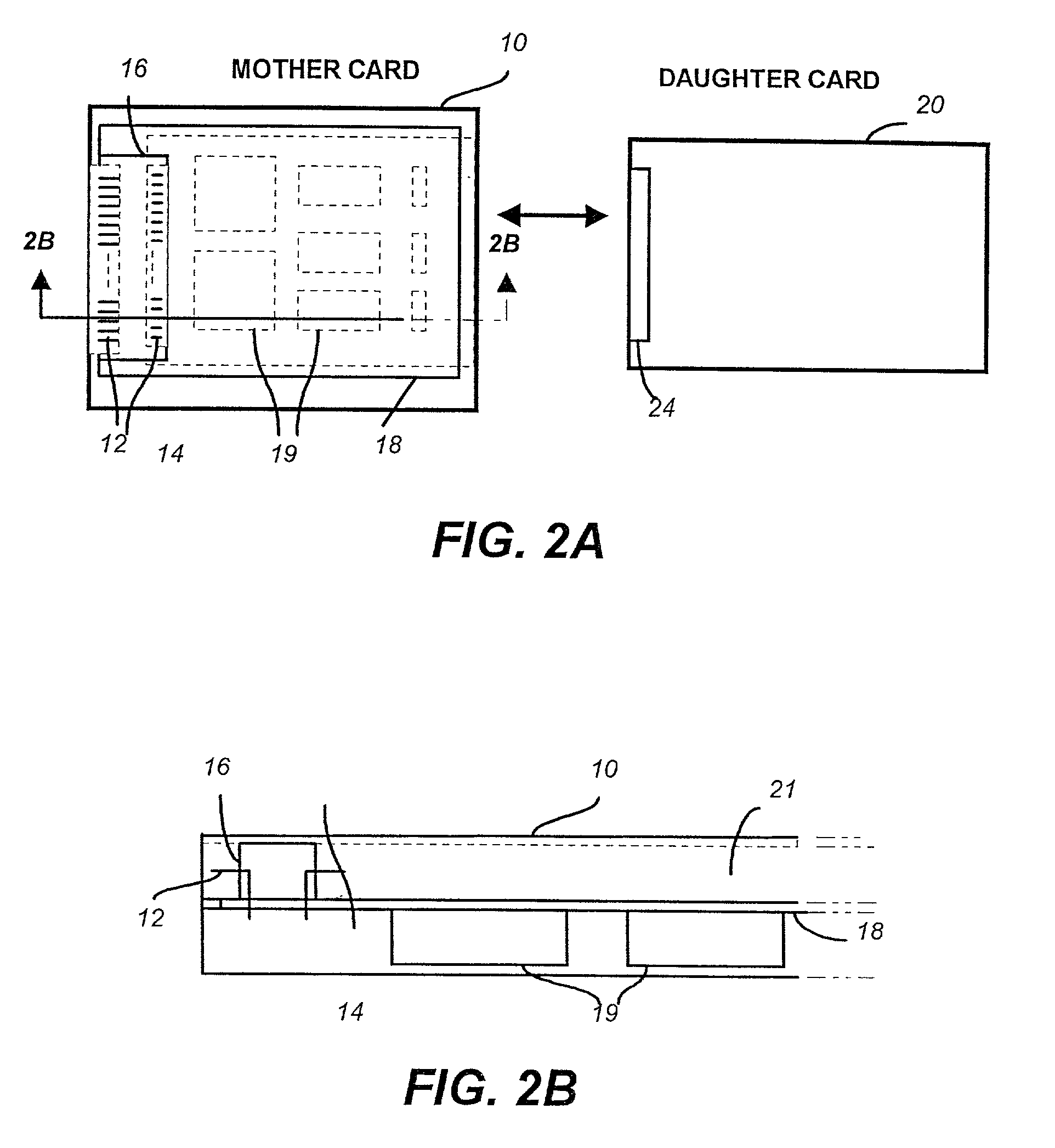

Removable mother/daughter peripheral card

InactiveUS7137011B1Add and decrease memory capacityMore cost-effective memory systemCoupling device connectionsSubstation/switching arrangement detailsFloppy diskDaughterboard

A peripheral card having a Personal Computer (“PC”) card form factor and removably coupled externally to a host system is further partitioned into a mother card portion and a daughter card portion. The daughter card is removably coupled to the mother card. In the preferred embodiment, a low cost flash “floppy” is accomplished with the daughter card containing only flash EEPROM chips and being controlled by a memory controller residing on the mother card. Other aspects of the invention includes a comprehensive controller on the mother card able to control a predefined set of peripherals on daughter cards connectable to the mother card; relocation of some host resident hardware to the mother card to allow for a minimal host system; a mother card that can accommodate multiple daughter cards; daughter cards that also operates directly with hosts having embedded controllers; daughter cards carrying encoded data and information for decoding it; and daughter cards with security features.

Owner:SANDISK TECH LLC

Instruments having an external working channel

Owner:INTUITIVE SURGICAL

Portable audio reproduction system

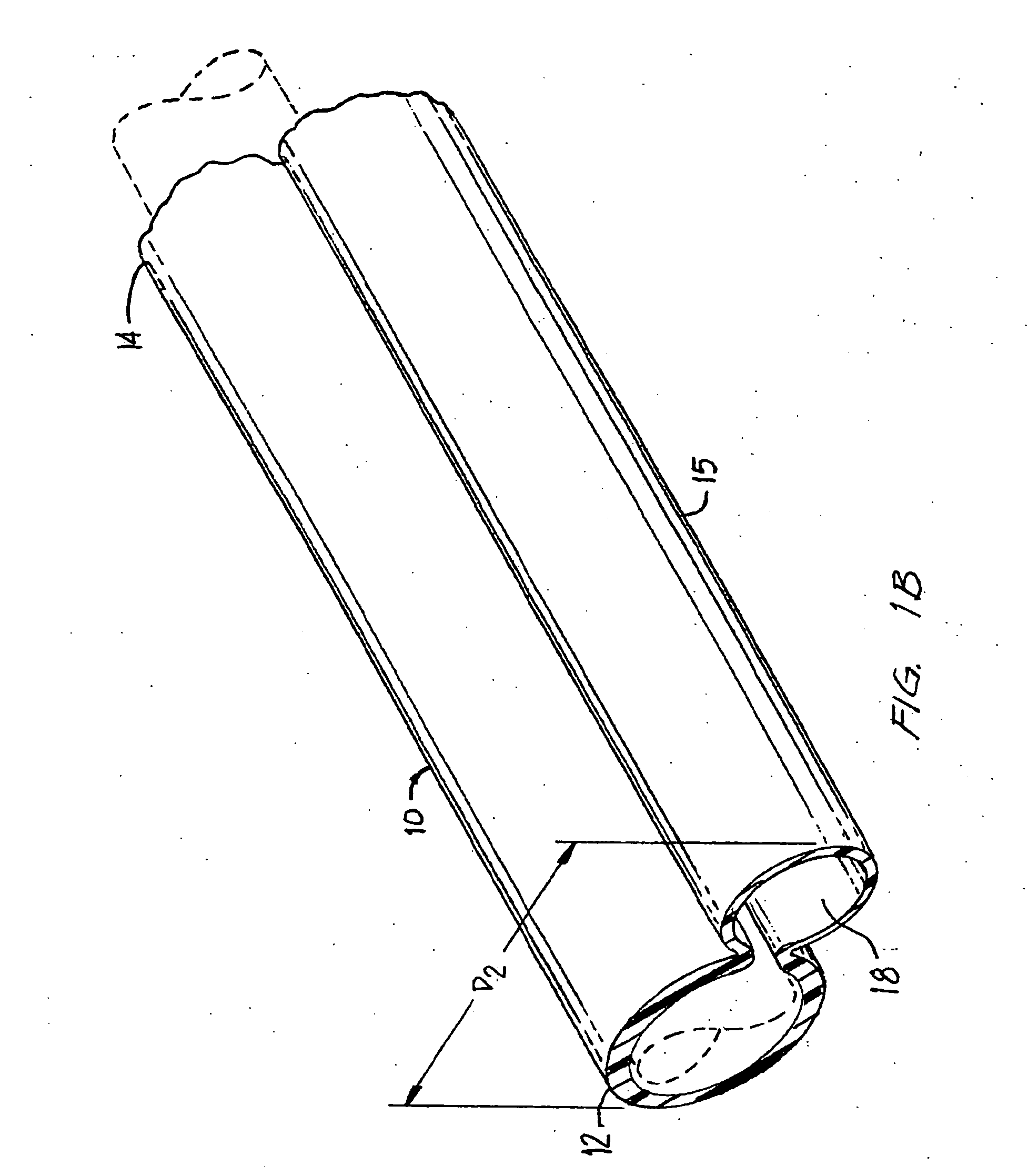

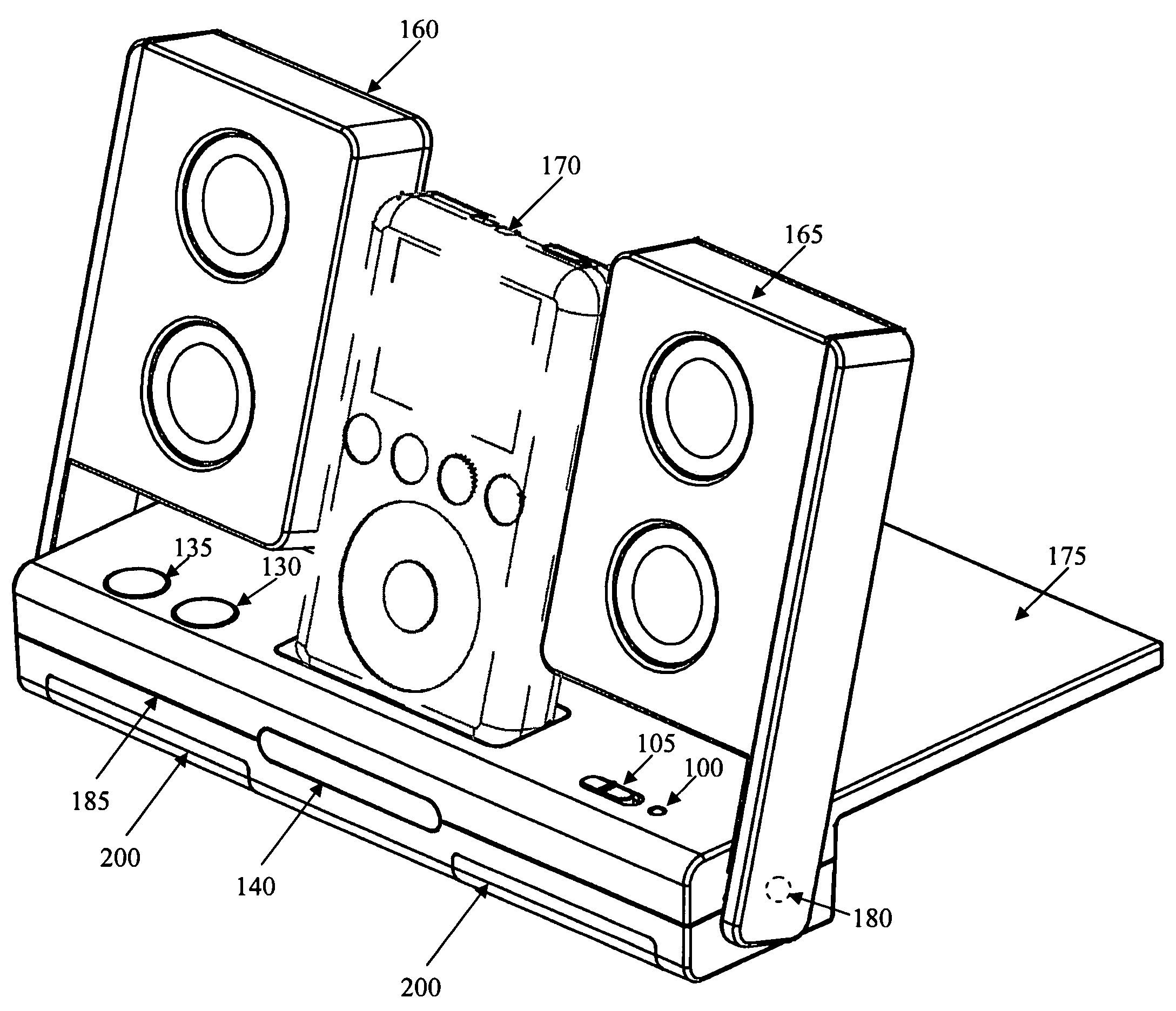

InactiveUS7095867B2Improve fidelityEnhance audio fidelity and reproduced frequency rangeDocking-station type assembliesLoudspeaker spatial/constructional arrangementsDocking stationAudio signal flow

A portable system capable of receiving audio signals from one or more sources and reproducing the signals via speakers contained therein. The portable audio reproduction system can include a docking station or similar means for communicatively coupling an audio device to the portable audio reproduction system, thereby reducing desktop clutter and simplifying connecting the portable audio reproduction system with the audio device. The speakers of the portable audio reproduction system can preferably be received within a base portion of the system, thereby protecting the speakers during transport and reducing the overall size of the system for improved portability. External connections may also be provided, thereby enabling the portable audio reproduction system to receive audio signals from additional sources, and a mixer allows the system to reproduce signals from a portable audio device and an auxiliary source, such as a computer.

Owner:ALTEC LANSING LLC

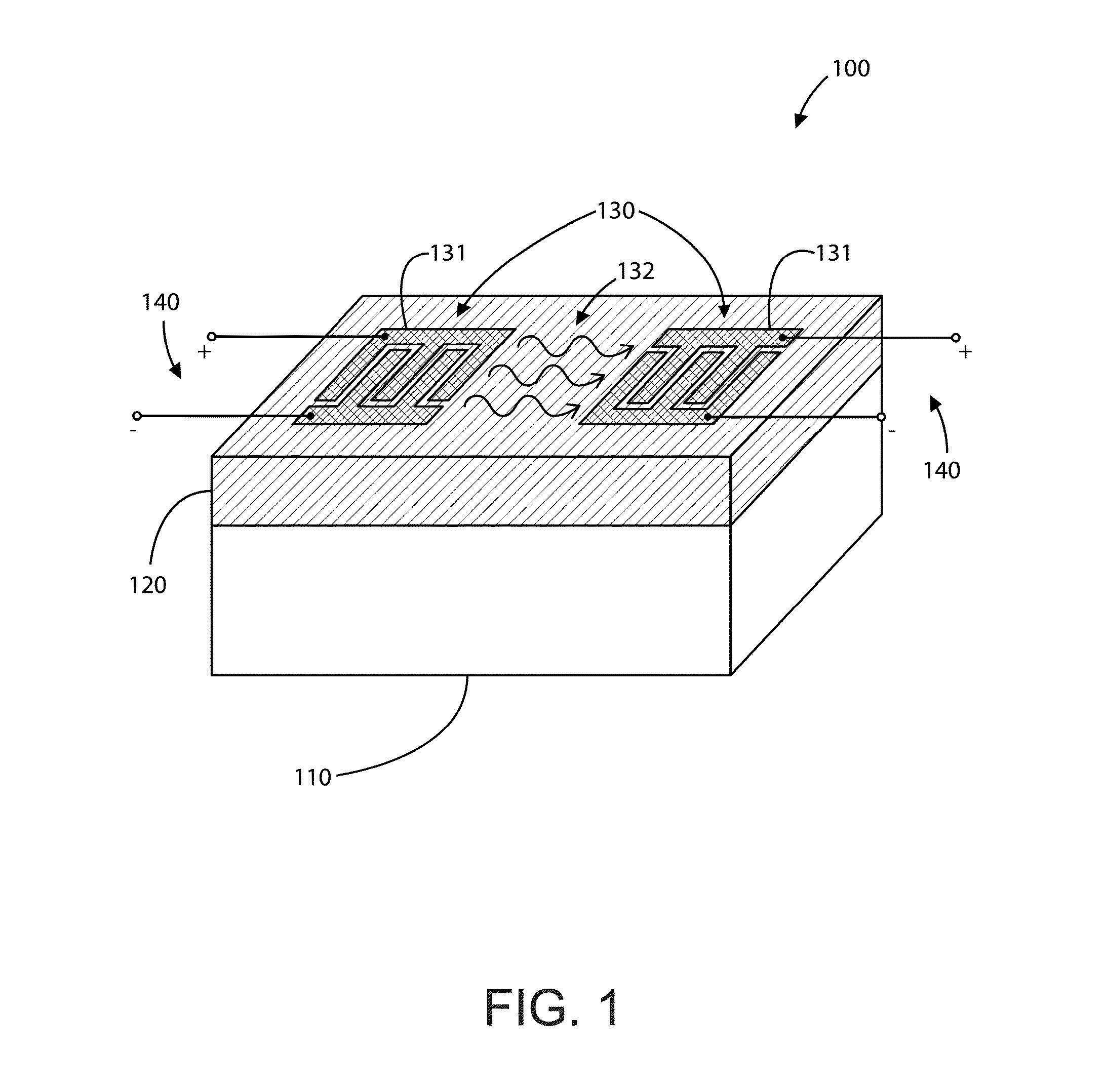

Single crystal acoustic resonator and bulk acoustic wave filter

ActiveUS20160028367A1AdvantageSimple and cost-effectivePiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesMetallic materialsCarbide

A method of wafer scale packaging acoustic resonator devices and an apparatus therefor. The method including providing a partially completed semiconductor substrate comprising a plurality of single crystal acoustic resonator devices provided on a silicon and carbide bearing material, each having a first electrode member, a second electrode member, and an overlying passivation material. At least one of the devices to be configured with an external connection, a repassivation material overlying the passivation material, an under metal material overlying the repassivation material. Copper pillar interconnect structures are then configured overlying the electrode members, and solder bump structures are form overlying the copper pillar interconnect structures.

Owner:AKOUSTIS INC

Semiconductor device incorporating a semiconductor constructing body and an interconnecting layer which is connected to a ground layer via a vertical conducting portion

InactiveUS7279750B2Deterioration of characteristic can be suppressedDownsize the electronic apparatusSemiconductor/solid-state device detailsNoise reduction constructionMetal foilSemiconductor

A semiconductor device includes metal foil to which a ground potential is applied, at a semiconductor constructing body provided on the metal foil and having a semiconductor substrate and a plurality of external connection electrodes provided on the semiconductor substrate. An insulating layer is provided around the semiconductor constructing body and has a thickness substantially equal to the semiconductor constructing body. An one upper interconnecting layer is provided on the semiconductor constructing body and insulating layer, and electrically connected to the external connection electrodes. A vertical conducting portion extends through the insulating layer and electrically connects the metal foil and upper interconnecting layer.

Owner:CMK

Light-emitting device and lighting apparatus incorporating same

ActiveUS8400051B2Reduce directivityEasy extractionIncadescent screens/filtersDischarge tube luminescnet screensLight equipmentLight emitting device

A light-emitting device is provided that can extract light in all directions and that has wide directivity. This light-emitting device includes: an elongated bar-shaped package extending sideways, the package being formed such that a plurality of leads are formed integrally with a first resin with part of the leads exposed; a light-emitting element that is fixed onto at least one of the leads and that is electrically connected to at least one of the leads; and a second resin sealing the light-emitting element. In the light-emitting device, the first resin and the second resin are formed of optically transparent resin, and the leads have outer lead portions used for external connection and protruding sideways from both left and right ends of the package.

Owner:USHIO DENKI KK

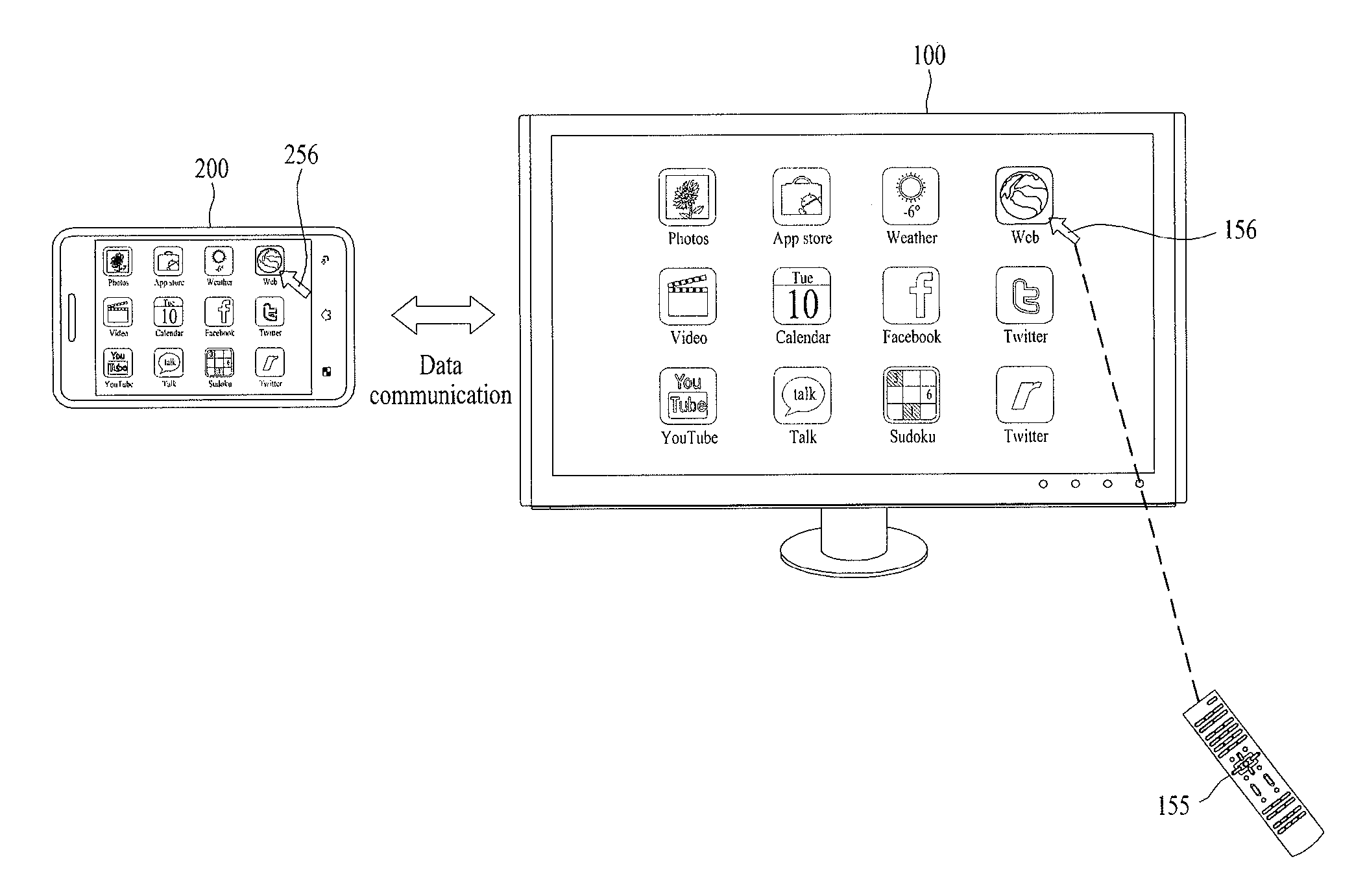

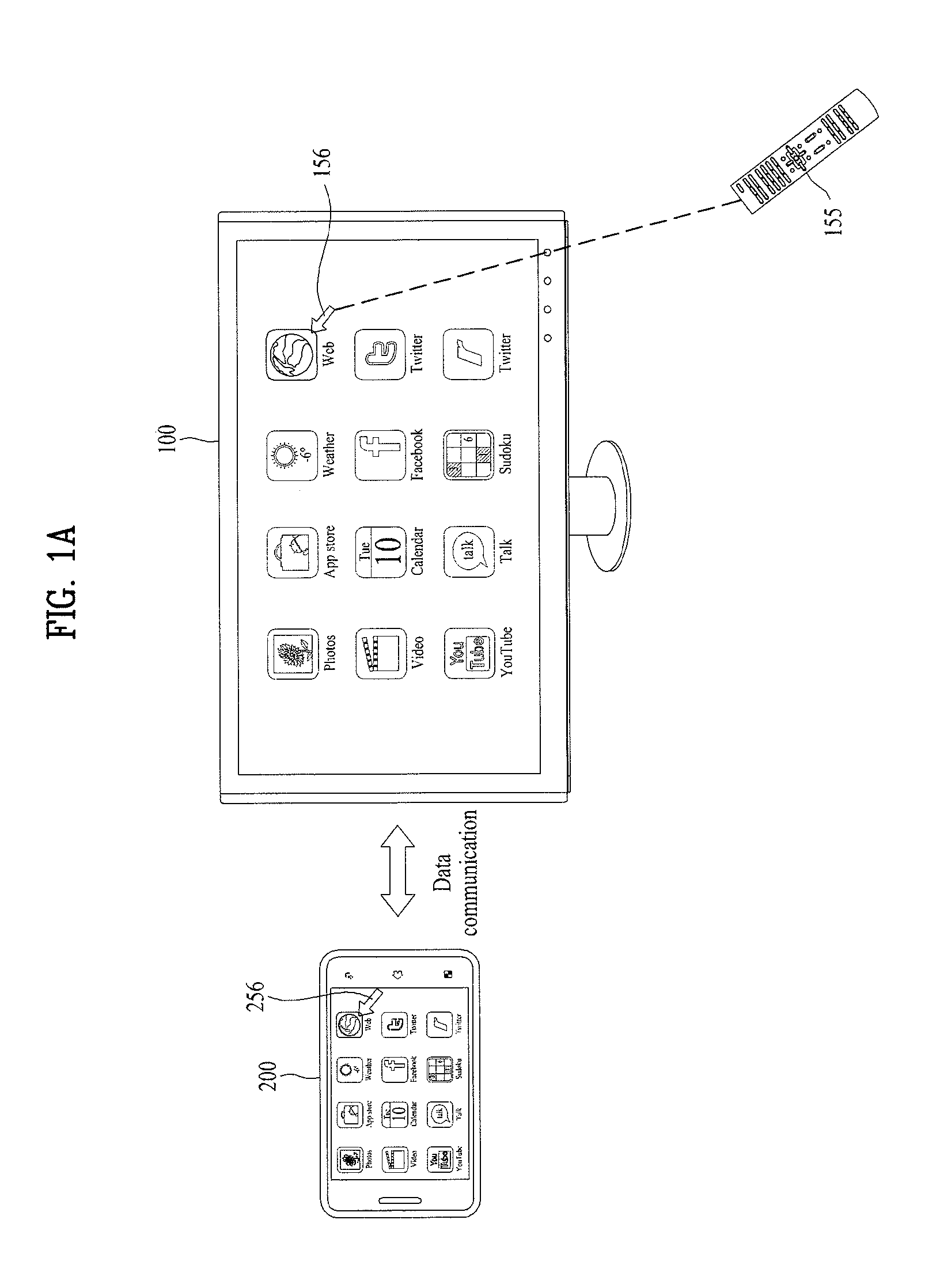

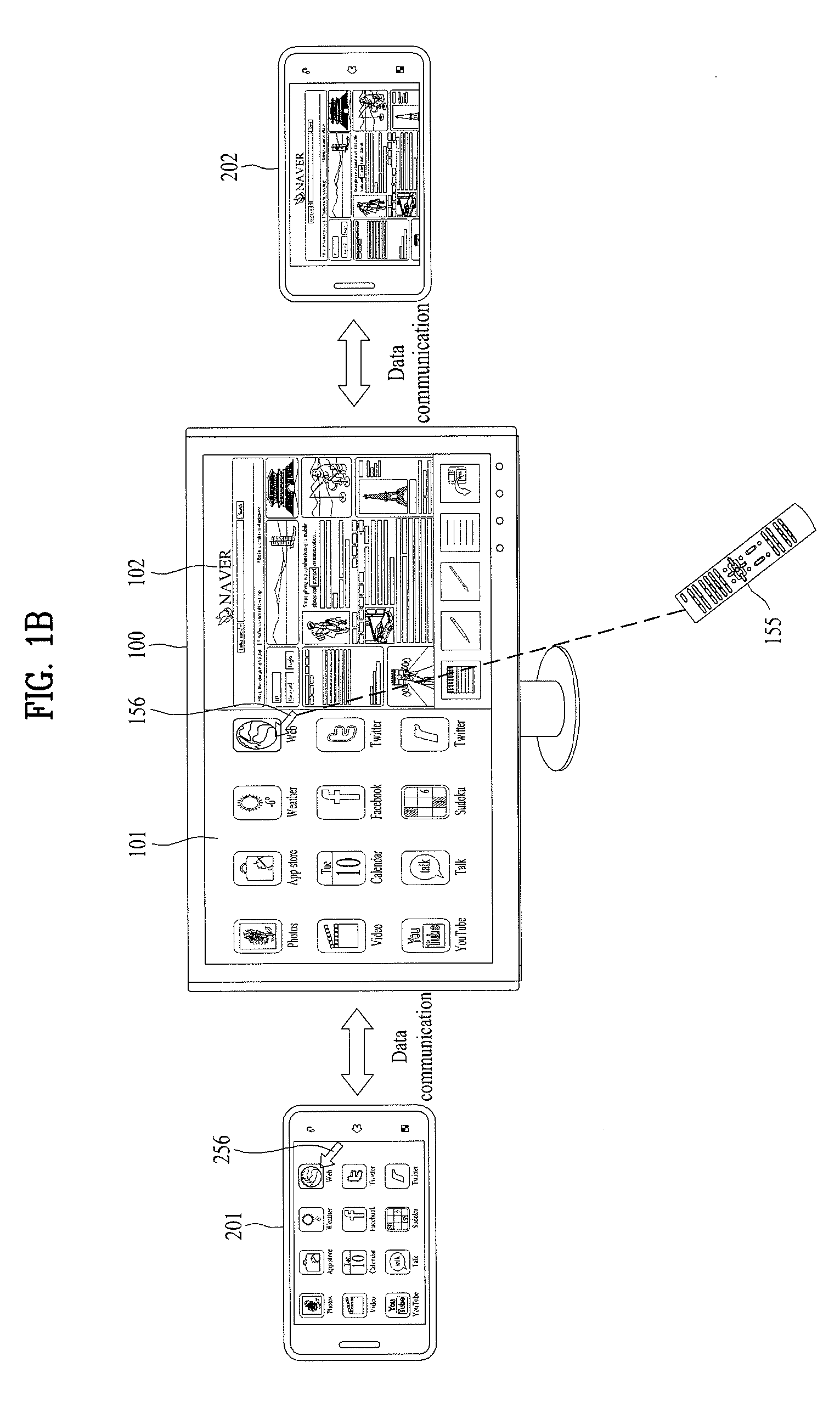

Mobile terminal, image display device and user interface provision method using the same

ActiveUS20140009394A1Effective controlTelevision system detailsDigital data processing detailsDisplay deviceMirror image

A method of controlling a plurality of mobile terminals connected to an externally connected image display device. The method includes transmitting screen information from a first mobile terminal to the image display device; transmitting screen information from a second mobile terminal to the image display device; displaying a first mirroring screen corresponding to the screen information of the first mobile terminal in a first region of a display of the image display device, and displaying a second mirroring screen corresponding to the screen information of the second mobile terminal in a second region of the display of the image display device; tracking a cursor on the display of the image display device input from an input unit of the image display device; and controlling the first mobile terminal from the image display device when the cursor is within the first region of the display and controlling the second mobile terminal from the image display device when the cursor is within the second region of the display.

Owner:LG ELECTRONICS INC

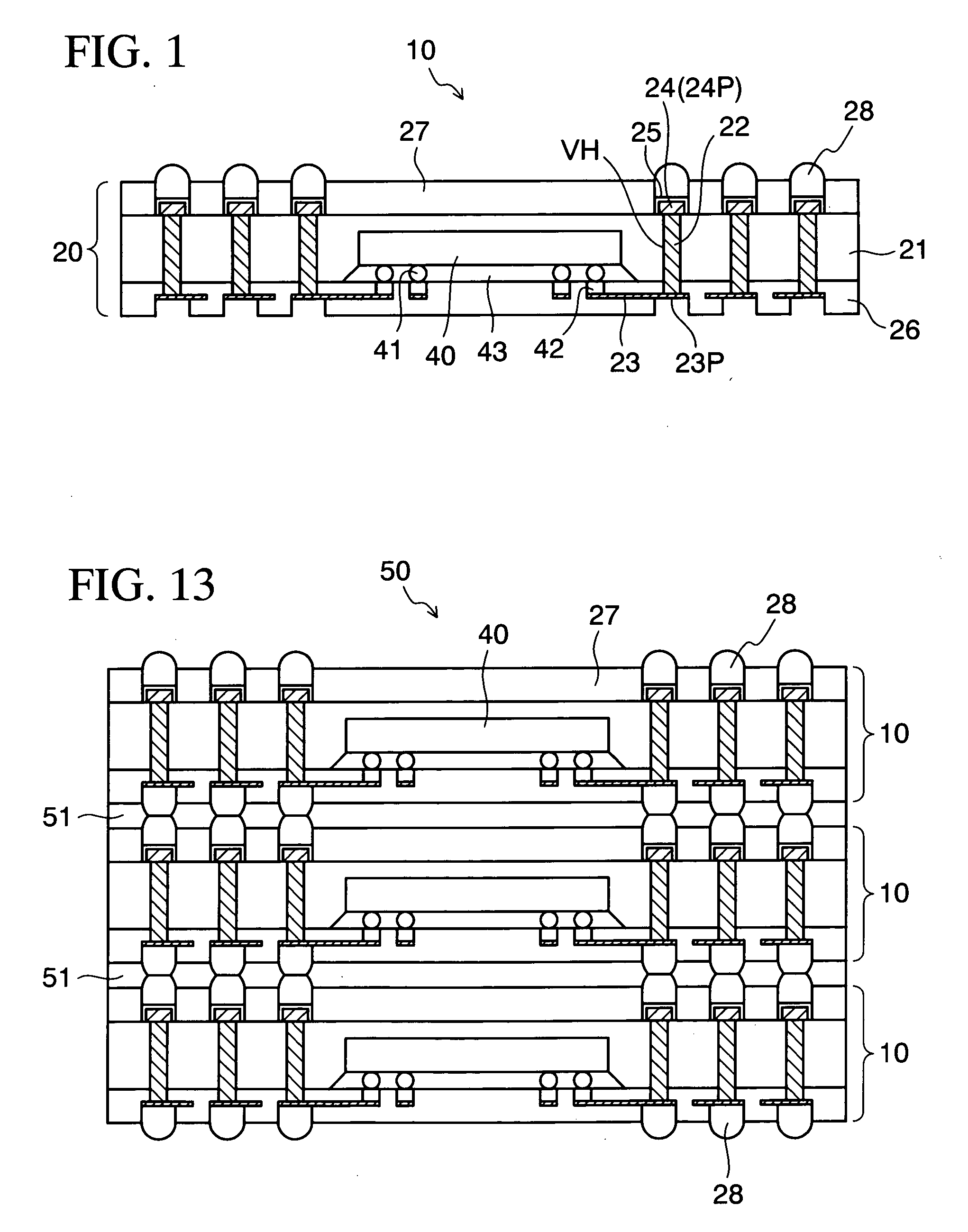

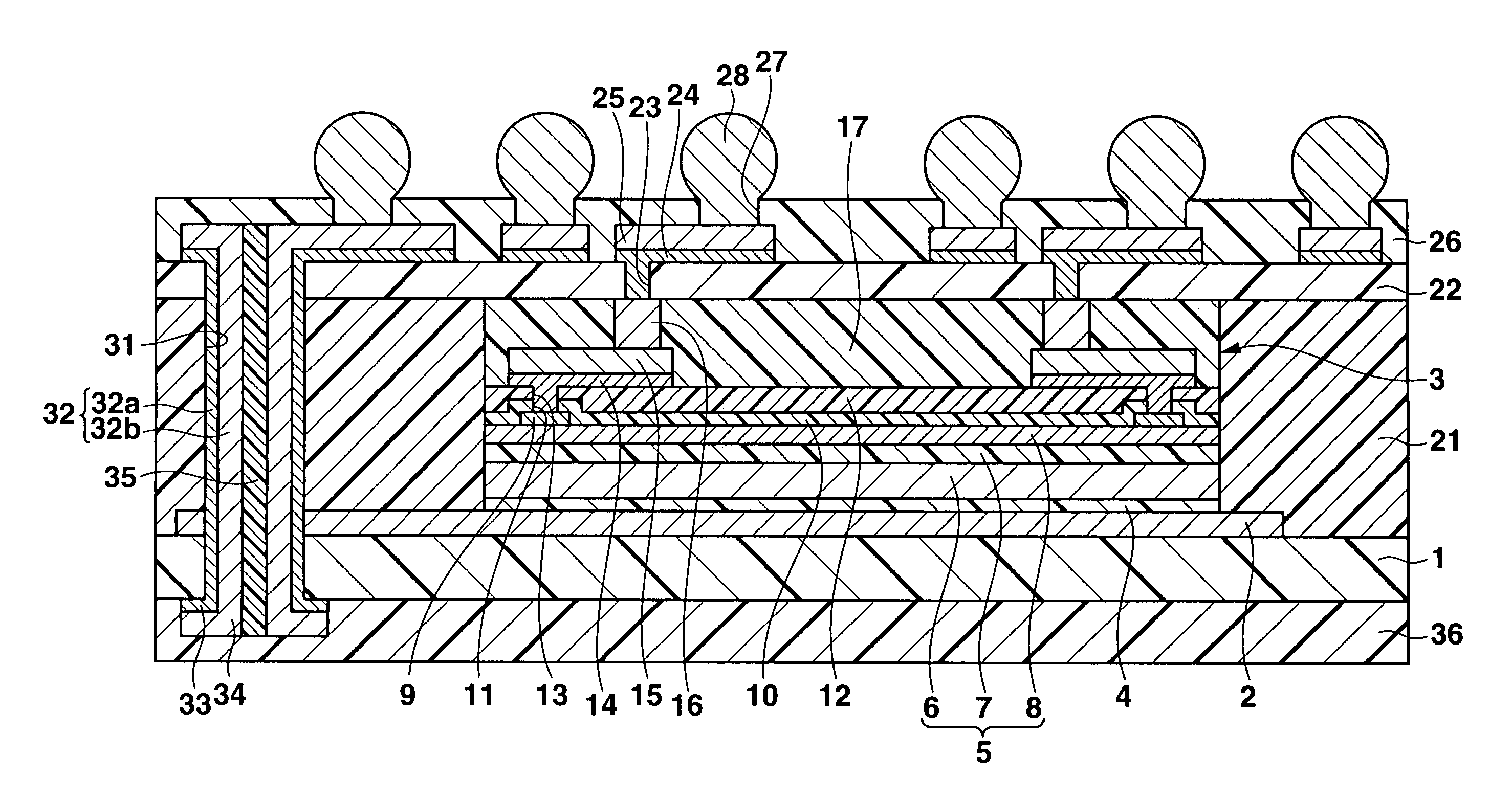

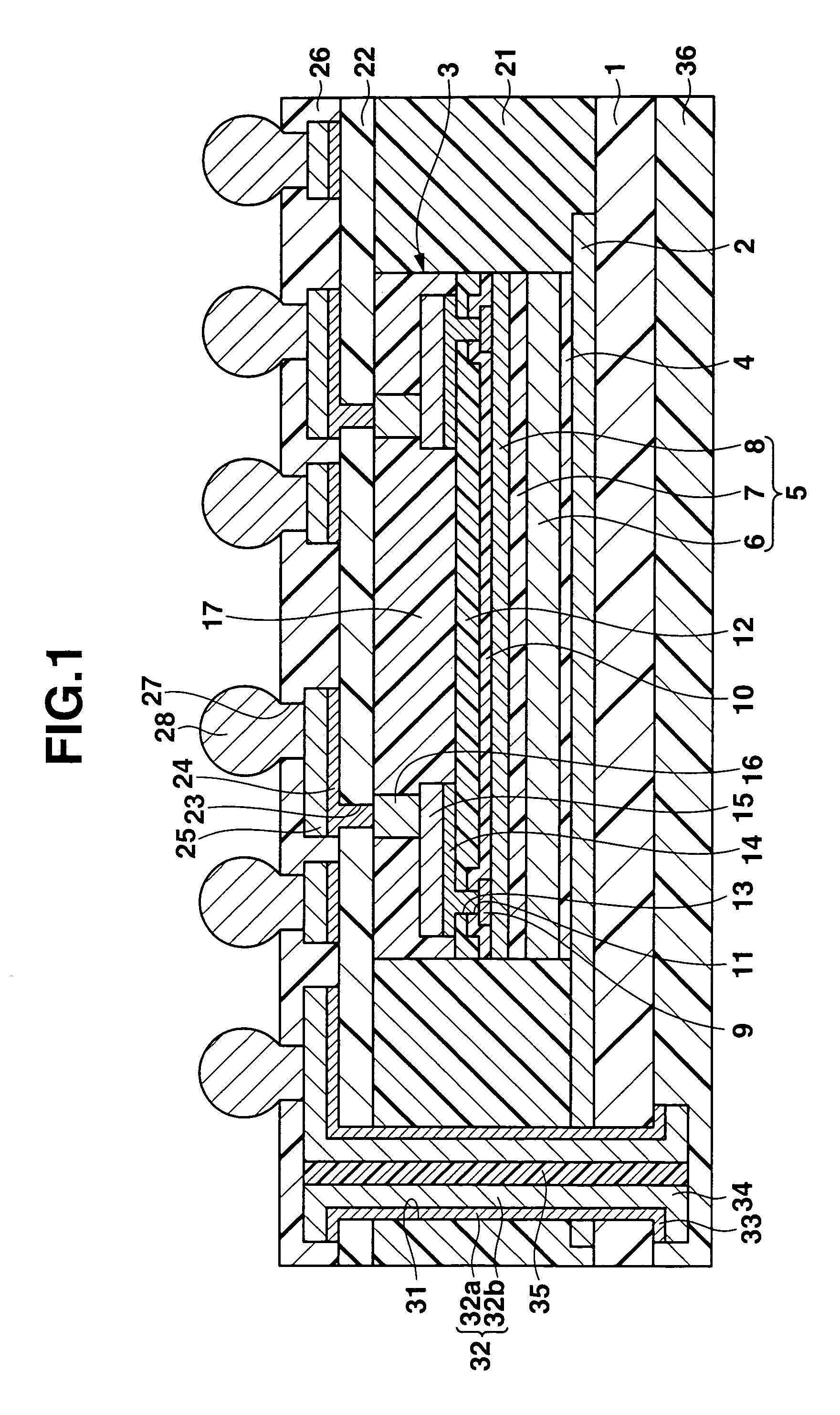

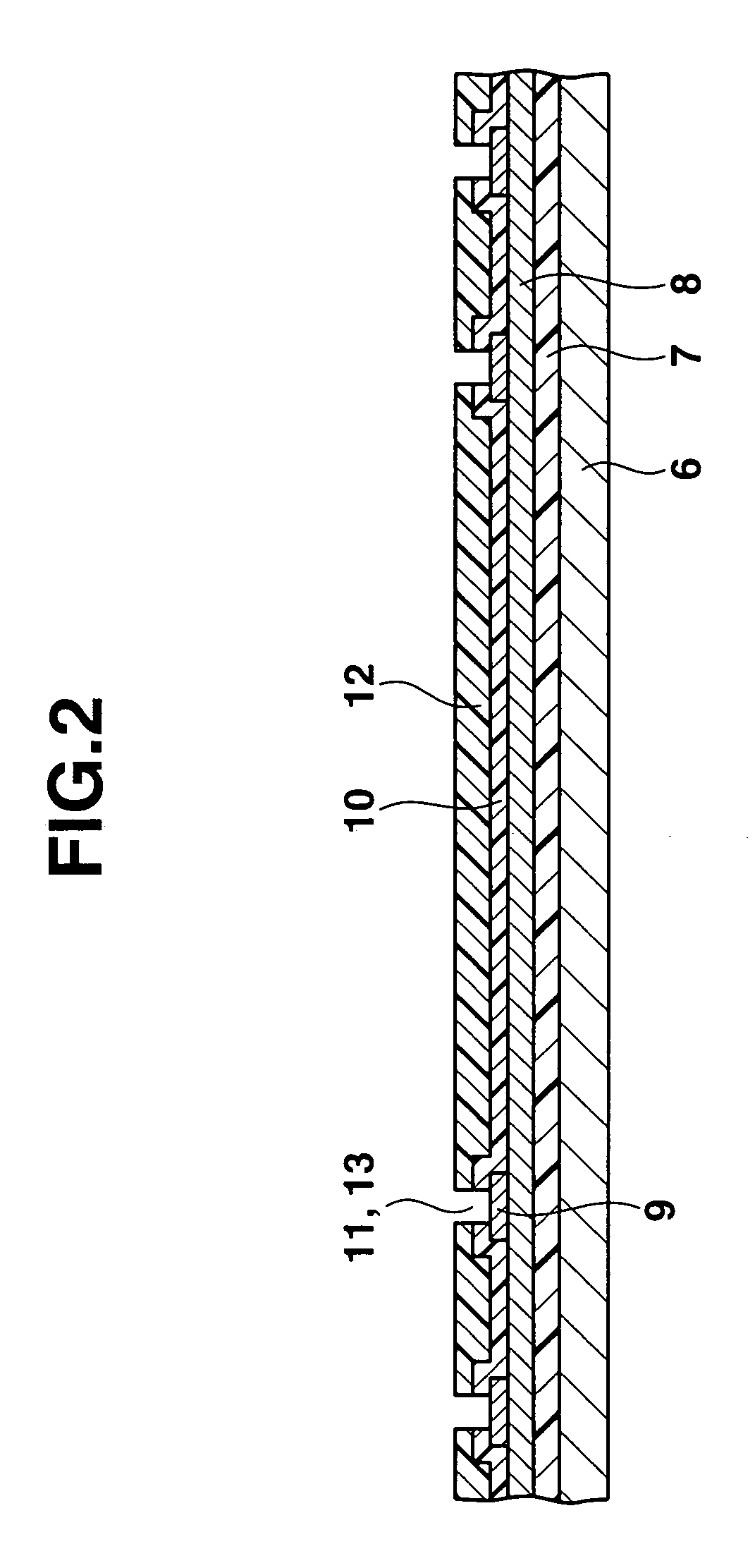

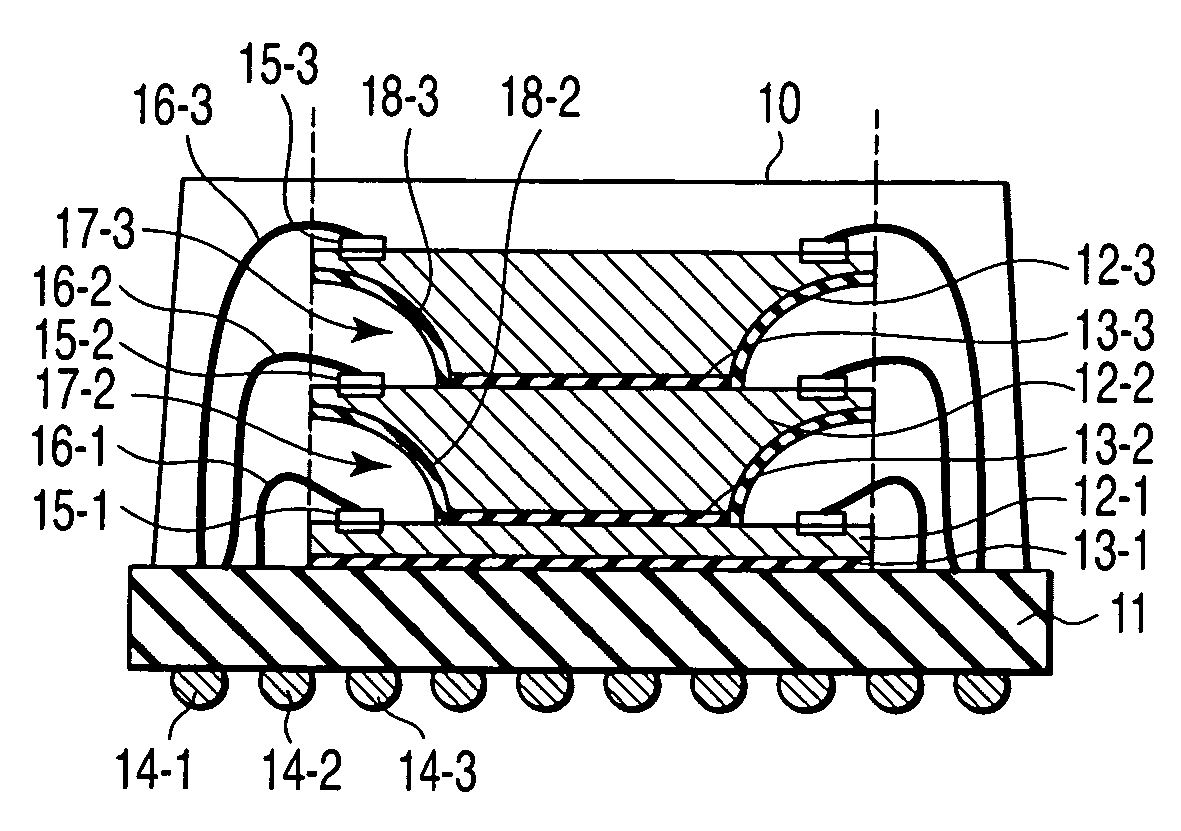

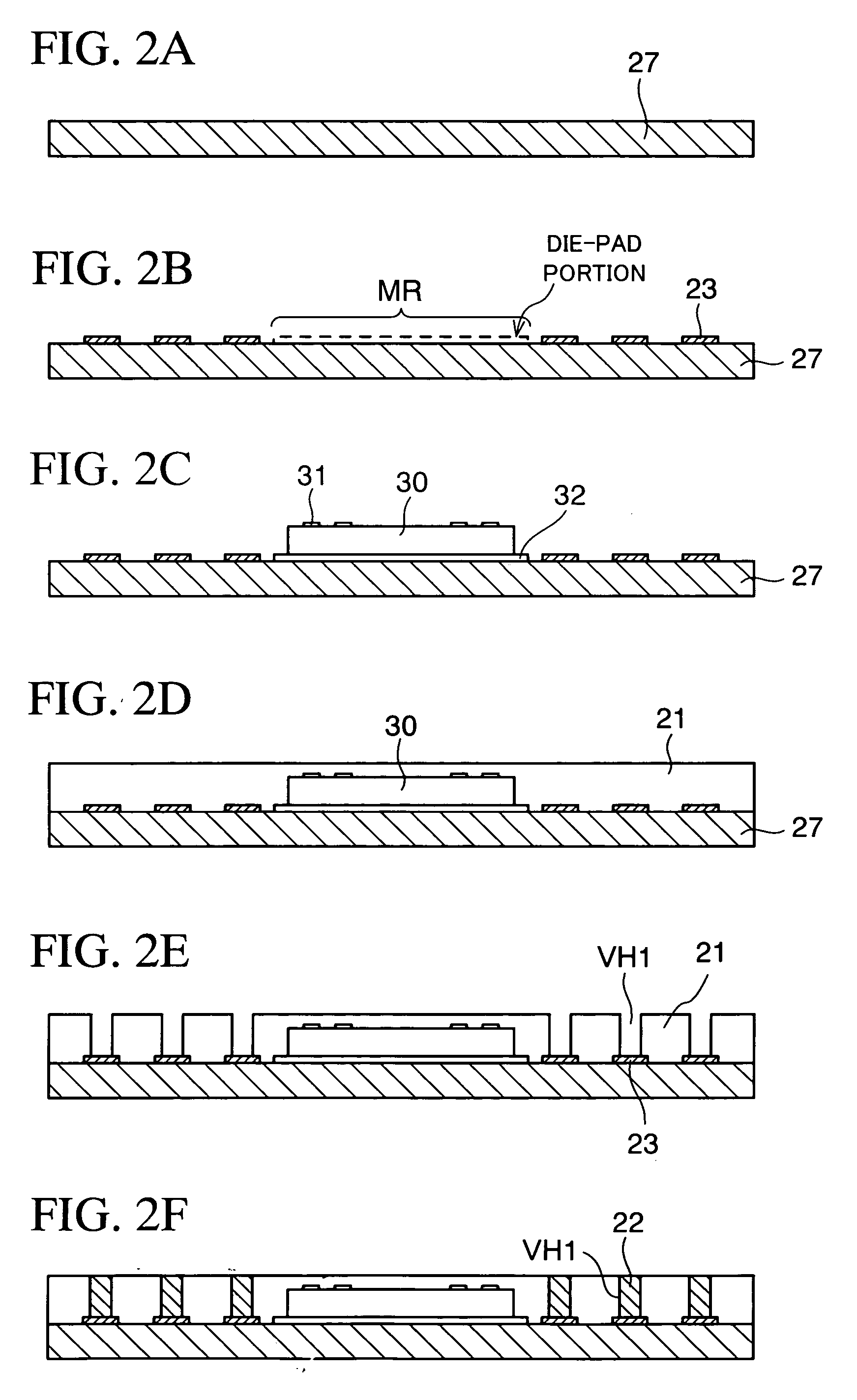

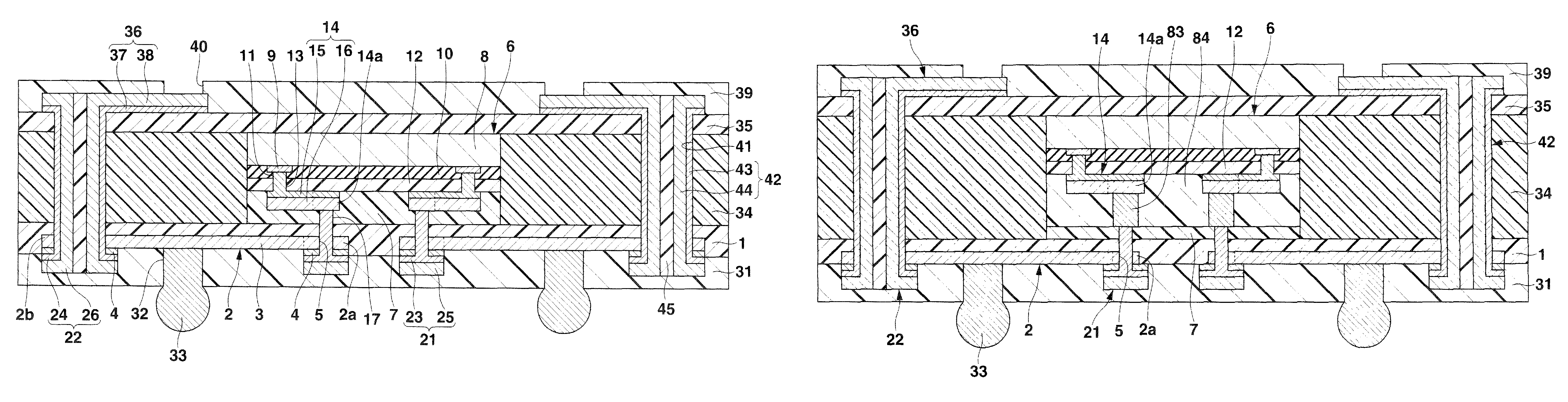

Semiconductor device having semiconductor chips stacked and mounted thereon and manufacturing method thereof

ActiveUS20060175697A1Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor chip

Chips are stacked and mounted on a circuit board having external connection electrodes and mounted thereon by wire bonding. At least one of the chips stacked on the chip includes overhung portions each of which has a start point inside bonding pads, is made thinner in a direction towards the outer periphery to an end point reaching the side wall and forms a space used to accommodate ball bonding portions between the overhung portion and the main surface of the chip arranged in the lower stage on a backside corresponding in position to the bonding pads, and insulating members formed to cover the overhung portions and prevent bonding wires of the chip arranged in the lower stage from being brought into contact with the upper-stage chip.

Owner:KIOXIA CORP

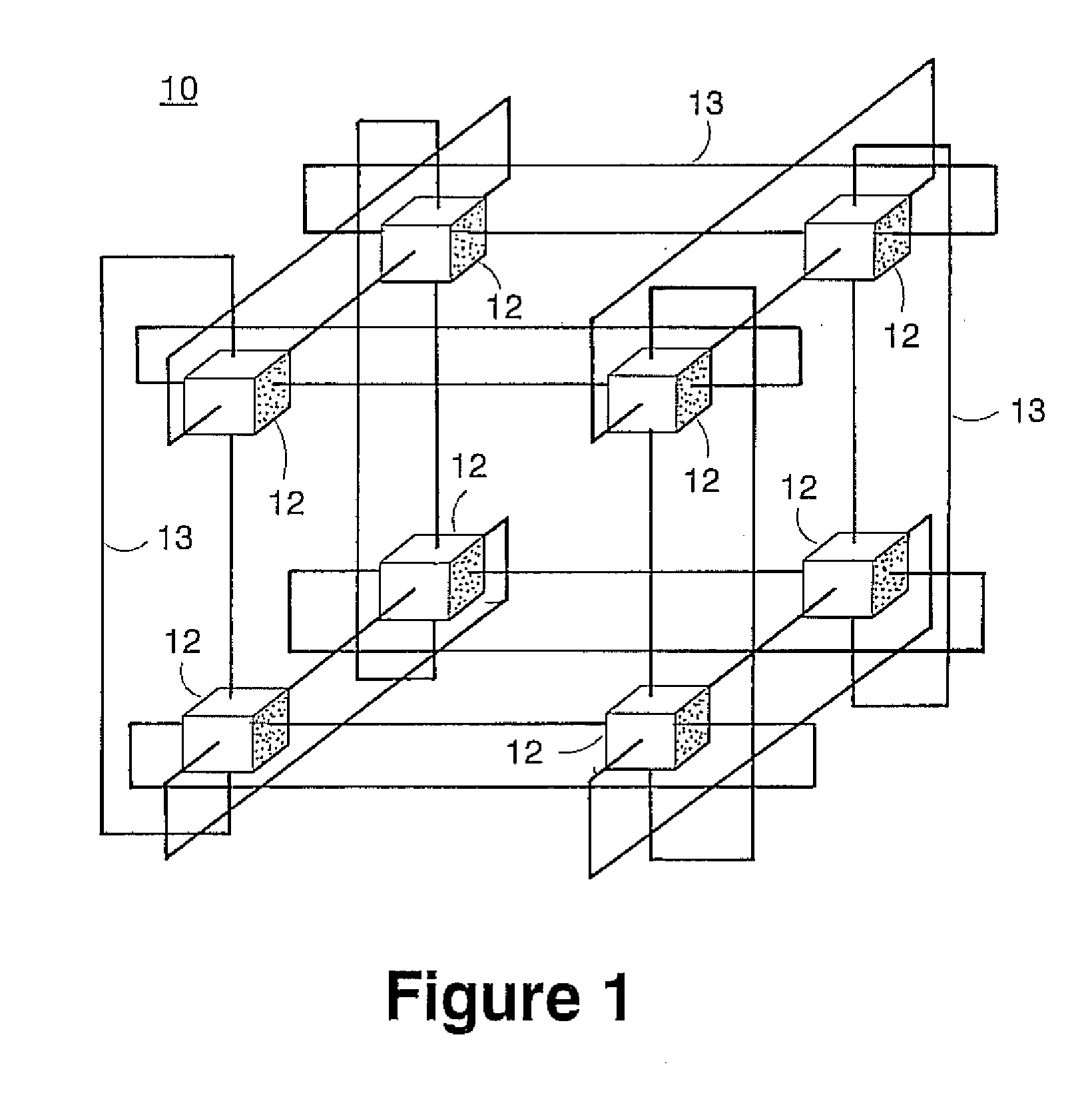

System and method for programmatic management of distributed computing resources

ActiveUS7886021B2Speed up developmentSpeeding up deliveryMultiple digital computer combinationsProgram controlWeb serviceStructure of Management Information

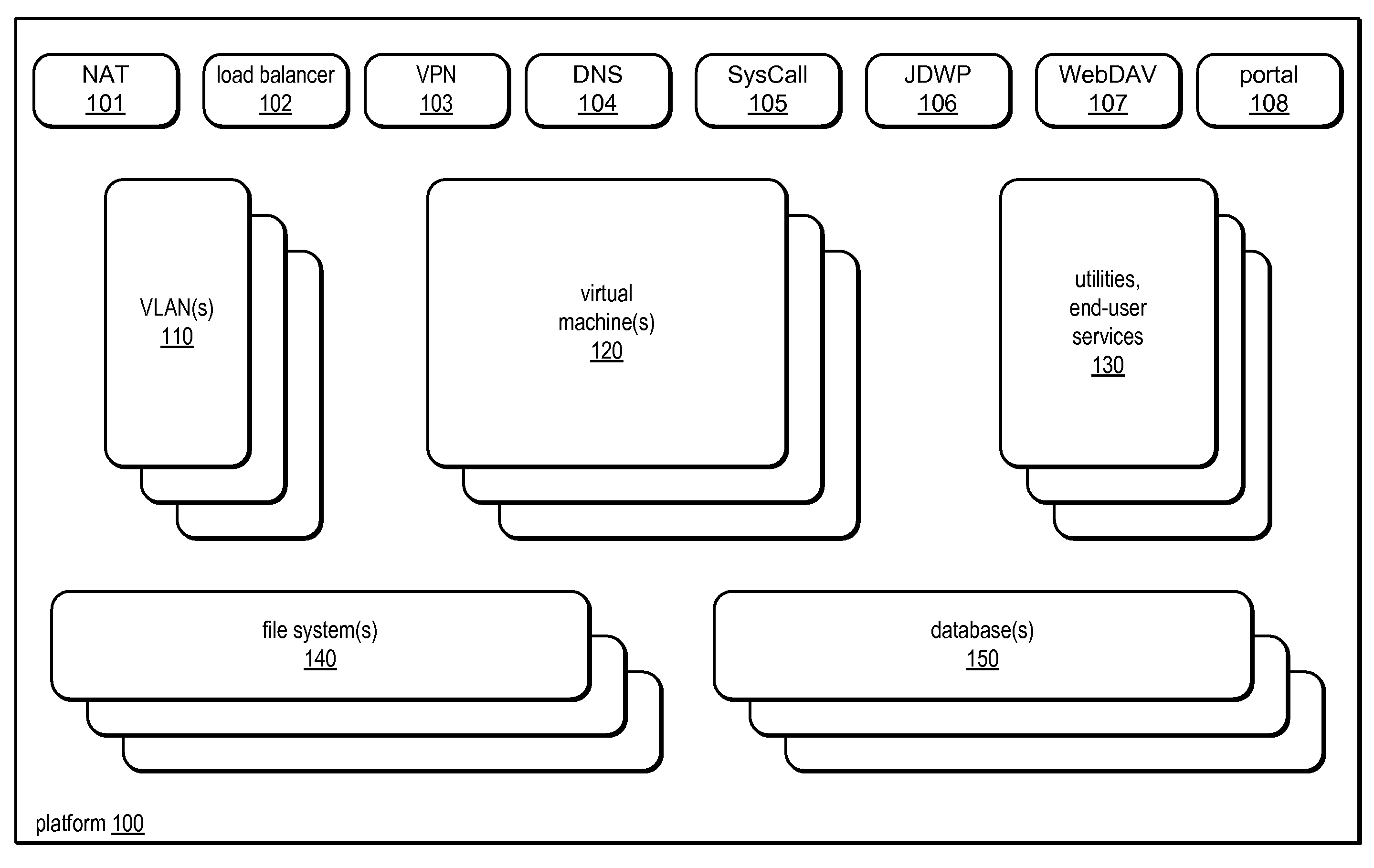

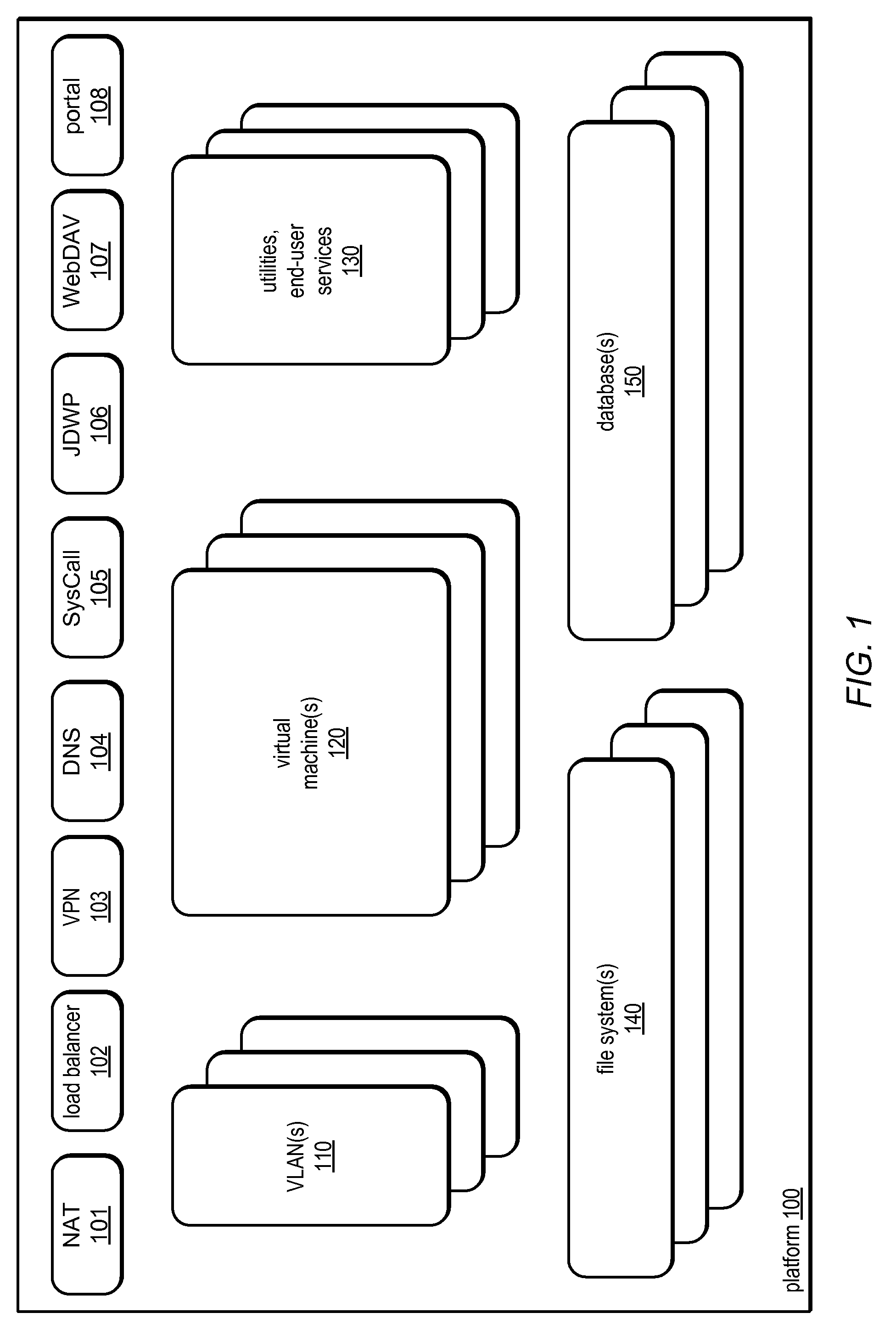

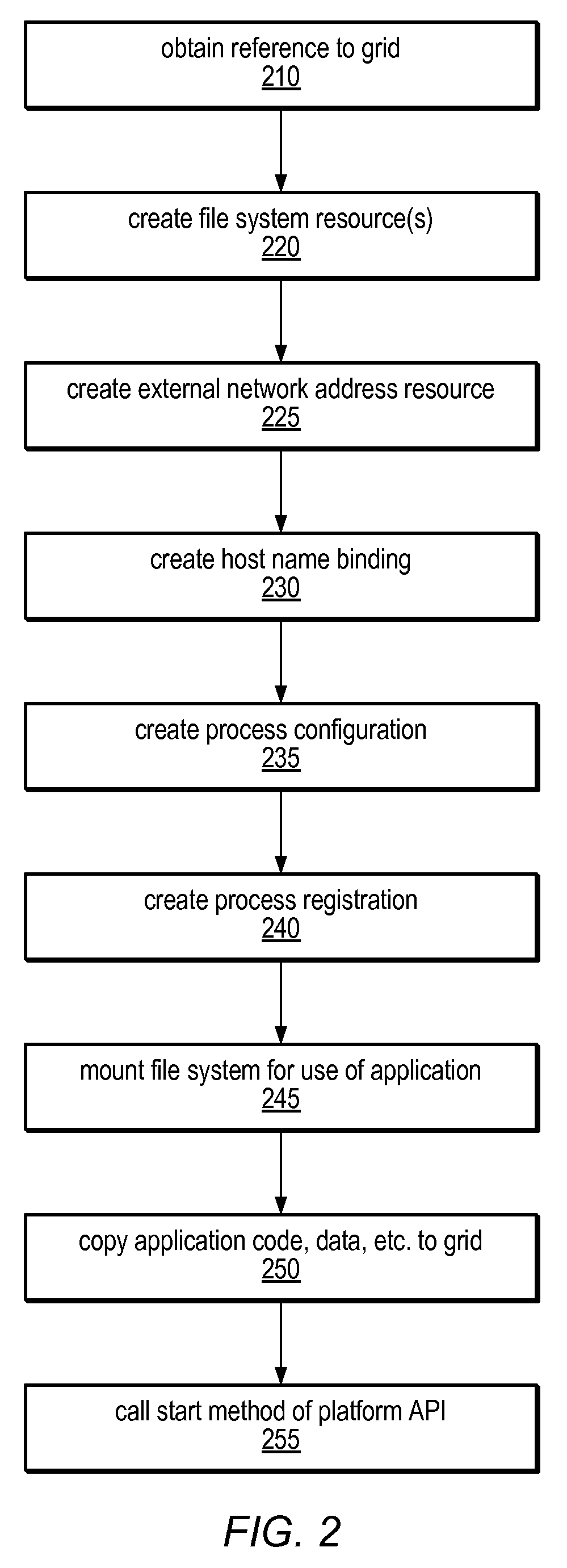

Systems and methods for providing a development and deployment platform for Software as a Service (SaaS) providers are disclosed. The platform may provide an application programming interface (API) through which customers may configure virtualized grids of language-level virtual machines (VMs), networks, and storage resources. A grid may be horizontally scalable and programmatically configurable by a customer and / or customer code. The platform may allow dynamic scaling of resources (up and down) to match changing demands, by allowing customers and / or customer code to programmatically alter their own system level structure at runtime, through the API. The grid may be accessed by both on-grid and off-grid processes, through internal and external connectivity resources provided by the platform. The platform may provide common utilities for end-user services, deployment operations, and development tasks (e.g., debugging), and may include frameworks and macro-components (e.g. web servers). The platform may host long-running Internet-based services and / or one-shot computational services.

Owner:ORACLE INT CORP

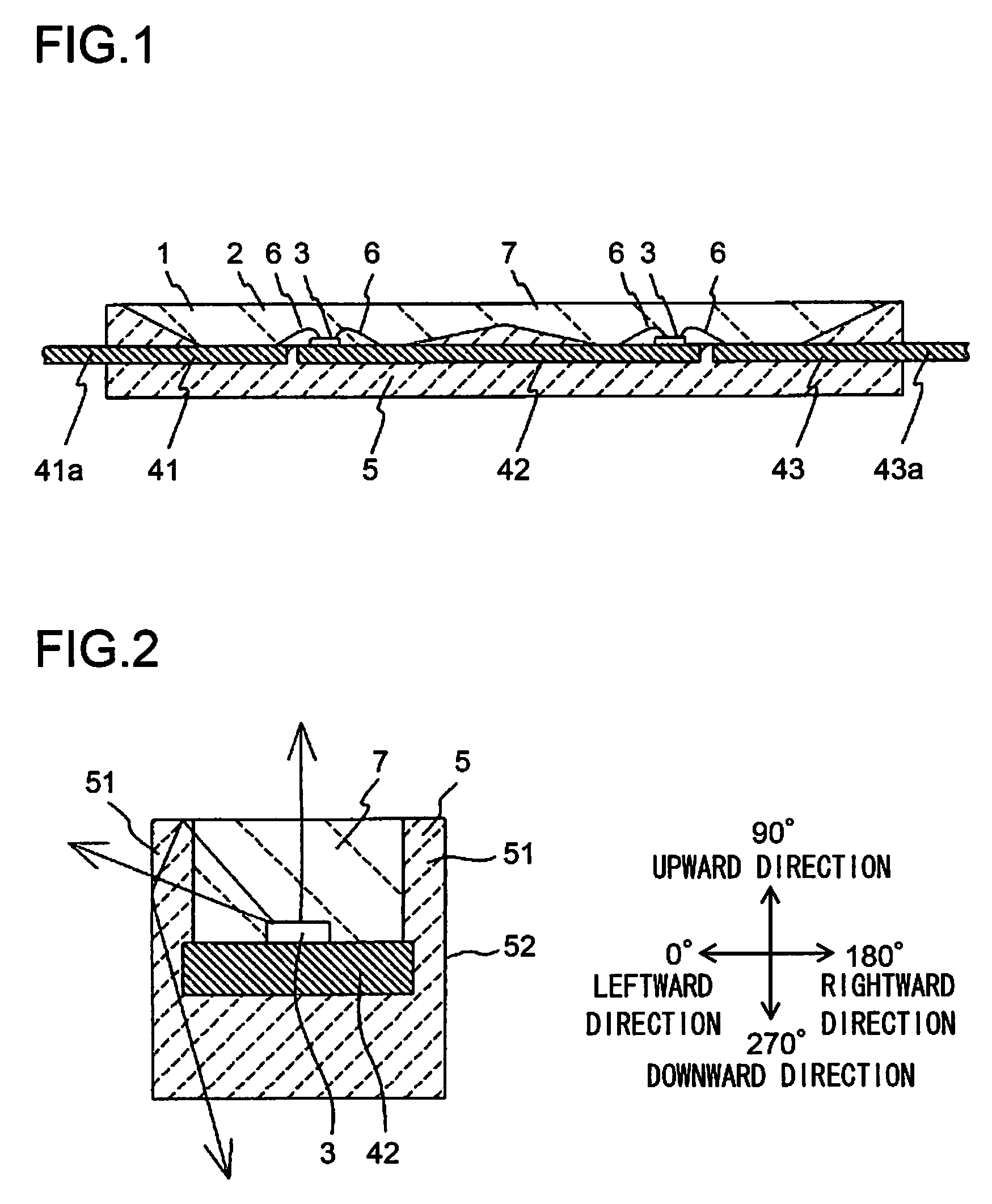

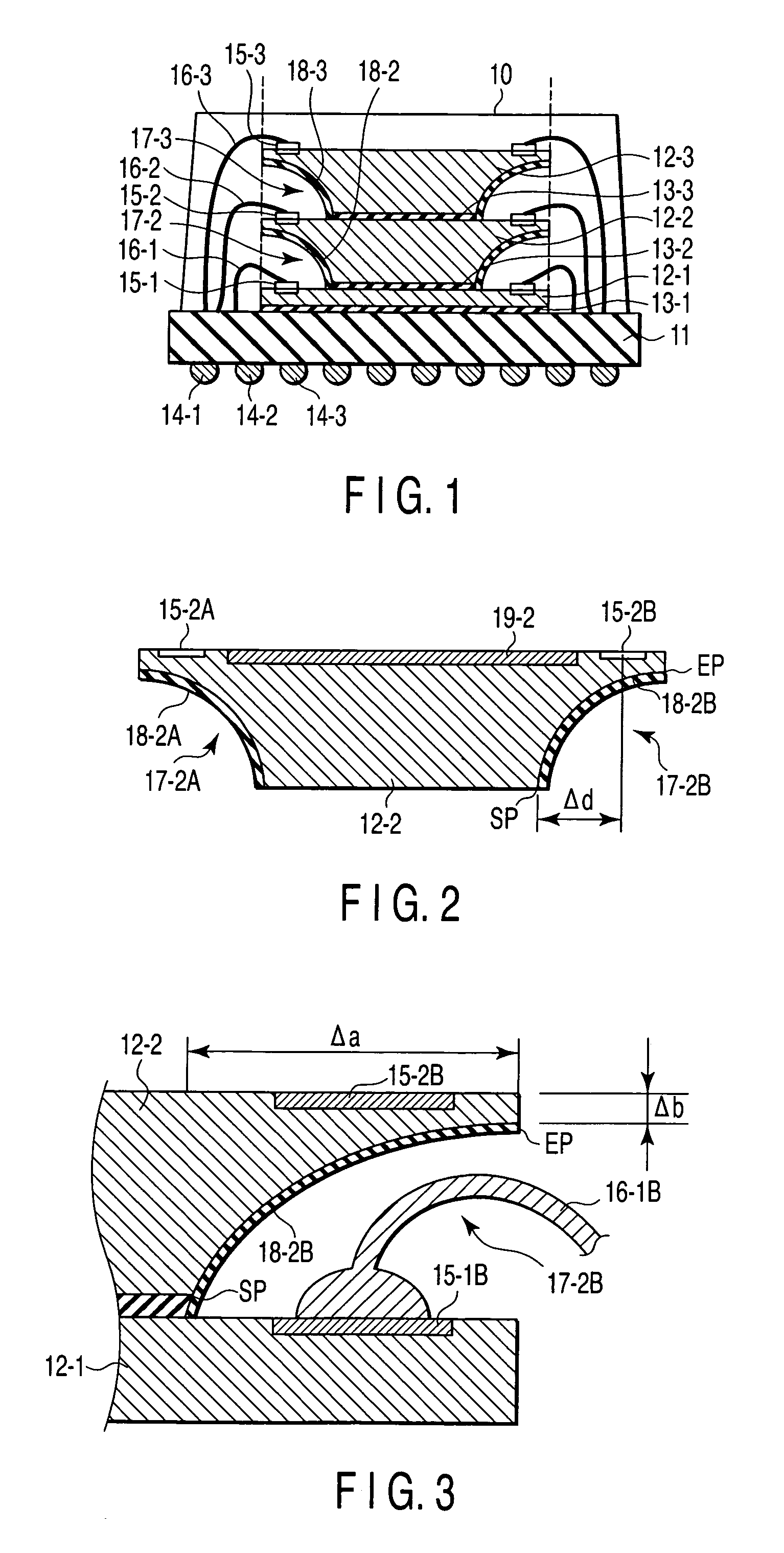

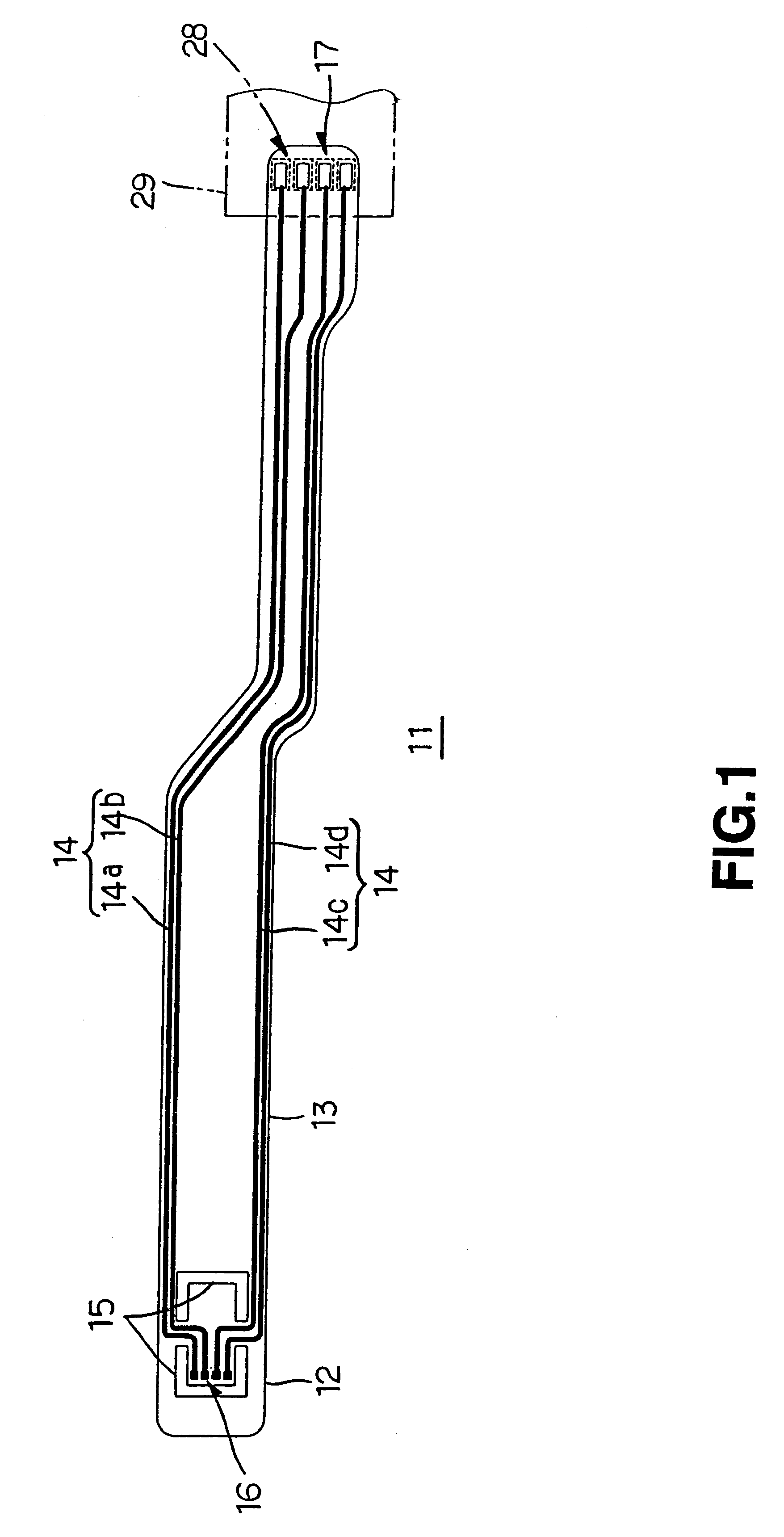

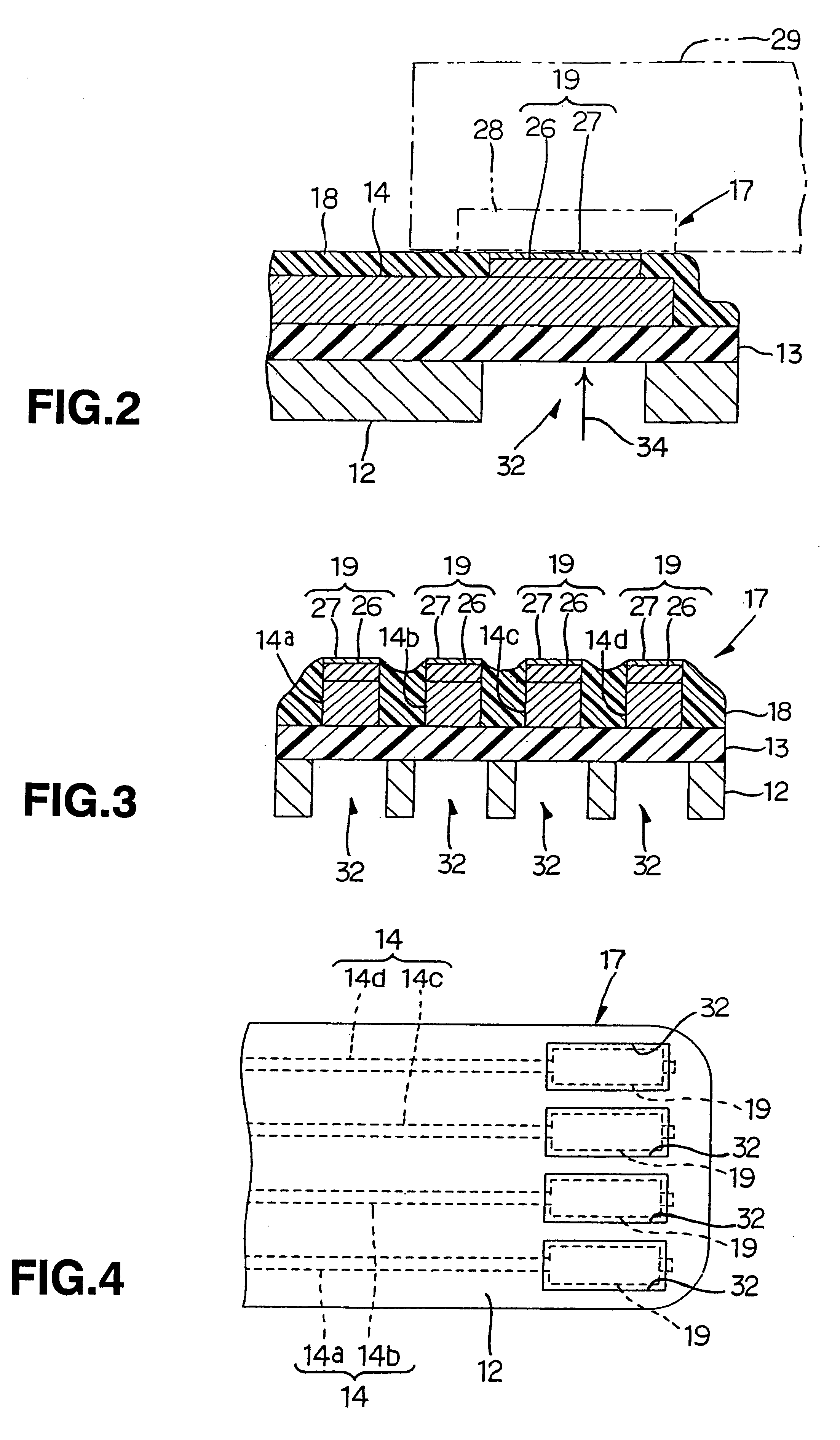

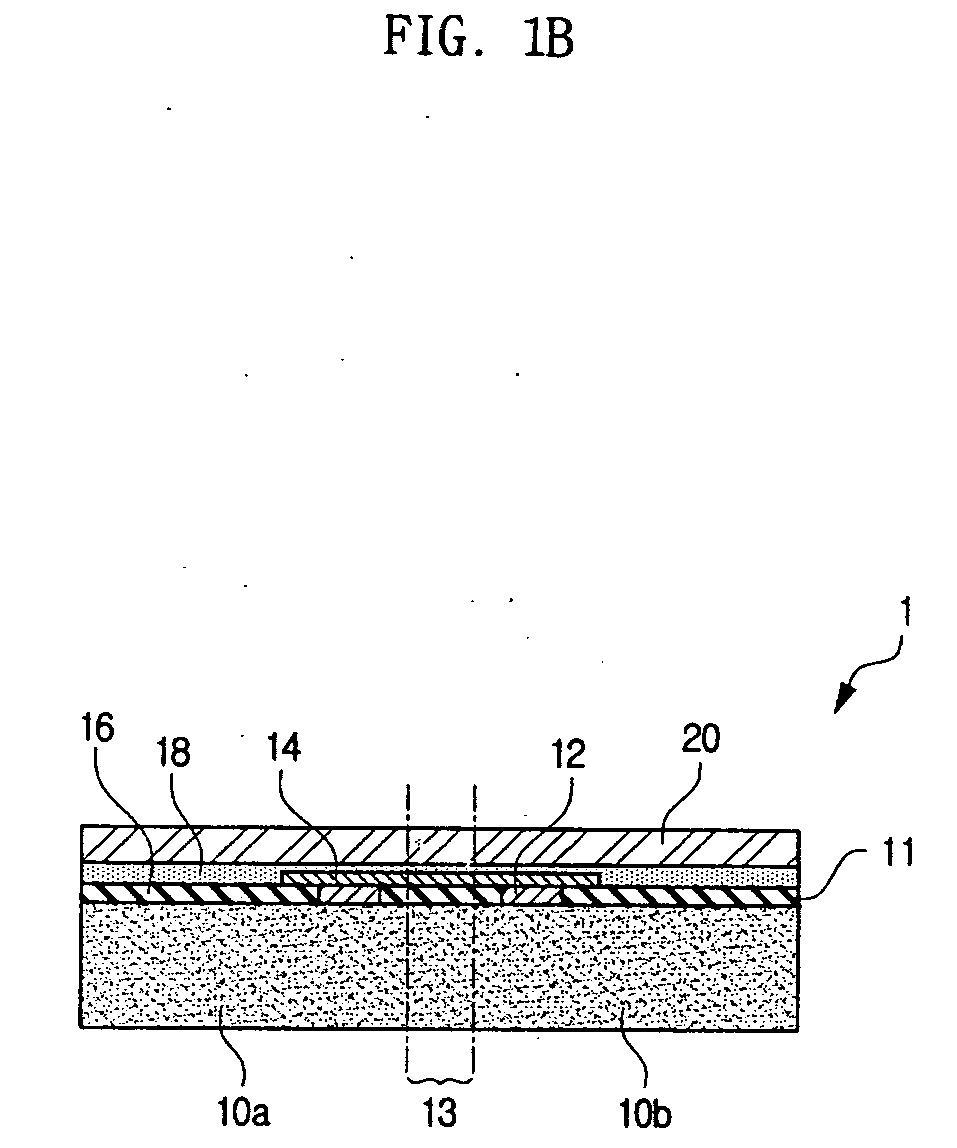

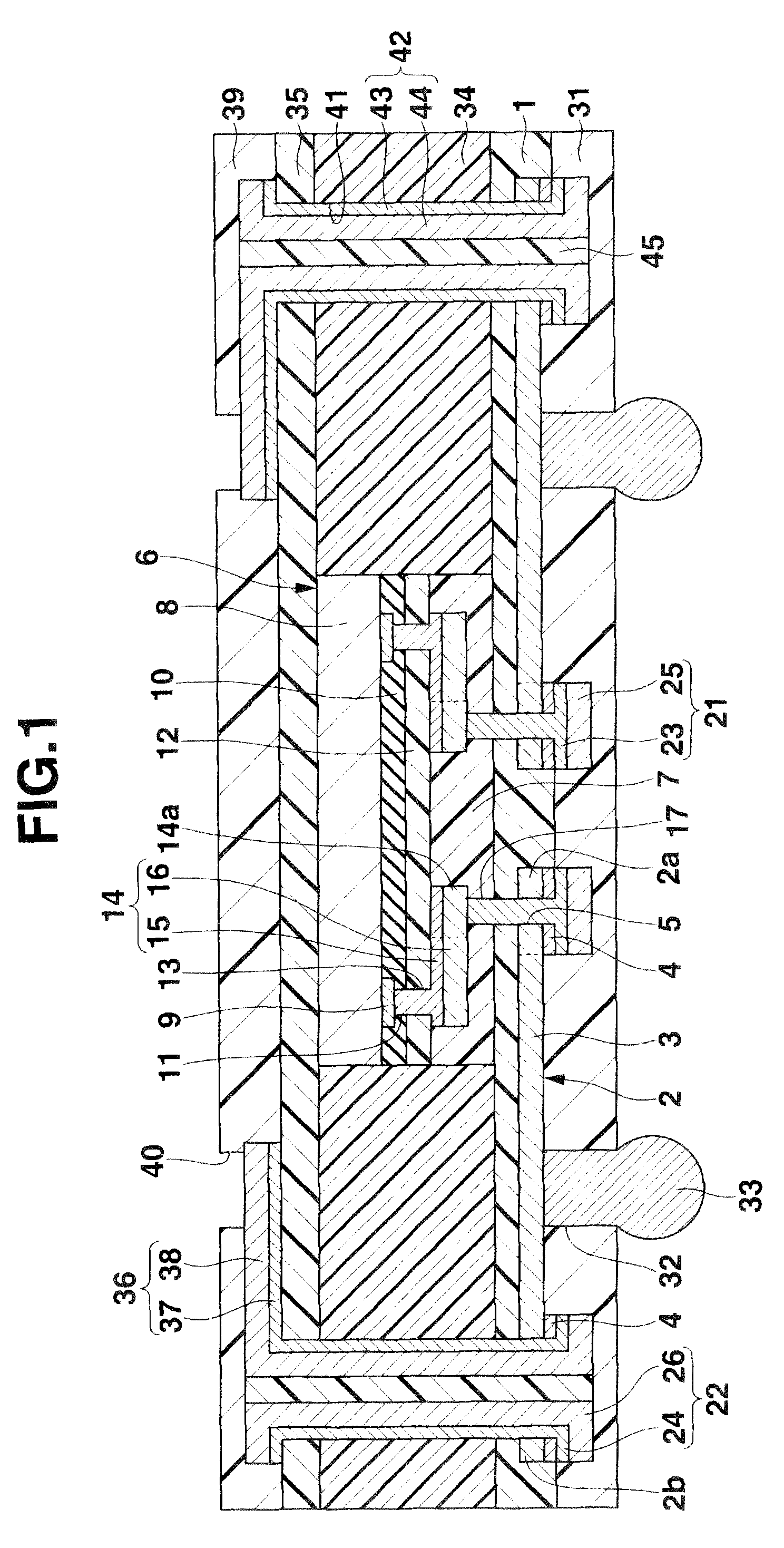

Suspension board with circuit

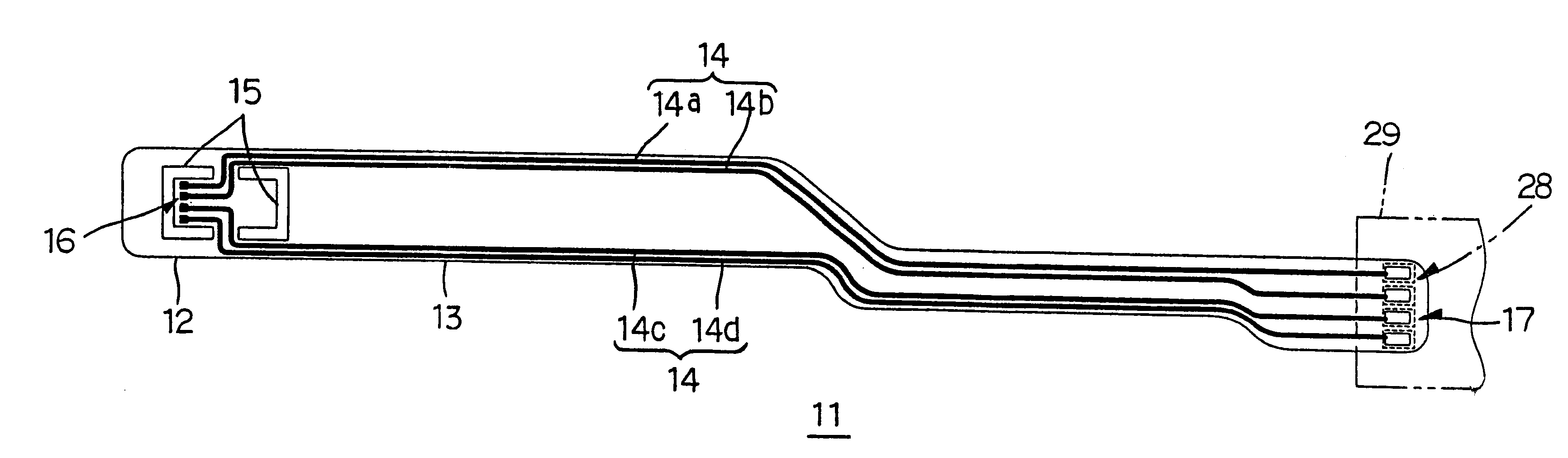

InactiveUS6399899B1High strengthSimple structureRelieving strain on wire connectionRecord information storageExternal connectionEngineering

To provide a suspension board with circuit that enables its terminals to be bonded to the other terminals with sufficient strength with simple structure, to ensure sufficient bonding reliability, the suspension board with circuit 11 includes a suspension board 12, a base layer 13 formed on the suspension board 12, and a conductive layer 14 formed on the base layer 13 and a cover layer 18 with which the conductive layer 14 is covered, wherein external connection terminals 17 to be bonded to terminals 28 of a read / write board 29 are formed without the suspension board 12 and / or the base layer 13 being formed.

Owner:NITTO DENKO CORP

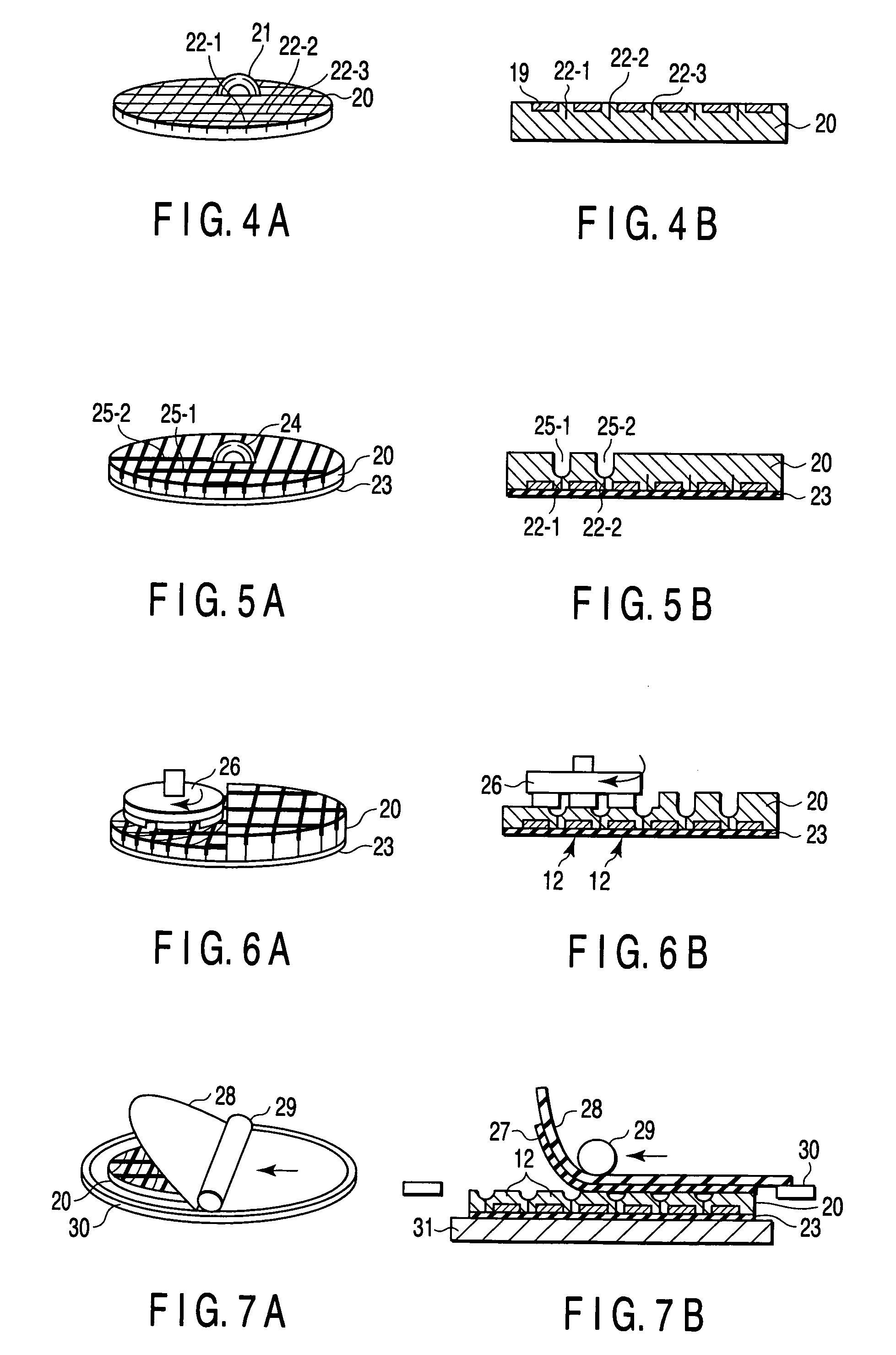

Method for manufacturing wafer level chip scale package using redistribution substrate

InactiveUS20060079019A1Increase widthIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringChip-scale package

The present invention provides a method for manufacturing a wafer level chip scale package using a redistribution substrate, which has patterned bump pairs connected by redistribution lines and formed on a transparent insulating substrate. The redistribution substrate is produced separately from a wafer and then bonded to the wafer. One part of each bump pair is in contact with a chip pad on the active surface of the wafer, and the other part coincides with one of holes formed in the wafer. Conductive lines are formed in the holes and on the non-active surface of the wafer. External connection terminals are formed on the conductive lines at the non-active surface.

Owner:EPWORKS

Semiconductor device and method of manufacturing the same

ActiveUS20050161833A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, one end of a conductor filled in the via hole is covered with a pad portion exposed to the outside, and a wiring layer connected to the other end of the conductor is formed. The portion (pad portion) of the wiring layer which correspond to the conductor is exposed from a protective film, or an external connection terminal is bonded to the top of the pad portion. Electrode terminals of the chip are connected to the wiring layer, and the opposite surface of the chip is exposed to the outside.

Owner:SHINKO ELECTRIC IND CO LTD

Semiconductor device having wiring line and manufacturing method thereof

InactiveUS8004089B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorLaser beams

On the lower surface of a semiconductor construct having an external connection electrode, there are formed an insulating film having a planar size greater than that of the semiconductor construct, and a metal layer and a mask metal layer having a connection pad portion in which a first opening corresponding to the external connection electrode is formed. A laser beam is applied using the mask metal layer as a mask, and a second opening is thereby formed in a part of the insulating film corresponding to the external connection electrode. Then, a connection conductor is formed to connect a wiring line to the external connection electrode via the second opening of the insulating film.

Owner:TERAMIKROS INC

Power module package having improved heat dissipating capability

InactiveUS7061080B2Efficiently dissipatedSimpler and cheap to manufactureSemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

A power module package is provided. The power module package includes a power circuit element, a control circuit element, a lead frame, a heat sink, and an epoxy molding compound (EMC). The control circuit element is connected to the power circuit and controls chips in the power circuit. The lead frame has external connecting means formed at the edges thereof, and a down set part, namely, formed between the external connecting means. The lead frame has a first surface to which the power circuit and the control circuit are attached, and a second surface used as a heat dissipating path, in particular, the power circuit is attached to the down set part. The heat sink which is closely attached to the down set part of the second surface of the lead frame by an adhesive. The EMC surrounds the power circuit, the control circuit, the lead frame and the heat sink, and exposes the external connecting means of the lead frame and a side of the heat sink.

Owner:SEMICON COMPONENTS IND LLC

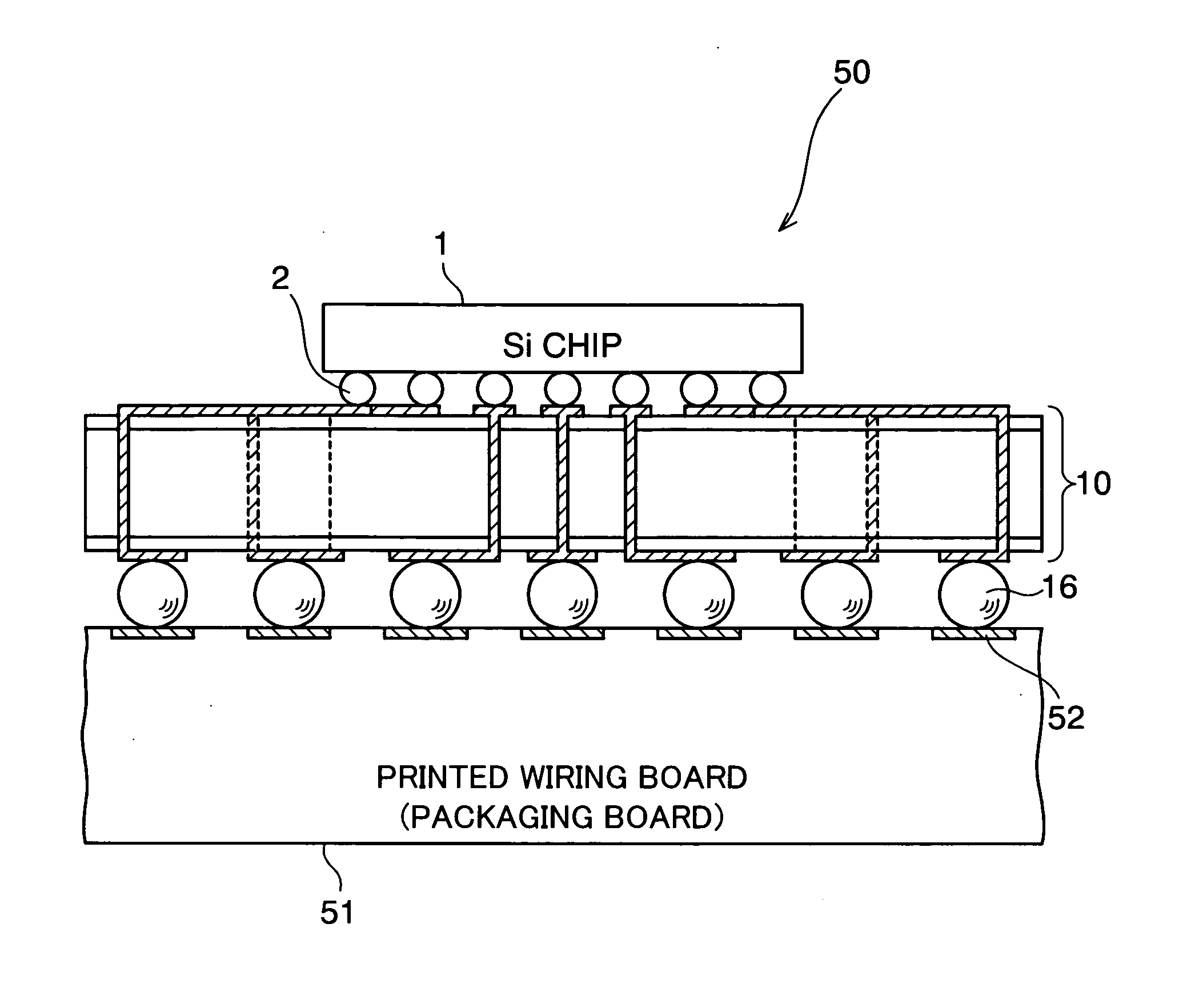

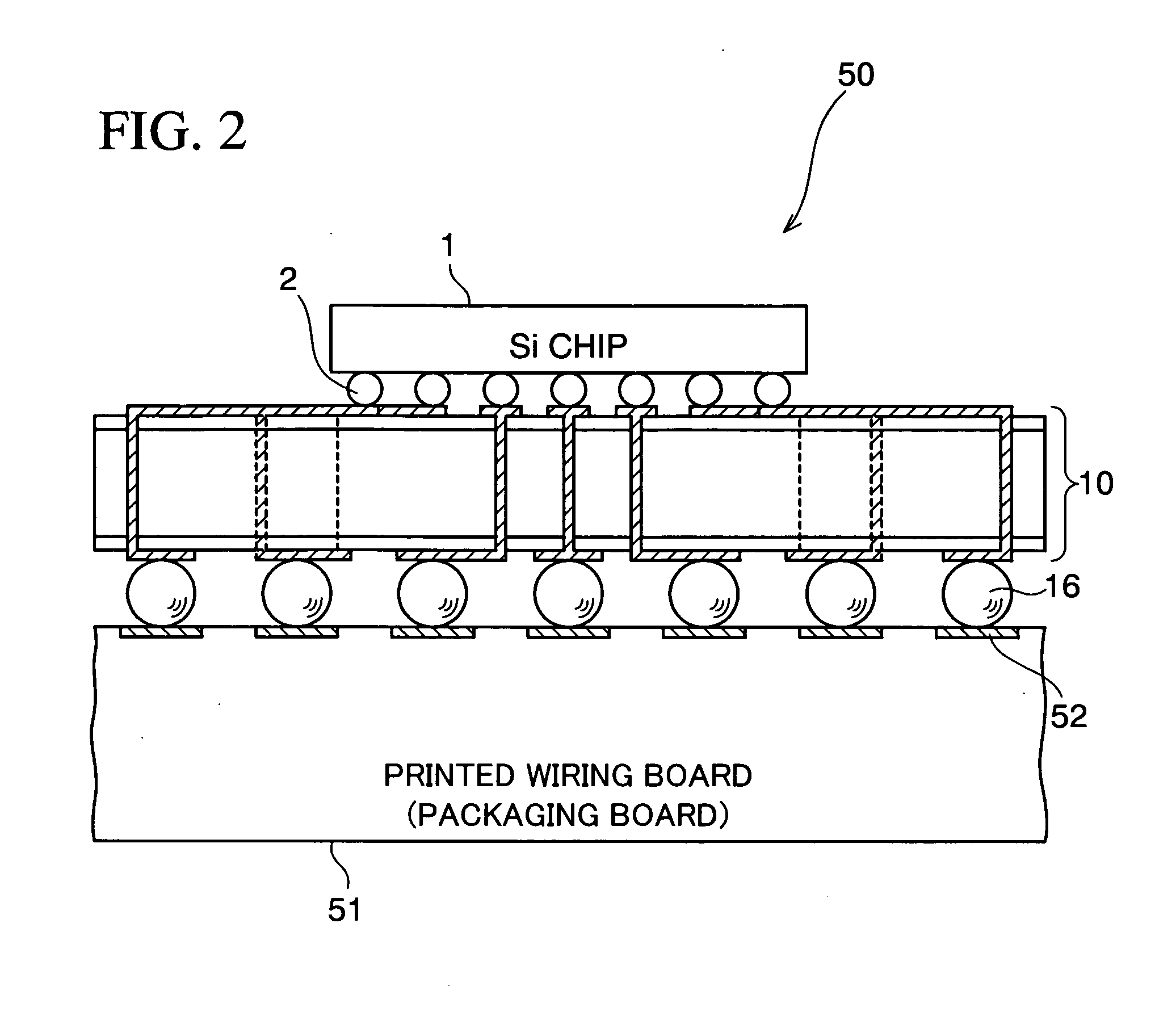

Interposer, method of fabricating the same, and semiconductor device using the same

ActiveUS20060001179A1Low costWell formedSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterposer

An interposer to be interposed between a semiconductor chip to be mounted thereon and a packaging board has an interposer portion made of a semiconductor and an interposer portion provided around the foregoing interposer portion integrally therewith. On both surfaces of the interposer portions, wiring patterns are formed via insulating layers. The wiring patterns are electrically connected via through holes formed at required positions in the interposer portions. The outer interposer portion is made of an insulator or a metal body. Further, external connection terminals are bonded to one surface of the interposer.

Owner:SHINKO ELECTRIC IND CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com