Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3959results about How to "Reduced footprint" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

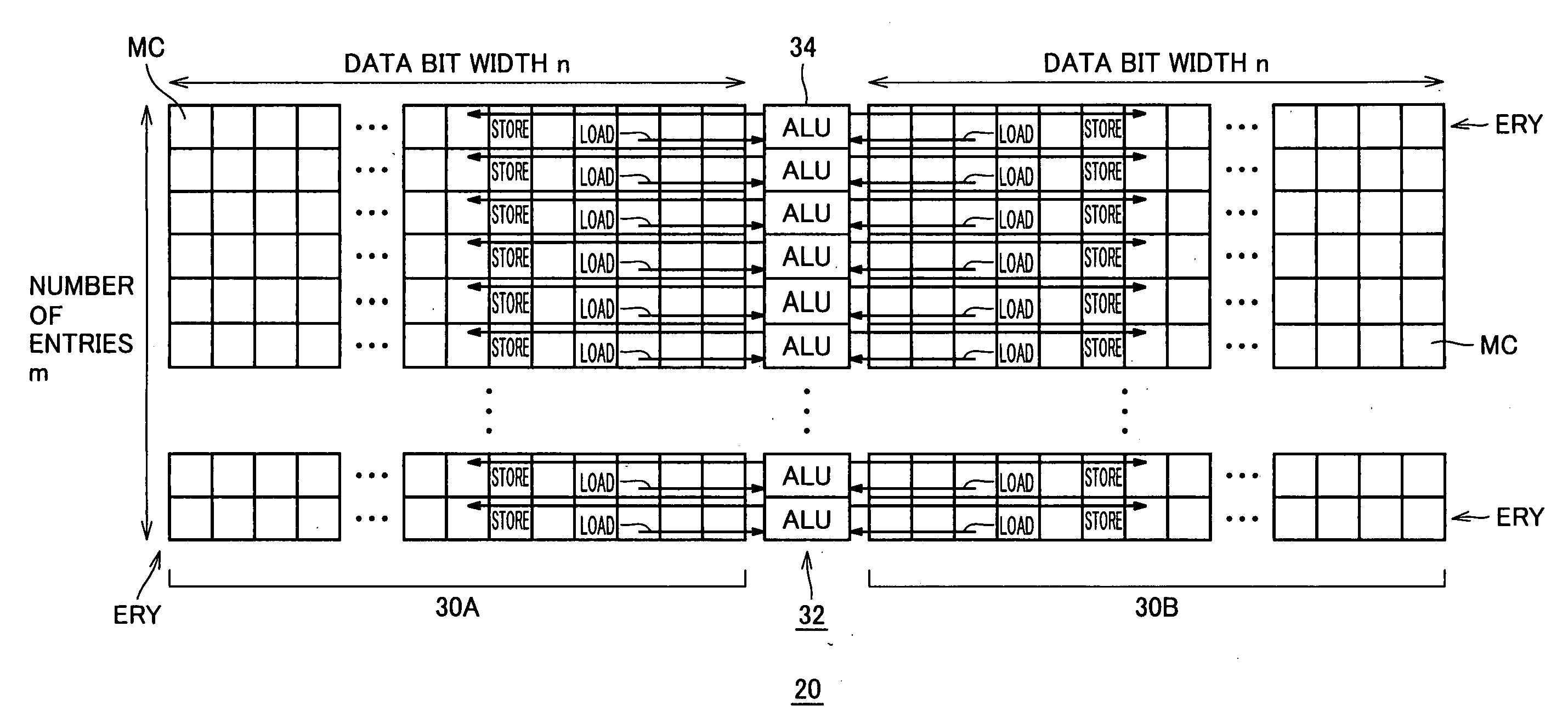

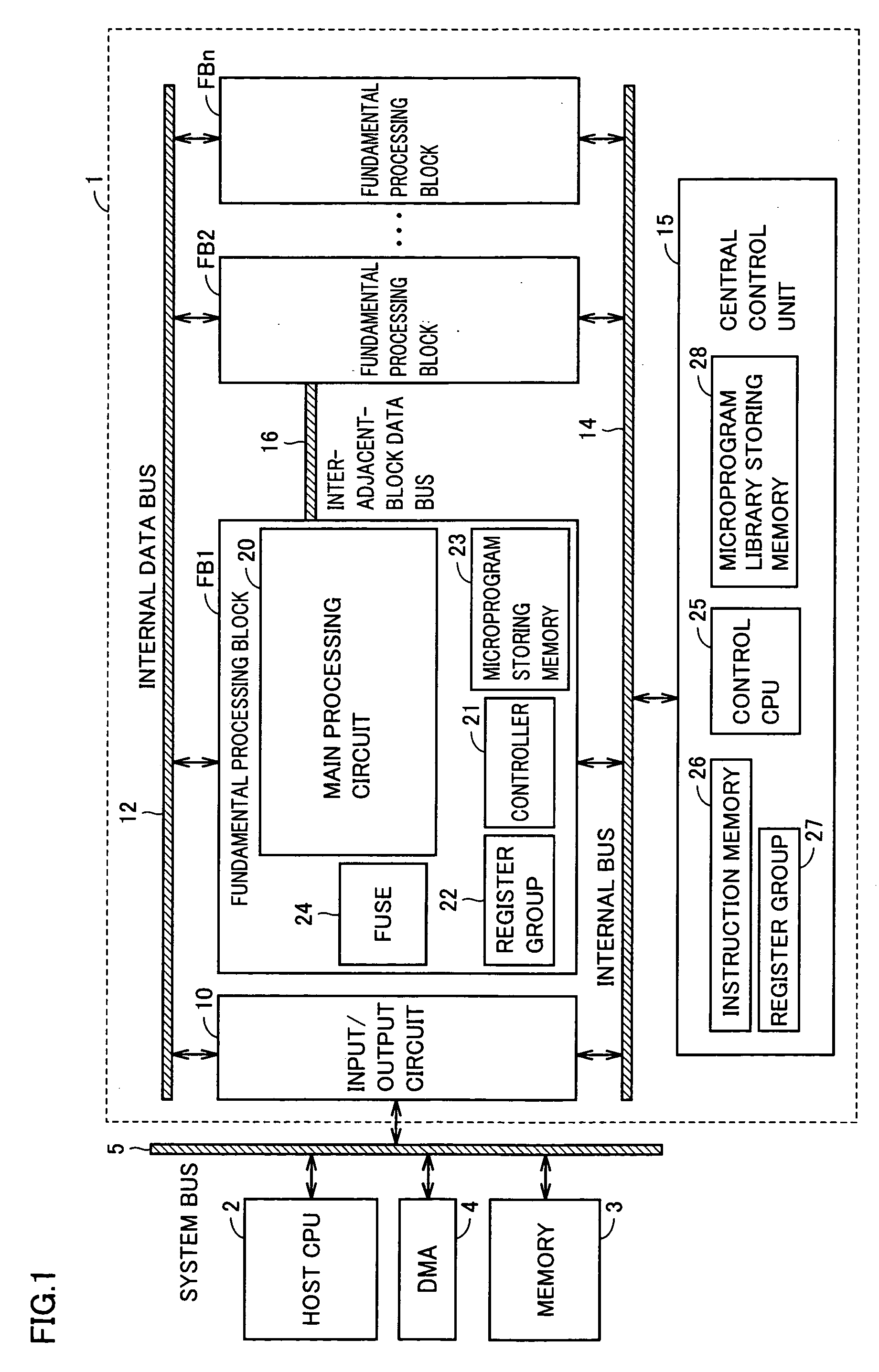

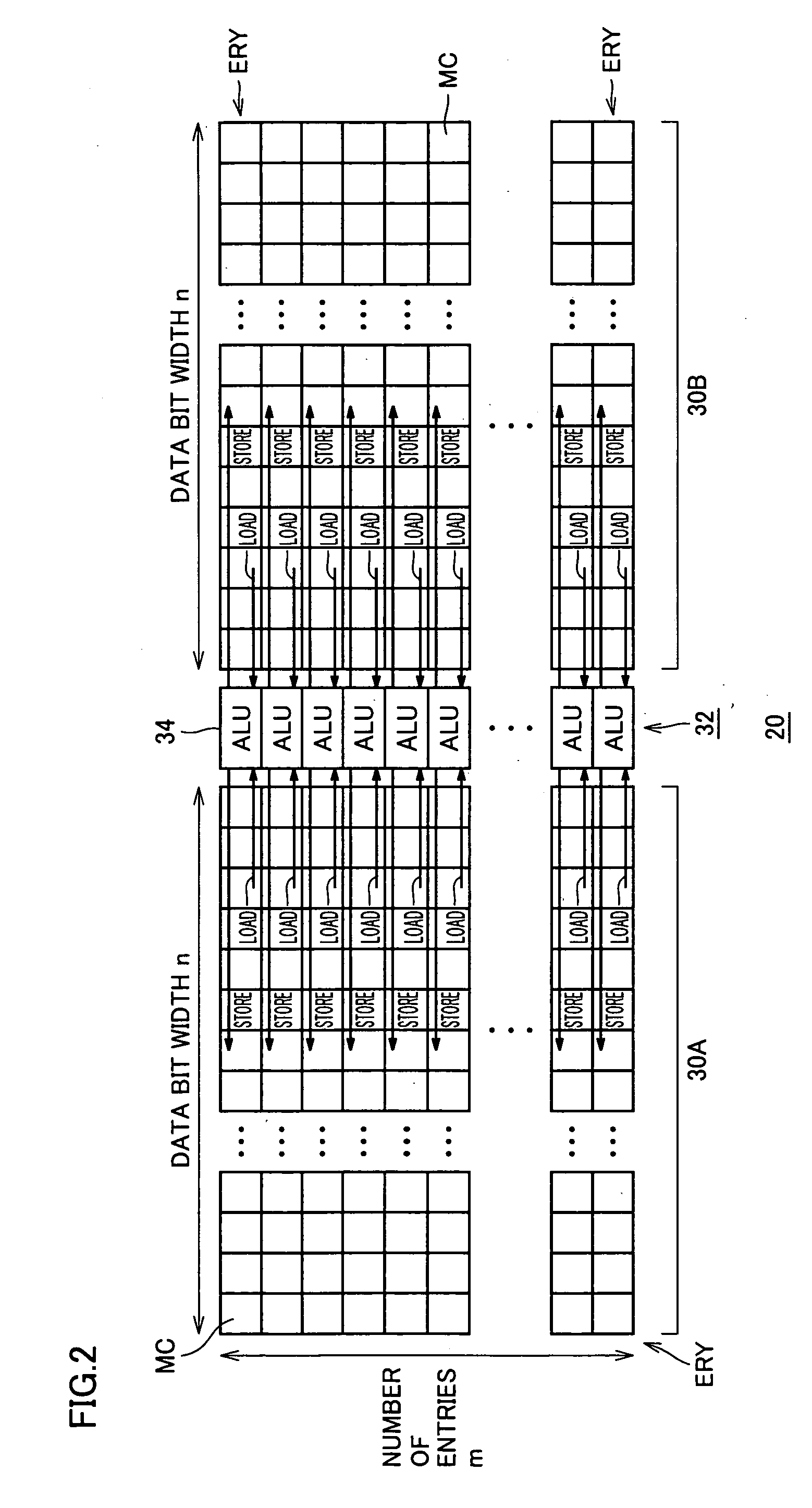

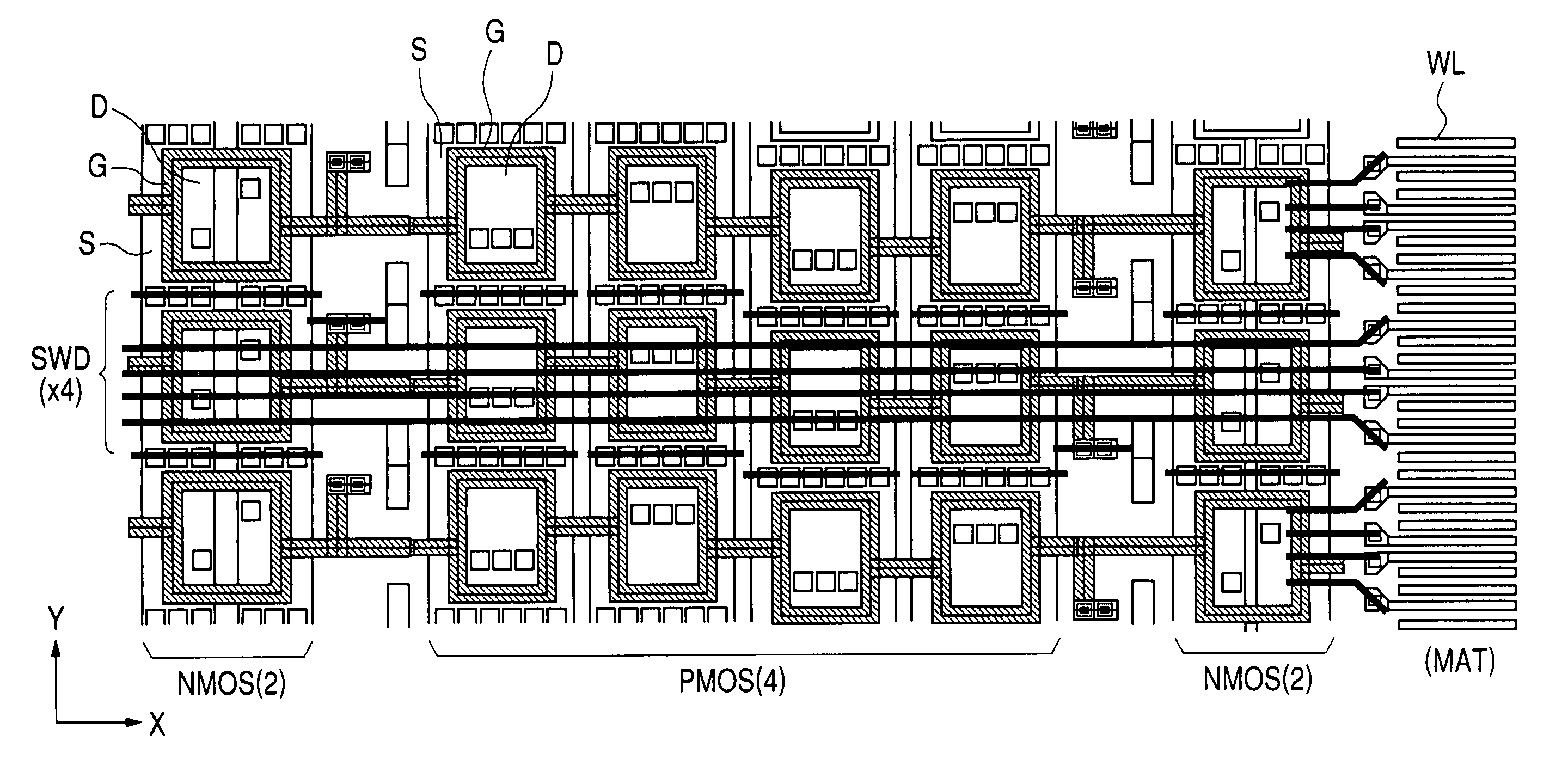

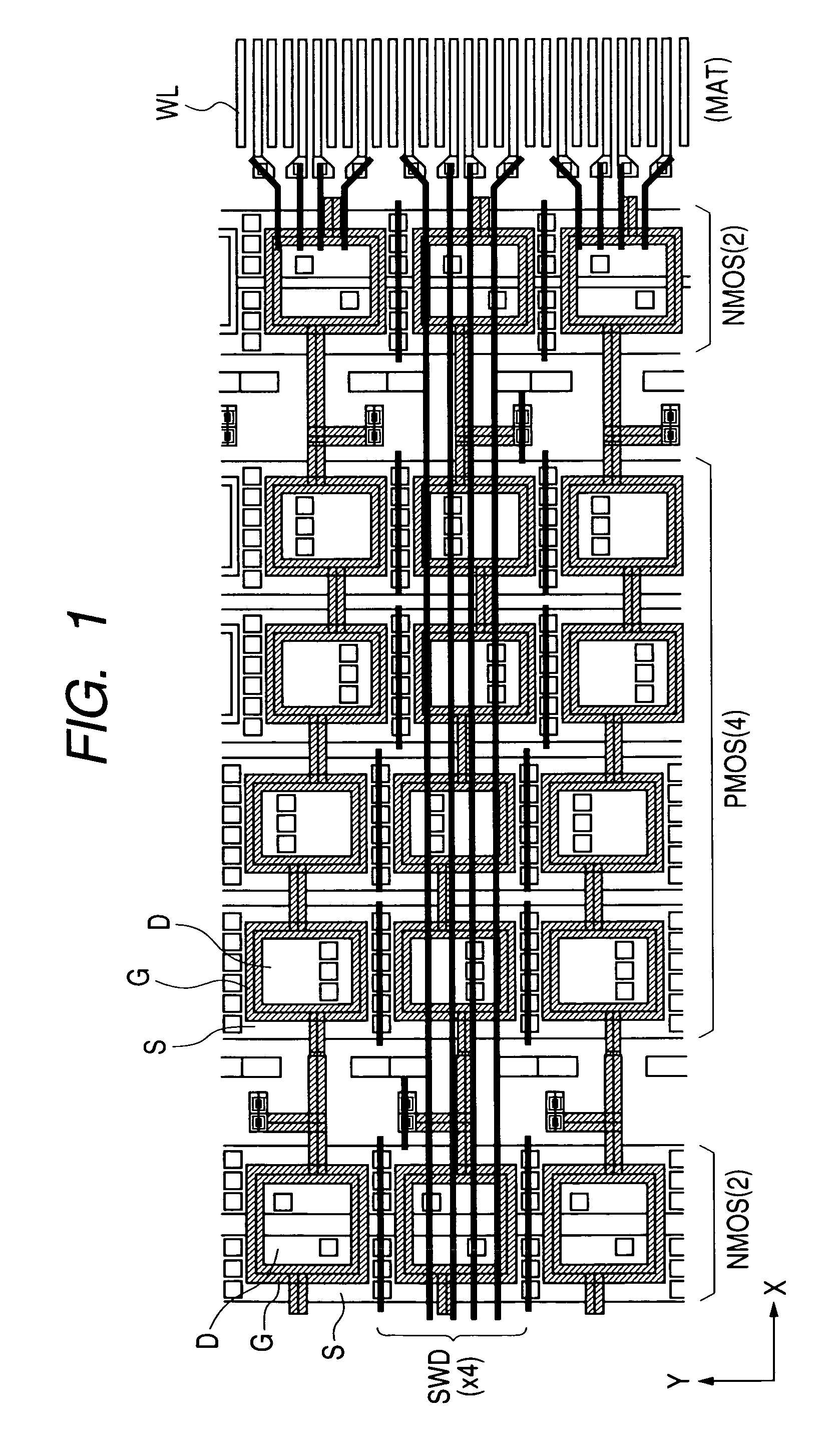

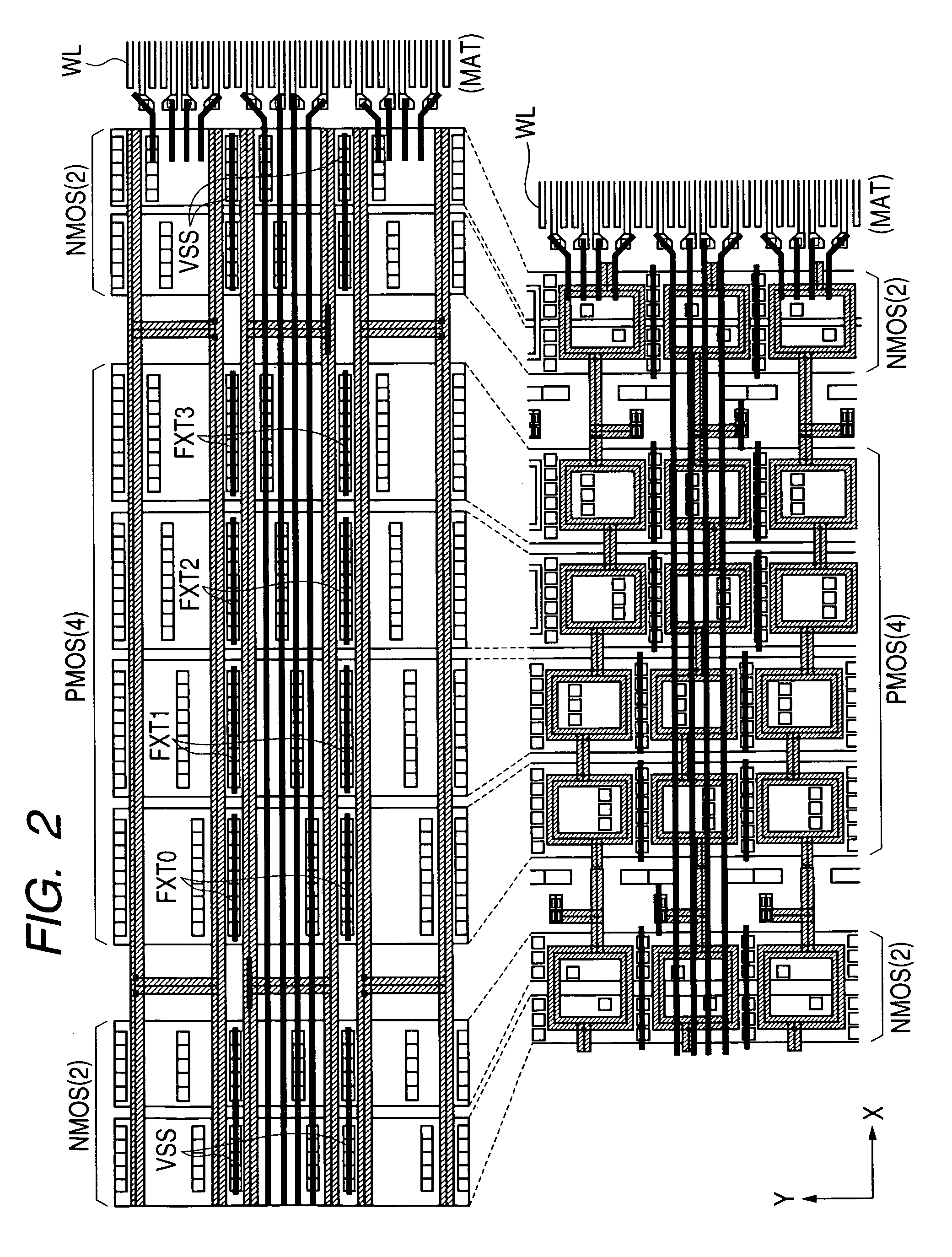

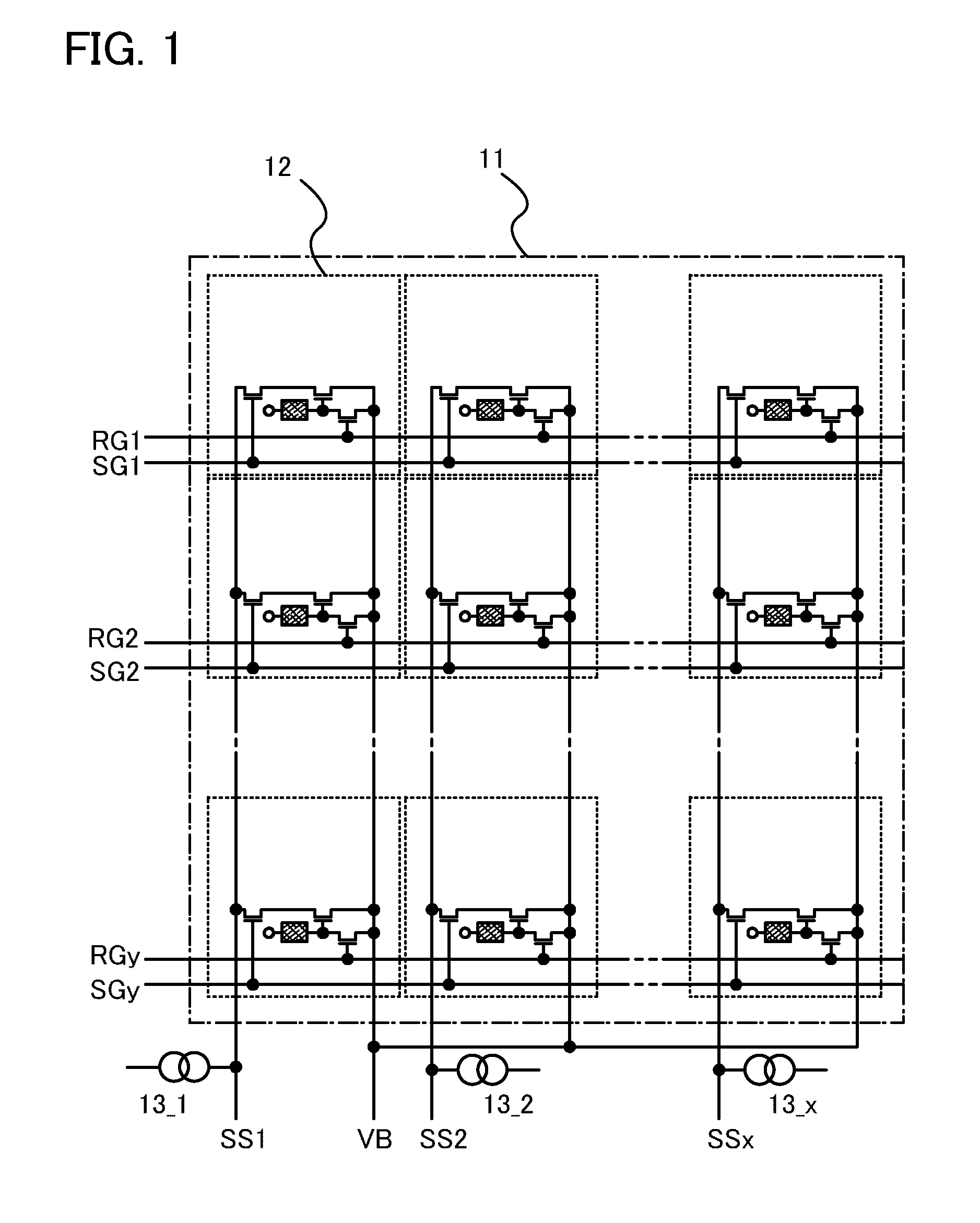

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

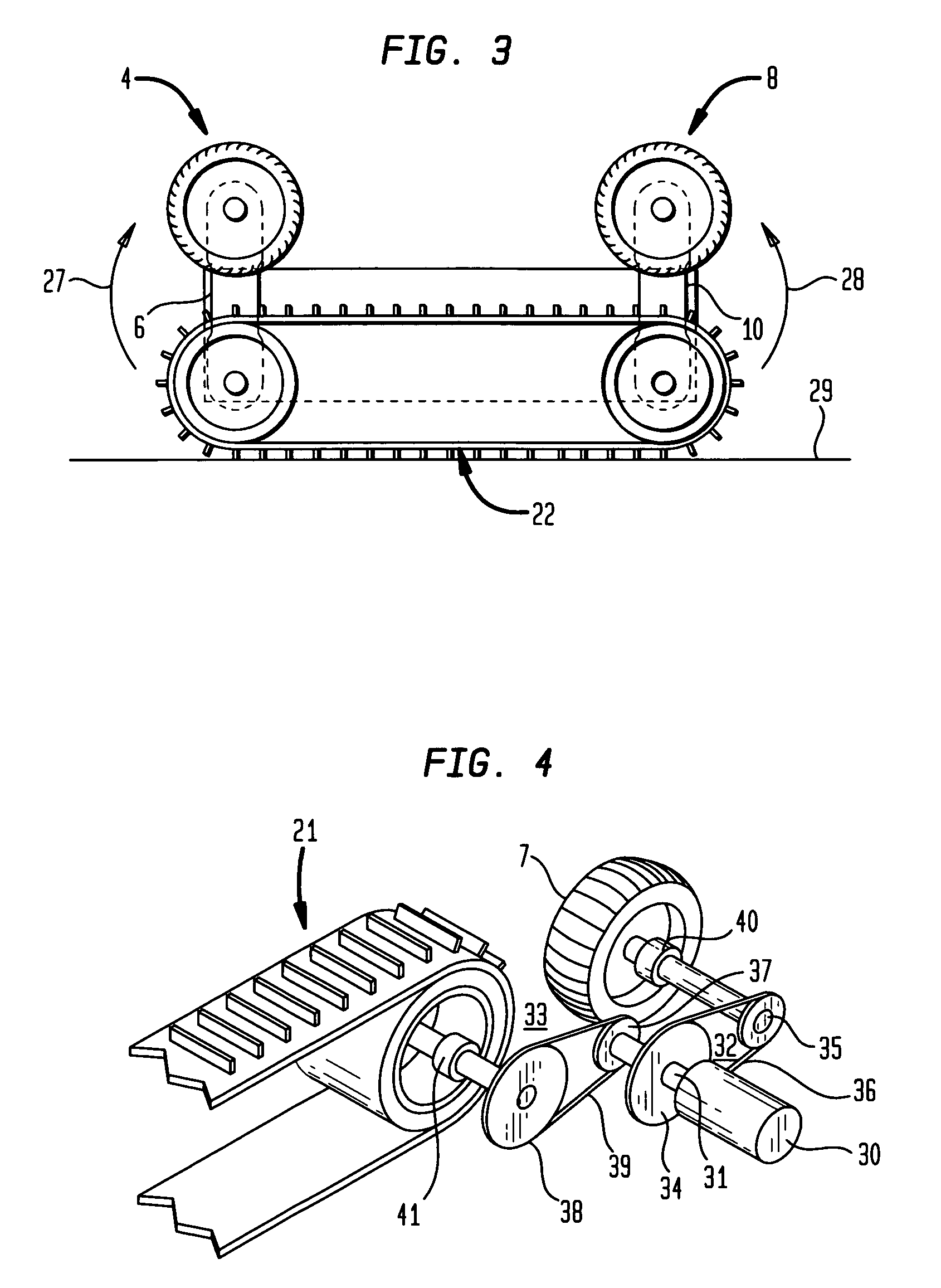

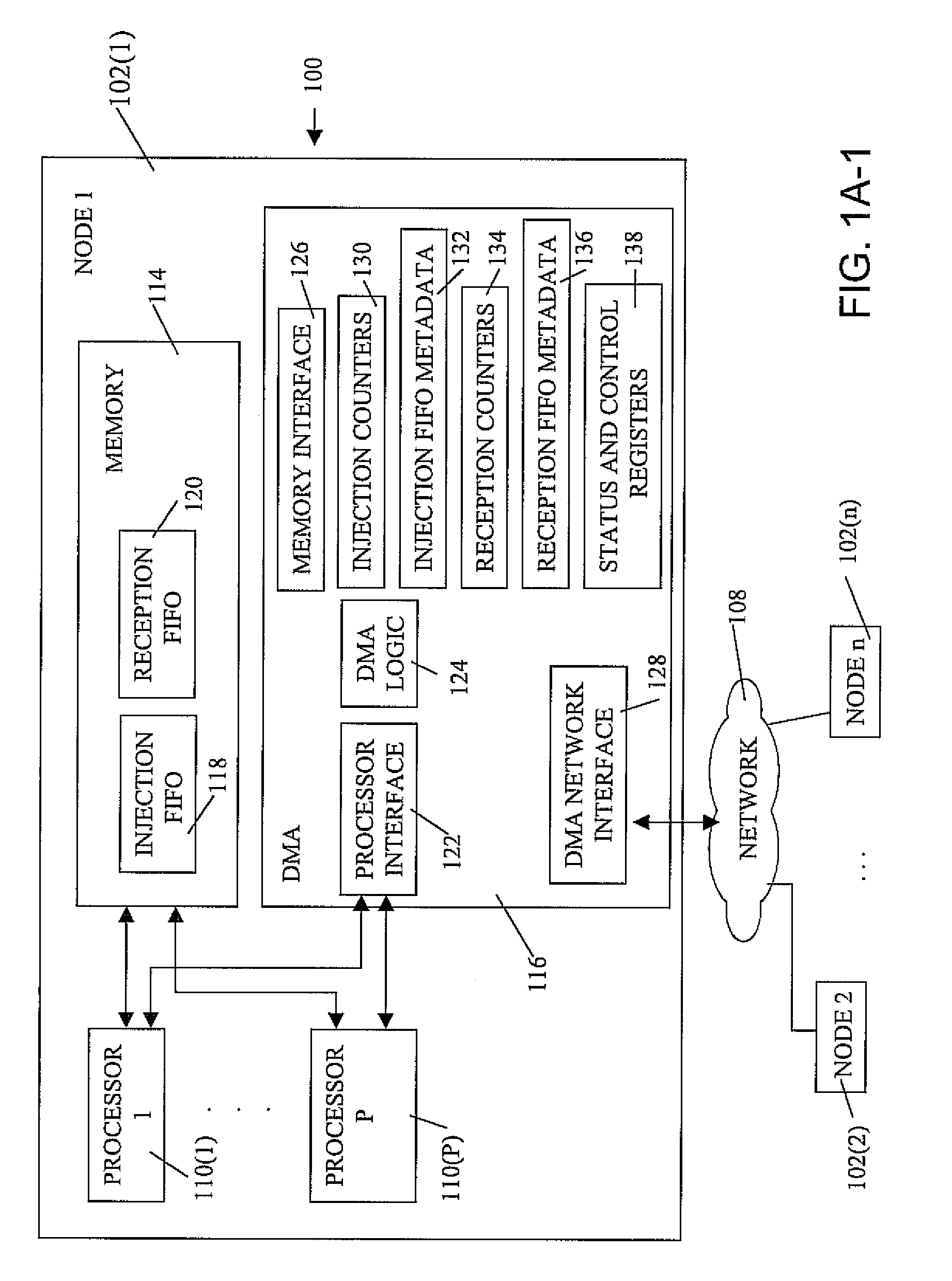

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

InactiveUS20050067620A1High bulk densityReduce chip footprintTransistorSemiconductor/solid-state device details3d integrated circuitCMOS

Three-dimensional (3D) integration schemes of fabricating a 3D integrated circuit in which the pFETs are located on an optimal crystallographic surface for that device and the nFETs are located on a optimal crystallographic surface for that type of device are provided. In accordance with a first 3D integration scheme of the present invention, first semiconductor devices are pre-built on a semiconductor surface of a first silicon-on-insulator (SOI) substrate and second semiconductor devices are pre-built on a semiconductor surface of a second SOI substrate. After pre-building those two structures, the structure are bonded together and interconnect through wafer-via through vias. In a second 3D integration scheme, a blanket silicon-on-insulator (SOI) substrate having a first SOI layer of a first crystallographic orientation is bonded to a surface of a pre-fabricating wafer having second semiconductor devices on a second SOI layer that has a different crystallographic orientation than the first SOI layer; and forming first semiconductor device on the first SOI layer.

Owner:GLOBALFOUNDRIES INC

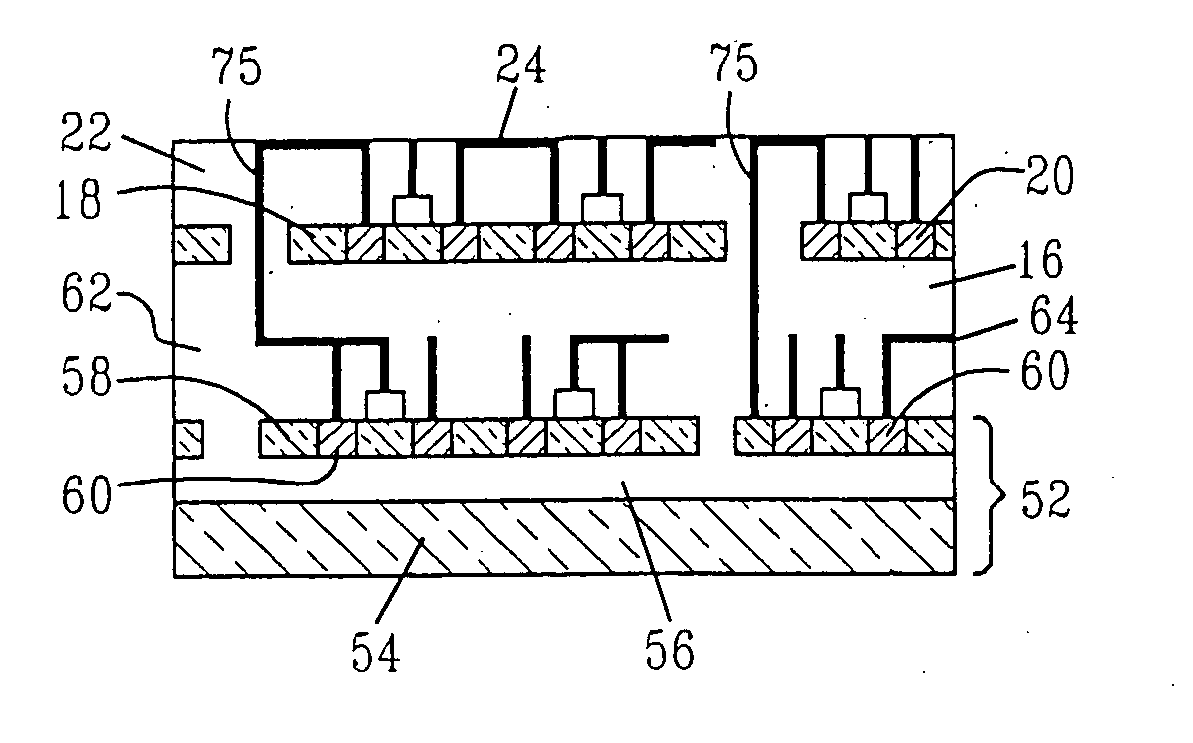

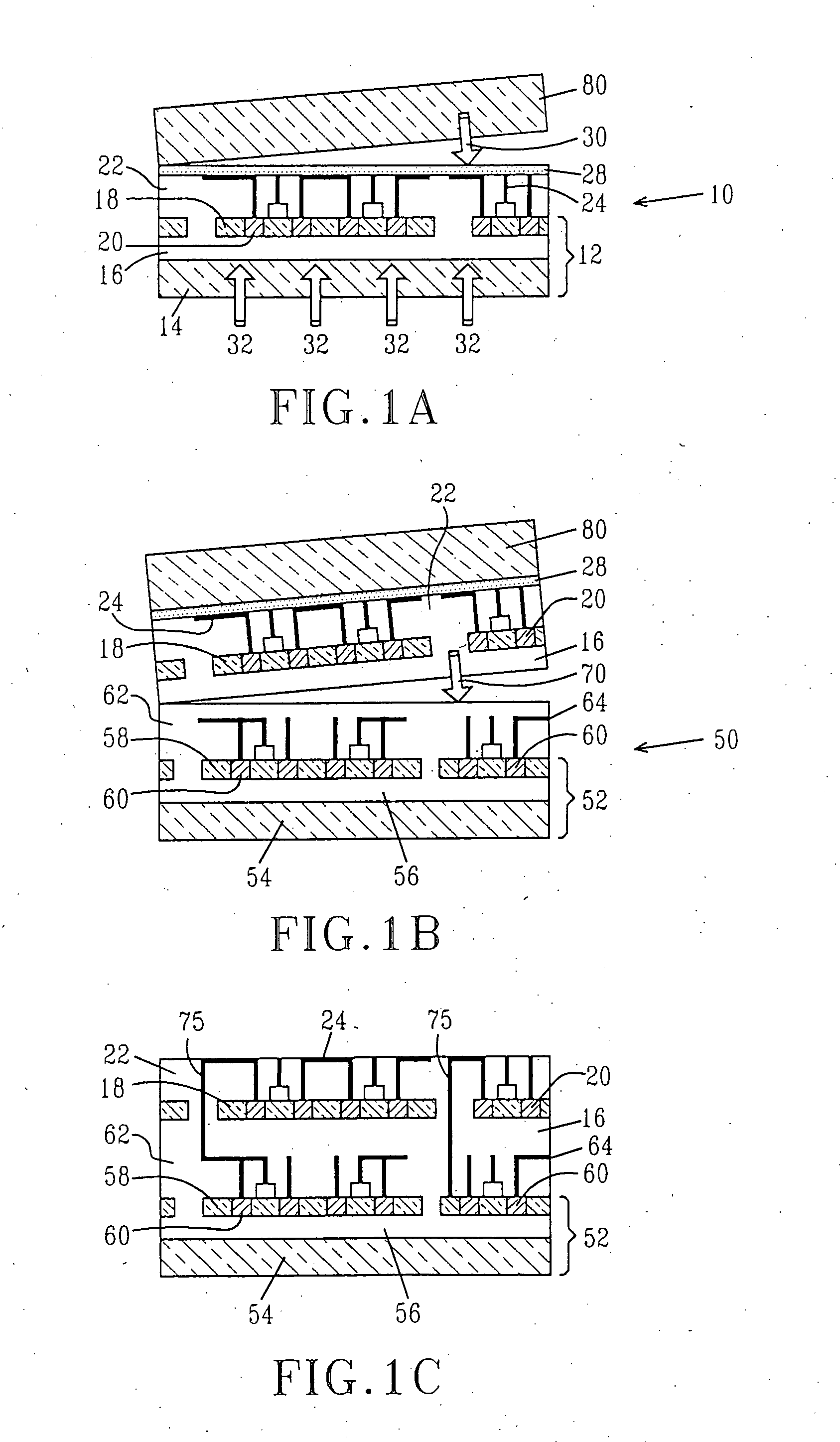

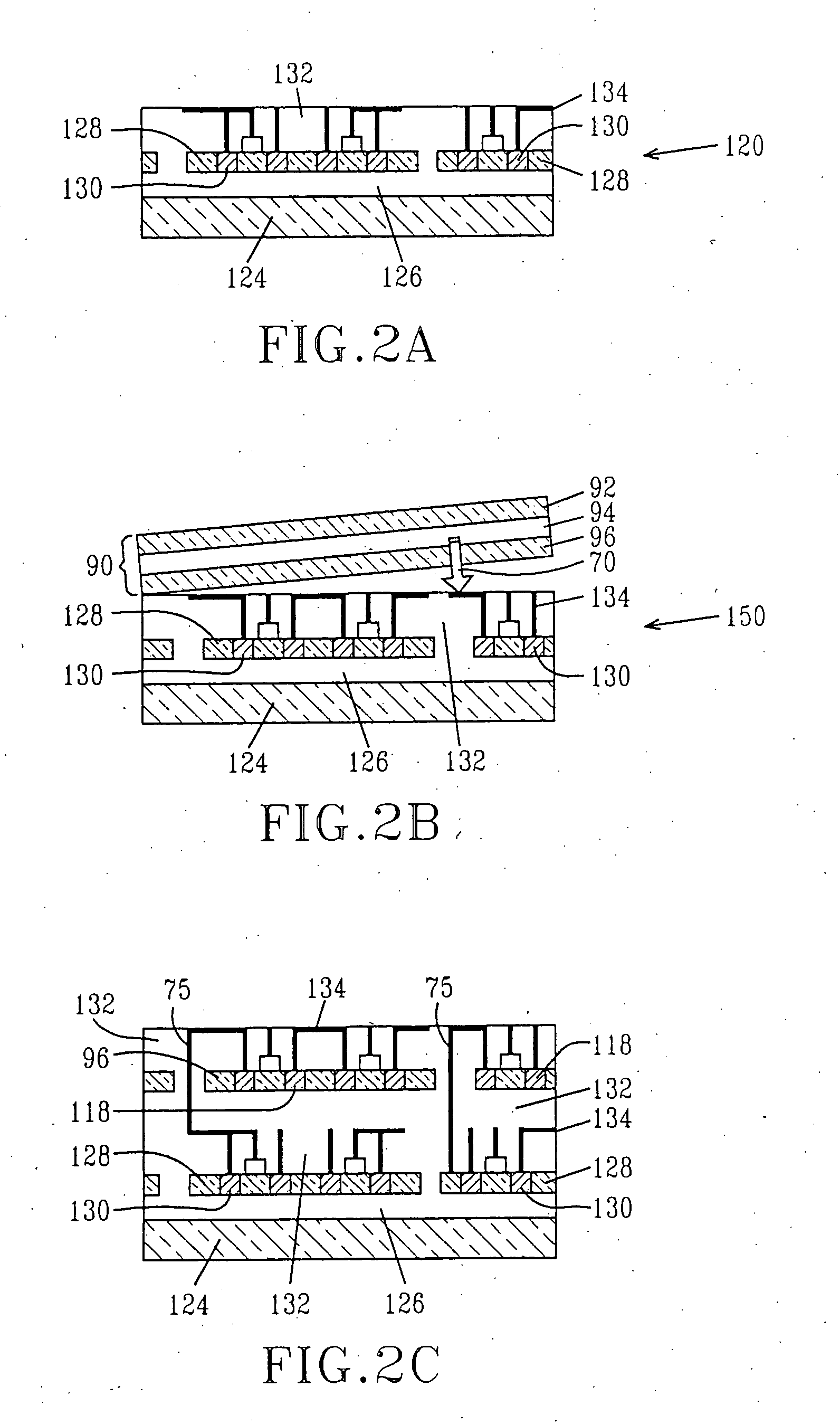

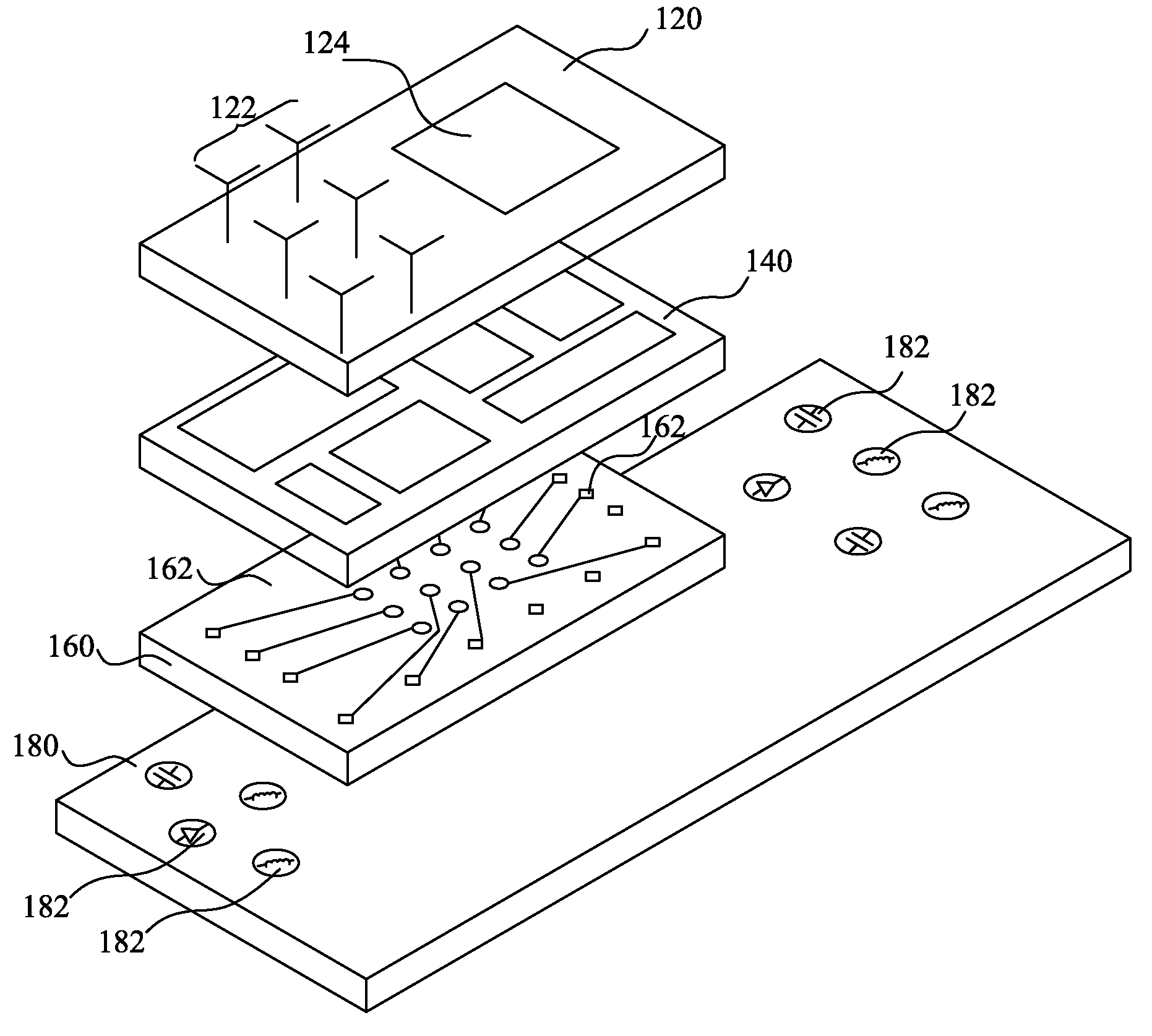

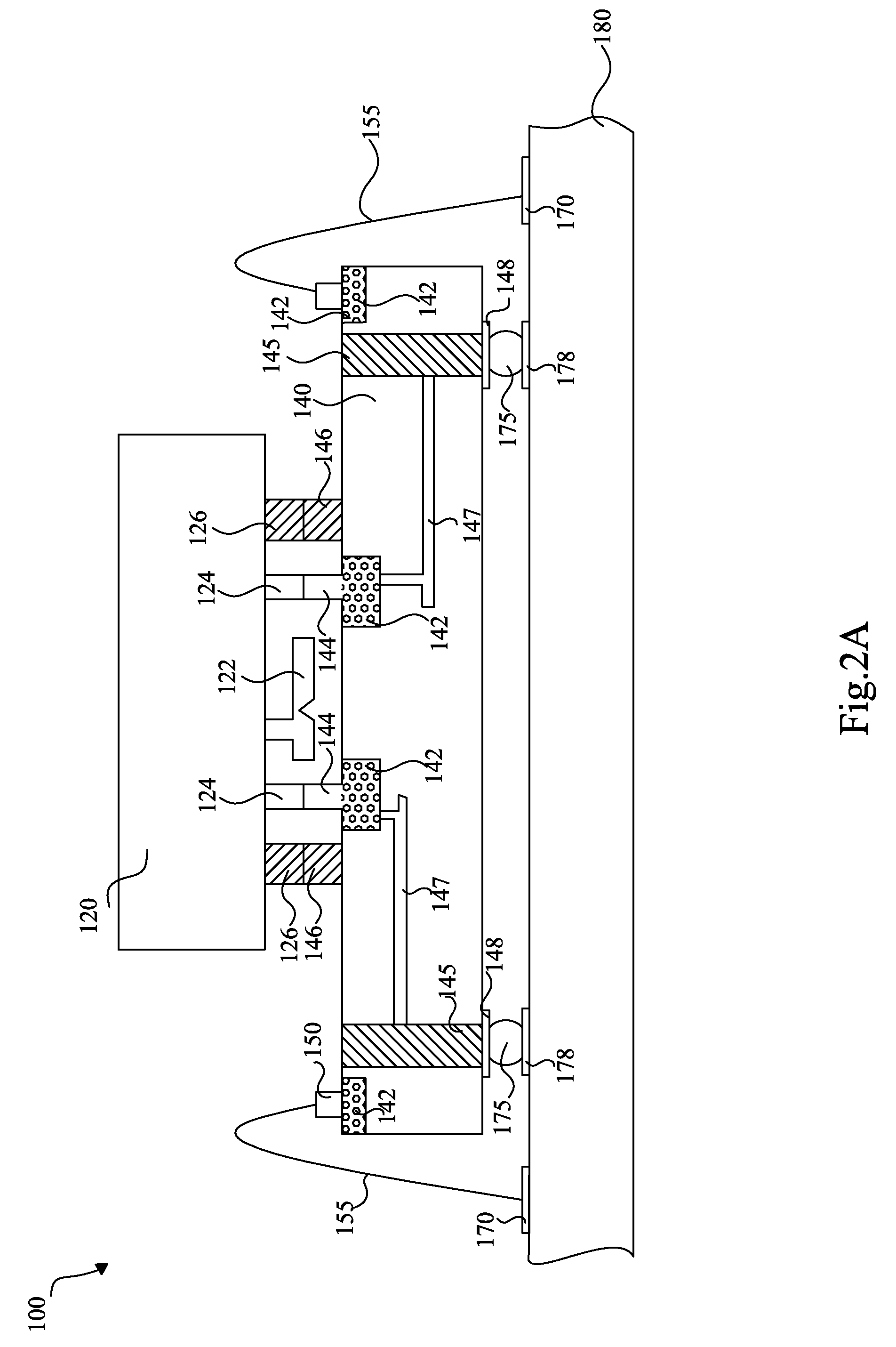

MEMS Packaging Including Integrated Circuit Dies

InactiveUS20090194829A1Highly integratedReduced package footprintSemiconductor/solid-state device detailsSolid-state devicesOn boardElectrical connection

MEMS packaging schemes having a system-on-package (SOP) configuration and a system-on-board (SOB) configuration are provided. The MEMS package comprises one or more MEMS dies, a cap section having one or more integrated circuit (IC) dies, and a packaging substrate or a printed circuit board (PCB) arranged in a stacking manner. Vertical connectors, such as through-silicon-vias (TSVs), are formed to provide short electrical connections between the various components. The MEMS packaging schemes enable higher integration density, reduced MEMS package footprints, reduced RC delays and power consumption.

Owner:TAIWAN SEMICON MFG CO LTD

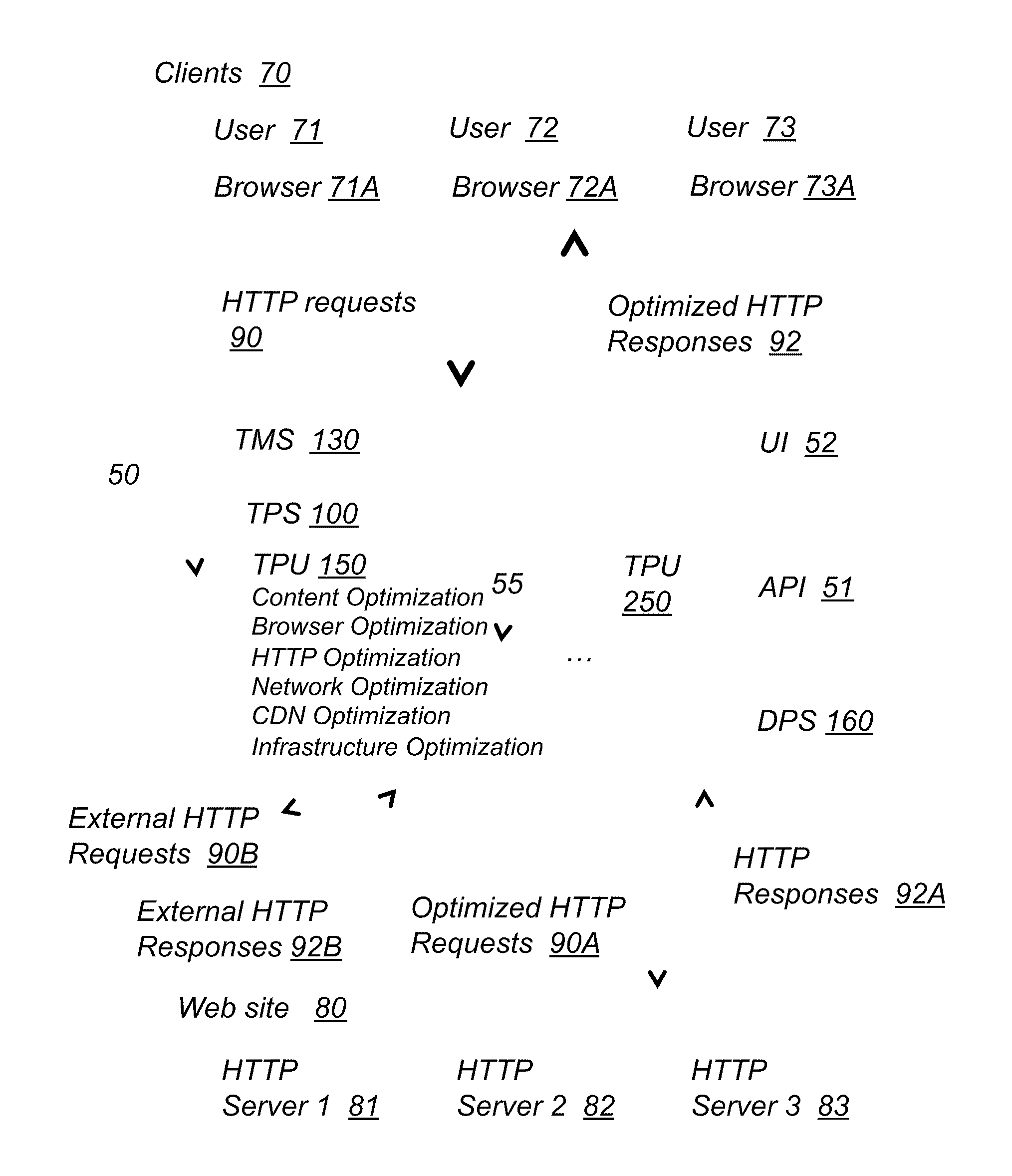

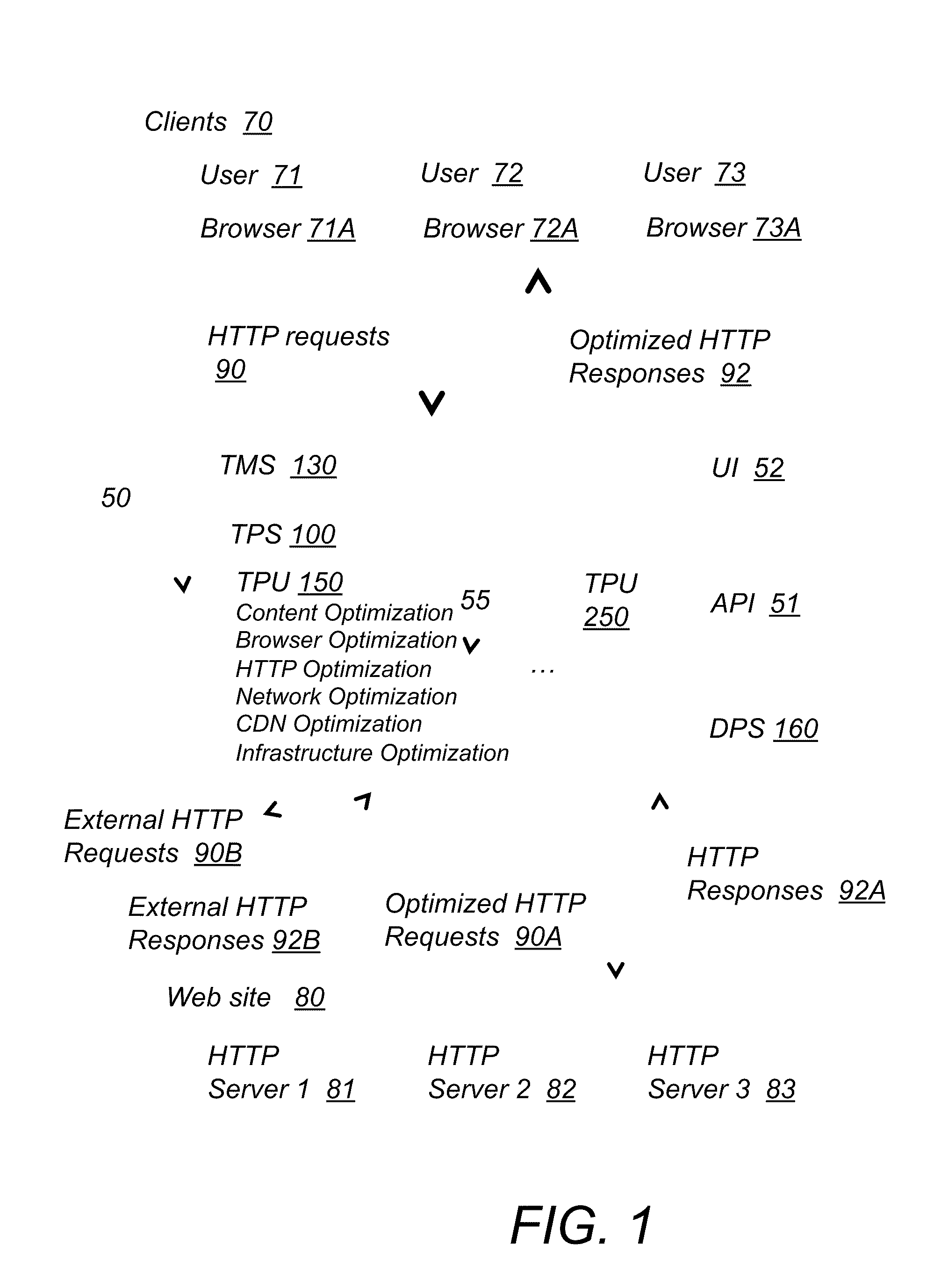

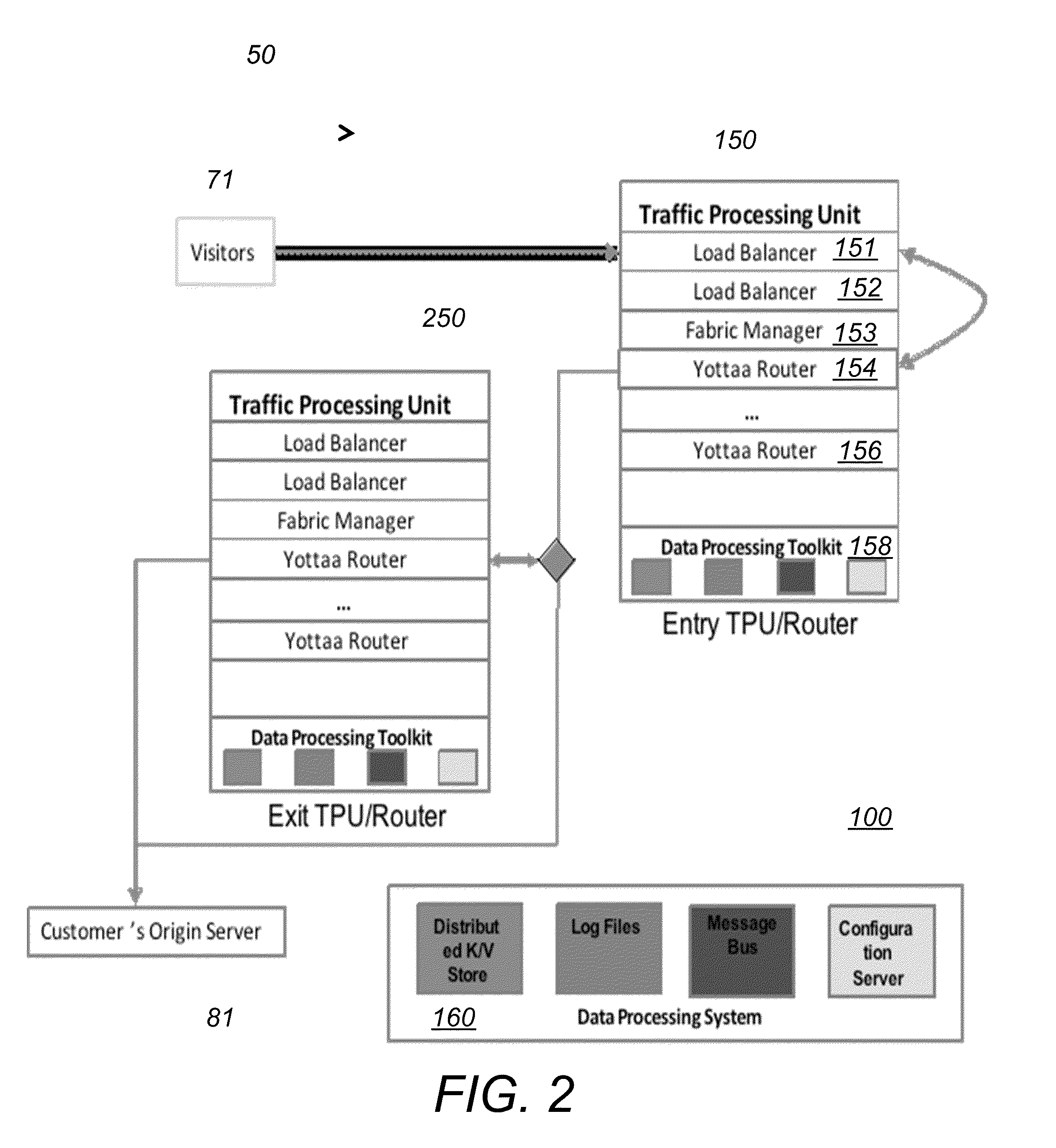

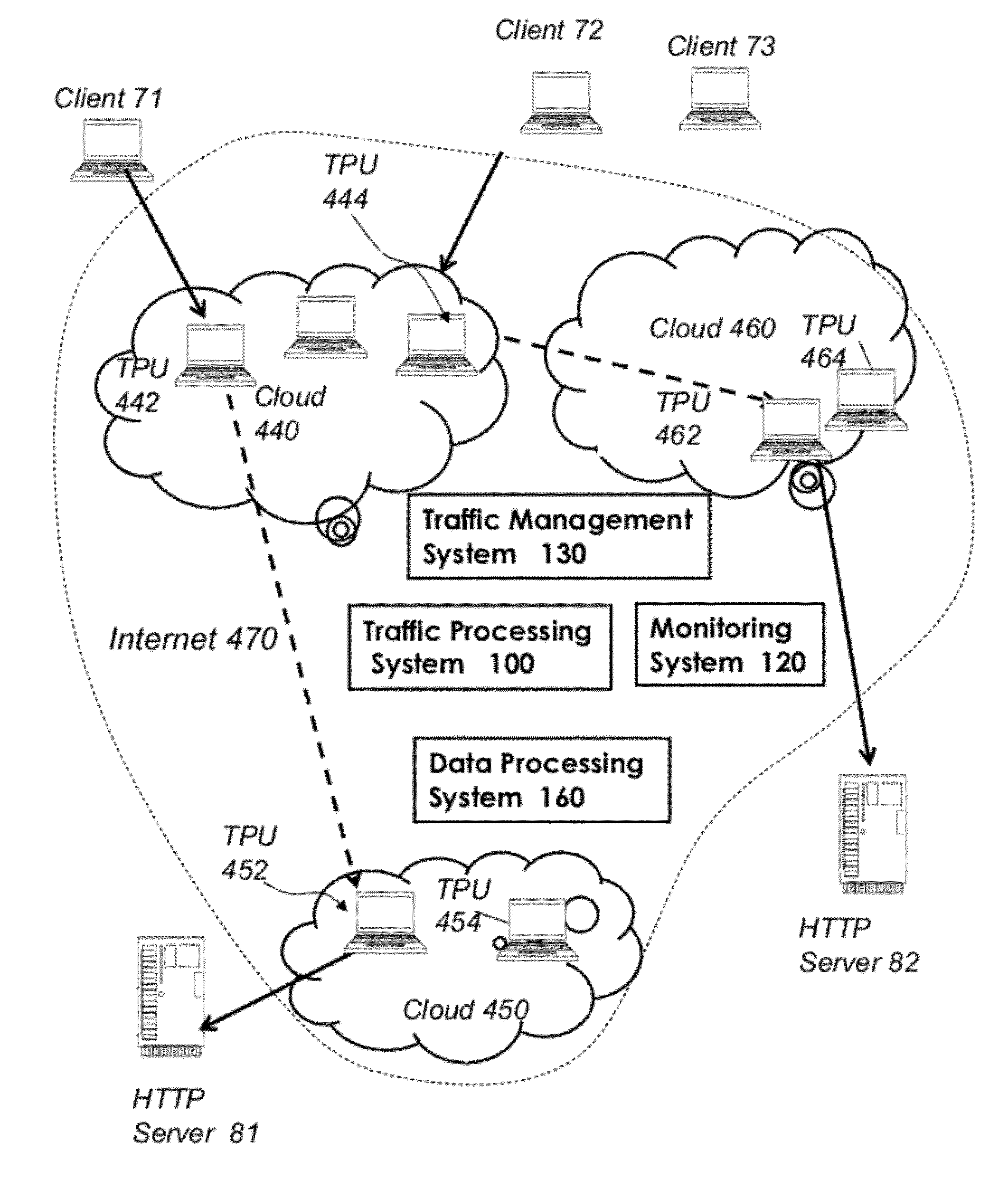

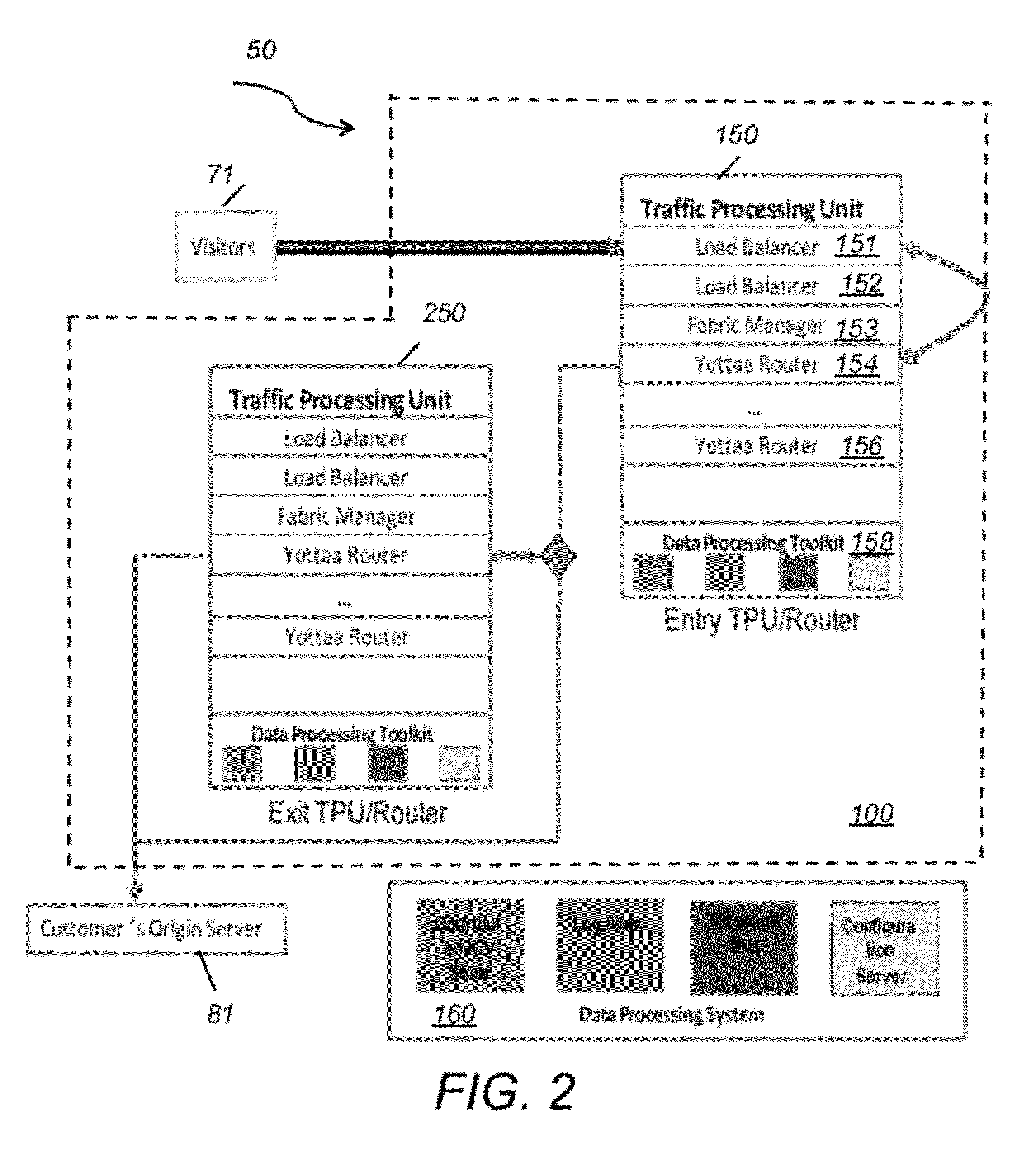

System and method for website performance optimization and internet traffic processing

ActiveUS20110137973A1Addressing slow performanceReduce in quantityMemory loss protectionError detection/correctionTraffic capacityWeb site

A system for optimizing the performance of a website that runs on one or more HTTP servers and is configured to receive HTTP requests from one or more clients via user agents and provide HTTP responses to the one or more clients includes an intermediary component configured to connect to the clients and the servers via network connections. The intermediary component includes a traffic management system (TMS) that includes means for managing HTTP requests originating from the clients and targeting the servers and HTTP responses originating from the servers and targeting the clients and means for redirecting the HTTP requests to the intermediary component. The intermediary component further includes a traffic processing system that includes means for receiving the redirected HTTP requests and the HTTP responses and means for applying optimization techniques to the redirected HTTP requests and the HTTP responses.

Owner:YOTTAA

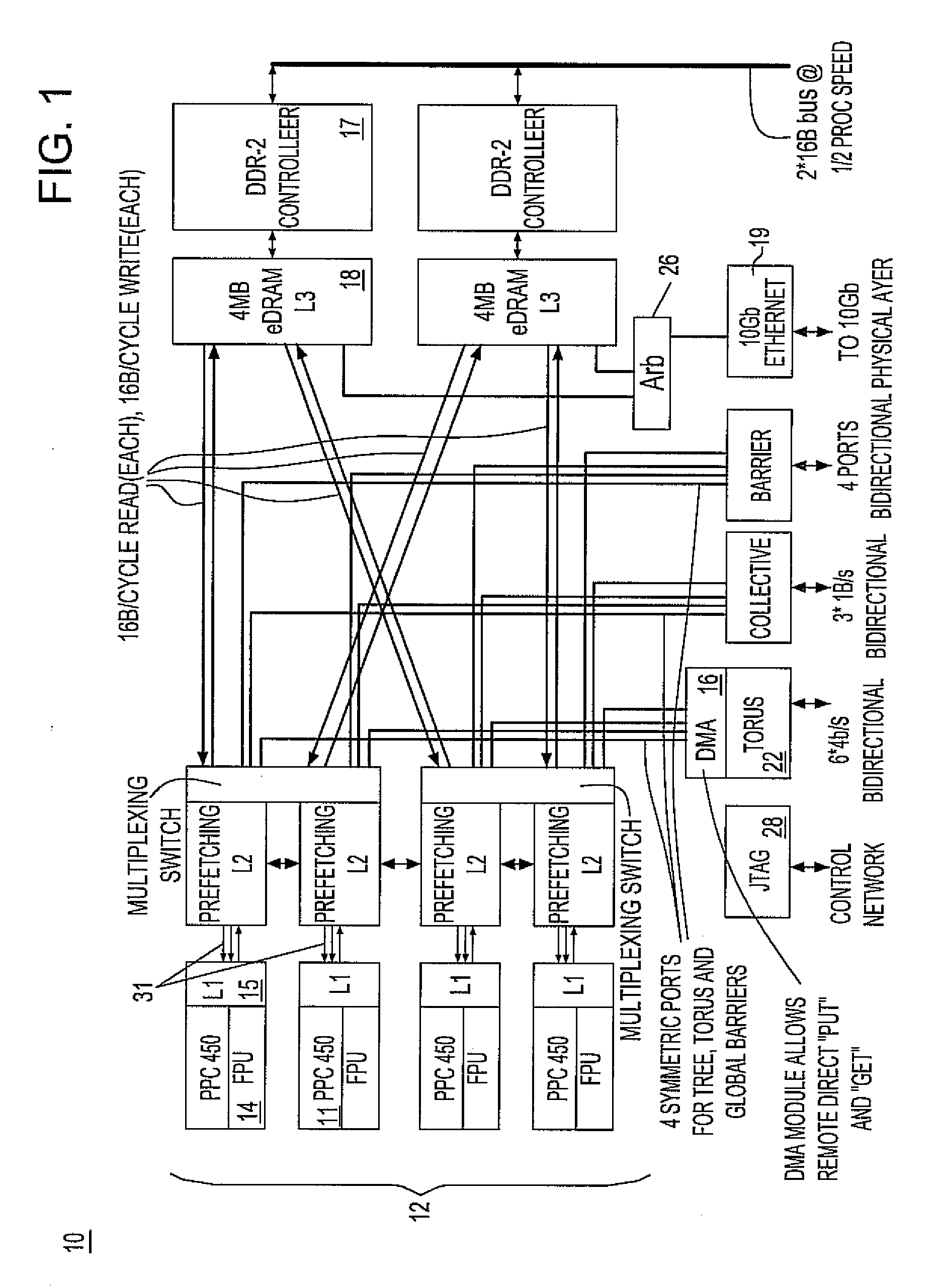

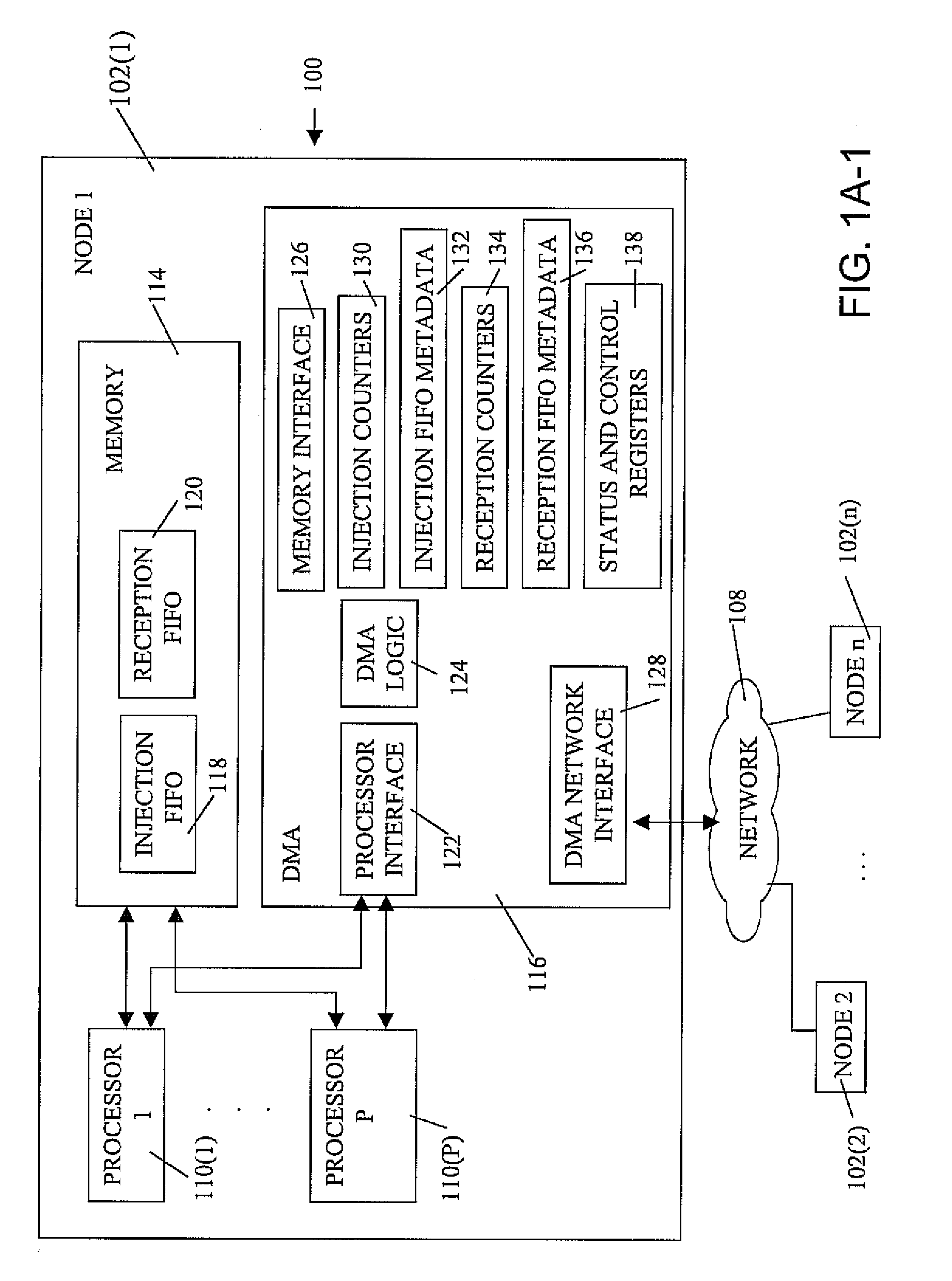

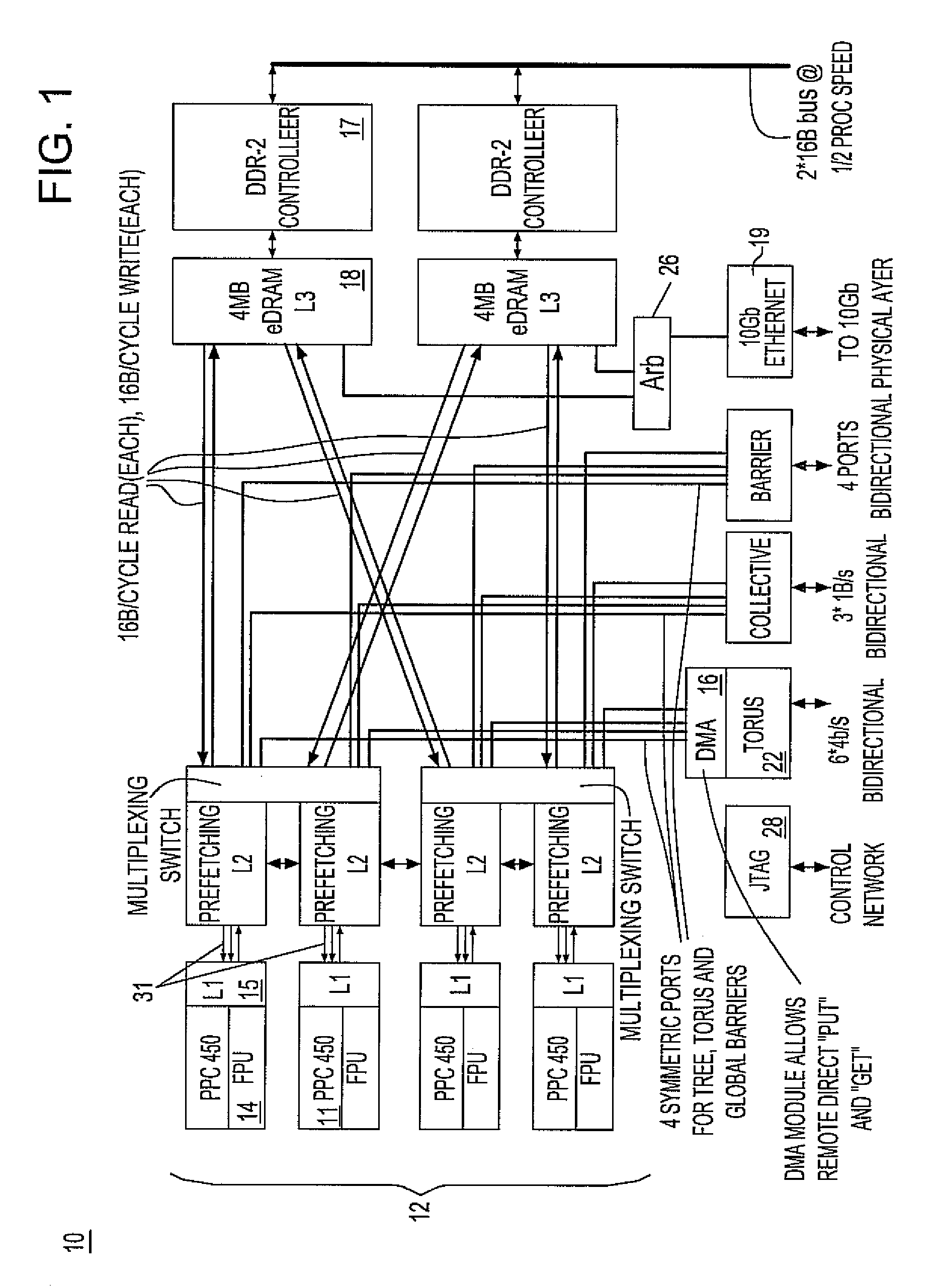

Ultrascalable petaflop parallel supercomputer

InactiveUS20090006808A1Massive level of scalabilityUnprecedented level of scalabilityProgram control using stored programsArchitecture with multiple processing unitsMessage passingPacket communication

A novel massively parallel supercomputer of petaOPS-scale includes node architectures based upon System-On-a-Chip technology, where each processing node comprises a single Application Specific Integrated Circuit (ASIC) having up to four processing elements. The ASIC nodes are interconnected by multiple independent networks that optimally maximize the throughput of packet communications between nodes with minimal latency. The multiple networks may include three high-speed networks for parallel algorithm message passing including a Torus, collective network, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. Novel use of a DMA engine is provided to facilitate message passing among the nodes without the expenditure of processing resources at the node.

Owner:IBM CORP

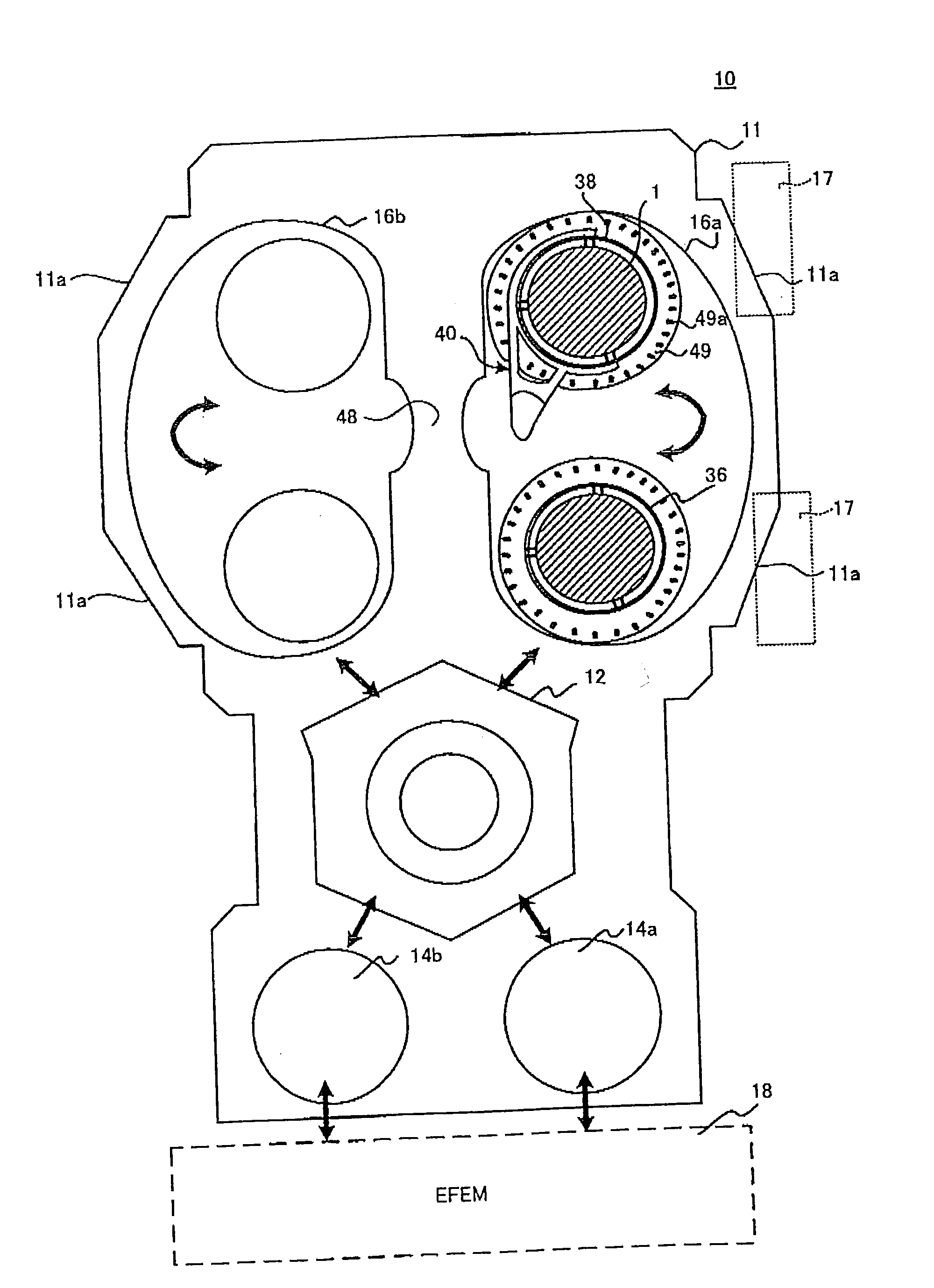

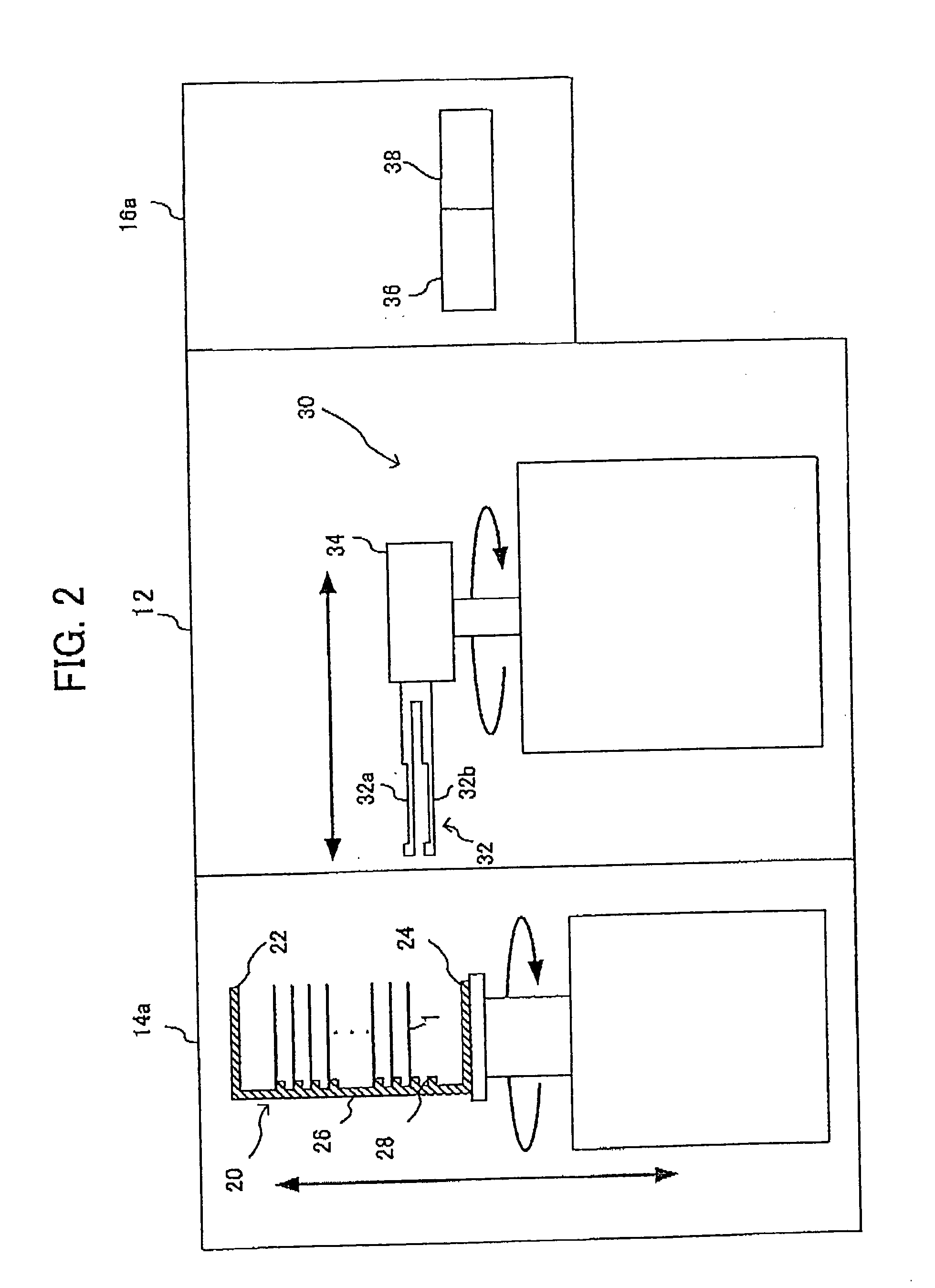

Substrate processing apparatus and substrate processing method

ActiveUS20100068414A1Improve throughputReduced footprintSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringMechanical engineering

A substrate processing apparatus includes a transport chamber and a processing chamber that processes substrates. The transport chamber has a first substrate transport member transporting the substrates from the transport chamber to the processing chamber. The processing chamber has a first processing unit which is adjacent to the transport chamber and has a first substrate placing base, a second processing unit which is adjacent to the other side of the transport chamber in the first processing unit and has a second substrate placing base, a second substrate transport member transporting the substrates between the first processing unit and the second processing unit, and a control unit controlling at least the second substrate transport member.

Owner:KOKUSA ELECTRIC CO LTD

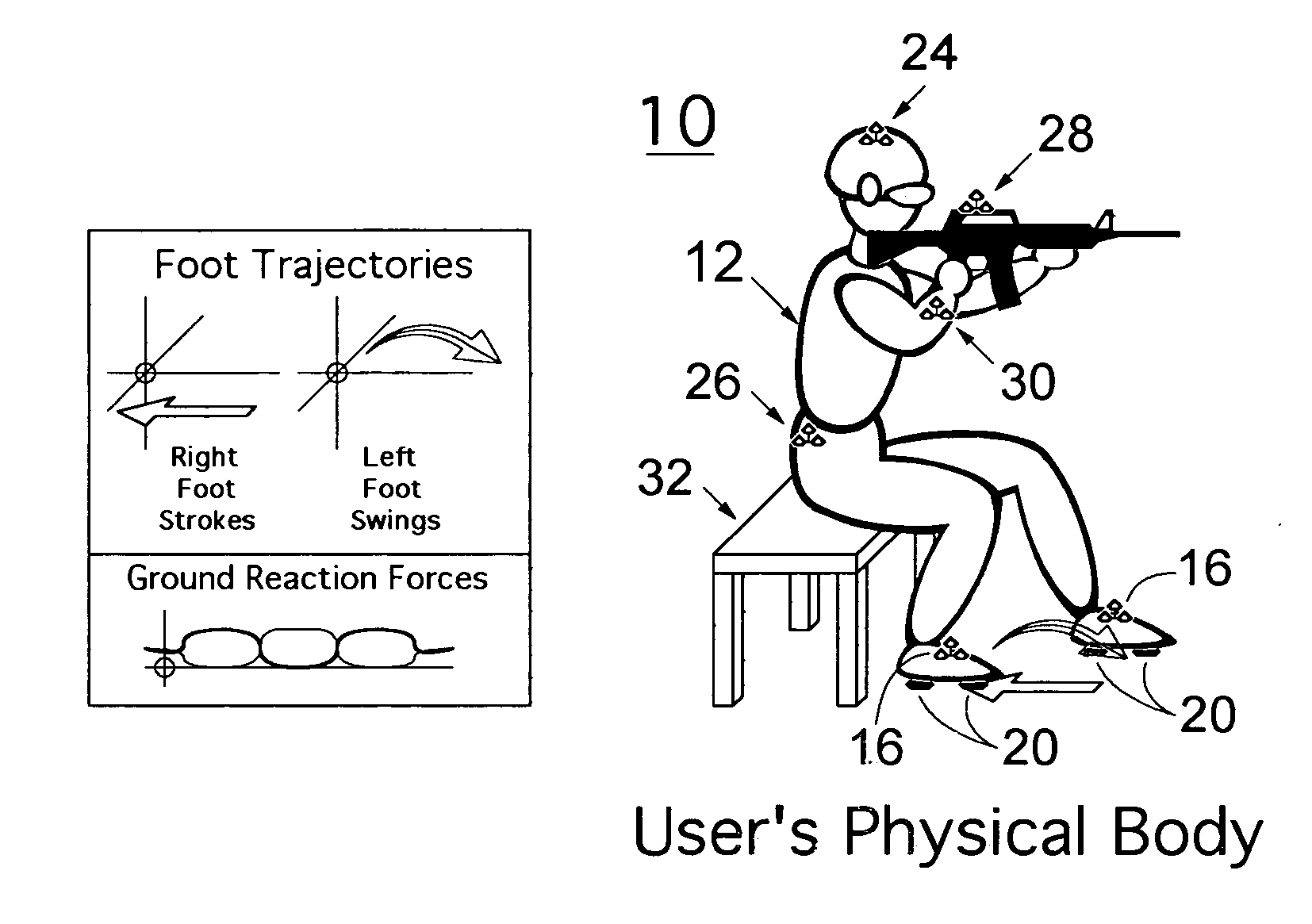

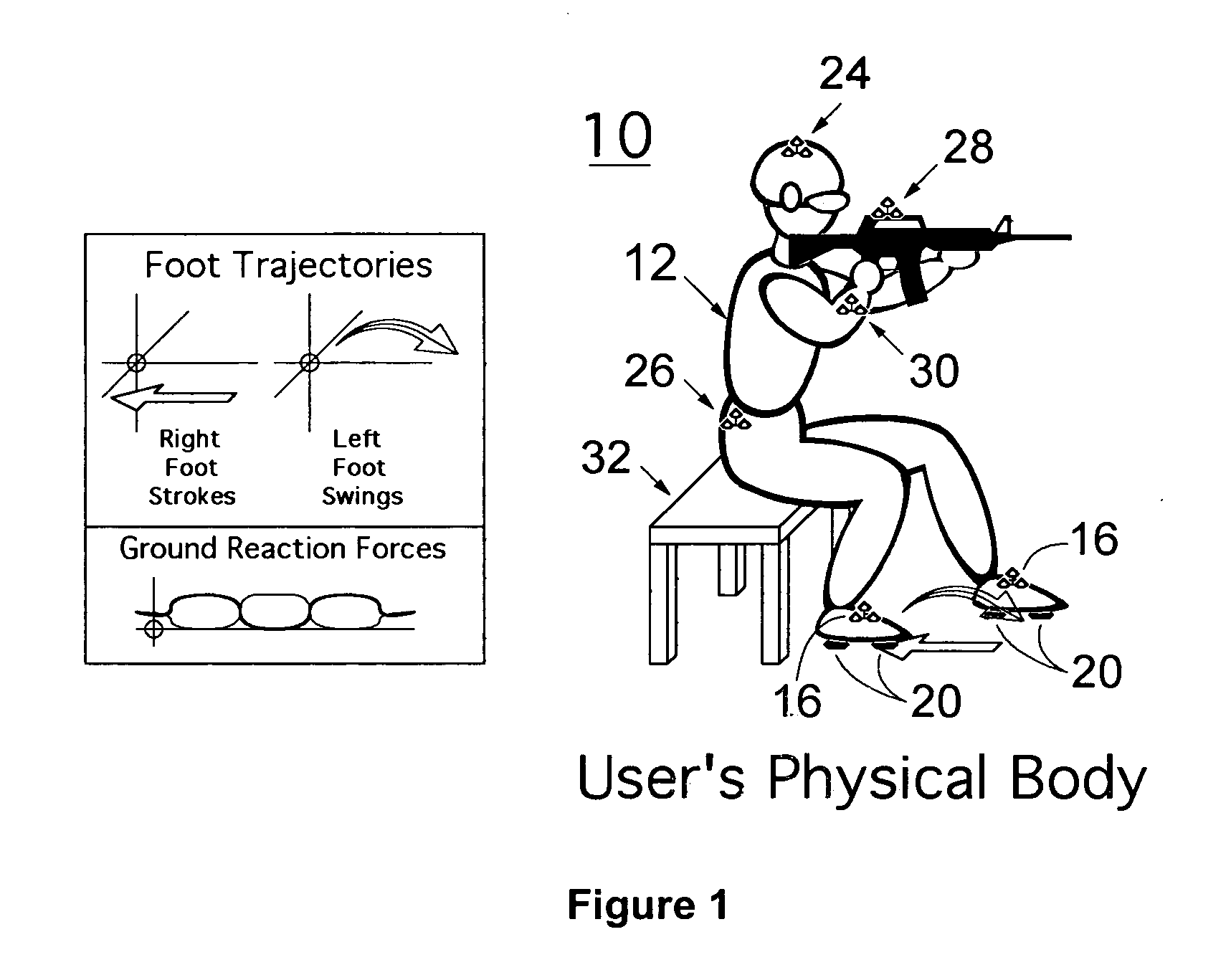

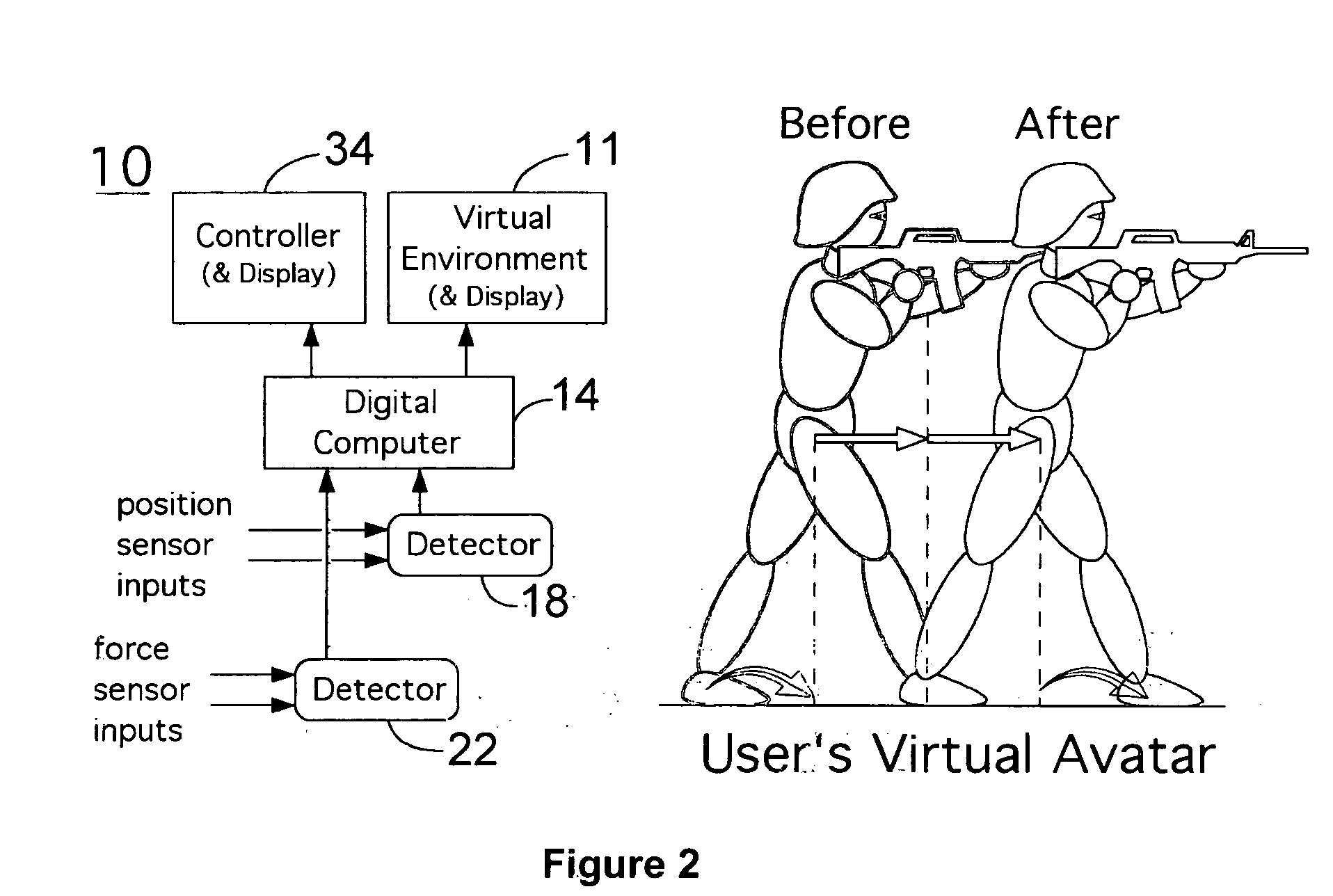

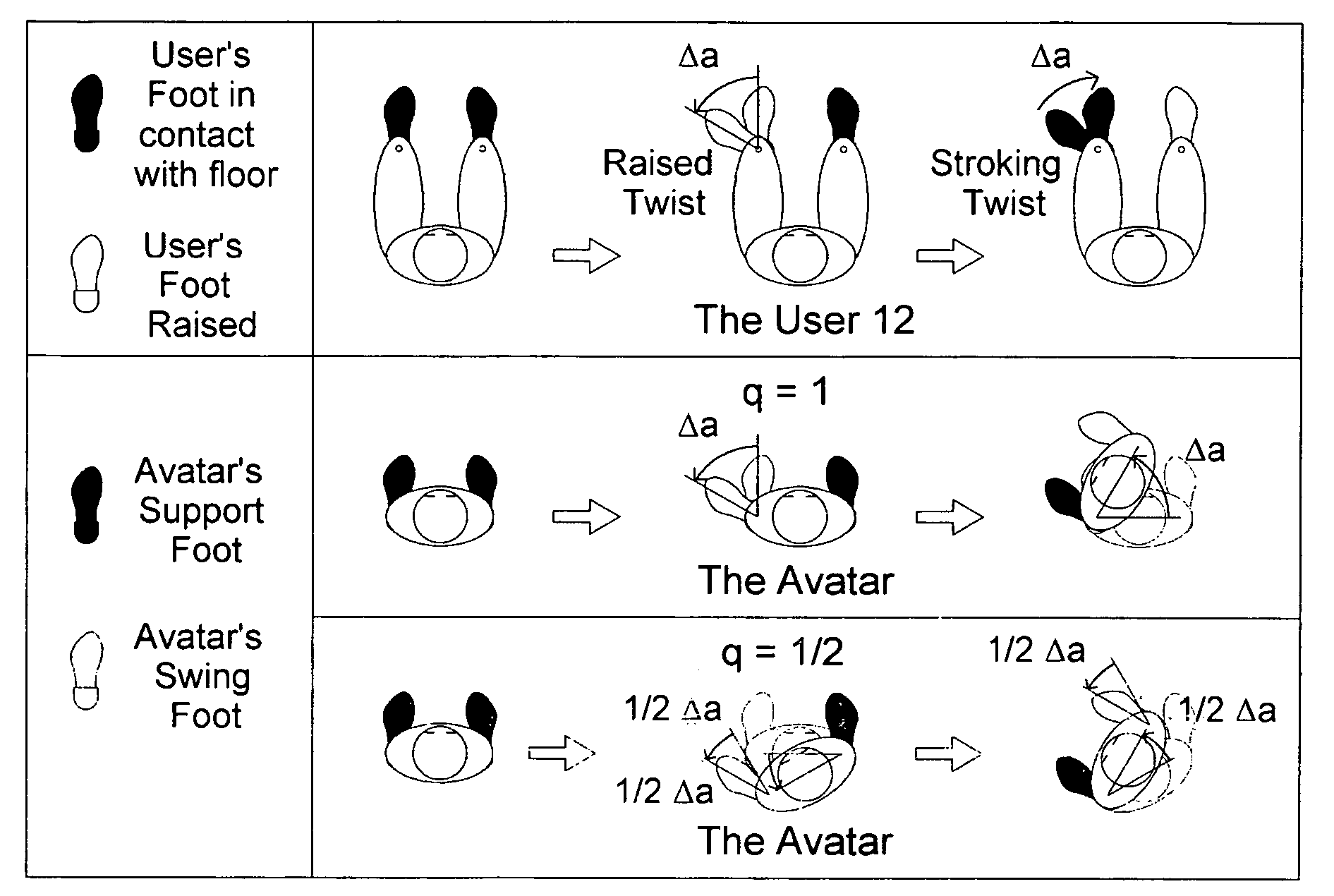

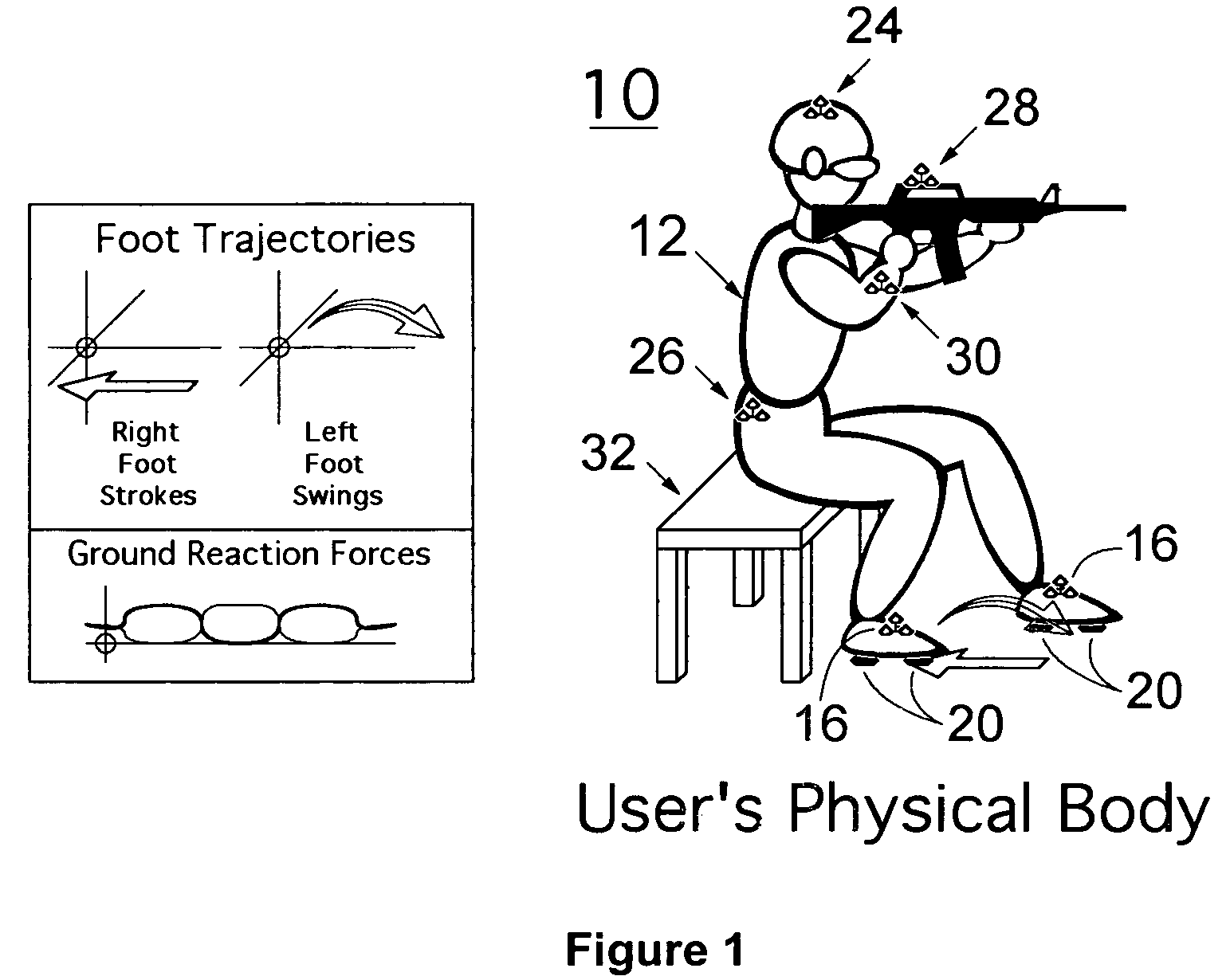

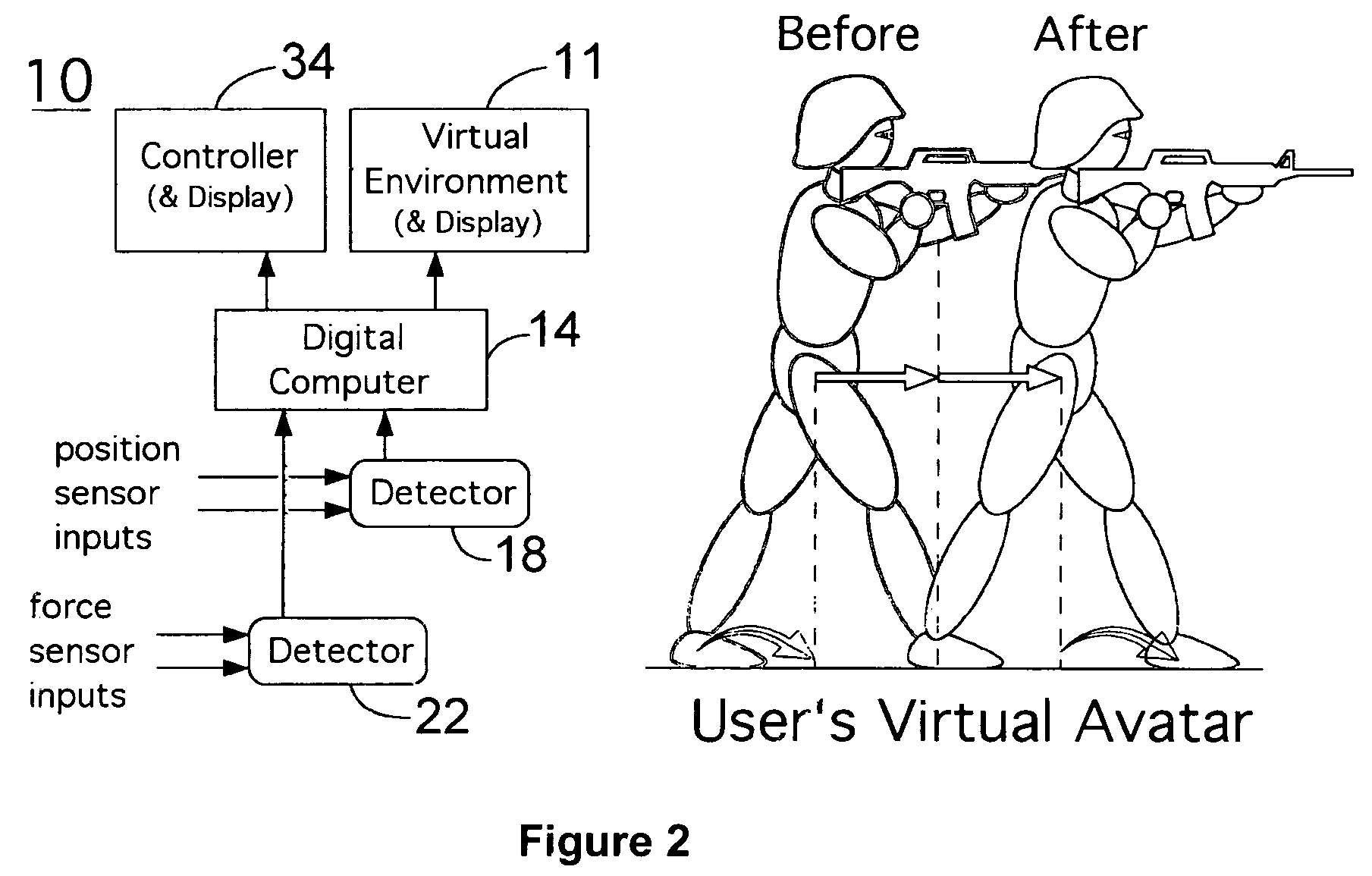

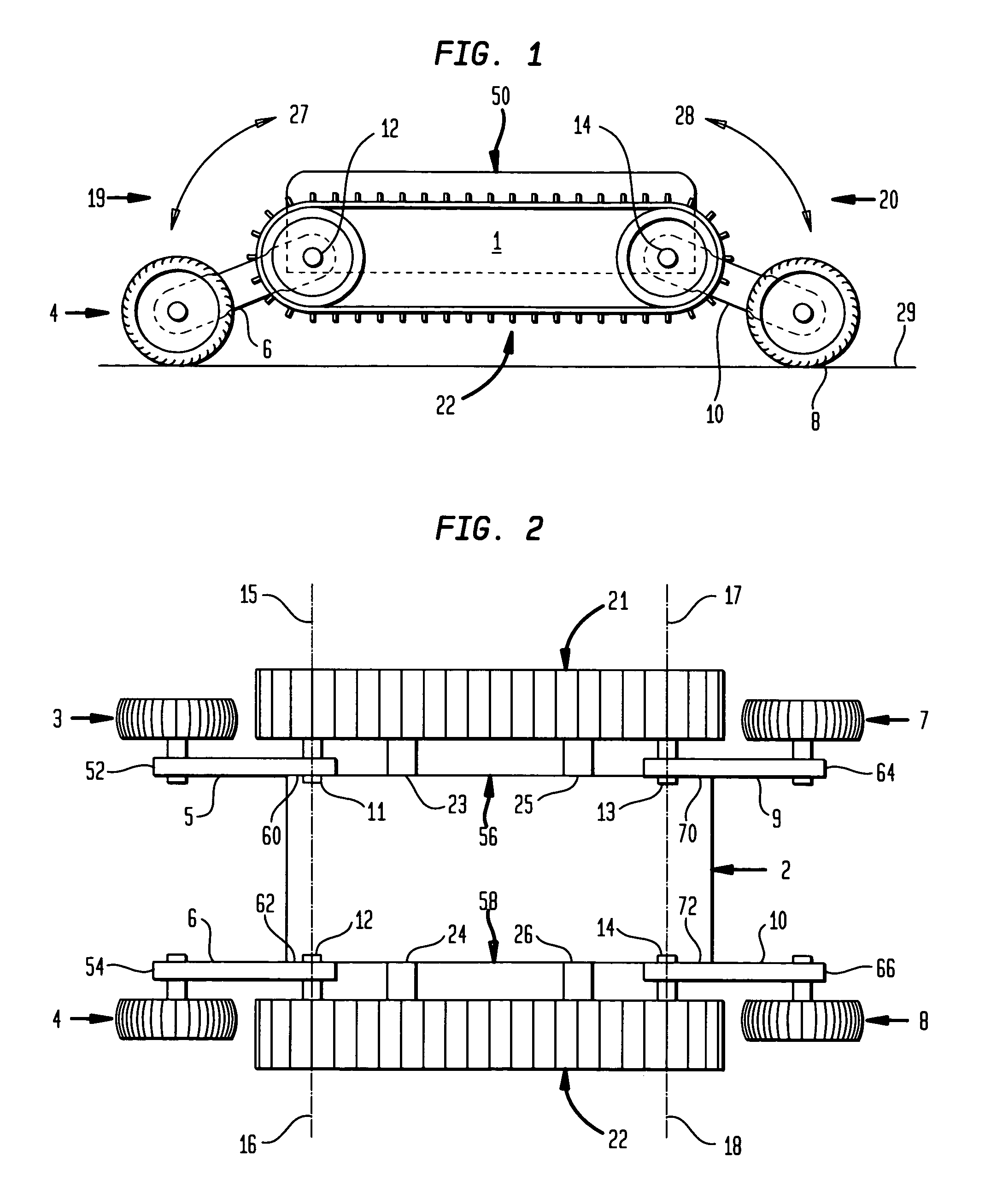

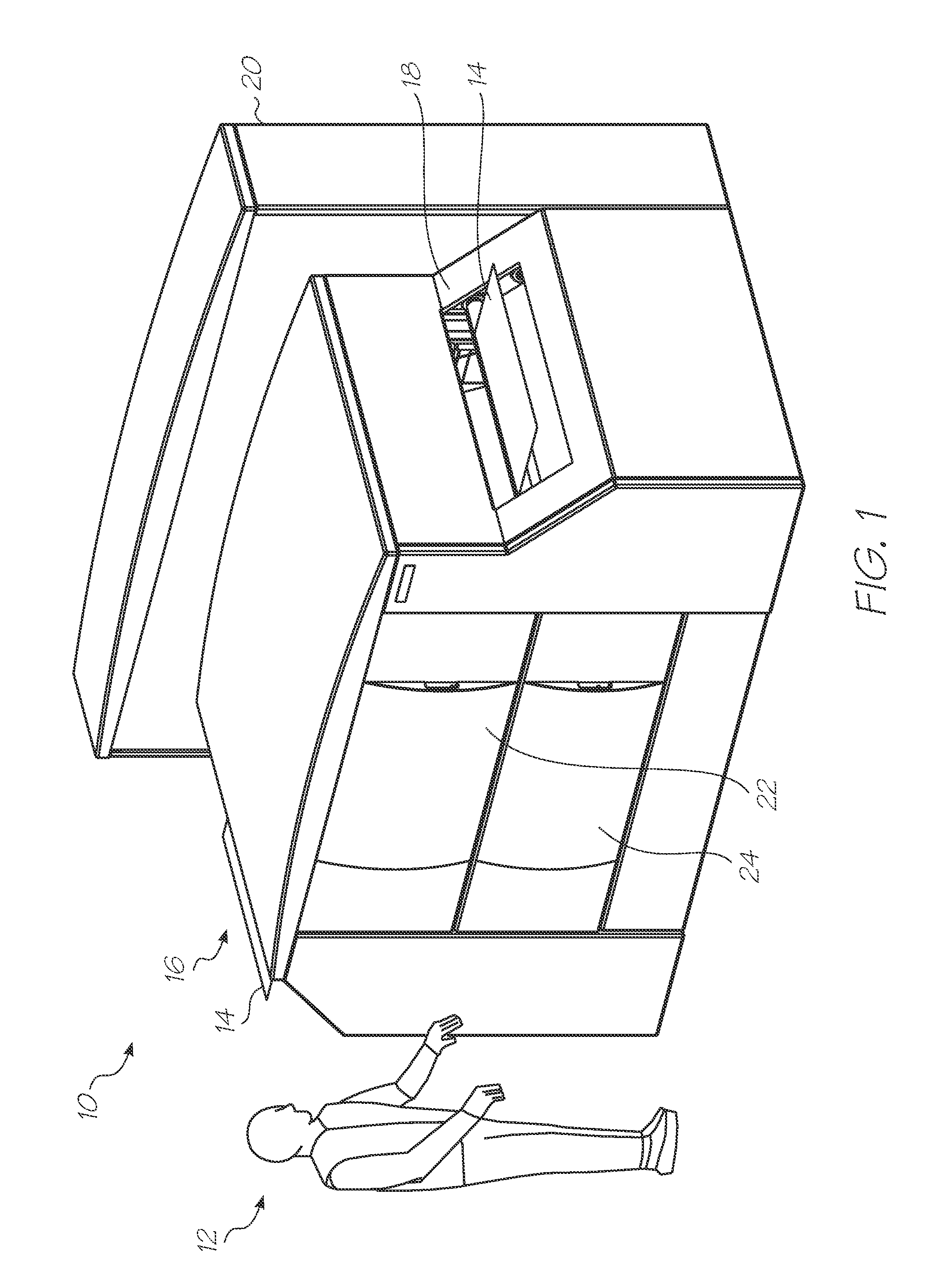

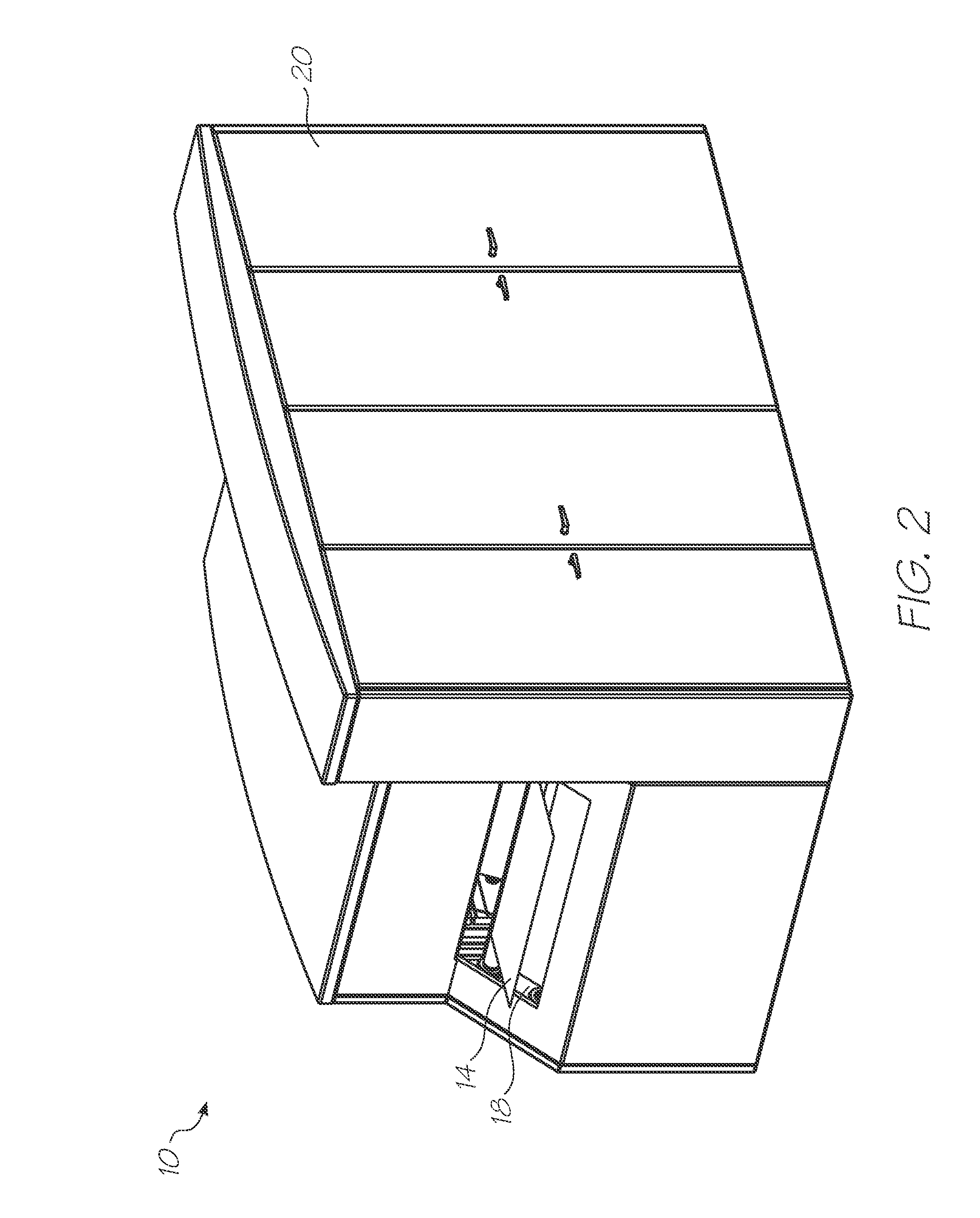

Simulated locomotion method and apparatus

InactiveUS20070003915A1Reduced footprintReduces vertical extentCosmonautic condition simulationsAnimationVirtual locomotionHuman–computer interaction

An apparatus for interfacing 3D movements of a user to control the locomotion of an avatar in a virtual environment includes a position tracker for tracking the position of a user's feet, with the foot motions including swinging and stroking; a computer programmed for (i) computing a direction and extent of motion of a reference in the virtual environment based on the foot positions and (ii) providing an avatar corresponding to the computed direction and extent of motion; and a display for displaying the avatar in the virtual environment. The apparatus accordingly uses the gestural motion of the user's feet while seated to simulate natural human locomotion. The gestural motions of stroking and swinging include translational and rotating movements, and are chosen to correspond to the actions of the feet and legs during natural human locomotion, providing natural control of virtual locomotion. The apparatus is also designed for controlling the locomotion of a remote vehicle.

Owner:USA AS REPRESENTED BY THE SEC OF THE NAVY THE

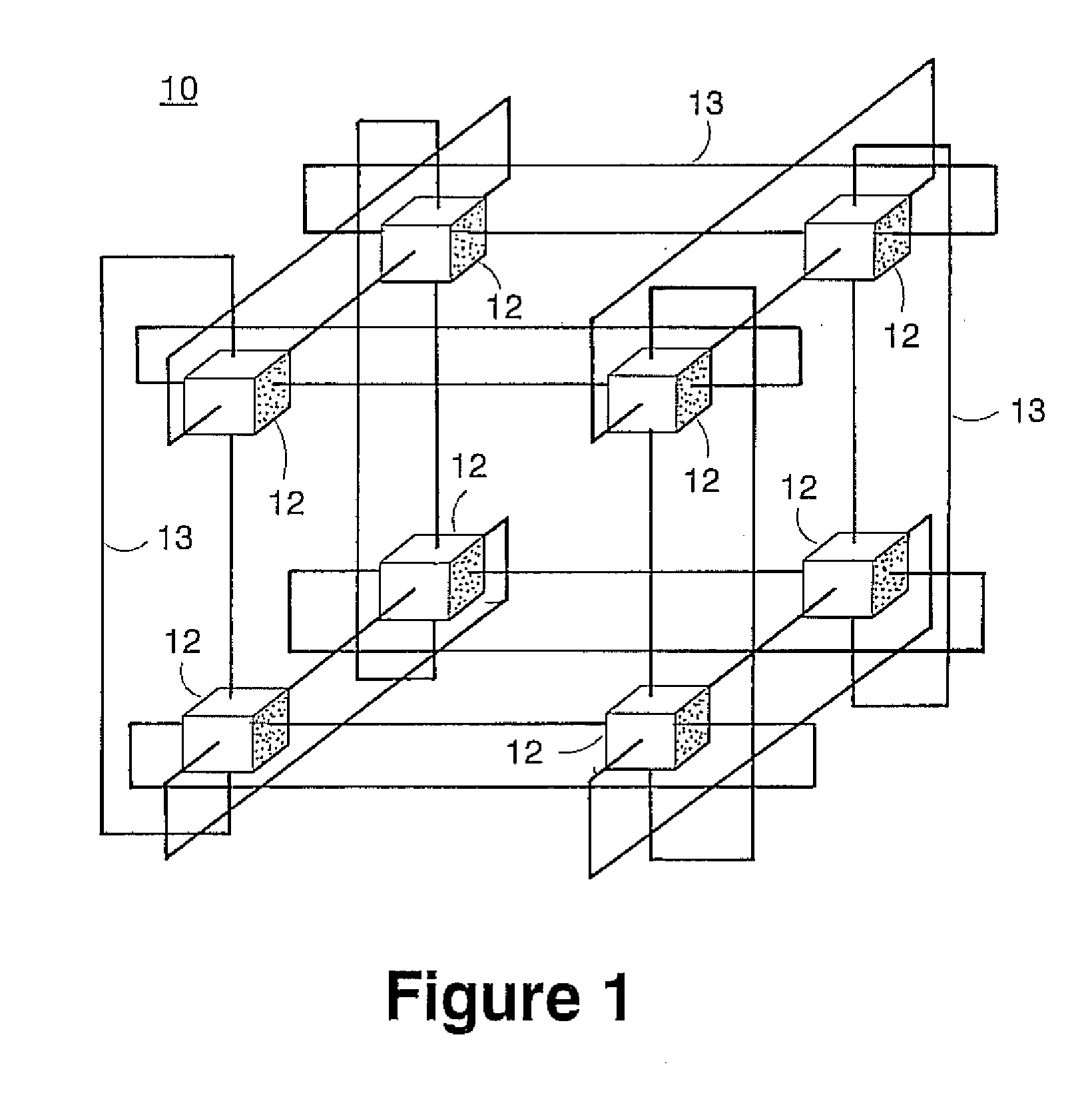

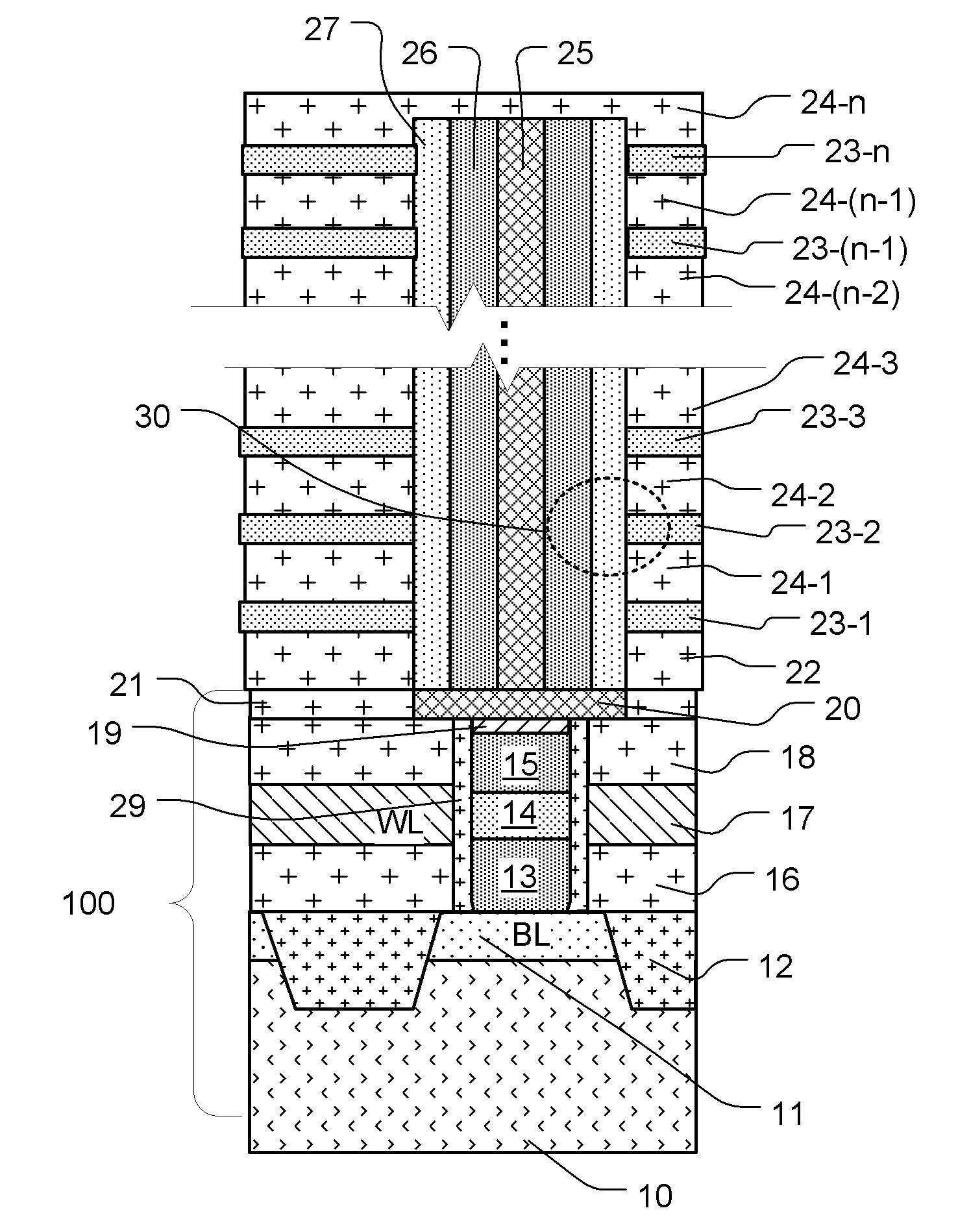

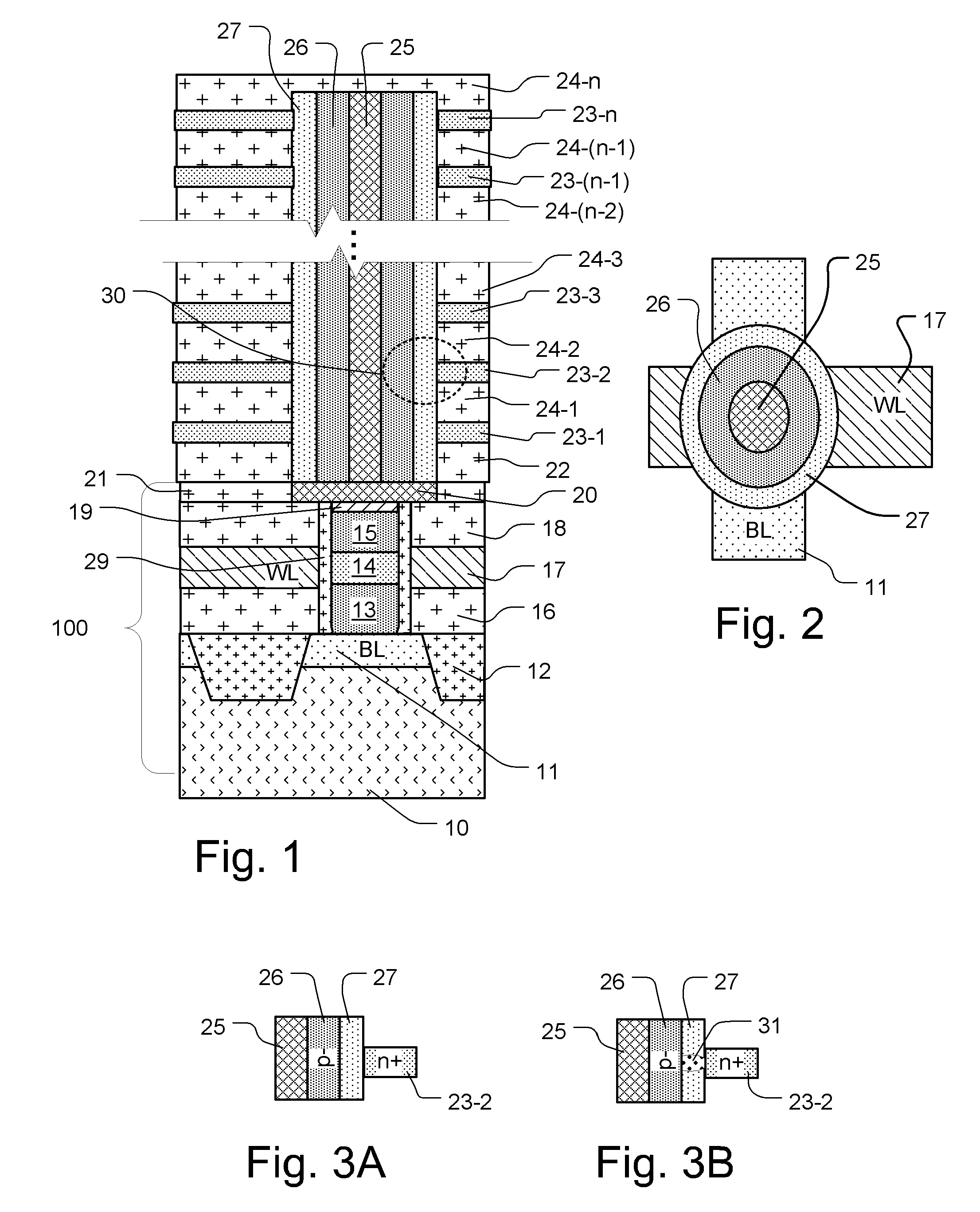

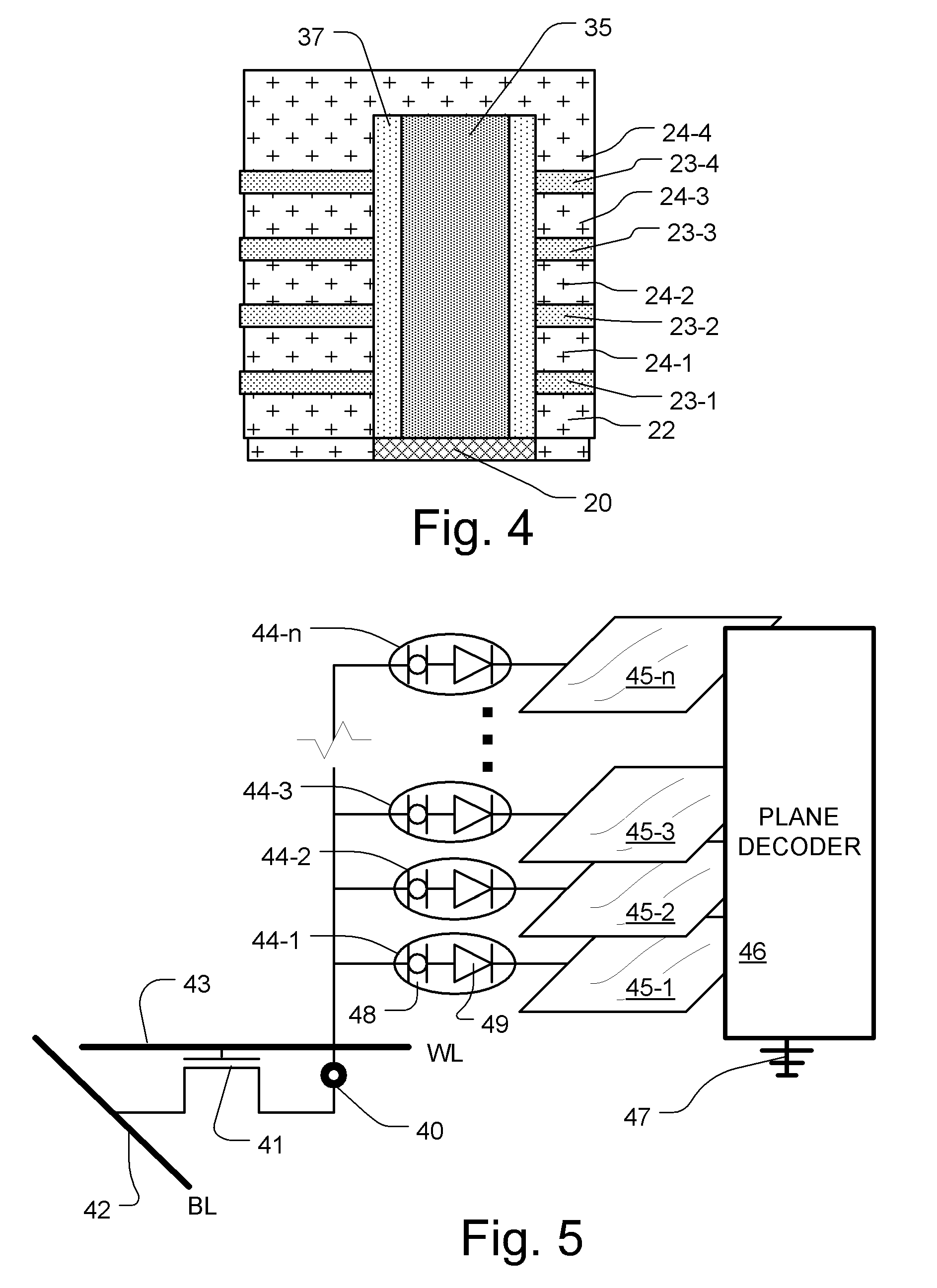

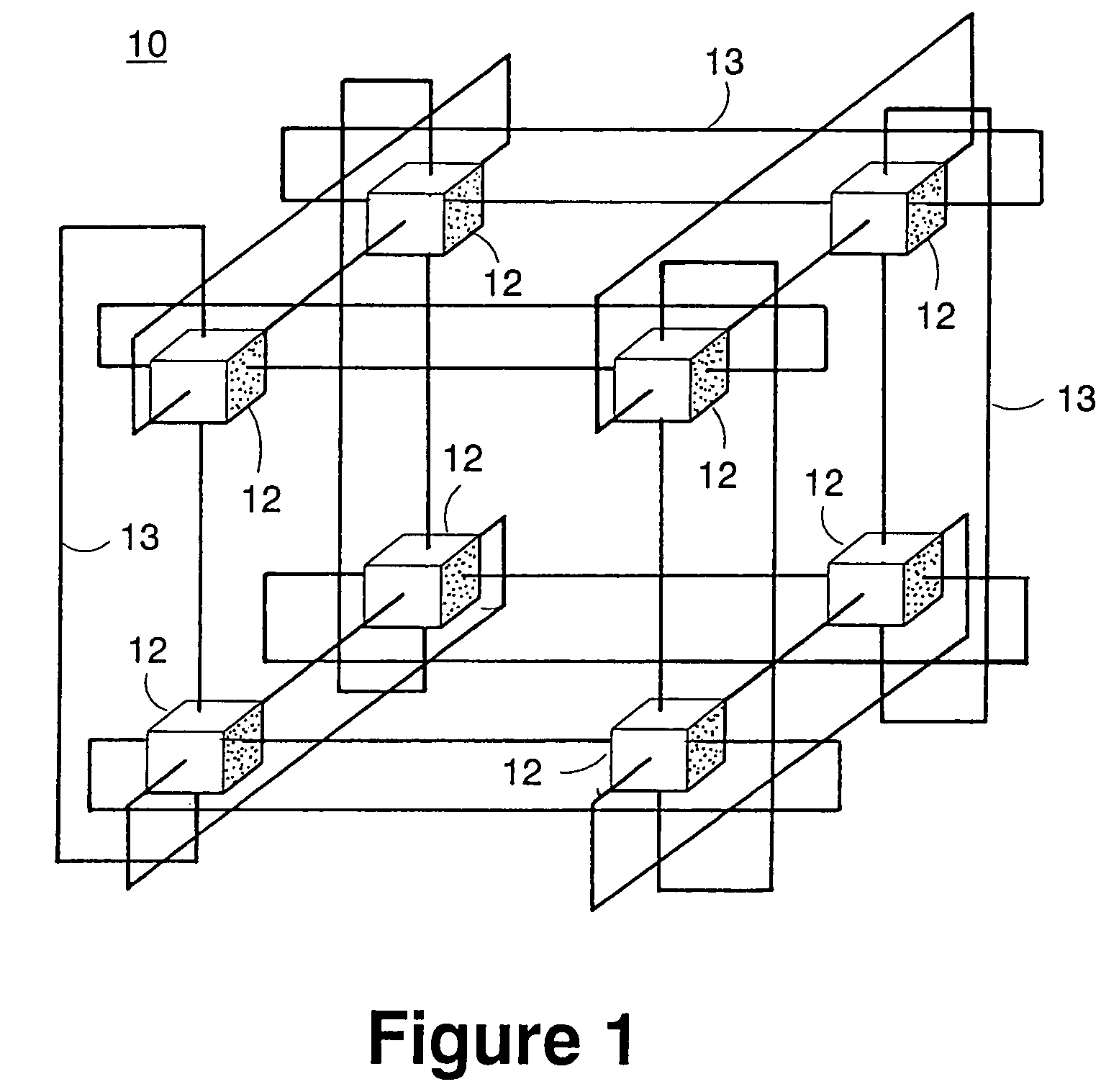

Integrated circuit 3D memory array and manufacturing method

ActiveUS20100270593A1Reduced footprintTransistorSemiconductor/solid-state device detailsBiomedical engineering3d memory

A 3D memory device is based on an array of electrode pillars and a plurality of electrode planes that intersect the electrode pillars at interface regions that include memory elements that comprise a programmable element and a rectifier. The electrode pillars can be selected using two-dimensional decoding, and the plurality of electrode planes can be selected using decoding on a third dimension.

Owner:MACRONIX INT CO LTD

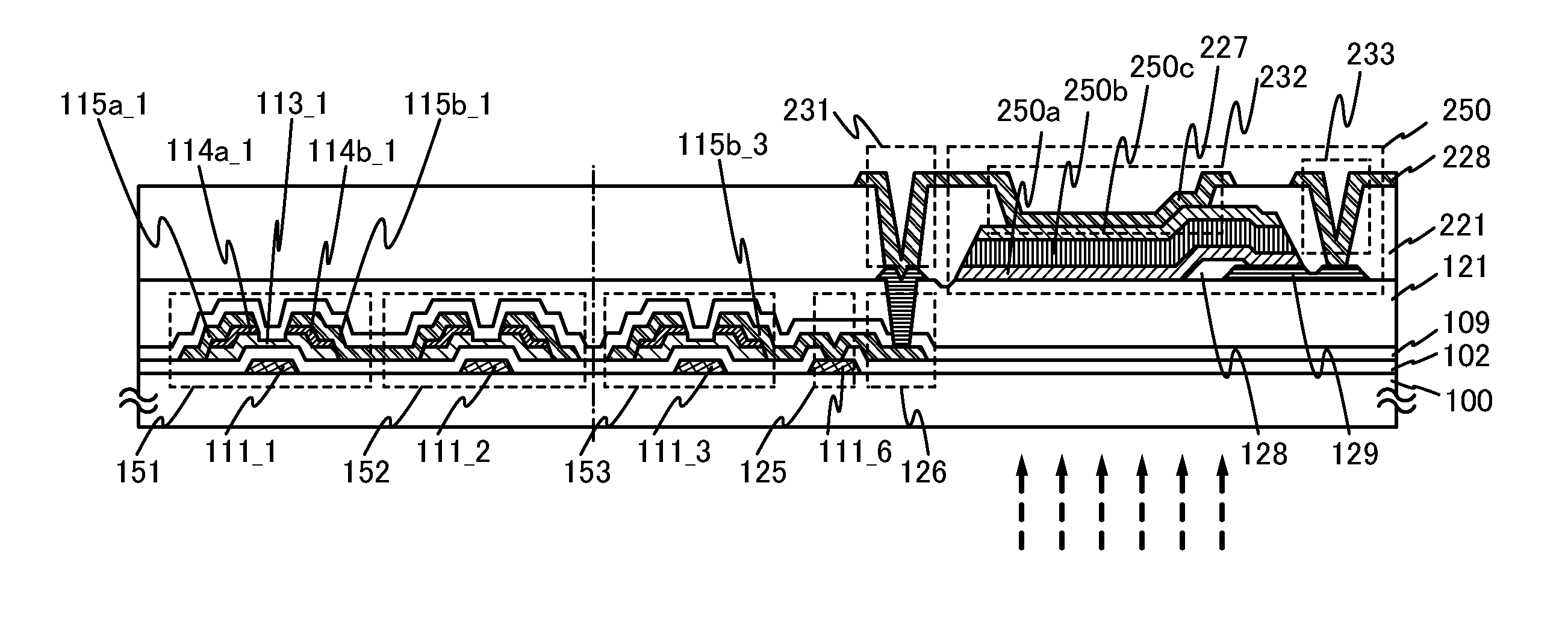

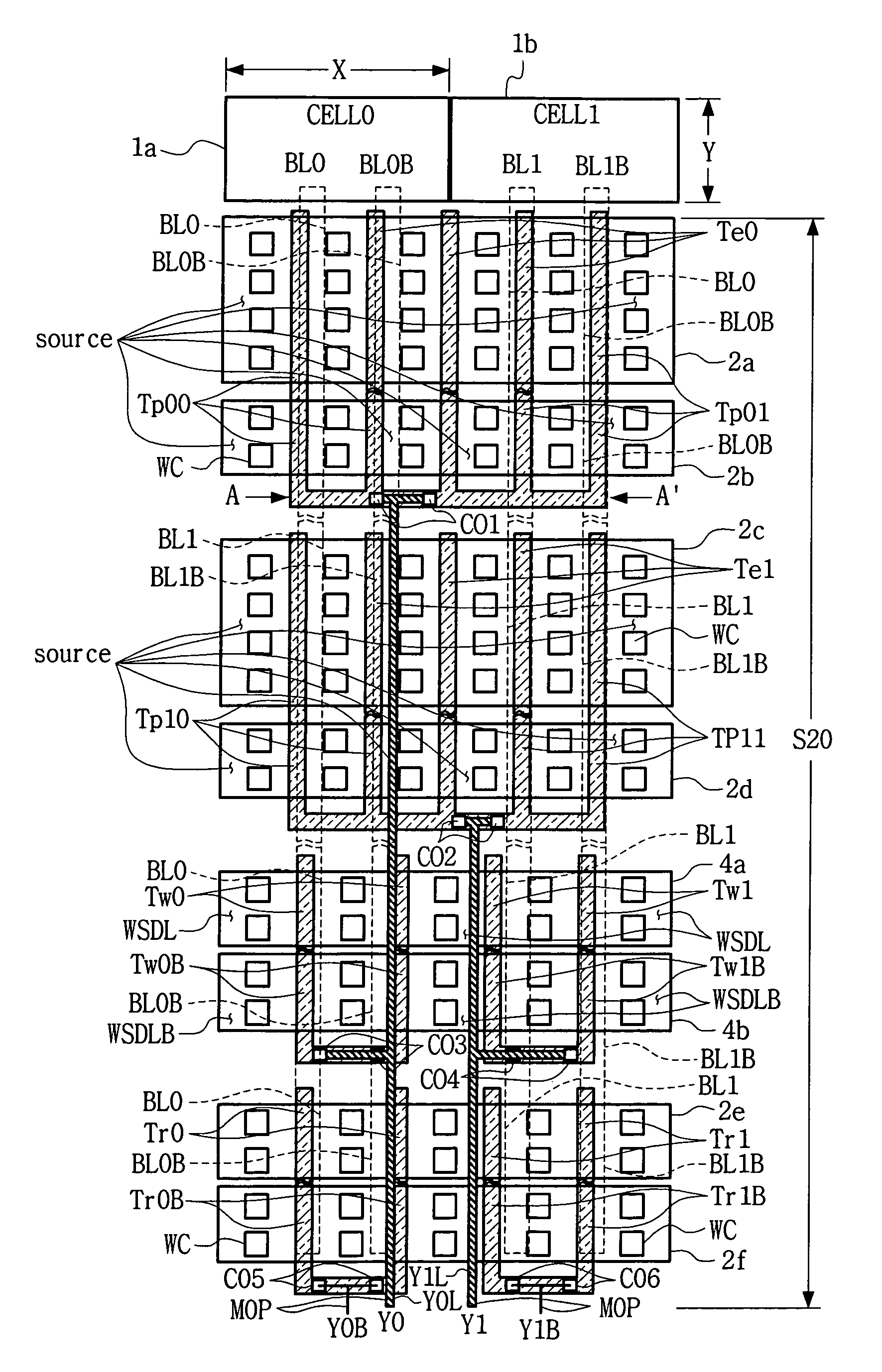

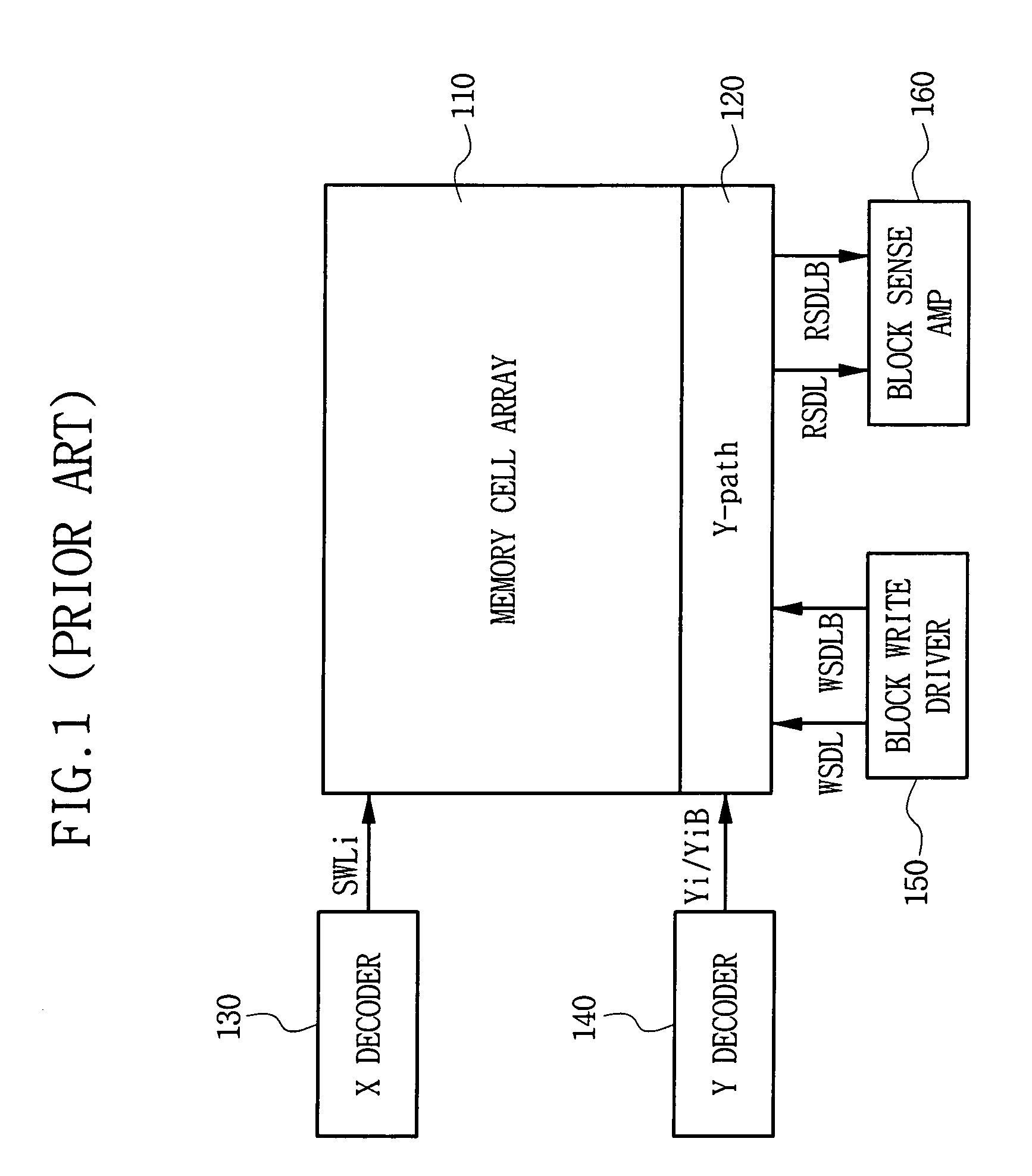

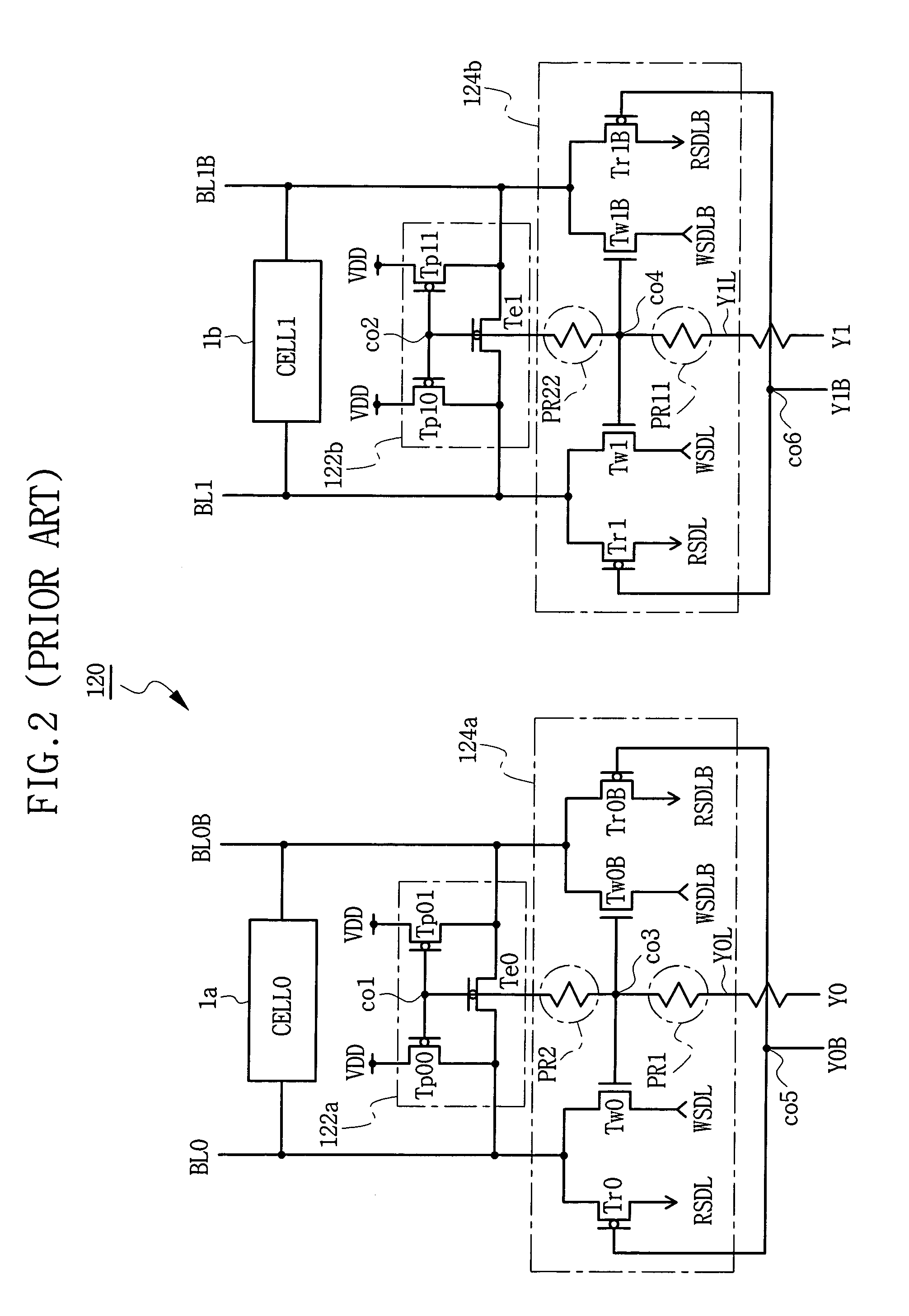

Semiconductor integrated circuit device

InactiveUS7016214B2Reduced footprintSuppress relative deviation of operation characteristicsTransistorSolid-state devicesMOSFETGate insulator

A semiconductor integrated circuit device capable of achieving higher integration and simplification of manufacturing processes is provided. Circuitry is provided which includes a first N-channel MOSFET and a first p-channel MOSFET each having a gate insulating dielectric film with a first film thickness, wherein a poly-silicon layer making up a gate electrode is doped with an N-type impurity. The circuitry also includes a second N-channel MOSFET having a gate insulator film with a second film thickness thinner than the first thickness, wherein an N-type impurity is doped into a polysilicon layer making up a gate electrode, and a second P-channel MOSFET with a P-type impurity being doped into a polysilicon layer making up a gate electrode. The gate electrodes of the first N-channel MOSFET and first P-channel MOSFET are integrally formed and mutually connected together.

Owner:HITACHI LTD

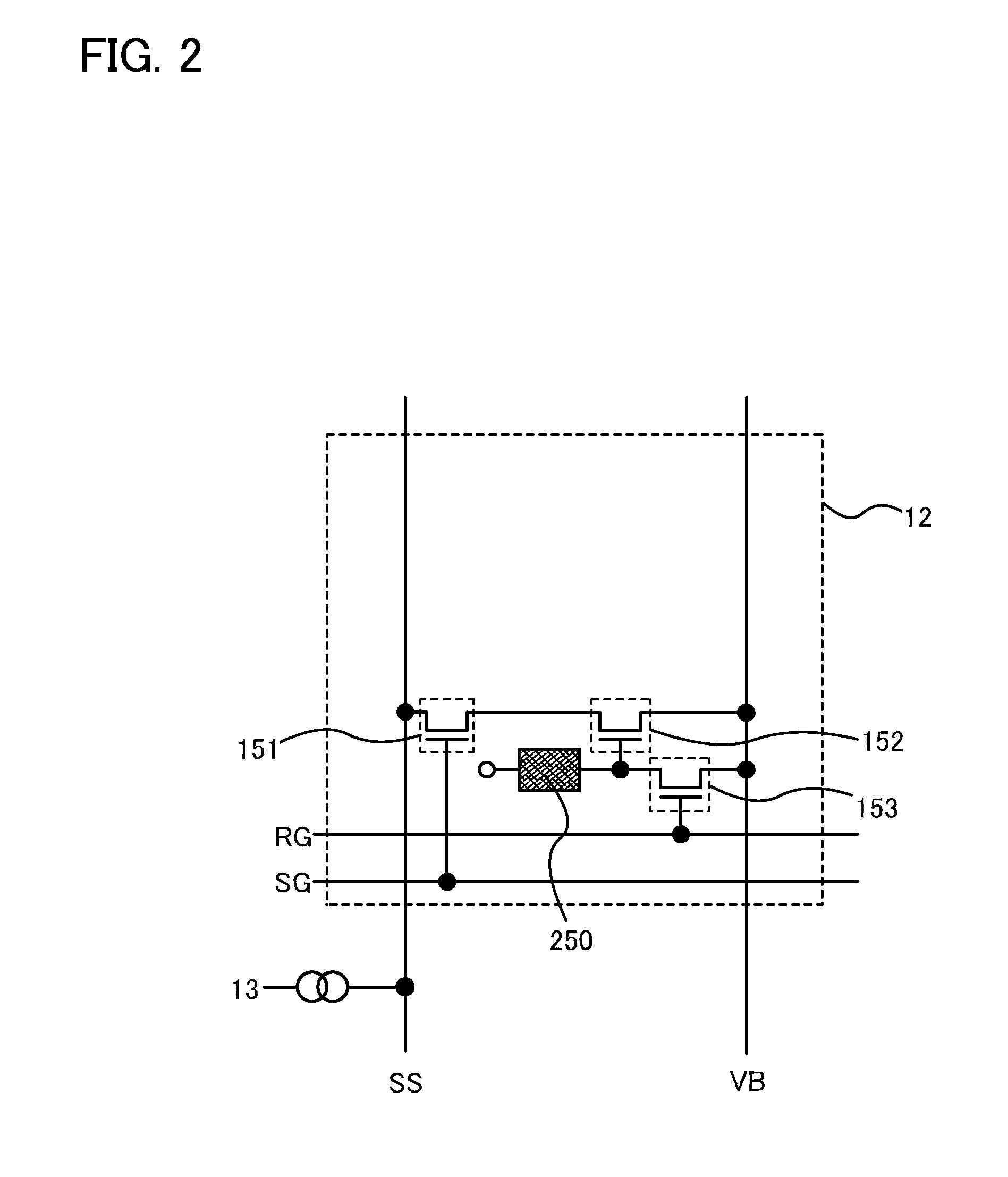

Photosensor and display device

ActiveUS20100134735A1Good reproducibilitySmall display unevennessTransistorStatic indicating devicesDriver circuitIndium

Thin film transistors including an oxide semiconductor containing indium, gallium, and zinc are easily arranged in a matrix over a large substrate and have small characteristic variations. With amplifier circuits and driver circuits of display elements which include the thin film transistors including an oxide semiconductor containing indium, gallium, and zinc with small characteristic variations, intensity distribution of light received by the photodiodes arranged in a matrix is converted into electrical signals with high reproducibility and output, and the display elements arranged in a matrix can be uniformly driven.

Owner:SEMICON ENERGY LAB CO LTD

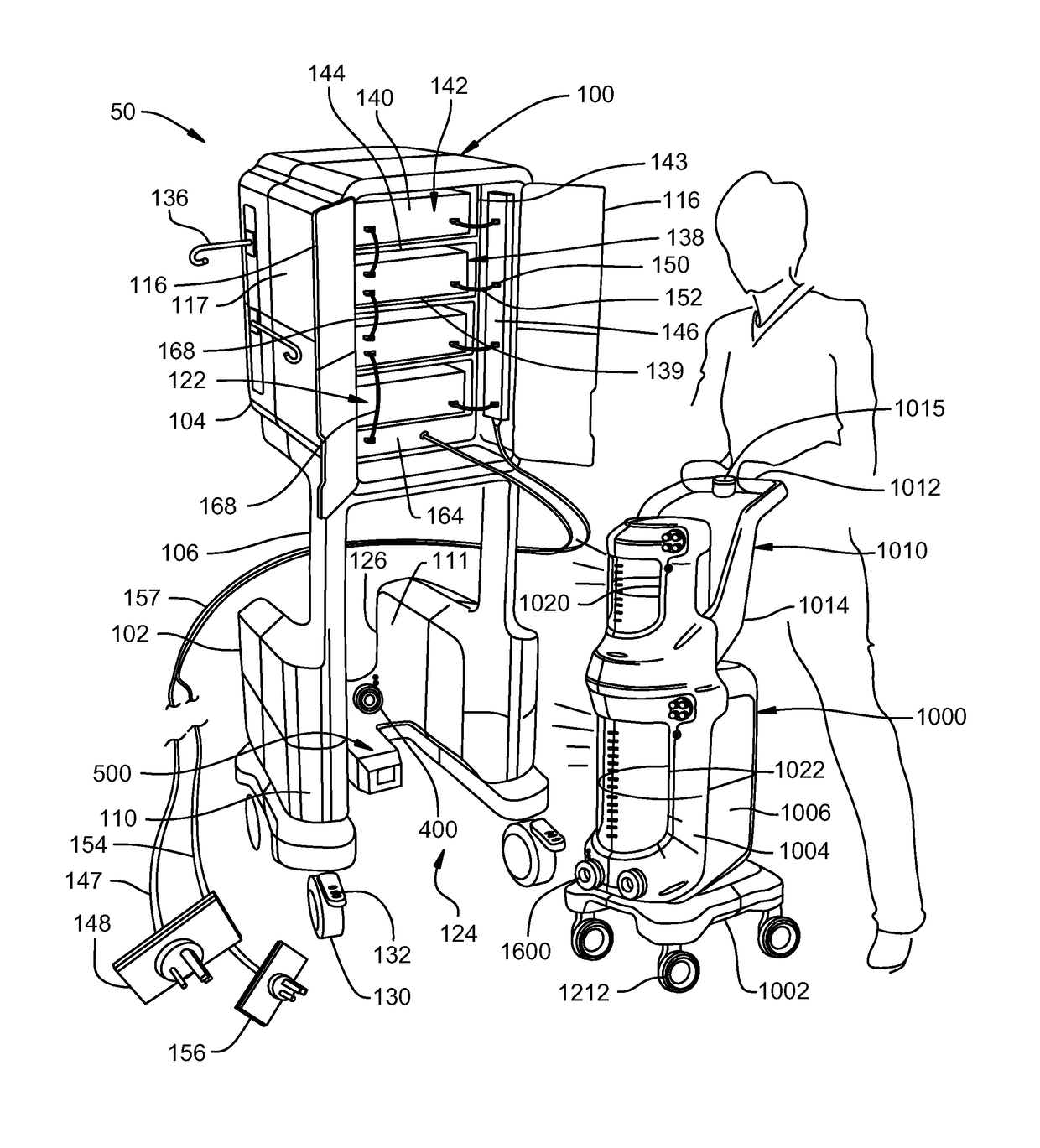

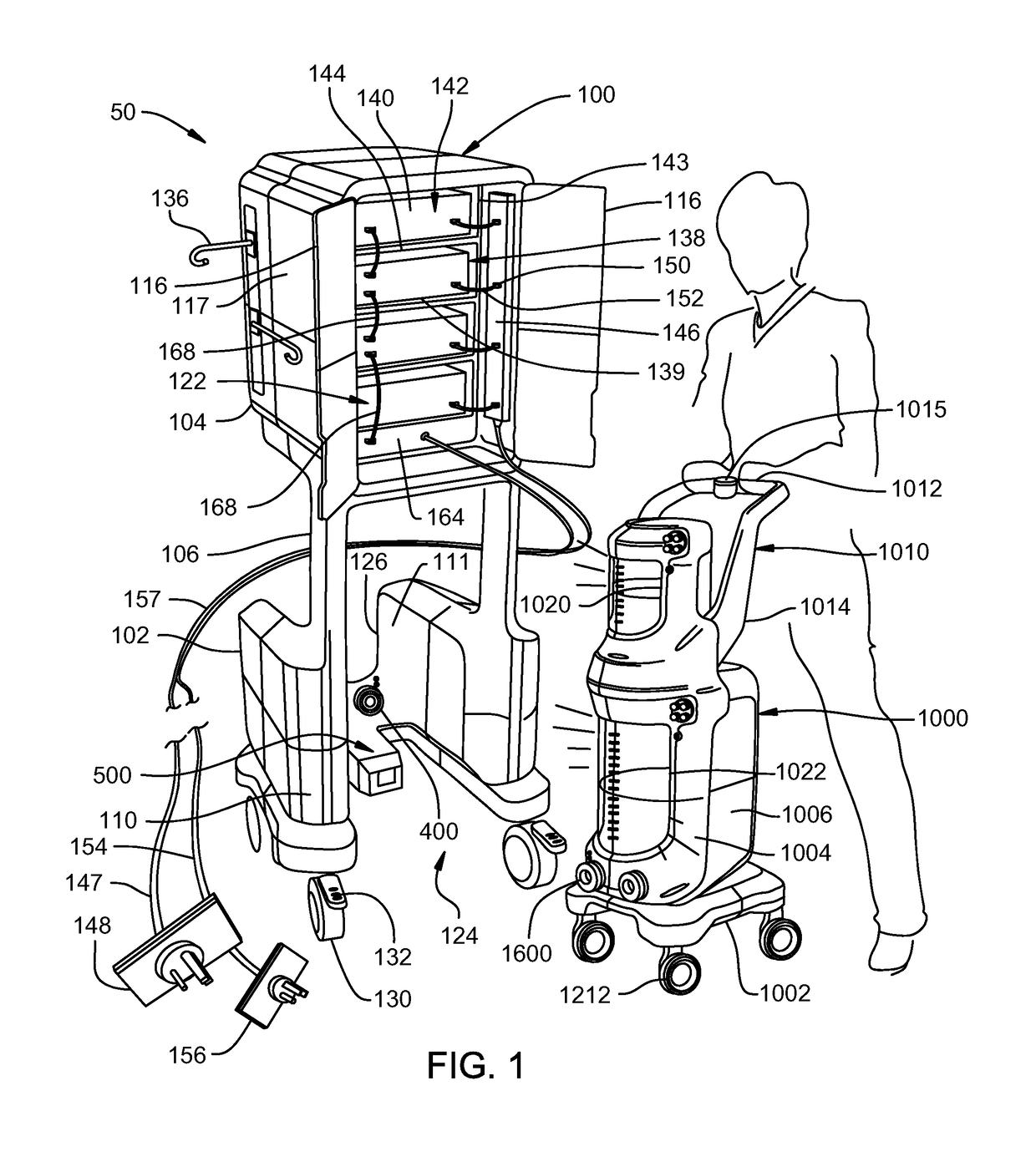

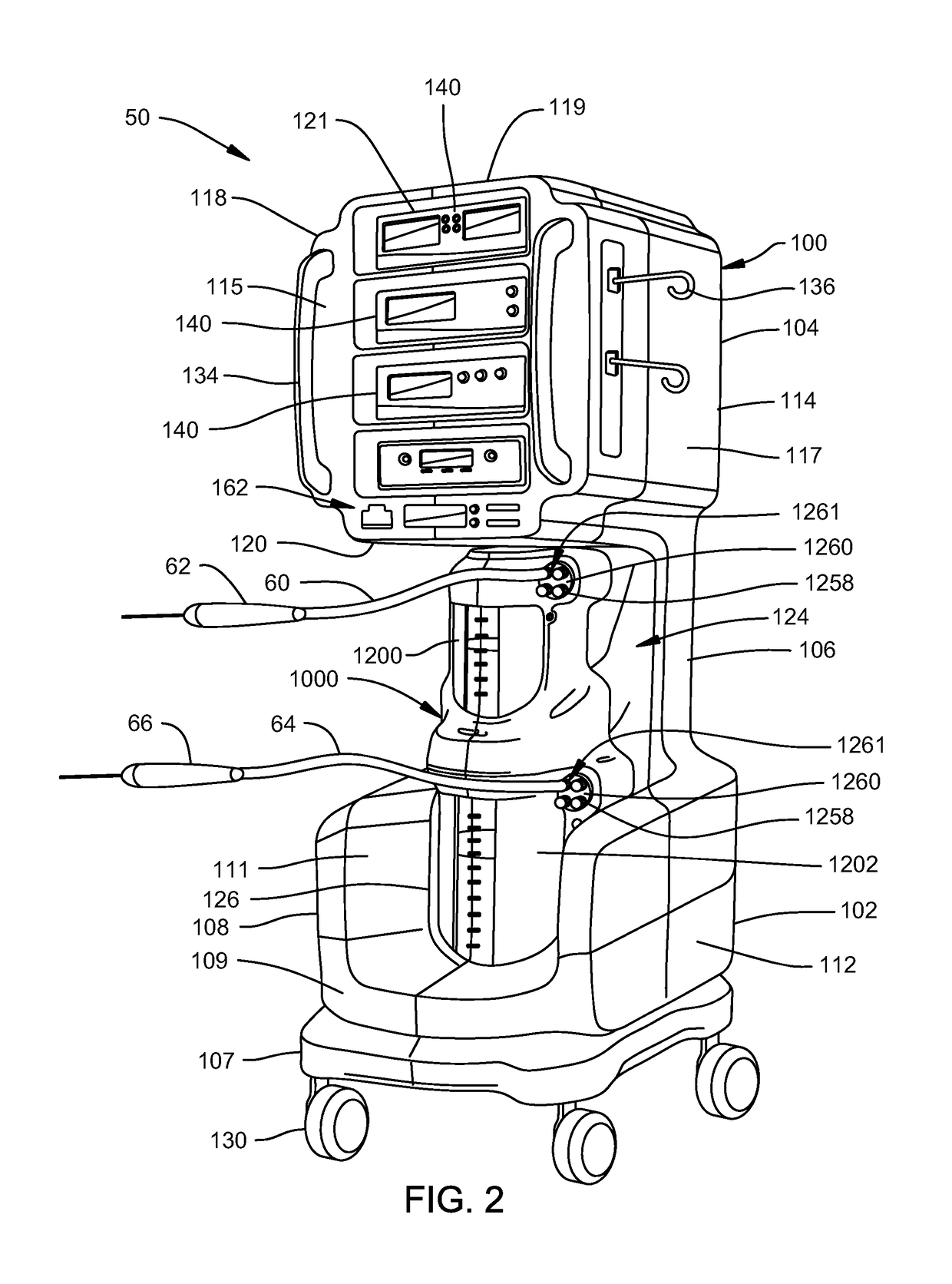

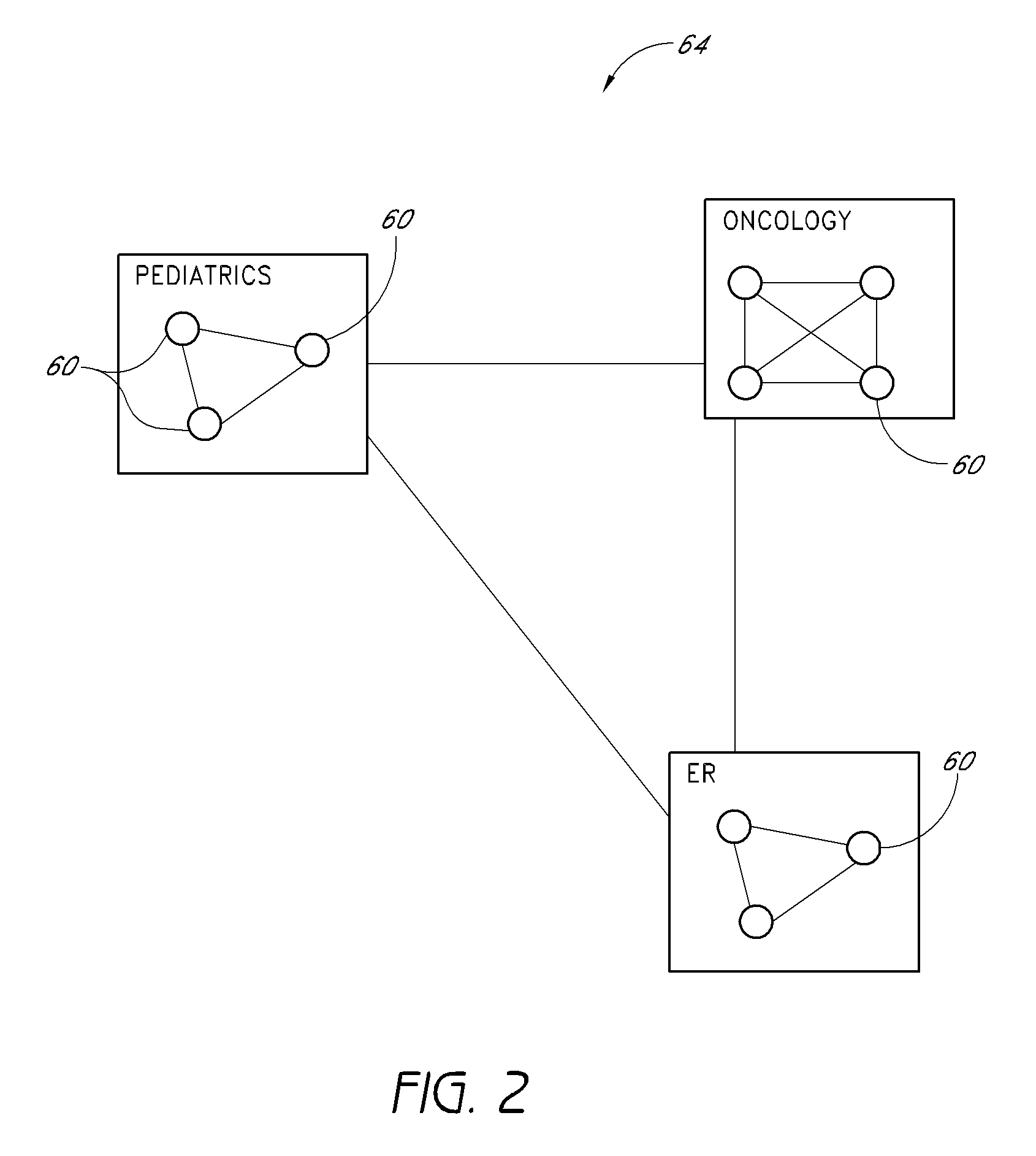

Mobile instrument assembly for use as part of a medical/surgical waste collection system, the assembly including a vacuum source to which a mobile waste collection cart can be releasably attached

ActiveUS10105470B2Reduces weight and sizeReduced footprintSurgical furnitureMedical devicesWaste collectionVacuum pump

A waste collection system for collecting waste during medical / surgical procedures including a mobile container cart with a waste container. A container cart is selectively coupled to a suction cart that includes a vacuum pump. The connection of the carts results in the connection of the vacuum pump to the waste container. The vacuum pump draws a vacuum that results in waste being drawn through a suction line into the waste container. The container cart holds instruments that can be removably attached to the container cart. This facilitates the configuration of the container cart for the specific procedure for which it is necessary to draw a suction.

Owner:STRYKER CORP

Simulated locomotion method and apparatus

InactiveUS7542040B2Reduced footprintReduces vertical extentCosmonautic condition simulationsAnimationVirtual locomotionLocation tracking

An apparatus for interfacing 3D movements of a user to control the locomotion of an avatar in a virtual environment includes a position tracker for tracking the position of a user's feet, with the foot motions including swinging and stroking; a computer programmed for (i) computing a direction and extent of motion of a reference in the virtual environment based on the foot positions and (ii) providing an avatar corresponding to the computed direction and extent of motion; and a display for displaying the avatar in the virtual environment. The apparatus accordingly uses the gestural motion of the user's feet while seated to simulate natural human locomotion. The gestural motions of stroking and swinging include translational and rotating movements, and are chosen to correspond to the actions of the feet and legs during natural human locomotion, providing natural control of virtual locomotion. The apparatus is also designed for controlling the locomotion of a remote vehicle.

Owner:USA AS REPRESENTED BY THE SEC OF THE NAVY THE

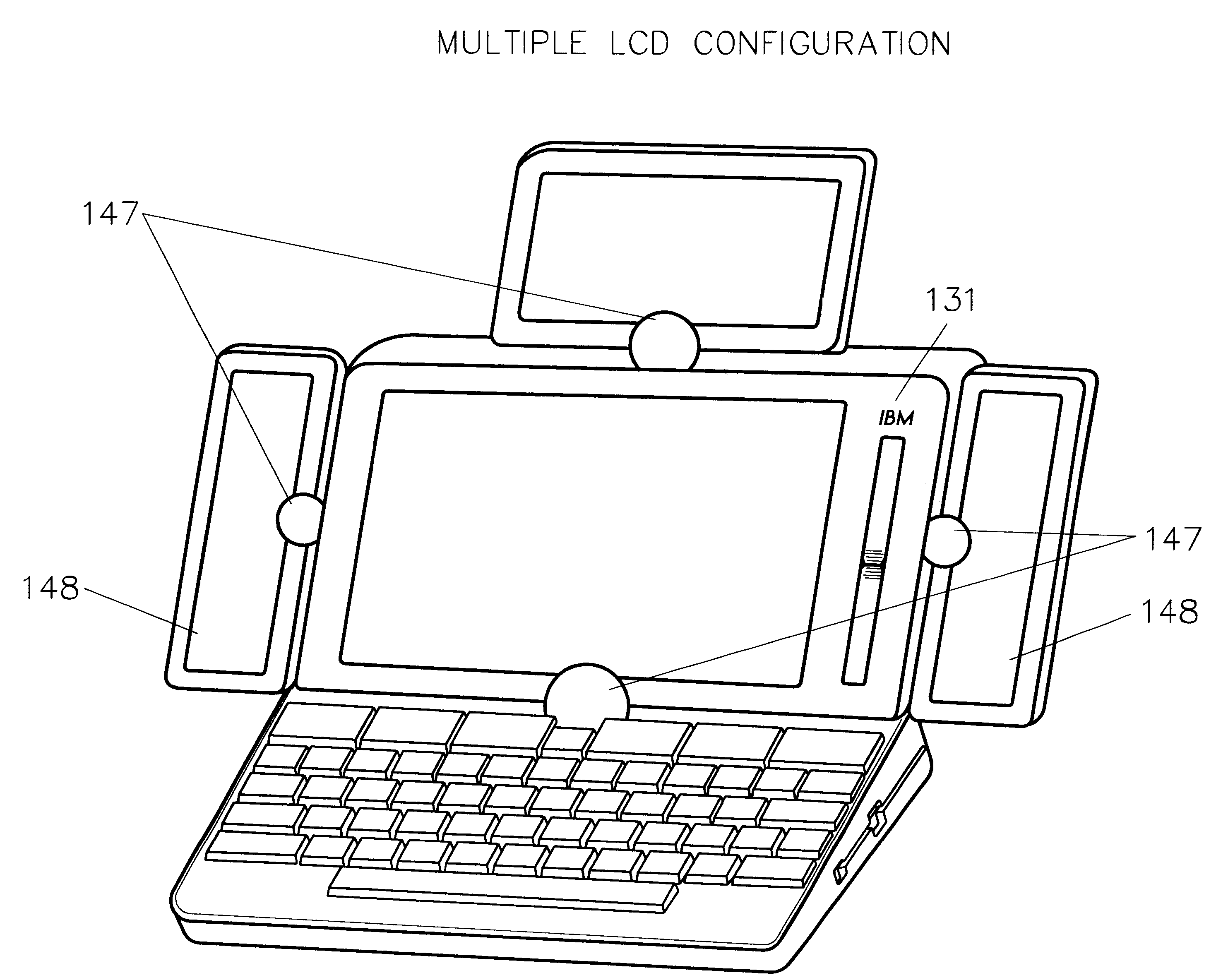

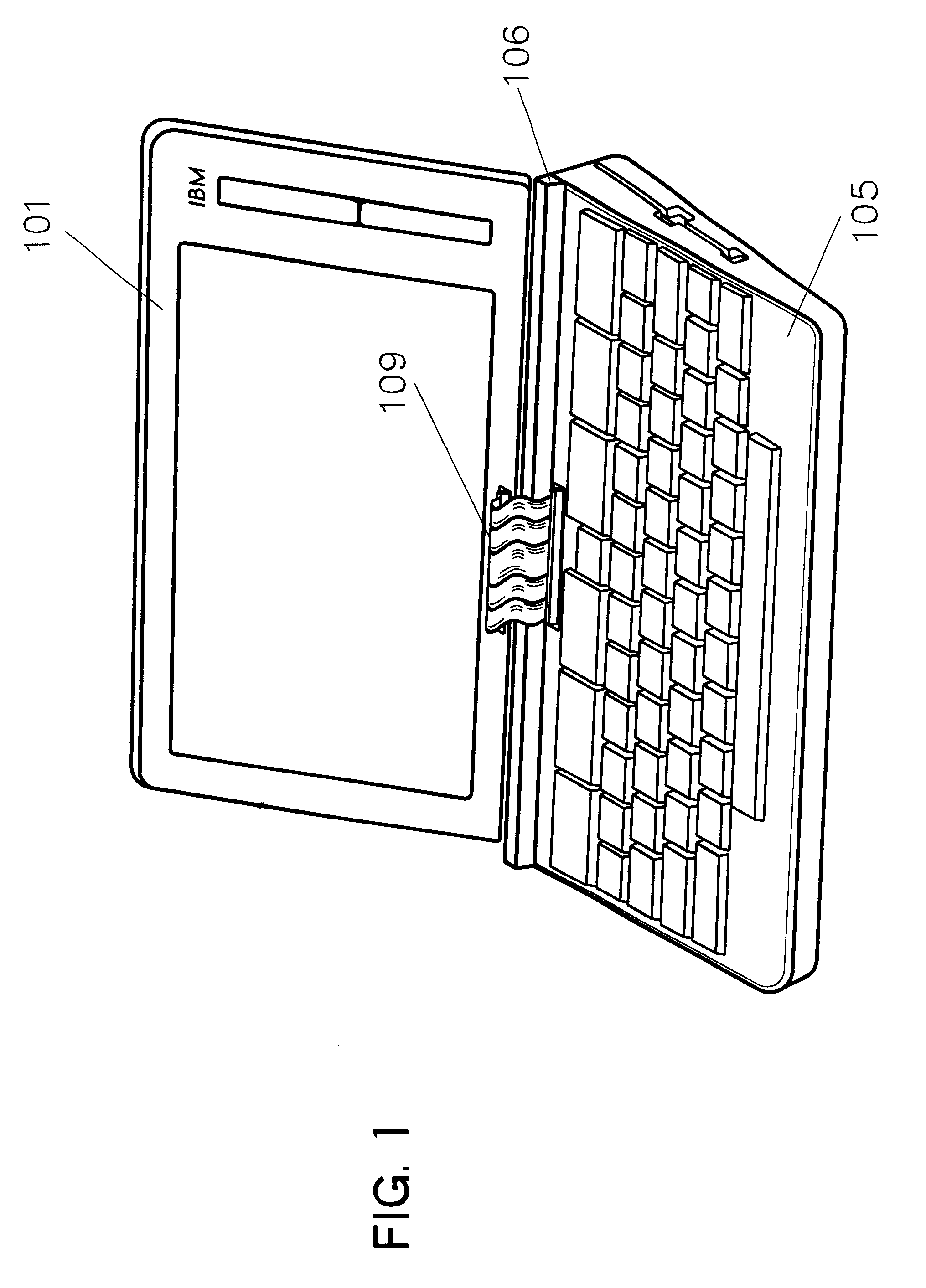

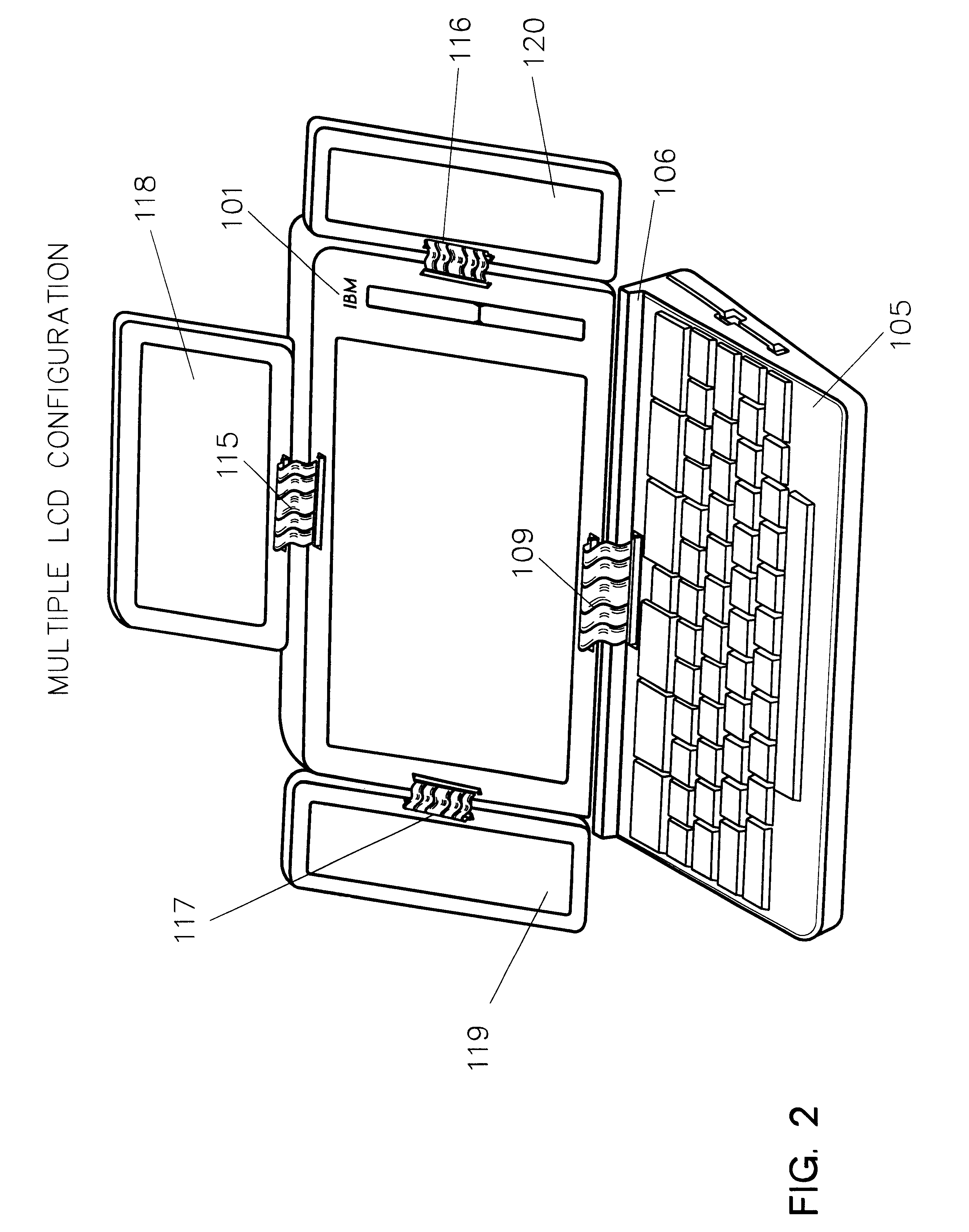

Pivotally extensible display device

InactiveUS6302612B1Reduced footprintImprove viewing effectYielding couplingCouplings for rigid shaftsLiquid-crystal displayDisplay device

An interface apparatus includes a base element, an interface element, and an attachment mechanism for attaching the interface element to the base element. The attachment mechanism is pivotable within a plurality of degrees of freedom. The interface element is an extensible member which is, in two of its embodiments, pivotally mounted so as to be rotatably adjustable about a pivot point with respect to a primary member. The primary member may be a base member or another display member. These members may be computer keyboards or displays, such as liquid crystal displays (LCDs), audio speakers, or the like such as are used in desk top or lap top computers and terminals.

Owner:VIDEOCON GLOBAL

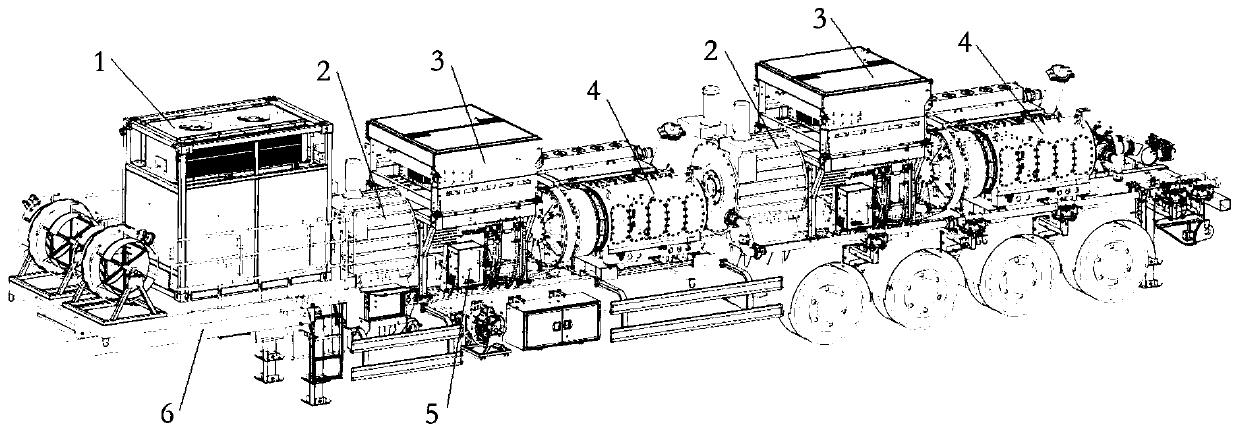

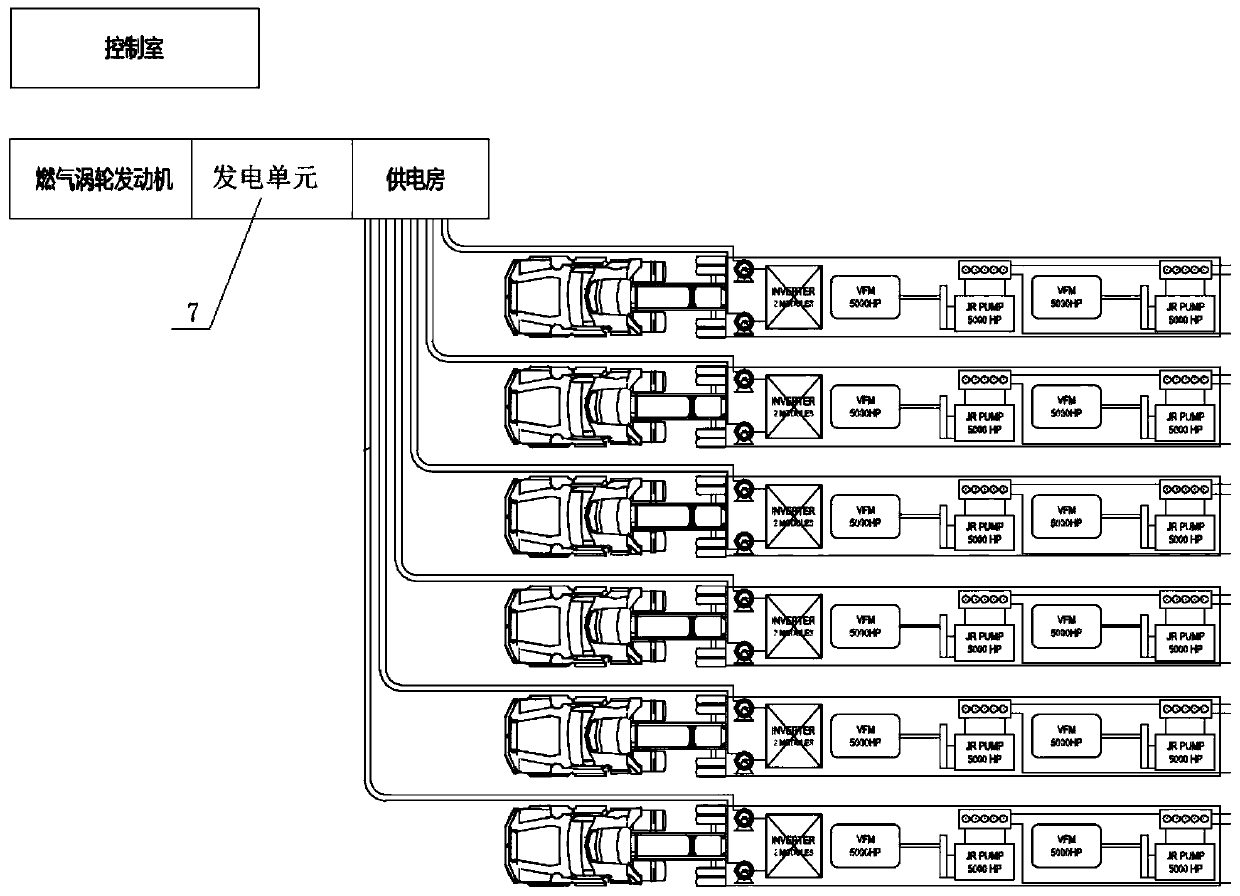

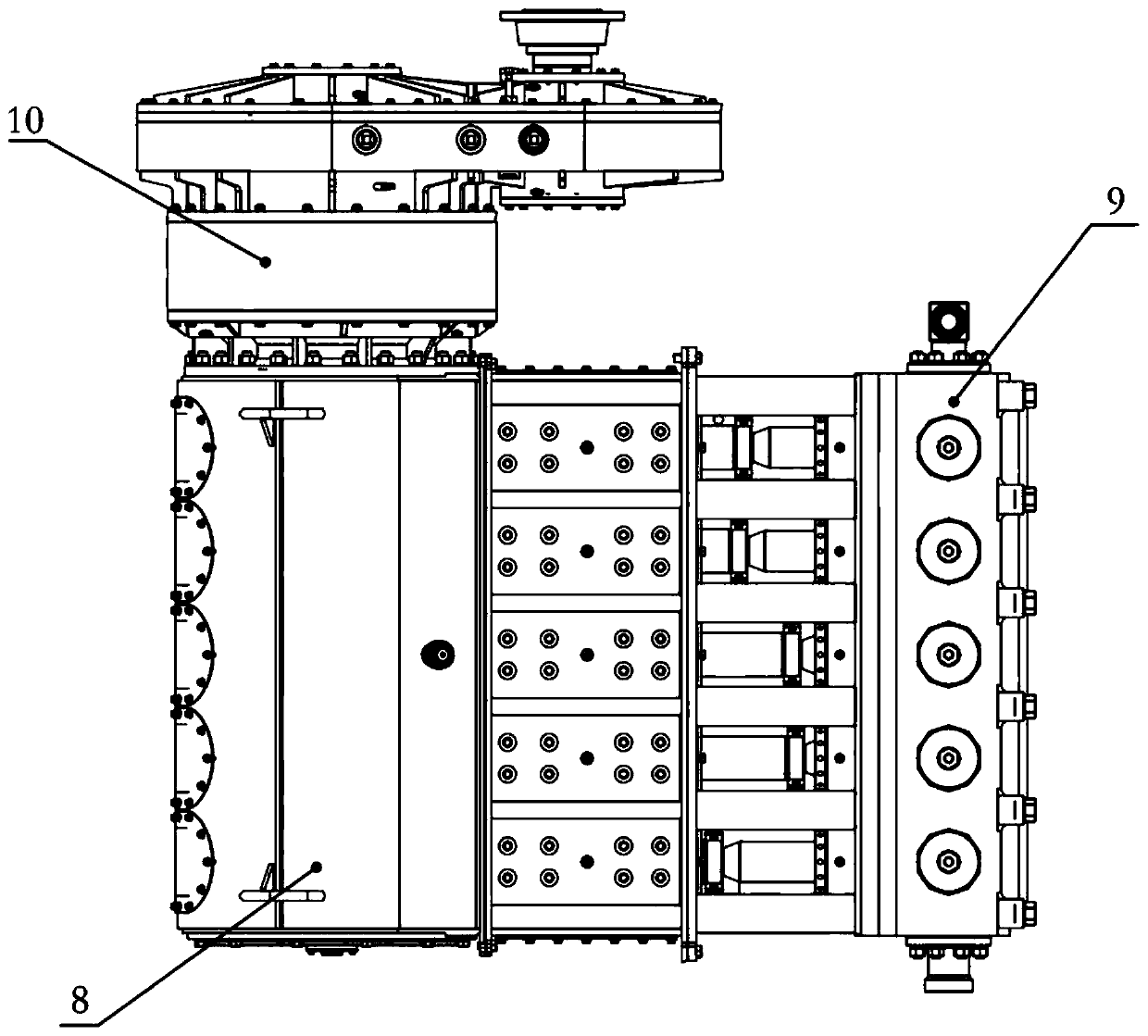

Electric drive fracturing semitrailer with dual engines and dual pumps

PendingCN109882144ARealized pump powerReduce investmentAssociation with control/drive circuitsPositive displacement pump componentsDrive shaftElectrical control

The invention discloses an electric drive fracturing semitrailer with dual engines and dual pumps. The electric drive fracturing semitrailer with the dual engines and the dual pumps comprises a semitrailer body, two plunger pumps, two radiators and an electrical control cabinet. The electric drive fracturing semitrailer with the dual engines and the dual pumps is characterized by further comprising two electromotorsand an inverter unit. The plunger pumps, the radiators, the electrical control cabinet, the electromotors and the inverter unit are integrated in the semitrailer body, the inverterunit is arranged on the gooseneck of the semitrailer body, the output end of the inverter unit individually drives the two electromotors, the other ends of the two electromotors are connected with theplunger pumps correspondingly, lubricating oil of the plunger pumps is cooled through the radiators, and local operation of the electric drive fracturing semitrailer with the dual engines and the dual pumps is realized through the electrical control cabinet. The electric drive fracturing semitrailer with the dual engine and the dual pump has the beneficial effects that the electromotors are adopted to drive the plunger pumps through a transmission shaft, the volume is small, and the economic efficiency, energy conservation and environment protection are achieved. The signal pump power of theplunder pumps is improved, design that the dual pumps are driven by the two electromotors is adopted by the whole fracturing device, the output power of the fracturing device is greatly improved, andthe using requirements are better met.

Owner:YANTAI JEREH PETROLEUM EQUIP & TECH CO LTD

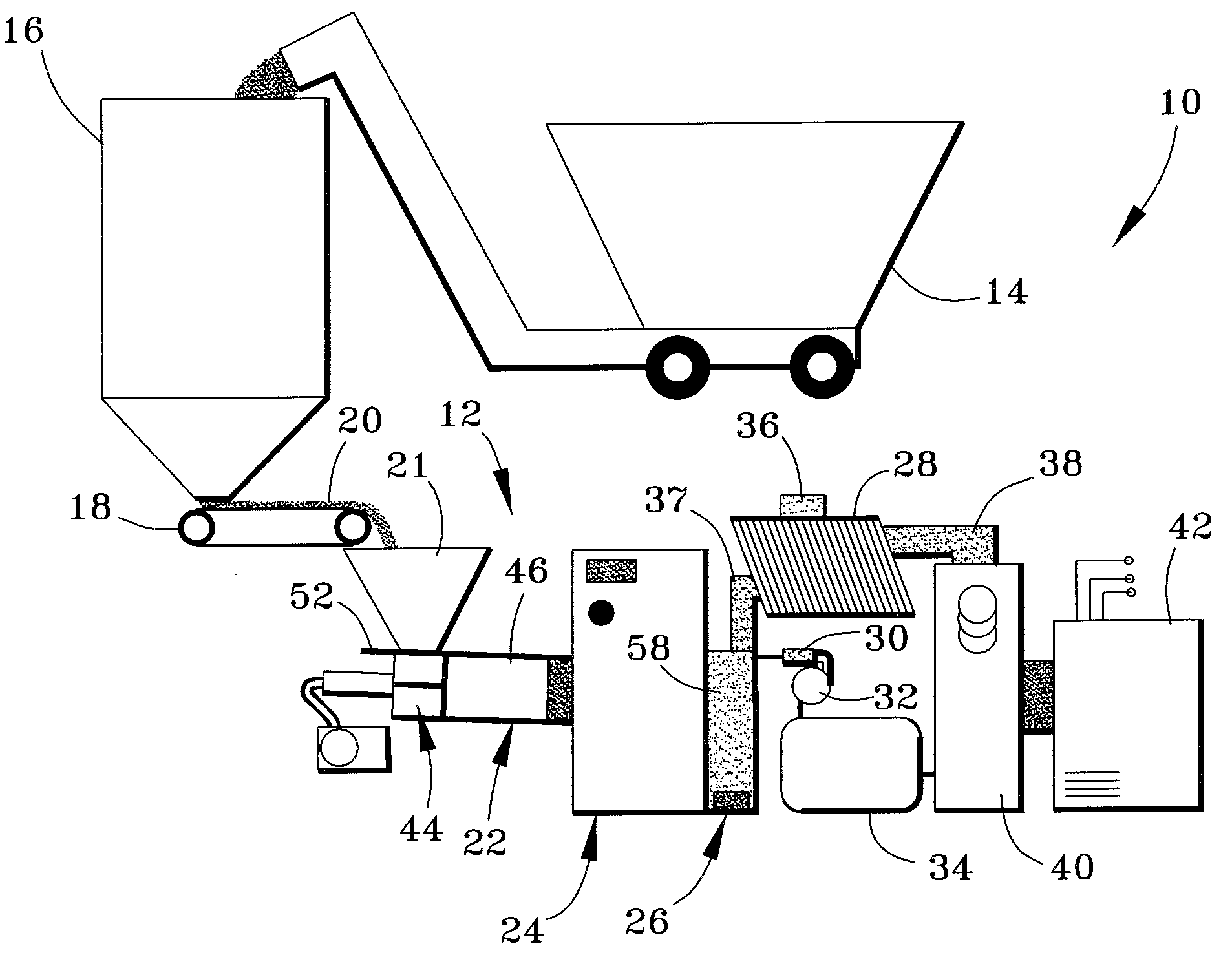

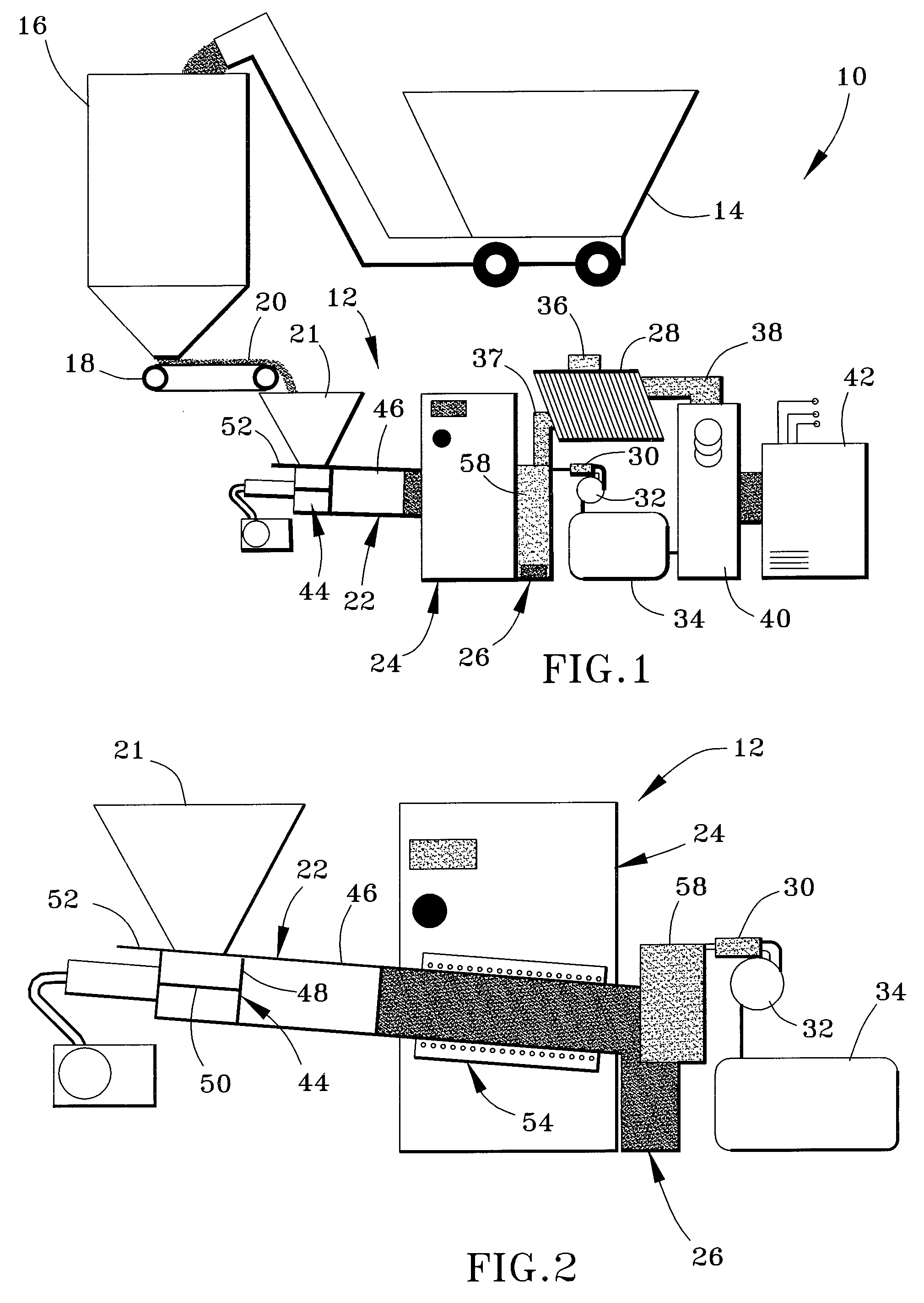

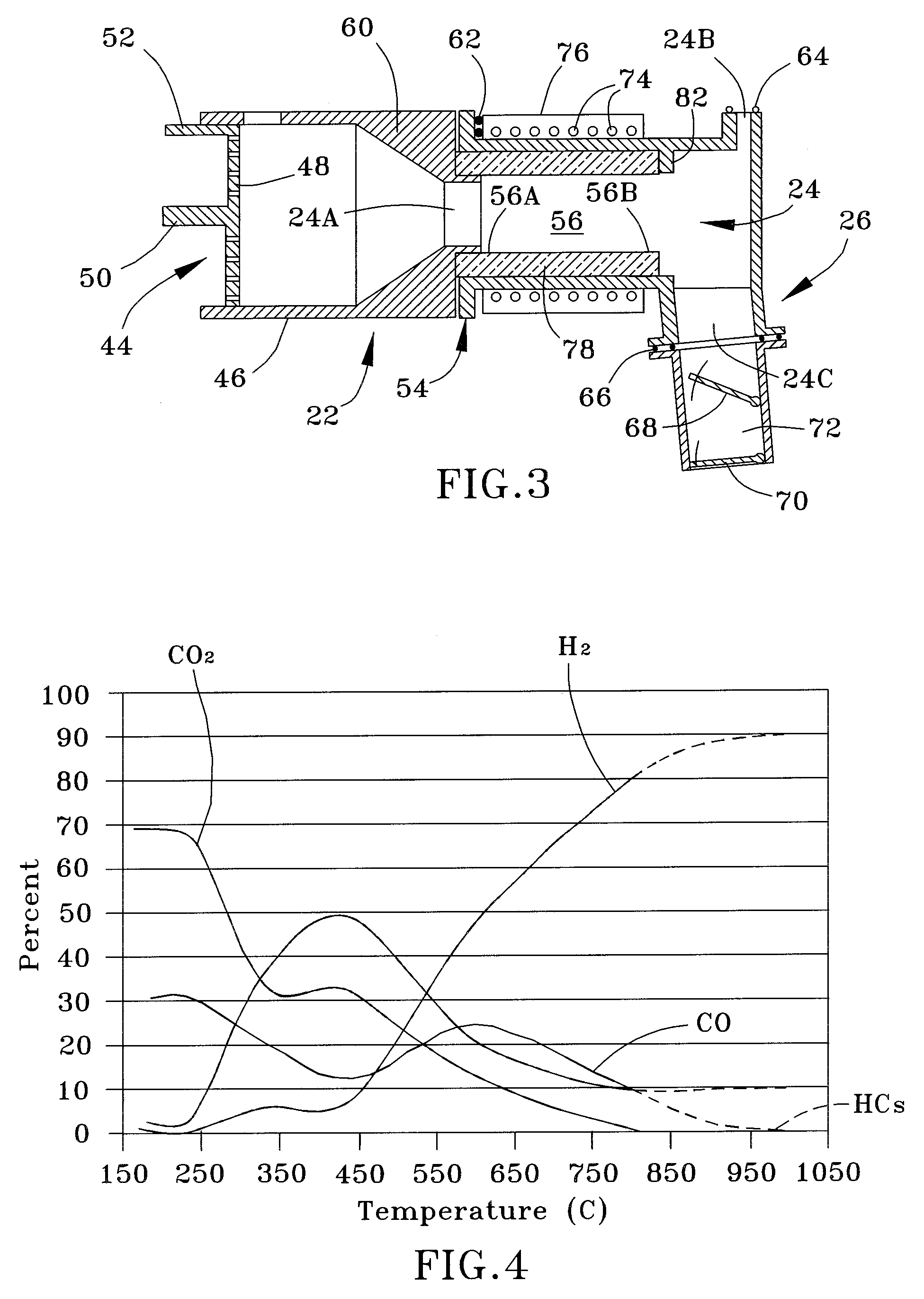

Process and system for syngas production from biomass materials

A process and system suitable for producing syngas from biomass materials. The process and system entail the compaction of a loose biomass material to remove air therefrom and form a compacted biomass material. The compacted biomass material is then introduced into a reactor and heated in the substantial absence of air so as not to combust the compacted biomass material. Instead, the compacted biomass material is heated to a temperature at which organic molecules within the compacted biomass material break down to form ash and gases comprising carbon monoxide and hydrogen gas. Thereafter, the carbon monoxide and hydrogen gas are released from the reactor, and the ash is removed from the reactor.

Owner:GREEN FORTRESS ENG INC

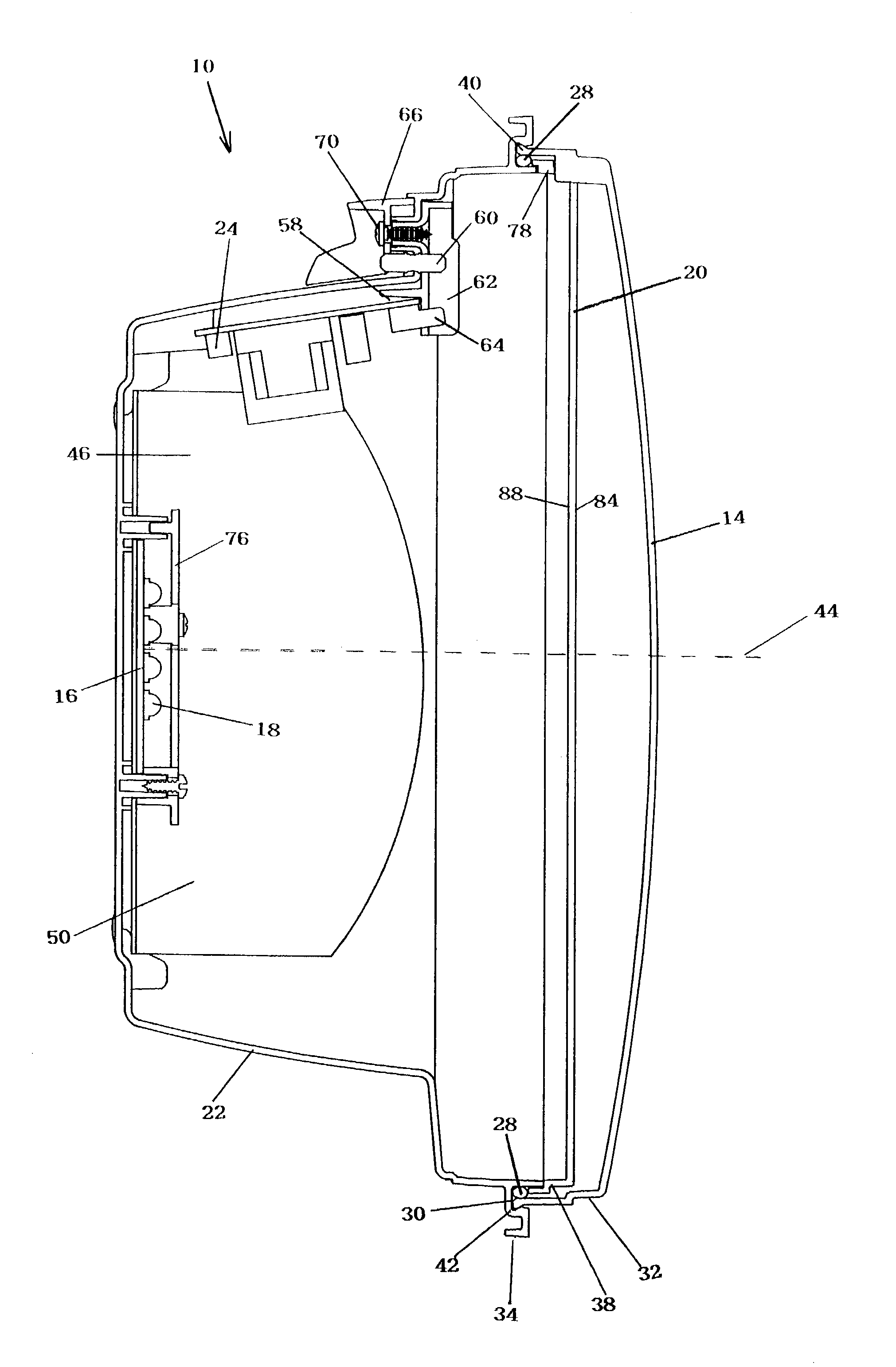

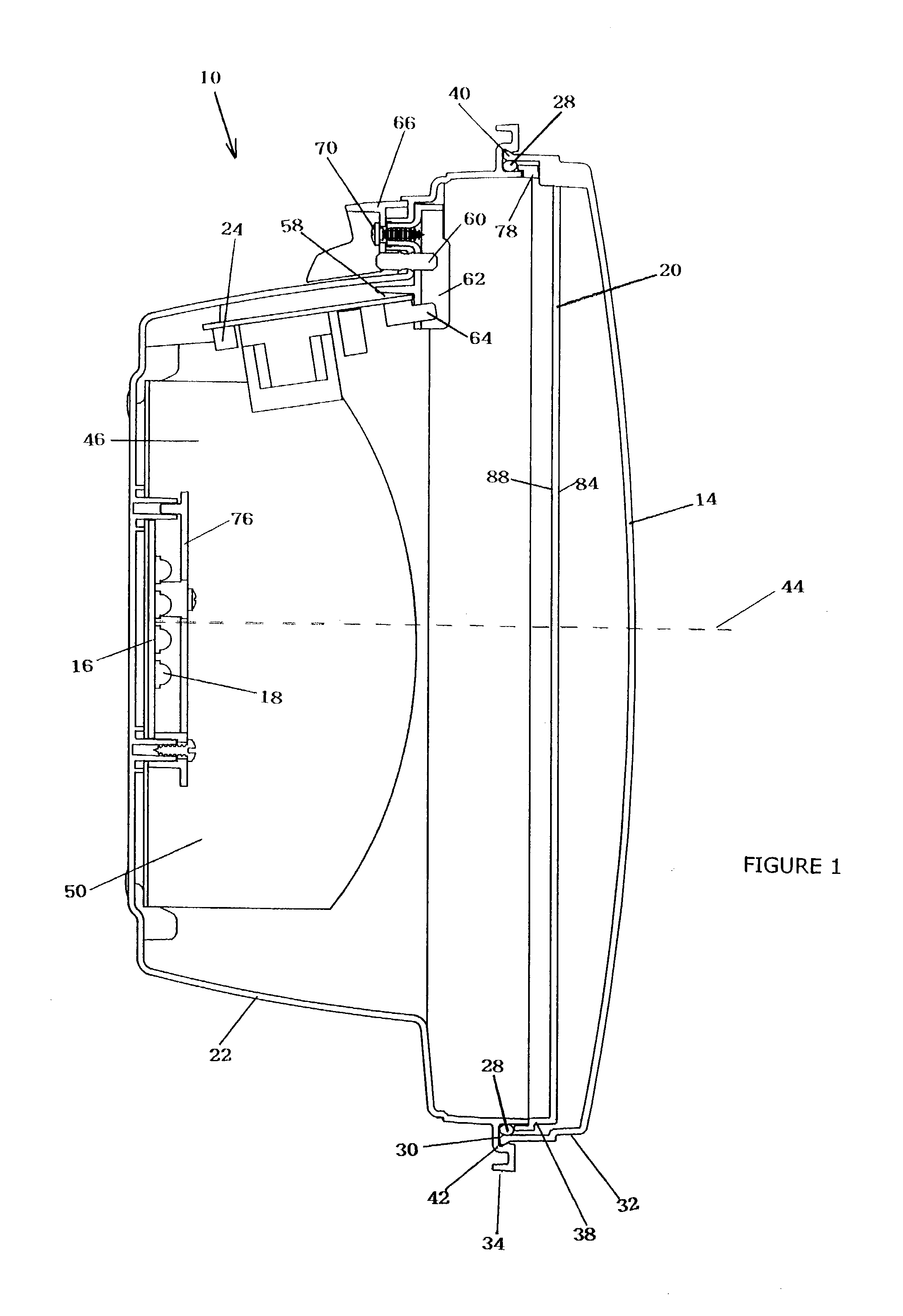

LED signal lamp

ActiveUS7237924B2Reduced footprintLighting support devicesPoint-like light sourceTotal internal reflectionOptical surface

An LED signal using a novel optical element to control the light distribution of a small LED light source. Light emitted by the LEDs illuminates the optical element. The optical element has a plurality of clusters, shaped along the x-, y- and z-axis to control the light. After the light is distributed, it encounters a second optical surface of the optical element, typically a fresnel surface. The light is controlled by the optical element.Optionally, a lens can be placed over each LED to control the light pattern of the LED. The lens has an entry face to direct the light to a total internal reflection surface on the side, which redirects the light to the exit face. The resulting signal is a uniform, efficient signal.

Owner:GE LIGHTING SOLUTIONS LLC

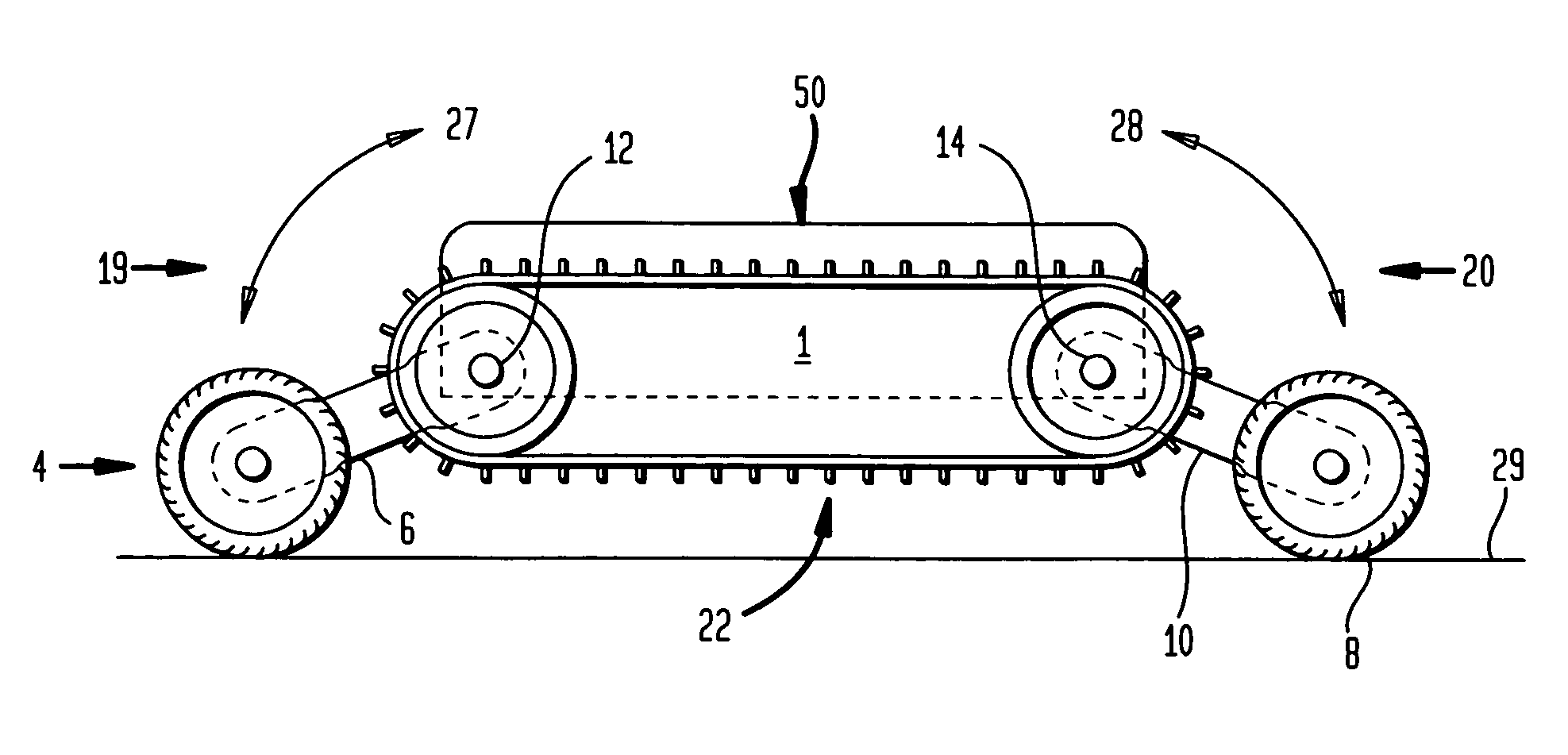

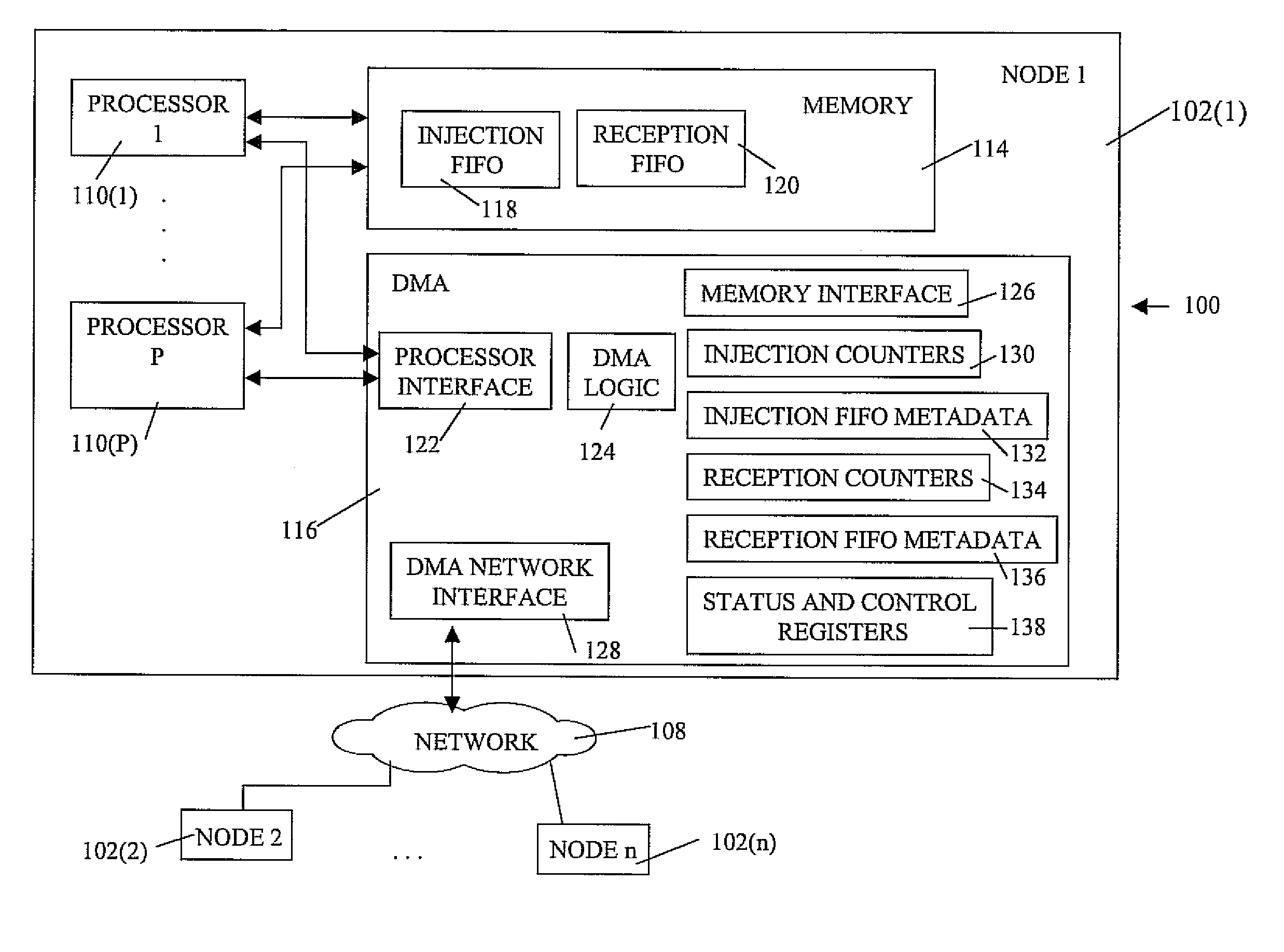

High mobility vehicle

InactiveUS7475745B1Reduces rolling lossExtended service lifeEndless track vehiclesManipulatorDrive wheelGear wheel

An embodiment of a high-mobility vehicle comprises a vehicle body, a track assembly attached to the vehicle body, arms pivotally attached to the vehicle body, and trackless drive wheels mounted on distal ends of the arms. Another embodiment of a high-mobility vehicle comprises a vehicle chassis, right and left drive motors attached to the vehicle chassis, right and left power transmission mechanisms having high torque and low torque sets of gears, track assemblies coupled to the high torque sets of gears, and trackless drive wheels coupled to the low torque sets of gears.

Owner:DEROOS BRADLEY G

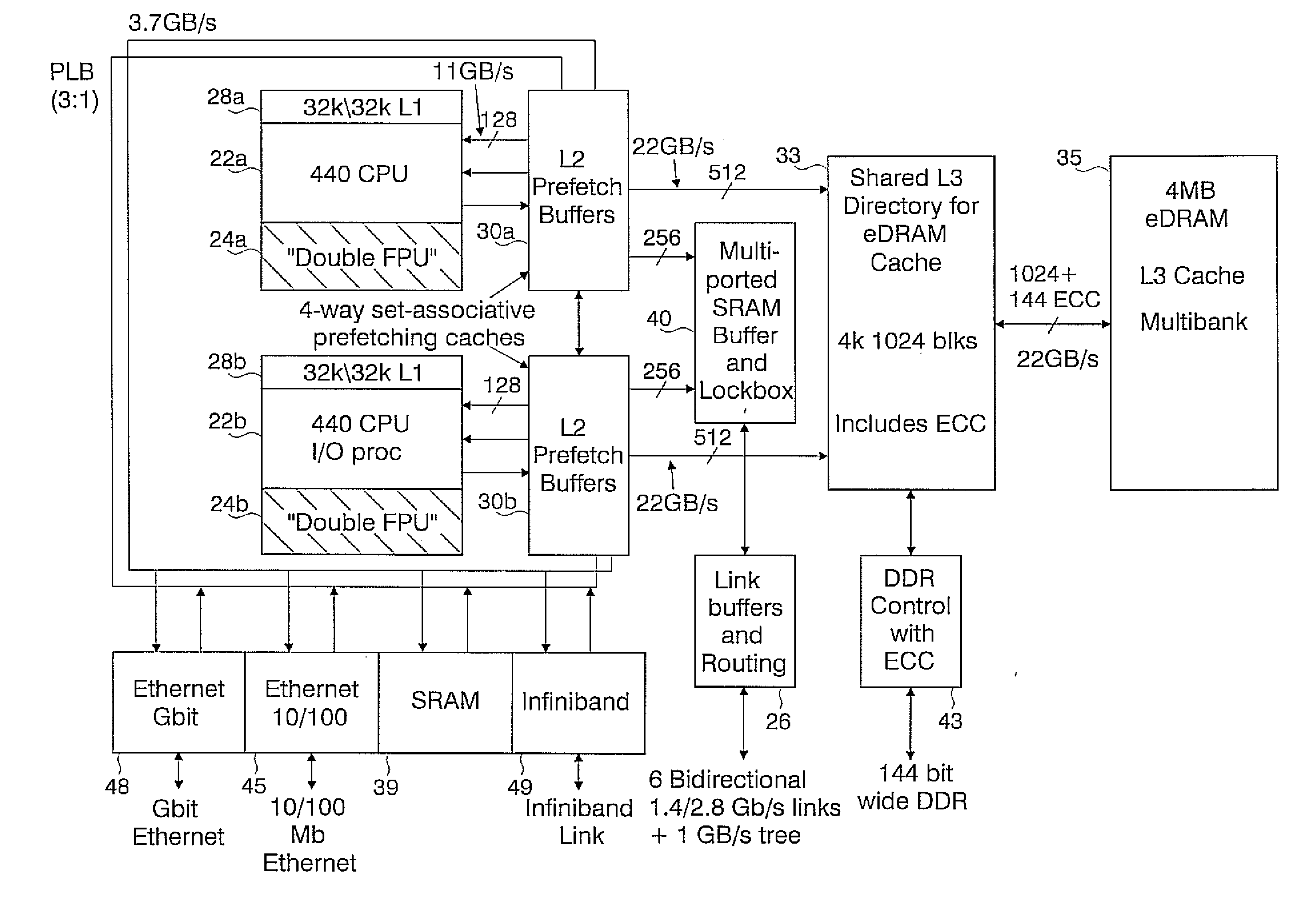

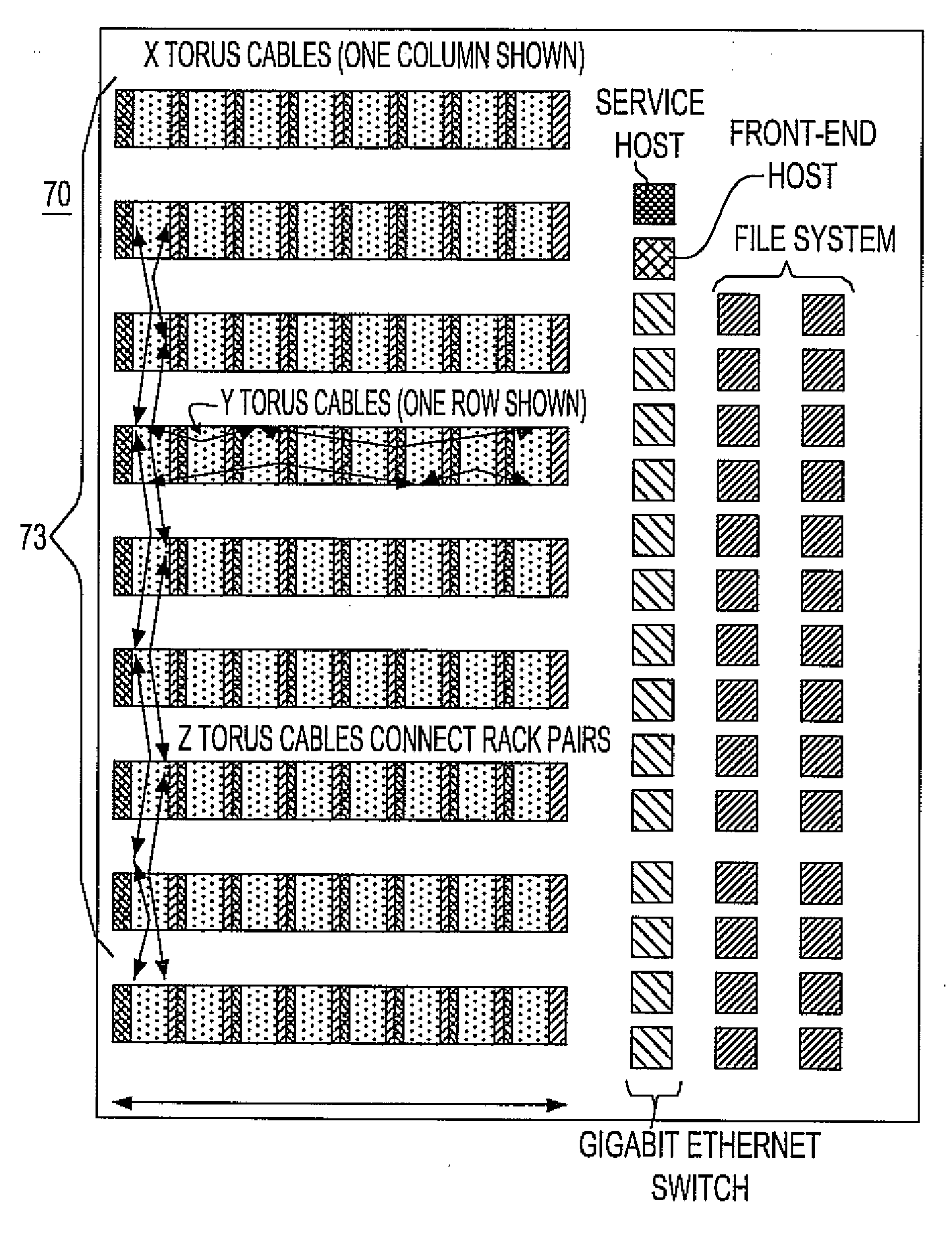

Ultrascalable petaflop parallel supercomputer

InactiveUS7761687B2Maximize throughputDelay minimizationGeneral purpose stored program computerElectric digital data processingSupercomputerPacket communication

A massively parallel supercomputer of petaOPS-scale includes node architectures based upon System-On-a-Chip technology, where each processing node comprises a single Application Specific Integrated Circuit (ASIC) having up to four processing elements. The ASIC nodes are interconnected by multiple independent networks that optimally maximize the throughput of packet communications between nodes with minimal latency. The multiple networks may include three high-speed networks for parallel algorithm message passing including a Torus, collective network, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. The use of a DMA engine is provided to facilitate message passing among the nodes without the expenditure of processing resources at the node.

Owner:INT BUSINESS MASCH CORP

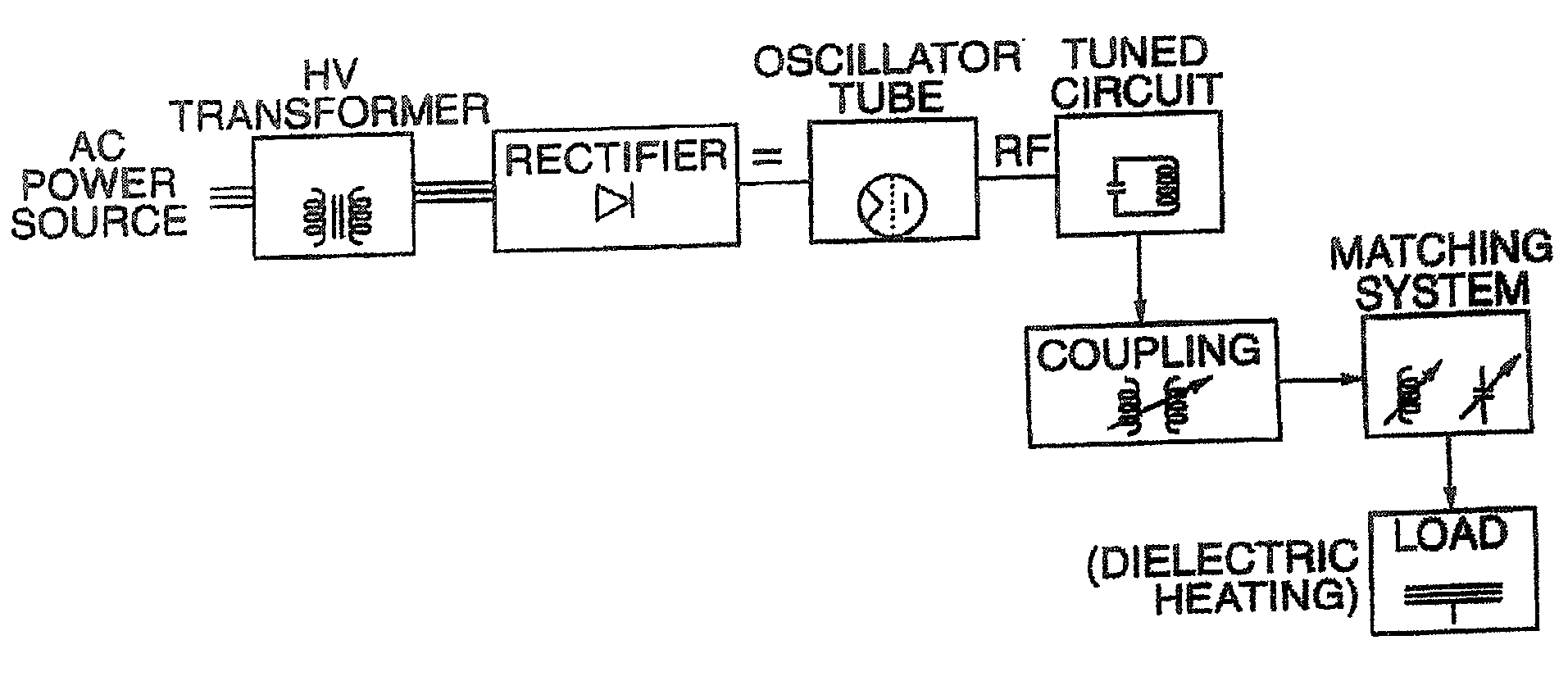

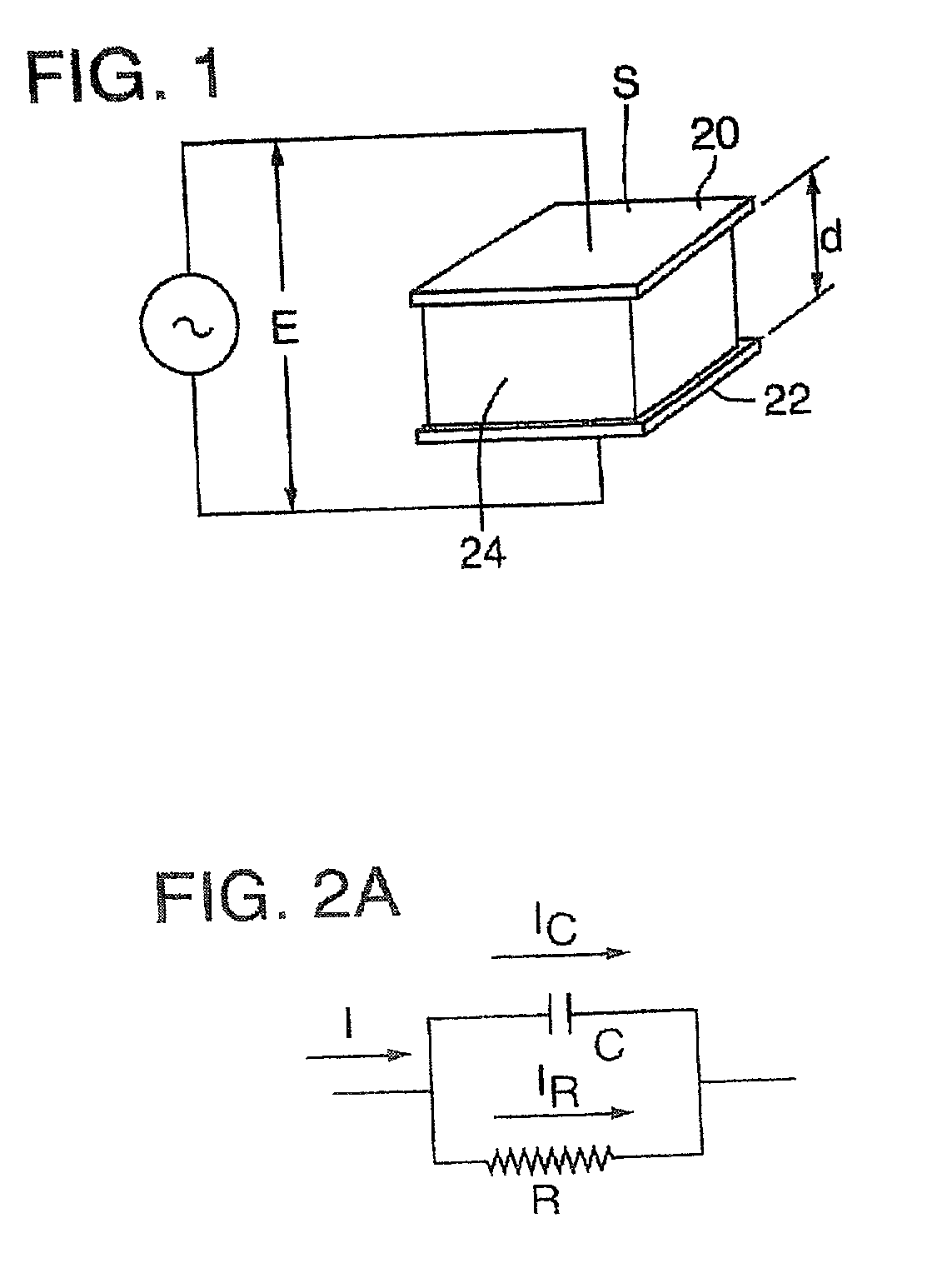

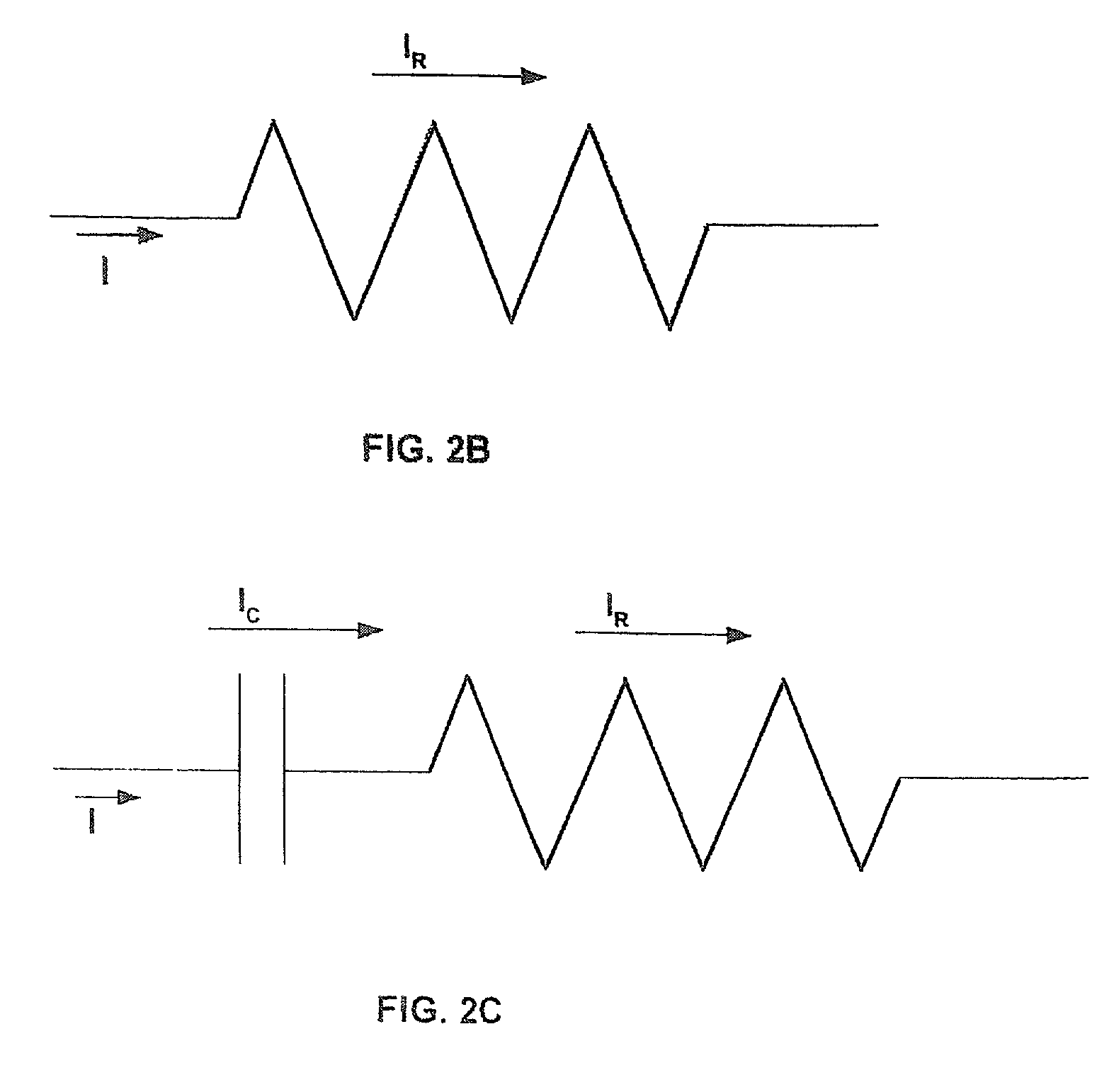

Variable frequency automated capacitive radio frequency (RF) dielectric heating system

InactiveUS20020047009A1Improve sealingLowering gap impedanceMeat/fish preservation by heatingDielectric heating circuitsRadio frequencyHeating system

A food product is heated by maintaining the food product in an AC electrical field generated by an RF signal. As the heating takes place, maximum energy is delivered to the food product using automatic impedance matching to adjust the rate of the process.

Owner:THE STATE OF OREGON ACTING BY & THROUGH THE OREGON STATE BOARD OF HIGHER EDUCATION ON BEHALF OF OREGON STATE UNIV +1

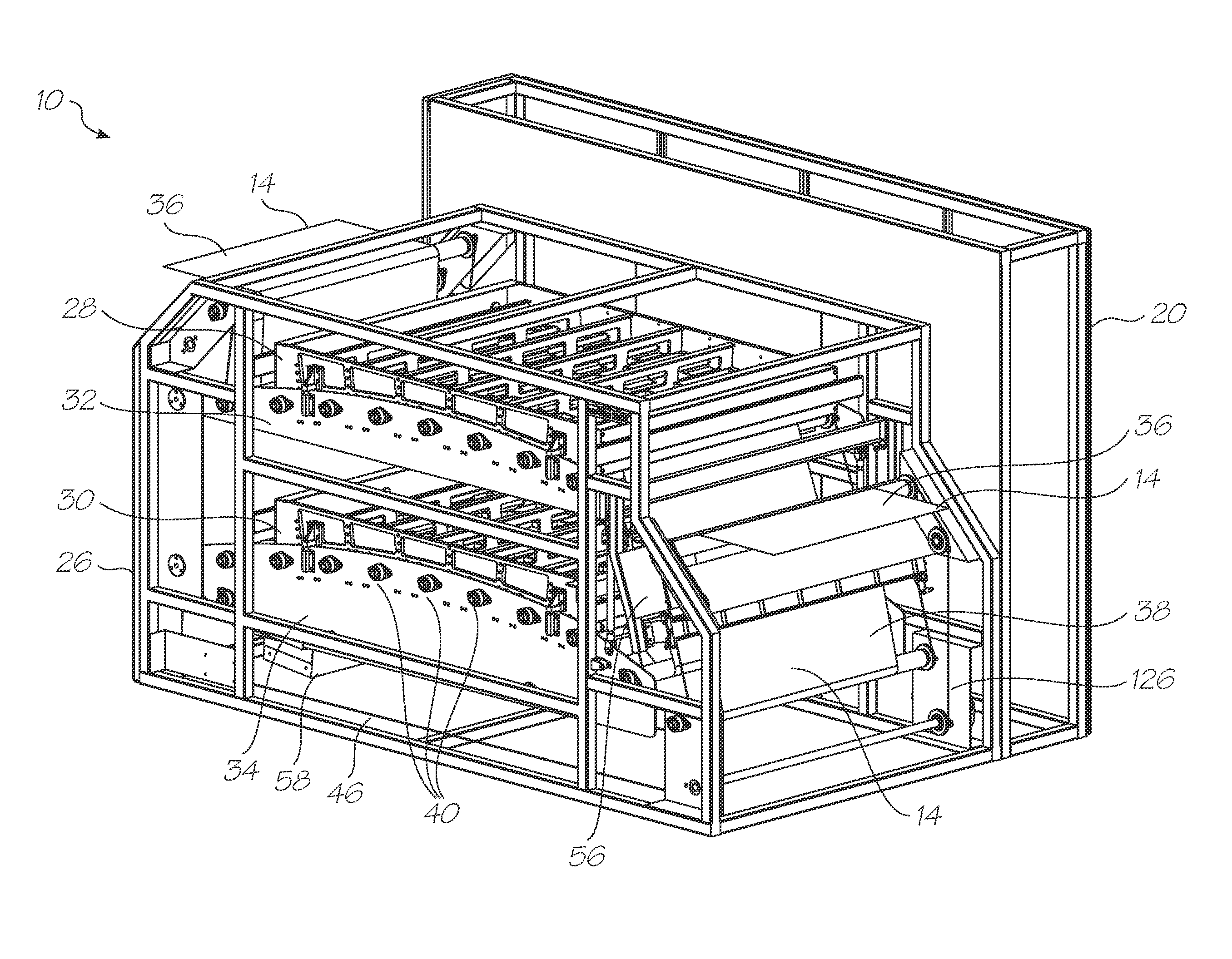

Continuous web printer for printing non-identical copies within a print run

ActiveUS20110043554A1Reduce the overall heightEasy to manufactureTypewritersOther printing apparatusEngineeringData entry

Owner:MEMJET TECH LTD

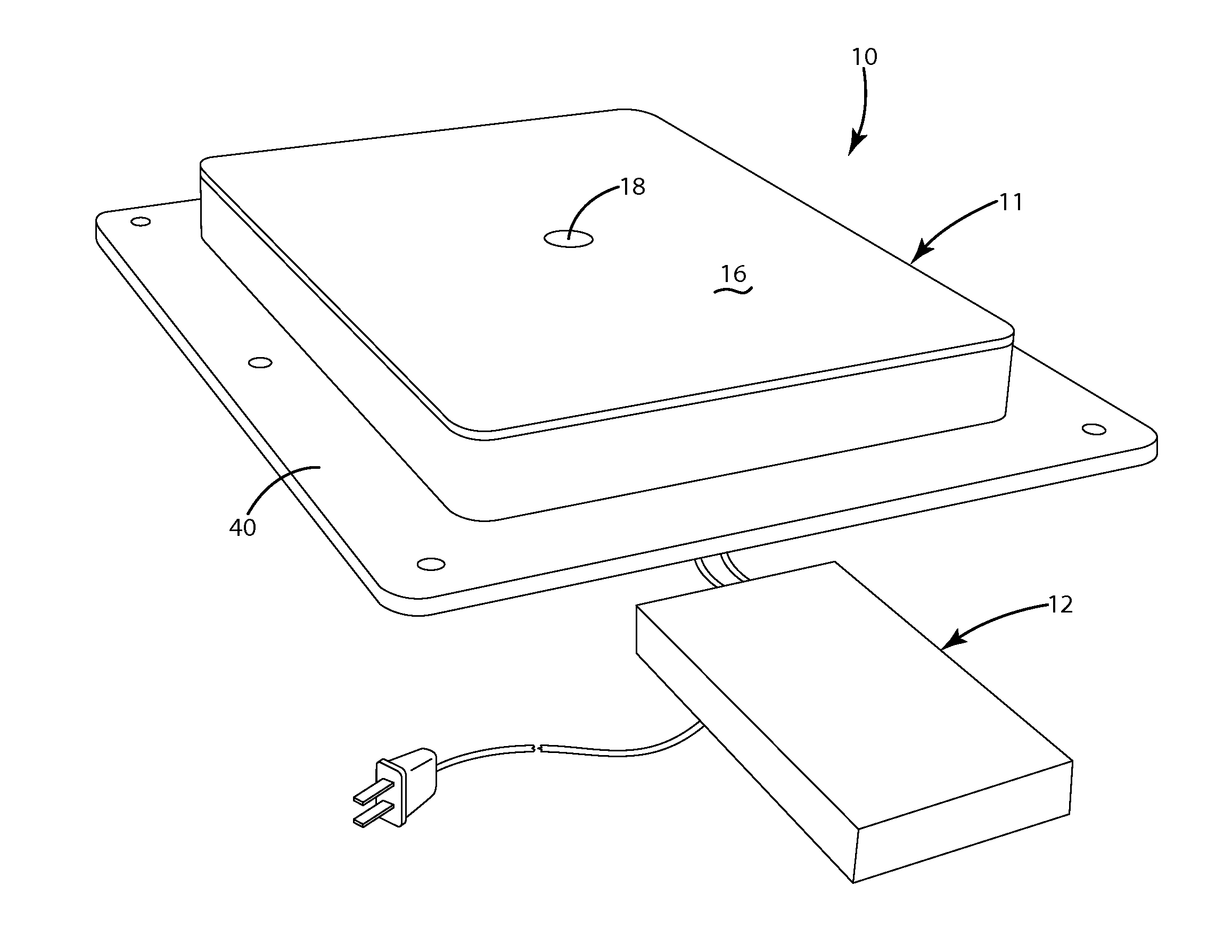

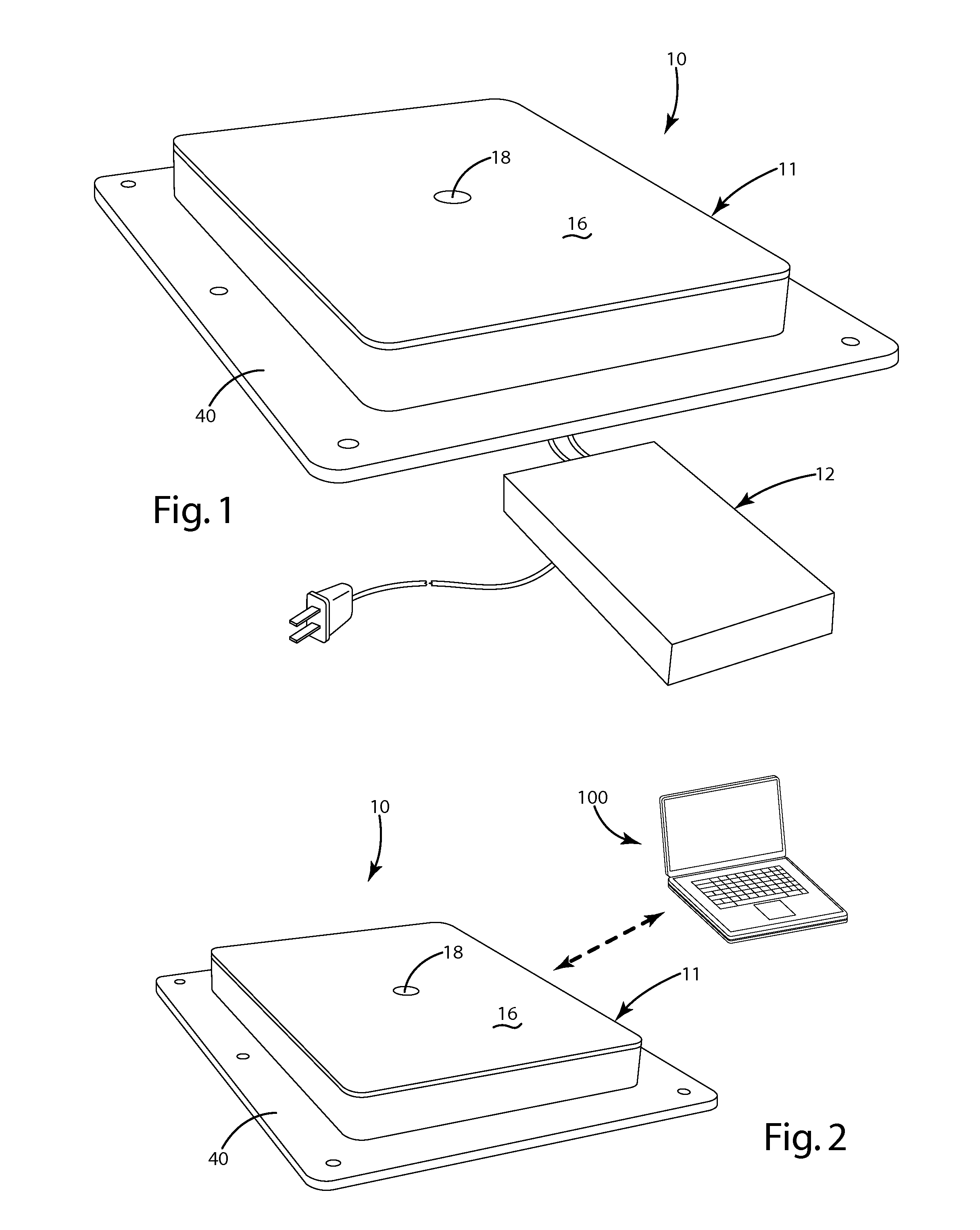

Inductive power supply

ActiveUS8373310B2Reduced footprintSimple mechanical structureBatteries circuit arrangementsElectromagnetic wave systemCharging stationMajor and minor

In one aspect, the present invention provides a wireless power supply having a plunger for mechanically interconnecting a remote device with the power supply. The plunger may be extendable / retractable to interfit with the remote device. In a second aspect, the present invention provides a wireless power supply with a movable primary that allows for close alignment between the primary and the secondary when the remote device is disposed within a range of different positions with respect to the charging surface. The movable primary may, for example, be coupled to the remote device by a peg, a plunger or a magnet. Alternatively, the position of the movable primary may be adjusted manually. In a third aspect, the present invention provides a charging bowl having a plurality of charging stations disposed about a common axis. Each charging station may include a movable primary that permits some freedom in positioning of the remote device on the charging surface. In a fourth aspect, the present invention provides a wireless power supply having a manually movable primary.

Owner:PHILIPS IP VENTURES BV

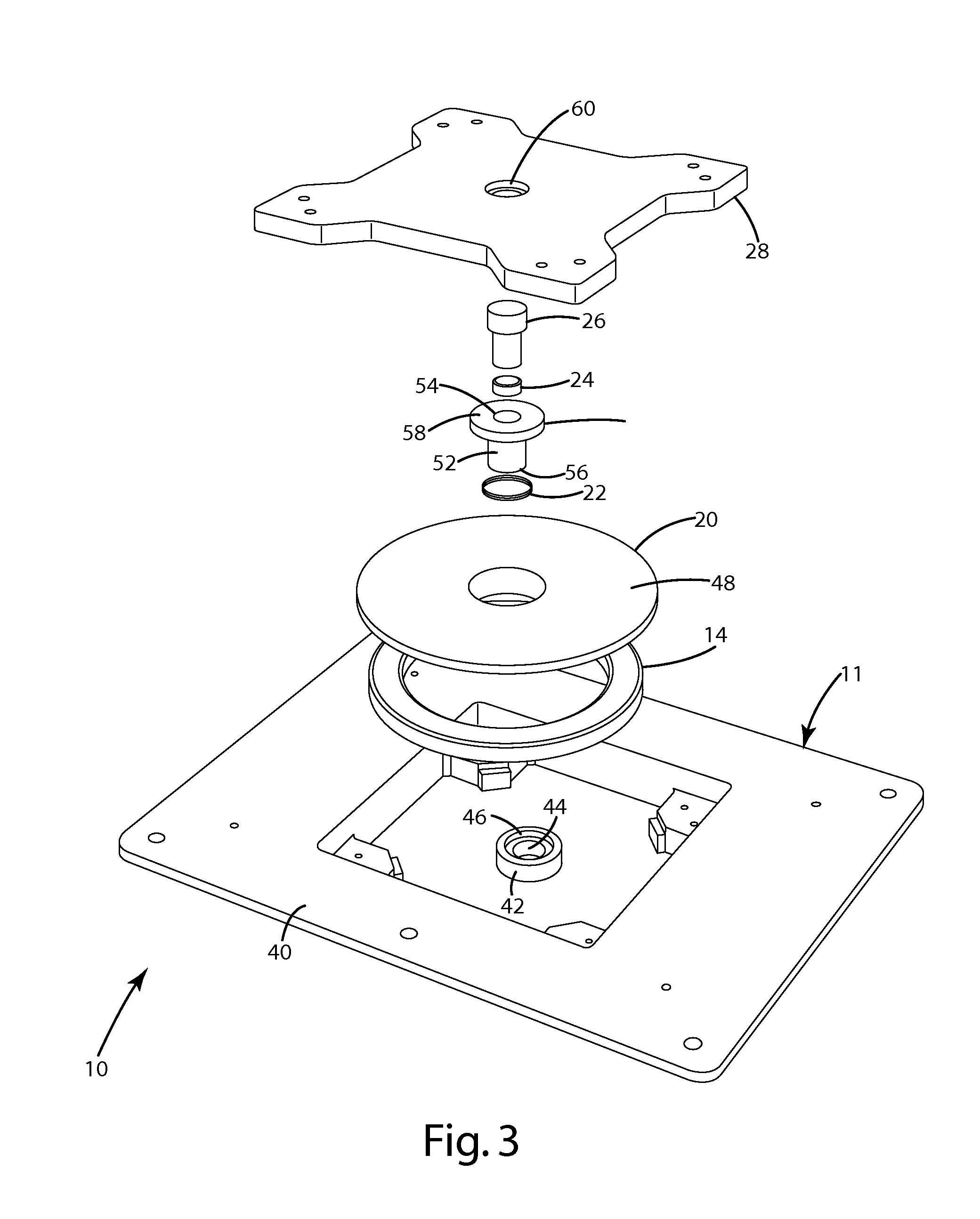

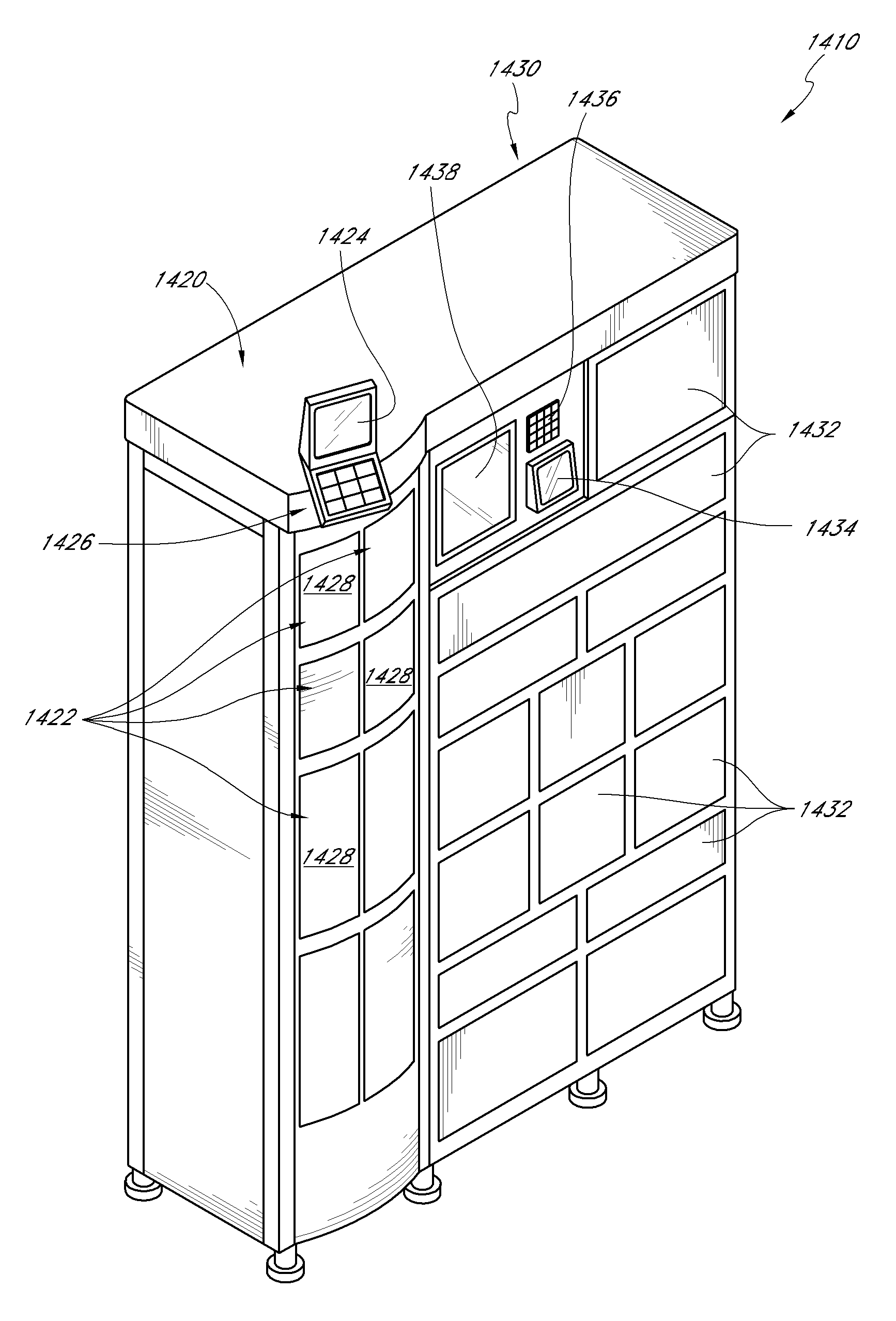

Combination disposal and dispensing apparatus and method

ActiveUS8195328B2Easy to classifyEncourages and facilitates complianceSurgical furnitureDiagnosticsMedical treatmentWaste management

A system and method related to dispensing and disposing medical items is provided. The dispensing portion is generally configured to dispense medical items stored within compartments based on dispensing instructions. The disposal portion is generally configured to sort waste items into a plurality of containers according to applicable rules and regulations governing the handling and / or disposal of such items. In some embodiments, a system comprises sorting stations each of which houses a number of disposable containers. Each station can identify an item of waste, determine the most appropriate container for the item, and facilitate disposal of the item in the appropriate container.

Owner:CAREFUSION 303 INC

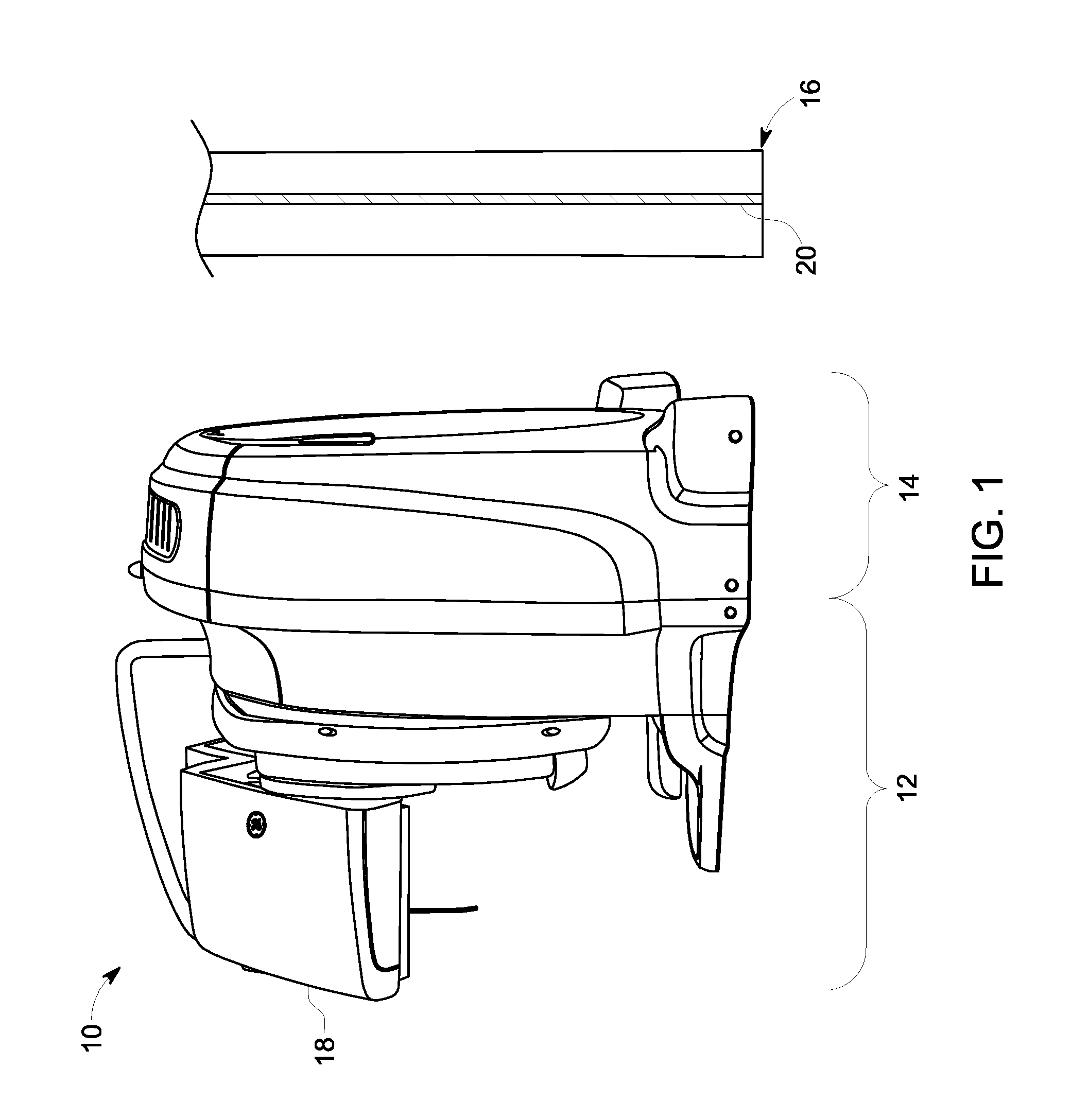

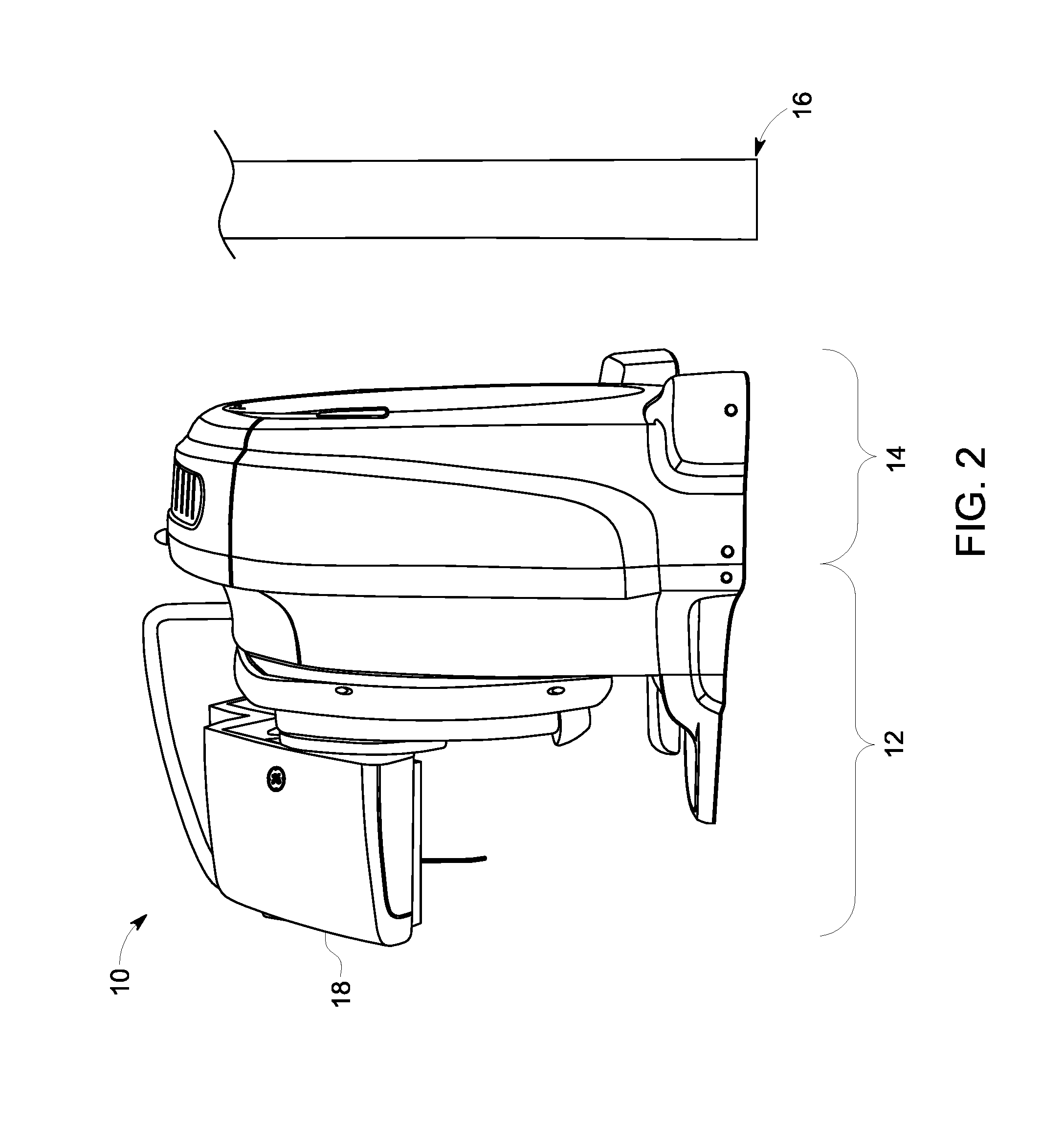

Ct system for use in multi-modality imaging system

InactiveUS20120256092A1Reduced footprintMaterial analysis using wave/particle radiationRadiation/particle handlingImaging qualityX-ray

A computed tomography (CT) imaging system is disclosed. The CT imaging system may be used in a multi-modality imaging context or other context. In one embodiment, the CT imaging system provides for both fast rotation of the rotating X-ray source and detection components and low dose of X-rays generated by the source providing several clinical and economic benefits such as low dose and sufficient image quality and no or insignificant investment in room shielding associated with diagnostic CT dose.

Owner:GENERAL ELECTRIC CO

System and method for website performance optimization and internet traffic processing

ActiveUS8112471B2Down capacityScale downMemory loss protectionError detection/correctionTraffic capacityNetwork connection

A system for optimizing the performance of a website that runs on one or more HTTP servers and is configured to receive HTTP requests from one or more clients via user agents and provide HTTP responses to the one or more clients includes an intermediary component configured to connect to the clients and the servers via network connections. The intermediary component includes a traffic management system (TMS) that includes means for managing HTTP requests originating from the clients and targeting the servers and HTTP responses originating from the servers and targeting the clients and means for redirecting the HTTP requests to the intermediary component. The intermediary component further includes a traffic processing system that includes means for receiving the redirected HTTP requests and the HTTP responses and means for applying optimization techniques to the redirected HTTP requests and the HTTP responses.

Owner:YOTTAA

Circuit wiring layout in semiconductor memory device and layout method

InactiveUS7564134B2Reduced footprintSmooth wiringTransistorSemiconductor/solid-state device detailsMOSFETMetal silicide

An improved circuit wiring layout provides smooth circuit wiring in a peripheral circuit region adjacent to a memory cell region of a semiconductor memory device, and eliminates a write-speed limiting factor. Forming a metal (instead of a metal silicided polysilicon) wiring layer to be connected to a gate layer, to transmit an electrical signal to the gates of FET (e.g., MOSFET (Metal Oxide Semiconductor Field Effect Transistor) transistors formed in the peripheral circuit region; the metal wiring layer is formed (e.g., using one metal damascene process), on a layer different from a word line layer formed on the gate layer (e.g., using another metal damascene process), thereby obtaining a layout of a peripheral circuit region having a reduced area and without using a silicide process.

Owner:SAMSUNG ELECTRONICS CO LTD

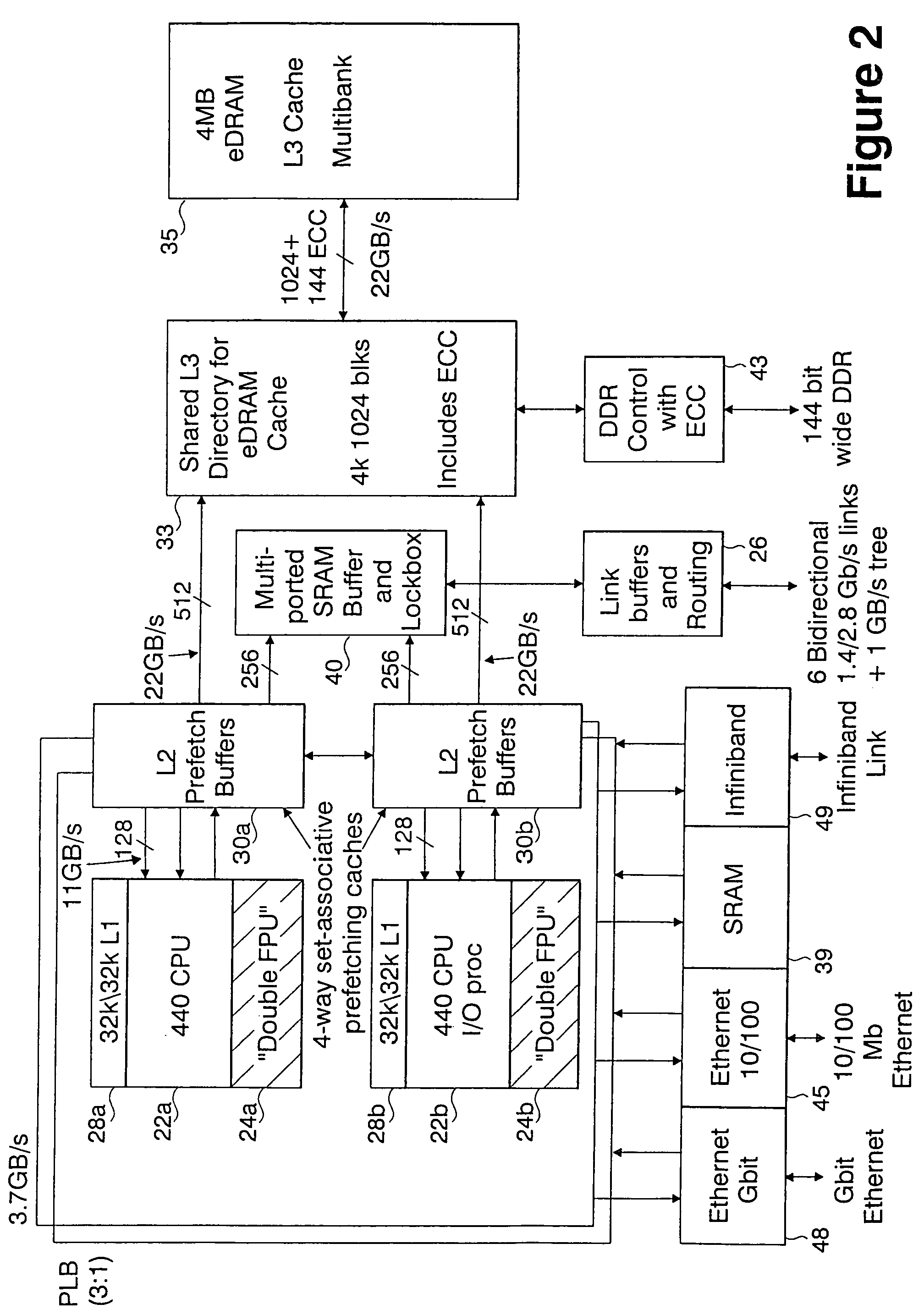

Massively parallel supercomputer

InactiveUS7555566B2Massive level of scalabilityUnprecedented level of scalabilityError preventionProgram synchronisationPacket communicationSupercomputer

A novel massively parallel supercomputer of hundreds of teraOPS-scale includes node architectures based upon System-On-a-Chip technology, i.e., each processing node comprises a single Application Specific Integrated Circuit (ASIC). Within each ASIC node is a plurality of processing elements each of which consists of a central processing unit (CPU) and plurality of floating point processors to enable optimal balance of computational performance, packaging density, low cost, and power and cooling requirements. The plurality of processors within a single node may be used individually or simultaneously to work on any combination of computation or communication as required by the particular algorithm being solved or executed at any point in time. The system-on-a-chip ASIC nodes are interconnected by multiple independent networks that optimally maximizes packet communications throughput and minimizes latency. In the preferred embodiment, the multiple networks include three high-speed networks for parallel algorithm message passing including a Torus, Global Tree, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. For particular classes of parallel algorithms, or parts of parallel calculations, this architecture exhibits exceptional computational performance, and may be enabled to perform calculations for new classes of parallel algorithms. Additional networks are provided for external connectivity and used for Input / Output, System Management and Configuration, and Debug and Monitoring functions. Special node packaging techniques implementing midplane and other hardware devices facilitates partitioning of the supercomputer in multiple networks for optimizing supercomputing resources.

Owner:IBM CORP

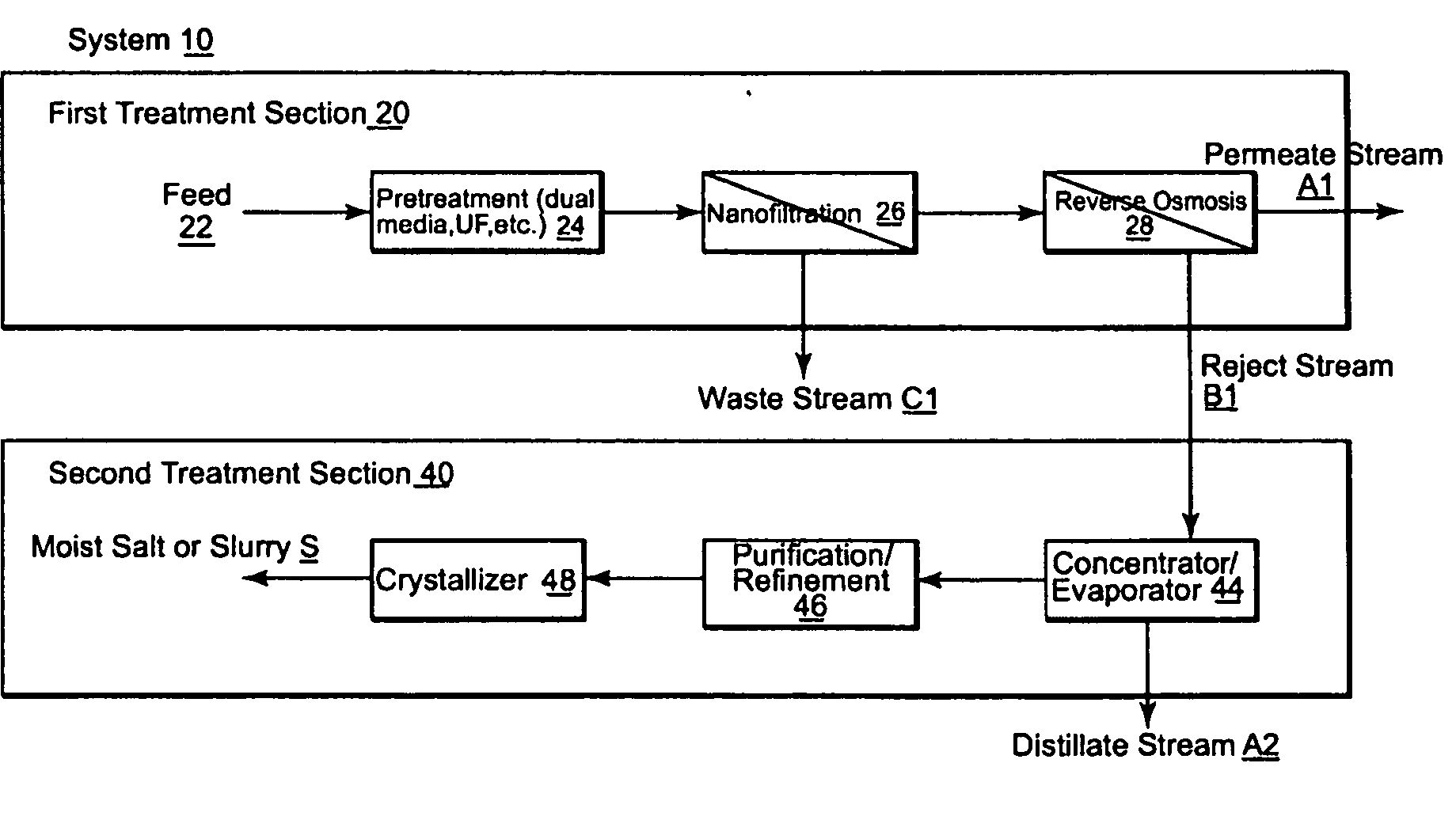

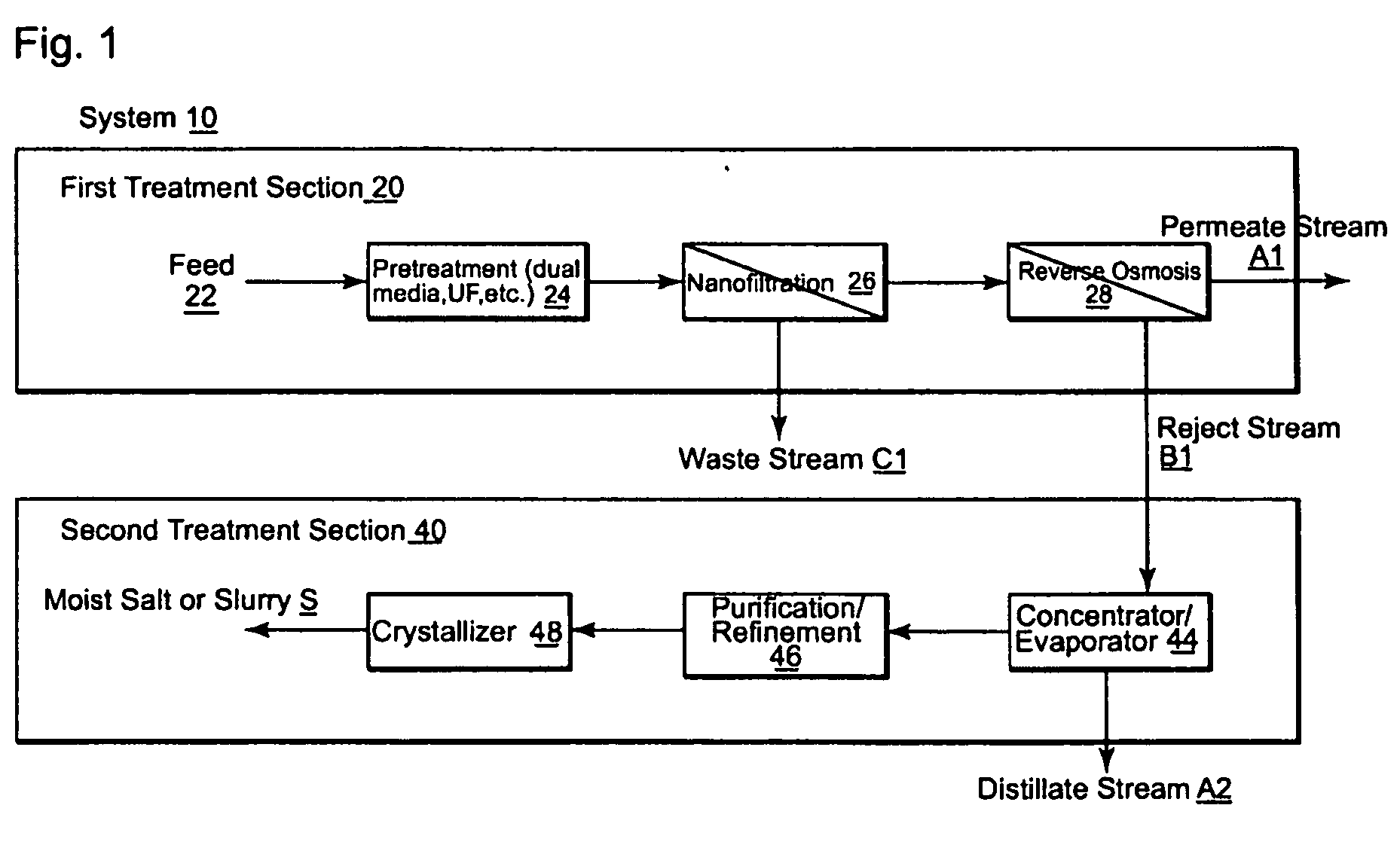

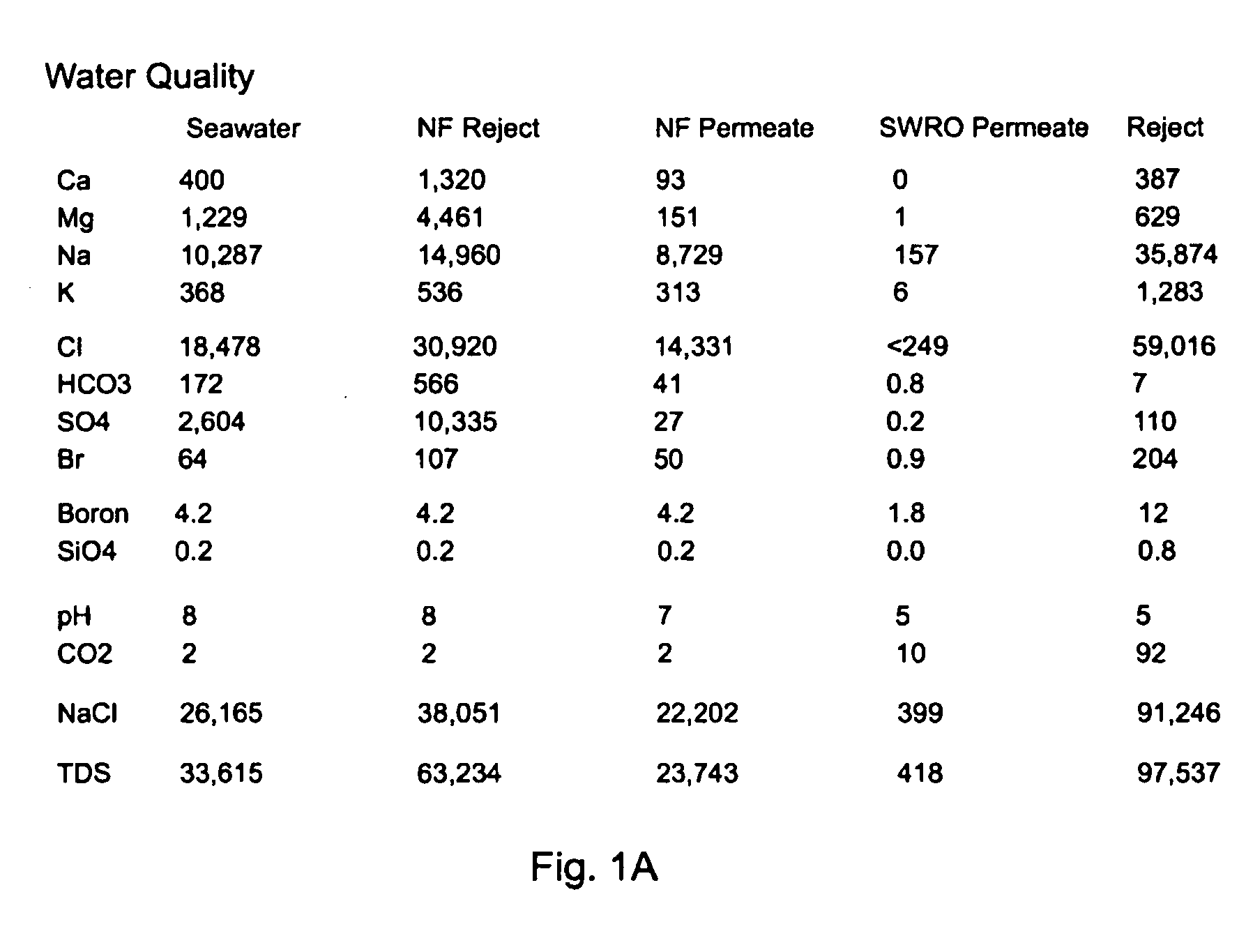

Water desalination plant and system for the production of pure water and salt

InactiveUS20100163471A1Large industrial capacitySimplified and cost-effective processSludge treatmentGeneral water supply conservationWater desalinationTotal dissolved solids

The present invention discloses a desalination plant that operates with a sea water or brackish water feed and produces a concentrated and selectively improved salt reject stream and a pure water permeate stream from a first treatment section that is arranged to produce primarily water at high recovery using membrane desalination processes. The reject stream from the first treatment line has a component distribution that is substantially reduced in native di- and polyvalent scaling ions, essentially depleted of sulfate, has substantially higher total dissolved solids than a traditional sea water reverse osmosis reject, yet is suitable for thermal treatment processes. The system may be enhanced by monovalent salt components. The unit may be integrated with a second treatment section, in which the first reject stream is further concentrated, purified, and processed to produce a high purity salt product.

Owner:GENERAL ELECTRIC CO

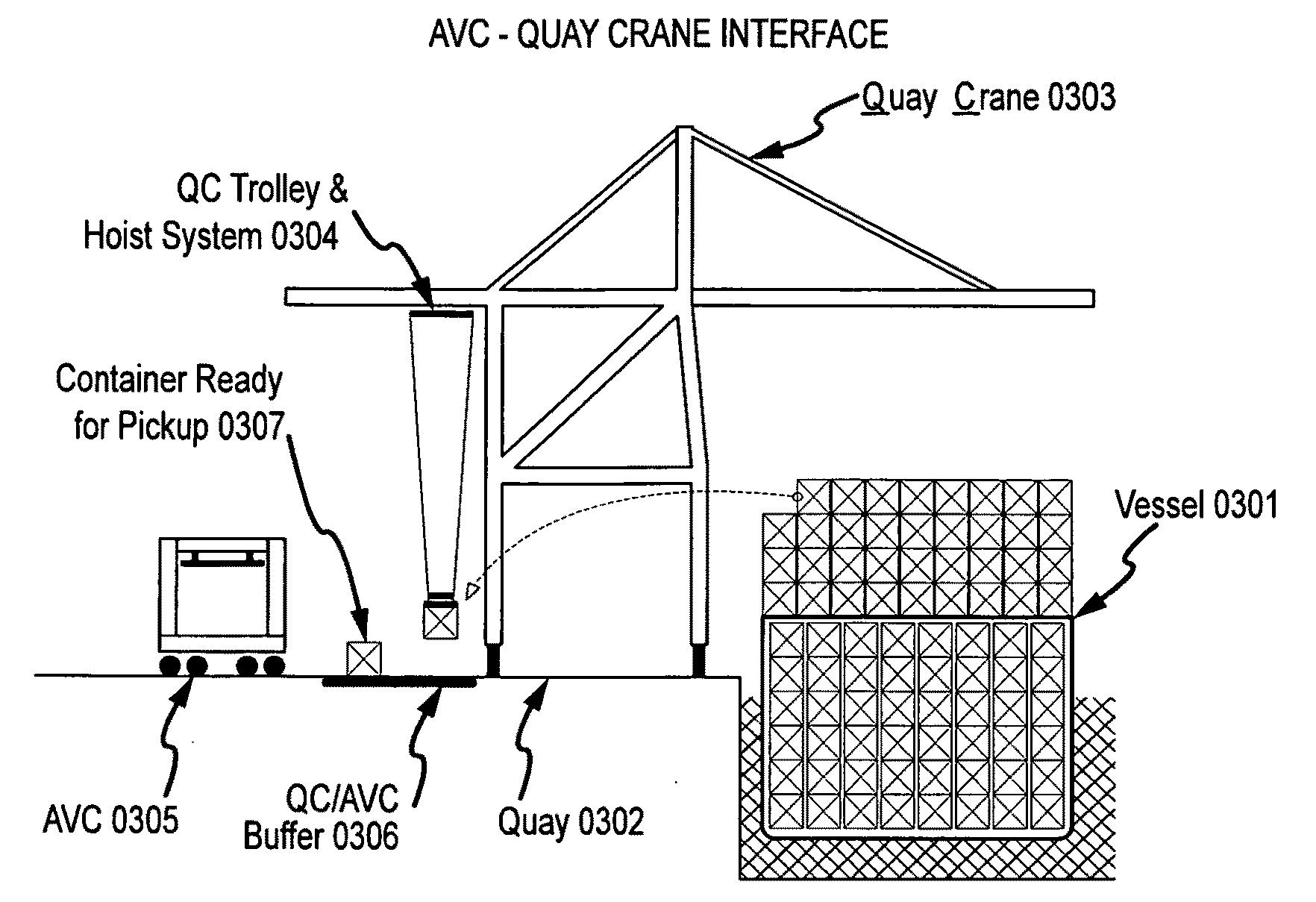

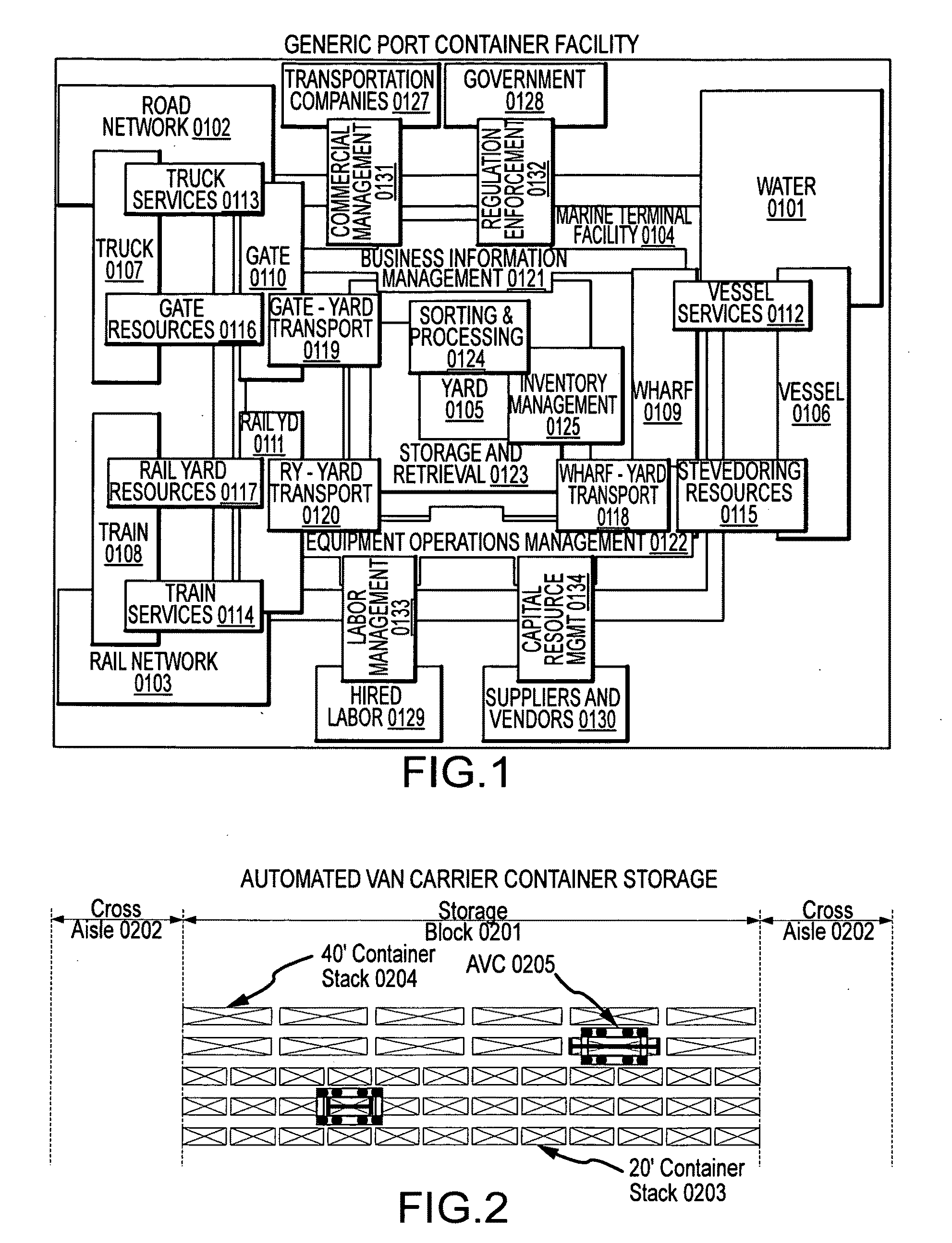

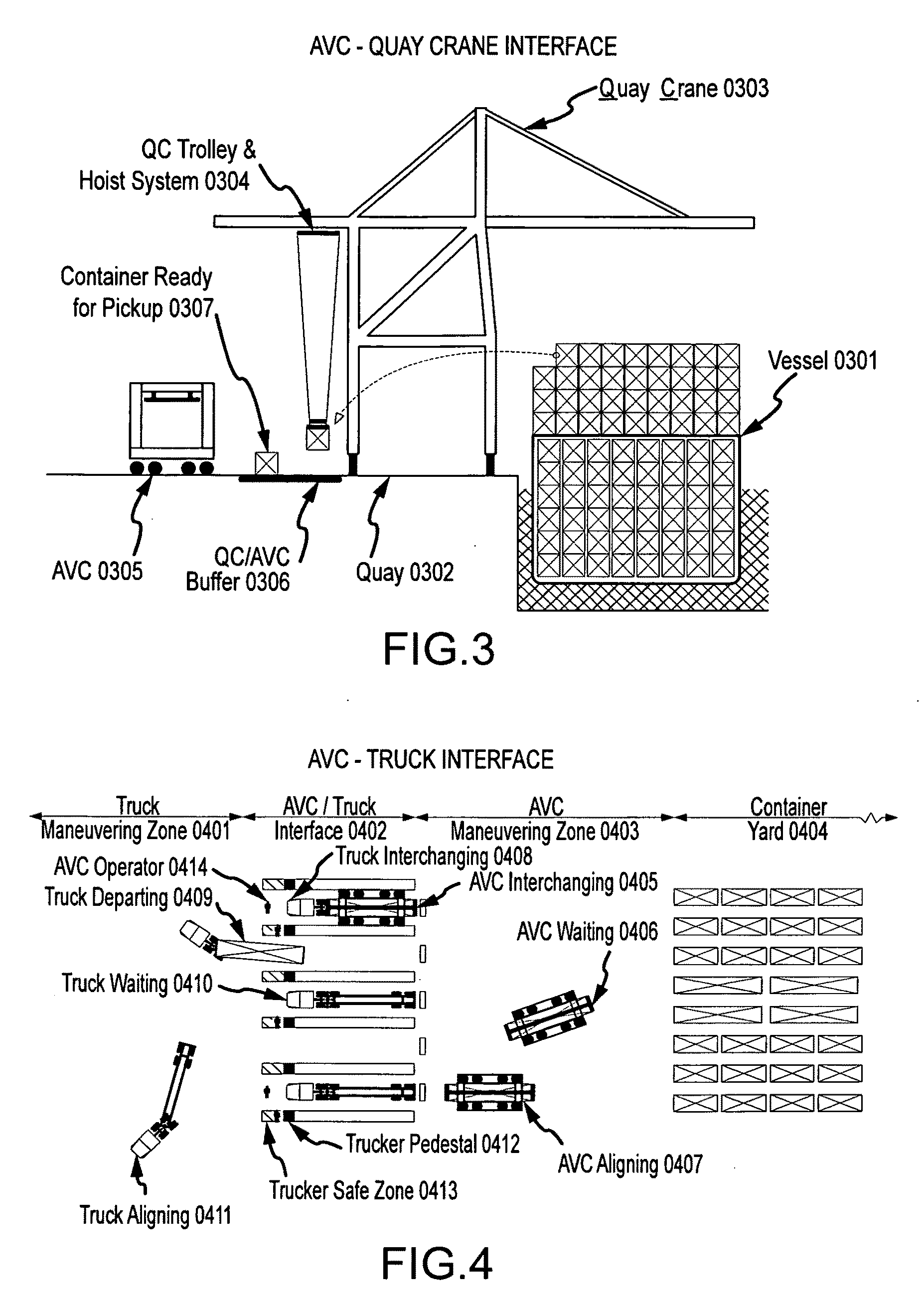

Automated marine container terminal and system

ActiveUS20100021272A1Isolation performanceReduce environmental footprintCargo handling apparatusDigital data processing detailsTruckRobot control

A system, equipment, and processes for extending the scope of automation in port container facilities, and thereby increasing port capacity within fixed land resources, increasing operational productivity, increasing safety, increasing the velocity and reliability of goods movement, increasing freight security, reducing negative environmental impacts, and reducing the overall cost of goods movement. A storage area is accessed by automated guided vehicles which receive and unload containerized loads. On the waterside, loads are exchanged between the vehicles and ships using quay cranes. On the ground transportation side, loads are exchanged between the vehicles and truck or rail carriers using semi automated or automated remote-controlled bridge cranes. Within the storage area, loads are exchanged between the vehicles and the storage facilities using automated stacking cranes. The vehicles are adapted to receive a cassette storage platform which in turn receives standard ISO containers. The vehicles also are adapted to receive one or more alternative platforms including a coning platform for workers to manage container coning, a reefer access and maintenance platform, and a worker transport platform. The use of a single vehicle type with interchangeable platforms allows for maximum flexibility and efficiency. The automation of the vehicle allows for complete contamination within the storage portion of the system.The system thus substantially extends the reach of automation to cover both landside and waterside intra-terminal transfer operations. By this extension, the interface of workers and machines is greatly reduced, increasing safety, productivity, security, and capacity. By this extension, the robotic control process can be fully optimized, increasing velocity and reliability while reducing the terminal's environmental footprint.

Owner:MARINE TERMINALS CORP

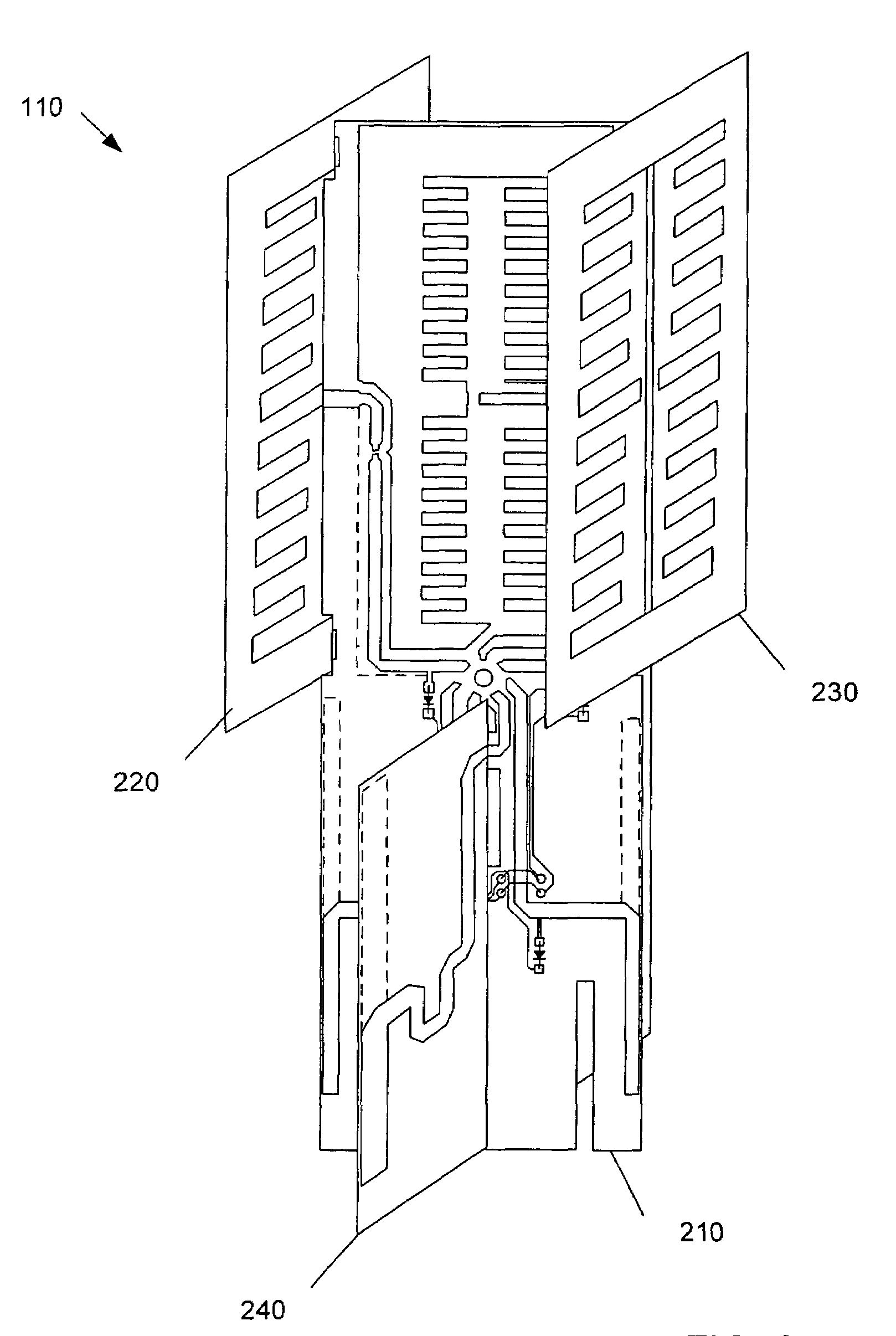

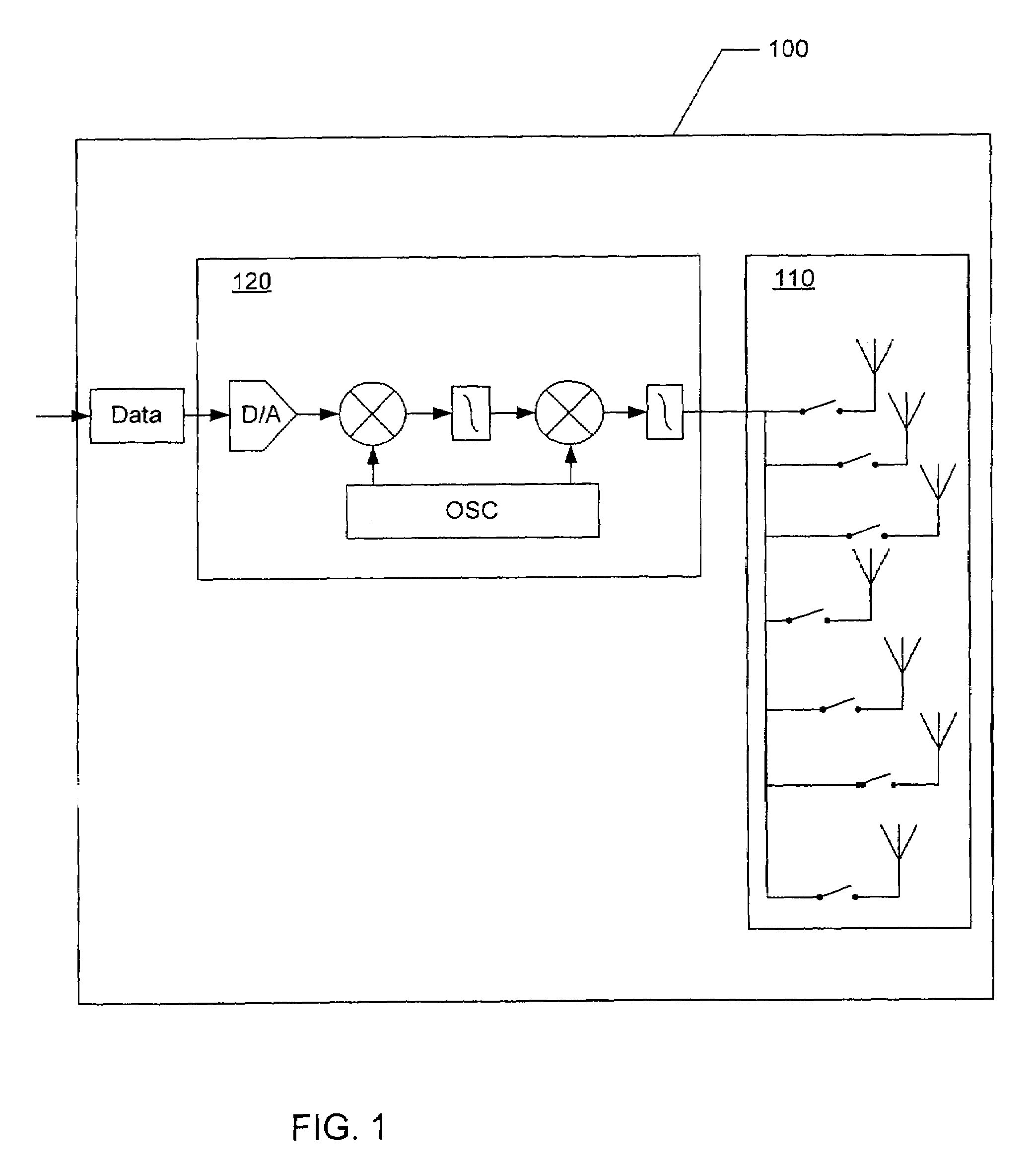

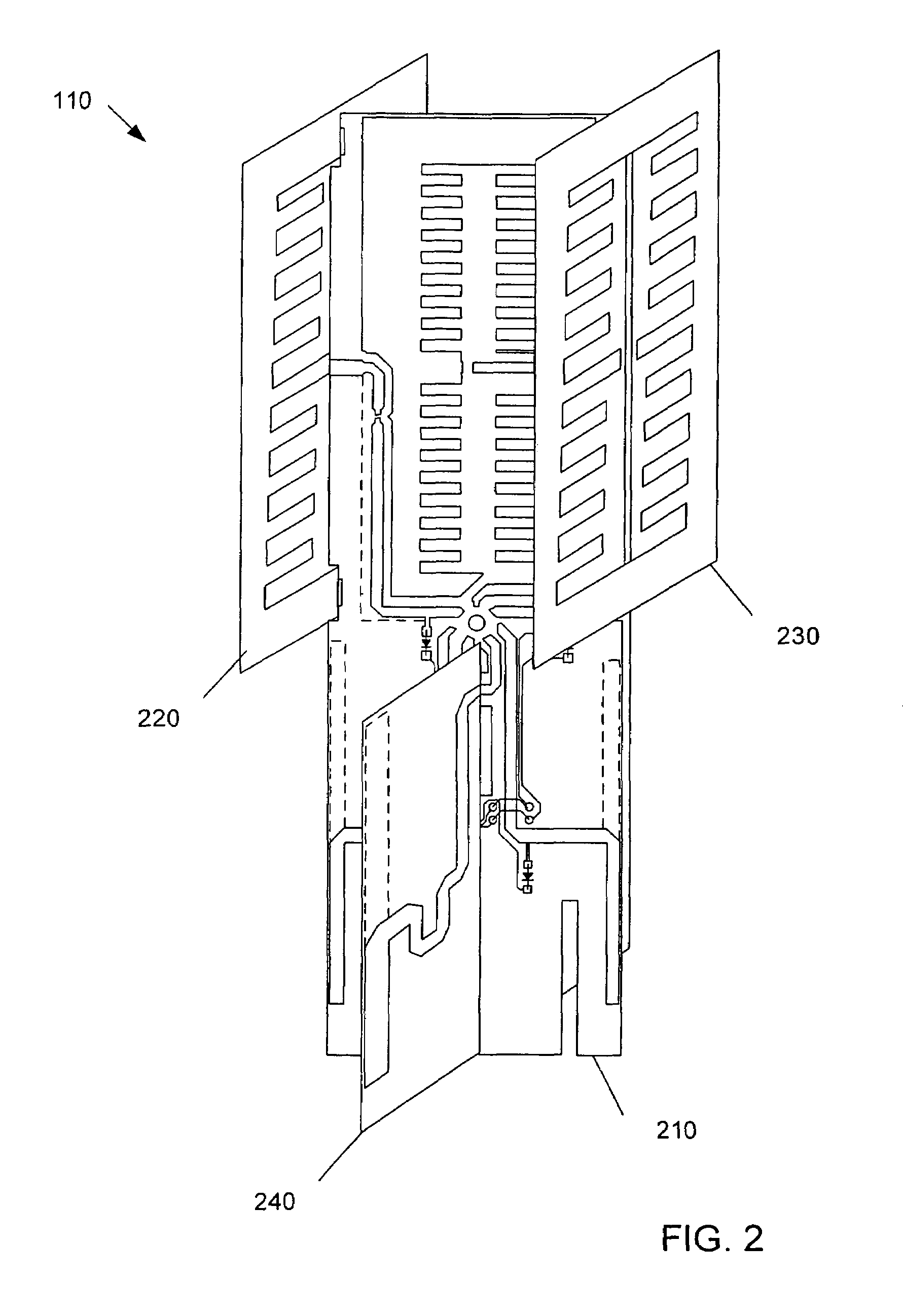

Coverage antenna apparatus with selectable horizontal and vertical polarization elements

ActiveUS7358912B1Reduced footprintAntenna arraysAntenna feed intermediatesAntenna elementHorizontal and vertical

An antenna apparatus comprises selectable antenna elements including a plurality of dipoles and / or a plurality of slot antennas (“slot”). Each dipole and / or each slot provides gain with respect to isotropic. The dipoles may generate vertically polarized radiation and the slots may generate horizontally polarized radiation. Each antenna element may have one or more loading structures configured to decrease the footprint (i.e., the physical dimension) of the antenna element and minimize the size of the antenna apparatus.

Owner:ARRIS ENTERPRISES LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com