Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

811 results about "3d memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Zero shrinkage smooth interface oxy-nitride and oxy-amorphous-silicon stacks for 3D memory vertical gate application

InactiveUS20130161629A1Reduce AlFx depositReduce AlFx buildingSolid-state devicesSemiconductor/solid-state device manufacturingDeposition temperatureAmorphous silicon

Methods are provided for depositing a stack of film layers for use in vertical gates for 3D memory devices, by depositing a sacrificial nitride film layer at a sacrificial film deposition temperature greater than about 550° C.; depositing an oxide film layer over the nitride film layer, at an oxide deposition temperature of about 600° C. or greater; repeating the above steps to deposit a film stack having alternating layers of the sacrificial films and the oxide films; forming a plurality of holes in the film stack; and depositing polysilicon in the plurality of holes in the film stack at a polysilicon process temperature of about 700° C. or greater, wherein the sacrificial film layers and the oxide film layers experience near zero shrinkage during the polysilicon deposition. Flash drive memory devices may also be made by these methods.

Owner:APPLIED MATERIALS INC

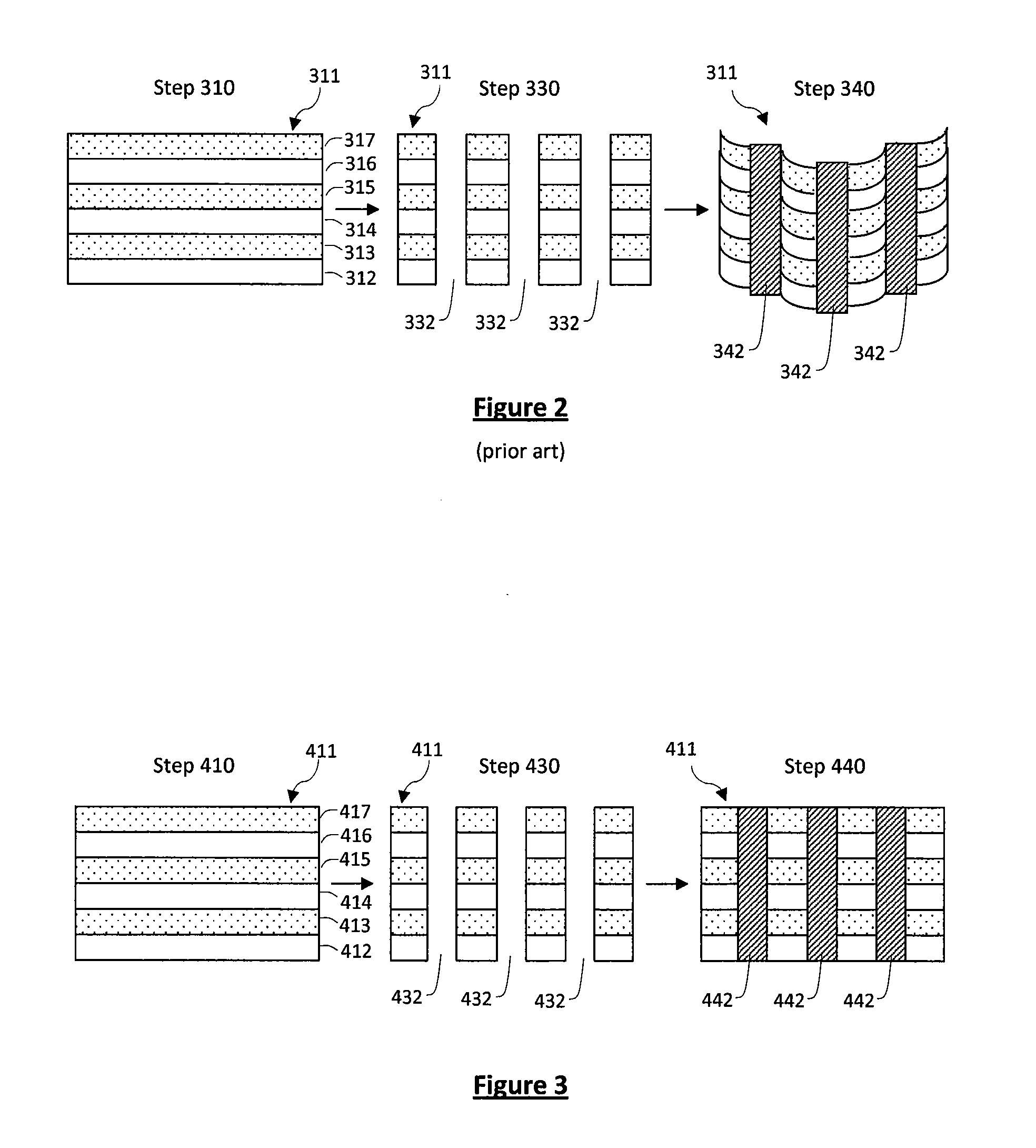

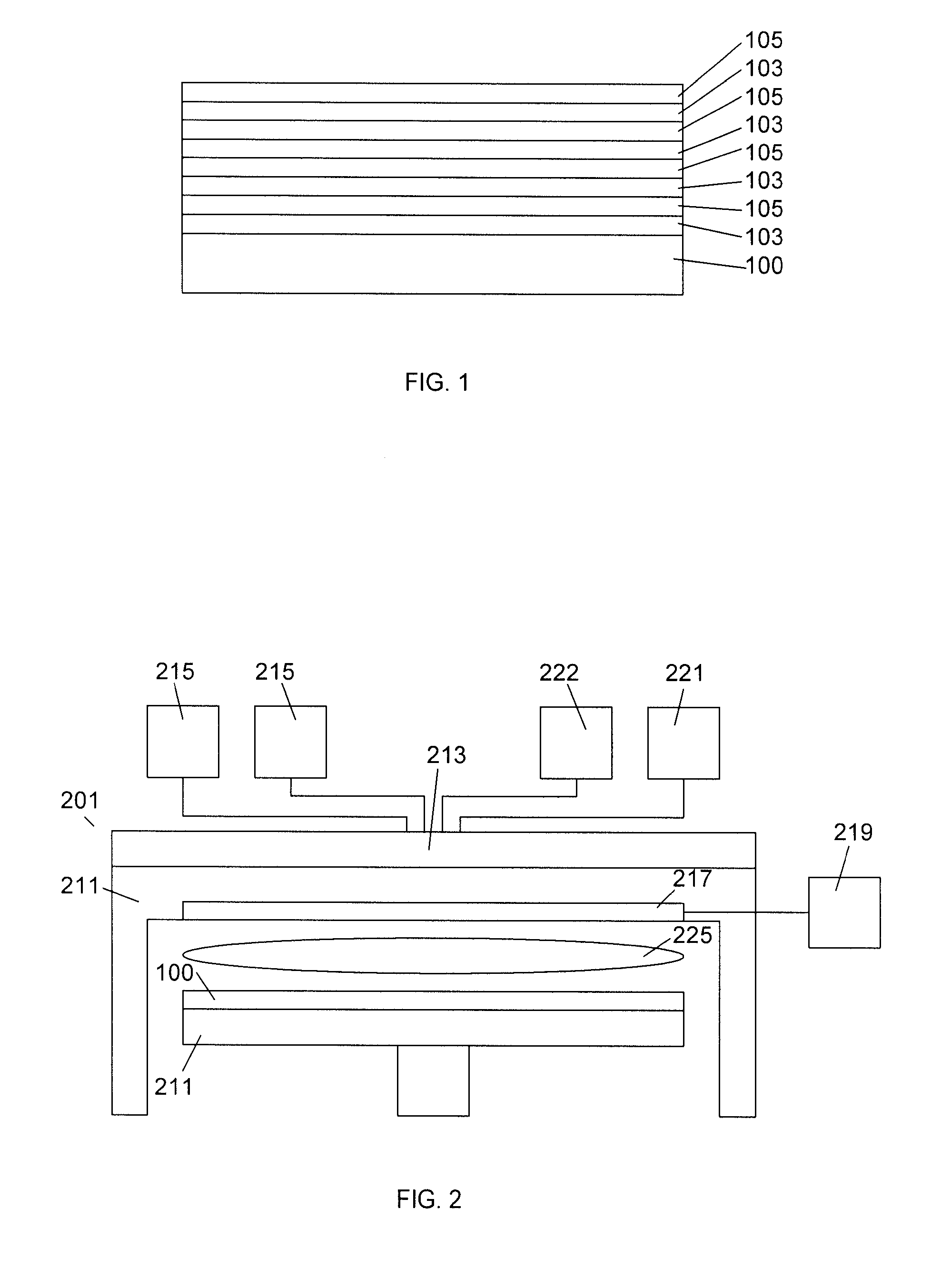

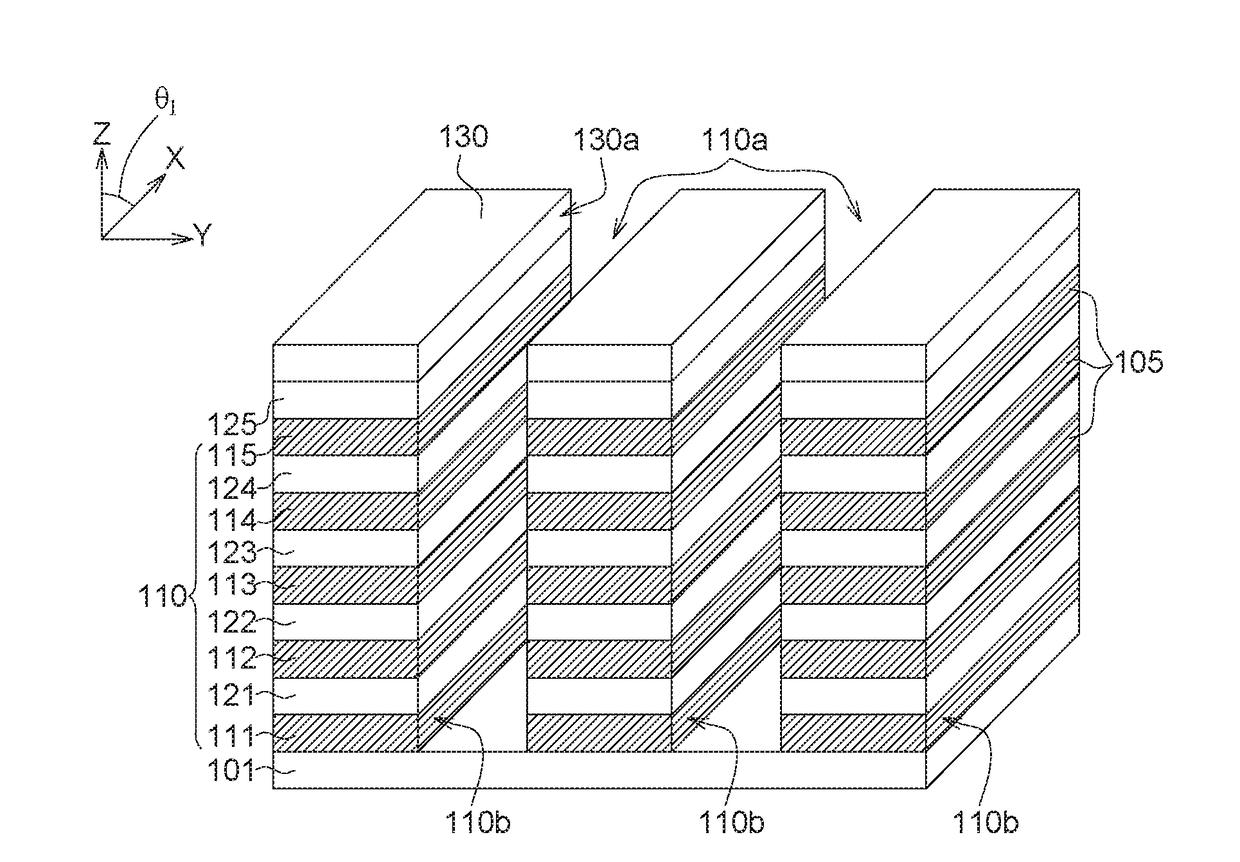

PECVD oxide-nitride and oxide-silicon stacks for 3D memory application

ActiveUS8076250B1Improve bonding interfaceAvoid layeringSemiconductor/solid-state device detailsSolid-state devicesMaterials science3d memory

A layer stack of different materials is deposited on a substrate in a single plasma enhanced chemical vapor deposition processing chamber while maintaining a vacuum. A substrate is placed in the processing chamber and a first processing gas is used to form a first layer of a first material on the substrate. A plasma purge and gas purge are performed before a second processing gas is used to form a second layer of a second material on the substrate. The plasma purge and gas purge are repeated and the additional layers of first and second materials are deposited on the layer stack.

Owner:APPLIED MATERIALS INC

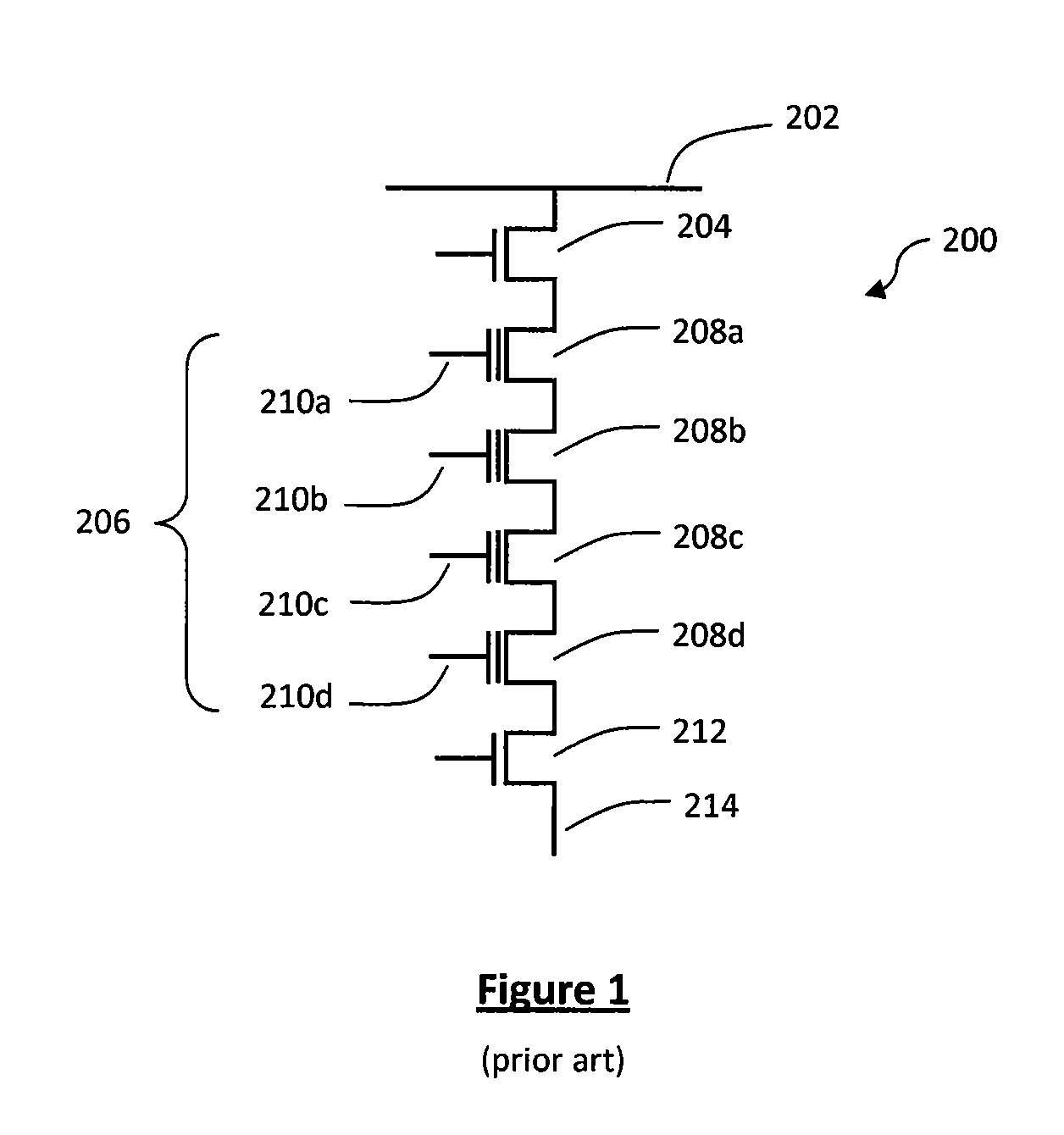

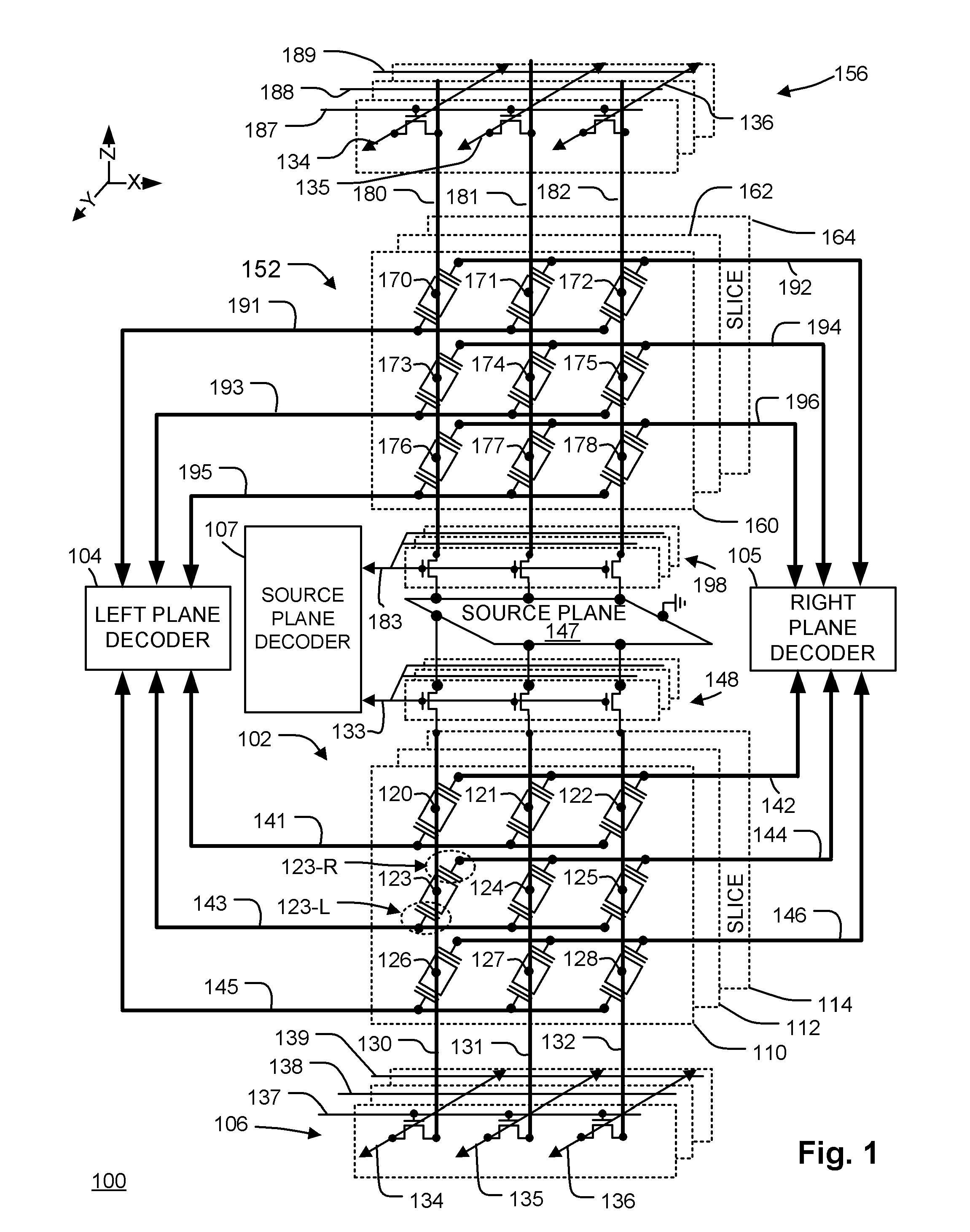

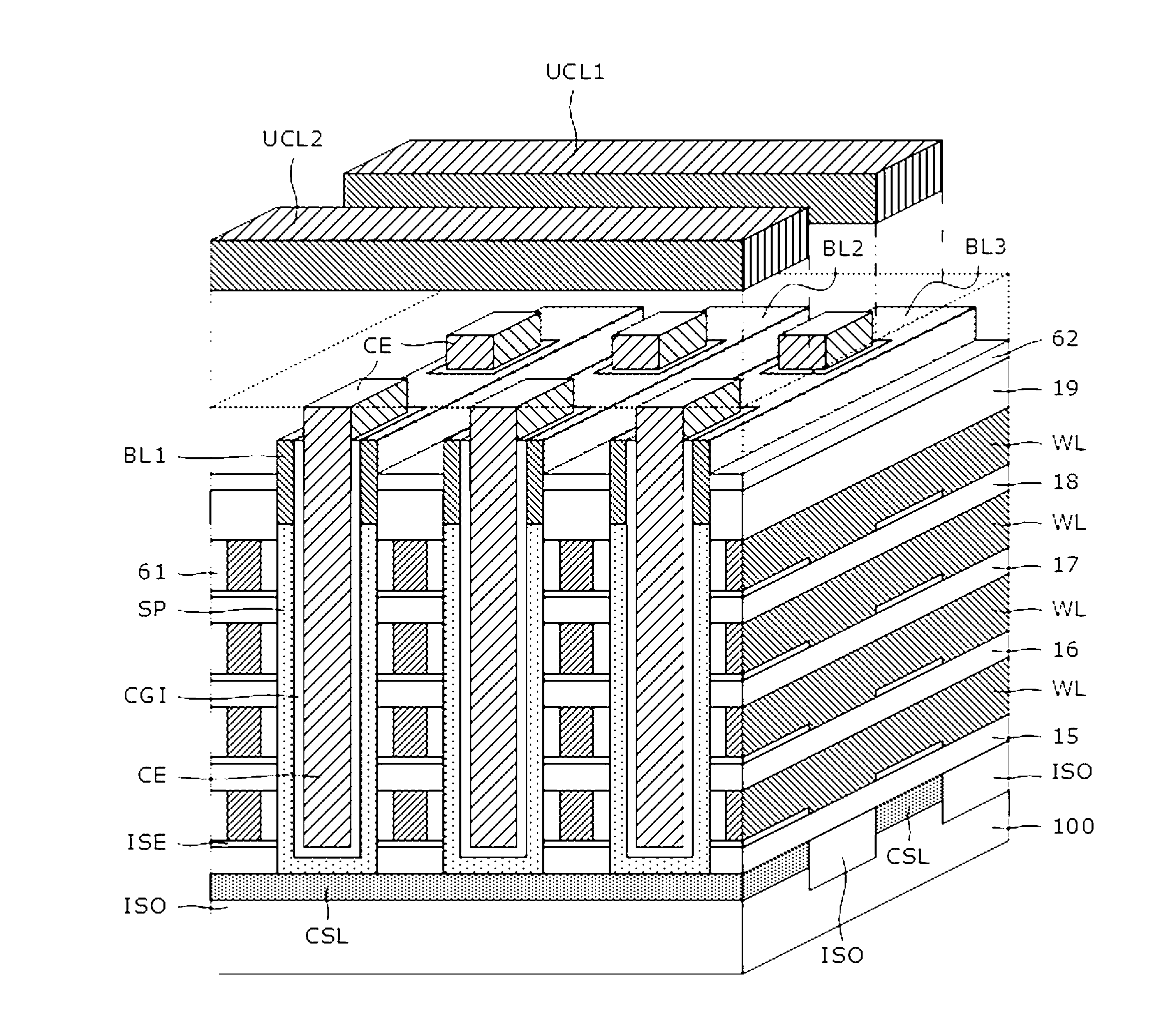

3D two-bit-per-cell NAND flash memory

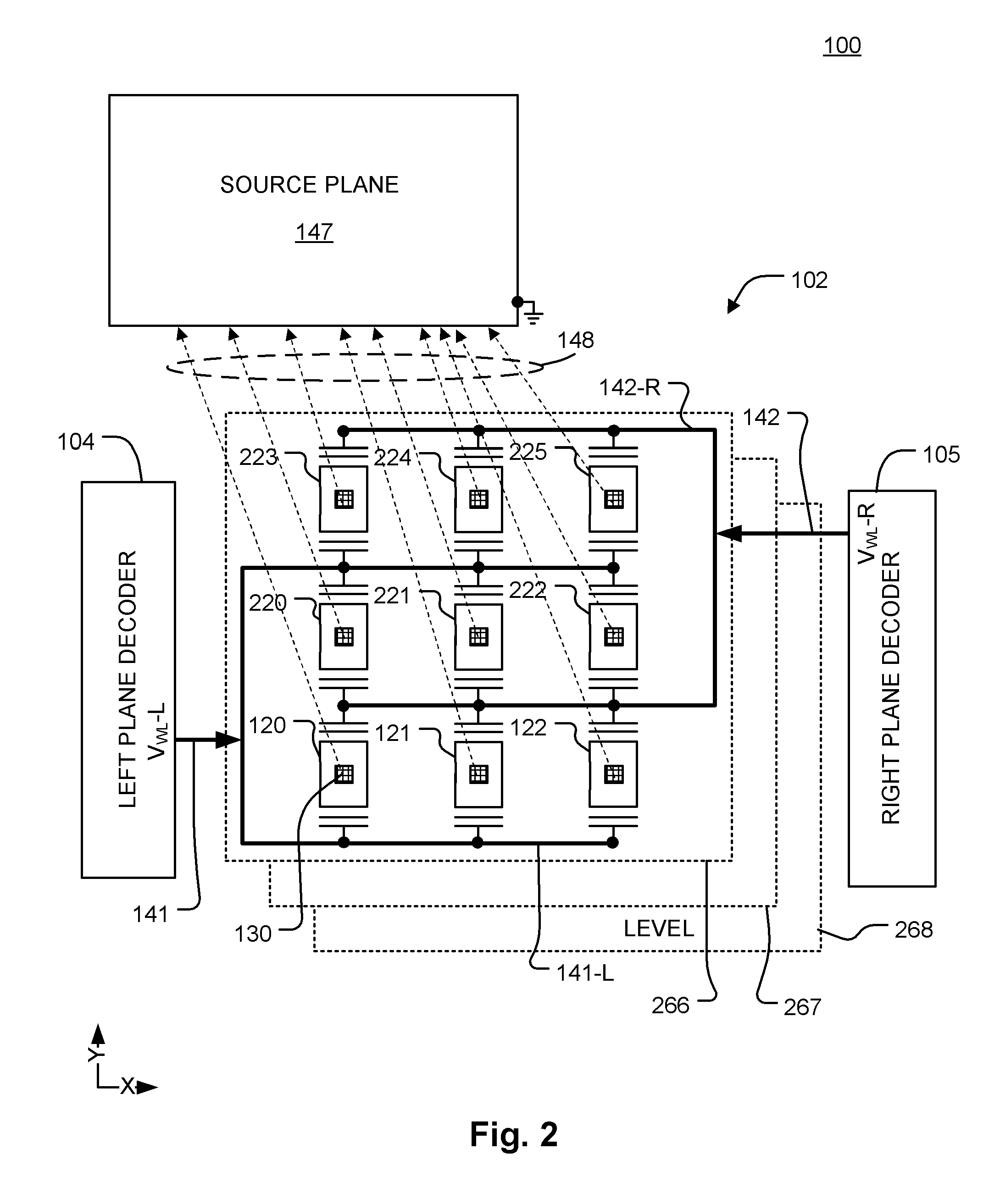

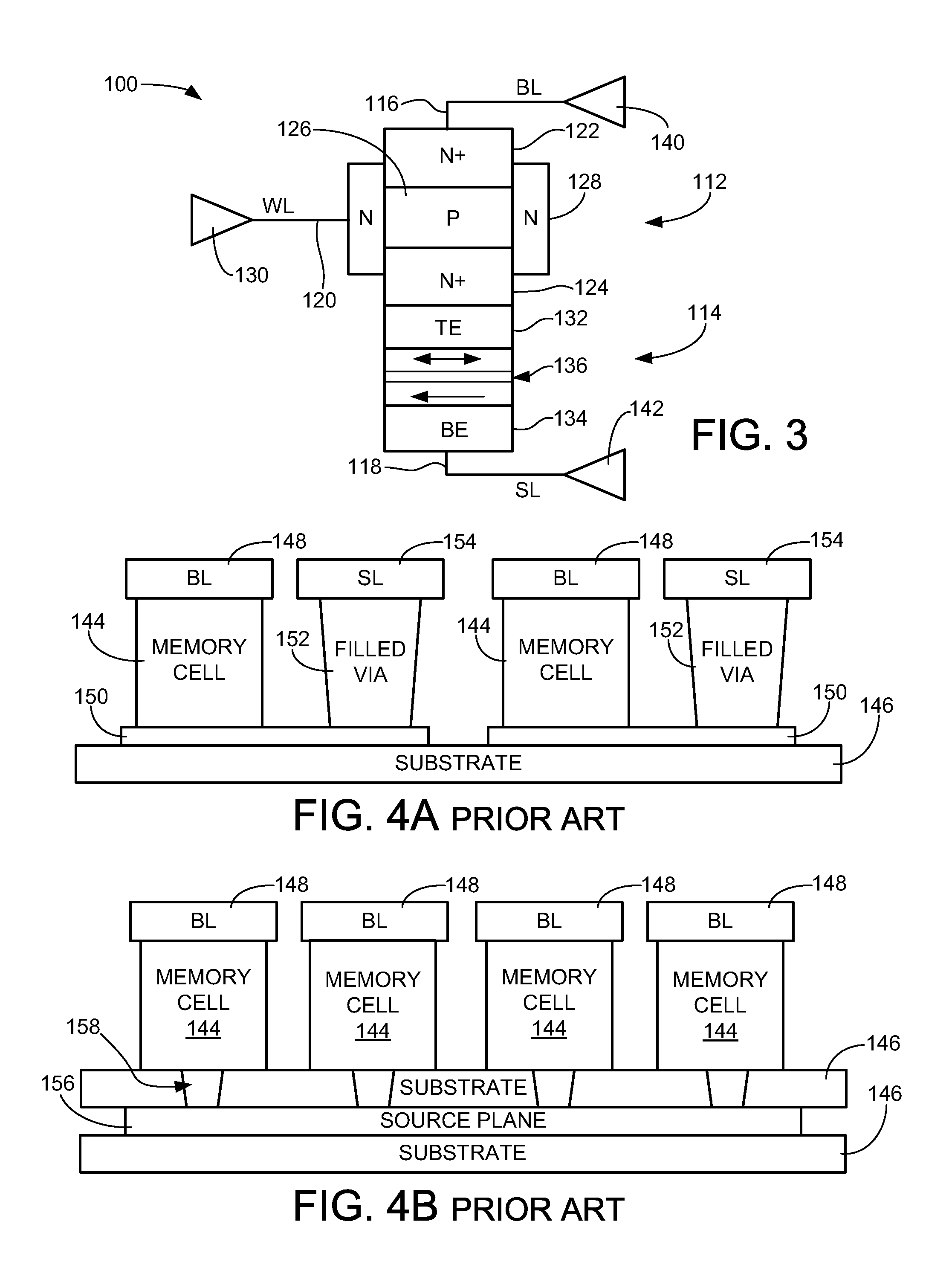

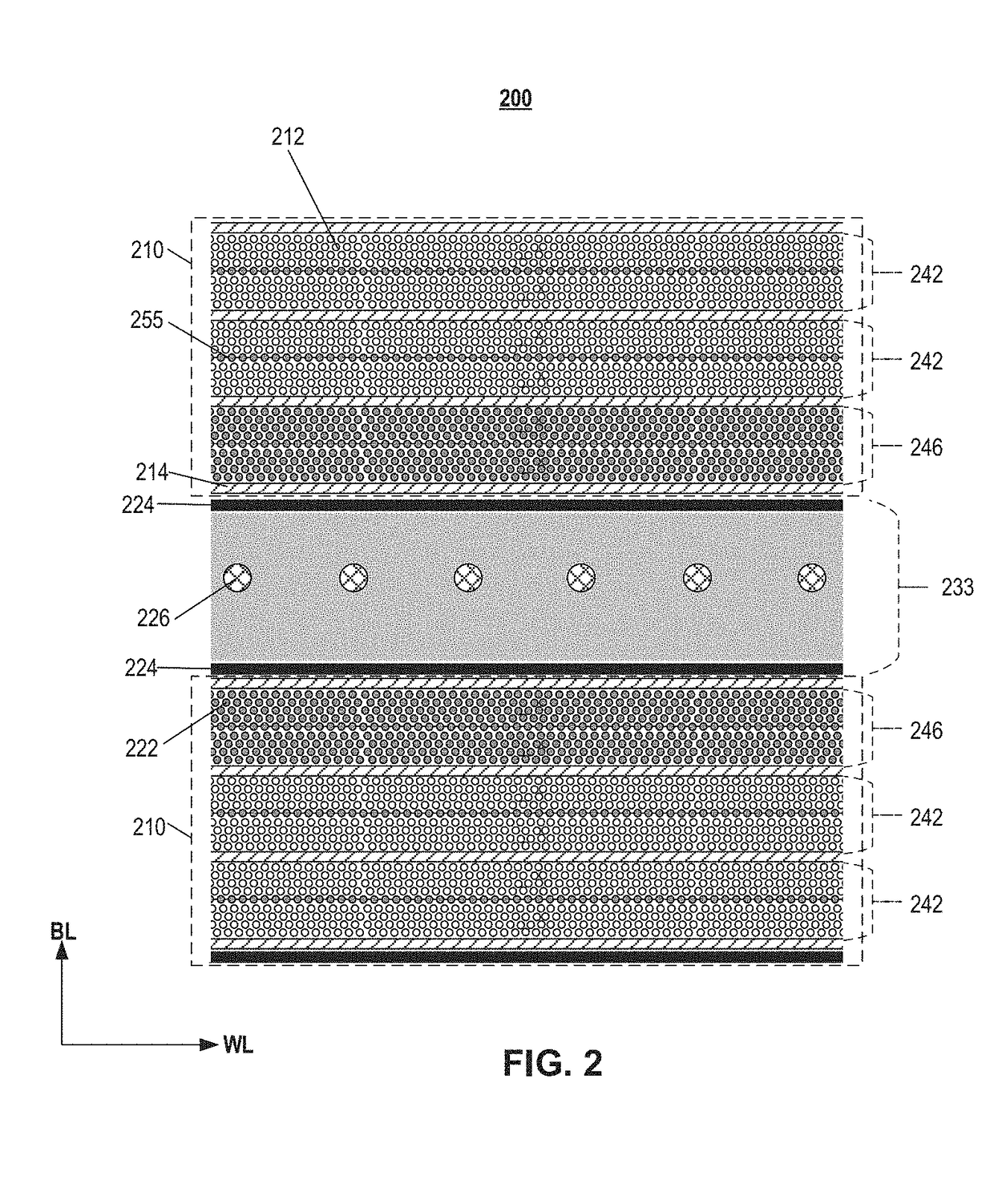

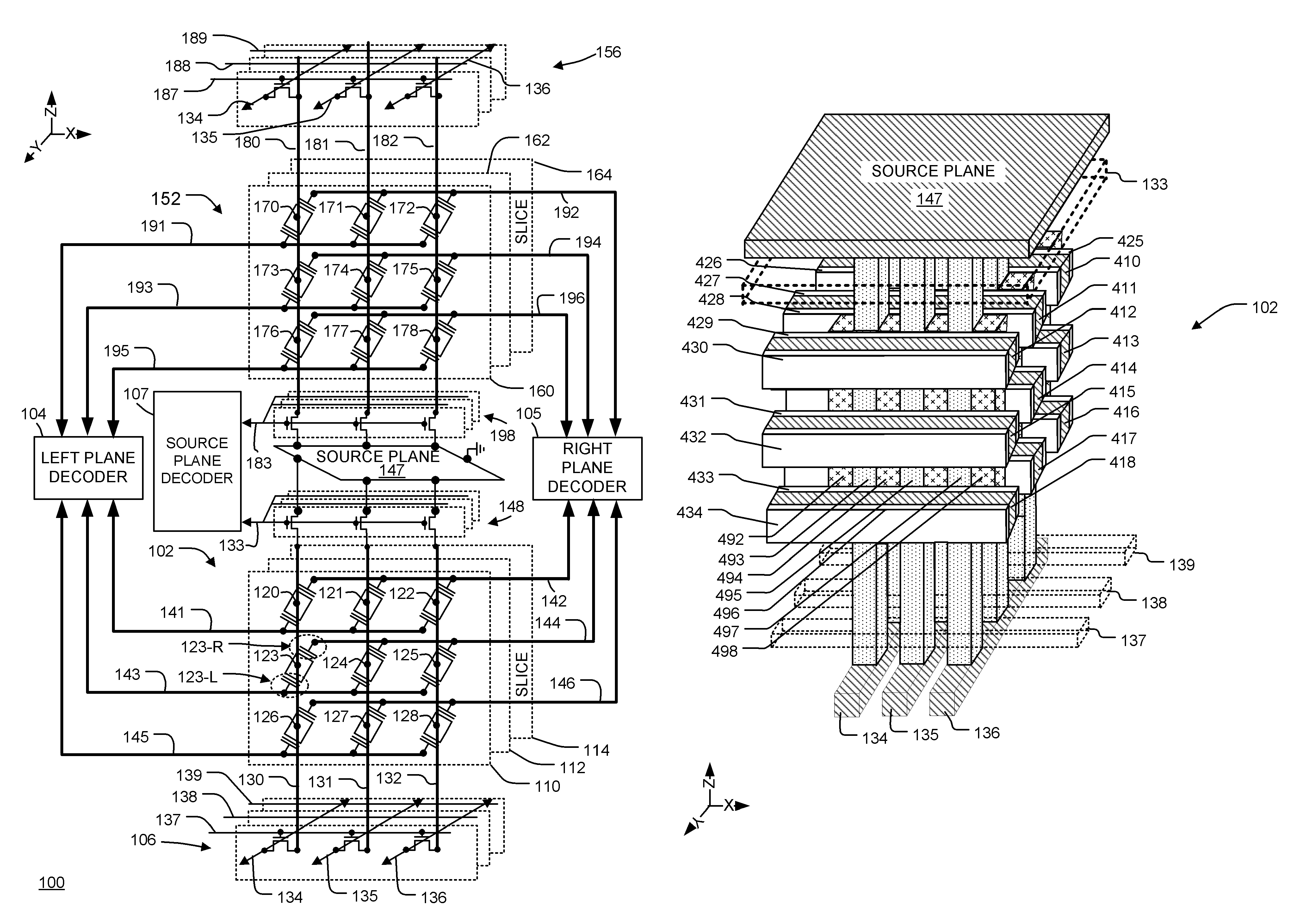

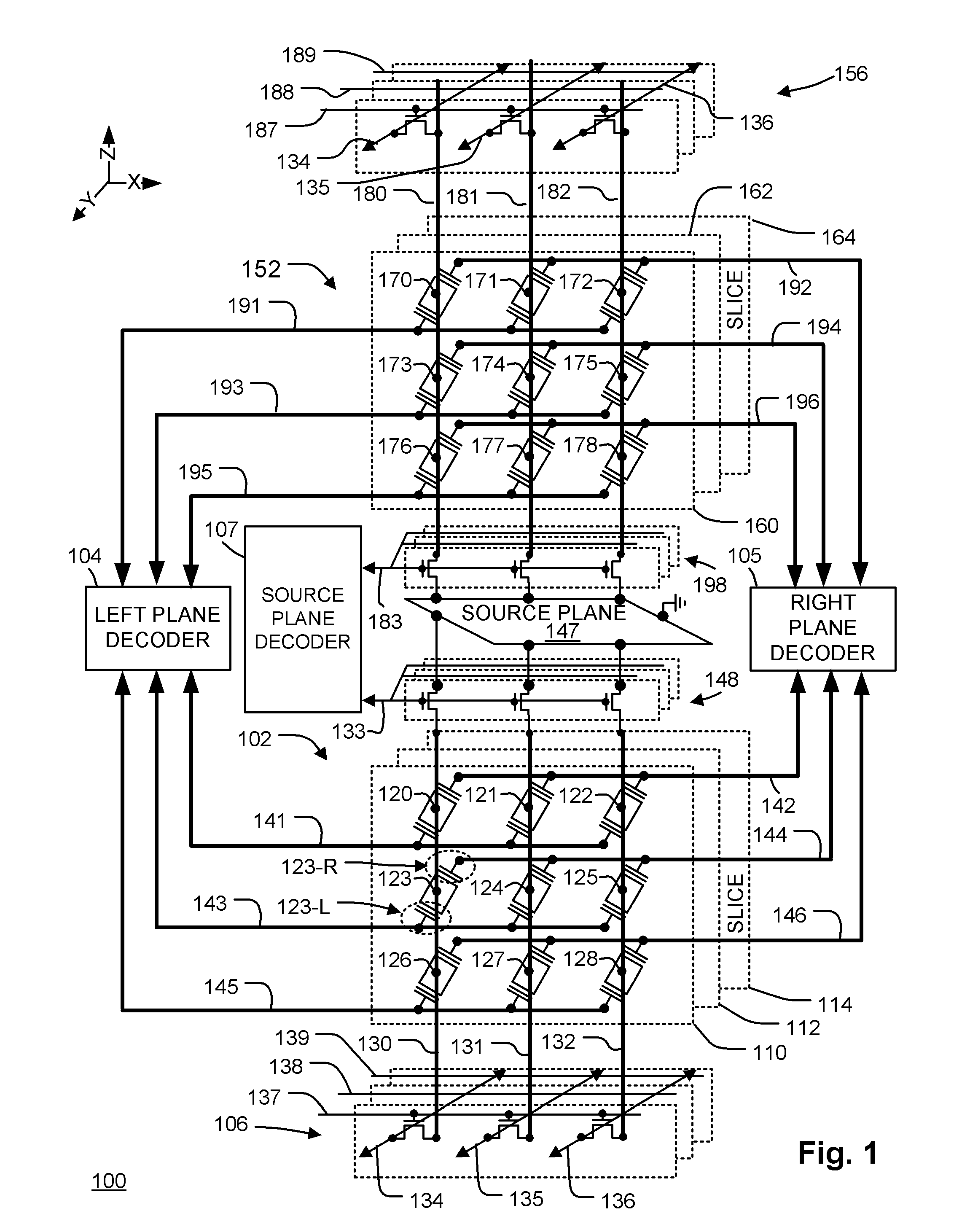

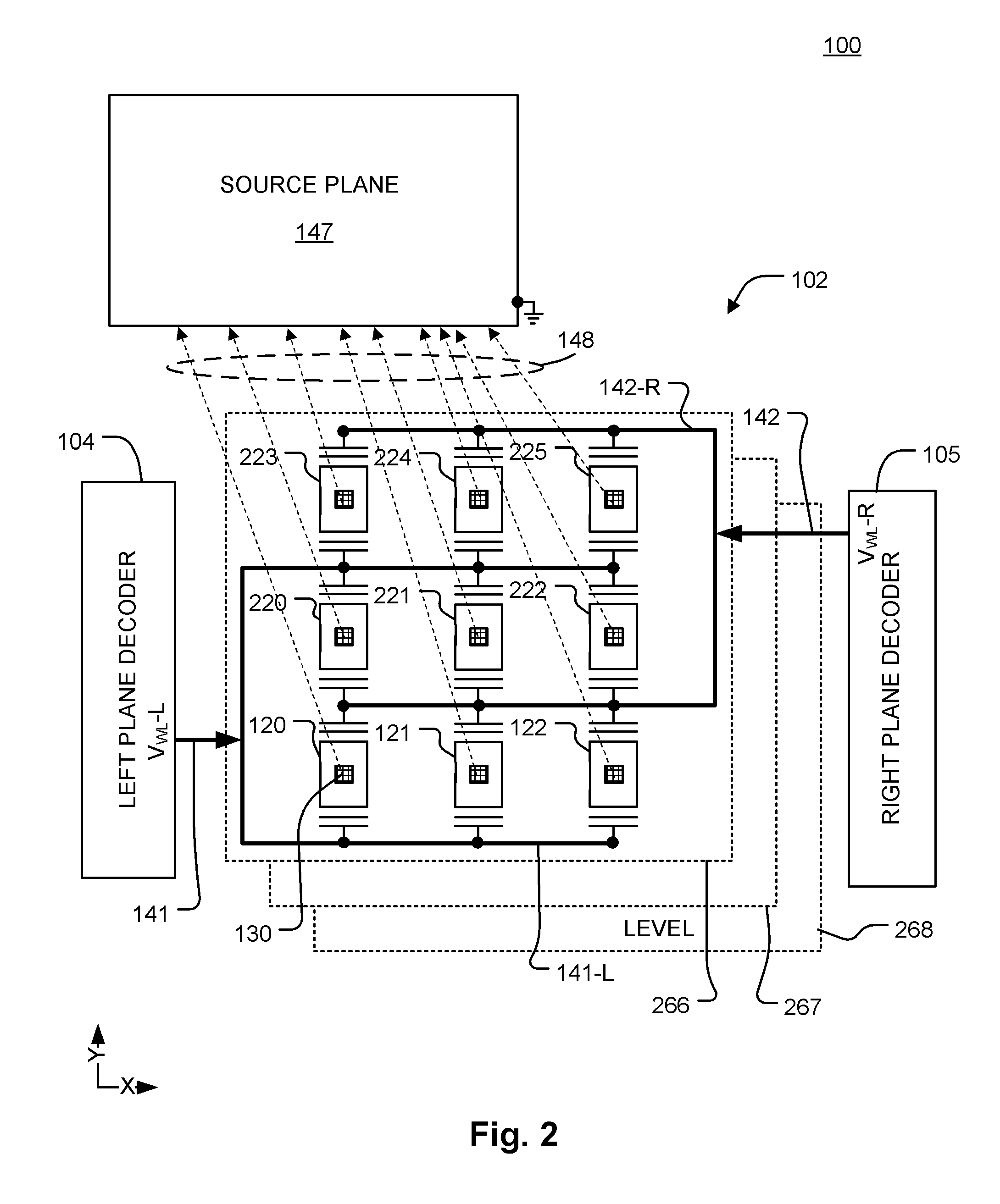

ActiveUS20110286283A1Few stepsHigh densitySolid-state devicesRead-only memoriesSource planePower flow

A 3D memory device is described which includes bottom and top memory cubes having respective arrays of vertical NAND string structures. A common source plane comprising a layer of conductive material is between the top and bottom memory cubes. The source plane is supplied a bias voltage such as ground, and is selectively coupled to an end of the vertical NAND string structures of the bottom and top memory cubes. Memory cells in a particular memory cube are read using current through the particular vertical NAND string between the source plane and a corresponding bit line coupled to another end of the particular vertical NAND string.

Owner:MACRONIX INT CO LTD

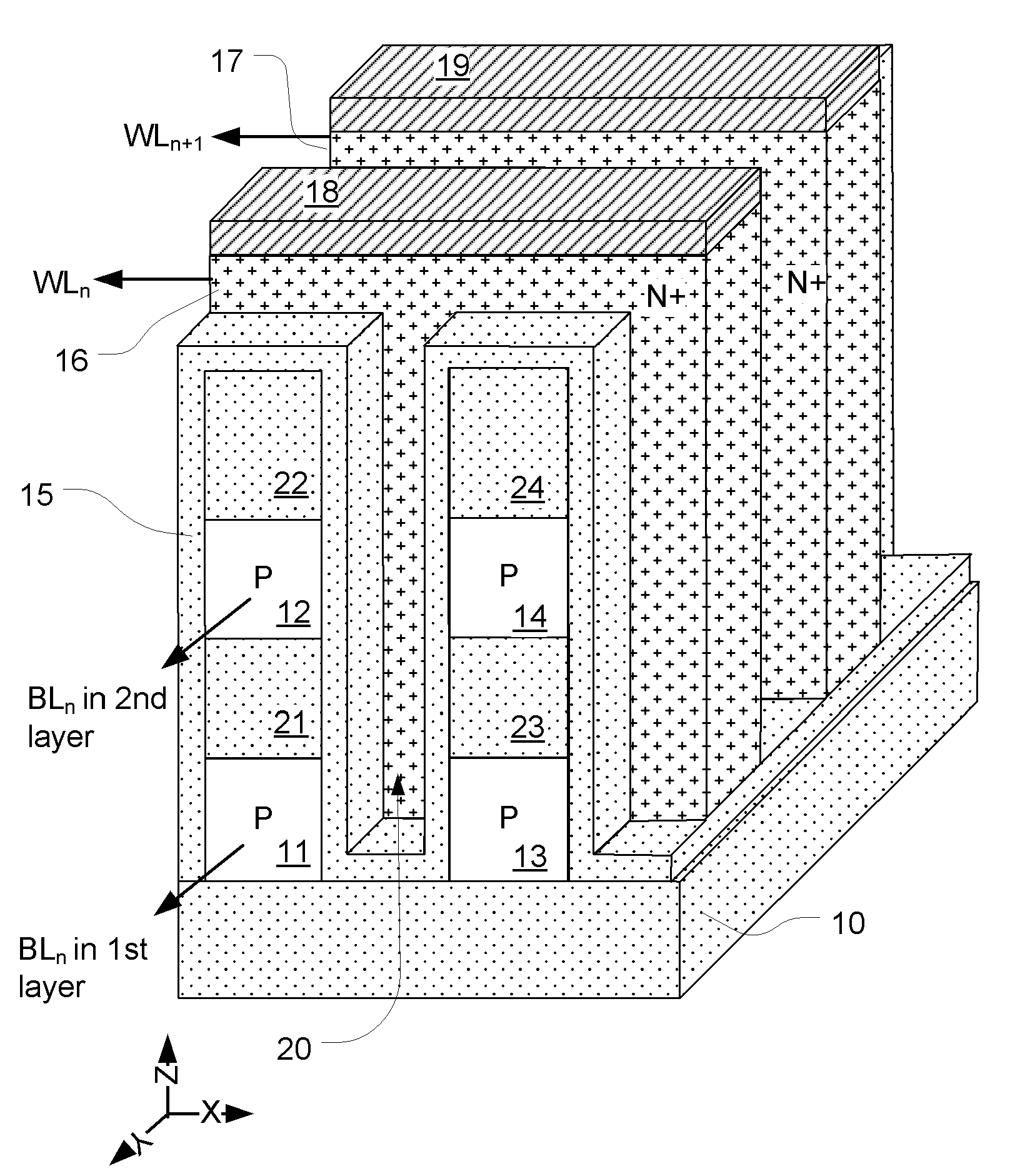

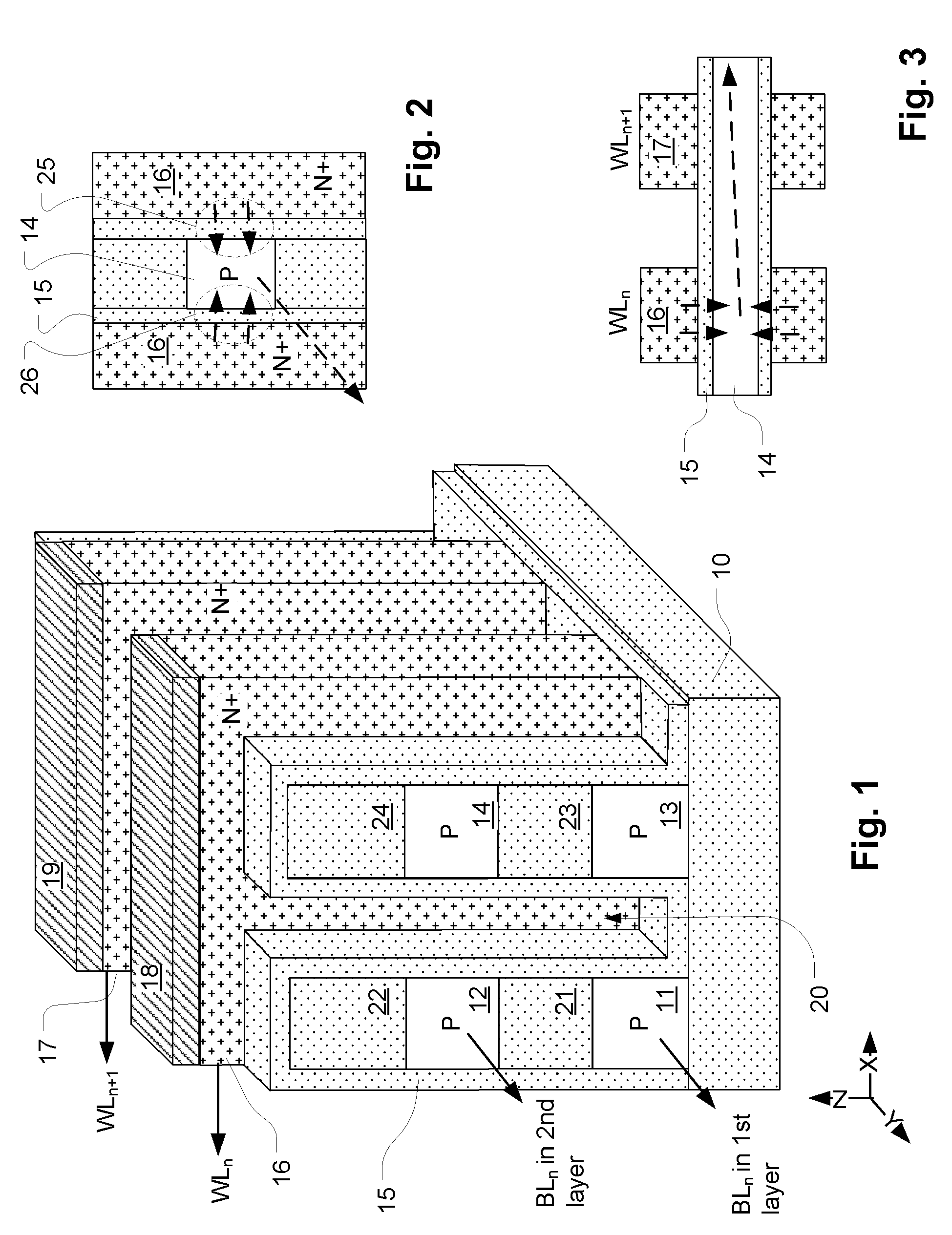

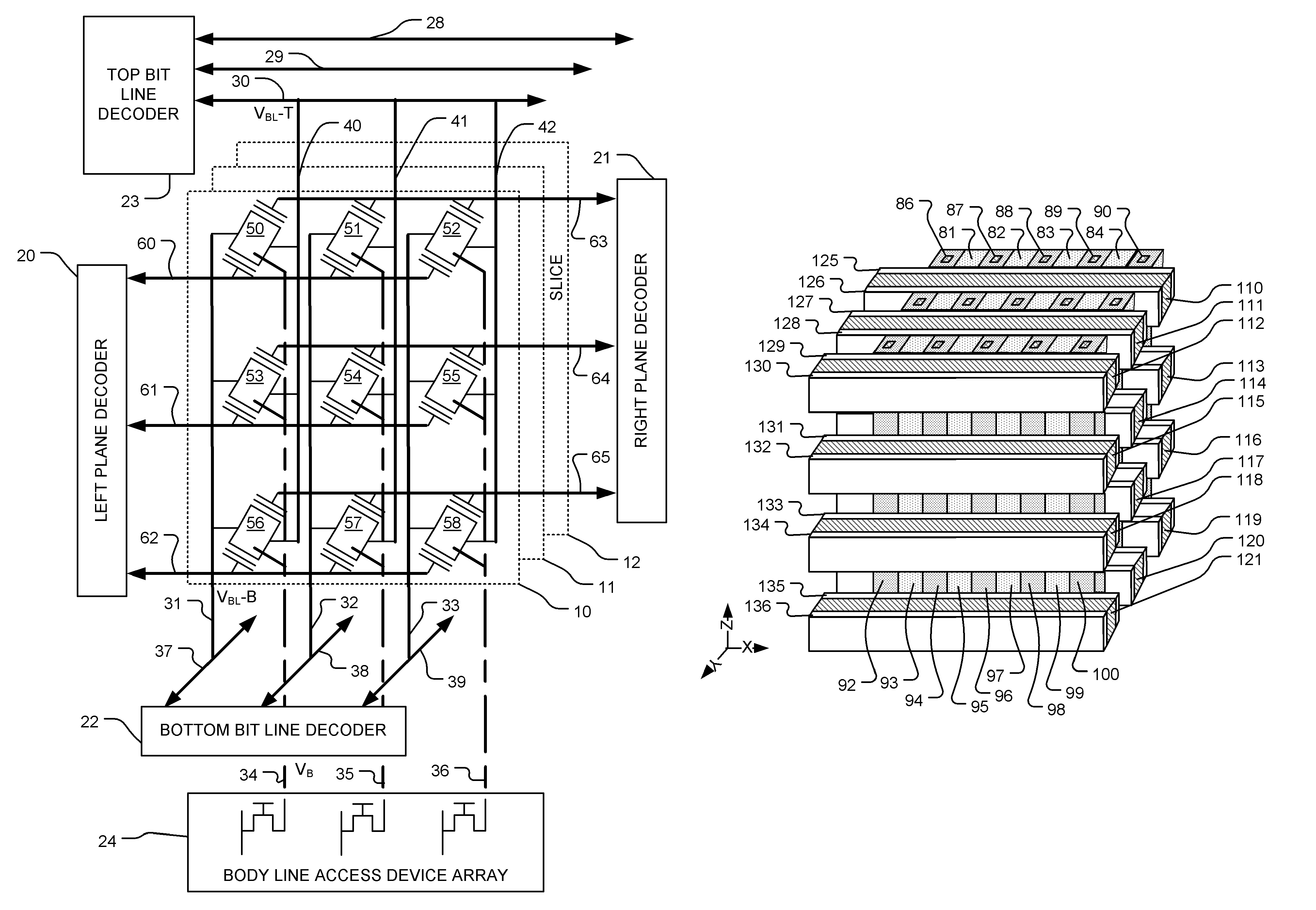

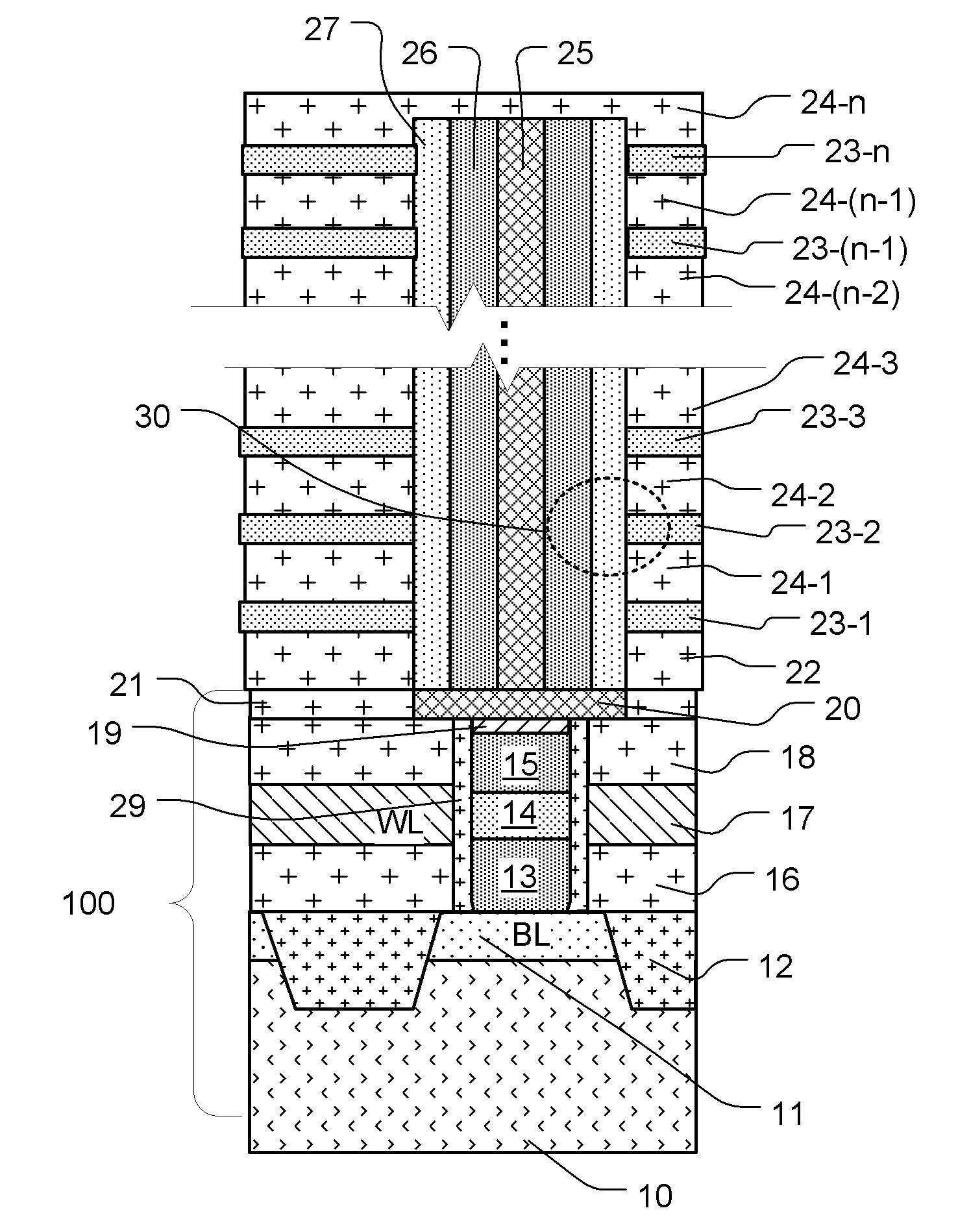

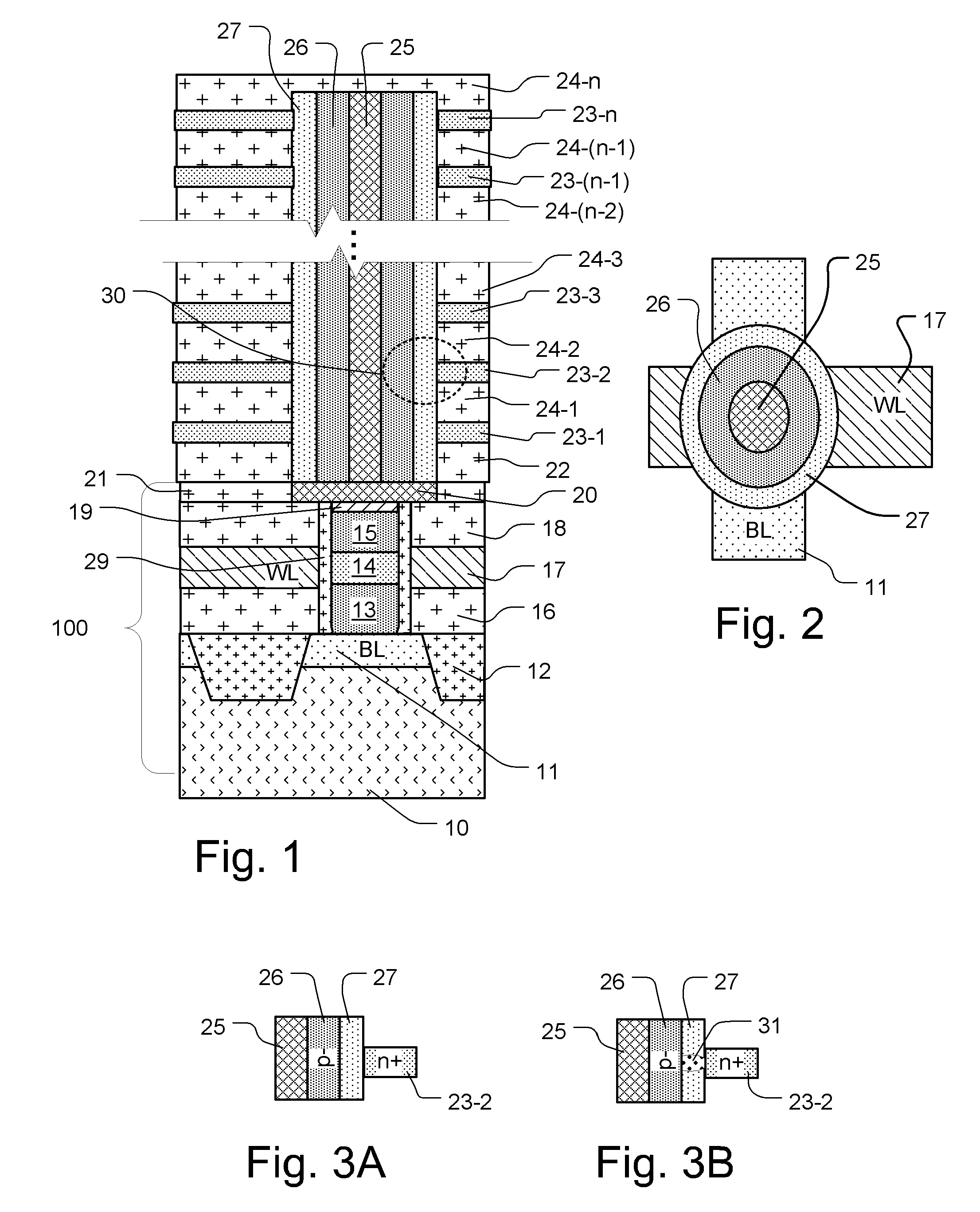

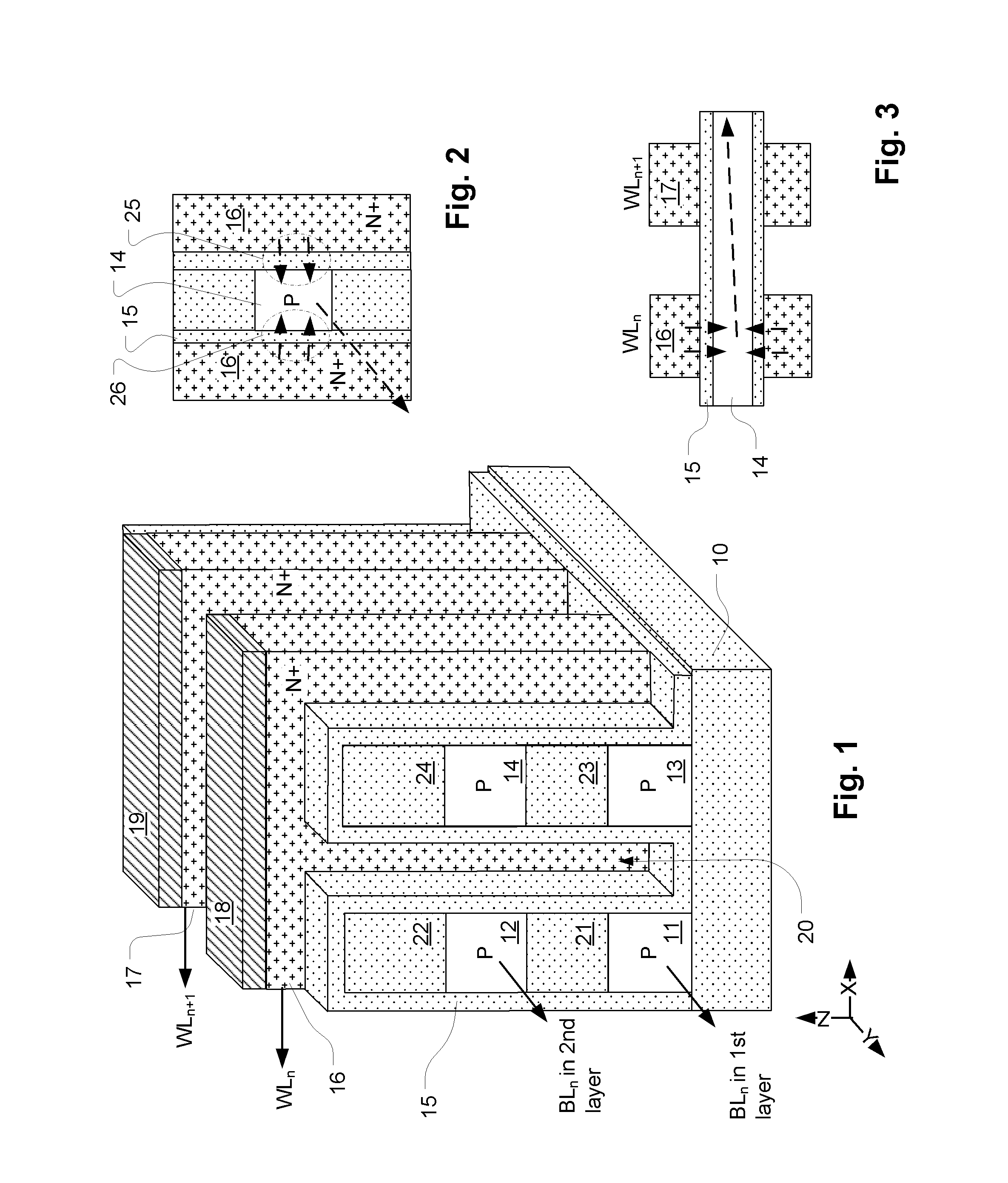

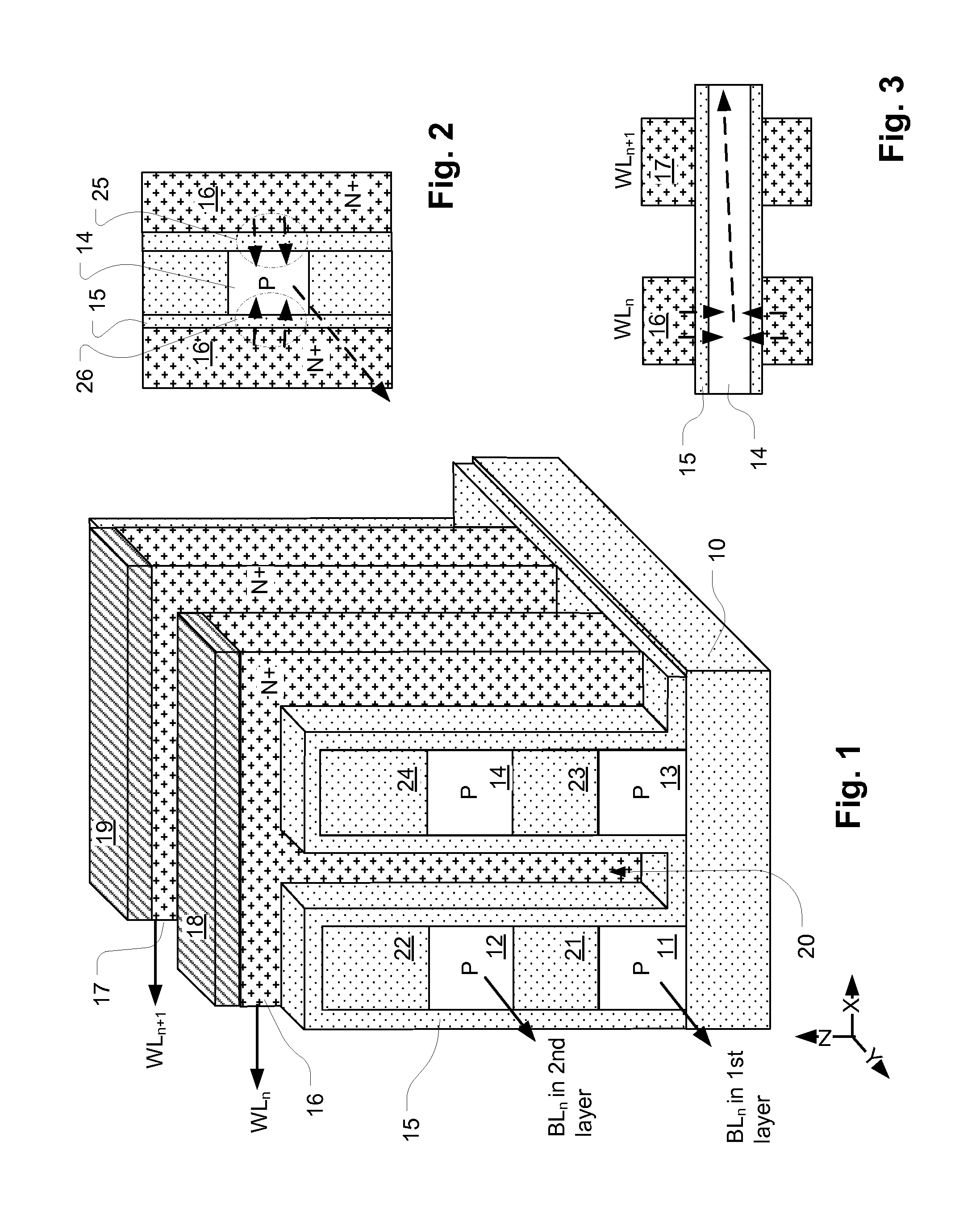

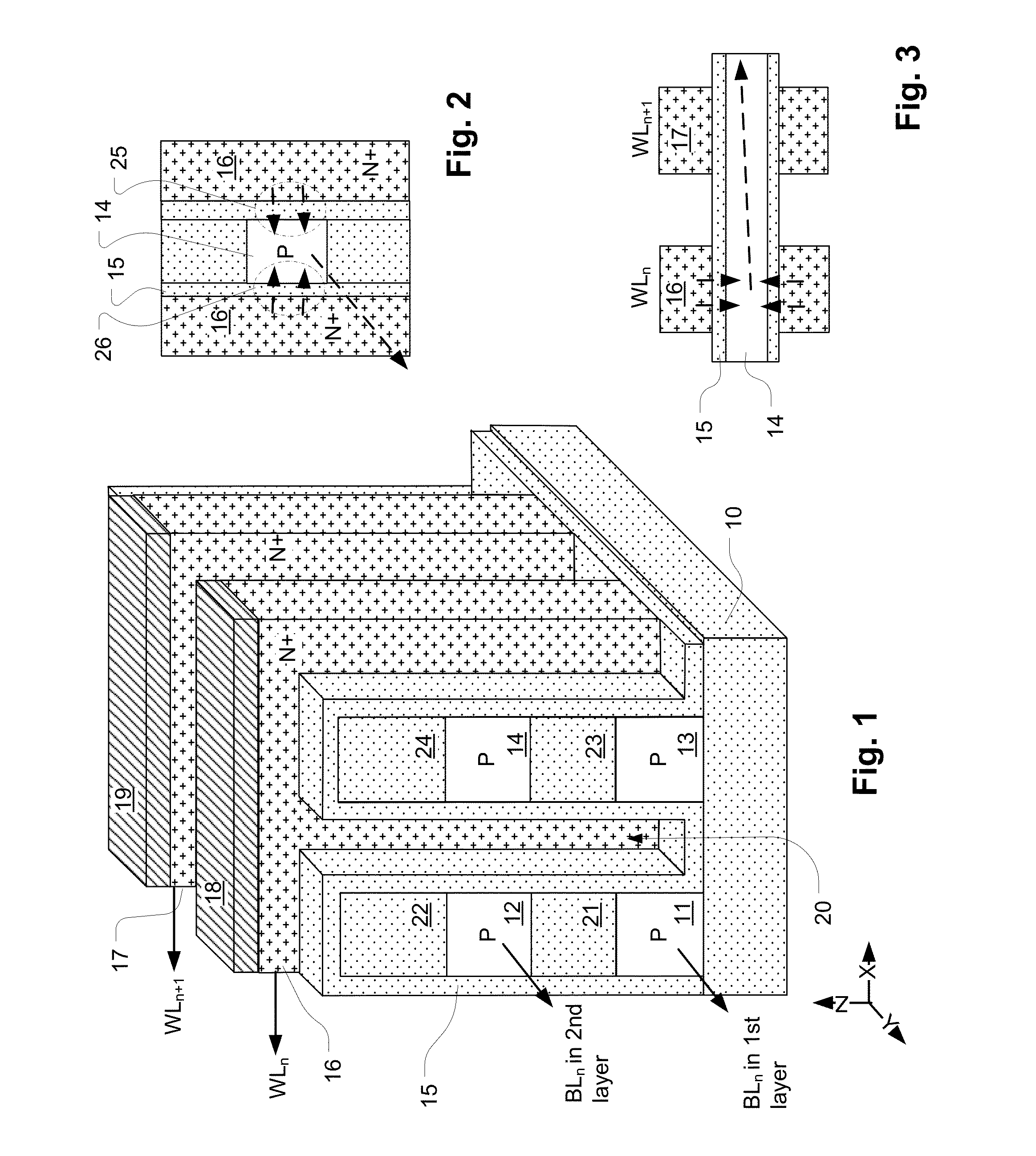

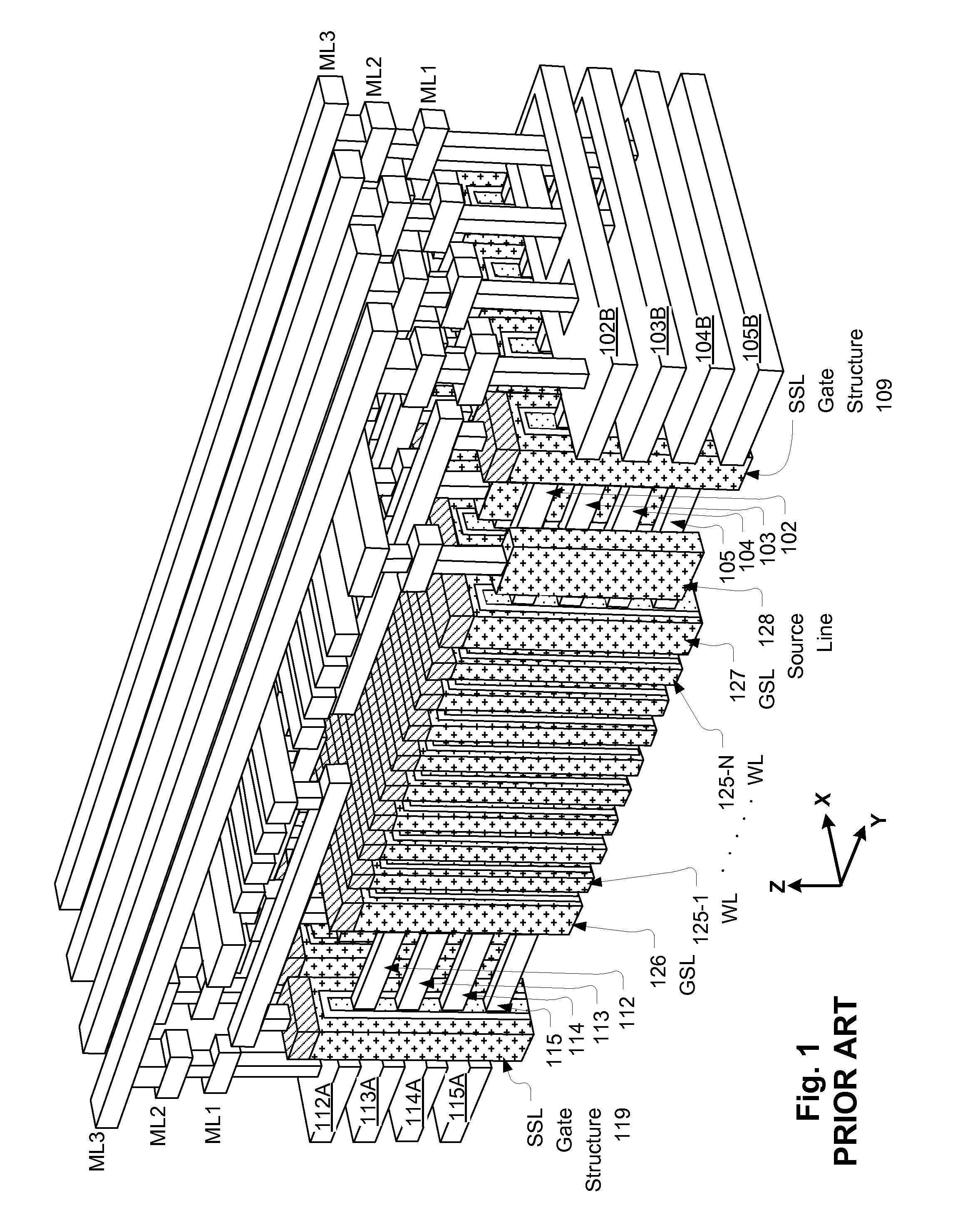

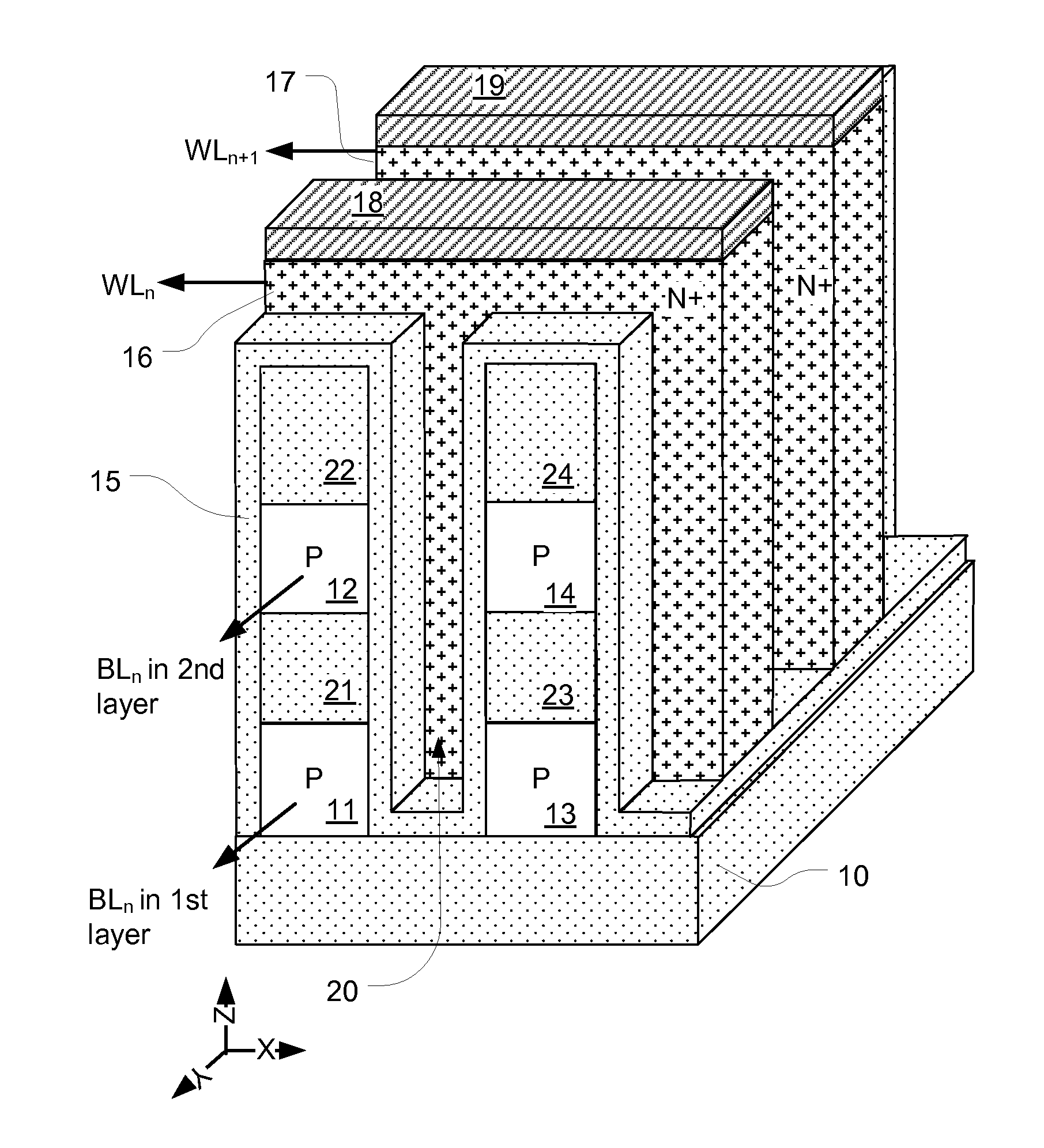

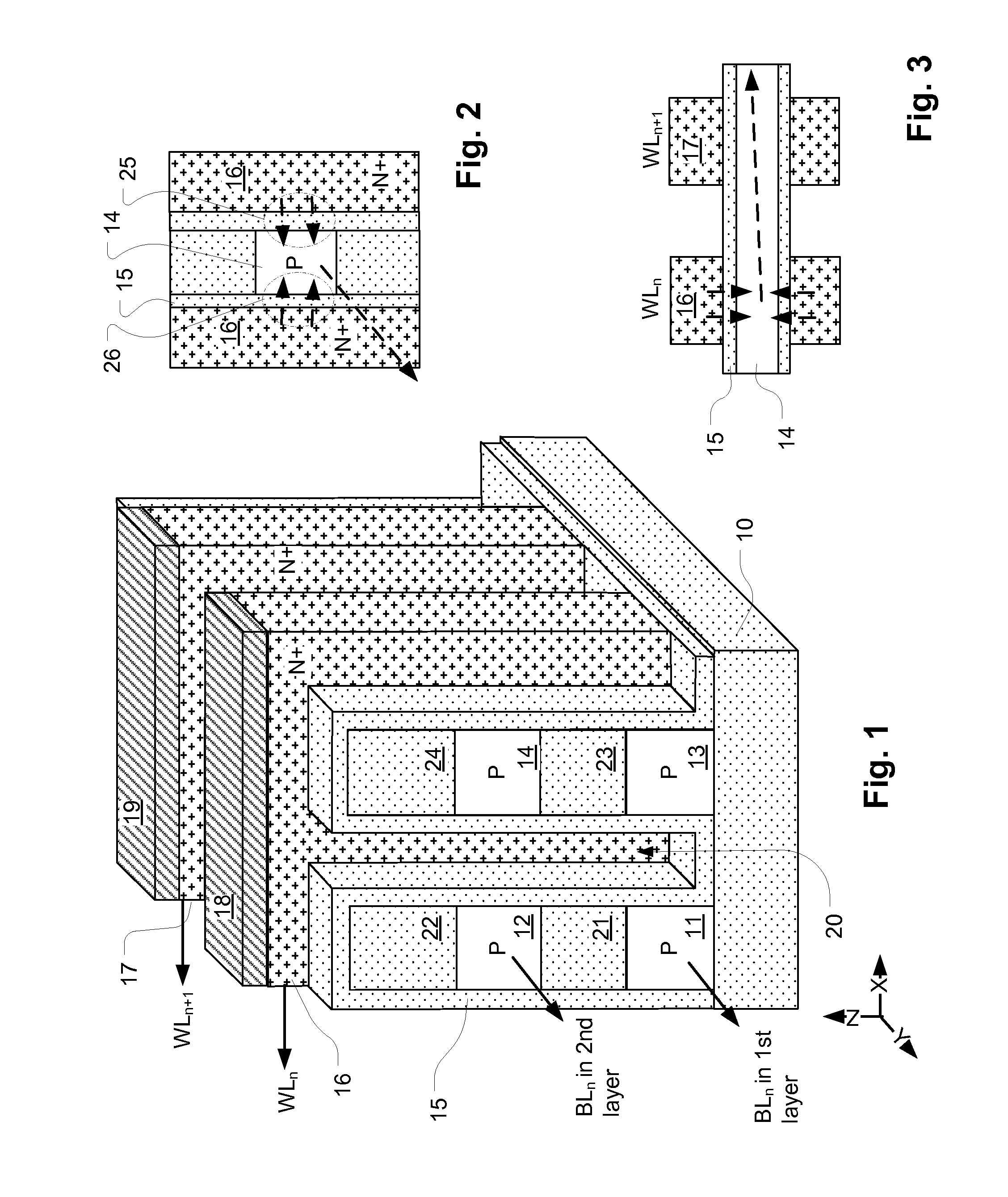

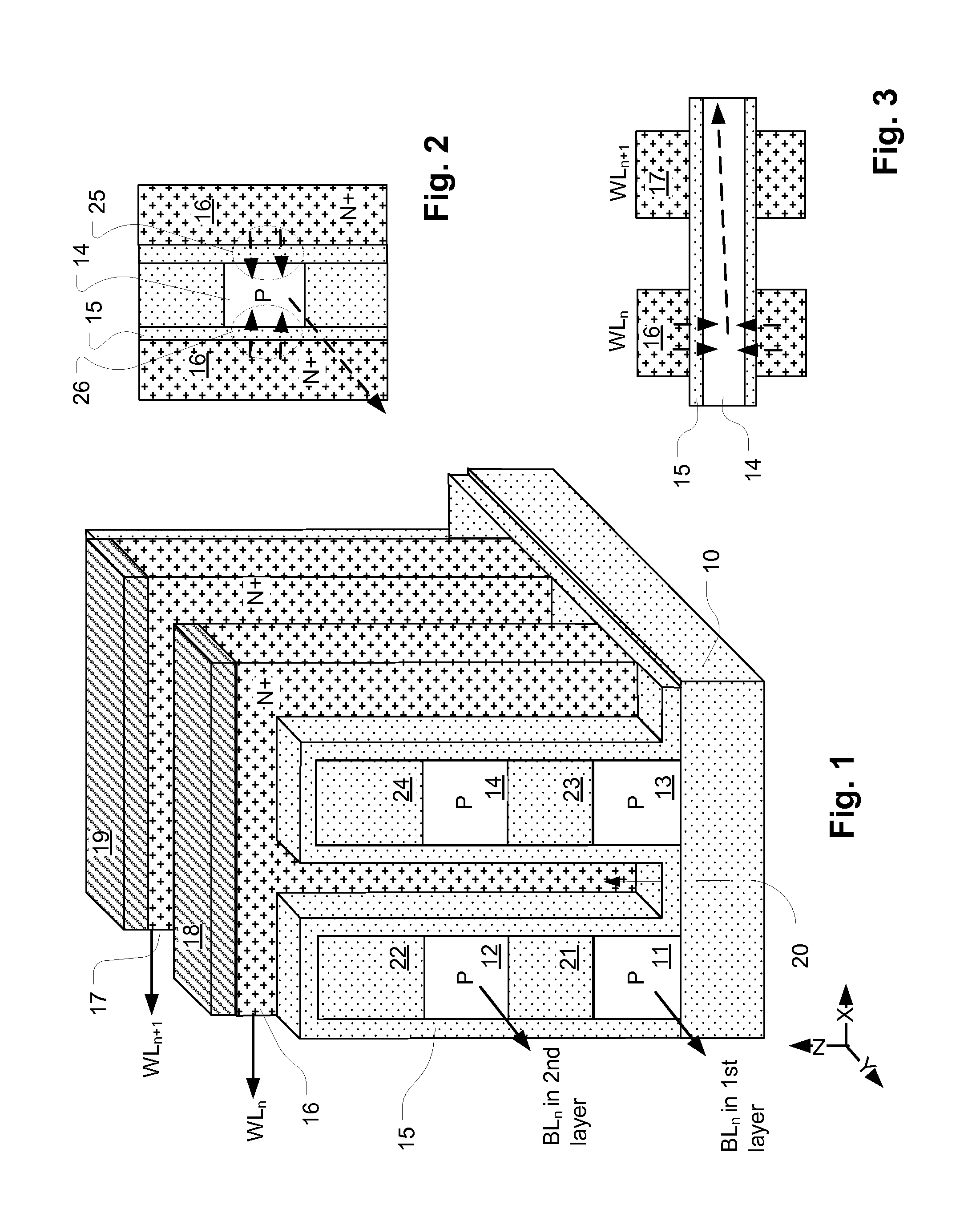

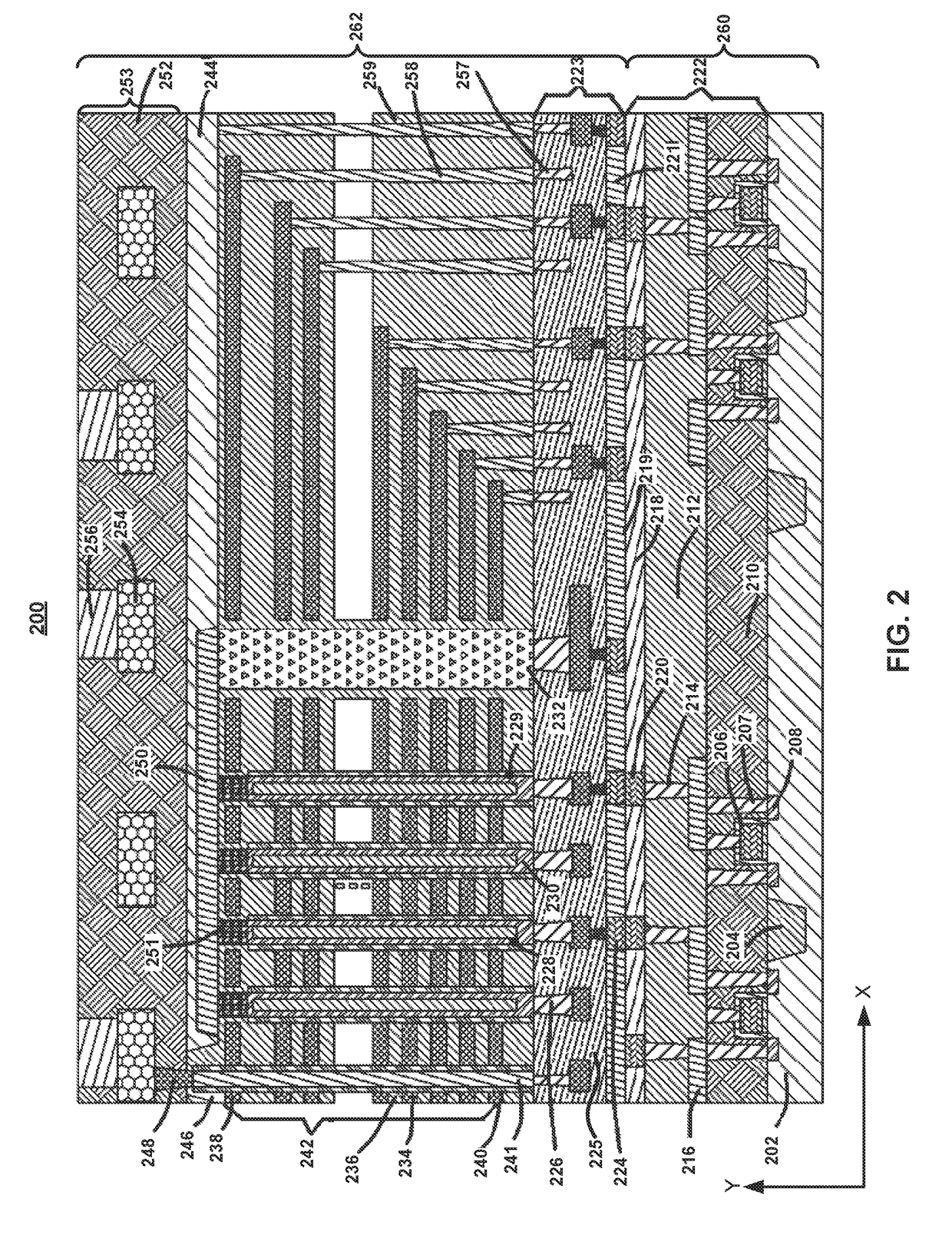

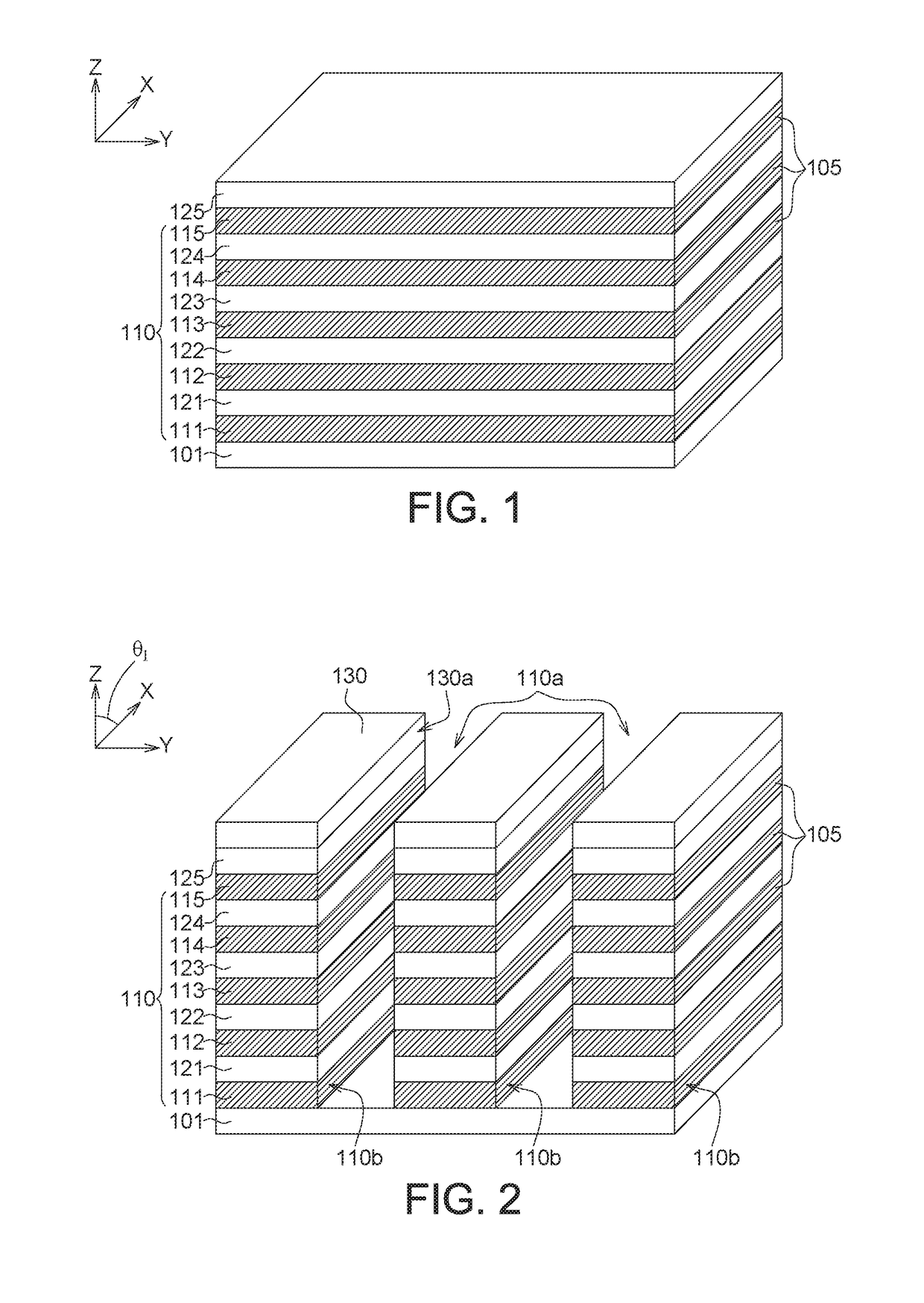

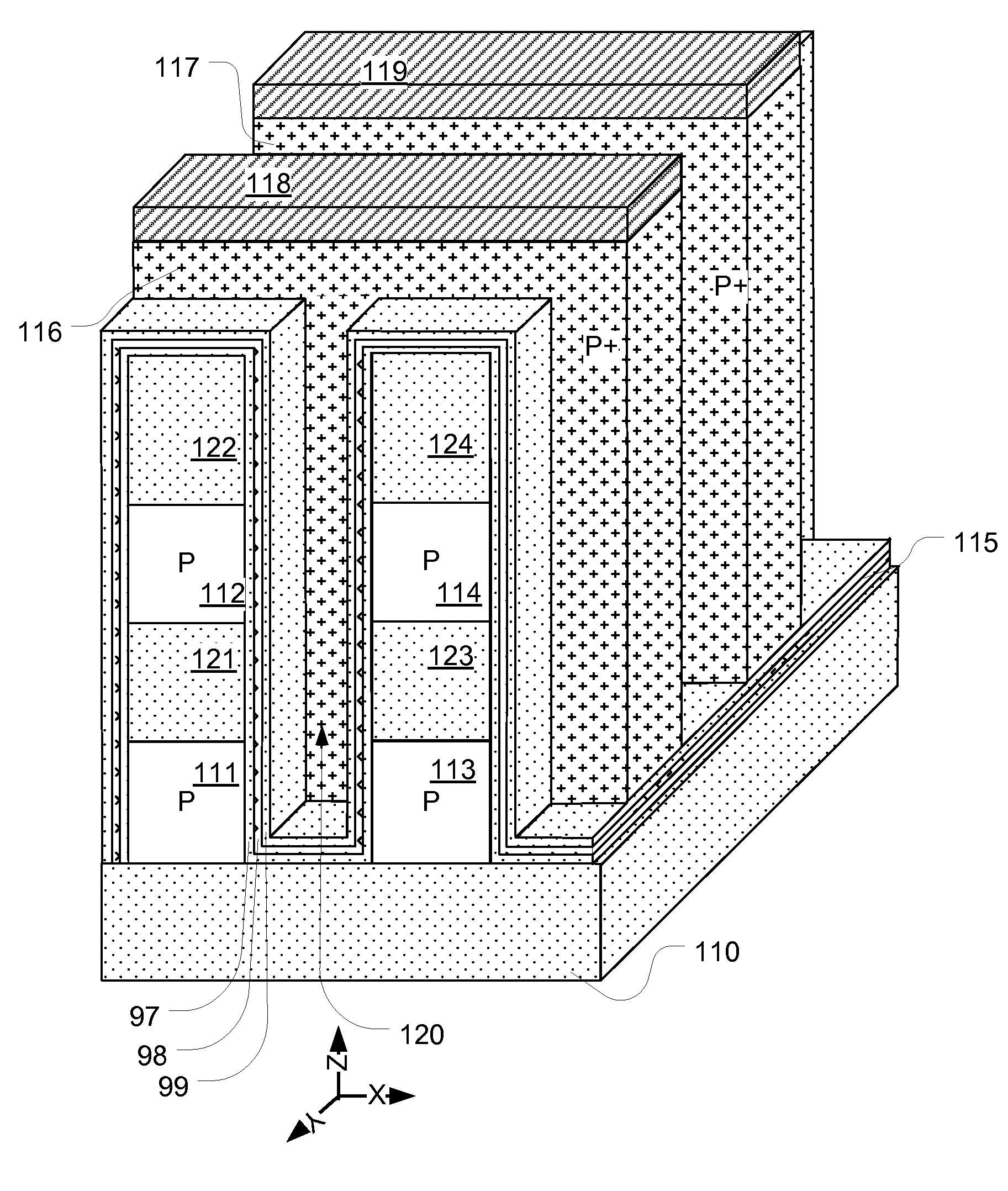

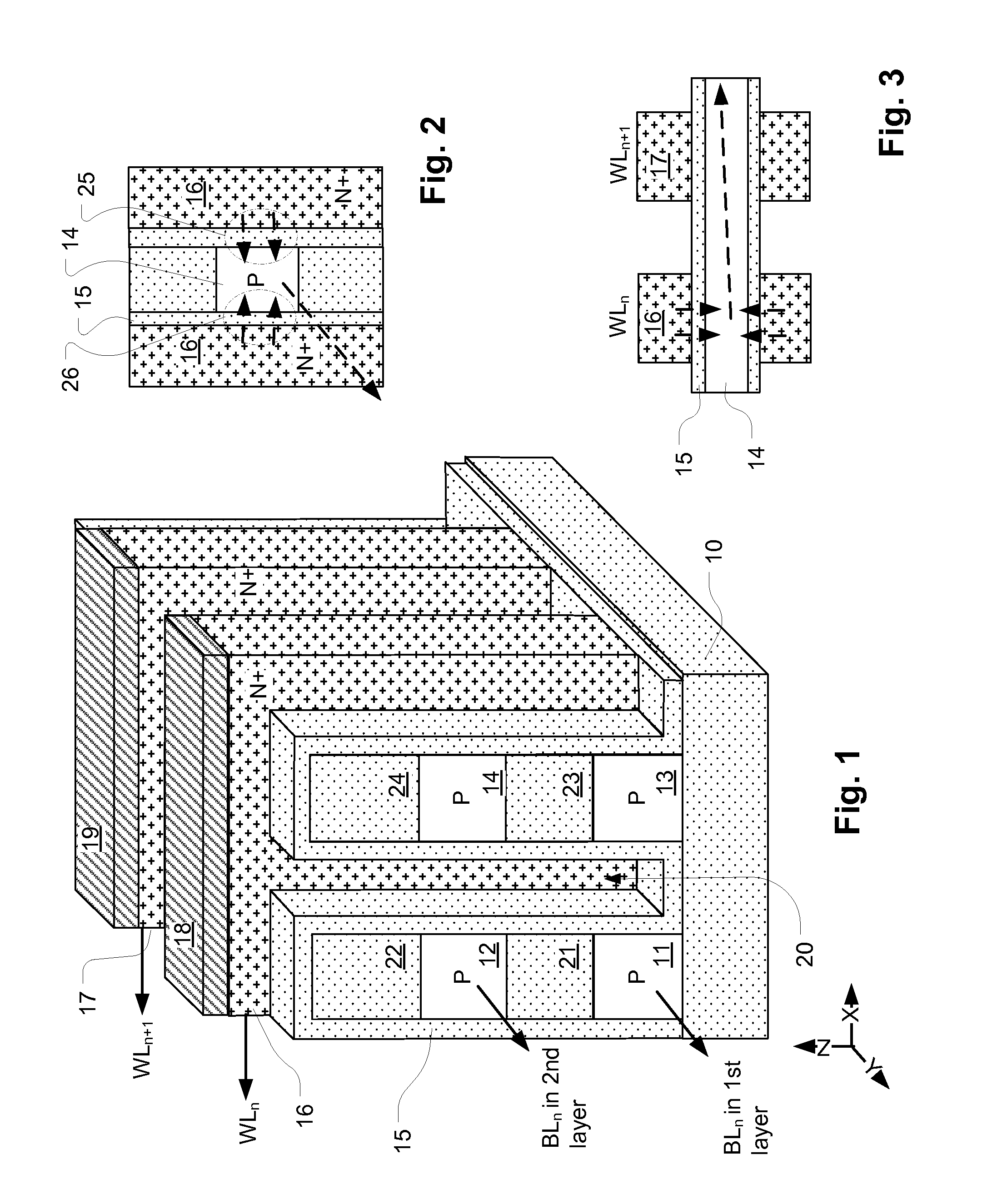

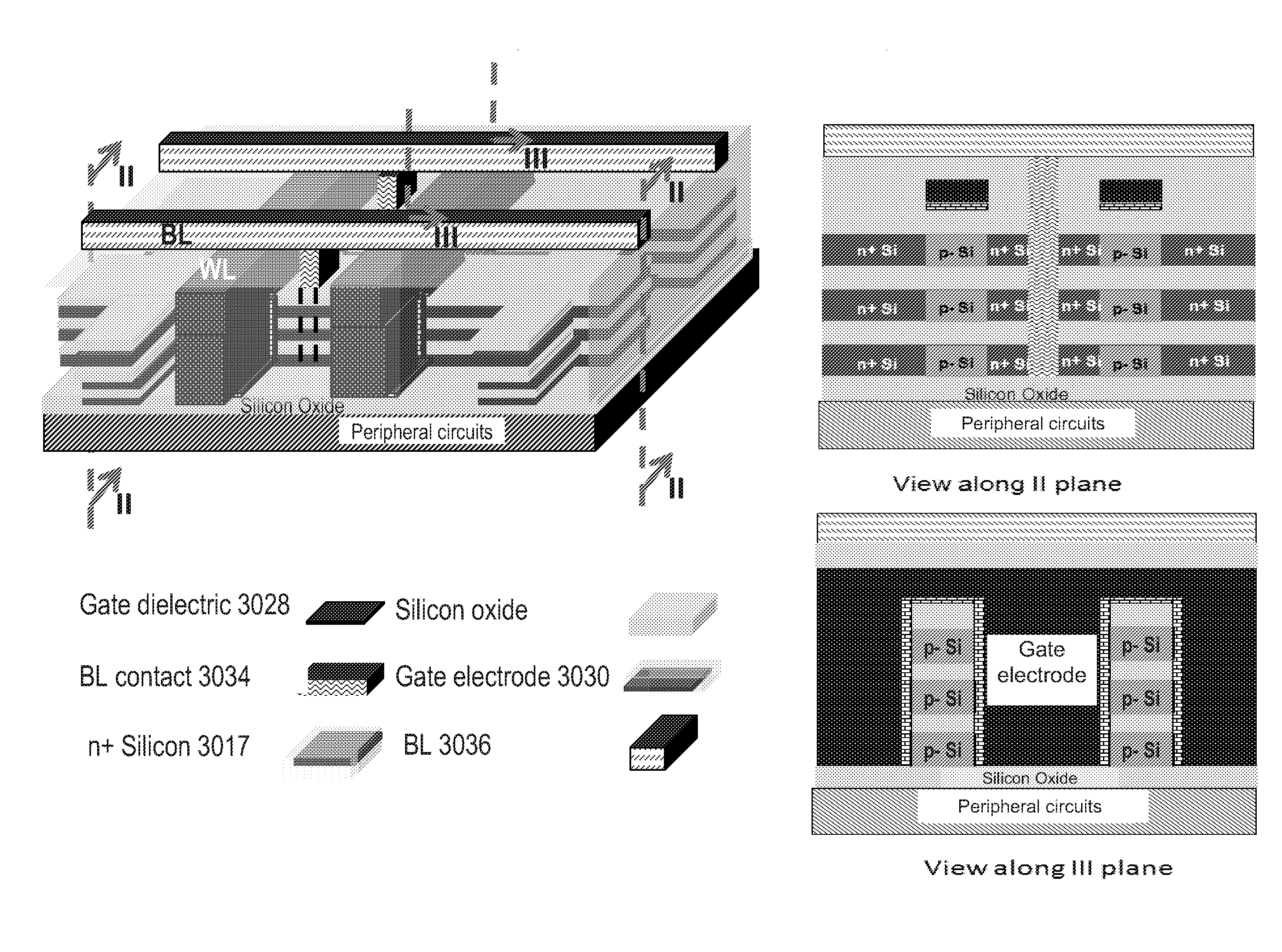

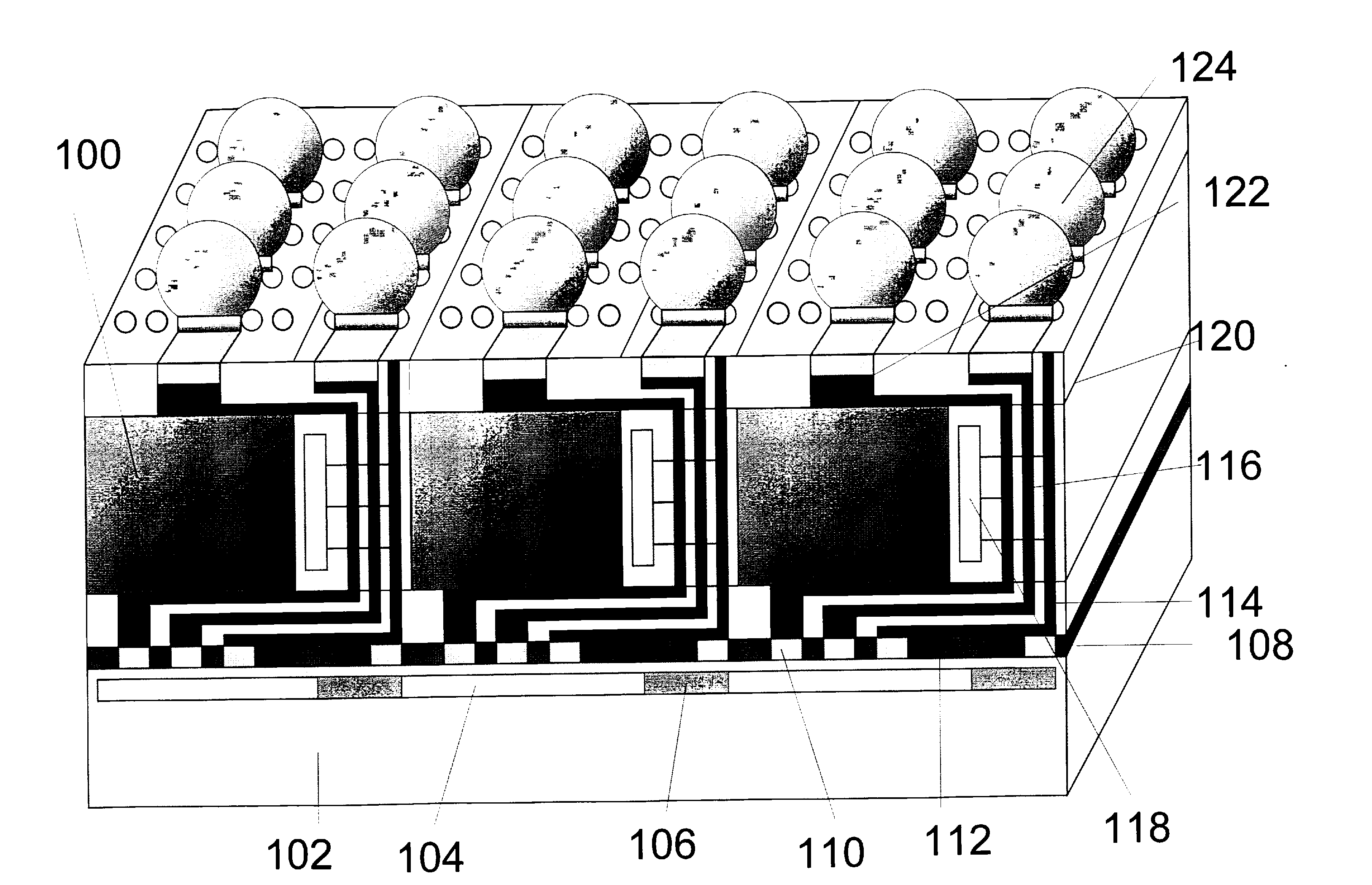

Integrated circuit self aligned 3D memory array and manufacturing method

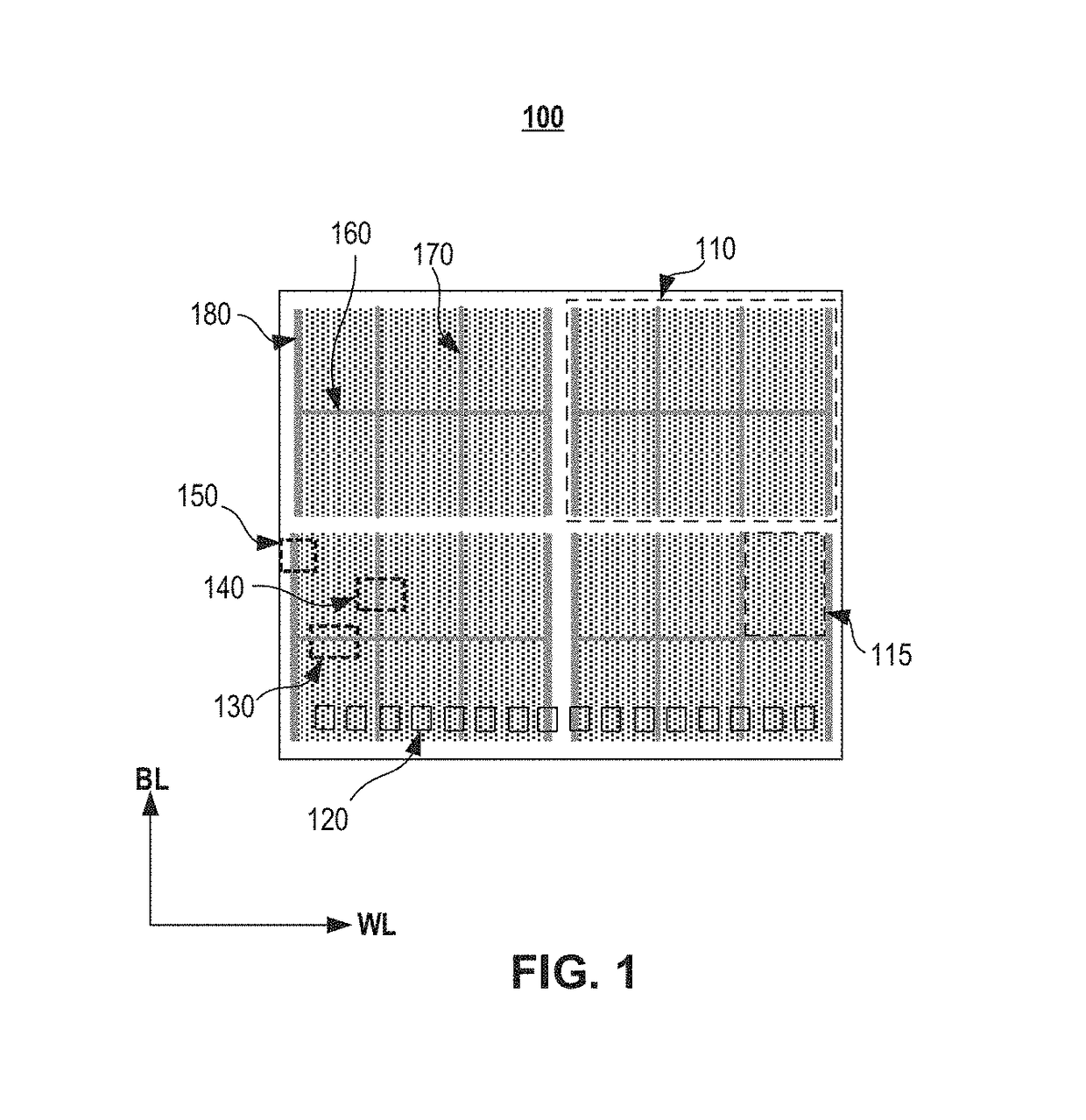

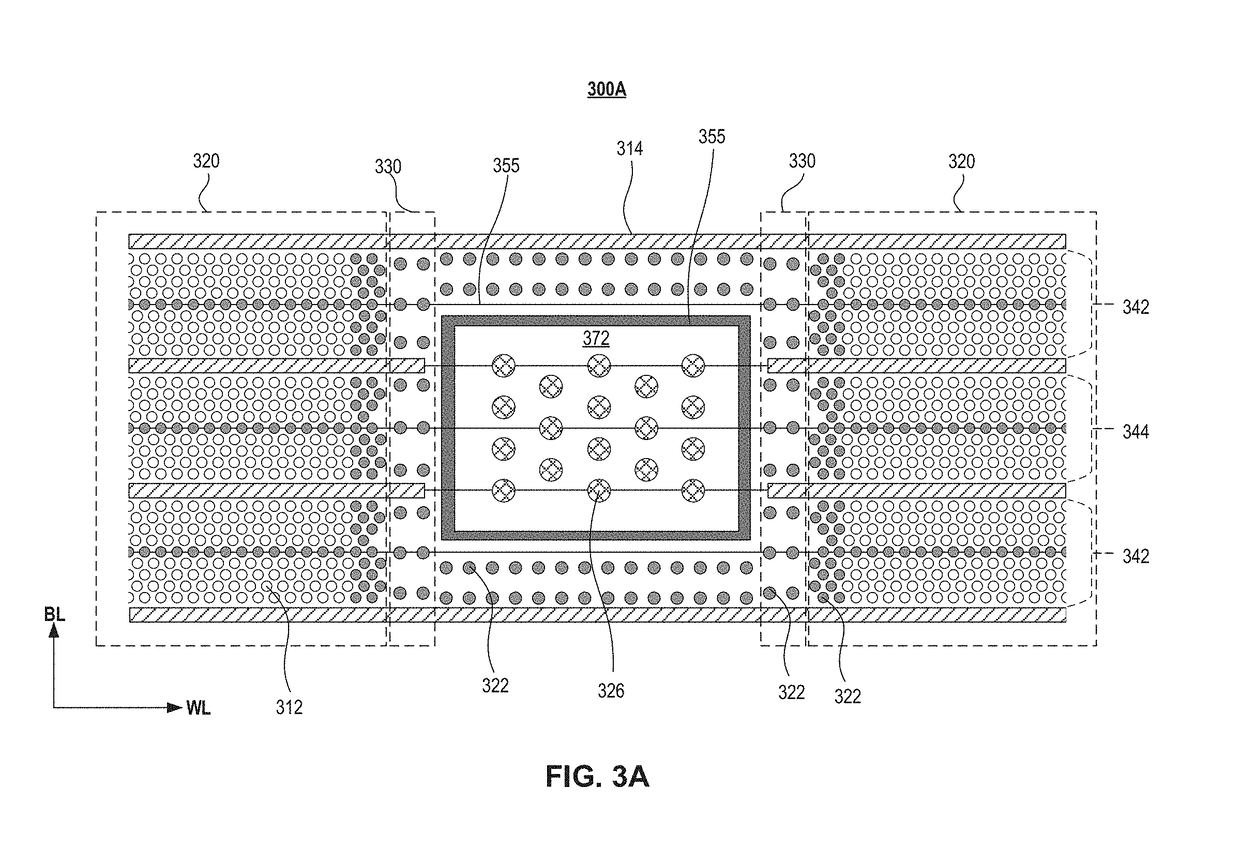

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

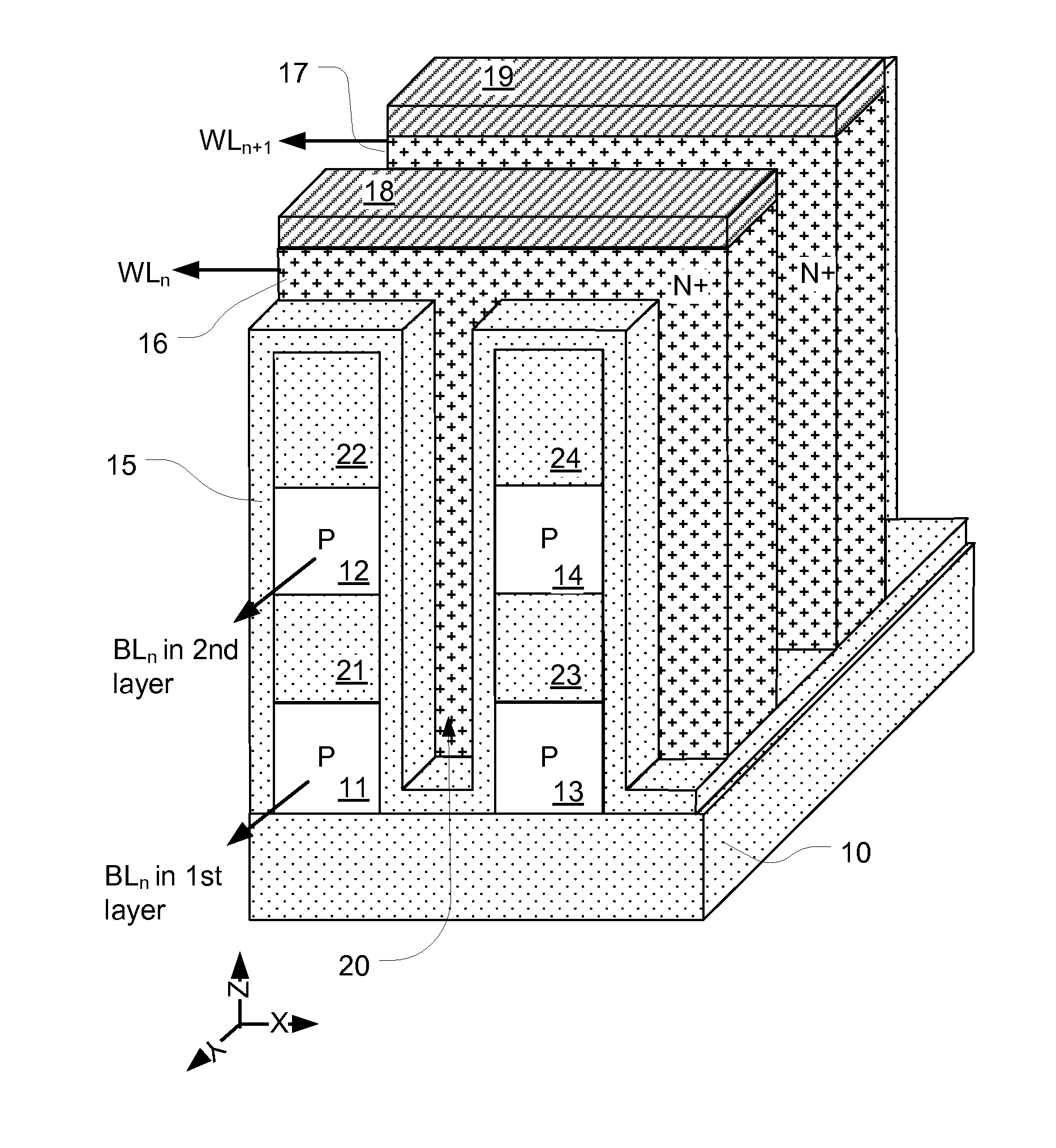

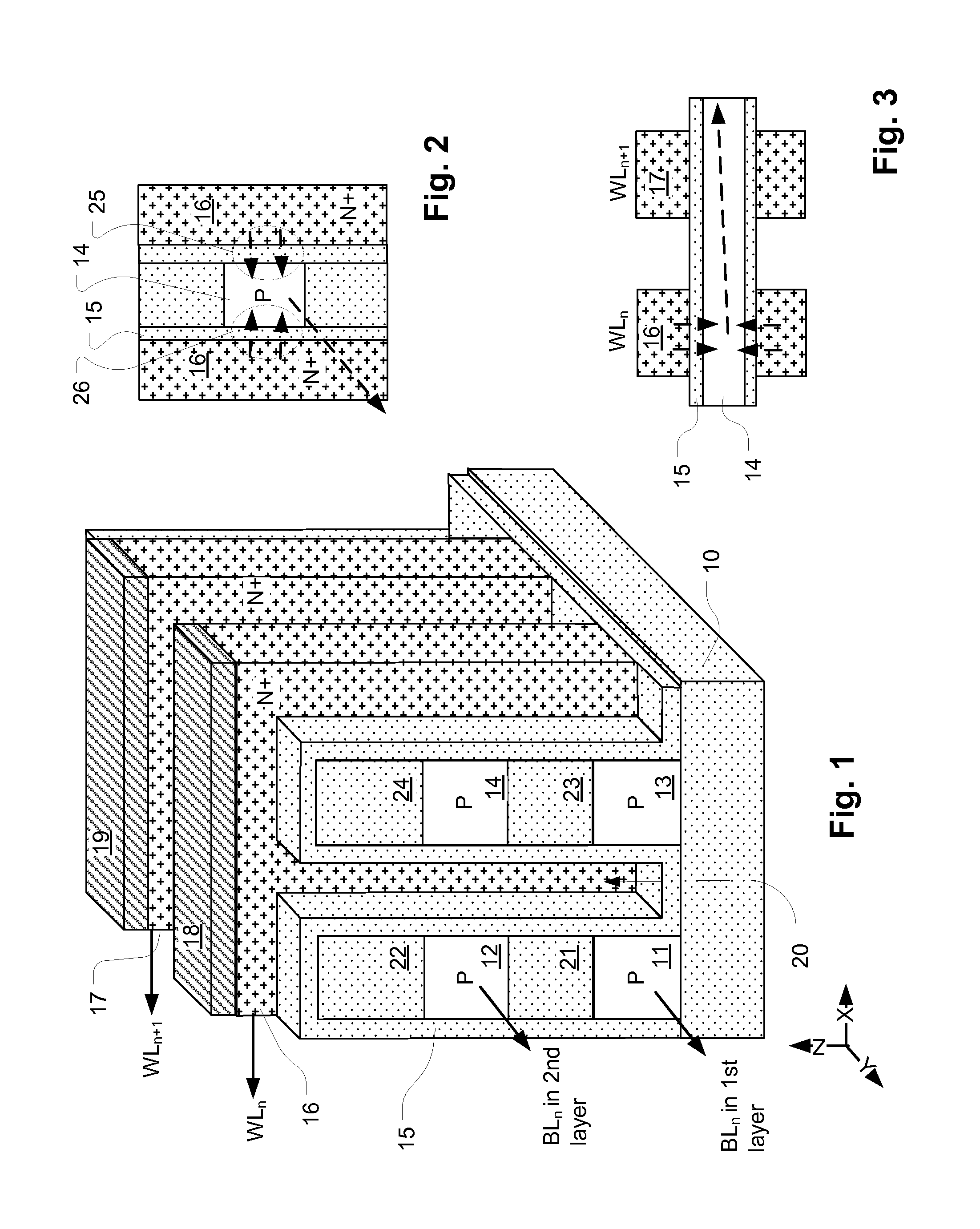

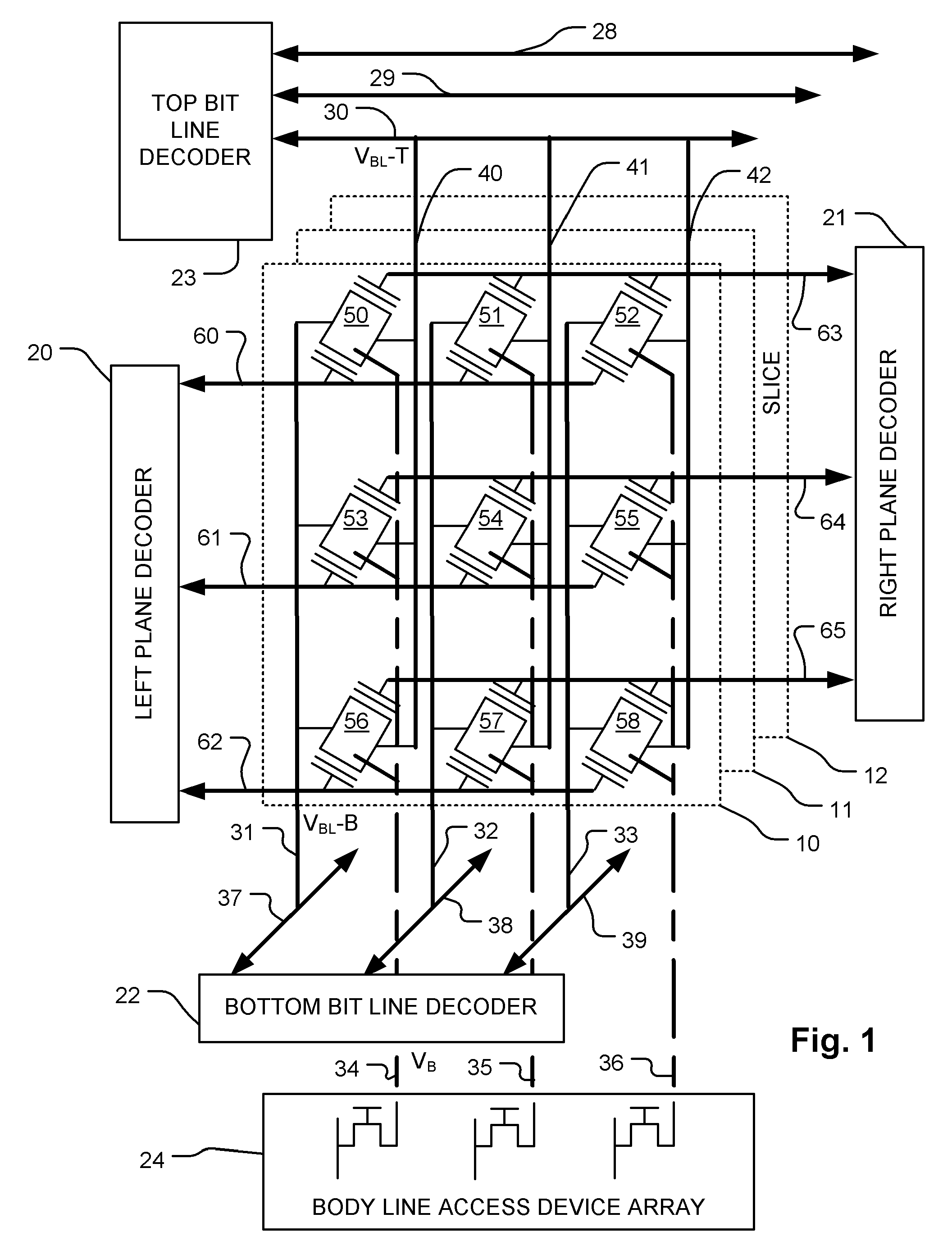

Memory Architecture of 3D NOR Array

A 3D memory device includes a plurality of ridge-shaped stacks of memory cells. Word lines are arranged over the stacks of memory cells. Bit lines structures are coupled to multiple locations along the stacks of memory cells. Source line structures are coupled to multiple locations along each of the semiconductor material strips of the stacks. The bit line structures and the source line structures are between adjacent ones of the word lines.

Owner:MACRONIX INT CO LTD

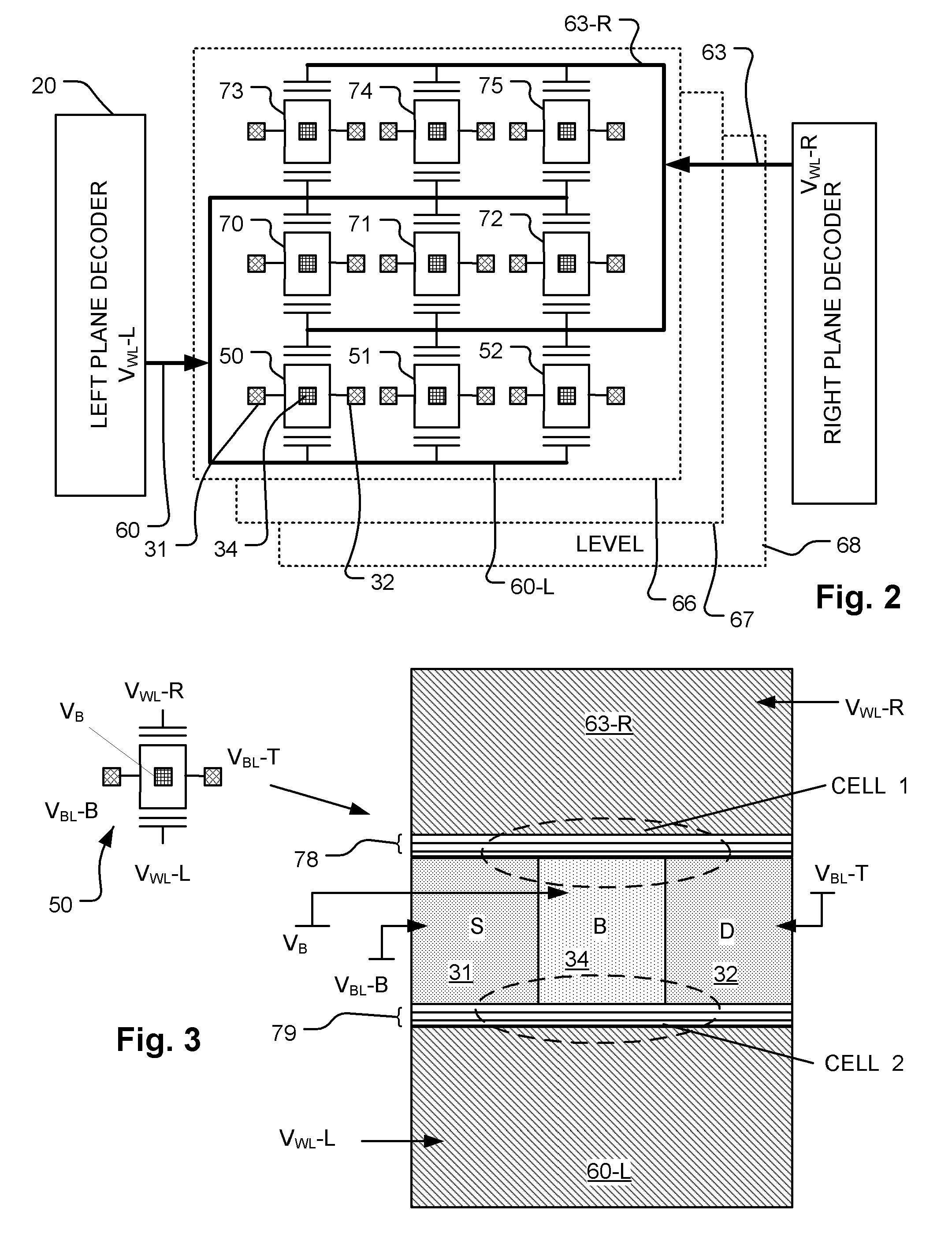

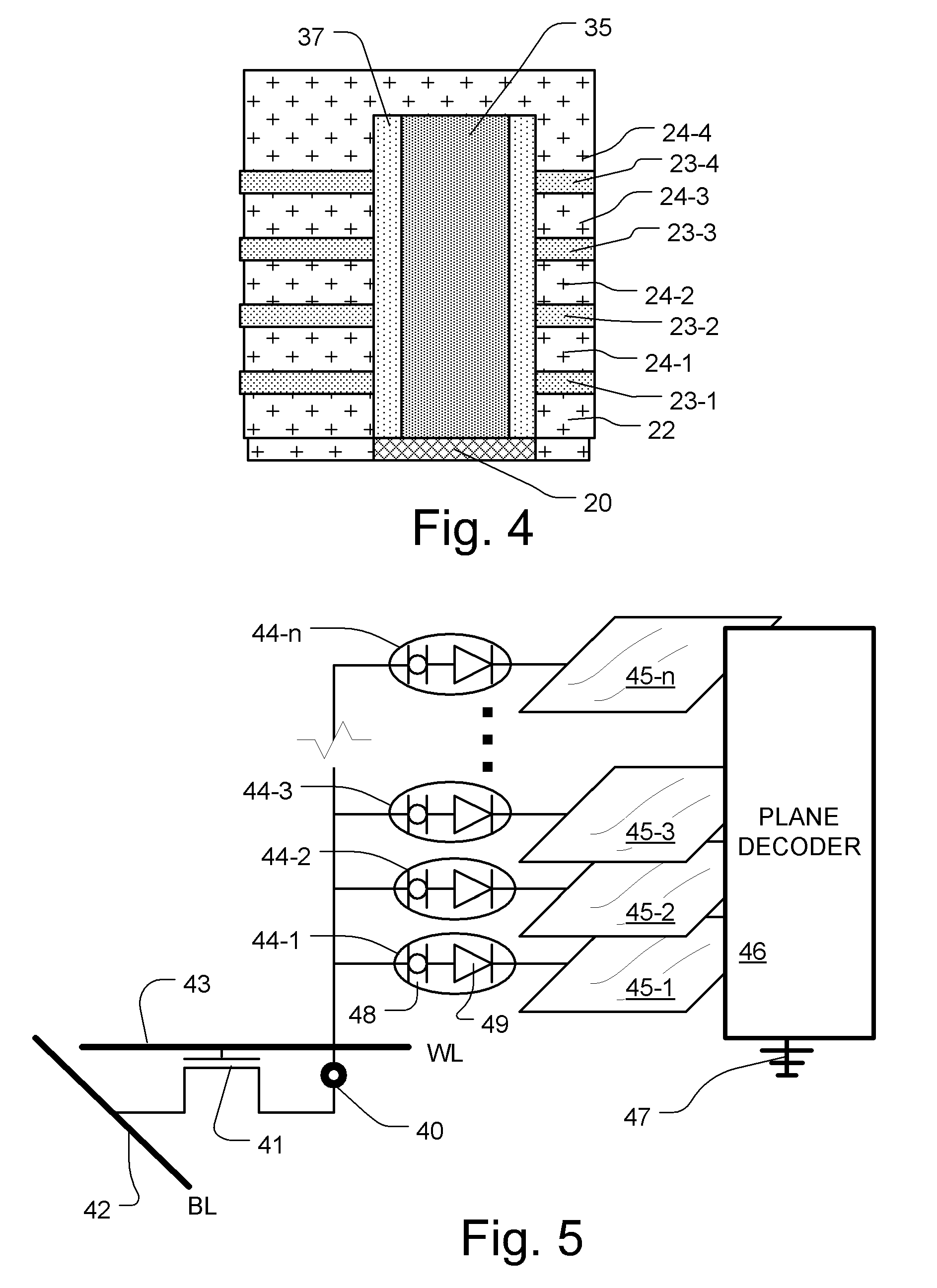

3D memory array arranged for FN tunneling program and erase

A 3D memory device includes an array of semiconductor body pillars and bit line pillars, dielectric charge trapping structures, and a plurality of levels of word line structures arranged orthogonally to the array of semiconductor body pillars and bit line pillars. The semiconductor body pillars have corresponding bit line pillars on opposing first and second sides, providing source and drain terminals. The semiconductor body pillars have first and second channel surfaces on opposing third and fourth sides. Dielectric charge trapping structures overlie the first and second channel surfaces, providing data storage sites on two sides of each semiconductor body pillar in each level of the 3D array. The device can be operated as a 3D AND-decoded flash memory.

Owner:MACRONIX INT CO LTD

3D memory array with vertical transistor

InactiveUS20120074466A1High densityImprove fill factorTransistorSolid-state devicesComputer science3d memory

A memory array includes a base circuitry layer and a plurality of memory array layers stacked sequentially to form the memory array. Each memory array layer is electrically coupled to the base circuitry layer. Each memory array layer includes a plurality of memory units. Each memory unit includes a vertical pillar transistor electrically coupled to a memory cell.

Owner:SEAGATE TECH LLC

Integrated circuit 3D memory array and manufacturing method

ActiveUS20100270593A1Reduced footprintTransistorSemiconductor/solid-state device detailsBiomedical engineering3d memory

A 3D memory device is based on an array of electrode pillars and a plurality of electrode planes that intersect the electrode pillars at interface regions that include memory elements that comprise a programmable element and a rectifier. The electrode pillars can be selected using two-dimensional decoding, and the plurality of electrode planes can be selected using decoding on a third dimension.

Owner:MACRONIX INT CO LTD

Integrated circuit self aligned 3D memory array and manufacturing method

ActiveUS20100226195A1Semiconductor/solid-state device detailsSolid-state devicesBit lineAudio power amplifier

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

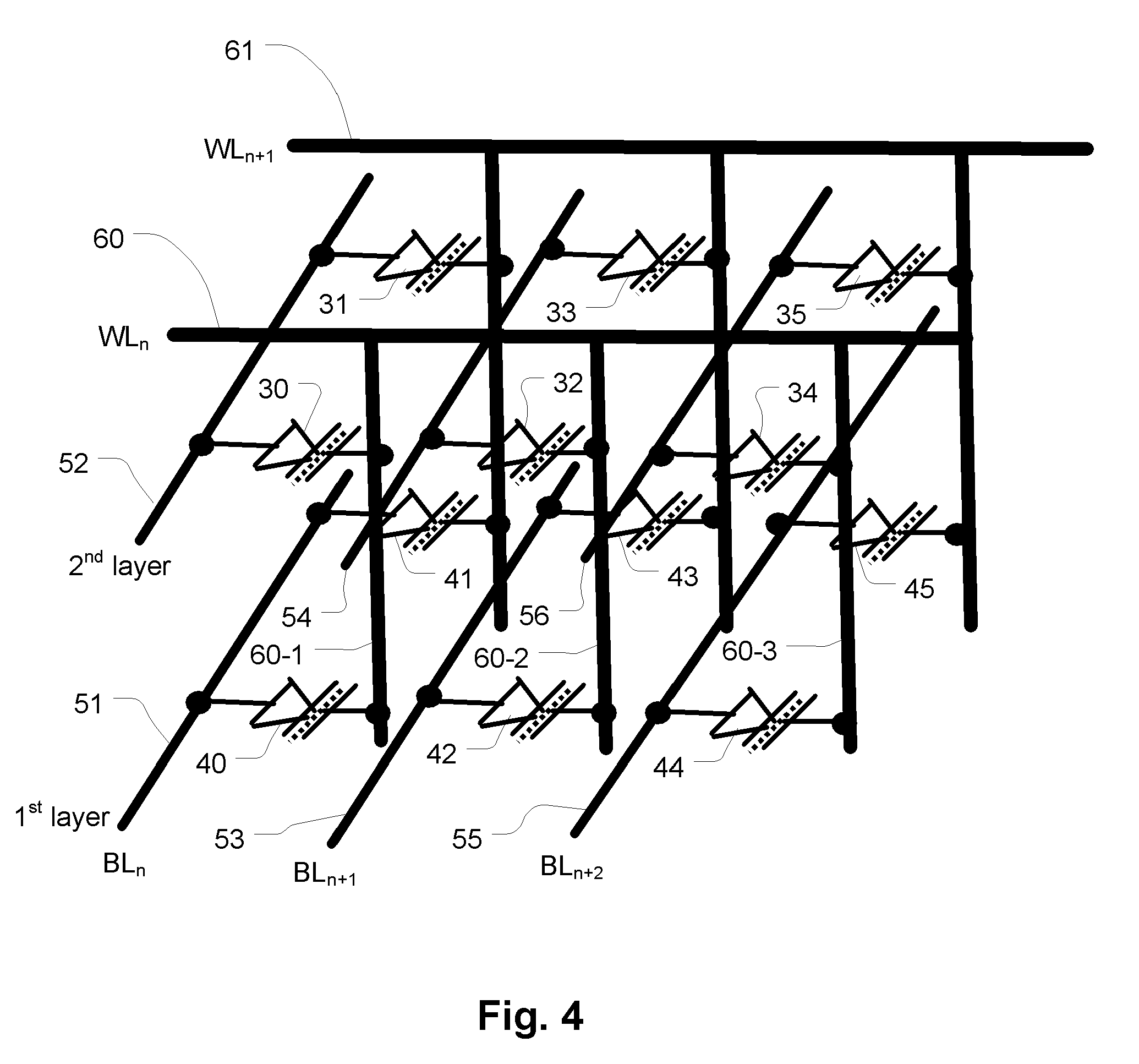

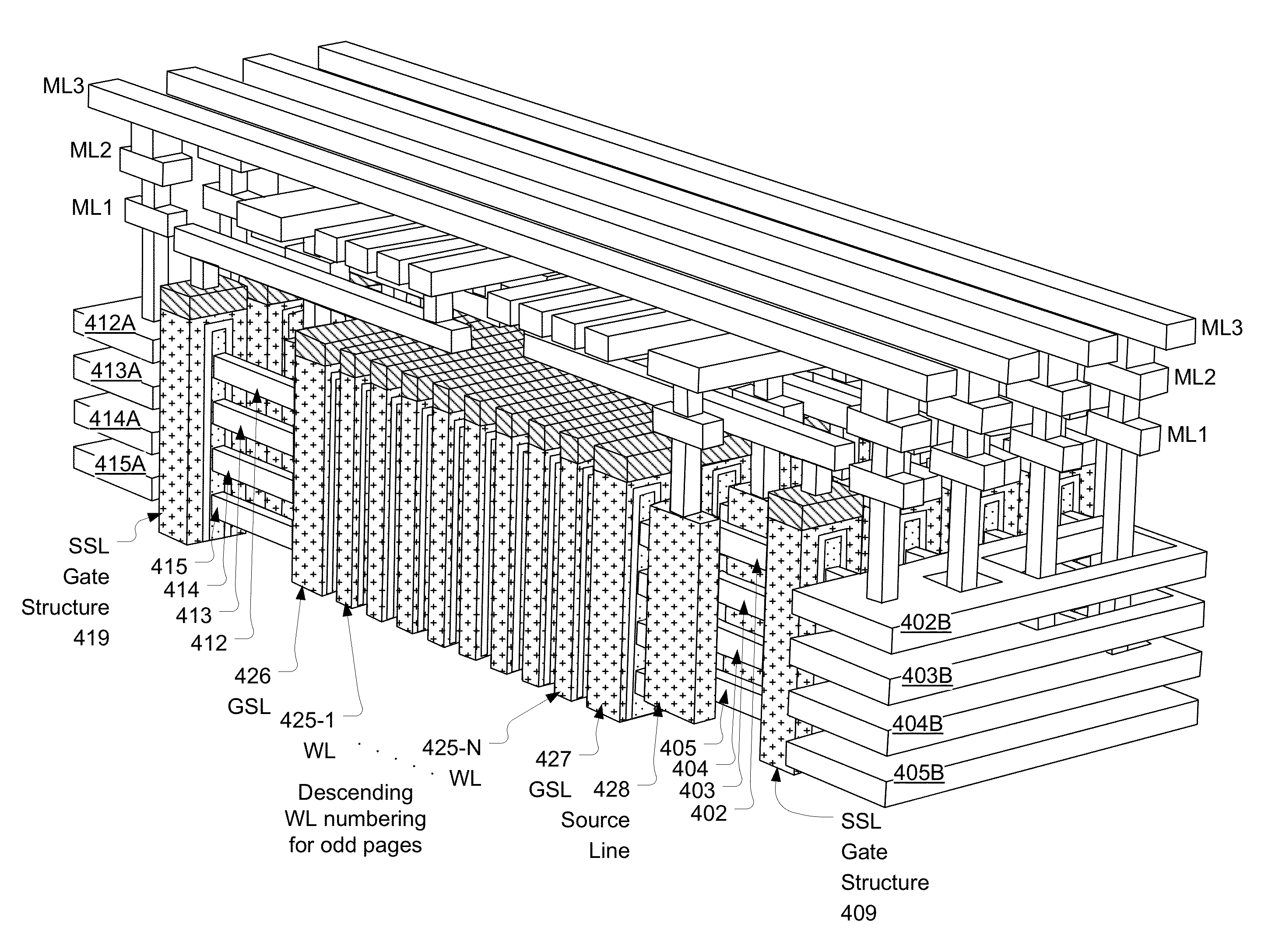

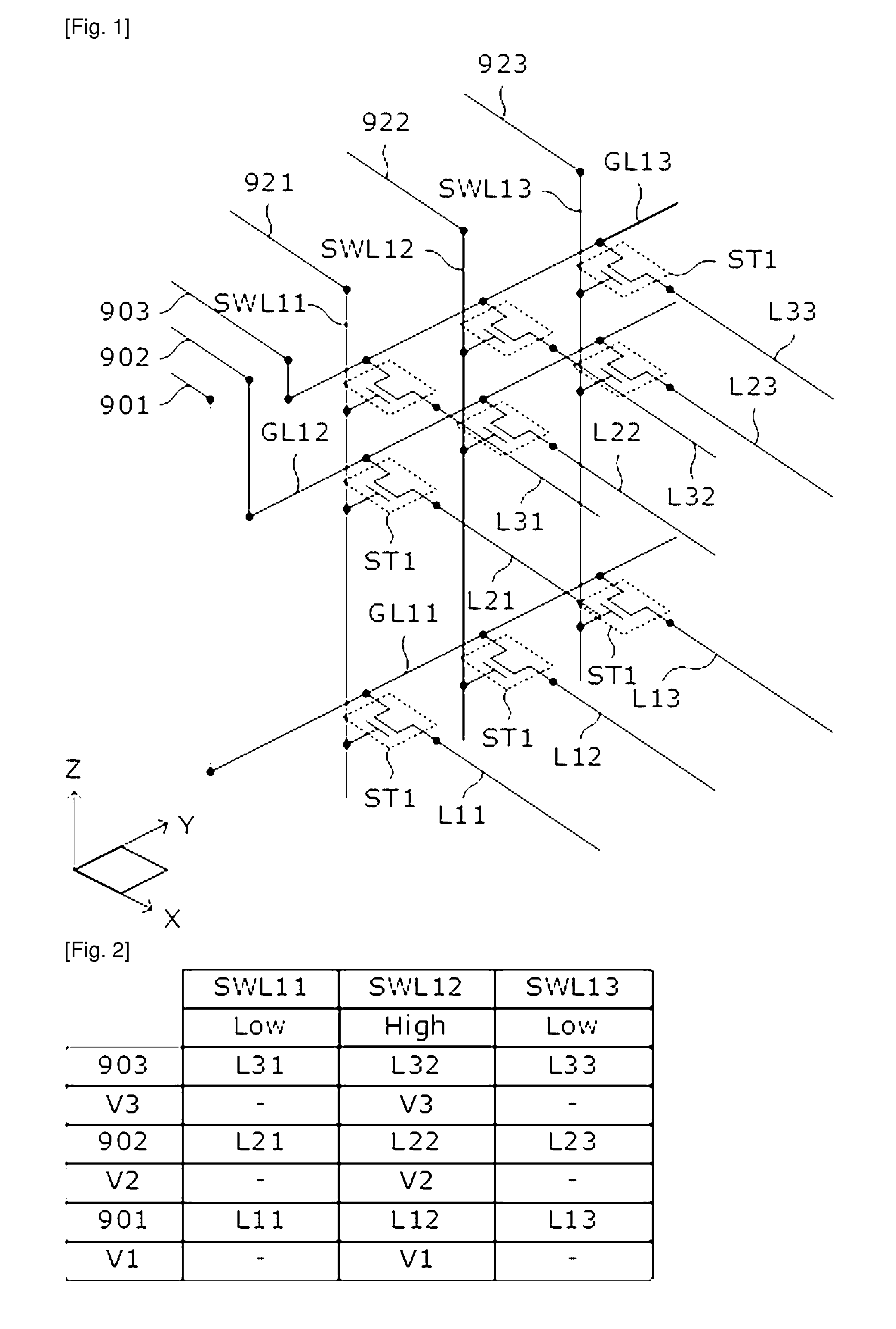

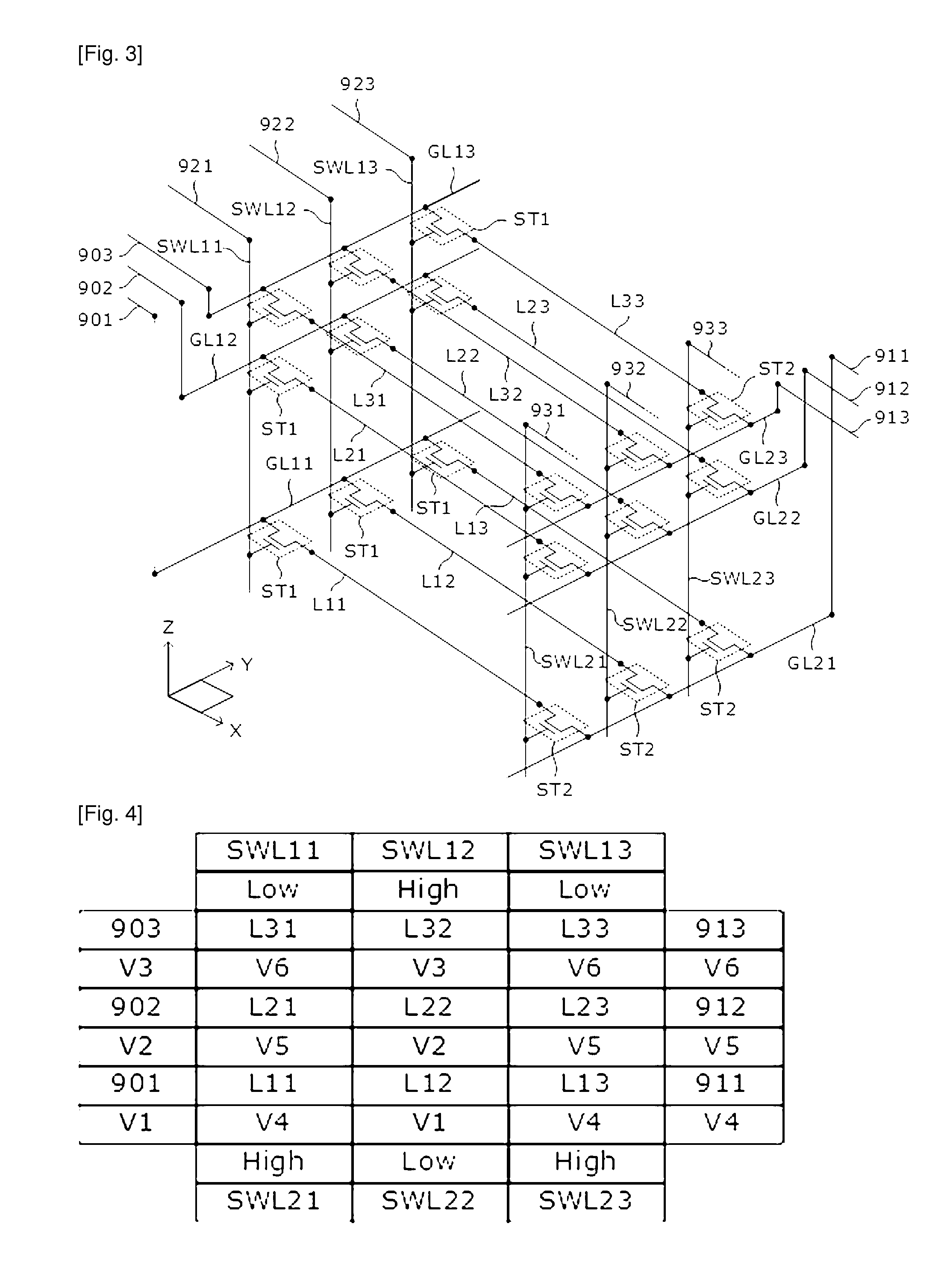

Memory Architecture of 3D Array With Alternating Memory String Orientation and String Select Structures

ActiveUS20120182806A1Increase pitchImproved gate structureSolid-state devicesRead-only memoriesArray data structureConductive materials

Owner:MACRONIX INT CO LTD

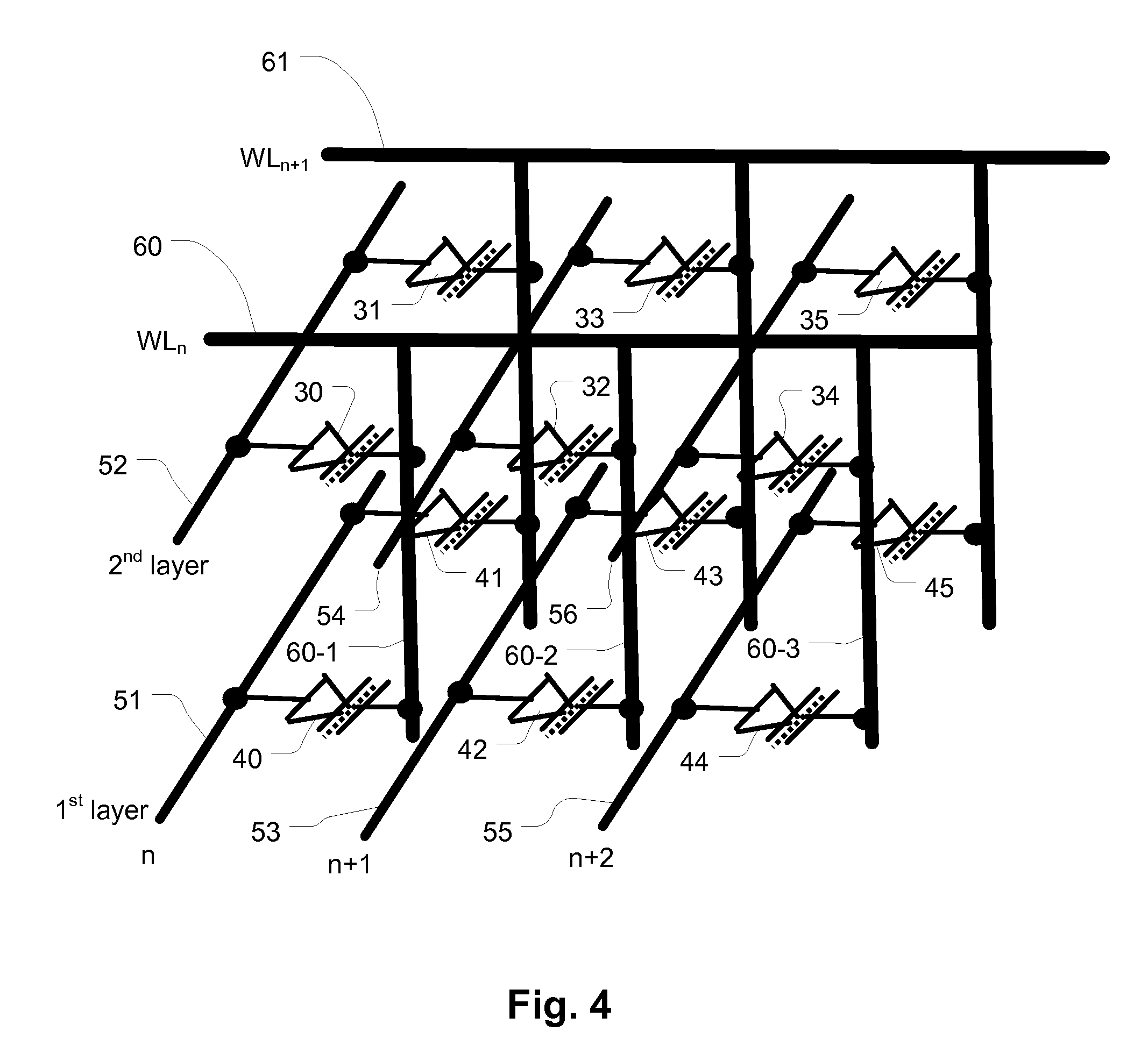

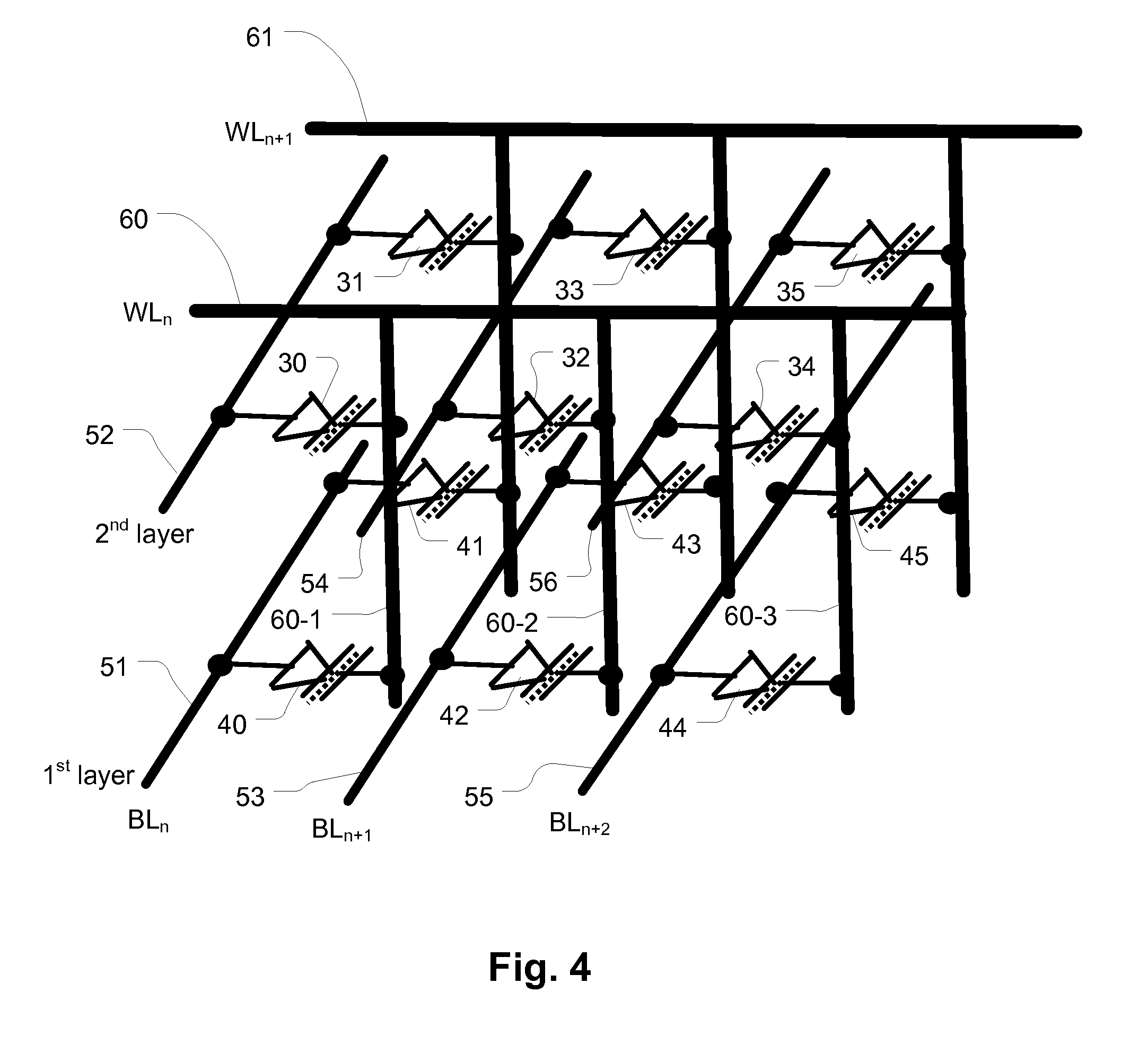

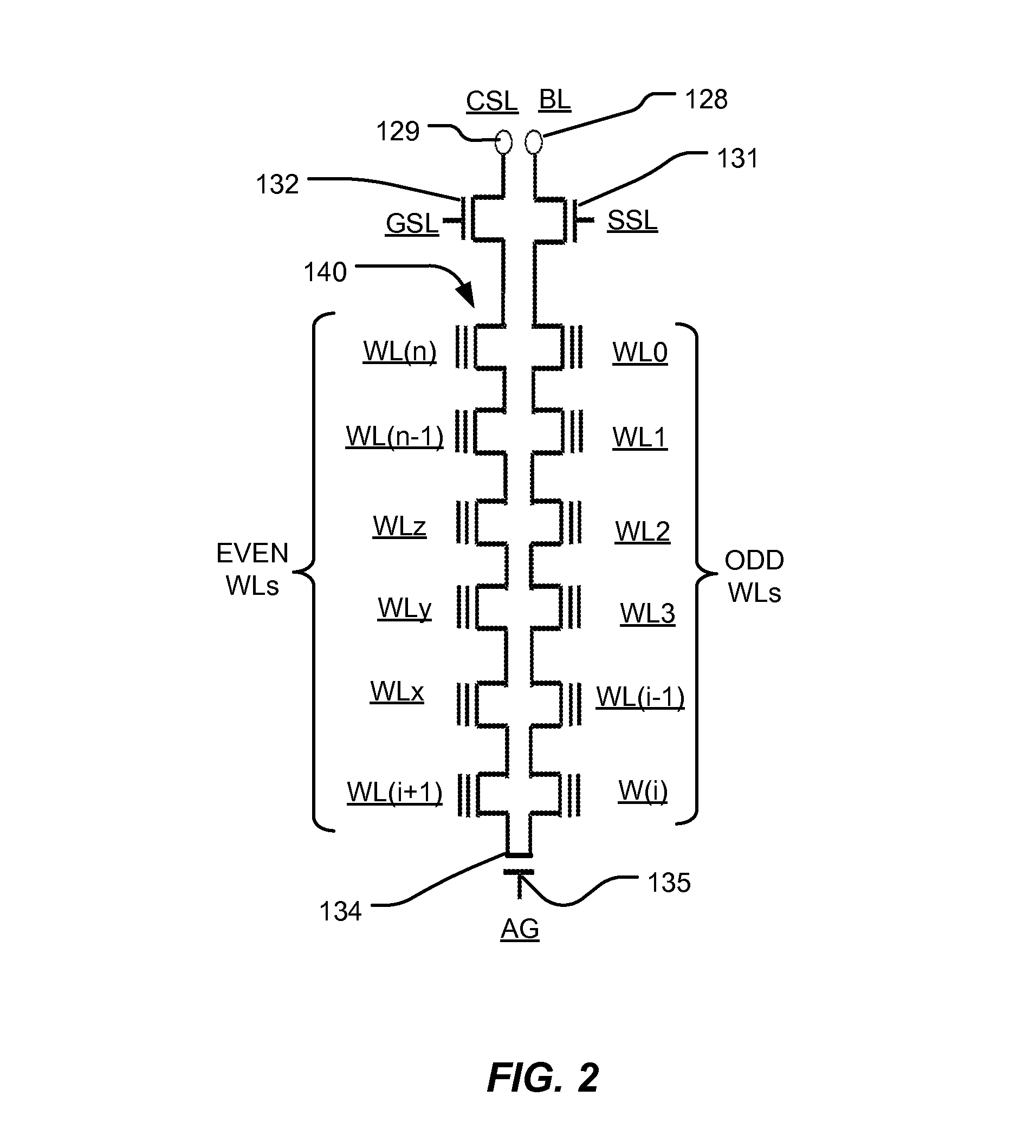

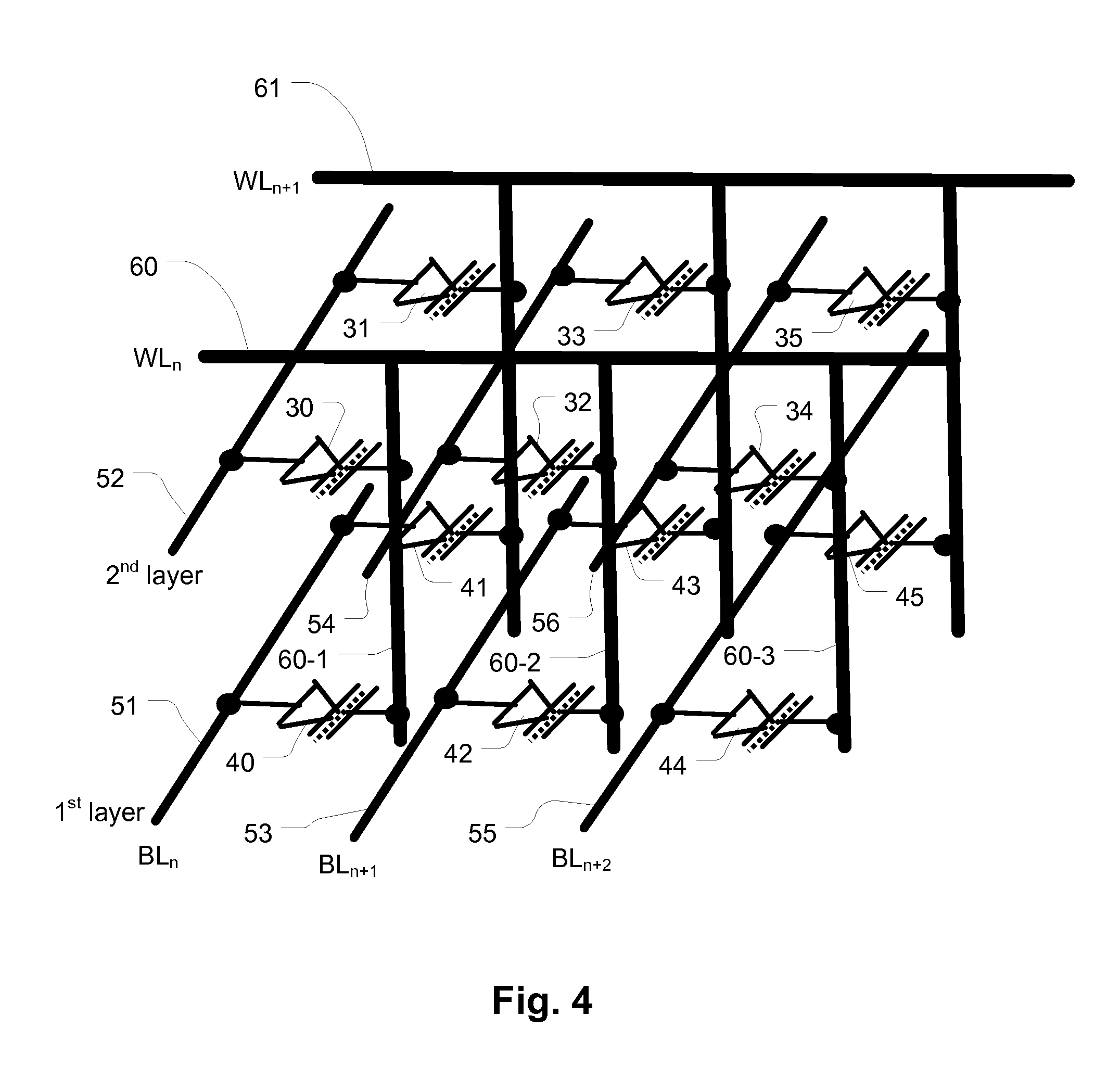

Memory architecture of 3D array with alternating memory string orientation and string select structures

ActiveUS8503213B2Increase pitchPitch is improvedSolid-state devicesRead-only memoriesAudio power amplifierConductive materials

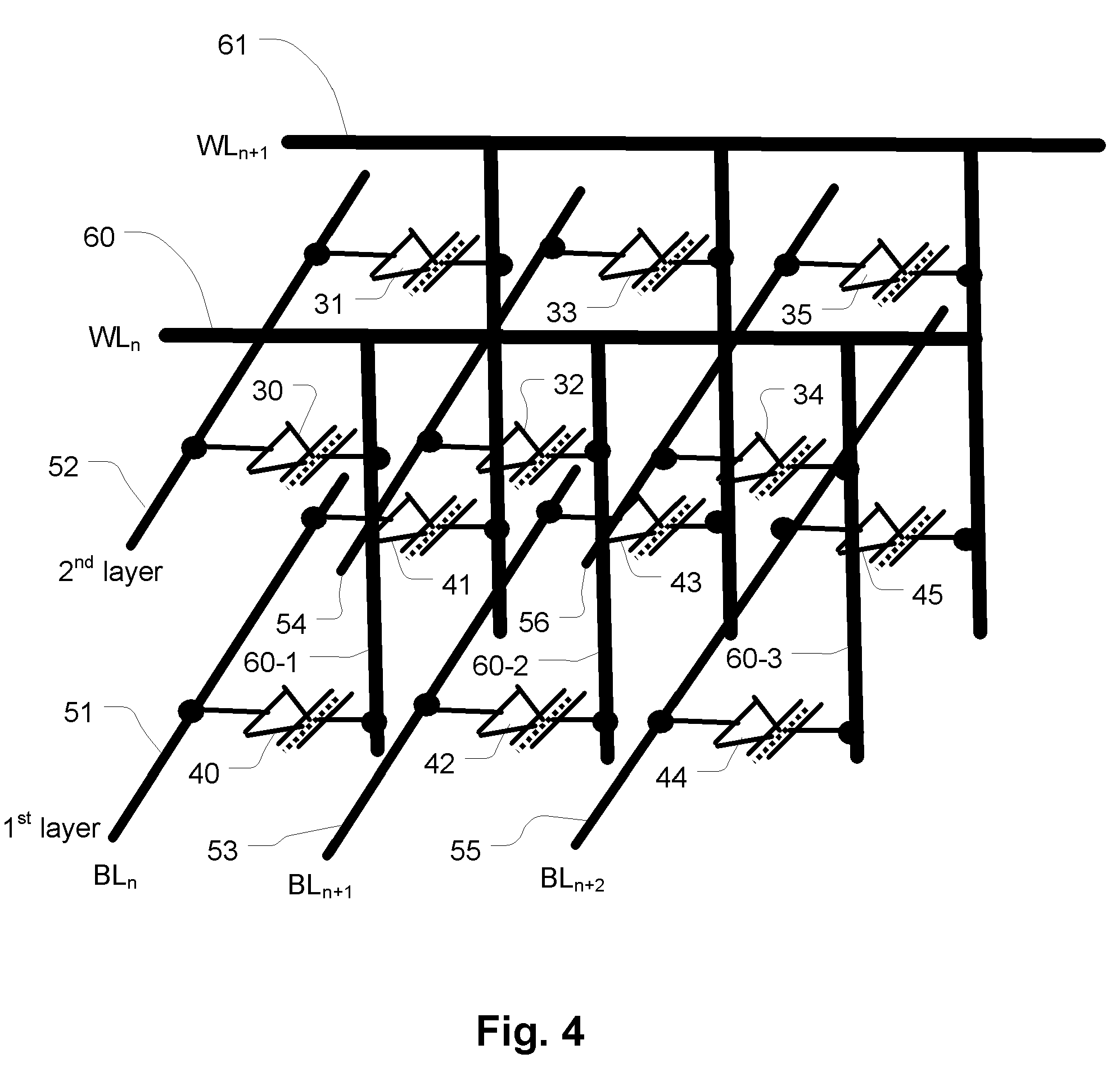

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. Diodes are connected to the bit lines at either the string select of common source select ends of the strings. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of word lines, which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the semiconductor strips on the stacks and the word lines.

Owner:MACRONIX INT CO LTD

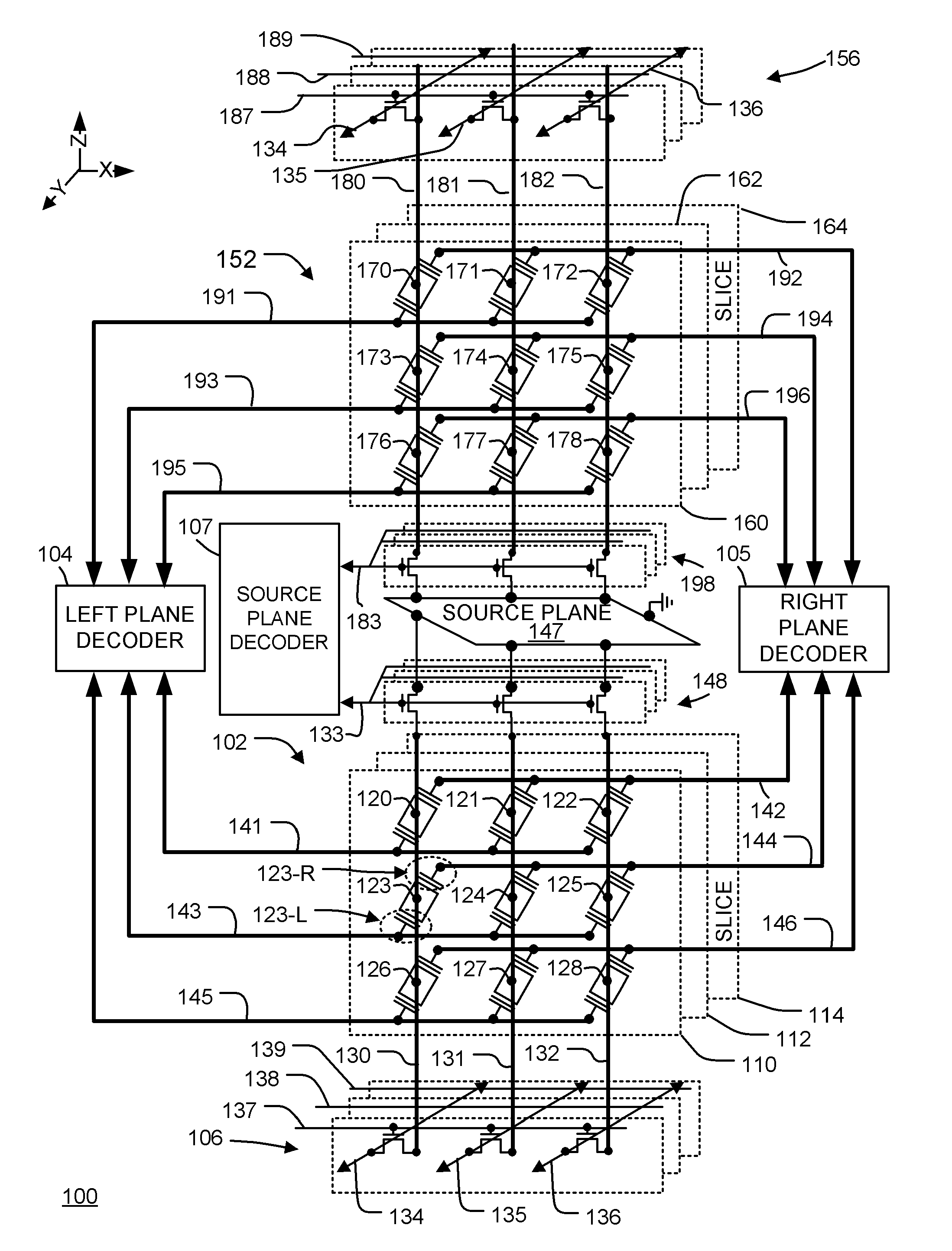

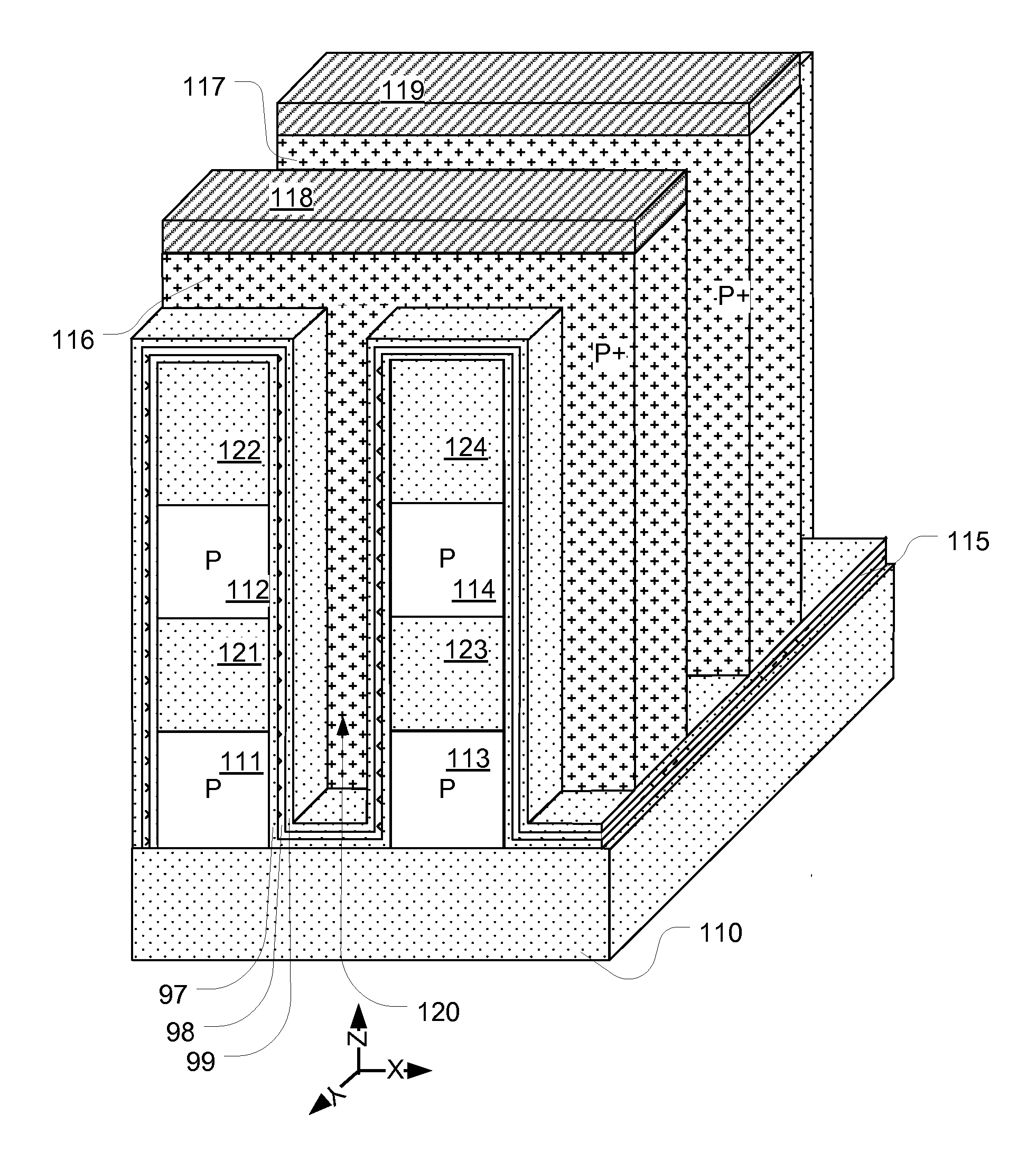

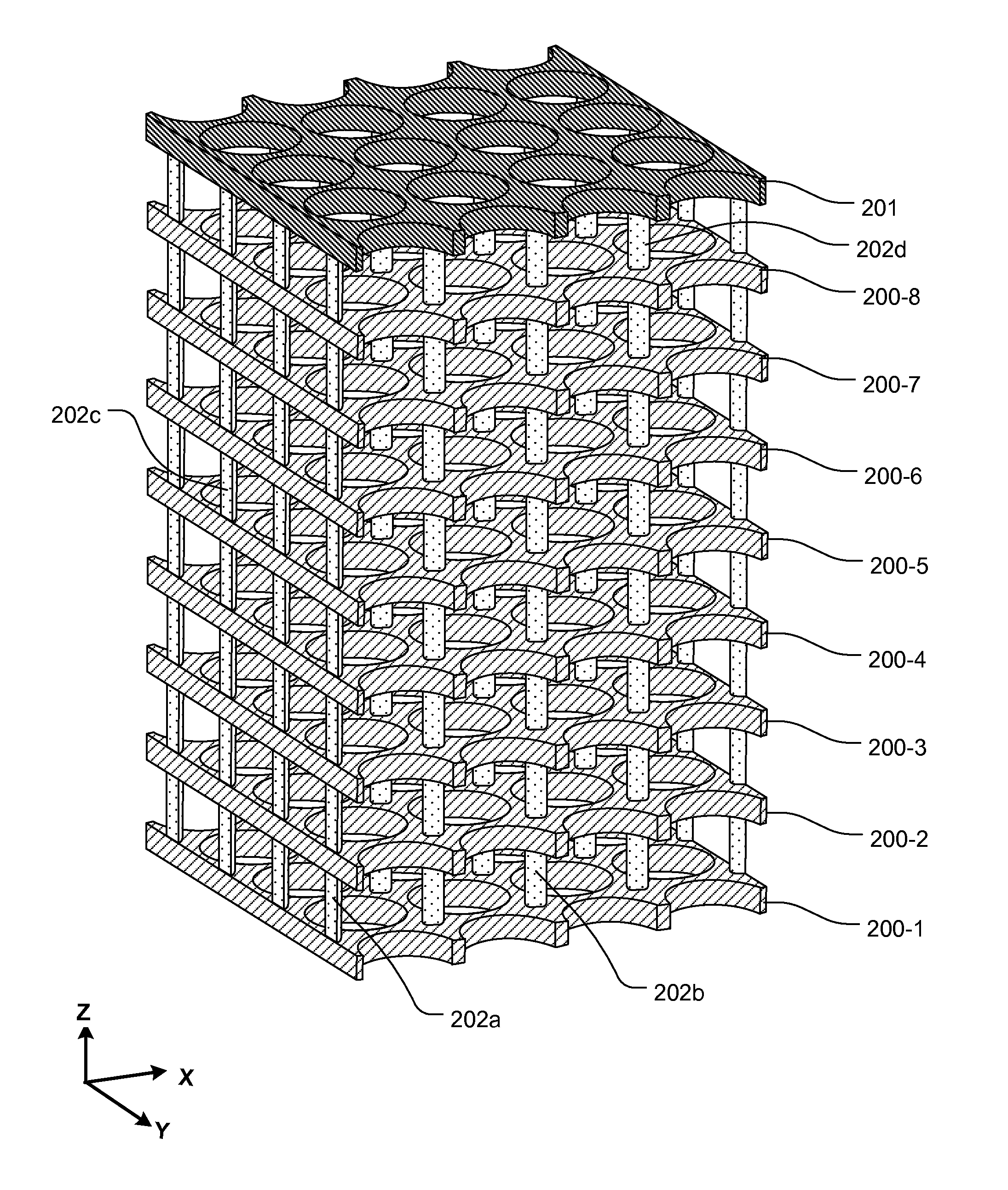

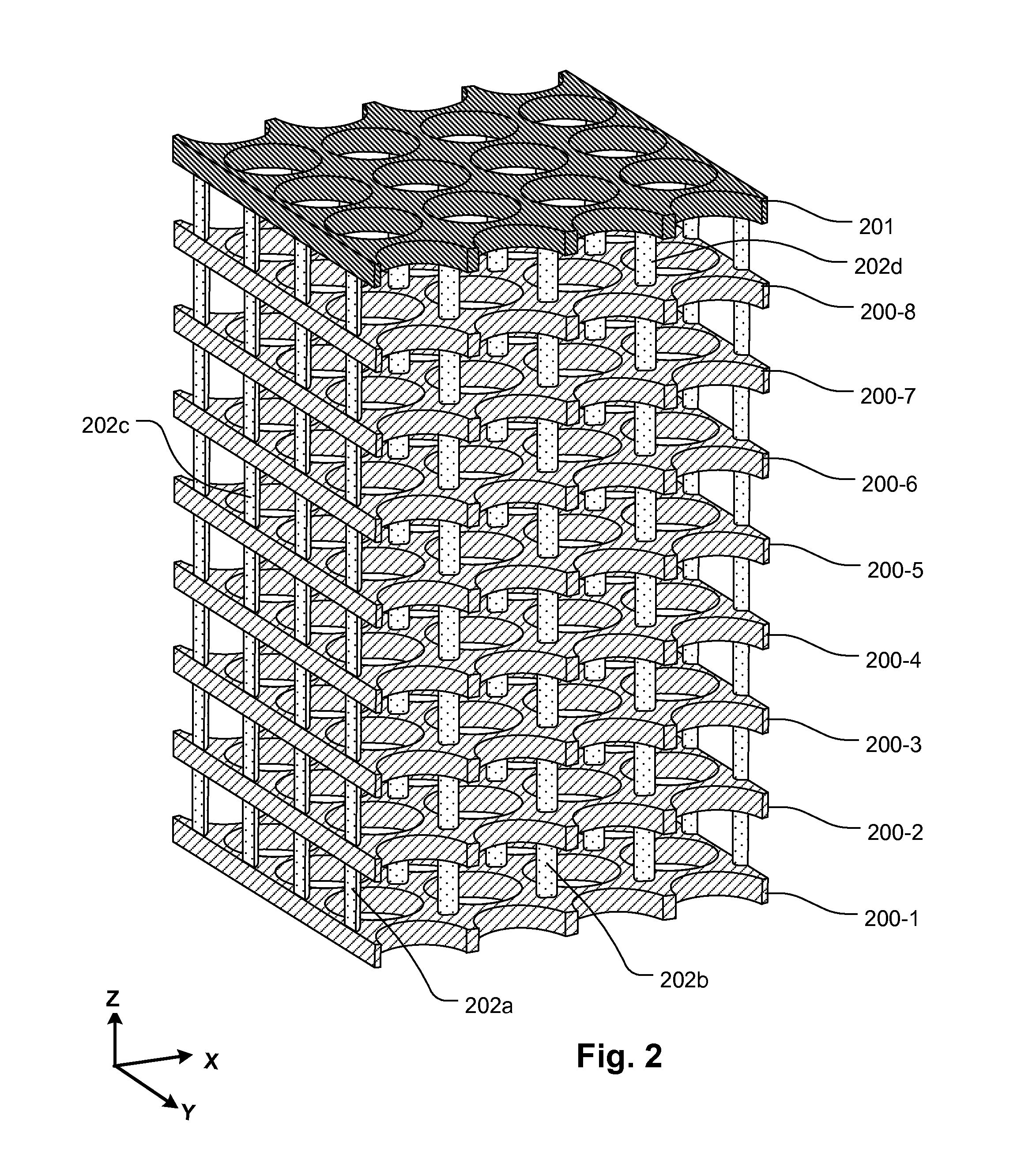

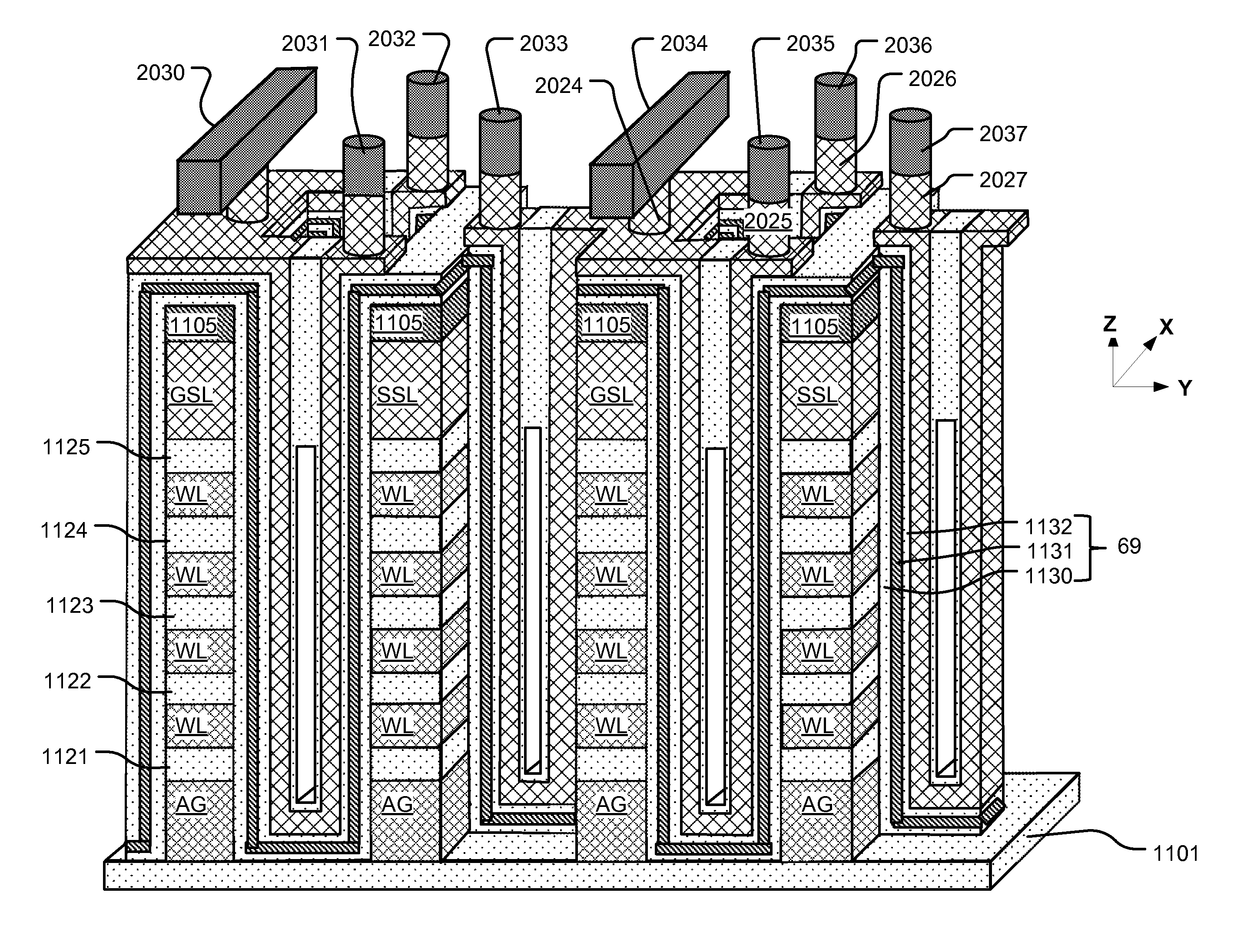

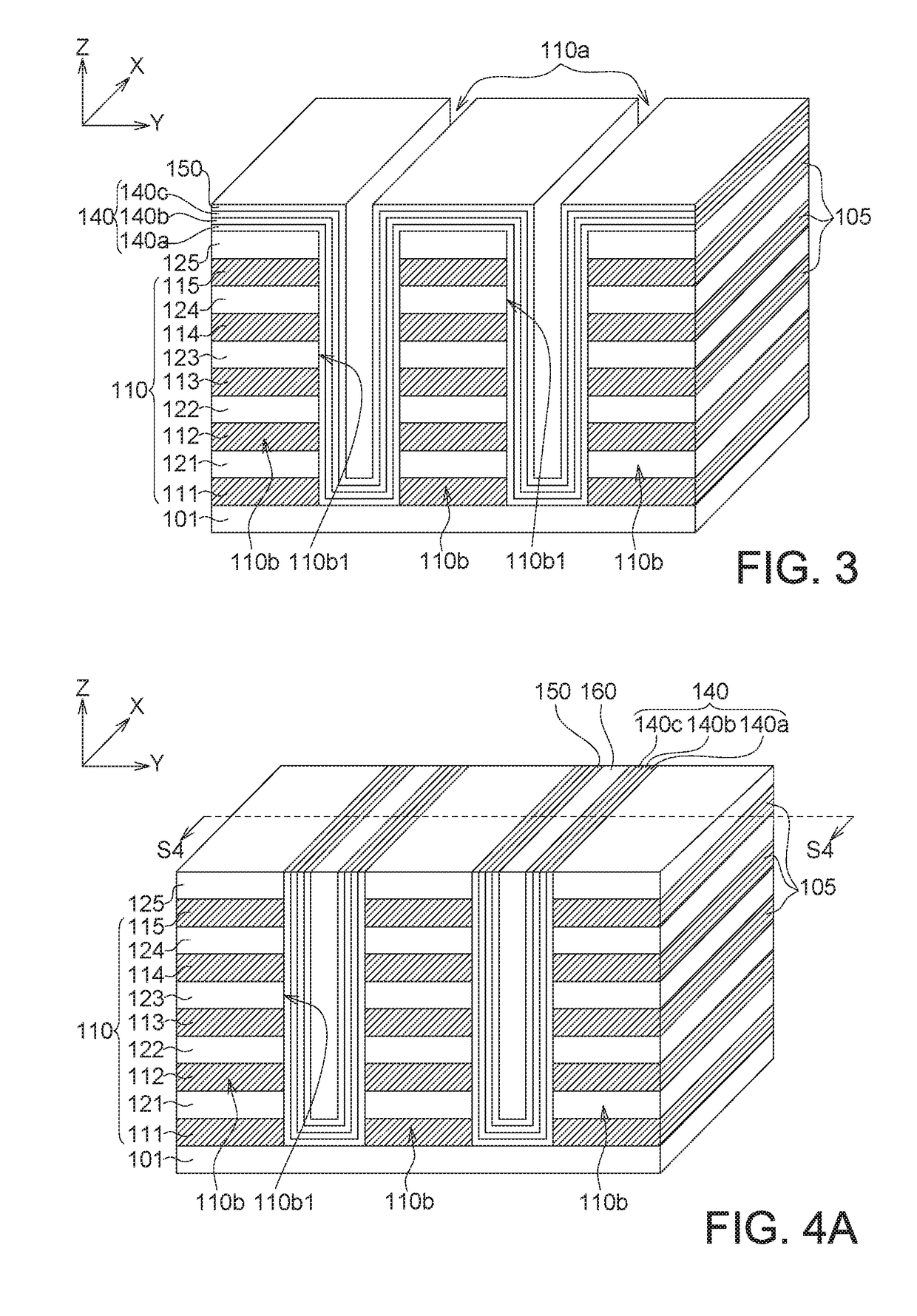

Vertical and 3D memory devices and methods of manufacturing the same

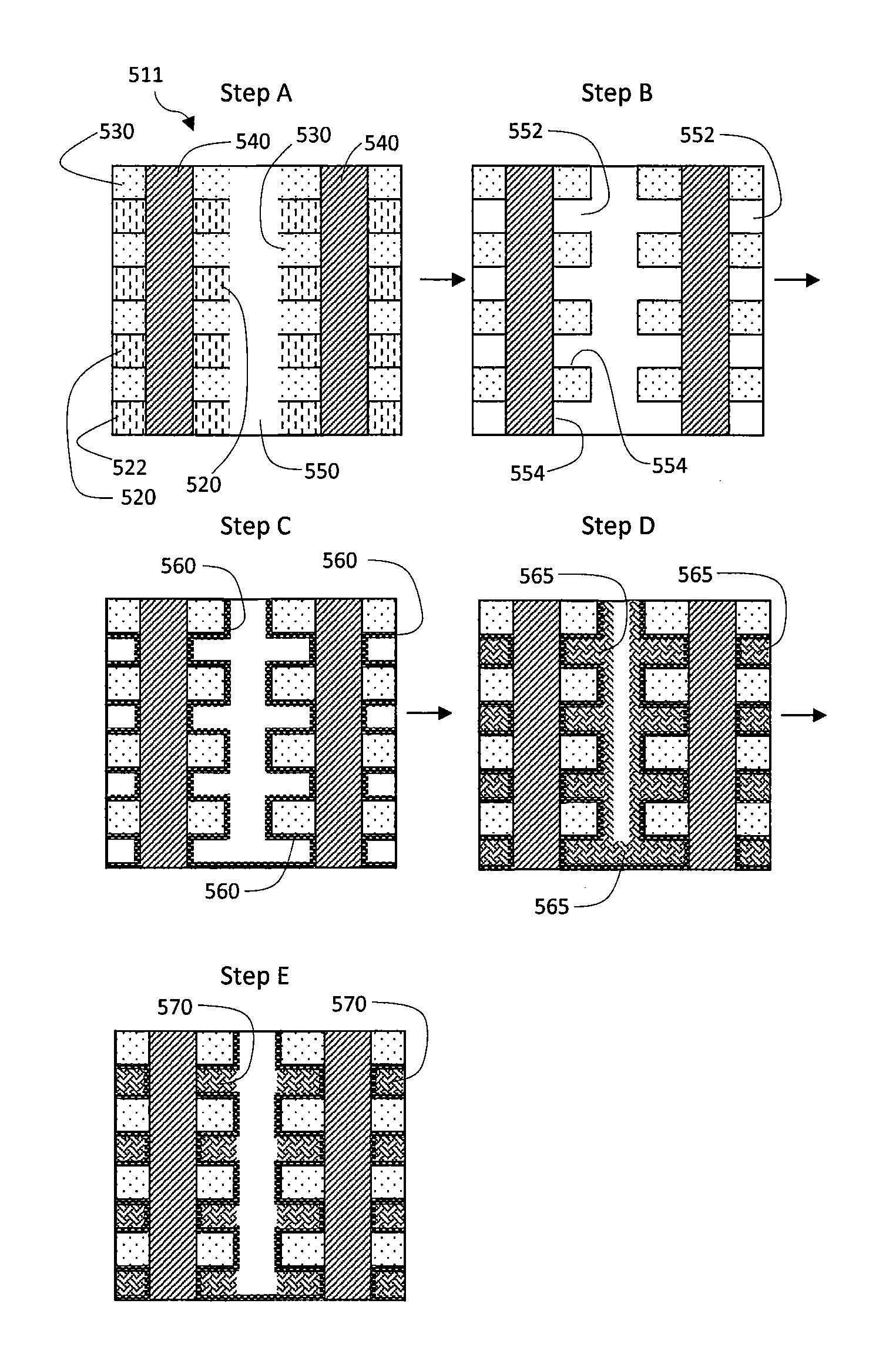

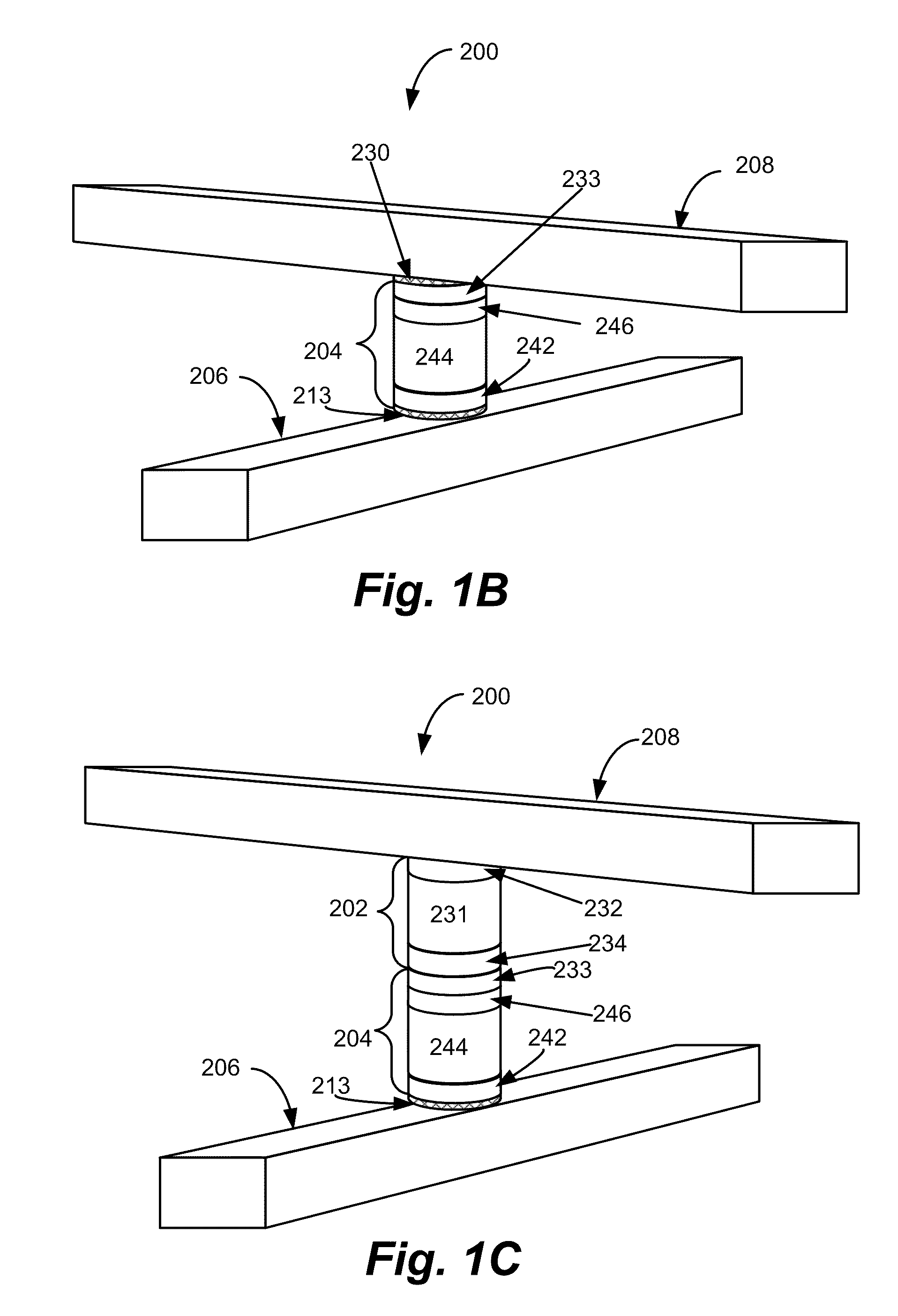

ActiveUS20160141299A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical slice

A memory device is described, which includes a block of memory cells comprising a plurality of stacks of horizontal active lines such as NAND string channel lines, with a plurality of vertical slices penetrated by, and surrounding, the horizontal active lines to provide a gate-all-around structure. A memory film is disposed between the horizontal active lines in the plurality of stacks and the vertical slices in the plurality of vertical slices. A 3D, horizontal channel, gate-all-around NAND flash memory is provided. A method for manufacturing a memory involves a buttress process. The buttress process enables horizontal channel, gate-all-around structures.

Owner:MACRONIX INT CO LTD

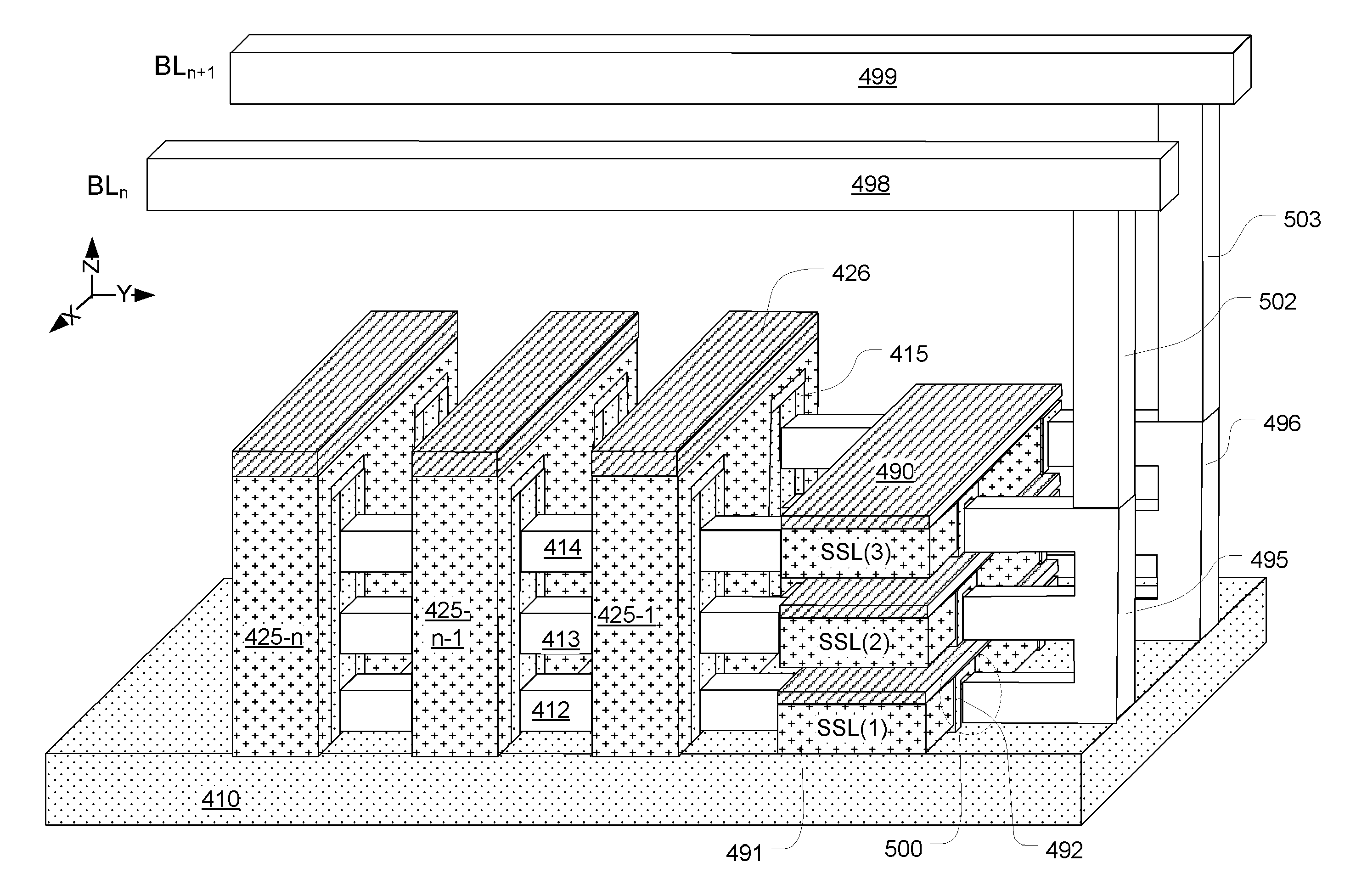

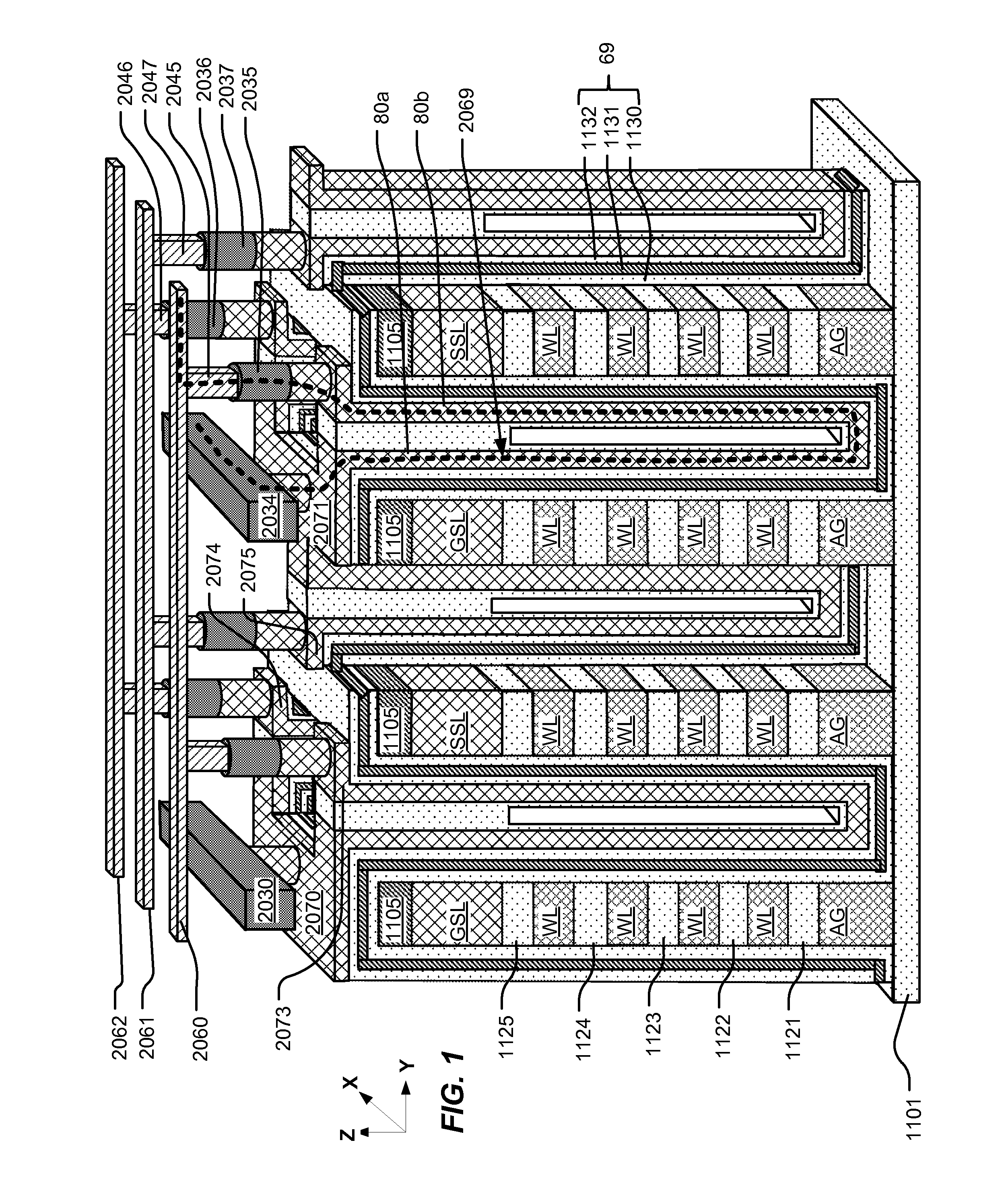

3D Memory Array With Improved SSL and BL Contact Layout

ActiveUS20120007167A1Semiconductor/solid-state device detailsSolid-state devicesAudio power amplifierSemiconductor materials

A 3D memory device includes a plurality of ridges, in some embodiments ridge-shaped, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the semiconductor material strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. In some embodiments, the 3D memory is made using only two critical masks for multiple layers. Some embodiments include a staircase-shaped structure positioned at ends of the semiconductor material strips. Some embodiments include SSL interconnects on a metal layer parallel to the semiconductor material strips, and further SSL interconnects on a higher metal layer, parallel to the word lines.

Owner:MACRONIX INT CO LTD

Reference line and bit line structure for 3D memory

A 3D NAND flash memory includes even and odd stacks of conductive strips. Some of the conductive strips in the stacks are configured as word lines. Data storage structures are disposed on the sidewalls of the even and odd stacks. Active pillars include even and odd semiconductor films on the data storage structures connected at the bottom ends so that the semiconductor films can be thin films having a U-shaped current path. An even pad connected to the even semiconductor film and an odd pad connected to the odd semiconductor film are disposed over the even and odd stacks respectively. A segment of a reference line is connected to the even pad, and an inter-level connector is connected to the odd pad. A segment of a bit line comprises an extension contacting the inter-level connector.

Owner:MACRONIX INT CO LTD

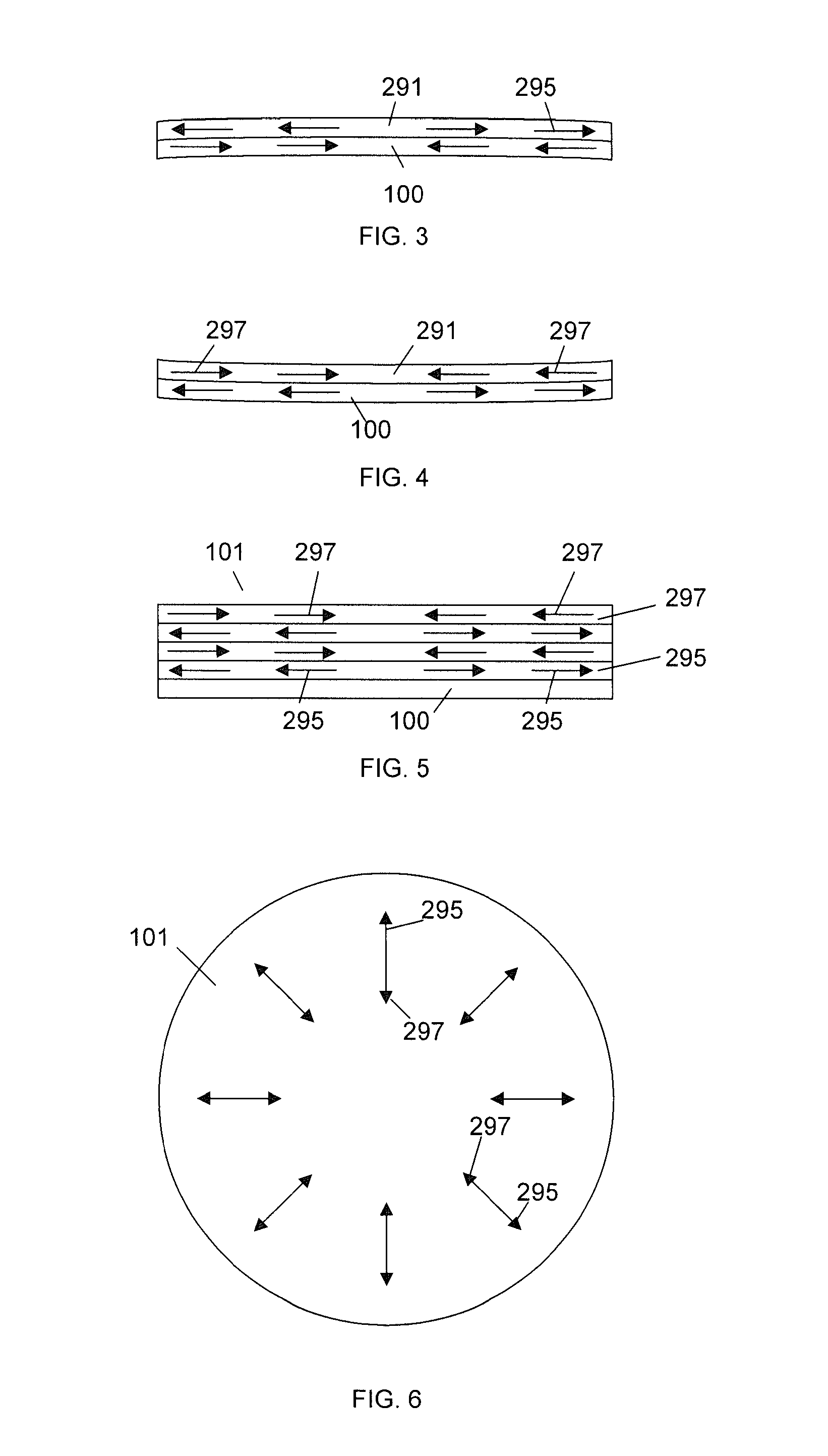

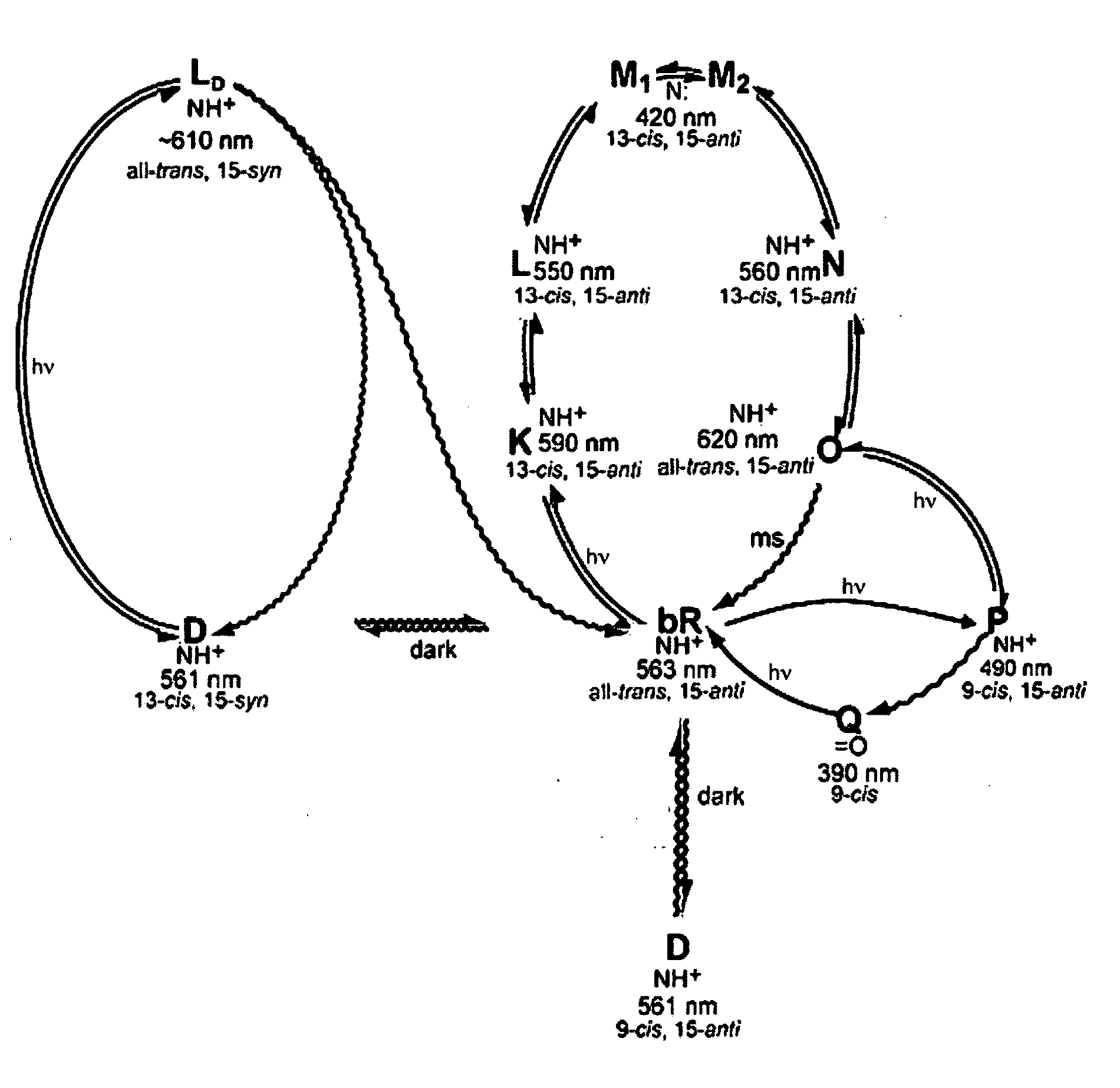

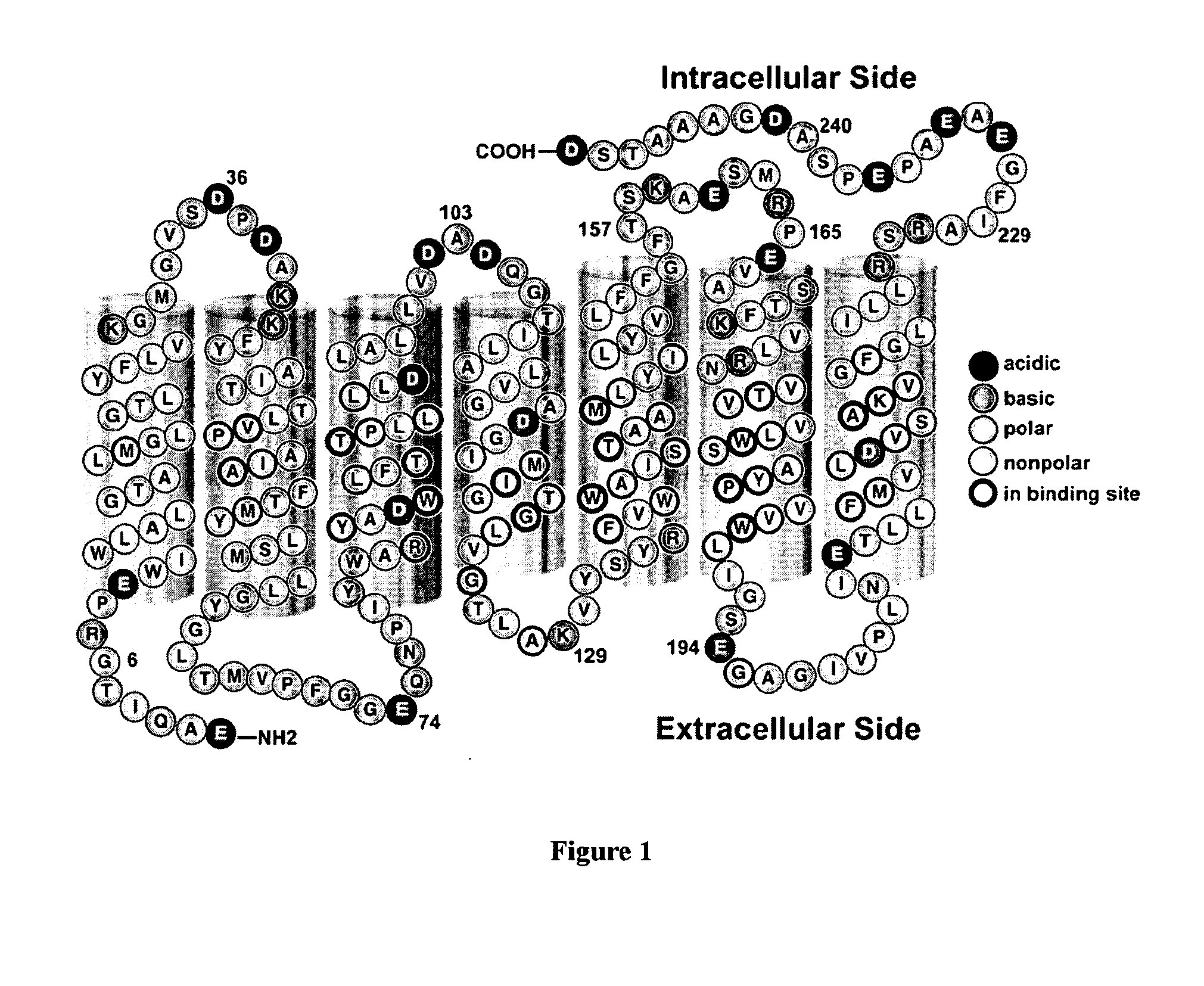

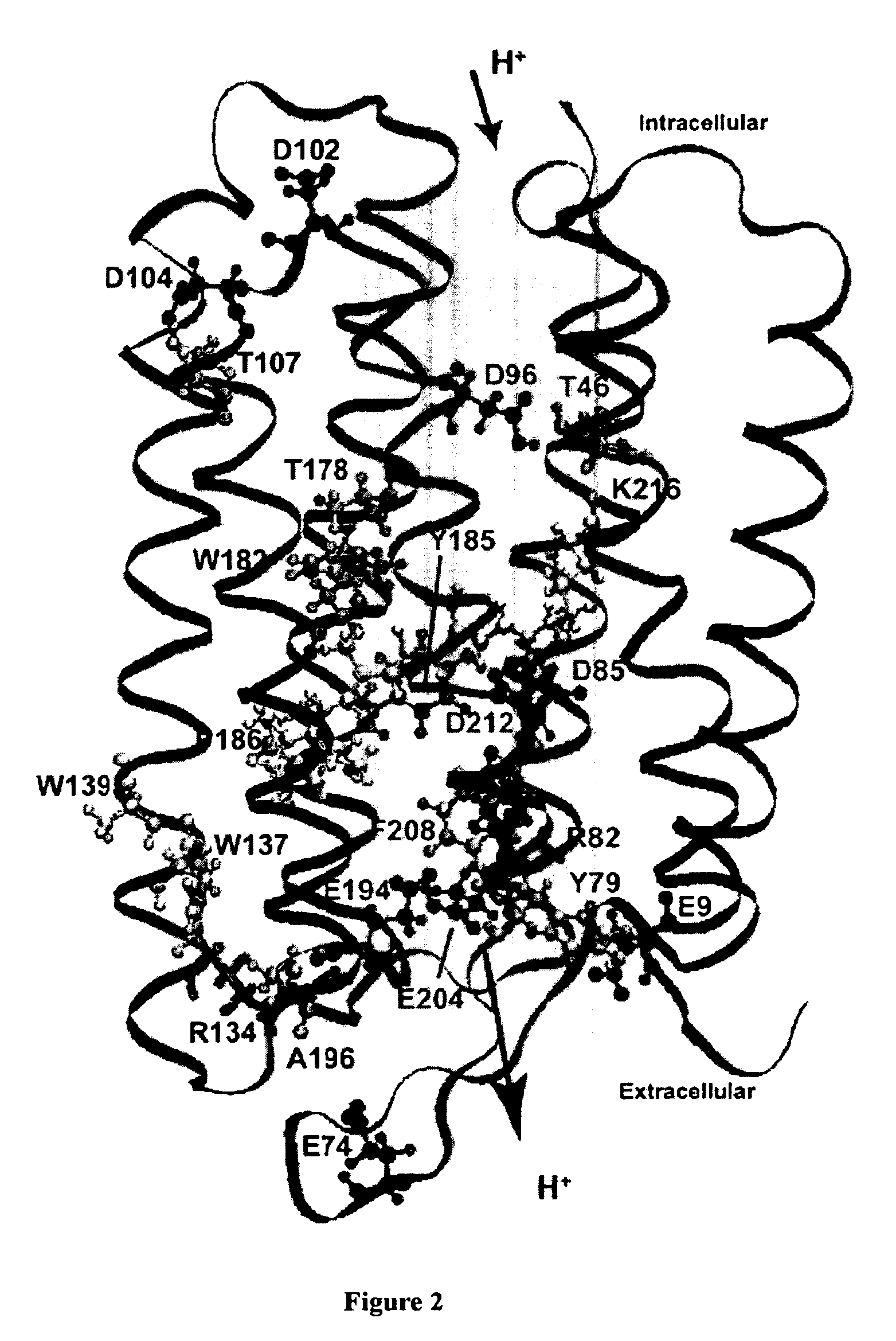

Bacteriorhodopsin Protein Variants and Methods of Use for Long Term Data Storage

ActiveUS20090268511A1High through-put storageEnhanced protein performanceNanoinformaticsPeptide preparation methodsLong term dataWild type

Bacteriorhodopsin protein variants and methods using the bacteriorhodopsin variants for performance in holographic and three-dimensional (3D) memory storage devices are described. The amino acid and chemical modifications of bacteriorhodopsin provided herein achieve greatly enhanced protein performance. The memory storage devices write, read and erase data proficiently. The bacteriorhodopsin protein variants are useful in optical memory storage and associative processor systems. Irradiation of the light-sensitive protein with light of known wavelength causes the protein to switch between different states. The variants enter the branched photocycle via a single or a two photon process and form the permanent ‘Q’ state more efficiently than the wild-type bacteriorhodopsin protein. This branching photocycle of the variants is exploited in the fabrication of 3D memory storage devices.

Owner:UNIV OF CONNECTICUT

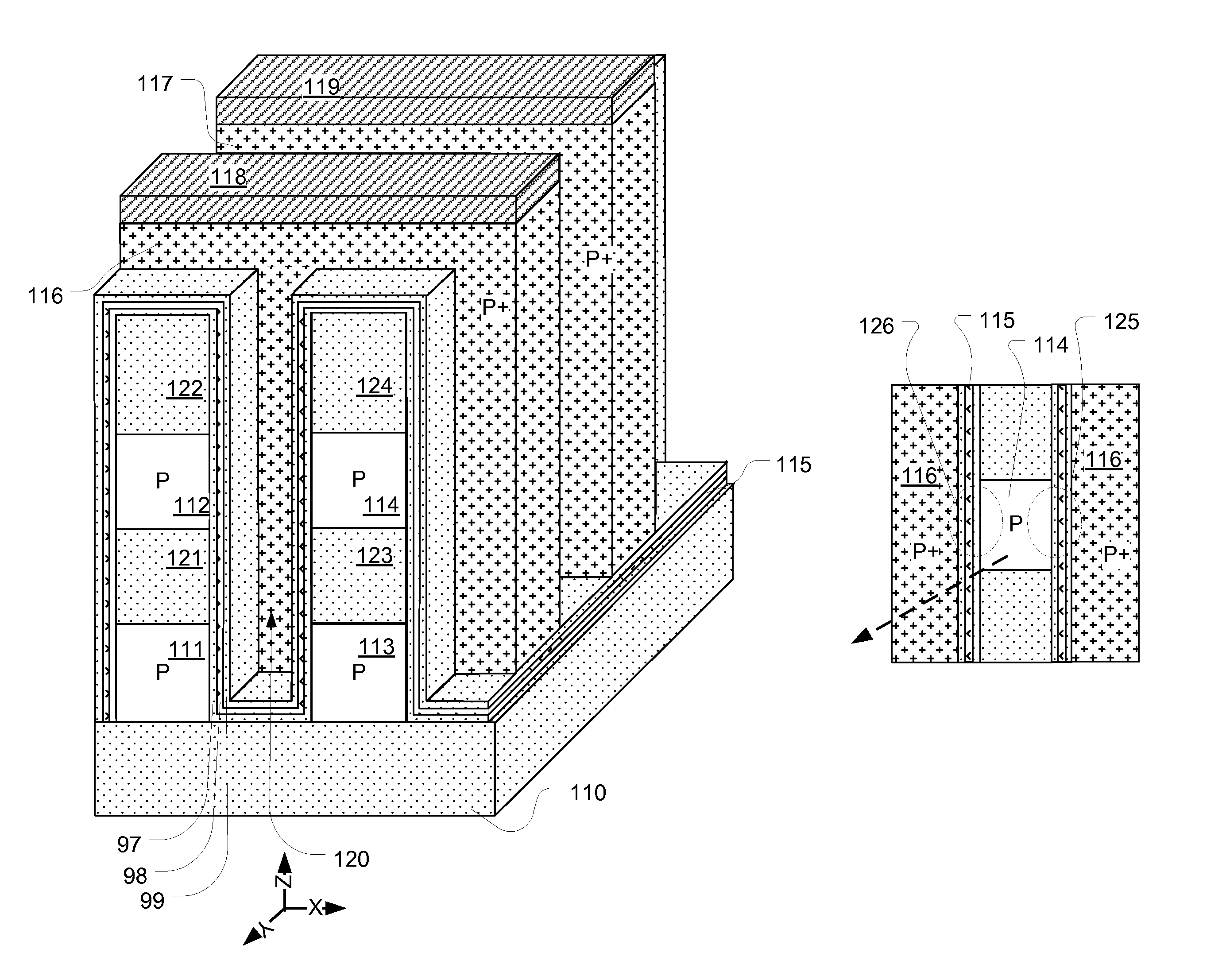

Memory architecture of 3D NOR array

A 3D memory device includes a plurality of ridge-shaped stacks of memory cells. Word lines are arranged over the stacks of memory cells. Bit lines structures are coupled to multiple locations along the stacks of memory cells. Source line structures are coupled to multiple locations along each of the semiconductor material strips of the stacks. The bit line structures and the source line structures are between adjacent ones of the word lines.

Owner:MACRONIX INT CO LTD

Magnetoresistive random access memory cell and 3D memory cell array

ActiveUS9218864B1Easy to implementImprove thermal stabilityDigital storageMagnetic stabilizationMagnetic reluctance

A novel three-terminal SOT-MRAM memory cell with a unique magnetic stabilization layer or structure is proposed. A complementary magnetic footprint of the data storage layer for the memory cell is able to be created within the magnetic stabilization layer or structure by the magnetic field from the storage layer to enhance the magnetic and thermal stability of the memory cell. Several designs for both perpendicular and in-plane SOT-MRAM memory cell have been invented. With proper wire connection and sensing arrangement, the proposed memory cell is capable of forming not only the 2D array but also 3D array.

Owner:GE YI +1

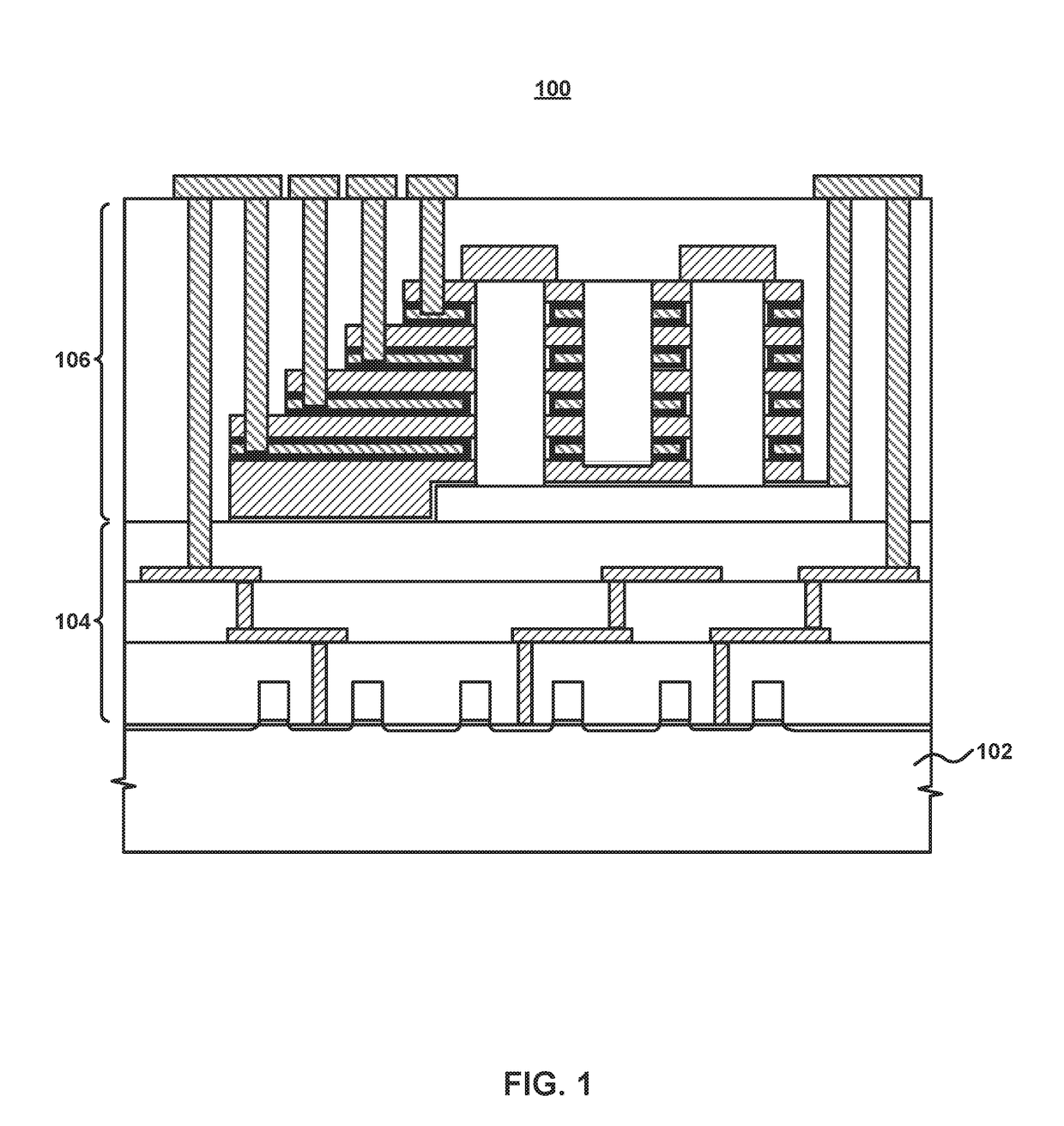

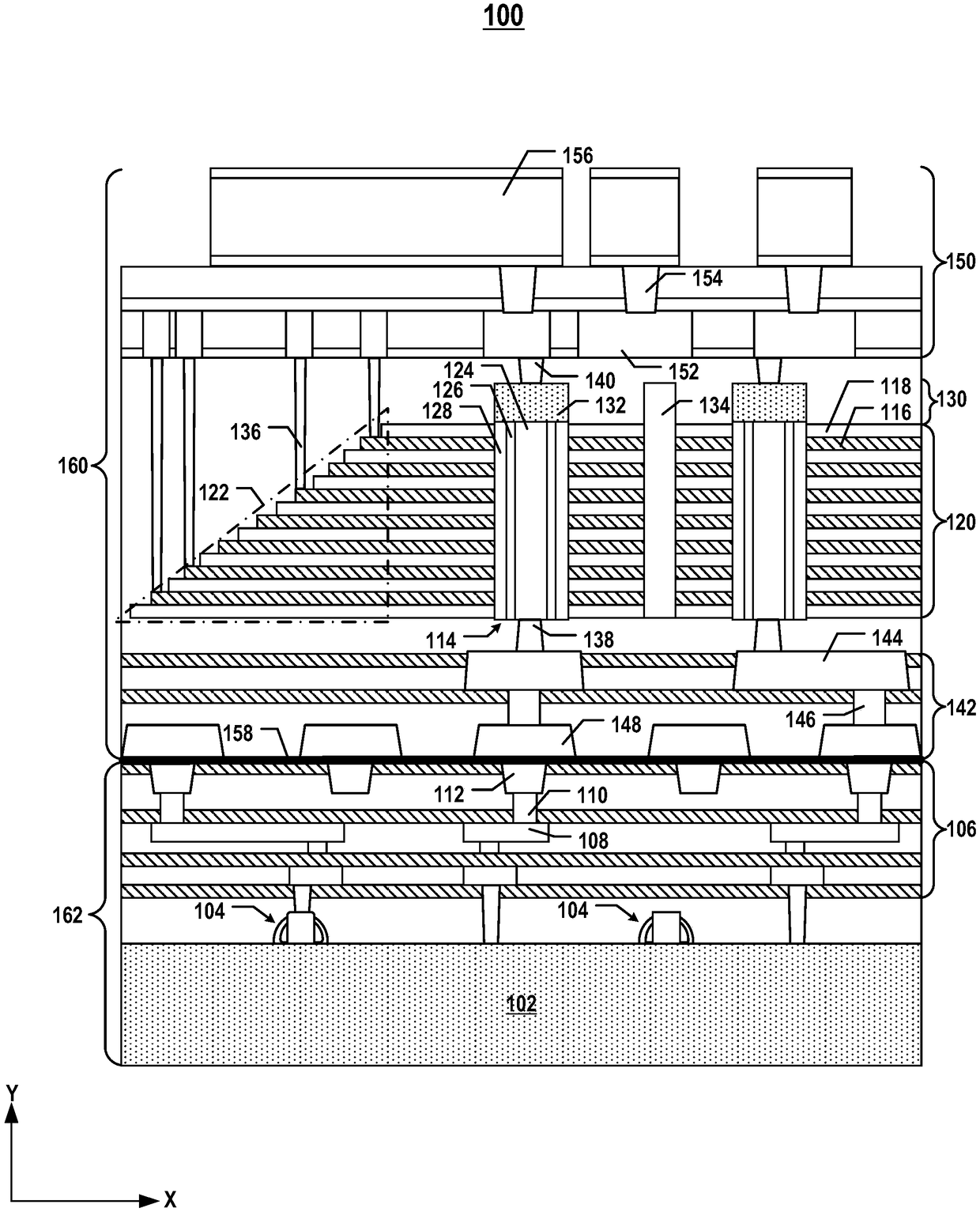

Three-dimensional memory devices and methods for forming the same

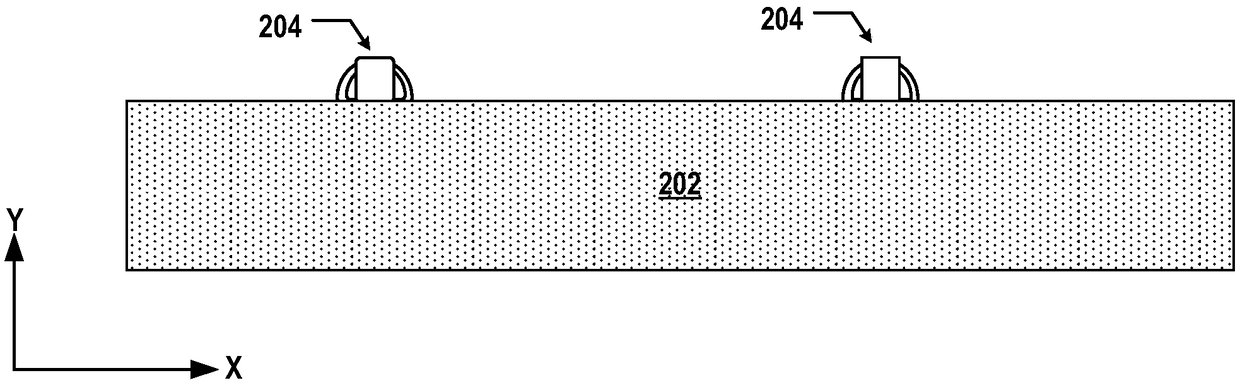

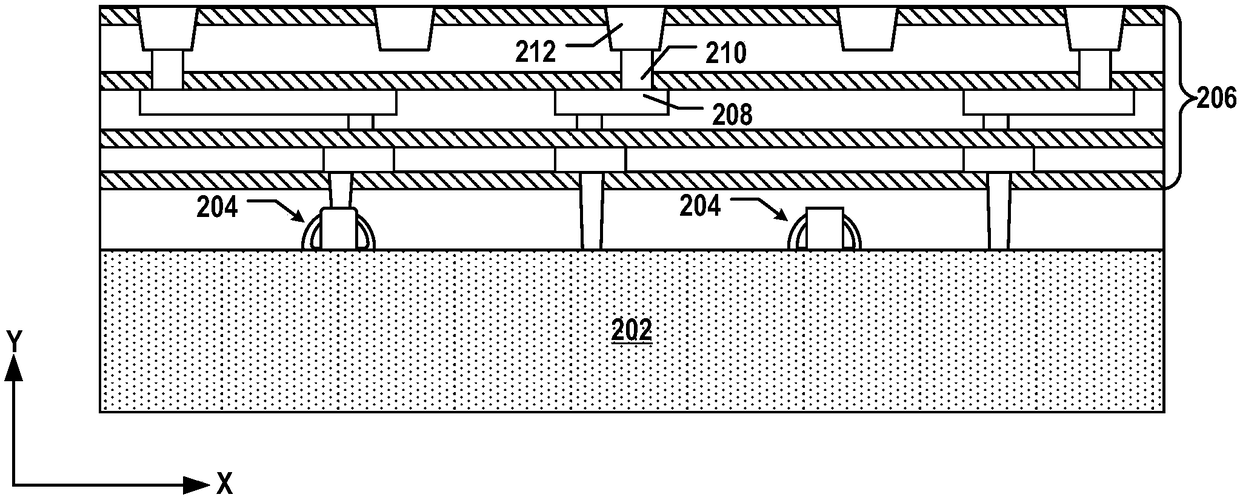

ActiveUS20190081069A1High bonding strengthPromote interdiffusionSemiconductor/solid-state device detailsSolid-state devicesBond interfaceCrystalline silicon

Embodiments of three-dimensional (3D) memory devices and methods for forming the 3D memory devices are disclosed. In an example, a NAND memory device includes a substrate, one or more peripheral devices on the substrate, a plurality of NAND strings above the peripheral devices, a single crystalline silicon layer above and in contact with the NAND strings, and interconnect layers formed between the peripheral devices and the NAND strings. In some embodiments, the NAND memory device includes a bonding interface at which an array interconnect layer contacts a peripheral interconnect layer.

Owner:YANGTZE MEMORY TECH CO LTD

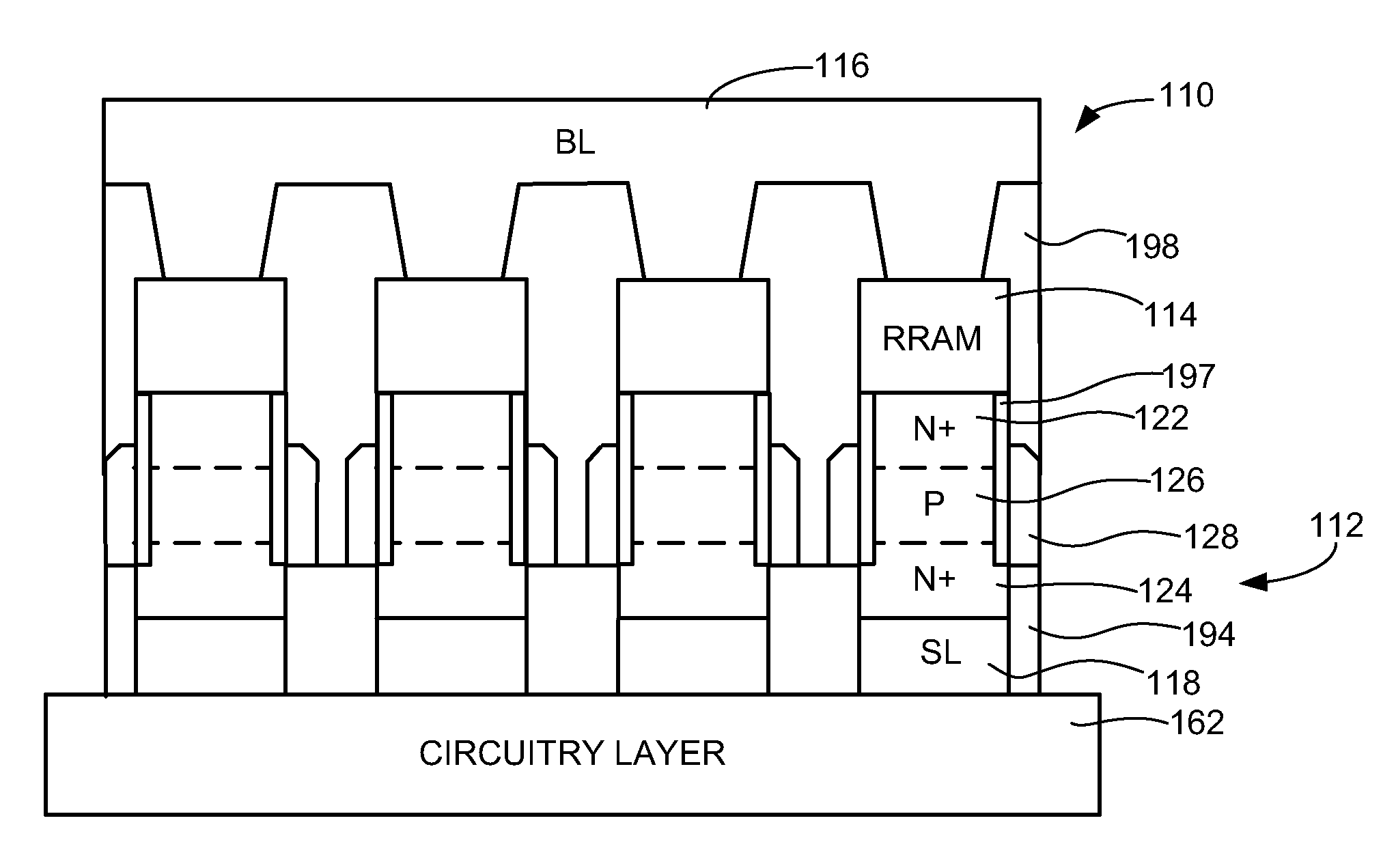

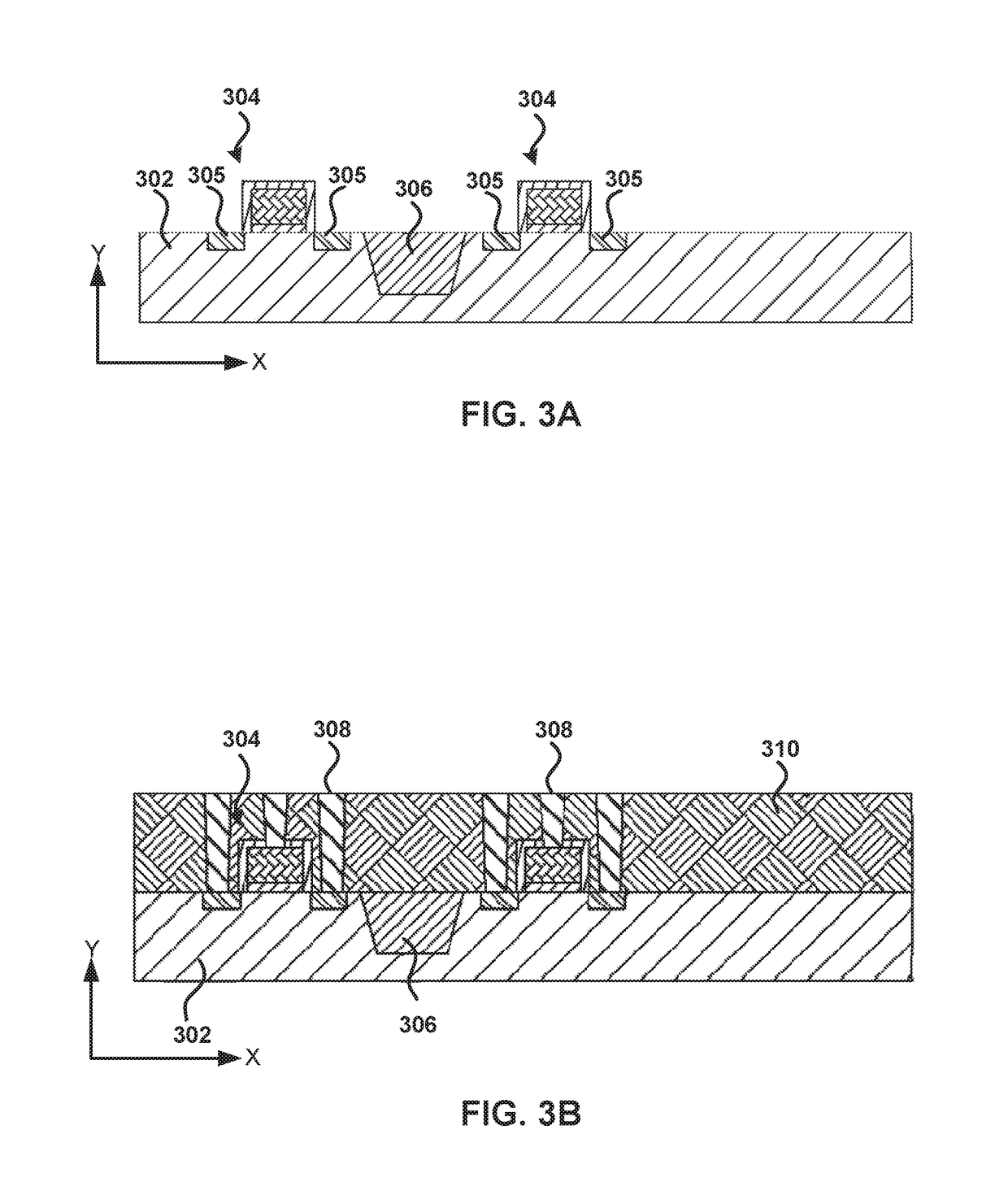

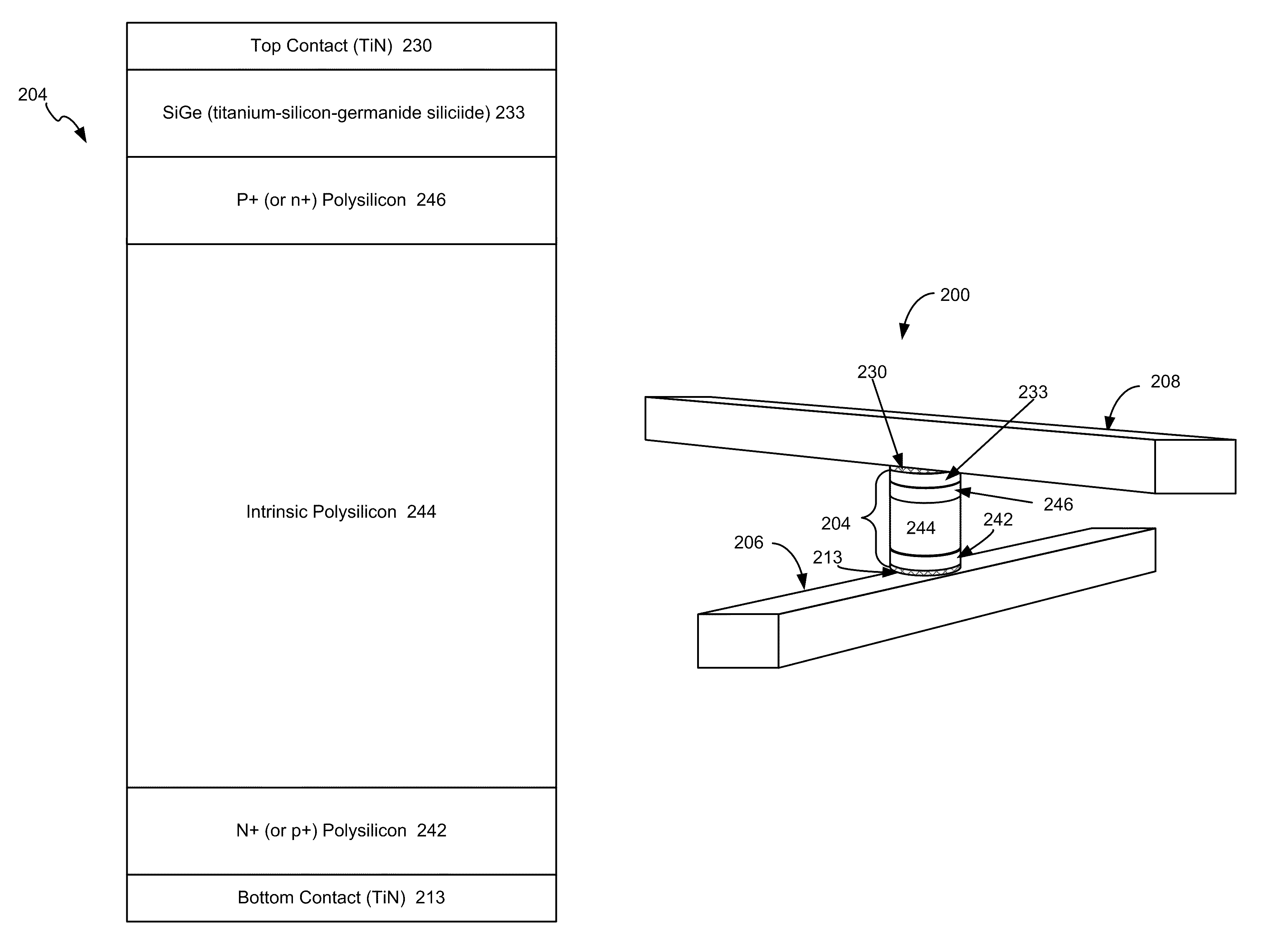

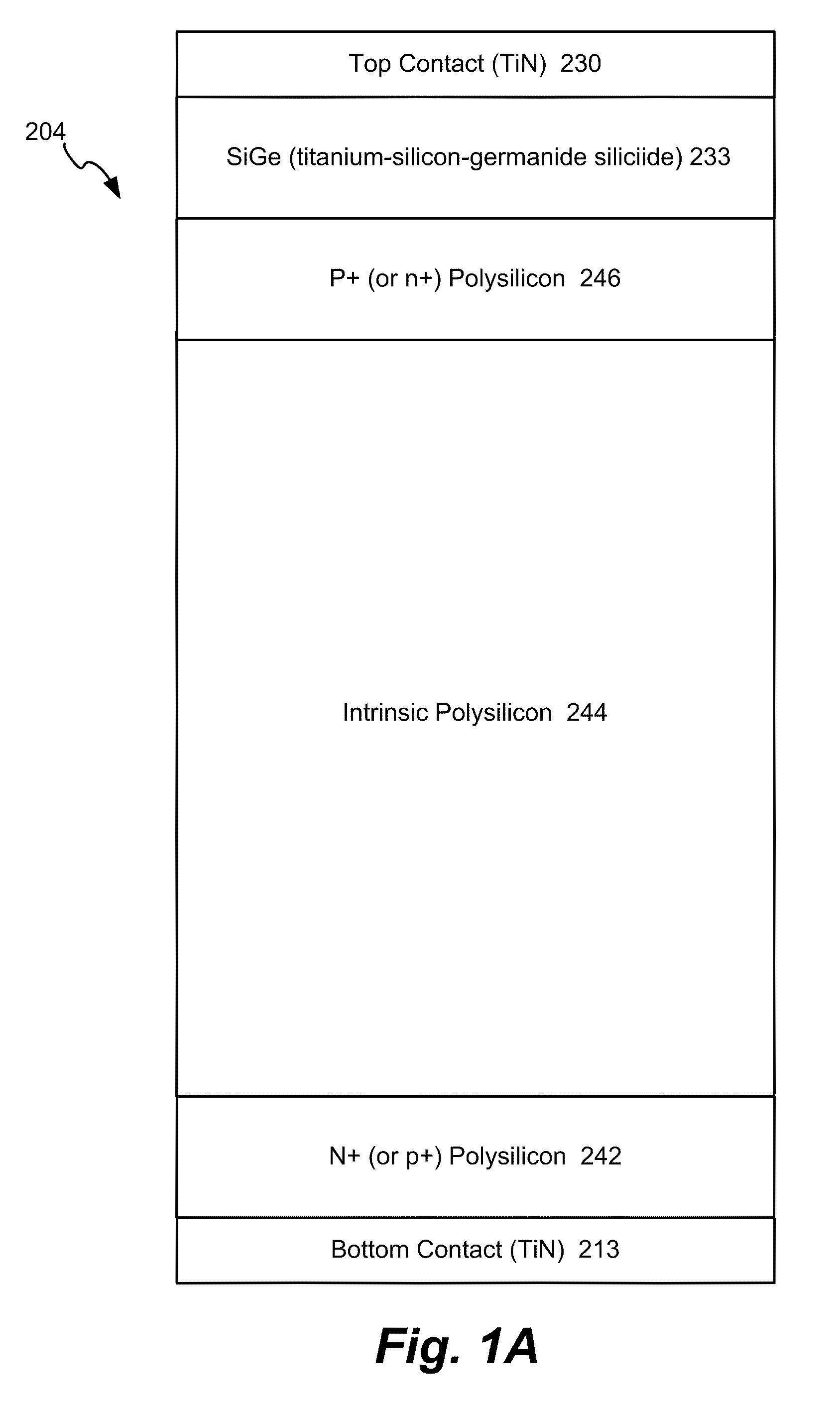

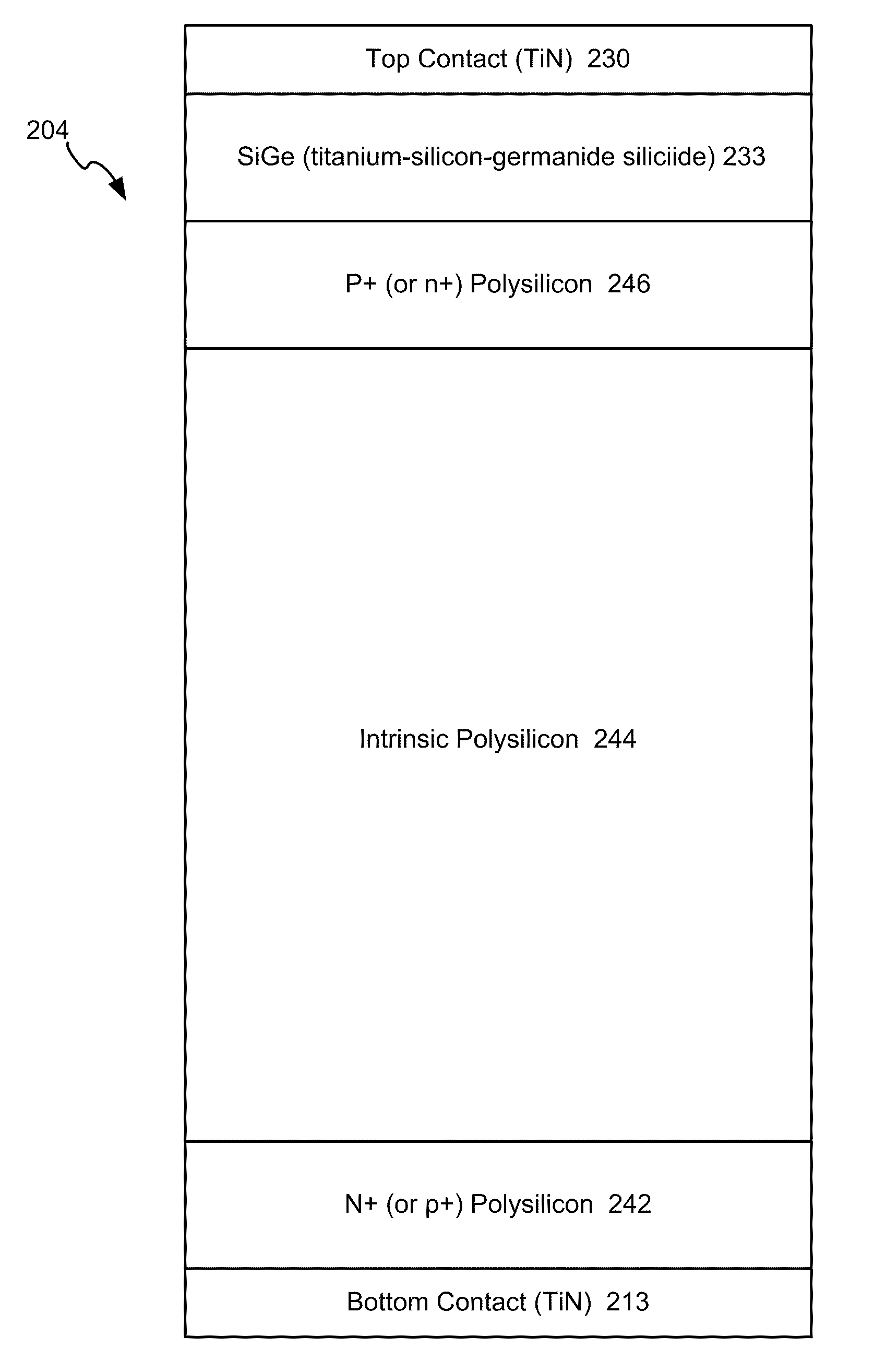

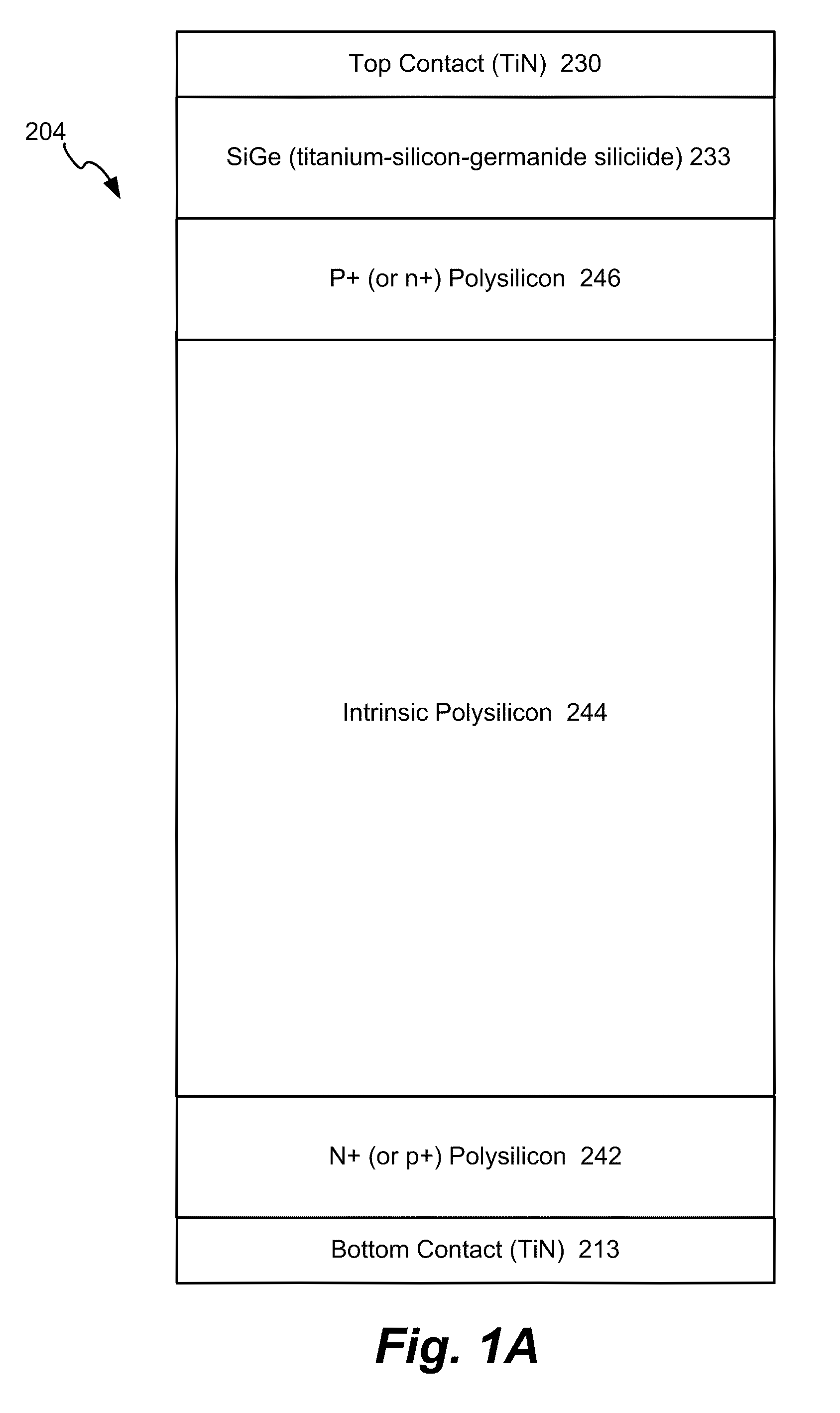

3D polysilicon diode with low contact resistance and method for forming same

ActiveUS8207064B2Solid-state devicesSemiconductor/solid-state device manufacturingPower flowReverse bias

A semiconductor p-i-n diode and method for forming the same are described herein. In one aspect, a SiGe region is formed between a region doped to have one conductivity (either p+ or n+) and an electrical contact to the p-i-n diode. The SiGe region may serve to lower the contact resistance, which may increase the forward bias current. The doped region extends below the SiGe region such that it is between the SiGe region and an intrinsic region of the diode. The p-i-n diode may be formed from silicon. The doped region below the SiGe region may serve to keep the reverse bias current from increasing as result of the added SiGe region. In one embodiment, the SiGe is formed such that the forward bias current of an up-pointing p-i-n diode in a memory array substantially matches the forward bias current of a down-pointing p-i-n diode which may achieve better switching results when these diodes are used with the R / W material in a 3D memory array.

Owner:SANDISK TECH LLC

Three dimensional memory device and method for fabricating the same

ActiveUS20180175051A1Reduce the impactReduce impactSolid-state devicesSemiconductor/solid-state device manufacturing3d memoryRidge

A 3D memory device includes a substrate, a ridge-shaped stack, a memory layer, a channel layer and a capping layer. The ridge-shaped stack includes a plurality of conductive strips extending along a first direction and stacked on the substrate. The memory layer is stacked on a vertical sidewall of the ridge-shaped stack along a second direction that forms a non-straight with the first direction. The channel layer is stacked on the memory layer along the second direction and has a narrow sidewall having a long side extending along the first direction. The capping layer is stacked on the narrow sidewall along a third direction that forms a non-straight angle with the second direction.

Owner:MACRONIX INT CO LTD

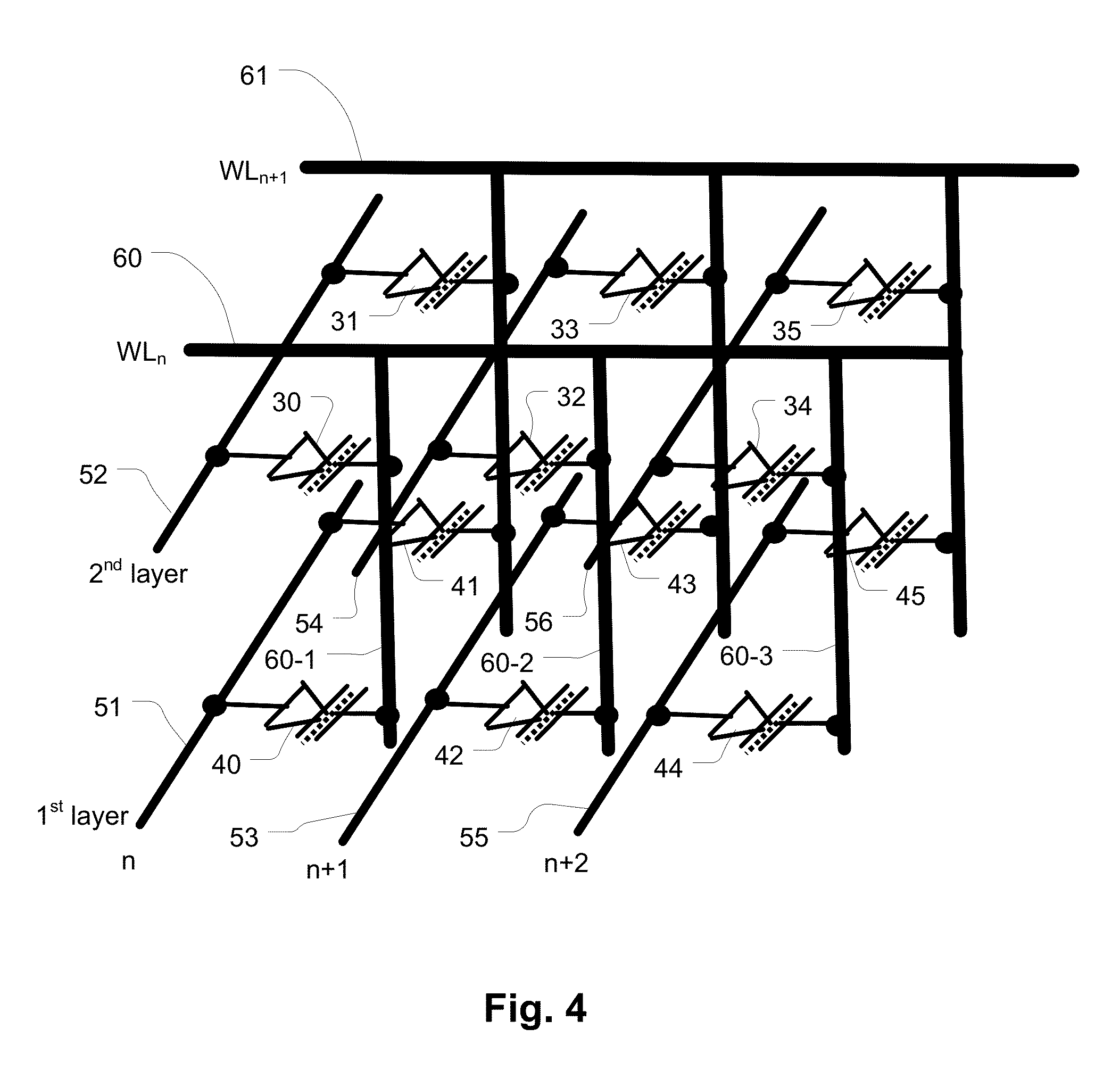

Memory Architecture of 3D Array With Diode in Memory String

Various embodiments are directed to 3D memory arrays that lack a select line and devices controlled by the select line between one of the source line and the bit line, and the memory cells. Diodes between the other of source line and the bit line, and the memory cells provide needed isolation from the memory cells.

Owner:MACRONIX INT CO LTD

Three-dimensional semiconductor device and methods of fabricating and operating the same

InactiveUS20110140070A1Easy to optimizeIncrease the areaSolid-state devicesRead-only memoriesElectrical connectionEngineering

Provided are three-dimensional semiconductor devices and methods of fabricating and operating the same. A device includes a connection node interposed between first and second nodes, a semiconductor pattern connected to the connection node, a plurality of memory elements connected to the semiconductor pattern, word lines connected to the memory elements, and a control electrode disposed opposite the semiconductor pattern. The control electrode selectively controls an electrical connection between the connection node and the memory element, thereby preventing an un-intended current path in a cross-point 3D memory device.

Owner:KIM SUNG DONG

3D polysilicon diode with low contact resistance and method for forming same

ActiveUS20110062557A1Solid-state devicesSemiconductor/solid-state device manufacturingReverse biasContact resistance

A semiconductor p-i-n diode and method for forming the same are described herein. In one aspect, a SiGe region is formed between a region doped to have one conductivity (either p+ or n+) and an electrical contact to the p-i-n diode. The SiGe region may serve to lower the contact resistance, which may increase the forward bias current. The doped region extends below the SiGe region such that it is between the SiGe region and an intrinsic region of the diode. The p-i-n diode may be formed from silicon. The doped region below the SiGe region may serve to keep the reverse bias current from increasing as result of the added SiGe region. In one embodiment, the SiGe is formed such that the forward bias current of an up-pointing p-i-n diode in a memory array substantially matches the forward bias current of a down-pointing p-i-n diode which may achieve better switching results when these diodes are used with the R / W material in a 3D memory array.

Owner:SANDISK TECH LLC

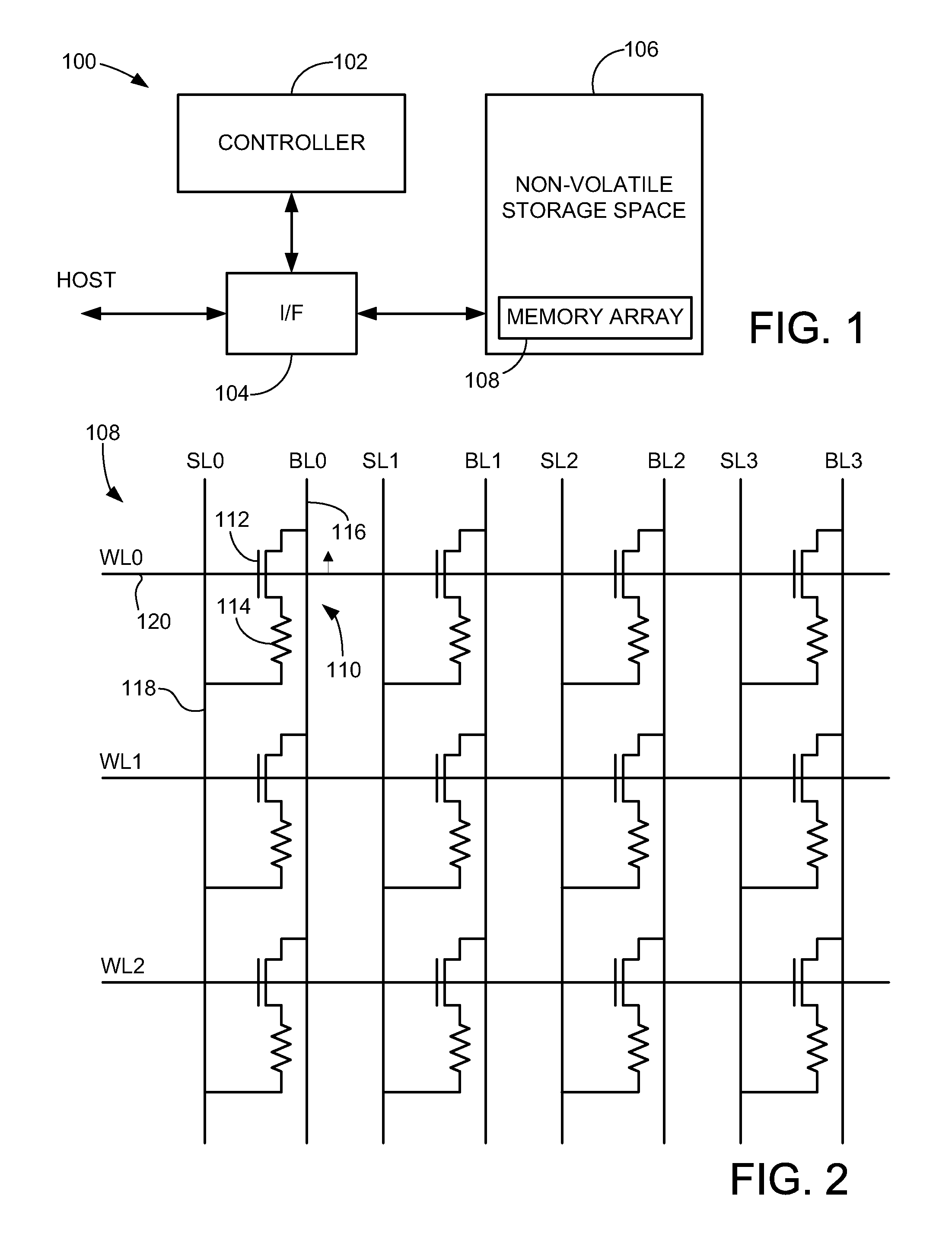

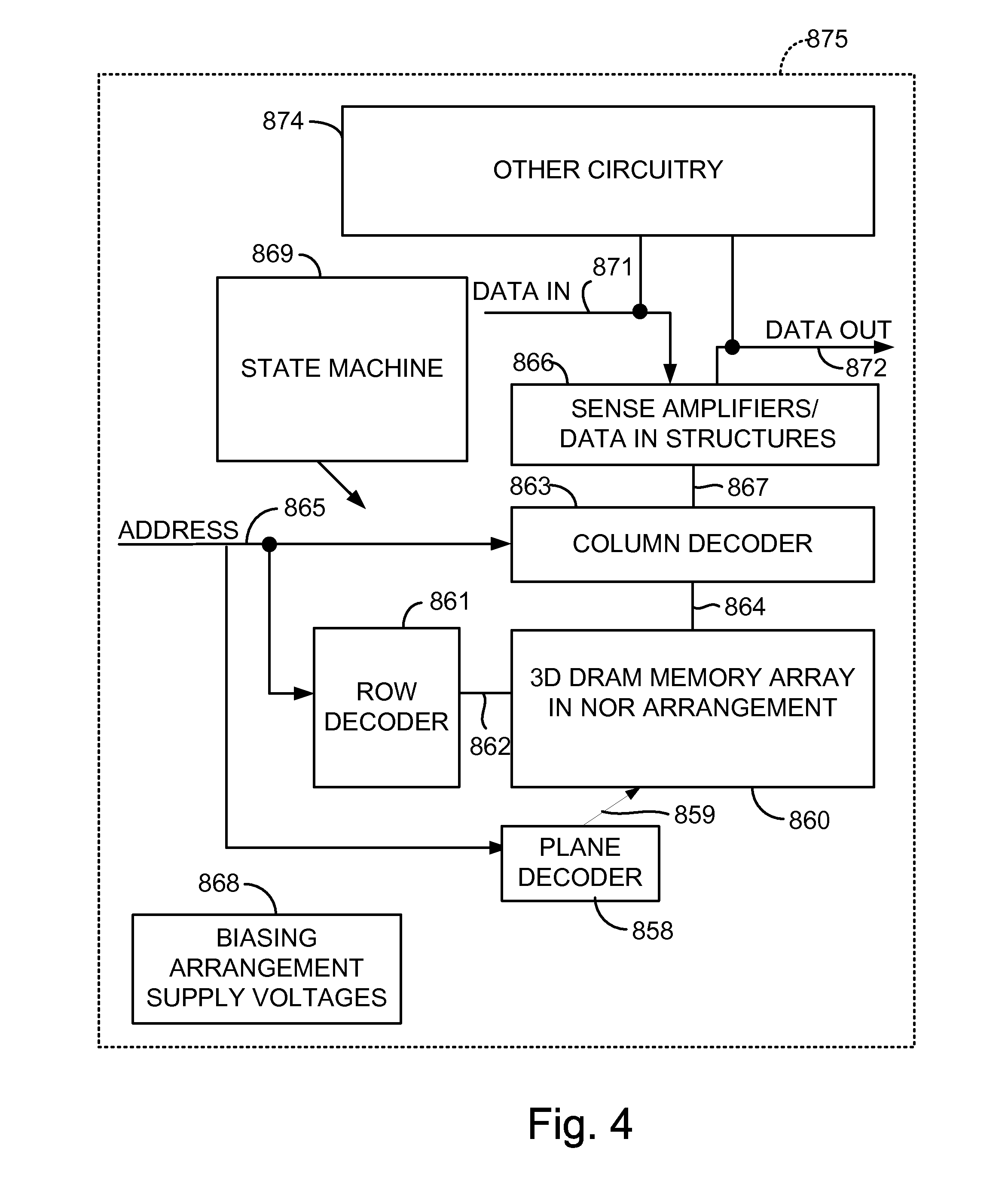

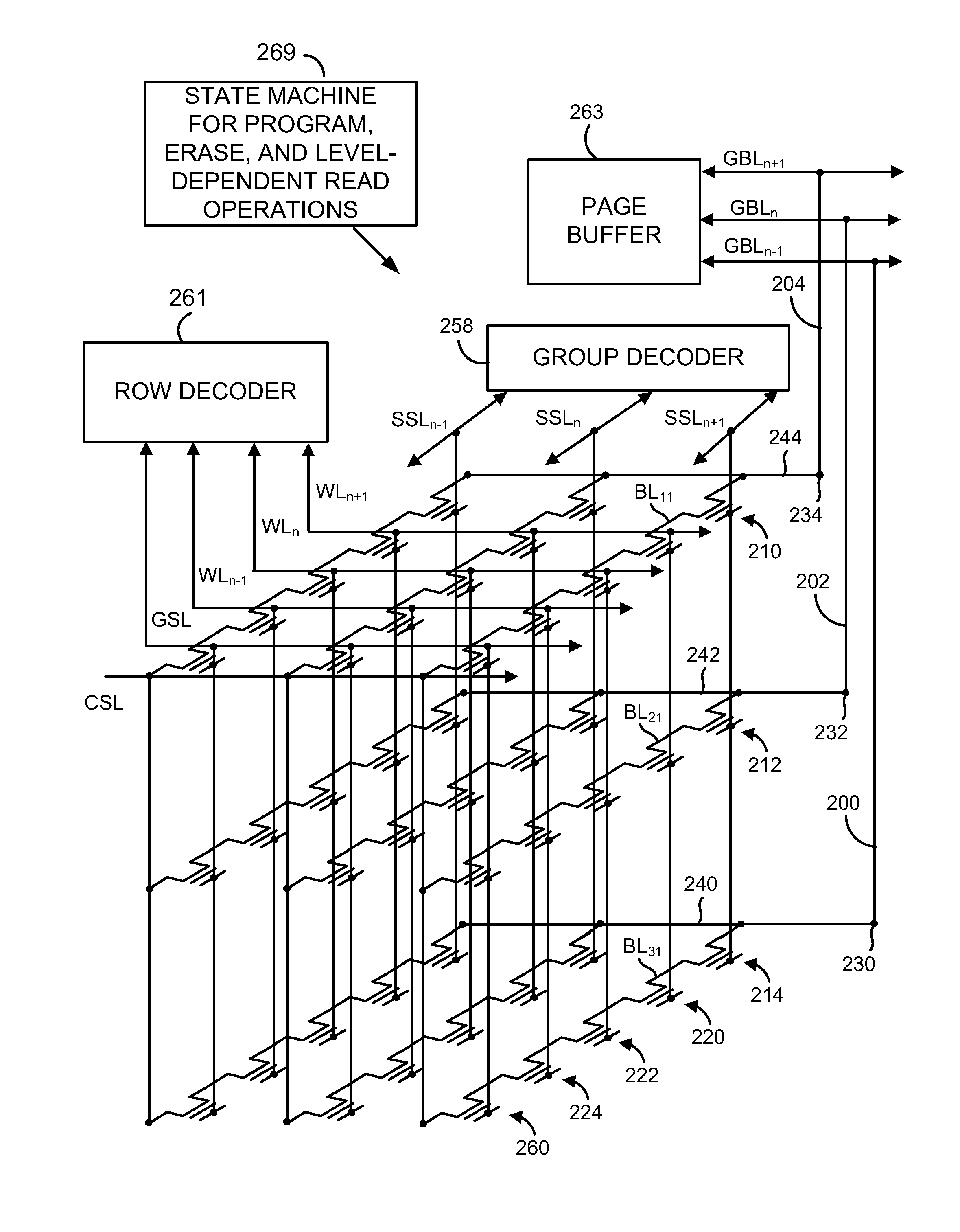

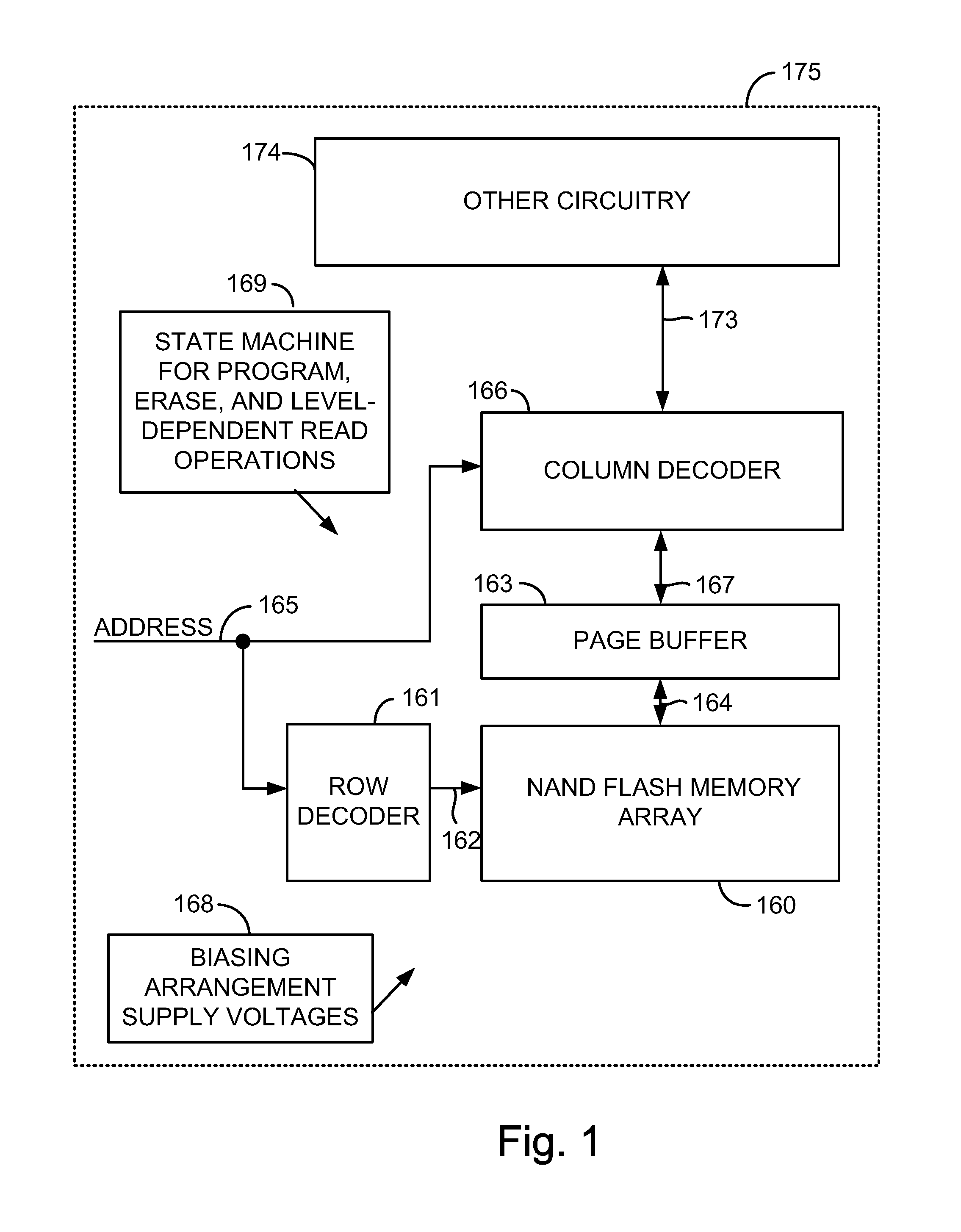

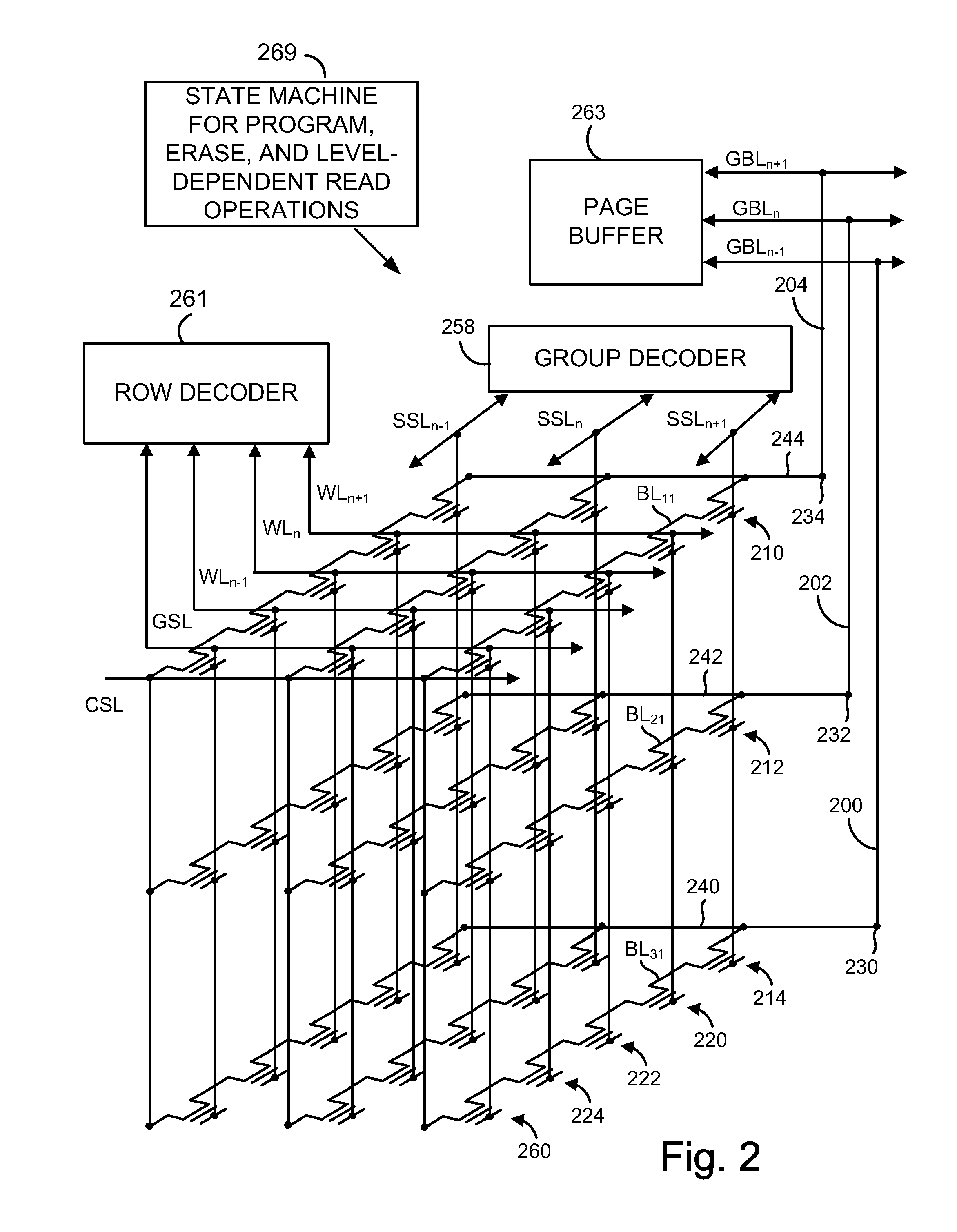

Architecture for a 3D memory array

ActiveUS20120182804A1Minimizing capacitance differenceMinimize the differenceSolid-state devicesRead-only memoriesBit lineCapacitance

Techniques are described herein for compensating for threshold voltage variations among memory cells in an array by applying different bias conditions to selected bit lines. Techniques are also described herein for connecting global bit lines to a variety of levels of memory cells in a 3D array, to provide for minimizing capacitance differences among the global bit lines.

Owner:MACRONIX INT CO LTD

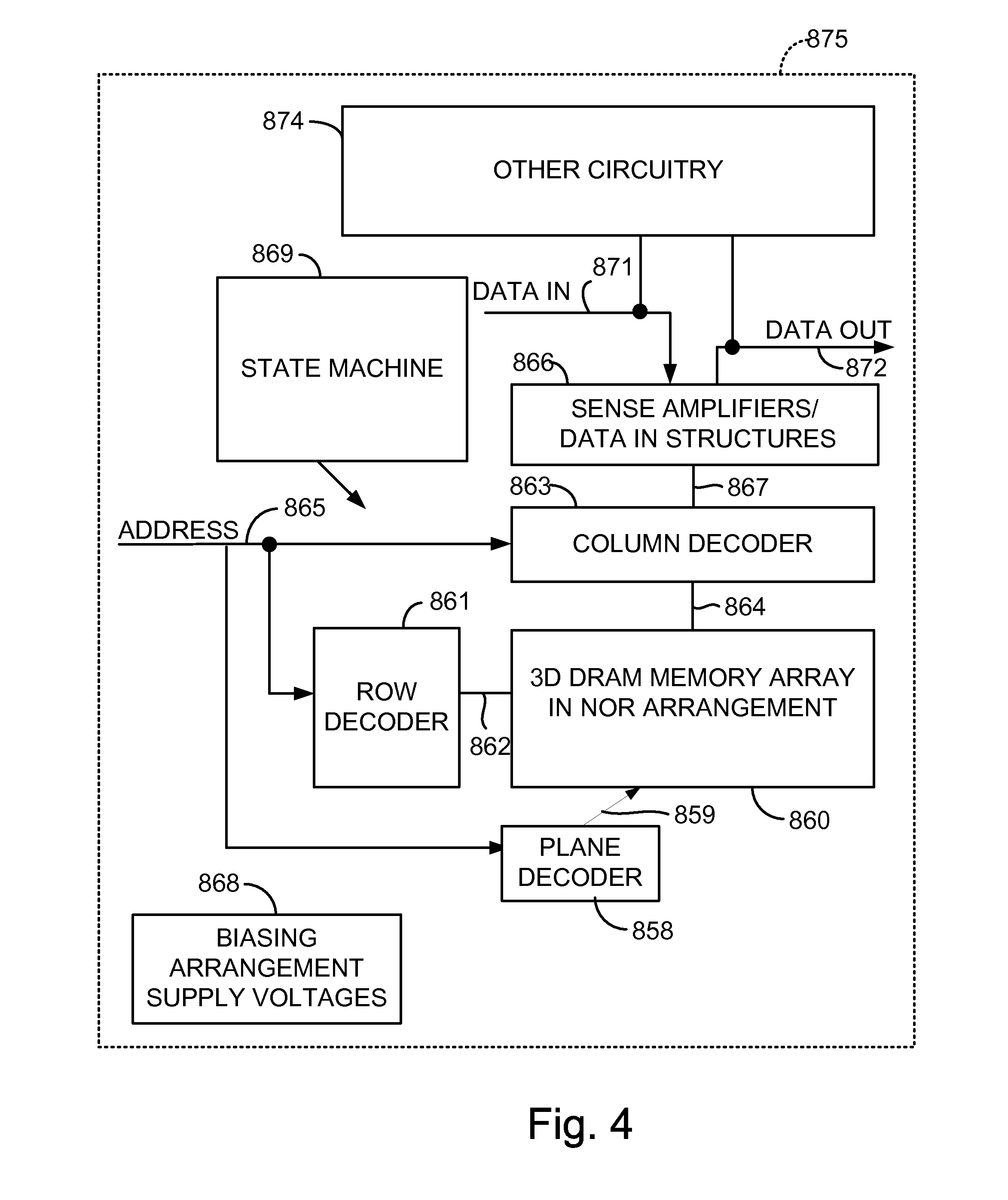

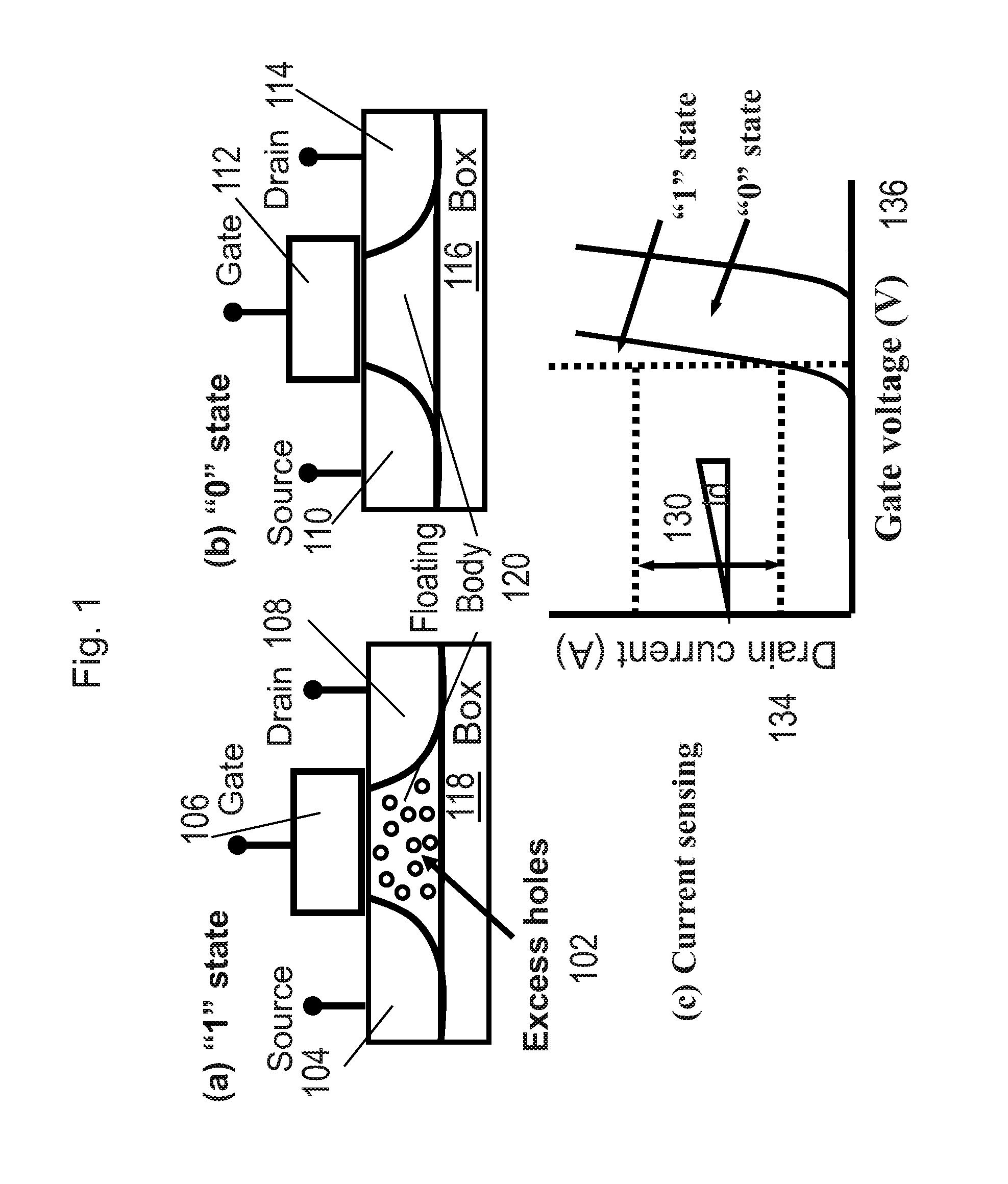

Method of maintaining a memory state

A method of maintaining a memory state of a 3D memory, wherein the memory includes at least a first cell and a second cell overlying the first cell, the method including: applying a back-bias to the first cell and the second cell without interrupting data access to the memory, and generating at least two stable floating body charge levels of the memory state.

Owner:MONOLITHIC 3D

Three-dimensional storage device

Embodiments of three-dimensional (3D) memory devices are disclosed. In an example, a 3D memory device includes a substrate, a peripheral device disposed on the substrate, a memory stacked layer disposed over the peripheral device and including a plurality of conductor / dielectric layer pairs, and a plurality of memory strings. Each memory string extends vertically through the memory stack layer andincludes a source select gate above the drain select gate and the drain select gate. The edges of the conductor / dielectric layer pairs along the vertical direction away from the substrate in the stepped structure of the storage stacked layer are staggered laterally toward the memory strings.

Owner:YANGTZE MEMORY TECH CO LTD

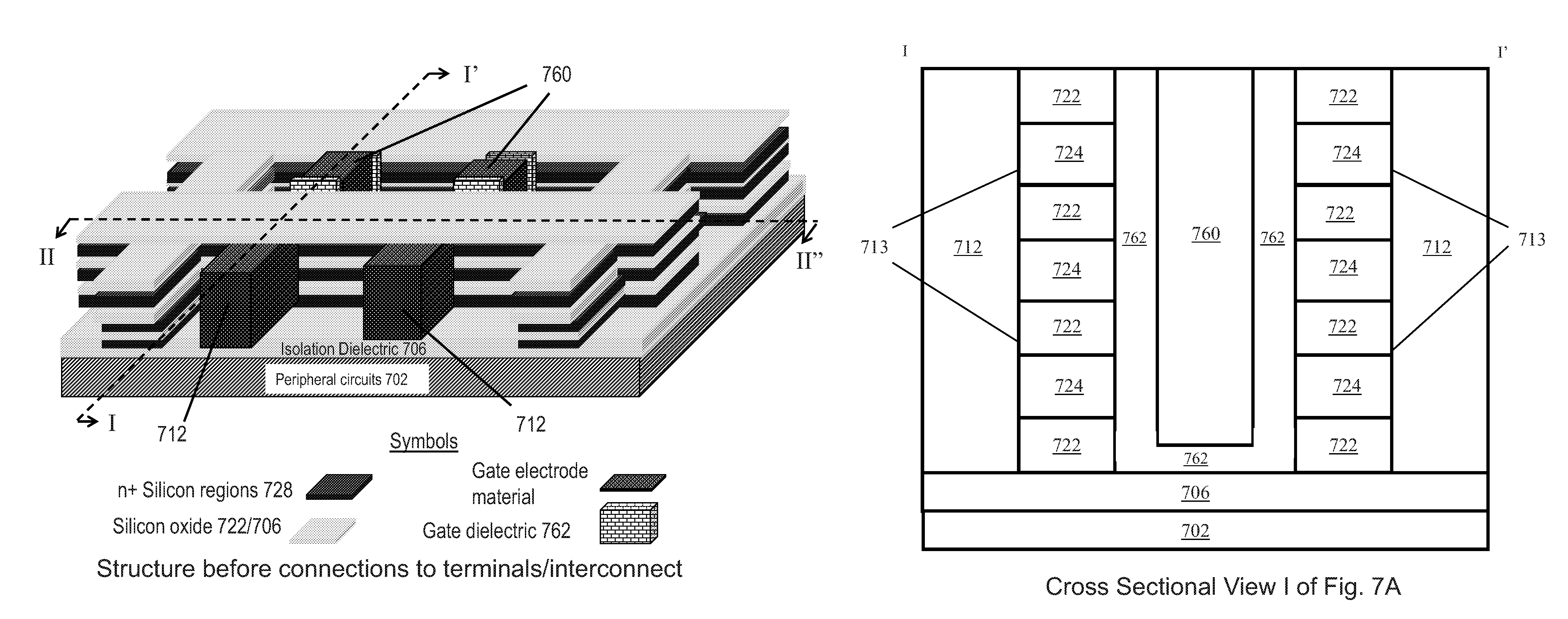

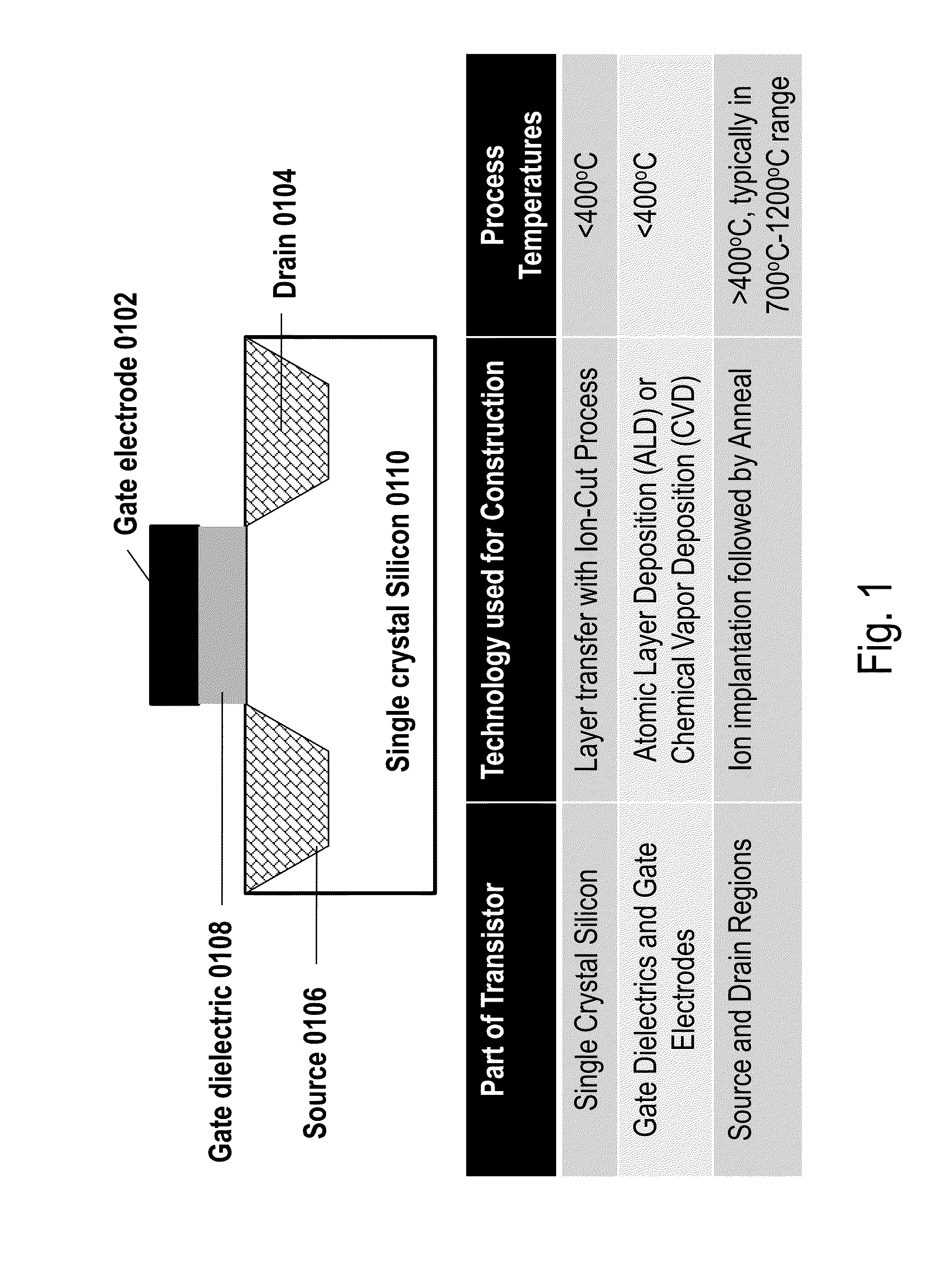

3D memory semiconductor device and structure

InactiveUS8581349B1TransistorSemiconductor/solid-state device detailsPower semiconductor deviceDevice material

A 3D memory device, including: a first memory layer including a first memory transistor with side gates; a second memory layer including a second memory transistor with side gates; and a periphery circuits layer including logic transistors for controlling the memory, the periphery circuits are covered by a first isolation layer, where the first memory layer includes a first monolithically mono-crystal layer directly bonded to a second isolation layer, and the second memory layer includes a second monolithically mono-crystal layer directly bonded to the second isolation layer, and the first mono-crystal layer is bonded on top of the first isolation layer, and the second memory transistor is self-aligned to the first memory transistor.

Owner:MONOLITHIC 3D

Hybrid bonding contact structure of three-dimensional memory device

ActiveUS20190057974A1Easy to etchLower Level RequirementsSemiconductor/solid-state device detailsSolid-state devicesElectricityArray data structure

Embodiments of through array contact structures of a 3D memory device and fabricating method thereof are disclosed. The memory device includes an alternating layer stack disposed on a first substrate. The alternating layer stack includes a first region including an alternating dielectric stack, and a second region including an alternating conductor / dielectric stack. The memory device further includes a barrier structure extending vertically through the alternating layer stack to laterally separate the first region from the second region, multiple through array contacts in the first region, each through array contact extending vertically through the alternating dielectric stack, an array interconnection layer in contact with the through array contacts, a peripheral circuit formed on a second substrate. and a peripheral interconnection layer on the peripheral circuit. The array interconnection layer is bonded on the peripheral interconnection layer, such that the peripheral circuit is electrically connected with at least one through array contact.

Owner:YANGTZE MEMORY TECH CO LTD

3D two bit-per-cell NAND flash memory

A 3D memory device includes bottom and top memory cubes having respective arrays of vertical NAND string structures. A common source plane comprising a layer of conductive material is between the top and bottom memory cubes. The source plane is supplied a bias voltage such as ground, and is selectively coupled to an end of the vertical NAND string structures of the bottom and top memory cubes. Memory cells in a particular memory cube are read using current through the particular vertical NAND string between the source plane and a corresponding bit line coupled to another end of the particular vertical NAND string.

Owner:MACRONIX INT CO LTD

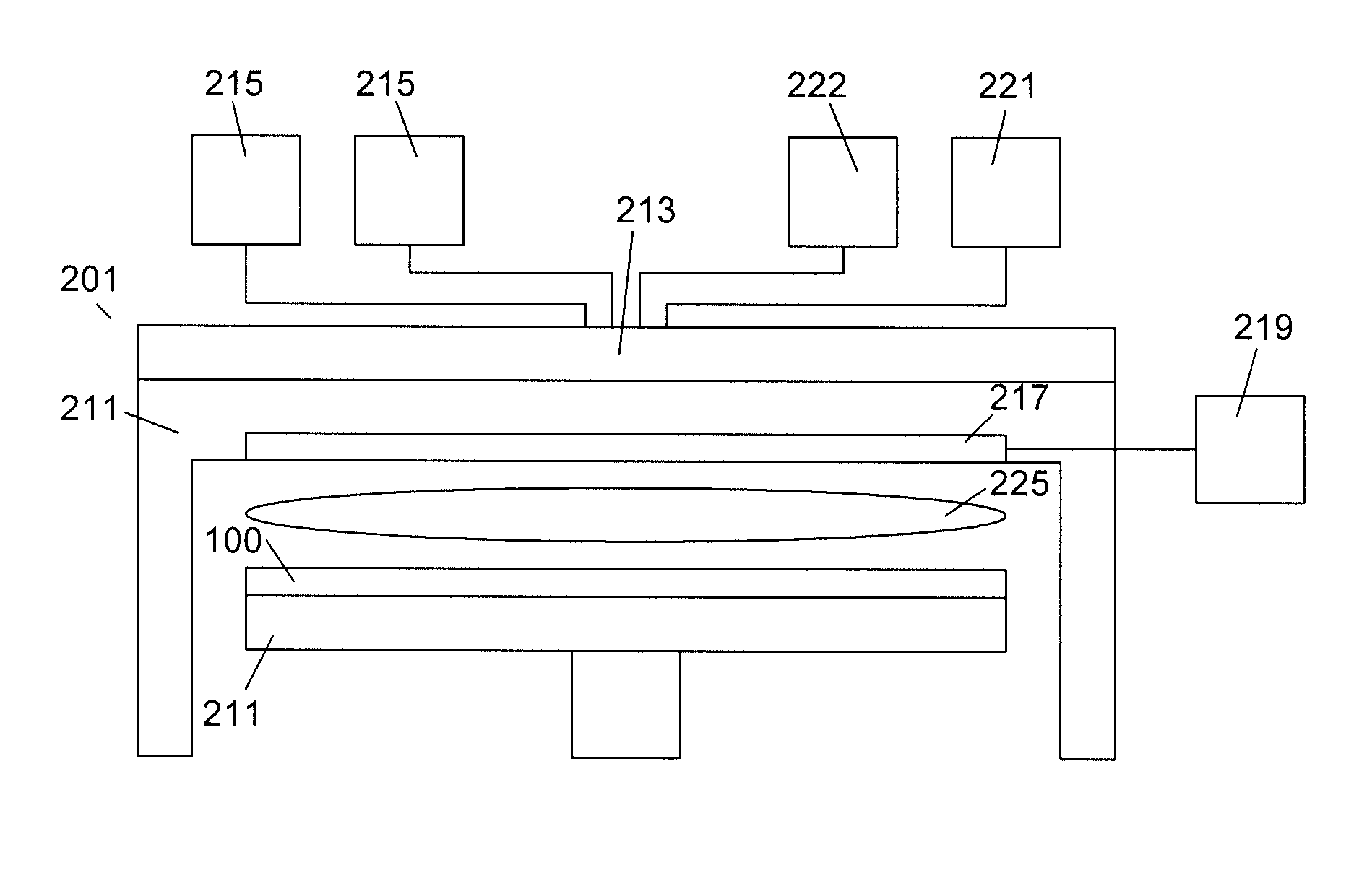

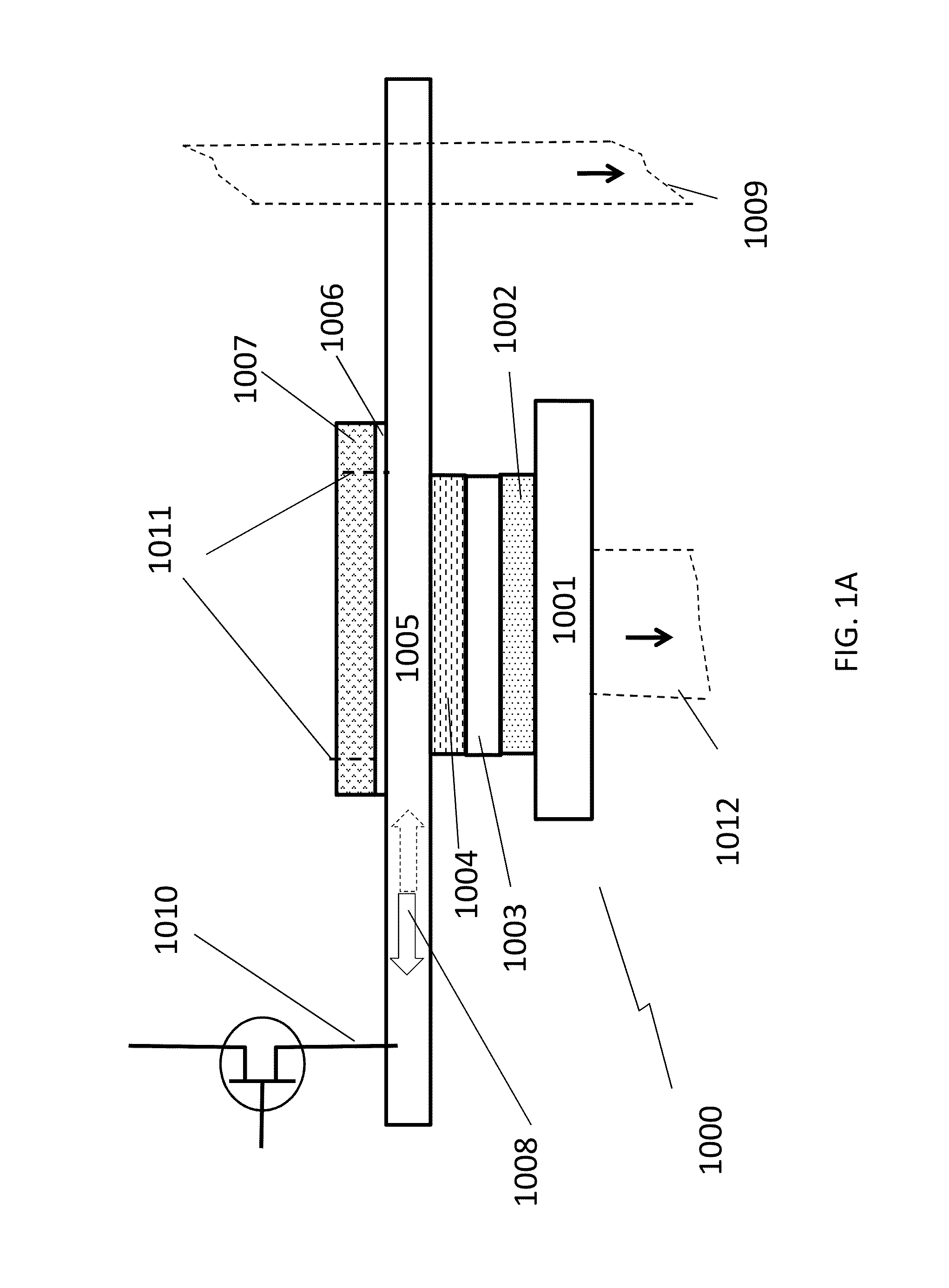

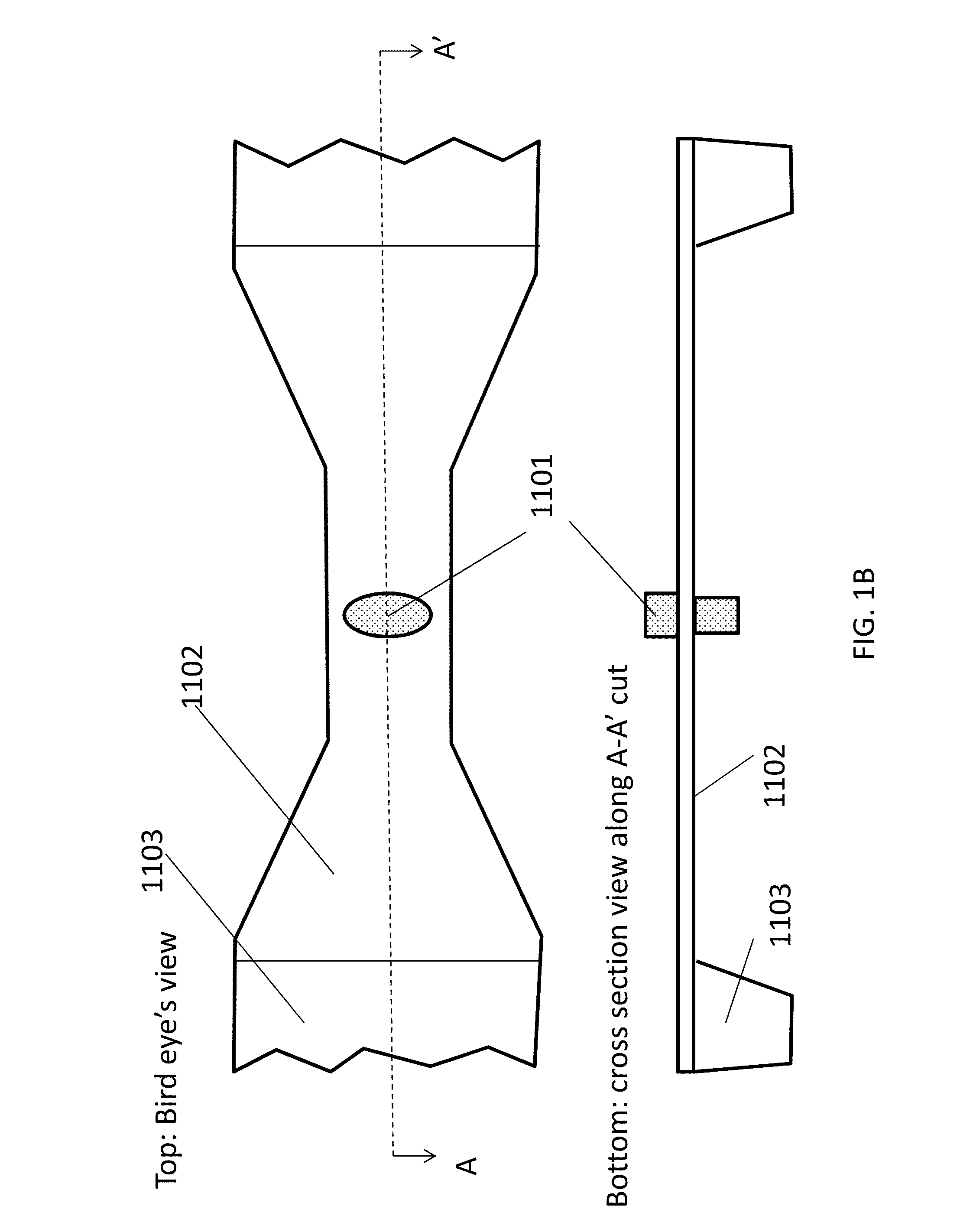

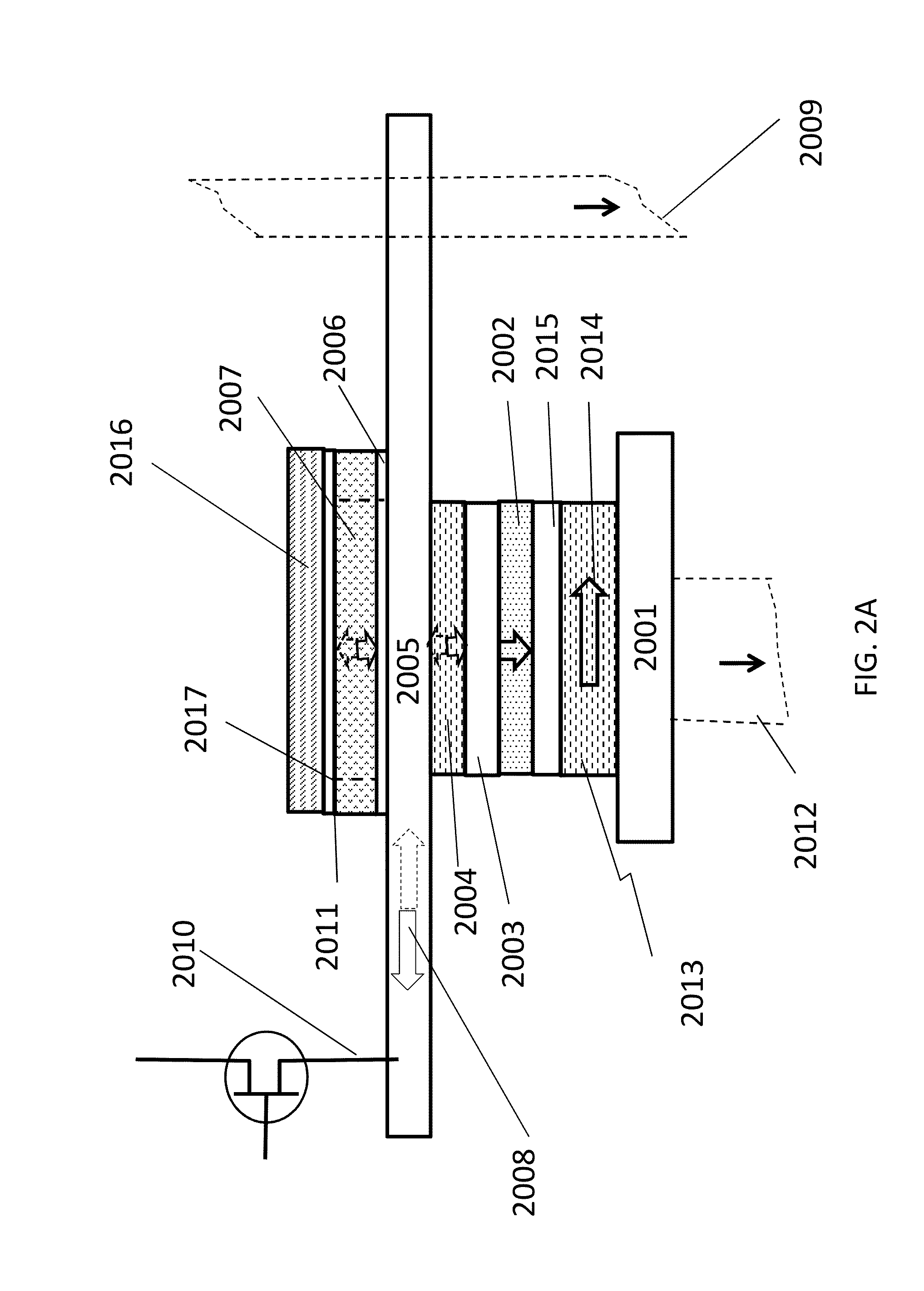

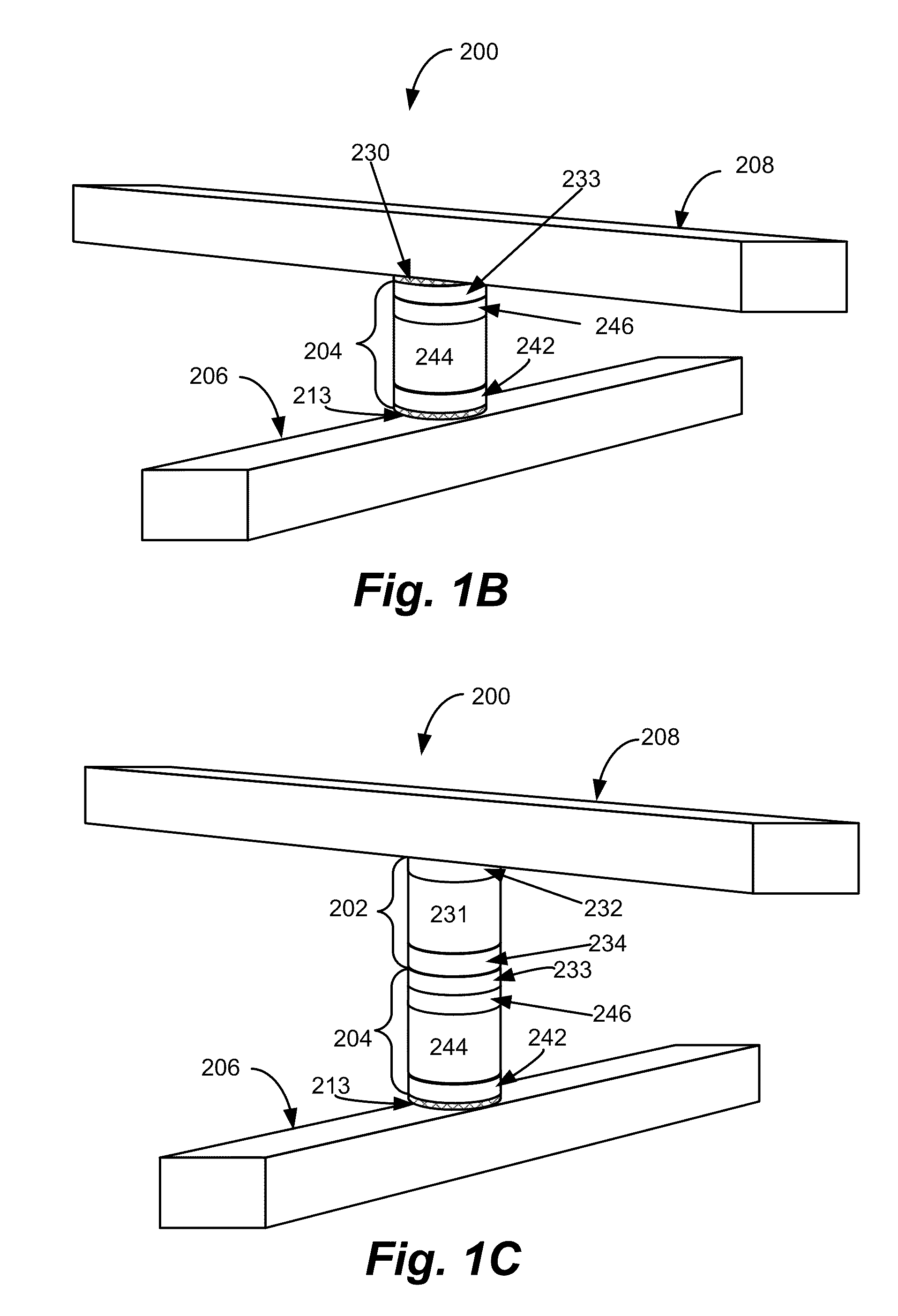

4d device process and structure

InactiveUS20110170266A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringUltra high density

a 4D device comprises a 2D multi-core logic and a 3D memory stack connected through the memory stack sidewall using a fine pitch T&J connection. The 3D memory in the stack is thinned from the original wafer thickness to no remaining Si. A tounge and groove device at the memory wafer top and bottom surfaces allows an accurate stack alignment. The memory stack also has micro-channels on the backside to allow fluid cooling. The memory stack is further diced at the fixed clock-cycle distance and is flipped on its side and re-assembled on to a template into a pseudo-wafer format. The top side wall of the assembly is polished and built with BEOL to fan-out and use the T&J fine pitch connection to join to the 2D logic wafer. The other side of the memory stack is polished, fanned-out, and bumped with C4 solder. The invention also comprises a process for manufacturing the device. In another aspect, the invention comprises a 4D process and device for over 50× greter than 2D memory density per die and an ultra high density memory.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com