Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

562 results about "Memory architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory architecture describes the methods used to implement electronic computer data storage in a manner that is a combination of the fastest, most reliable, most durable, and least expensive way to store and retrieve information. Depending on the specific application, a compromise of one of these requirements may be necessary in order to improve another requirement. Memory architecture also explains how binary digits are converted into electric signals and then stored in the memory cells. And also the structure of a memory cell.

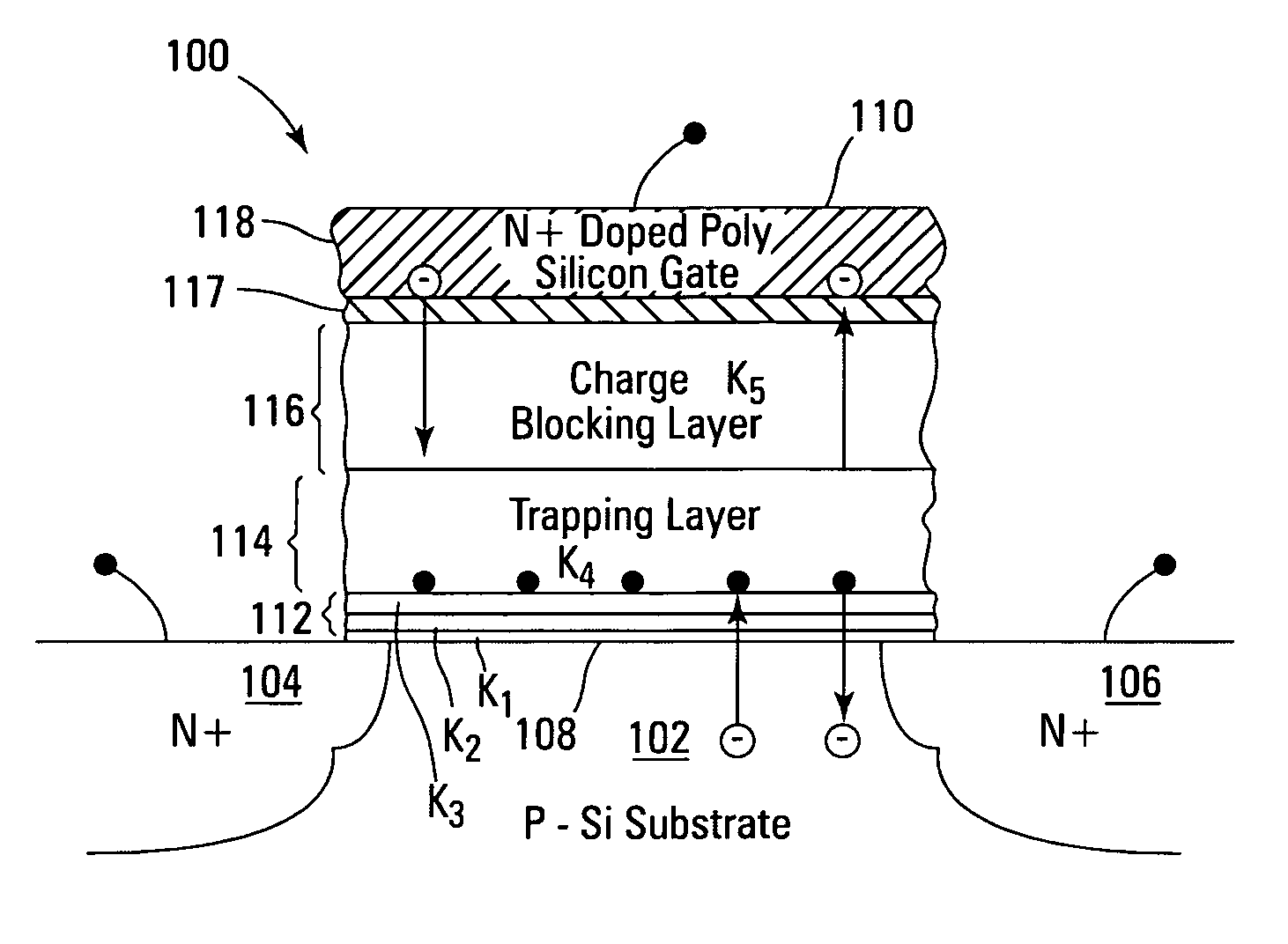

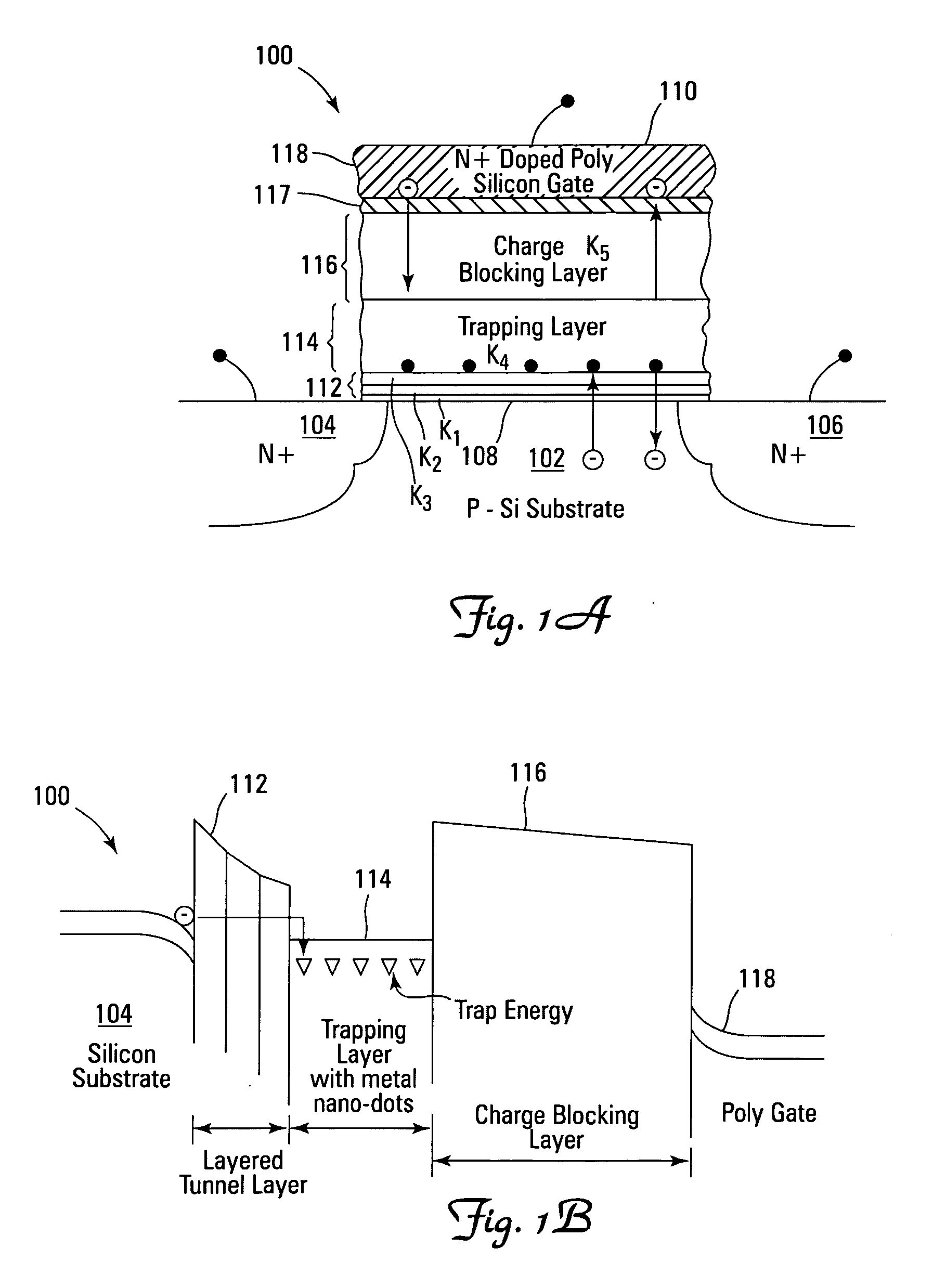

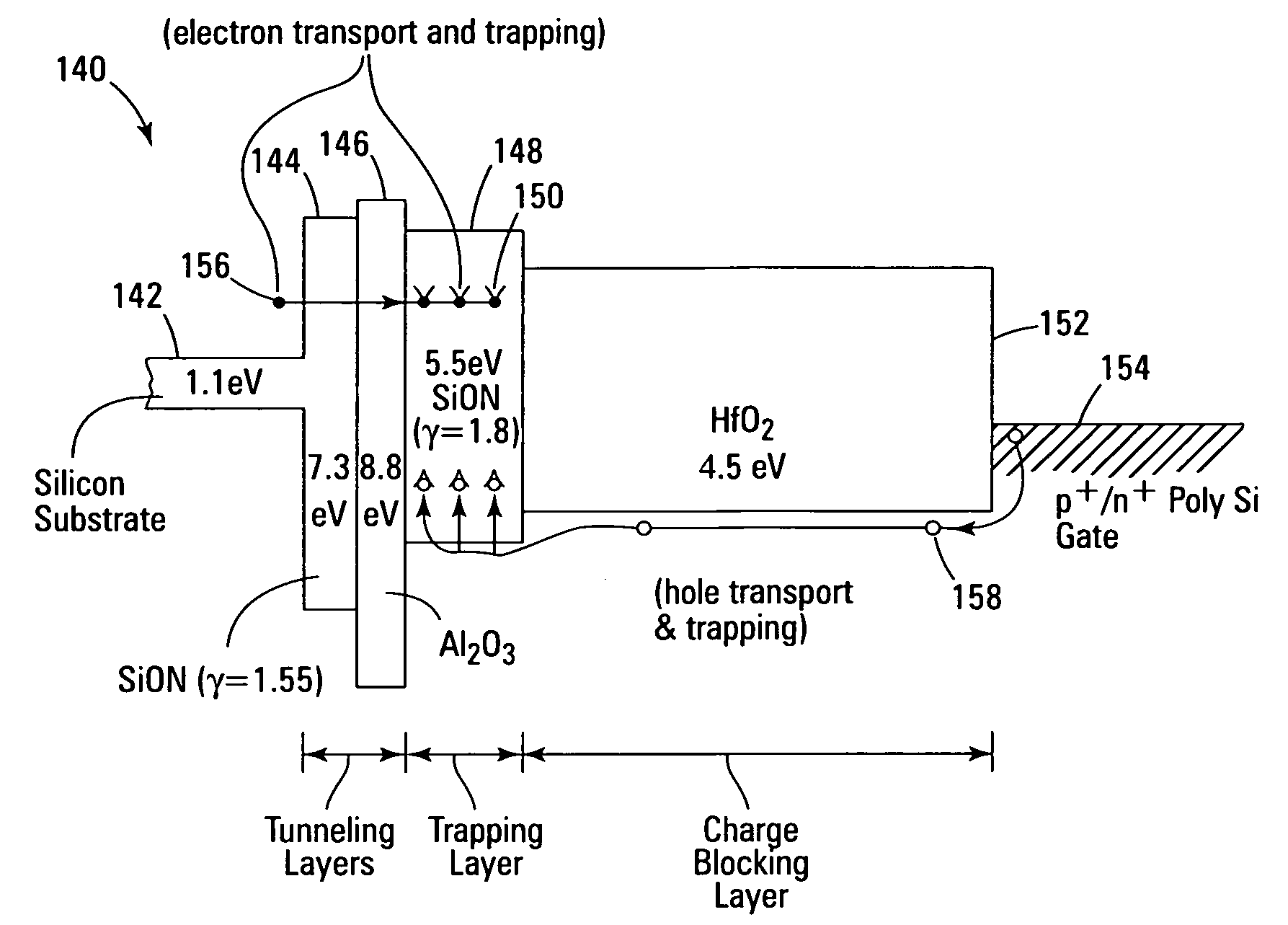

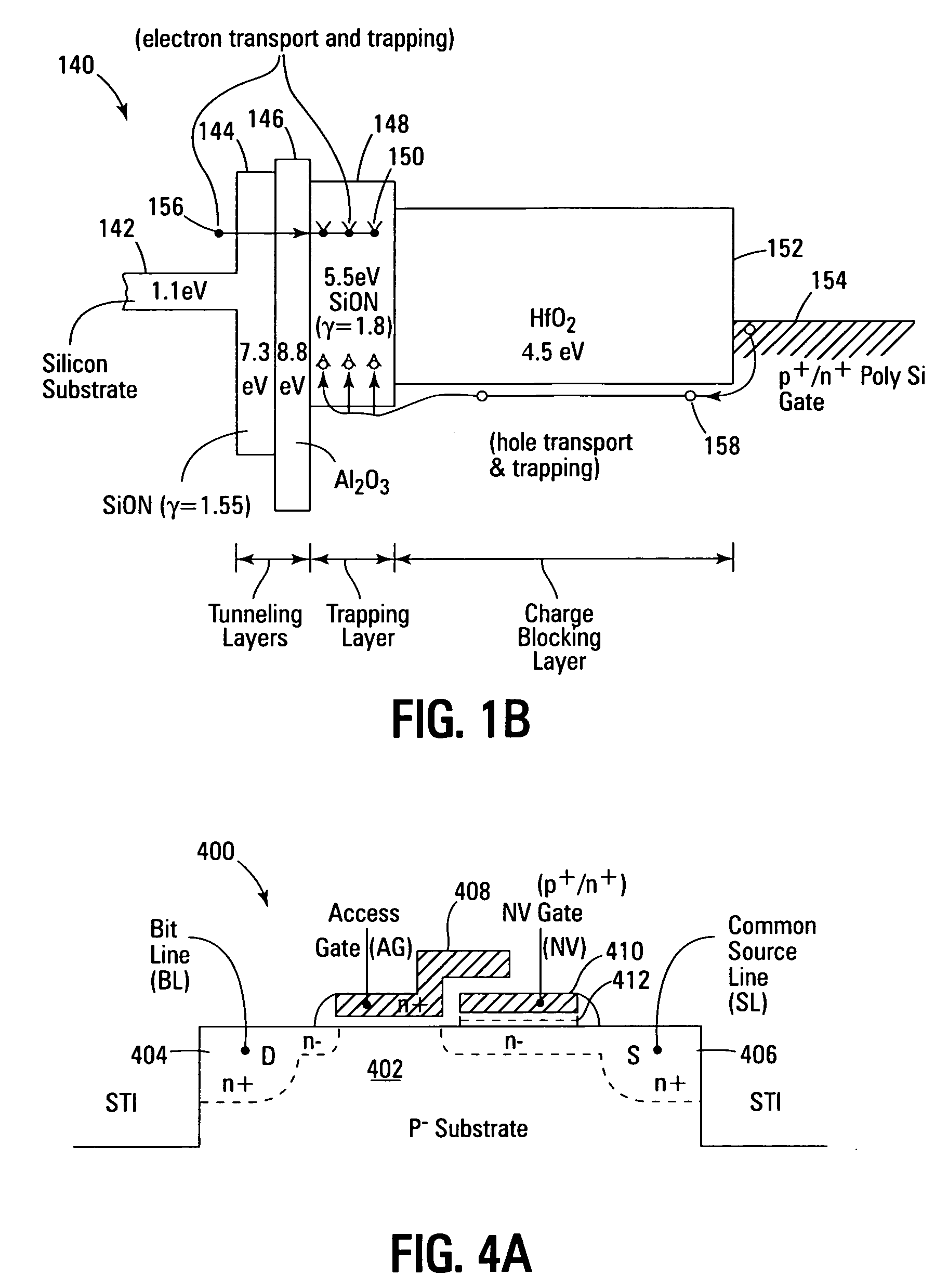

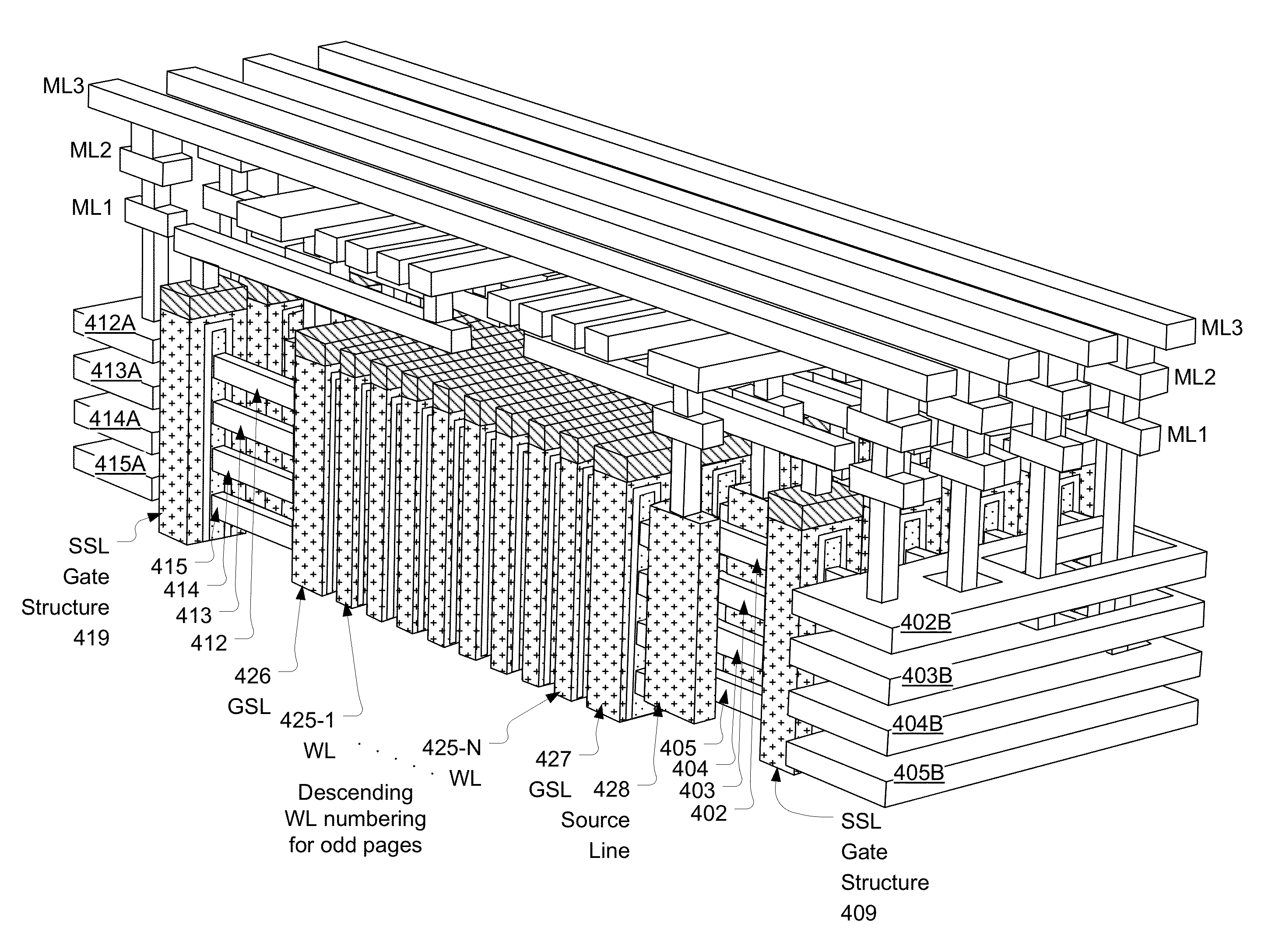

Novel low power non-volatile memory and gate stack

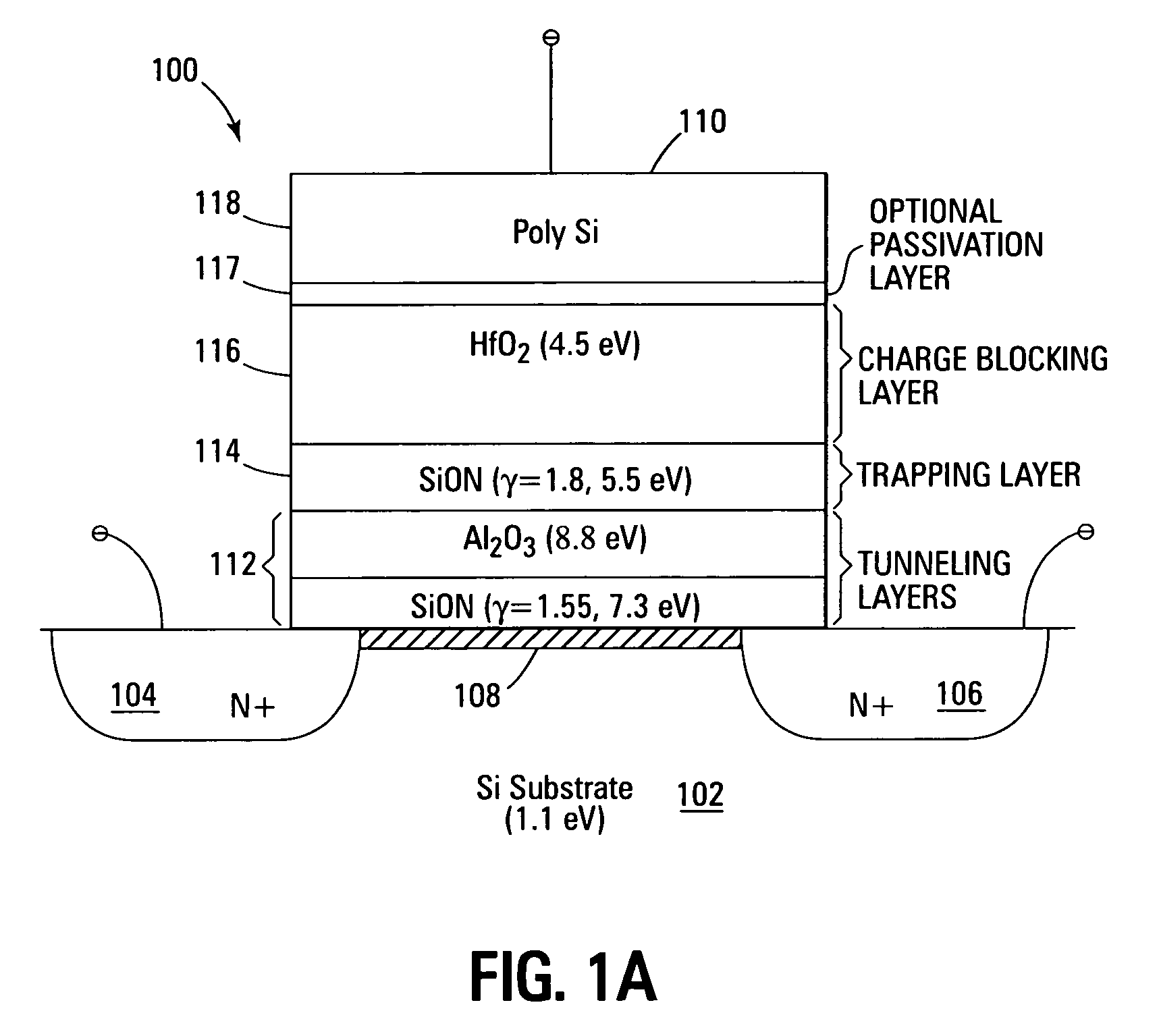

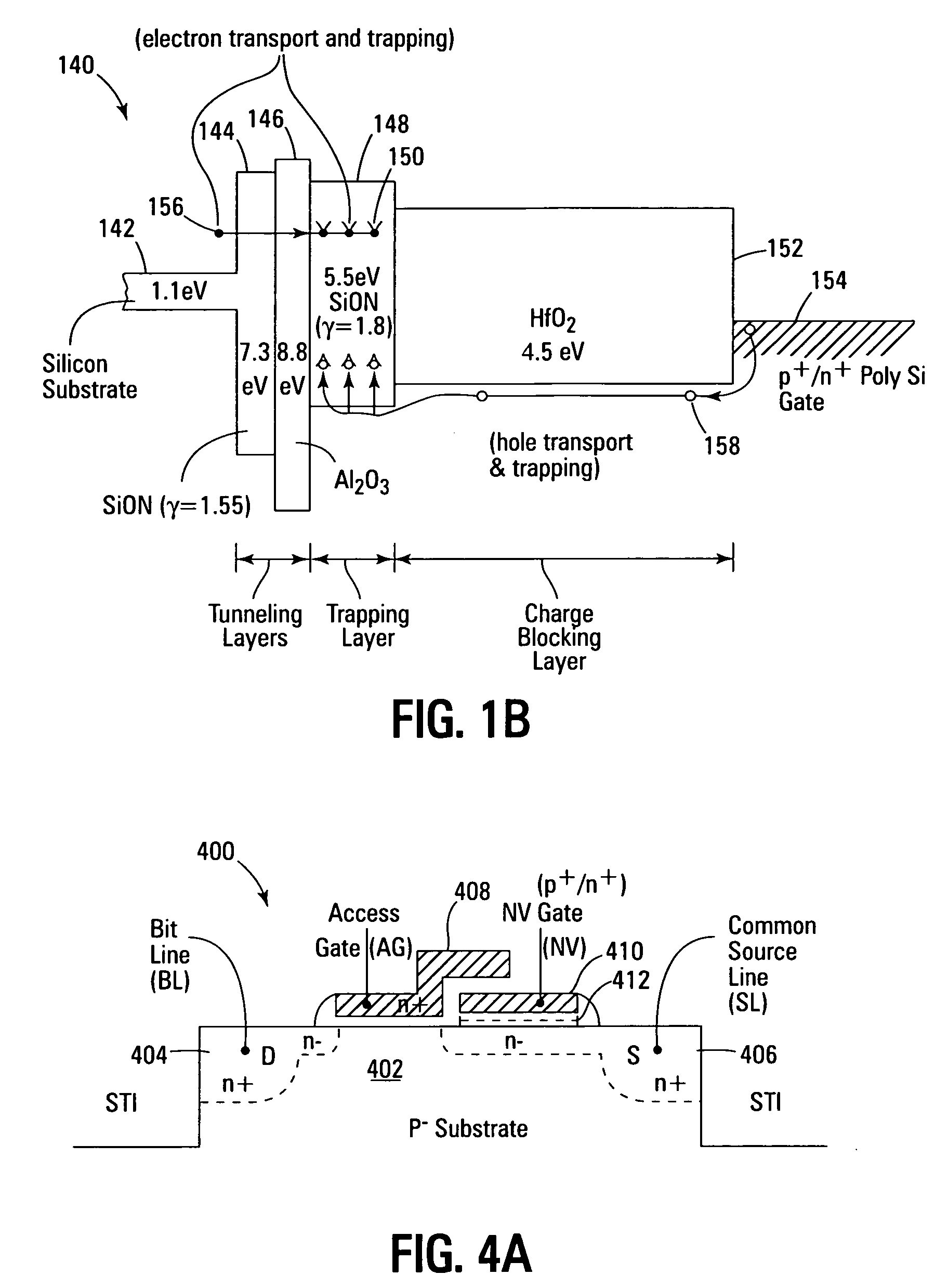

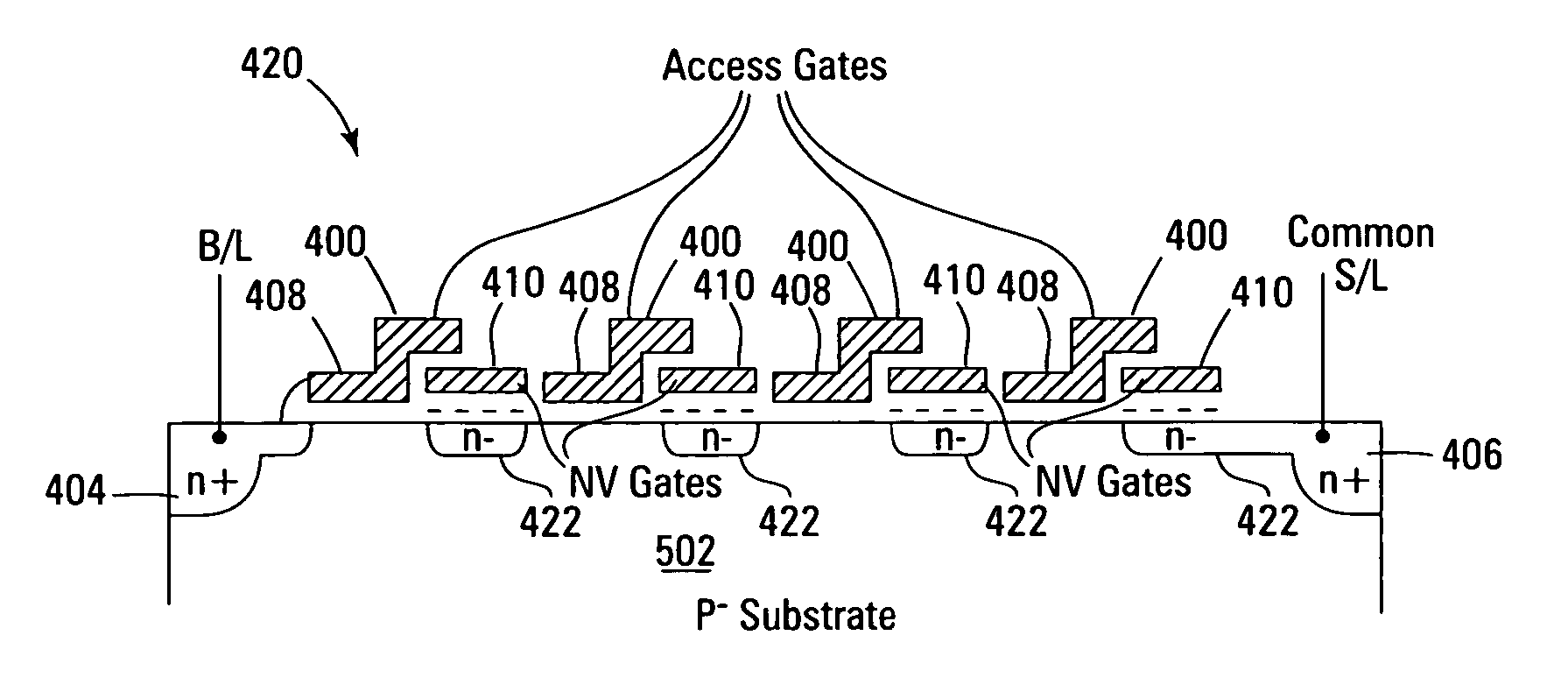

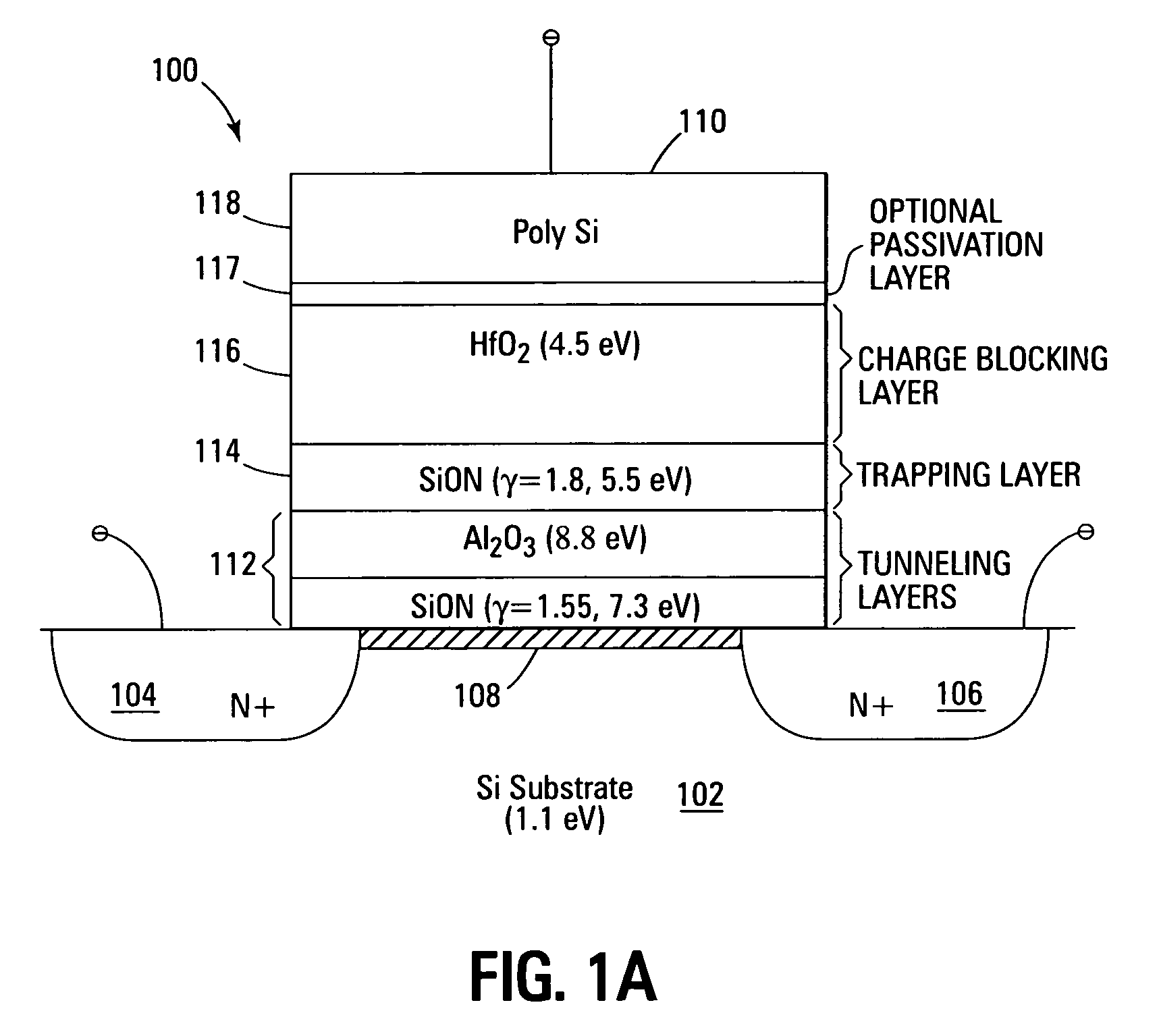

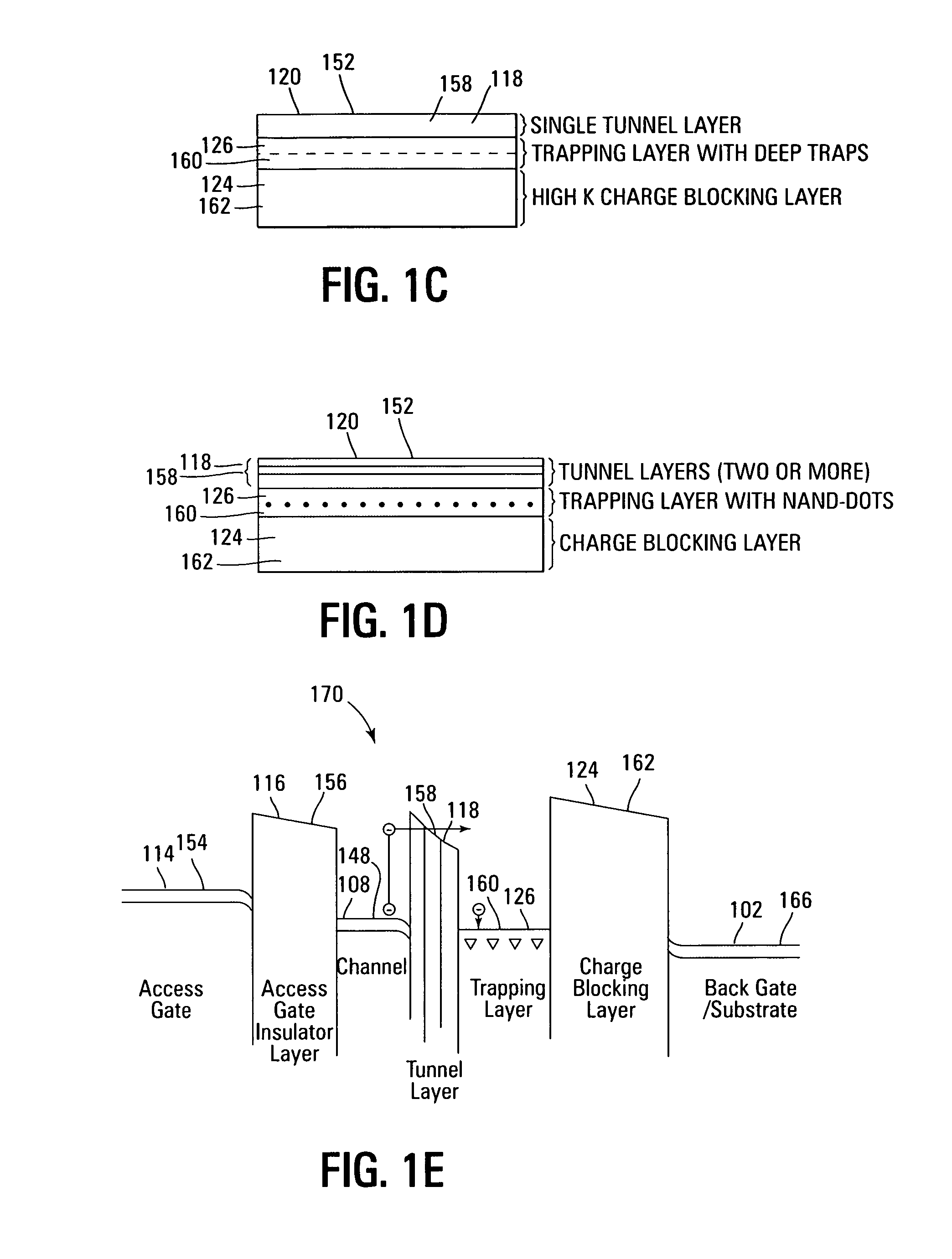

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

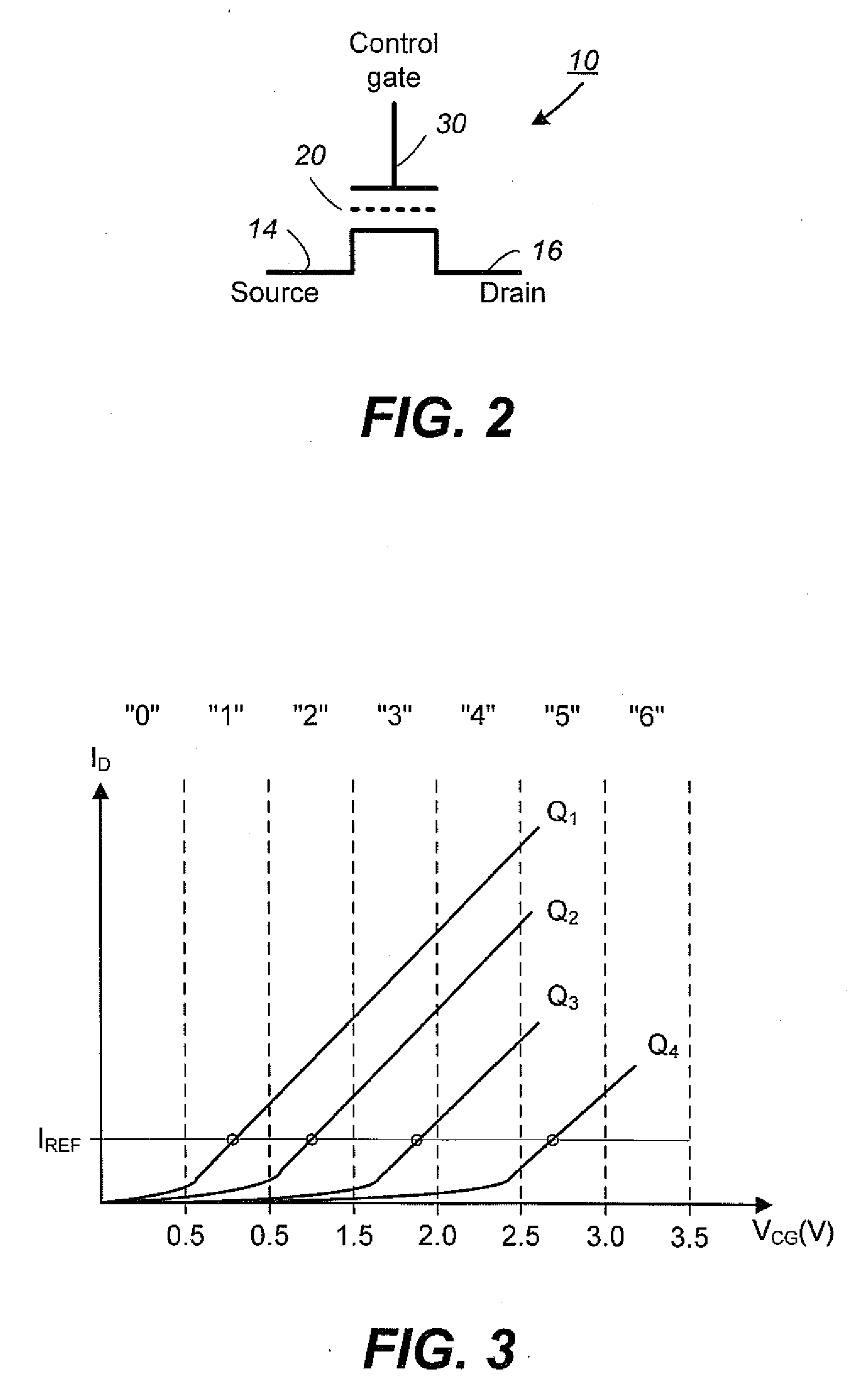

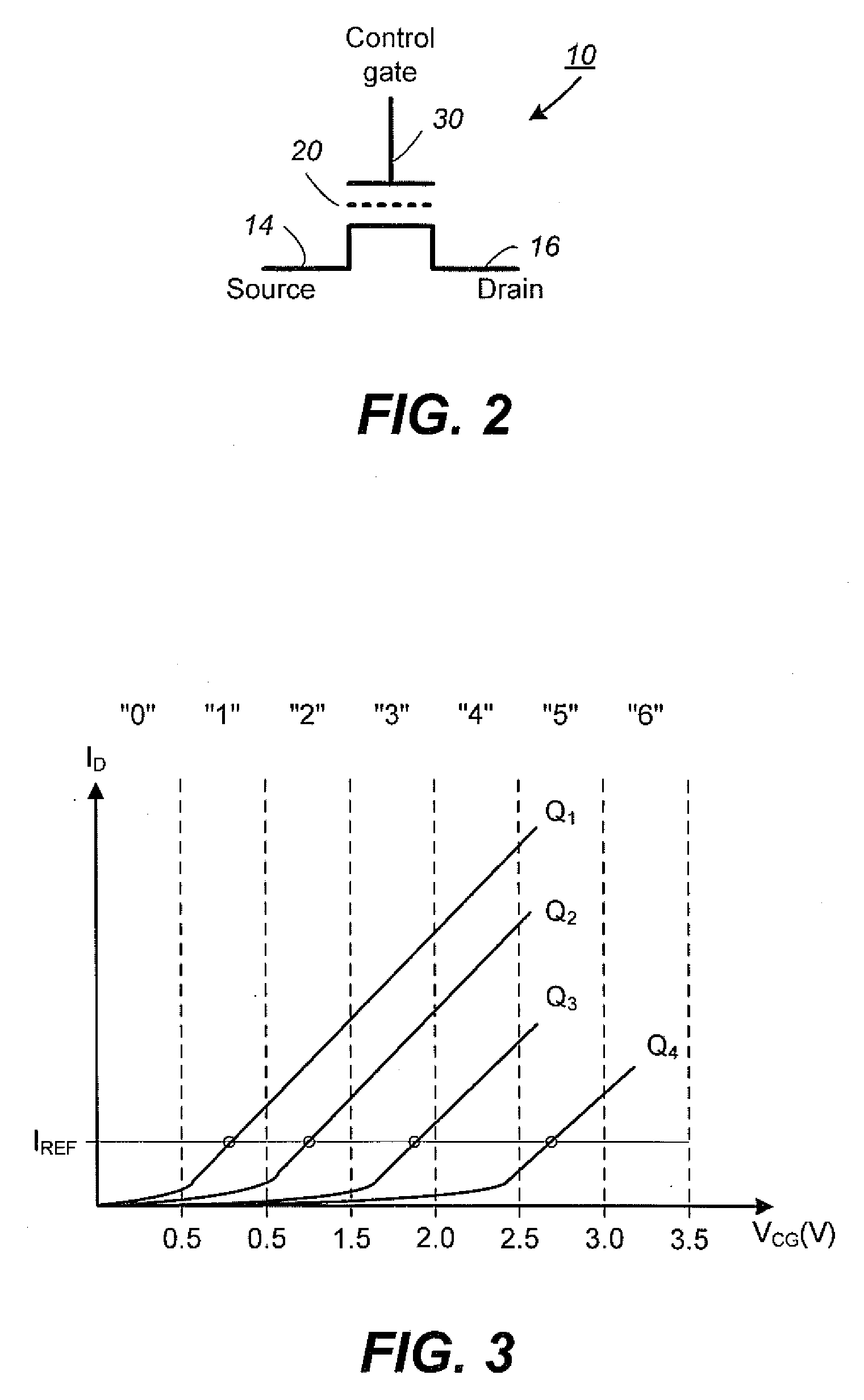

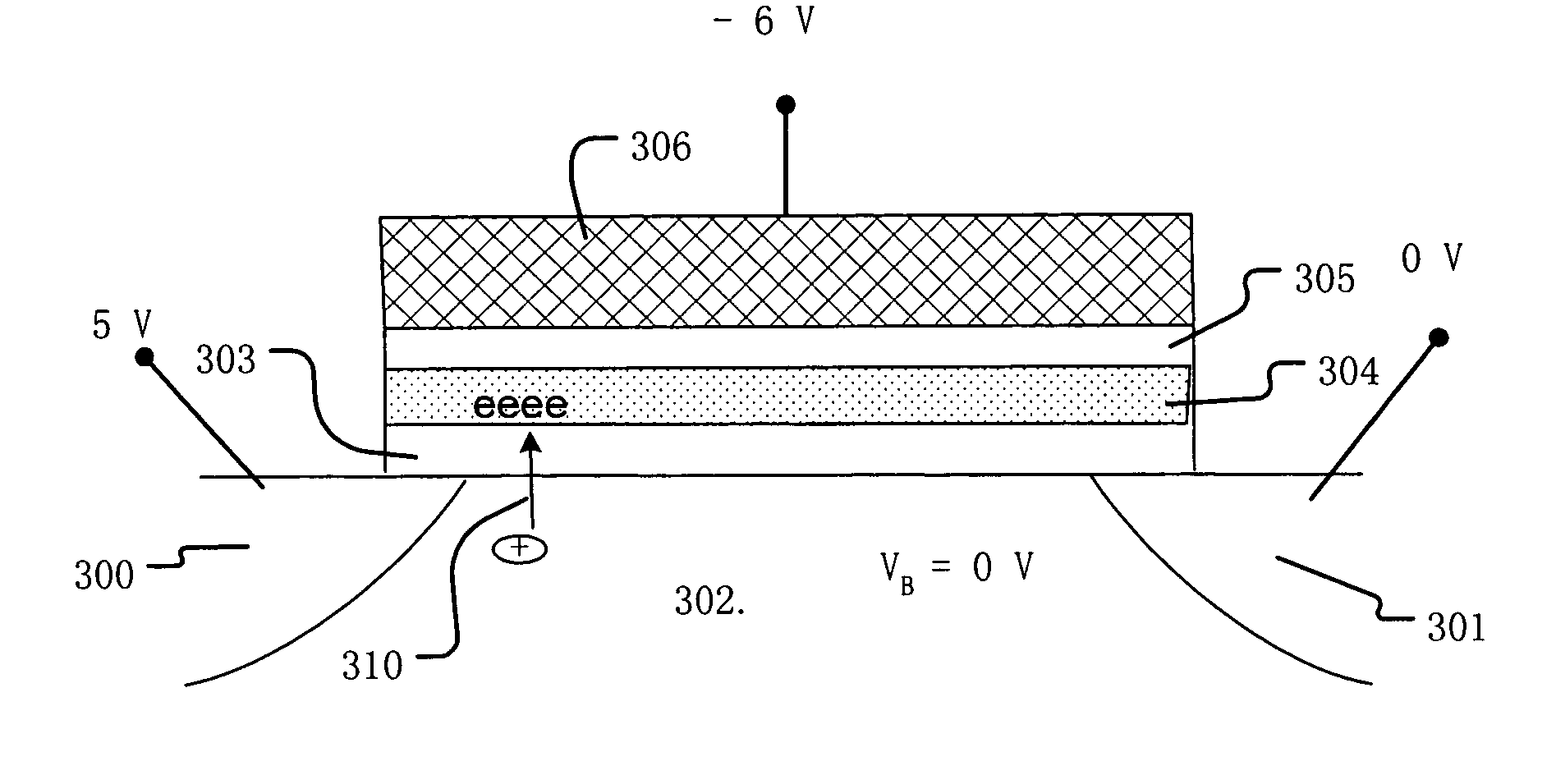

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

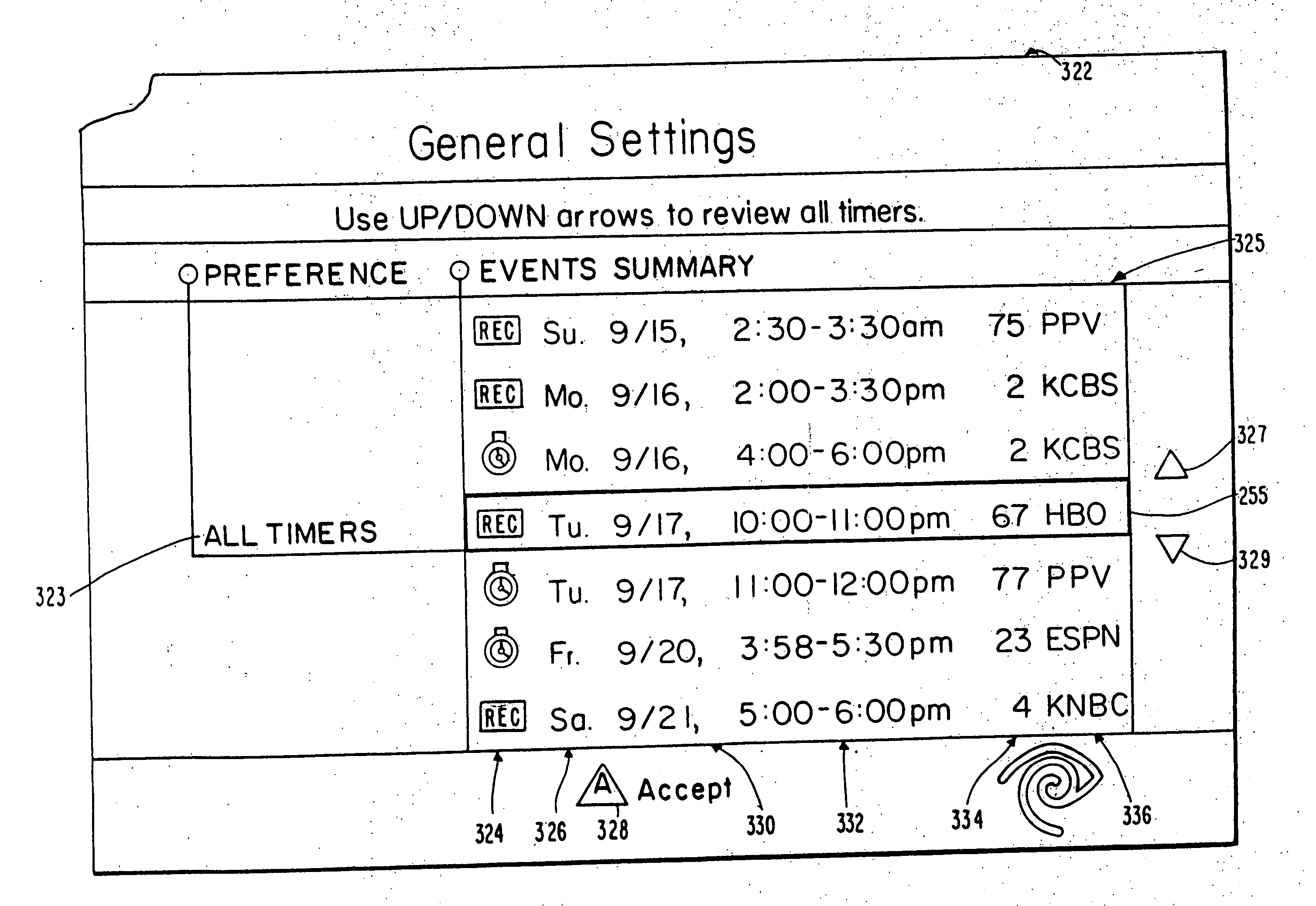

Interactive television program guide display

InactiveUS20050015804A1Increase the number ofEnhanced signalTelevision system detailsTelevision system scanning detailsThe InternetHybrid fibre-coaxial

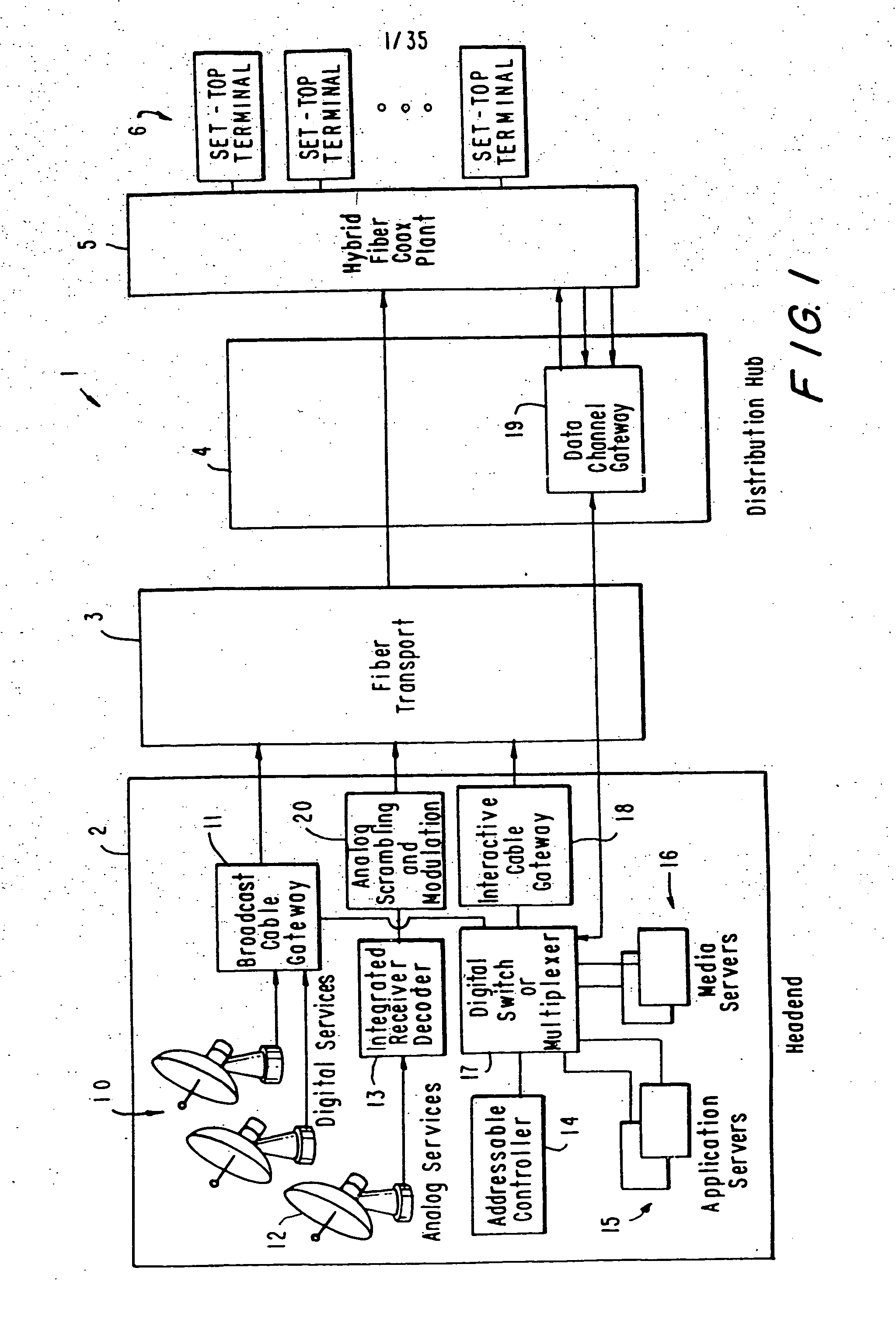

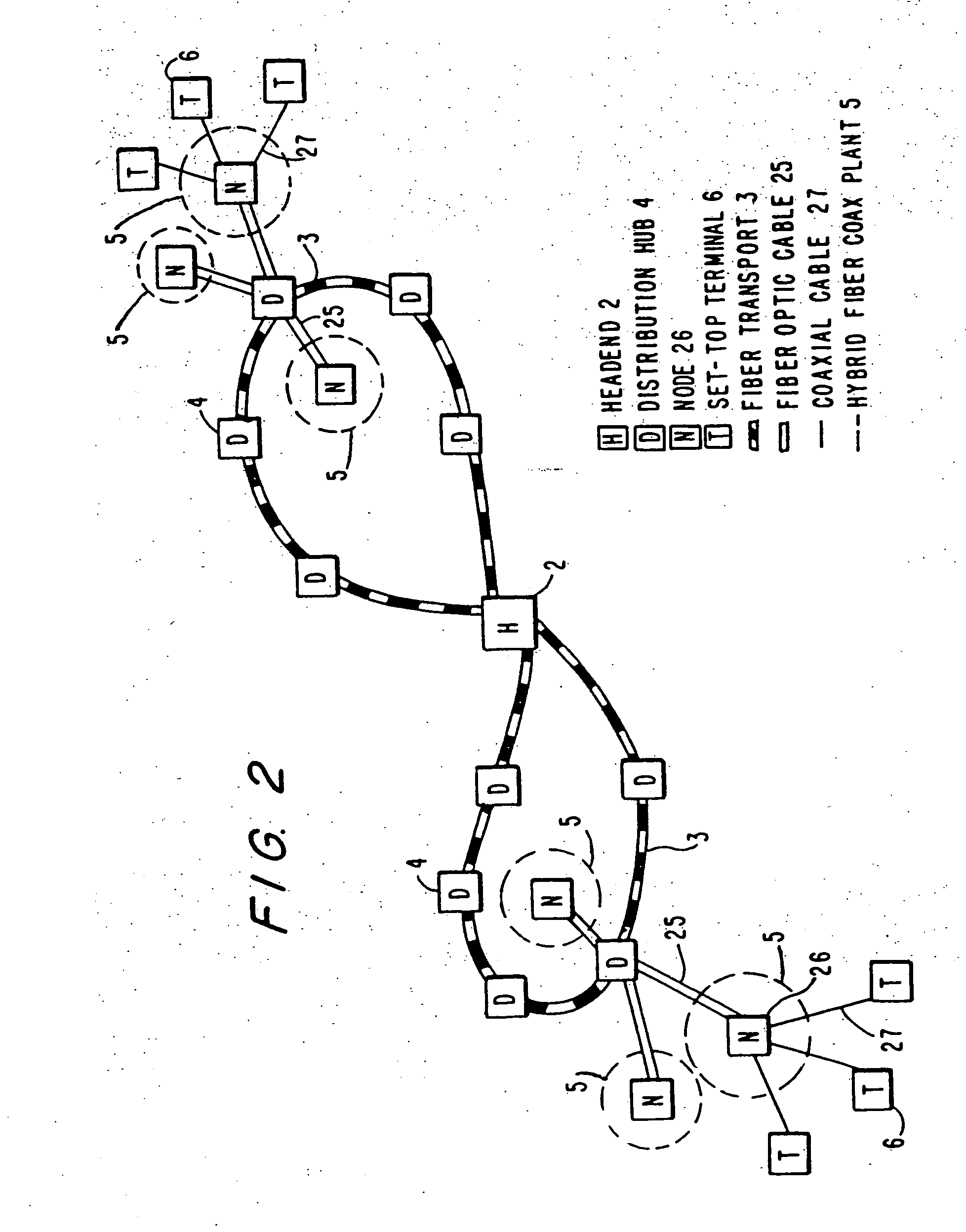

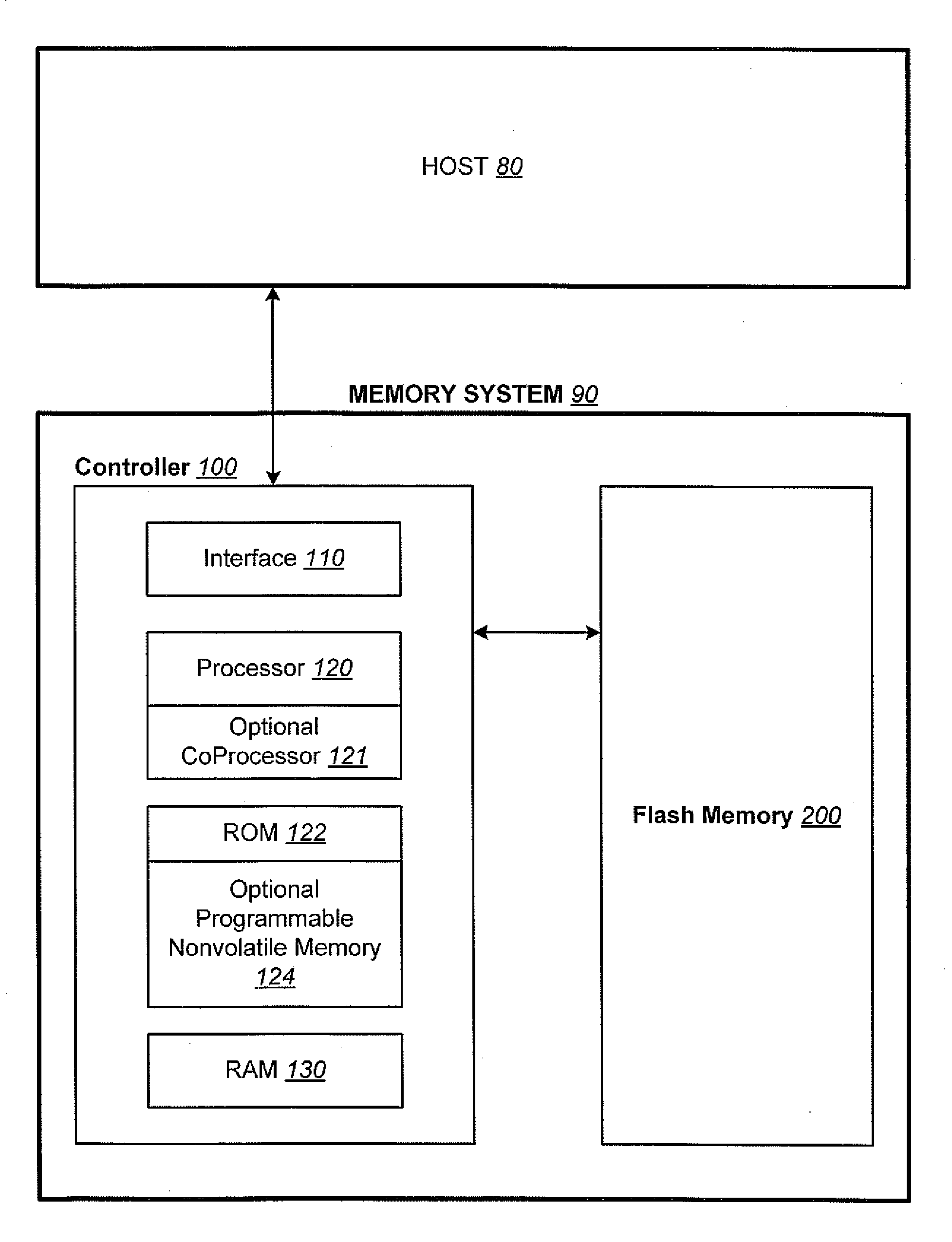

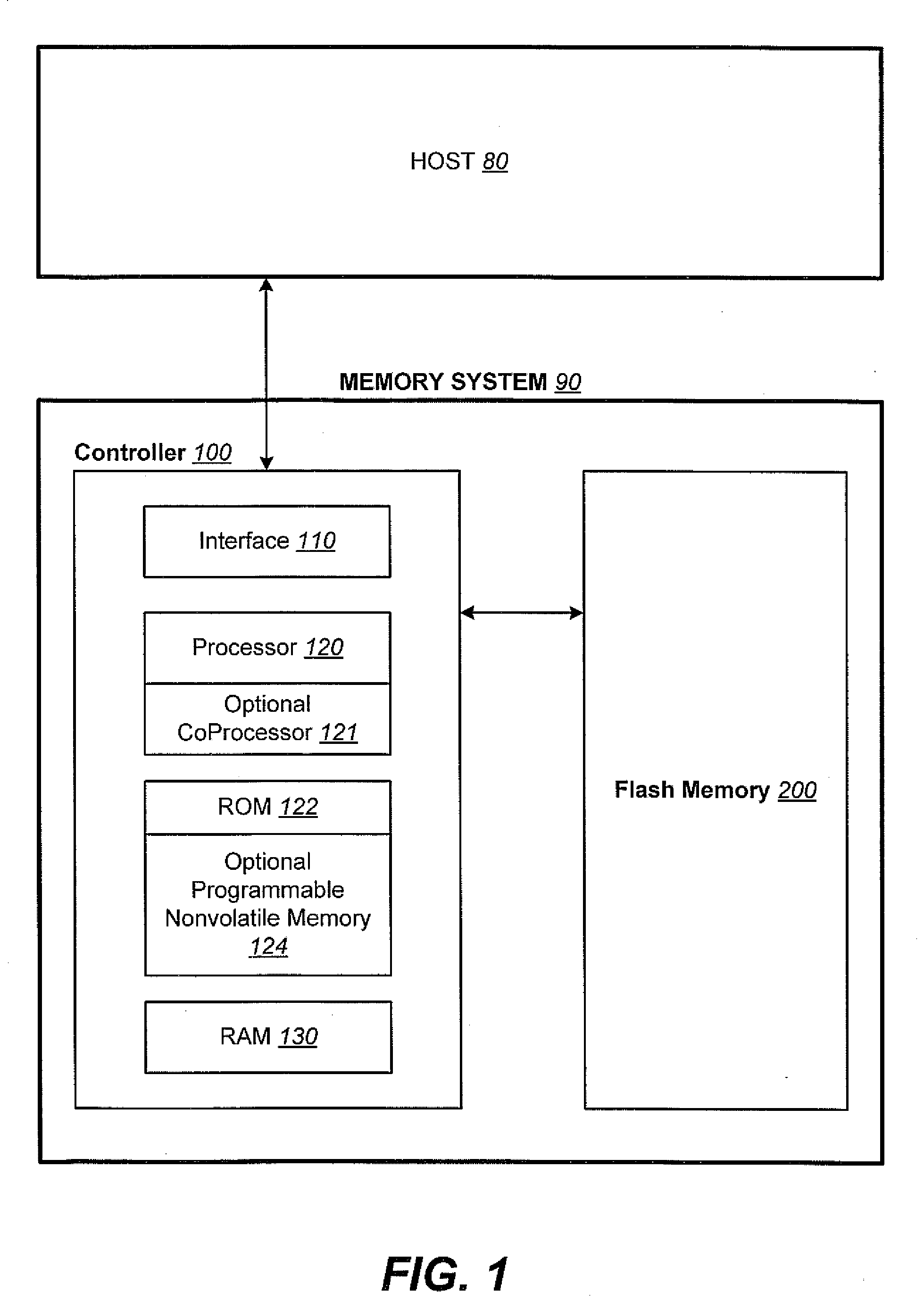

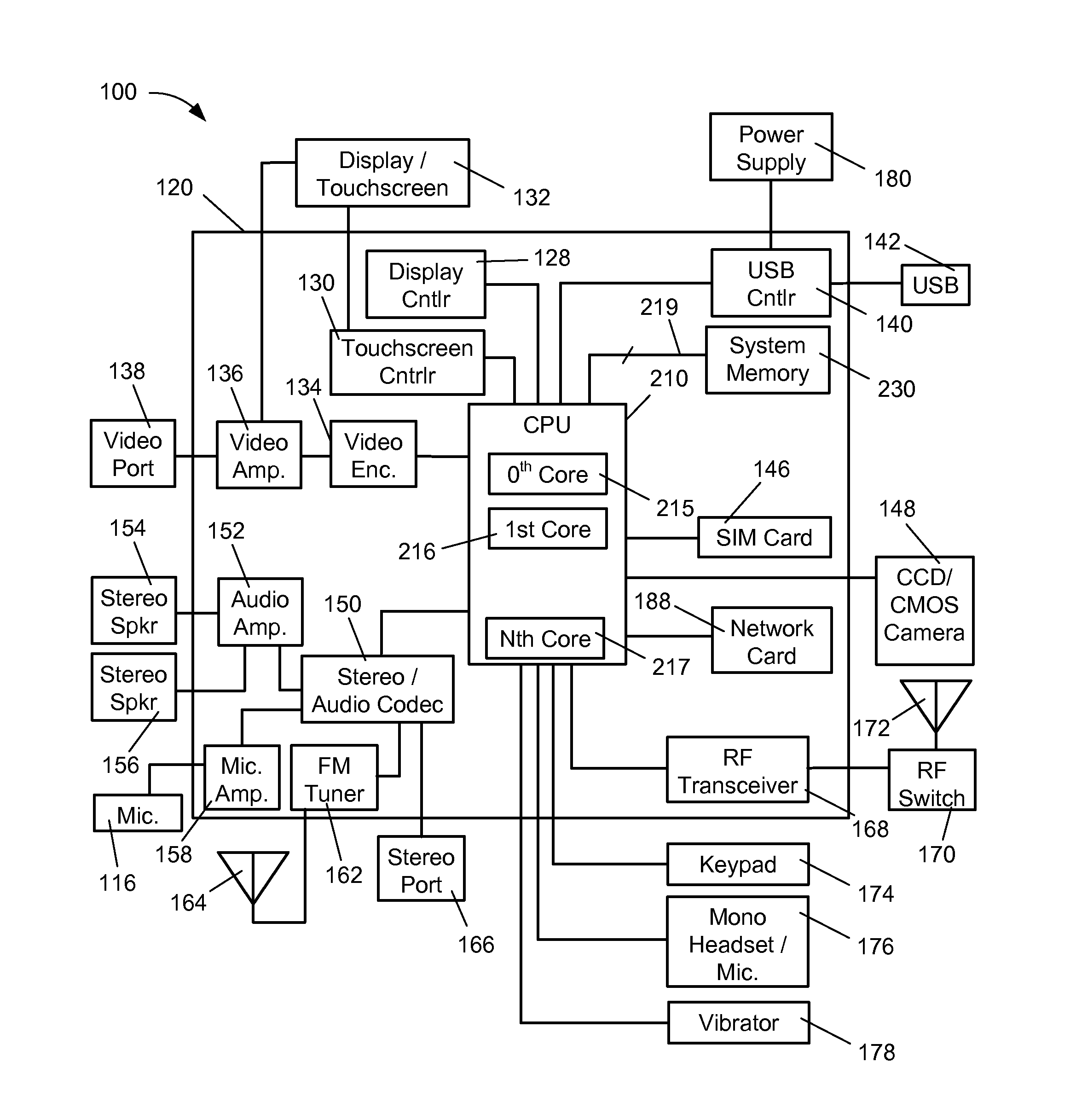

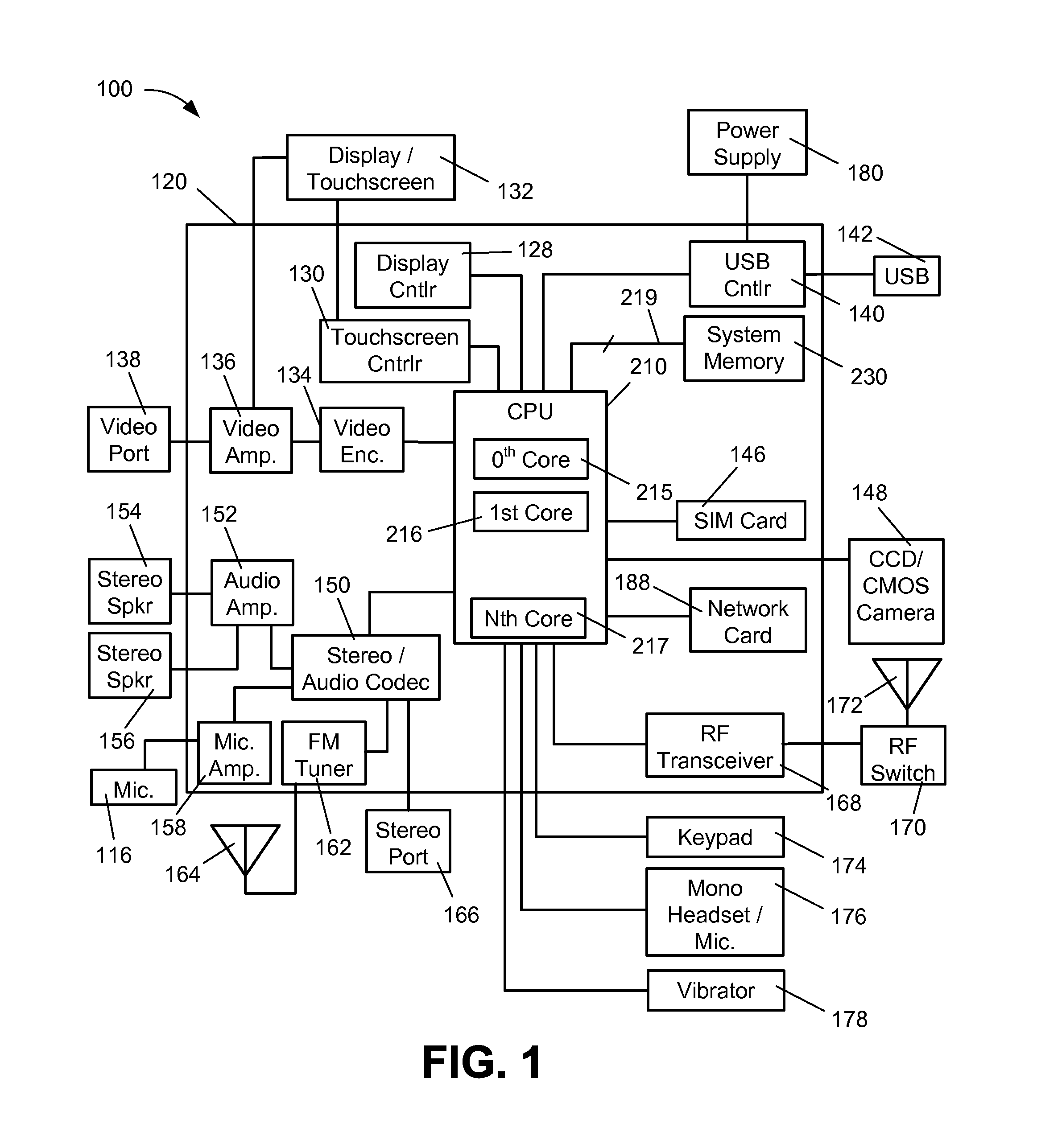

A full service cable television system and method are provided. The system comprises a cable headend, at least one fiber transport, at least one distribution hub, at least one hybrid fiber coax plant, and a plurality of set-top terminals. The system delivers television programs, advanced cable services, and online services. Programs and services are transmitted to the set-top terminals in both digital and analog formats to maintain downward compatibility with existing systems. The set-top terminal includes a central processing unit, a unified memory architecture, a memory management unit, communications circuitry, I / O control circuitry, and audio and video output circuitry. Through these components, the set-top terminal provides advanced cable services such as a comprehensive channel navigator, an interactive program guide, impulse Pay-Per-View, Near-Video-On-Demand and Video-On-Demand programming, and advanced configuration controls. The set-top terminal also provides online services such as World Wide Web browsing, Internet e-mail, and home shopping.

Owner:TIME WARNER CABLE ENTERPRISES LLC

Non-Volatile Memory and Method With Write Cache Partitioning

ActiveUS20100172180A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationRead-only memoriesMultilevel memoryGranularity

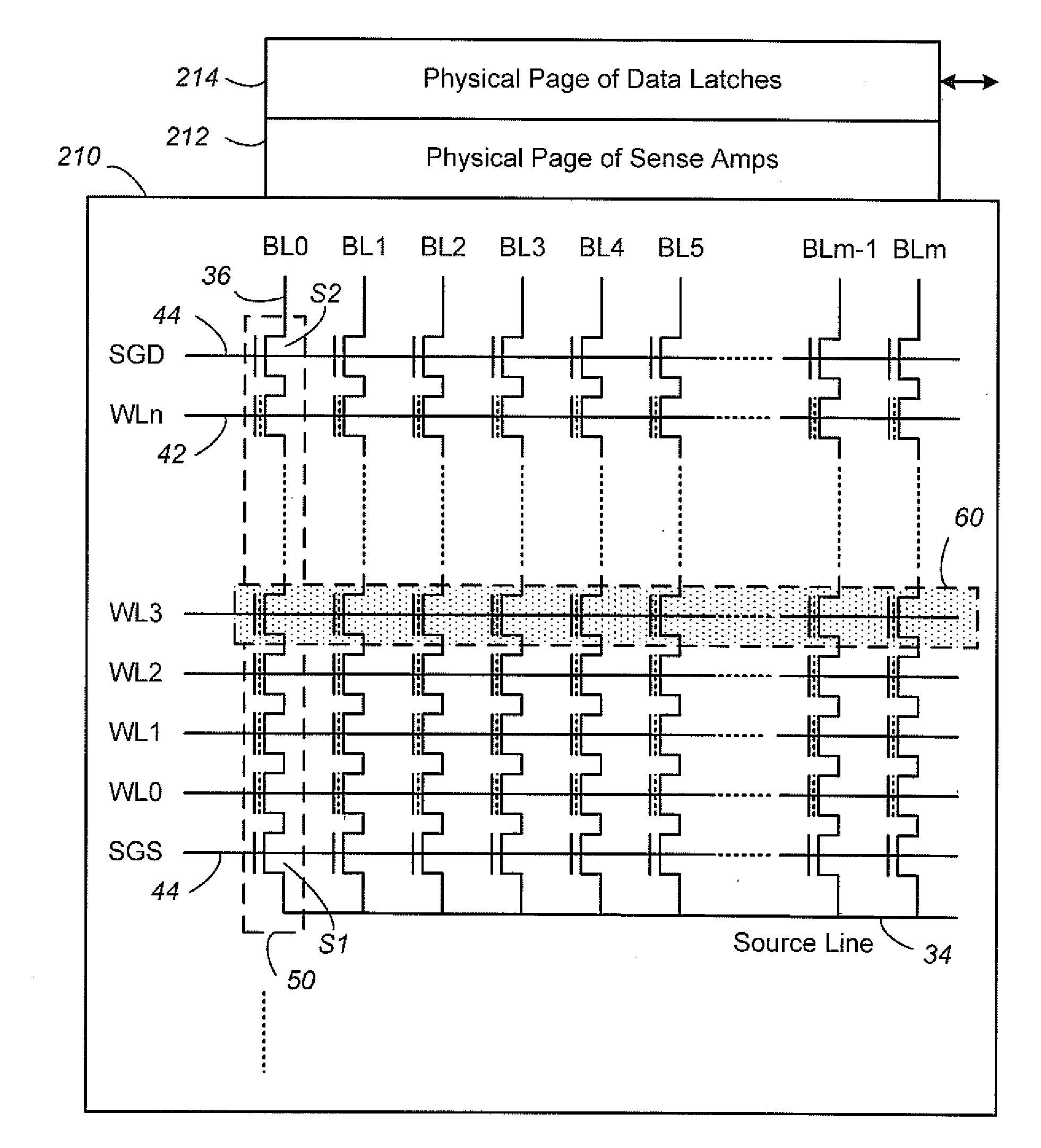

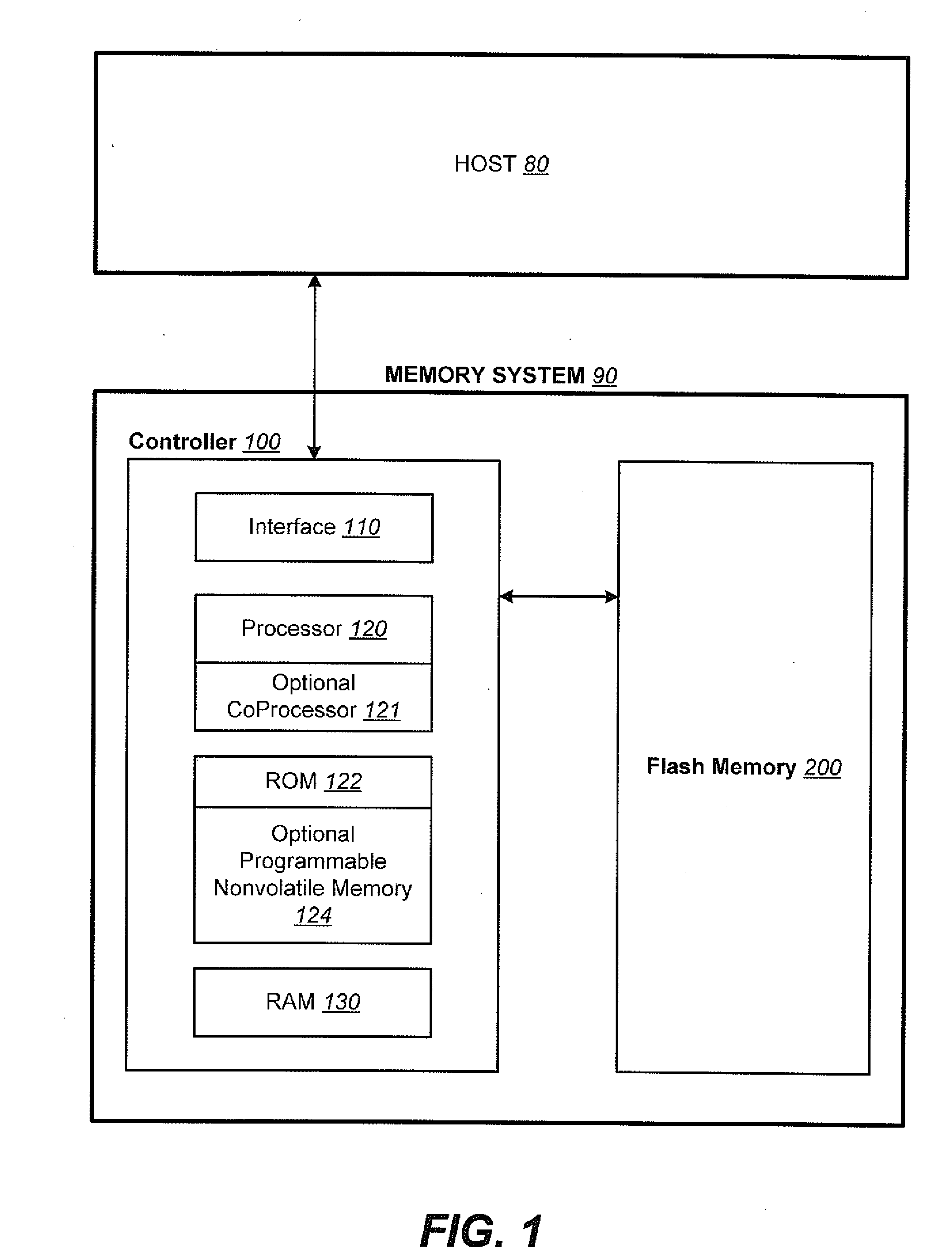

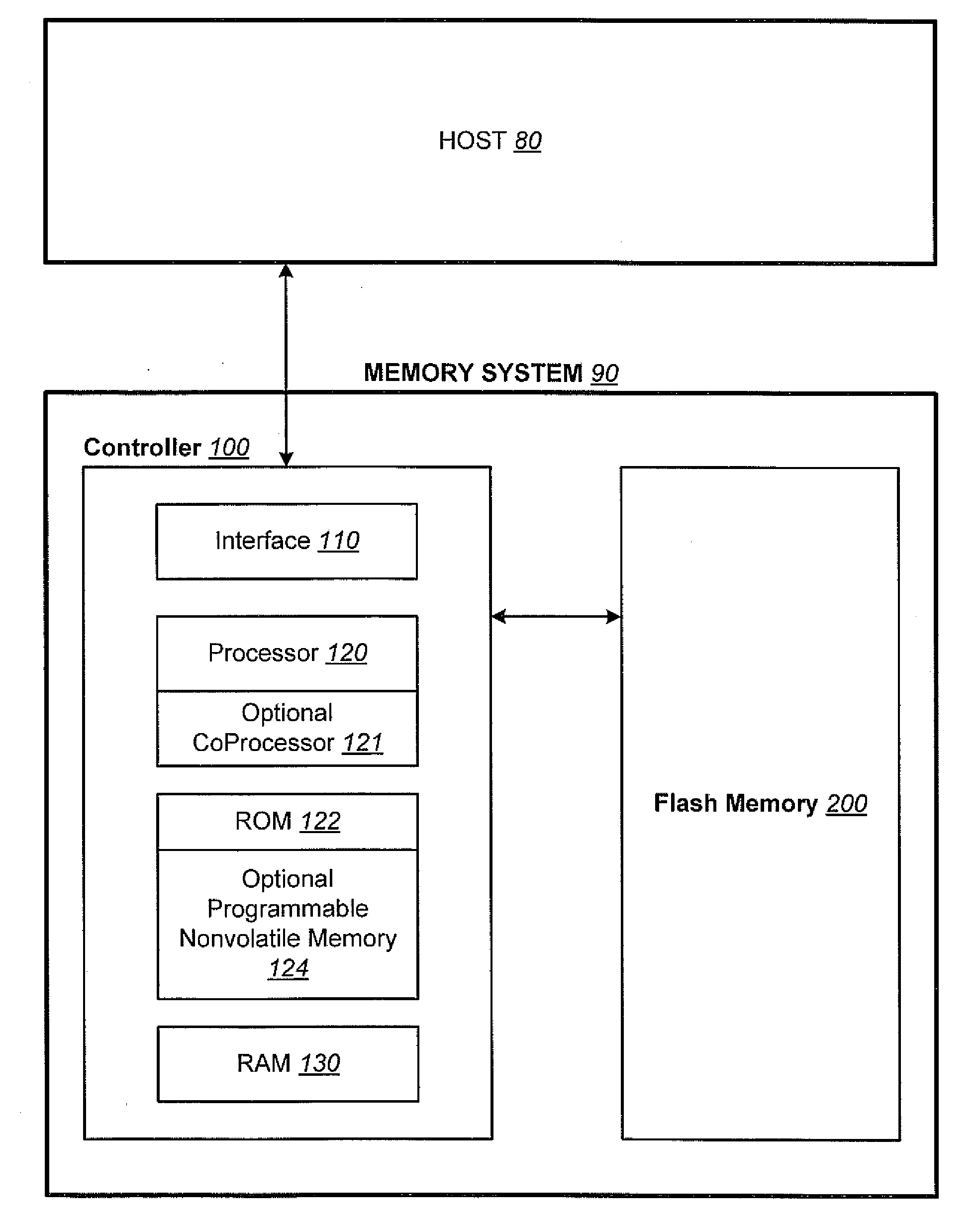

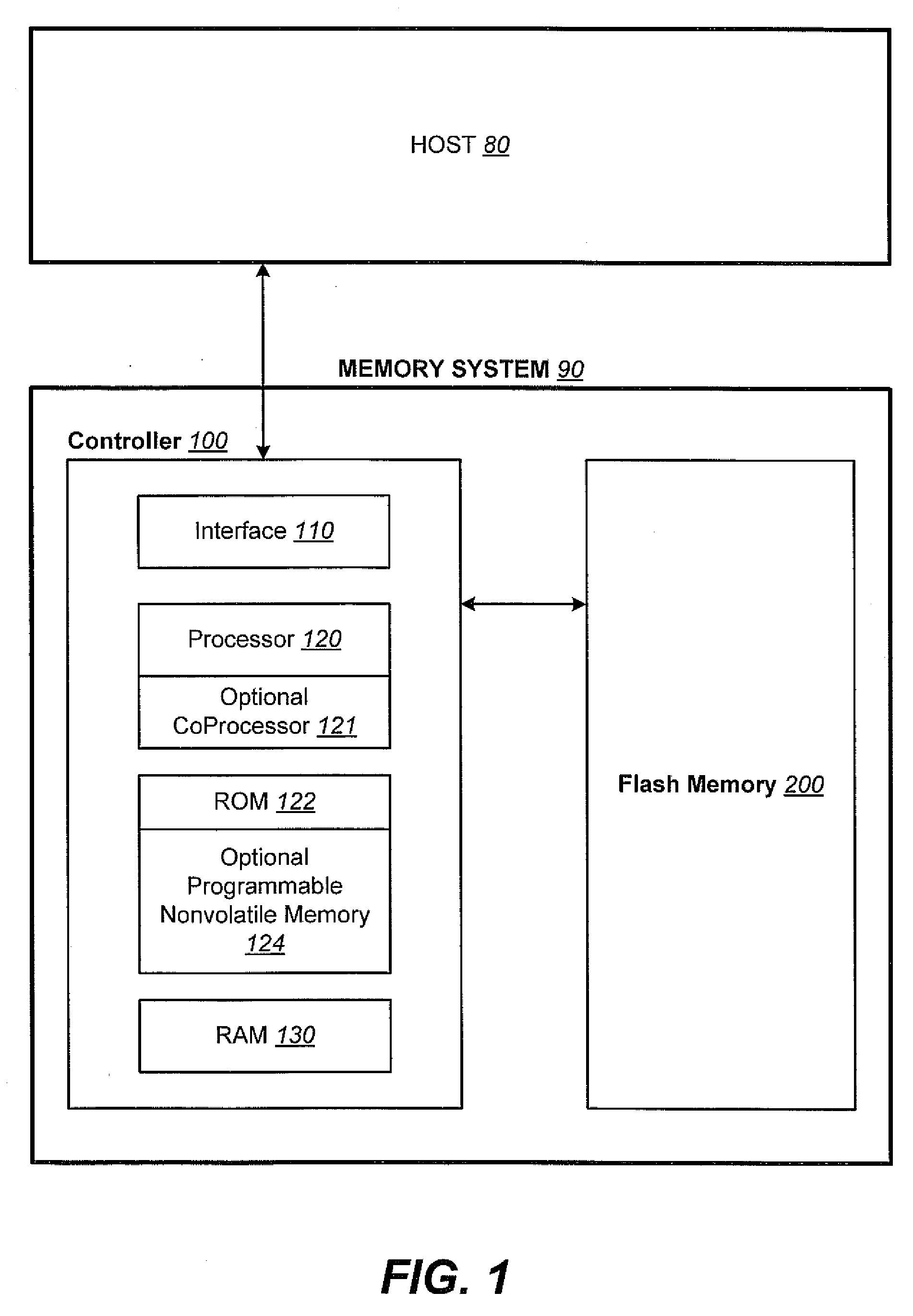

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. Decisions to write data to the cache memory or directly to the main memory depend on the attributes and characteristics of the data to be written, the state of the blocks in the main memory portion and the state of the blocks in the cache portion.

Owner:SANDISK TECH LLC

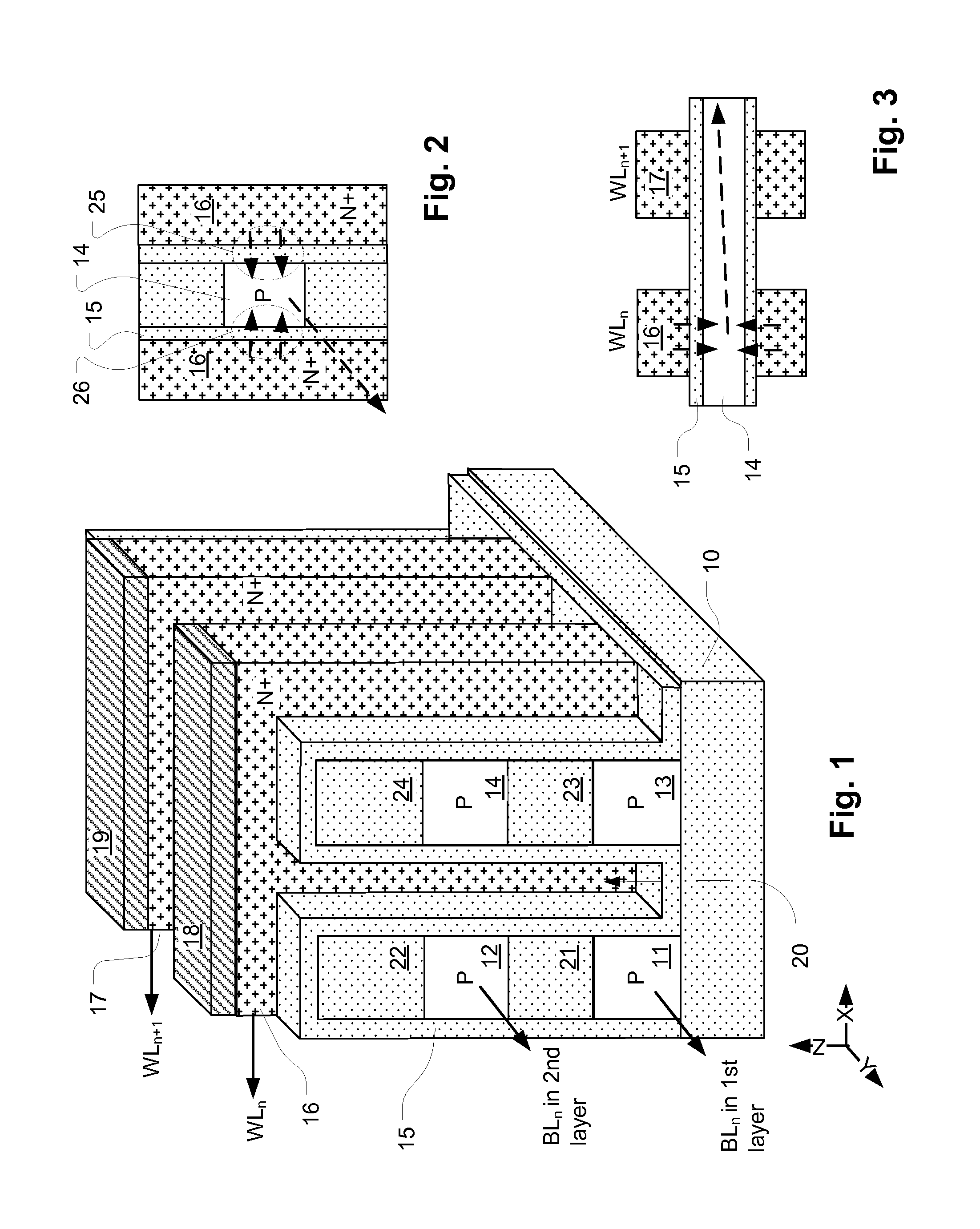

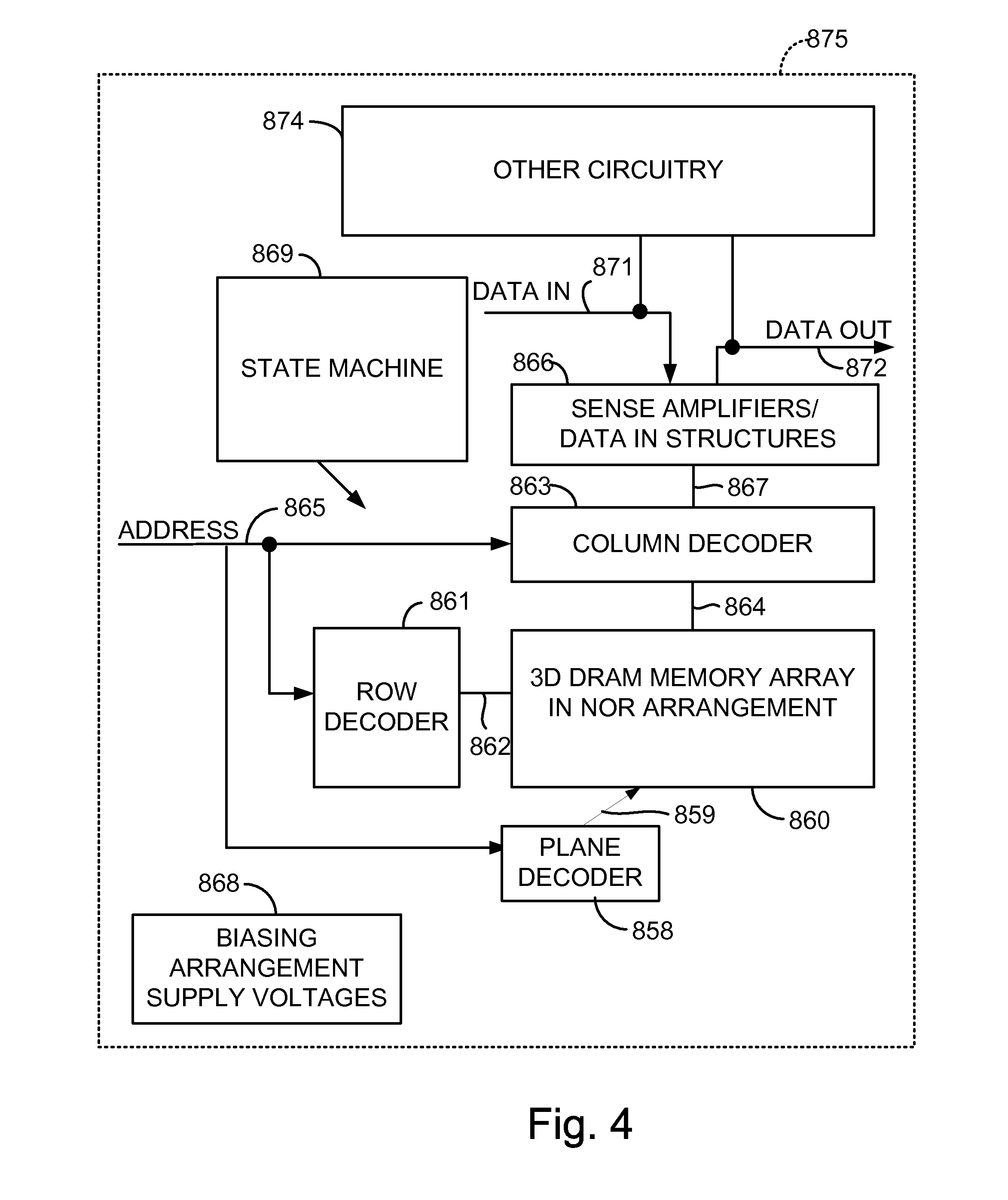

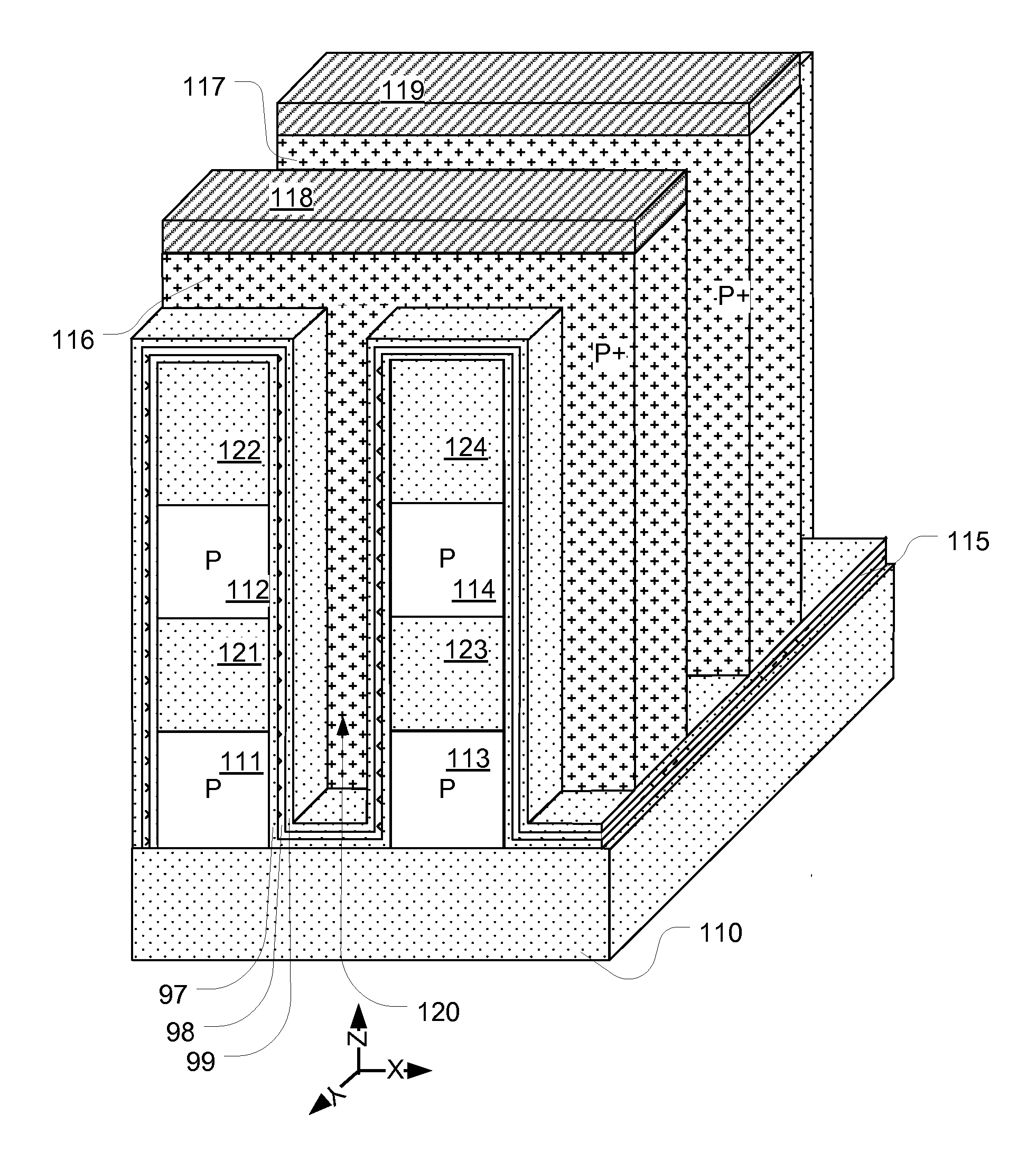

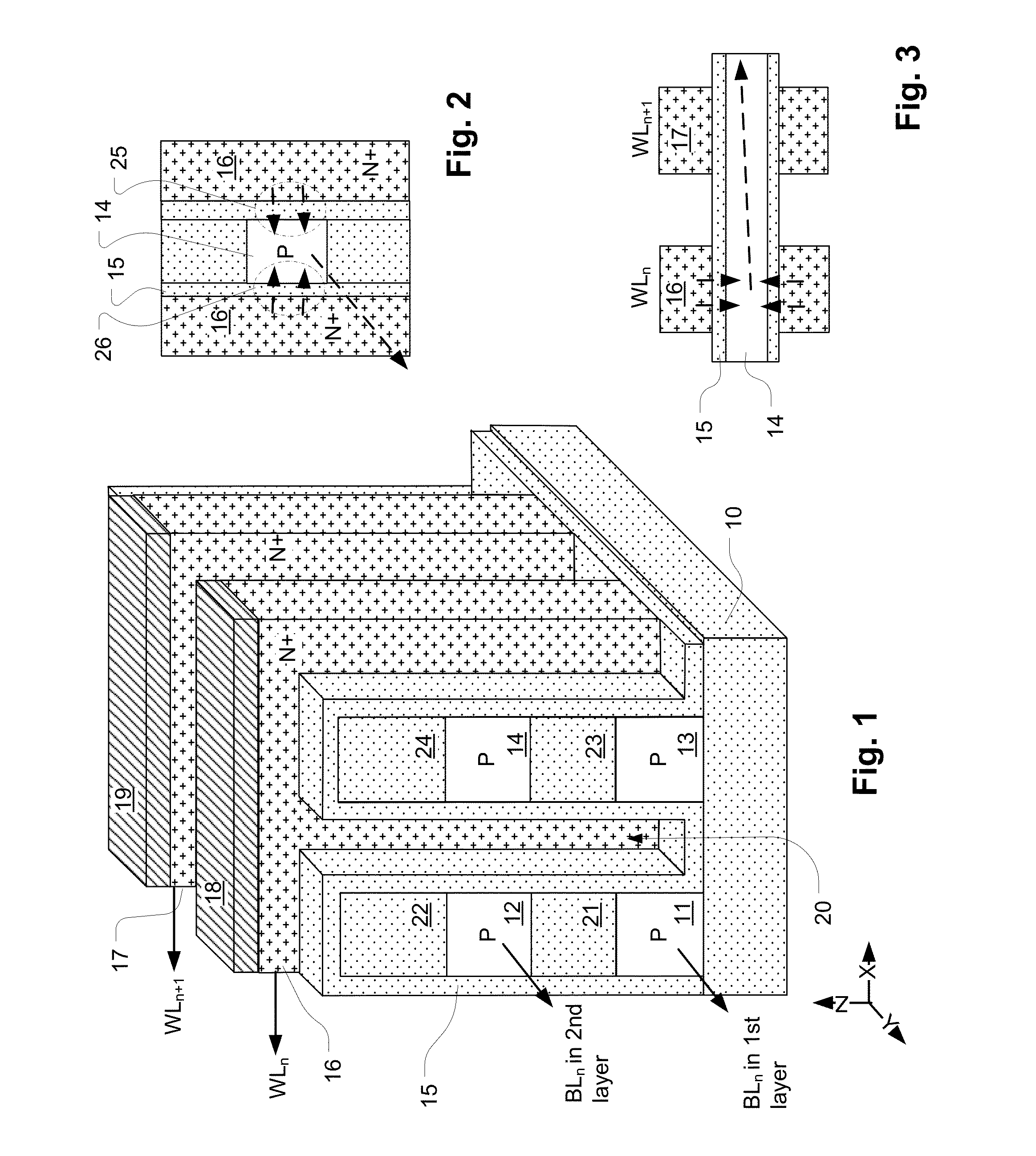

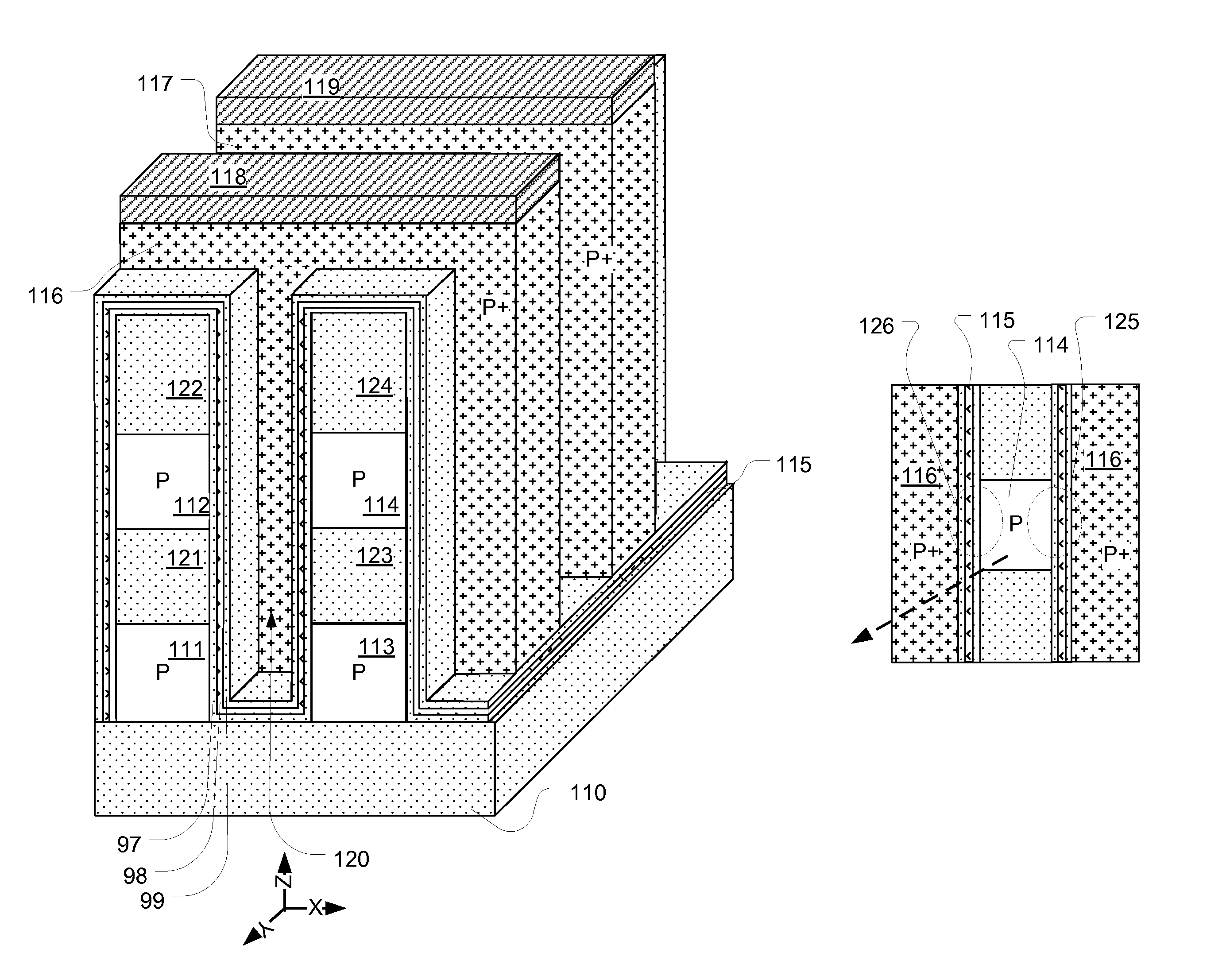

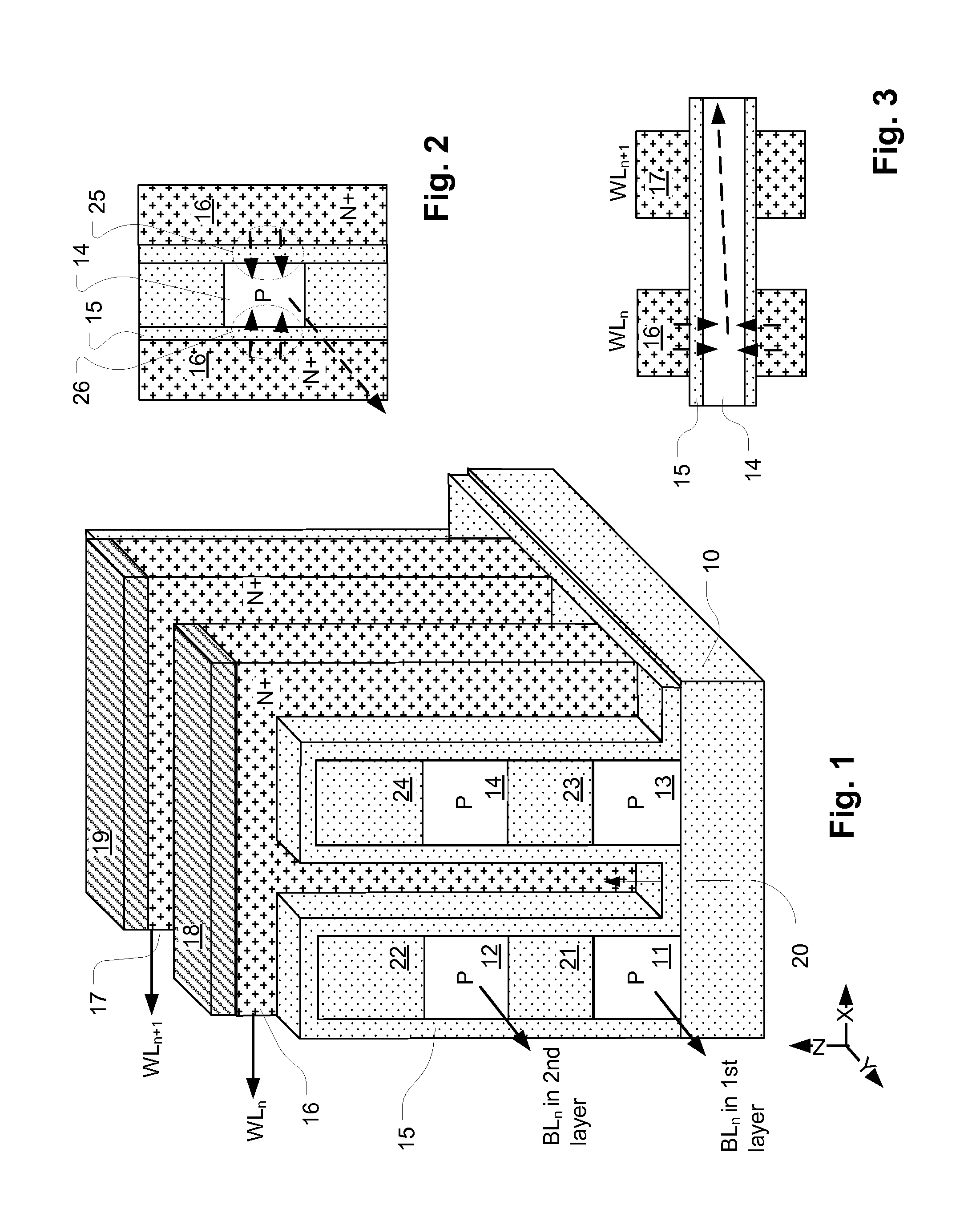

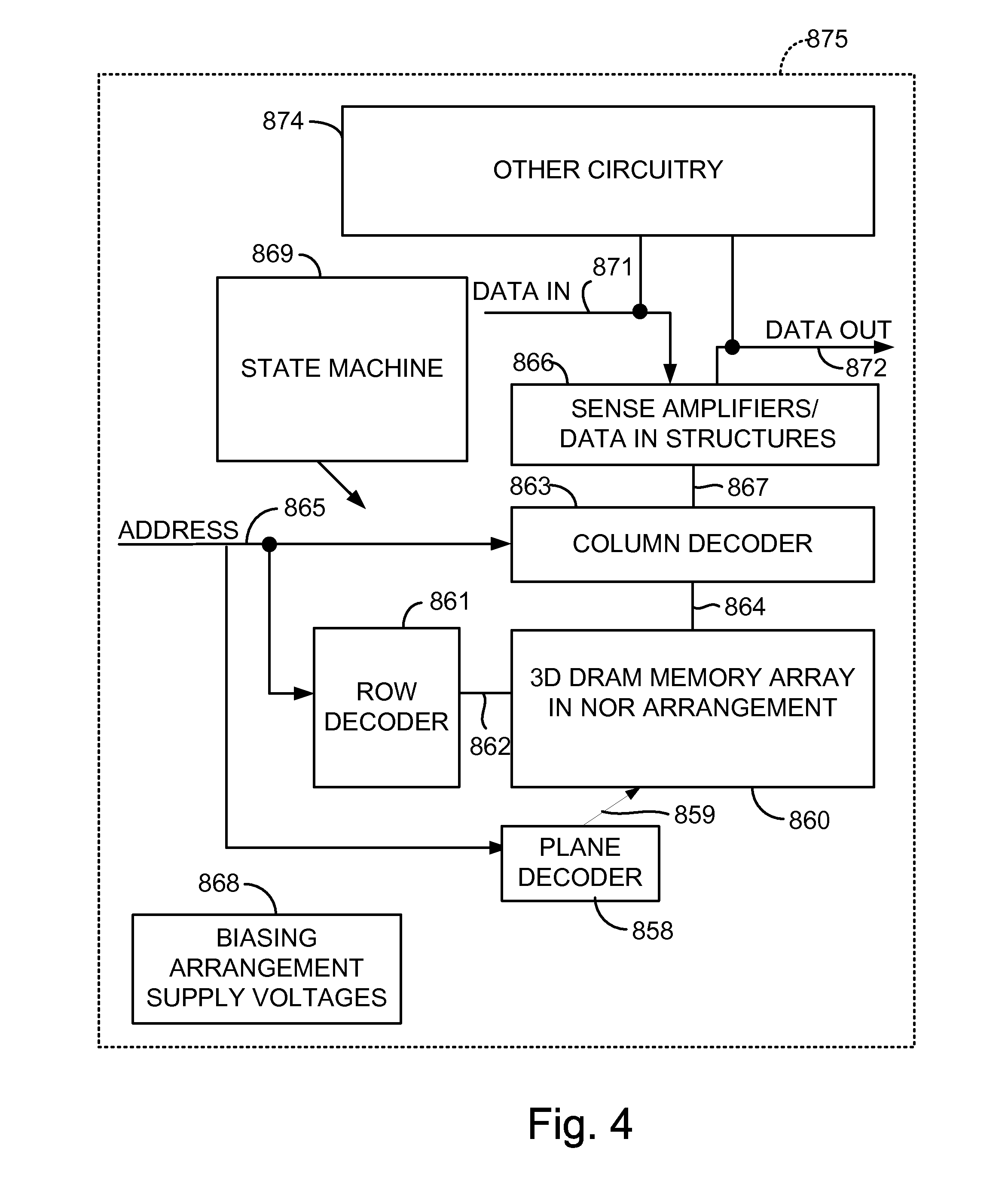

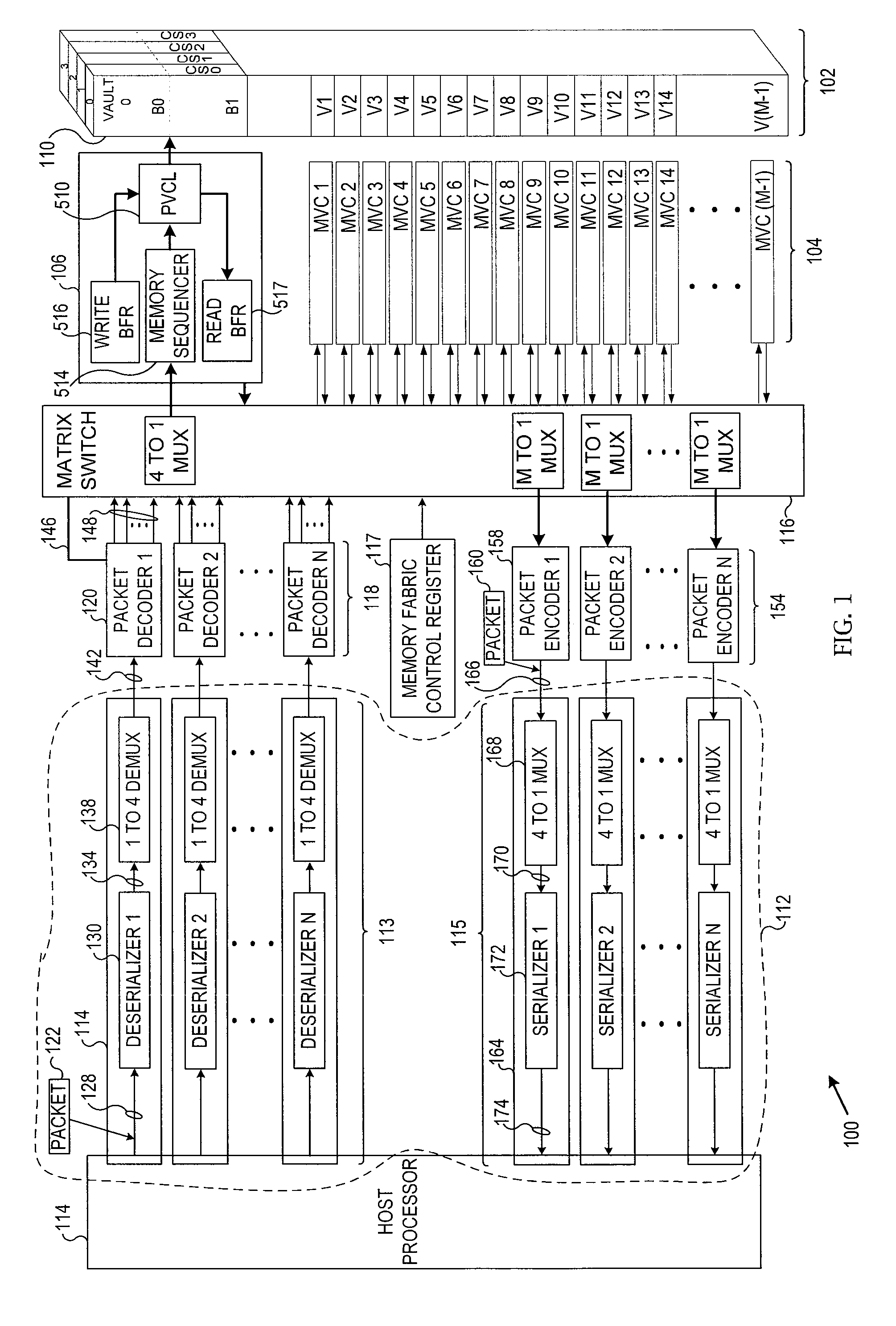

Memory Architecture of 3D NOR Array

A 3D memory device includes a plurality of ridge-shaped stacks of memory cells. Word lines are arranged over the stacks of memory cells. Bit lines structures are coupled to multiple locations along the stacks of memory cells. Source line structures are coupled to multiple locations along each of the semiconductor material strips of the stacks. The bit line structures and the source line structures are between adjacent ones of the word lines.

Owner:MACRONIX INT CO LTD

Non-Volatile Memory and Method With Write Cache Partition Management Methods

InactiveUS20100174847A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationMemory adressing/allocation/relocationGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. The cache memory has a capacity dynamically increased by allocation of blocks from the main memory in response to a demand to increase the capacity. Preferably, a block with an endurance count higher than average is allocated. The logical addresses of data are partitioned into zones to limit the size of the indices for the cache.

Owner:SANDISK TECH LLC

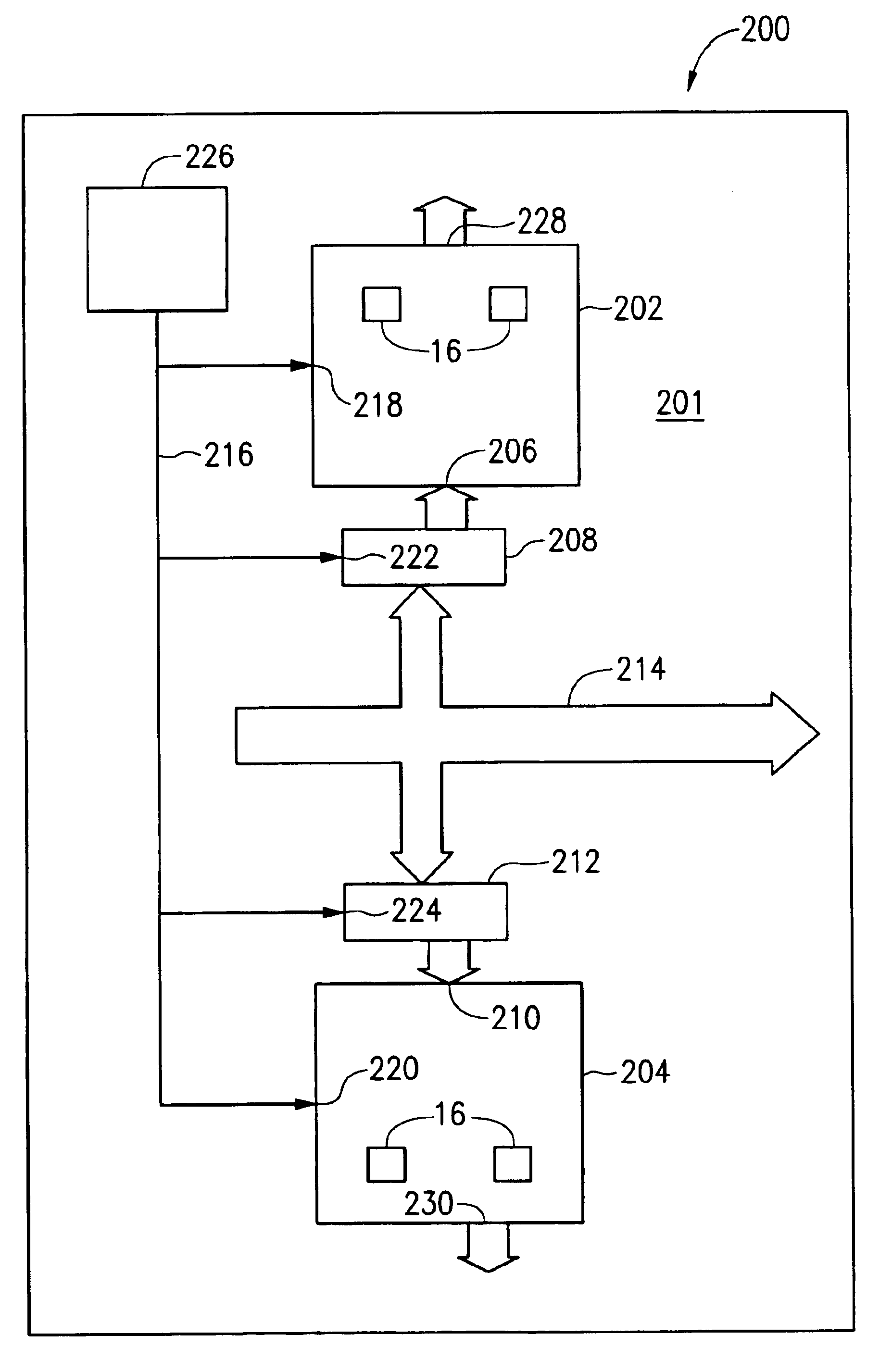

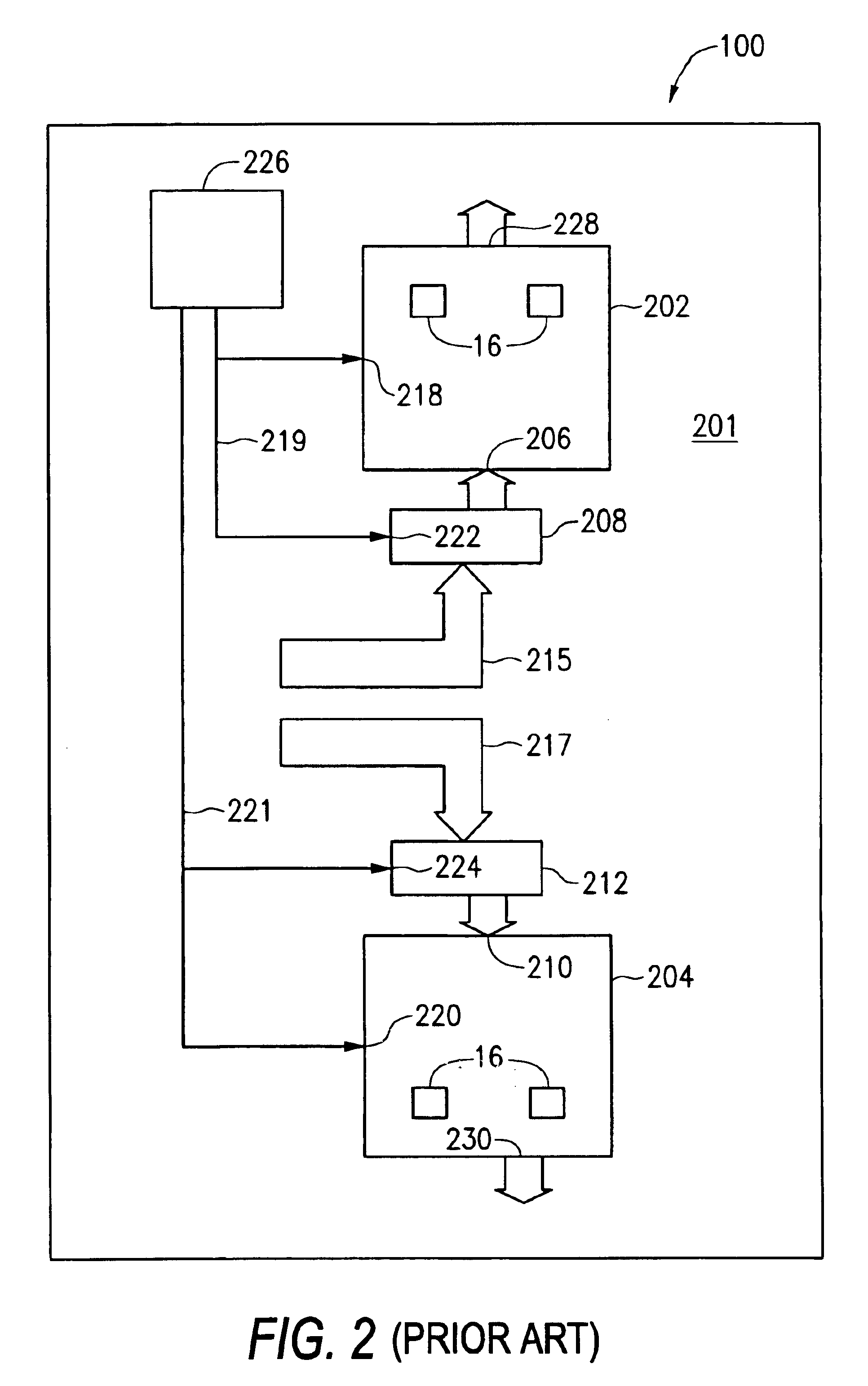

System and method for uniform interleaving of data across a multiple-channel memory architecture with asymmetric storage capacity

ActiveUS20150100746A1Memory adressing/allocation/relocationShared memory architectureCache-only memory architecture

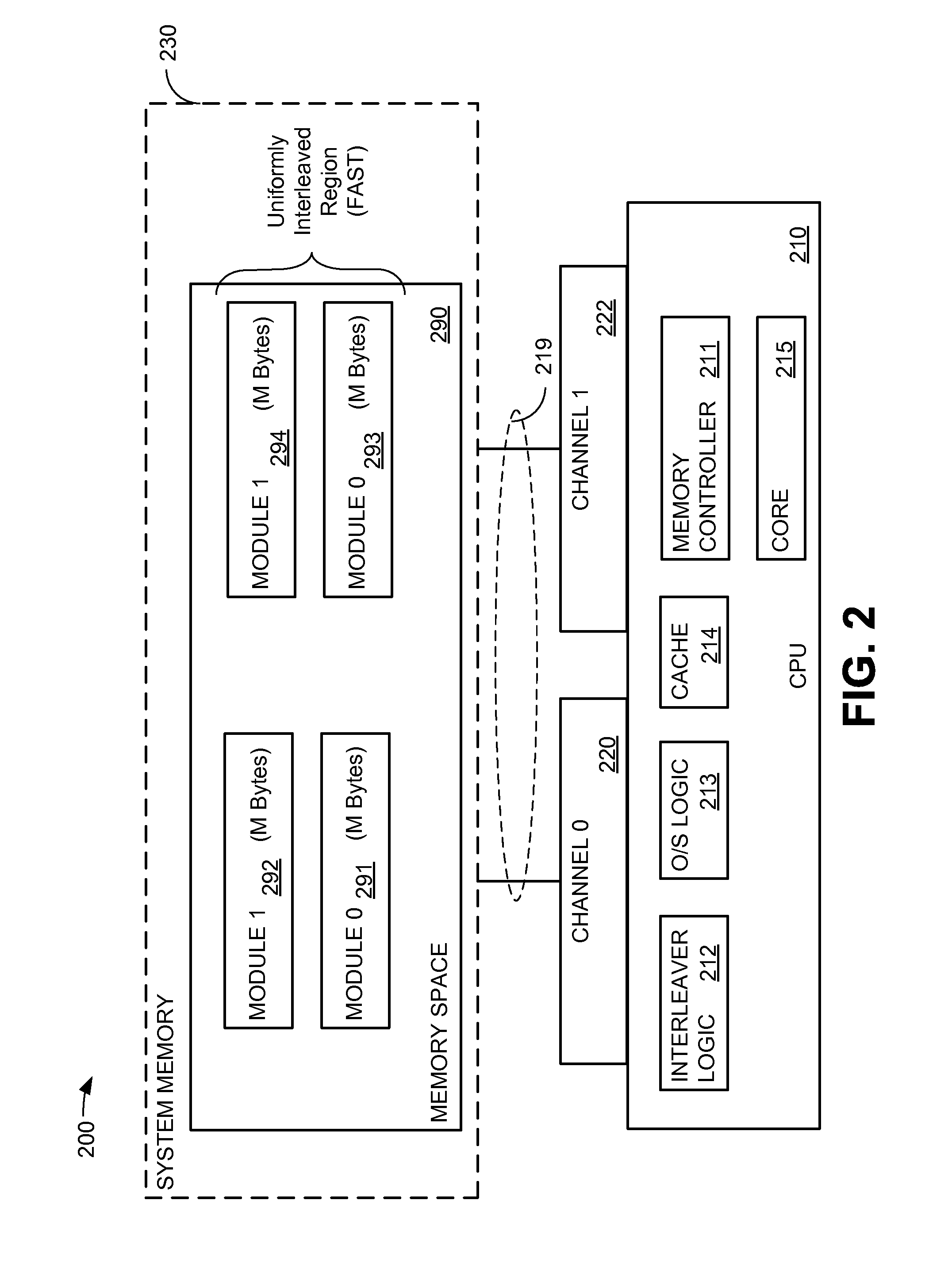

Systems and methods for uniformly interleaving memory accesses across physical channels of a memory space with a non-uniform storage capacity across the physical channels are disclosed. An interleaver is arranged in communication with one or more processors and a system memory. The interleaver identifies locations in a memory space supported by the memory channels and is responsive to logic that defines virtual sectors having a desired storage capacity. The interleaver accesses the asymmetric storage capacity uniformly across the virtual sectors in response to requests to access the memory space.

Owner:QUALCOMM INC

Multi-channel memory architecture

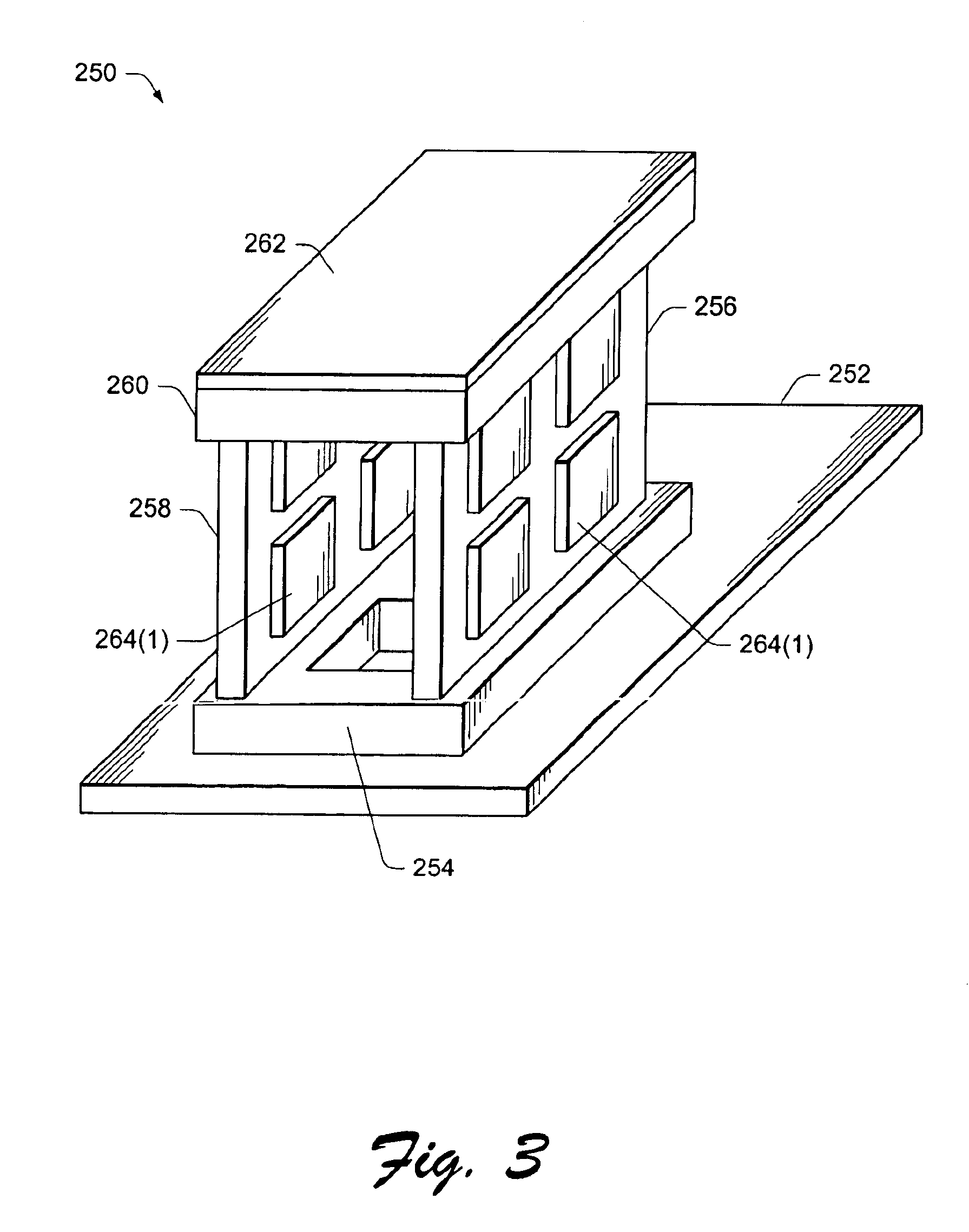

InactiveUS6853557B1Circuit arrangements on support structuresPrinted circuit aspectsElectrical conductorEngineering

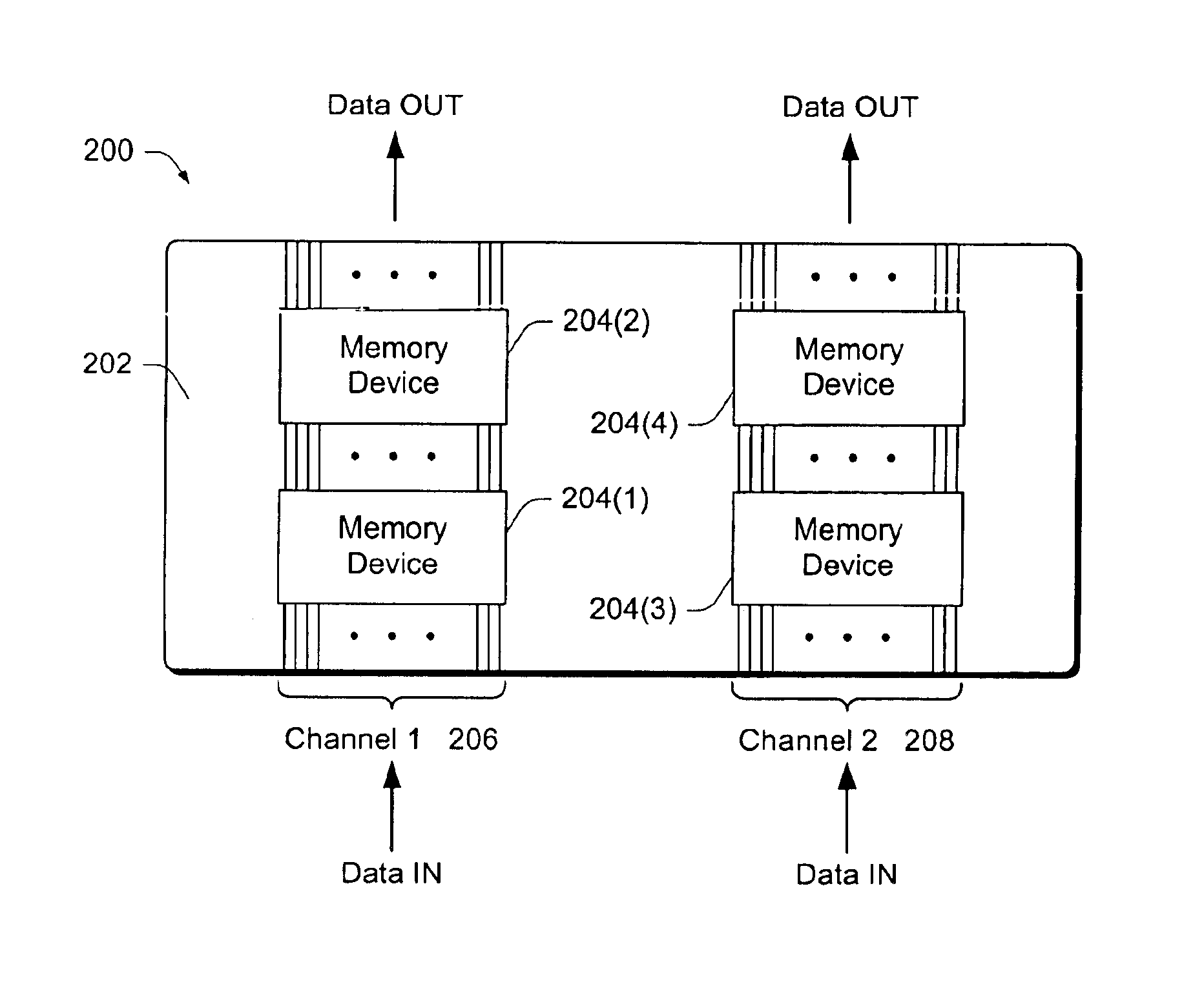

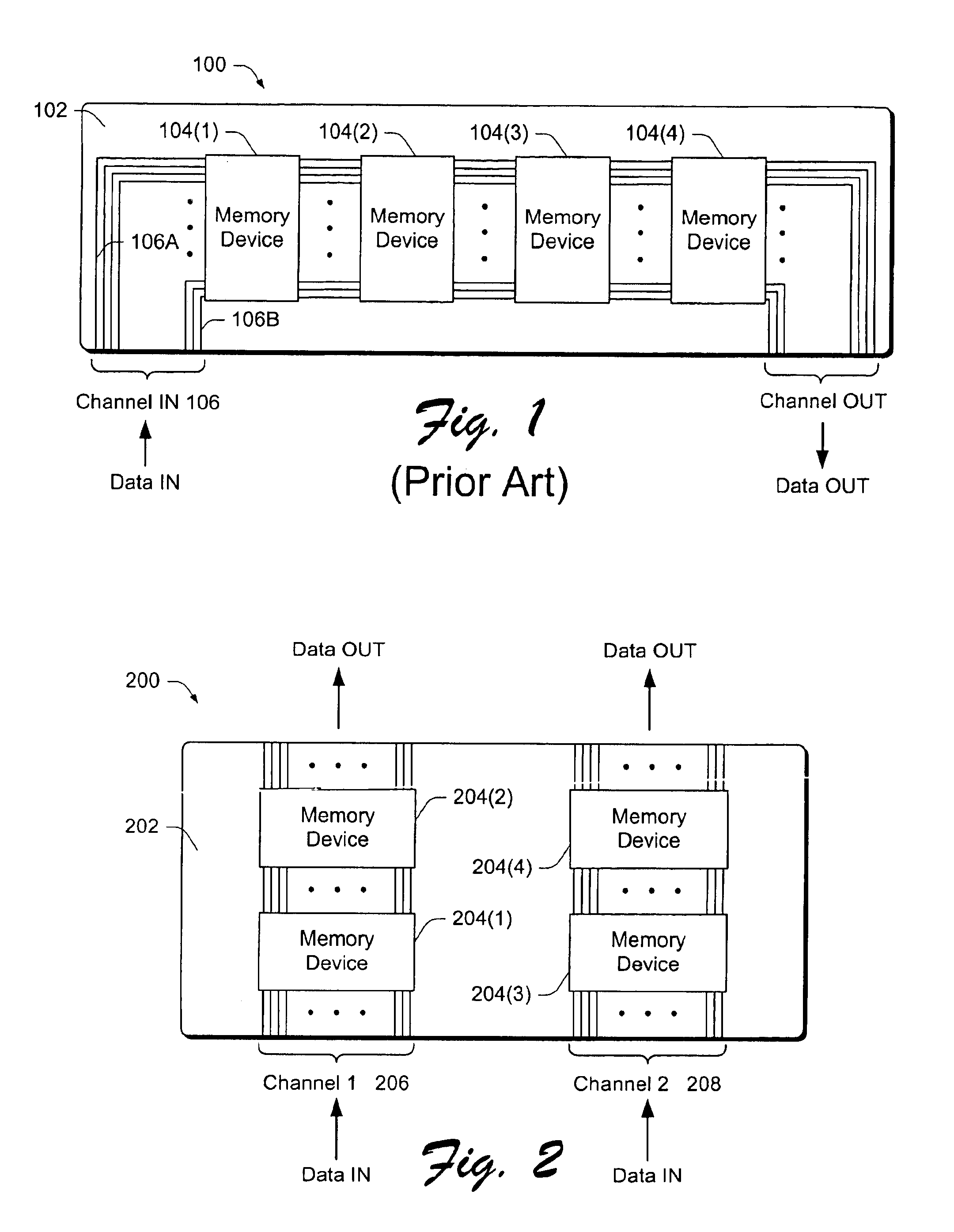

A memory architecture includes a first substrate containing multiple memory devices and a first channel portion extending across the first substrate. The architecture further includes a second substrate containing multiple memory devices and a second channel portion extending across the second substrate. A connector couples the first channel portion to the second channel portion to form a single channel. The connector includes a first slot that receives an edge of the first substrate and a second slot that receives an edge of the second substrate. Another connector has a pair of slots that receive opposite edges of the first and second substrates. The channel portions extend across the substrates in a substantially linear path. Each channel portion includes multiple conductors having lengths that are approximately equal.

Owner:RAMBUS INC

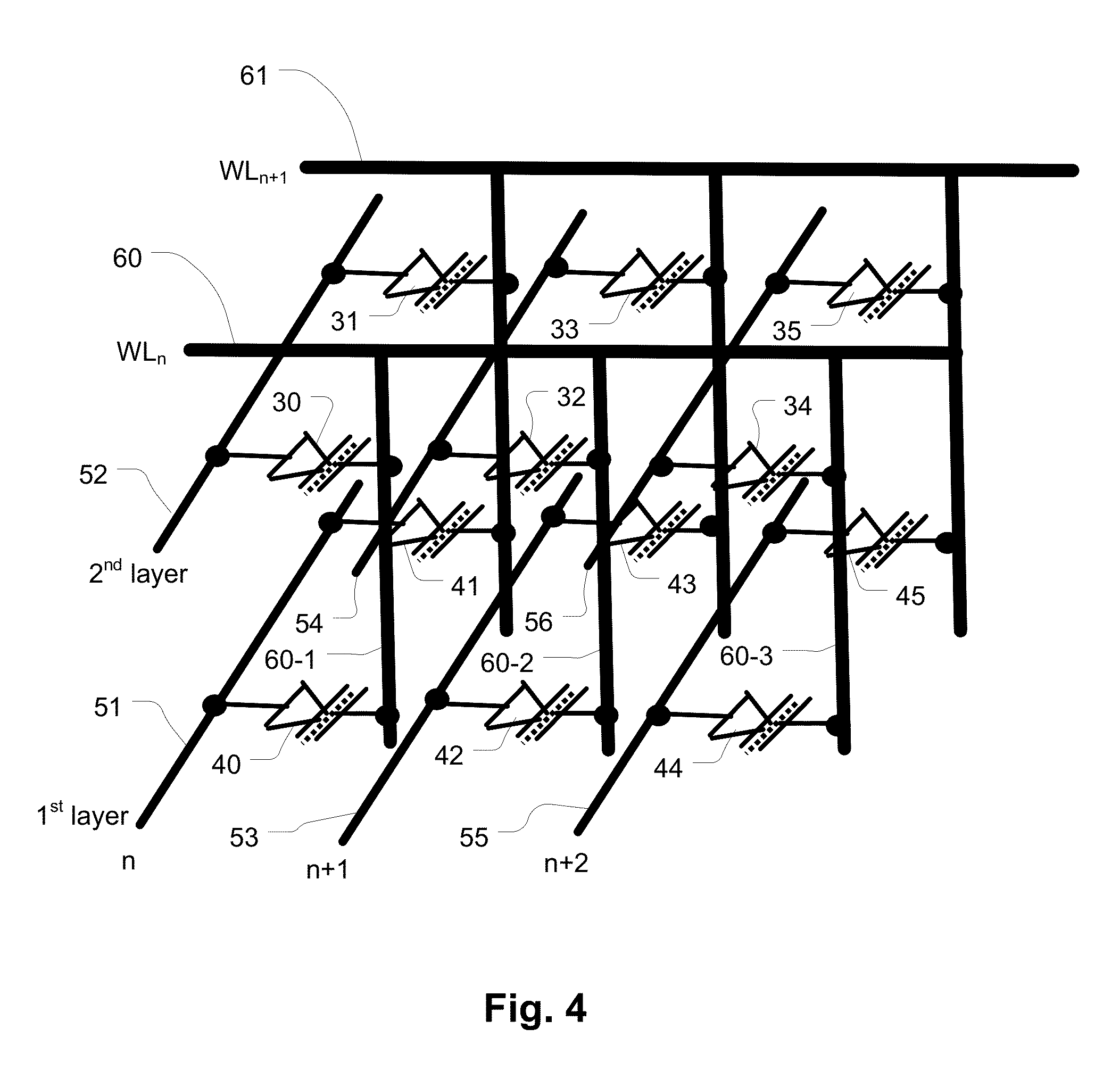

Memory Architecture of 3D Array With Alternating Memory String Orientation and String Select Structures

ActiveUS20120182806A1Increase pitchImproved gate structureSolid-state devicesRead-only memoriesArray data structureConductive materials

Owner:MACRONIX INT CO LTD

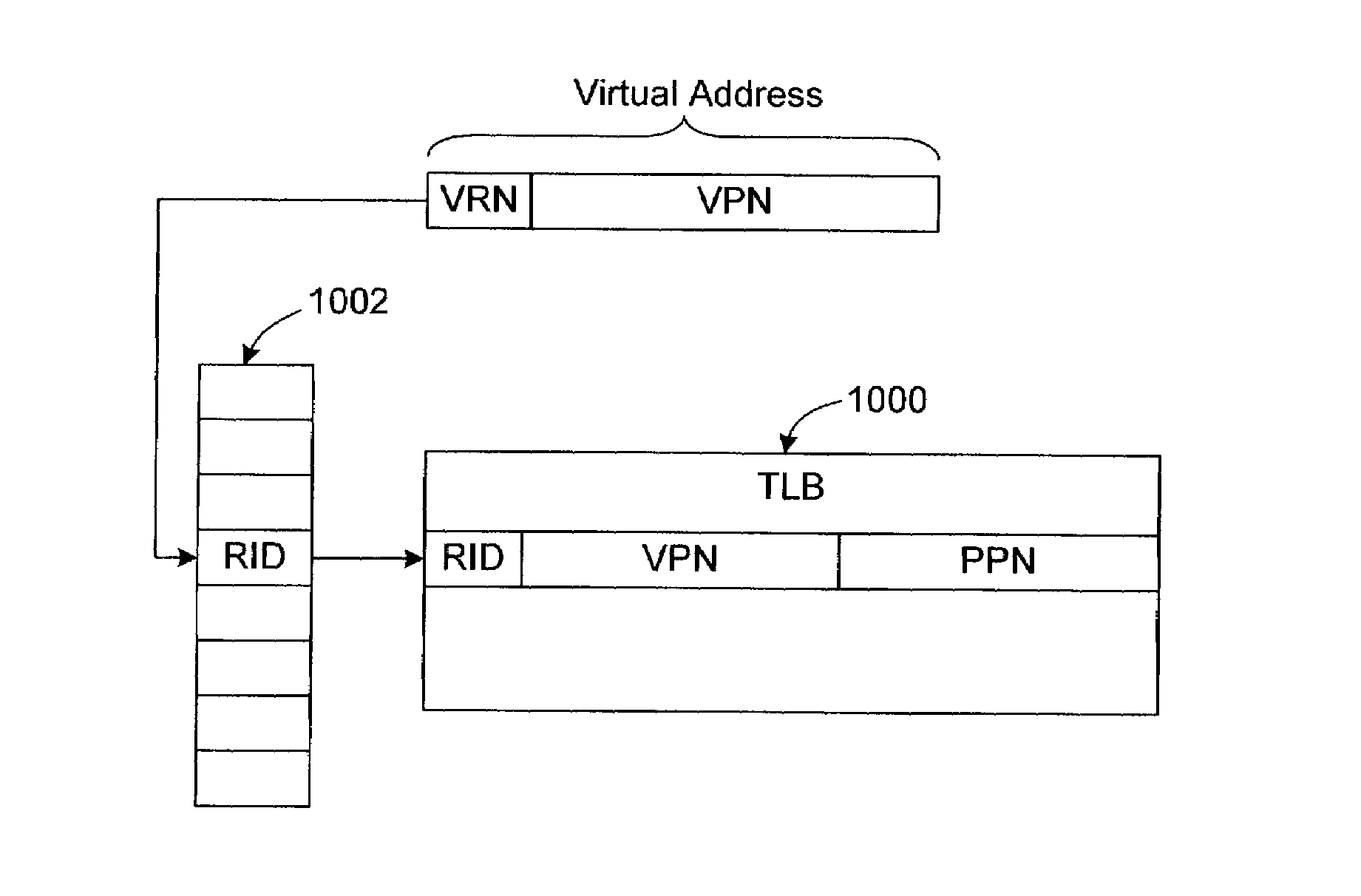

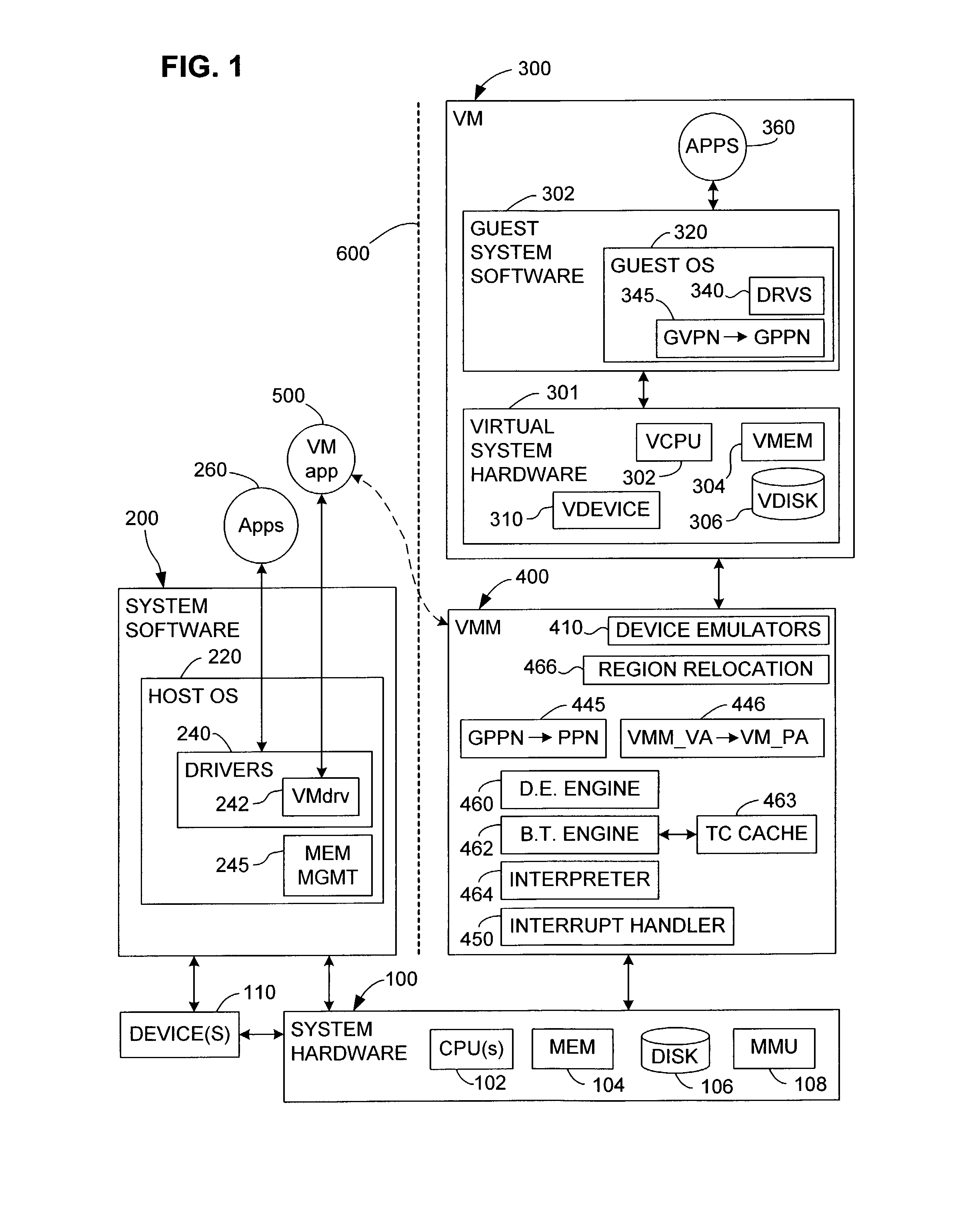

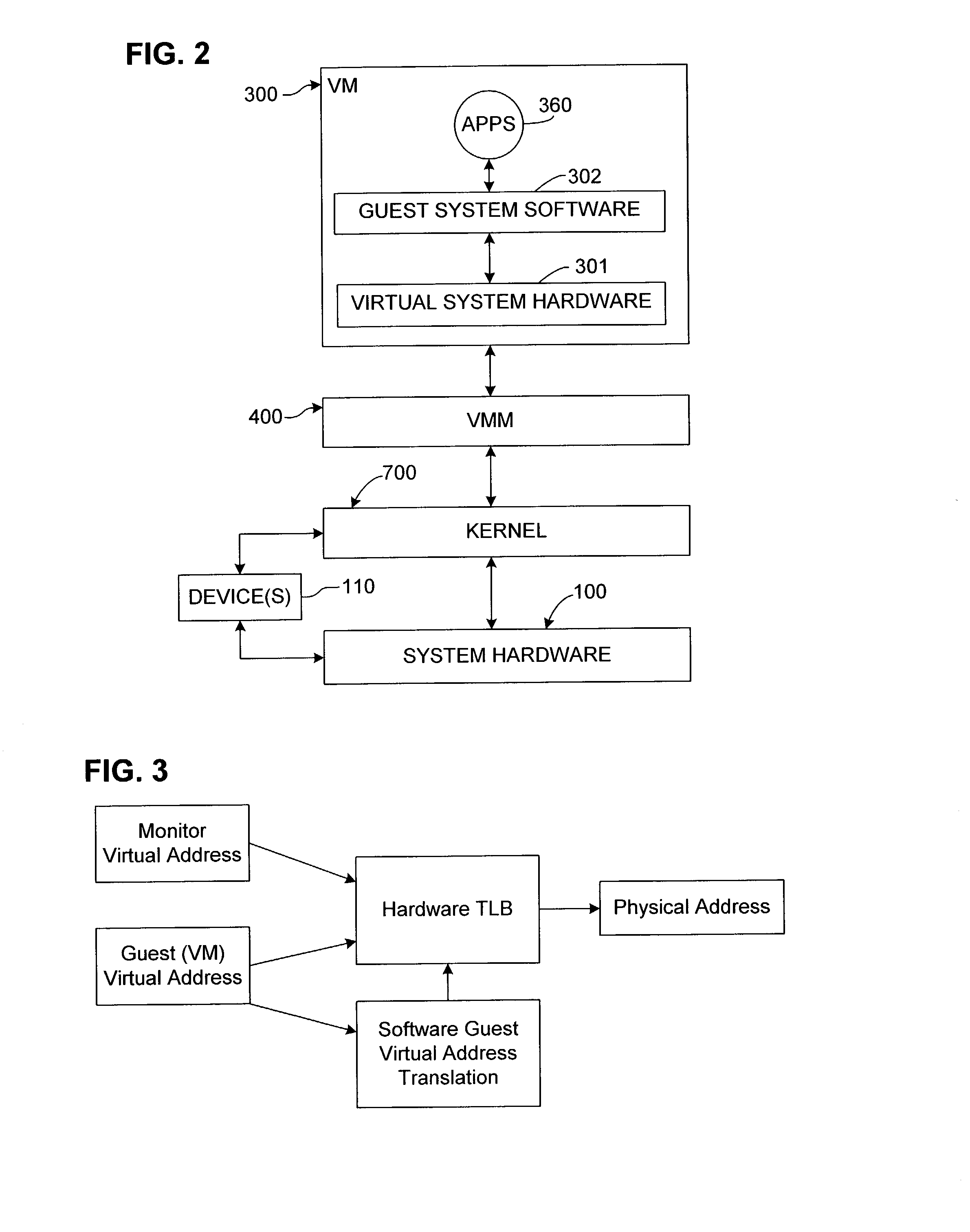

Virtualization system for computers with a region-based memory architecture

ActiveUS7089377B1Efficient sharingSoftware simulation/interpretation/emulationMemory systemsVirtualizationProcessor register

In a computer system with a non-segmented, region-based memory architecture, such as Intel IA-64 systems, two or more sub-systems share a resource, such as a virtual-to-physical address mapping and need to have overlapping regions of the virtual address space for accessing different physical addresses. Virtual addresses include a portion that is used to identify which region the issuing sub-system wants to access. For example, the region-identifying portion of virtual addresses may select a region register whose contents point to a virtual-to-physical address mapping for the corresponding region. To protect a second sub-system S2 from a first S1, whenever the S1 issues an address in a region occupied by S2, the region for the S2 is changed. This allows S1 to issue its addresses without change. In a preferred embodiment of the invention, S2 is a virtual machine monitor (VMM) and S1 is a virtual machine running on the VMM.

Owner:VMWARE INC

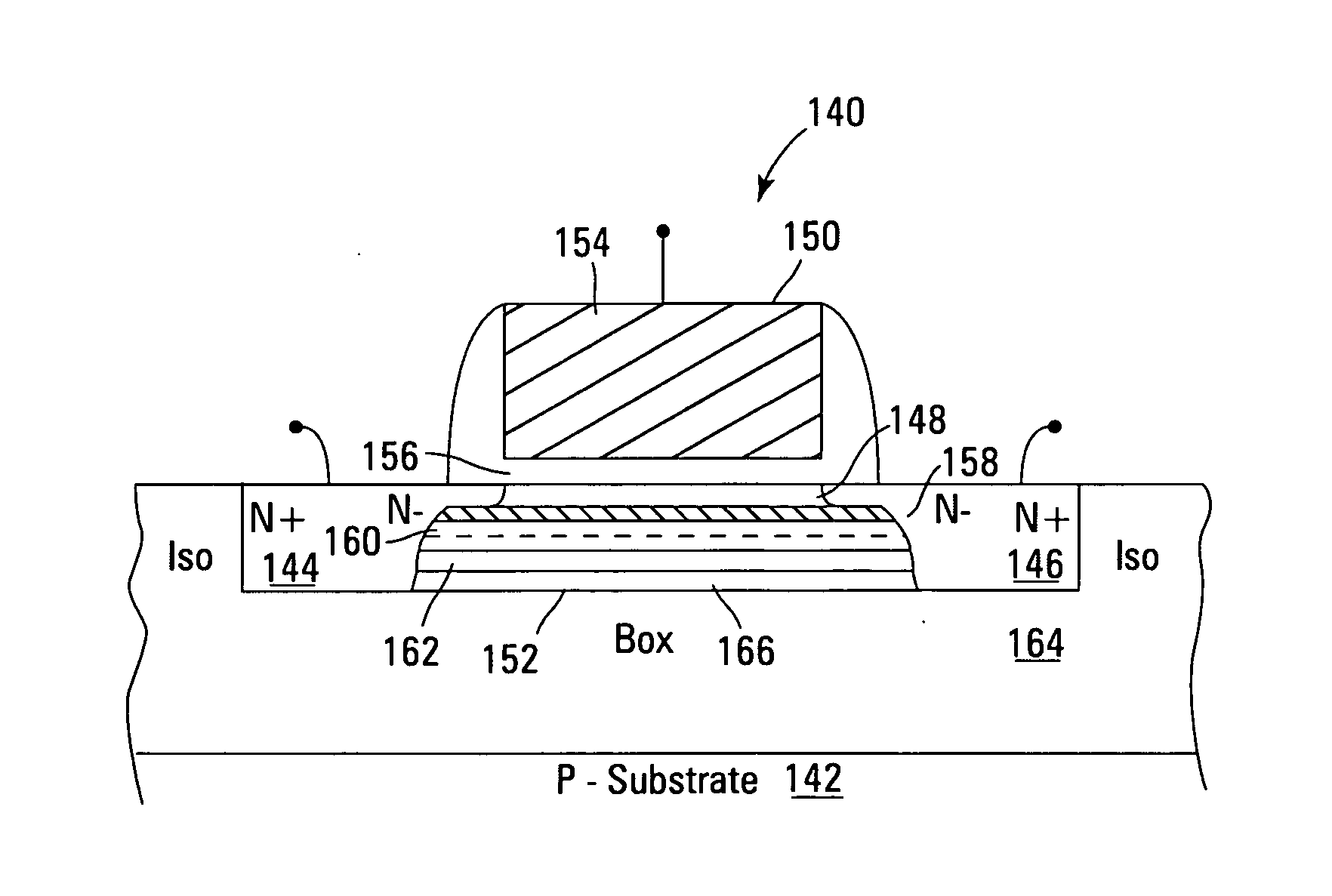

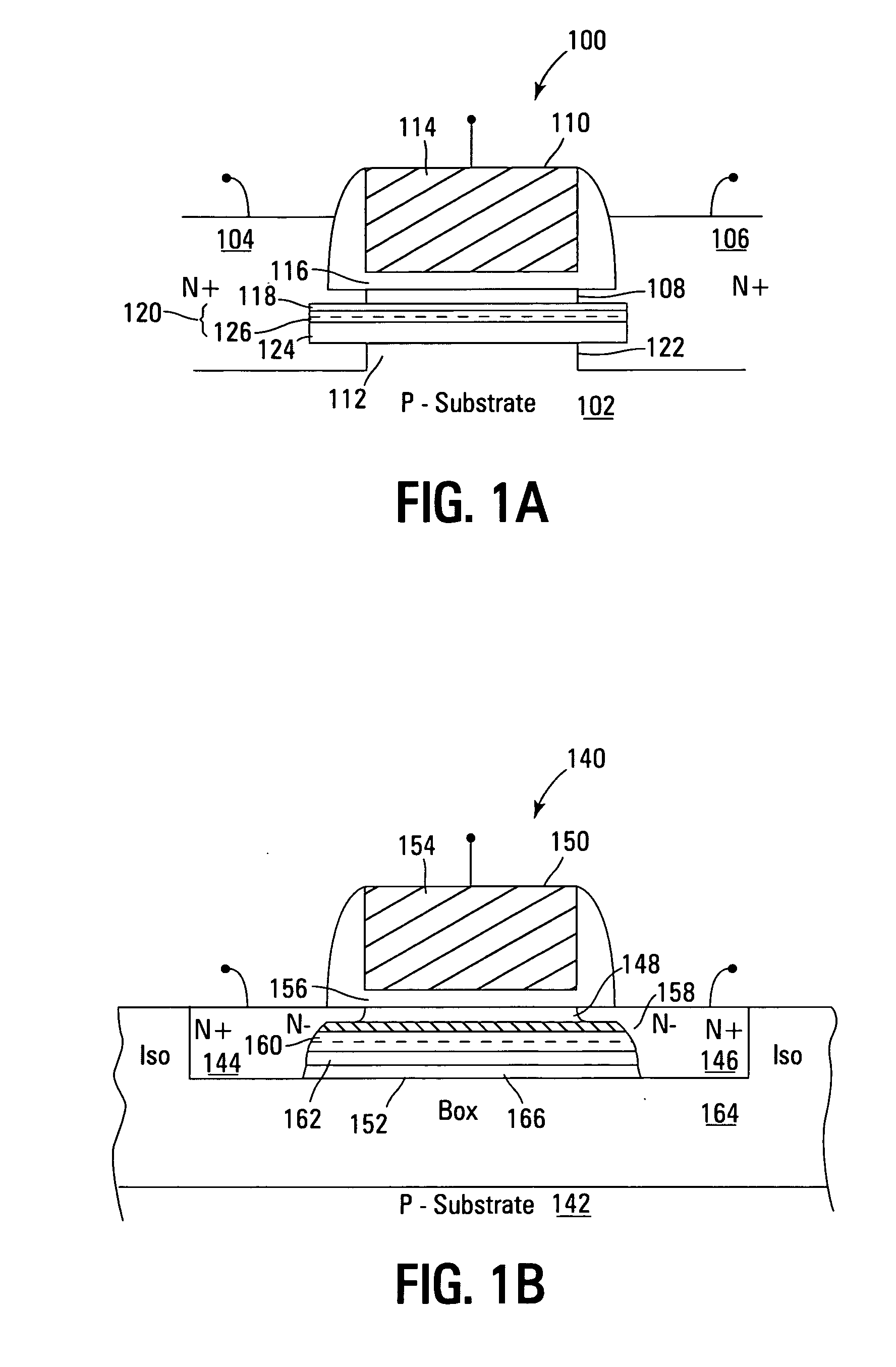

Band-engineered multi-gated non-volatile memory device with enhanced attributes

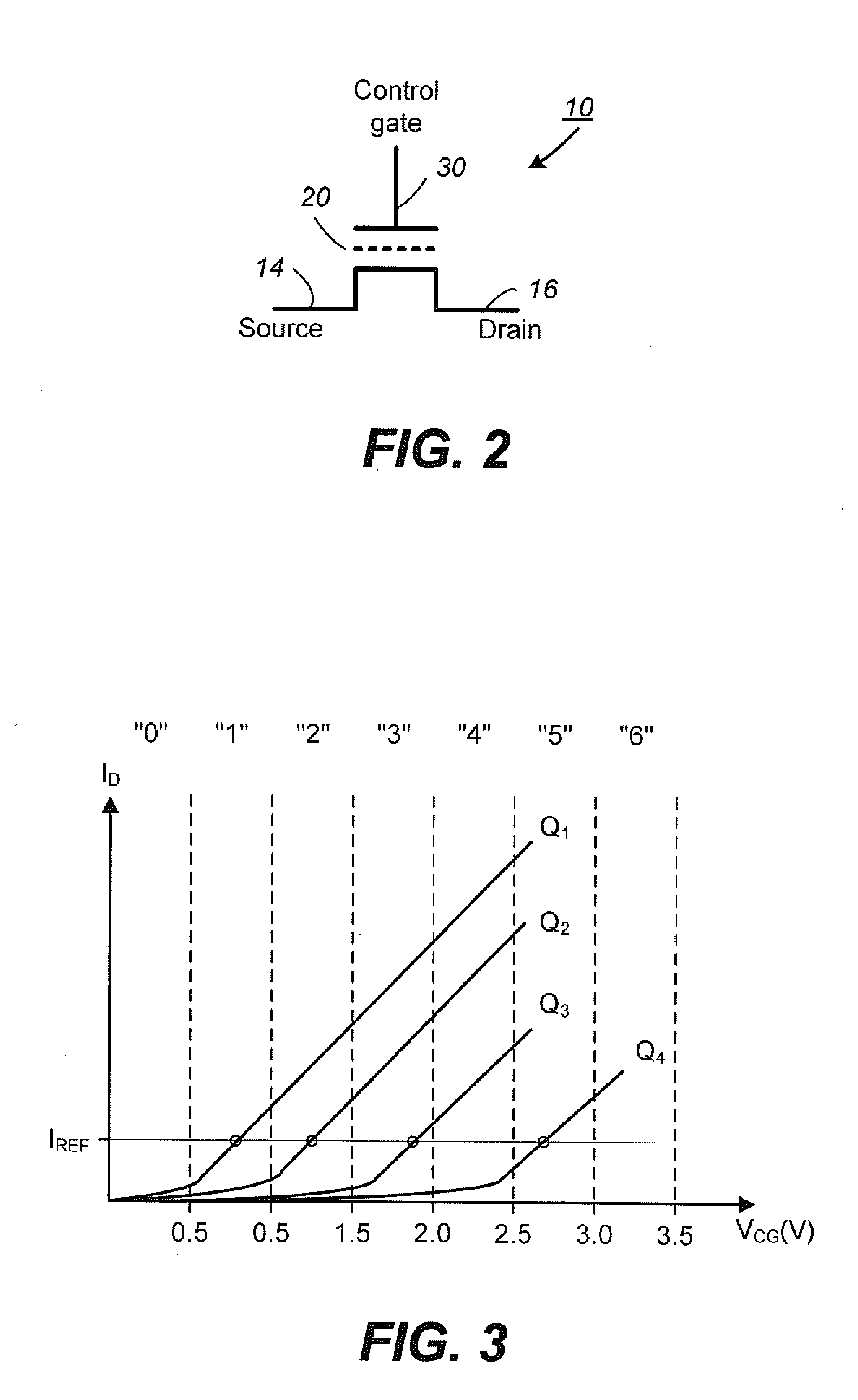

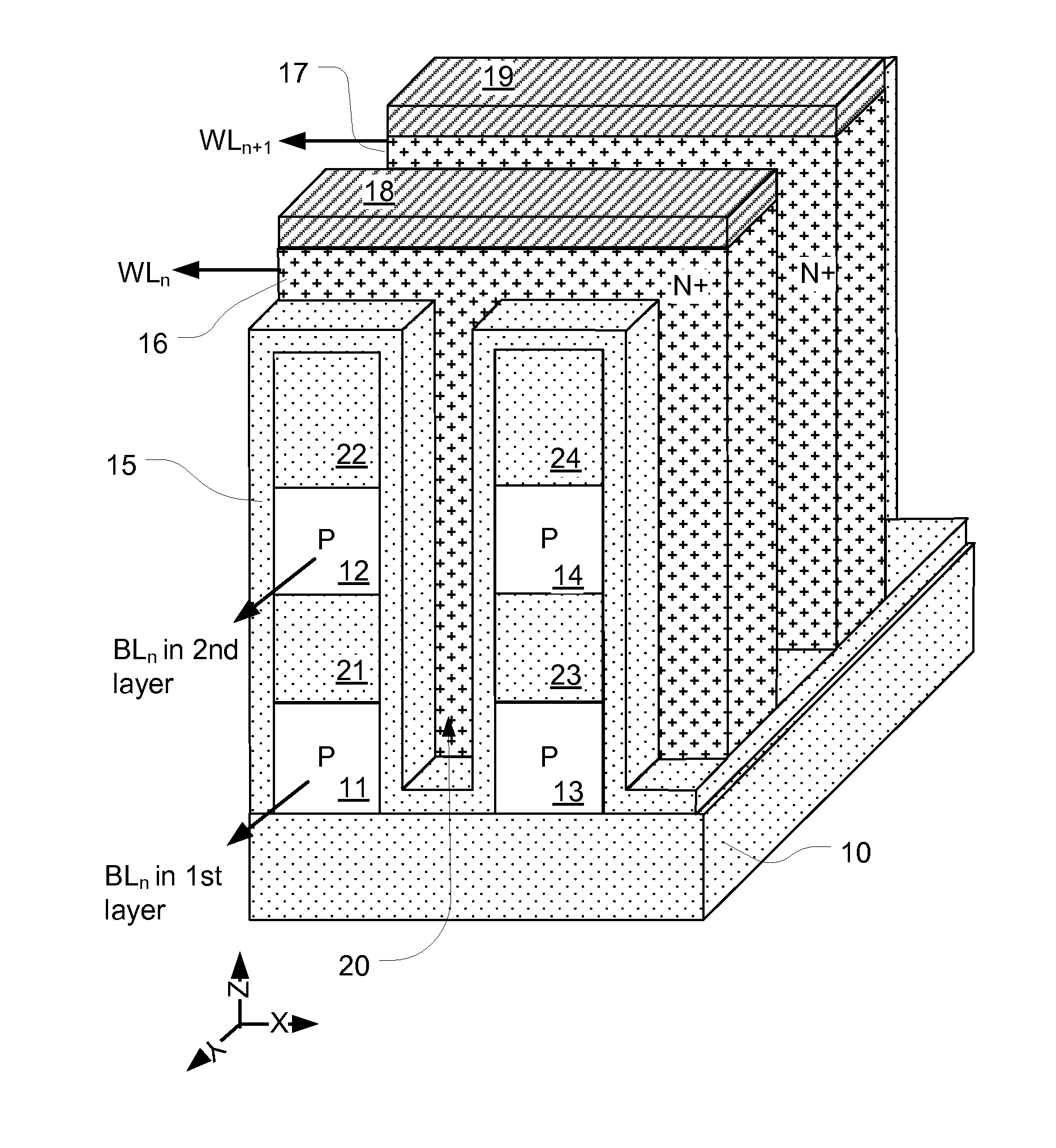

ActiveUS7279740B2Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

Band-engineered multi-gated non-volatile memory device with enhanced attributes

ActiveUS20060258090A1Reduce harmExcellent charge retentionSolid-state devicesRead-only memoriesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in floating gate memory cells in NOR or NAND memory architectures that allow for direct tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory cells of the present invention also allow multiple bit storage in a single memory cell, and allow for programming and erase with reduced voltages. A positive voltage erase process via hole tunneling is also provided.

Owner:MICRON TECH INC

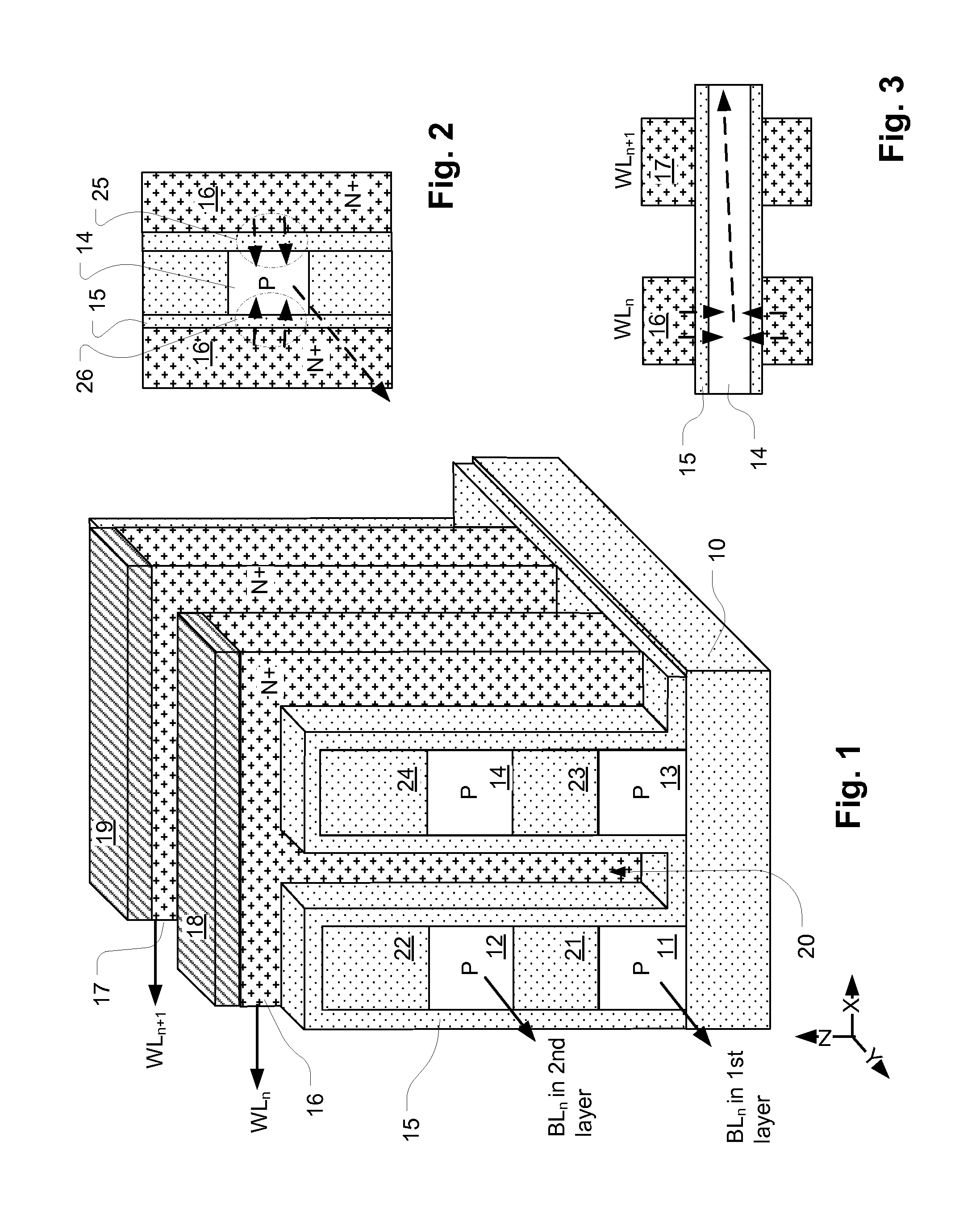

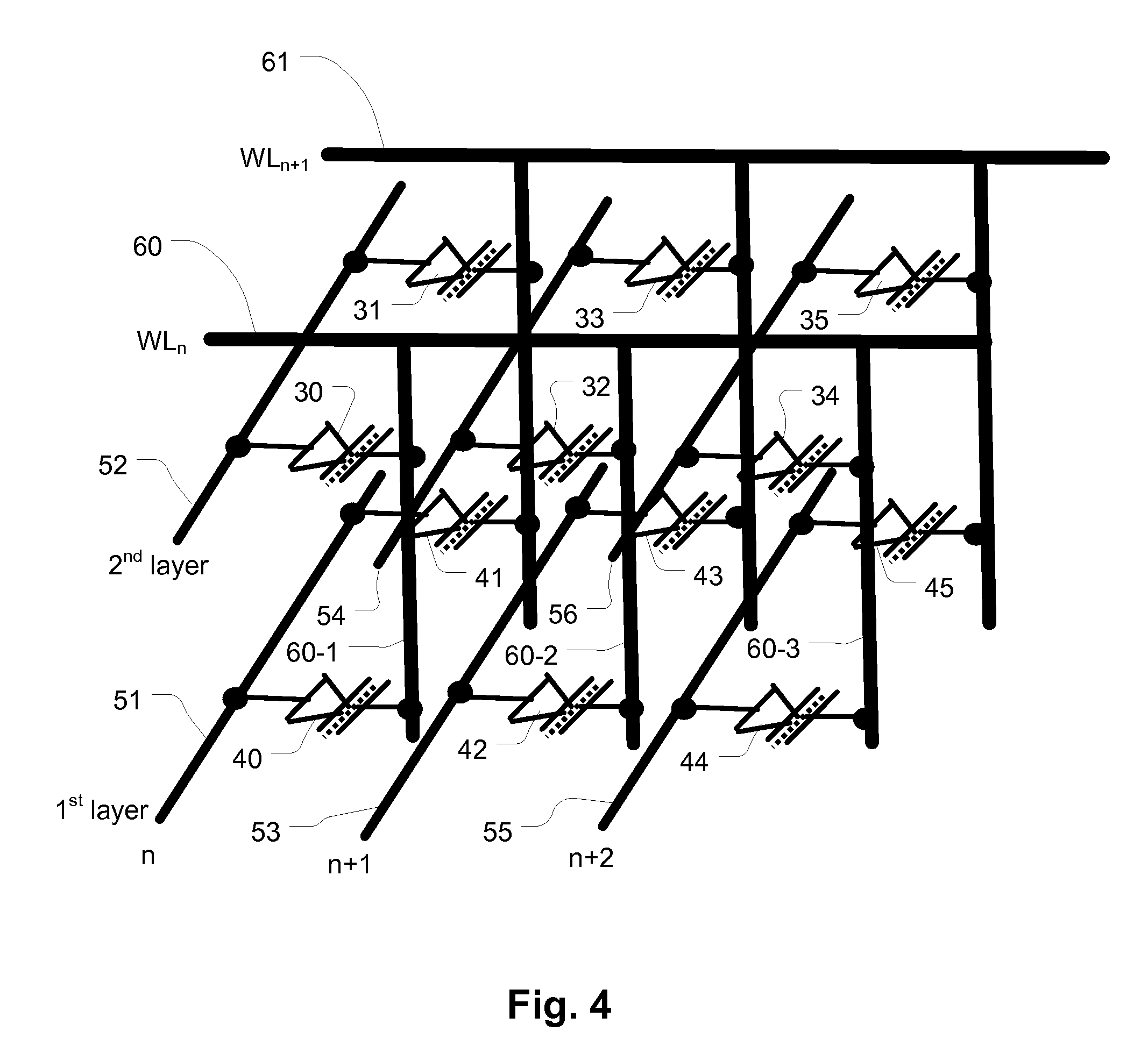

Memory architecture of 3D array with alternating memory string orientation and string select structures

ActiveUS8503213B2Increase pitchPitch is improvedSolid-state devicesRead-only memoriesAudio power amplifierConductive materials

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. Diodes are connected to the bit lines at either the string select of common source select ends of the strings. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of word lines, which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the semiconductor strips on the stacks and the word lines.

Owner:MACRONIX INT CO LTD

Nonvolatile Memory With Write Cache Having Flush/Eviction Methods

ActiveUS20100174846A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationEnergy efficient ICTGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. Decisions to archive data from the cache memory to the main memory depend on the attributes of the data to be archived, the state of the blocks in the main memory portion and the state of the blocks in the cache portion.

Owner:SANDISK TECH LLC

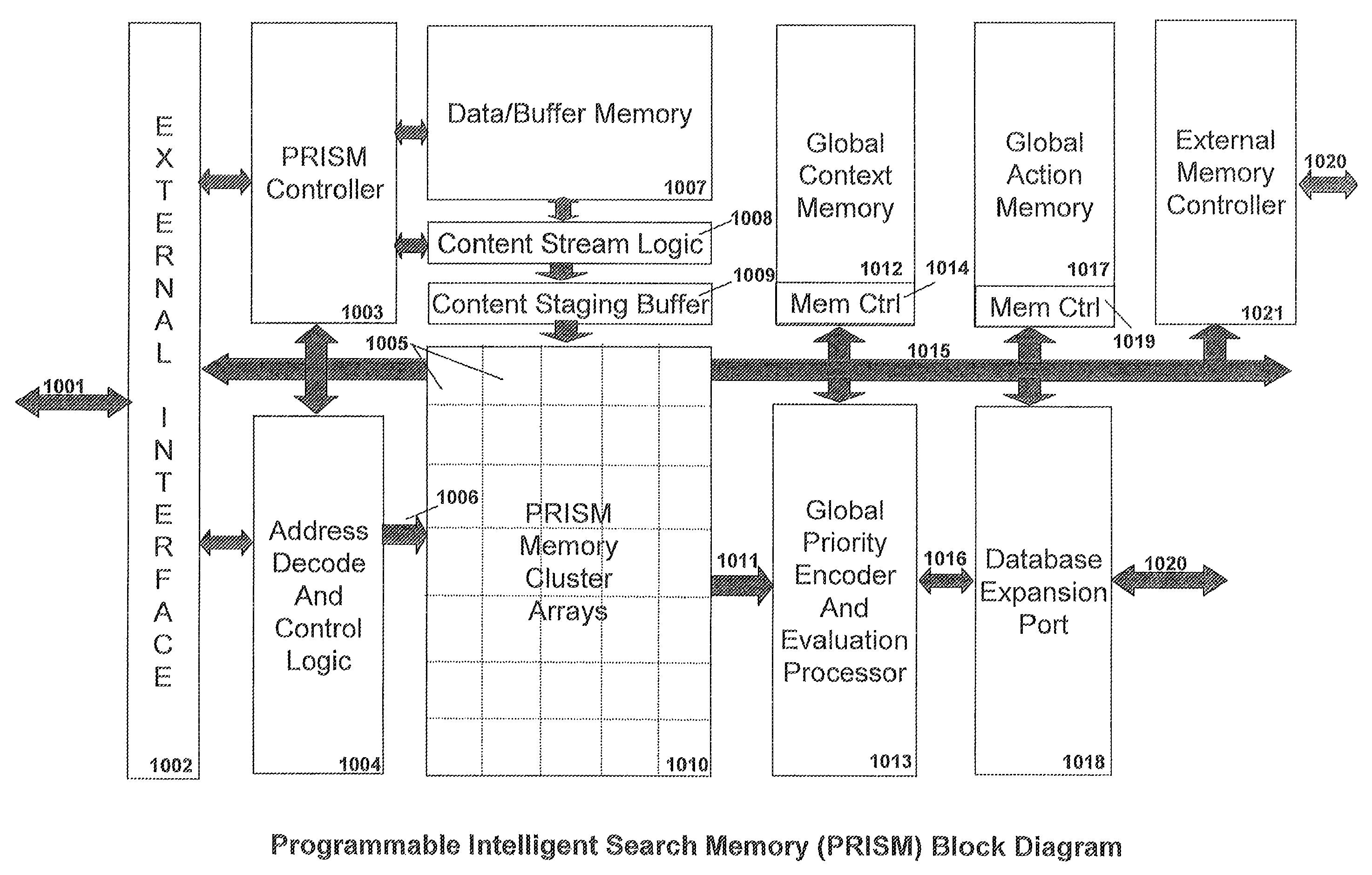

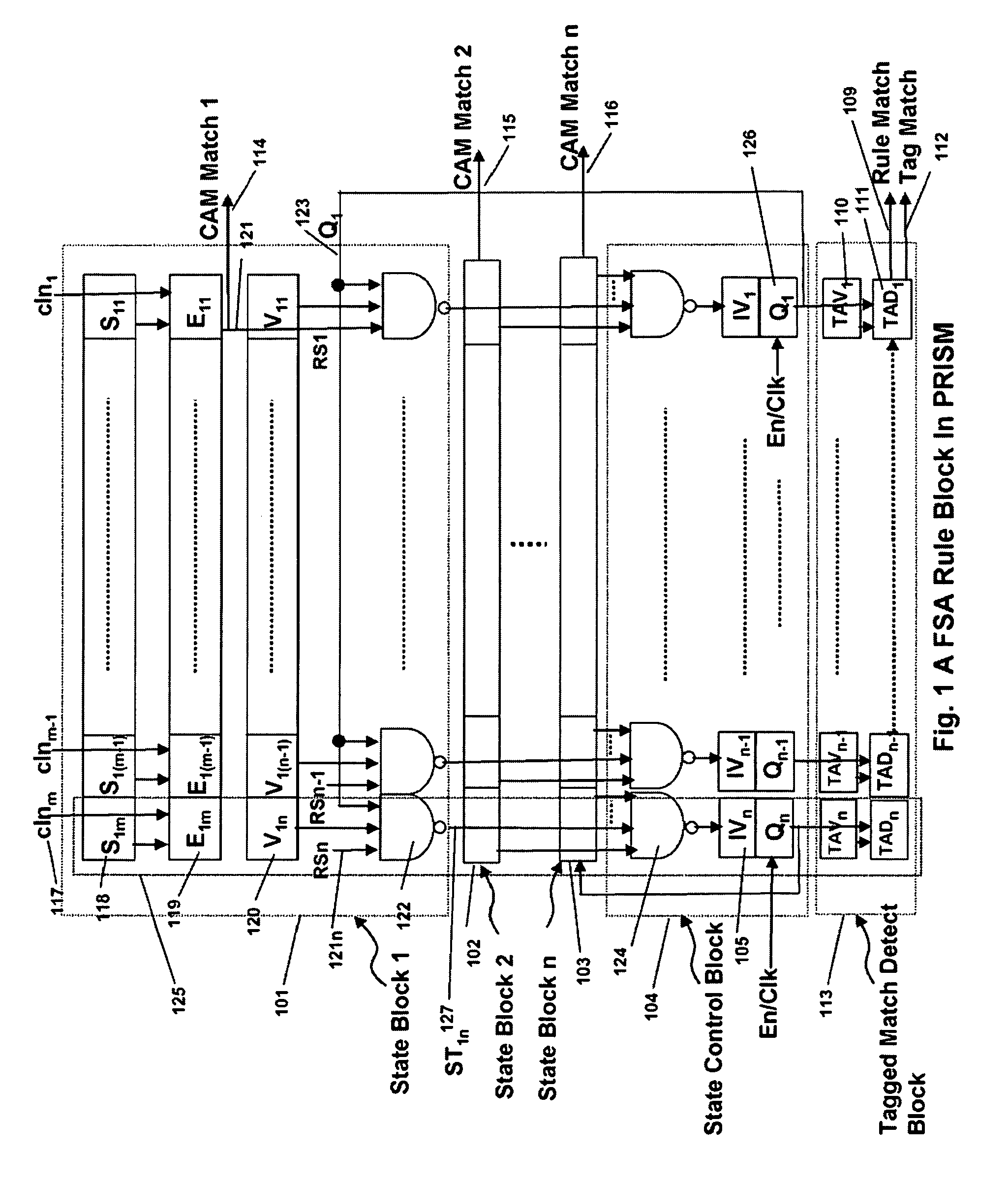

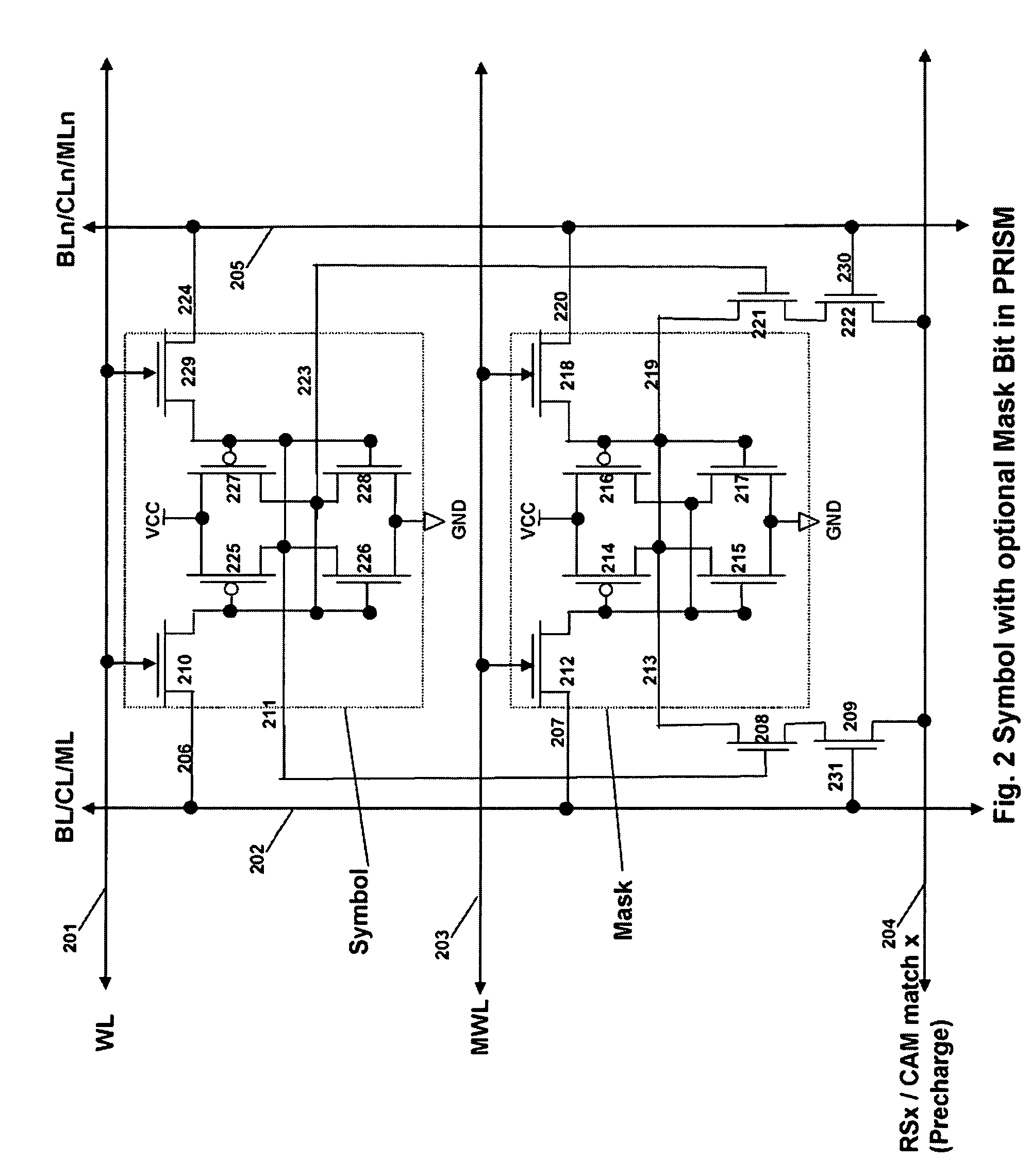

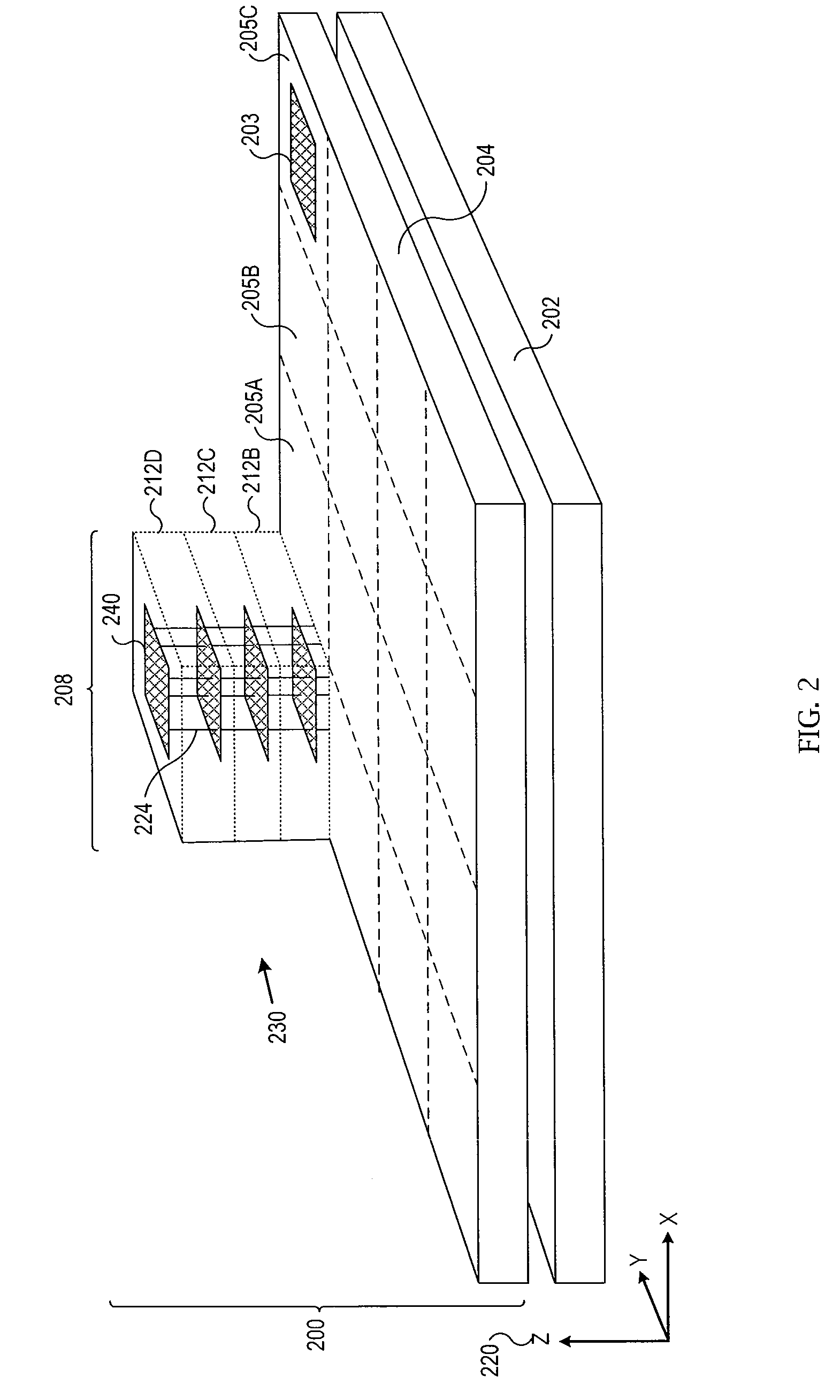

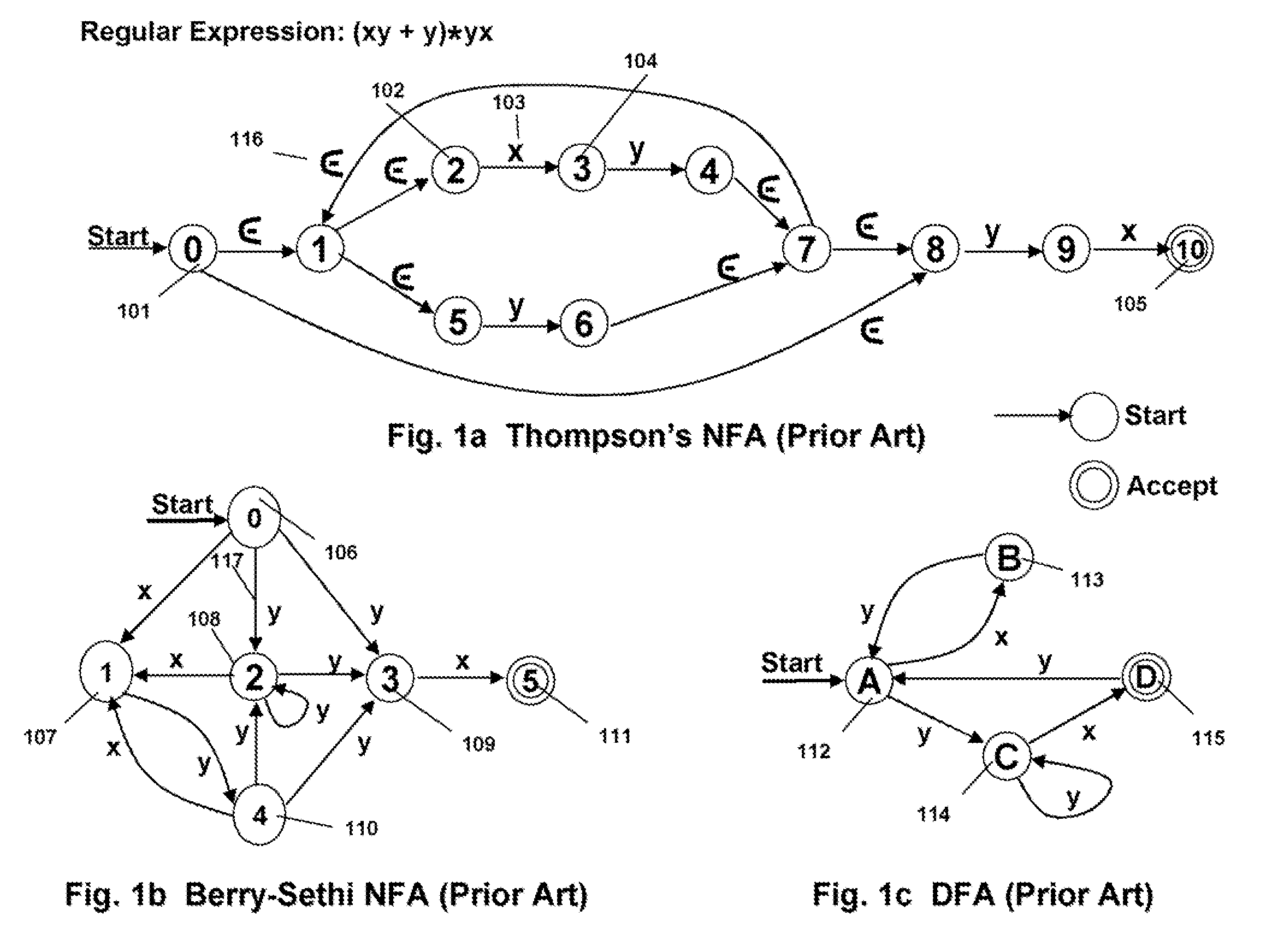

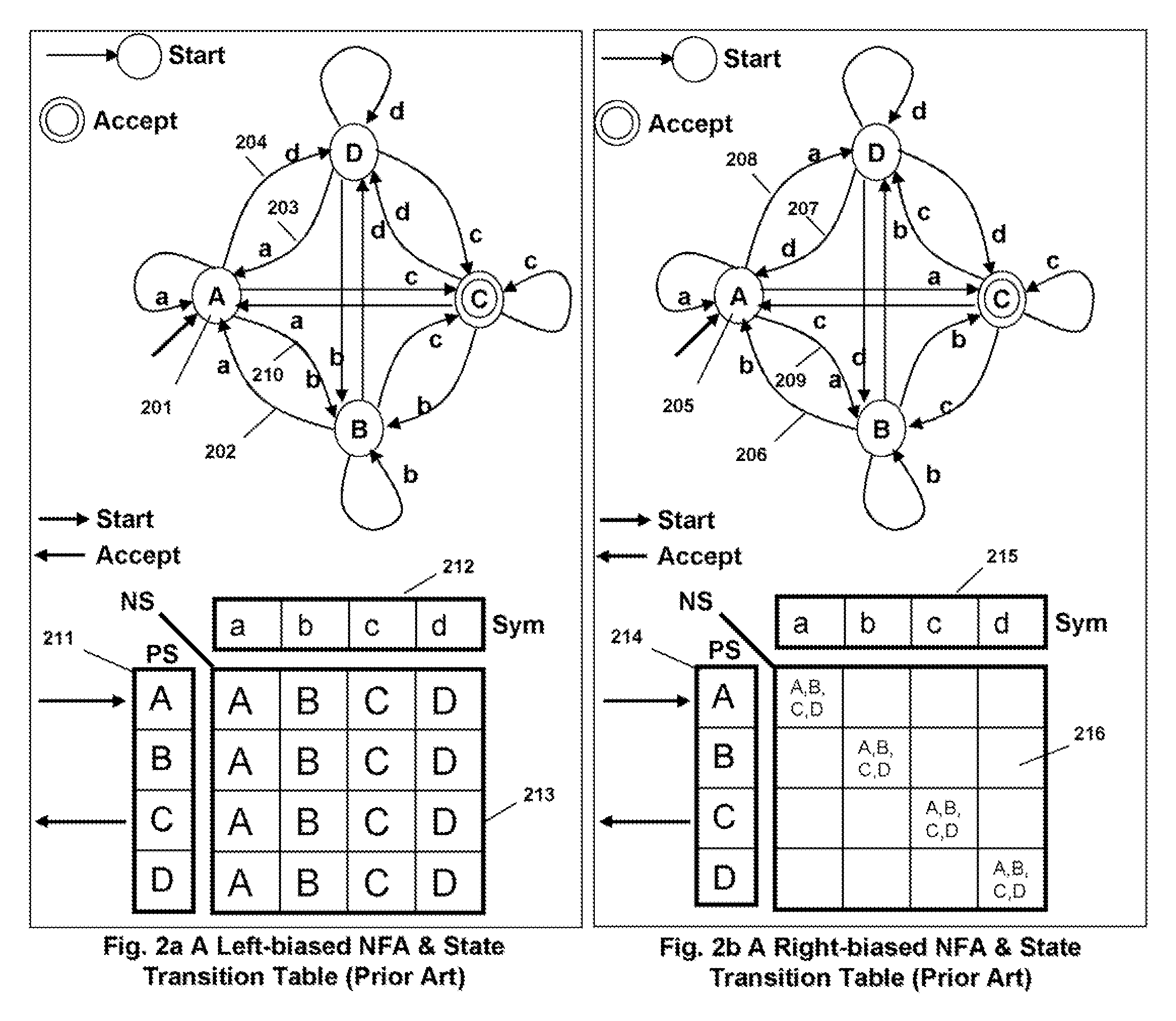

Complex symbol evaluation for programmable intelligent search memory

ActiveUS7827190B2Efficient and compact realizationDigital data information retrievalDigital data processing detailsTerm memoryMemory architecture

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable Intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken. Content search rules comprise of regular expressions which are converted to finite state automata and then programmed in PRISM for evaluating content with the search rules. The PRISM memory provides features for complex regular expression symbols like range detection, complement control, bit masking and the like and enables complex symbols and compact regular expression representation.

Owner:INFOSIL INC

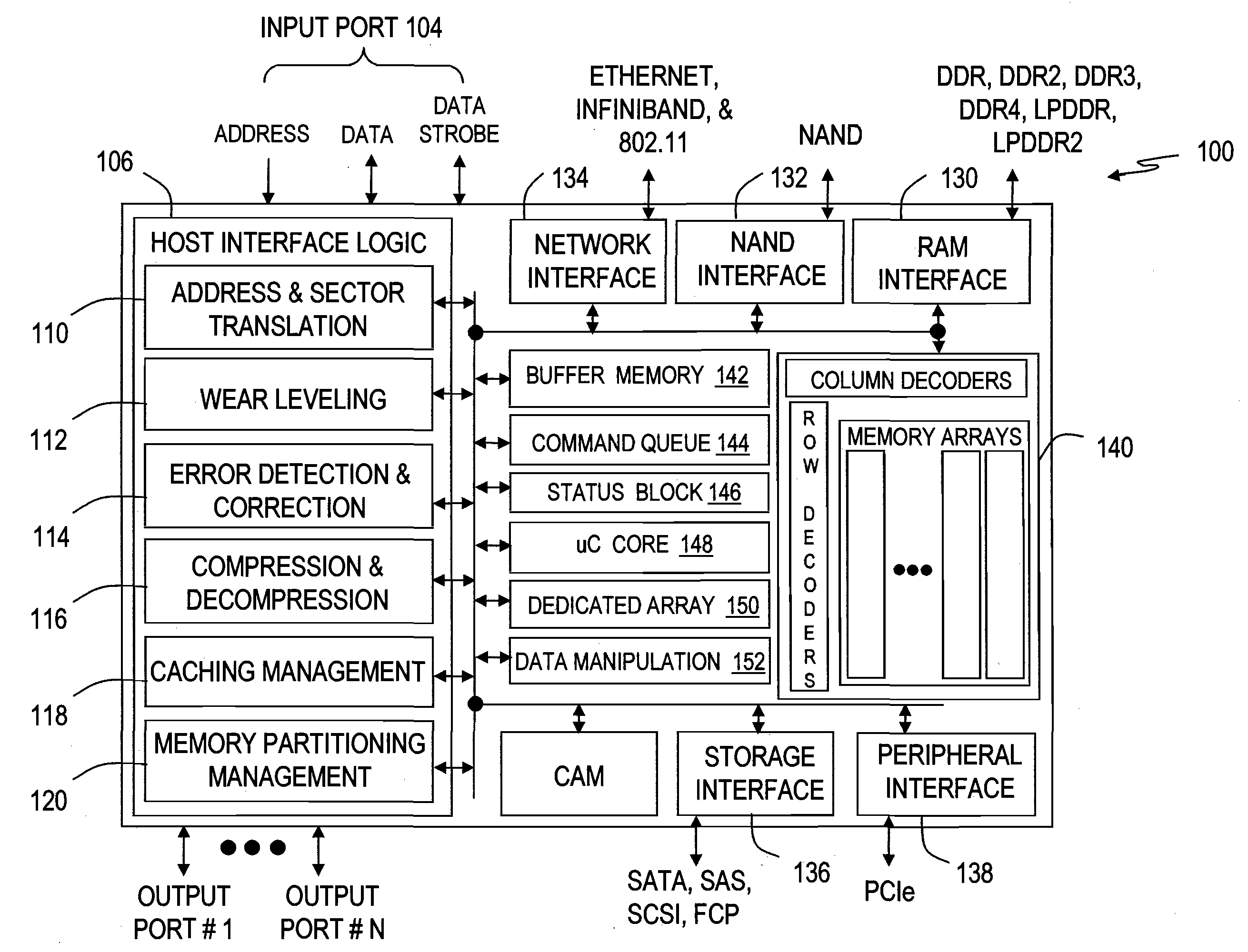

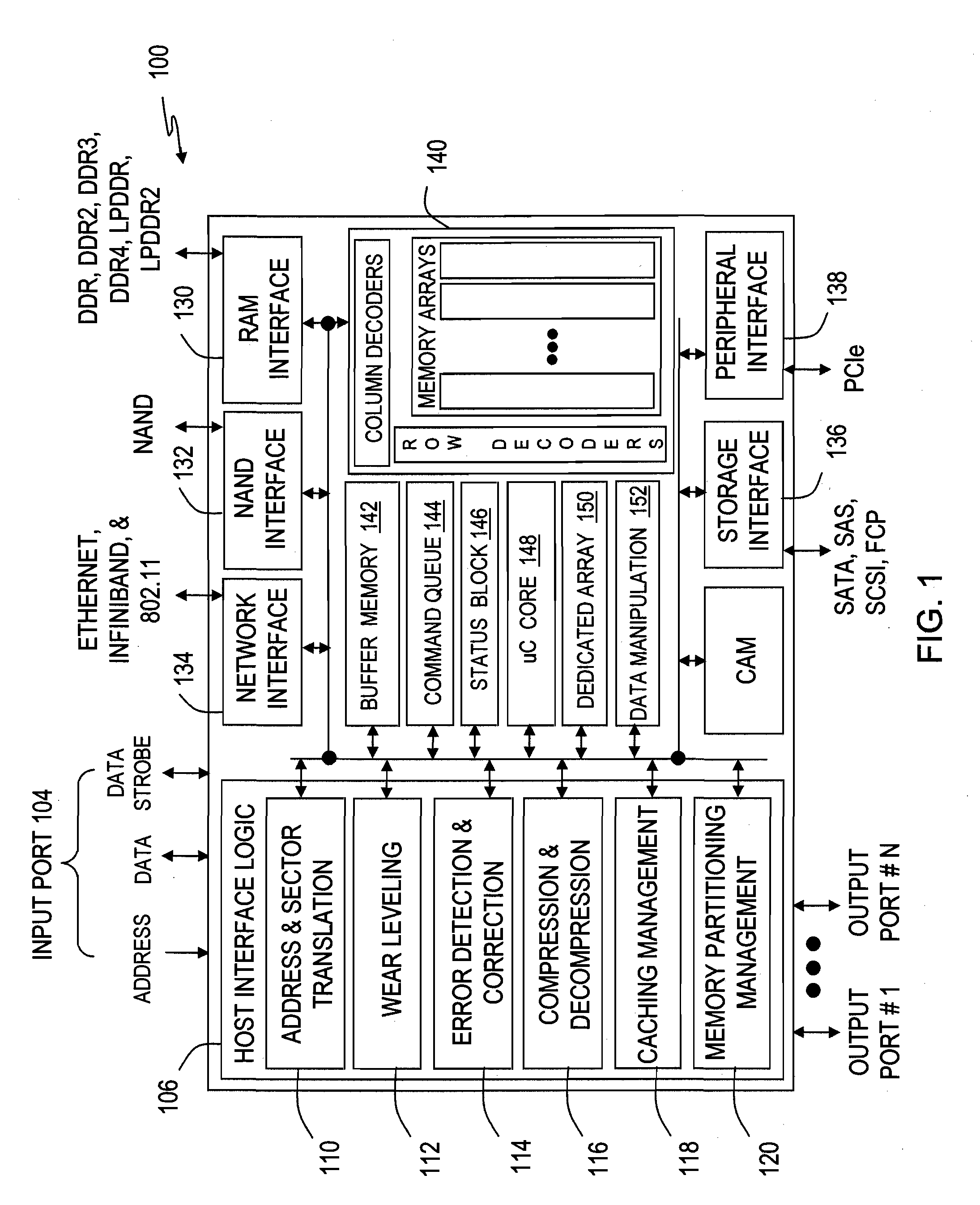

Memory device for a hierarchical memory architecture

ActiveUS20100318718A1Energy efficient ICTInput/output to record carriersPhase-change memoryComputer architecture

A hierarchical memory device having multiple interfaces with different memory formats includes a Phase Change Memory (PCM). An input port and an output port connect the hierarchical memory device in a daisy-chain hierarchy or a hierarchical tree structure with other memories. Standard non-hierarchical memory devices can also attach to the output port of the hierarchical memory device.

Owner:MICRON TECH INC

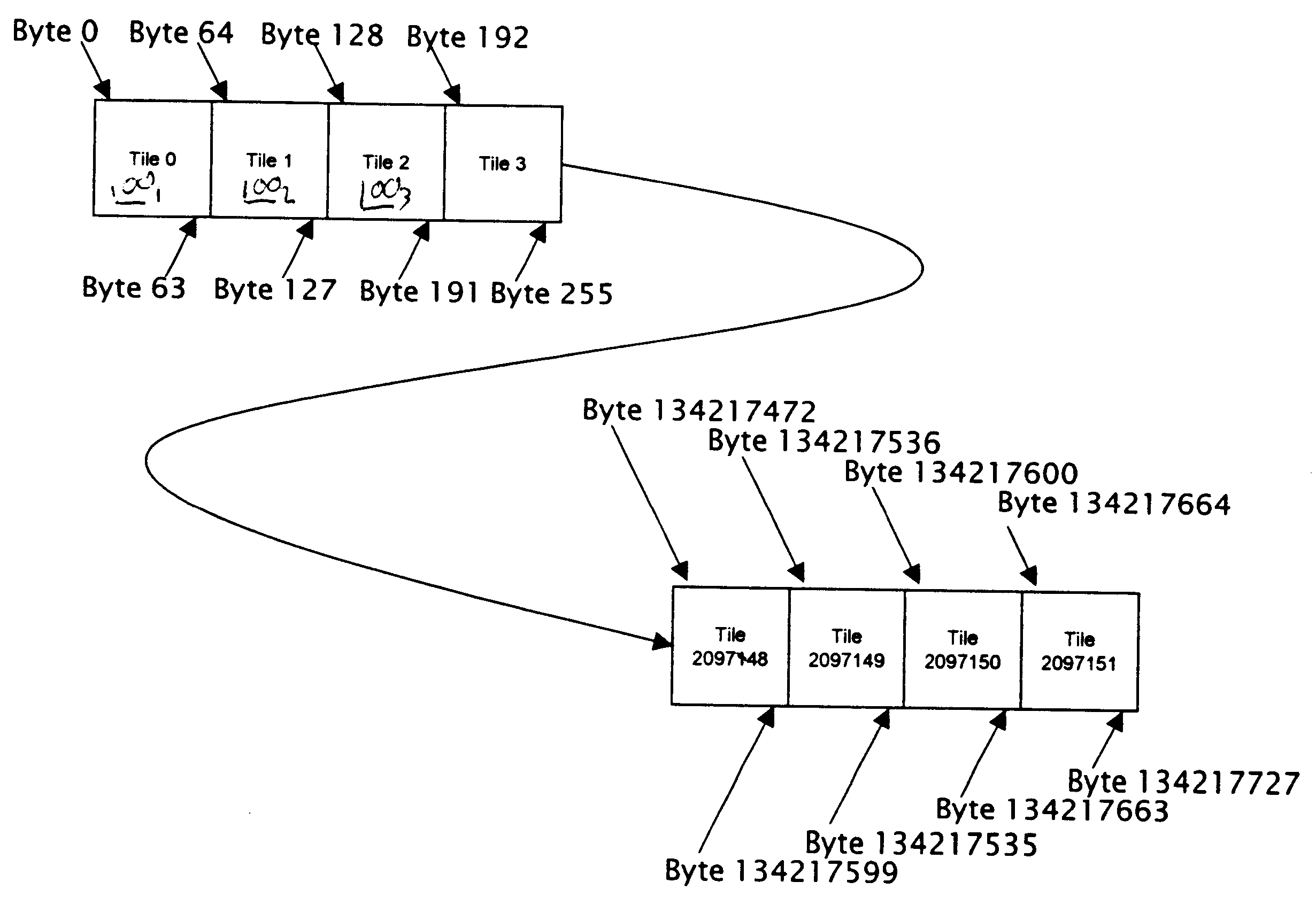

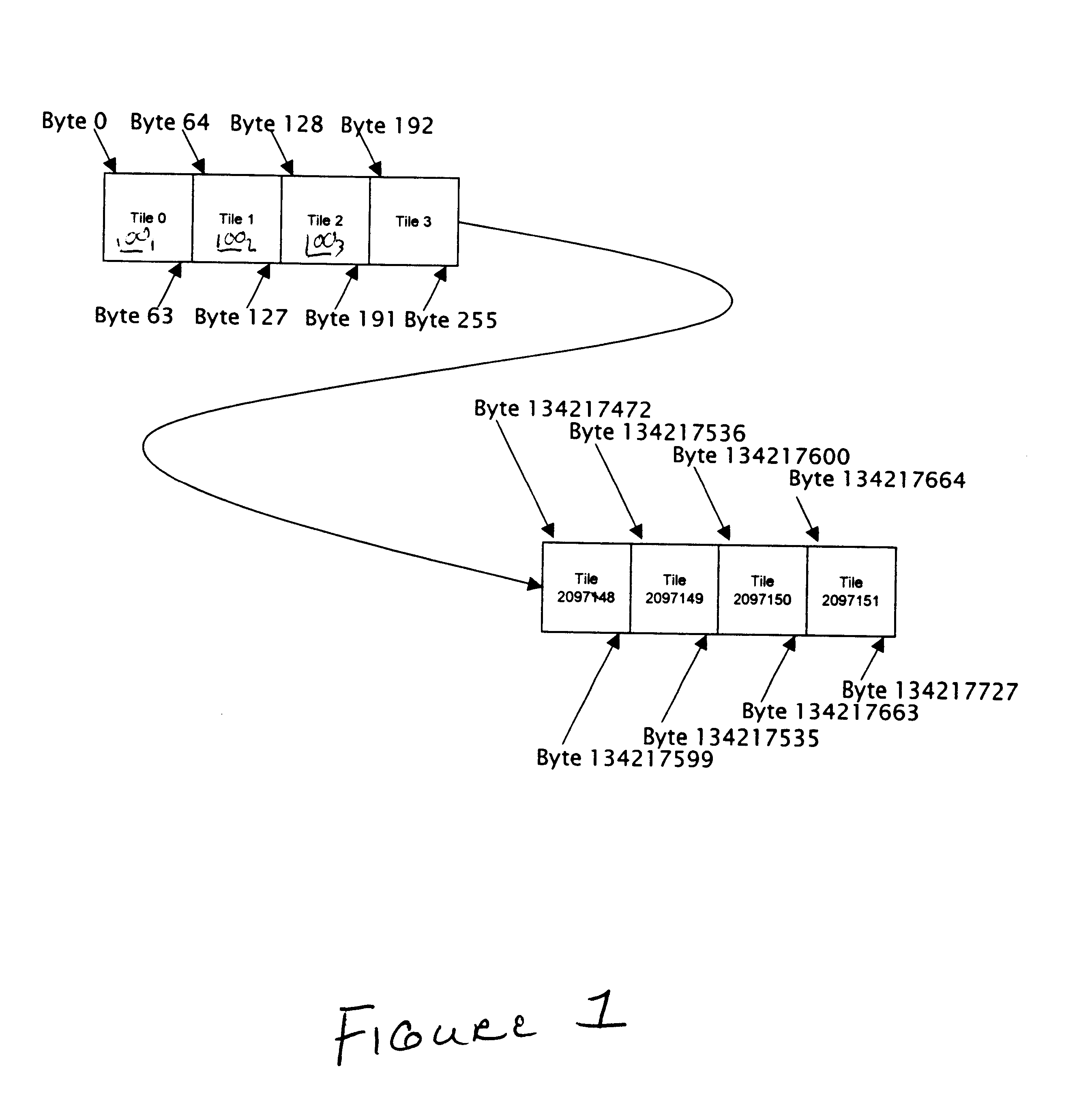

Planar byte memory organization with linear access

InactiveUS6847370B2Memory adressing/allocation/relocationCathode-ray tube indicatorsGraphicsMemory architecture

A graphics memory architecture in which row addresses are permuted, in a basically tile-oriented storage architecture, so that fast parallel access is provided both by scanlines (for video operations) and also by tiles (for graphics operations).

Owner:XUESHAN TECH INC

Cache memory architecture with on-chip tag array and off-chip data array

InactiveUS6247094B1Memory architecture accessing/allocationMemory adressing/allocation/relocationCache-only memory architectureMemory architecture

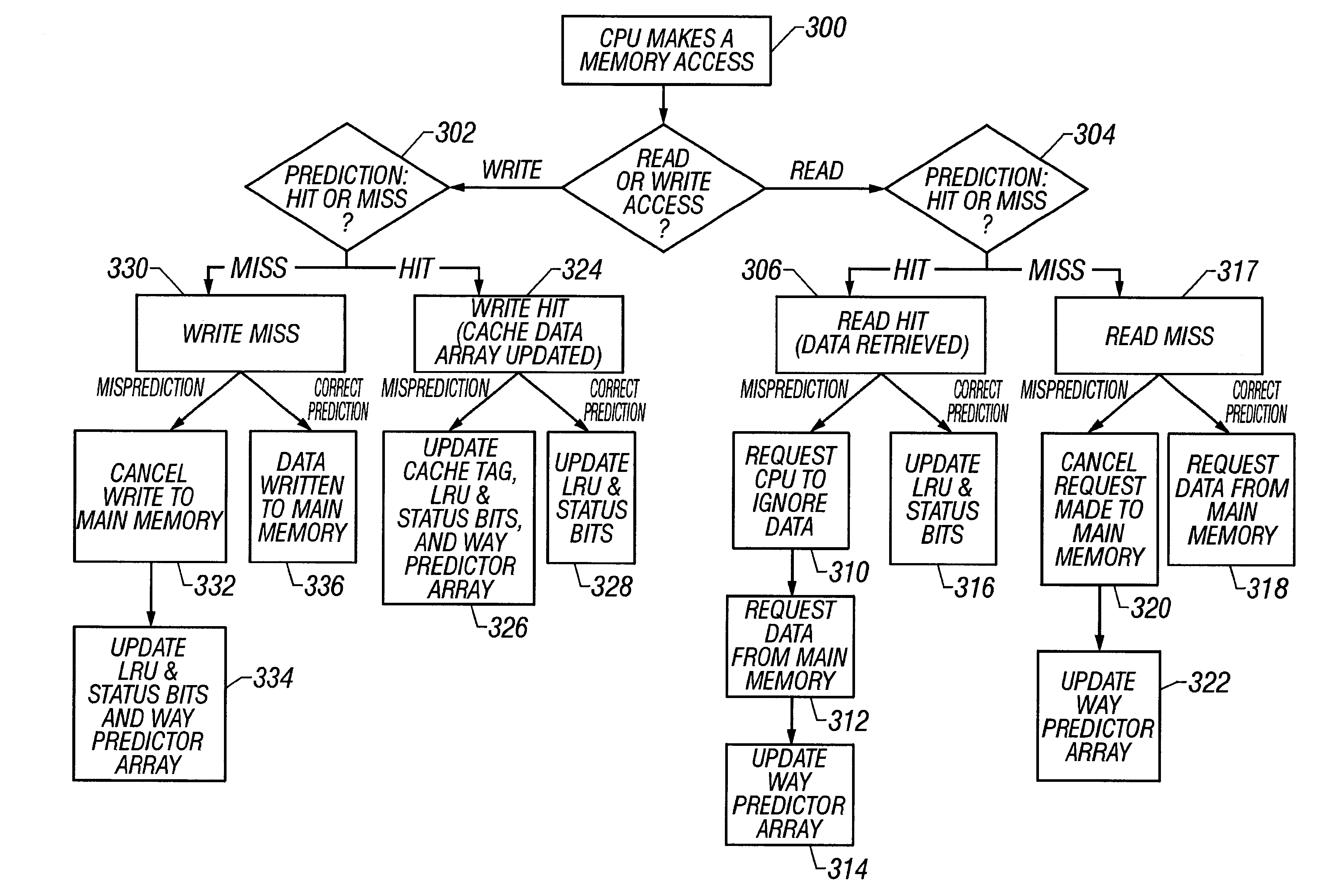

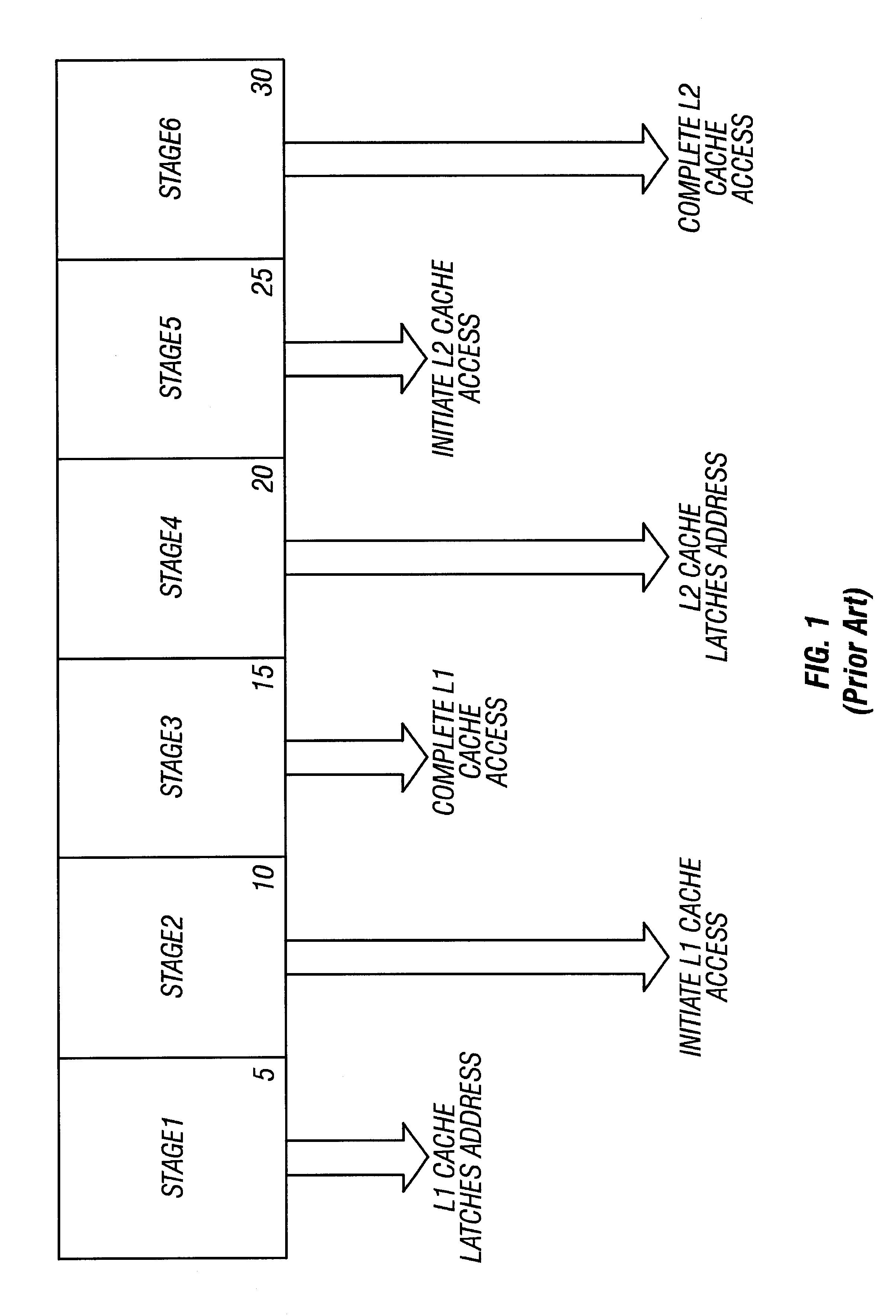

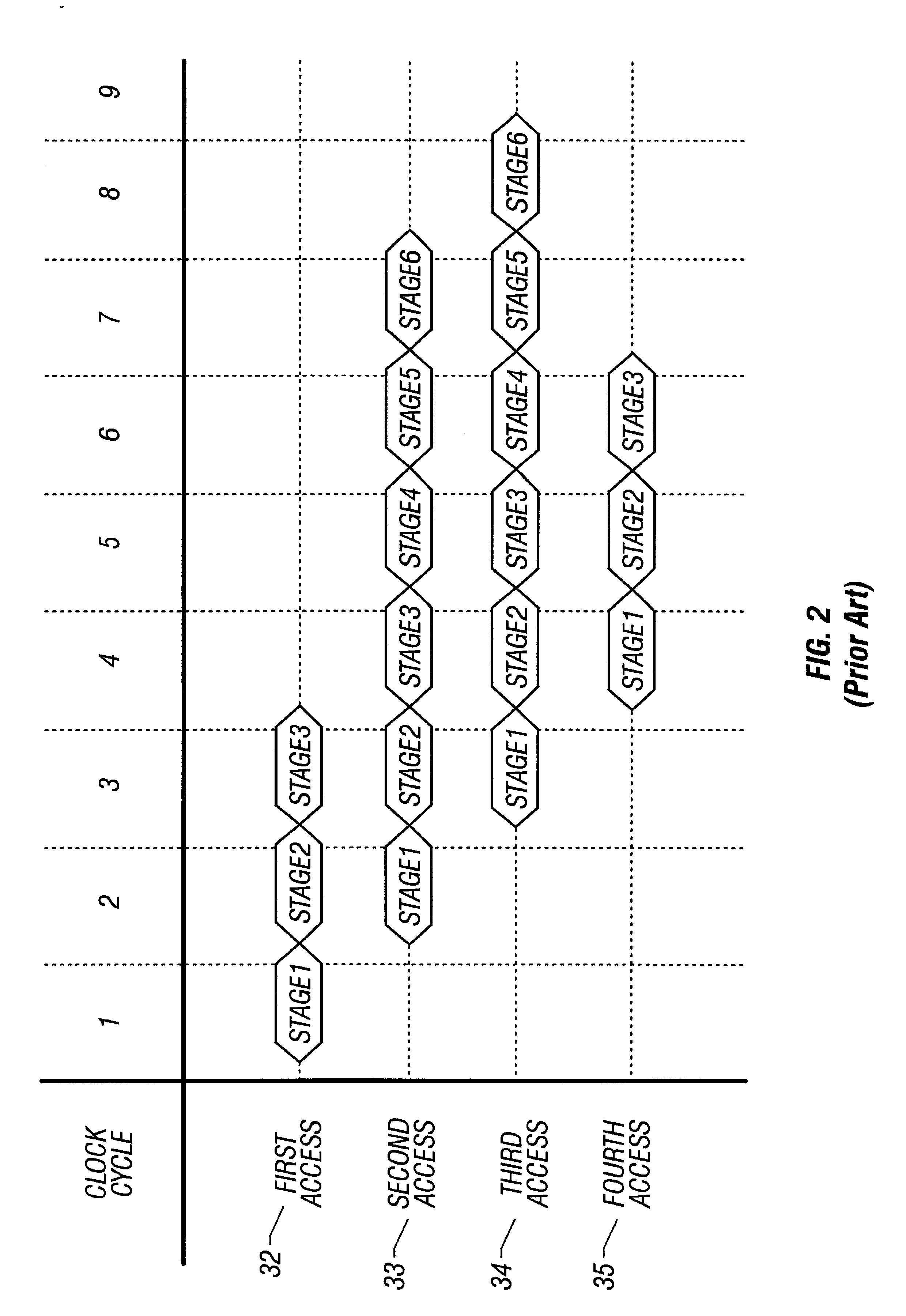

The present invention provides an improved cache memory architecture with way prediction. The improved architecture entails placing the address tag array of a cache memory on the central processing unit core (i.e. the microprocessor chip), while the cache data array remains off the microprocessor chip. In addition, a way predictor is provided in conjunction with the improved memory cache architecture to increase the overall performance of the cache memory system.

Owner:INTEL CORP

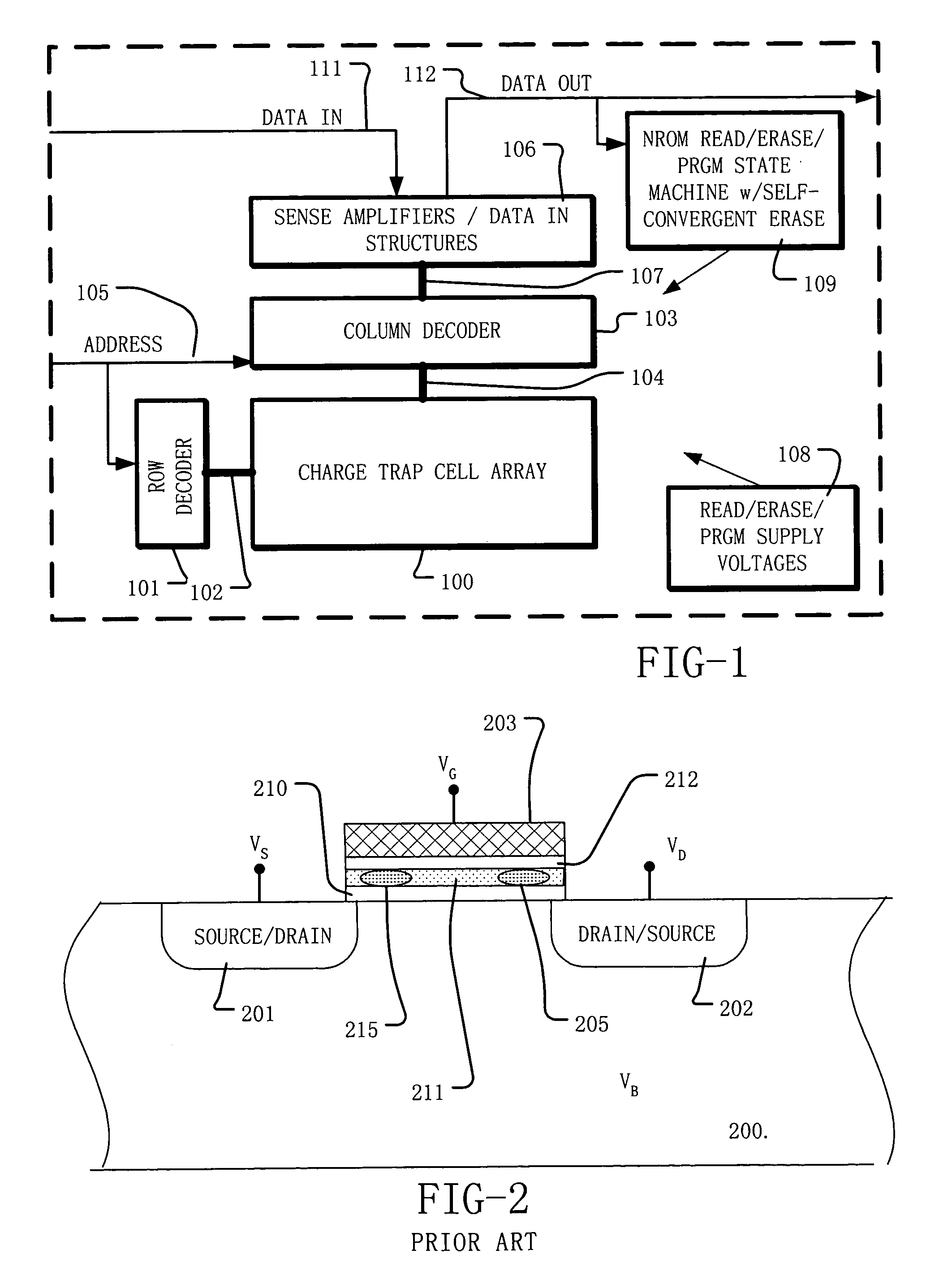

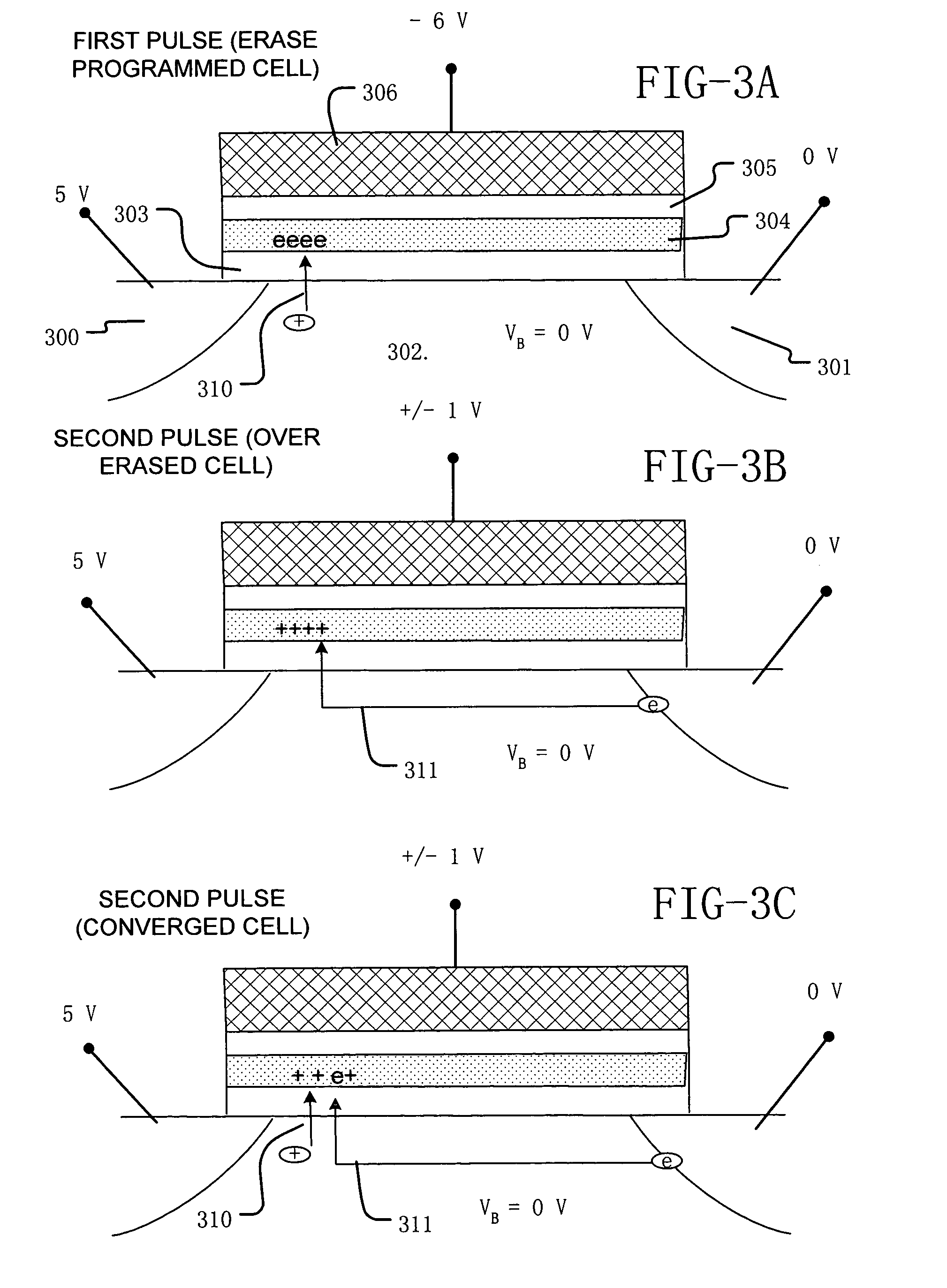

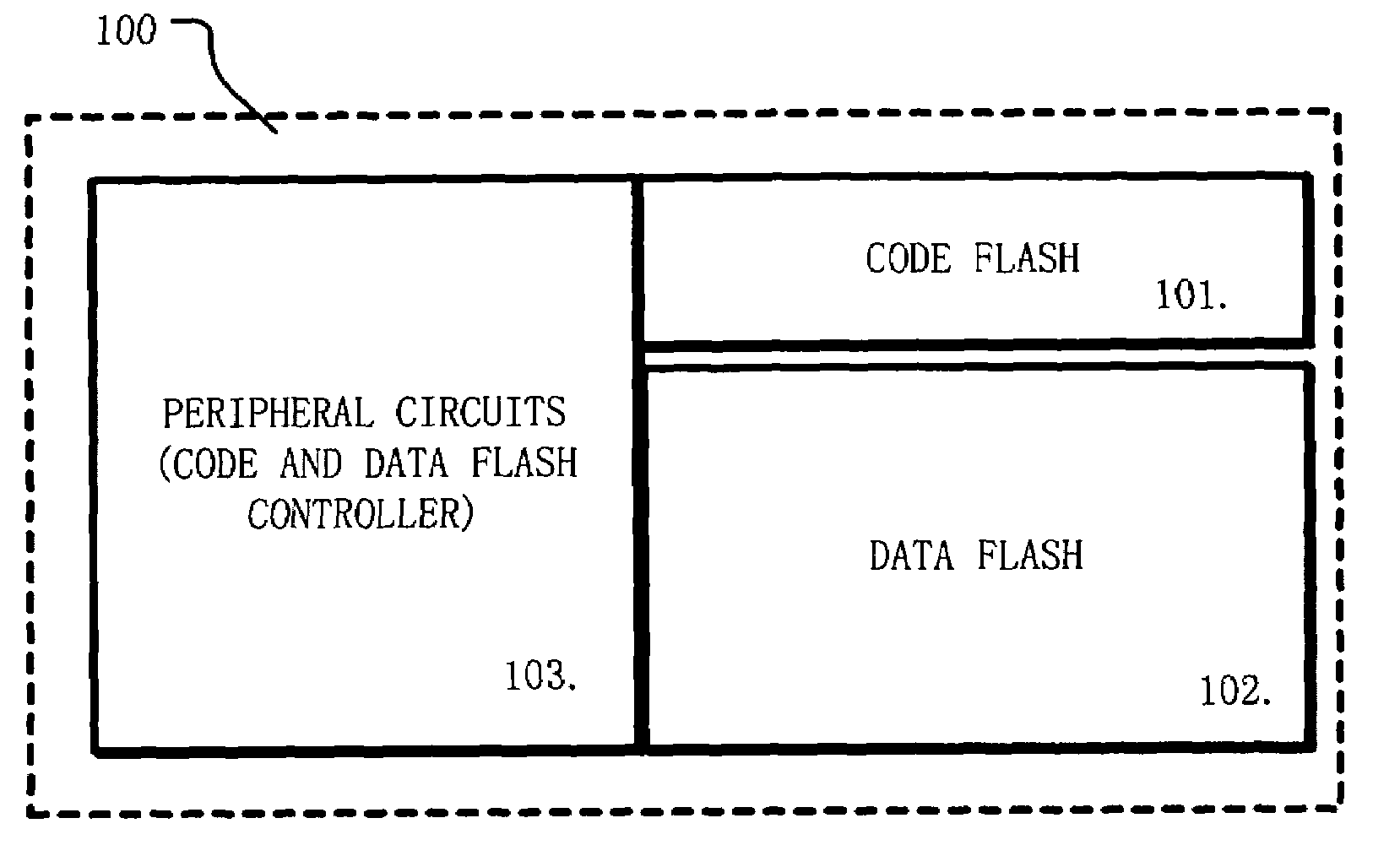

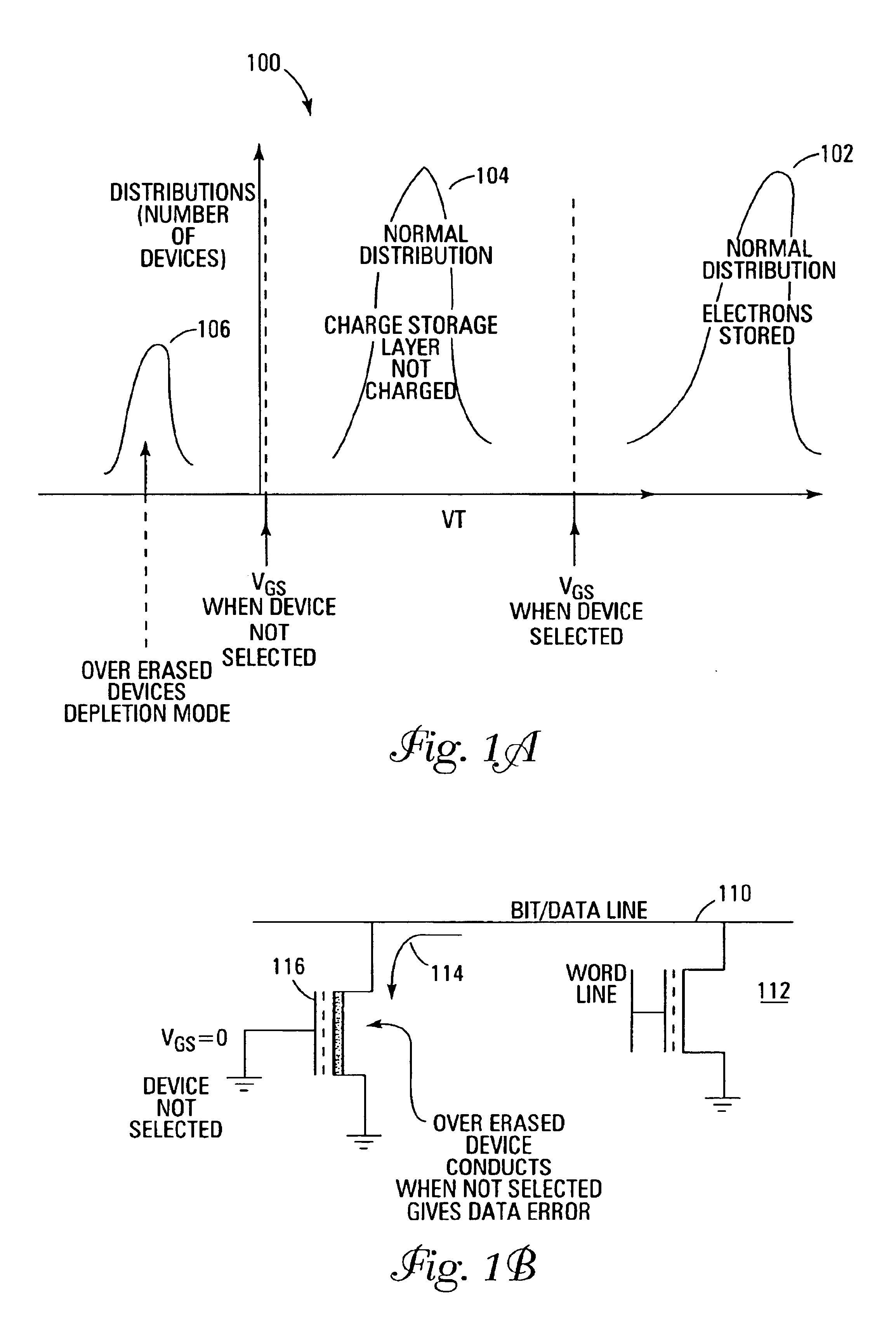

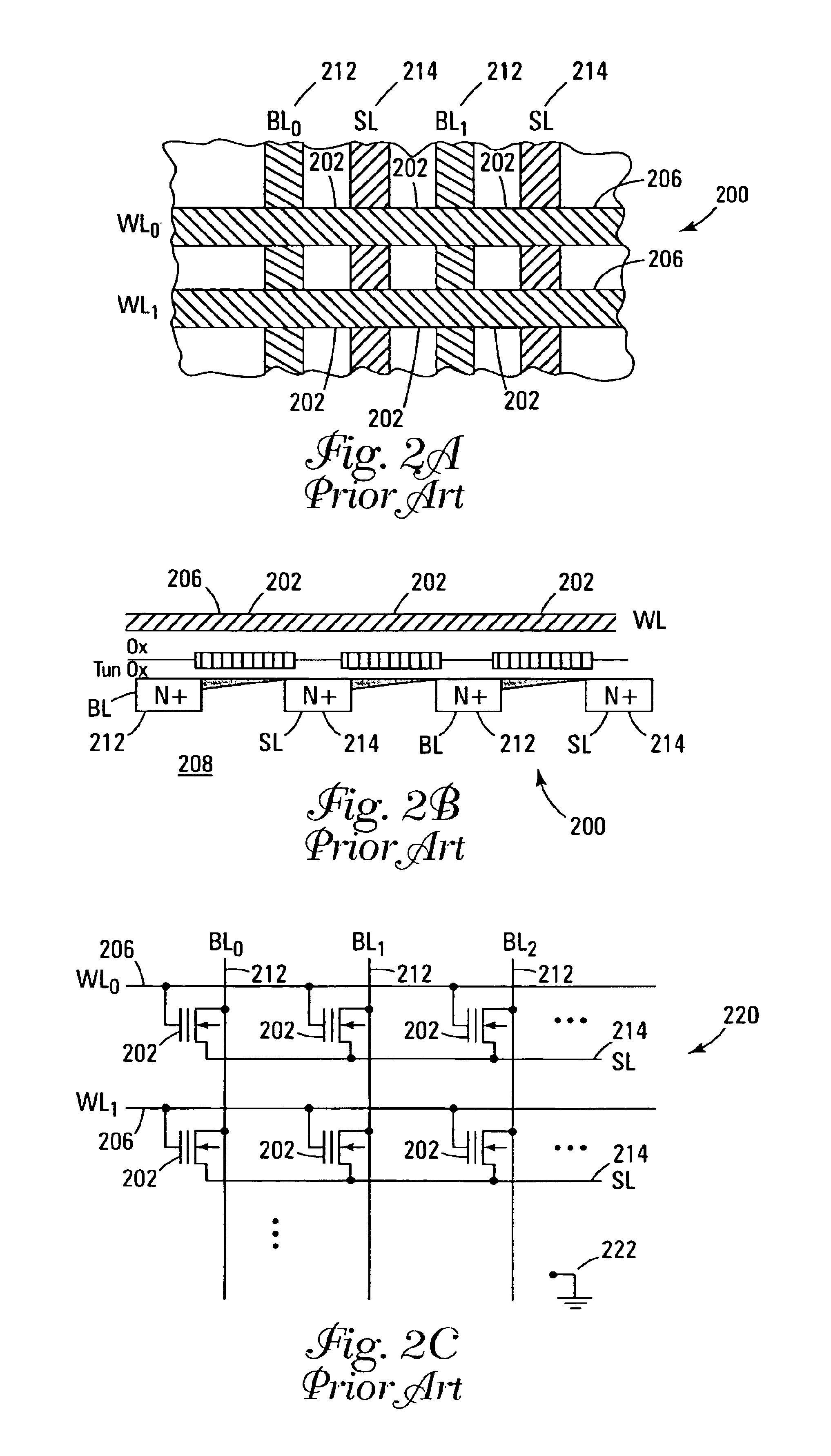

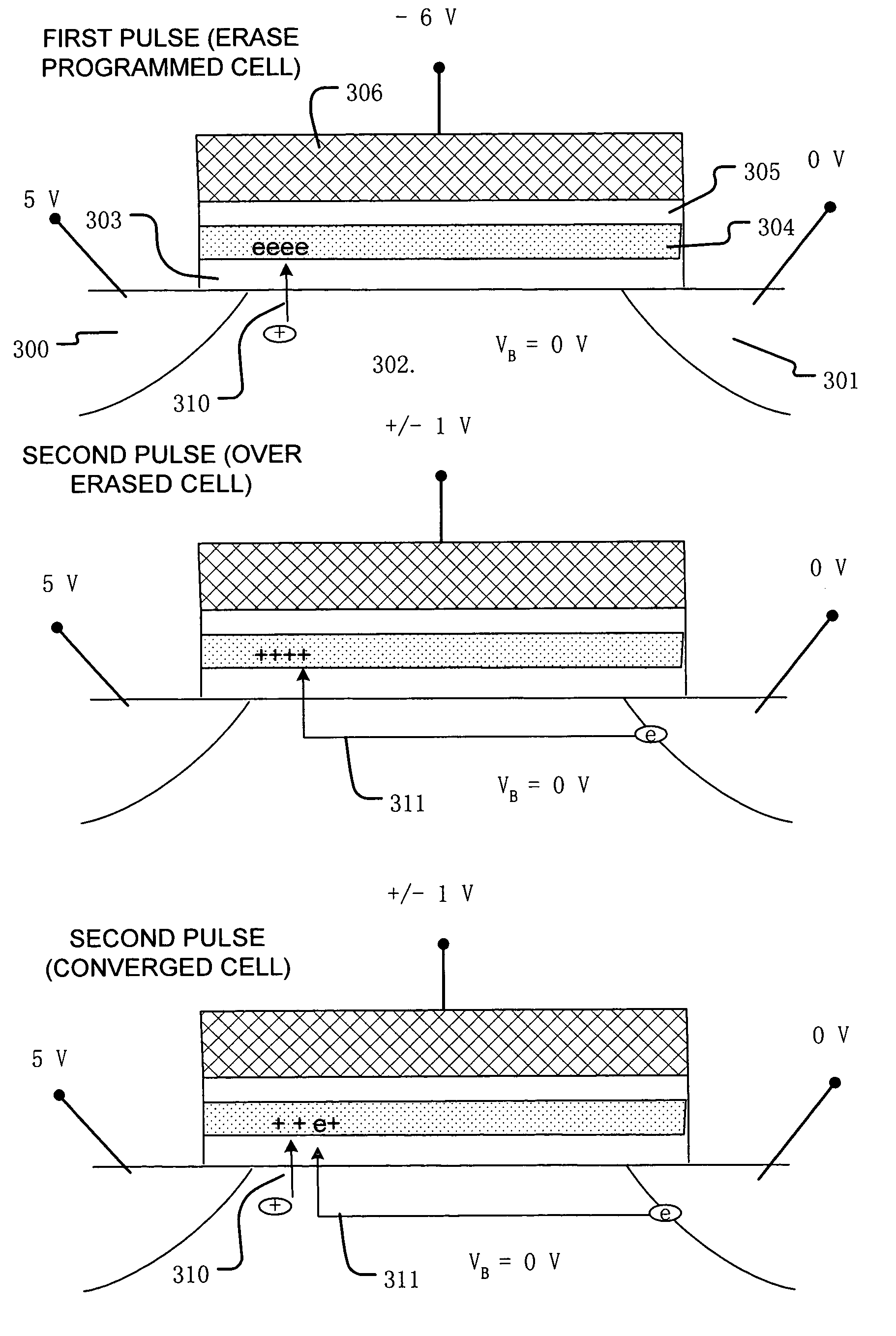

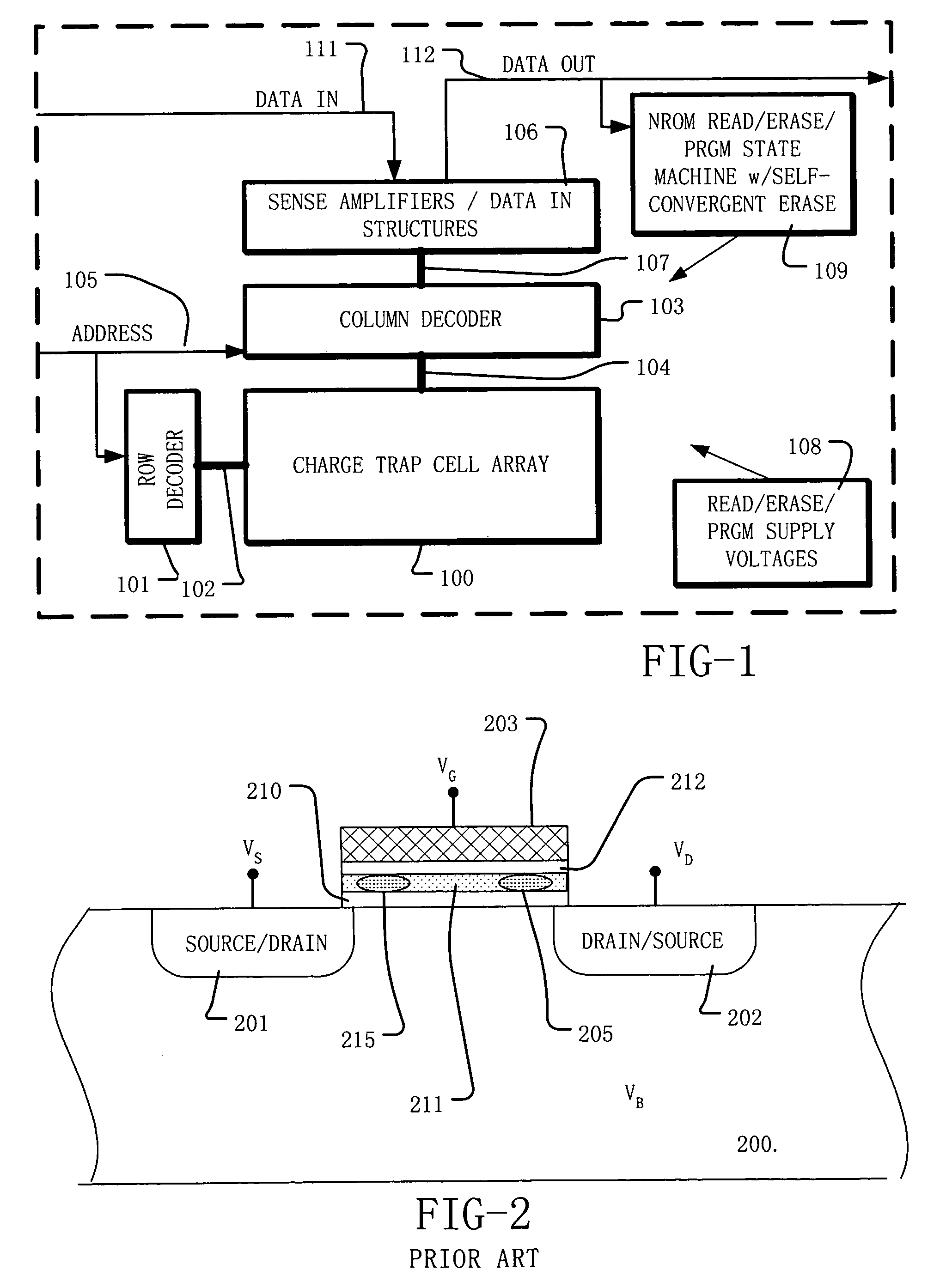

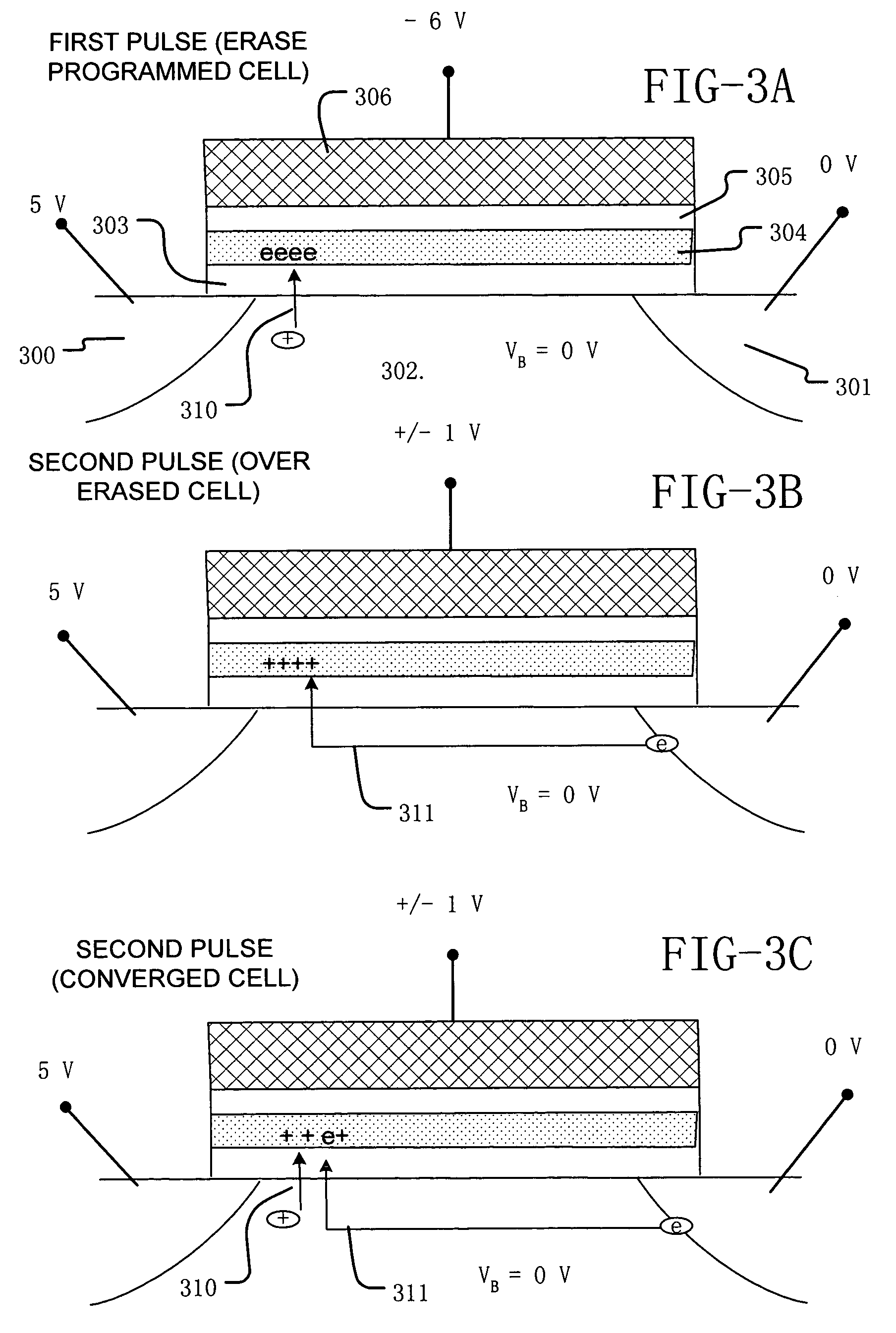

Method and system for self-convergent erase in charge trapping memory cells

ActiveUS20050237813A1Reduce negative chargeNegatively chargedTransistorRead-only memoriesTrappingEngineering

A process and a memory architecture for operating a charge trapping memory cell is provided. The method for operating the memory cell includes establishing a high threshold state in the memory cell by injecting negative charge into the charge trapping structure to set a high state threshold. The method includes using a self-converging biasing procedure to establish a low threshold state for the memory cell by reducing the negative charge in the charge trapping structure to set the threshold voltage for the cell to a low threshold state. The negative charge is reduced in the memory cell by applying a bias procedure including at least one bias pulse. The bias pulse balances charge flow into and out of the charge trapping layer to achieve self-convergence on a desired threshold level. Thereby, an over-erase condition is avoided.

Owner:MACRONIX INT CO LTD

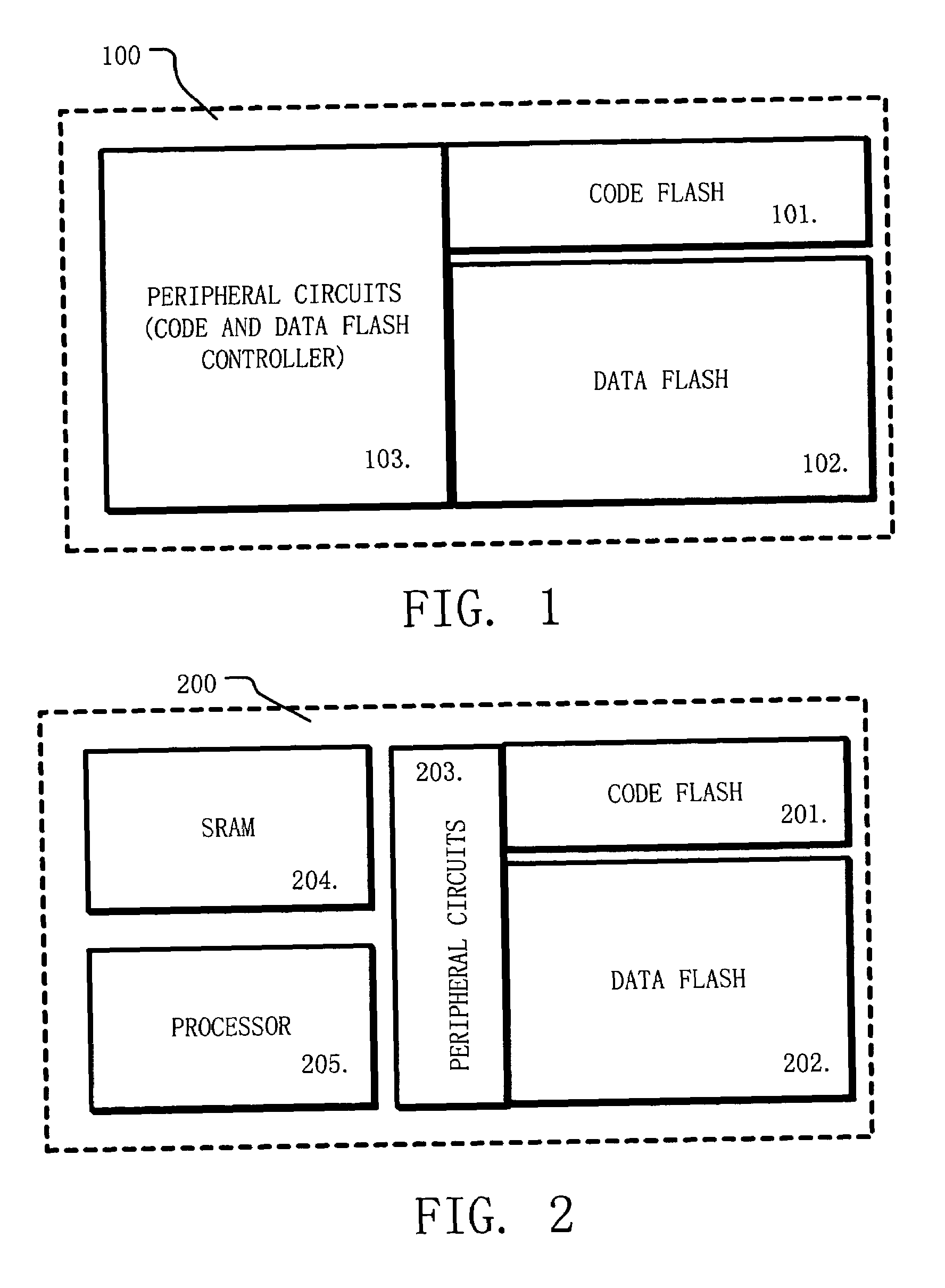

Integrated code and data flash memory

ActiveUS7158411B2Easy to manufactureLow costTransistorSolid-state devicesMemory architectureNon-volatile memory

A memory architecture for an integrated circuit comprises a first memory array configured to store data for one pattern of data usage and a second memory array configured to store data for another pattern of data usage. The first and second memory arrays comprise charge storage based nonvolatile memory cells having substantially the same structure in both arrays. A first operation algorithm adapted for example for data flash applications is used for programming, erasing and reading data in the first memory array. A second operation algorithm adapted for example for code flash applications is used for programming, erasing and reading data in the second memory array, wherein the second operation algorithm is different than the first operation algorithm. Thus, one die with memory for both code flash and data flash applications can be easily manufactured using a simple process, at low cost and high yield.

Owner:MACRONIX INT CO LTD

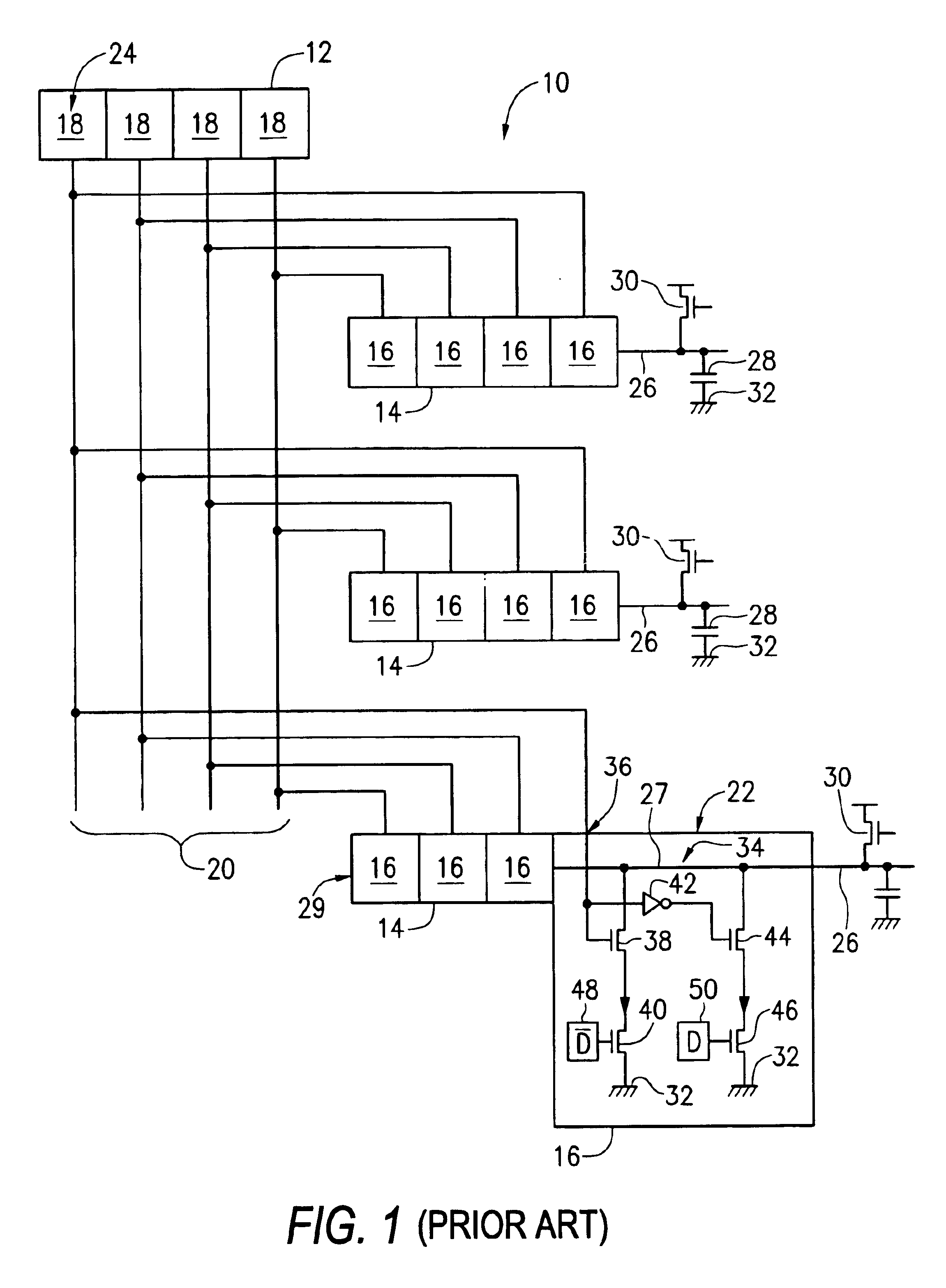

CAM memory architecture and a method of forming and operating a device according to a CAM memory architecture

InactiveUS6906938B2Lower requirementOptimized areaDigital storageMemory systemsControl signalControl data

A method for a content addressable memory that includes receiving a first data value for evaluation at a first memory block during a first time interval, receiving a second data value for evaluation at a second memory block during a second time interval and evaluating said both the first and second data values during a third time interval. According to one embodiment of the invention the first and second time intervals are separate so that the first and second data blocks receive unique data out of phase with one another from a single address bus. Evaluation of both data values takes place substantially simultaneously in the respective memory blocks. Also included is a device architecture and a device adapted to control data transfer to two CAM memory blocks in response to alternate phase transitions of a control signal.

Owner:ROUND ROCK RES LLC

Memory architecture of 3D NOR array

A 3D memory device includes a plurality of ridge-shaped stacks of memory cells. Word lines are arranged over the stacks of memory cells. Bit lines structures are coupled to multiple locations along the stacks of memory cells. Source line structures are coupled to multiple locations along each of the semiconductor material strips of the stacks. The bit line structures and the source line structures are between adjacent ones of the word lines.

Owner:MACRONIX INT CO LTD

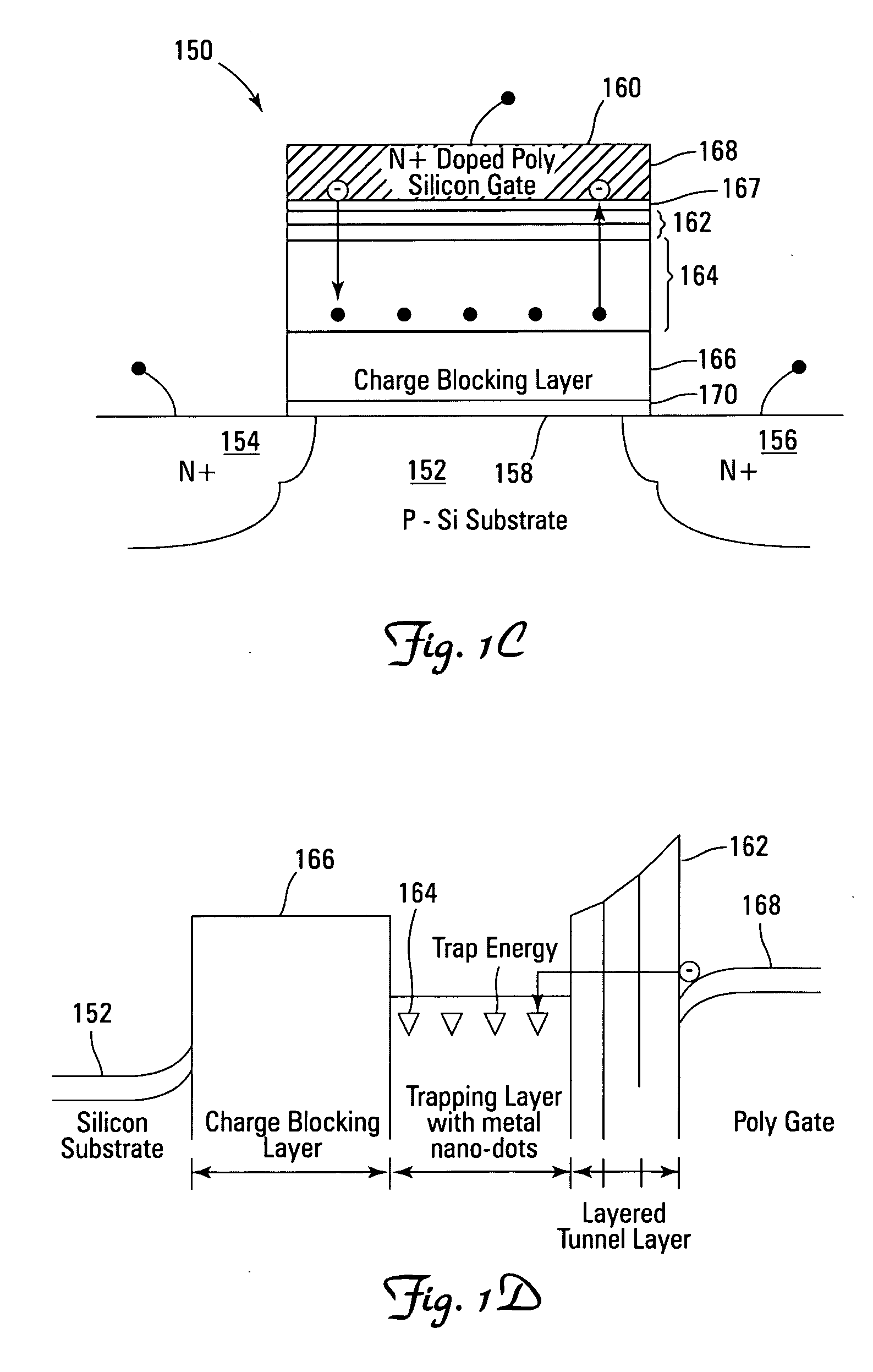

Back-side trapped non-volatile memory device

ActiveUS20060284236A1Efficient eraseReduce voltageNanoinformaticsSolid-state devicesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that utilize back-side trapped floating node memory cells with band-gap engineered gate stacks with asymmetric tunnel barriers. Embodiments of the present invention allow for direct tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention and reduces the possibility of damage to the channel / insulator interface. The direct tunneling program and efficient erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory device embodiments of the present invention are presented that are arranged in NOR or NAND memory architecture arrays. Memory cell embodiments of the present invention also allow multiple levels of bit storage in a single memory cell, and allow for programming and erase with reduced voltages.

Owner:MICRON TECH INC

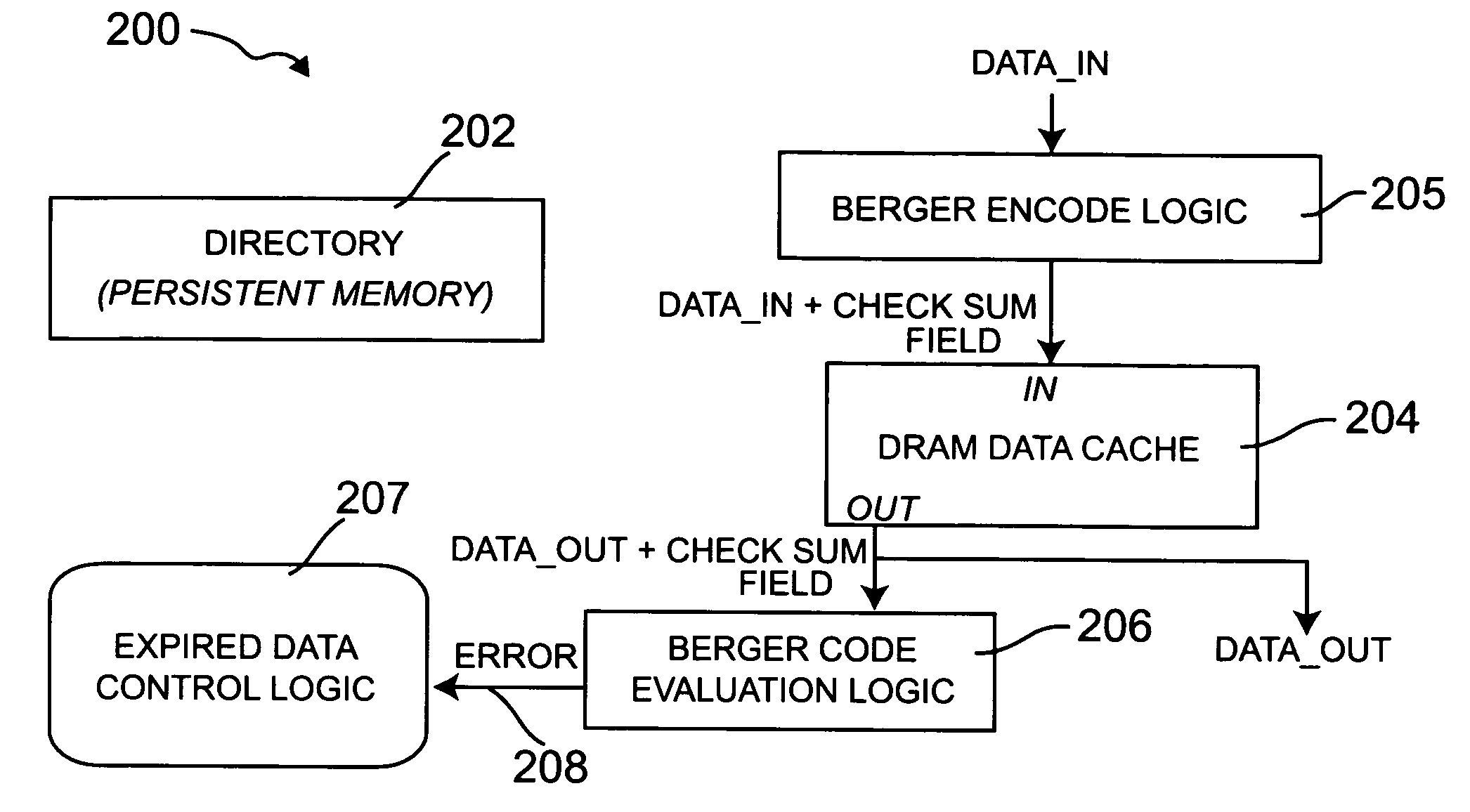

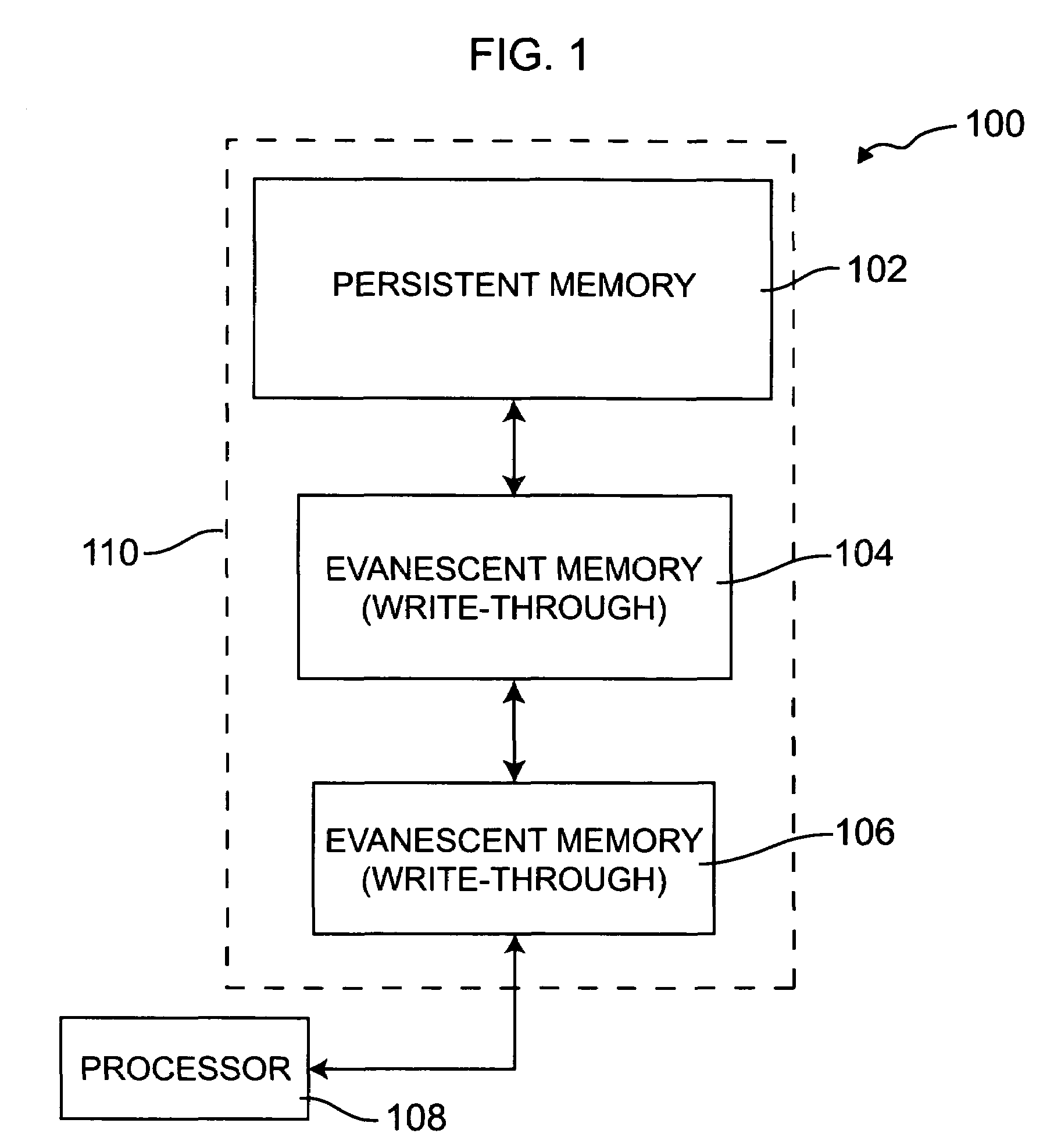

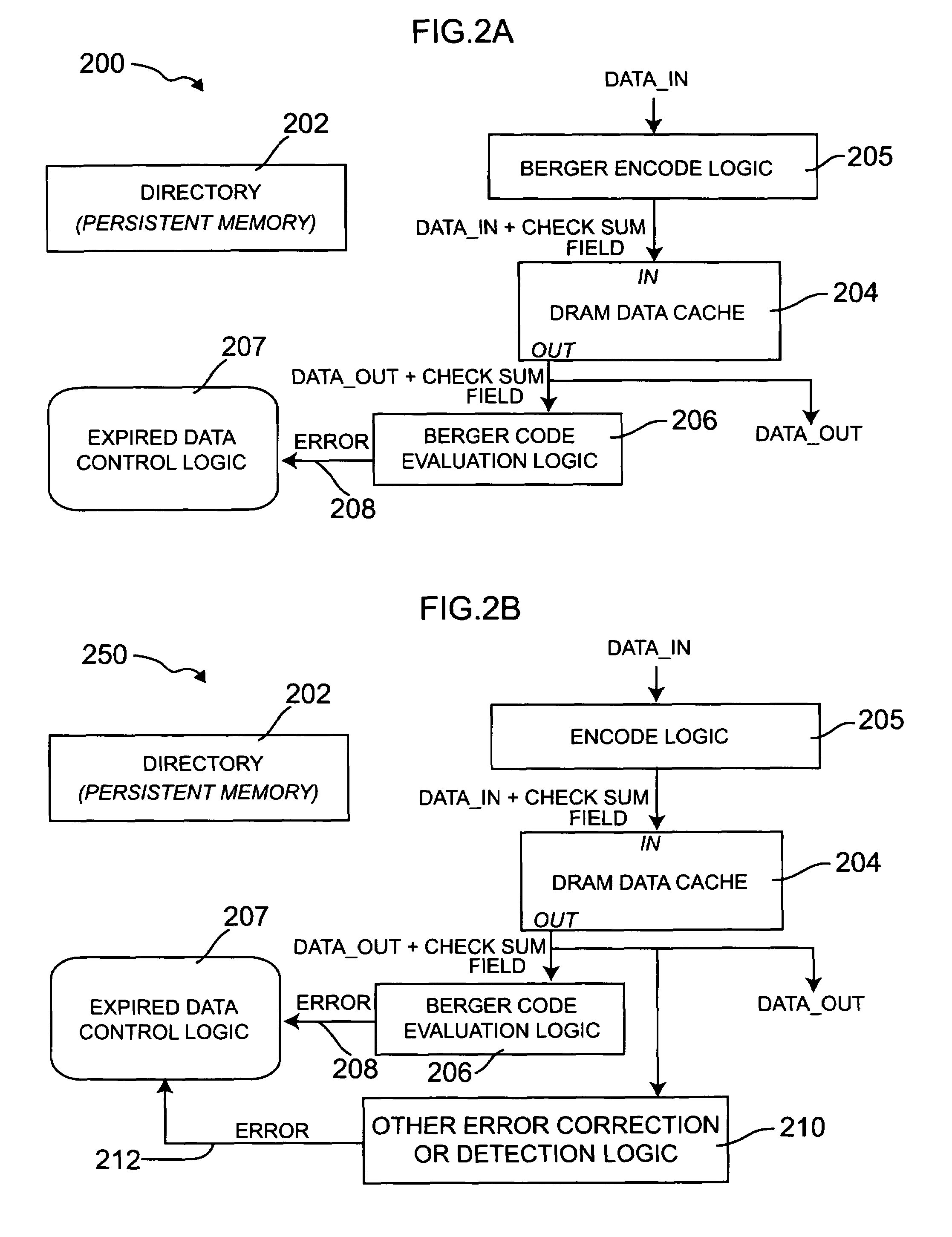

Dynamic memory architecture employing passive expiration of data

ActiveUS7290203B2Reduce manufacturing costUsed in environmentMemory architecture accessing/allocationEnergy efficient ICTDynamic storageEngineering

Apparatus for passively tracking expired data in a dynamic memory includes an error encoding circuit operative to receive an input data word and to generate an encoded data word which is stored in the dynamic memory. The apparatus further includes a decoding circuit operative to receive an encoded data word from the dynamic memory, to detect at least one or more unidirectional errors in the input data word read from the dynamic memory, and to generate an error signal when at least one error is detected, the error signal indicating that the input data word contains expired data. Control circuitry included in the apparatus is configured for initiating one or more actions in response to the error signal.

Owner:GLOBALFOUNDRIES U S INC

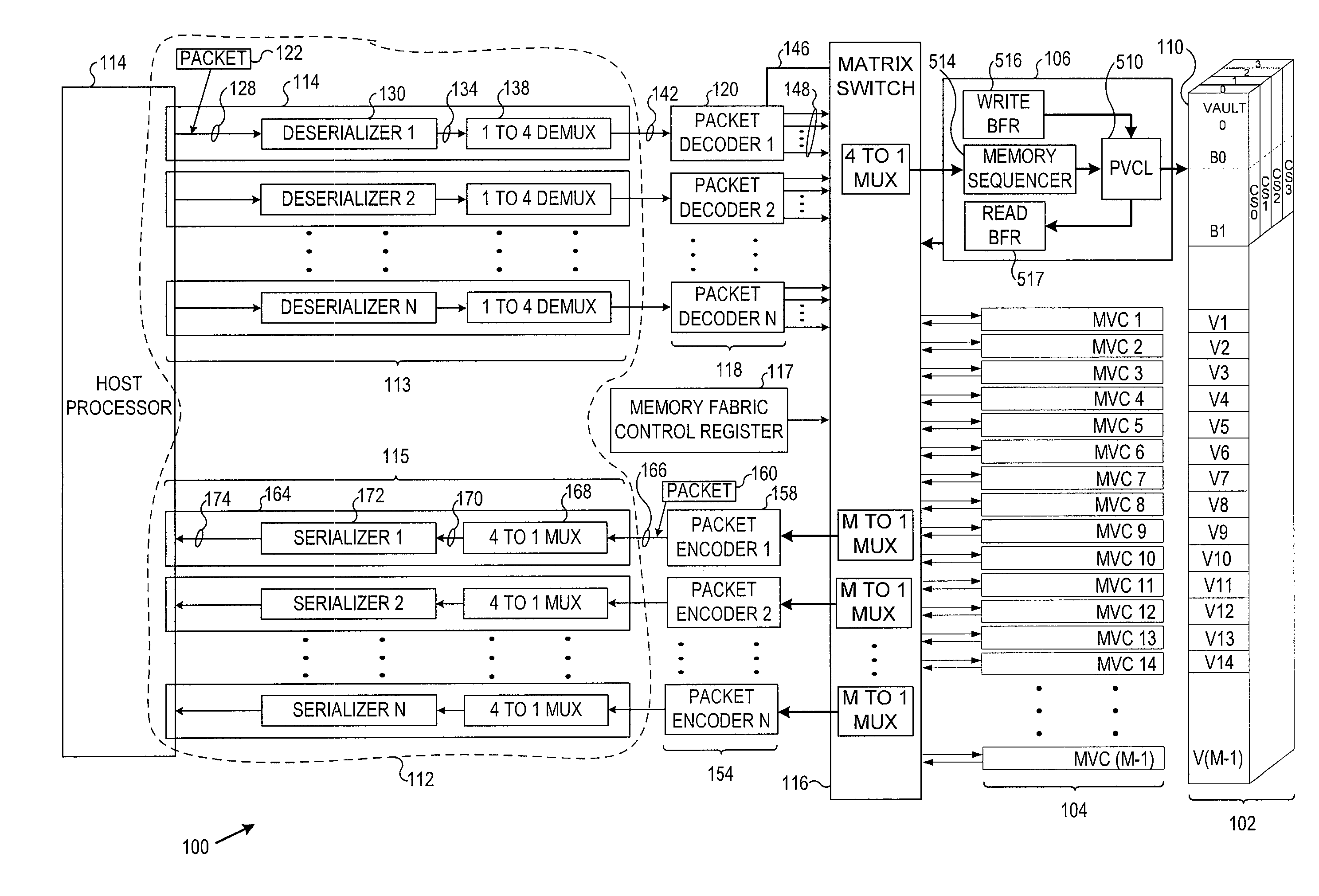

Multi-serial interface stacked-die memory architecture

ActiveUS7978721B2Energy efficient ICTTime-division multiplexTelecommunications linkCommunication link

Systems and methods disclosed herein substantially concurrently transfer a plurality of streams of commands, addresses, and / or data across a corresponding plurality of serialized communication link interfaces (SCLIs) between one or more originating devices or destination devices such as a processor and a switch. At the switch, one or more commands, addresses, or data corresponding to each stream can be transferred to a corresponding destination memory vault controller (MVC) associated with a corresponding memory vault. The destination MVC can perform write operations, read operations, and / or memory vault housekeeping operations independently from concurrent operations associated with other MVCs coupled to a corresponding plurality of memory vaults.

Owner:MICRON TECH INC

Embedded Programmable Intelligent Search Memory

ActiveUS20080140661A1Reduce classification overheadImprove performanceDigital data information retrievalDigital data processing detailsMulti processorMemory architecture

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken The PRISM content search memory is embedded in a single core or multi-core processors or in multi-processor systems to perform content search. PRISM accelerates content search by offloading the content search tasks from the processors. Content search rules comprise of regular expressions which are converted to finite state automata and then programmed in PRISM for evaluating content with the search rules.

Owner:INFOSIL INC

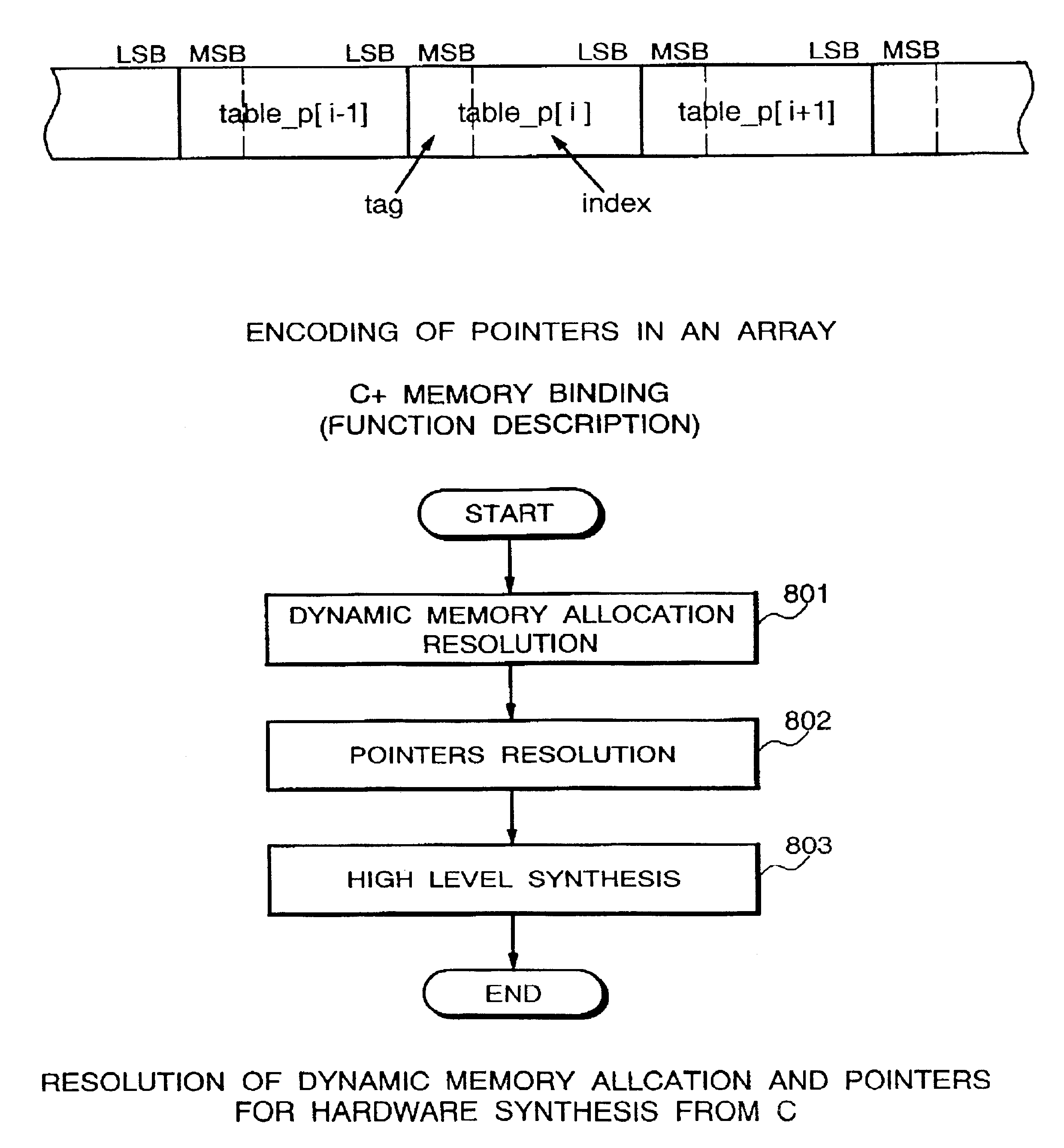

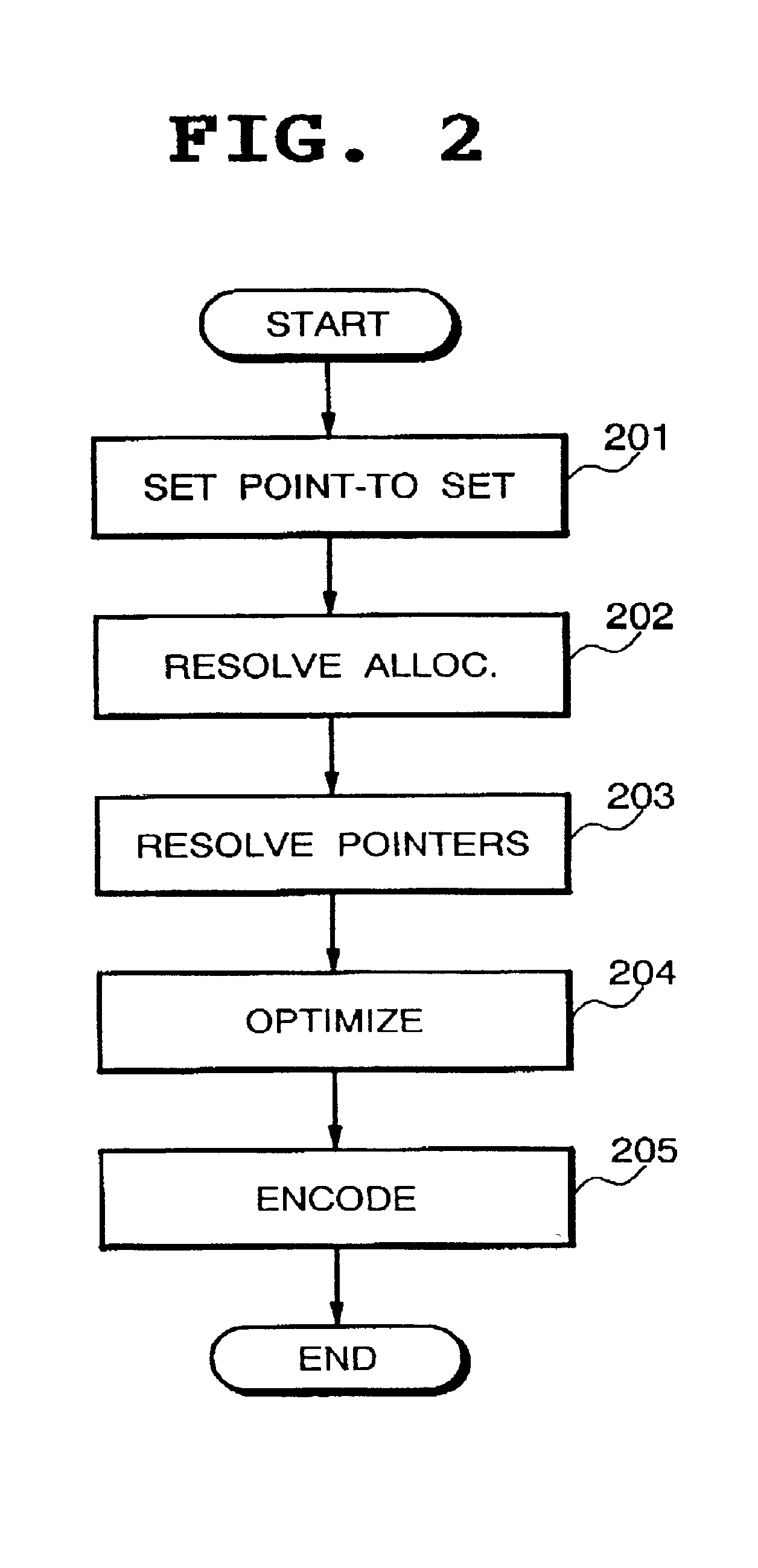

Resolution of dynamic memory allocation/deallocation and pointers

InactiveUS6467075B1CAD circuit designSoftware simulation/interpretation/emulationSoftware systemTheoretical computer science

One of the greatest challenges in C / C++-based design methodology is to efficiently map C / C++ models into hardware. Many of the networking and multimedia applications implemented in hardware or mixed hardware / software systems are making use of complex data structures stored in one or multiple memories. As a result, many of the C / C++ features which were originally designed for software applications are now making their way into hardware. Such features include dynamic memory allocation / deallocation and pointers used to manage data. This inventors present a solution for efficiently mapping arbitrary C code with pointers and malloc / free into hardware. This solution fits current memory management methodologies. It consists of instantiating a hardware allocator tailored to an application and a memory architecture. This work also supports the resolution of pointers without restriction on the data structures. An implementation using the SUIF framework is presented, followed by some case studies such as the realization of a video filter.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV +1

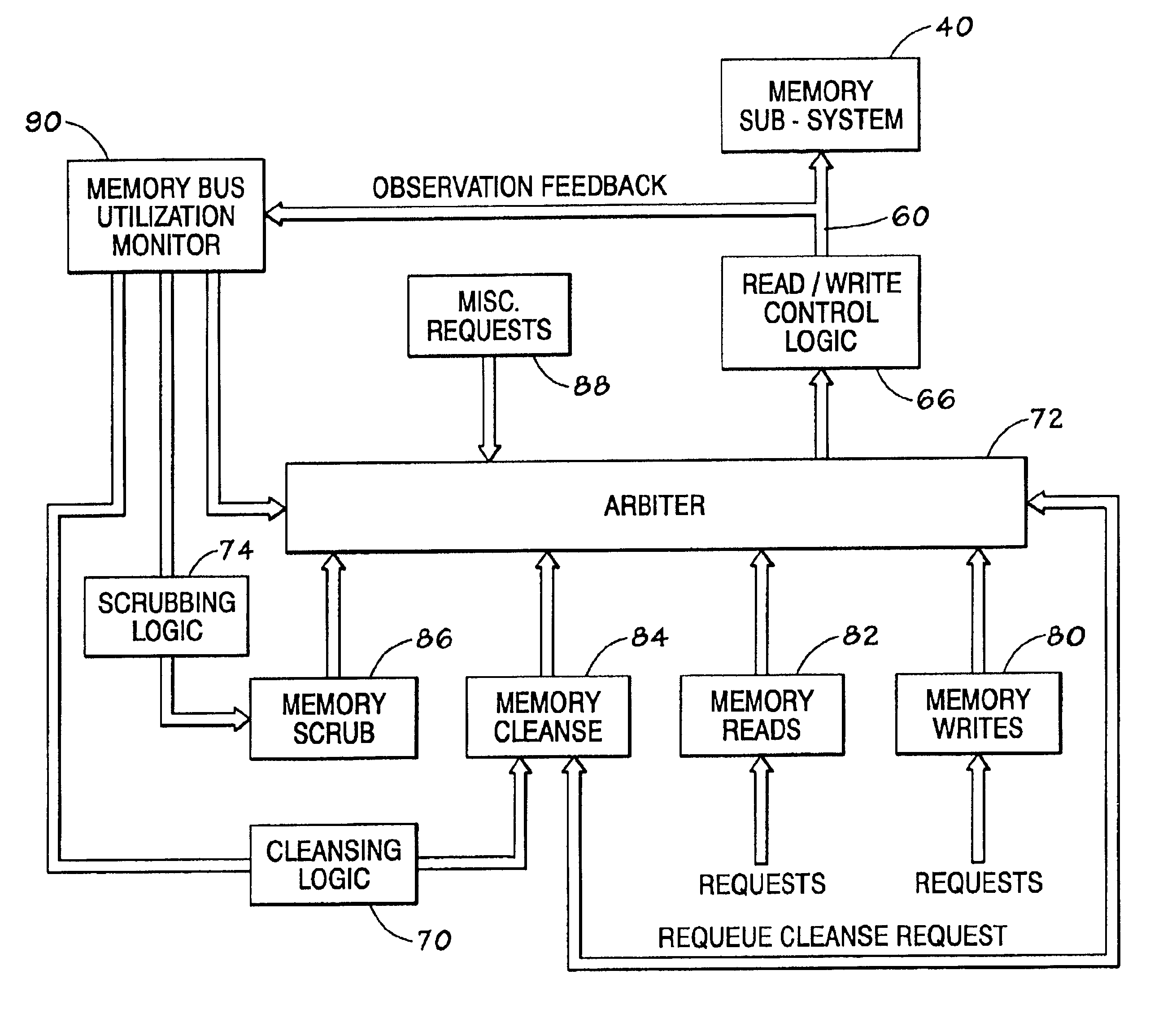

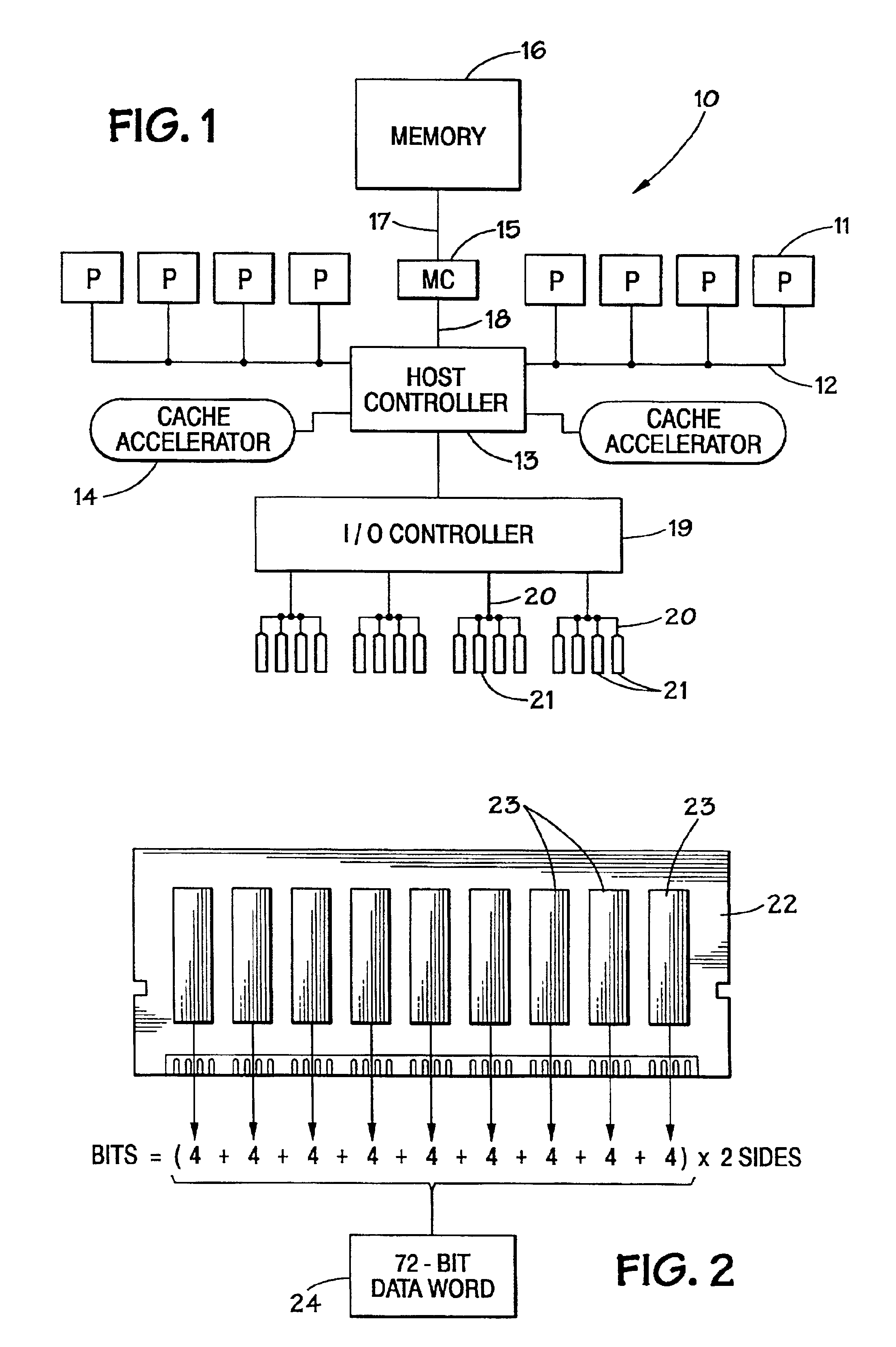

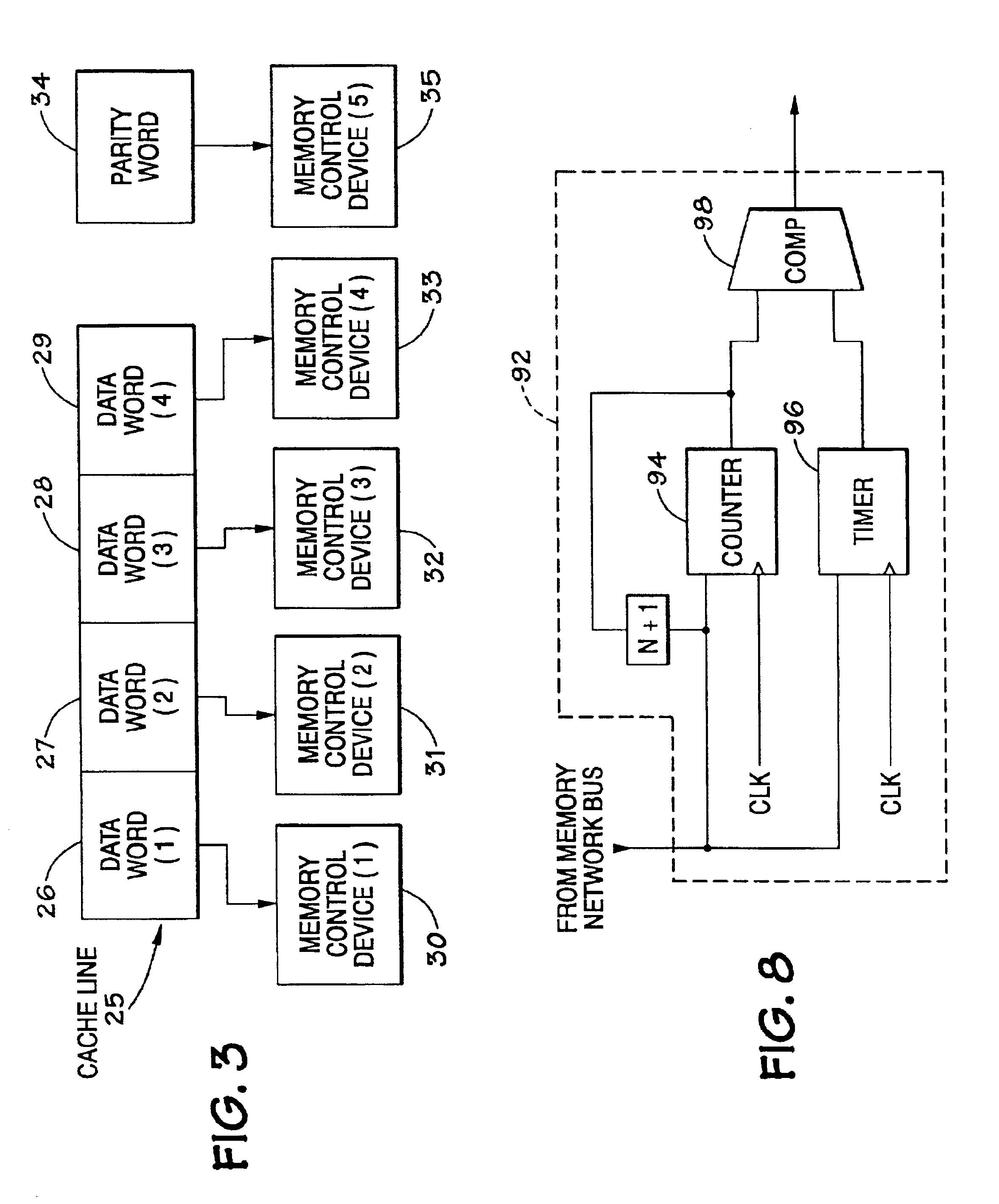

Memory sub-system error cleansing

Owner:HEWLETT PACKARD DEV CO LP

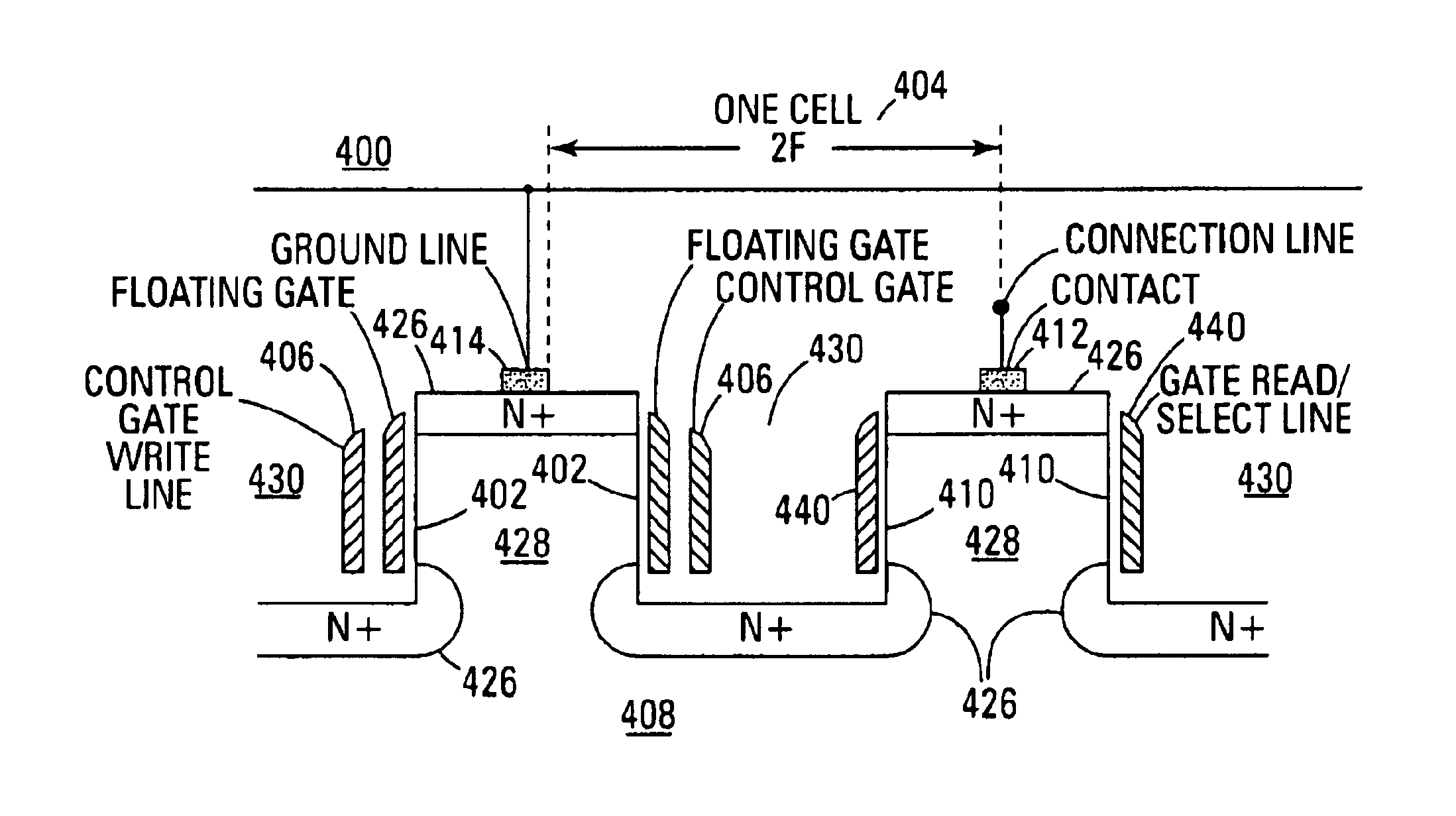

Vertical device 4F2 EEPROM memory

ActiveUS6878991B1Promotes its utilizationImproved high density memory deviceTransistorSolid-state devicesBit lineHigh density

EEPROM memory devices and arrays are described that facilitate the use of vertical floating gate memory cells and select gates in NOR or NAND high density memory architectures. Memory embodiments of the present invention utilize vertical select gates and floating gate memory cells to form NOR and NAND architecture memory cell strings, segments, and arrays. These memory cell architectures allow for improved high density memory devices or arrays with integral select gates that can take advantage of the features semiconductor fabrication processes are generally capable of and allow for appropriate device sizing for operational considerations. The memory cell architectures also allow for mitigation of disturb and overerasure issues by placing the floating gate memory cells behind select gates that isolate the memory cells from their associated bit lines and / or source lines.

Owner:MICRON TECH INC

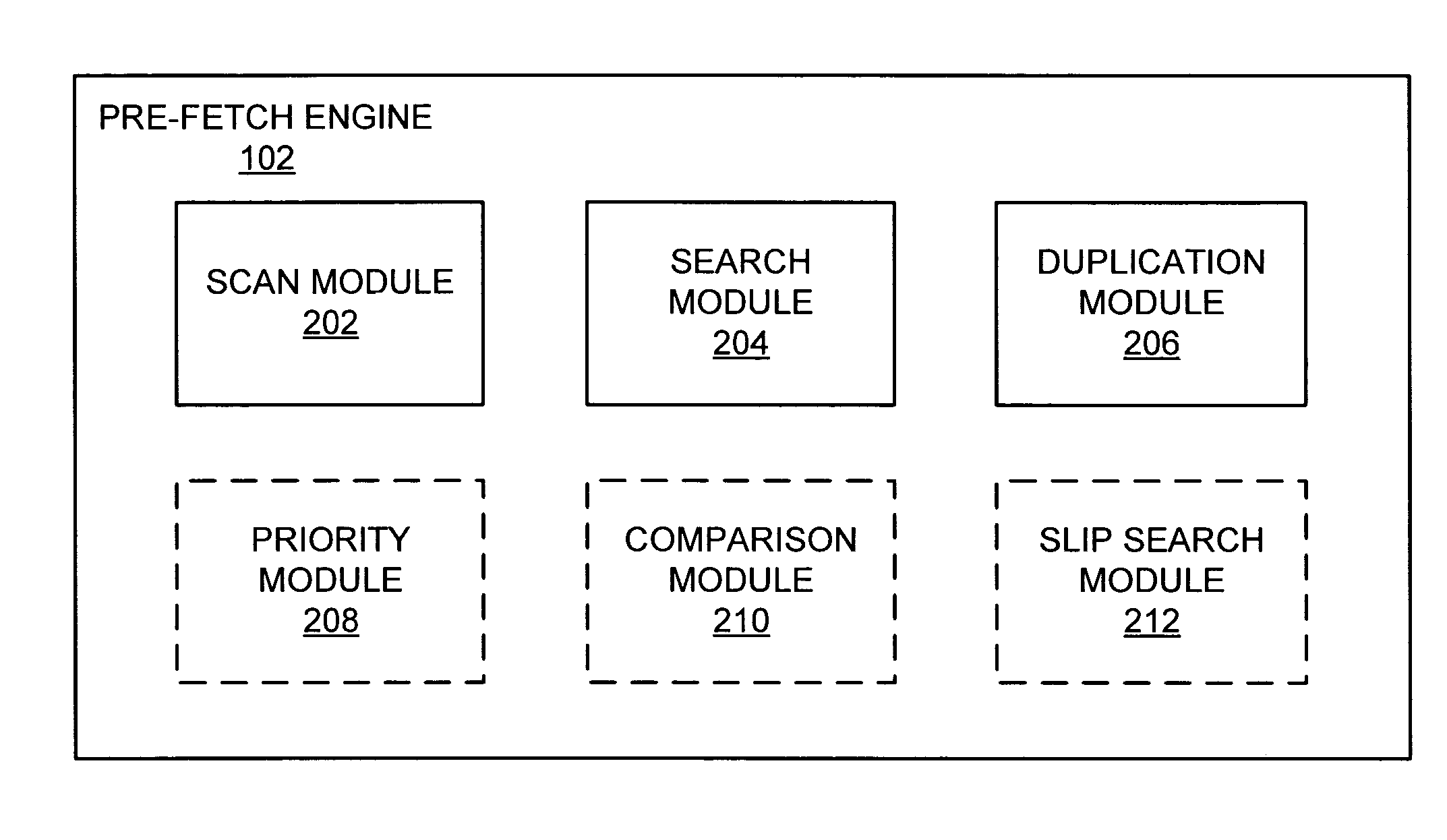

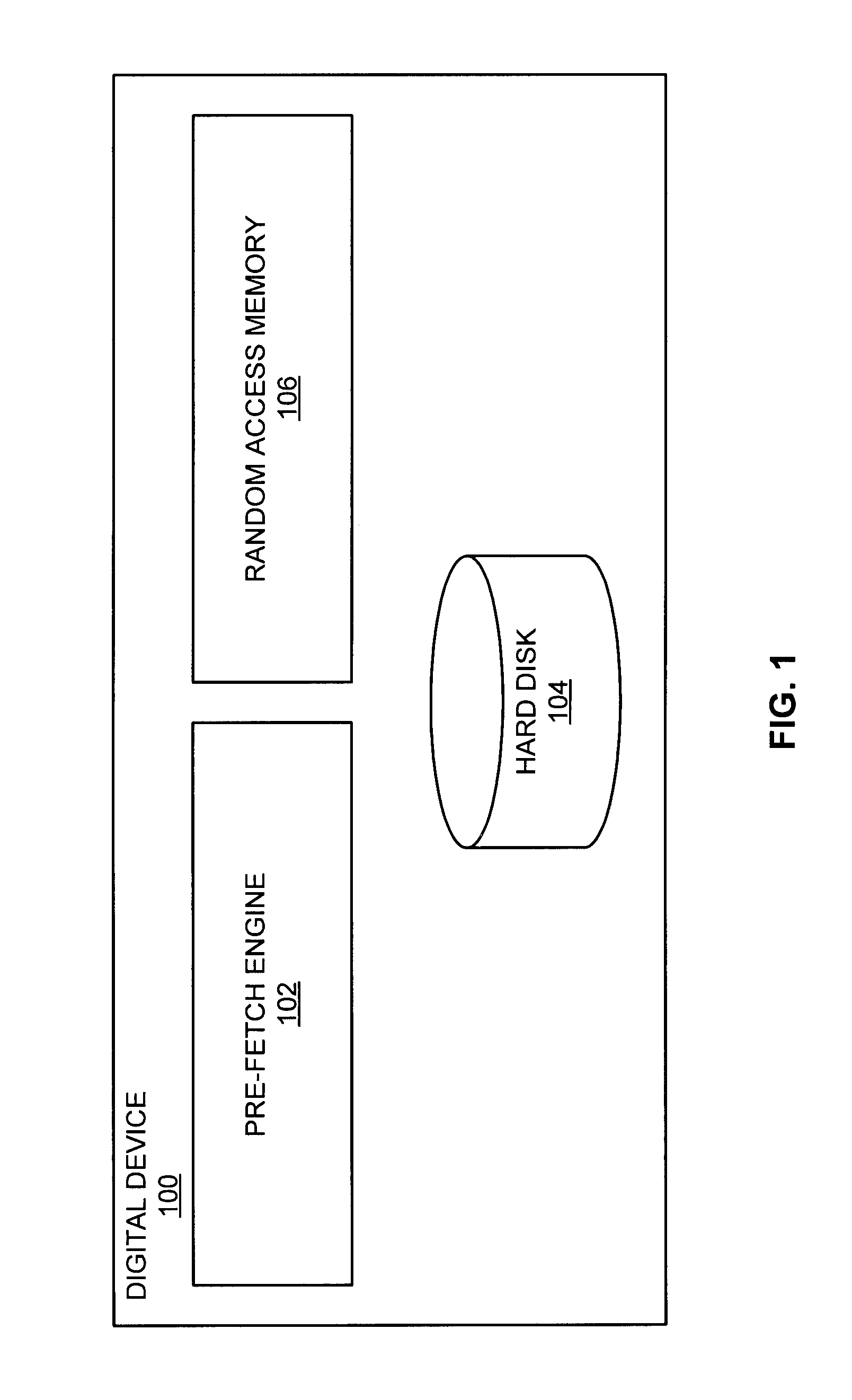

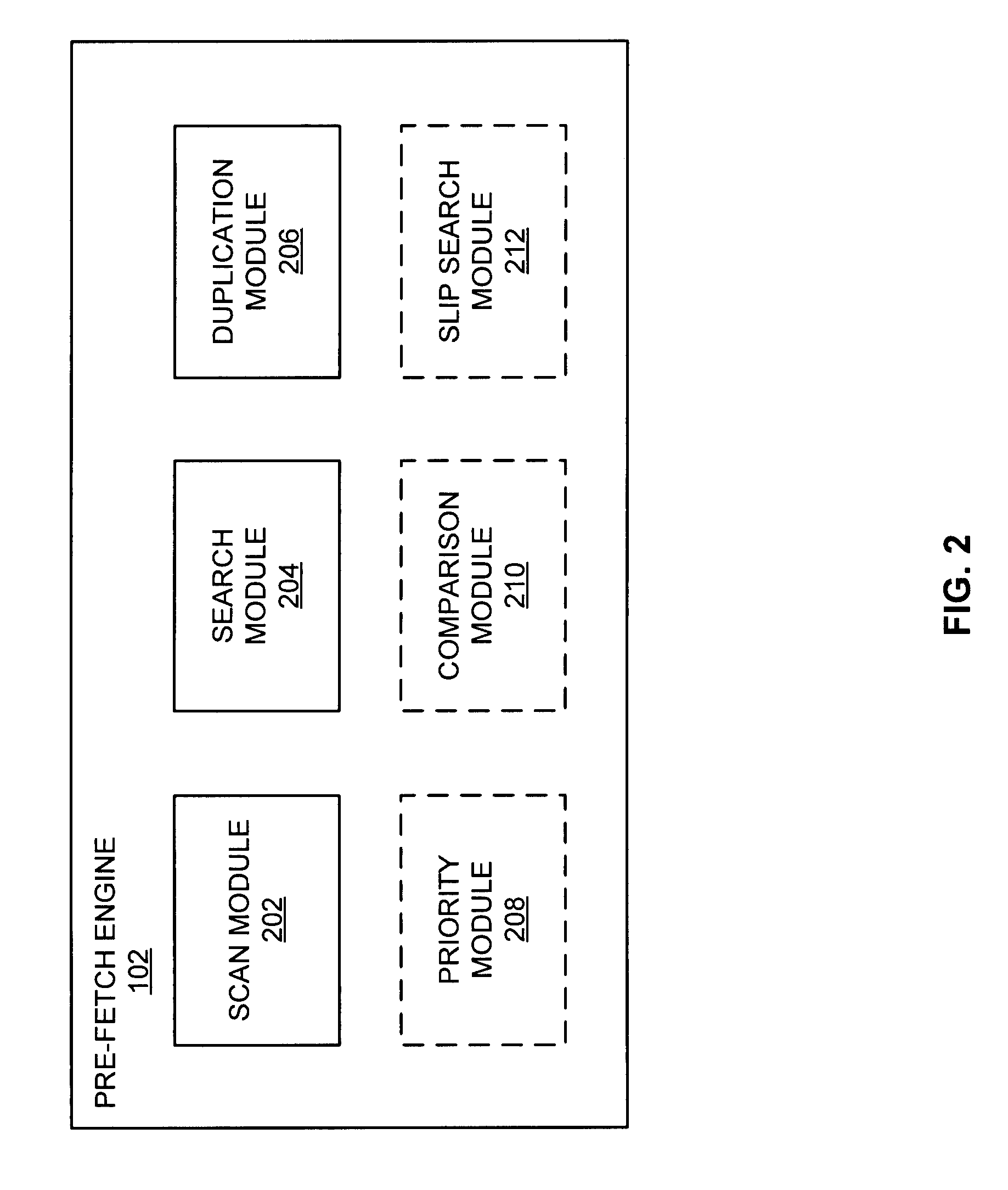

Pre-fetching data into a memory

Systems and methods for pre-fetching of data in a memory are provided. By pre-fetching stored data from a slower memory into a faster memory, the amount of time required for data retrieval and / or processing may be reduced. First, data is received and pre-scanned to generate a sample fingerprint. Fingerprints stored in a faster memory that are similar to the sample fingerprint are identified. Data stored in the slower memory associated with the identified stored fingerprints is copied into the faster memory. The copied data may be compared to the received data. Various embodiments may be included in a network memory architecture to allow for faster data matching and instruction generation in a central appliance.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Method and system for self-convergent erase in charge trapping memory cells

A process and a memory architecture for operating a charge trapping memory cell is provided. The method for operating the memory cell includes establishing a high threshold state in the memory cell by injecting negative charge into the charge trapping structure to set a high state threshold. The method includes using a self-converging biasing procedure to establish a low threshold state for the memory cell by reducing the negative charge in the charge trapping structure to set the threshold voltage for the cell to a low threshold state. The negative charge is reduced in the memory cell by applying a bias procedure including at least one bias pulse. The bias pulse balances charge flow into and out of the charge trapping layer to achieve self-convergence on a desired threshold level. Thereby, an over-erase condition is avoided.

Owner:MACRONIX INT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com