Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

587 results about "Finite state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

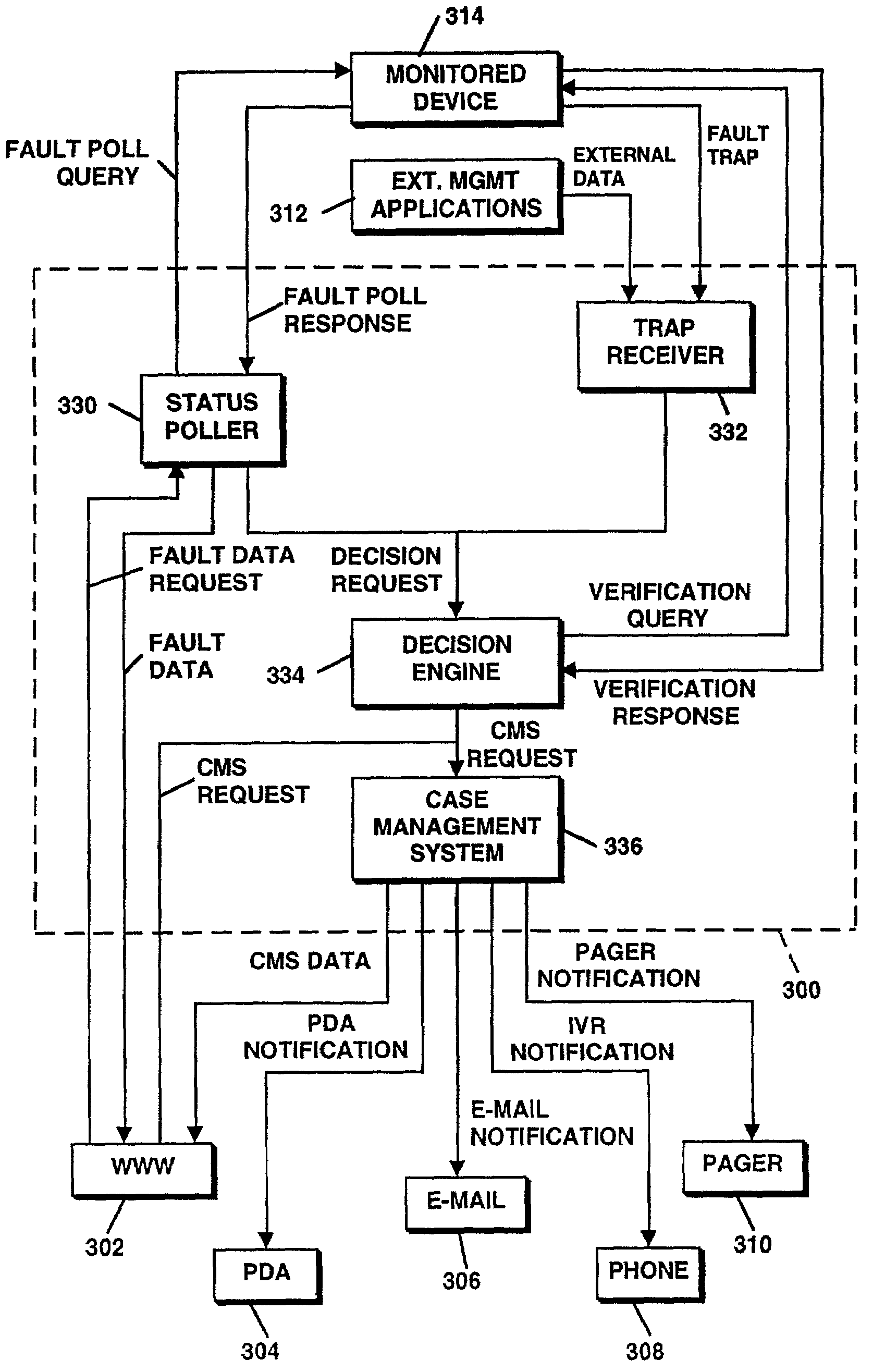

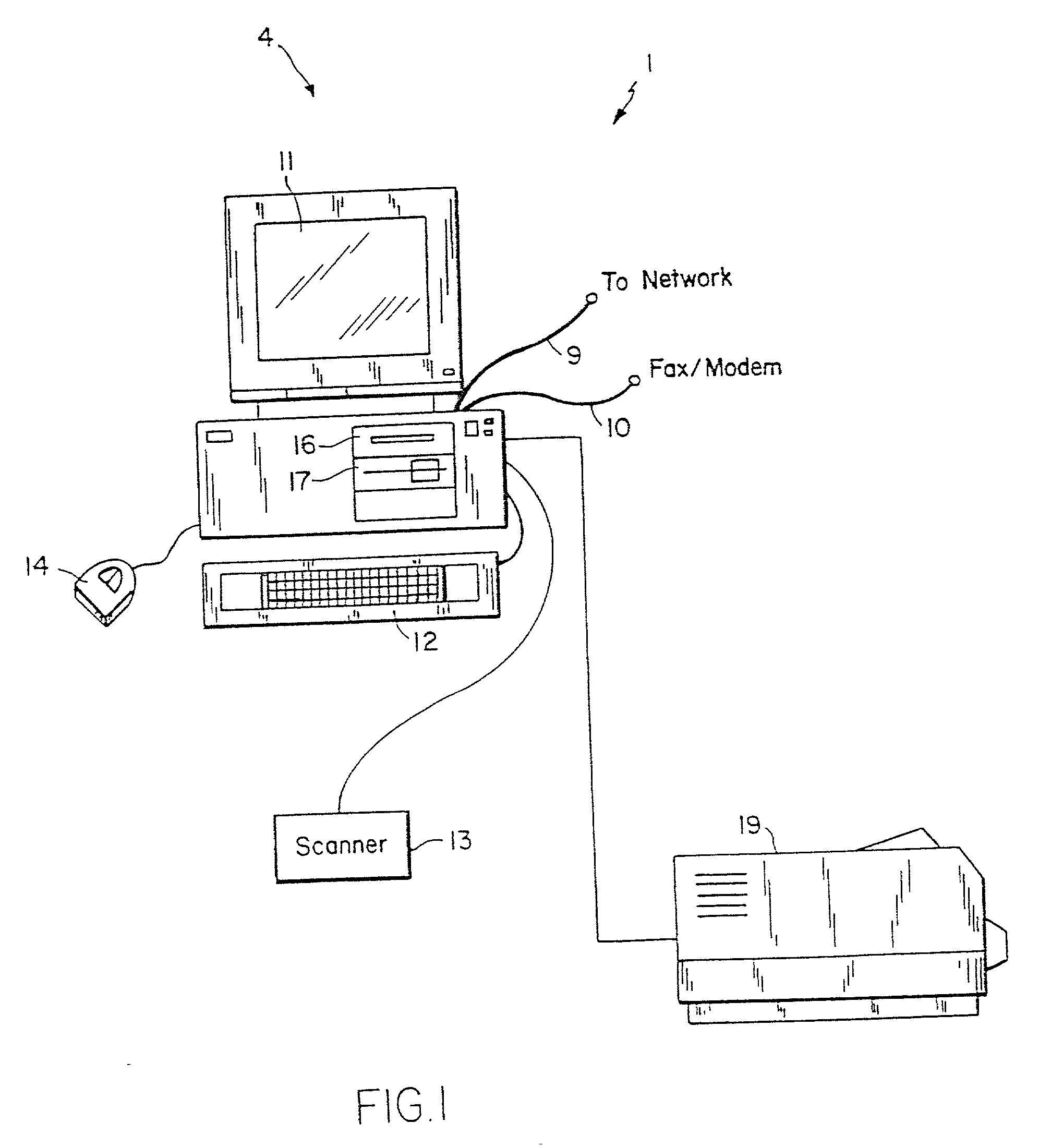

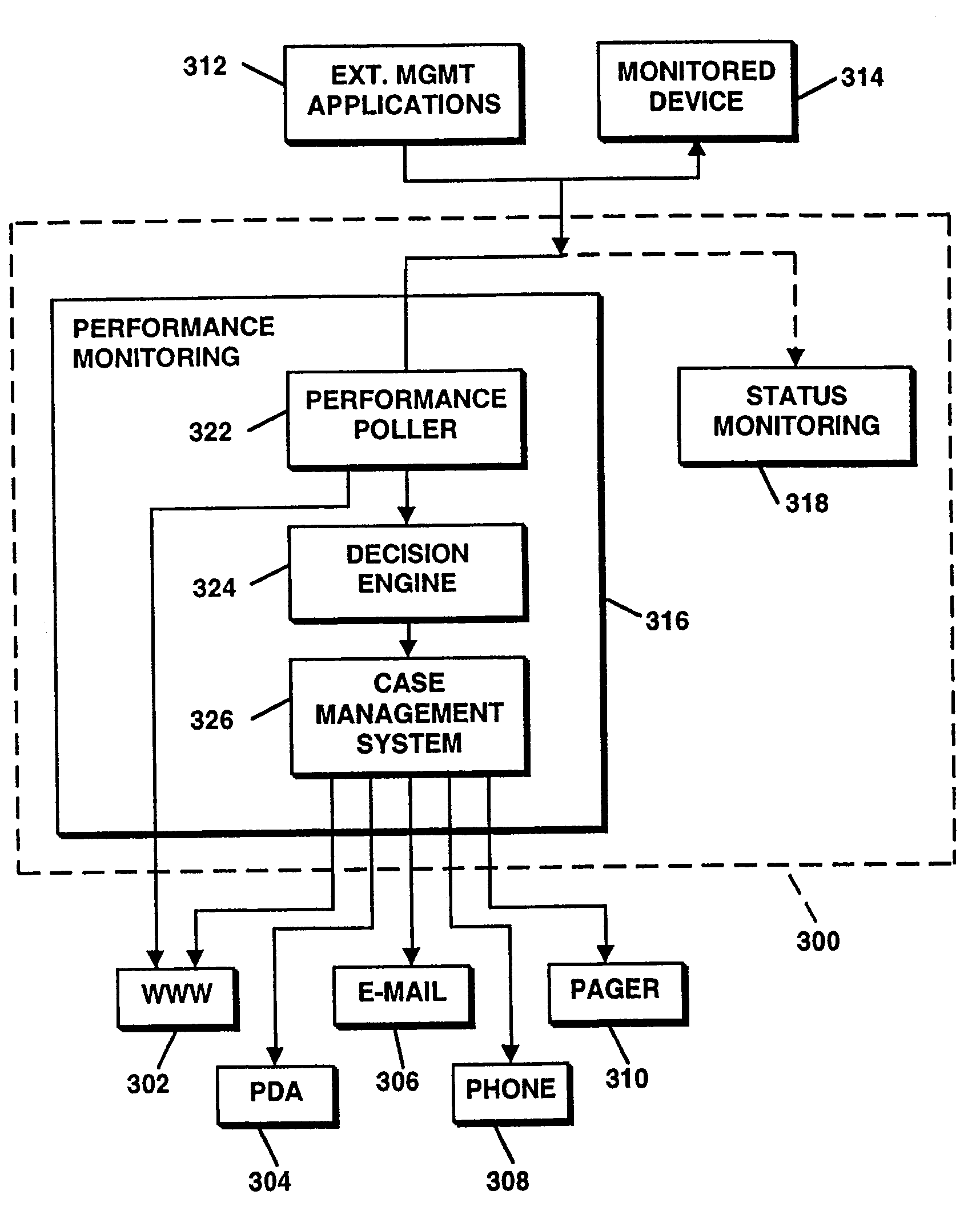

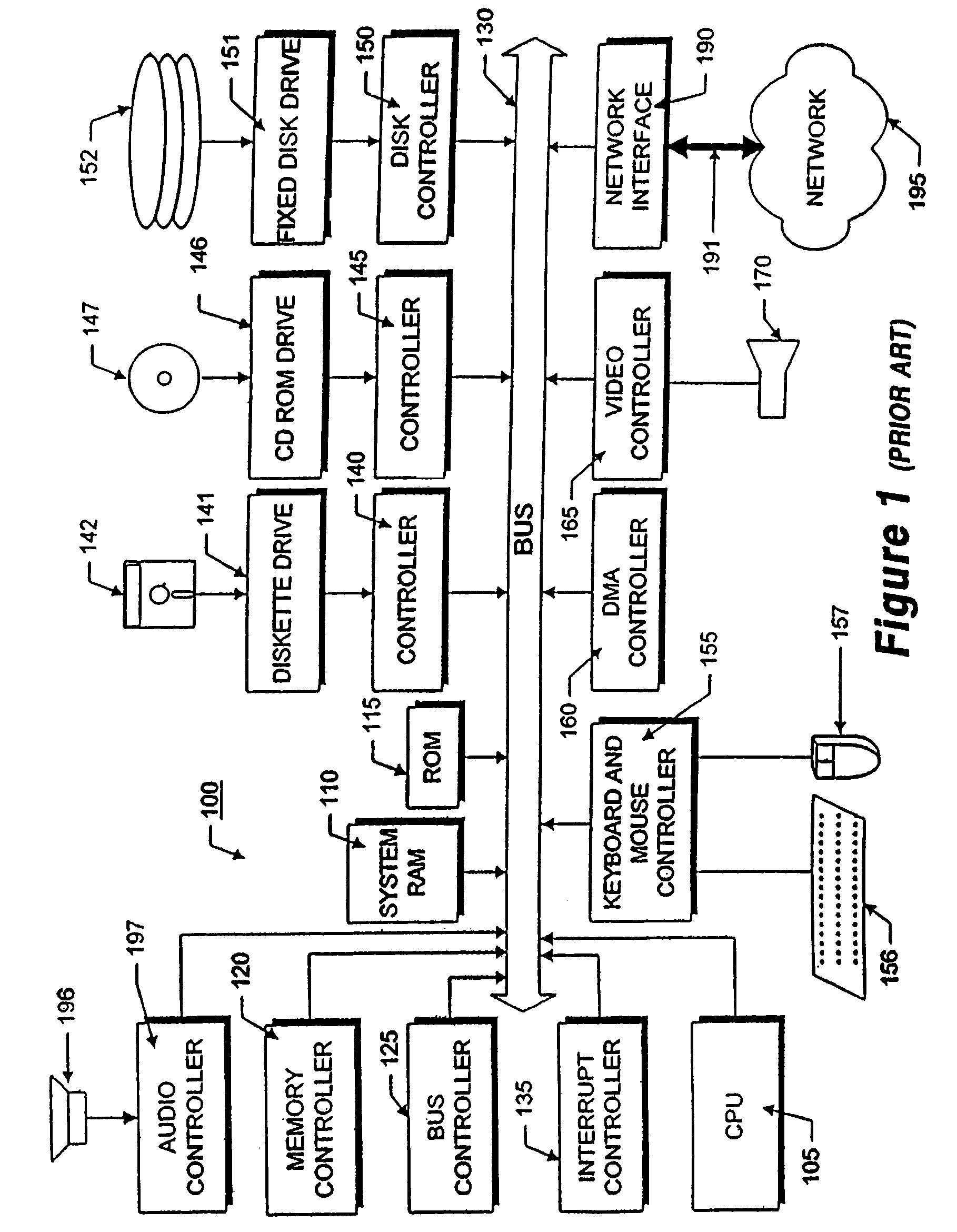

Method and apparatus for identifying problems in computer networks

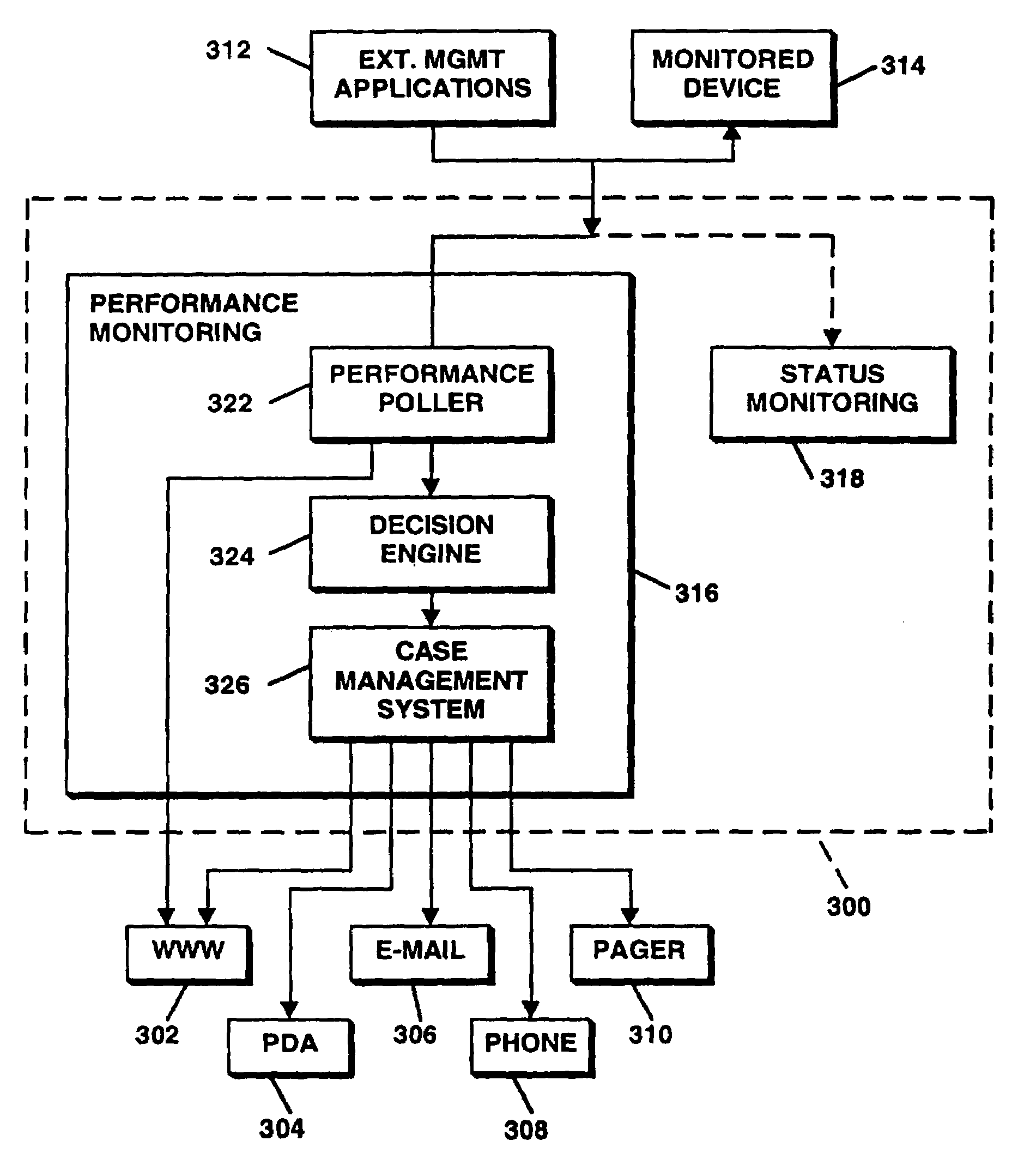

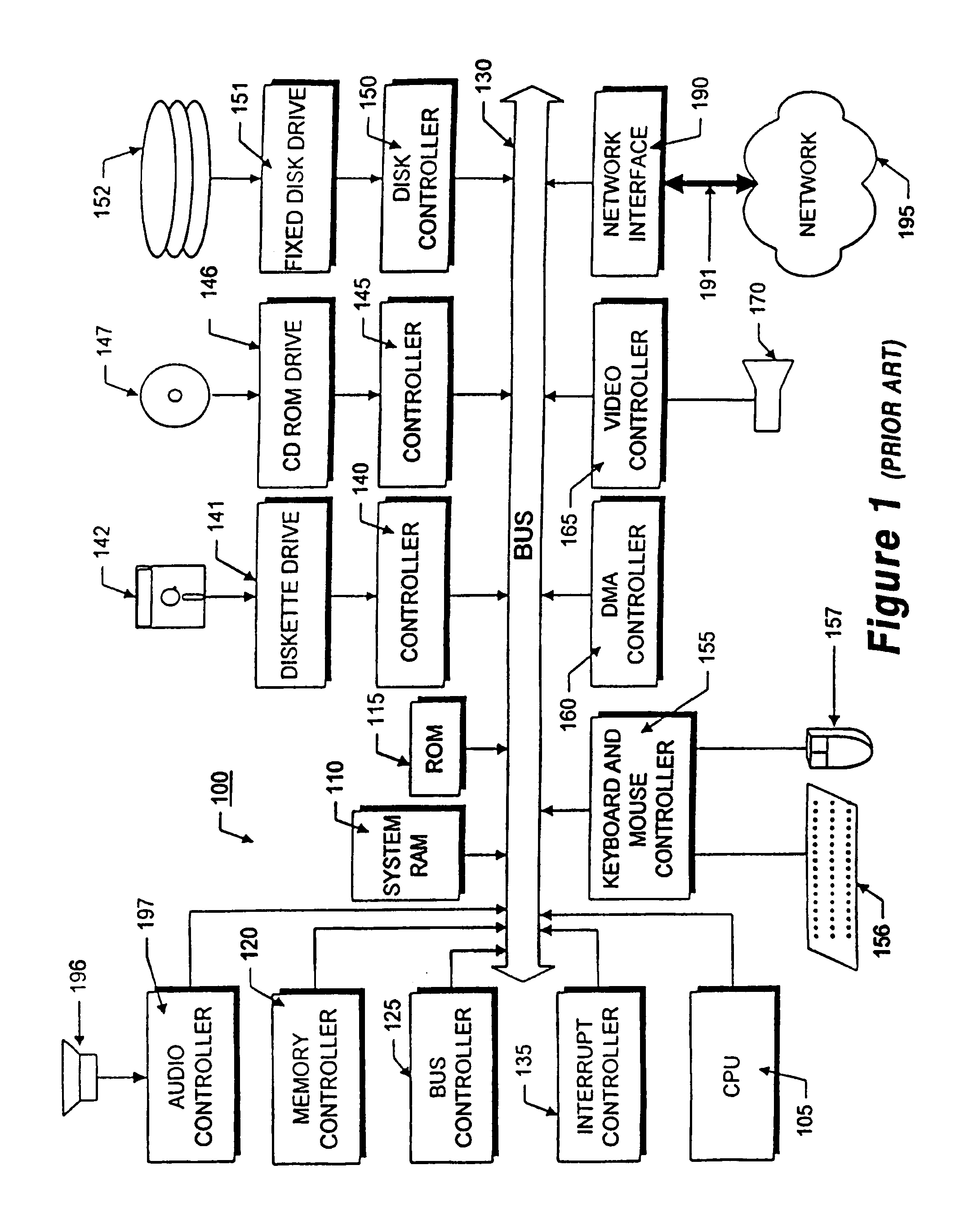

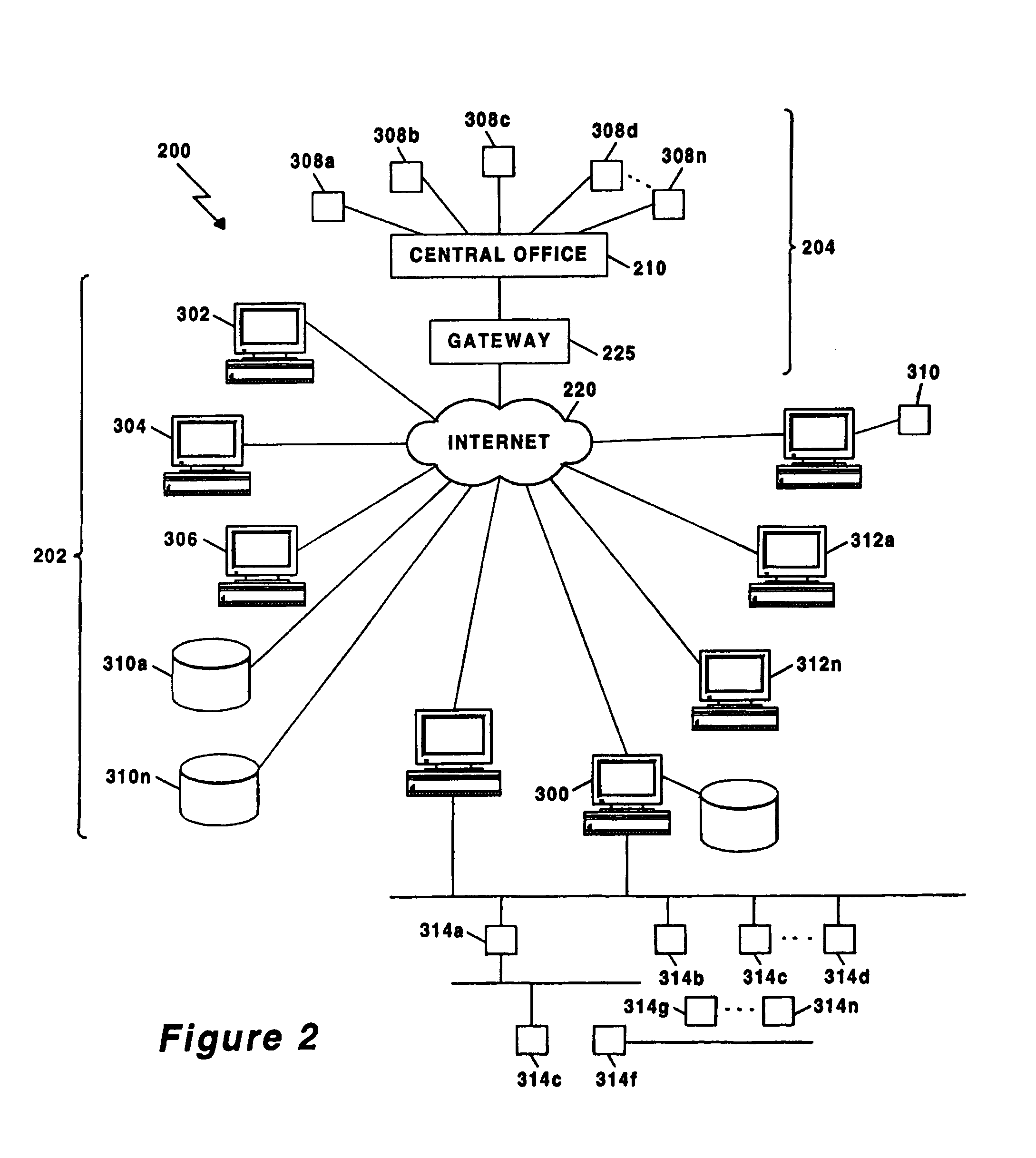

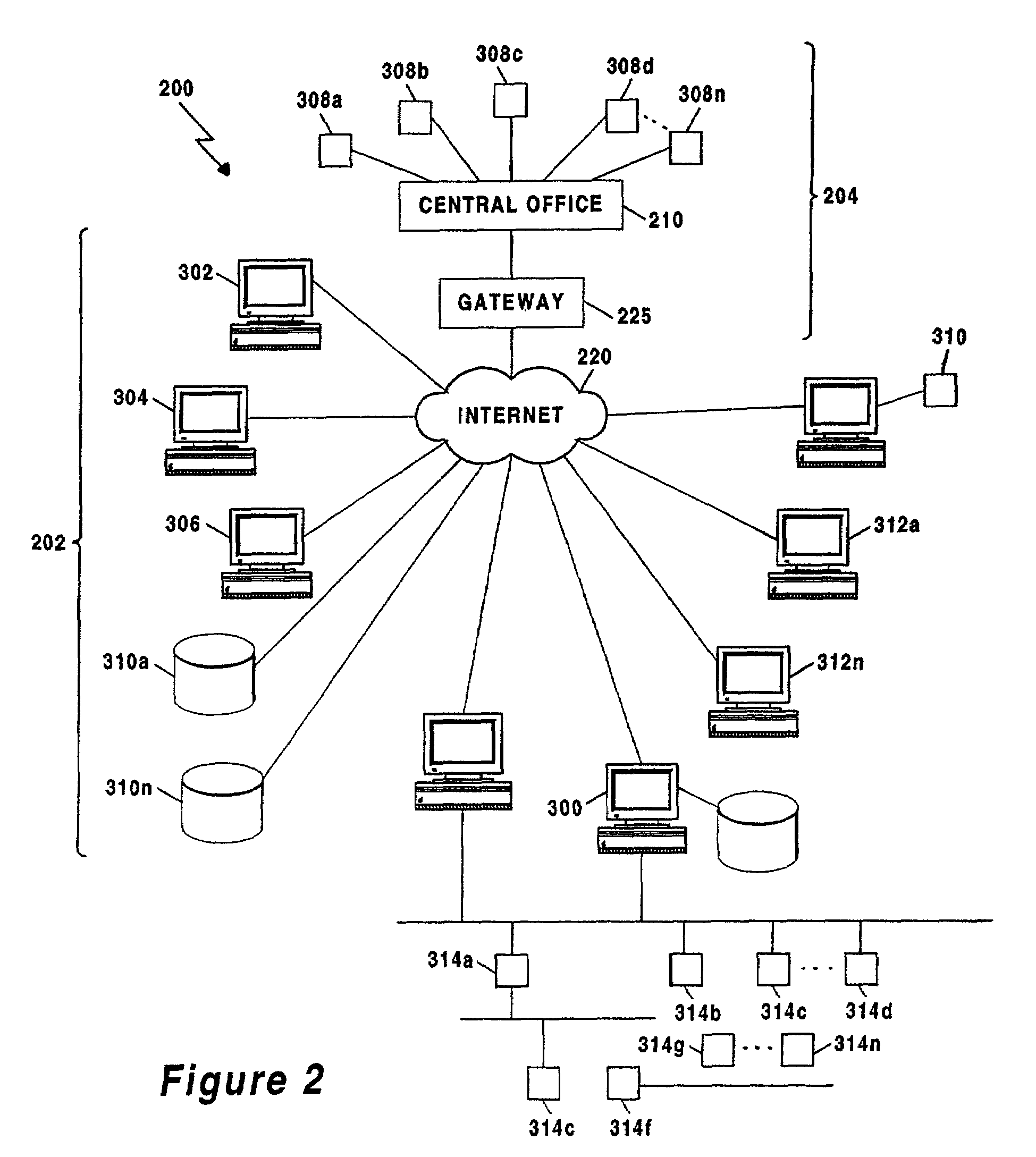

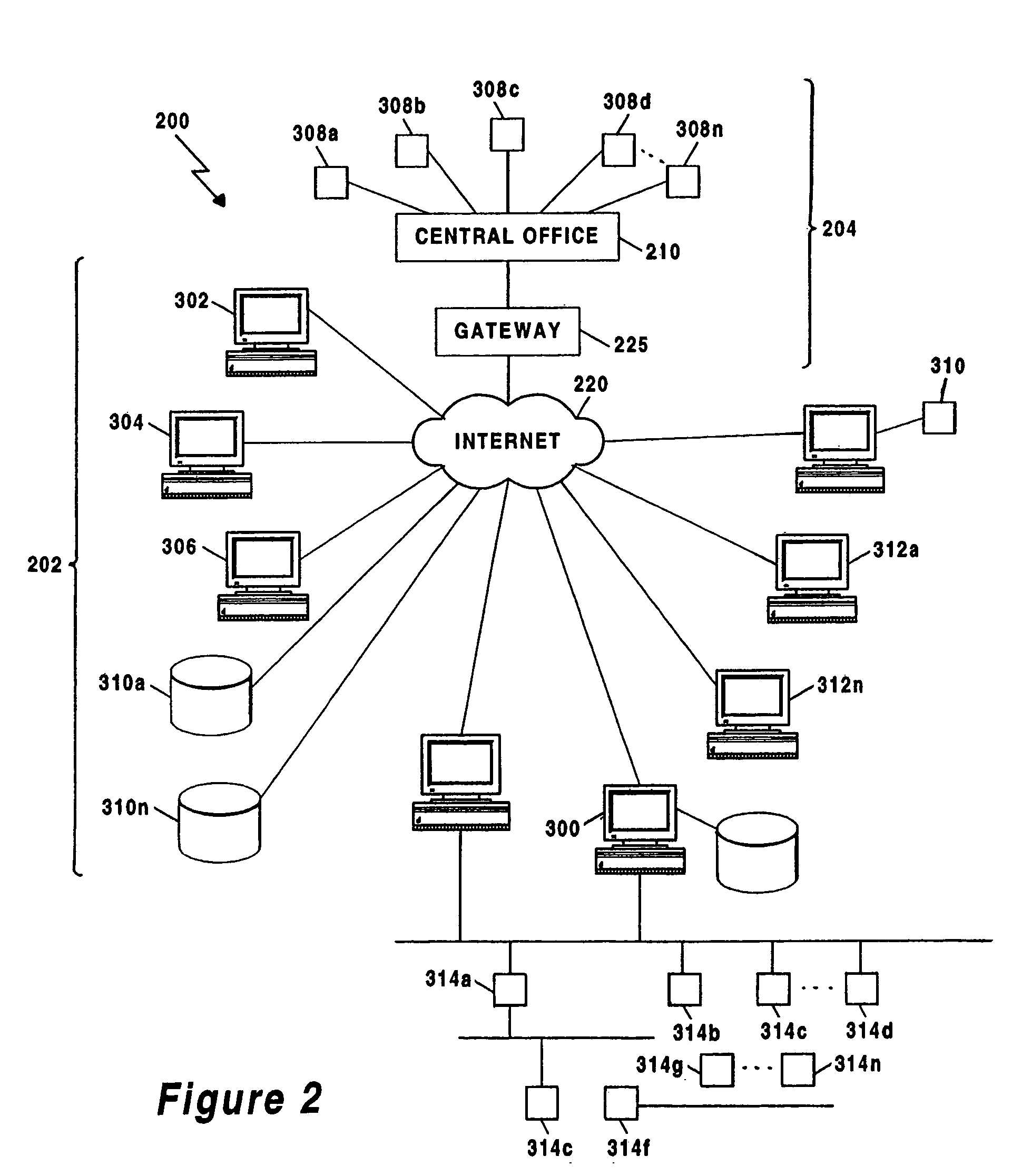

A network appliance for monitoring, diagnosing and documenting problems among a plurality of devices and processes (objects) coupled to a computer network utilizes periodic polling and collection of object-generated trap data to monitor the status of objects on the computer network. The status of a multitude of objects is maintained in memory utilizing virtual state machines which contain a small amount of persistent data but which are modeled after one of a plurality of finite state machines. The memory further maintains dependency data related to each object which identifies parent / child relationships with other objects at the same or different layers of the OSI network protocol model. A decision engine verifies through on-demand polling that a device is down. A root cause analysis module utilizes status and dependency data to locate the highest object in the parent / child relationship tree that is affected to determine the root cause of a problem. Once a problem has been verified, a “case” is opened and notification alerts may be sent out to one or more devices. A user interface allows all objects within the network to be displayed with their respective status and their respective parent / child dependency objects in various formats.

Owner:OPTANIX INC

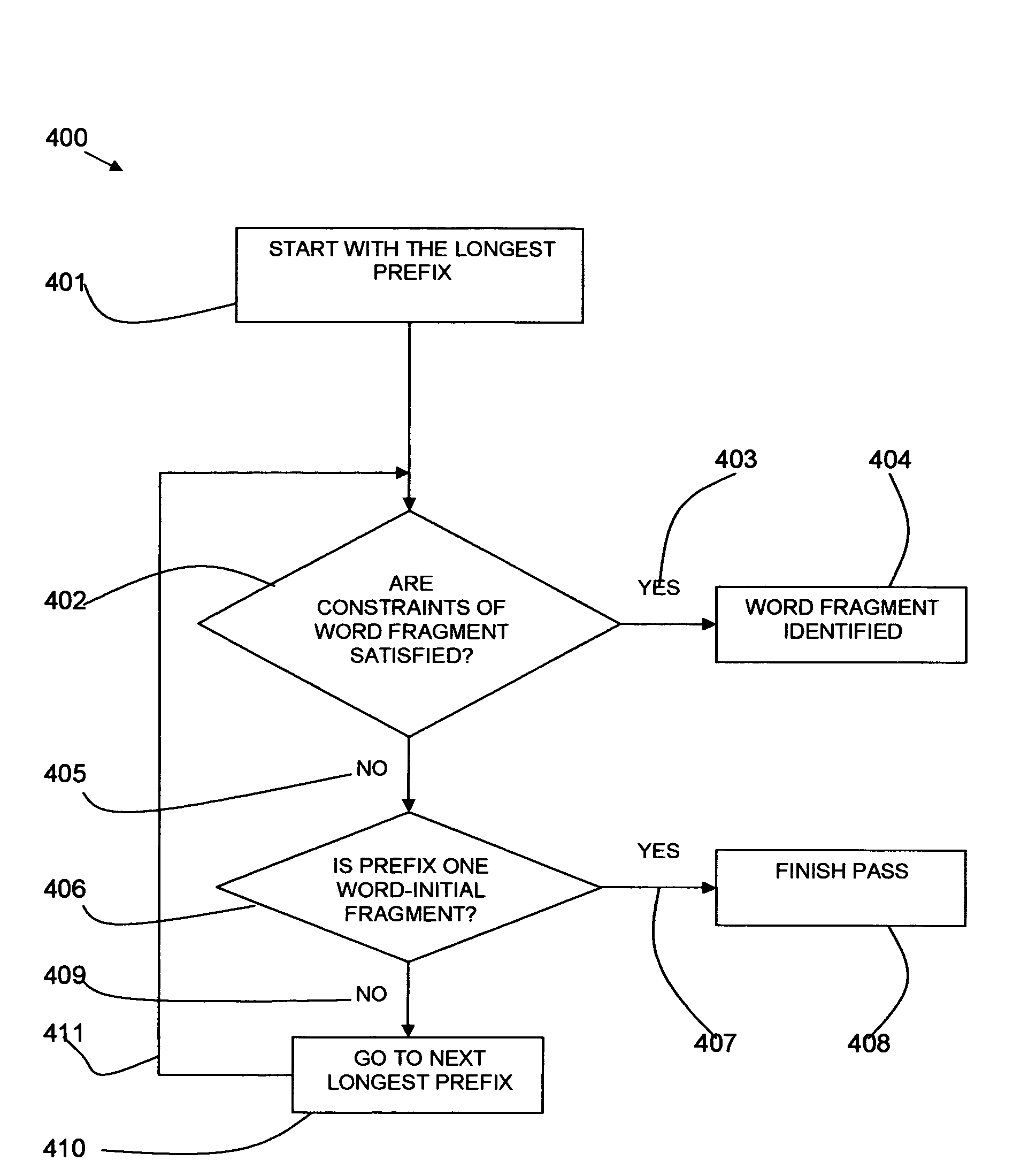

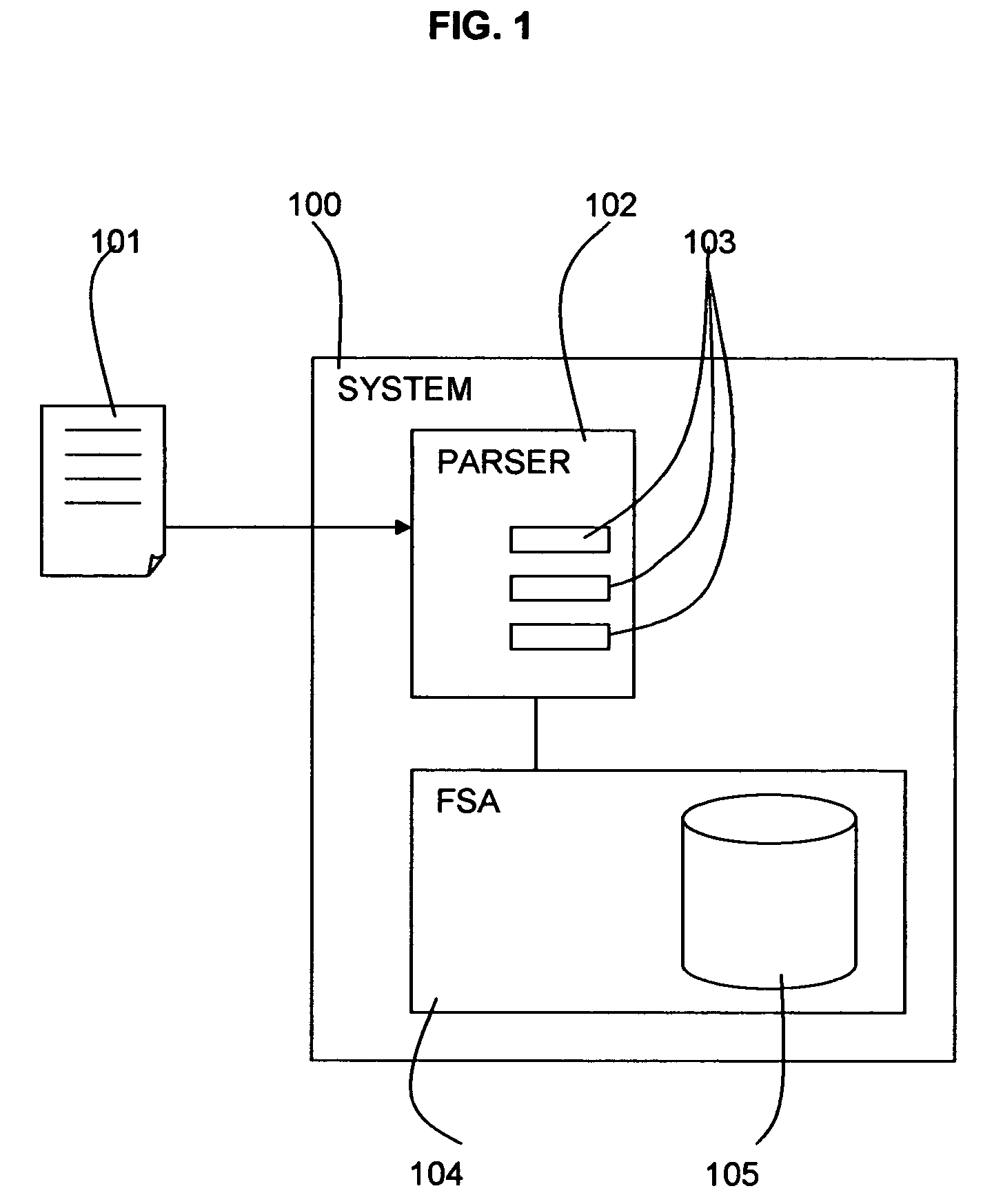

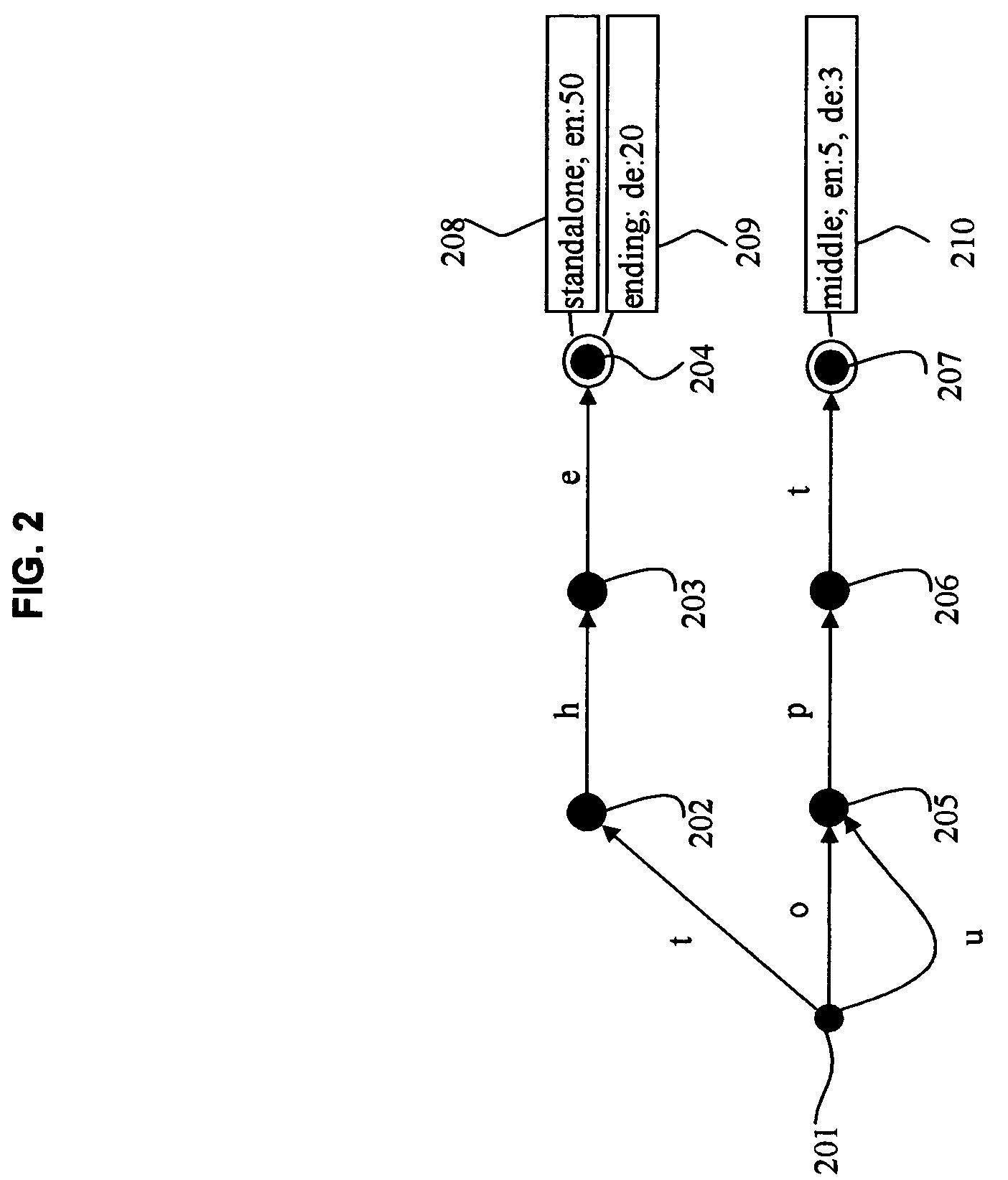

Method and system for language identification

InactiveUS7818165B2Computationally efficientNatural language data processingSpecial data processing applicationsFeature setRelevant information

A method and system for language identification are provided. The system includes a feature set of a plurality of character strings of varying length with associated information. The associated information includes one or more significance scores for a character string for one or more of a plurality of languages. Means are provided for detecting character strings from the feature set within a token from an input text. The system uses a finite-state device and the associated information is provided as glosses at the final nodes of the finite-state device for each character string. The associated information can also include significance scores based on linguistic rules.

Owner:LINKEDIN

Method and apparatus for maintaining the status of objects in computer networks using virtual state machines

ActiveUS7197561B1Error detection/correctionMultiple digital computer combinationsVirtual finite-state machineFinite-state machine

A network appliance for monitoring, diagnosing and documenting problems among a plurality of devices and processes (objects) coupled to a computer network utilizes periodic polling and collection of object-generated trap data to monitor the status of objects on the computer network. The status of a multitude of objects is maintained in memory utilizing virtual state machines which contain a small amount of persistent data but which are modeled after one of a plurality of finite state machines. The memory further maintains dependency data related to each object which identifies parent / child relationships with other objects at the same or different layers of the OSI network protocol model. A decision engine verifies through on-demand polling that a device is down. A root cause analysis module utilizes status and dependency data to locate the highest object in the parent / child relationship tree that is affected to determine the root cause of a problem. Once a problem has been verified, a “case” is opened and notification alerts may be sent out to one or more devices. A user interface allows all objects within the network to be displayed with their respective status and their respective parent / child dependency objects in various formats.

Owner:OPTANIX INC

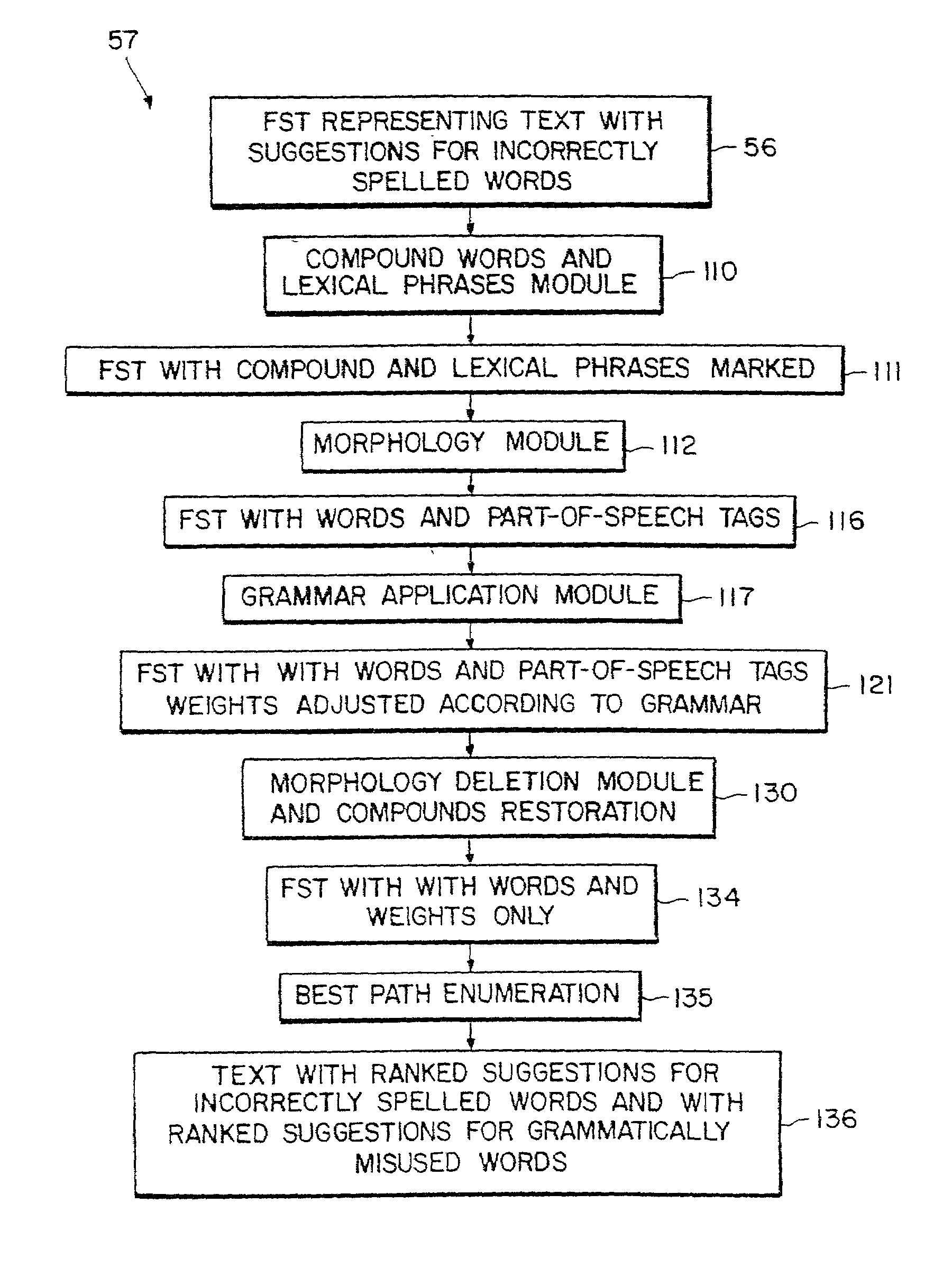

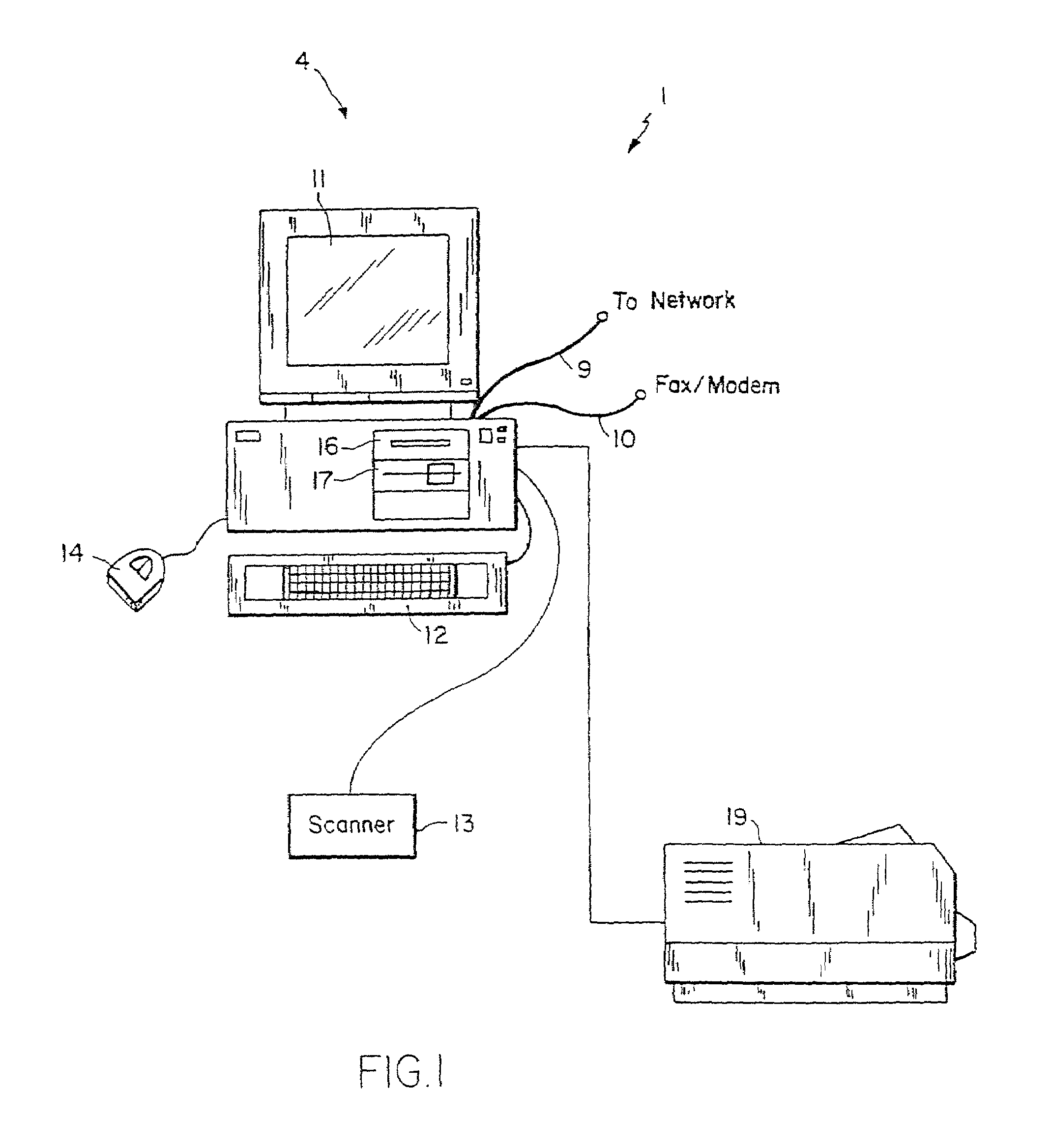

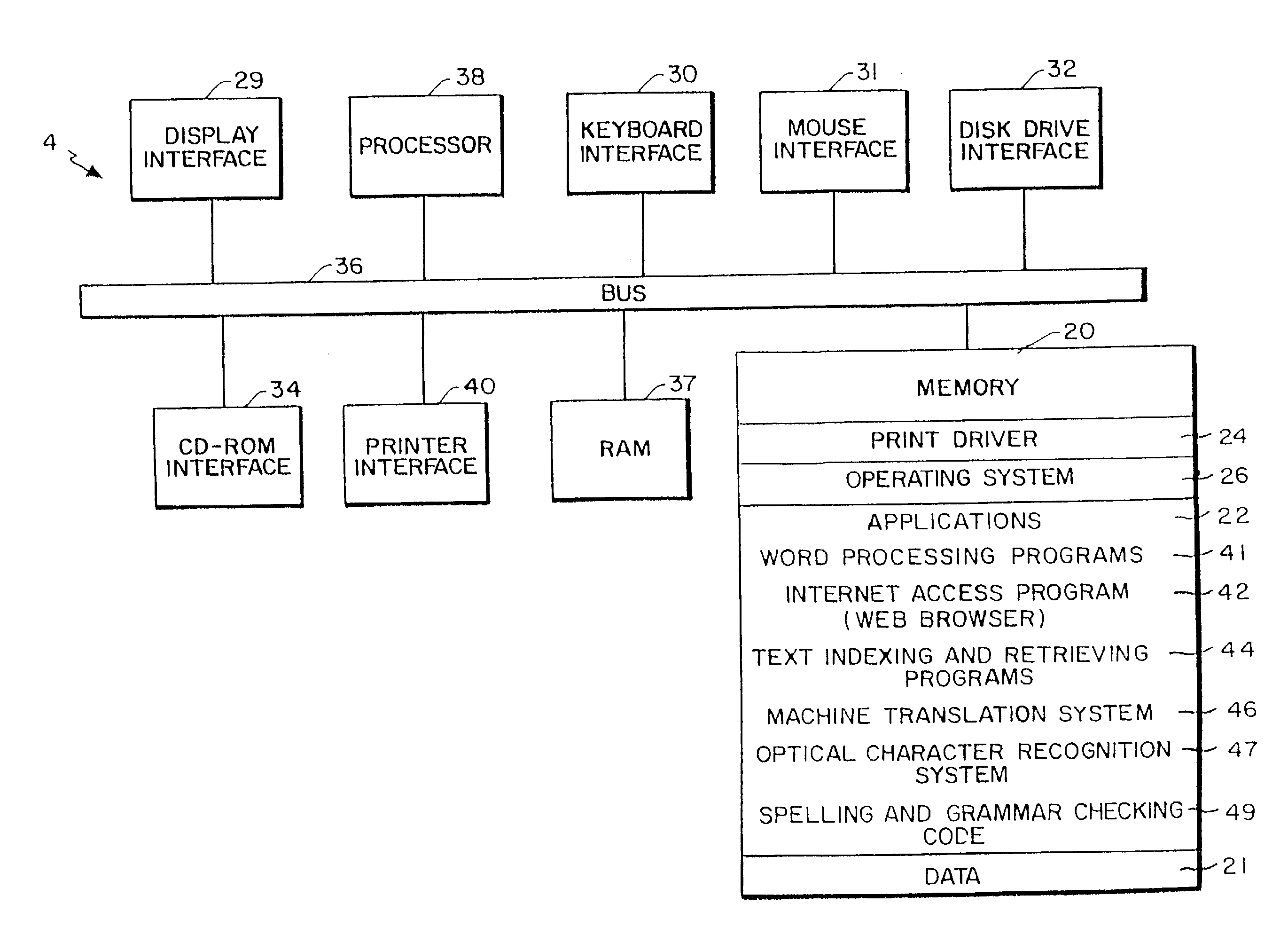

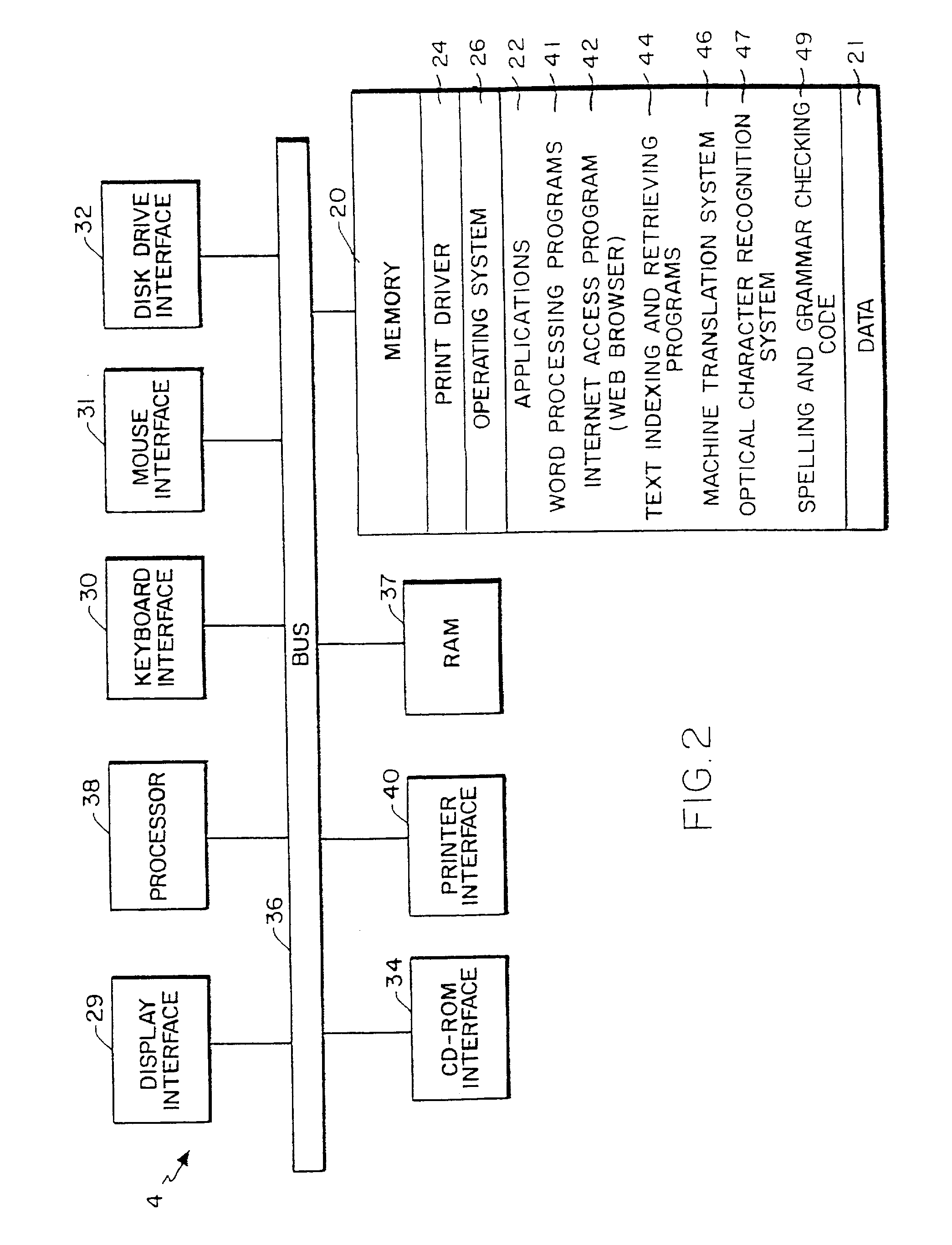

Spelling and grammar checking system

InactiveUS7243305B2Data processing applicationsDigital computer detailsFinite-state machineFinite state

System of correcting misspelled words in input text detects a misspelled word in the input text, determines a list of alternative words for the misspelled word, and ranks the list of alternative words based on a context of the input text. In certain embodiments, finite state machines (FSMs) are utilized in the spelling and grammar correction process, storing one or more lexicon FSMs, each of which represents a set of correctly spelled reference words. Storing the lexicon as one or more FSMs facilitates those embodiments of the invention employing a clinet-server architecture. The input text to be corrected may also be encoded as a FSM, which includes alternative word(s) for word(s) in need of correction along with associated weights. The invention adjusts the weights by taking into account the grammatical context in which the word appears in the input text. In certain embodiments the modification is performed by applying a second FSM to the FSM that was generated for the input text, where the second FSM encodes a grammatically correct sequence of words, thereby generating an additional FSM.

Owner:GLOBAL INFORMATION RES TECH

Spelling and grammar checking system

InactiveUS20040093567A1Data processing applicationsNatural language data processingFinite-state machineEngineering

System of correcting misspelled words in input text detects a misspelled word in the input text, determines a list of alternative words for the misspelled word, and ranks the list of alternative words based on a context of the input text. In certain embodiments, finite state machines (FSMs) are utilized in the spelling and grammar correction process, storing one or more lexicon FSMs, each of which represents a set of correctly spelled reference words. Storing the lexicon as one or more FSMs facilitates those embodiments of the invention employing a clinet-server architecture. The input text to be corrected may also be encoded as a FSM, which includes alternative word(s) for word(s) in need of correction along with associated weights. The invention adjusts the weights by taking into account the grammatical context in which the word appears in the input text. In certain embodiments the modification is performed by applying a second FSM to the FSM that was generated for the input text, where the second FSM encodes a grammatically correct sequence of words, thereby generating an additional FSM.

Owner:GLOBAL INFORMATION RES TECH

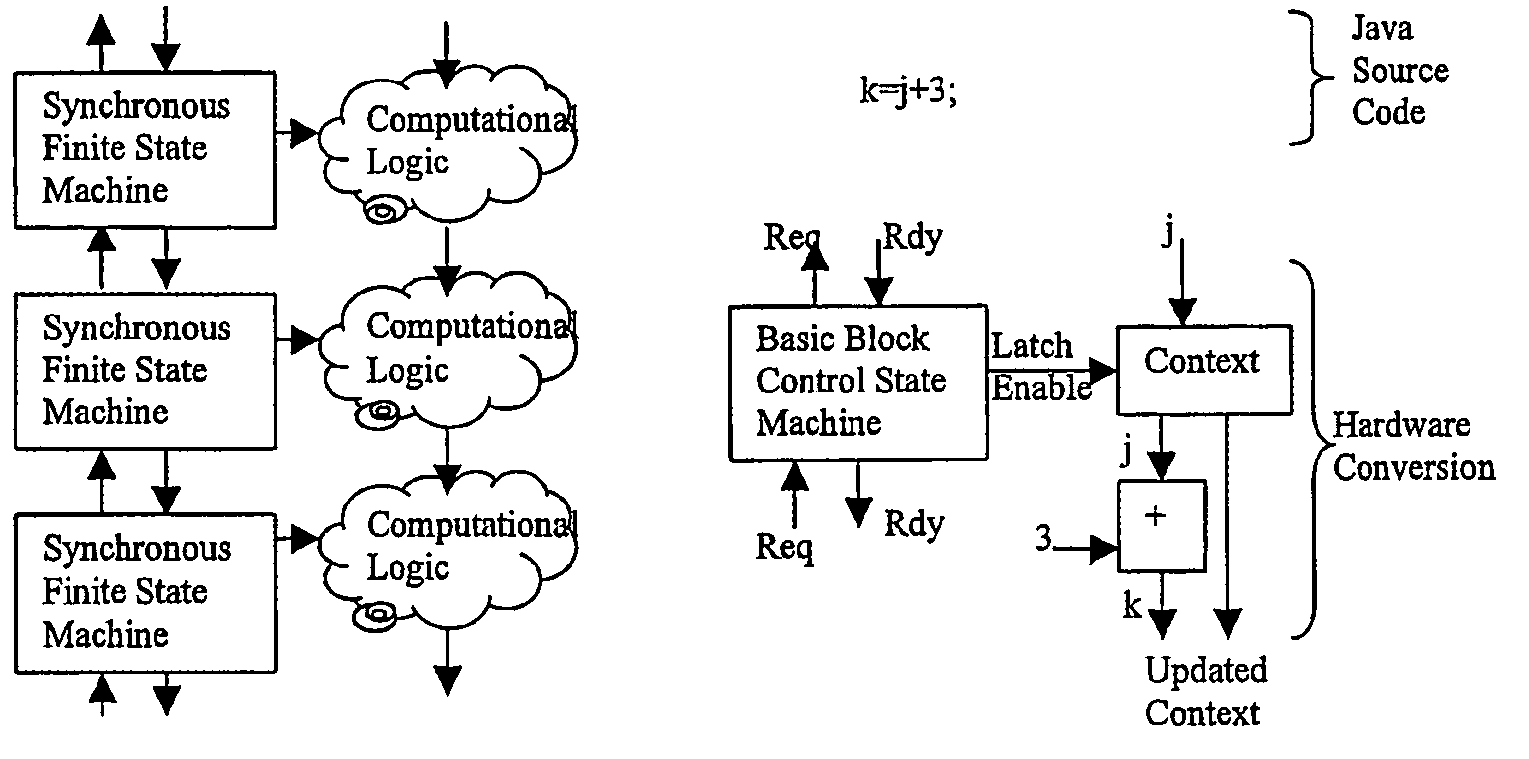

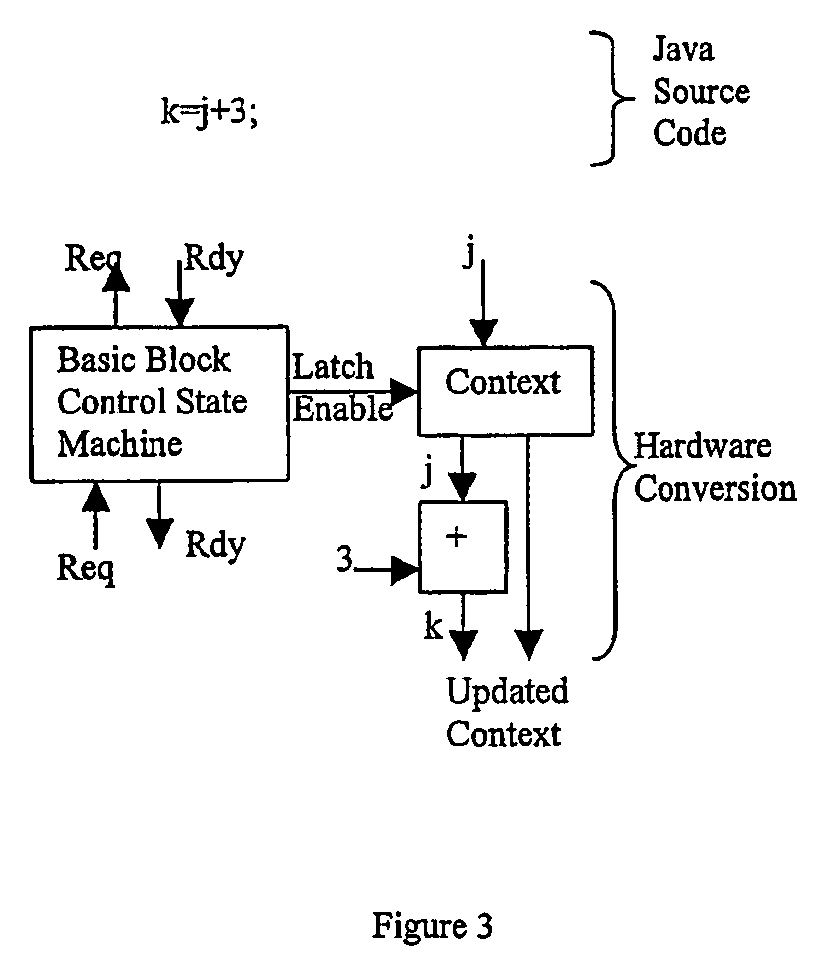

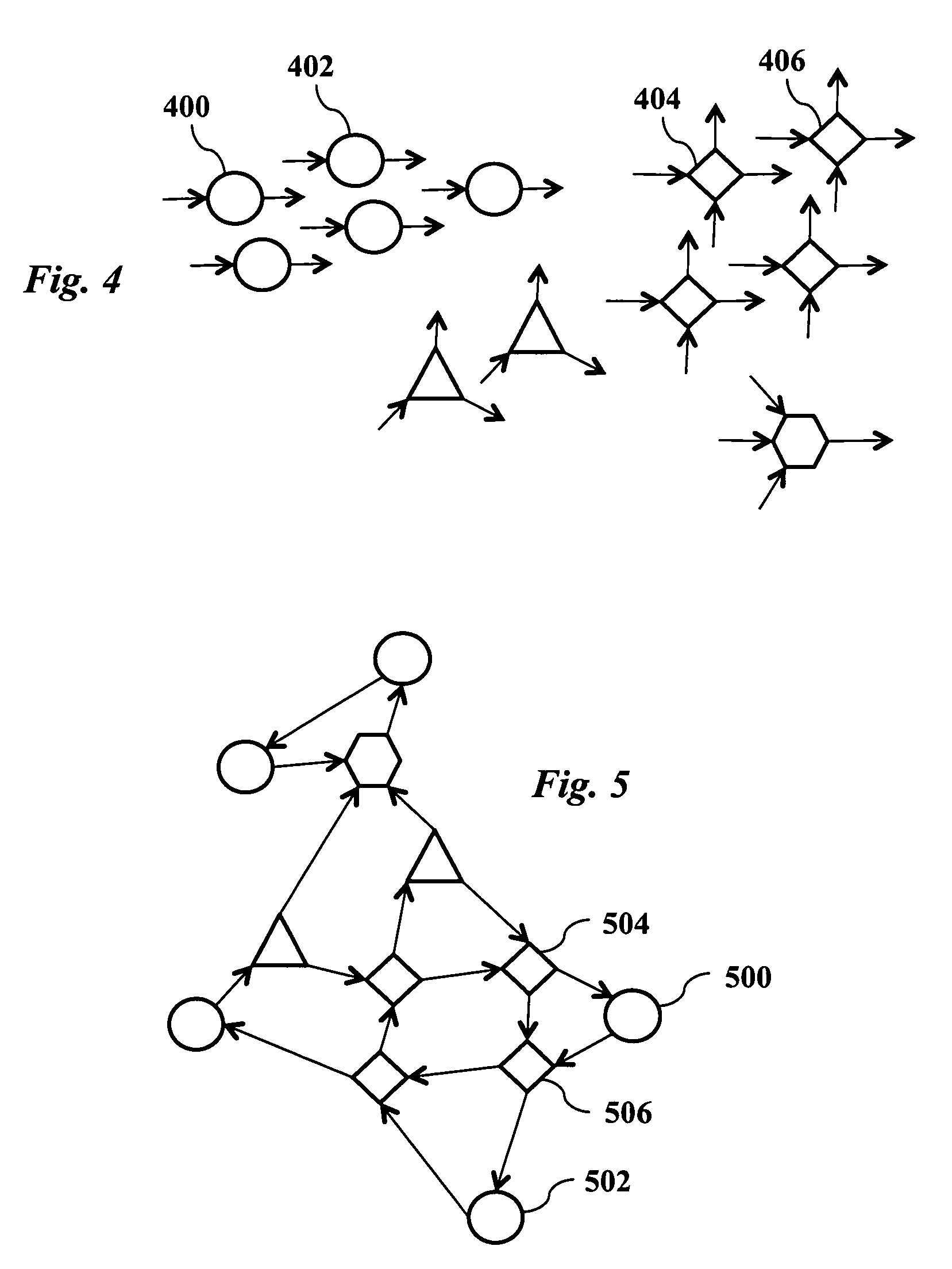

System of finite state machines

InactiveUS7224185B2Enough timeConcurrent instruction executionMultiple digital computer combinationsSufficient timeComputational logic

A system of finite state machines built with asynchronous or synchronous logic for controlling the flow of data through computational logic circuits programmed to accomplish a task specified by a user, having one finite state machine associated with each computational logic circuit, having each finite state machine accept data from either one or more predecessor finite state machines or from one or more sources outside the system and furnish data to one or more successor finite state machines or a recipient outside the system, excluding from consideration in determining a clock period for the system logic paths performing the task specified by the user, and providing a means for ensuring that each finite state machine allows sufficient time to elapse for the computational logic circuit associated with that finite state to perform its task.

Owner:CAMPBELL JOHN +1

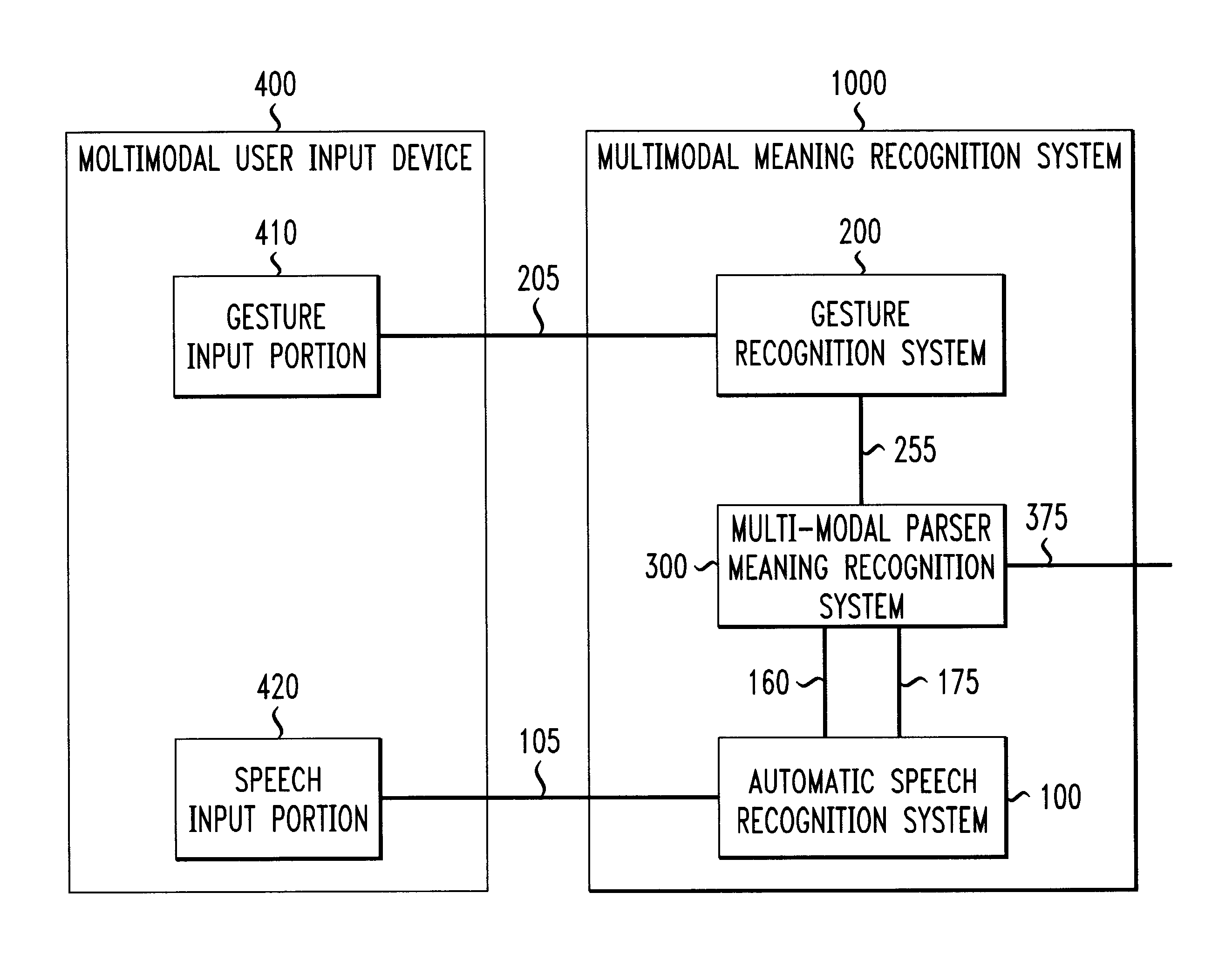

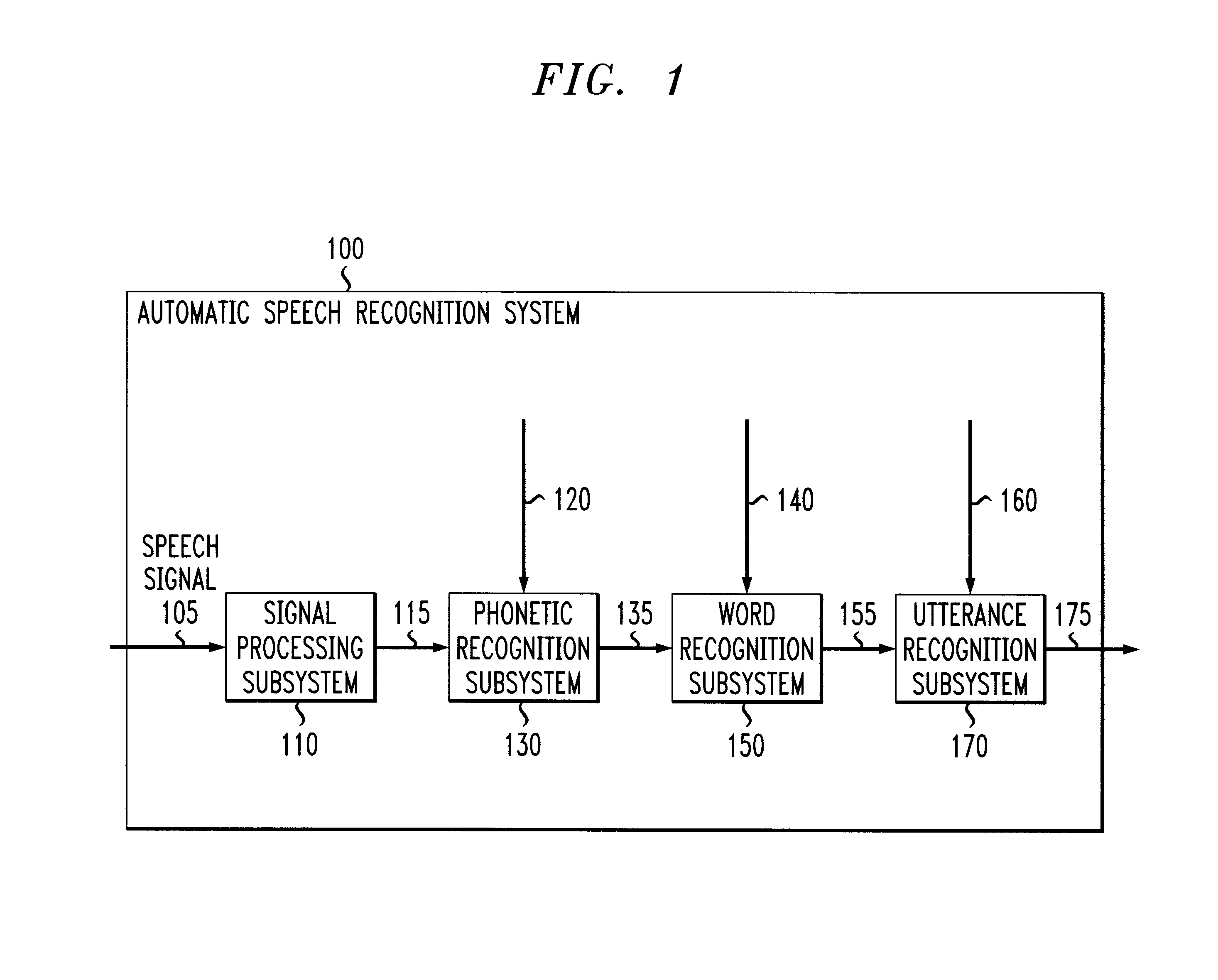

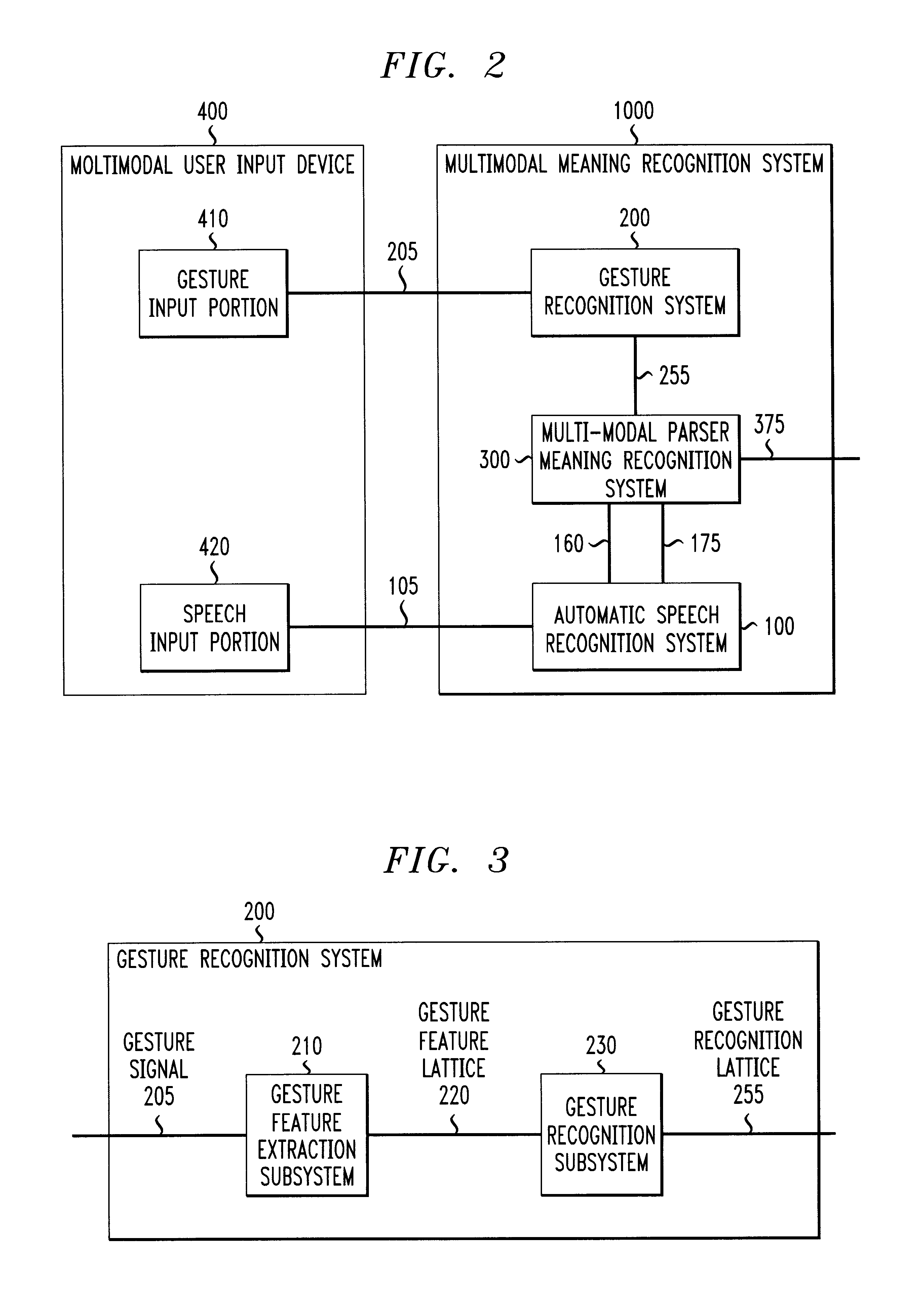

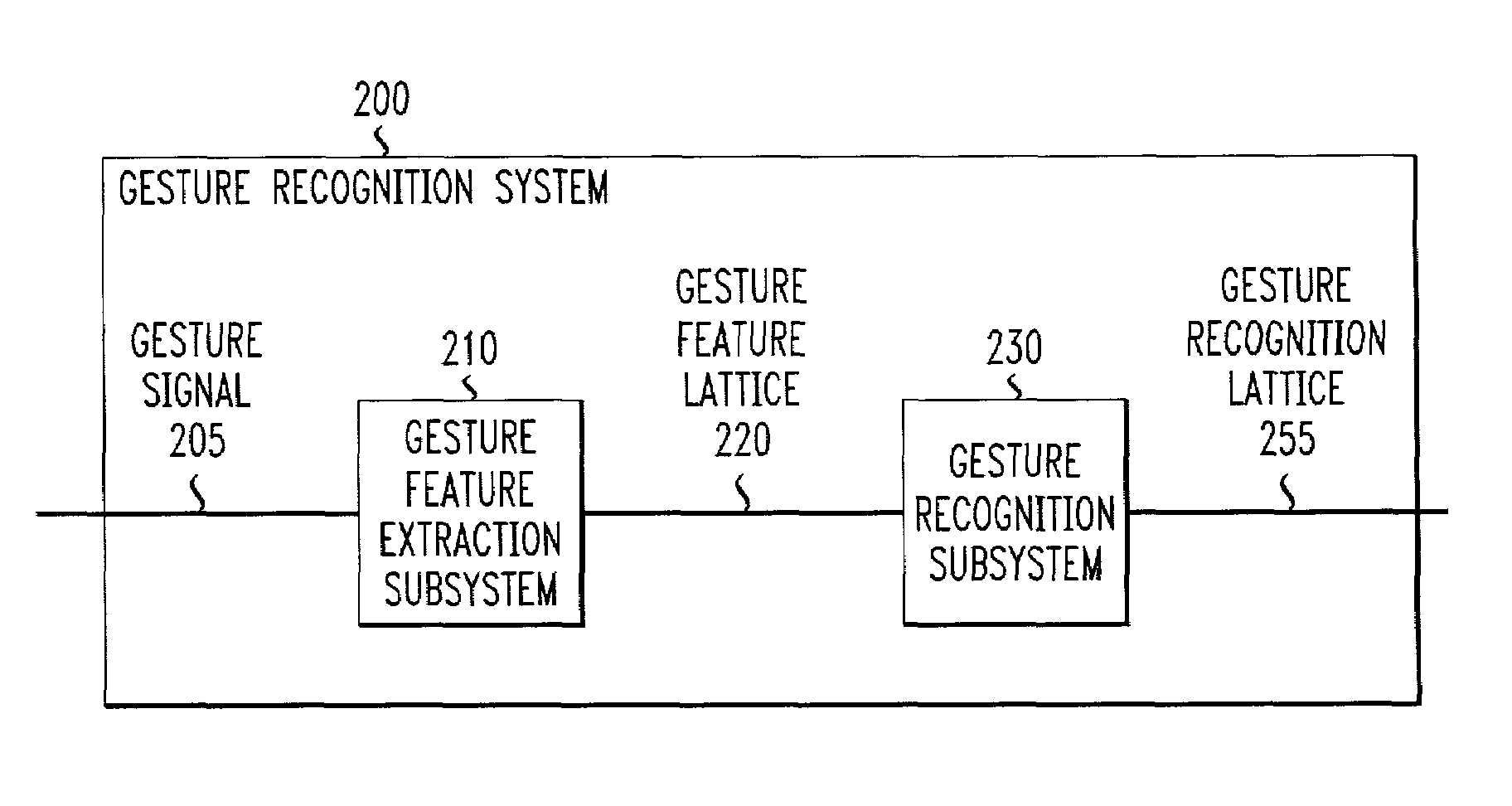

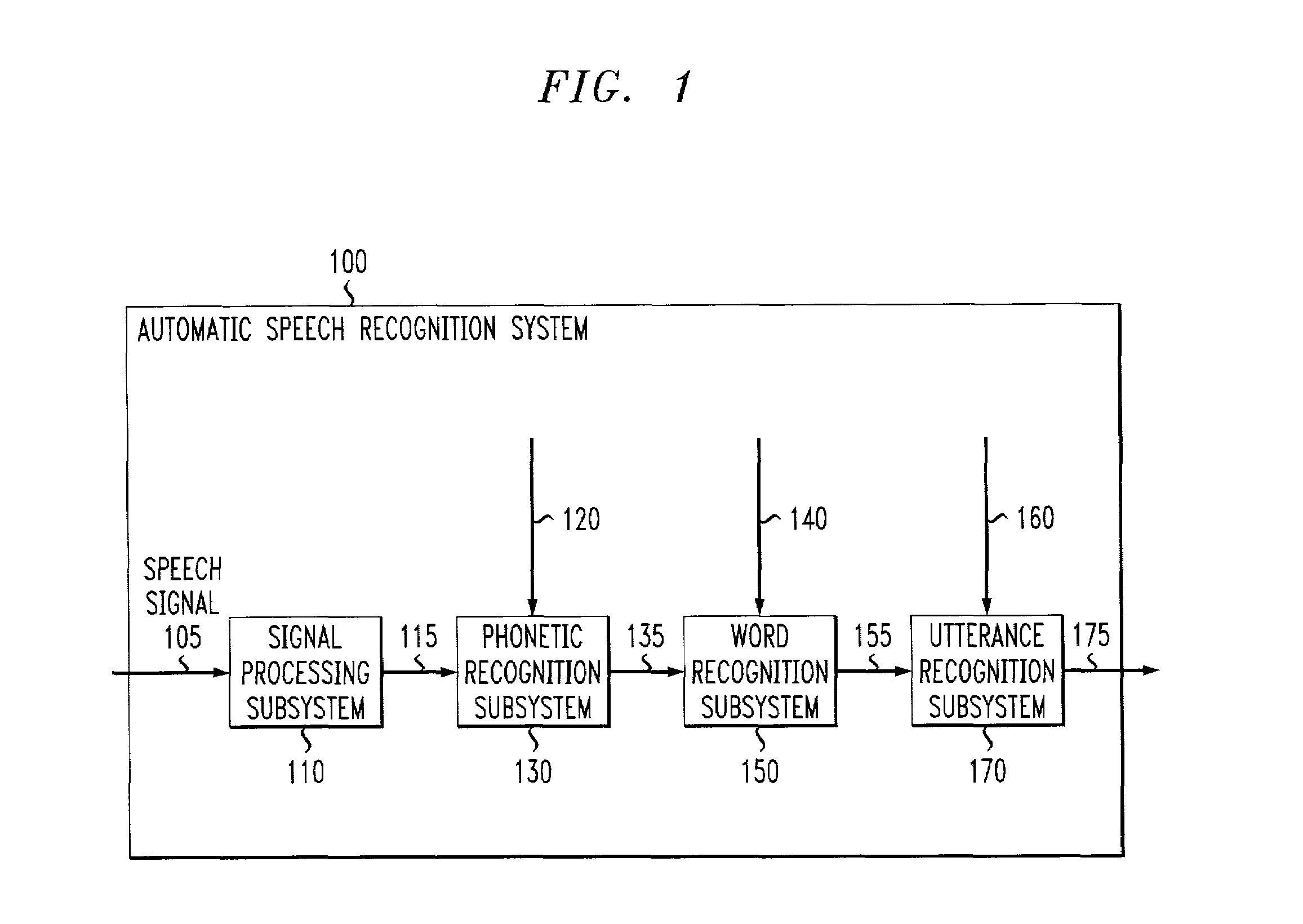

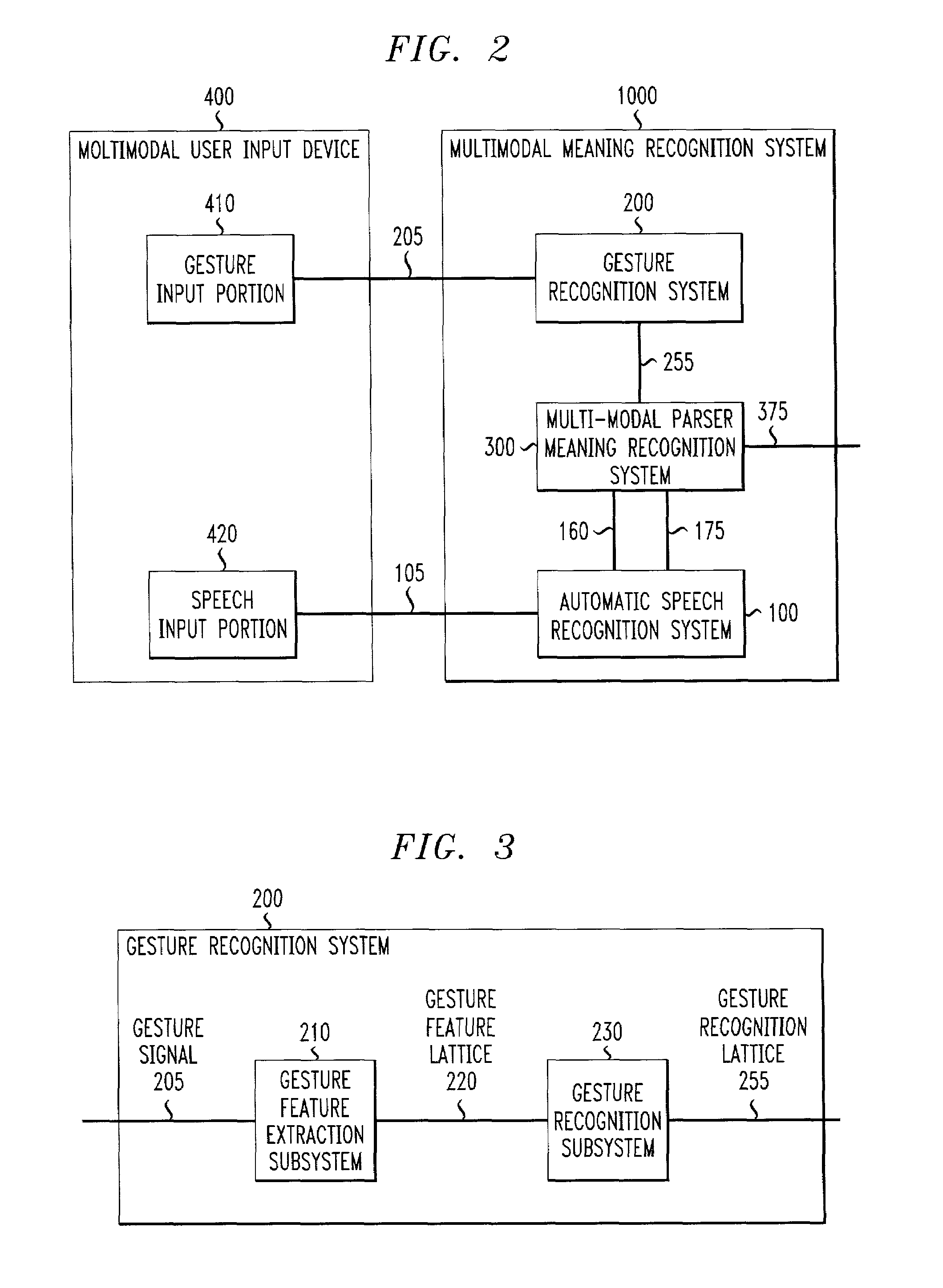

Systems and methods for extracting meaning from multimodal inputs using finite-state devices

InactiveUS6868383B1Computational complexity is reducedCharacter and pattern recognitionSpeech recognitionSpeech inputAutomatic speech

Multimodal utterances contain a number of different modes. These modes can include speech, gestures, and pen, haptic, and gaze inputs, and the like. This invention use recognition results from one or more of these modes to provide compensation to the recognition process of one or more other ones of these modes. In various exemplary embodiments, a multimodal recognition system inputs one or more recognition lattices from one or more of these modes, and generates one or more models to be used by one or more mode recognizers to recognize the one or more other modes. In one exemplary embodiment, a gesture recognizer inputs a gesture input and outputs a gesture recognition lattice to a multimodal parser. The multimodal parser generates a language model and outputs it to an automatic speech recognition system, which uses the received language model to recognize the speech input that corresponds to the recognized gesture input.

Owner:INTERACTIONS LLC (US)

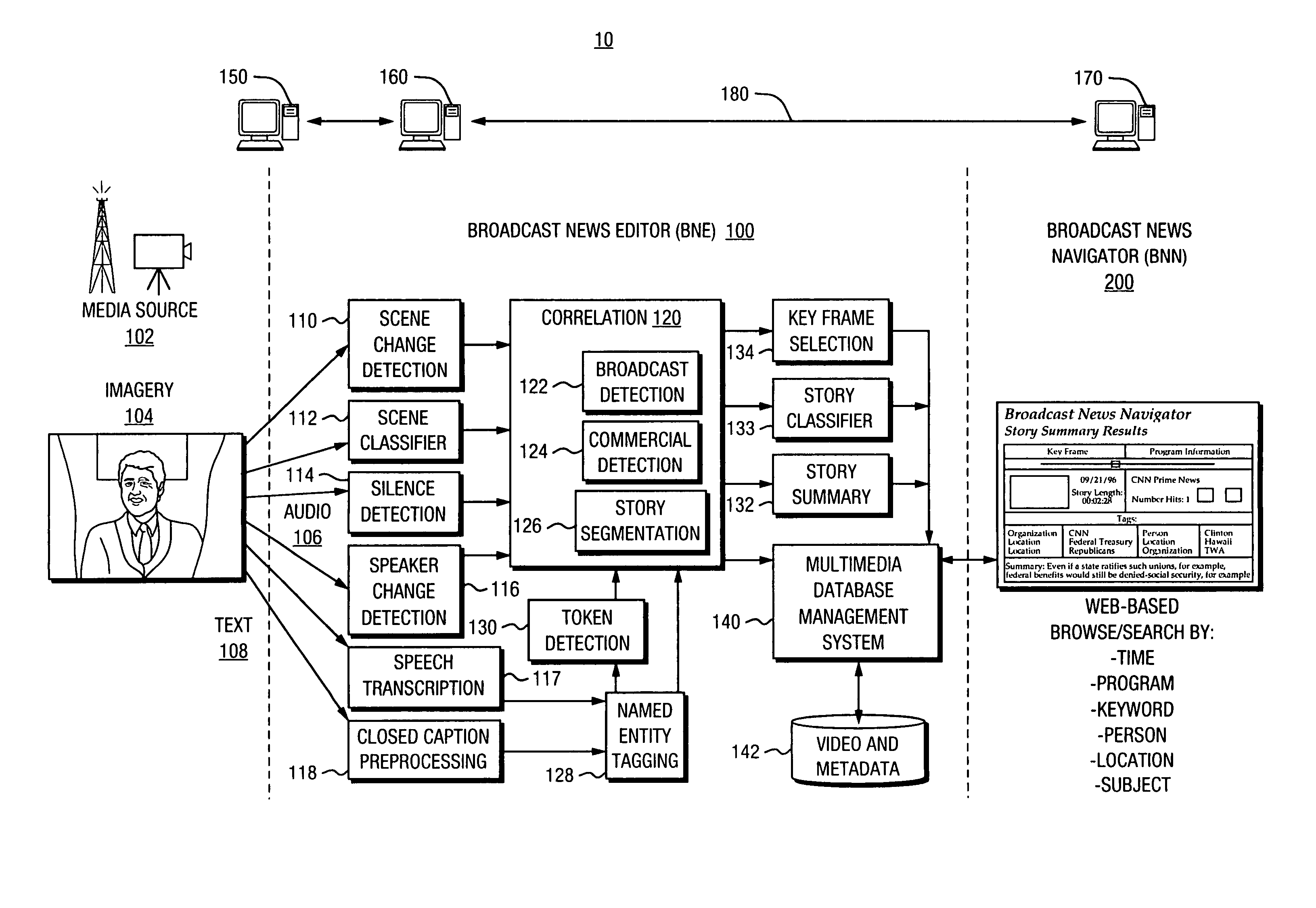

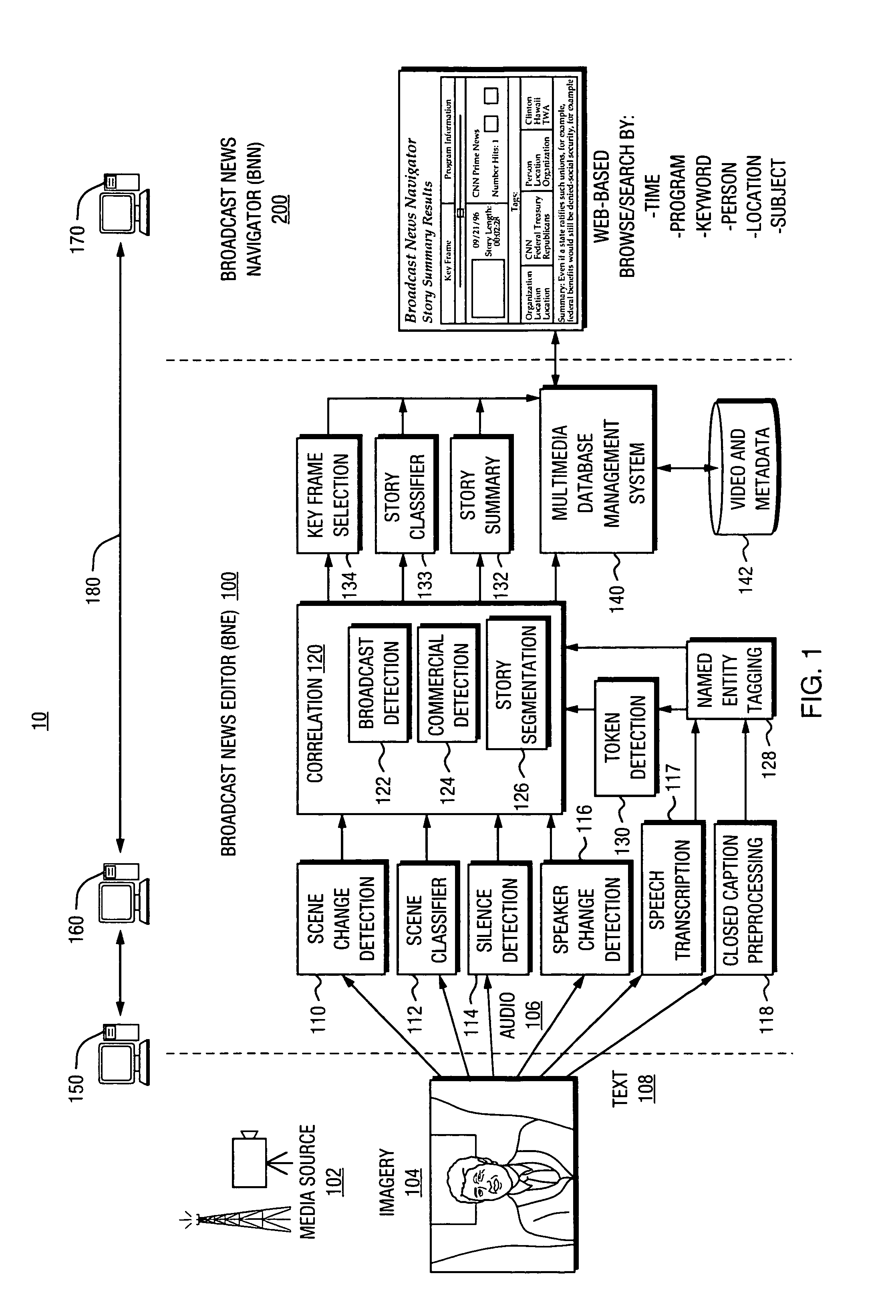

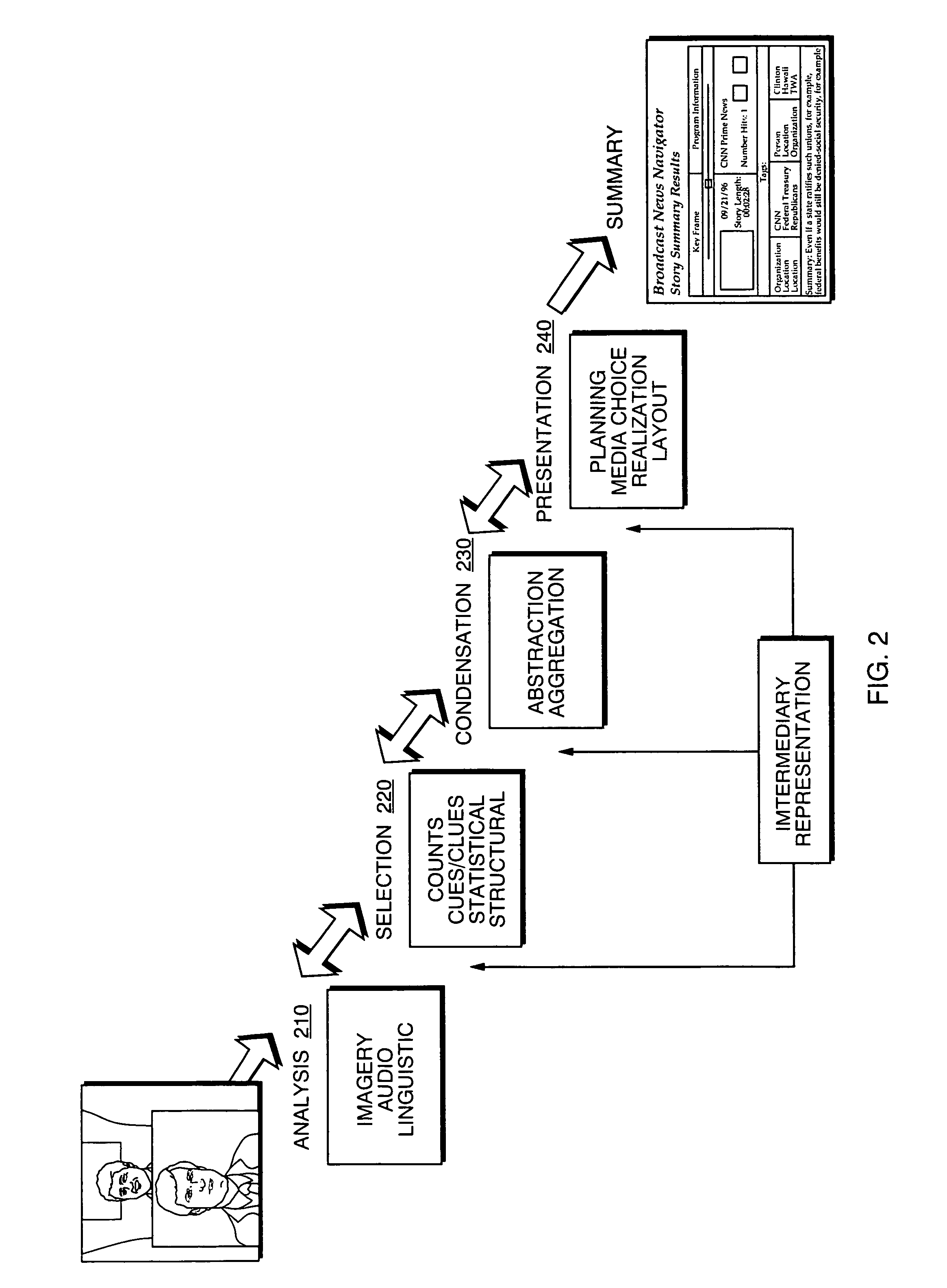

Automated segmentation and information extraction of broadcast news via finite state presentation model

InactiveUS7765574B1More efficientMore timelyTelevision system detailsDigital data information retrievalWeb browserPublic information

Owner:OAKHAM TECH

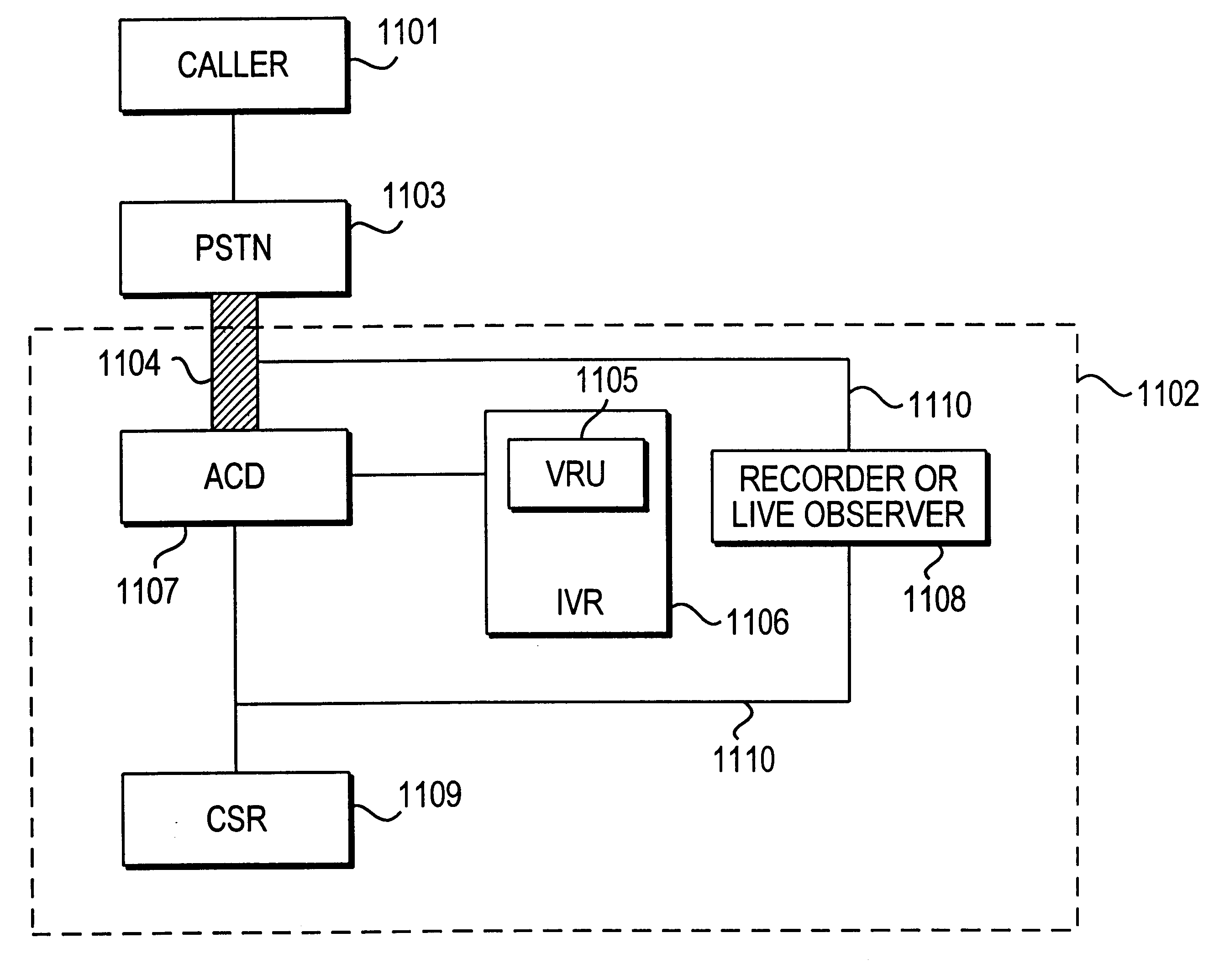

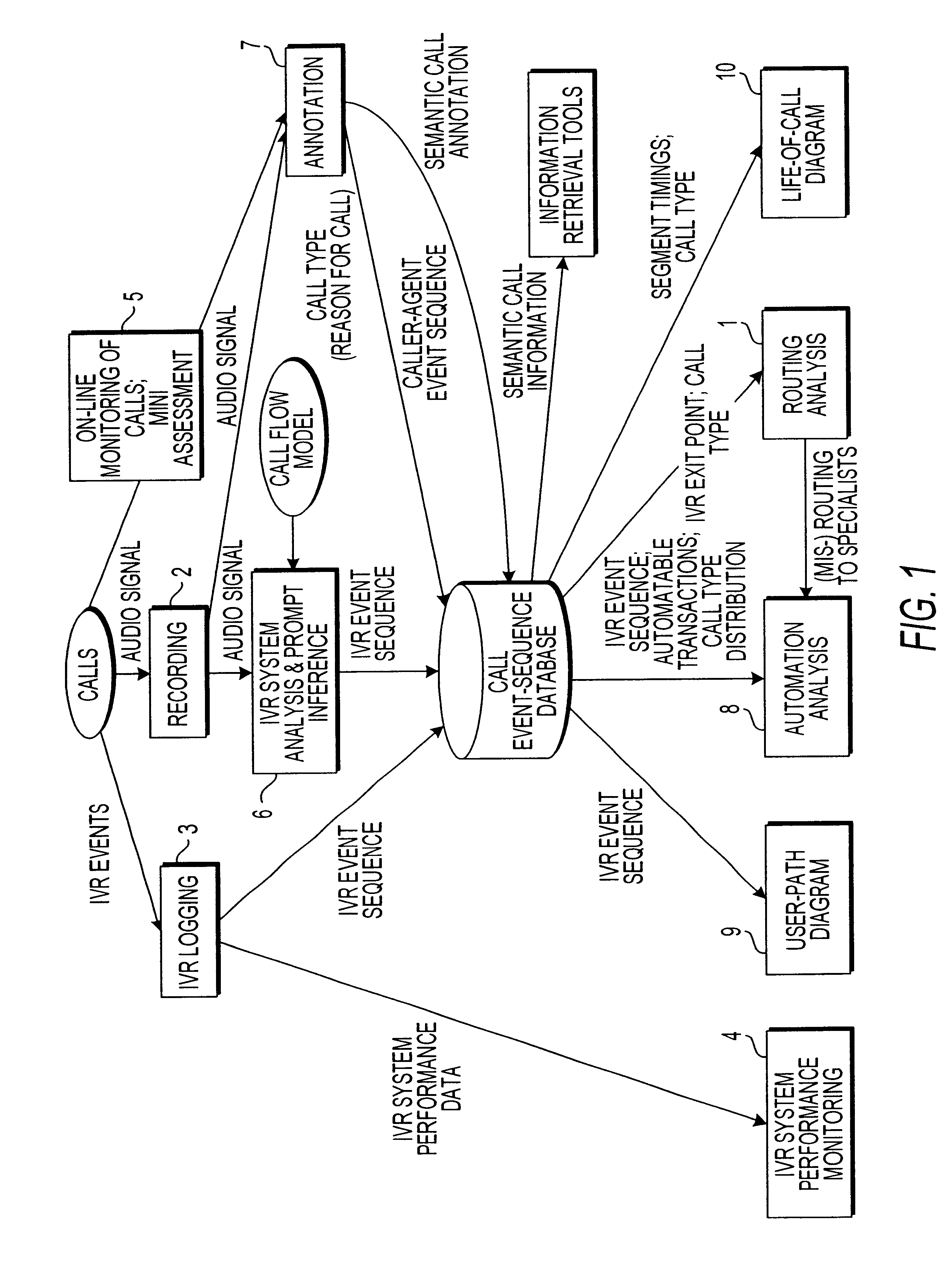

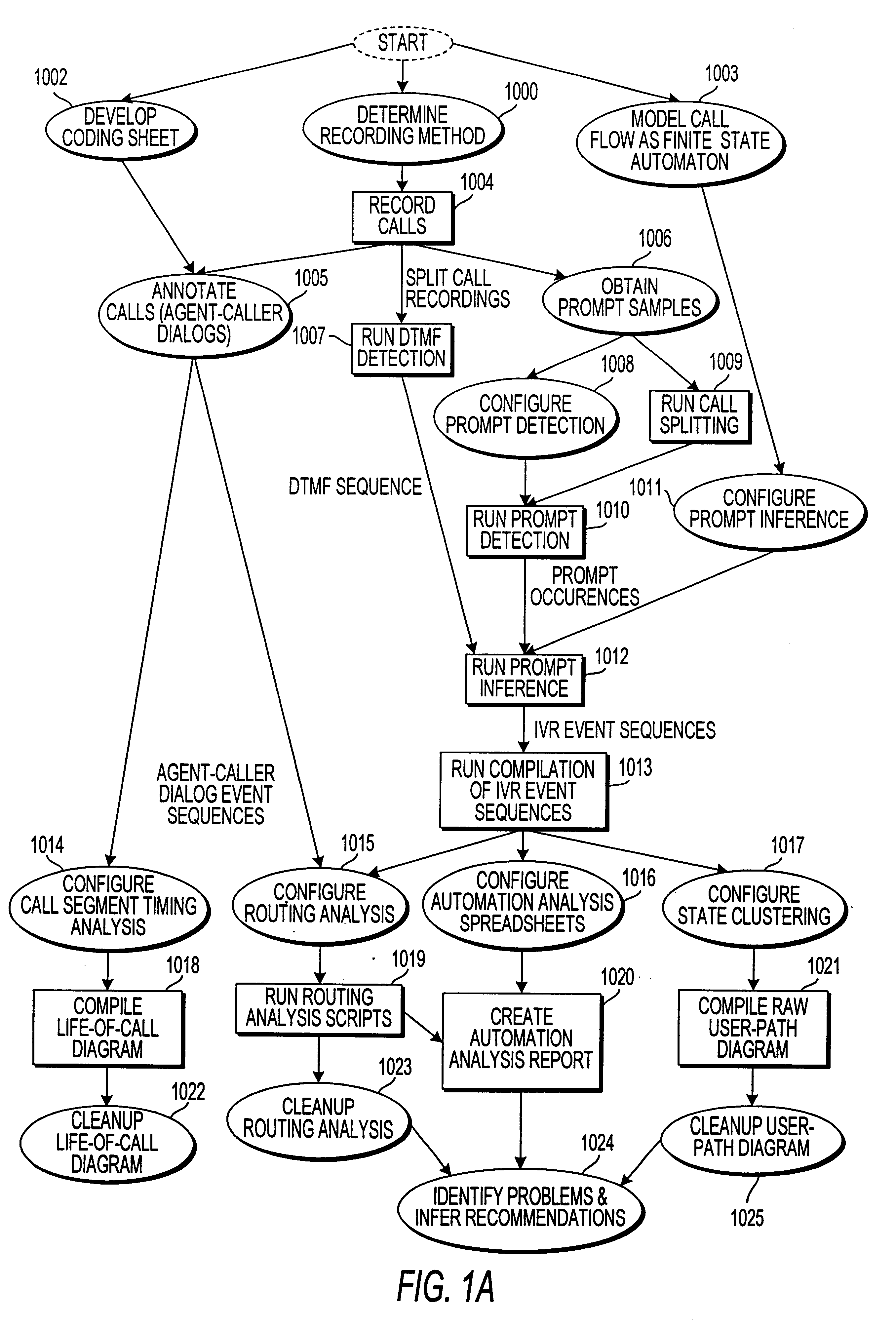

Apparatus and method for analyzing an automated response system

InactiveUS6823054B1Automatic call-answering/message-recording/conversation-recordingSpecial service for subscribersSpeech inputAutomaton

A system for analyzing an interactive voice response (IVR) system of a call processing center determines a complete sequence of events occurring within the IVR system. The IVR system being operable to automatically accept calls from callers and respond to input from the callers. The system models a call flow of the IVR system as a non-deterministic finite-state automaton. A recording of a plurality of calls to the call processing center is split, such that each of plural calls to the call center is in one audio file. For a plurality of calls, the system detects a complete sequence of DTMF and / or speech input to the IVR system, detects selected prompts issued by the IVR system, and inputs the detected sequence of DTMF and / or speech input as well as the detected prompts issued by the IVR system into the finite-state automaton to determine a call-event sequence for that call. The call-event sequence includes information regarding how that call left the IVR system.

Owner:VERIZON PATENT & LICENSING INC +1

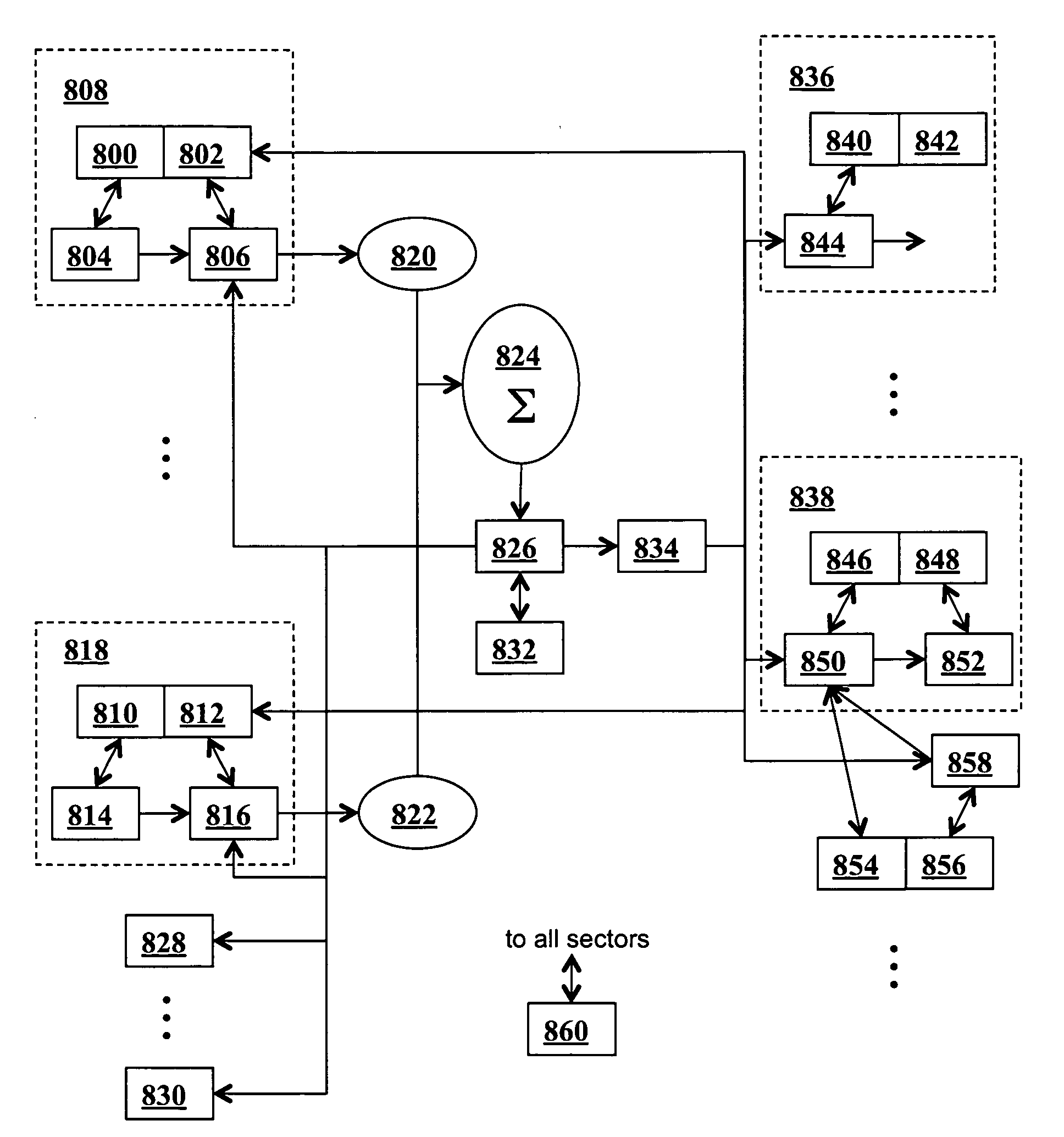

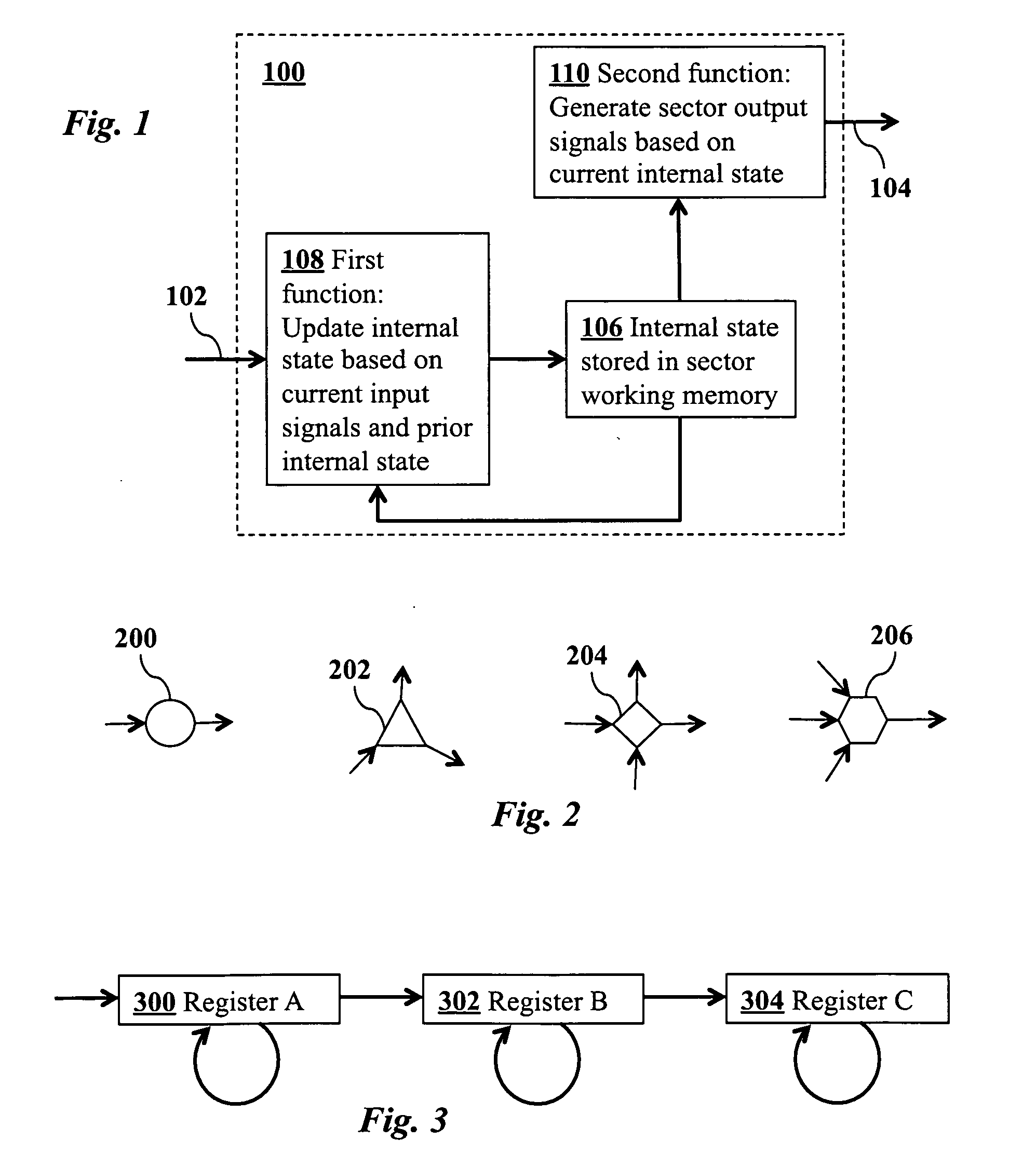

Method for efficiently simulating the information processing in cells and tissues of the nervous system with a temporal series compressed encoding neural network

ActiveUS20110016071A1Effective simulationExact reproductionDigital computer detailsDigital dataInformation processingNervous system

A neural network simulation represents components of neurons by finite state machines, called sectors, implemented using look-up tables. Each sector has an internal state represented by a compressed history of data input to the sector and is factorized into distinct historical time intervals of the data input. The compressed history of data input to the sector may be computed by compressing the data input to the sector during a time interval, storing the compressed history of data input to the sector in memory, and computing from the stored compressed history of data input to the sector the data output from the sector.

Owner:CORTICAL DATABASE

Finite state encoders and decoders for vector signaling codes

ActiveUS8718184B1Channel dividing arrangementsModulated-carrier systemsCommunications systemComputer science

In a chip-to-chip communication system and apparatus, a set of physical signals to be conveyed over a communication bus is provided, and mapped to a codeword of a vector signaling code using the physical signals and a state information, wherein a codeword is representable as a vector of plurality of real-valued components, and wherein a vector signaling code is a set of codewords in which the components sum to zero and for which there is at least one component and at least three codewords having different values in that component; and wherein the state information is a plurality of information present in continuous or discrete form which may have been obtained from previous codewords transmitted over the communication bus.

Owner:KANDOU LABS

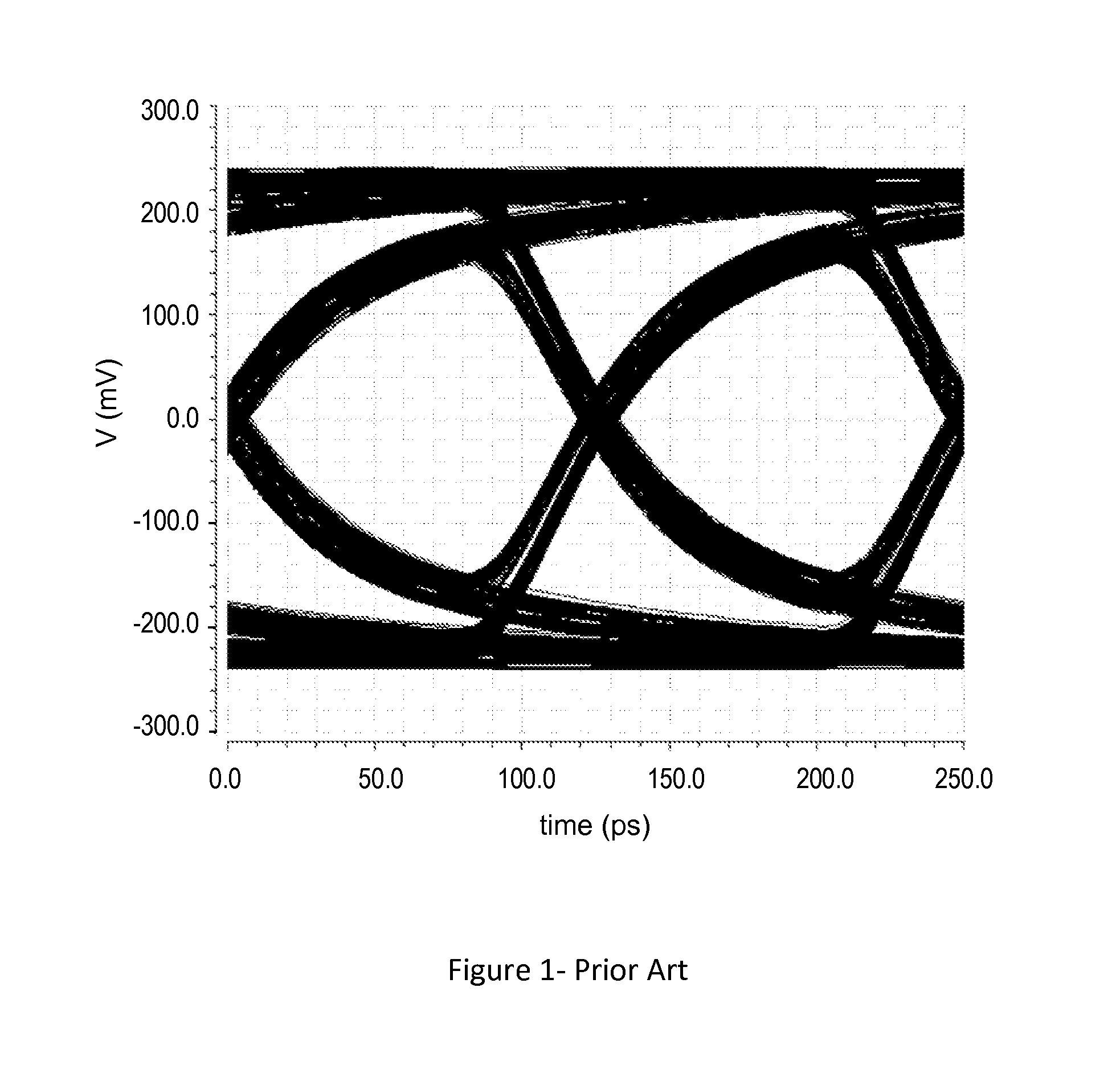

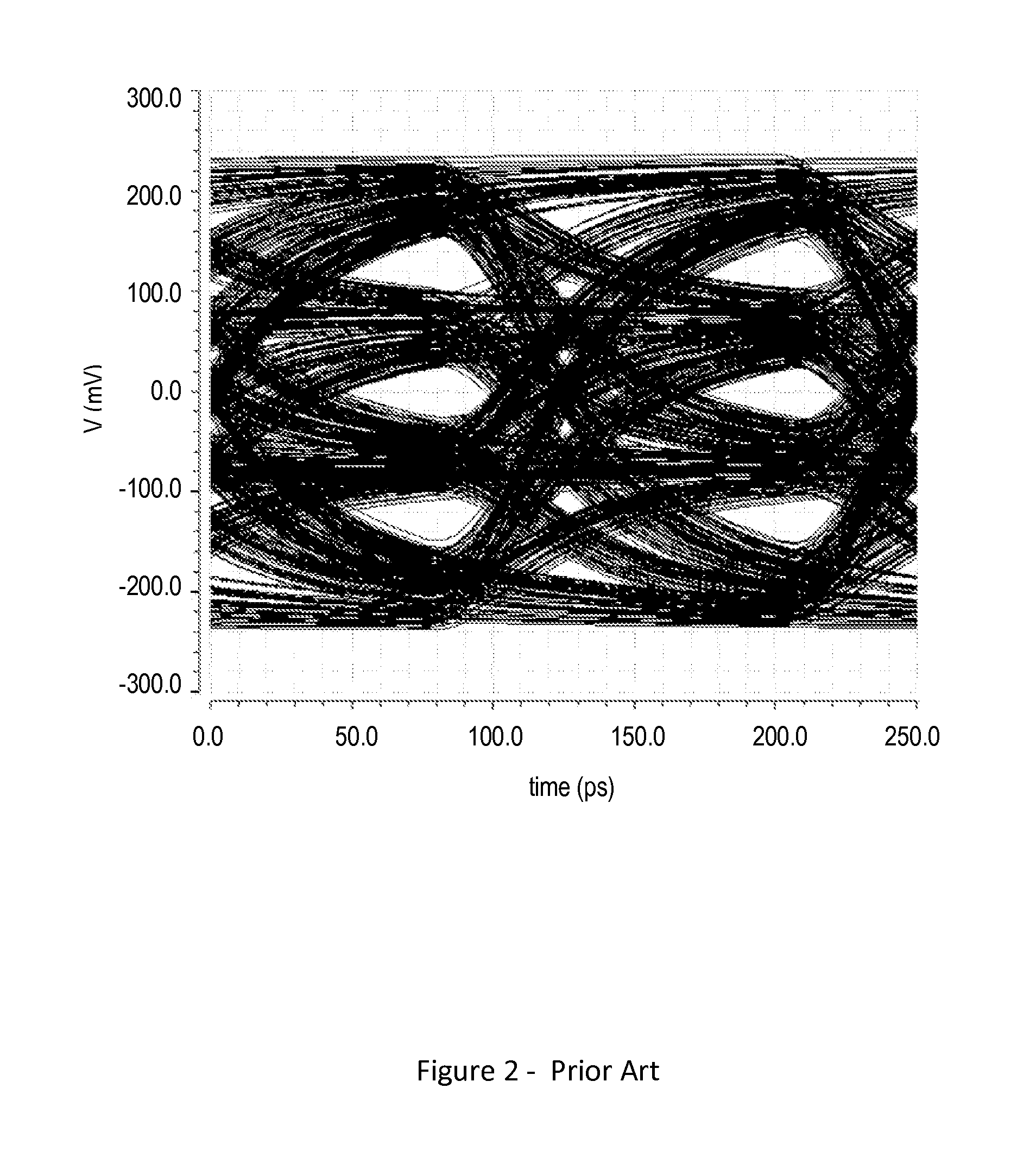

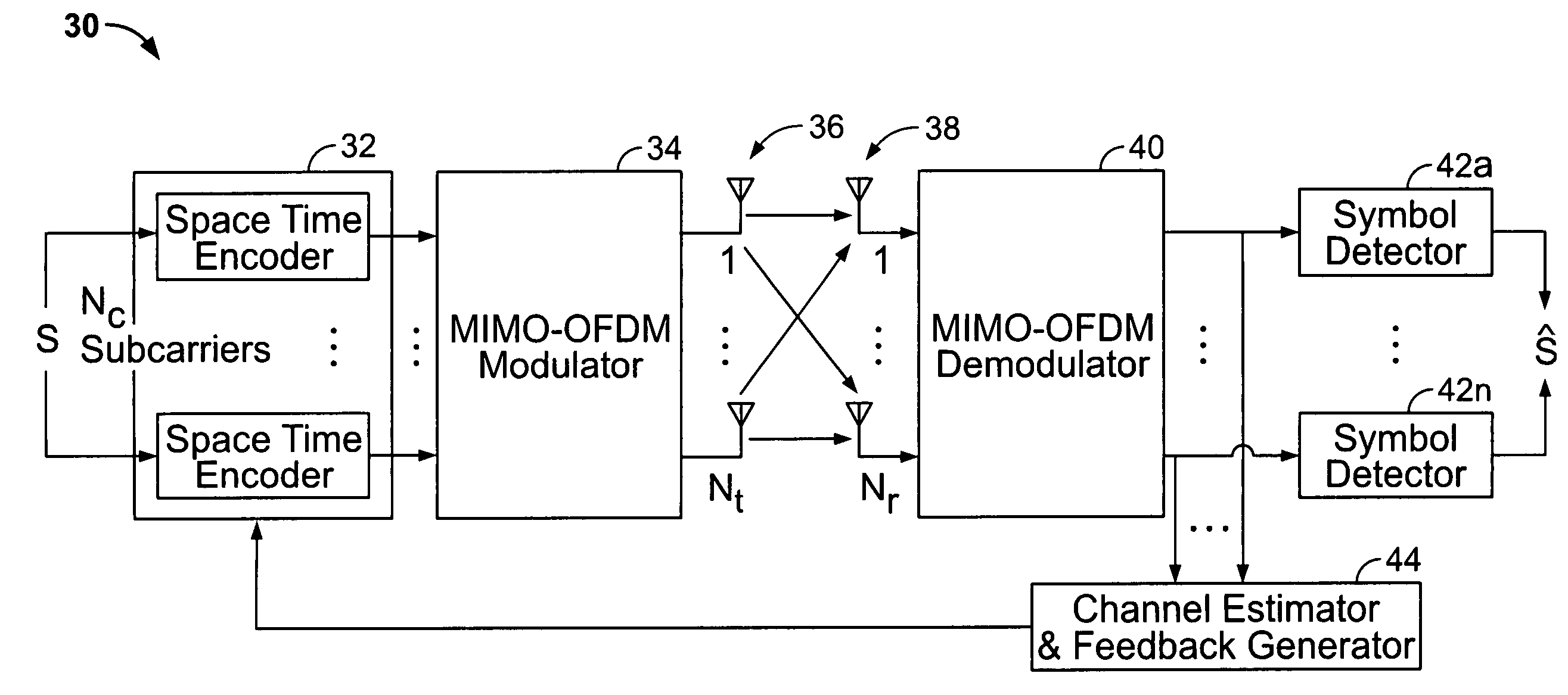

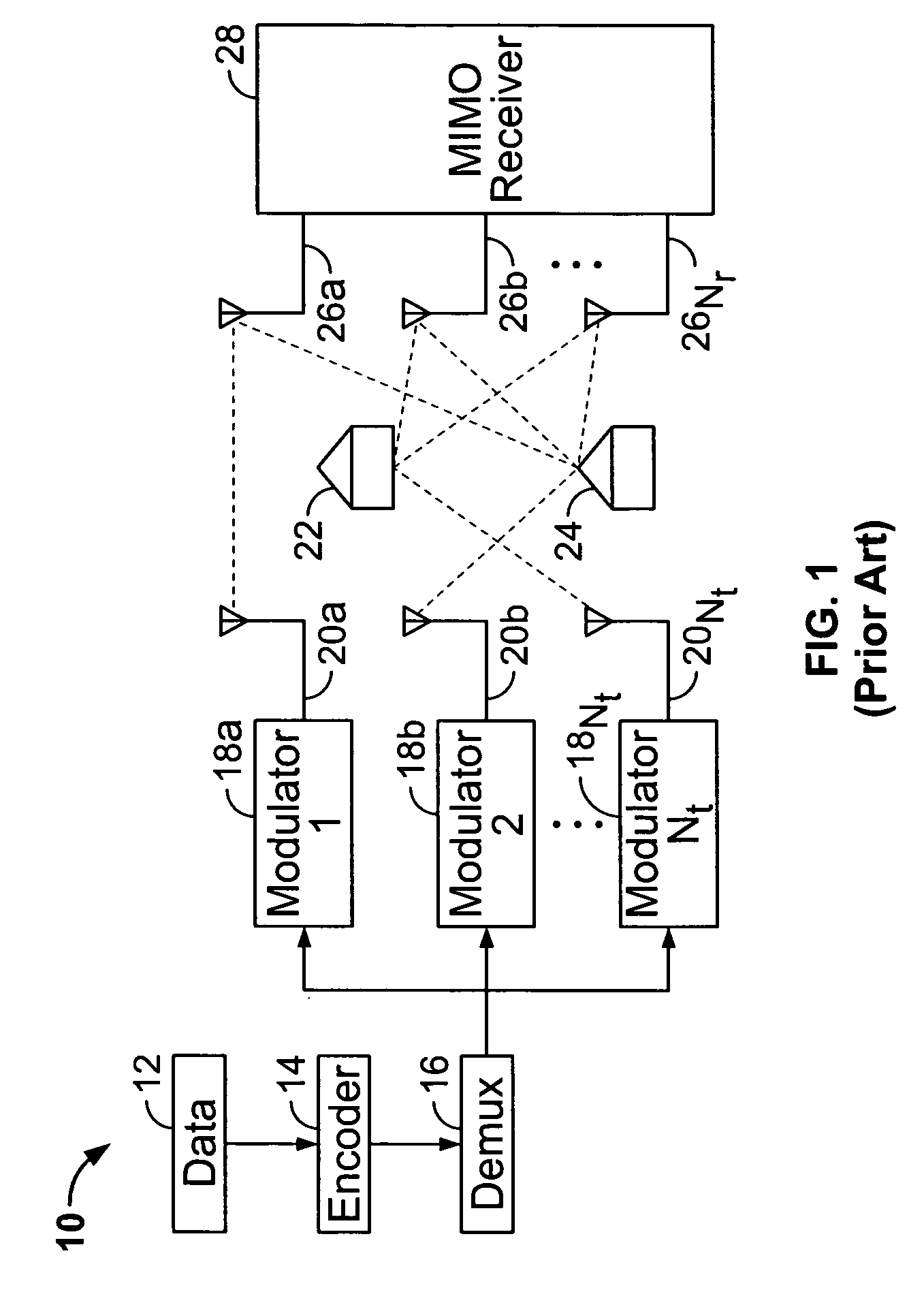

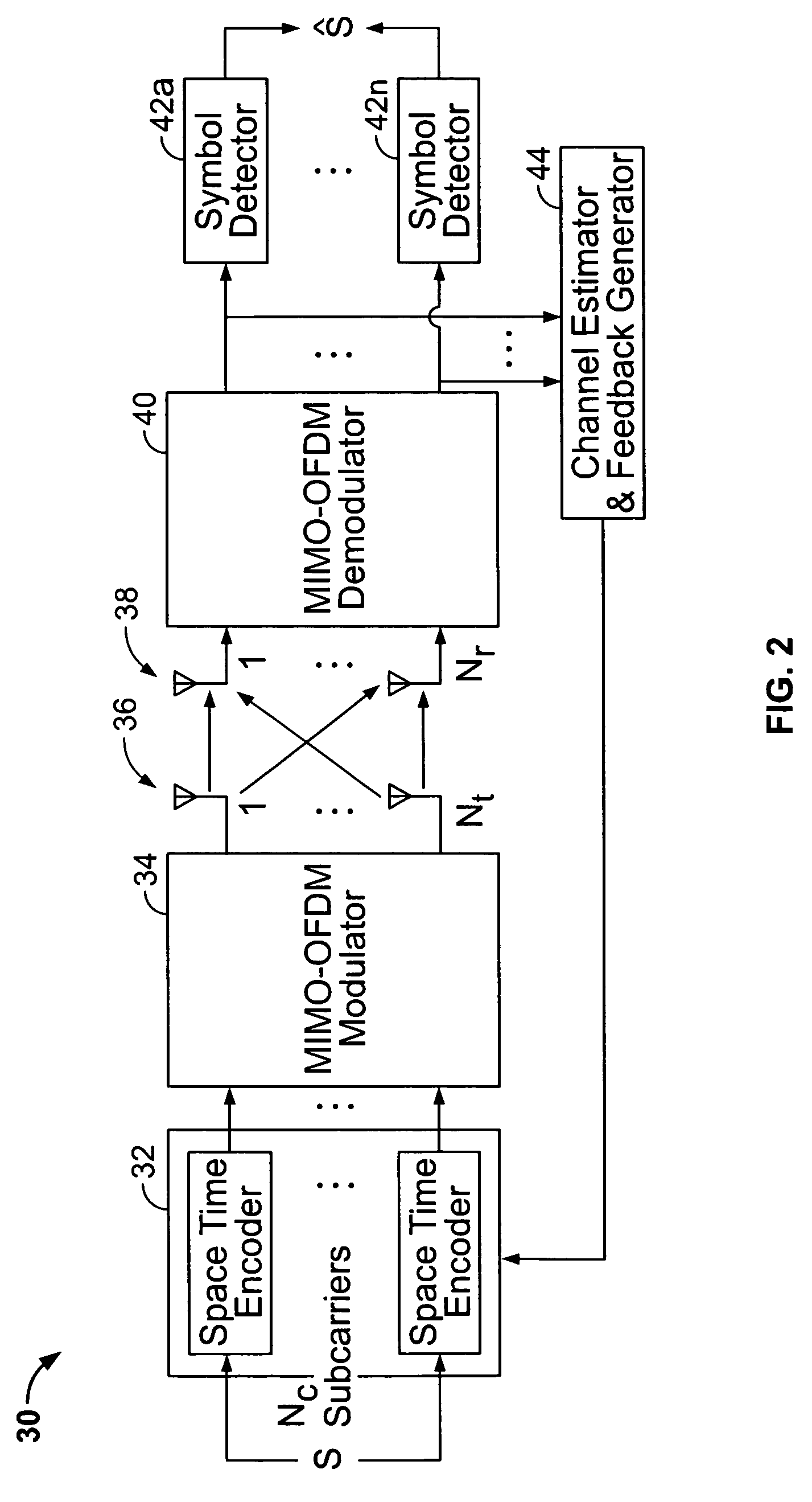

Recursive and trellis-based feedback reduction for MIMO-OFDM with rate-limited feedback

InactiveUS20070297529A1Reduce feedbackMaintain performanceModulated-carrier systemsDiversity/multi-antenna systemsCarrier signalDynamic programming

Techniques are provided for reducing feedback while maintaining performance in a MIMO-OFDM system. The disclosed techniques employ finite-rate feedback methods that uses vector quantization compression. The disclosed methods / techniques generally involve: receiving a plurality of symbols from a plurality of sub-carriers at a receiver; selecting a plurality of indices of codewords corresponding to a codebook of pre-coding weighting matrices for the sub-carriers based on vector quantization compression of the codewords; and transmitting the selected indices over a wireless channel to a transmitter. Finite state vector quantization feedback makes use of a finite state vector quantizer (FSVQ), which is a recursive vector quantizer (VQ) with a finite number of states. In finite state vector quantization feedback, optimal precoding matrices (beamforming vectors) are selected sequentially across subcarriers. In a trellis-based feedback method, the optimal precoding matrices are selected at the same time for all subcarriers by searching for the optimum choice of matrices along a trellis using the Viterbi algorithm (dynamic programming).

Owner:UNIV OF CONNECTICUT

Method and apparatus for identifying problems in computer networks

A network appliance for monitoring, diagnosing and documenting problems among a plurality of devices and processes (objects) coupled to a computer network utilizes periodic polling and collection of object-generated trap data to monitor the status of objects on the computer network. The status of a multitude of objects is maintained in memory utilizing virtual state machines which contain a small amount of persistent data but which are modeled after one of a plurality of finite state machines. The memory further maintains dependency data related to each object which identifies parent / child relationships with other objects at the same or different layers of the OSI network protocol model. A decision engine verifies through on-demand polling that a device is down. A root cause analysis module utilizes status and dependency data to locate the highest object in the parent / child relationship tree that is affected to determine the root cause of a problem. Once a problem has been verified, a “case” is opened and notification alerts may be sent out to one or more devices. A user interface allows all objects within the network to be displayed with their respective status and their respective parent / child dependency objects in various formats.

Owner:OPTANIX INC

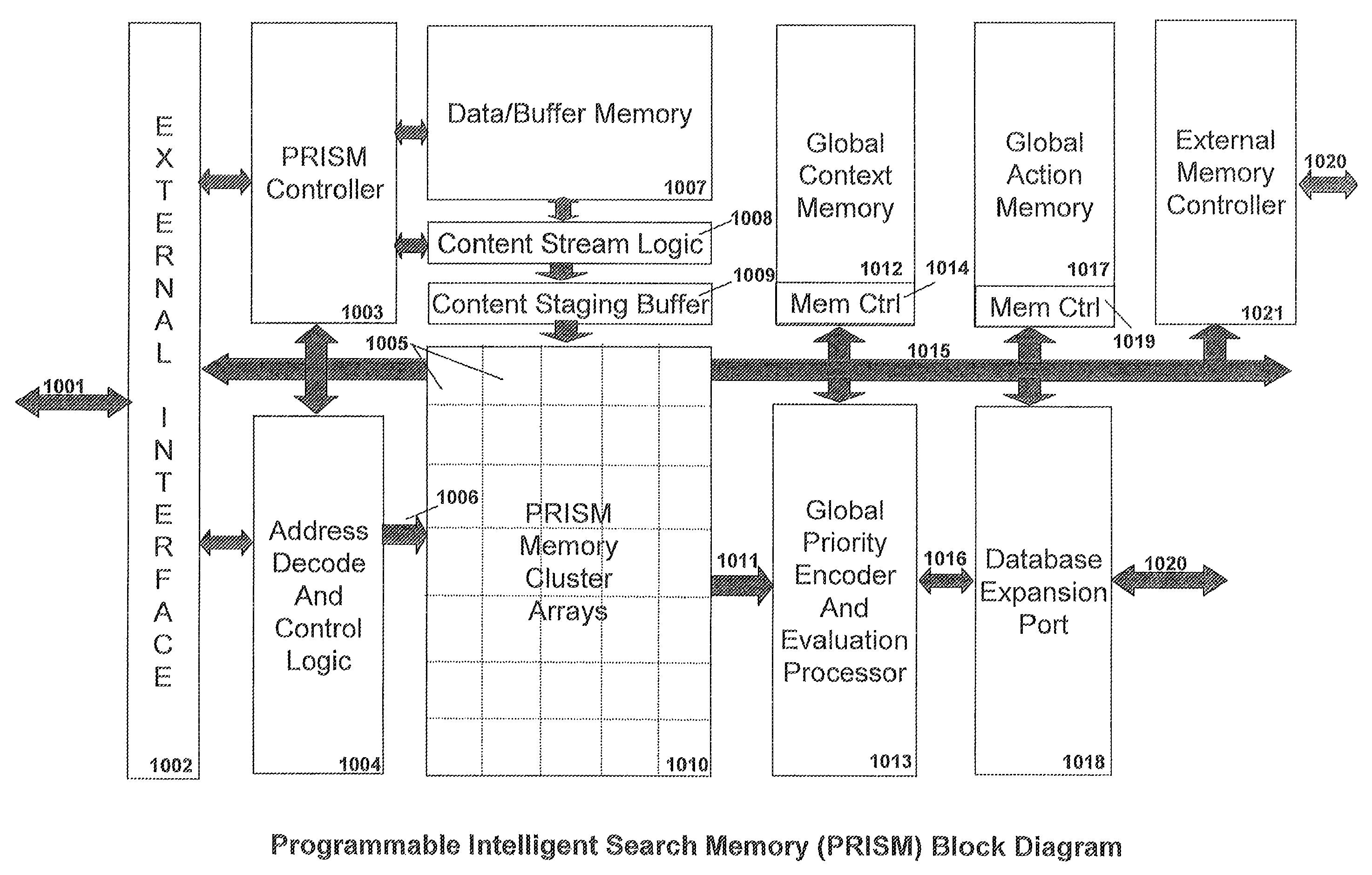

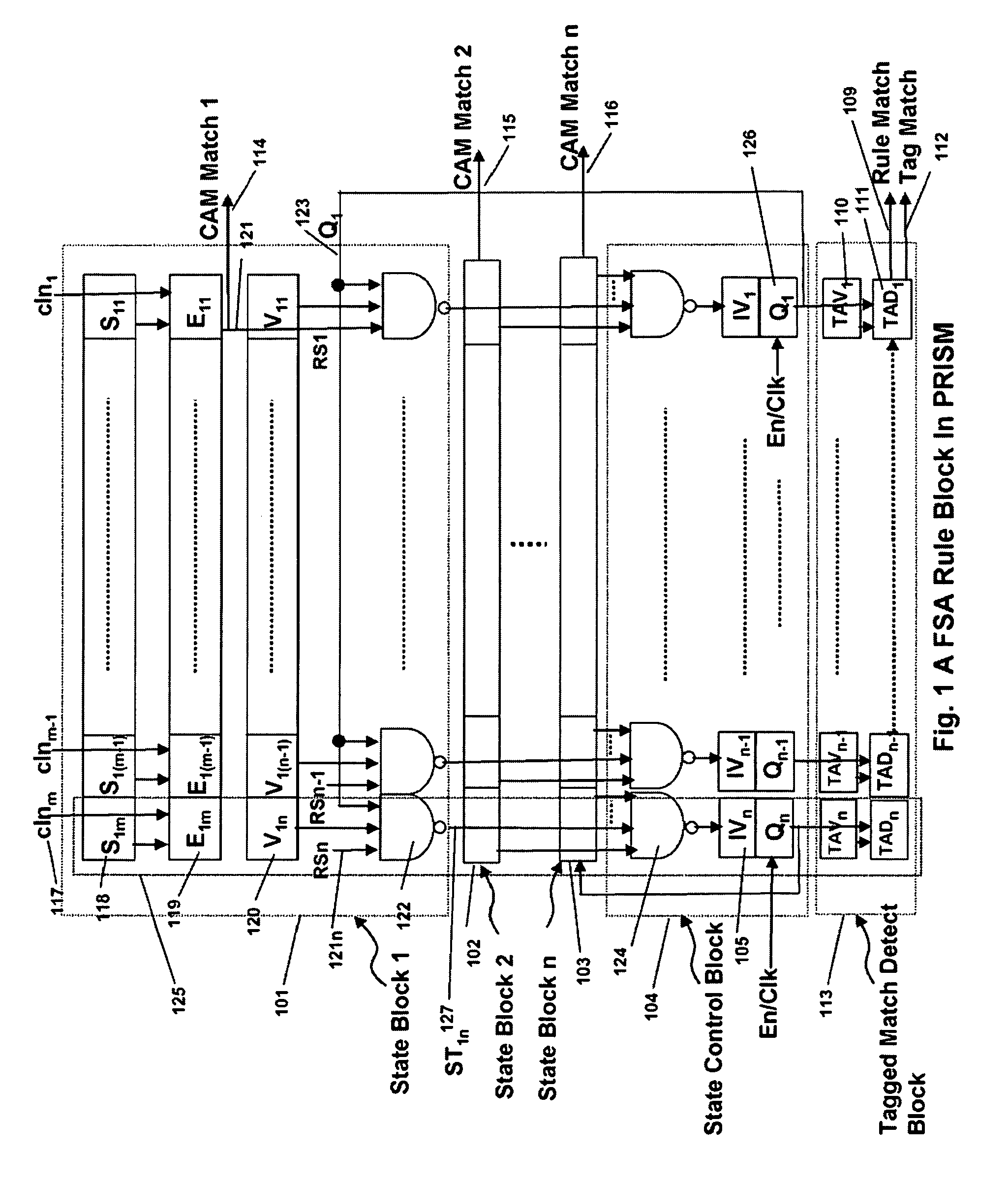

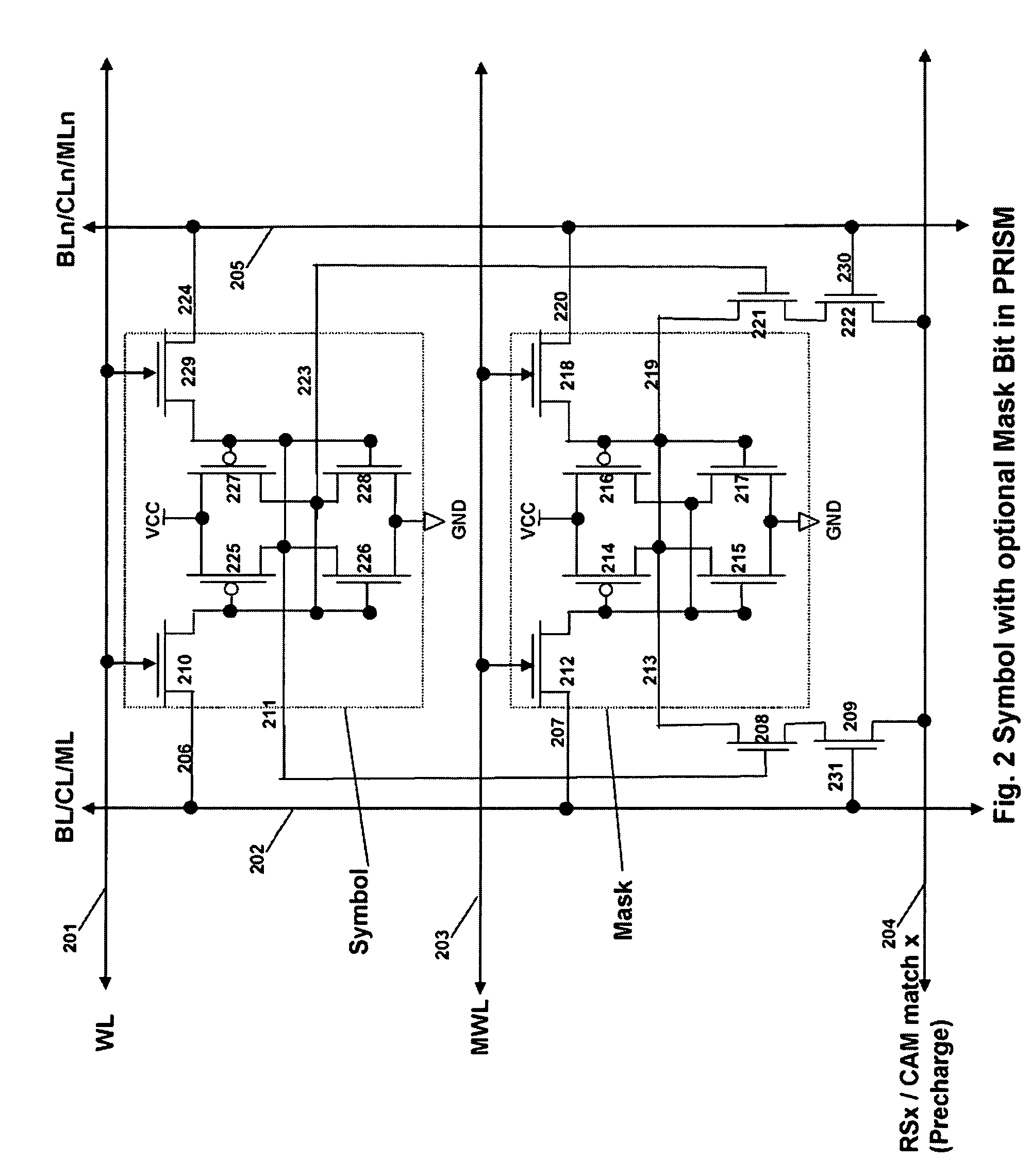

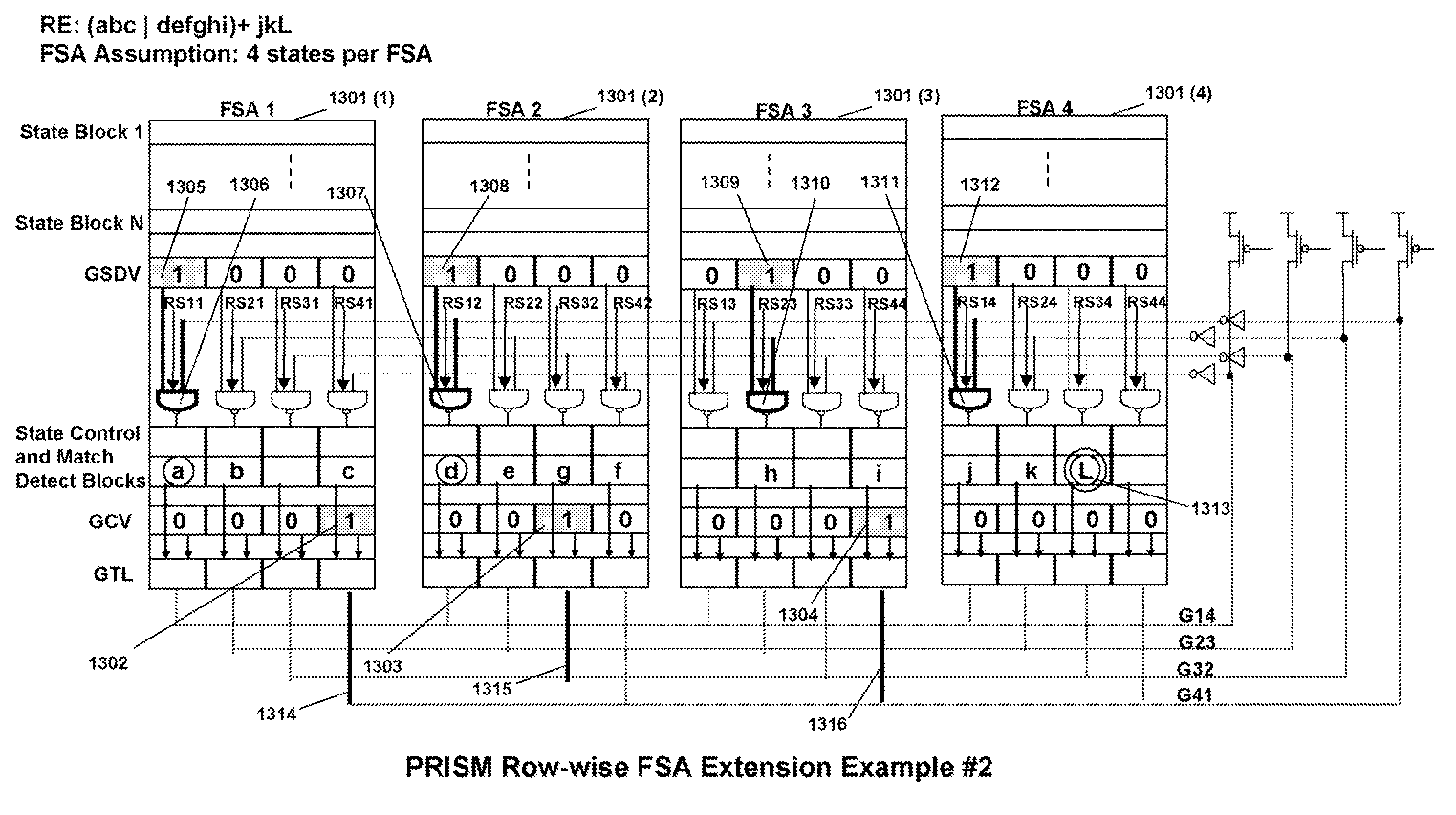

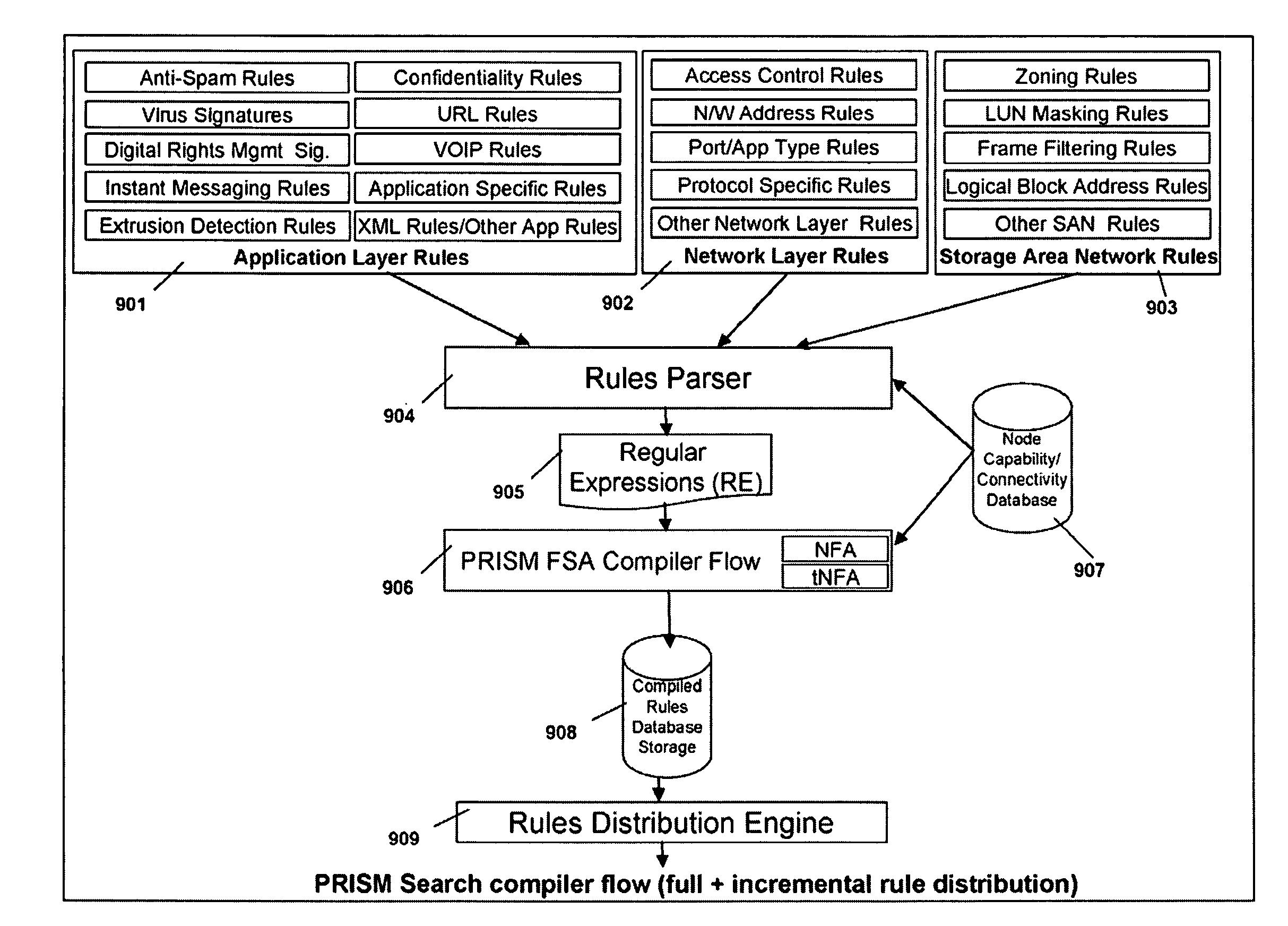

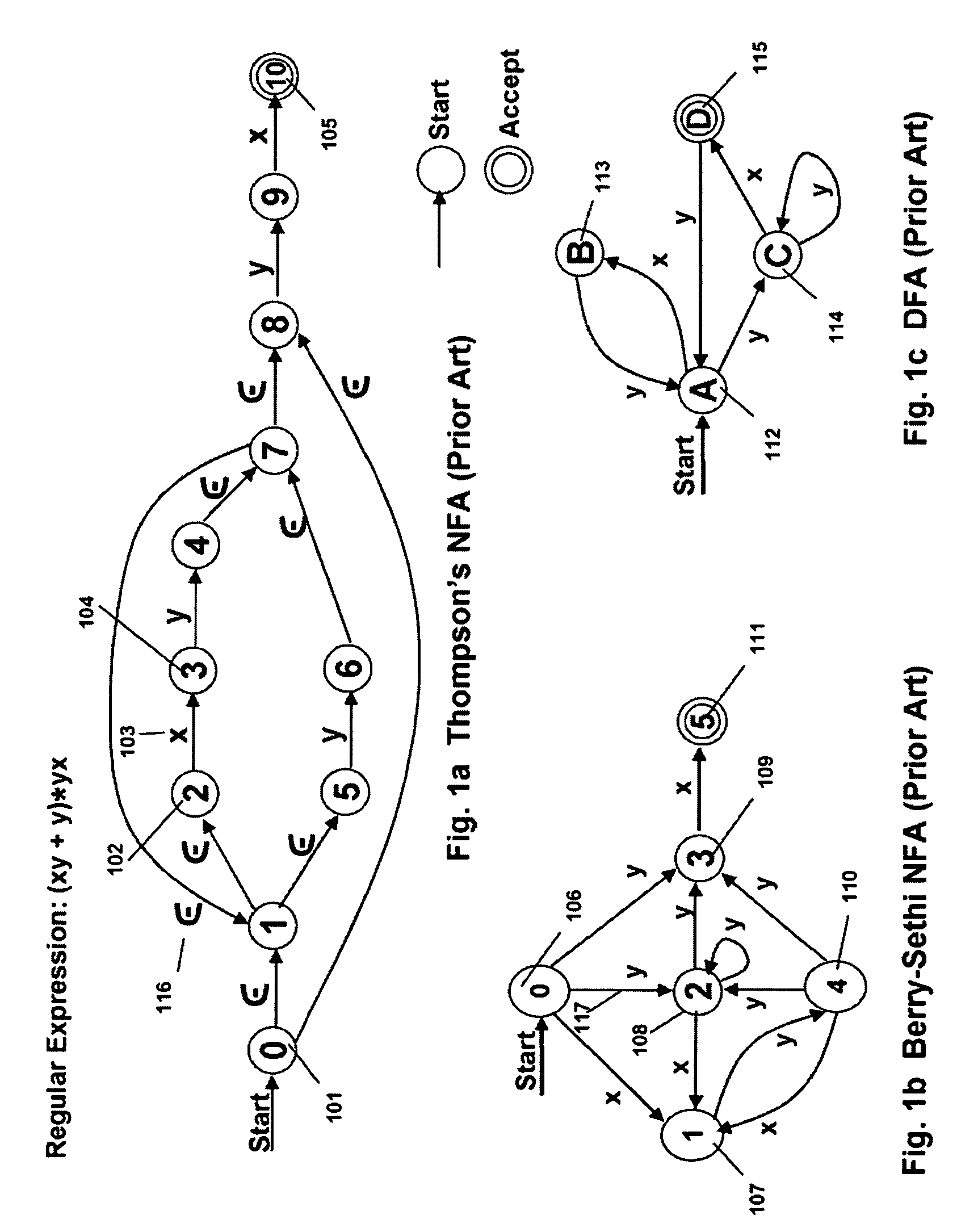

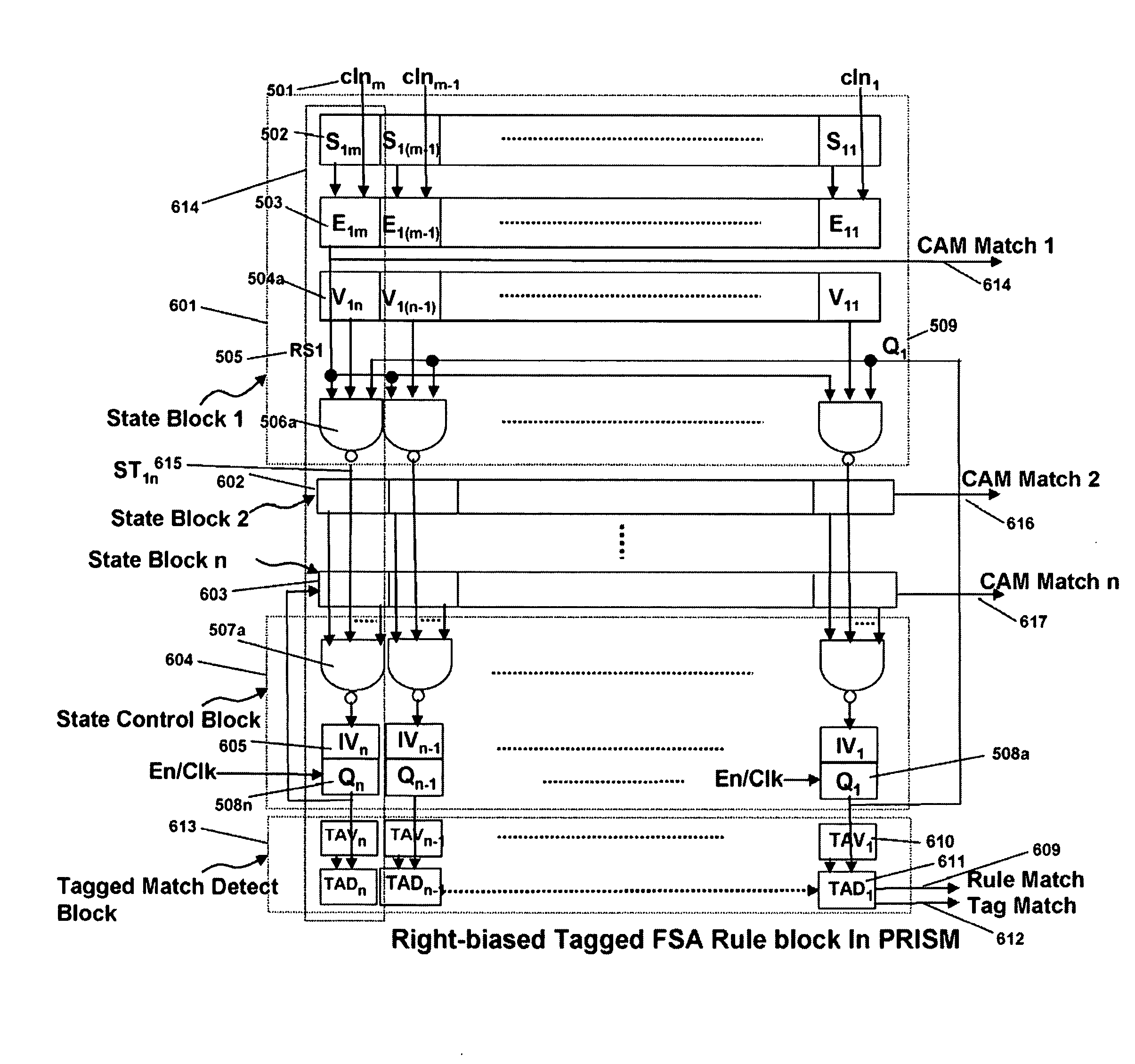

Complex symbol evaluation for programmable intelligent search memory

ActiveUS7827190B2Efficient and compact realizationDigital data information retrievalDigital data processing detailsTerm memoryMemory architecture

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable Intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken. Content search rules comprise of regular expressions which are converted to finite state automata and then programmed in PRISM for evaluating content with the search rules. The PRISM memory provides features for complex regular expression symbols like range detection, complement control, bit masking and the like and enables complex symbols and compact regular expression representation.

Owner:INFOSIL INC

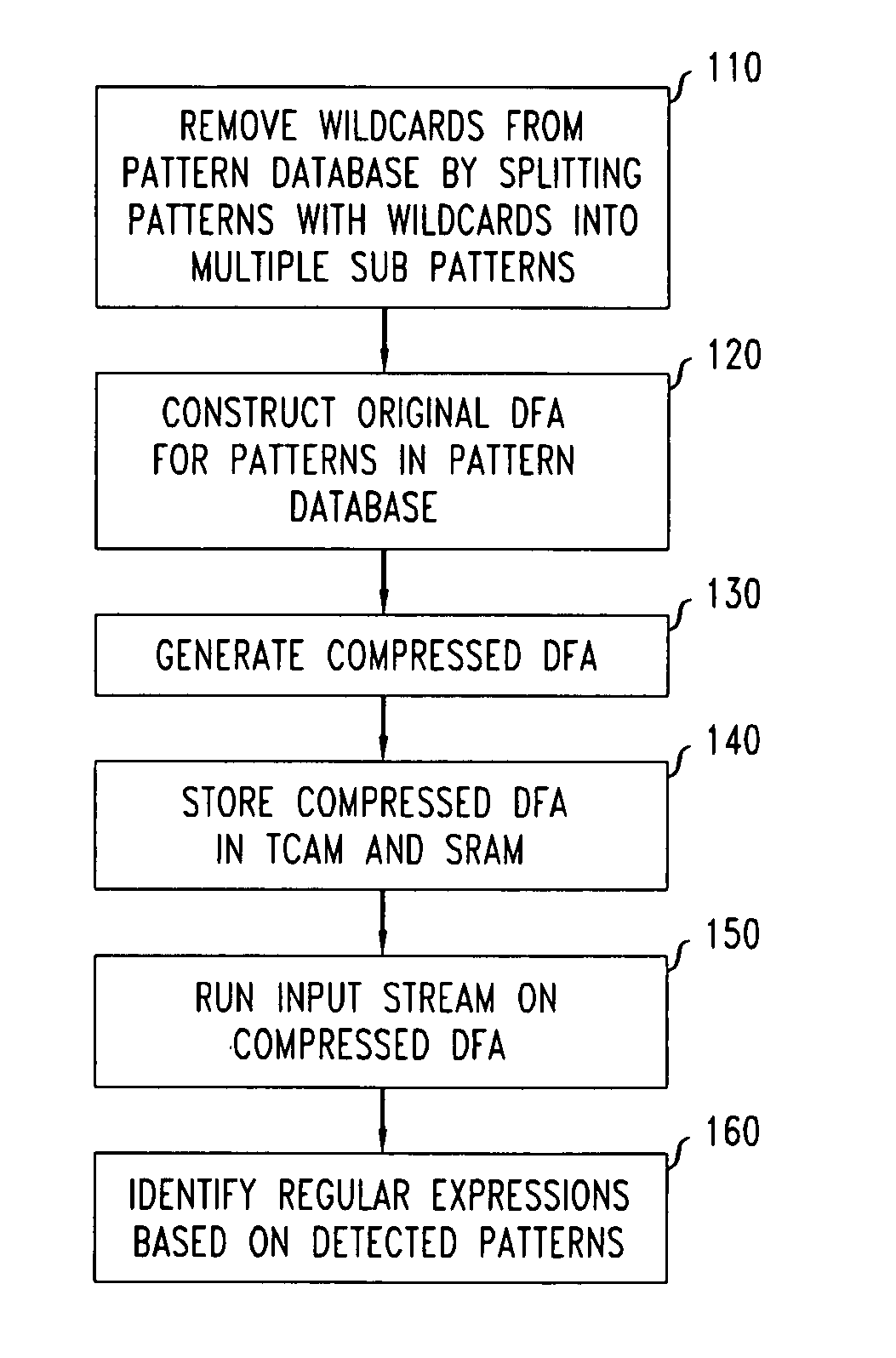

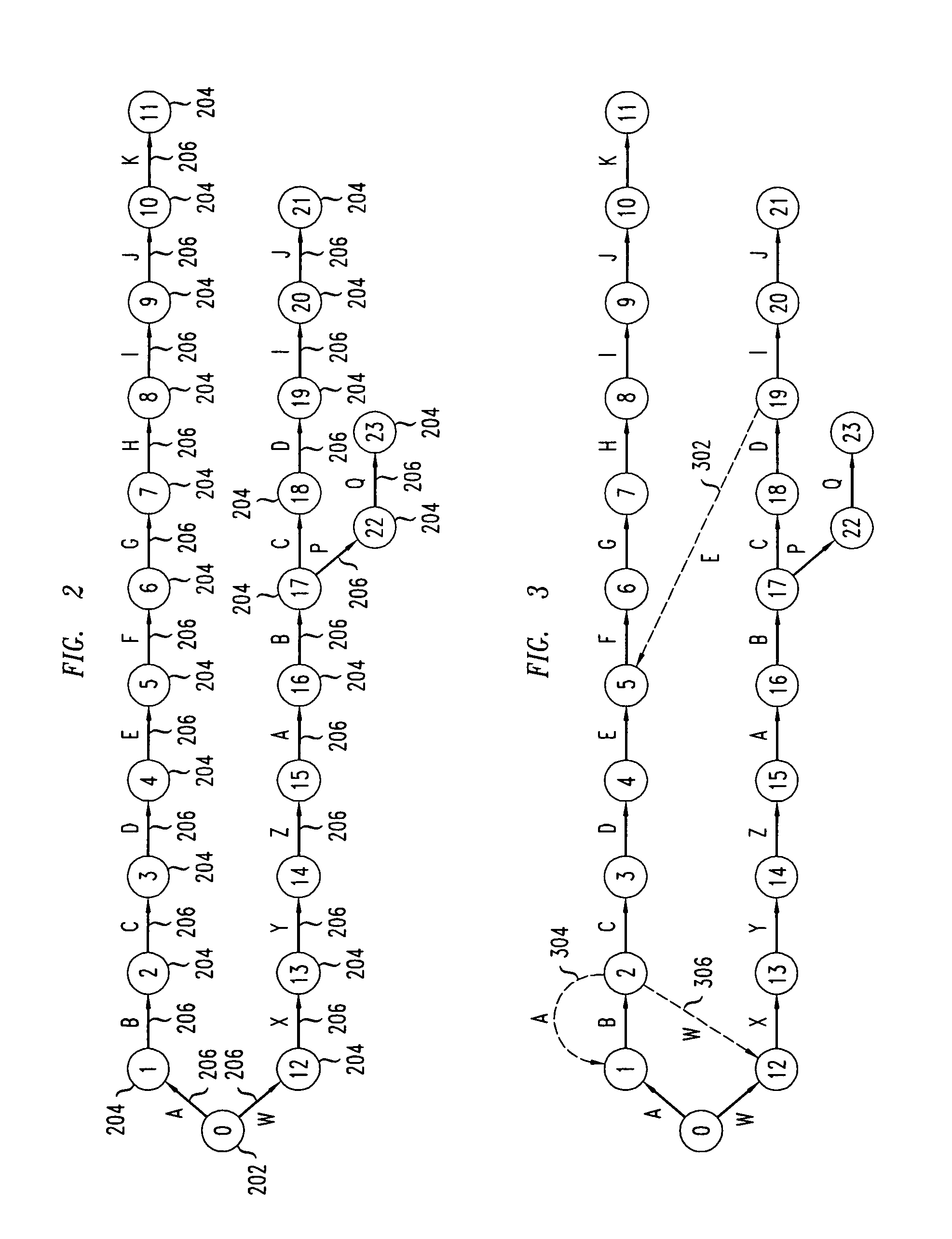

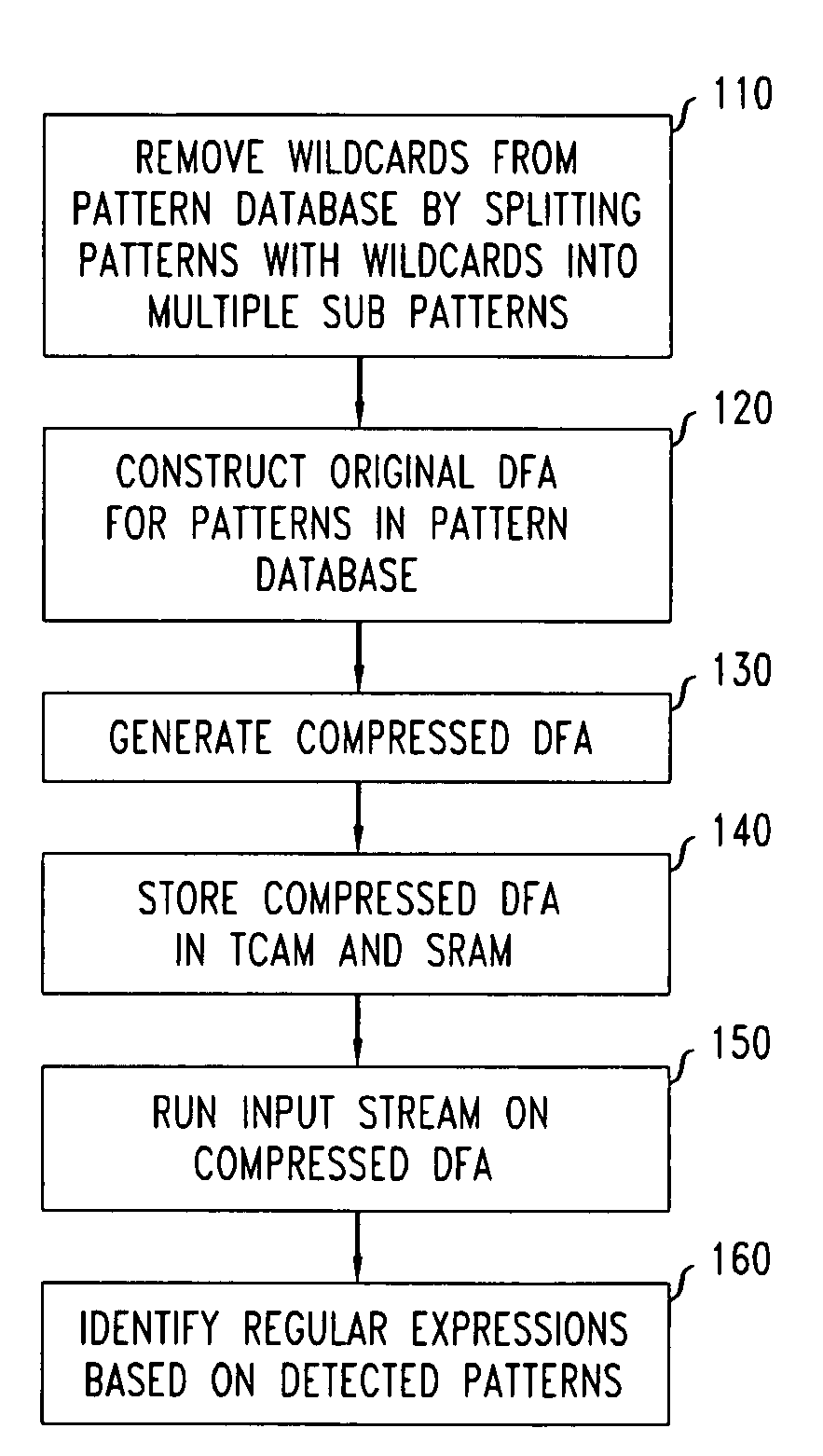

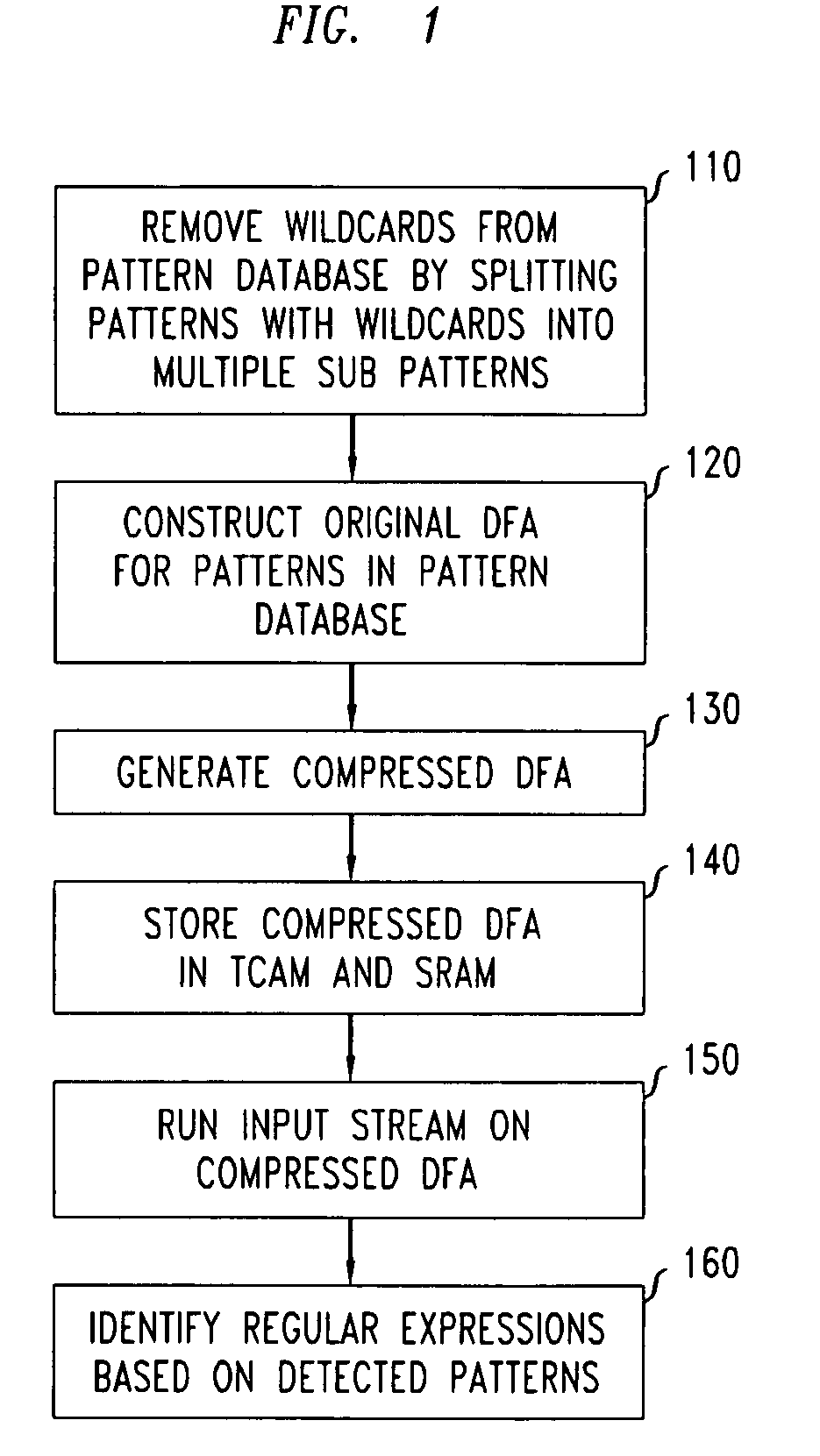

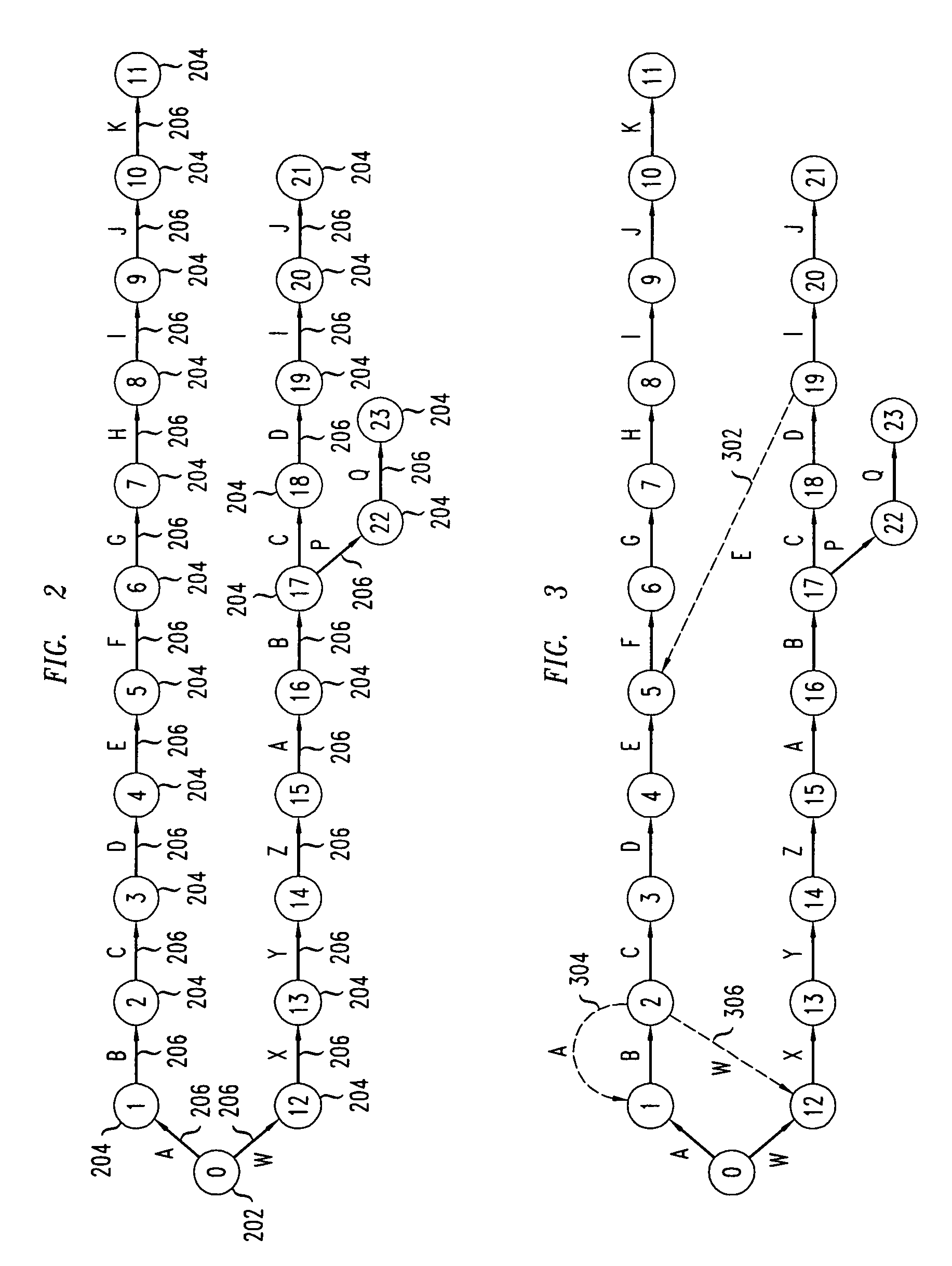

Method and system for multi-character multi-pattern pattern matching

ActiveUS20080046423A1High pattern matching speedEasy to implementData processing applicationsDigital data information retrievalPattern matchingTernary content addressable memory

Disclosed is a method and system for multi-character multi-pattern pattern matching. In the multi-character multi-pattern pattern matching method, patterns in an input stream are detected by transitioning between states of a “compressed deterministic finite state automaton (DFA)”, with each transition based on multiple characters of the input stream. The compressed DFA is created by compressing an original DFA, such as an Aho-Corasick DFA, such that each state of the compressed DFA represents multiple consecutive states of the original DFA and each transition between the states of the compressed DFA is a combination of all of the transitions between the multiple consecutive states of the original DFA. This method can be implemented using a Ternary Content-Addressable Memory (TCAM) to store the transitions of the compressed DFA and compares the transitions with multiple characters of an input stream at a time to detect patterns in the input stream.

Owner:ALGOGENE FINANCIAL TECHNOLOGY COMPANY LIMITED

Embedded Programmable Intelligent Search Memory

ActiveUS20080140661A1Reduce classification overheadImprove performanceDigital data information retrievalDigital data processing detailsMulti processorMemory architecture

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken The PRISM content search memory is embedded in a single core or multi-core processors or in multi-processor systems to perform content search. PRISM accelerates content search by offloading the content search tasks from the processors. Content search rules comprise of regular expressions which are converted to finite state automata and then programmed in PRISM for evaluating content with the search rules.

Owner:INFOSIL INC

Systems and methods for extracting meaning from multimodal inputs using finite-state devices

ActiveUS7069215B1Reduce computational complexityComputational complexity is reducedCharacter and pattern recognitionSpeech recognitionComputation complexitySemantic representation

Finite-state systems and methods allow multiple input streams to be parsed and integrated by a single finite-state device. These systems and methods not only address multimodal recognition, but are also able to encode semantics and syntax into a single finite-state device. The finite-state device provides models for recognizing multimodal inputs, such as speech and gesture, and composes the meaning content from the various input streams into a single semantic representation. Compared to conventional multimodal recognition systems, finite-state systems and methods allow for compensation among the various input streams. Finite-state systems and methods allow one input stream to dynamically alter a recognition model used for another input stream, and can reduce the computational complexity of multidimensional multimodal parsing. Finite-state devices provide a well-understood probabilistic framework for combining the probability distributions associated with the various input streams and for selecting among competing multimodal interpretations.

Owner:INTERACTIONS LLC (US)

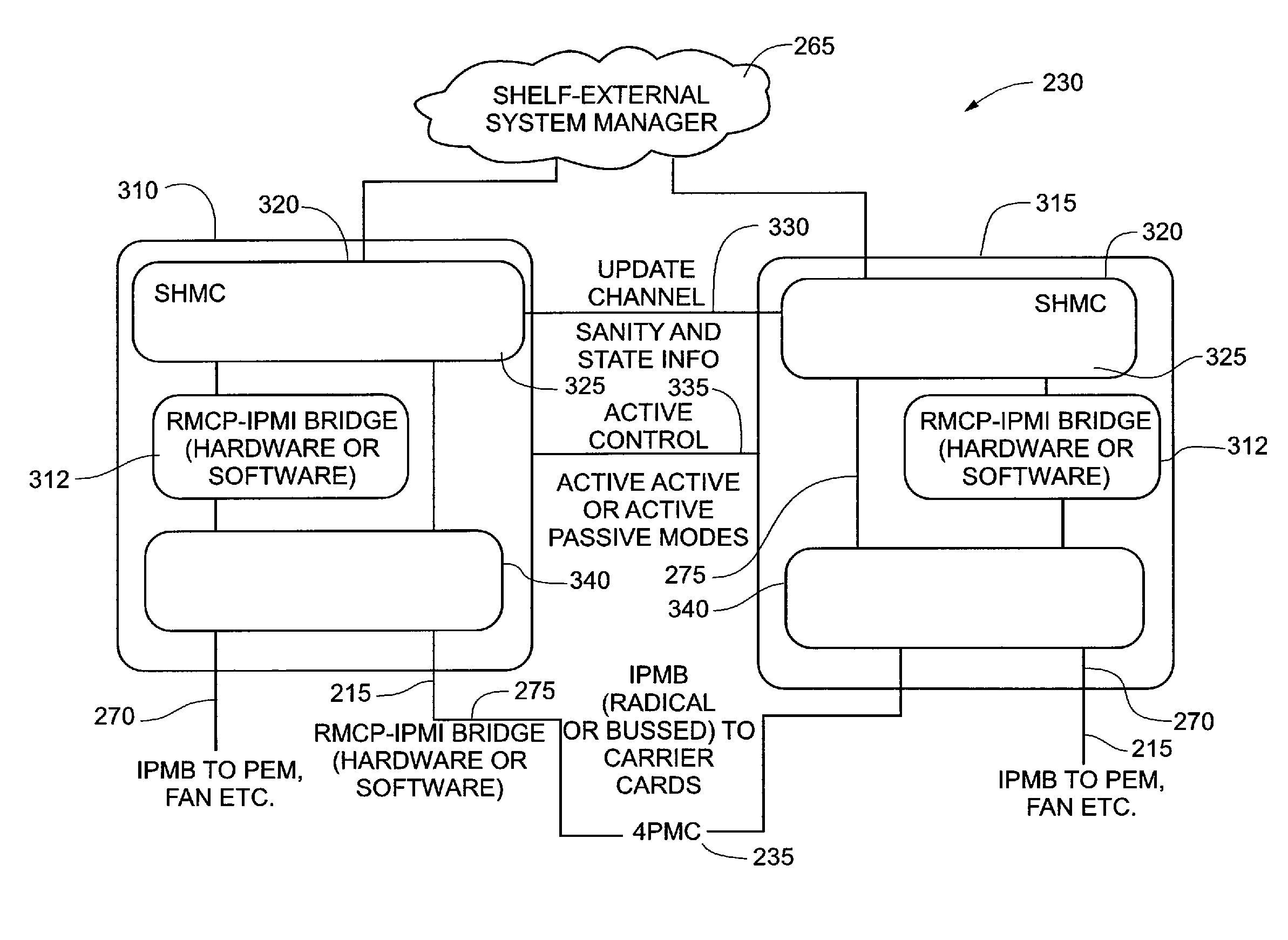

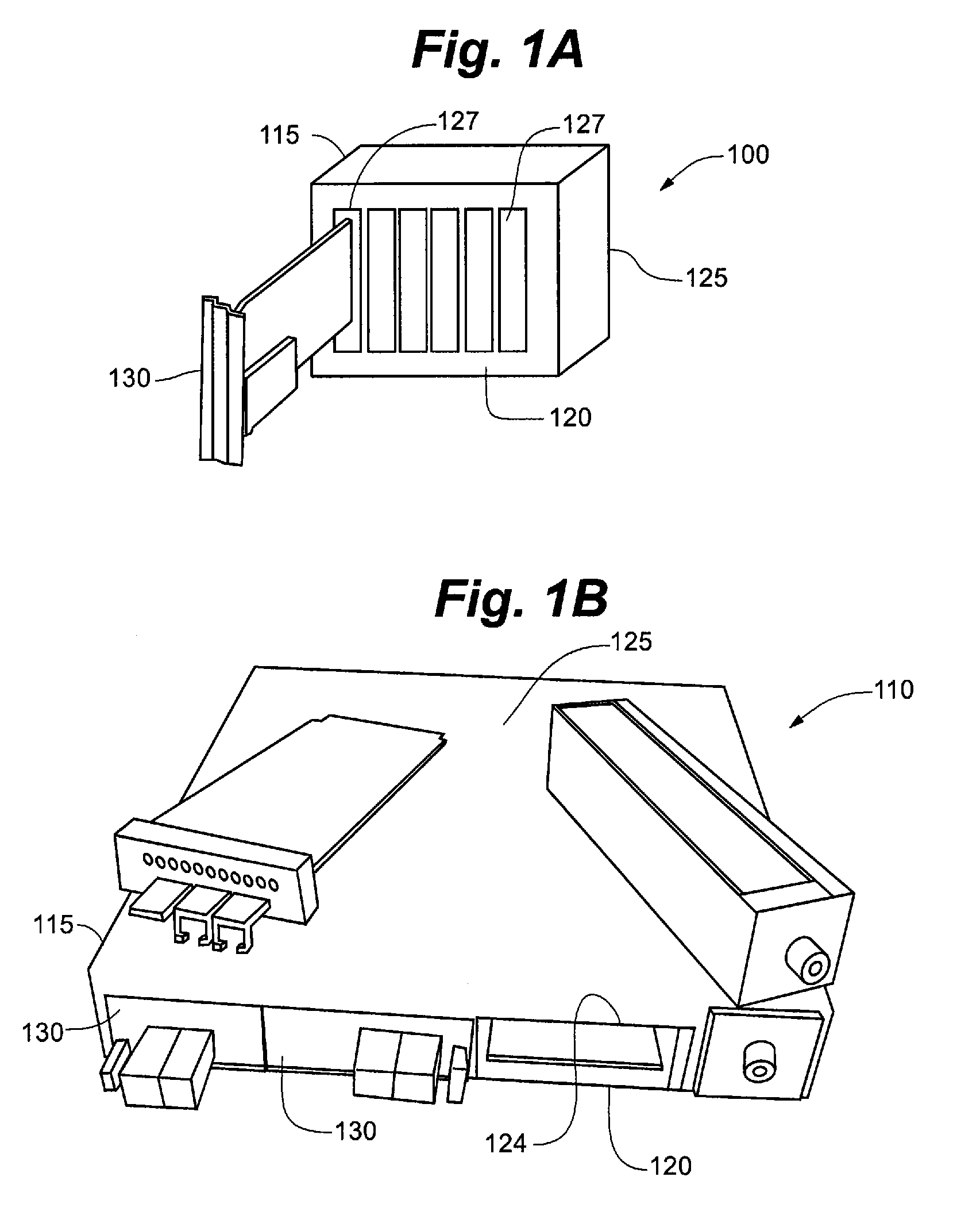

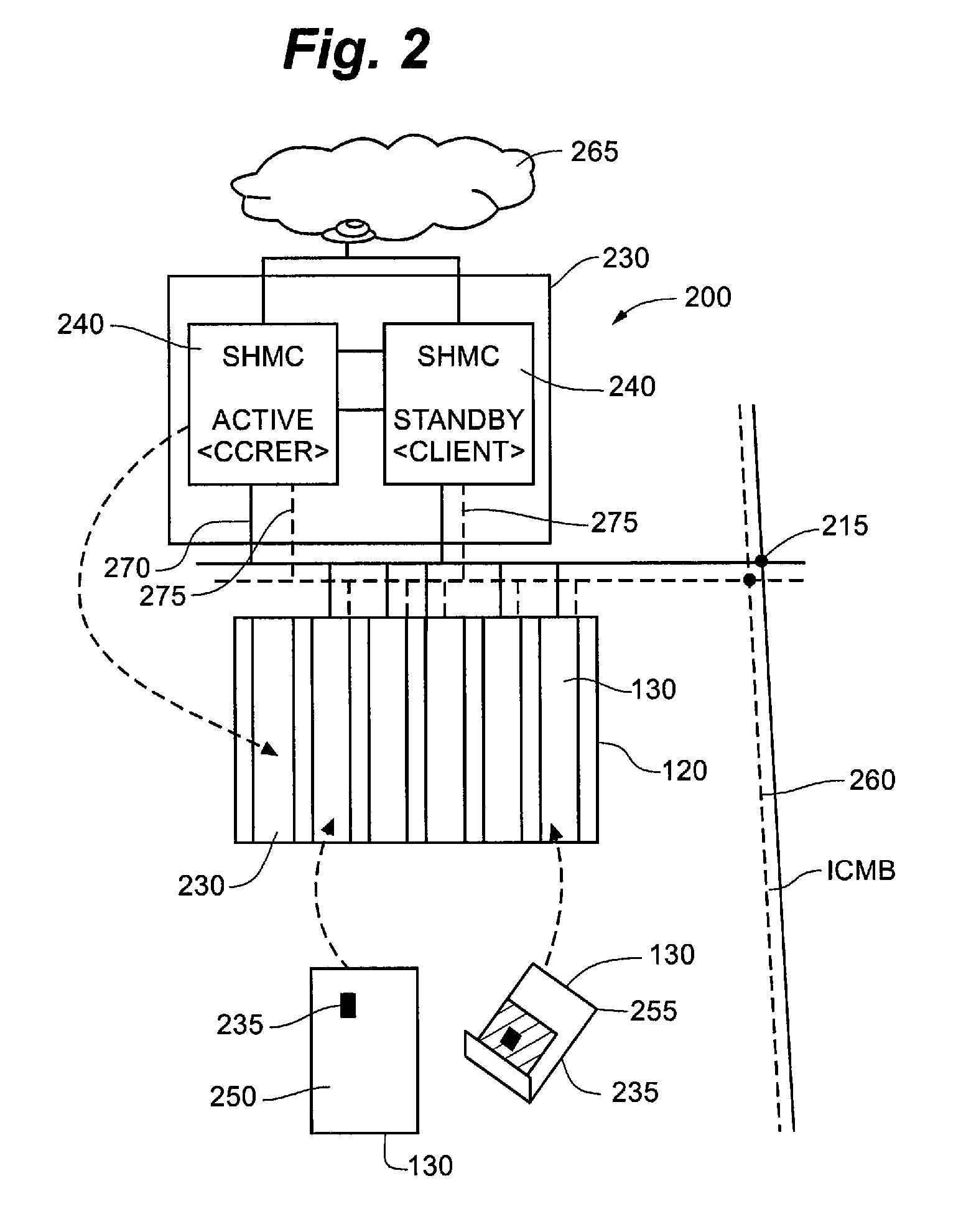

Shelf management controller with hardware/software implemented dual redundant configuration

InactiveUS7827442B2Safety arrangmentsElectric controllersController architectureIntelligent Platform Management Interface

A fault tolerant, multi-protocol shelf management controller architecture that is extensible provides an intelligent platform management interface that is version indifferent as well as programmable and reconfigurable. The shelf management controller is arranged in a dual redundant configuration in a client-server mode and has a message driven configuration with the messages conforming to the Intelligent Platform Management Interface (IPMI) specification as extended by PICMG 3.0. In one embodiment, each shelf management controller includes at least one bit stream processor comprising sequenced stage machines implementing one or more finite state machines associated with one or more devices that are under control of the shelf management controller. The finite state machines could be hardware or software based. The shelf management controller is also modeled as a layered architecture that includes an IPMI API layer. The IPMI API layer enables the shelf manager to interface with legacy and future IPMI specifications.

Owner:RPX CORP

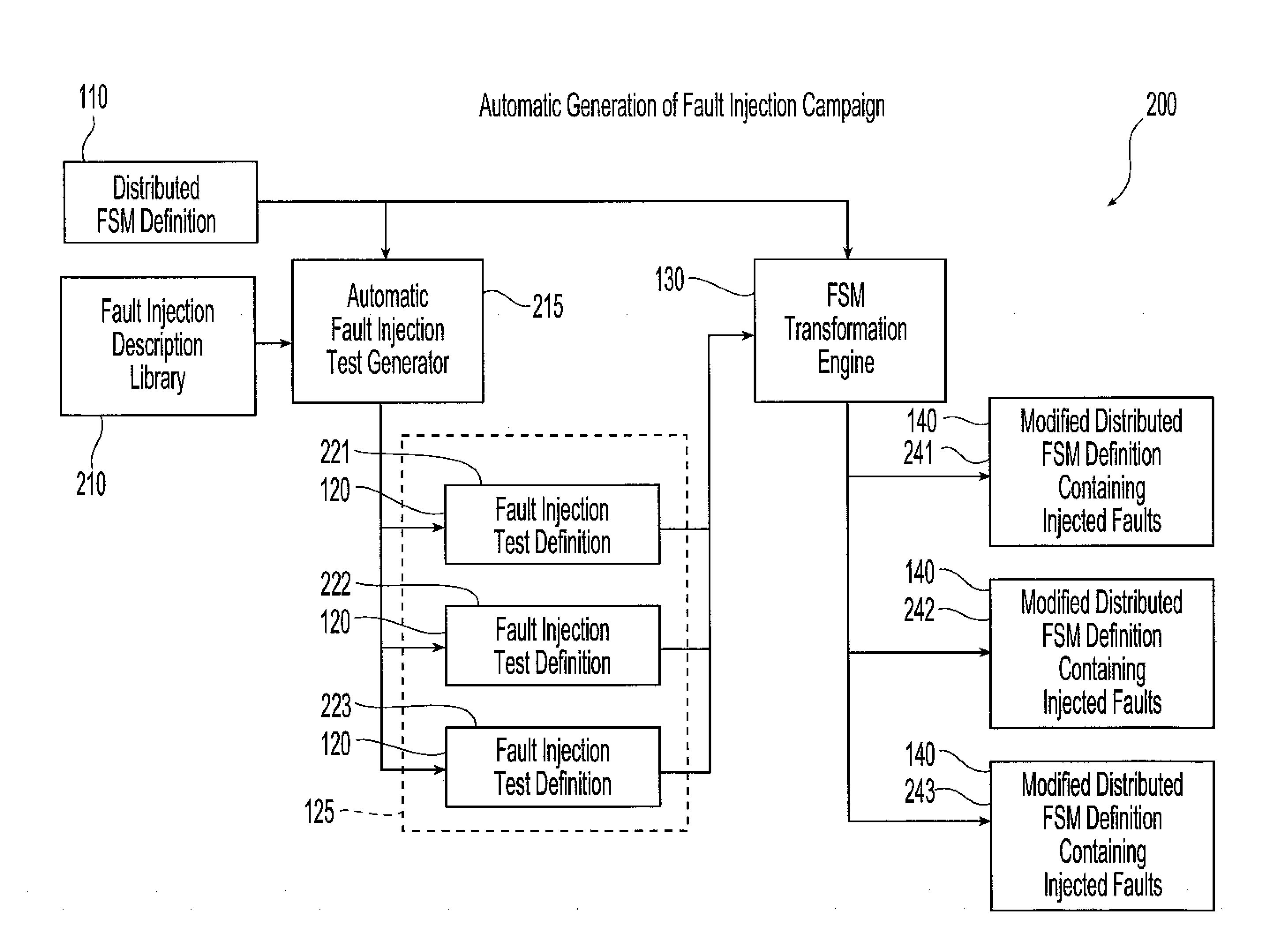

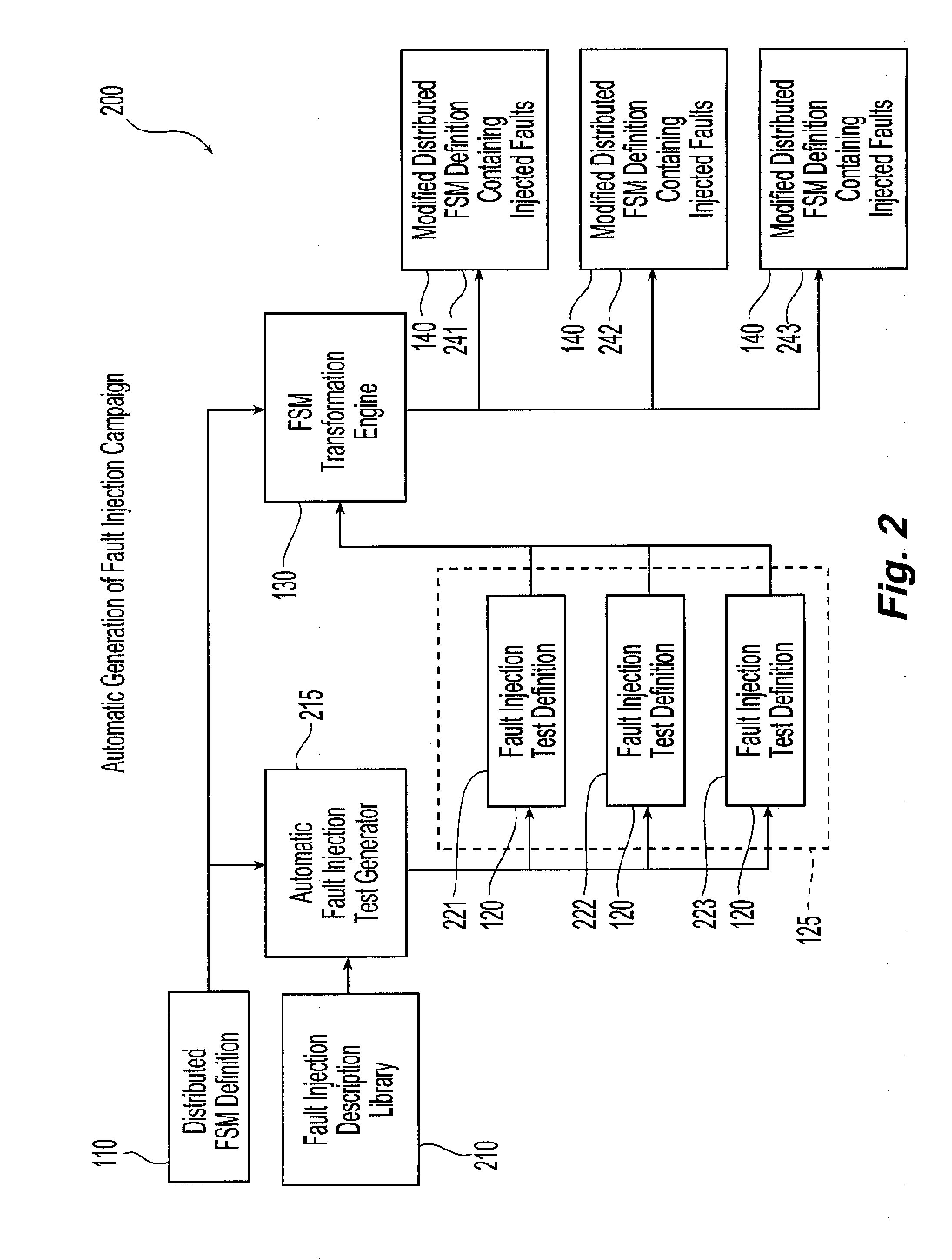

Distributed fault injection mechanism

InactiveUS20080215925A1Validating the robustness of a distributed computing systemEasy injectionError detection/correctionGraphicsGraphical user interface

Methods and systems are provided for testing distributed computer applications using finite state machines. A finite state machine definition for use in a distributed computer system is combined with the fault injections definitions contained within a fault injection campaign that is created for testing the computer application employing that finite state machine. The definition and combination of the finite state machine definition and the fault injection campaign is carried out automatically or manually, for example using a graphical user interface. This combination creates at least one modified finite state machine definition containing the desired injected faults. The modified finite state machine definition is separate from the originally identified finite state machine definition, and the originally identified finite state machine remains intact without injected faults. Trigger points within the finite state machine definition are identified for each fault injection test definition, and the modified finite state machine definition containing the fault injection test definition associated with a given trigger point are used in place of the original finite state machine definition upon detection of that trigger point during runtime of the finite state machine definition.

Owner:IBM CORP

FSA Context Switch Architecture for Programmable Intelligent Search Memory

ActiveUS20090049230A1Reduce overheadSoap detergents with organic compounding agentsDigital data information retrievalMemory architectureAutomaton

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable Intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken. Content search rules comprise of regular expressions which are converted to finite state automata (FSA) and then programmed in PRISM for evaluating content with the search rules. PRISM architecture comprises of a plurality of programmable PRISM Search Engines (PSE) organized in PRISM memory clusters that are used simultaneously to search content presented to PRISM. A context switching architecture enables transitioning of PSE states between different input contexts.

Owner:INFOSIL INC

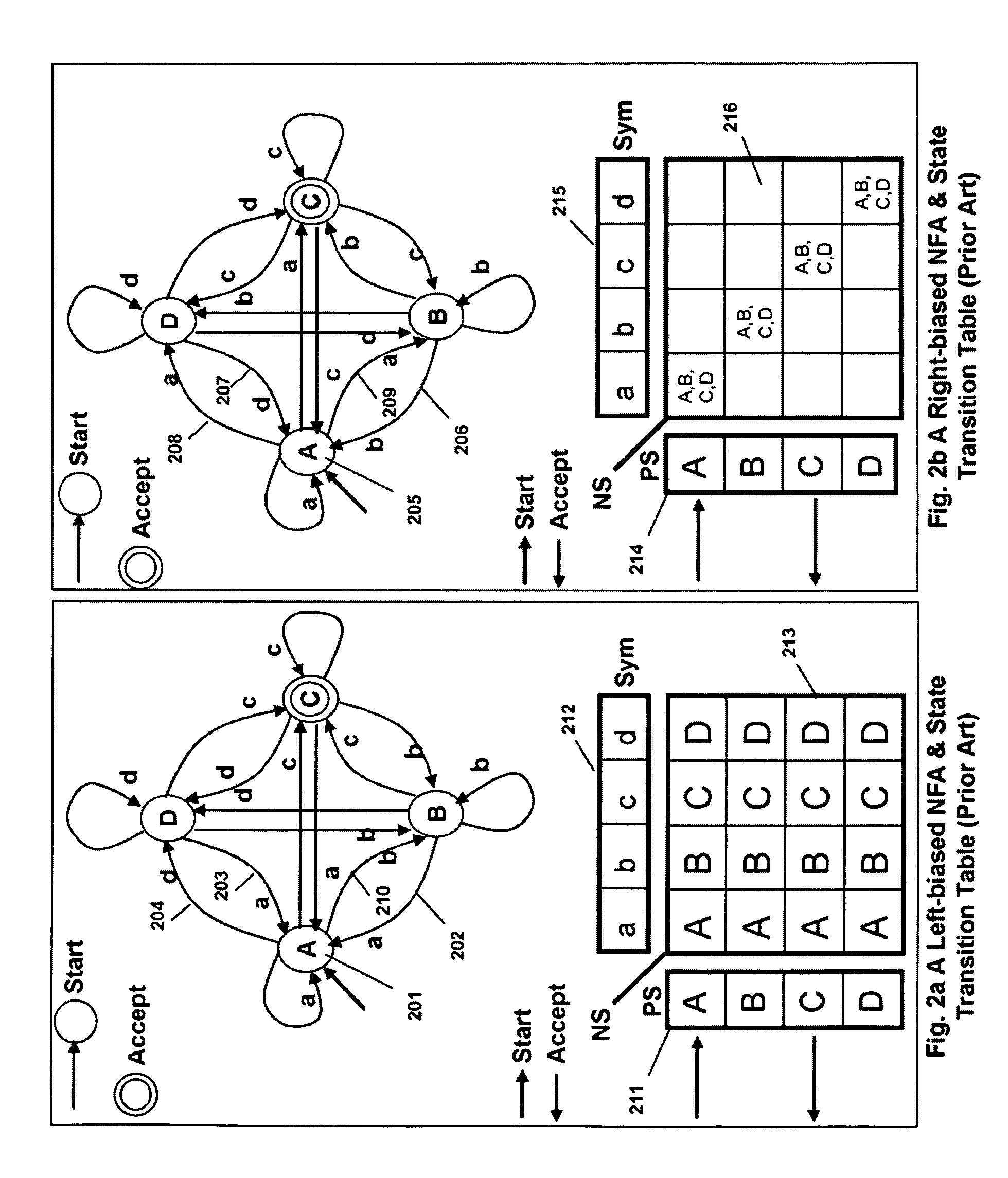

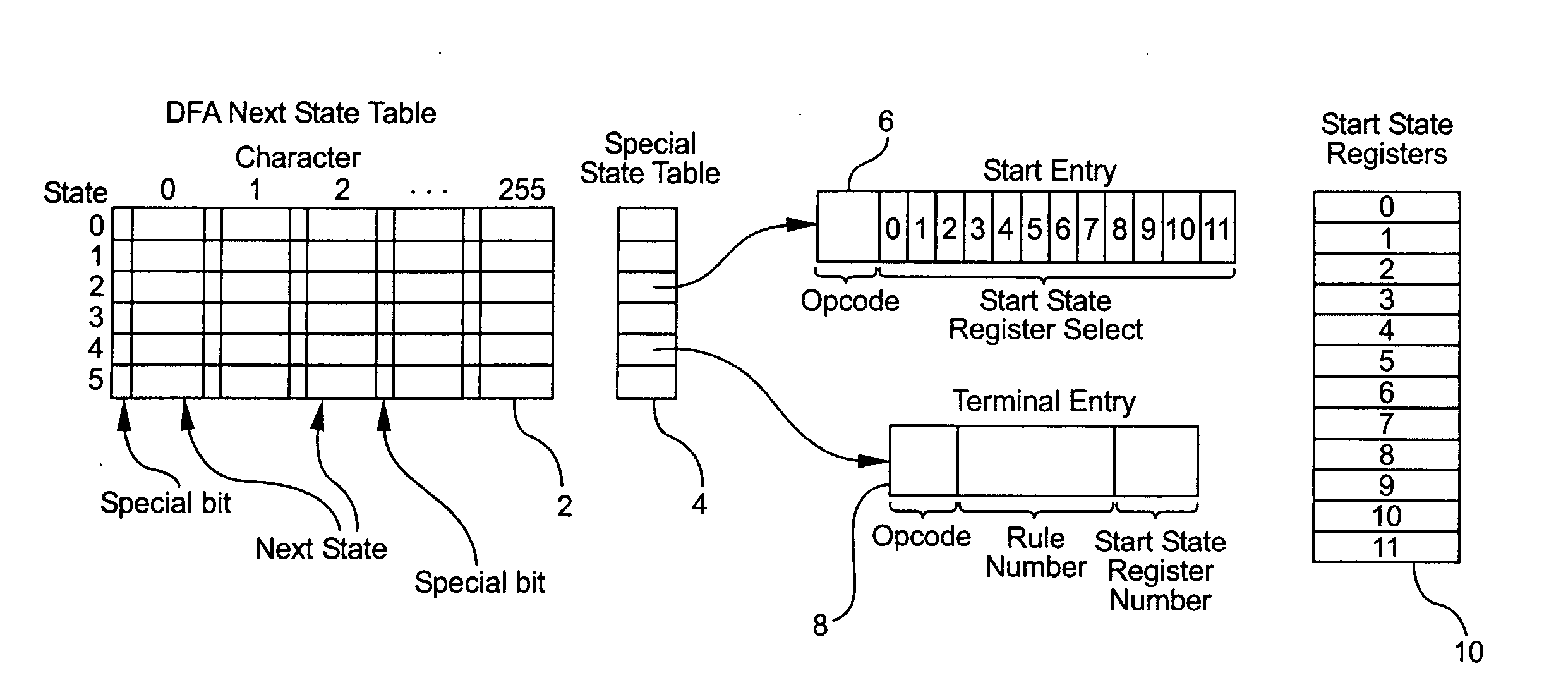

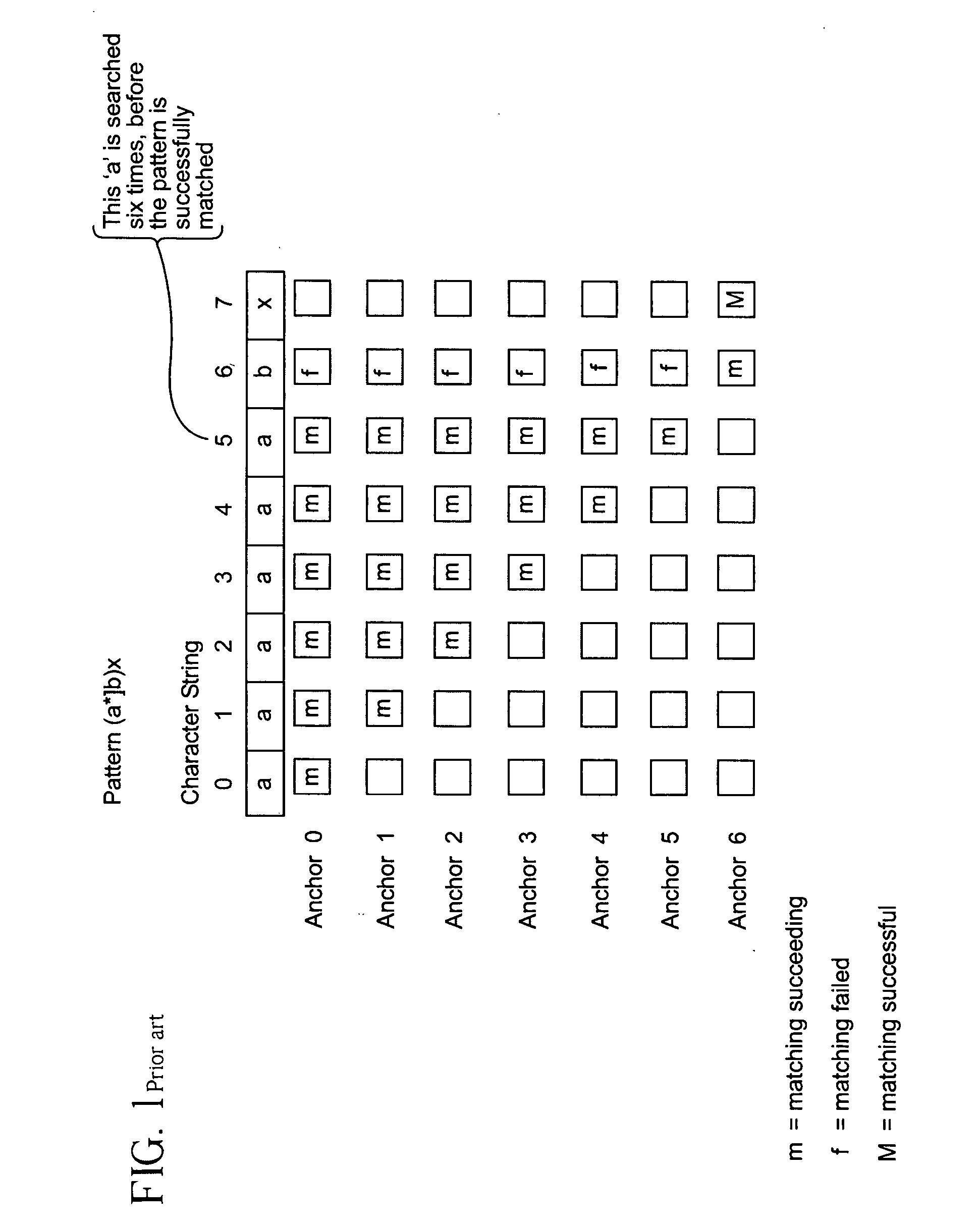

System and method for determining the start of a match of a regular expression

InactiveUS20080077587A1Overcome disadvantagesData processing applicationsDigital data information retrievalAutomatonRegular expression

A system for determining the start of a match of a regular expression has a special state table which contains start state entries and terminal state entries; a plurality of start state registers for storing offset information indicative of the start of a match of the regular expression; a deterministic finite state automaton (DFA) next state table which, given the current state and an input character, returns the next state. The DFA next state table includes a settable indicator for any next state table entry which indicates whether to perform a lookup into the special state table. A compiler loads values into the special state table based on the regular expression.

Owner:RAMBUS INC

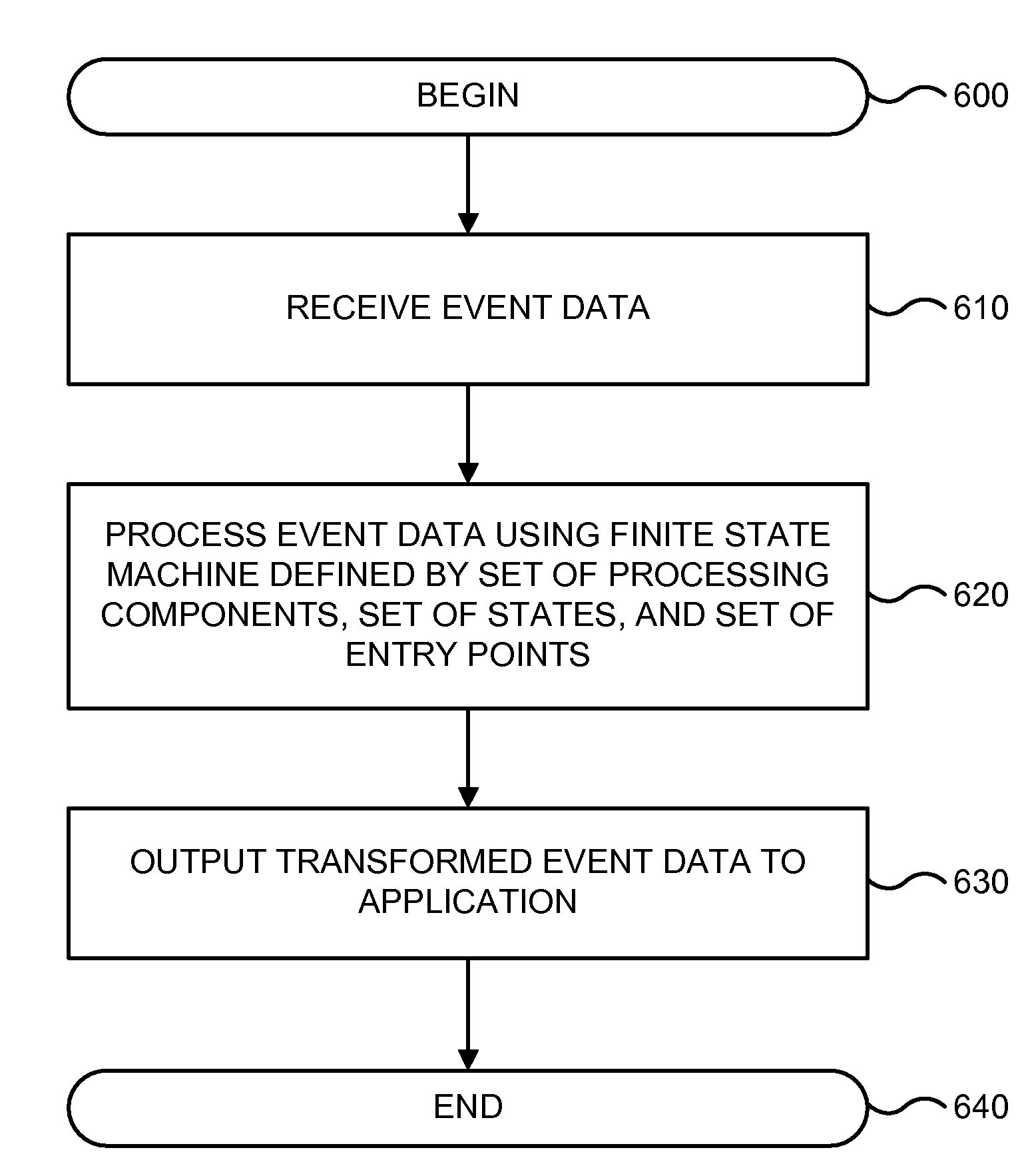

Event Processing Finite State Engine and Language

In various embodiments, a method for processing event streams includes receiving a finite state machine defined in response to a set of processing components, a set of states, and a set of entry points. Event data associated with an event stream is also received. The event data is processes according to the finite state machine to generate an event.

Owner:ORACLE INT CORP

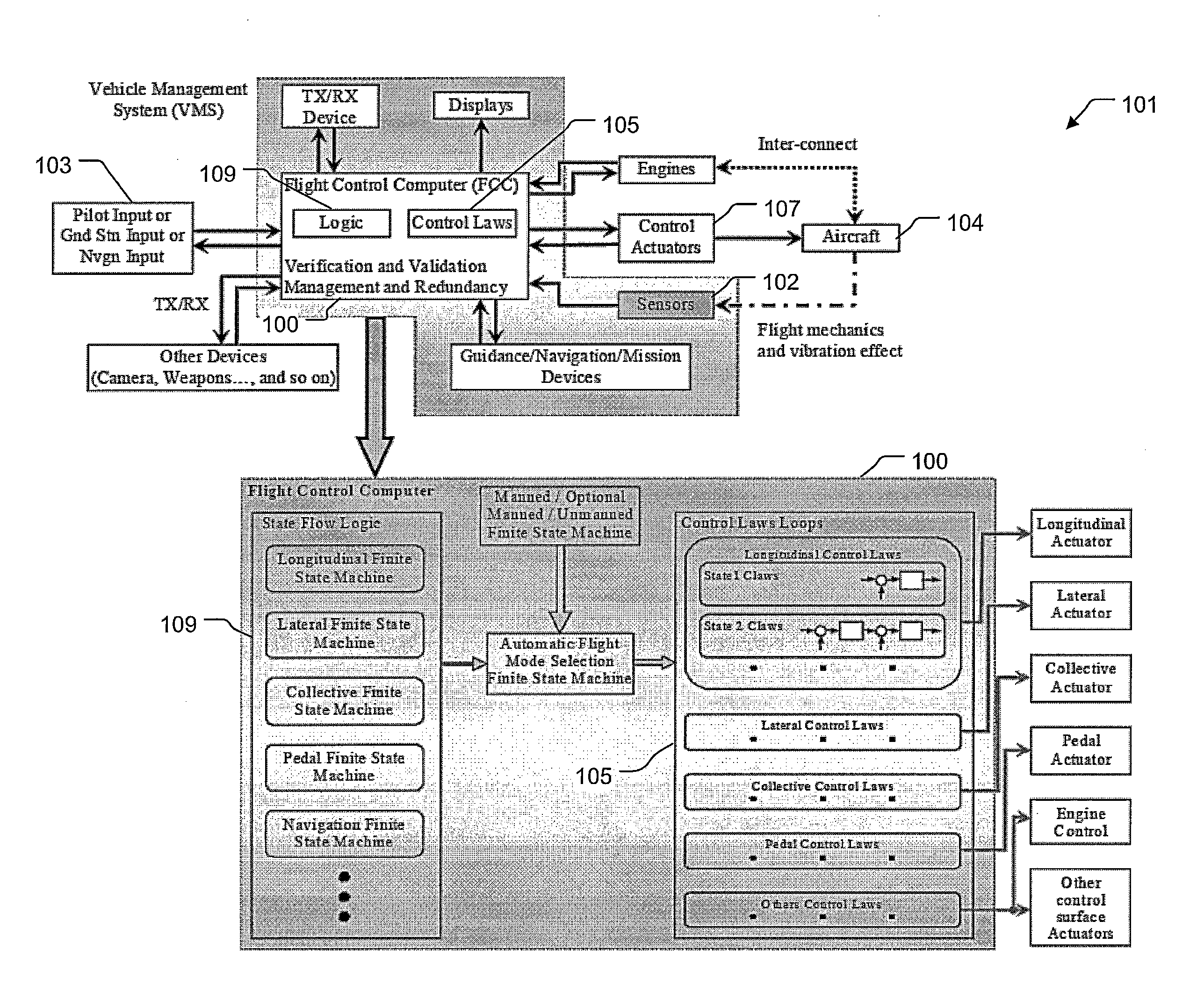

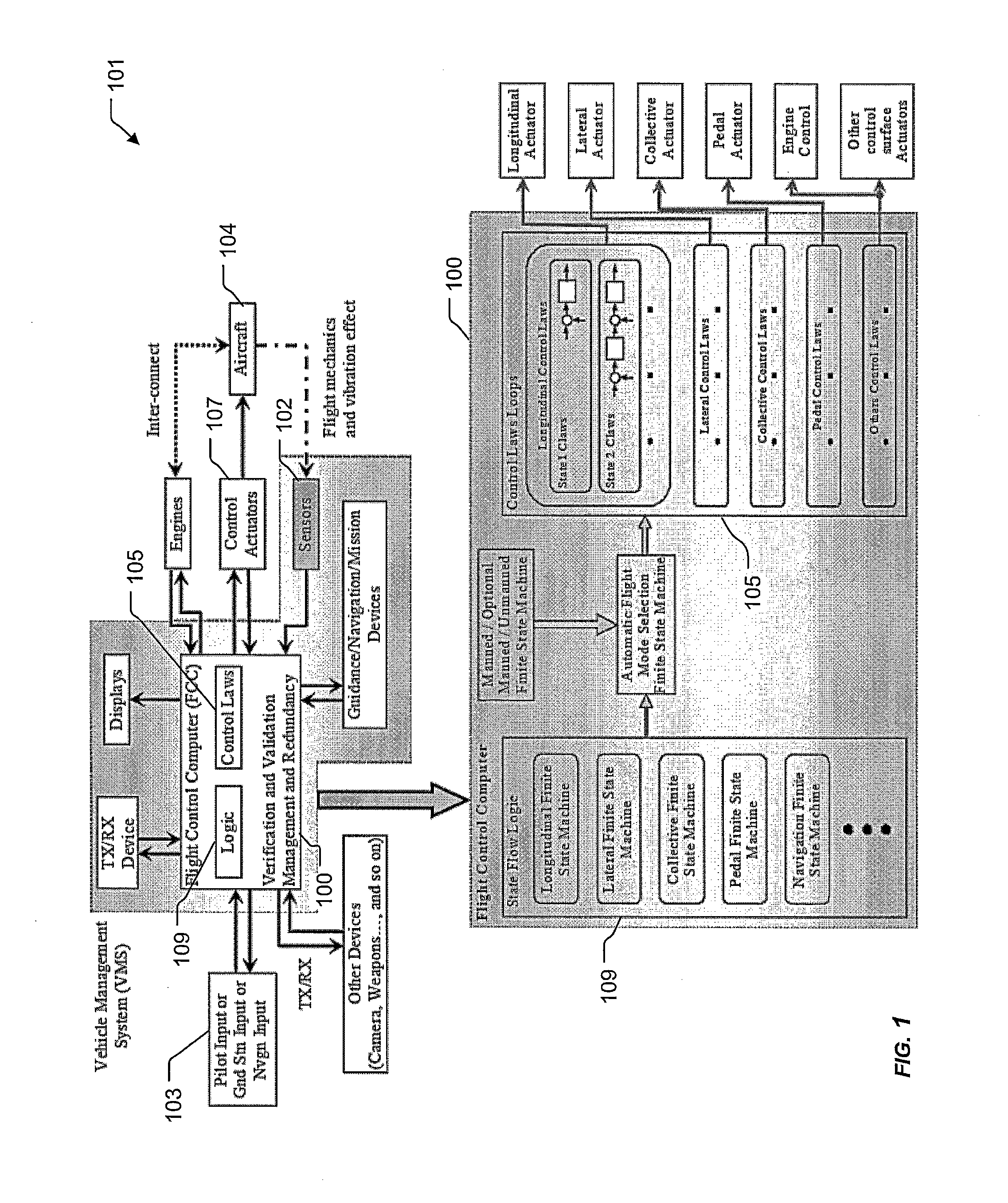

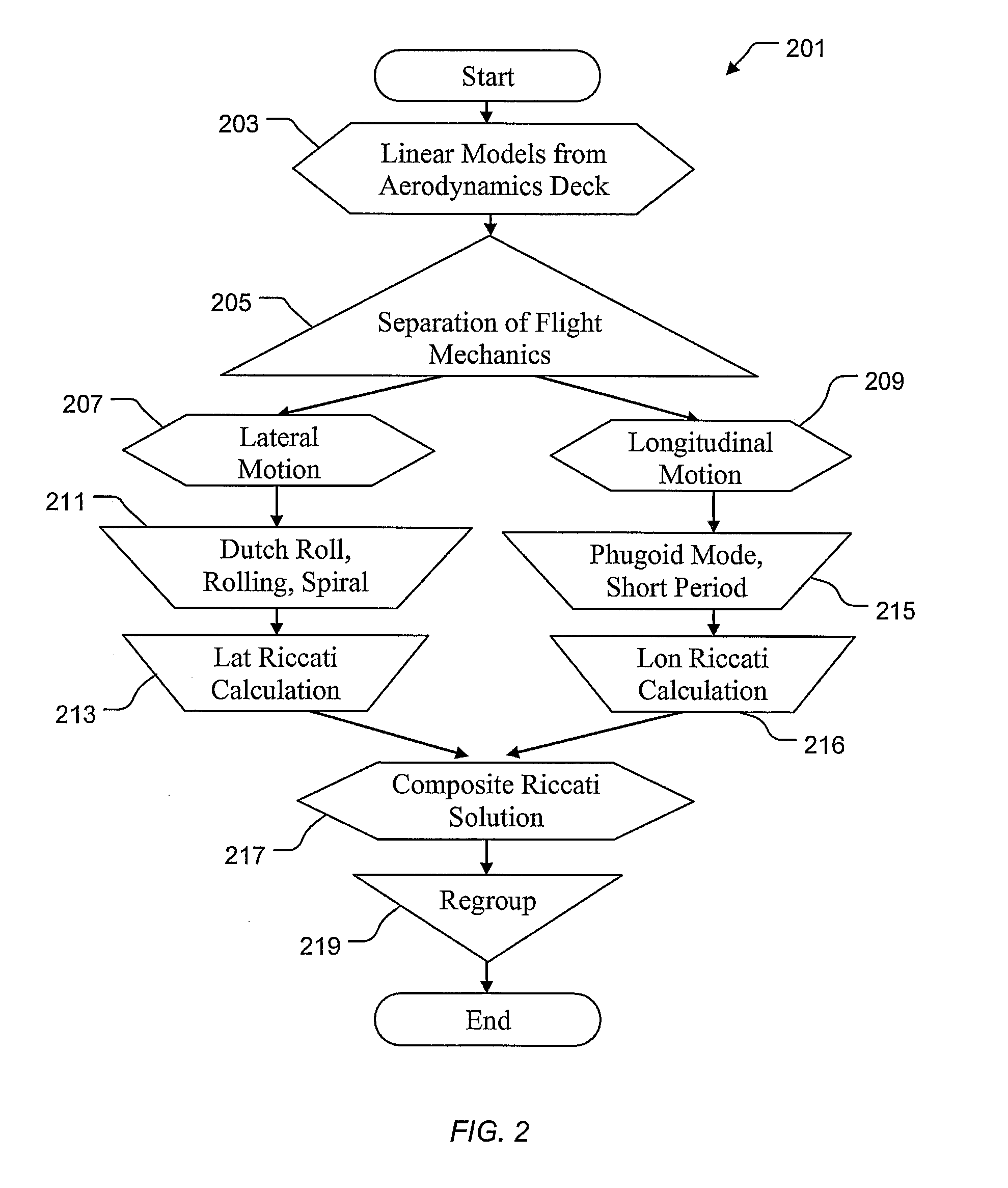

Vehicle management system using finite state machines

A system includes a plurality of actuators and a management system operably associated with the plurality electronic and mechanical devices. The management architecture includes interfaces configured to the entire electronics and mechanics to provide a parameter to a computer. The computer includes a control and management architecture using modular finite state flow designs configured to analyze the parameter. The computer with a plurality of finite state machines can conduct a plurality of control laws operably associated with one or more actuators for finite functions of mobility. The method includes matching the parameter with the finite state machine and controlling the actuator via control law operably associated with finite state machine. The method can therefore be achieved either manually, semi-autonomously and autonomously with seamless and switchless control using a central control computer with integration of electronic and mechanic sensors and devices.

Owner:TEXTRON INNOVATIONS

Attribute-based word modeling

An attribute-based speech recognition system is described. A speech pre-processor receives input speech and produces a sequence of acoustic observations representative of the input speech. A database of context-dependent acoustic models characterize a probability of a given sequence of sounds producing the sequence of acoustic observations. Each acoustic model includes phonetic attributes and suprasegmental non-phonetic attributes. A finite state language model characterizes a probability of a given sequence of words being spoken. A one-pass decoder compares the sequence of acoustic observations to the acoustic models and the language model, and outputs at least one word sequence representative of the input speech.

Owner:MULTIMODAL TECH INC

Compiler for Programmable Intelligent Search Memory

ActiveUS20080140600A1Efficient and compact realizationReduce overheadDigital data information retrievalDigital storageMemory architectureAutomaton

Memory architecture provides capabilities for high performance content search. Content search rules comprise of regular expressions which are compiled to finite state automata and then programmed in Programmable Intelligent Search Memory (PRISM) for evaluating content with the search rules. A compiler compiles the content search rules for evaluation by PRISM memory. The PRISM memory architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable Intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken.

Owner:INFOSIL INC

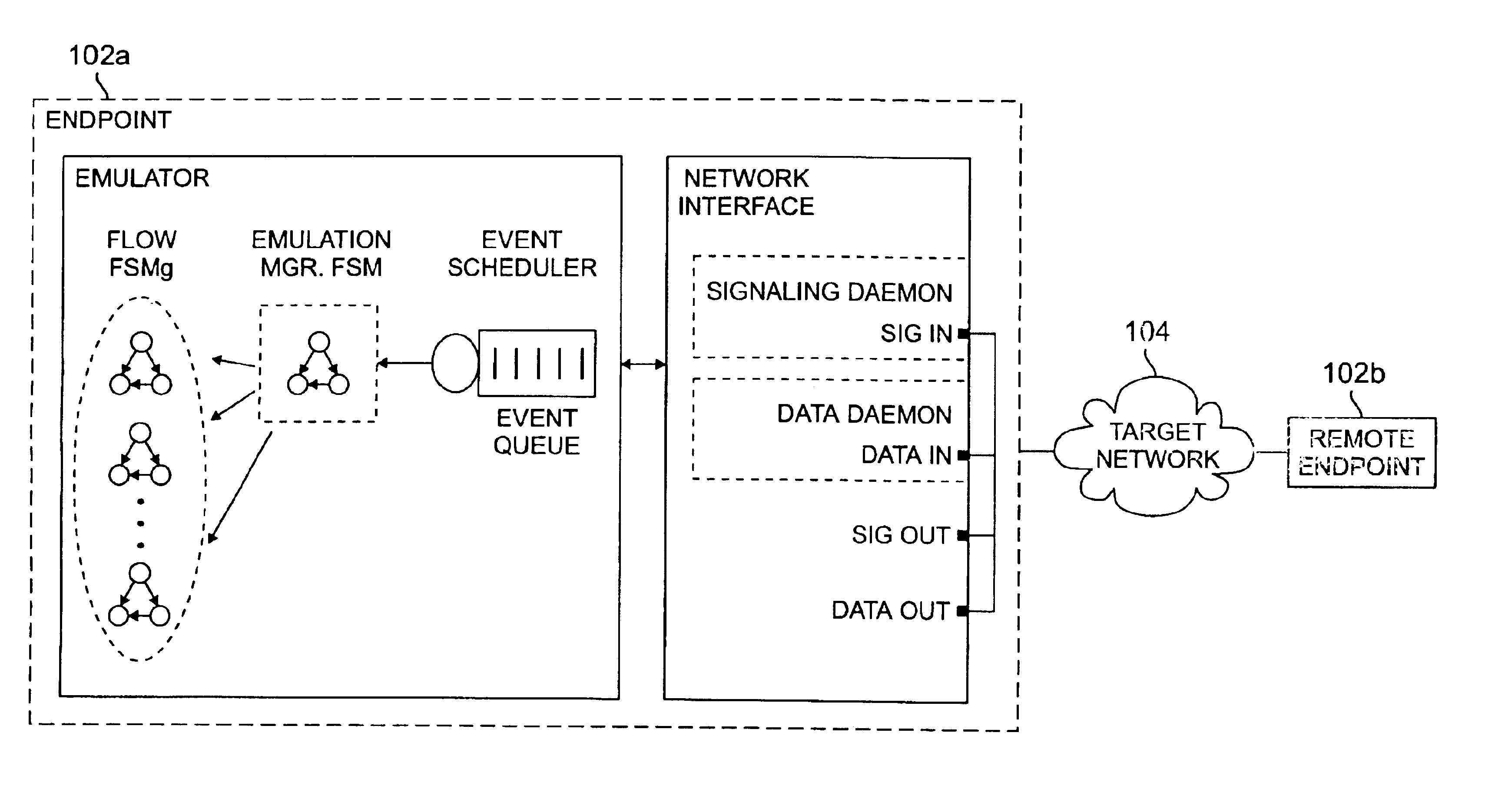

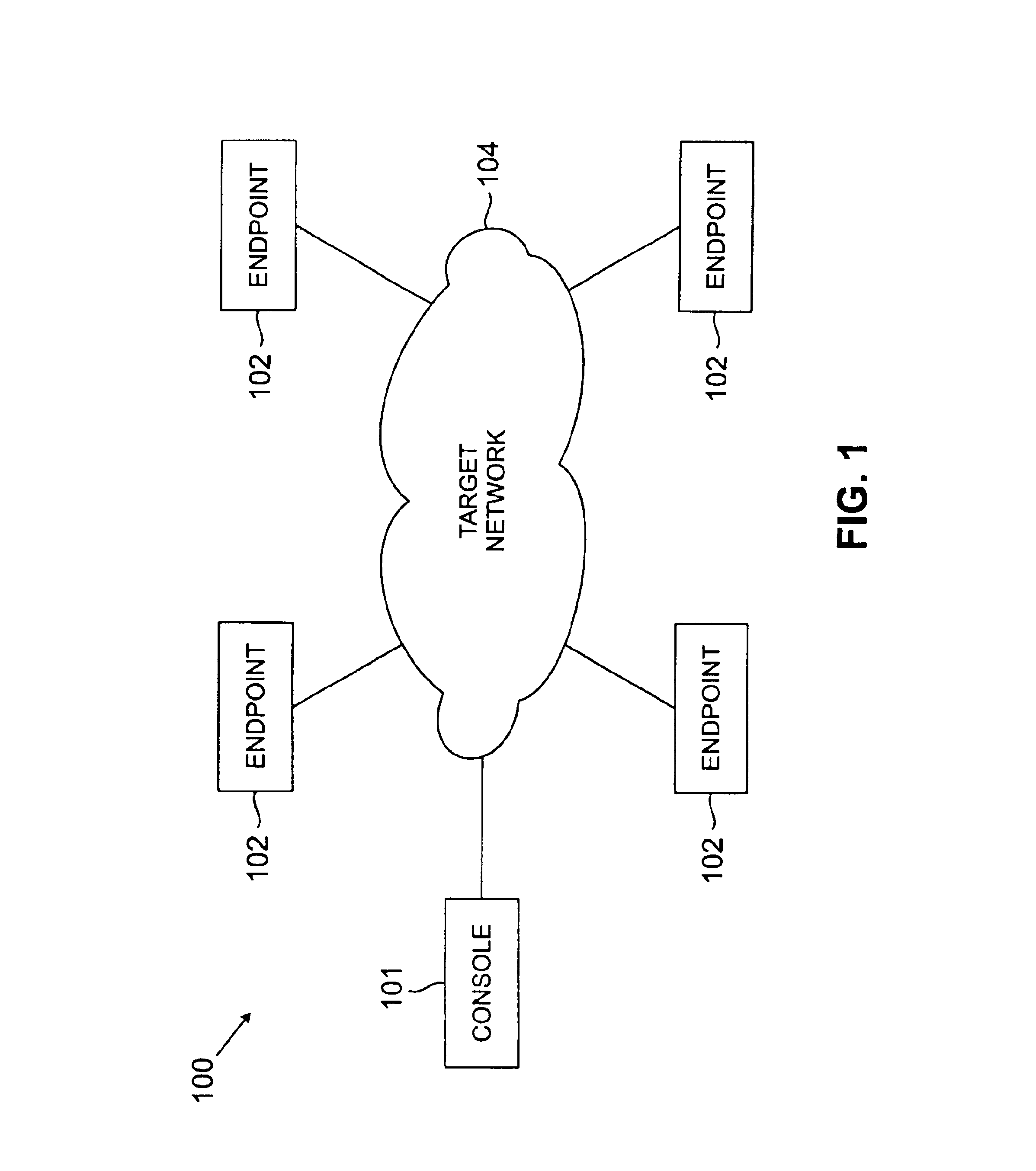

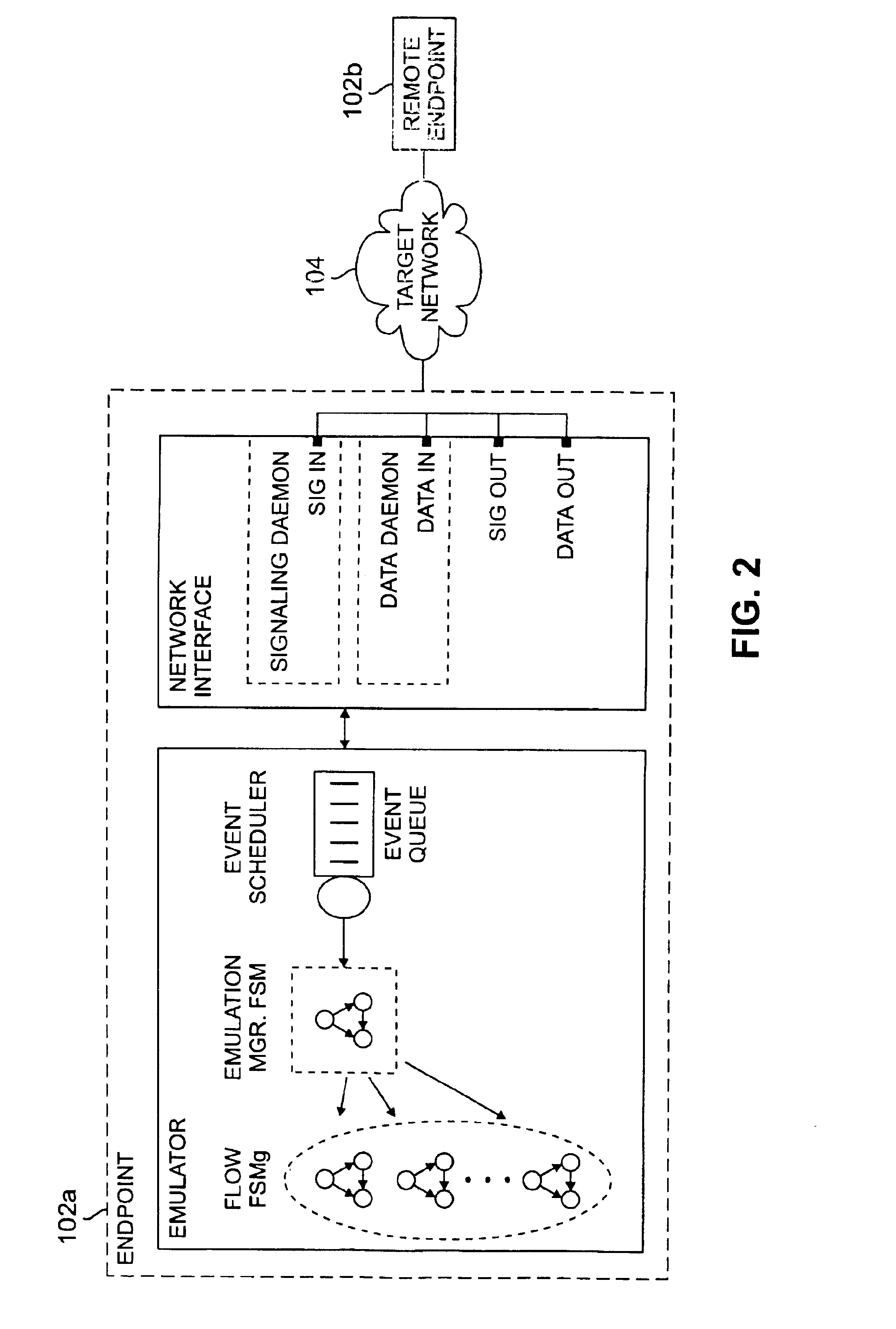

Framework for flexible and scalable real-time traffic emulation for packet switched networks

An implementation framework, including methodologies and the architecture, for a real-time traffic emulation for packet switched networks. The framework uses extended finite state machines to model the traffic flows that are to be emulated. A simple yet flexible FMS-based scripting language is proposed to describe these flows. An event-driven approach to schedule CPU among flows is also adopted.

Owner:LUCENT TECH INC +1

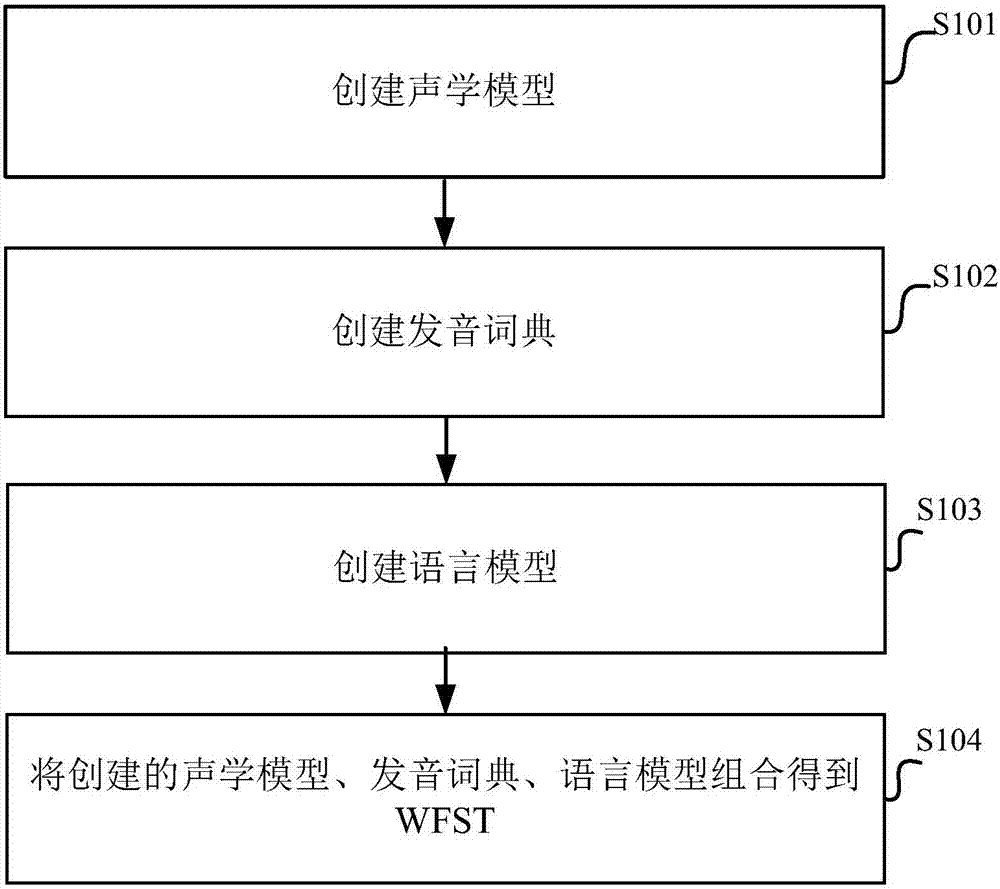

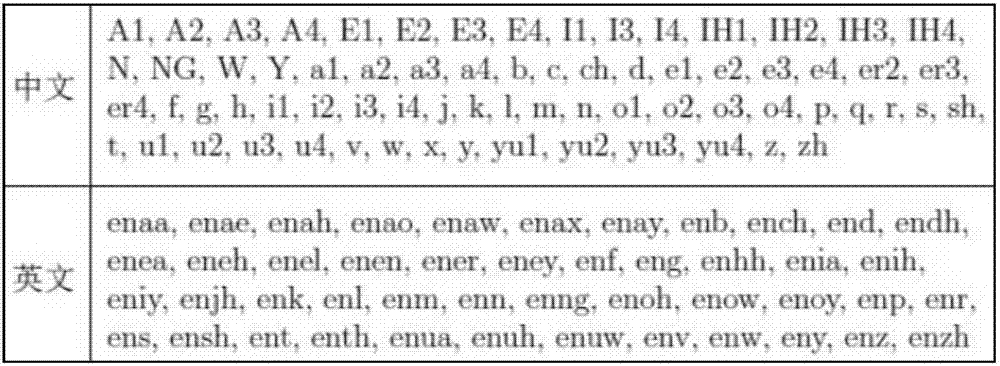

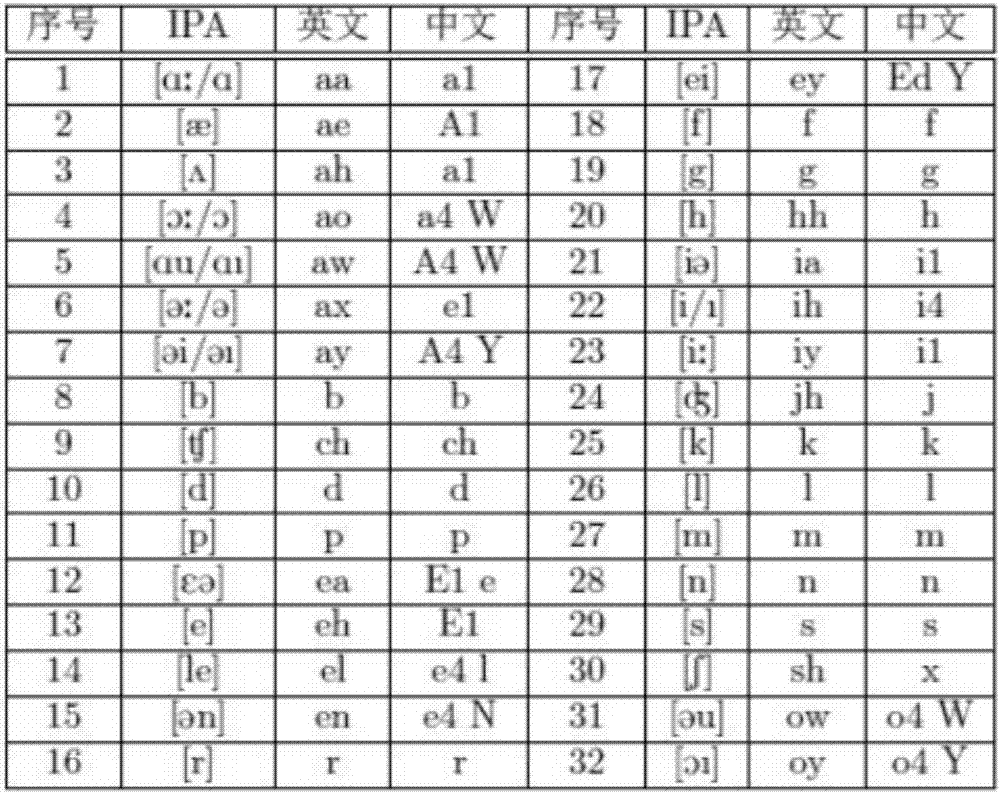

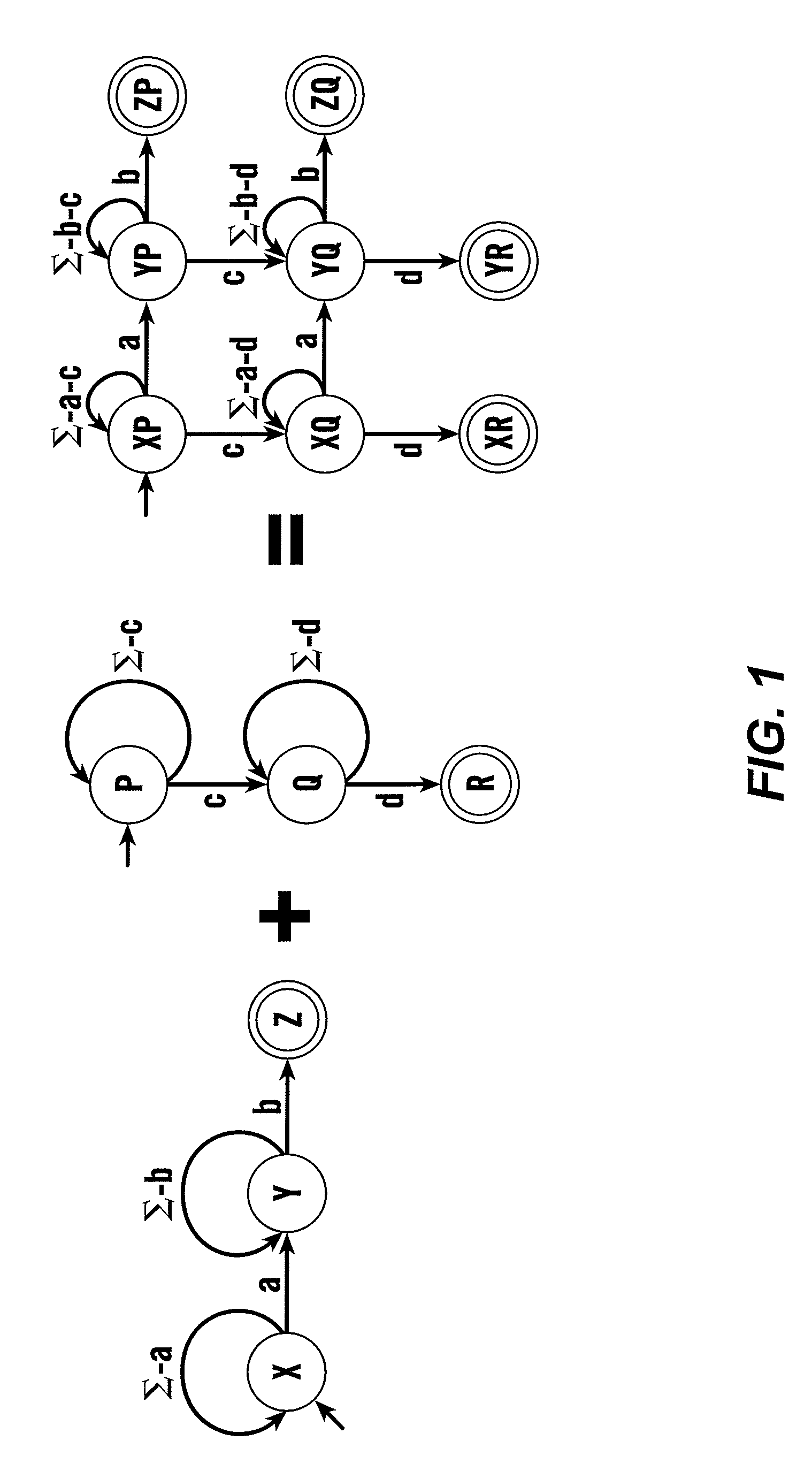

Voice recognition method, device and system and terminal

ActiveCN107195296AIn line with pronunciation habitsImprove recognition accuracySpeech recognitionFeature extractionAcoustic model

The embodiment of the invention provides a voice recognition method, device and system and a terminal. The method comprises the steps that voice to be recognized is received; feature extraction is performed on the voice to be recognized so as to obtain feature information; and the feature information is inputted to a weighted finite state transducer WFST to be recognized, the WFST is obtained by the pre-created combination of an acoustic model, a pronunciation dictionary and a language model, all the first language phonemes and second language phonemes in the acoustic model have the corresponding relationship, and phonetic notation of all the first language vocabularies in the pronunciation dictionary is performed by the second language phonemes. With application of the scheme, the voice recognition accuracy can be enhanced.

Owner:ALIBABA GRP HLDG LTD

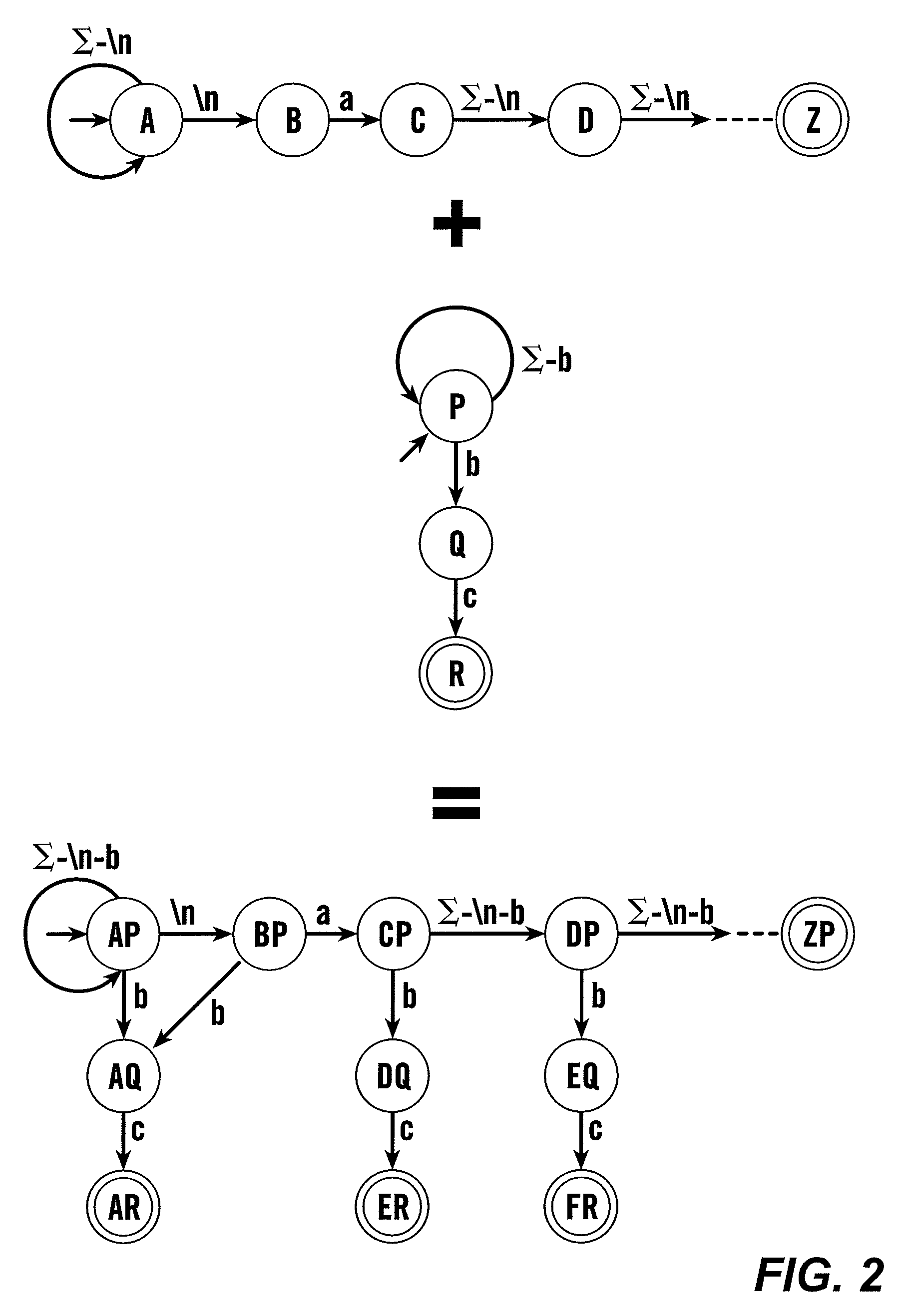

Extended finite state automata and systems and methods for recognizing patterns using extended finite state automata

Deterministic finite automata (DFAs) are popular solutions to deep packet inspection because they are fast and DFAs corresponding to multiple signatures are combinable into a single DFA. Combining such DFAs causes an explosive increase in memory usage. Extended finite automata (XFAs) are an alternative to DFAs that avoids state-space explosion problems. XFAs extend DFAs with a few bytes of “scratch memory” used to store bits and other data structures that record progress. Simple programs associated with automaton states and / or transitions manipulate this scratch memory. XFAs are deterministic in their operation, are equivalent to DFAs in expressiveness, and require no custom hardware support. Fully functional prototype XFA implementations show that, for most signature sets, XFAs are at least 10,000 times smaller than the DFA matching all signatures. XFAs are 10 times smaller and 5 times faster or 5 times smaller and 20 times faster than systems using multiple DFAs.

Owner:WISCONSIN ALUMNI RES FOUND

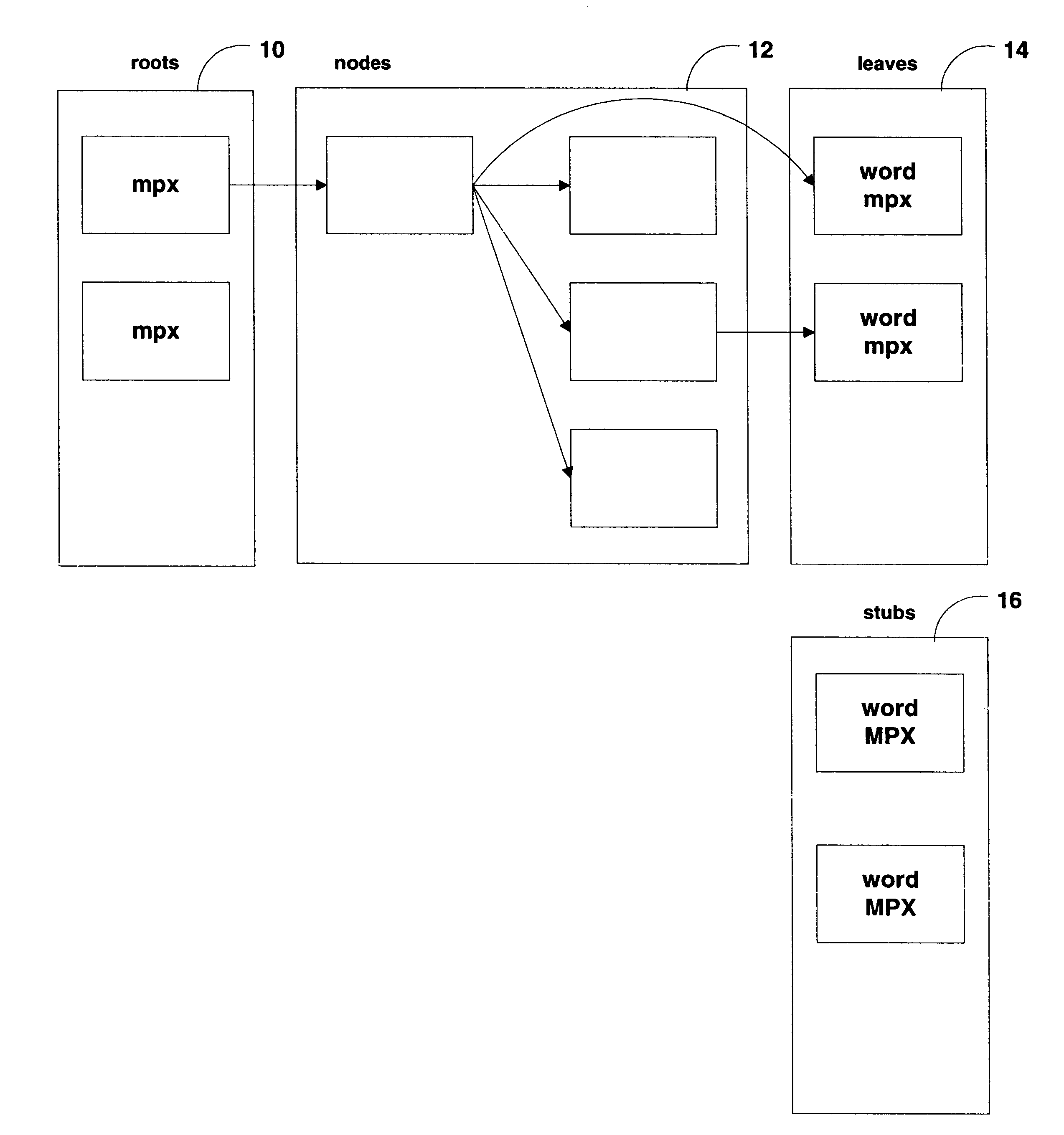

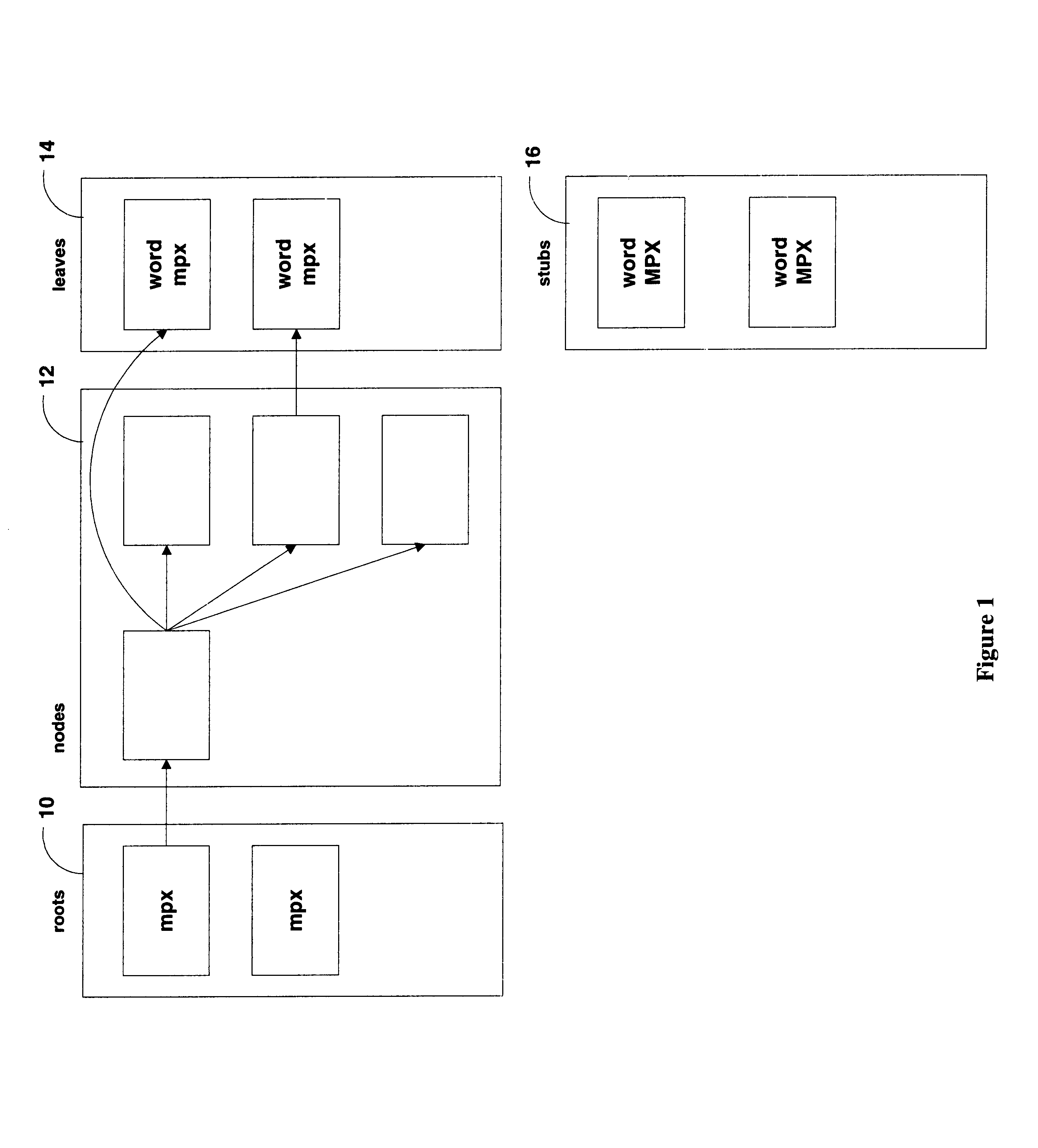

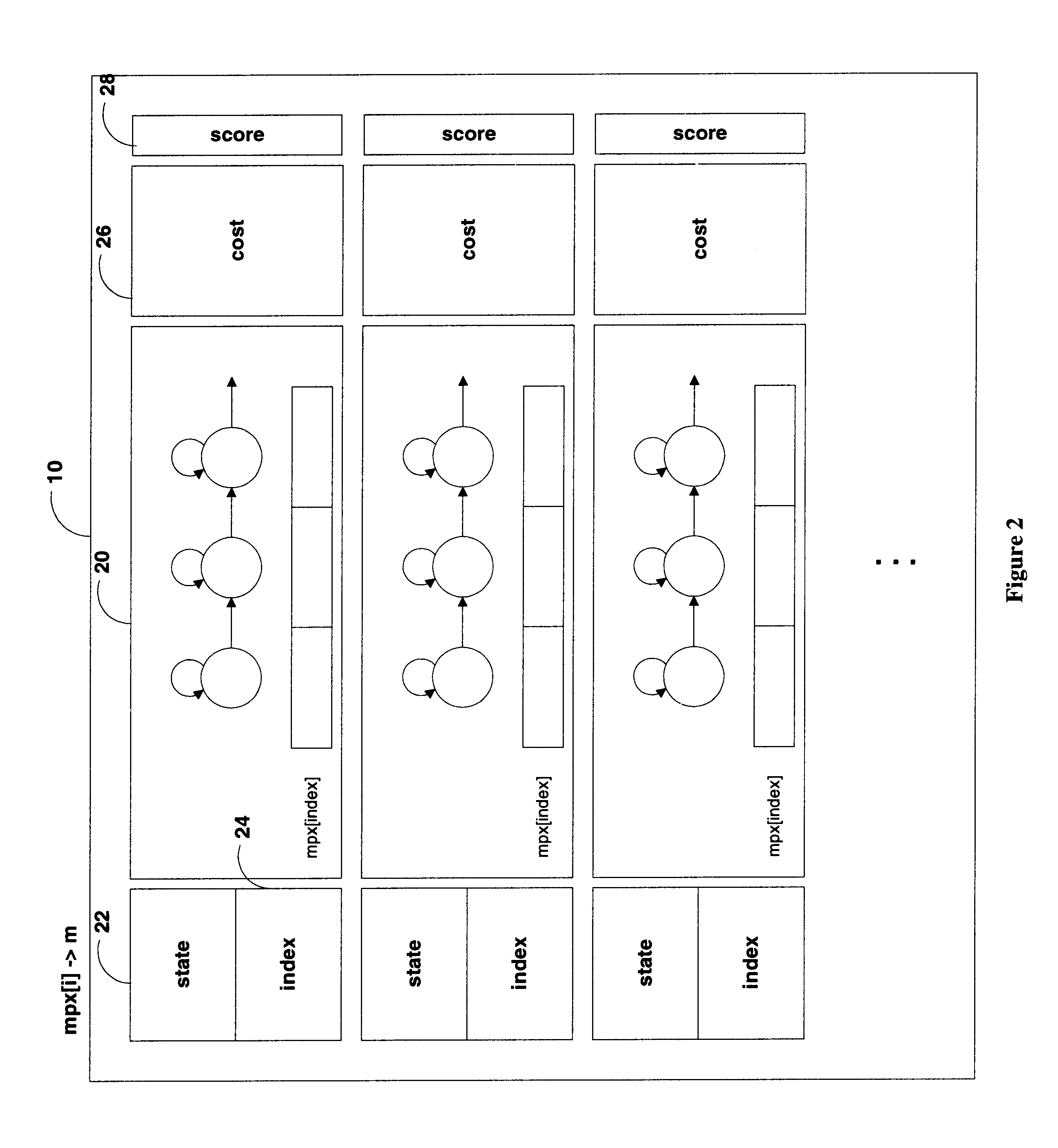

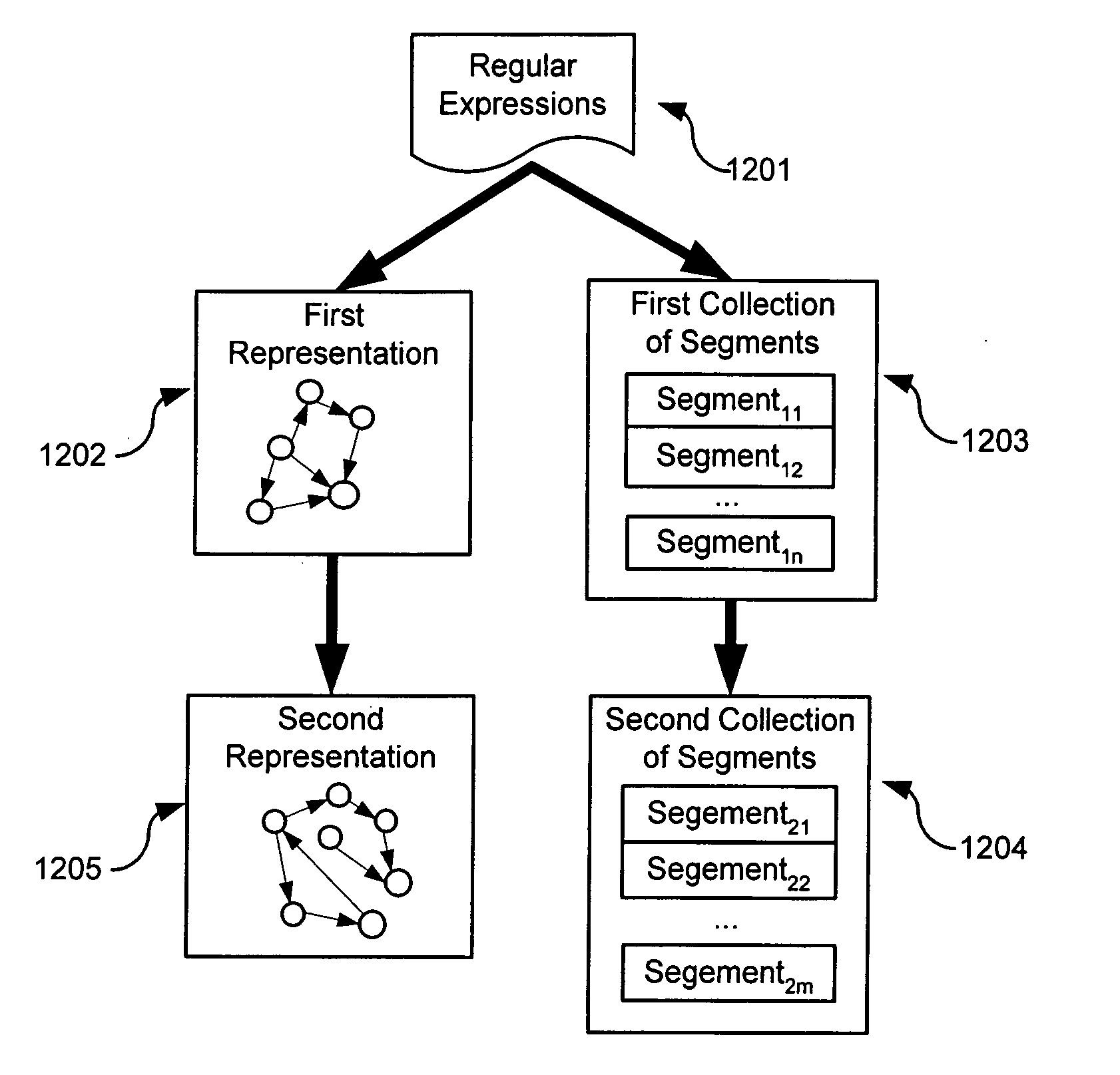

Method for transformation of regular expressions

InactiveUS20060085389A1Reduce memory requirementsDigital data information retrievalDigital data processing detailsSemanticsTerm memory

A method and apparatus for transforming regular expressions into a less resource intensive representation is disclosed. The method and apparatus converts a collection of regular expressions into a multi-level representation in which the memory requirements of the lowest level representation is reduced when compared with a conventional finite state automaton representation. The method and apparatus converts a collection of regular expressions into a collection of segments and a higher level representation in a way that retains the semantics of the original set of regular expressions. This transformation is performed through the use of an intermediate form. The resulting representation and collection admit an implementation which avoids the potentially costly memory requirements of a traditional implementation of the original expressions.

Owner:SENSORY NETWORKS +1

Method and system for multi-character multi-pattern pattern matching

ActiveUS7725510B2Increase speedEasy to implementData processing applicationsDigital data information retrievalPattern matchingTernary content addressable memory

Disclosed is a method and system for multi-character multi-pattern pattern matching. In the multi-character multi-pattern pattern matching method, patterns in an input stream are detected by transitioning between states of a “compressed deterministic finite state automaton (DFA)”, with each transition based on multiple characters of the input stream. The compressed DFA is created by compressing an original DFA, such as an Aho-Corasick DFA, such that each state of the compressed DFA represents multiple consecutive states of the original DFA and each transition between the states of the compressed DFA is a combination of all of the transitions between the multiple consecutive states of the original DFA. This method can be implemented using a Ternary Content-Addressable Memory (TCAM) to store the transitions of the compressed DFA and compares the transitions with multiple characters of an input stream at a time to detect patterns in the input stream.

Owner:ALGOGENE FINANCIAL TECHNOLOGY COMPANY LIMITED

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com