Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

791 results about "Fault injection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fault injection is a testing technique which aids in understanding how [virtual/real] system behaves when stressed in unusual ways. This technique is based on simulation's or experiment's result, thus it may be more valid (or closer to reality) compared to statistical methods.

Distributed fault injection mechanism

InactiveUS20080215925A1Validating the robustness of a distributed computing systemEasy injectionError detection/correctionGraphicsGraphical user interface

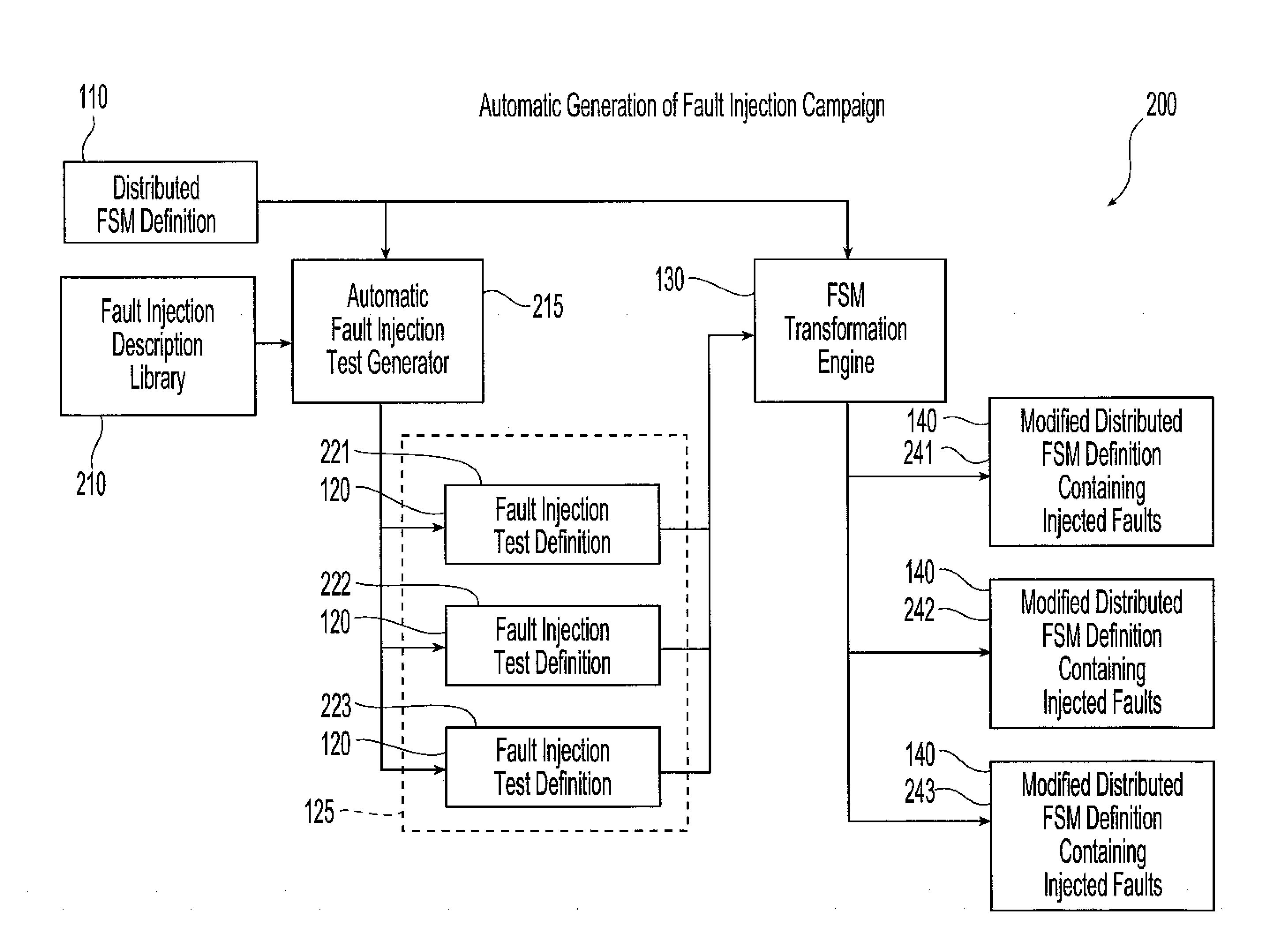

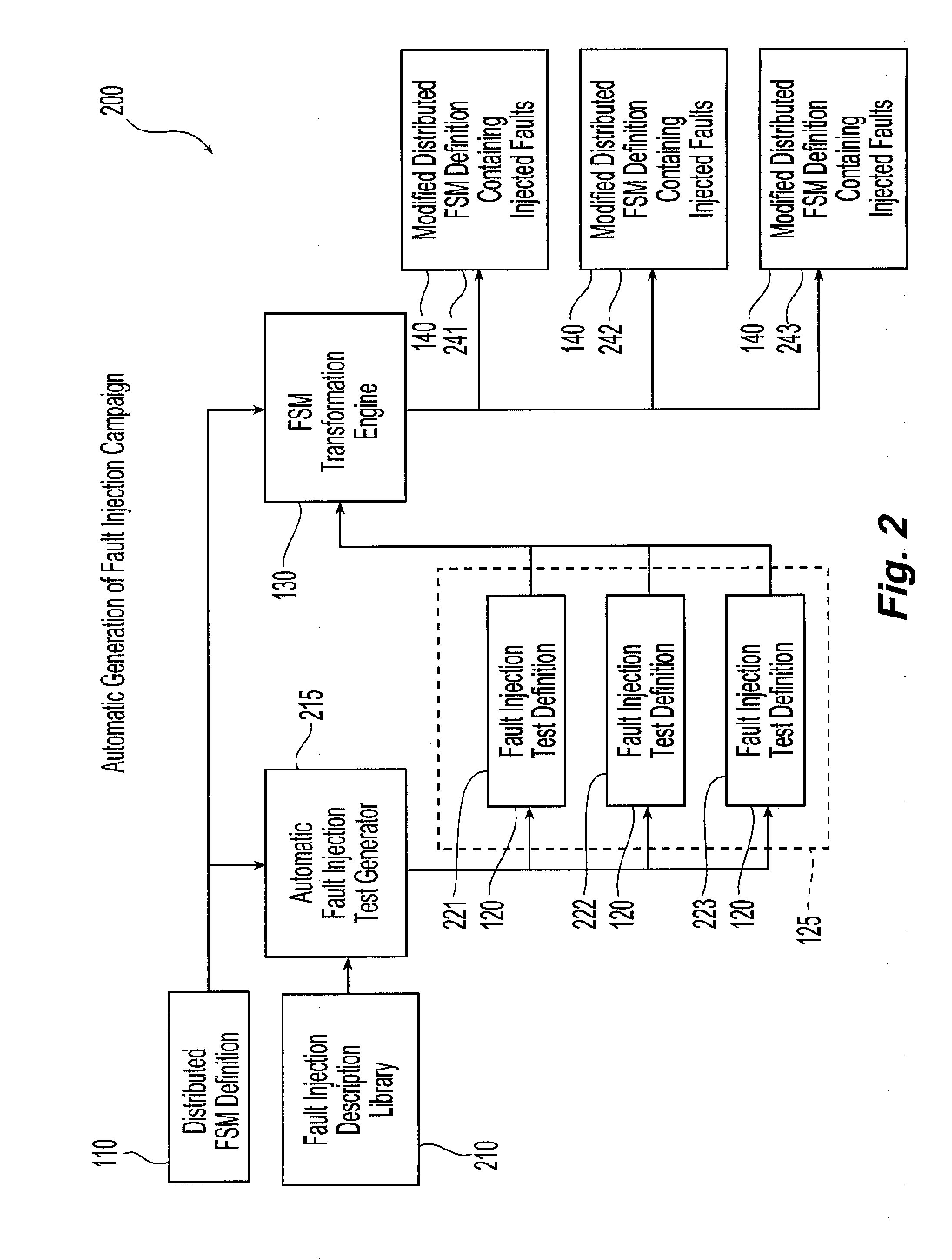

Methods and systems are provided for testing distributed computer applications using finite state machines. A finite state machine definition for use in a distributed computer system is combined with the fault injections definitions contained within a fault injection campaign that is created for testing the computer application employing that finite state machine. The definition and combination of the finite state machine definition and the fault injection campaign is carried out automatically or manually, for example using a graphical user interface. This combination creates at least one modified finite state machine definition containing the desired injected faults. The modified finite state machine definition is separate from the originally identified finite state machine definition, and the originally identified finite state machine remains intact without injected faults. Trigger points within the finite state machine definition are identified for each fault injection test definition, and the modified finite state machine definition containing the fault injection test definition associated with a given trigger point are used in place of the original finite state machine definition upon detection of that trigger point during runtime of the finite state machine definition.

Owner:IBM CORP

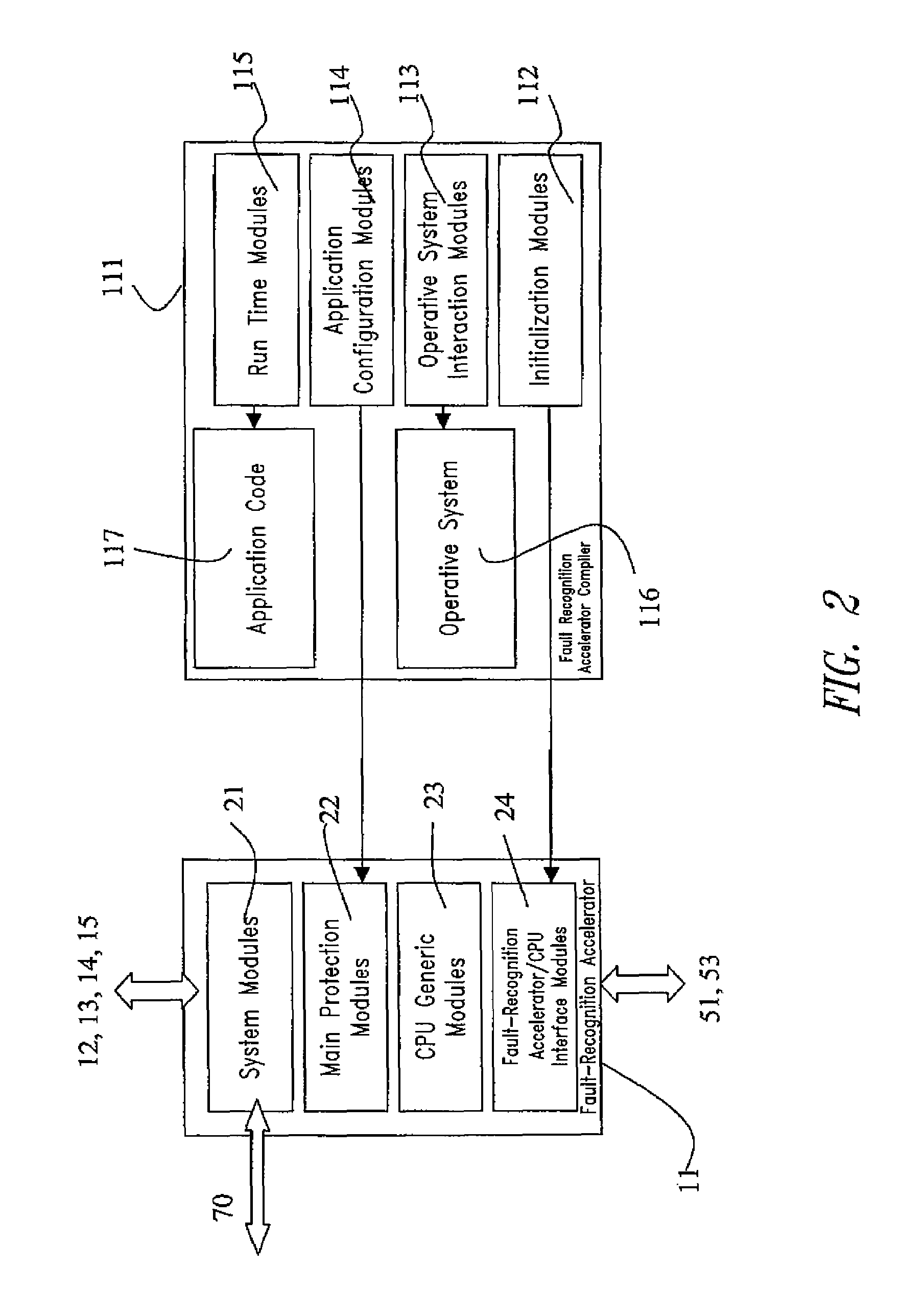

Dependable microcontroller, method for designing a dependable microcontroller and computer program product therefor

ActiveUS7472051B2Improve reliabilityEfficient use ofAnalogue computers for electric apparatusHardware monitoringMicrocontrollerFault tolerance

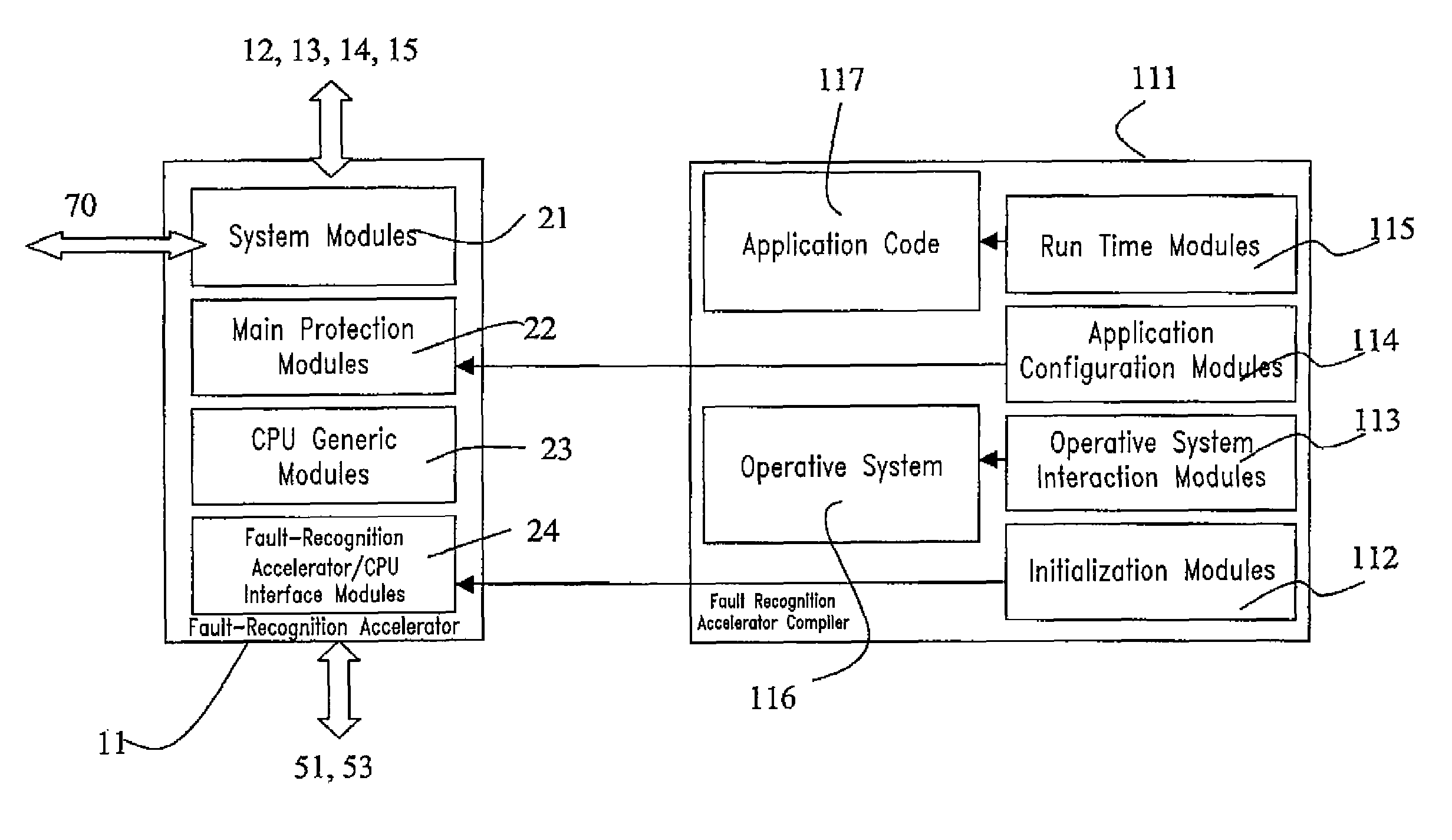

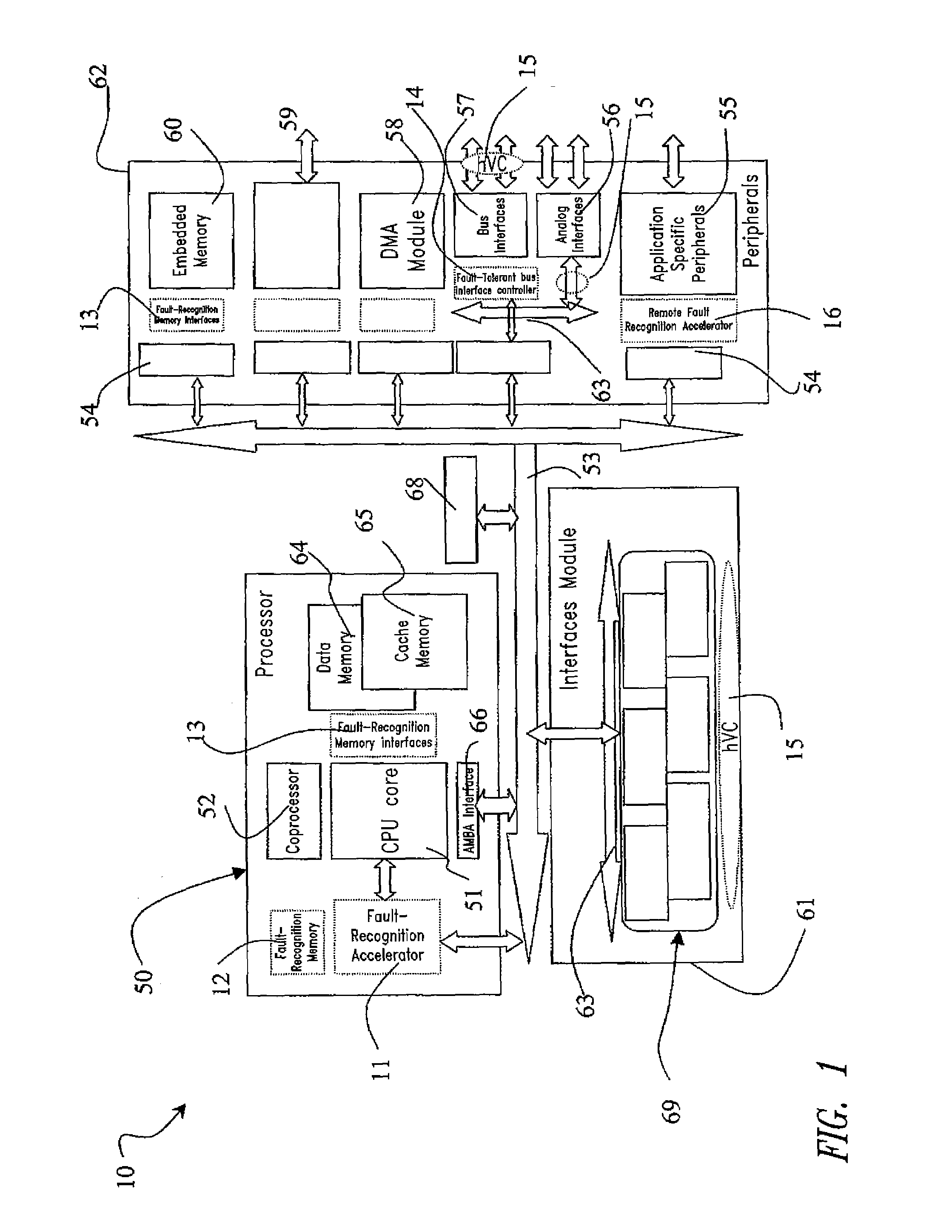

A microcontroller comprising a central processing unit and a further fault processing unit suitable for performing validation of operations of said central processing unit. The further fault processing unit is external and different with respect to said central processing unit and said further fault processing unit comprises at least a module for performing validation of operations of said central processing unit and one or more modules suitable for performing validation of operations of other functional parts of said microcontroller. Validation of operations of said central processing unit is performed by using one or more of the following fault tolerance techniques: data shadowing; code&flow signature; data processing legality check; addressing legality check; ALU concurrent integrity checking; concurrent mode / interrupt check. The proposed microcontroller is particularly suitable for application in System On Chip (SoC) and was developed by paying specific attention to the possible use in automotive System On Chip. The invention also includes a method for designing and verify such fault-robust system on chip, and a fault-injection technique based on e-language.

Owner:TAHOE RES LTD

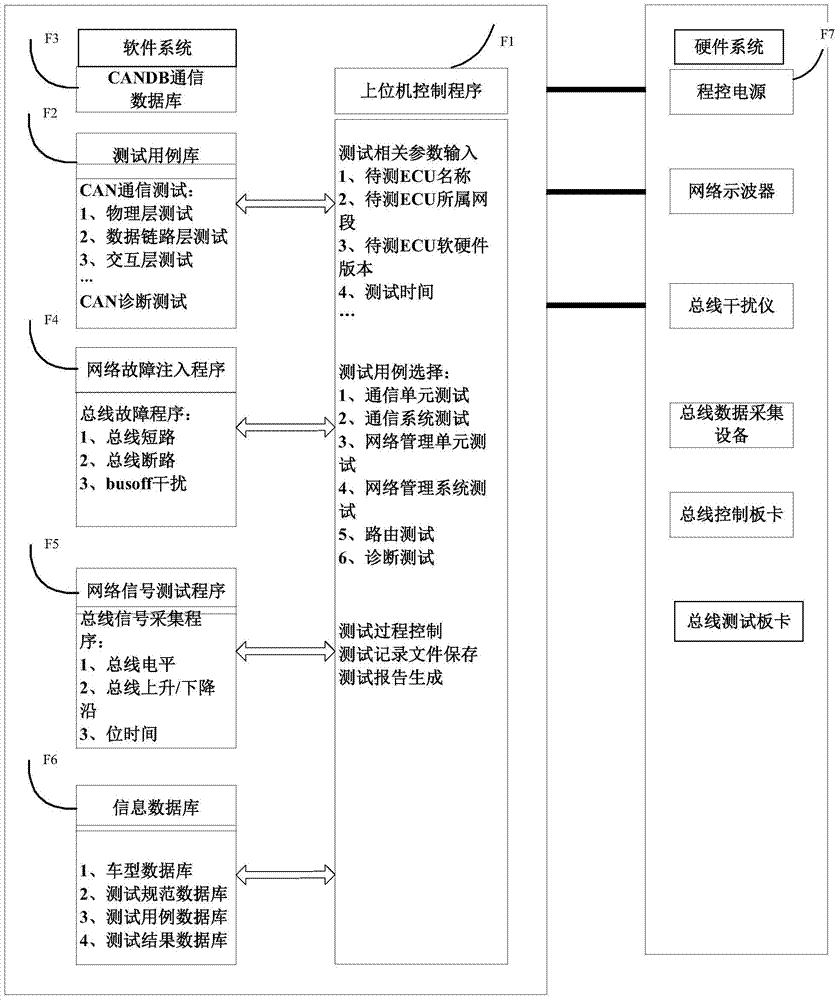

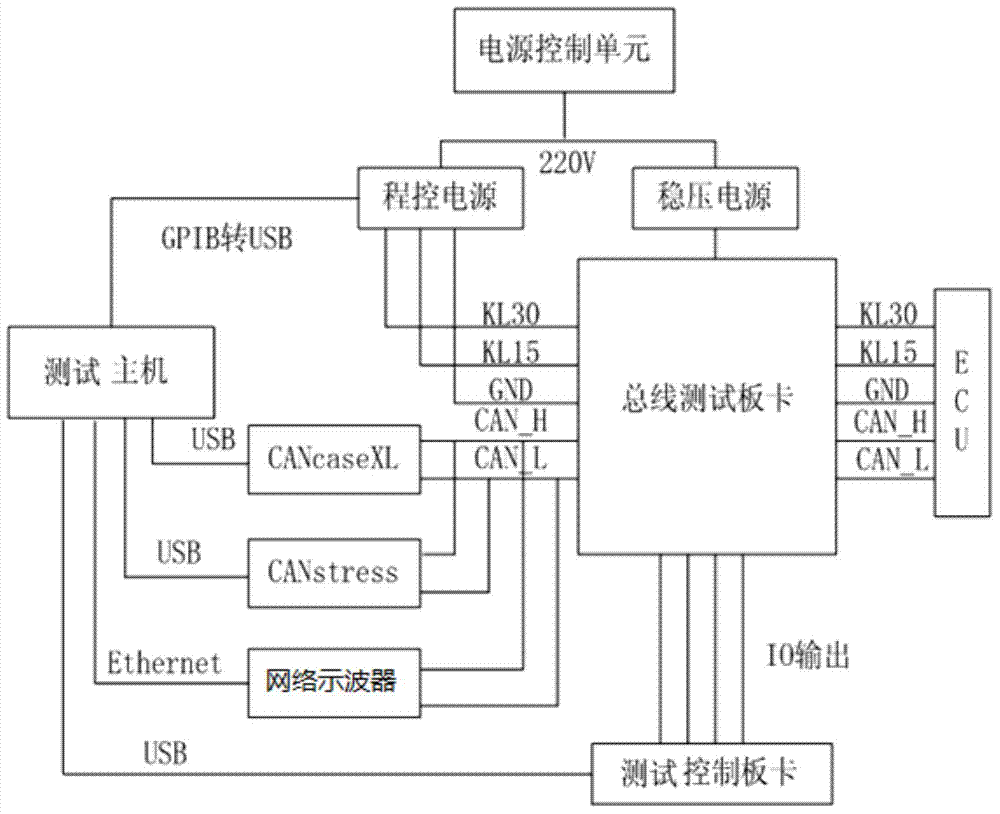

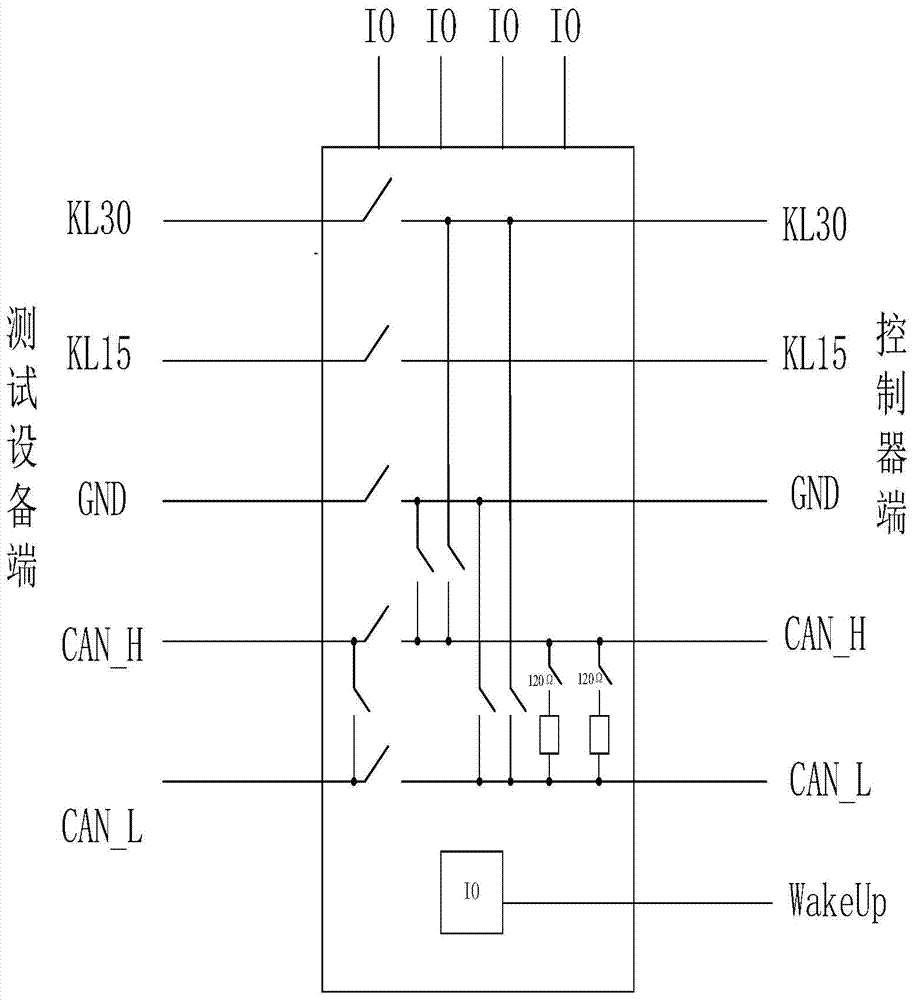

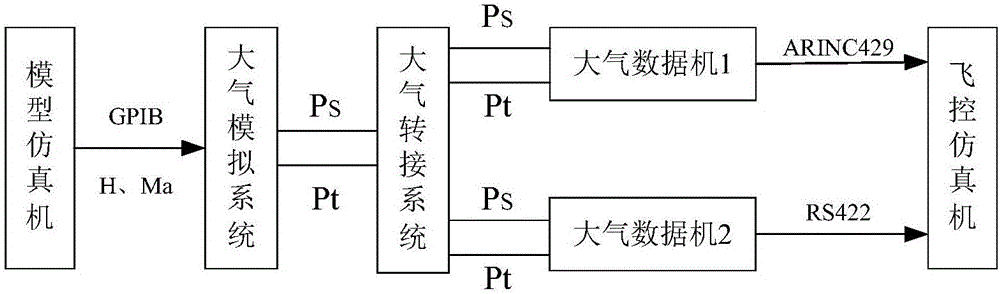

Automatic vehicle-mounted electronic control unit CAN bus communication testing device and system

InactiveCN104298224AReduce duplication of effortAffect accuracyElectric testing/monitoringData acquisitionTest fixture

The invention relates to an automatic vehicle-mounted electronic control unit CAN bus communication testing device. A testing host of the device controls a programmable power supply to output different amplitudes of voltages according to working requirements of an ECU; physical layer testing signals of a CAN bus are output to a network oscilloscope to be displayed, and physical layer testing data are transmitted to the testing host through the network oscilloscope; ECU testing data are transmitted to the testing host through a bus data acquisition device; the testing host records, analyzes and evaluates the testing data of the ECU and the CAN bus to generate a test report. A bus interferometer is used for interfering with bus waveforms of the tested ECU in real time. The testing host controls on-off states of relays of a bus testing board card through a testing control card board to execute the bus fault injection operation. By means of the automatic vehicle-mounted electronic control unit CAN bus communication testing device, various defects of a manual test are overcome, unnecessary repeated labor of a vehicle-mounted network engineer is reduced, and the testing result is accurate.

Owner:CHINA FIRST AUTOMOBILE

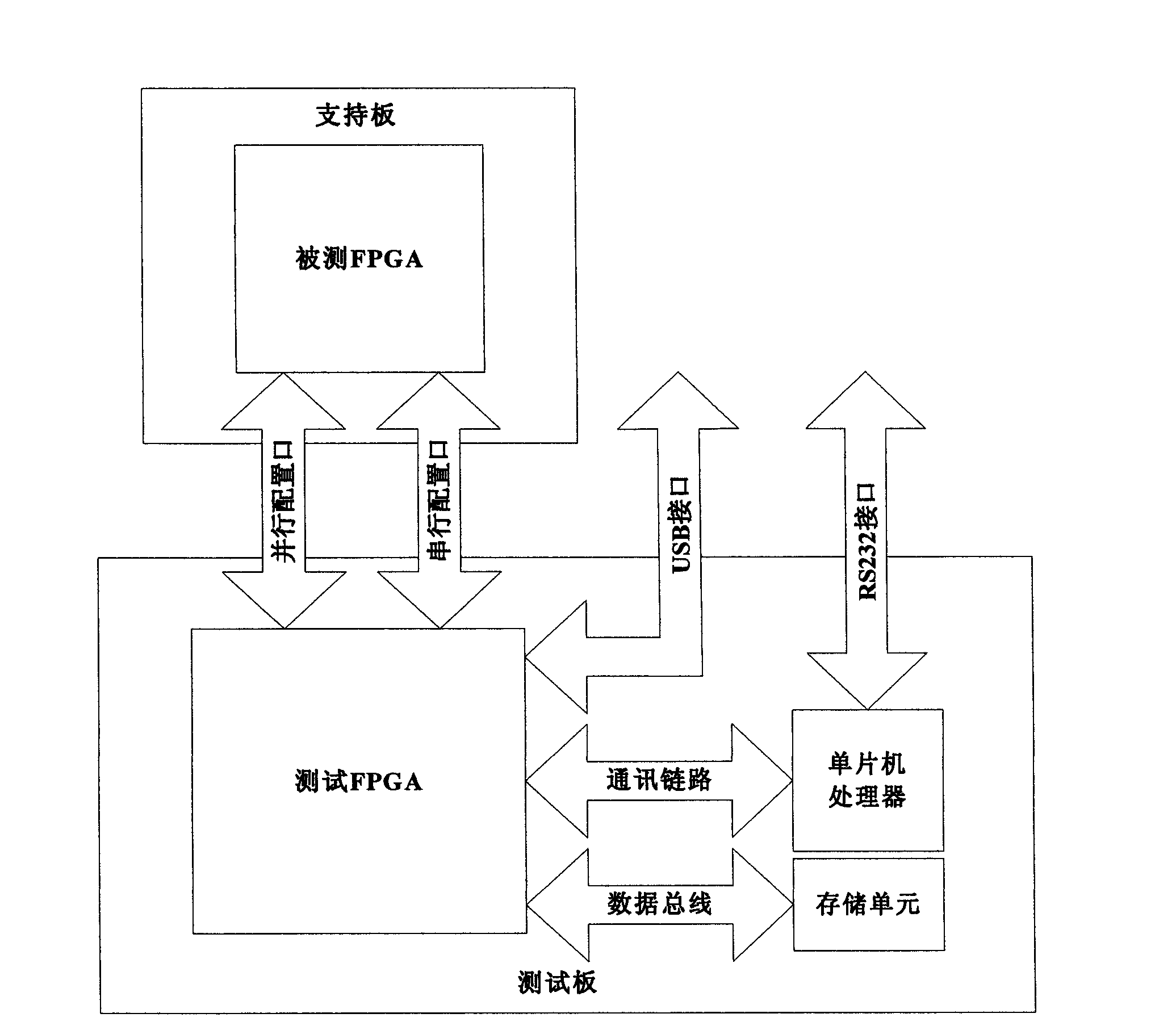

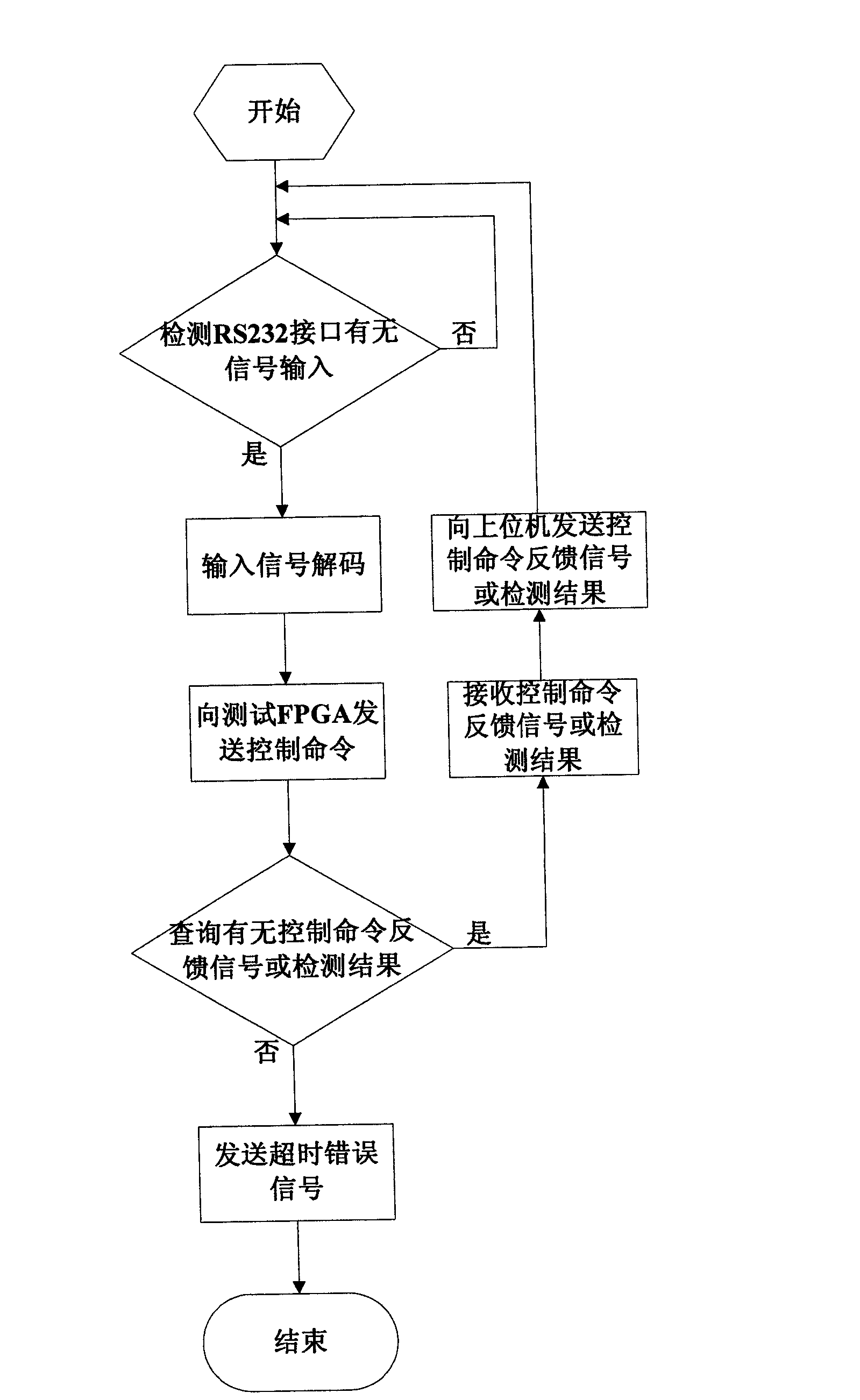

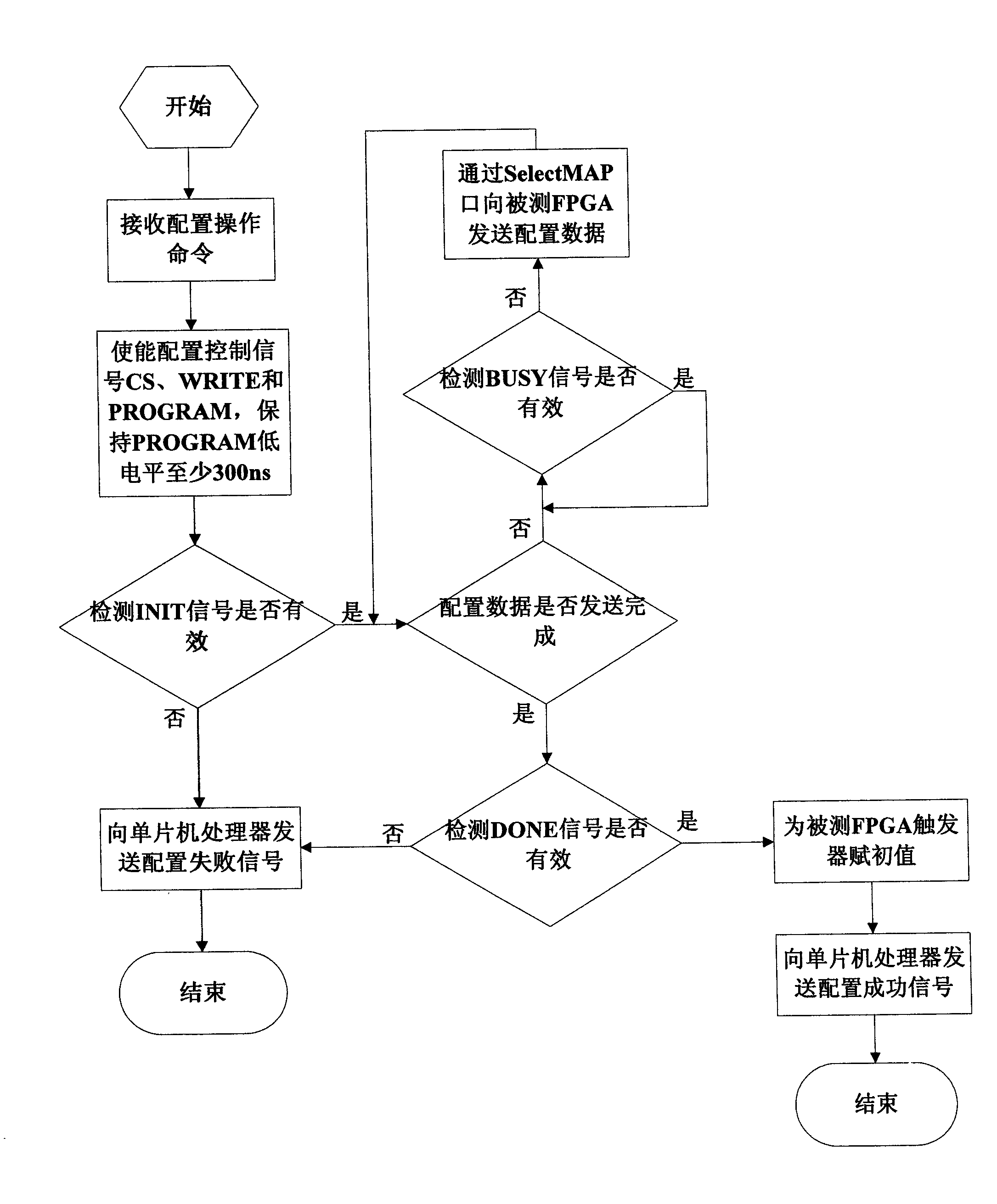

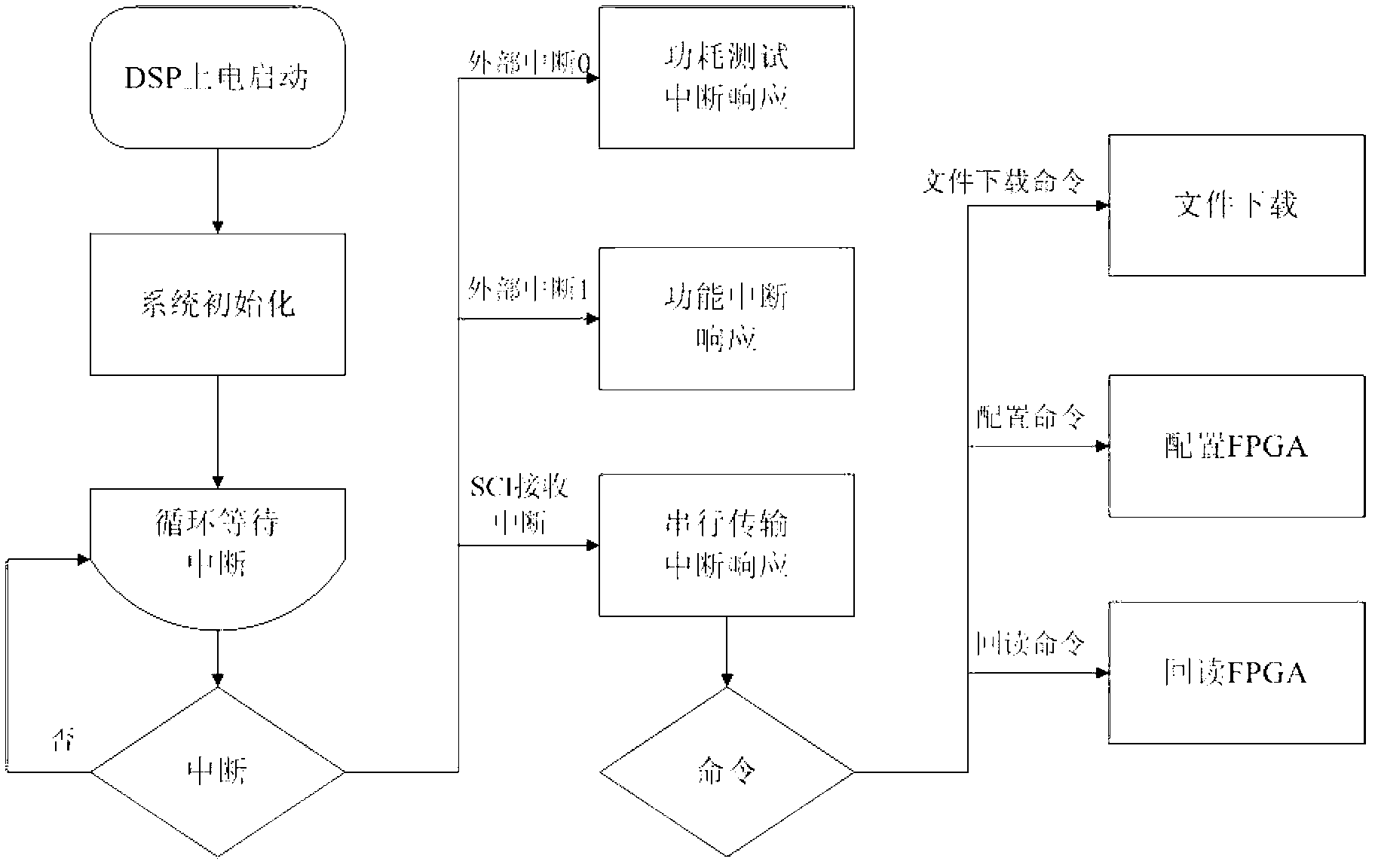

Test system and method for single event effect of SRAM (System Random Access Memory) type FPGA (Field Programmable Gate Array)

ActiveCN102332307AEasy to operateImplement rollover detectionStatic storagePilot systemRandom access memory

The invention provides a test system and method for a single event effect of an SRAM (System Random Access Memory) type FPGA (Field Programmable Gate Array). The test system comprises a single chip microcomputer processor, an RS232 interface circuit, a USB (Universal Serial Bus) interface circuit, a test FPGA and a storage unit. The test system and method can be used for fault injection tests of a configuration memory and a BRAM (Battery Random Access Memory) of the SRAM type FPGA, and single event function interrupting detection, single event locking detection and single event turning detection including single event turning detection for a configuration storage region, the BRAM and a trigger of the SRAM type FPGA are realized. The invention has the advantages of simplicity in operation, entirety in detection, high accuracy, good real-time property and strong universality.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

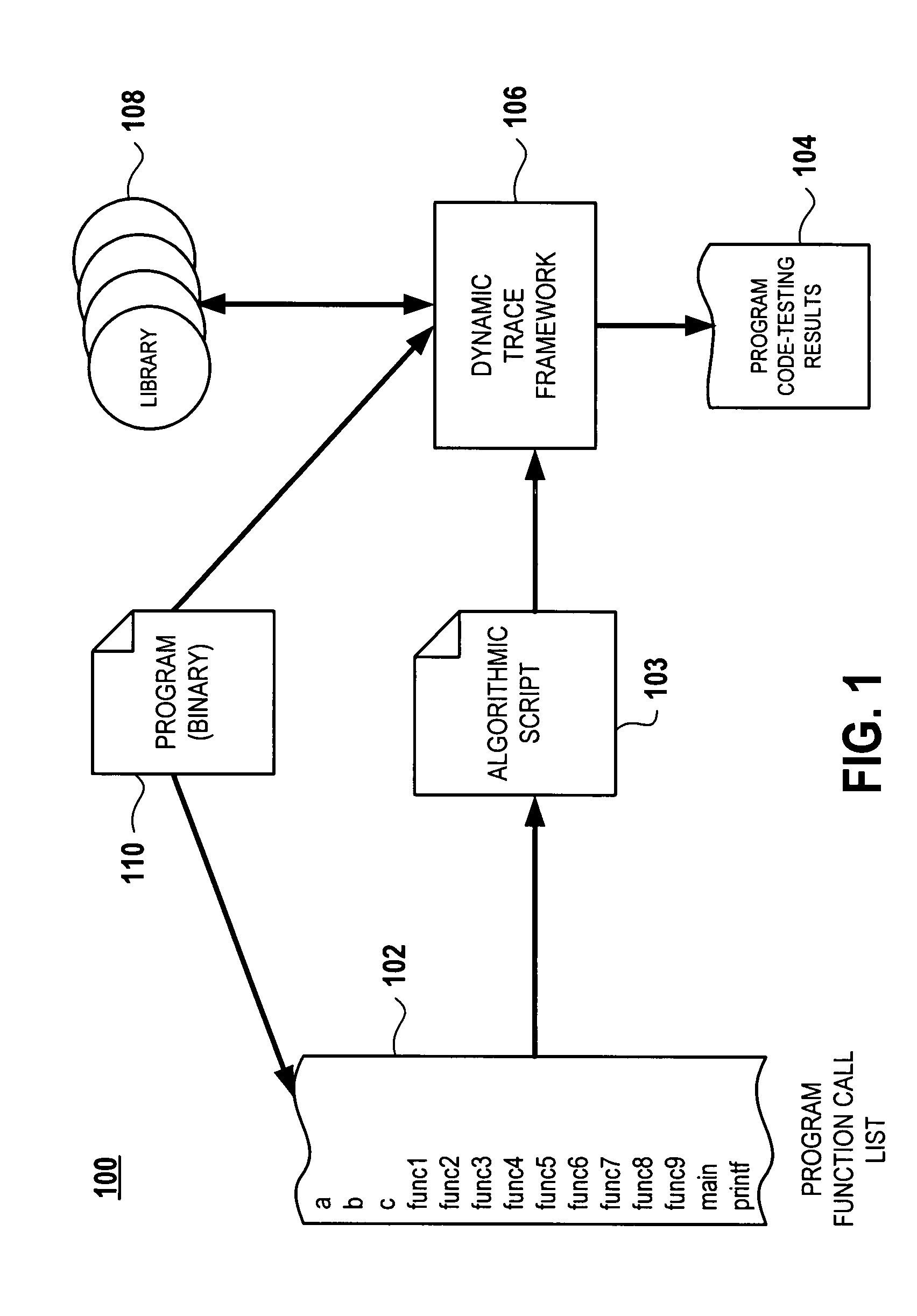

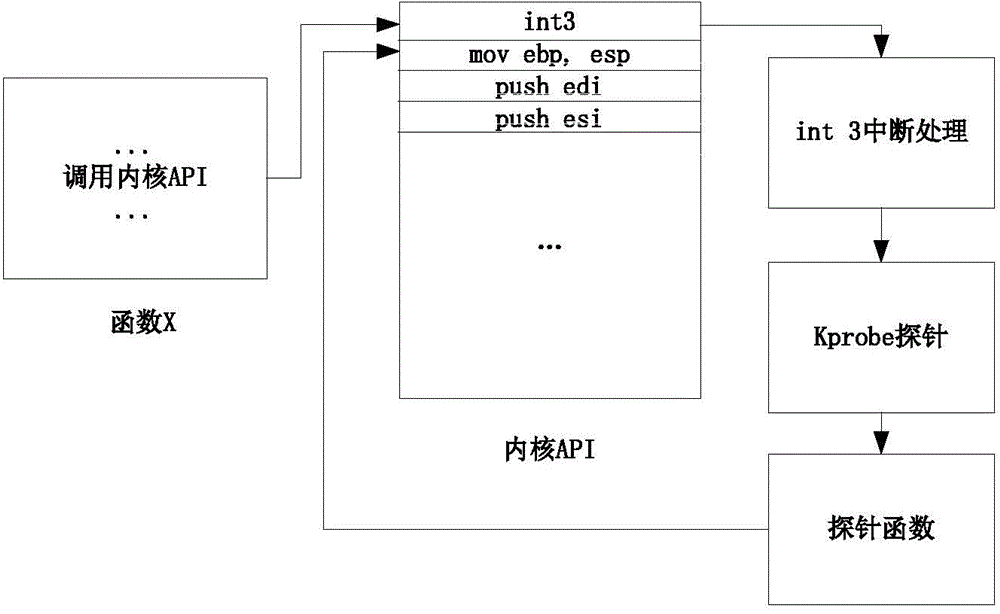

Dynamic fault injection during code-testing using a dynamic tracing framework

ActiveUS7757215B1Error detection/correctionSpecific program execution arrangementsSoftware faultSource code

An approach is provided for performing software fault injection code testing in a framework that allows testers to place flexible tracing and monitoring actions into algorithmic scripts which provide instructions for dynamically switching called software program functions to corresponding fault injected functions during program execution and that allows testers to perform fault injection testing without requiring modification or access to the underlying source code of the software program being tested. The framework suspends execution of the software program when certain conditions are met, removes any existing linking to called functions, changes the software program's runtime dynamic linking, performs any other instructions provided by the algorithmic script, and then resumes the software program's execution until execution of the program is complete or until the framework is again instructed to change the software program's runtime dynamic linking.

Owner:ORACLE INT CORP

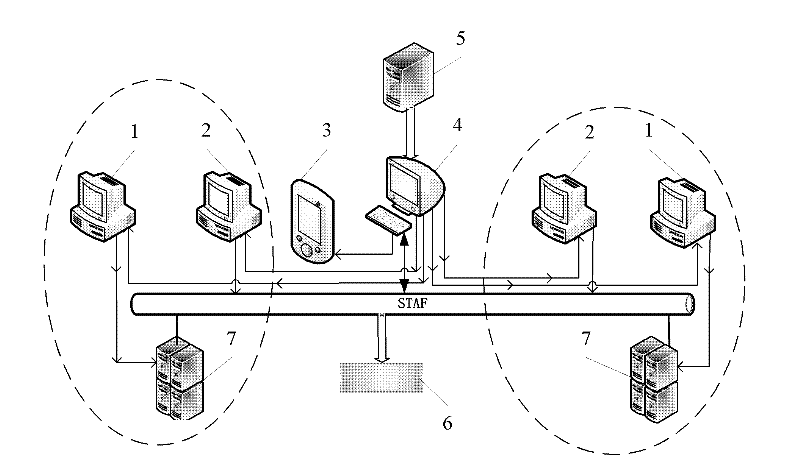

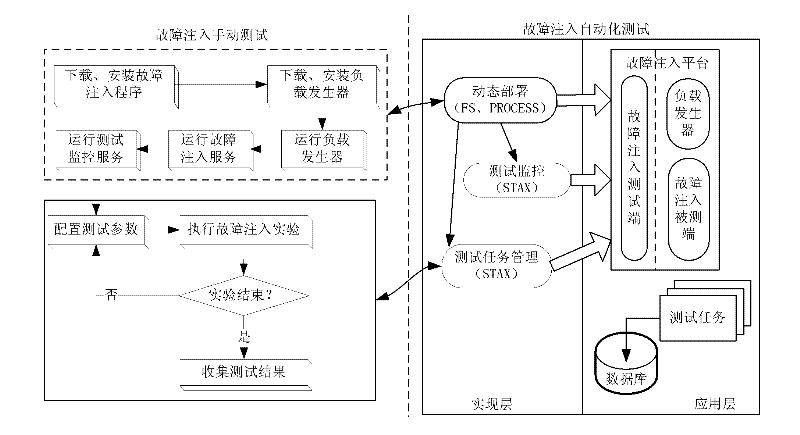

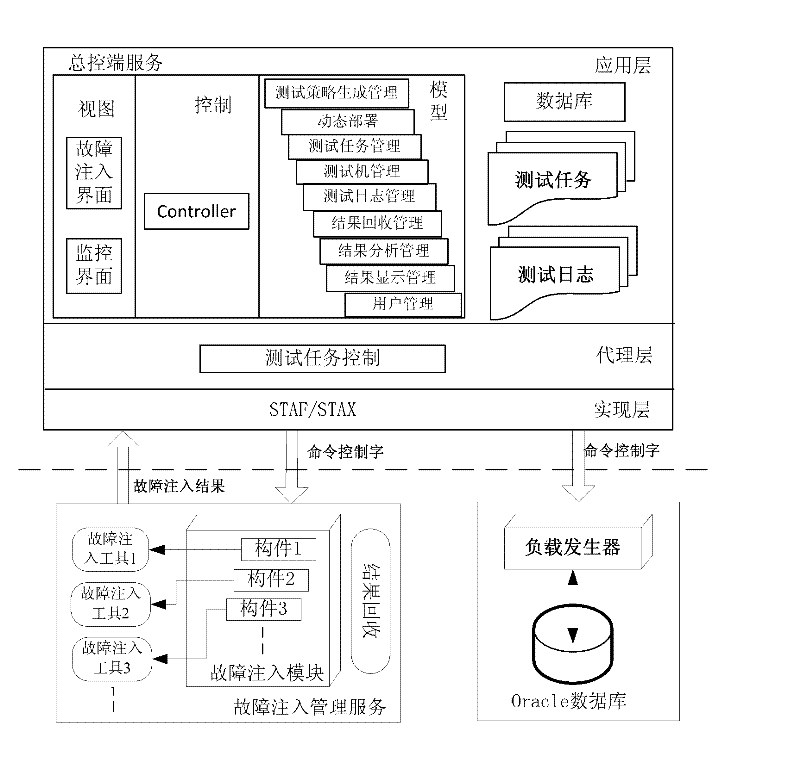

Software testing automation framework (STAF)-based fault injection automation testing platform and method for high-end fault-tolerant computer

InactiveCN102354298AImprove scalabilityImprove maintainabilitySoftware testing/debuggingRelational databaseSoftware engineering

The invention discloses a software testing automation framework (STAF)-based fault injection automation testing platform and an STAF-based fault injection automation testing method for a high-end fault-tolerant computer, and relates to a fault injection technology. The invention provides a fault injection automation testing platform and a fault injection automation testing method, which are applicable for the high-end fault-tolerant computer. The method is implemented by adopting an embedded software distributed testing environment. An application layer in software is an application program operated in general control end service, manages data and information in an automation testing process by utilizing a relational database and a file system, and provides a friendly graphic interface; a proxy layer is operated between the application layer and a realization layer to realize task proxy, and takes charge of executing an automation testing task submitted by a user from the interface; and the realization layer packages the communication among an automation testing control server and testing proxies of various platforms, and executes specific operations of various automation tests. The STAF-based fault injection automation testing platform is a distributed and automatic fault injection platform which is constructed on the basis of an open source automation testing tool STAF, and can integrate various software fault injection tools.

Owner:HARBIN INST OF TECH

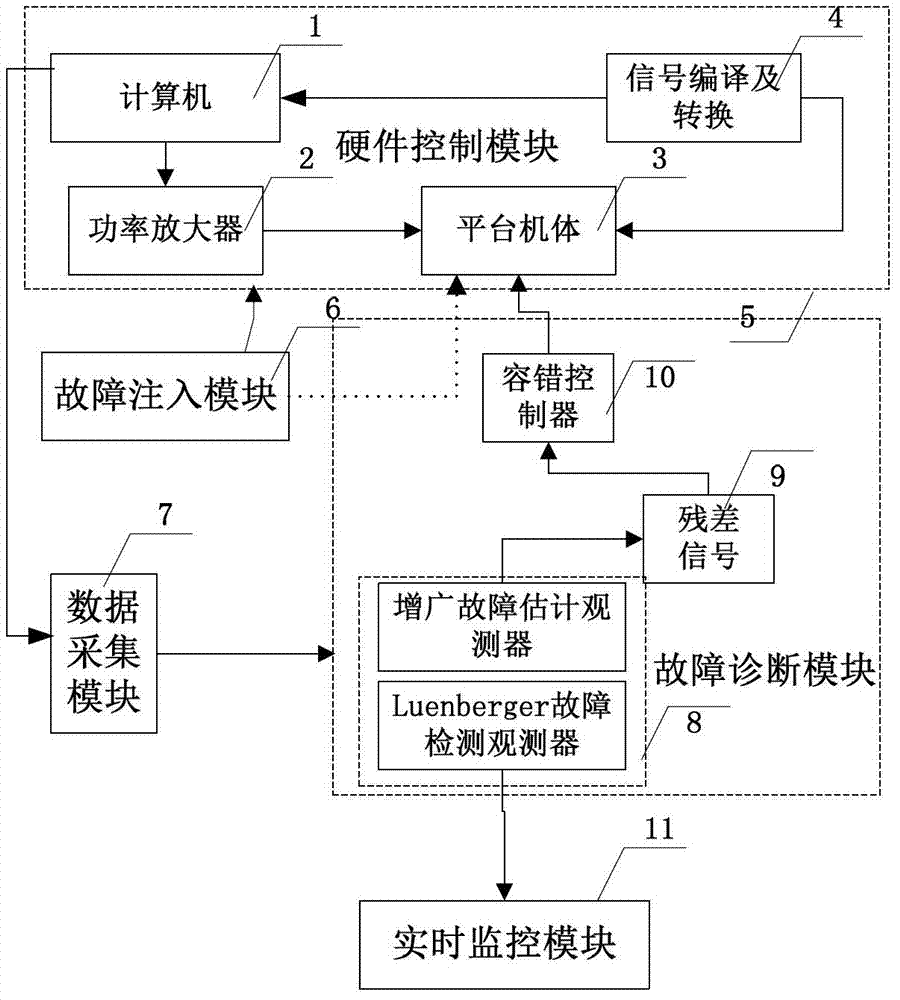

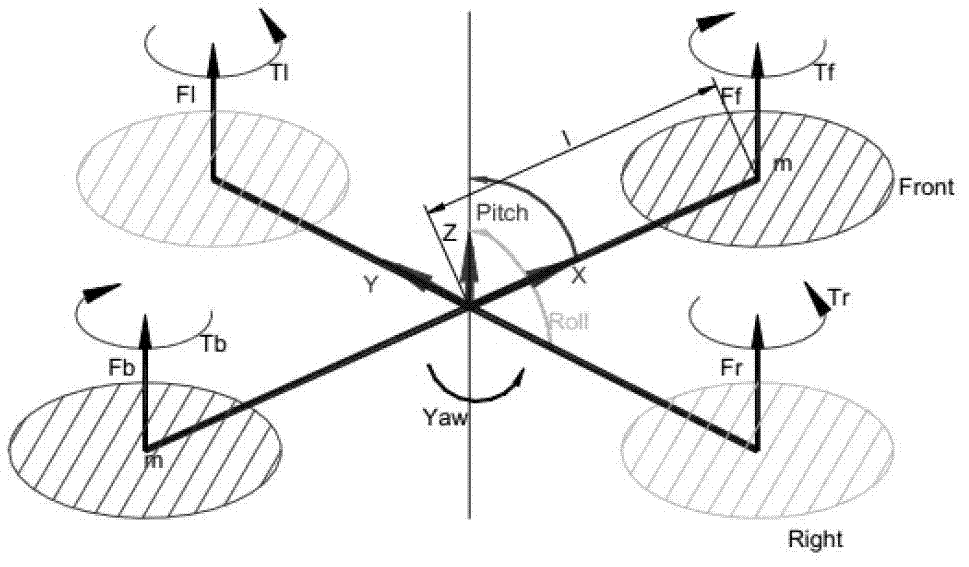

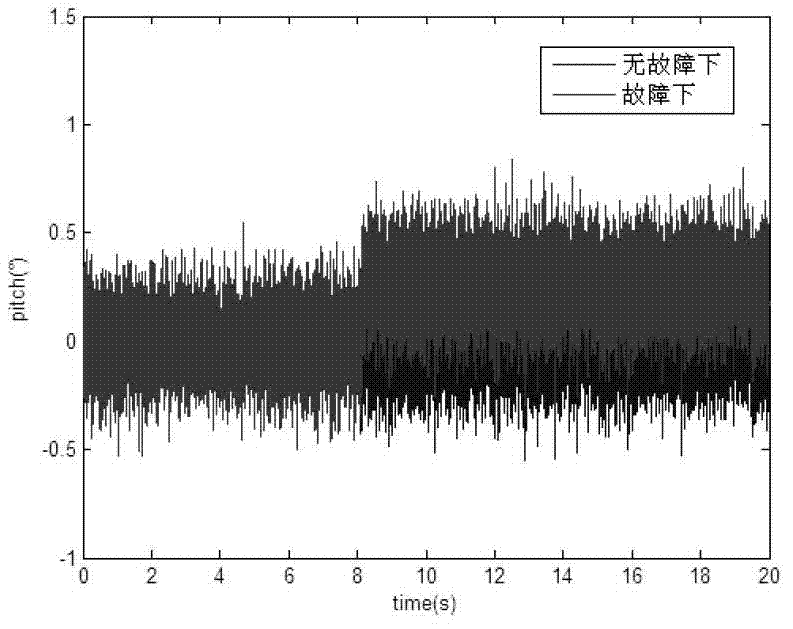

A plurality of united observer based fault diagnosis and fault-tolerant control device and method

ActiveCN102854874AAvoid serious coupling problemsAvoid errorsElectric testing/monitoringAviationDiagnosis methods

The invention discloses a plurality of united observer based fault diagnosis and fault-tolerant control device and a method and belongs to the field of aerospace. The plurality of united observer based fault diagnosis and fault-tolerant control device comprises following modules of a fault injection module, a fault diagnosis module, a real time monitoring module and a hardware control module. According to the method, the problem that traditional observer based fault diagnosis methods are limited by conditions is mainly solved, the operation is simple, the implementability is high, and the method can be used for diagnosing faults of actuating mechanisms of a four rotor wing helicopter and verifying feasibility of state monitoring.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Partial fault tolerant stream processing applications

InactiveUS20110239048A1Error detection/correctionSpecific program execution arrangementsFault toleranceDriving assessment

In one embodiment, the invention comprises partial fault tolerant stream processing applications. One embodiment of a method for implementing partial fault tolerance in a stream processing application comprising a plurality of stream operators includes: defining a quality score function that expresses how well the application is performing quantitatively, injecting a fault into at least one of the plurality of operators, assessing an impact of the fault on the quality score function, and selecting at least one partial fault-tolerant technique for implementation in the application based on the quantitative metric-driven assessment.

Owner:IBM CORP

CBTC (Communications Based Train Control) signal system simulation testing platform

The invention provides a CBTC (Communications Based Train Control) signal system simulation testing platform, which comprises a signal bus, a simulation vehicle-mounted and simulation vehicle system, a simulation station, a simulation rail side system, a three-dimensional vision system and a testing platform management system, wherein the simulation vehicle-mounted and simulation vehicle system, the simulation station, the simulation rail side system, the three-dimensional vision system and the testing platform management system are mutually connected through the signal bus. By applying the invention, an integral solution including vehicle, scheduling and signal systems can be checked and demonstrated; a signal system can be subjected to function and performance tests indoors, and failure injection conditions which can not be simulated in various sites can be carried out indoors, thus testing means are enriched and safety of the system is improved; and simulation checking under the condition of multiple vehicles can be passed, a method for analyzing the railway operation capability is deeply researched, and the reference is provided for the layout of signal devices.

Owner:TRAFFIC CONTROL TECH CO LTD

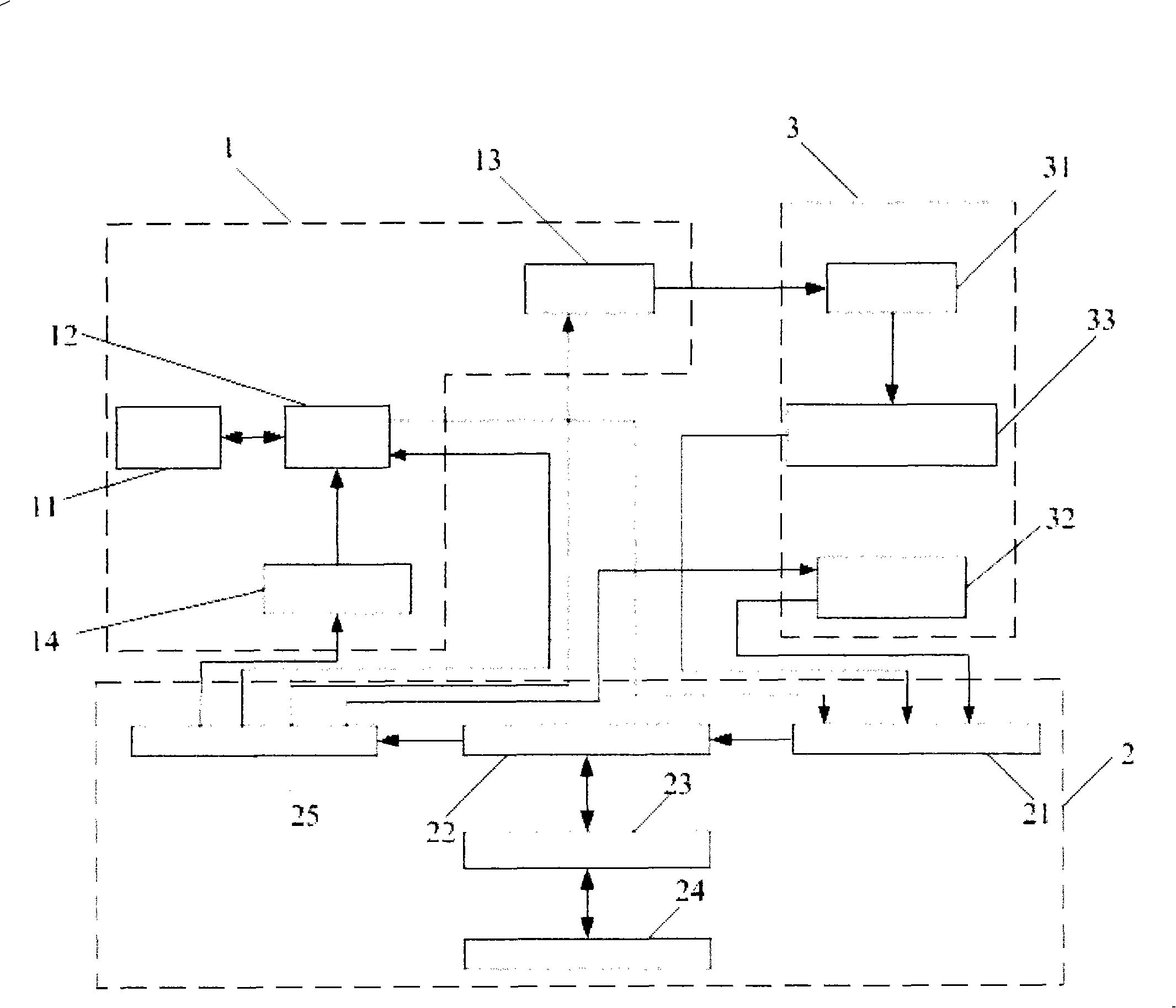

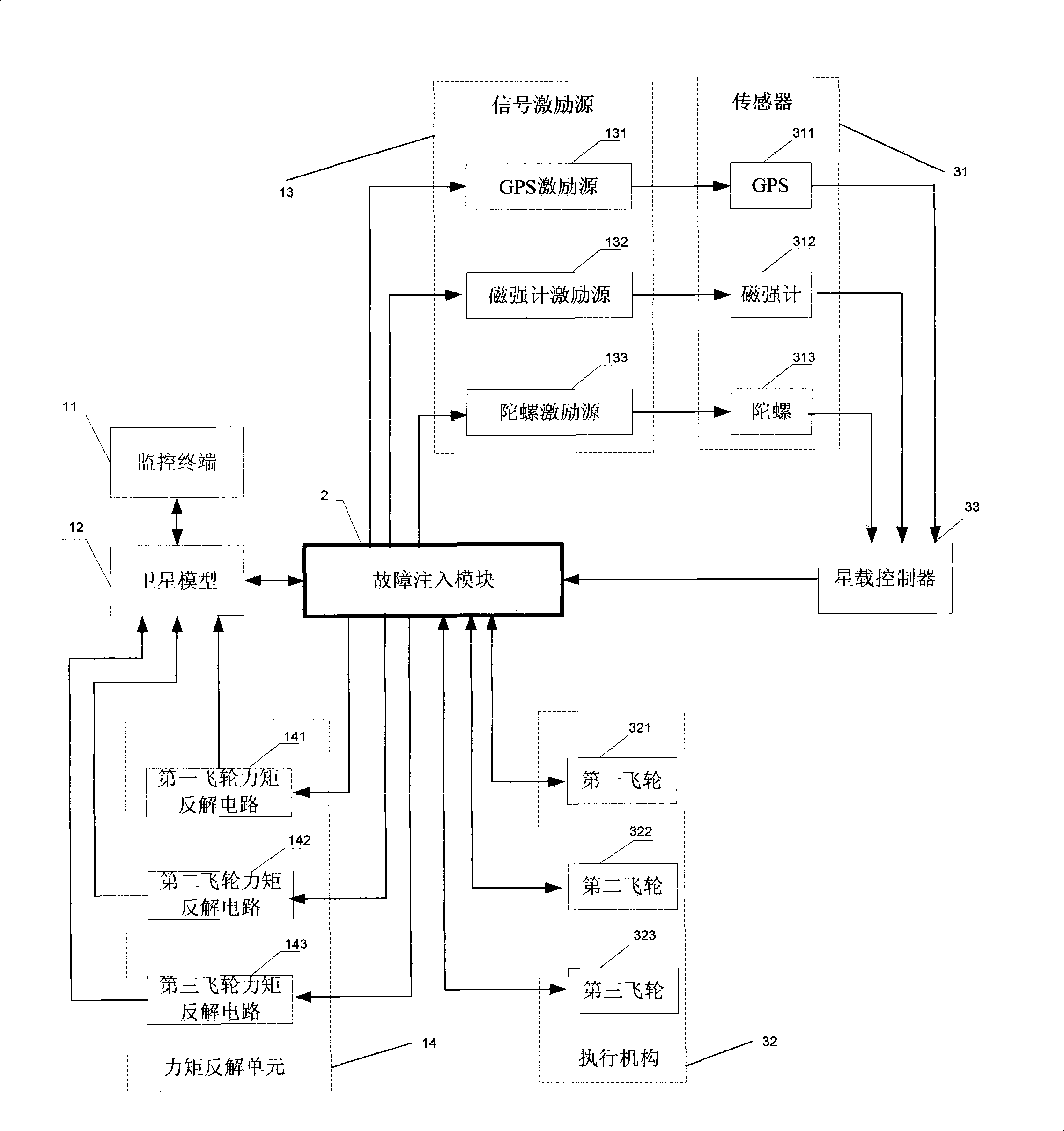

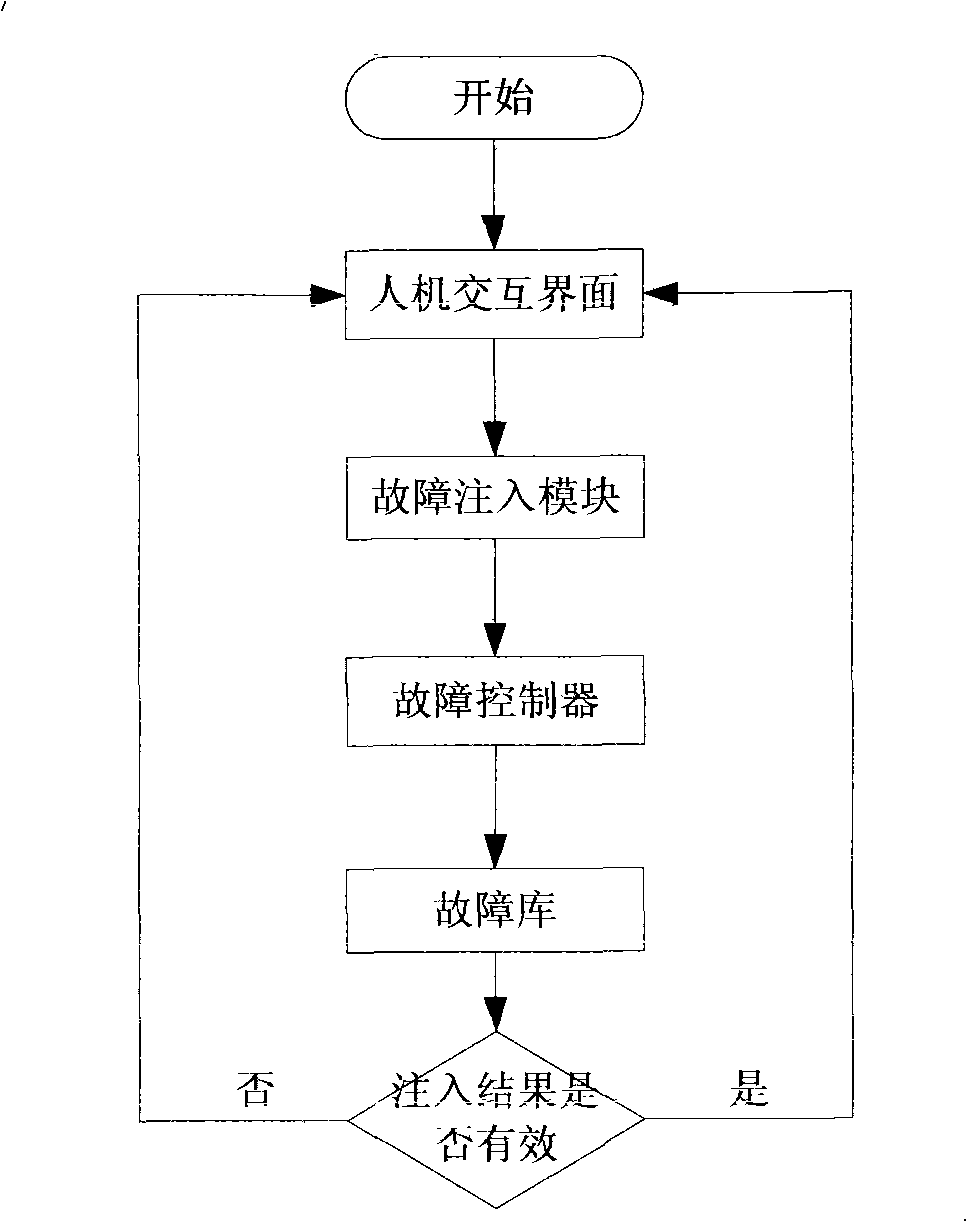

Simulation test equipment and method for moonlet attitude control reliability validation

InactiveCN101344788AWithout breaking integrityImprove test accuracyElectric testing/monitoringControl signalPrice ratio

Simulation test equipment for validating the reliability of satellite attitude control and a test method thereof belong to the field of satellite attitude control. The test equipment comprises a ground simulation support module, a fault injection module and a satellite-born module, wherein, the ground simulation support module includes a monitoring terminal, a satellite model, a signal exciting source and a moment reverse-solution unit; the fault injection module includes an analog-to-digital converter, a signal transfer circuit, a fault injection processor, a man-machine interface unit and a digital-to-analog converter; and the satellite-born module includes a sensor, a satellite-born controller and an actuator. The test method comprises the following steps of: fault model setting; satellite initialization; orbit and attitude information renewal; the satellite-born controller collects signals of the sensor and outputs actuator command signals to the fault injection module; the actuator receives actuator pseudo command signals and outputs feedback signals to the fault injection module; the moment reverse-solution unit collects the pseudo feedback signals output by the fault injection module and outputs moment control signals to the satellite model. The equipment and the method of the invention have high feasibility and high performance-price ratio.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

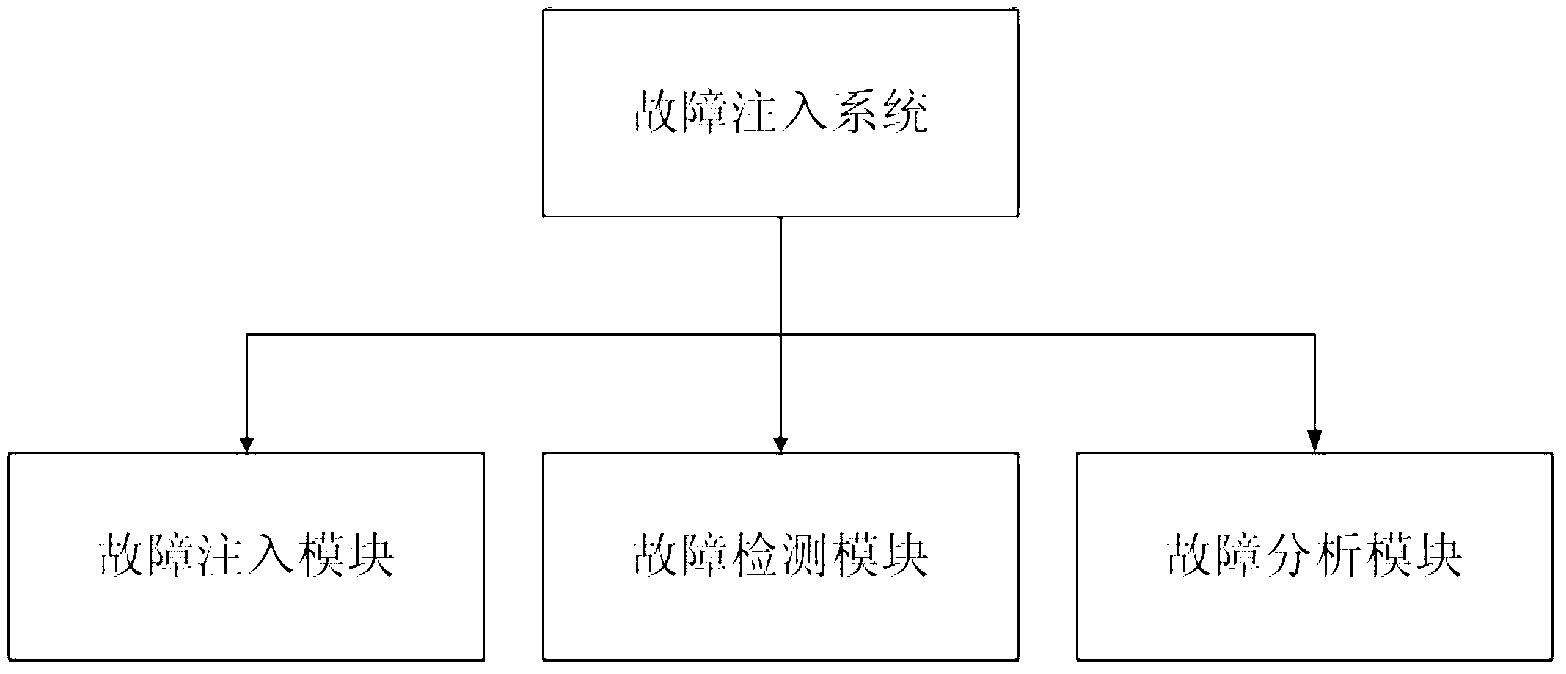

Fault simulation system and fault analysis method for single event upset

InactiveCN103198868ANo damageThrottling flow timeStatic storageSpecial data processing applicationsComputer moduleFault analysis

The invention relates to a fault simulation system and a fault analysis method for single event upset in a large scale integrated circuit SRAM-type FPGA (Field Programmable Gate Array). The fault simulation system comprises a host computer and a control board, wherein the control board comprises a fault injection module, a fault detecting module and a fault analyzing module. The fault simulation system and the fault analysis method provided by the invention are flexible to use, low in cost, high in simulation precision, fast in simulation speed and free from any physical damage to a chip.

Owner:NORTHWEST INST OF NUCLEAR TECH

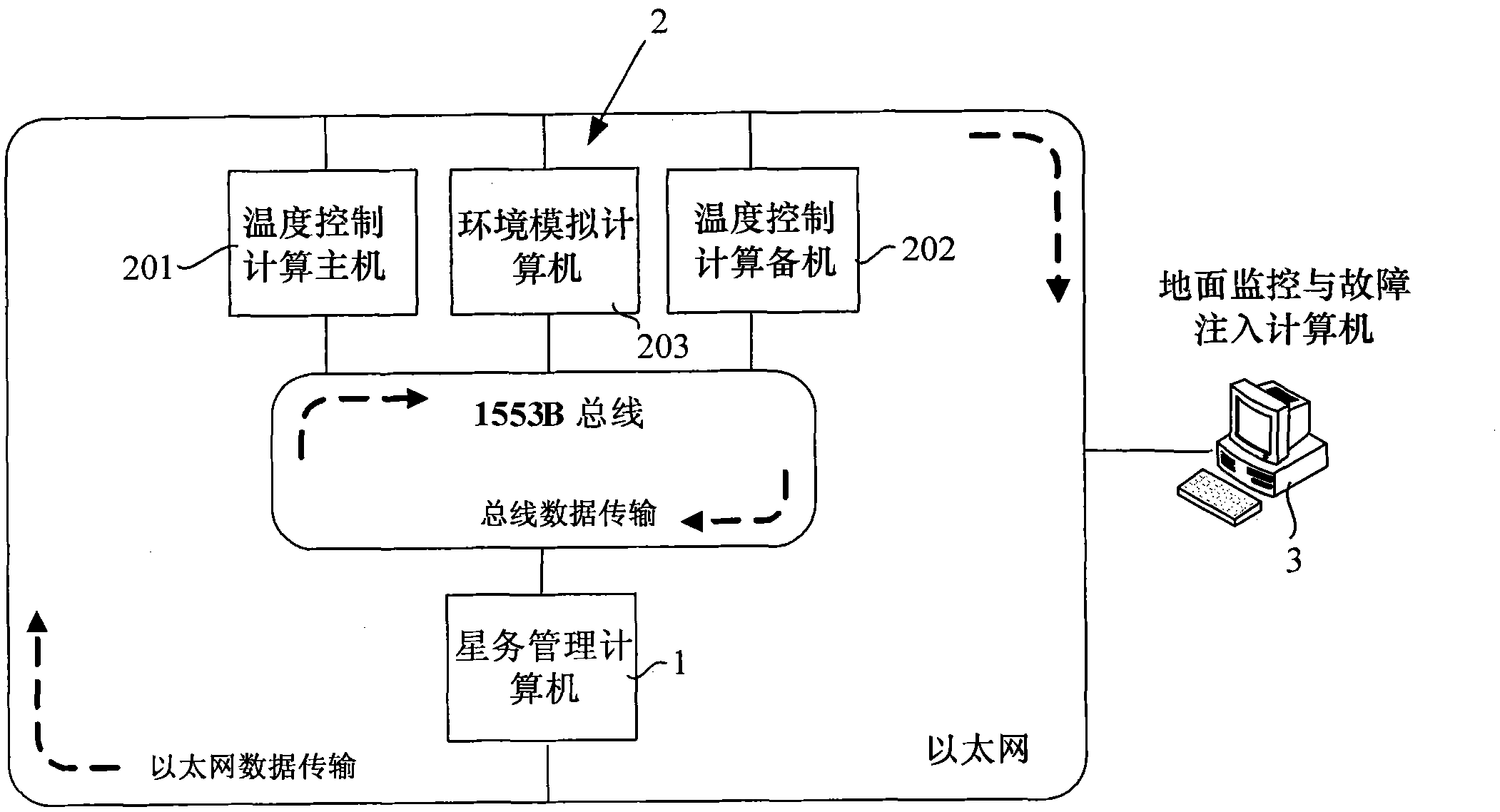

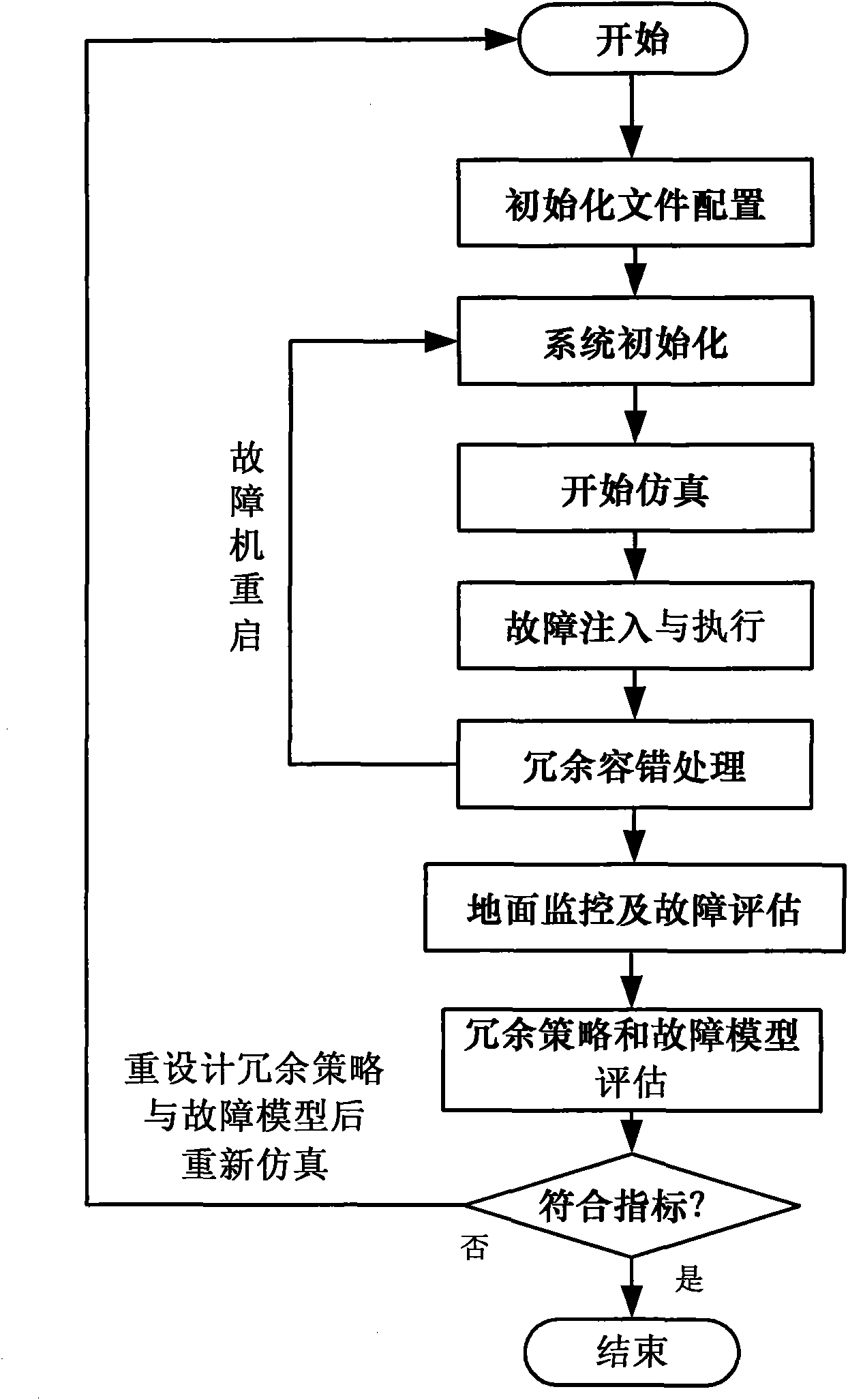

Embedded satellite-borne fault-tolerant temperature control system and verification method thereof

InactiveCN101819445AIn line with the development trendWith real development prospectsTemperatue controlError detection/correctionFault toleranceTemperature control

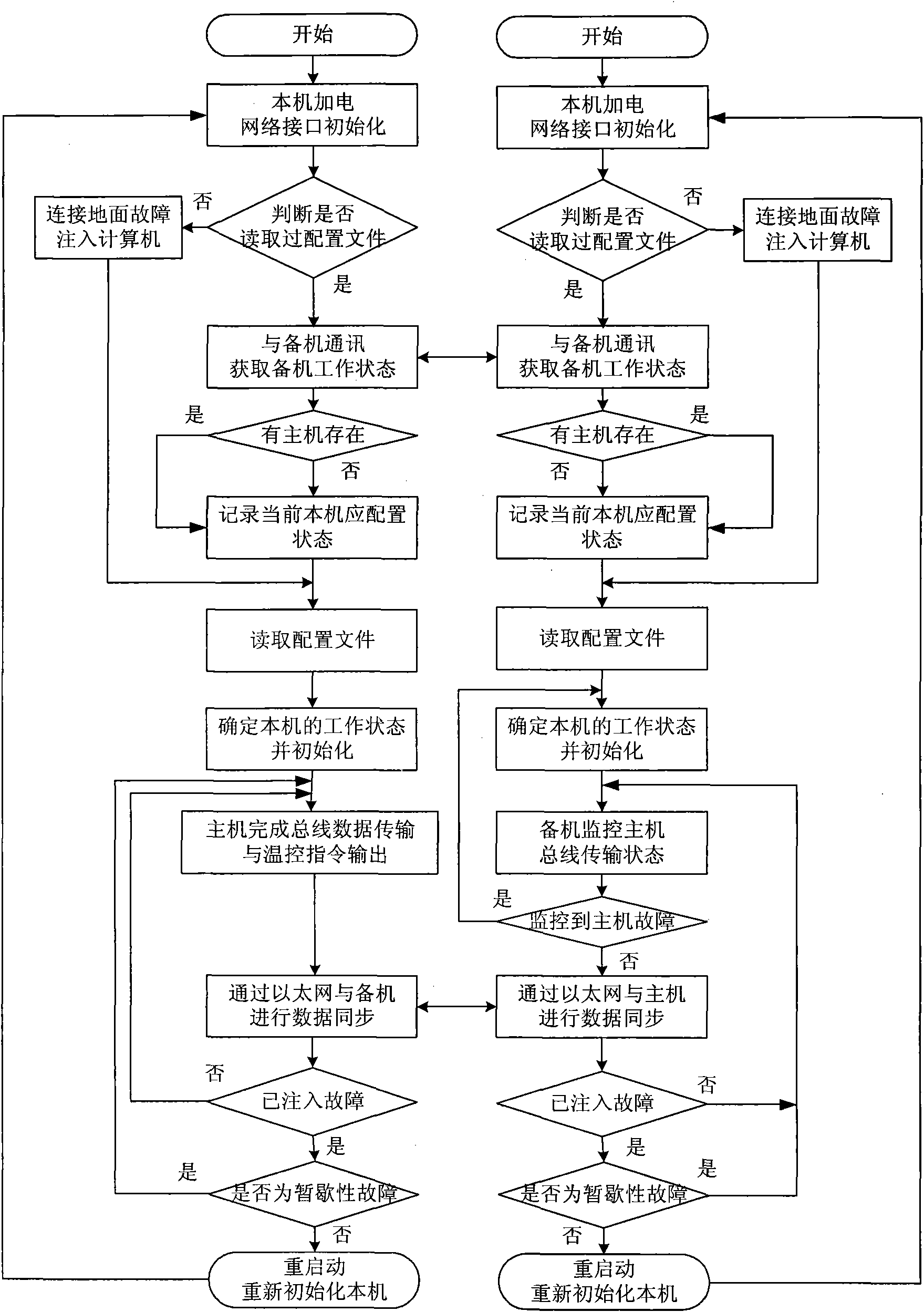

The invention discloses an embedded satellite-borne fault-tolerant temperature control system and a verification method thereof. The system comprises a satellite management computer, an on-satellite temperature control system and a ground monitoring and fault injection computer; the on-satellite temperature control system comprises a temperature control calculation host machine, a temperature control calculation standby machine and an environmental simulation computer; and the temperature control calculation host machine and the temperature control calculation standby machine are temperature control computers. The verification method comprises the following steps of: 1, initializing a file allocation; 2, initializing the system; 3, beginning simulation; 4, injecting and executing a fault; 5, processing redundant fault tolerance; 6, monitoring the ground and evaluating the fault; and 7, evaluating a fault model and a redundancy strategy of the temperature control system. The fault injection and the verification process of the whole running stage of the real satellite-borne temperature control system are completely realized; and the method is simple, convenient and reliable, and greatly reduces the test time and expense for the practical system.

Owner:BEIHANG UNIV

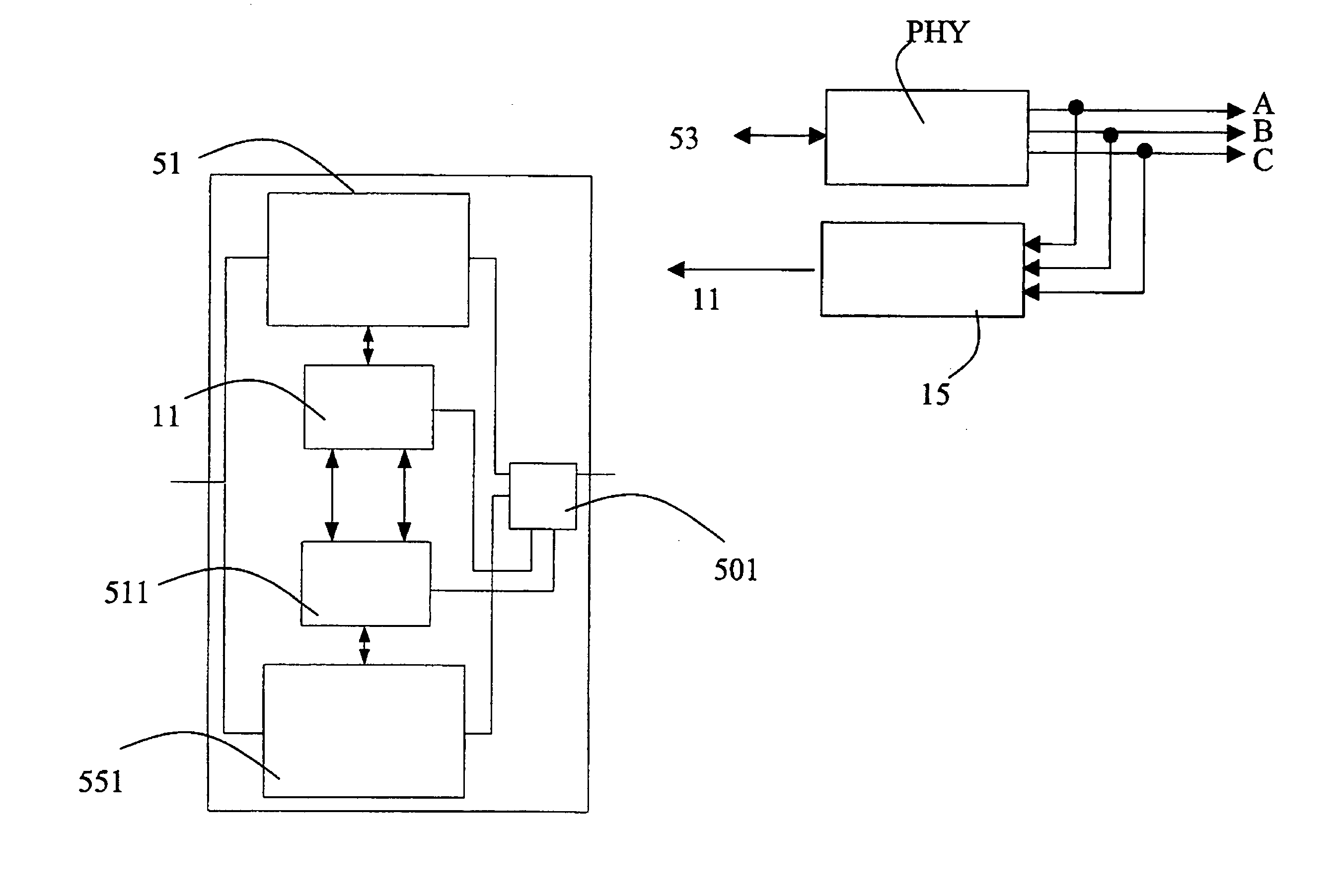

Dependable microcontroller, method for designing a dependable microcontroller and computer program product therefor

ActiveUS20050050387A1Reduced area overheadLow low latency controlAnalogue computers for electric apparatusHardware monitoringMicrocontrollerFault tolerance

A microcontroller comprising a central processing unit and a further fault processing unit suitable for performing validation of operations of said central processing unit. The further fault processing unit is external and different with respect to said central processing unit and said further fault processing unit comprises at least a module for performing validation of operations of said central processing unit and one or more modules suitable for performing validation of operations of other functional parts of said microcontroller. Validation of operations of said central processing unit is performed by using one or more of the following fault tolerance techniques: data shadowing; code&flow signature; data processing legality check; addressing legality check; ALU concurrent integrity checking; concurrent mode / interrupt check. The proposed microcontroller is particularly suitable for application in System On Chip (SoC) and was developed by paying specific attention to the possible use in automotive System On Chip. The invention also includes a method for designing and verify such fault-robust system on chip, and a fault-injection technique based on e-language.

Owner:TAHOE RES LTD

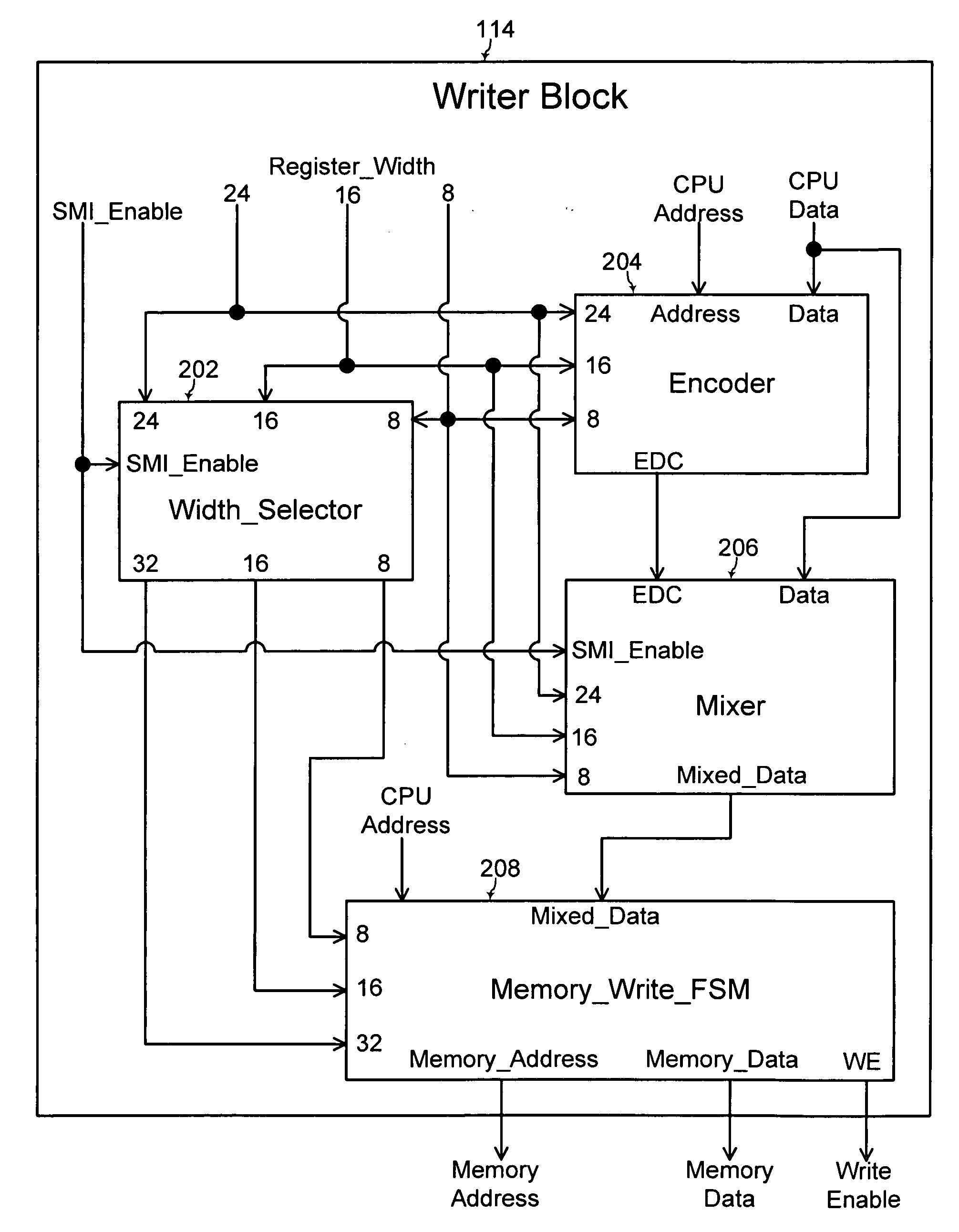

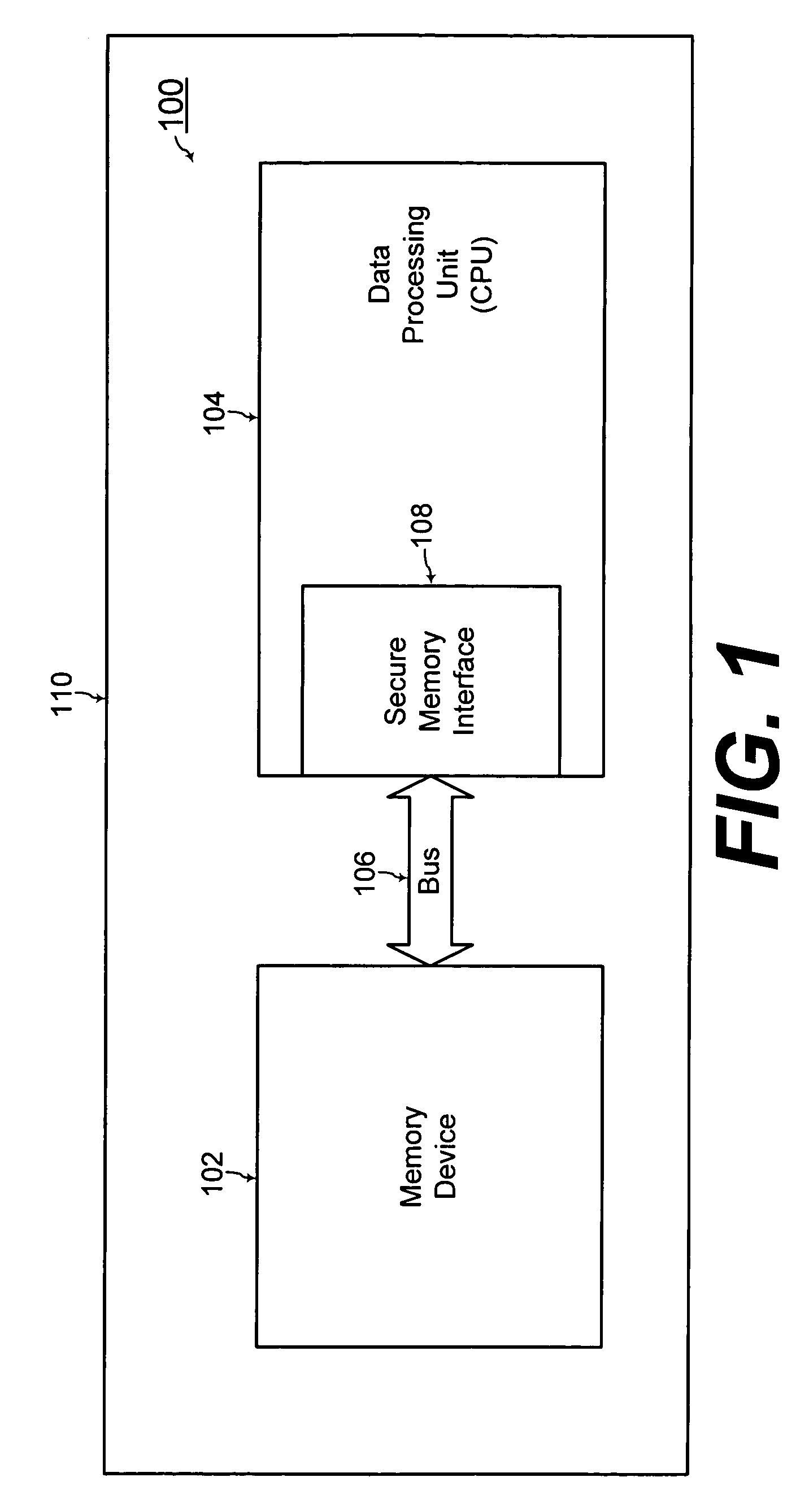

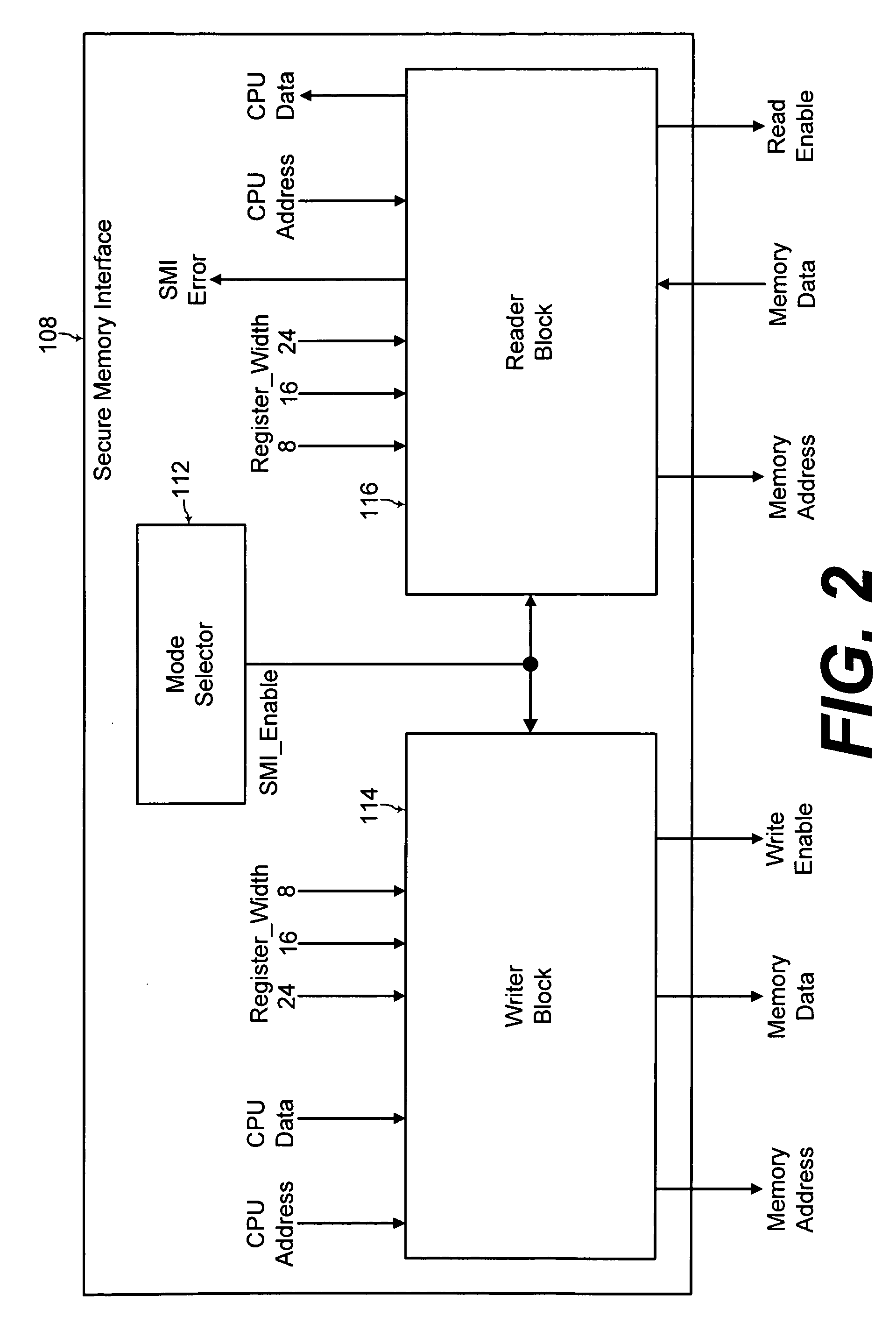

Secure memory interface

ActiveUS20100082927A1Efficient detectionEasy accessDigital computer detailsUnauthorized memory use protectionMain processing unitMemory interface

A secure memory interface includes a reader block, a writer block, and a mode selector for detecting fault injection into a memory device when a secure mode is activated. The mode selector activates or deactivates the secure mode using memory access information from a data processing unit. Thus, the data processing unit flexibly specifies the amount and location of the secure data stored into the memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

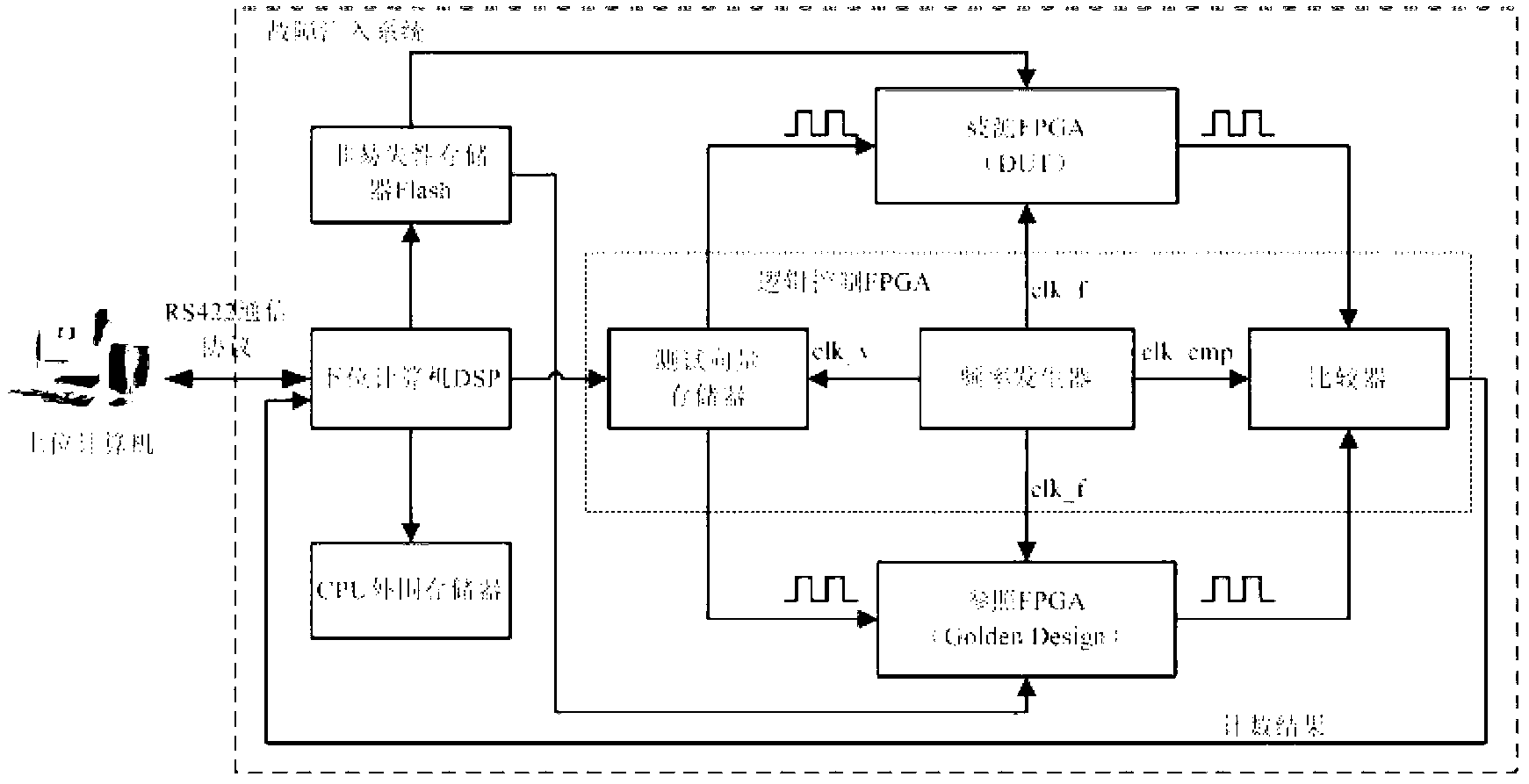

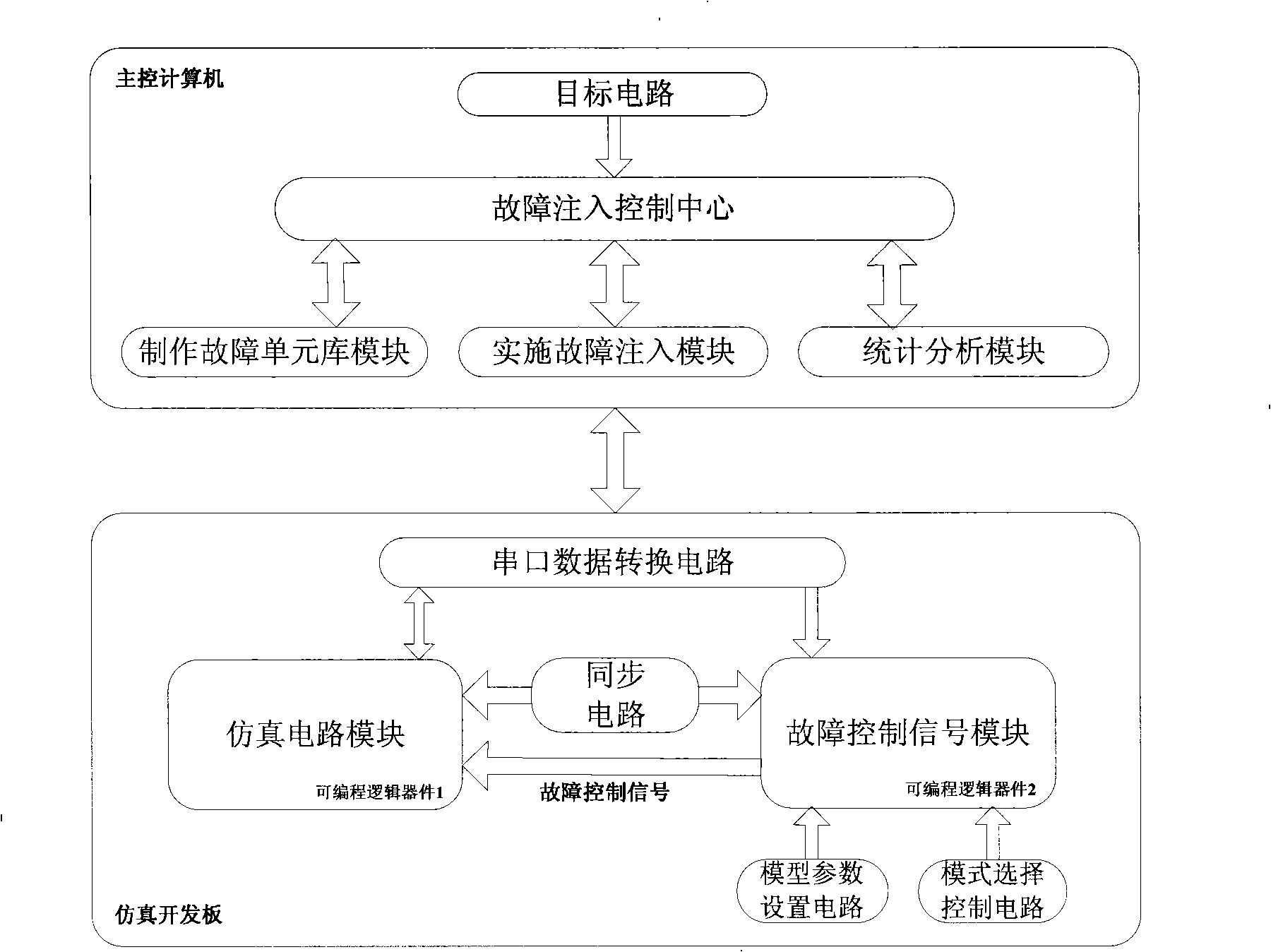

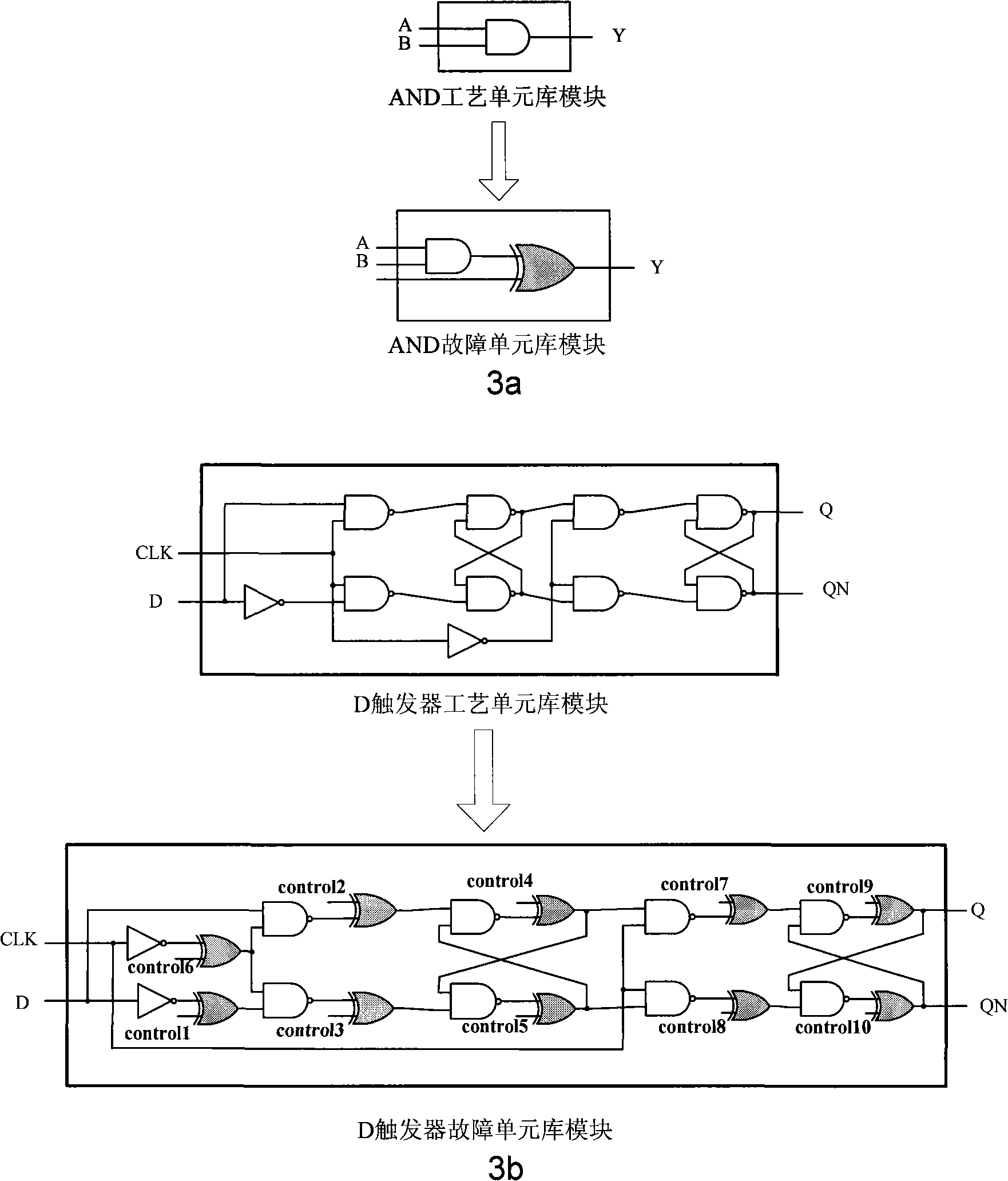

Fault injection system and method for verifying anti-single particle effect capability

InactiveCN101281555AHigh fault injection coverageHigh performance reference valueSpecial data processing applicationsControl signalStatistical analysis

The invention relates to a fault injection system for verifying anti-single-particle-effect ability. A fault unit library fabrication module modifies a process unit library of an objective circuit to a fault unit library of the objective circuit; a fault injection implementation module modifies the gate level HDL codes of the objective circuit, generates a non-fault circuit and a fault circuit, maps the modified codes to the fault unit library, counts the number of the fault terminals of the codes and sends to a fault control signal module; a synchronous circuit realizes clock synchronization of a simulation circuit module and a fault control signal module; the fault control signal module generates a fault control signal and sends to the fault circuit of the simulation circuit module; the simulation circuit module loads the non-fault circuit and the fault circuit, provides input signals to the two circuits, provides the control signal to the non-fault circuit, compares the outputs of the two circuits and sends the comparison result and the fault control signal to a statistical analysis module to record, the statistical analysis module calculates the error rate and sensitivity of each node.

Owner:BEIJING MXTRONICS CORP +1

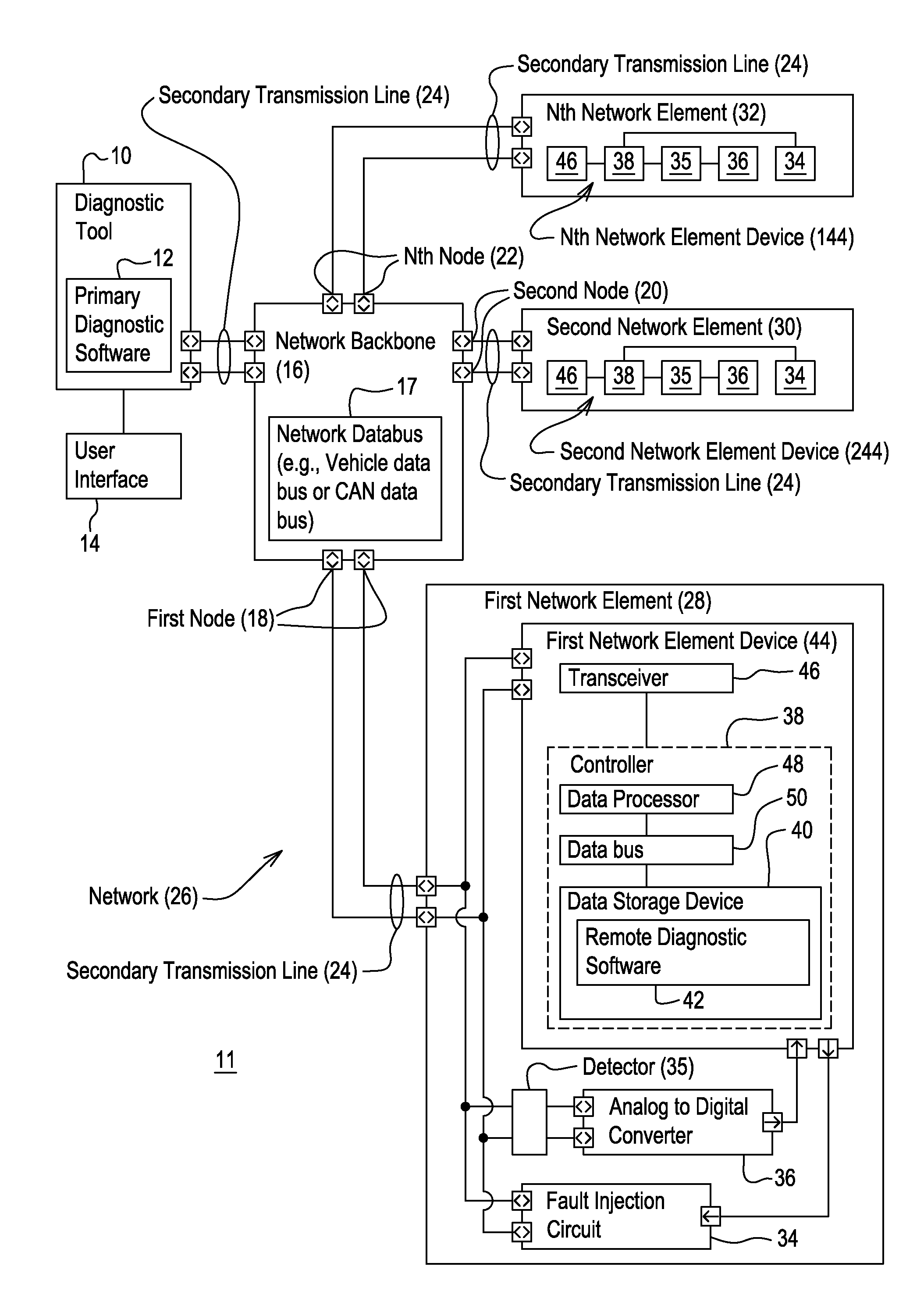

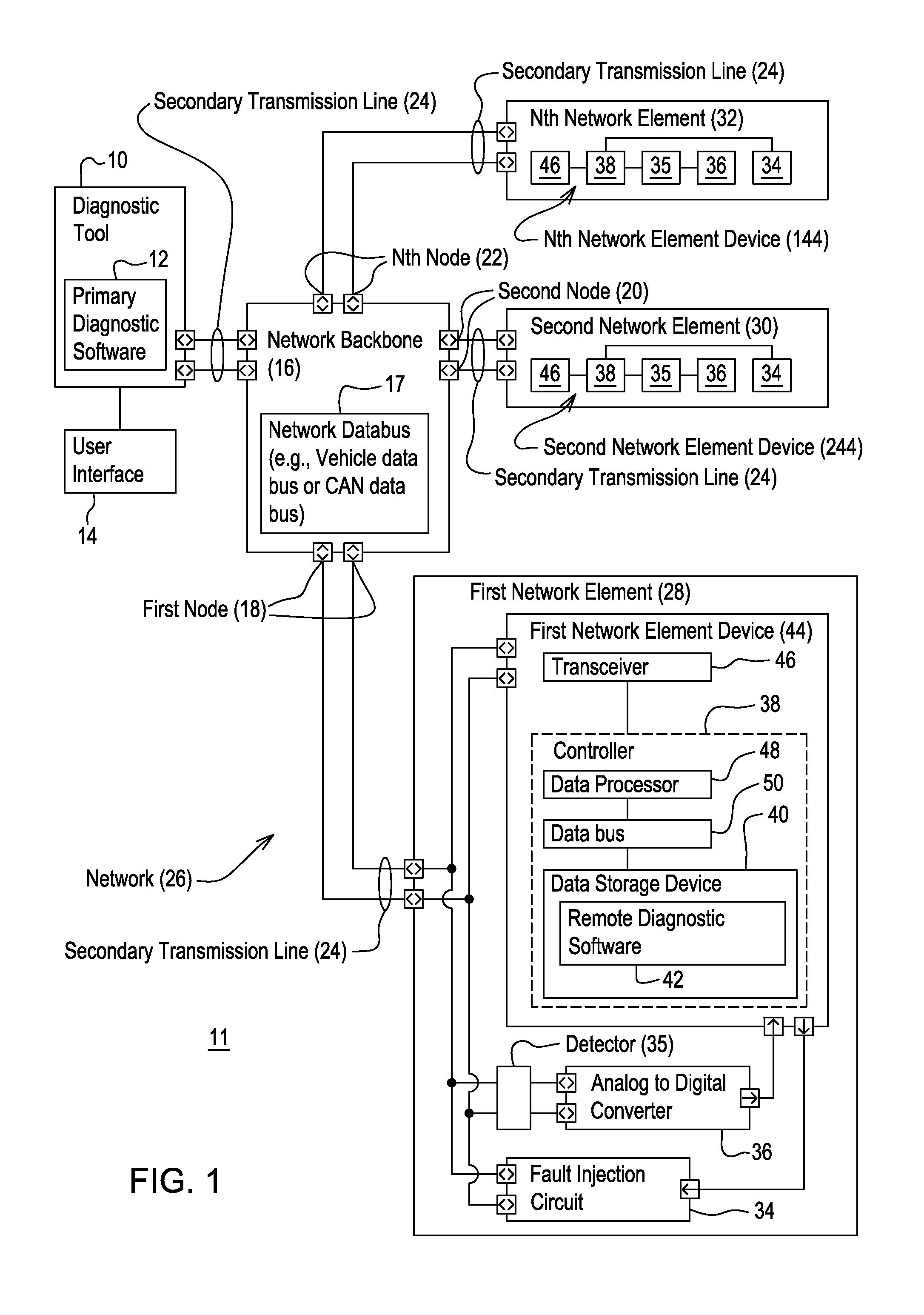

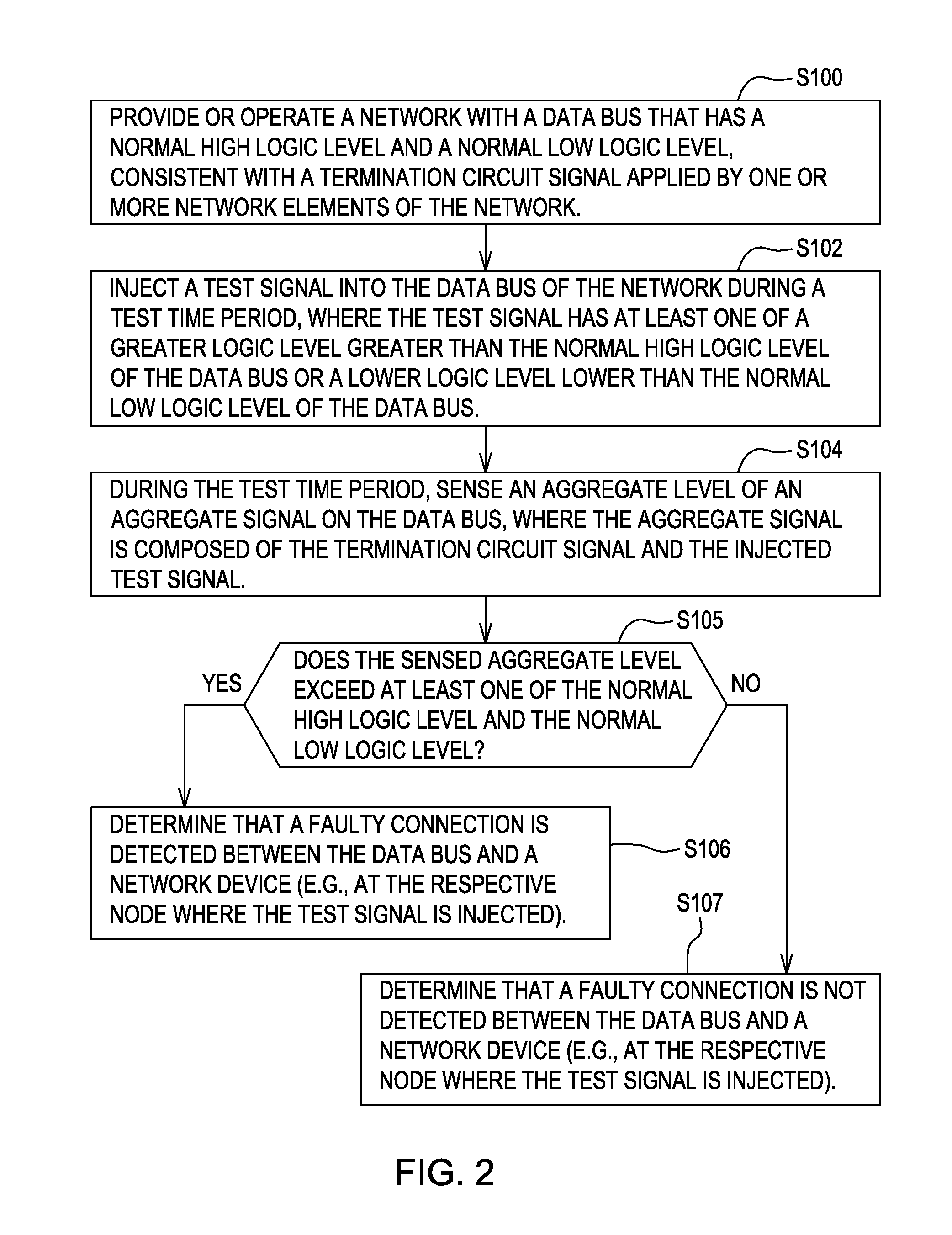

Method and system for diagnosing a fault or open circuit in a network

A fault injection circuit injects a test signal into a data bus with a normal high logic level and a normal low logic level. The test signal has a greater logic level greater than the normal high logic level of the data bus or a lower logic level lower than the normal low logic level of the data bus. An analog-to-digital converter is coupled to a voltage level detector for sensing an aggregate level of an aggregate signal on the data bus. The aggregate signal is composed of the termination circuit signal and the test signal. A diagnostic tool determines whether a faulty connection between the data bus and a network device exists, where the sensed aggregate level exceeds at least one of the normal high logic level and the normal low logic level.

Owner:DEERE & CO

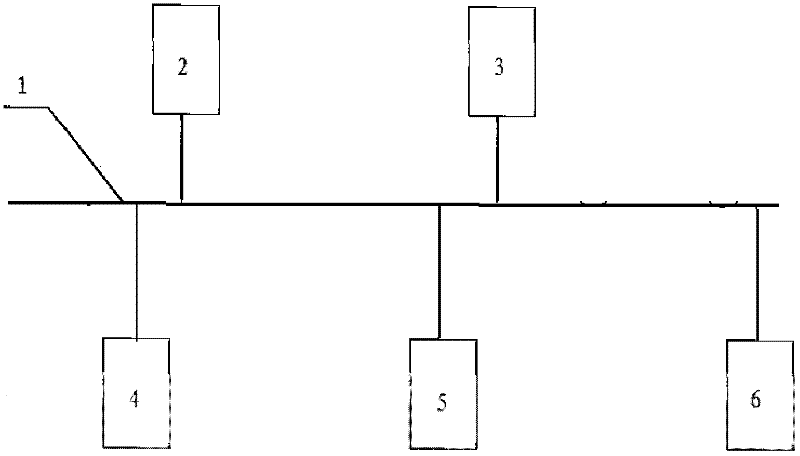

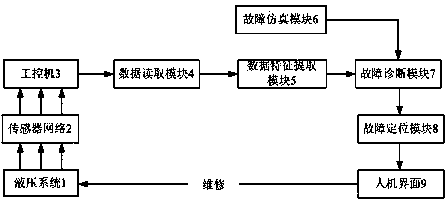

Online fault diagnosis method for hydraulic system

InactiveCN104061208AGuaranteed accuracyAccurate fault locationFluid-pressure actuator testingHuman–machine interfaceFeature extraction

The invention discloses an online fault diagnosis method for a hydraulic system. A sensor network (2) and an industrial personal computer (3) are used for acquiring a signal of a key position of the hydraulic system (1). Meanwhile, a system model is established for the hydraulic system (1), and fault injection simulation is carried out to obtain a simulation result serving as fault simulation data in a fault simulation module (6). The key characteristic information of the data provided by a data reading module (4) is found by a data characteristic extraction module (5), and fault diagnosis is carried out through a fault diagnosis module (7). A fault positioning module (8) can be used for positioning the fault according to fault information obtained by the fault diagnosis module (7), and providing a fault diagnosis result, fault causes, a detection flow and fault elimination measures, which are all displayed on a human-computer interface (9). According to the method, the false fault alarm rate is reduced, the capacities such as early warning are improved, and the method plays an important role in improvement of the reliability of the hydraulic system of product equipment.

Owner:BEIJING MECHANICAL EQUIP INST

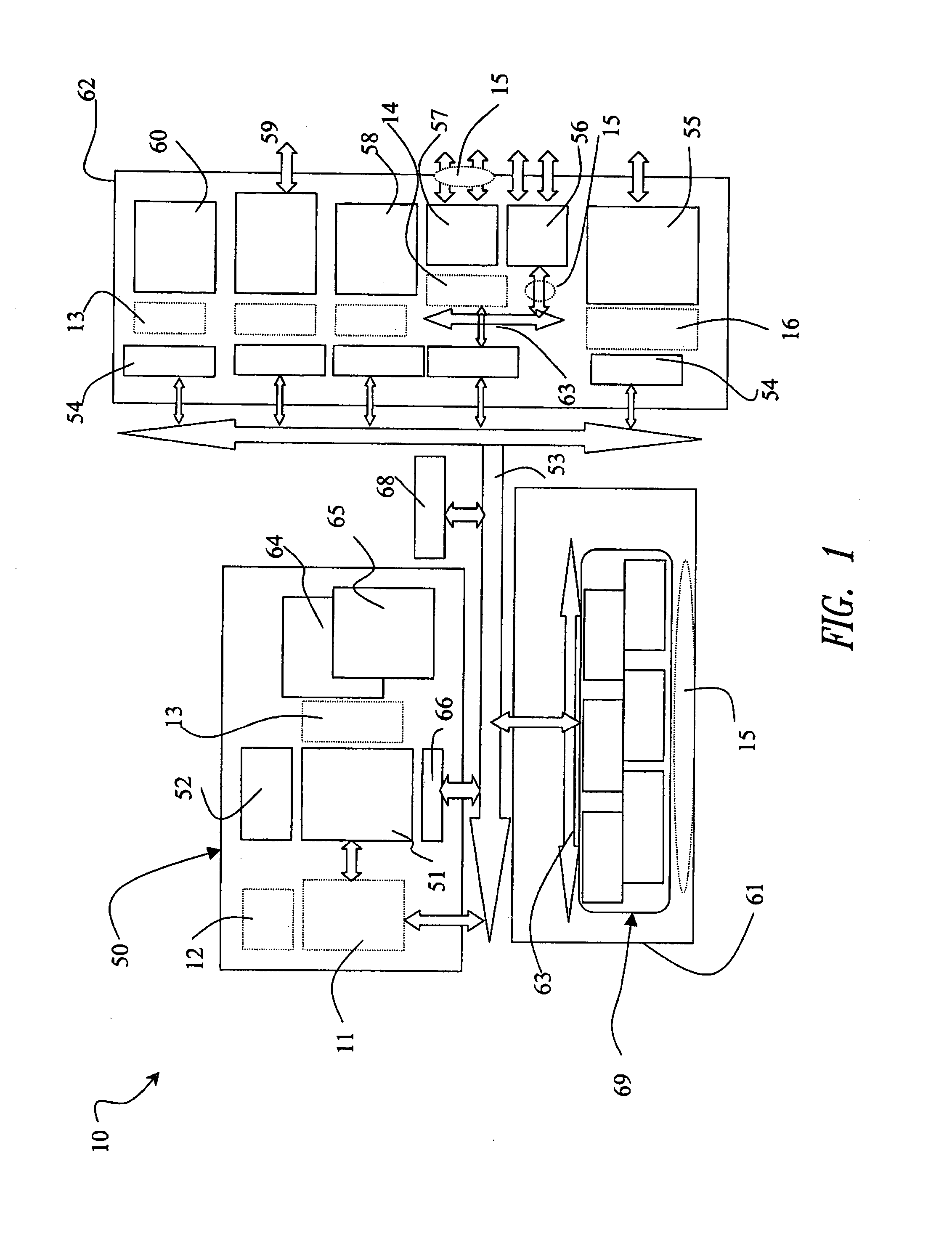

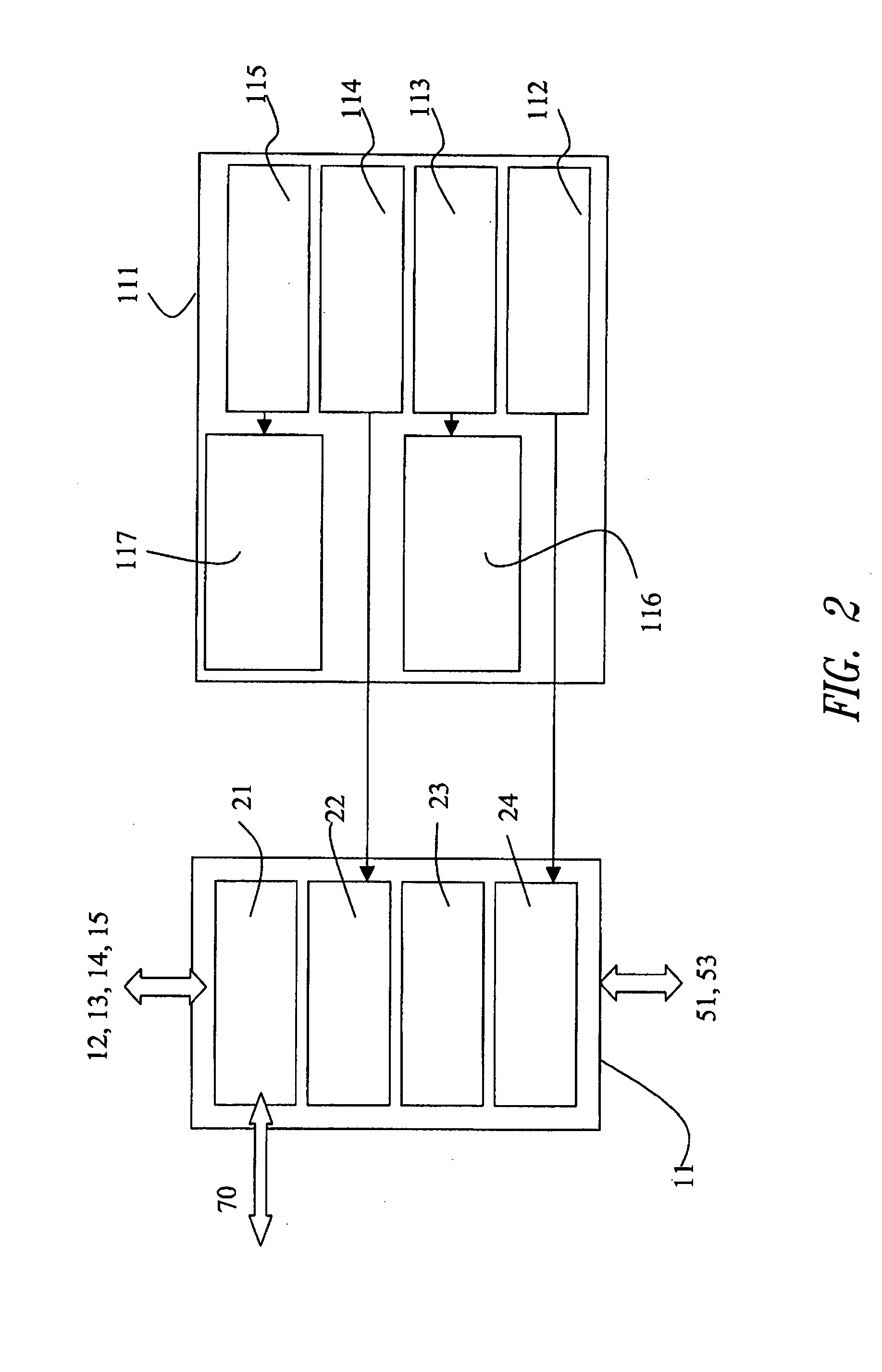

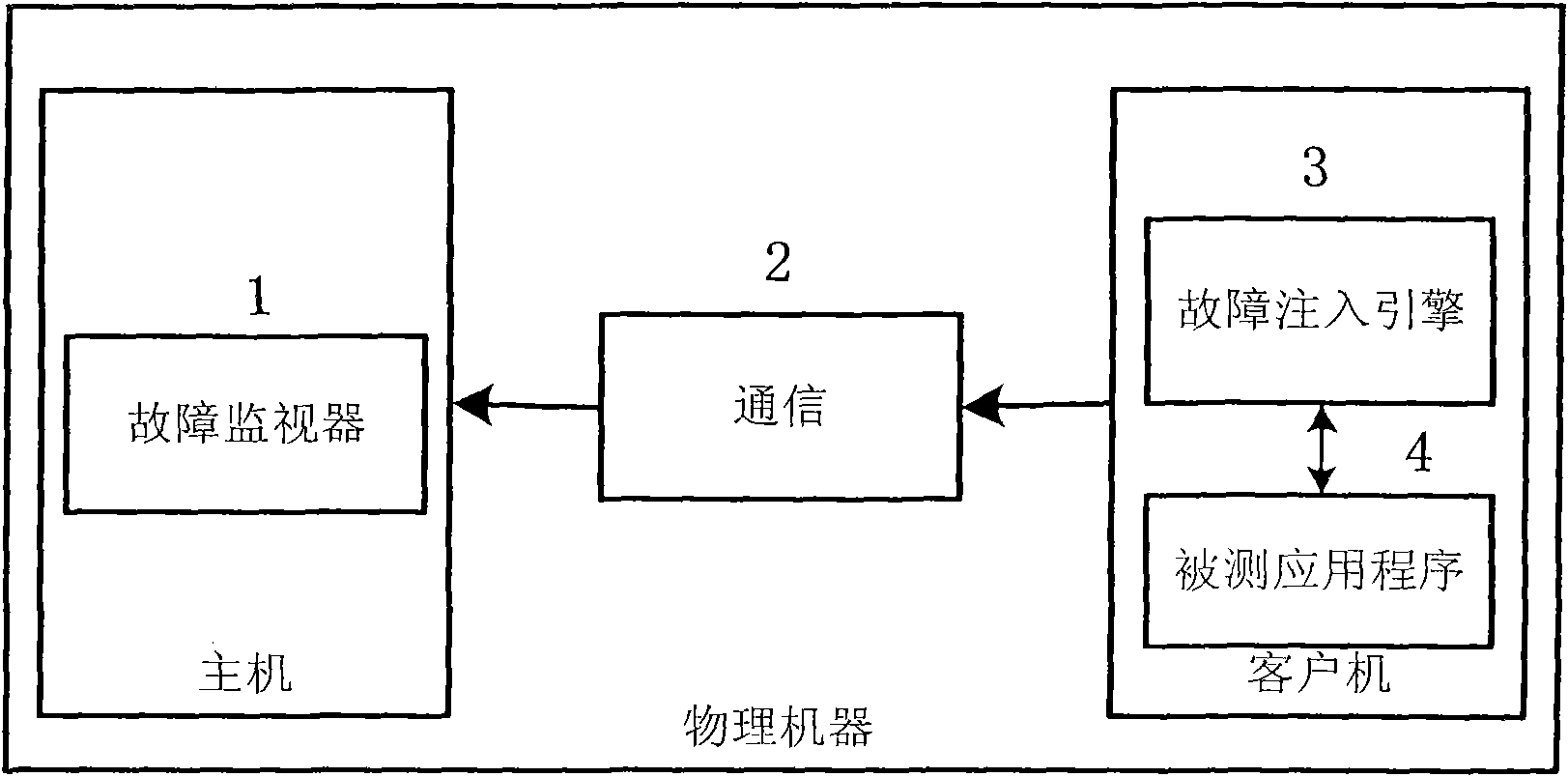

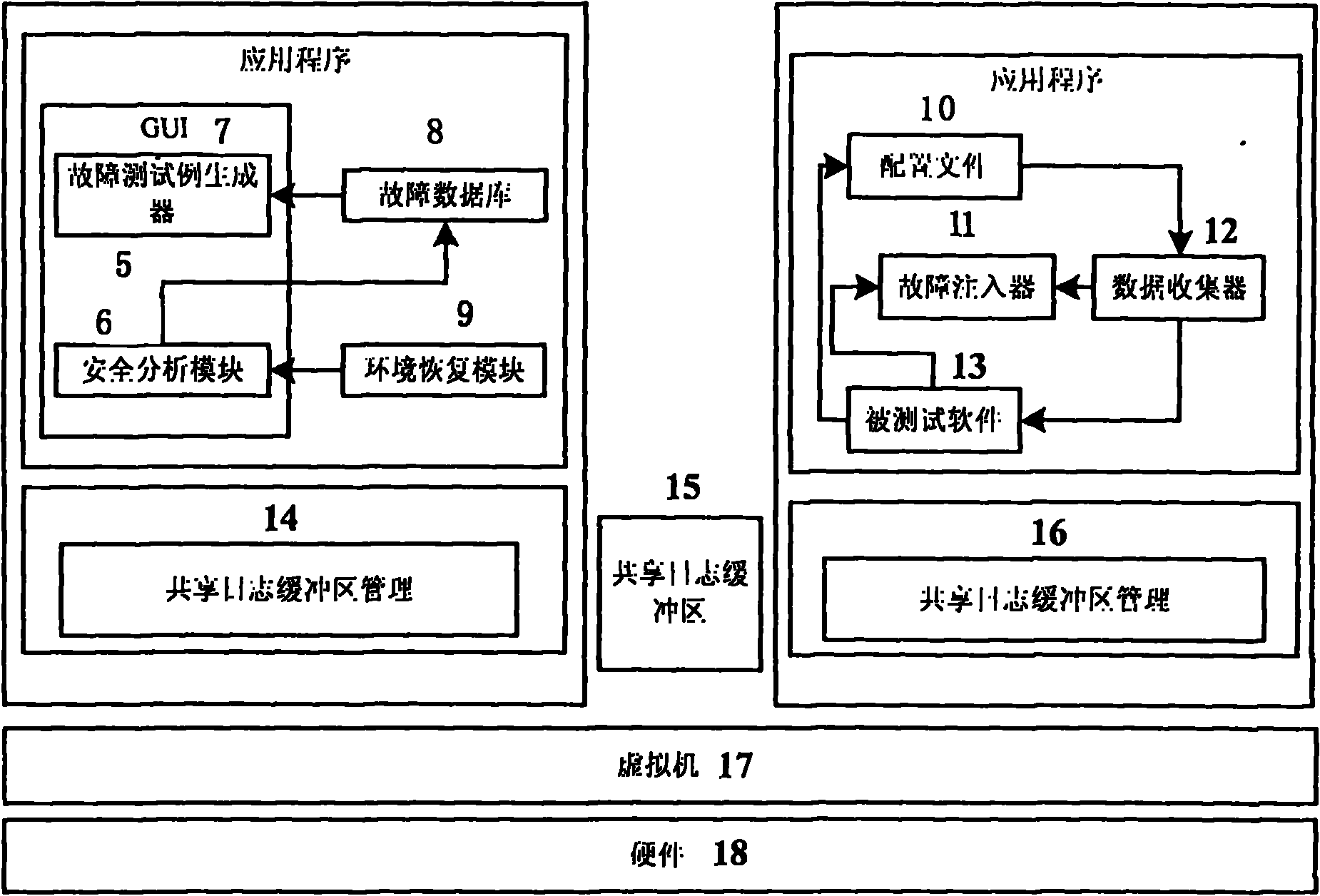

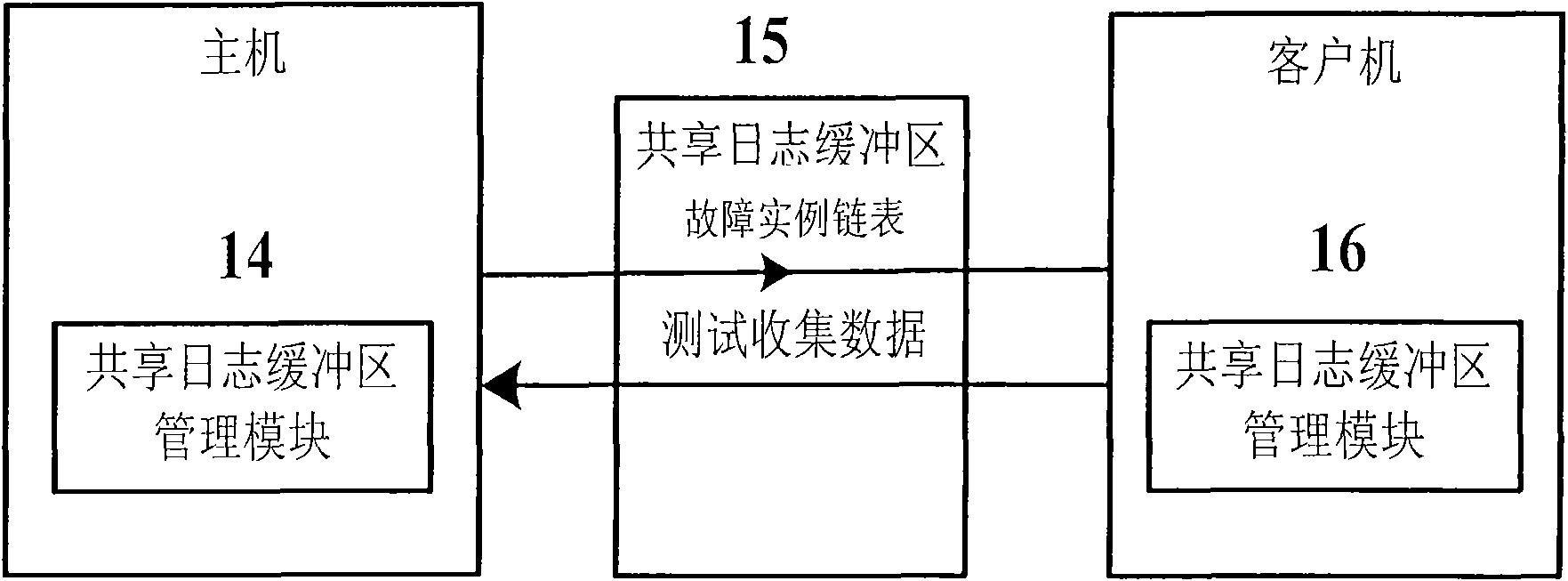

Method for fault-injection test based on virtual machine

The invention provides a method for using a virtual machine to improve the performance in software-testing based on fault injection. Based on the EAI (environment-application interaction) model put forward by WENLIANG DU, Syracuse University (US), the fault injection is carried out on the interaction point of the application program and the environment thereof in the invention to disturb the environment and further test the software vulnerability, thus reducing the semantic difference between the injected fault and the actual fault, reducing the number of test cases and respectively achieving the two functional parts of the test tool at the host and guest of the virtual machine; and based on the shared files between the virtual machine and the guest, and the backup and recovery mechanism of the virtual machine, the invention can improve the robustness and flexibility of the test tool. The tool generated by the method comprises an application program configuration file (10), a fault test case generator (5), a security analysis module (6), a graphical user interface (7), an environment recovery module (9), a fault injector (11) and a data collector (12), wherein the tool further comprises software (13) to be tested and shared memory auxiliary modules (14), (15) and (16) of the virtual machine for sharing the data related to the tests. The method of the invention is capable of effectively detecting and simulating the security breaches in the software and improving the security of the software.

Owner:曾凡平 +2

Semiconductor integrated circuit, circuit function veryfication device and method of veryfying circuit function

InactiveUS20100251043A1Detecting faulty computer hardwareStatic storageComputer scienceBuilt-in self-test

A semiconductor integrated circuit has a data generation circuit configured to generate first data used for function verification of a built-in self test circuit and a built-in redundancy allocation circuit of a memory, a failure data generation circuit configured to generate second data for conducting a built in self test by inverting at least one bit of the first data based on a failure injection indication signal, and a timing circuit configured to adjust timing of at least one of the first and the second data in order to use one of the first and the second data as writing data to the memory and to use the other as an output expected value compared with data read out from the memory.

Owner:KK TOSHIBA

Flight control simulation system with fault diagnosis capability for unmanned helicopter

InactiveCN106444429ARealize simulationHighly replaceableSimulator controlGround installationsRemote controlMathematical model

The invention provides a flight control simulation system with fault diagnosis capability for an unmanned helicopter. The flight control simulation system with fault diagnosis capability for an unmanned helicopter comprises a simulation general control console, a simulation computer, a flight control management system, a sensor system, physical effect equipment, a servo system, a remote control and remote measurement system, and a task load system, wherein the simulation general control console controls the simulation computer to carry on a power on test, model generation and injection of fault model; the simulation computer selects simulation and interference model and simulates fault injection to carry on flight simulation; the flight control management system receives the information of sensors and the remote control and remote measurement system; the servo system realizes the real reaction of an operating mechanism; and the sensor system transmits the acquired sensor information to the flight control management system. For the flight control simulation system with fault diagnosis capability for an unmanned helicopter, the simulation computer can be embedded into different aircraft mathematical models, so that simulation of a plurality of aircrafts can be realized. For the flight control simulation system with fault diagnosis capability for an unmanned helicopter, the servo system and the sensor system can access a real steering engine of aircraft and real sensors so as to develop the steering engine of aircraft, to make a test flight for the steering engine of aircraft, and detecting working of the sensors.

Owner:BEIHANG UNIV

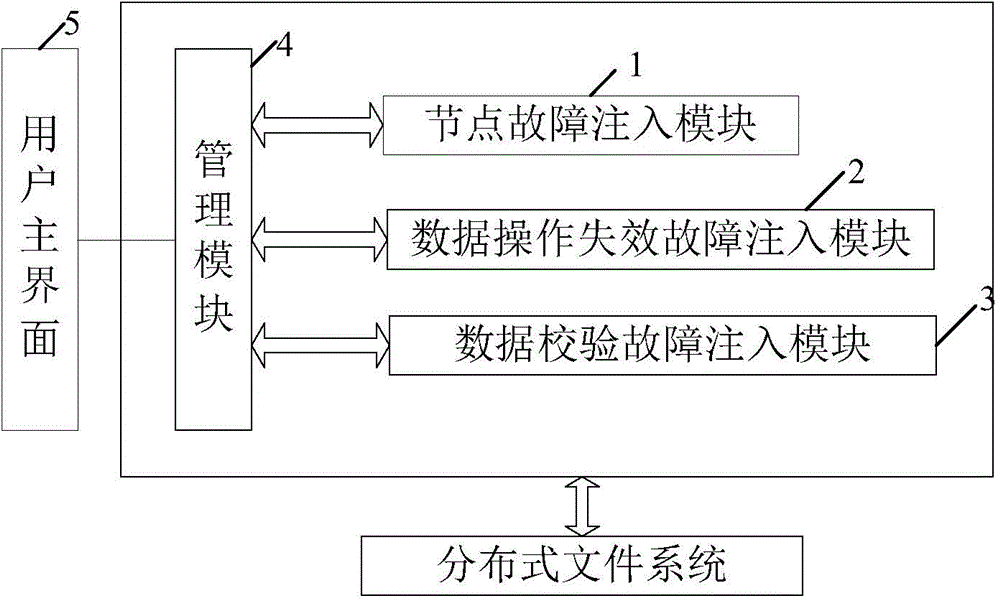

Cloud environment distributed file system reliability test suite

InactiveCN104461865AGuaranteed reliabilitySoftware testing/debuggingDistributed File SystemData operations

The invention provides a cloud environment distributed file system reliability test suite, and relates to the field of cloud computing. The test suite aims to solve the problems that in an existing distributed system, a suite for testing distributed file system reliability lacks, preparation for problems occurring in the distributed system can not be made in advance, and reliability of the system is low. A management module of the test suite is used for calling a corresponding node fault injection module, a data operation failure fault injection module and a data intended effect fault injection module according to operation commands of test staff, collecting fault injection results of the node fault injection module, the data operation failure fault injection module and the data intended effect fault injection module and feeding back the fault injection results to the test staff through a user main interface. The user main interface is used for being located between the test staff and the management module, providing a man-machine interaction interface, receiving commands of a user and feeding back the fault injection results. The cloud environment distributed file system reliability test suite can be used for fault injection of the cloud environment distributed file system.

Owner:HARBIN INST OF TECH

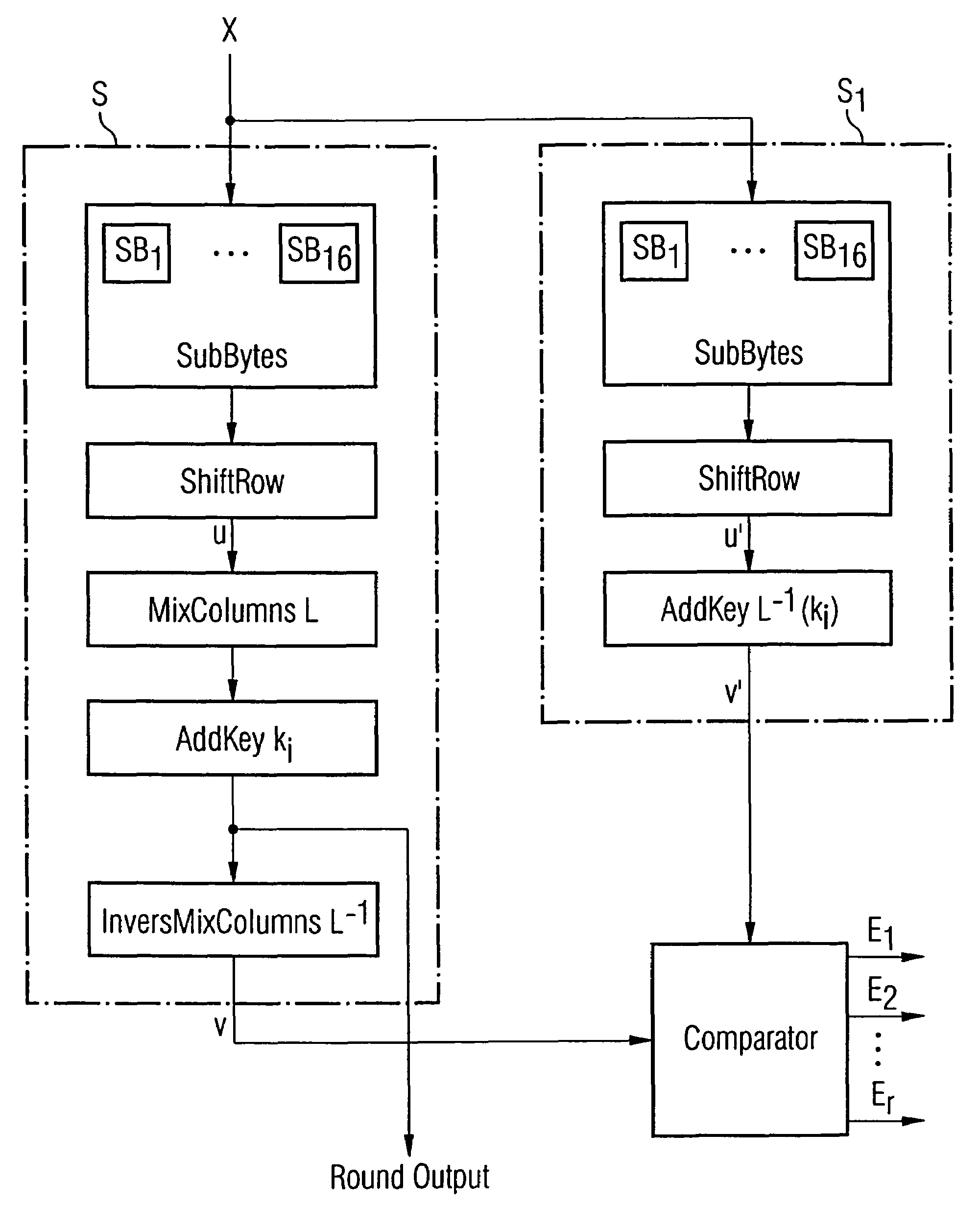

Cryptographic unit and method for operating a crytographic unit

ActiveUS7694156B2Improve featuresUnauthorized memory use protectionHardware monitoringComputer hardwareSignal on

A cryptographic unit includes a first processing unit for determining an output signal on the basis of the AES algorithm and for determining a first comparison signal, a second processing unit for determining a second comparison signal, and a release unit for providing the output signal, wherein the release unit is designed to perform a defense measure against an external tapping of the output signal when the first comparison signal is not related to the second comparison signal in a predetermined relationship. The first comparison signal is determined in a different way as compared to the second comparison signal, so that, in the case of the injection of faults into the cryptographic unit, these faults may be detected very easily.

Owner:INFINEON TECH AG

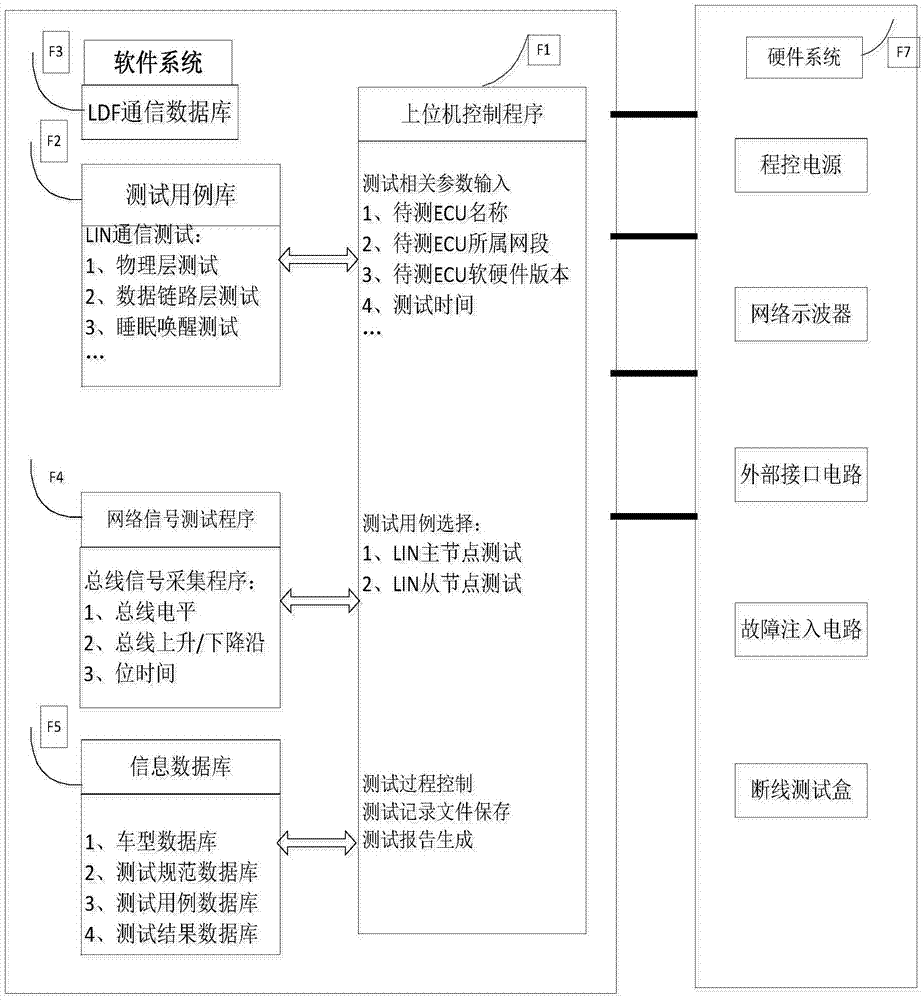

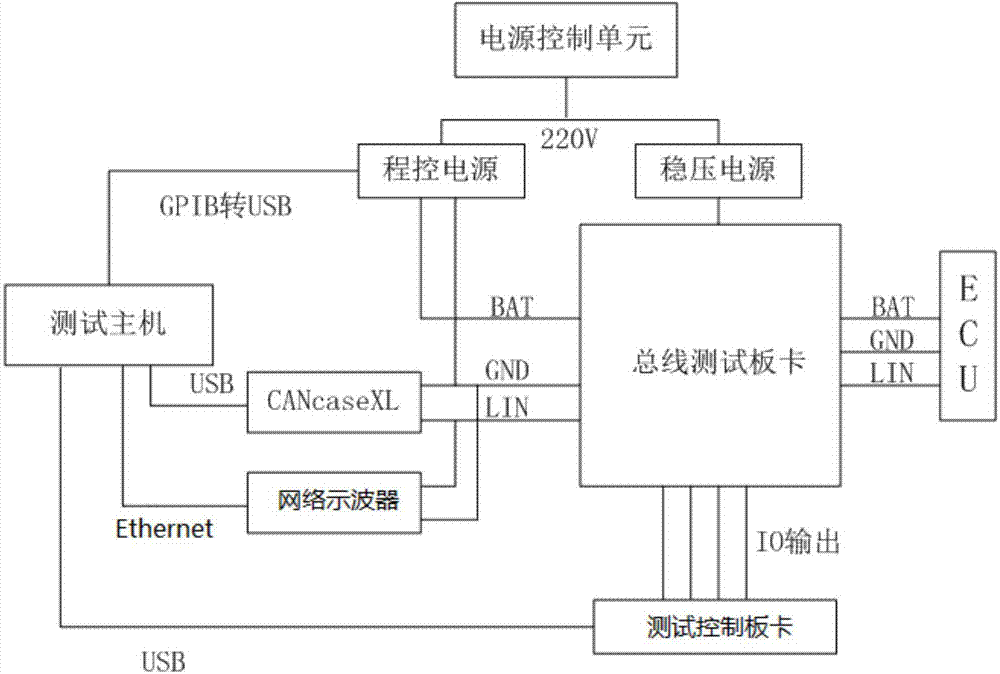

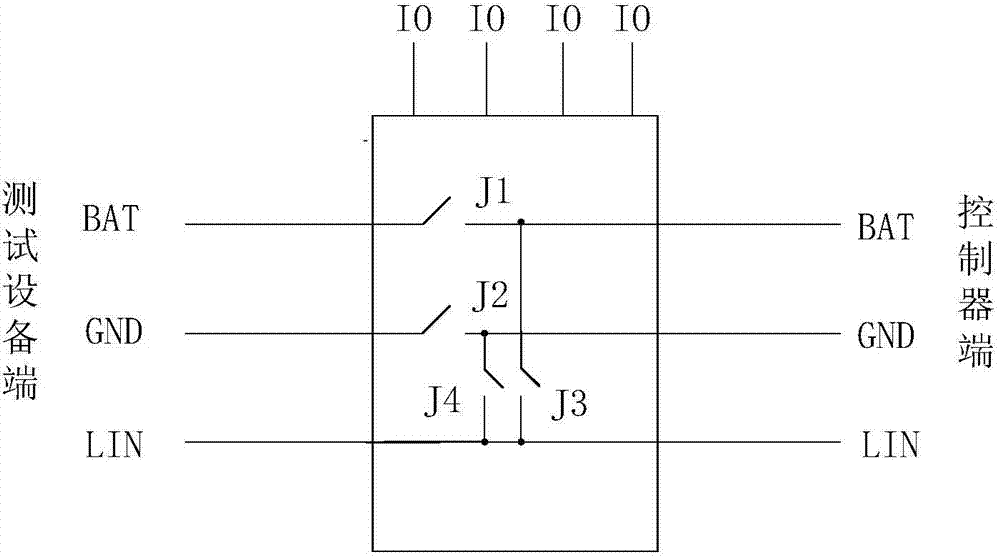

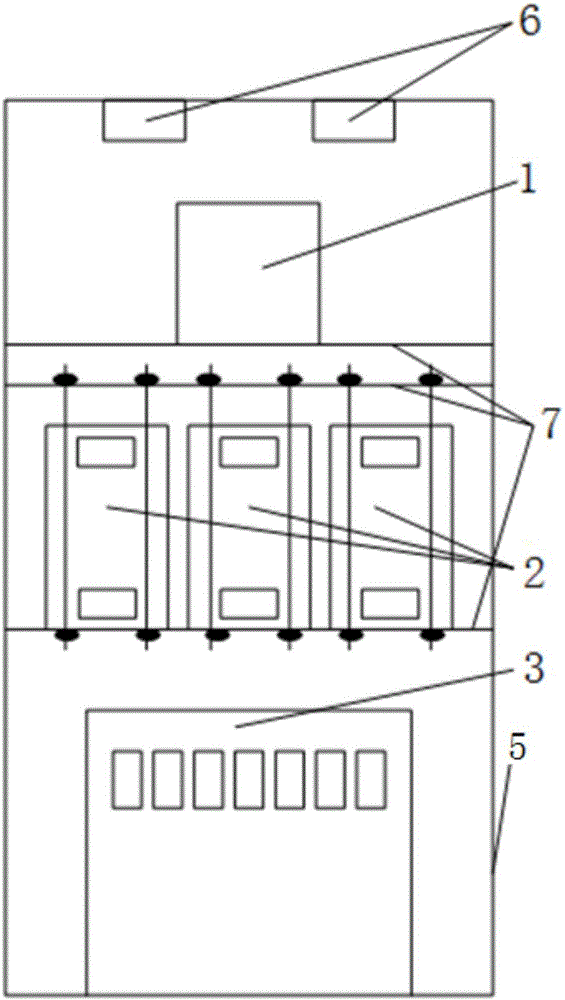

Vehicle-mounted electronic control unit LIN bus communication automatic testing device and system

InactiveCN104267715AReduce duplication of effortAffect accuracyElectric testing/monitoringBus masteringTest fixture

The invention relates to a vehicle-mounted electronic control unit LIN bus communication automatic testing device. A test host of the device controls a programmable power supply to output voltages of different amplitudes according to the work needs of an ECU. The physical layer testing signal of a LIN bus is output to a network oscilloscope to be displayed, and physical layer testing data are transmitted to the test host through the network oscilloscope. ECU testing data are transmitted to the test host through bus data collecting equipment. The test host records, analyzes and evaluates the testing data of the ECU and the LIN bus to generate a test report. The test host controls all relays of a bus test board card to be connected or disconnected through a bus control board card to execute bus fault injection operation. According to the vehicle-mounted electronic control unit LIN bus communication automatic testing device, various defects of manual testing are overcome, unnecessary repeated labor of a vehicle-mounted network engineer is reduced, and the test result is precise.

Owner:CHINA FIRST AUTOMOBILE

Saber-based circuit failure simulation analyzing method

ActiveCN102156760AImproving Failure Simulation EfficiencySpecial data processing applicationsModelSimHemt circuits

The invention provides a Saber-based circuit failure simulation analyzing method. The method is characterized by comprising the following steps: 1, performing Saber circuit function modeling and simulation; 2, determining the failure mode of a device to be simulated; 3, modeling the failure; 4, injecting the failure; 5, simulating a failed circuit to generate a failure simulation result; 6, setting a failure criterion; and 7, giving a failure analyzing result. Regarding the problem that the conventional circuit failure simulation can be only used for digital circuits, the method provides a practical failure simulation method based on the digital-analog hybrid simulation platform Saber. Furthermore, many failure simulation models which cannot be solved by predecessors are added, and 48 failure modes can be simulated. Realization of automatic failure injection greatly improves the failure simulation efficiency. The direct interface between Saber and failure simulation is broken through,and an effective signal failure determination method is provided.

Owner:苏州天航长鹰科技发展有限公司

Fault injection method and system

InactiveUS20050050393A1Electronic circuit testingError detection/correctionProcessor registerComputer science

A method and system are disclosed for fault injection using Boundary Scan resources compliant with 1149.1, while operating in system mode. The system has two register circuits, one, for storing and updating fault selection data and another, for storing and updating fault injection values.

Owner:LUCENT TECH INC

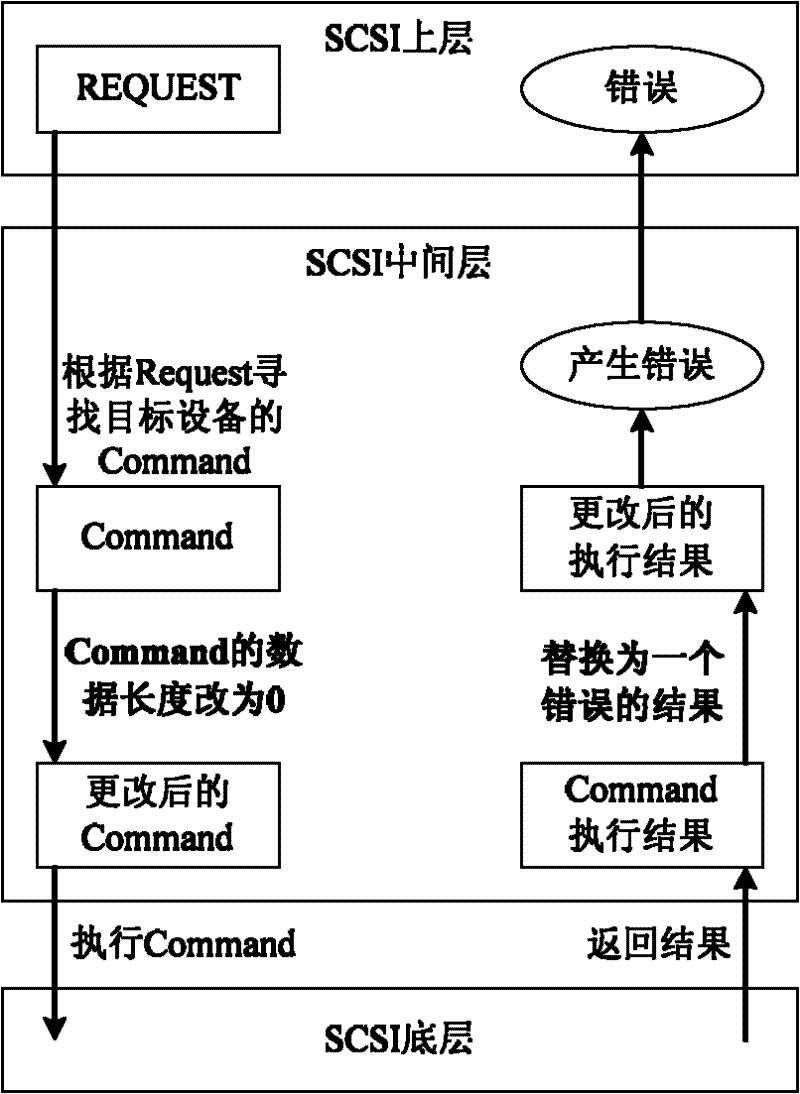

Fault injection tool based on scsi driver layer

InactiveCN102270173AConvenient and flexible way to simulate fault injectionFault Behavior RealSoftware testing/debuggingMass storageSCSI

A fault injection tool based on the SCSI driver layer, involving fault injection technology. The invention provides a fault injection tool for mass storage for detecting quality of mass storage. The fault injection command input interface in the fault injection tool is used to provide an external fault configuration file input interface, generate and send a fault injection command to the kernel; the kernel module runs in the kernel state, and is used to intercept and rewrite according to the received fault injection command The queuecommand function of the SCSI command is used to implement fault injection; and the device registration information is printed to the kernel log during the fault loading process, and the fault information is printed to the kernel log after the fault is injected; the multipath device number matching viewing interface is used to view the Compare the device with the kernel log and multipath configuration information, and obtain the registration number ID corresponding to each path of the multipath device in the tool. This tool enables more fault simulations.

Owner:HARBIN INST OF TECH

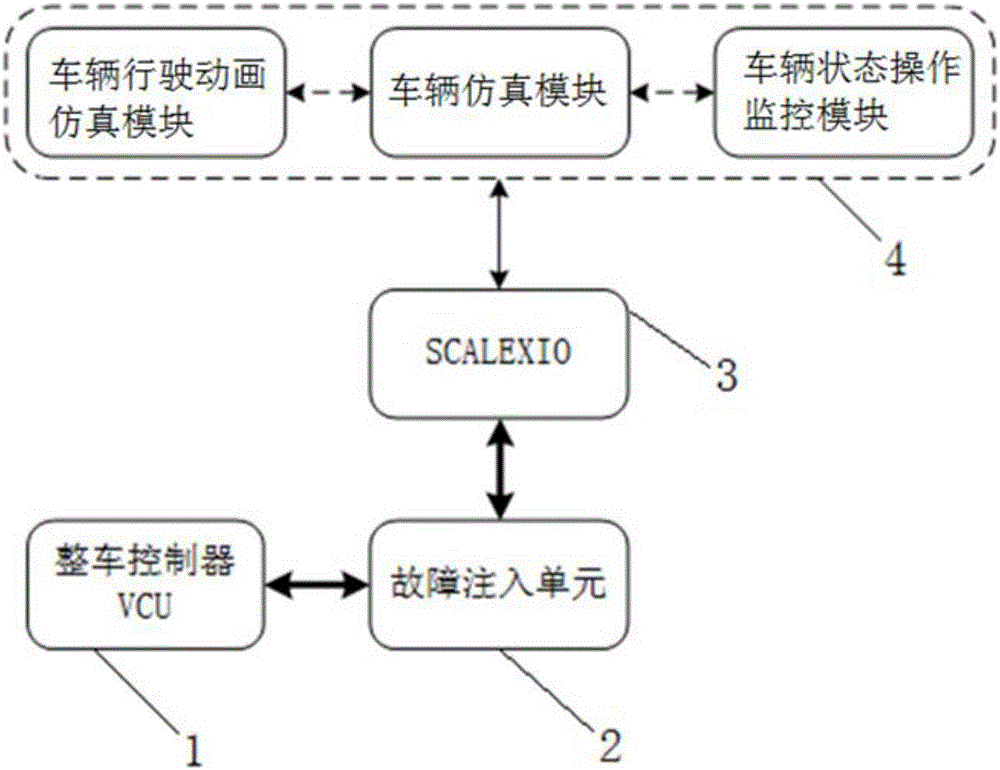

Hardware-in-the-loop test system for whole vehicle controller for electric vehicle and test method

PendingCN106444721AGood value for moneyDoes not occupy a large areaElectric testing/monitoringTest efficiencyAnimation

The invention discloses a hardware-in-the-loop test system for a whole vehicle controller for an electric vehicle and a test method. The hardware-in-the-loop test system comprises a whole electric vehicle controller, a fault injection hardware unit, an SCALEXIO, and a vehicle simulating module, a vehicle driving animation simulating module and a vehicle state operating and monitoring module in a computer. Connection and communication among the SCALEXIO, the fault injection hardware unit and the whole electric vehicle controller is achieved through a wire harness, and connection and communication between the SCALEXIO and the computer is achieved through a network line; through the corresponding SCALEXIO software in the computer, SCALEXIO channel selection is achieved, and communications of a vehicle simulating model, vehicle driving animation and vehicle state operation and monitoring interact in the computer. The hardware-in-the-loop test system can effectively save the development time and reduce the development cost of the whole vehicle controller, can achieve performance testing on the whole vehicle controller under the limit driving condition of the vehicle, can achieve systematic, integrated and automatic testing on the whole vehicle controller and generate a test report, effectively reduces the testing cost and improves the testing efficiency.

Owner:NANJING YUEBOO POWER SYST CO LTD

System for testing error detection circuits

ActiveUS20140019818A1Electronic circuit testingLogical operation testingMaster processorReliability engineering

A system for testing an error detection circuit includes a fault injection unit for operating the error detection circuit in a fault injection mode. A fault is inserted in either of a primary or a redundant processor. Output signals generated by the primary and redundant processors are compared and checked for a mismatch and the error detection circuit outputs a test signal based on the comparison result.

Owner:NXP USA INC

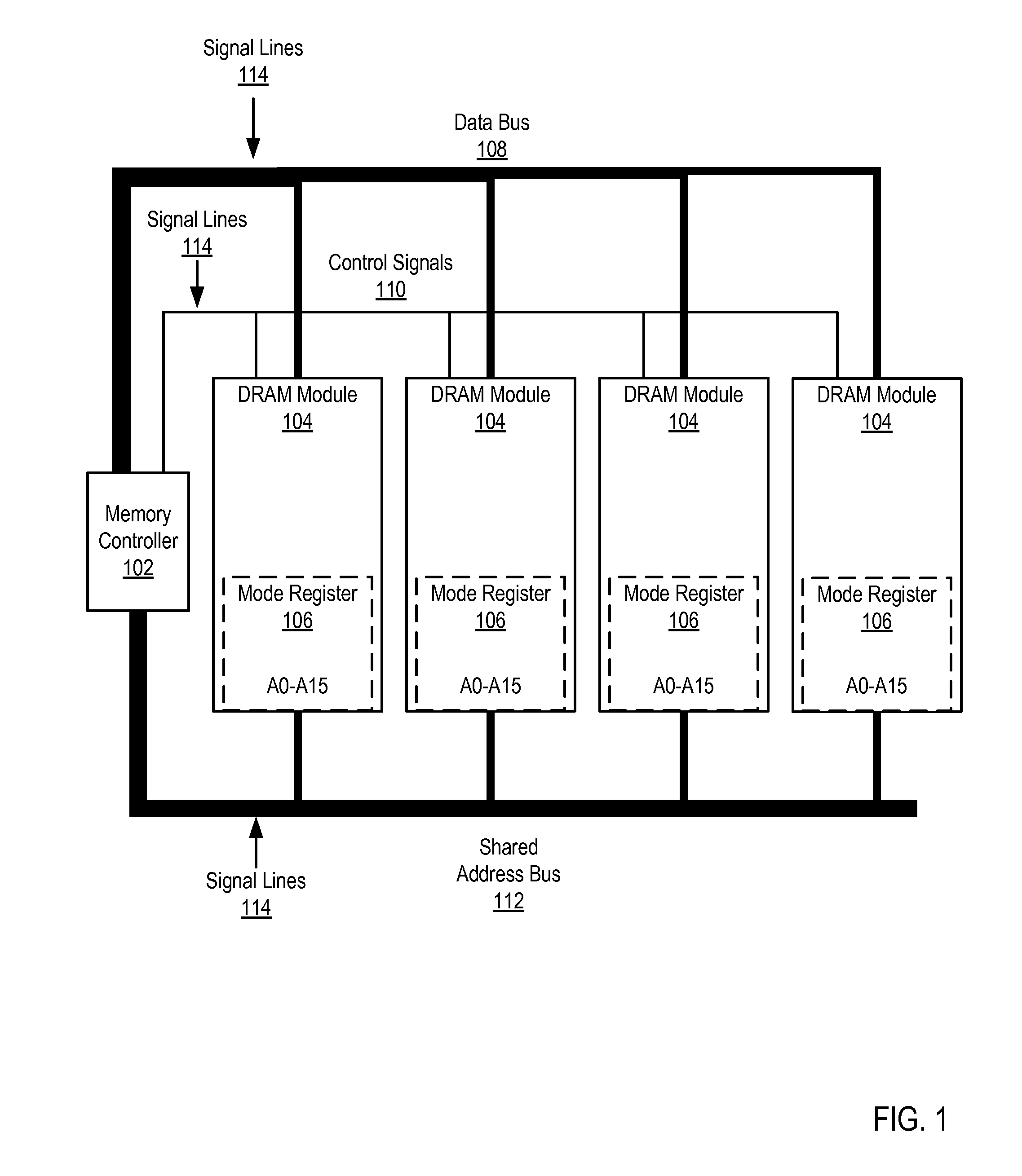

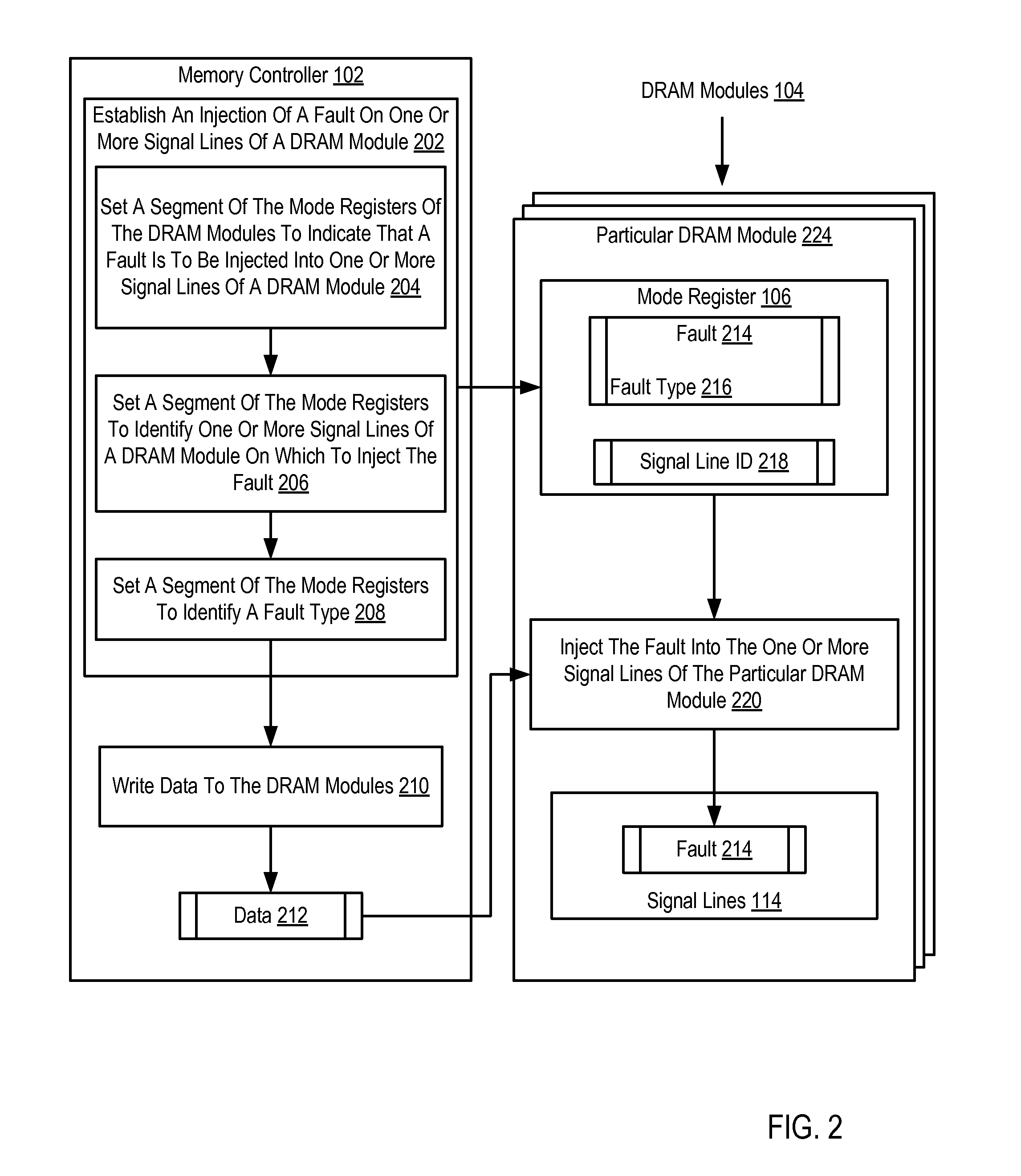

Fault Injection In Dynamic Random Access Memory Modules For Performing Built-In Self-Tests

Fault injection in dynamic random access memory (‘DRAM’) modules for performing built-in self-tests (‘BISTs’) including establishing, in the mode registers of the DRAM modules by the memory controller through the shared address bus, an injection of a fault into one or more signal lines of a DRAM module, the fault characterized by a fault type; writing data by the memory controller through a data bus to the DRAM modules, the data identifying a particular DRAM module; and responsive to receiving the data, injecting, by the particular DRAM module, the fault characterized by the fault type into the one or more signal lines of the particular DRAM module.

Owner:LENOVO GLOBAL TECH INT LTD

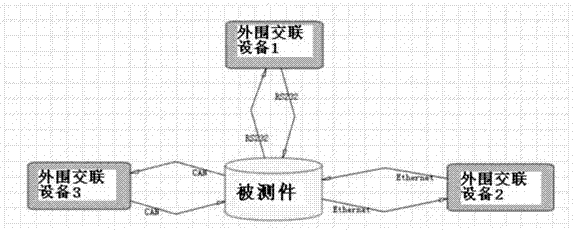

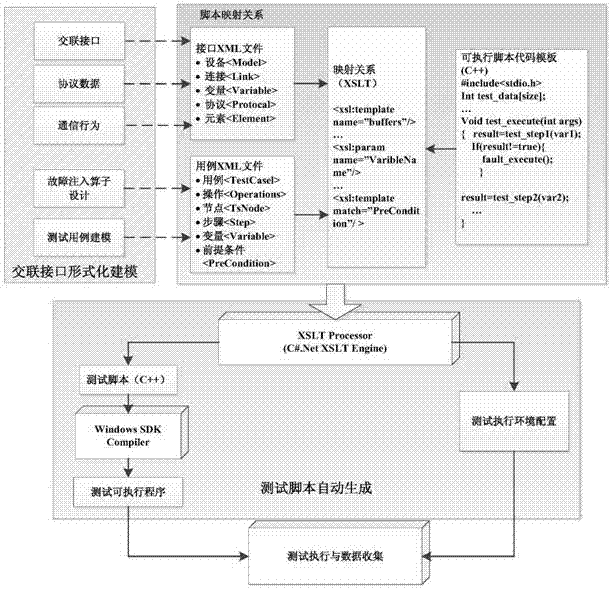

Interface-oriented automatic test method for software fault injection

InactiveCN107368408ALower requirementImprove versatilitySoftware testing/debuggingTest scriptData modeling

The invention provides an interface-oriented automatic test method for software fault injection, and aims at realizing the automatic test of interface fault injection. The method comprises the following steps of: firstly carrying out cross-linkage interface modeling, communication behavior modeling and protocol data modeling; designing a fault injection operator and carrying out test case modeling; automatically generating an XML-format test case on the basis of the model; and finally automatically generating the test case into a test script of C++ language on the basis of XSLT, calling windows SDK to automatically generate a test program and automatically executing the test program, realizing result collection through a Windows pipeline technology, and evaluating the test result so as to complete the fault injection test of the whole cross-linkage interface. According to the method, universality and usability realized by an interface fault injection test tool are effectively improved, the interface test efficiency is improved and the test cost is reduced.

Owner:中国船舶工业综合技术经济研究院

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com