Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

994 results about "Main processing unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Main Processing Unit (MPU) The portion of the PES which interprets or executes the (main part of the) Application Program. The MPU may include power supply, memory, and I/Os.

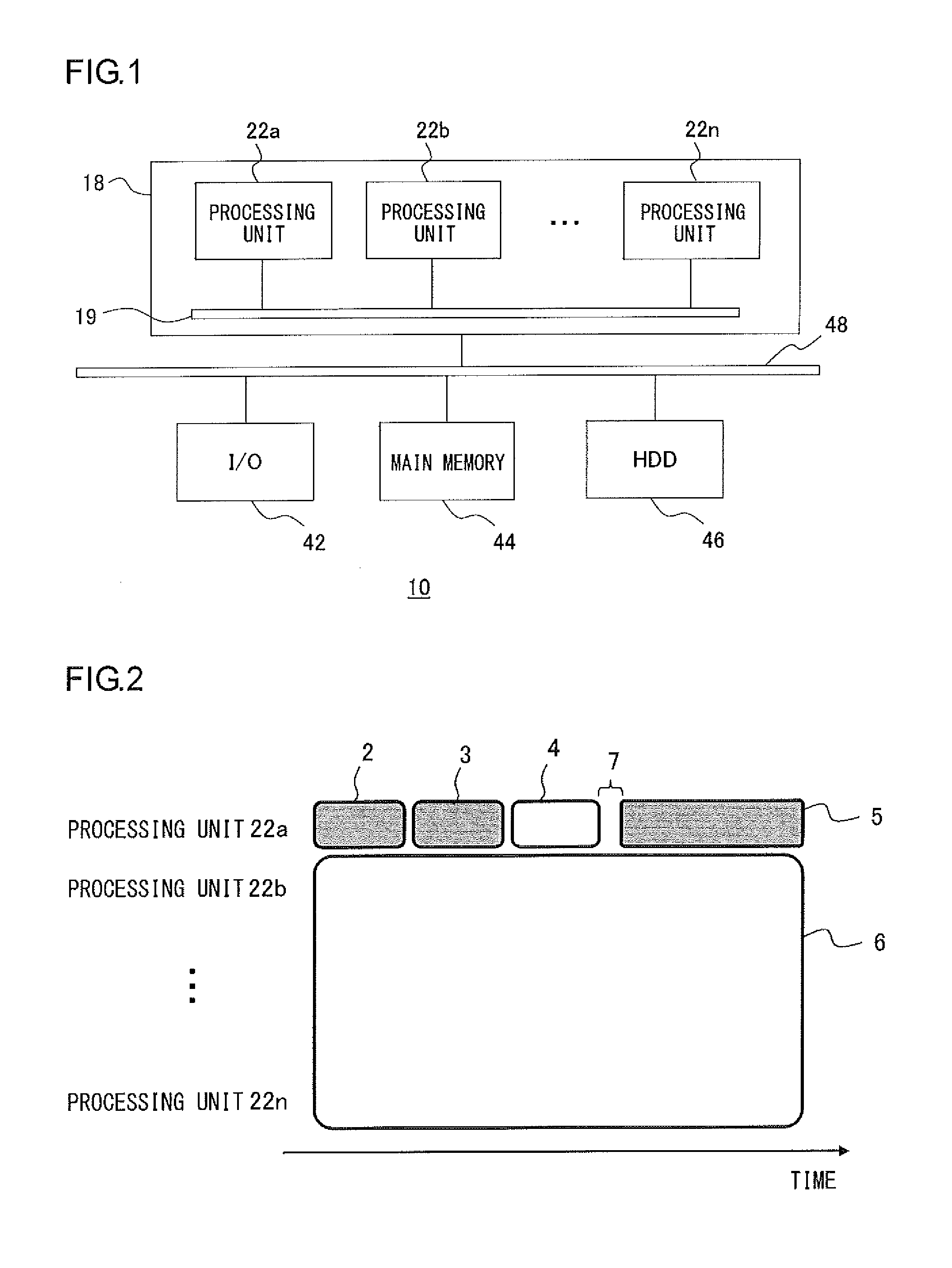

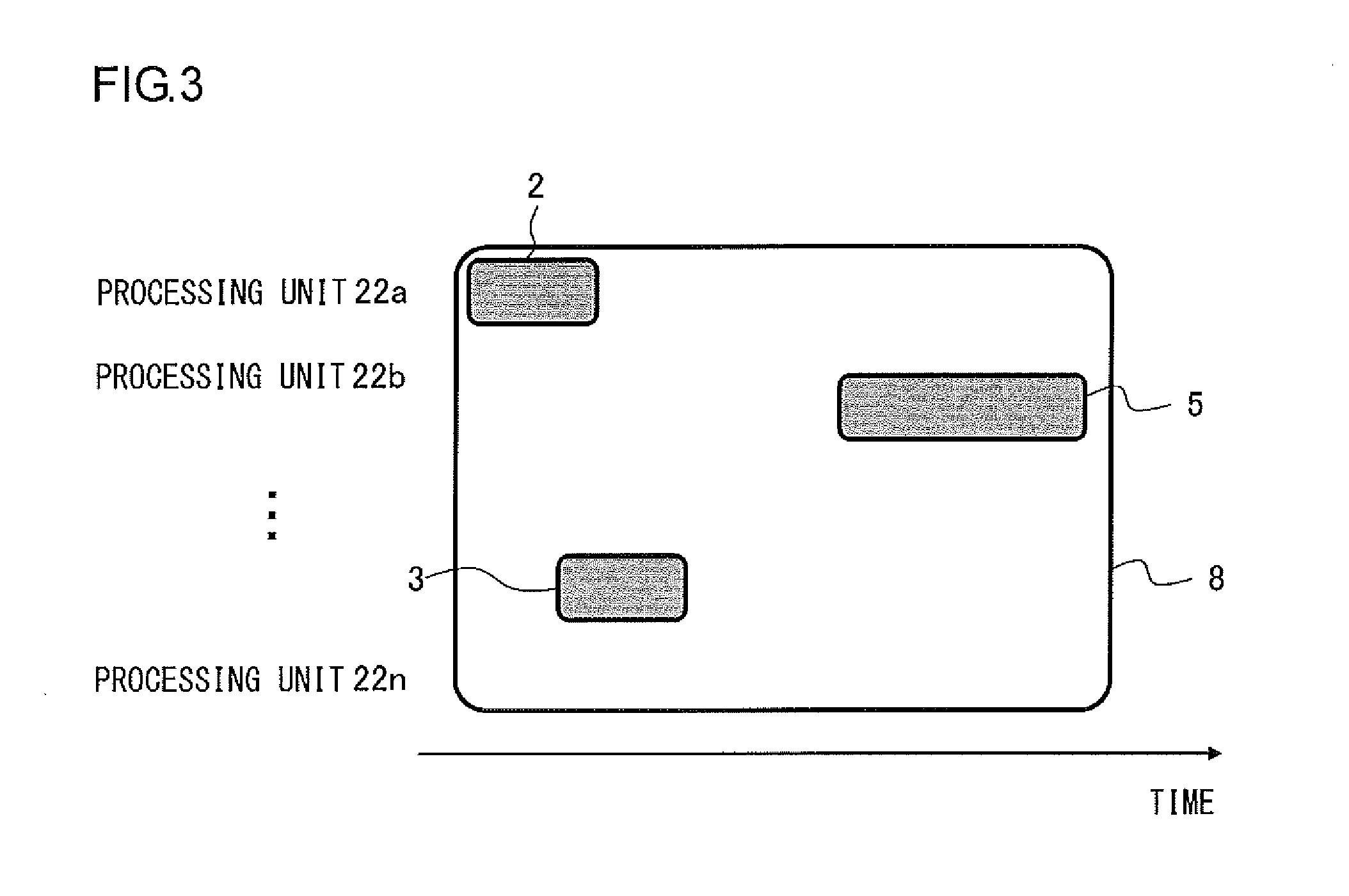

Information processing device and information processing method

ActiveUS20110302587A1Efficient execution of parallelEfficient executionMultiprogramming arrangementsMemory systemsMain processing unitInformation processing

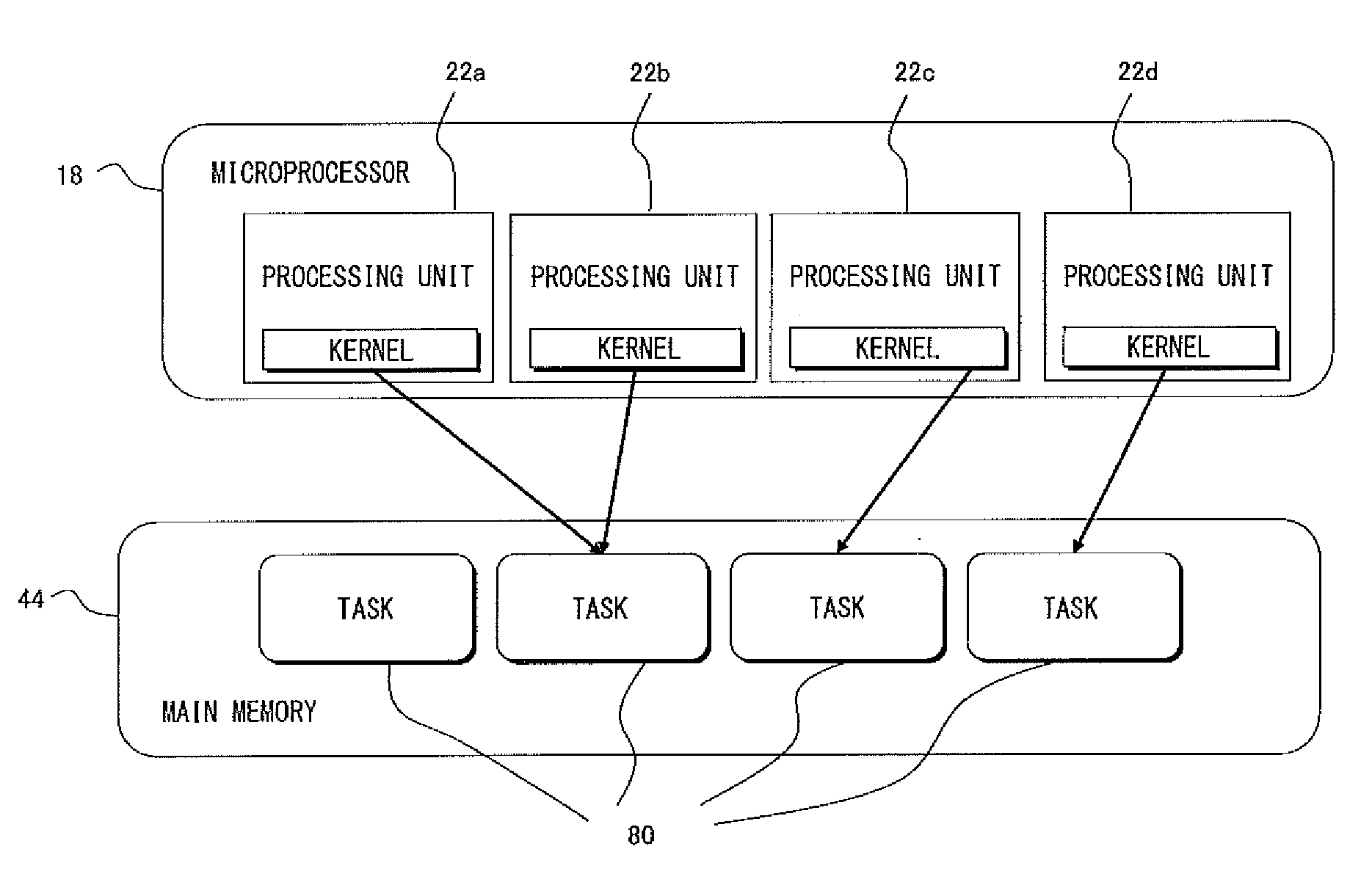

A system-level management unit generates a system processing and makes a processing request to a task allocation unit of a user-level management unit. The task allocation unit schedules the system processing according to a procedure of an introduced user-level scheduling. A processing unit assigned to execute the system processing sends a notification of acceptability of the system processing to a main processing unit, by halts an application task in appropriate timing or when the processing of the current task is completed. When the notification is received within the time limit for execution, the system-level management unit has the processing unit start the system processing.

Owner:SONY COMPUTER ENTERTAINMENT INC

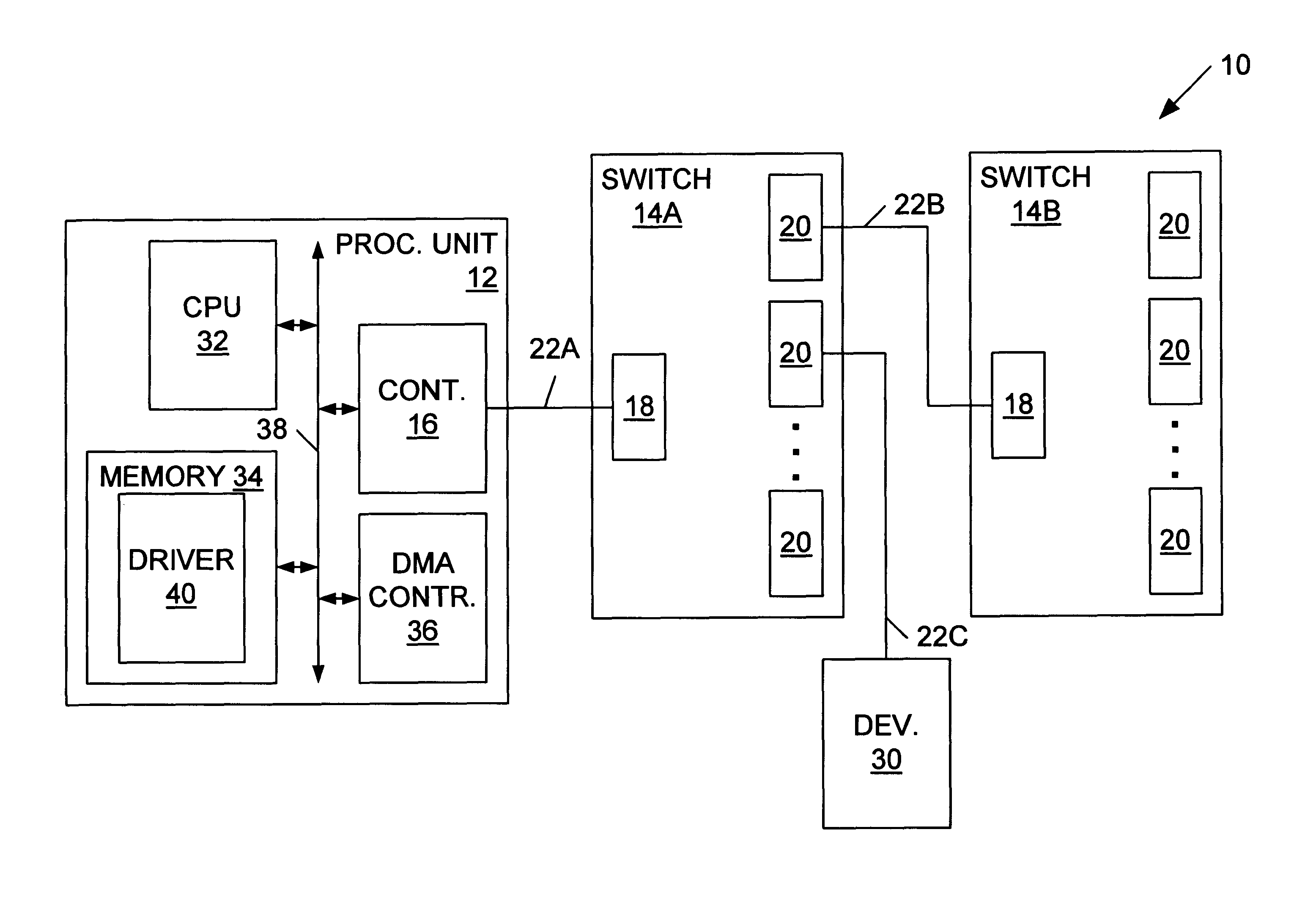

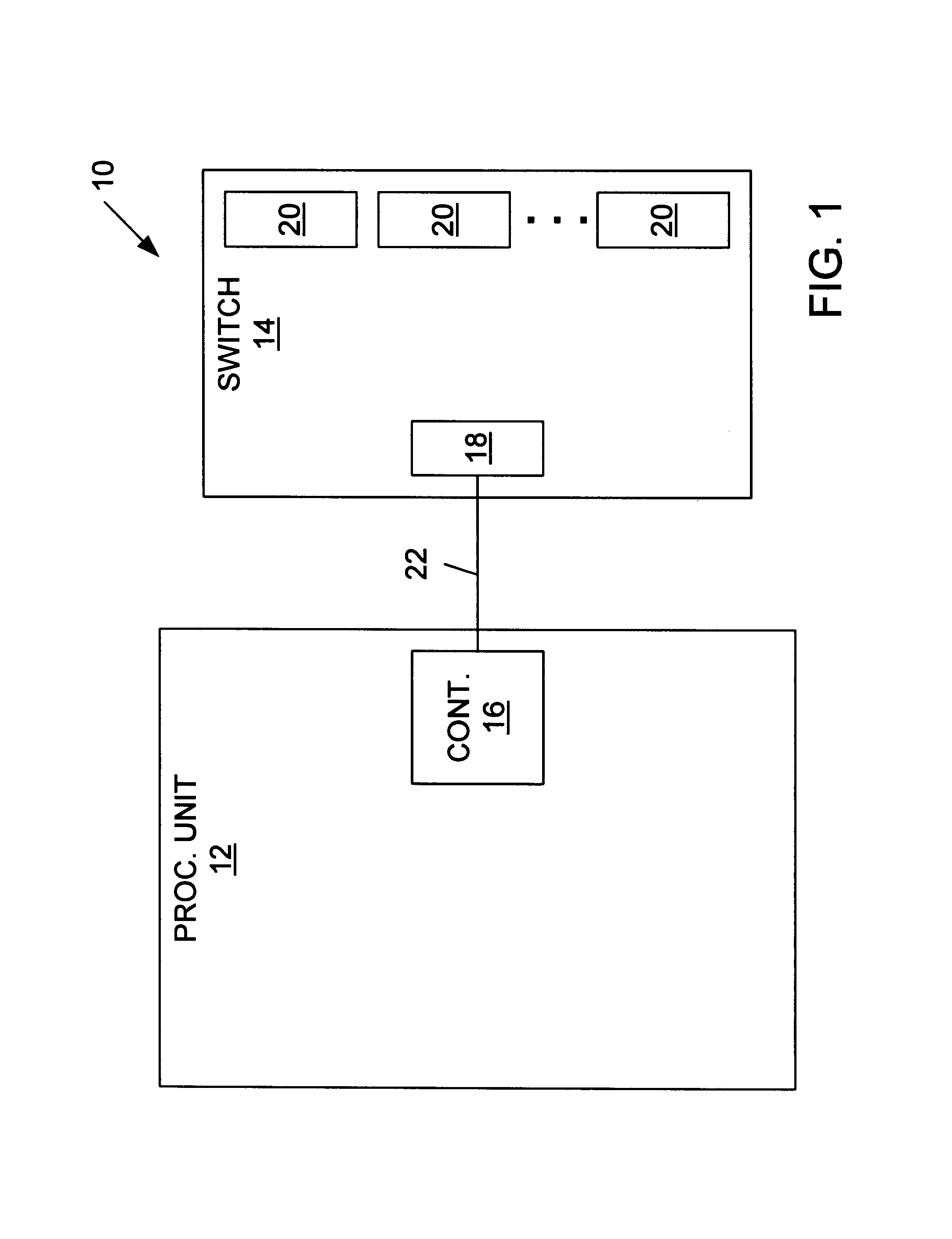

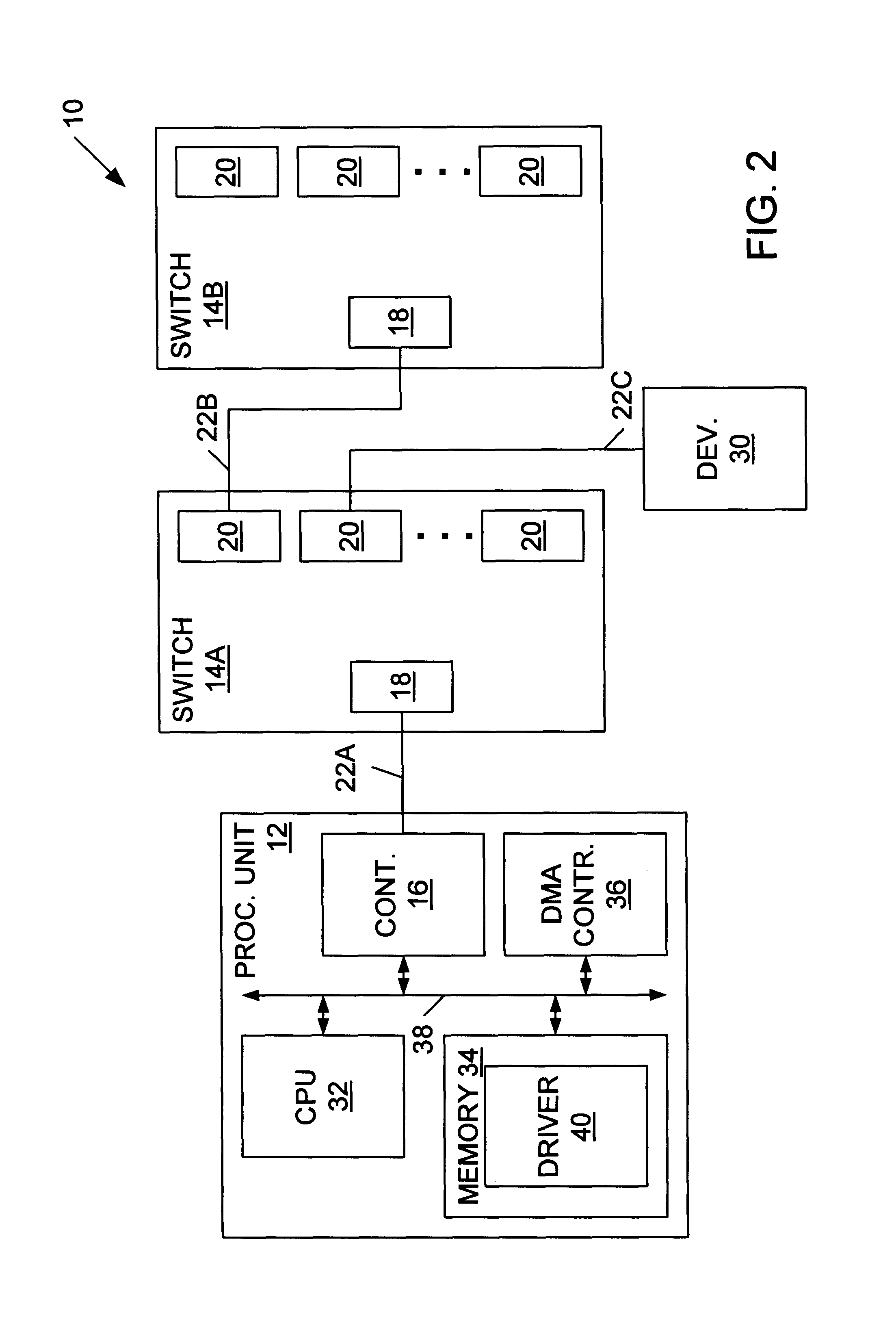

Data exchange methods for a switch which selectively forms a communication channel between a processing unit and multiple devices

InactiveUS6845409B1Reduce processing overheadReduce overheadMultiplex system selection arrangementsInput/output to record carriersMain processing unitDirect memory access

A switch is presented including a host input / output (I / O) port adapted for coupling to a controller, multiple device I / O ports each adapted for coupling to at least one device, and logic coupled between the host I / O port and the device I / O ports configured to selectively form a communication channel between the host I / O port and one of the device I / O ports. The switch may operate in a connected mode and a disconnected mode. When in the switch is in the disconnected mode, the logic may not form a communication channel between the host I / O port and any of the device I / O ports. In an ATA embodiment, the switch may comply with an AT attachment (ATA) standard, and thus be an ATA switch. The host I / O port may be adapted for coupling to an ATA controller, the device I / O ports may be adapted for coupling to at least one ATA device, and the logic may selectively form an ATA communication channel between the host I / O port and one of the device I / O ports. Several methods for exchanging data between a processing unit coupled to the host I / O port of the switch and one or more devices coupled to device I / O ports of the switch are described. Several methods for performing direct memory access (DMA) transfers to move data between a memory of the processing unit and one or more of the devices are also described.

Owner:ORACLE INT CORP

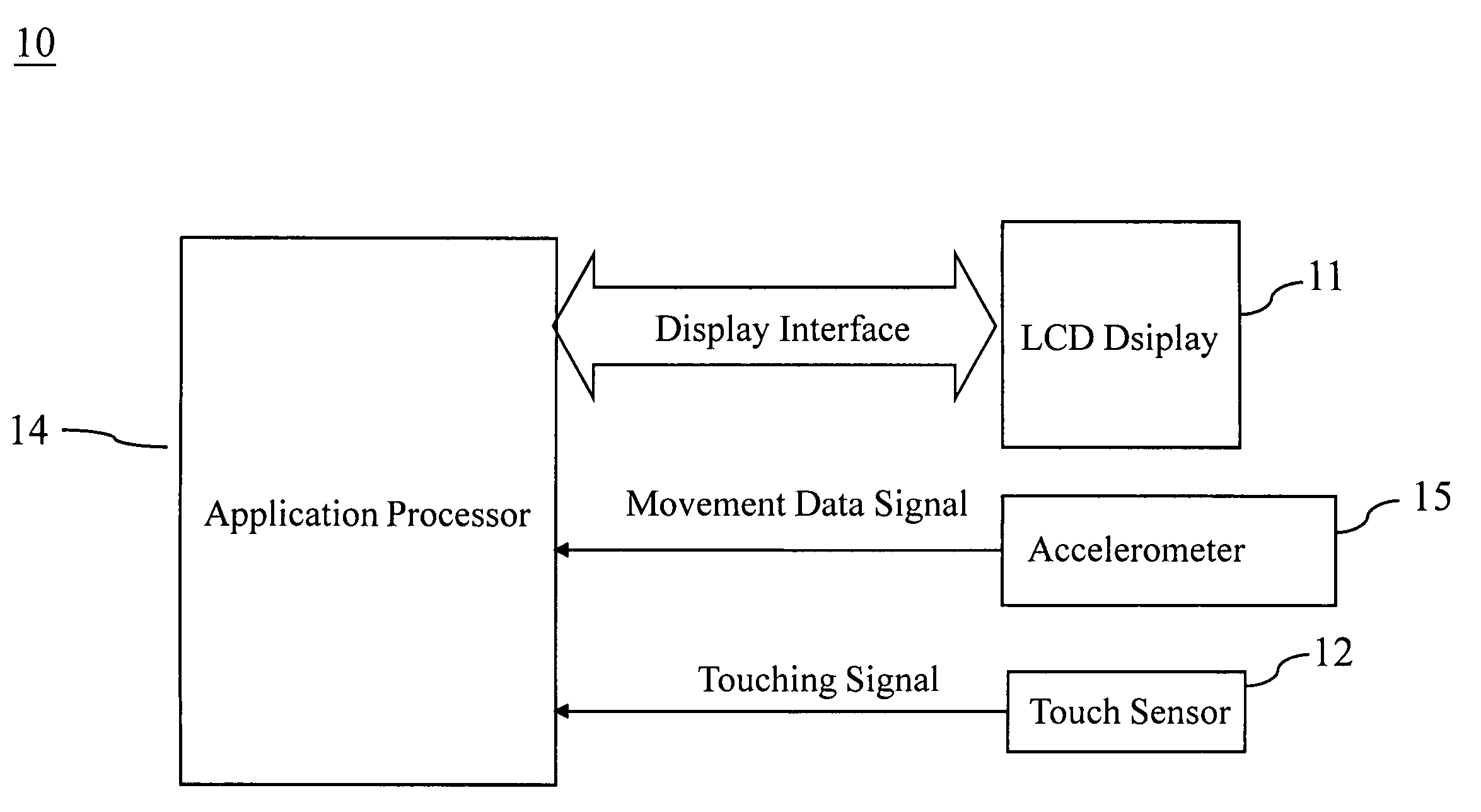

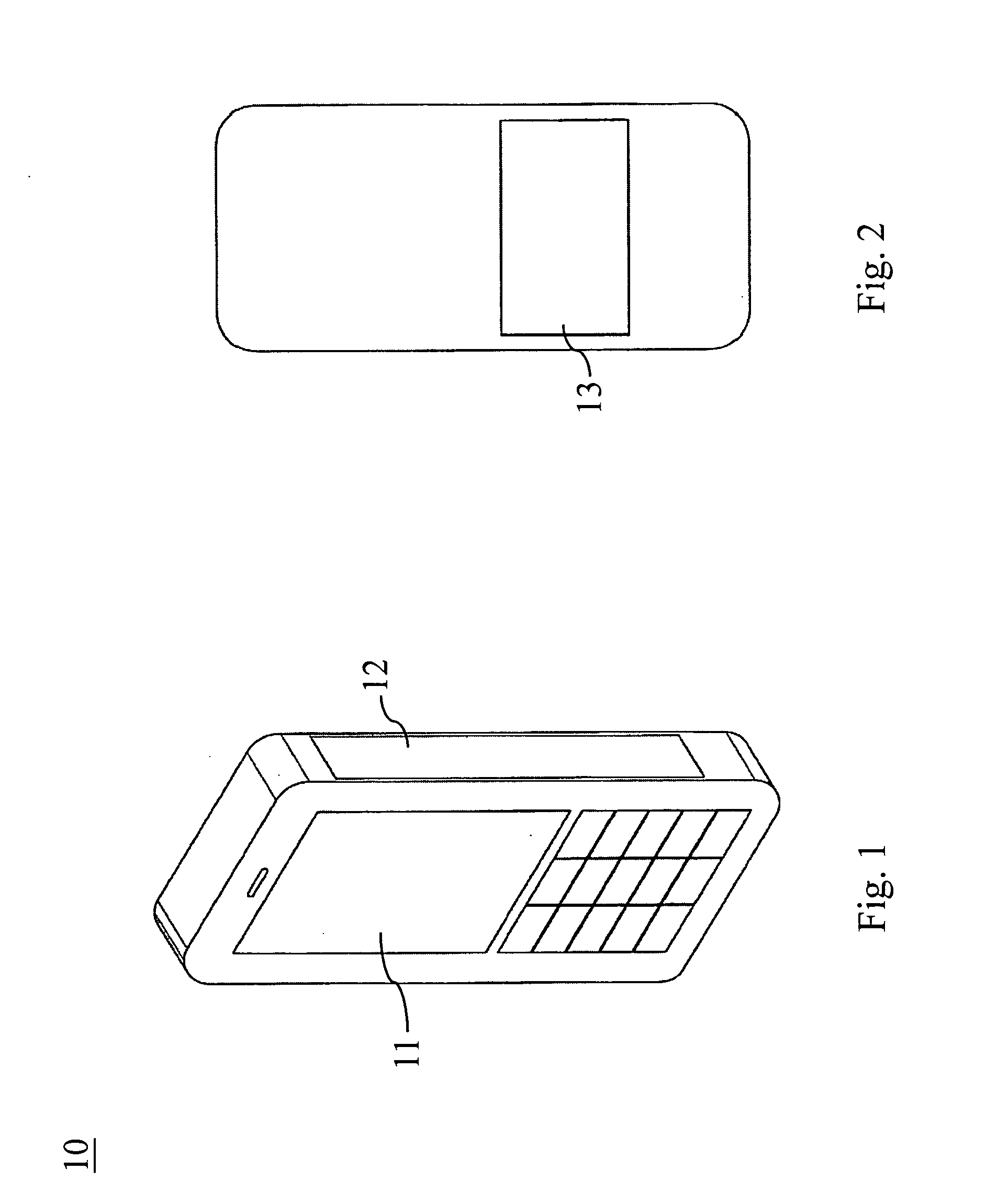

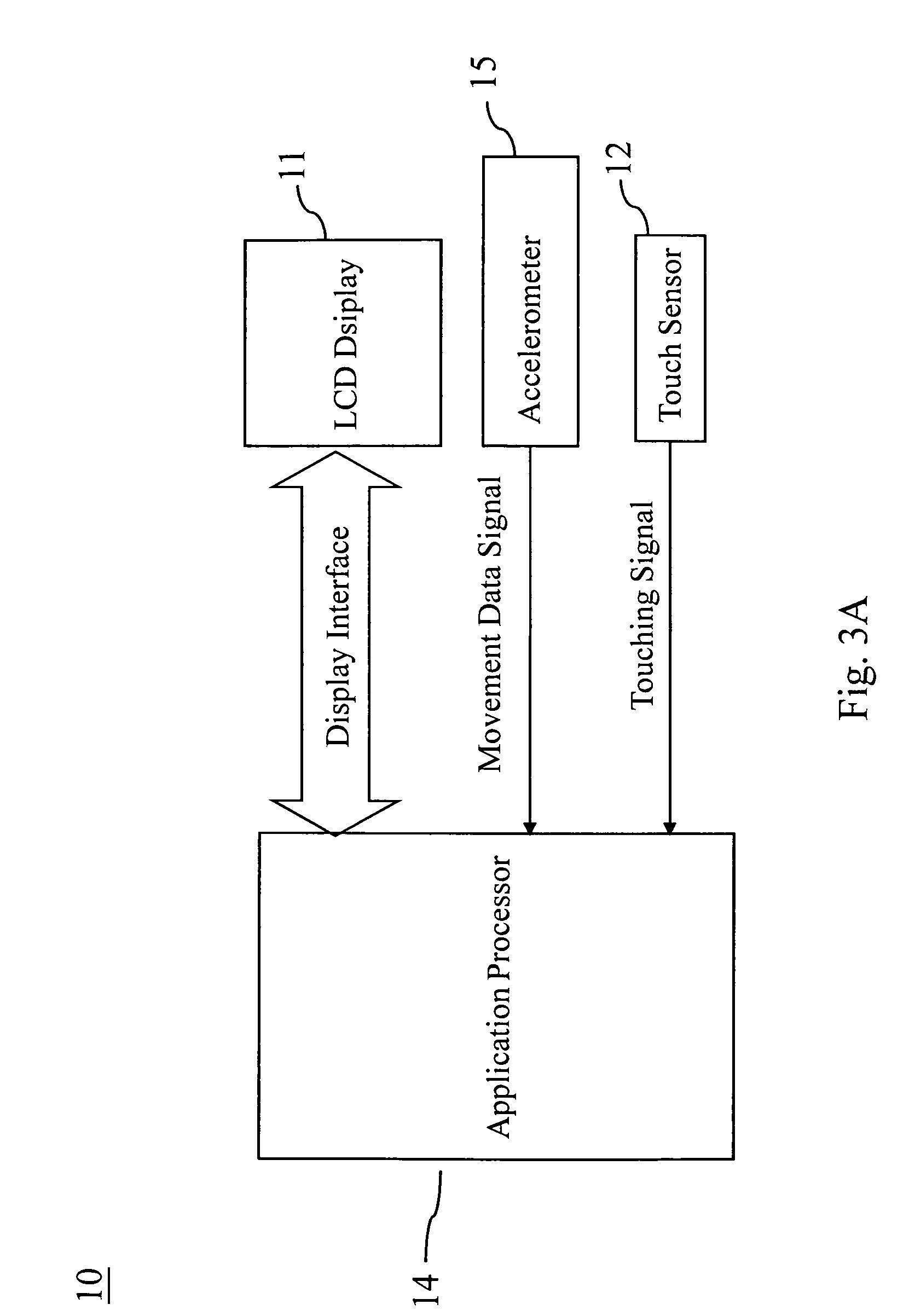

Portable electronis device and the mode switching method thereof

InactiveUS20100013778A1Less powerPower managementDetails for portable computersElectricityMain processing unit

The present invention relates to a portable electronic device which can be switched between a first mode and a second mode. The portable electronic device comprises a first sensor to detect a touch on the portable electronic device and generate a first signal based on such touch, a second sensor to detect a movement of the portable electronic device and generate a second signal based on such movement, and a processing unit which electrically connects the first sensor and the second sensor. When the portable electronic device is in the first mode, the processing unit switches the portable electronic device to the second mode based on the first and second signals. In addition, the present invention provides a mode switching method that enables the portable electronic device to determine whether to enter or exit from the sleep mode.

Owner:HTC CORP

Methods and apparatus for processor task migration in a multi-processor system

ActiveUS20050188372A1Program initiation/switchingResource allocationMain processing unitMulti processor

Methods and apparatus are provided for executing processor tasks on a multi-processing system. The multi-processing system includes a plurality of sub-processing units and a main processing unit that may access a shared memory. Each sub-processing unit includes an on-chip local memory separate from the shared memory. The methods and apparatus contemplate: providing that the processor tasks be copied from the shared memory into the local memory of the sub-processing units in order to execute them, and prohibiting the execution of the processor tasks from the shared memory; and migrating at least one processor task from one of the sub-processing units to another of the sub-processing units.

Owner:SONY COMPUTER ENTERTAINMENT INC

Method and apparatus for sharing memory space across mutliple processing units

A method and apparatus for sharing memory space of multiple memory units by multiple processing units are described. In an embodiment, a method includes storing a set of data across more than one of at least two memory units upon determining that the number of sets of data is static. The method also includes storing the set of data within a single memory unit of the at least two memory units upon determining that the set of data is dynamic.

Owner:TELEFON AB LM ERICSSON (PUBL)

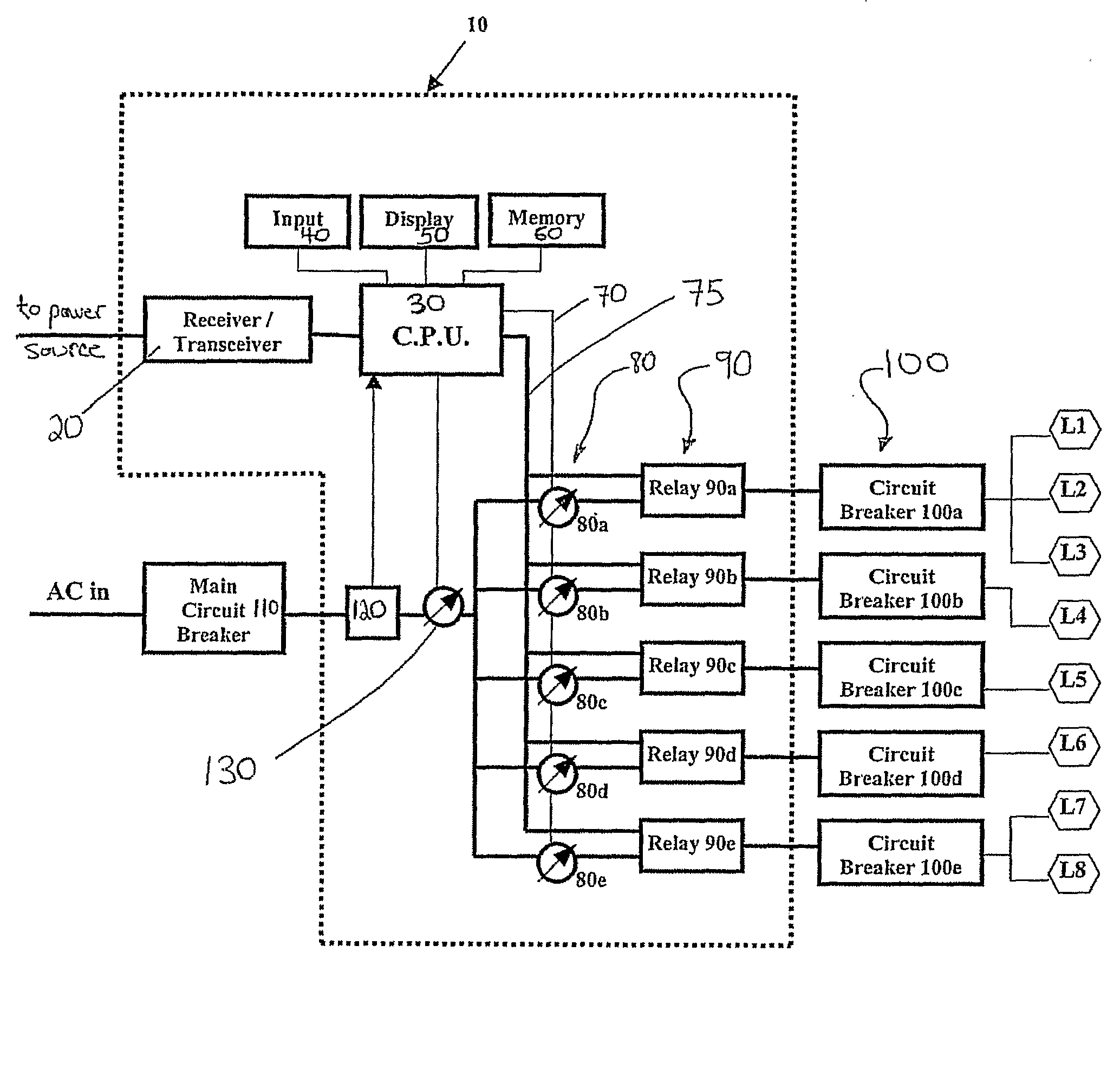

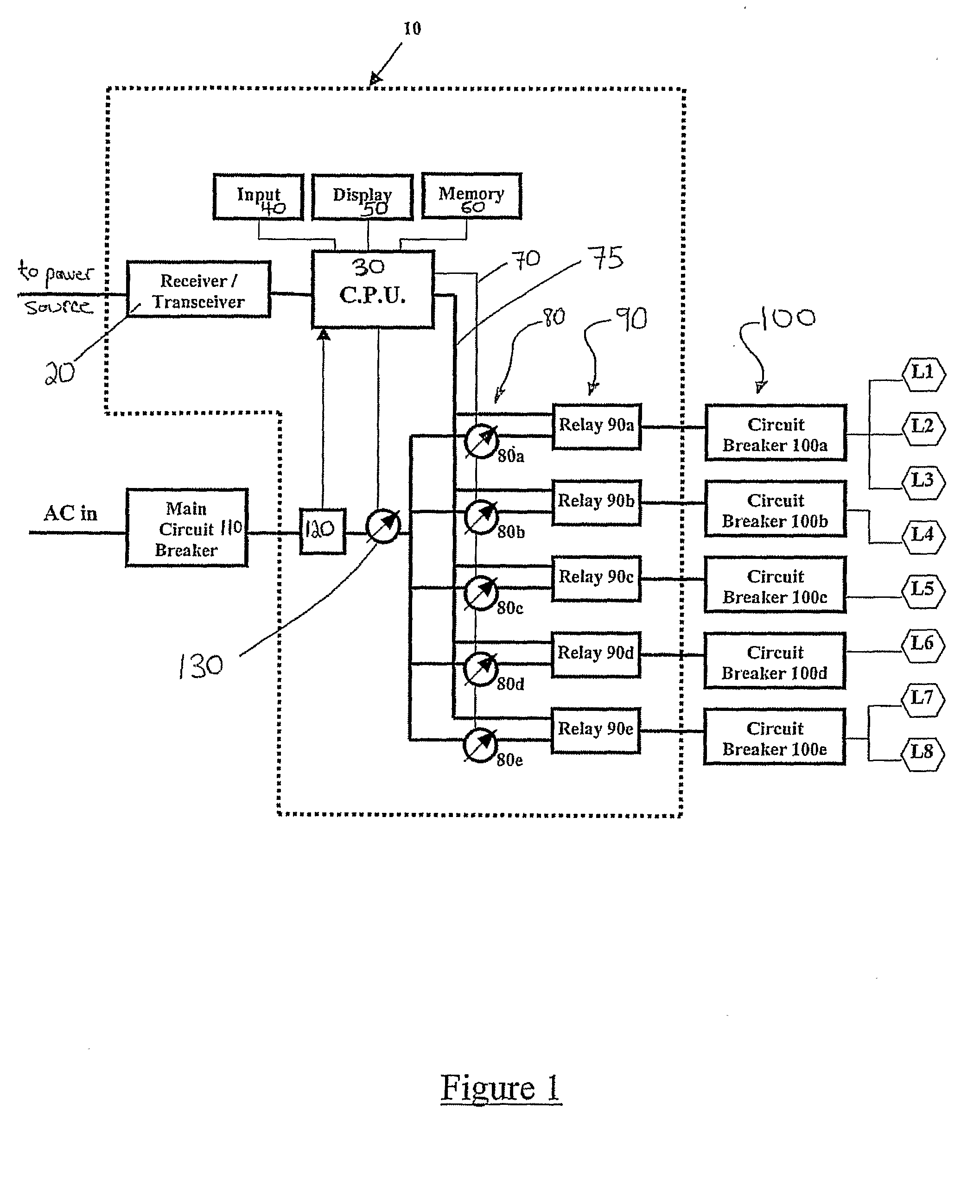

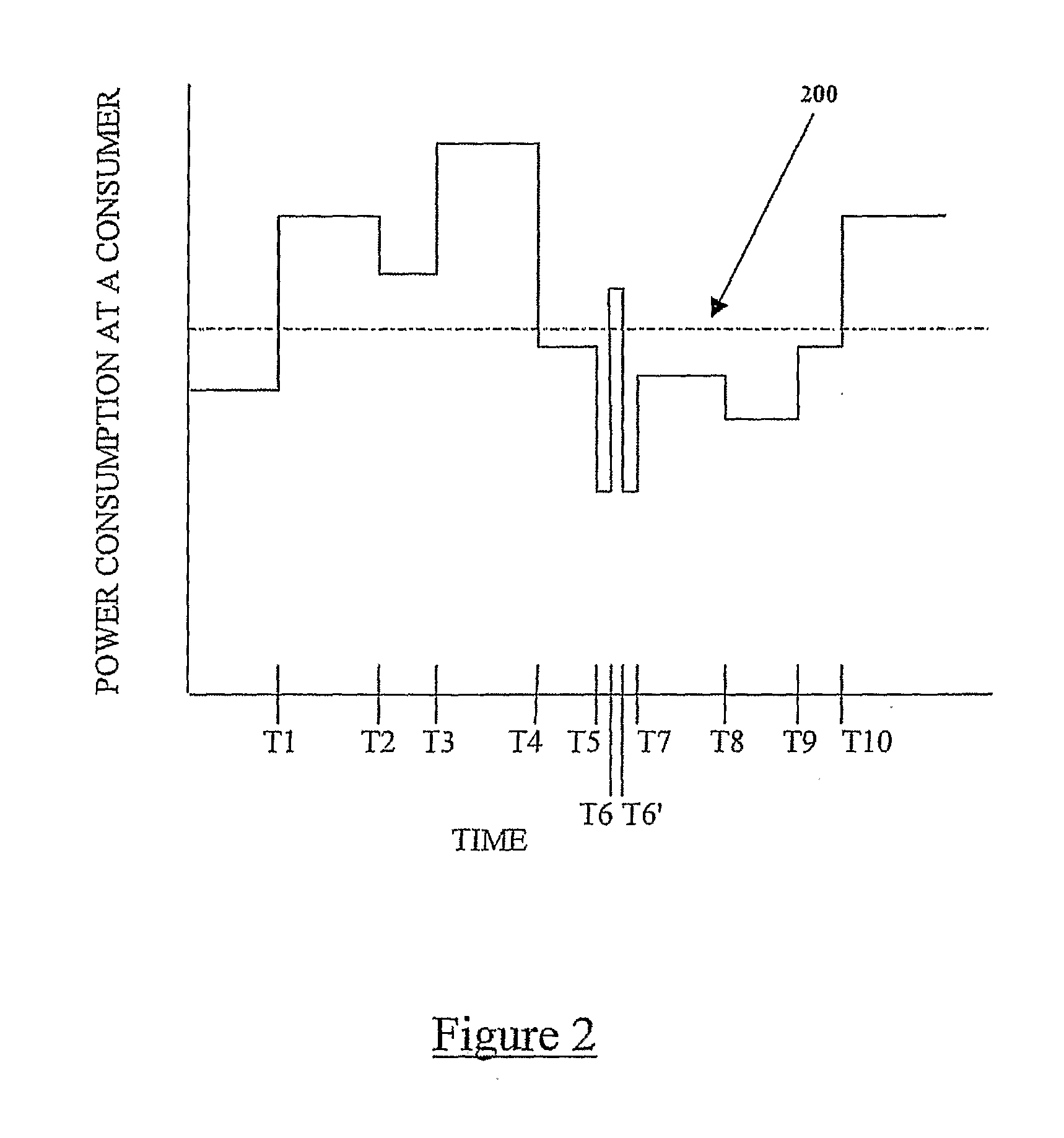

Flexible electric load management system and method therefore

InactiveUS20090018706A1Reduce power consumptionMechanical power/torque controlLevel controlMain processing unitCurrent sensor

A system for controlling electricity consumption of an electricity consumer having a plurality of loads, including: (a) a main central processing unit, connected to a power source, and adapted to receive a signal therefrom; (b) a memory associated with the processing unit; (c) controlled relay assemblies connected to a plurality of loads via local circuit breakers, each assembly including: (i) a relay, responsive to the processing unit; (ii) a current sensor, electrically connected to the relay, the relay and the current sensor being electrically associated with the processing unit, and (iii) an electrical line having a first end connecting the relay assembly to the power source, and having a second end connecting to a local circuit breaker connected to at least one load; wherein each current sensor is adapted to provide, to the processing unit, data pertaining to current drawn via a particular local circuit breaker, and wherein the processing unit is configured to command the relay based on the signal received from the power source, and based on a set of rules provided to the processing unit, the set of rules including load priority information, such that each relay opens or closes in response to the command from the processing unit, so as to shut off or restore power to the electrical line.

Owner:COMPUTERIZED ELECTRICITY SYST LTD

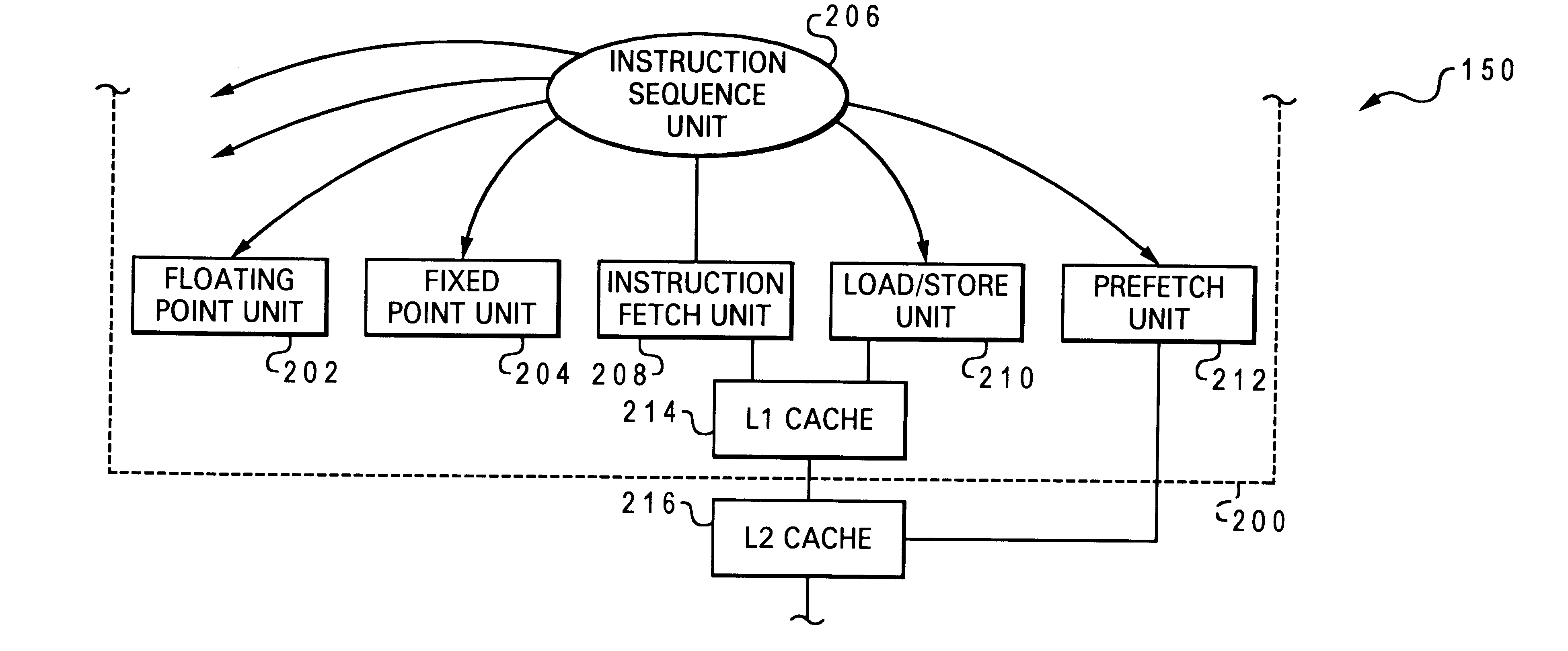

Optimized cache allocation algorithm for multiple speculative requests

A method of operating a computer system is disclosed in which an instruction having an explicit prefetch request is issued directly from an instruction sequence unit to a prefetch unit of a processing unit. In a preferred embodiment, two prefetch units are used, the first prefetch unit being hardware independent and dynamically monitoring one or more active streams associated with operations carried out by a core of the processing unit, and the second prefetch unit being aware of the lower level storage subsystem and sending with the prefetch request an indication that a prefetch value is to be loaded into a lower level cache of the processing unit. The invention may advantageously associate each prefetch request with a stream ID of an associated processor stream, or a processor ID of the requesting processing unit (the latter feature is particularly useful for caches which are shared by a processing unit cluster). If another prefetch value is requested from the memory hiearchy and it is determined that a prefetch limit of cache usage has been met by the cache, then a cache line in the cache containing one of the earlier prefetch values is allocated for receiving the other prefetch value.

Owner:IBM CORP

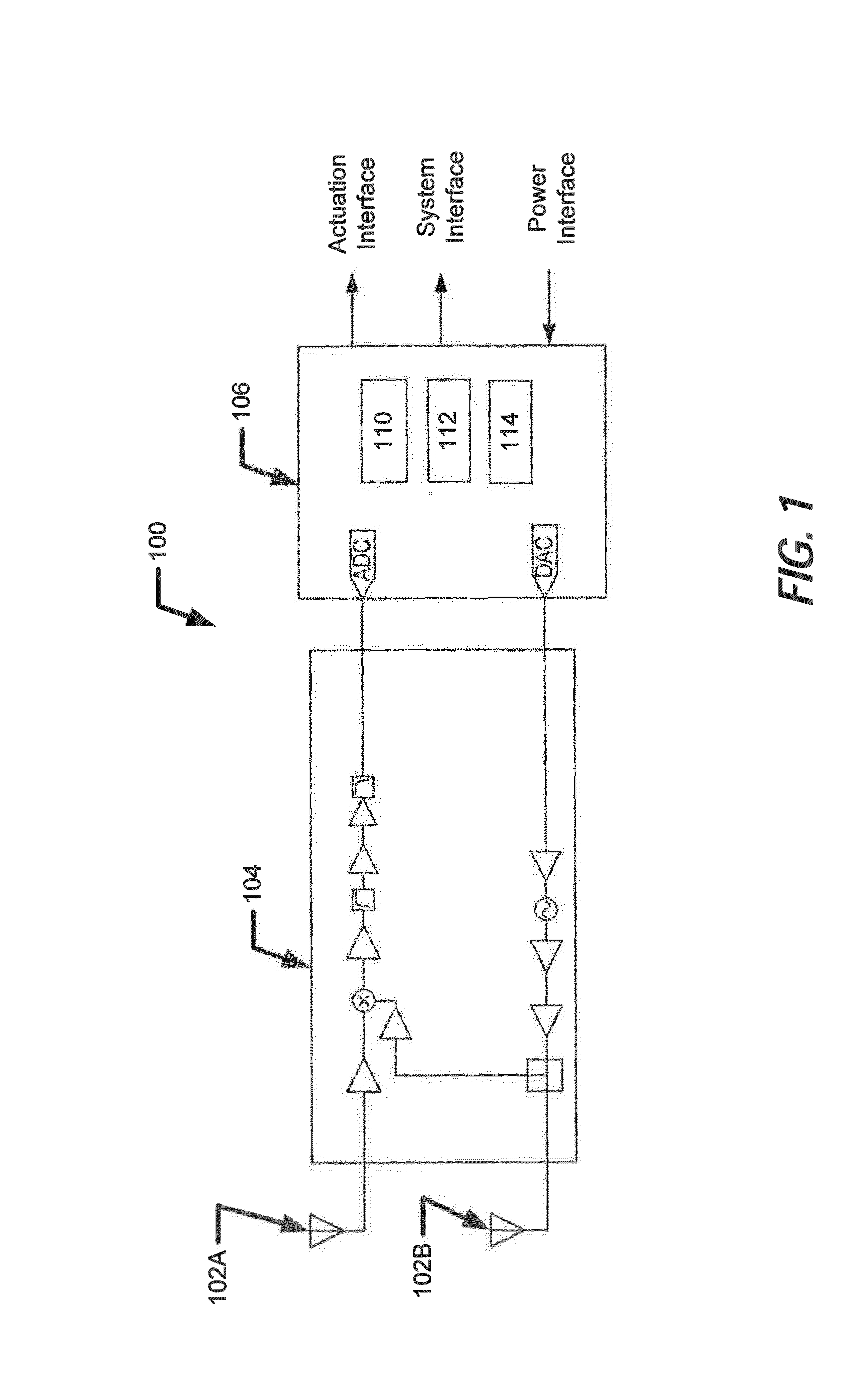

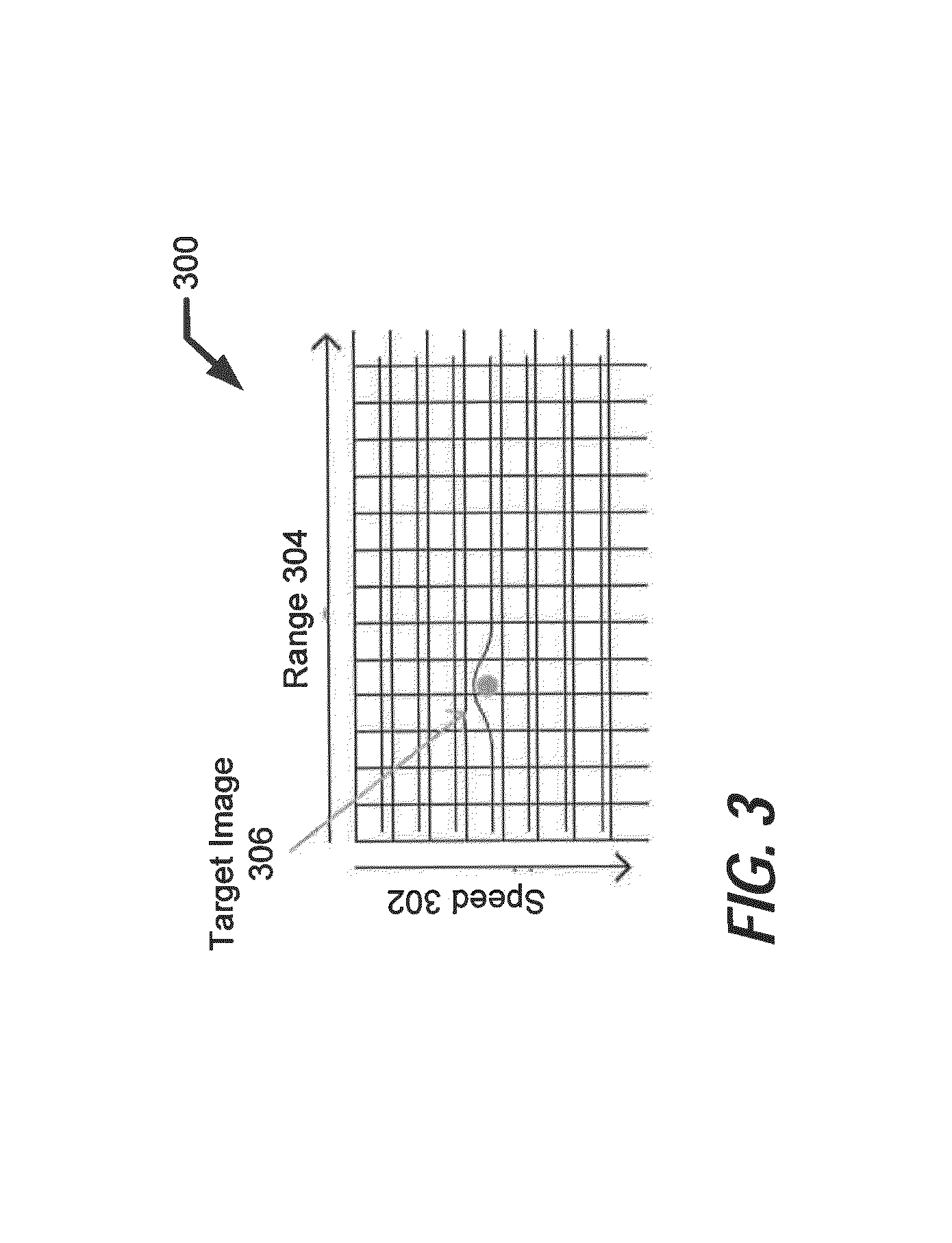

Proximity sensor

A forward-looking proximity sensor comprises one or more antenna elements mounted on a carrier platform in a lateral direction of said carrier platform, said antenna elements being configured to transmit a modulated signal in a direction of travel of said carrier platform, said antenna elements receiving a reflected portion of said modulated signal from said target; and a processing unit configured to generate said modulated signal based on a baseband signal and a carrier signal, said processing unit further determining characteristics of said target based on said reflected portion of said modulated signal, said characteristics of said target indicating a range of said target and at least one feature of said target.

Owner:TECHNOLOGY SERVICE CORPORATION

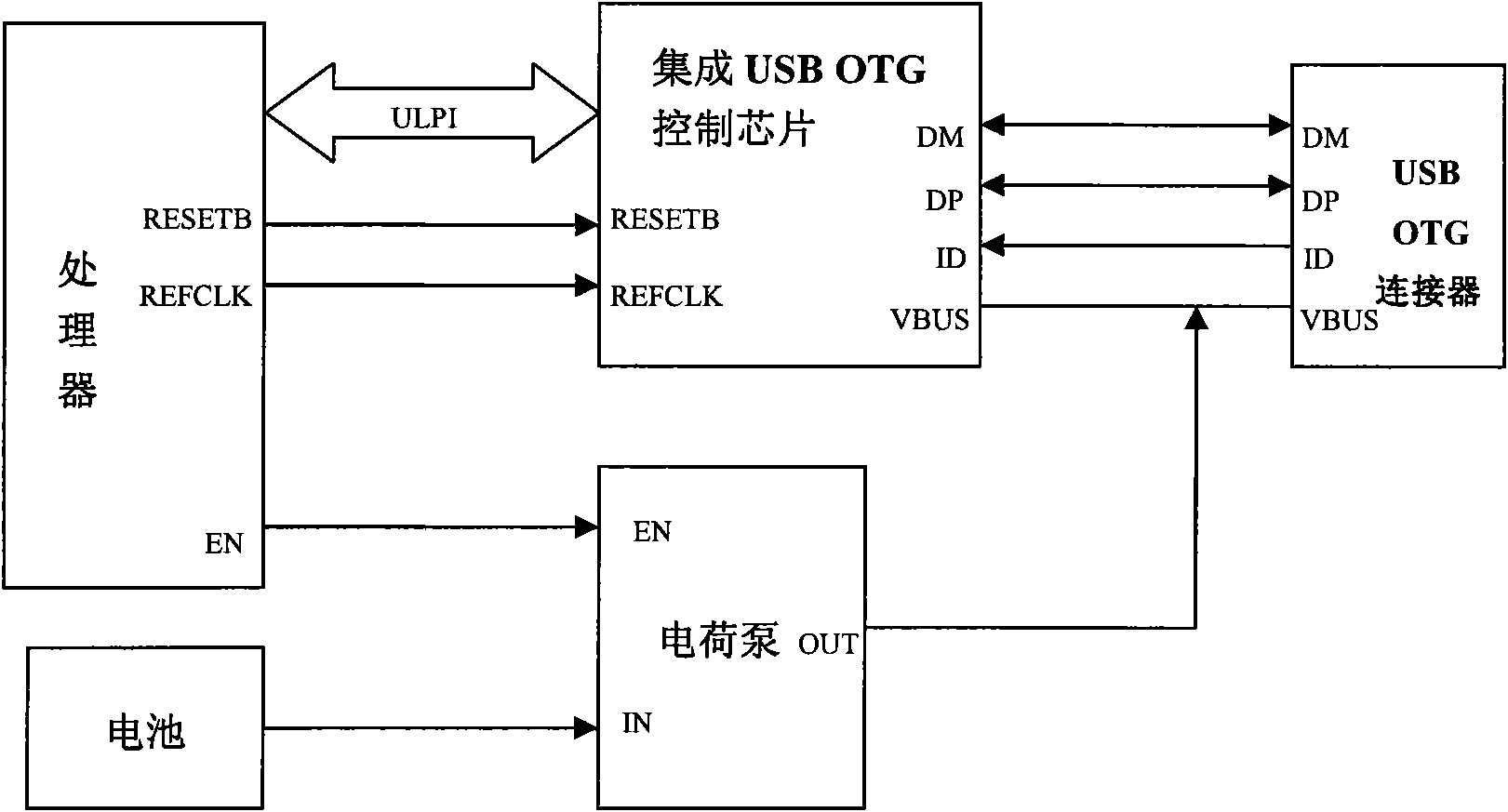

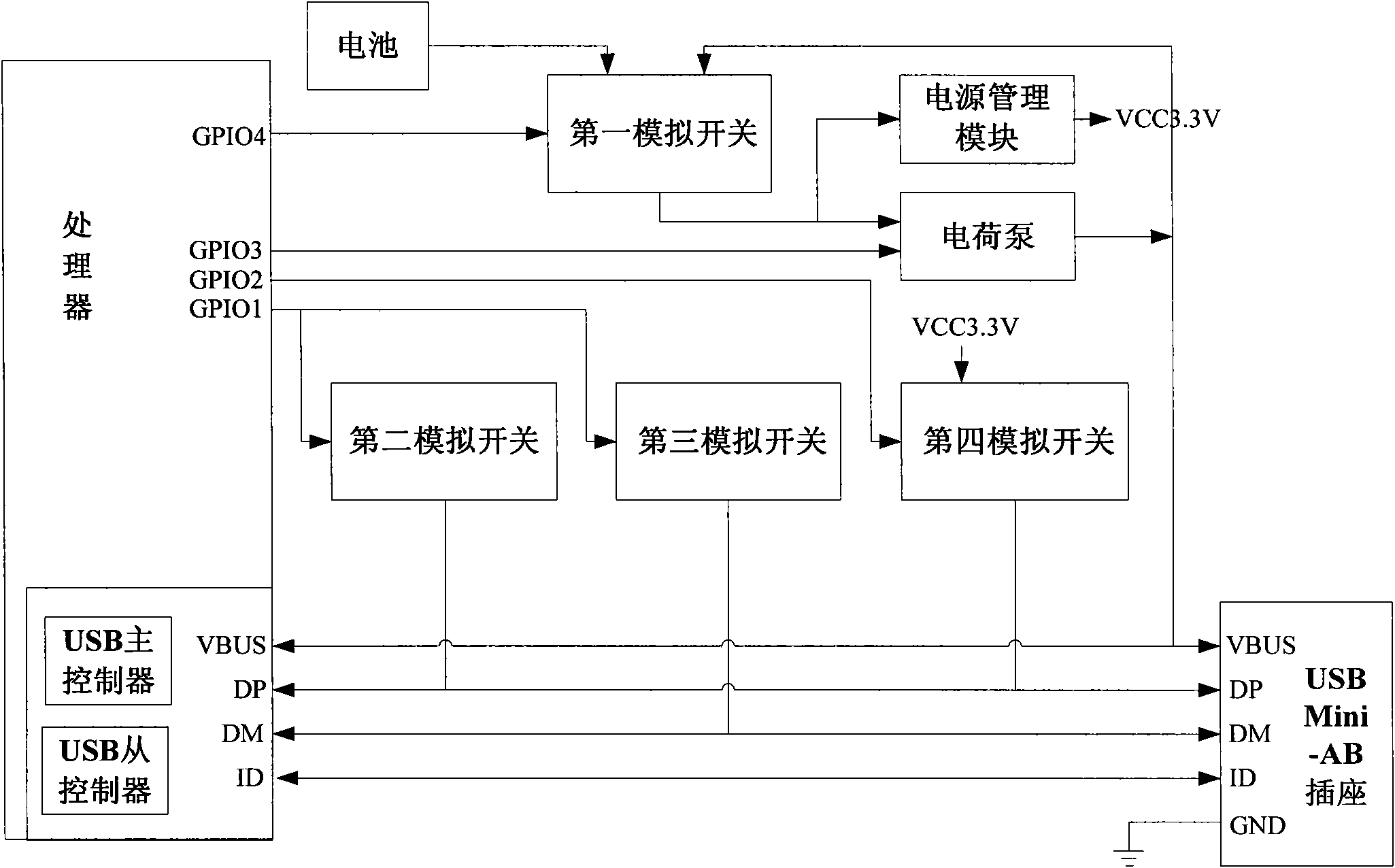

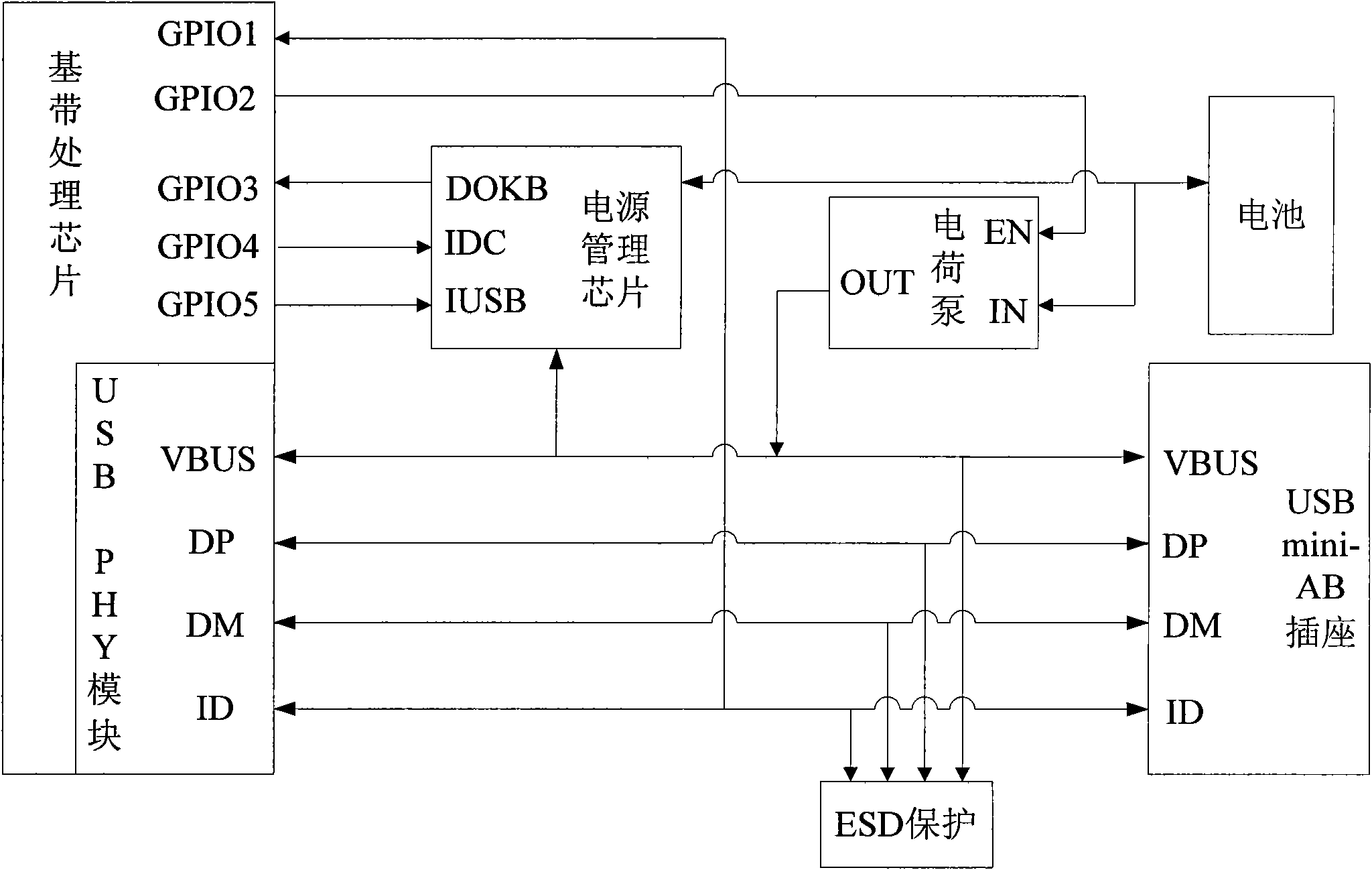

Method and device for realizing USB OTG function on electronic equipment

ActiveCN101901201AEasy to controlReduce power consumptionEnergy efficient ICTPower supply for data processingMain processing unitPhysical layer

The invention discloses a method and a device for realizing USB OTG function on electronic equipment. When external electronic equipment is connected with a USB OTG connecting unit, each pin state of the USB OTG connecting unit triggers a main processing unit to open or close a USB physical layer module. When the USB physical layer module is opened, the USB physical layer module executes identification and configuration on the external electronic equipment, and notifies the main processing unit of executing power supply operation. By designing the external electronic equipment identification flow and the detection closing flow, the method and the device for realizing the USB OTG function can identify a charger, USB master equipment and USB slave equipment, and can reasonably close the USB physical layer module inside the main processing unit when the external electronic equipment is not plugged. The device overcomes the defects of the conventional USB OTG schemes, and has the characteristics of simple control, no occupancy of a system bus, and low power consumption so as to prolong the standby time.

Owner:ZTE CORP

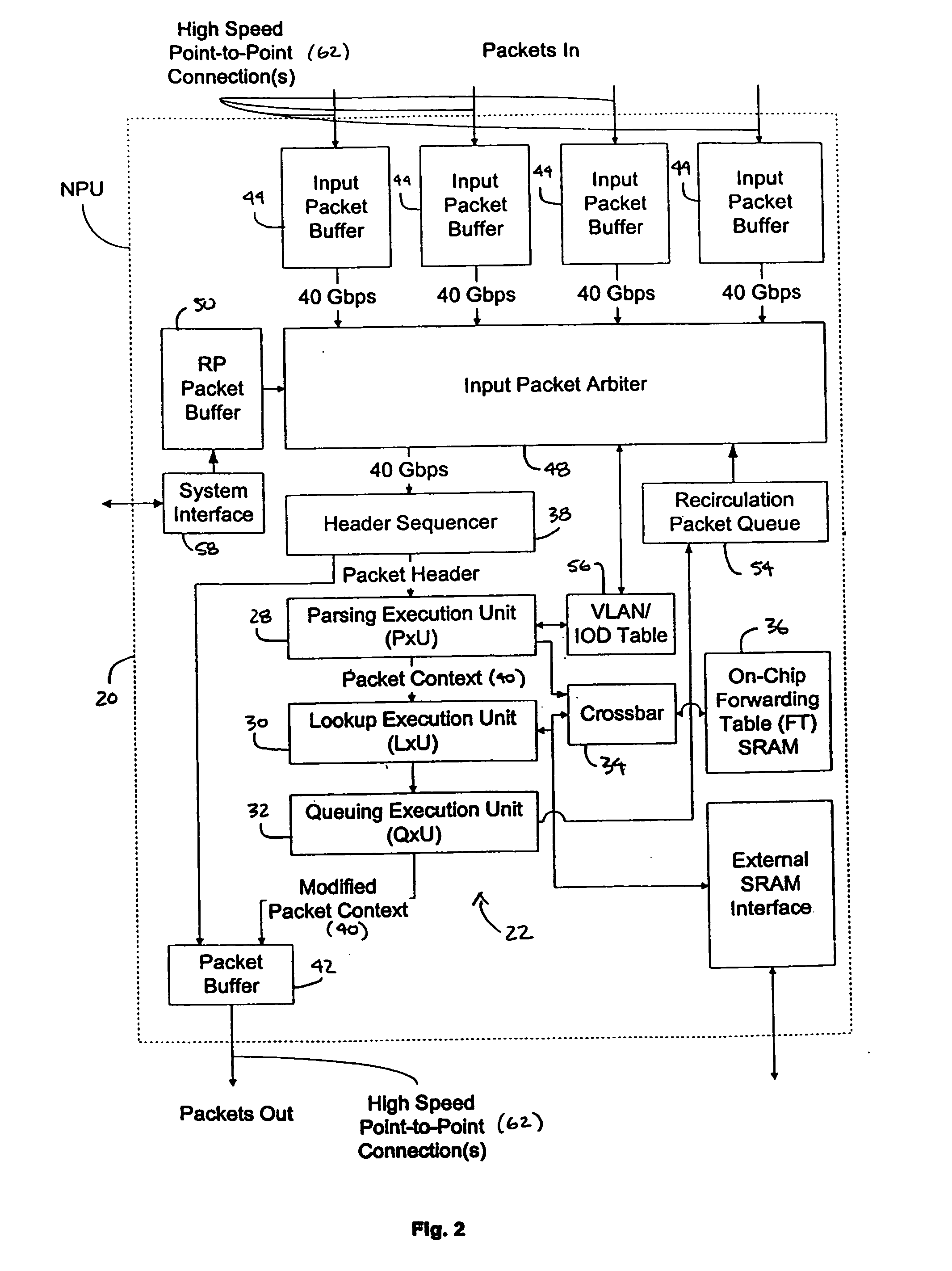

Processing unit for efficiently determining a packet's destination in a packet-switched network

InactiveUS20060117126A1Input is hugeEliminate needTransmissionElectric digital data processingMain processing unitSingle stage

A processor for use in a router, the processor having a systolic array pipeline for processing data packets to determine to which output port of the router the data packet should be routed. In one embodiment, the systolic array pipeline includes a plurality of programmable functional units and register files arranged sequentially as stages, for processing packet contexts (which contain the packet's destination address) to perform operations, under programmatic control, to determine the destination port of the router for the packet. A single stage of the systolic array may contain a register file and one or more functional units such as adders, shifters, logical units, etc., for performing, in one example, very long instruction word (vliw) operations. The processor may also include a forwarding table memory, on-chip, for storing routing information, and a cross bar selectively connecting the stages of the systolic array with the forwarding table memory.

Owner:CISCO TECH INC

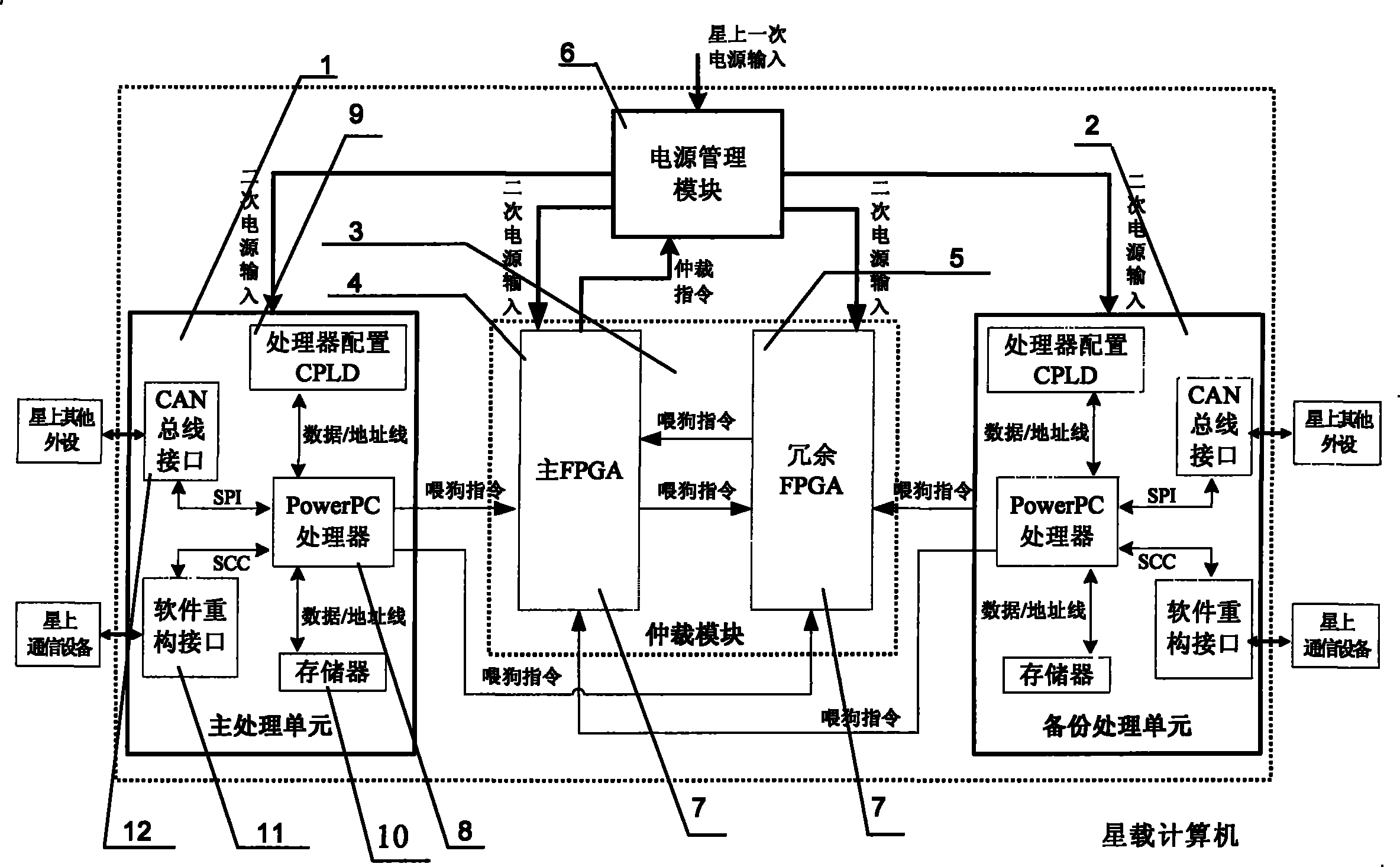

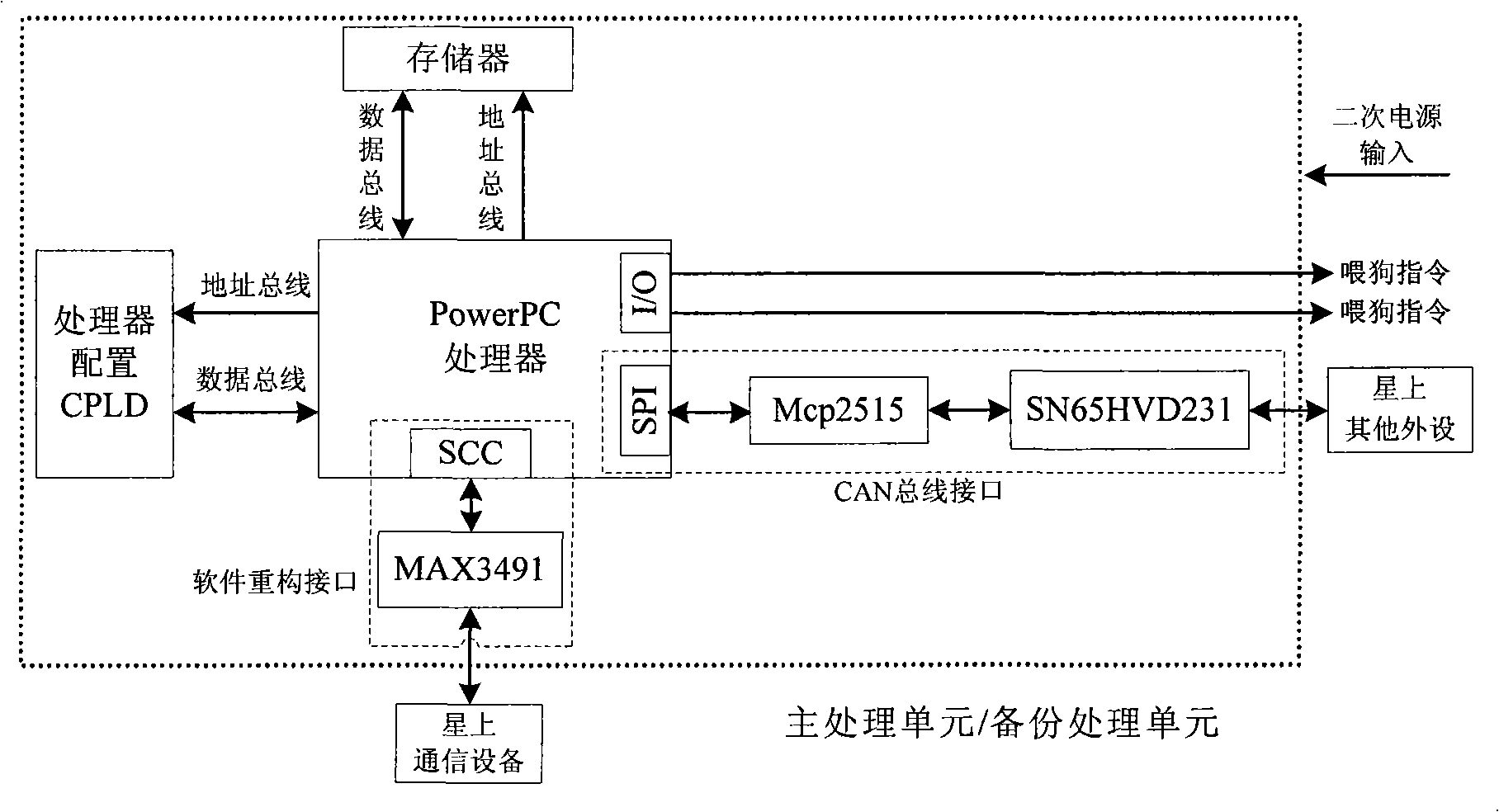

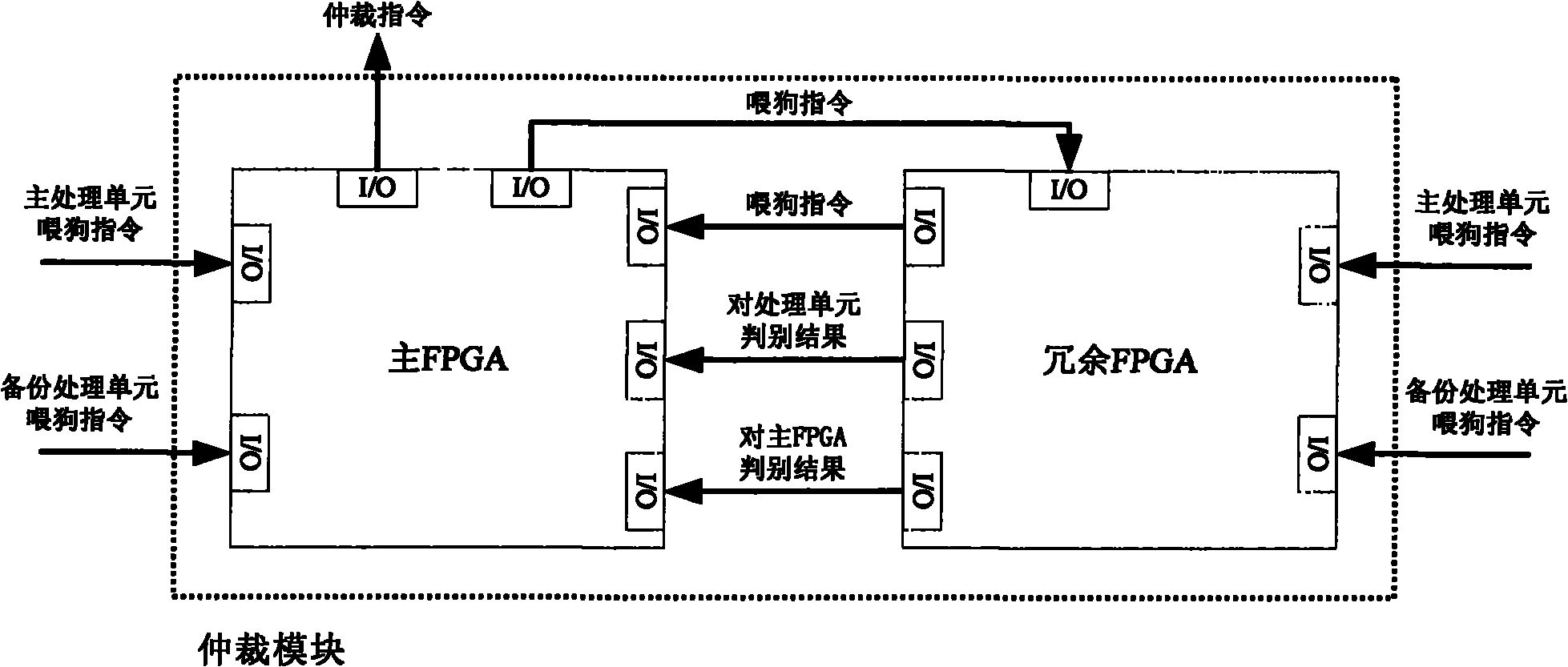

Reconfigurable on-board computer of redundancy arbitration mechanism

InactiveCN101833536AImprove software and hardware configurationFlexibleArchitecture with multiple processing unitsMain processing unitElectronic systems

The invention relates to a reconfigurable on-board computer of a redundancy arbitration mechanism. The reconfigurable on-board computer consists of a main processing unit, a backup processing unit, an arbitration module and a power supply management module, wherein by adopting a double-computer cold backup mode and based on a Power PC processor and a software configurable interface, the main processing unit and the backup processing unit can realize software configuration of the on-board computer through satellite-to-ground links. Algorithms of failure detection, self-check and double-computer switching arbitration of the on-board computer are stored in the arbitration module; the arbitration module consists of two sets of FPGA, which detect failures of the main processing unit and the backup processing unit, performs internal self-check in real time respectively, form failure judgment on the main processing unit and the backup processing unit and the redundancy arbitration of the double-computer switching, and finally report the arbitration results such as restoration, switching and the like to the power supply management module in an instruction format for performing. The reconfigurable on-board computer performs cold backup design on the main processing unit and the backup processing unit, and performs failure detection and double-computer switching by using the arbitration module, so that the reconfigurable on-board computer has the advantages of high processing capacity, flexible function, high reliability, low energy consumption, and the computer has important value in the development of electronic systems of micro / nano satellites.

Owner:BEIHANG UNIV

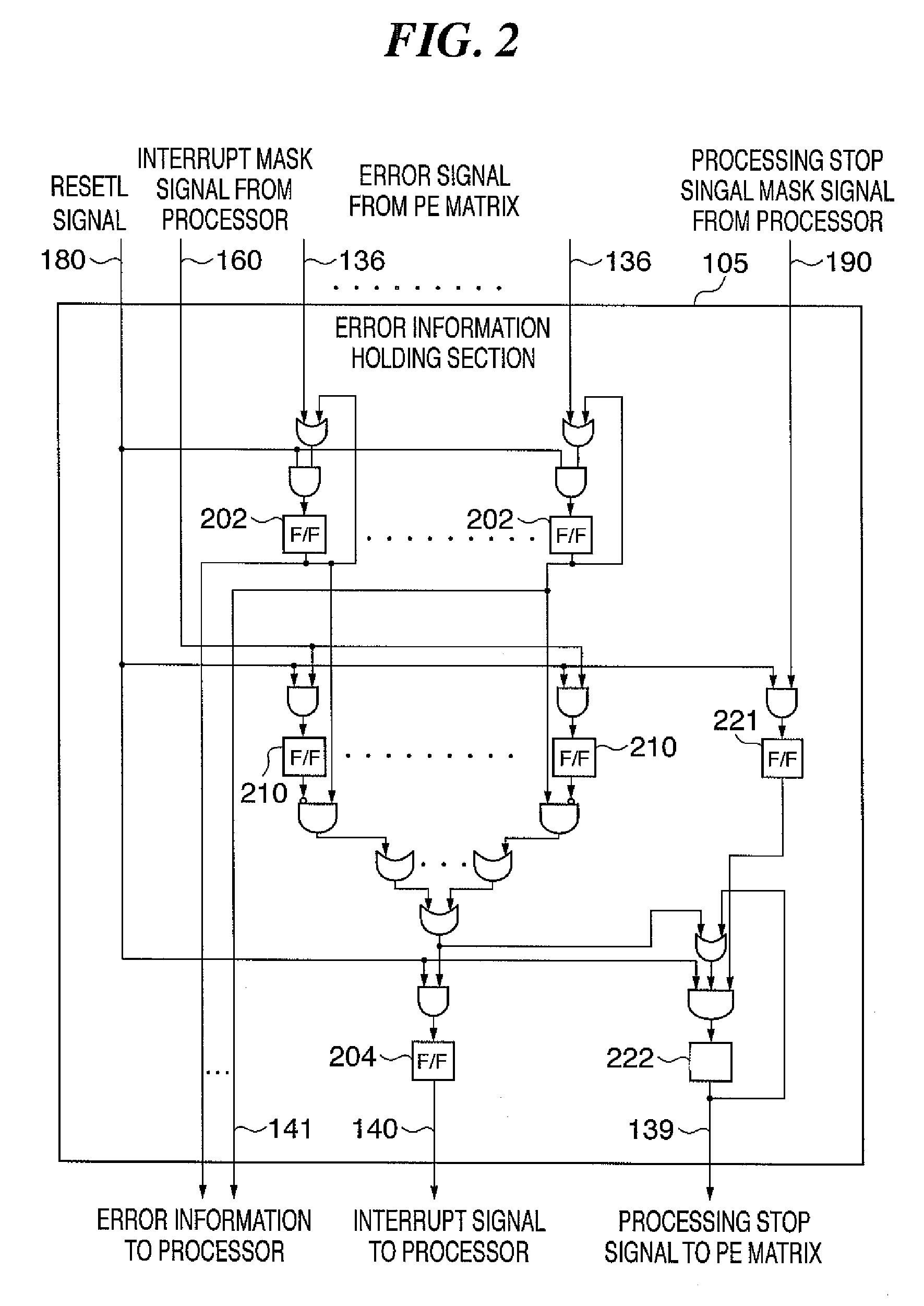

Reconfigurable processor and reconfiguration method executed by the reconfigurable processor

InactiveUS20070180315A1Error detection/correctionSpecial data processing applicationsMain processing unitParallel computing

A reconfigurable processor which is capable of carrying out or continuing processing even after occurrence of an error in a data processing unit within the reconfigurable processor. The reconfigurable processor has a processing element matrix comprised of a plurality of processing elements. The reconfigurable processor reconfigures the processing element matrix according to an error of the processing element matrix.

Owner:CANON KK

Monitoring operational data in data processing systems

InactiveUS20050015773A1Reduce the impactEfficient delimiting of data collectionError detection/correctionMultiprogramming arrangementsData processing systemMain processing unit

A data processing apparatus includes a set of components for monitoring data relating to the operation of a plurality of data processing units. Each data processing unit includes connection points for connecting to others of the data processing units and an operational data processing component for processing data. The set of components includes event listeners located at the connection points for detecting events within the flow of processing operations at the data processing units.

Owner:IBM CORP

Defining characteristics between processing systems

InactiveUS6202095B1Reduce in quantityMore efficientResource allocationMultiple digital computer combinationsMain processing unitData processing system

Disclosed is a system for indicating system capabilities. A first processing unit, such as a control unit, receives a command from a second processing unit, such as a host system, indicating capabilities of the first processing unit. The first processing unit determines common capabilities indicated in the command that are also available in the first processing unit and indicates in a data structure, such as a bitmap data structure, the common capabilities. The first processing unit then signals the second processing unit of the change in system status.

Owner:IBM CORP

Cross-chip communication mechanism in distributed node topology

InactiveUS20040215929A1Promote disseminationSubstation/switching arrangement detailsElectric digital data processingTransmission protocolMain processing unit

A method of communicating between processing units on different integrated circuit chips in a multi-processor computer system by issuing a command from a source processing unit to a destination processing unit, receiving the command at the destination processing unit while the destination processing unit is processing program instructions, and accessing registers in clock-controlled components of the destination processing unit without interrupting processing of the program instructions by the destination processing unit. The access may be a read from status or mode registers of the destination processing unit, or write to control or mode registers. Many processing units can be interconnected in a ring topology, and the access command can be passed from the source processing unit through several other processing units before reaching the destination processing unit. Each of the processing units is assigned a respective, unique identification number (PID) in addition to one or more optional "special" tags which are not necessarily unique, and an external command (XSCOM) interface on a given chip recognizes only those commands that include the corresponding chip tag, unless the command is a broadcast. Commands may be directed to subgroups of processors by implementing masks against the PID, selected portion of the PID, or other "special" tag in a broadcast fashion. The XSCOM interface also has the ability to block any broadcast command (e.g., reset) to itself when that command was issued by its associated processing unit (a "Block Self" mode). The processing units are interconnected via a fabric bus, and the XSCOM interface preferably uses an additional communications line that follows the topology of the fabric bus or could alternately use command / data packets across the existing fabric transmission protocol. The service processor has access to this command interface through an external port (e.g. JTAG) and assembly code running on the processing unit has access to the command interface via special assembly code sequences.

Owner:IBM CORP

Offloading operations for maintaining data coherence across a plurality of nodes

InactiveUS20080065835A1Reduce the burden onFree resourceTransmissionMemory systemsData coherenceMain processing unit

Offloading data coherence operations from a primary processing unit(s) executing instantiated code responsible for data coherence in a shared-cache cluster to a data coherence offload engine reduces resource consumption and allows for efficient sharing of data in accordance with the data coherence protocol. Some of the data coherence operations, such as consulting and maintaining a directory, generating messages, and writing a data unit can be performed by a data coherence offload engine. The data coherence offload engine indicates availability of the data unit in the memory to the appropriate instantiated code. Hence, the instantiated code (the corresponding primary processing unit) is no longer burdened with some of the work load of data coherence operations. Migration of tasks from a primary processing unit(s) to data coherence offload engines allows for efficient retrieval and writing of a requested data unit.

Owner:SUN MICROSYSTEMS INC

Method and apparatus for dispersed storage memory device selection

InactiveUS20110078373A1Digital data information retrievalMemory adressing/allocation/relocationMain processing unitOperational system

A method begins when a dispersed storage (DS) processing unit of a DS unit has at least one of DS unit operational data and DS unit operating system algorithm to store. The method continues with the DS processing unit encoding at least a portion of the at least one of DS unit operational data and DS unit operating system algorithm in accordance with an error coding dispersal storage function to produce a plurality of data slices. The method continues with the DS processing unit storing at least some of the plurality of data slices in memory devices of the DS unit in accordance with the error coding dispersal storage function.

Owner:PURE STORAGE

Electronic atomization hookah

There is provided an electronic atomization hookah comprising a) a shell comprising a shell body, a shell top portion and a shell bottom portion, where the shell body defines a shell internal cavity and comprises a first nozzle defining a first passage inside the cavity and configured to receive a smoking hose, and where the shell top portion comprises a first slot and the shell bottom portion comprises a second slot; b) a liquid supplying container, an atomizer and at least one battery arranged within the shell internal cavity, where the atomizer is in contact with the container for heating a liquid contained therein when activated such that a mist is formed as a function of the heating, and where the container comprises a first opening in communication with the first passage for allowing output of the mist therethrough; c) a hollow tube having a tube bottom extremity and a tube top extremity, where the hollow tube bottom extremity is coupled to the first slot and forms a substantially airtight seal therewith; d) a jar comprising a substantially flat base and a jar top portion configured to be demountably coupled to the second slot; e) a hookah head having a top portion and a bottom portion, where the head bottom portion is configured to be coupled to the tube top extremity and forms a substantially airtight seal therewith; and f) a main processing unit and a sensor located within the hookah head, where the main processing unit is connected to the sensor, to the at least one battery and to the atomizer, such that, when a user inhales using the smoking hose, a variation of pressure is detected by the sensor and an electrical signal is automatically transmitted by the main processing unit to the atomizer for activation.

Owner:MAGIC HERBAL R L

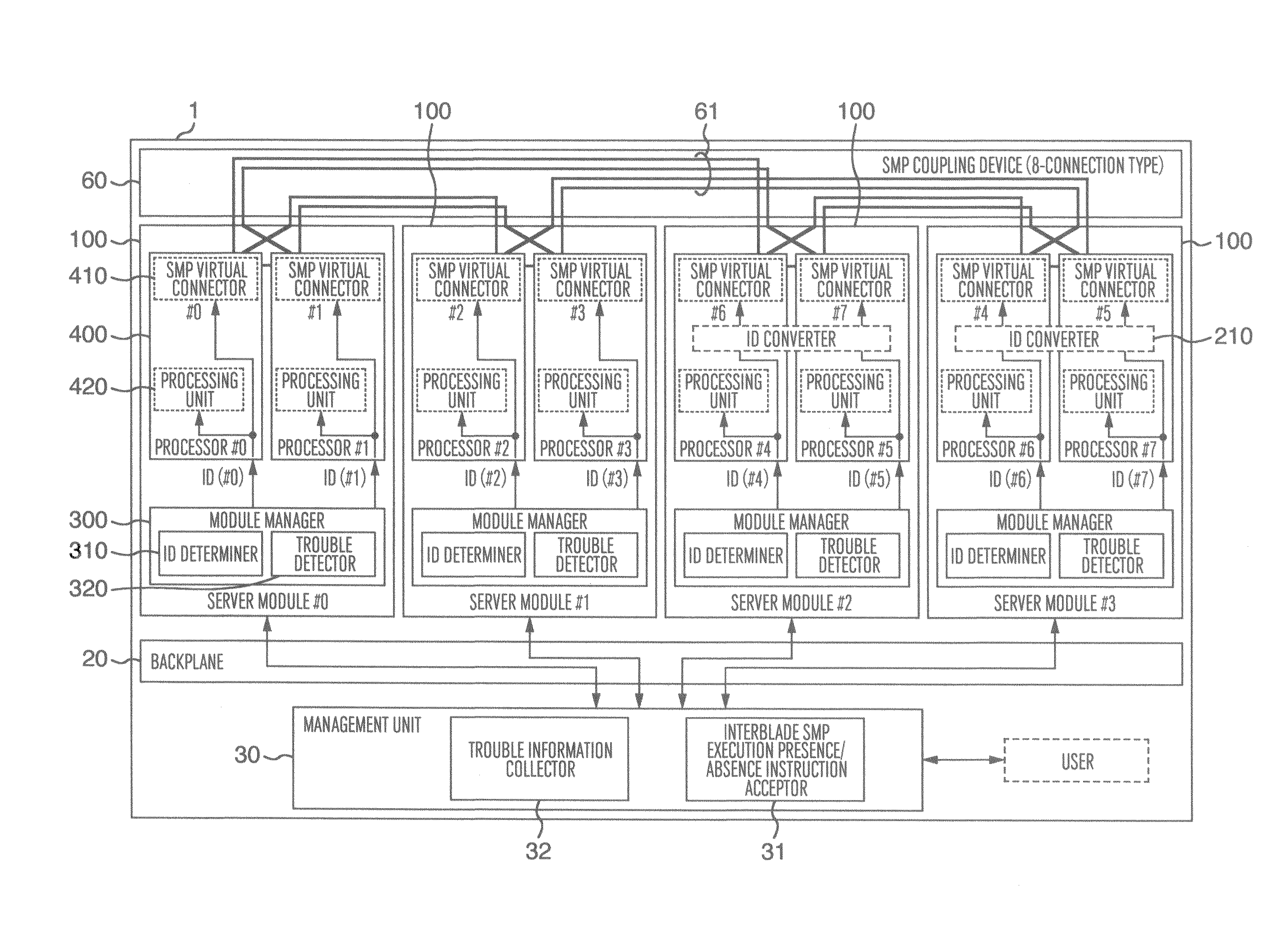

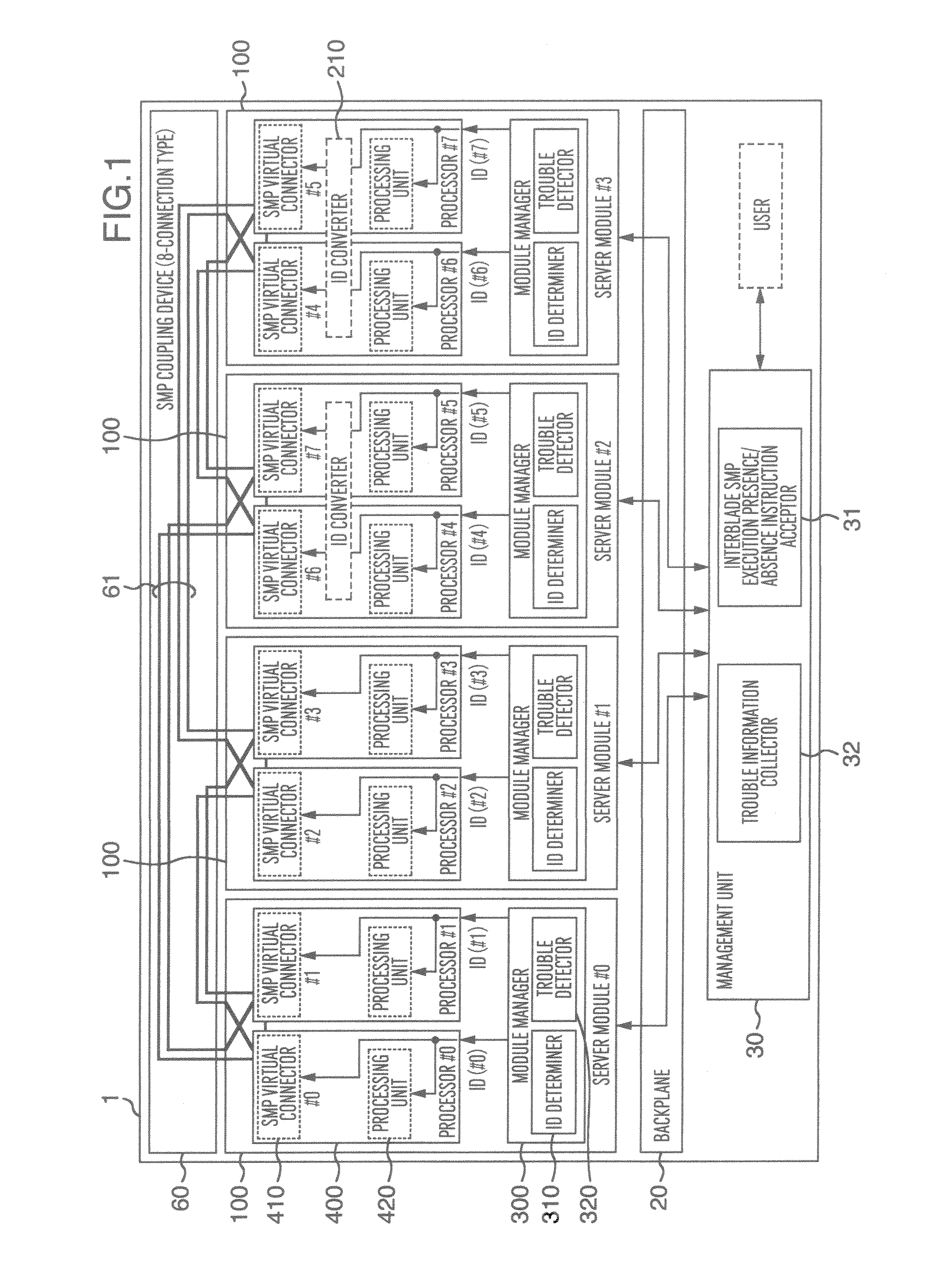

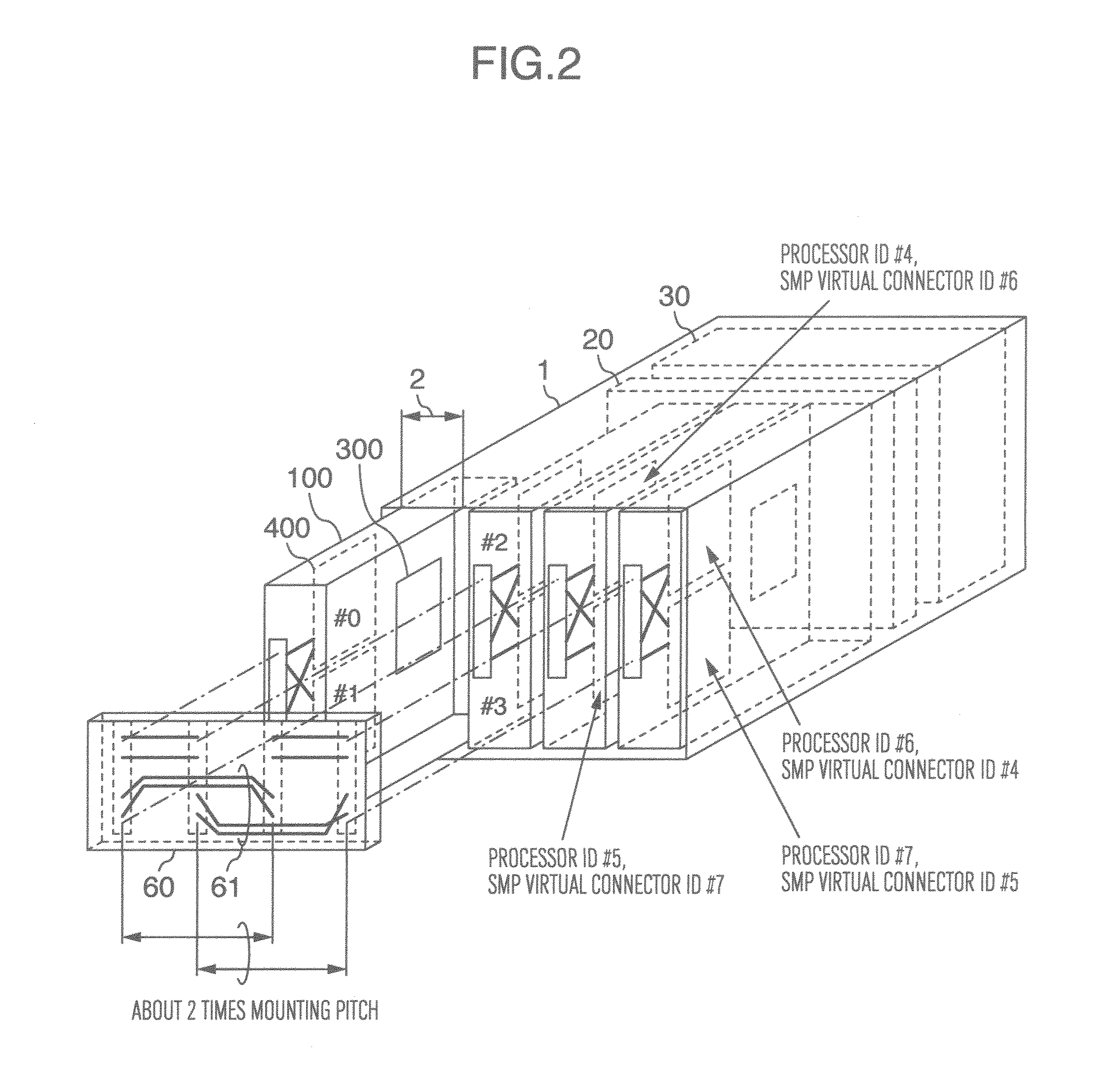

Blade server apparatus

ActiveUS8745275B2Shorten the line lengthImprove signal transmission qualityGeneral purpose stored program computerInput/output processes for data processingMain processing unitBlade server

A blade server apparatus including a plurality of server modules, a backplane for mounting the plurality of server modules thereon, and an SMP coupling device having wiring lines to SMP couple the plurality of server modules. Each of the server modules has one or more processors controlled by firmware and a module manager for managing its own server module, the module manager has an ID determiner for informing each processor of a processor ID, each processor has a processing unit and an SMP virtual connecting unit for instructing ones of wiring lines of the SMP coupling device through which a packet received from the processing unit is to be transmitted, and an ID converter for converting the processor ID and informing it to the SMP virtual connecting unit is provided within the firmware.

Owner:HITACHI LTD

Portable three-dimensional temperature field reconstruction system based on infrared thermal imager and depth camera

InactiveCN107067470AImprove reconstruction effectProof of validity3D modellingMain processing unitPoint cloud

The invention relates to a portable three-dimensional temperature field reconstruction system based on an infrared thermal imager and a depth camera, which comprises a main processing unit, a temperature information acquisition unit and a three-dimensional point cloud information acquisition unit, wherein the main processing unit realizes data processing and software running by using a contained GPU device; the temperature information acquisition module realizes acquisition for object surface temperature information; and the three-dimensional point cloud information acquisition module realizes acquisition for object surface three-dimensional space information, the object surface temperature information and the object surface three-dimensional space information are transmitted to the main processing unit so as to be processed, and the processed information is displayed through a visualization upper computer. The portable three-dimensional temperature field reconstruction system can perform three-dimensional modeling on a scene online in real time, can enable infrared temperature field information to be fused with a three-dimensional model, and is significantly improved in construction effect compared with an operation of independently using an RGB-D depth camera or an infrared thermal imager.

Owner:NORTHEASTERN UNIV

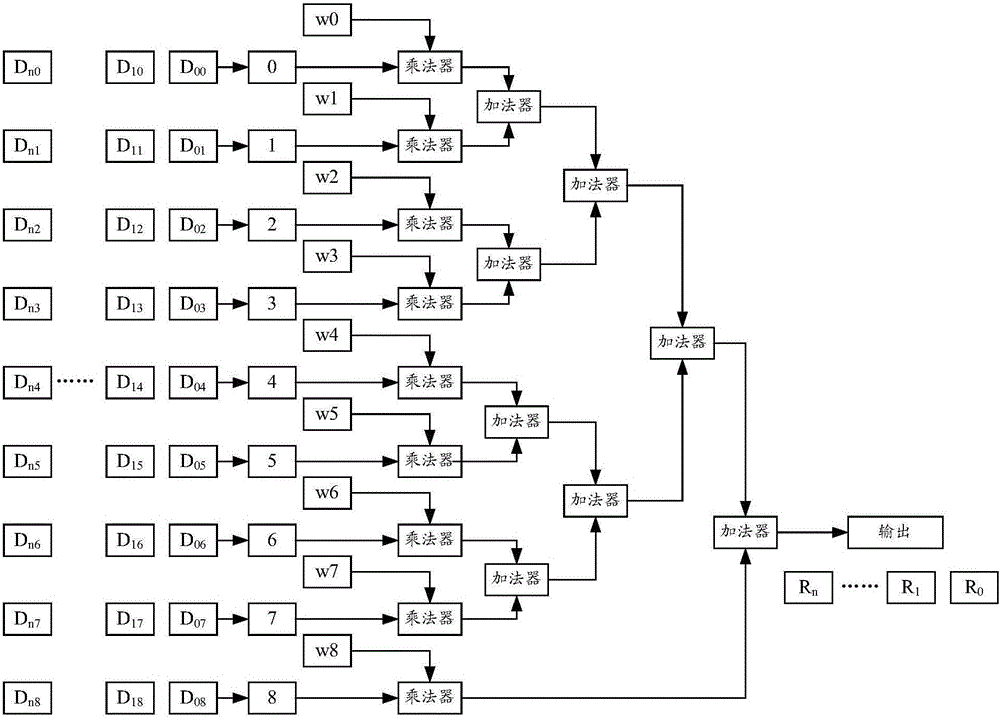

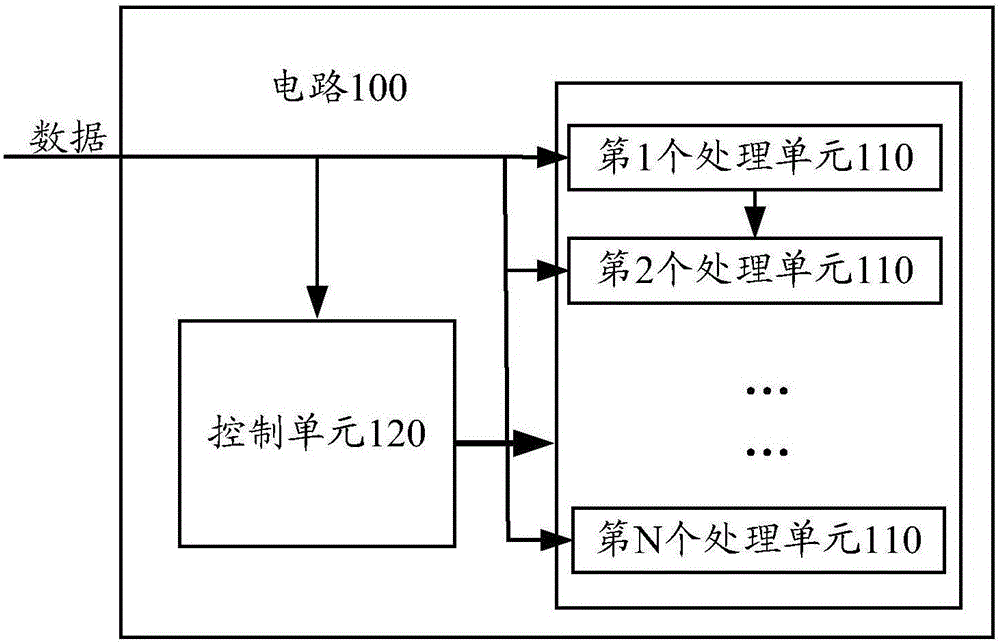

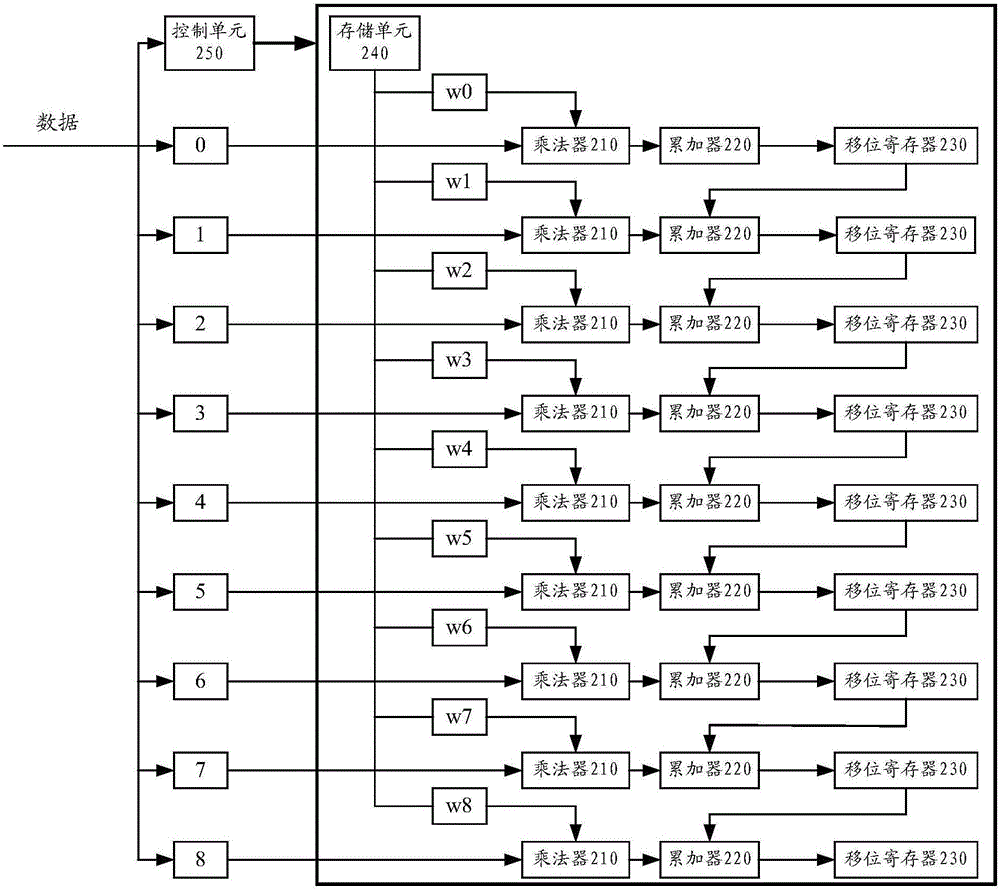

Circuit for processing data, image processing system, and method and apparatus for processing data

InactiveCN106127302AReduce power consumptionAchieve sharingDigital data processing detailsConcurrent instruction executionMain processing unitImaging processing

The embodiments of the invention disclose a circuit for processing data, an image processing system, and a method and apparatus for processing data. The circuit comprises a control unit and N processing units. The control unit and each processing unit among the N processing units are connected with a data transmission unit, each processing unit is used for processing the same data output successively by the data transmission unit, and the output end of an i-th processing unit among the N processing units is connected with the input end of an (i+1)th processing unit, wherein N is an integer greater than 1, and the value scope of i is an integer ranging from 1 to N-1. The control unit is used for, when it is determined that data to be processed output by the data transmission unit is 0, controlling the N processing units to be all at a closed state. The circuit, the system, the method and the apparatus provided by the embodiments of the invention can reduce circuit power consumption while realizing convolution operation.

Owner:HANGZHOU HUAWEI DIGITAL TECH

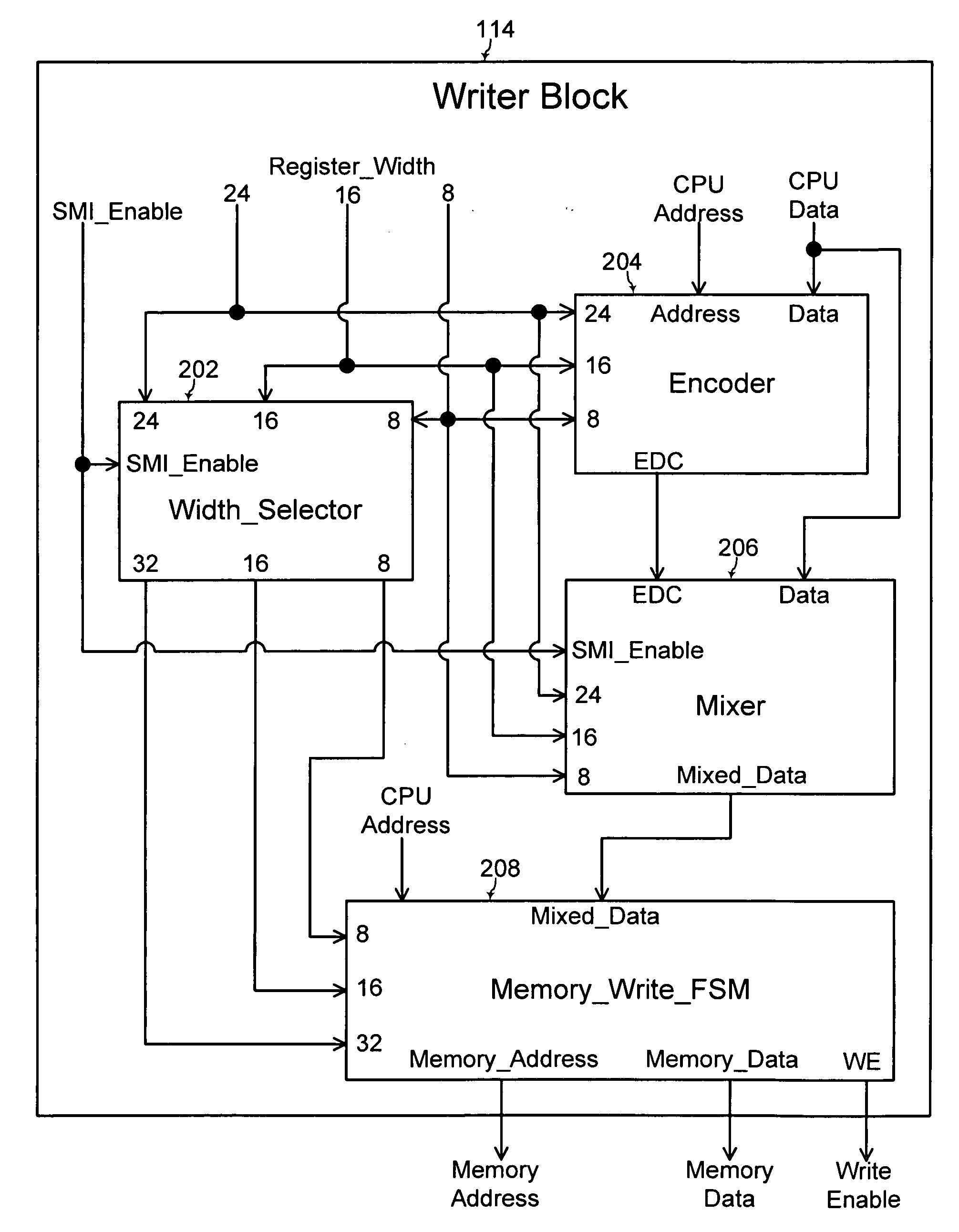

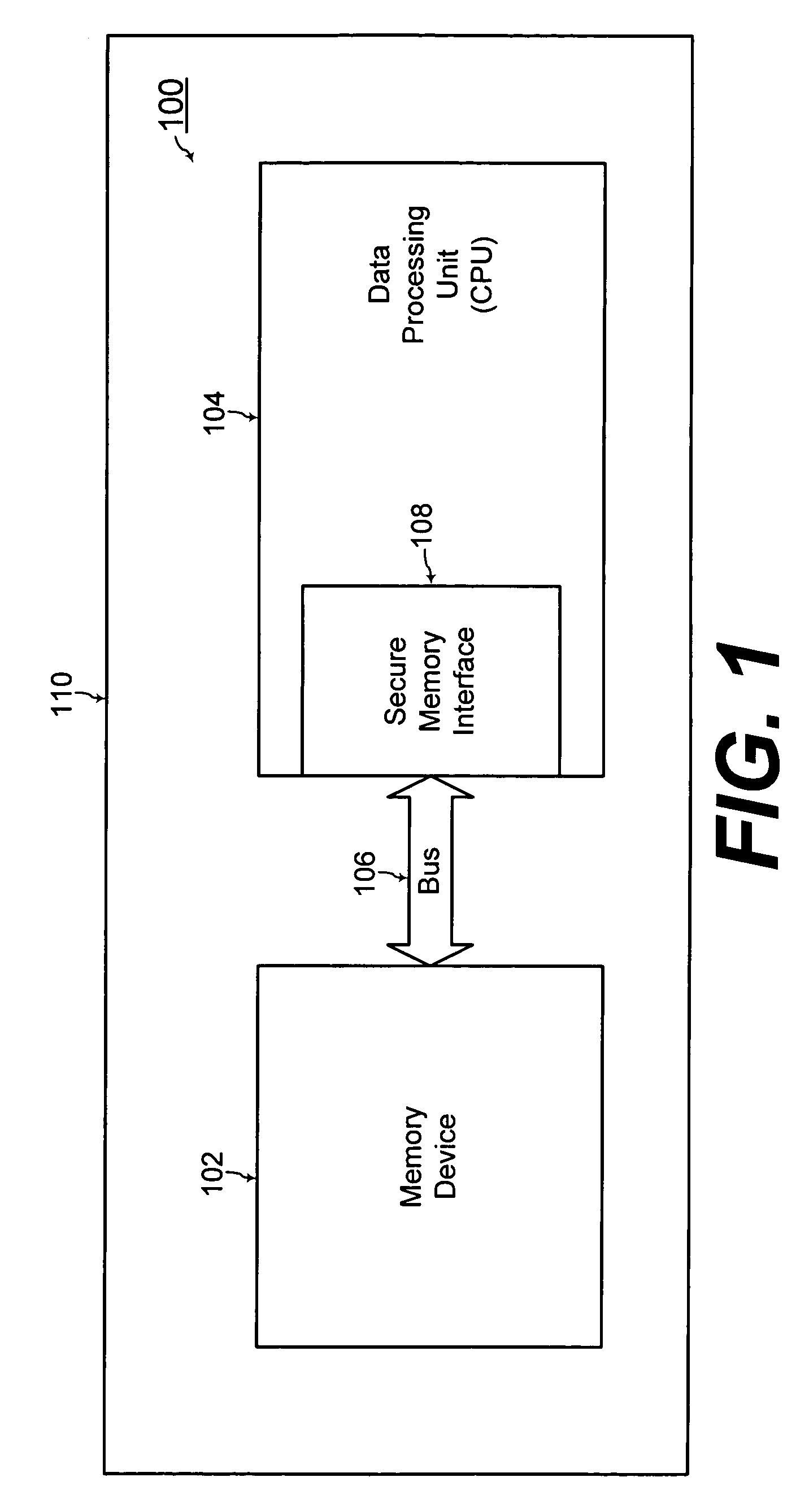

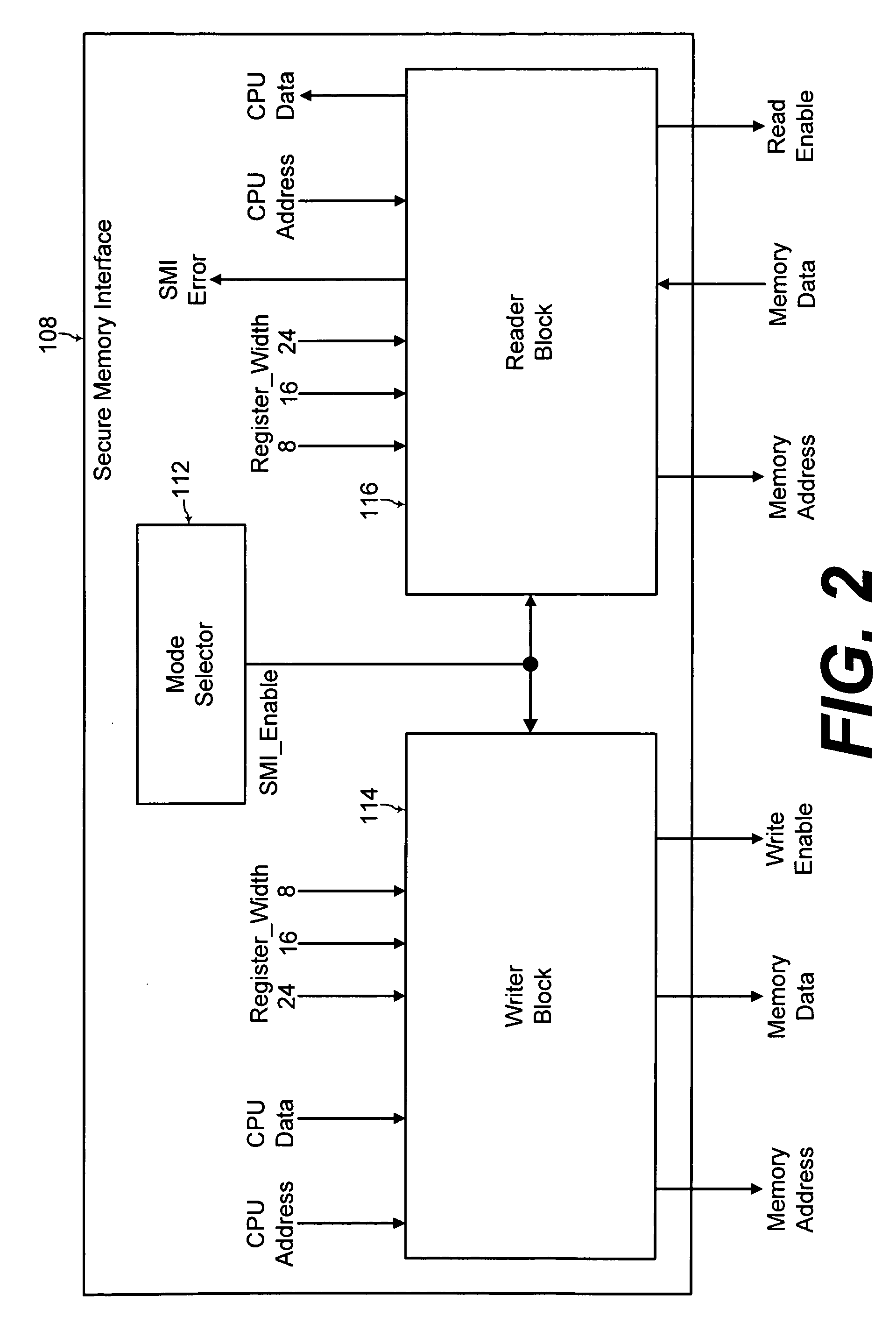

Secure memory interface

ActiveUS20100082927A1Efficient detectionEasy accessDigital computer detailsUnauthorized memory use protectionMain processing unitMemory interface

A secure memory interface includes a reader block, a writer block, and a mode selector for detecting fault injection into a memory device when a secure mode is activated. The mode selector activates or deactivates the secure mode using memory access information from a data processing unit. Thus, the data processing unit flexibly specifies the amount and location of the secure data stored into the memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

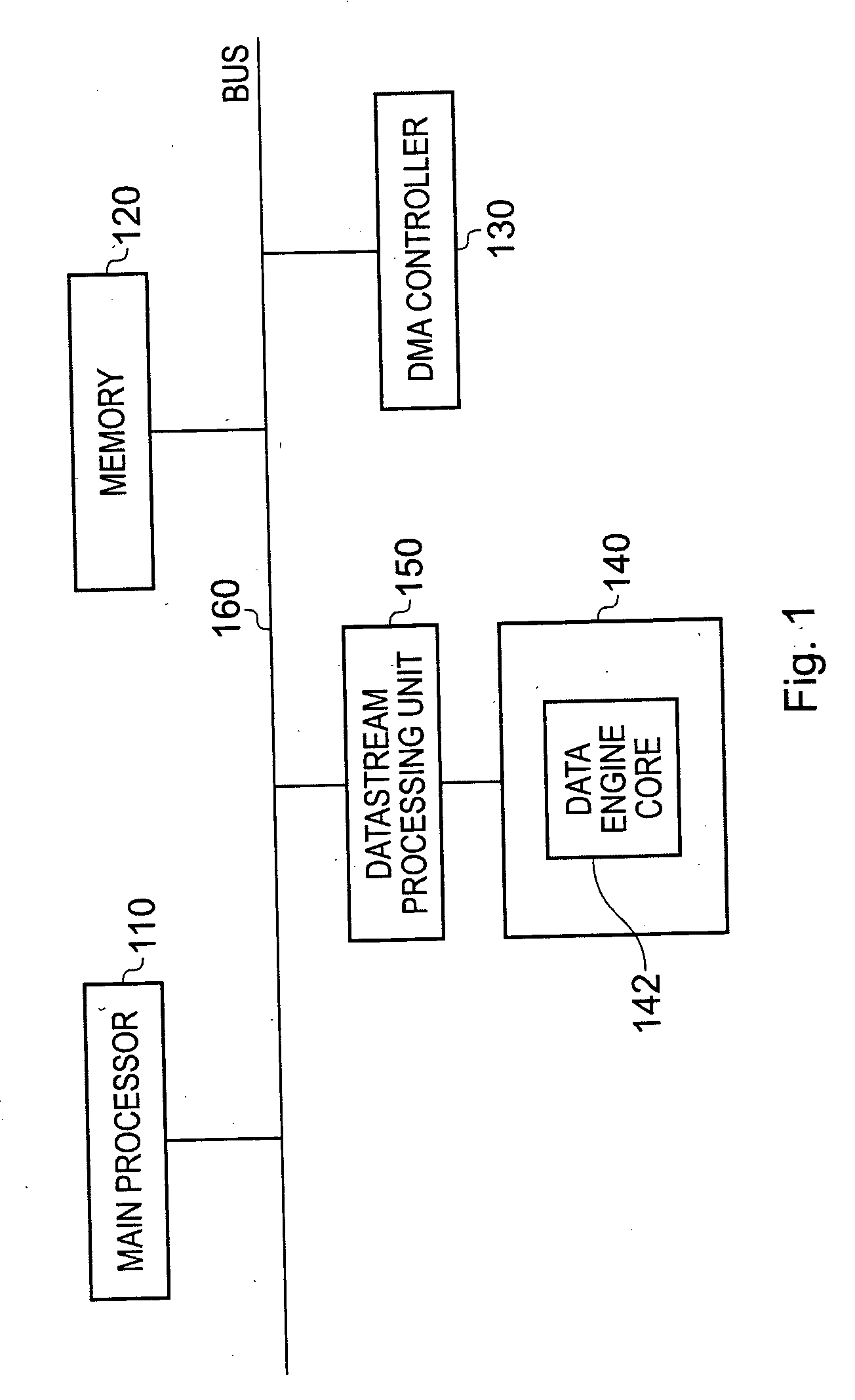

Data processing system

ActiveUS20060251092A1Lighten the computational burdenReduce the burden onGeneral purpose stored program computerData switching by path configurationData processing systemMain processing unit

A data processing system is provided comprising a main processor operable to perform a plurality of data processing tasks, a data engine having a data engine core operable to perform a number of said plurality of data processing tasks on behalf of said main processor and a data stream processing unit providing a data communication path between said main processing unit and said data engine core. The data stream processing unit has a control interface operable to receive from said data engine core at least one command and a data stream controller operable to receive at least one input data stream and to perform at least one operation on said at least one input data stream to generate at least one output data stream comprising a sequence of data elements. The data stream processing unit is responsive to said at least one command from said data engine core to control said data stream controller to perform said at least one operation.

Owner:ARM LTD

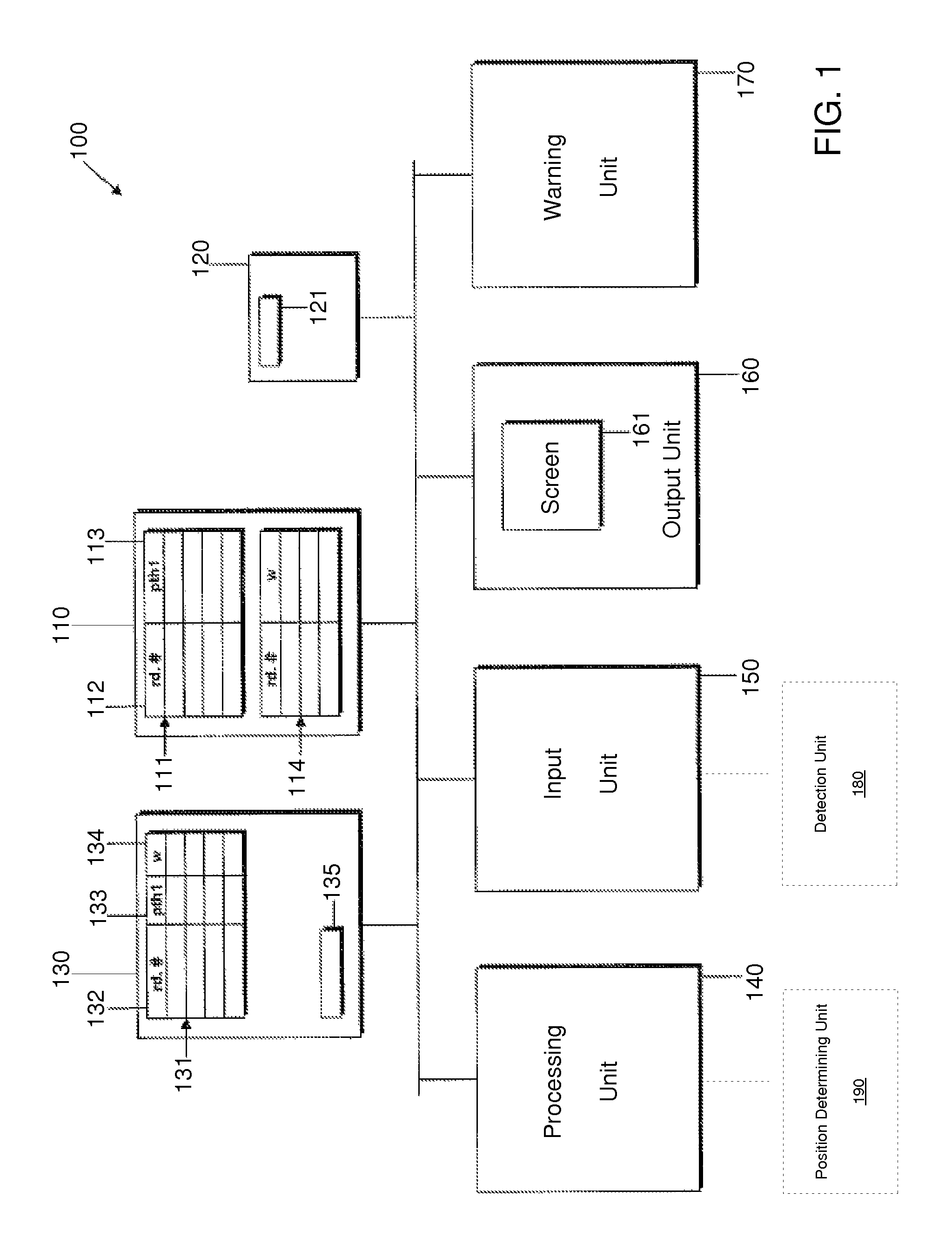

Route determination and driver warning system

ActiveUS7761227B2Instruments for road network navigationRoad vehicles traffic controlMain processing unitDriver/operator

A system for determining a route and for warning a driver of a vehicle and corresponding methods are provided. The systems include storage units that store road segment passage restriction data and vehicle passage restriction data. The systems further include a working memory unit and a processing unit that determine a route to be displayed on an output unit or that provide a warning signal output, depending upon both the vehicle passage restriction data and the road segment passage restriction data.

Owner:HARMAN BECKER AUTOMOTIVE SYST

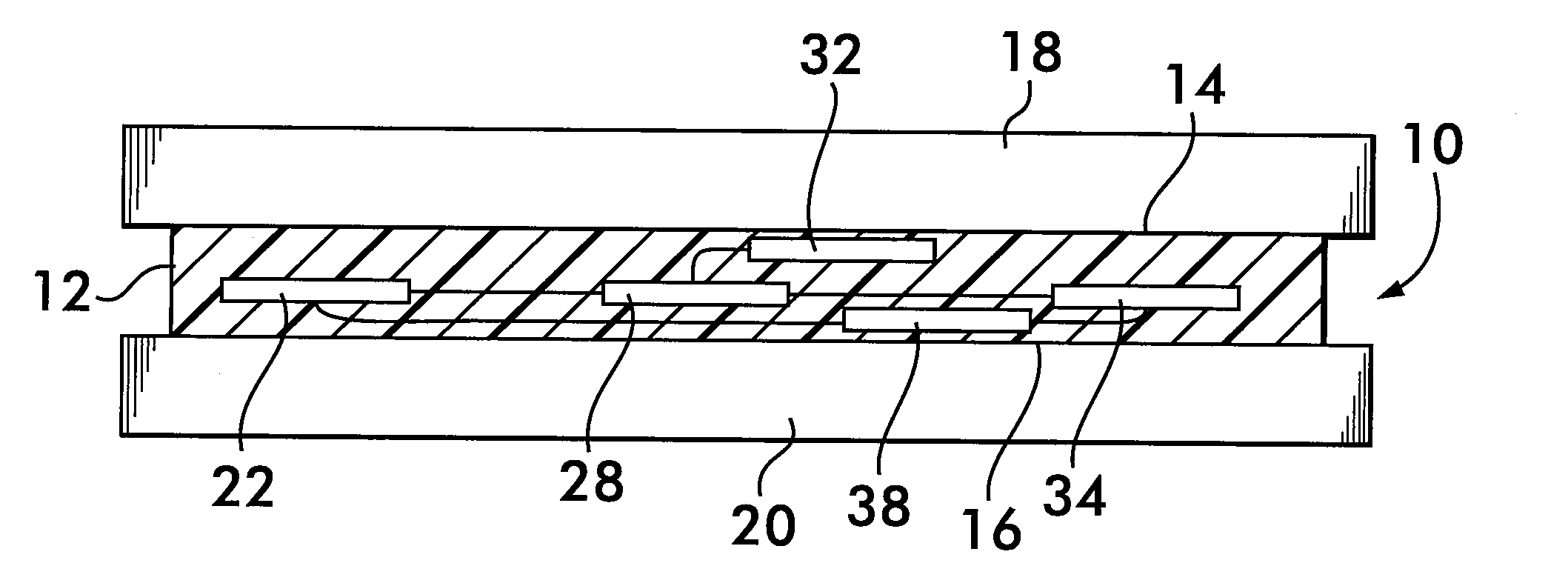

Sensor interface

ActiveUS20070255509A1Bearing assemblyMeasurement apparatus componentsMain processing unitElectronic component

A sensor interface is disclosed including a flexible substrate in which are embedded sensors for measuring physical parameters such as temperature, displacement, velocity, acceleration, stress, strain, pressure and force present between objects such as a railcar bearing and a truck side frame. The substrate is positioned between the objects of interest Electronic components such as a data processing unit, a data storage device, a communication device and a power source may also be embedded within the substrate. The electronic devices communicate with one another and the sensors to process signals generated by the sensors indicative of the parameters being measured.

Owner:AMSTED RAIL CO INC

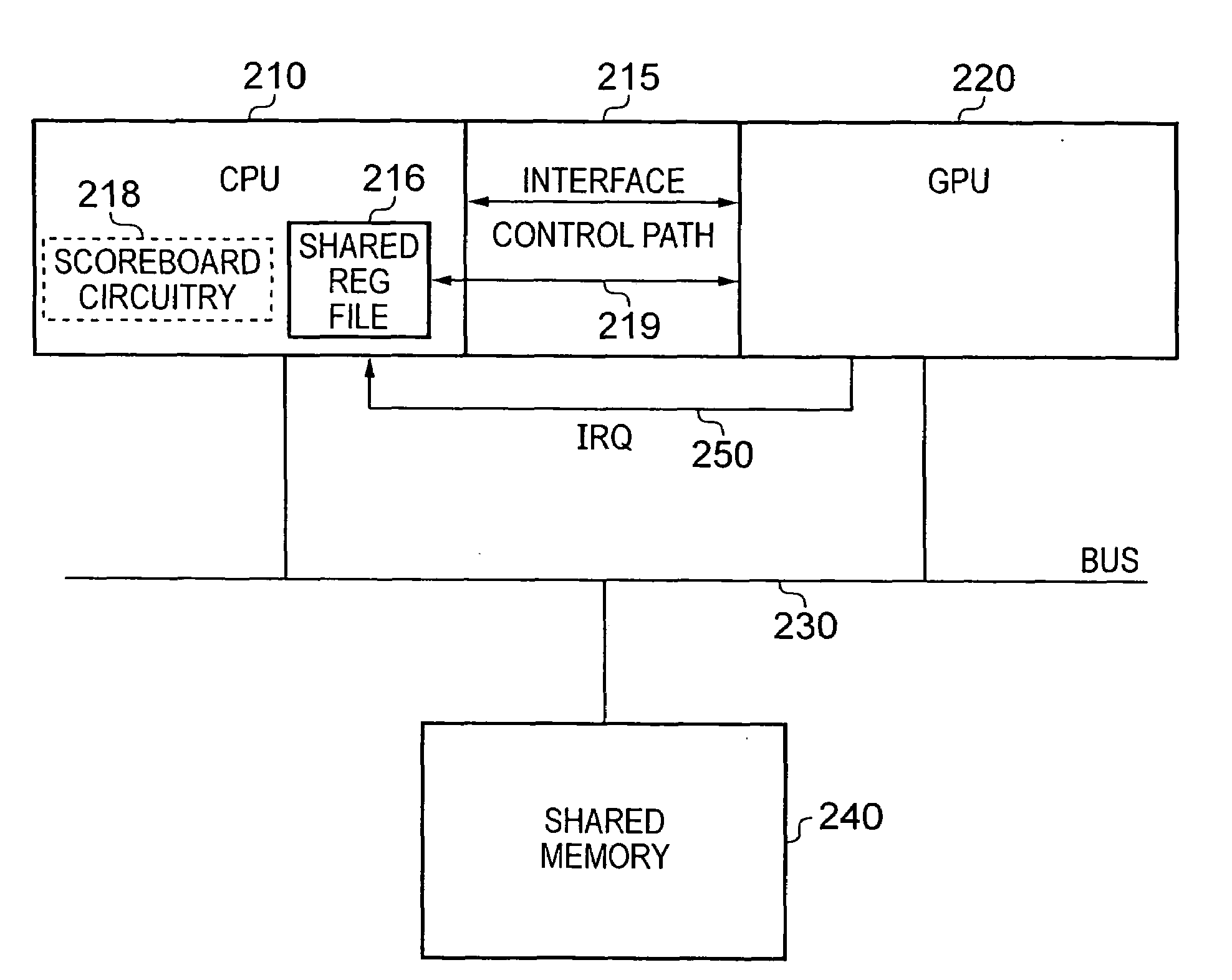

Apparatus and method for communicating between a central processing unit and a graphics processing unit

ActiveUS20100045682A1Delay minimizationRaise priorityMultiple digital computer combinationsProcessor architectures/configurationComputational scienceGraphics

Owner:ARM LTD

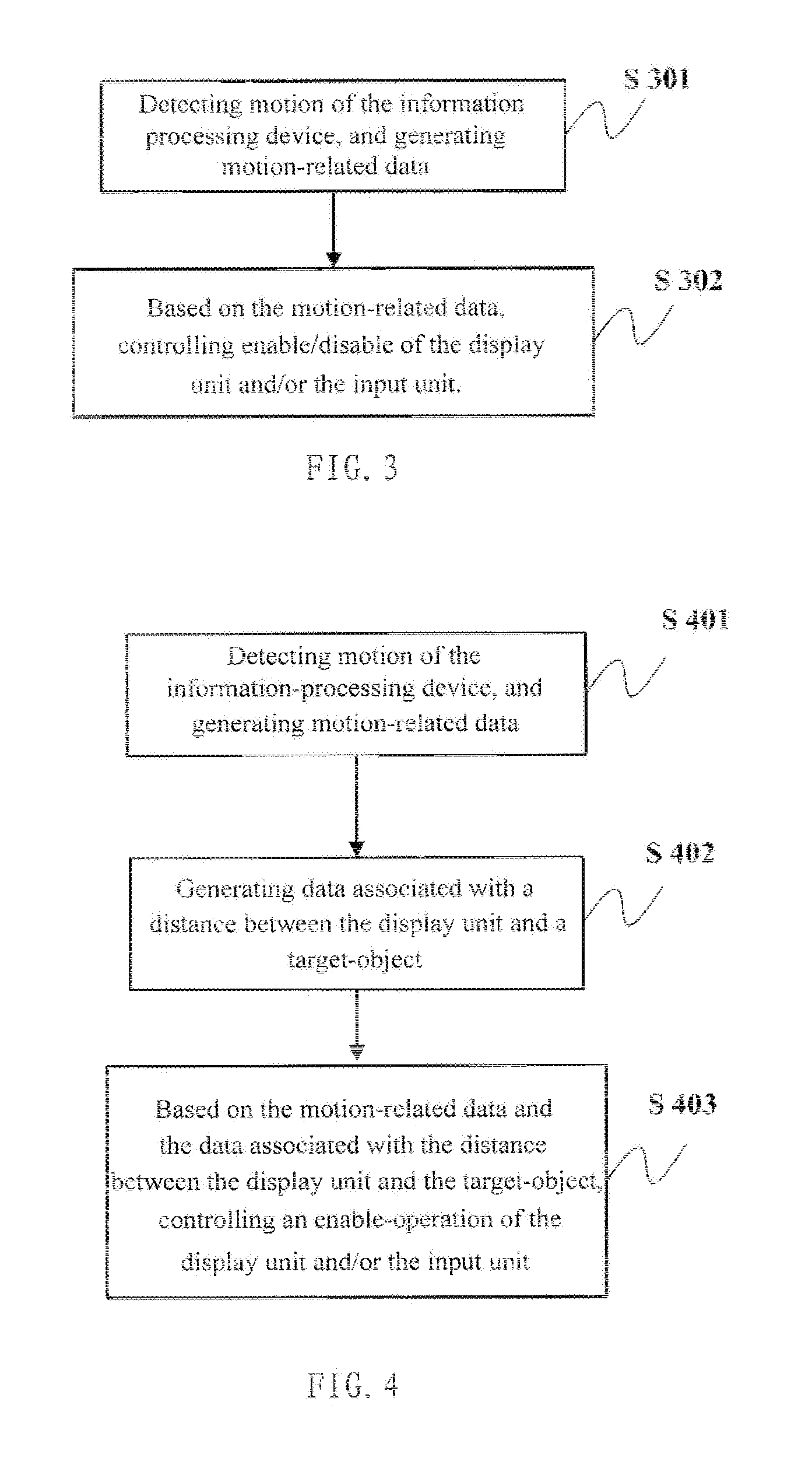

Information Processing Device And Control Method Thereof

ActiveUS20130147712A1Improve user experienceReduce power consumptionEnergy efficient ICTPower managementMain processing unitInformation processing

An information processing device and a control method applied to the information processing device is described. The information processing device includes a display unit configured to display images; an input unit configured to receive inputs from a user; a motion detecting unit configured to detect motion of the information processing device and to generate data related to the motion; and a processing unit connected to the display unit, the input unit and the motion detecting unit. The processing unit is configured to receive the motion-related data from the motion detecting unit, and enable / disable of the display unit and / or the input unit based on the data related to the motion.

Owner:LENOVO SOFTWARE +1

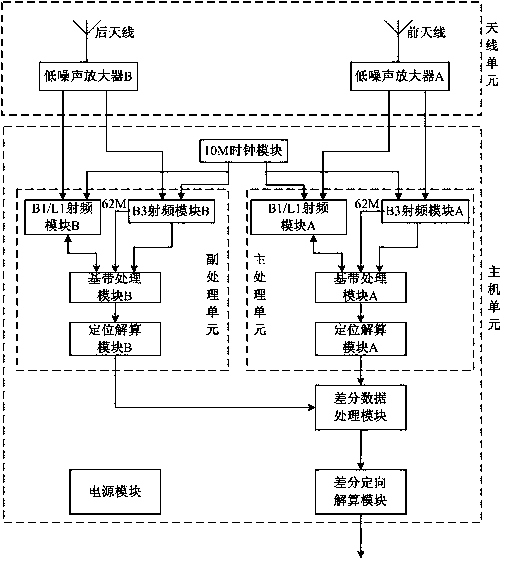

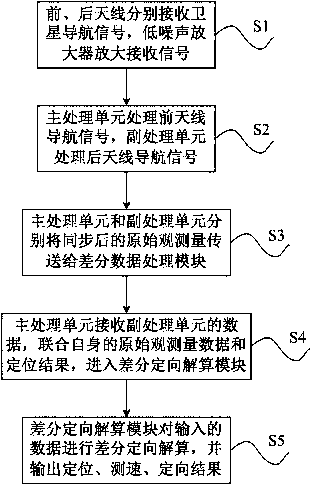

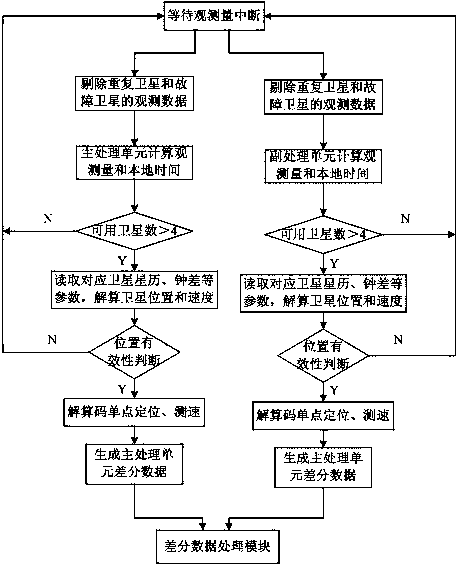

Carrier phase differential-based dual-antenna integrated positioning and orientation system and method

ActiveCN104297772AEliminate errorsHigh precisionSatellite radio beaconingMain processing unitComputer module

The invention relates to a carrier phase differential-based dual-antenna integrated positioning and orientation system and method. The system includes an antenna unit and a host unit, wherein the antenna unit is provided with two antennas which receive satellite navigation signals simultaneously, and the host unit comprises a main processing unit, an auxiliary processing unit, a differential data processing module and a differential orientation calculation module. The main processing unit and the auxiliary processing unit process signals received by corresponding antennas, and transmit synchronized original observed quantity to the differential data processing module after positioning is accomplished; the main processing unit and the auxiliary processing unit transmit respective original observed quantity data and positioning results to the differential orientating calculation module so that calculation can be performed; and finally, positioning, velocity measurement and orientation results of a whole unit can be obtained. With the dual-antenna integrated design adopted, the system of the invention has the advantages of small size, reliable use, high orientation precision, no time accumulated error and long stable working time; and differential calculation can be completed through a real-time calculation method, and the position and course results of a carrier can be obtained in a static state or dynamic state, and primary orientation time is short, and real-time performance is high.

Owner:CHENGDU GUOXING COMM

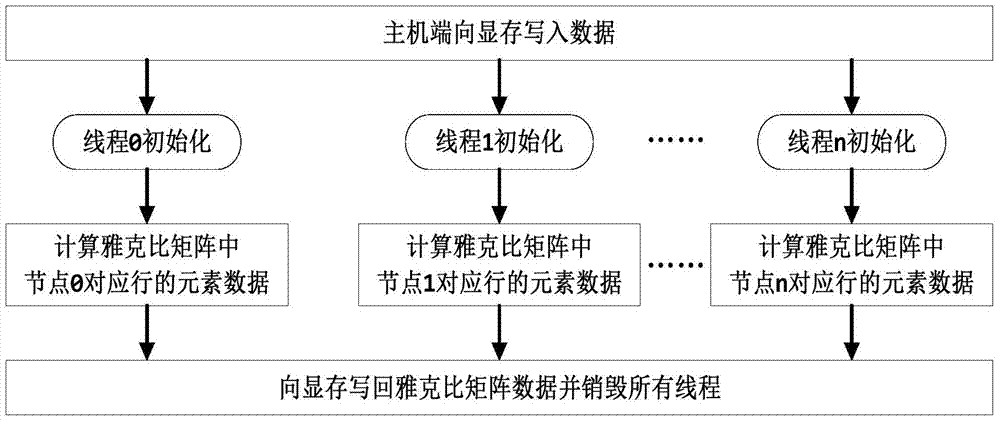

GPU (graphic processing unit) based parallel power flow calculation system and method for large-scale power system

ActiveCN103617150ARealize the loop iterative processImplement parallel build methodsComplex mathematical operationsMain processing unitArithmetic processing unit

The invention relates to a GPU (graphic processing unit) based parallel power flow calculation system and method for a large-scale power system. The system comprises a symbol Jacobian matrix forming and decomposing module, an initialization module, a power flow equation right-hand side calculation module, a jacobian matrix assignment module, an LU decomposing module and a forward and backward substitution module; the symbol Jacobian matrix forming and decomposing module is located on a host side, and the host side transmits calculating data to an equipment side; the power flow equation right-hand side calculation module, the jacobian matrix assignment module, the LU decomposing module and the forward and backward substitution module are sequentially connected on the equipment side. The method includes (1) transmitting data needed by calculation to the host side entirely; (2) generating a symbol Jacobian matrix and performing symbol composition on the symbol Jacobian matrix; (3) transmitting a decomposition result by the host side to the equipment side; (4) executing power flow equation right-hand side calculation; (5) executing Jacobian matrix assignment; (6) executing LU decomposition; (7) executing forward and backward substitution.

Owner:STATE GRID CORP OF CHINA +1

Paravirtualized virtual GPU

ActiveUS20130091500A1Improve system performanceMinimal interventionSoftware simulation/interpretation/emulationMemory systemsMain processing unitParallel computing

An embodiment of the invention sets forth a primary processing unit, a secondary processing unit coupled to the primary processing unit and accessible via a plurality of channels and a plurality of guest virtual machines executing on the primary processing unit. Each guest virtual machine includes a driver associated with the secondary processing unit, and a privileged virtual machine executing on the primary processing unit and configured to allocate a different set of channels of the plurality of channels to each of the drivers included in the guest virtual machines, where a first set of channels allocated to a first driver enables the first driver to access the secondary processing unit without conflicting with any of the other and with minimal performance overhead by directly accessing the secondary processing unit channels.

Owner:NVIDIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com