Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

295results about How to "Shorten the line length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

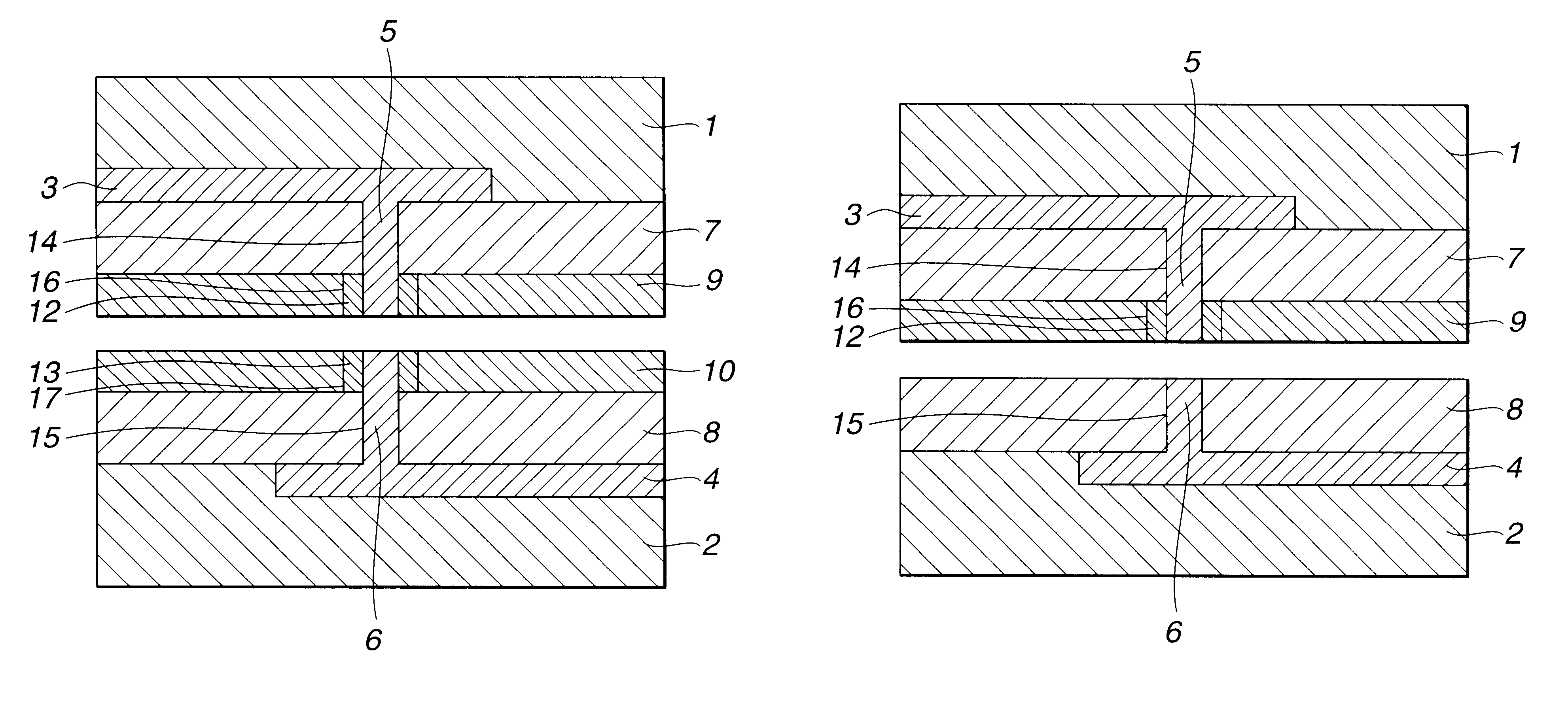

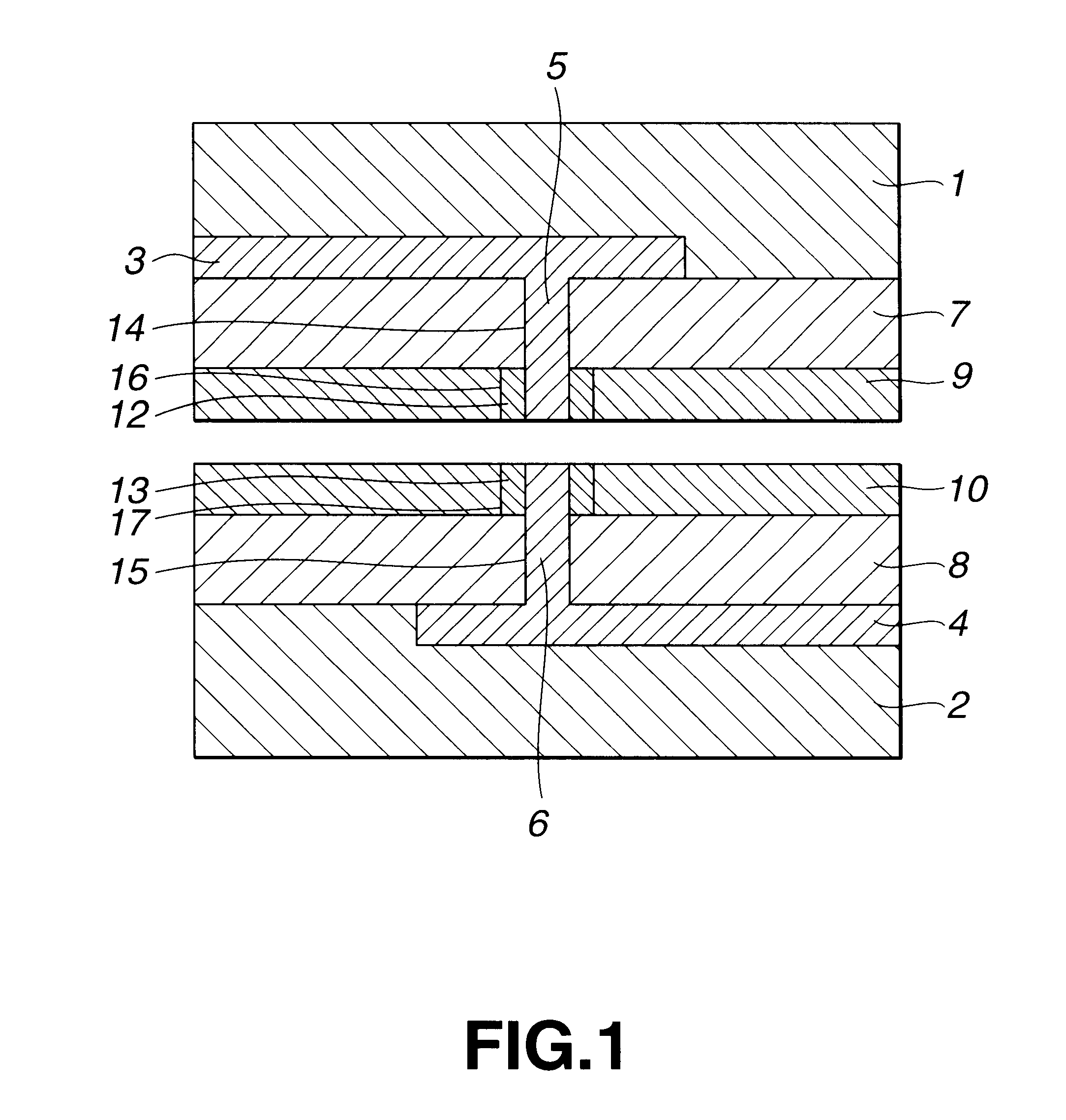

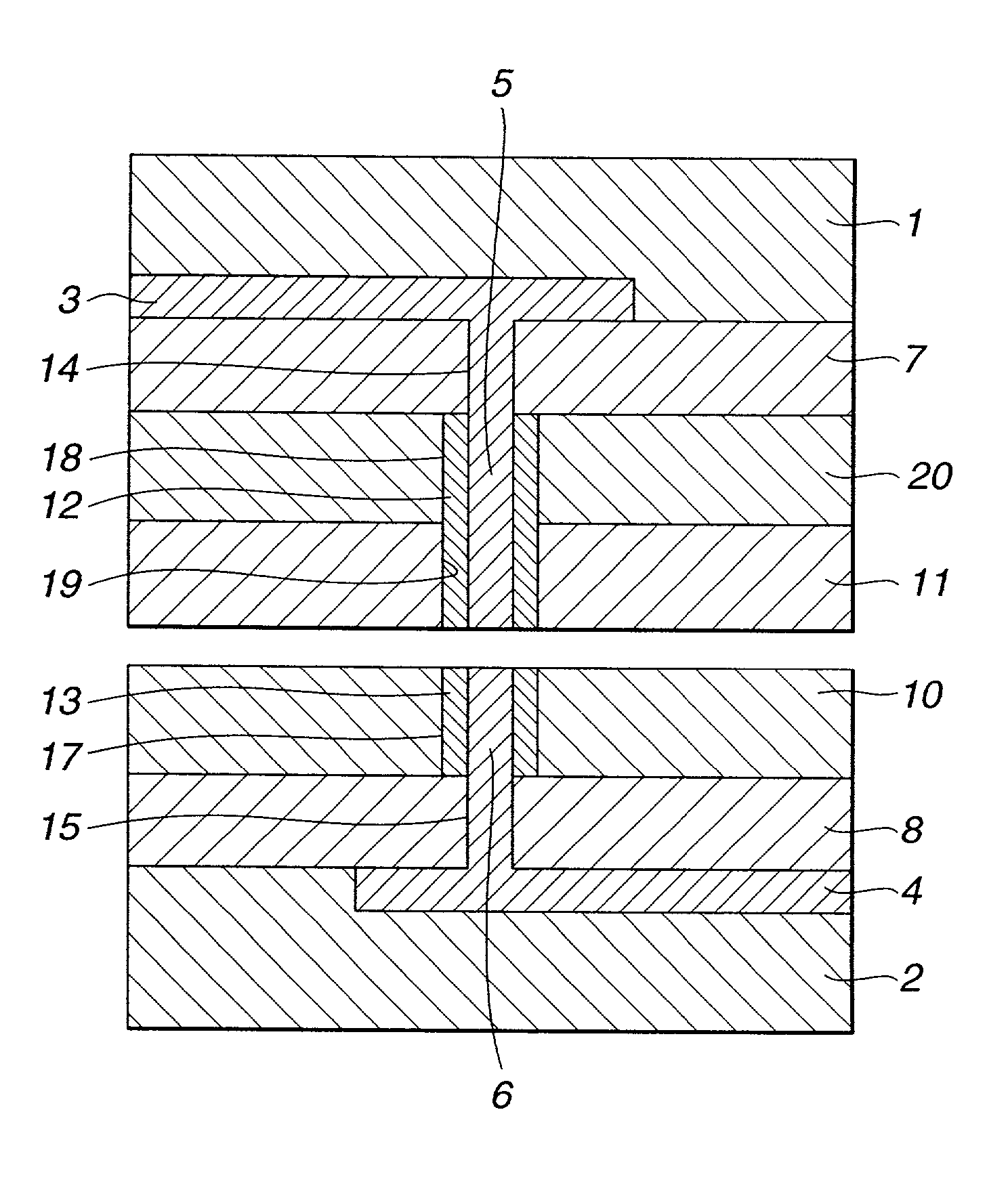

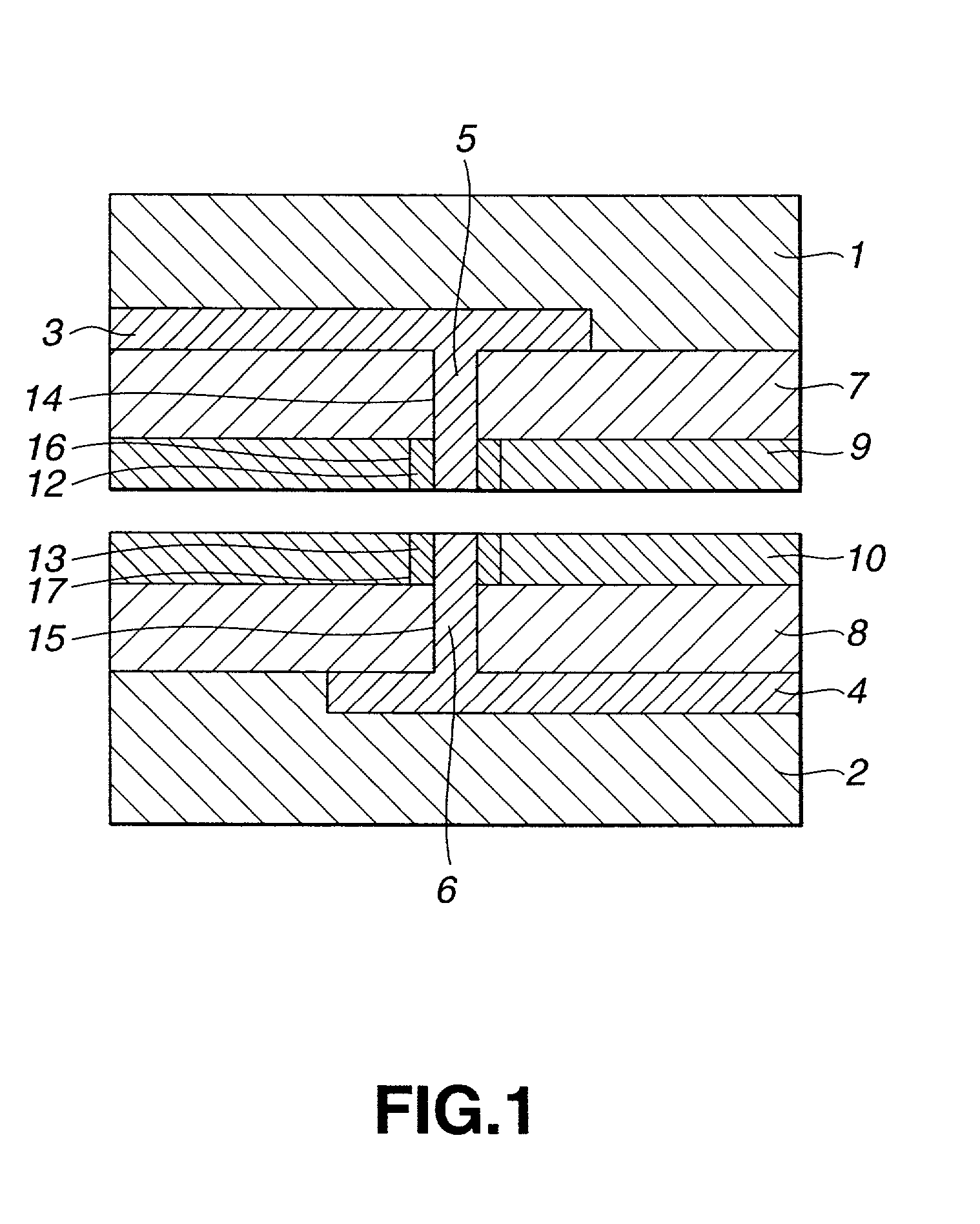

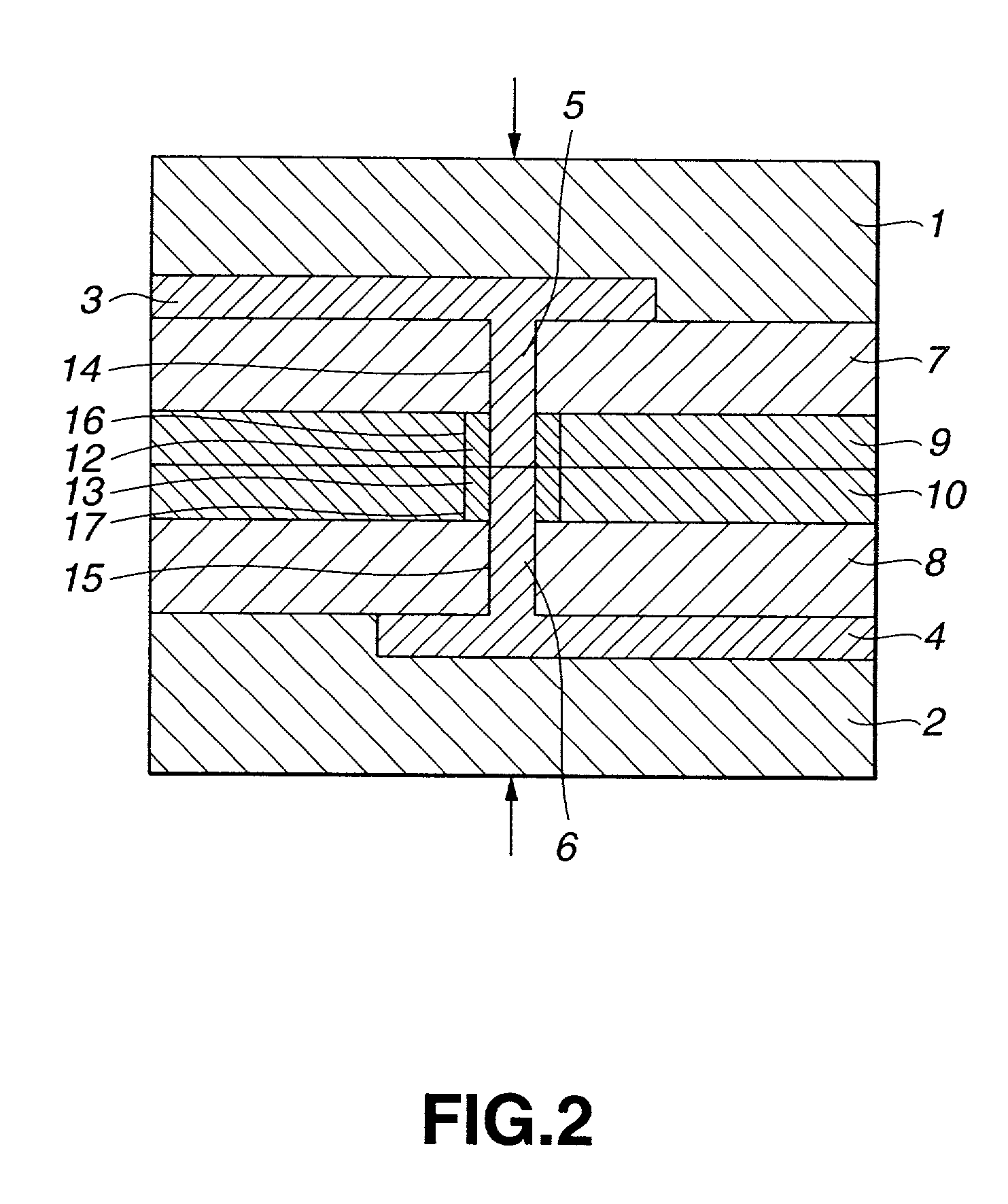

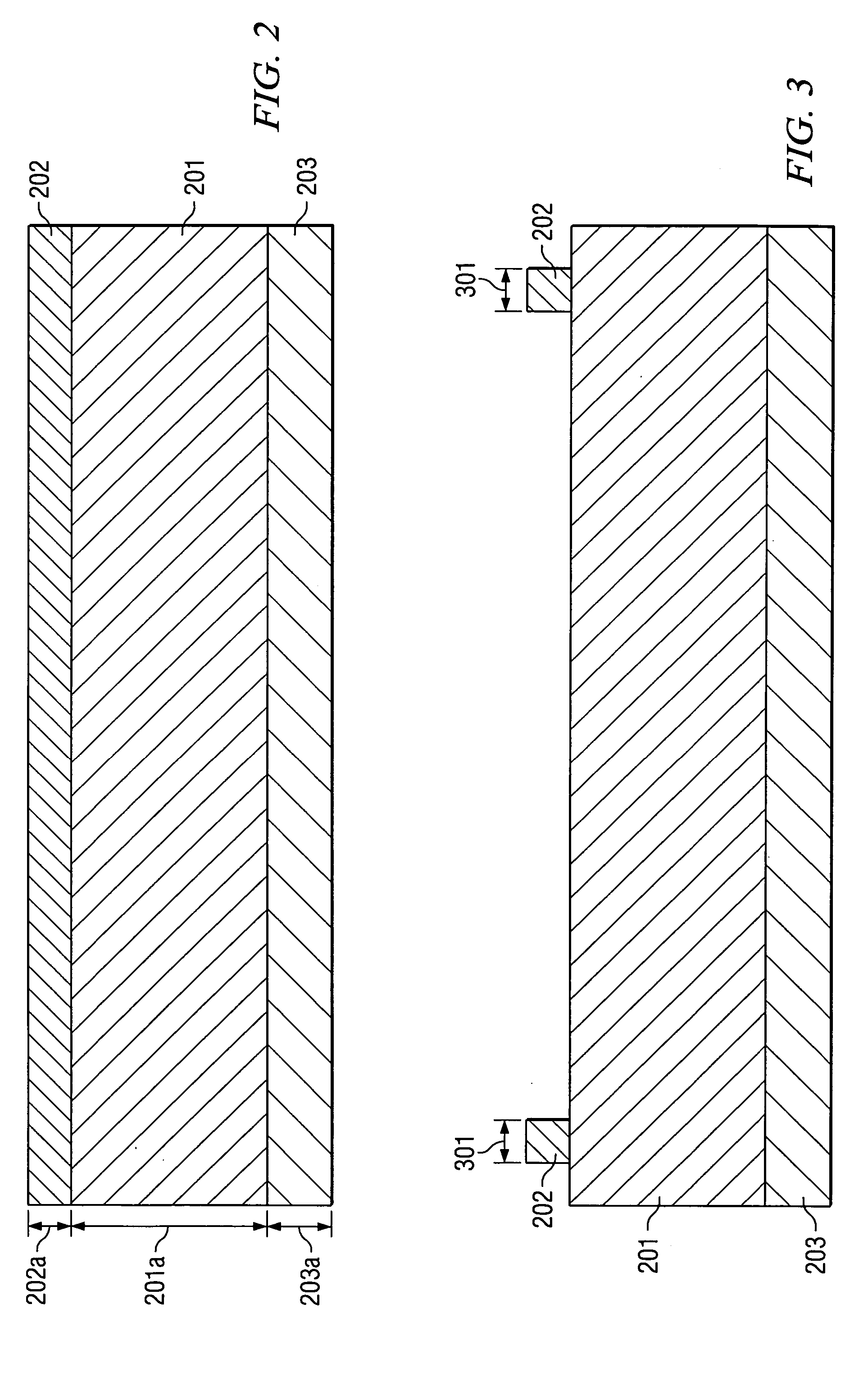

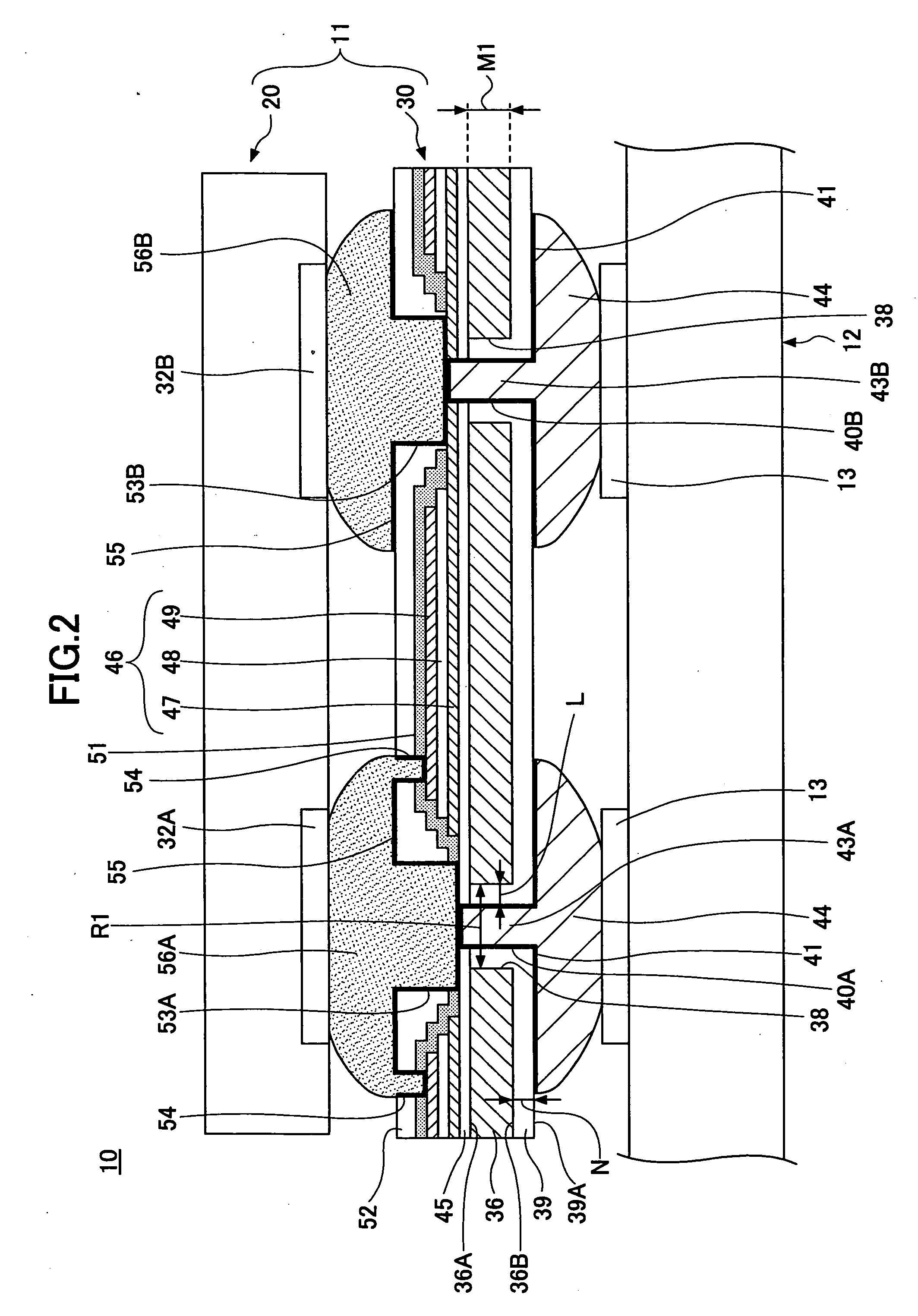

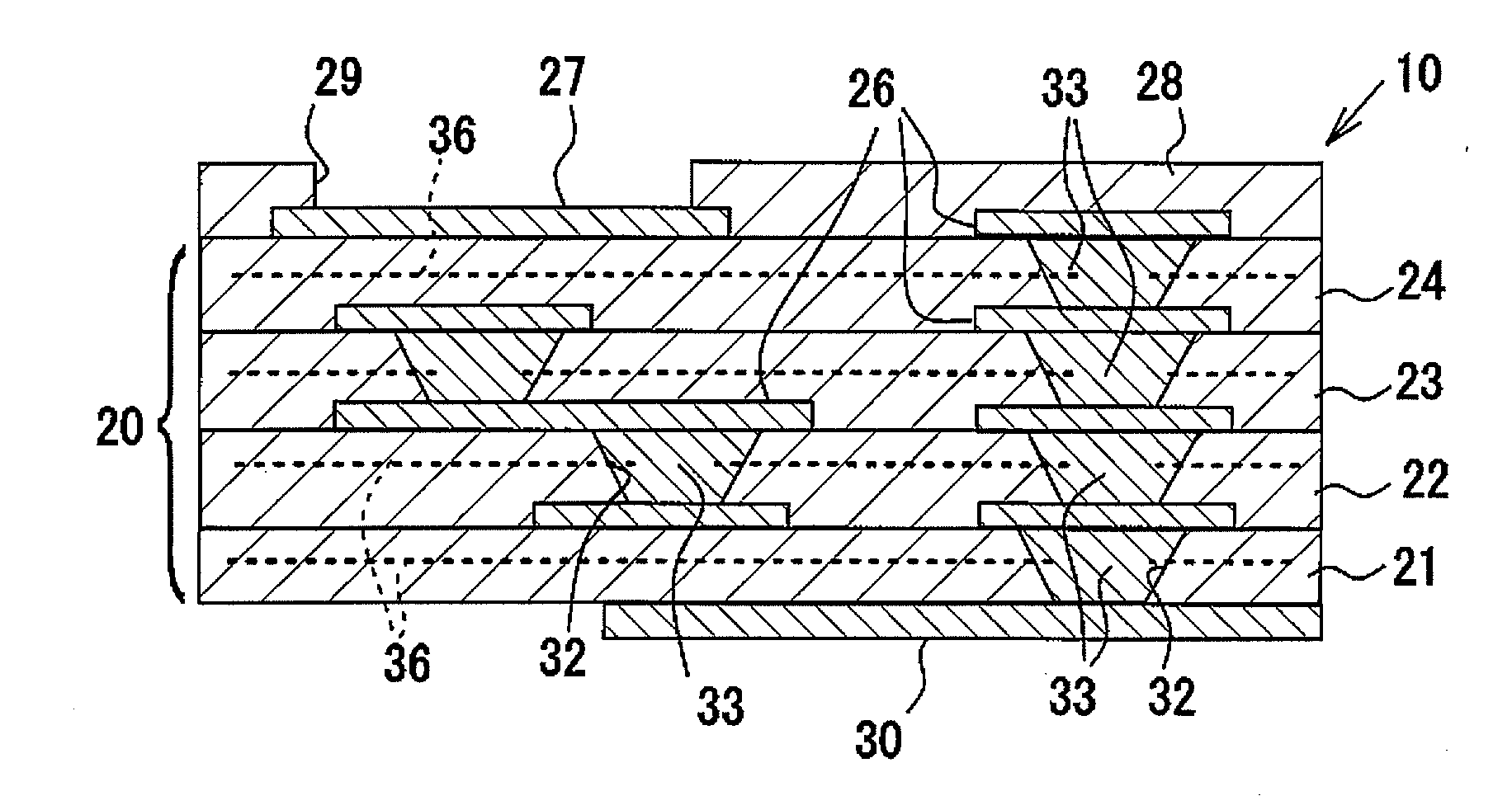

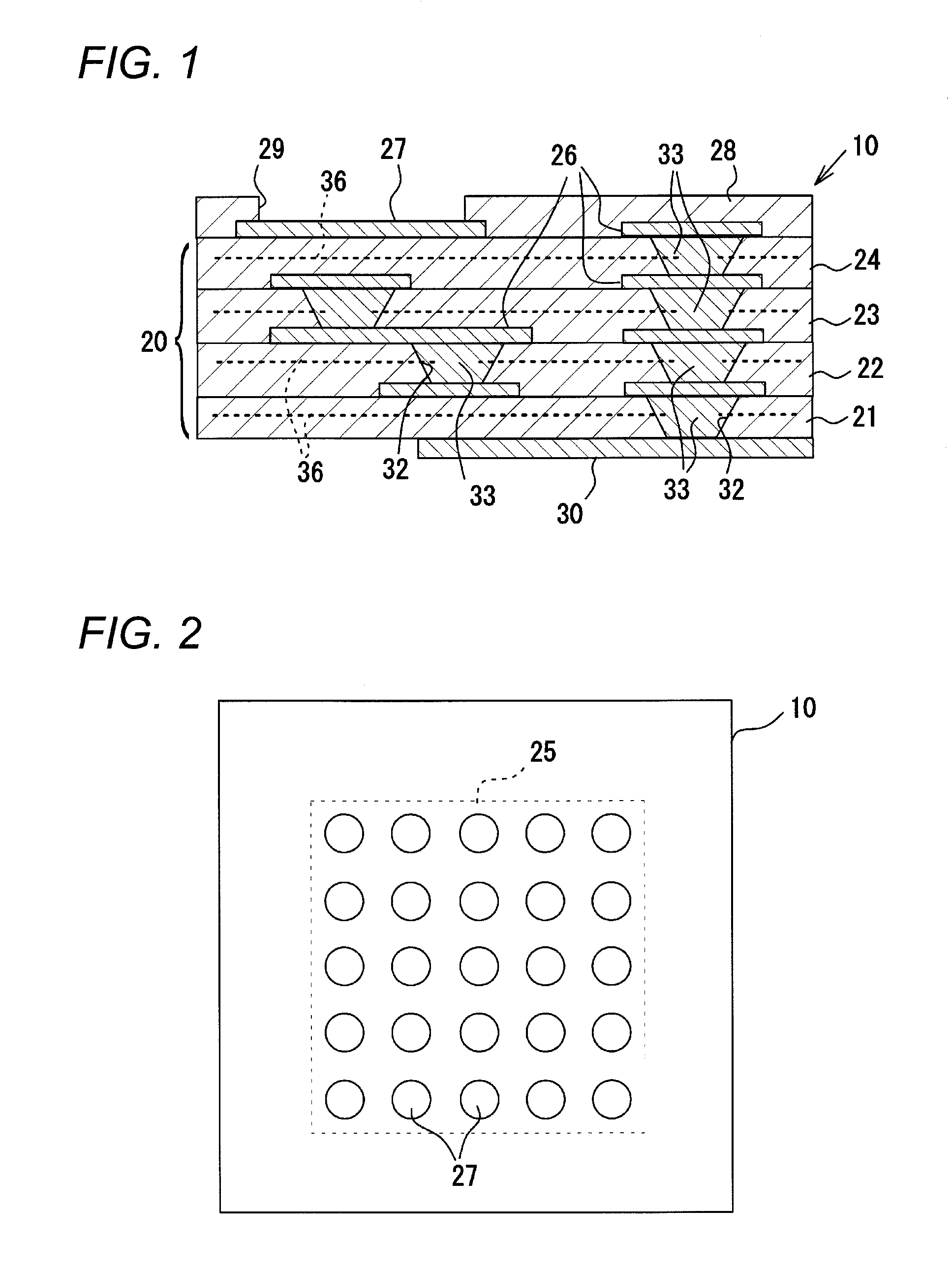

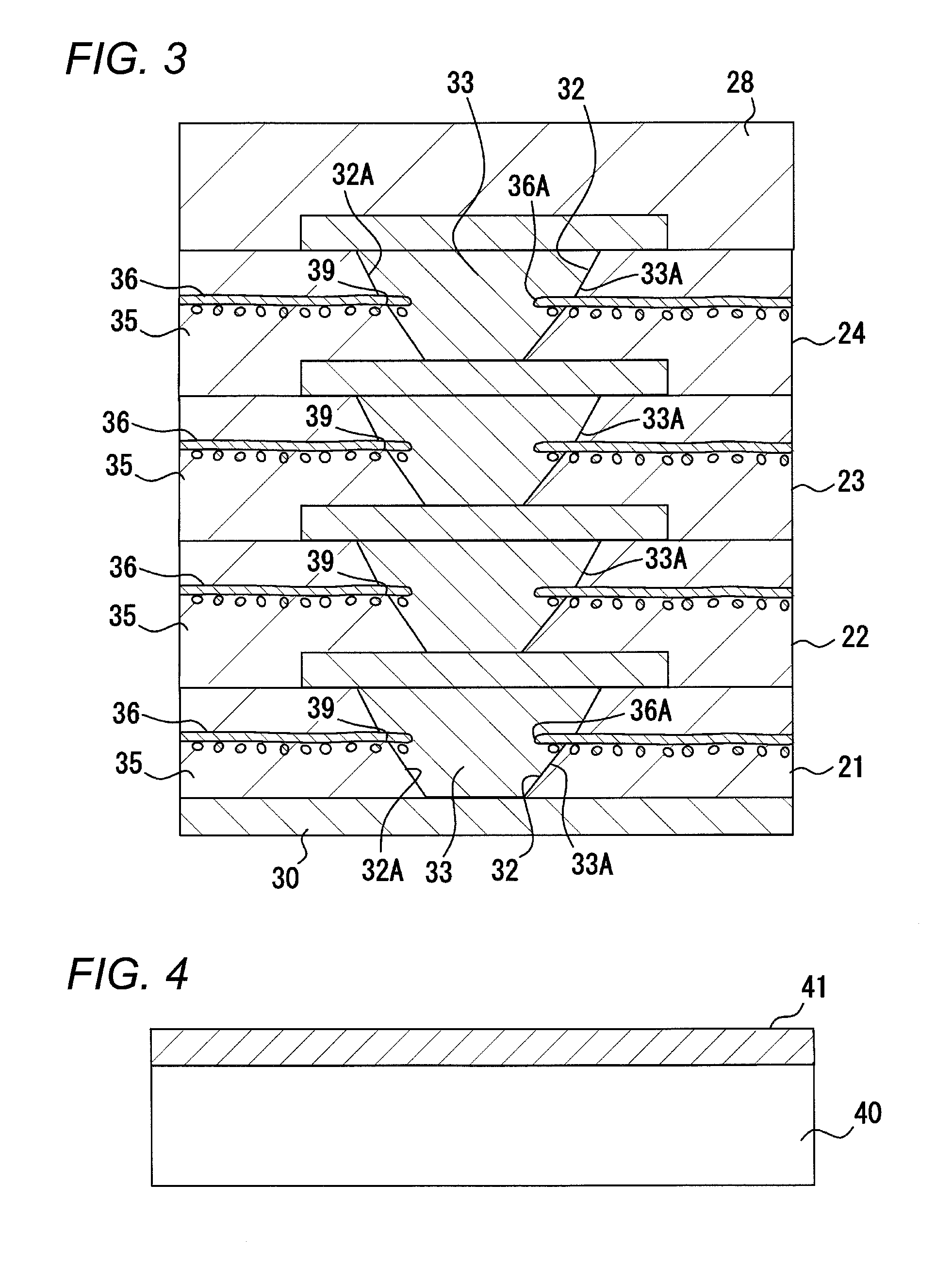

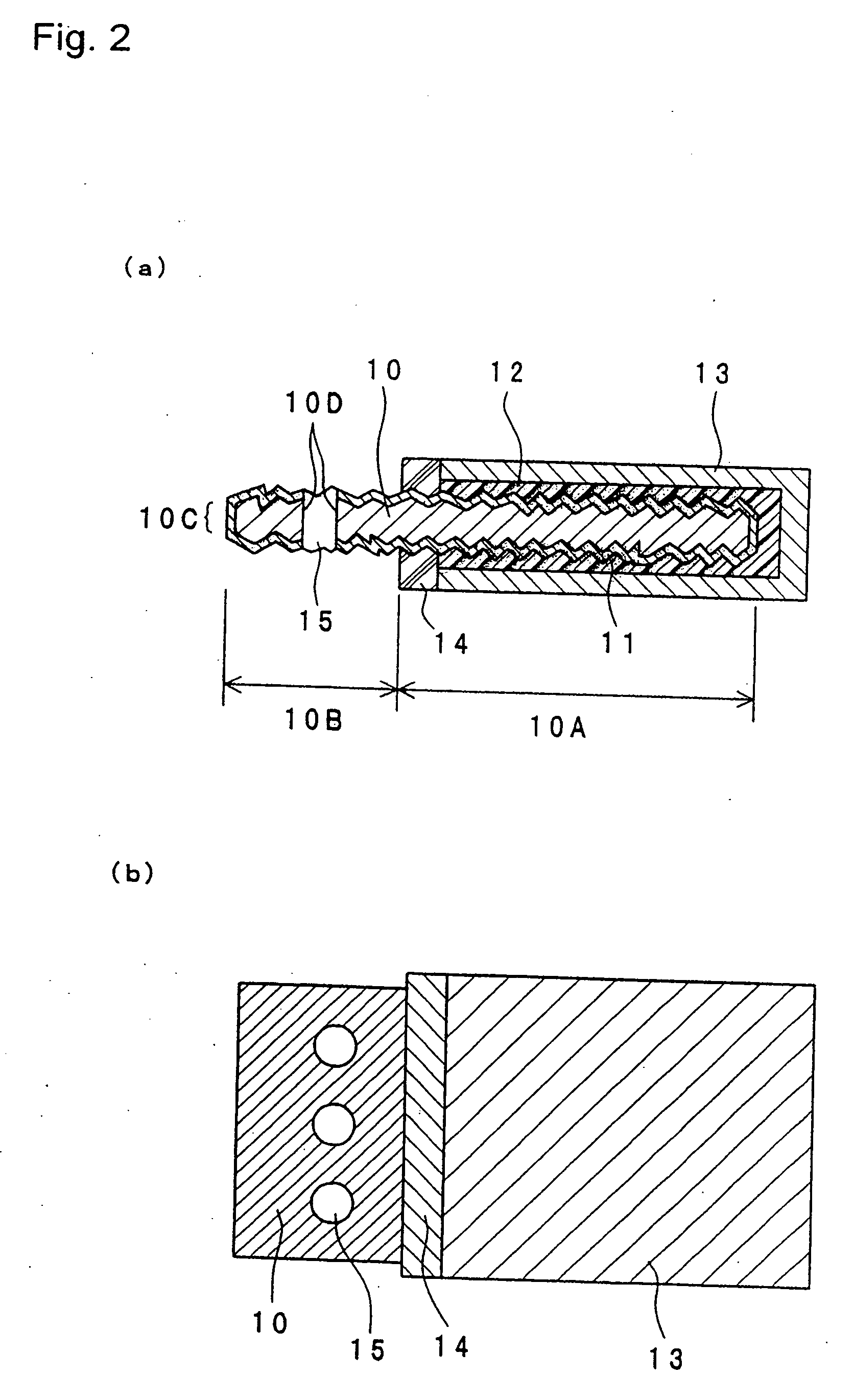

Interconnect structure for stacked semiconductor device

InactiveUS6465892B1Shorten the line lengthEasy to produceSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

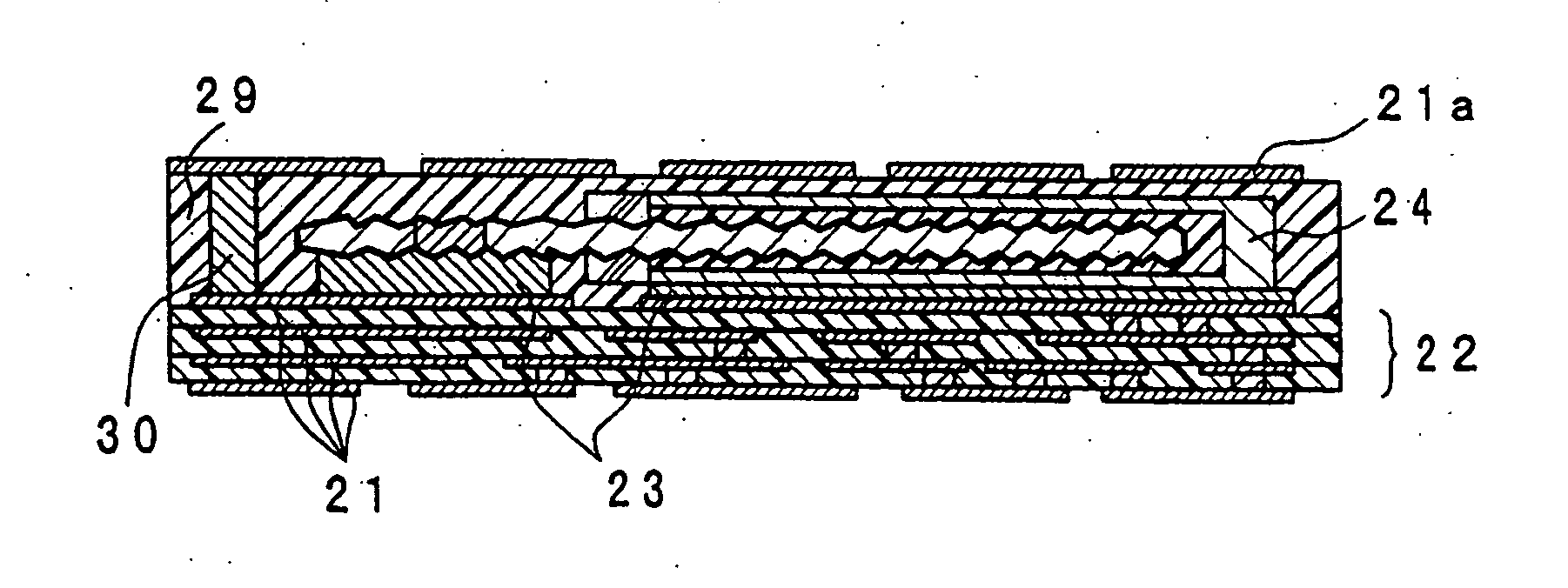

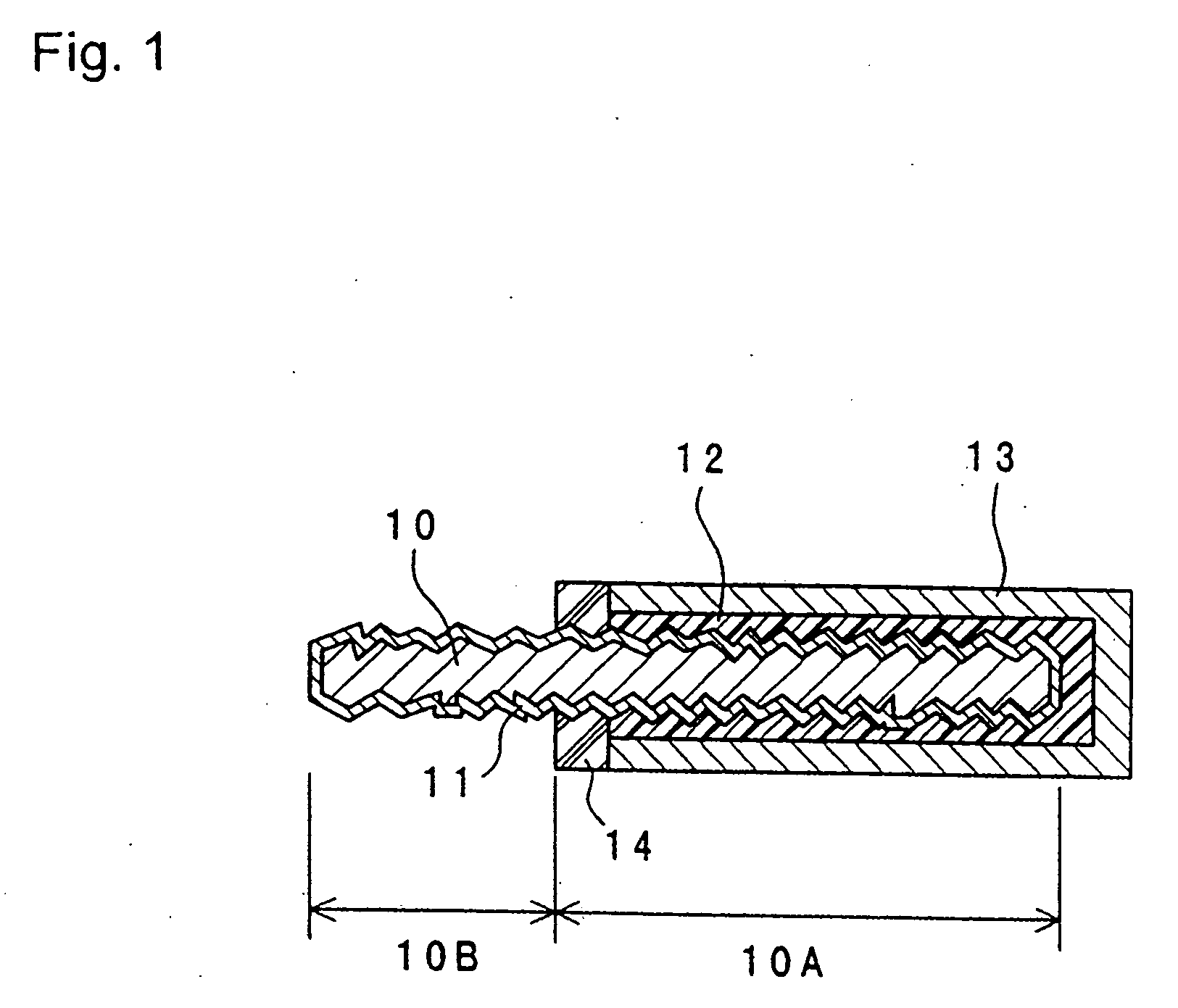

In a multi-layer interconnection structure, the wiring length is to be reduced, and the interconnection is to be straightened, at the same time as measures need to be taken against radiation noise. To this end, there is disclosed a semiconductor device in which plural semiconductor substrates, each carrying semiconductor elements, are bonded together. On each semiconductor substrate is deposited an insulating layer through which is formed a connection wiring passed through the insulating layer so as to be connected to the interconnection layer of the semiconductor element. On a junction surface of at least one of the semiconductor substrates is formed an electrically conductive layer of an electrically conductive material in which an opening is bored in association with the connection wiring. The semiconductor substrates are bonded together by the solid state bonding technique to interconnect the connection wirings formed on each semiconductor substrate.

Owner:LAPIS SEMICON CO LTD +9

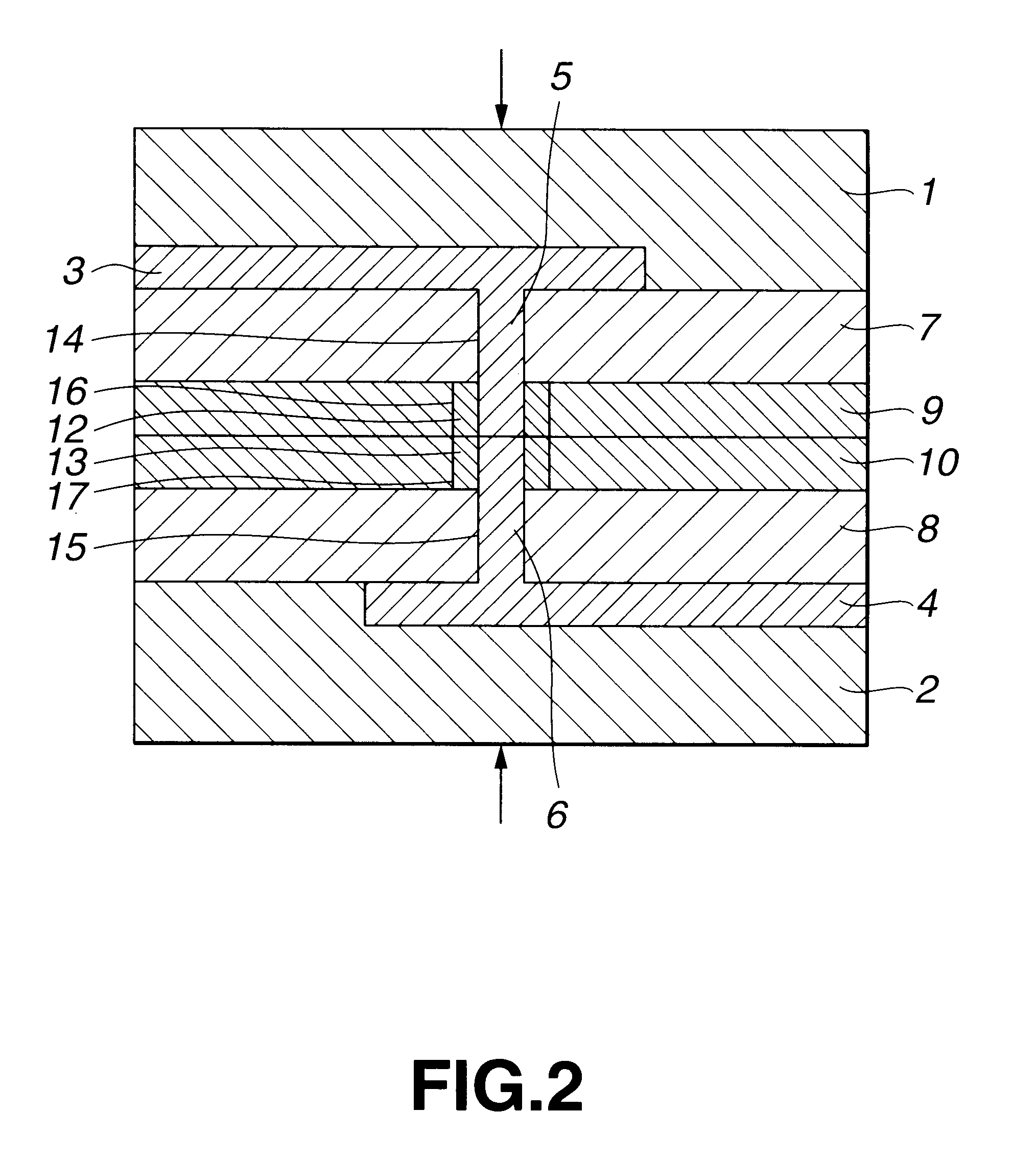

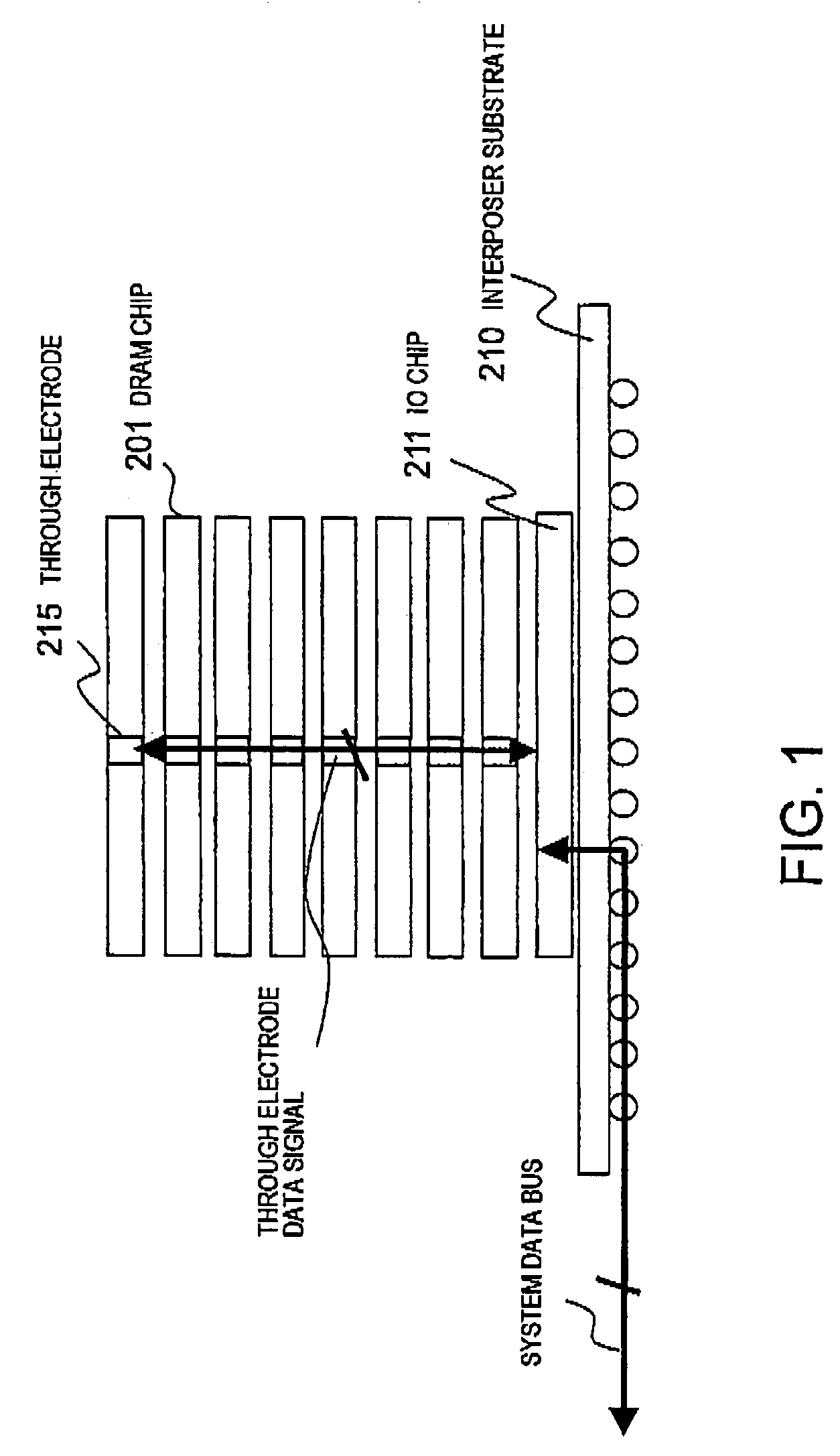

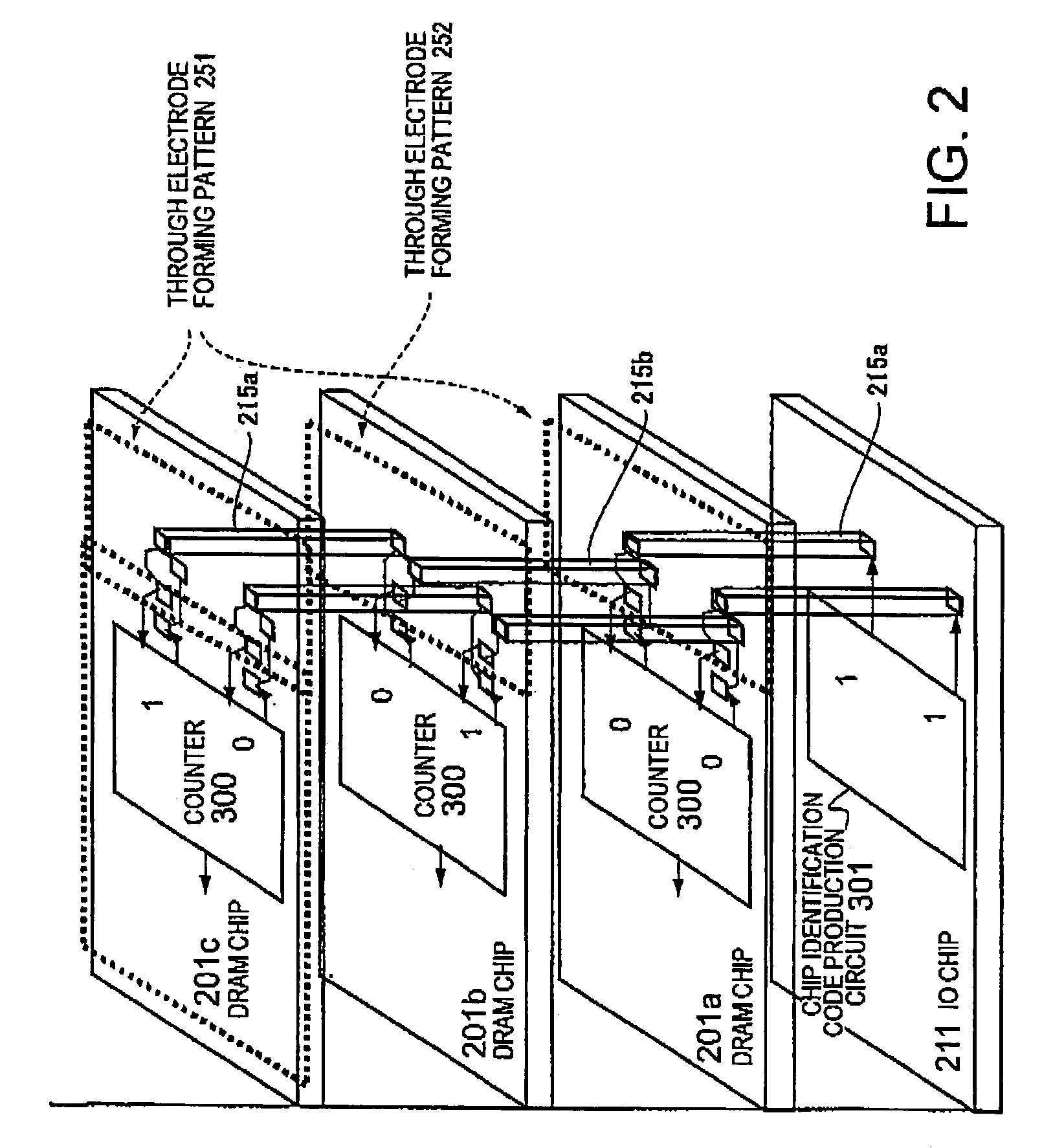

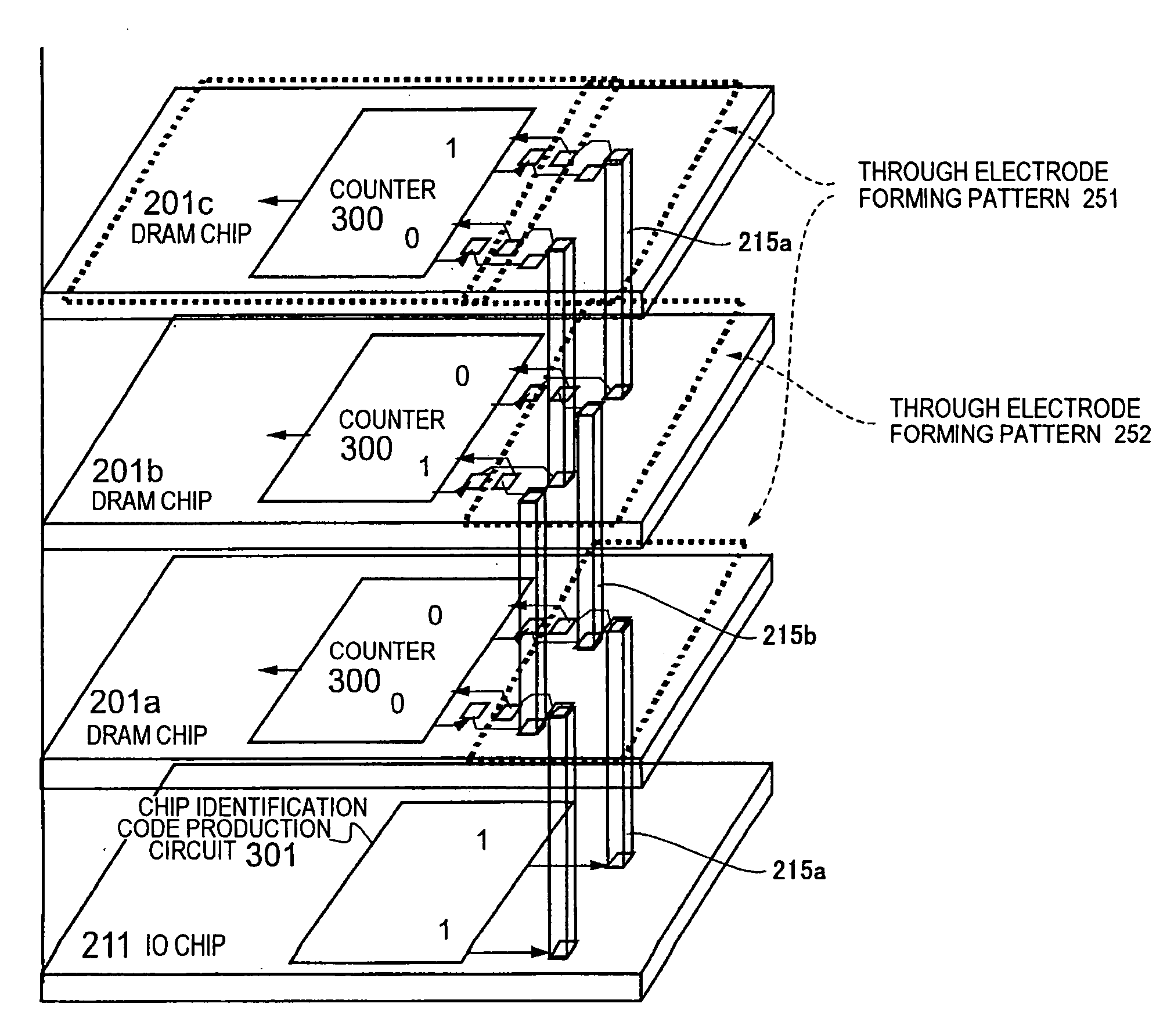

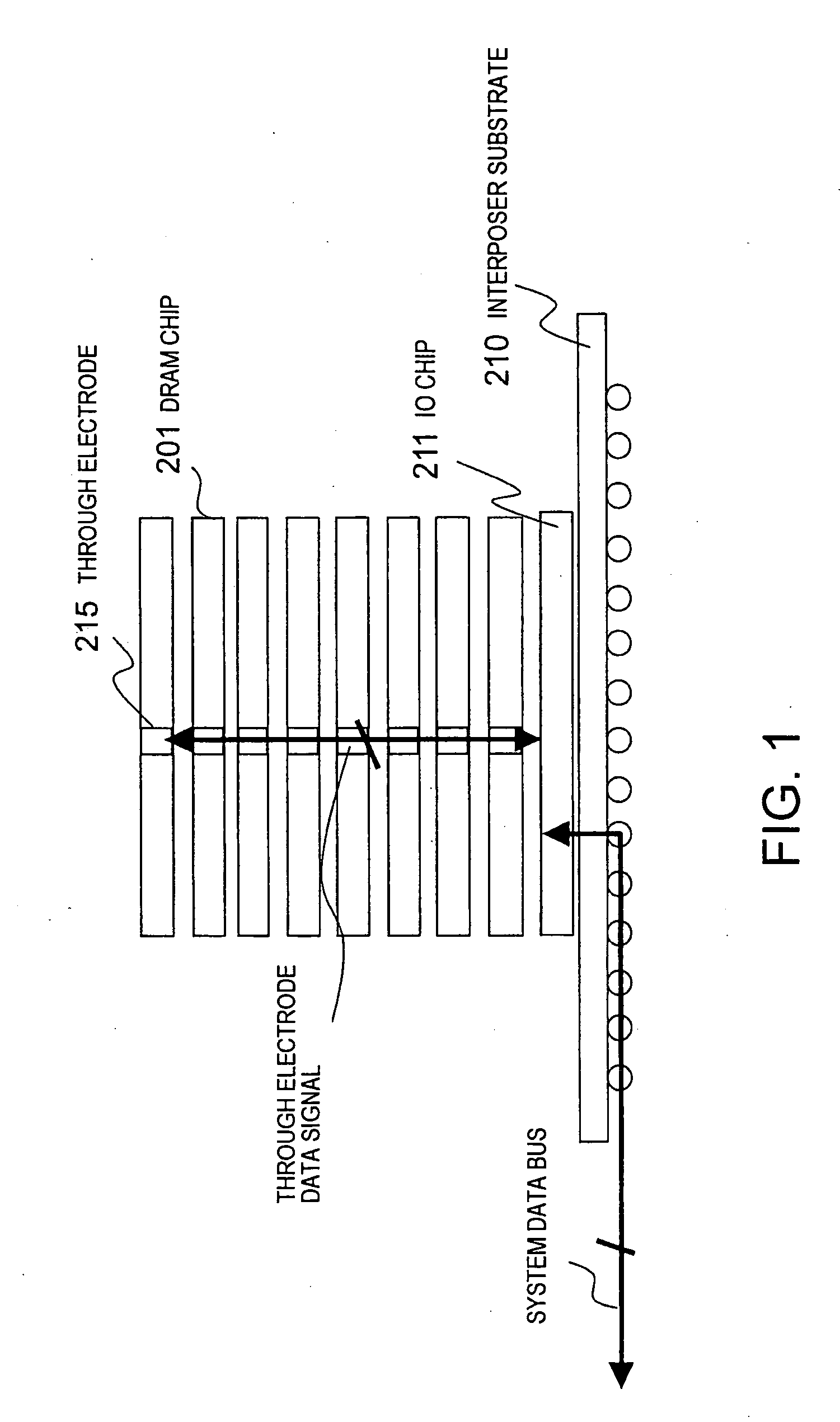

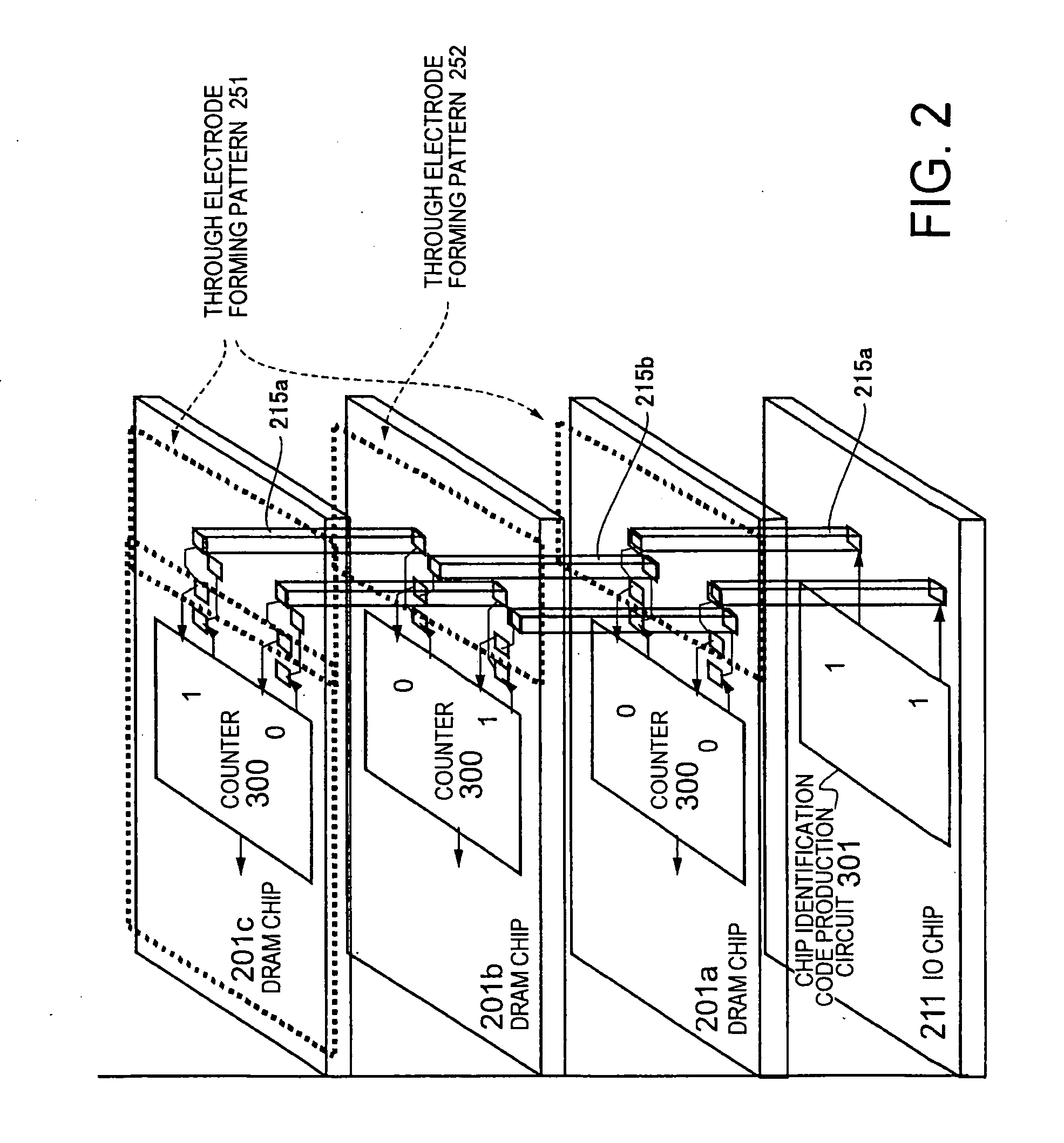

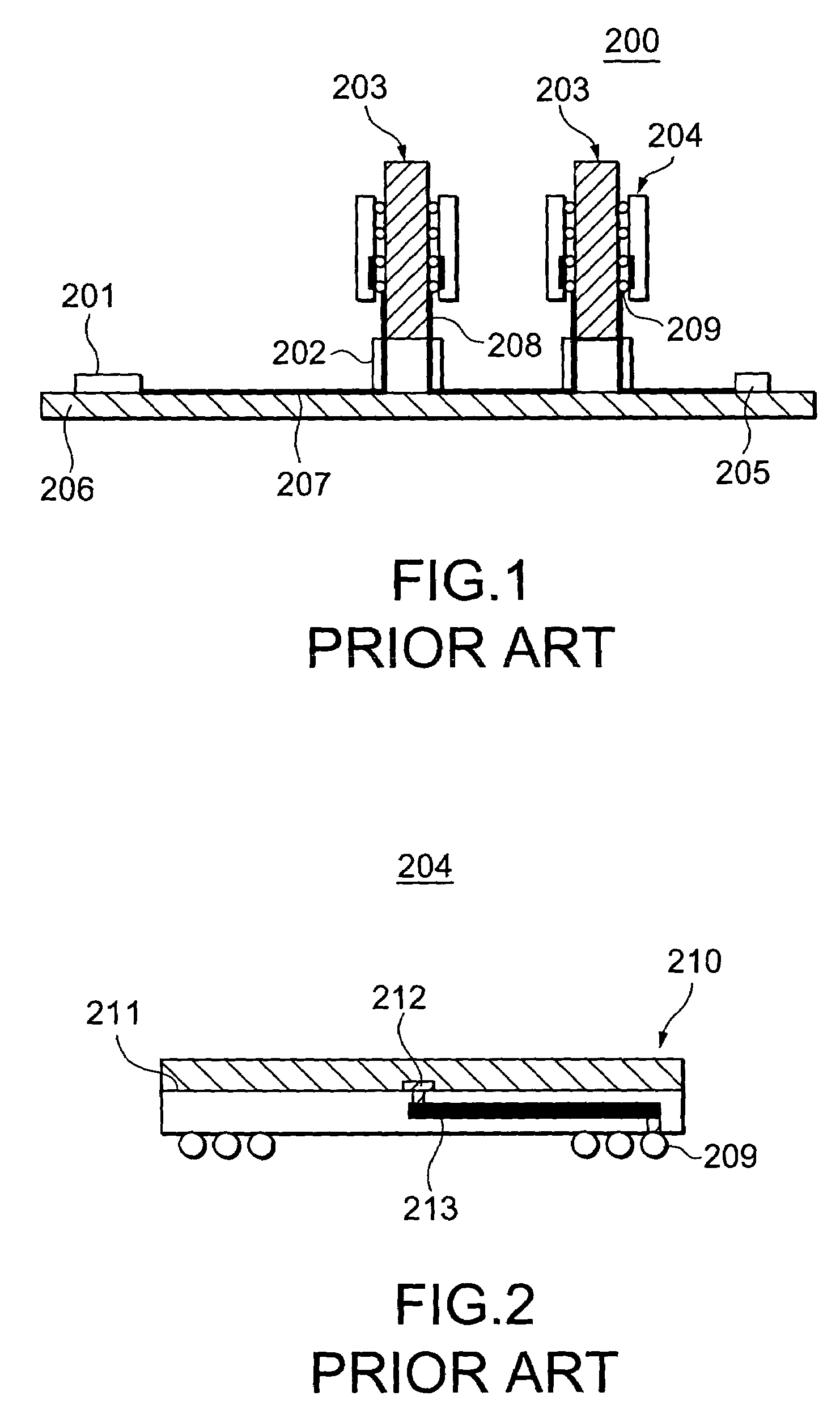

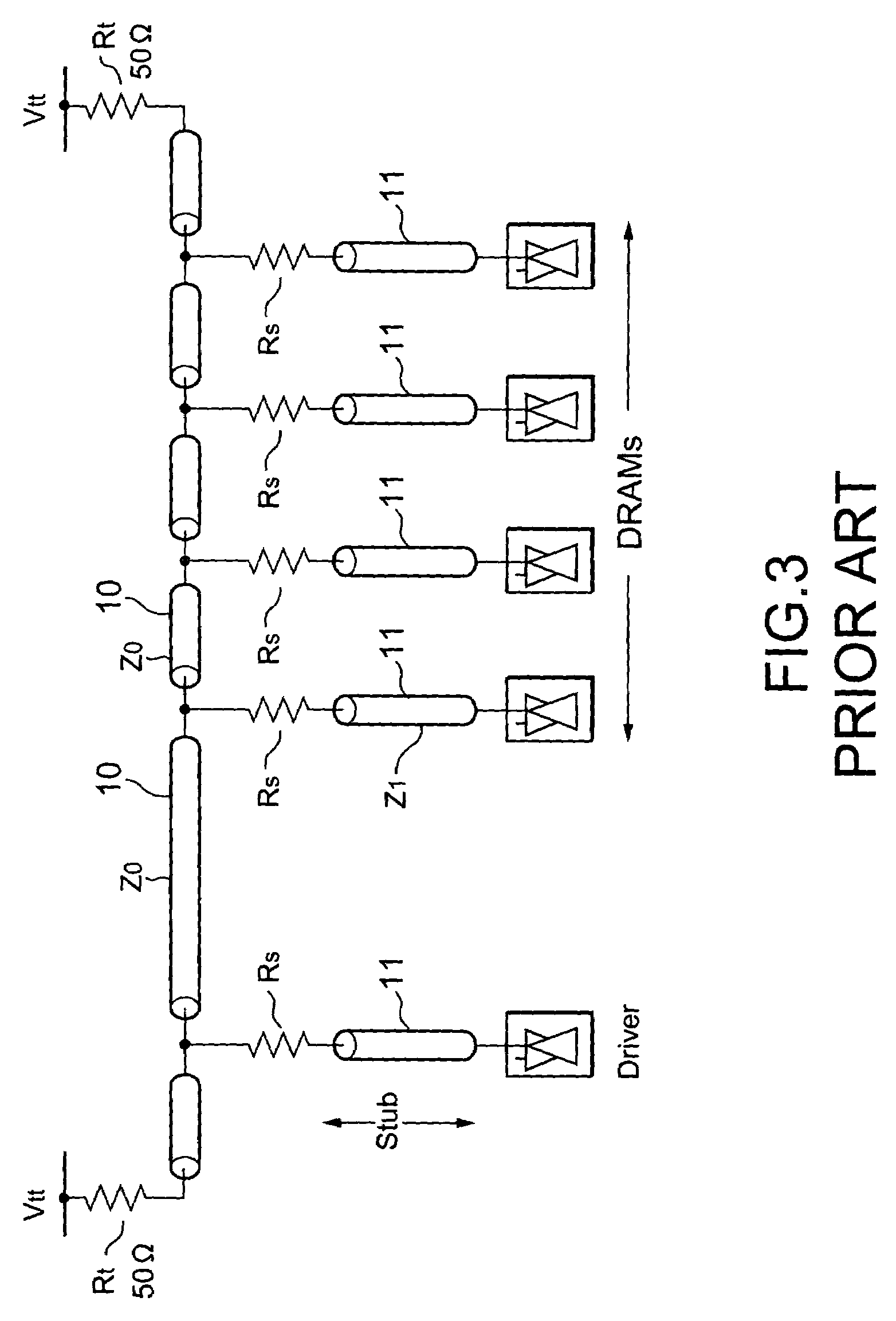

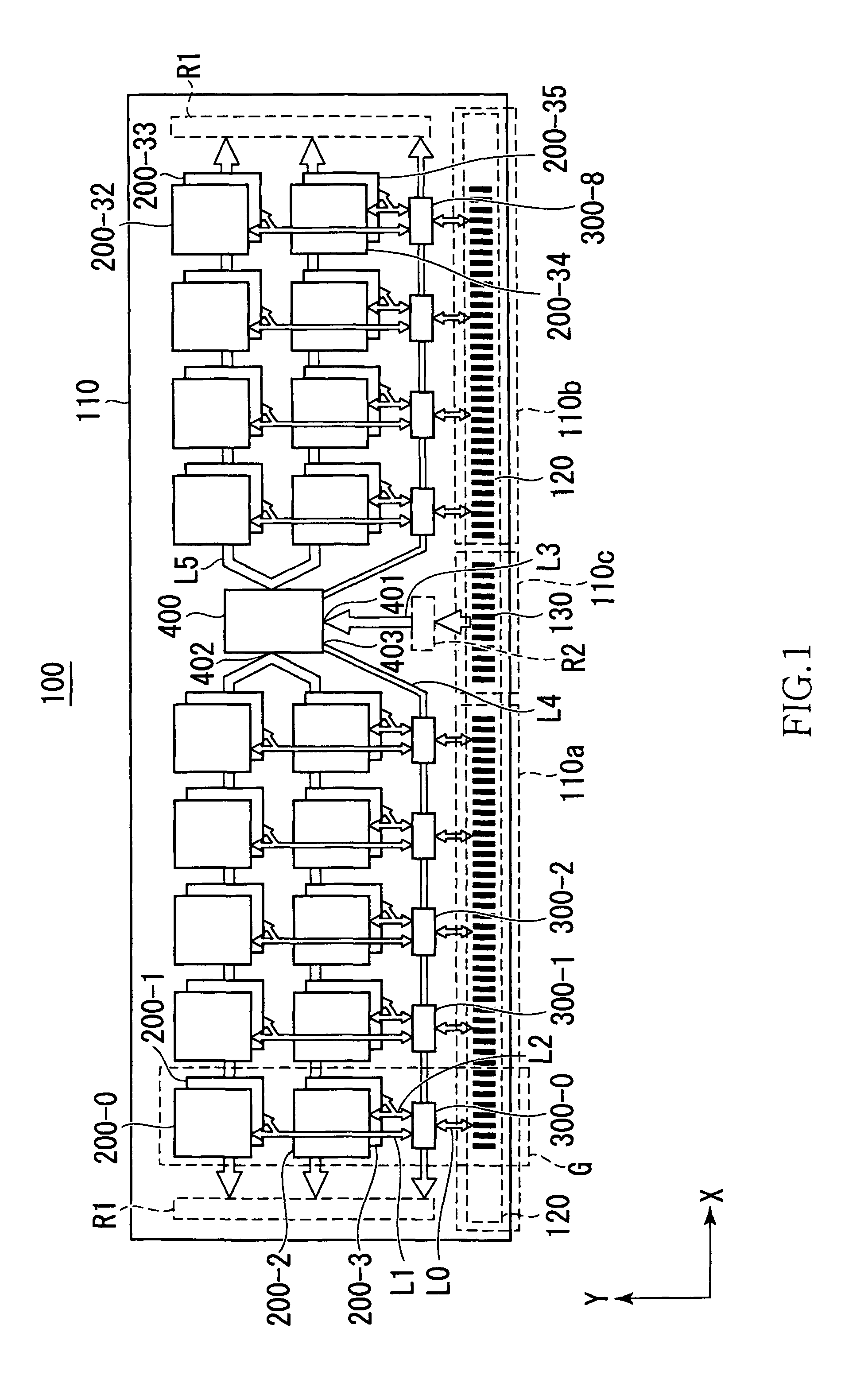

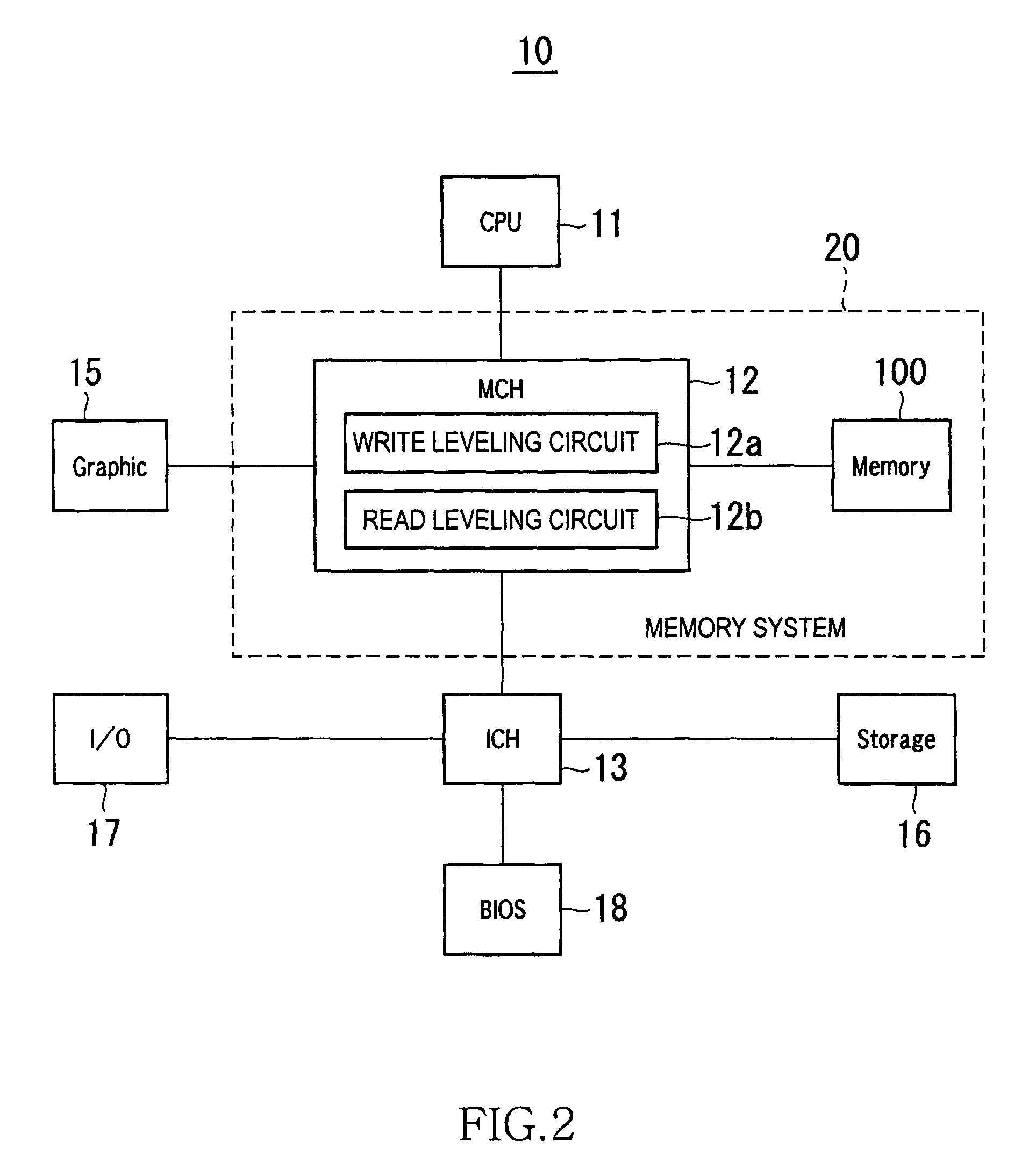

Memory module and memory system

ActiveUS7123497B2Increase chanceVarious problemDomestic stoves or rangesLighting and heating apparatusData signalComputer module

In a memory module including a plurality of DRAM chips which transmit / receive a system data signal with a predetermined data width and at a transfer rate and which transmit / receive an internal data signal having a larger data width and a lower transfer rate as compared with the system data signal, it has become clear that there is a restriction on the transfer rate of the system data signal and that speeding-up cannot be expected. A current consumption in a plurality of DRAMs constituting the memory module is large, and this is also a factor for hindering the speeding-up. There is obtained a memory module in which a plurality of DRAM chips are stacked on an IO chip and in which each DRAM chip is connected to the IO chip by a through electrode and which comprises a constitution for mutually converting the system data signal and the internal data signal in each DRAM chip by the IO chip. In this constitution, a wiring between the DRAM chips can be shortened, and DLL having a large current consumption may be disposed only on the IO chip.

Owner:LONGITUDE LICENSING LTD

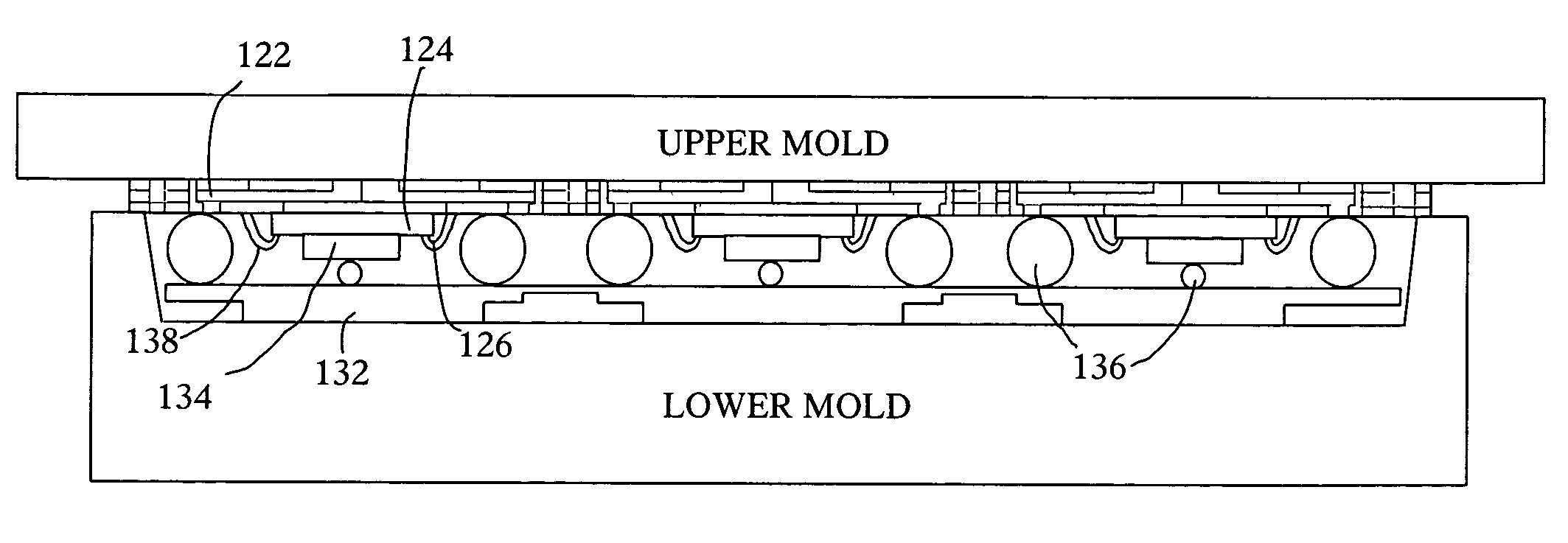

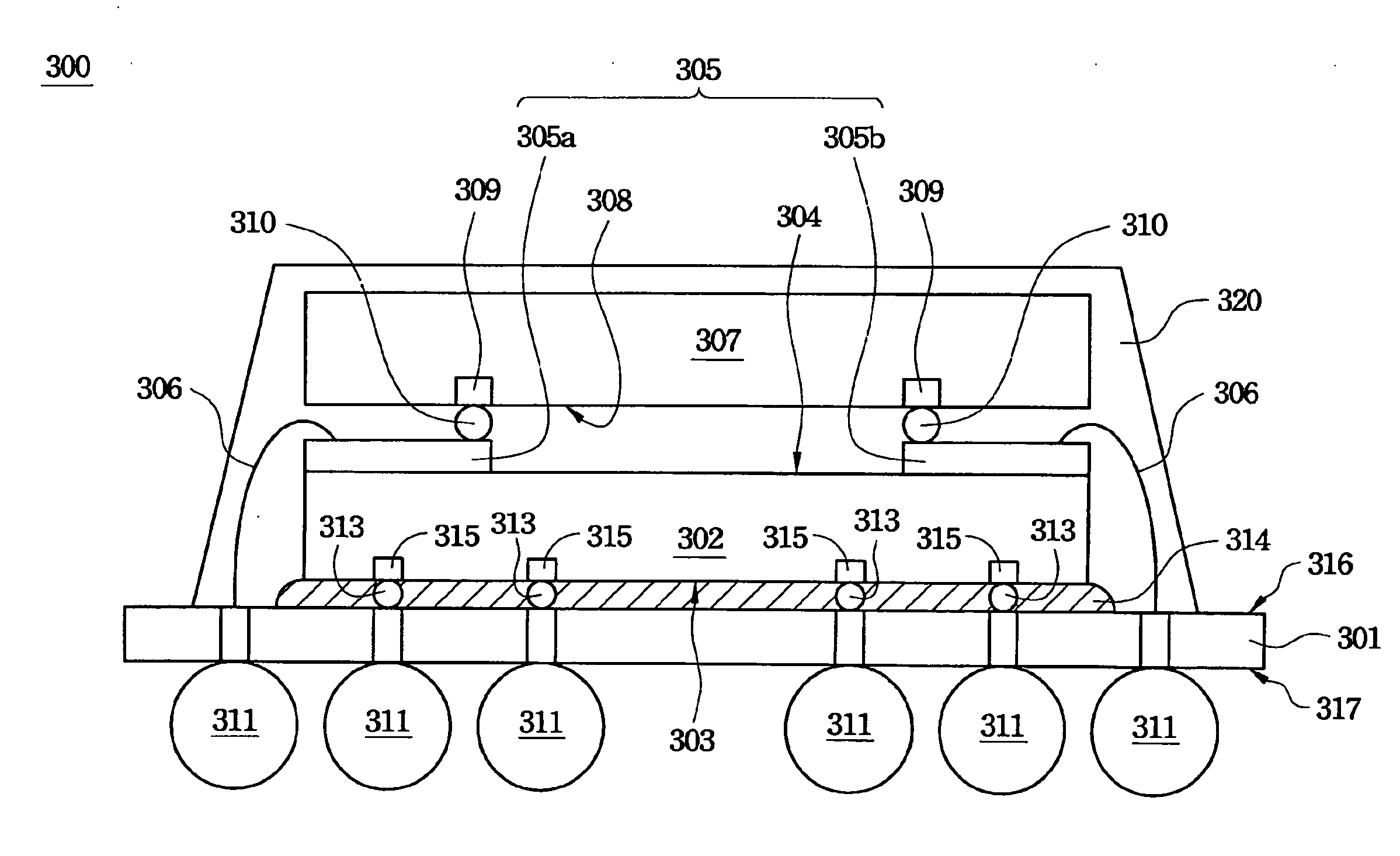

Ball grid array package and process for manufacturing same

InactiveUS6987032B1Inhibiting mold flashReducing mold flashSemiconductor/solid-state device detailsSolid-state devicesBall grid arraySemiconductor

A ball grid array package is manufactured by mounting a semiconductor die to a first surface of a substrate and mounting a die adapter to the semiconductor die. The semiconductor die is wire bonded to ones of conductive traces of the substrate. A collapsible spacer is mounted to the substrate and the substrate is releasably clamped to an upper side of a mold cavity. A heat spreader and at least one collapsible spacer are placed in the mold cavity such that the collapsible spacer is disposed between the heat spreader and the substrate. A molding compound is molded in the mold, thereby molding the semiconductor die, the substrate, the wire bonds, the die adapter, the at least one collapsible spacer and the heat spreader into the molding compound to provide a molded package. A ball grid array is formed on a second surface of the substrate, bumps of the ball grid array being electrically connected to the conductive traces and the integrated circuit package is singulated.

Owner:UTAC HEADQUARTERS PTE LTD

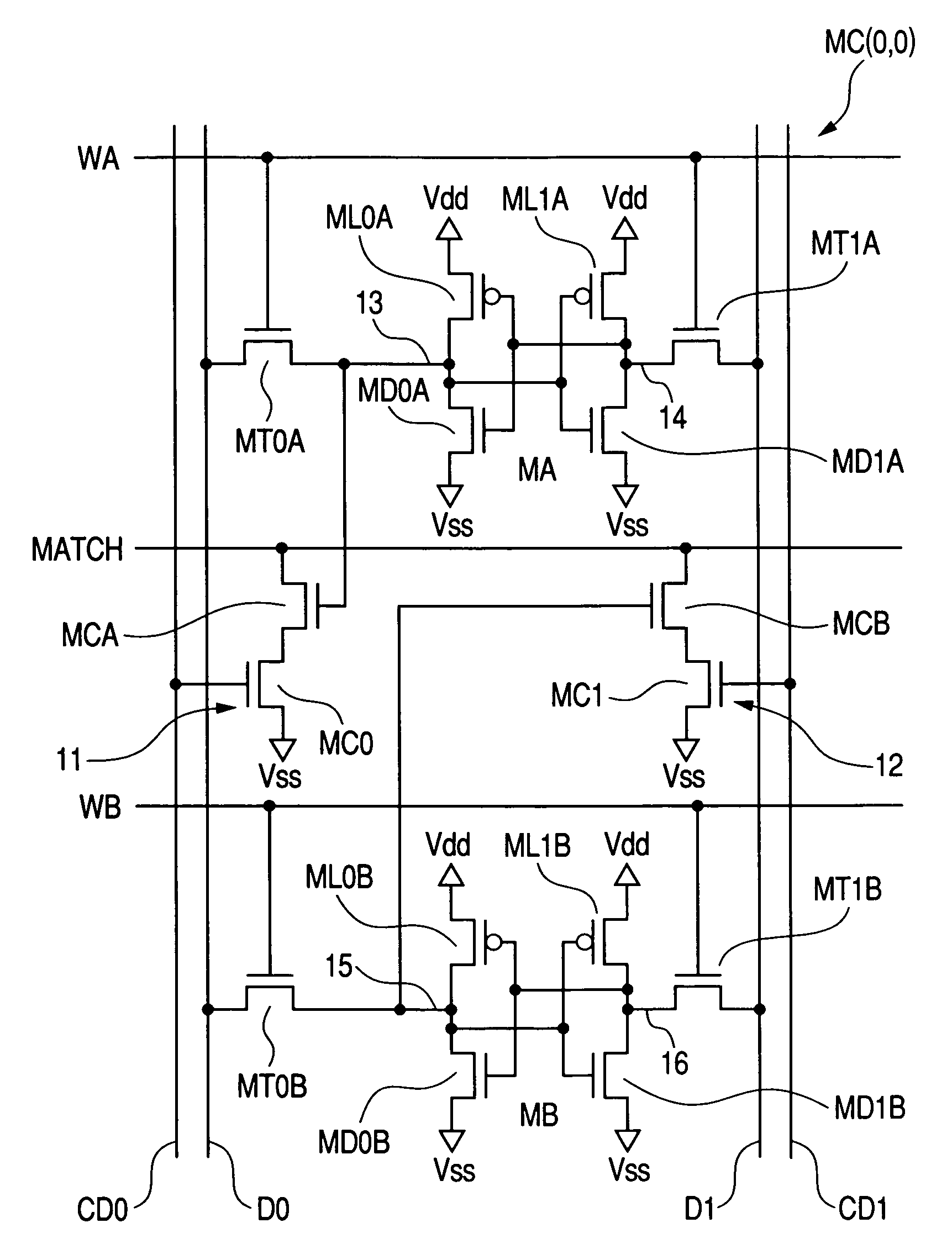

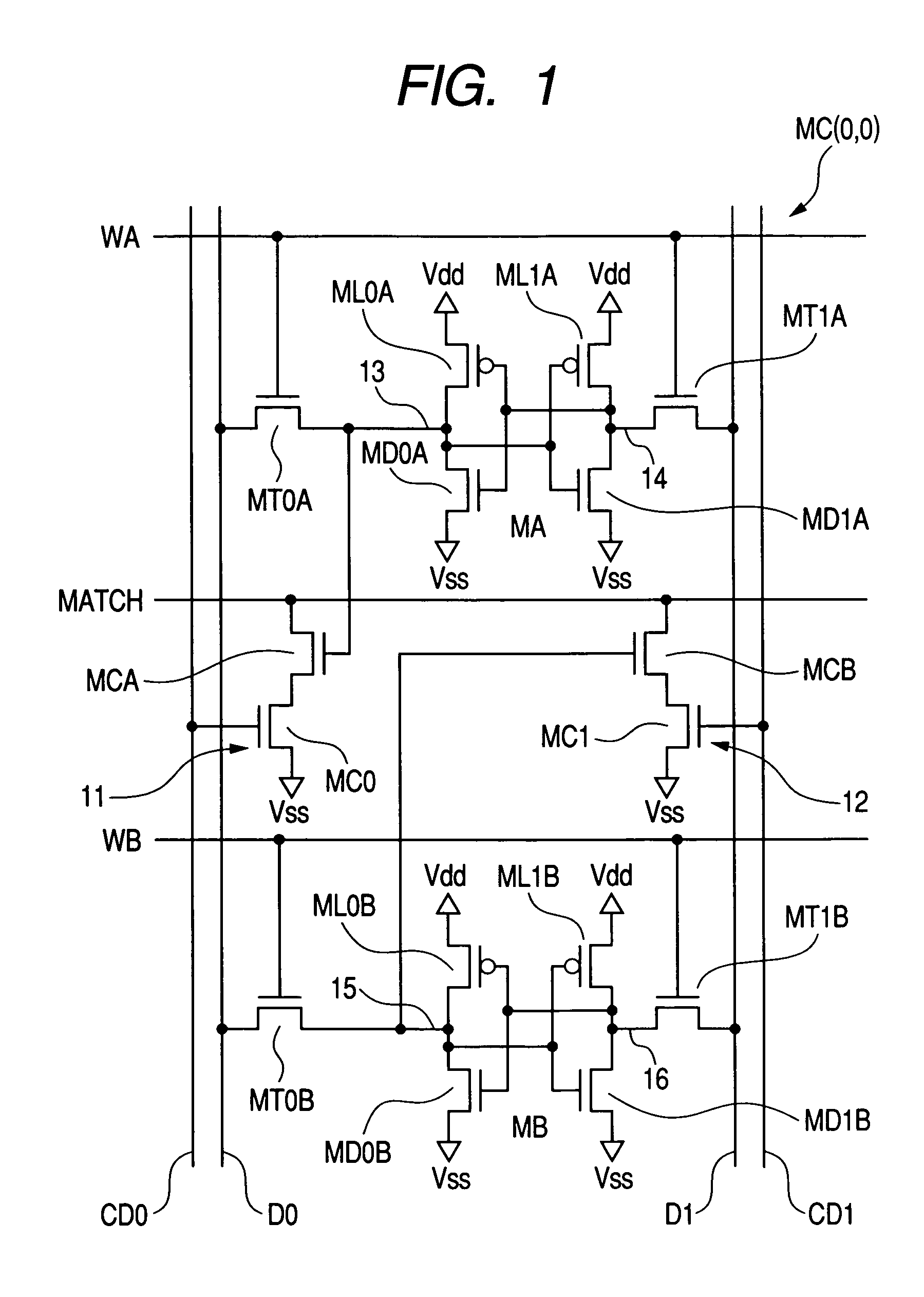

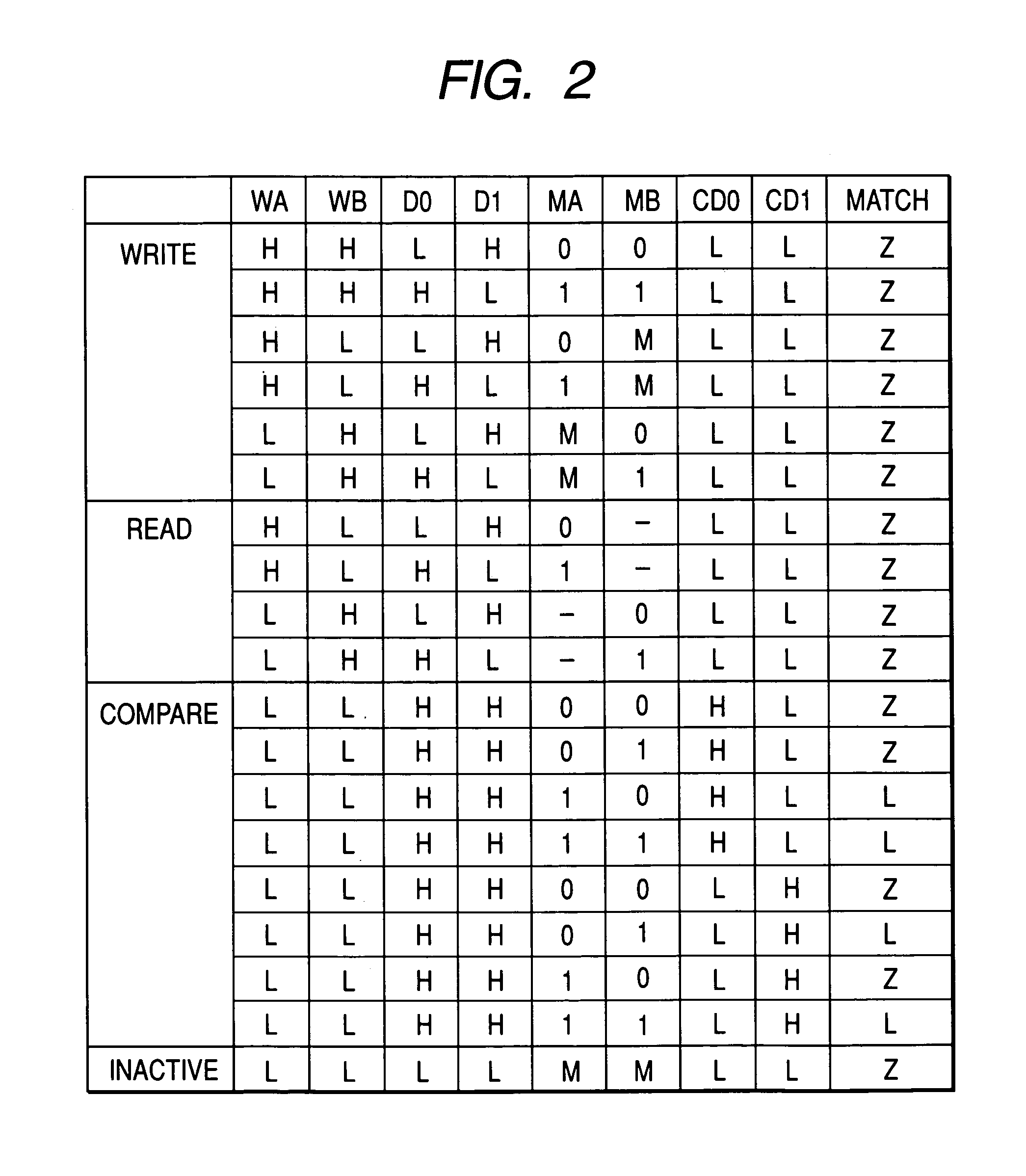

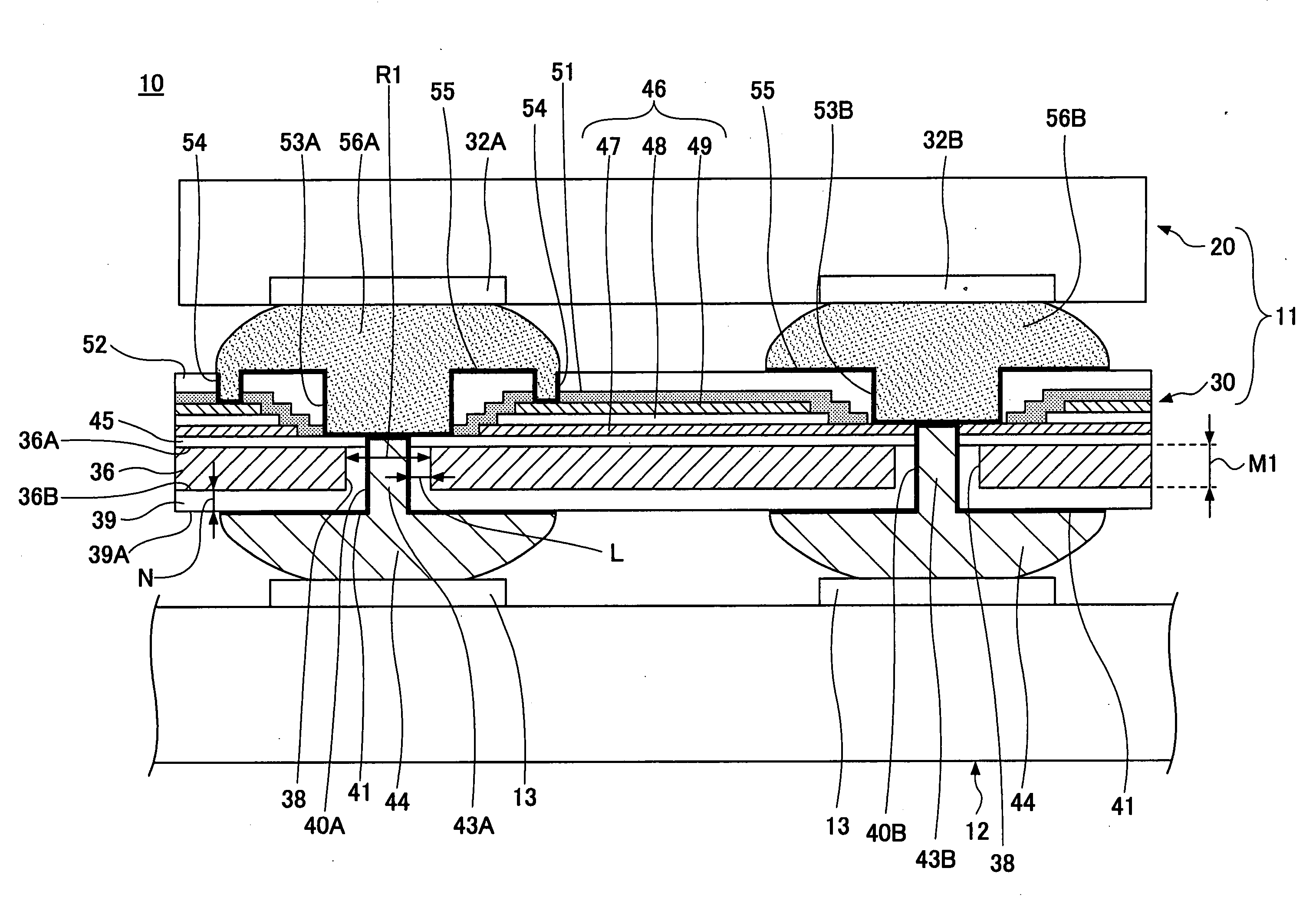

Semiconductor device

InactiveUS7009862B2Reduce manufacturing costIncrease productionTransistorSolid-state devicesProcess conditionsDiffusion layer

Data lines (D0, D1) are shared by a first storage portion (MA) and a second storage portion (MB), and furthermore, a first transistor (MC0) coupled to a first comparison data portion (CD0) and a second transistor (MCA) coupled to the storage node of a first storage portion are connected in series to form a first comparing circuit (11), and a third transistor (MC1) coupled to a second comparison data line (CD1) and a fourth transistor (MCB) coupled to the storage node of the second storage portion are connected in series to form a second comparing circuit (12). Consequently, it is possible to enhance a symmetry in the layout of a diffusion layer and a wiring layer and to achieve the easiness of a layout in which a memory cell is line symmetrical with respect to a center line passing through a center thereof. Thus, a manufacturing process condition can easily be optimized and a variation in a manufacturing process can be reduced so that the microfabrication of the memory cell can be achieved.

Owner:HITACHI LTD

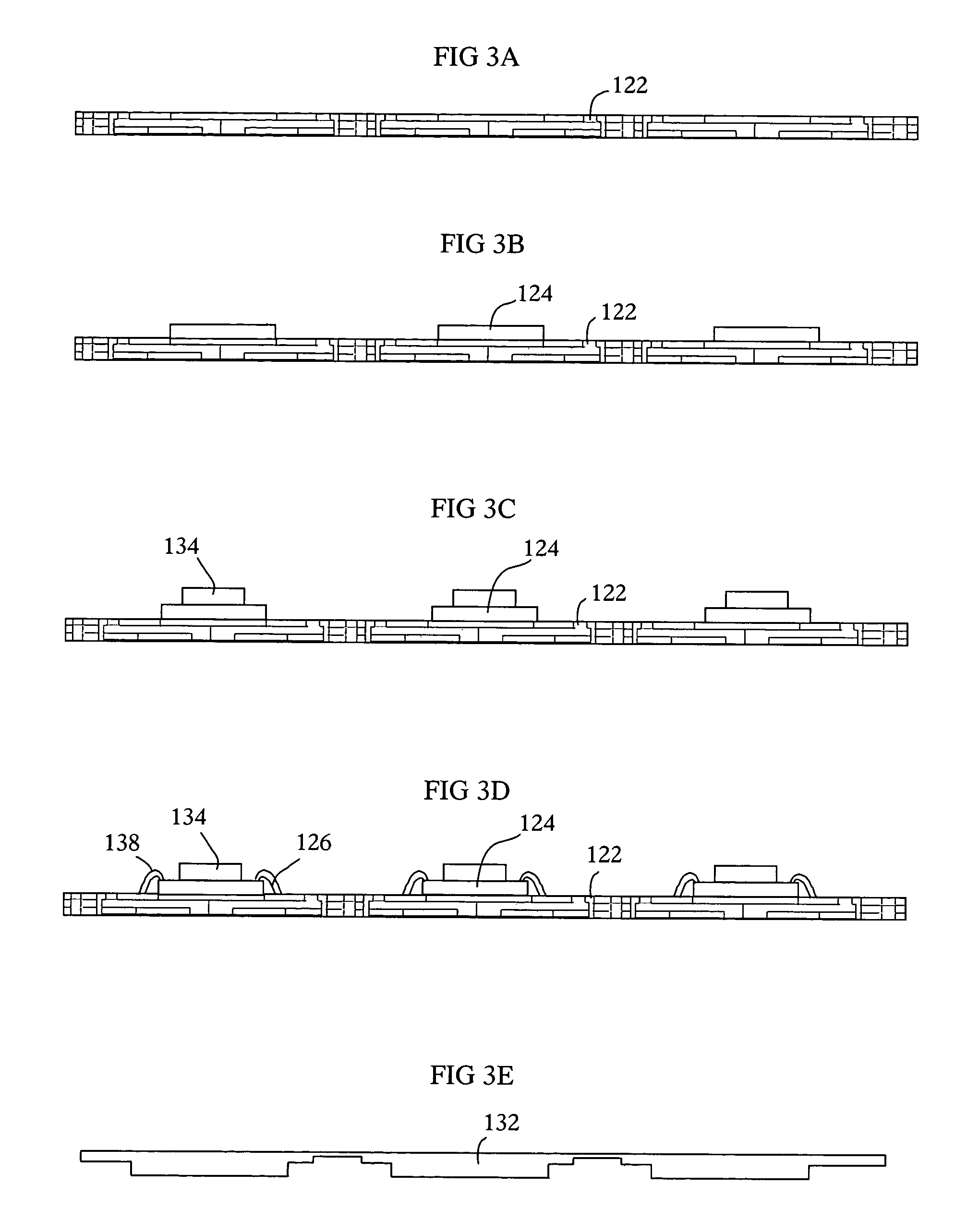

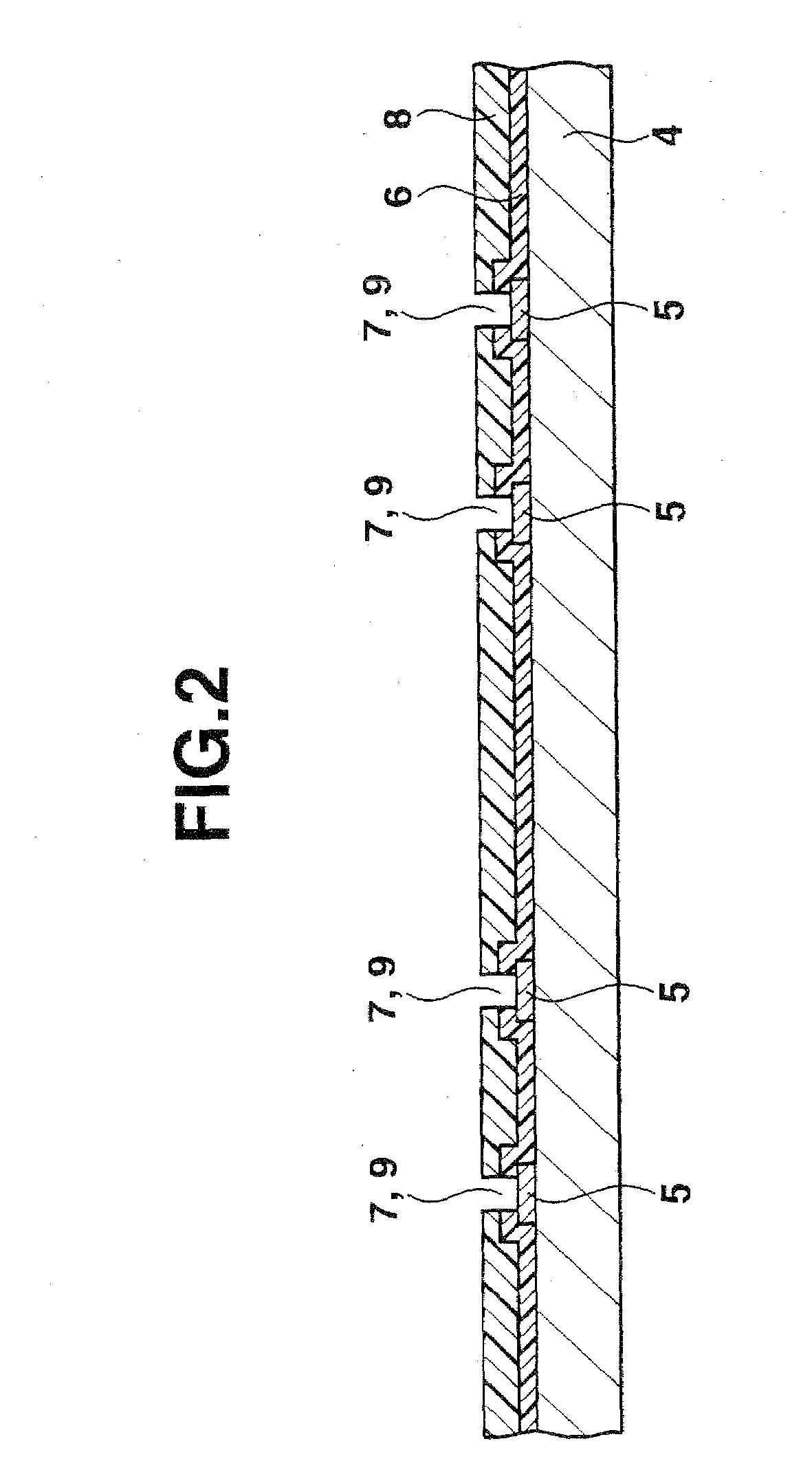

Method for manufacturing an interconnect structure for stacked semiconductor device

InactiveUS20020074670A1Shorten the line lengthEasy to produceSemiconductor/solid-state device detailsSolid-state devicesInterconnectionSemiconductor device

In a multi-layer interconnection structure, the wiring length is to be reduced, and the interconnection is to be straightened, at the same time as measures need to be taken against radiation noise. To this end, there is disclosed a semiconductor device in which plural semiconductor substrates, each carrying semiconductor elements, are bonded together. On each semiconductor substrate is deposited an insulating layer through which is formed a connection wiring passed through the insulating layer so as to be connected to the interconnection layer of the semiconductor element. On a junction surface of at least one of the semiconductor substrates is formed an electrically conductive layer of an electrically conductive material in which an opening is bored in association with the connection wiring. The semiconductor substrates are bonded together by the solid state bonding technique to interconnect the connection wirings formed on each semiconductor substrate.

Owner:LAPIS SEMICON CO LTD +1

Memory module and memory system

ActiveUS20060262587A1Increase chanceTotal current dropDomestic stoves or rangesLighting and heating apparatusData signalTerm memory

In a memory module including a plurality of DRAM chips which transmit / receive a system data signal with a predetermined data width and at a transfer rate and which transmit / receive an internal data signal having a larger data width and a lower transfer rate as compared with the system data signal, the transfer rate of the system data signal is restricted. Current consumption in DRAMs constituting the memory module is large, hindering speed increases. For this memory module, a plurality of DRAM chips are stacked on an IO chip. Each DRAM chip is connected to the IO chip by a through electrode, and includes a constitution for mutually converting the system data signal and the internal data signal in each DRAM chip by the IO chip. Therefore, wiring between the DRAM chips can be shortened, and DLL having a large current consumption may be disposed only on the IO chip.

Owner:LONGITUDE LICENSING LTD

Chip-Stacked Package Structure

InactiveUS20080265397A1Extend length and radianSmall sizeSemiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

A chip stacked package structure and applications are provided, wherein the chip stacked package structure comprises a substrate, a first chip, a patterned circuit layer and a second chip. The substrate has a first surface and an opposite second surface. The first chip with a first active area and an opposite first rear surface is electrically connected to first surface of substrate by a flip chip bonding process. The patterned circuit layer set on the dielectric layer is electrically connected to the substrate via a bonding wire. The second chip set on the patterned circuit layer has a second active area and a plurality of second pads formed on the second active area, wherein the second bonding pad is electrically connected to the patterned circuit layer.

Owner:CHIPMOS TECH INC +1

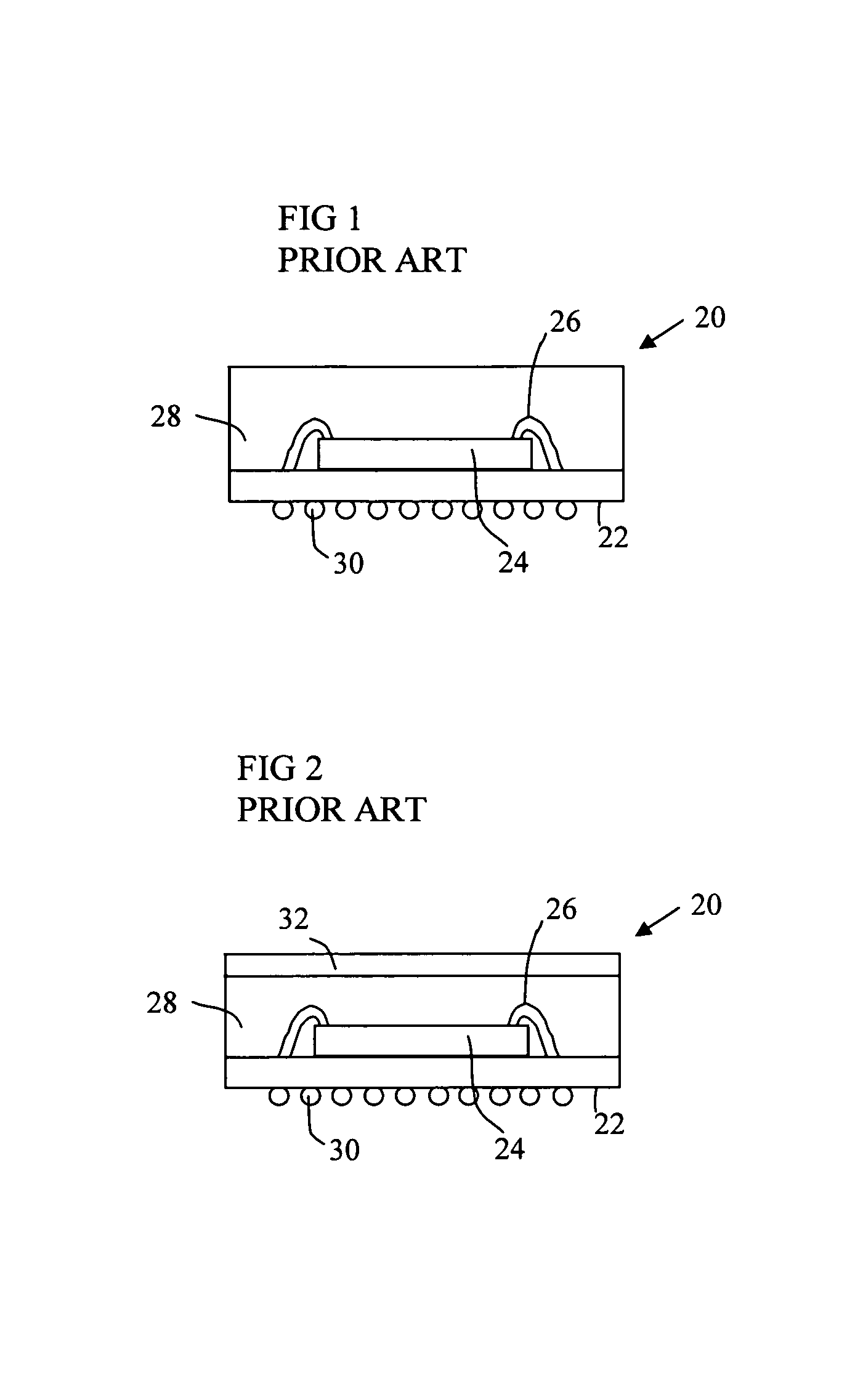

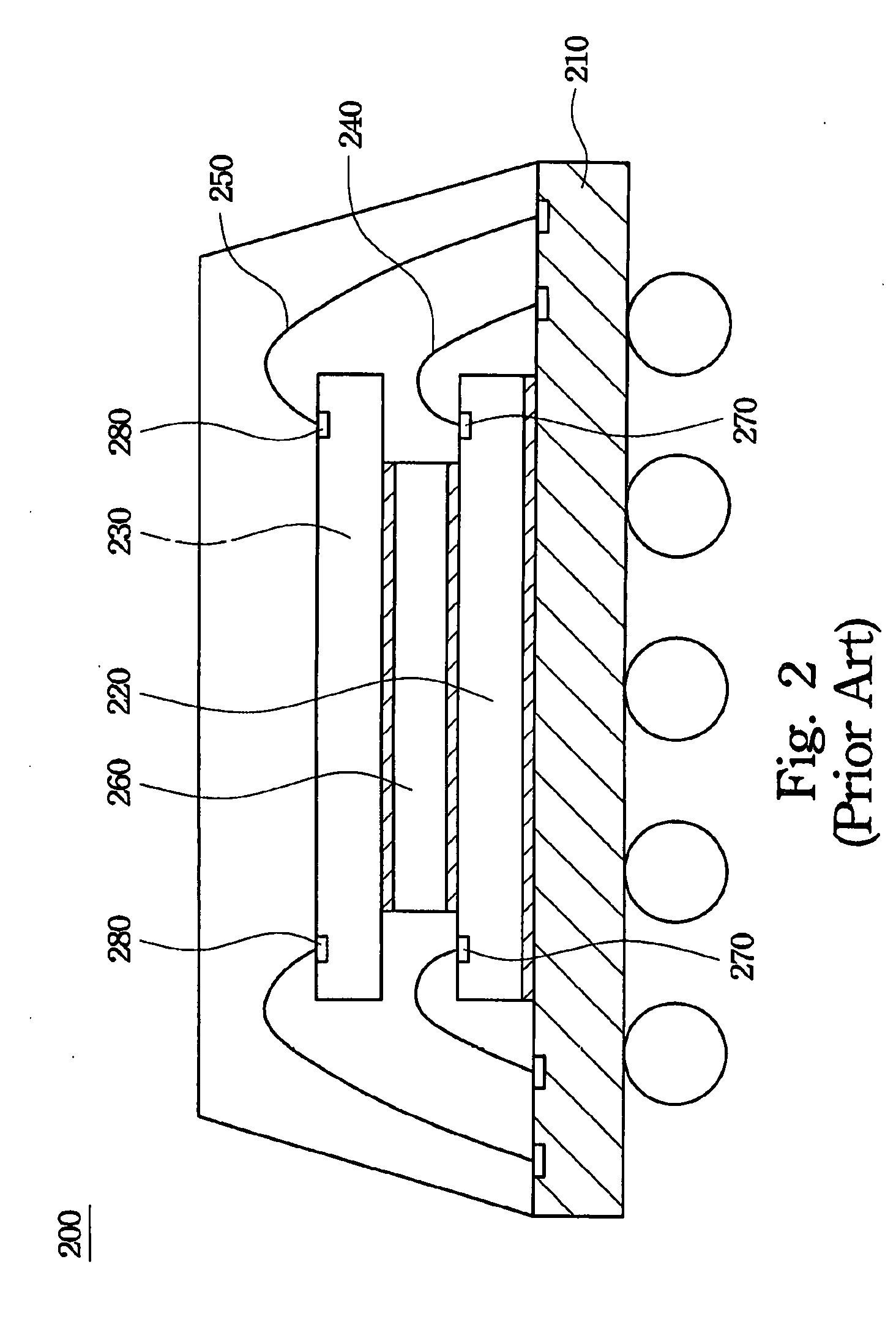

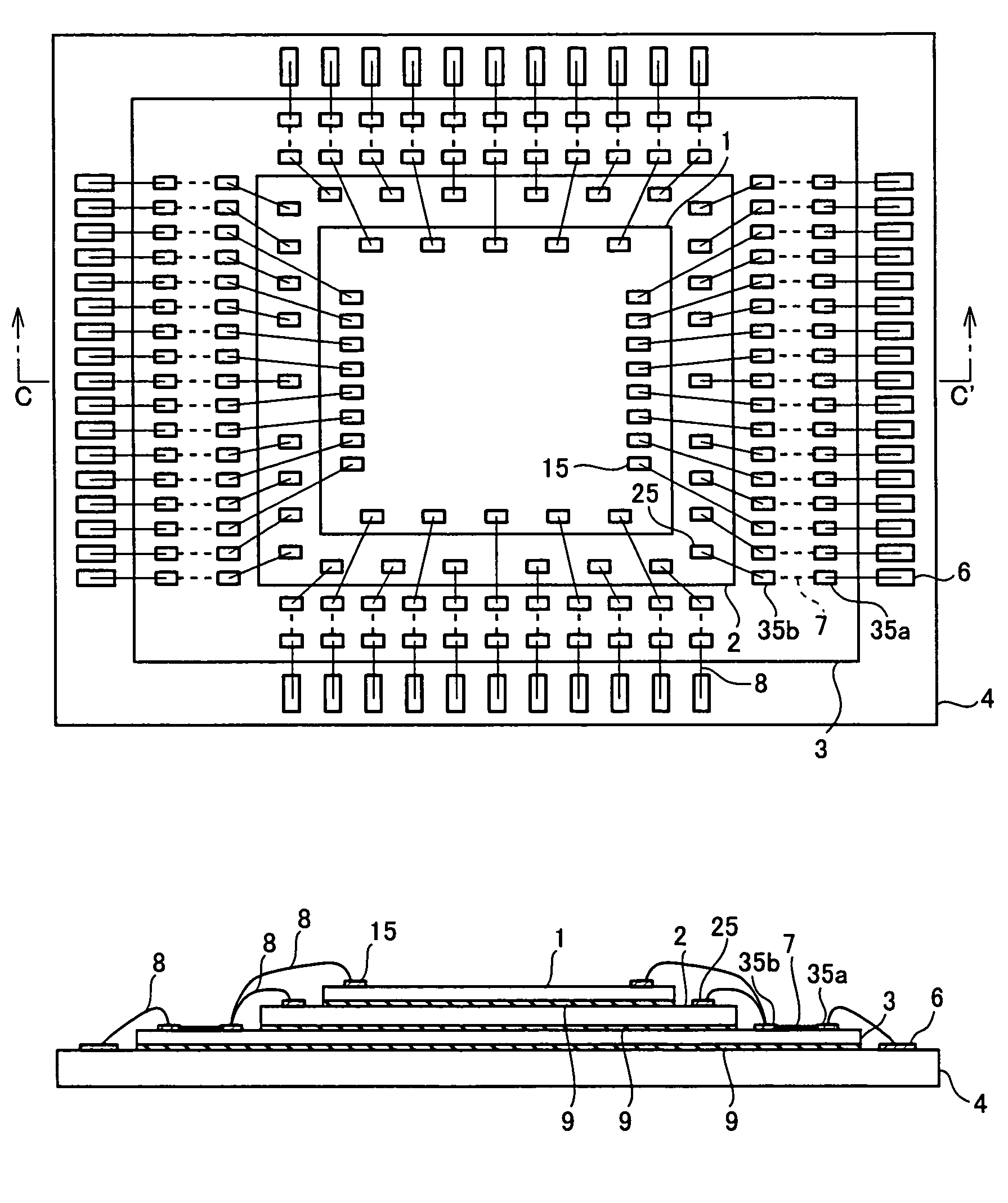

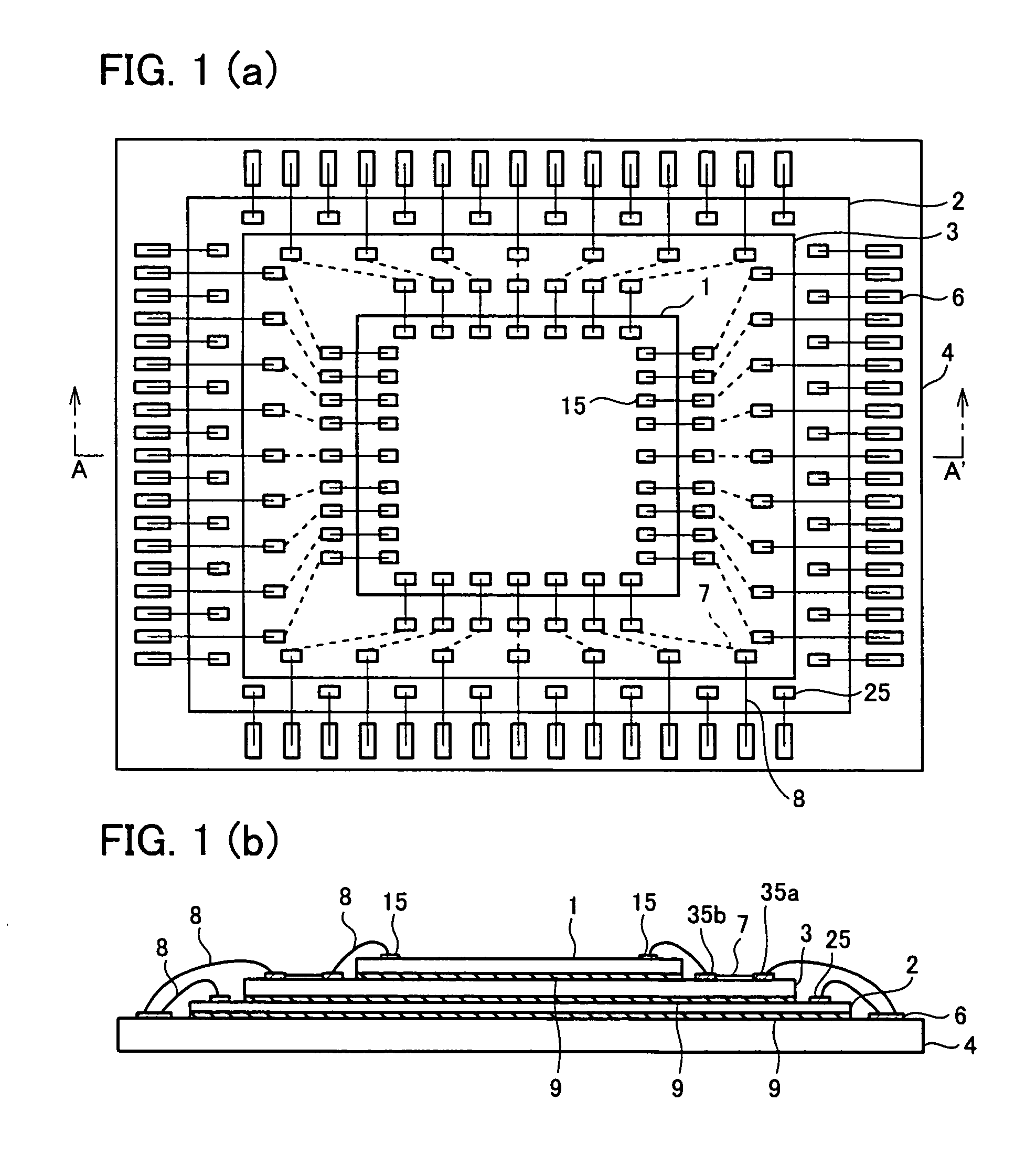

Semiconductor device

ActiveUS6979905B2Prevents wire bonding strengthInhibition strengthSemiconductor/solid-state device detailsSolid-state devicesElectric propertiesEngineering

In a semiconductor device in which a semiconductor chip is stacked on a substrate, an interposer chip having wirings is provided under the semiconductor chip. A bonding pad of the semiconductor chip is electrically connected to a bonding terminal provided on the substrate via the interposer chip by wire bonding. The interposer chip prevents a semiconductor element formed in the semiconductor chip from deteriorating in terms of an electric property and from being physically damaged. Further, the wire bonding strength does not drop. Moreover, it is possible to form a fine wiring pitch for relaying a wire-bonding wire.

Owner:SHARP KK

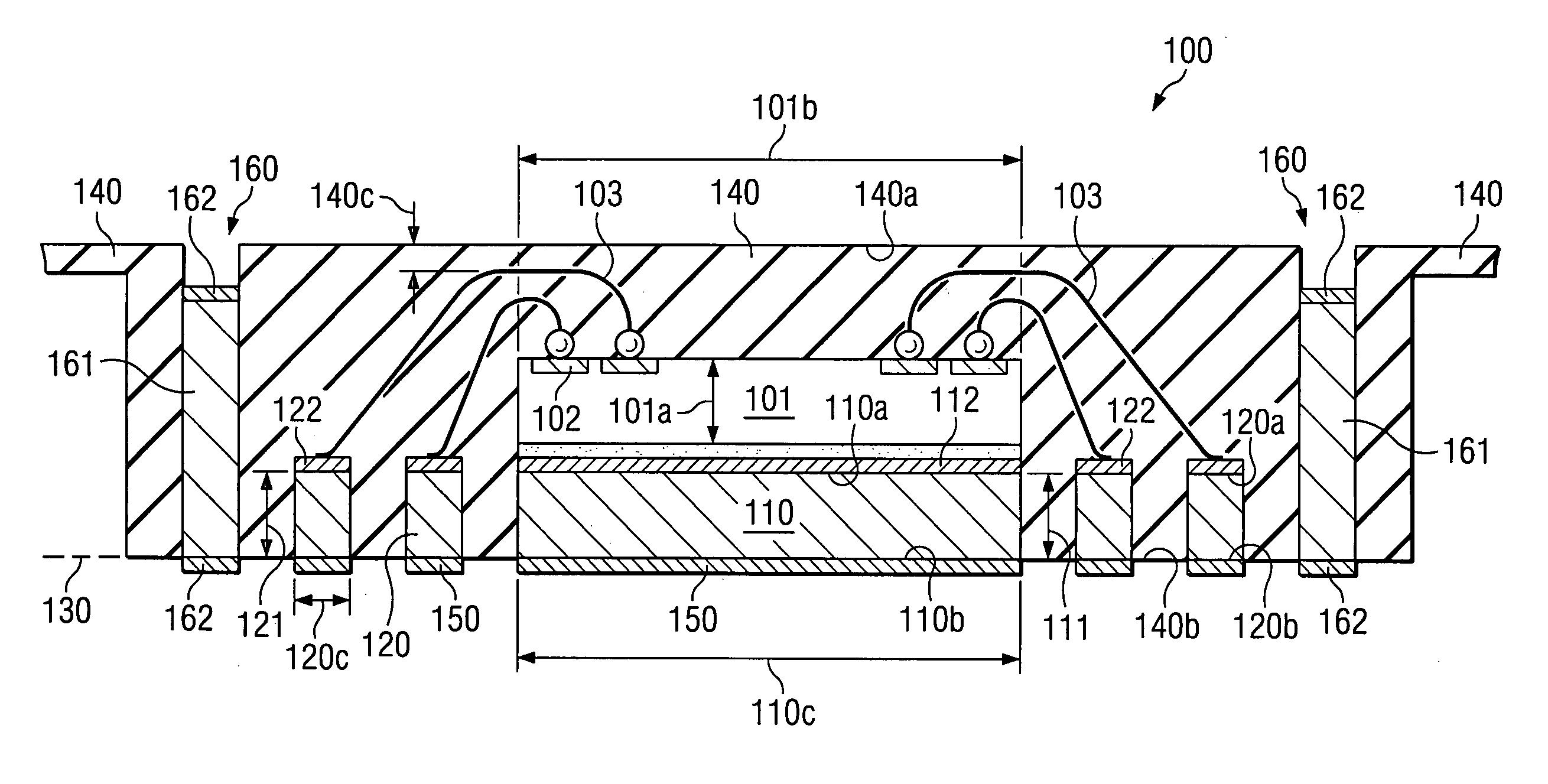

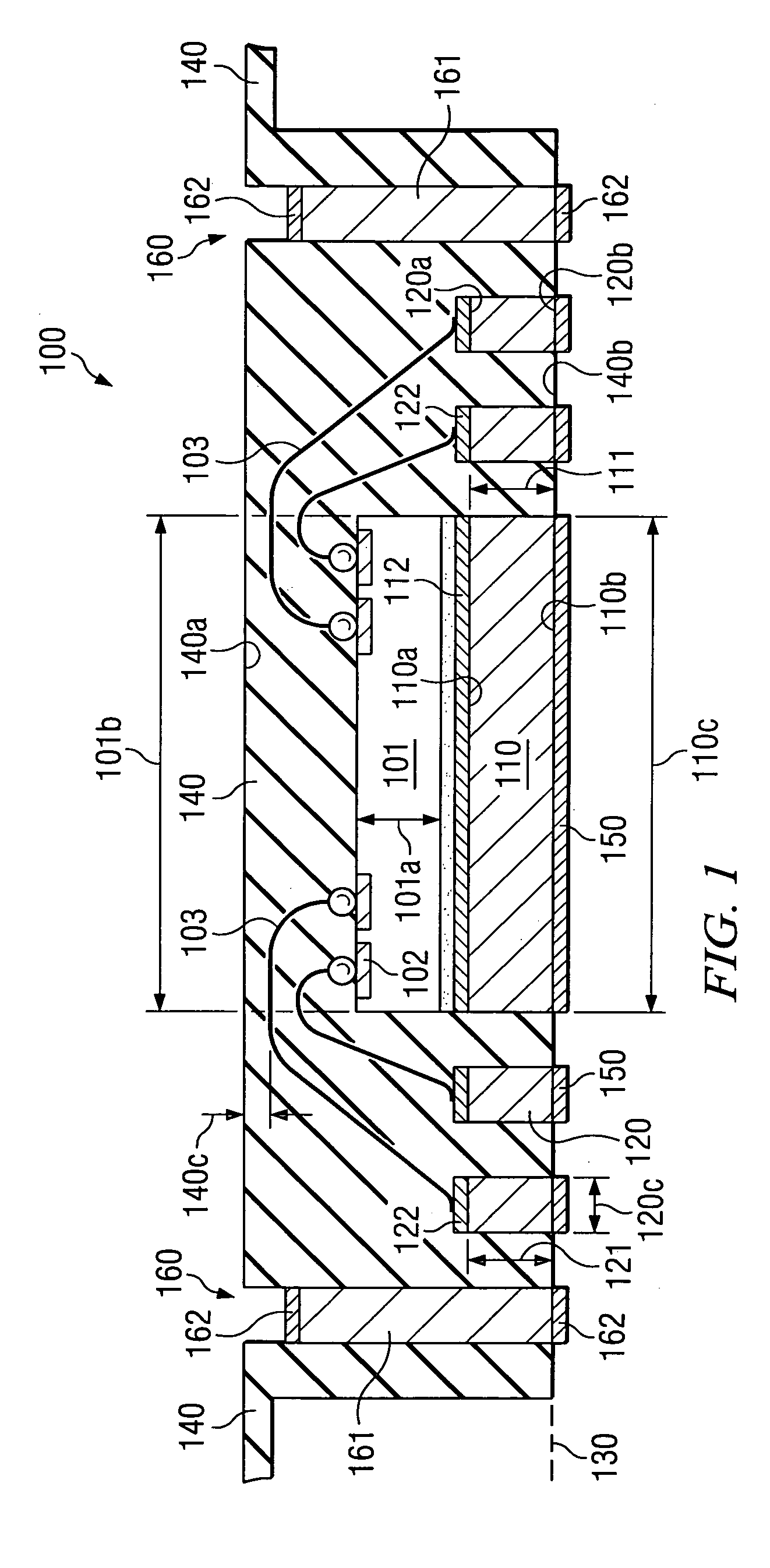

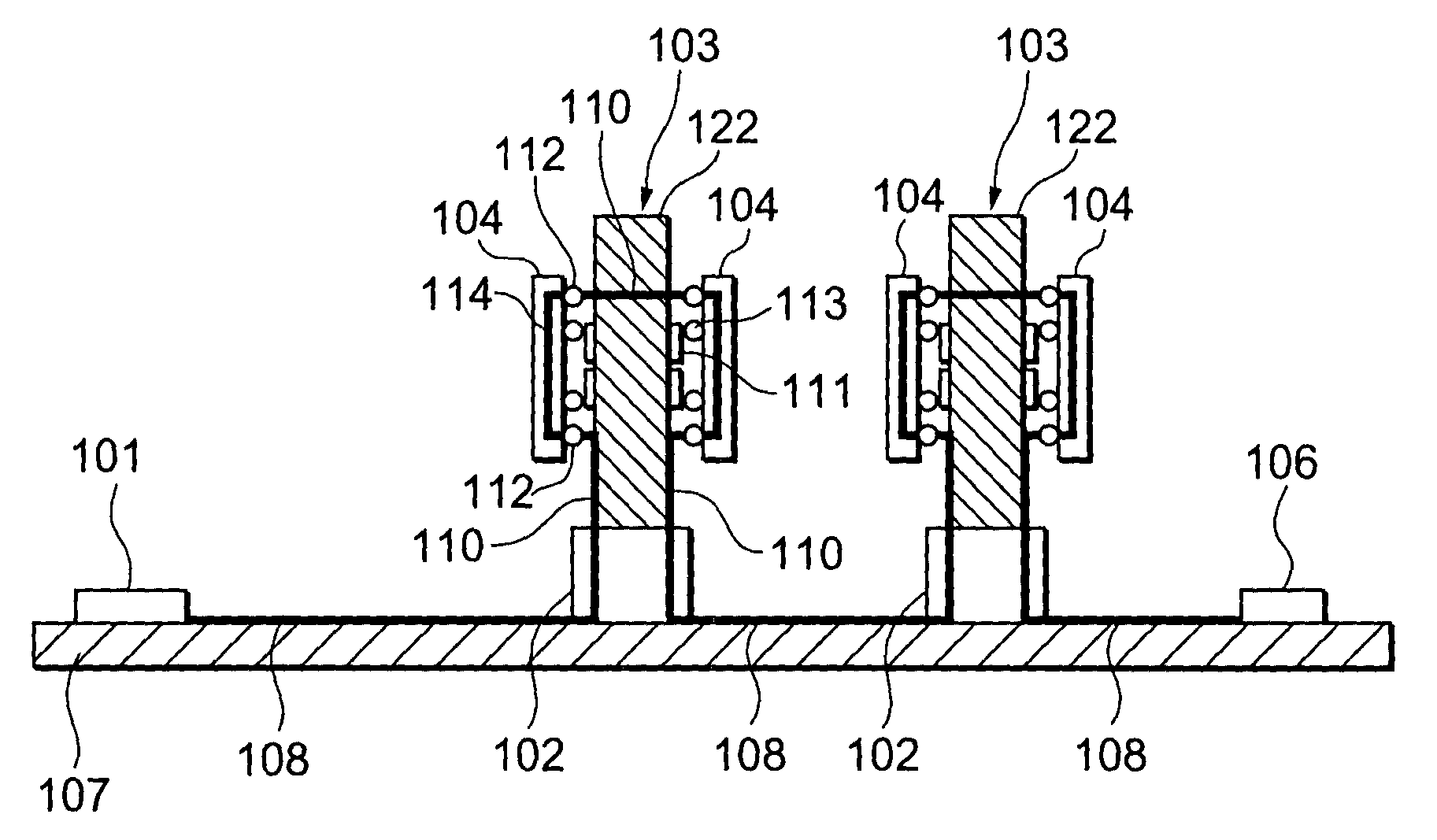

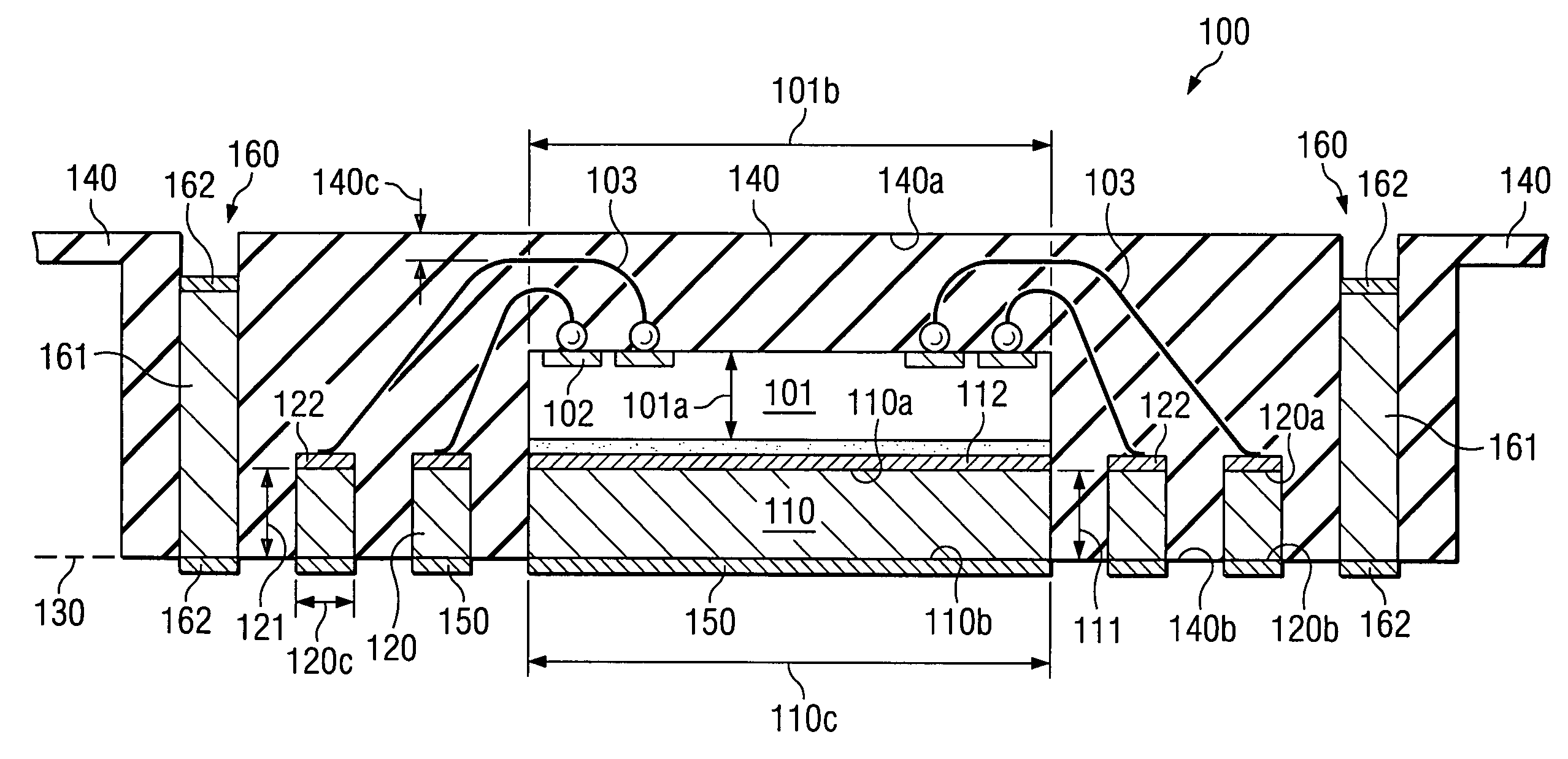

Structure and method of molded QFN device suitable for miniaturization, multiple rows and stacking

ActiveUS20070090524A1Excellent thermal device performanceImprove speed performanceSemiconductor/solid-state device detailsSolid-state devicesLead bondingMiniaturization

A semiconductor device comprising a semiconductor chip (101) assembled on a first copper cuboid (110); the cuboid has sides of a height (111). The device further has a plurality of second copper cuboids (120) suitable for wire bond attachment; the second cuboids have sides of a height (121) substantially equal to the height of the first cuboid. The back surfaces of all cuboids are aligned in a plane (130). Encapsulation compound (140) is adhering to and embedding the chip, the wire bonds, and the sides of all cuboids so that the compound forms a first surface (140b) aligned with the plane of the back cuboid surfaces and a second surface (140a) above the embedded wires. For devices intended for stacking, the devices further comprise a plurality of vias (160) through the encapsulation compound from the first to the second compound surfaces; the vias are filled with copper, and the via locations are matching between the devices-to-be-stacked.

Owner:TEXAS INSTR INC

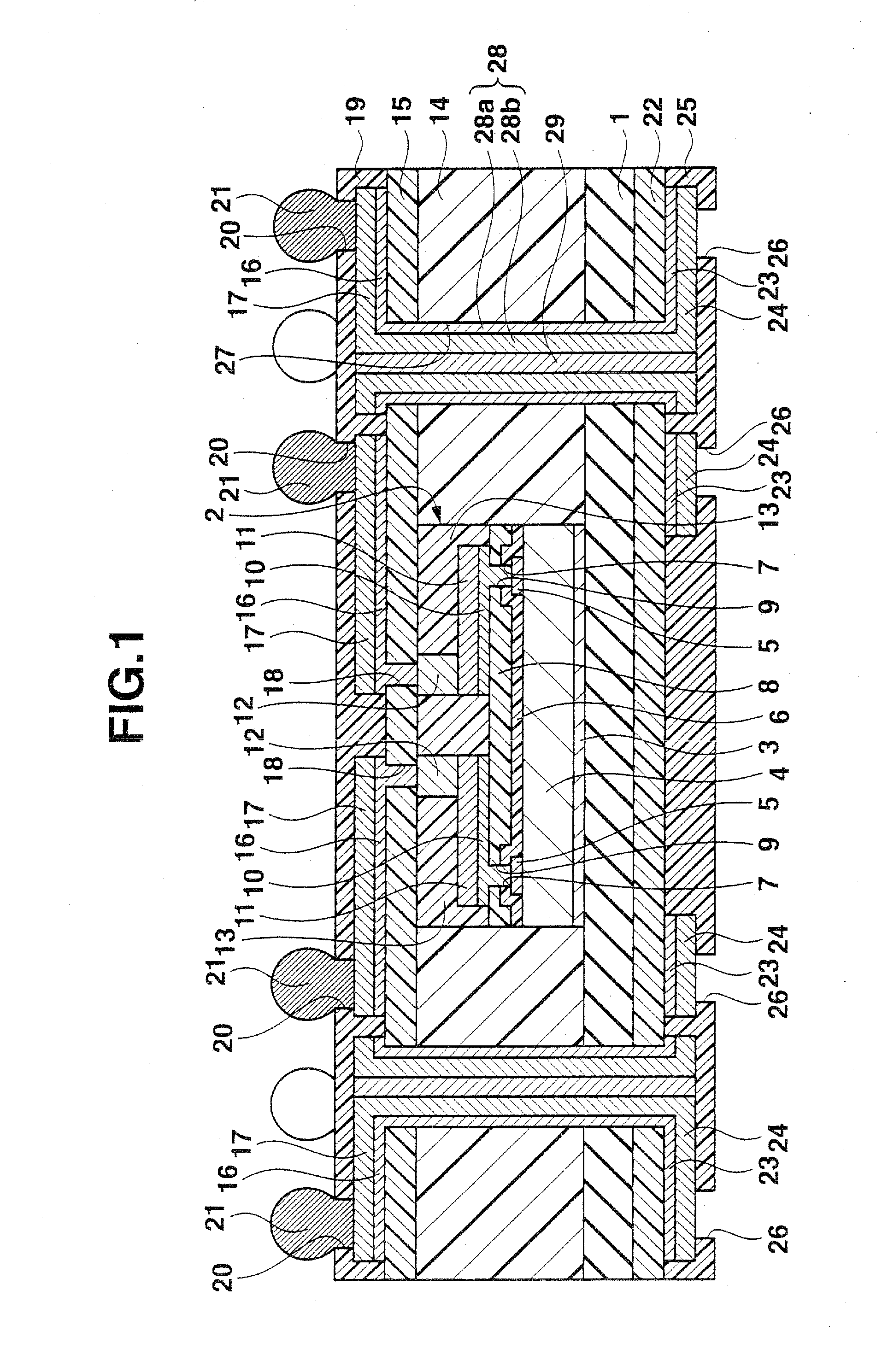

Semiconductor package including connected upper and lower interconnections, and manufacturing method thereof

InactiveUS20080166836A1Improve connection reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package includes a base plate, at least one semiconductor constructing body which is formed on one surface of the base plate and has a plurality of external connection electrodes formed on a semiconductor substrate, an insulating layer which is formed on one surface of the base plate around the semiconductor constructing body, upper interconnections which are formed on the insulating layer and each includes at least one interconnection layer, at least some of the upper interconnections are connected to the external connection electrodes of the semiconductor constructing body, lower interconnections which are formed on the other surface of the base plate and each includes at least one interconnection layer, and at least some of the lower interconnections which are electrically connected to the upper interconnections.

Owner:CMK +1

Semiconductor device, method of manufacturing the same, capacitor structure, and method of manufacturing the same

InactiveUS20060180938A1Lower impedanceReduce inductanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A semiconductor device is disclosed that includes an interposer and a semiconductor chip. The interposer includes a Si substrate; multiple through vias provided through an insulating material in corresponding through holes passing through the Si substrate; a thin film capacitor provided on a first main surface of the Si substrate so as to be electrically connected to the through vias; and multiple external connection terminals provided on a second main surface of the Si substrate so as to be electrically connected to the through vias. The second main surface faces away from the first main surface. The semiconductor chip is provided on one of the first main surface and the second main surface so as to be electrically connected to the through vias. The Si substrate has a thickness less than the diameter of the through holes.

Owner:FUJITSU LTD

Semiconductor unit having two device terminals for every one input/output signal

InactiveUS7633147B2Shorten the lengthShorten the line lengthFinal product manufactureSemiconductor/solid-state device detailsMemory chipEngineering

A semiconductor unit constituting a memory device has a memory chip, a package substrate having three wiring layers. Power-supply surfaces (VDD surface) and (GND surface) are wired on the package substrate while an intra-package DQ bus is wired on an intermediate layer between both of the power-supply surfaces. The memory device has two DQ pins every one intra-package DQ bus. The intra-package DQ bus is connected to a signal terminal pad of the memory chip through a via hole. In view of the two DW pins, a via hole for connecting the intra-package DQ bus with the signal terminal pad constitutes a branch wire.

Owner:KOMORO MURATA MFG +1

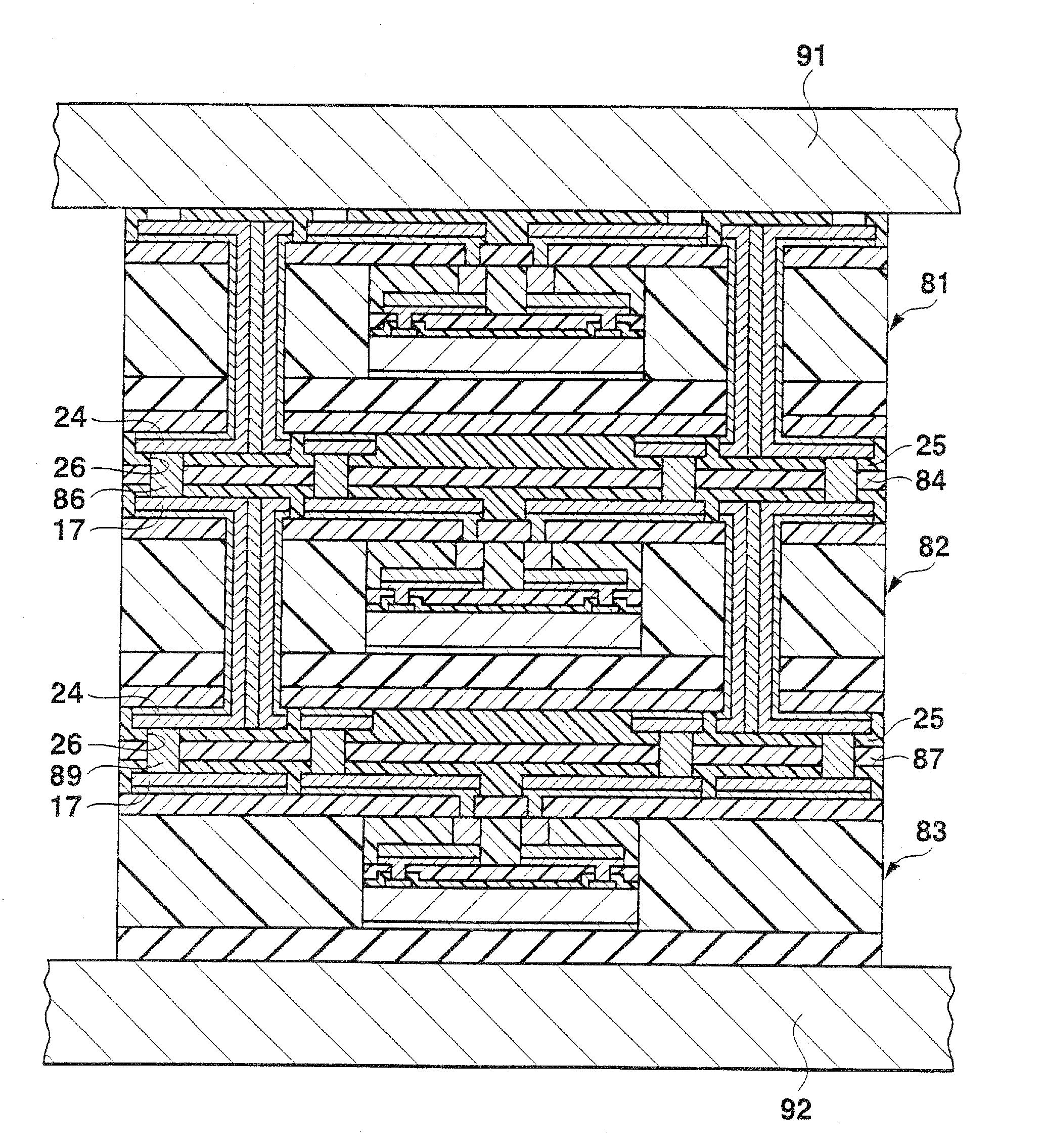

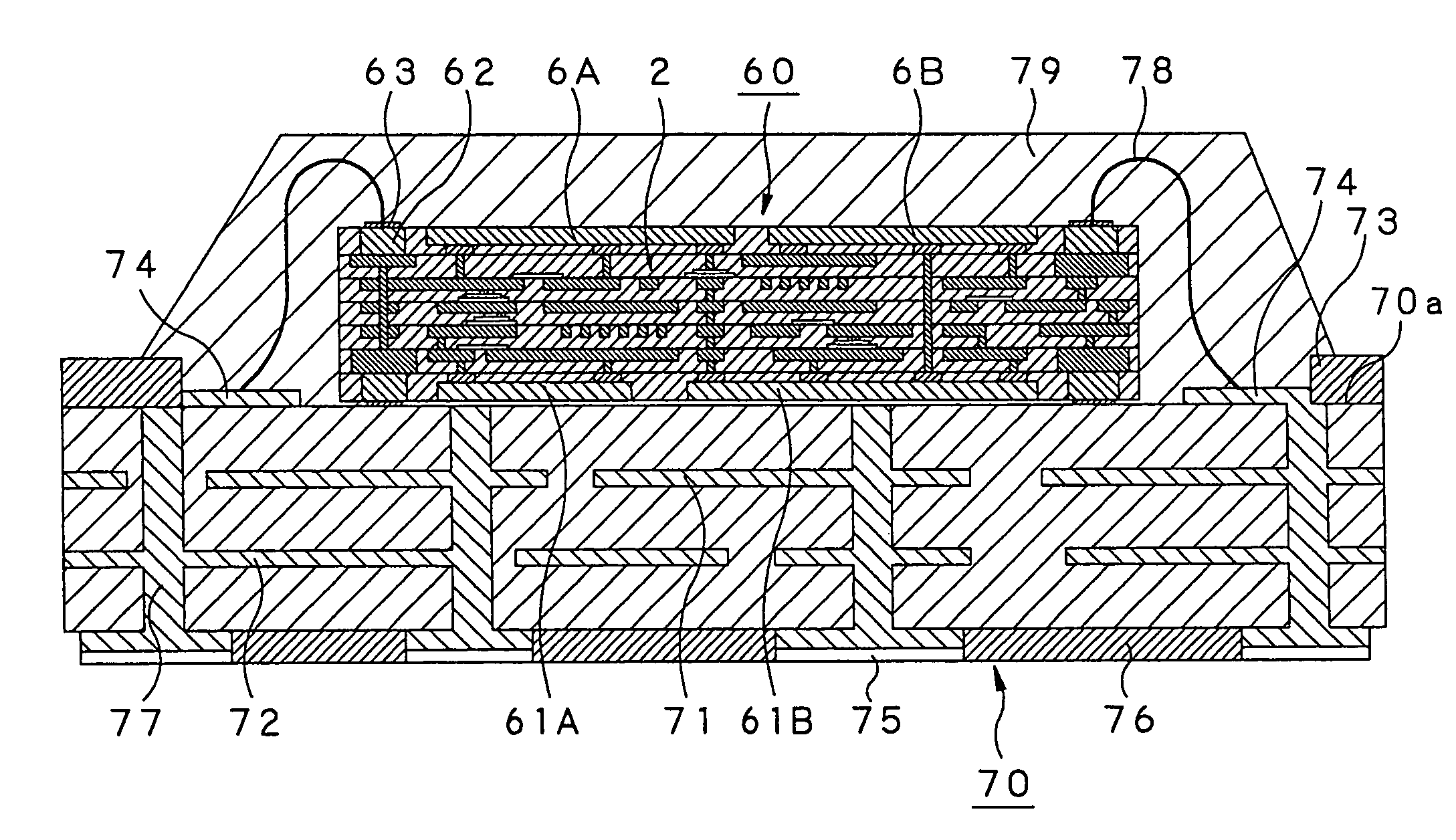

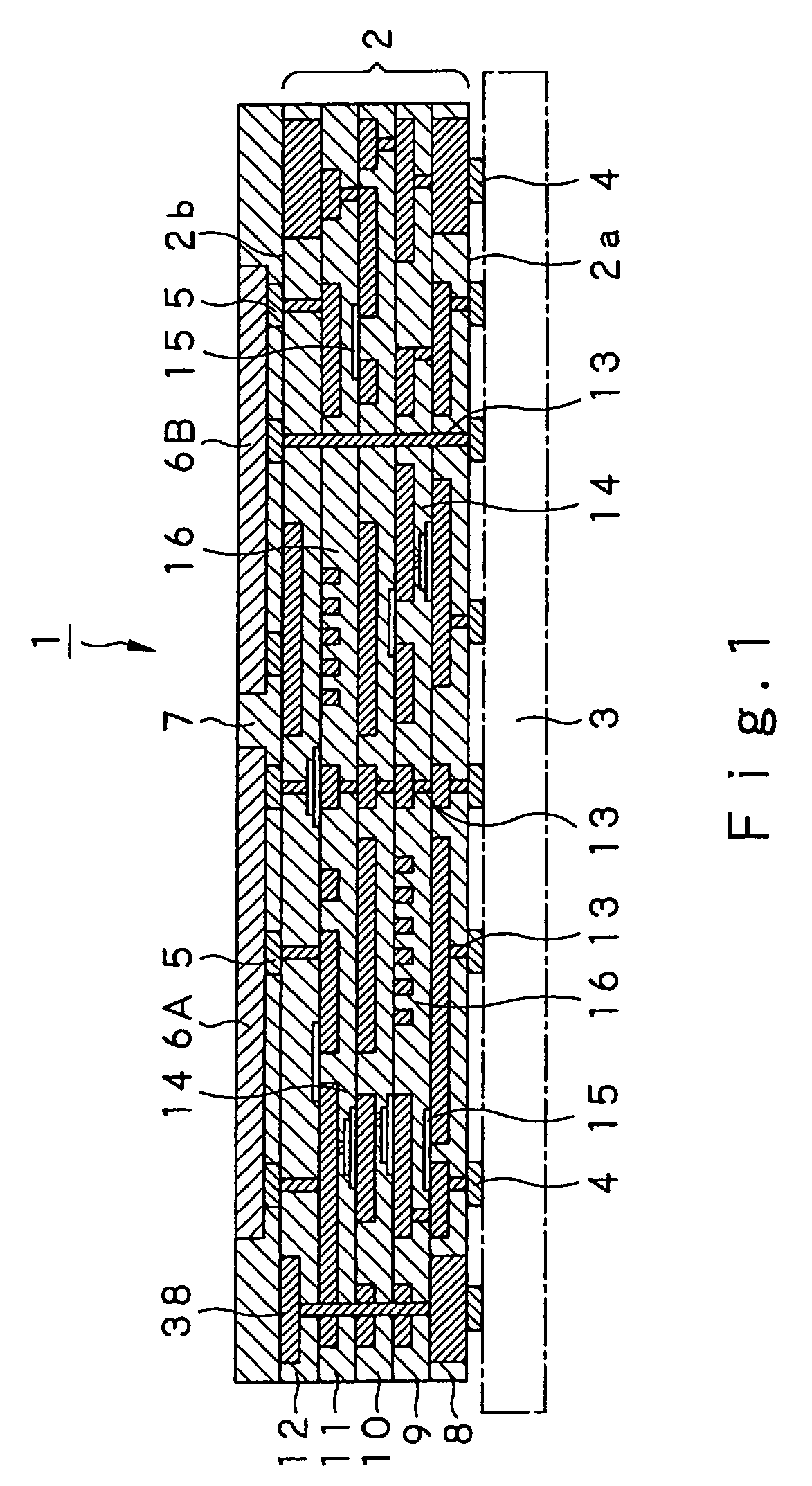

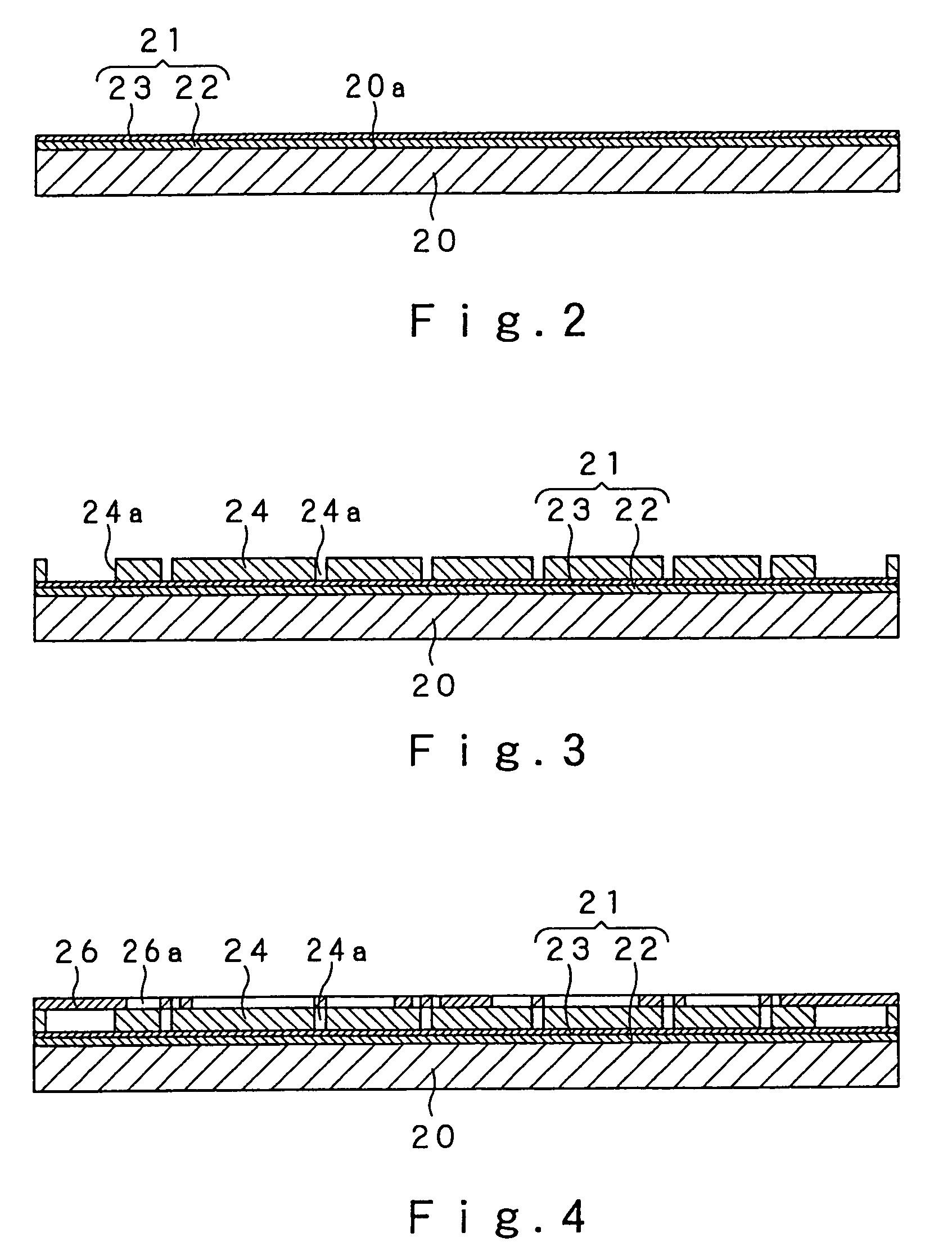

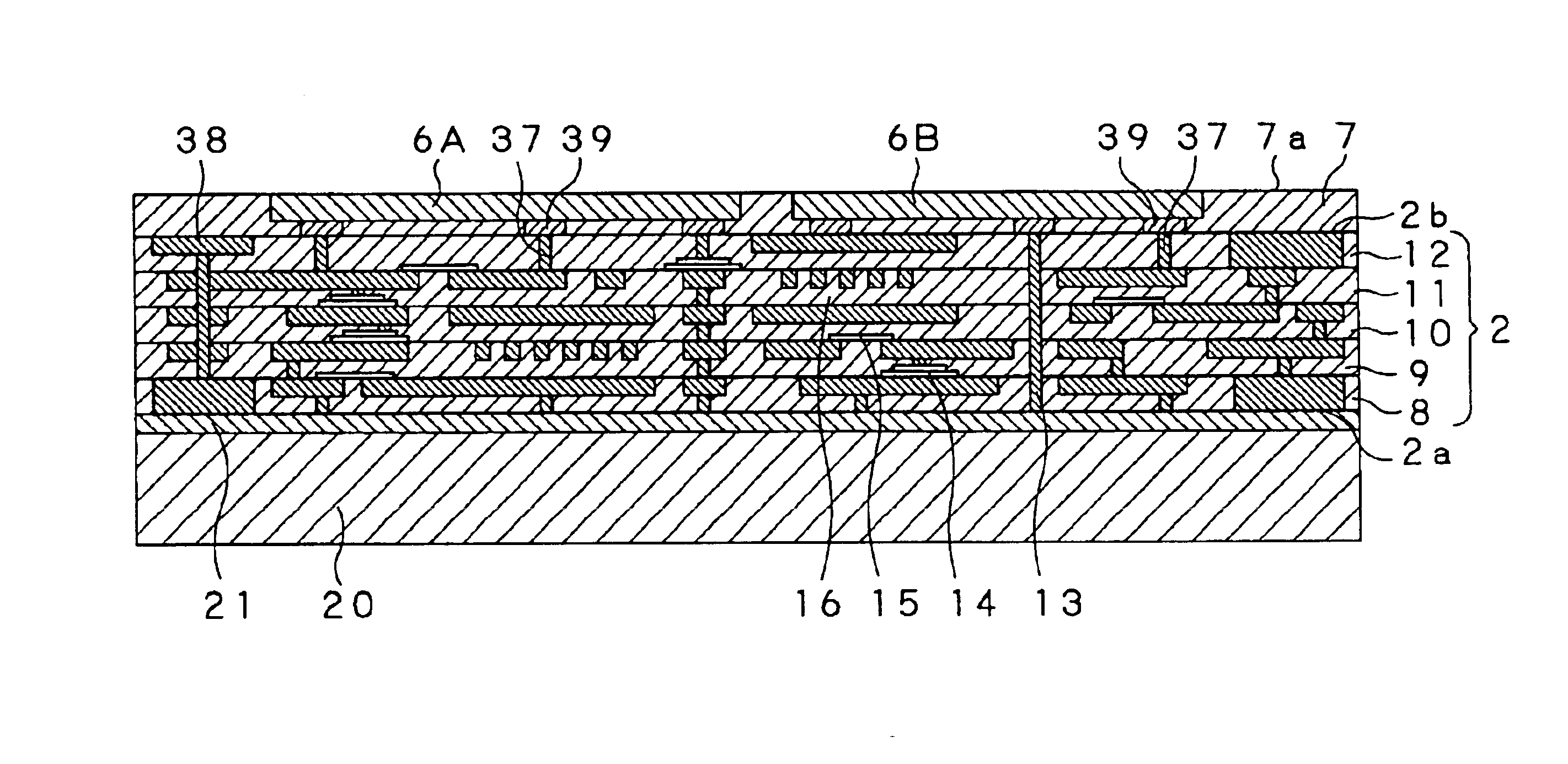

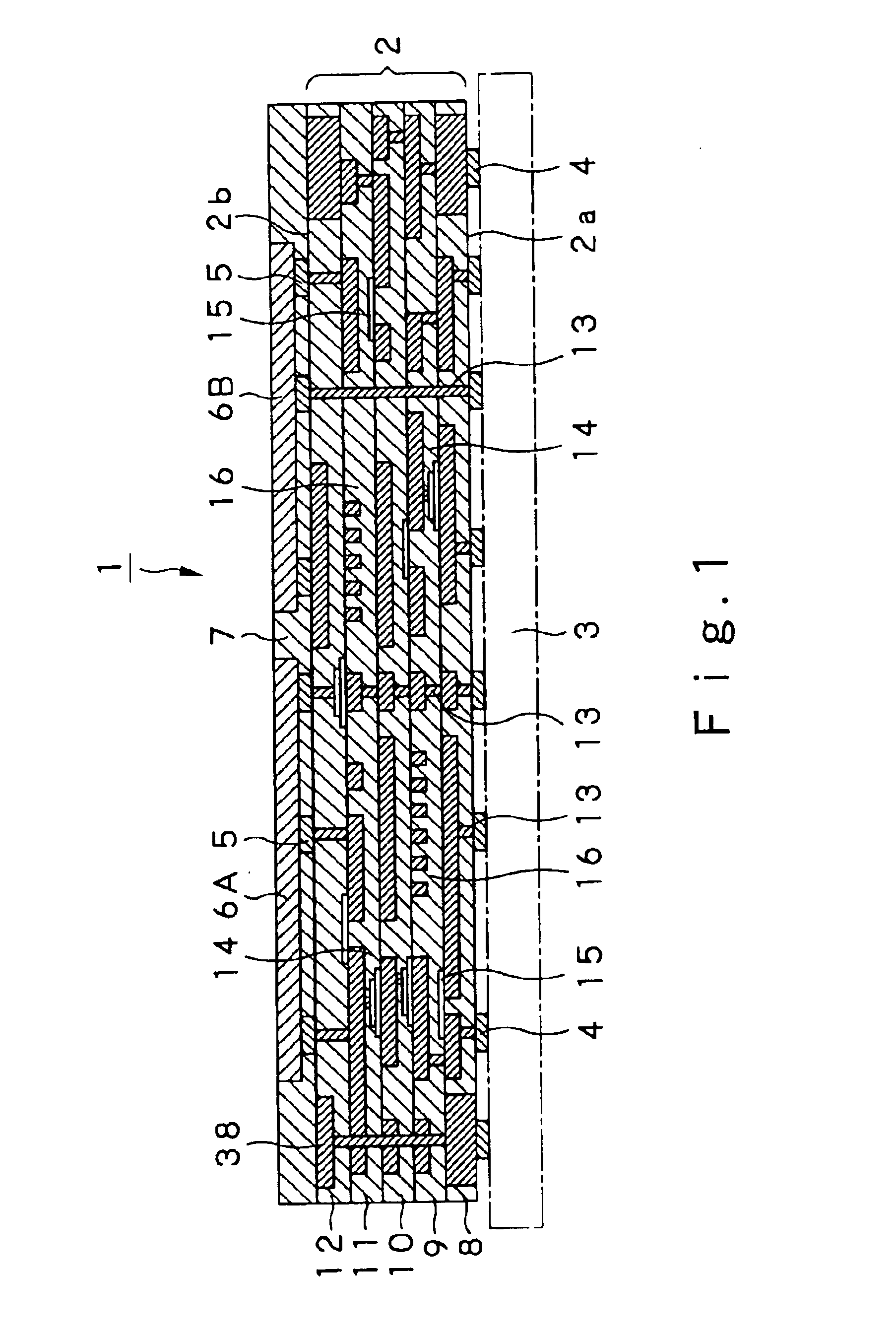

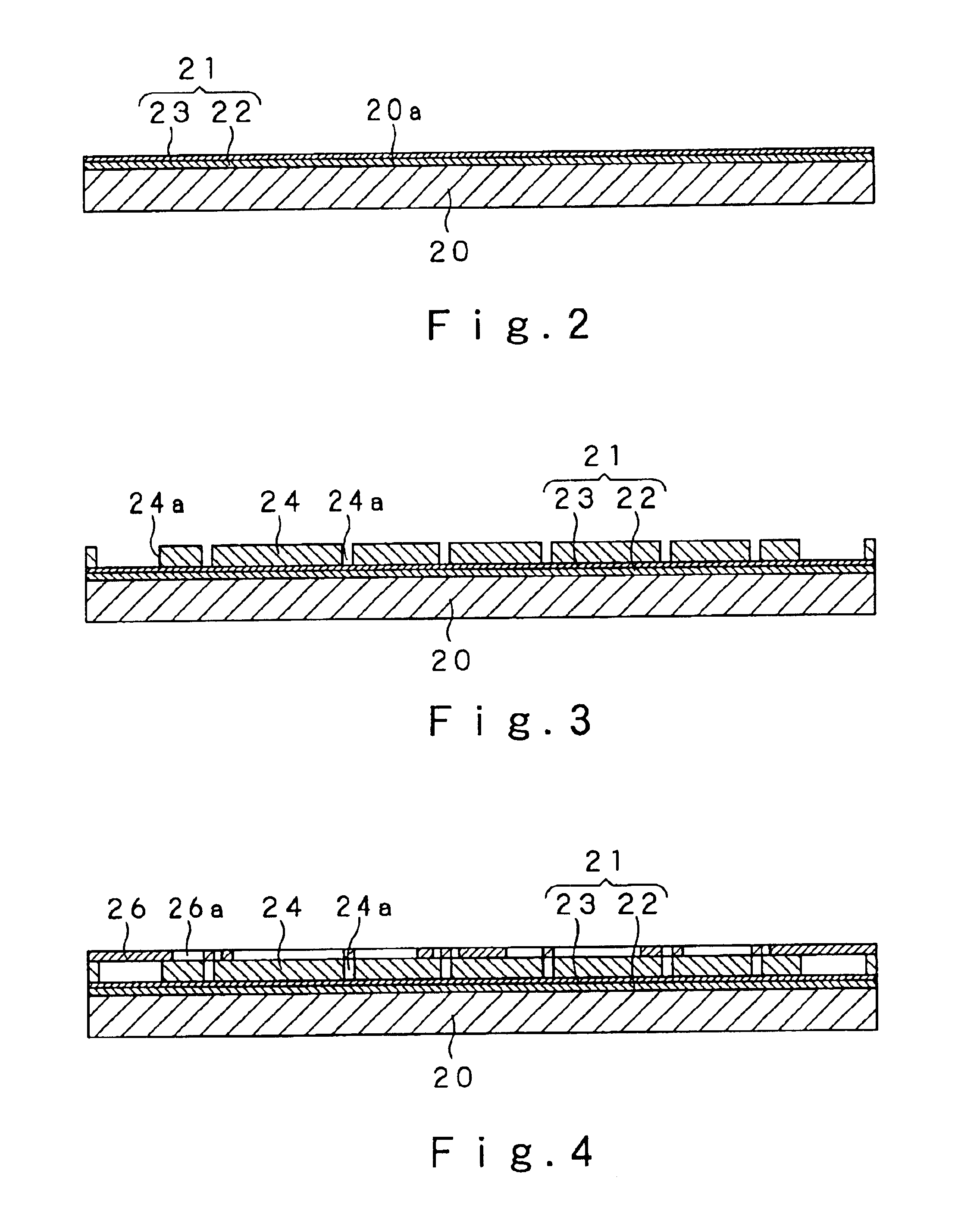

Multi-chip circuit module and method for producing the same

InactiveUS7193311B2Overcome problemsHigh densitySemiconductor/solid-state device detailsSolid-state devicesInter layerSemiconductor chip

A multi-chip circuit module on which semiconductor chips are loaded and which is provided with circuit patterns, input / output terminals or the like for interconnecting the semiconductor chips. A multi-layered wiring section (2) is formed by respective unit wiring layers (8) to (12) in such a manner that an upper unit wiring layer is layered on a surface-planarized subjacent unit wiring layer and connected to one another by inter-layer connection by a via-on-via structure. A semiconductor chip (6) mounted on this multi-layer wiring section (2) is polished along with the sealing resin layer (7) for reducing the thickness.

Owner:SONY CORP

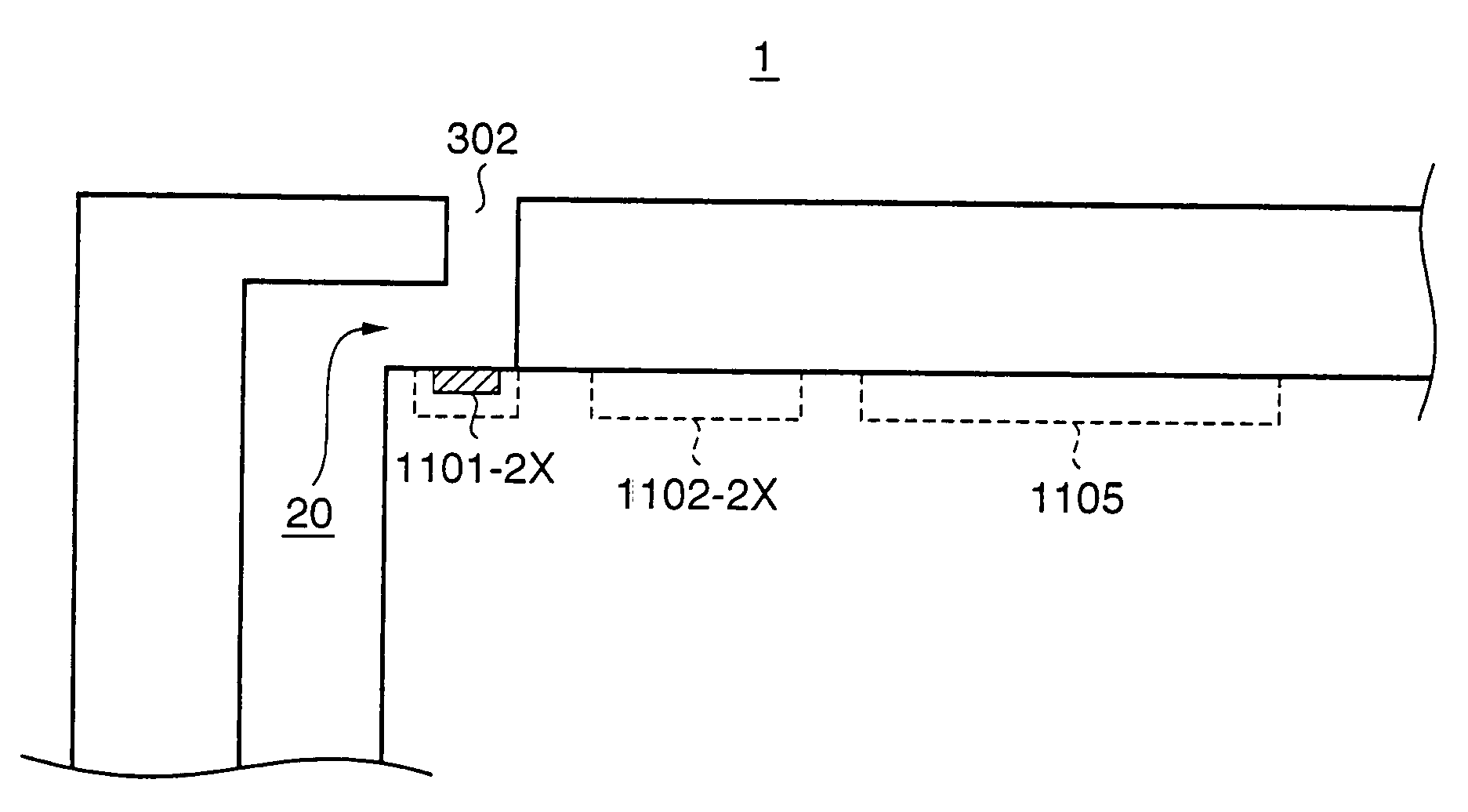

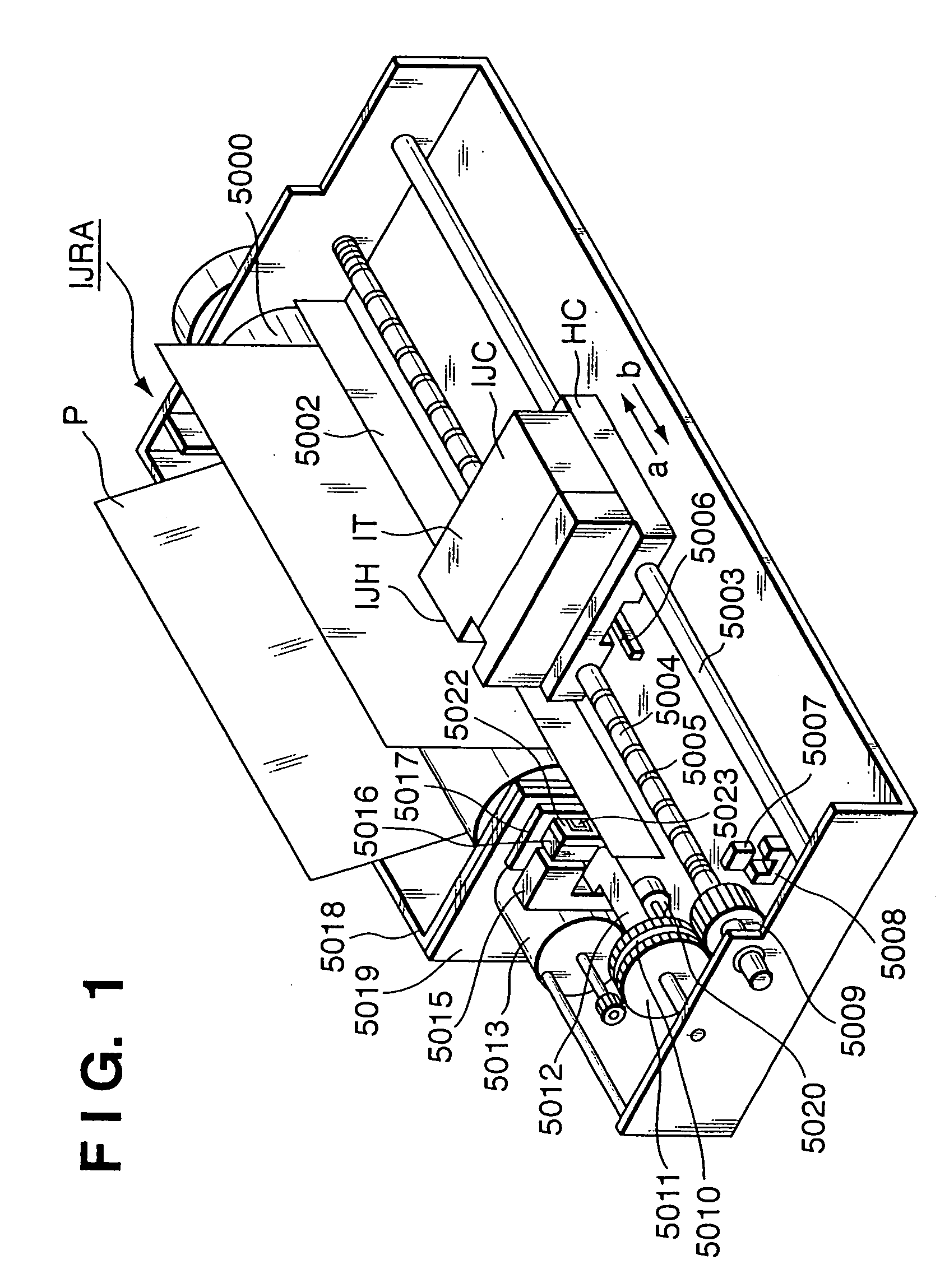

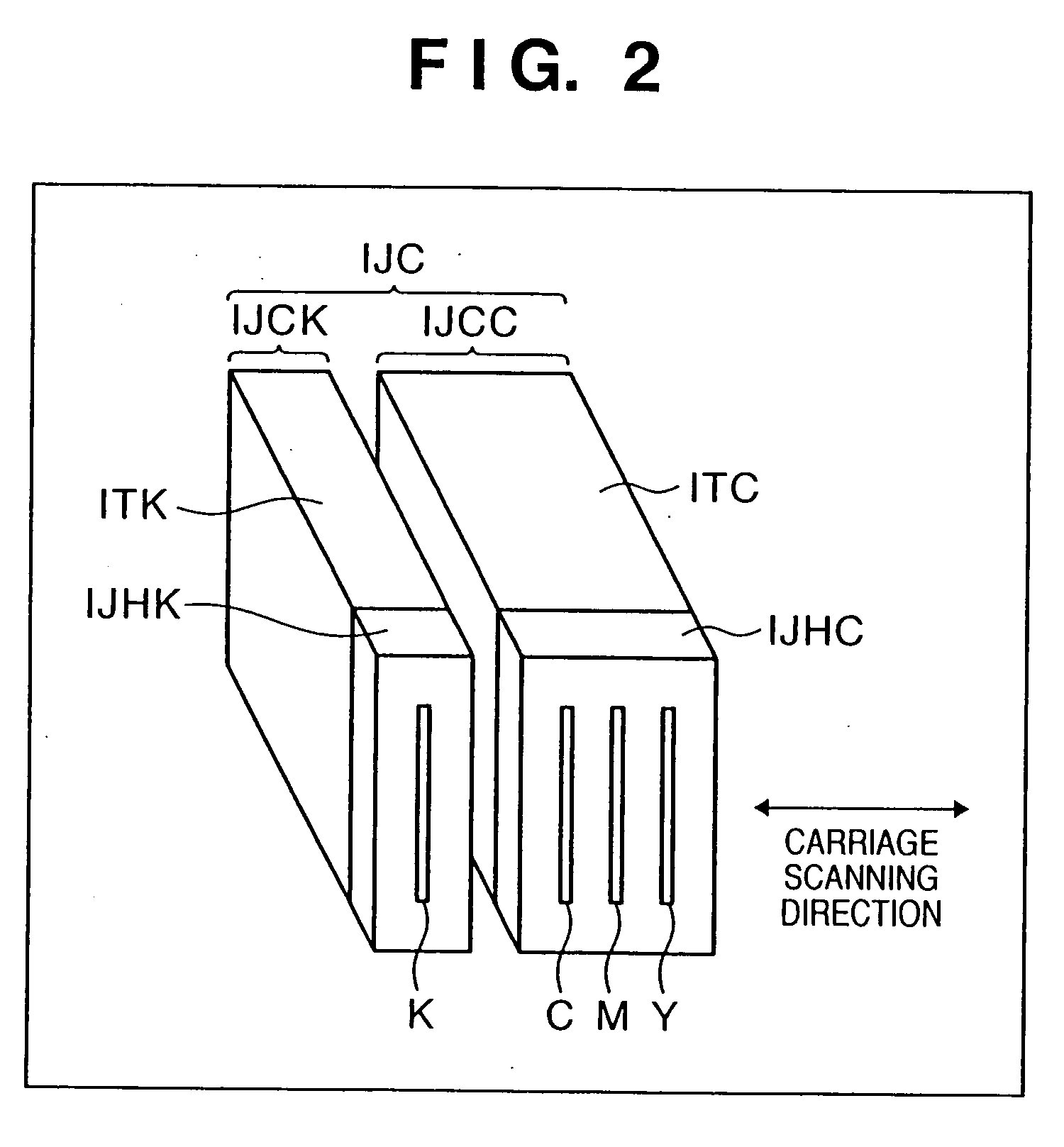

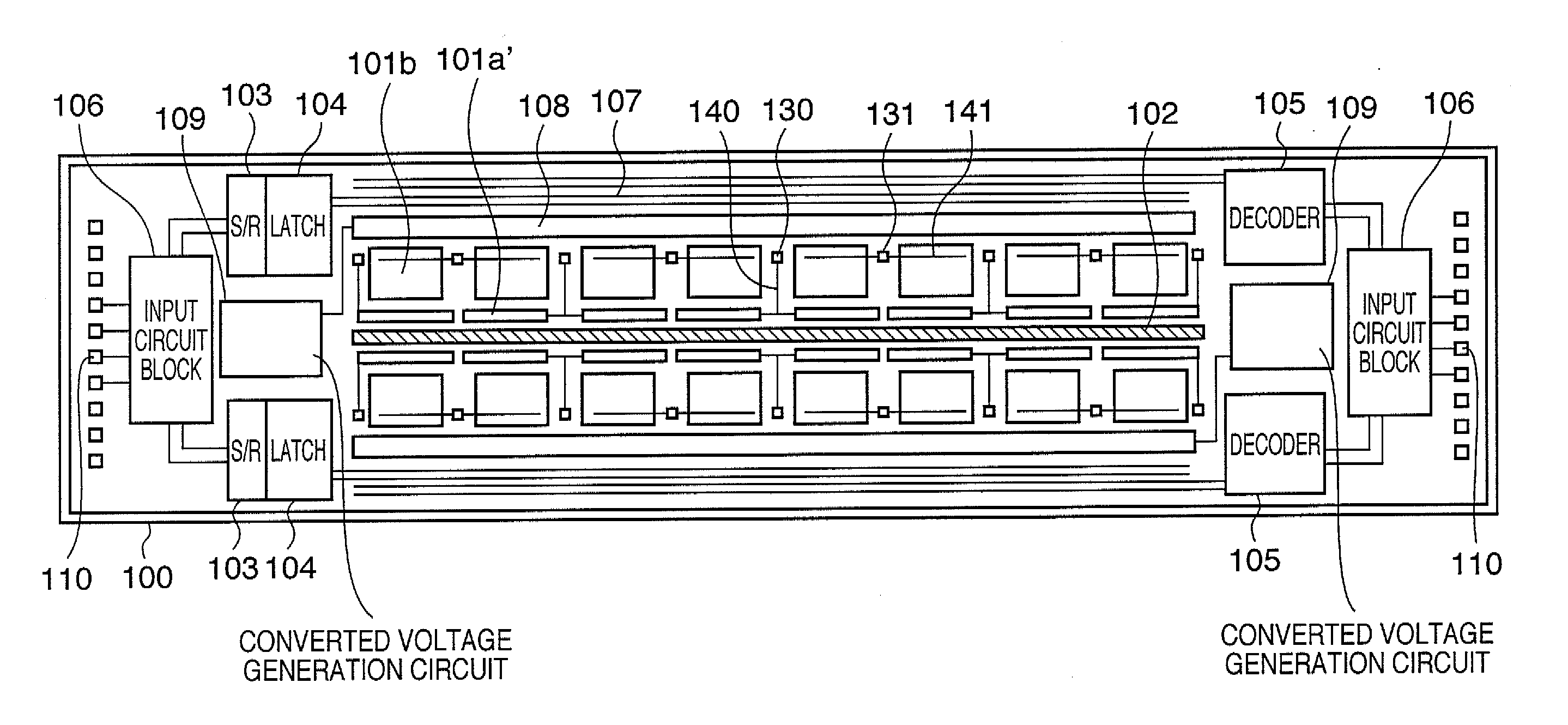

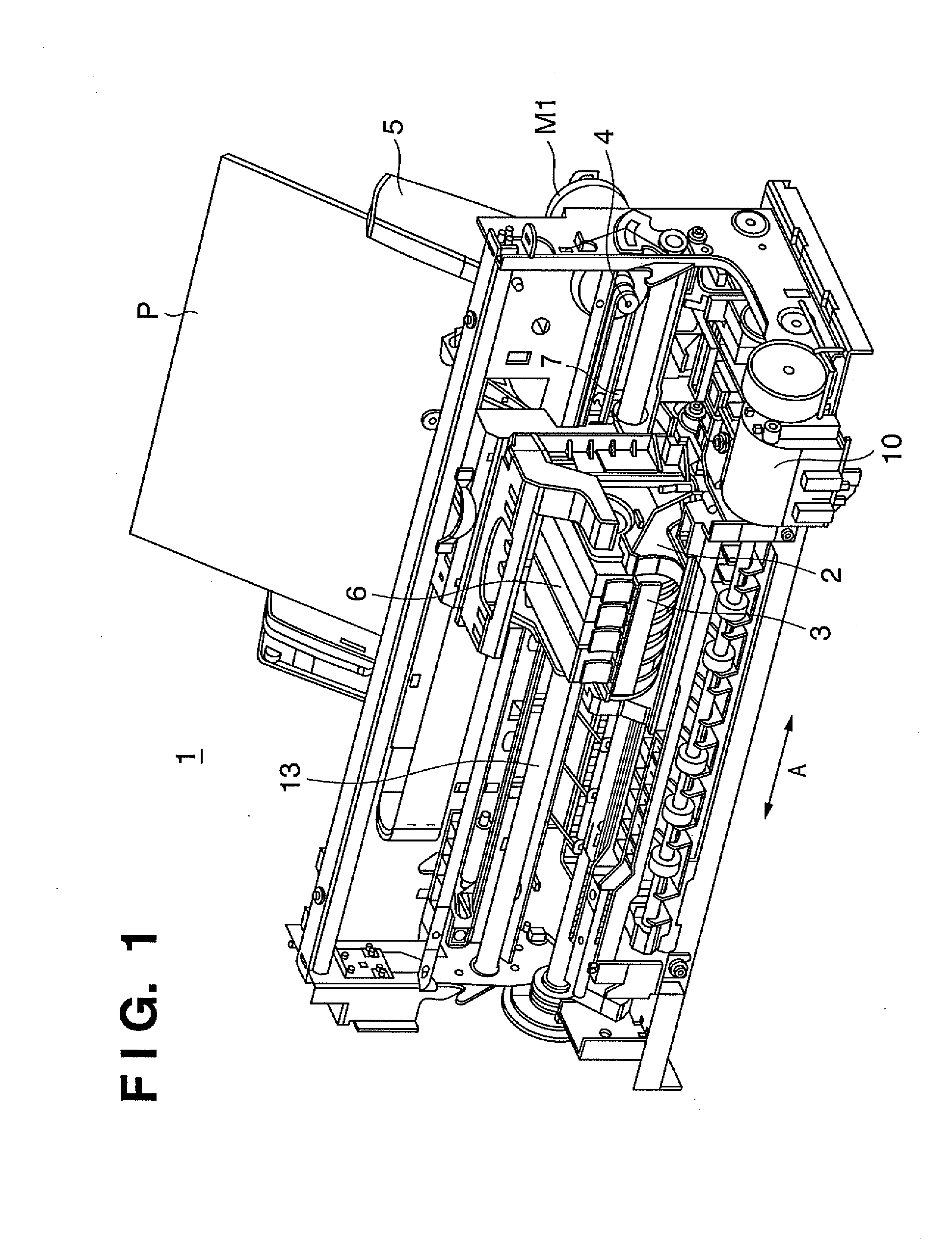

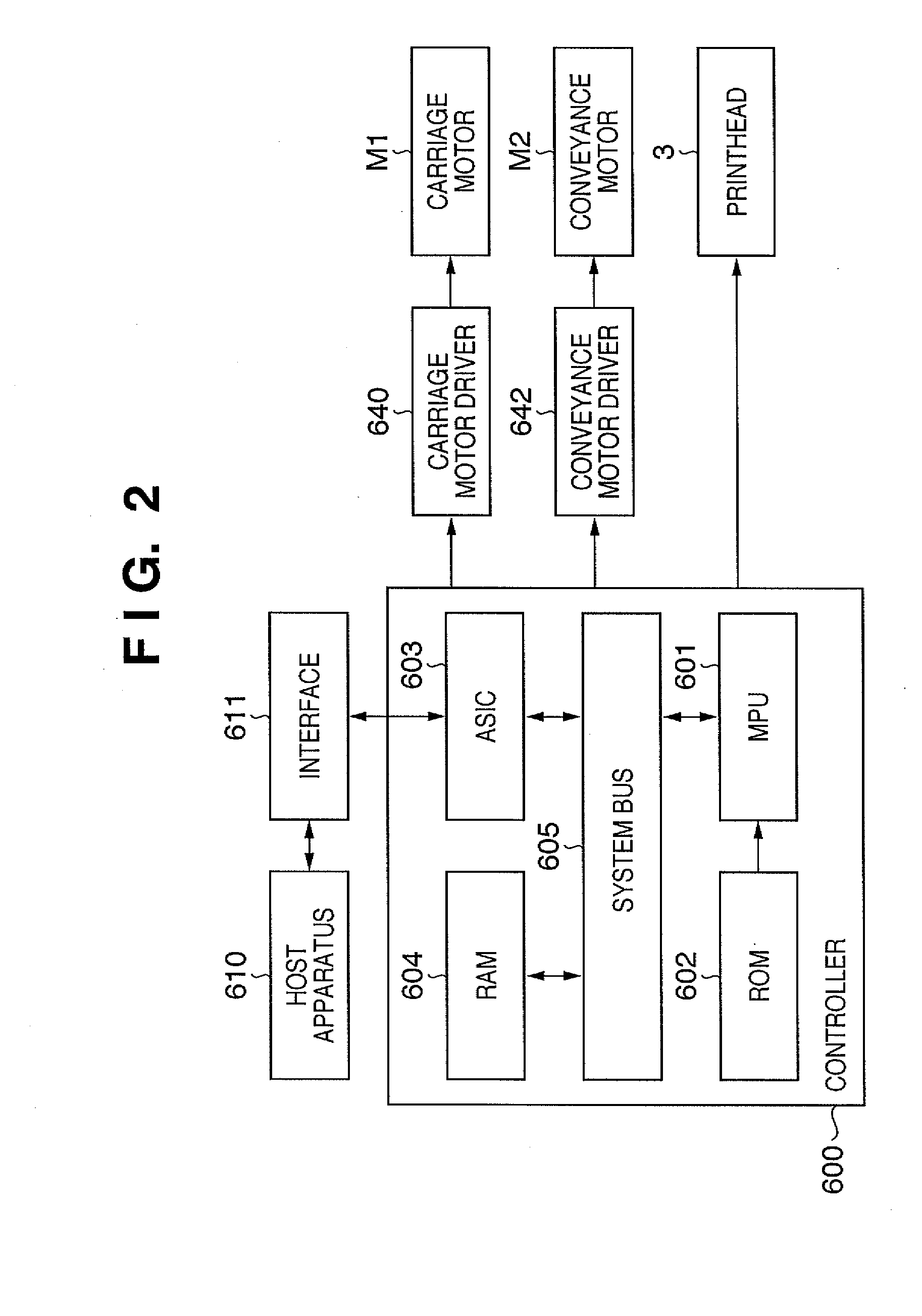

Printhead substrate, printhead, head cartridge, and printing apparatus

An object of this invention is to provide a driving circuit layout which suppresses an increase in the area of a head substrate in an inkjet printhead adopting a constant electric current driving method. To achieve this object, a plurality of printing elements and a plurality of switching elements which are very large in number are arrayed in the longitudinal direction of a head substrate. A terminal which receives a driving signal and a control signal that are used to drive the plurality of printing elements is arranged at the end of the board in the widthwise direction of the board. A electric current source for supplying a predetermined electric current is interposed in an area between these two areas.

Owner:CANON KK

Method for producing a multi-chip circuit module including a multi-layered wiring section utilizing a via-on-via structure

InactiveUS6919226B2Problem can be overcomeOvercome problemsSemiconductor/solid-state device detailsSolid-state devicesEngineeringInput/output

A multi-chip circuit module on which semiconductor chips are loaded and which is provided with circuit patterns, input / output terminals or the like for interconnecting the semiconductor chips. A multi-layered wiring section (2) is formed by respective unit wiring layers (8) to (12) in such a manner that an upper unit wiring layer is layered on a surface-planarized subjacent unit wiring layer and connected to one another by inter-layer connection by a via-on-via structure. A semiconductor chip (6) mounted on this multi-layer wiring section (2) is polished along with the sealing resin layer (7) for reducing the thickness.

Owner:SONY CORP

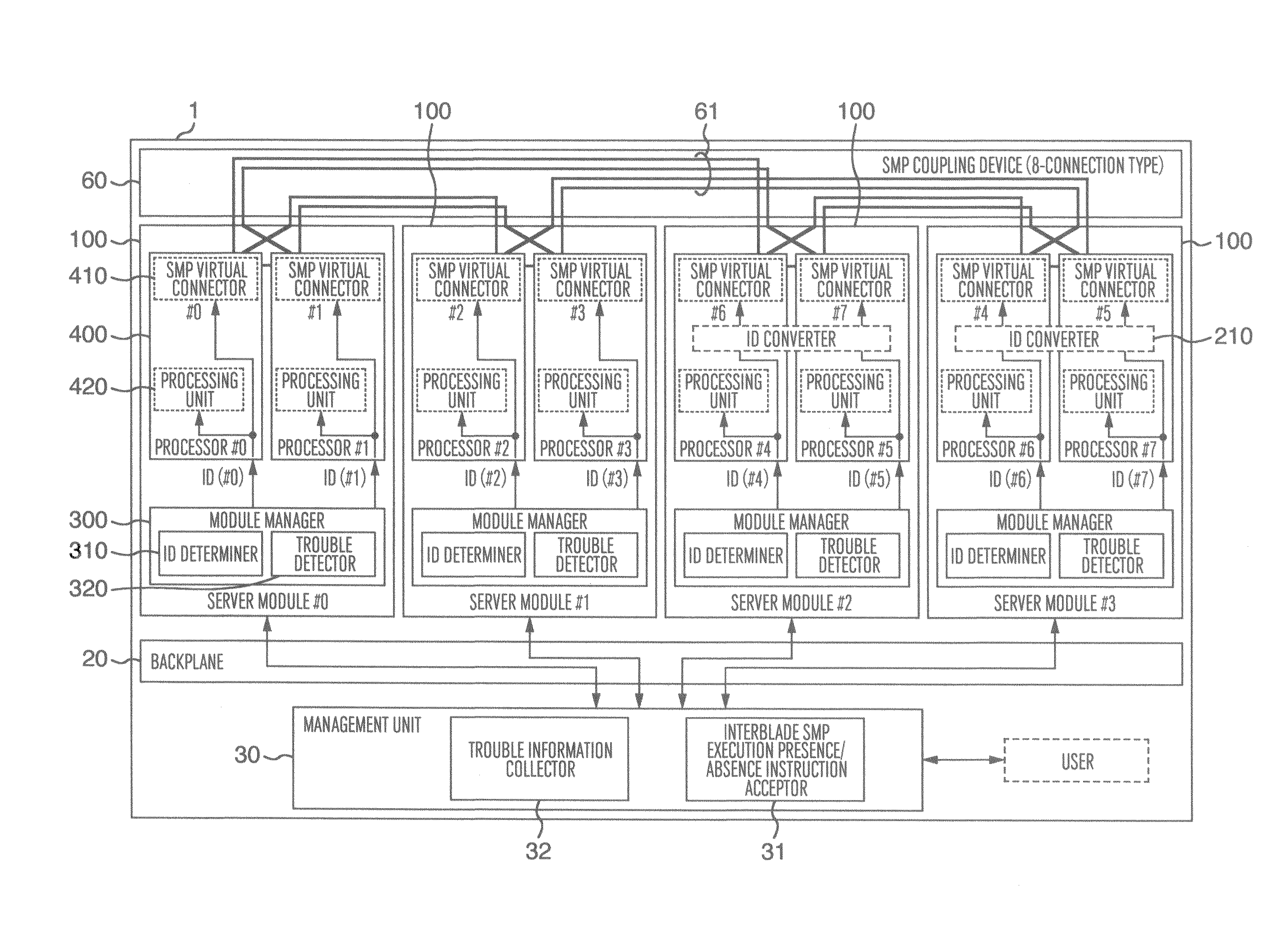

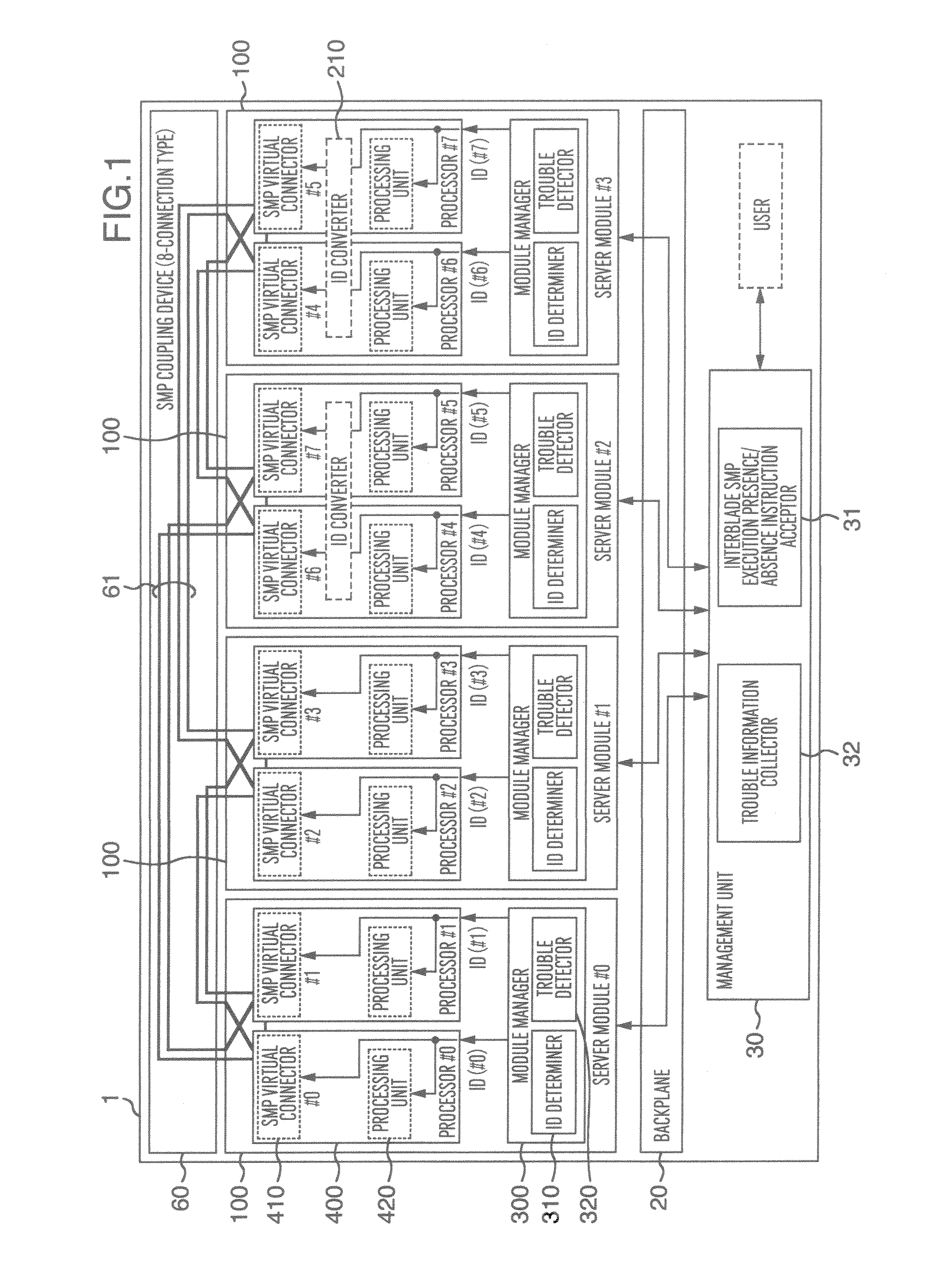

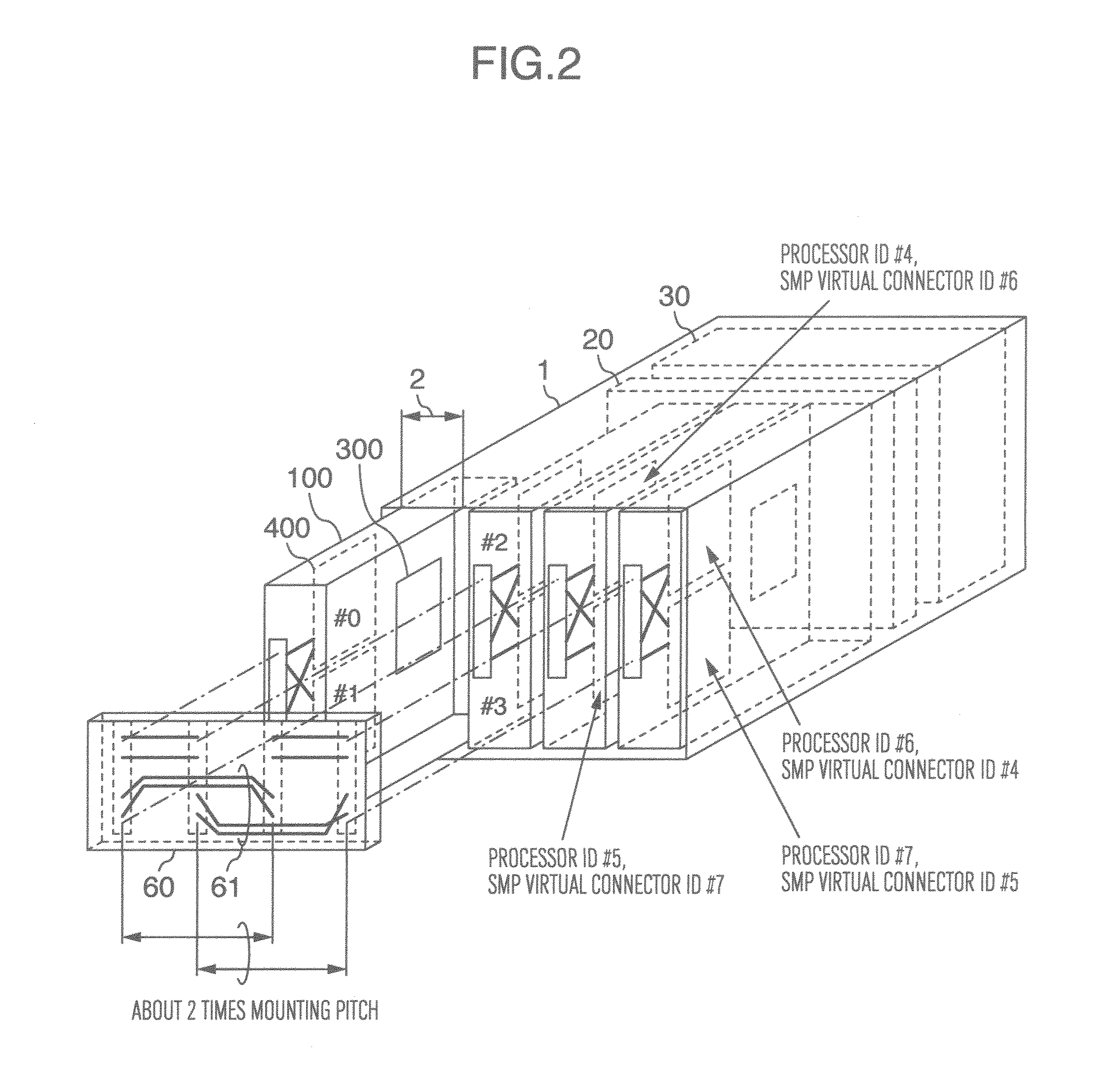

Blade server apparatus

ActiveUS8745275B2Shorten the line lengthImprove signal transmission qualityGeneral purpose stored program computerInput/output processes for data processingMain processing unitBlade server

A blade server apparatus including a plurality of server modules, a backplane for mounting the plurality of server modules thereon, and an SMP coupling device having wiring lines to SMP couple the plurality of server modules. Each of the server modules has one or more processors controlled by firmware and a module manager for managing its own server module, the module manager has an ID determiner for informing each processor of a processor ID, each processor has a processing unit and an SMP virtual connecting unit for instructing ones of wiring lines of the SMP coupling device through which a packet received from the processing unit is to be transmitted, and an ID converter for converting the processor ID and informing it to the SMP virtual connecting unit is provided within the firmware.

Owner:HITACHI LTD

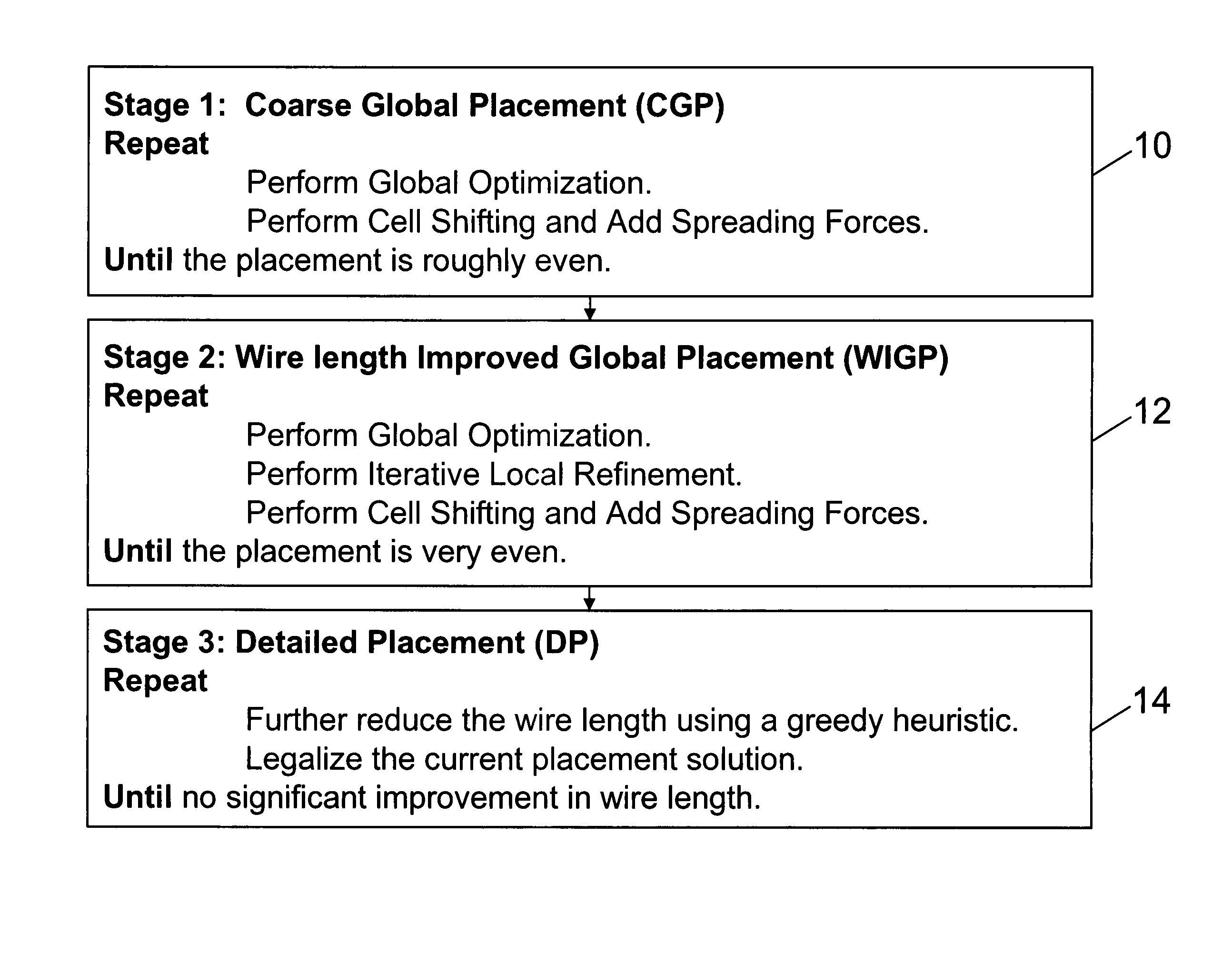

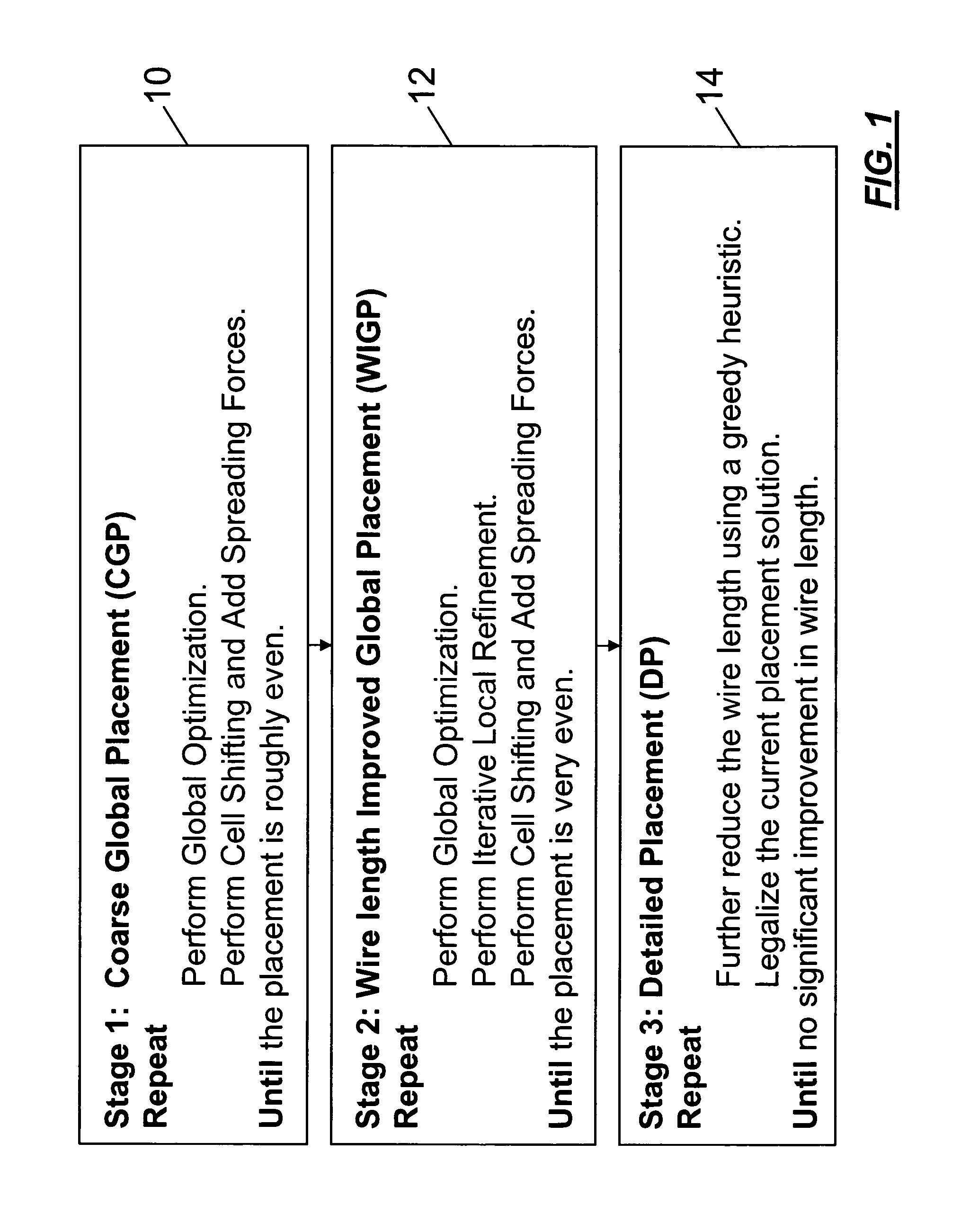

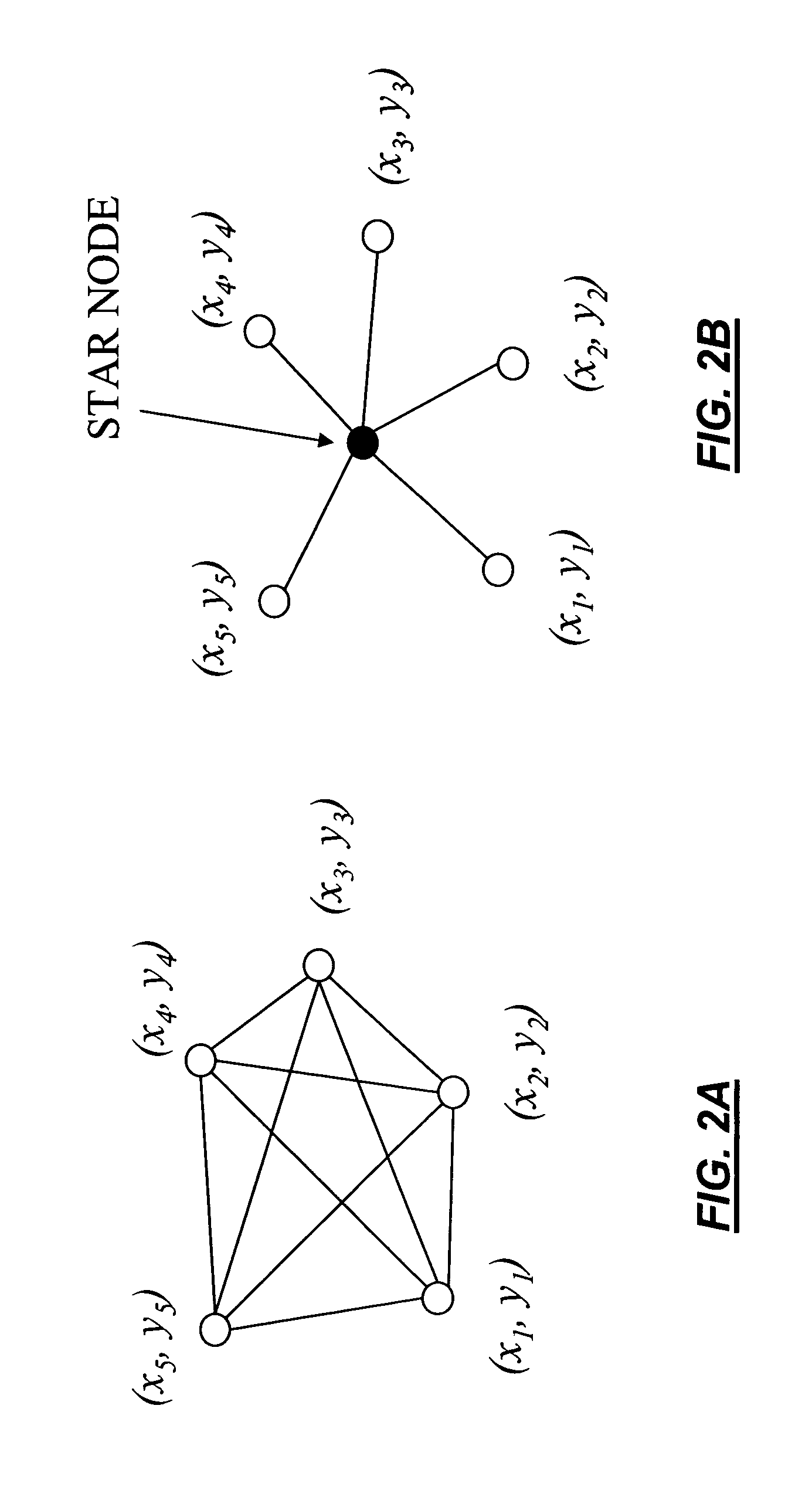

Fastplace method for integrated circuit design

InactiveUS7266796B1Fast and iterative and flat placement methodEliminates cellComputer aided designSoftware simulation/interpretation/emulationEngineeringObject function

A method for efficient analytical placement of standard cell designs includes obtaining a placement of cells using a wirelength objective function, modifying the placement of cells by cell shifting to redistribute cells to thereby reduce cell overlap, and refining the placement of cells to thereby reduce wirelength using a half-perimeter bounding rectangle-measure. Preferably the wirelength the wirelength objective function is a quadratic objective function which is solved using a hybrid net model. The hybrid net model preferably uses a clique model for two-pin and three-pin nets and a star model for nets having at least four pins. The use of the hybrid net model reduces a number of non-zero entries in a connectivity matrix.

Owner:IOWA STATE UNIV RES FOUND

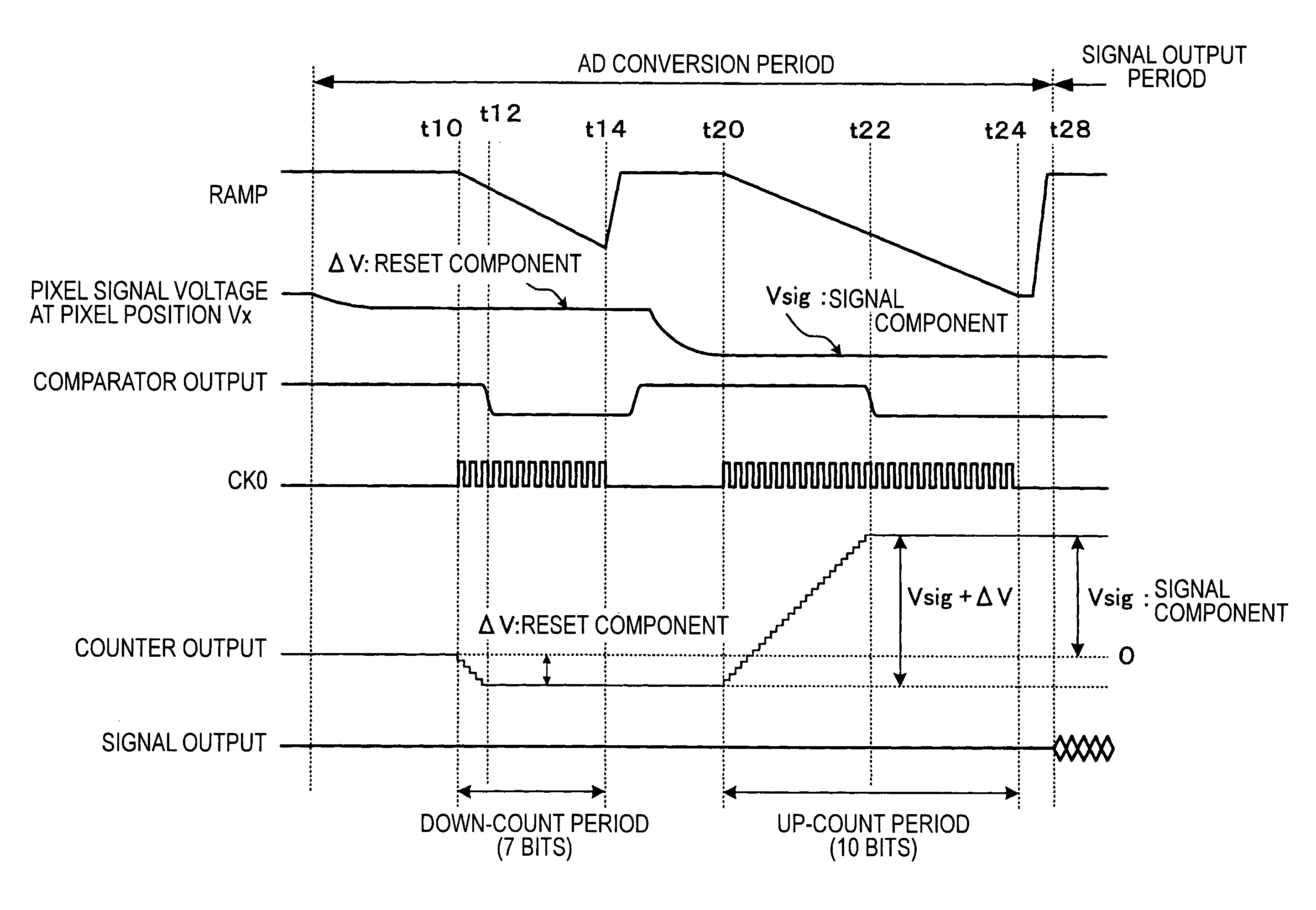

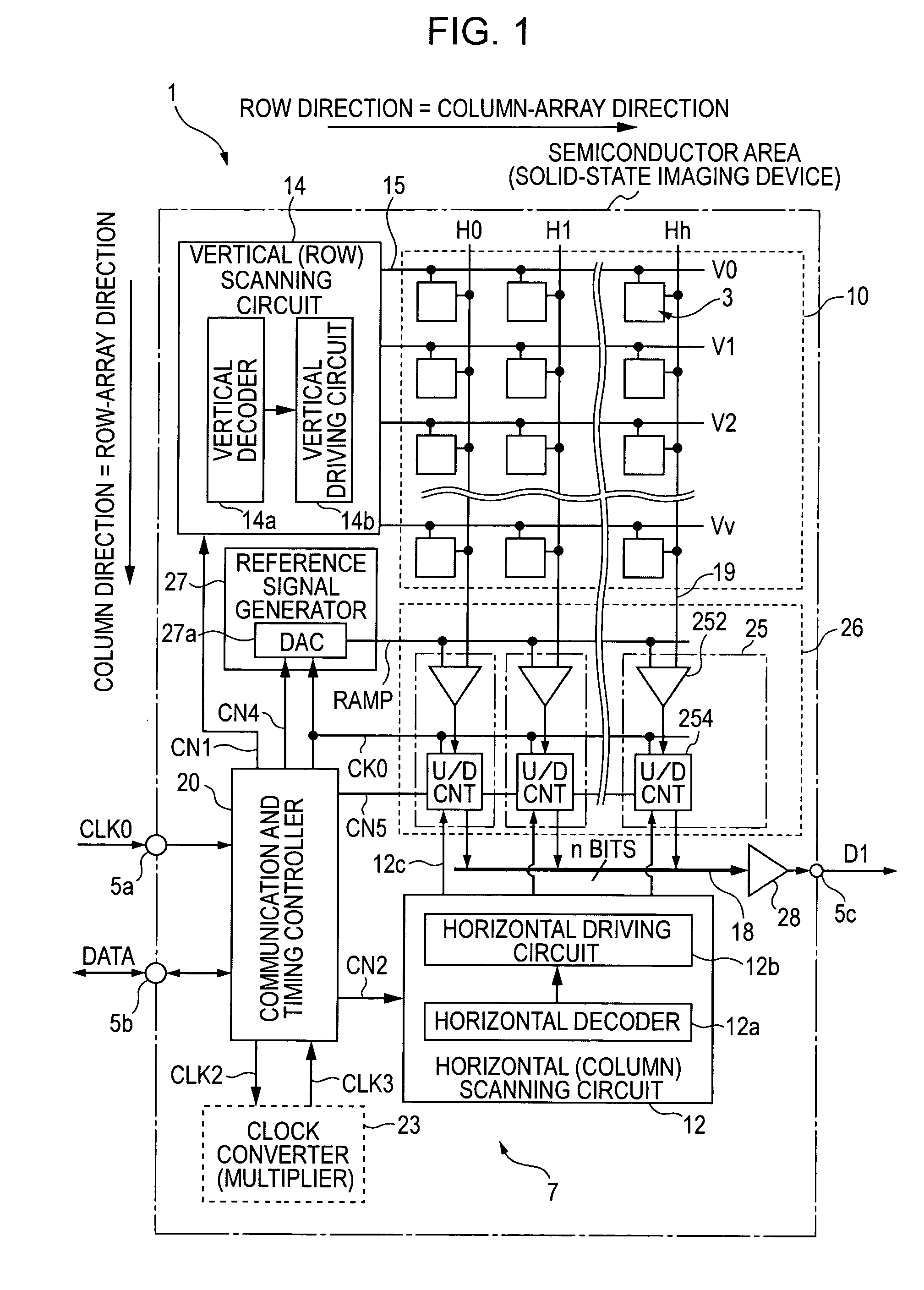

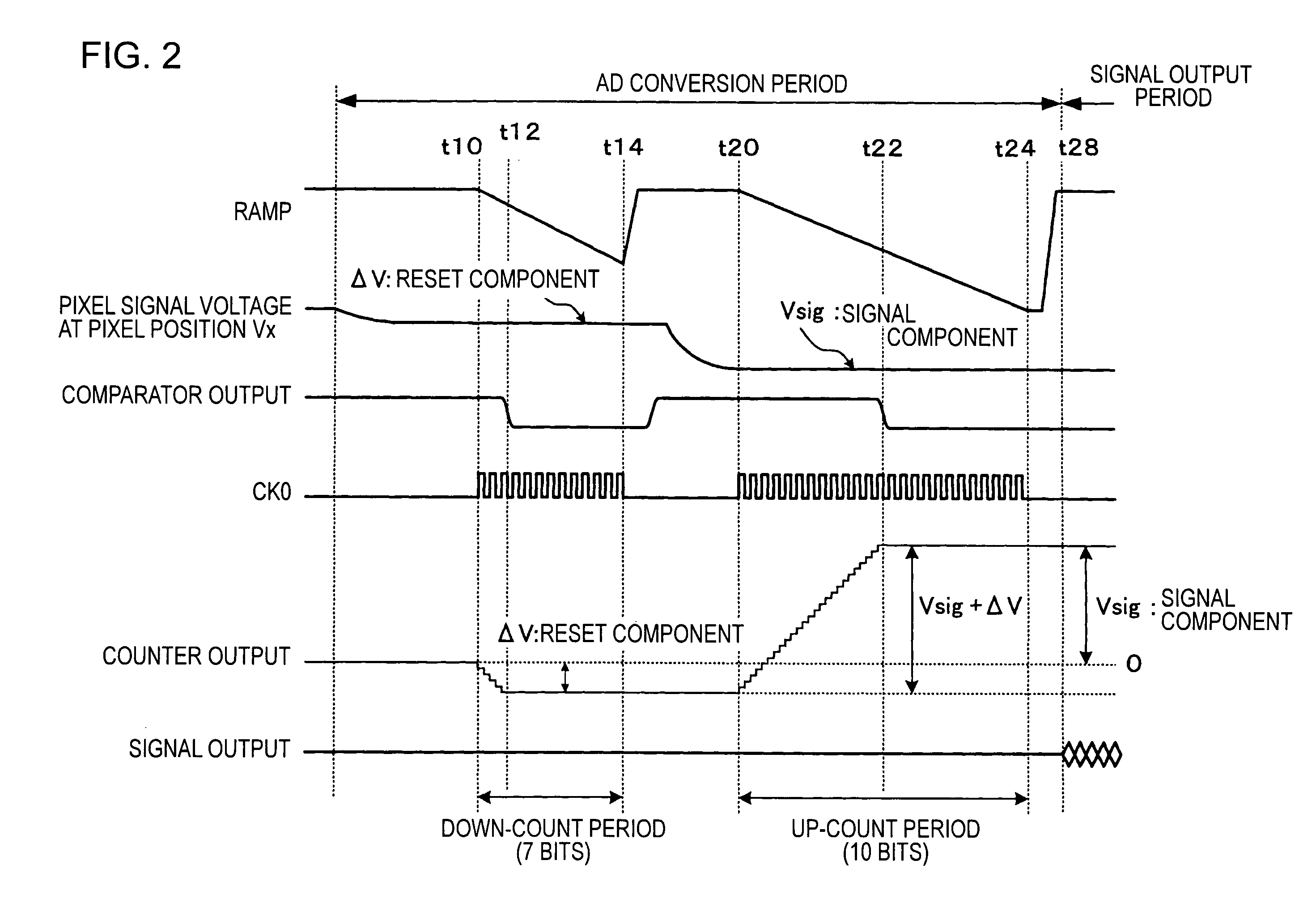

Analog-to-digital conversion method, analog-to-digital converter, semiconductor device for detecting distribution of physical quantity, and electronic apparatus

ActiveUS20060097902A1Increase currentImprove noiseTelevision system detailsElectric signal transmission systemsDigital dataA d converter

In an analog-to-digital conversion method for converting a difference signal component representing a difference between a reference component and a signal component in an analog signal to be processed into digital data, in a first process, a signal corresponding to one of the reference component and the signal component is compared with a reference signal for conversion into the digital data. Concurrently with the comparison, counting is performed in one of a down-count mode and an up-count mode, and a count value at a time of completion of the comparison is held. In a second process, a signal corresponding to the other one of the reference component and the signal component is compared with the reference signal. Concurrently with the comparison, counting is performed in the other one of the down-count mode and the up-count mode, and a count value at a time of completion of the comparison is held.

Owner:SONY CORP

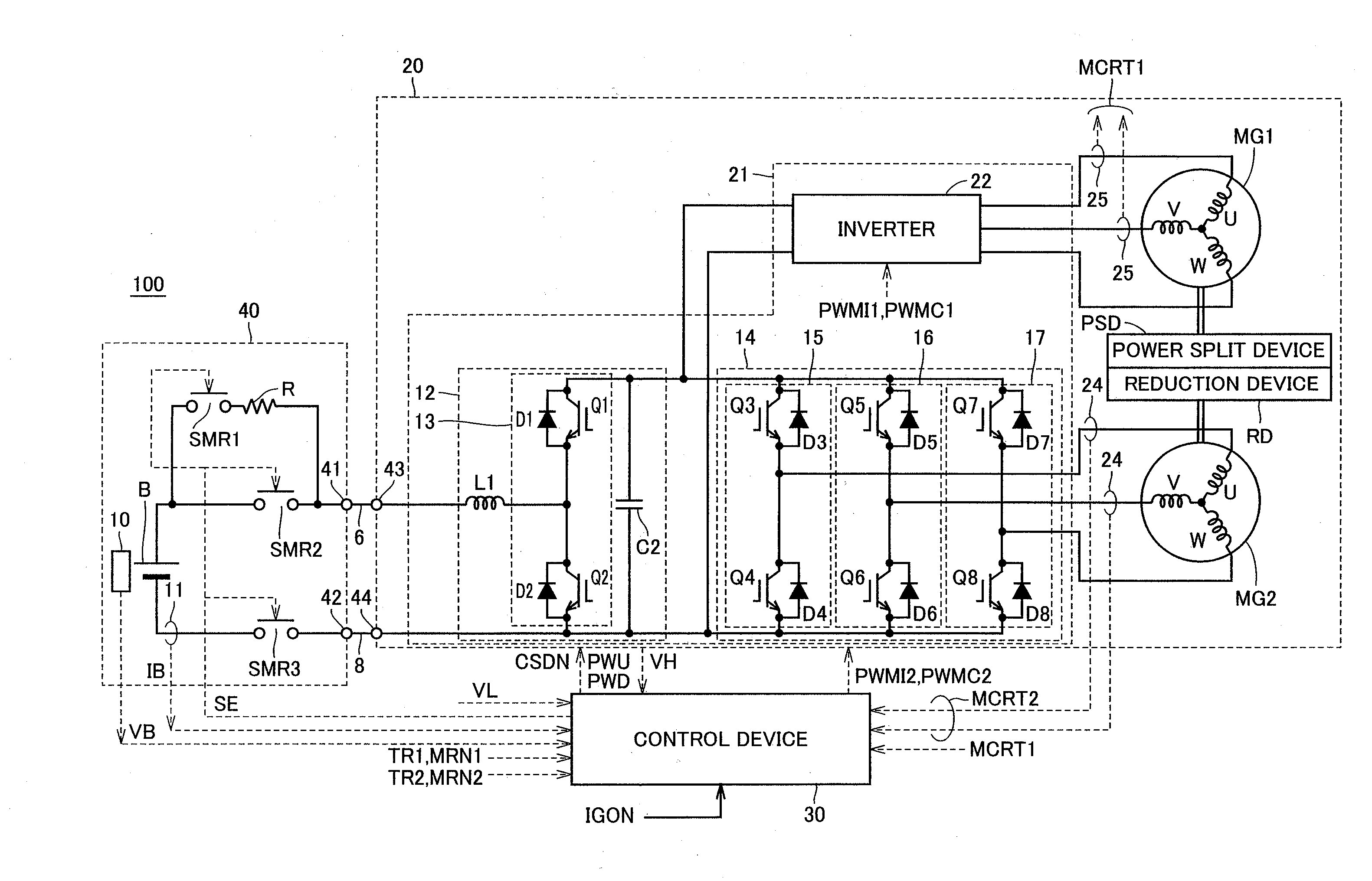

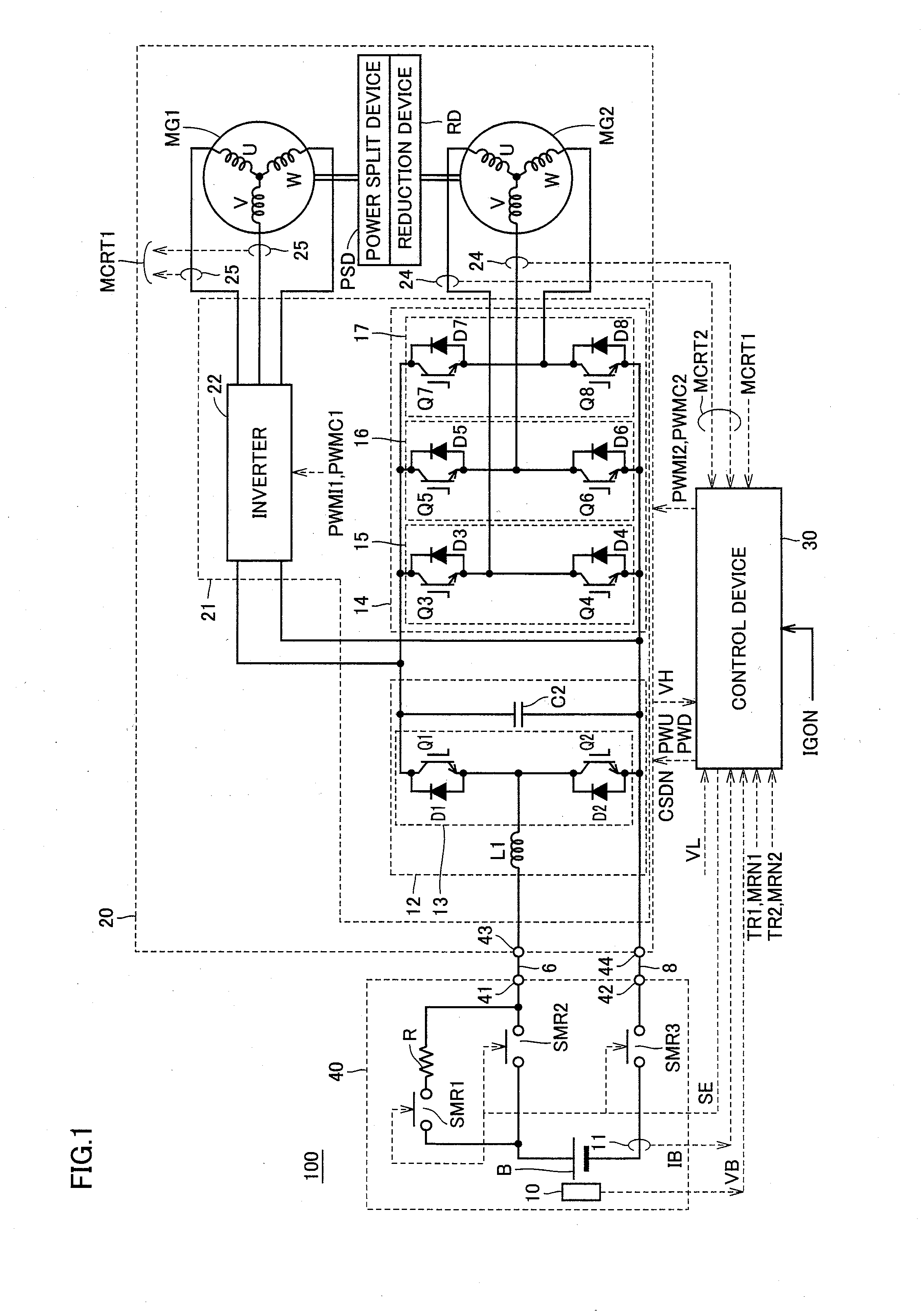

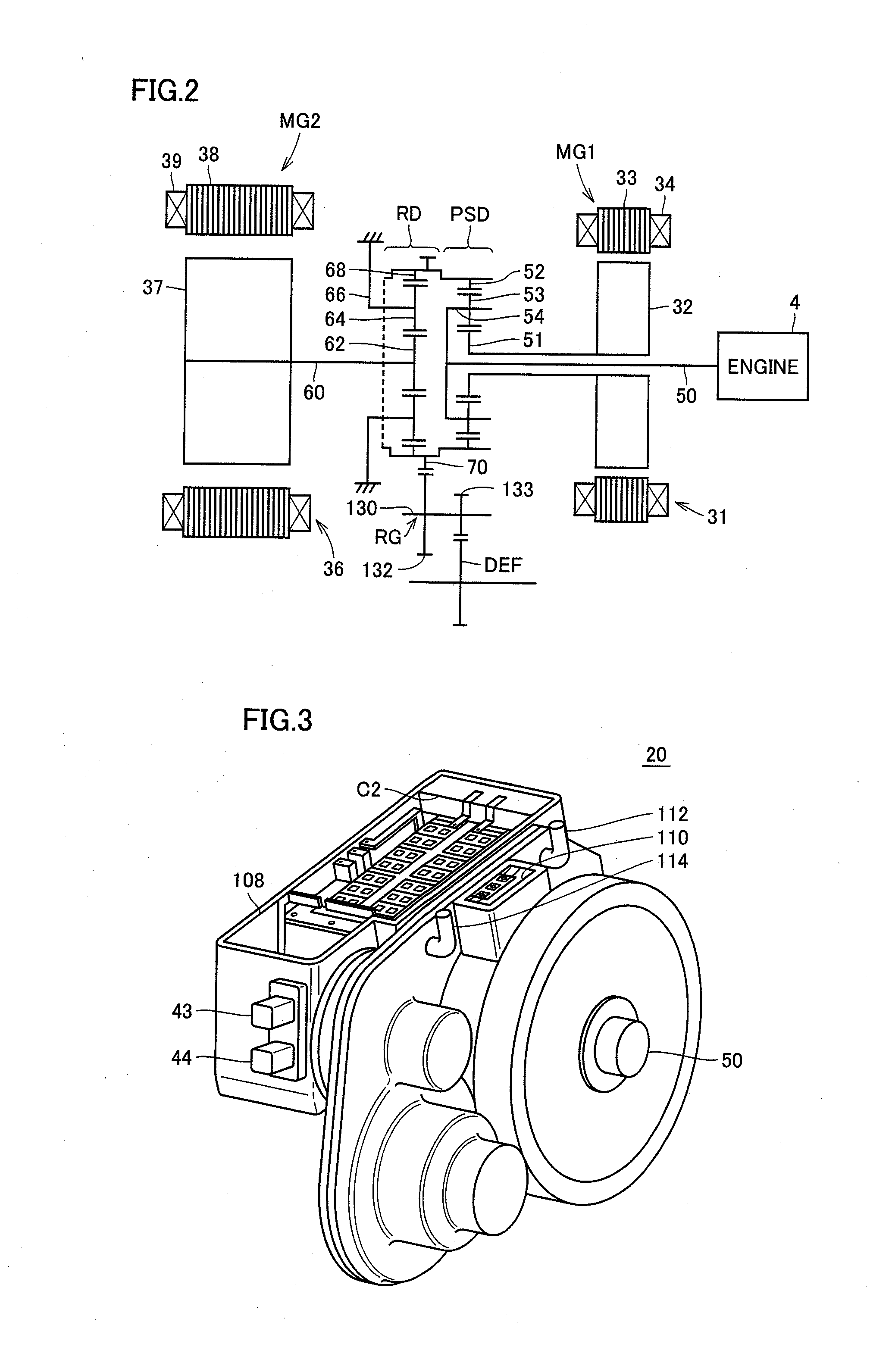

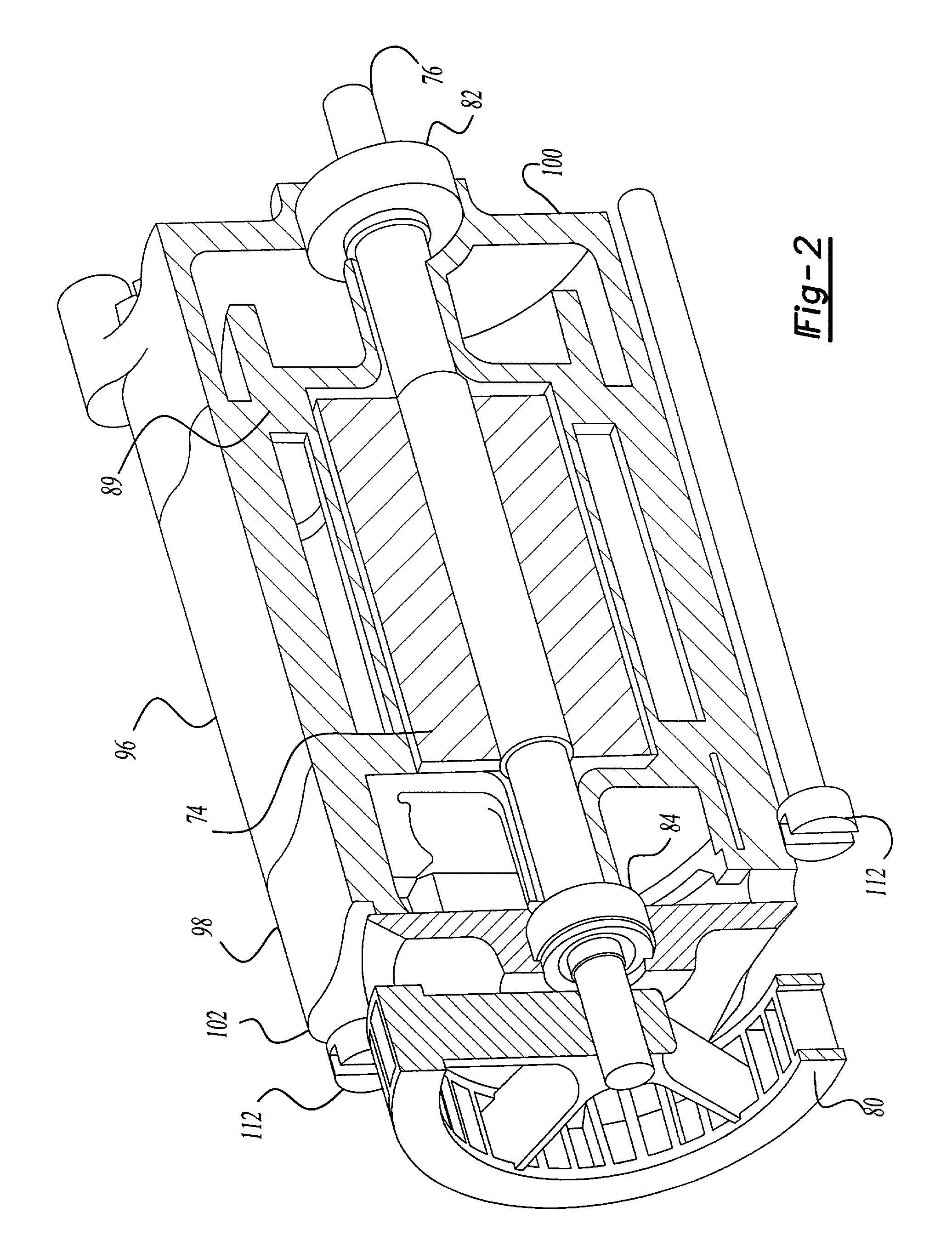

Vehicle drive device

InactiveUS20100072865A1Reduce surge voltageShorten the line lengthHybrid vehiclesTransformers/inductances coolingVoltage converterConverters

A vehicle drive device includes a motor generator (MG2), a power control unit controlling the motor generator (MG2), and a case housing the motor generator (MG2) and the power control unit. The power control unit includes a first inverter driving the motor generator (MG2) and a voltage converter boosting a power supply voltage to apply the voltage to the first inverter. A reactor L1 which is a component of the voltage converter is disposed such that at least a portion of a core comes into contact with the case for heat exchange. Consequently, the heat is dissipated to the case having a large heat capacity for integral housing, to thereby allow the heat dissipation performance of the reactor (L1) arranged in the limited space to be ensured.

Owner:TOYOTA JIDOSHA KK

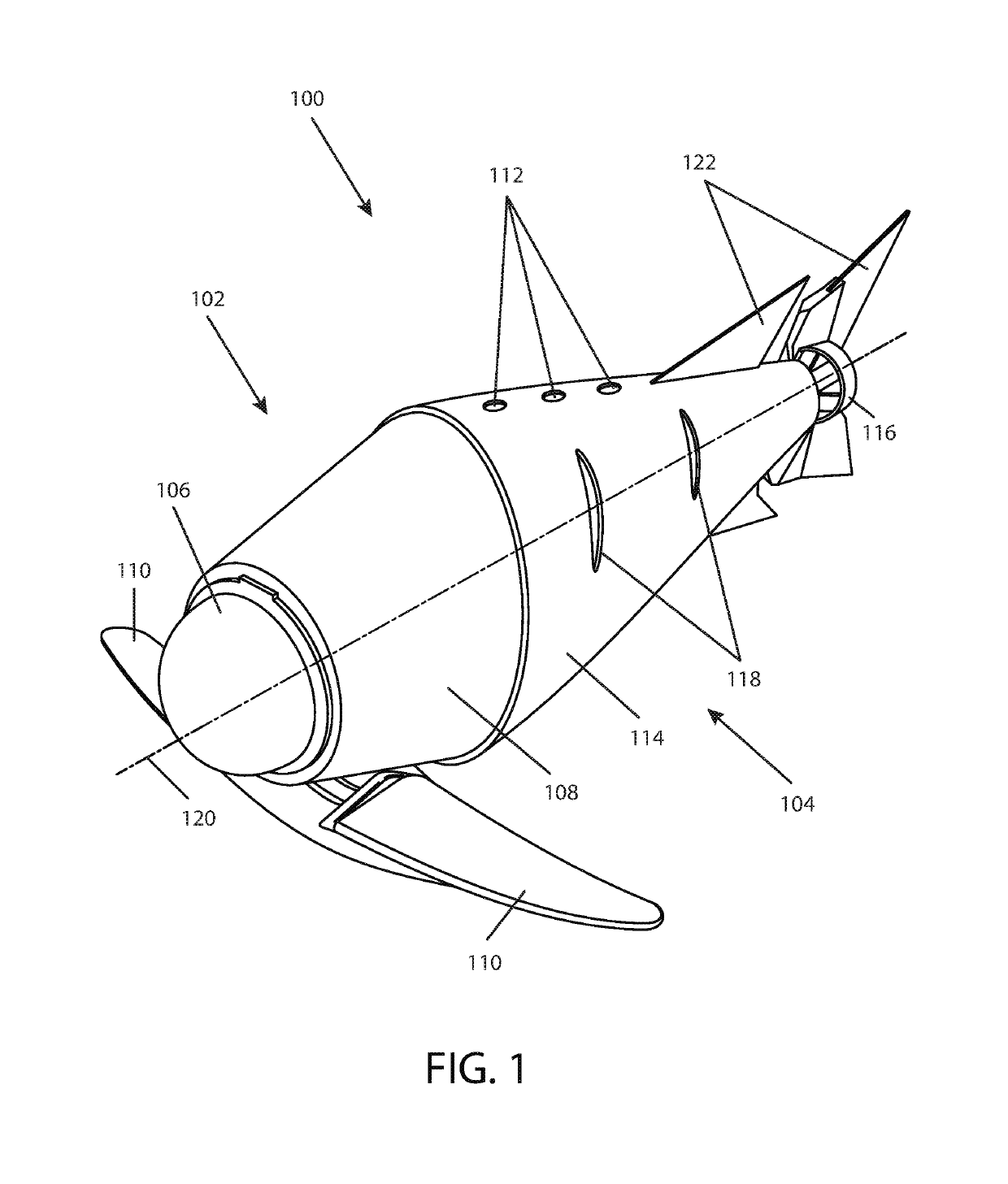

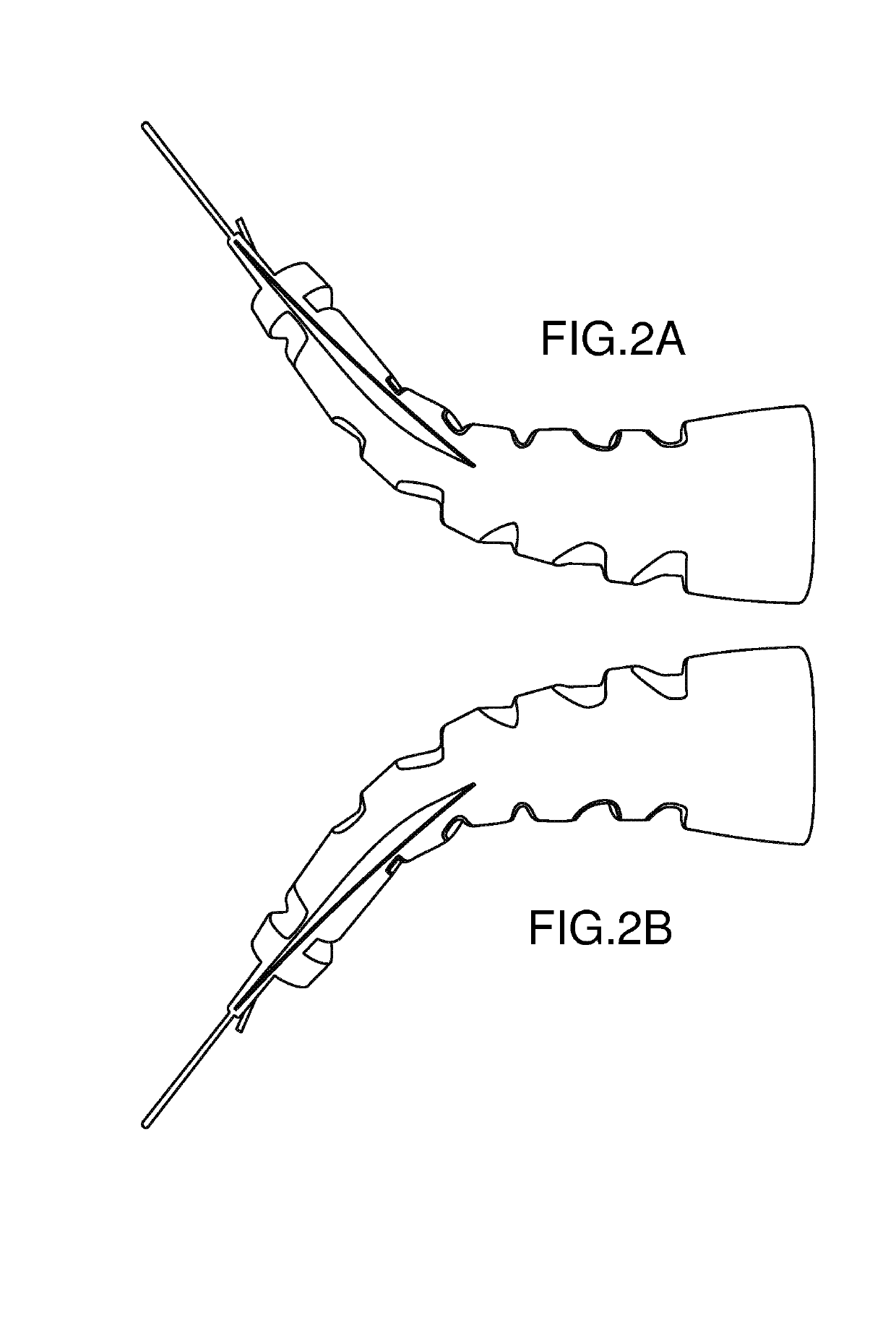

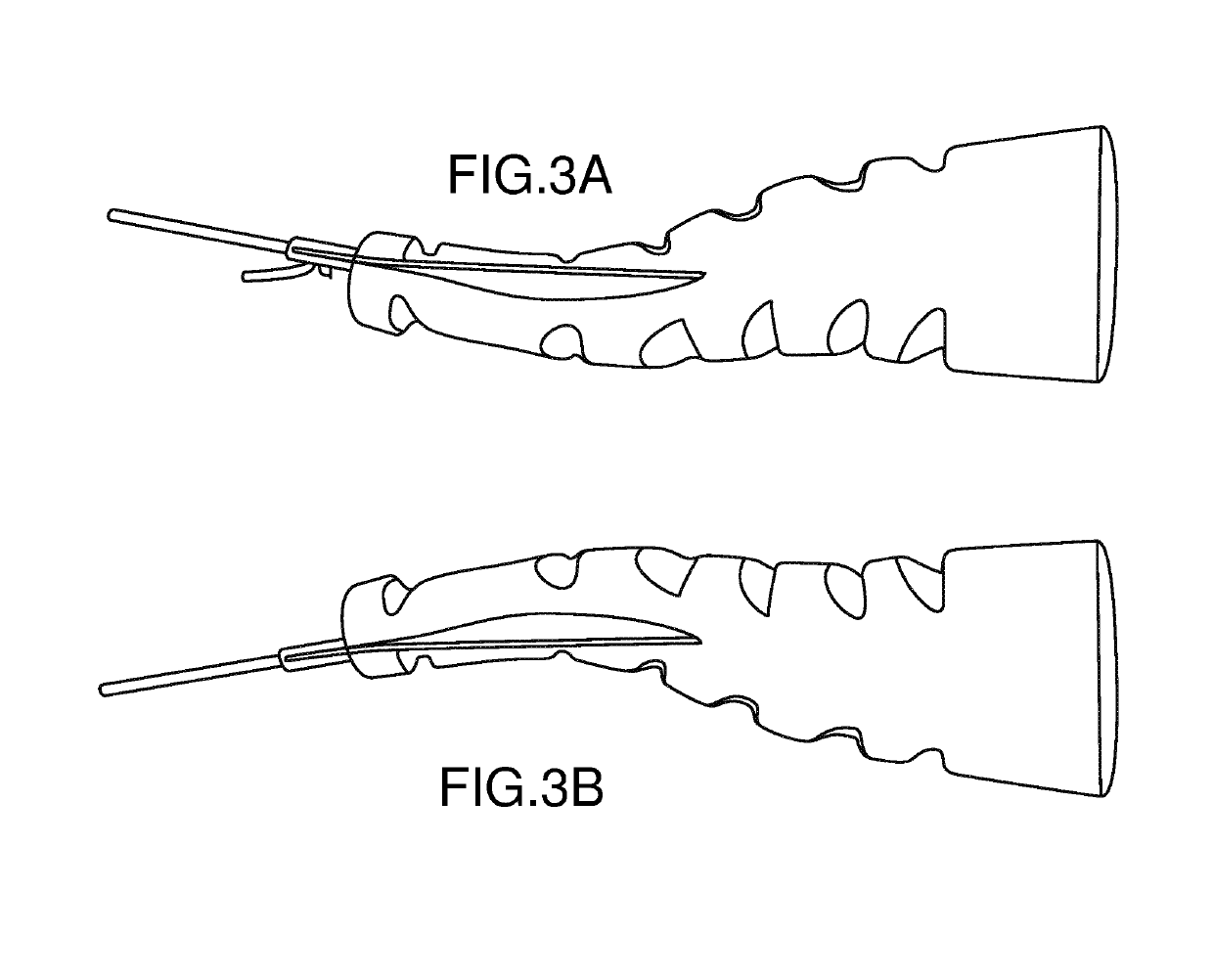

Modular biomimetic underwater vehicle

ActiveUS20190135393A1Simple and robust mechanismComparable and good performanceImage enhancementImage analysisMarine engineeringModularity

Embodiments of the present invention are directed to a modular, biomimetic, underwater vehicle capable of propulsion using one or more tail undulation methods, such as anguilliform or carangiform propulsion methods.

Owner:AQUAAI CORP

Structure and method of molded QFN device suitable for miniaturization, multiple rows and stacking

ActiveUS7504716B2Robust and flexible methodologyShorten the line lengthSemiconductor/solid-state device detailsSolid-state devicesLead bondingMiniaturization

A semiconductor device comprising a semiconductor chip (101) assembled on a first copper cuboid (110); the cuboid has sides of a height (111). The device further has a plurality of second copper cuboids (120) suitable for wire bond attachment; the second cuboids have sides of a height (121) substantially equal to the height of the first cuboid. The back surfaces of all cuboids are aligned in a plane (130). Encapsulation compound (140) is adhering to and embedding the chip, the wire bonds, and the sides of all cuboids so that the compound forms a first surface (140b) aligned with the plane of the back cuboid surfaces and a second surface (140a) above the embedded wires. For devices intended for stacking, the devices further comprise a plurality of vias (160) through the encapsulation compound from the first to the second compound surfaces; the vias are filled with copper, and the via locations are matching between the devices-to-be-stacked.

Owner:TEXAS INSTR INC

Brushless DC motor

InactiveUS7058291B2Reduce cost of producingProcedure is complexSynchronous motors startersWindingsHigh power densityMagnetic flux

A system and method for reducing the cost of producing a brushless DC motor (58) is presented. The brushless DC motor (58) provides higher power density and efficiency with an increased tool run time. The brushless DC motor (58) includes a rotor assembly (72) that has an unmagnetized permanent magnet (74) affixed to a shaft. The permanent magnet (74) remains unmagnetized until the motor is partially assembled. A plurality of coils (94) for producing a magnetic field are wound about the rotor assembly (72). The coils (94) include end turns that enclose the rotor assembly (72) such that the rotor assembly (72) is not removable. Since the windings (94) are wound with the rotor assembly (72) already enclosed, the windings (94) do not require large end coils to allow subsequent insertion of the rotor (72). Minimizing the end coils reduces the length of wire required per turn, thereby reducing the resistance of the winding (94). Also, since the permanent magnet (74) is unmagnetized when the coils (94) are wound around the rotor assembly (72) the winding process is simplified by not coupling energy into the wire which would influence the winder operation. The wound assembly is inserted into a stator stack (96) comprised of magnetic material that provides a magnetic flux return path for the magnetic flux generated by the permanent magnet (74). Using an unmagnetized permanent magnet (74) facilitates easy insertion of the wound assembly into the stator stack (96), reduces the accumulation of magnetic debris during the manufacturing process, and permits the motor assembly to be sealed prior to magnetizing the permanent magnet (74).

Owner:BLACK & DECKER INC

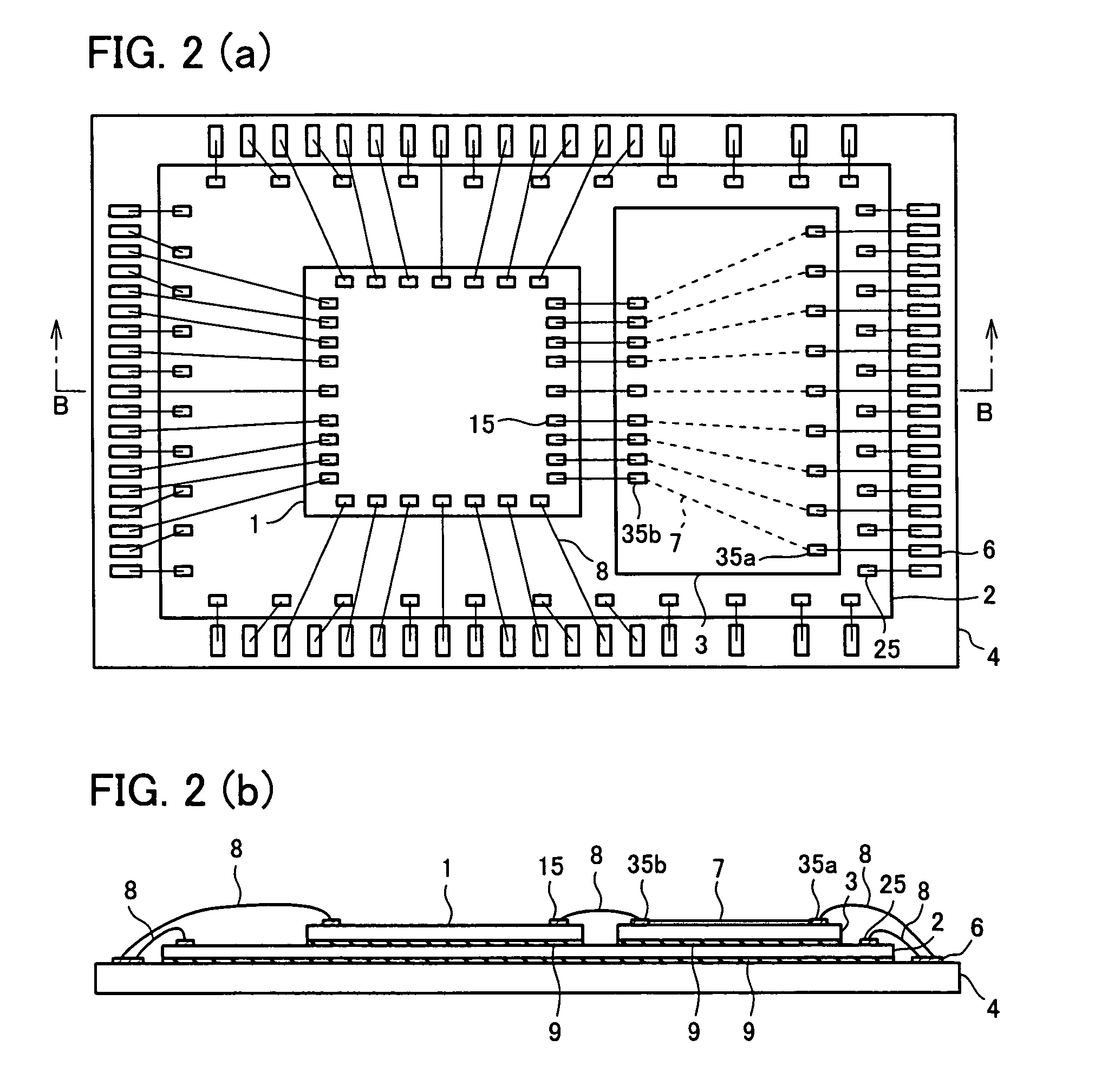

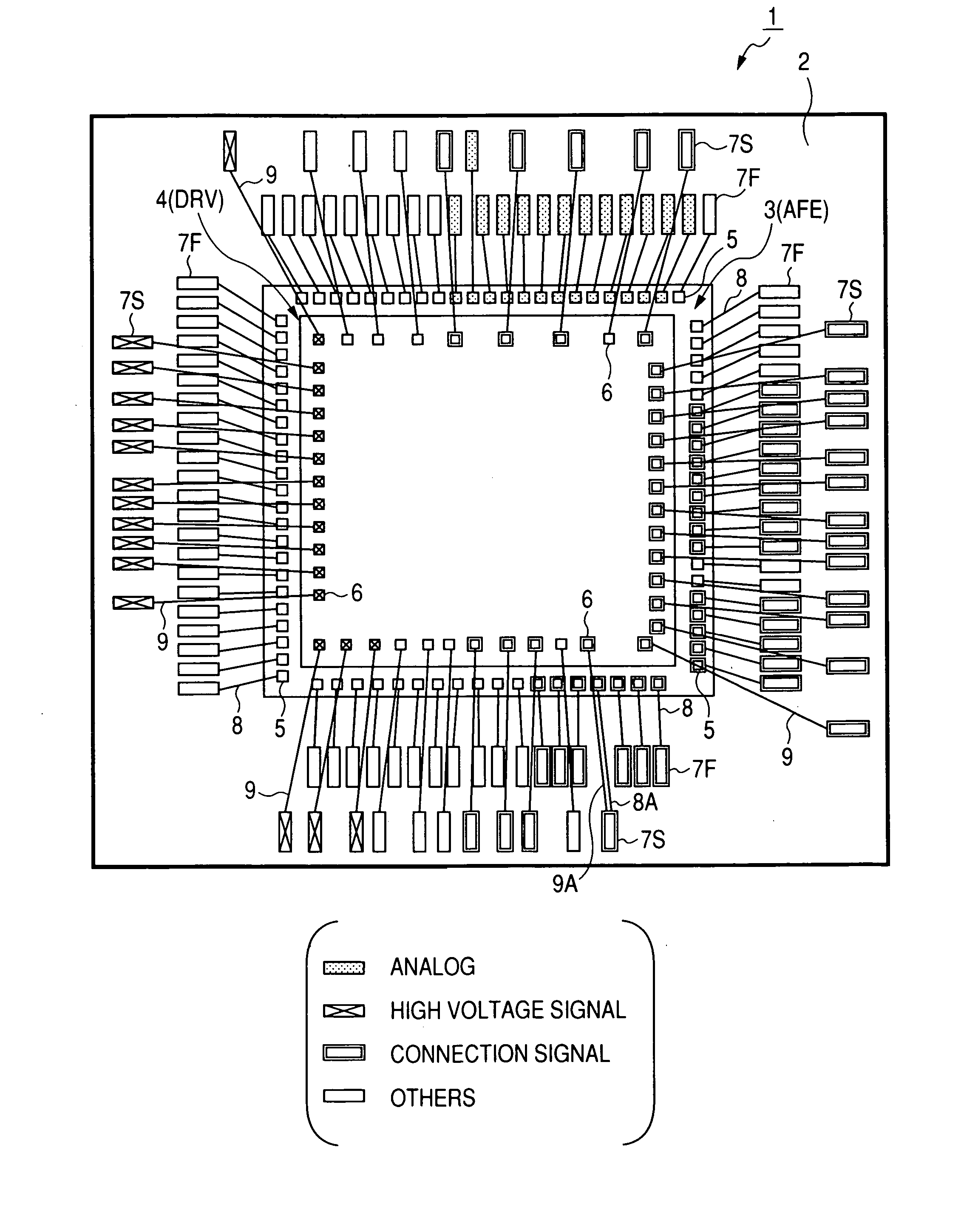

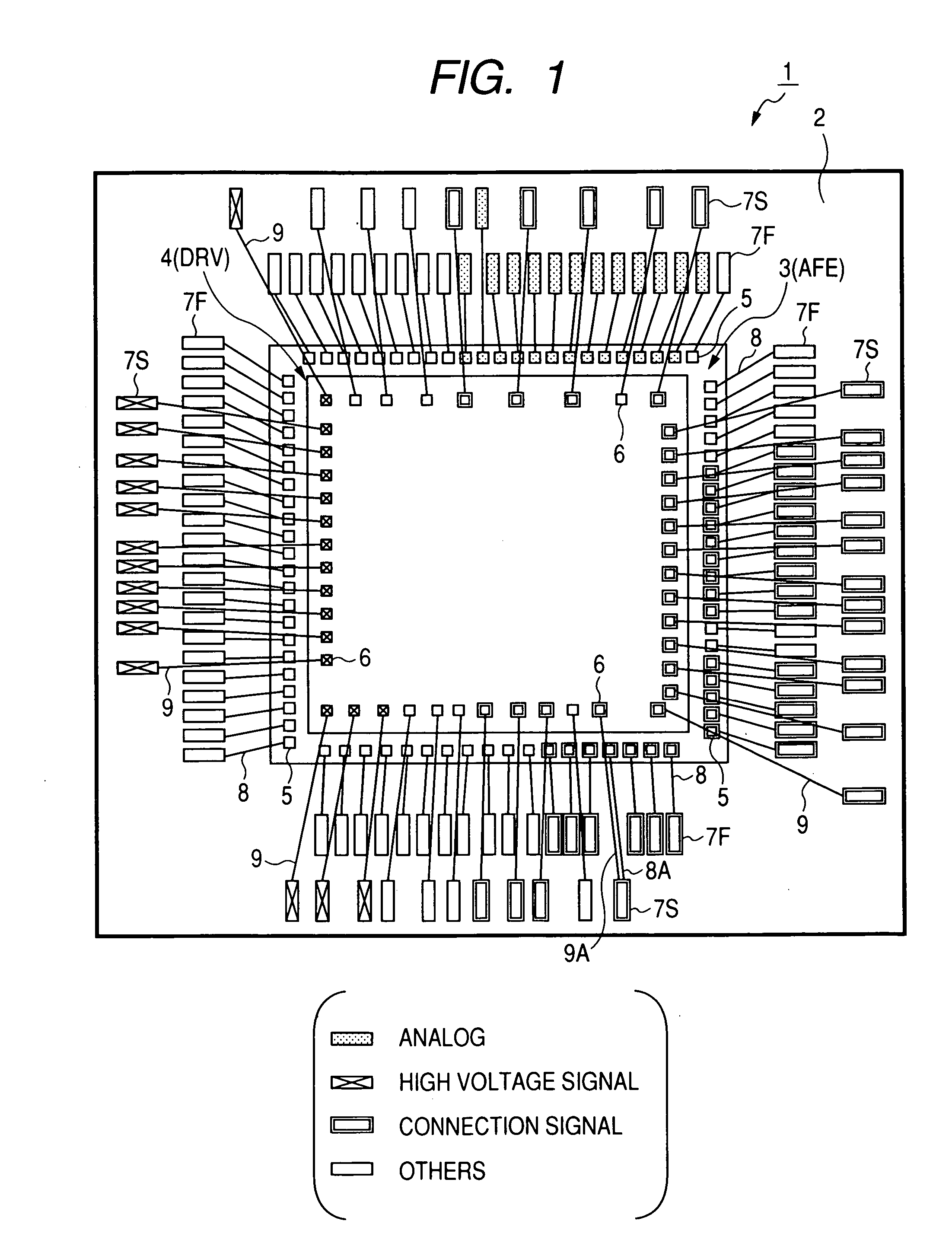

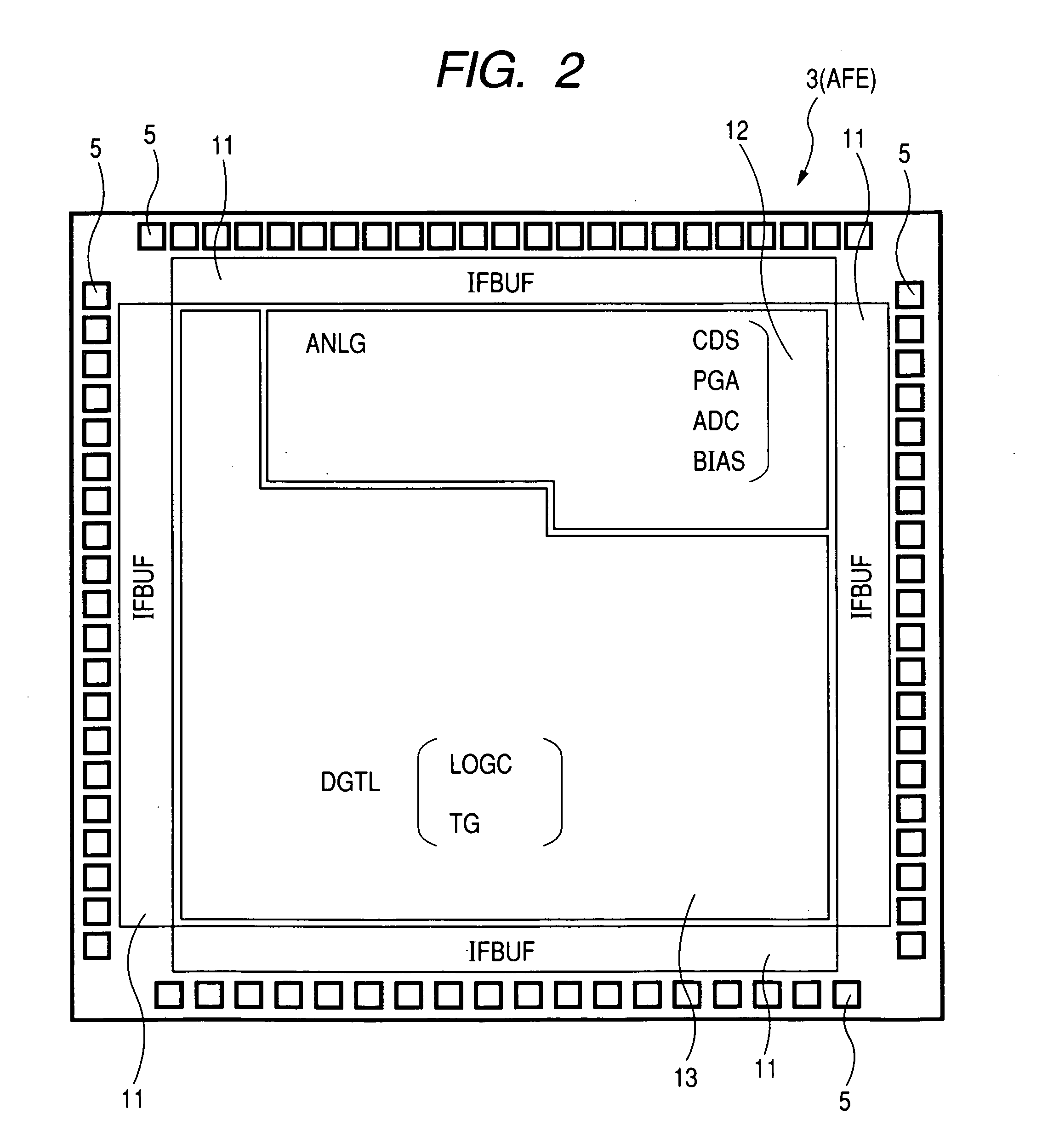

Semiconductor device and an image sensing device

InactiveUS20060220673A1Increased SiSI deterioration due coupling noise or the like can be thereby restrainedReliability increasing modificationsSemiconductor/solid-state device detailsDevice materialSemiconductor chip

SI in a semiconductor device in which a plurality of semiconductor chips differing in withstand voltage or in noise immunity, such as a multi-chip module, is to be improved. The semiconductor device comprises a first semiconductor chip and a second semiconductor chip mounted over a package substrate which has a plurality of bonding pads arranged along the edges. The first semiconductor chip has a plurality of bonding pads for analog signals, and the second semiconductor chip has a plurality of bonding pads for high-voltage signals. The edges along which the bonding pads for analog signals are arranged and the edges along which the bonding pads for high-voltage signals are arranged are disposed along mutually different edges of the package substrate. Adjoining of electrodes or wirings for high voltage signals and those for analog signals over the package substrate can be easily avoided, and SI deterioration can be thereby restrained.

Owner:RENESAS ELECTRONICS CORP

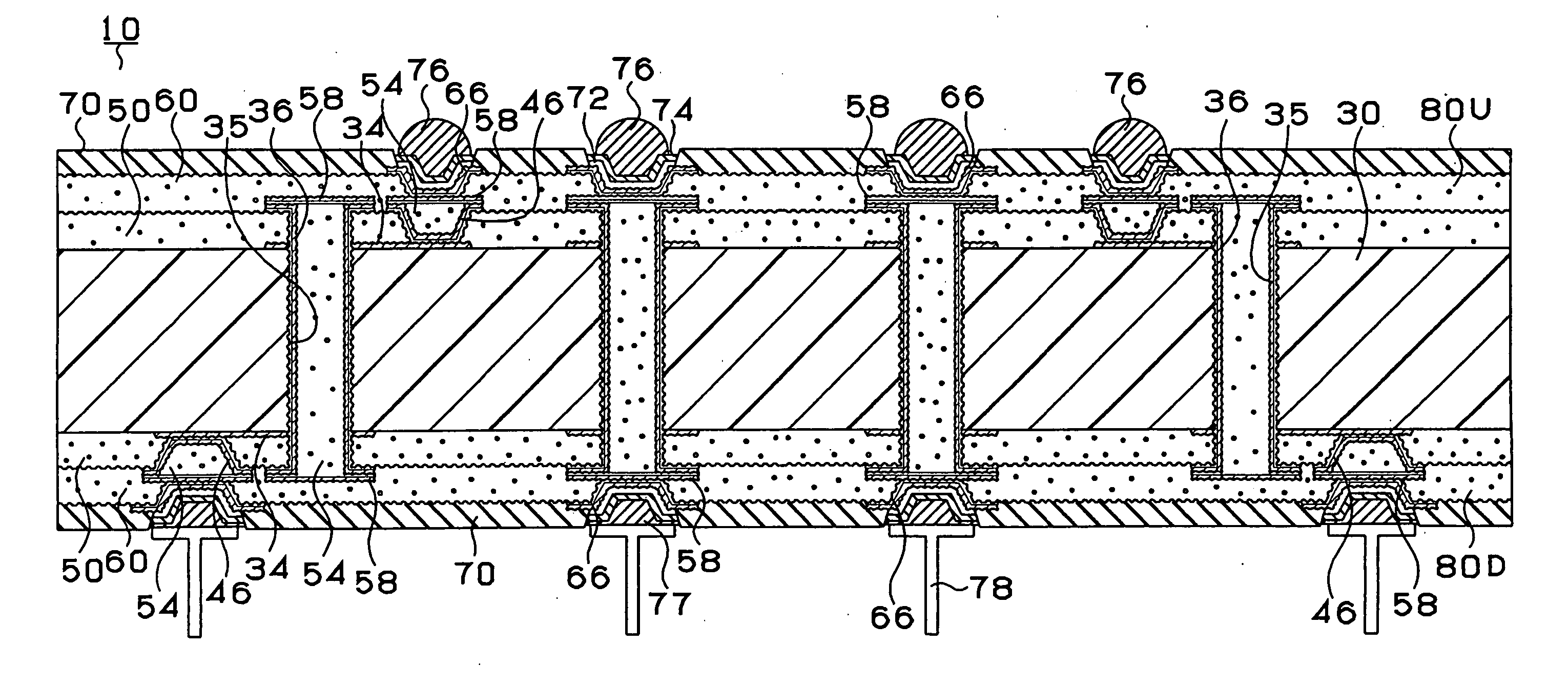

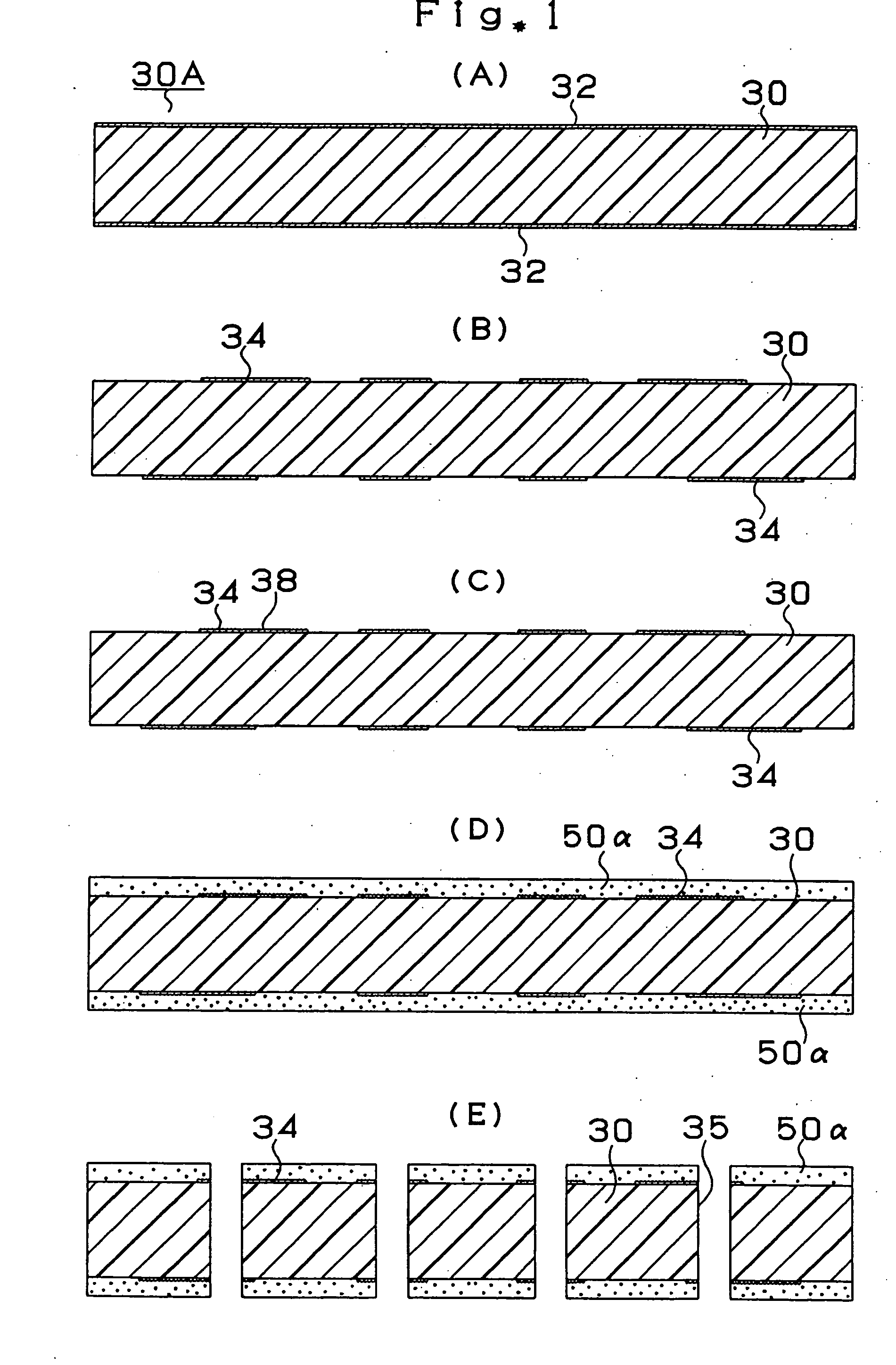

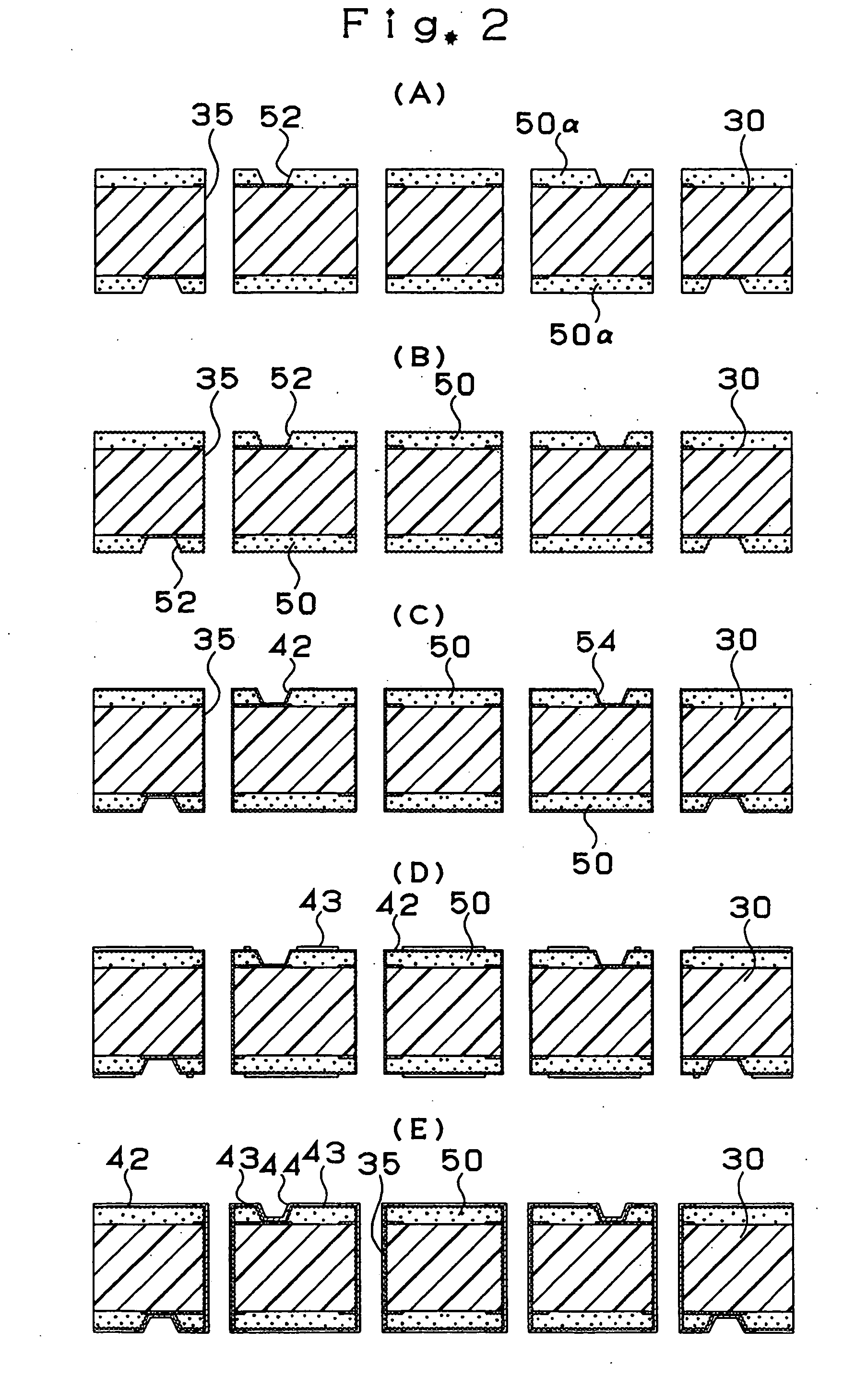

Multi-layer printed circuit board and method of manufacturing multi-layer printed circuit board

InactiveUS20050189136A1Shorten the line lengthIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesEngineeringPrinted circuit board

Through holes 36 are formed to penetrate a core substrate 30 and lower interlayer resin insulating layers 50, and via holes 66 are formed right on the through holes 36, respectively. Due to this, the through holes 36 and the via holes 66 are arranged linearly, thereby making it possible to shorten wiring length and to accelerate signal transmission speed. Also, since the through holes 36 and the via holes 66 to be connected to solder bumps 76 (conductive connection pins 78), respectively, are directly connected to one another, excellent reliability in connection is ensured.

Owner:IBIDEN CO LTD

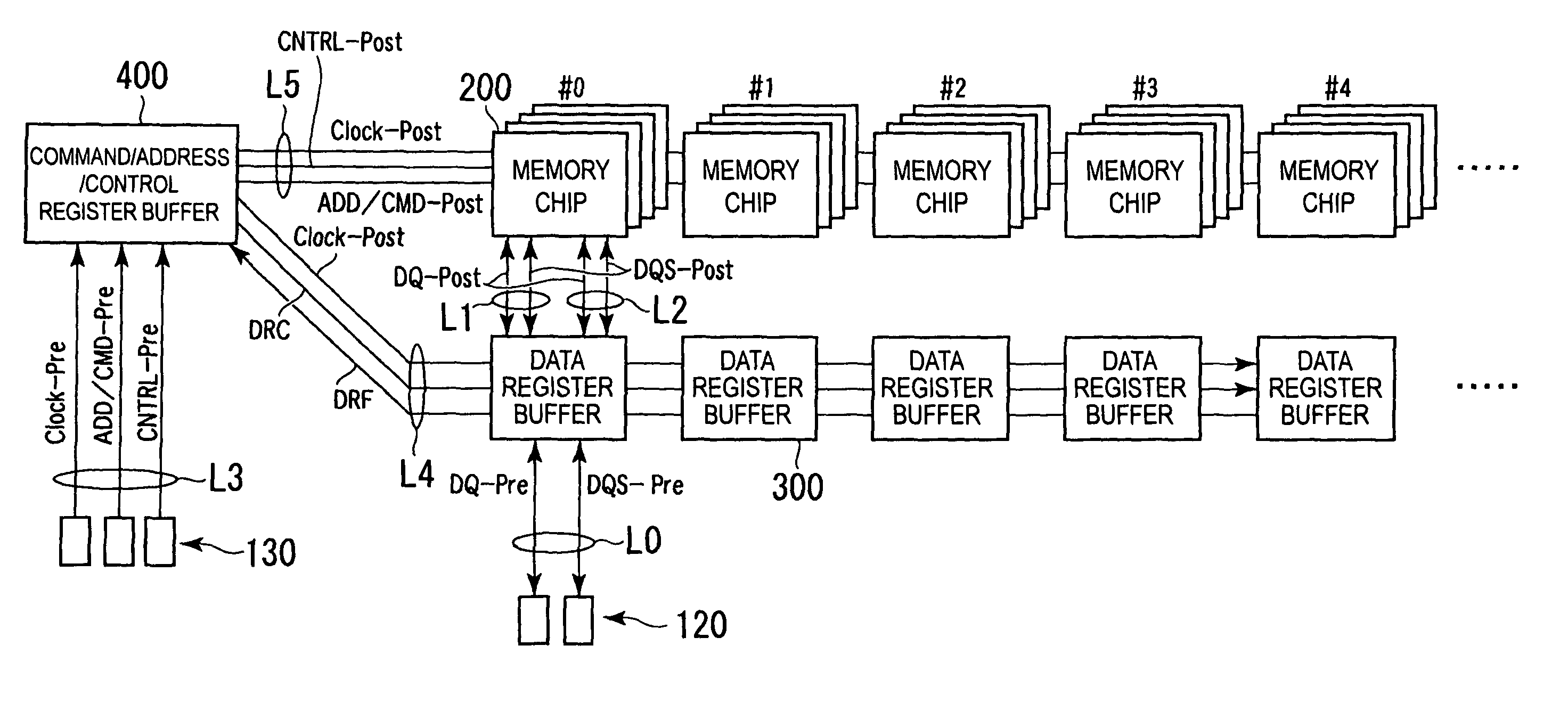

Load reduced memory module and memory system including the same

ActiveUS8422263B2Improve signal qualityLine lengthSolid-state devicesDigital storageMemory chipControl signal

A memory module includes a plurality of memory chips, a plurality of data register buffers, and a command / address / control register buffer mounted on a module PCB. The data register buffers perform data transfers with the memory chips. The command / address / control register buffer performs buffering of a command / address / control signal and generates a control signal. The buffered command / address / control signal is supplied to the memory chips, and the control signal is supplied to the data register buffers. According to the present invention, because line lengths between the data register buffers and the memory chips are shortened, it is possible to realize a considerably high data transfer rate.

Owner:LONGITUDE LICENSING LTD

Multilayer wiring board

InactiveUS20090229874A1High bonding strengthImprove production yieldPrinted circuit aspectsPrinted circuit manufactureEpoxyElectrical conductor

A coreless wiring board has no core board but a laminated structure in which a conductor layer and resin insulating layers are alternately laminated into a multilayer. Each of the resin insulating layers is formed to contain a glass cloth in an epoxy resin. A plurality of via holes taking a shape of an inverse truncated cone and having steps on internal wall surfaces is formed to penetrate each of the resin insulating layers, and a filled via conductor for electrically connecting the conductors is formed in each of the via holes.

Owner:NGK SPARK PLUG CO LTD

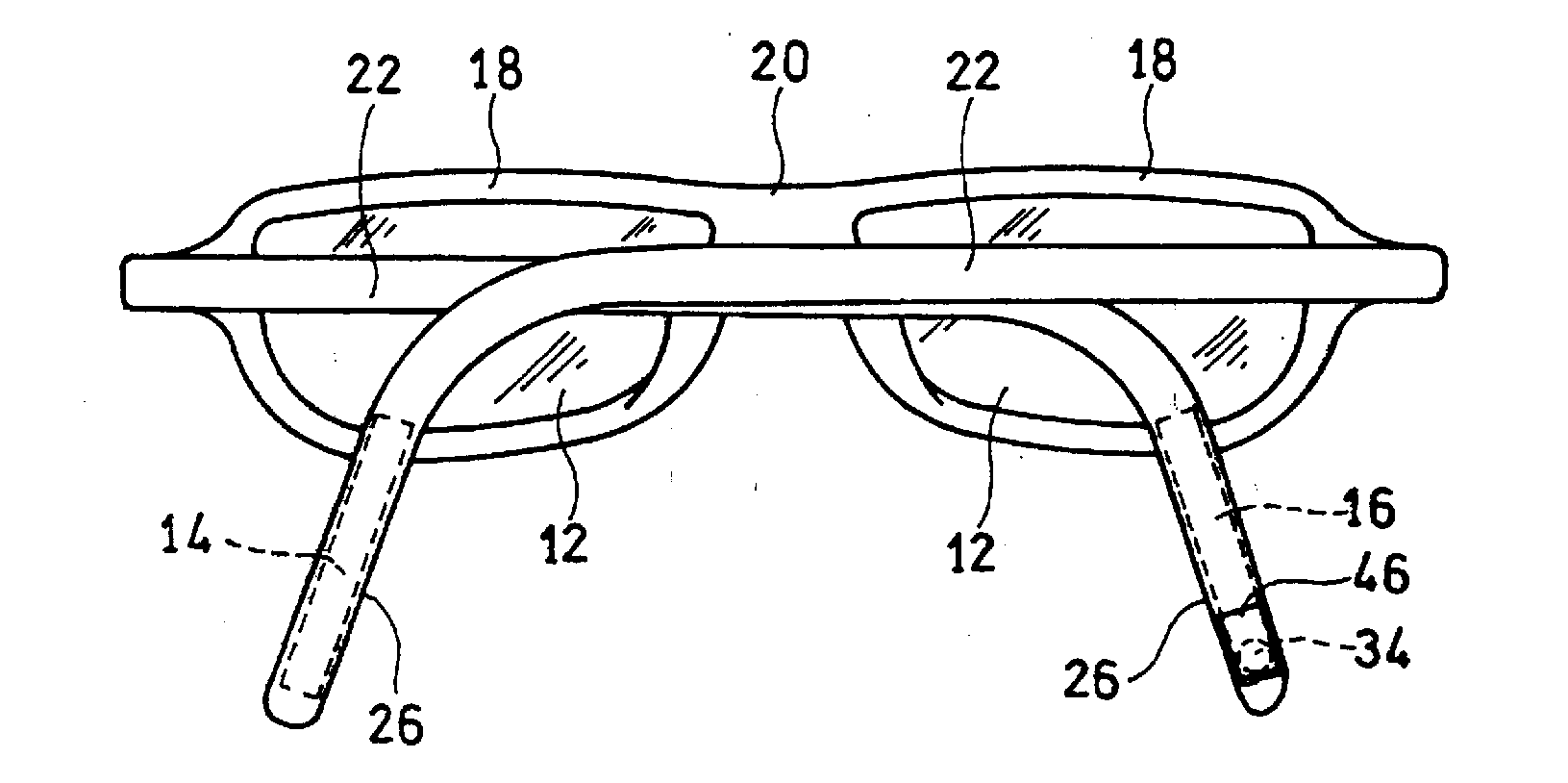

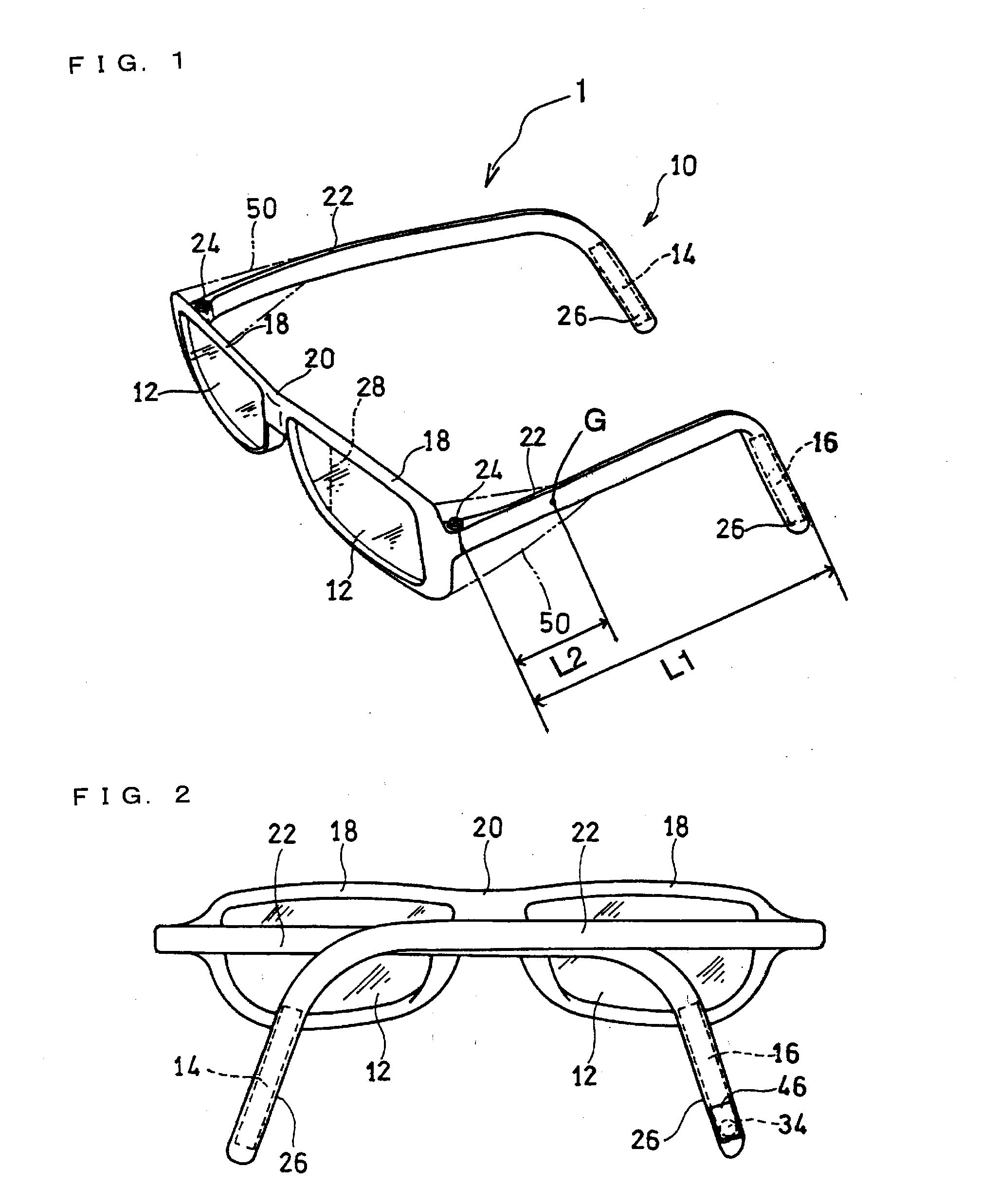

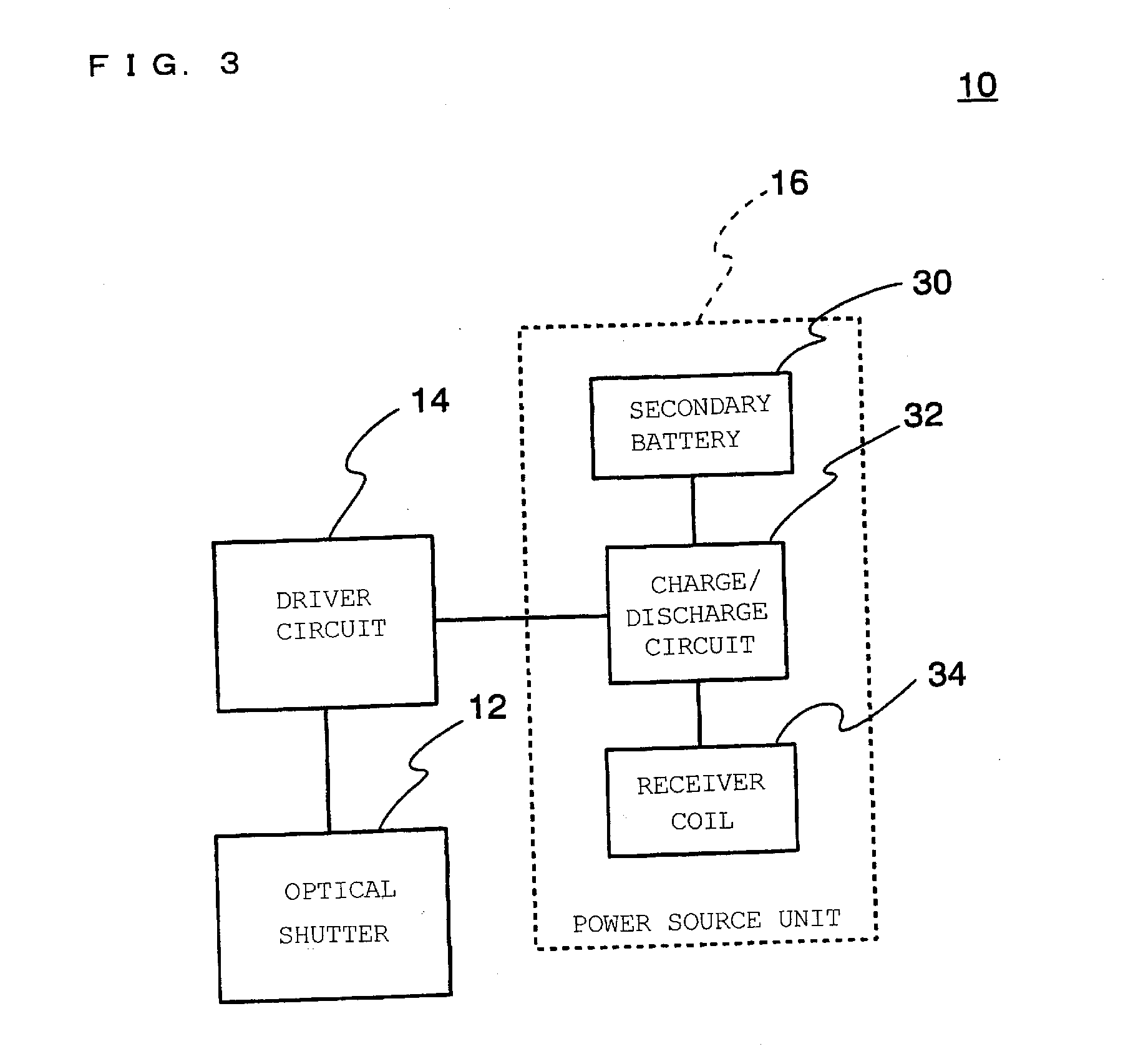

Optical device and charging system including the same

InactiveUS20130120706A1Simple designImprove efficiencyTelevision system detailsNon-optical adjunctsDriver circuitElectricity

An optical device including: one or more optical components configured to be electrically actuated such that light transmission states are variable, a driver circuit for the optical components, a power source unit for driving the optical components, a pair of rims for supporting the optical components, a pair of temples having front and rear ends and being connected at the front ends to the pair of rims, and a pair of earpieces formed at the rear ends of the pair of temples. The power source unit includes a secondary battery, and a power receiver coil for charging the secondary battery. The secondary battery includes a case made of a non-magnetic material.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

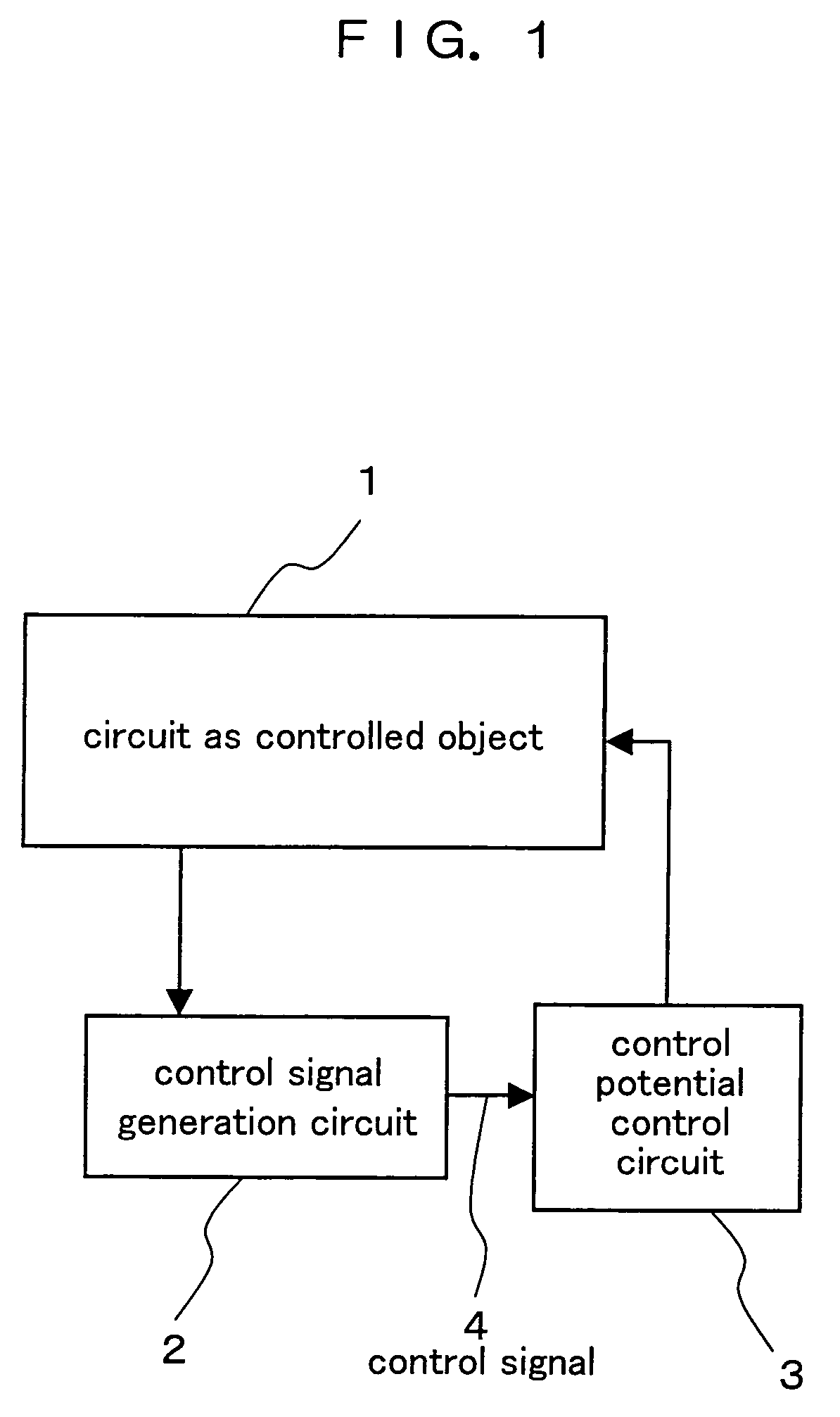

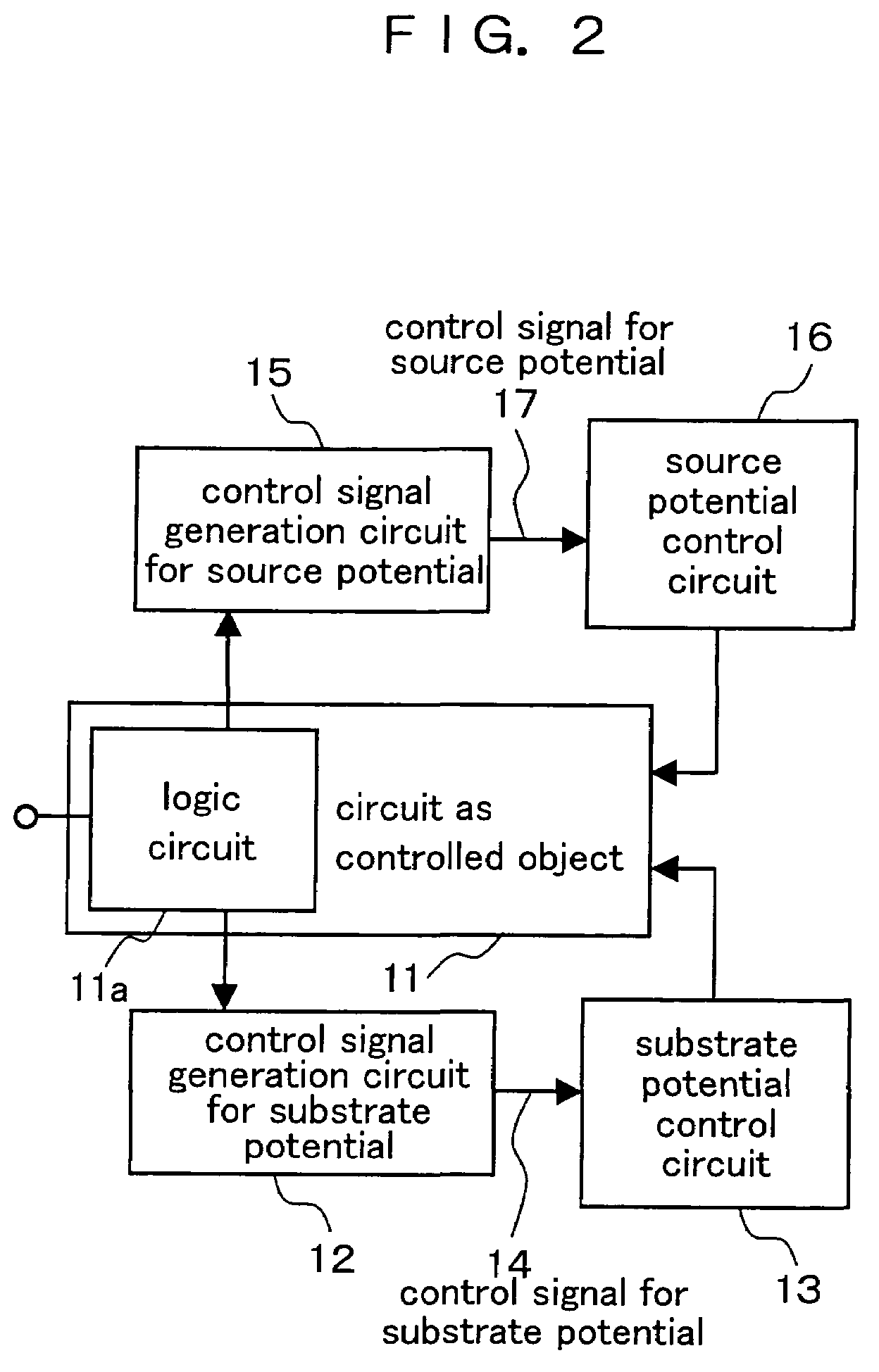

Semiconductor integrated circuit

ActiveUS7123076B2Improve the immunitySignificant valuePower reduction in field effect transistorsTransistorControl signalControl circuit

A semiconductor integrated circuit according to the present invention comprises a circuit as a controlled object including an MOS transistor, wherein a control potential (at least one of a substrate potential and source potential) is to be controlled, a control signal generation circuit for generating a control signal with respect to the control potential based on an internal signal of the circuit as the controlled object, and a control potential control circuit for controlling the control potential (substrate potential / source potential) of the MOS transistor based on the control signal.

Owner:SOCIONEXT INC

Capacitor and method for producing the same, and circuit board with a built-in capacitor and method for producing the same

InactiveUS20070022590A1Improve connection reliabilityReduce connection resistancePrinted circuit assemblingLiquid electrolytic capacitorsDielectricElectrically conductive adhesive

Owner:PANASONIC CORP

Head substrate, printhead, head cartridge, and printing apparatus

InactiveUS20080129791A1Reduce power lossShortening of durable service life can be preventedInking apparatusOther printing apparatusEngineeringDriven element

The purpose of this invention is to provide a head substrate capable of increasing layout efficiency. To achieve this purpose, an ink supply channel is arranged, and a plurality of printing element arrays are arranged on at least one side of the ink supply channel, and a plurality of driving element arrays are arranged adjacent to the plurality of printing element arrays. A plurality of power supply pads and a plurality of ground pads are arranged in areas between the plurality of driving element arrays.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com