Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33835 results about "Data lines" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Information (often called data) inside a computer, as well as on the board used in this tutorial, is exchanged among the various components by means of metallic conductors called data lines. A group of data lines is called a data bus. Each data line carries a unit of data called a bit. A bit can be on or off.

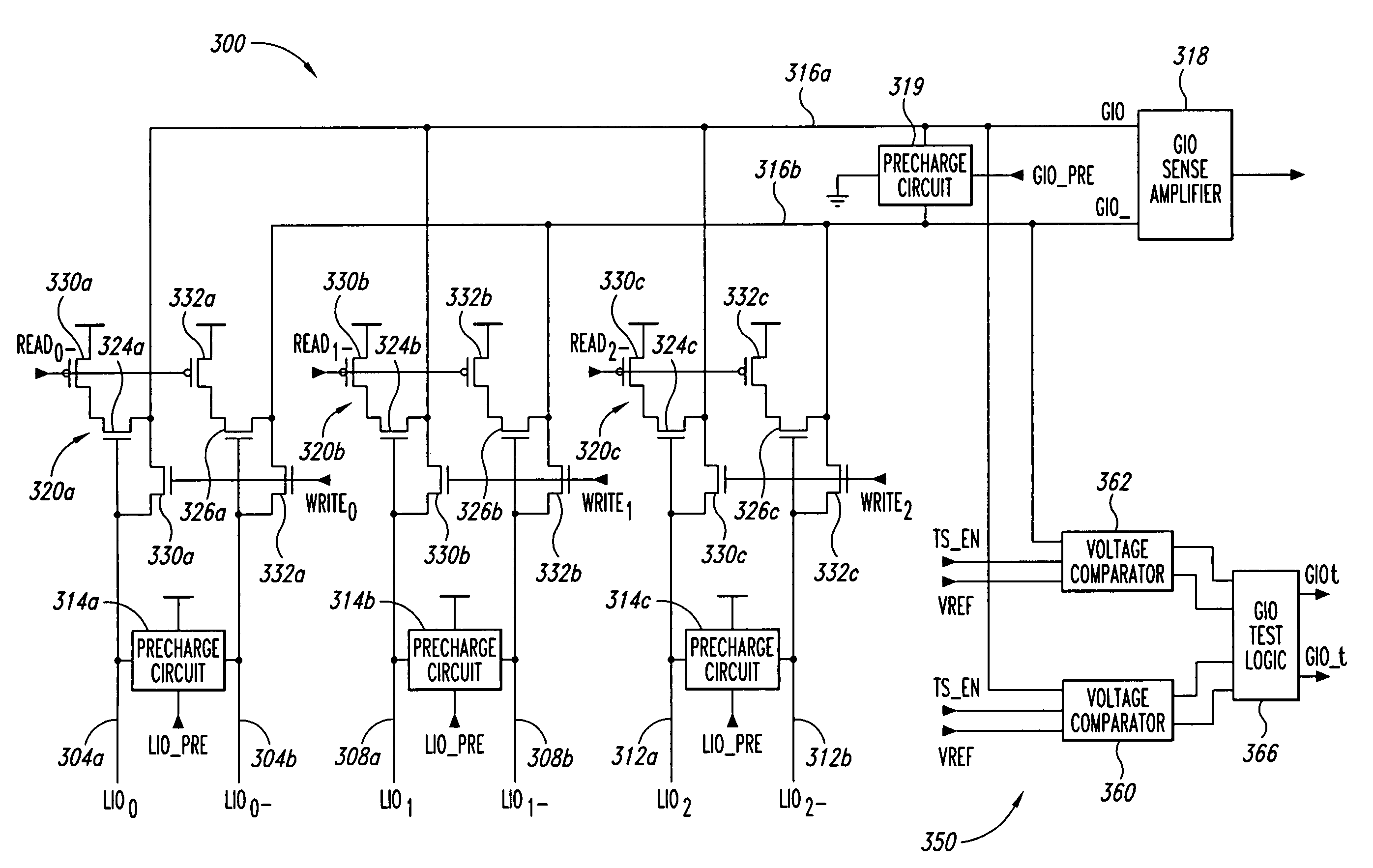

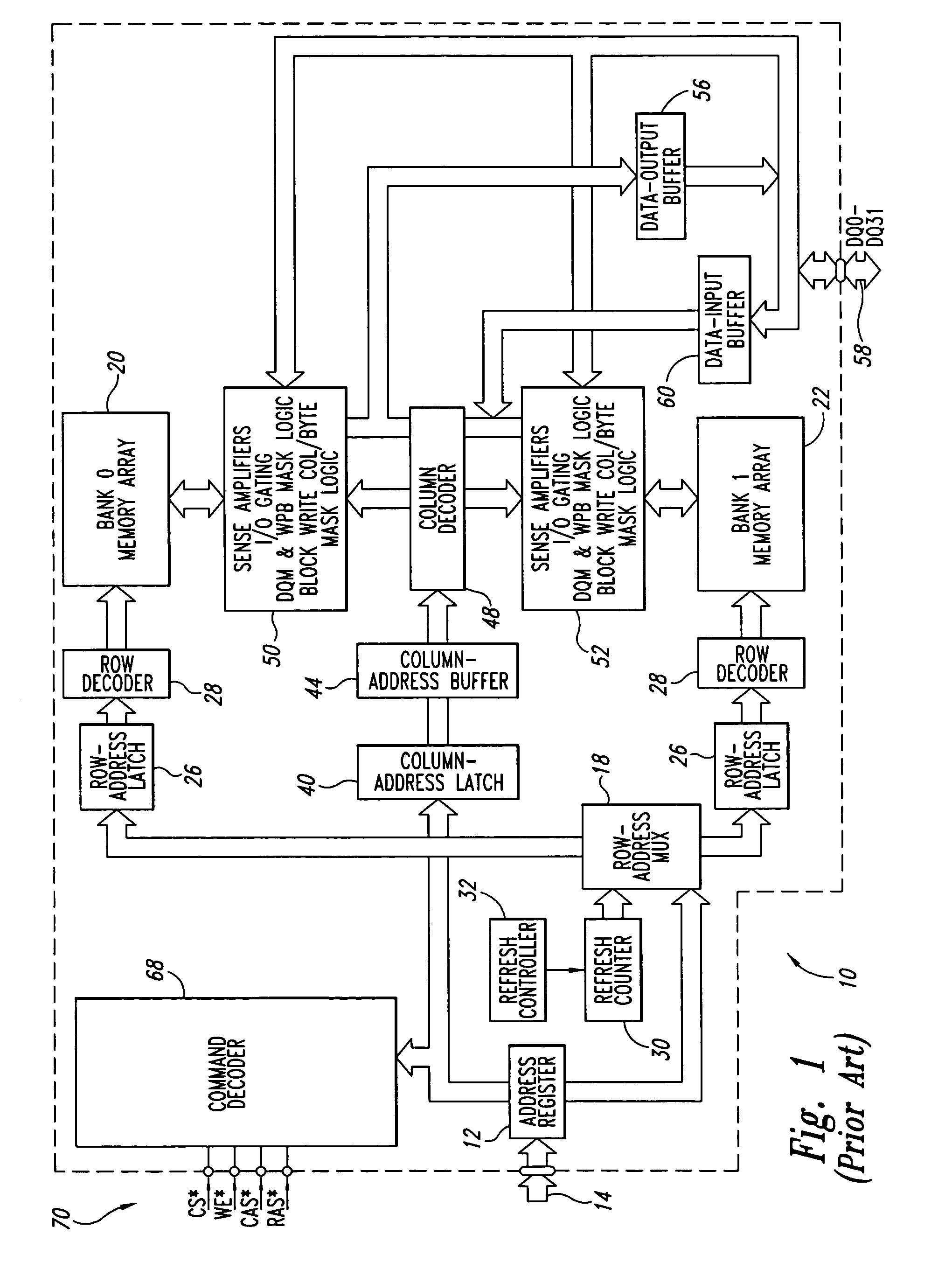

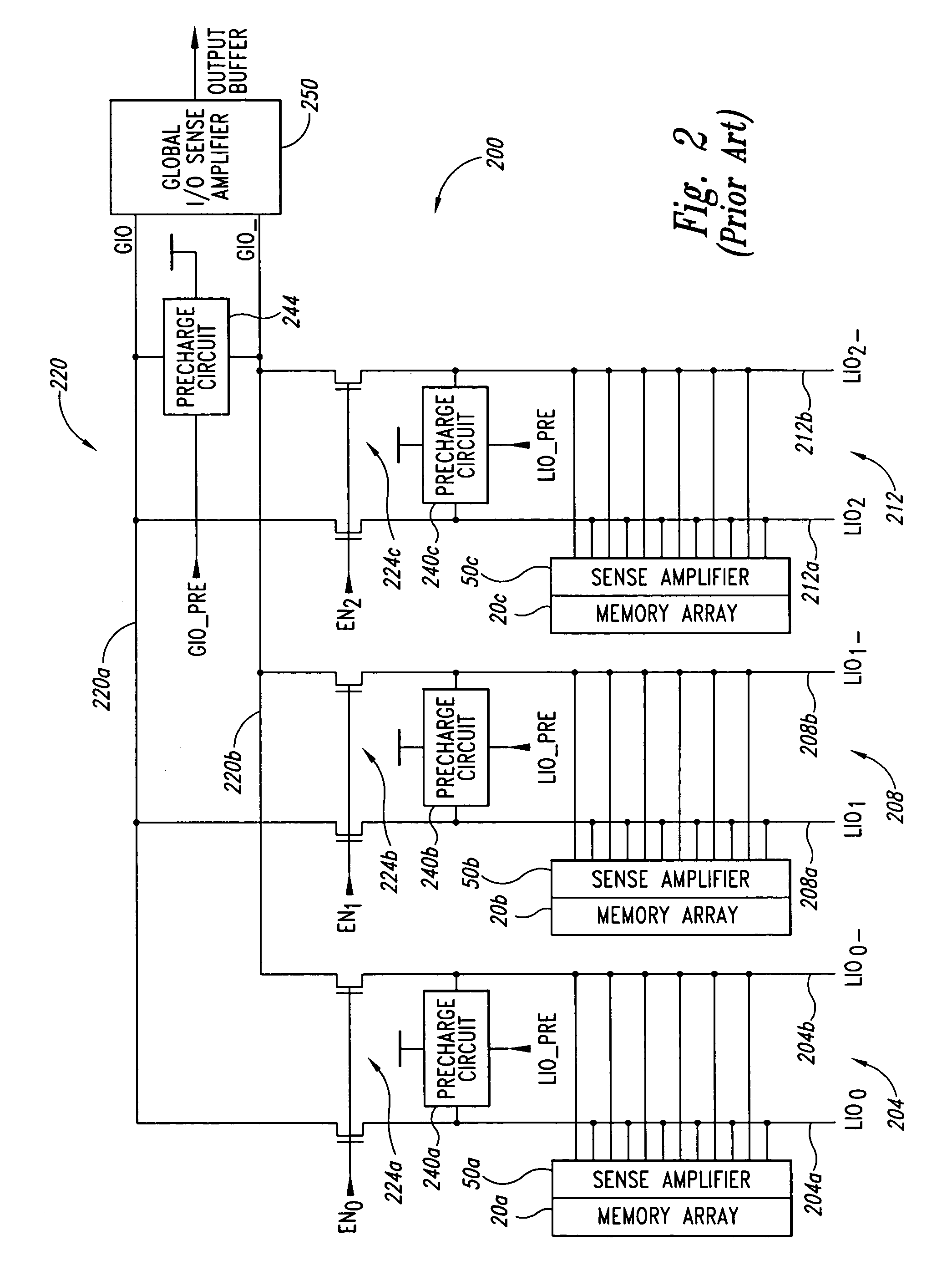

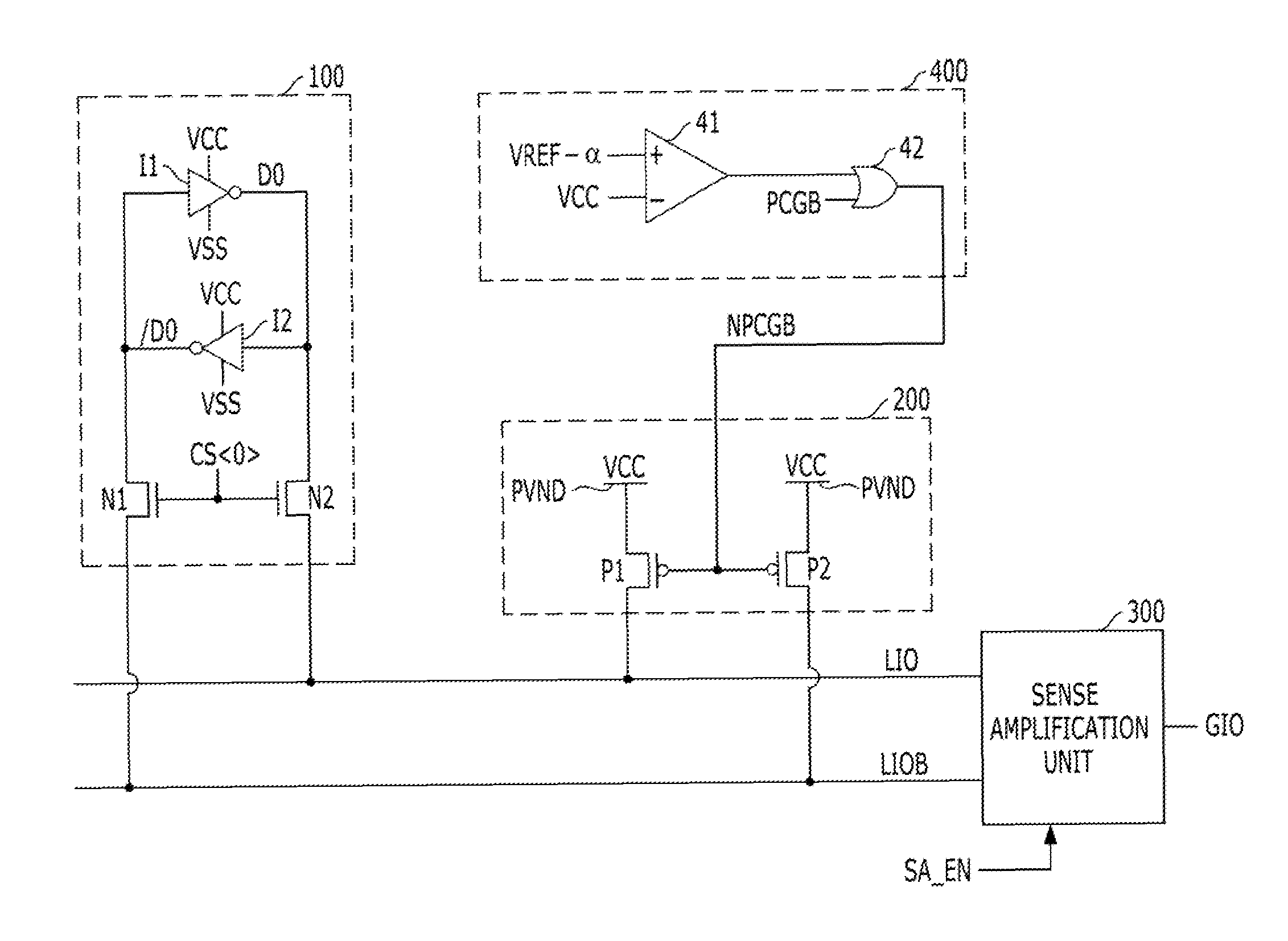

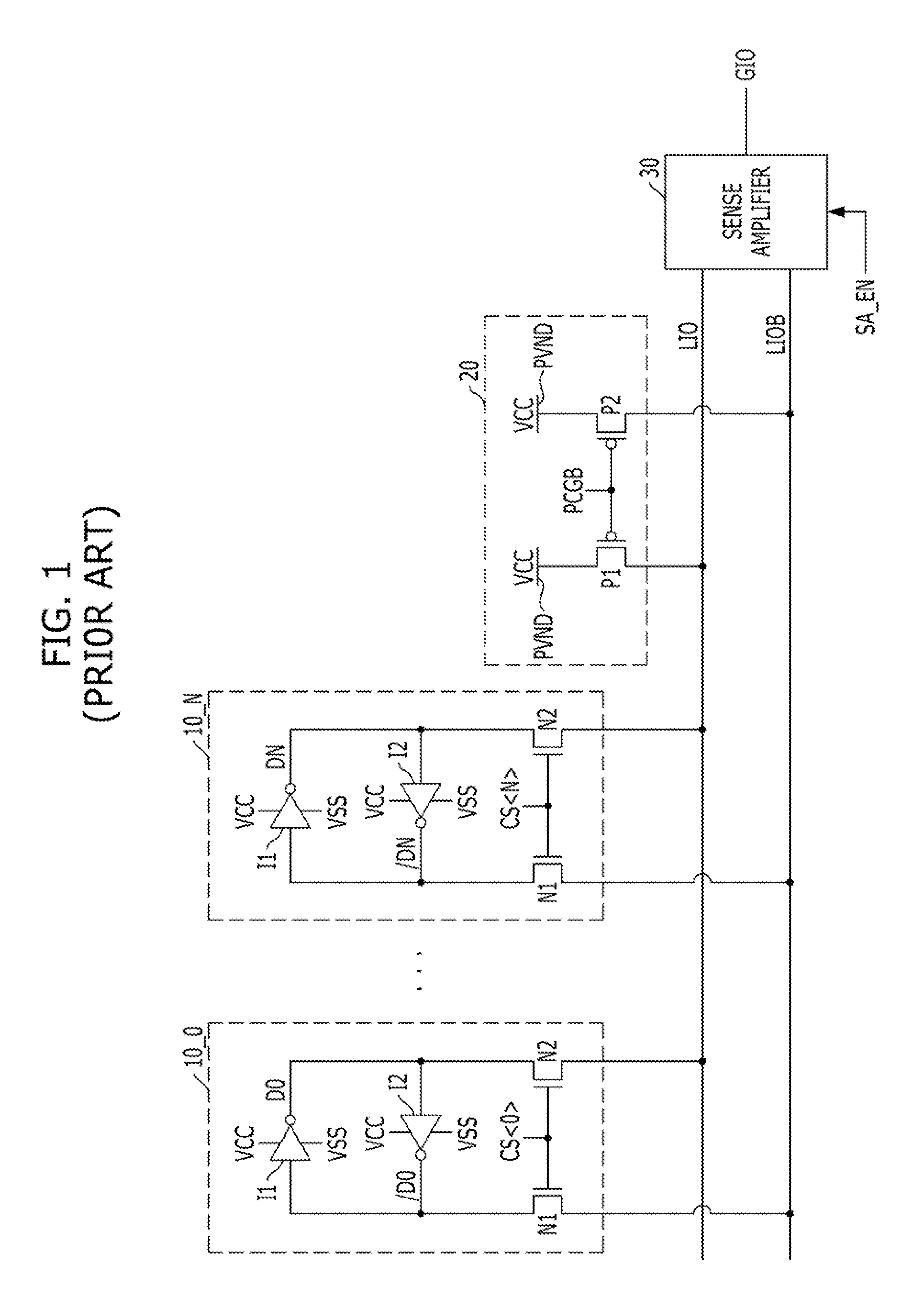

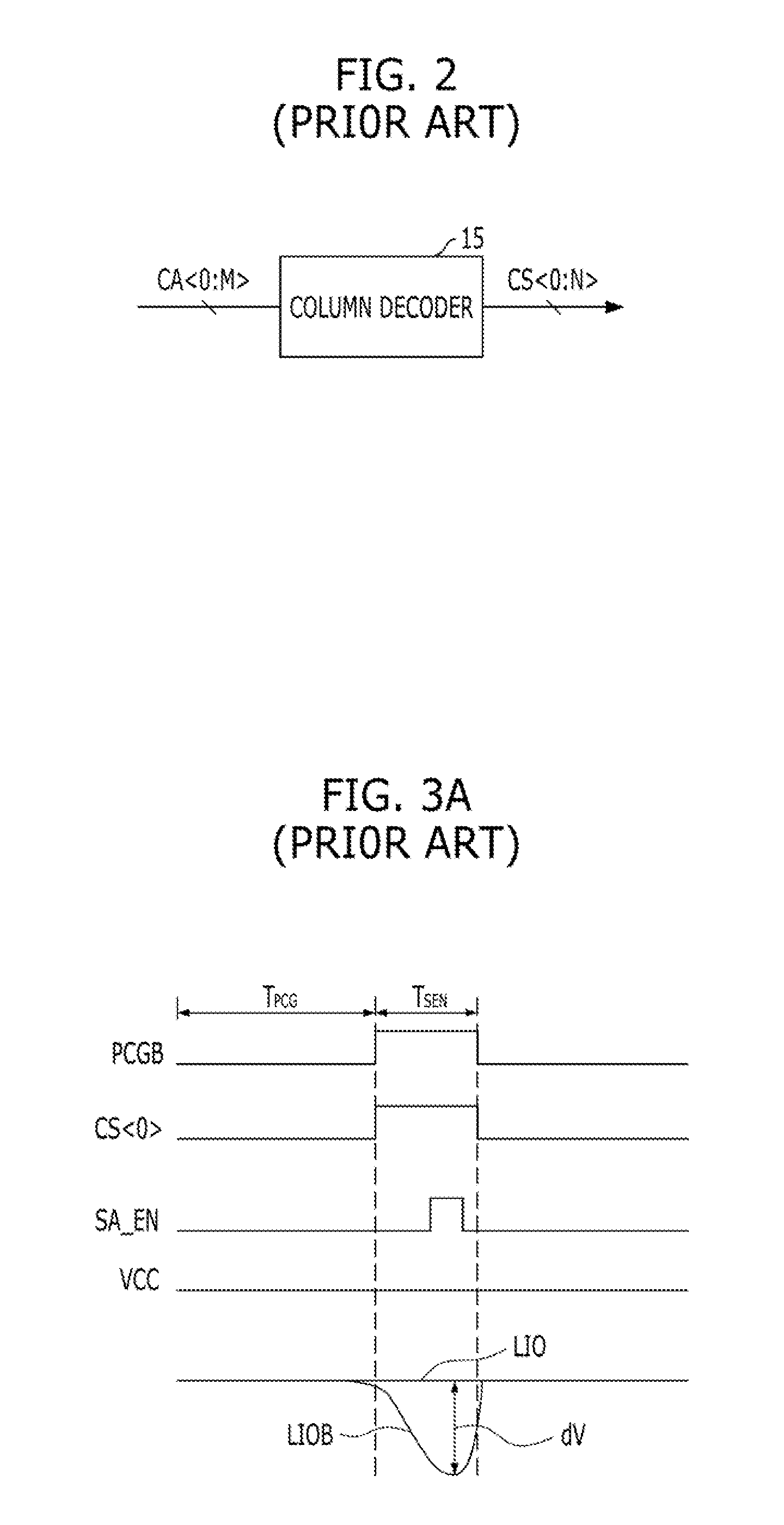

Data path having grounded precharge operation and test compression capability

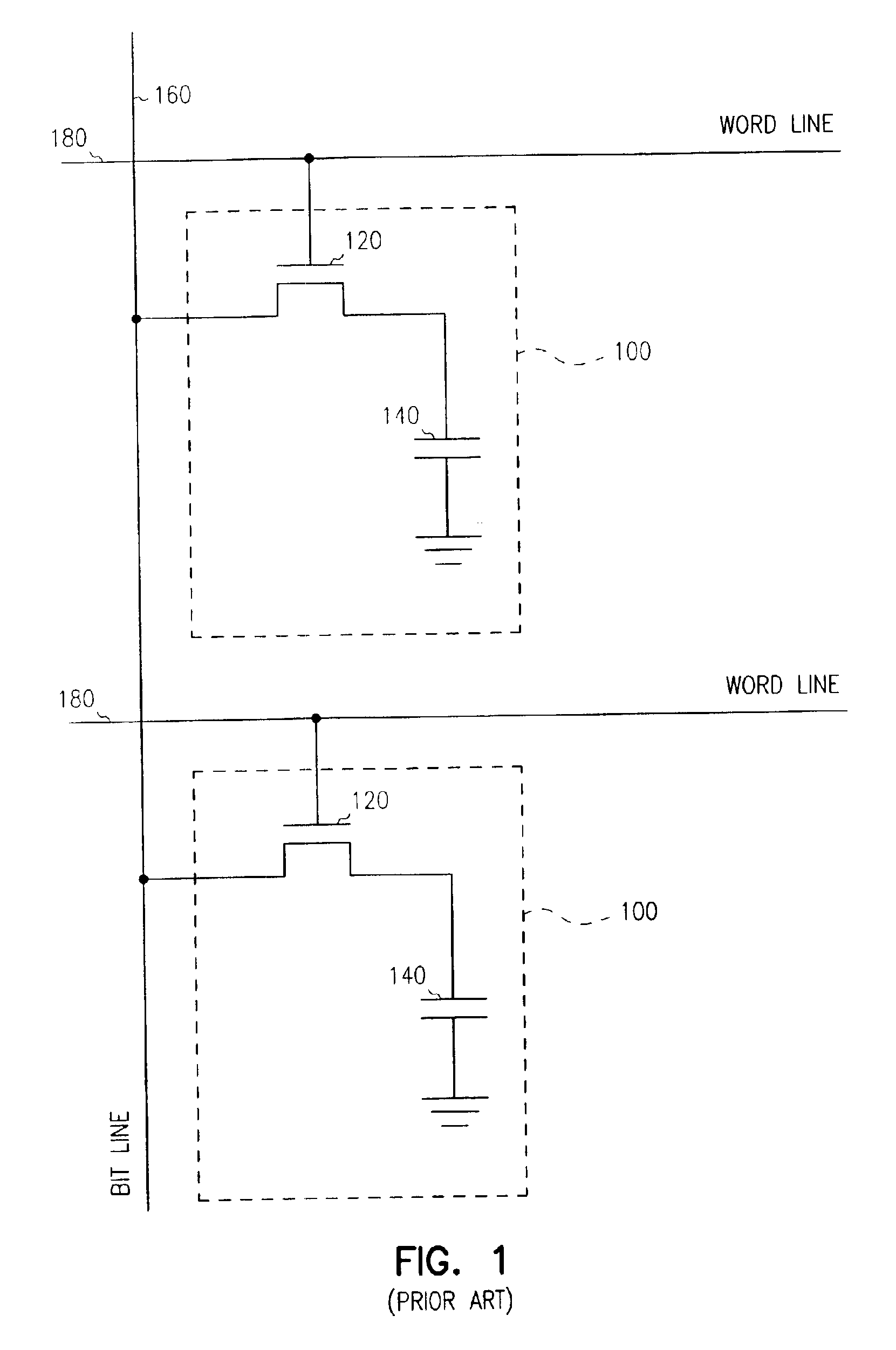

A data path for coupling data between a memory cell and an input / output (IO) line sense amplifier. An IO line coupling circuit is coupled to a pair of global data lines and a pair of local data lines to couple and decouple each of the global data lines to and from a voltage supply based on the voltage levels of the local data lines for the memory read operation. For the memory write operation, the IO line coupling circuit couples and decouples each of the global data lines to and from a respective one of the local data lines. The data path also includes a first precharge circuit coupled to the global data lines to couple the global data lines to ground to precharge the signal lines prior to a memory read or write operation, and can further include a test compression circuit coupled to the global data lines.

Owner:MOSAID TECH

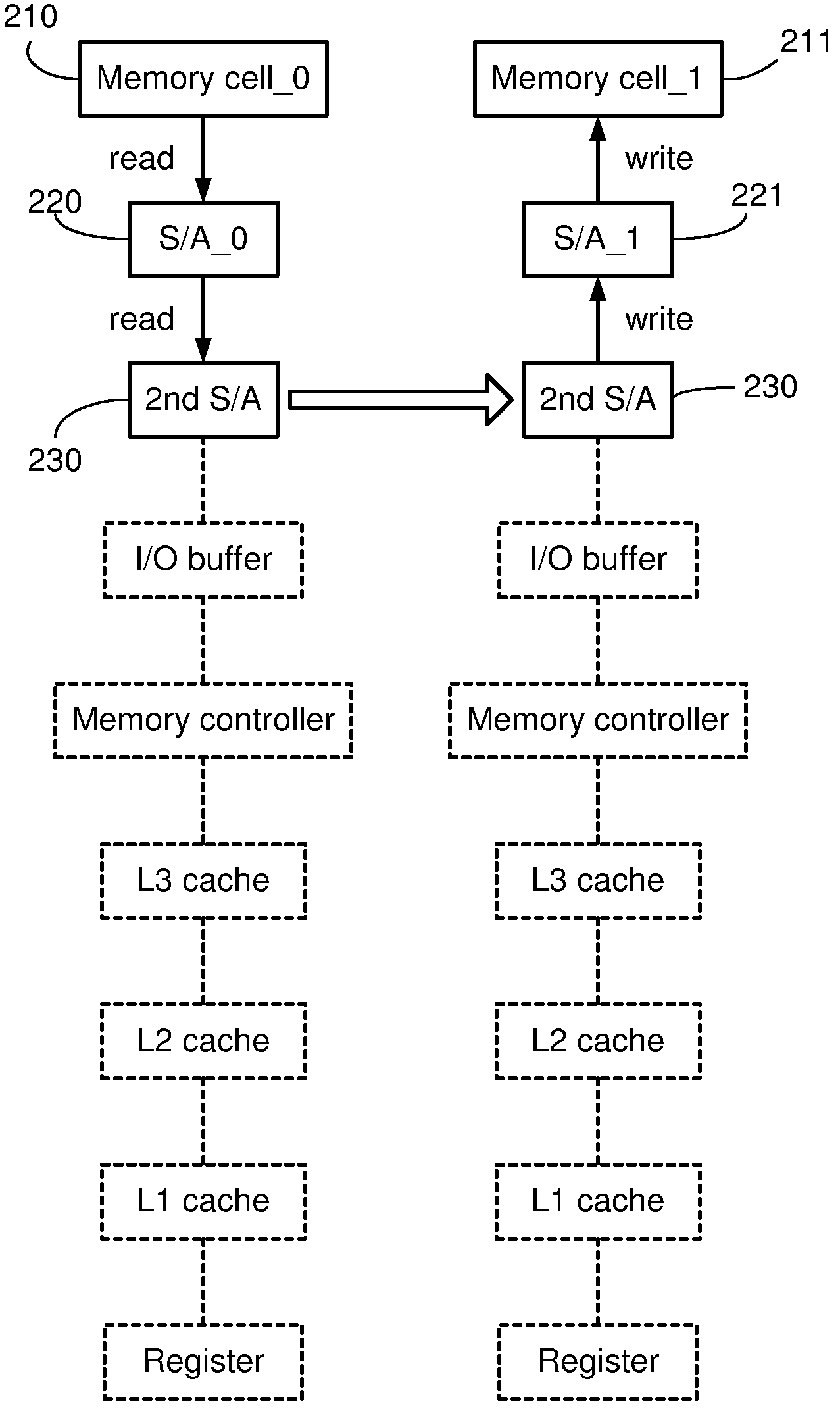

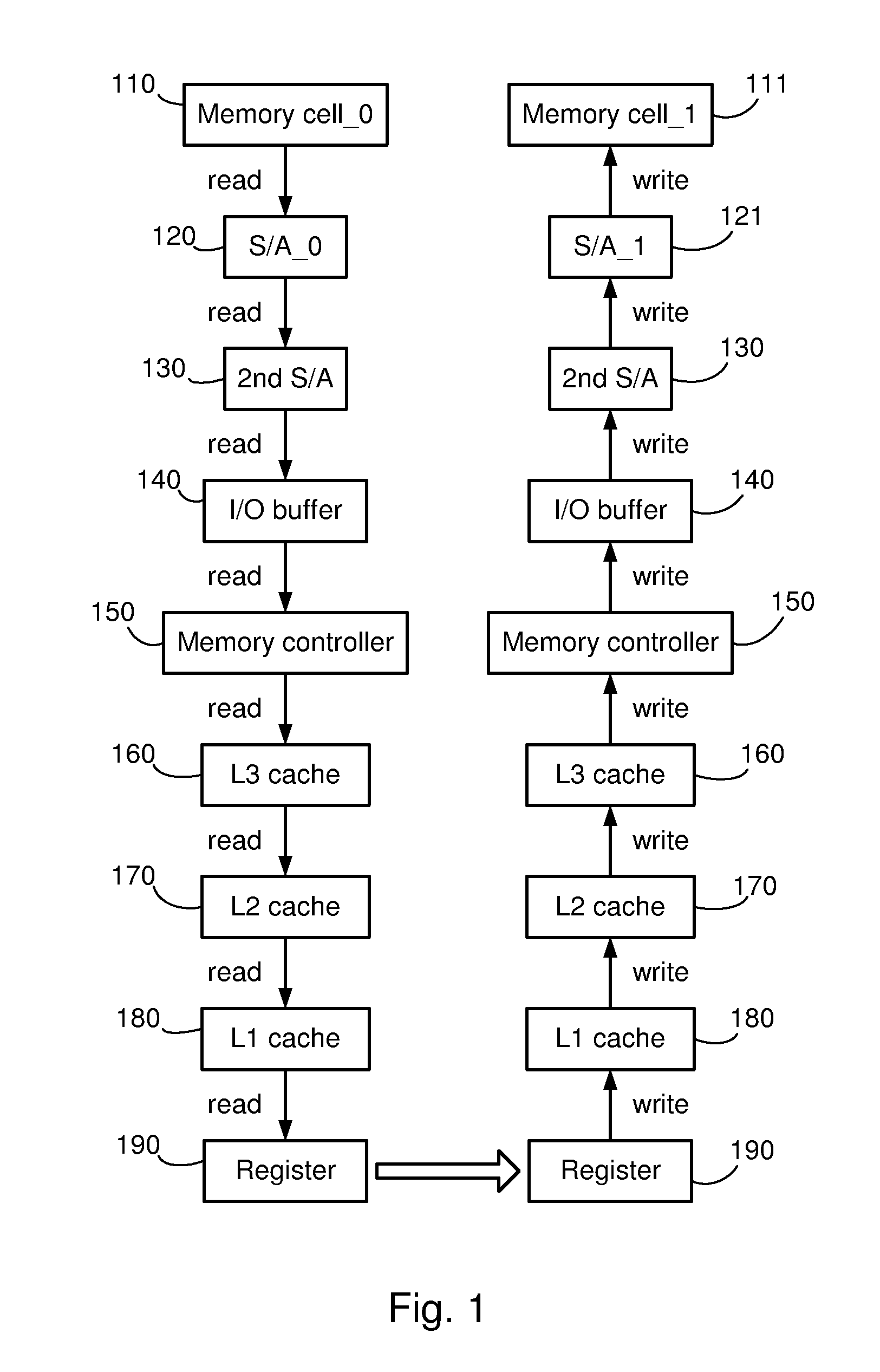

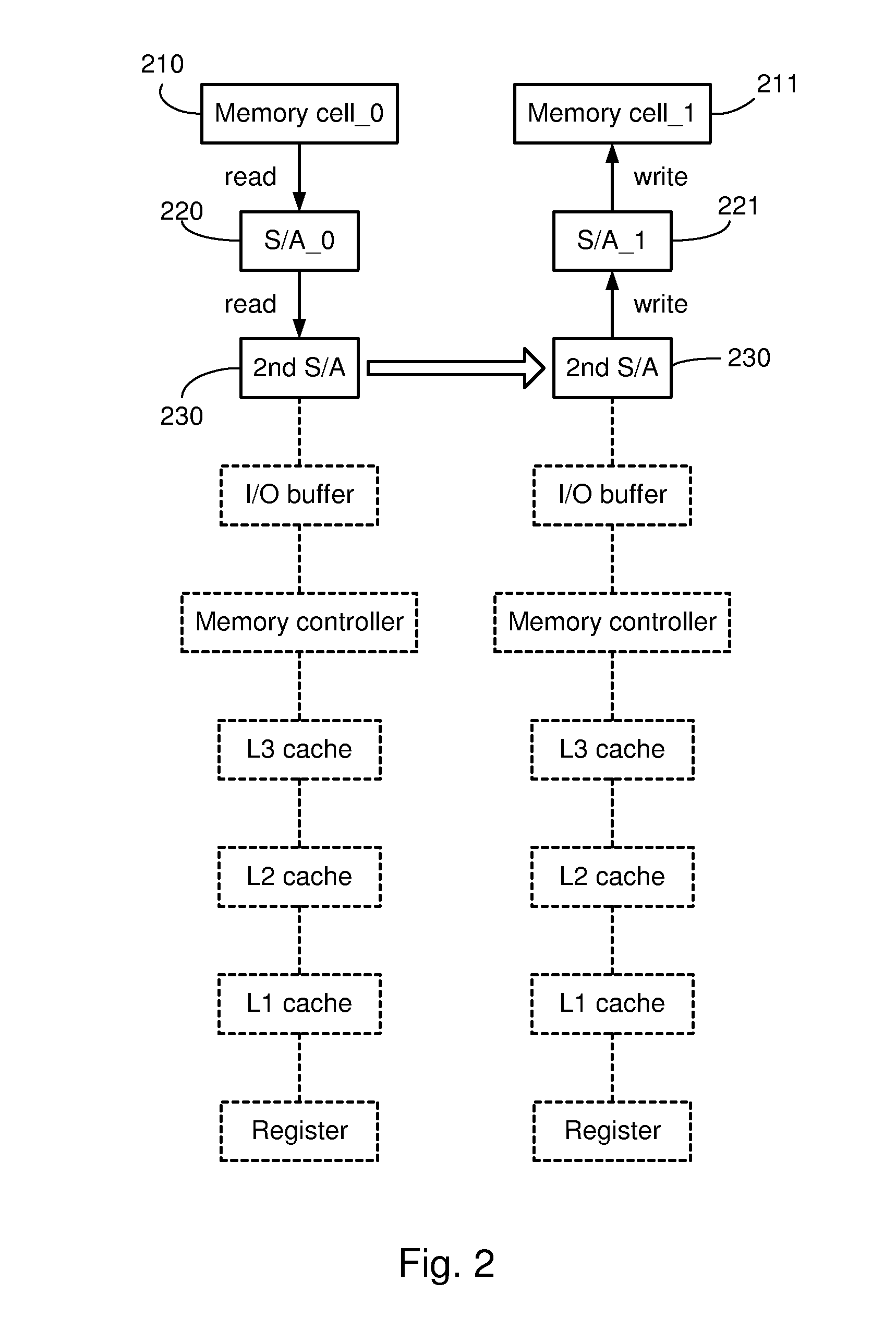

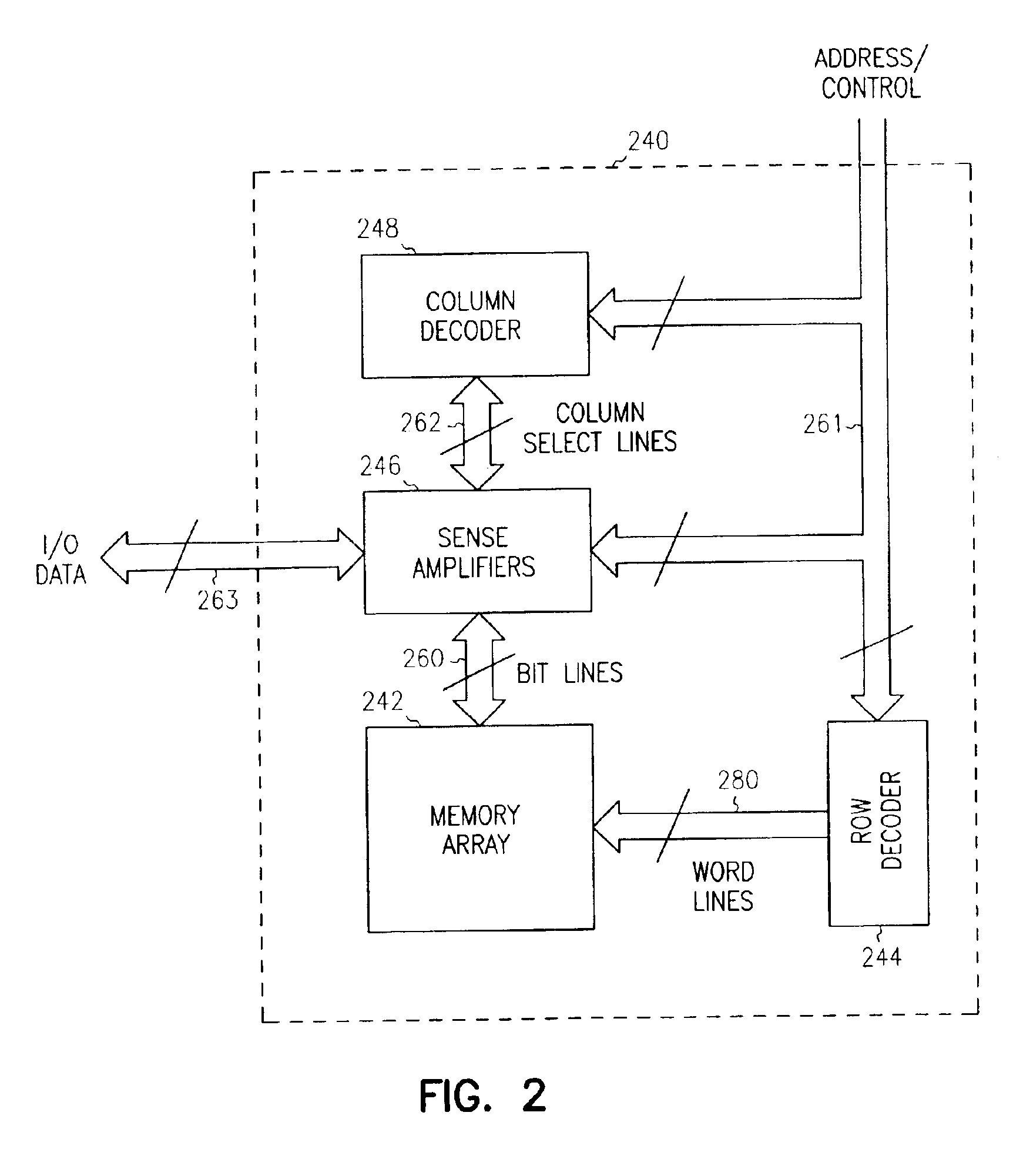

Systems and methods for data transfers between memory cells

Systems and methods for reducing the latency of data transfers between memory cells by enabling data to be transferred directly between sense amplifiers in the memory system. In one embodiment, a memory system uses a conventional DRAM memory structure having a pair of first-level sense amplifiers, a second-level sense amplifier and control logic for the sense amplifiers. Each of the sense amplifiers is configured to be selectively coupled to a data line. In a direct data transfer mode, the control logic generates control signals that cause the sense amplifiers to transfer data from a first one of the first-level sense amplifiers (a source sense amplifier) to the second-level sense amplifier, and from there to a second one of the first-level sense amplifiers (a destination sense amplifier.) The structure of these sense amplifiers is conventional, and the operation of the system is enabled by modified control logic.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

Precharge circuit and non-volatile memory device

A precharge circuit includes a precharge unit configured to apply a voltage of a precharge voltage terminal to a data line during a precharge operation, and a sensing unit configured to disable the precharge unit by sensing the voltage of the precharge voltage terminal, The precharge circuit may control a precharge operation by sensing a change in the voltage level of the precharge voltage terminal.

Owner:SK HYNIX INC

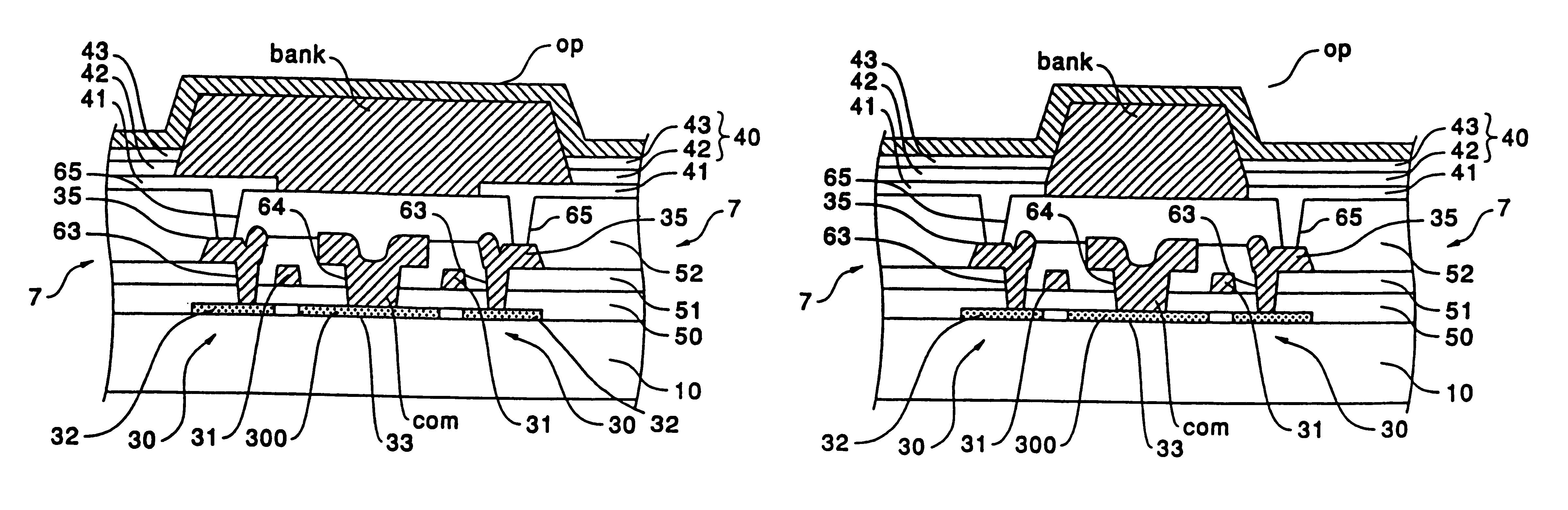

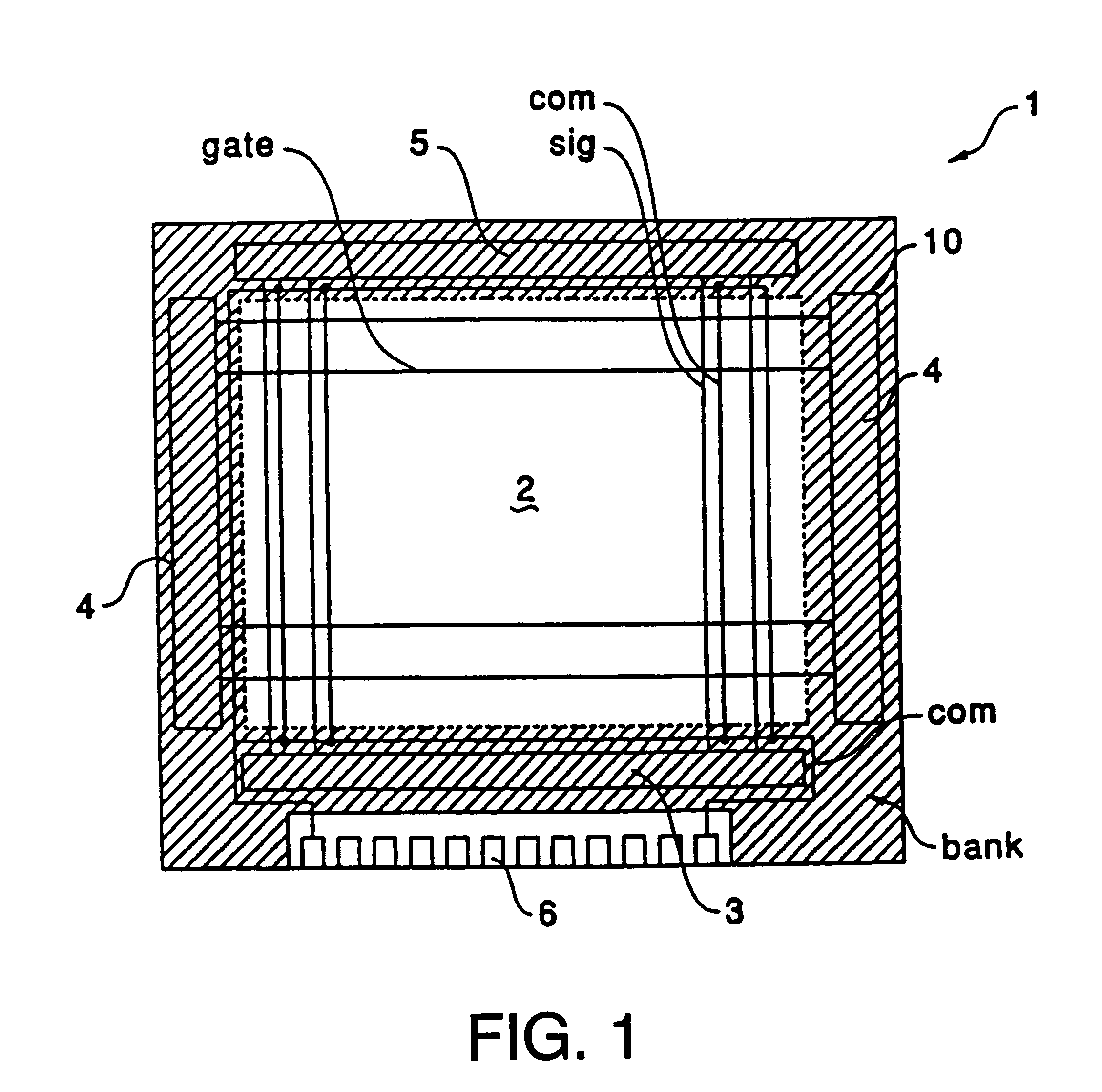

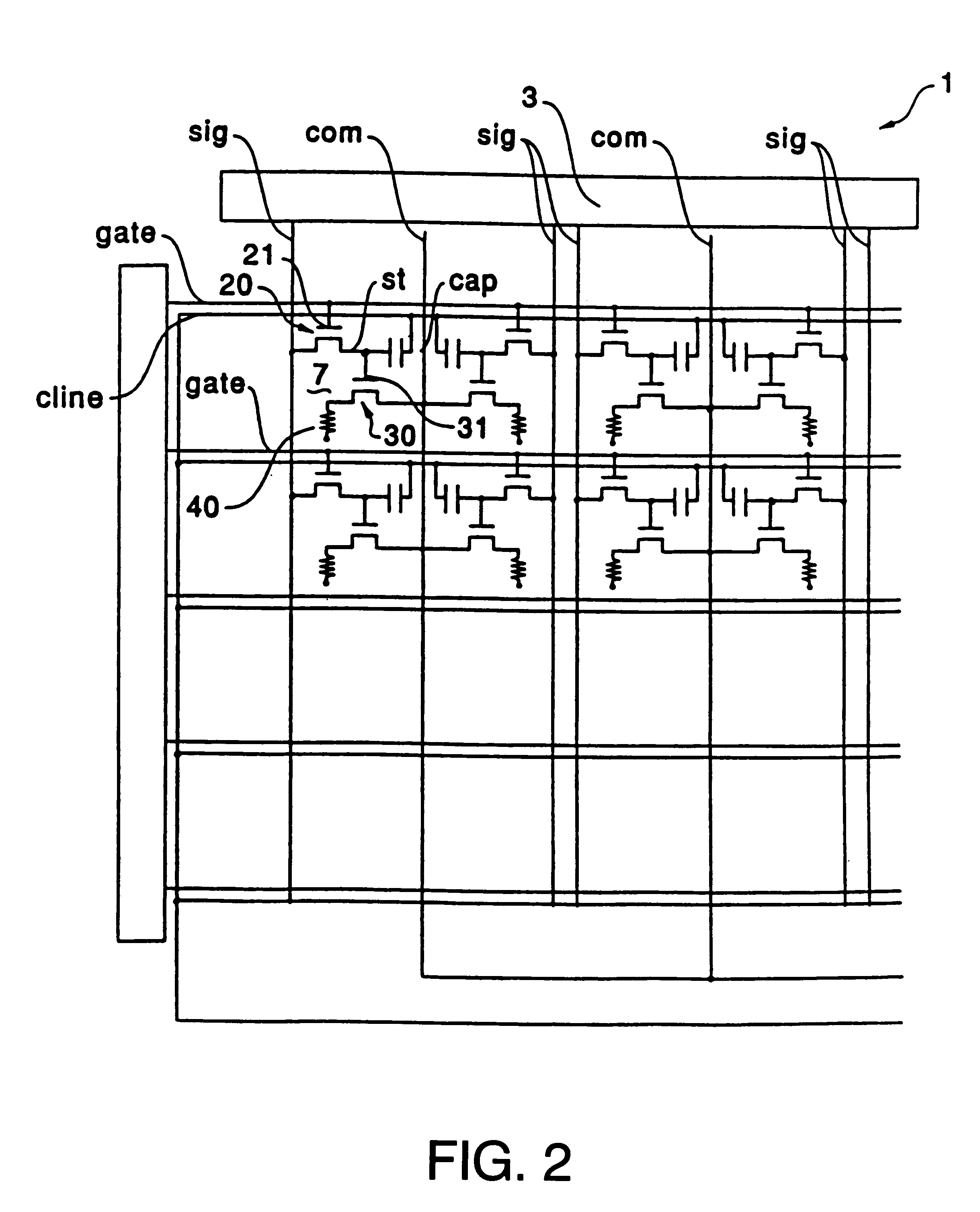

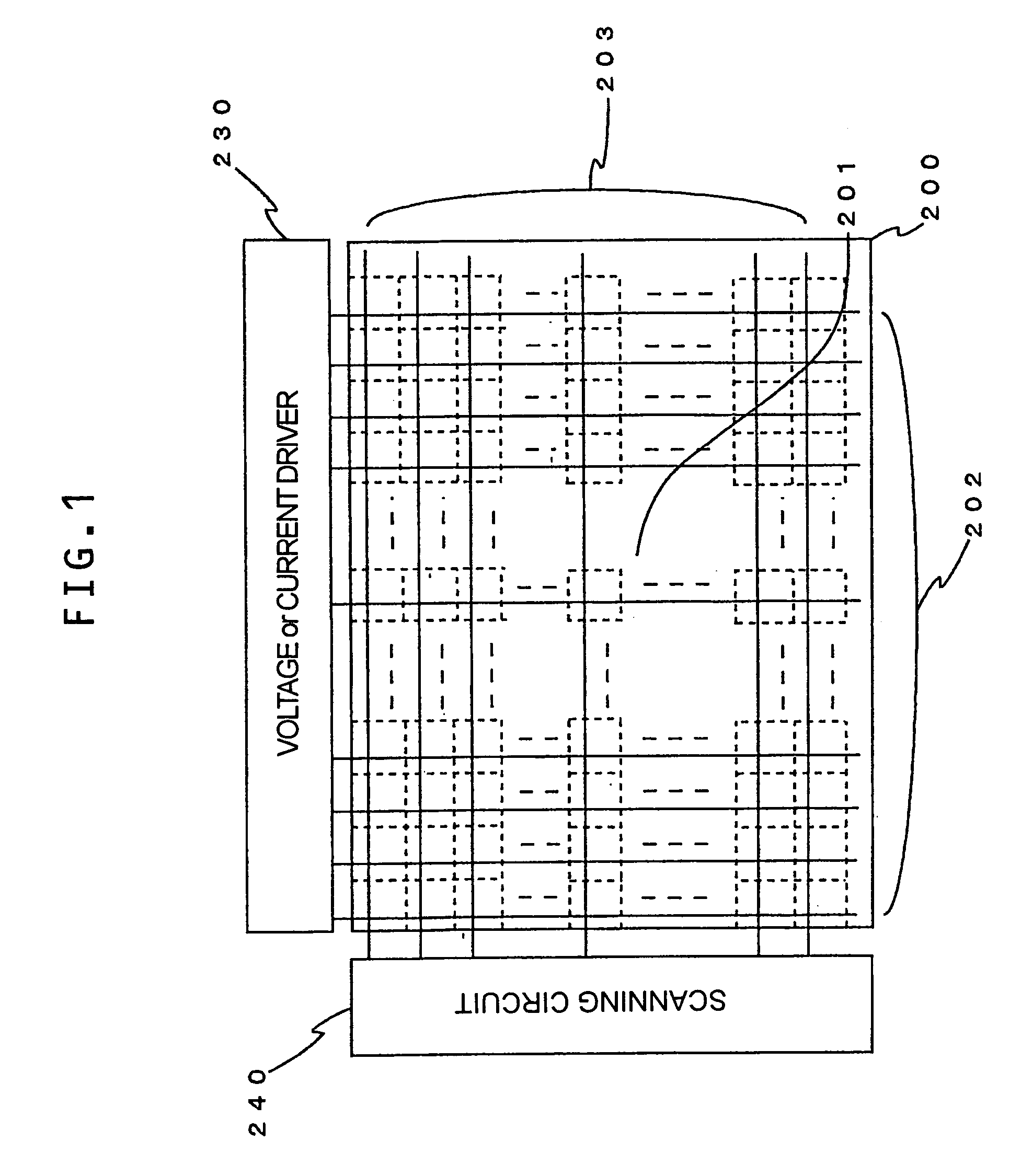

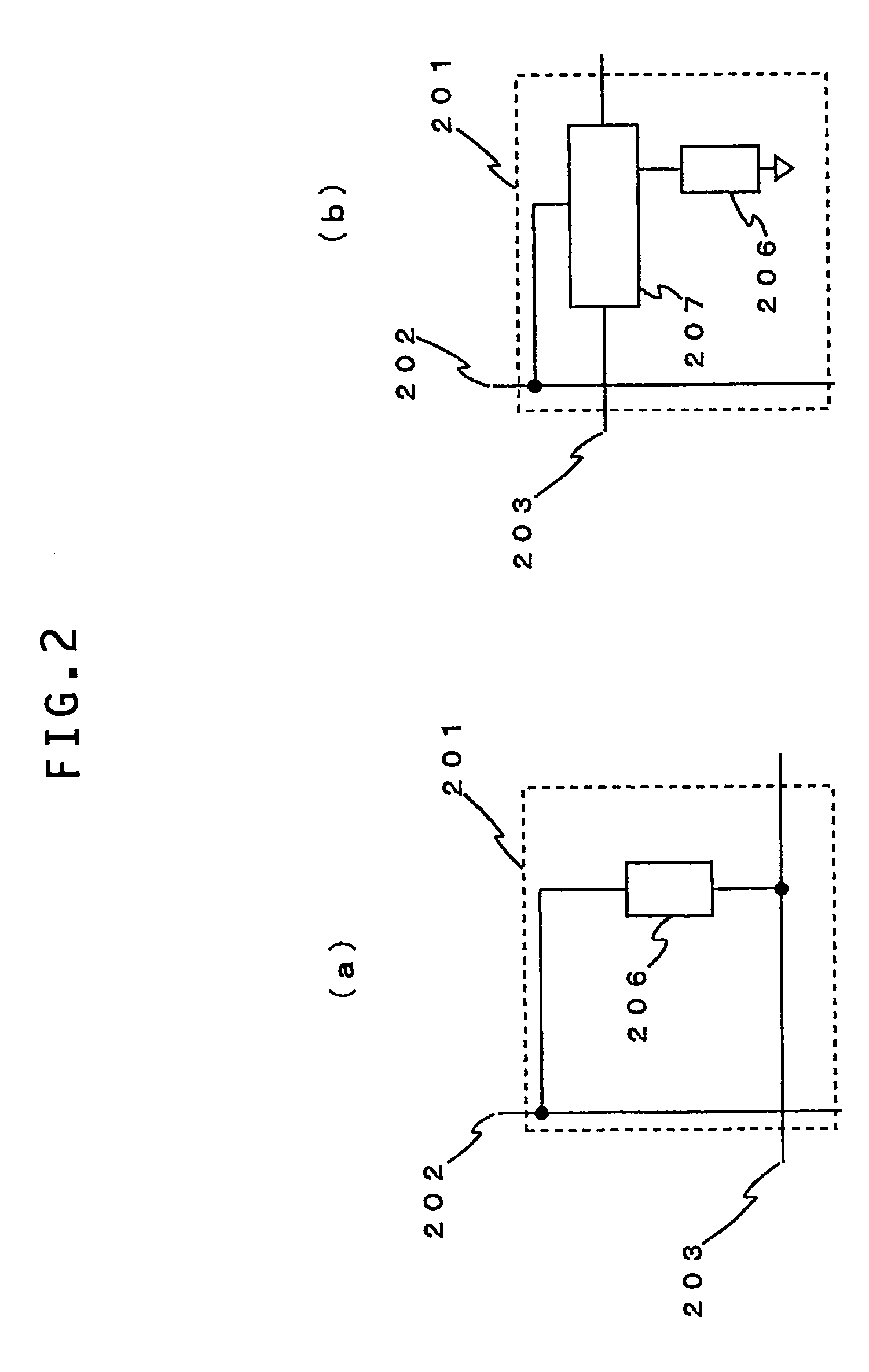

Display device

The invention provides a display device in which parasitic capacitance associated with data lines and driving circuits is prevented using a bank layer whose primary purpose is to define areas on a substrate in which an organic semiconductor film is formed. When the organic semiconductor film for forming a luminescent element such as an electroluminescent element or an LED is formed is formed in pixel regions (7), the organic semiconductor film is formed in the areas surrounded by the bank layer (bank) formed of a black resist. The bank layer (bank) is also formed between an opposite electrode (op) and data lines (sig) for supplying an image signal to first TFTs (20) and holding capacitors (cap) in the pixel regions (7) thereby preventing parasitic capacitance associated with the data lines (sig).

Owner:INTELLECTUAL KEYSTONE TECH LLC

Method of manufacturing semiconductor device

ActiveUS20080299758A1Reduces yield and reliabilityReduce capacitySemiconductor/solid-state device detailsSolid-state devicesHigh densityDevice material

A high-density N-type diffusion layer 116 formed in a separation area 115 makes it possible to reduce a collector current flowing through a parasitic NPN transistor 102. Thus, a normal CMOS process can be used to provide a driving circuit and a data line driver which make it possible to improve resistance to possible noise occurring between adjacent terminals, while controlling a chip size.

Owner:PANNOVA SEMIC

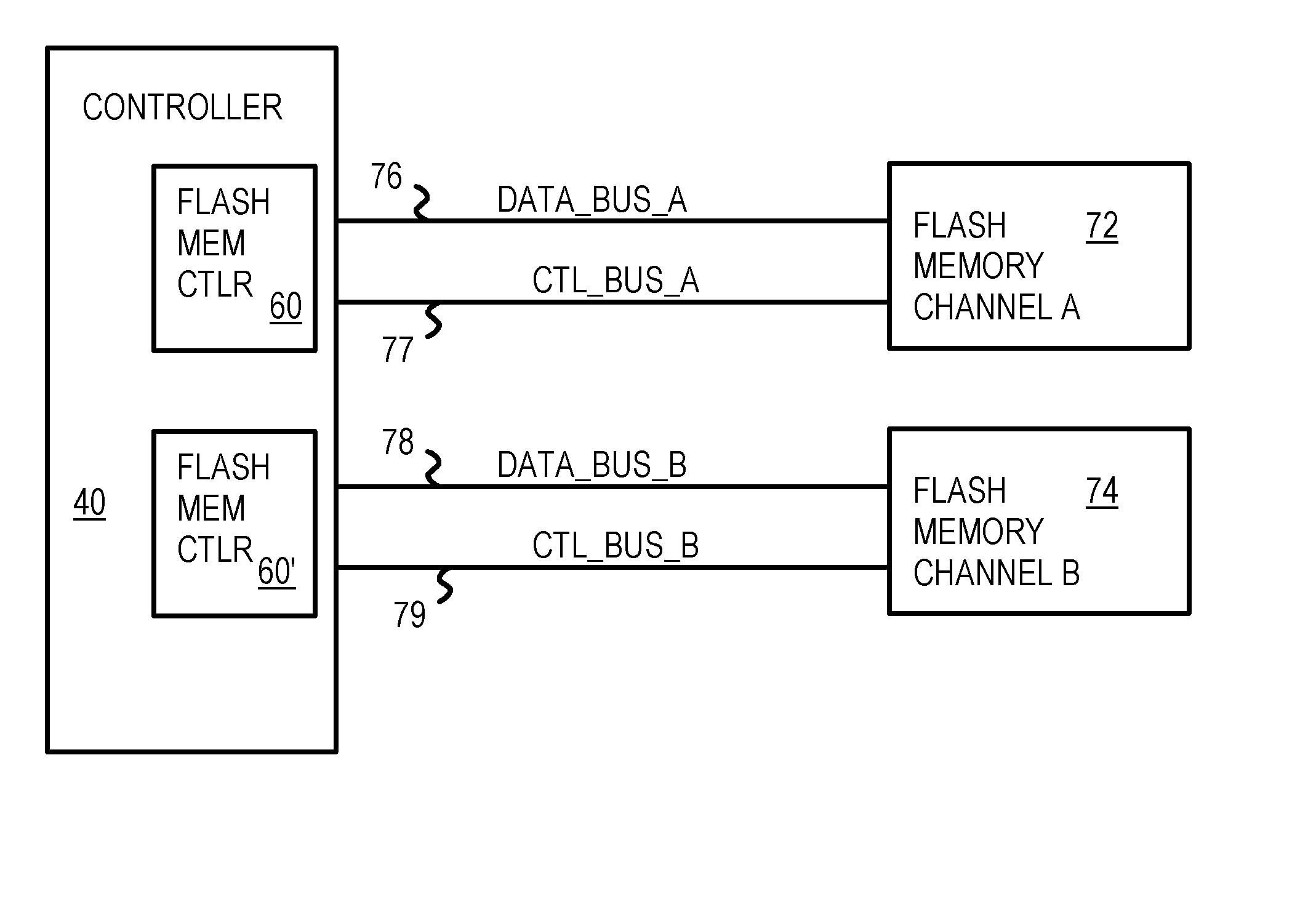

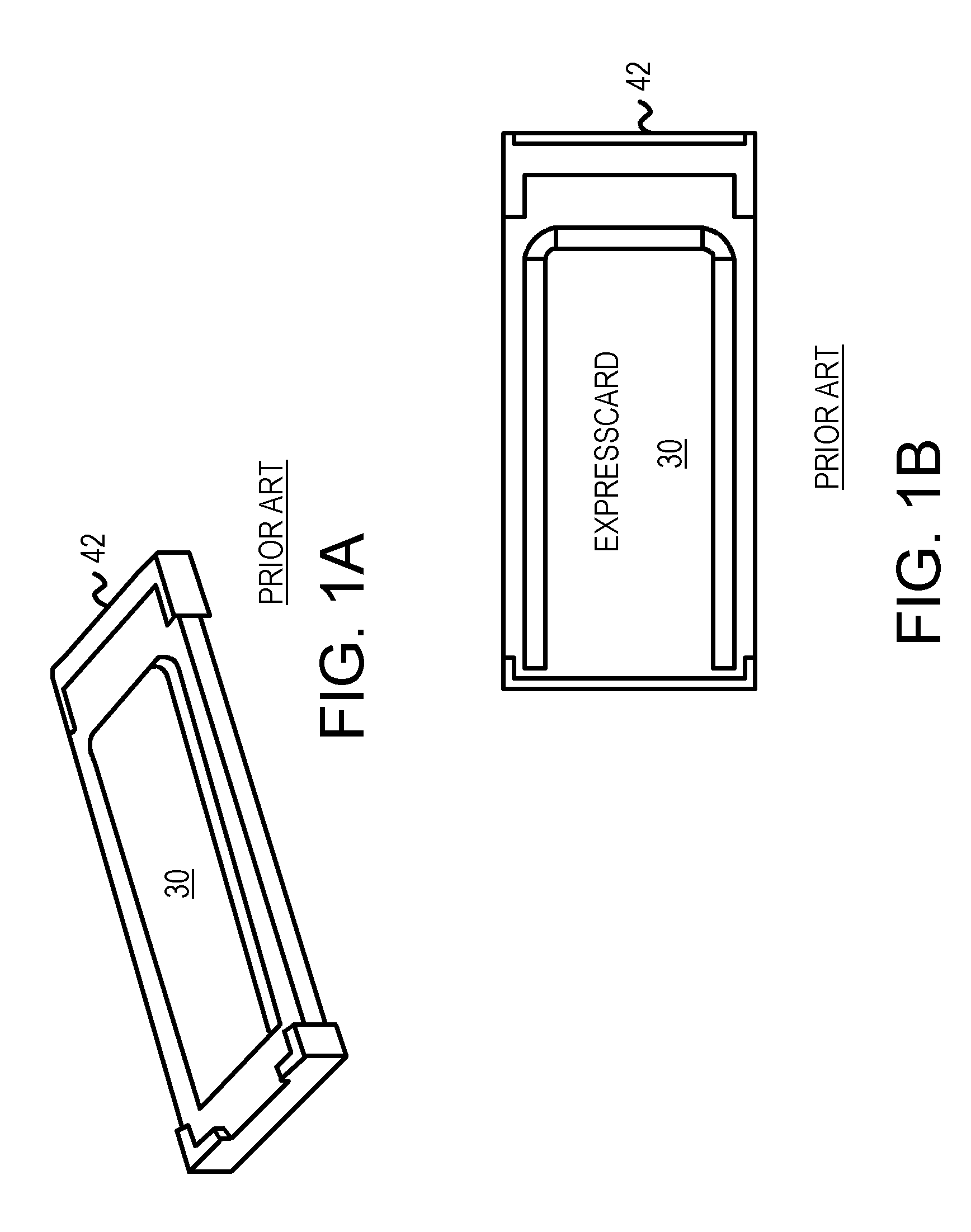

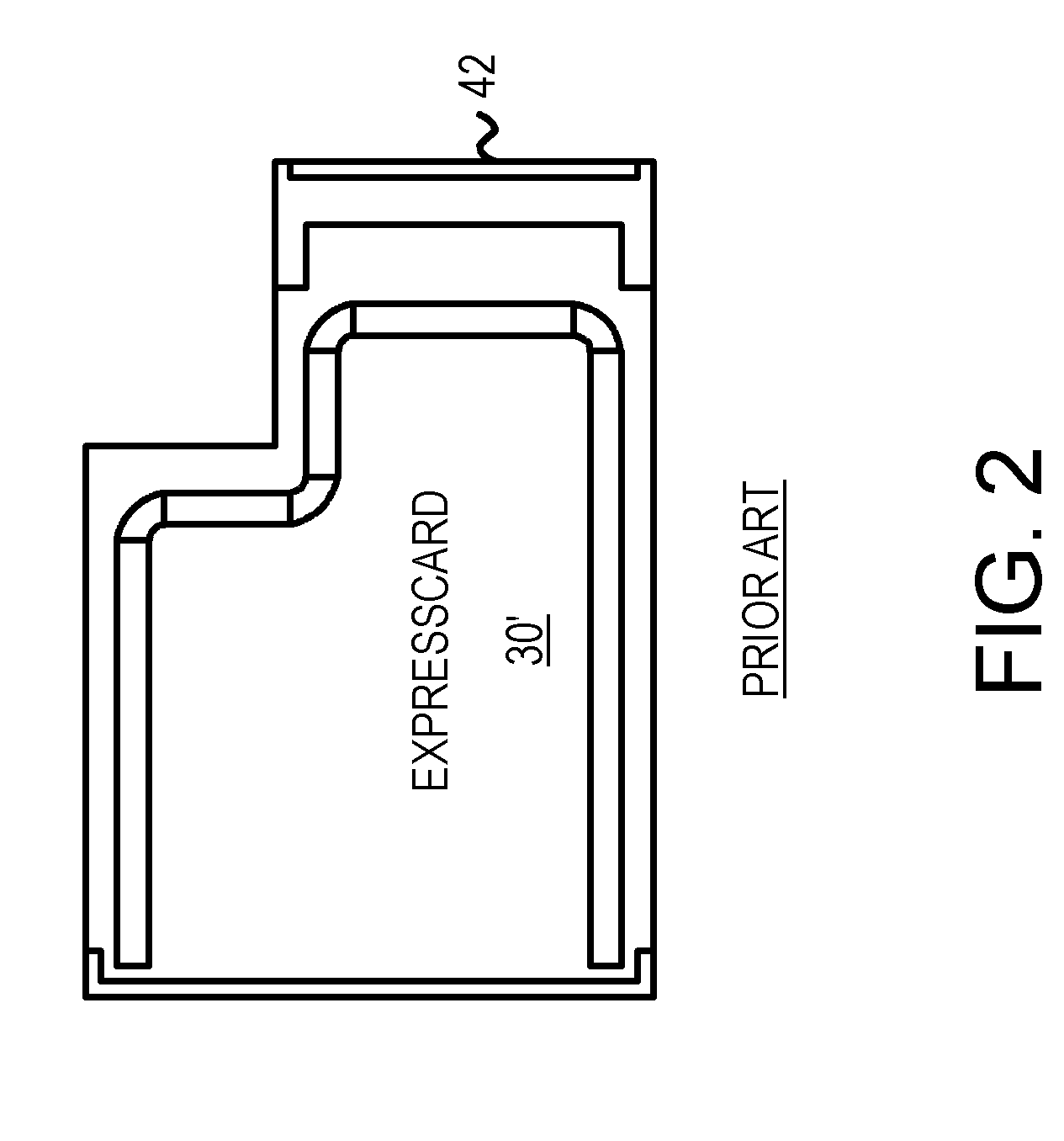

ExpressCard with On-Card Flash Memory with Shared Flash-Control Bus but Separate Ready Lines

An ExpressCard contains flash memory. The ExpressCard has an ExpressCard connector that plugs into a host, such as a personal computer, digital camera, or personal digital assistant (PDA). A controller chip on the ExpressCard uses a pair of differential Universal-Serial-Bus (USB) data lines in the connector to communicate with the USB host, or can use PCI Express, Firewire, or other protocols. One or more flash-memory chips on the ExpressCard are controlled by a flash-memory controller in the controller chip. Two or more channels of a flash bus have a shared control bus but separate ready lines. The separate ready lines allow flash-memory chips in the two channels to finish operations at different times.

Owner:SUPER TALENT ELECTRONICS

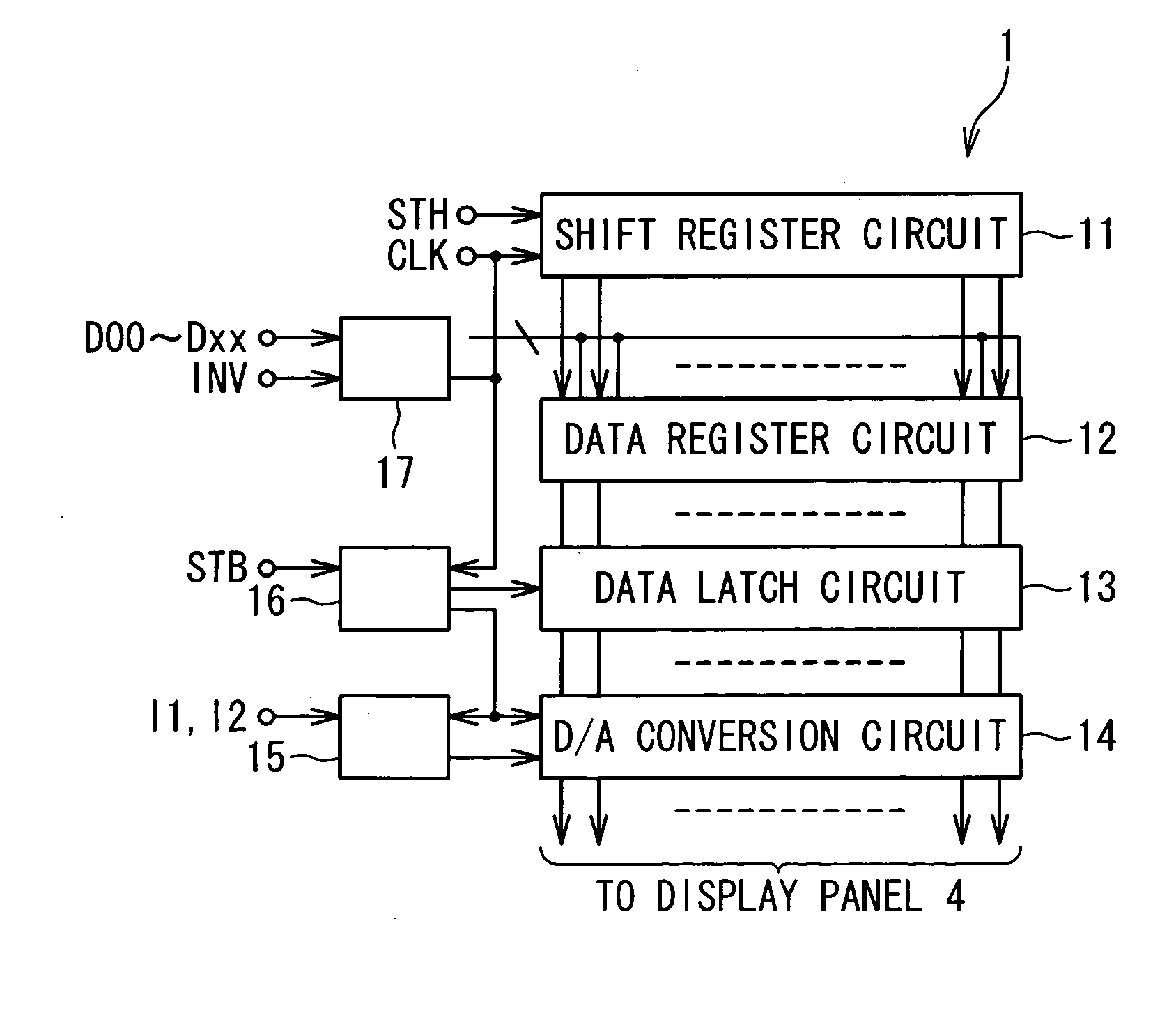

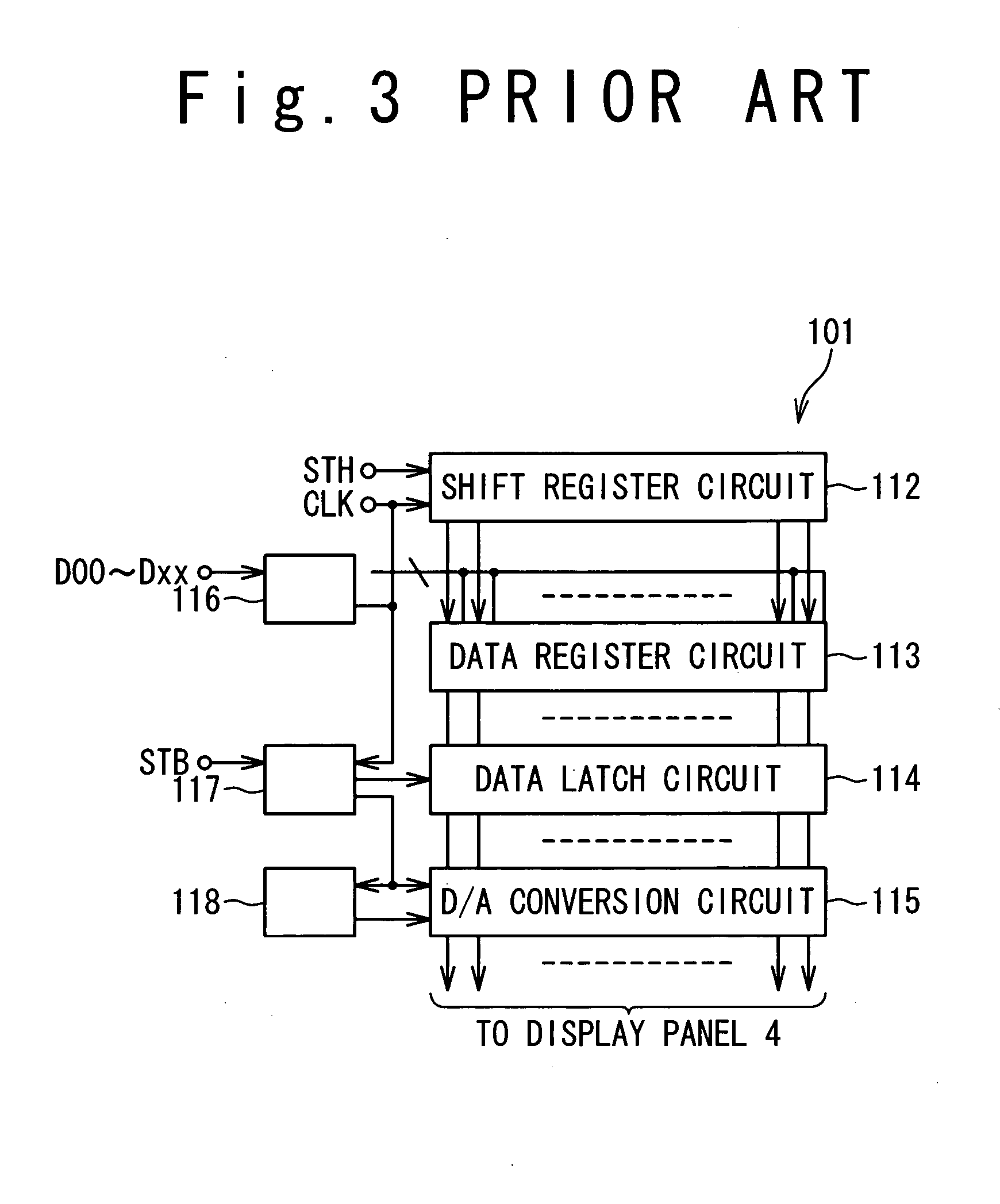

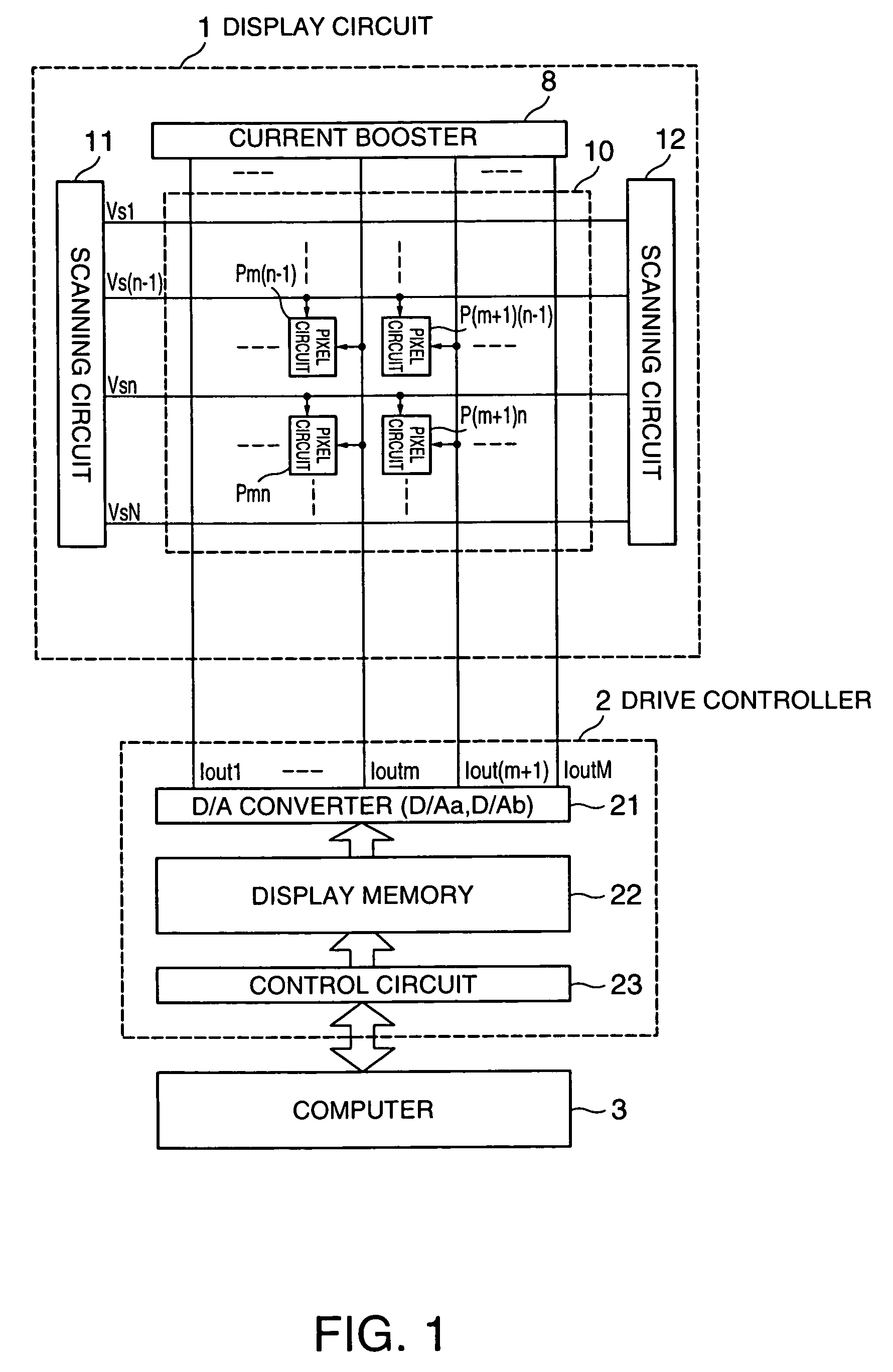

Display apparatus, and driving circuit for the same

ActiveUS20050168416A1Electroluminescent light sourcesSolid-state devicesCurrent driverElectrical current

A drive circuit for a display apparatus includes a gradation voltage generation circuit and a D / A conversion circuit. The gradation voltage generation circuit generates a plurality of different first gradation voltages and a plurality of different second gradation voltages. The D / A conversion circuit drives a light emitting element of a pixel through a data line with a gradation voltage based on one of the first gradation voltages as a first specific gradation voltage in a precharge period and drives the light emitting element of the pixel through the data line with a gradation current based on one of the second gradation voltages as a second specific gradation voltage. The D / A conversion circuit includes a voltage driver to drive the light emitting element, and a current driver to drive the light emitting element.

Owner:RENESAS ELECTRONICS CORP

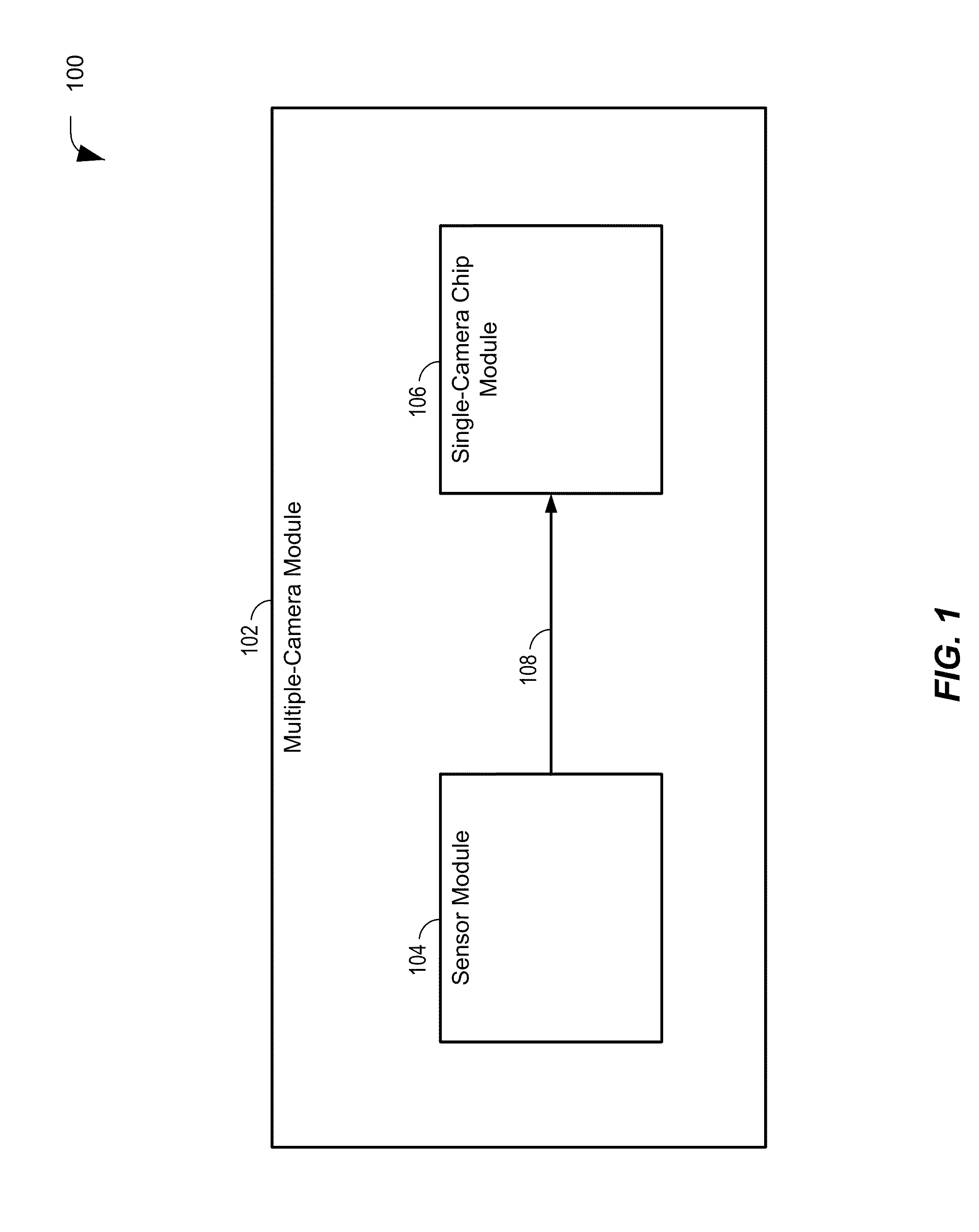

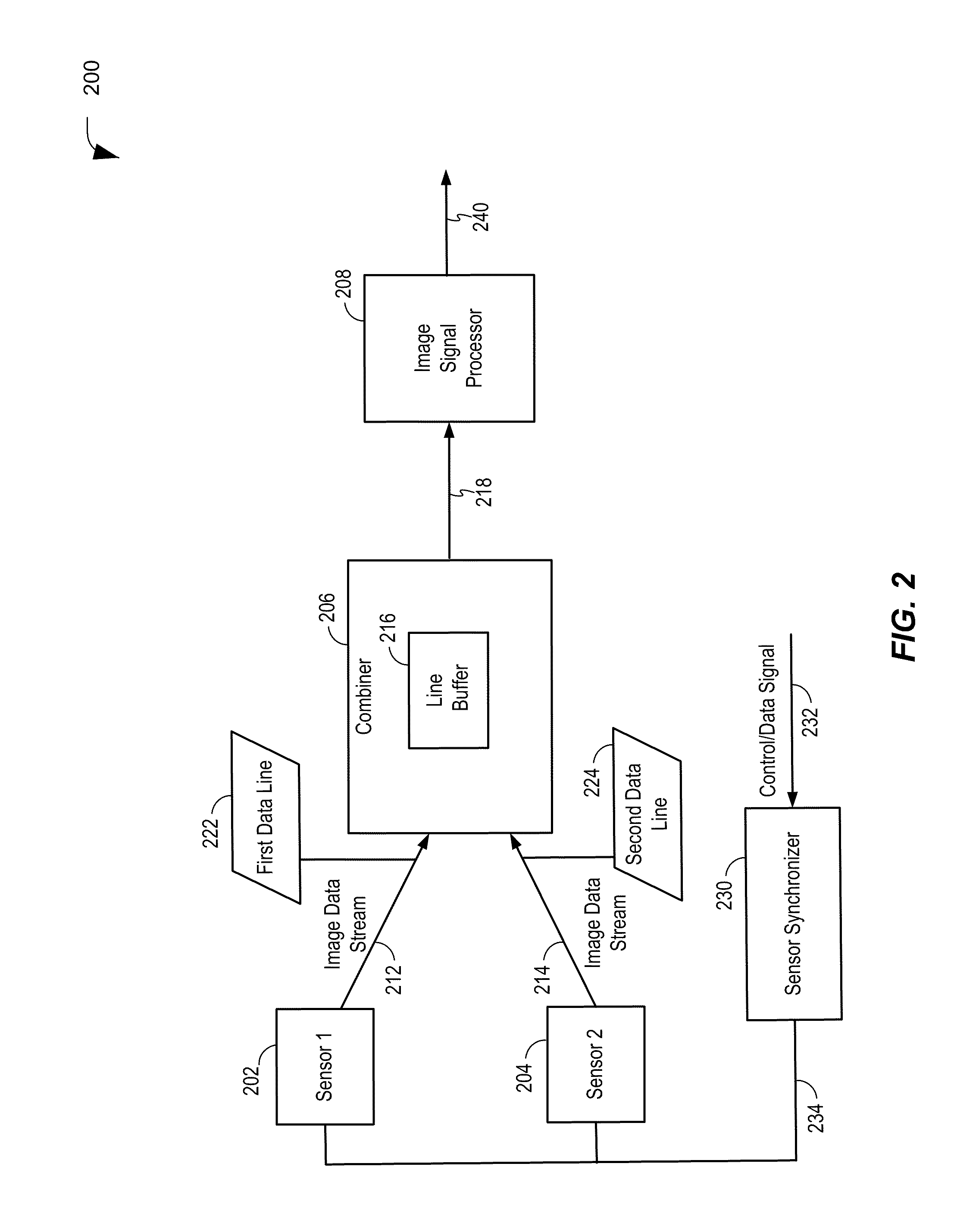

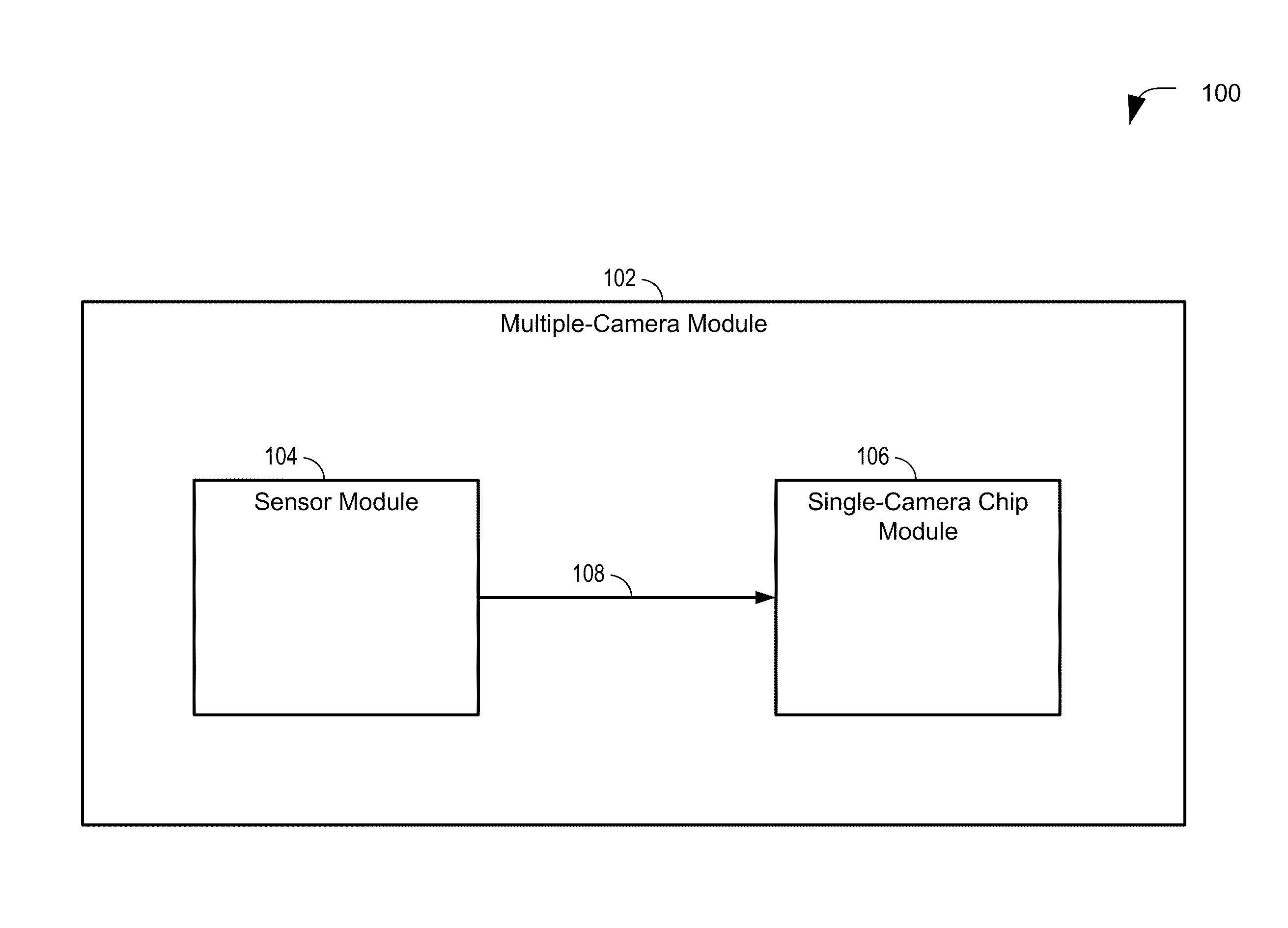

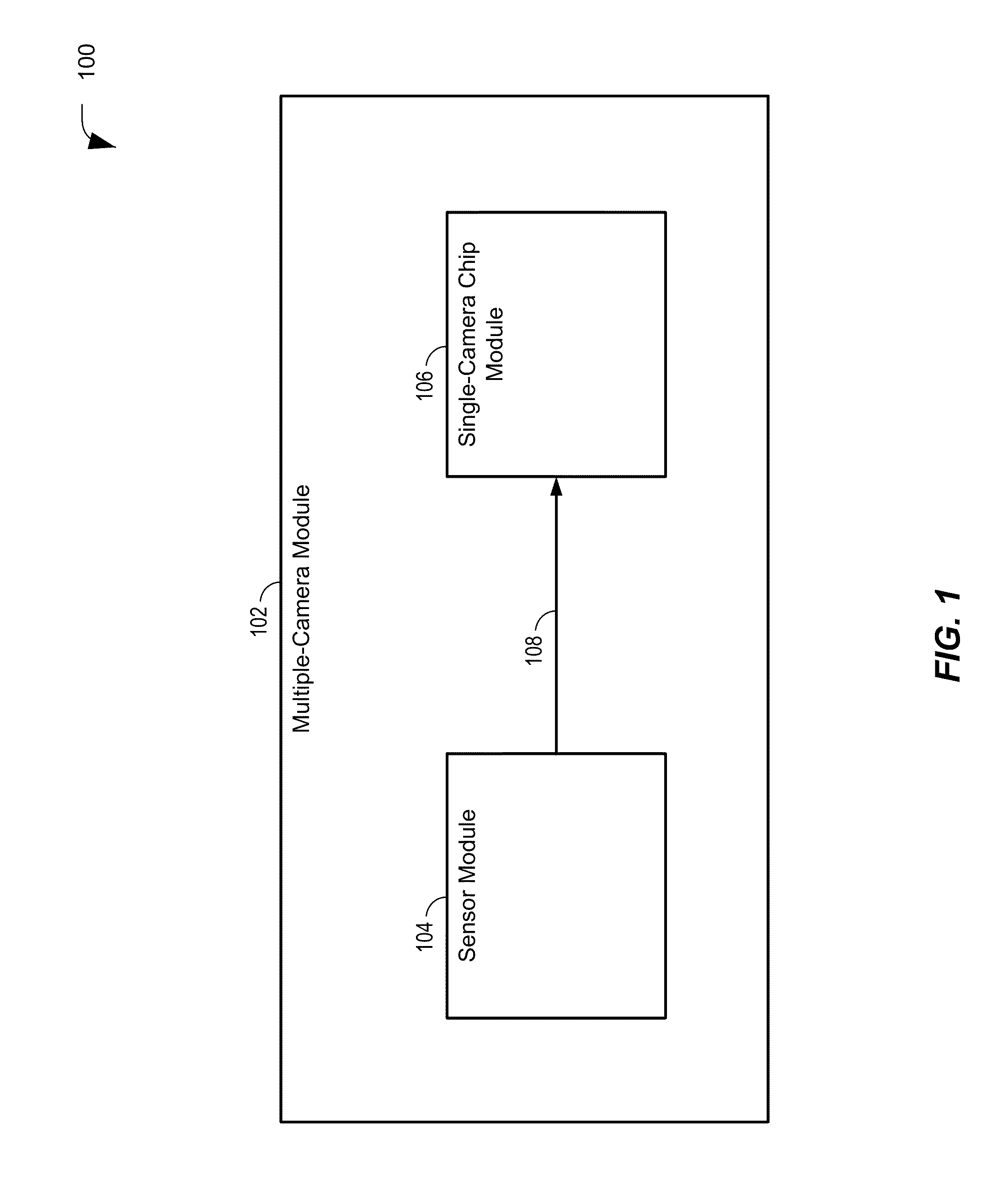

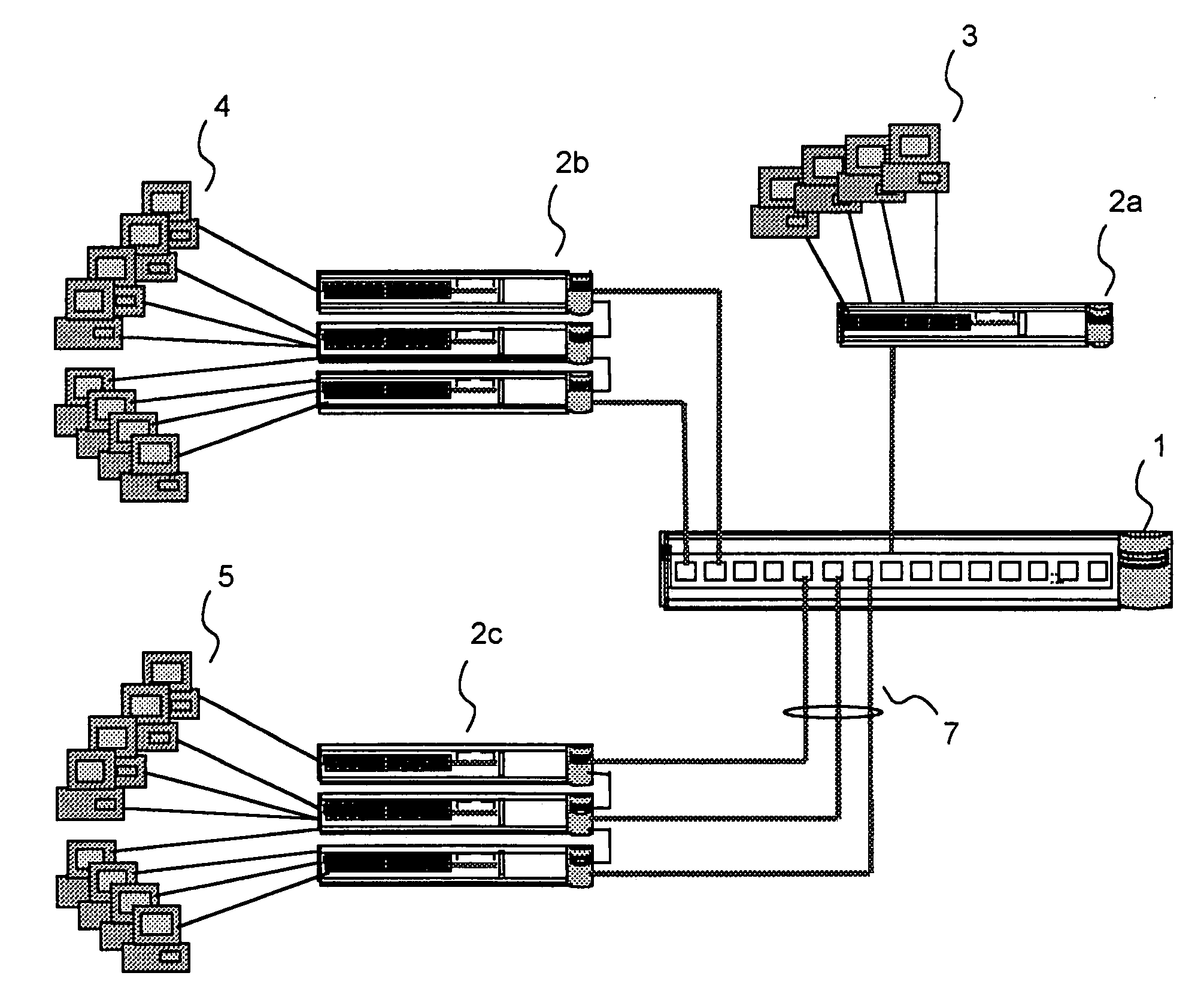

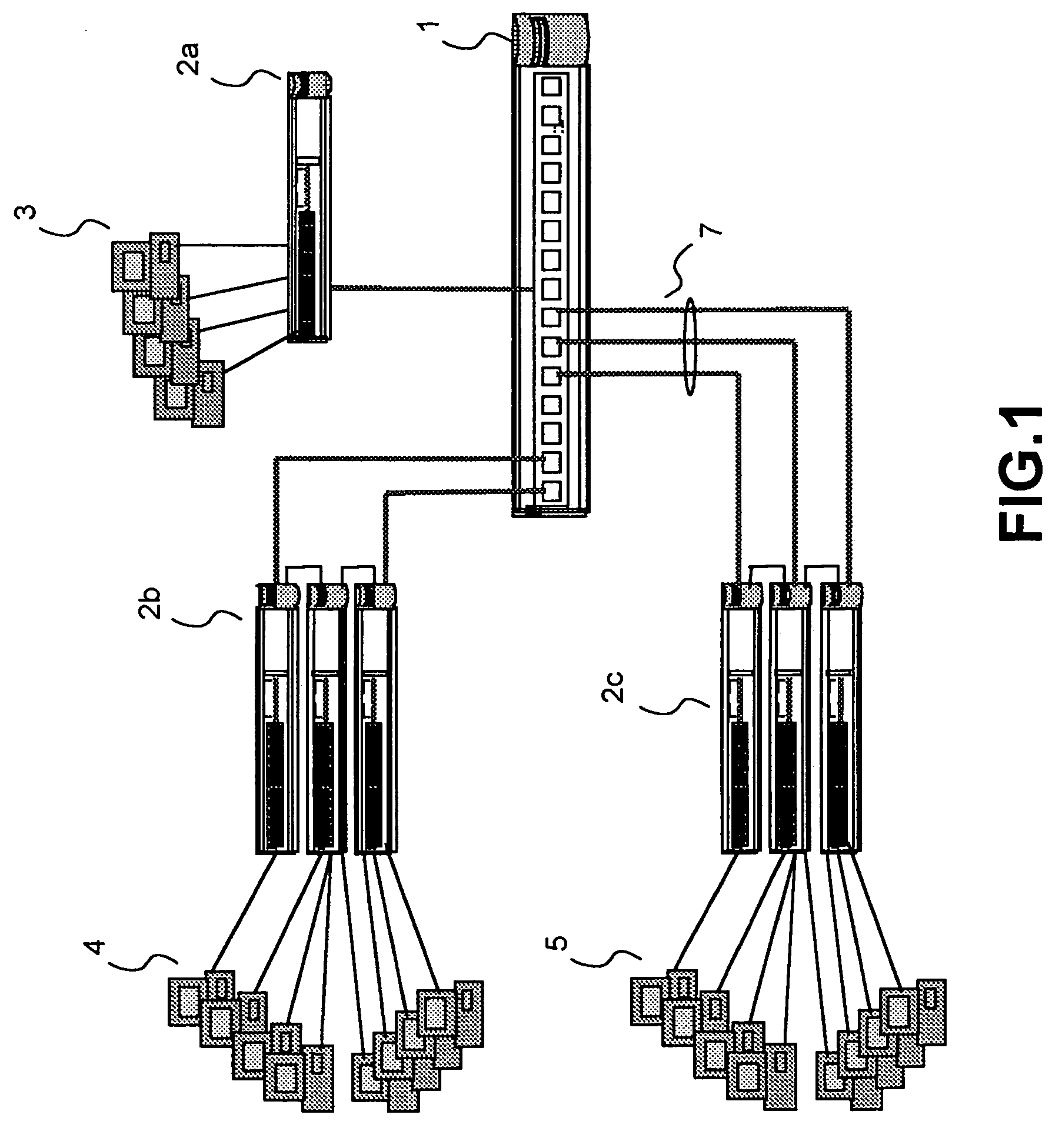

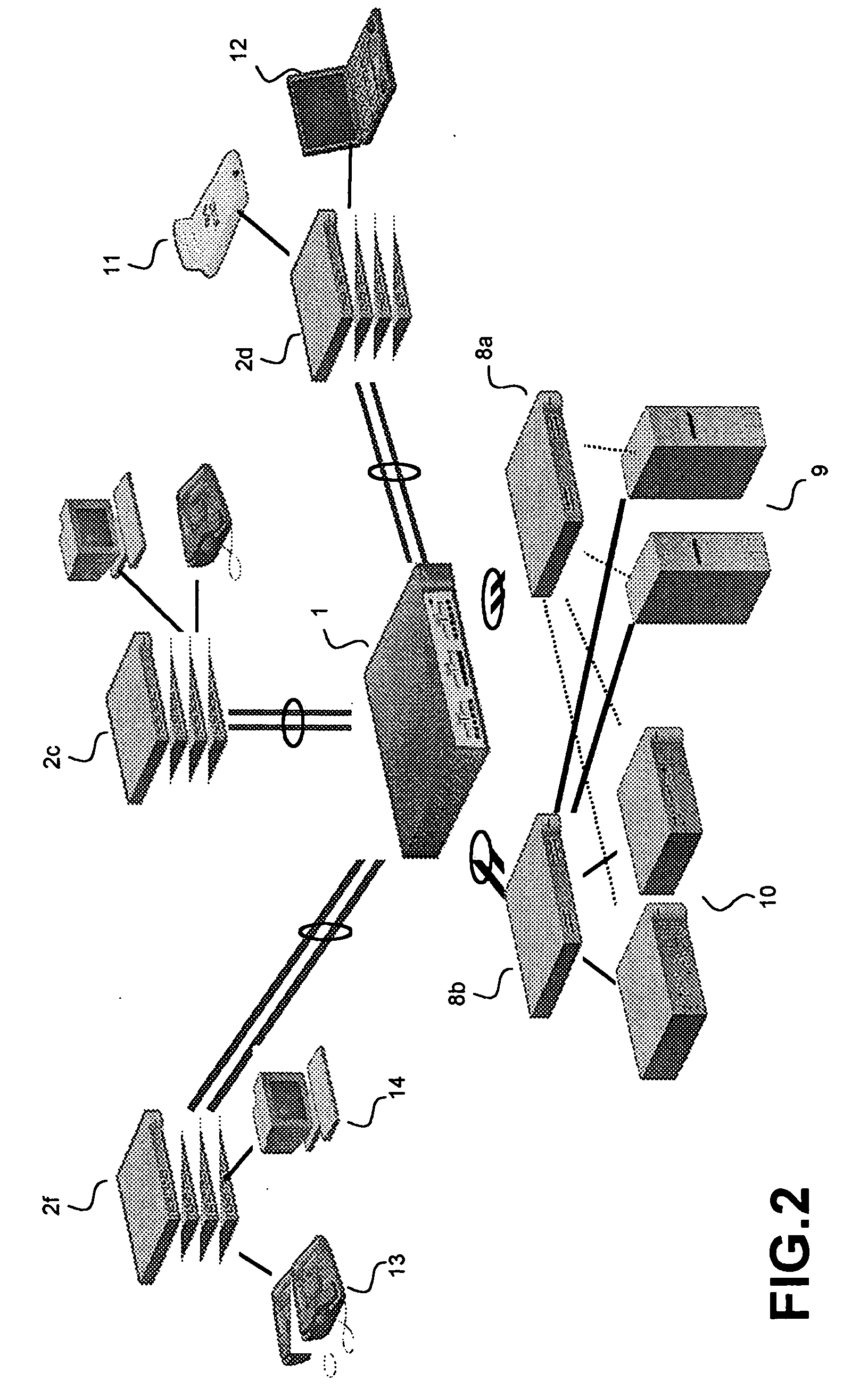

Combining data from multiple image sensors

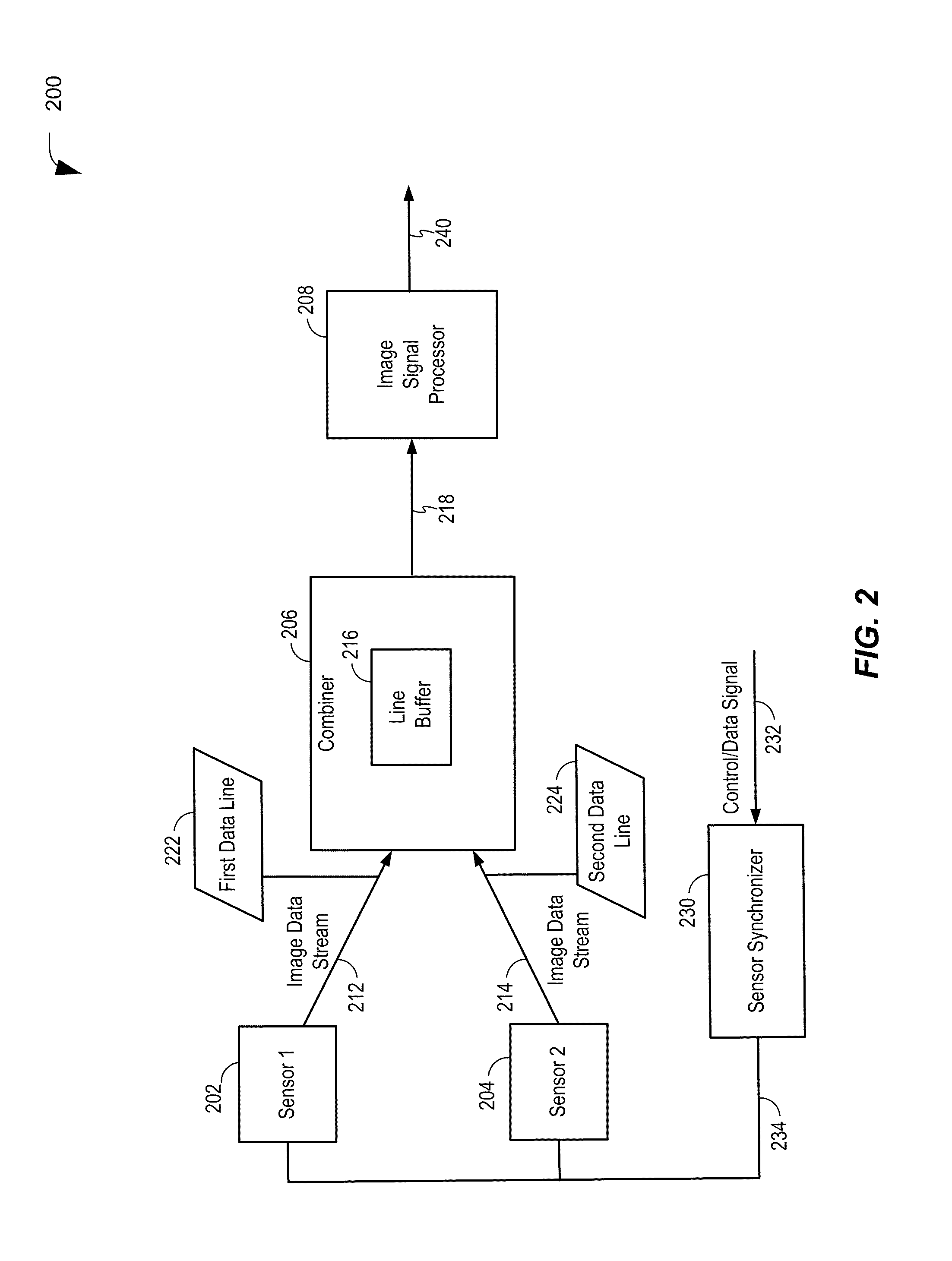

InactiveUS20110242342A1Avoid pollutionTelevision system detailsSteroscopic systemsControl signalMultiple sensor

A method of combining data from multiple sensors is disclosed. The method includes providing a common control signal to multiple image sensors to be synchronized. The method further includes receiving a first data line from a first image sensor of the multiple image sensors, receiving a second data line from a second image sensor of the multiple image sensors, and combining the first data line and the second data line to generate a synchronized data line.

Owner:QUALCOMM INC

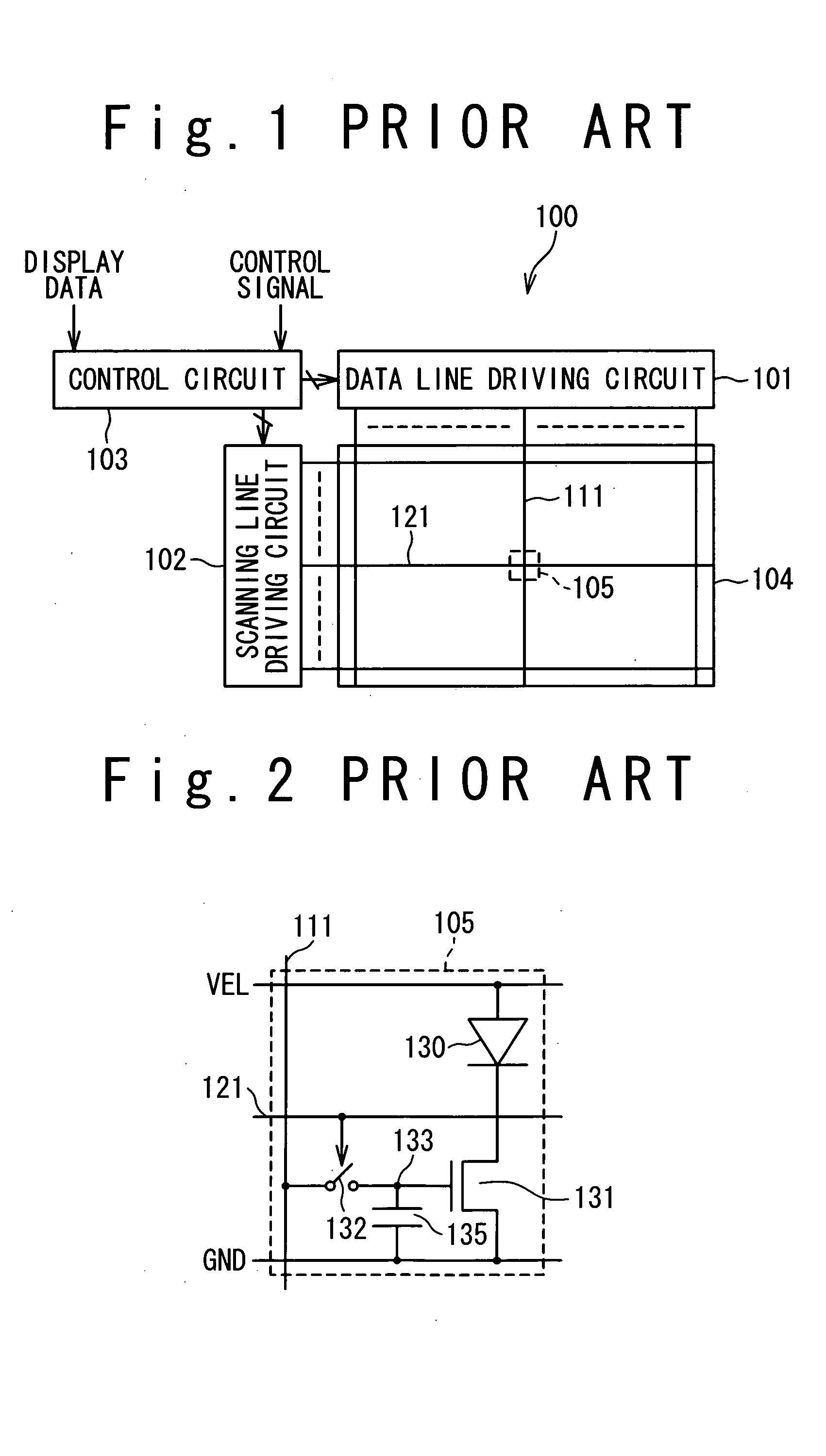

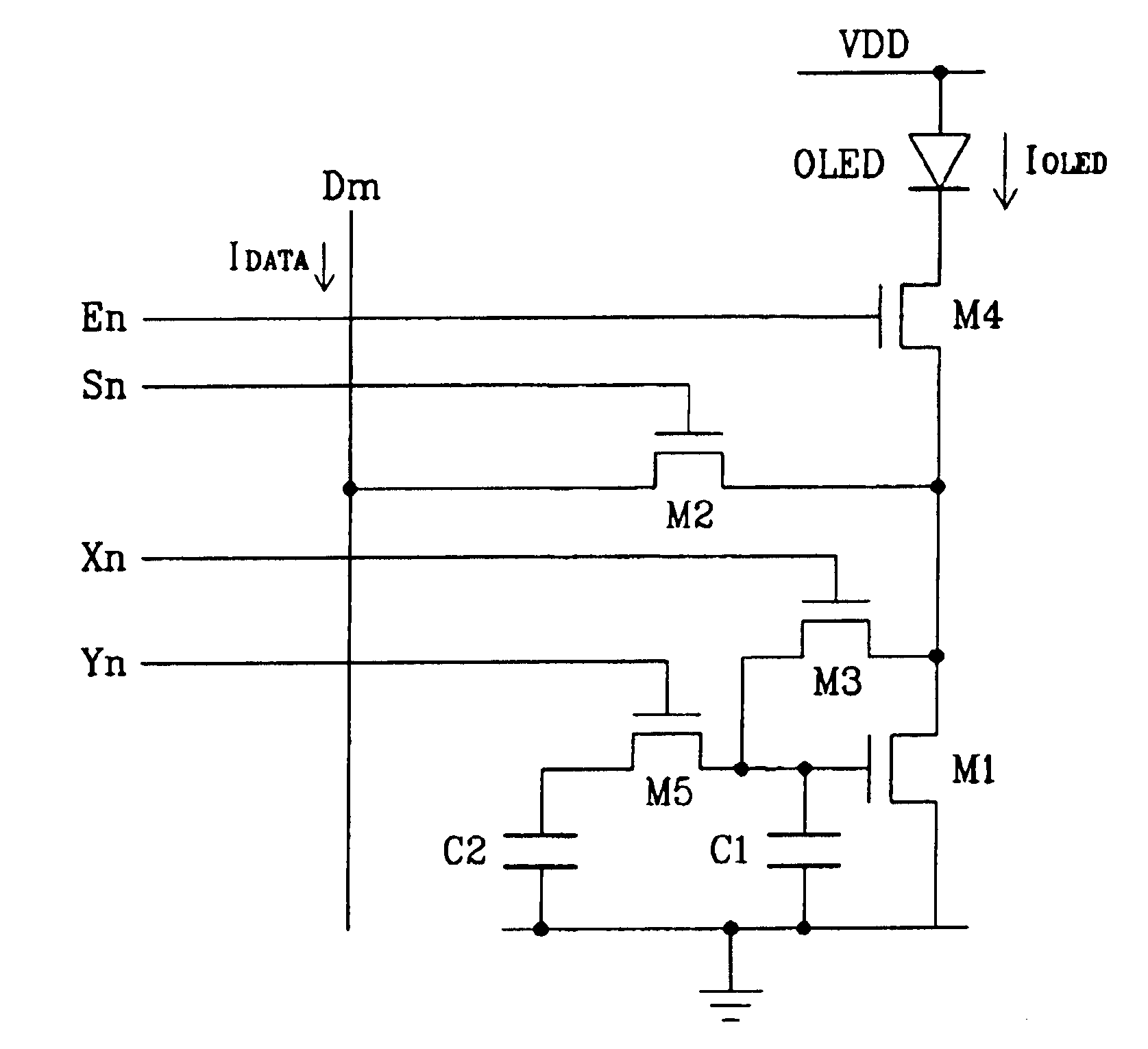

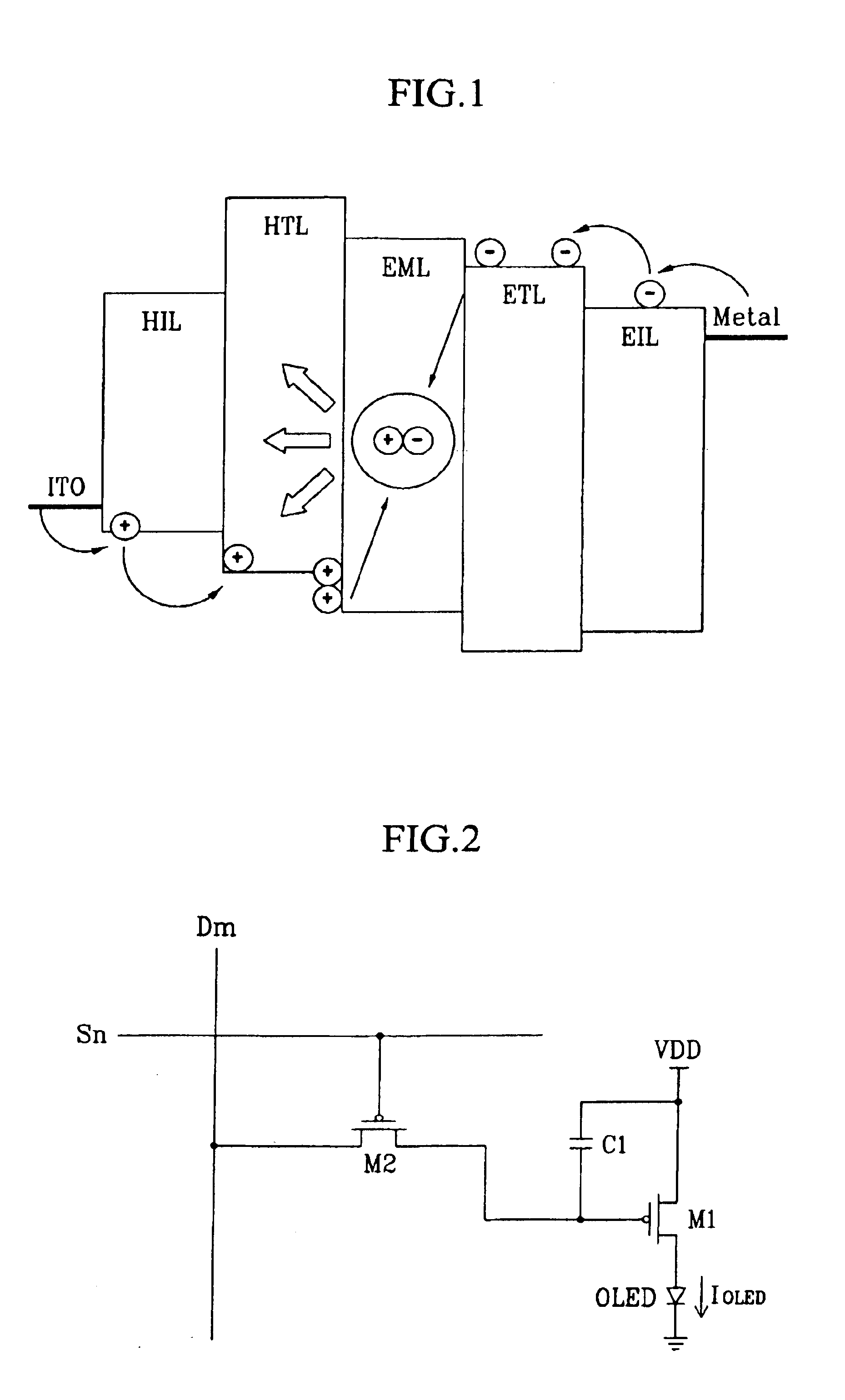

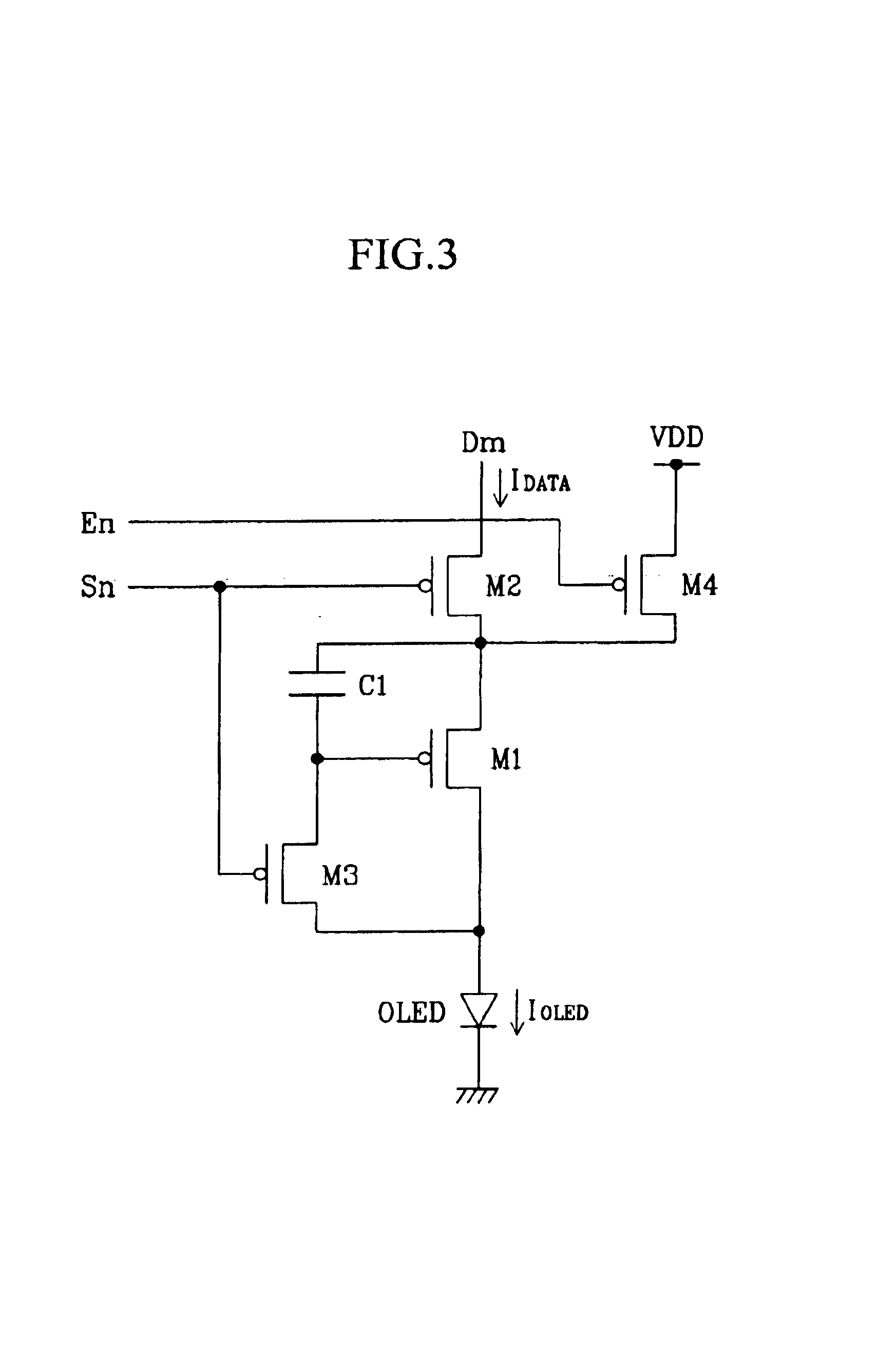

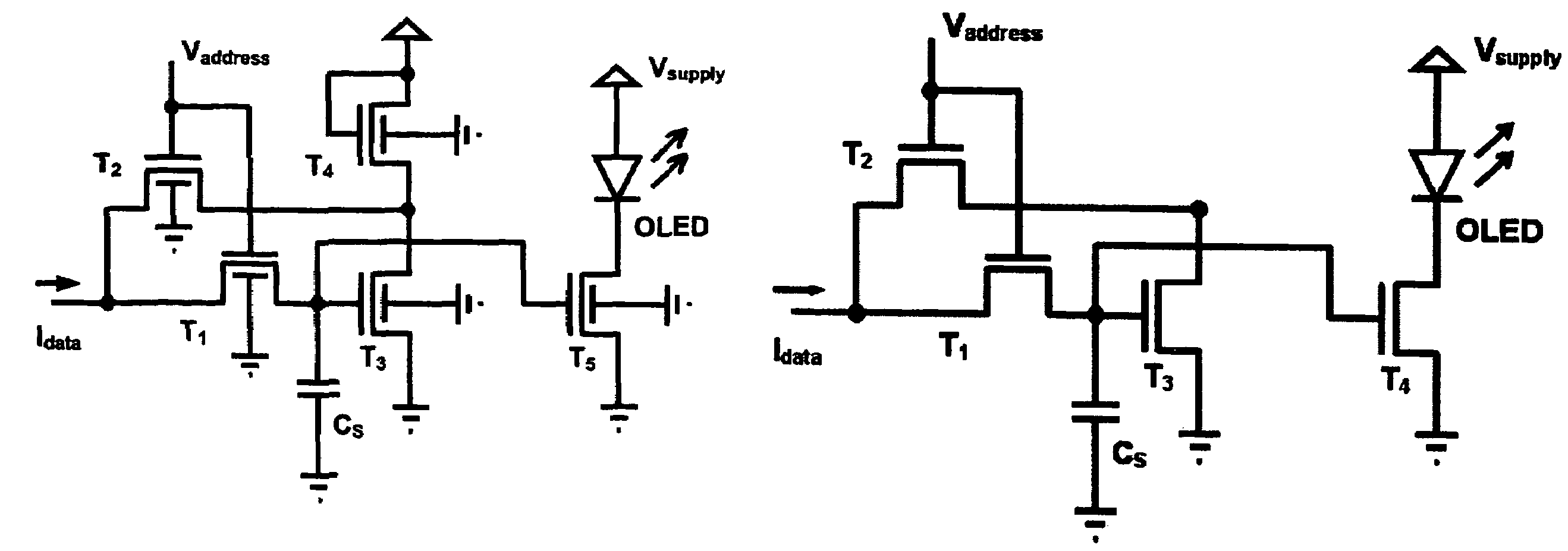

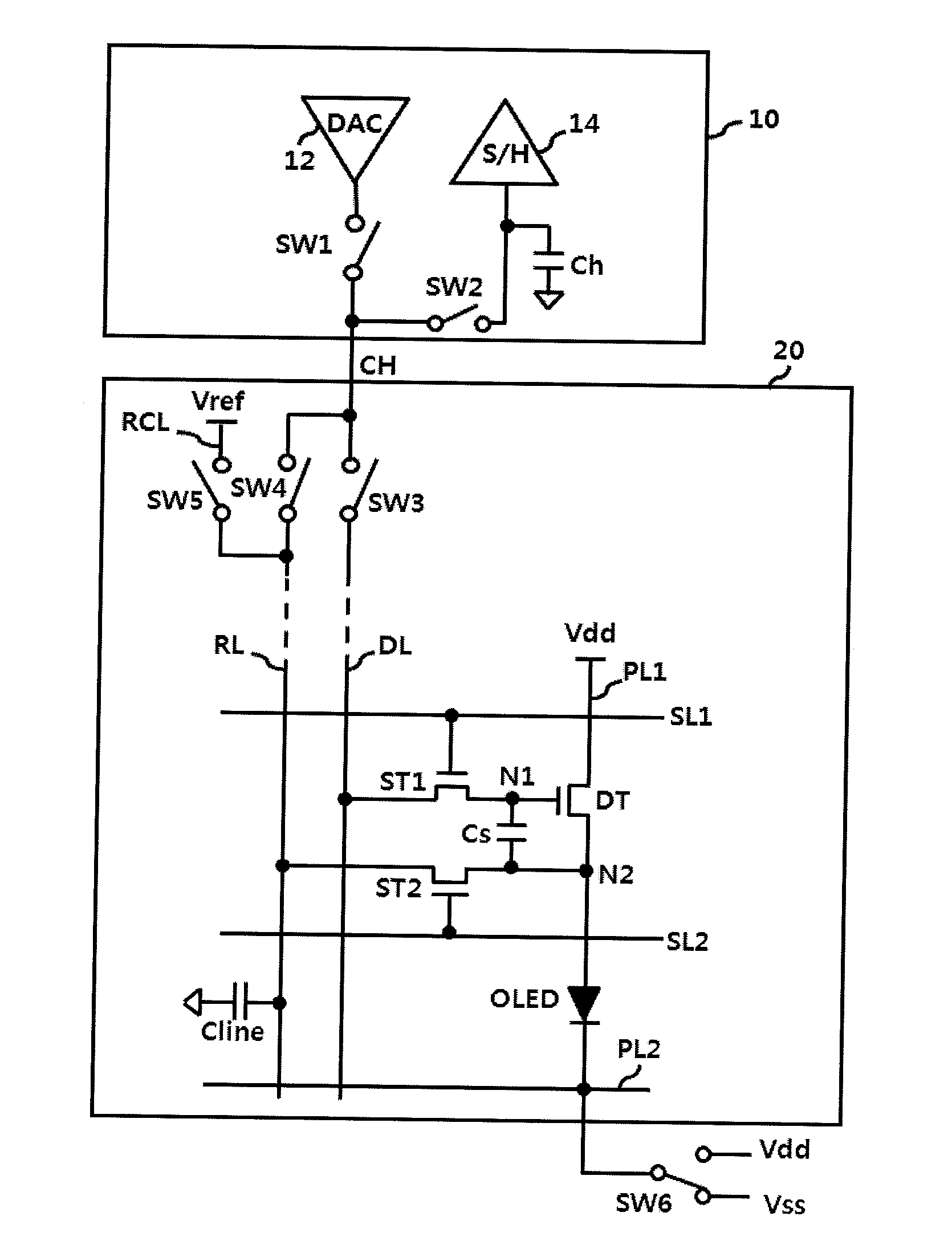

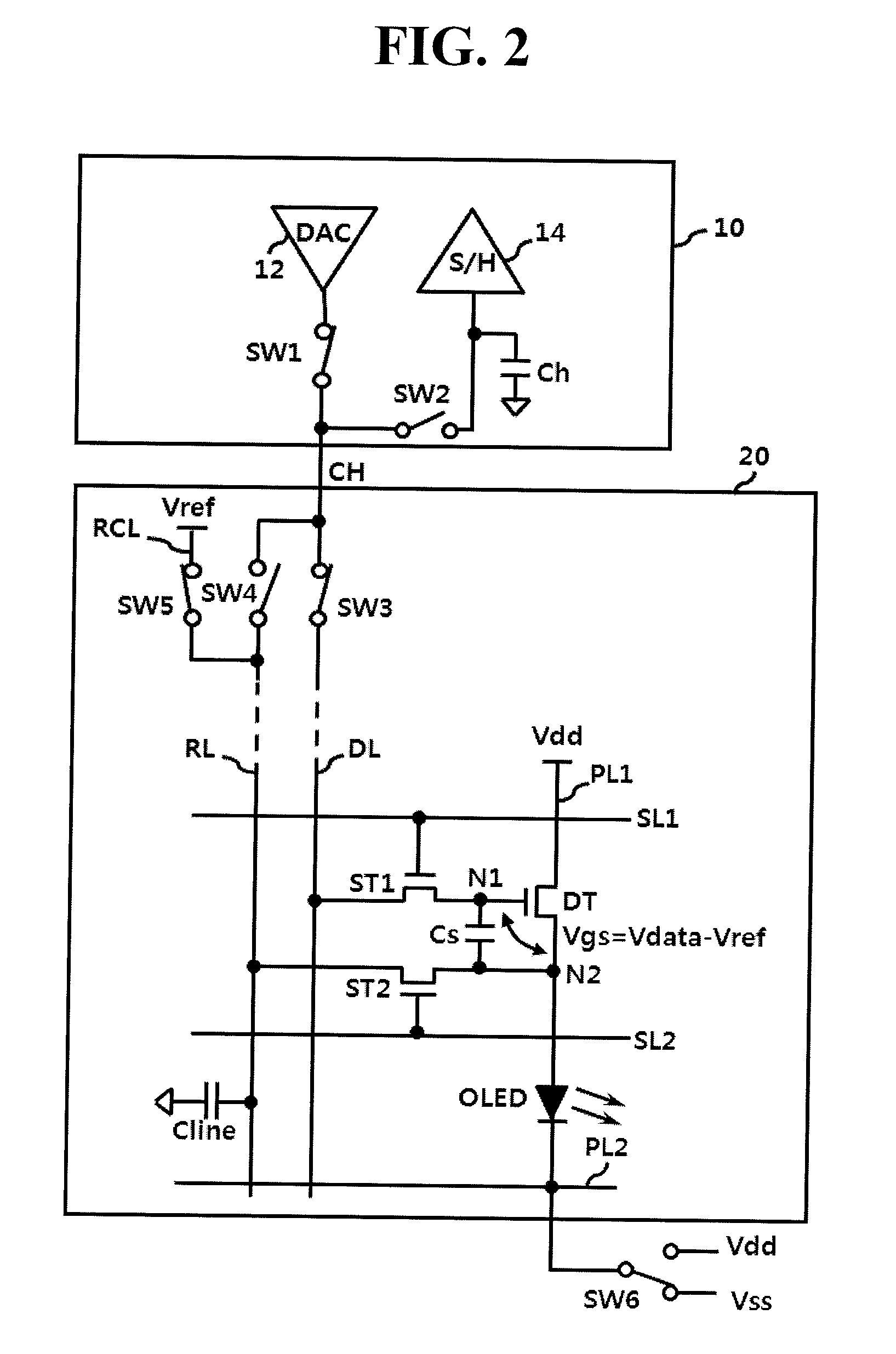

Light emitting display, display panel, and driving method thereof

A light emitting display for compensating for the threshold voltage of transistor or mobility and fully charging a data line. A transistor and first through third switches are formed on a pixel circuit of an organic EL display. The transistor supplies a driving current for emitting an organic EL element (OLED). The first switch diode-connects the transistor. A first storage unit stores a first voltage corresponding to a threshold voltage of the transistor. A second switch transmits a data current in response to a select signal. A second storage unit stores a second voltage corresponding to the data current. A third switch transmits the driving current to the OLED. A third voltage determined by coupling of the first and second storage units is applied to a transistor to supply the driving current to the OLED.

Owner:SAMSUNG DISPLAY CO LTD

Combining data from multiple image sensors

InactiveUS20110242355A1Avoid pollutionTelevision system detailsSteroscopic systemsComputer graphics (images)Control signal

A method of combining data from multiple sensors is disclosed. The method includes providing a common control signal to multiple image sensors. Each of the multiple image sensors is responsive to the common control signal to generate image data. The method also includes receiving synchronized data output from each of the multiple image sensors, combining the synchronized data output from each of the multiple image sensors to generate a synchronized data line, and providing the synchronized data line to an image processor via a single camera input of the image processor.

Owner:QUALCOMM INC

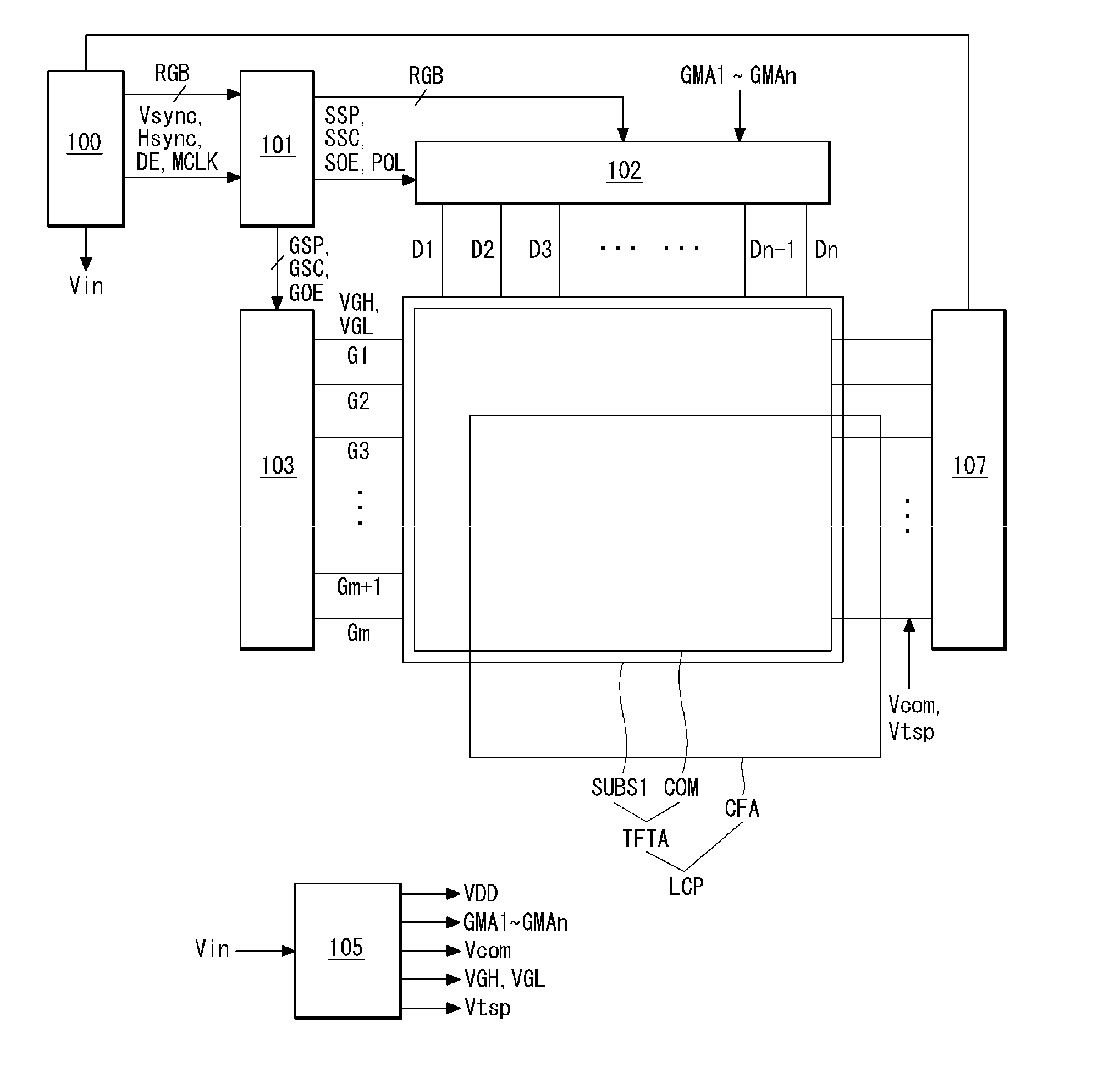

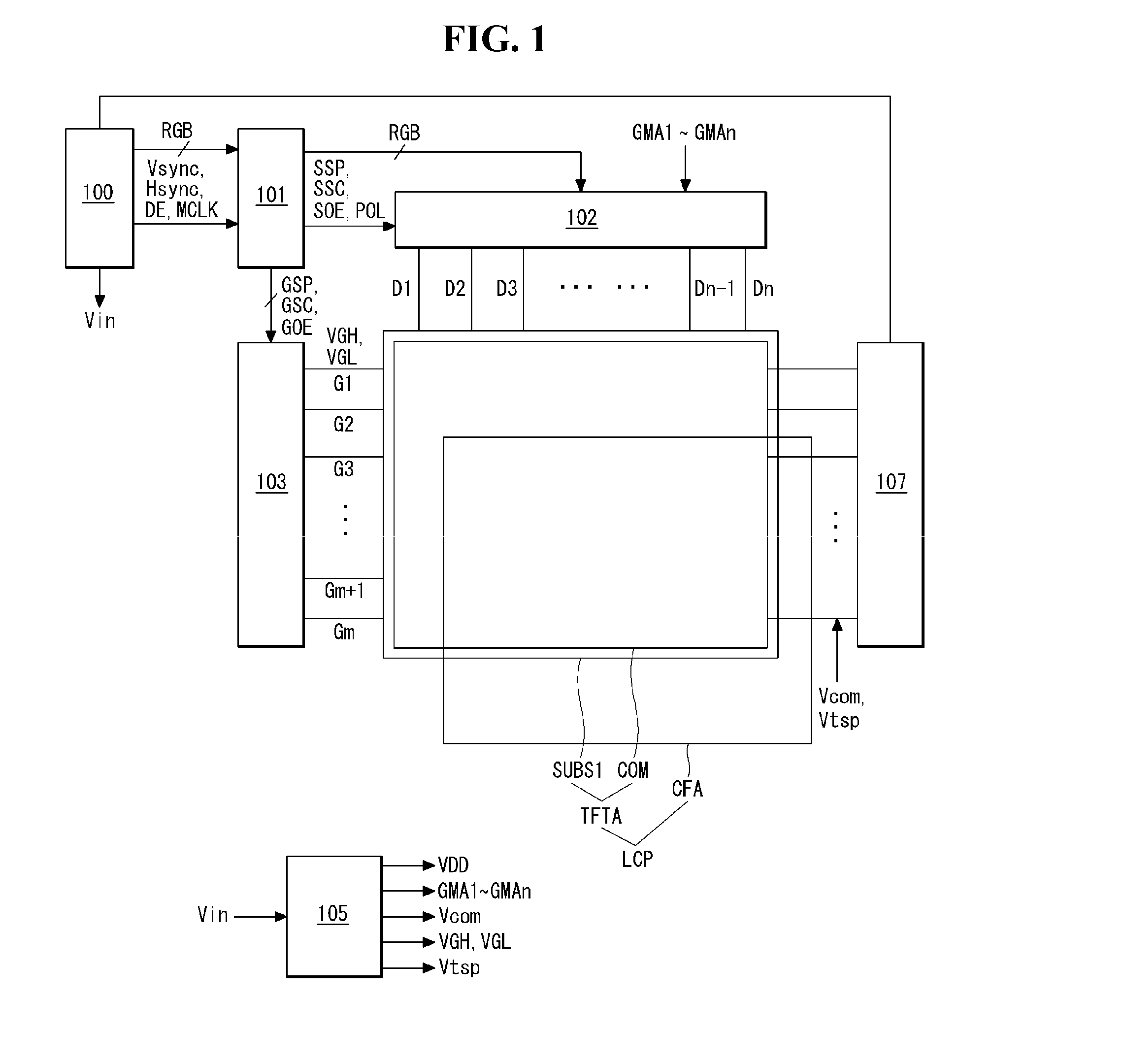

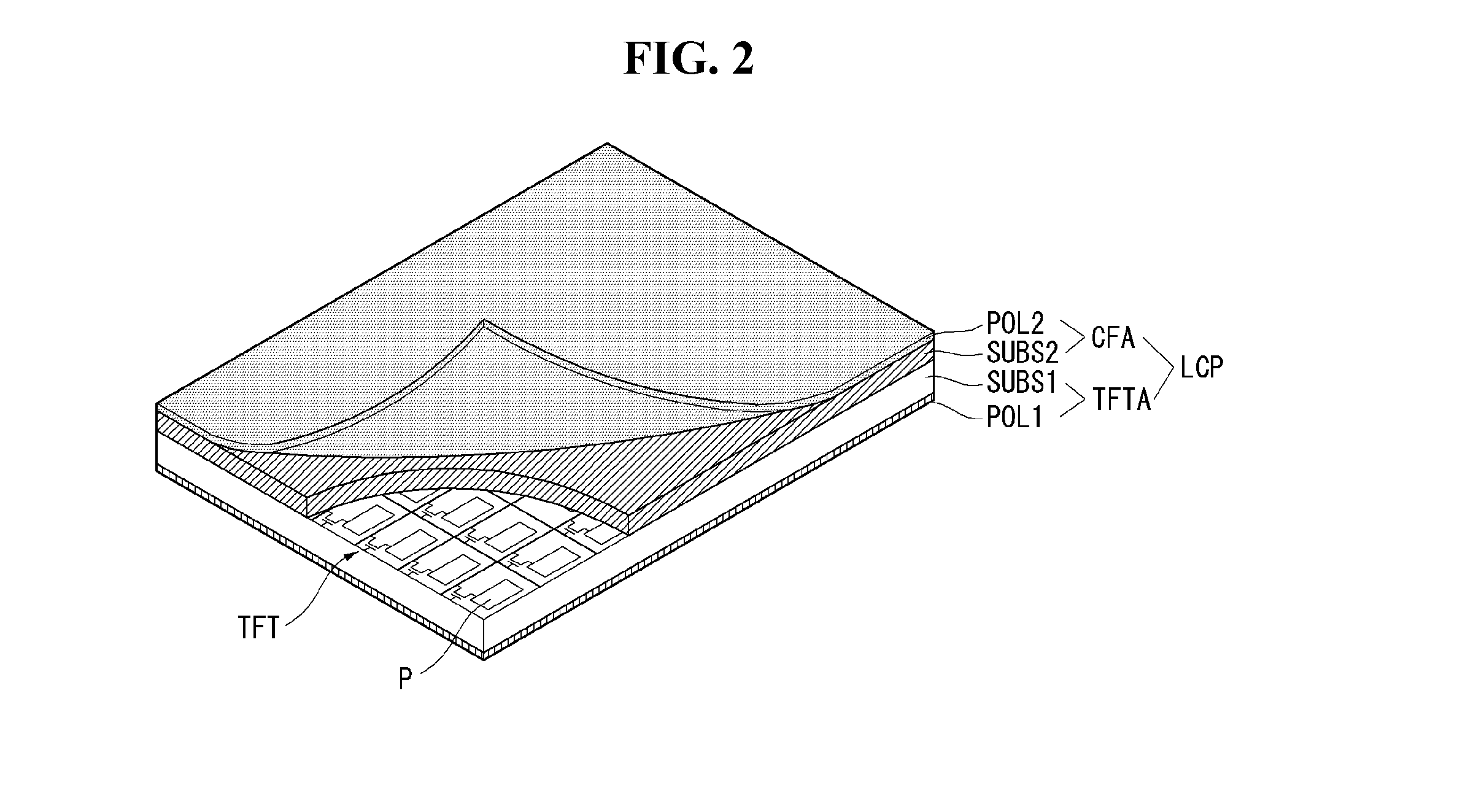

Touch sensor integrated display device

ActiveUS20120218199A1Reduce thicknessIncreased durabilityStatic indicating devicesNon-linear opticsDisplay deviceEngineering

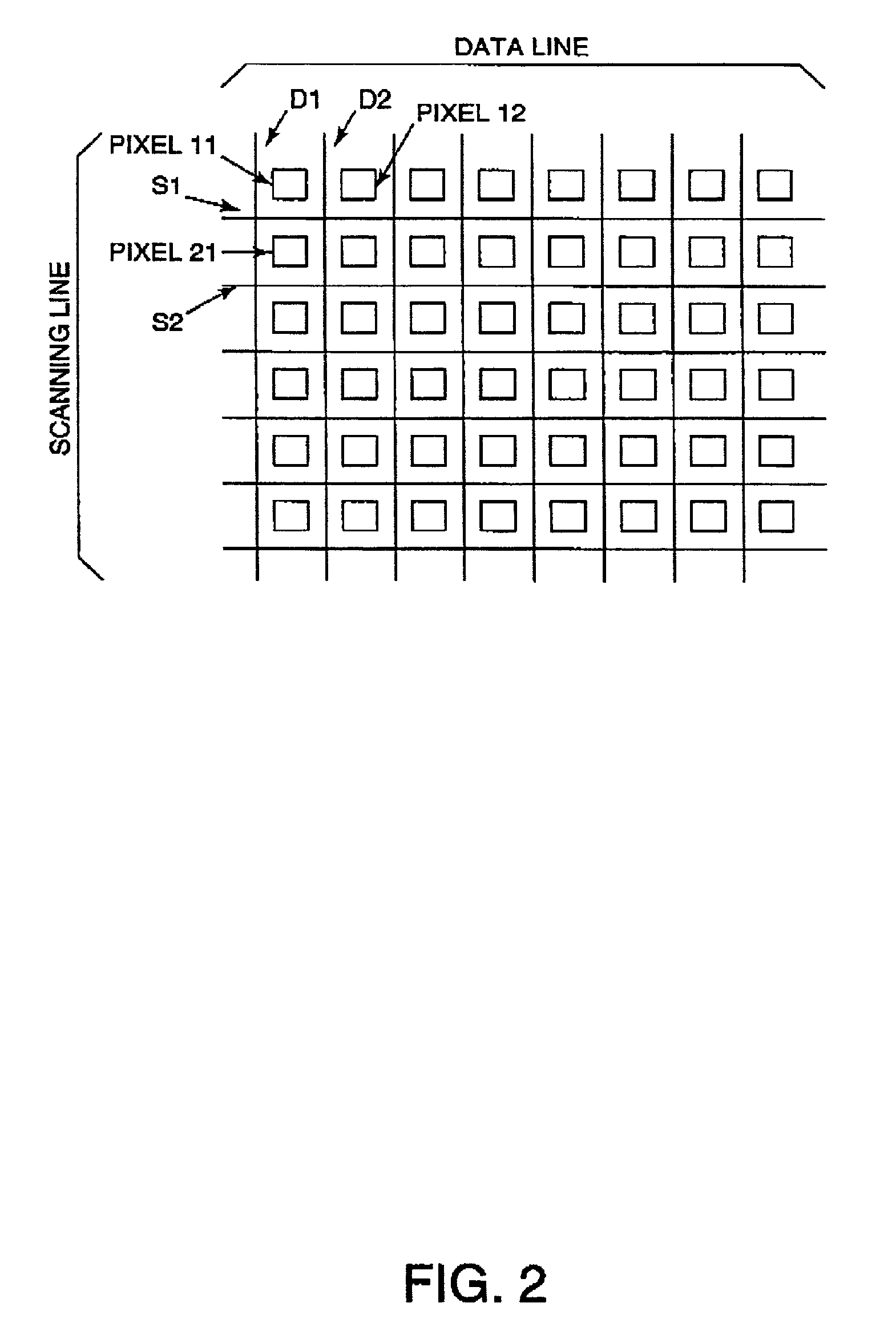

A touch sensor integrated display device is provided comprising gate lines and data lines formed on a substrate to be intersected with each other, a plurality of pixel electrodes formed at intersections between the gate lines and the data lines, and a common electrode formed to overlap the plurality of pixel electrodes through an insulating film disposed between the common electrode and the plurality of pixel electrodes, wherein the common electrode includes at least two touch electrodes, each of which is connected to at least one of signal lines arranged in one of a first direction and a second direction crossing the first direction.

Owner:LG DISPLAY CO LTD

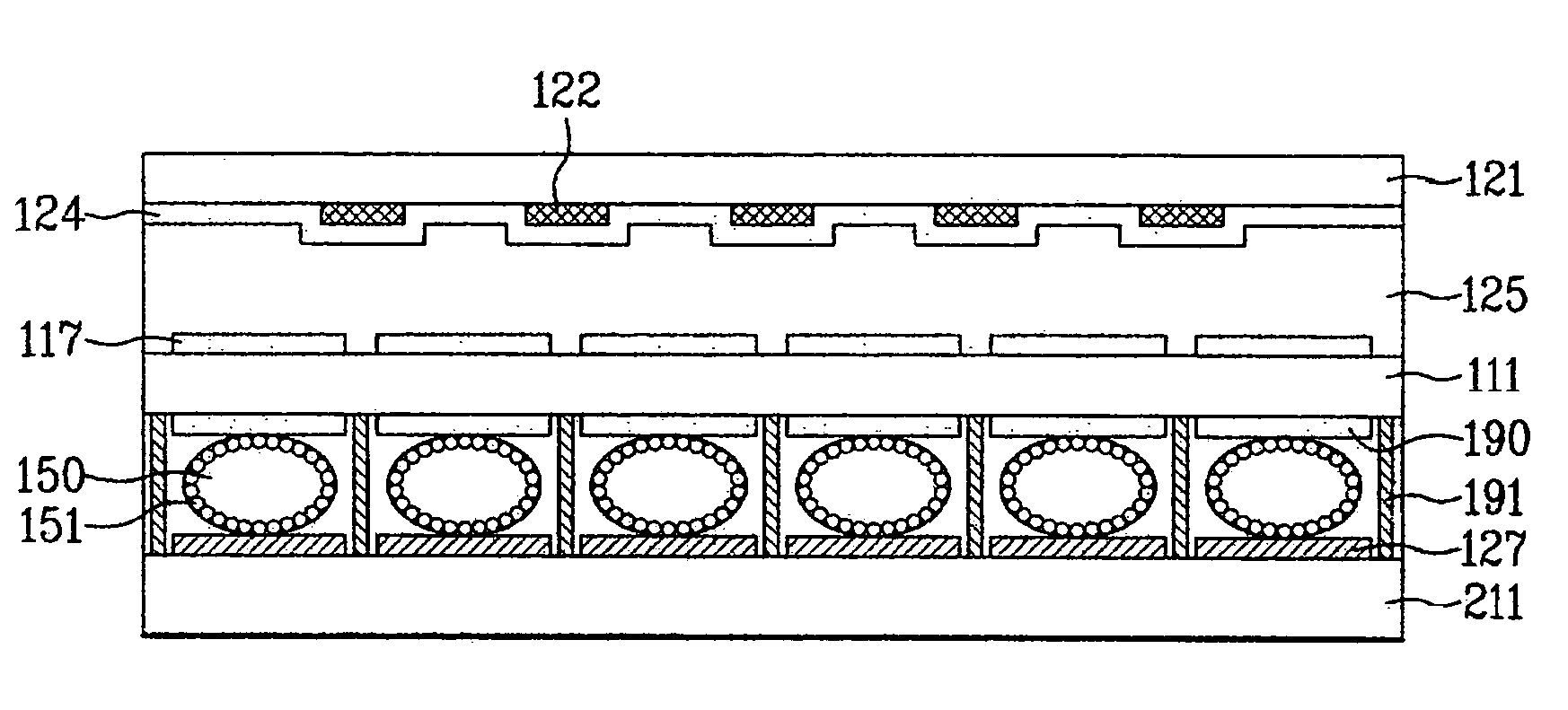

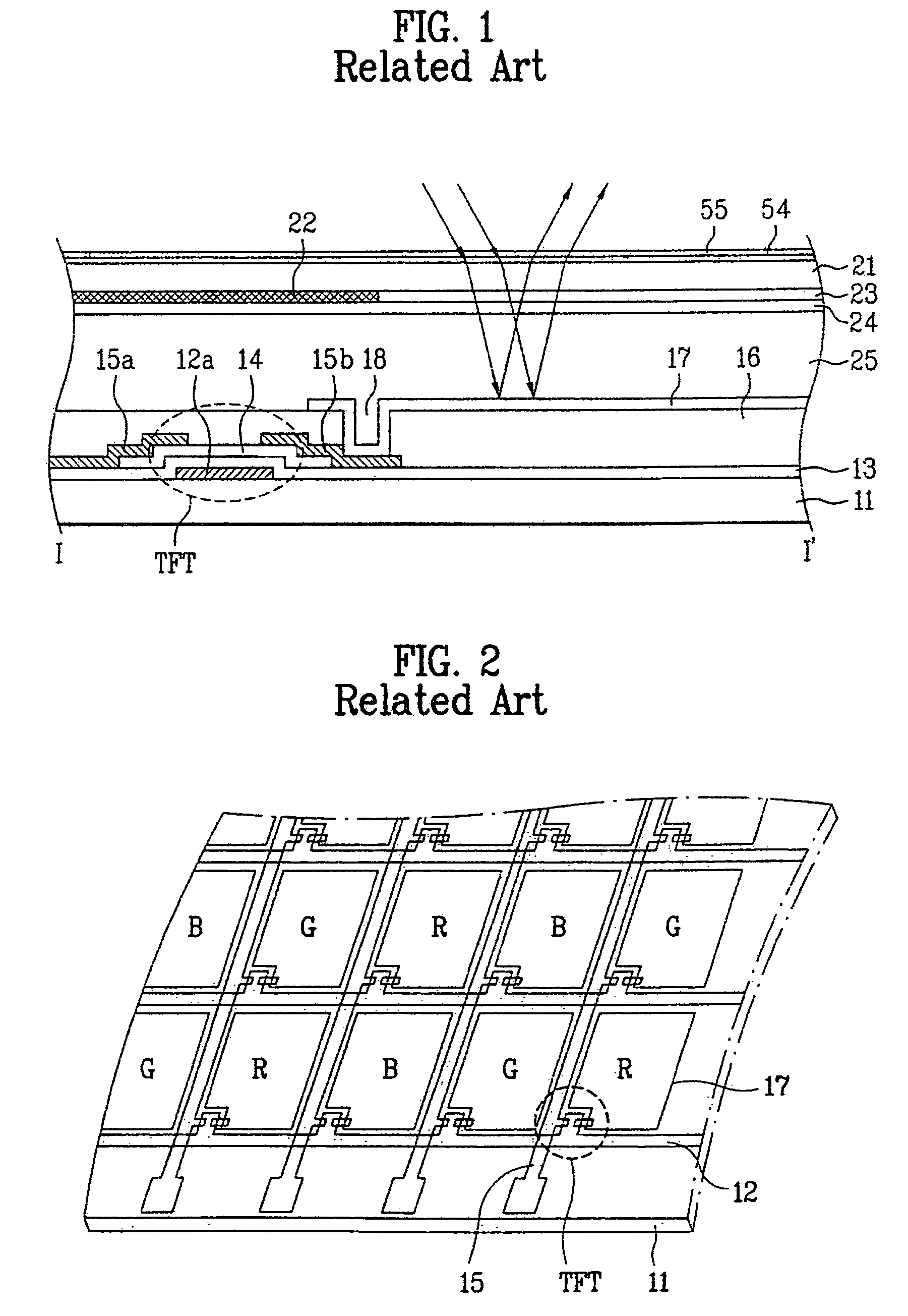

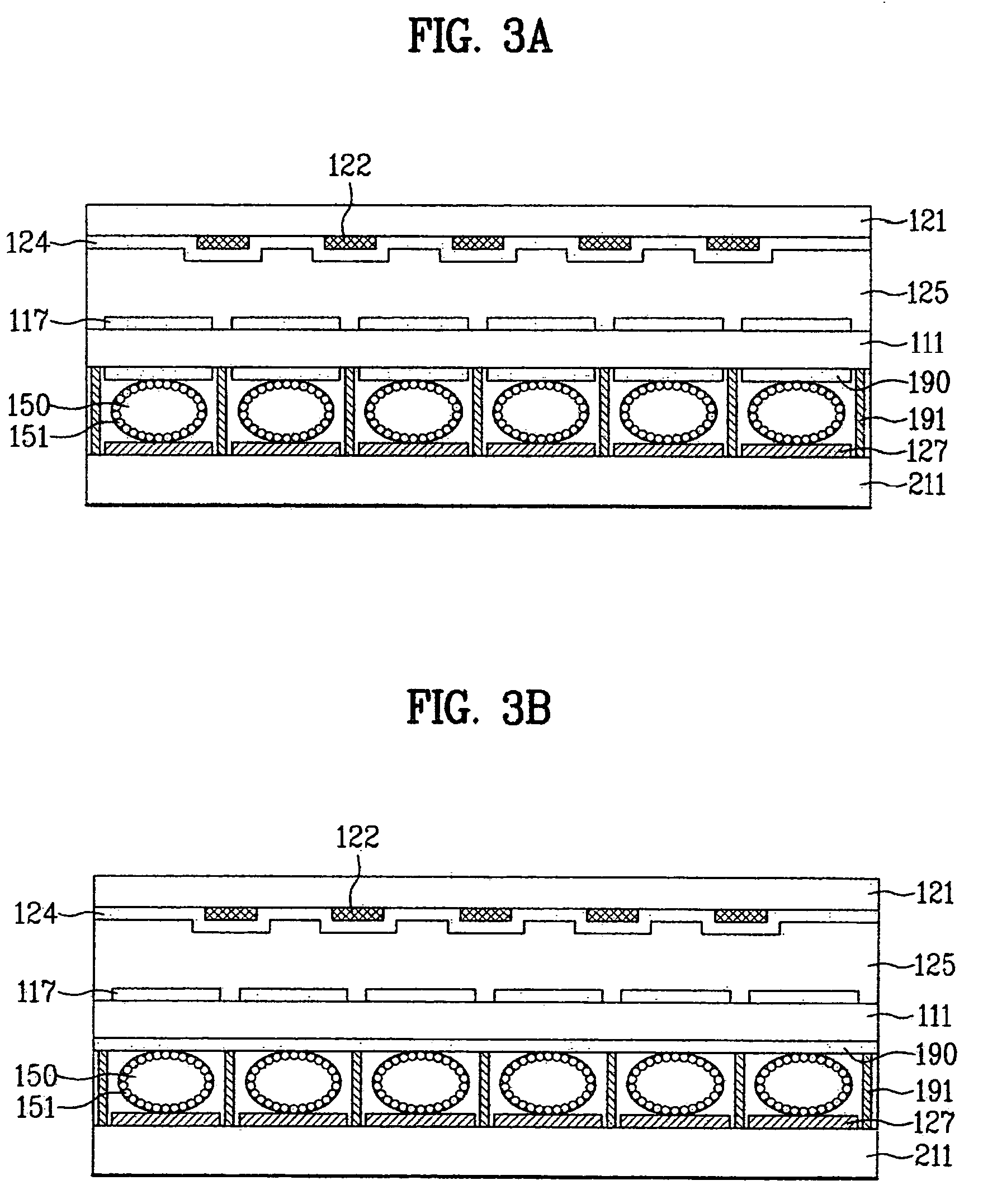

Reflective type liquid crystal display device and fabrication method thereof

ActiveUS7548291B2High resolutionTransistorStatic indicating devicesLiquid-crystal displayImage resolution

Owner:E INK CORPORATION

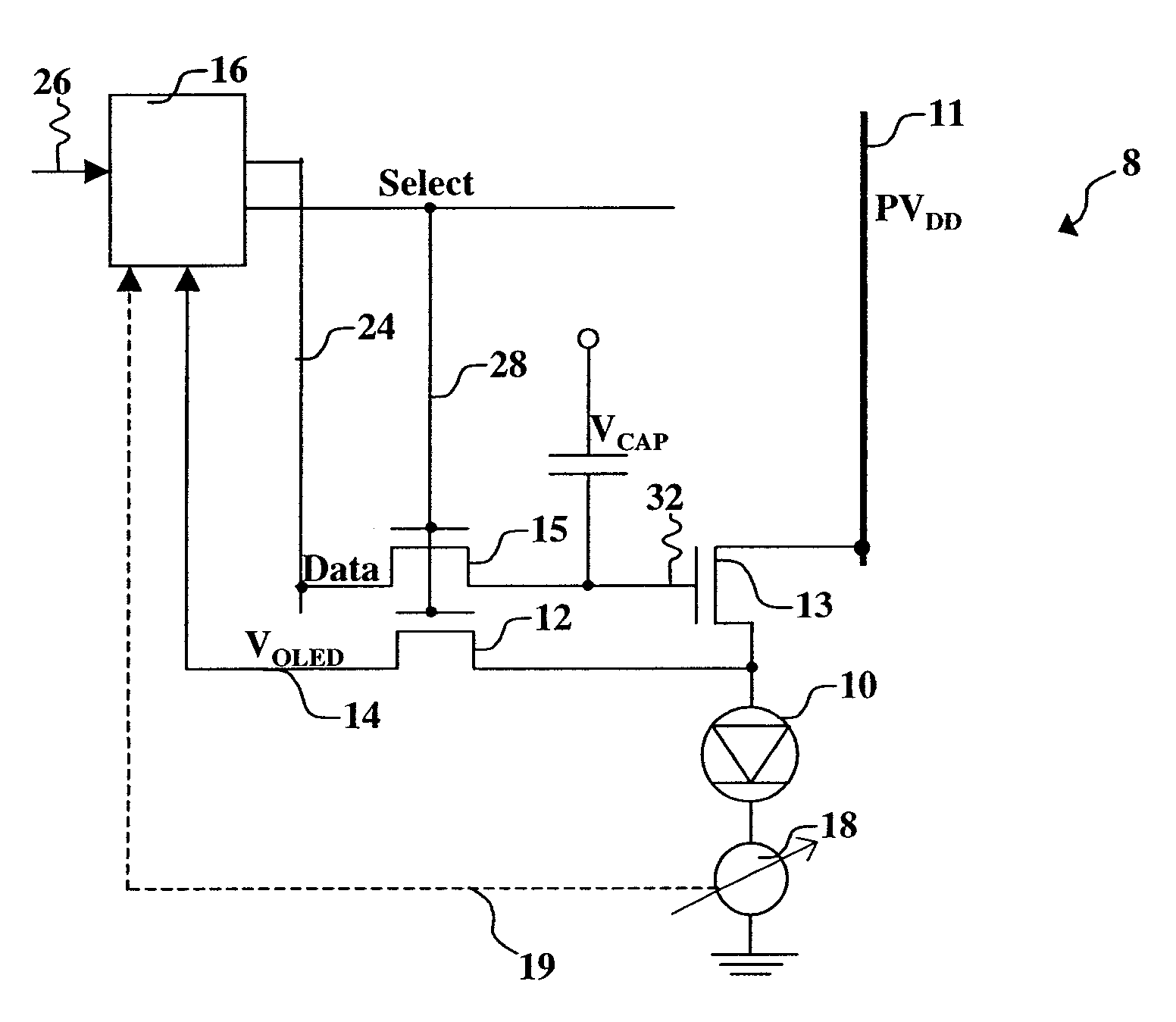

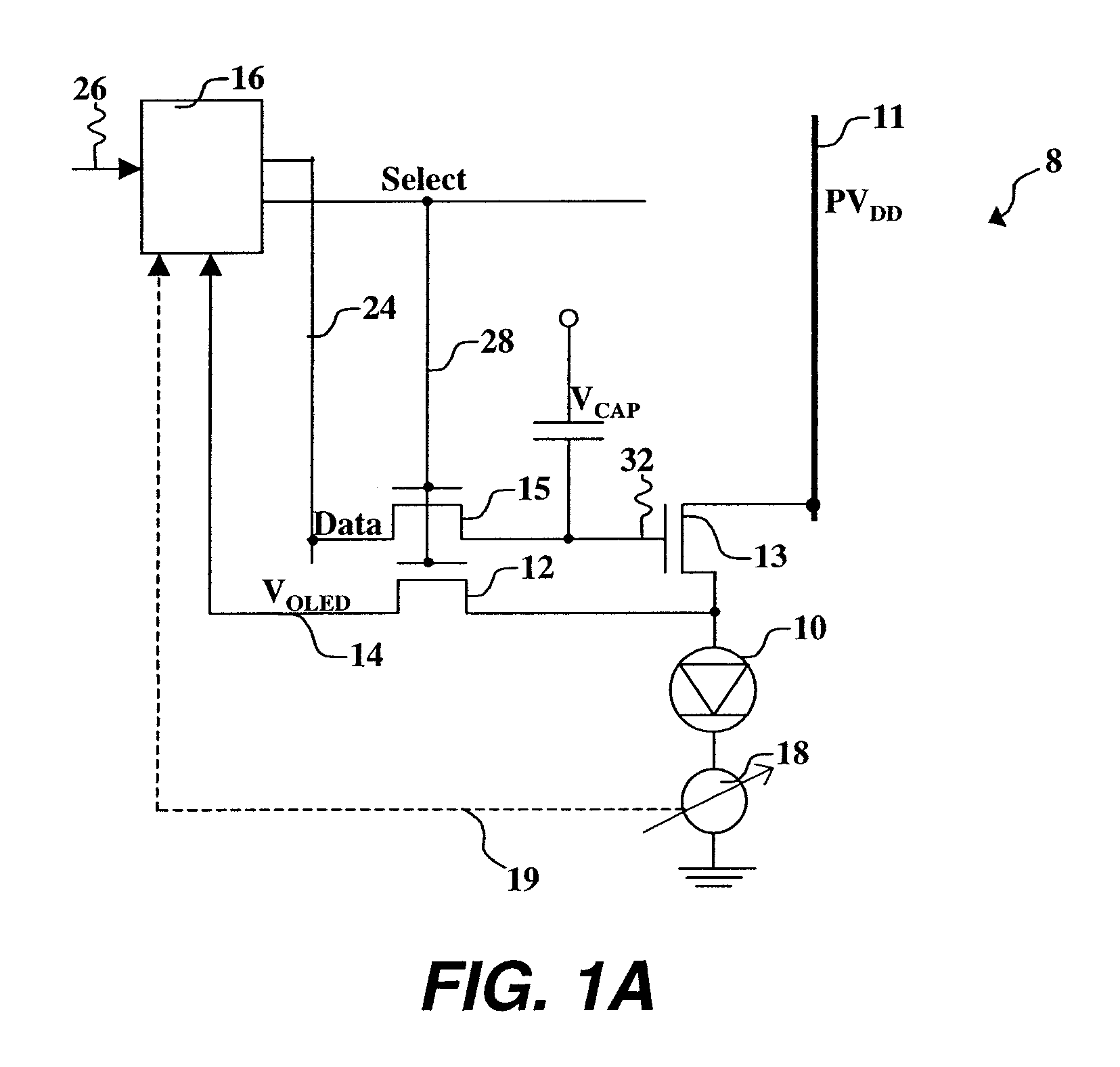

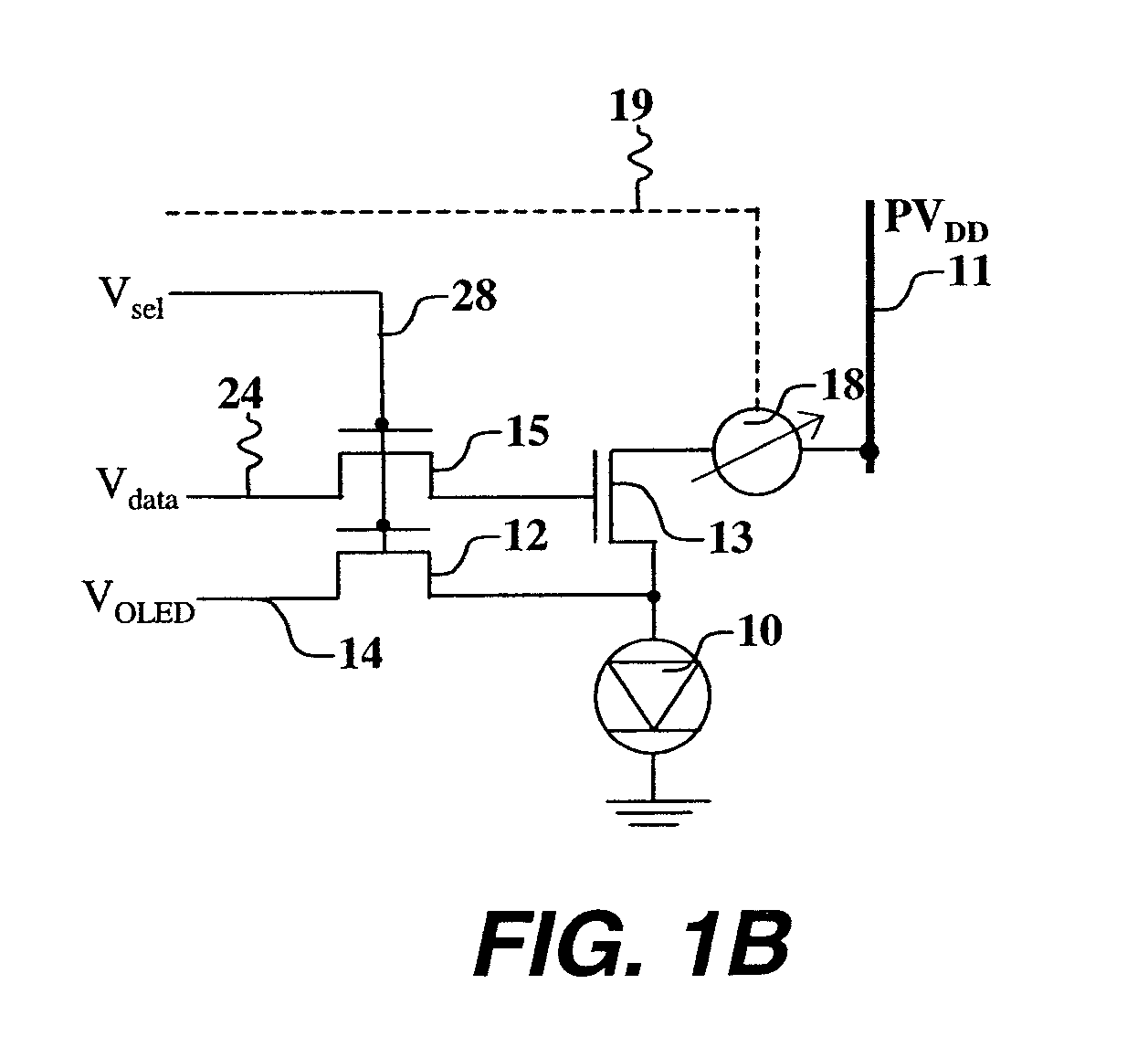

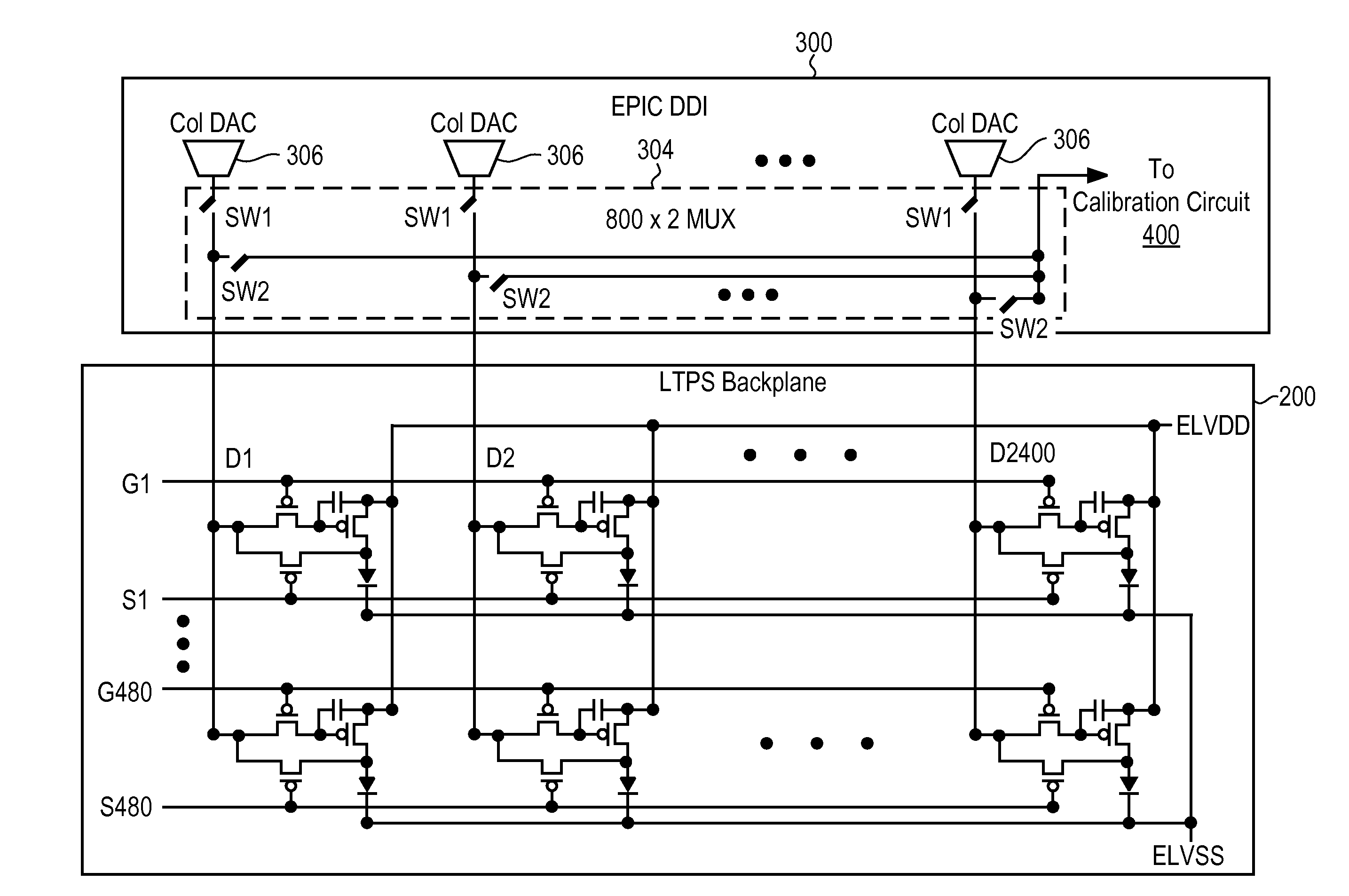

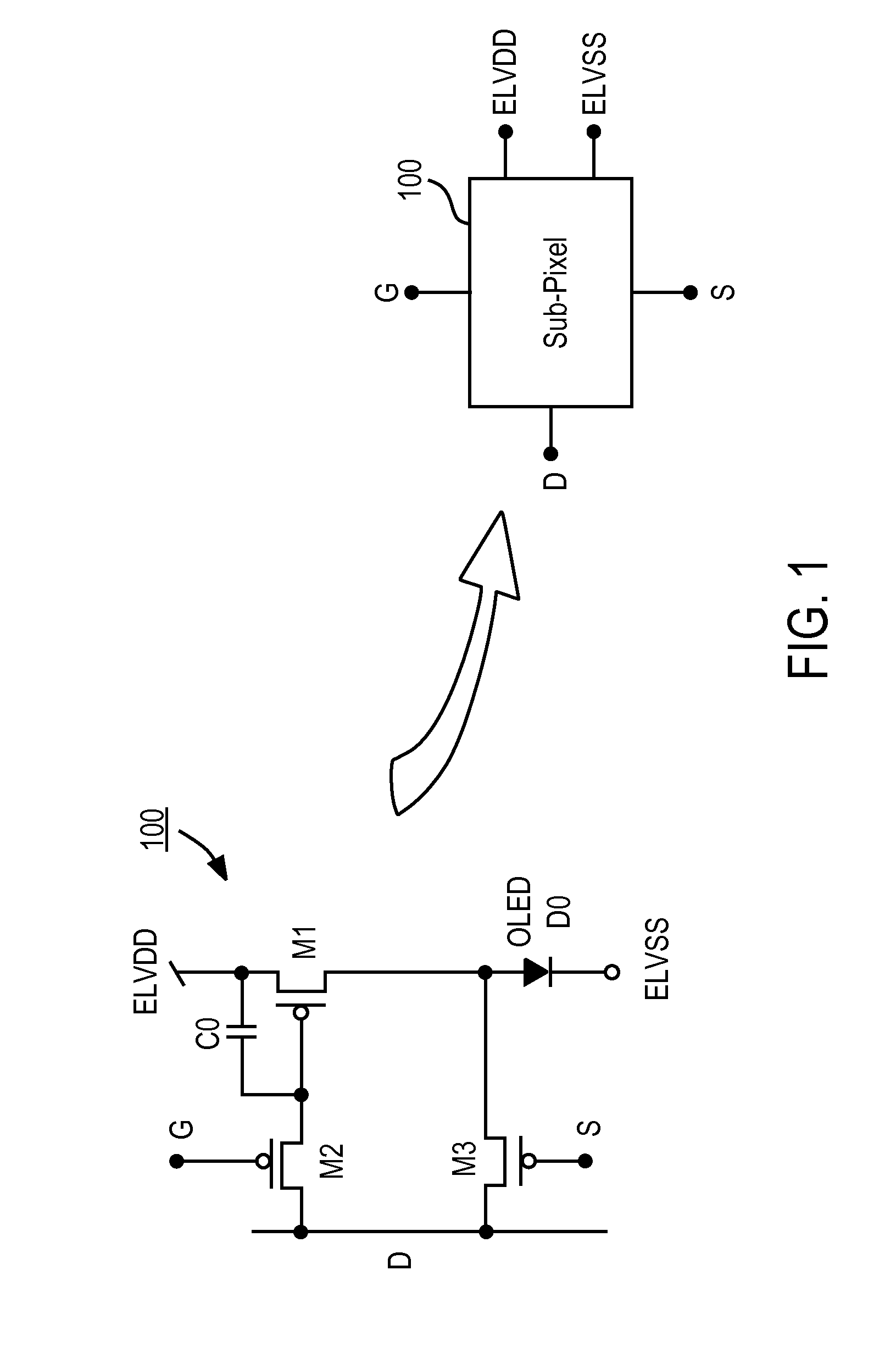

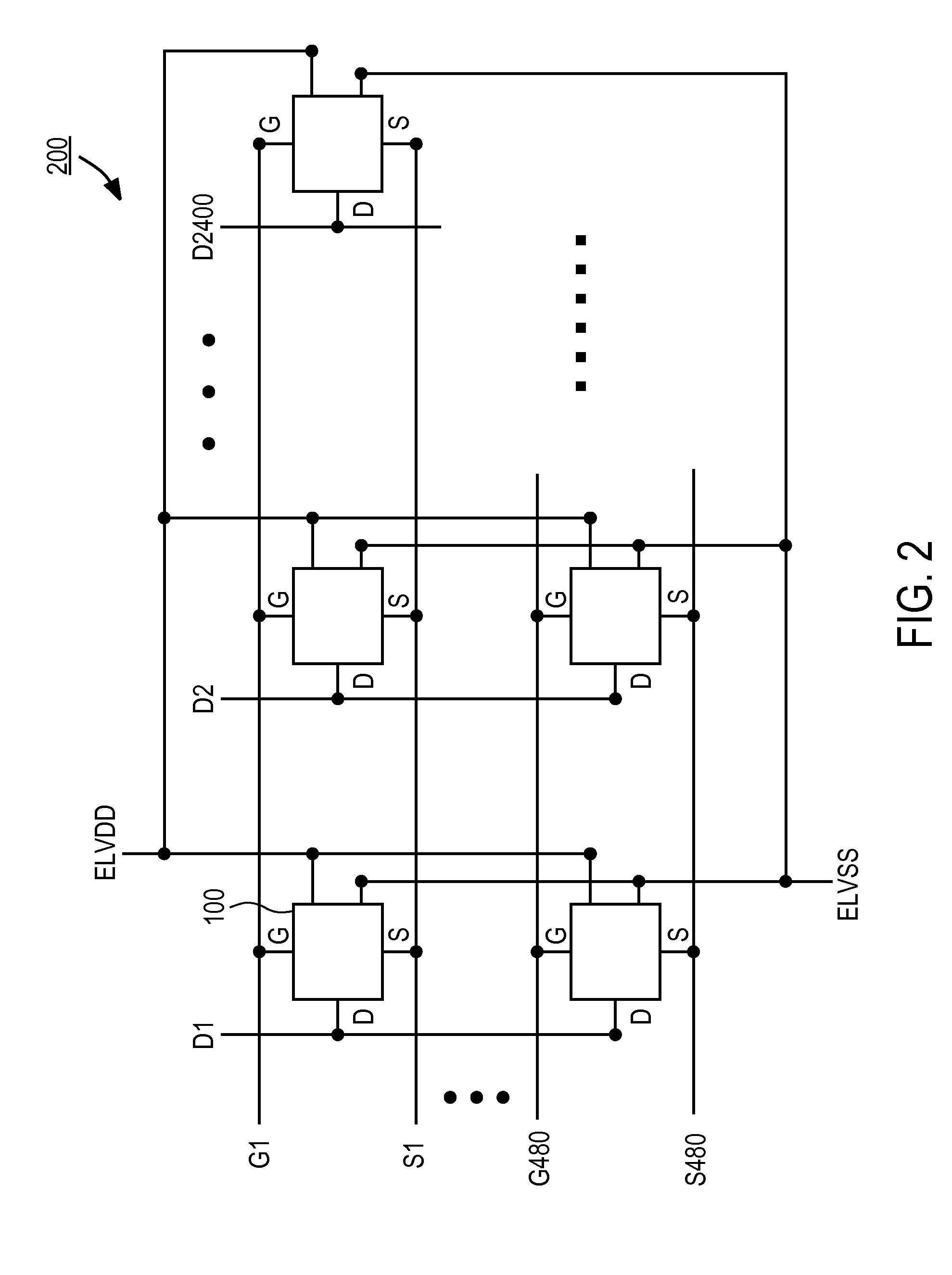

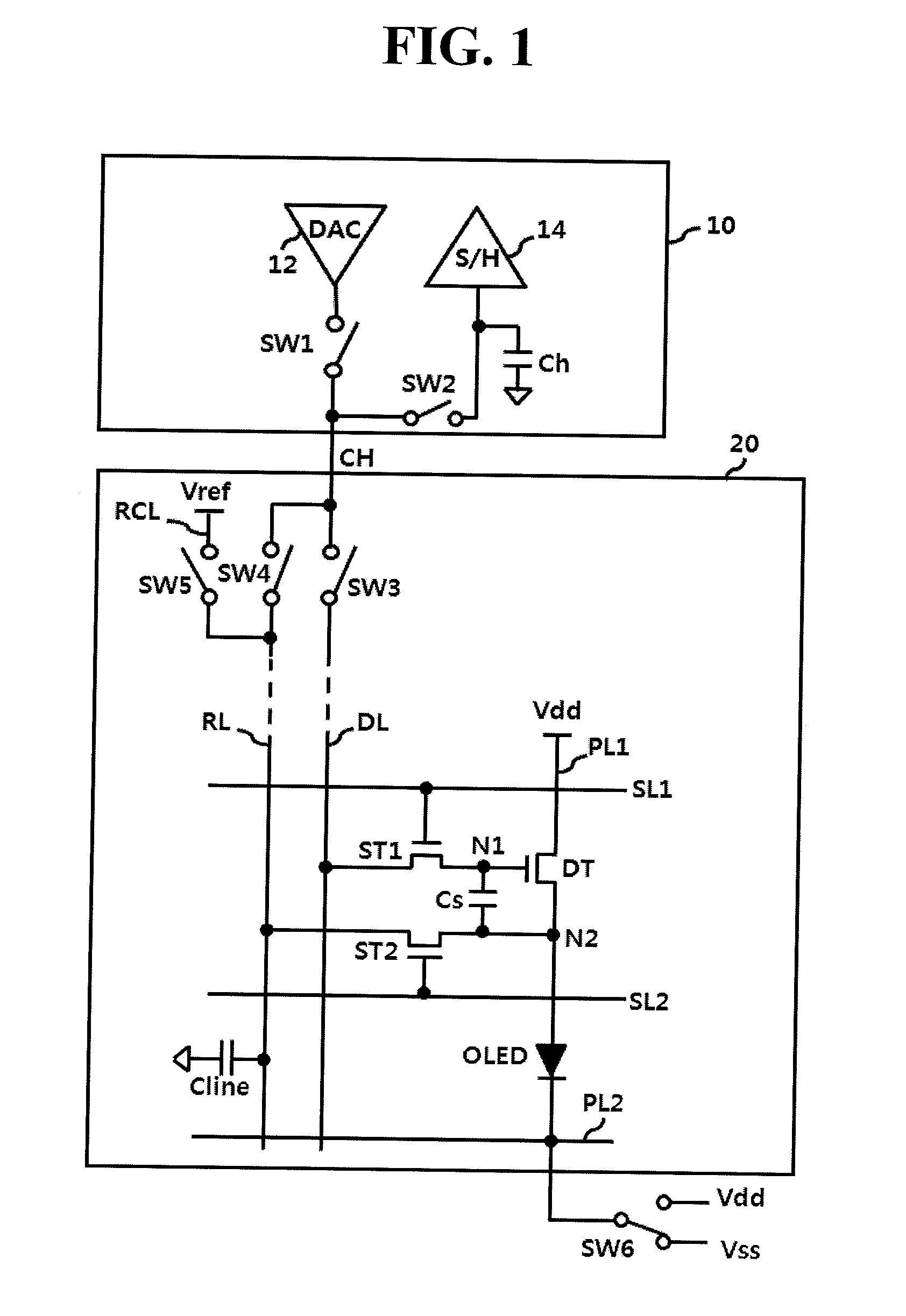

OLED display with aging and efficiency compensation

ActiveUS7355574B1Simple currentSimple voltageCathode-ray tube indicatorsInput/output processes for data processingHemt circuitsBrightness perception

Compensated drive circuit adjusting for changes in the threshold voltage of a drive transistor and for aging of an OLED device, comprising: a data line carrying analog data representative of the brightness level, and a select line; the drive transistor connected to a power supply and to the OLED device such that when the select line is activated and a voltage from the data line is applied to the gate electrode of such transistor and current proportional to the applied voltage will flow through the drain and source electrodes through the OLED device; circuitry for measuring first and second parameters associated with the drive circuitry and responsive to the measured first and second parameters for computing offset voltages to adjust for changes in the threshold voltage of the drive transistors and for aging of the OLED device.

Owner:GLOBAL OLED TECH

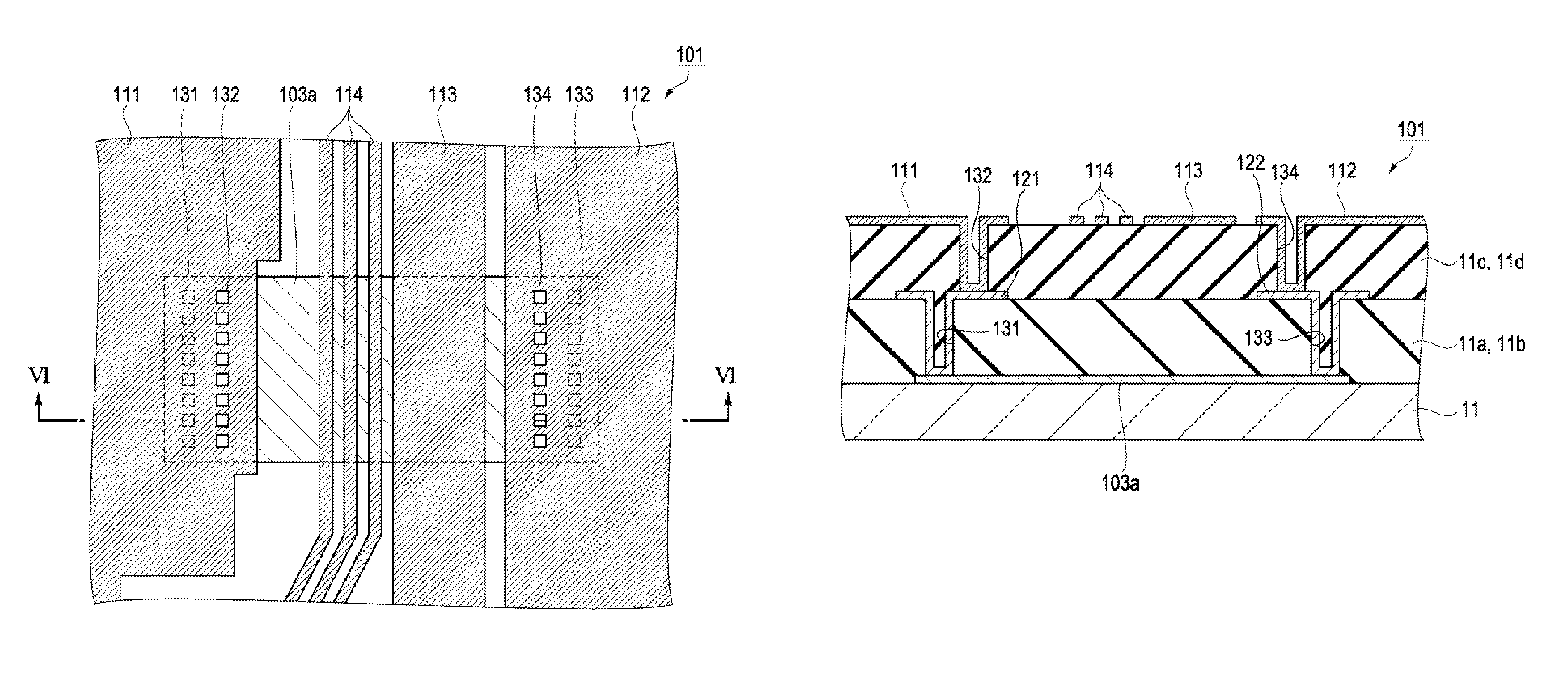

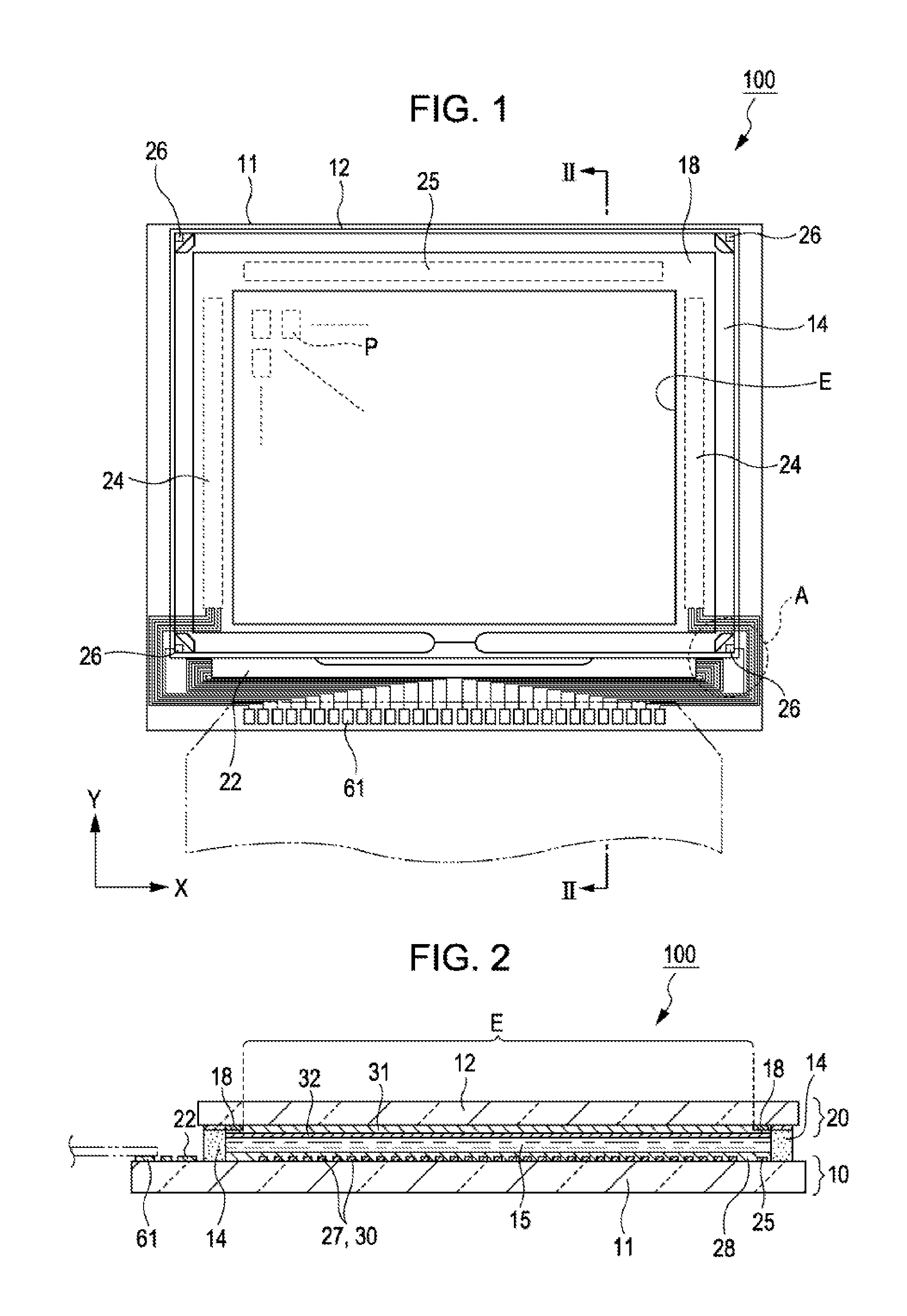

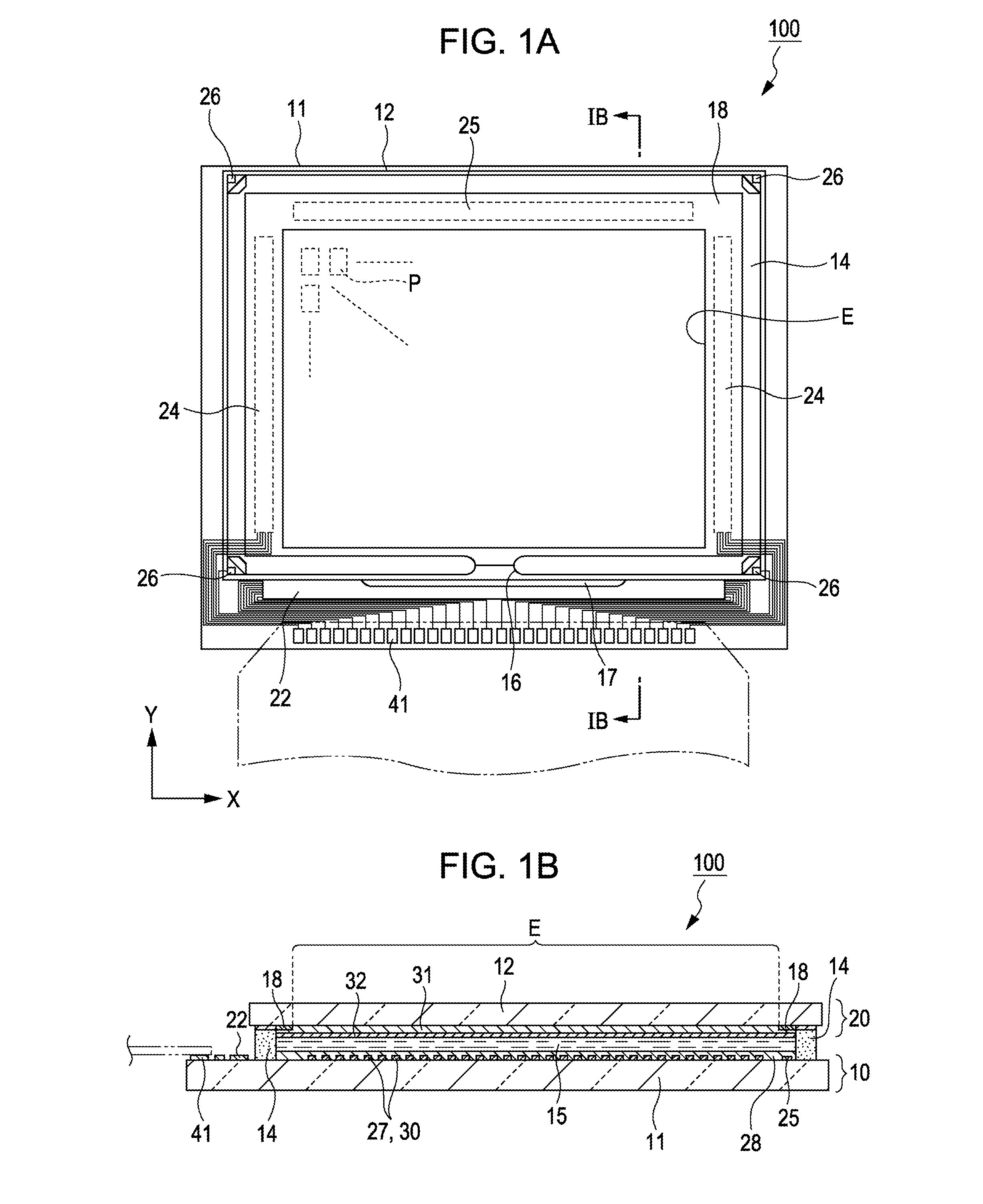

Electro-optical device and electronic apparatus

ActiveUS8803867B2Improve reliabilityCathode-ray tube indicatorsNon-linear opticsElectricityElectrical conductor

A liquid crystal device includes a scanning line driving circuit, a data line driving circuit, a first VDD power supply wiring line that supplies power to the data line driving circuit, a second VDD power supply wiring line that supplies power to the scanning line driving circuit, and a common wiring line that electrically connects the first VDD power supply wiring line and the second VDD power supply wiring line to each other in an integrated manner. The common wiring line includes electrical conductors, a wiring line, and contact holes.

Owner:SEIKO EPSON CORP

Electro-optical device and electronic apparatus

Disclosed is a pixel electrode which is electrically connected to a scanning line electrically connected to a gate electrode, a data line electrically connected to a data line side source and drain region, and a pixel electrode side source and drain region; and a capacitance element which has a first capacitance electrode which is electrically connected to a capacitance line, a second capacitance electrode which is provided to oppose the first capacitance electrode, and a dielectric layer which is interposed between the first capacitance electrode and the second capacitance electrode, where the first capacitance electrode is arranged to be covered with the dielectric layer and the second capacitance electrode between a layer where the transistor, the scanning line, and the data line are provided and a layer where the pixel electrode is provided.

Owner:138 EAST LCD ADVANCEMENTS LTD

Display apparatus, display driving apparatus and method for driving same

ActiveUS20080074413A1Current/voltage measurementCathode-ray tube indicatorsVoltage converterVoltage generator

A light-emitting element capable of emitting light having a preferred gradation level depending on display data. During a precharge period, a data driver applies a precharge voltage to a capacitor via a data line. After the application of the precharge voltage, a voltage converter reads a first reference voltage Vref(t1) and a second reference voltage Vref(t2) to generate a compensation voltage based on a difference between the respective reference voltages. Based on the compensation voltage, a voltage calculator compensates an original gradation level voltage Vorg having a value in accordance with display data generated by a gradation level voltage generator. The voltage calculator generates a compensated gradation level voltage Vpix corresponding to a variation amount of an element characteristic for a transistor Tr13 for driving light emission to apply the compensated gradation level voltage Vpix to a data line Ld.

Owner:SOLAS OLED LTD

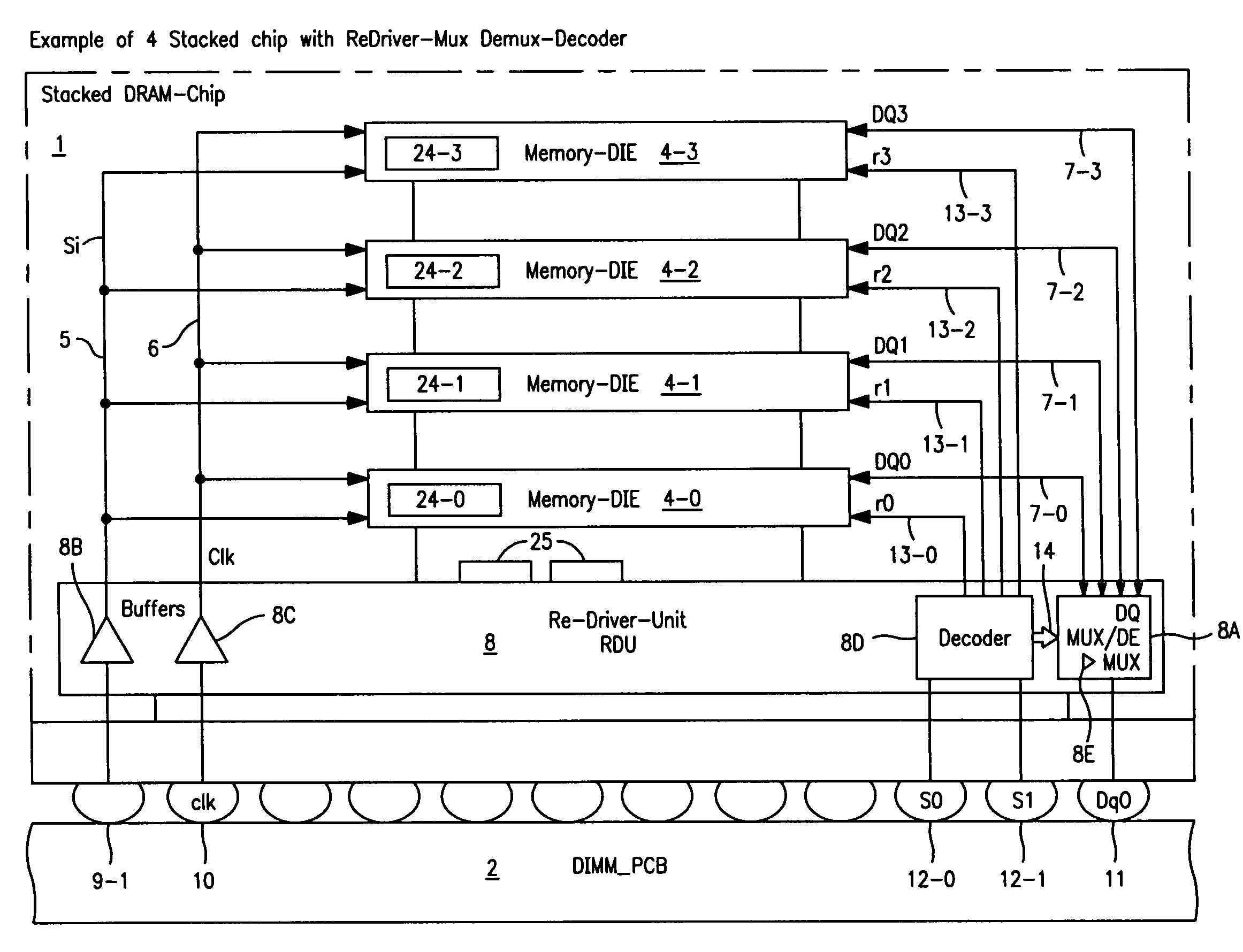

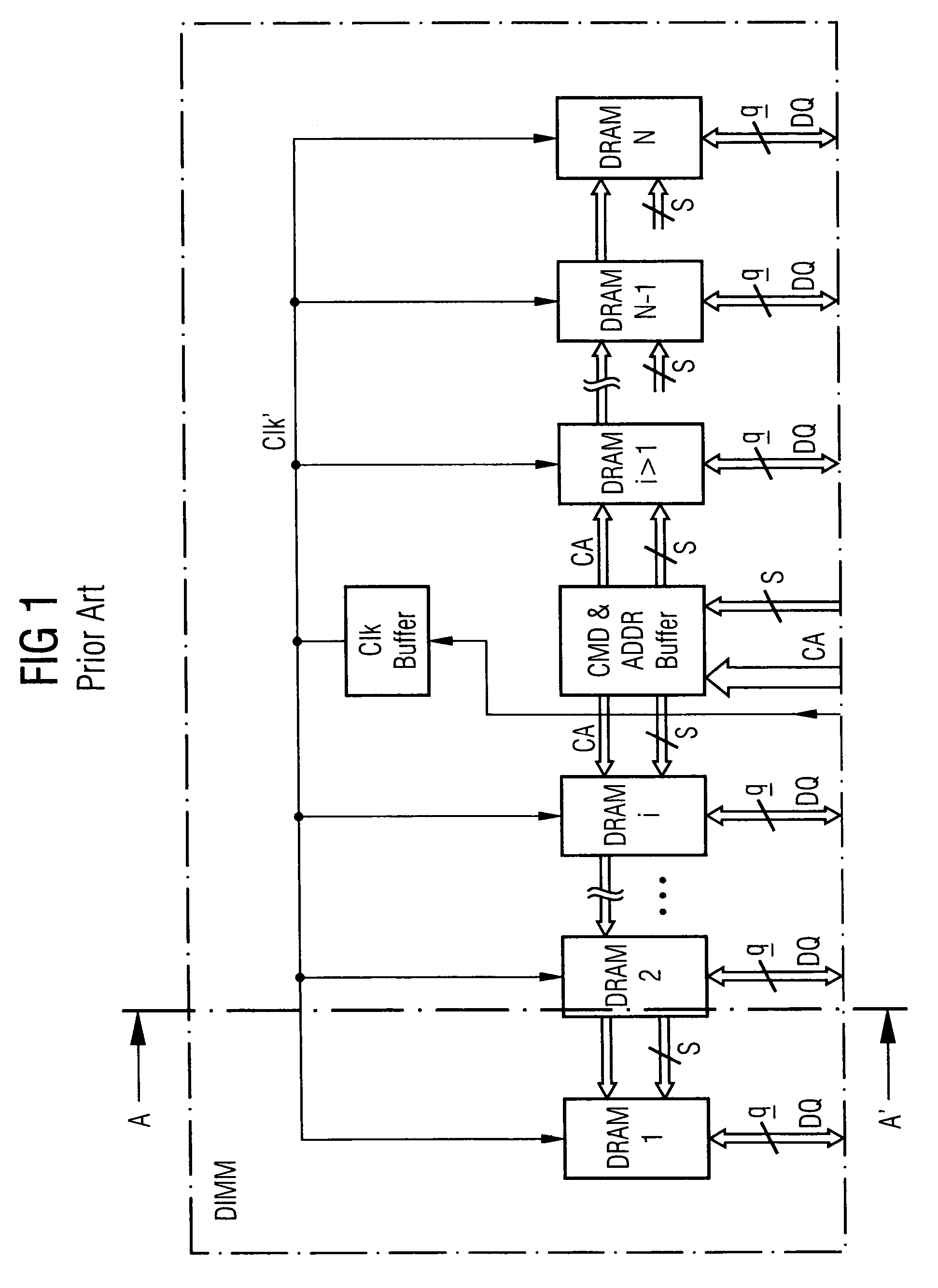

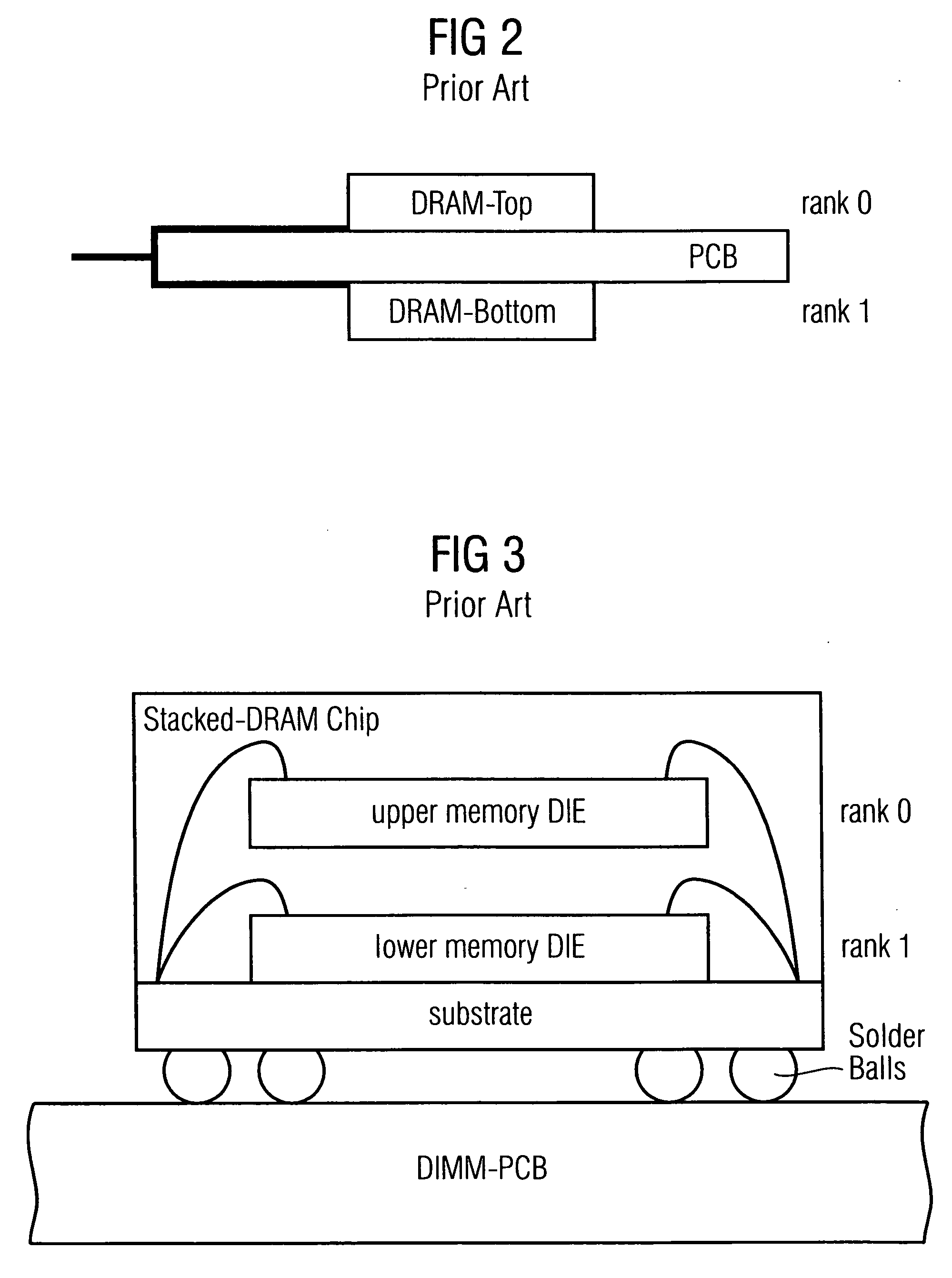

Stacked DRAM memory chip for a dual inline memory module (DIMM)

ActiveUS7200021B2Increase the number ofSmall sizeSemiconductor/solid-state device detailsNanoinformaticsInternal memoryMemory chip

A stacked DRAM memory chip for a Dual In Line Memory Module (DIMM) is disclosed. According to one aspect, the DRAM memory chip comprises at least four stacked DRAM memory dies. Further, the memory dies are each selectable by a corresponding internal memory rank signal. Each memory die comprises an array of memory cells. A common internal address bus is provided for addressing the memory cells and is connected to all stacked DRAM memory dies. Internal data buses are provided for writing data into the memory cells and reading data out of the memory cells of the DRAM memory dies. An integrated redriving unit comprises buffers for all internal address lines provided for driving external address signals applied to address pads of the DRAM memory chip. A multiplexer / demultiplexer switches the internal data lines of the selected DRAM memory die. A memory rank decoder selects a corresponding memory die.

Owner:POLARIS INNOVATIONS LTD

Electronic apparatus, electronic system, and driving method for electronic apparatus

InactiveUS7310092B2Accurate brightnessIncreasing costElectroluminescent light sourcesSolid-state devicesElectronic systemsData signal

An electronic apparatus includes unit circuits provided with electronic devices, data lines connected to the unit circuits, a first output device to output, as a first output, a current or a voltage corresponding to an externally supplied data signal, a second output device to output, as a second output, a current or a voltage corresponding to the magnitude of the first output, and a selection supply device to select one of or both the first output from the first output device and the second output from the second output device and to supply the selected output to the data line. With this configuration, the image reproducibility in a low-luminance / low-grayscale display area of a display apparatus using EL devices is enhanced.

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

Correction of aging in amoled display

The data line voltage on the data line of the AMOLED sub-pixels is measured while the OLED is being driven by a reference current, in order to determine the age of the OLED in the sub-pixel. The pixel transistor serves as a current source for driving the OLED in the sub-pixel with the reference current. The data line voltage is substantially equal to the forward voltage VF(aged) of the aged OLED being driven at the reference current. The forward voltage VF (un-aged) of a reference (un-aged) OLED sub-pixel also measured at the reference current, and is subtracted from the measured OLED diode forward voltage VF (aged) to obtain their difference ΔVF=VF(aged)−VF(un-aged). ΔVF is an indicator of the age of the OLED in the sub-pixel, and is used as an index to a look-up-table that stores the corresponding aging offset data for generating the incremental pixel current needed to maintain constant luminance in the aged OLED pixel.

Owner:SILICONFILE TECH INC

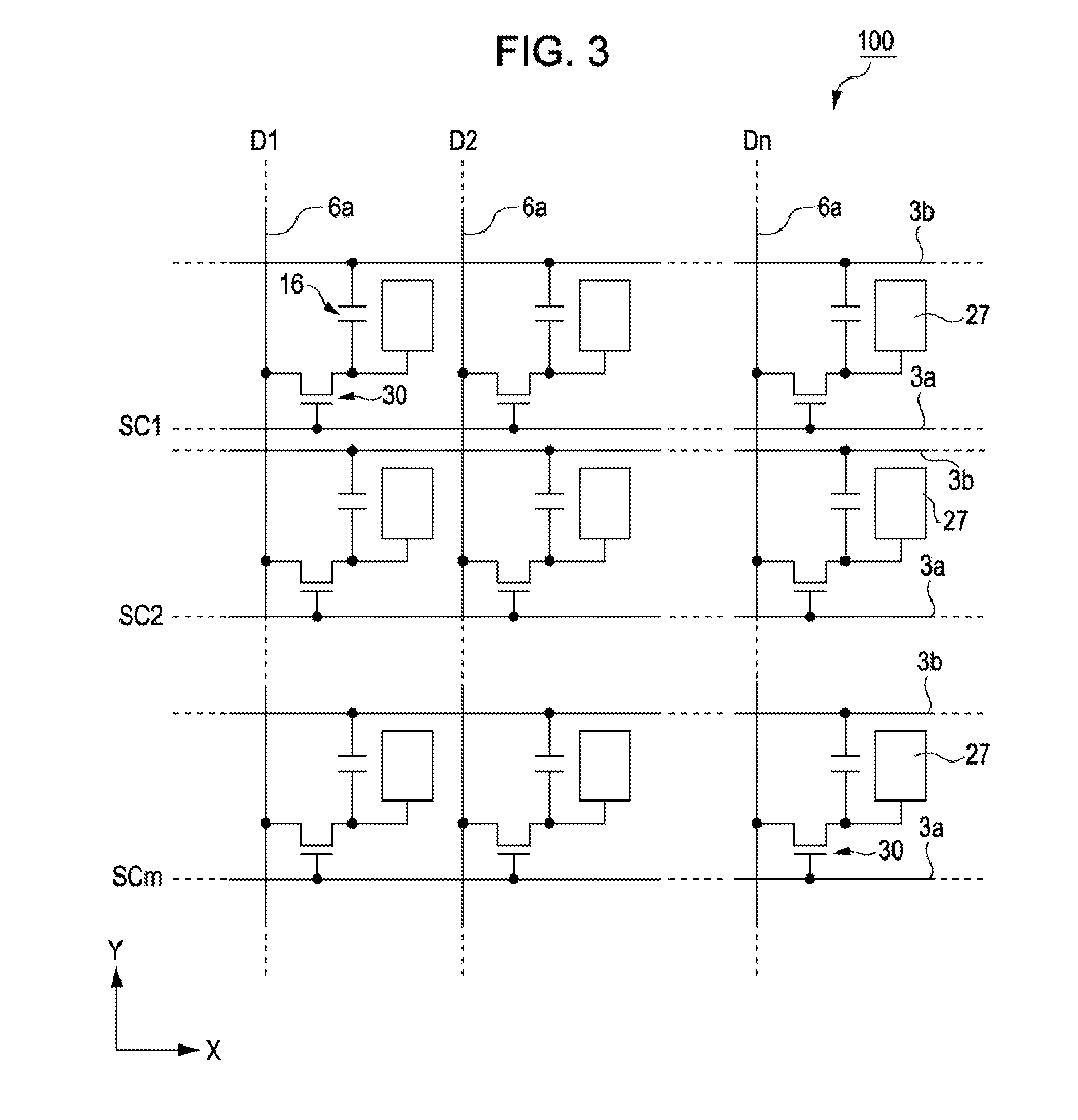

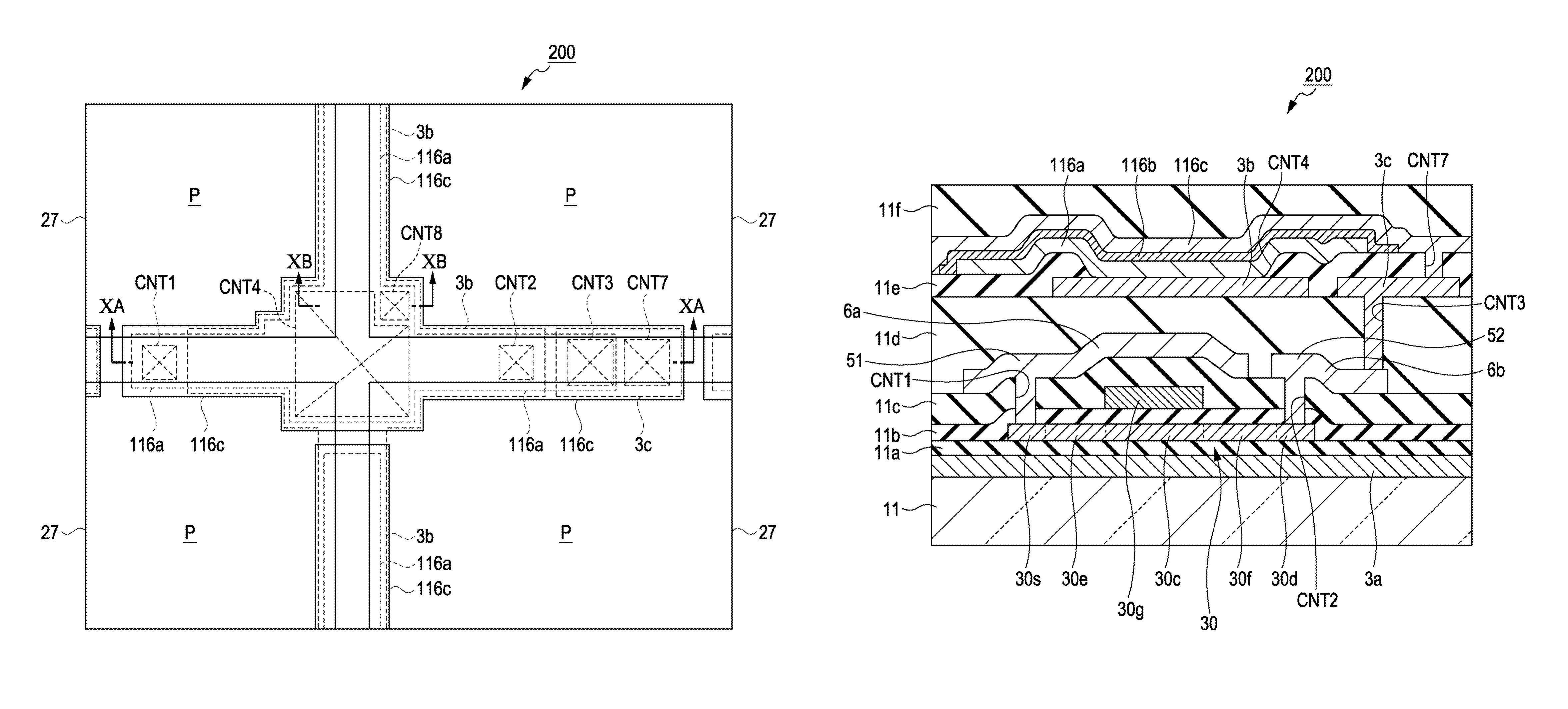

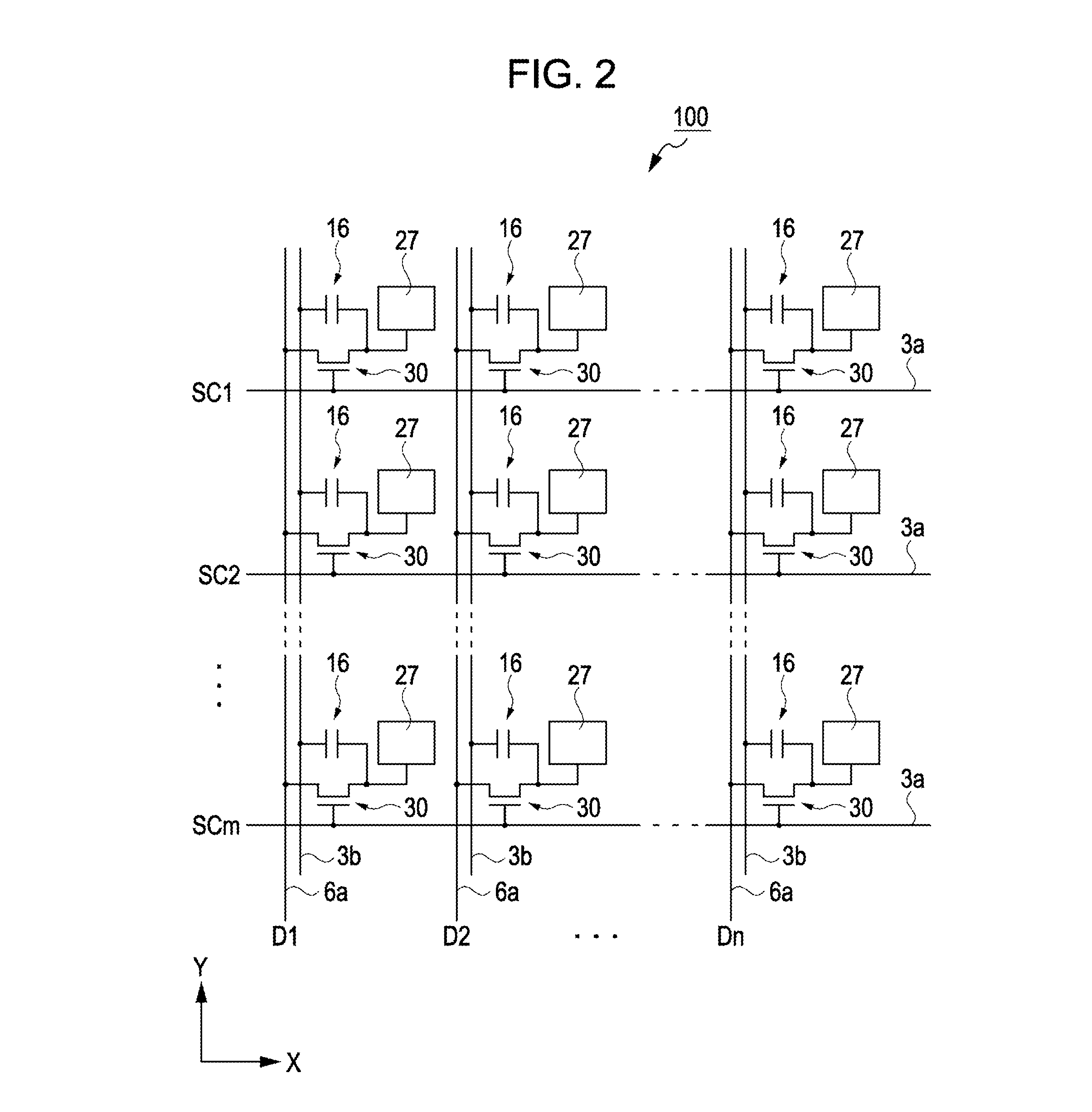

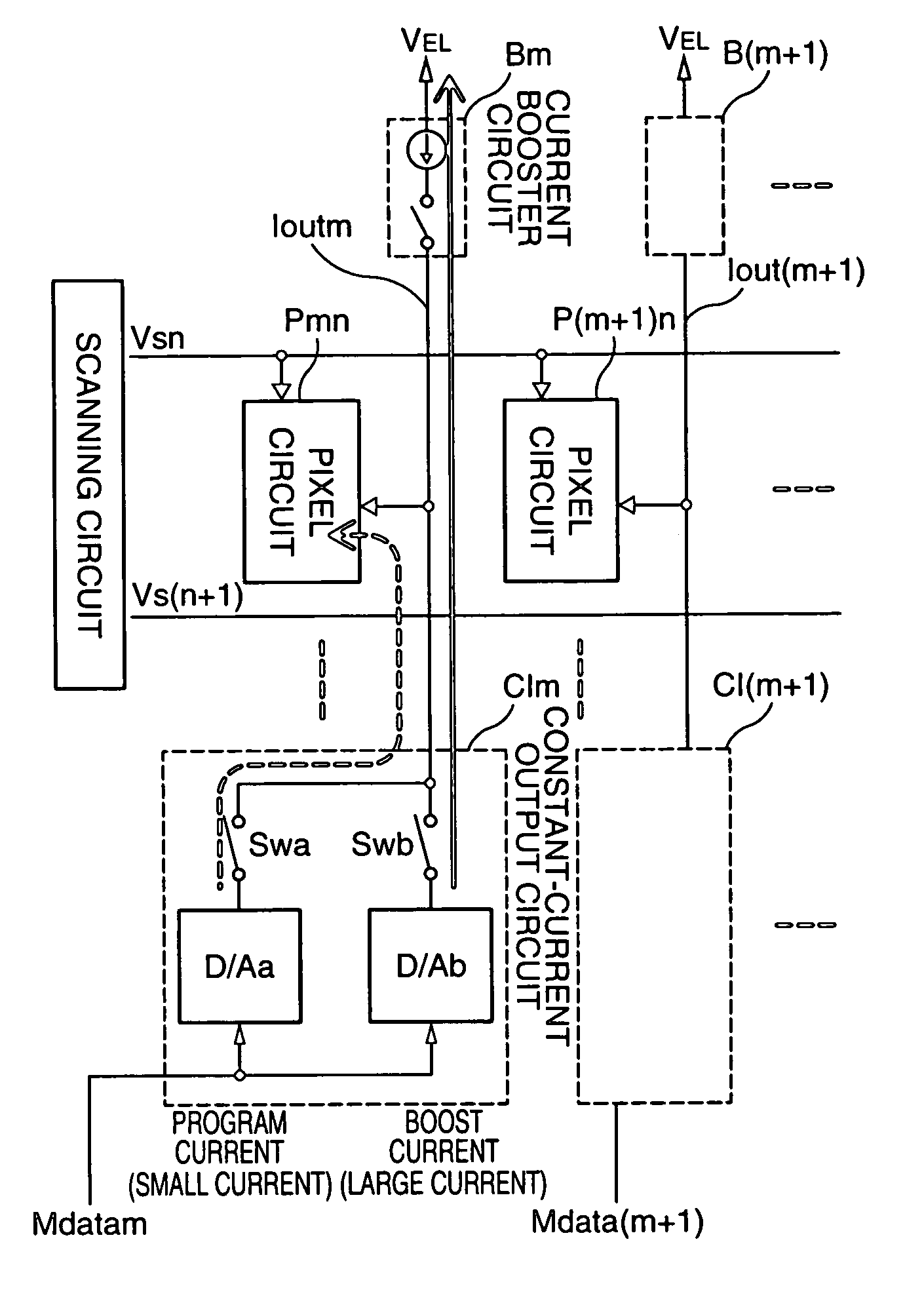

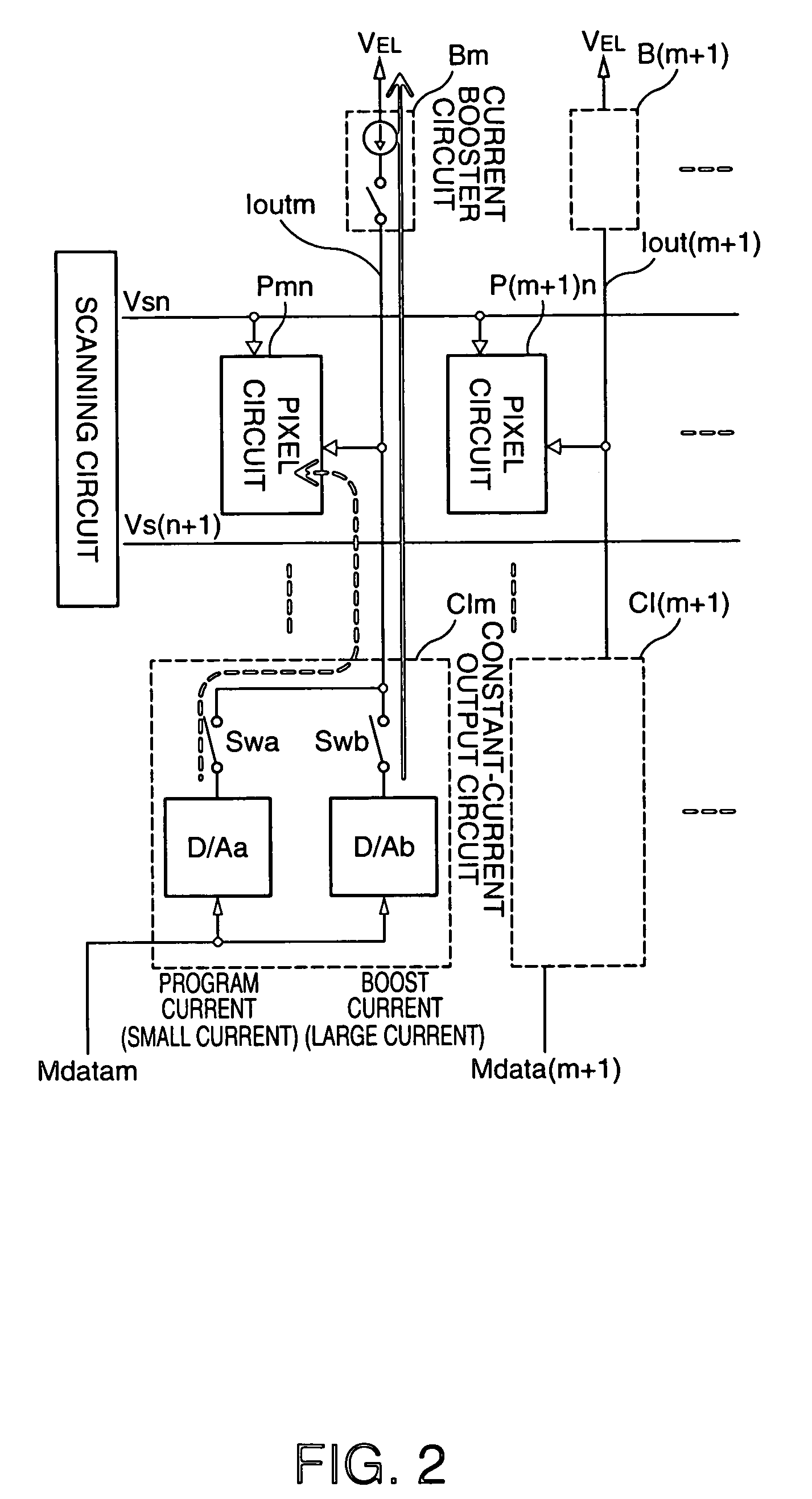

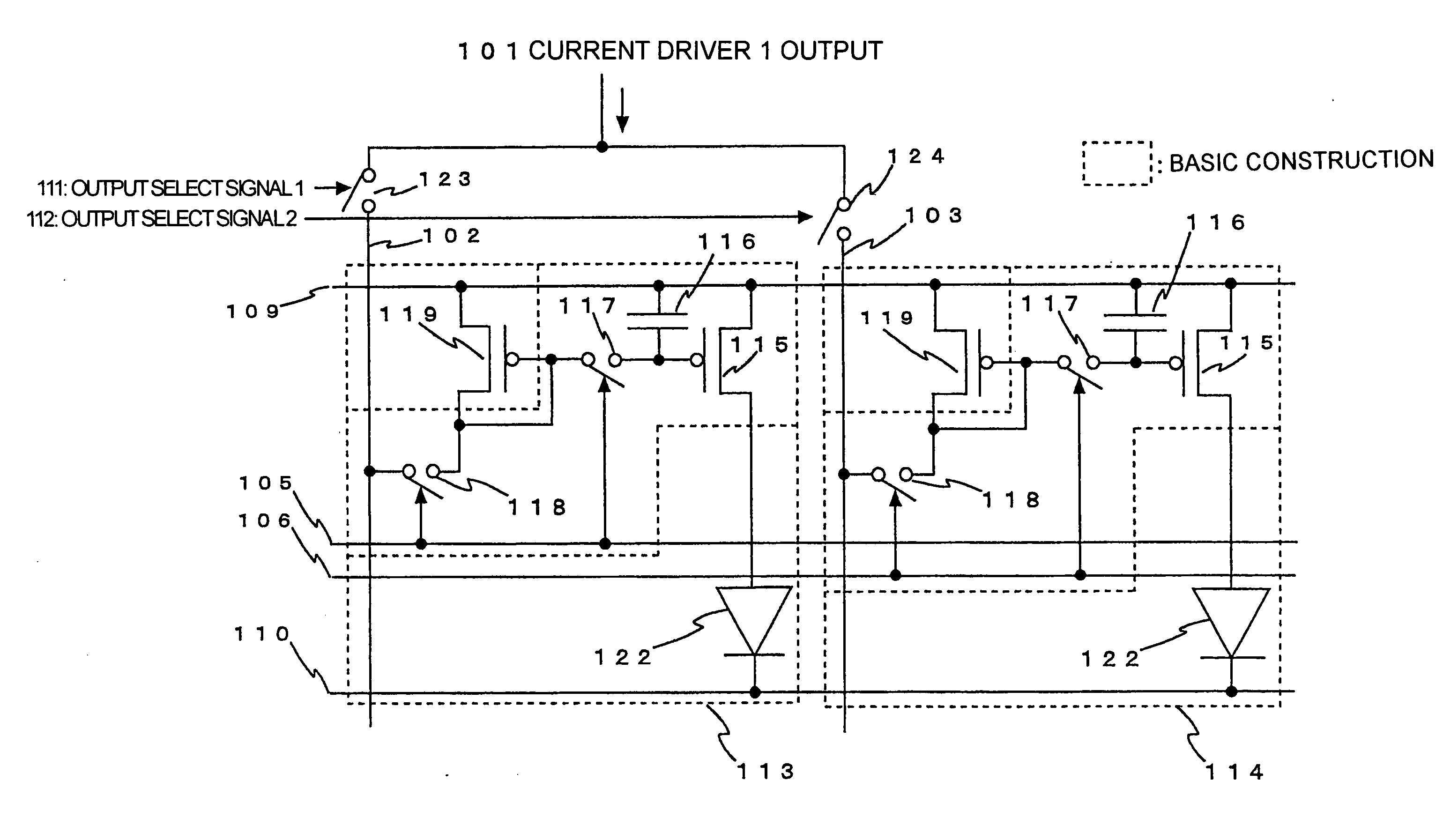

Semiconductor device provided with matrix type current load driving circuits, and driving method thereof

A semiconductor device to which active drive current programming is applied, comprising current load cells each having a current load and a current load driving circuit, which are arranged in a matrix, capable of reducing the circuit scale of a current driver with little change made in the structure of the current load driving circuit, and a driving method of the same. A current load cell (113, 114) includes a current load driving circuit which is provided with a transistor (115) connected in series with a current load (122) between first and second power supplies (109, 110); a capacitance (116) connected between the control terminal of the transistor (115) and the first power supply (109); and switches (117, 118) connected between the control terminal of the transistor (115) and a corresponding data line. The output (101) of a current driver is connected to a plurality of data lines via a selector (123, 124), and the plural data lines connected to one output of the current driver via the selector and at least one of the switches of each of the current load cells corresponding to the respective data lines are drive-controlled in a time division manner during one horizontal period.

Owner:HANNSTAR DISPLAY CORPORATION

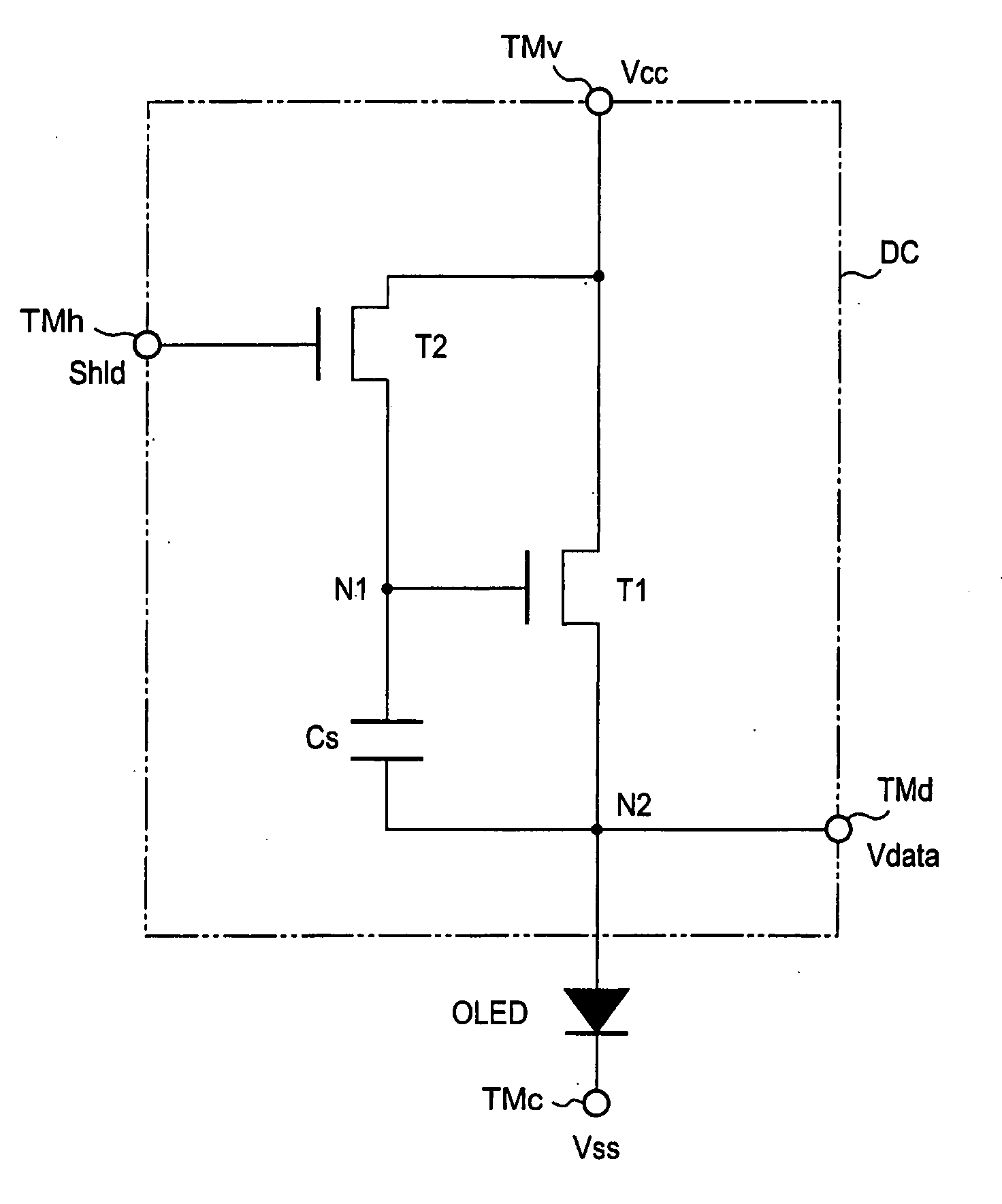

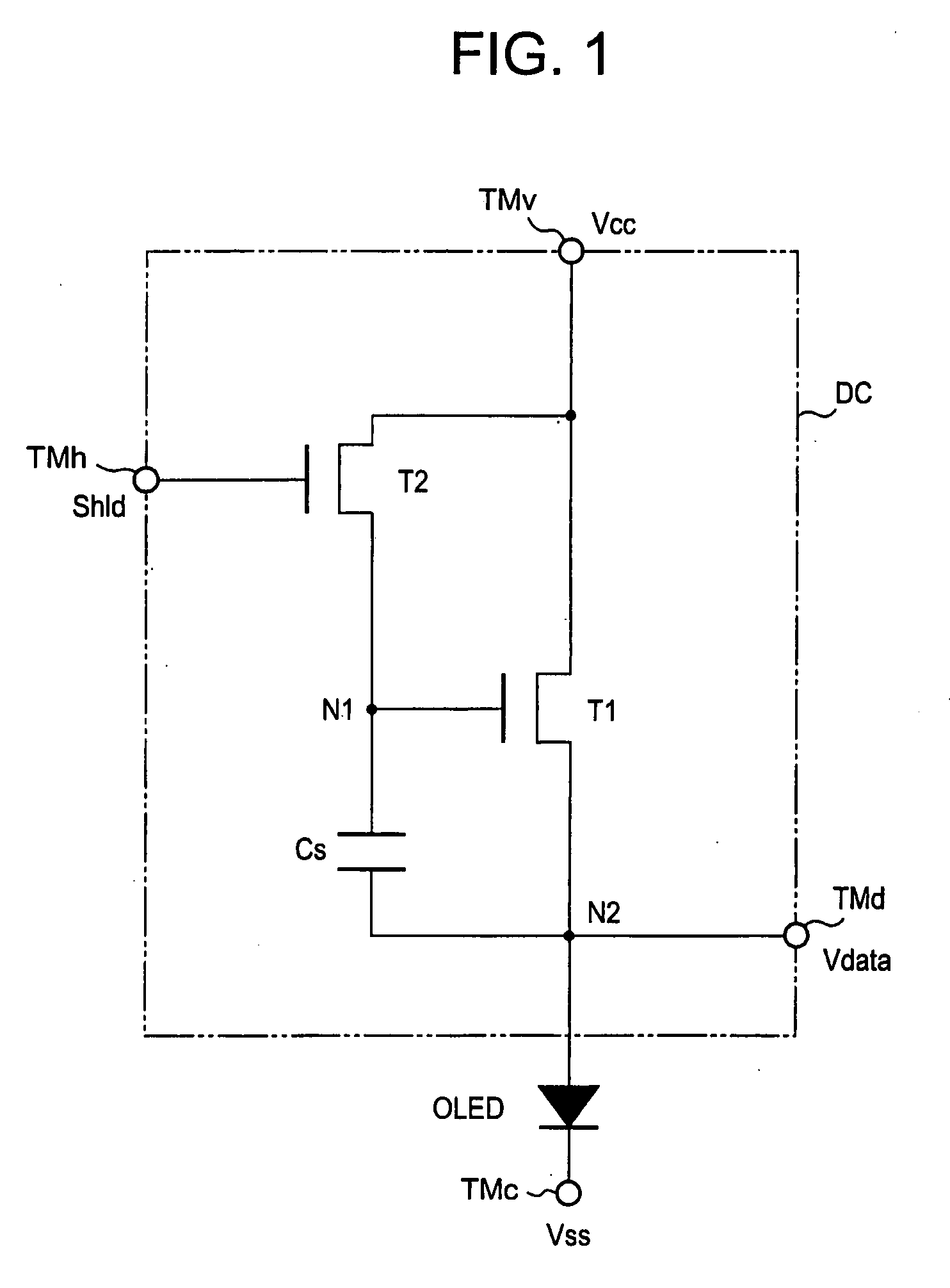

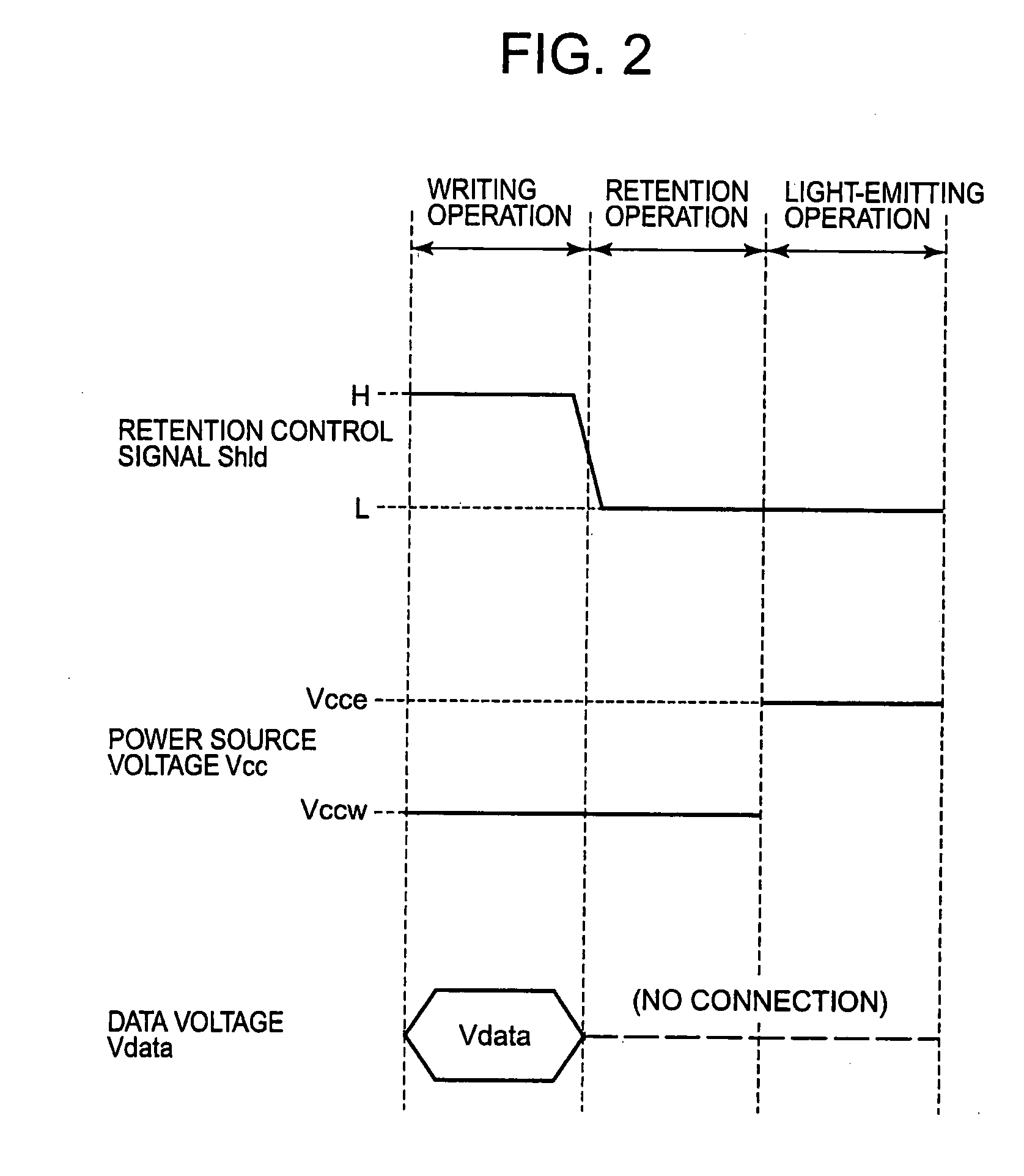

Pixel driver circuit and pixel circuit having the pixel driver circuit

InactiveUS7569849B2Static indicating devicesElectroluminescent light sourcesDriver circuitLight-emitting diode

A pixel driver circuit for driving a light-emitting element and a pixel circuit having the pixel driver circuit are provided. The pixel driver circuit includes a data line, address lines, switch thin film transistors, feedback thin film transistors and drive thin film transistors. The pixel circuit may include an organic light emitting diode, which is driven by the pixel driver circuit.

Owner:IGNIS INNOVATION

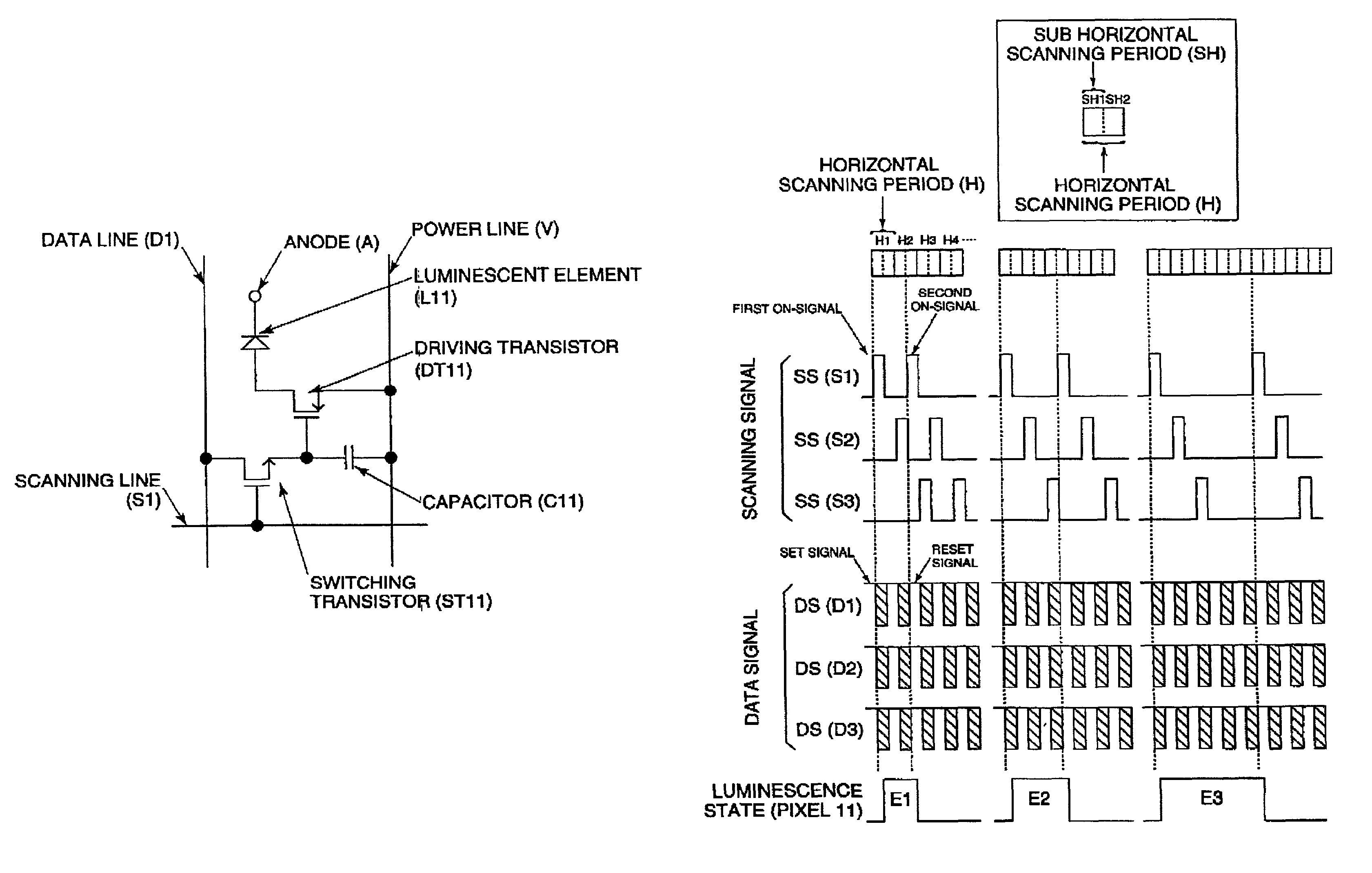

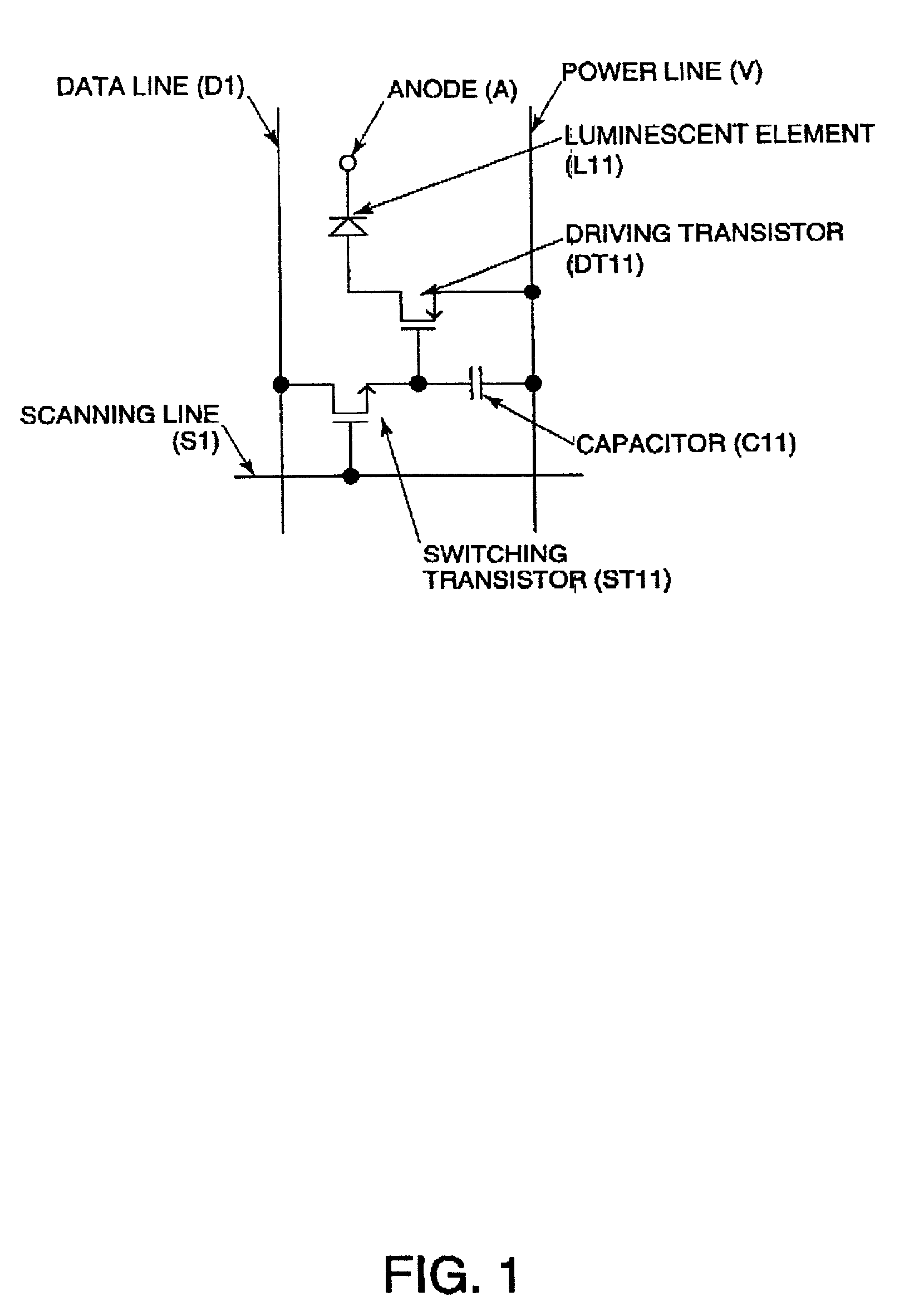

Driving method for electro-optical device, electro-optical device, and electronic apparatus

InactiveUS7315295B2Efficient implementationReduce power consumptionStatic indicating devicesSolid-state devicesTime ratioTransistor

The invention provides a method for implementing a multi-level display of an electro-optical device according to a time ratio gray-scale method without providing reset lines. In an electro-optical device that includes, at an intersection of a scanning line and a data line, an electro-optical element, a driving transistor that drives the electro-optical element, and a switching transistor that controls the driving transistor, a gray-scale is obtained by performing a plurality of set-reset operations. Each set-reset operation includes: a setting step of supplying an on-signal to the switching transistor via the scanning line, and of supplying a set signal to select a conducting state or a non-conducting state of the driving transistor to the driving transistor via the data line and the switching transistor in accordance with the one signal; and a resetting step of supplying an on-signal to the switching transistor via the scanning line, and of supplying a reset signal to select the non-conducting state of the driving transistor to the driving transistor via the data line and the switching transistor in accordance with the one signal.

Owner:BOE TECH GRP CO LTD

System and method for the management of power supplied over data lines

ActiveUS20040230846A1Configuring power of Ethernet devicesSpecial service provision for substationVolume/mass flow measurementNetwork switchEthernet

A system for providing power over data lines, particularly Ethernet data lines, comprises a network switch including a multiplicity of ports each of which is capable of supplying power in addition to data packets, a controllable power source which is coupled to said ports for supplying power thereto and a processor which is coupled to control the supply of power by the power source. The processor is programmed to guarantee the supply of power to selected ports and to allow or inhibit the supply of power to ports other than the selected ports, having regard to a specified limit on the supply of power by the controllable power source and the total guaranteed power to the selected ports.

Owner:VALTRUS INNOVATIONS LTD +1

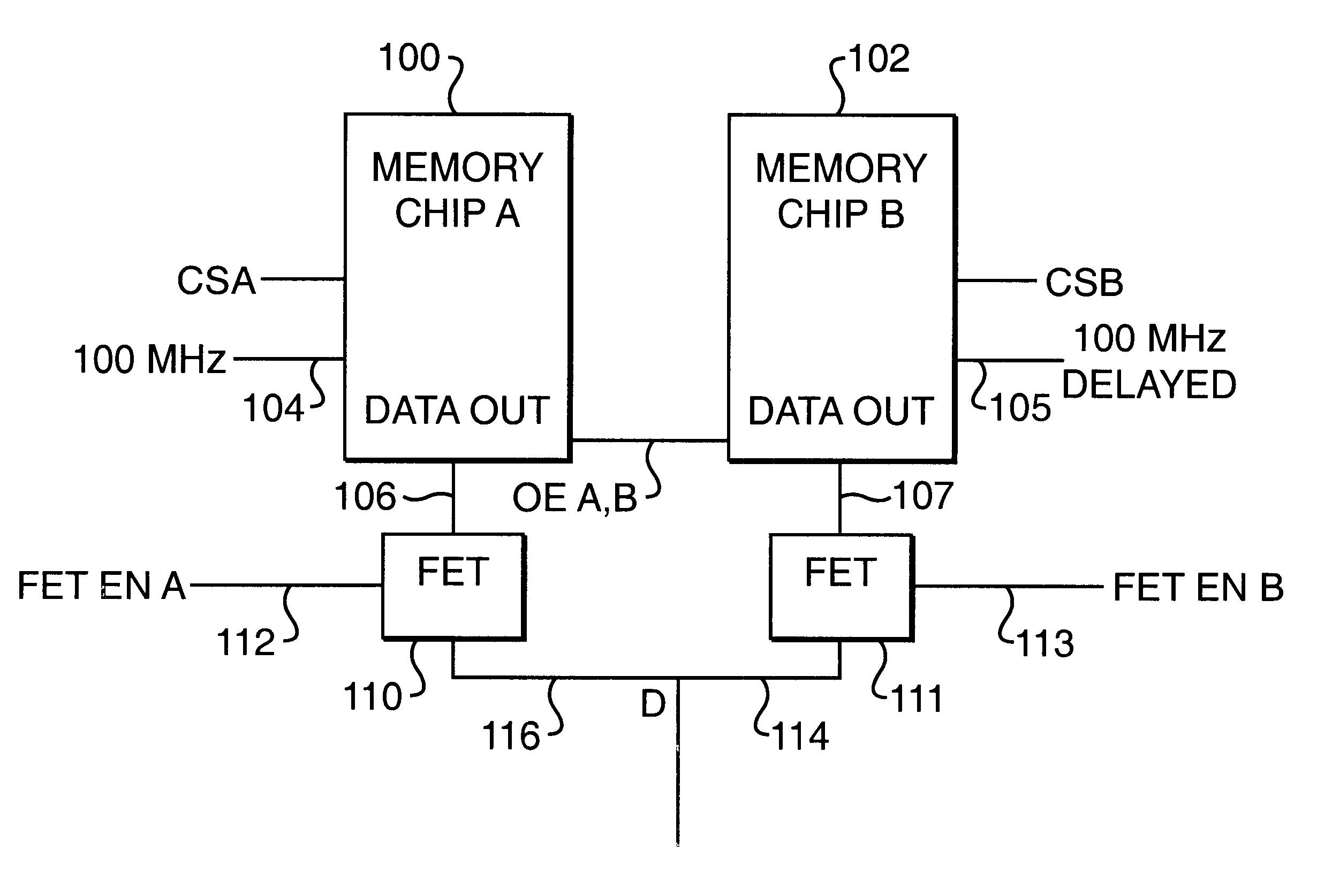

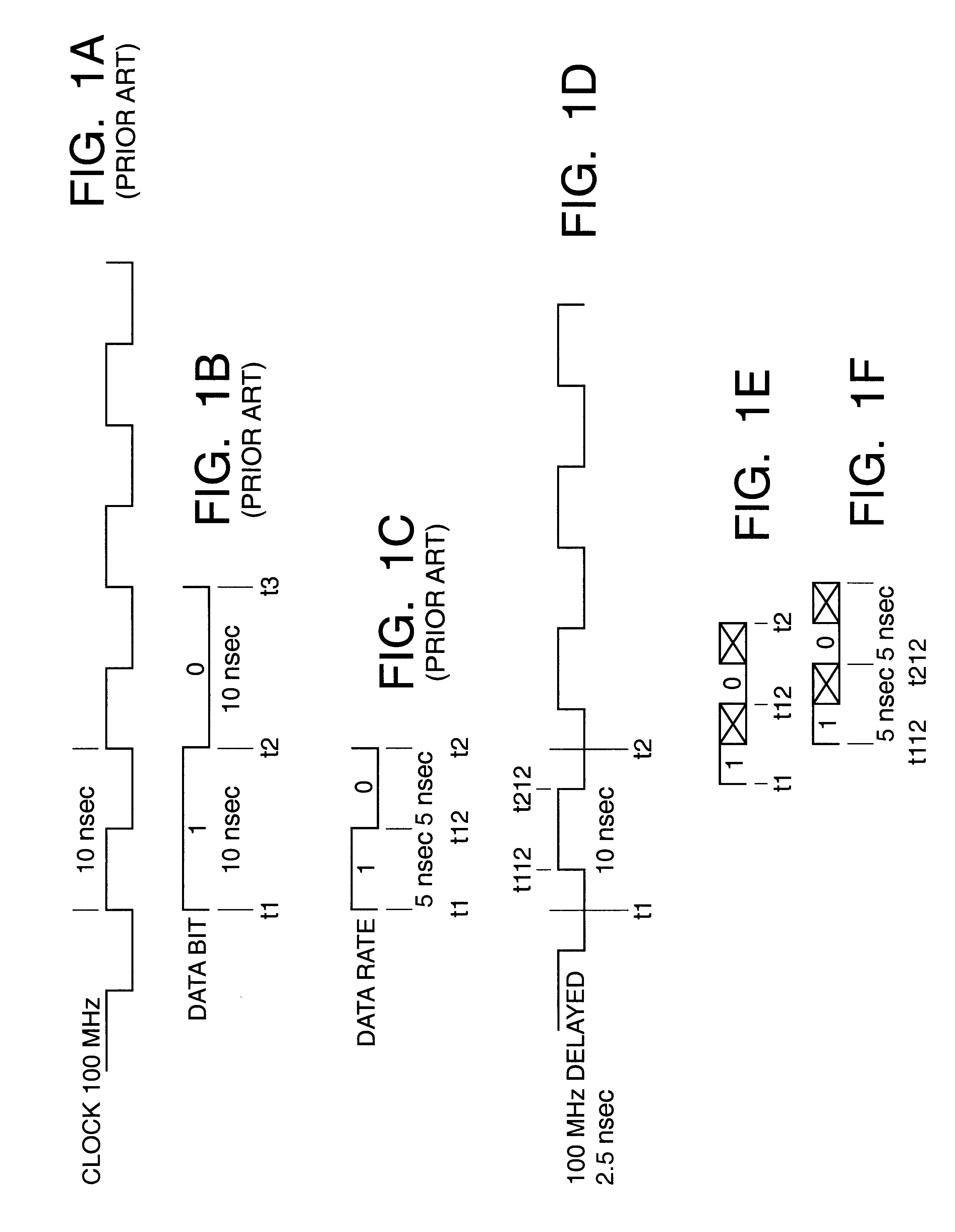

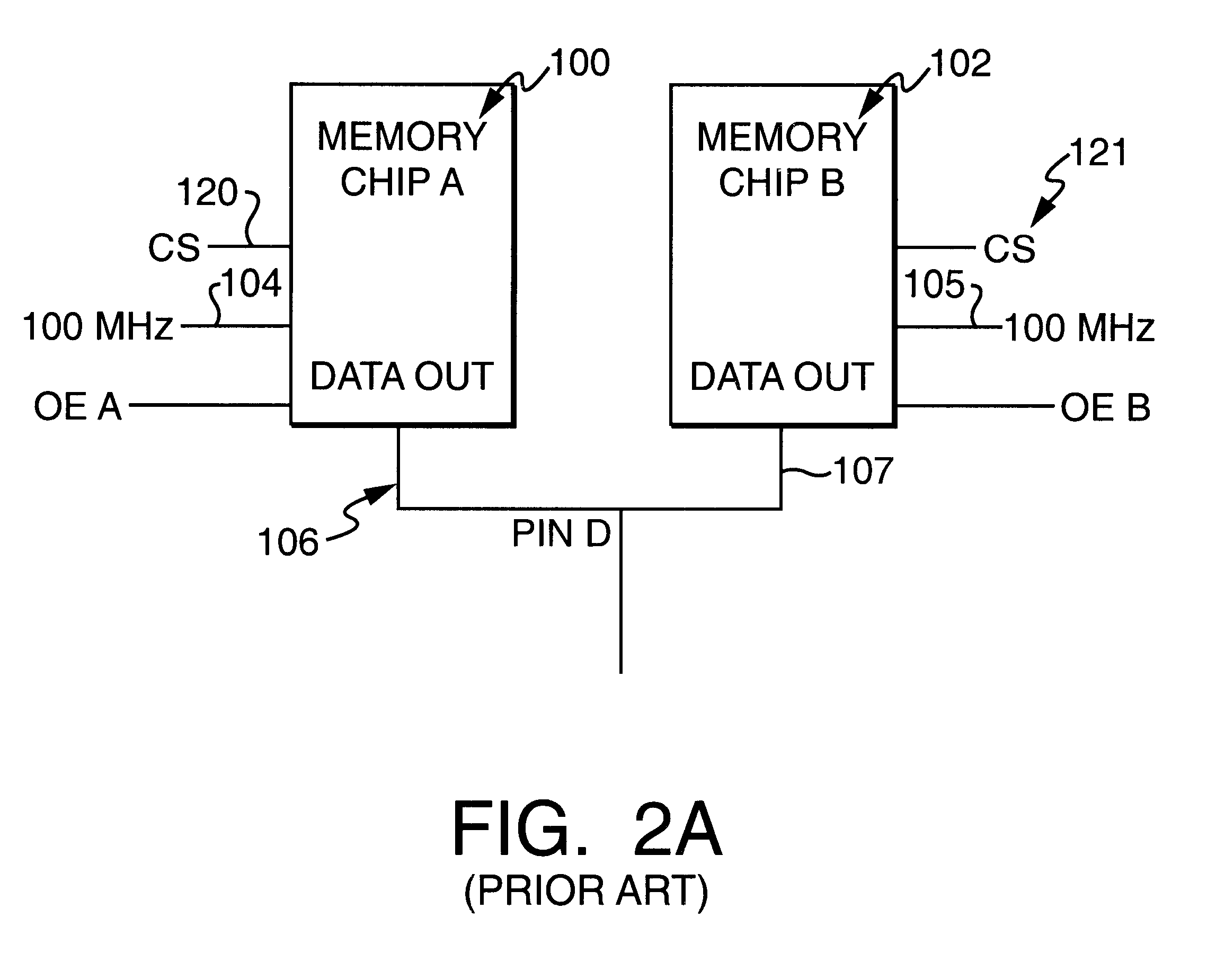

Memory system using FET switches to select memory banks

A computer memory system provides a double data rate (DDR) memory output while requiring memory chips with only half the frequency limit of the prior art DDR memory chips. The system contains a first memory bank having data lines and a second memory bank having data lines. The first and second memory banks are associated with first and second clock signals, respectively, where the second clock signal is delayed from the first clock signal such that the data lines of the first memory bank are connected to a data bus in synchronism with the first clock signal while the data lines of the second memory bank are connected with the data bus in synchronism with the second clock signal. In one embodiment, a first FET switch connects the data lines of the first memory bank with the data bus and a second FET switch connects the data lines of the second memory bank with the data bus. The second FET switch is connected to the data bus at a time delayed from the beginning after the start of each clock cycle of the second clock signal. As a result, the data bus is never connected to the data lines of both memory banks at the same time, but rather, the data bus is alternately connected with the first memory bank and then the second memory bank.

Owner:FOOTHILLS IP LLC

Organic light emitting diode display device for pixel current sensing and pixel current sensing method thereof

ActiveUS20130050292A1Increase speedSimple structureCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceVoltage reference

An OLED display device which can sense a current of each pixel at high speed by a simple structure in order to compensate for luminance non-uniformity and a pixel current sensing method thereof are discussed. The OLED display device includes a display panel including pixels, each including a light emitting element and a pixel circuit for independently driving the light emitting element, a data driver for driving a data line connected to the pixel circuit using a data voltage, floating one of the data line, a reference line for supplying a reference voltage to the pixel circuit, and a power line for supplying a power to the pixel circuit to use the floated line as a current sensing line, sensing a voltage corresponding to a pixel current of the pixel circuit flowing to the current sensing line, and outputting the sensing voltage, in a sensing mode.

Owner:LG DISPLAY CO LTD

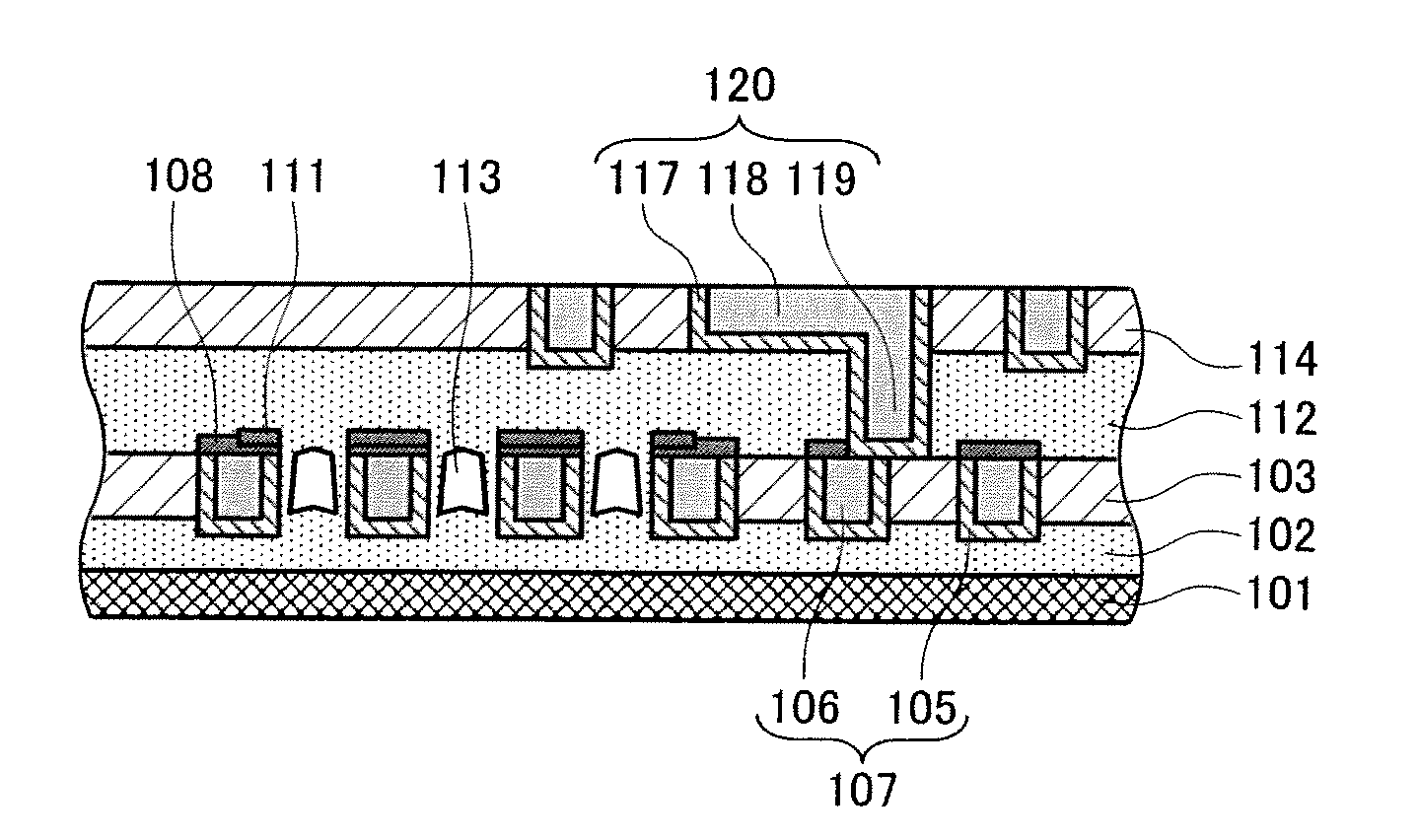

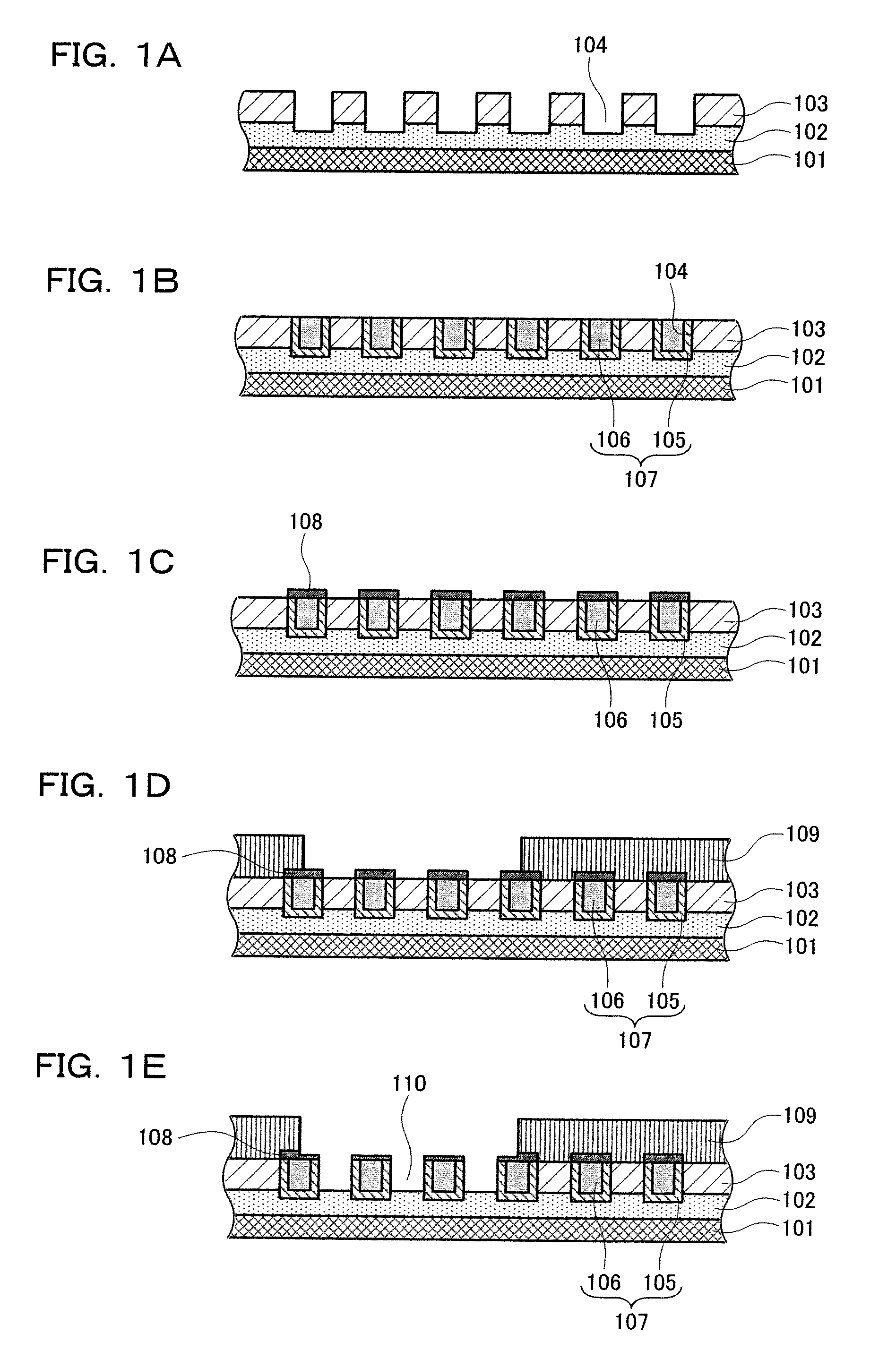

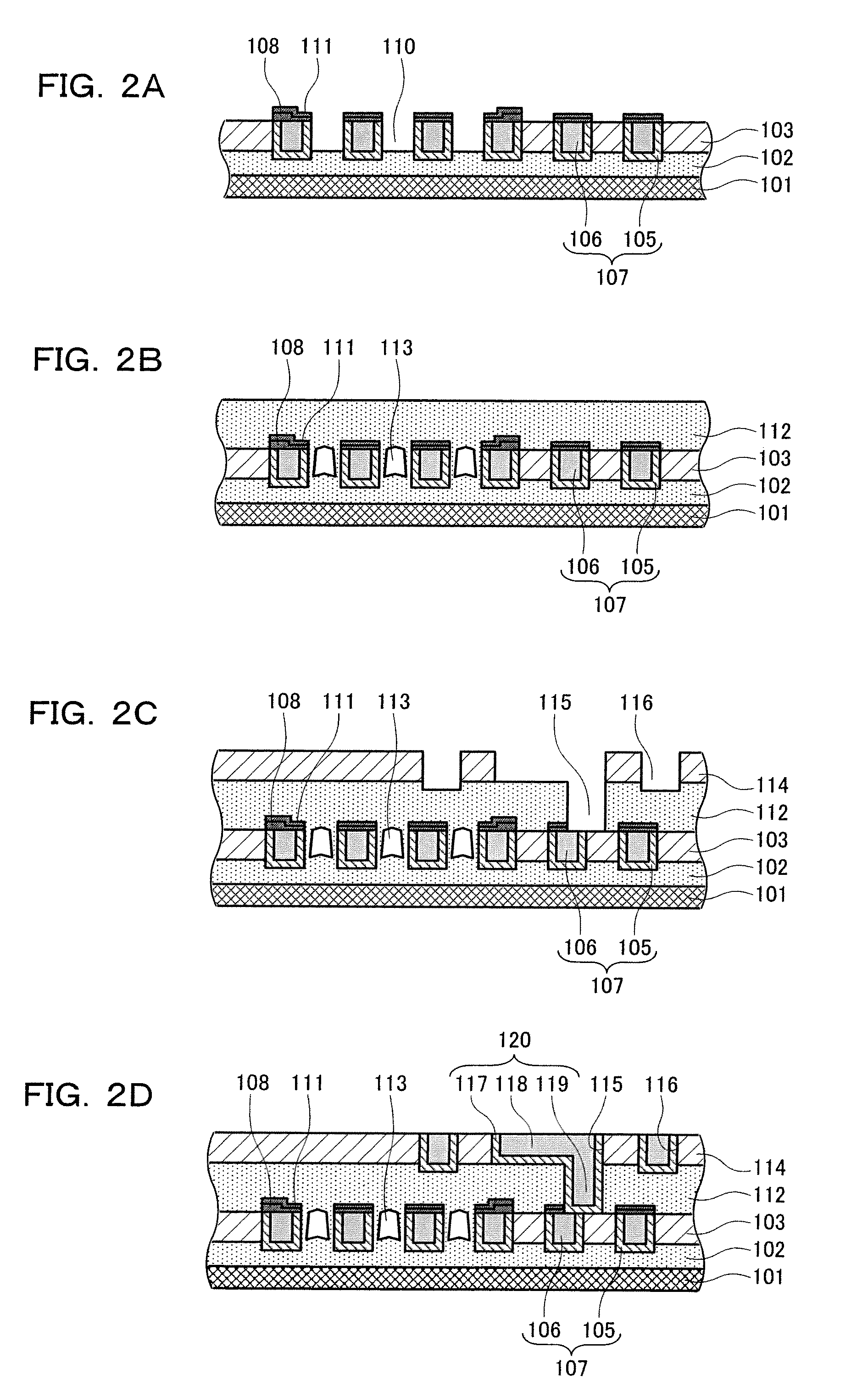

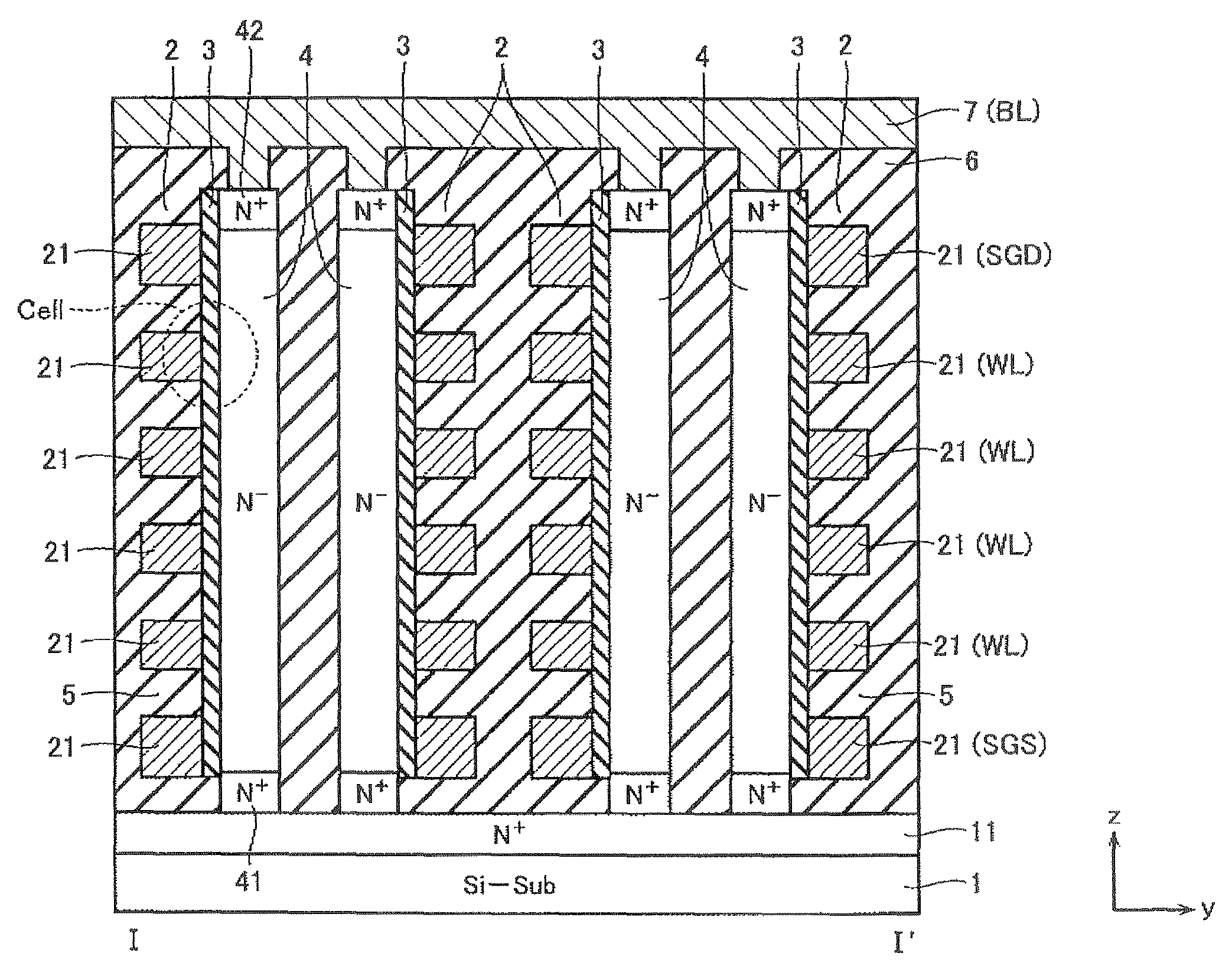

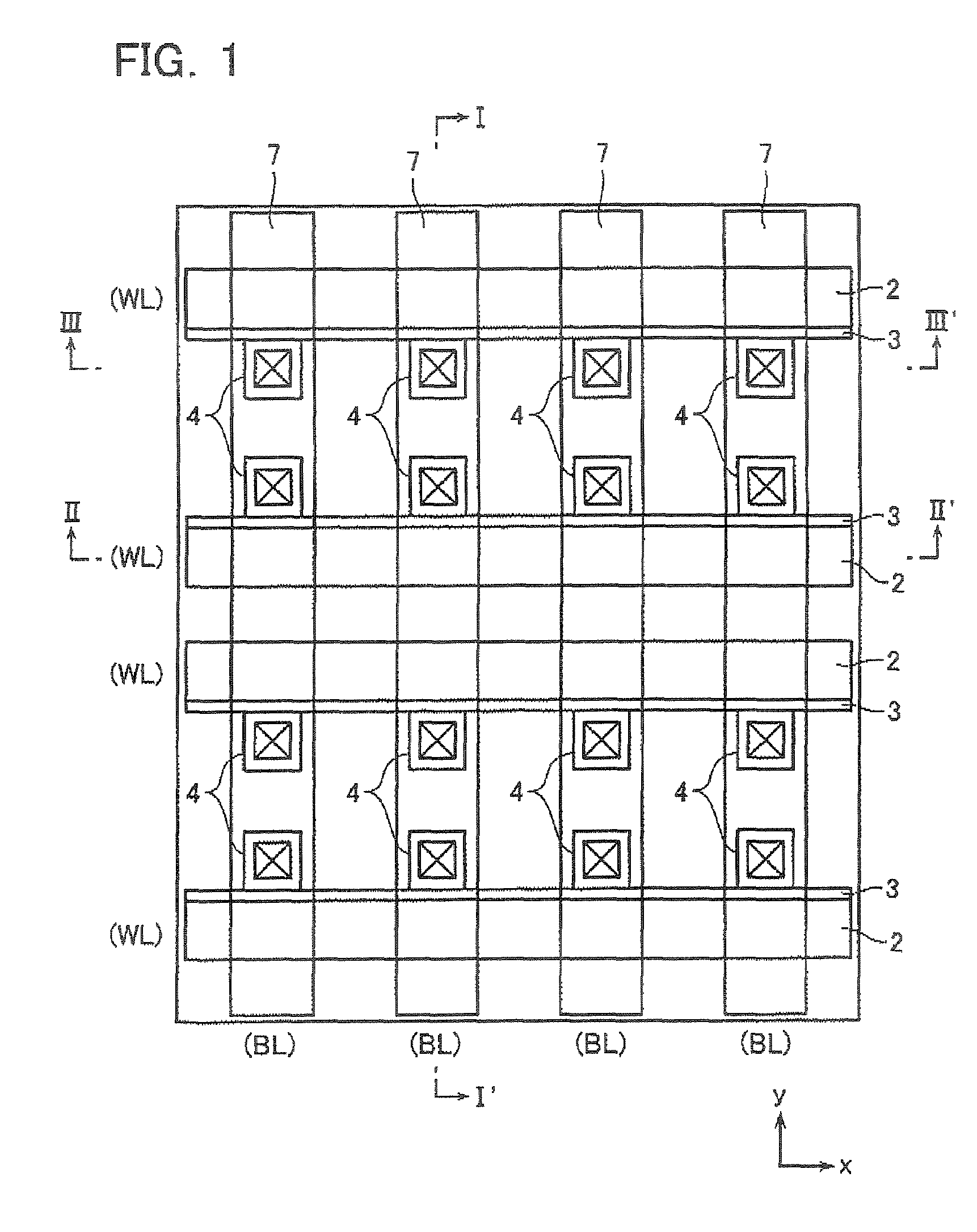

Semiconductor memory device including pillar-shaped semiconductor layers and a method of fabricating the same

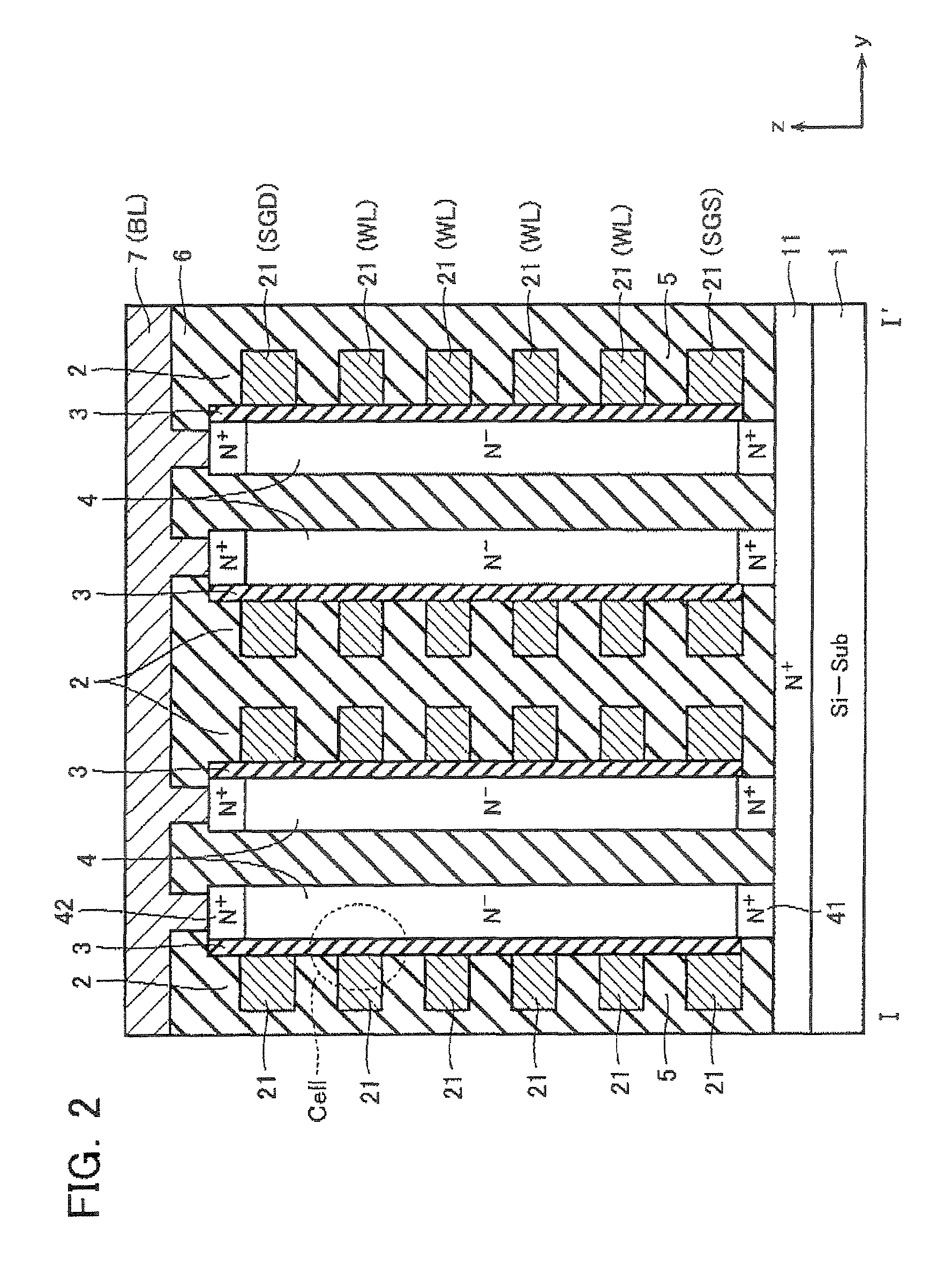

A semiconductor memory device includes: a semiconductor substrate, on which an impurity diffusion layer is formed in a cell array area; a gate wiring stack body formed on the cell array area, in which multiple gate wirings are stacked and separated from each other with insulating films; a gate insulating film formed on the side surface of the gate wiring stack body, in which an insulating charge storage layer is contained, pillar-shaped semiconductor layers arranged along the gate wiring stack body, one side surfaces of which are opposed to the gate wiring stack body via the gate insulating film, each pillar-shaped semiconductor layer having the same conductivity type as the impurity diffusion layer; and data lines formed to be in contact with the upper surfaces of the pillar-shaped semiconductor layers and intersect the gate wirings.

Owner:KK TOSHIBA

Integrated multi-touch surface having varying sensor granularity

ActiveUS20080309631A1Easy inputFine granularityDigital data processing detailsSubstation equipmentGranularityComputer science

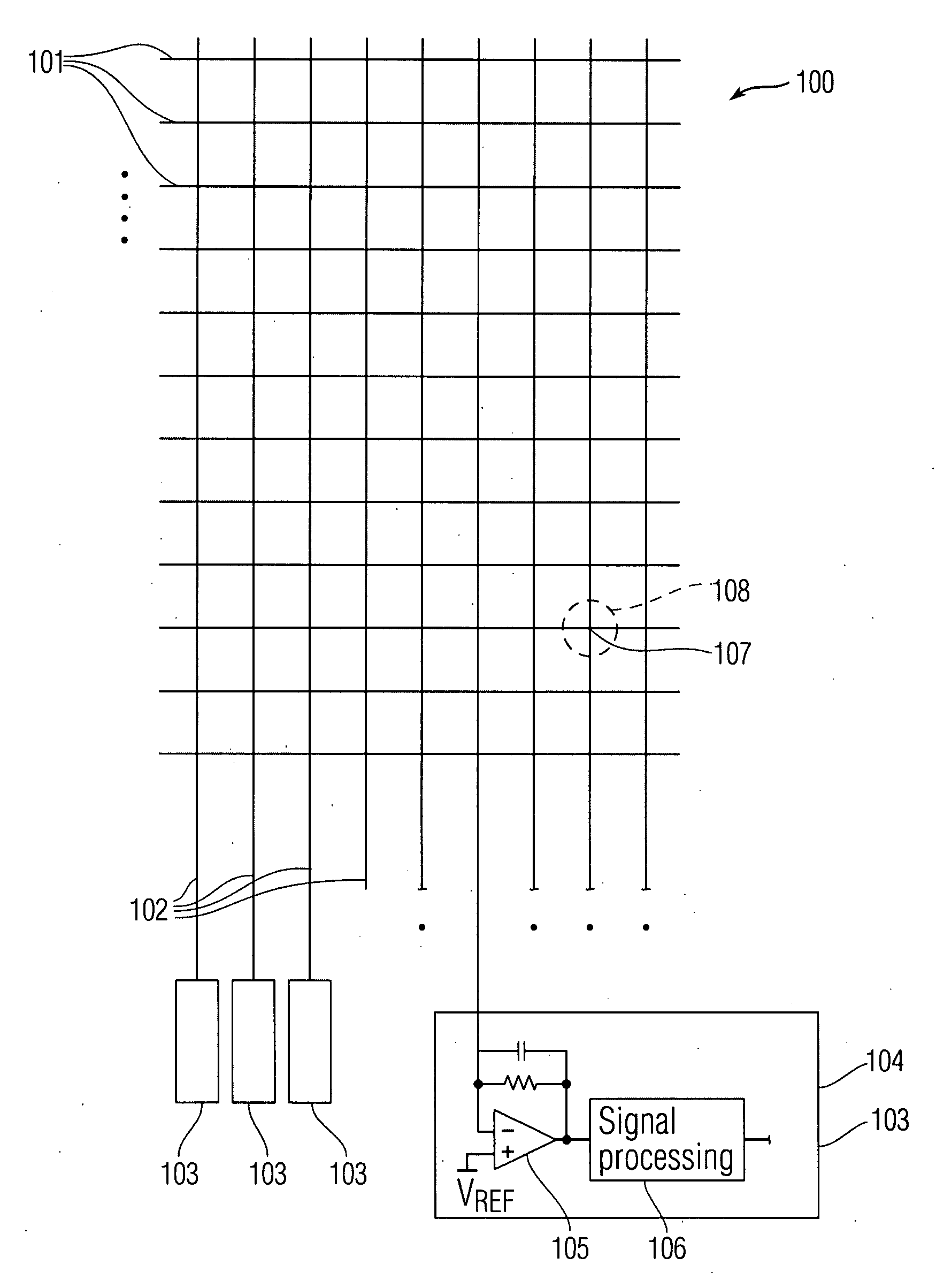

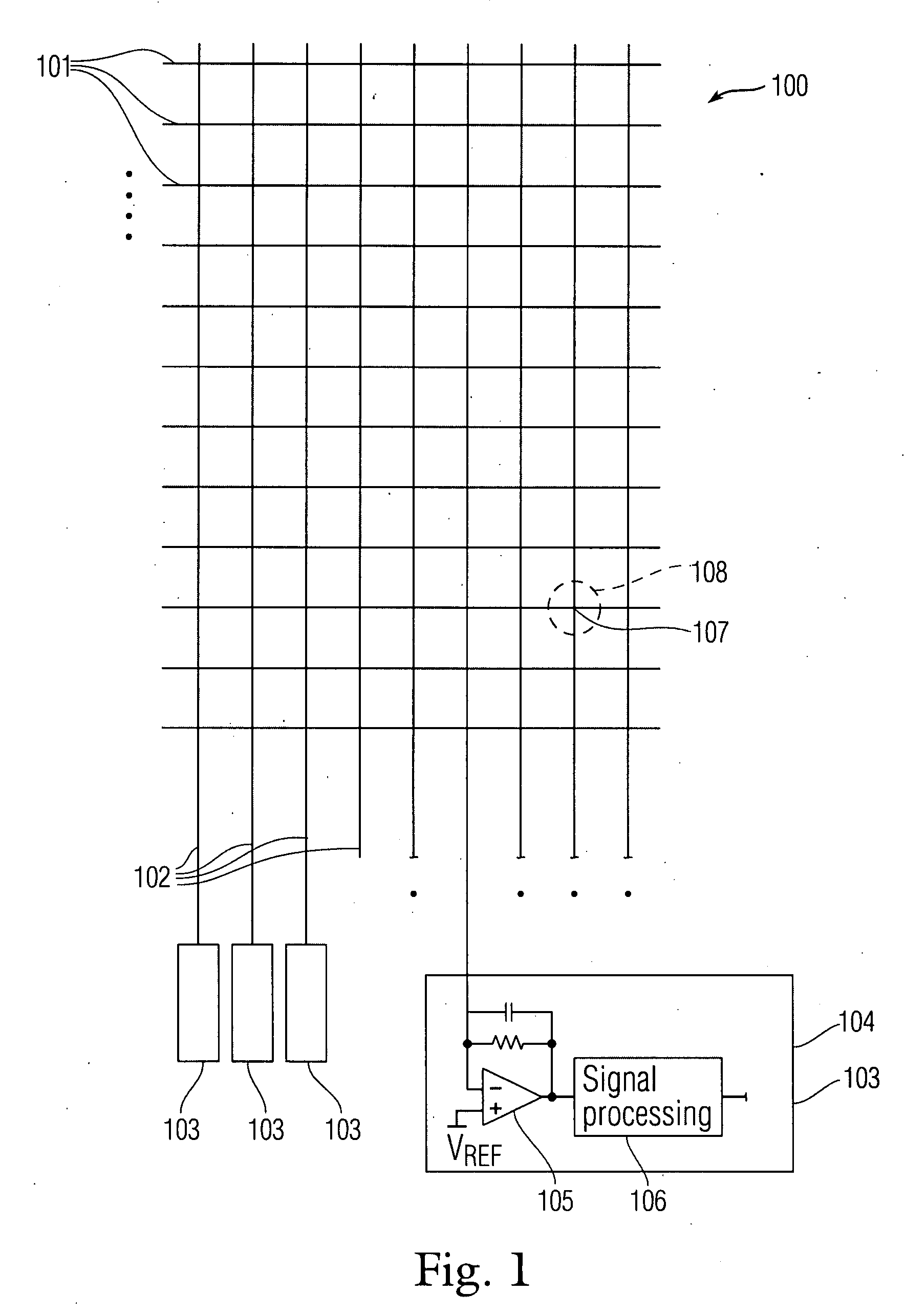

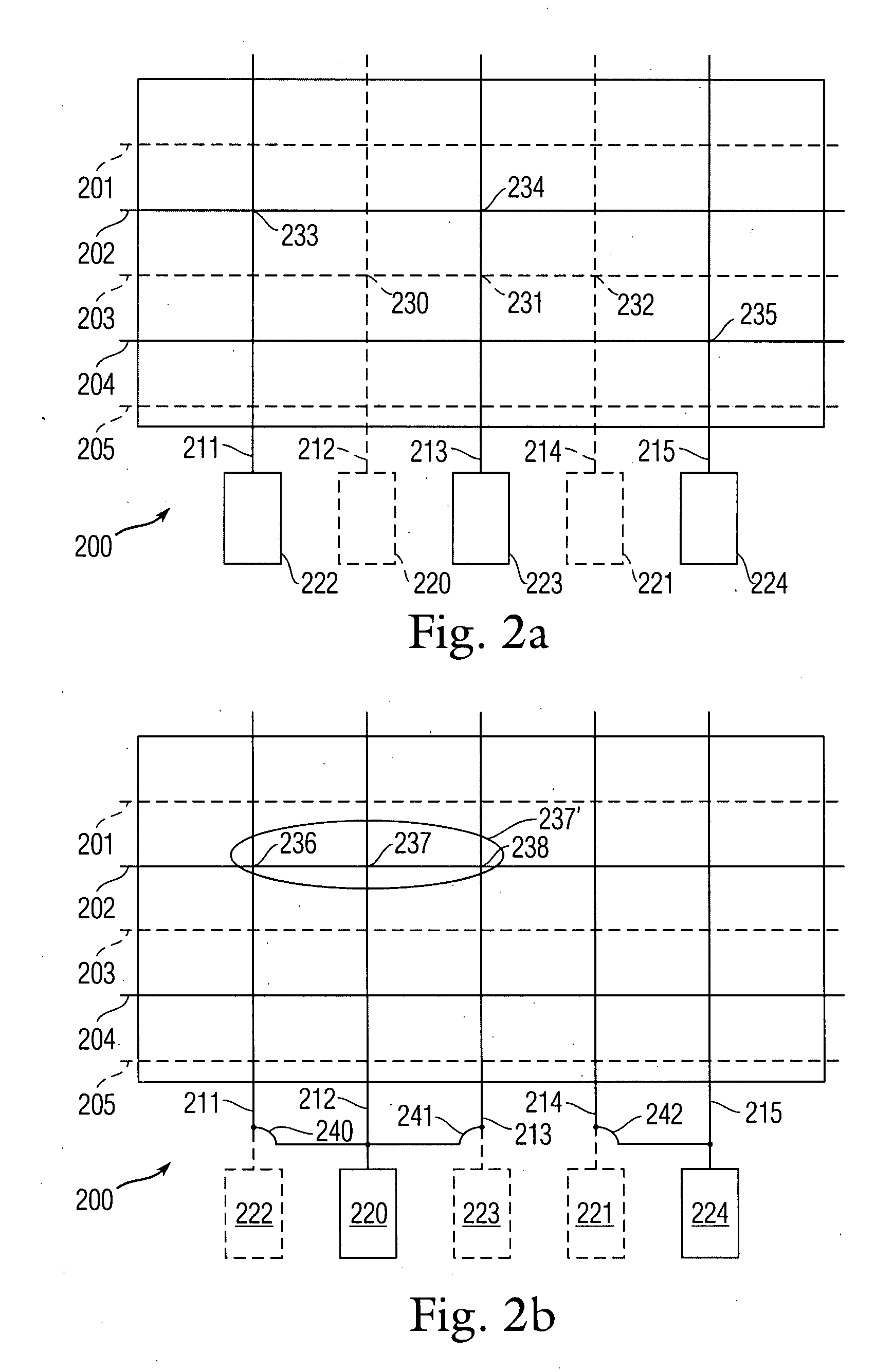

This relates to an event sensing device that includes an event sensing panel and is able to dynamically change the granularity of the panel according to present needs. Thus, the granularity of the panel can differ at different times of operation. Furthermore, the granularity of specific areas of the panel can also be dynamically changed, so that different areas feature different granularities at a given time. This also relates to panels that feature different inherent granularities in different portions thereof. These panels can be designed, for example, by placing more stimulus and / or data lines in different portions of the panel, thus ensuring different densities of pixels in the different portions. Optionally, these embodiments can also include the dynamic granularity changing features noted above.

Owner:APPLE INC

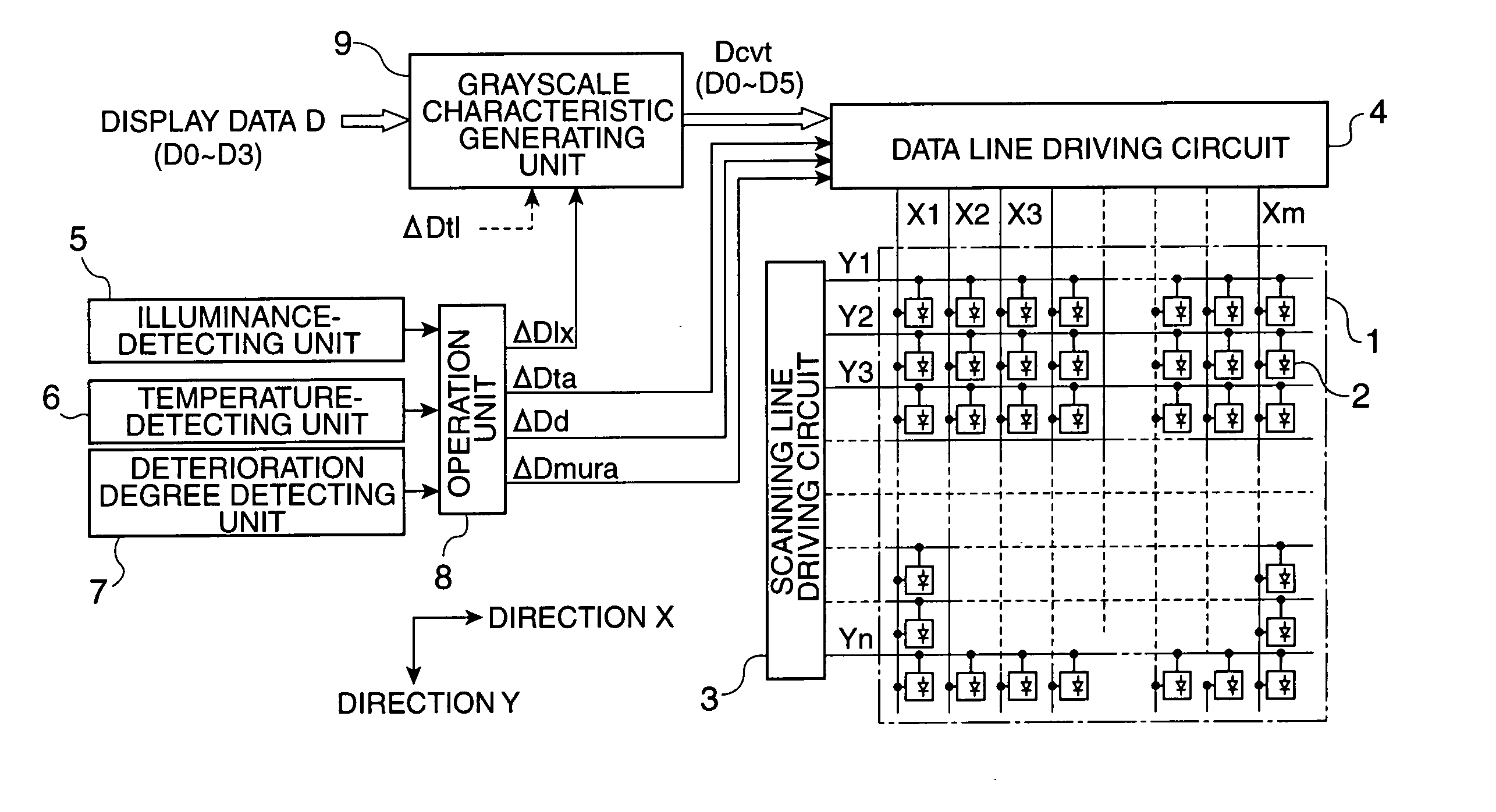

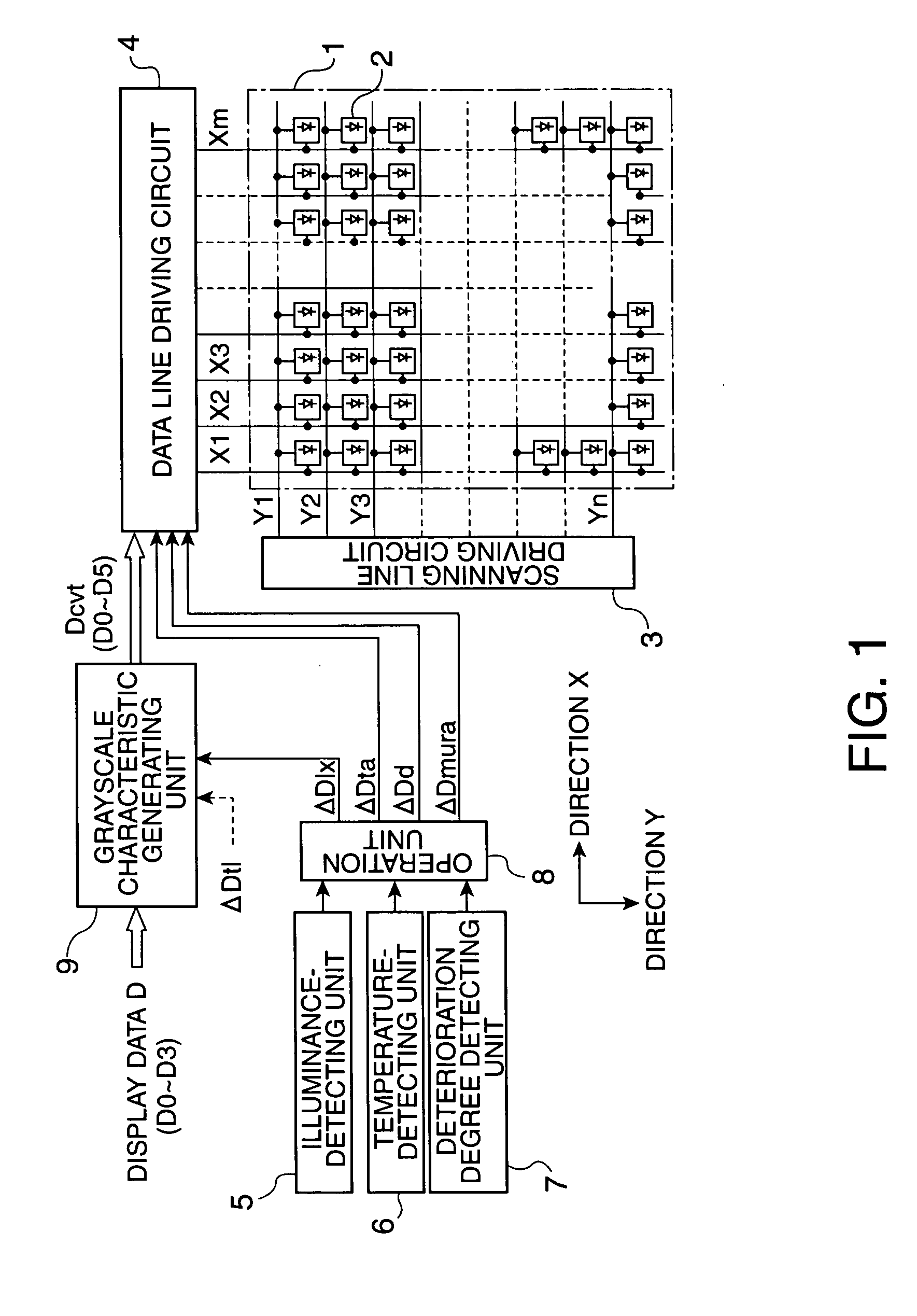

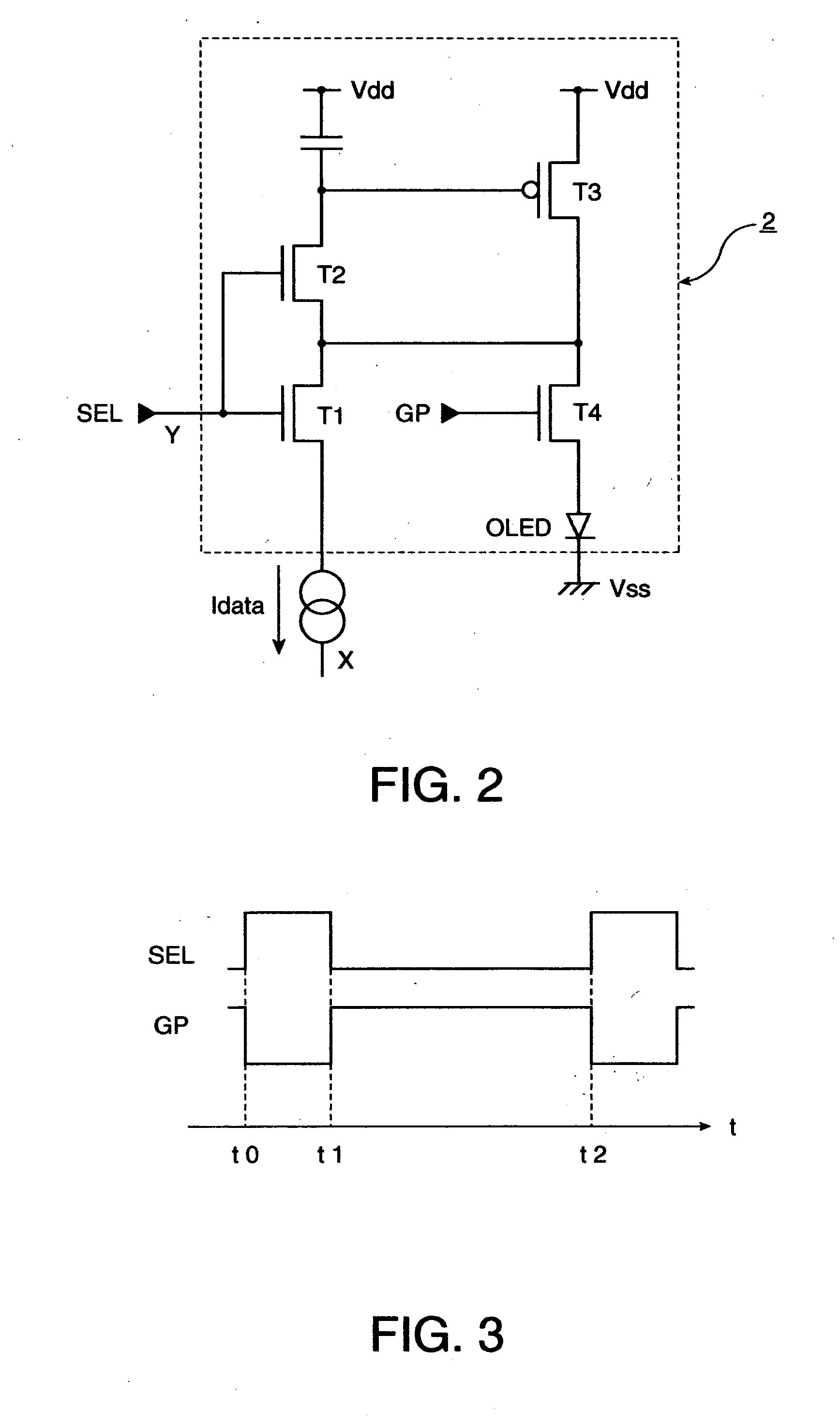

Electro-optical device, method of driving electro-optical device, and electronic apparatus

The invention provides an electro-optical device that stabilizes display quality by performing correction processing corresponding to a plurality of disturbance factors. Specifically, a grayscale characteristic generating unit can generate conversion data having grayscale characteristics obtained by changing the grayscale characteristics of display data that defines the grayscales of pixels with reference to a conversion table whose description contents include correction factors. A data line driving circuit can drive the pixels after correcting the grayscale characteristics of the conversion data by the correction factors using other processing different from the that performed by the grayscale characteristic generating unit.

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

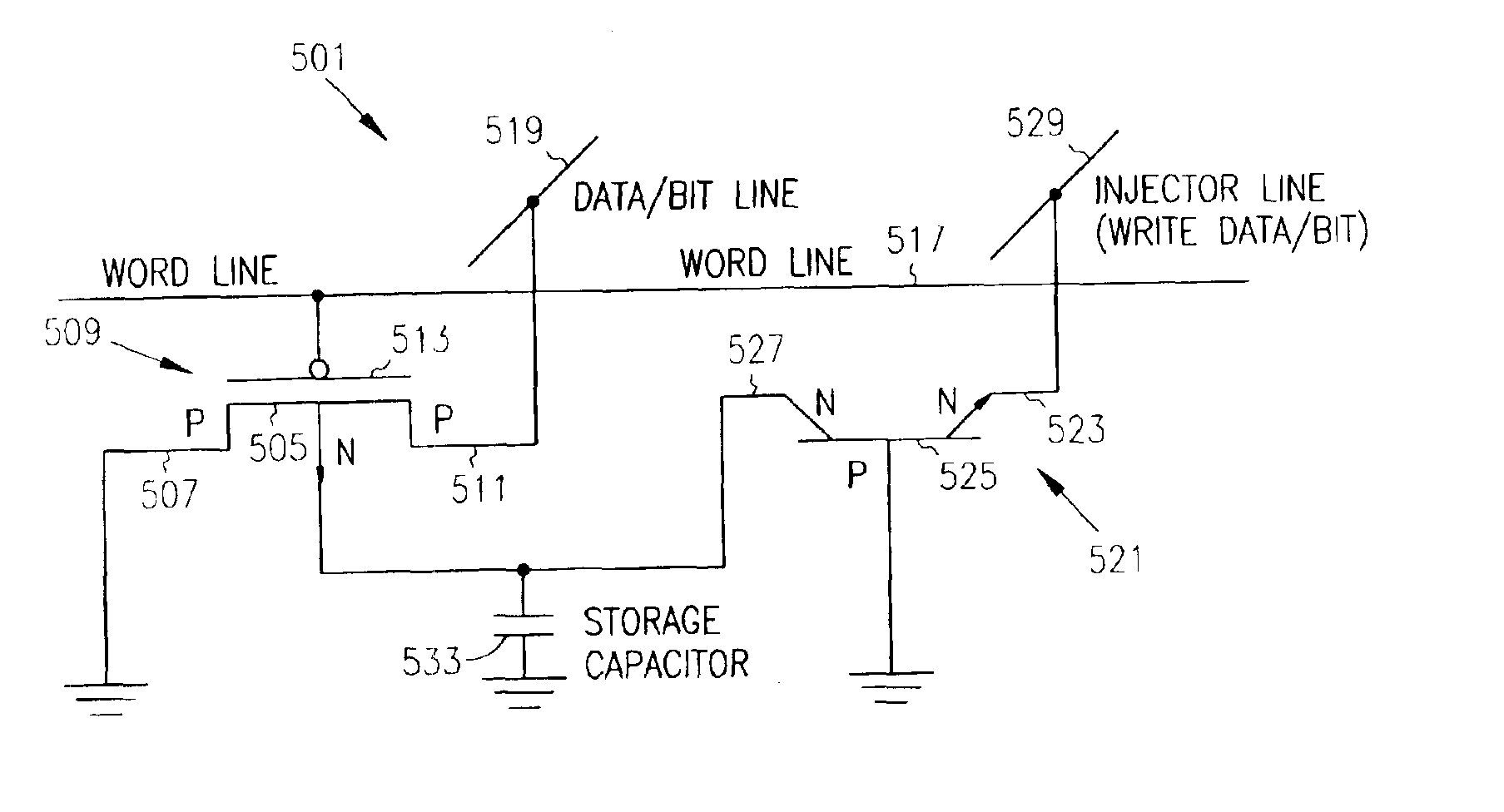

Embedded DRAM gain memory cell having MOS transistor body provided with a bi-polar transistor charge injecting means

A high density horizontal merged MOS-bipolar gain memory cell is realized for DRAM operation. The gain cell includes a horizontal MOS transistor having a source region, a drain region, and a floating body region therebetween. The gain cell includes a horizontal bi-polar transistor having an emitter region, a base region and a collector region. The collector region for the horizontal bi-polar transistor serves as the floating body region for the horizontal MOS transistor. A gate opposes the floating body region and is separated therefrom by a gate oxide. The emitter region for the horizontal bi-polar transistor is coupled to a write data line.

Owner:MICRON TECH INC

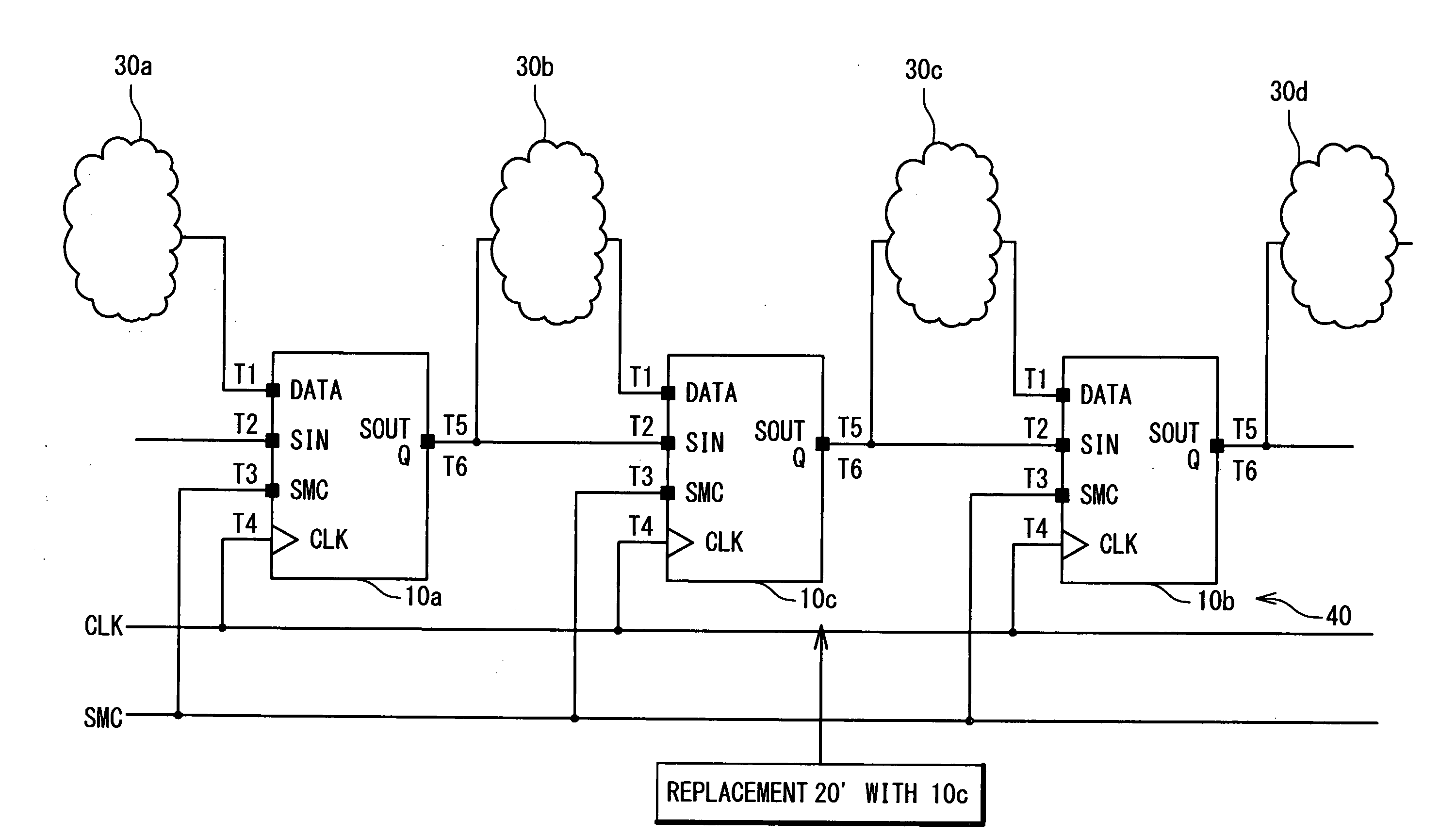

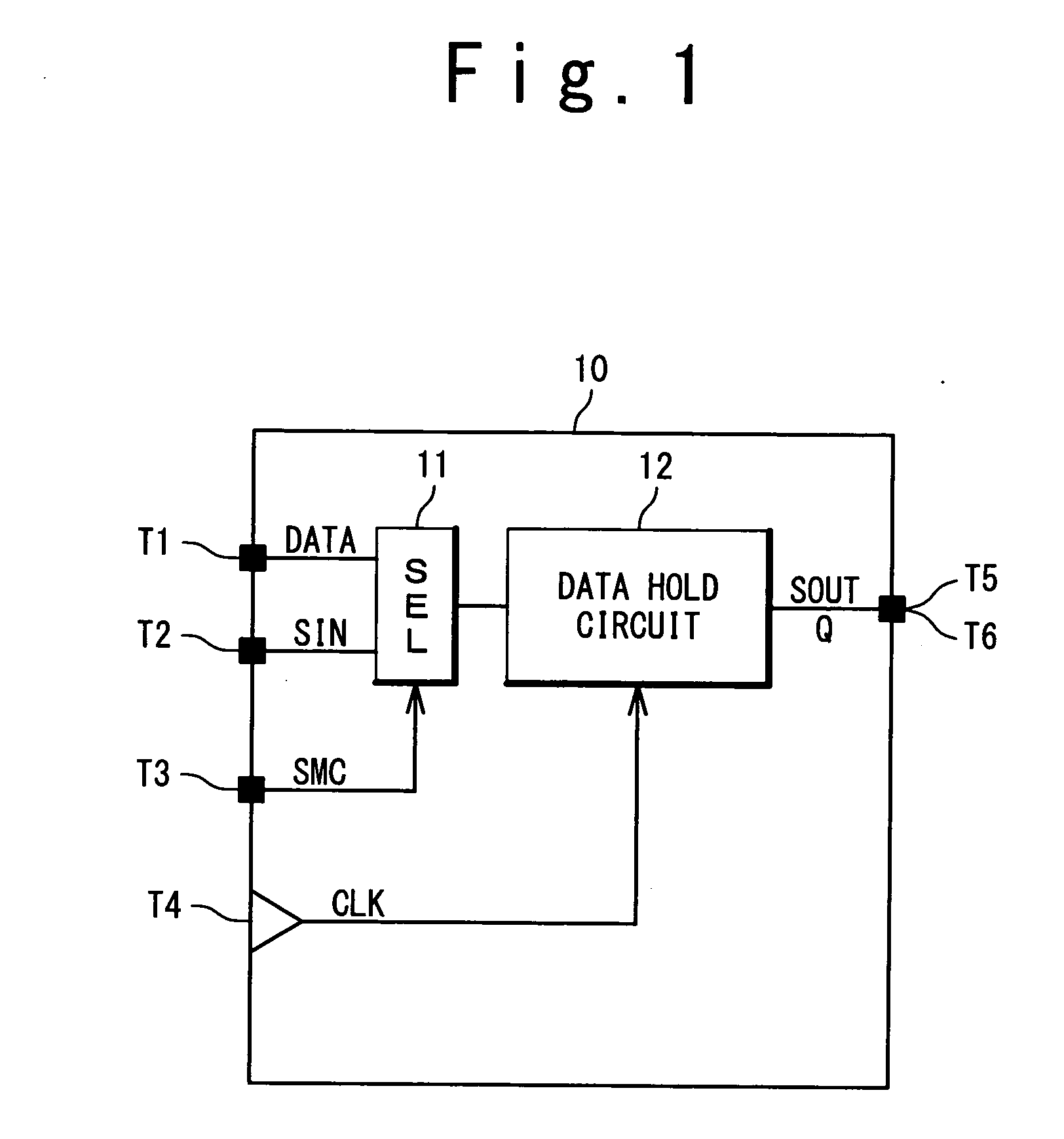

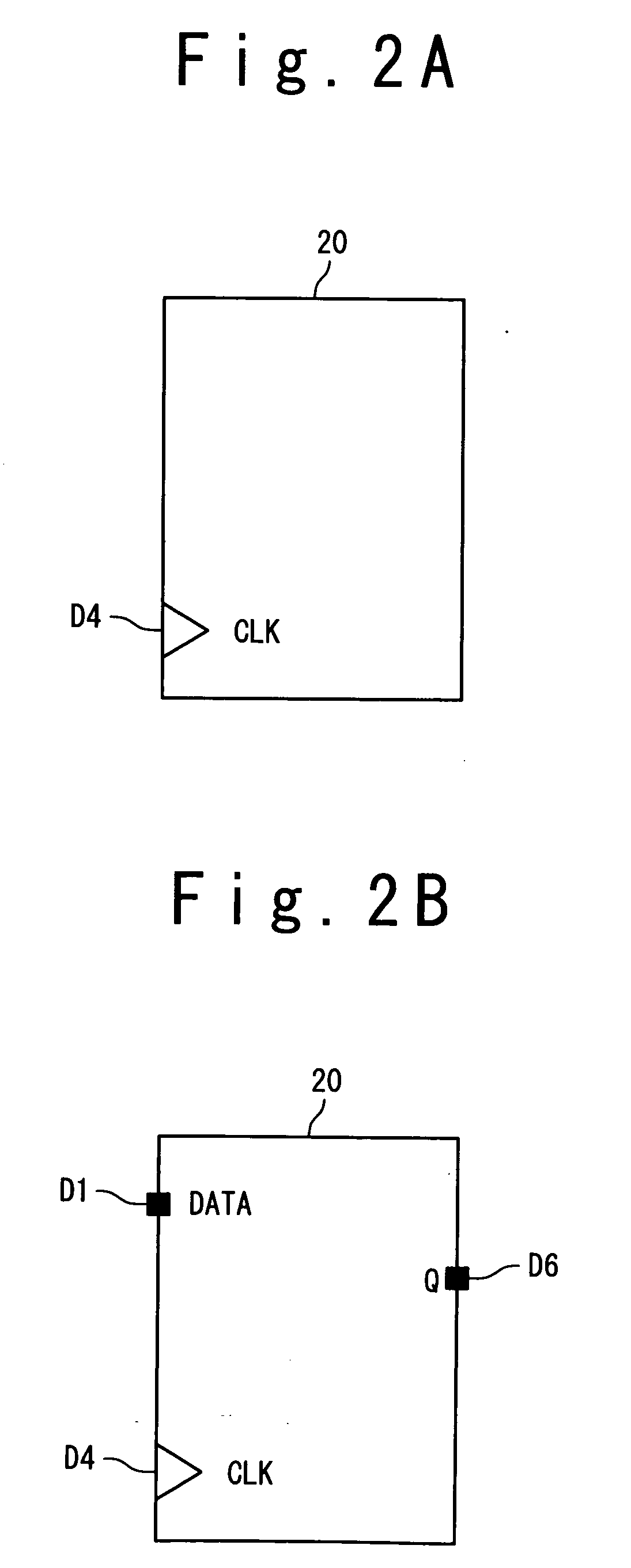

Integrated circuit design based on scan design technology

InactiveUS20090032899A1Effect of power consumption reduction is enhancedReduce power consumptionElectronic circuit testingSolid-state devicesEngineeringCircuit design

An integrated circuit is provided with a scan chain including a scan flip-flop and a dummy block. The dummy block has a clock terminal receiving a clock signal, a scan input terminal connected to a scan data line within the scan chain, and a scan output terminal connected to another scan data line within the scan chain. The dummy block is configured to output data on the scan output terminal in response to input data fed to the scan input terminal, not responsively to the clock signal.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com