Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1660 results about "Control bus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, a control bus is part of the system bus, used by CPUs for communicating with other devices within the computer. While the address bus carries the information about the device with which the CPU is communicating and the data bus carries the actual data being processed, the control bus carries commands from the CPU and returns status signals from the devices. For example, if the data is being read or written to the device the appropriate line (read or write) will be active (logic one).

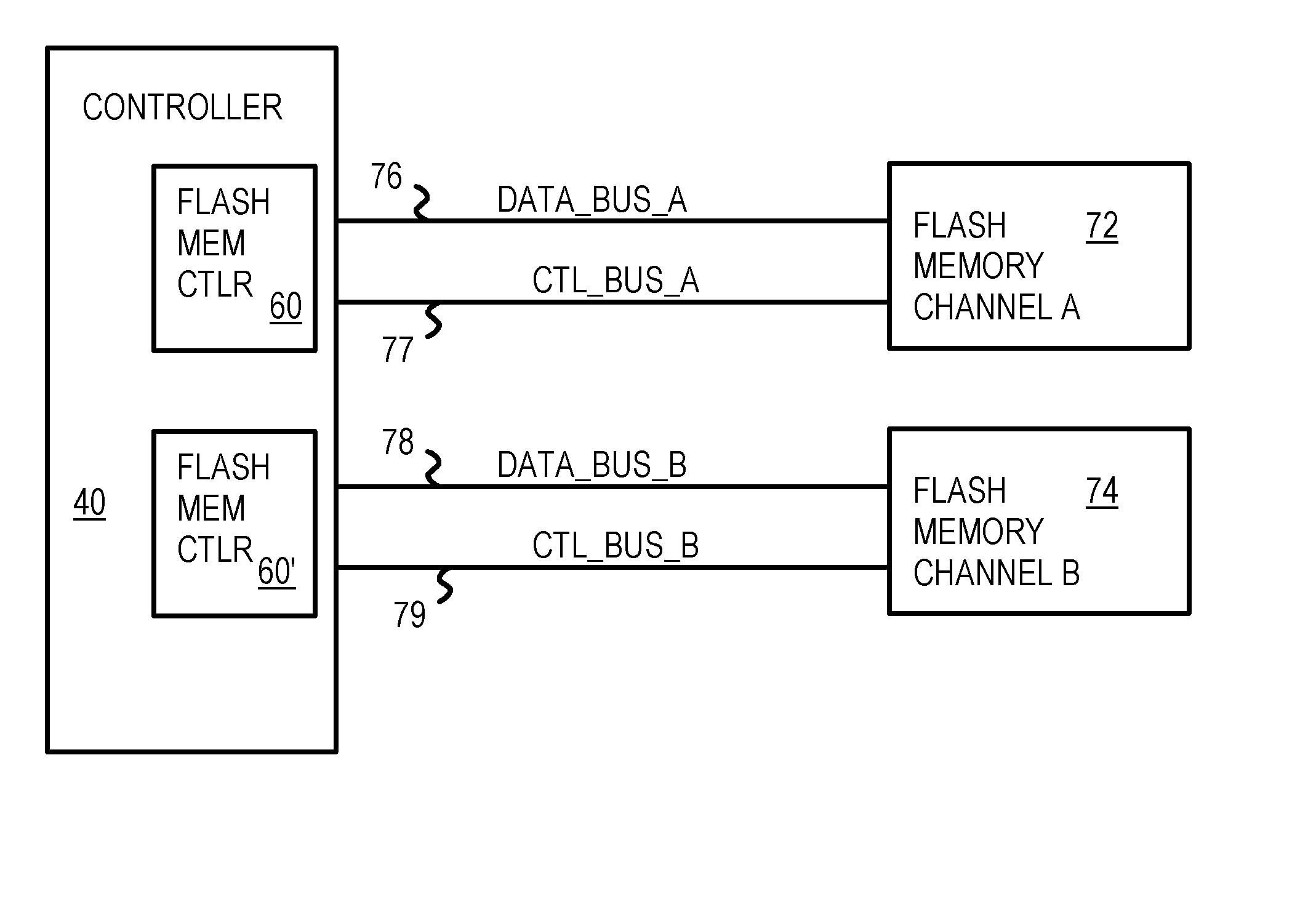

ExpressCard with On-Card Flash Memory with Shared Flash-Control Bus but Separate Ready Lines

An ExpressCard contains flash memory. The ExpressCard has an ExpressCard connector that plugs into a host, such as a personal computer, digital camera, or personal digital assistant (PDA). A controller chip on the ExpressCard uses a pair of differential Universal-Serial-Bus (USB) data lines in the connector to communicate with the USB host, or can use PCI Express, Firewire, or other protocols. One or more flash-memory chips on the ExpressCard are controlled by a flash-memory controller in the controller chip. Two or more channels of a flash bus have a shared control bus but separate ready lines. The separate ready lines allow flash-memory chips in the two channels to finish operations at different times.

Owner:SUPER TALENT ELECTRONICS

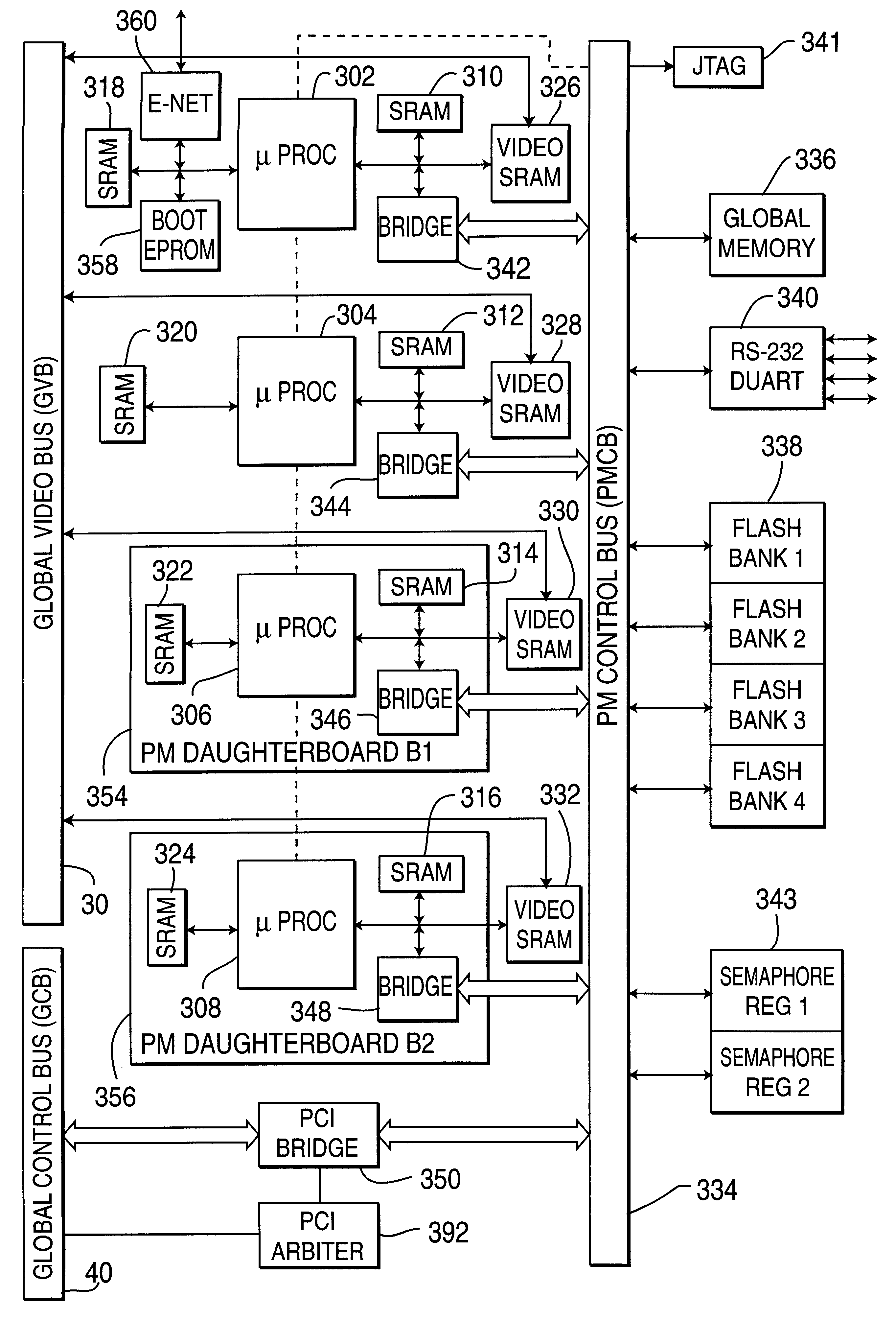

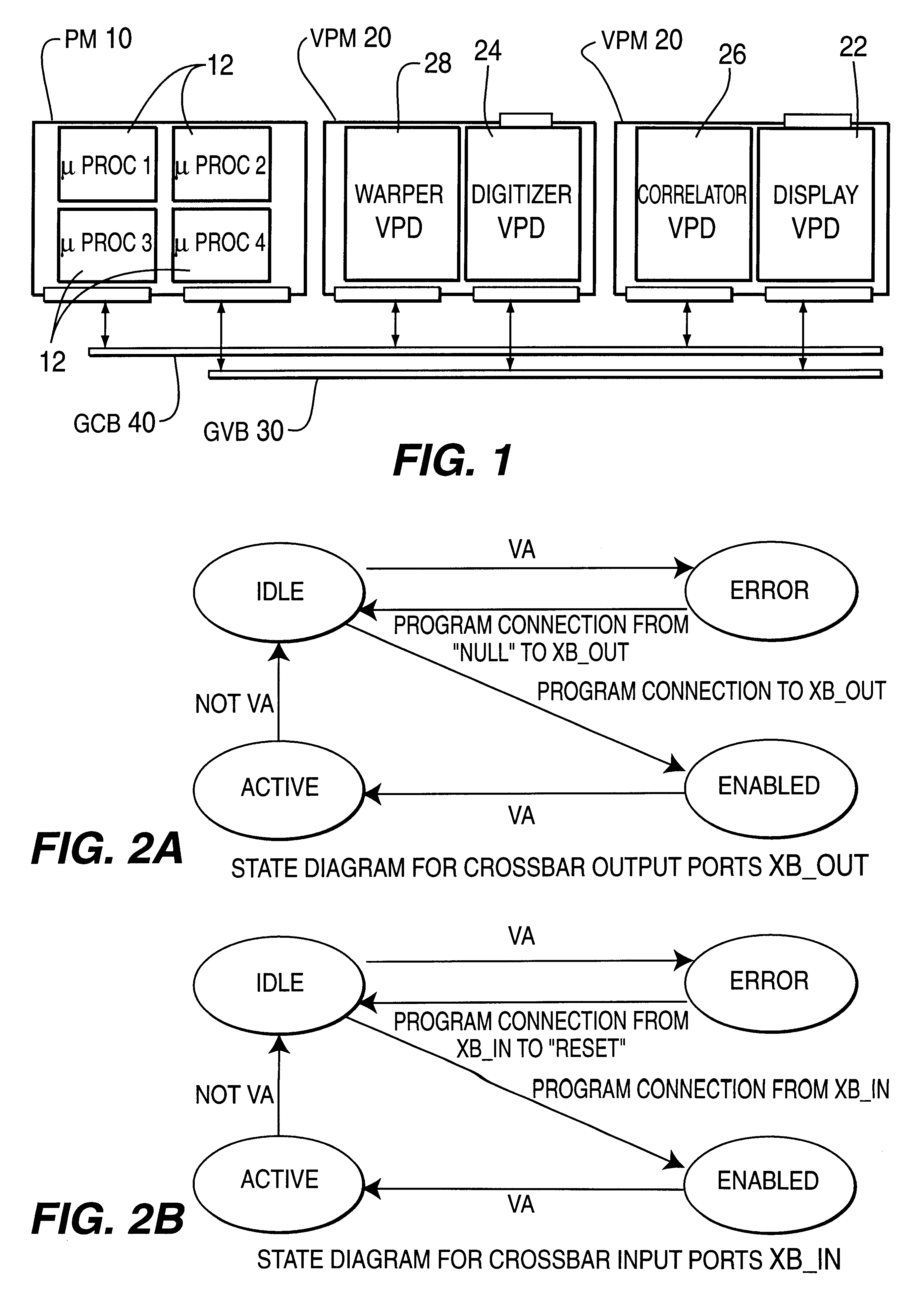

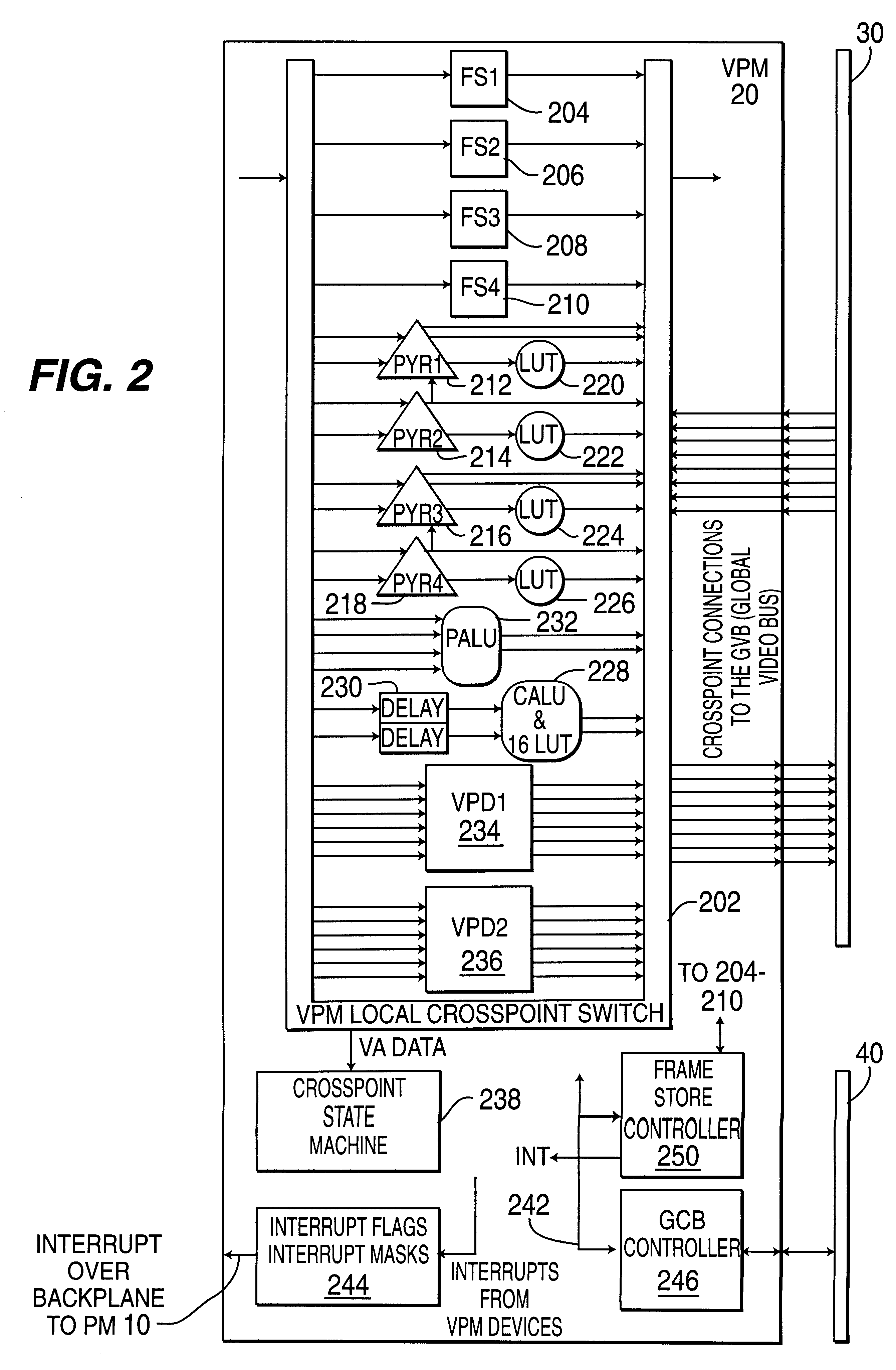

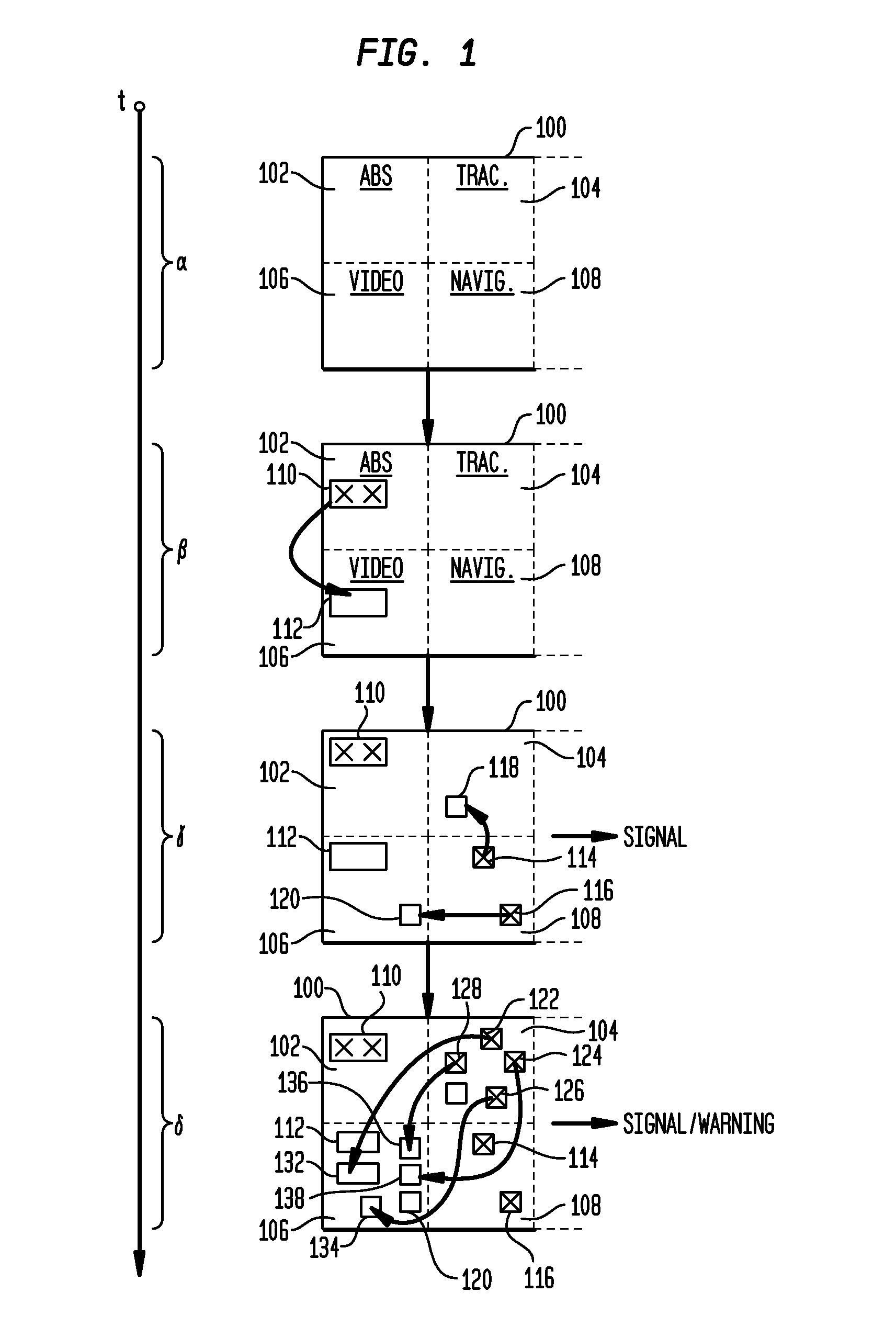

Modular parallel-pipelined vision system for real-time video processing

InactiveUS6188381B1Easy to operateReduce control overheadTelevision system detailsColor signal processing circuitsProcess moduleHandling system

A real-time modular video processing system (VPS) which can be scaled smoothly from relatively small systems with modest amounts of hardware to very large, very powerful systems with significantly more hardware. The modular video processing system includes a processing module containing at least one general purpose microprocessor which controls hardware and software operation of the video processing system using control data and which also facilitates communications with external devices. One or more video processing modules are also provided, each containing parallel pipelined video hardware which is programmable by the control data to provide different video processing operations on an input stream of video data. Each video processing module also contains one or more connections for accepting one or more daughterboards which each perform a particular image processing task. A global video bus routes video data between the processing module and each video processing module and between respective processing modules, while a global control bus provides the control data to / from the processing module from / to the video processing modules separate from the video data on the global video bus. A hardware control library loaded on the processing module provides an application programming interface including high level C-callable functions which allow programming of the video hardware as components are added and subtracted from the video processing system for different applications.

Owner:SARNOFF CORP

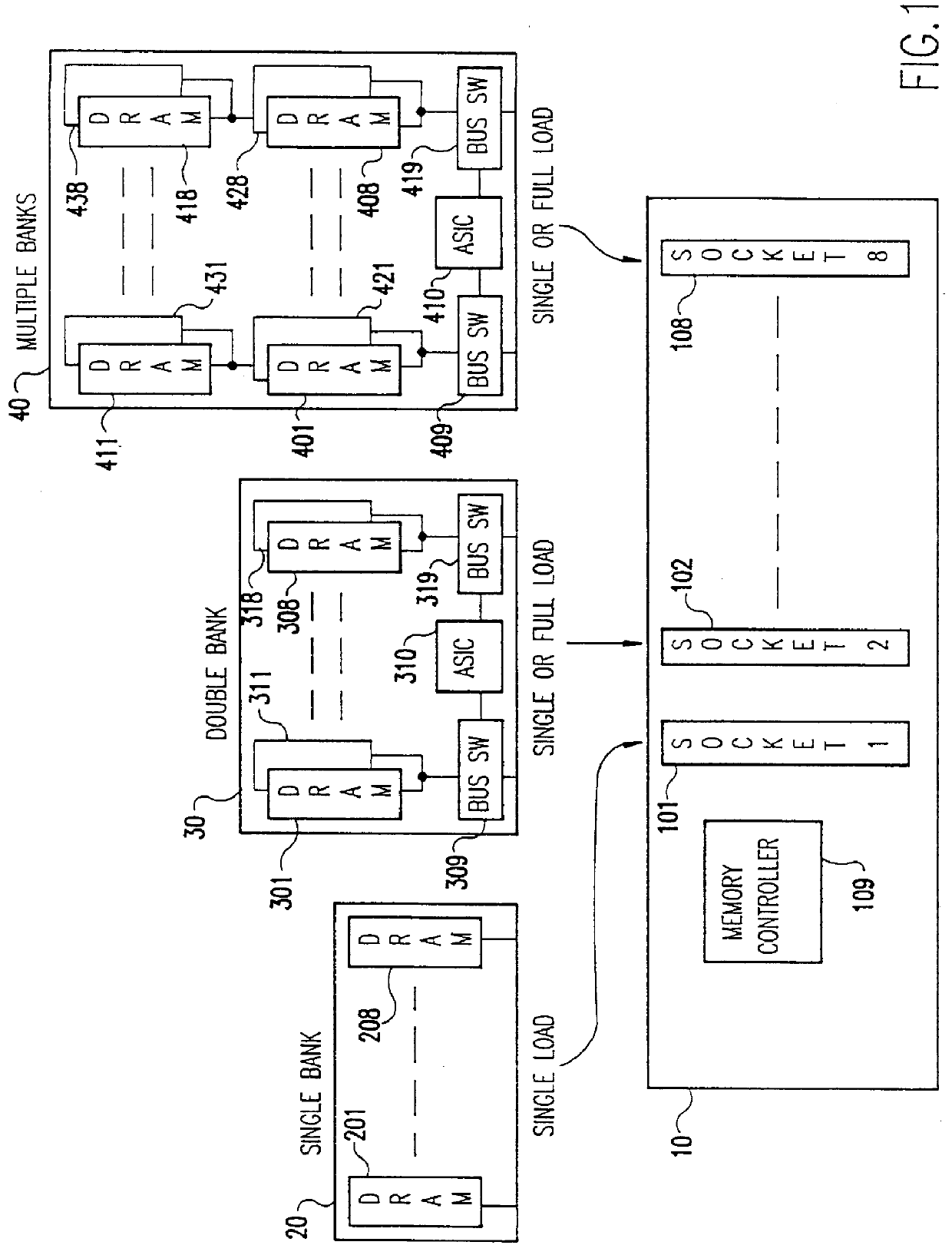

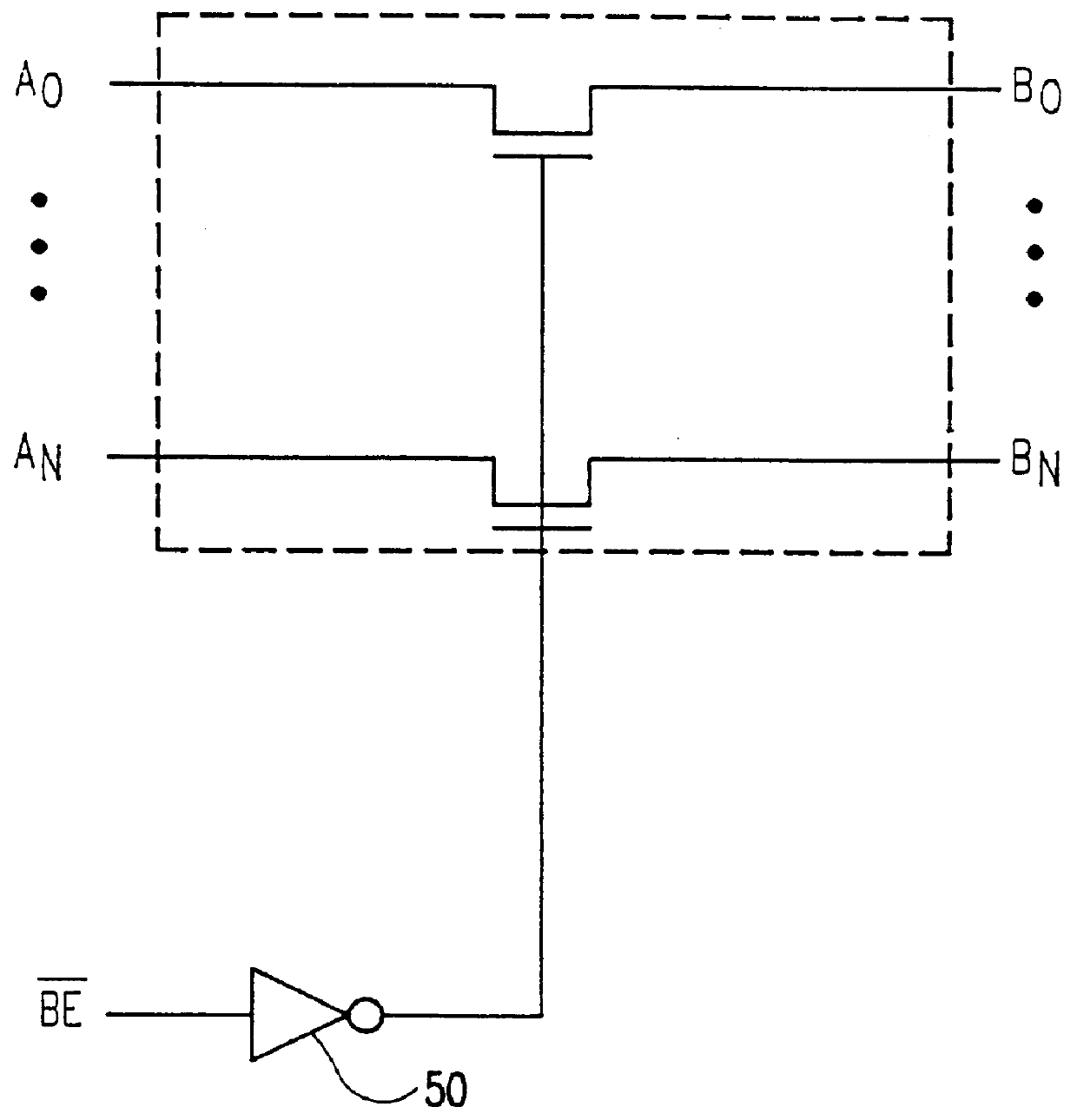

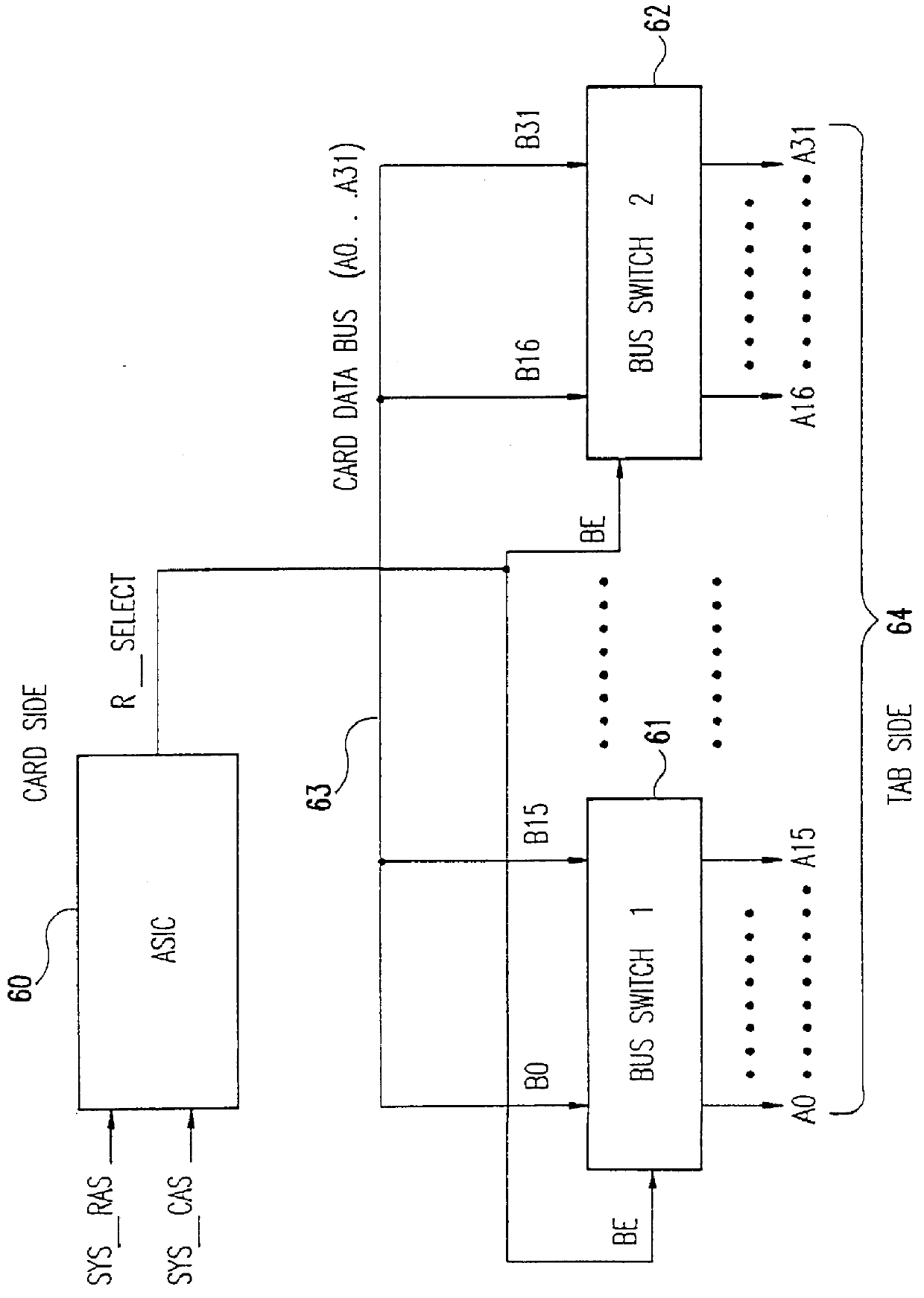

High density memory module with in-line bus switches being enabled in response to read/write selection state of connected RAM banks to improve data bus performance

InactiveUS6070217AMaximize memory densityReduce signal reflectionMemory adressing/allocation/relocationSolid-state devicesCapacitanceBiological activation

Data line loading on high density modules with multiple DRAMs is minimized permitting the maximum memory density of systems of otherwise limited density to be increased without an ensuing performance degradation due to data line capacitive loading. First the single or dual in-line memory module (SIMM or DIMM) includes in-line bus switches. The bus switches are between the SIMM or DIMM module tabs (system) and random access memory devices (RAM) and are either in a high impedance (off) or active state depending on the READ / WRITE state of the RAM. When in the high impedance state, the effective loading of the module is that of the bit switch device. The logic for determining the READ / WRITE state may be embedded in an application specific integrated circuit (ASIC) that monitors bus activity and controls activation of the bus switches, be provided by a memory controller or, generated by the RAM itself. The bus switches are active when the RAM is performing a read or a write and inactive otherwise. The RAM is Fast Page Mode (FPM) and Extended Data Output (EDO) or Synchronous DRAM (SDRAM).

Owner:IBM CORP

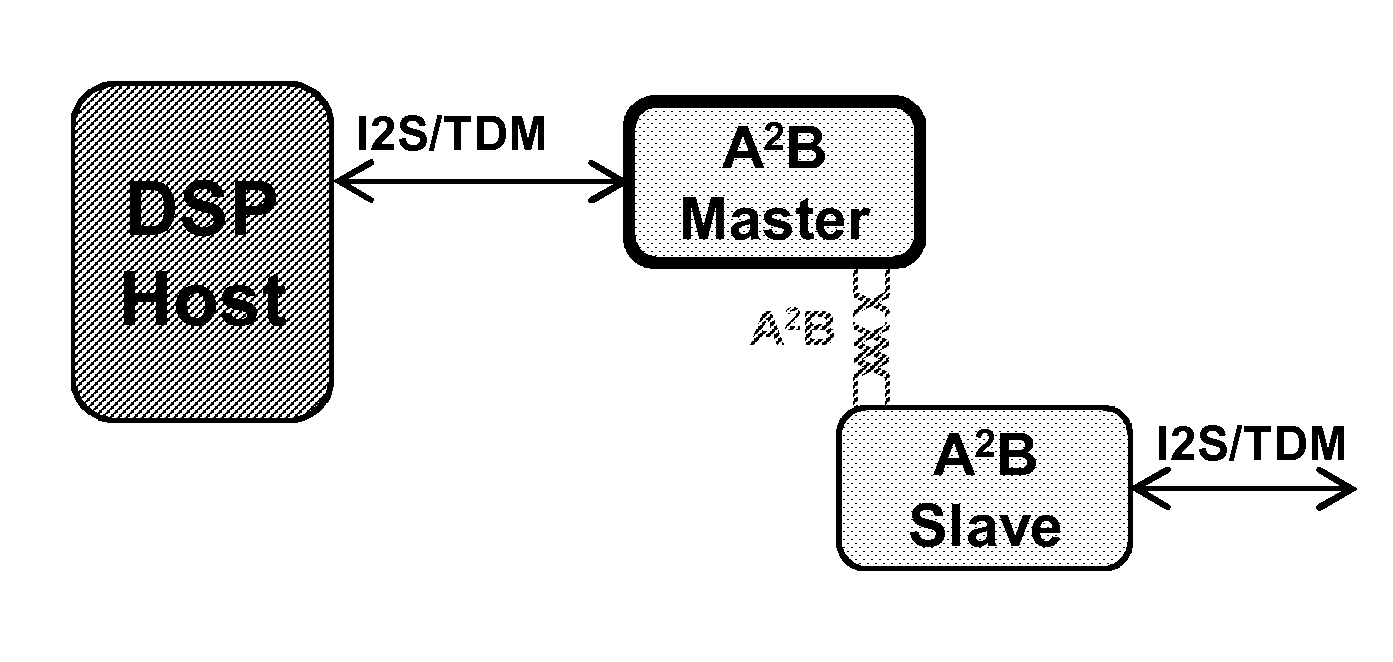

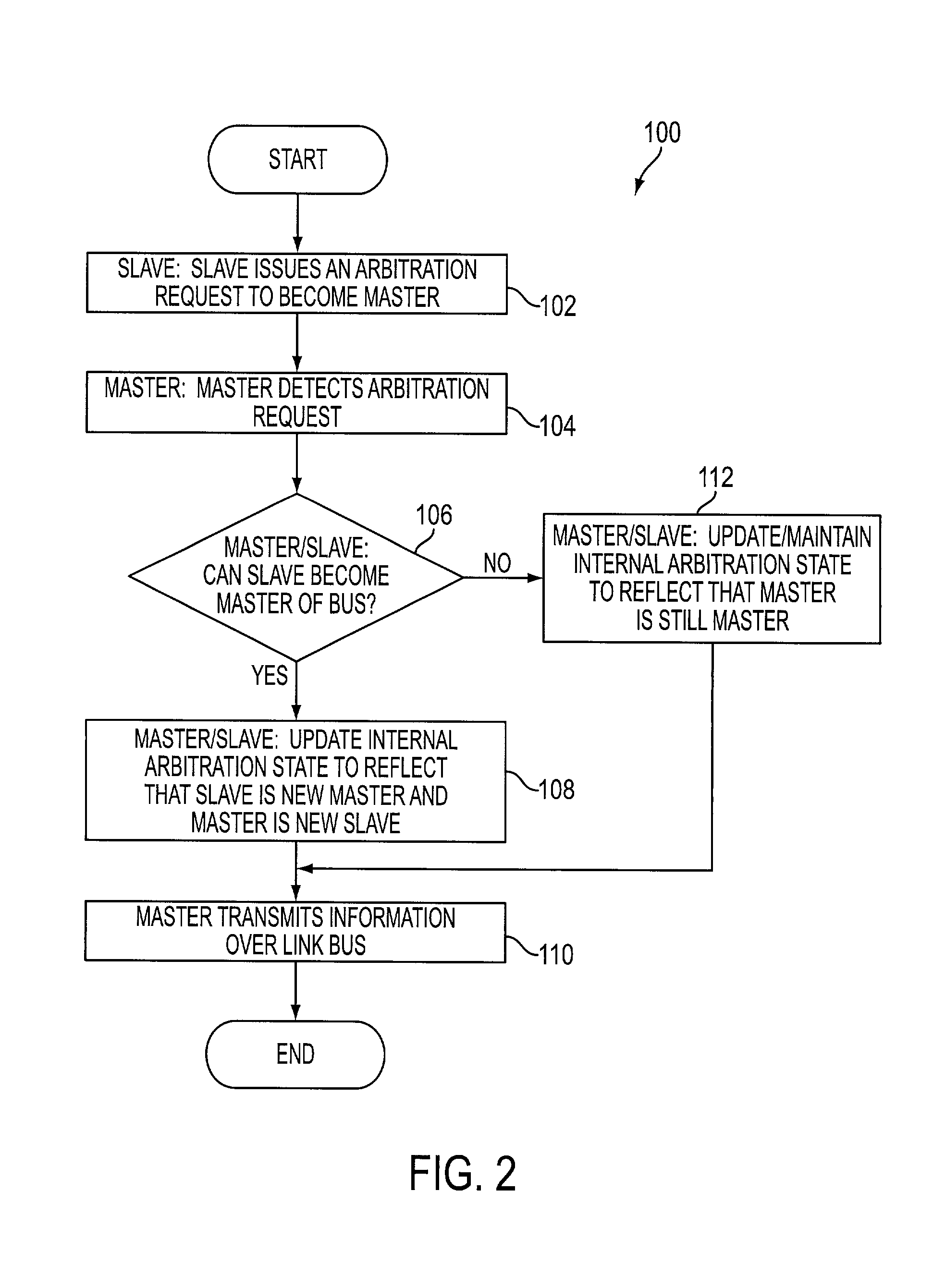

Methods for Discovery, Configuration, and Coordinating Data Communications Between Master and Slave Devices in a Communication System

ActiveUS20130124763A1Energy efficient ICTEfficient power electronics conversionCommunications systemControl bus

Various embodiments of the present invention methods for discovery, configuration, and coordinating data communications between master and slave devices in a communication system. Exemplary embodiments are described with reference to a two-wire point-to-point bus system, although the method can be used in other communication systems. Provisions are included for controlling the sequential powering of the bus and slave devices.

Owner:ANALOG DEVICES INC

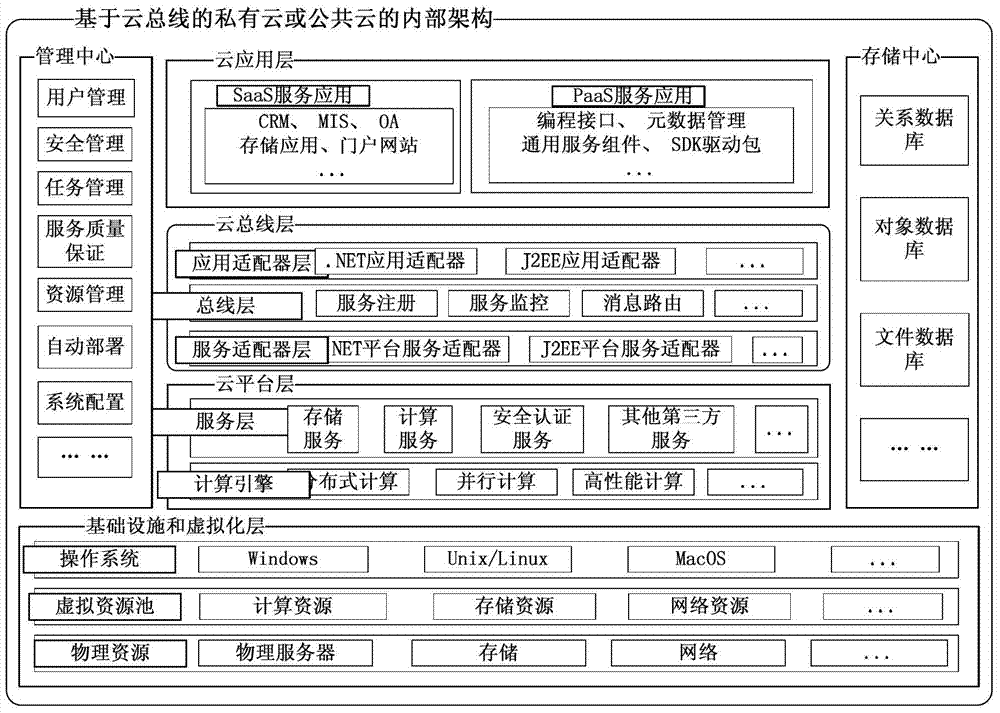

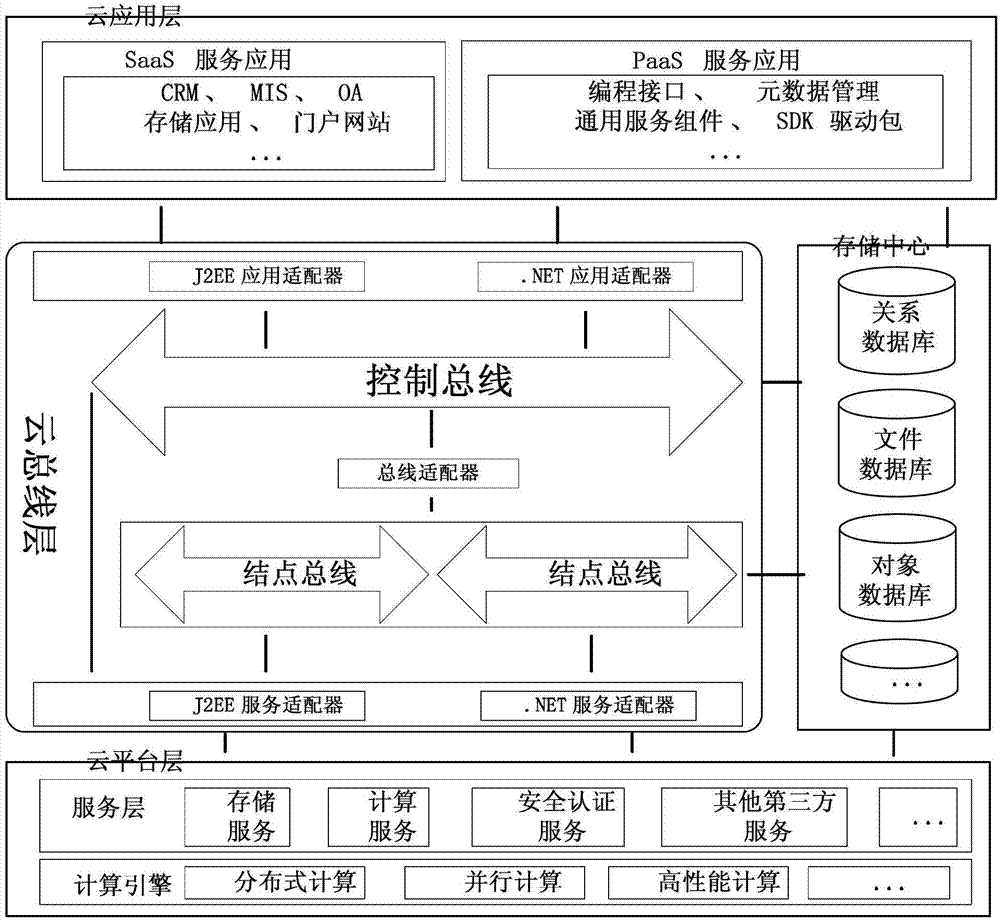

Hybrid cloud computing system based on cloud bus and realization method of hybrid cloud computing system

The invention discloses a hybrid cloud computing system based on a cloud bus and a realization method of the hybrid cloud computing system. The system is based on a local private cloud, one or more public clouds are integrated, the internal constitution of the local private cloud is consistent with that of the public cloud, both the internal constitution of the local private cloud and the internal constitution of the public cloud comprise an infrastructure, a virtualization layer, a cloud platform layer, a cloud bus layer, a cloud application layer, a management center and a storage center, wherein the hardware resources on a bottom layer are grouped into a virtual cluster through the infrastructure and the virtualization layer so as to provide different virtual resources to the superior layer; the cloud platform is used for operating a web application program or a service and utilizing an open interface to carry out the secondary development and application integration; and the cloud bus layer is used for managing and monitoring various services on the cloud platform layer and is a hub for connecting the cloud application layer and the cloud platform layer, and the cloud bus layer is established on the basis of SOA (service oriented architecture) concept and comprises a control bus, a plurality of node buses and an adapter. Due to the adoption of the hybrid cloud computing system, the migration of the existing IT (internet) environment of an enterprise to a cloud computing environment can be accelerated, the investment can be reduced, and the resource can be adequately utilized.

Owner:SOUTH CHINA UNIV OF TECH

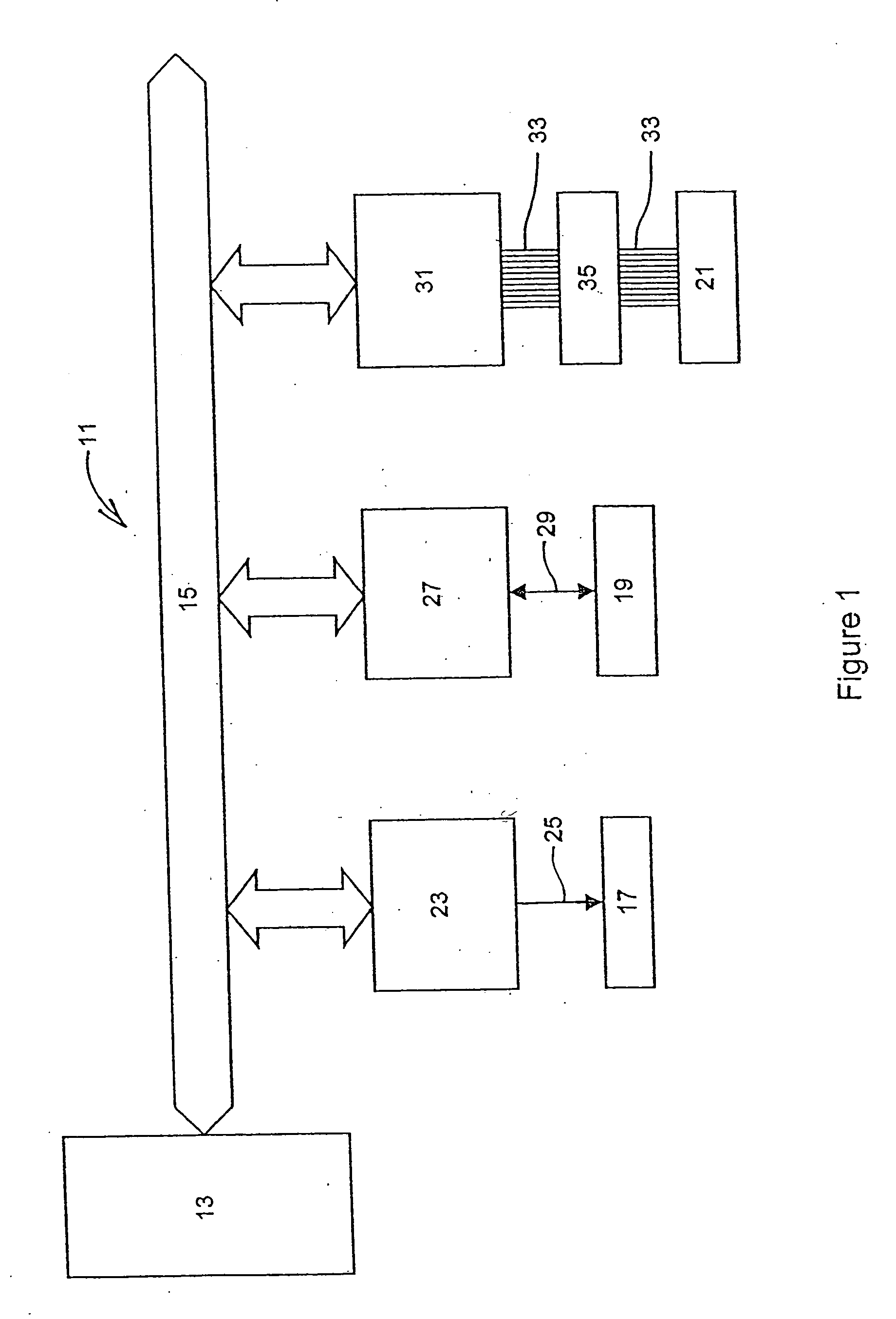

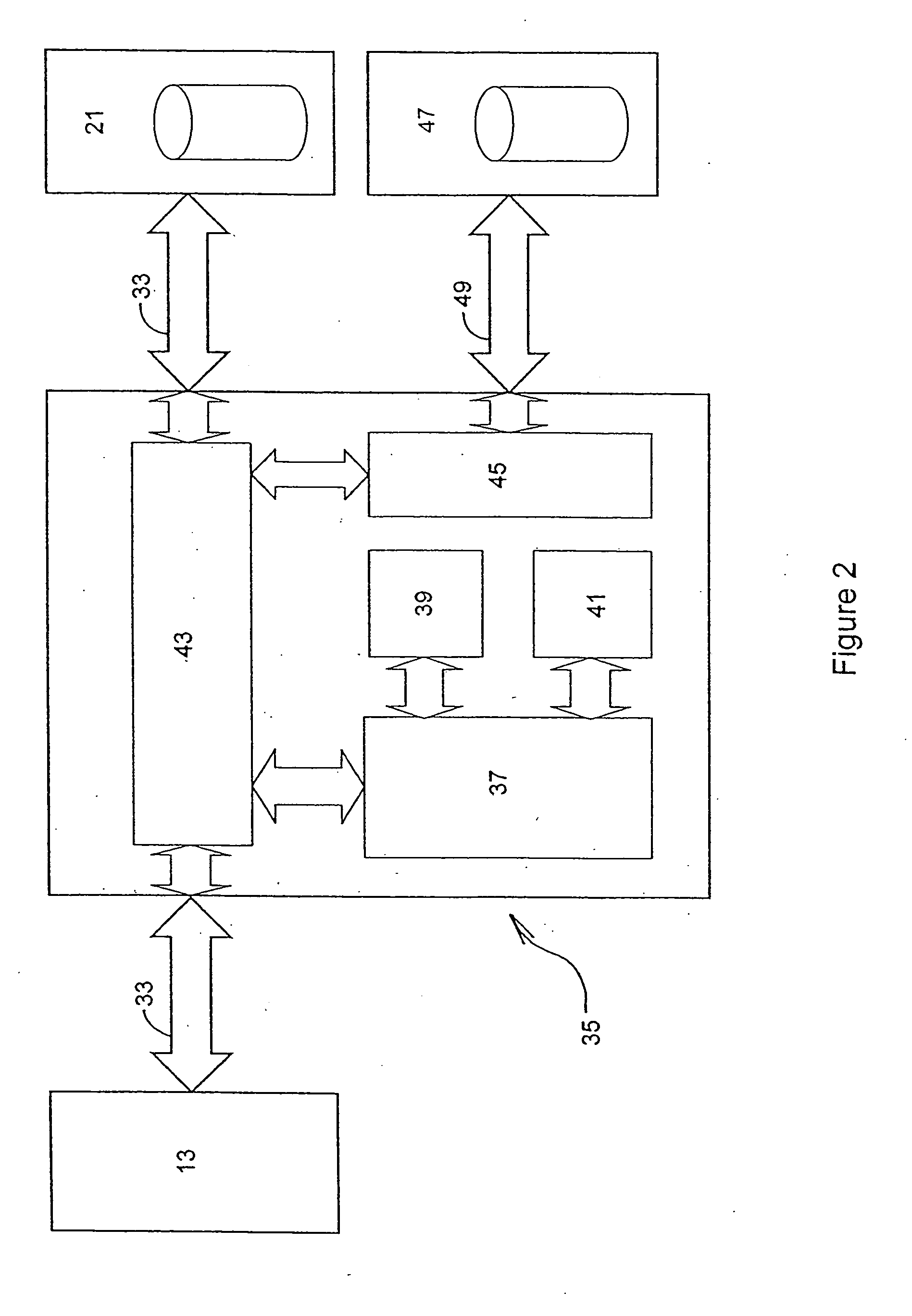

Security system and method for computers

InactiveUS20050091522A1Improve protectionPrevent unauthorized accessDigital data processing detailsLiftersData accessComputer memory

A computer security device (35) comprising a processor (37) that is independent of the host CPU (13) for controlling access between the host CPU (13) and the storage device (21). A program memory (41) that is independent of the computer memory and the storage device (21) unalterably stores and provides computer programs for operating the processor (37) in a manner so as to control access to the storage device (21). The security device (35) is connected only in line with the data access channel (33) between the host CPU (13) and the storage device (21), and off the main data and control bus (15) of the host CPU (13). All data access by the host CPU (13) to the data storage device (21) is blocked before initialization of the security device (35) and is intercepted immediately after the initialization under the control of the processor (37). The processor (37) effects independent control of the host CPU (13) and configuration of the computer (11) to prevent unauthorized access to the storage device (21) during the interception phase. All users of the computer (11) are authenticated with a prescribed profile of access to the storage device (21) and data access to the storage device remains blocked until a user of the computer (11) is correctly authenticated.

Owner:SECURE SYST LTD

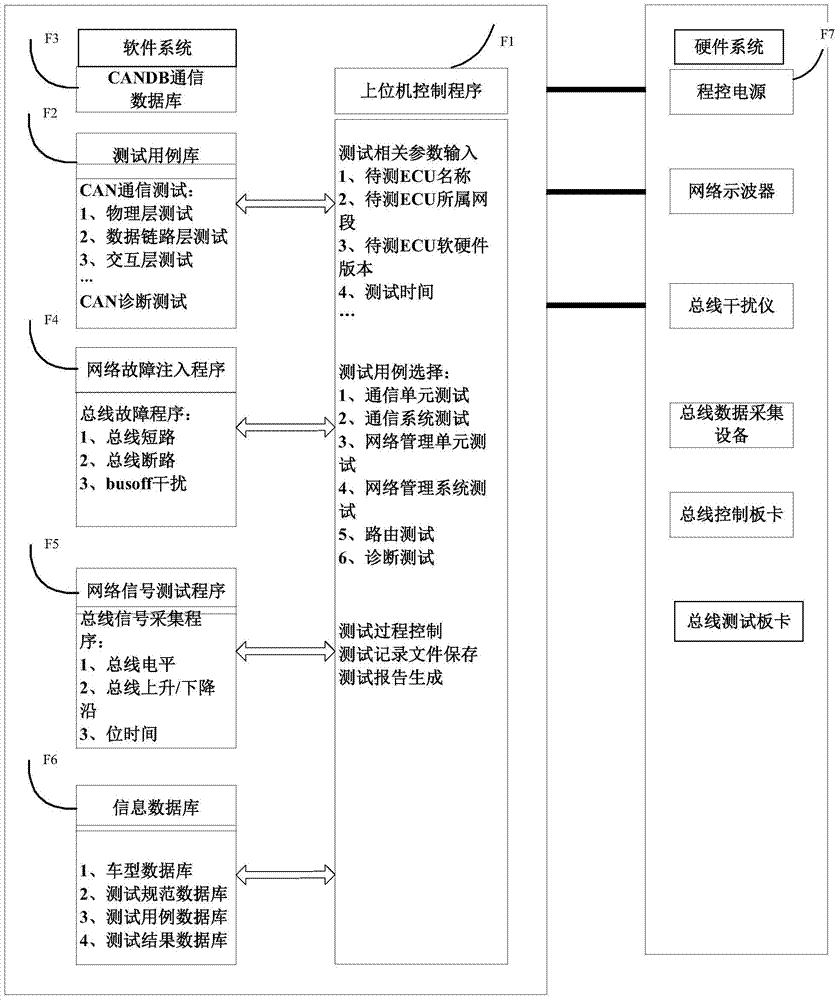

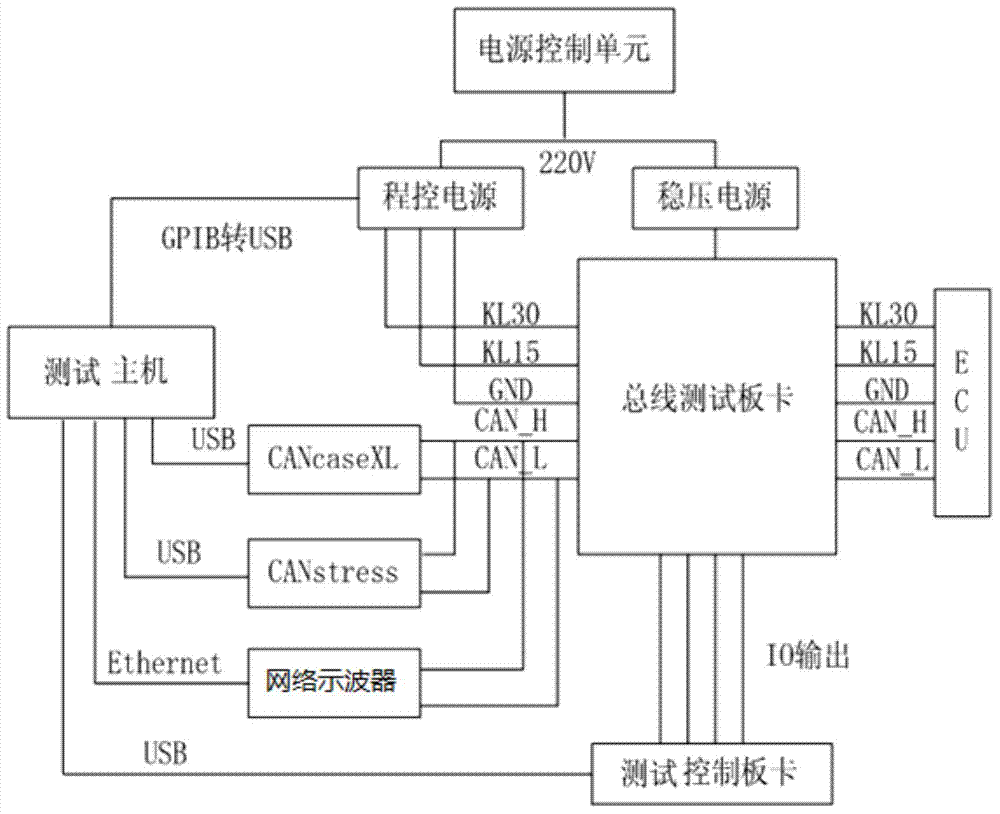

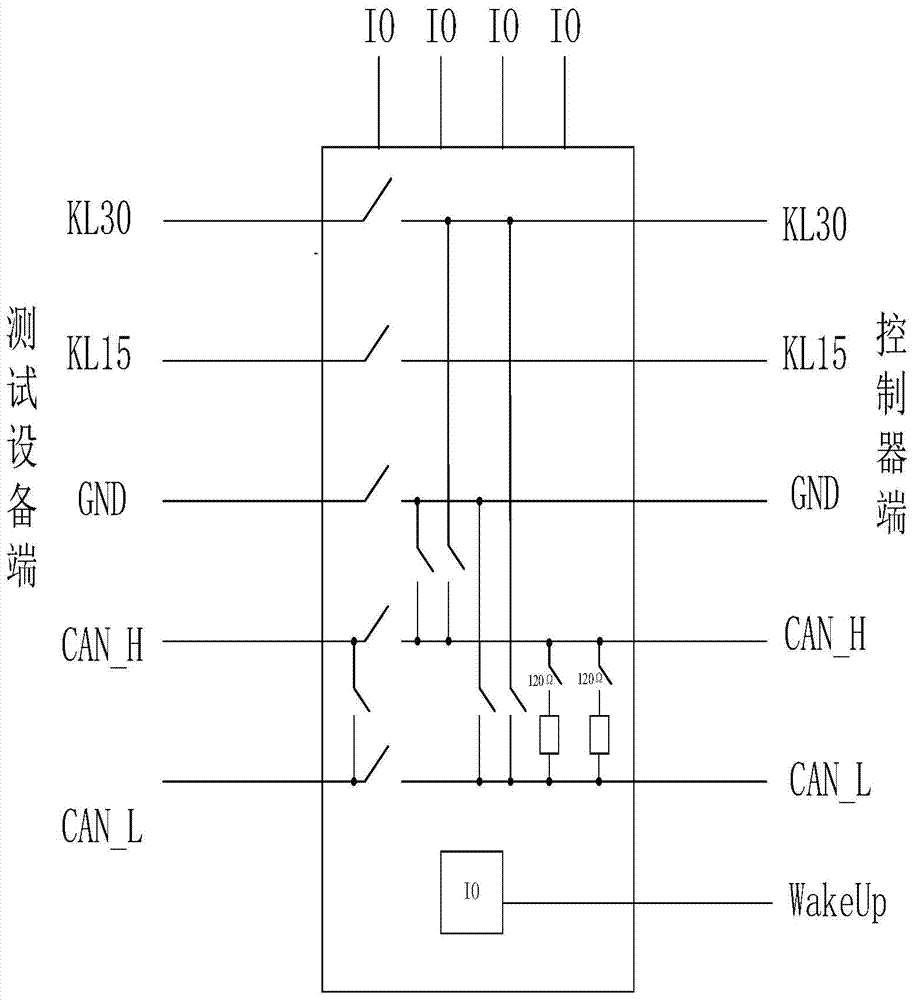

Automatic vehicle-mounted electronic control unit CAN bus communication testing device and system

InactiveCN104298224AReduce duplication of effortAffect accuracyElectric testing/monitoringData acquisitionTest fixture

The invention relates to an automatic vehicle-mounted electronic control unit CAN bus communication testing device. A testing host of the device controls a programmable power supply to output different amplitudes of voltages according to working requirements of an ECU; physical layer testing signals of a CAN bus are output to a network oscilloscope to be displayed, and physical layer testing data are transmitted to the testing host through the network oscilloscope; ECU testing data are transmitted to the testing host through a bus data acquisition device; the testing host records, analyzes and evaluates the testing data of the ECU and the CAN bus to generate a test report. A bus interferometer is used for interfering with bus waveforms of the tested ECU in real time. The testing host controls on-off states of relays of a bus testing board card through a testing control card board to execute the bus fault injection operation. By means of the automatic vehicle-mounted electronic control unit CAN bus communication testing device, various defects of a manual test are overcome, unnecessary repeated labor of a vehicle-mounted network engineer is reduced, and the testing result is accurate.

Owner:CHINA FIRST AUTOMOBILE

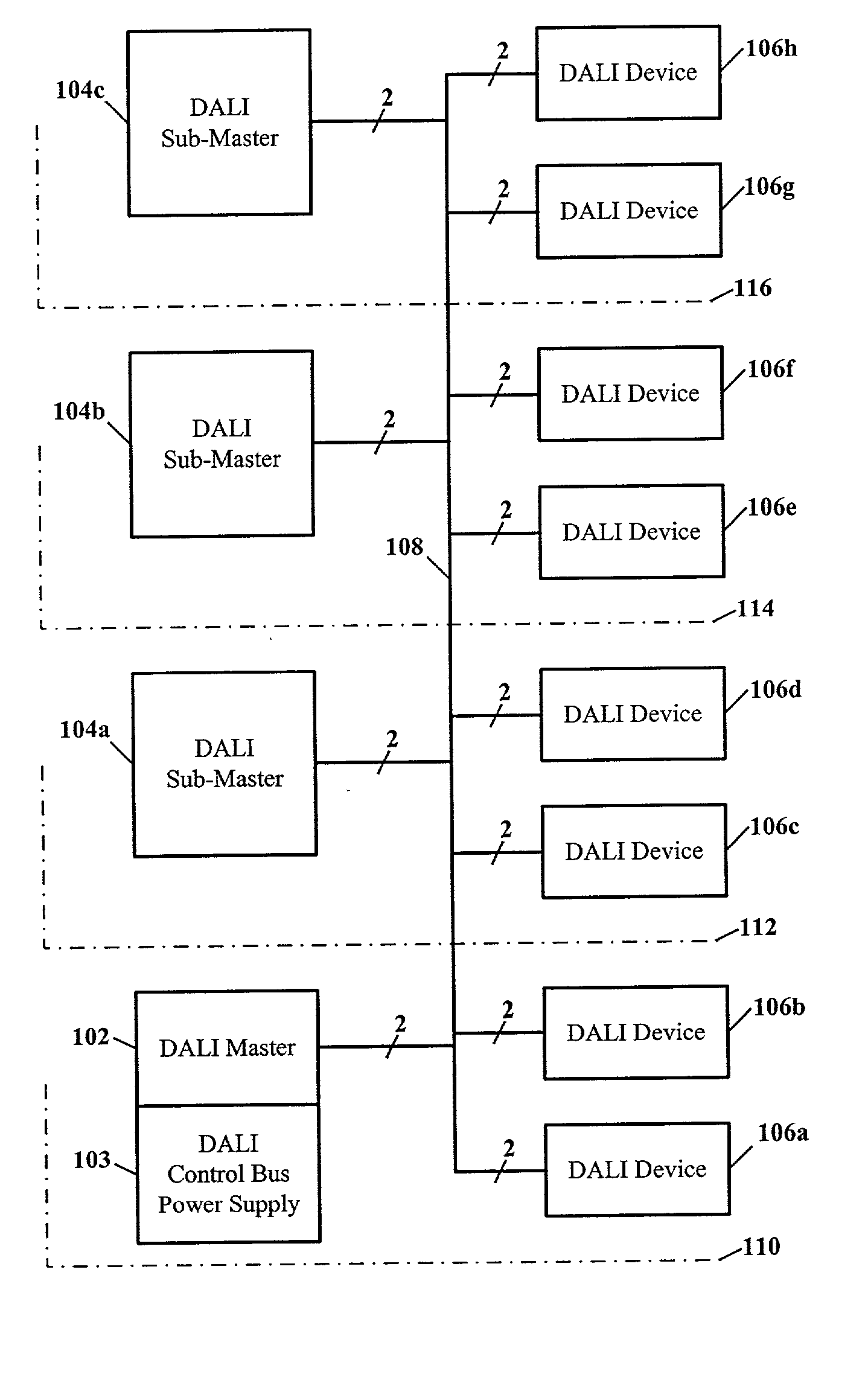

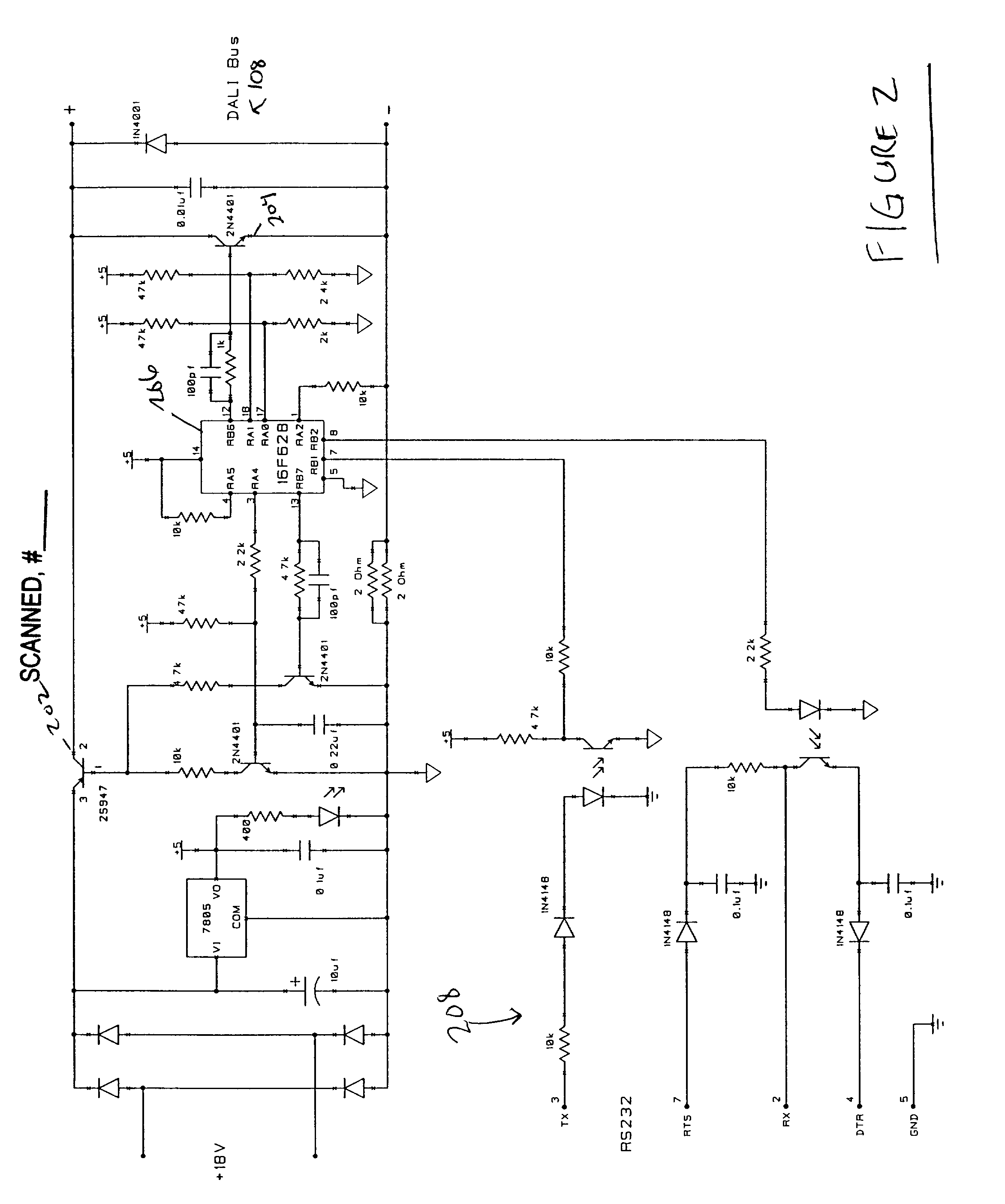

Multiple master digital addressable lighting interface (DALI) system, method and apparatus

InactiveUS20030036807A1Low costElectrical apparatusComputer controlCost effectivenessLight equipment

A Digital Addressable Lighting Interface (DALI) master and DALI control bus power supply in combination with at least one DALI sub-master are connected to a single DALI control bus. The single DALI control bus may have a plurality of DALI slave devices, e.g., luminaries connected thereto and disbursed throughout a plurality of offices and / or rooms. The DALI master and the at least one DALI sub-master allow local control of the lighting in each office or room while maintaining the simplicity and cost effectiveness of a single DALI control bus system. Collision of commands sent simultaneously by two or more DALI masters may be detected and the corrupted commands retransmitted.

Owner:MICROCHIP TECH INC

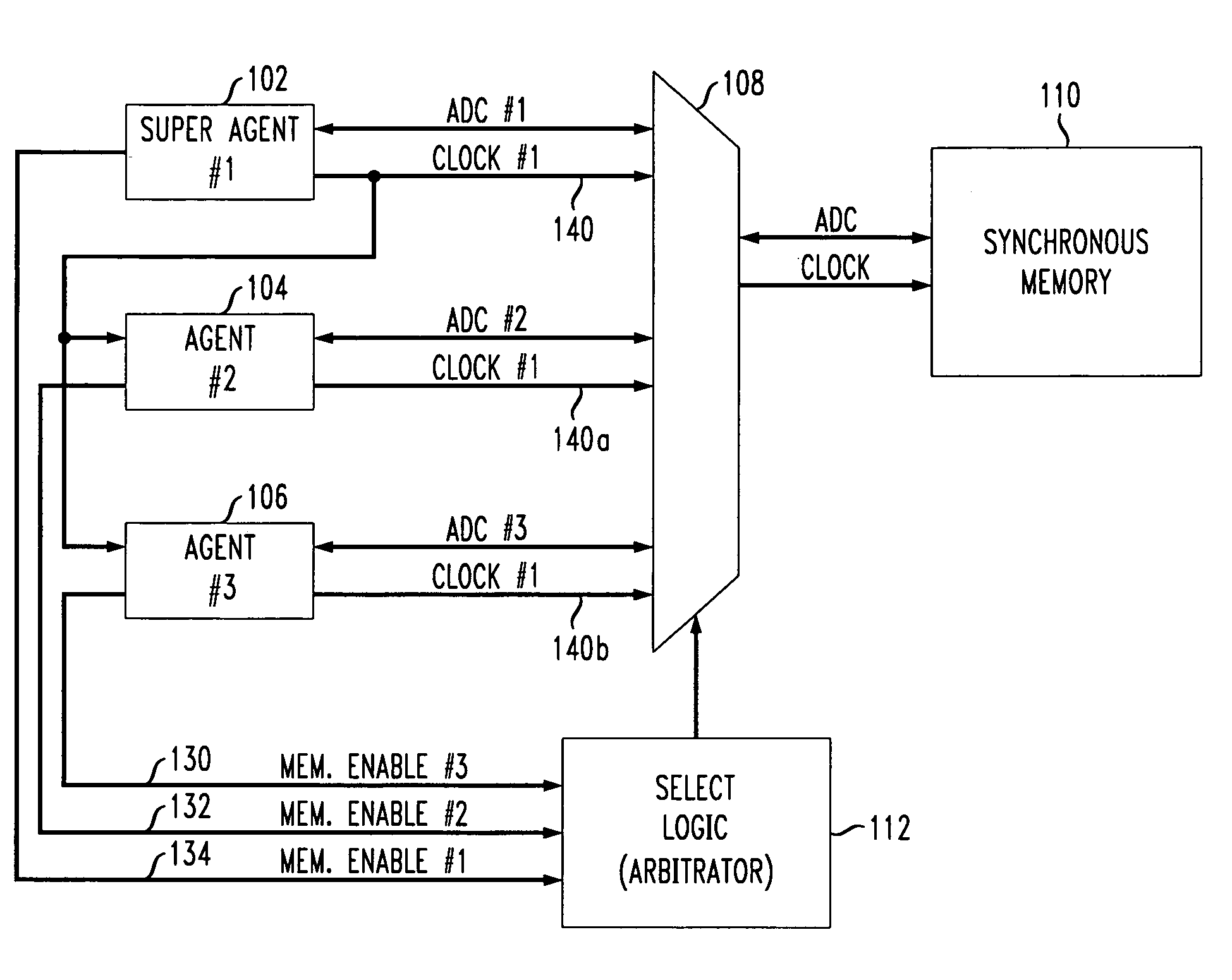

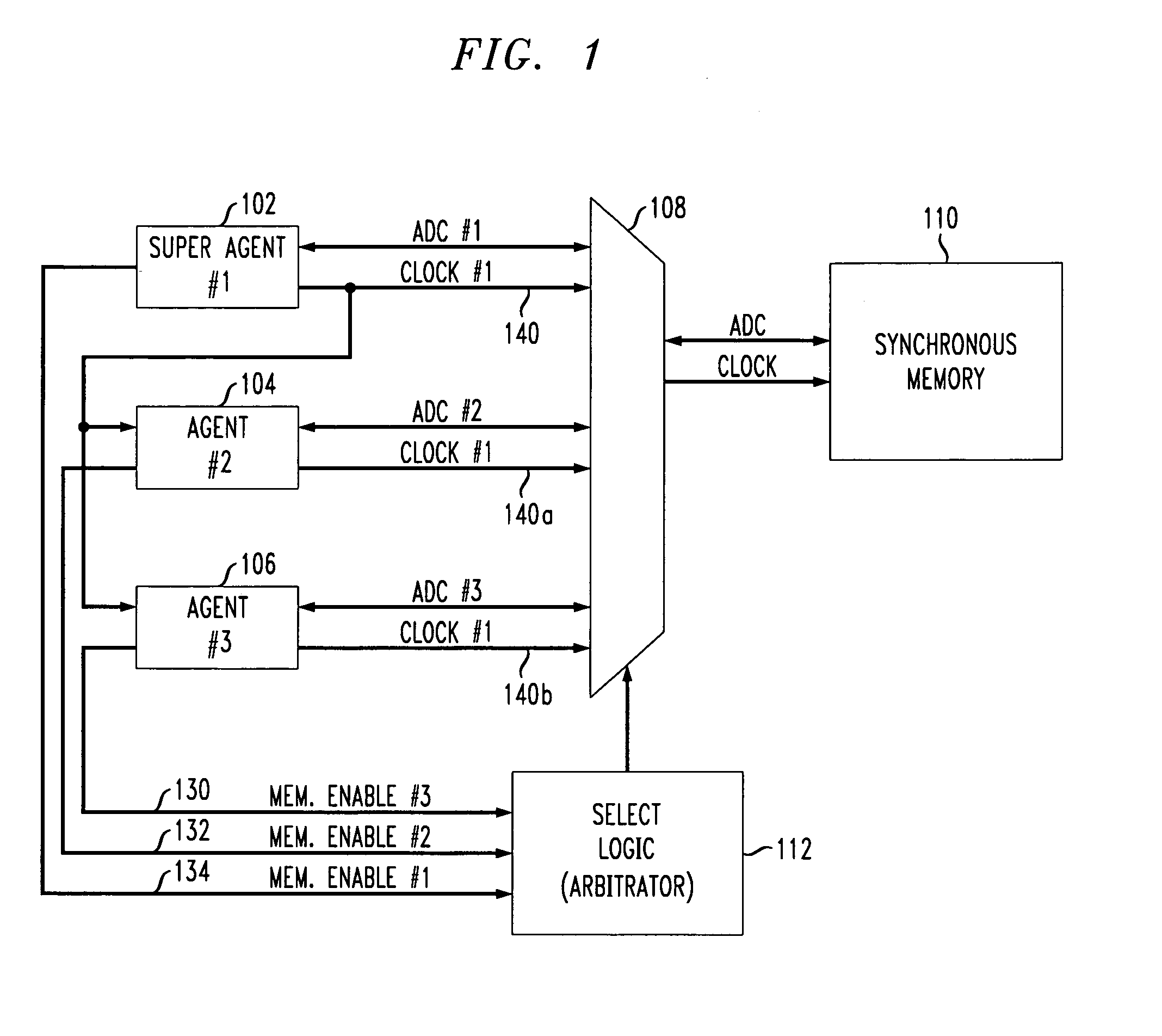

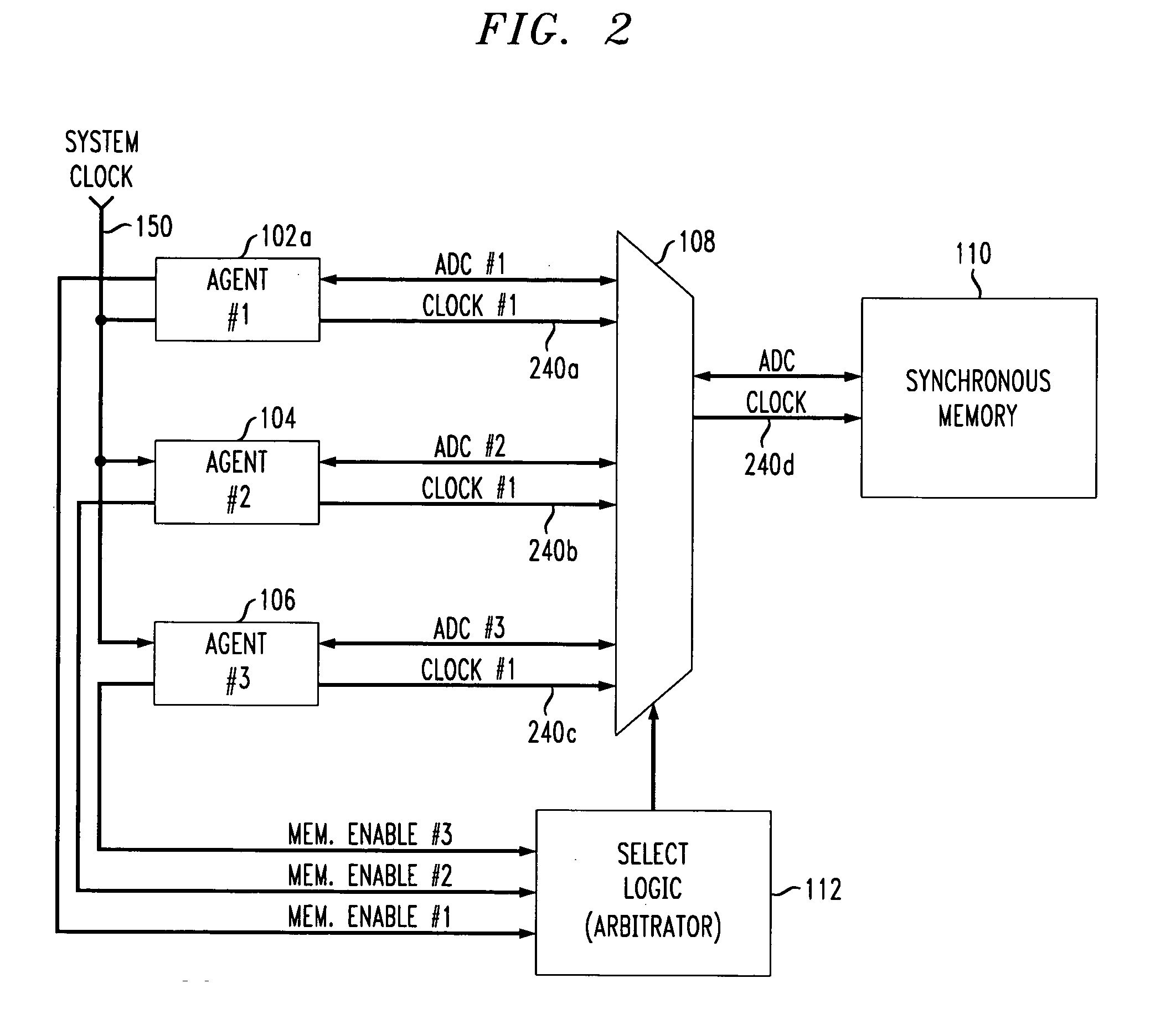

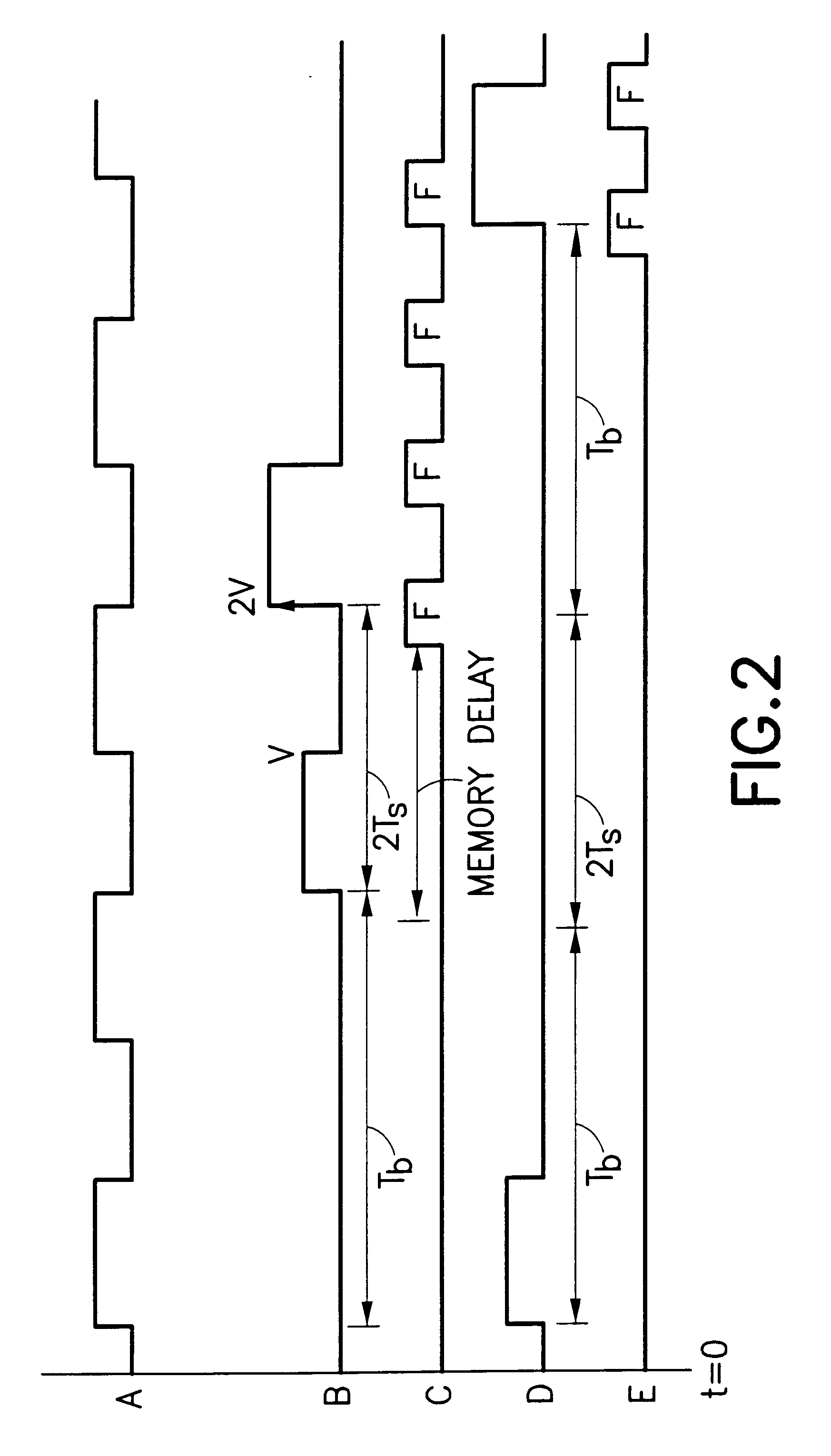

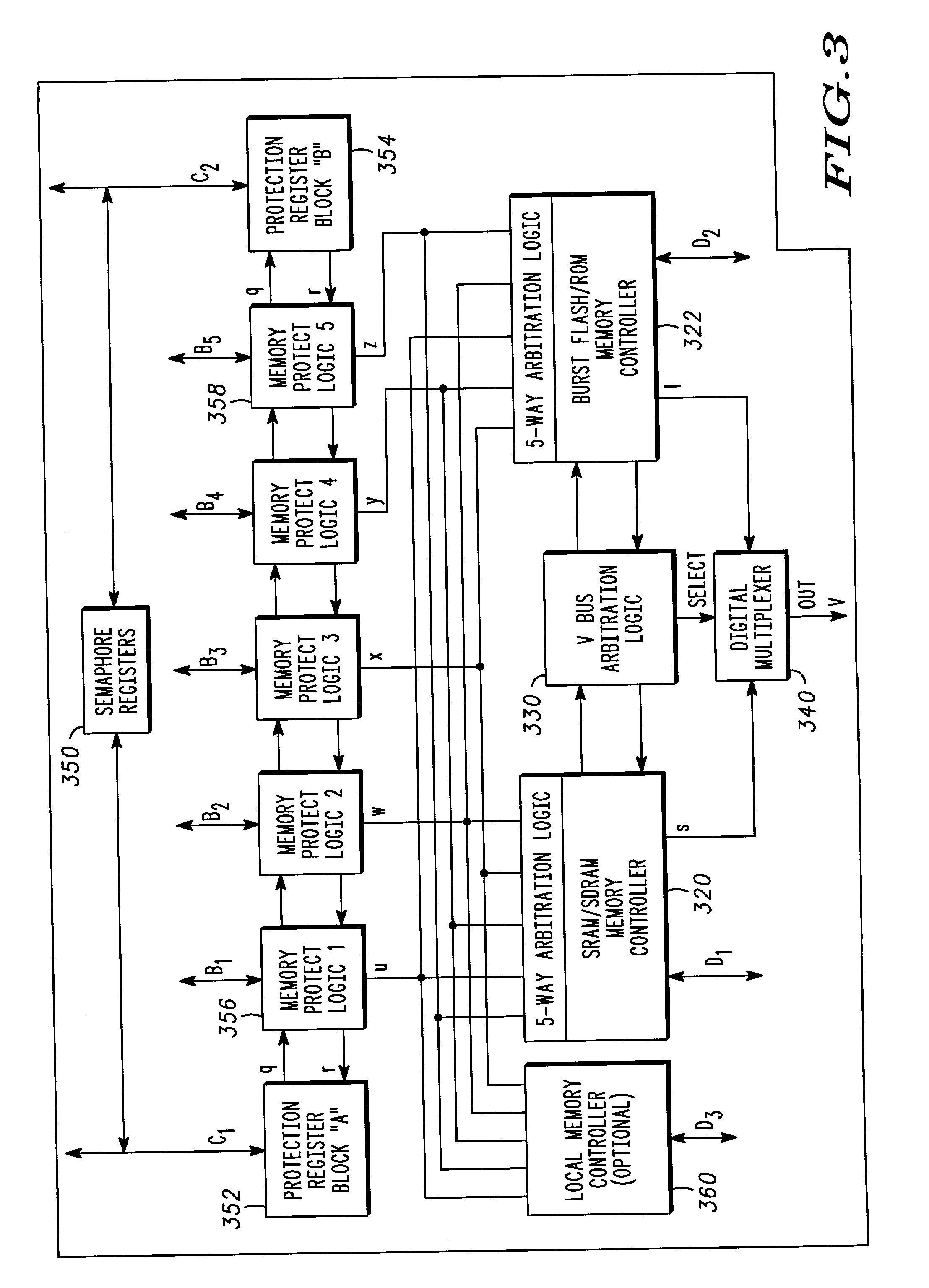

Dynamic partitioning of memory banks among multiple agents

A multiple agent system providing each of a plurality of agents, e.g., processors, to access a shared synchronous or asynchronous memory. In the case of synchronous memory, the clock signal from a super agent selected from among the plurality of agents provides a memory access clock signal to the other agents accessing the same shared memory. The other agents synchronize their respective address, data and control busses to those of the super agent, and output a representation of the same clock signal to the shared memory. In another aspect of the present invention, the shared memory is partitioned for use from among a plurality of groups of agents, each agent group comprising one or more agents. Any one of the agents may update a configuration register to flexibly reconfigure the amount of shared memory available to the agents as necessary.

Owner:AGERE SYST INC

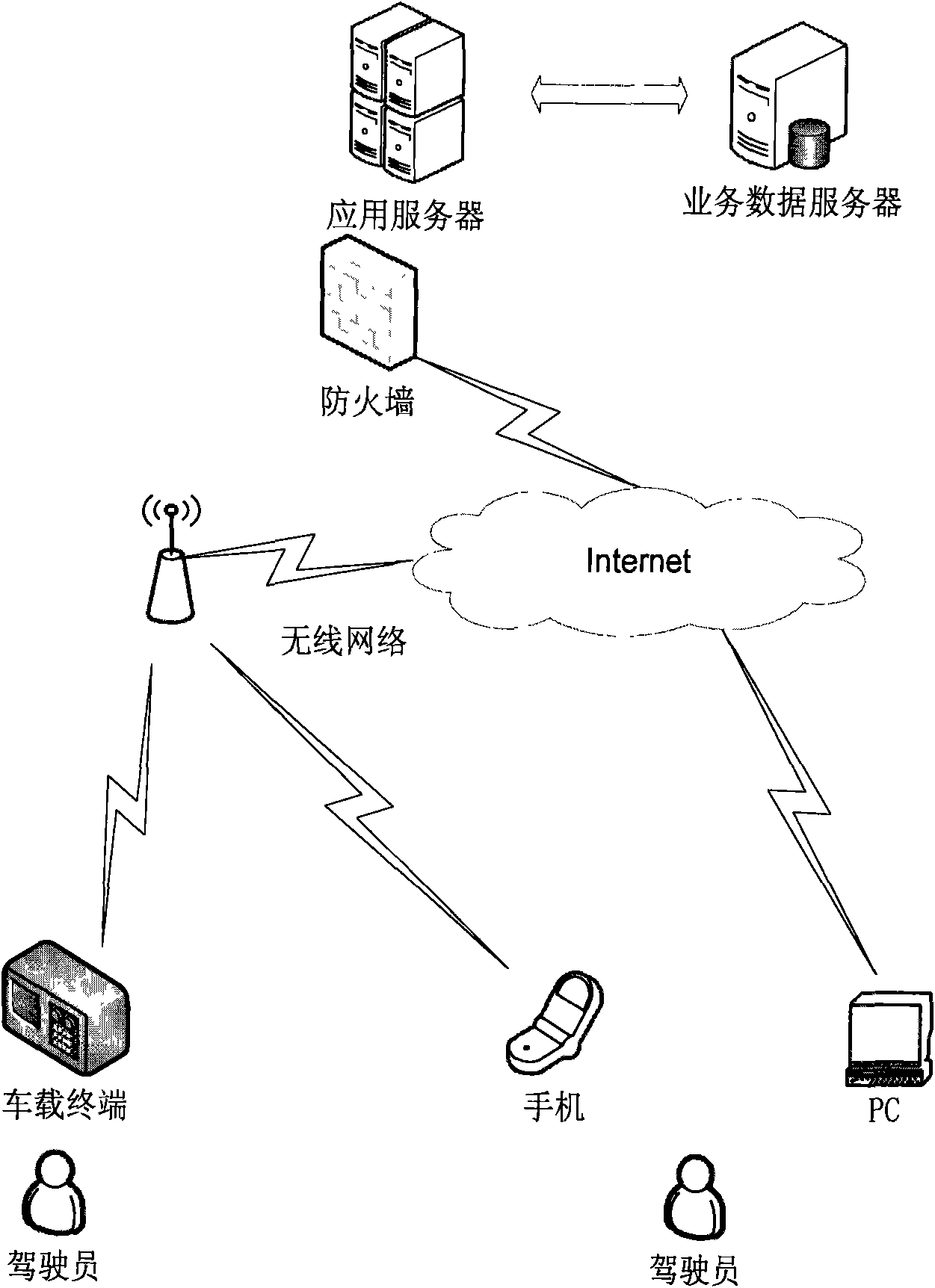

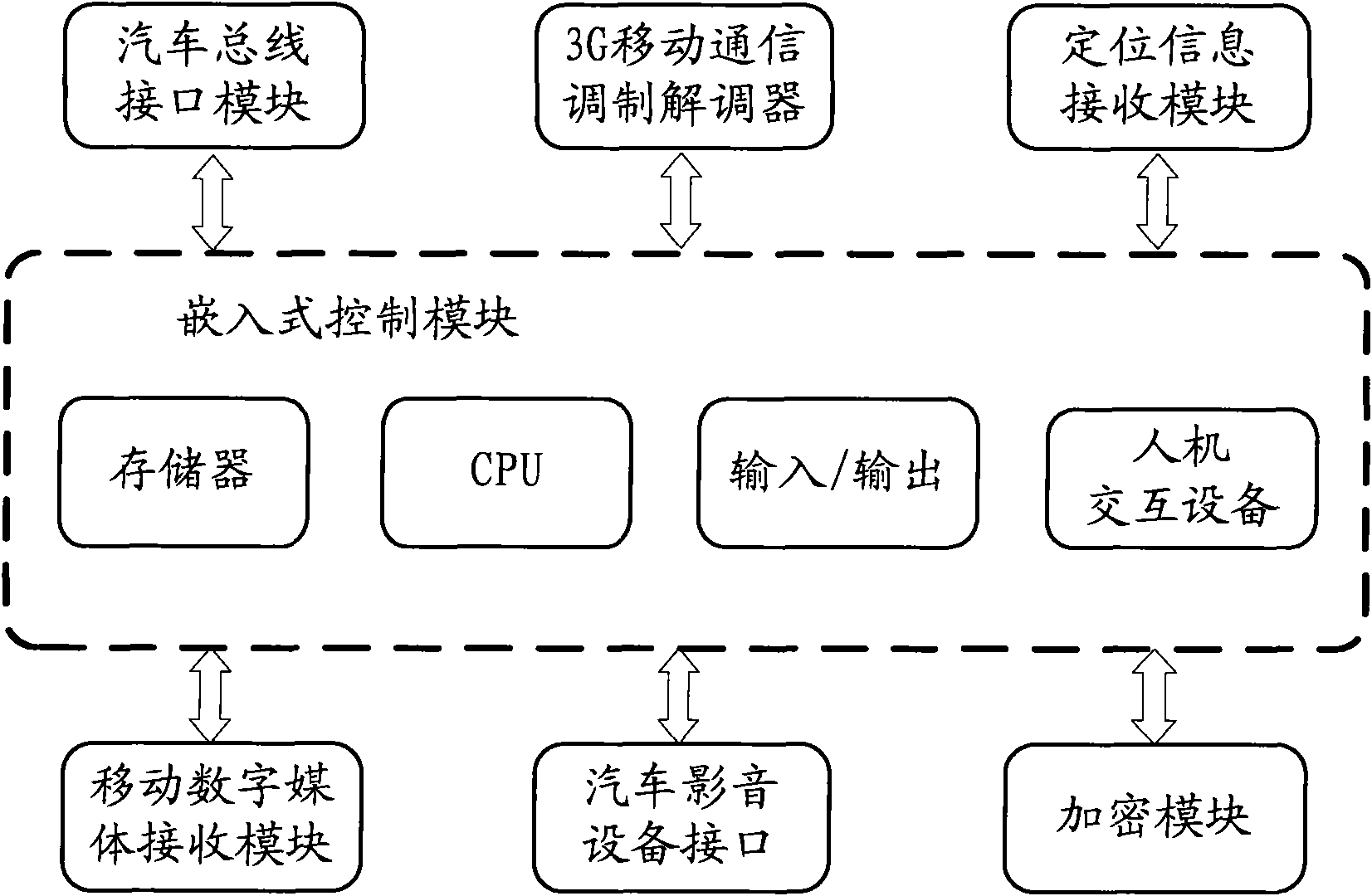

Vehicle real-time information system based on the third-generation mobile communication

InactiveCN101621735AReal-time analysisEnable security posture assessmentInstruments for road network navigationWireless commuication servicesTime informationModem device

The invention relates to a vehicle comprehensive information system based on the third-generation (3G) mobile communication, comprising a server and a vehicle-loaded terminal communicating with each other via a 3G network. The vehicle-loaded terminal comprises a vehicle bus interface module, a 3G mobile communication modem module and an embedded-type control module, and the server comprises an information receiving module, an information storage module, a function module and an information issuing module. The vehicle bus interface module is accessed to an inside control bus of a vehicle through an OBD interface, obtains the vehicle running information and transmits the information to the embedded-type control module; the embedded-type control module obtains and processes the vehicle running information and communicates interactively with the server through the 3G mobile communication modem module connected with the embedded-type control module; the information reception module receives the information of the vehicle-loaded terminal transmitted by the 3G network; the information storage module stores the information of the information receiving module and the application information; the function module is used for realizing the application functions of vehicle positioning, map navigation, real-time path plan, theft prevention of vehicles and the like; and the information issuing module is used for transmitting information provided by the server to the vehicle-loaded terminal.

Owner:赵阳 +2

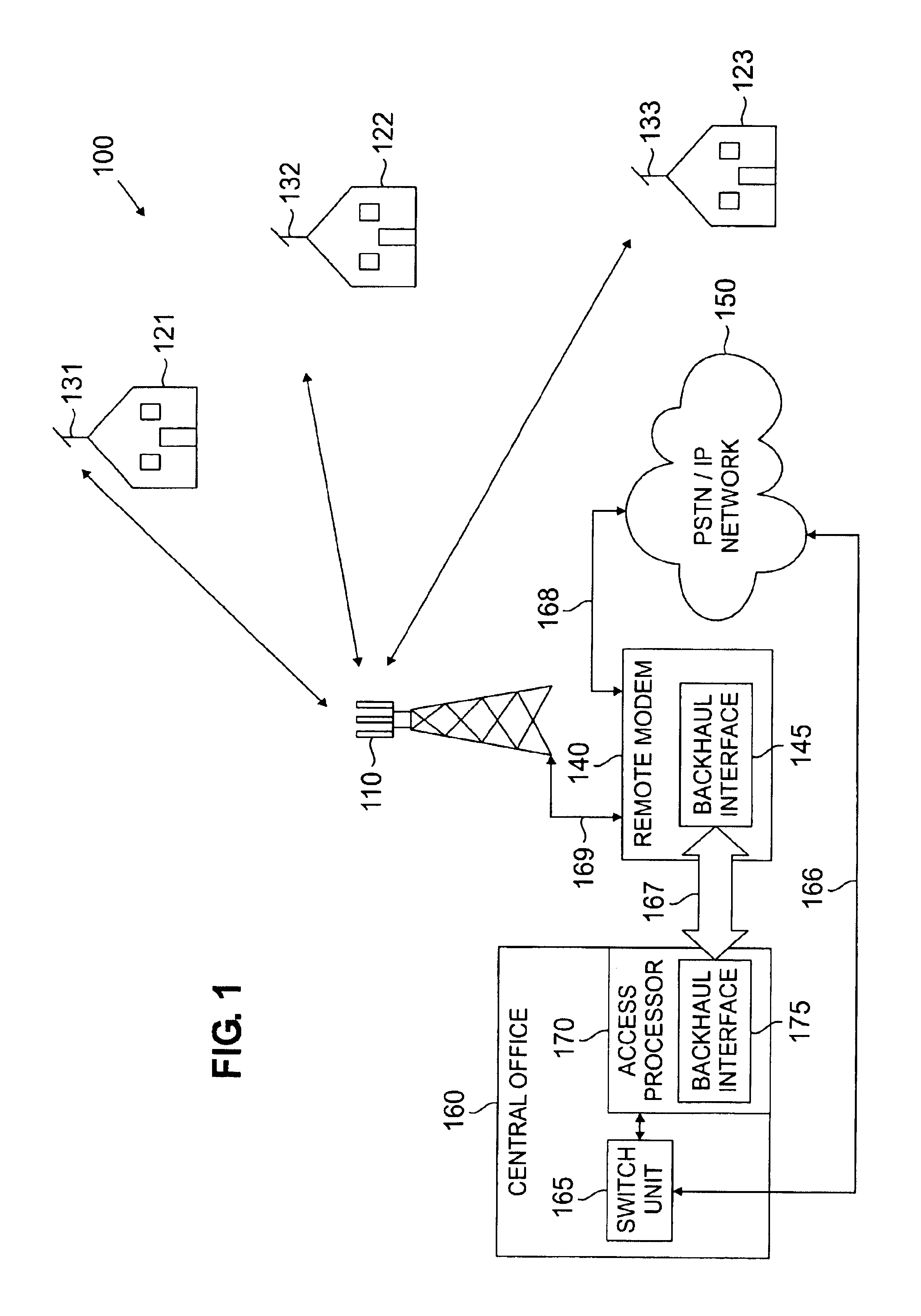

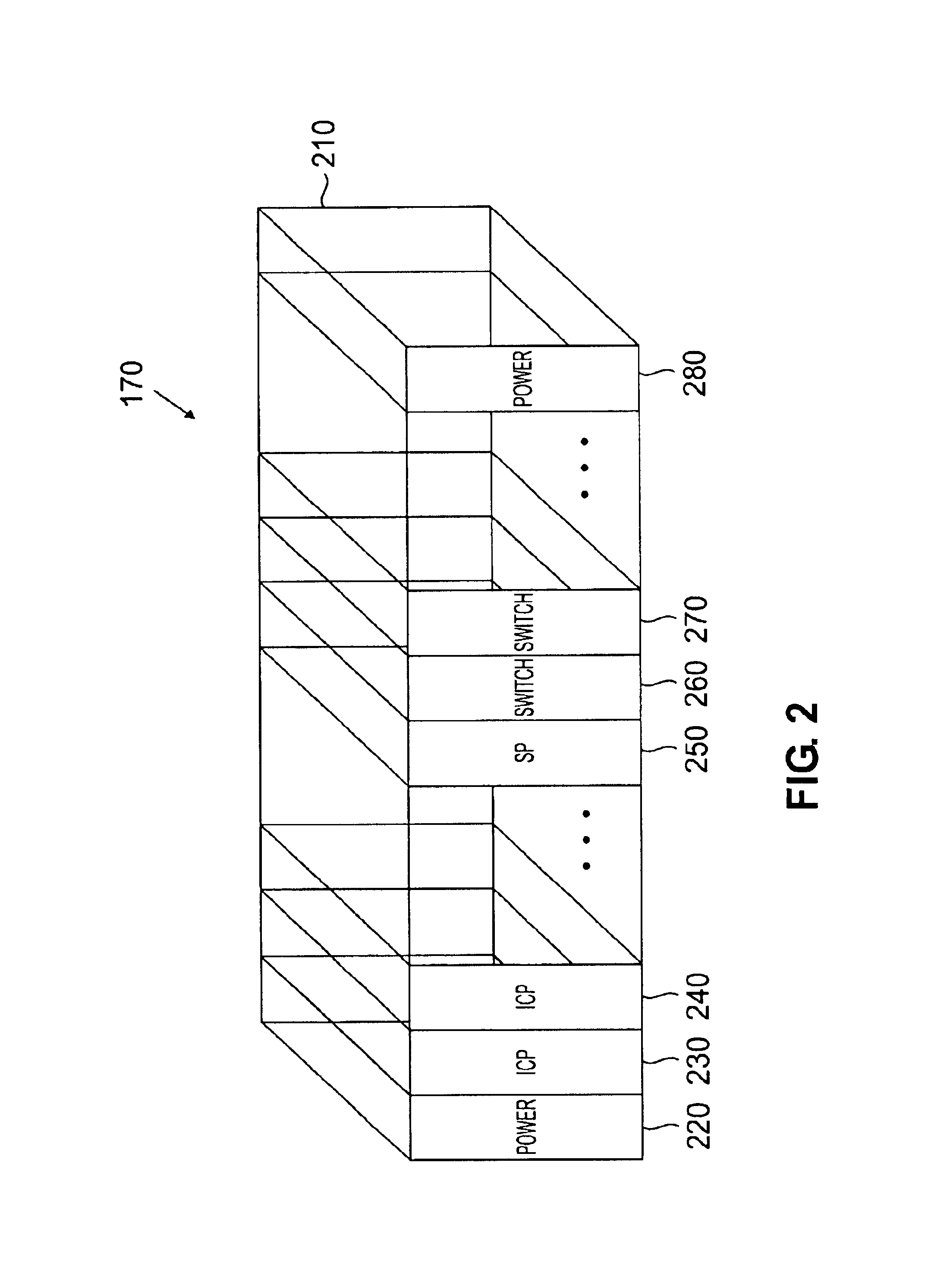

System and method for providing an improved common control bus for use in on-line insertion of line replaceable units in wireless and wireline access systems

InactiveUS6925516B2Error preventionDigital data processing detailsModem deviceProgrammable logic device

There is disclosed a system and method for providing an improved common control bus for use in the on-line insertion of line replaceable units (such as circuit board cards) into a backplane of a processor shelf, a modem shelf, or a similar type of equipment. The present invention increases the number of device locations that a common control bus can access. The present invention comprises a complex programmable logic device on a circuit board card that is coupled to a common control bus. The complex programmable logic device is capable of selectively coupling to the common control bus each one of a plurality of device locations on the circuit board card. The complex programmable logic device controls data access to and from each device that is coupled to the common control bus.

Owner:RAZE TECH

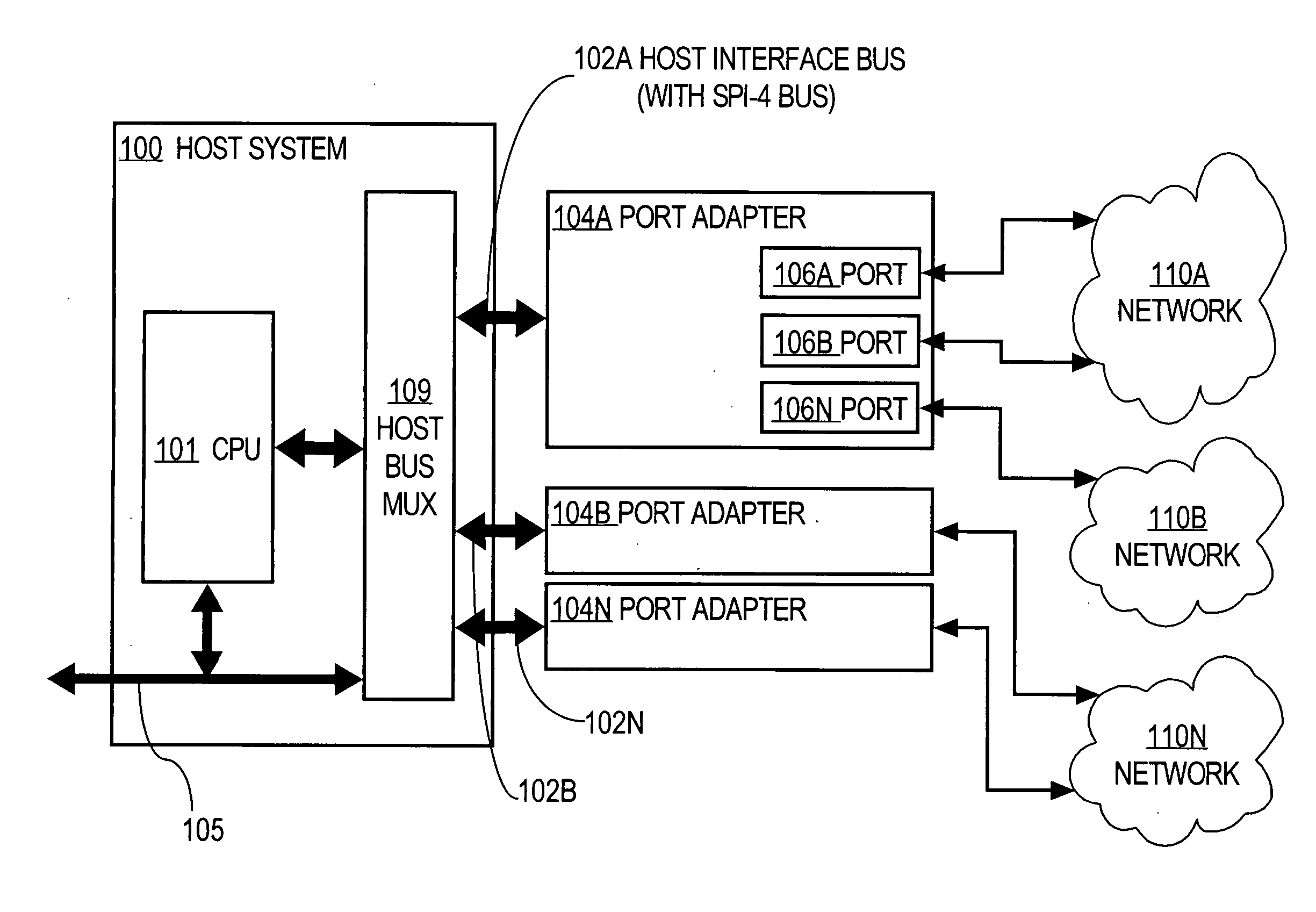

Port adapter for high-bandwidth bus

InactiveUS20050149651A1Prevent potentially high currentPrevent corruptionTime-division multiplexData switching by path configurationHigh bandwidthBandwidth requirement

Owner:CISCO TECH INC

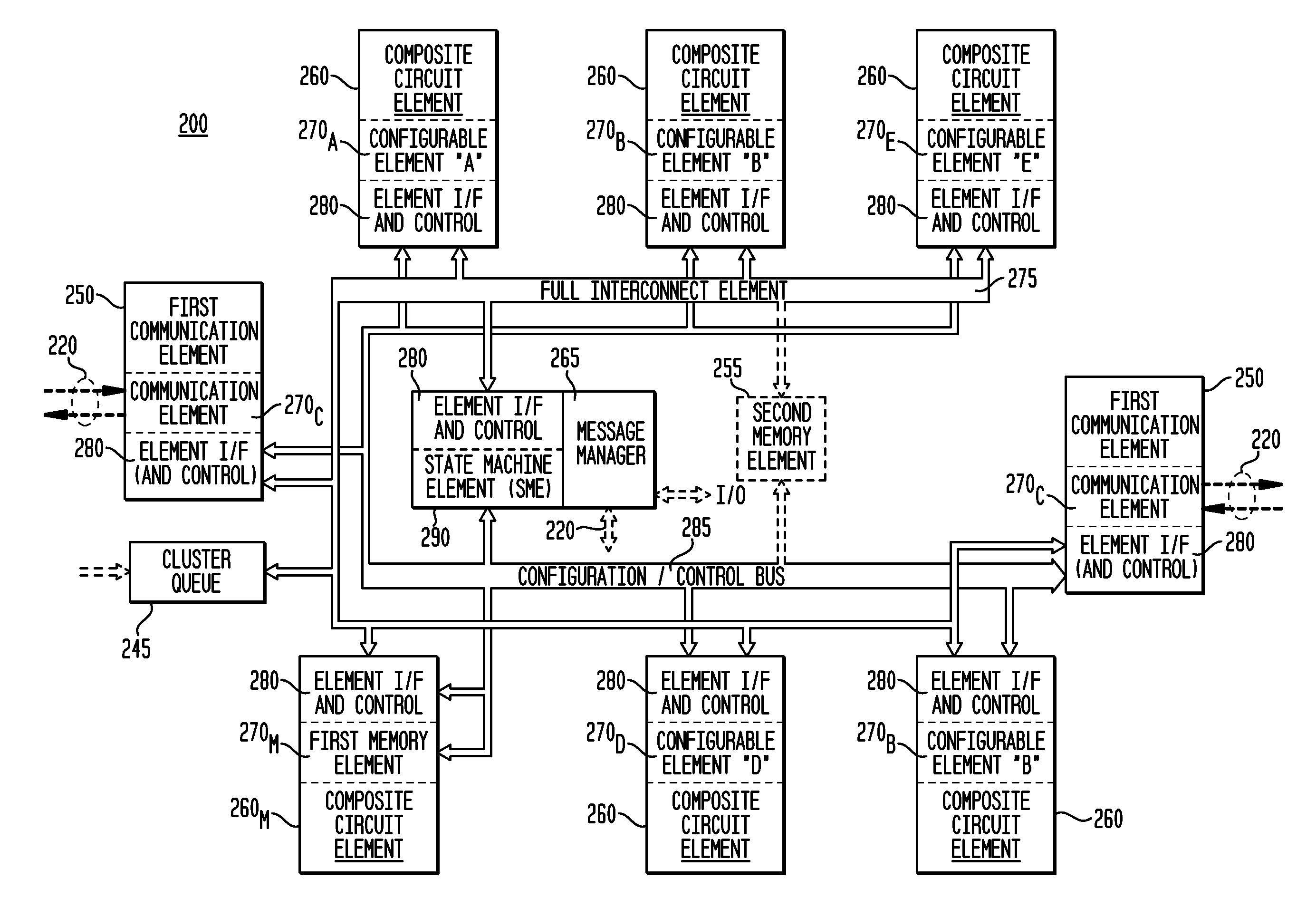

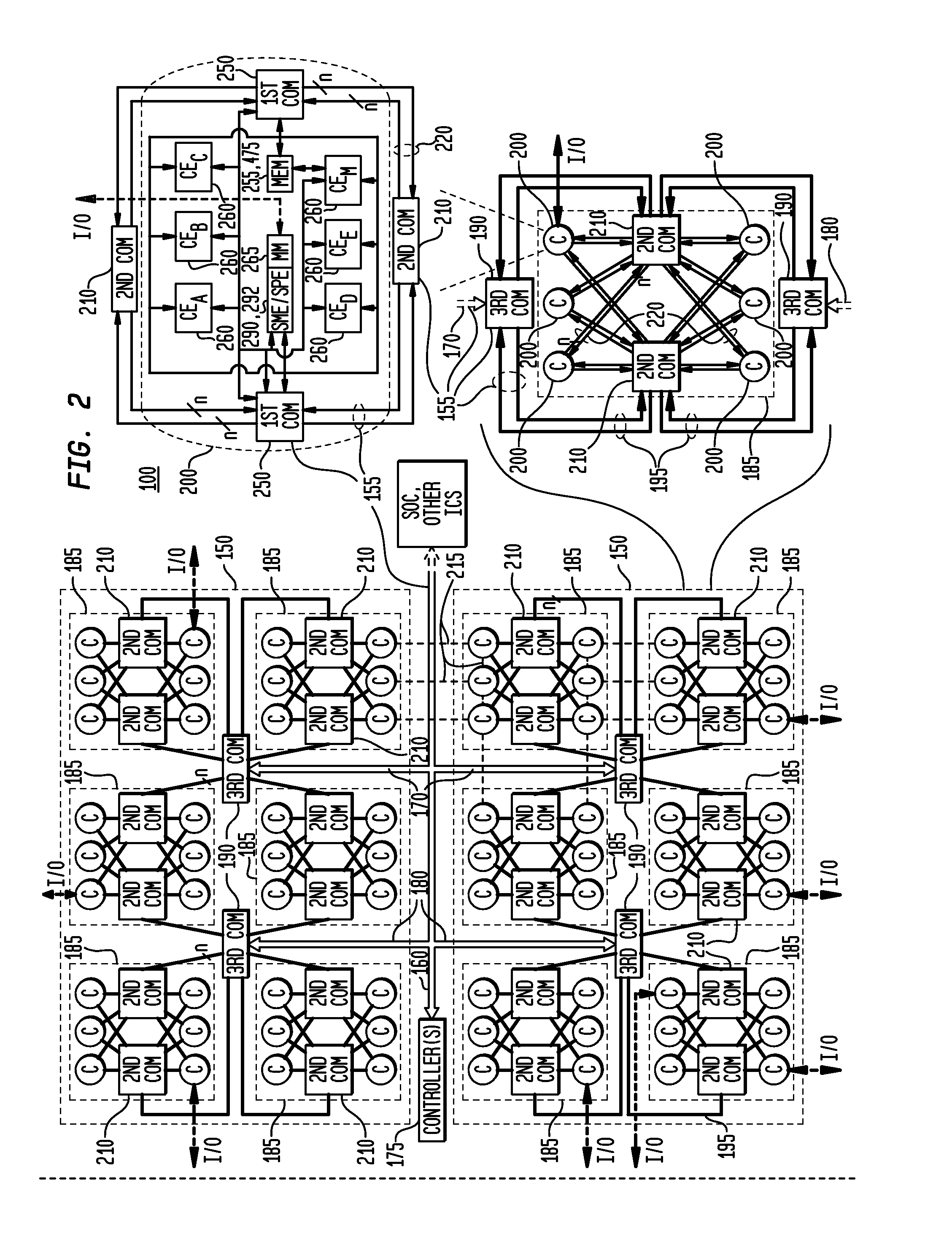

Reconfigurable Integrated Circuit Architecture With On-Chip Configuration and Reconfiguration

InactiveUS20120131288A1Significant resiliencyError detection/correctionFail-safe circuitsComputer architectureProcessor register

The exemplary embodiments provide a reconfigurable integrated circuit capable of on-chip configuration and reconfiguration, comprising: a plurality of configurable composite circuit elements; a configuration and control bus; a memory; and a sequential processor. Each composite circuit element comprises: a configurable circuit; and an element interface and control circuit, the element interface and control circuit comprising an element controller and at least one configuration and control register to store one or more configuration and control words. The configuration and control bus is coupled to the plurality of configurable composite circuit elements, and comprises a plurality of address and control lines and a plurality of data lines. The sequential processor can write configurations to the configuration and control registers of an addressed configurable composite circuit element to configure or reconfigure the configurable circuit.

Owner:ELEMENT CXI

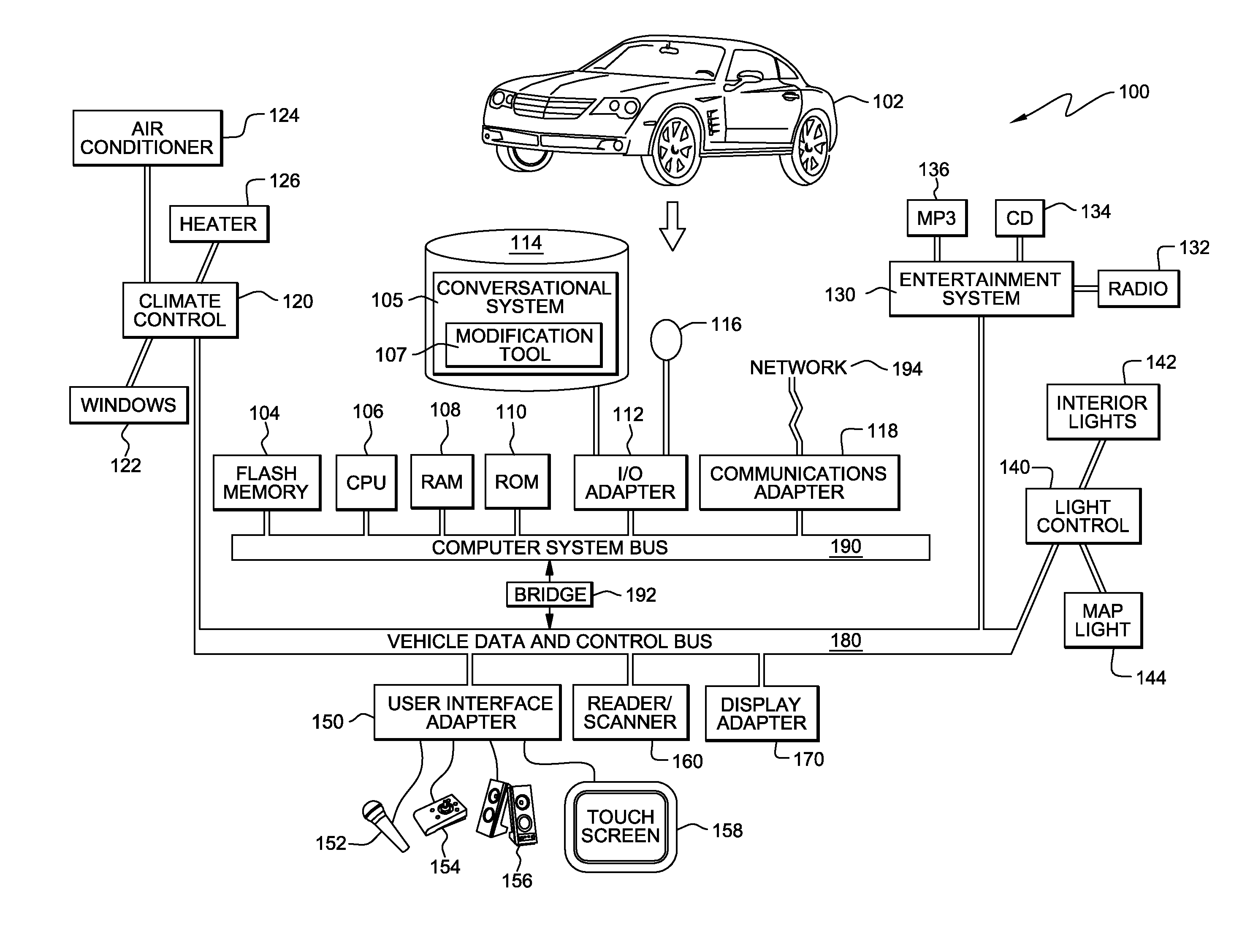

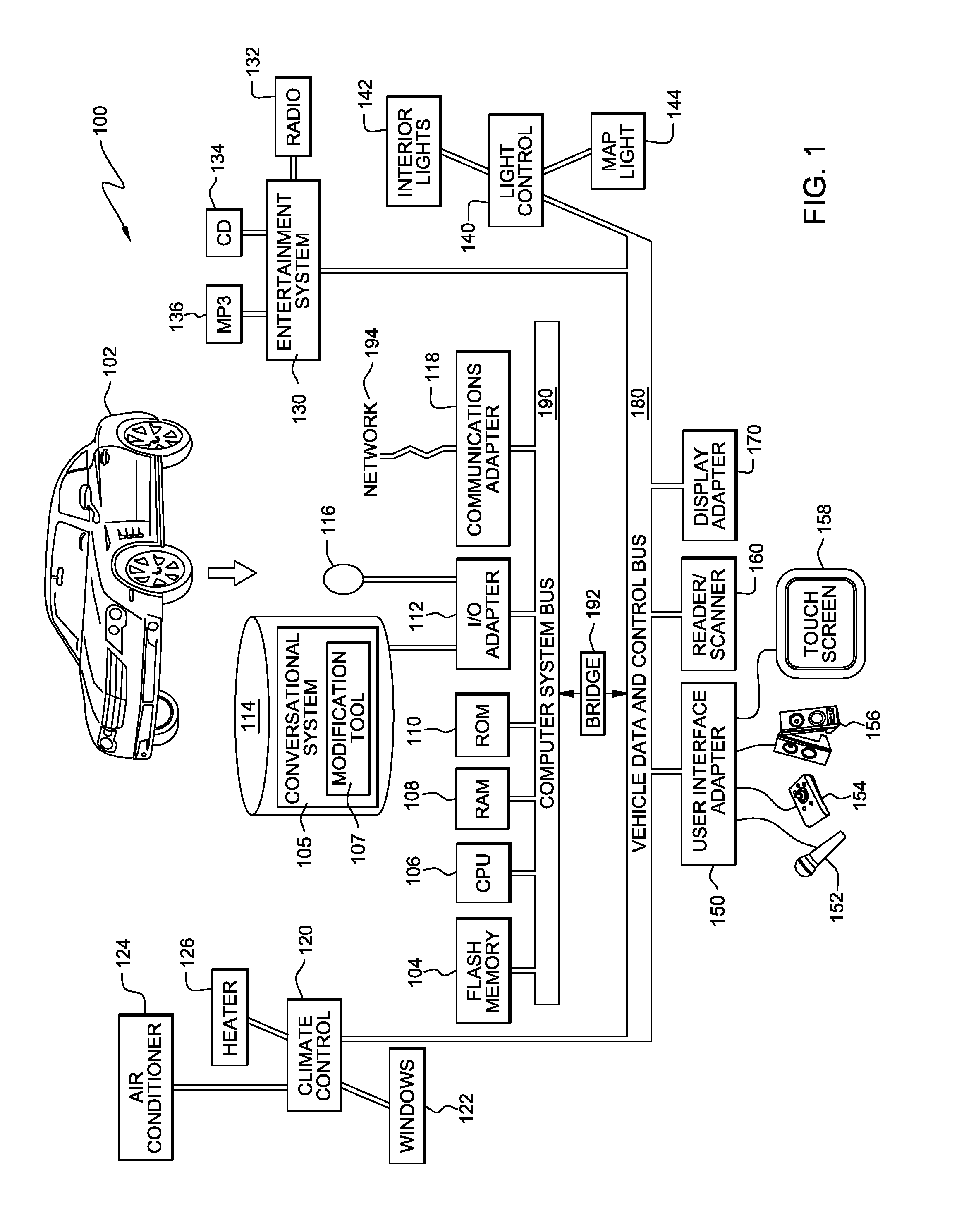

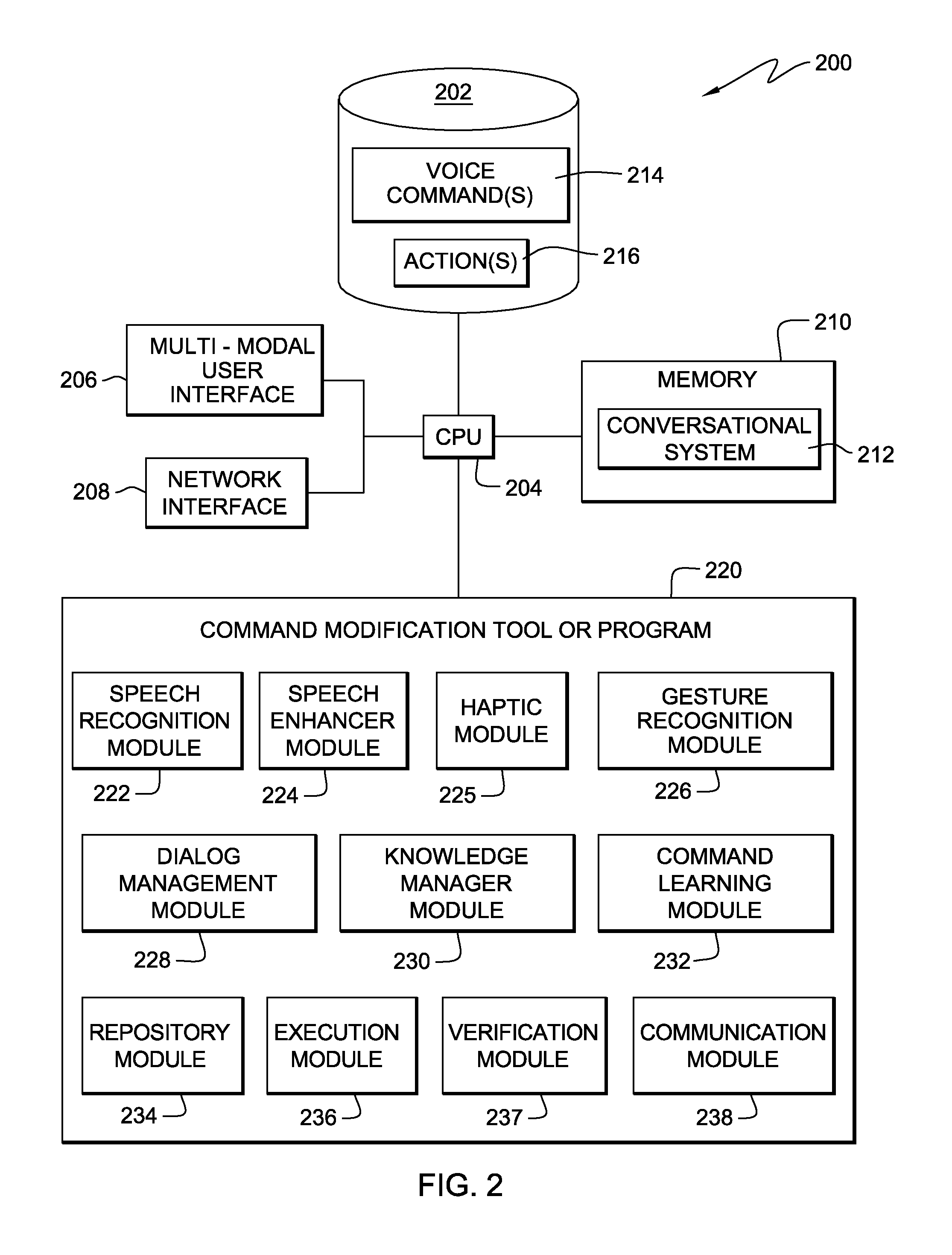

Machine, system and method for user-guided teaching and modifying of voice commands and actions executed by a conversational learning system

A machine, system and method for user-guided teaching and modifications of voice commands and actions to be executed by a conversational learning system. The machine includes a system bus for communicating data and control signals received from the conversational learning system to a computer system, a vehicle data and control bus for connecting devices and sensors in the machine, a bridge module for connecting the vehicle data and control bus to the system bus, machine subsystems coupled to the vehicle data and control bus having a respective user interface for receiving a voice command or input signal from a user, a memory coupled to the system bus for storing action command sequences learned for a new voice command and a processing unit coupled to the system bus for automatically executing the action command sequences learned when the new voice command is spoken.

Owner:NUANCE COMM INC

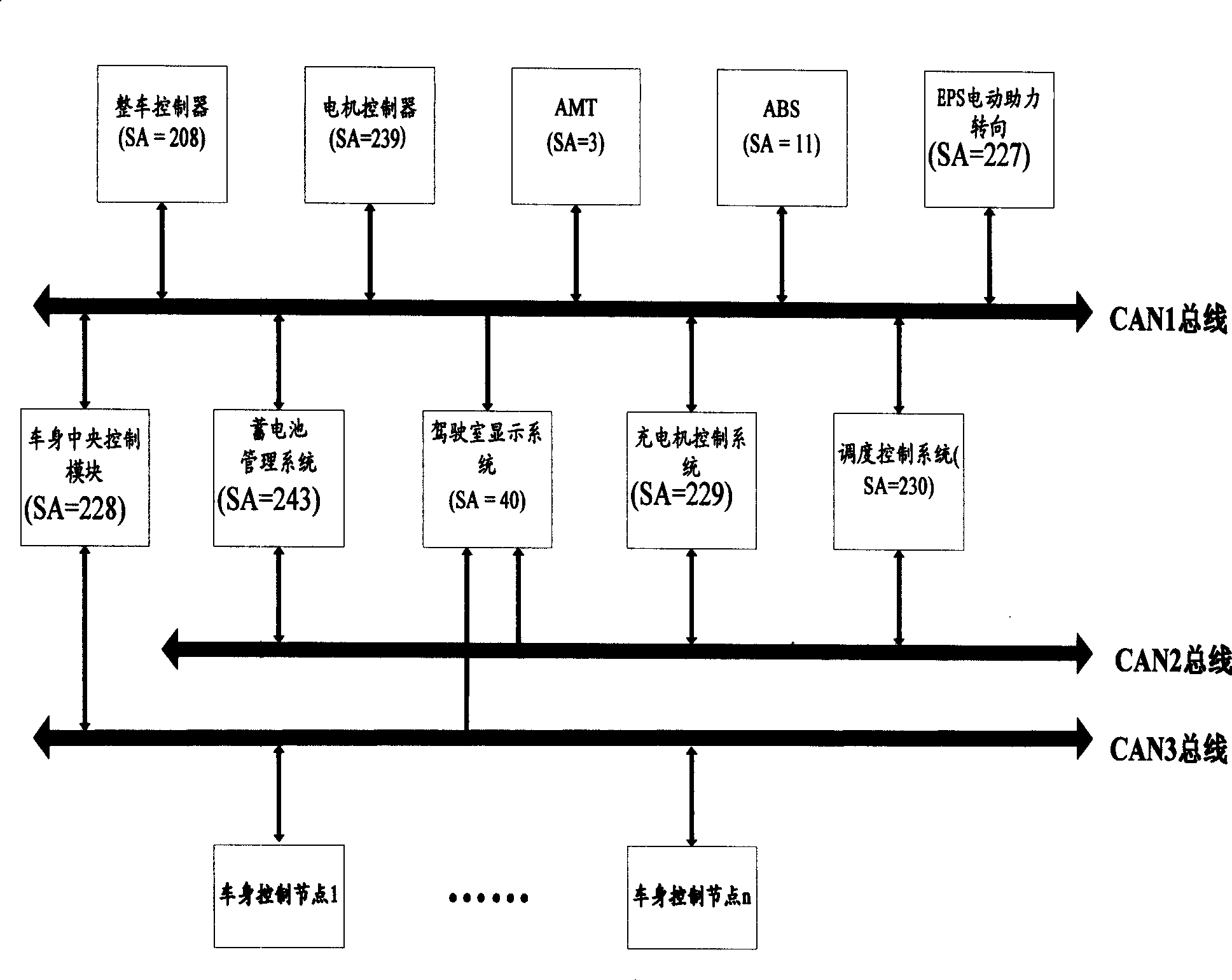

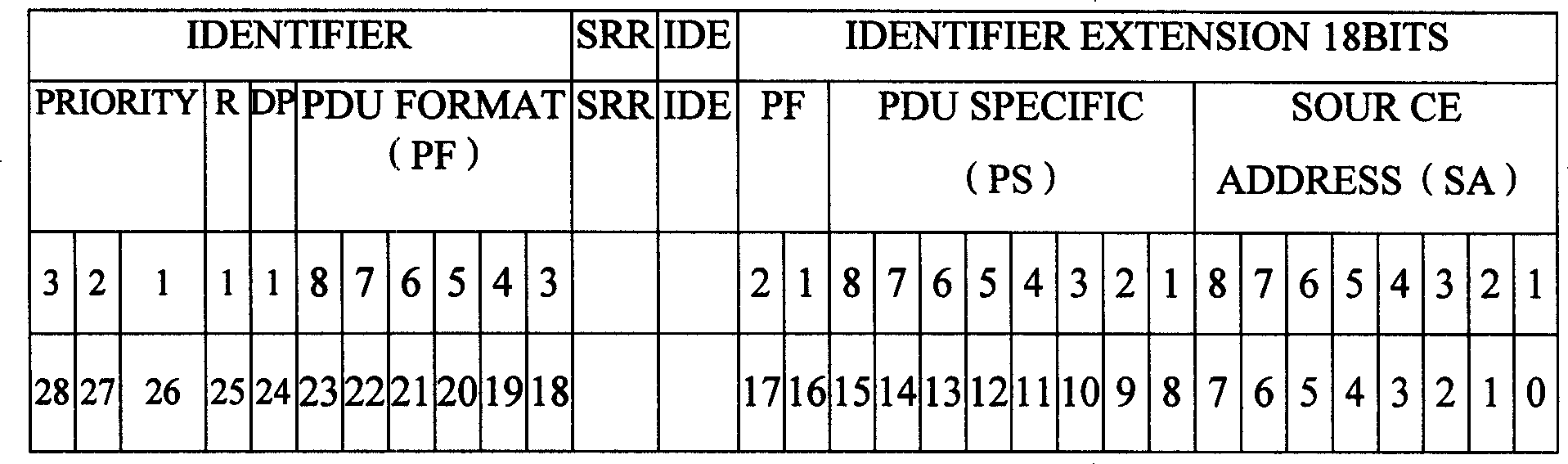

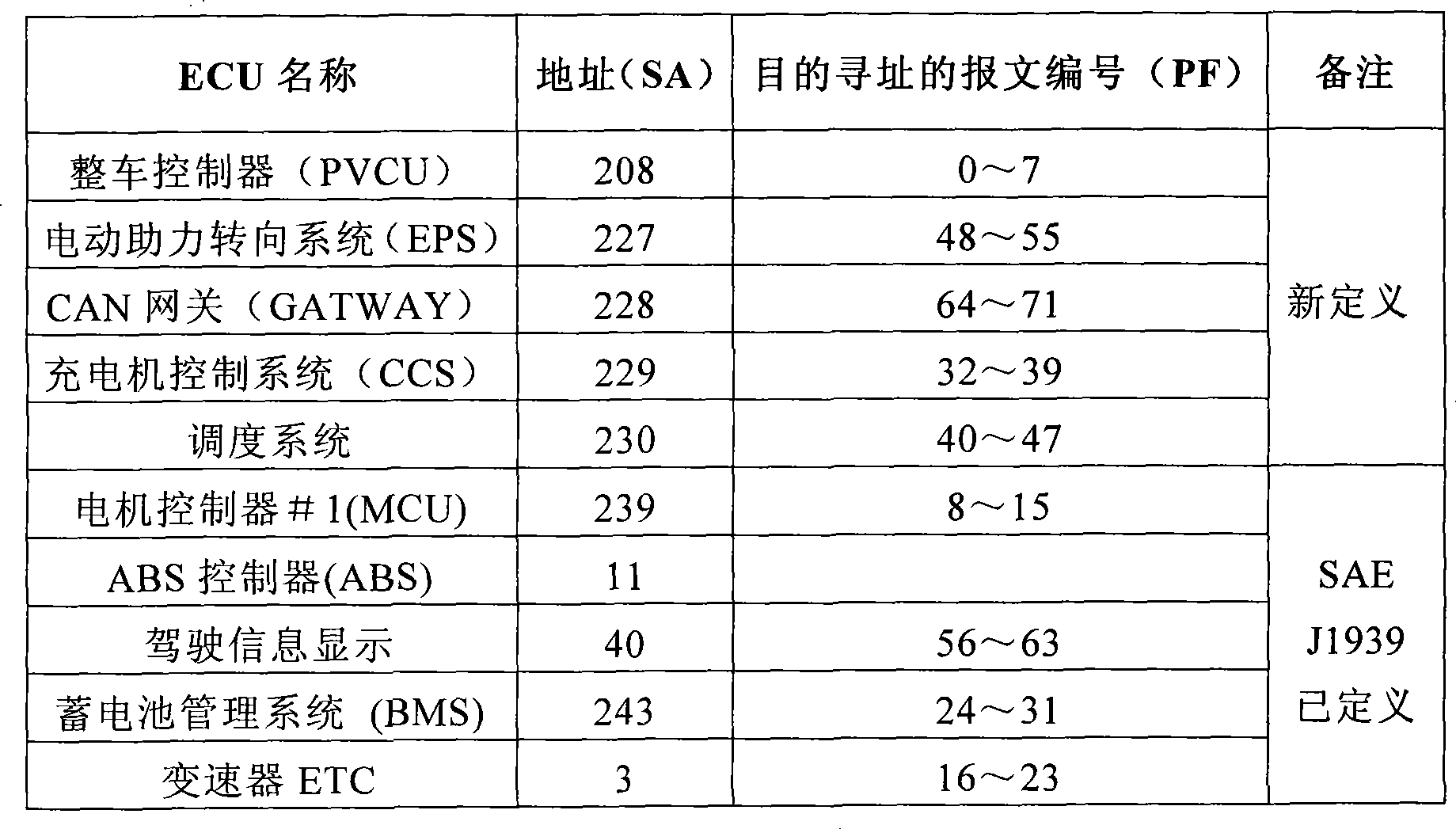

Pure electric motor coach communication system and method based on three CAN bus

InactiveCN101417636AAdd control nodeReduce load rateElectric/fluid circuitBus networksPower batteryLow speed

The invention provides a pure electric passenger vehicle communication system based on three ways of CAN buses, comprising a plurality of controllers and three ways of CAN buses, wherein, the CAN buses comprise three ways of CAN buses which are coupled with the plurality of controllers and consist of a CAN1 bus, a CAN2 bus, and a CAN3 bus; the CAN1 bus is a high-speed CAN bus and used for the control of a power system; the CAN2 bus is a high-speed CAN bus and used for the transmission of power battery monometer data; and the CAN3 bus is a low-speed CAN bus, provided with a plurality of vehicle body control nodes, and used for achieving the information collection and control of each part of the vehicle body. The system causes the loading rate of the power system control bus to be greatly reduced, ensures the real-time performance of the control, and improves the driving safety of the electric vehicle.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

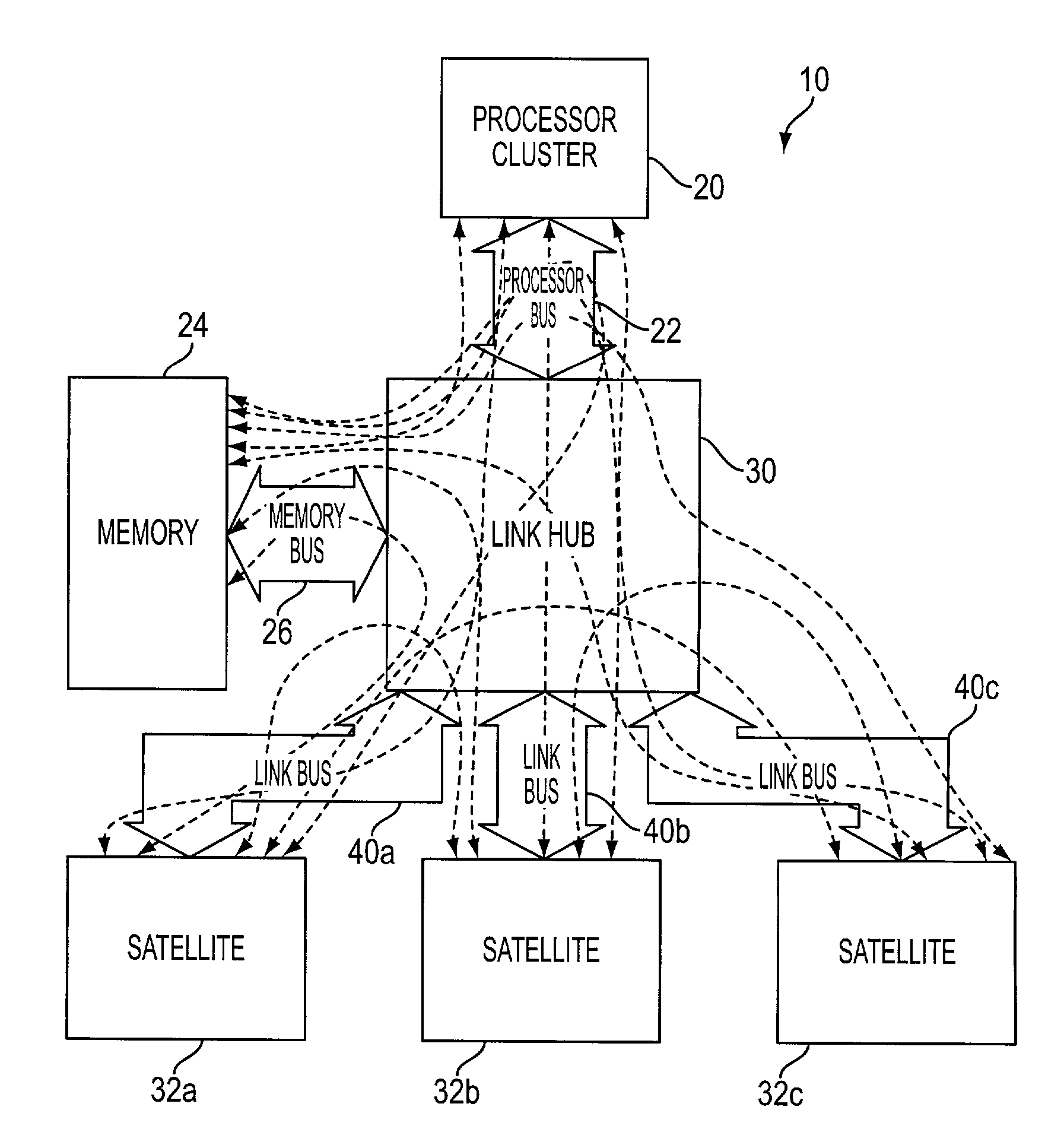

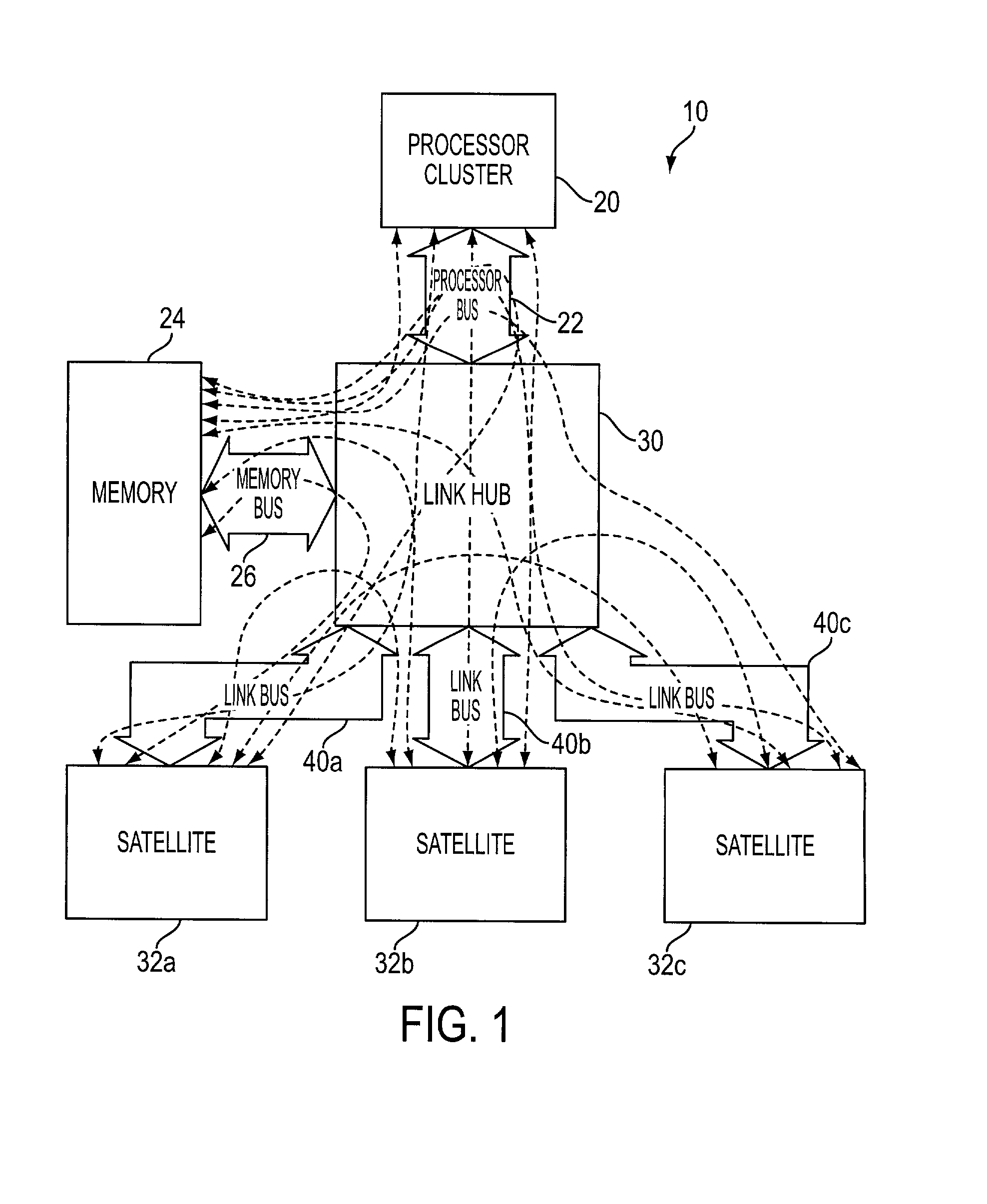

Arbitration method for a source strobed bus

InactiveUS6993612B2Minimize the numberLow costTime-division multiplexMemory systemsComputerized systemComputer science

A hub based computer system having a central hub that communicates with a plurality of satellite devices over respective link buses. Each link bus is substantially the same and adheres to a predefined link bus protocol. The satellite devices are also connected to industry standard buses / devices. The central hub also communicates with a processor and system memory over additional buses. Each link bus includes a status line that allows each device connected to the same link bus to request control of the bus. The link bus protocol establishes a window in which the status signal may convey arbitration request information in a time-multiplexed manner. The protocol further includes a method of determining whether control of the bus can be transferred to a different device. Each device takes part in the decision process and thus, the arbitration method of the invention is decentralized.

Owner:MICRON TECH INC

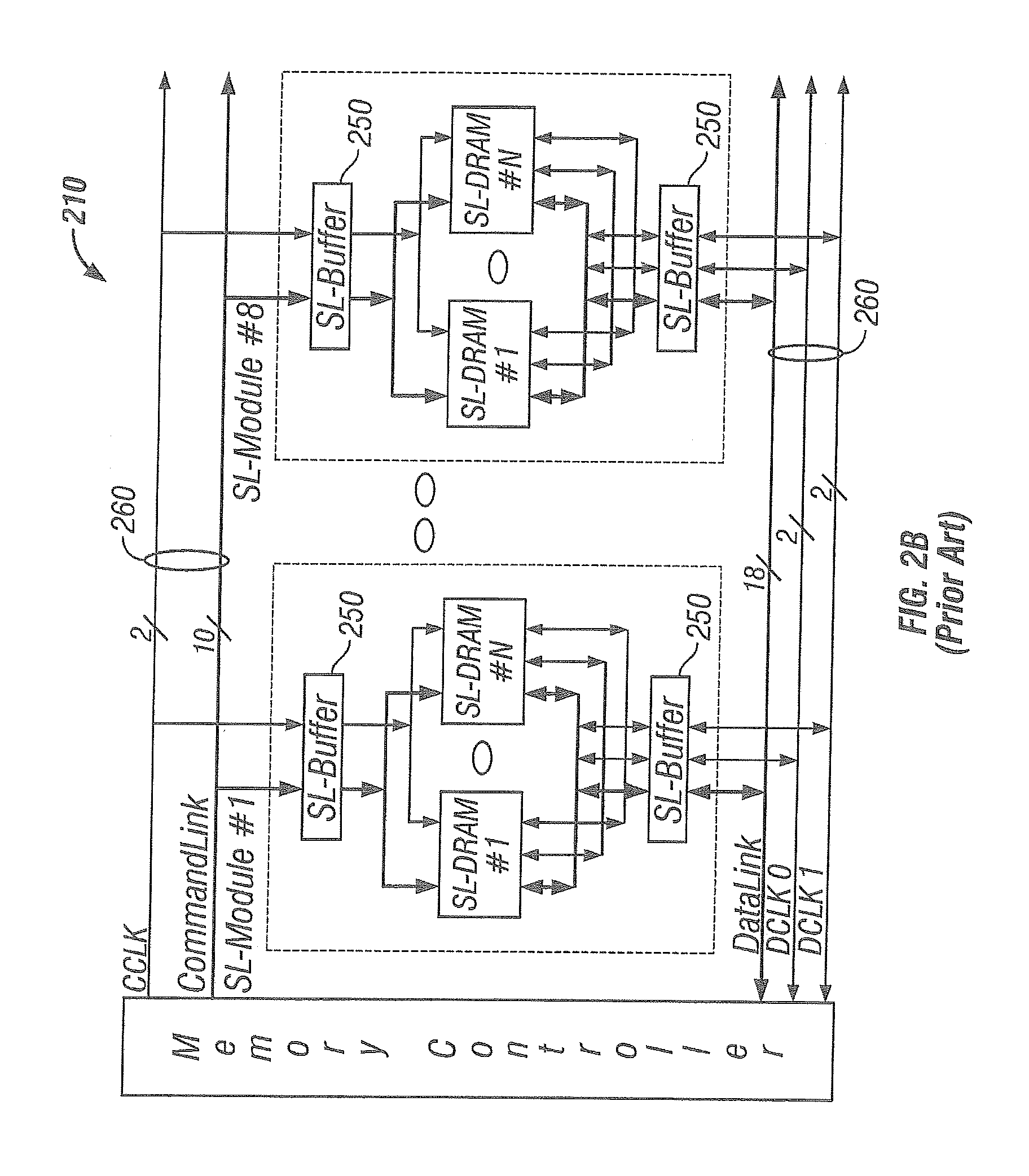

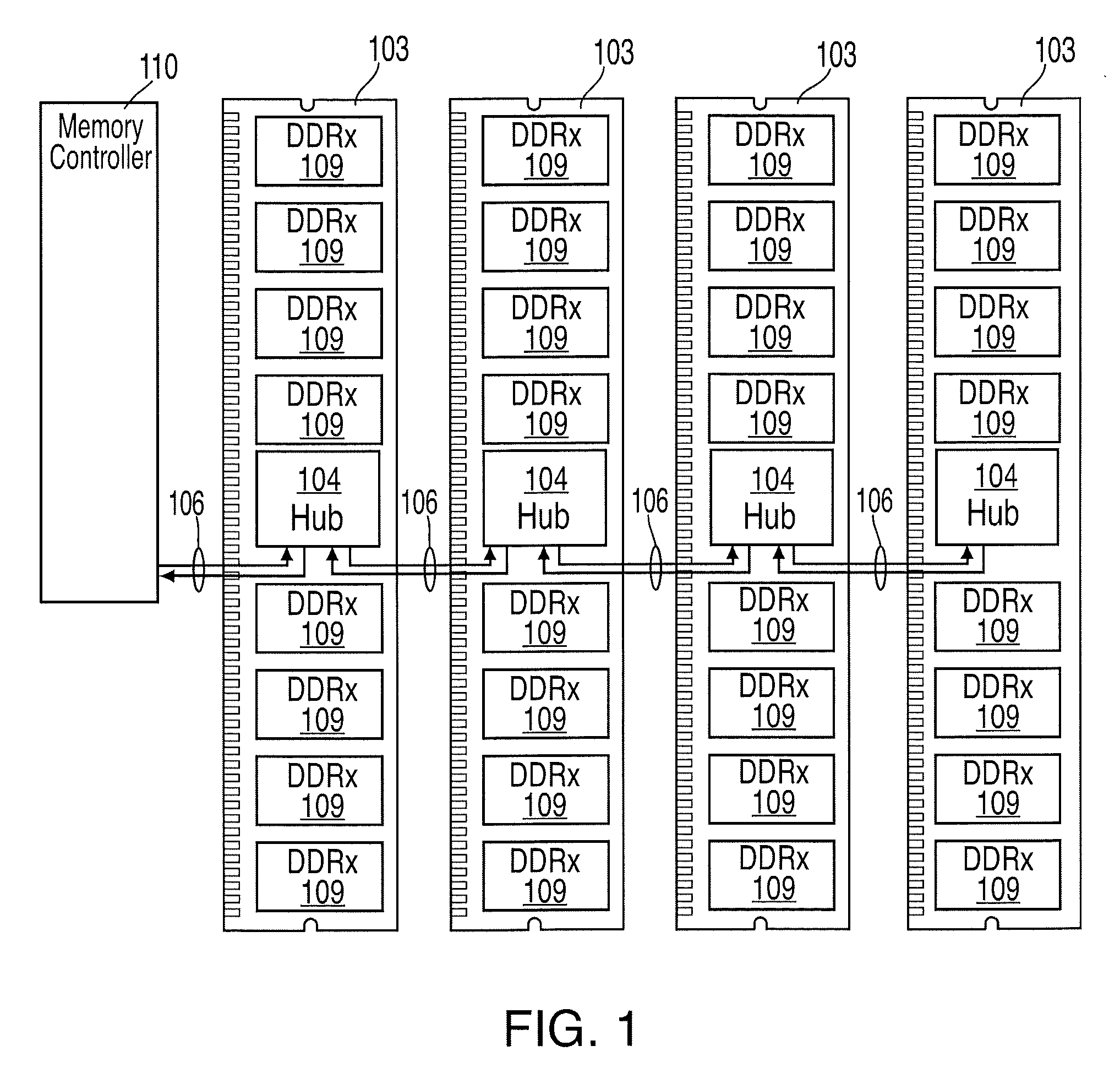

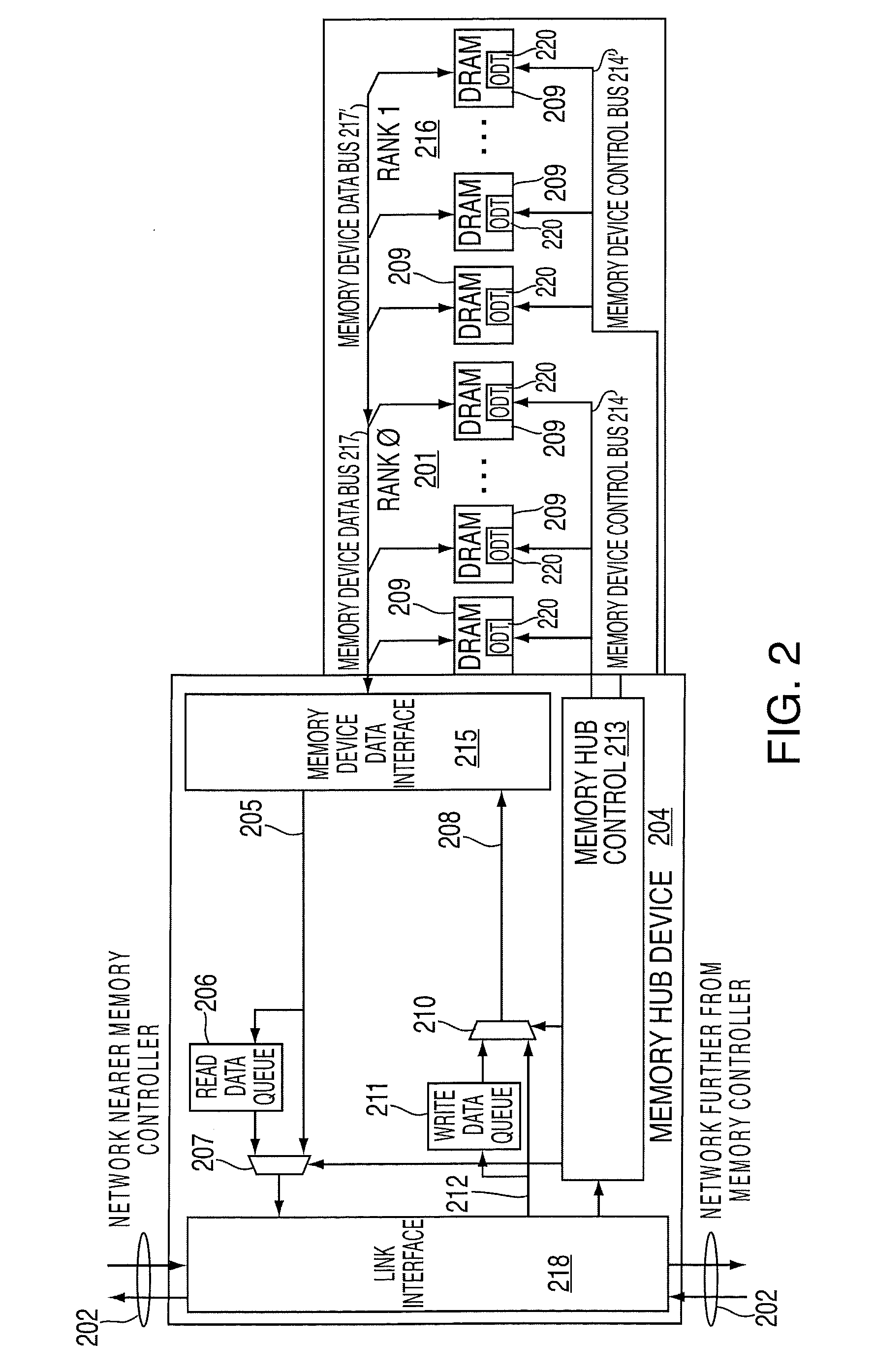

Buffered Memory Having A Control Bus And Dedicated Data Lines

InactiveUS20080034130A1Memory adressing/allocation/relocationDigital storageInterconnect topologyMultiplexer

A memory system architecture / interconnect topology includes a configurable width buffered module having a configurable width buffer device. The configurable width buffer device is coupled to at least one memory device on the configurable width memory module. The configurable width buffer device includes an interface and a configurable serialization circuit capable of varying a data path width or a number of contacts used at the interface of the configurable width buffer device in accessing the at least one memory device. In an alternate embodiment of the present invention, a multiplexer / demultiplexer circuit is provided. A state storage provides a data width for the configurable width buffer and a SPD provides the configurable width buffer and / or module capabilities to the memory system.

Owner:RAMBUS INC

Method and apparatus for verifying the integrity of control module operation

A control module (100) includes a first signal processing unit (102) that is coupled to a second signal processing unit (114) by a control bus (130), an address bus (131) and a data bus (132). The control module conveys seed value addresses (108) and expected result addresses (110) over the address bus, seed values (118) and verification set output values (107) over the data bus, and compares each verification set output value to an expected result (120), thereby allowing the control module to determine whether the first signal processing unit, the control bus, the address bus, and the data bus are collectively functioning correctly. By properly selecting the seed value addresses, expected result addresses, seed values, and expected results (and correspondingly, verification set output values), proper operation of each line of the address bus and control bus may be individually verified.

Owner:TEMIC AUTOMOTIVE OF NORTH AMERICA

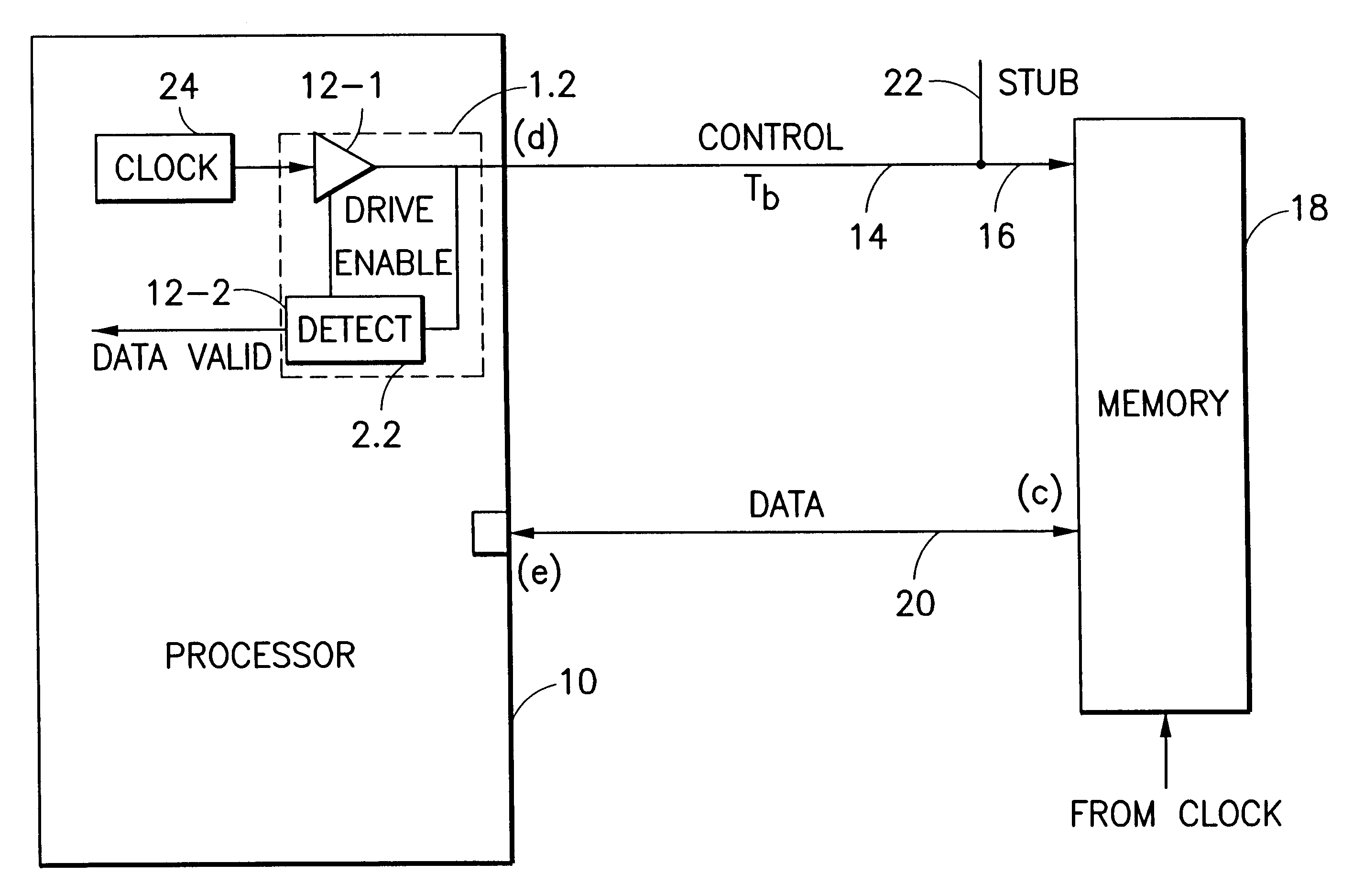

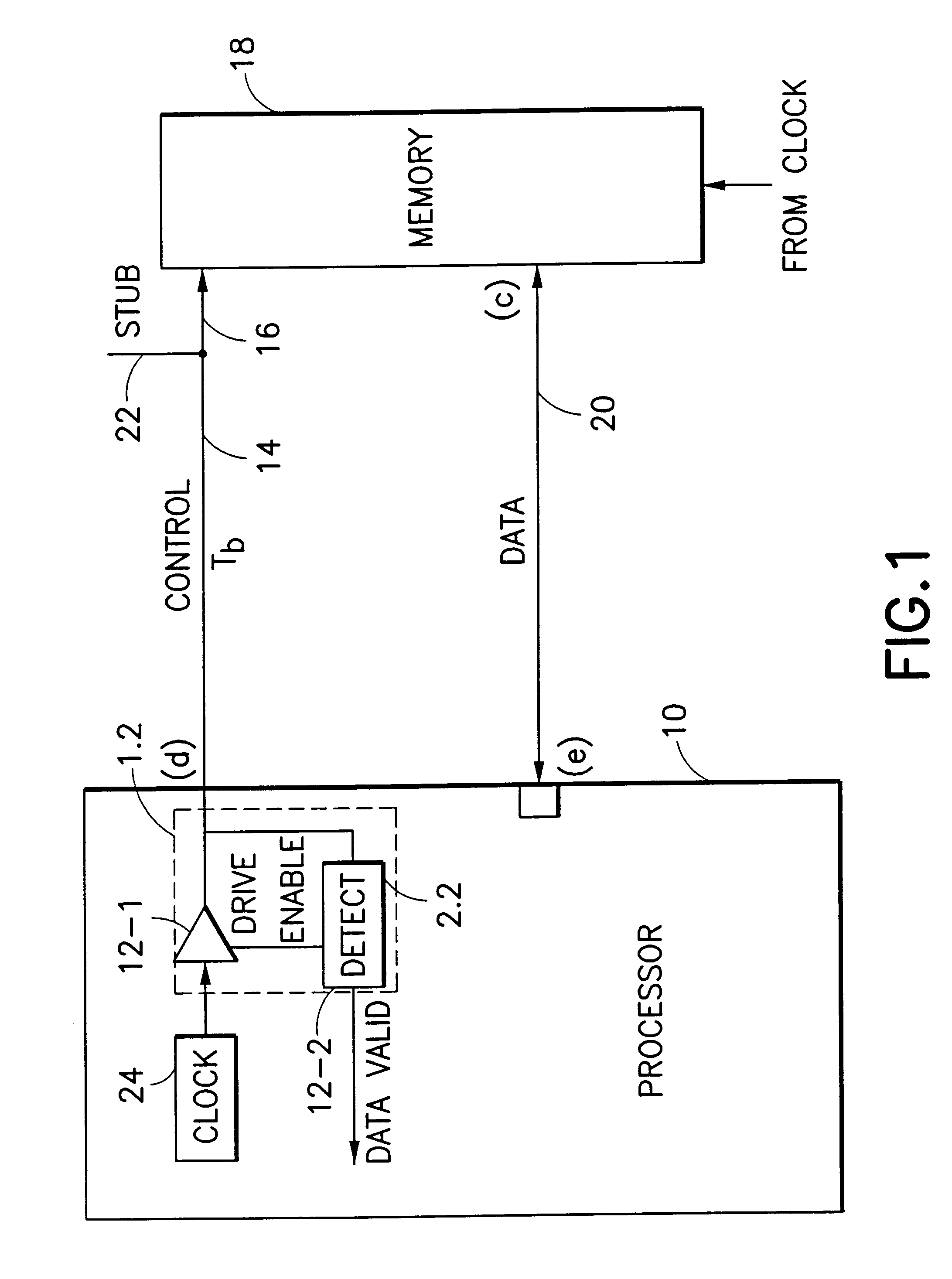

High frequency valid data strobe

InactiveUS6177807B1Reliability increasing modificationsElectronic switchingDetector circuitsControl signal

A processor with a memory send / received control circuit including a bus drive circuit and a detector circuit connected via control bus line to the control input of the memory. A data input line, or output line, or data input / output line is connected between the processor and the memory. A transmission line stub having a length that is incrementally variable is connected to the memory control input side of the control line 14. The impedance Z0 of the transmission line stub is equal to that of the control line and is open circuited at the end which results in voltage doubling to achieve high speed synchronization between control signals and data signals and to ensure valid data at high clock rates.

Owner:IBM CORP

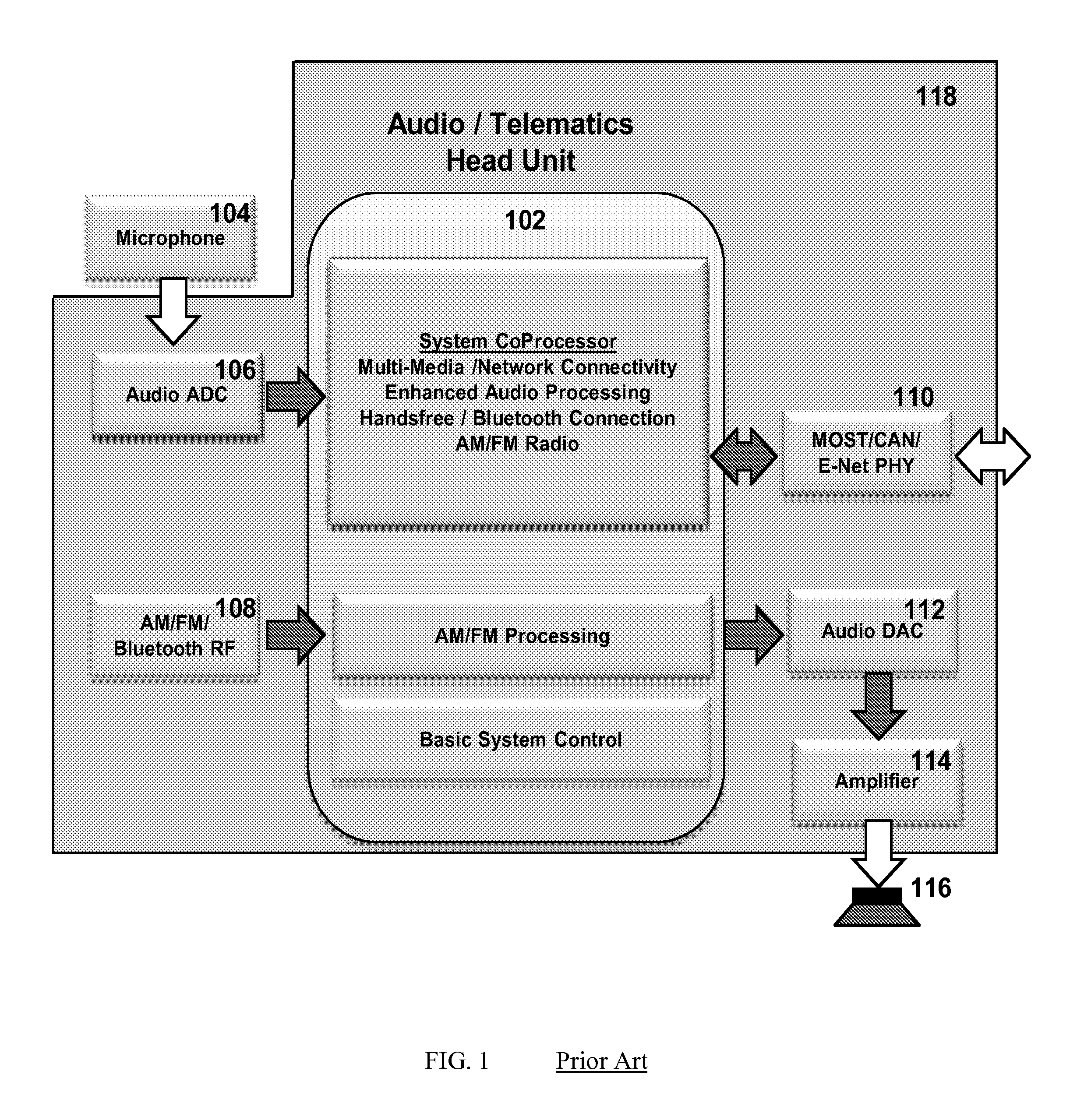

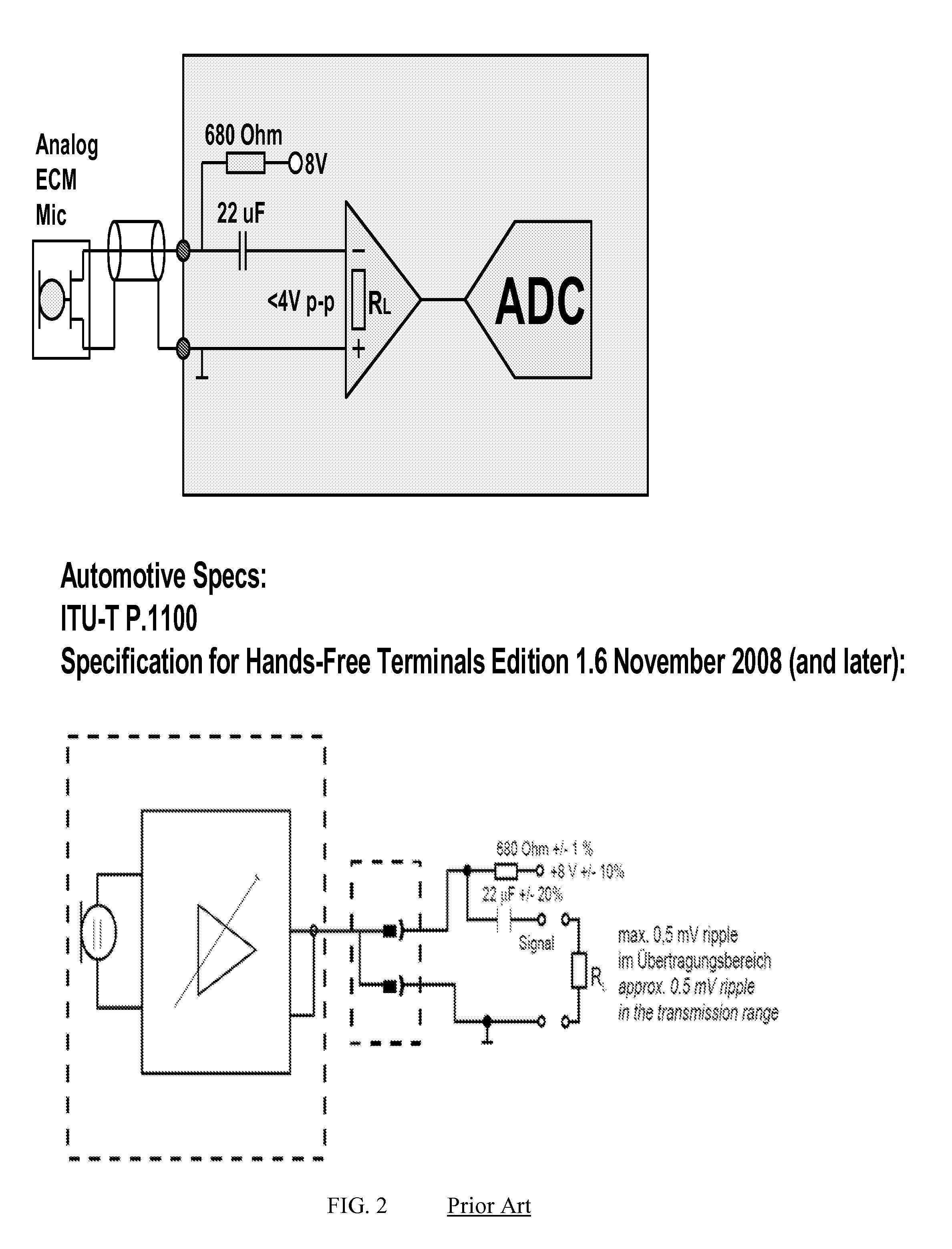

Mobile wireless communication device architectures and methods therefor

A wireless communications architecture having first and second synchronous memory devices coupled to a virtual channel memory controller by corresponding first and second data buses, and a shared address and control bus interconnecting the virtual channel memory controller and the first and second synchronous memory devices. The first and second synchronous memory devices are addressed with the shared address bus, and the first and second memory locations are accessed via the first and second data buses, respectively.

Owner:APPLE INC

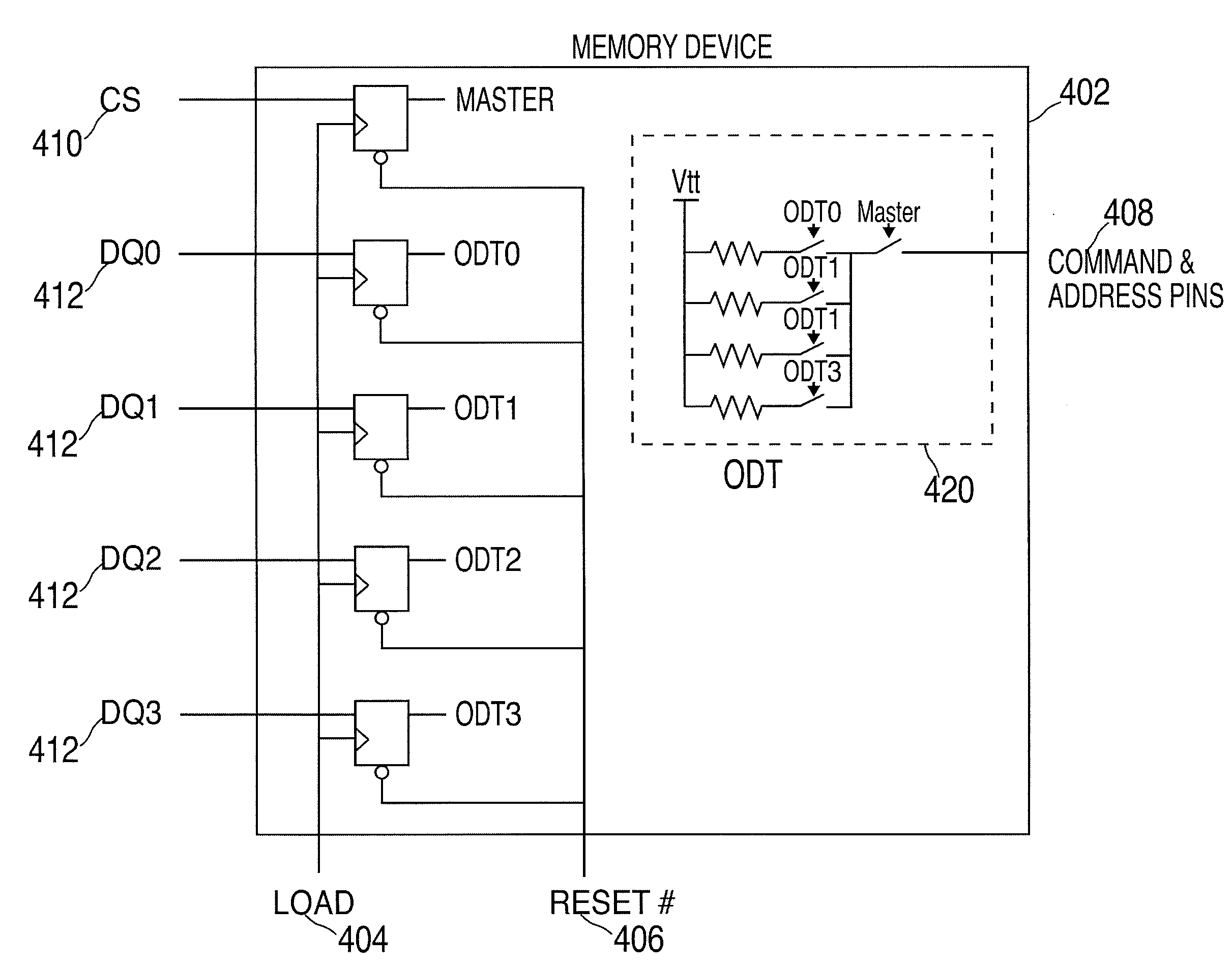

System for providing on-die termination of a control signal bus

ActiveUS20090273960A1Reliability increasing modificationsElectronic switchingControl signalControl bus

A system for providing on-die termination (ODT) of a control signal bus. The system includes a memory device that includes a plurality of data bus connectors, one or both of a load signal connector and a reset signal connector, a control bus connector, an ODT, and a mechanism. The ODT is in communication with the control bus connector, and the ODT provides a level of termination resistance to a control bus connected to the control bus connector. The mechanism latches data received via the data bus connectors in response to a signal received via one or both of the load signal connector and the reset signal connector. The data is utilized to set the level of termination resistance provided by the ODT.

Owner:GLOBALFOUNDRIES US INC

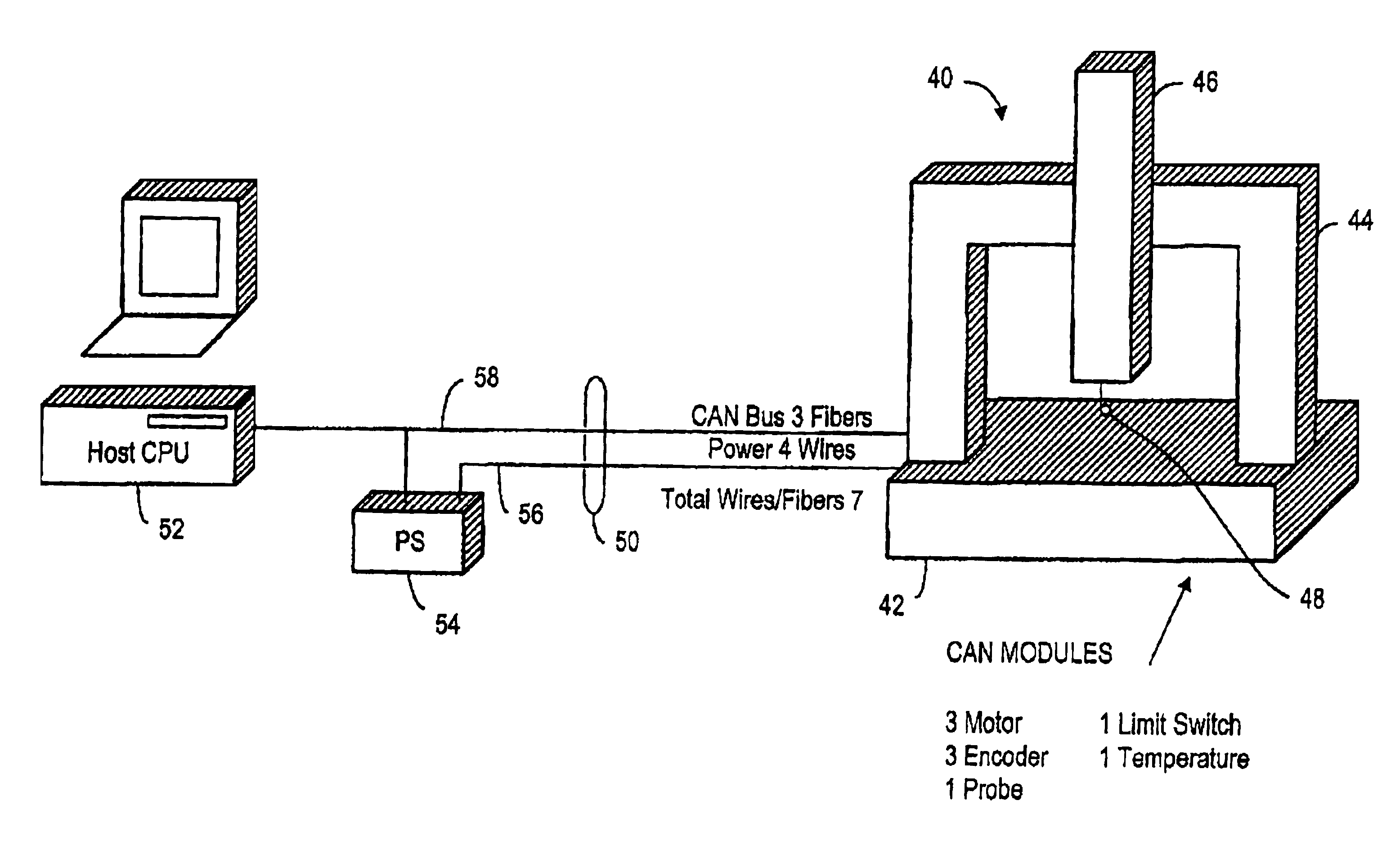

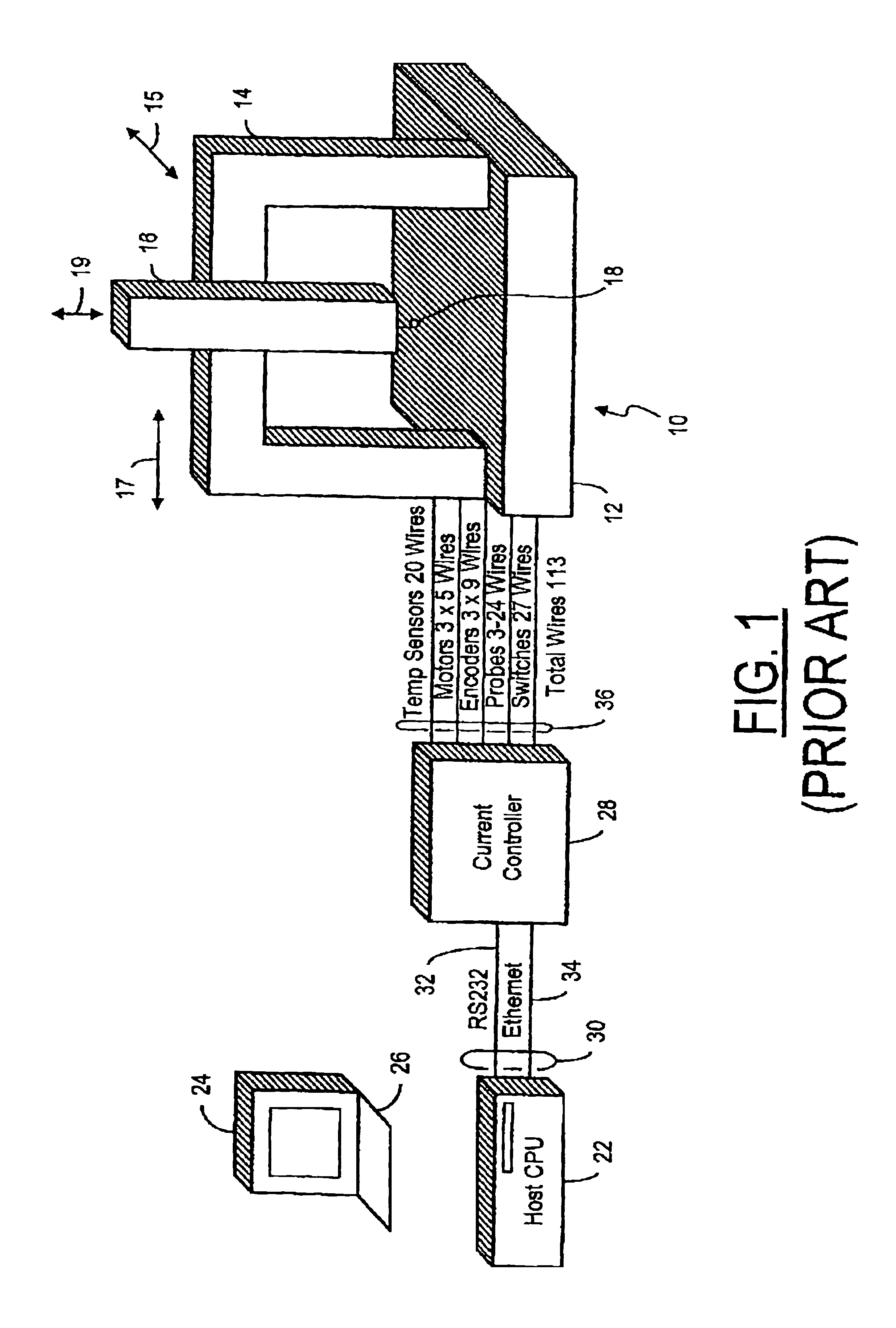

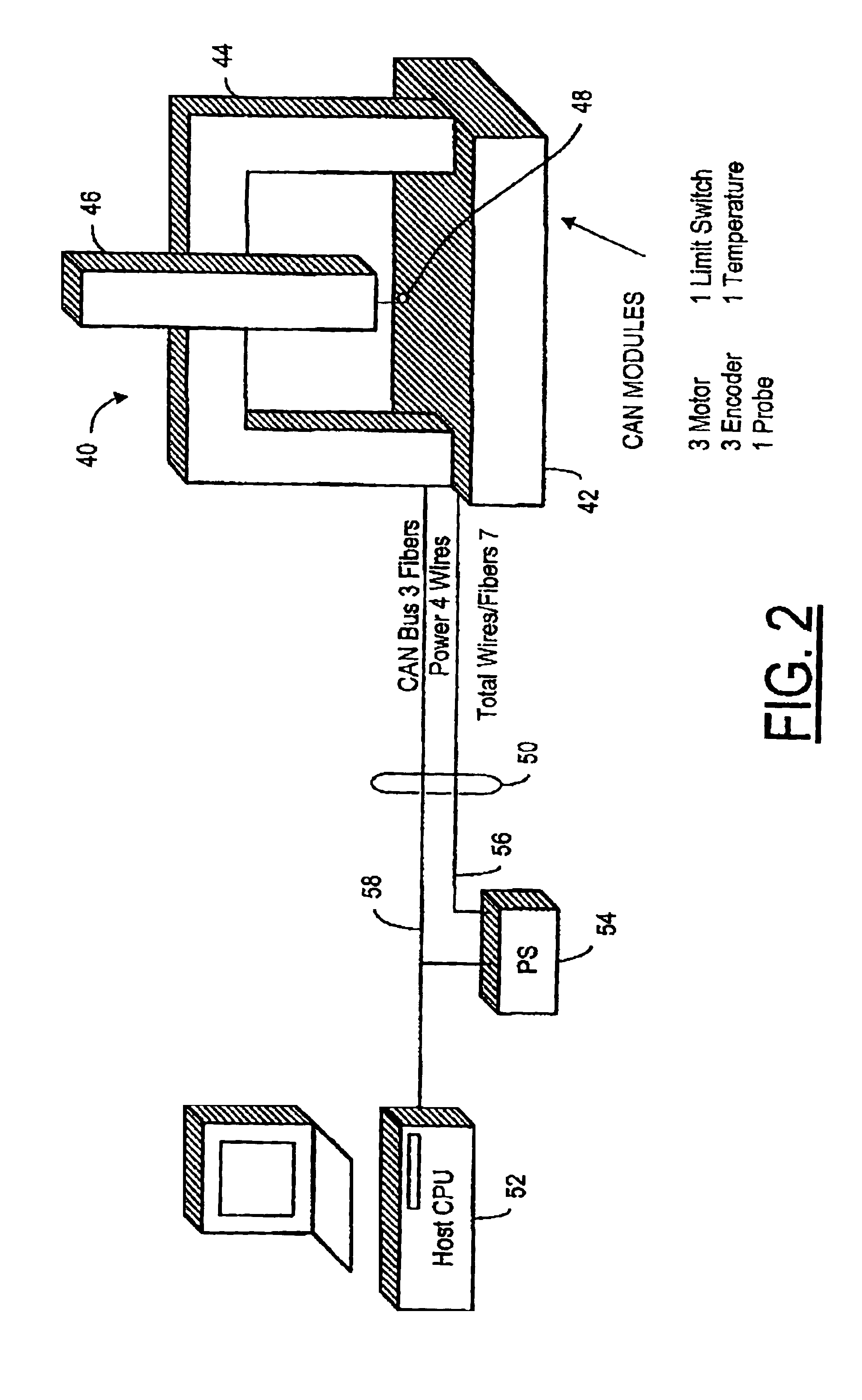

Communication method and common control bus interconnecting a controller and a precision measurement assembly

InactiveUS6948255B2Reduce cable dragImprove servo performanceFeeler-pin gaugesUsing subsonic/sonic/ultrasonic vibration meansControl busEmbedded system

The number and weight of wires interconnecting a host and / or controller with a precision measurement assembly is reduced using a common or shared bus. The bus may be entirely electrical or may include optical fibers to reduce EMI susceptibillty. A custom bus or a known serial network bus such as CAN or SIRCOS may be used.

Owner:HEXAGON TECH CENT GMBH

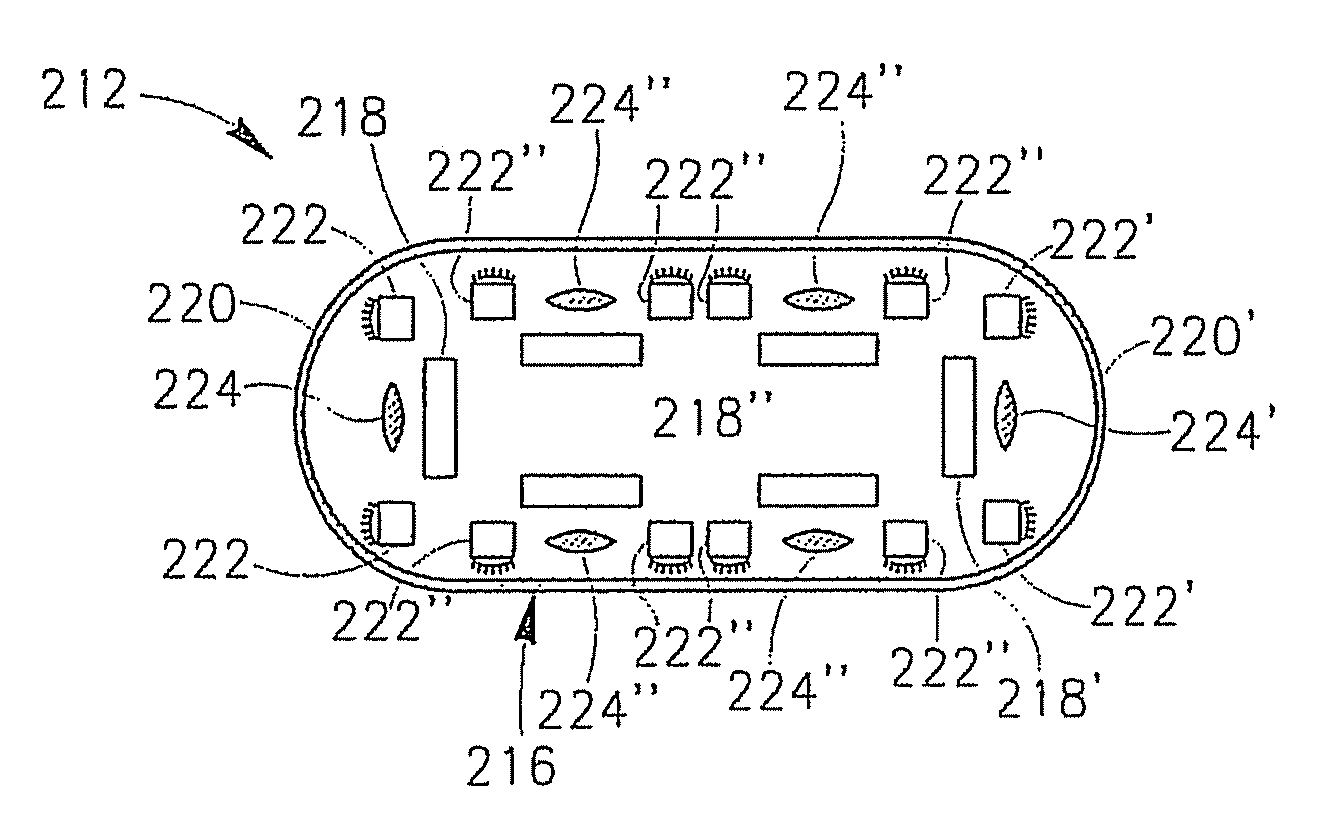

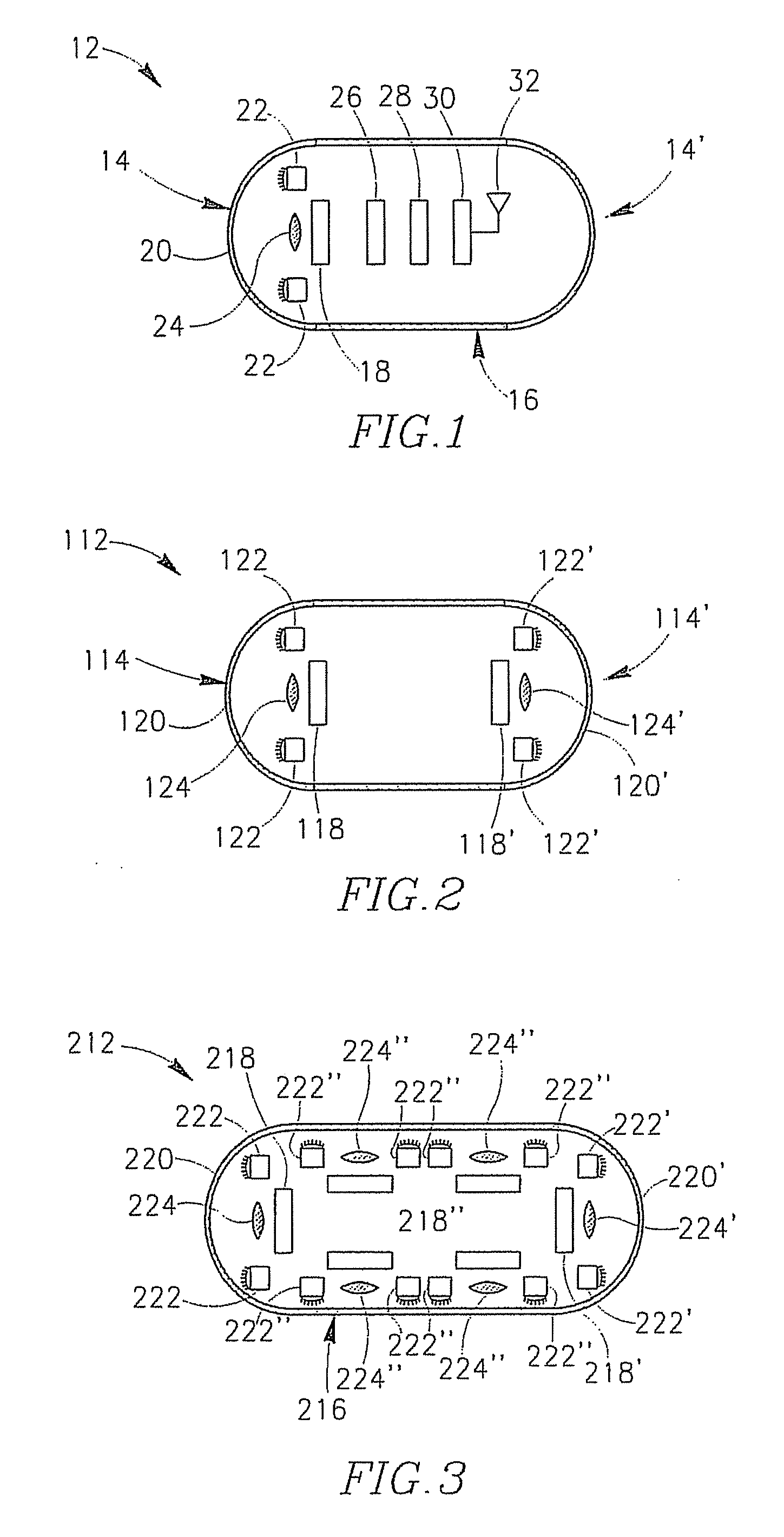

In-vivo sensing device and method for communicating between imagers and processor thereof

InactiveUS20100013914A1Reduce power consumptionLower Level RequirementsEndoscopesColor television detailsIn vivoComputer science

Owner:GIVEN IMAGING LTD

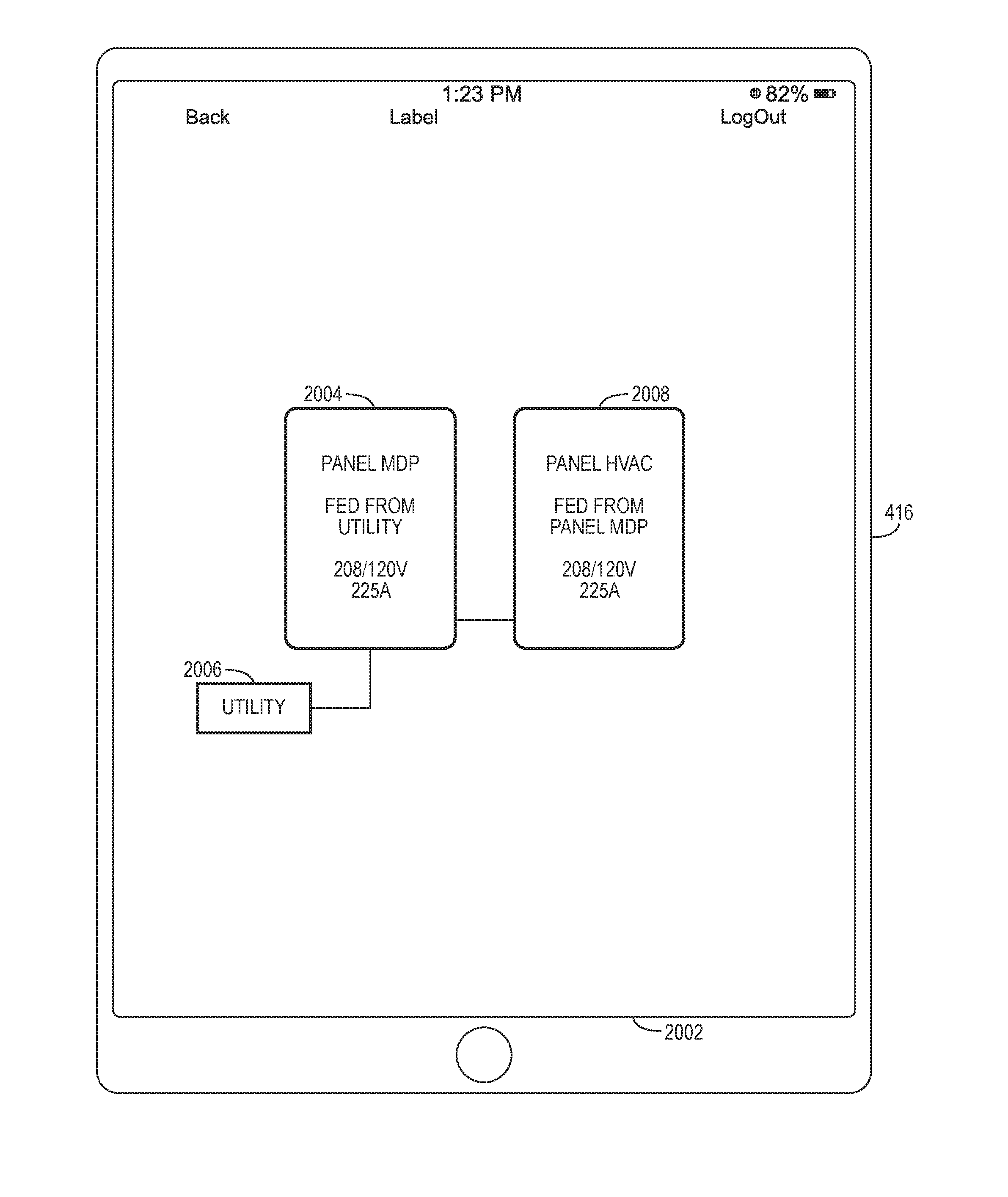

Dynamic coordination of protection devices in electrical distribution systems

ActiveUS20160294179A1Programme controlParameter calibration/settingElectricityDistribution power system

A dynamically coordinatable electrical distribution system includes a plurality of intelligently-controlled protection devices (PDs), a communication and control bus (comm / control) bus, and a central computer. The plurality of intelligently-controlled PDs is configured to protect a plurality of associated electrical loads from faults, developing faults, and other undesired electrical anomalies. Each of the PDs further has electrically adjustable time-current characteristics. The intelligently-controlled PDs are communicatively coupled to the comm / control bus and configured to report current data representative of real-time currents flowing through their respective loads to the central computer, via the comm / control bus. The central computer is configured to communicate with the plurality of PDs over the comm / control bus and dynamically coordinate the time-current characteristics of the plurality of PDs based on the current data it receives from the PDs.

Owner:ATOM POWER INC

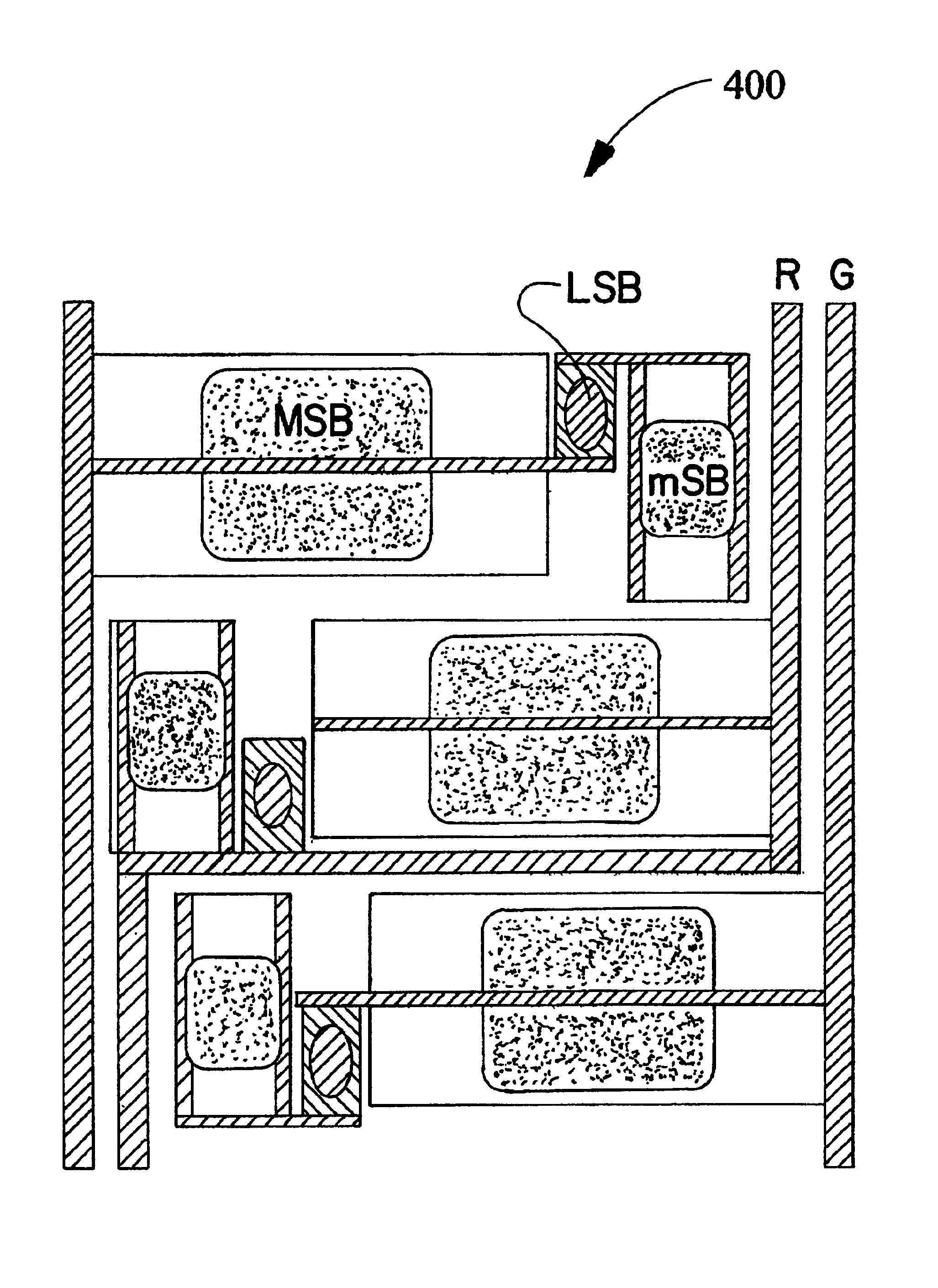

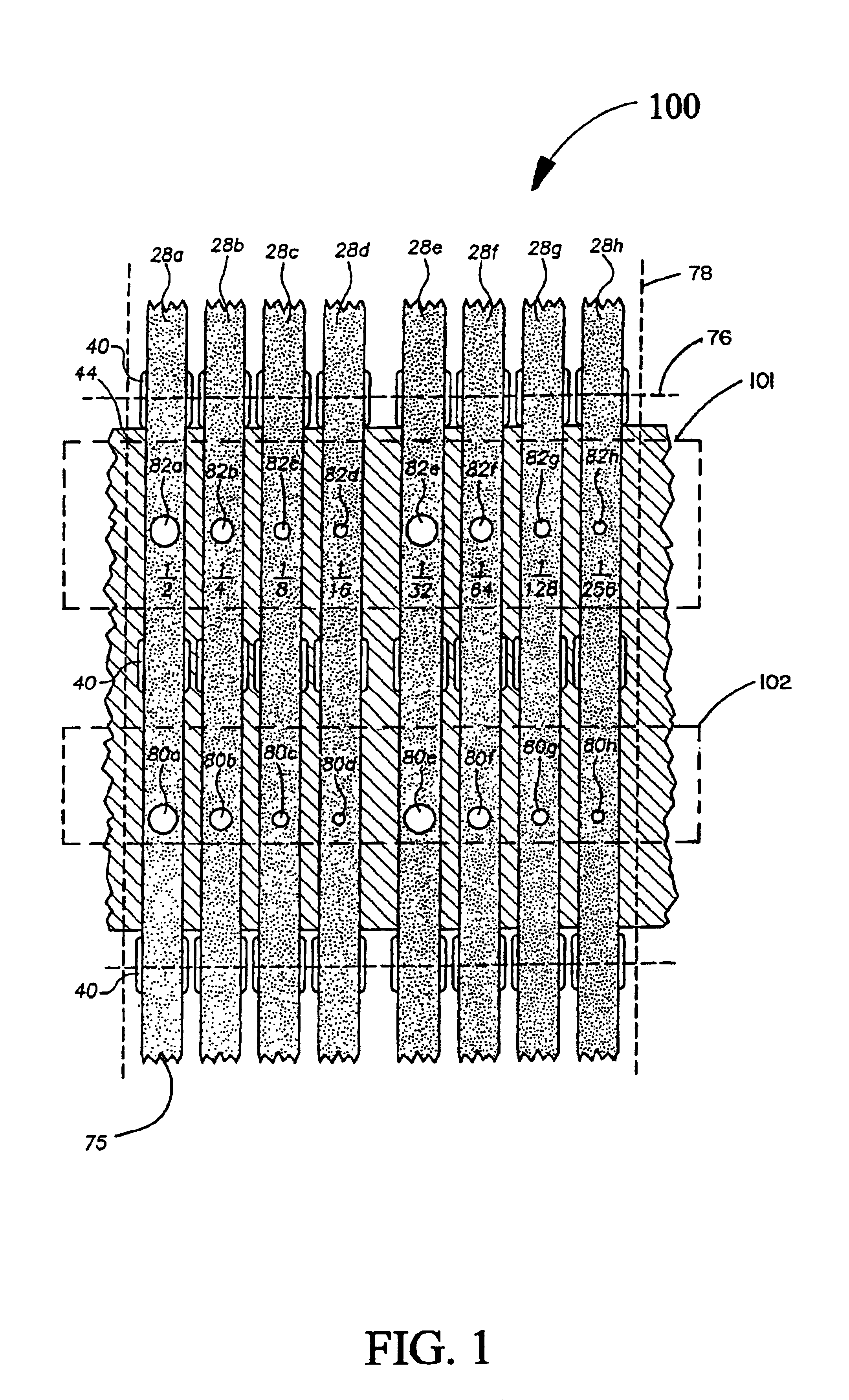

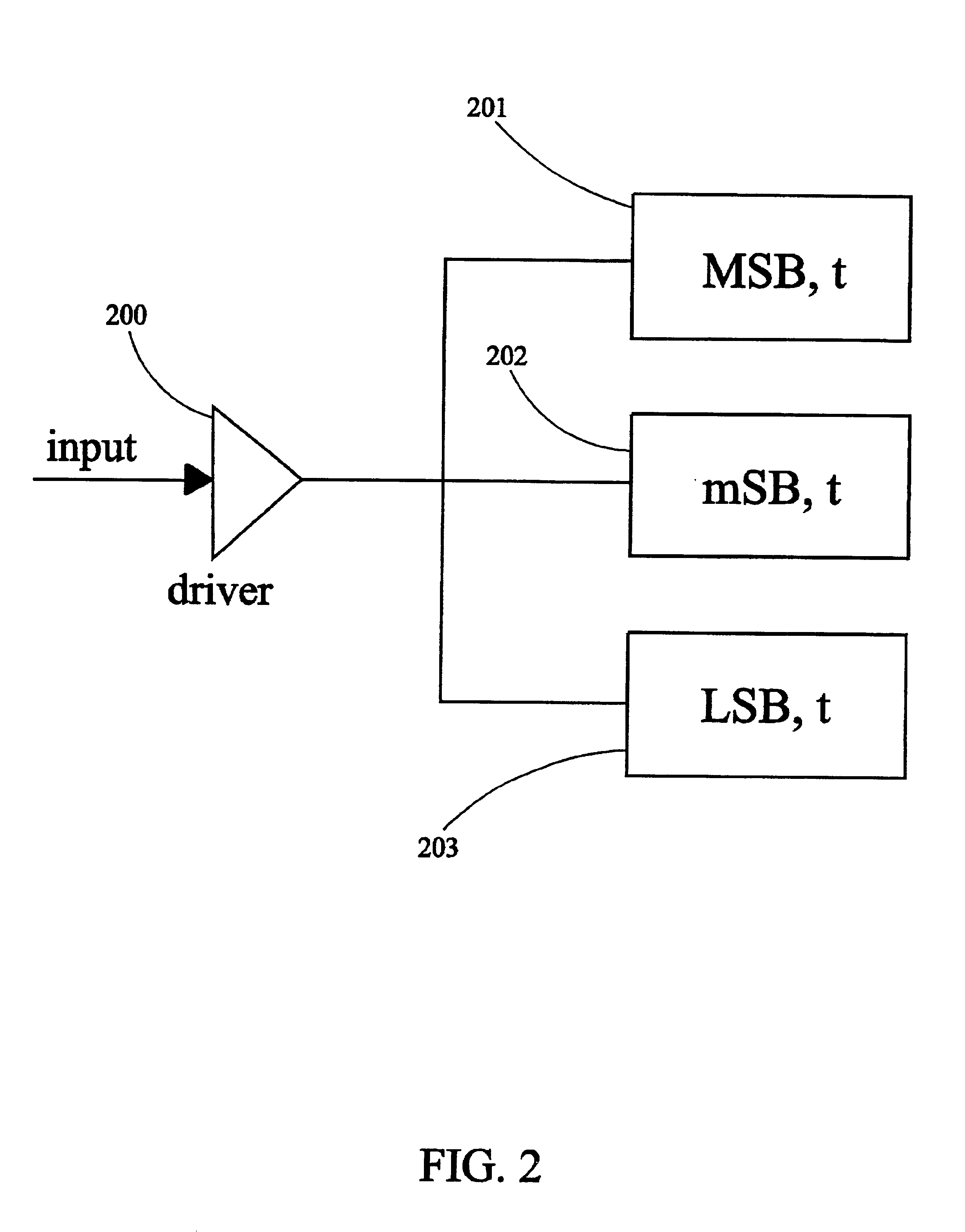

Method and apparatus for reducing driver count and power consumption in micromechanical flat panel displays

InactiveUS6879307B1Reducing driver countCathode-ray tube indicatorsInput/output processes for data processingEngineeringBiological activation

A micromechanical panel display driver is shown in which only one driver and control bus are needed for each color. Furthermore, the elements are made with uniform film thicknesses, thereby minimizing the number of steps needed to fabricate the display. Here 6 bits are provided with temporal and aperture weighting. The use of temporal weighting generally requires the activation of most pixels twice / frame, which consumes considerable power. It should also be possible to eliminate temporal weighting by redistributing the contact area into a larger number of aperture weights and by adding a row electrode. Here pixels are activated only in response to a charge in the image. This generally reduces the drive power, since many pixels in a typical image do not change from frame to frame.

Owner:THE GOVERNMENT OF THE US SEC THE AIR FORCE

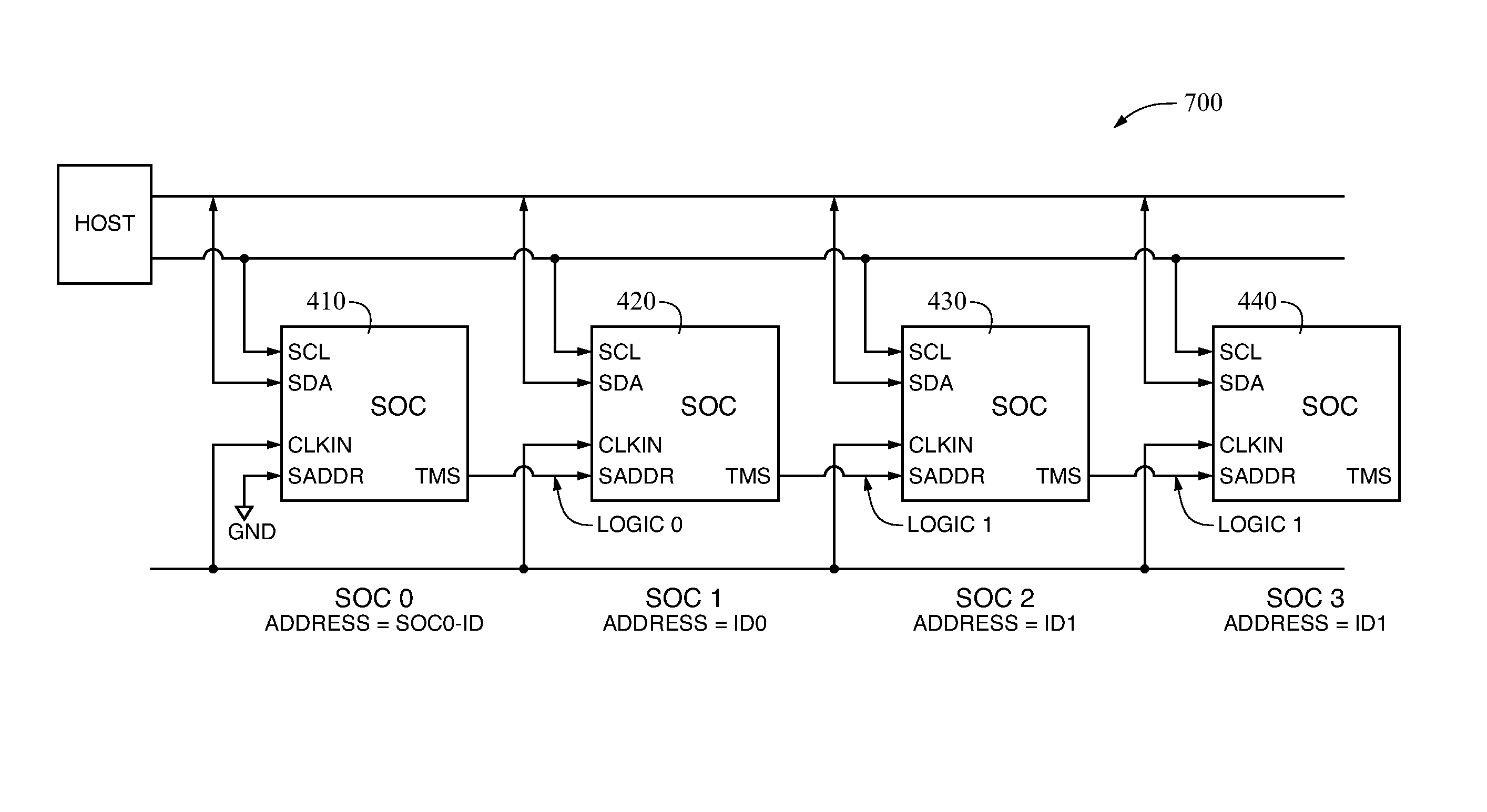

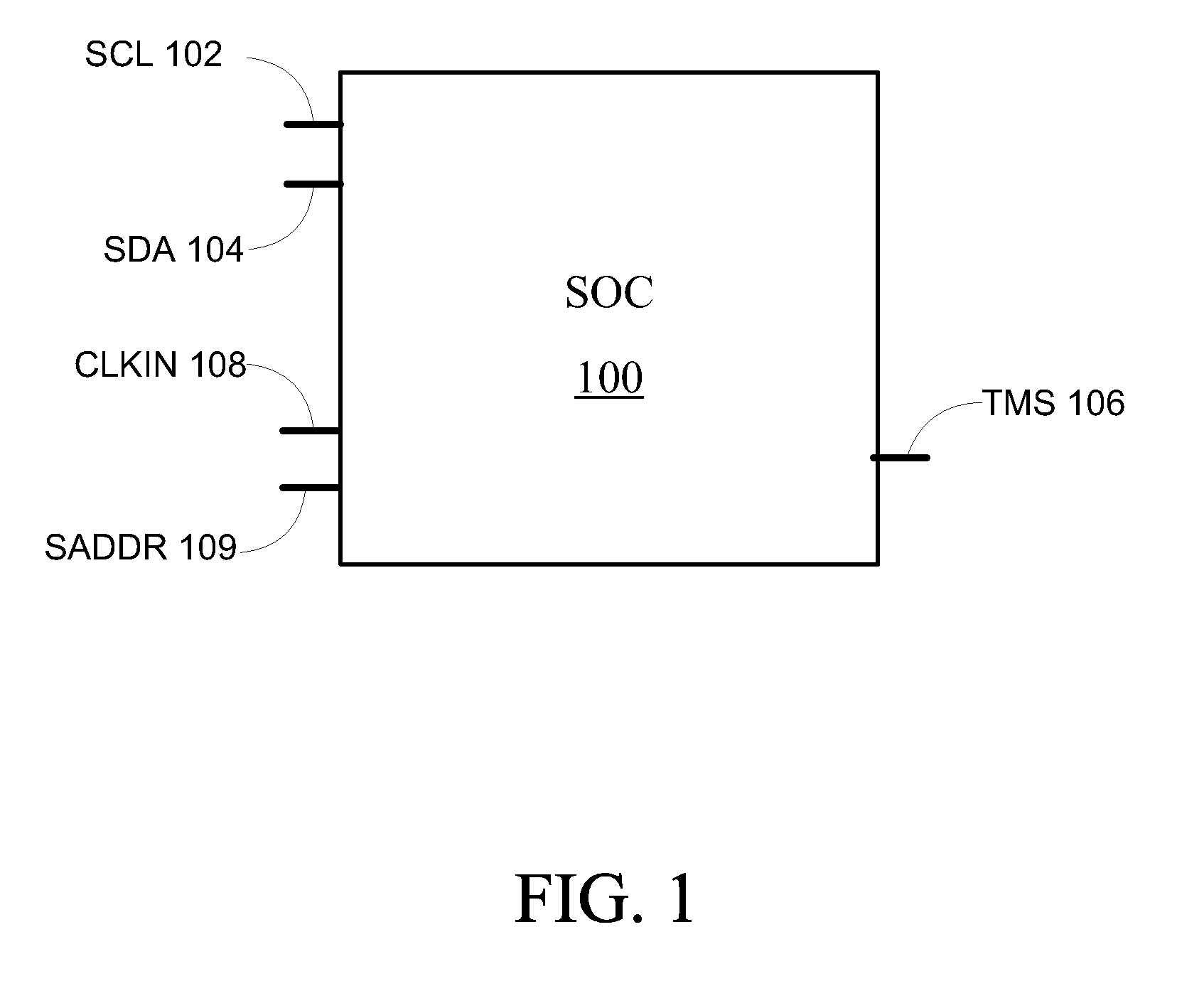

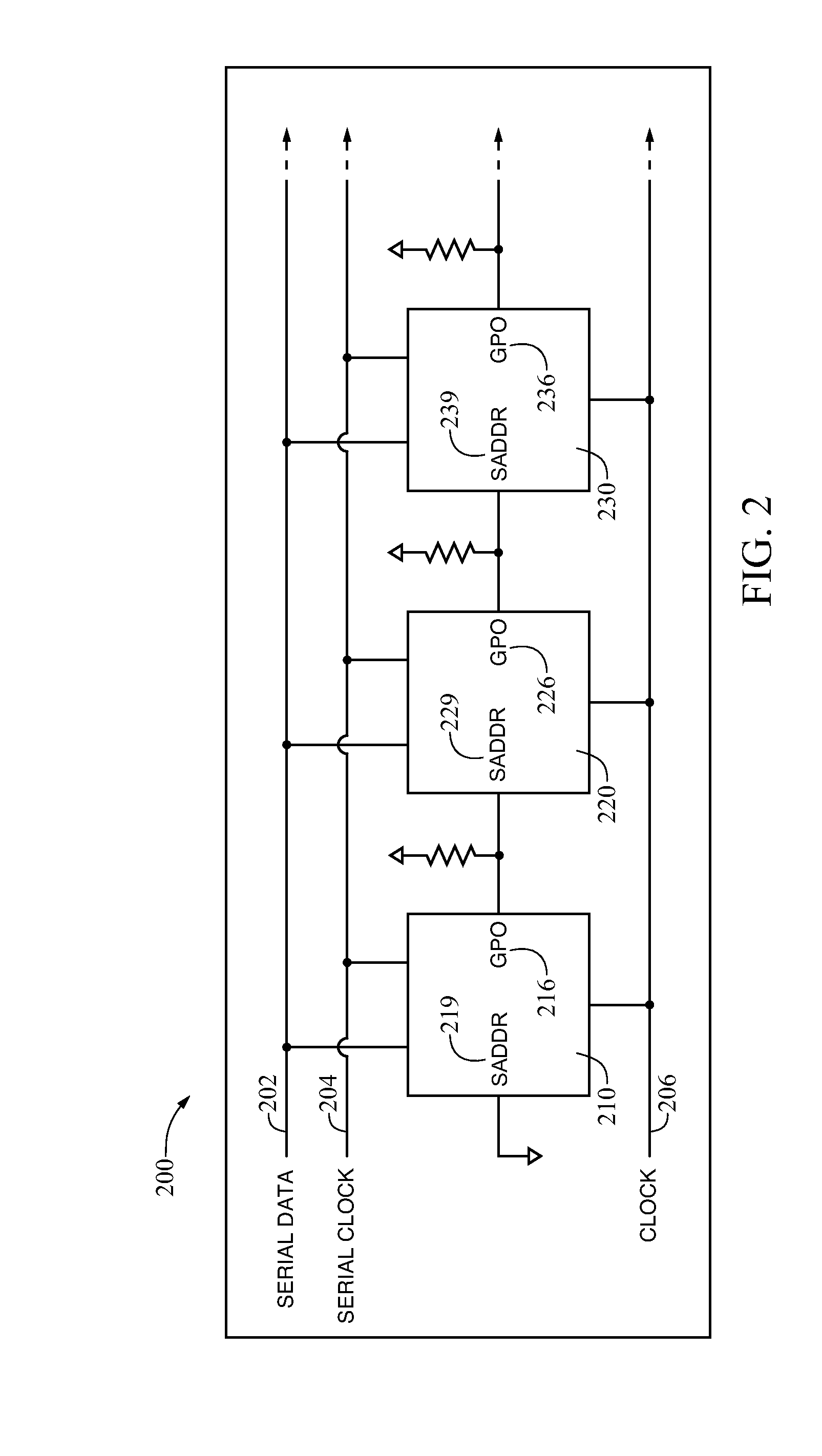

Systems and methods for addressing and synchronizing multiple devices

ActiveUS8205017B2Circuit arrangementsInput/output processes for data processingComputer hardwareVia device

This is generally directed to systems and methods for control of two or more devices through a shared control bus. For example, the devices can be coupled to a host system through the control bus. In some embodiments, the devices can be configured by the host system through address select pins of the devices. For example, the host system can sequentially program each device to change its default address to a unique address. In some embodiments, an event can be propagated through each device, thus resulting in each device receiving the event at a different time. In some embodiments, configuration by the host system can include programming each device with a value representing its own position in the chain. In this case, a device can use this value to delay its response to the event, thereby allowing all the devices in the chain to respond to the event simultaneously.

Owner:SEMICON COMPONENTS IND LLC

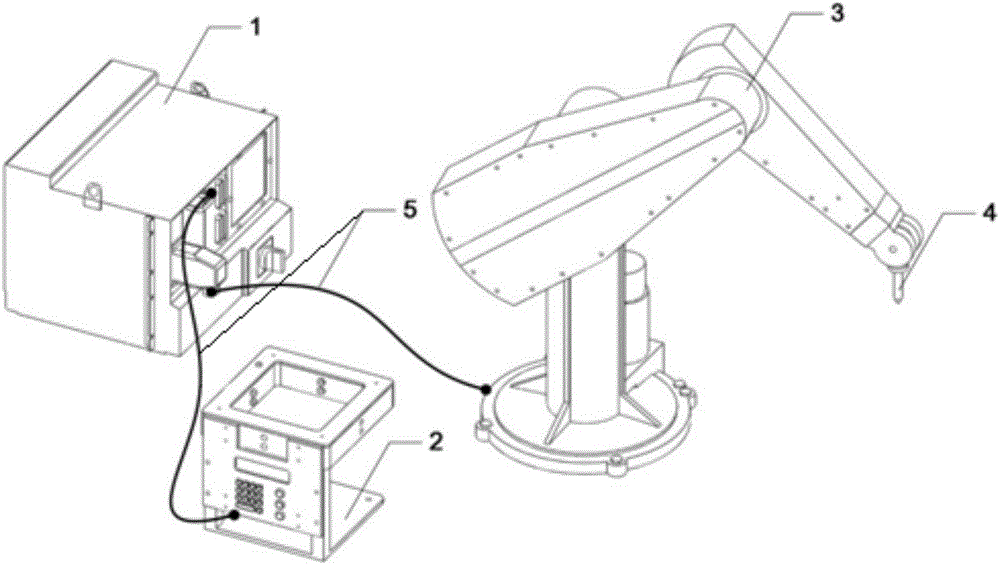

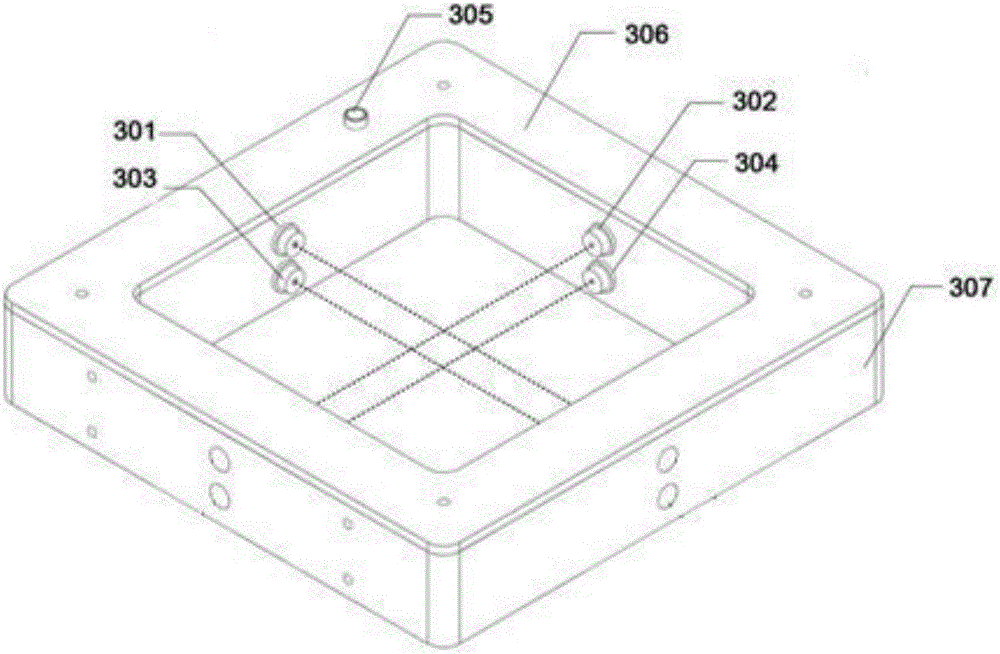

TCP online quick calibration method and device applied to industrial robot

ActiveCN105945948AImprove working accuracyReduce downtime for maintenanceProgramme controlProgramme-controlled manipulatorProduction lineComputer science

The invention discloses a TCP online quick calibration method and device applied to an industrial robot. The device comprises a control cabinet, a TCP calibration device, the industrial robot, a terminal tool and control buses; the control cabinet is separately connected with the TCP calibration device and the industrial robot through the control buses; the terminal tool is mounted on the industrial robot; the TCP calibration device includes a TCP detecting device, a calibration controller and a mounting base; the TCP detecting device is fixedly mounted on one side of the industrial robot through the mounting base; and a measuring plane is parallel to a XOY plane of an industrial robot base coordinate system. According to on-off signals of a correlation photoelectric sensor, the pose data of a flange is recorded, and the pose deviations of the terminal tool in X / Y axis and Z axis directions are calculated and compensated; and through multiple times of repeated operations, the TCP calibration errors are reduced, the operation precision of the industrial robot is effectively improved, the stop maintenance time of the industrial robot is reduced, and the automation degree of an industrial production line is improved.

Owner:南京速之海自动化设备有限公司

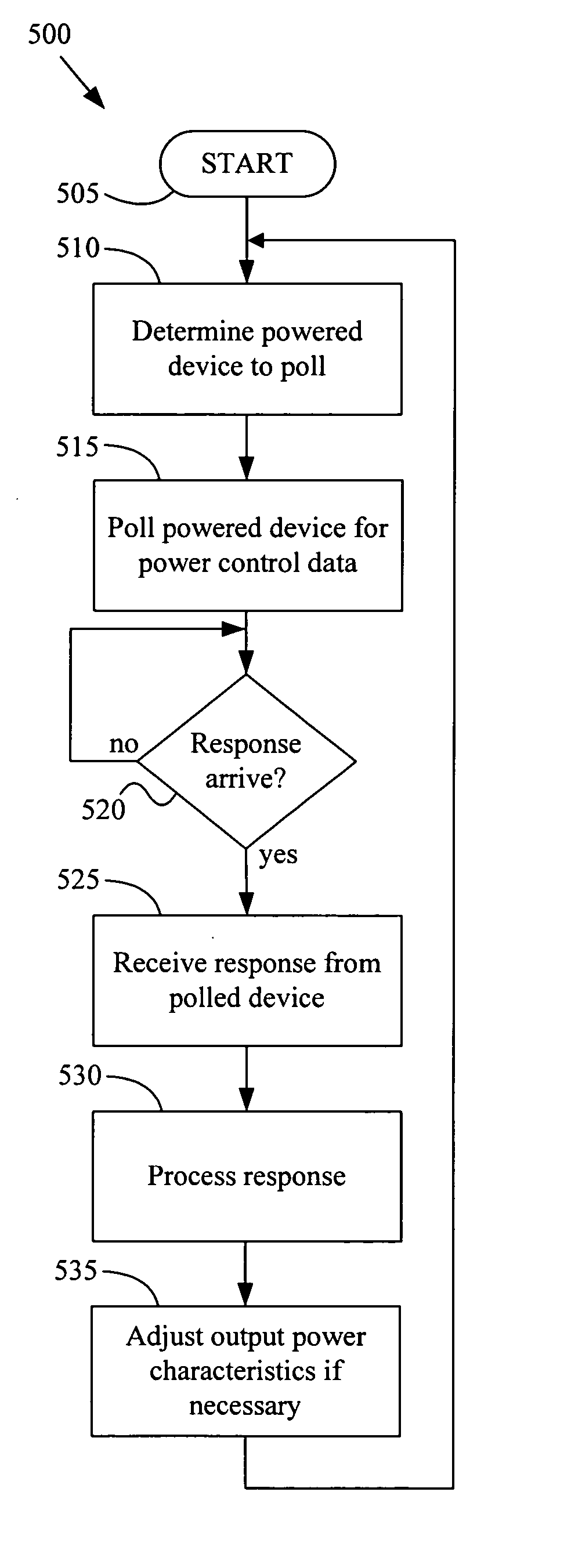

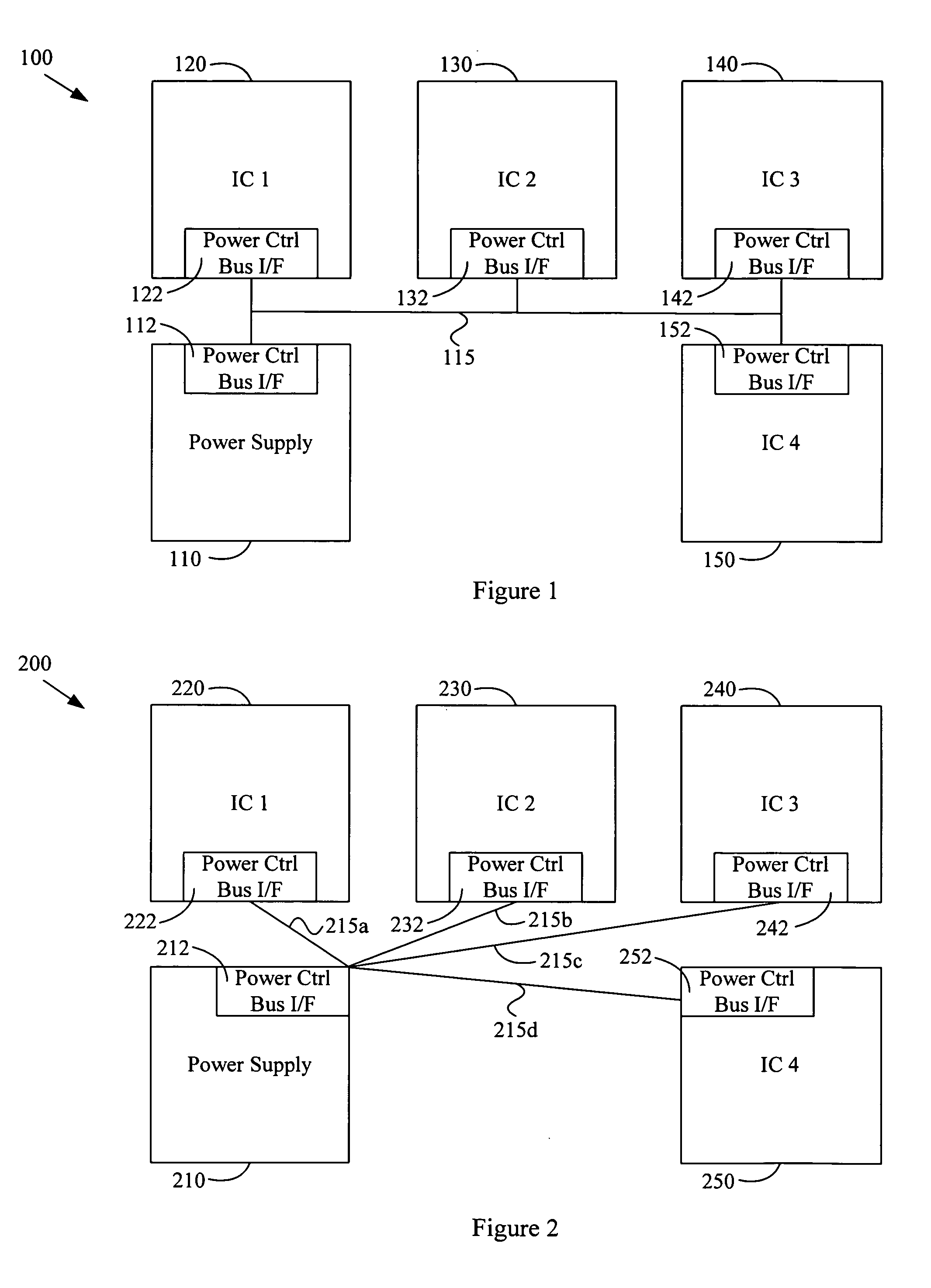

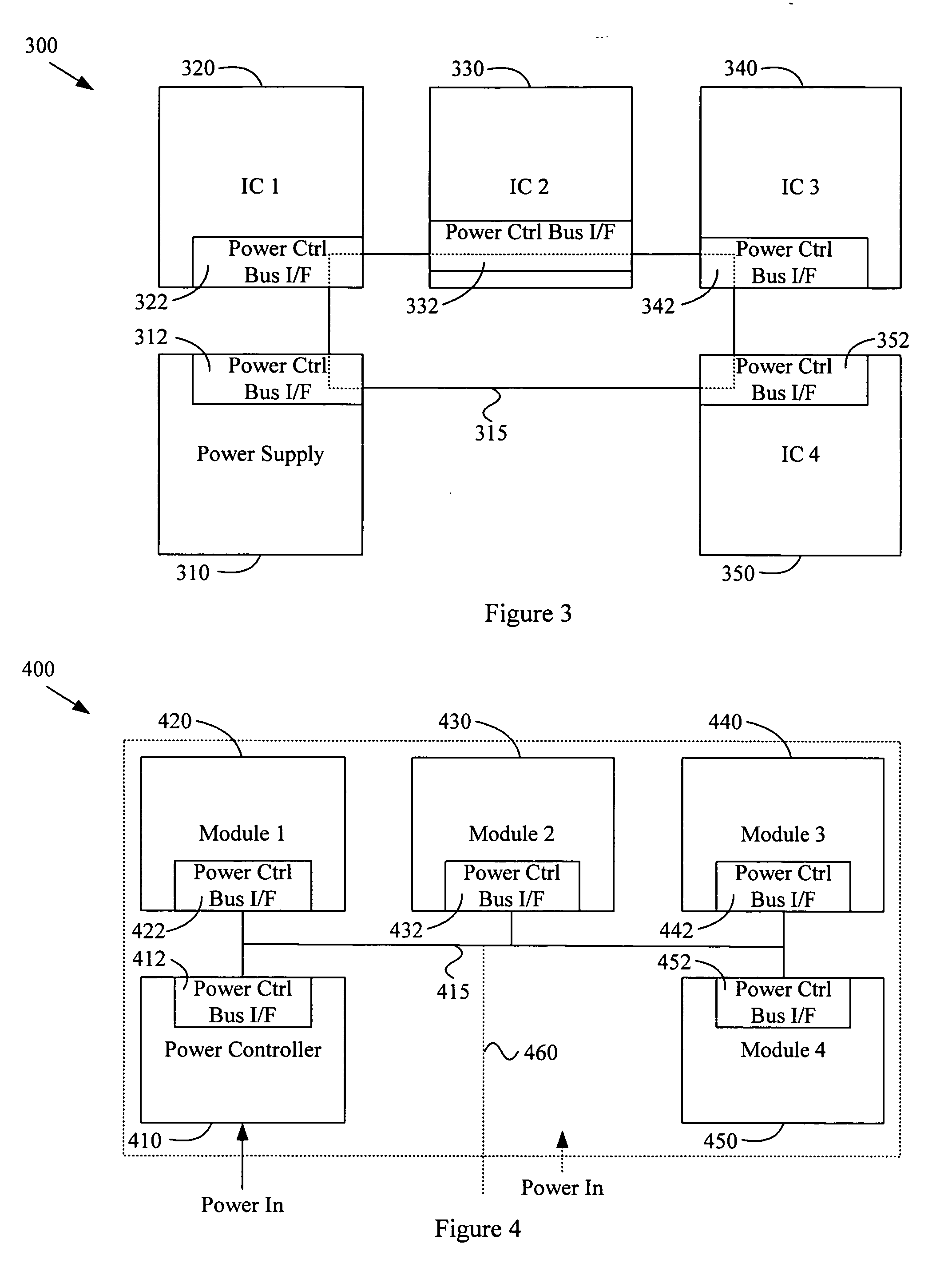

Power control bus

ActiveUS20050289374A1Volume/mass flow measurementPower supply for data processingControl dataEngineering

A circuit and method utilizing a power control data bus for implementing power control. Various aspects of the present invention provide an electrical circuit that comprises a power supply circuit that outputs electrical power. The electrical circuit may also comprise an integrated circuit that receives electrical power from the power supply circuit. The electrical circuit may also comprise a power control data bus, which communicatively couples a power control data bus interface of the power supply circuit and a power control data bus interface of the integrated circuit. The power control data bus may, for example, carry power control data between the integrated circuit and the power supply circuit. Various aspects of the present invention also provide a method that comprises communicating power control data over a power control data bus and utilizing the power control data to control characteristics of electrical power provided to an integrated circuit or module.

Owner:AVAGO TECH INT SALES PTE LTD

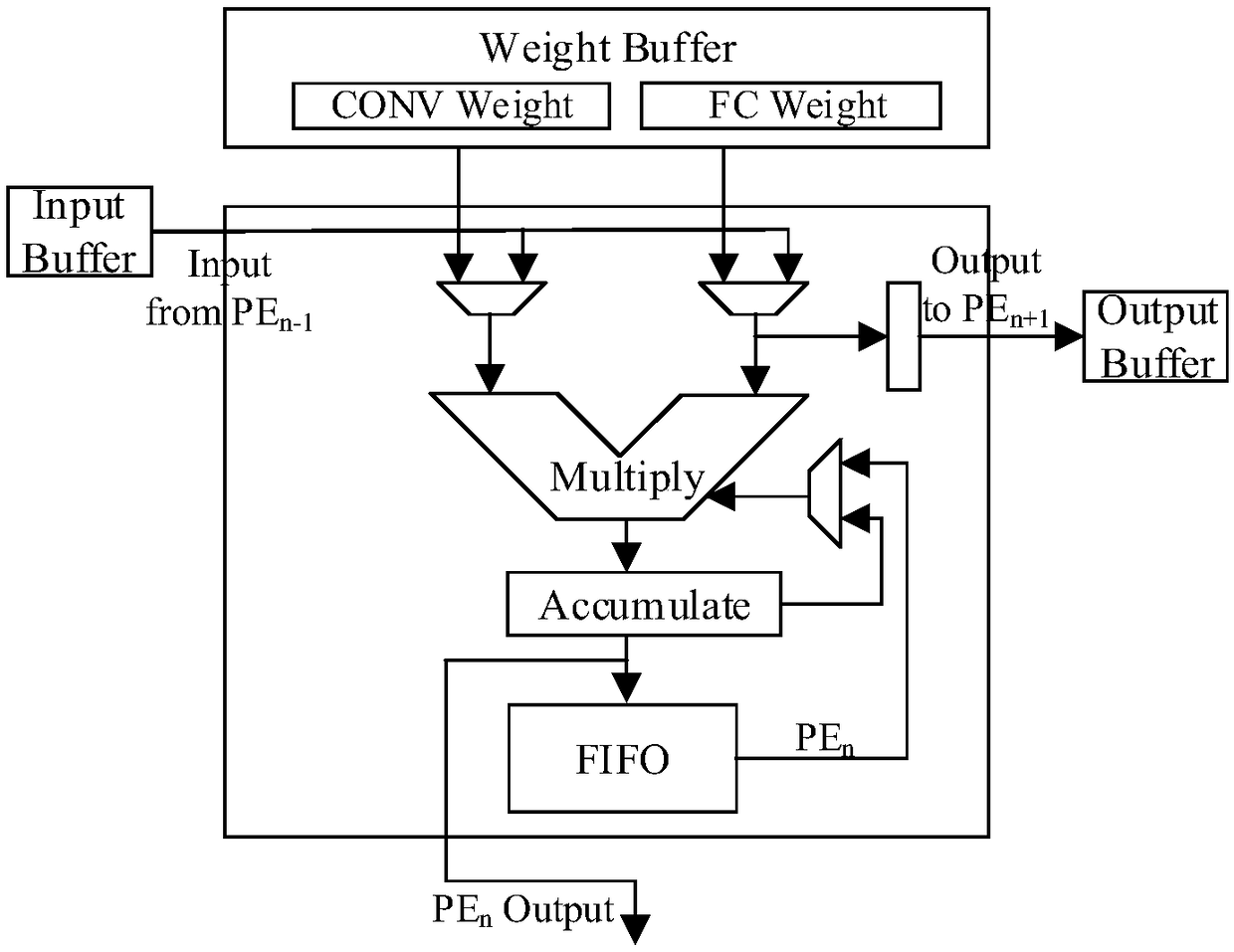

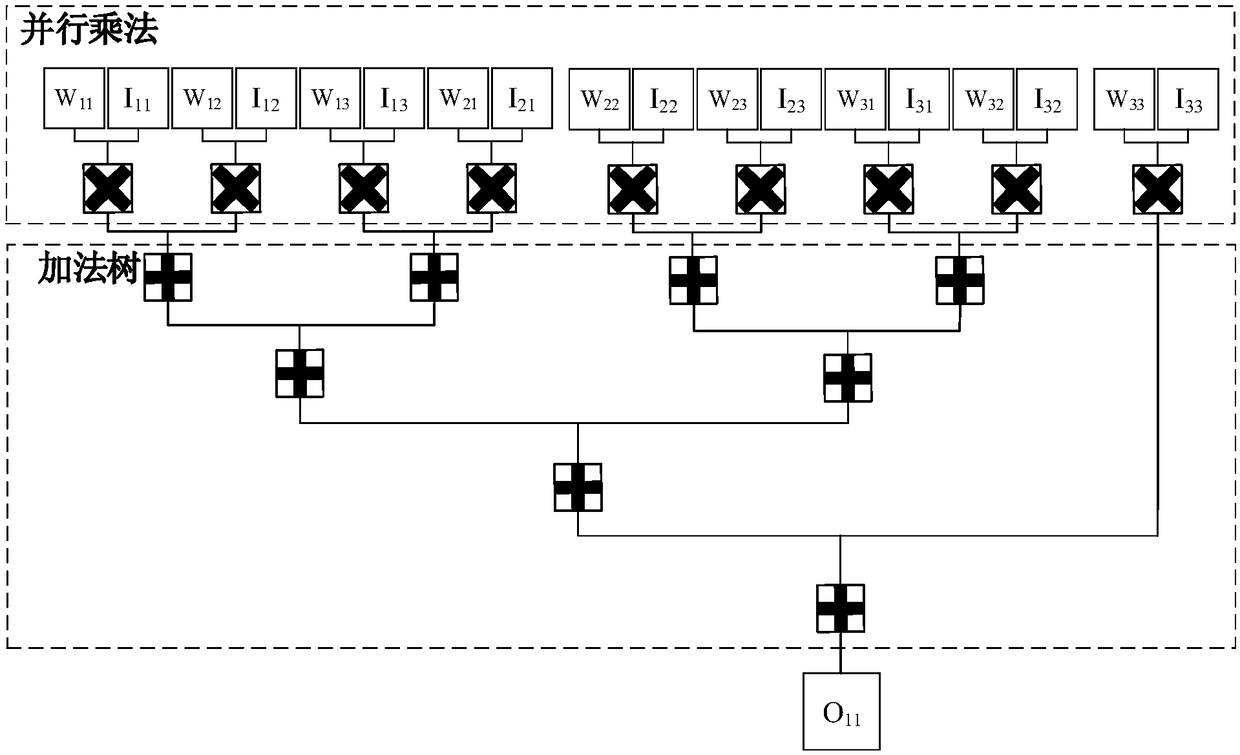

Convolutional-neural-network accelerating system based on field-programmable gate array

InactiveCN108665059AImprove resource utilizationImprove performanceNeural architecturesProduction lineExternal storage

The invention discloses a convolutional-neural-network accelerating system based on a field-programmable gate array. The convolutional-neural-network accelerating system comprises a general processor,the field-programmable gate array, a storage module, a data bus and a control bus, wherein the general processor is a soft core of a reduced instruction set, and is responsible for starting an accelerator, being in communication with a host terminal, conducting time measurement and the like; a DDR3 DRAM serves as an external storage of the accelerator system; an AXI4-Lite bus is used for demand transmission, and an AXI4 bus is used for data transmission; the field-programmable gate array comprises multiple processing engines (PE), and each processing engine adopts a most-suitable fragment unfolding strategy to correspond to calculation of one layer in the convolutional neural network; all the processing engines are mapped onto a same FPGA chip, and therefore different layers can simultaneously work in a production line mode. Compared with an existing convolutional-neural-network accelerating system, the convolutional-neural-network accelerating system based on the field-programmable gate array can obtain higher energy efficiency benefit.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

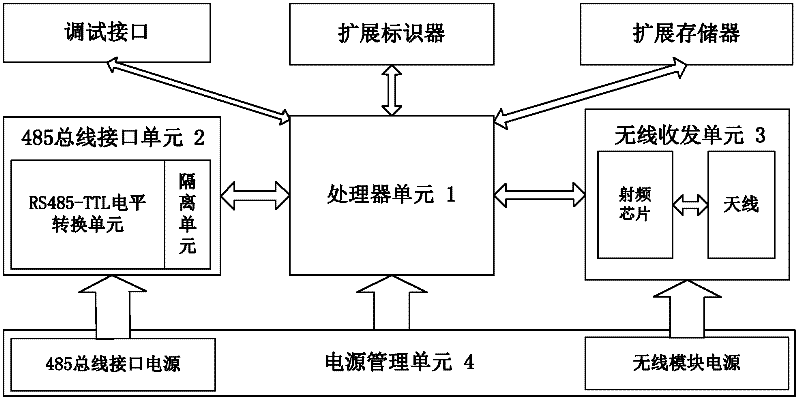

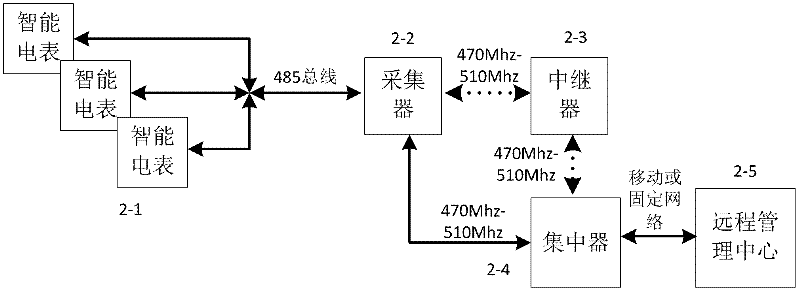

Gatherer device of wireless ad-hoc network meter reading system, and operation method

InactiveCN102693615ALow investment costGood value for moneyTransmission systemsElectricityPower Management Unit

A gatherer device of wireless ad-hoc network meter reading system comprises a processor unit, a 485 bus interface unit, a wireless transmitting-receiving unit, and a power supply managing unit; wherein the processor unit is responsible for operation and control of the whole device, the 485 bus interface unit is used for connecting one or multiple electric meters, the wireless transmitting-receiving unit is responsible for interacting data and commands with a concentrator of the wireless ad-hoc network meter reading system, and the power supply managing unit supplies power for the whole device. An operation method of the gatherer device comprises that a command is received by the wireless transmitting-receiving unit and transmitted to the processor unit for processing, that the processor unit sends a request frame to an electric meter, that the processor unit receives a response frame from the electric meter and analyzes the response frame to acquire information of electricity consumption, and that finally the information of electricity consumption is returned to the concentrator through the wireless transmitting-receiving unit. The device and the method in the invention solve problems that the prior micropower wireless communication meter reading manners have much channel interferences, and are relatively low in security, relatively short in communication distances and not well in penetrating capabilities. Furthermore, the device has the advantages of low cost, high cost performance, good instantaneity, safety and reliability, and use and maintenance conveniences.

Owner:NANJING TOP NODES SENSOR NETWORKS TECH +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com