Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1227 results about "Complex programmable logic device" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A complex programmable logic device (CPLD) is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both. The main building block of the CPLD is a macrocell, which contains logic implementing disjunctive normal form expressions and more specialized logic operations.

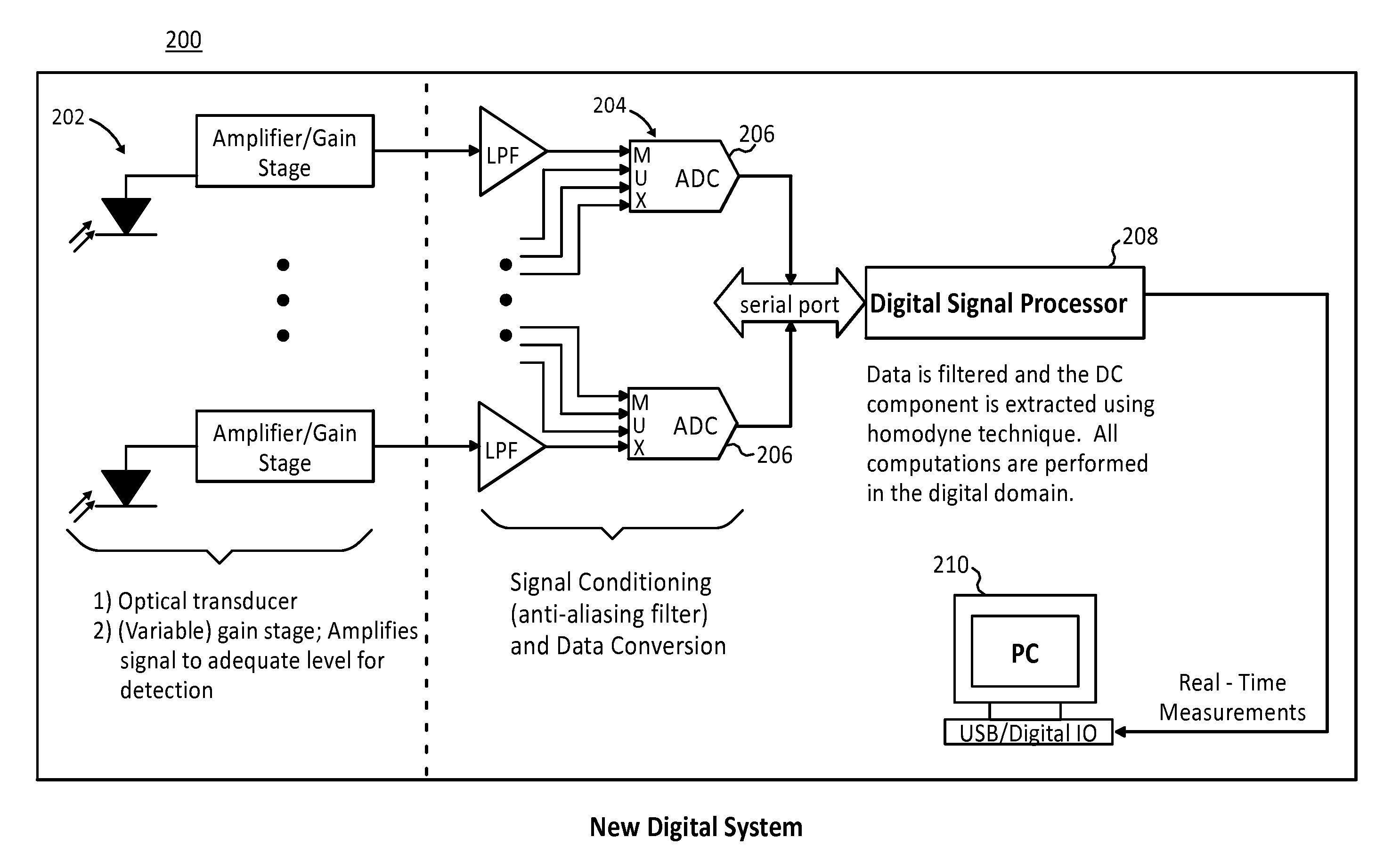

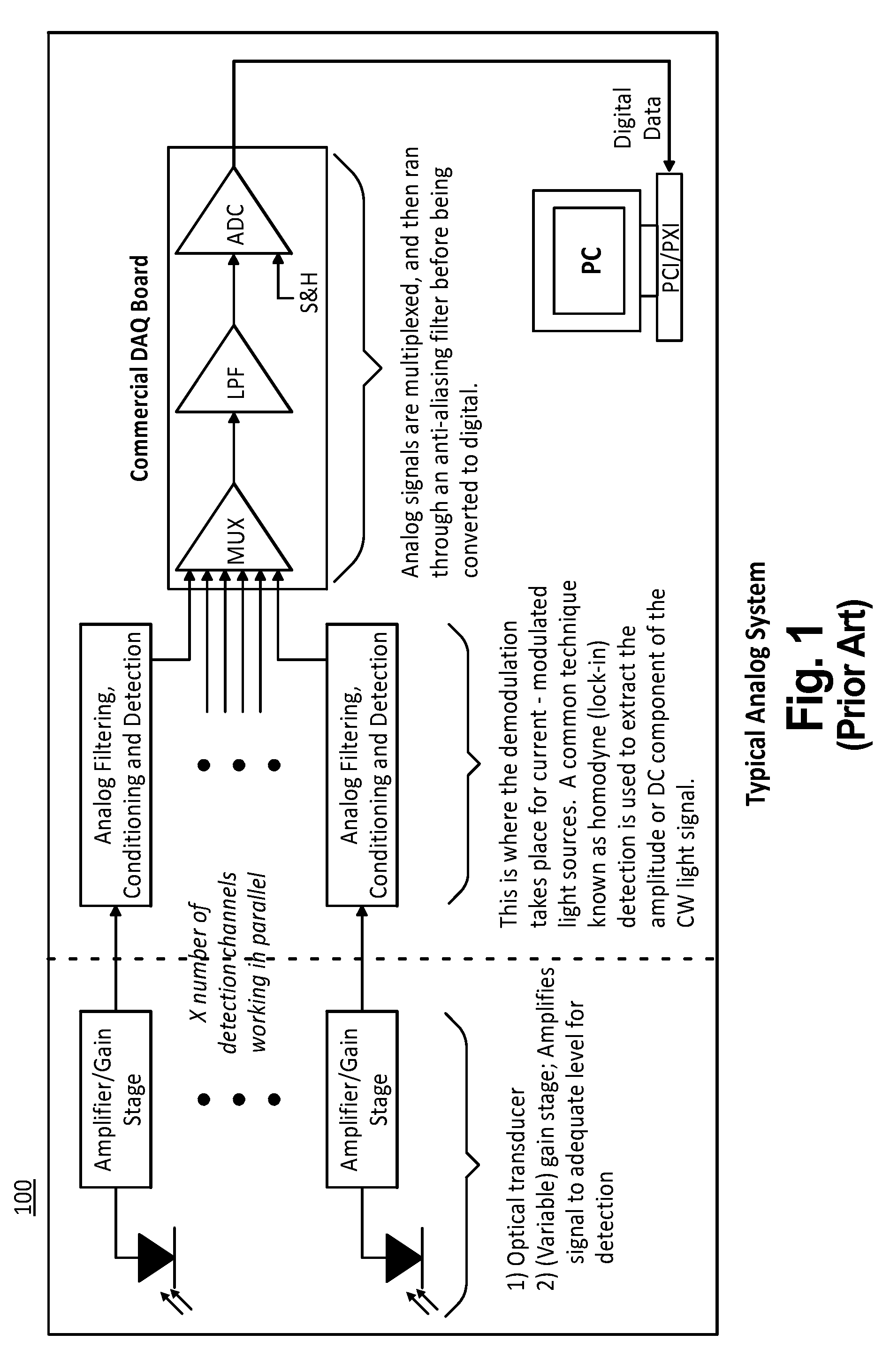

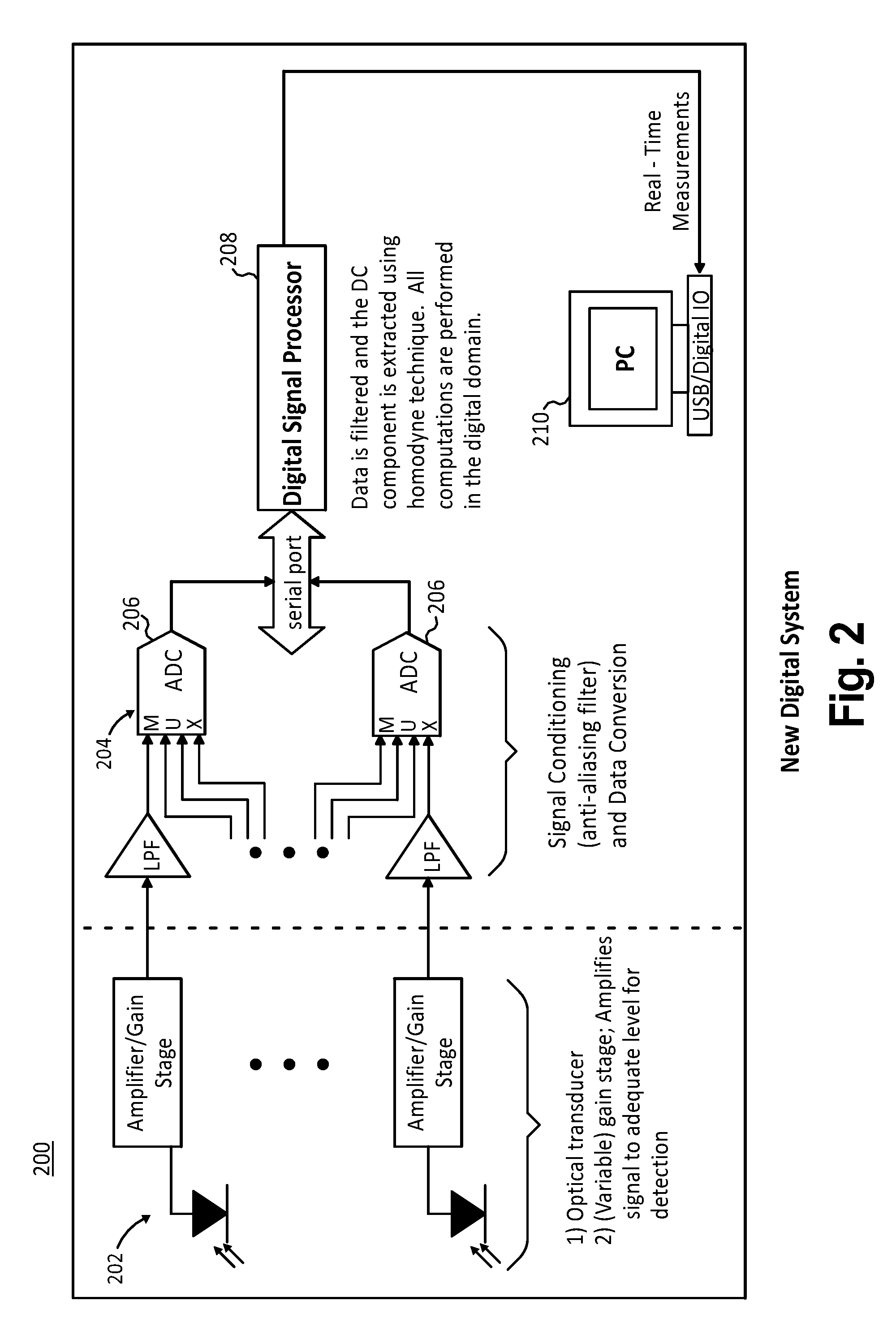

Digital signal processor-based detection system, method, and apparatus for optical tomography

ActiveUS7463362B2Easy accessScattering properties measurementsUsing optical meansDigital signal processingAverage filter

The present invention provides systems, methods and apparatuses that perform digital detection for use in optical tomography. Methods and systems are provided in which digital lock-in detection is performed using an algorithm that employs a phase-independent quadrature technique. Methods and systems are provided in which a unique manipulation of an ordinary averaging filter optimized for sources discrimination and the consequent sampling constraints is presented as a novel filtering scheme for the lock-in detection. Systems and apparatuses are provided which include a digital signal processor which performs digital lock-in detection and an integrated complex programmable logic device for timing control. Apparatuses are provided which include an instrument having an integrated digital signal processor for performing digital processing and detection for use in optical tomography.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK +1

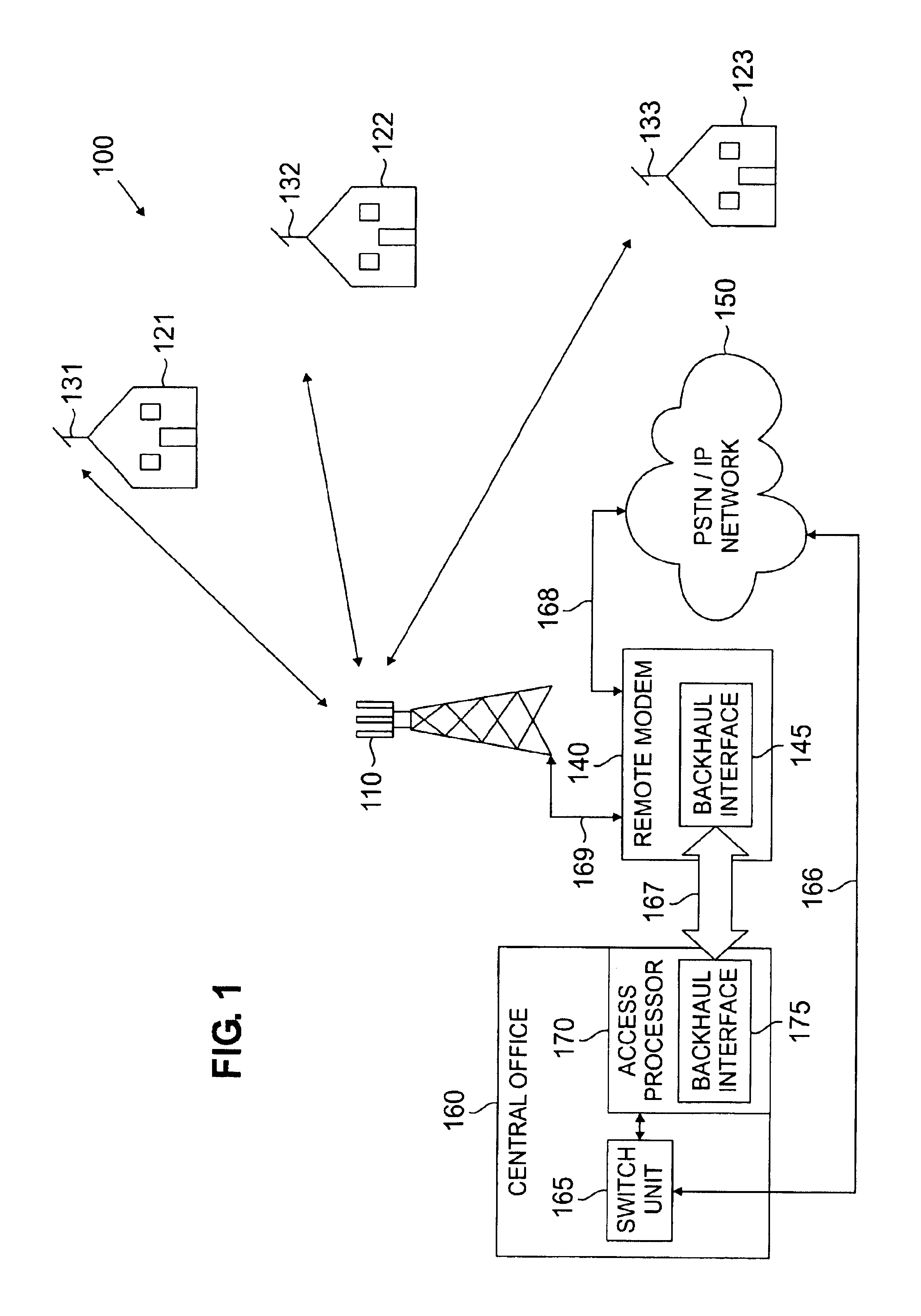

System and method for providing an improved common control bus for use in on-line insertion of line replaceable units in wireless and wireline access systems

InactiveUS6925516B2Error preventionDigital data processing detailsModem deviceProgrammable logic device

There is disclosed a system and method for providing an improved common control bus for use in the on-line insertion of line replaceable units (such as circuit board cards) into a backplane of a processor shelf, a modem shelf, or a similar type of equipment. The present invention increases the number of device locations that a common control bus can access. The present invention comprises a complex programmable logic device on a circuit board card that is coupled to a common control bus. The complex programmable logic device is capable of selectively coupling to the common control bus each one of a plurality of device locations on the circuit board card. The complex programmable logic device controls data access to and from each device that is coupled to the common control bus.

Owner:RAZE TECH

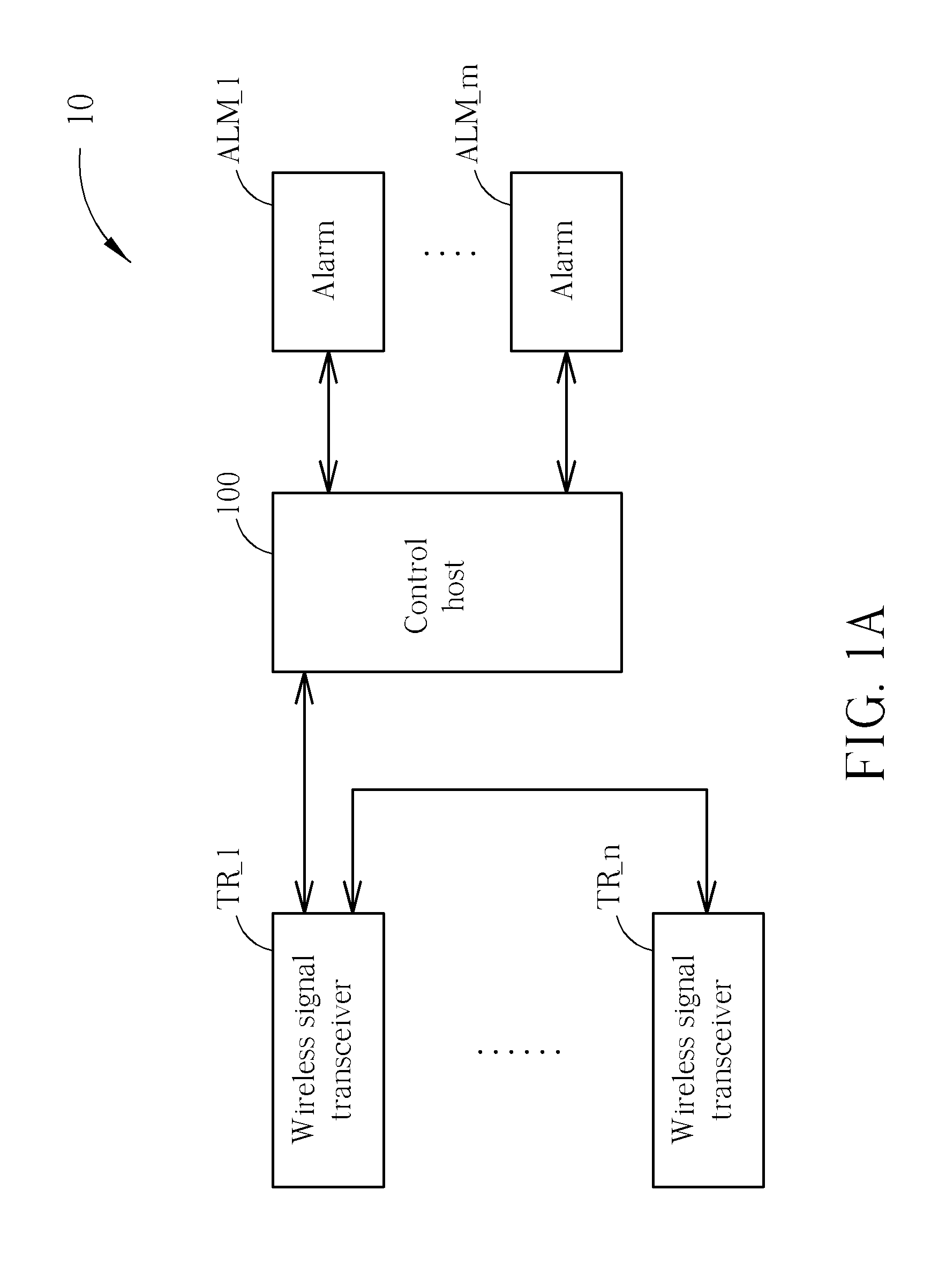

Wireless Signal Transceiver and Blind Spot Detection System

InactiveUS20120154173A1Anti-collision systemsRadio wave reradiation/reflectionDigital signal processingTransceiver

A wireless signal transceiver for a blind spot detection system includes a first substrate, a radio-frequency processing unit formed on the first substrate for transmitting a wireless signal and receiving a reflecting signal of the transmitted wireless signal, and a complex programmable logic device controlled by a digital signal processor for controlling operations of the radio-frequency processing unit according to at least a control command of the digital signal processor, so as to detect whether an object exists within a specific range.

Owner:WISTRON NEWEB

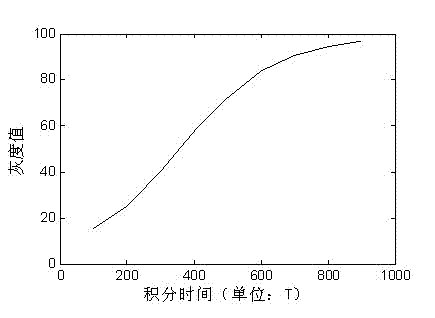

Infrared focal plane array blind pixel detection method based on integral time adjustment

The invention requests to protect an infrared focal plane array blind pixel detection method based on integral time adjustment, belongs to the technical field of signal detection. Aiming at the condition limitation that the traditional blind pixel detection method based on a standard black body radiation source depends on an expensive black body and a fixed dark room and the blind pixel detectioncannot be performed as required anytime anywhere, the invention provides a method of flexibly and conveniently adjusting a response output value of the infrared focal plane array in different integral time through a CPLD (complex programmable logic device) programming, computing a response rate of each detection unit according to the response output value and detecting the blind pixel according to the blind pixel definition. The detection unit response output value, the blind pixel detection and the blink pixel compensation in different integral time are recorded. The method provided by the invention has a simple implementation process, and has application and spread value in the IRFPA (infrared focal plane array) blind pixel detection.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

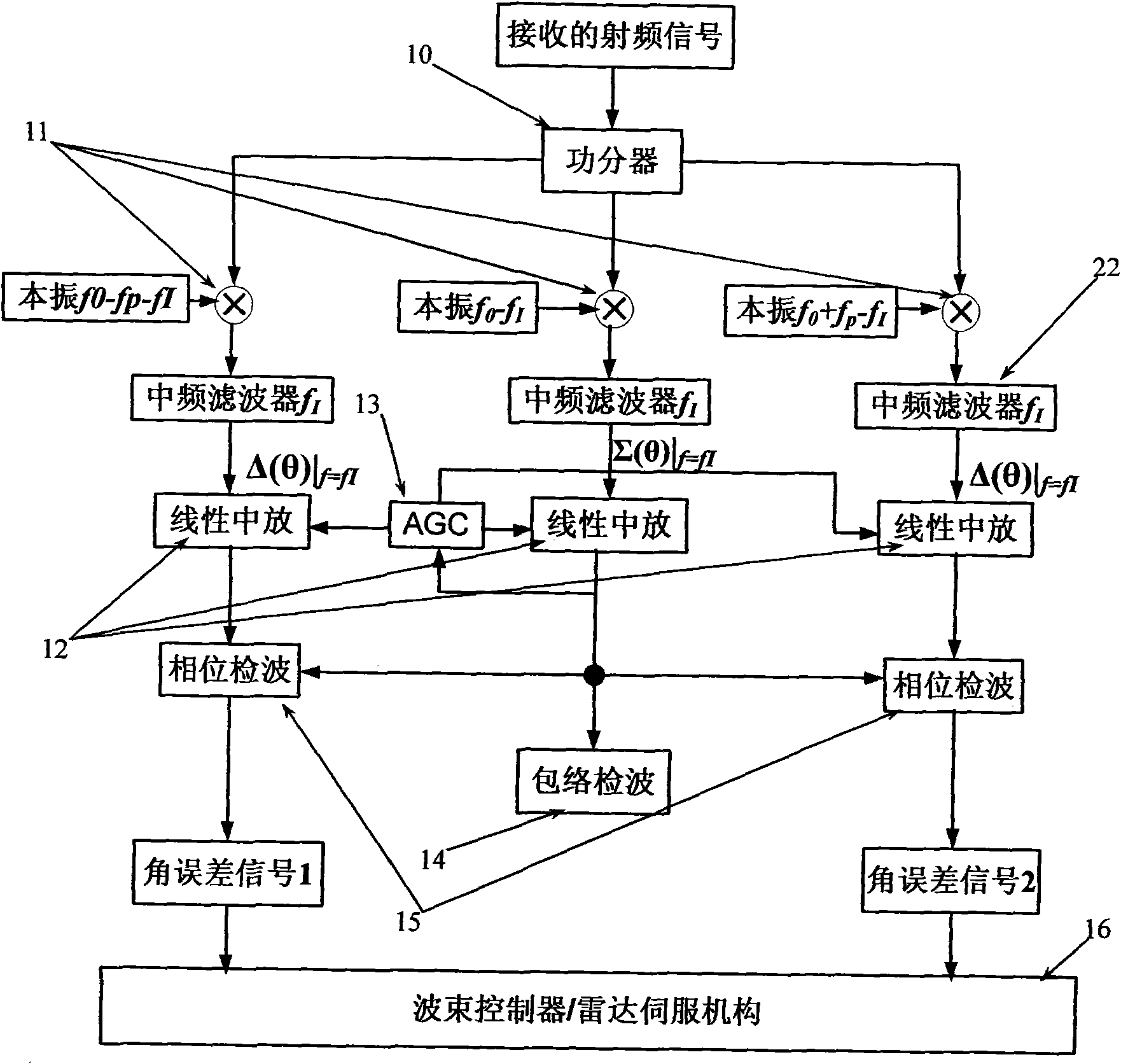

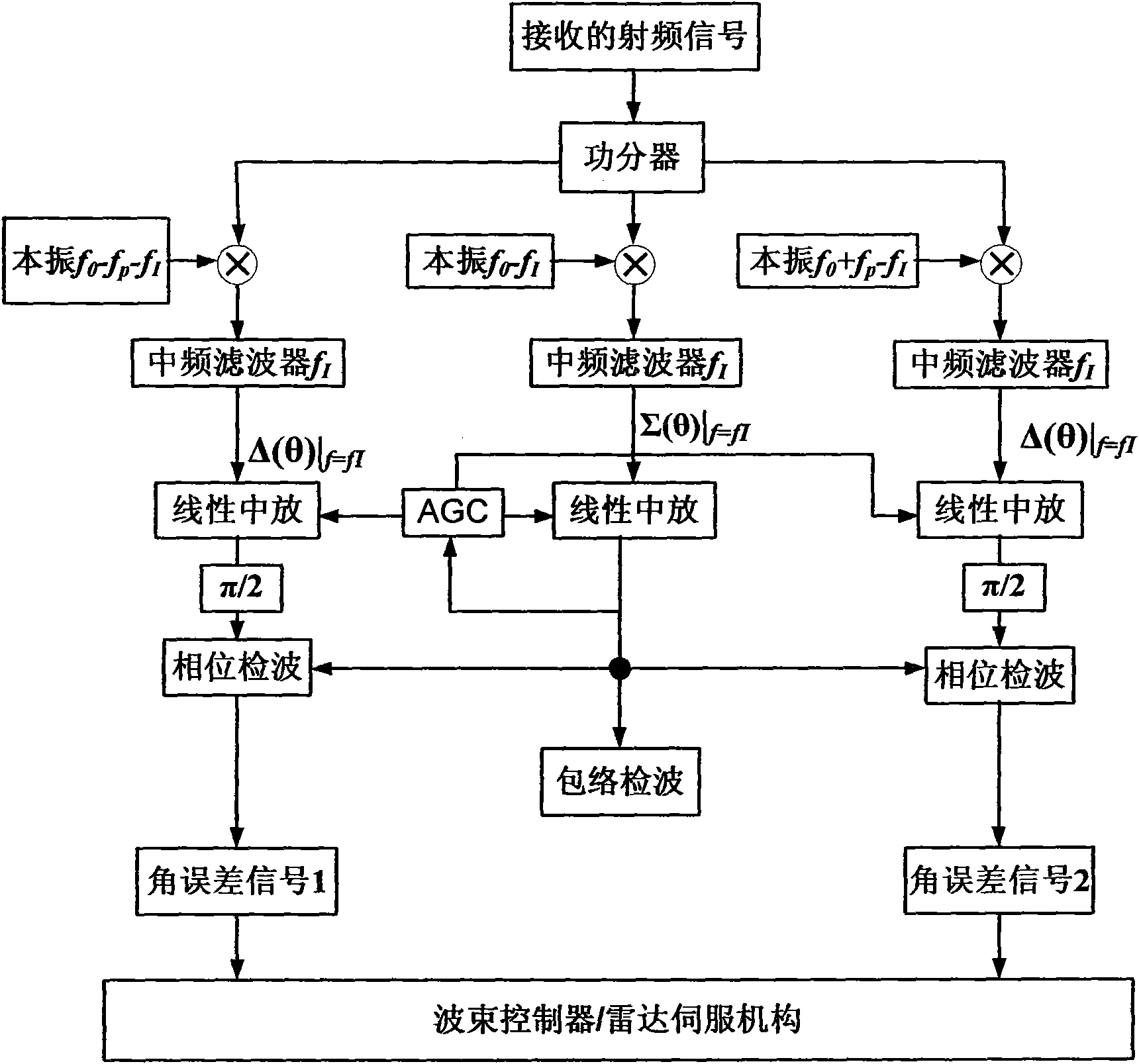

Monopulse radar system based on time modulation antenna array

InactiveCN101587188ACompact structureBeam performance is easily adjustableRadio wave reradiation/reflectionRadar systemsIntermediate frequency

The invention discloses a phased array monopulse radar system based on the time modulation antenna array technology. The basic scheme of the invention comprises an antenna array comprising a plurality of array antenna units, a high-speed radio frequency switch controlled by a complex programmable logic device, a radar receiver, and the like; based on the basic scheme, a power-divider, a mixer, and an intermediate frequency amplifier are reasonably added in the radar receiver, and an amplitude detector, a phase detector and the like are reasonably added at a data processing terminal to form various improved schemes of the invention. With the invention, sum beams and difference beams are easily generated simultaneously, therefore, the transmission of simultaneous frequency diversity signals can be easily realized, and difference beams of higher performance (beam gain, null depth, slope of zero, and the like) can be easily obtained. The invention can be widely used in the phased array monopulse radar systems having application background adding radar reconnaissance difficulty of enemy, or used in radar systems of other target angle measurement and precision angle tracking.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

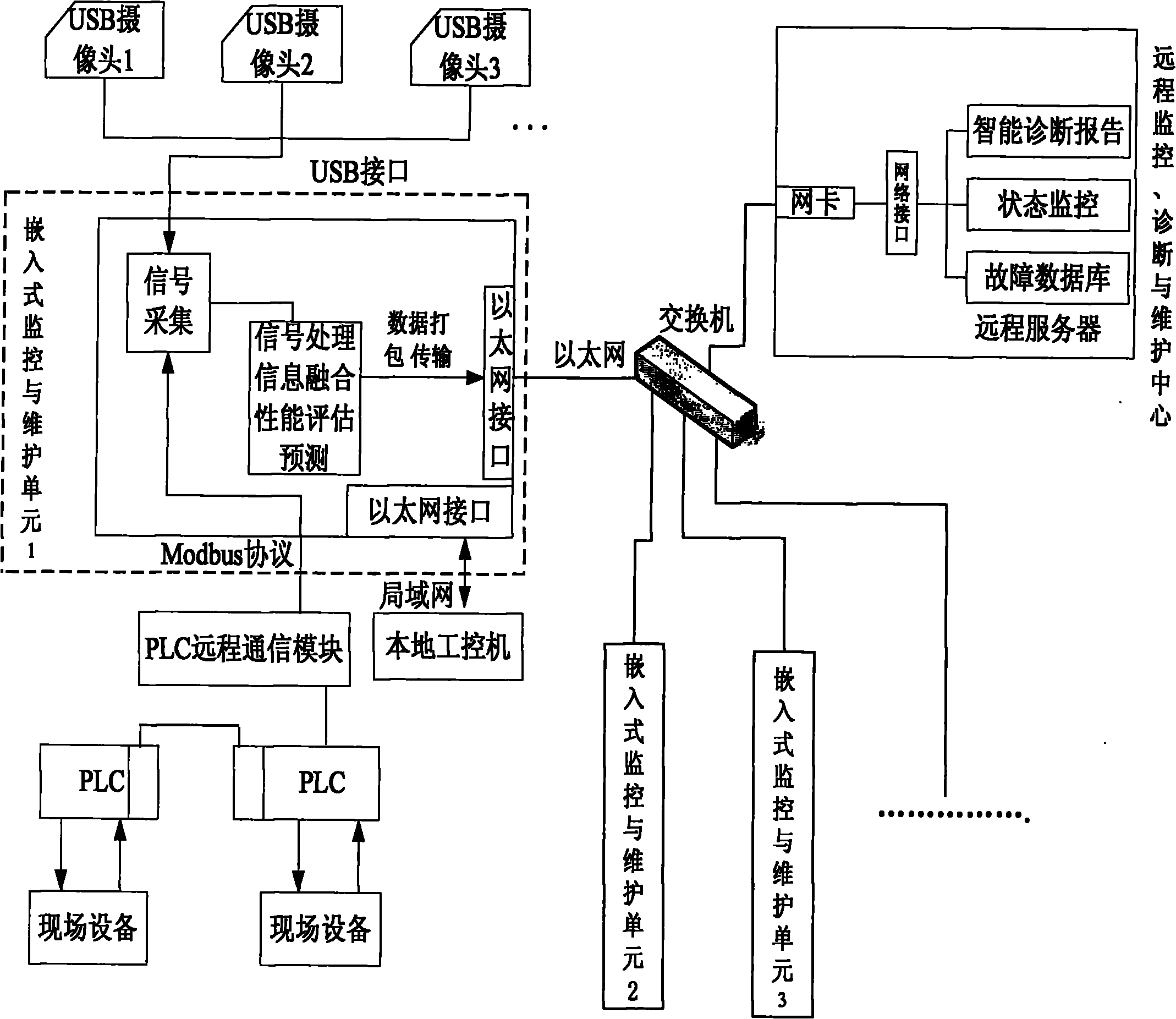

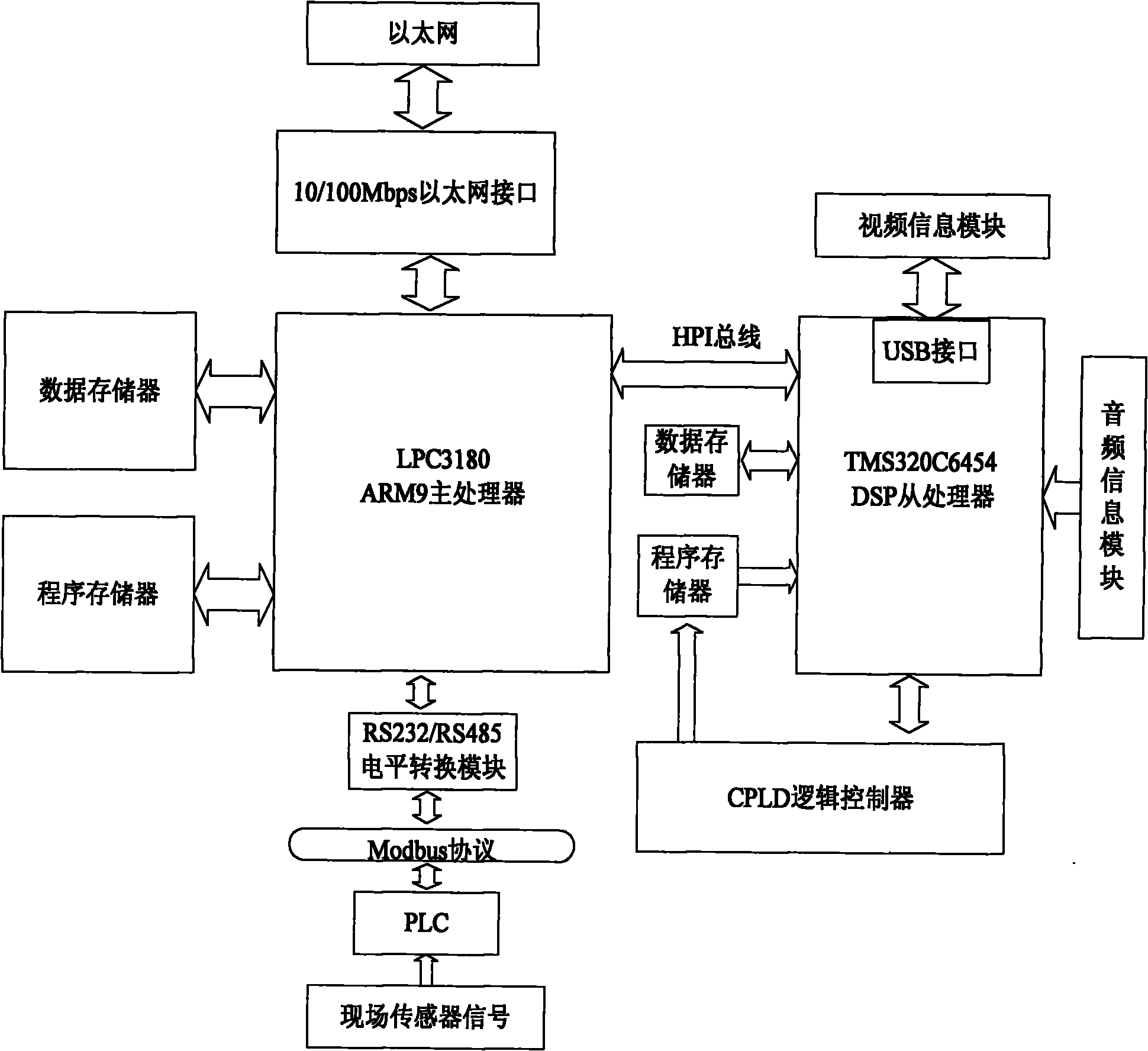

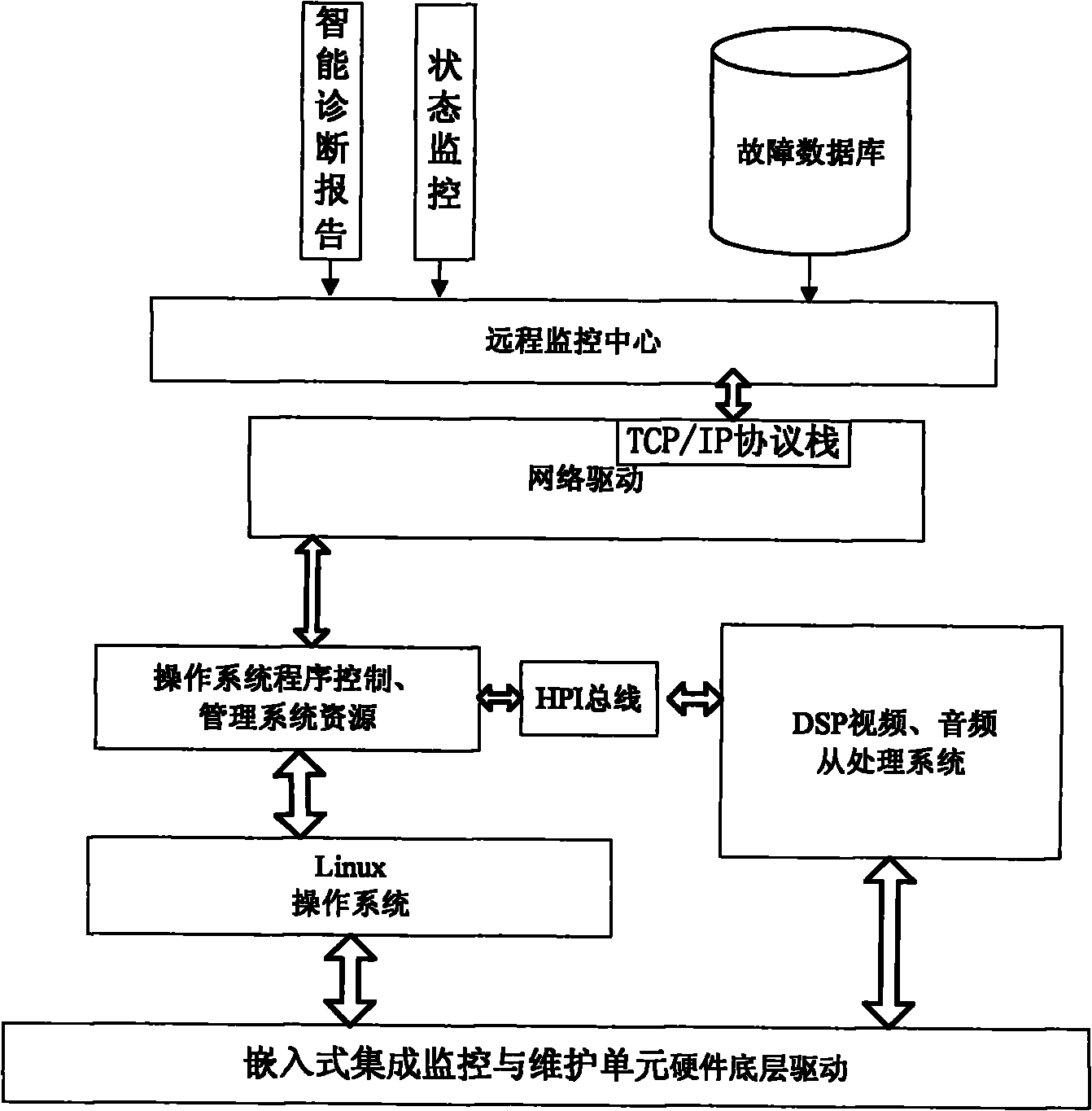

Embedded type integrated monitoring and maintenance system of concrete block forming production line

InactiveCN101782755AImprove efficiencyMeet real-time row requirementsComputer controlSimulator controlComplex programmable logic deviceUSB

The invention discloses an embedded type integrated monitoring and maintenance system of a concrete block forming production line, which is based on a B / S (browser / server) mode network function structure model, comprises various on-site signal acquisition modules, an embedded type monitoring and maintenance unit and a remote monitoring diagnosis and maintenance center, and concretely comprises anARM9 main processor, a DSP (digital signal processor) slave processor, an Ethernet module, an USB (universal serial bus) camera module, a RS-232 / RS-485 level switch module, a data storage module, a program storage module, a video information module, an audio information module, an HPI (hardware platform interface) bus, a CPLD (complex programmable logic device) logic controller module, a local industrial personal computer (IPC) and a remote server. The invention has the advantages of low cost, strong portability, high configurability, complete functions, compact system and modularized design,and can meet the real-time requirement of high-speed data.

Owner:NANJING UNIV OF SCI & TECH

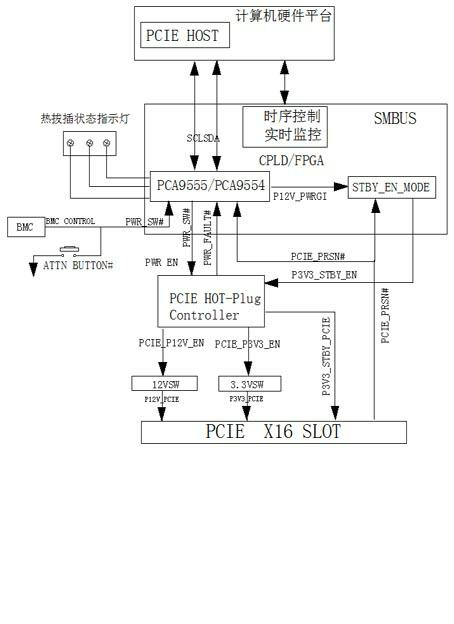

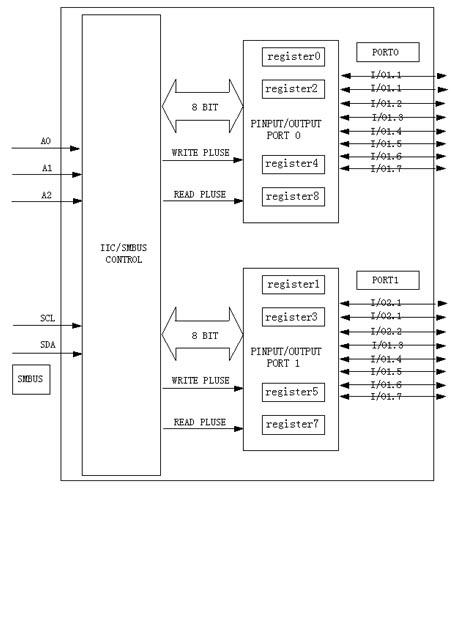

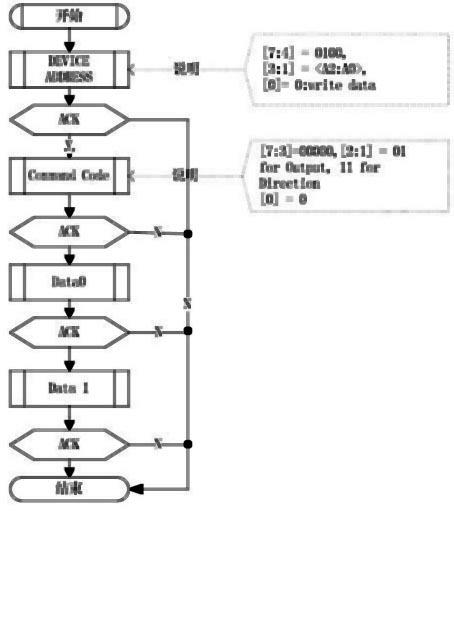

Method for realizing hot-plug of PCIE equipment by CPLD or FPGA

ActiveCN102662903AAvoid situations that shut down your computer systemImprove reliabilityEnergy efficient computingElectric digital data processingSequence controlProgrammable logic device

The invention provides a method for realizing hot-plug of PCIE (Peripheral Component Interconnect Express) equipment by CPLD (Complex Programmable Logic Device) or FPGA (Field Programmable Gate Array). A hardware system comprises PCIE HOST, CPLD / FPGA, PCIE HOT-PLUG CONTROLLER, and a PCIE insertion groove co-constructed system hardware platform, wherein multiple PCA9555 functional modules are hung under the PCIE HOST, and the function of converting SMBUS (System Management Bus) into GPIO (General Purpose Input / Output) is simulated in the CPLD / FPGA by the PCA9555 functional modules; different PCA9555 are distinguished by addresses A2, A1 and A0; the PCIE HOST communicates with the PAC9555 by the SMBUS; and the sequence control of a computer system and the hot-plug control of the PCIE equipment are integrated, and the PCA9555 function is realized by a programmable logic device CPLD / FPGA. Therefore, PCA9555 chips are not needed, the device use is reduced, the system cost is lowered, the power consumption is reduced, the board card space is saved, the computer system is lower in power consumption, and the reliability, stability and expandability are improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

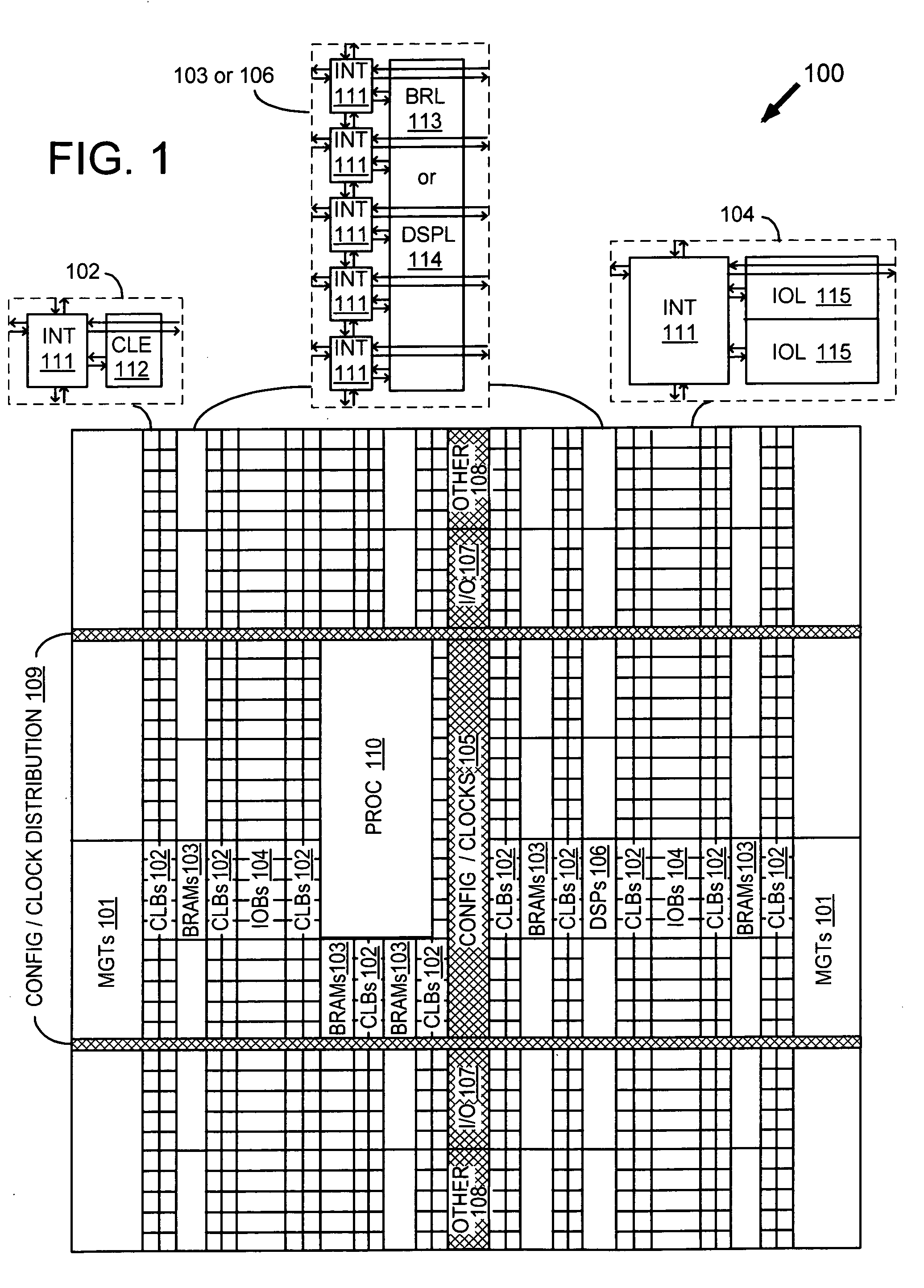

Method and apparatus for providing secure intellectual property cores for a programmable logic device

ActiveUS7890917B1CAD circuit designSpecial data processing applicationsIntellectual propertyProgrammable logic device

Method and apparatus for providing secure intellectual property (IP) cores for a programmable logic device (PLD) are described. An aspect of the invention relates to a method of securely distributing an IP core for PLDs. A circuit design is generated for the IP core, the circuit design being re-locatable in a programmable fabric for PLDs. The circuit design is encoded to produce at least one partial configuration bitstream. Implementation data is generated for utilizing the IP core as a reconfigurable module in top-level circuit designs. The at least one partial configuration bitstream and the implementation data are delivered to users of the PLDs.

Owner:XILINX INC

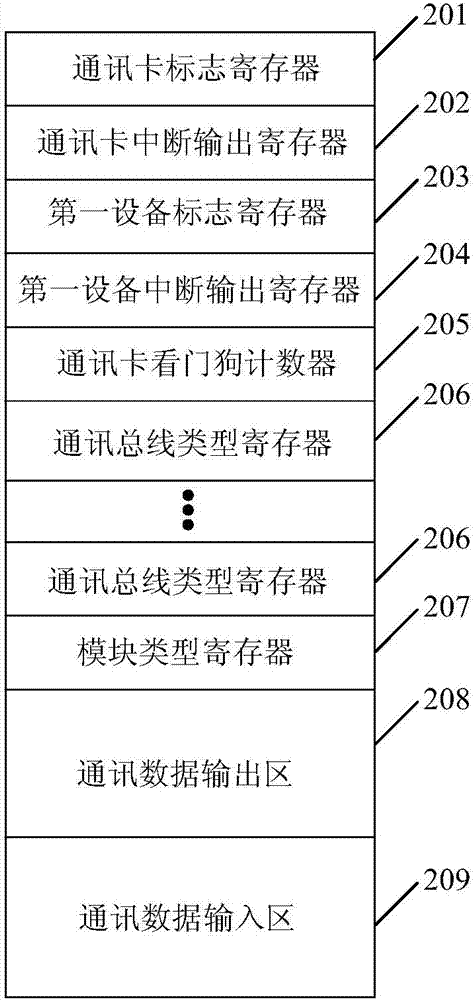

Board system and FPGA (Field Programmable Logic Array) online update method of communication interface cards

ActiveCN103559053AReduce design costImprove scalabilityProgram loading/initiatingCommunication interfaceComplex programmable logic device

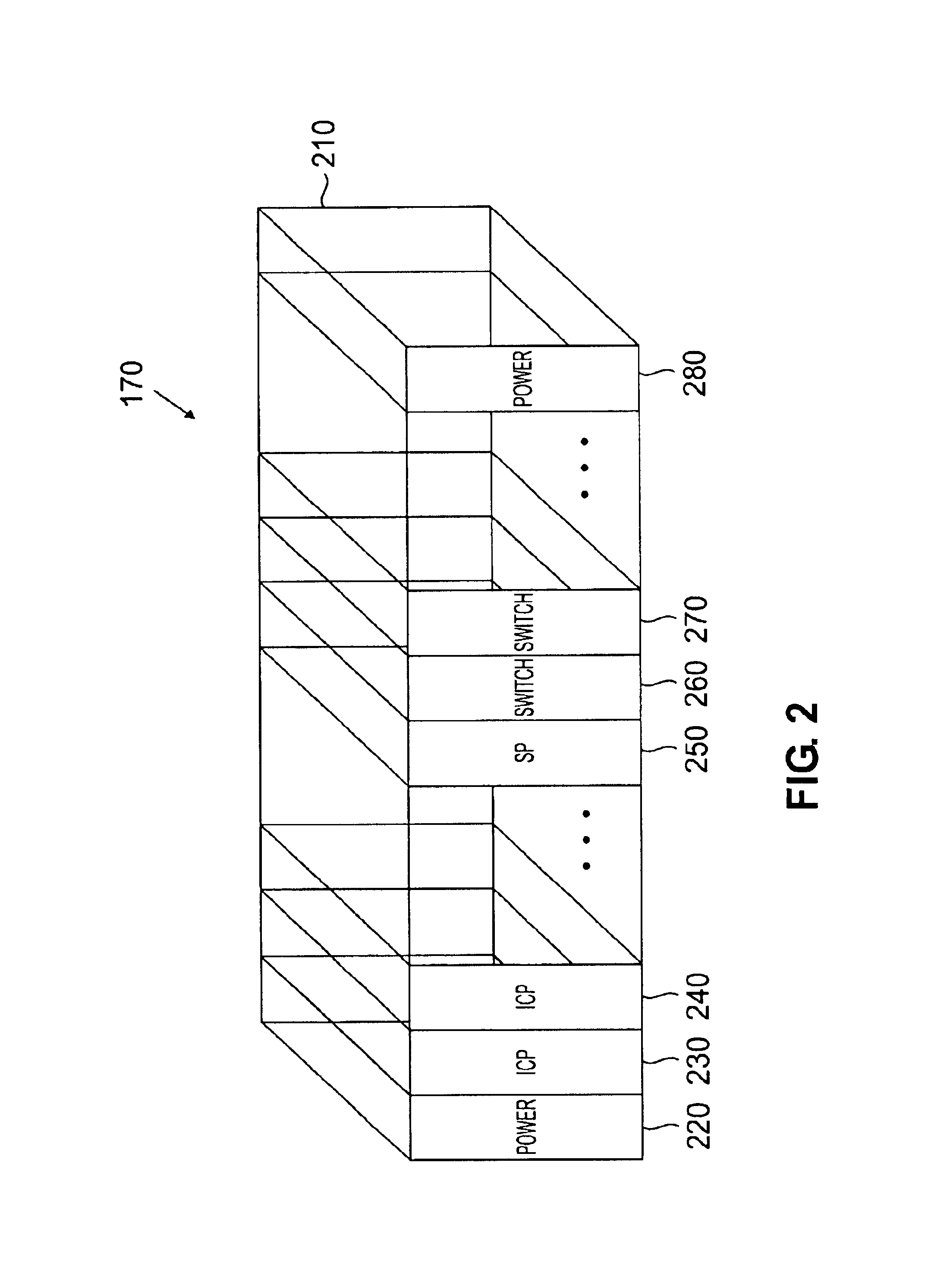

The invention relates to the technical field of communication and discloses a board system, aiming at solving the problems that an FPGA (Field Programmable Logic Array) online update mode is inapplicable for the FPGA online update of a separated type system of a motherboard plus multiple communication interface cards in the prior art, and the update mode is high in cost and low in reliability. The system comprises a motherboard and n interface cards, wherein the motherboard comprises a CPU (Center Processing Unit), a CPLD (Complex Programmable Logic Device) unit and n slot positions; each slot position is connected with the CPLD unit; the CPLD unit is connected with the CPU; the n interface cards are connected onto the n slot positions in a plugging and one-to-one correspondence way through n connectors so as to realize signal interconnection with the motherboard; as an integer, n is greater than or equal to 2; the CPLD unit comprises a gating module and a counting module; the interface cards comprise an FPGA unit, a selector switch, a main flash module and a slave flash module; the main flash module and the slave flash module are connected with the FPGA unit through the selector switch. In addition, the invention also discloses an FPGA online update method of the communication interface cards, which is applicable for the separated type system of the motherboard plus the multiple interface cards.

Owner:MAIPU COMM TECH CO LTD

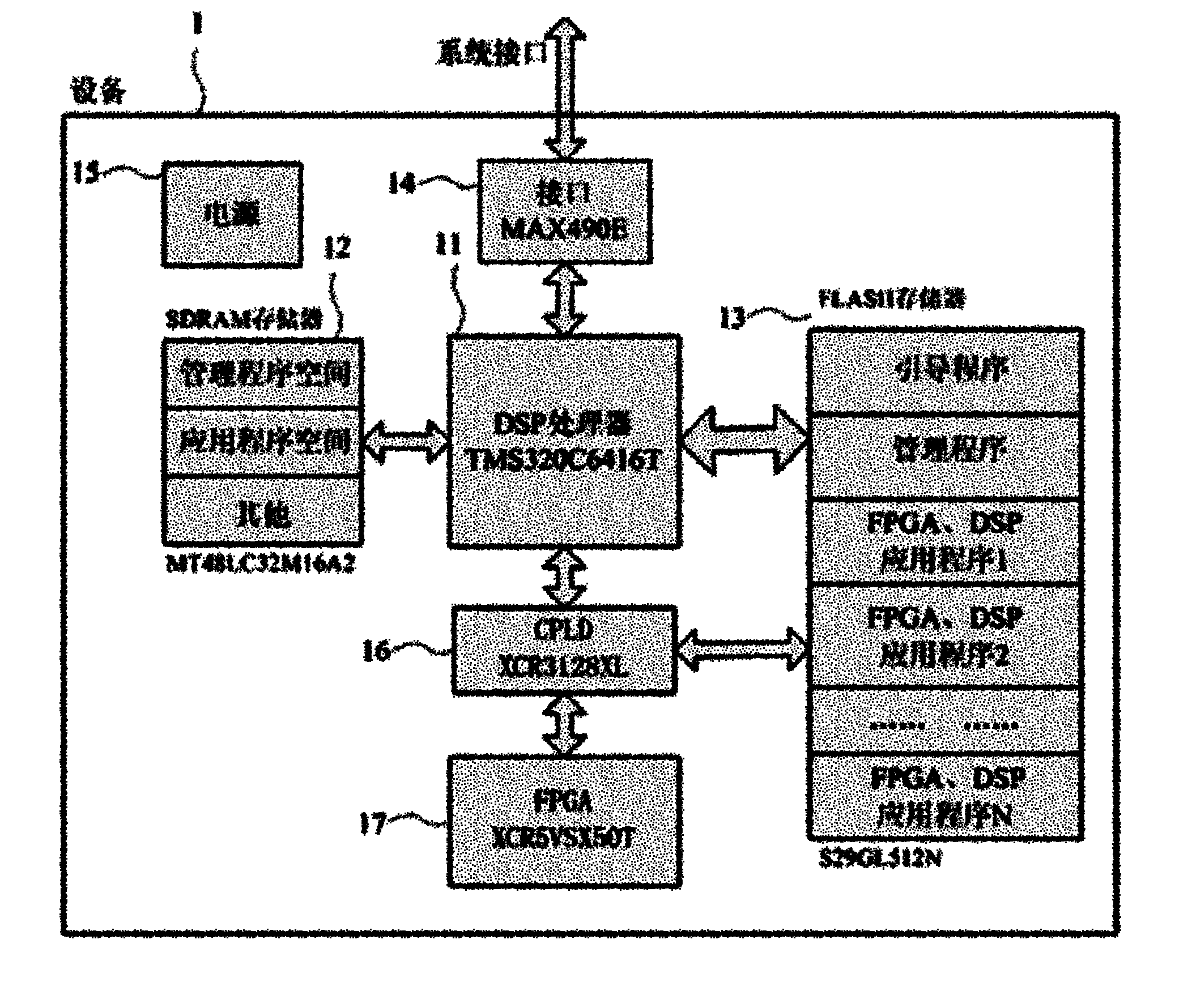

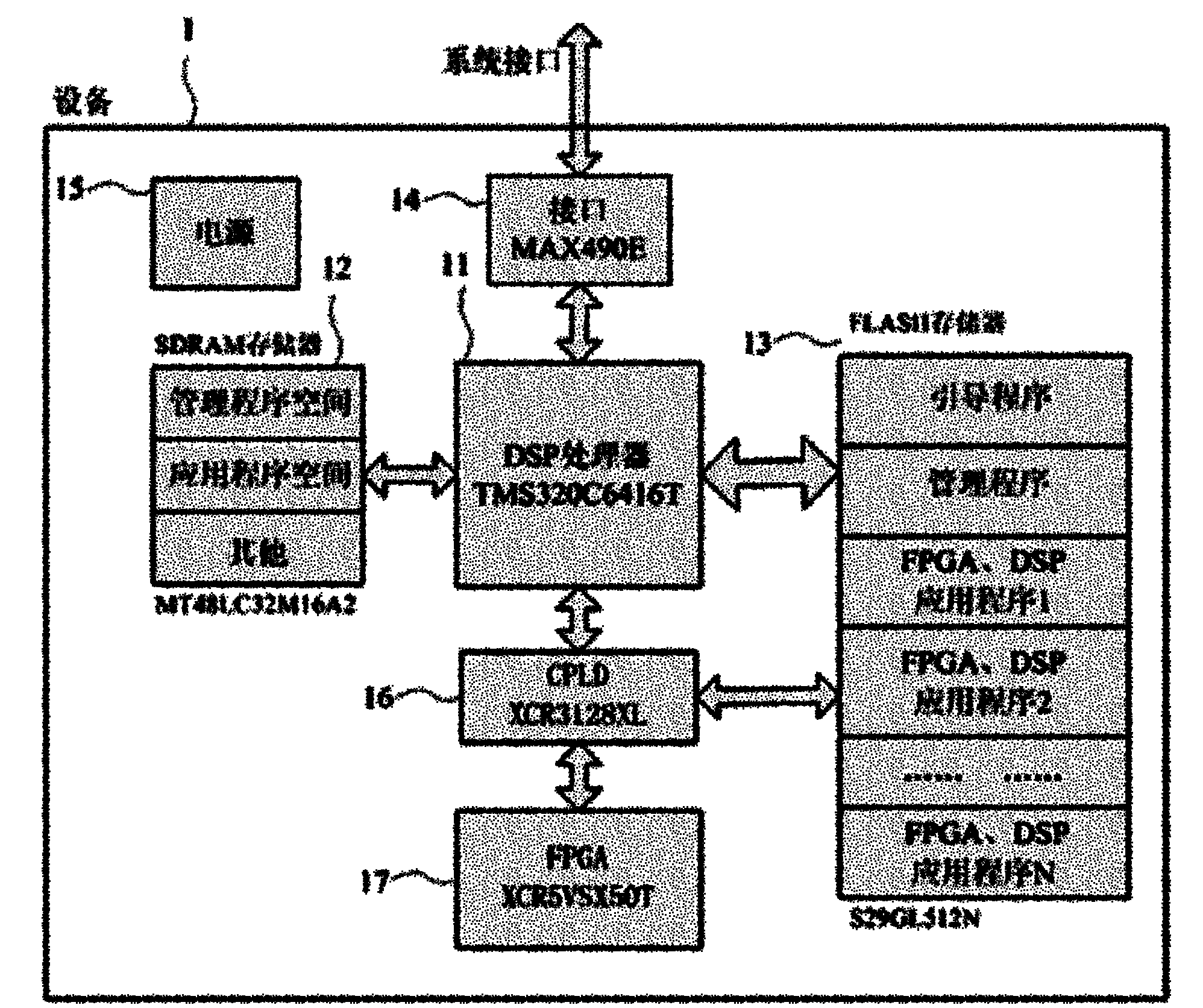

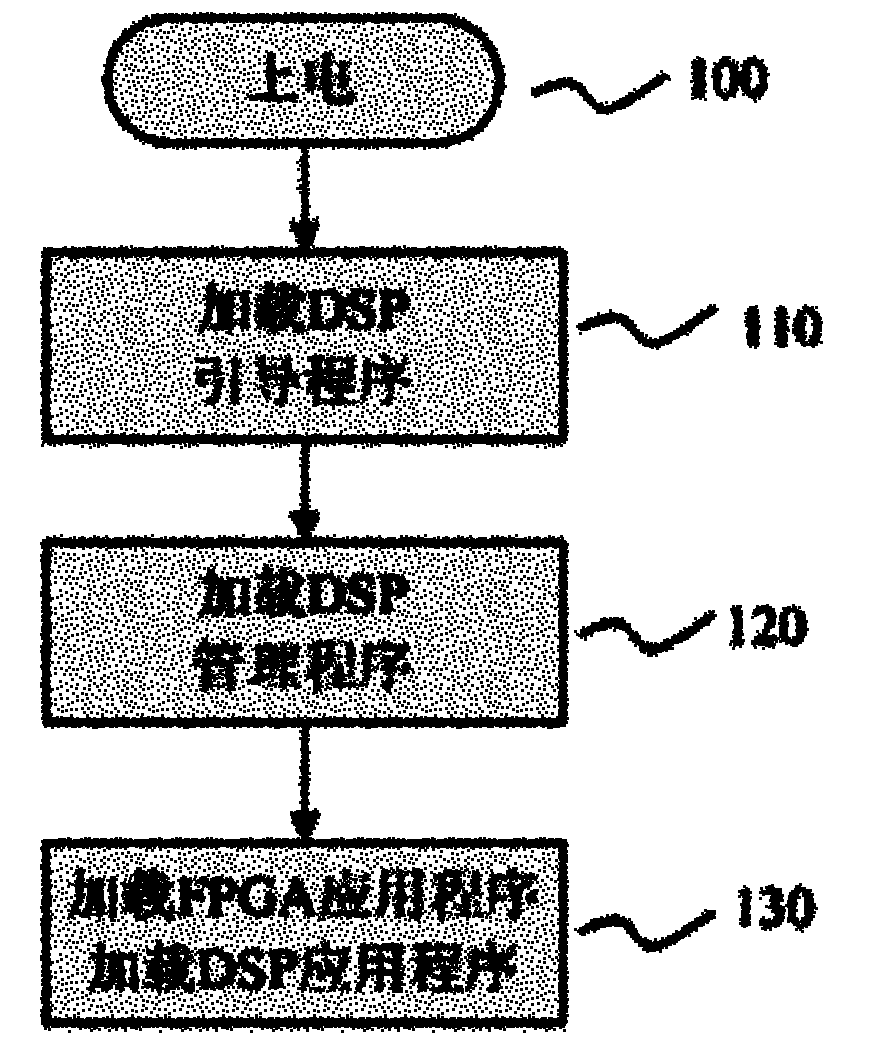

Method and system for dynamically loading processor application programs

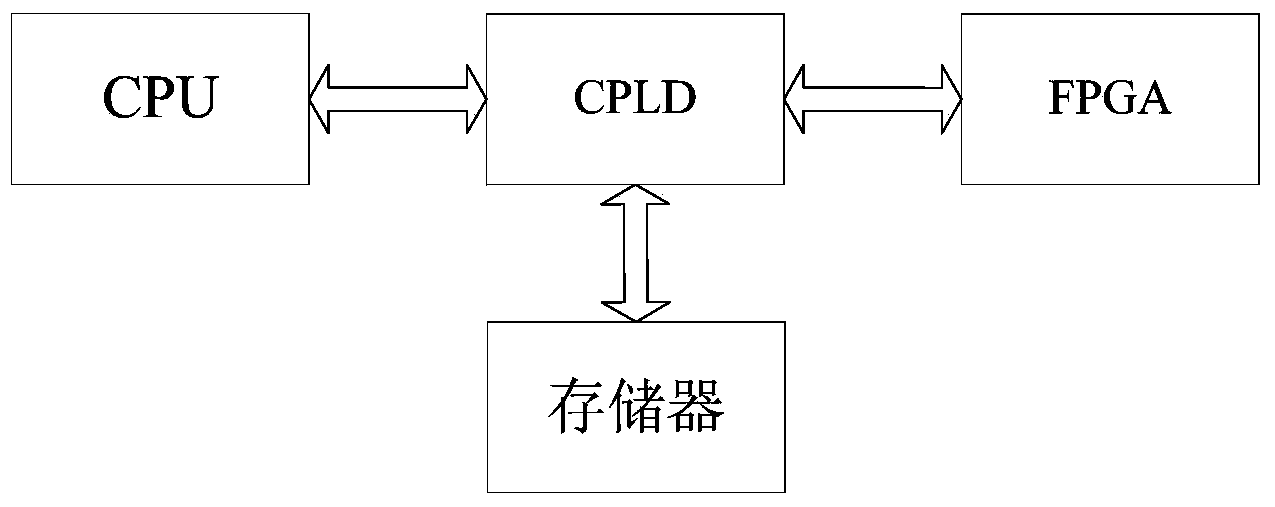

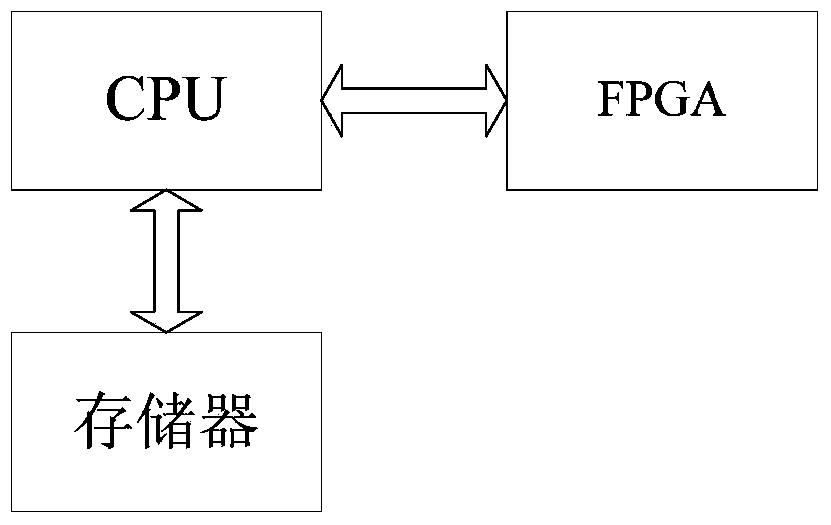

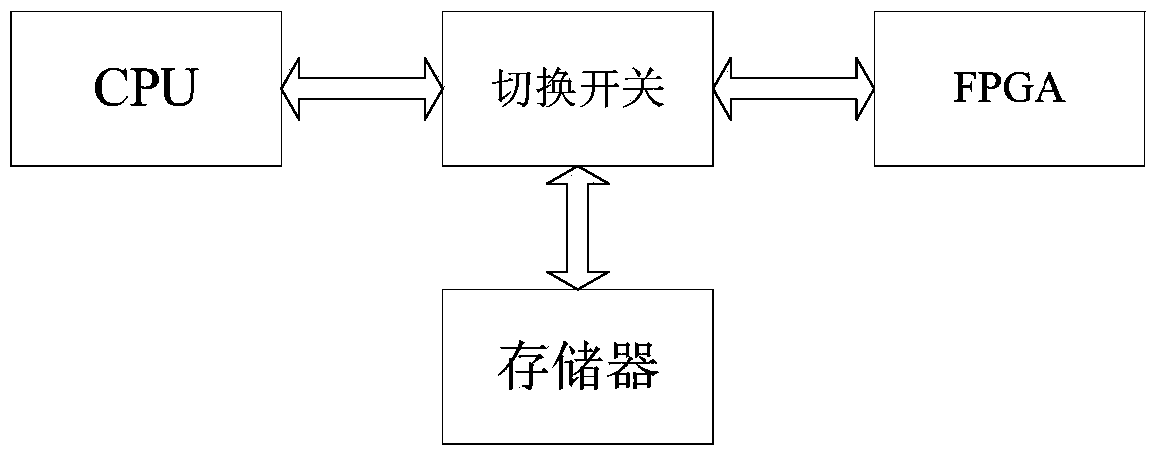

InactiveCN101901156AEasy to implementEasy to reuseProgram loading/initiatingSynchronous dynamic random-access memoryComplex programmable logic device

The invention relates to a technique for dynamically loading processor application programs and a hardware system for realizing the technique. The system mainly comprises a digital signal processor (DSP) 11, a field programmable gate array (FPGA) processor 17, a complex programmable logic device (CPLD) 16, a FLASH memory 13, a synchronous dynamic random access memory (SDRAM) 12, an interface chip14 and a power module 15, wherein fixed programs in the FLASH memory 13 comprise a DSP bootstrap program, a DSP management program and a plurality of FPGA and DSP application programs. A method for implementing the system has the characteristics that: dynamic loading and on-line updating of the FPGA application program and the DSP application program are realized by using the management program; the jump among the bootstrap program, the management program and the application programs is realized by the DSP technique so as to complete the dynamic loading function; and the FPGA is taken over bythe CPLD so as to configure a bus and the FPGA application program is loaded by combining the DSP.

Owner:SICHUAN JIUZHOU ELECTRIC GROUP

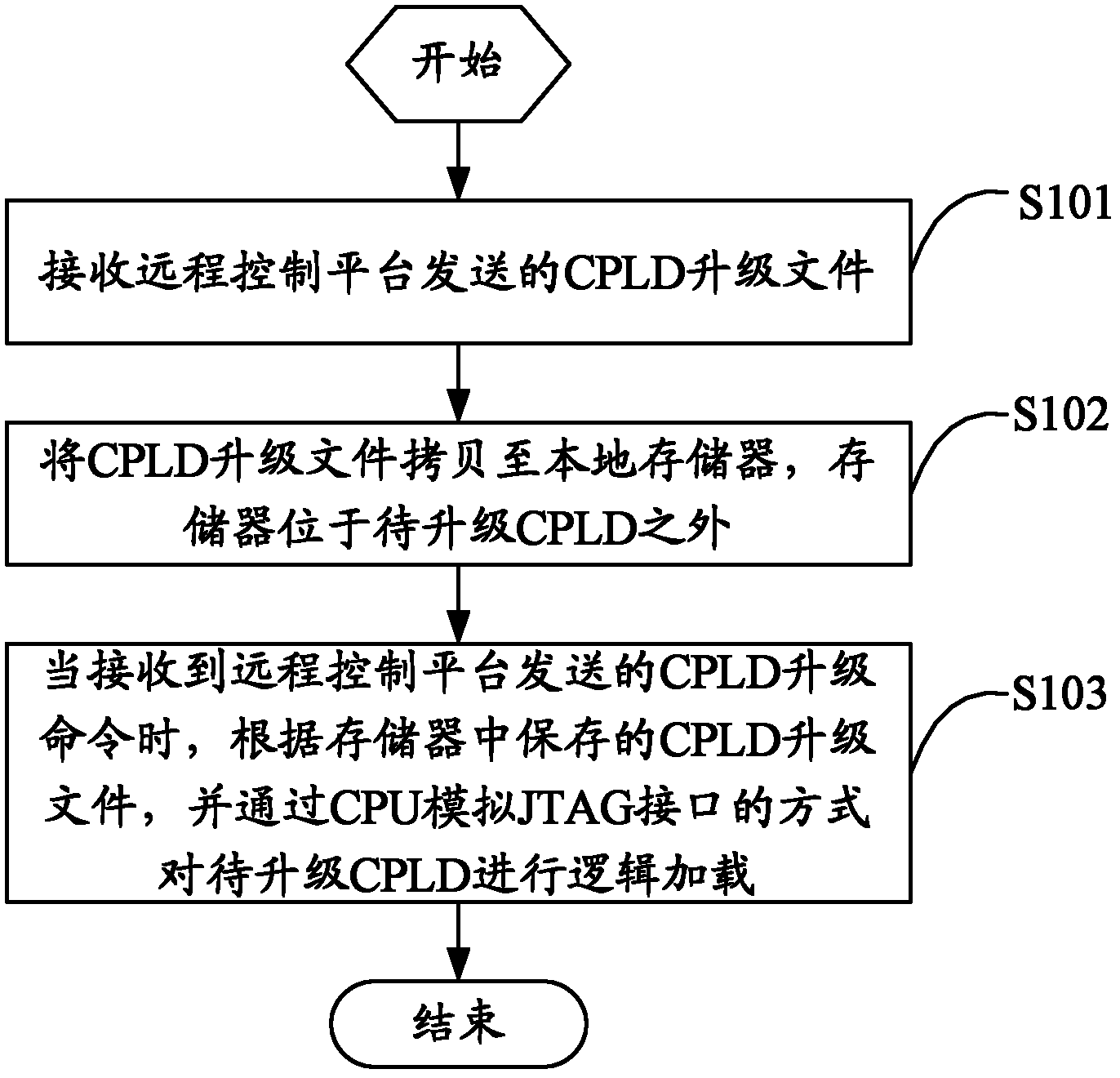

Online CPLD (Complex Programmable Logic Devices) upgrading method, device and business veneer

InactiveCN102662701AImprove reliabilitySimple methodProgram loading/initiatingRemote controlComplex programmable logic device

The invention relates to an online CPLD (Complex Programmable Logic Devices) upgrading method, an online CPLD upgrading device and a business veneer. The method comprises the following steps: receiving a CPLD upgrading file sent by a remote control platform; and copying the CPLD upgrading file to a local storage, and when receiving the CPLD upgrading instruction sent by the remote control platform, logically loading a CPLD to be upgraded through a CPU (Central Processing Unit) in a manner of simulating a JTAG (Joint Test Action Group) interface according to the CPLD upgrading file stored in the storage. According to the invention, remote upgrading on on-site equipment CPLD can be realized without depending on the internal logics of the CPLD to be upgraded, and CPLD of all factories can be compatible by adopting the upgrading manner of simulating the JTAG interface, so that the universality is good; furthermore, in the online upgrading process, if the abnormal conditions of reset or power failure of the CPU occur, the CPLD, whose online upgrading is not completed, can still be reloaded for upgrading when the system is restarted, so that the online upgrading reliability of the CPLD is improved.

Owner:ZTE CORP

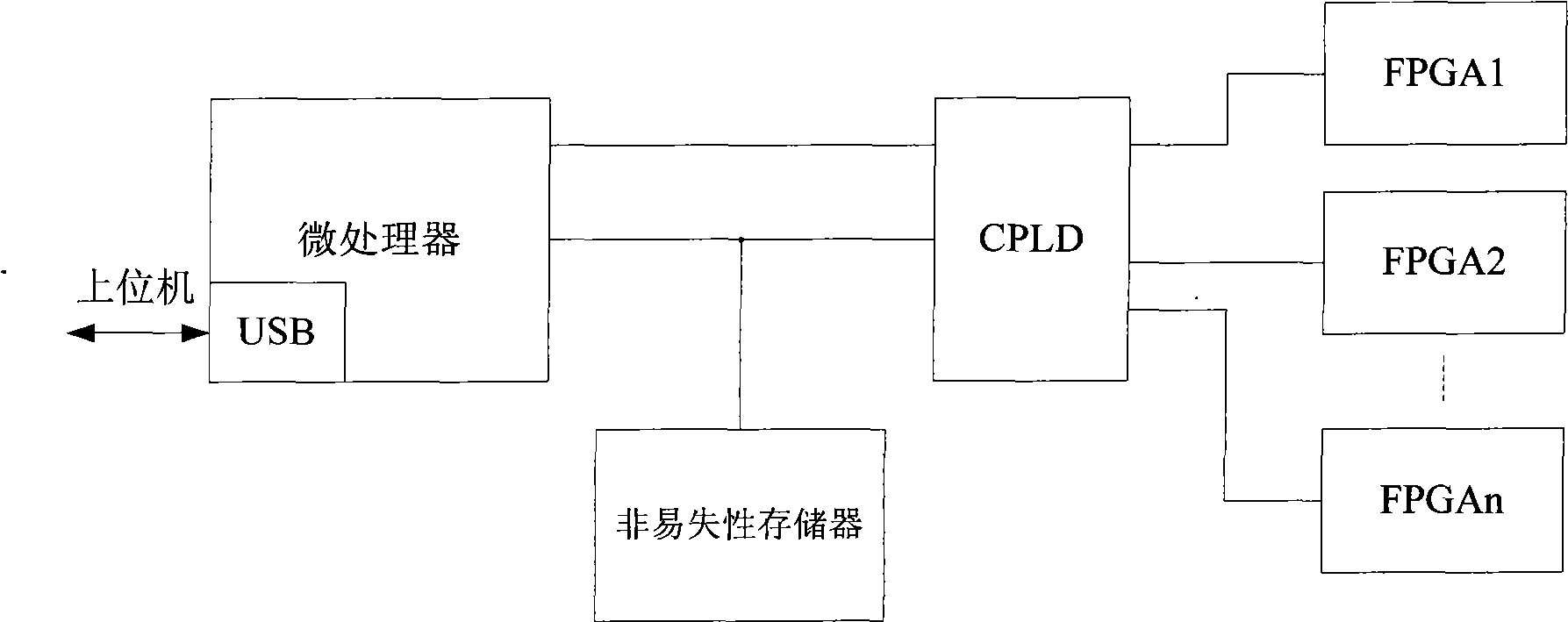

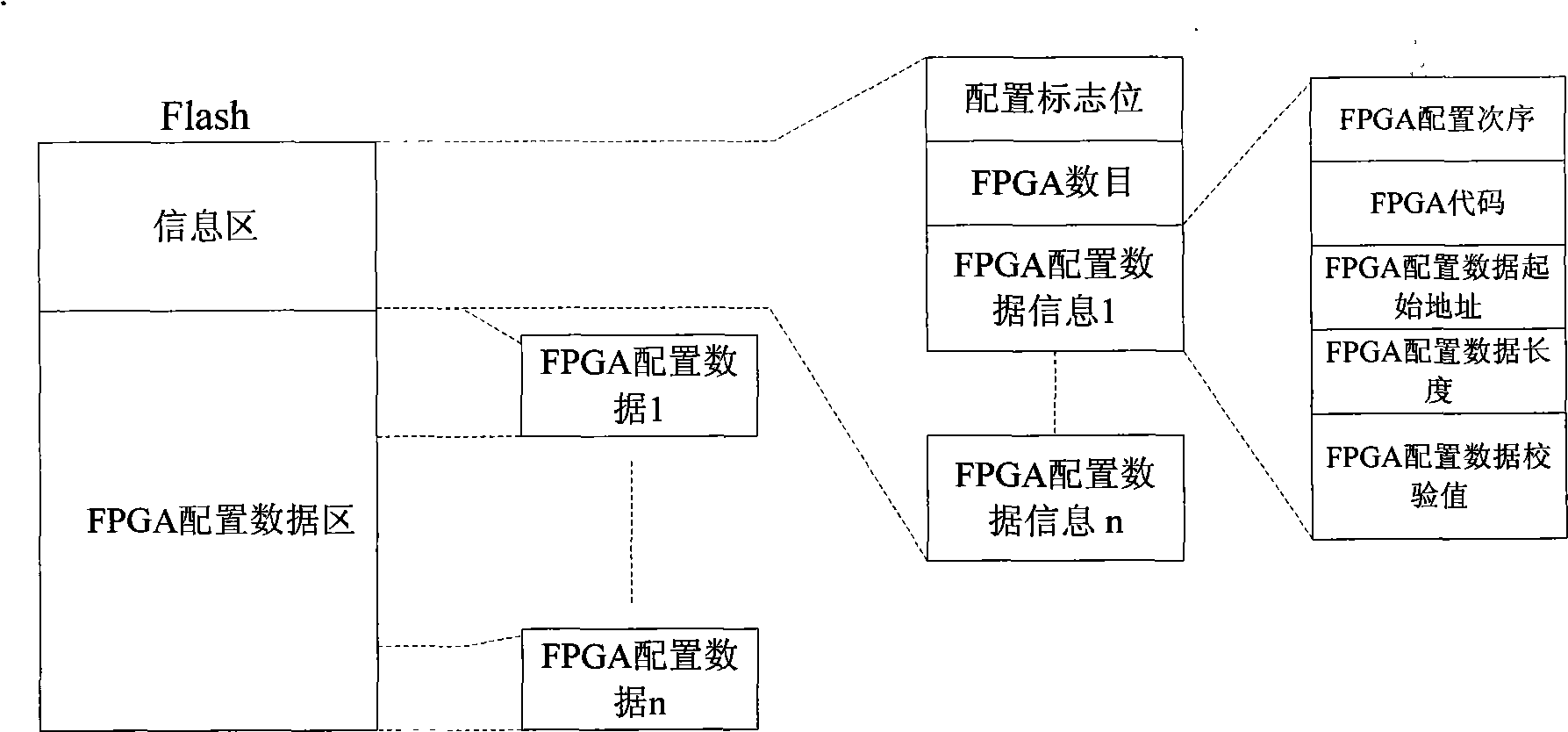

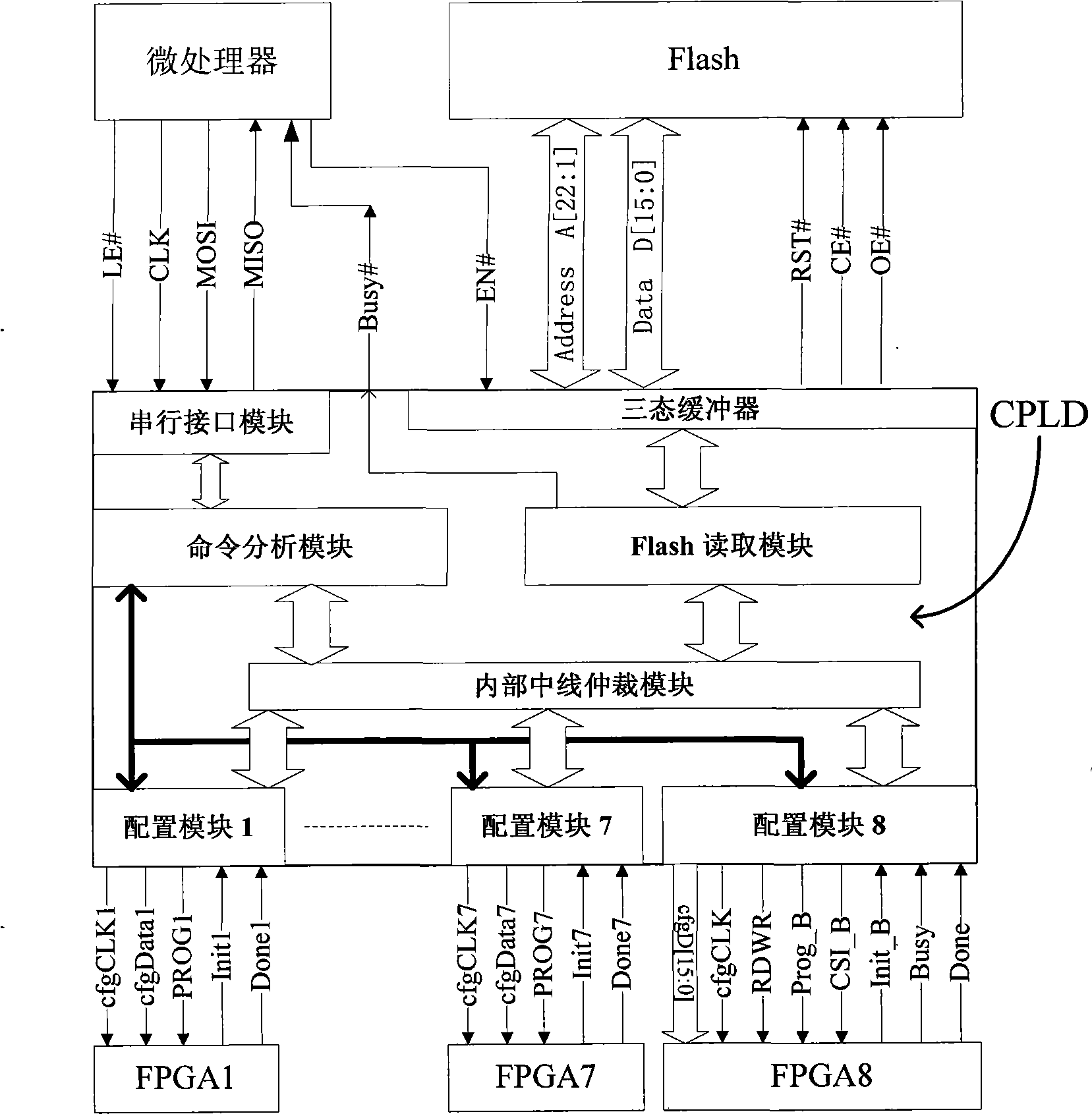

System for unified configuration and management of FPGA chip in equipment

InactiveCN101485576ARealize unified configurationRealize managementUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsComplex programmable logic deviceFpga chip

The invention discloses a system for unified configuration and management of FPGA chips inside equipment. The system comprises a configuration and management logic component and at least one field programmable gate array (FPGA) chip, wherein the configuration and management logic component is connected with the FPGA, and comprises a microprocessor, a nonvolatile memory and a complex programmable logic device (CPLD) which are connected with each another; the CPLD is connected with the FPGA; and the configuration and management logic component is used to realize the configuration of one or more pieces of the FPGA in a serial mode or a parallel mode. The system realizes unified configuration and management of the FPGA chips inside the equipment and greatly increases the configuration efficiency of the FPGA chips inside the equipment, thereby increasing equipment efficiency during use and maintenance.

Owner:SHENZHEN LANDWIND IND

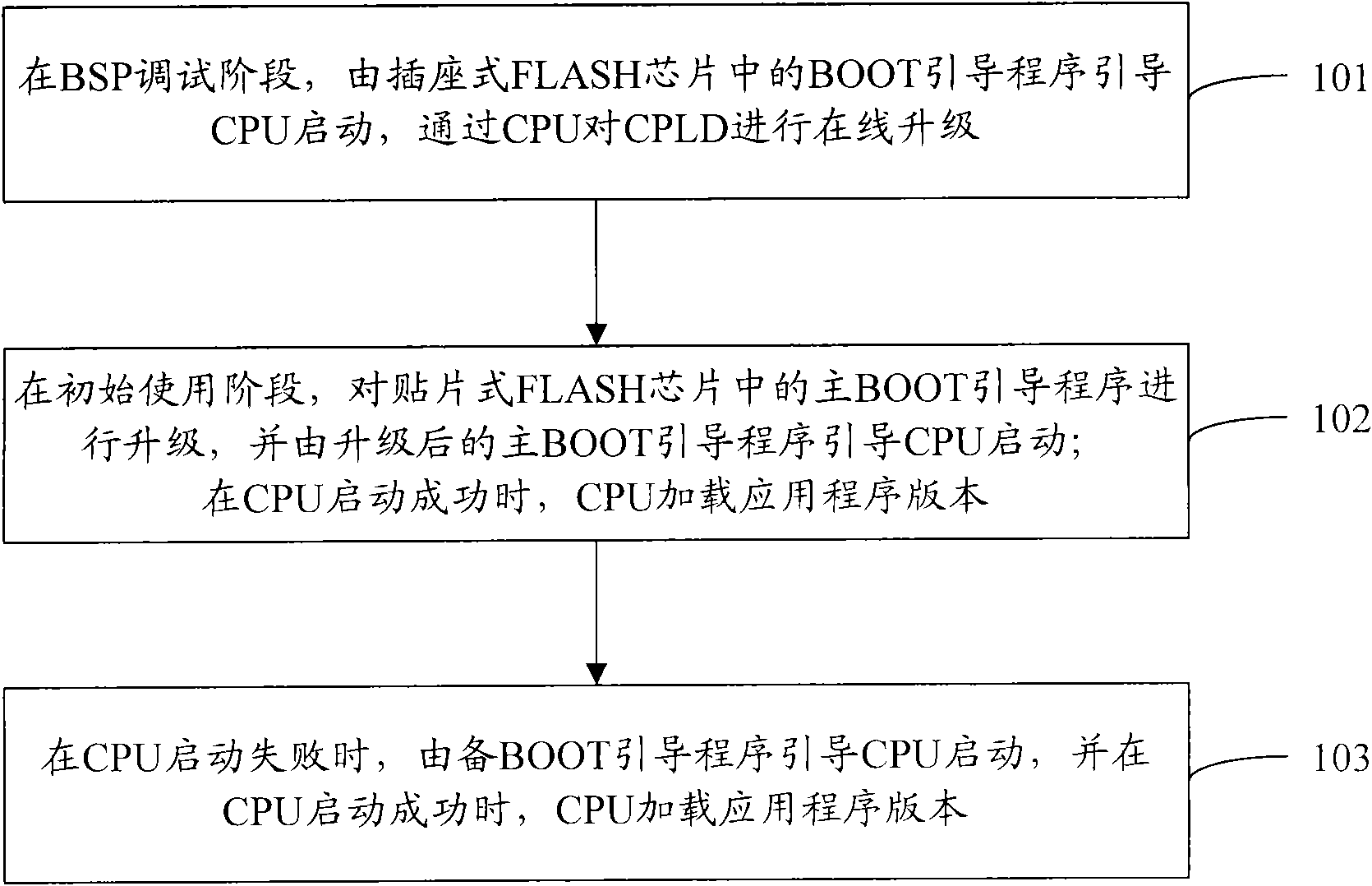

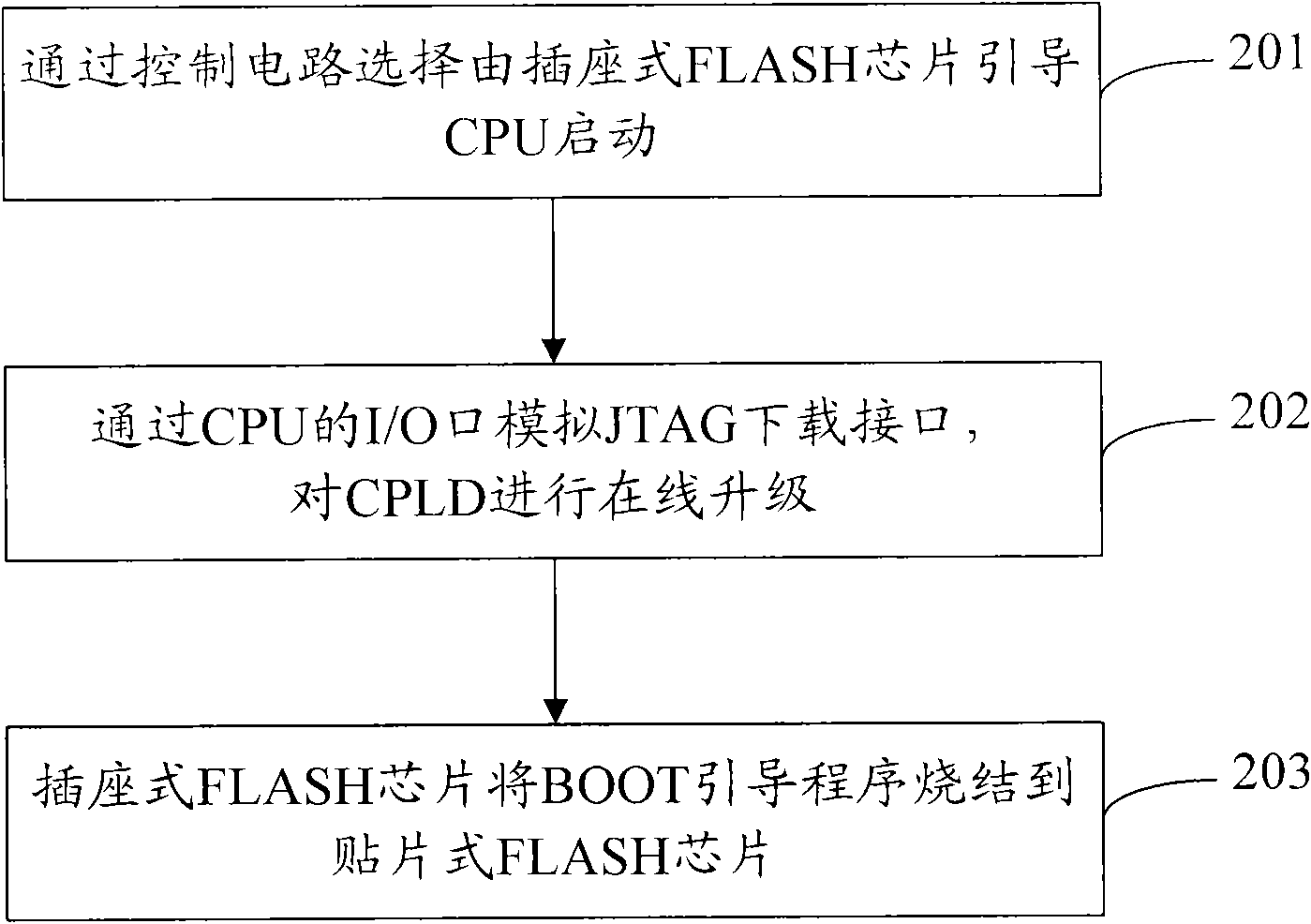

Upgrading and backup method and device for embedded system

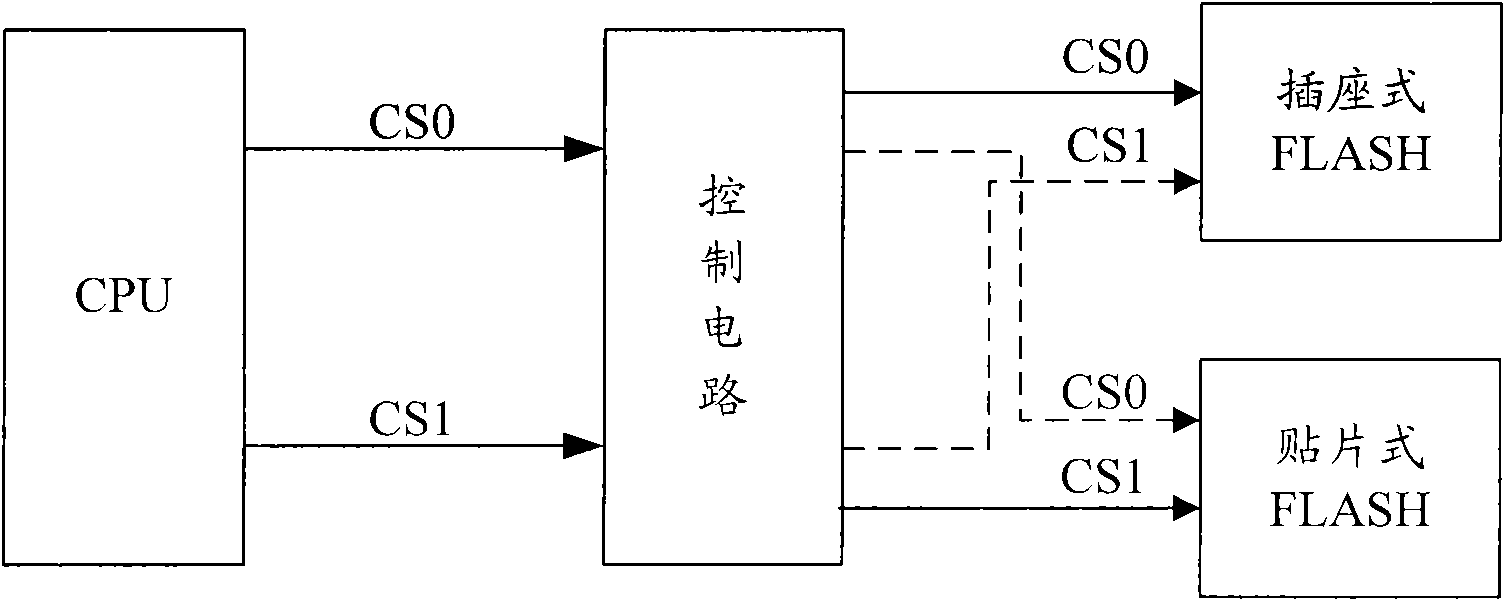

InactiveCN102073517AReliable remote upgradeSave resourcesProgram loading/initiatingRedundant operation error correctionBoard support packageSurface mounting

The invention discloses an upgrading and backup method and device for an embedded system. The method comprises the following steps of: in a BSP (Board Support Package) debugging stage, booting a CPU (Central Processing Unit) to start by a BOOT program in a socket type FLASH chip and upgrading a CPLD (Complex Programmable Logic Device) on line through the CPU; in an initial use stage, upgrading a main BOOT program in a surface mount type FLASH chip, booting the CPU to start by the upgraded main BOOT program, and loading application program version by the CPU when the CPU starts successfully; and when the CPU is failed to start, booting the CPU to start by a standby BOOT program, and loading the application program version by the CPU when the CPU starts successfully. By the invention, the embedded system can be reliably, simply and conveniently upgraded with low cost.

Owner:ZTE CORP

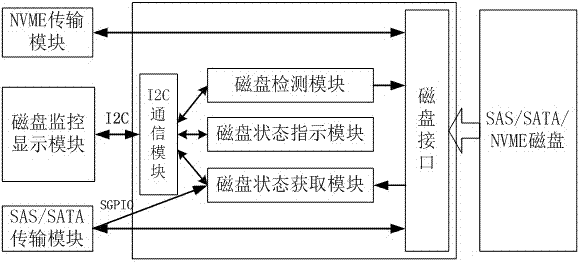

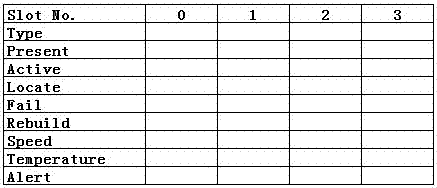

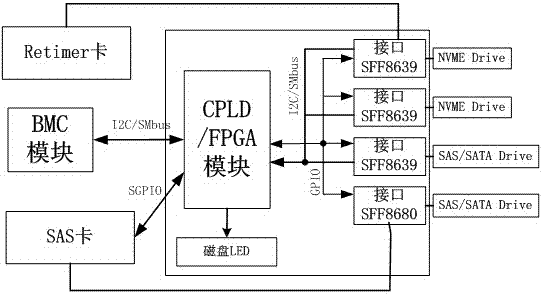

Disk monitoring system and method

InactiveCN106970866ARealize real-time monitoringRealize intelligent judgmentHardware monitoringElectricityStatistical analysis

The invention discloses a disk monitoring system and method. The system comprises a disk monitoring display module, a CPLD (Complex Programmable Logic Device) or FPGA (Field Programmable Gate Array) module, a disk interface module, an SAS (Statistical Analysis System) / SATA (Serial Advanced Technology Attachment) transmission module and an NVME transmission module. After the method and the system are started and electrified, a disk detection module carries out detection distinguishing on the type and the amount of connected disks. The system has the advantages that different types of disk states are monitored, monitoring functions are comprehensive and uniform, an implementation way is simple and reliable and clients can conveniently check.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

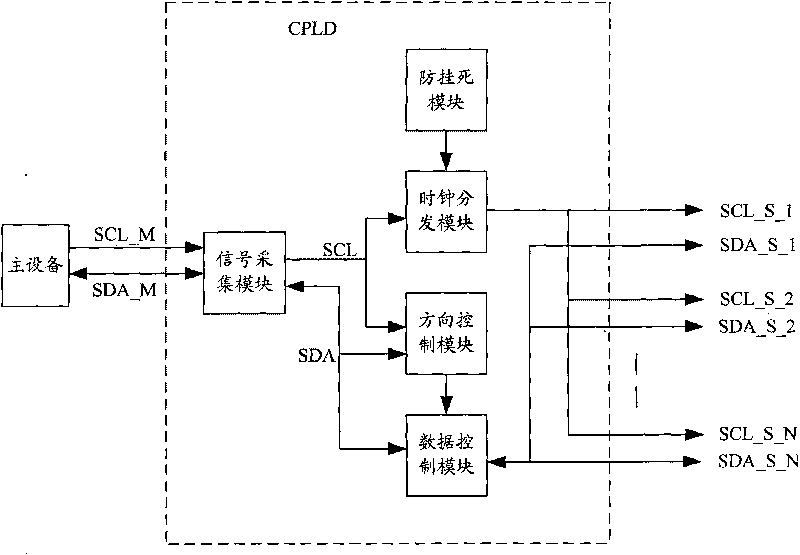

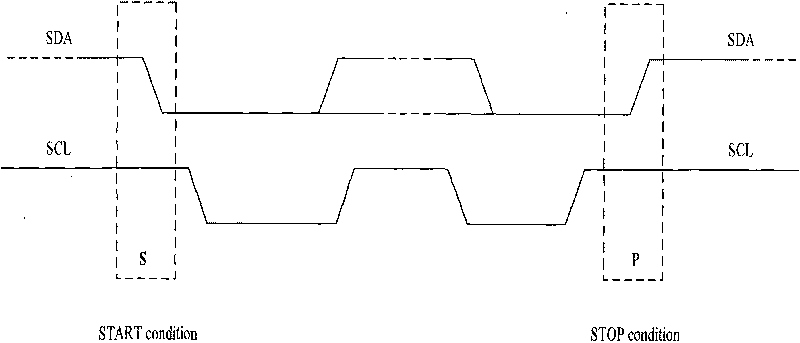

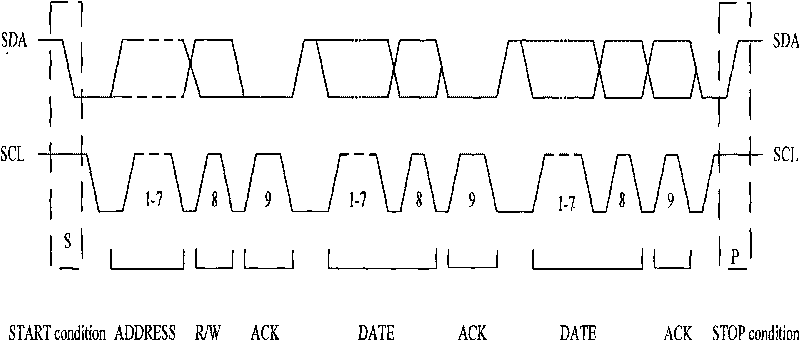

System and method for realizing I2C bus control

ActiveCN101763331AReduce Design ComplexityImprove signal qualityElectric digital data processingProgrammable logic deviceSingle plate

The invention discloses a system for realizing I2C bus control. In the system, a complex programmable logic device (CPLD) is used for dividing SCL signals acquired from an Inter-integrated circuit (I2C) bus of master equipment into a plurality of paths and expanding the divided signals to the I2C bus of slave equipment, and between SDA signals acquired from the I2C buses of the master equipment and the slave equipment, judging a current data state and determining the direction of current SDA signals. The invention also discloses a method for realizing the I2C bus control, which comprises the following steps: dividing the SCL signals acquired from the Inter-integrated circuit (I2C) bus of the master equipment into the plurality of paths, and expanding the divided signals to the I2C bus of the slave equipment; and between the SDA signals of the I2C buses of the master equipment and the slave equipment, judging the current data state and determining the direction of the current SDA signals. The method and the system of the invention can reduce cost and the design complexity of a single board.

Owner:ZTE CORP

A Fault Detection and Protection Circuit for Brushless DC Motor

InactiveCN102290790AEmergency protective circuit arrangementsDynamo-electric machine testingProcess moduleComputer module

The invention discloses a fault detecting and protective circuit of a brushless direct current motor, which comprises a three-phase current signal detecting module, a stator winding open-phase fault switching module, a Hall sensor signal detecting module, a stator winding overcurrent detecting module, a CPLD (Complex Programmable Logic Device) fault processing module and a winding current cutting module, wherein the three-phase current signal detecting module is used for detecting a three-phase signal of a direct-current motor; the Hall sensor signal detecting module is used for detecting and reshaping an output signal of the Hall sensor; the stator winding overcurrent detecting module is used for collecting winding currents and comparing the winding currents with a set value; and the CPLD (Complex Programmable Logic Device) fault processing module is used for logically processing the three-phase signal, a Hall reshaping signal and a overcurrent fault signal and respectively sending signals to the stator winding open-phase fault switching module and the winding current cutting module. The circuit can increase the reliability of a controller of the brushless direct current motor, can protect a stator winding, a Hall sensor and a stator winding after open-phase faults of the stator winding, the Hall sensor and the stator winding and prevents the stator winding, the Hall sensor and the stator winding from being damaged due to the faults.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

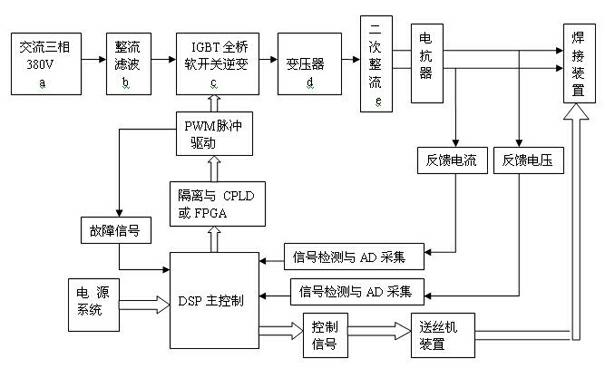

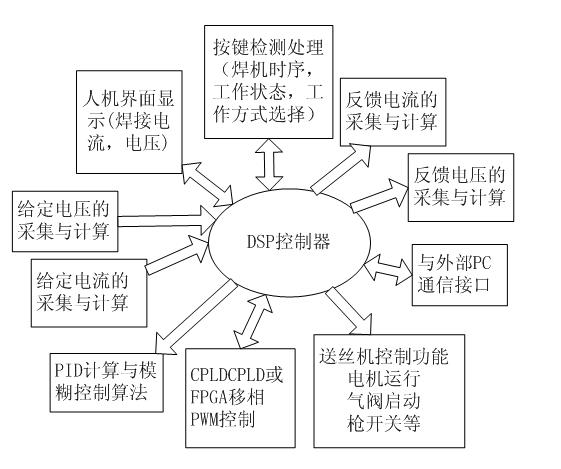

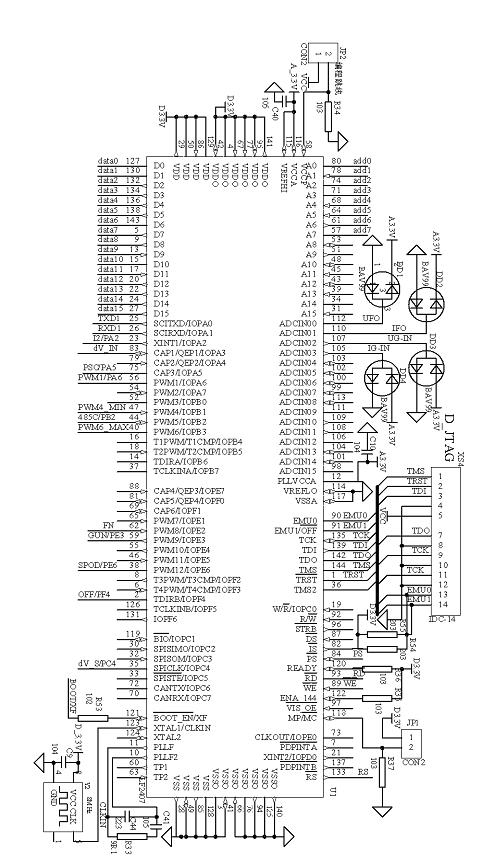

Multifunctional digitized welding machine

InactiveCN102350569ABeautiful shapeImprove dynamic response performanceArc welding apparatusFull bridgeTransformer

The invention relates to a multifunctional digitized welding machine, which comprises a full-bridge type inversion main circuit, a control circuit and a soft switch PWM (Pulse-Width Modulation) driving circuit, wherein the full-bridge type inversion main circuit is composed of an IGBT (Insulated Gate Bipolar Translator); the soft switch PWM driving circuit of a symmetric carrier is based on a CPLD (Complex Programmable Logic Device) or FPGA (Field Programmable Gate Array); the inversion main circuit comprises a rectifying filtering module, an IGBT full-bridge inversion module, a main transformer and a secondary rectifying filtering module; the control circuit comprises a DSP (Digital Signal Processor) control processor, a manual idle-dropping circuit, a regulating, detecting and sampling circuit for a feedback current and voltage signal outputted by the welding machine, a collecting and setting circuit for a feeding speed and given voltage of the welding machine, a display circuit for an interface and parameter of an external keyboard and a communication circuit connected to a PC (Personal Computer); the regulating, detecting and sampling circuit for the feedback current and voltage signal outputted by the welding machine comprises a Hall voltage sensor for detecting a feedback arc voltage outputted by the welding machine and a Hall current sensor for detecting an output current of the welding machine; and the collecting and setting circuit for the feeding speed and given voltage of the welding machine comprises a collecting circuit for a given voltage and given current, namely the feeding speed, on a panel of a feeder.

Owner:PANDA ELECTRONICS GROUP +2

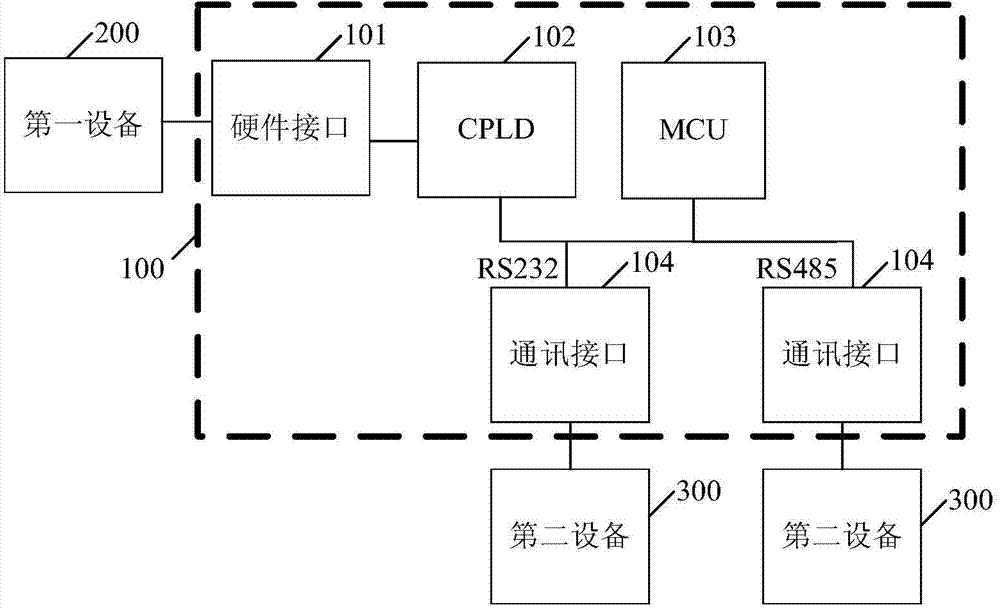

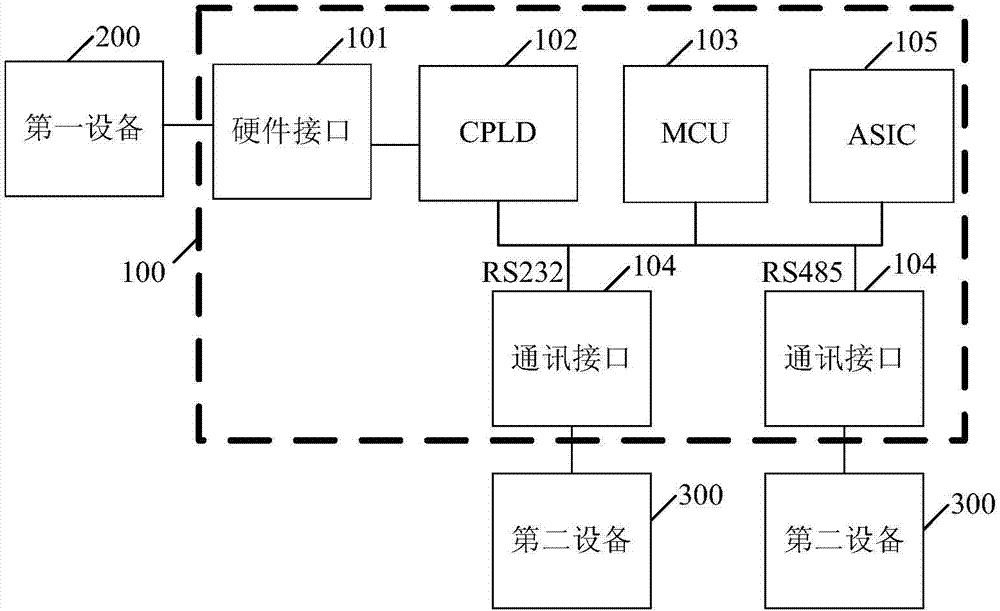

Card and method for converting communication protocols

InactiveCN104753958AAchieve deliveryExchangeTransmissionCommunication interfaceComplex programmable logic device

The invention provides a card and a method for converting communication protocols. The card and the method have the advantages that the diversified communication protocols can be adopted for a plurality of second devices, data can be received by a plurality of communication interfaces, can be forwarded to an MCU (micro-control unit) and then are respectively analyzed and converted by the MCU, then the second devices can be communicated with first devices via CPLD (complex programmable logic device) and hardware interfaces, and accordingly the communication protocols can be simultaneously transmitted and exchanged by the single card for converting the communication protocols; another card for converting the communication protocols in the prior art can be omitted, and accordingly problems of high cost and multiple interfaces in procedures for converting diversified protocols in the prior art can be solved.

Owner:SHENZHEN INVT ELECTRIC

Power supply management system and method for server

InactiveUS20130311795A1Volume/mass flow measurementPower supply for data processingSupply managementControl signal

A management system includes two motherboards assigned with different identities, a complex programmable logic device (CPLD), and a switch unit. Each motherboard includes a baseboard management controller (BMC) employed to receive a control signal from a client. The BMC outputs an operation signal corresponding to the control signal and an identity of the motherboard. The CPLD is configured to store the control signal and the identity as a record in a priority list, and determine whether the priority list is a void list. The CPLD outputs a switch signal according to the identity of the record obtained from the priority list in response to the priority list not being a void list. The switch unit is configured to receive the switch signal from the CPLD, and enable a power supply unit to power the corresponding motherboard.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

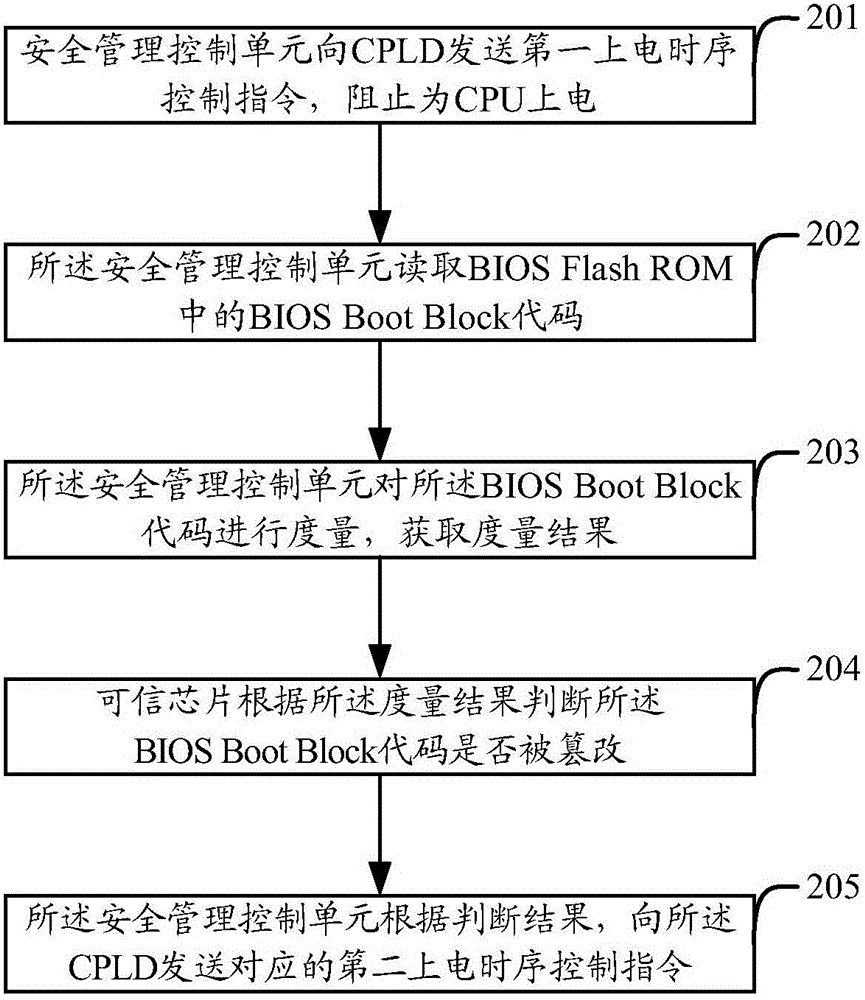

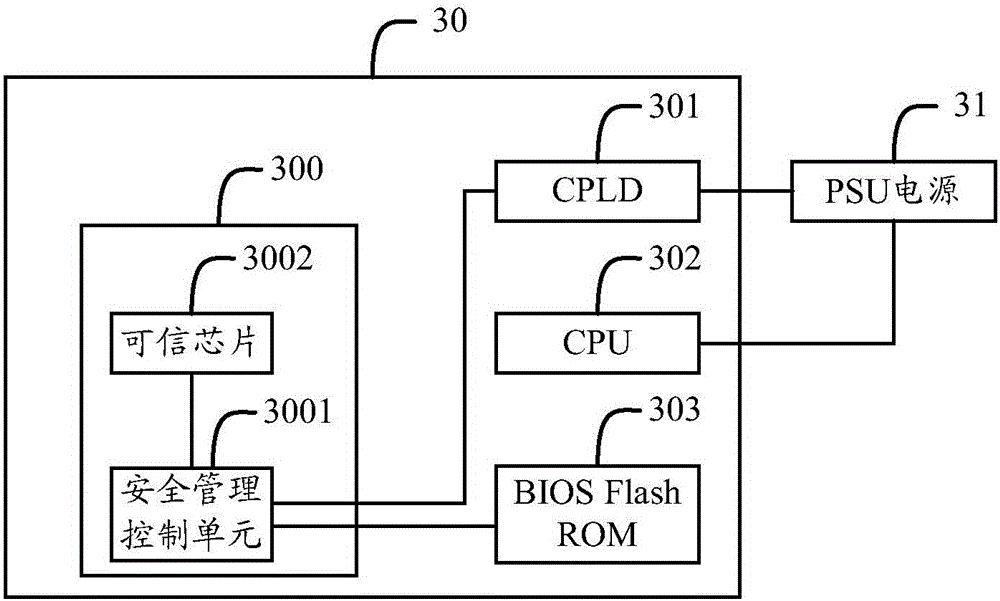

Trustworthy measurement apparatus and method

InactiveCN105160255AEnsure safetyImprove securityPlatform integrity maintainanceElectricityBlock code

The invention provides a trustworthy measurement apparatus and method. The apparatus comprises a security management control unit and a trusted chip, wherein the security management control unit is connected with the trusted chip as well as a complex programmable logic device (CPLD) and a basic input output system flash read only memory (BIOS Flash ROM) on an external mainboard, and is used for sending a first power-on time sequence control instruction to the CPLD for preventing a CPU from being powered on after a trustworthy server is powered on, reading a BIOS Boot Block code in the BIOS Flash ROM, measuring the BIOS Boot Block code, sending a measurement result to the trusted chip, receiving a judgment result of the trusted chip and sending a corresponding second power-on time sequence control instruction to the CPLD; and the trusted chip is used for receiving the measurement result sent by the security management control unit, judging whether the BIOS Boot Block code is tampered, and sending the judgment result to the security management control unit. According to the scheme, the security of the trustworthy server can be improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

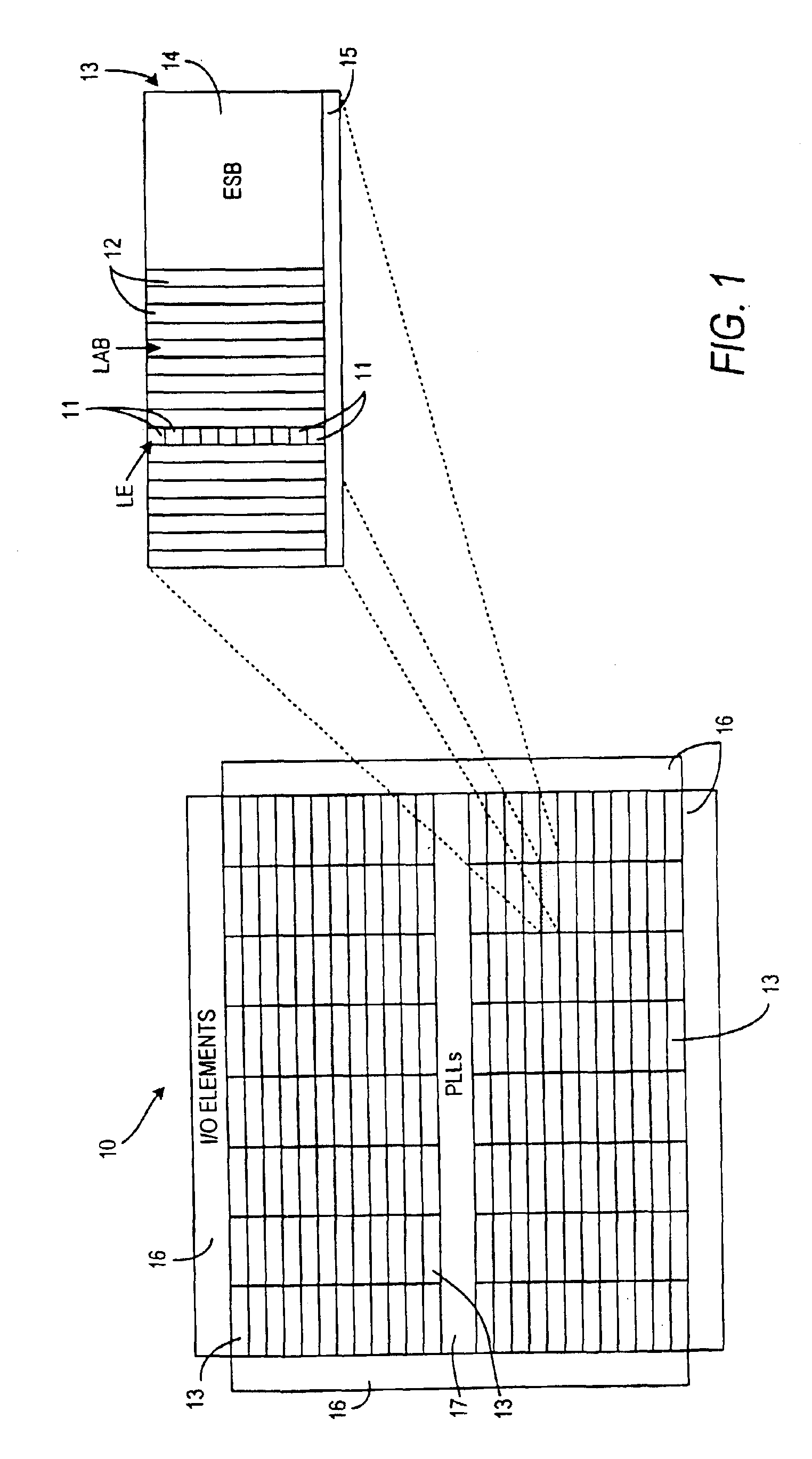

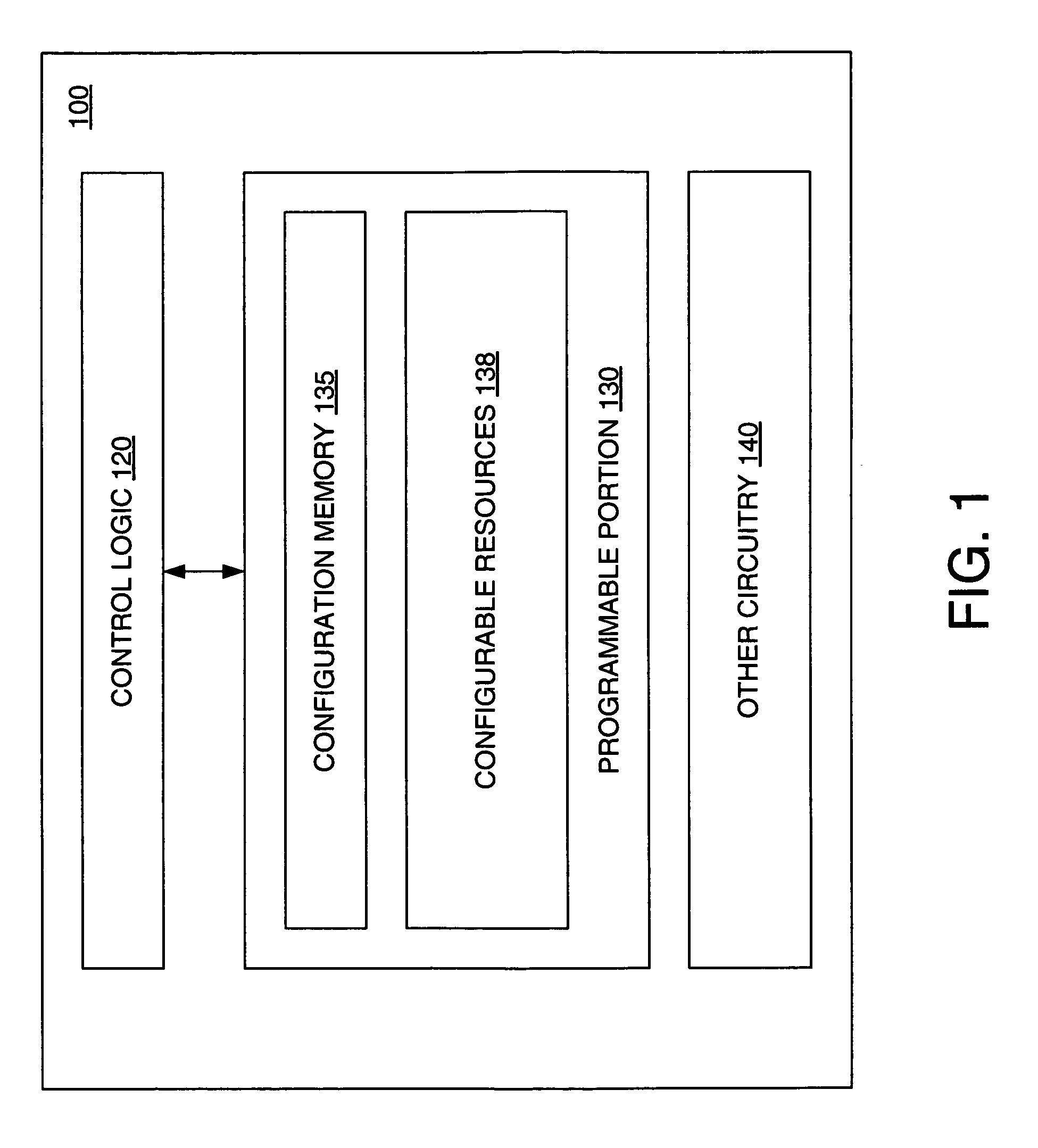

Mask-programmable logic device with building block architecture

InactiveUS6988258B2Reduce in quantityMinimize wasteSpecial data processing applicationsLogic circuits using elementary logic circuit componentsProgrammable logic deviceComplex programmable logic device

A mask-programmable logic device includes logical building blocks that can be connected together to form various logical units for programmable logic. Functionality of a comparable conventional programmable logic device can be provided with fewer gates in this way than by providing all of the gates normally present on that comparable conventional programmable logic device, resulting in fewer unused gates in the devices once mask-programmed.

Owner:ALTERA CORP

Hot-redundancy CAN (Controller Area Network)-bus high-fault-tolerance control terminal and method based on dual DSPs (Digital Signal Processors)

ActiveCN103149907ALower latencyImprove reliabilityTotal factory controlProgramme total factory controlFault toleranceArea network

The invention relates to a hot-redundancy CAN (Controller Area Network)-bus high-fault-tolerance control terminal and method based on dual DSPs (Digital Signal Processors), belonging to the field of automation and control. The terminal and the method are used for solving the problems of control failure, data loss, transmission timeout and the like easily caused due to the fact that control terminals of existing distributed control systems mostly adopt cold backup and the problem that the existing fault tolerance mechanism is not perfect enough. The terminal comprises a digital-analog I / O (Input / Output) board and a dual-redundancy DSP control board, wherein the dual-redundancy DSP control board comprises a master DSP, a slave DSP, a first CAN transceiving module, a second CAN transceiving module, a third CAN transceiving module and a fourth CAN transceiving module, the digital-analog I / O board comprises a power supply module, an ADC (Analog to Digital Converter) module, a first RS232 (Recommended Standard 232) communication module, a second RS232 communication module, a CPLD (Complex Programmable Logic Device), a PWM (Pulse Width Modulation) module and a PWM filtering and self-inspection module, the master DSP and the slave DSP form redundancy, and the failure of controllers is solved by two manners comprising self inspection and mutual inspection.

Owner:HARBIN INST OF TECH

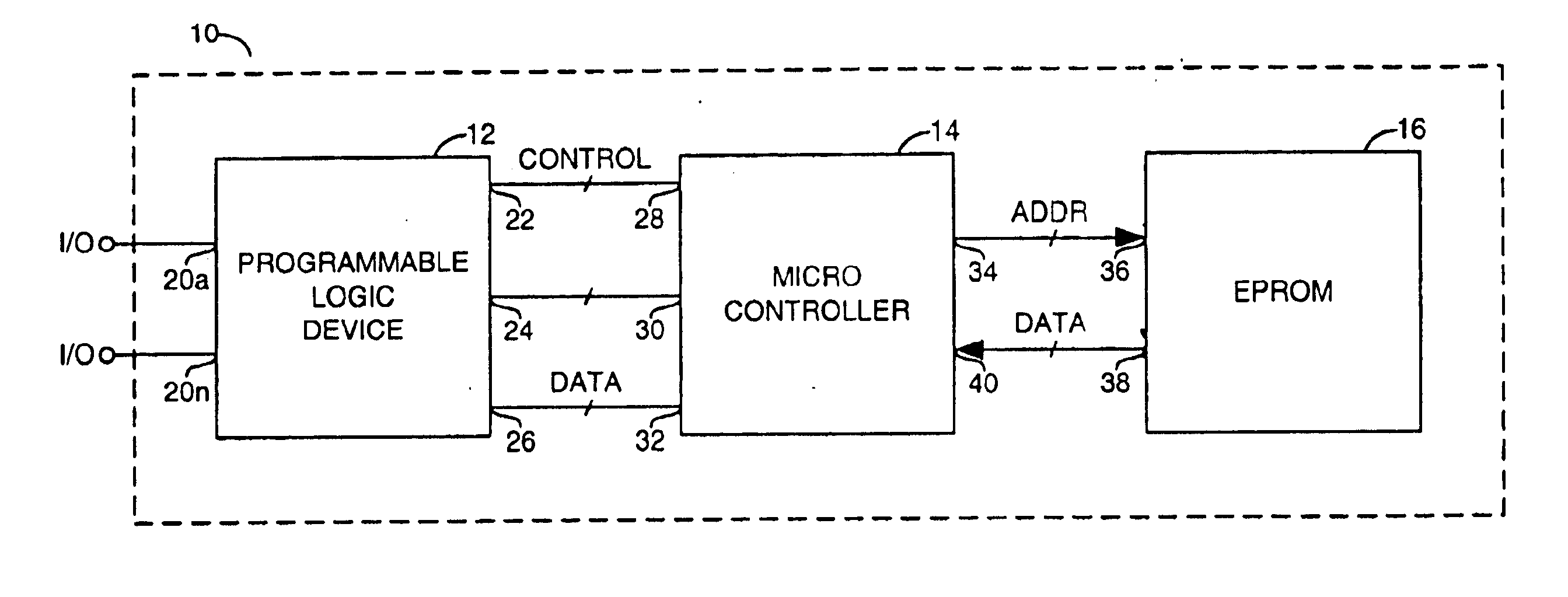

Microcontroller with programmable logic on a single chip

InactiveUS6898101B1Static storageArchitecture with single central processing unitMicrocontrollerErasable programmable logic device

A programmable logic device, a memory device and a microcontroller manufactured on a single integrated circuit chip. In one example, the programmable logic device may comprise one or more macrocells each comprising an input / output macrocell or a buried macrocell. In another example, the programmable logic device may be a complex programmable logic device (CPLD) or a programmable logic array (PLA).

Owner:MONTEREY RES LLC

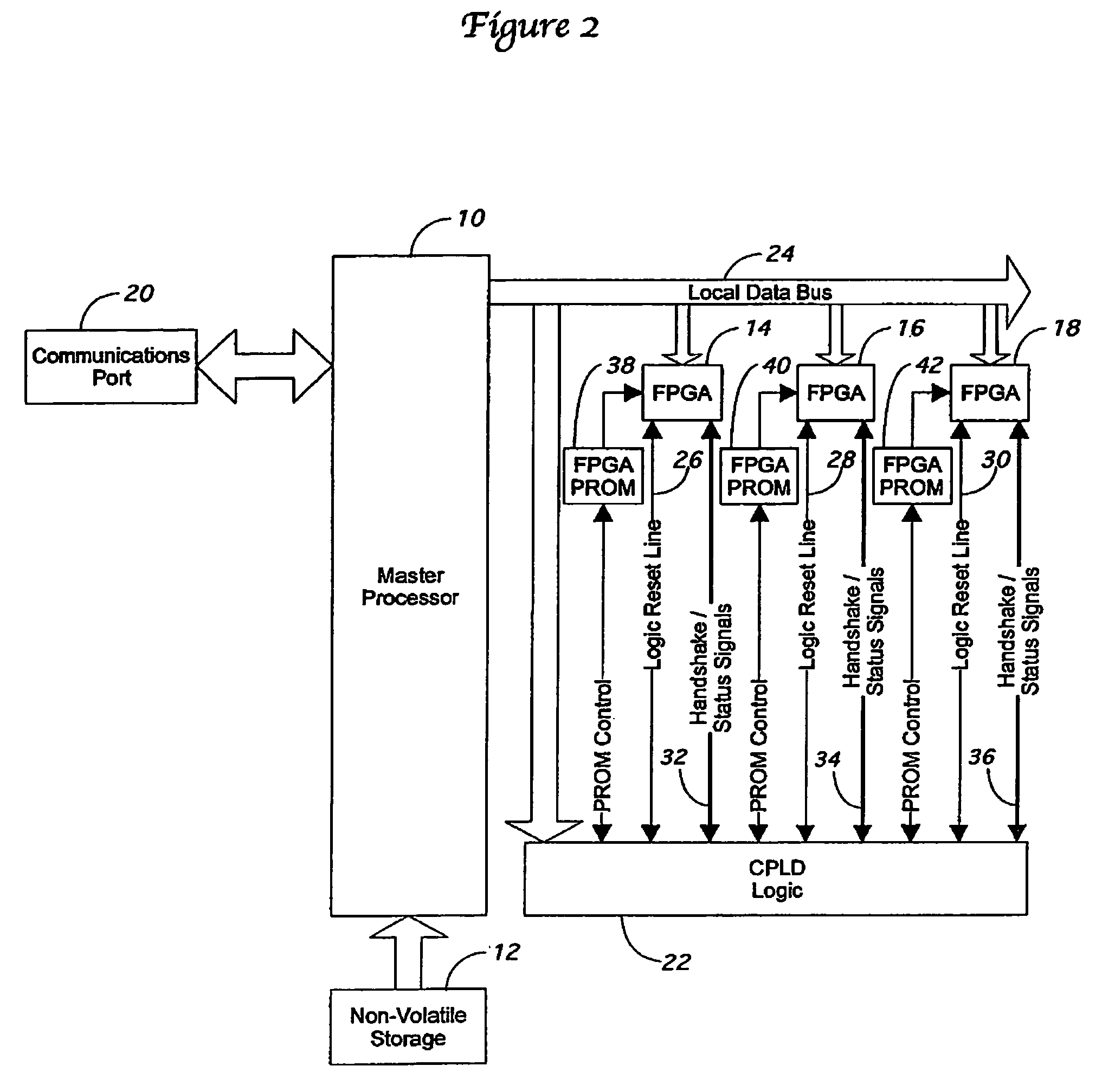

Method and apparatus for configuring a programmable logic device

InactiveUS7146598B2Minimal numberDrain can be reducedElectronic circuit testingData resettingProgrammable logic deviceErasable programmable logic device

A method and apparatus for configuring multiple first programmable logic devices from a single memory includes a microprocessor, and a second programmable logic device containing the interface logic for the first programmable device and the microprocessor. The present invention allows multiple FPGAs to be programmed from a single memory structure under the control of the microprocessor thereby using fewer components than systems dedicating a separate memory to each FPGA. A communications port allows new configurations to be downloaded to the microprocessor memory. In addition, the present invention can be used in combination with standard systems with each FPGA having its own memory, with the microprocessor being able to select between the central microprocessor memory and the local memory for programming each FPGA.

Owner:MCDATA SERVICES CORP +1

General vibration signal measuring system of fan

ActiveCN102155984AReal-time and accurate reflection of vibration statusEliminate the problem of energy leakageVibration measurement in solidsSystems designMonitoring system

The invention discloses a general vibration signal measuring system of a fan, wherein the system realizes the variable frequency multi-channel synchronous sampling function for automatically tracking revolving speed based on phase signals. Site phase signals can be effectively identified and regulated by adopting two-way peak detection superimposing technique for phase signals, thereby improving the adaptability of field application of products. A general signal access circuit is designed to be a compatible circuit which is capable of enabling a plurality of vibration sensor signals of circuits to be compatible, realizing the synchronous, fast and high-precise sampling of signals, and being suitable for the state monitoring system design of large rotation machineries in various industrialsites. The A / D (analogue / digital) sampling frequency can be adjusted automatically according to the revolving speed by a CPLD (complex programmable logic device) logic control circuit; the single-board multi-channel synchronous sampling is realized, and multi-board card multi-channel synchronous sampling is also realized. The measuring system has the characteristics of strong generality, reliableperformance, high precision, simple configuration and the like.

Owner:BEIJING SIFANG JIBAO AUTOMATION

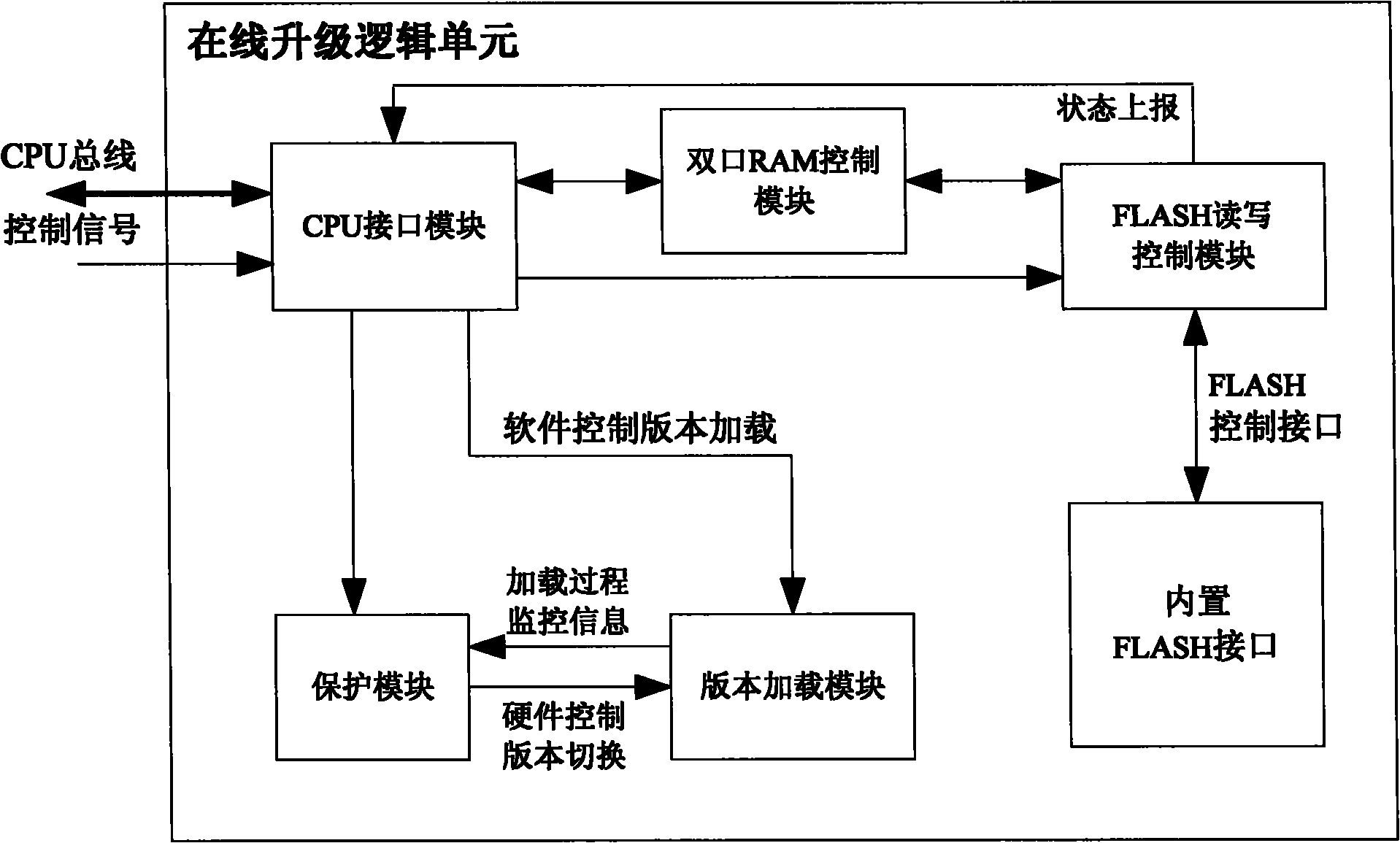

Device and method for dynamically upgrading complex programmable logic device (CPLD)

InactiveCN101853172AReduce the impactFast Version SwitchingProgram loading/initiatingProgrammable logic deviceComplex programmable logic device

The invention discloses a device and a method for dynamically upgrading a complex programmable logic device (CPLD), wherein a service one-board processor acquires background CPLD version information from a remote background network management platform and compares the background CPLD version information with the version information of the CPLD operating in the single board and the working version information saved in an on-chip FLASH user data area; if the background CPLD version information is inconsistent with the version information of the CPLD operating in the single board and the working version information saved in the on-chip FLASH user data area, a version downloading process is carried out, the acquired background CPLD version file is written in an on-chip FLASH working version area of a CPLD chip, and the working version information of the user data area is updated; and a version loading module of a logic unit is upgraded on line, and the background CPLD version is acquired from the working version area for loaded according to a command for switching and loading the working version. The invention has simple circuit, only an on-chip FLASH of the CPLD is utilized, other tasks of the service processor can be normally executed in the on-line upgrading process, and version switching can be completed quickly.

Owner:ZTE CORP

Integrated circuit pin testing device

ActiveCN105510763AImplement pin testSimple structureElectronic circuit testingMicrocontrollerProgrammable logic device

The invention discloses an integrated circuit pin testing device. The integrated circuit pin testing device comprises a main board and an expansion board. A first output end of a microcontroller arranged on the main board is electrically connected with an input end of a complex programmable logic device arranged on the expansion board and is used for transmitting a received test instruction to the complex programmable logic device. An output end of the complex programmable logic device is electrically connected with a first input end of a switch module. A first output end of the switch module is electrically connected with a tested pin of a tested integrated circuit. The complex programmable logic device controls a corresponding switch in the switch module to be switched on according to the test instruction. A second output end of the microcontroller is electrically connected with an input end of a constant-current source, and an output end of the constant-current source is electrically connected with a second input end of the switch module. The microcontroller controls the constant-current source to input corresponding test current to the tested pin after receiving the test instruction. By the integrated circuit pin testing device, the problems of large size and low portability due to structural complexity of an internal hardware circuit of a traditional OS (open / short) tester are effectively solved.

Owner:ALLWINNER TECH CO LTD

Remote dynamic loading system and method for processor program on basis of FPGA (Field Programmable Gate Array) or CPLD (complex programmable logic device) controller

ActiveCN103389669ALower requirementSimple processProgramme controlComputer controlCommunication unitProgrammable logic device

The invention provides a remote dynamic loading system and method for a processor program on the basis of an FPGA or a CPLD controller. The system comprises an upper computer, a communication unit, an FPGA or a CPLD controller unit, a processer unit and a parallel volatile storage unit, wherein the processor program is stored in the upper computer, the program and a control command are packaged into data frames, identifiers are added, and the data frames are transmitted to the communication unit; the communication unit receives the program and the control command from the upper computer and sends the program and the control command to the FPGA or CPLD controller unit; and the FPGA or CPLD controller unit manages an external bus of the processer unit and receives the data frames from the communication unit at the same time, writes the program into the parallel volatile storage unit according to identifiers and contents of the data frames, and controls the processor to jump to an address where the program is in and start working. According to the system and the method, remote and dynamic loading is performed on the processor on the premise that a storage is not subjected to flash curing.

Owner:THE 715TH RES INST OF CHINA SHIPBUILDING IND CORP

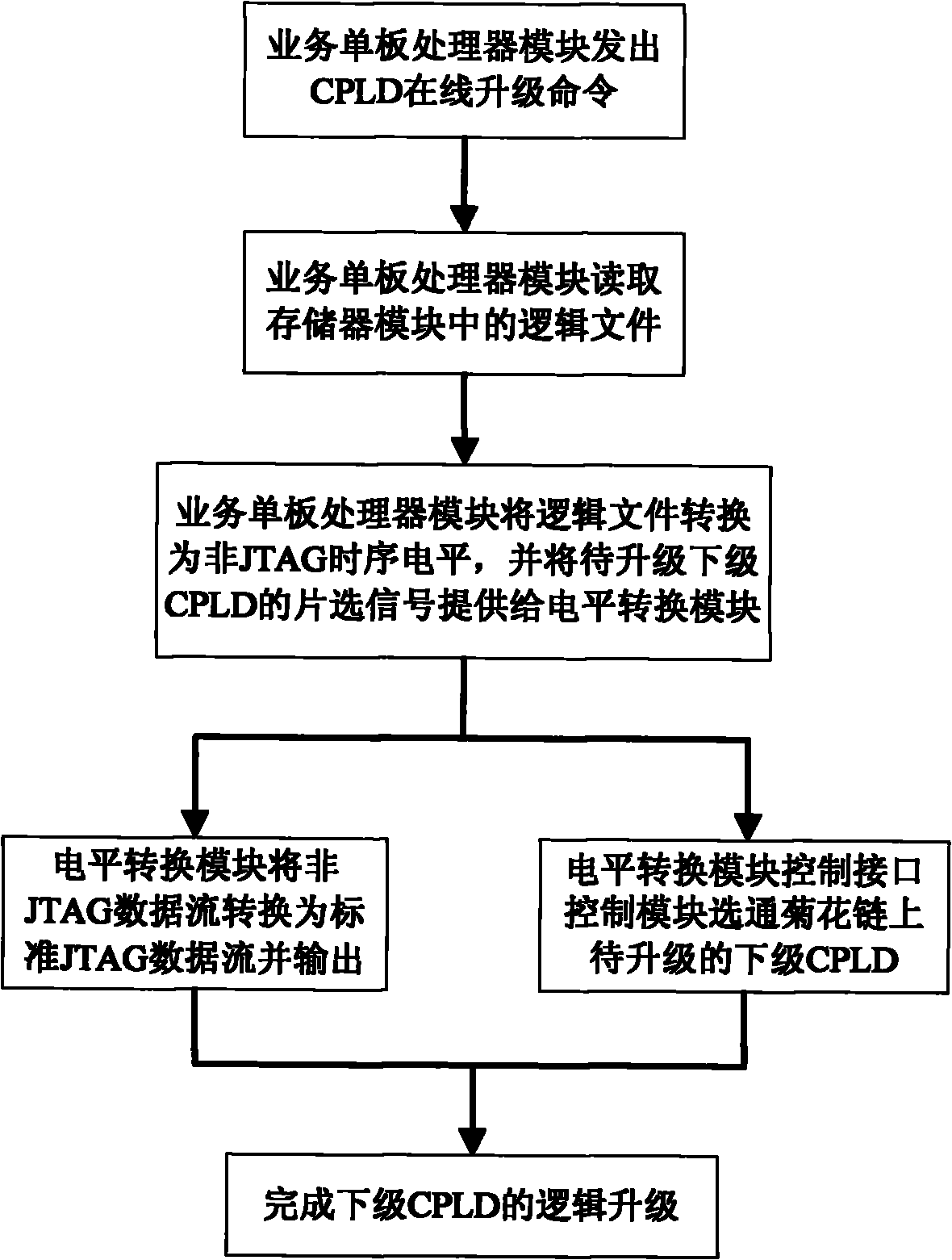

Method and device for upgrading complex programmable logic device on line

InactiveCN101894029AApplicable logic online upgradeEasy to update onlineProgram loading/initiatingProcessor registerProgrammable logic device

The invention discloses a method and a device for upgrading a complex programmable logic device on line. The method comprises: storing a to-be-upgraded CPLD logic file in a binary format, and converting the to-be-upgraded CPLD logic file in the binary format into a JTAG time sequence electrical level when the CPLD is to be upgraded; according to a non-JTAG time sequence electrical level, simulating a standard JTAG time sequence electrical level by using a register; and gating a subordinate CPLD of the to-be-upgraded CPLD, and writing the standard JTAG time sequence electrical level into the to-be-upgraded CPLD to complete the online upgrade of the to-be-upgraded CPLD. When the method and the device are used, the CPLD device can be upgraded on line directly without cable sintering.

Owner:ZTE CORP

Design security for configurable devices

ActiveUS7345502B1Fail-safe circuitsElectrical testingProgrammable logic deviceComplex programmable logic device

Methods and structures for design security in configurable devices are described. In some embodiments, a configurable device may be placed in an unsecured mode allowing for access to configuration data and other diagnostic functions during development and production phases. Once the device is finalized, it may be placed in a secure mode that disables a configuration path and enables a bypass path, thereby securing the configuration data. In some embodiments, the configurable device may be a programmable logic device, such as a complex programmable logic device.

Owner:XILINX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com