Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

59248results about "Energy efficient computing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

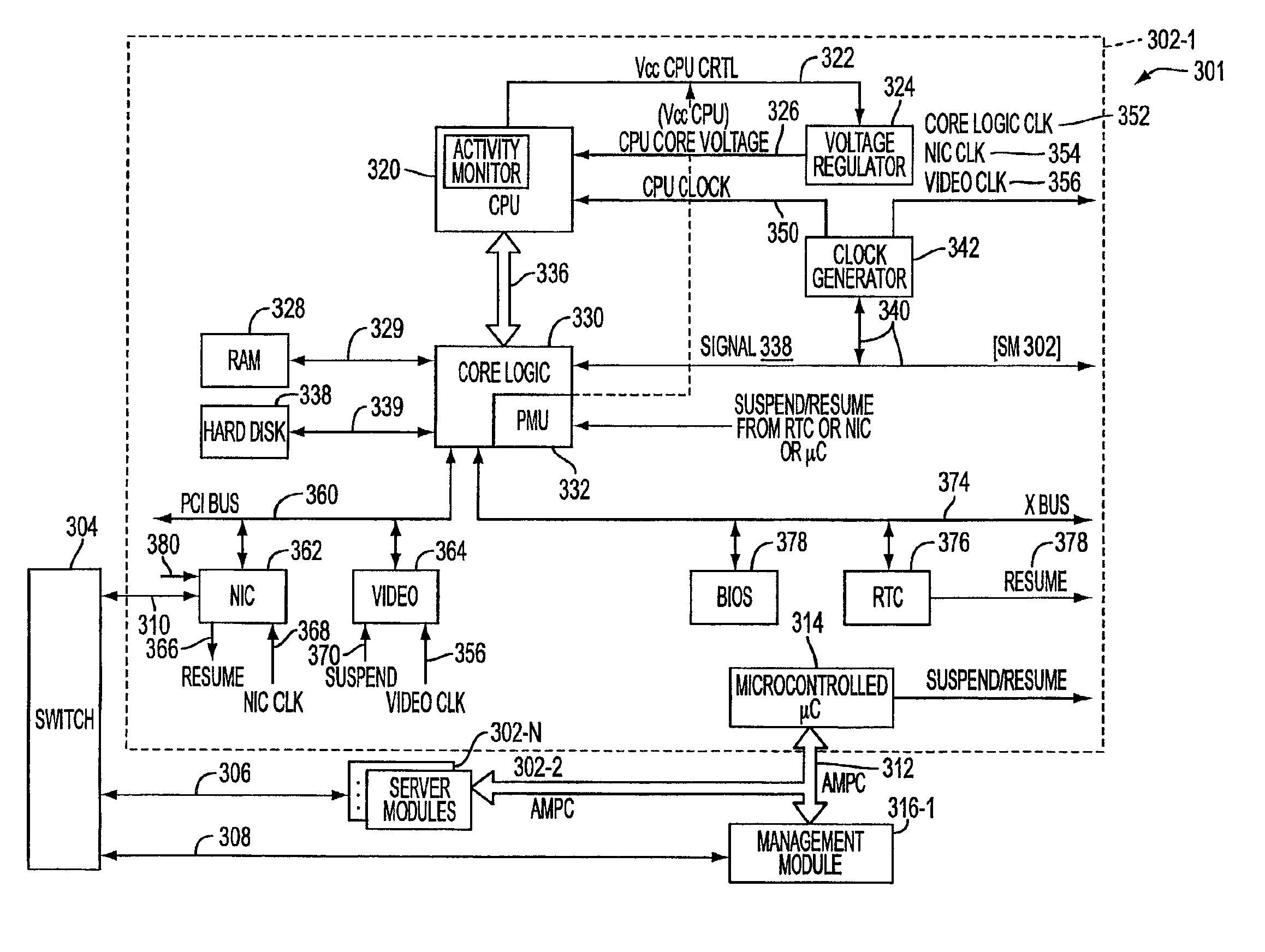

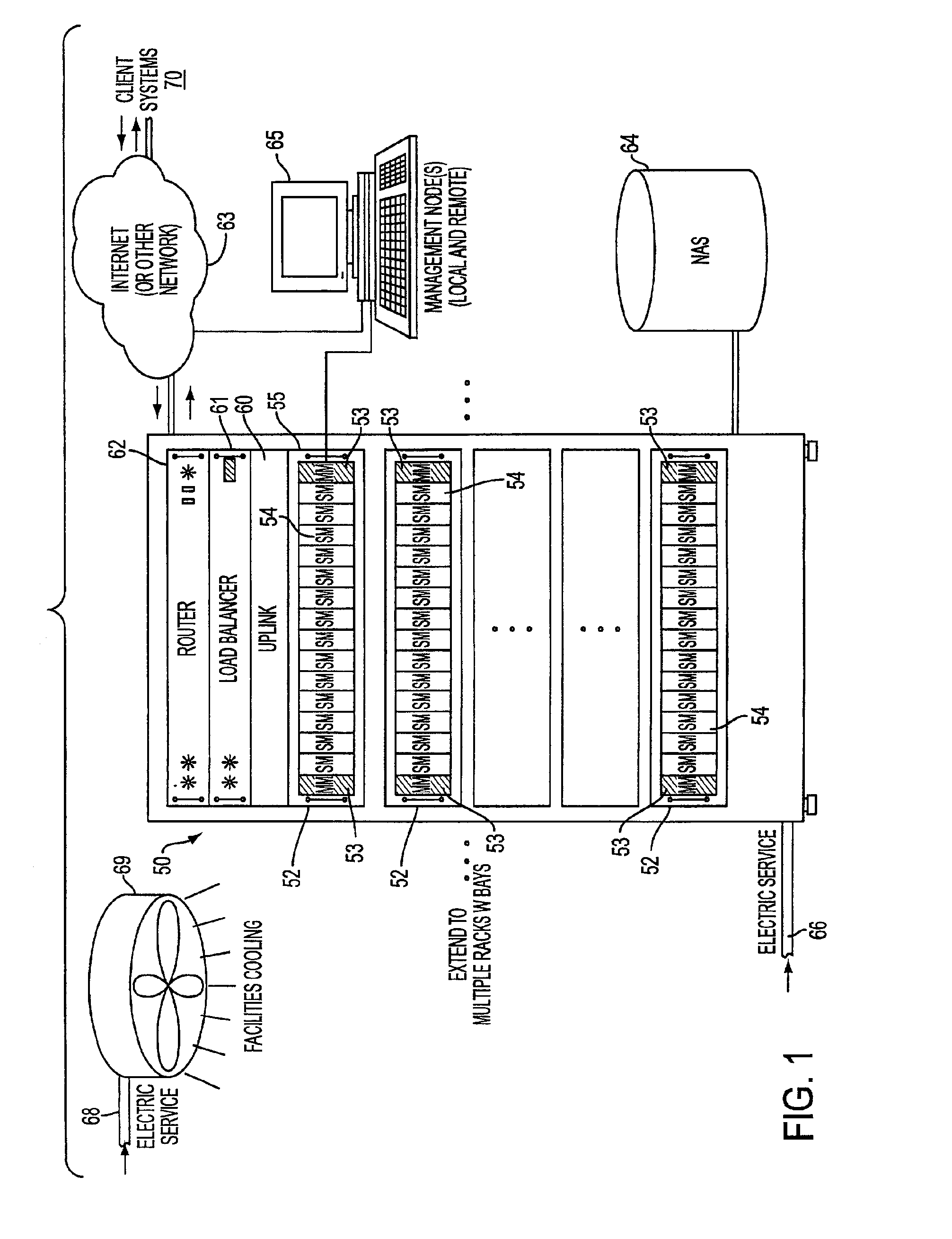

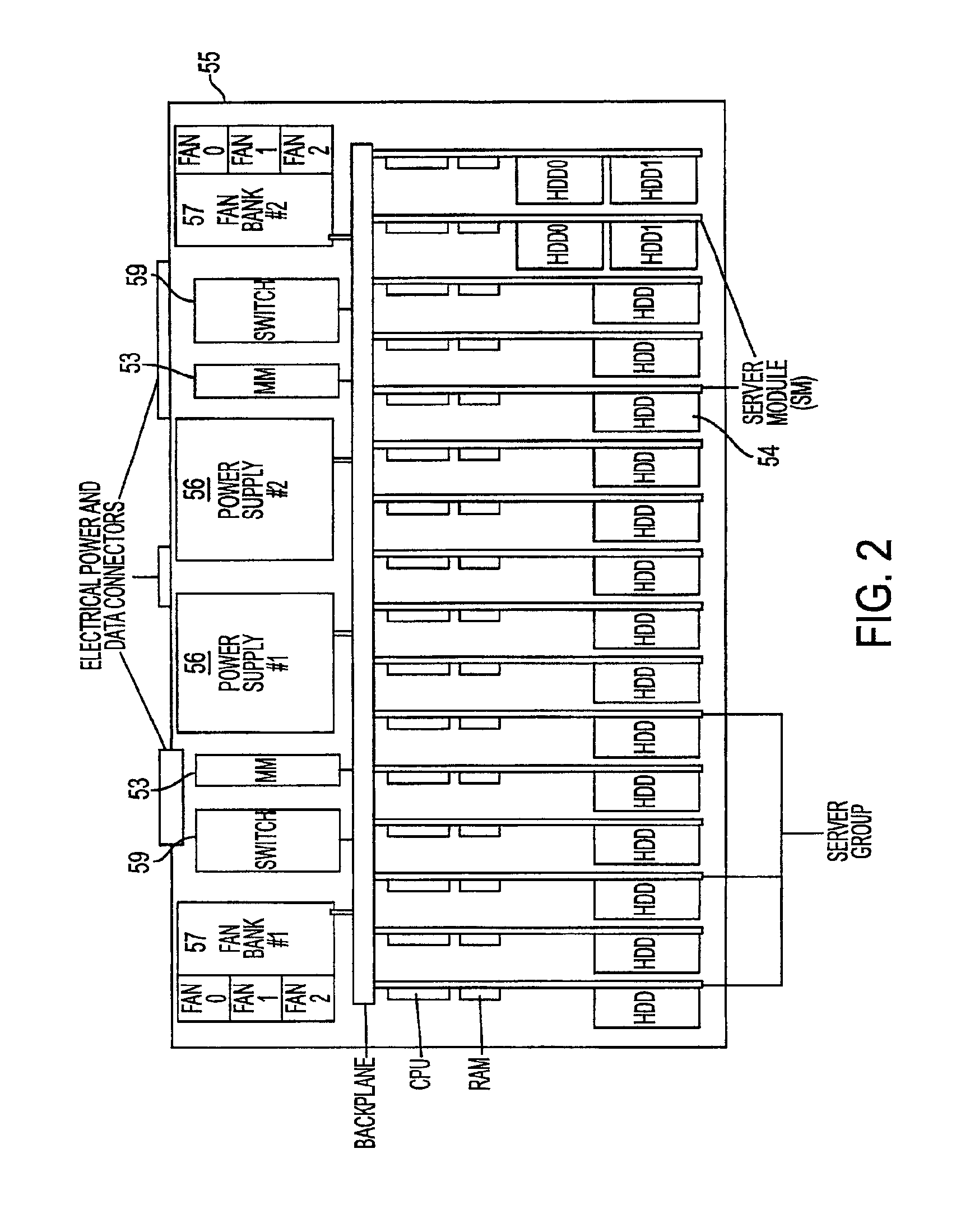

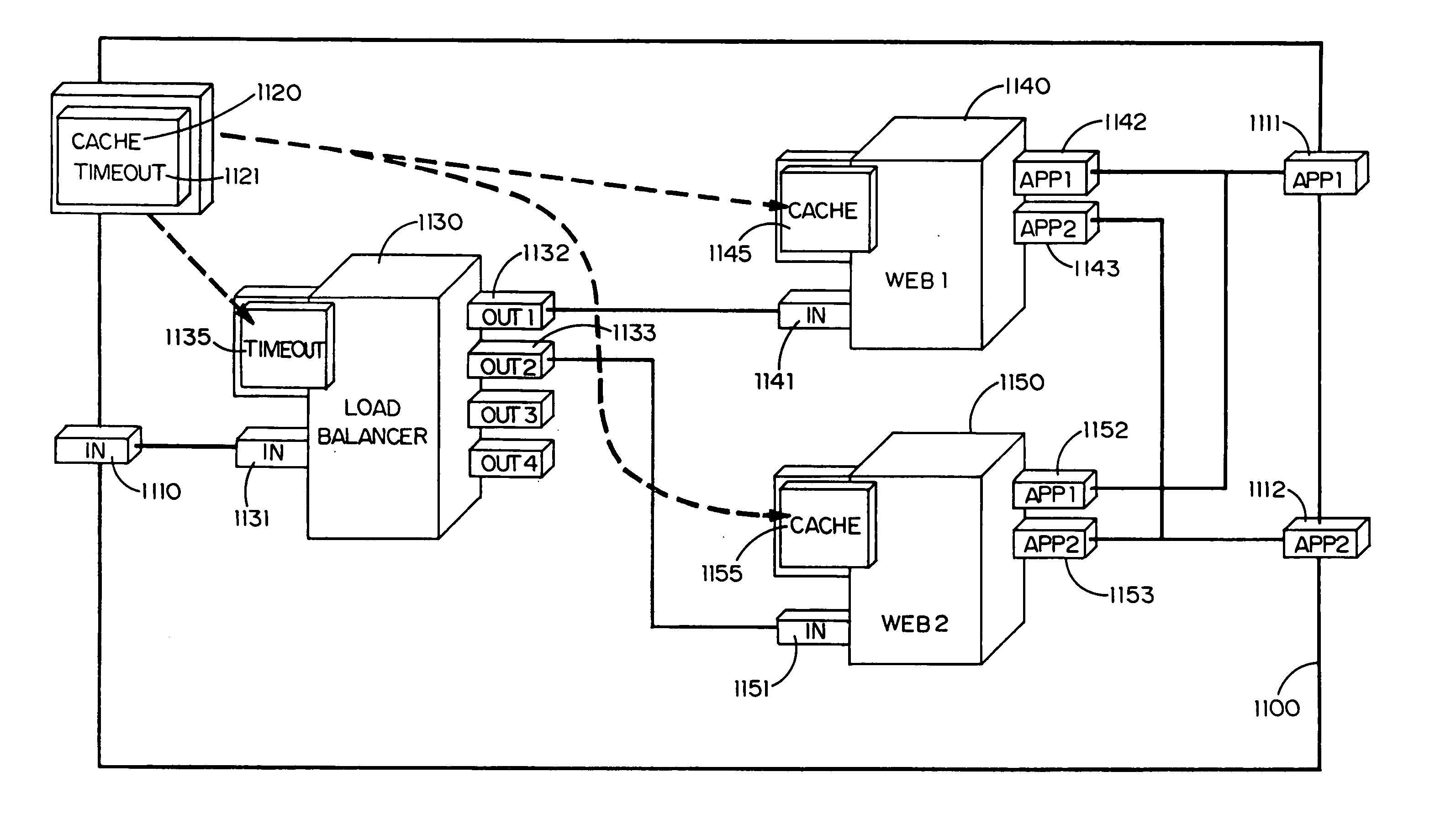

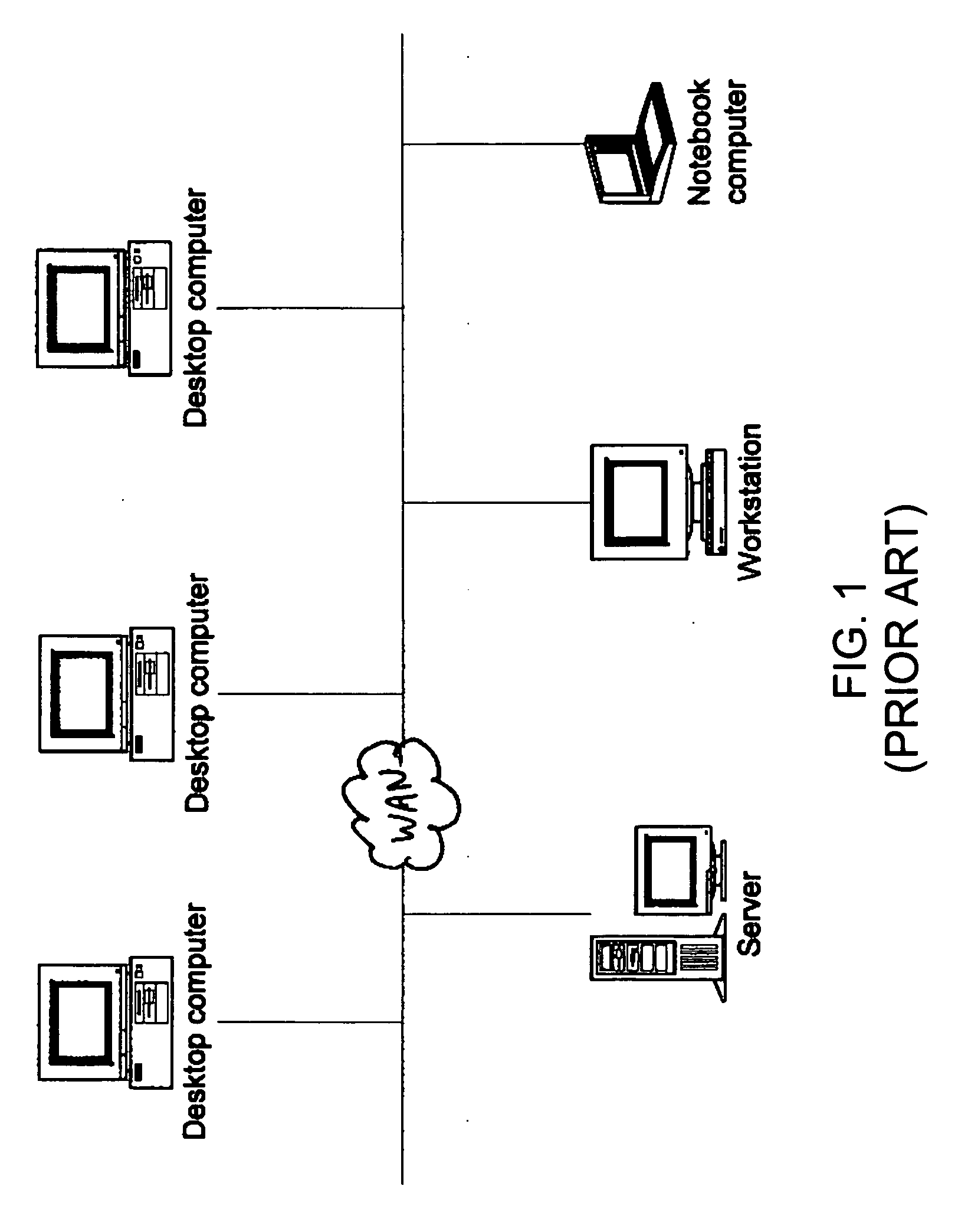

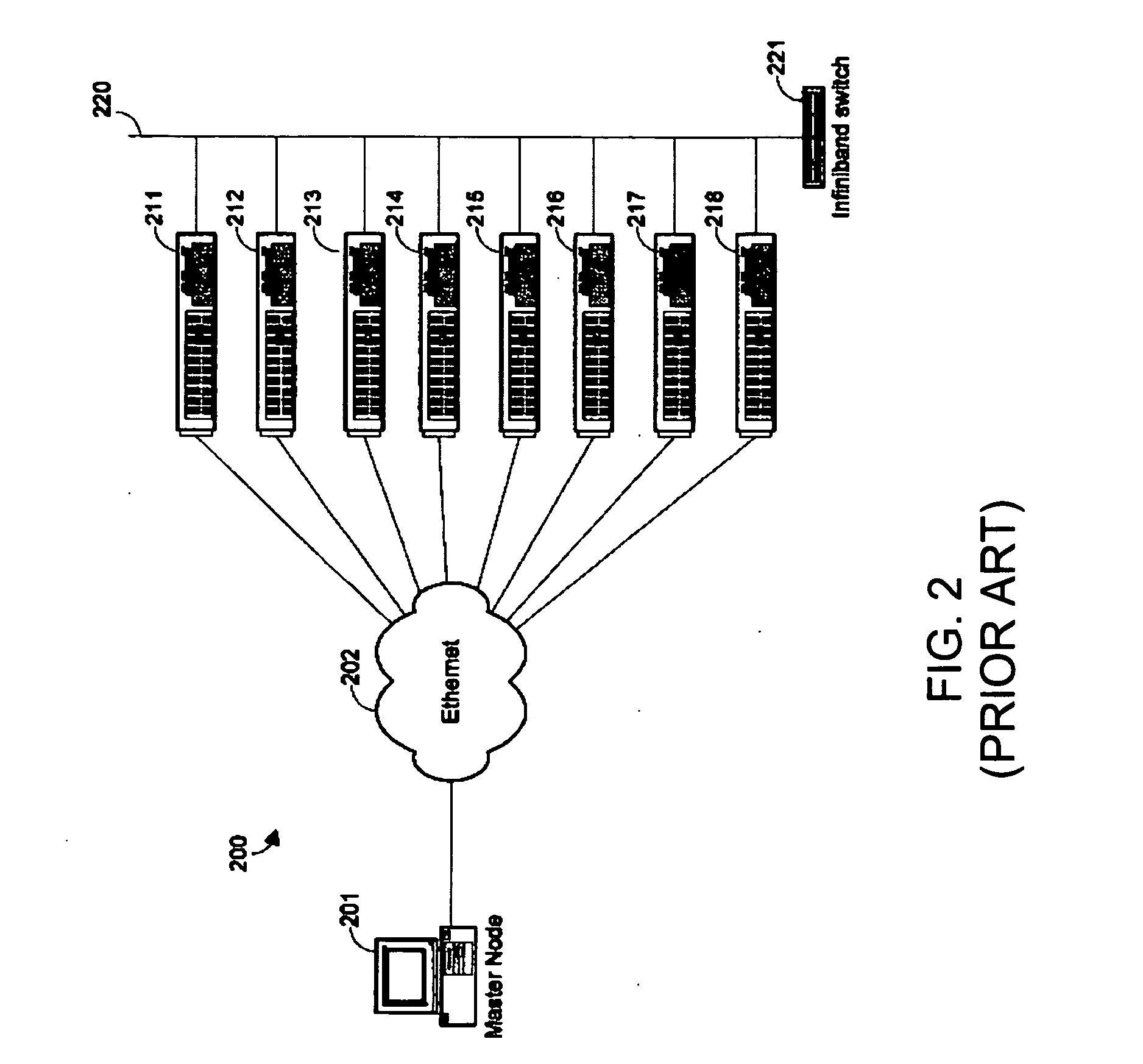

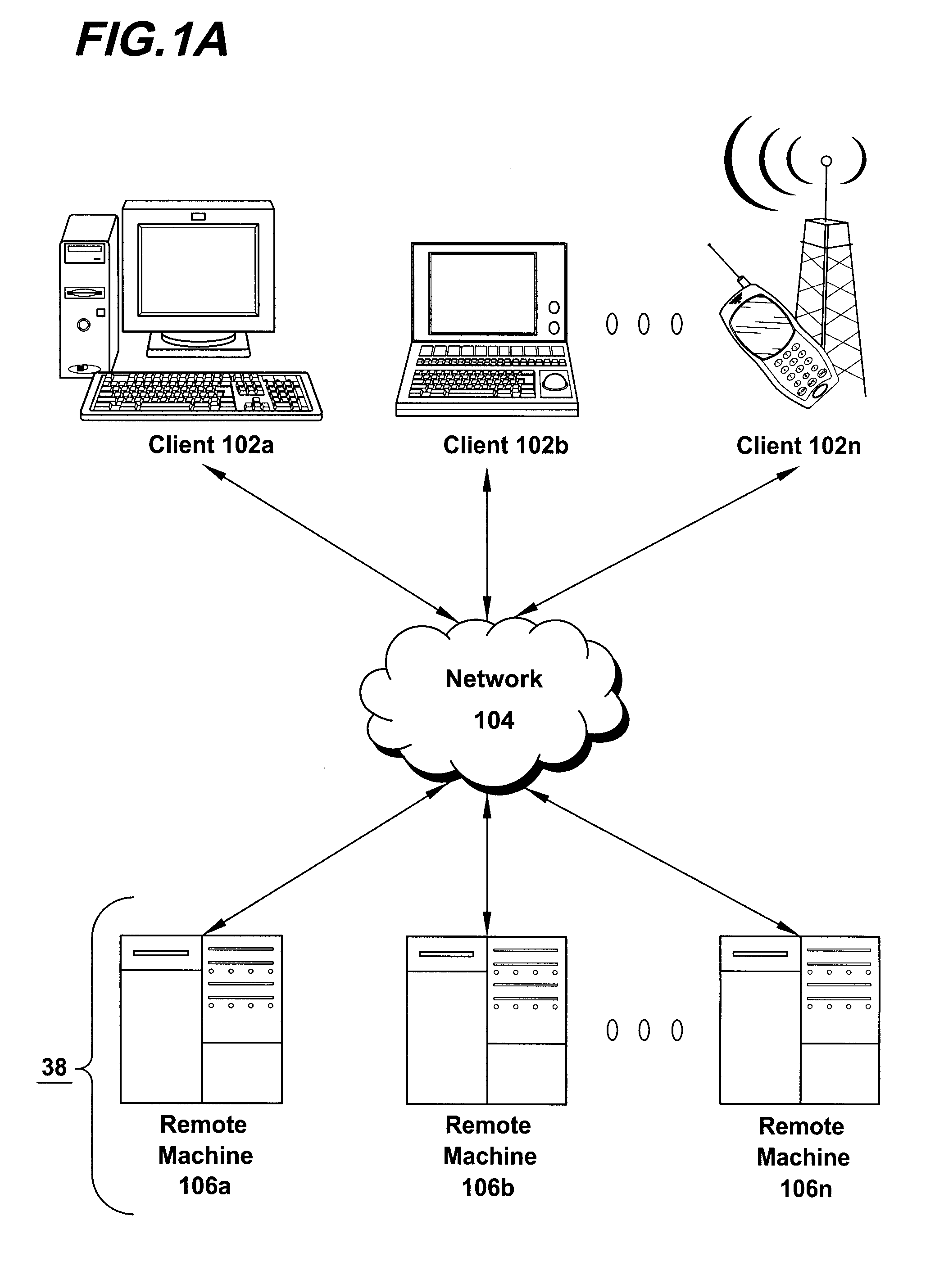

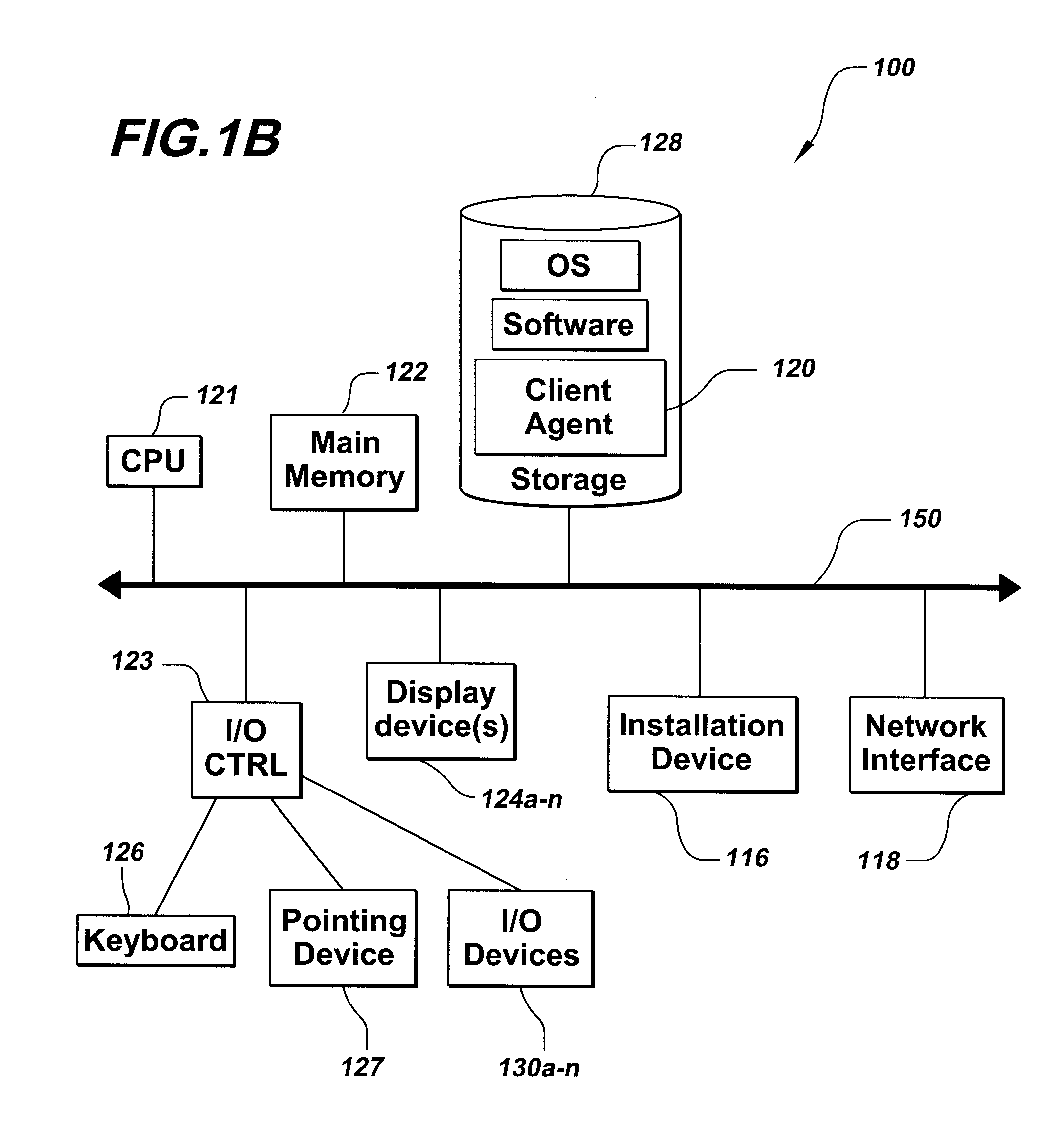

System, method, and architecture for dynamic server power management and dynamic workload management for multi-server environment

InactiveUS6859882B2Save energyConserving methodEnergy efficient ICTVolume/mass flow measurementNetwork architectureWorkload management

Network architecture, computer system and / or server, circuit, device, apparatus, method, and computer program and control mechanism for managing power consumption and workload in computer system and data and information servers. Further provides power and energy consumption and workload management and control systems and architectures for high-density and modular multi-server computer systems that maintain performance while conserving energy and method for power management and workload management. Dynamic server power management and optional dynamic workload management for multi-server environments is provided by aspects of the invention. Modular network devices and integrated server system, including modular servers, management units, switches and switching fabrics, modular power supplies and modular fans and a special backplane architecture are provided as well as dynamically reconfigurable multi-purpose modules and servers. Backplane architecture, structure, and method that has no active components and separate power supply lines and protection to provide high reliability in server environment.

Owner:HURON IP

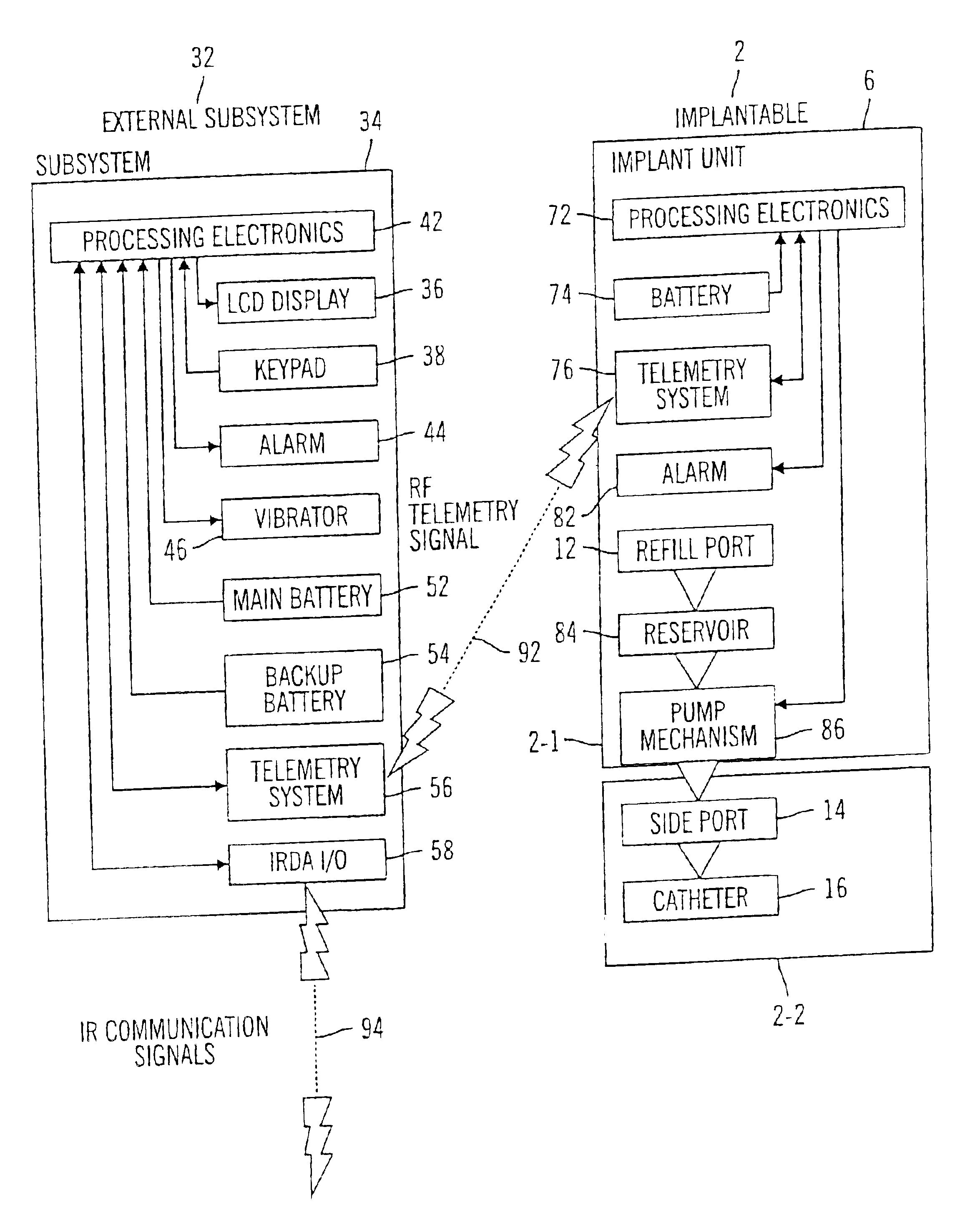

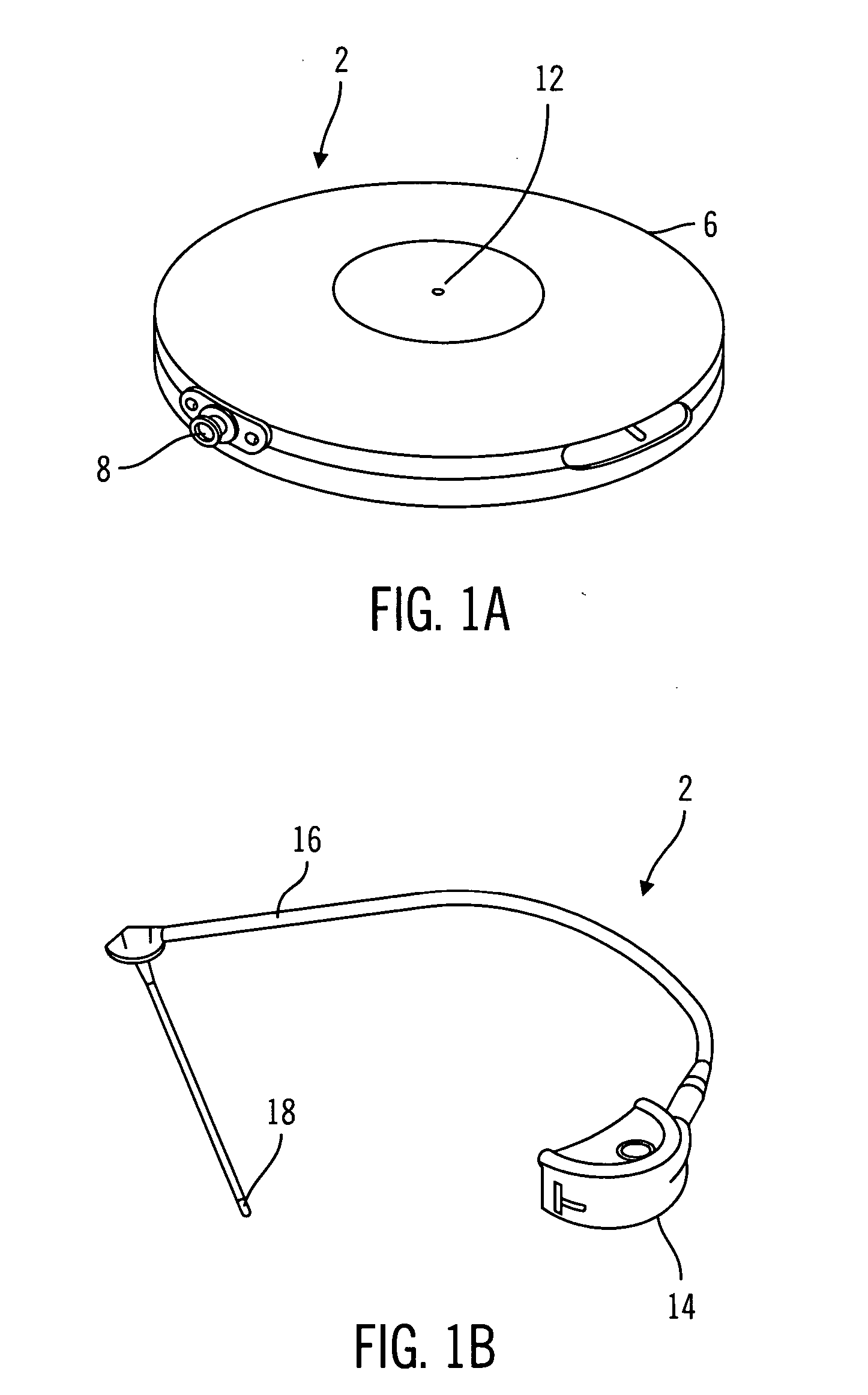

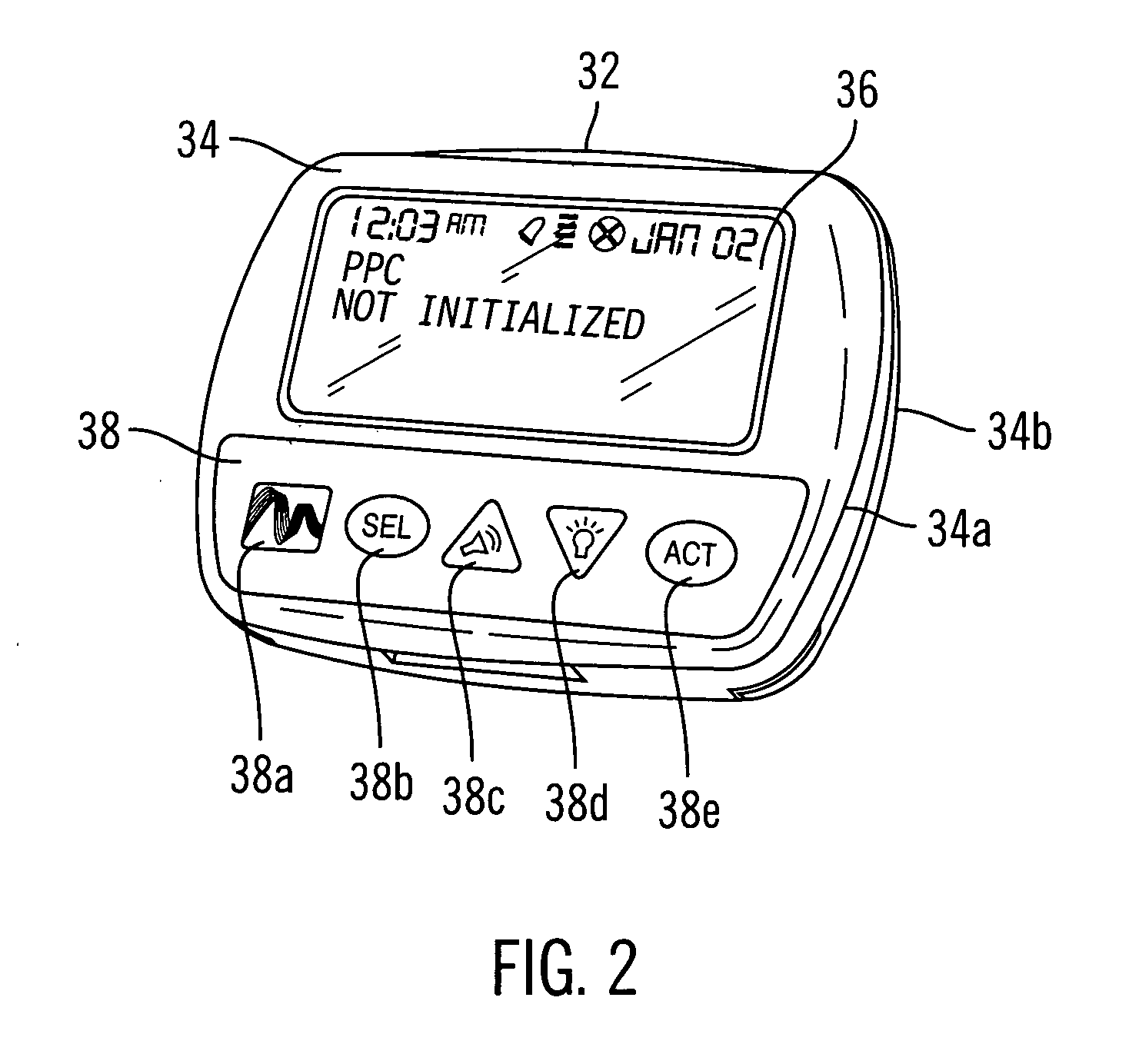

Ambulatory medical apparatus and method using a telemetry system with predefined reception listening

InactiveUS6950708B2Reduce power consumptionConsuming and burdensomeEnergy efficient ICTElectrotherapyAmbulatoryStart time

An implanted medical device (e.g. infusion pump) and an external device communicate with one another via telemetry messages that are receivable only during windows or listening periods. Each listening period is open for a prescribed period of time and is spaced from successive listening periods by an interval. The prescribed period of time is typically kept small to minimize power consumption. To increase likelihood of successful communication, the window may be forced to an open state, by use of an attention signal, in anticipation of an incoming message. To further minimize power consumption, it is desirable to minimize use of extended attention signals, which is accomplished by the transmitter maintaining an estimate of listening period start times and attempting to send messages only during listening periods. In the communication device, the estimate is updated as a result of information obtained with the reception of each message from the medical device.

Owner:MEDTRONIC MIMIMED INC

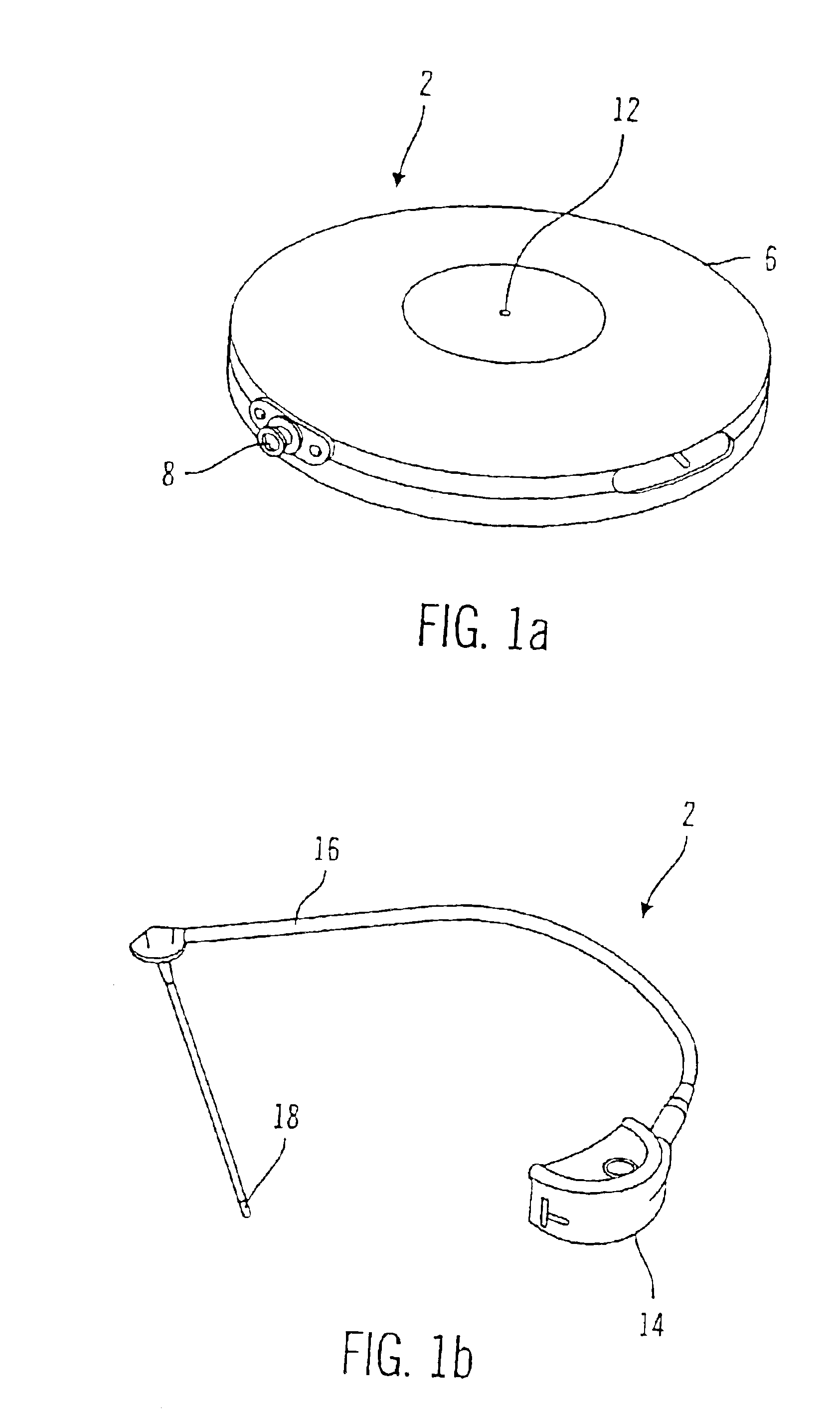

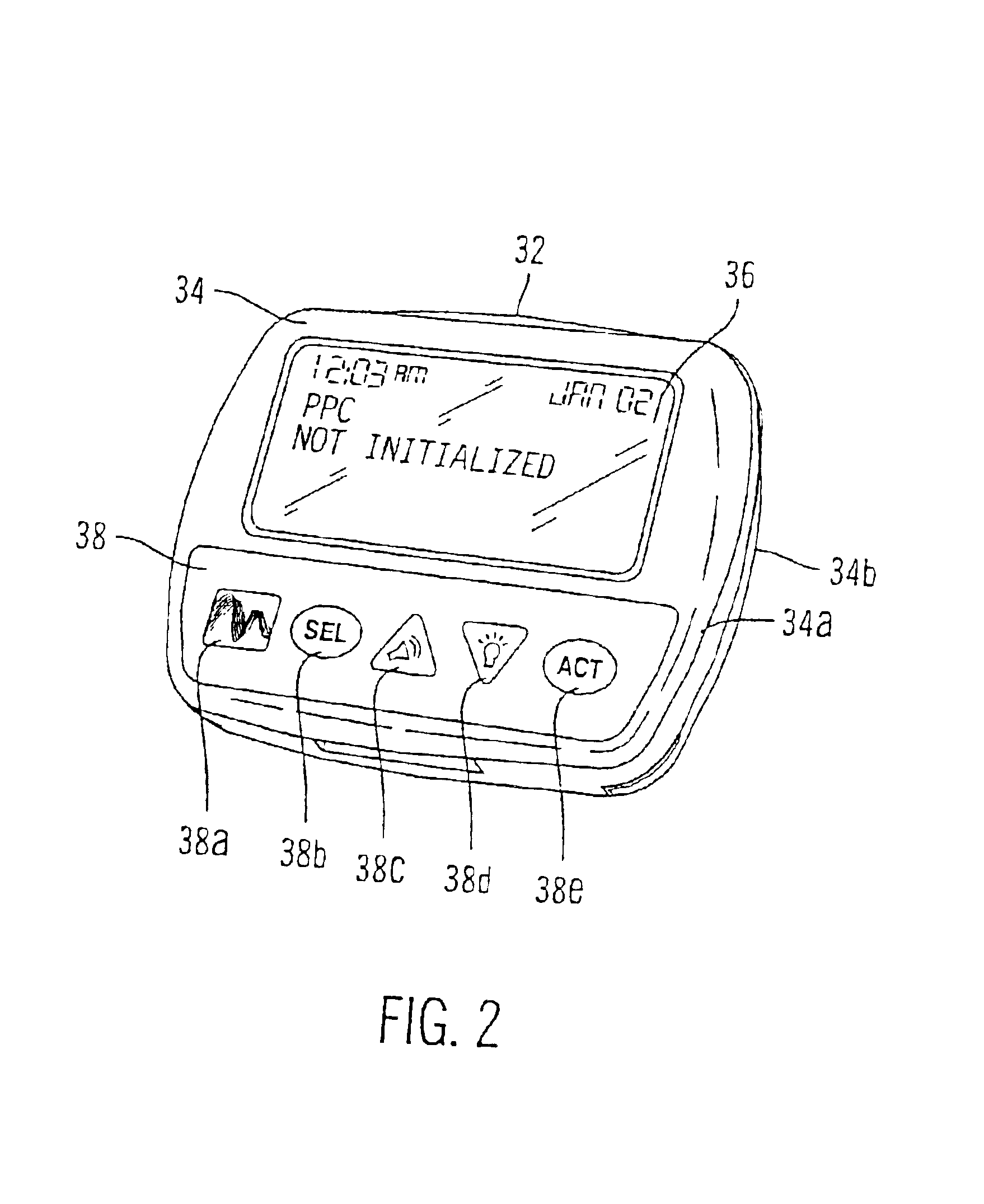

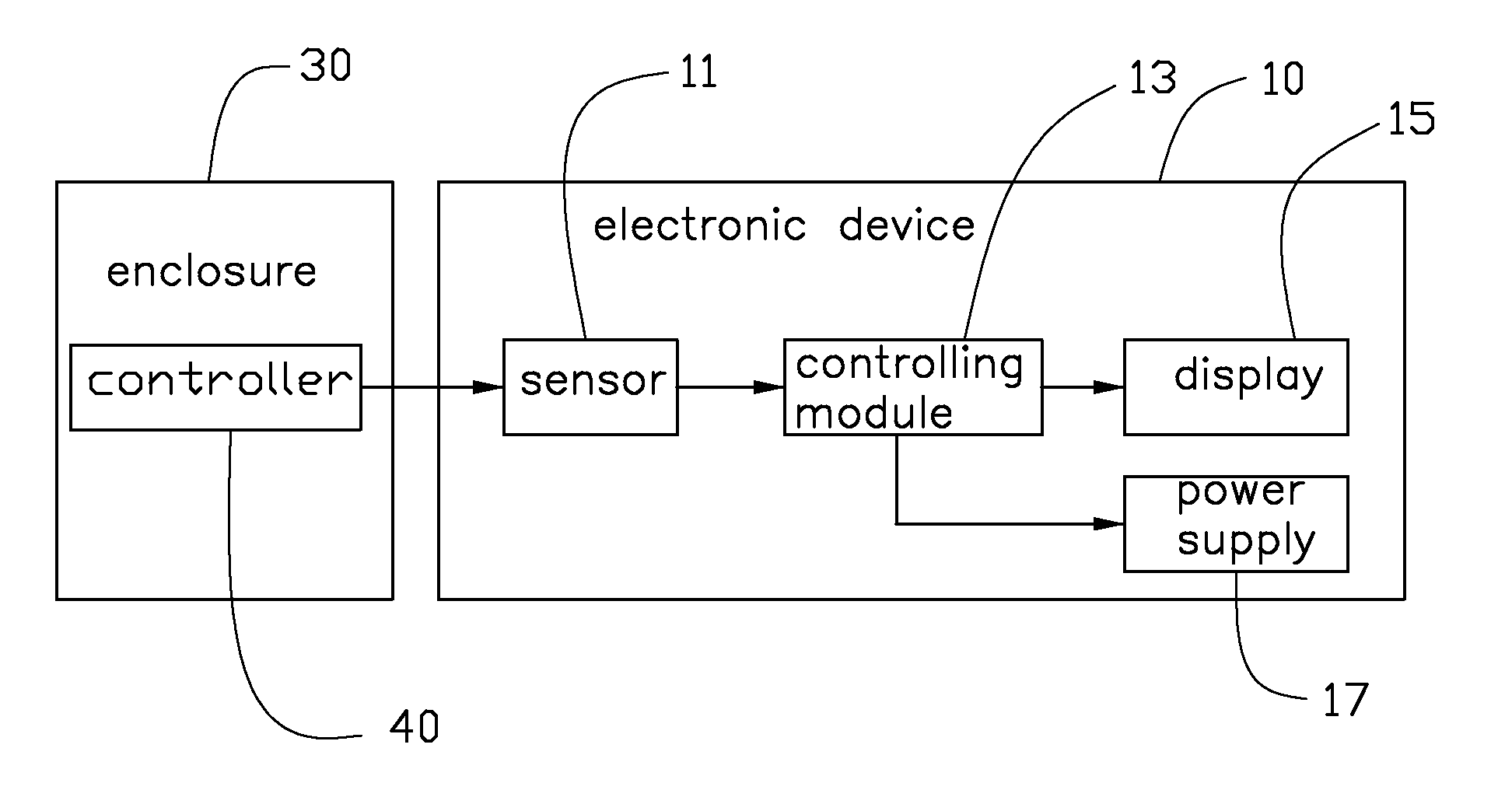

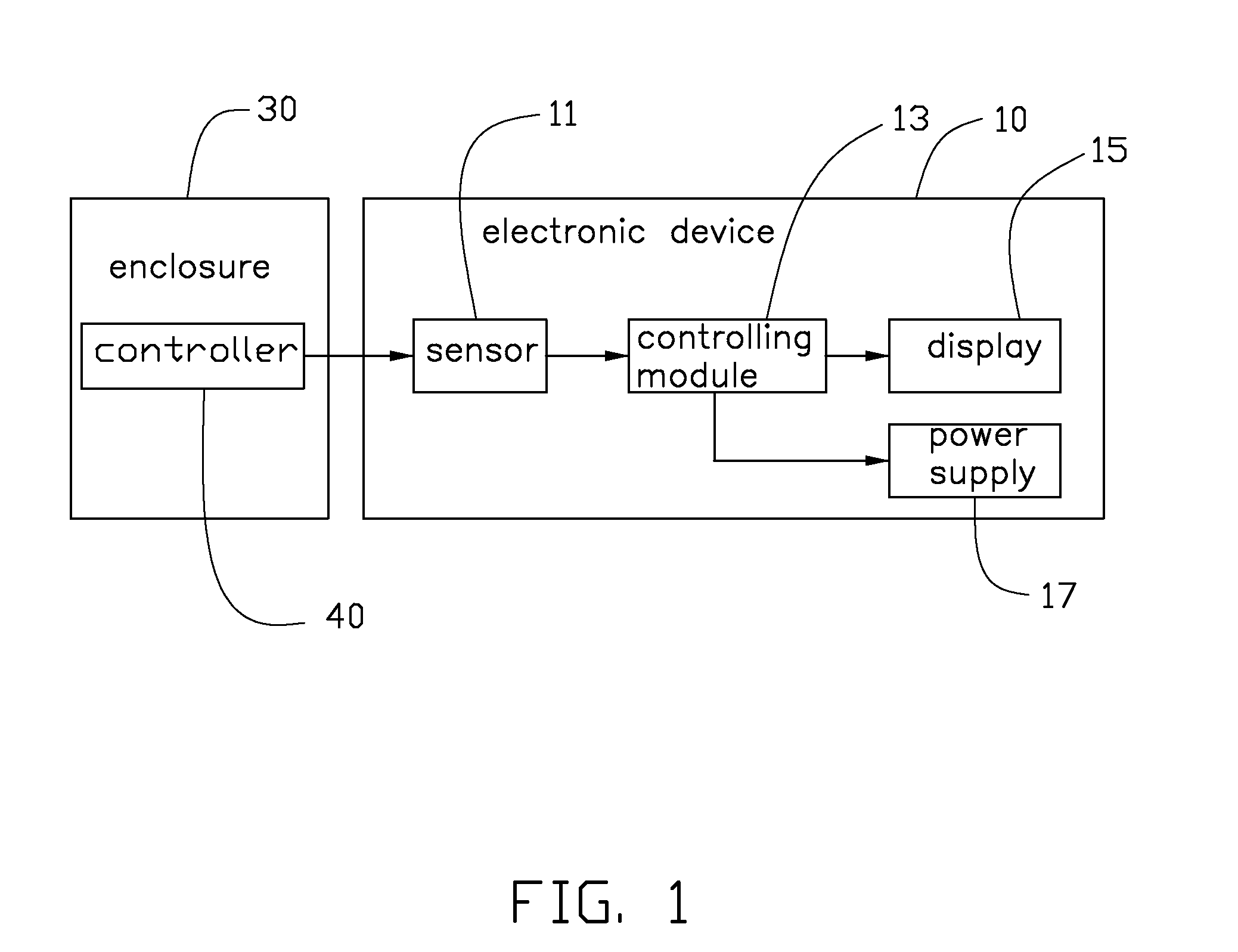

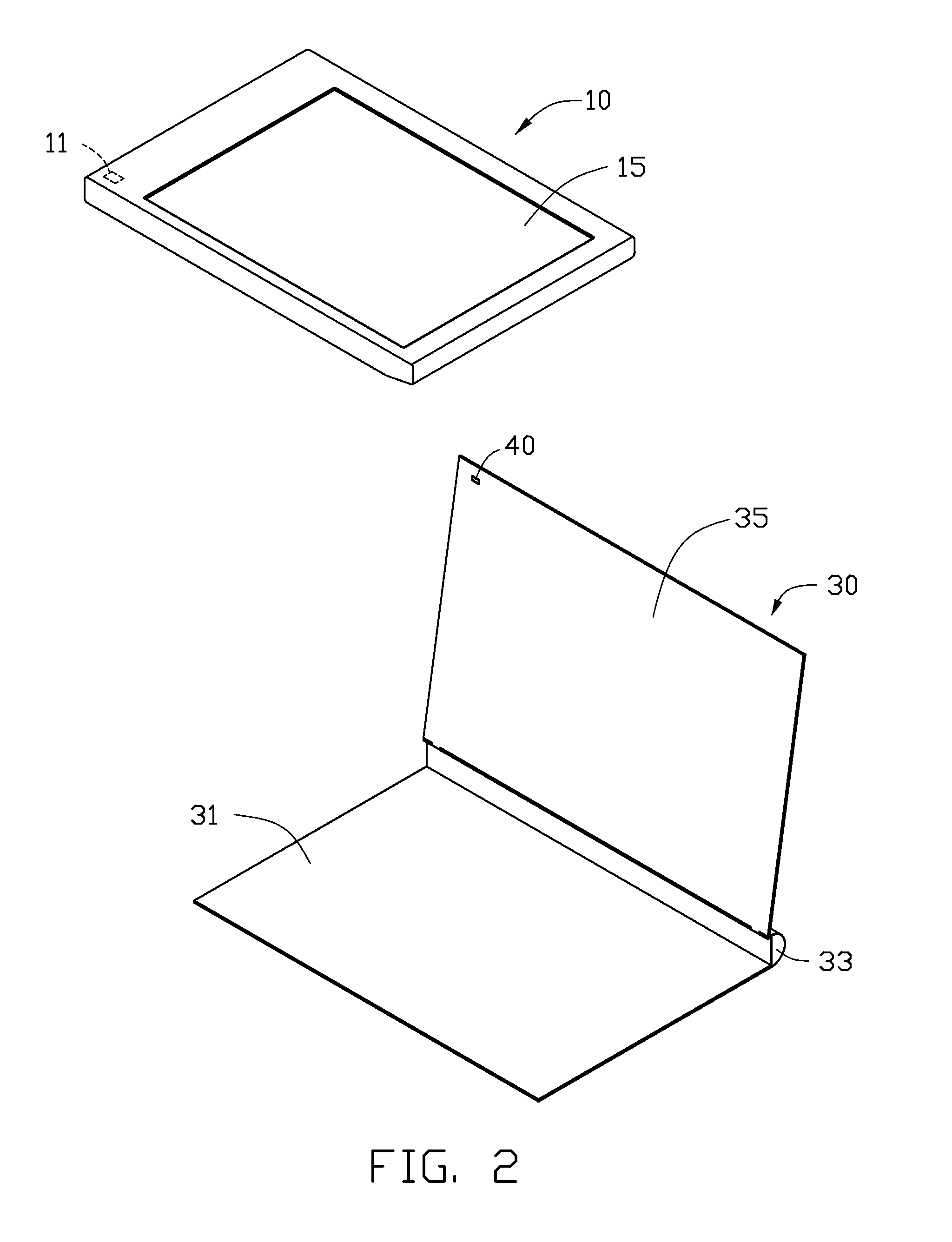

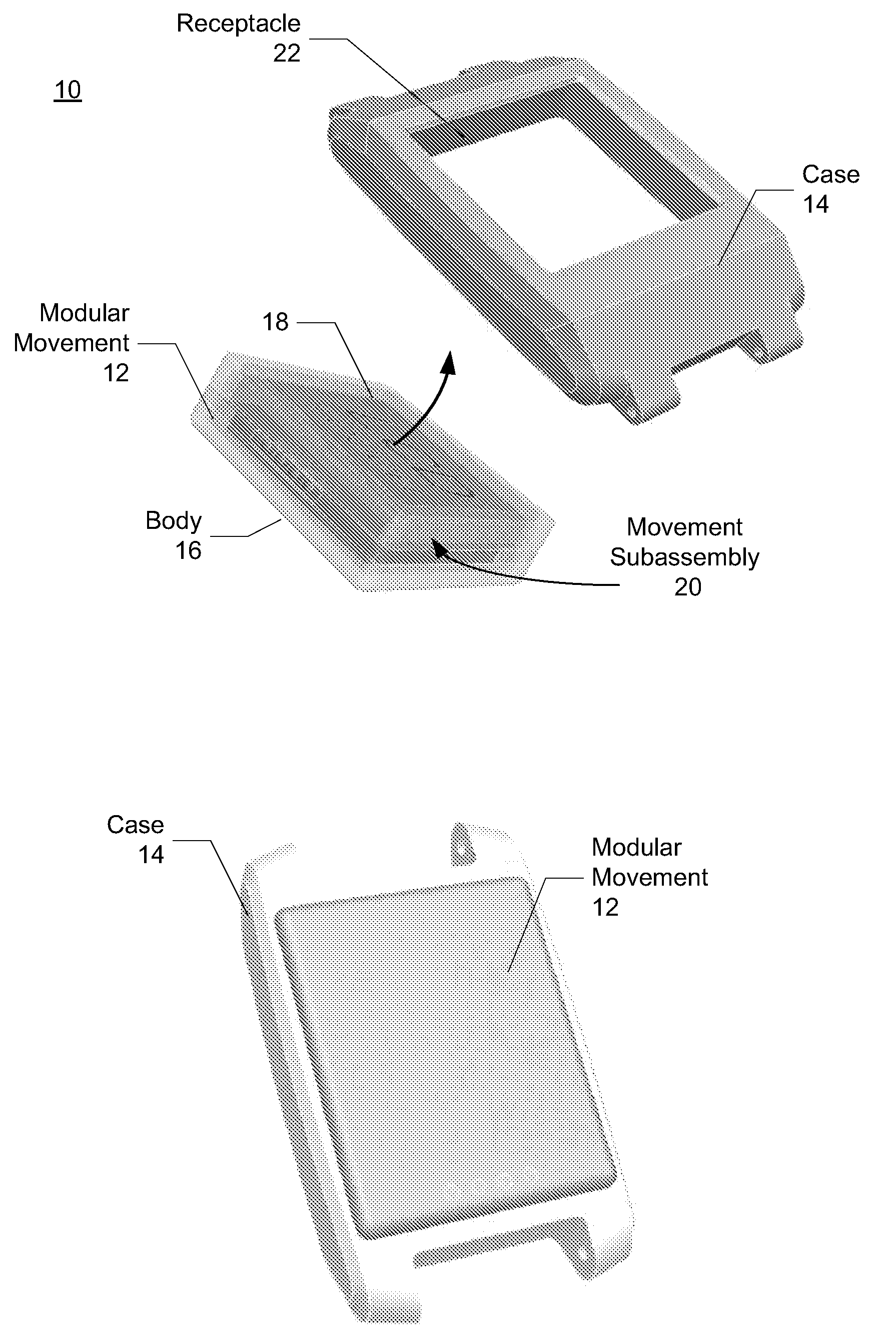

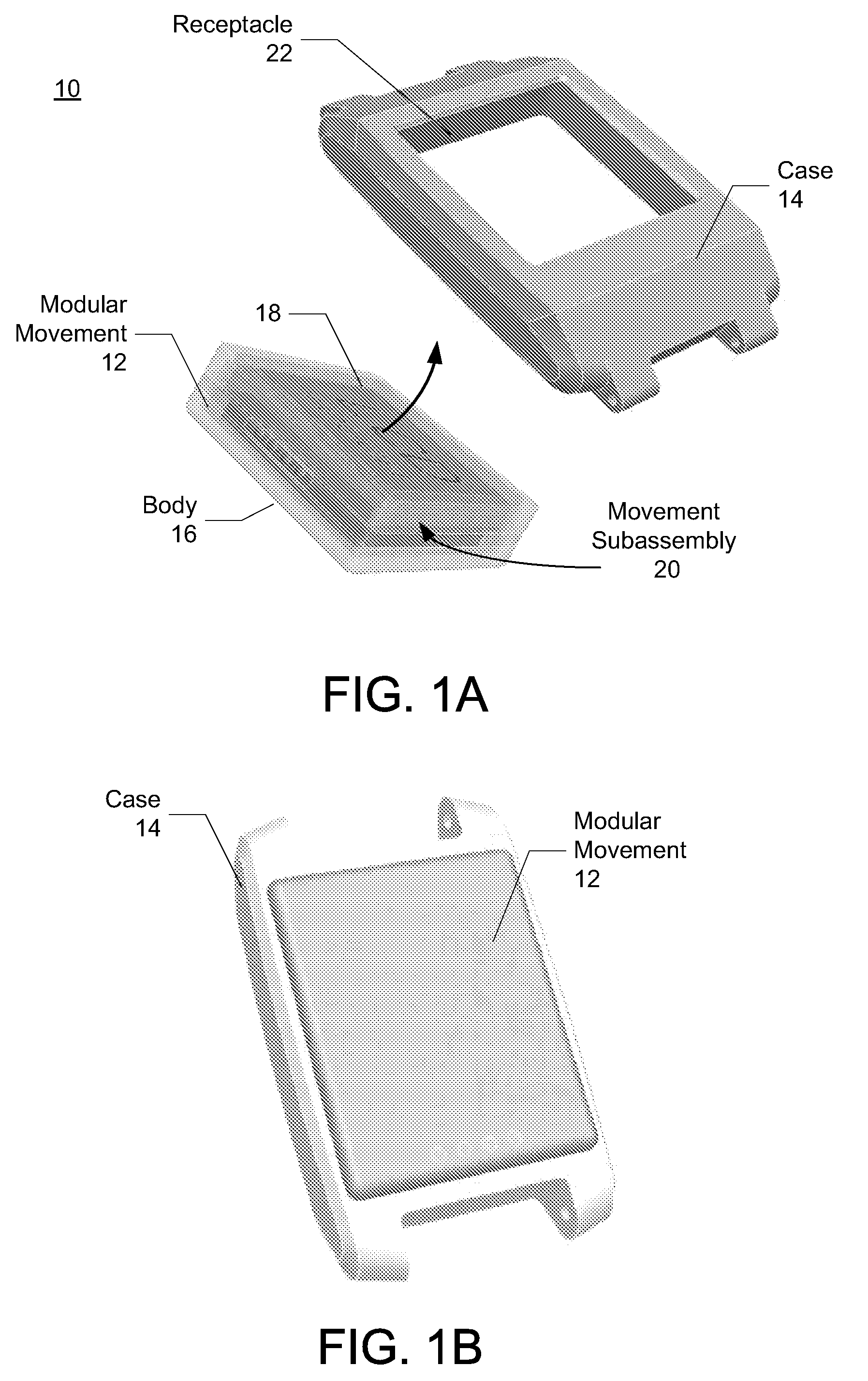

Electronic device assembly

An electronic device assembly includes an electronic device and an enclosure receiving the electronic device. The electronic device includes a display and a sensor. The enclosure includes a cover and a controller attached to the cover. The cover is rotatable relative to the electronic device between a first position and a second position. In the first position, the cover covers the electronic device, and the controller controls the sensor transmitting a first signal to the electronic device, for turning off a power supplied to the display. In the second position, the electronic device is exposed, and the controller controls the sensor transmitting a second signal to the electronic device, for turning on the power of the display.

Owner:HON HAI PRECISION IND CO LTD

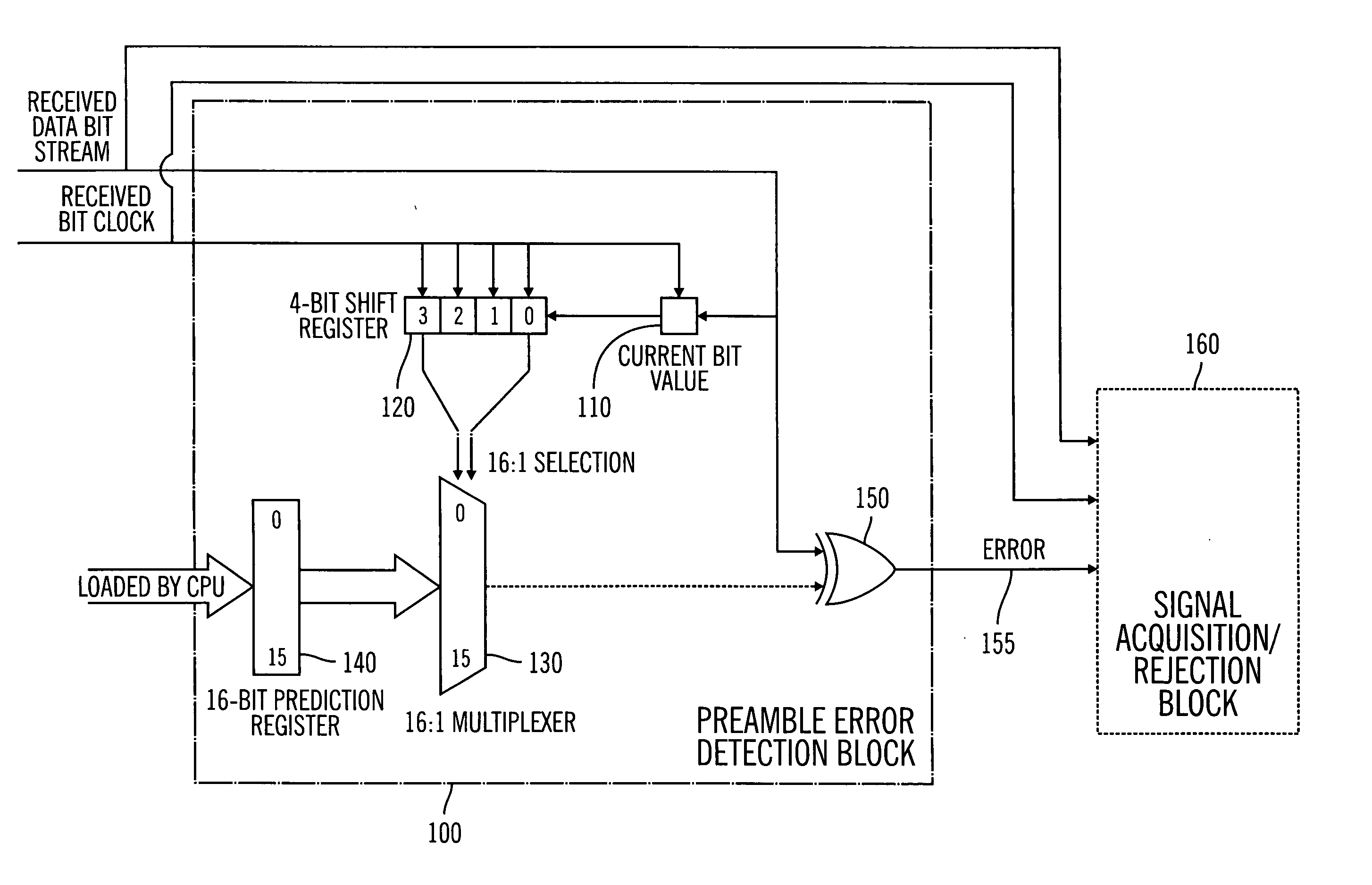

Rapid discrimination preambles and methods for using the same

InactiveUS20050195930A1Sync fastLess power consumptionEnergy efficient ICTElectrotherapyComputer hardwareSystems approaches

A system, method and program are disclosed for achieving rapid bit synchronization in low power medical device systems. Messages are transmitted via telemetry between a medical device and a communication device. The synchronization scheme uses a portion of a unique preamble bit pattern to identify the communication device allowing for economical communications with a minimum expenditure of energy. A special set of preamble bit patterns are utilized for their unique synchronization properties making them particularly suited for rapid bit synchronization. These unique preamble bit patterns further provide simplification to the preamble error detection logic.

Owner:MEDTRONIC MIMIMED INC

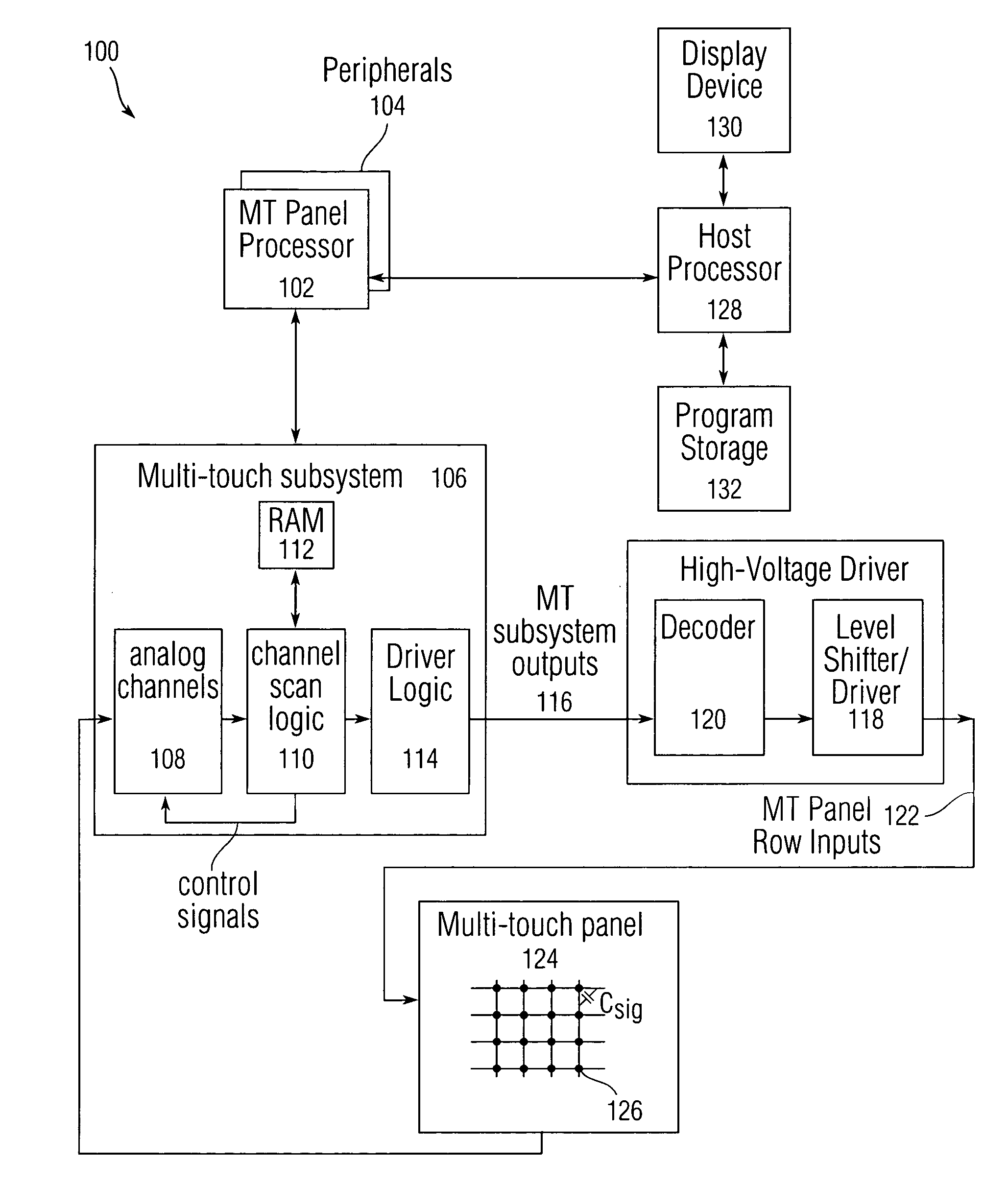

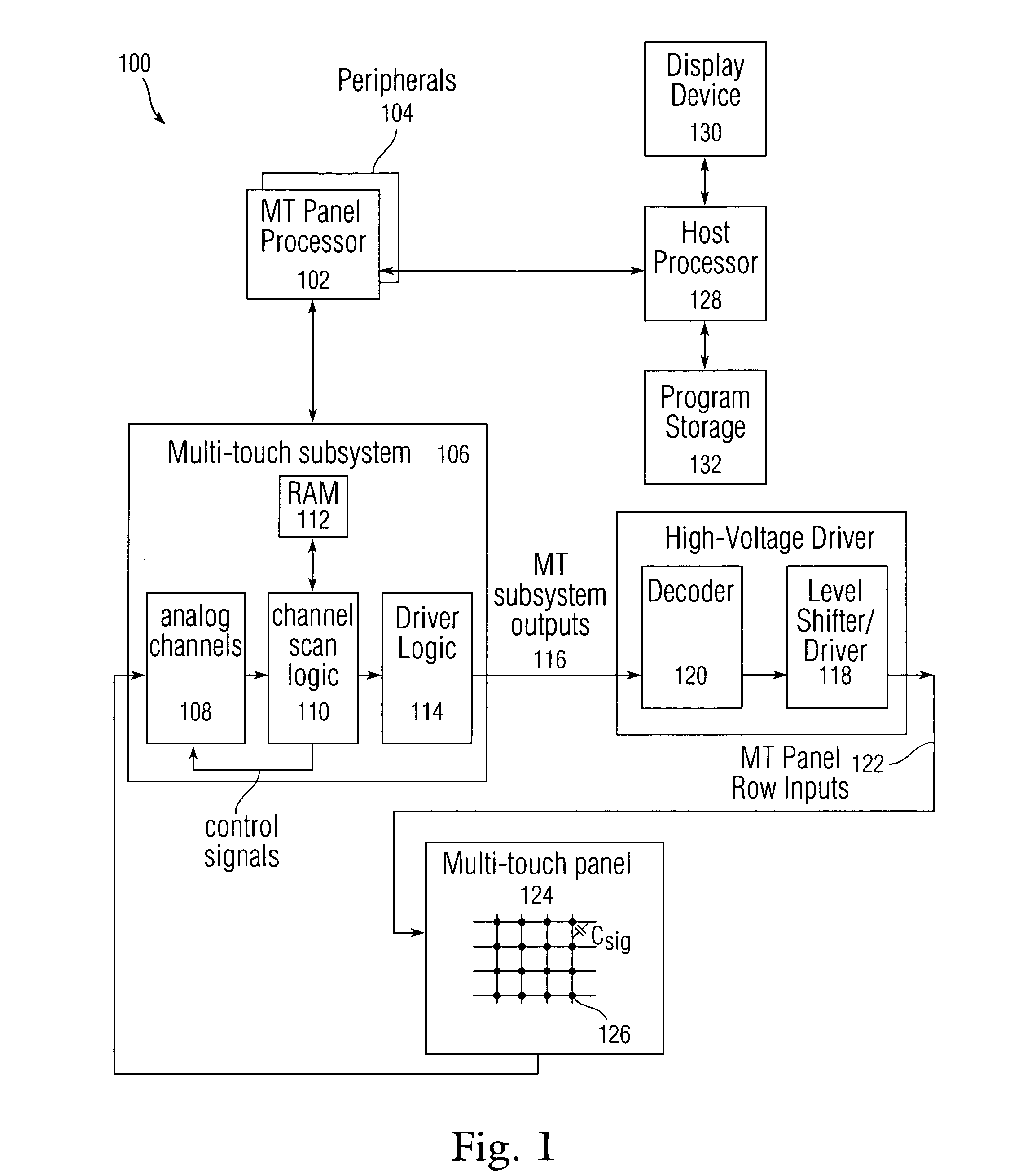

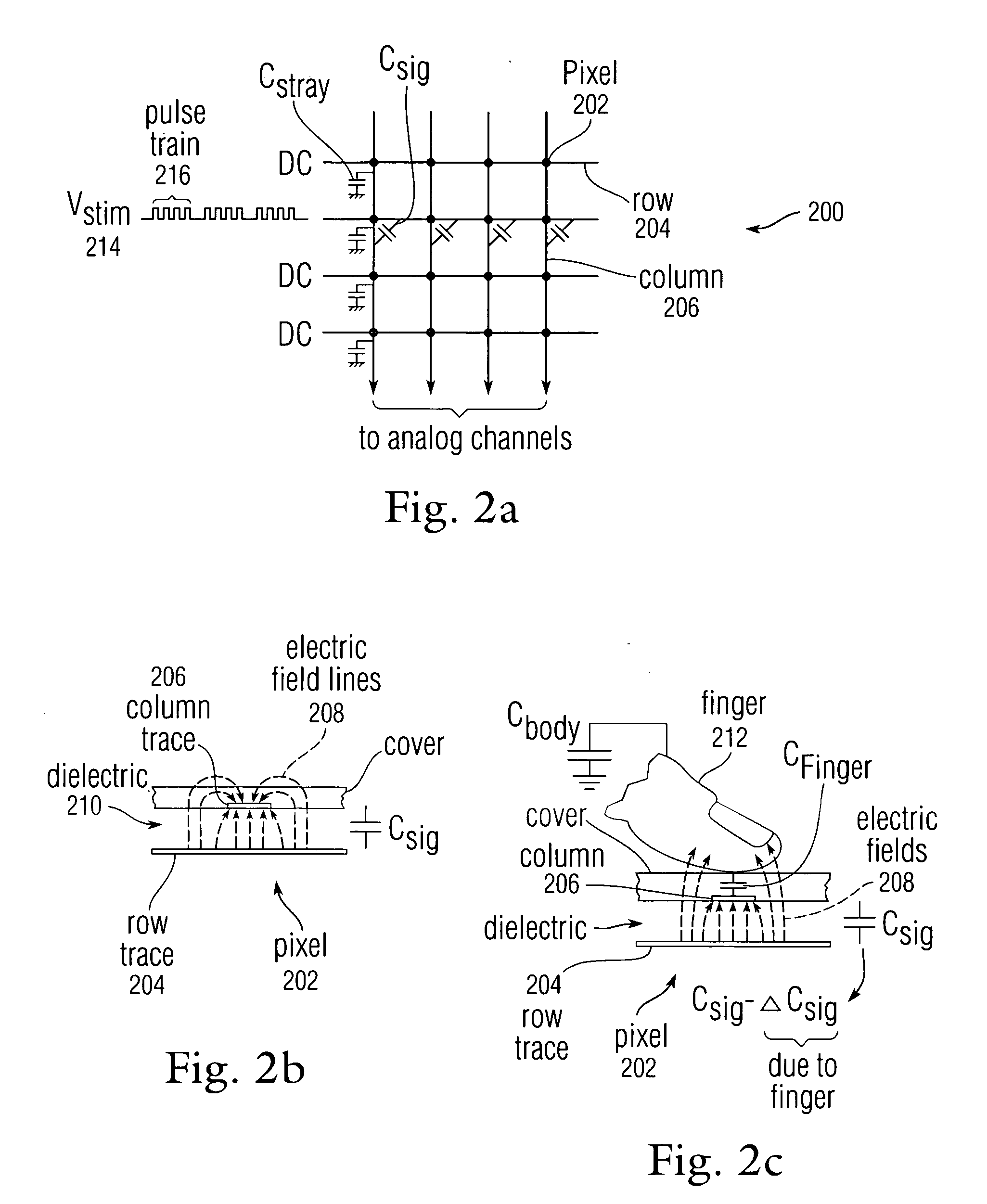

Proximity and multi-touch sensor detection and demodulation

ActiveUS20080158172A1Brightening displayDisplay delayEnergy efficient ICTPower network operation systems integrationProximity sensorEngineering

The use of one or more proximity sensors in combination with one or more touch sensors in a multi-touch panel to detect the presence of a finger, body part or other object and control or trigger one or more functions in accordance with an “image” of touch provided by the sensor outputs is disclosed. In some embodiments, one or more infrared (IR) proximity sensors can be driven with a specific stimulation frequency and emit IR light from one or more areas, which can in some embodiments correspond to one or more multi-touch sensor “pixel” locations. The reflected IR signal, if any, can be demodulated using synchronous demodulation. In some embodiments, both physical interfaces (touch and proximity sensors) can be connected to analog channels in the same electrical core.

Owner:APPLE INC

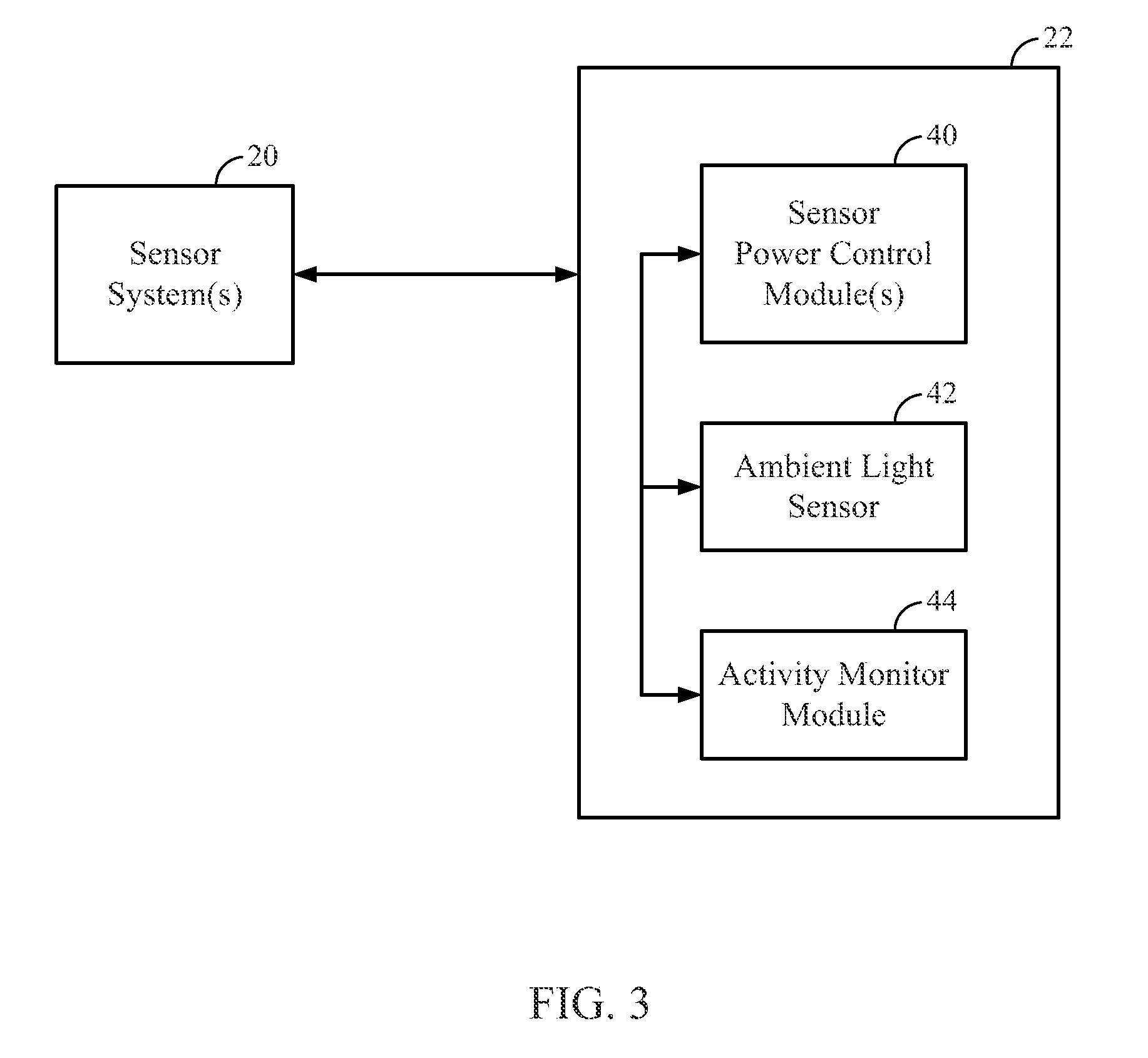

Using ambient light sensor to augment proximity sensor output

ActiveUS20080167834A1Energy efficient ICTDigital data processing detailsData processing systemProximity sensor

Apparatuses and methods to sense proximity of an object and operate a proximity sensor of a portable device. In some embodiments, a method includes receiving an ambient light sensor (ALS) output, and altering, based on the ALS output, an effect of a proximity sensor output on control of a proximity determination. The ALS sensor and the proximity sensor may be located adjacent to an earpiece of a portable device. In some cases, the proximity determination may be a proximity of an object to the proximity sensor, and altering the effect may include changing the proximity of the object from a proximity greater than a first threshold to a proximity less than the first threshold. Other apparatuses and methods and data processing systems and machine readable media are also described.

Owner:APPLE INC

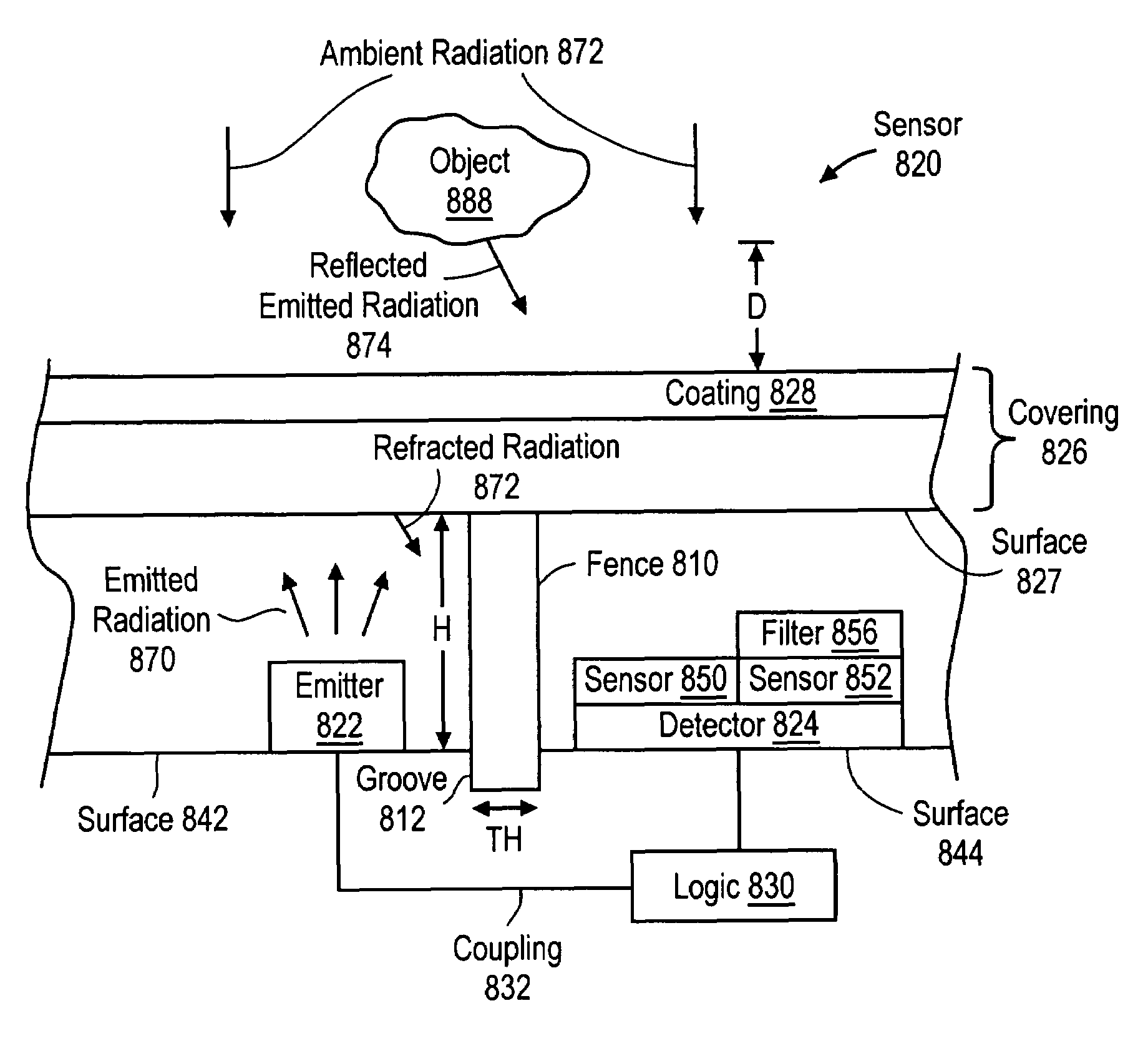

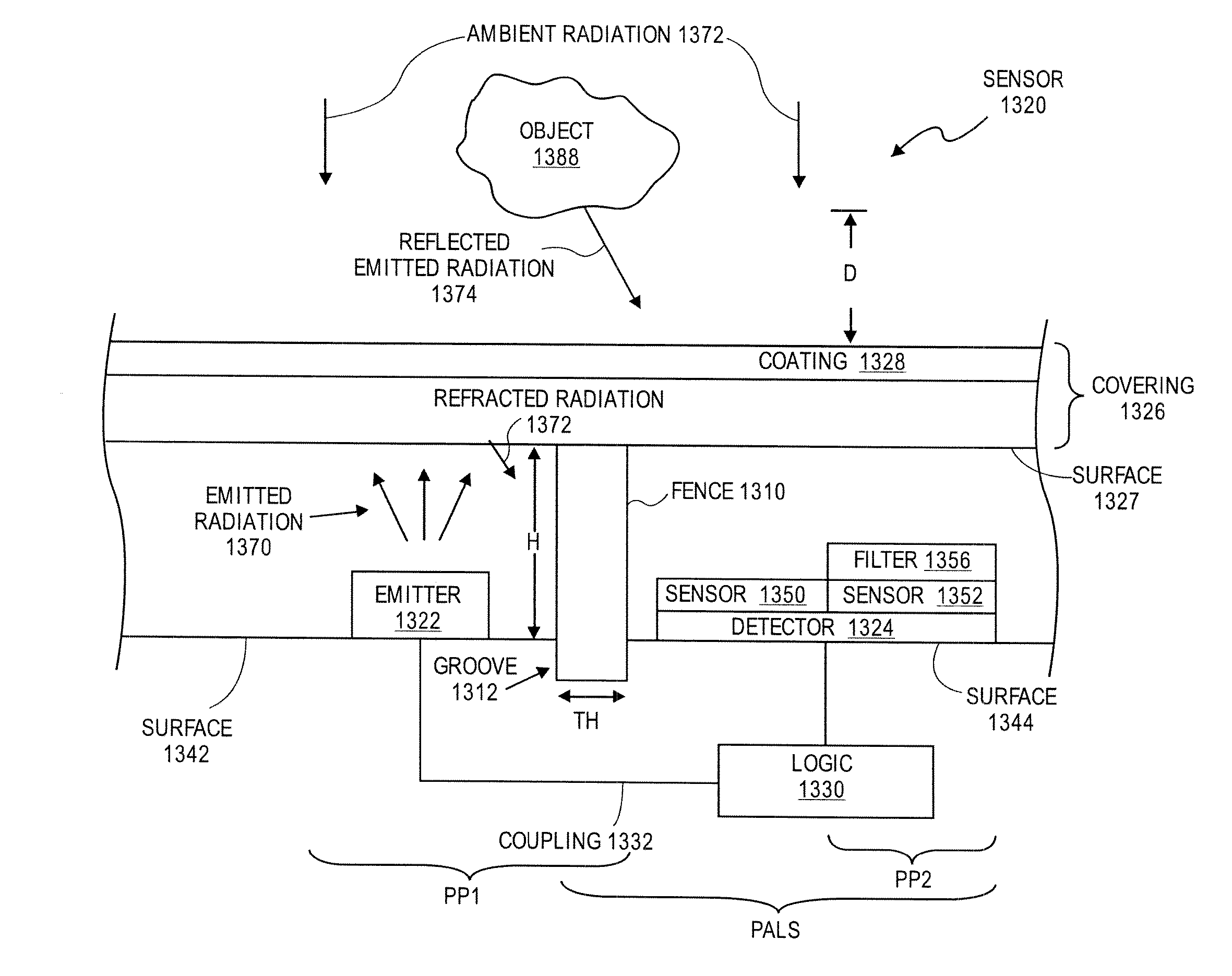

Integrated proximity sensor and light sensor

Apparatuses and methods to sense proximity and to detect light. In one embodiment, an apparatus includes an emitter of electromagnetic radiation and a detector of electromagnetic radiation; the detector has a sensor to detect electromagnetic radiation from the emitter when sensing proximity, and to detect electromagnetic radiation from a source other than the emitter when sensing visible light. The emitter may be disabled at least temporarily to allow the detector to detect electromagnetic radiation from a source other than the emitter, such as ambient light. In one implementation, the ambient light is measured by measuring infrared wavelengths. Also, a fence having a non-IR transmissive material disposed between the emitter and the detector to remove electromagnetic radiation emitted by the emitter. Other apparatuses and methods and data processing systems and machine readable media are also described.

Owner:APPLE INC

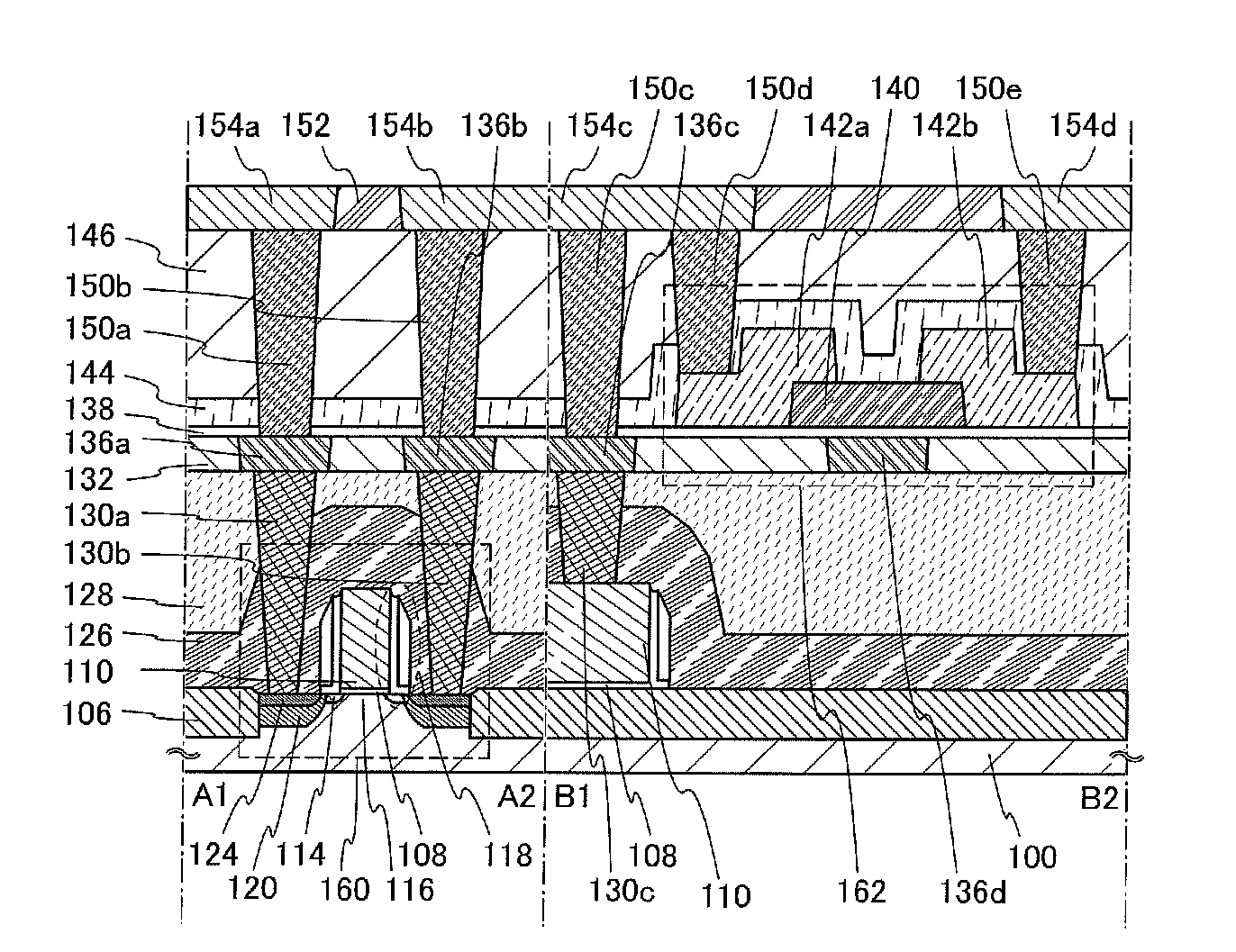

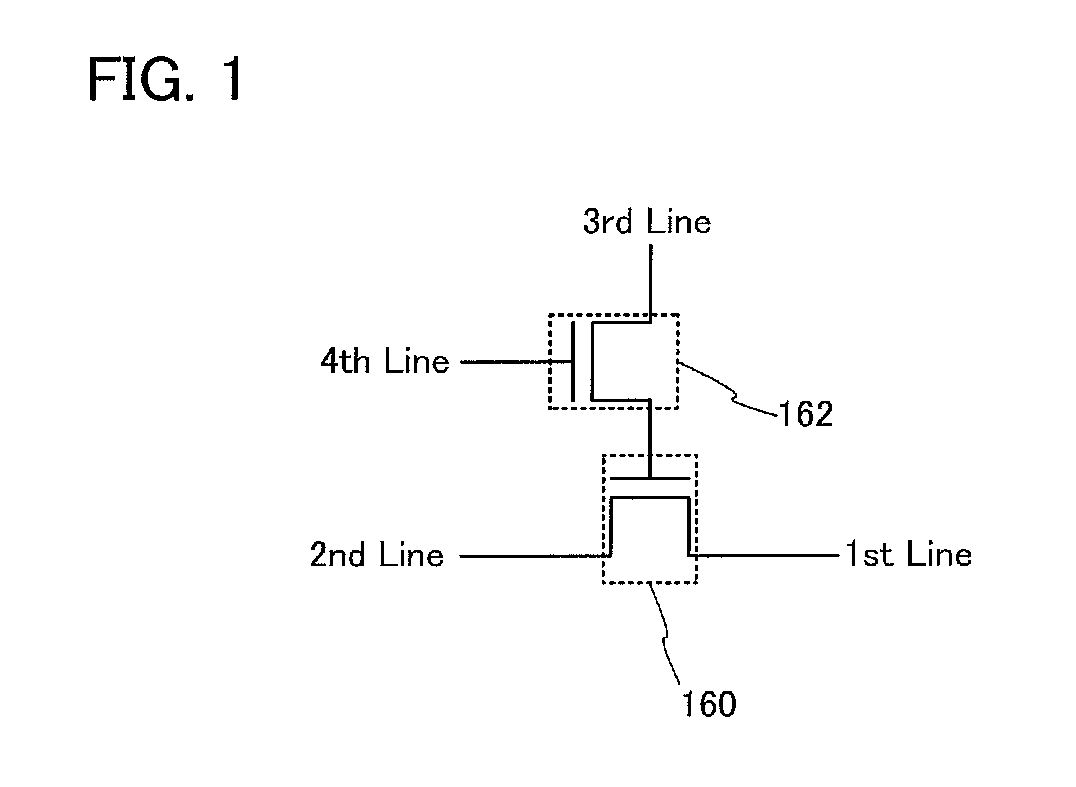

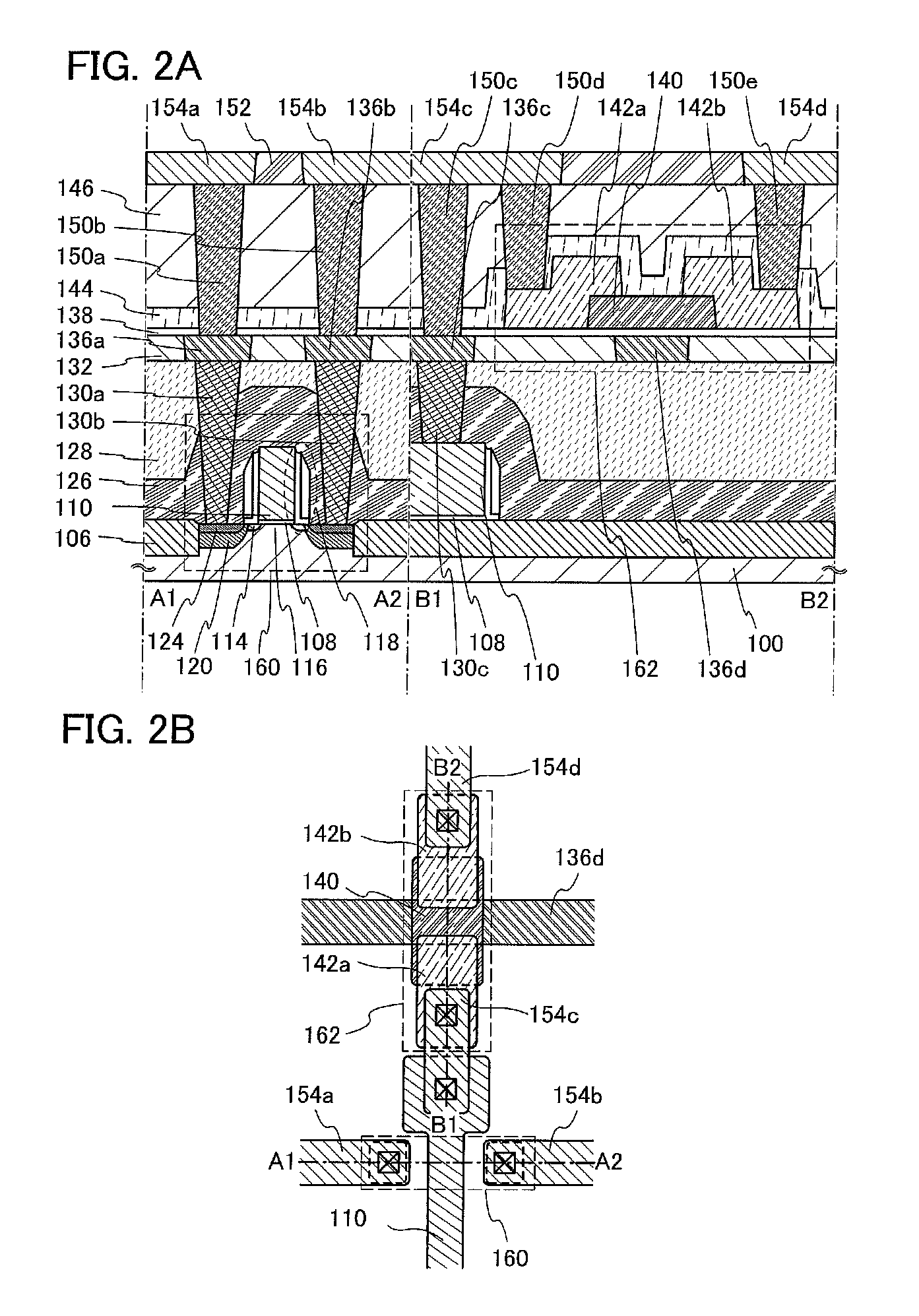

Semiconductor device

ActiveUS20110101351A1Reduce power consumptionFrequency of refresh can be lowSolid-state devicesRead-only memoriesSemiconductor materialsData storing

Disclosed is a semiconductor device capable of functioning as a memory device. The memory device comprises a plurality of memory cells, and each of the memory cells contains a first transistor and a second transistor. The first transistor is provided over a substrate containing a semiconductor material and has a channel formation region in the substrate. The second transistor has an oxide semiconductor layer. The gate electrode of the first transistor and one of the source and drain electrodes of the second transistor are electrically connected to each other. The extremely low off current of the second transistor allows the data stored in the memory cell to be retained for a significantly long time even in the absence of supply of electric power.

Owner:SEMICON ENERGY LAB CO LTD

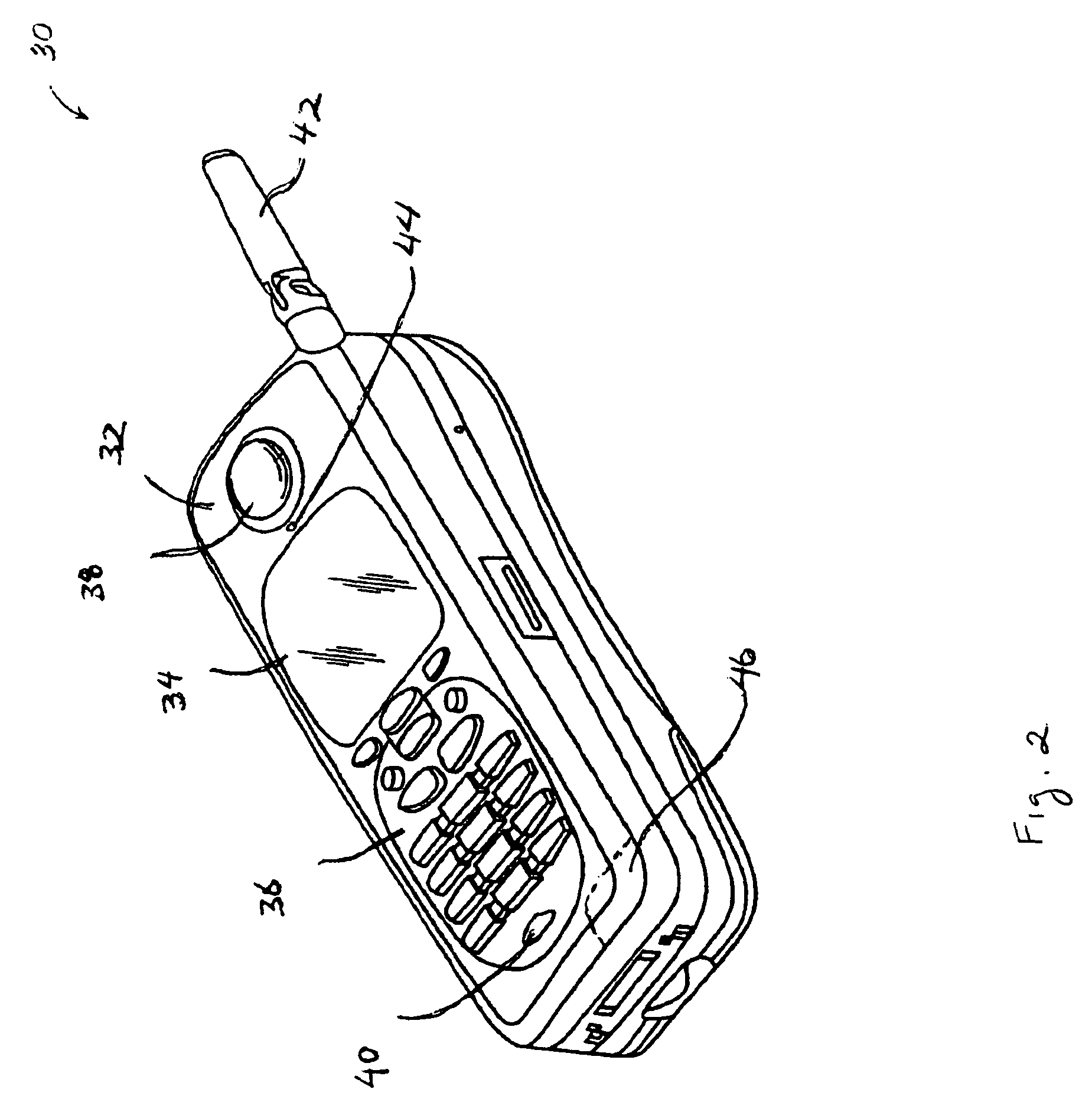

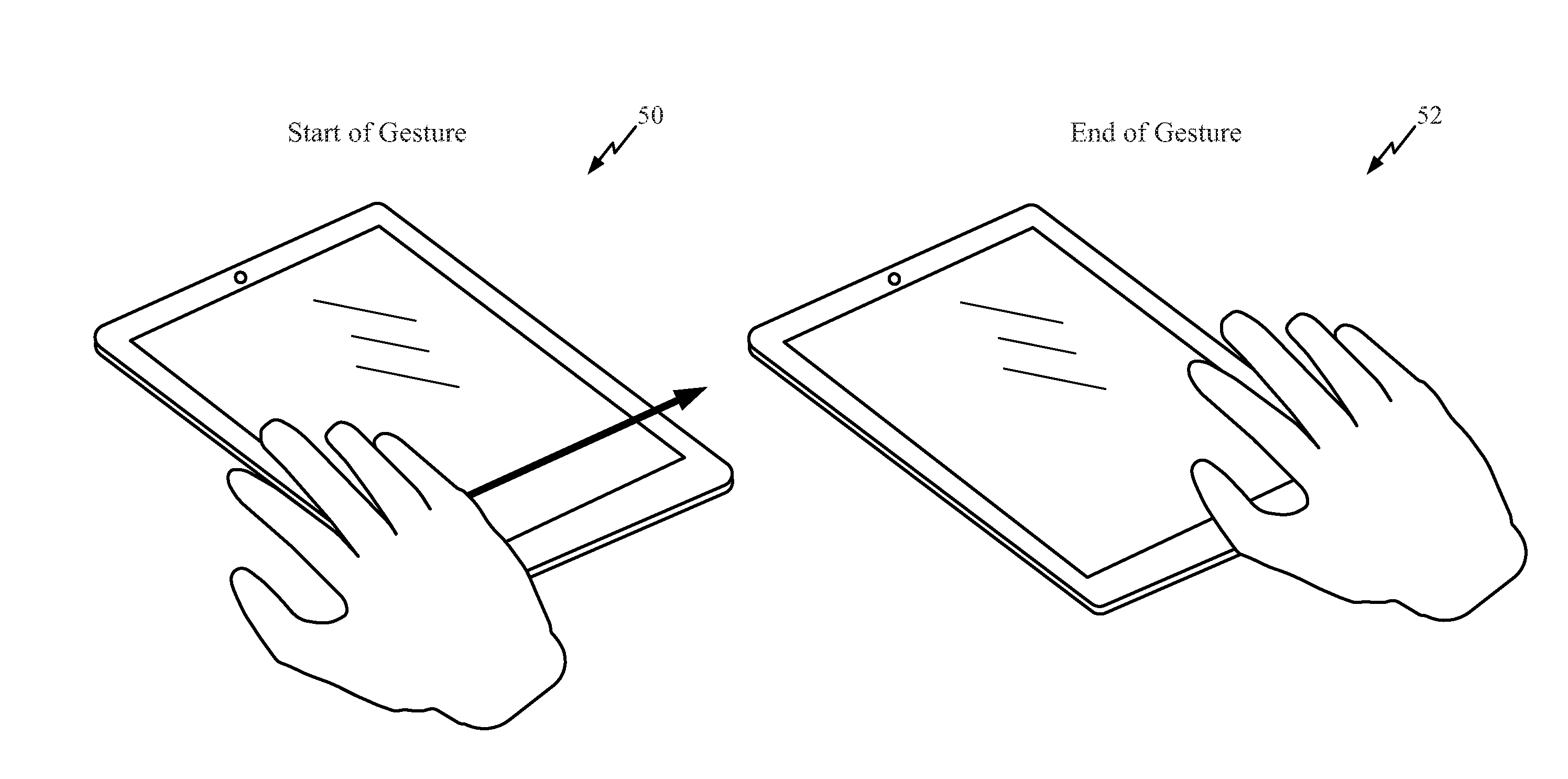

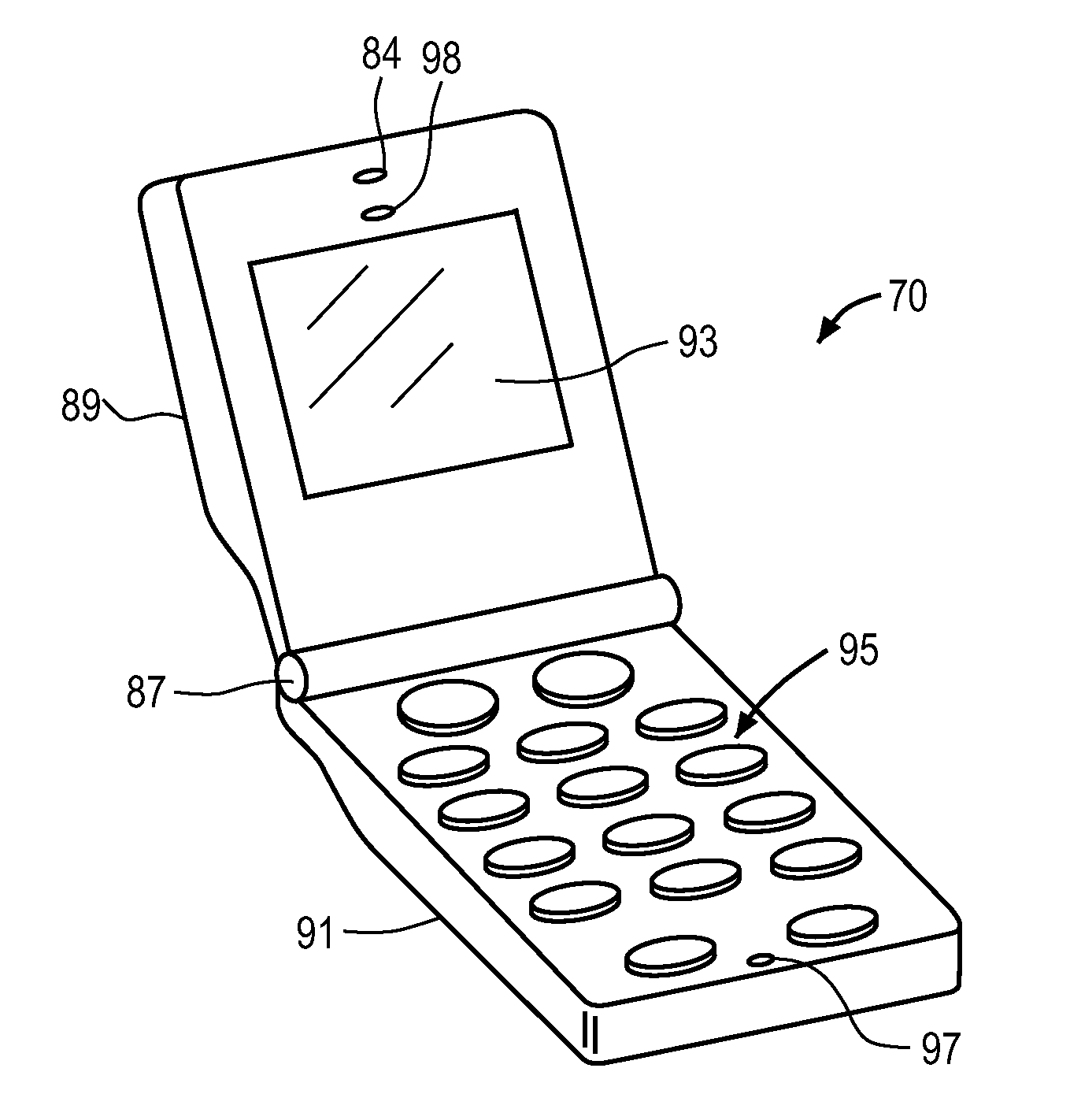

Methods and apparatus for contactless gesture recognition

InactiveUS20110310005A1Reduce wearImprove aestheticsInput/output for user-computer interactionEnergy efficient ICTProximity sensorHuman–computer interaction

Systems and methods are described for performing contactless gesture recognition for a computing device, such as a mobile computing device. An example technique for managing a gesture-based input mechanism for a computing device described herein includes identifying parameters of the computing device relating to accuracy of gesture classification performed by the gesture-based input mechanism and managing a power consumption level of at least an infrared (IR) light emitting diode (LED) or an IR proximity sensor of the gesture-based input mechanism based on the parameters of the computing device.

Owner:QUALCOMM INC

Using ambient light sensor to augment proximity sensor output

ActiveUS7957762B2Energy efficient ICTDigital data processing detailsData processing systemProximity sensor

Apparatuses and methods to sense proximity of an object and operate a proximity sensor of a portable device. In some embodiments, a method includes receiving an ambient light sensor (ALS) output, and altering, based on the ALS output, an effect of a proximity sensor output on control of a proximity determination. The ALS sensor and the proximity sensor may be located adjacent to an earpiece of a portable device. In some cases, the proximity determination may be a proximity of an object to the proximity sensor, and altering the effect may include changing the proximity of the object from a proximity greater than a first threshold to a proximity less than the first threshold. Other apparatuses and methods and data processing systems and machine readable media are also described.

Owner:APPLE INC

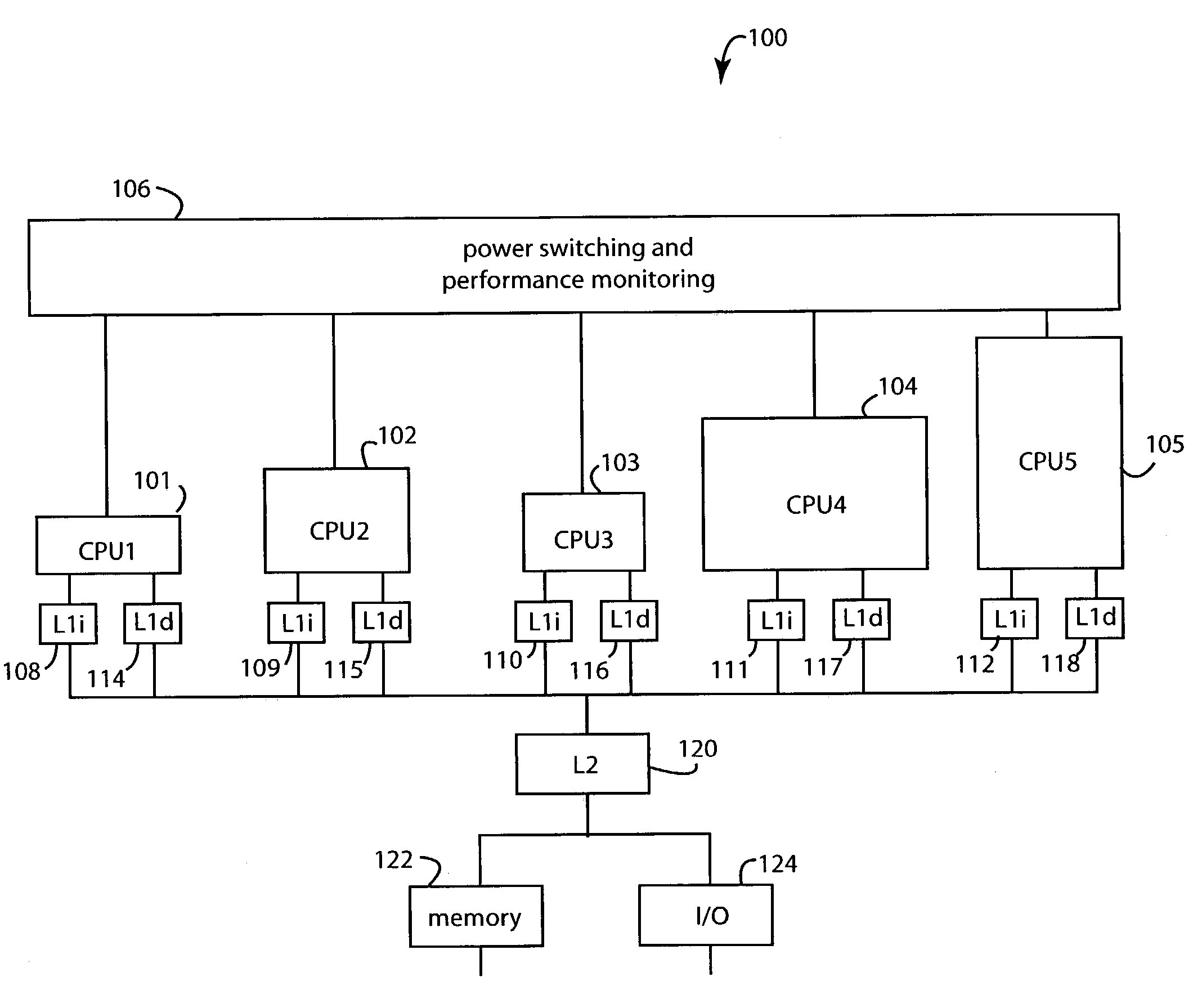

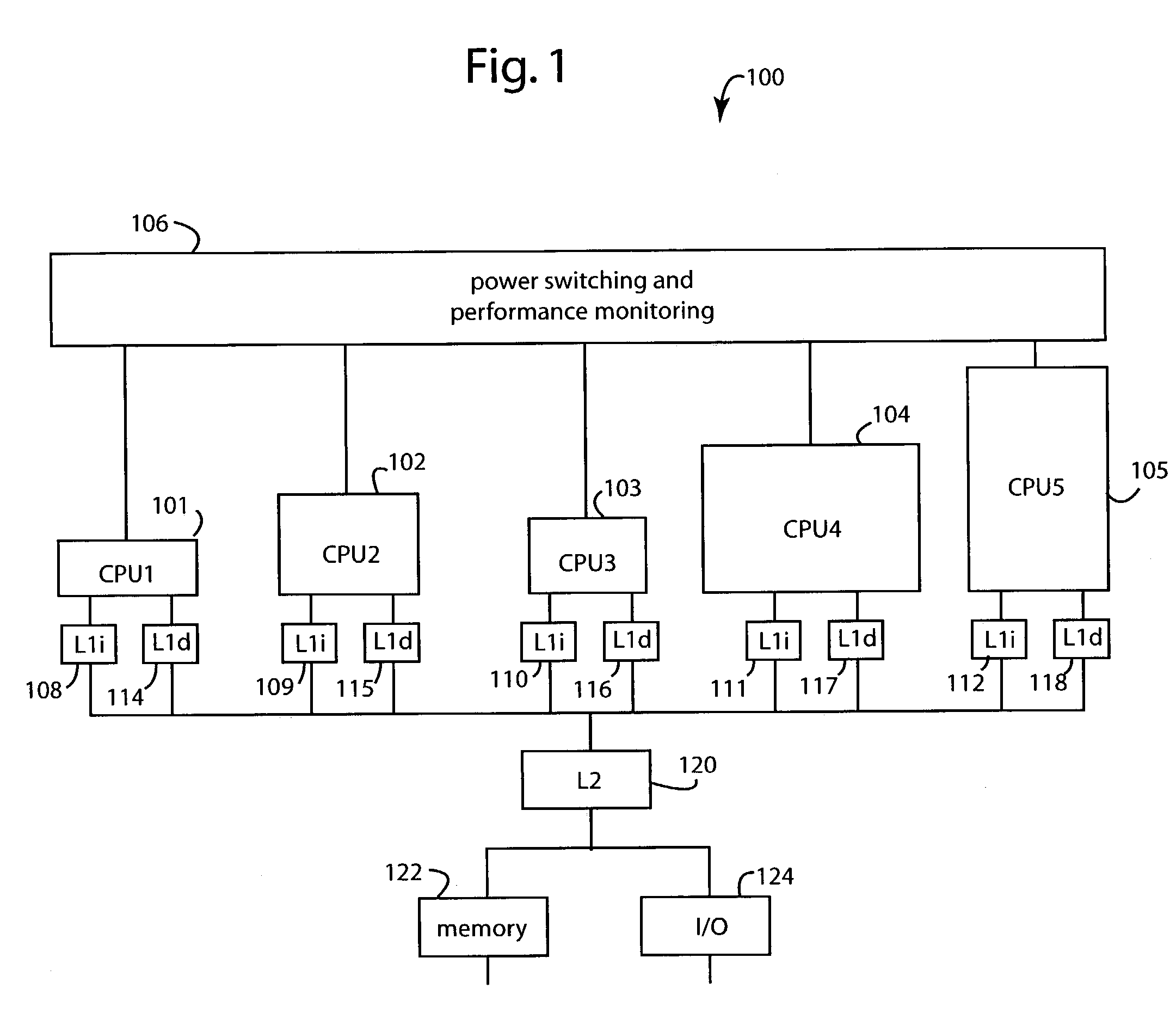

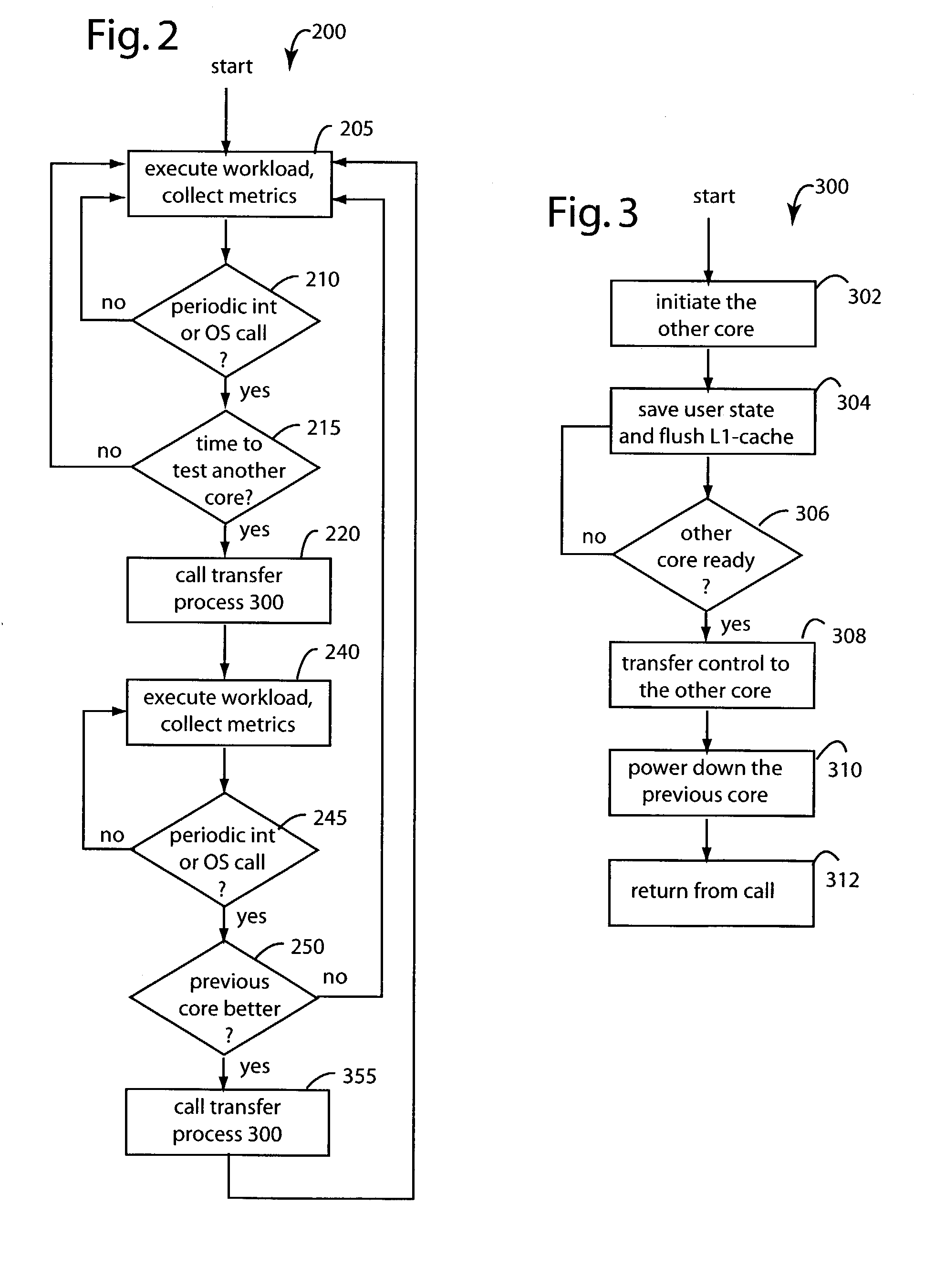

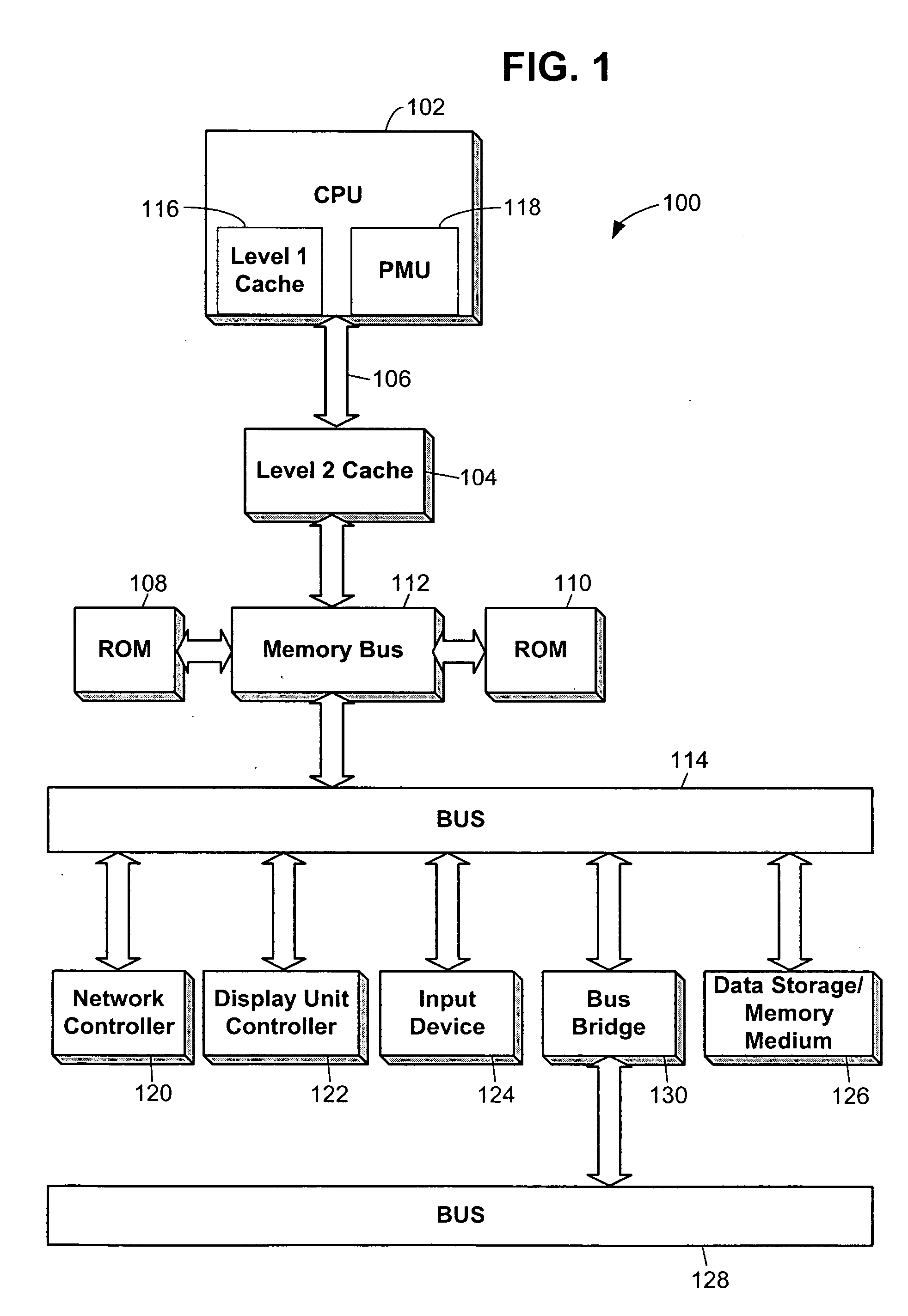

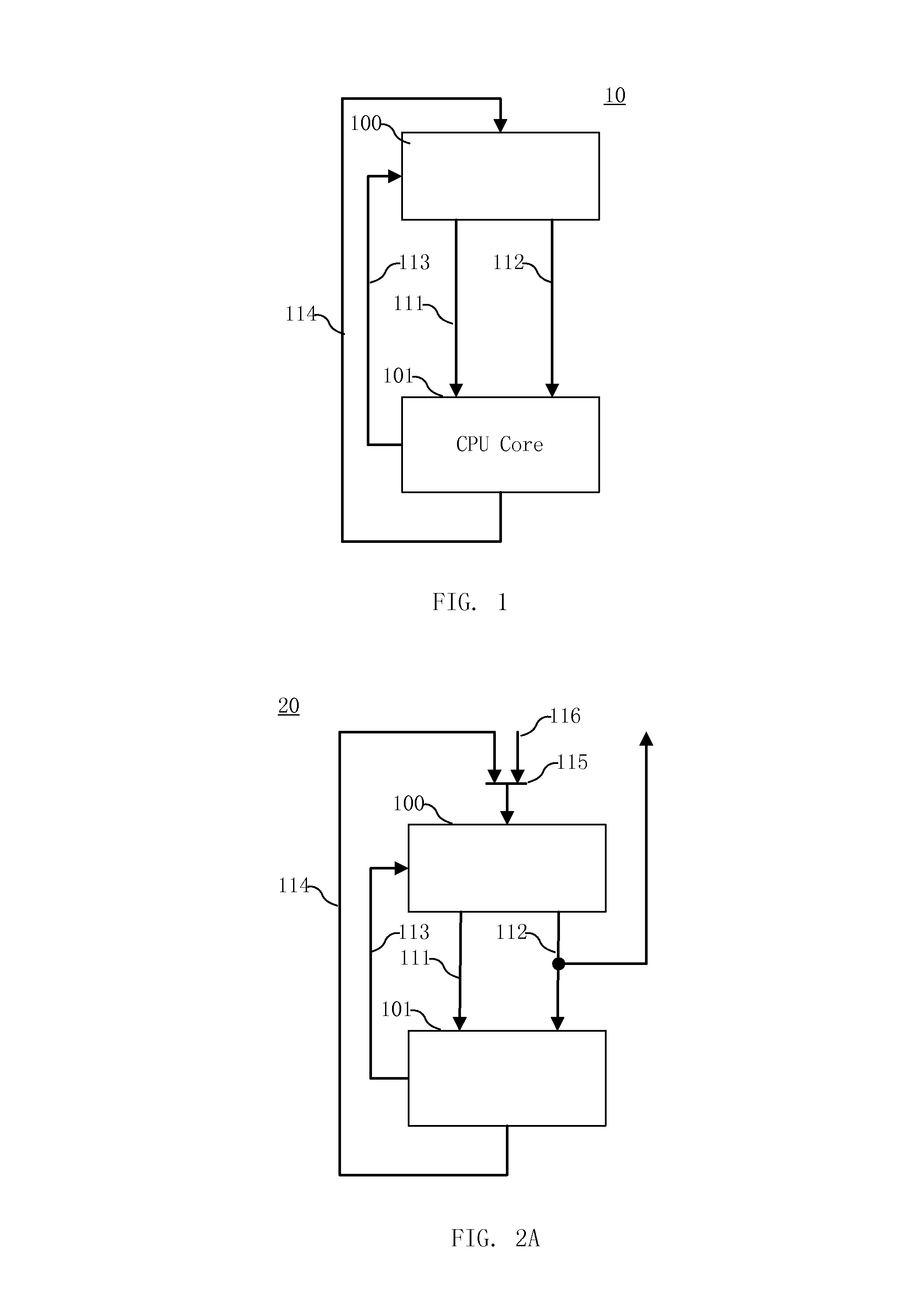

Dynamically selecting processor cores for overall power efficiency

ActiveUS7093147B2Save battery powerSave powerEnergy efficient ICTVolume/mass flow measurementOperating pointParallel computing

A computer system for conserving operating power includes a number of computer hardware processor cores that differ amongst themselves in at least in their respective operating power requirements and processing capabilities. A monitor gathers performance metric information from each of the computer hardware processor cores that is specific to a particular run of application software then executing. A workload transfer mechanism transfers the executing application software to a second computer hardware processor core in a search for reduced operating power. A transfer delay mechanism is connected to delay a subsequent transfer of the executing application software if the system operating power may be conserved by such delay.

Owner:HEWLETT PACKARD DEV CO LP

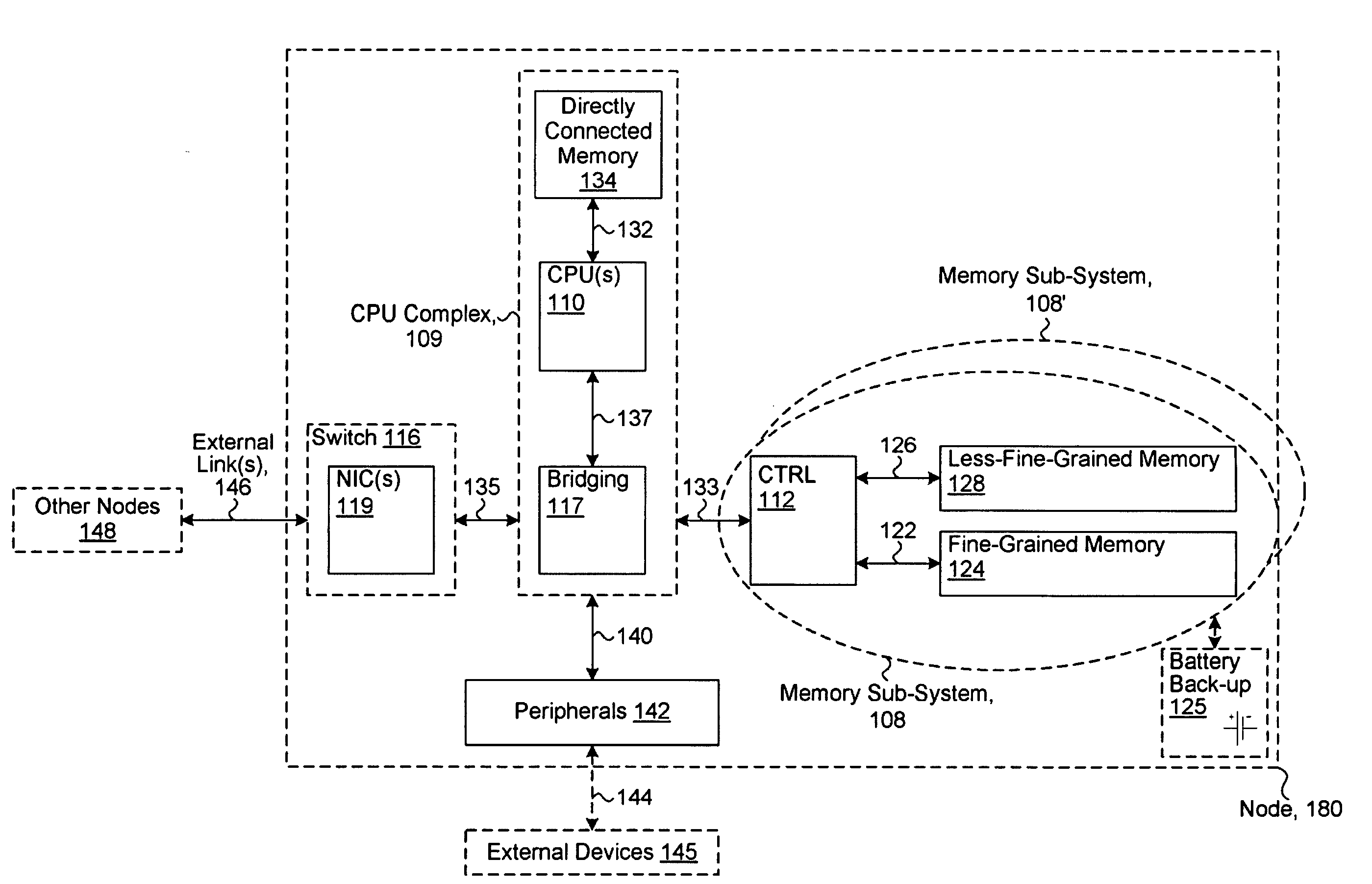

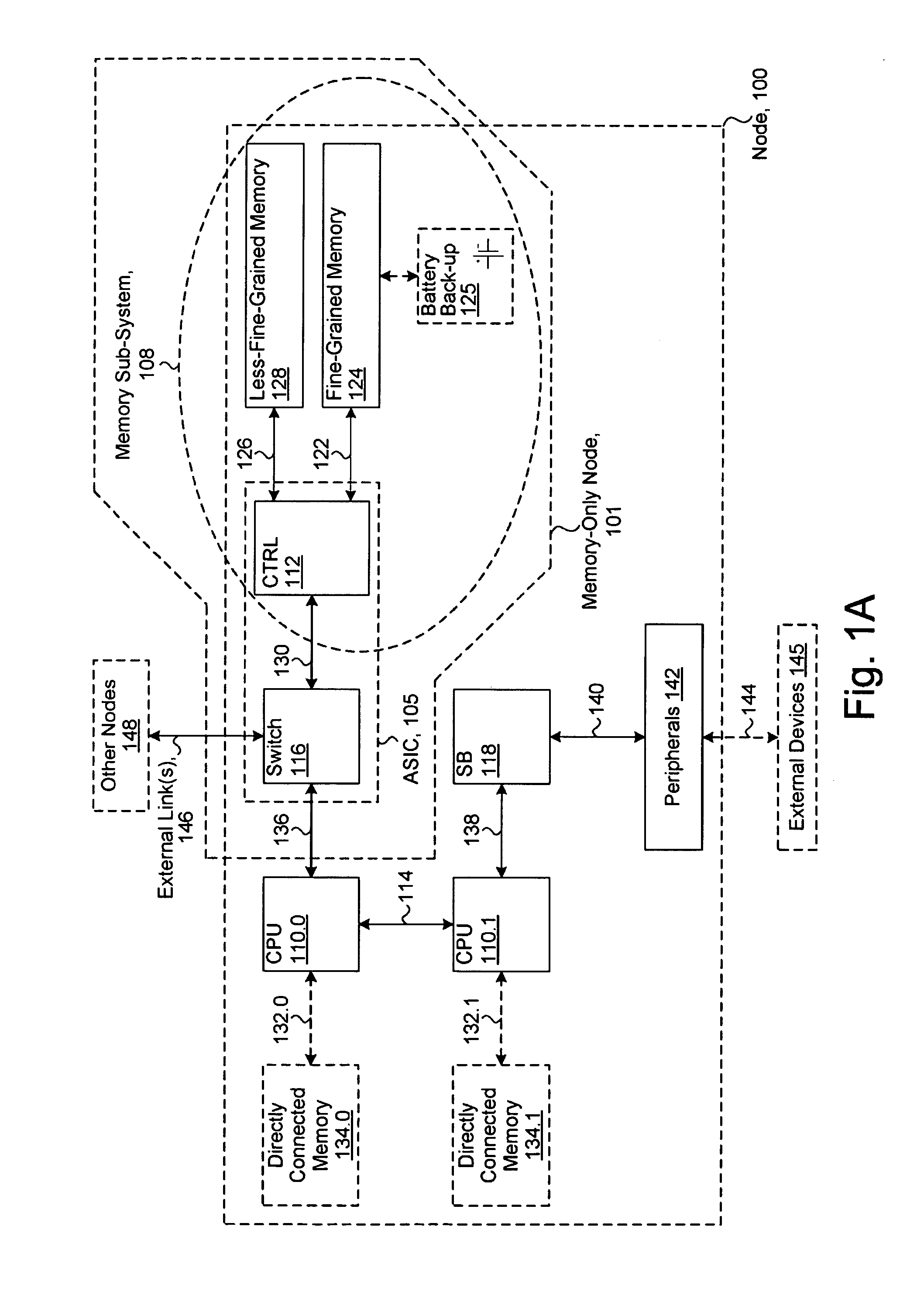

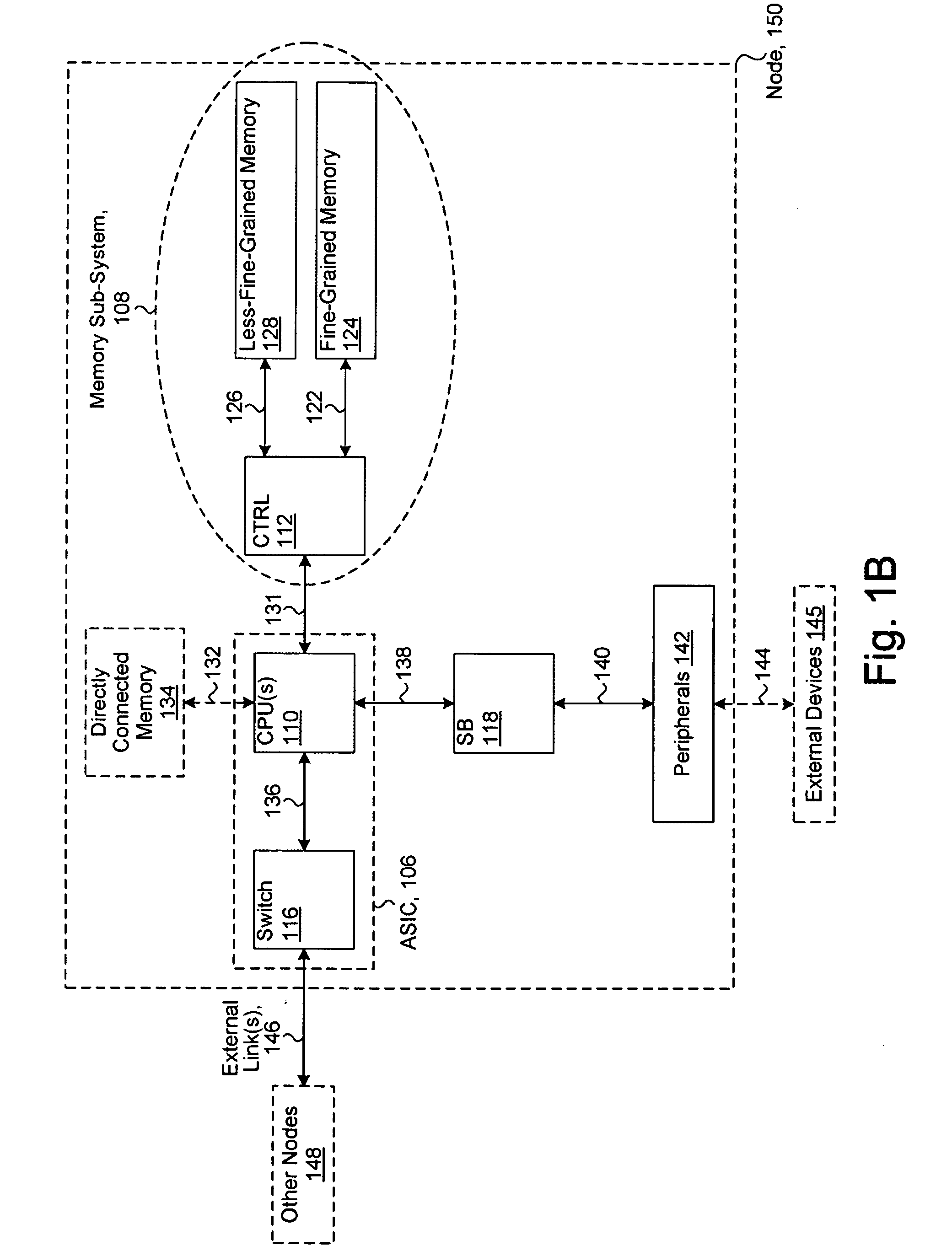

System including a fine-grained memory and a less-fine-grained memory

ActiveUS20080301256A1Memory architecture accessing/allocationEnergy efficient ICTData processing systemWrite buffer

A data processing system includes one or more nodes, each node including a memory sub-system. The sub-system includes a fine-grained, memory, and a less-fine-grained (e.g., page-based) memory. The fine-grained memory optionally serves as a cache and / or as a write buffer for the page-based memory. Software executing on the system uses n node address space which enables access to the page-based memories of all nodes. Each node optionally provides ACID memory properties for at least a portion of the space. In at least a portion of the space, memory elements are mapped to locations in the page-based memory. In various embodiments, some of the elements are compressed, the compressed elements are packed into pages, the pages are written into available locations in the page-based memory, and a map maintains an association between the some of the elements and the locations.

Owner:SANDISK TECH LLC

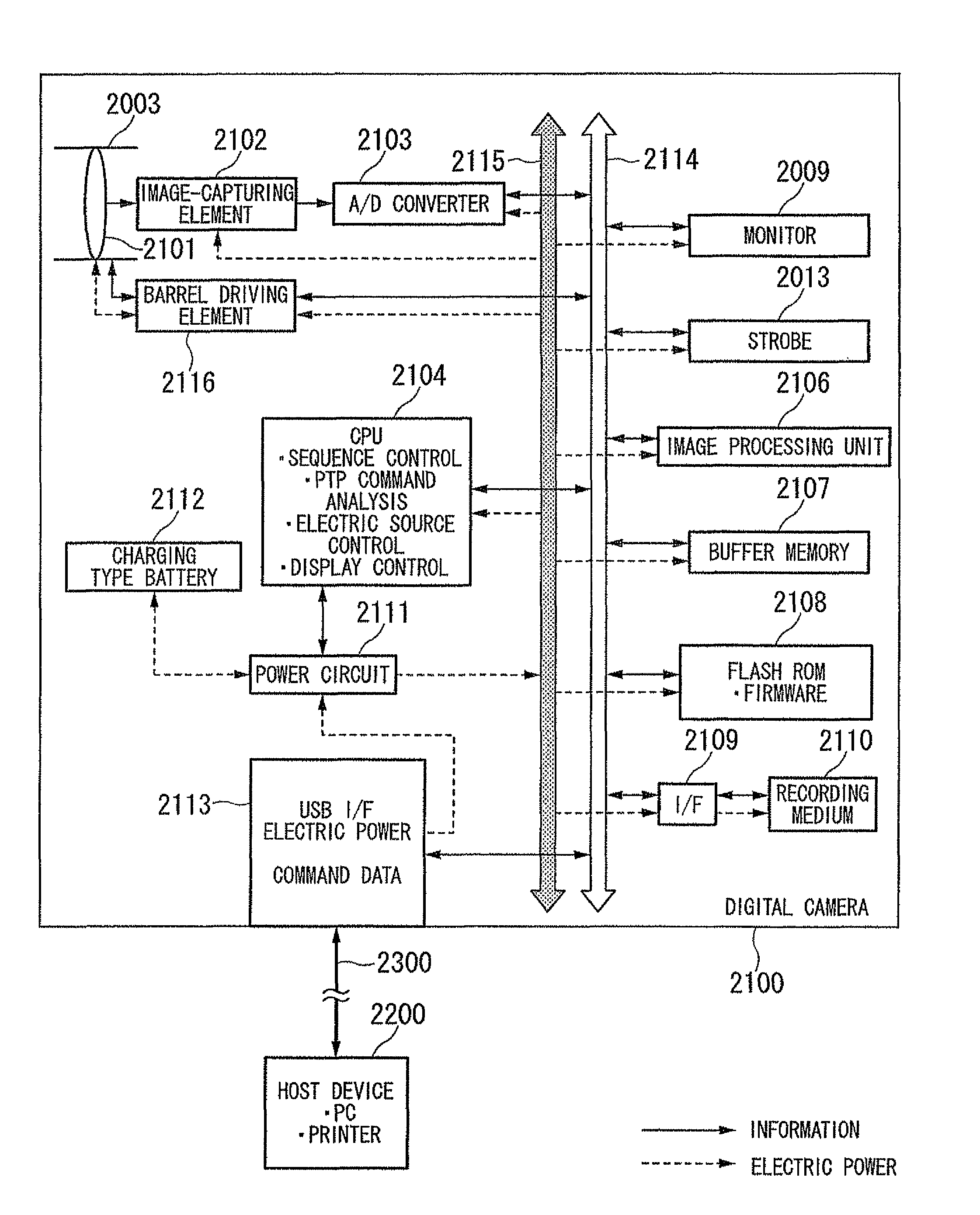

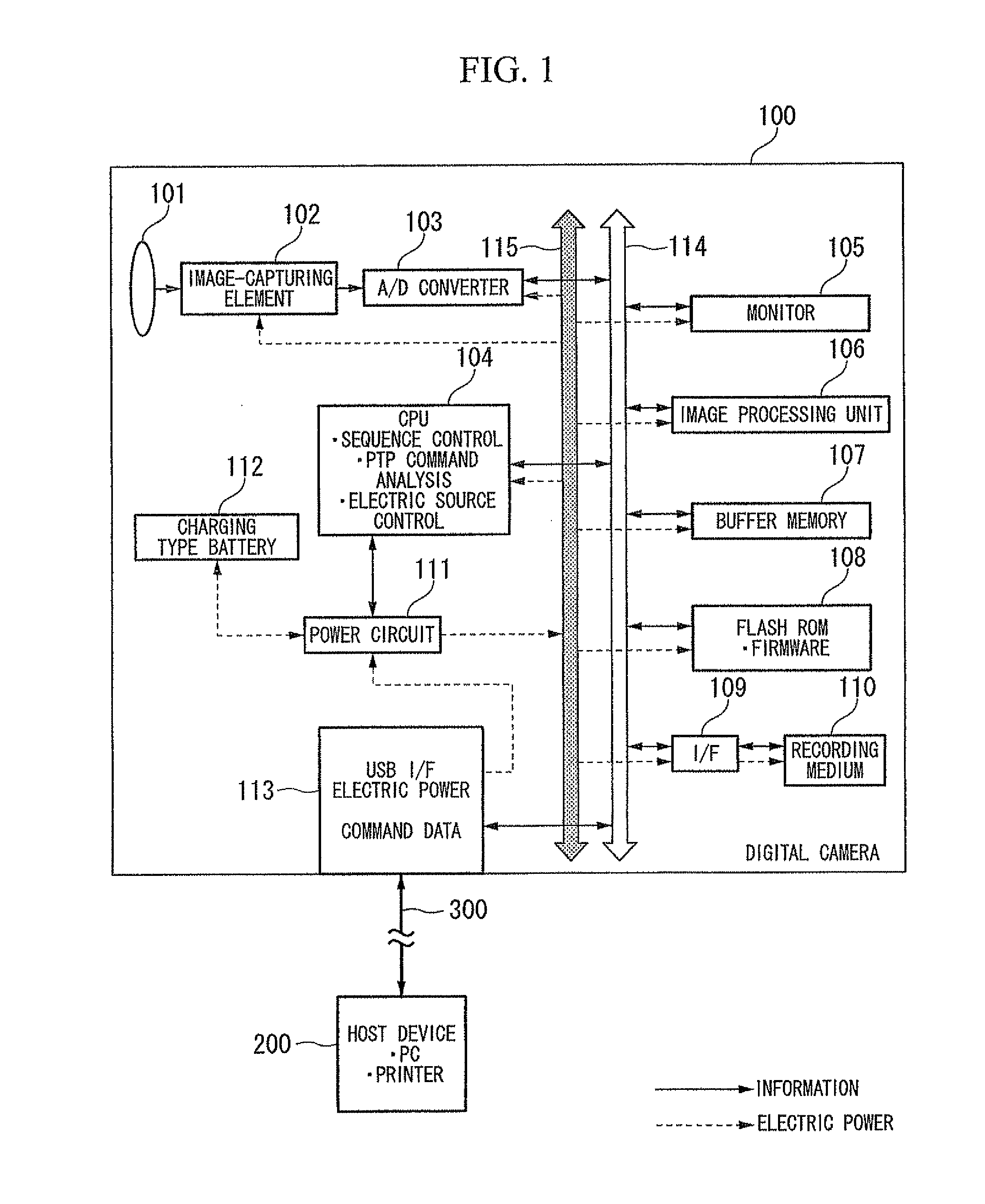

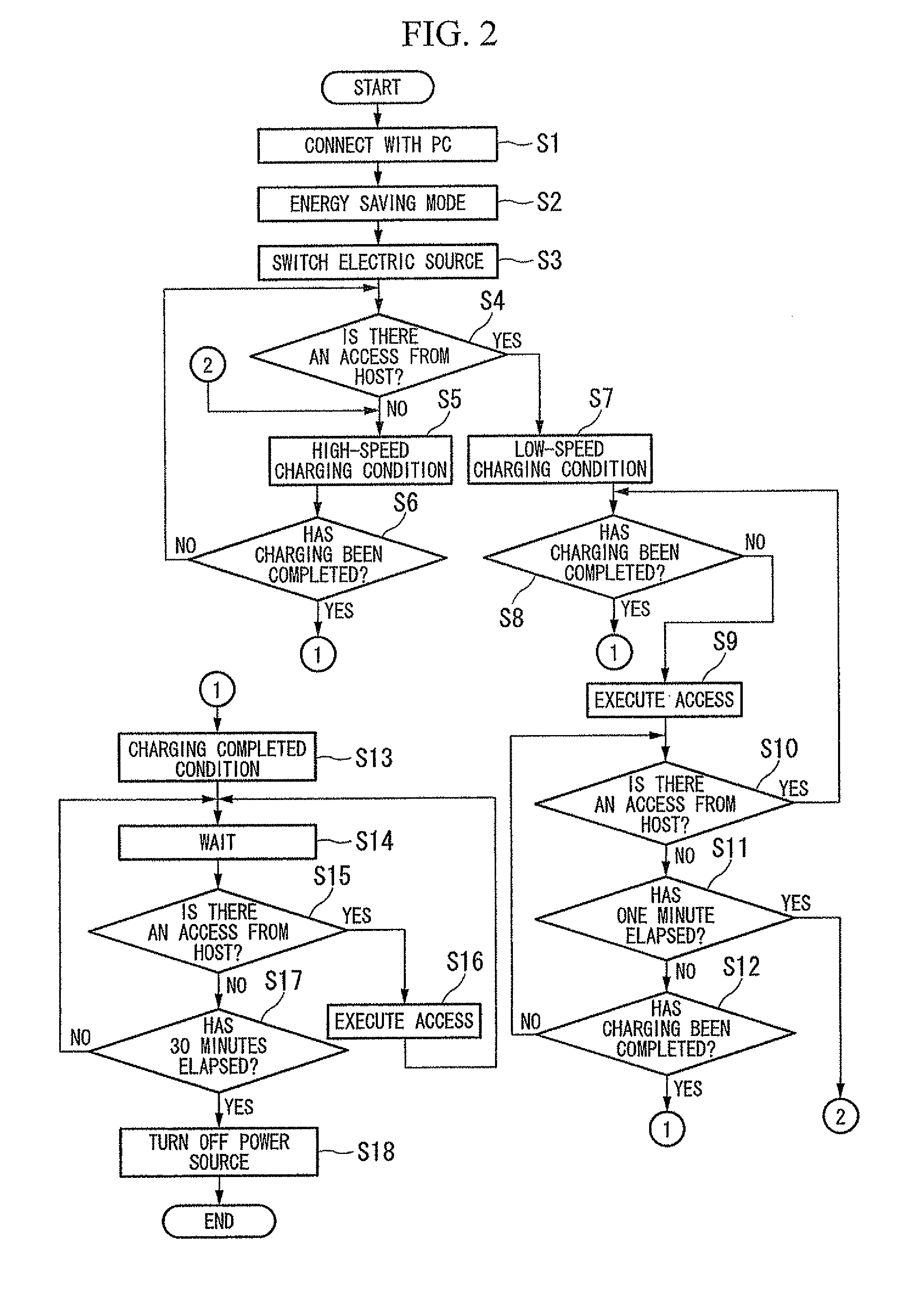

Electronic device, and method controlling electronic power supply

InactiveUS9030166B2Appropriately executedAppropriate performanceEnergy efficient ICTBatteries circuit arrangementsElectrical batteryEngineering

An electric device including: a connecting unit connected to a connection line supplying an electric power of a predetermined rating and transmitting and receiving an information; a charging unit conducting a charging of a charging battery connected to an own device, by the electric power supplied by the connection line; an electric supplying unit supplying an electric power to a recording medium storing an information; a reading-and-writing unit performing a reading-and-writing operation of the recording medium; and an electronic source controlling unit performing a control of the electric power supplied to the charging unit, when the reading-and-writing unit performs the reading-and-writing operation of the recording medium, according to an access request to the recording medium via the connection line.

Owner:NIKON CORP

Apparatus, method and system for rapid delivery of distributed applications

ActiveUS20070078988A1Virtualized networkFirmly connectedEnergy efficient ICTMultiple digital computer combinationsVirtualizationVirtual device

An apparatus, method and system are disclosed for visually constructing and rapidly delivering distributed applications. The system includes a virtual appliance apparatus and a composite appliance apparatus, as well as a system for virtualizing hardware resources and for provisioning, executing and scaling distributed applications.

Owner:CA TECH INC

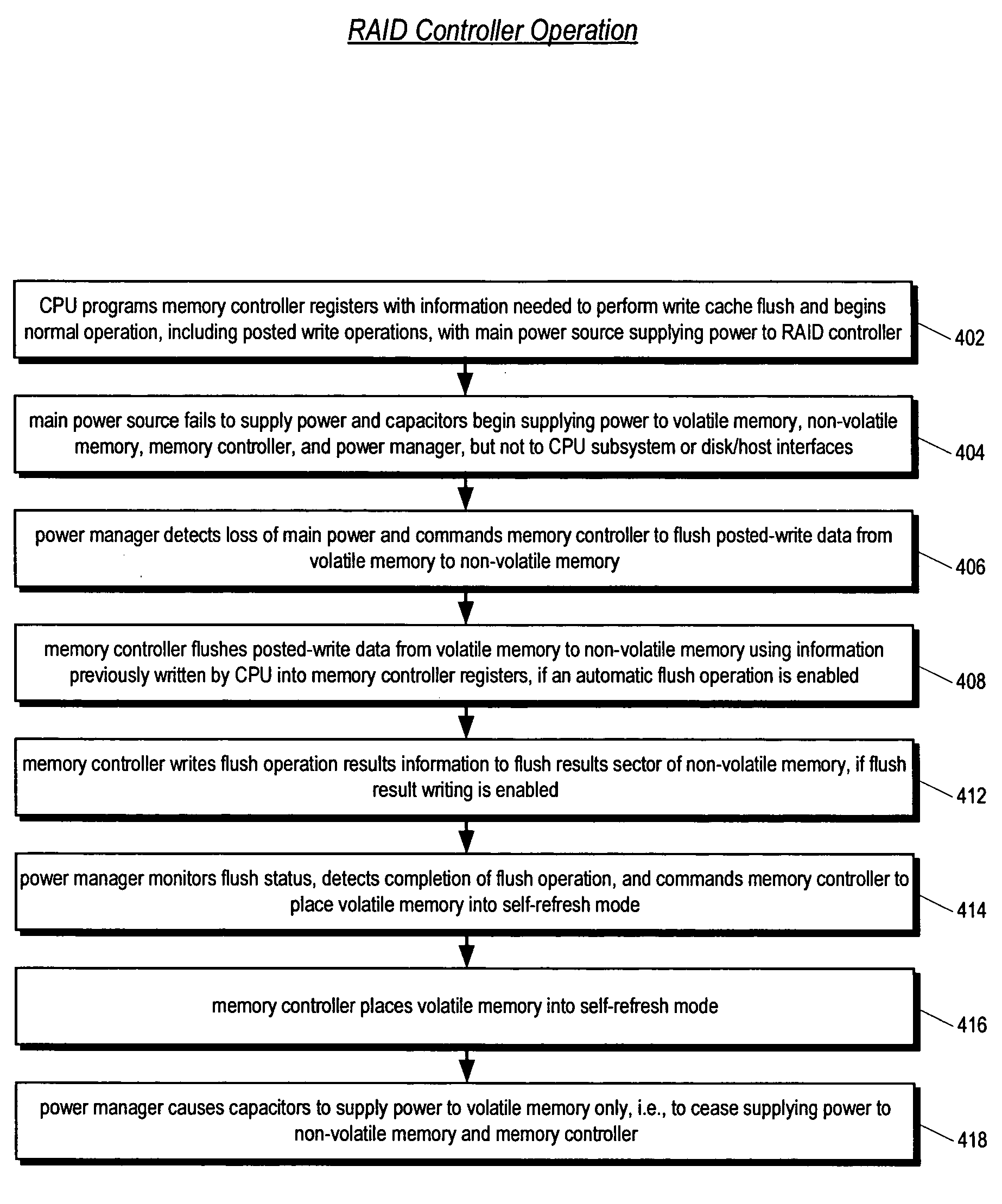

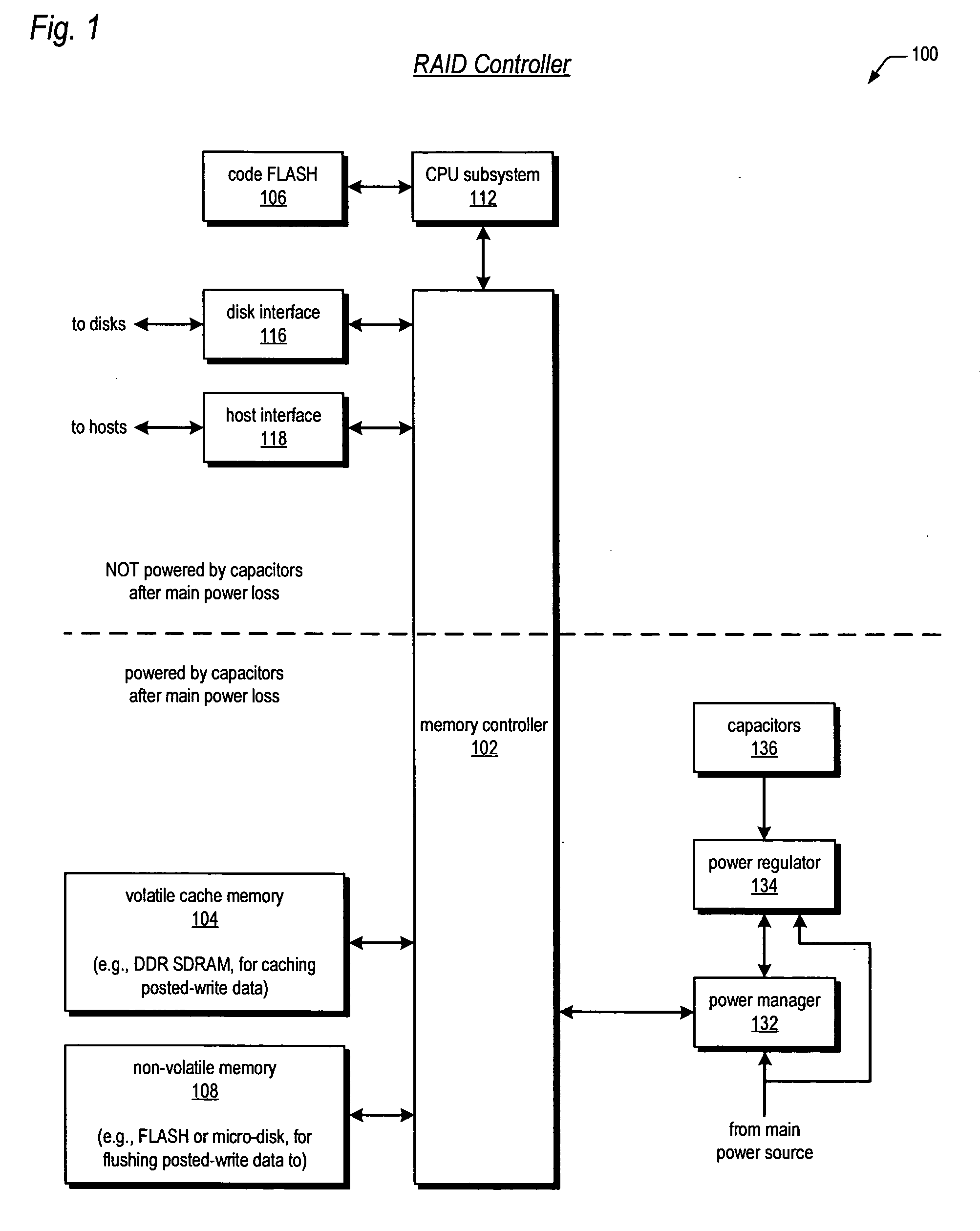

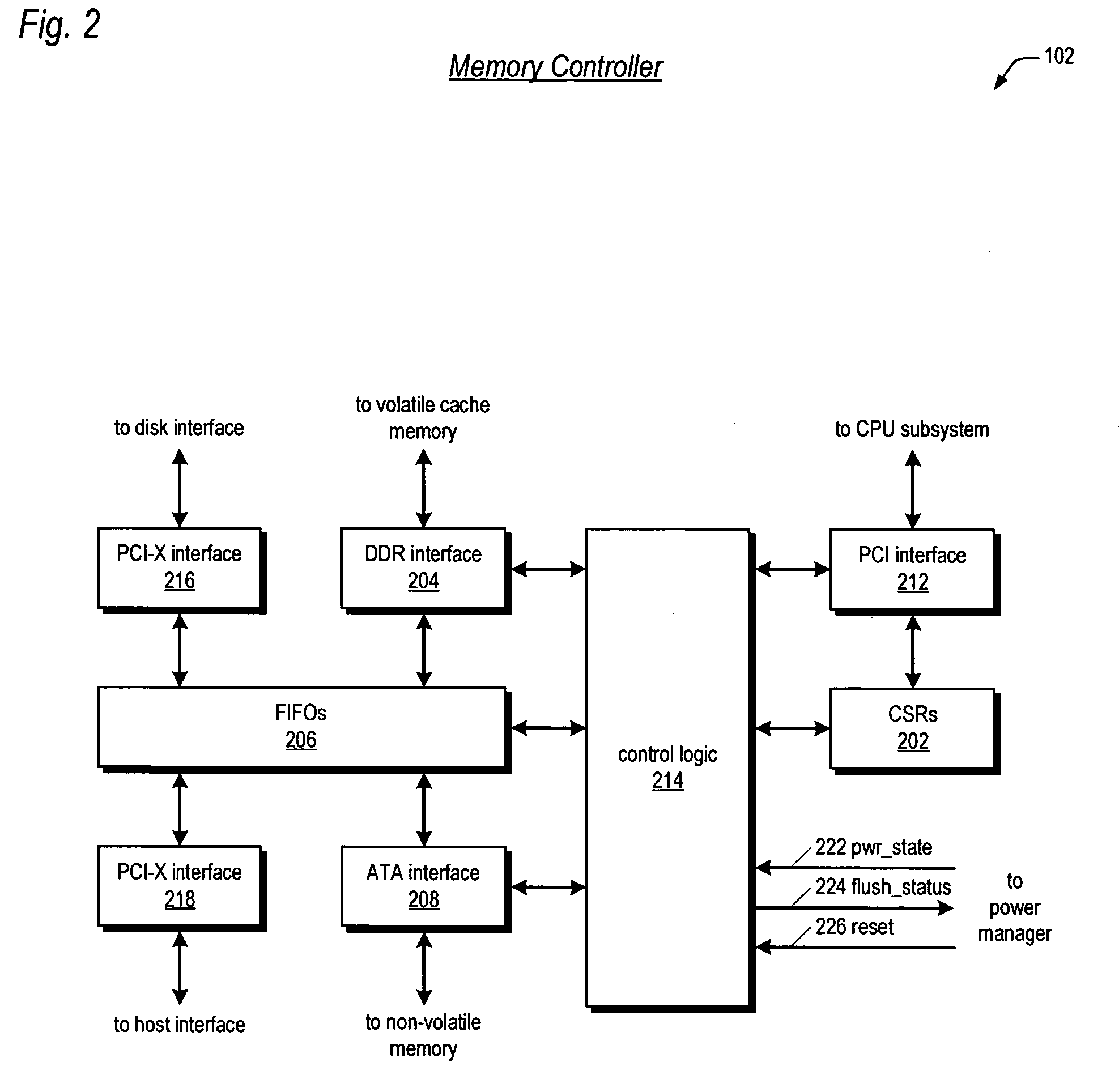

Raid controller using capacitor energy source to flush volatile cache data to non-volatile memory during main power outage

InactiveUS20060015683A1Reduces amount of energy storage capacity requirementLess expensiveEnergy efficient ICTMemory loss protectionRAIDStored energy

A write-caching RAID controller is disclosed. The controller includes a CPU that manages transfers of posted-write data from host computers to a volatile memory and transfers of the posted-write data from the volatile memory to storage devices when a main power source is supplying power to the RAID controller. A memory controller flushes the posted-write data from the volatile memory to the non-volatile memory when main power fails, during which time capacitors provide power to the memory controller, volatile memory, and non-volatile memory, but not to the CPU, in order to reduce the energy storage requirements of the capacitors. During main power provision, the CPU programs the memory controller with information needed to perform the flush operation, such as the location and size of the posted-write data in the volatile memory and various flush operation characteristics.

Owner:DOT HILL SYST

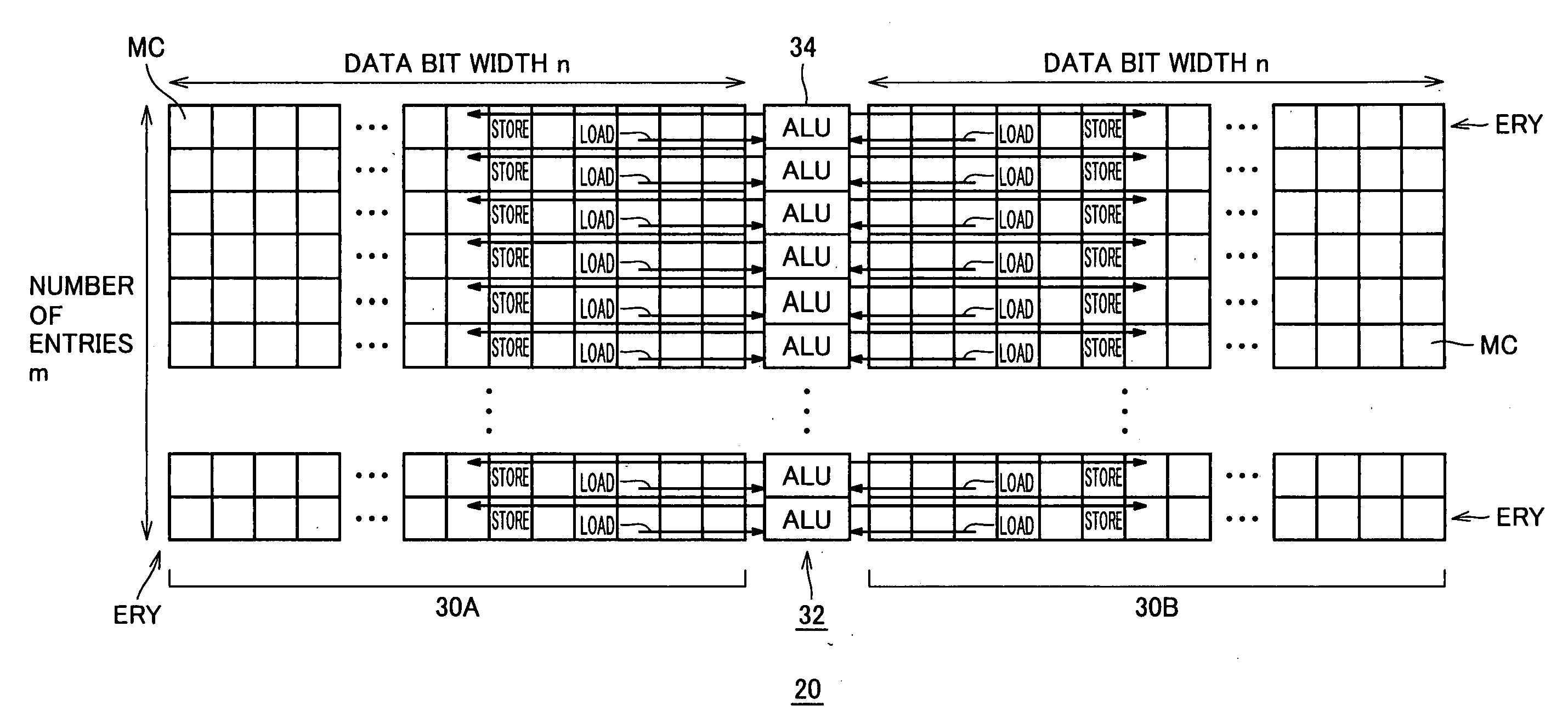

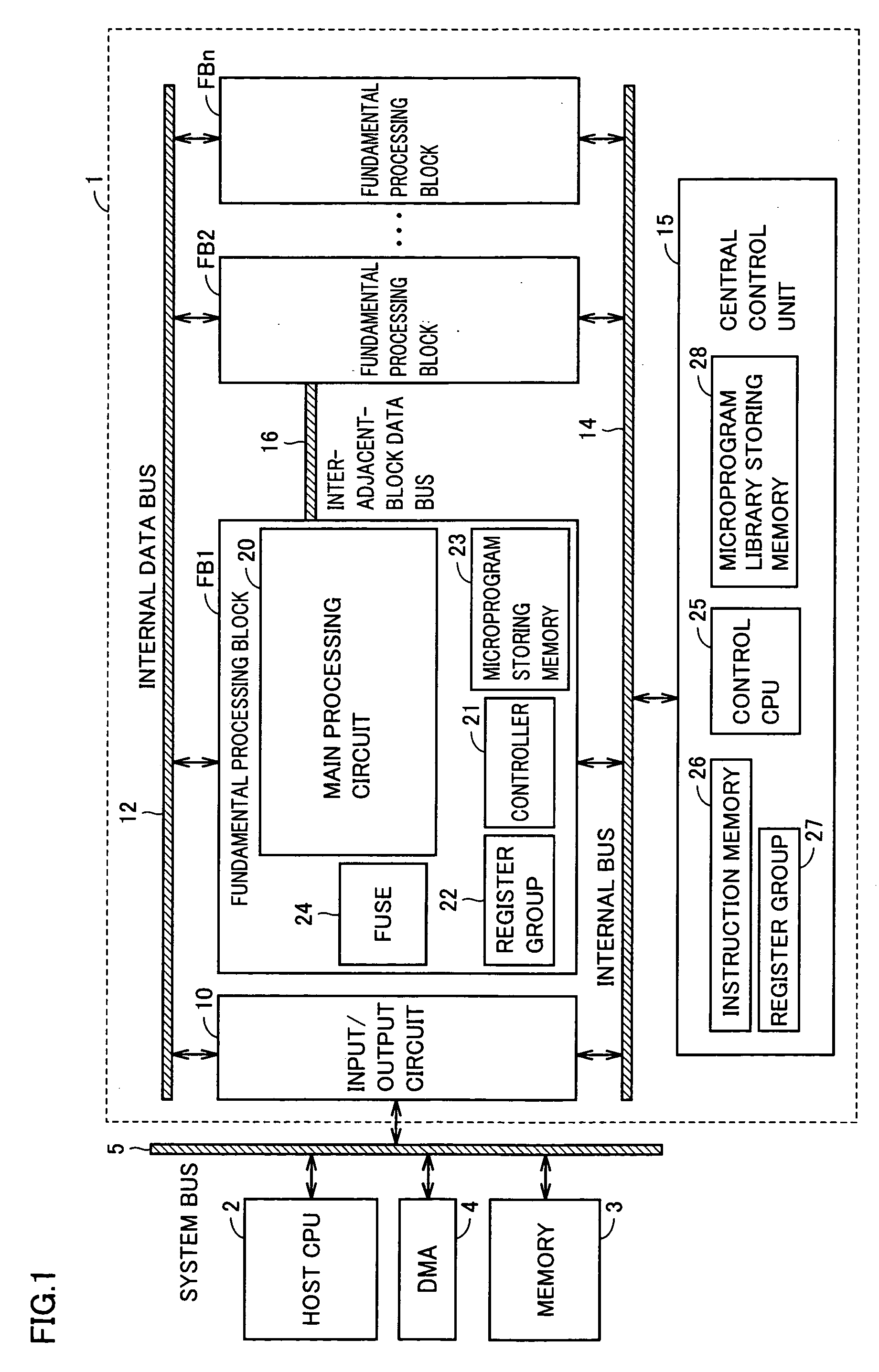

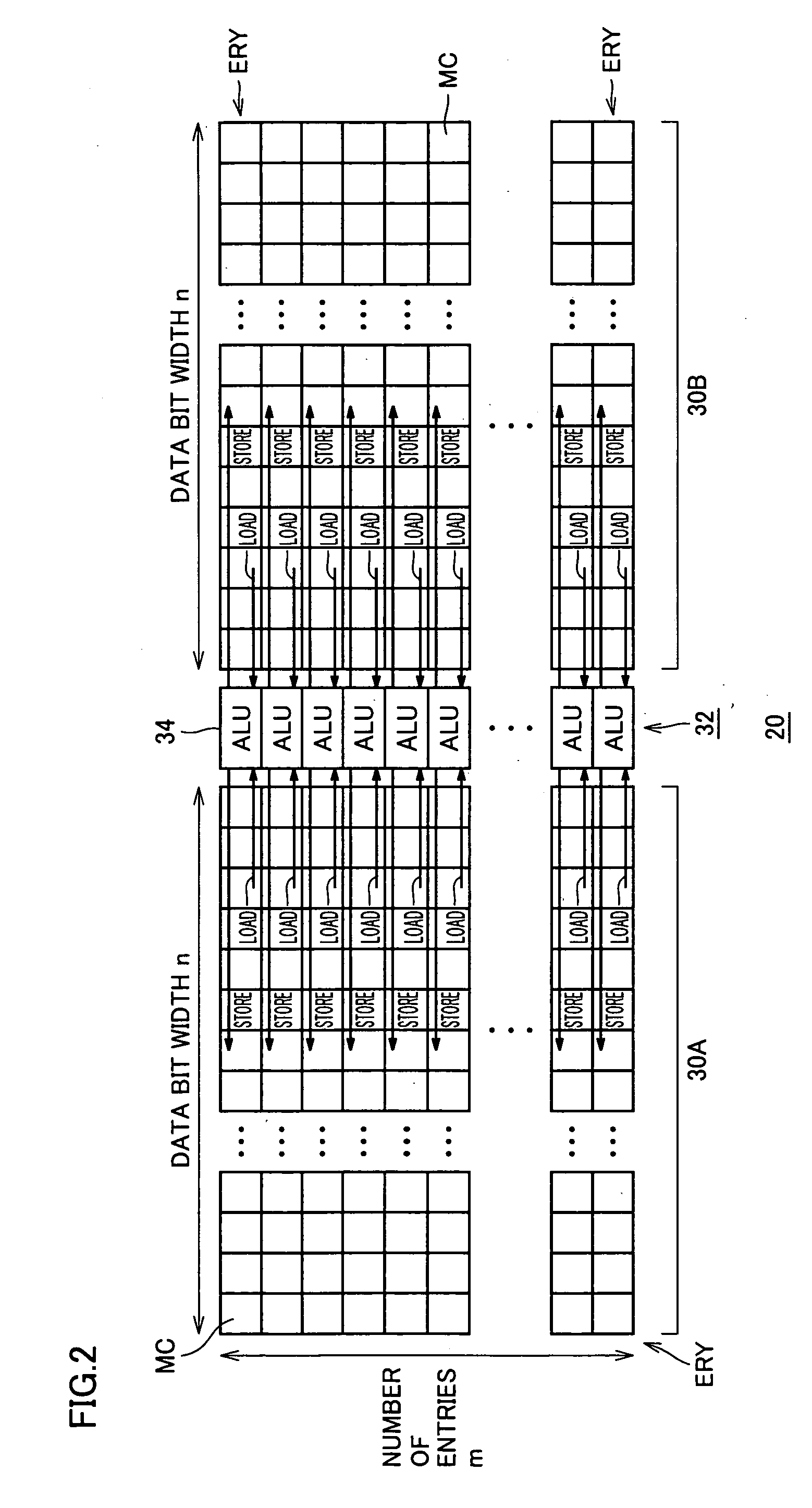

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

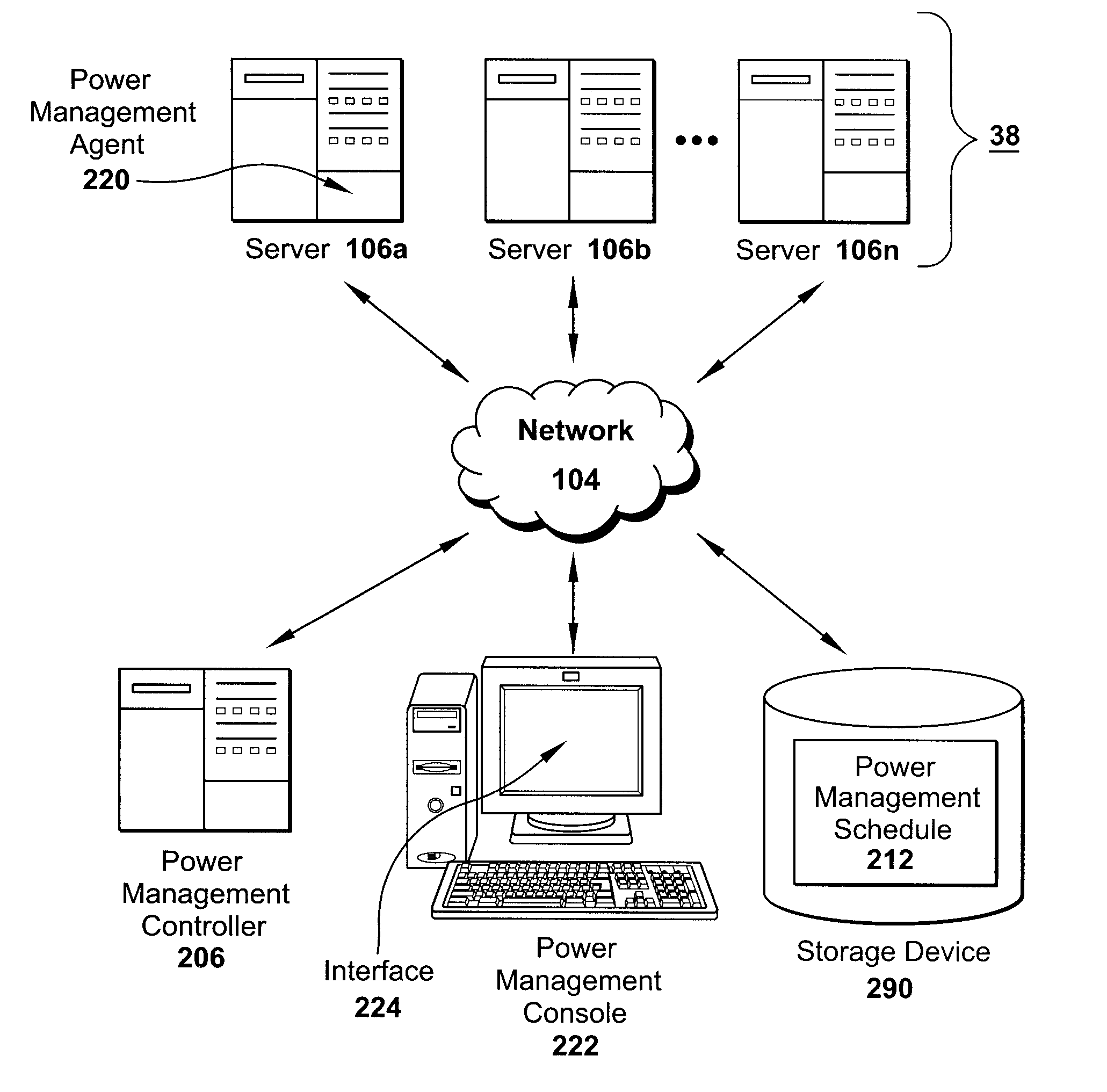

Systems and Methods to Adaptively Load Balance User Sessions to Reduce Energy Consumption

InactiveUS20090106571A1Energy efficient ICTDigital data processing detailsPower modeProgram planning

A method for adaptively load balancing user sessions to reduce energy consumption includes identifying a session type for each of a plurality of user sessions. A server group is defined, providing access to a subset of the user sessions having a common session type. A power management schedule is also defined for the server group. The method includes consolidating, onto at least one server in the server group, the subset of user sessions. In still another aspect, a method for reducing energy consumption by dynamically managing power modes for a plurality of servers, includes monitoring, via a power monitoring agent, a level of load on one of the servers. A power management console generates a power management schedule for a server, responsive to the monitored level of load. Responsive to the power management schedule, a power management controller dynamically controls a level of power for the server.

Owner:CITRIX SYST INC

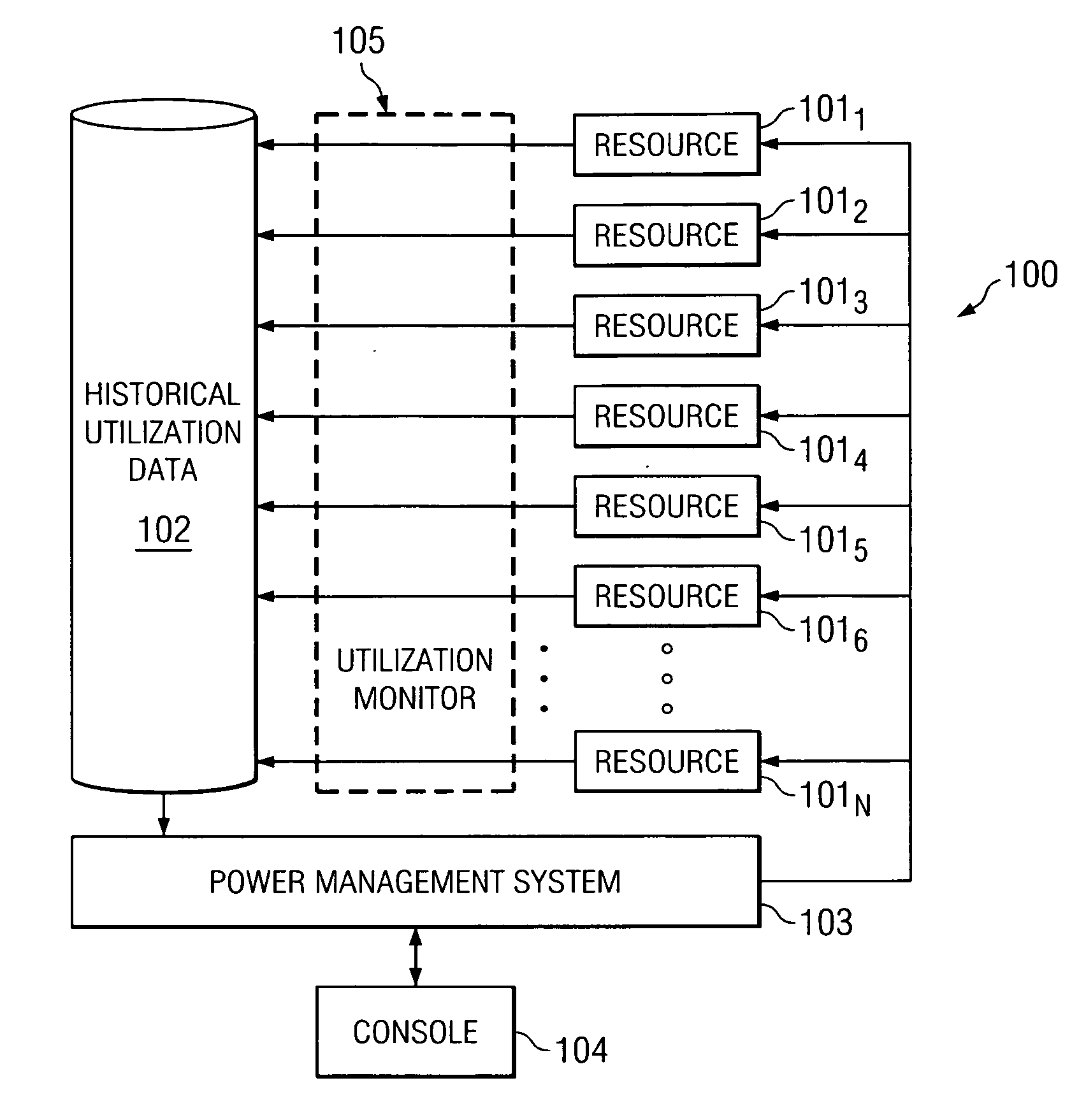

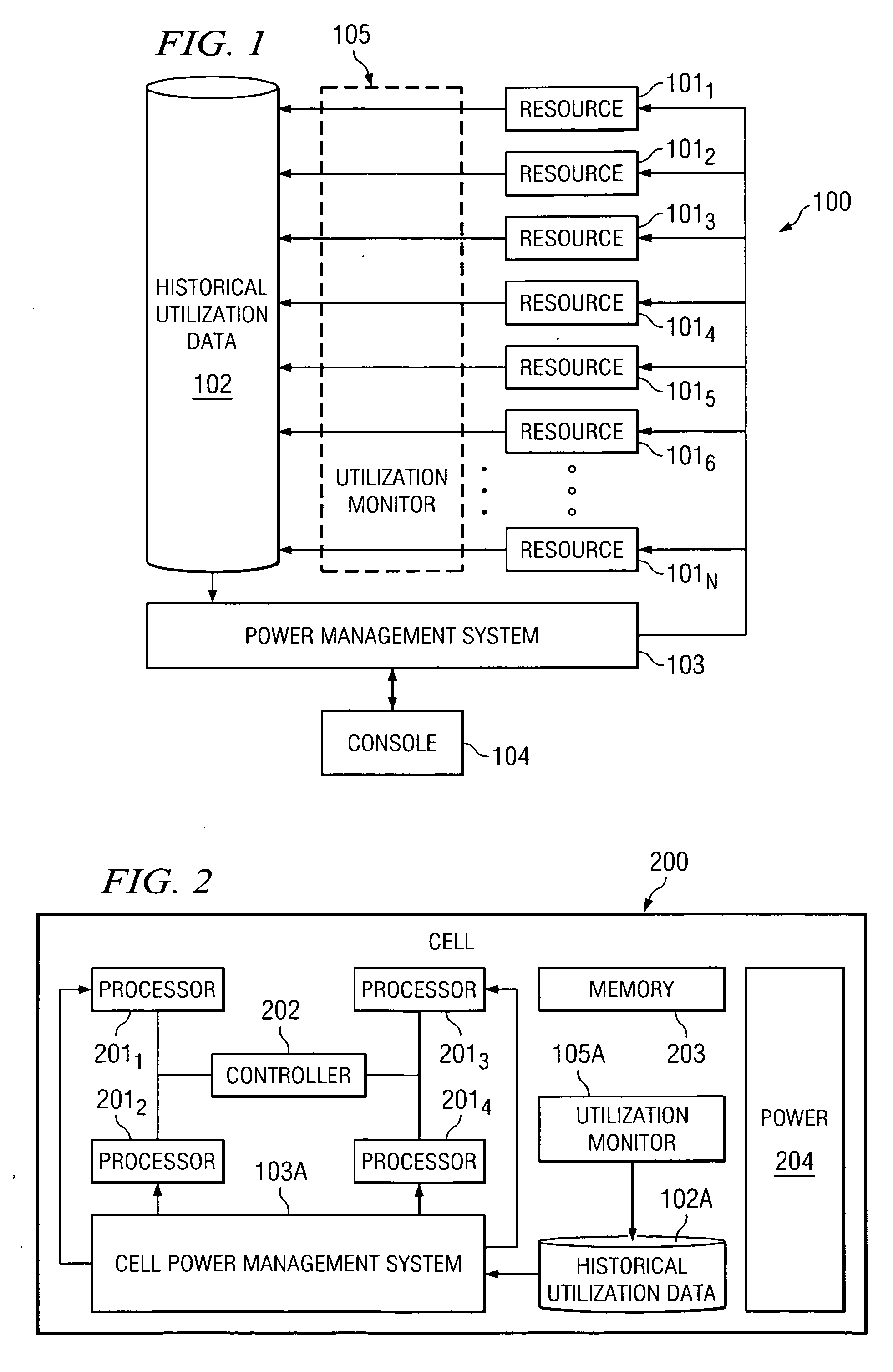

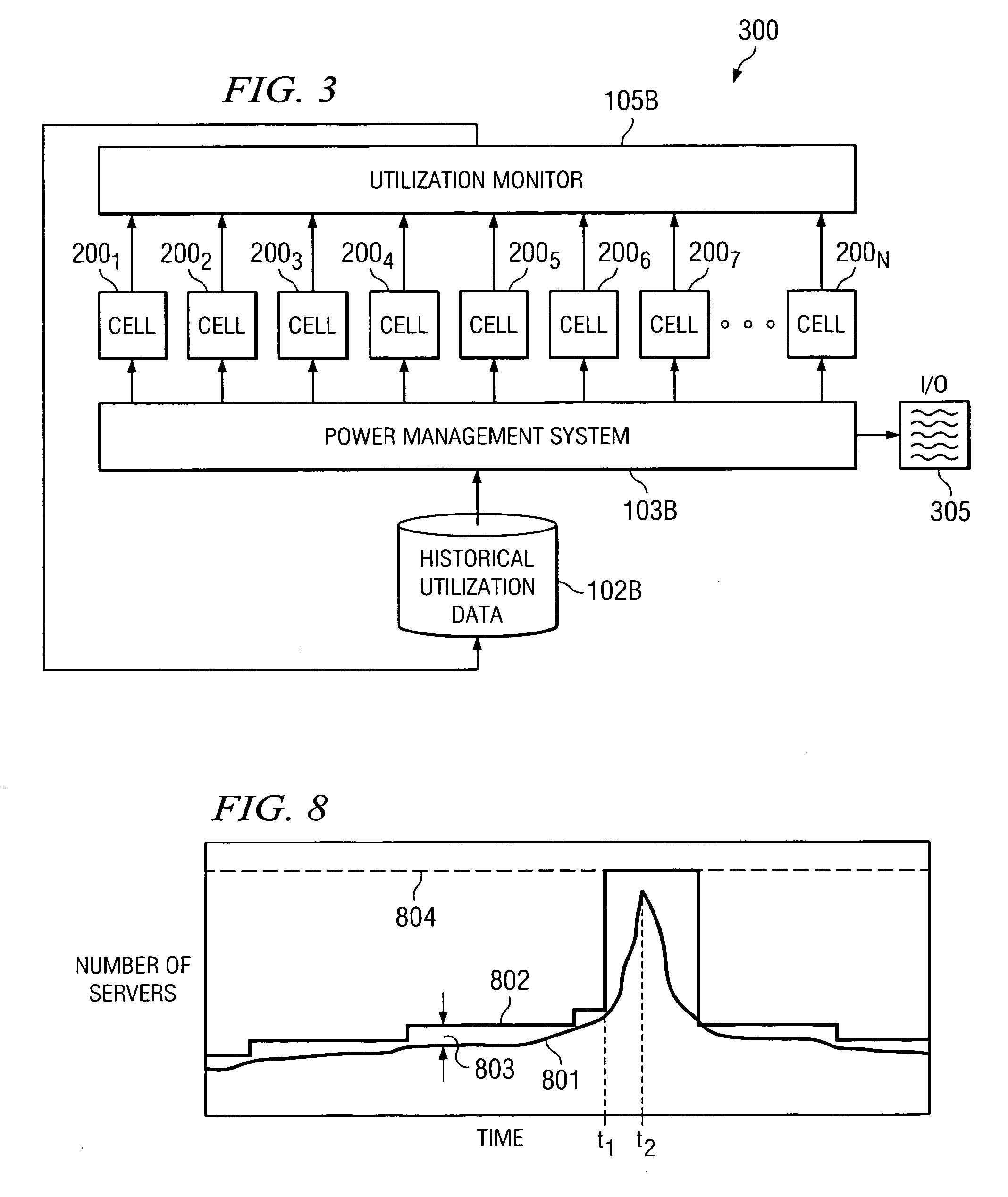

System and method for controlling power to resources based on historical utilization data

ActiveUS20060184287A1Energy efficient ICTMechanical power/torque controlResource basedSystem configuration

A method comprises collecting utilization data for a resource, and predicting by a power management system, based on the collected utilization data, future utilization of the resource. The method further comprises controlling, by the power management system, power to the resource, based at least in part on the predicted future utilization of the resource. In one embodiment, the utilization data is collected for a plurality of resources that are operable to perform tasks, and the method further comprises determining, by the power management system, how many of the resources are needed to provide a desired capacity for servicing the predicted future utilization of the resources for performing the tasks. The method further comprises configuring, by the power management system, ones of the resources exceeding the determined number of resources needed to provide the desired capacity in a reduced power-consumption mode.

Owner:MOSAID TECH

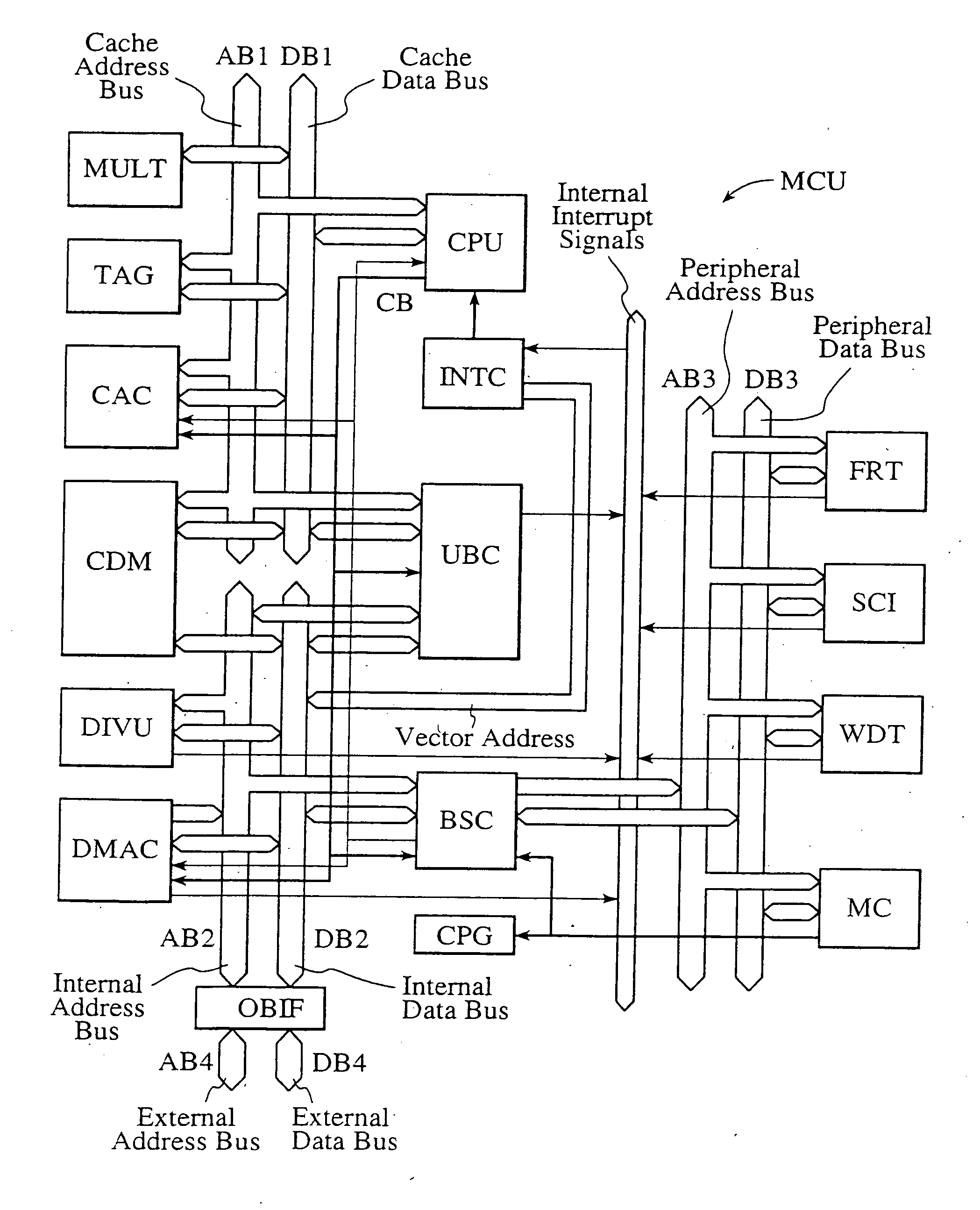

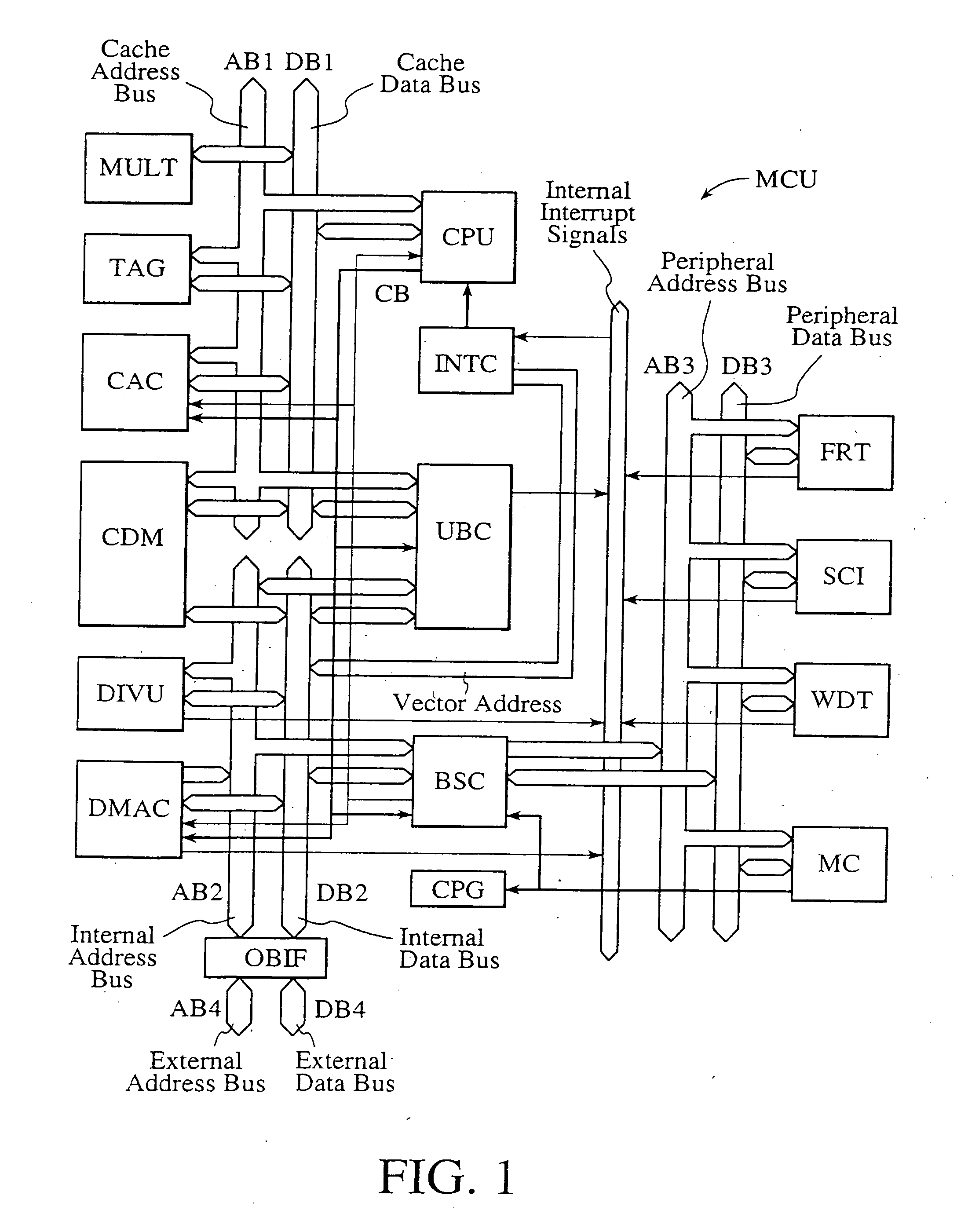

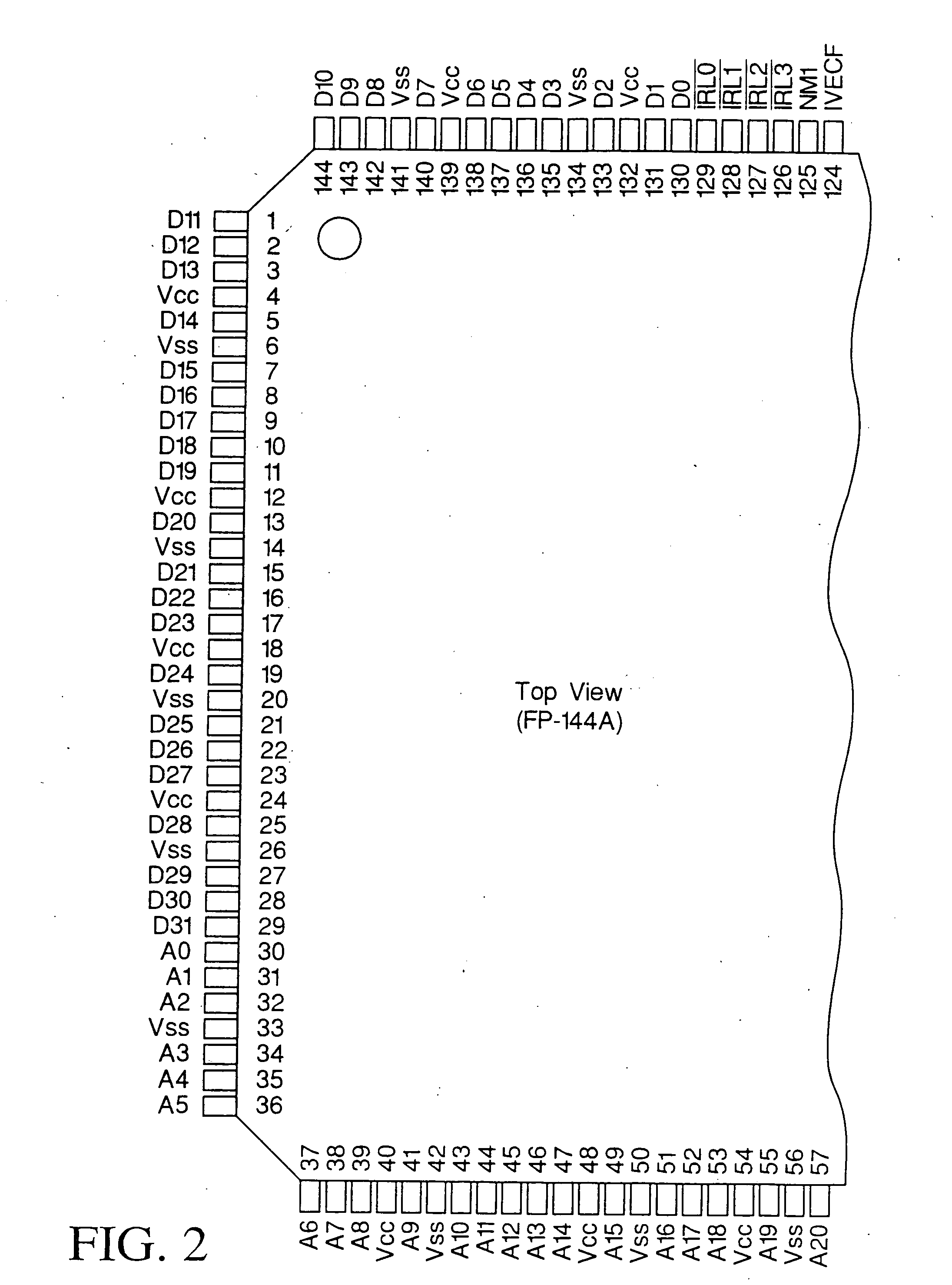

Single-chip microcomputer

InactiveUS20120023281A1Multiple functionsPerformance multiplePower managementEnergy efficient ICTMicrocontrollerMicrocomputer

A single-chip microcomputer comprising: a first bus having a central processing unit and a cache memory connected therewith; a second bus having a dynamic memory access control circuit and an external bus interface connected therewith; a break controller for connecting the first bus and the second bus selectively; a third bus having a peripheral module connected therewith and having a lower-speed bus cycle than the bus cycles of the first and second buses; and a bus state controller for effecting a data transfer and a synchronization between the second bus and the third bus. The single-chip microcomputer has the three divided internal buses to reduce the load capacity upon the signal transmission paths so that the signal transmission can be accomplished at a high speed. Moreover, the peripheral module required to have no operation speed is isolated so that the power dissipation can be reduced.

Owner:KAWASAKI SHUMPEI +8

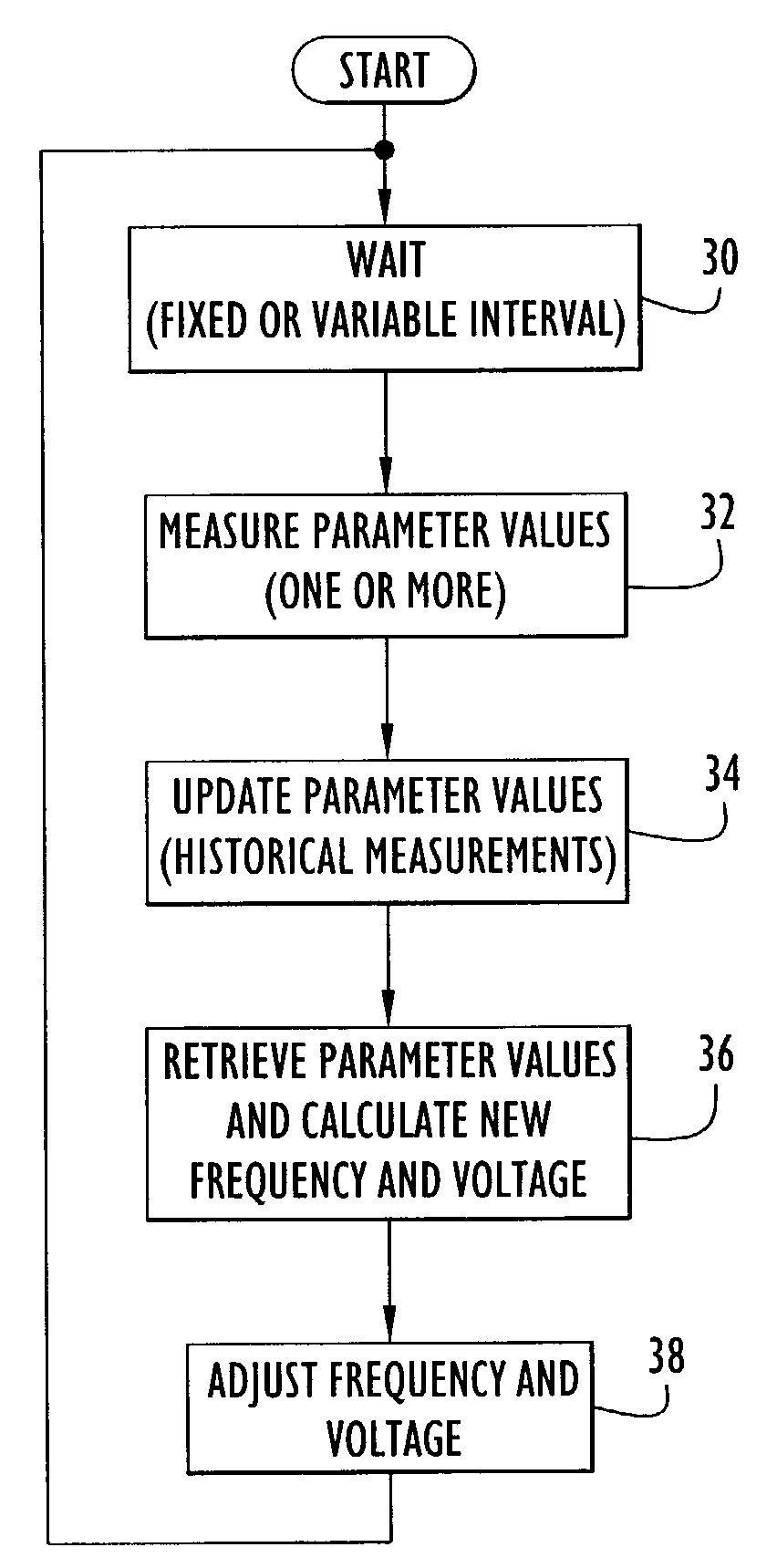

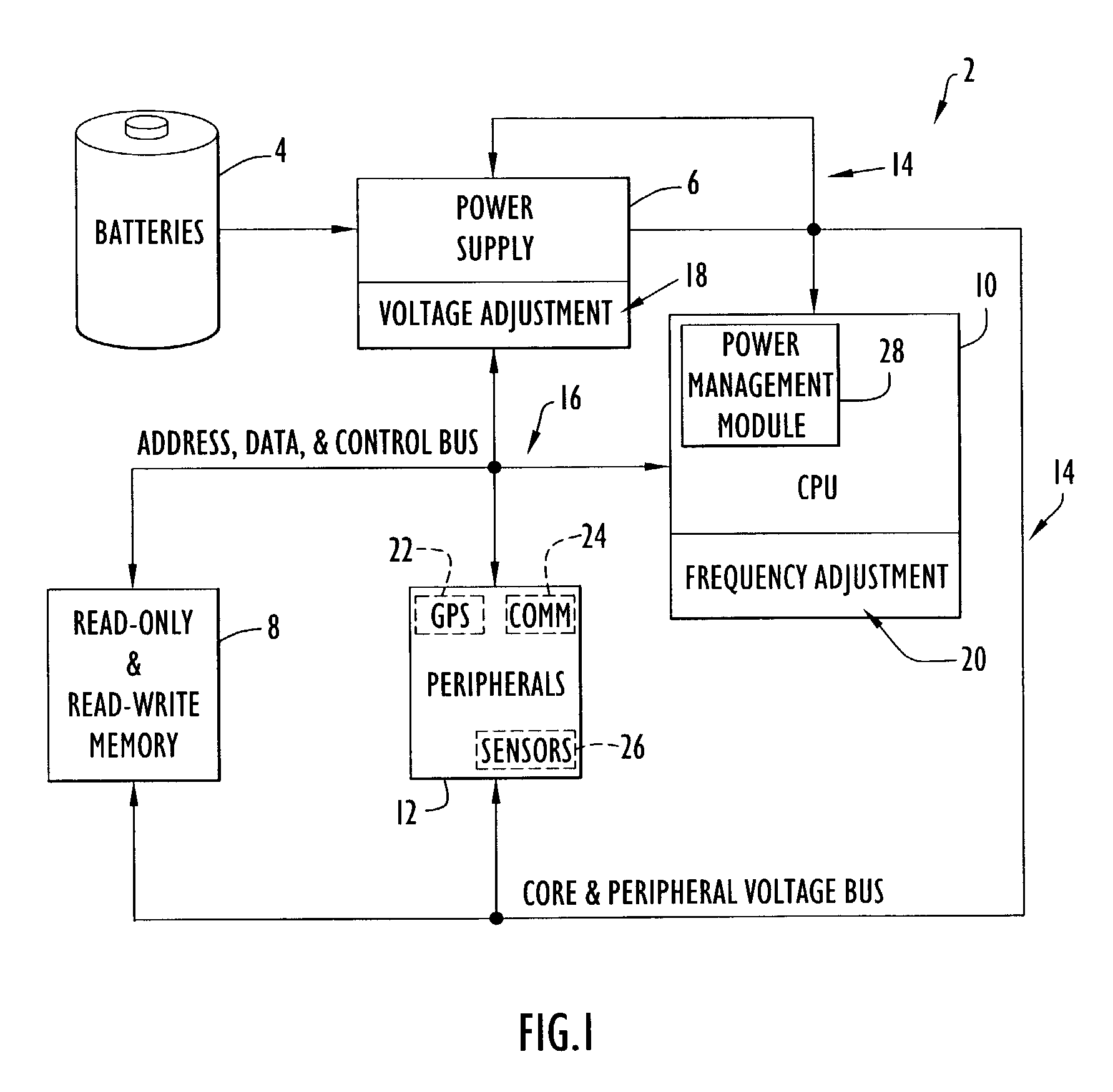

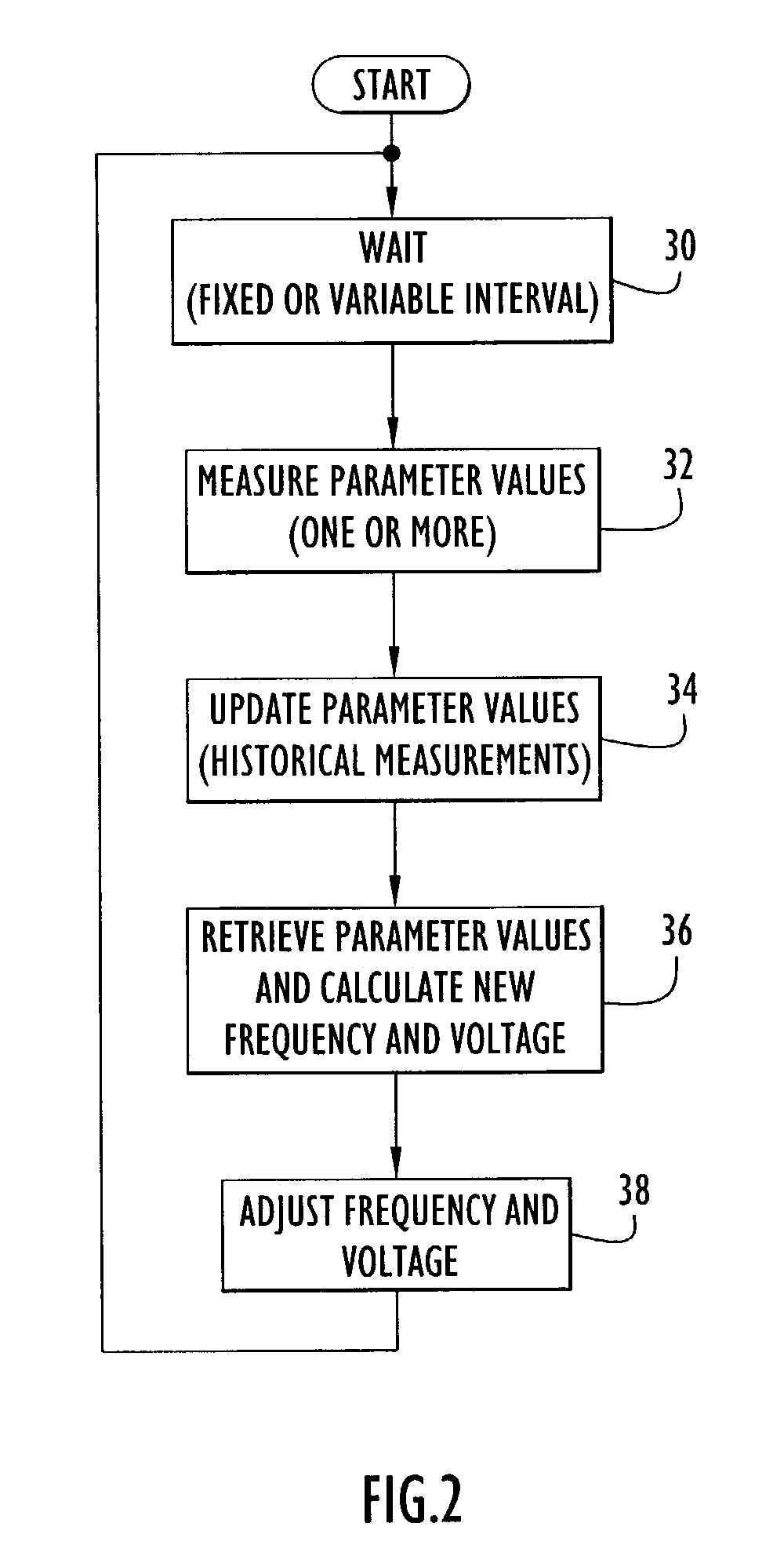

Method and apparatus for optimizing performance and battery life of electronic devices based on system and application parameters

InactiveUS7111179B1Reduce power consumptionExtending device operating lifeEnergy efficient ICTBatteries circuit arrangementsOperational systemElectrical battery

An electronic device (e.g., computer system, etc.) employing dynamic power management of the present invention adjusts power consumption in accordance with an analysis of parameters and events occurring over one or more time-periods. Preferably, the electronic device monitors microprocessor, operating system, peripheral and / or device-level events and adjusts run-time parameters, such as microprocessor clock frequency and voltage, to reduce power consumption with minimal perceived degradation in performance.

Owner:MOSAID TECH

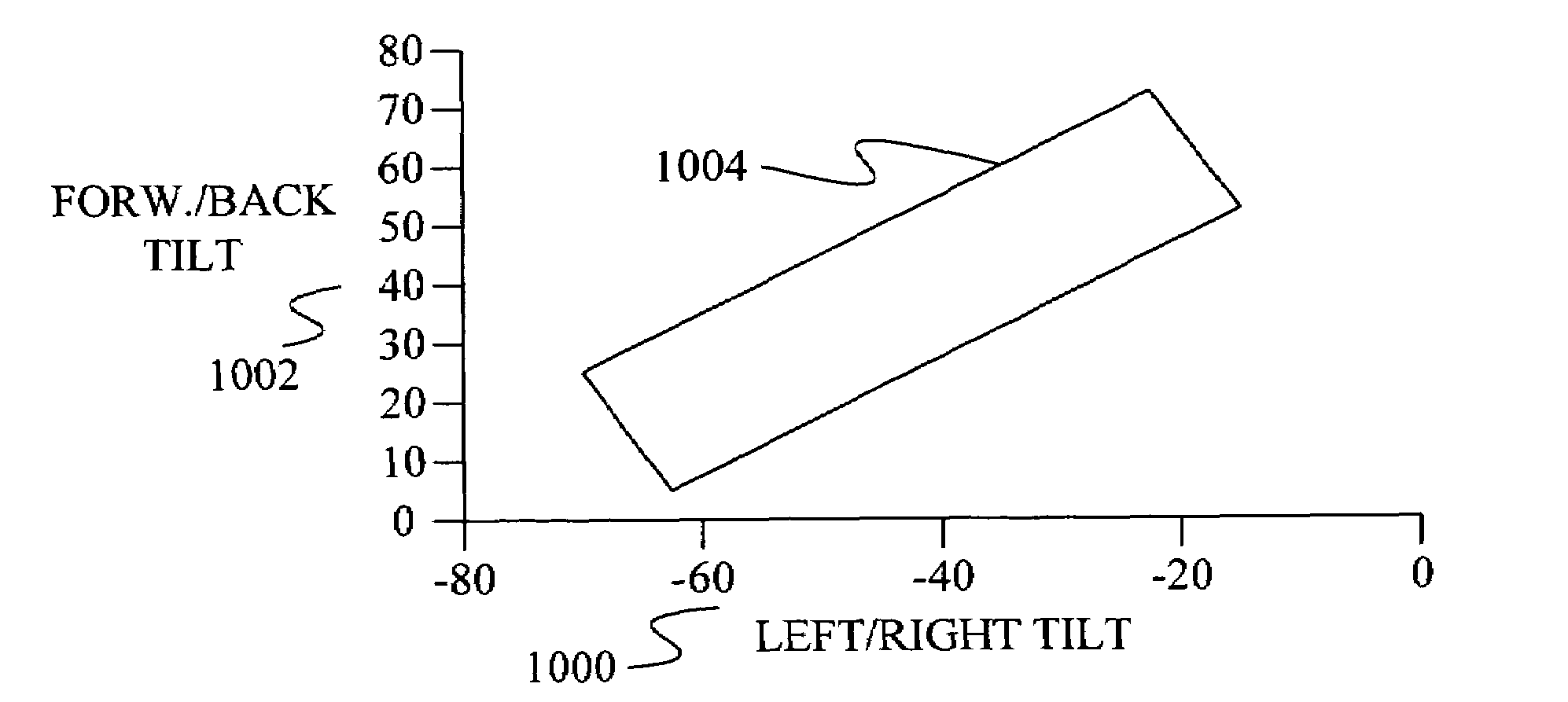

Gesture-based power management of a wearable portable electronic device with display

InactiveUS20090195497A1Energy efficient ICTDigital data processing detailsDisplay deviceEmbedded system

Methods and systems for providing gesture-based power management for a wearable portable electronic device with display are described. An inertial sensor is calibrated to a reference orientation relative to gravity. Motion of the portable device is tracked with respect to the reference orientation, and the display is enabled when the device is within a viewable range, wherein the viewable range is a predefined rotational angle range in each of x, y, and z axis, to a user based upon a position of the device with respect to the reference orientation. Furthermore, the display is turned off if an object is detected within a predetermined distance of the display for a predetermined amount of time.

Owner:GOOGLE LLC

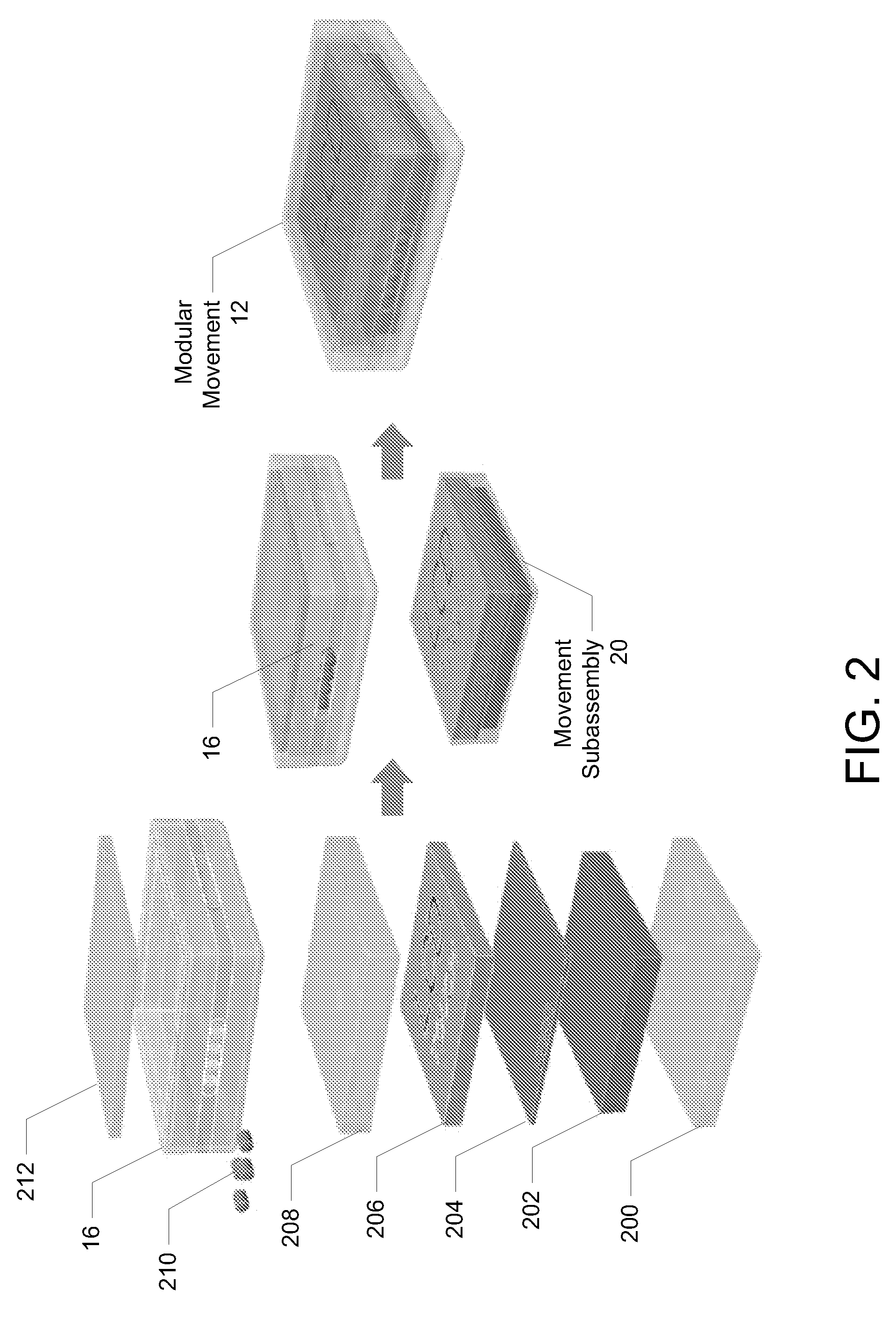

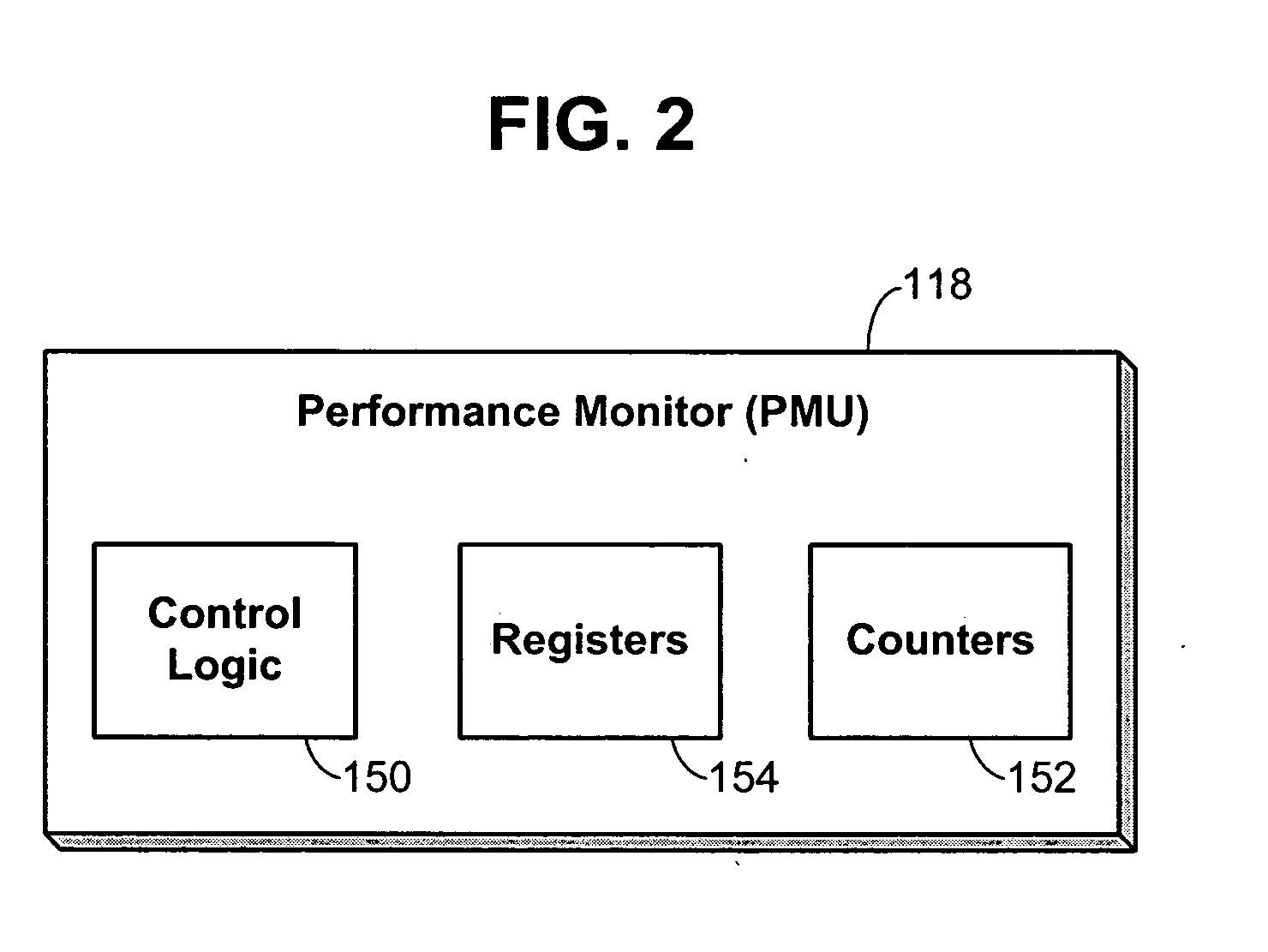

Performance monitoring based dynamic voltage and frequency scaling

Voltage and frequency scaling techniques that are based upon monitored data are provided. The techniques may be used to better manage the power and energy consumption of a processor in an embedded system, such as a cellular telephone, personal data assistant, smart device, or the like. The techniques may be used with processors that offer a performance monitoring capability. The performance monitor may monitor thread-level utilization at runtime. Instructions per cycle and memory references per cycle are example metrics that may be monitored by the performance monitor. The voltage and frequency scaling techniques may adjust the operating voltage and operating frequency of the processor based on the values of these two metrics. For example, the techniques may include accessing a voltage and frequency scheduler lookup table. The techniques may be employed with non-embedded systems, as well, embedded systems.

Owner:TAHOE RES LTD

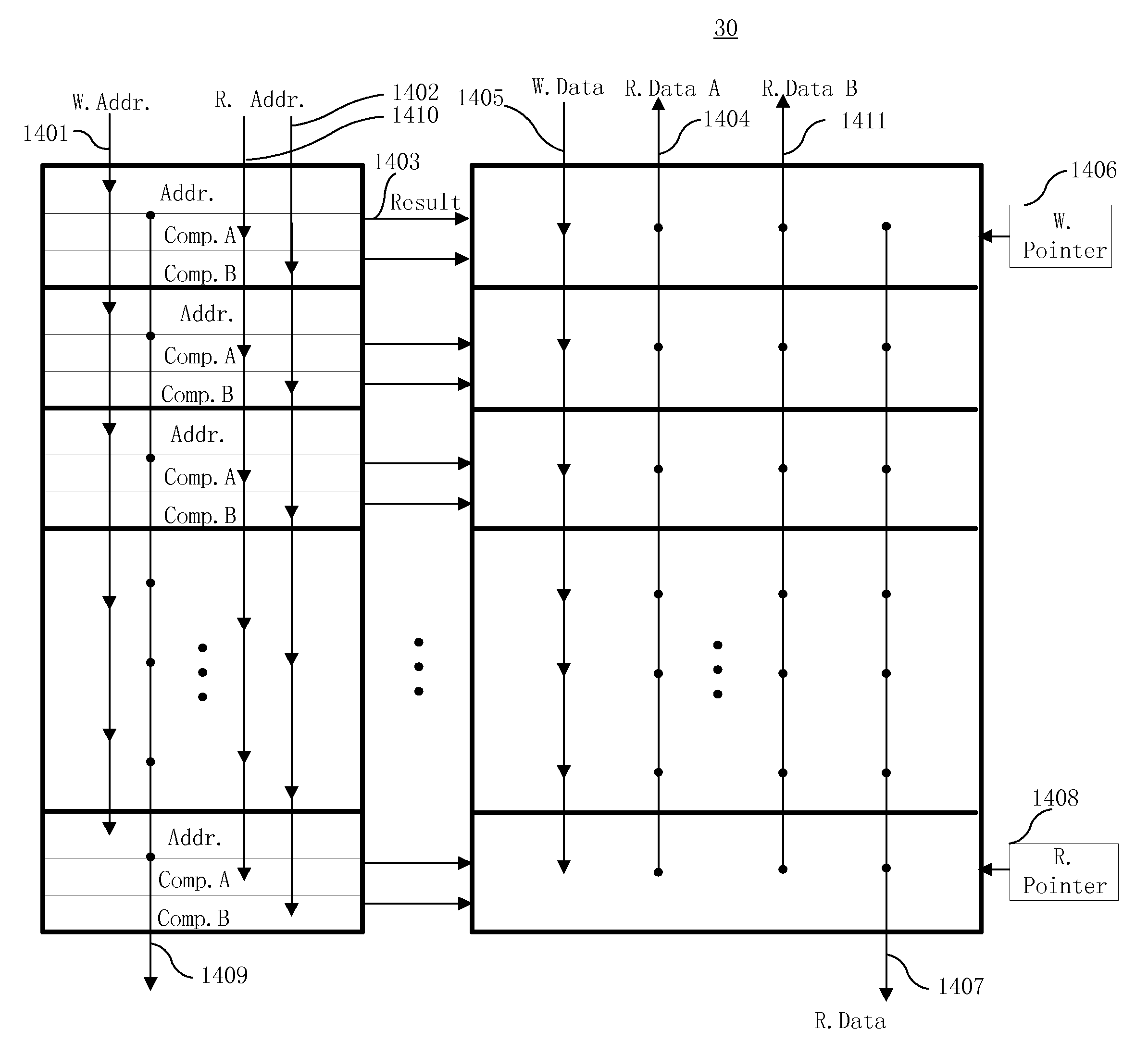

Processor-cache system and method

ActiveUS9047193B2Shorten the counting processEfficient and uniform structureEnergy efficient ICTRegister arrangementsAddress generation unitProcessor register

A digital system is provided. The digital system includes an execution unit, a level-zero (L0) memory, and an address generation unit. The execution unit is coupled to a data memory containing data to be used in operations of the execution unit. The L0 memory is coupled between the execution unit and the data memory and configured to receive a part of the data in the data memory. The address generation unit is configured to generate address information for addressing the L0 memory. Further, the L0 memory provides at least two operands of a single instruction from the part of the data to the execution unit directly, without loading the at least two operands into one or more registers, using the address information from the address generation unit.

Owner:SHANGHAI XINHAO MICROELECTRONICS

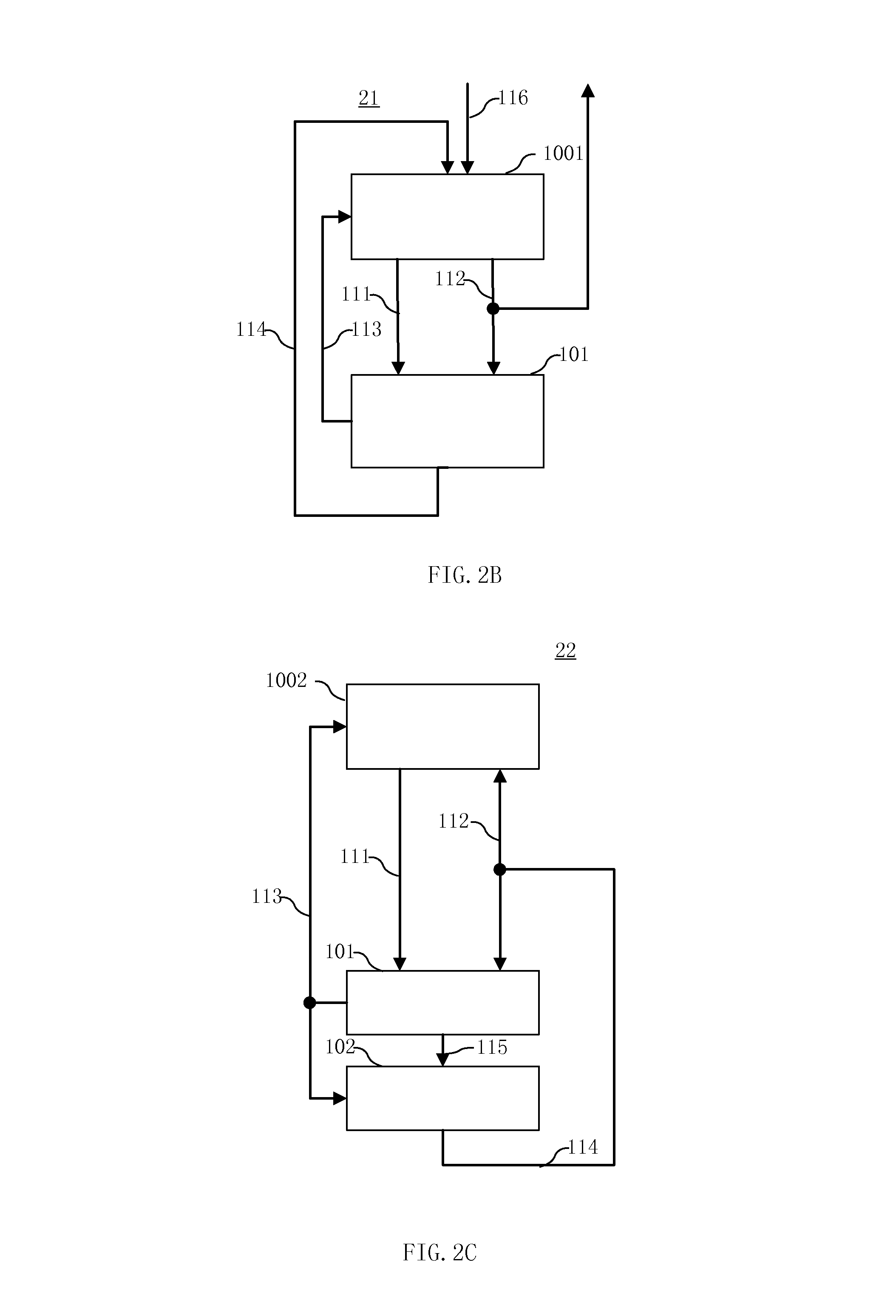

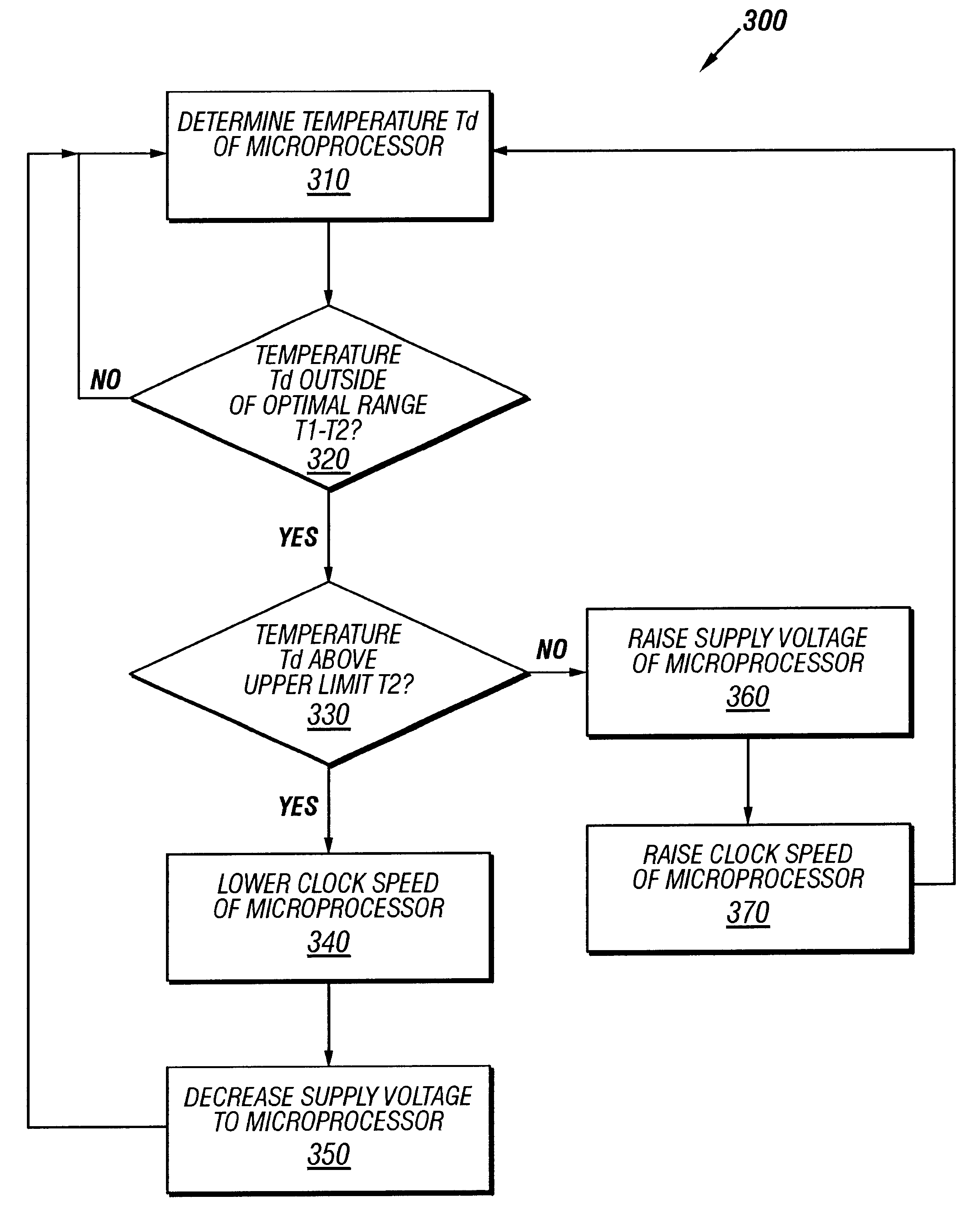

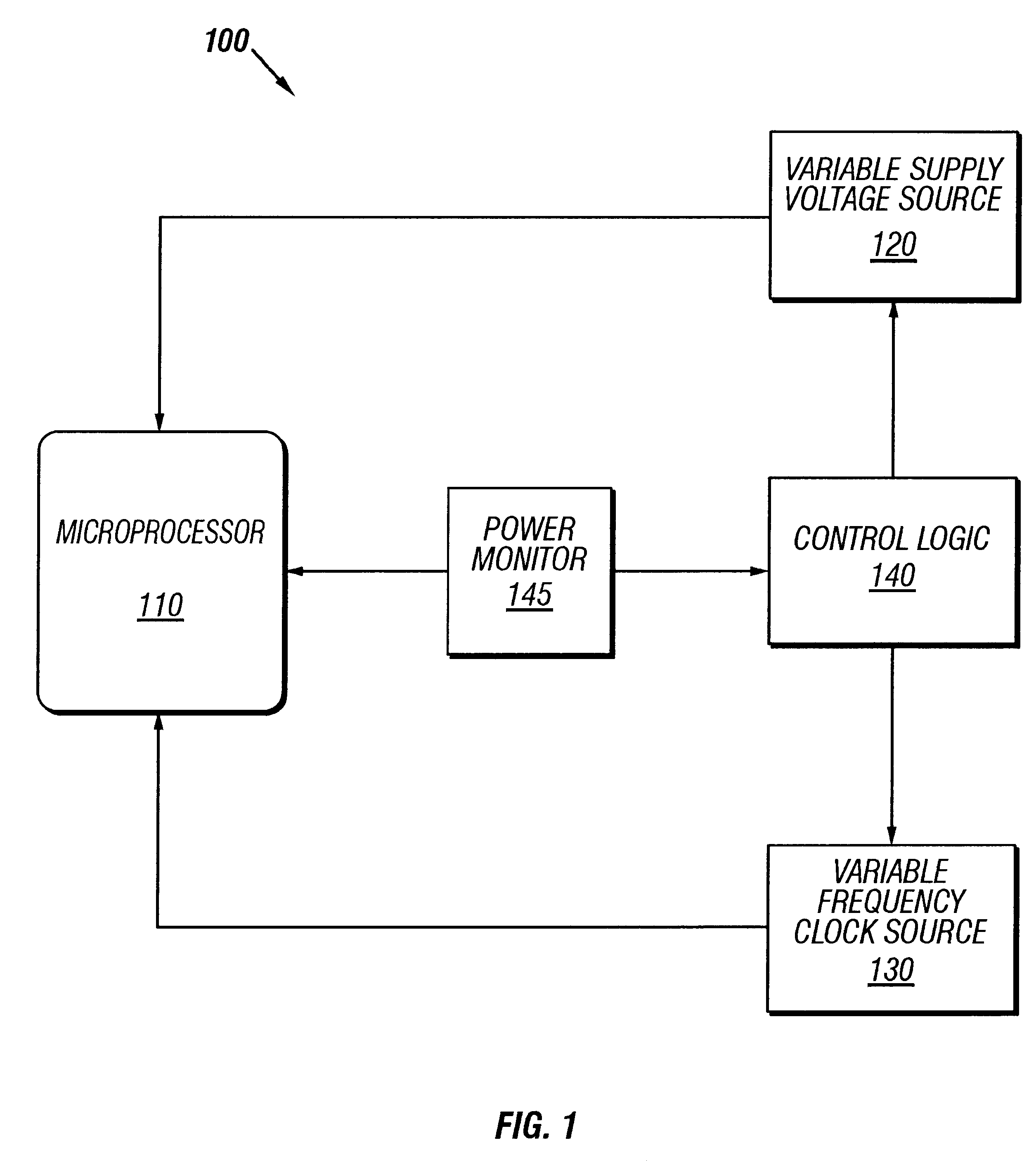

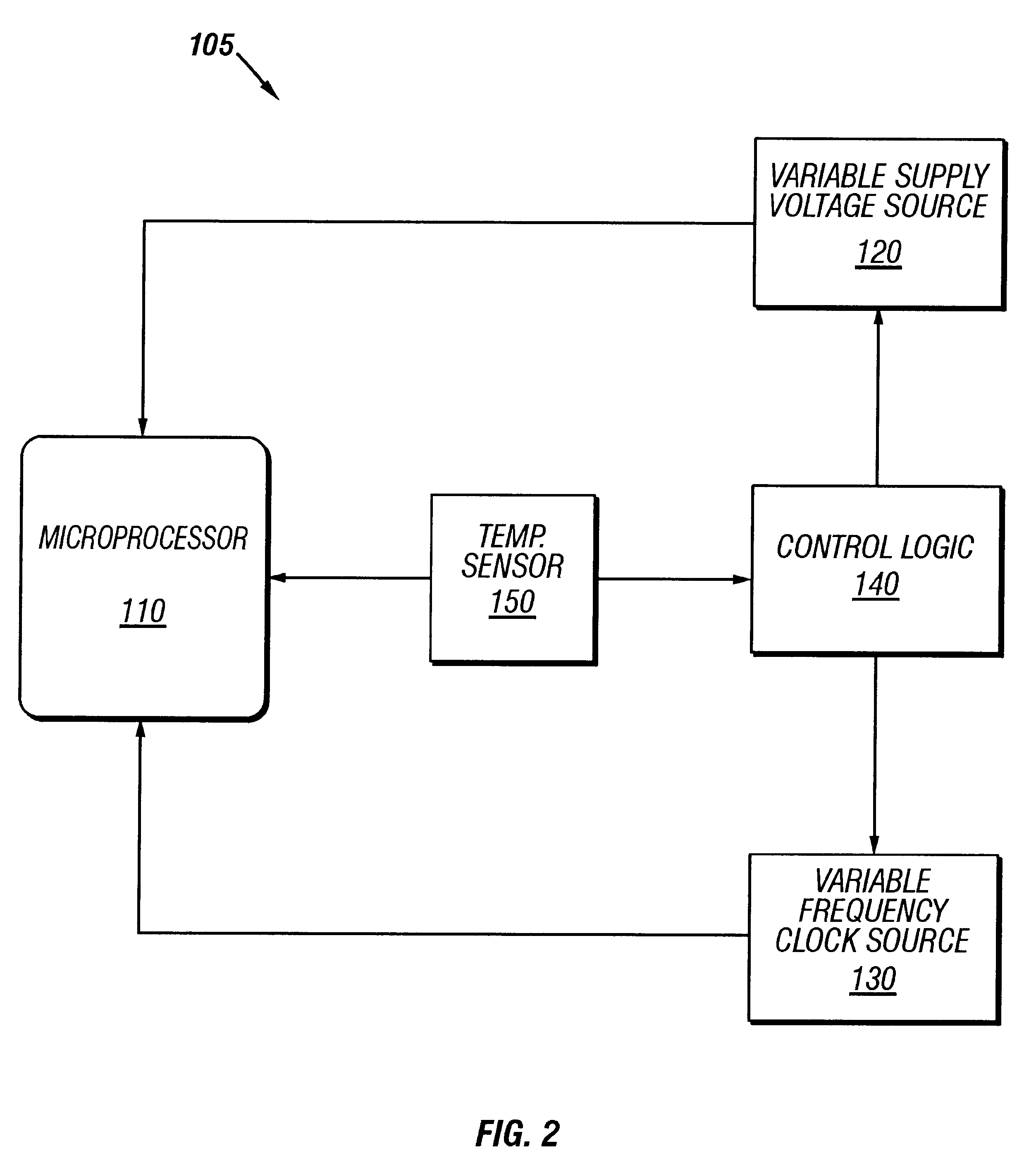

Method and apparatus for power throttling in a microprocessor using a closed loop feedback system

A method and apparatus for power throttling in a microprocessor. A voltage source supplies voltage to the microprocessor, and a clock source operates the microprocessor at a desired frequency. In one embodiment, a power monitor is configured to measure the short term power consumption of the microprocessor. In another embodiment, a temperature sensor measures the temperature of the microprocessor. Control logic is coupled to the voltage source and the clock source. The control logic receives an indication of the power consumption or temperature, as applicable, and compares it to a predetermined value. In response to the comparison, the control logic varies the supply voltage and the frequency.

Owner:INTEL CORP

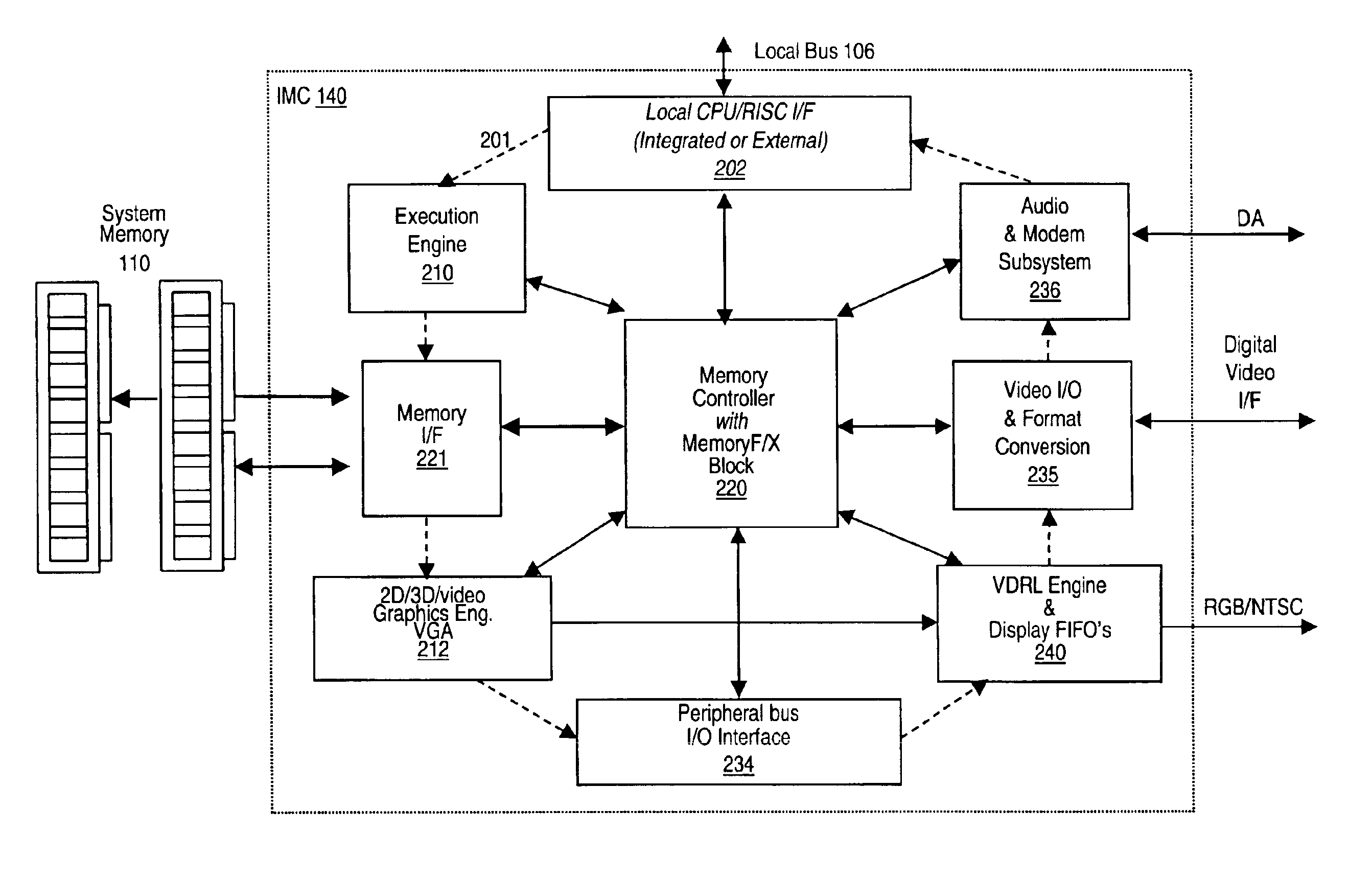

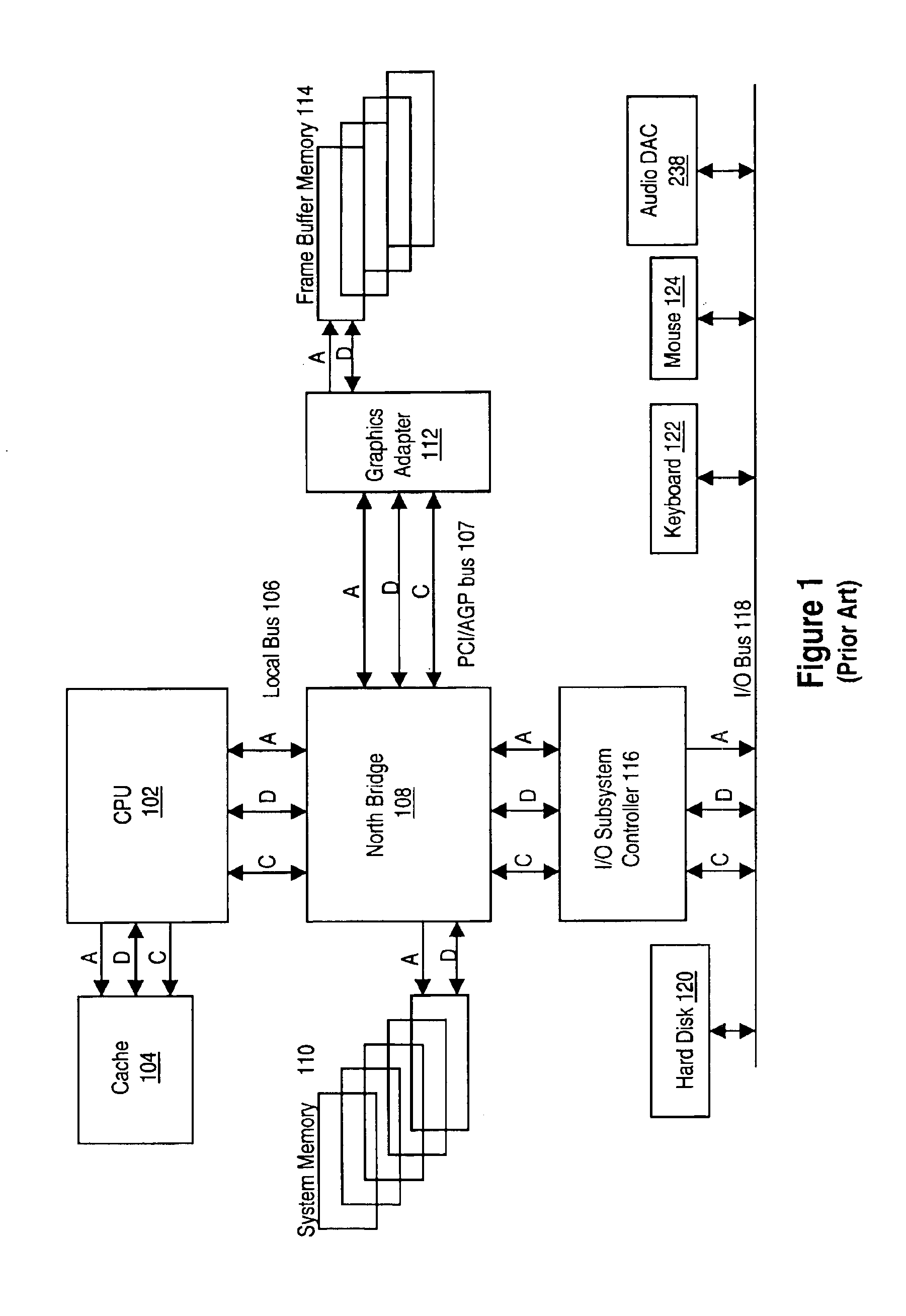

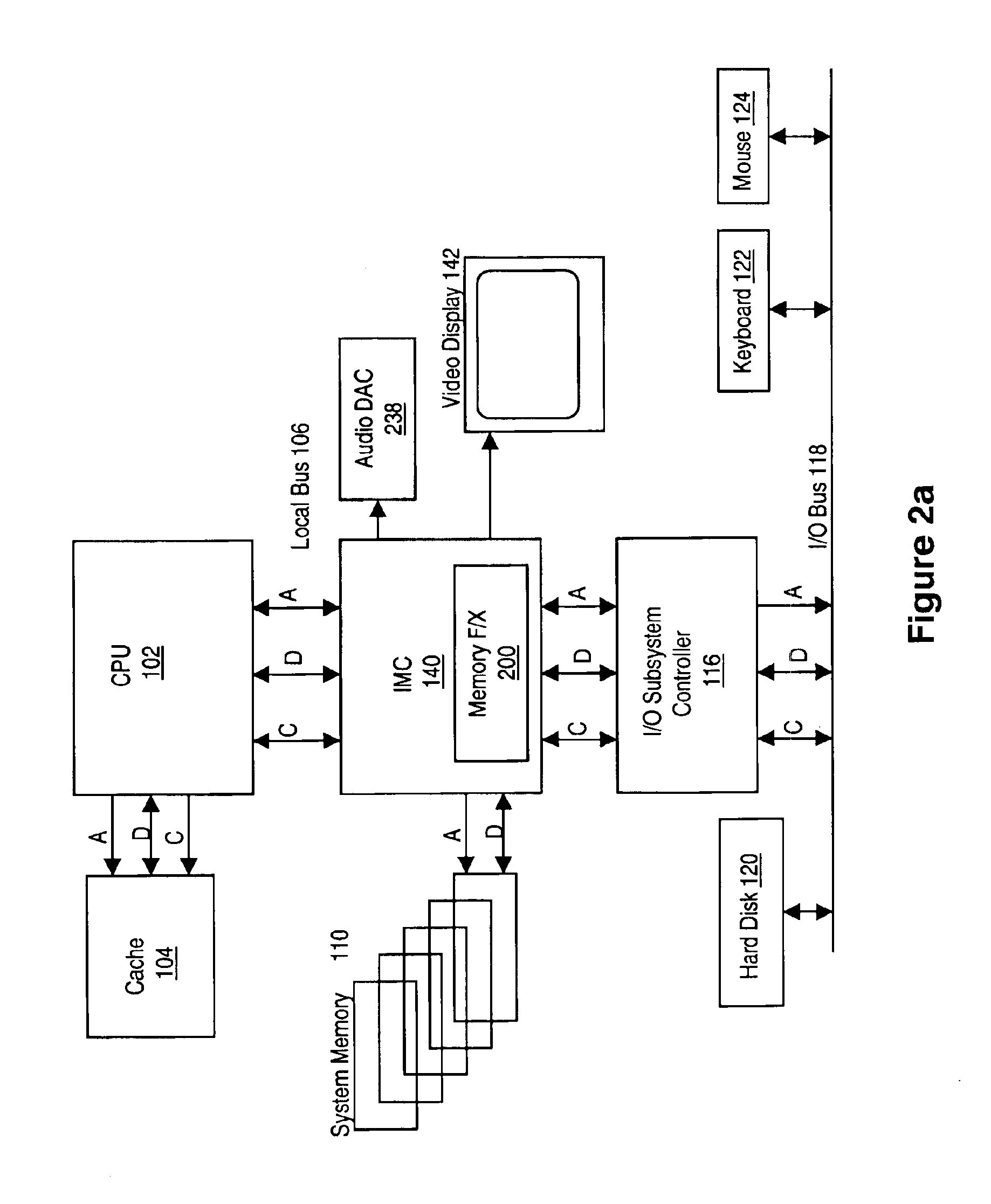

Memory module including scalable embedded parallel data compression and decompression engines

InactiveUS6879266B1Low costSmall data storage requirementMemory architecture accessing/allocationEnergy efficient ICTParallel compressionParallel computing

An memory module including parallel data compression and decompression engines for improved performance. The memory module includes MemoryF / X Technology. To improve latency and reduce performance degradations normally associated with compression and decompression techniques, the MemoryF / X Technology encompasses multiple novel techniques such as: 1) parallel lossless compression / decompression; 2) selectable compression modes such as lossless, lossy or no compression; 3) priority compression mode; 4) data cache techniques; 5) variable compression block sizes; 6) compression reordering; and 7) unique address translation, attribute, and address caches. The parallel compression and decompression algorithm allows high-speed parallel compression and high-speed parallel decompression operation. The memory module-integrated data compression and decompression capabilities remove system bottlenecks and increase performance. This allows lower cost systems due to smaller data storage, reduced bandwidth requirements, reduced power and noise.

Owner:INTELLECTUAL VENTURES I LLC

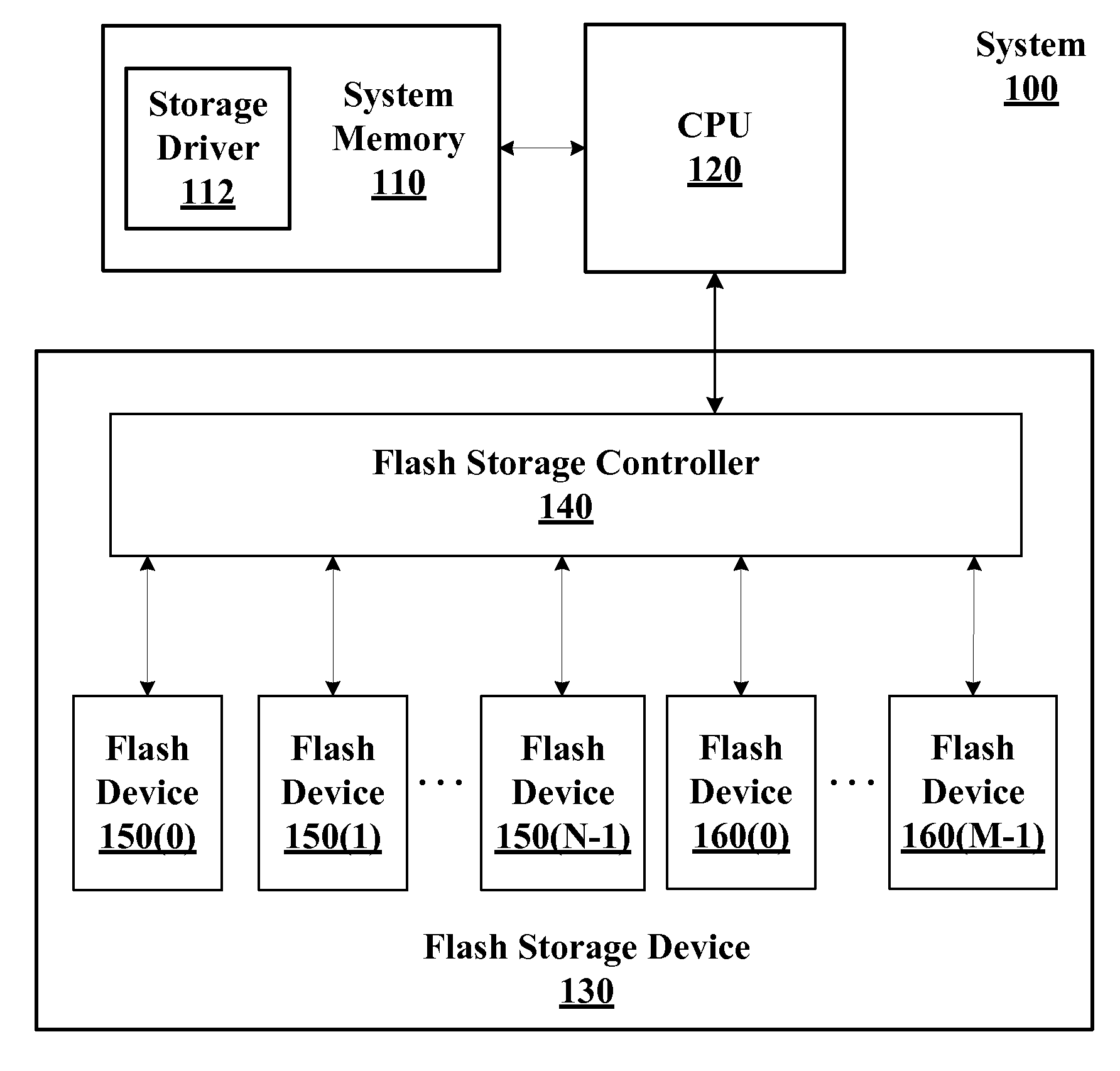

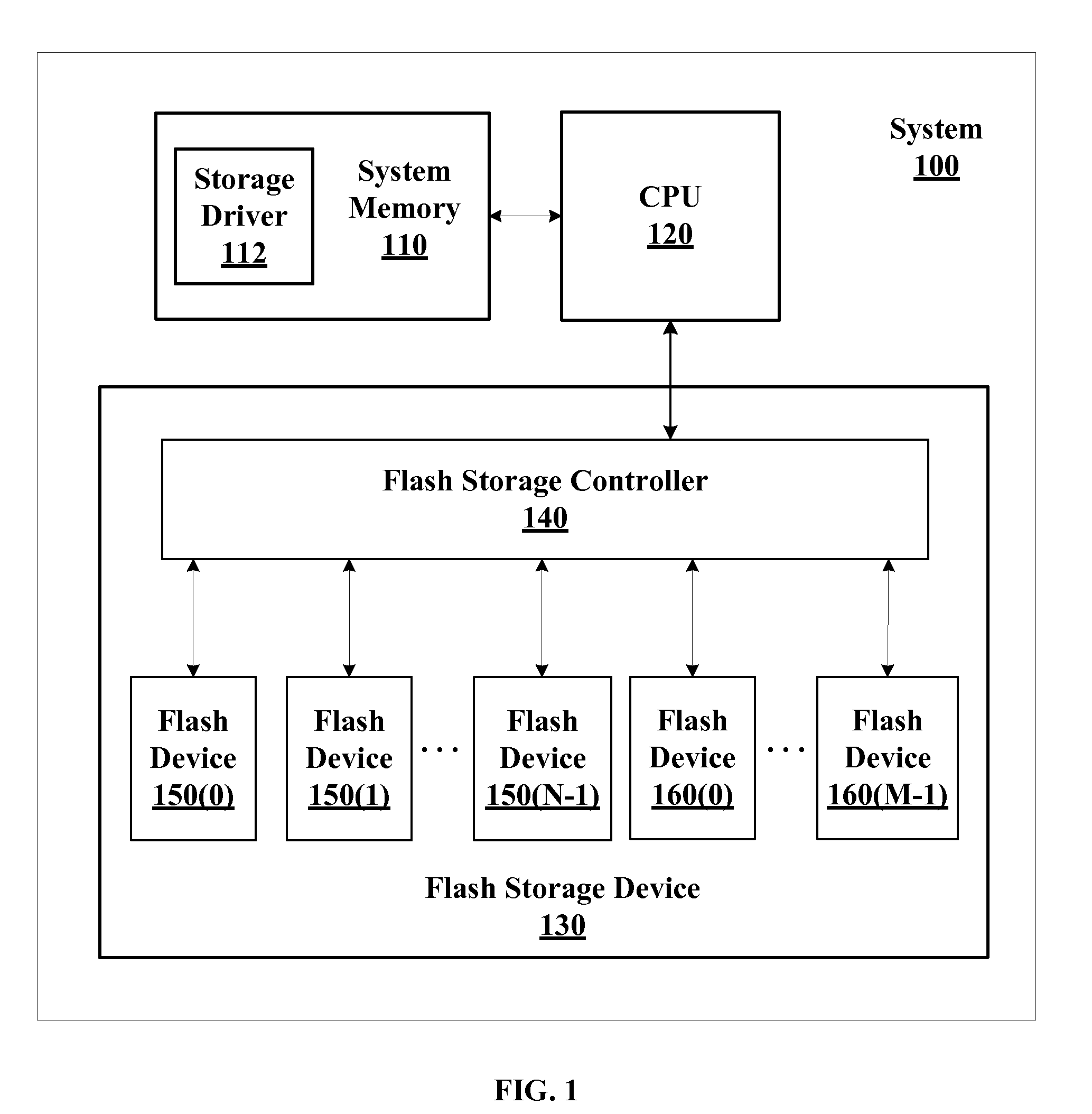

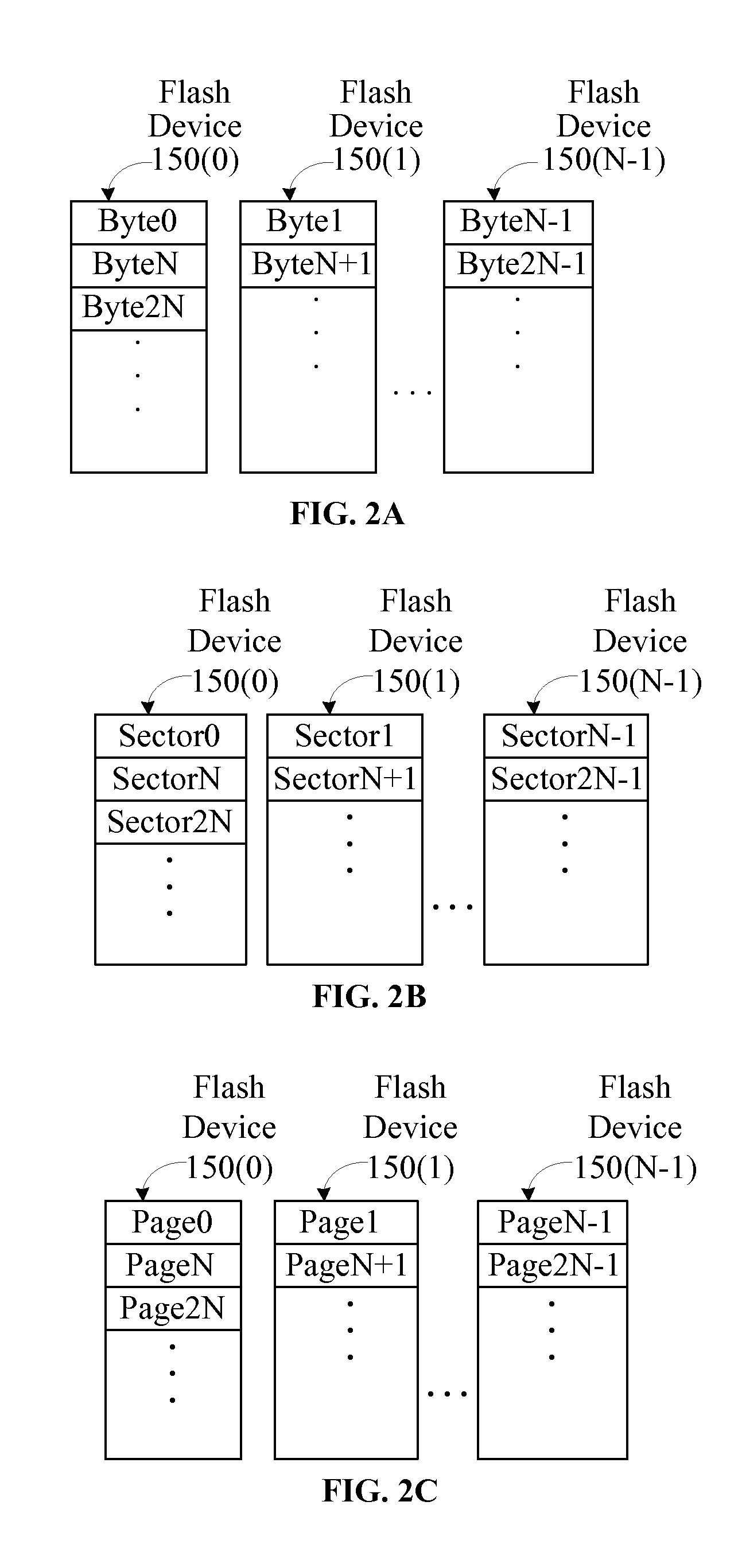

Flash devices with raid

InactiveUS20090172335A1Improve reliabilityImprove performanceMemory architecture accessing/allocationEnergy efficient ICTRAIDHard disc drive

Methods and apparatus of the present invention include multiple flash storage devices that are configured to form a single storage device that is flexible and scalable. Reliability and performance are improved while keeping the power consumption benefits compared to conventional hard disk drives.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

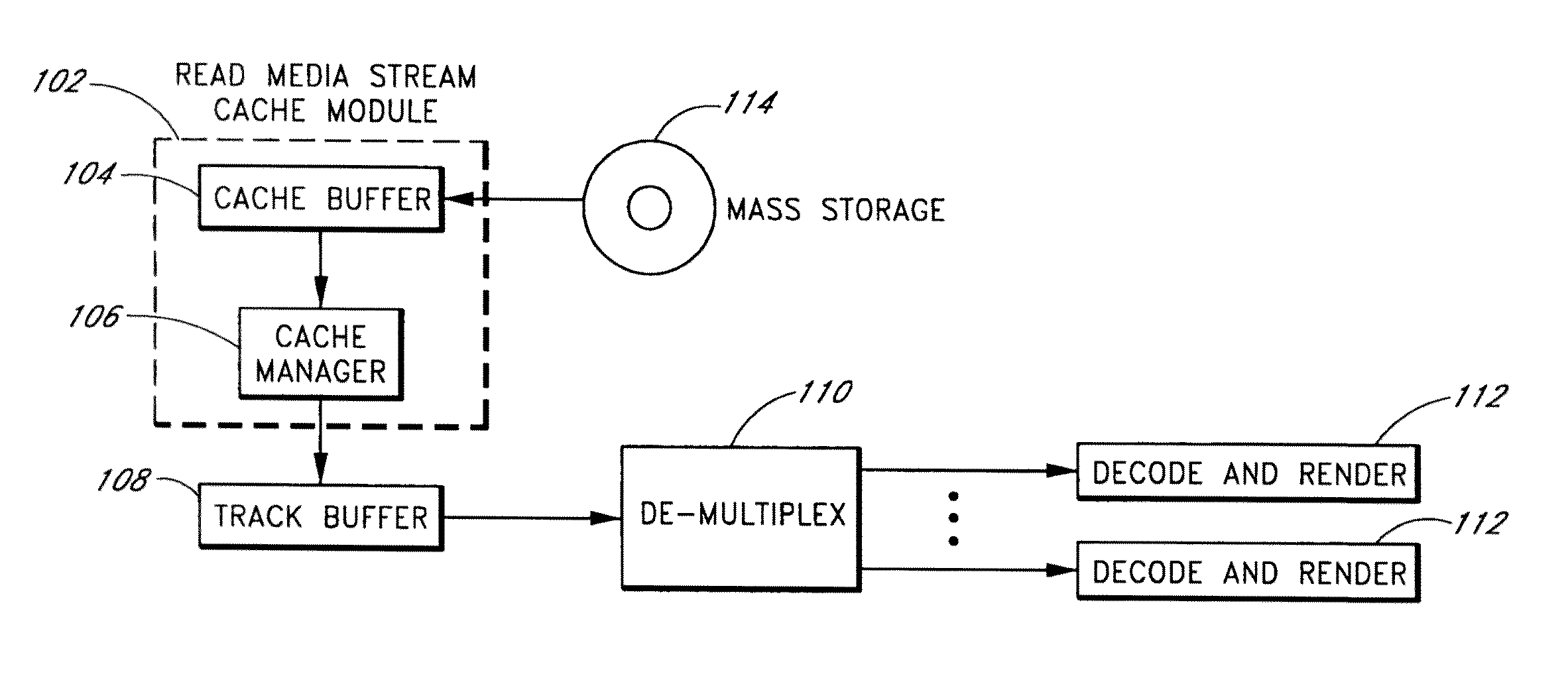

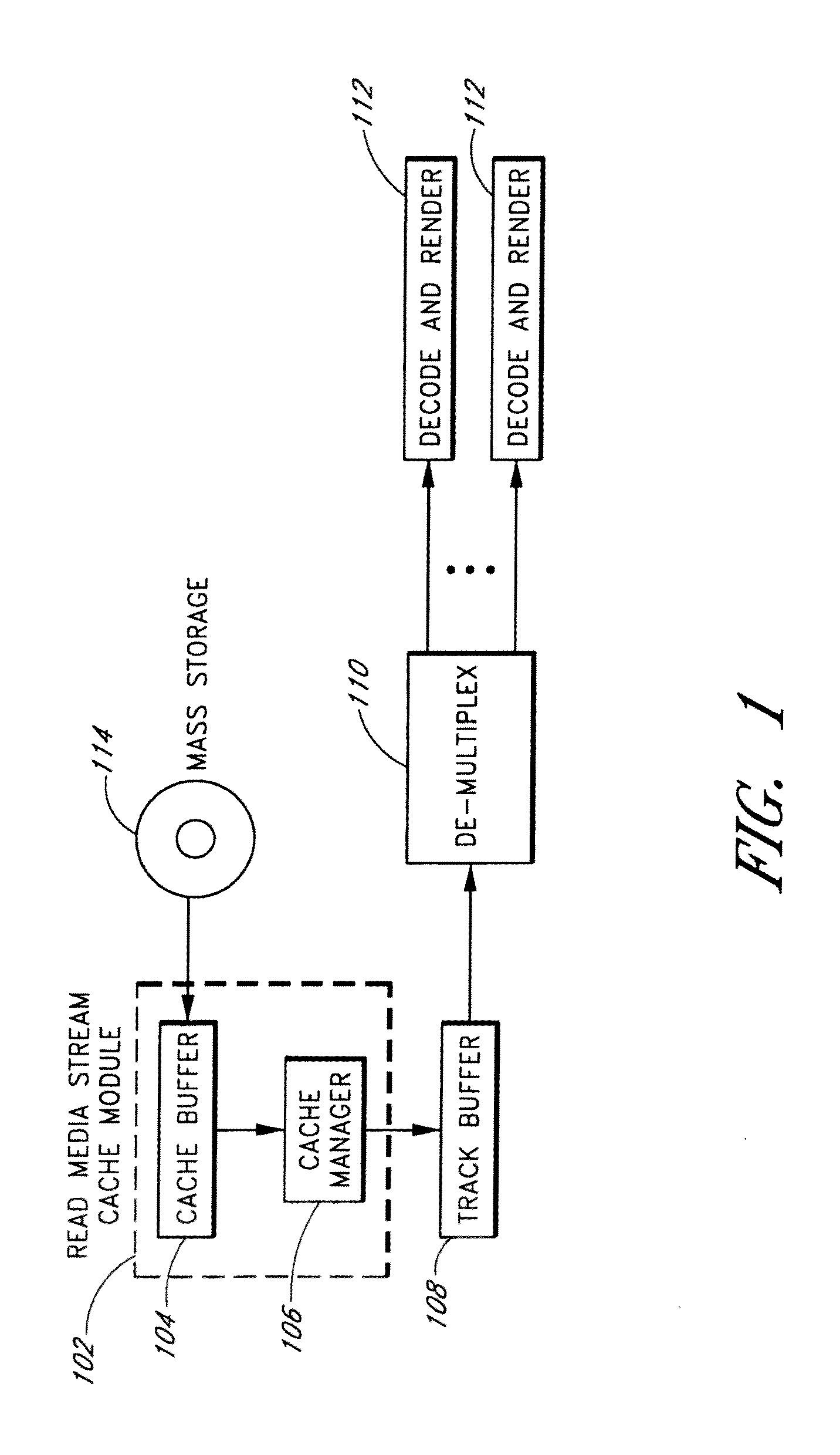

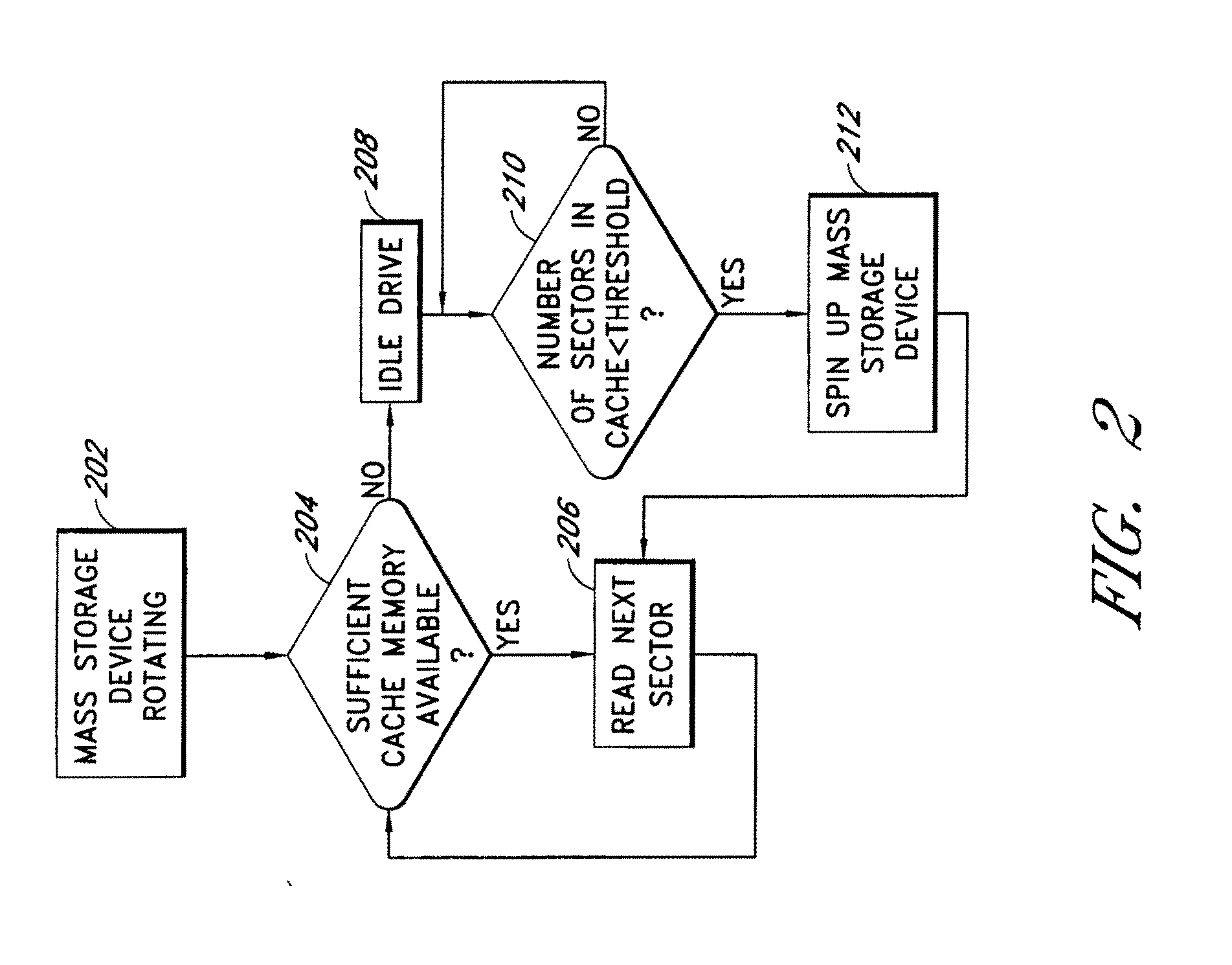

System and Method for Caching Multimedia Data

InactiveUS20100332754A1Data augmentationImprove functionalityMemory architecture accessing/allocationEnergy efficient ICTParallel computingData system

Systems and methods are provided for caching media data to thereby enhance media data read and / or write functionality and performance. A multimedia apparatus, comprises a cache buffer configured to be coupled to a storage device, wherein the cache buffer stores multimedia data, including video and audio data, read from the storage device. A cache manager coupled to the cache buffer, wherein the cache buffer is configured to cause the storage device to enter into a reduced power consumption mode when the amount of data stored in the cache buffer reaches a first level.

Owner:COREL CORP

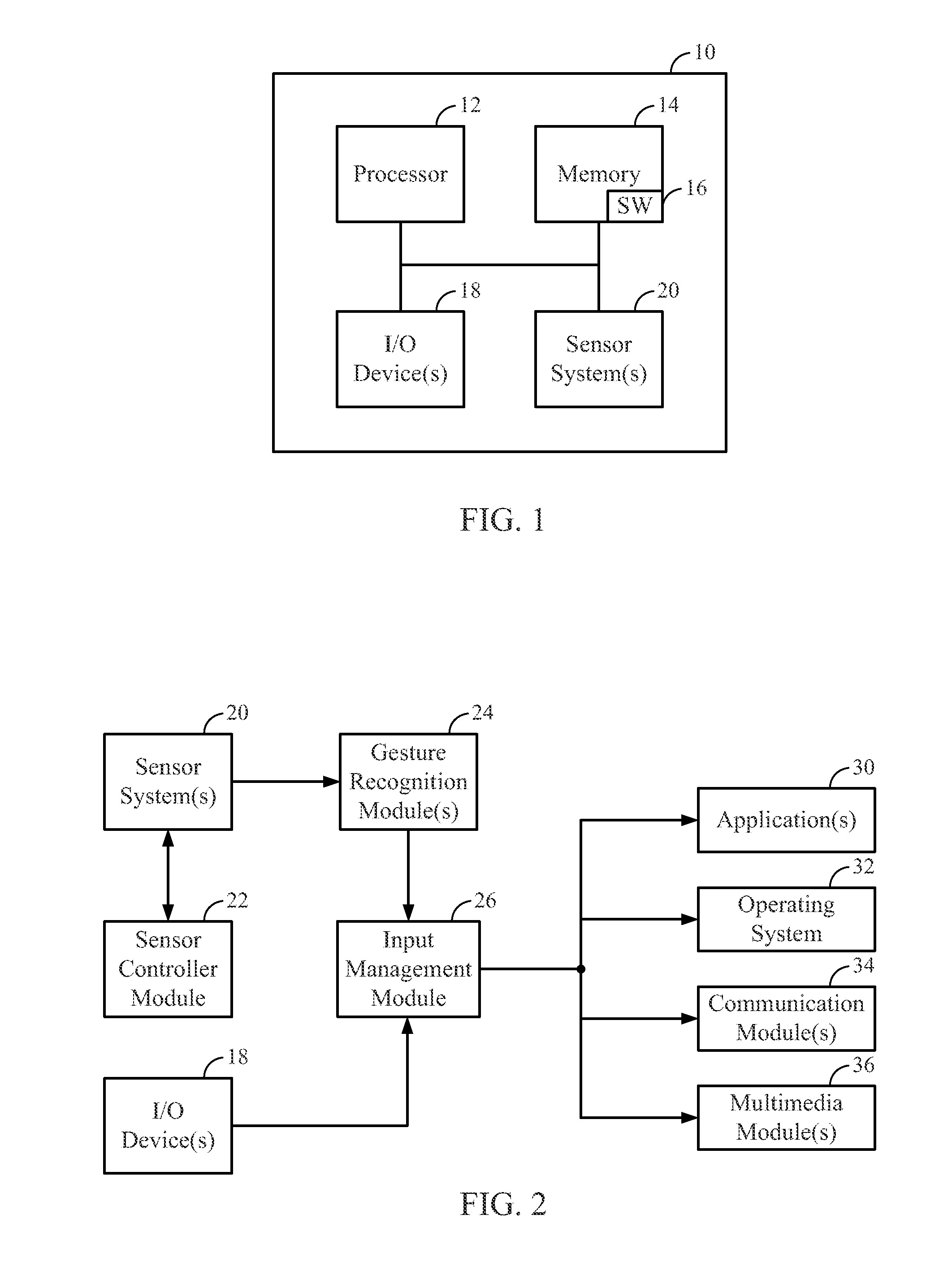

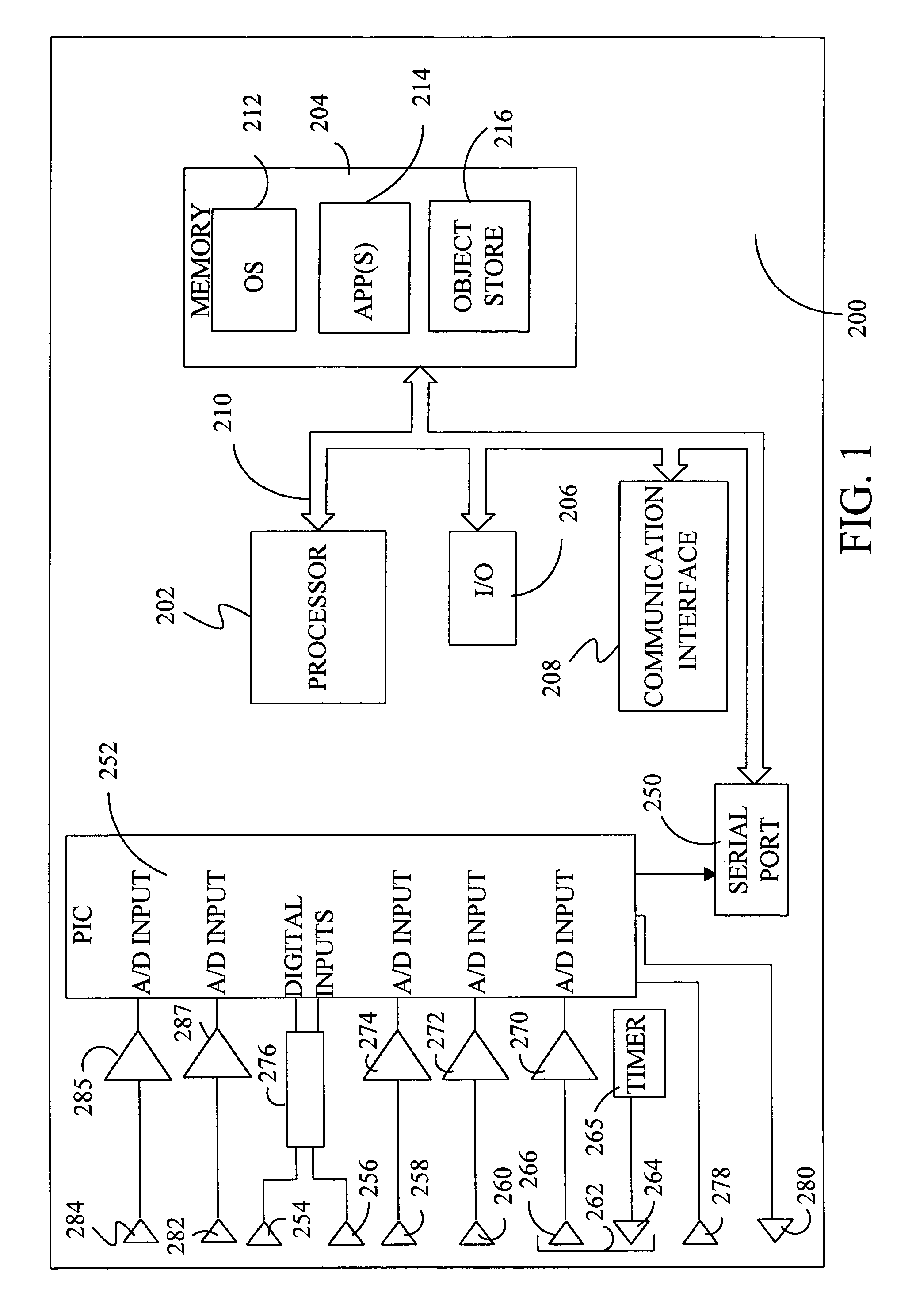

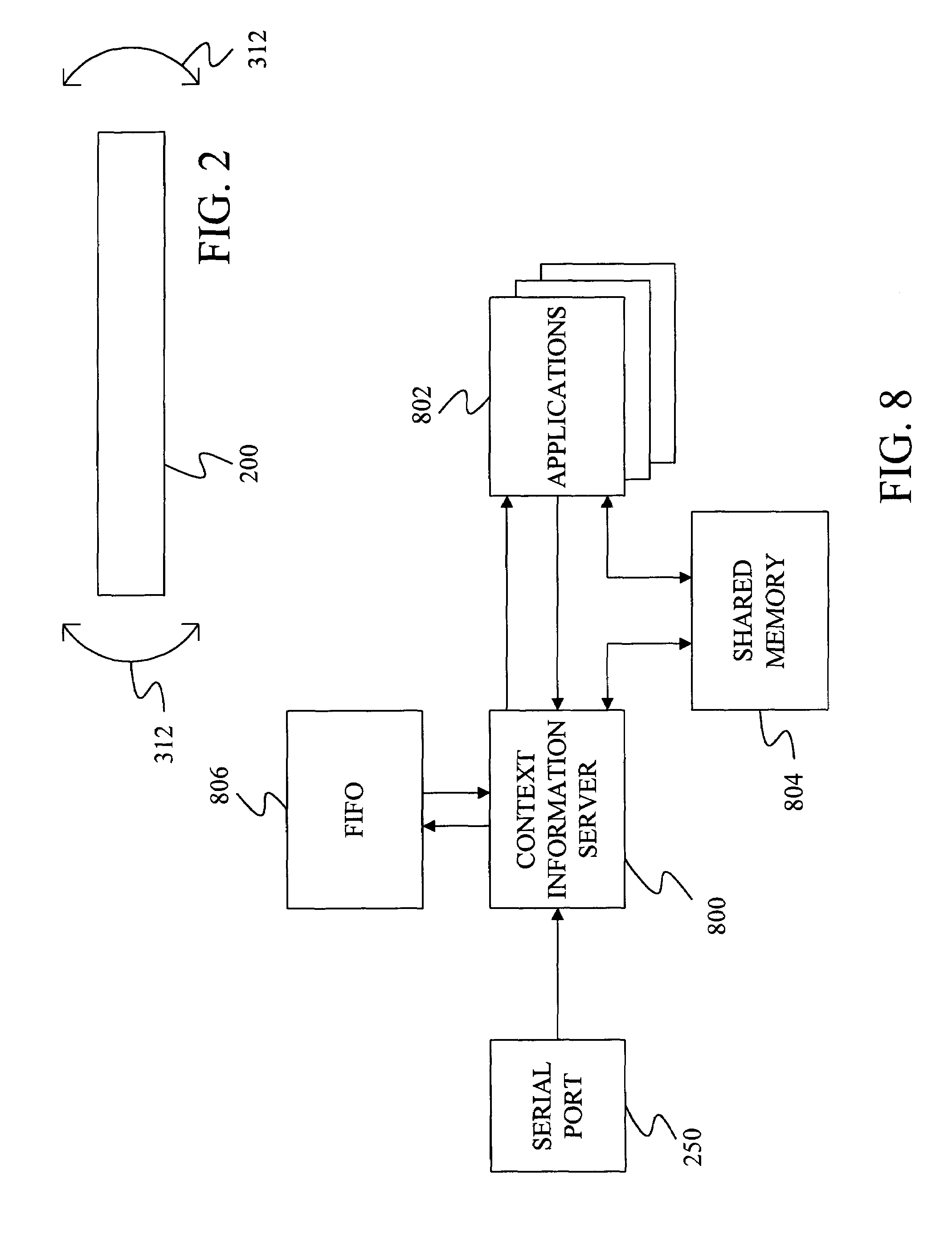

Method and apparatus using multiple sensors in a device with a display

In a device having a display, at least one sensor signal is generated from a sensor in the device. One or more context values are then generated from the sensor signal. The context values indicate how the device is situated relative to one or more objects. At least one of the context values is then used to control the operation of one or more aspects of the device.

Owner:MICROSOFT TECH LICENSING LLC

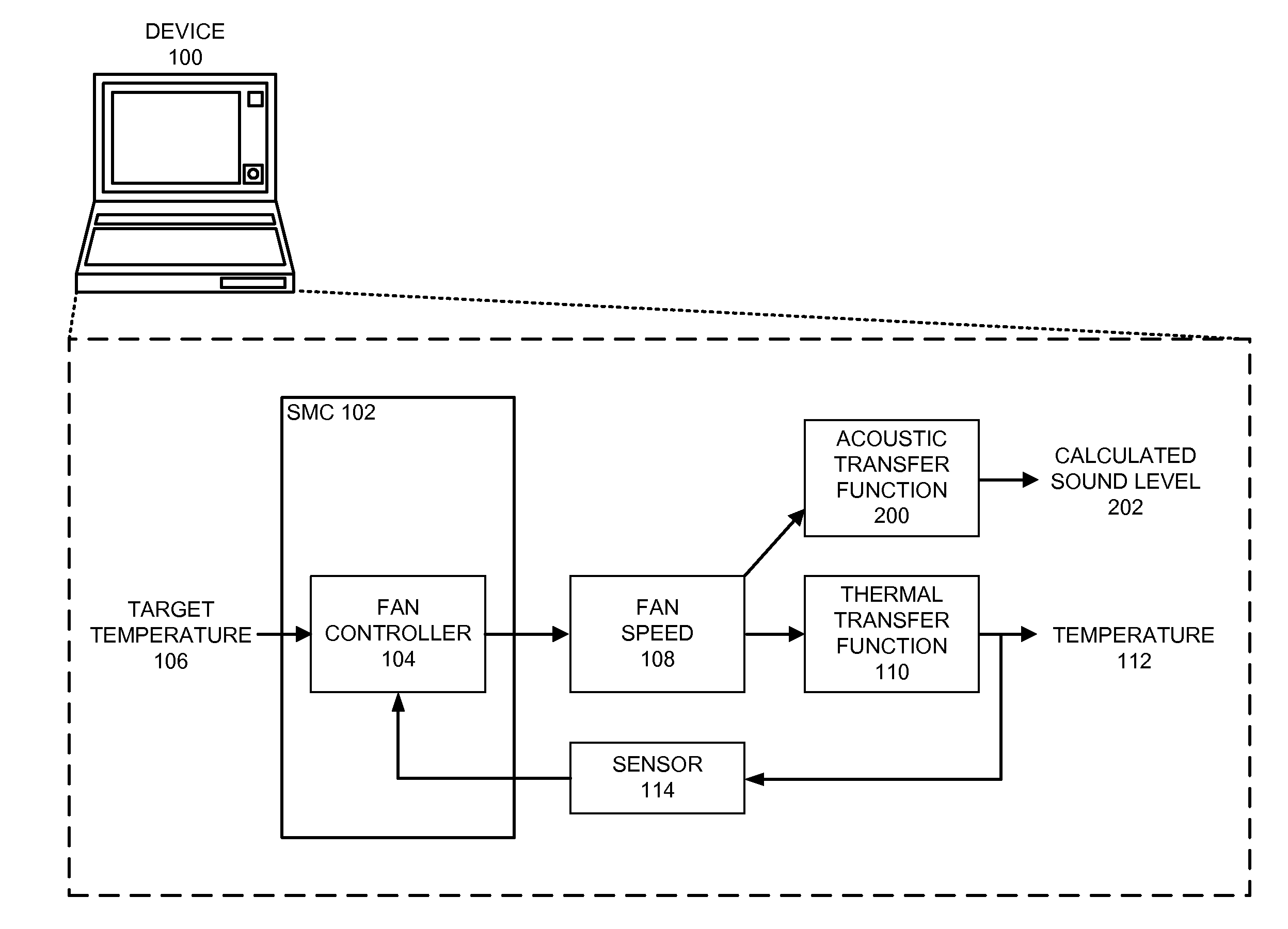

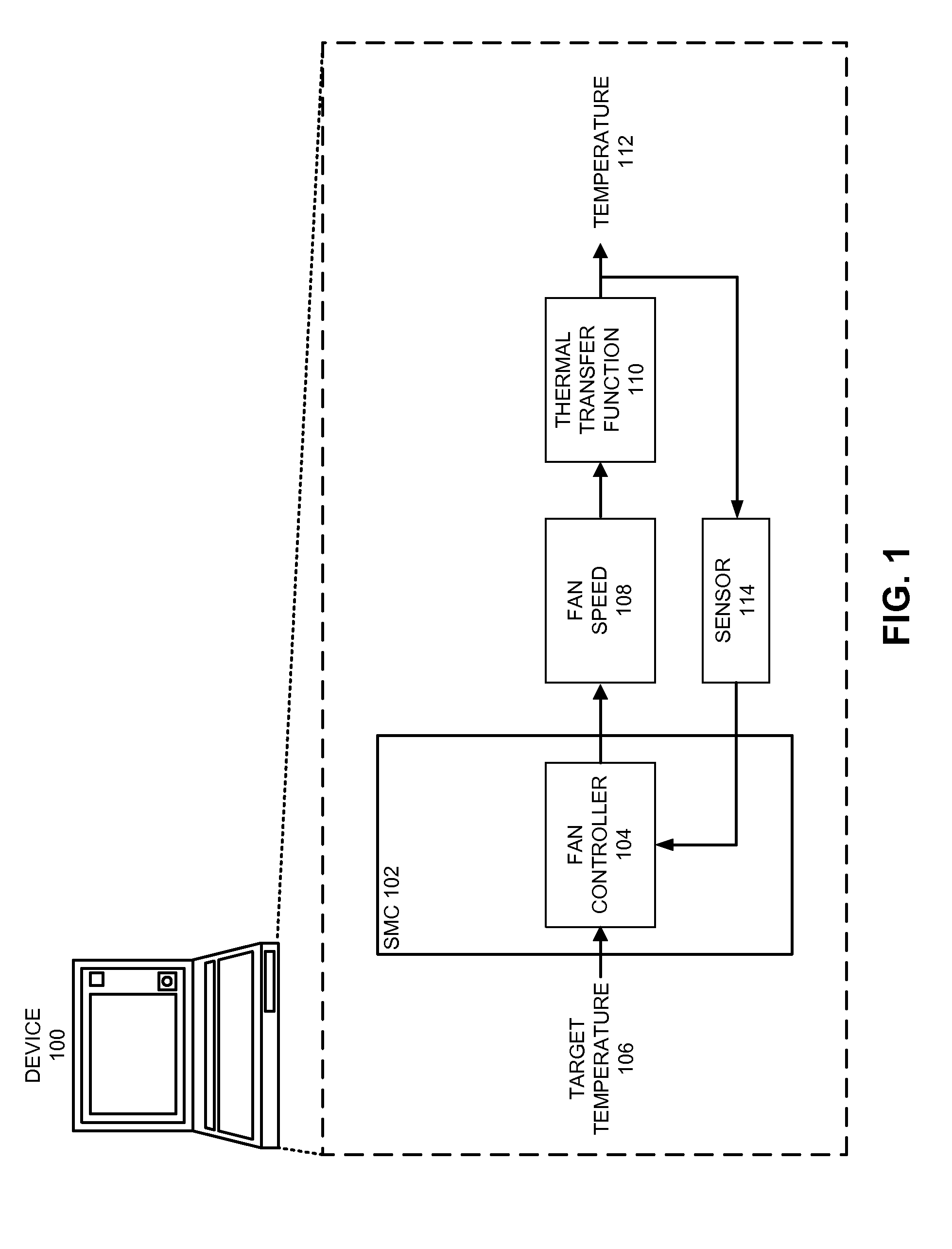

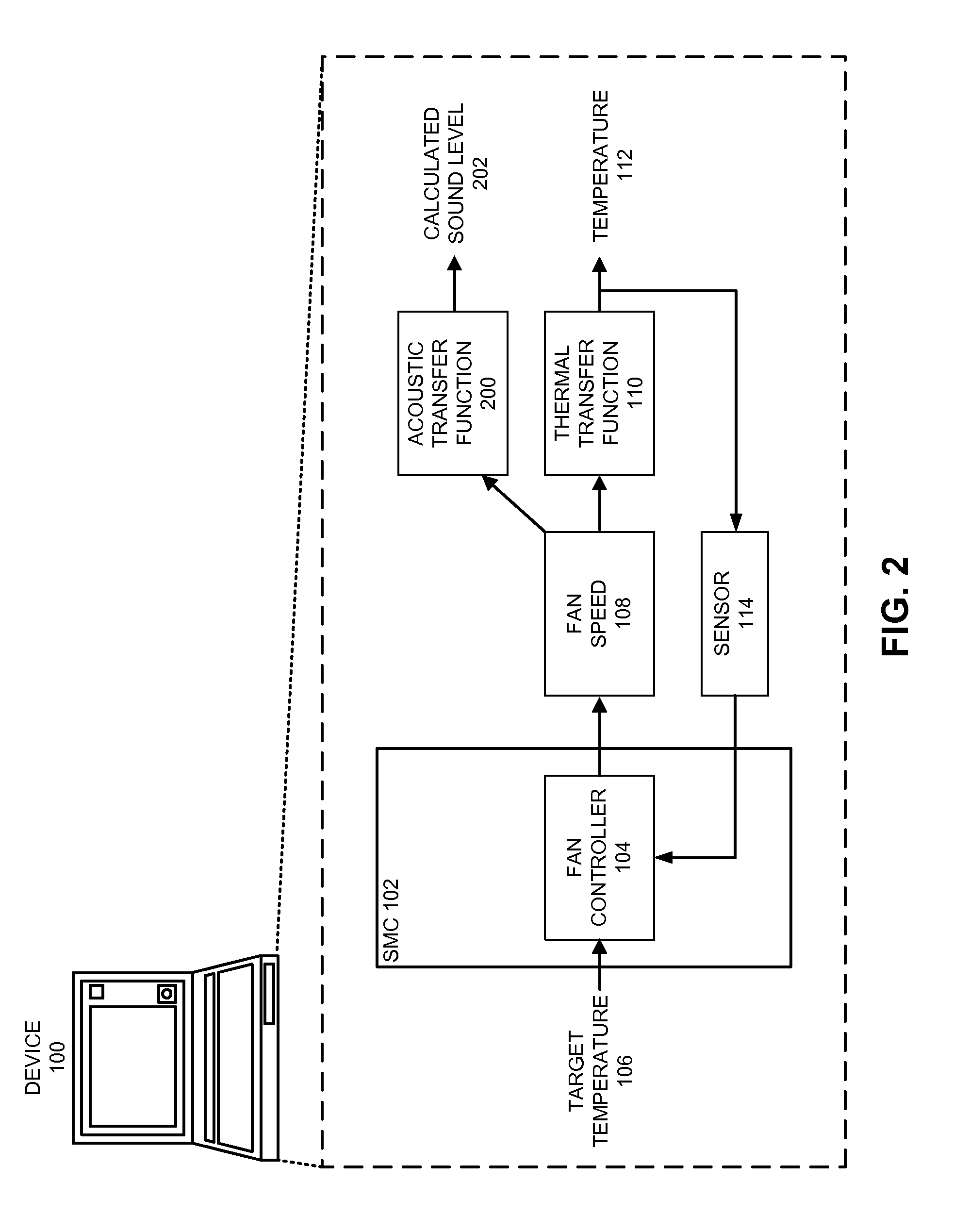

Reducing annoyance by managing the acoustic noise produced by a device

ActiveUS20090092261A1Less worryReduce user annoyanceEnergy efficient ICTEar treatmentAcousticsNoise estimation

One embodiment of the present invention provides a system that reduces annoyance by managing the acoustic noise produced by a device. During operation, the system receives a set of acoustic characteristics for noise-producing components within the device. The system then uses these acoustic characteristics to estimate the acoustic noise being generated by each of these noise-producing components. Next, the system aggregates this set of acoustic noise estimates to produce an aggregate estimate for the acoustic noise produced by the device. The system then analyzes this aggregate estimate using an acoustic annoyance model to determine the acoustic annoyance level. The system then adjusts a setting in the device to manage the acoustic annoyance level produced by the device.

Owner:APPLE INC

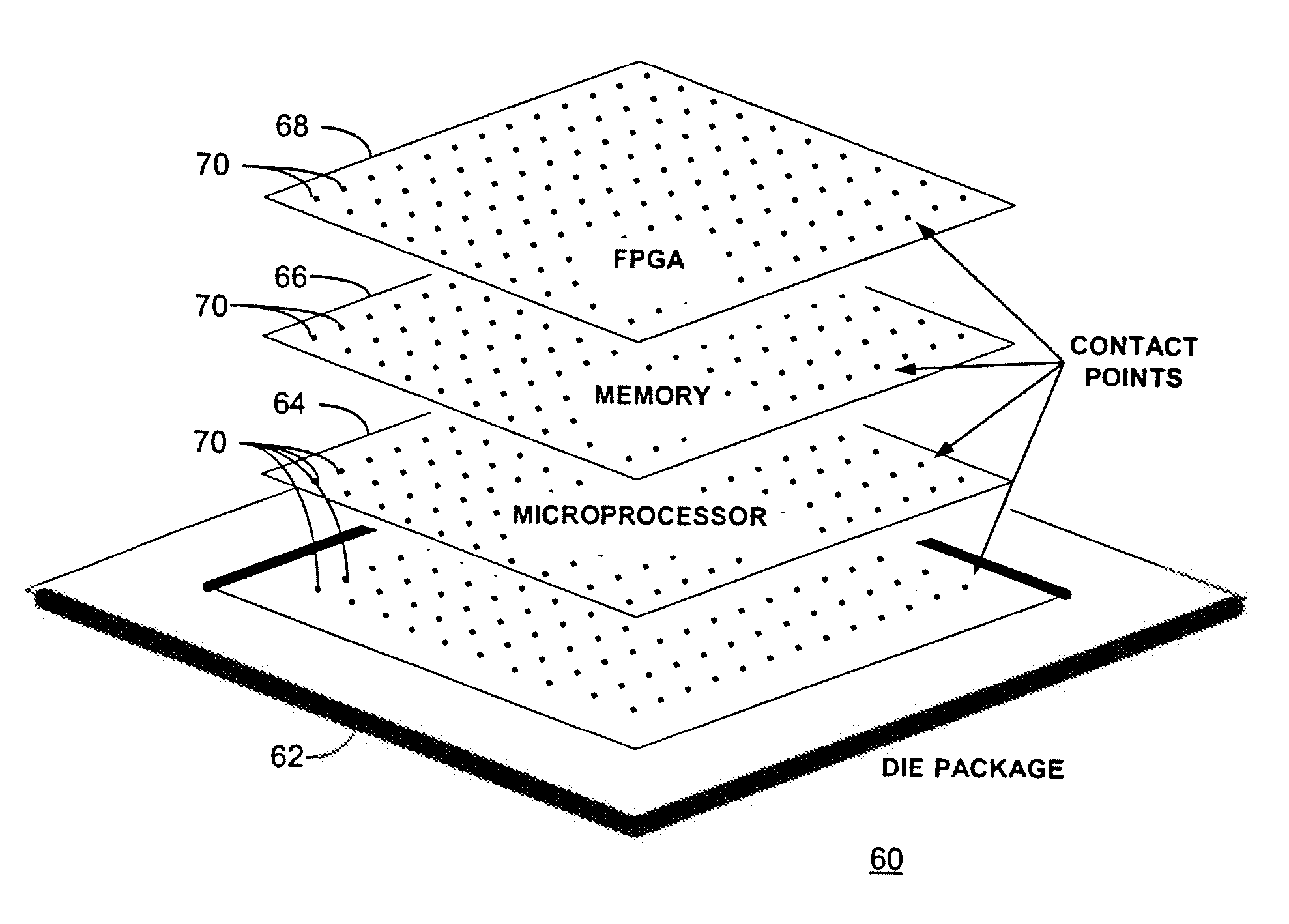

Reconfigurable processor module comprising hybrid stacked integrated circuit die elements

InactiveUS20060195729A1Energy efficient ICTError detection/correctionEngineeringField-programmable gate array

A reconfigurable processor module comprising hybrid stacked integrated circuit (“IC”) die elements. In a particular embodiment disclosed herein, a processor module with reconfigurable capability may be constructed by stacking one or more thinned microprocessor, memory and / or field programmable gate array (“FPGA”) die elements and interconnecting the same utilizing contacts that traverse the thickness of the die. The processor module disclosed allows for a significant acceleration in the sharing of data between the microprocessor and the FPGA element while advantageously increasing final assembly yield and concomitantly reducing final assembly cost.

Owner:ARBOR GLOBAL STRATEGIES LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com