Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1978results about "Register arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

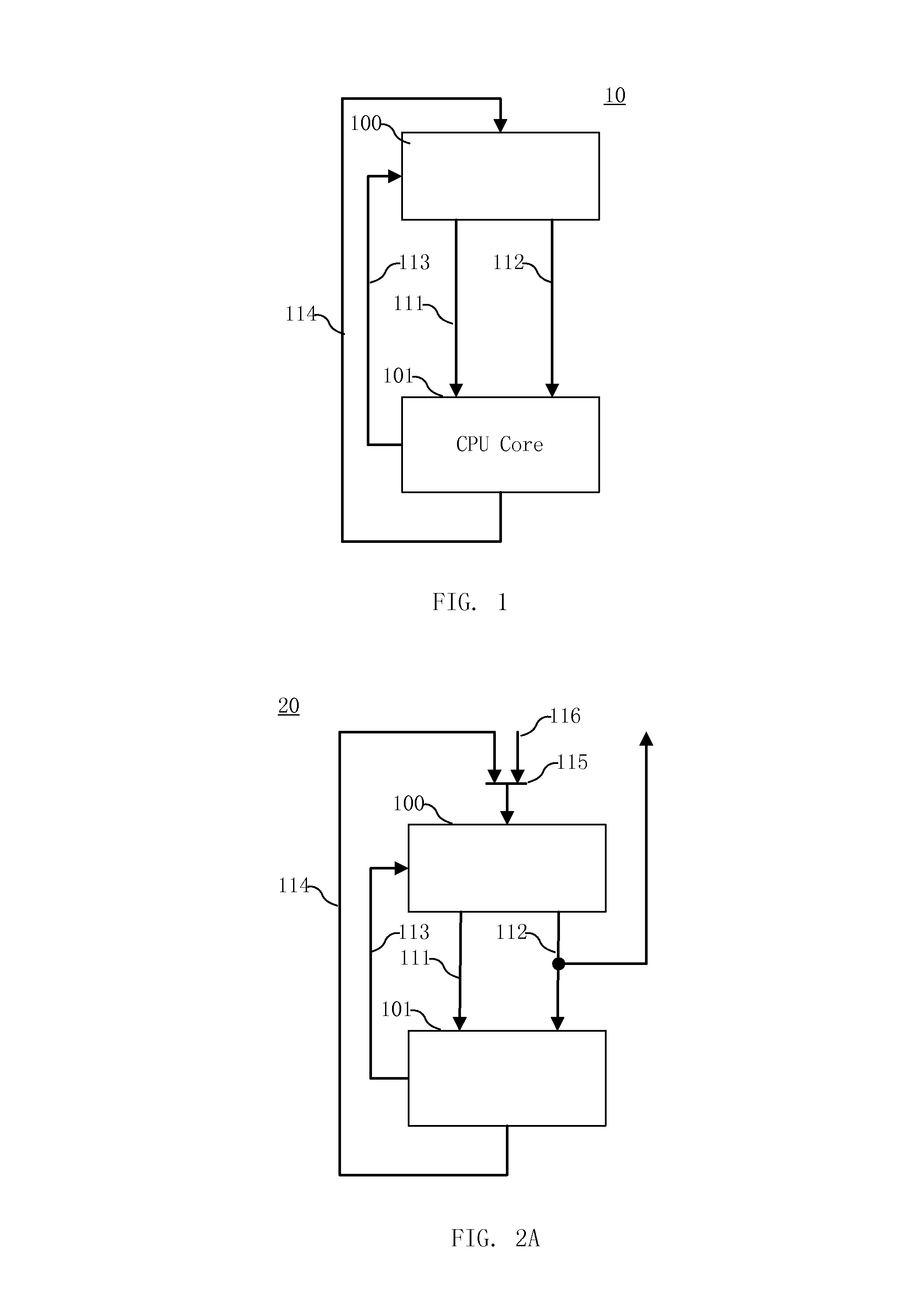

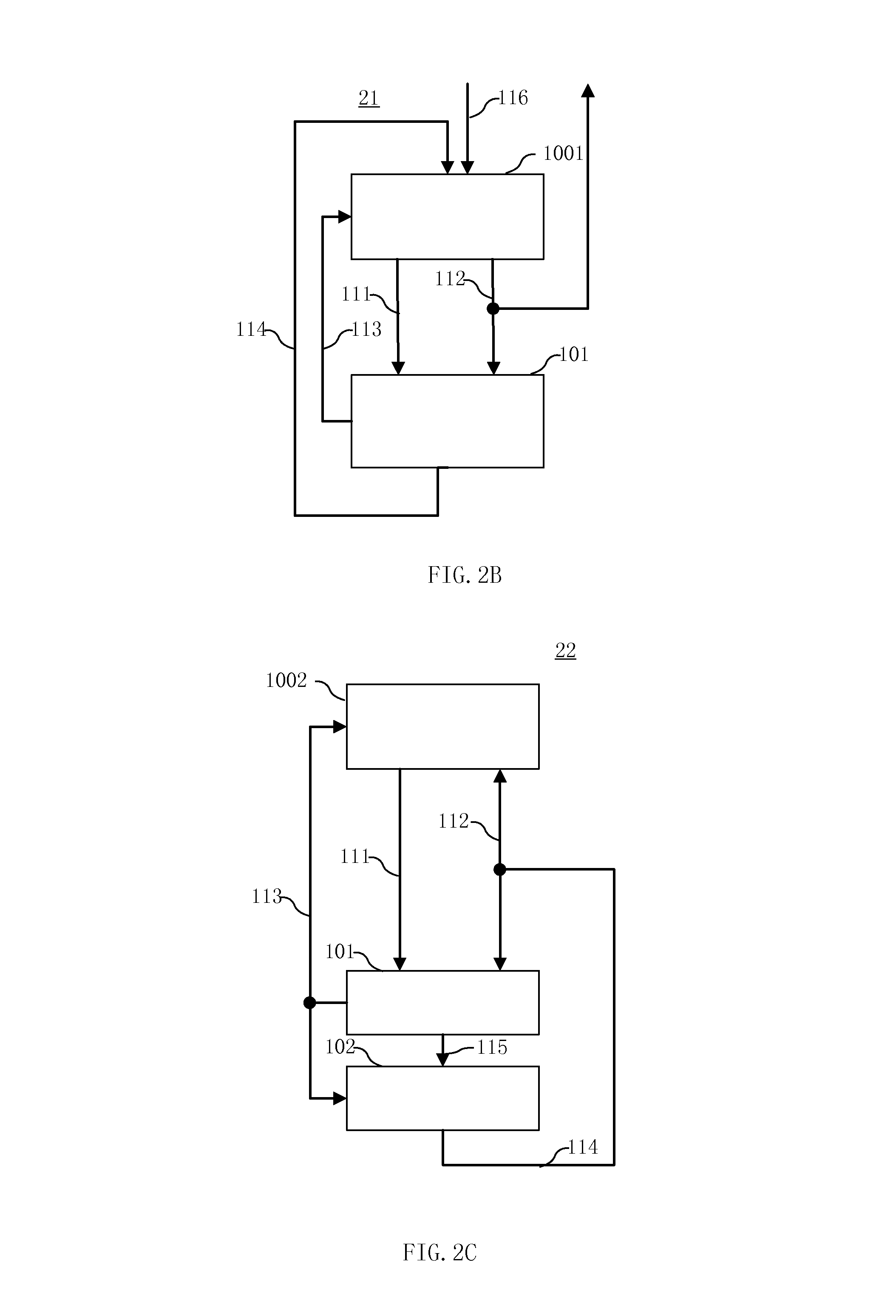

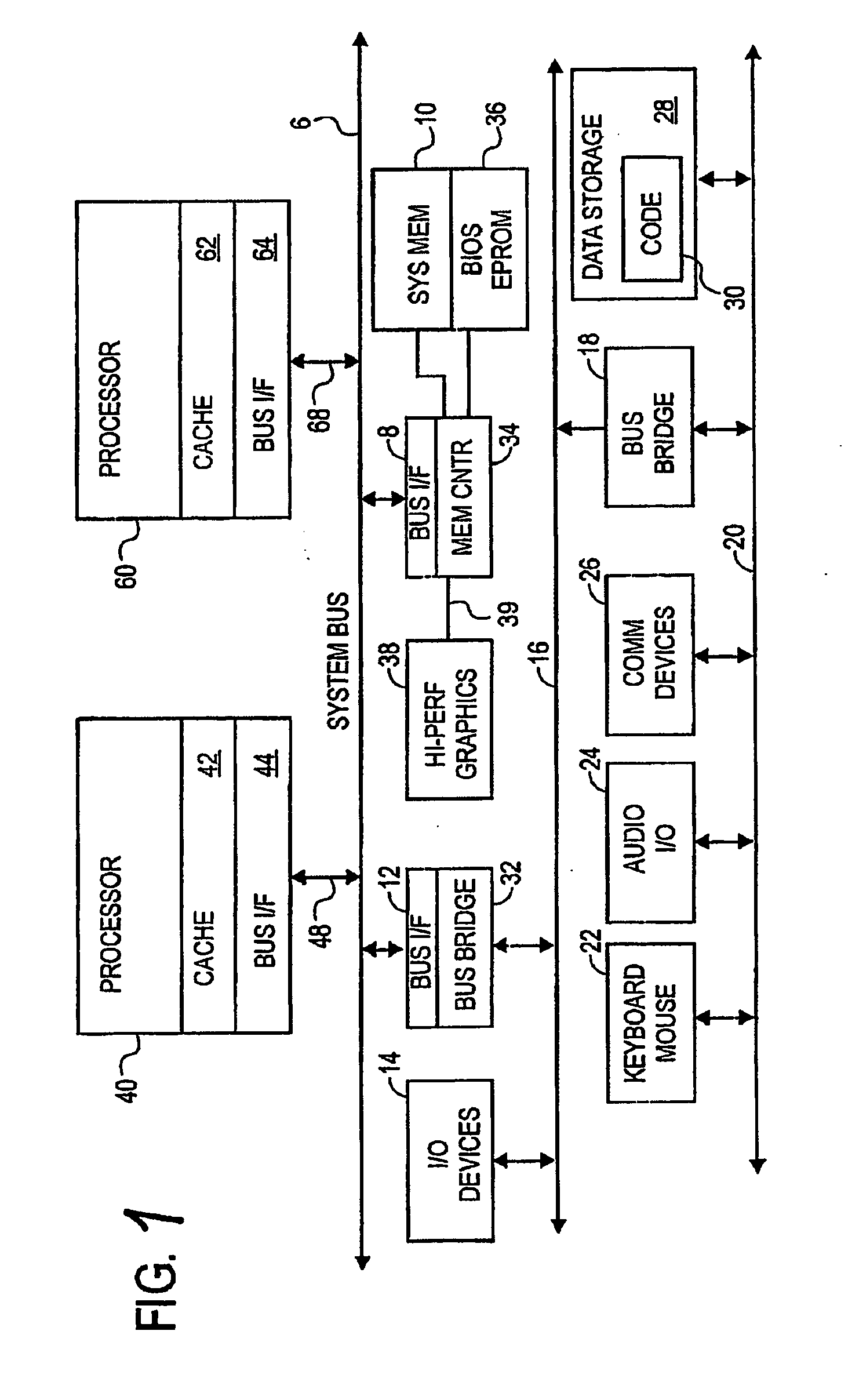

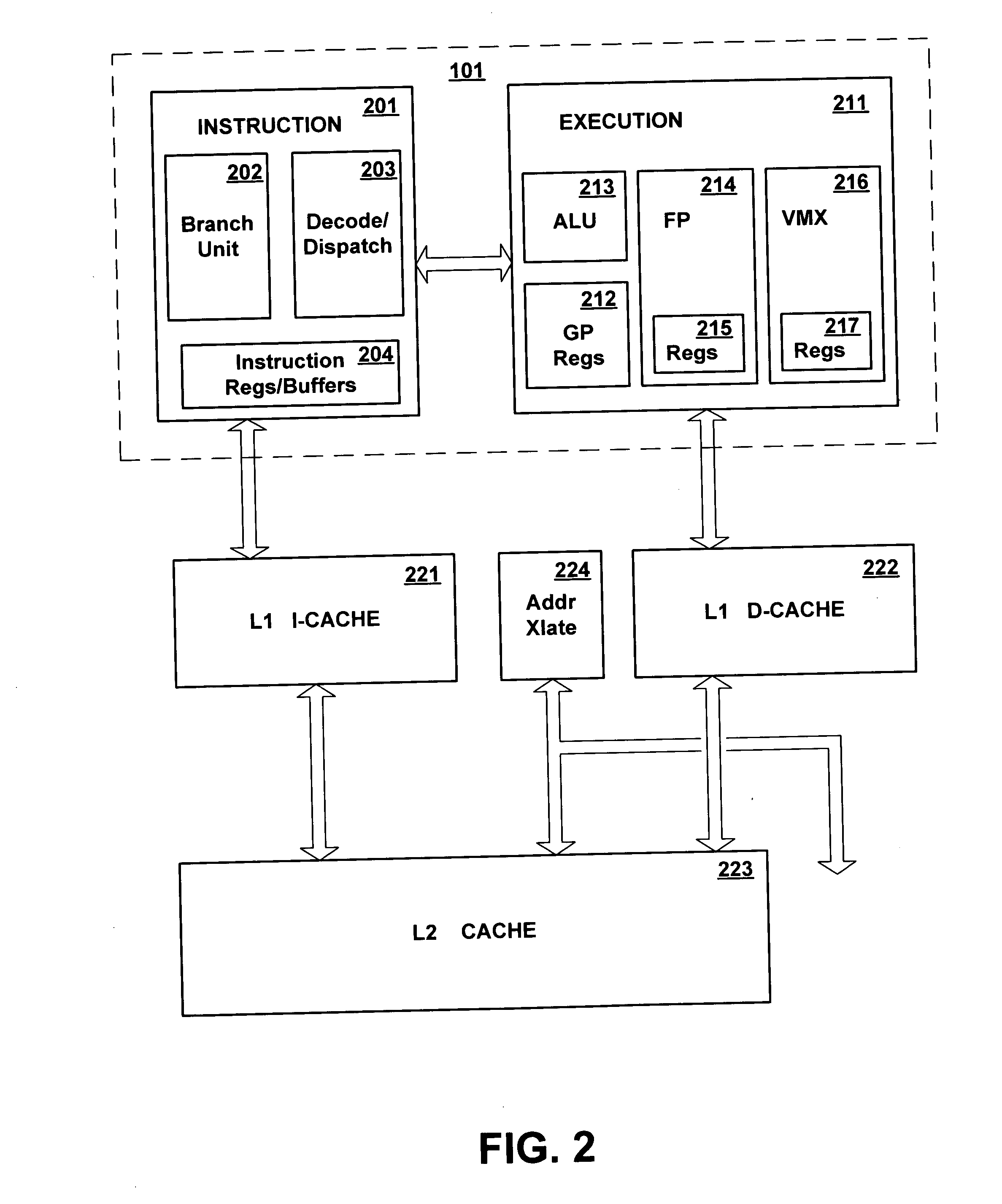

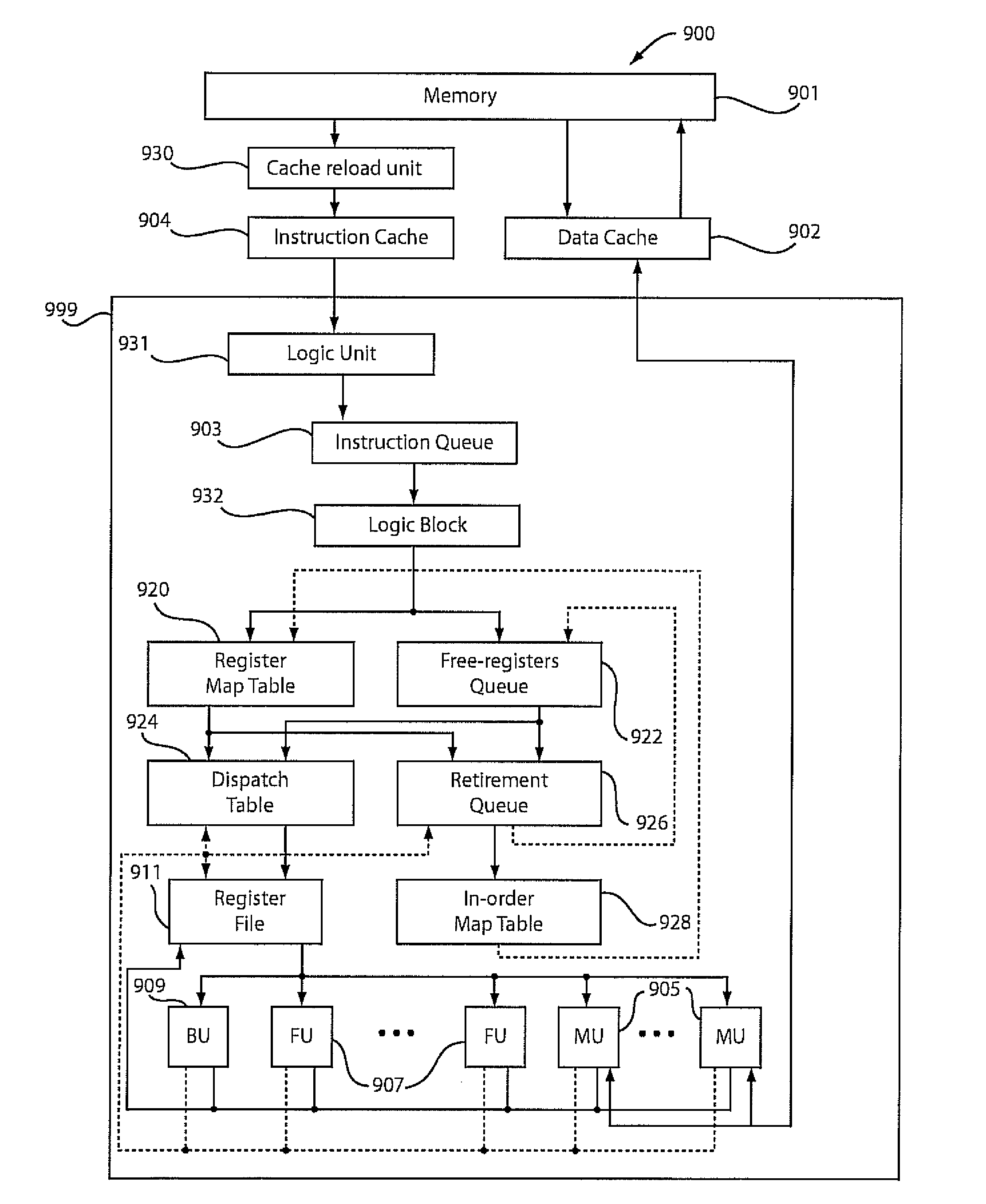

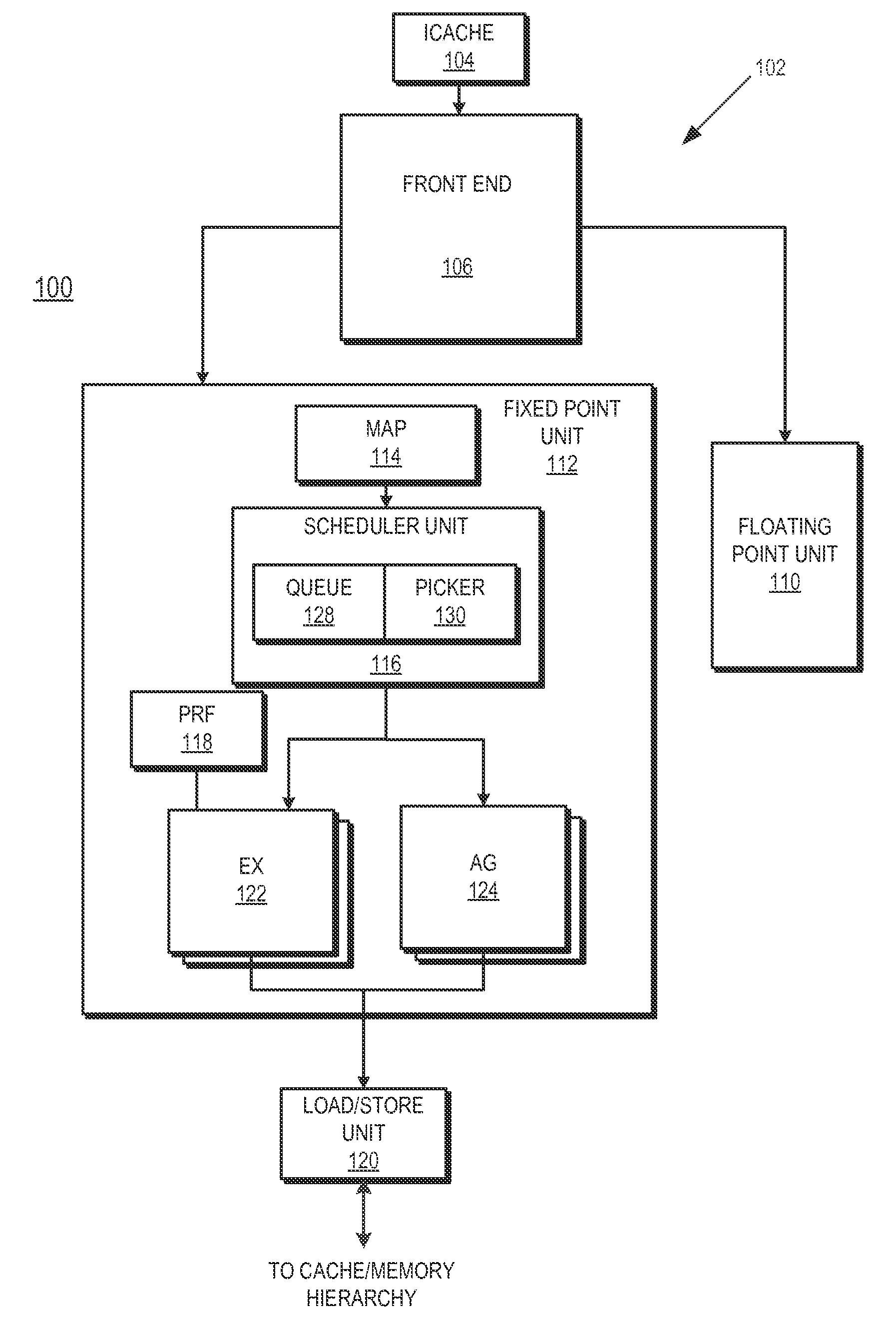

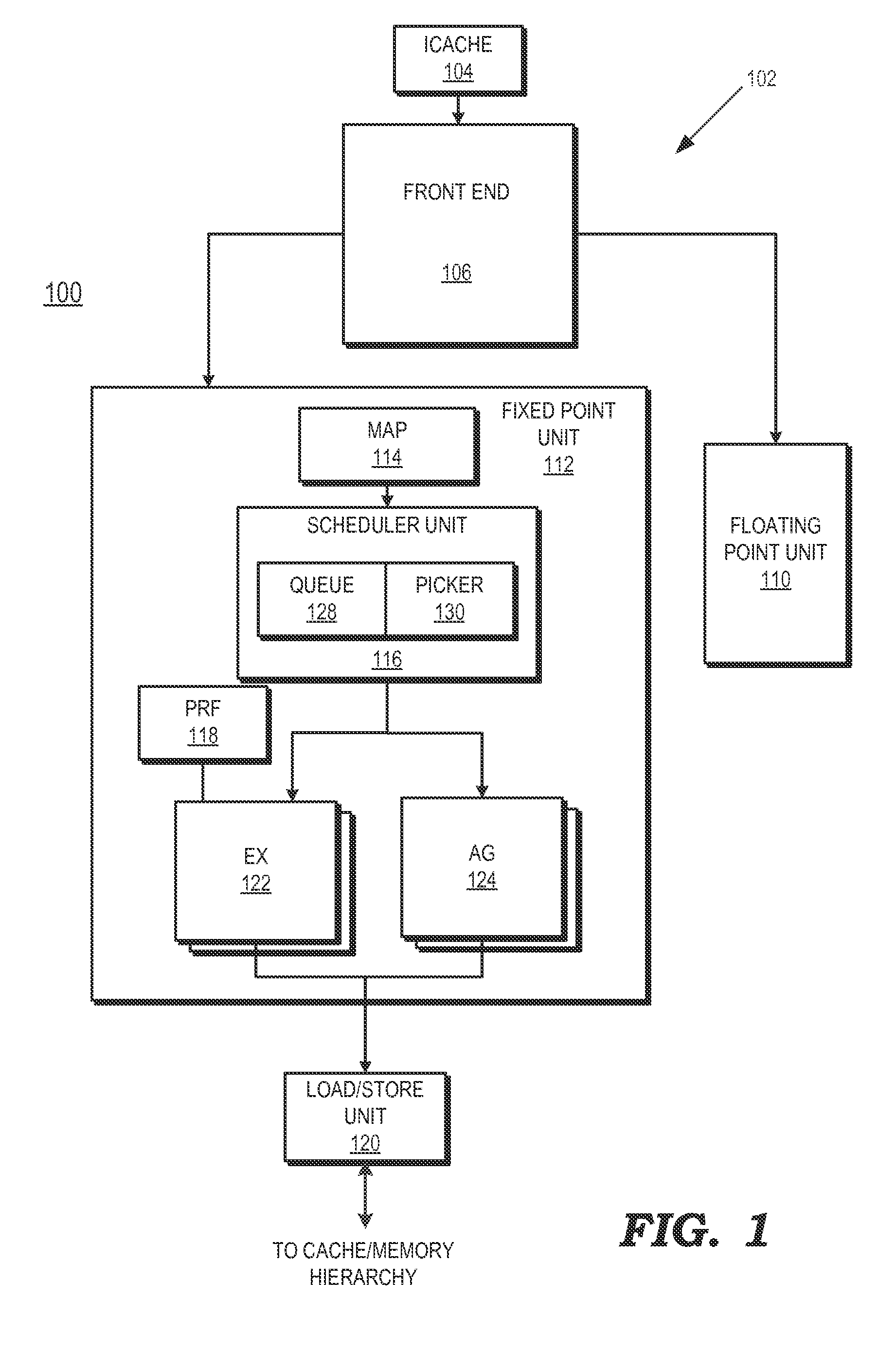

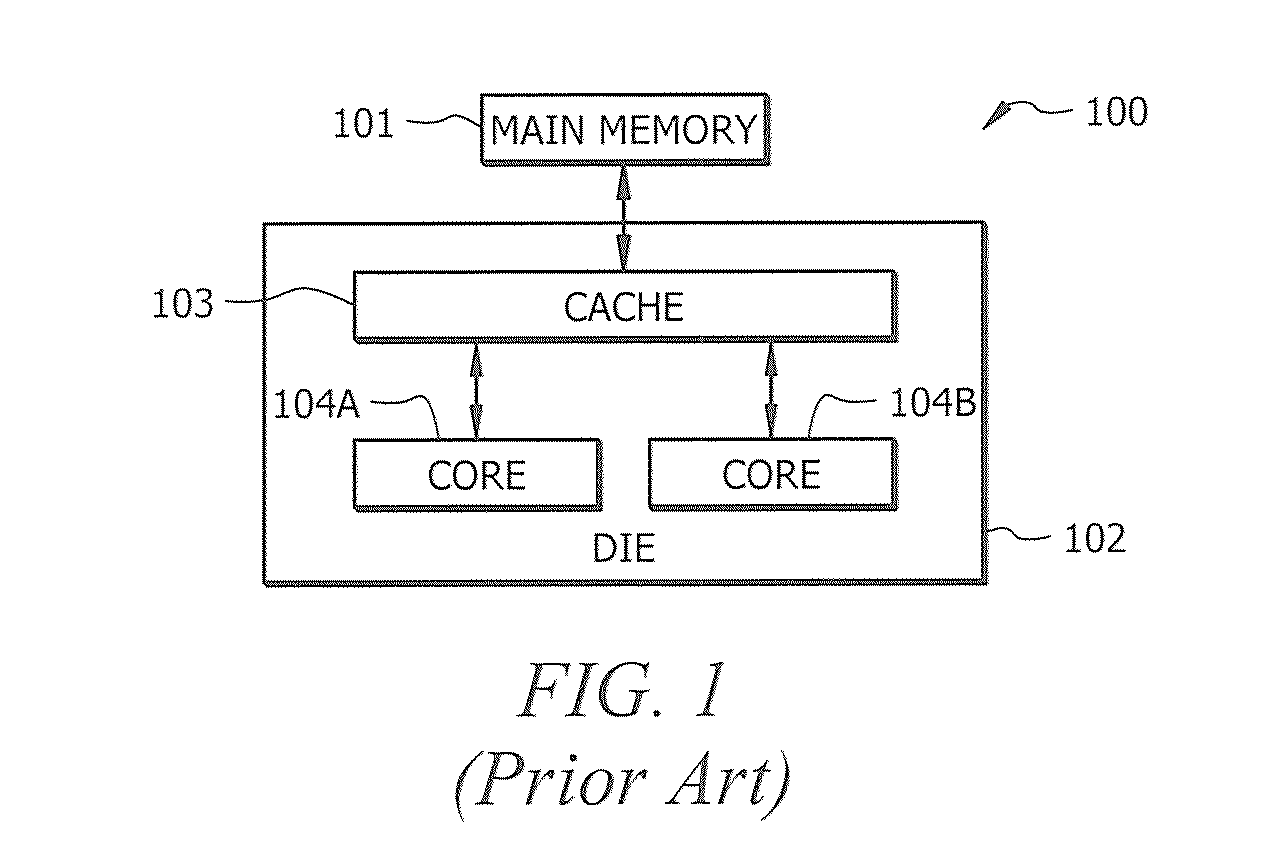

Processor-cache system and method

ActiveUS9047193B2Shorten the counting processEfficient and uniform structureEnergy efficient ICTRegister arrangementsAddress generation unitProcessor register

Owner:SHANGHAI XINHAO MICROELECTRONICS

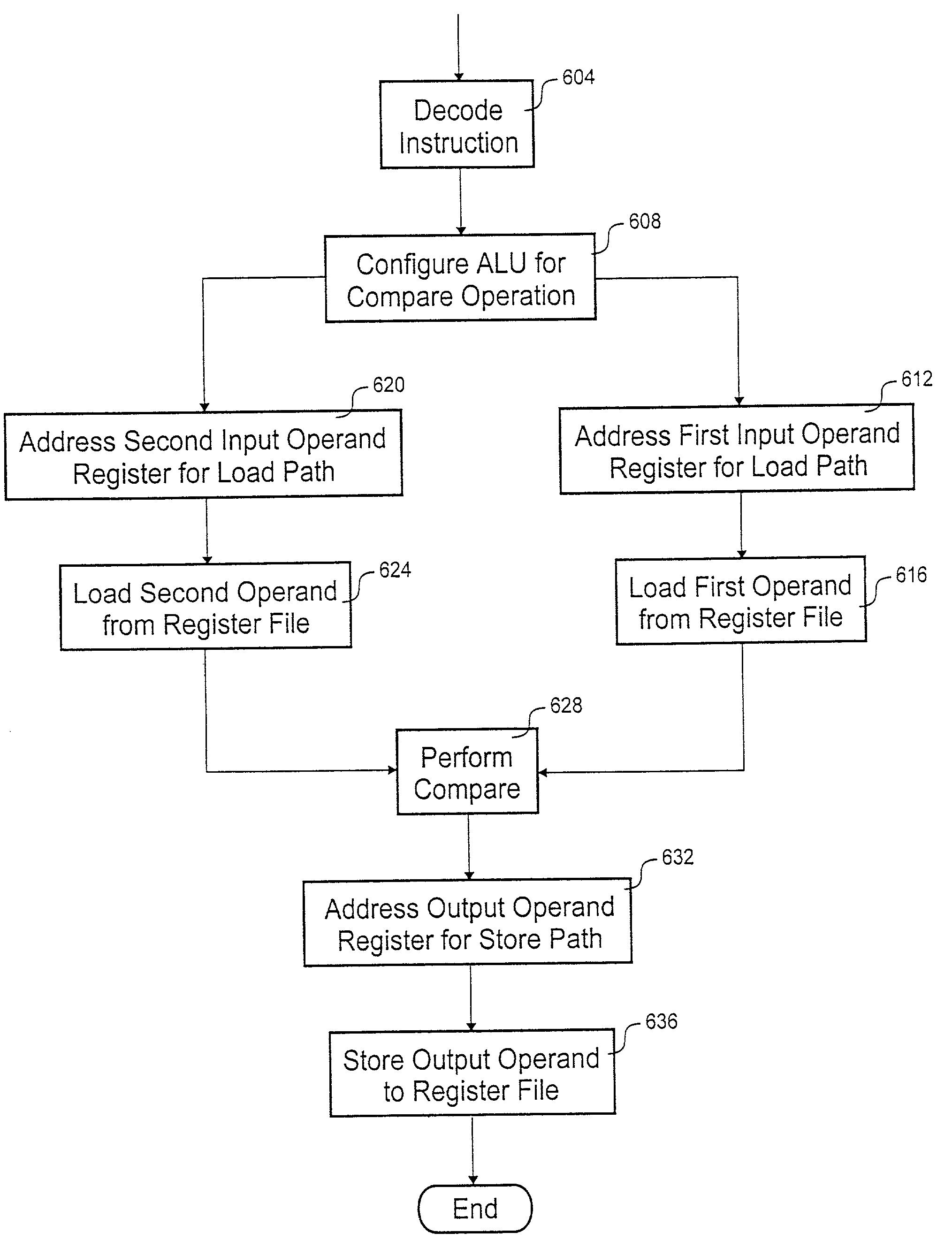

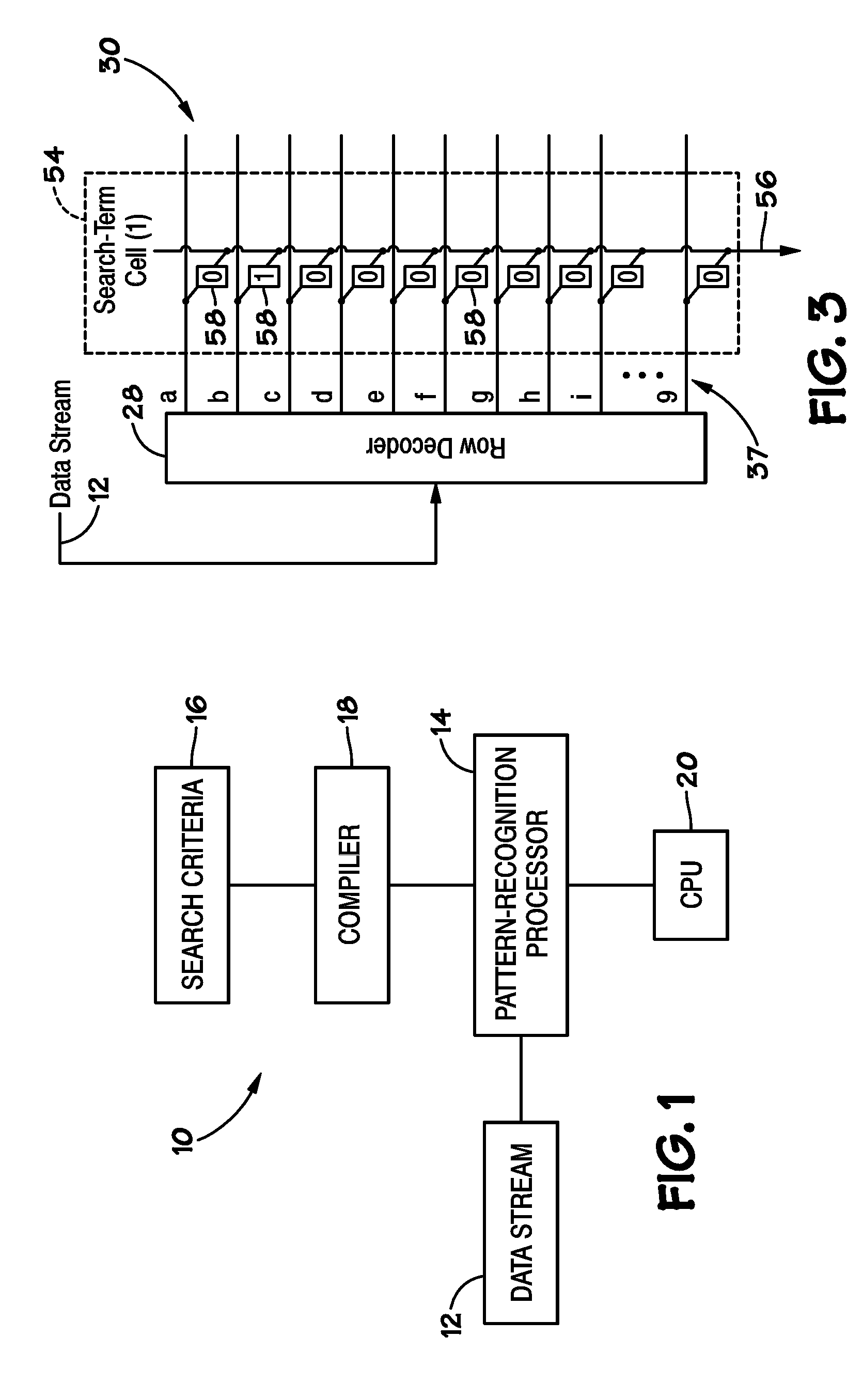

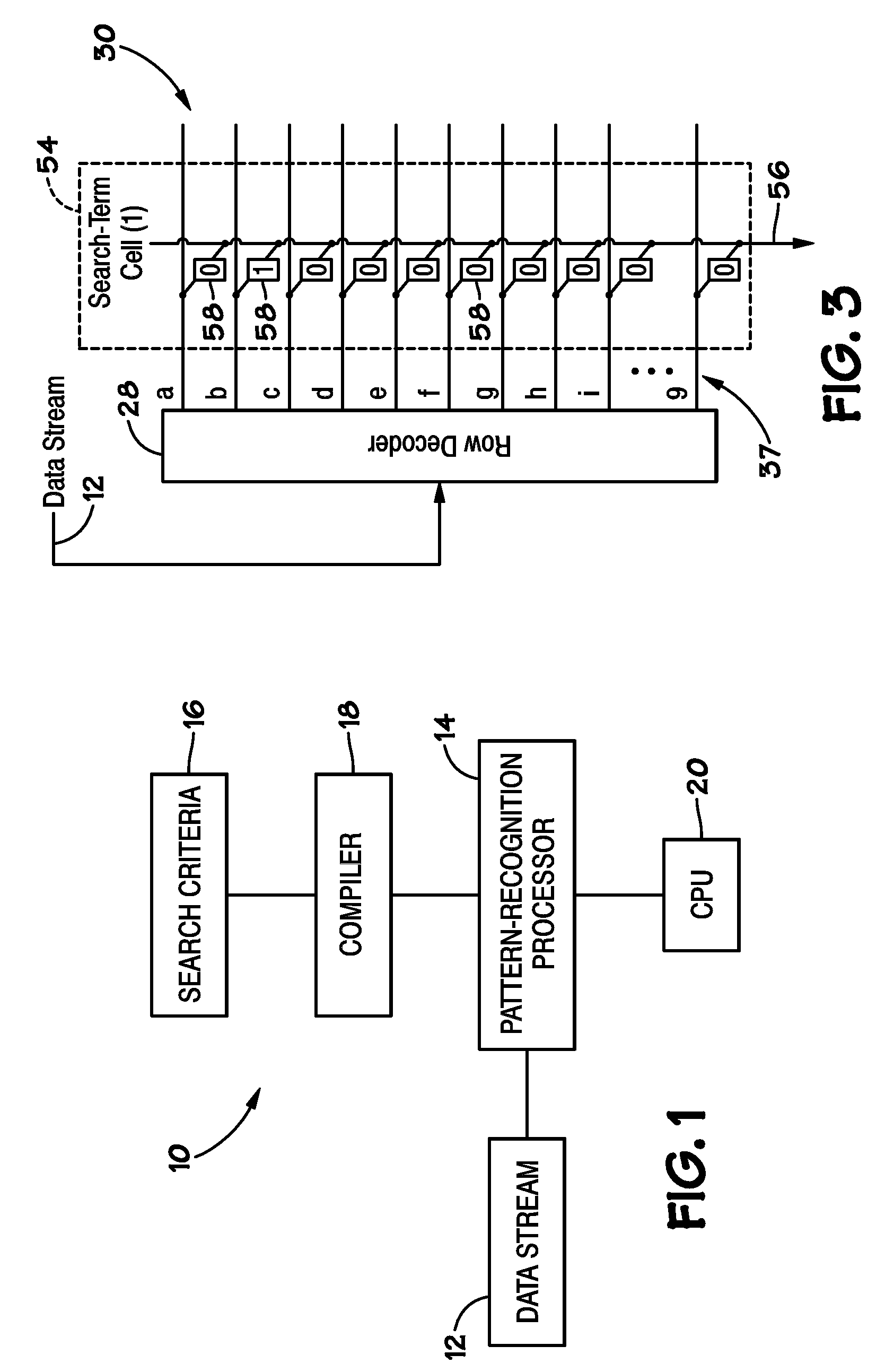

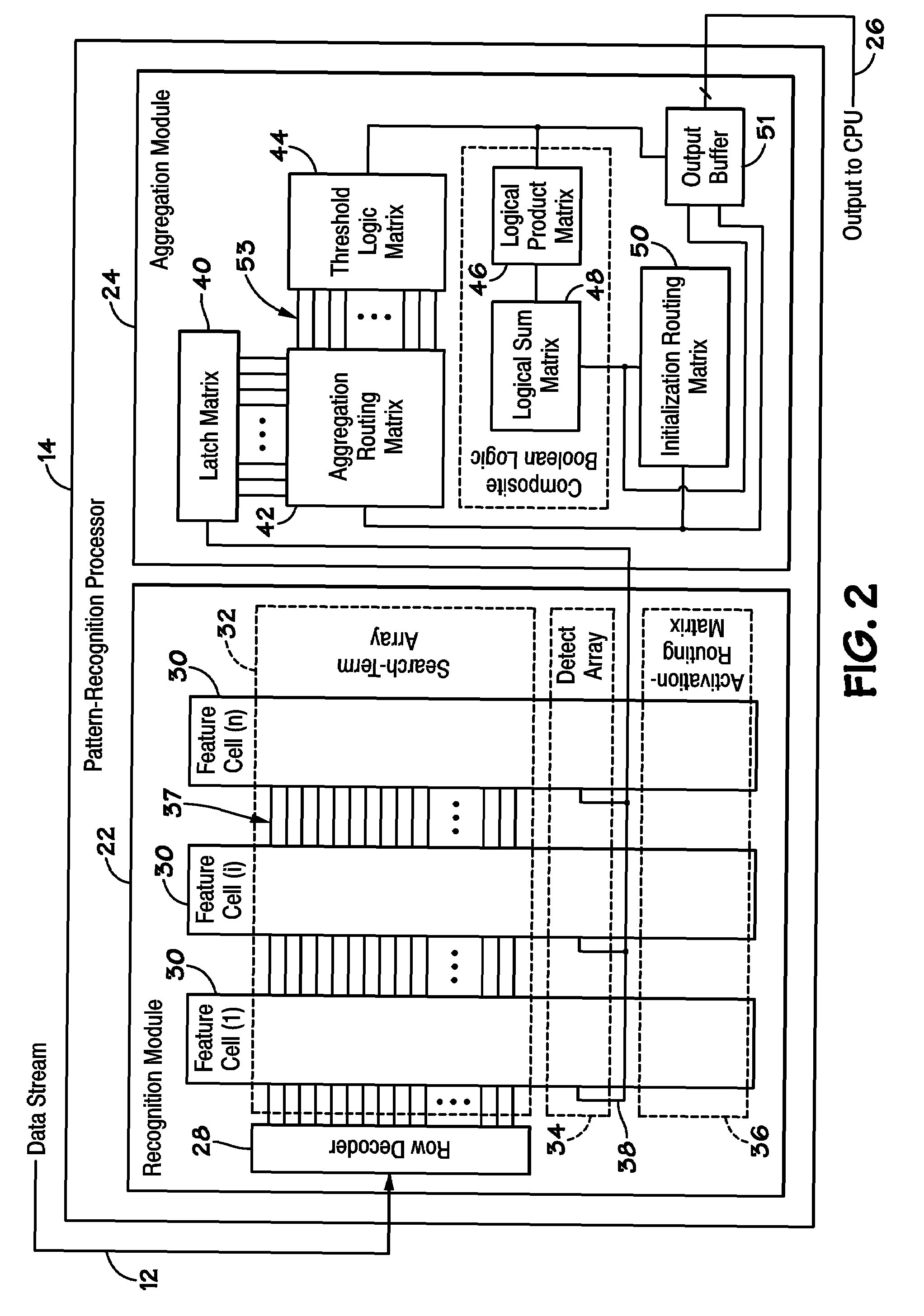

Processing architecture having a compare capability

Owner:ORACLE INT CORP

Microprocessors

Owner:TEXAS INSTR INC

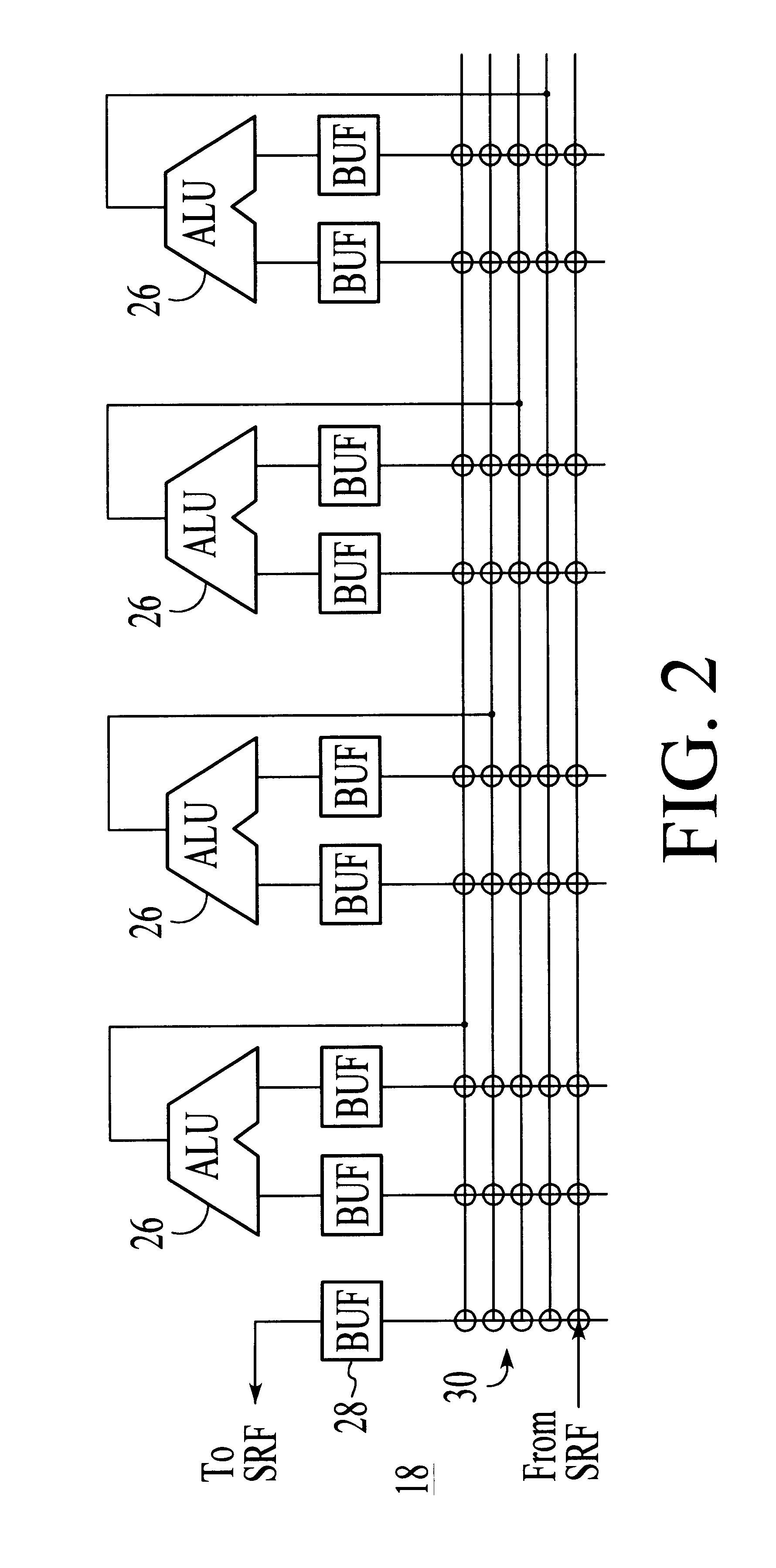

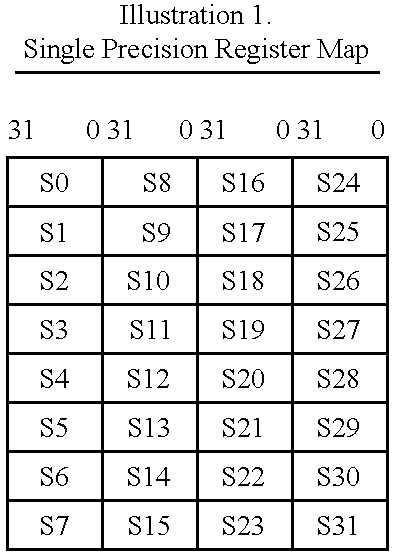

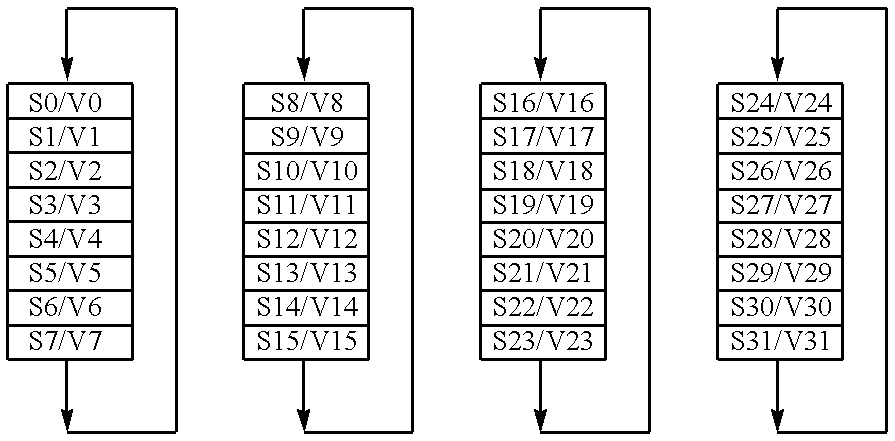

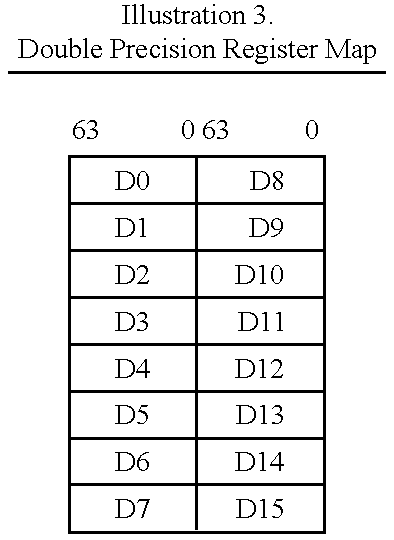

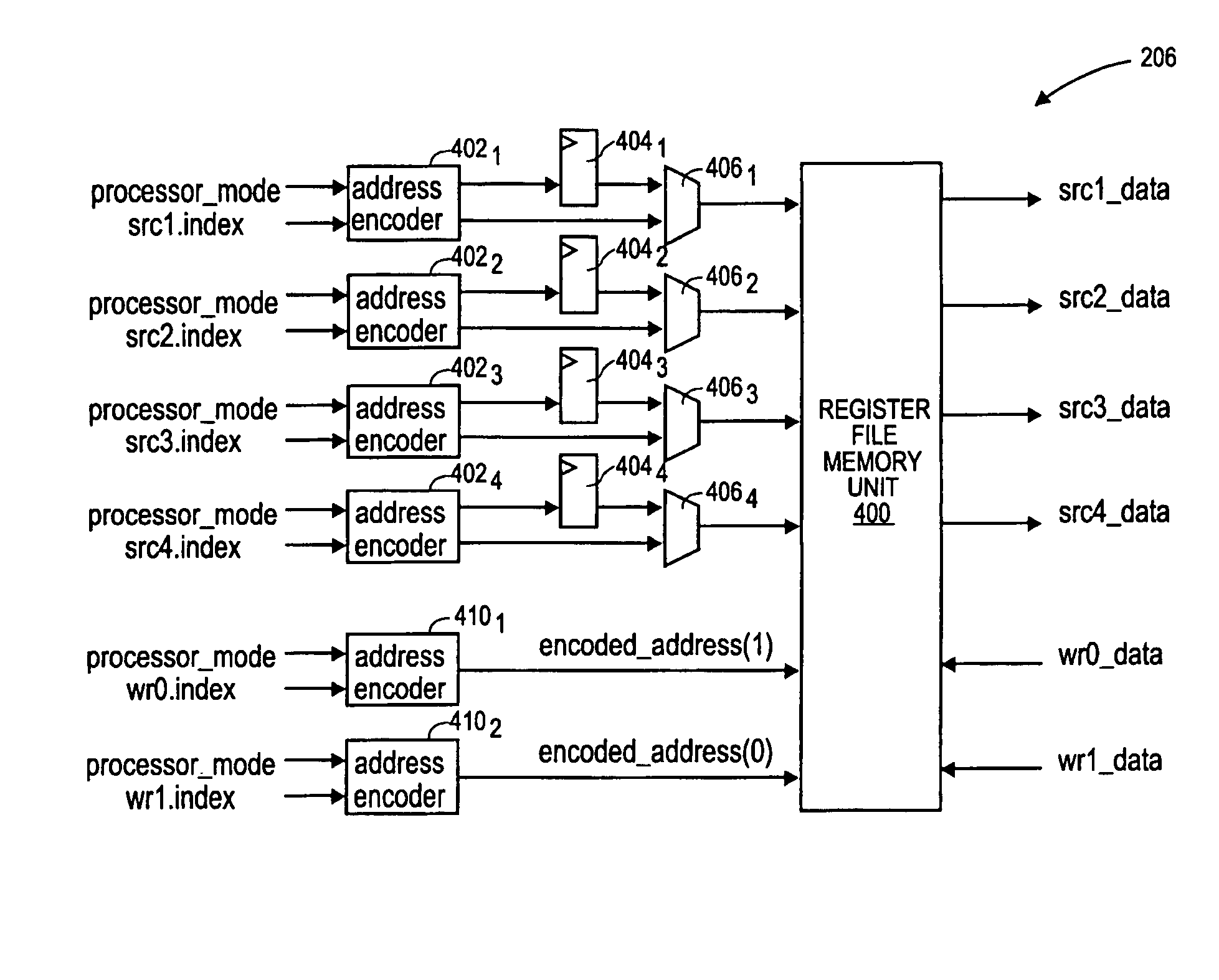

SIMD datapath coupled to scalar/vector/address/conditional data register file with selective subpath scalar processing mode

InactiveUS6839828B2Not compromise SIMD data processing performanceReduce consumptionRegister arrangementsDigital data processing detailsProcessor registerOperation mode

Owner:INTEL CORP

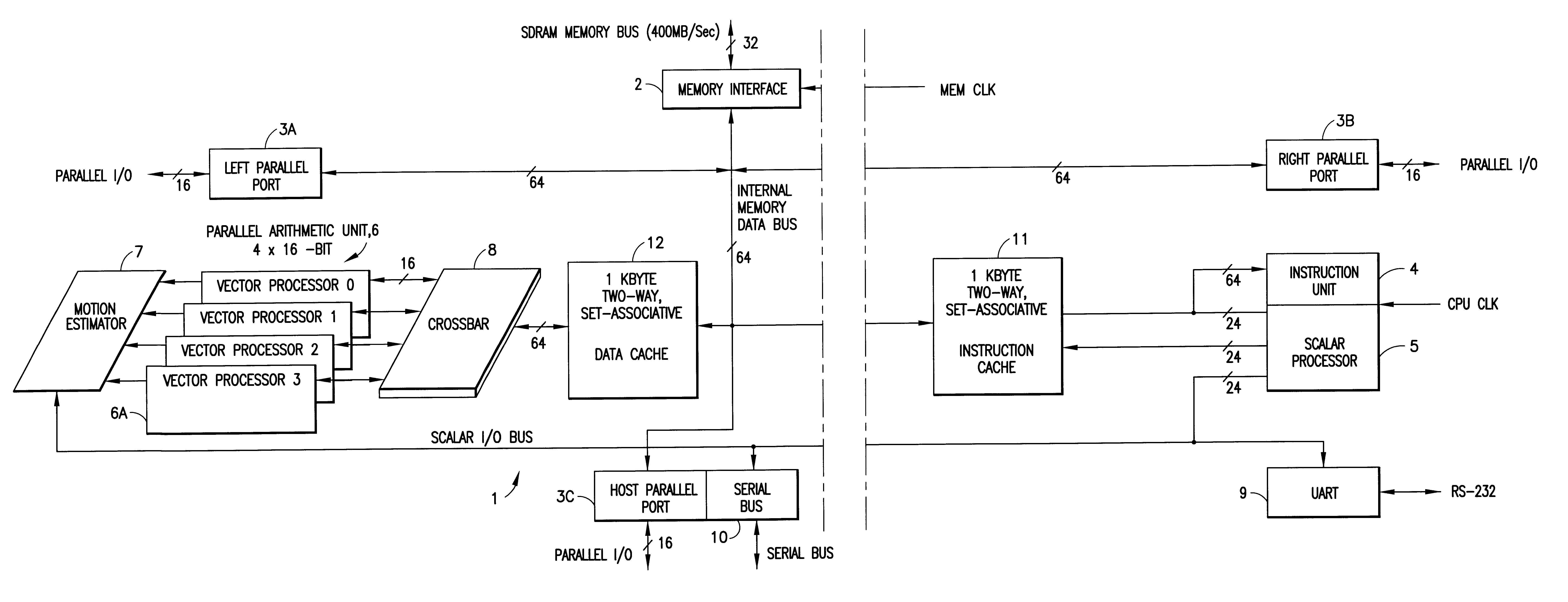

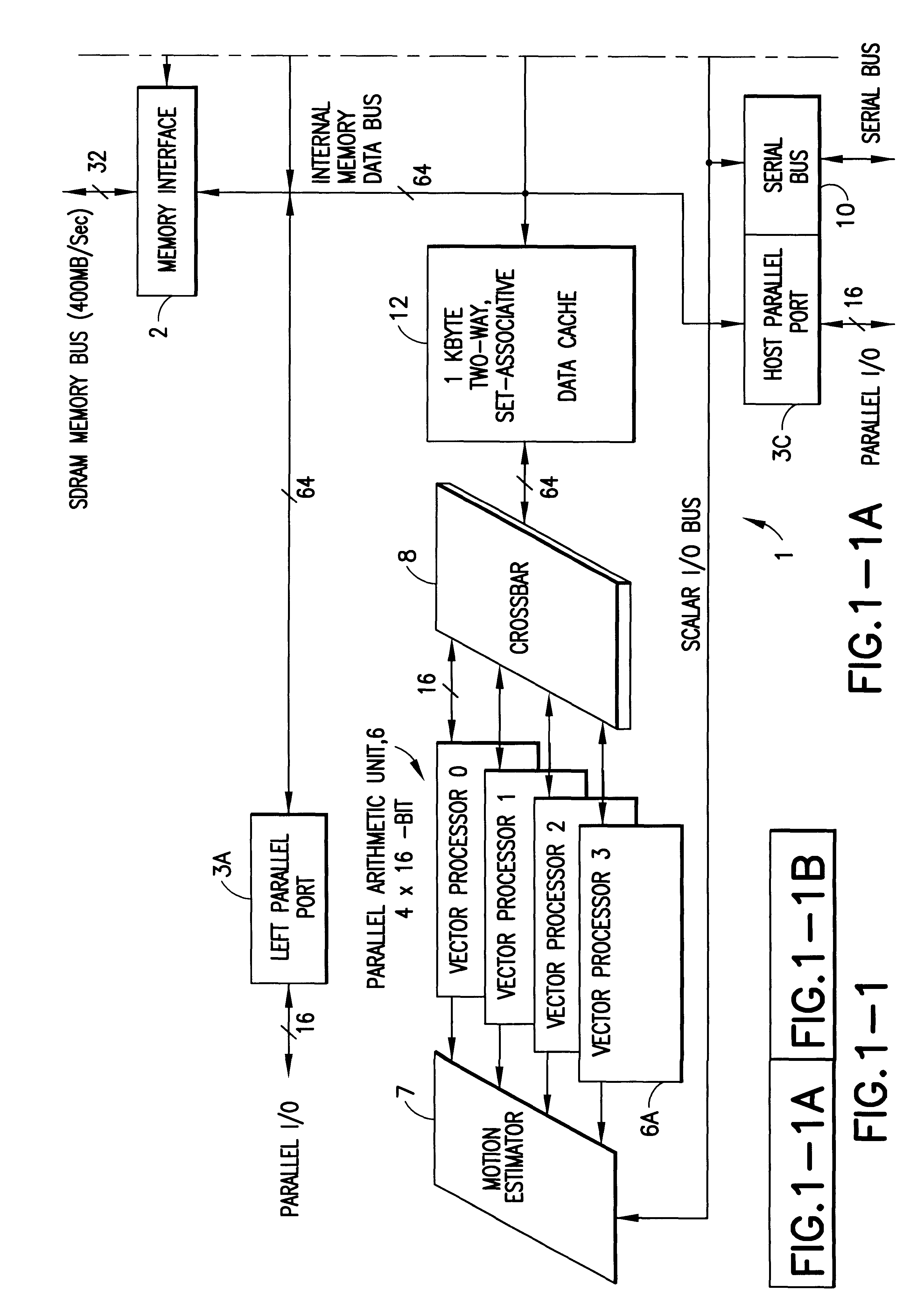

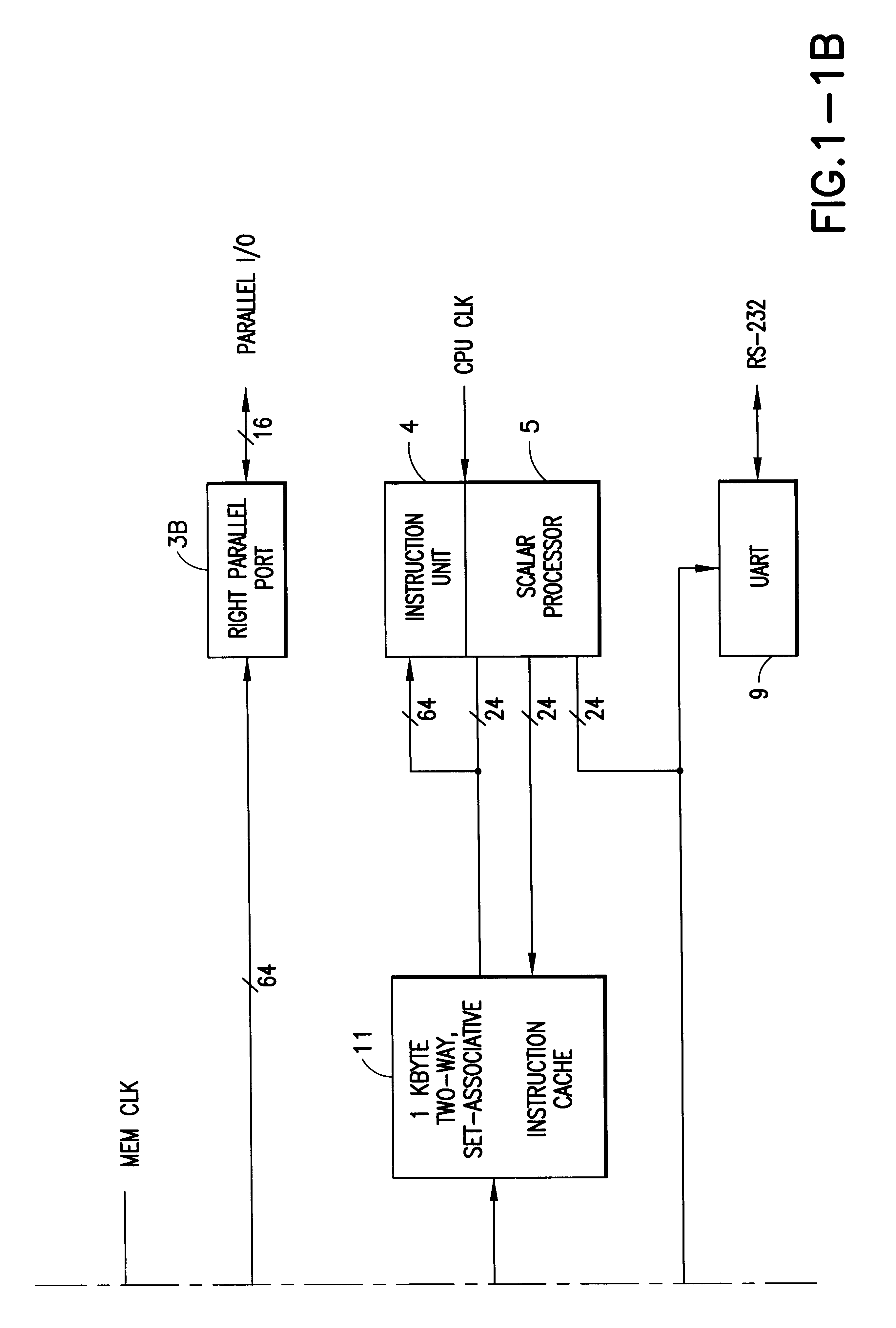

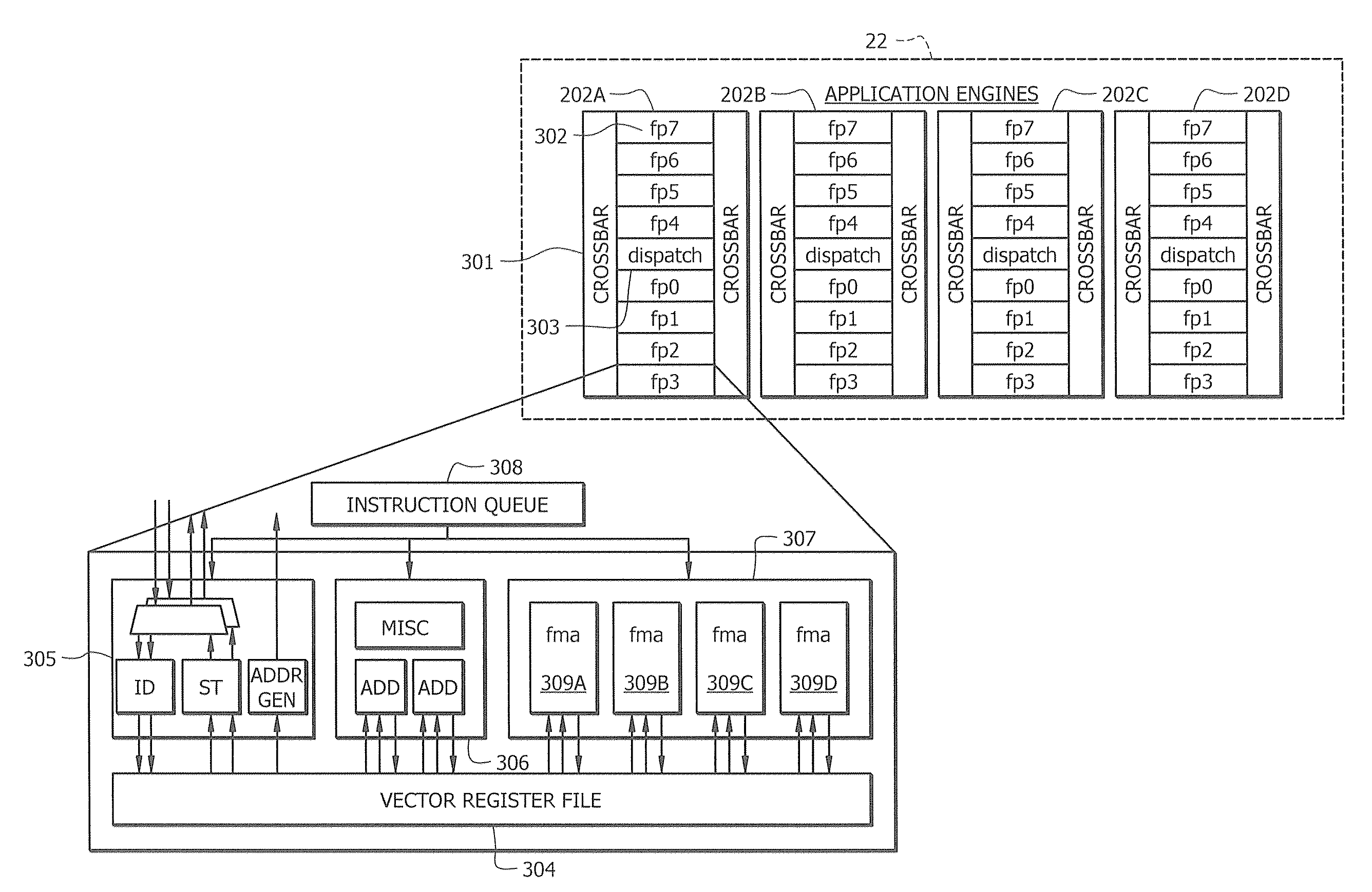

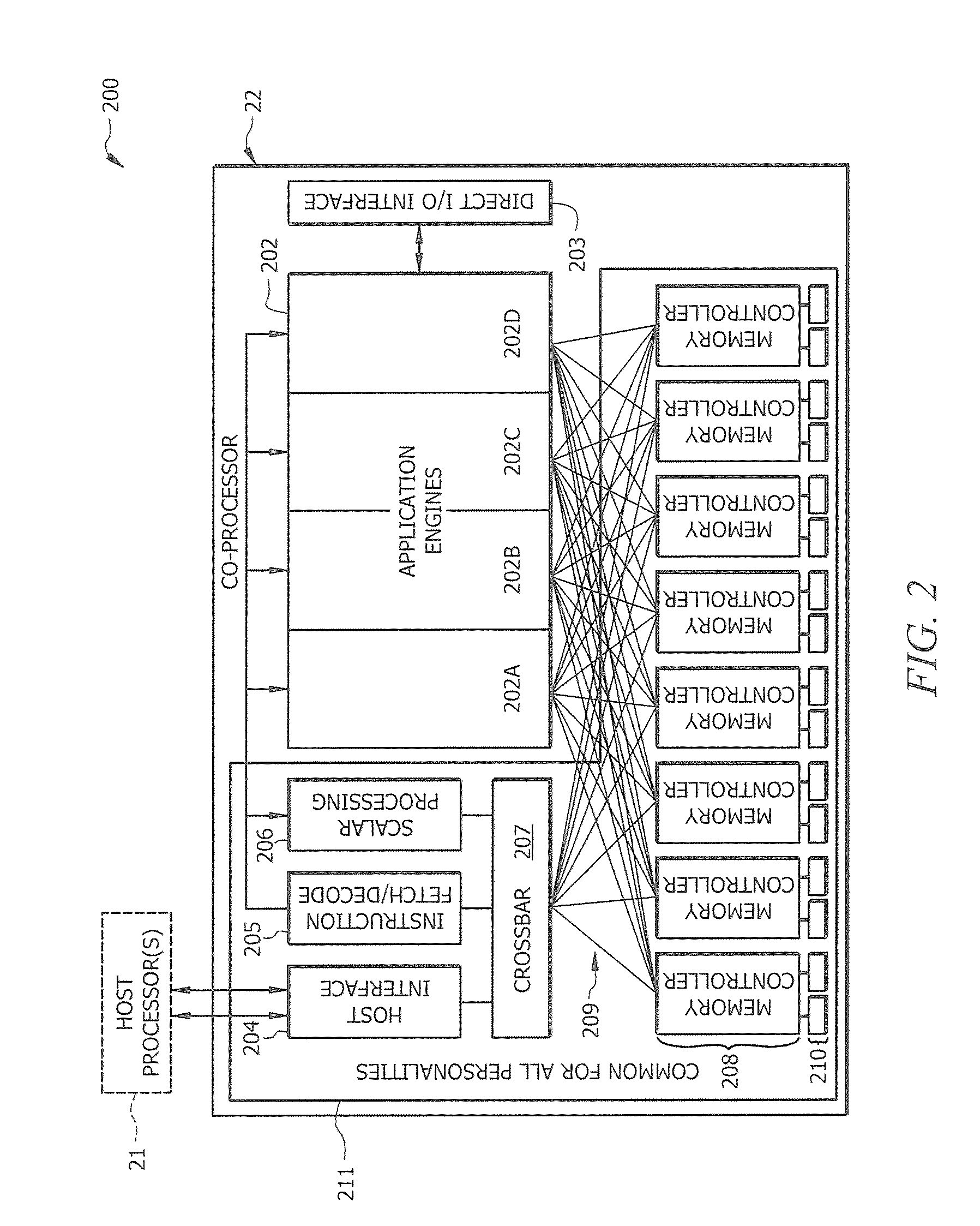

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

Owner:CUFER ASSET LTD LLC

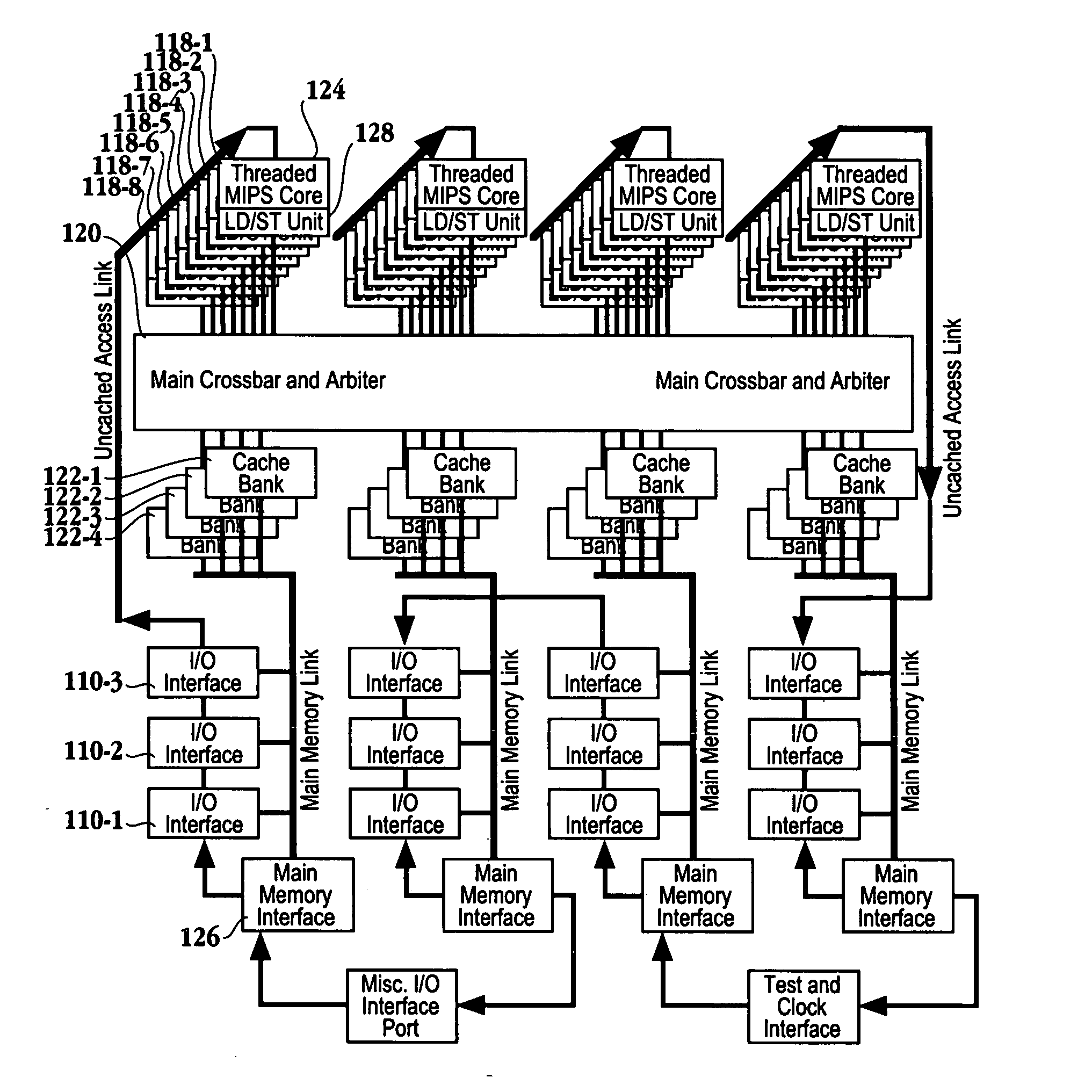

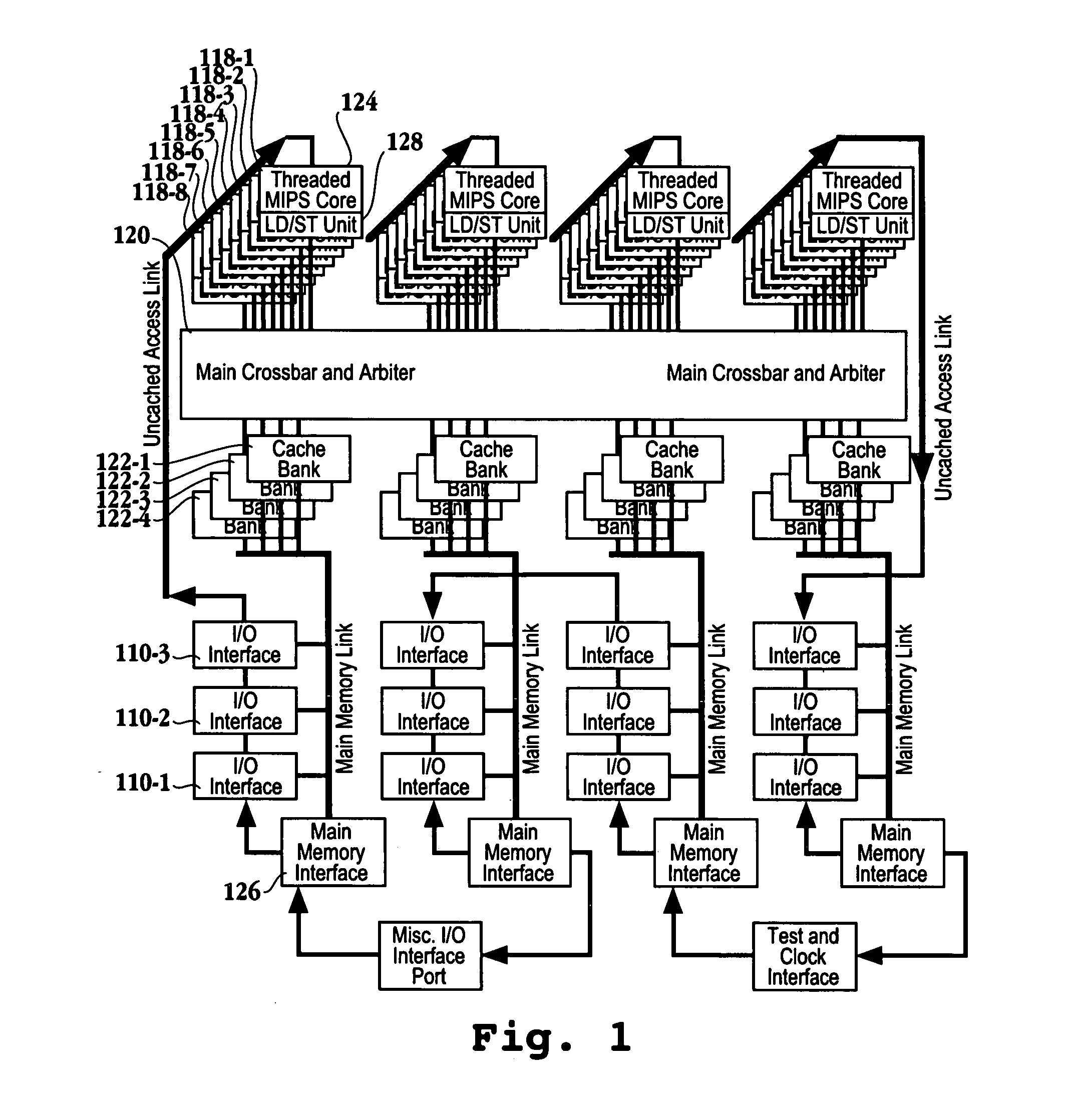

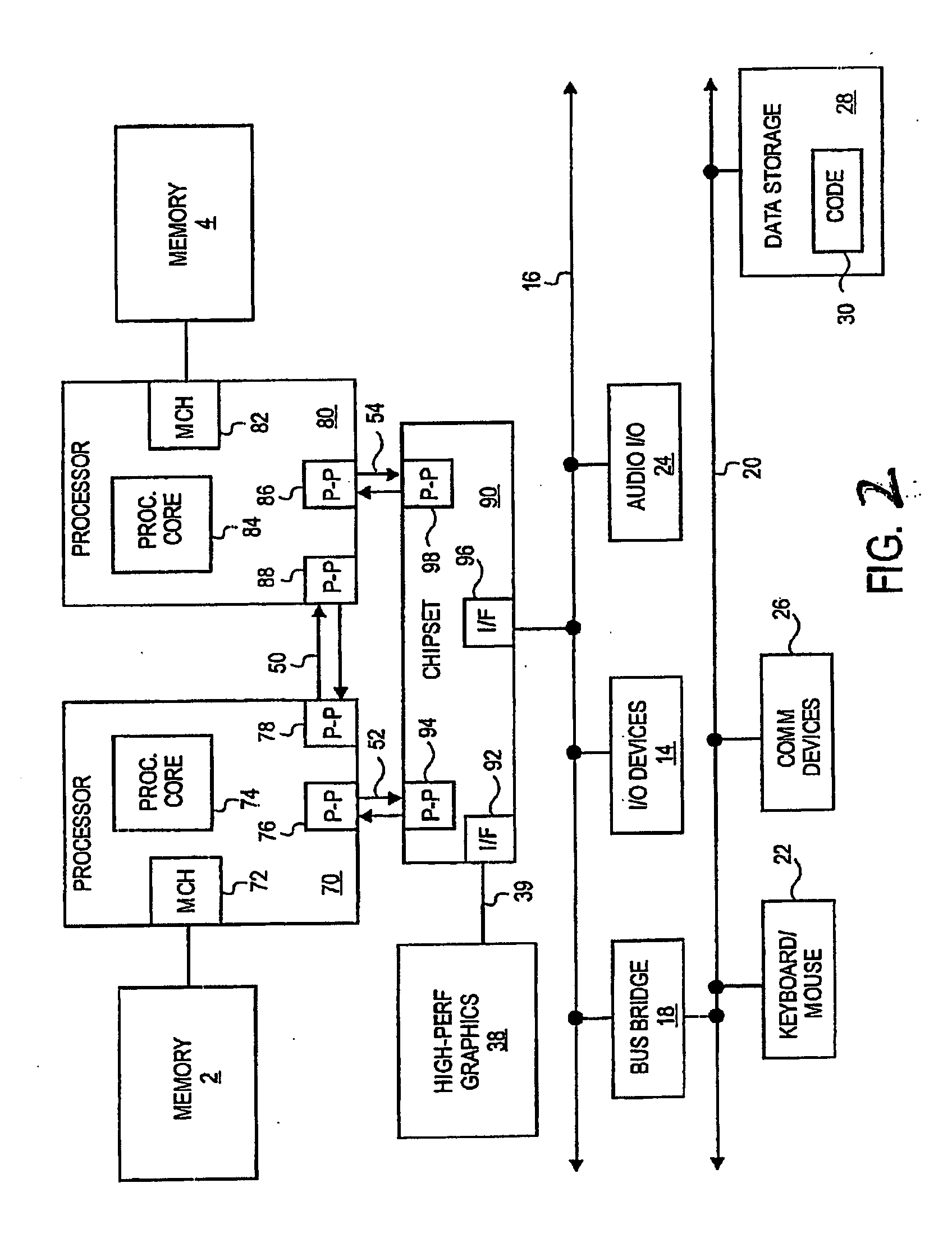

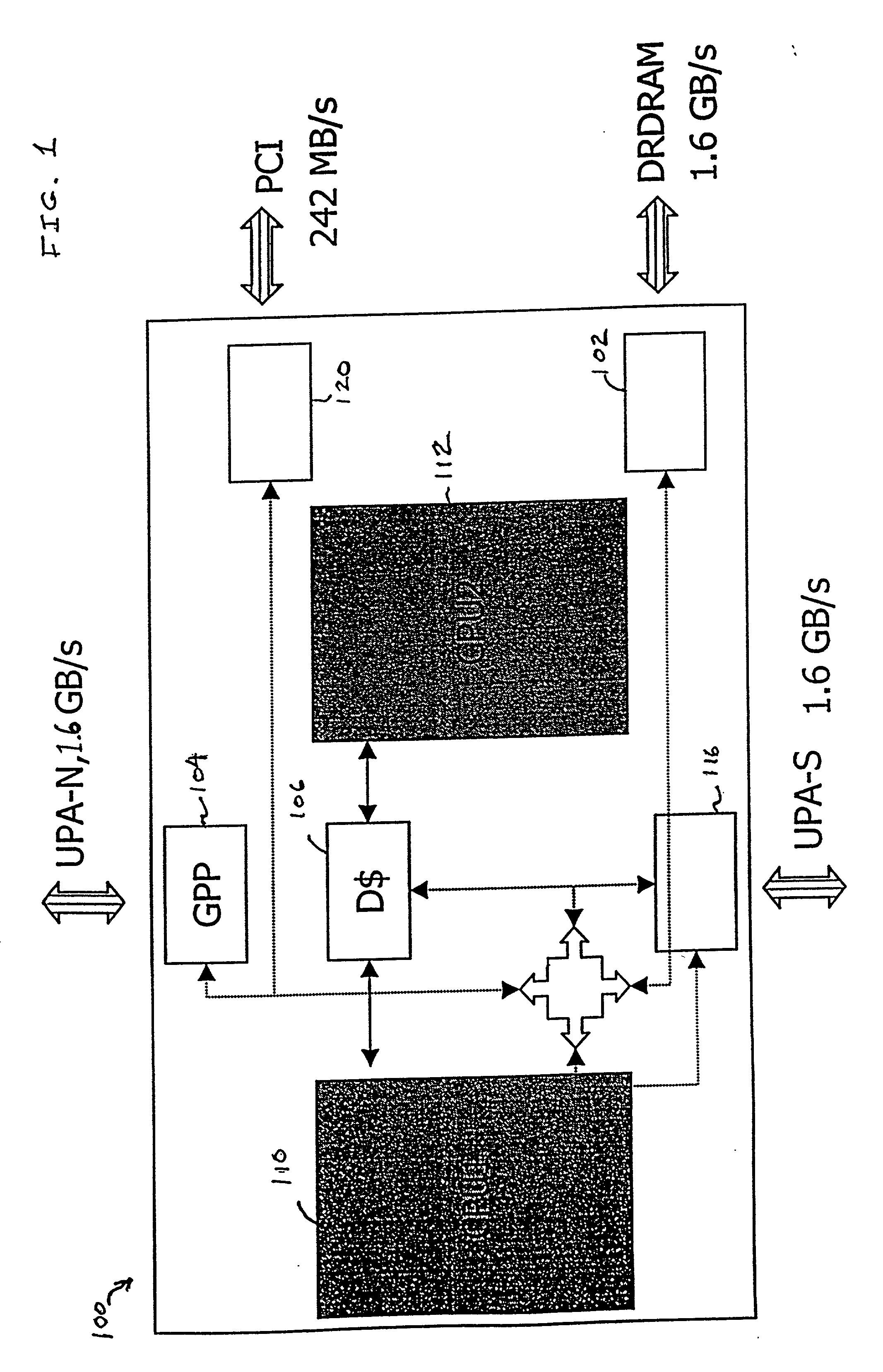

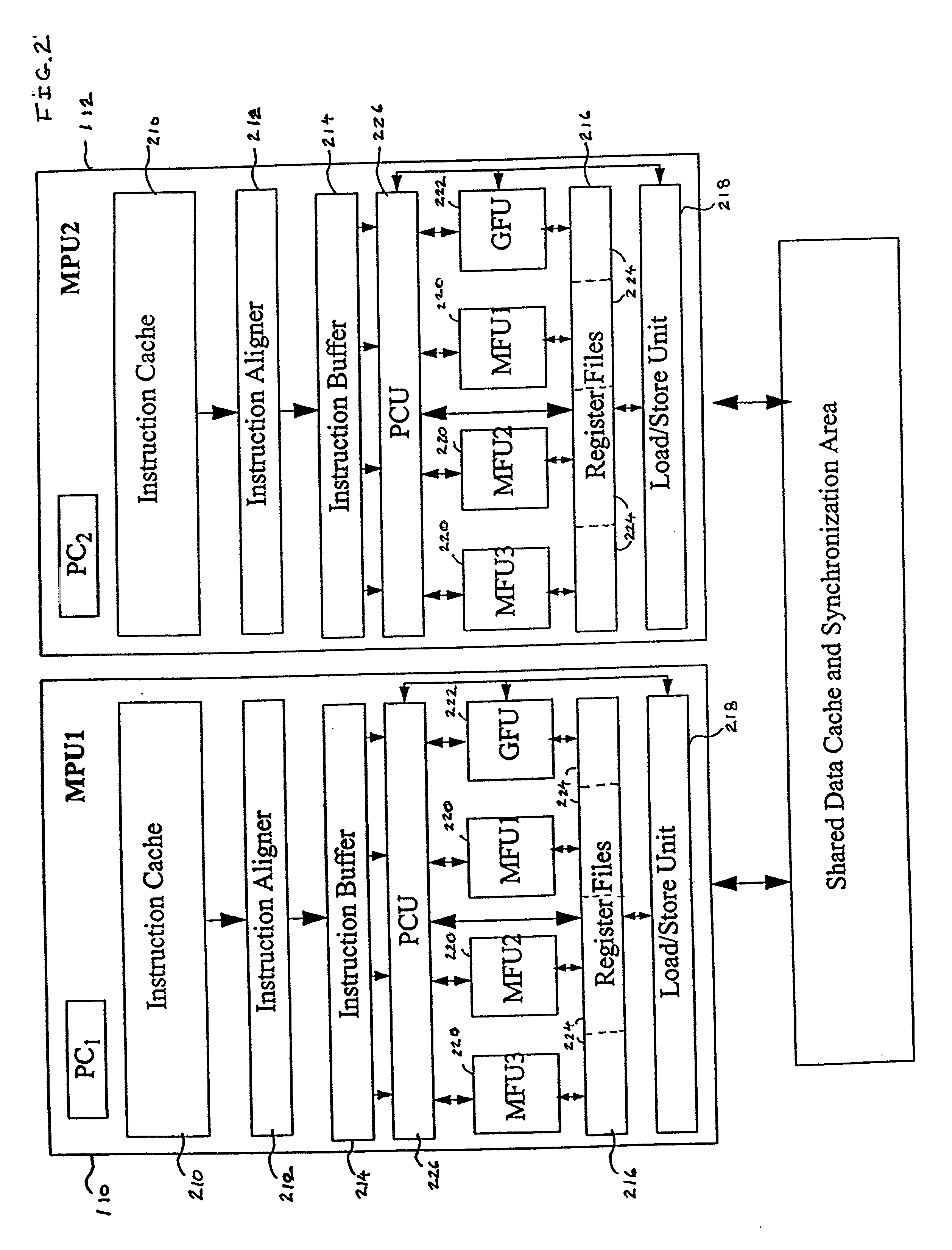

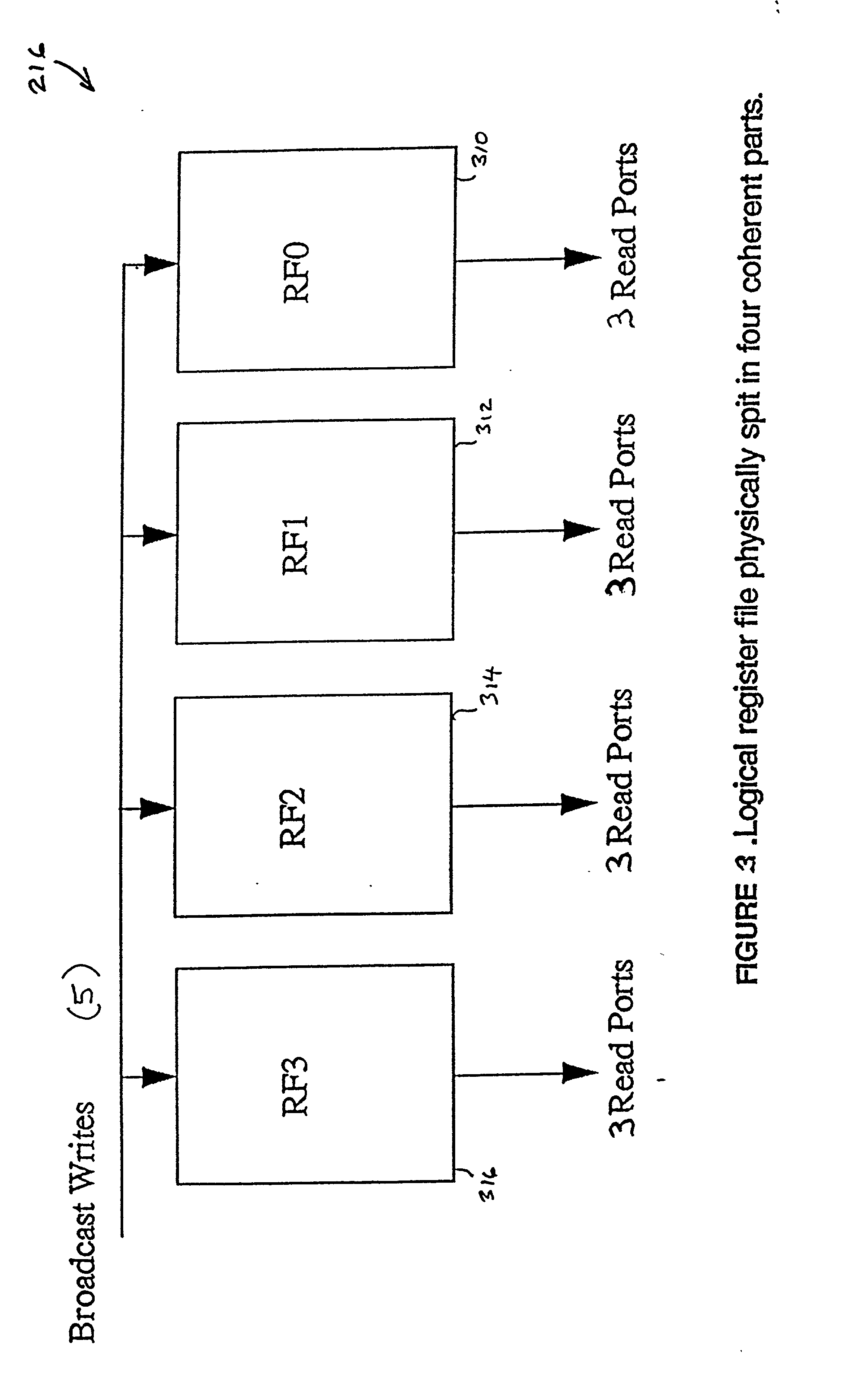

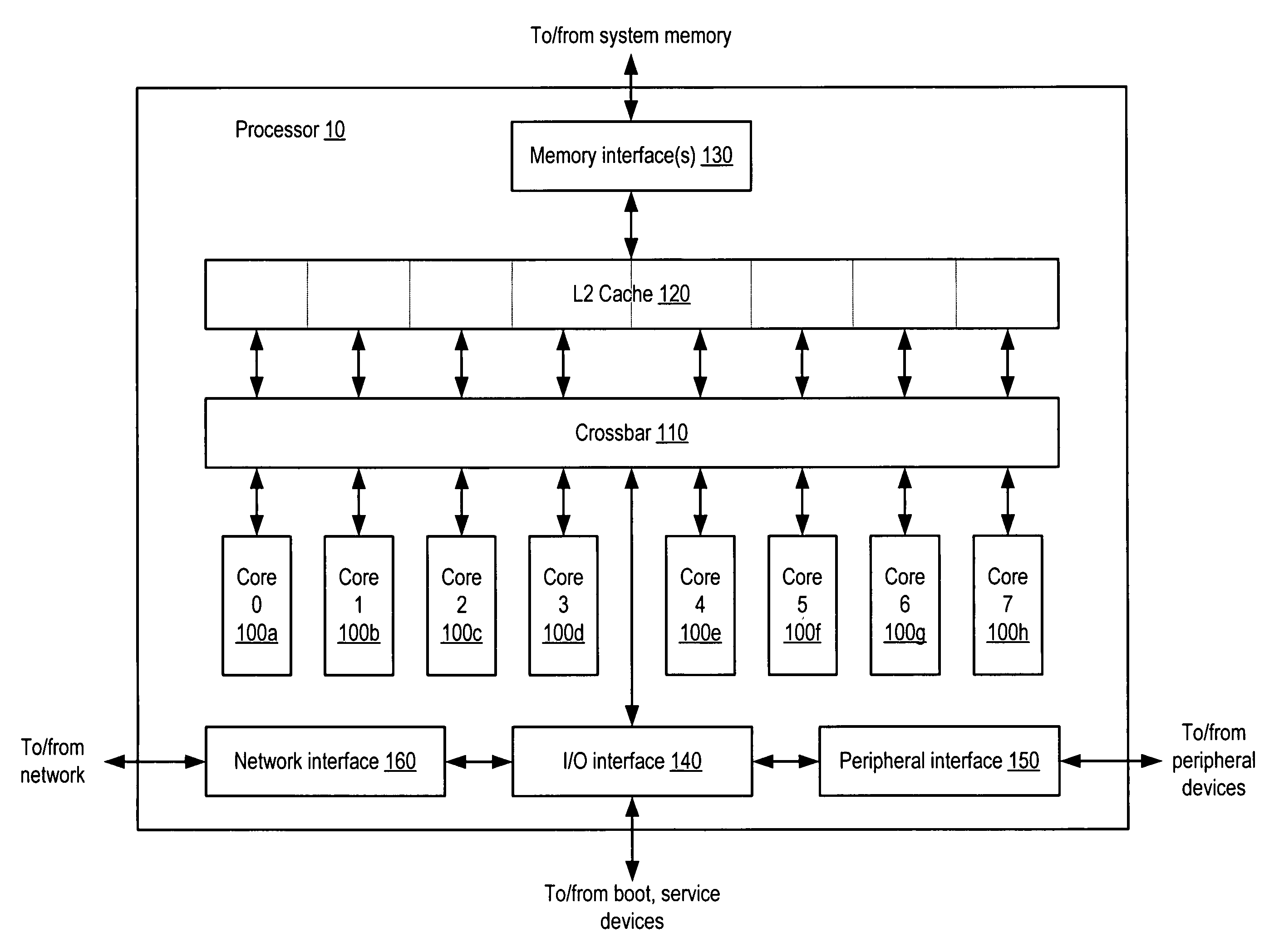

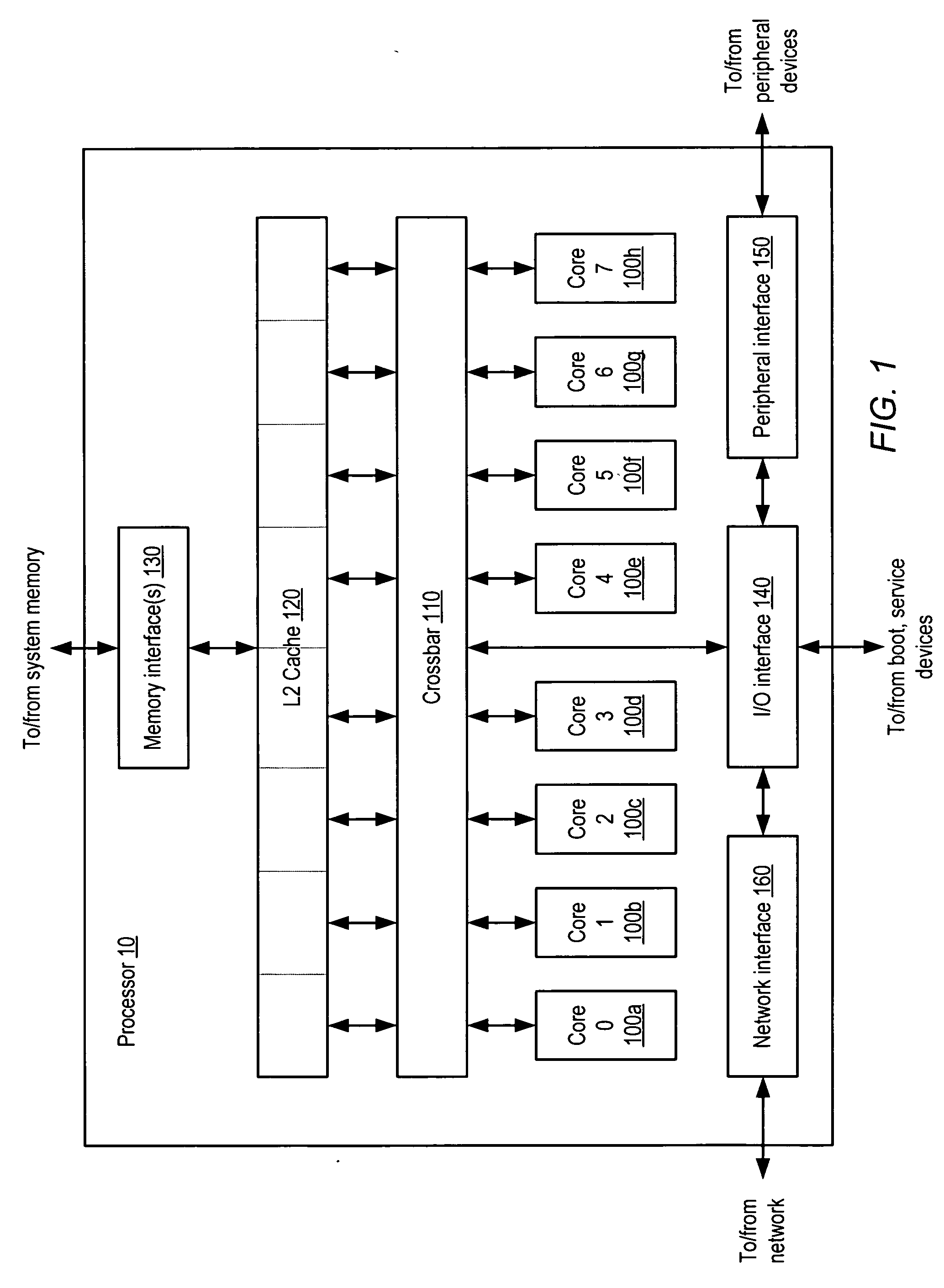

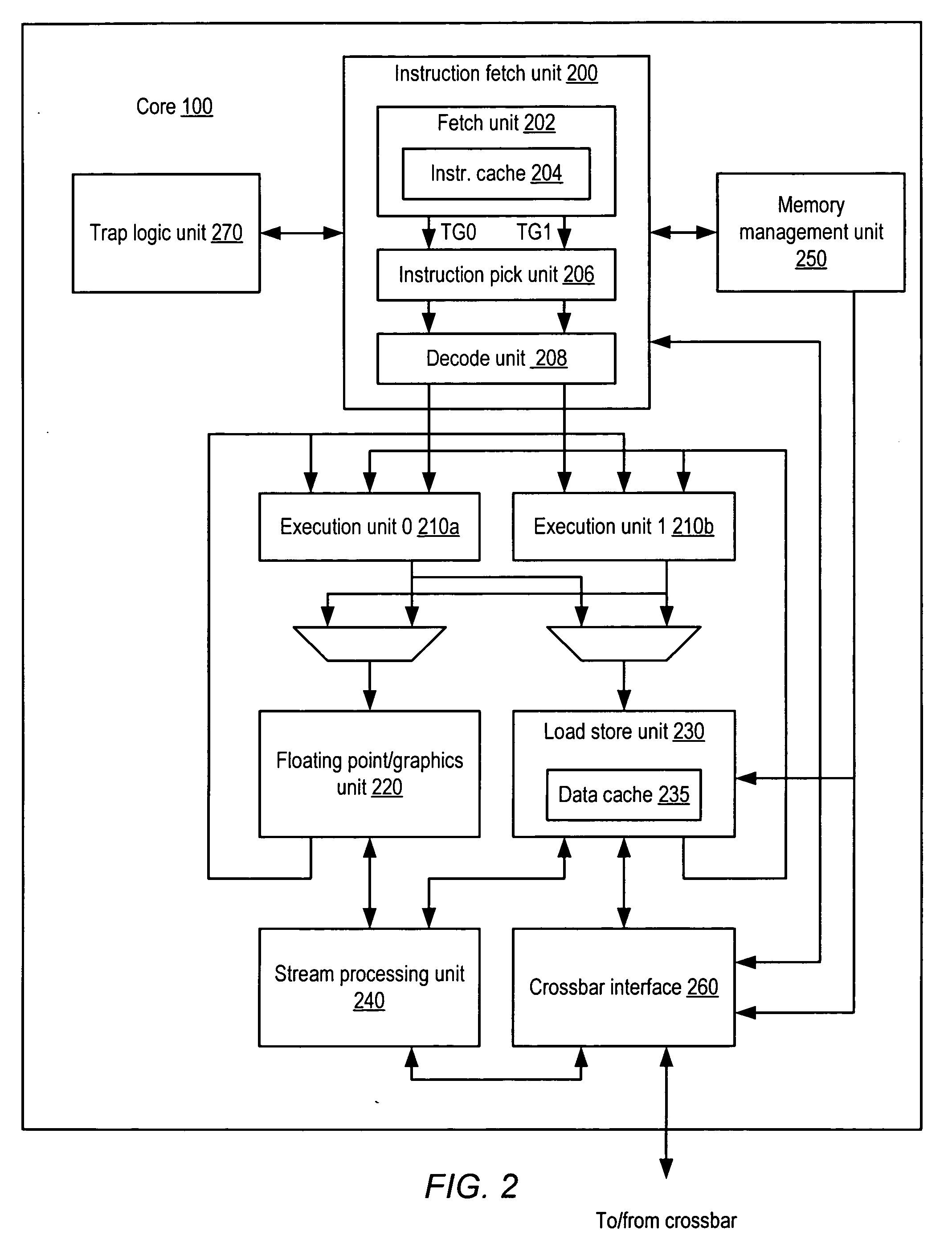

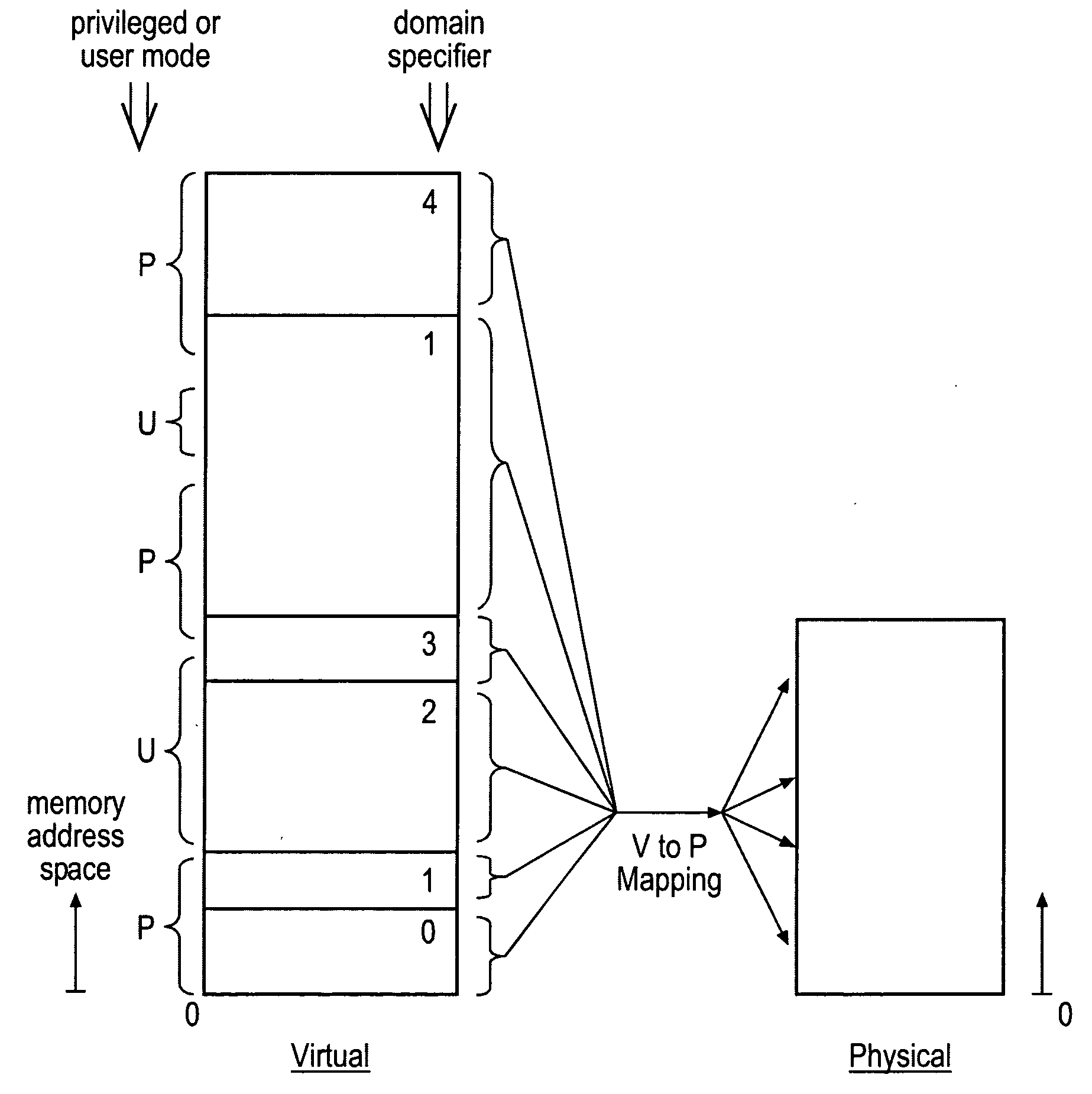

Multi-core multi-thread processor

ActiveUS20050044319A1Easy accessRegister arrangementsMemory adressing/allocation/relocationMemory interfaceParallel computing

Owner:ORACLE INT CORP

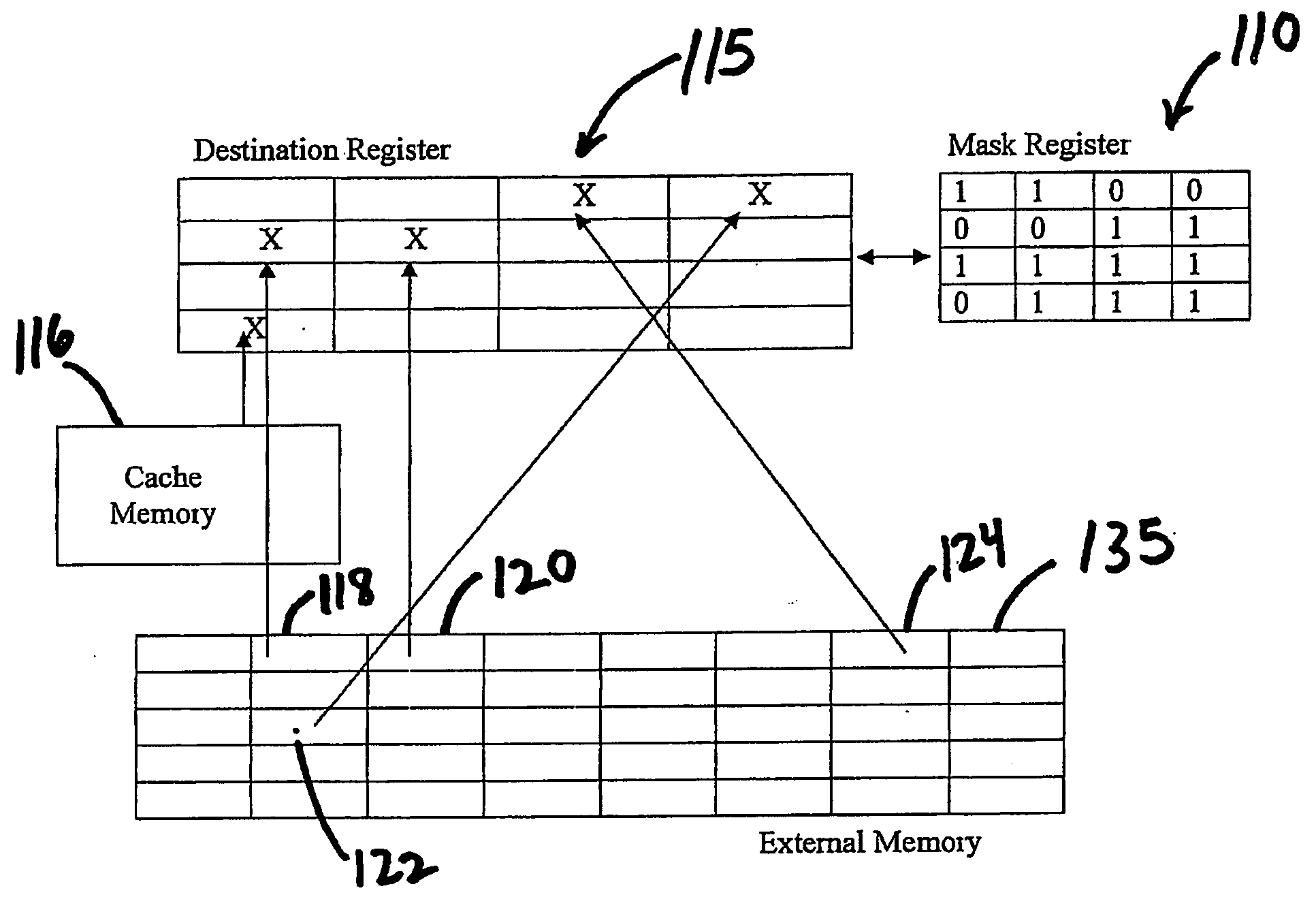

Device, system, and method for gathering elements from memory

InactiveUS20090172364A1Memory architecture accessing/allocationRegister arrangementsData fieldData element

Owner:INTEL CORP

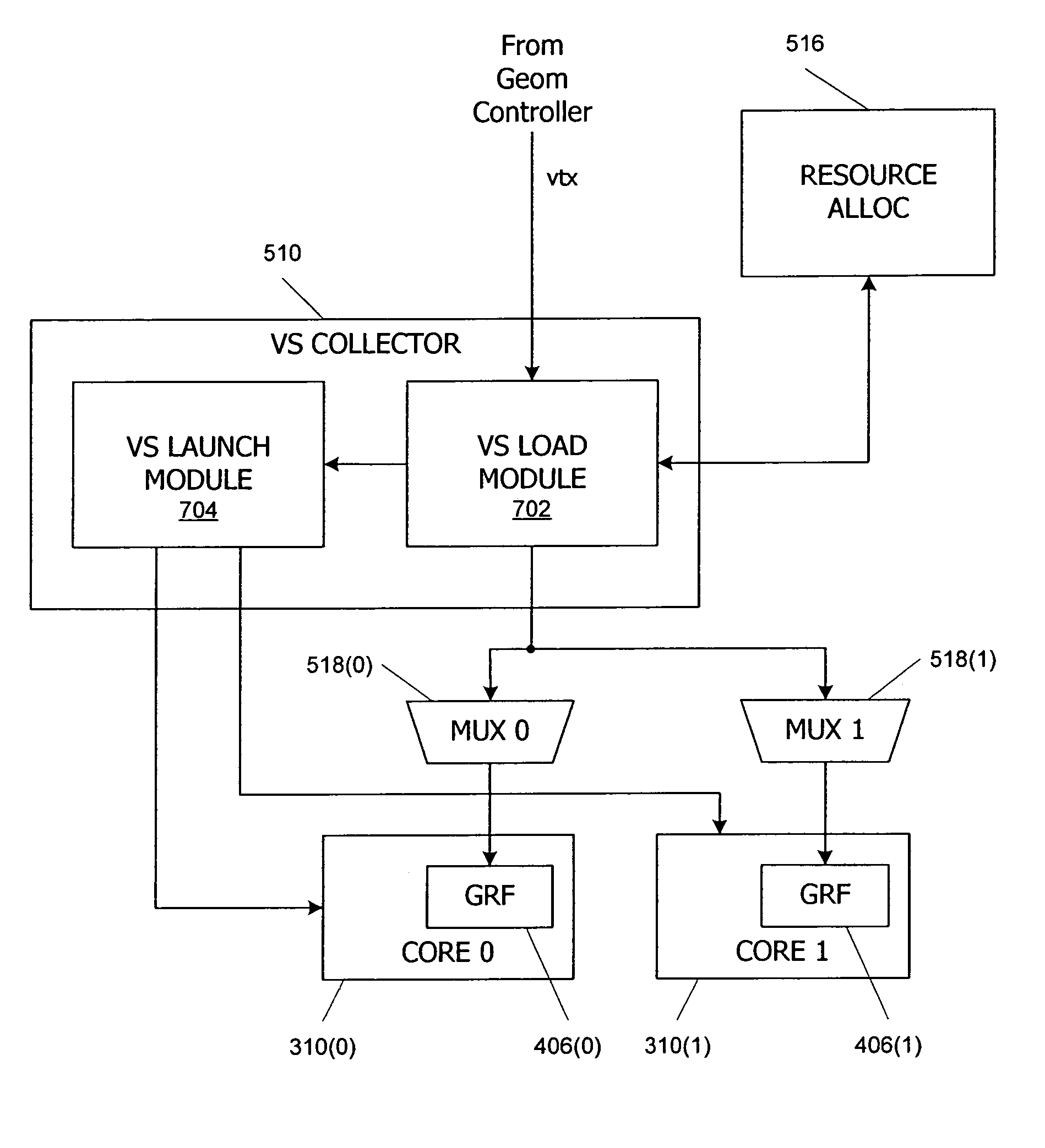

Multithreaded SIMD parallel processor with loading of groups of threads

ActiveUS7447873B1Management loadRegister arrangementsGeneral purpose stored program computerProcessing coreProcessor register

Owner:NVIDIA CORP

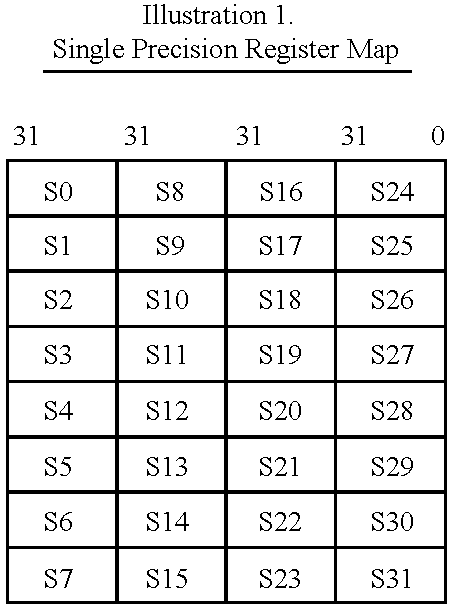

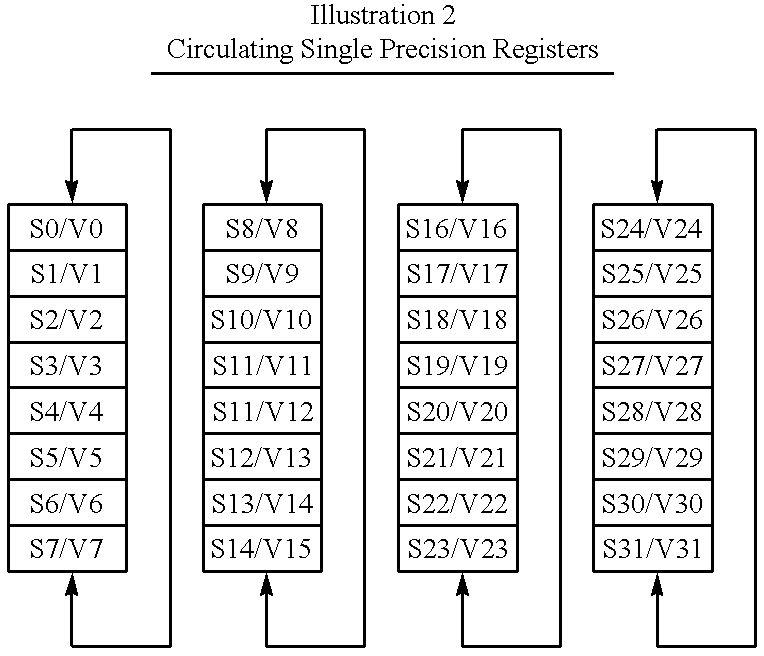

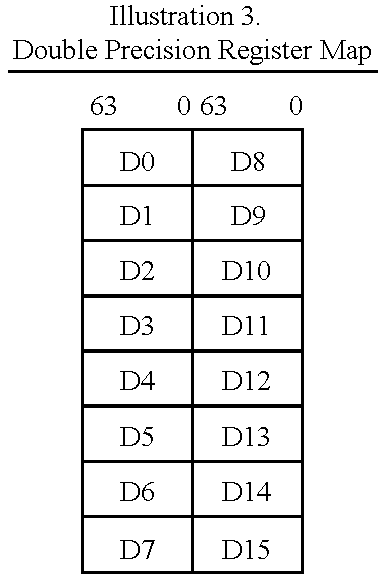

Coprocessor opcode division by data type

InactiveUS6247113B1Easy to scaleReduced hardware coprocessorRegister arrangementsGeneral purpose stored program computerData processing systemCoprocessor

Owner:ARM LTD

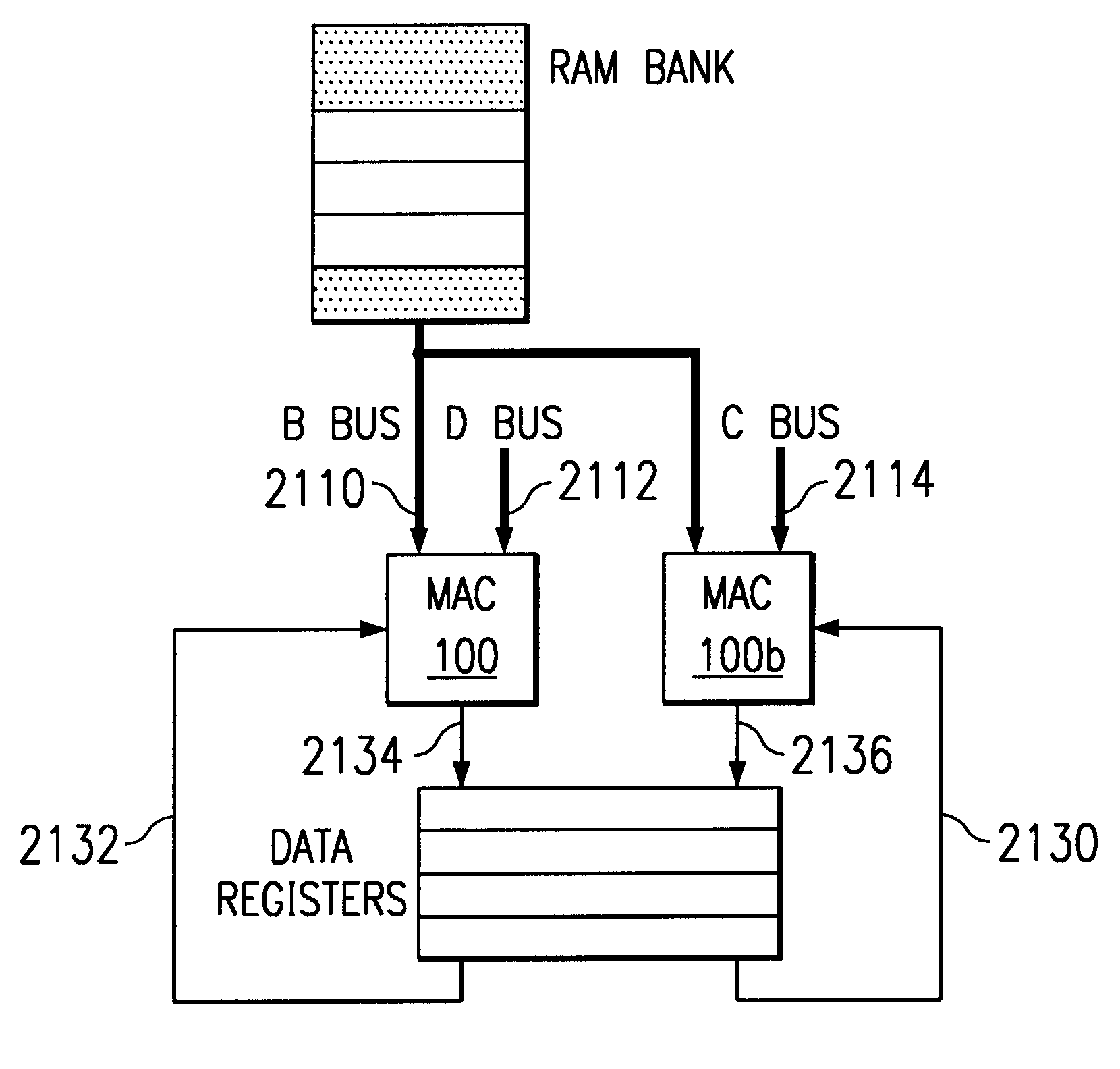

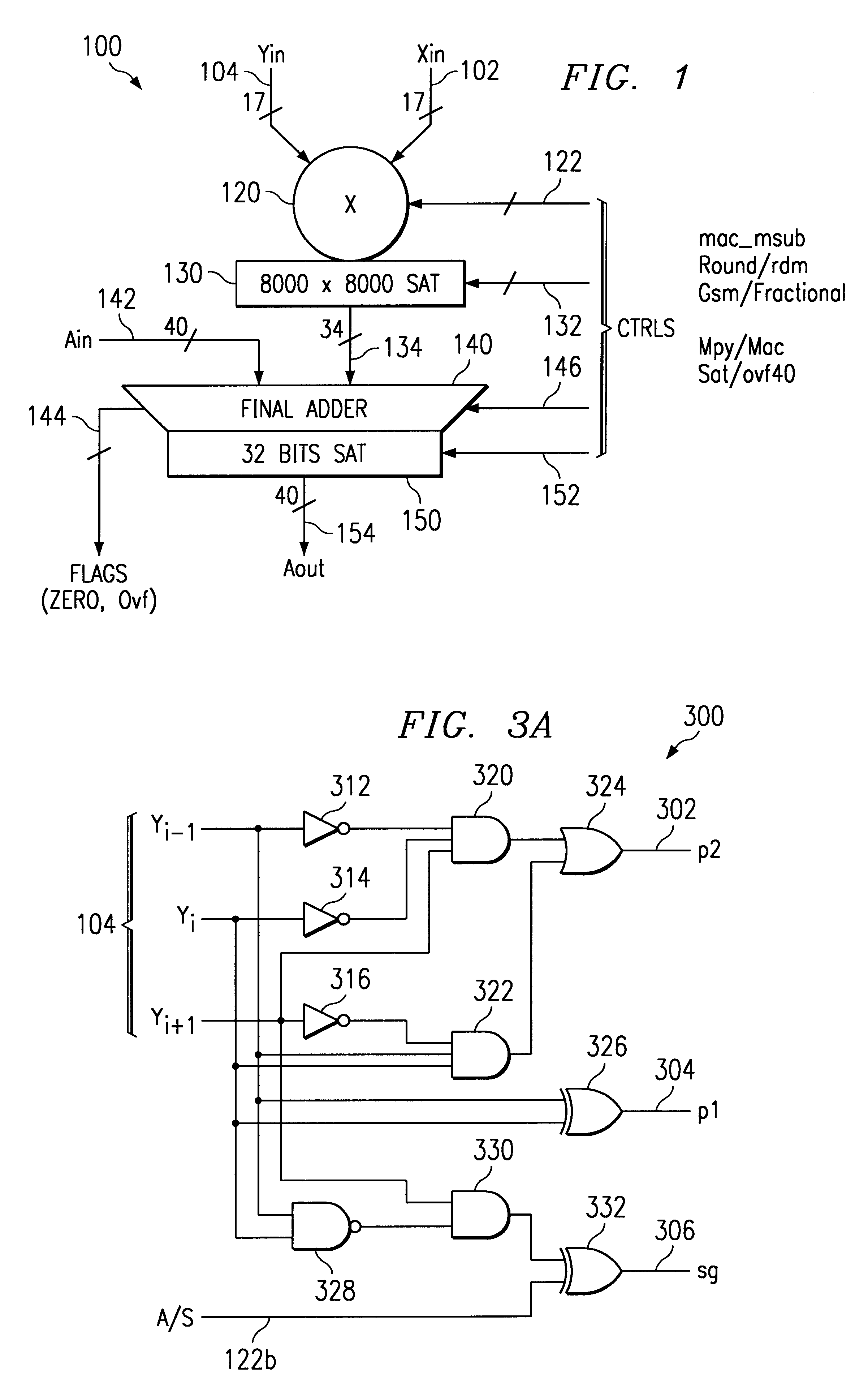

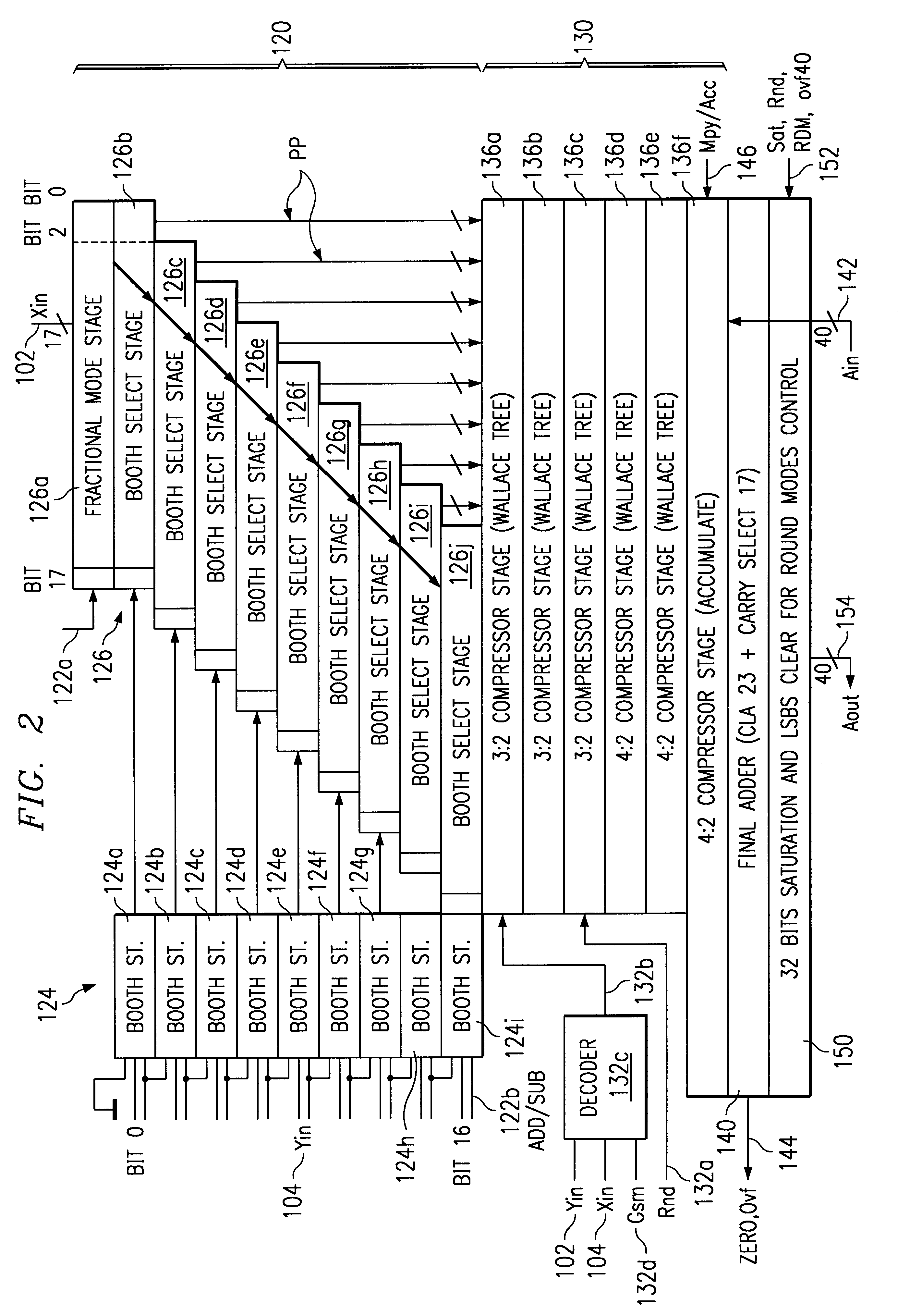

Multiplier accumulator circuits

Owner:TEXAS INSTR INC

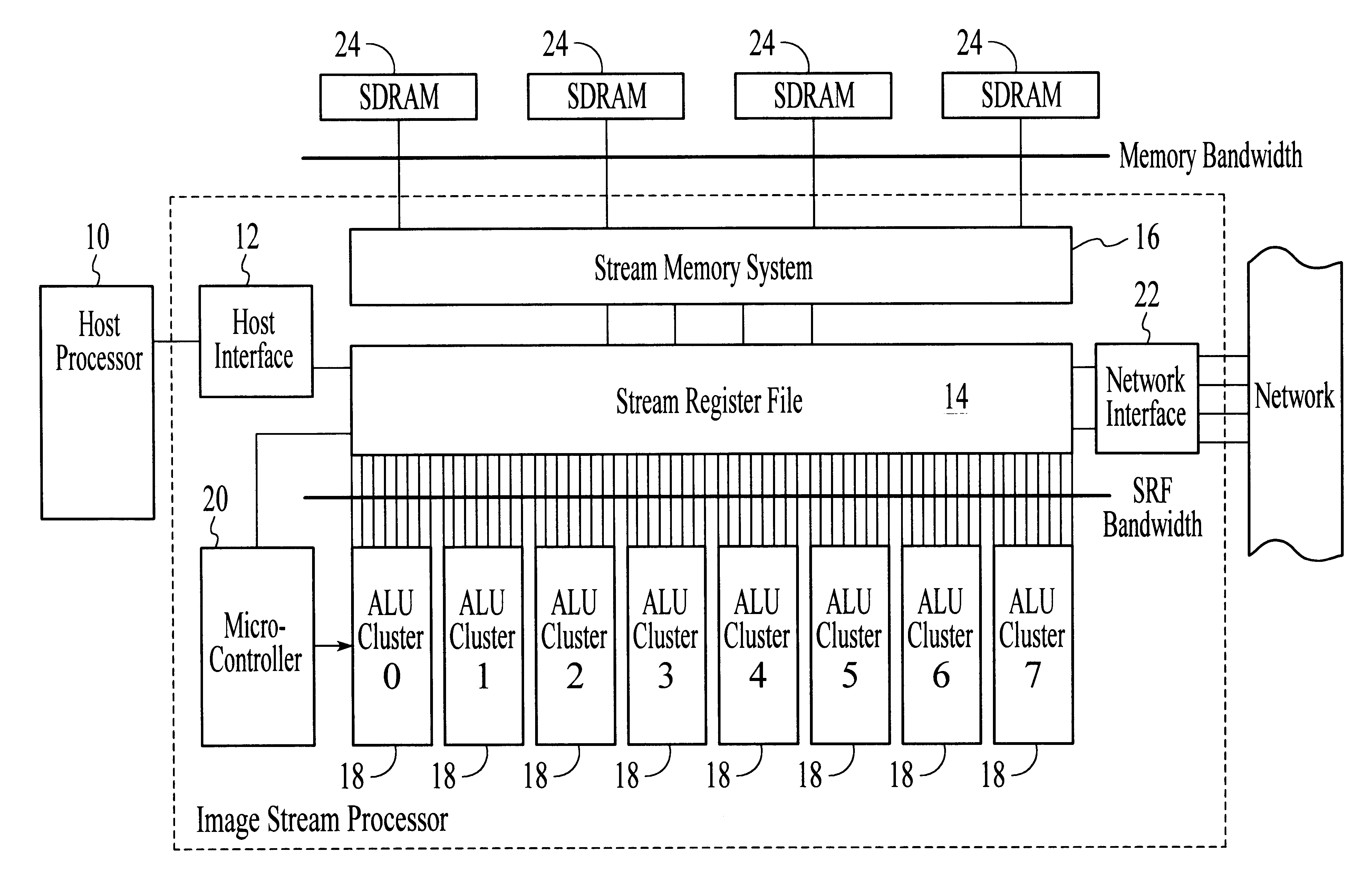

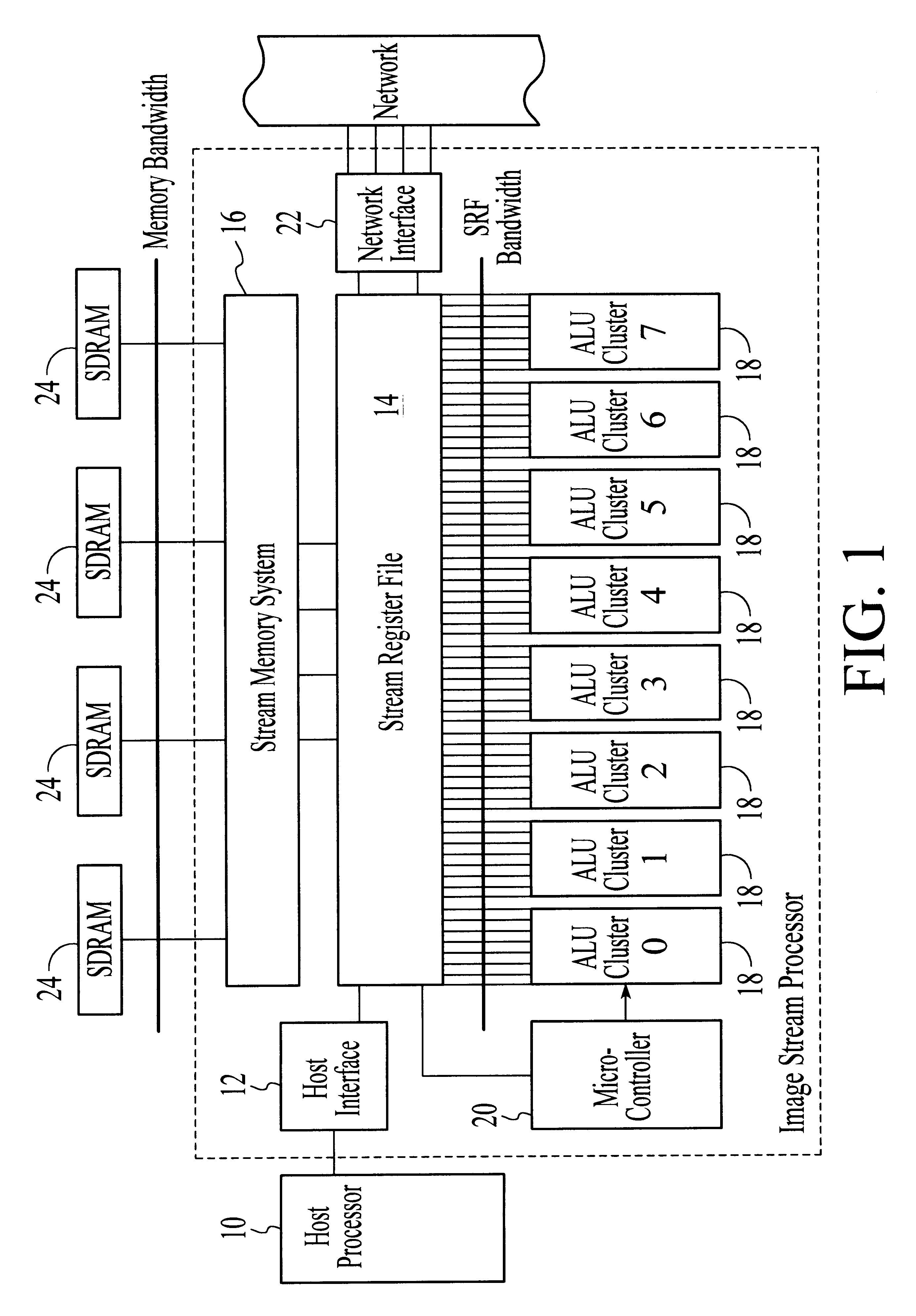

System and method for performing compound vector operations

InactiveUS6192384B1Reduce bandwidth requirementsMinimize the numberOperational speed enhancementRegister arrangementsOperating instructionImaging processing

Owner:THE BOARD OF TRUSTEES OF THE LELAND +1

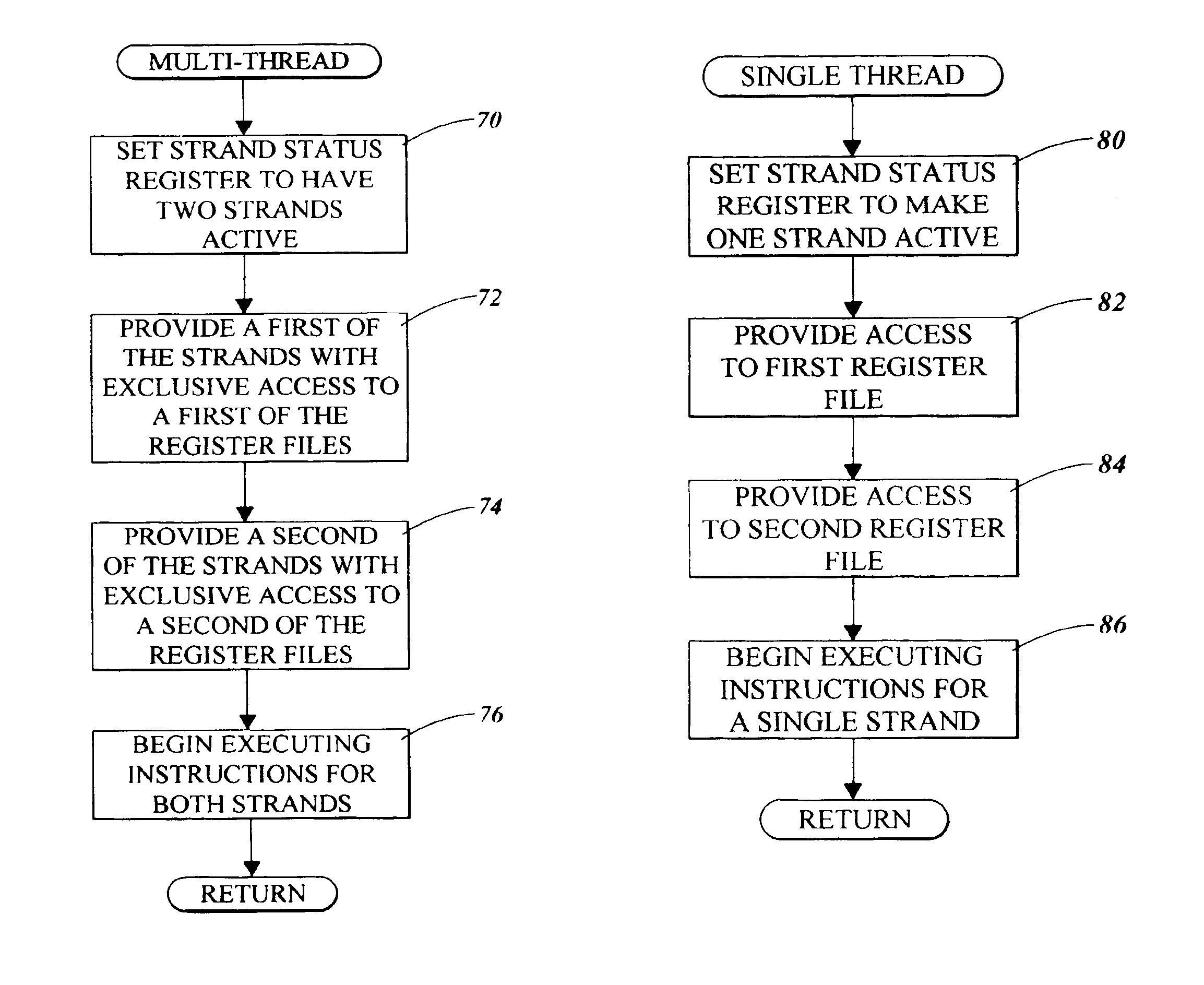

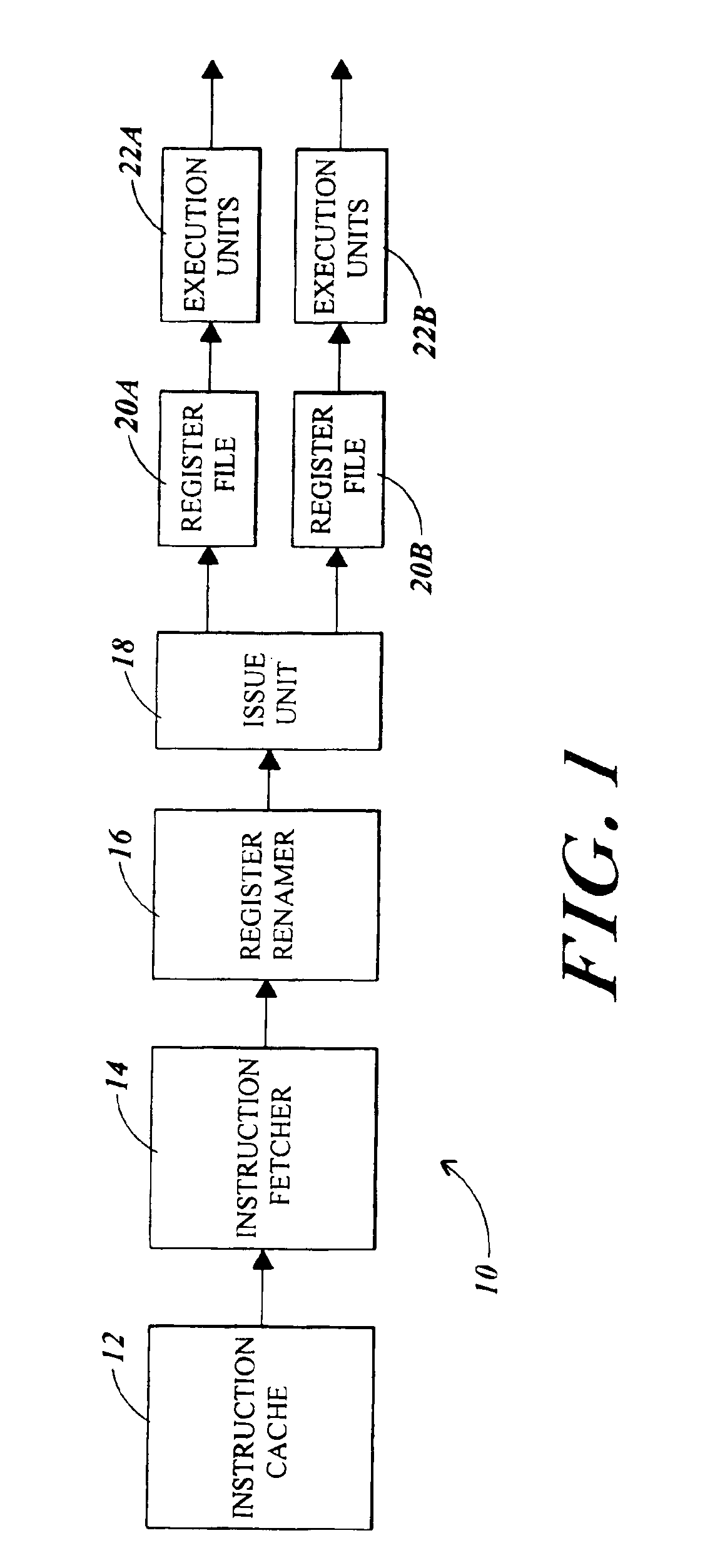

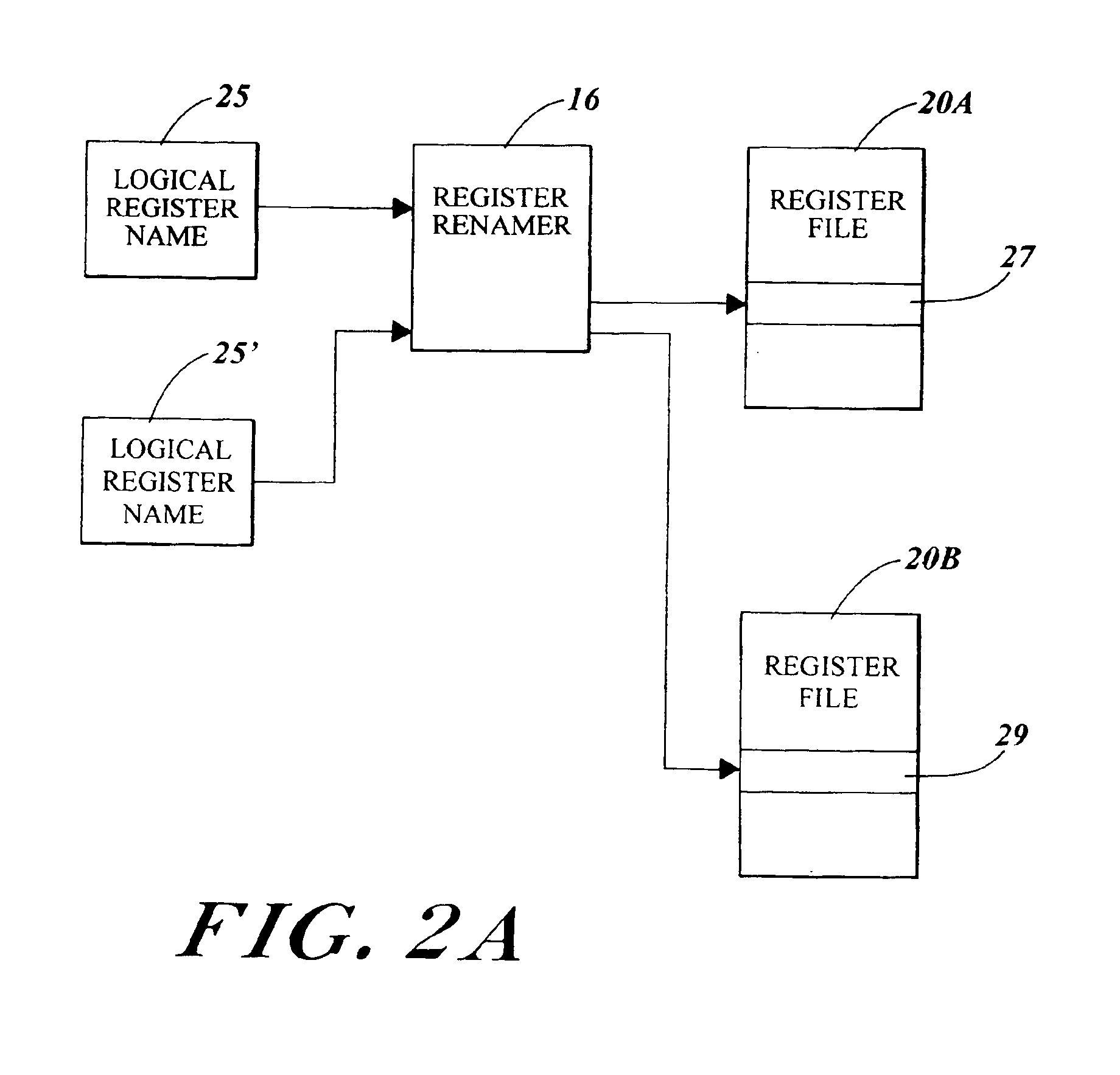

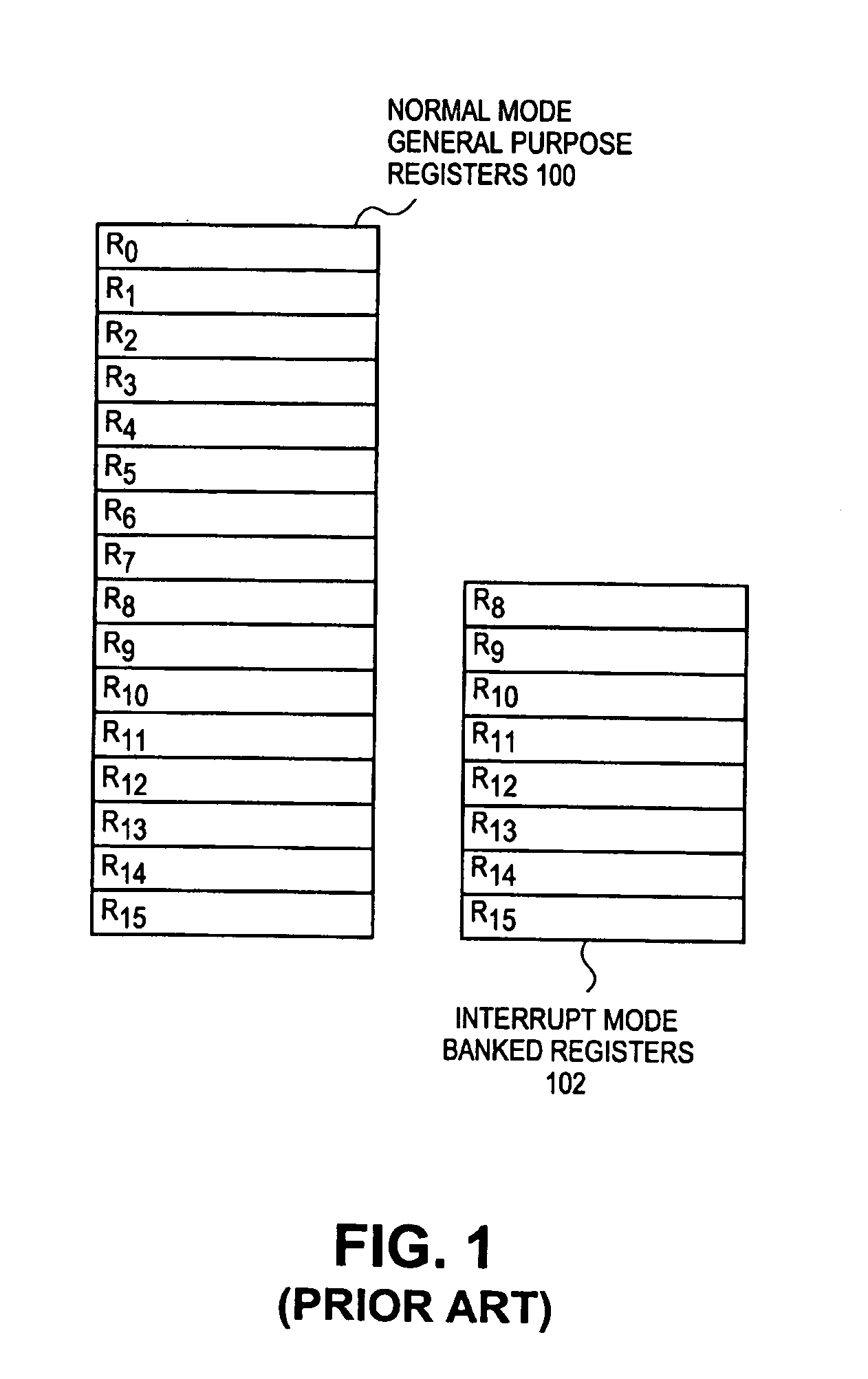

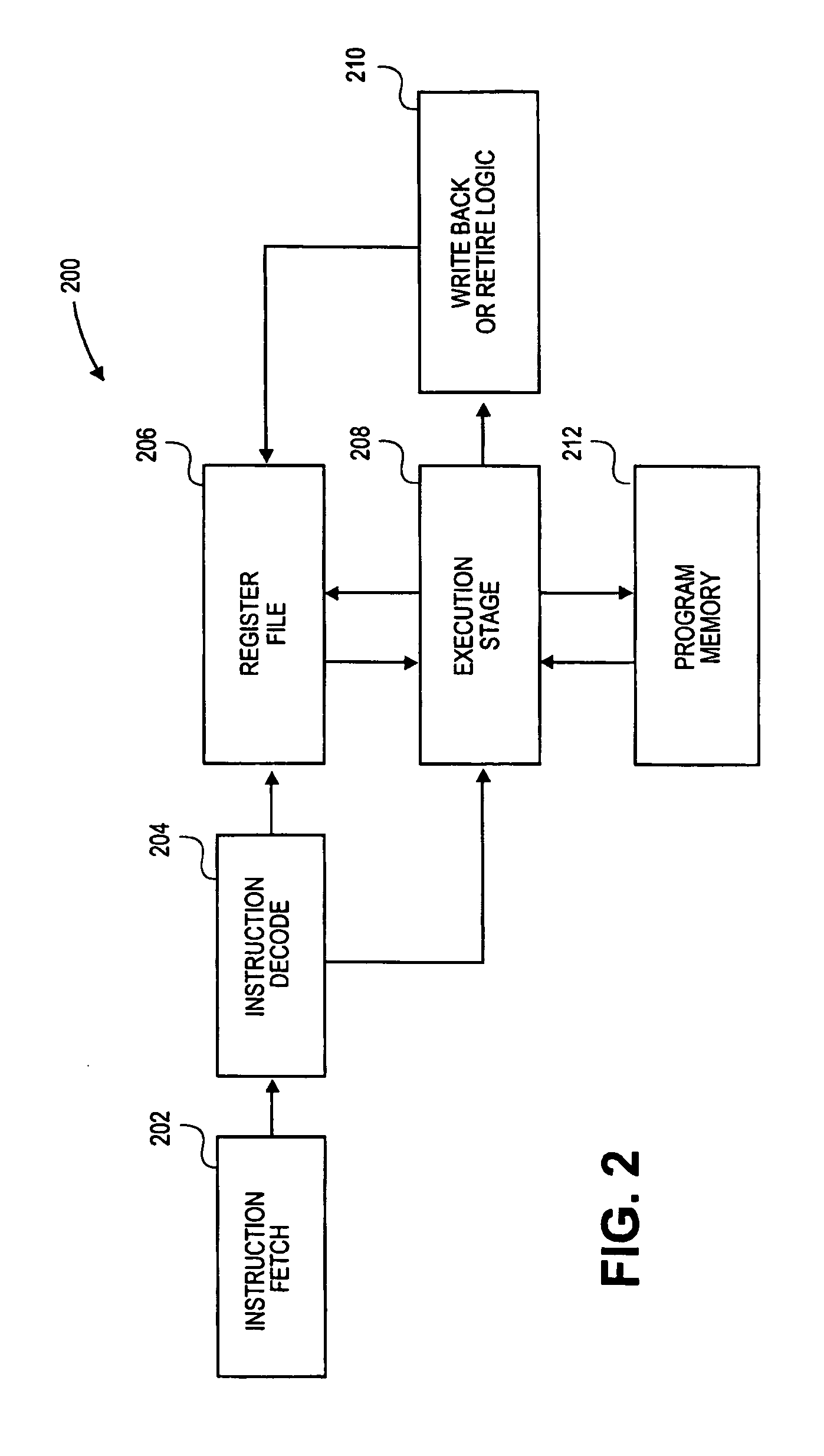

Microprocessor and method for giving each thread exclusive access to one register file in a multi-threading mode and for giving an active thread access to multiple register files in a single thread mode

InactiveUS6954846B2Maximize issue rateRegister arrangementsUnauthorized memory use protectionMicroprocessorExclusive access

Owner:ORACLE INT CORP

Vector register addressing

InactiveUS6332186B1Without complexityWithout costRegister arrangementsInstruction analysisMemory addressProcessing Instruction

Owner:ARM LTD

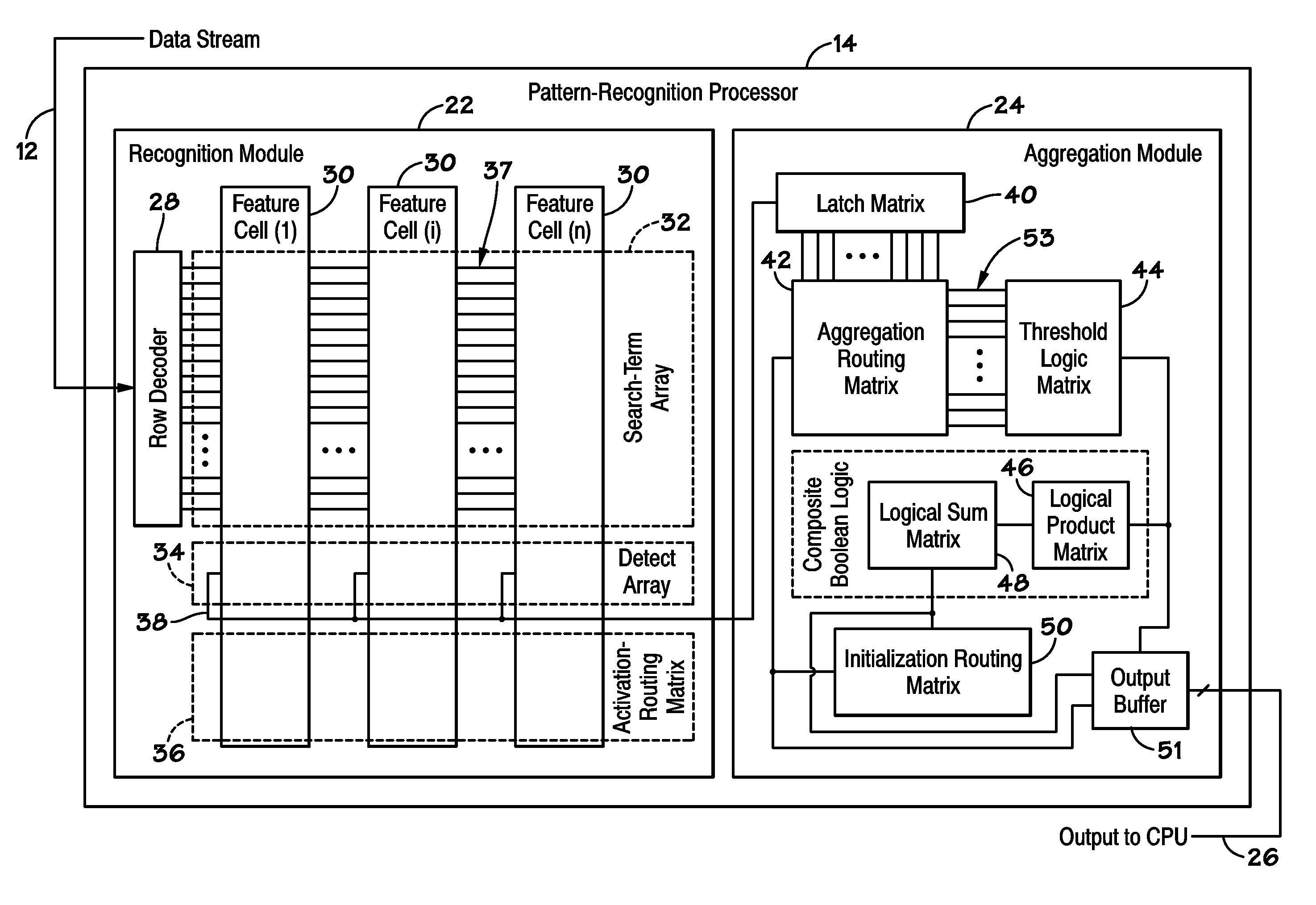

Indirect Register Access Method and System

ActiveUS20100100691A1Memory architecture accessing/allocationRegister arrangementsAccess methodProcessor register

Owner:MICRON TECH INC

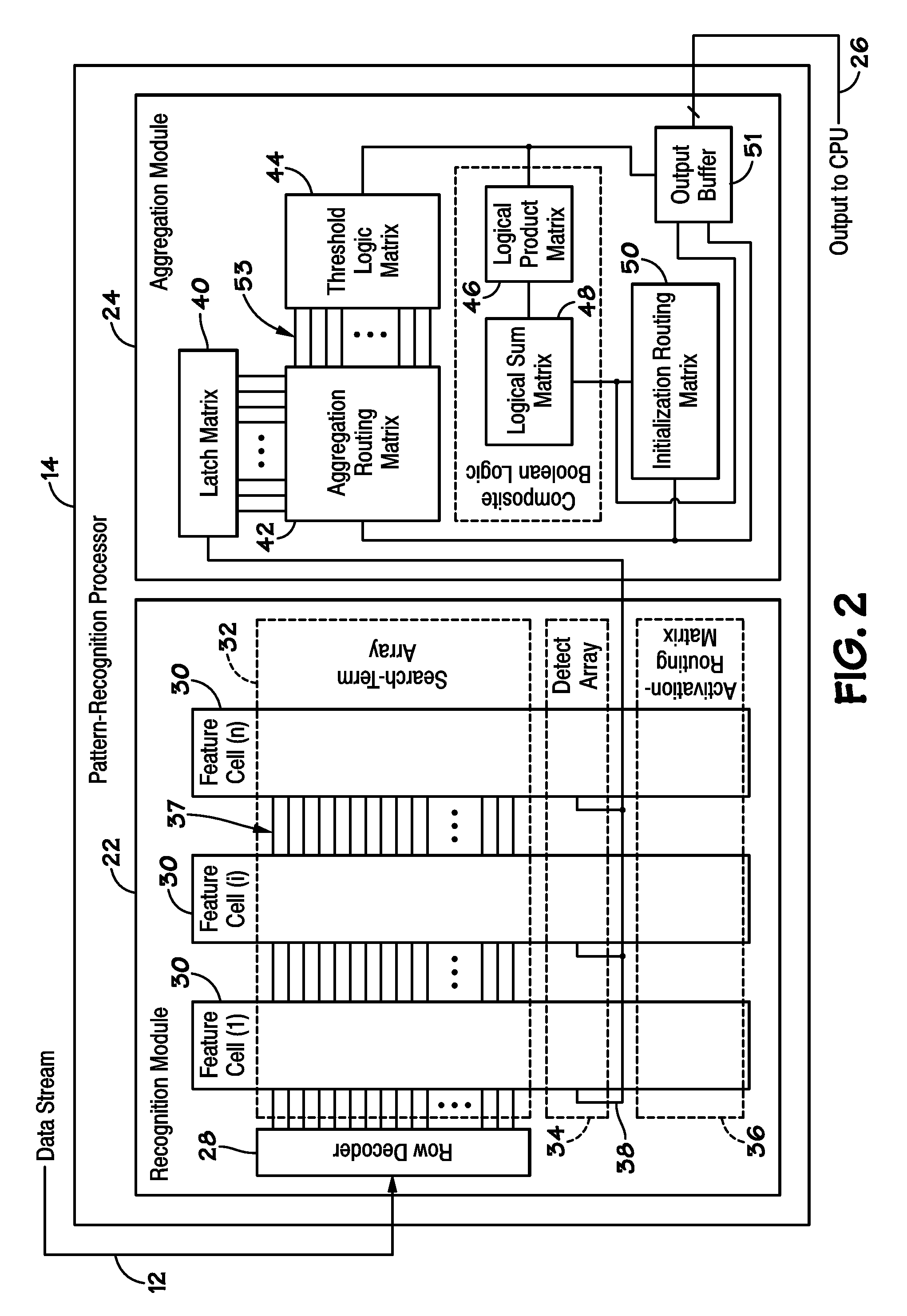

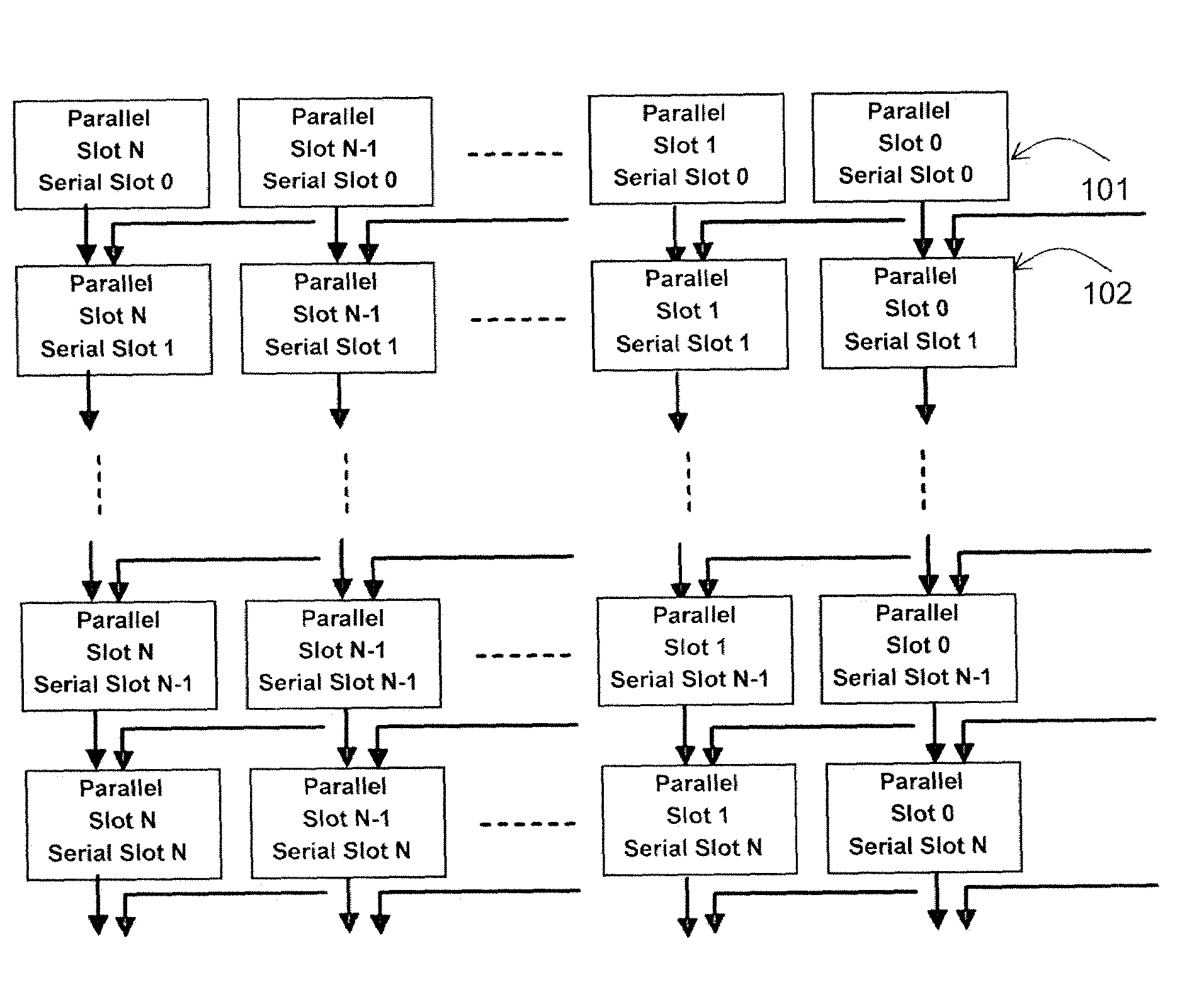

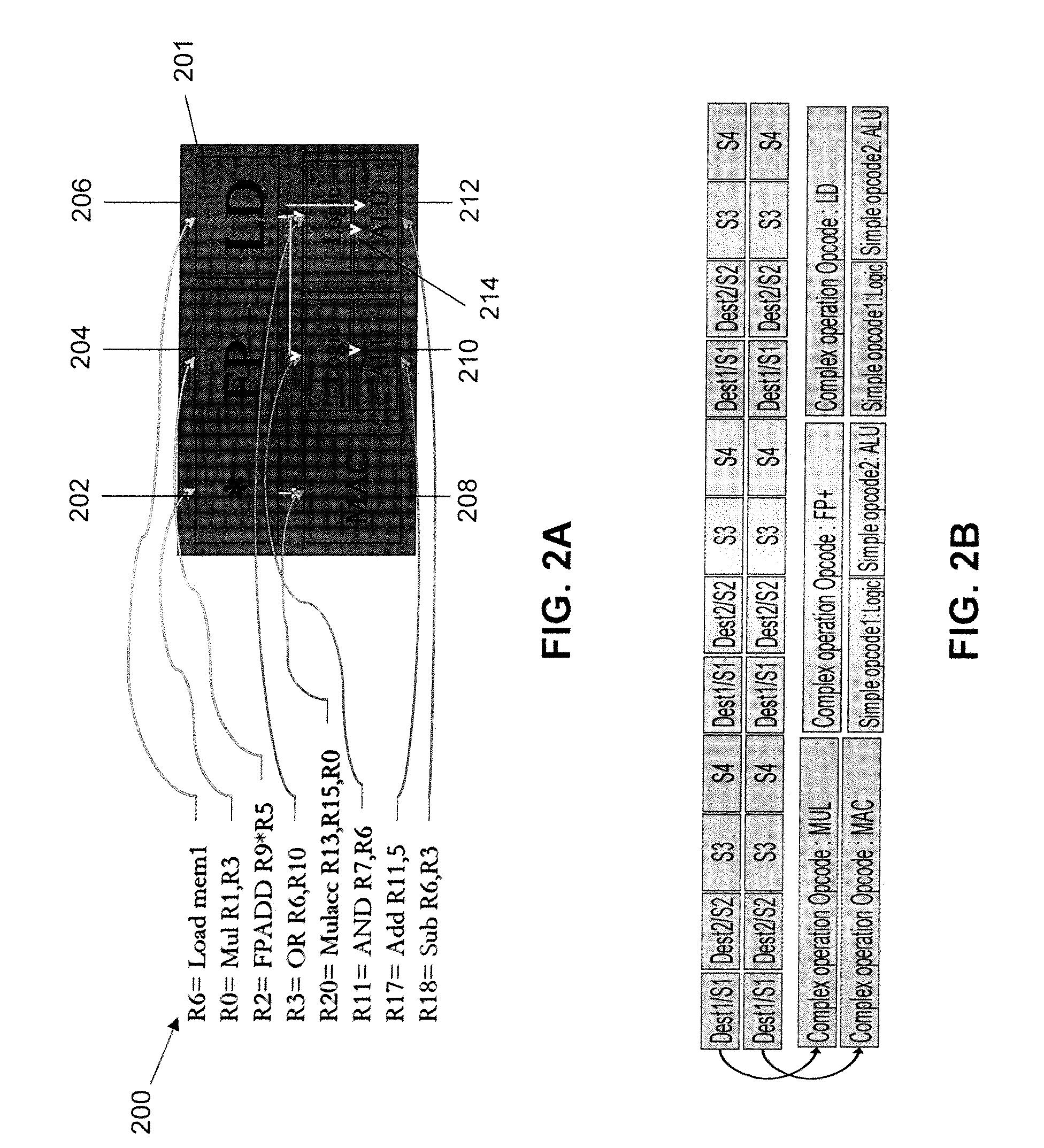

Apparatus and Method for Processing an Instruction Matrix Specifying Parallel and Dependent Operations

ActiveUS20090113170A1Single instruction multiple data multiprocessorsRegister arrangementsParallel computingMatrix manipulation

Owner:INTEL CORP

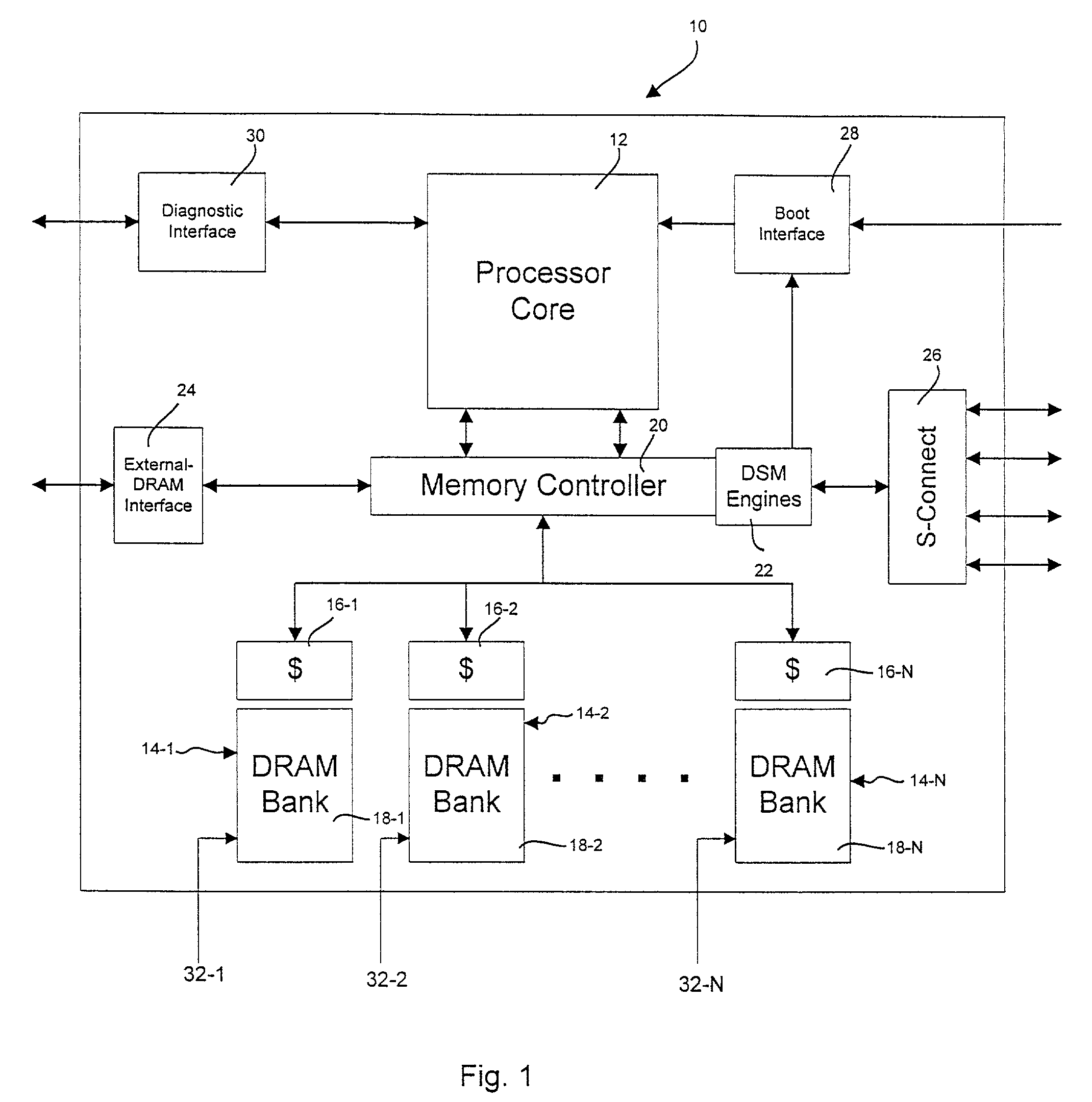

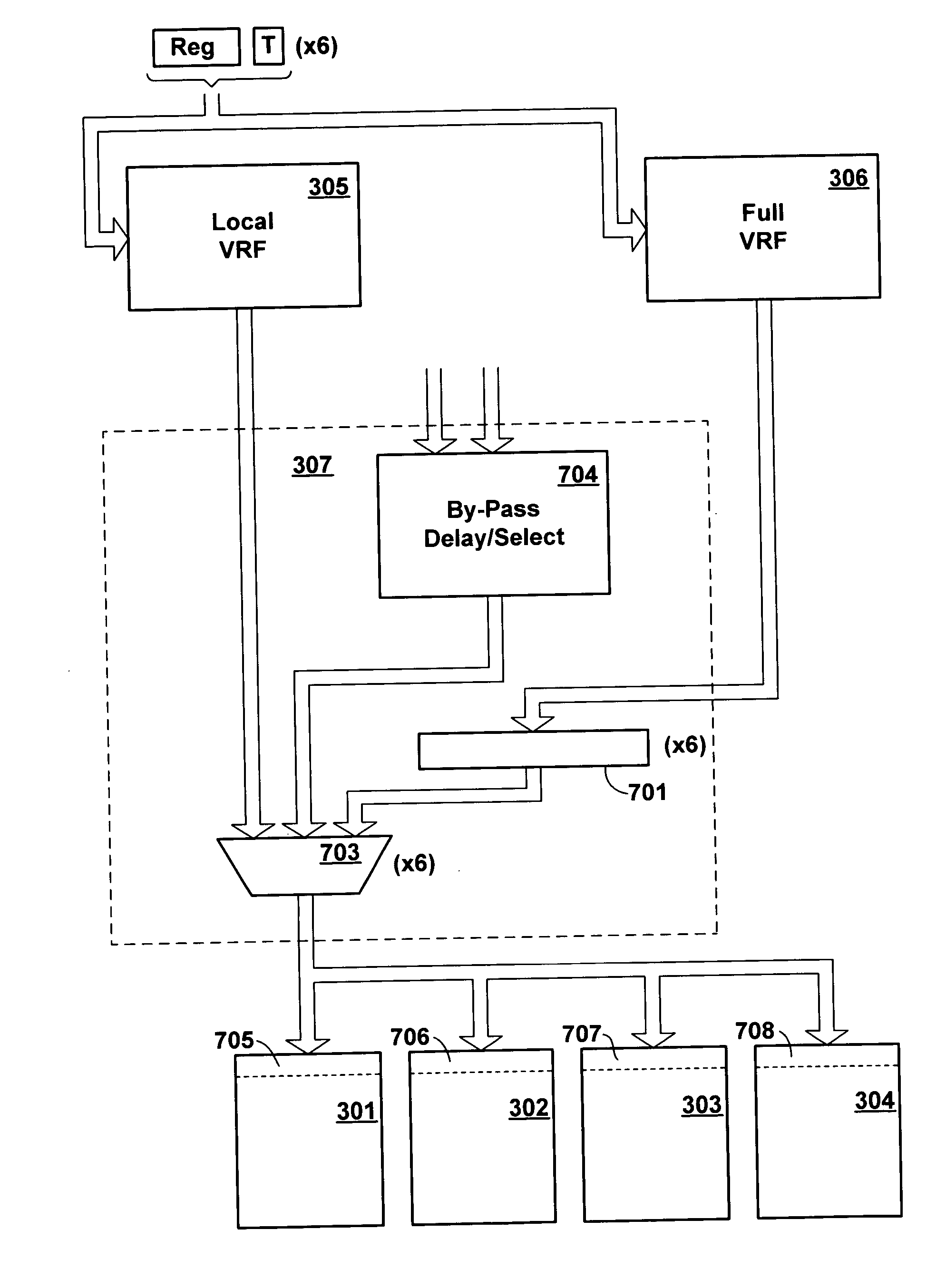

Digital data processing apparatus having multi-level register file

InactiveUS20050289299A1Faster access latency timeSlow access latency timeRegister arrangementsMemory adressing/allocation/relocationDigital dataMemory bank

Owner:IBM CORP

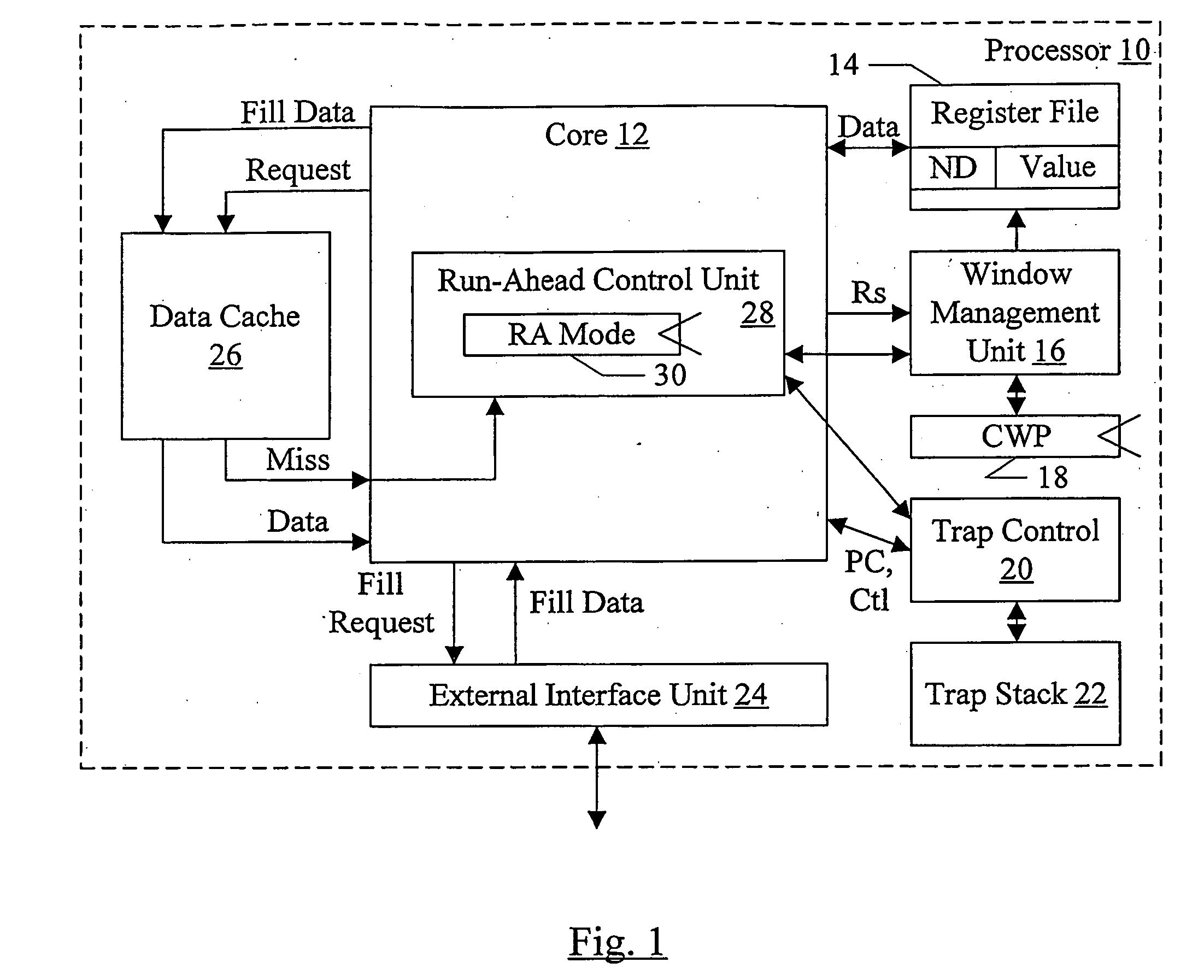

Using windowed register file to checkpoint register state

InactiveUS20080016325A1Register arrangementsDigital computer detailsSpeculative executionManagement unit

Owner:SUN MICROSYSTEMS INC

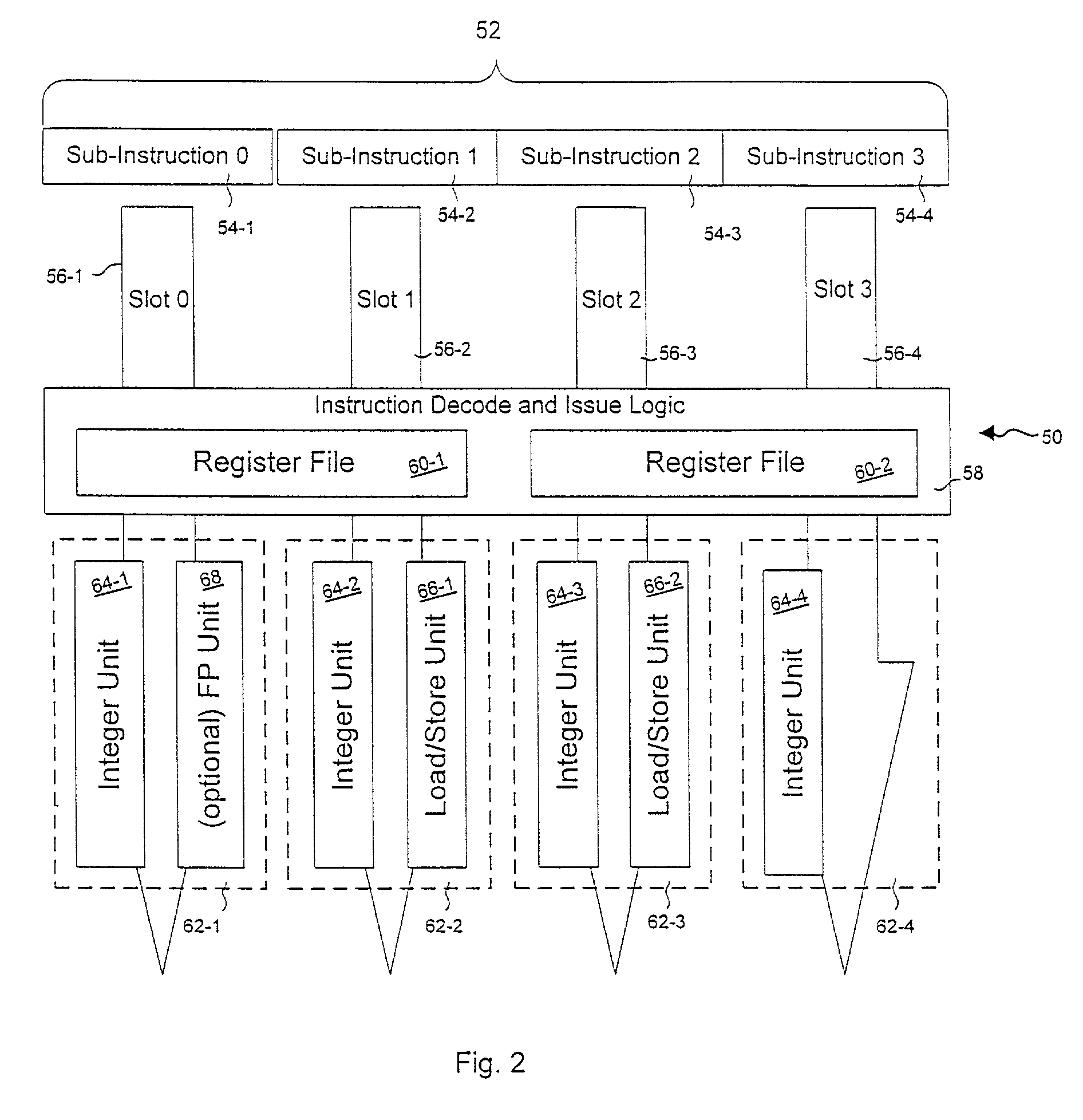

Local and global register partitioning in a vliw processor

InactiveUS20010042190A1Register arrangementsDigital computer detailsProcessor registerVery long instruction word

Owner:ORACLE INT CORP

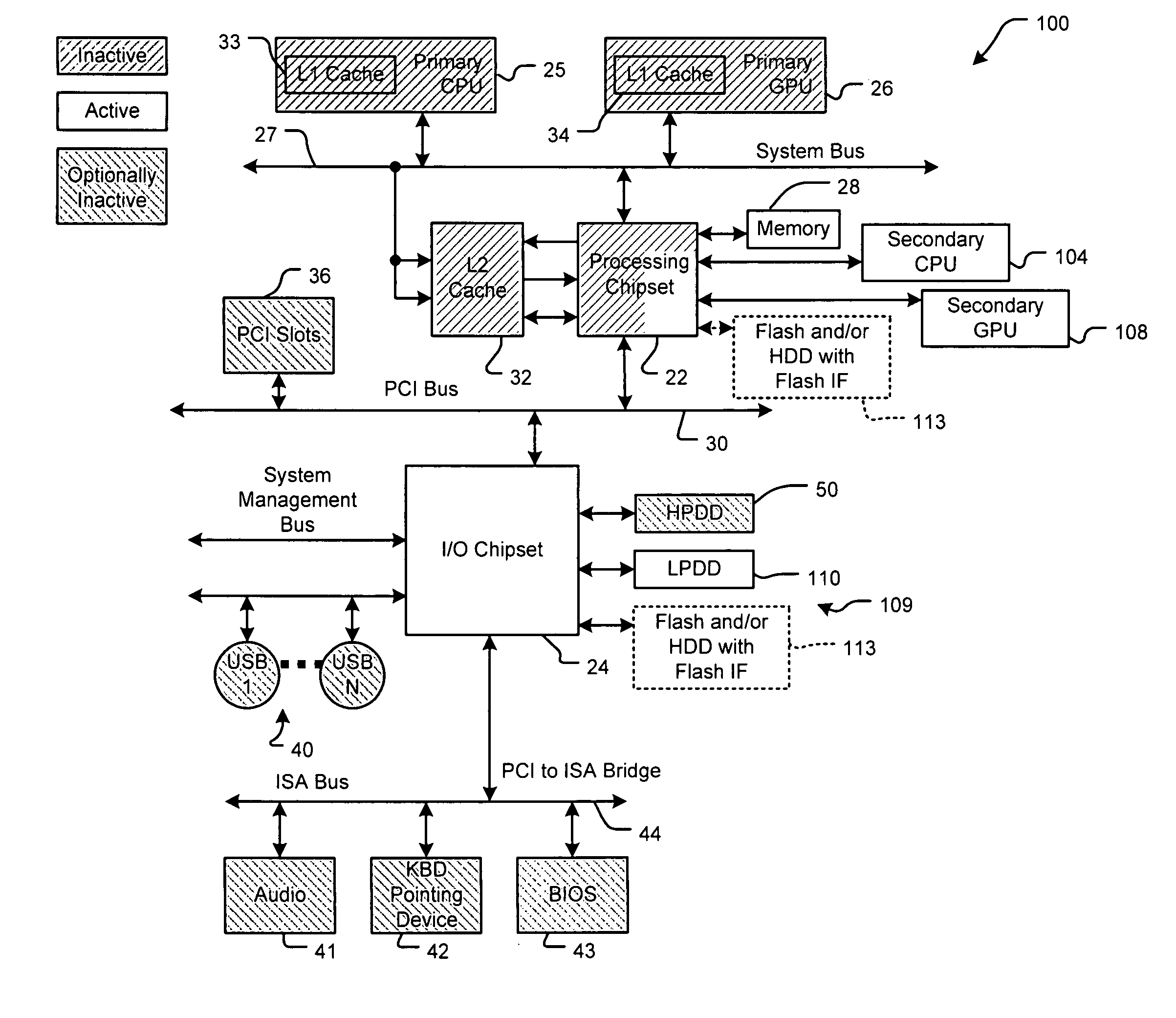

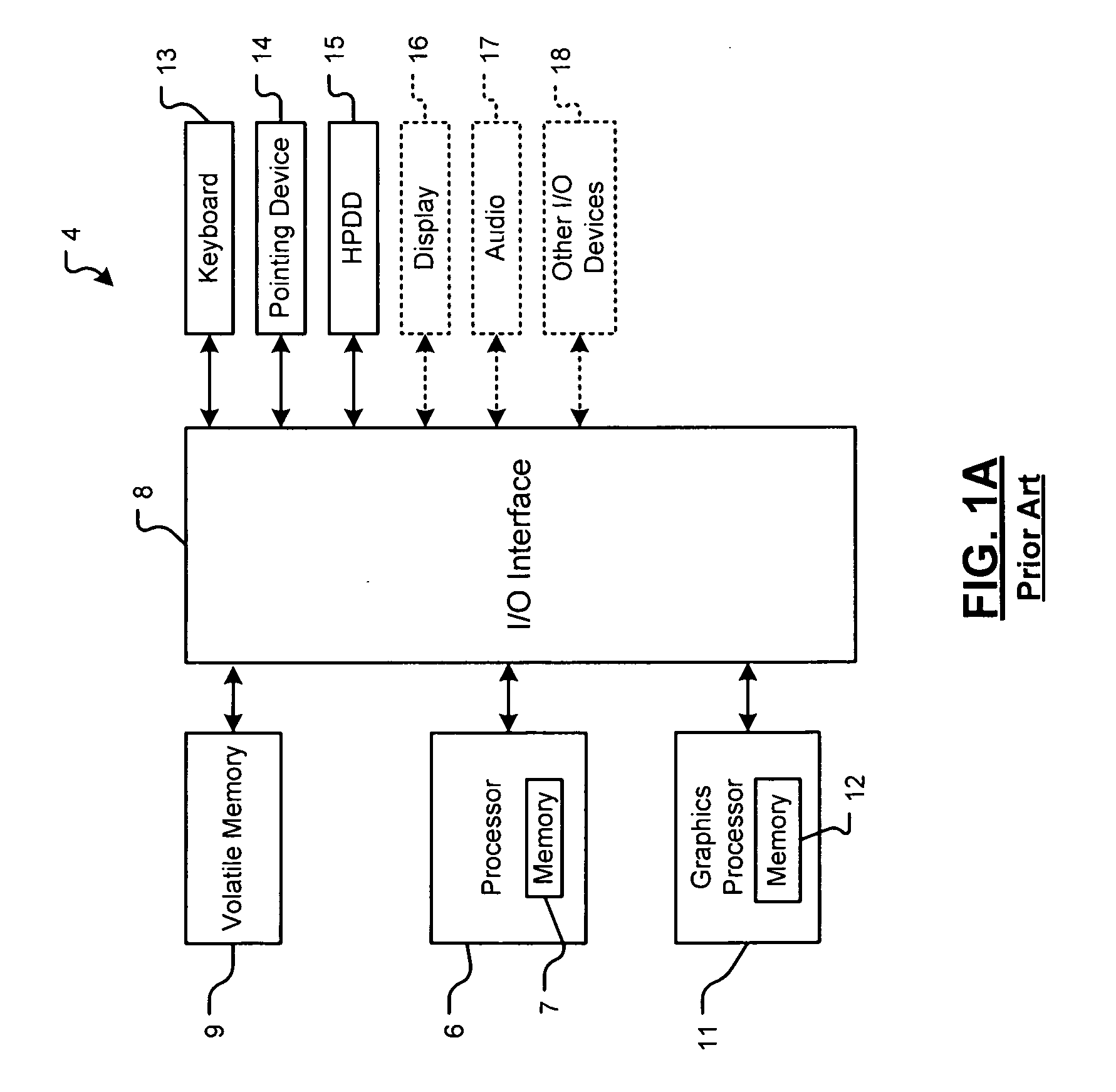

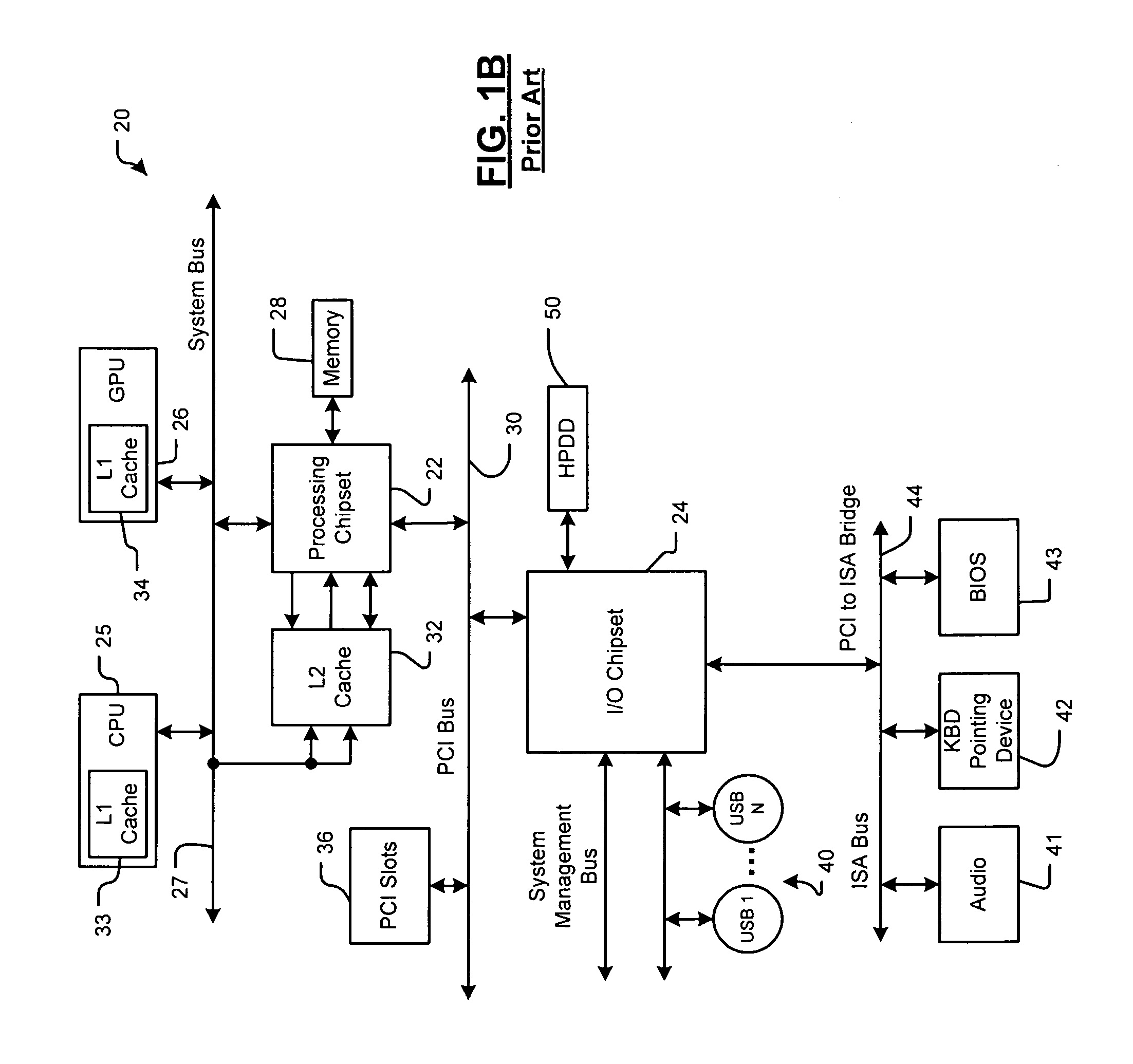

System with high power and low power processors and thread transfer

Owner:SUTARDJA SEHAT

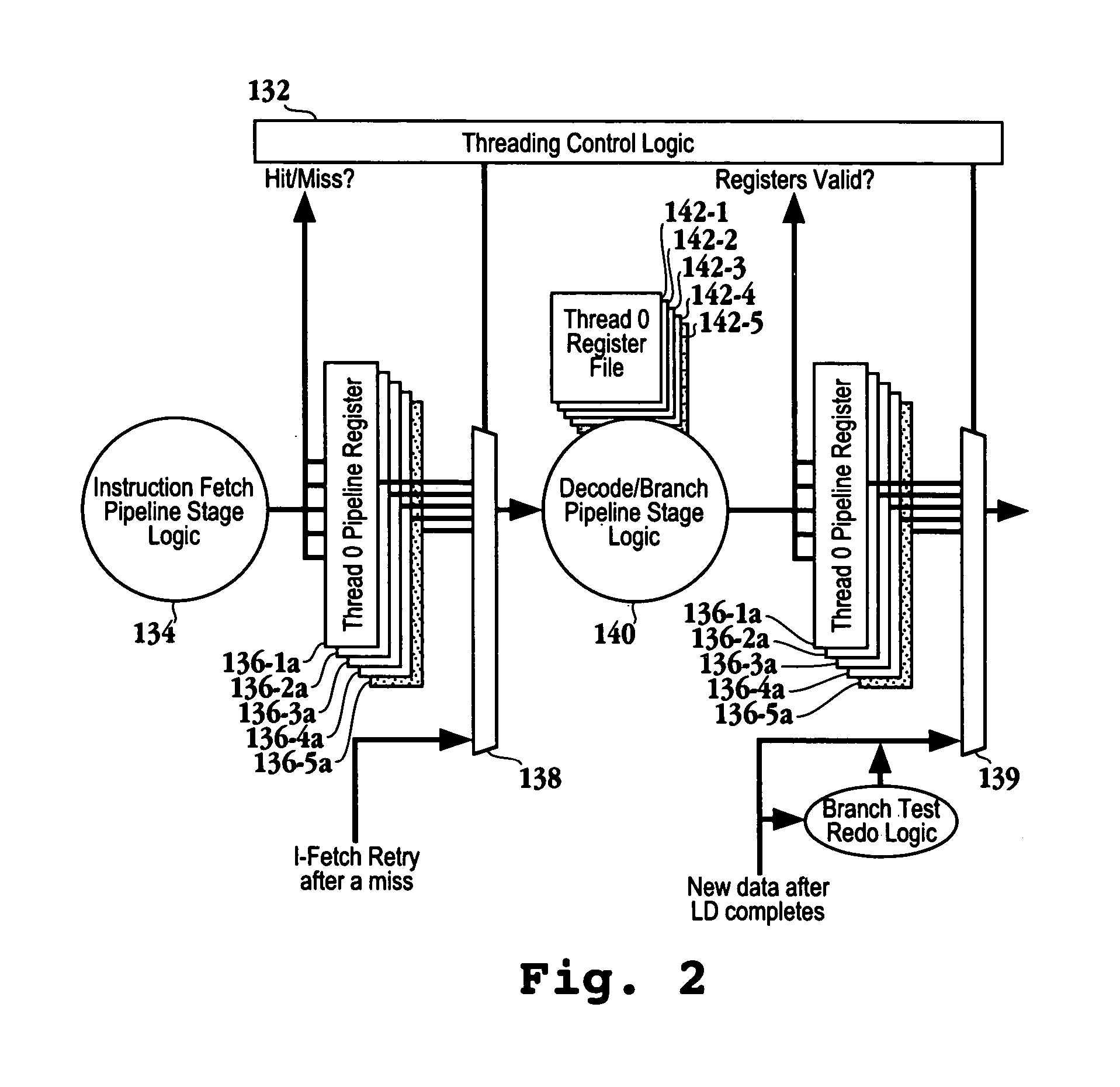

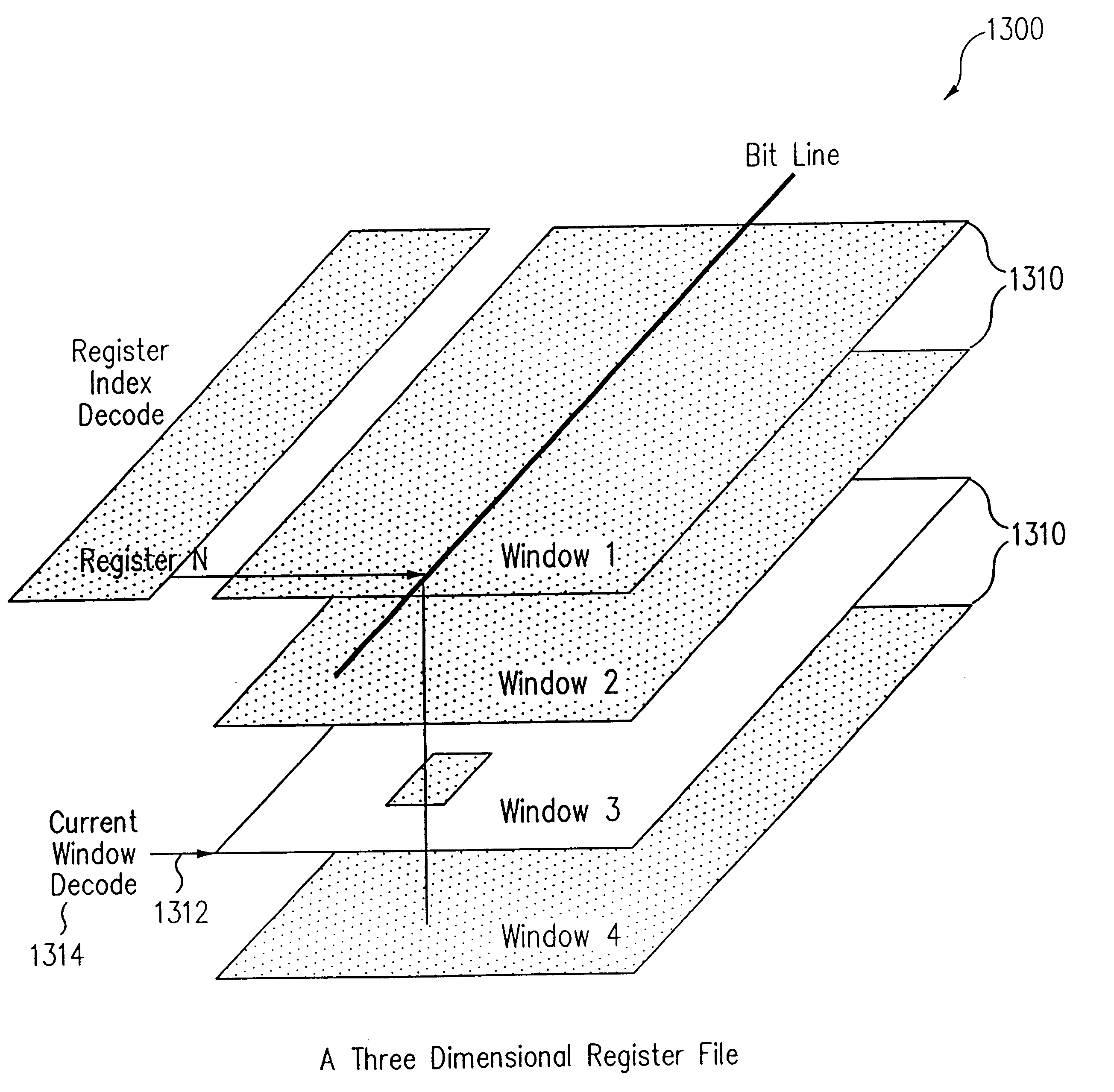

Vertically and horizontally threaded processor with multidimensional storage for storing thread data

InactiveUS6351808B1Register arrangementsDigital computer detailsMultidimensional scalingProcessor register

Owner:ORACLE INT CORP

System and Method of Indirect Register Access

ActiveUS20100100714A1Register arrangementsDigital computer detailsProcessor registerComputer science

Owner:MICRON TECH INC

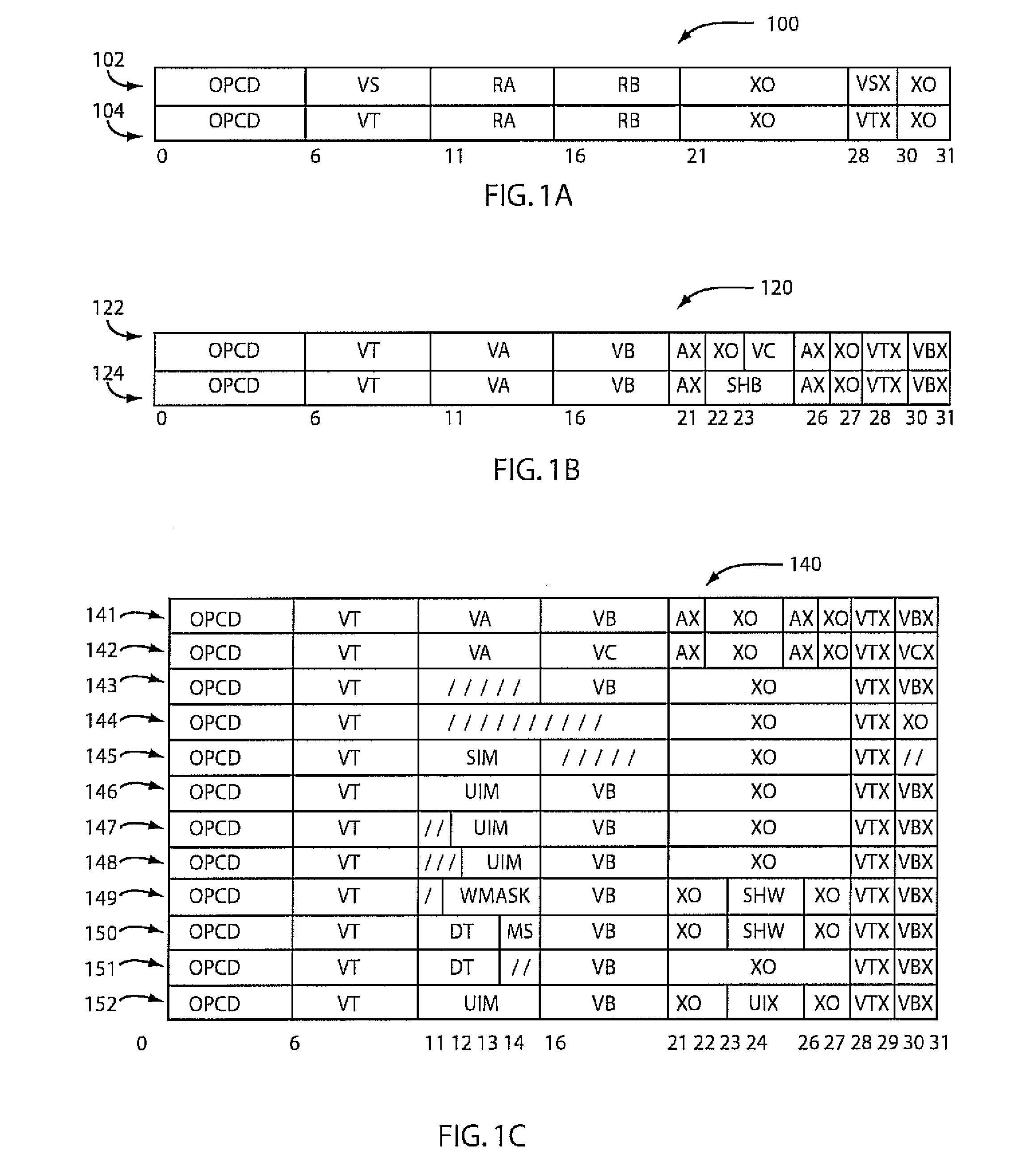

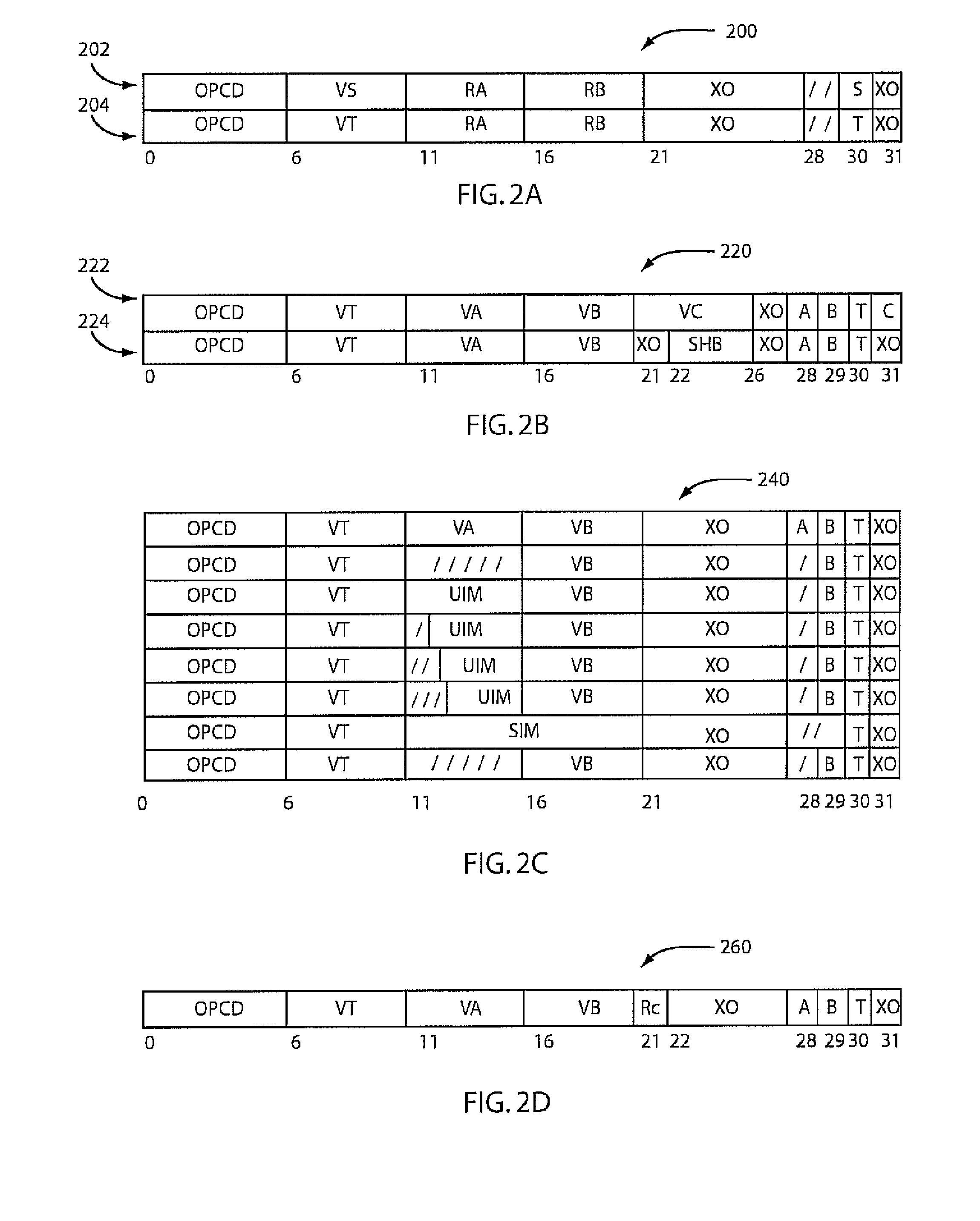

Implementing instruction set architectures with non-contiguous register file specifiers

ActiveUS20080189519A1Register arrangementsInstruction analysisProcessing InstructionProcessor register

Owner:INT BUSINESS MASCH CORP

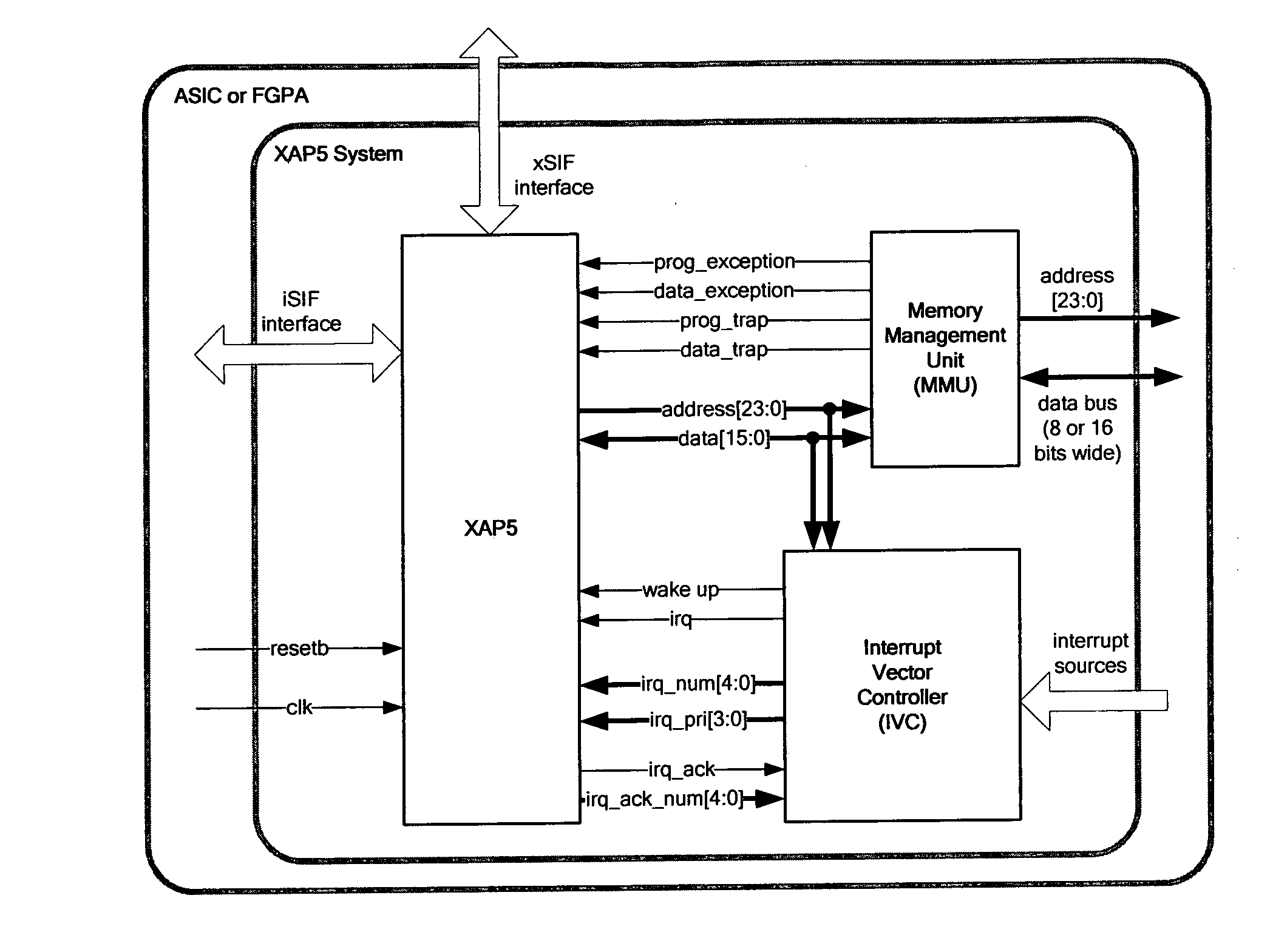

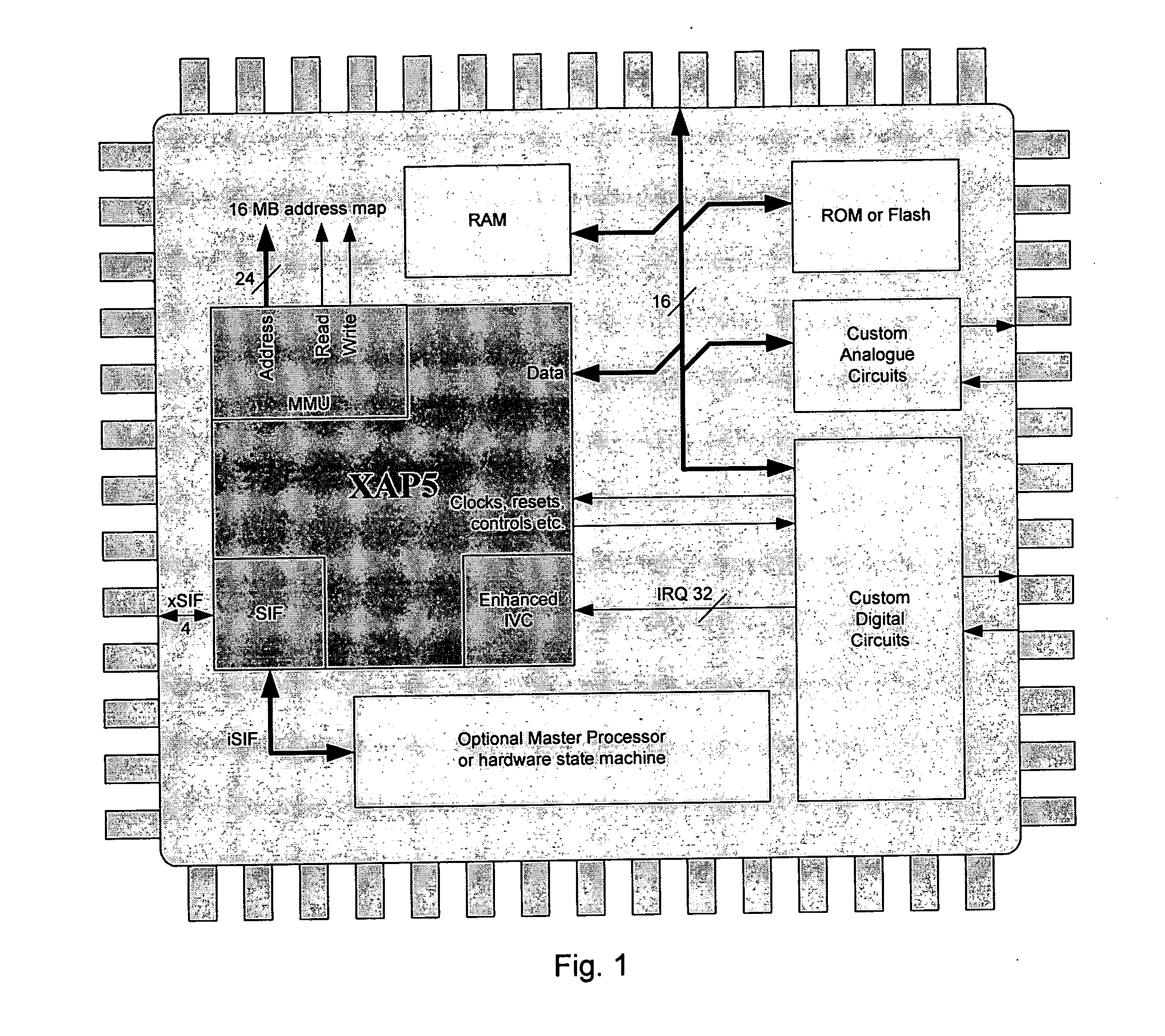

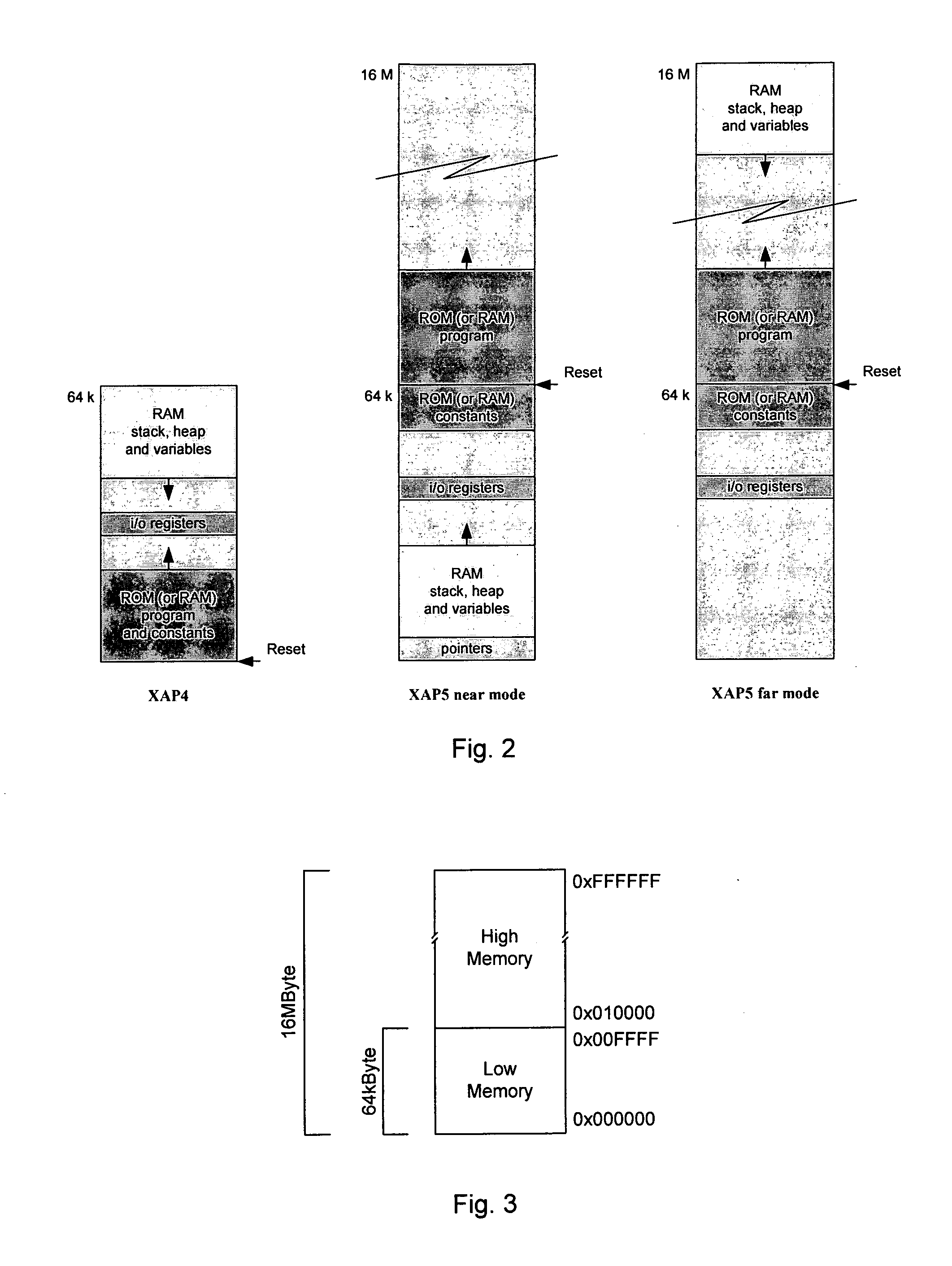

Data processing apparatus

ActiveUS20100293342A1Simple structureSmall spacingConditional code generationRegister arrangementsInstruction setContent-addressable memory

Owner:CAMBRIDGE CONSULTANTS LTD

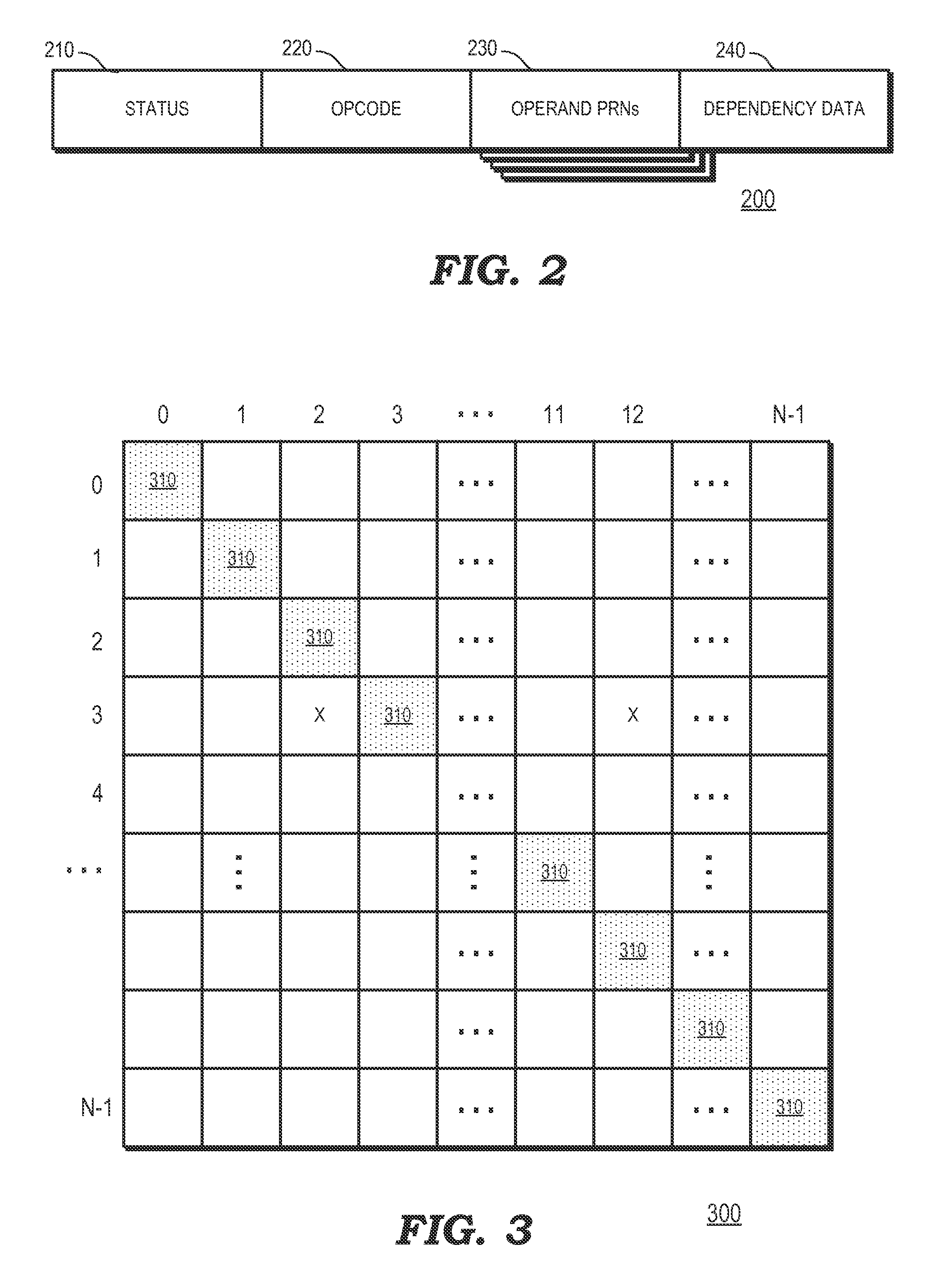

Dependent instruction suppression

ActiveUS20140380024A1Register arrangementsDigital computer detailsDependency informationLoad instruction

A method includes suppressing execution of at least one dependent instruction of a load instruction by a processor using stored dependency information responsive to an invalid status of the load instruction. A processor includes an execution unit to execute instructions and a scheduler. The scheduler is to select for execution in the execution unit a load instruction having at least one dependent instruction and suppress execution of the at least one dependent instruction using stored dependency information responsive to an invalid status of the load instruction.

Owner:ADVANCED MICRO DEVICES INC

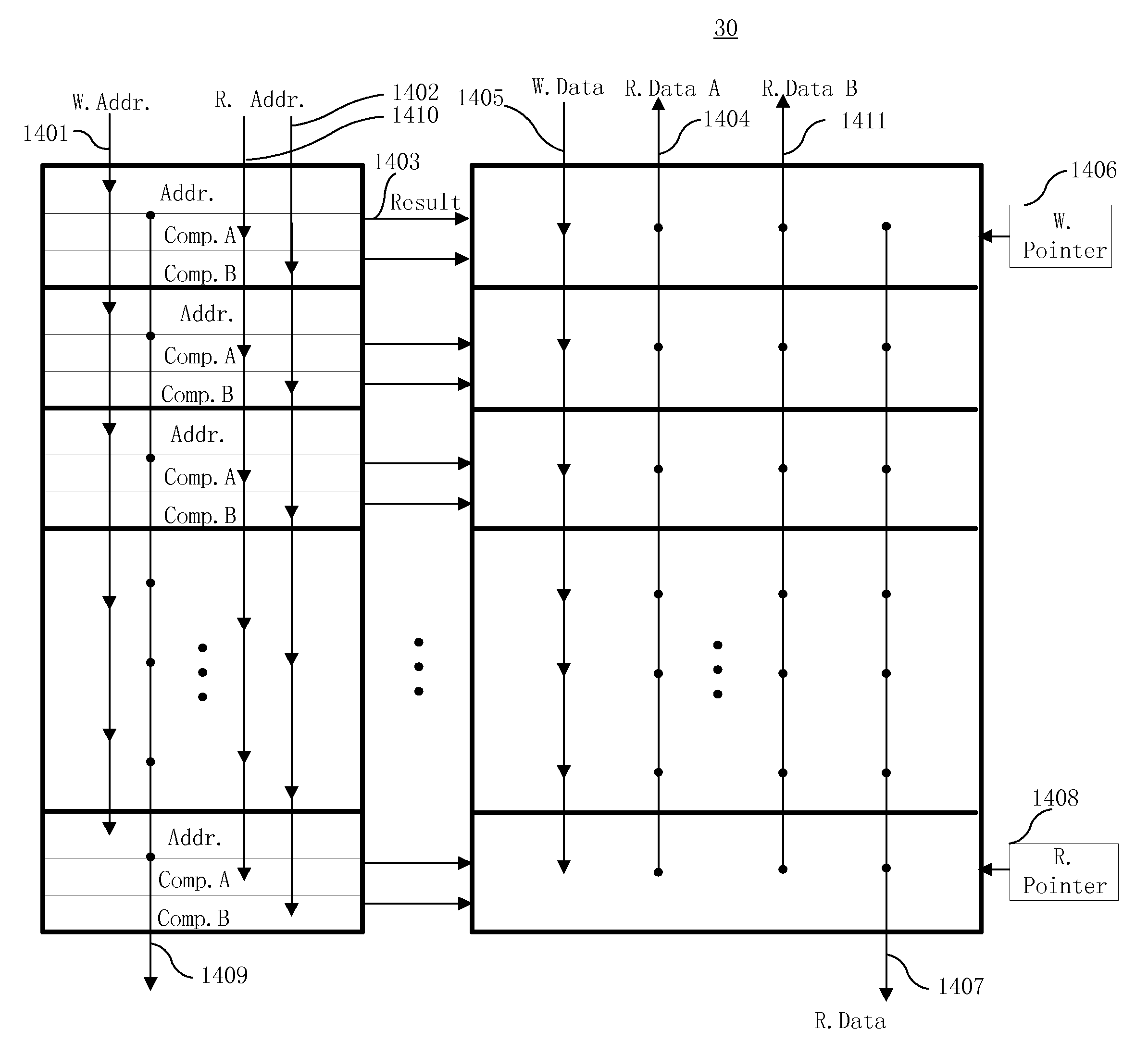

Memory mapped register file and method for accessing the same

InactiveUS7558942B1Register arrangementsGeneral purpose stored program computerData processing systemProcessing Instruction

Owner:MARVELL ASIA PTE LTD

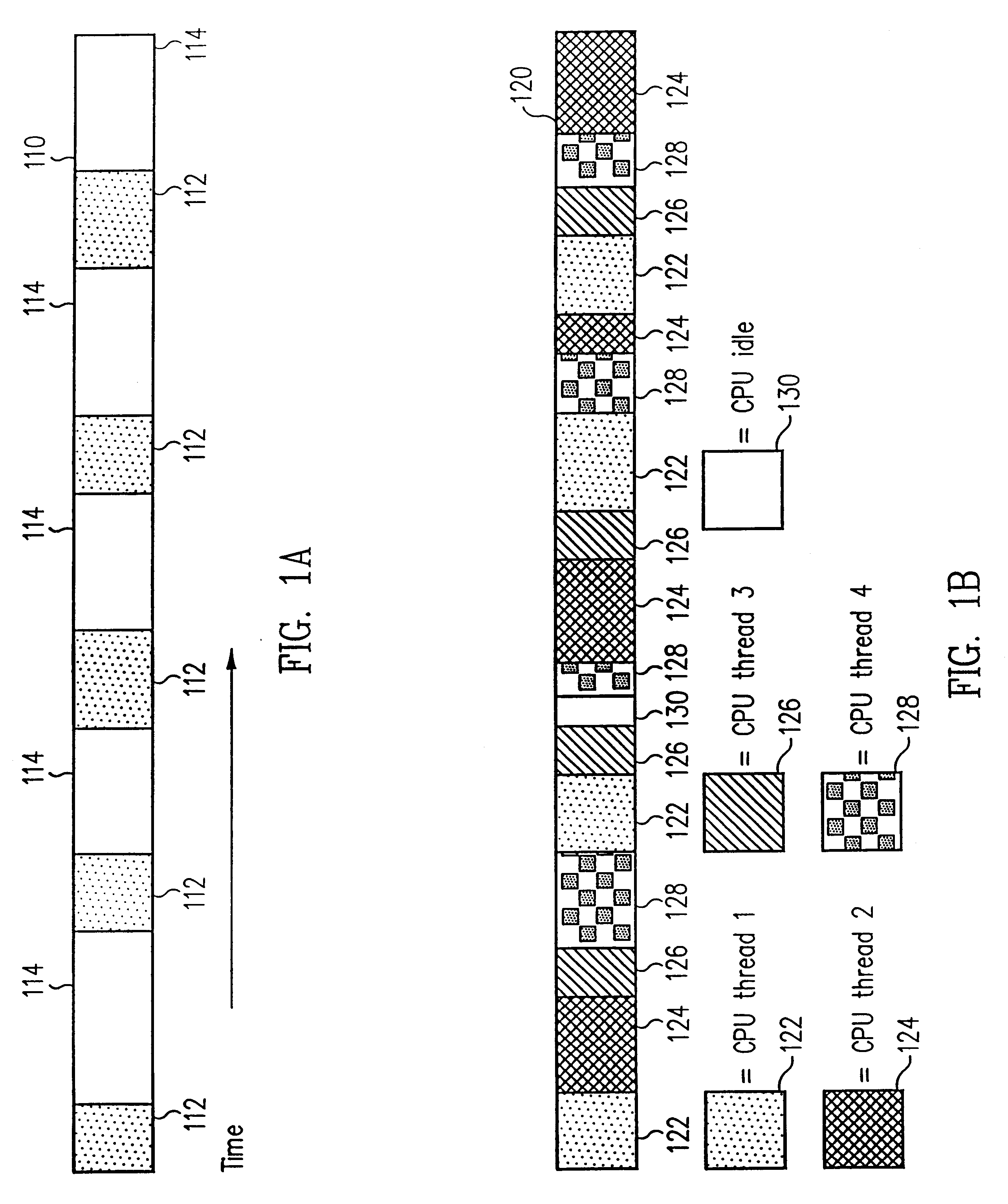

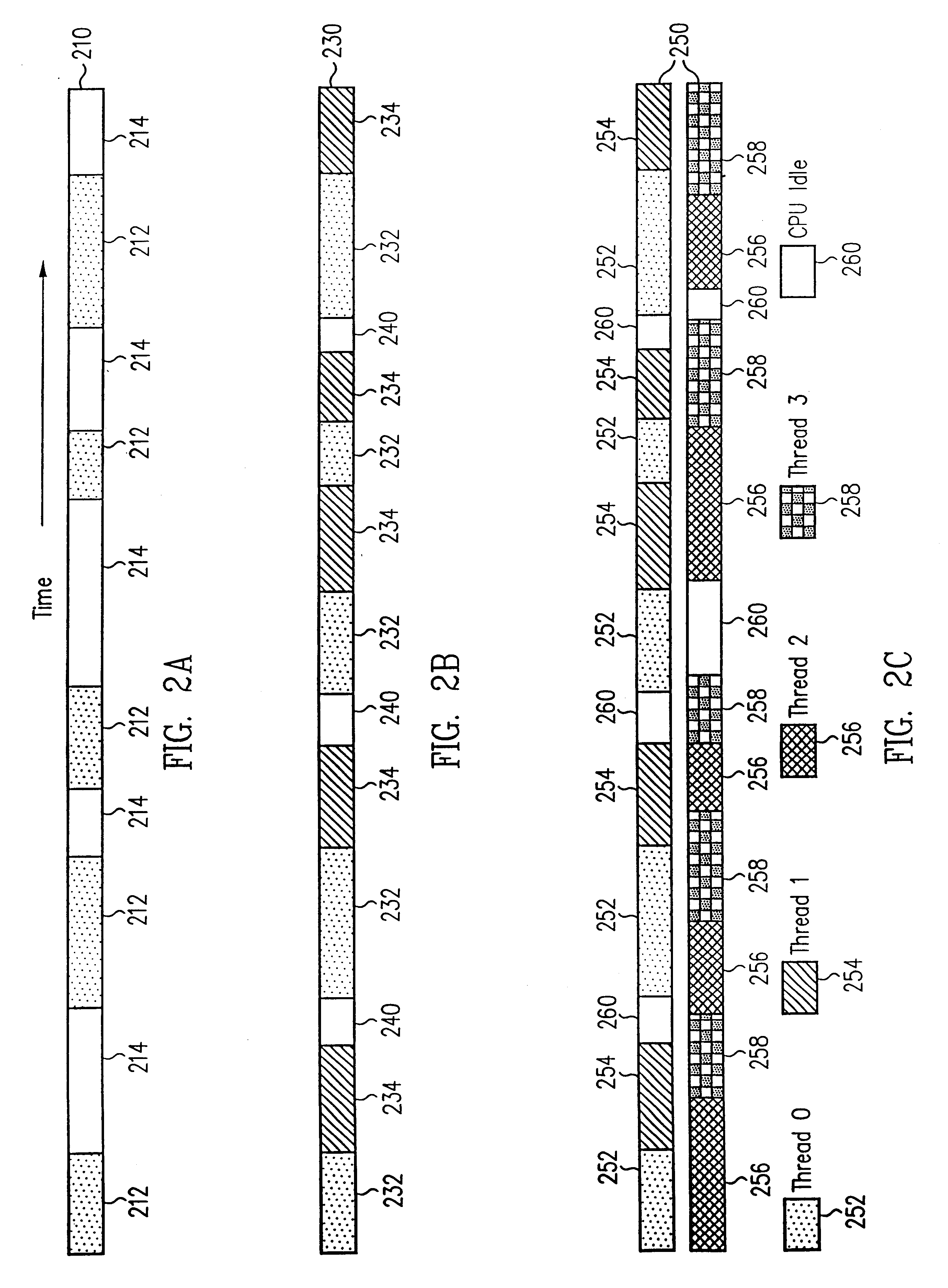

Method and appratus for power throttling in a multi-thread processor

ActiveUS20060020831A1Save powerRegister arrangementsVolume/mass flow measurementControl powerParallel computing

A method and apparatus for controlling power consumption in a processor. In one embodiment, a processor includes a pipeline. The pipeline includes logic for fetching instructions, issuing instructions, and executing instructions. The processor also includes a power management unit. The power management unit is configured to input M stalls into the pipeline every N instruction cycles (where M and N are integer value and wherein M is less than N).

Owner:SUN MICROSYSTEMS INC

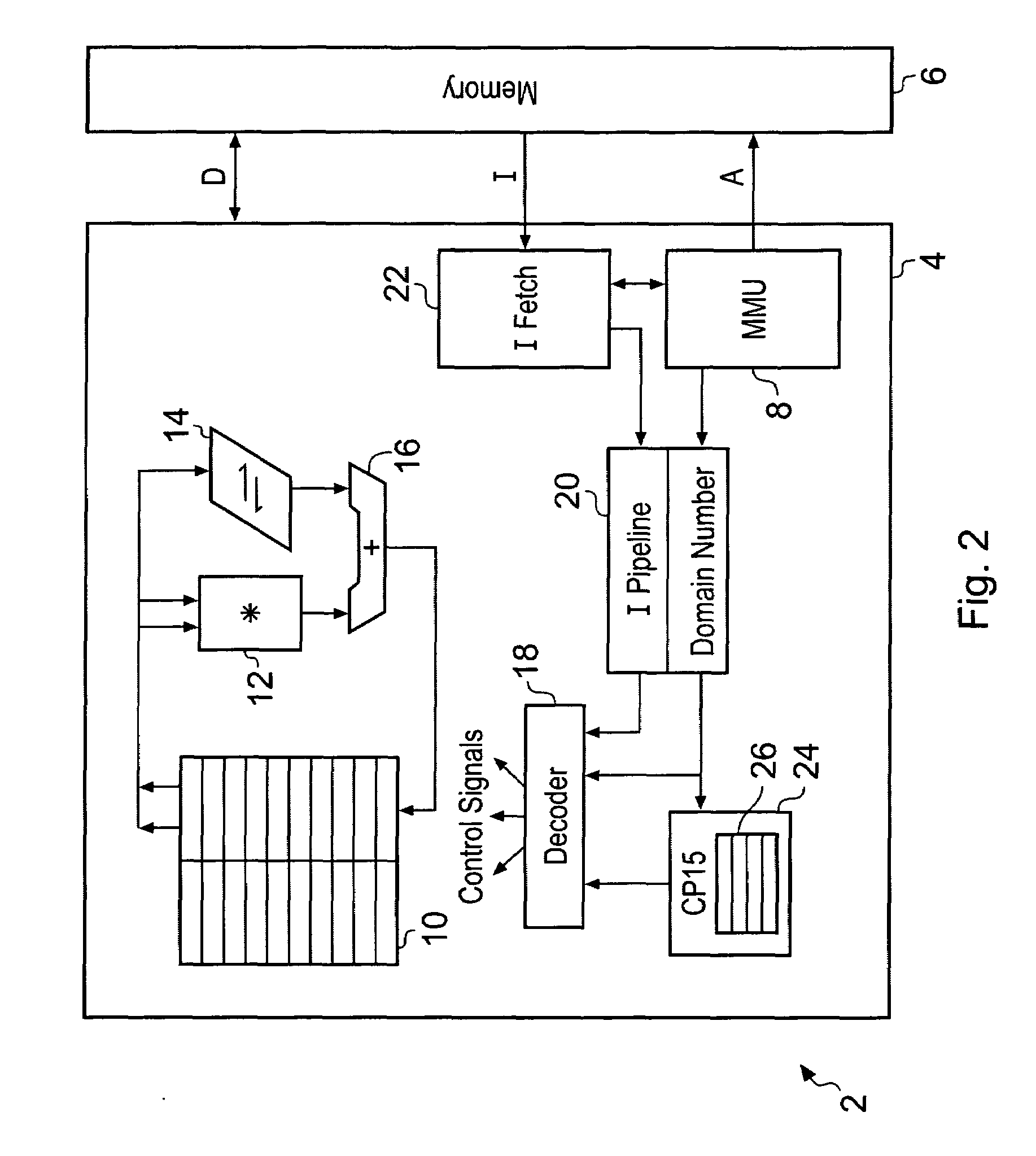

Protected function calling

ActiveUS20080250216A1Improve securityAchieve backward compatibilityMemory architecture accessing/allocationRegister arrangementsMemory addressParallel computing

Owner:ARM LTD

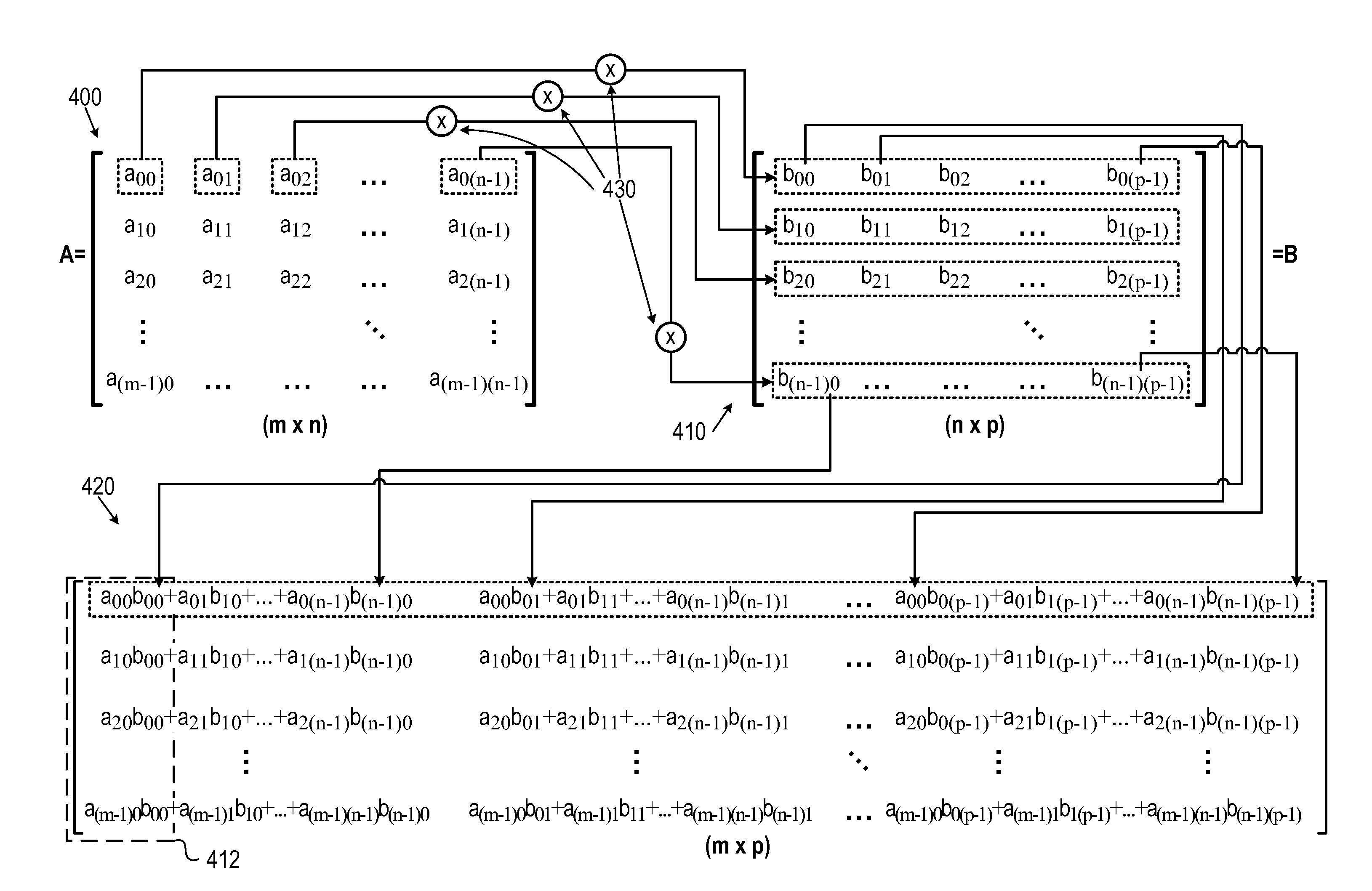

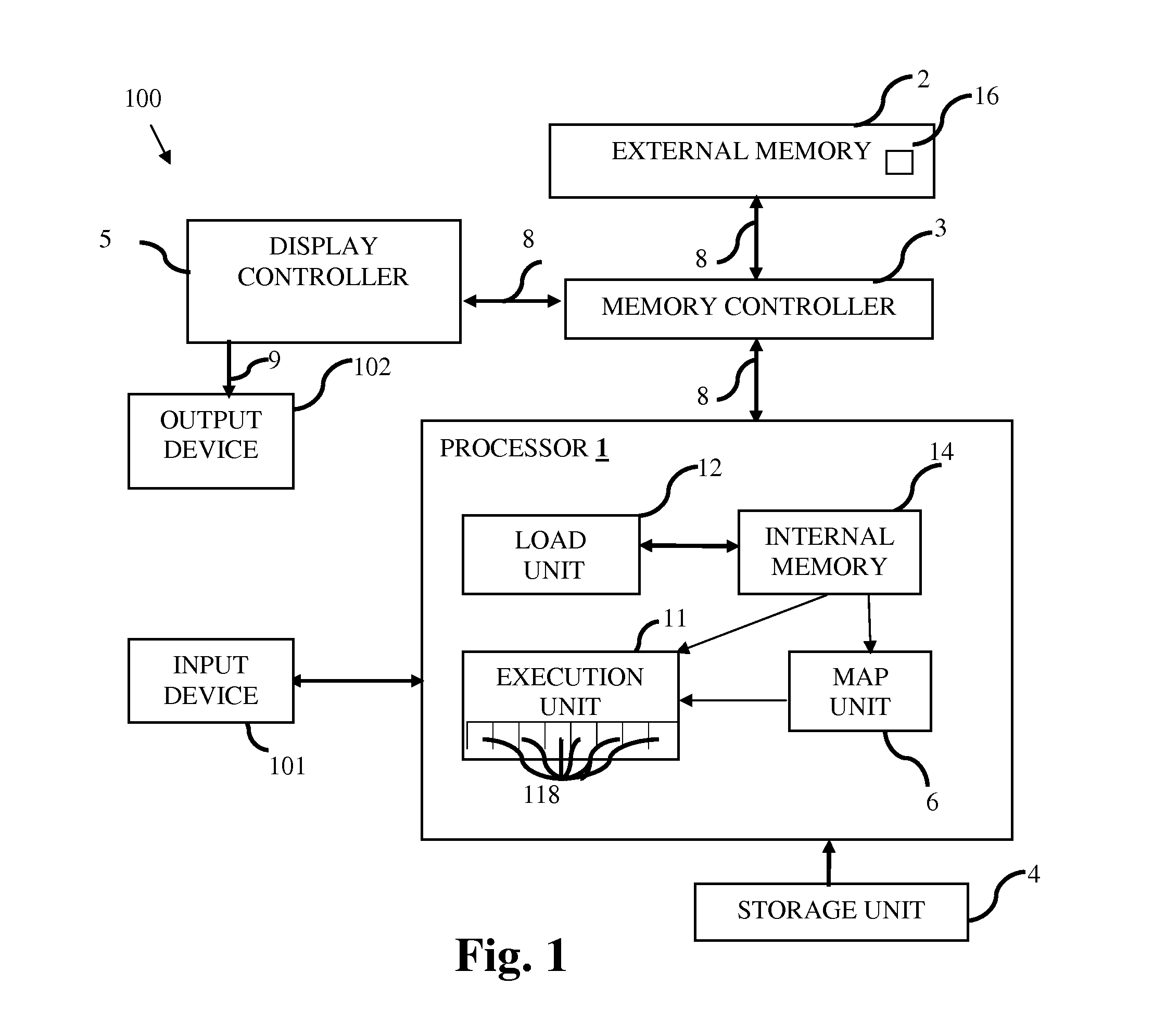

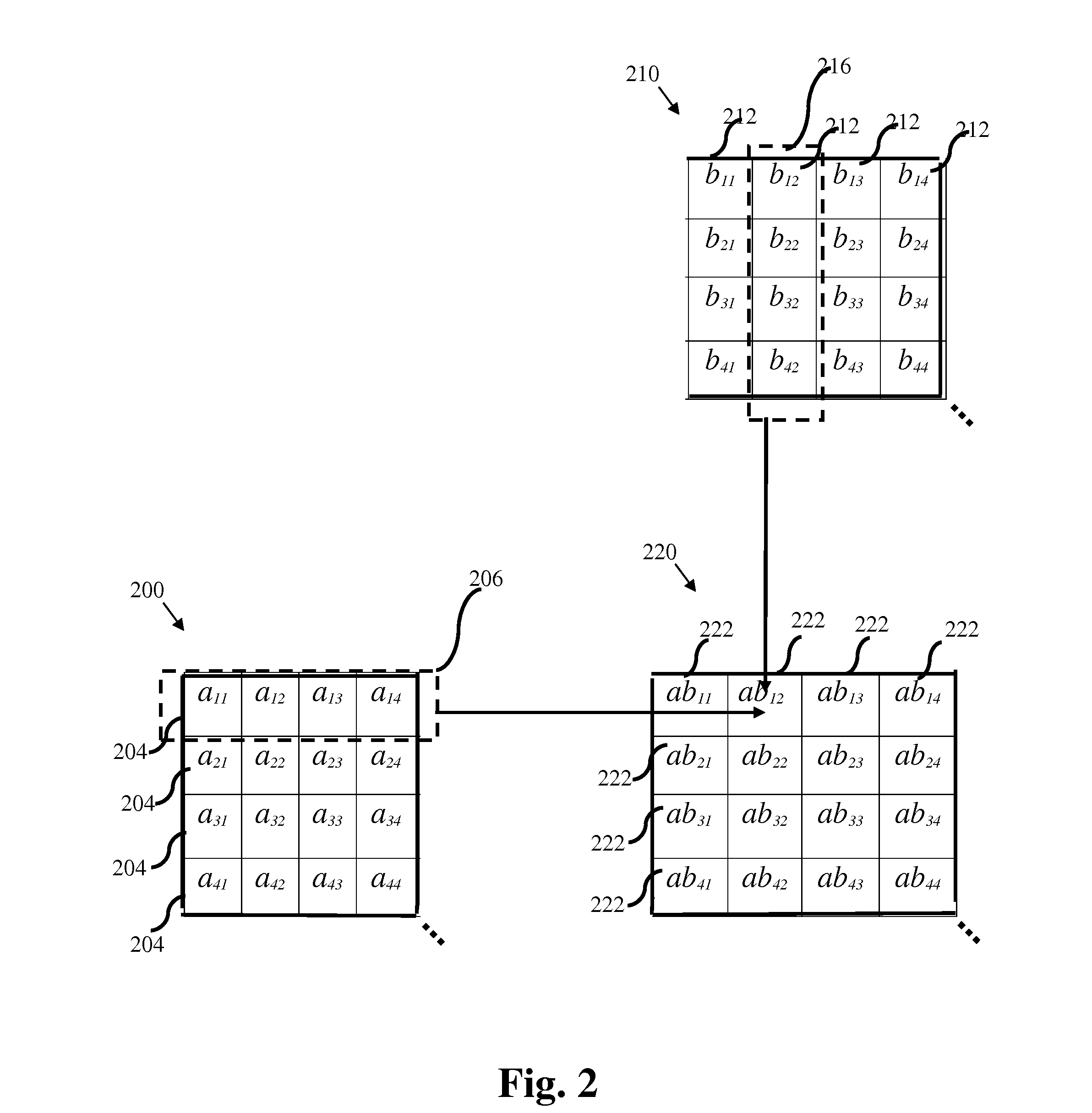

System, device, and method for multiplying multi-dimensional data arrays

InactiveUS20120113133A1Register arrangementsComputation using non-contact making devicesArray data structureSingle element

Owner:CEVA D S P LTD

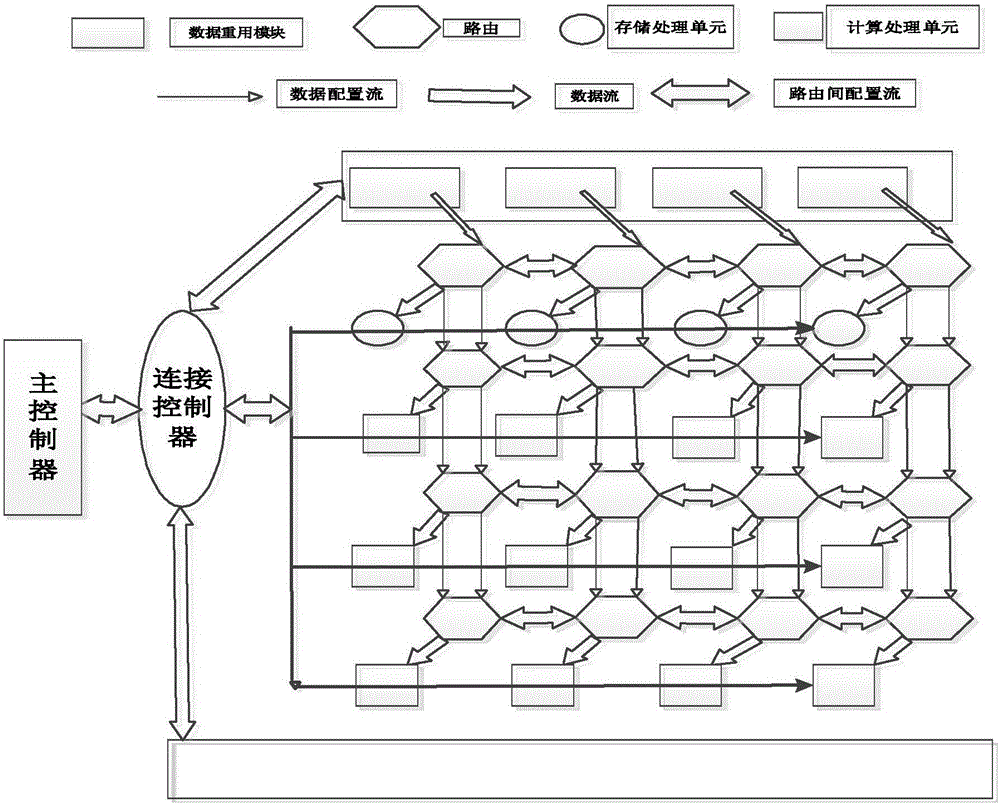

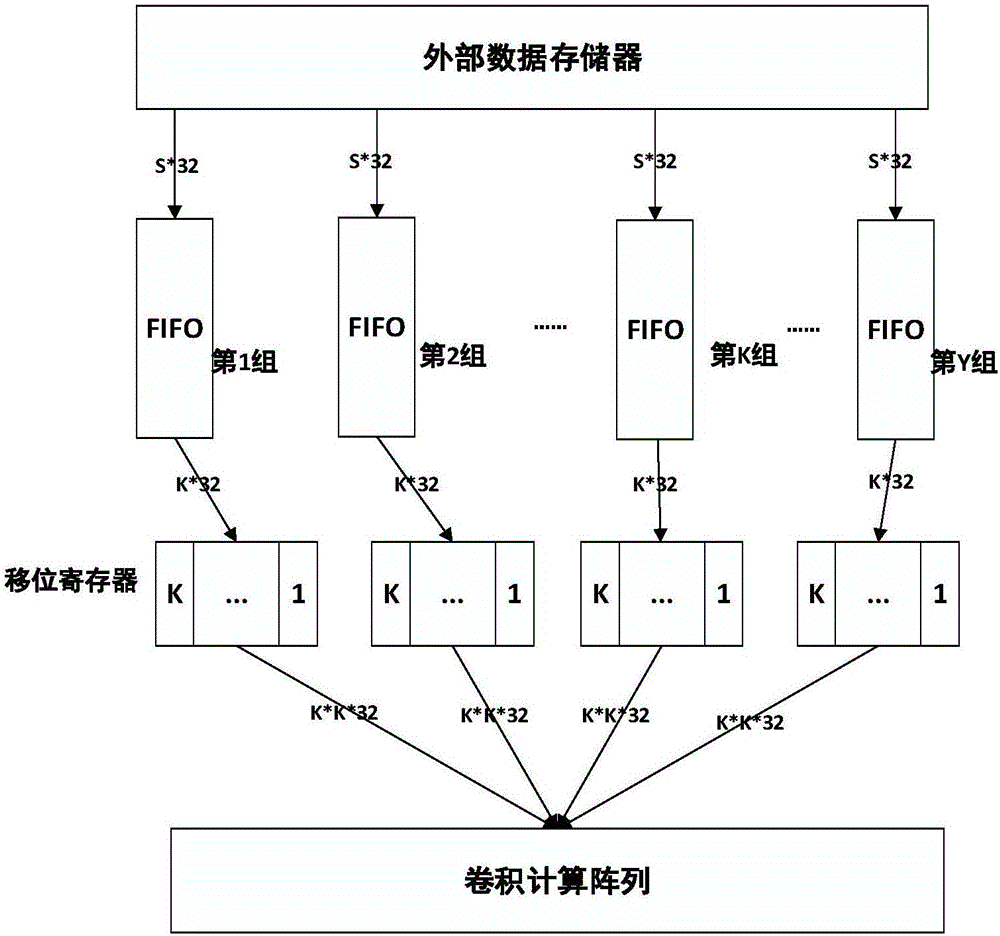

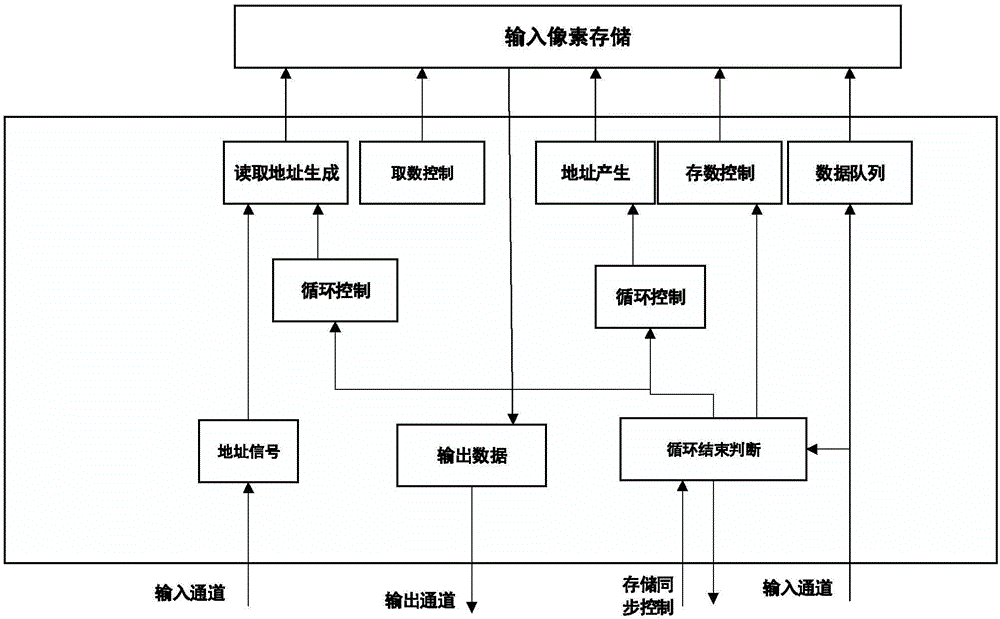

System for circular convolution calculation data reuse of convolutional neural network

InactiveCN106250103ARegister arrangementsConcurrent instruction executionProcessor registerComputation process

Owner:SOUTHEAST UNIV

Dynamically-selectable vector register partitioning

InactiveUS20100115233A1Register arrangementsProgram control using wired connectionsProcessor registerMulti processor

Owner:CONVEY COMP

Popular searches

Energy efficient computing Comparison of digital values Specific program execution arrangements Memory systems Computation using denominational number representation Handling data according to predetermined rules Current supply arrangements Number-of-one counters Next instruction address formation Power supply for data processing

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap