Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

52 results about "Wallace tree" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

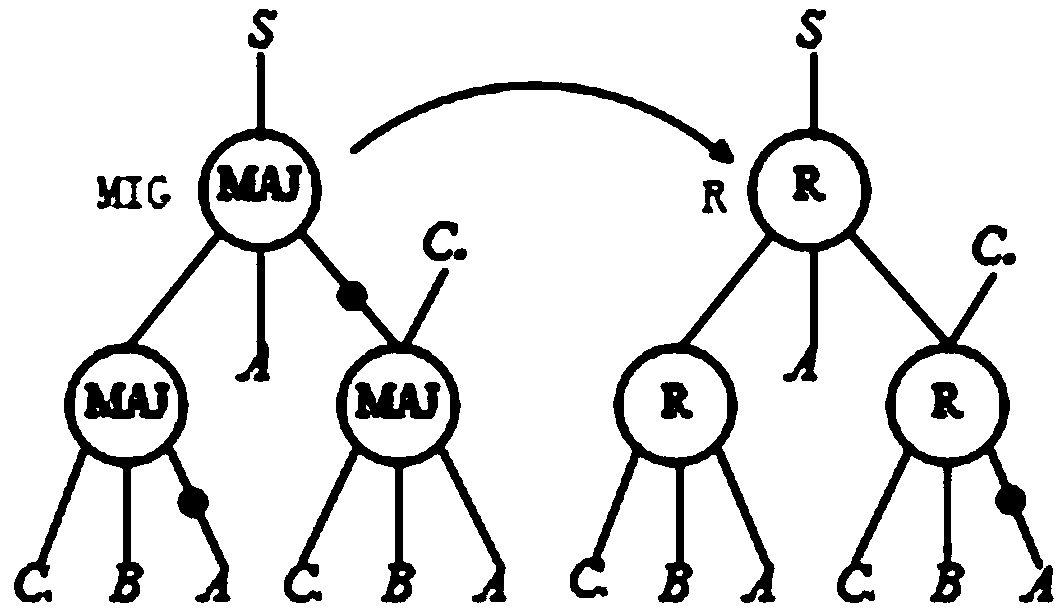

Inventor

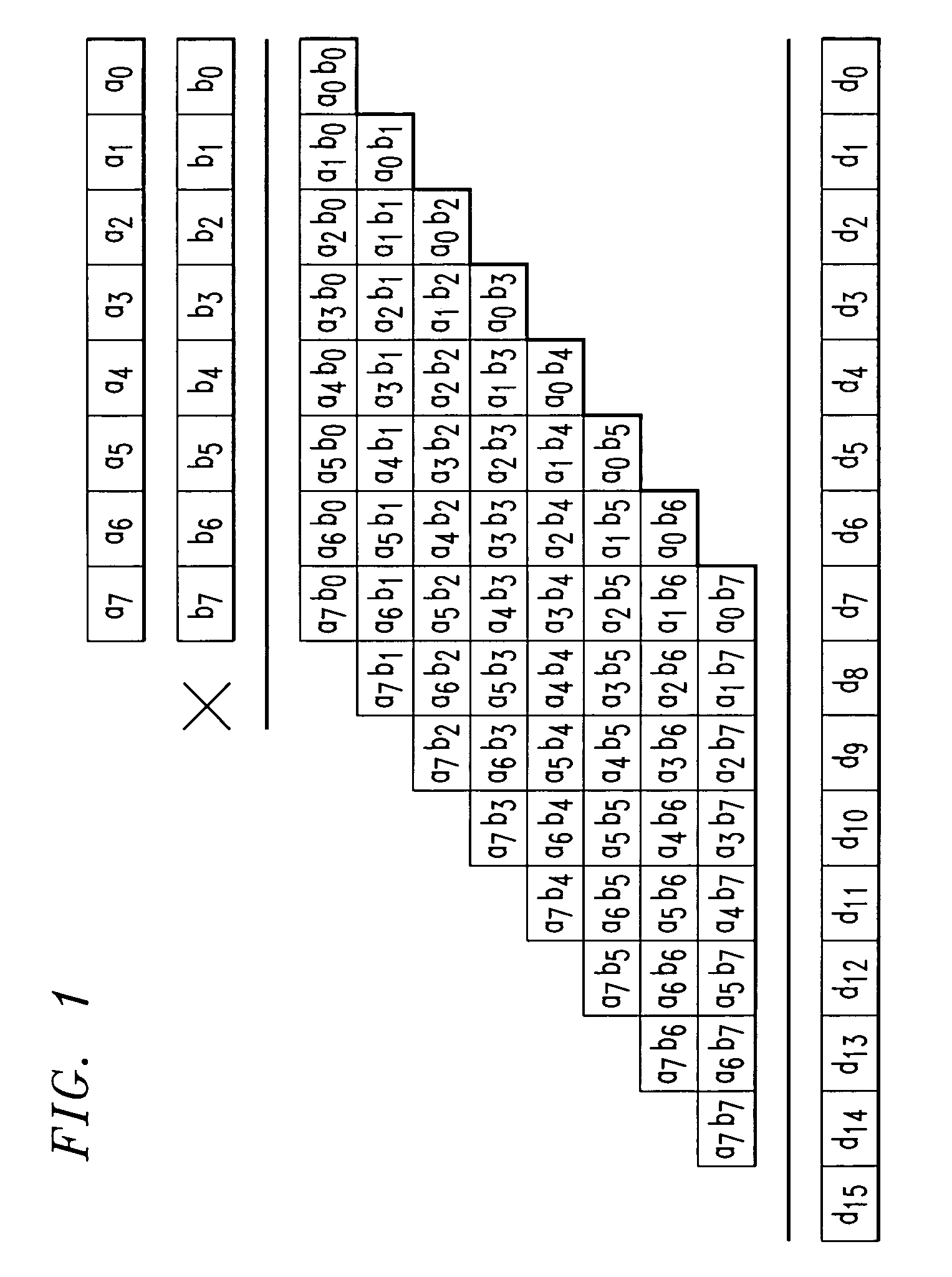

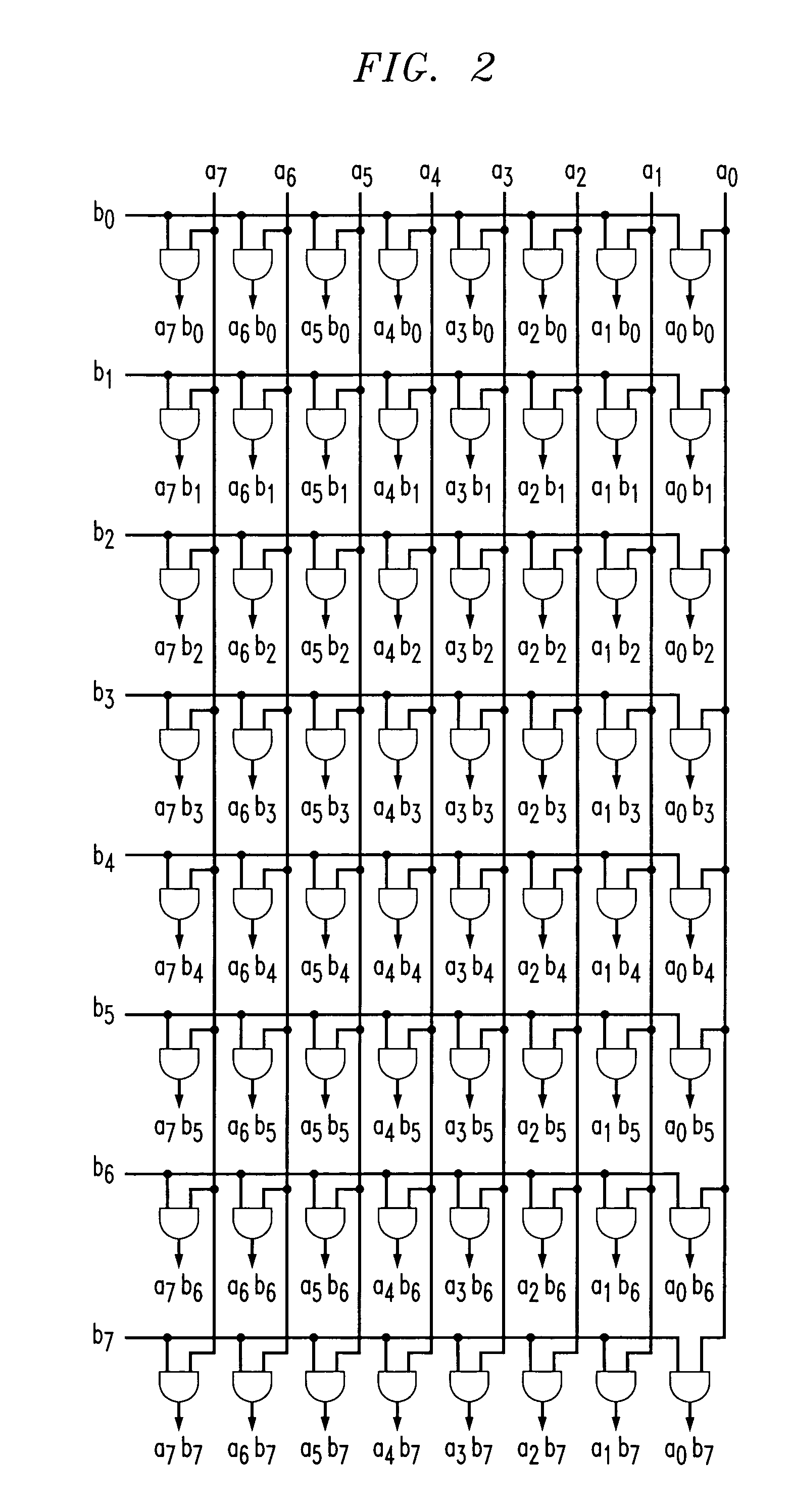

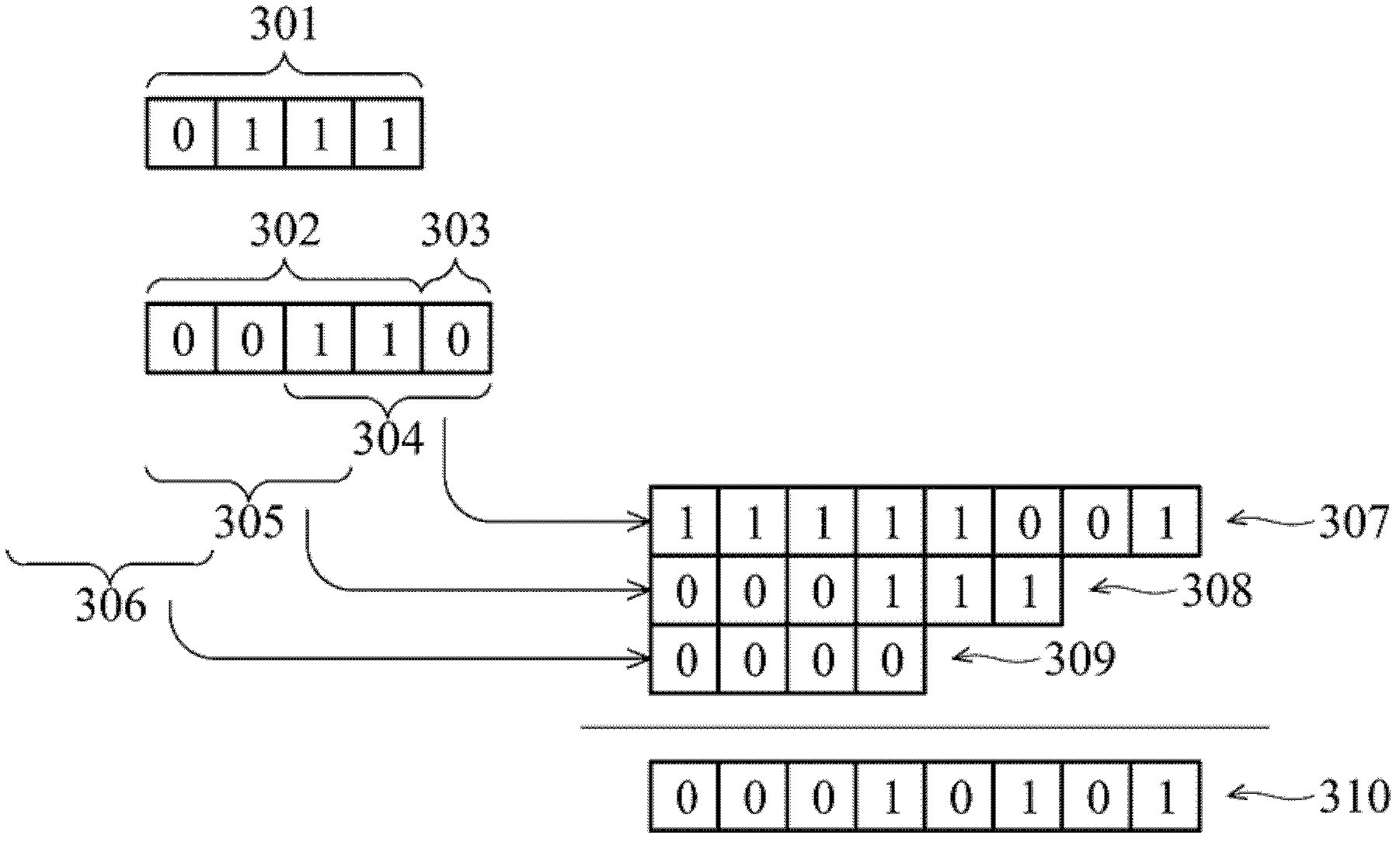

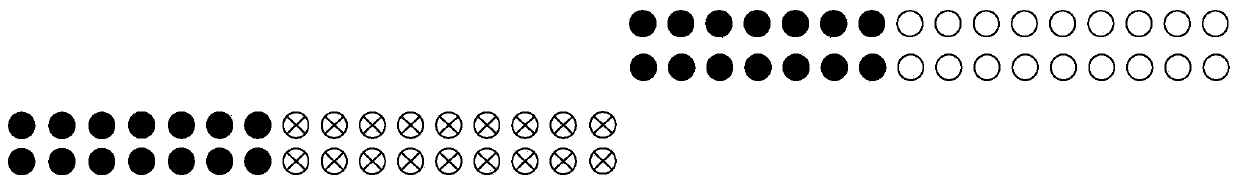

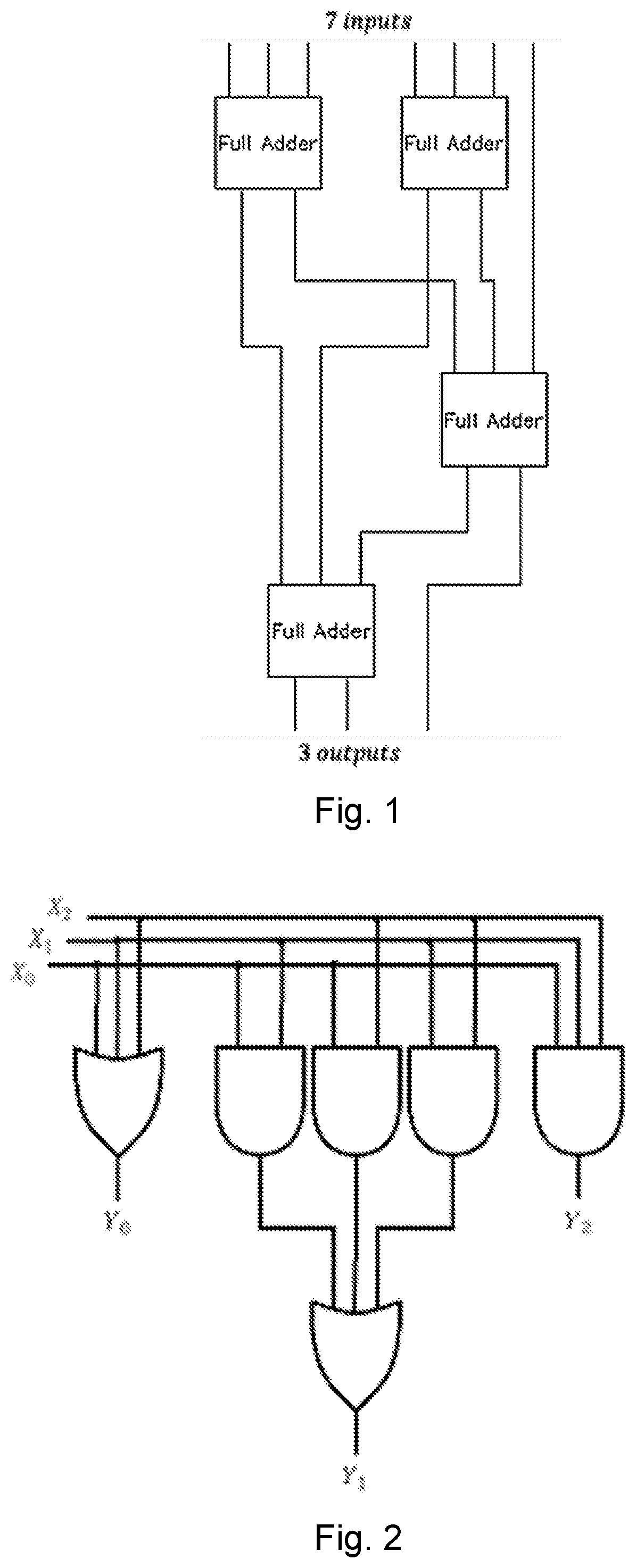

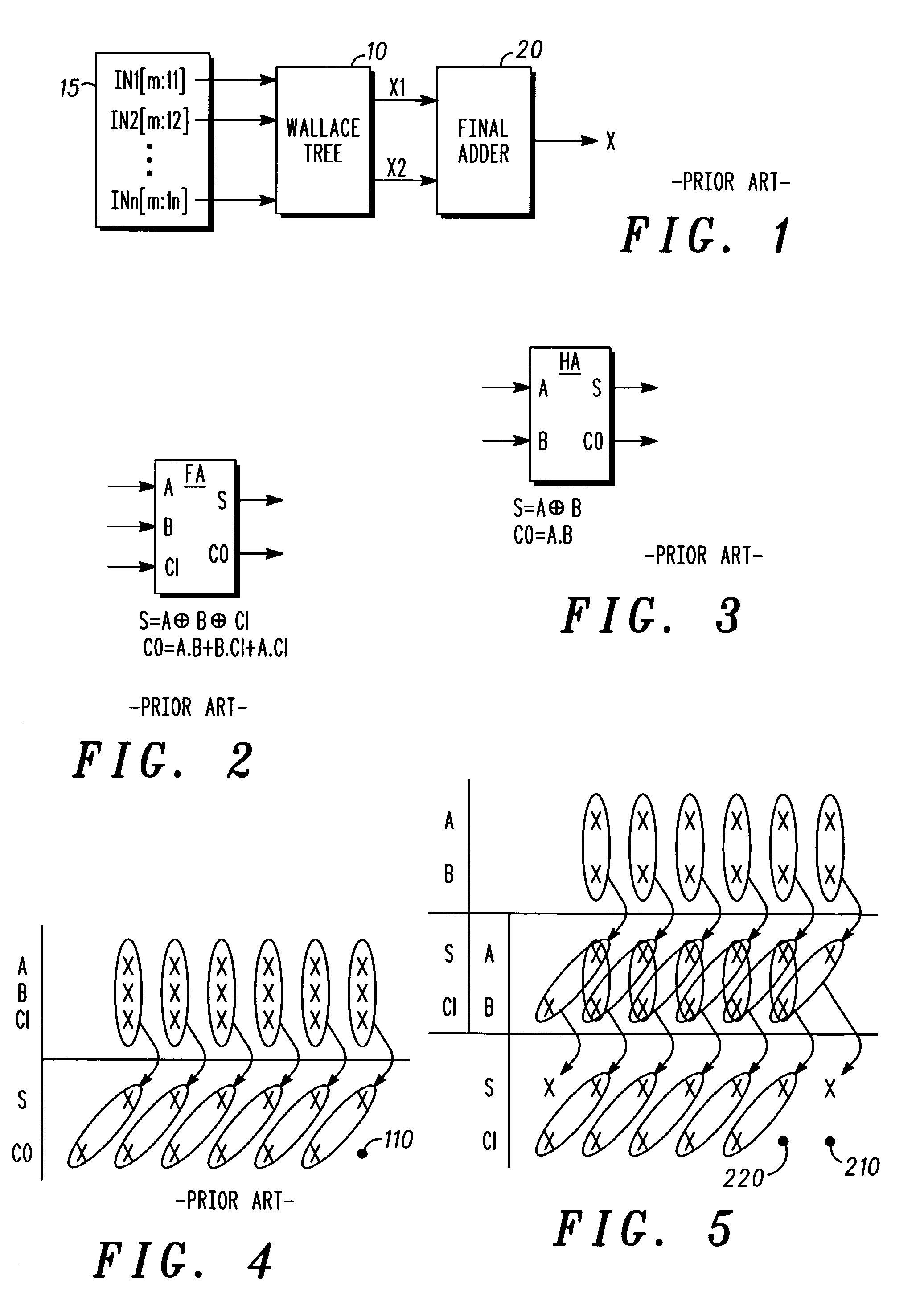

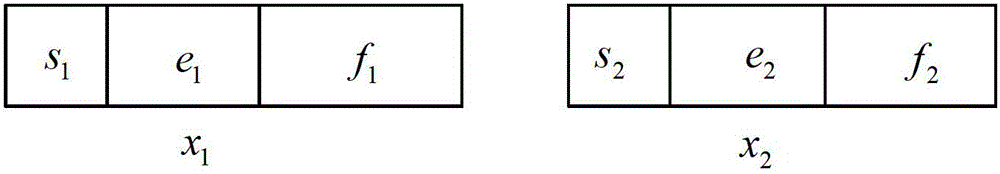

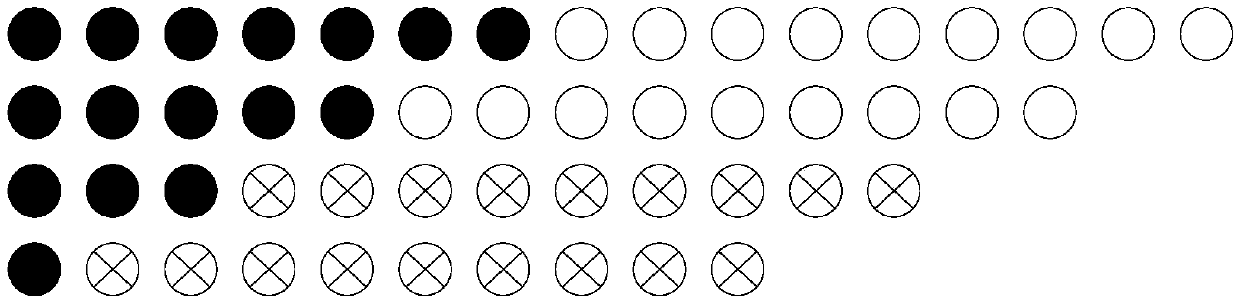

A Wallace tree is an efficient hardware implementation of a digital circuit that multiplies two integers, devised by Australian Computer Scientist Chris Wallace in 1964. The Wallace tree has three steps: Multiply (that is – AND) each bit of one of the arguments, by each bit of the other, yielding n² results. Depending on position of the multiplied bits, the wires carry different weights, for example wire of bit carrying result of a₄b₃ is 128 (see explanation of weights below).

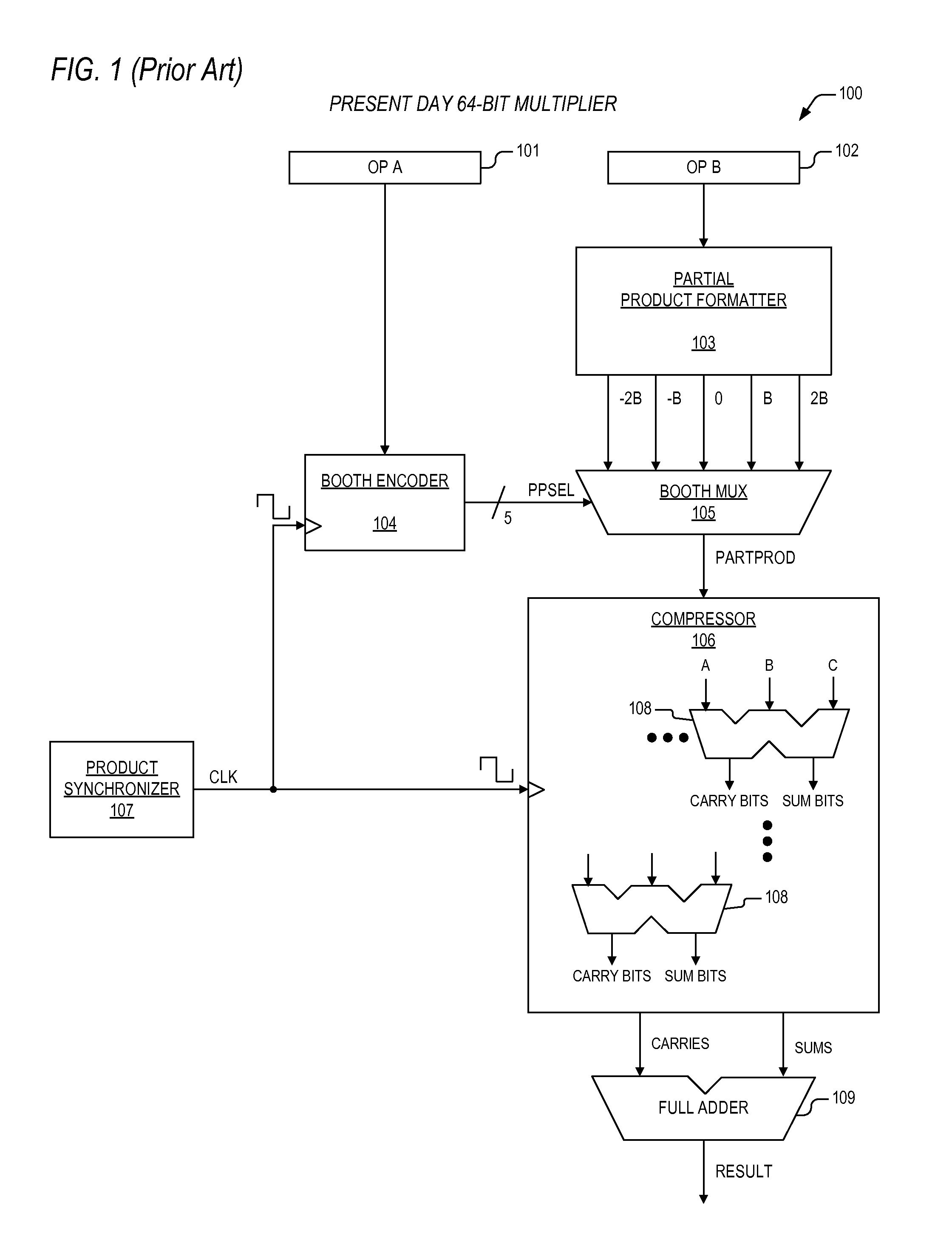

Multiplier accumulator circuits

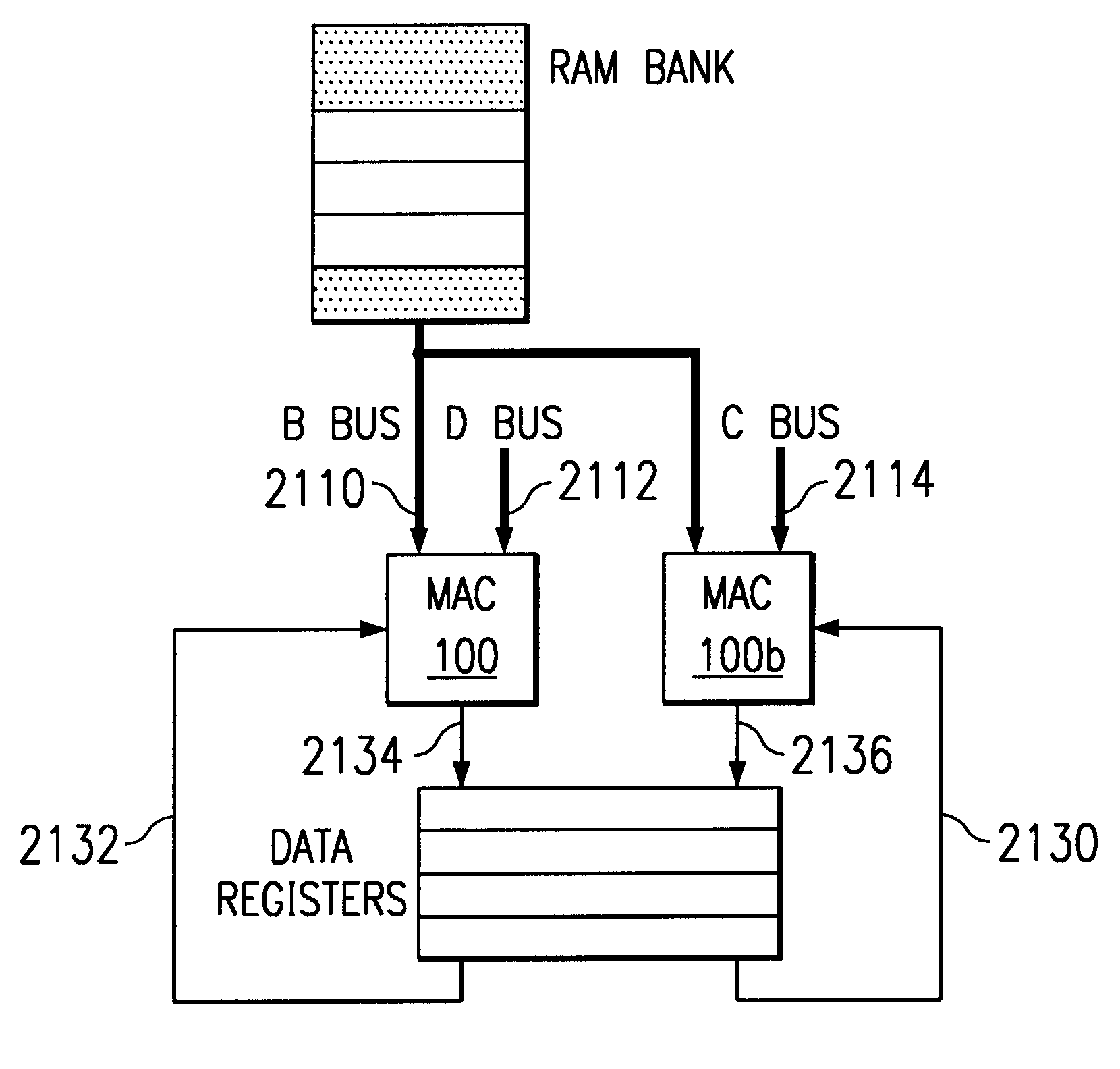

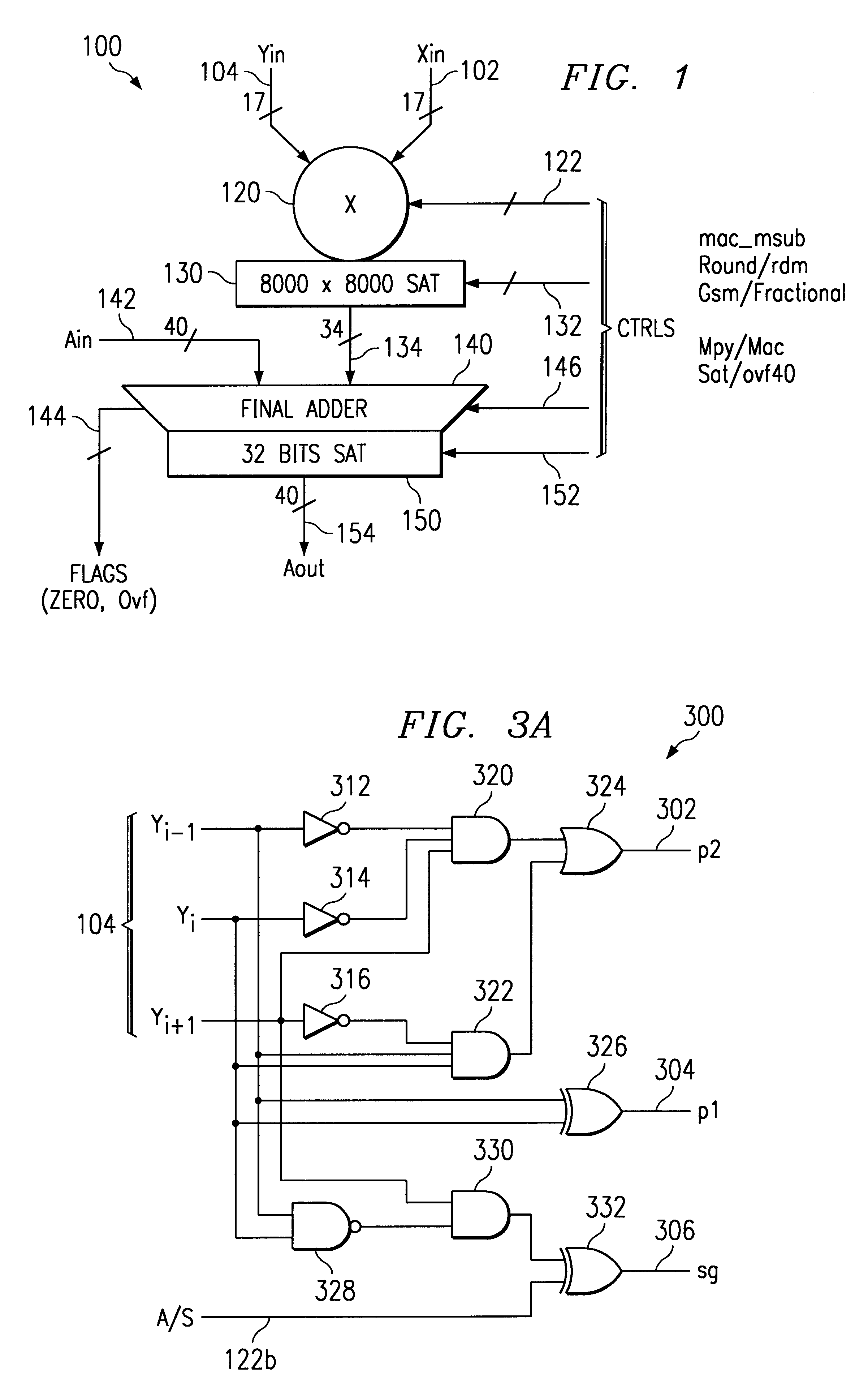

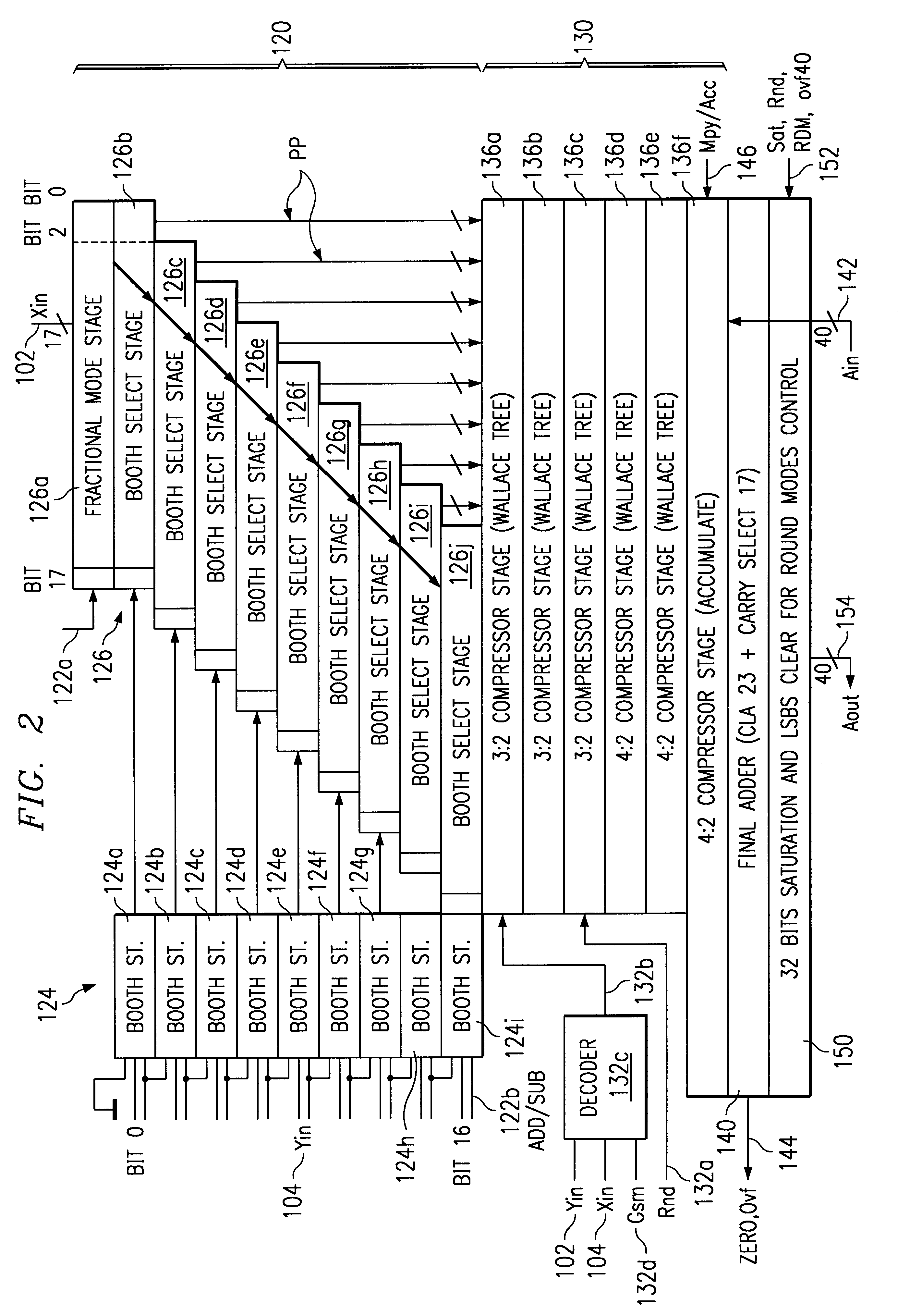

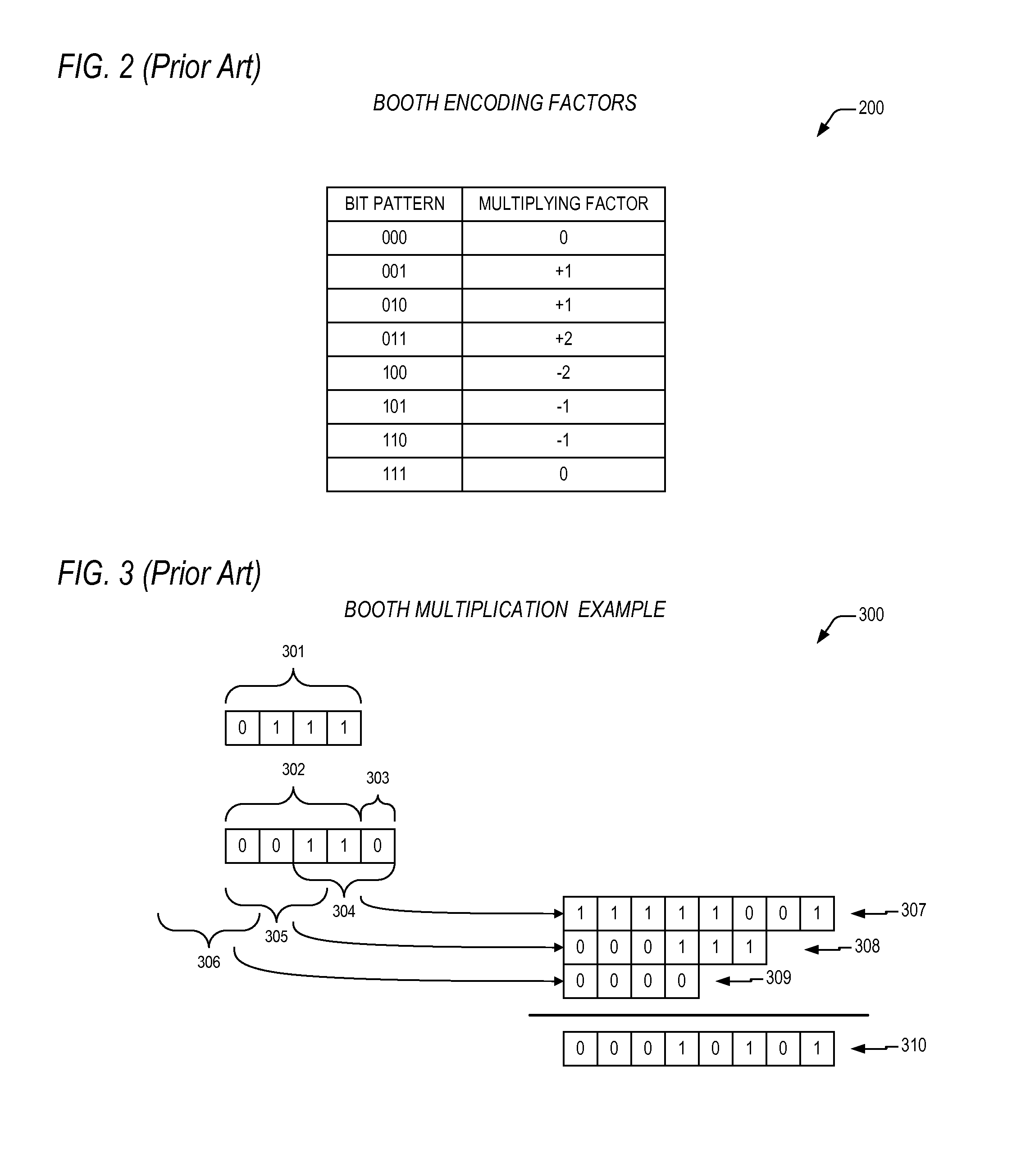

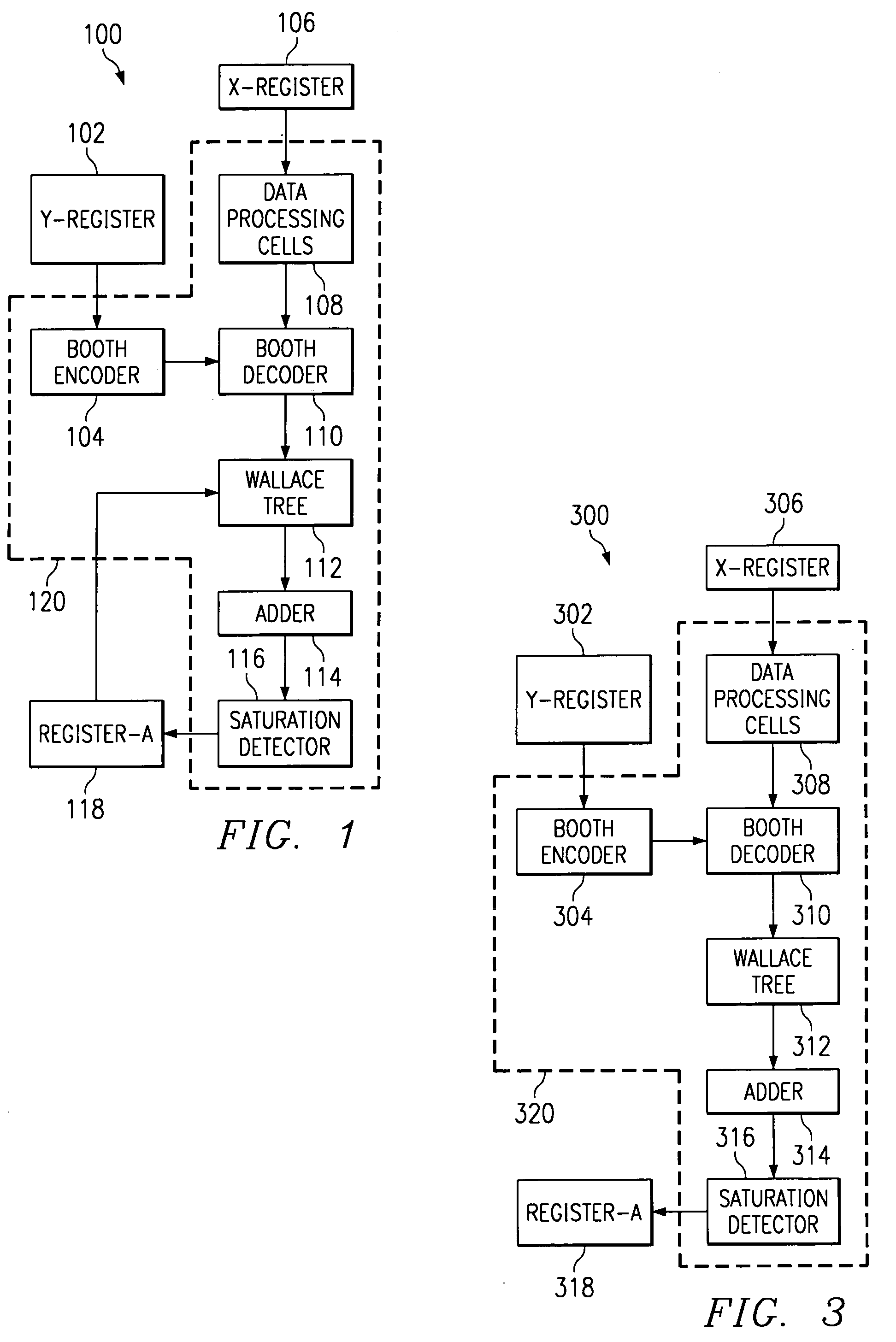

A multiply-accumulate (MAC) unit, having a first binary operand X, a second binary operand Y, a third binary operand, Booth recode logic for generating a plurality of partial products from said first and second operands, a Wallace tree adder for reducing the partial products and for selectively arithmetically combining the reduced partial products with said third operand, a final adder for generating a final sum, and a saturation circuitry for selectively rounding or saturating said final sum is provided. A dual MAC unit is also provided.

Owner:TEXAS INSTR INC

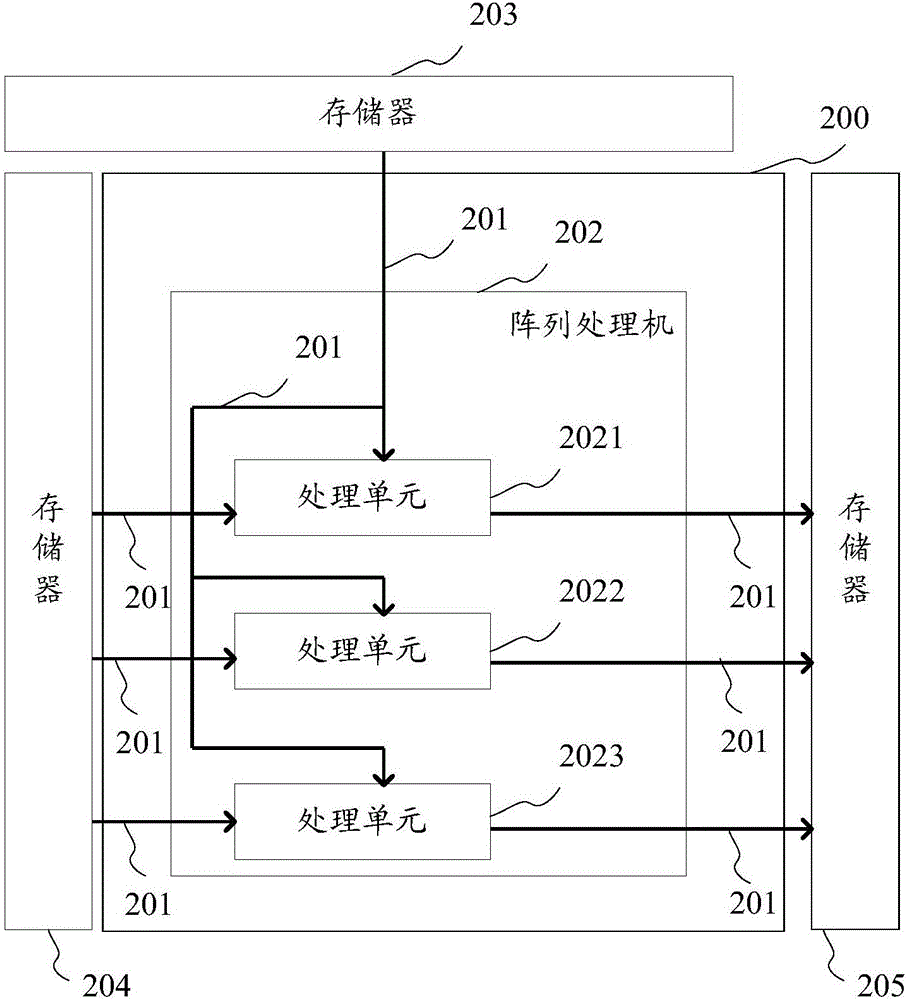

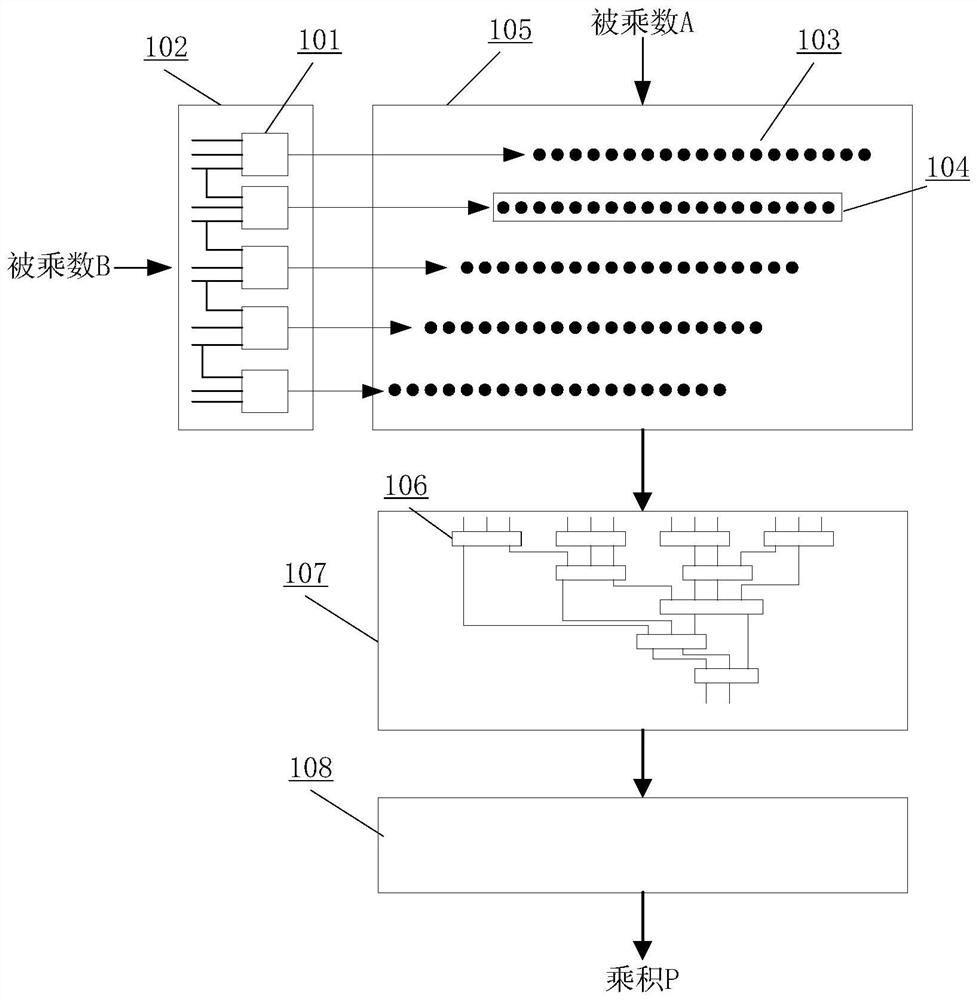

Processor and method for executing matrix multiplication on processor

ActiveCN106445471AProcessing speedImprove versatilityDigital data processing detailsProgram controlWallace treeParallel computing

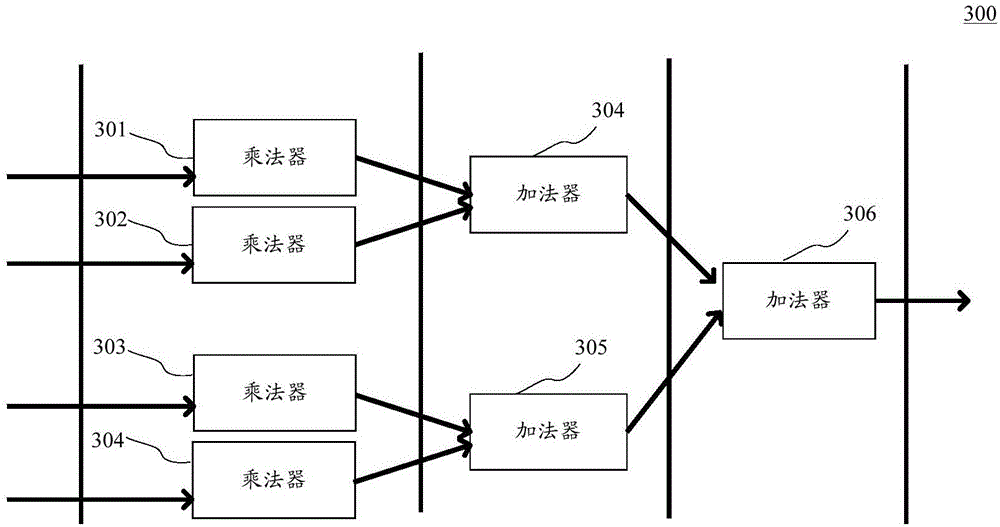

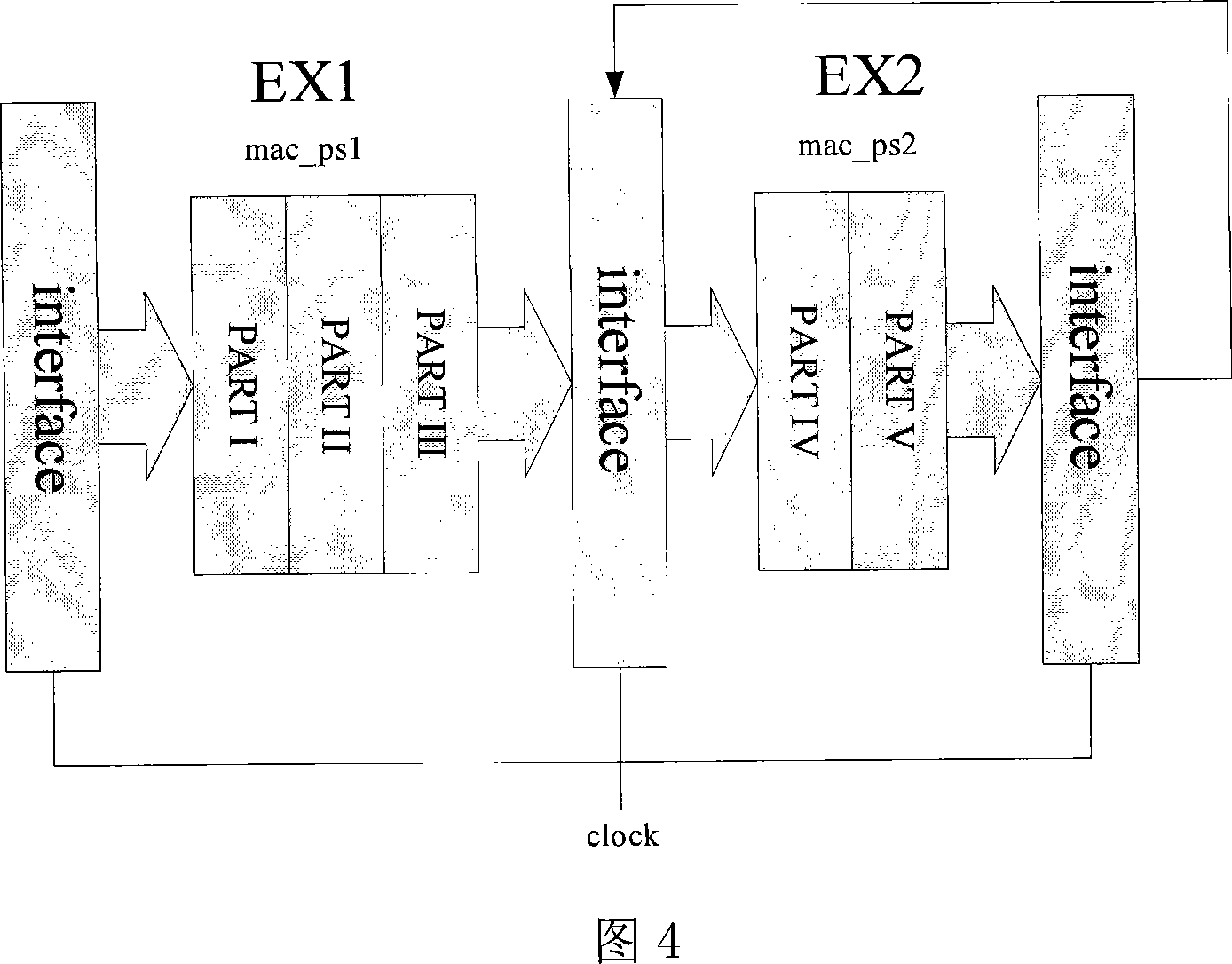

The invention discloses a processor and a method for executing matrix multiplication on the processor. The processor comprises a data bus and an array processor composed of k processing units. The data bus is used for reading n columns of row vectors in sequence from M*N multiplicand matrixes, inputting the row vectors to the processing units in the array processor, reading n*k sub-matrixes from N*K multiplier matrixes, inputting column vectors of the sub-matrixes into the corresponding processing units in the array processor, and outputting results obtained through multiplication executed by the processing units. Each processing unit in the array processor is used for executing parallel vector multiplication on the input row vectors and the column vectors, and each processing unit comprises a Wallace tree multiplying unit composed of n multiplying units and n-1 adders. The implementation mode improves processing efficiency of matrix multiplication.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

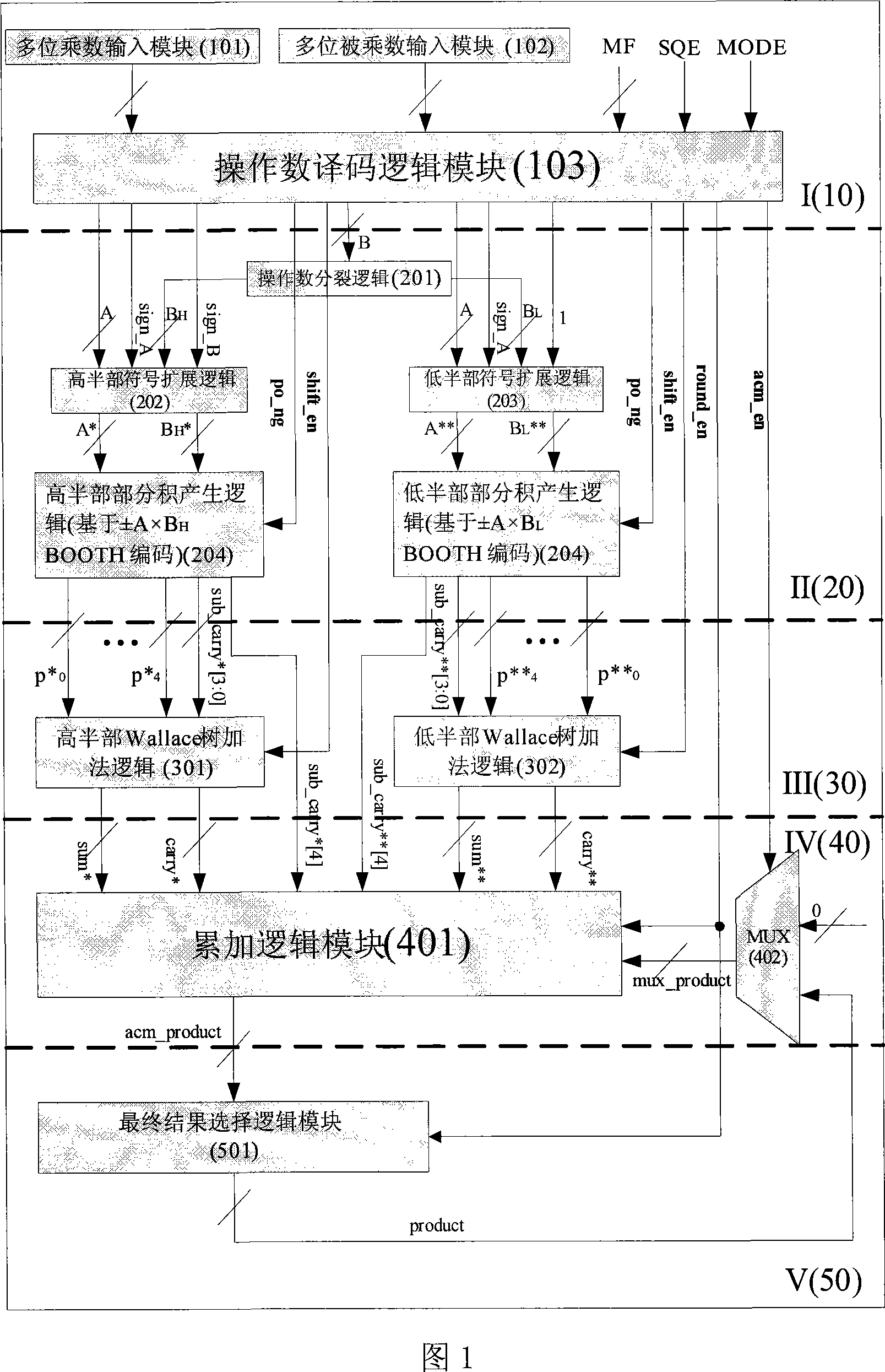

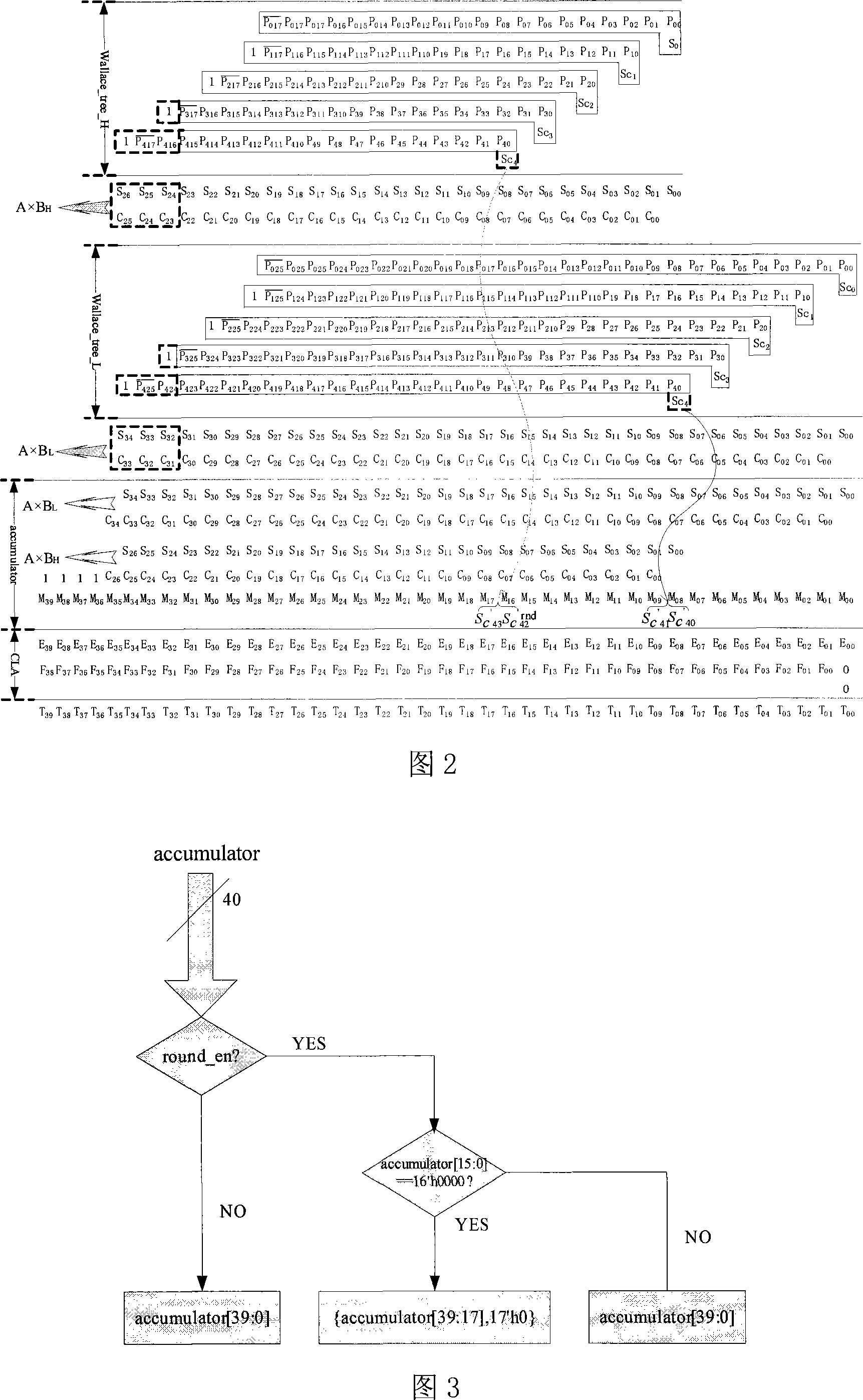

Multiply adding up device

InactiveCN101082860ASatisfy the limit of bit widthReduce latencyDigital data processing detailsWallace treeComputer architecture

The invention discloses a multiplication accumulation device of multiple multiplication accumulating patterns in the modern digital signal processor, which comprises the following parts: operand decoding unit, partial product generating unit, Wallace tree-typed addition unit, accumulation unit and final result unit, wherein the predecoding unit, partial product generating unit, Wallace tree-typed addition unit, accumulation unit and final result unit are connected sequently. The invention modifies the BOOTH coded algorism to affirm the precision of system, which reduces the time delay of entire MAC.

Owner:ZHEJIANG UNIV

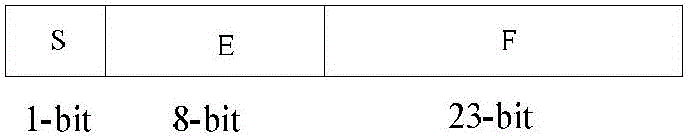

Multiplier and cipher circuit

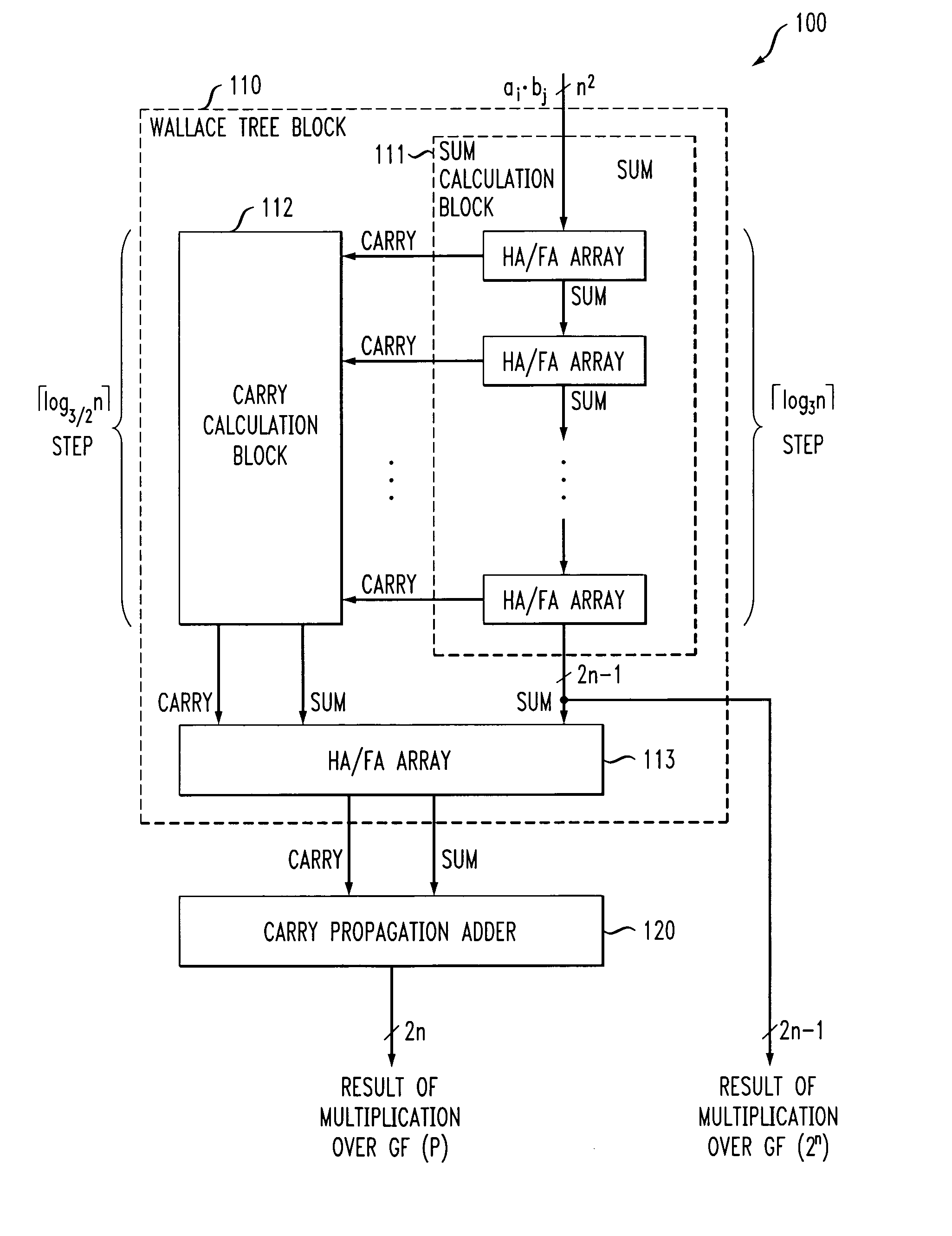

InactiveUS8244790B2Increase in circuit sizeComputation using non-contact making devicesDigital computer detailsWallace treeCarry propagation

A multiplier circuit is disclosed including a Wallace tree block and a carry propagation adder. The Wallace tree block includes a sum calculation block adding partial products for each digit and a carry calculation block adding carries obtained in the addition by the sum calculation block. In the case of multiplication over an extension field (finite field GF(2n)) of two, a result of calculation by the sum calculation block is outputted. The carry propagation adder adds the result of calculation by the sum calculation block and a result of calculation by the carry calculation block. In the case of multiplication for integers (finite field GF(p)), a result of calculation by the carry propagation adder is outputted.

Owner:IBM CORP

No-carry multiplication device and processing method thereof

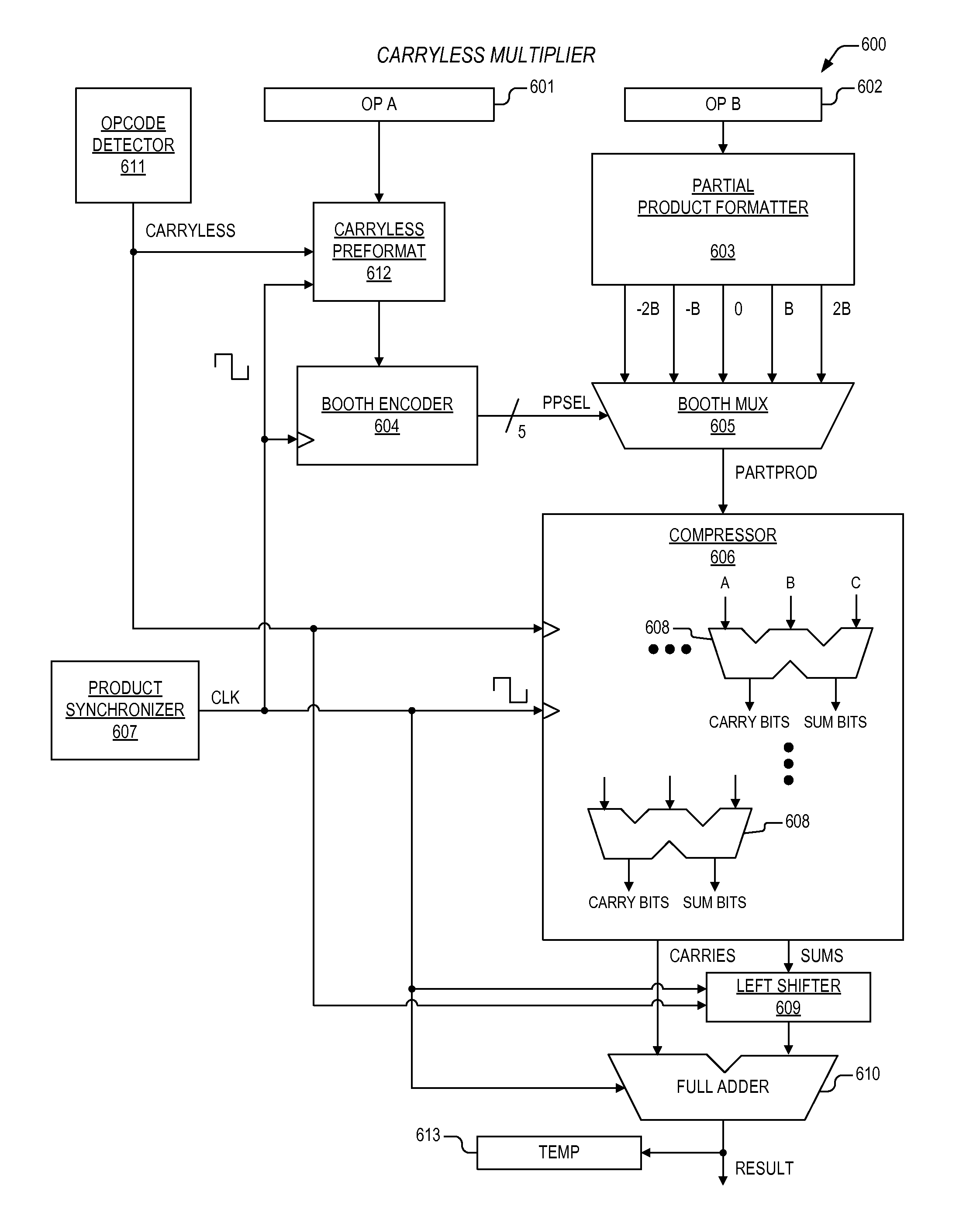

The invention provides a no-carry multiplication device and a processing method thereof. The device includes a no-carry pre-format unit, a Booth encoder, a reducer, a left shift device and an XOR gate. The no-carry pre-format unit receives a multiplier operand and formats the multiplier operand into multiple parts. The Booth encoder receives and judges the parts, and selects multiple first part product of a multiplicand operand. By using the parts, multiple second part product of the multiplicand operand can be avoided to select. The second part product causes carry bit. The reducer couples with the Booth encoder. The first part product is totalized through a plurality of carry storage summators. The carry storage summators generate a plurality of totaling bits and a plurality of carry bits. The carry storage summators are arranged in a Wallace tree architecture. When a no-carry multiplying is in execution, the carry bits can not be enabled. The left shift device couples with the reducer and shifts output of the reducer at least one bit. The XOR gate couples with the reducer and the left shift device for XOR operation and generates a no-carry multiplication result.

Owner:VIA TECH INC

Multiply-add method and multiply-add apparatus

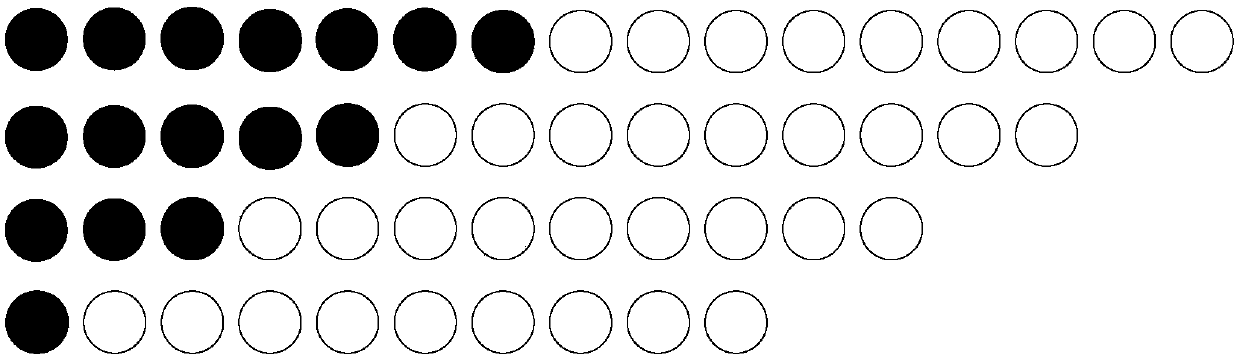

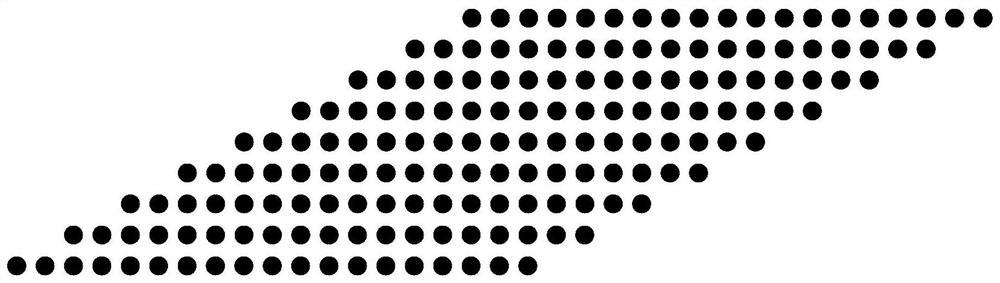

ActiveCN101986260AEasy to optimize layoutReduce areaDigital data processing detailsWallace treePartial product

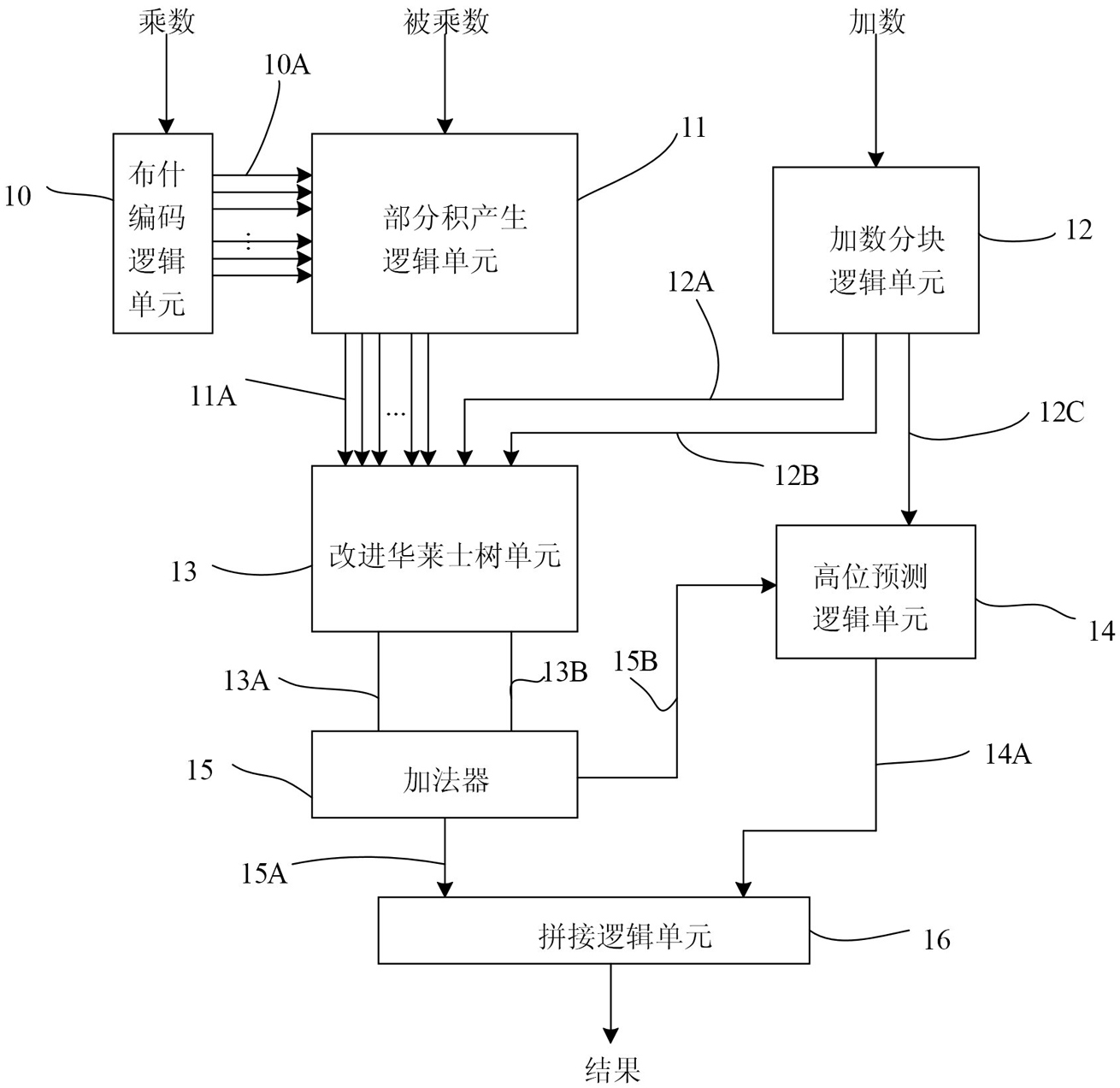

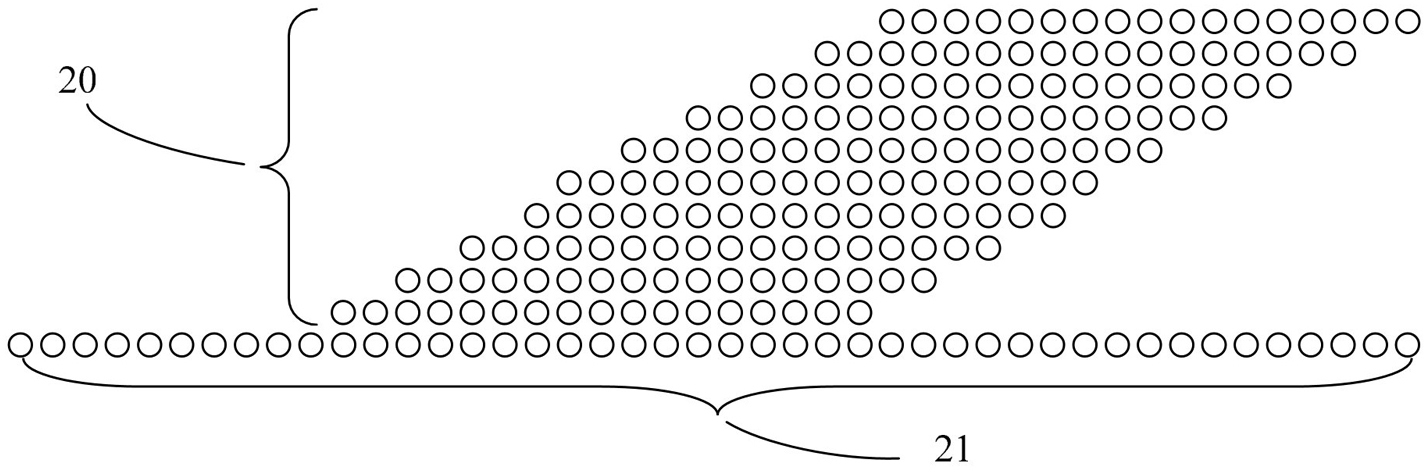

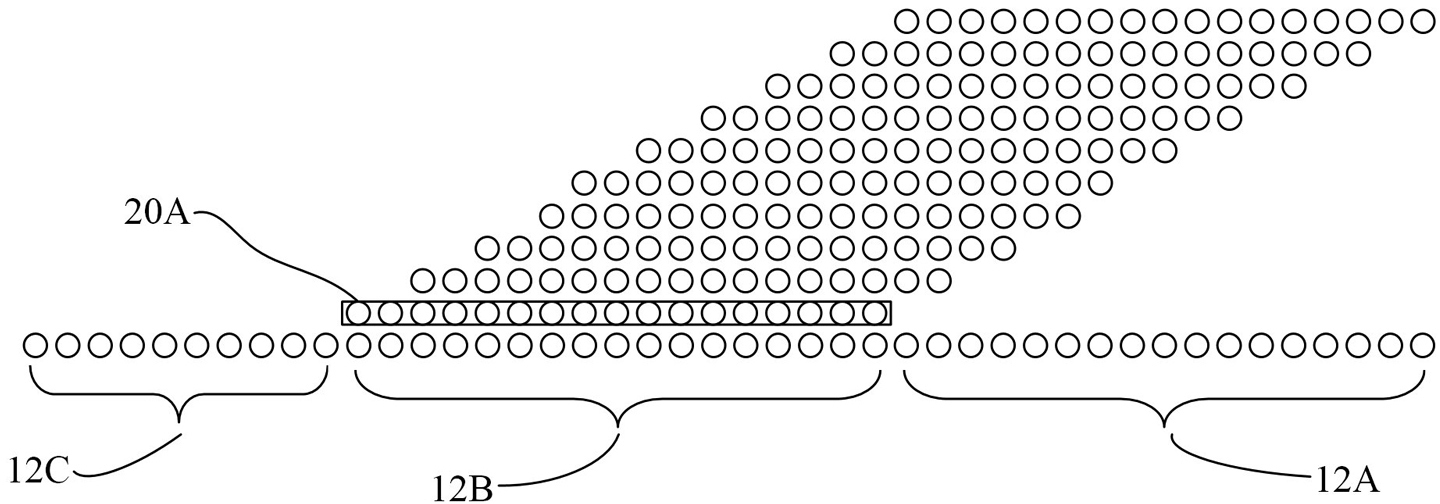

The invention disclose a multiply-add method and multiply-add apparatus, the method comprises the following steps: (1) a multiplier generates a plurality of control signals through a Bush coding logical unit, a multiplicand serves as the input of a partial product generating logical unit, and a partial product is generated; (2) an addend obtains a lower-order intercepting part, an intermediate part and a higher-order intercepting part through an addend partitioning logical unit; the lower-order intercepting part, the intermediate part and the partial product serve as the input of an improved Wallace tree unit, the obtained result serves as the input of an adder, and a lower-order result and a control signal are generated; 3 the higher-order intercepting part obtains a higher-order result through a higher-order forecasting logical unit; and (4) the lower-order result and the higher-order result obtains a final result through a matching logical unit. The multiply-add apparatus comprise the Bush coding logical unit, the partial product generating logical unit, the addend partitioning logical unit, the adder, the higher-order forecasting logical unit, the improved Wallace tree unit and the matching logical unit. The invention has the advantages of simple and compact structure, low cost, quick arithmetic speed, stabilization, reliability, and the like.

Owner:NAT UNIV OF DEFENSE TECH

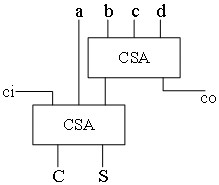

Summation path circuit of carry-save adder and carry-save adder

ActiveCN103761066AEasy constructionOutput delay equalizationComputation using non-contact making devicesTransmission gateWallace tree

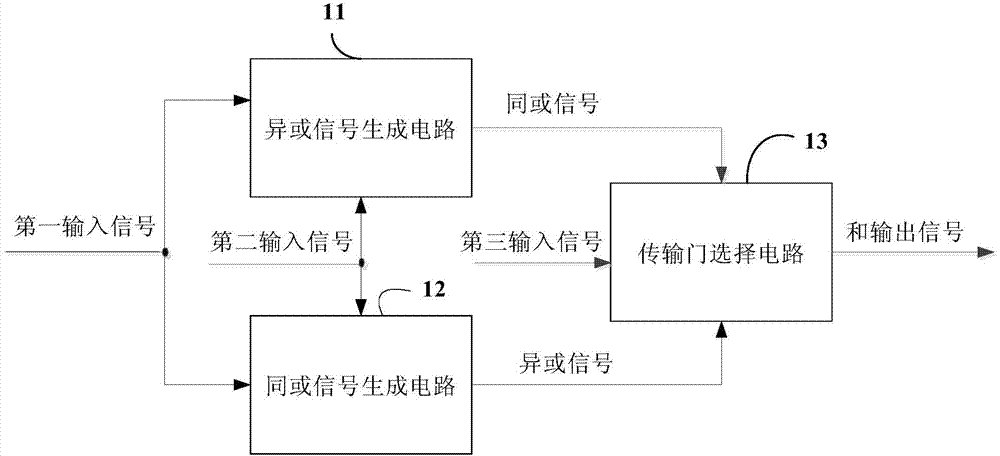

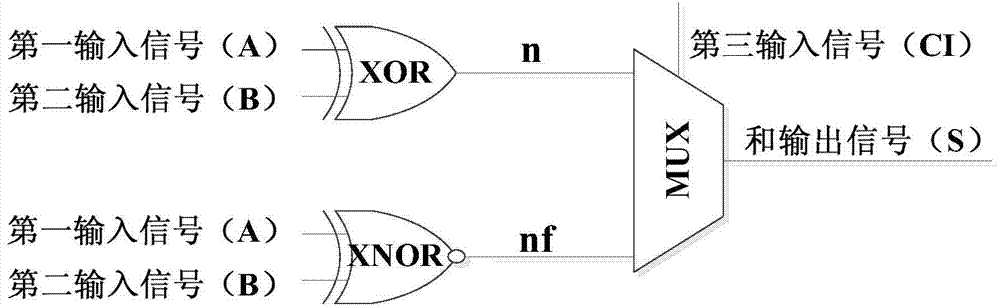

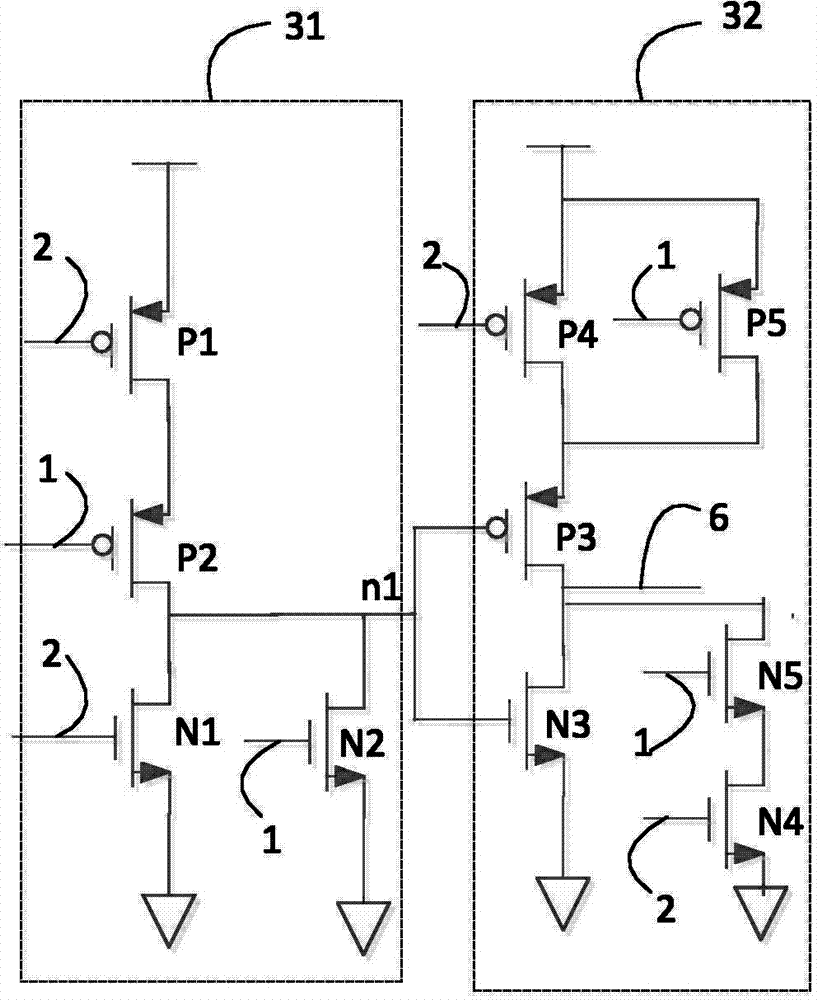

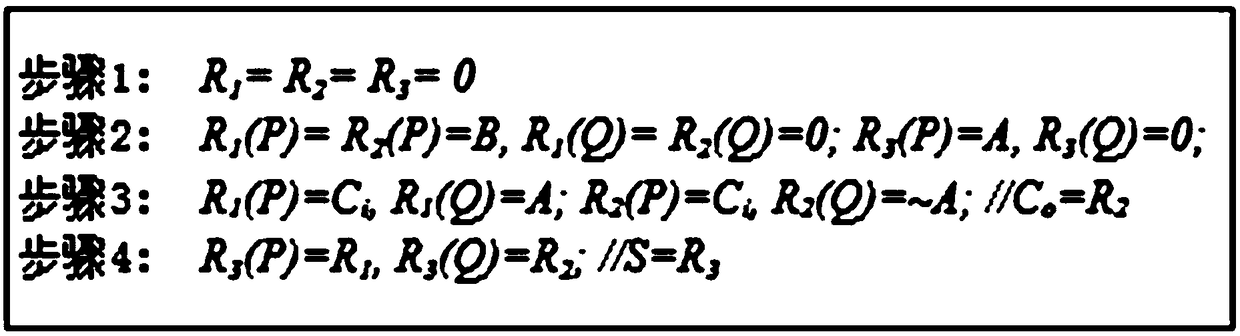

The invention provides a summation path circuit of a carry-save adder and the carry-save adder. The summation path circuit of the carry-save adder comprises an exclusive-or signal generating circuit, a not-exclusive-or signal generating circuit and a transmission gate selection circuit, wherein the exclusive-or signal generating circuit and the not-exclusive-or signal generating circuit synchronously produce exclusive-or signals and not-exclusive-or signals of a first input signal and a second input signal, the transmission gate selection circuit is used for generating and outputting signals according to the exclusive-or signals, the not-exclusive-or signals and a third input signal. The summation path circuit achieves synchronous output of the exclusive-or signals of the first input signal and the second input signal and the not-exclusive-or signals of the first input signal and the second input signal through the exclusive-or signal generating circuit and the not-exclusive-or signal generating circuit so as to enable output relay of the input signals from the rising edge to the falling edge to be balanced and small and facilitate establishing of Wallace trees.

Owner:LOONGSON TECH CORP

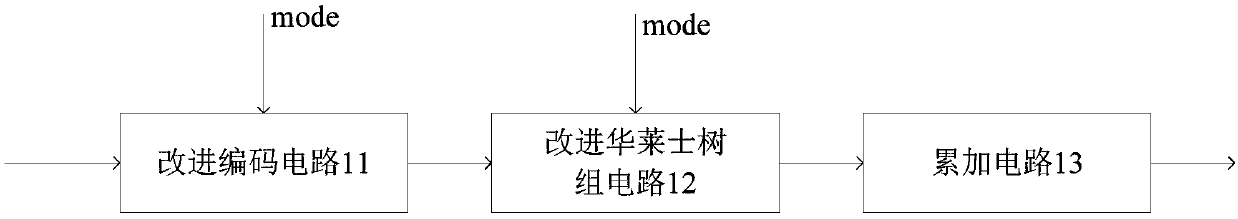

Multiplier, data processing method and chip

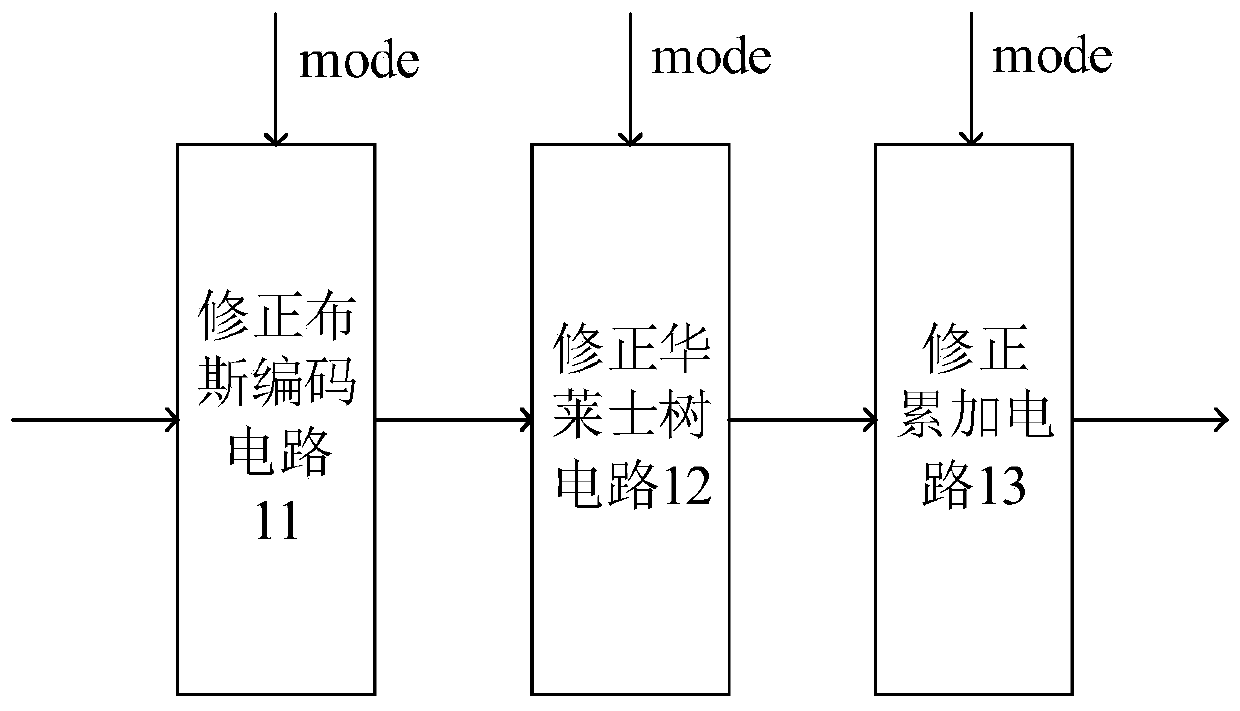

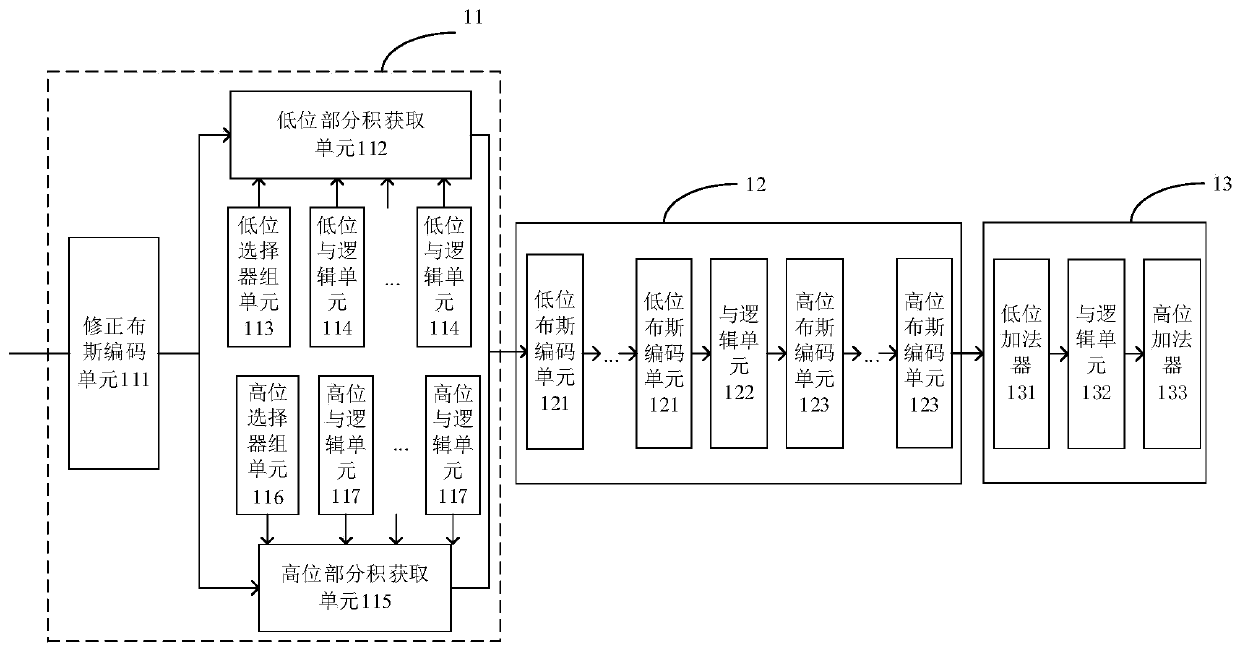

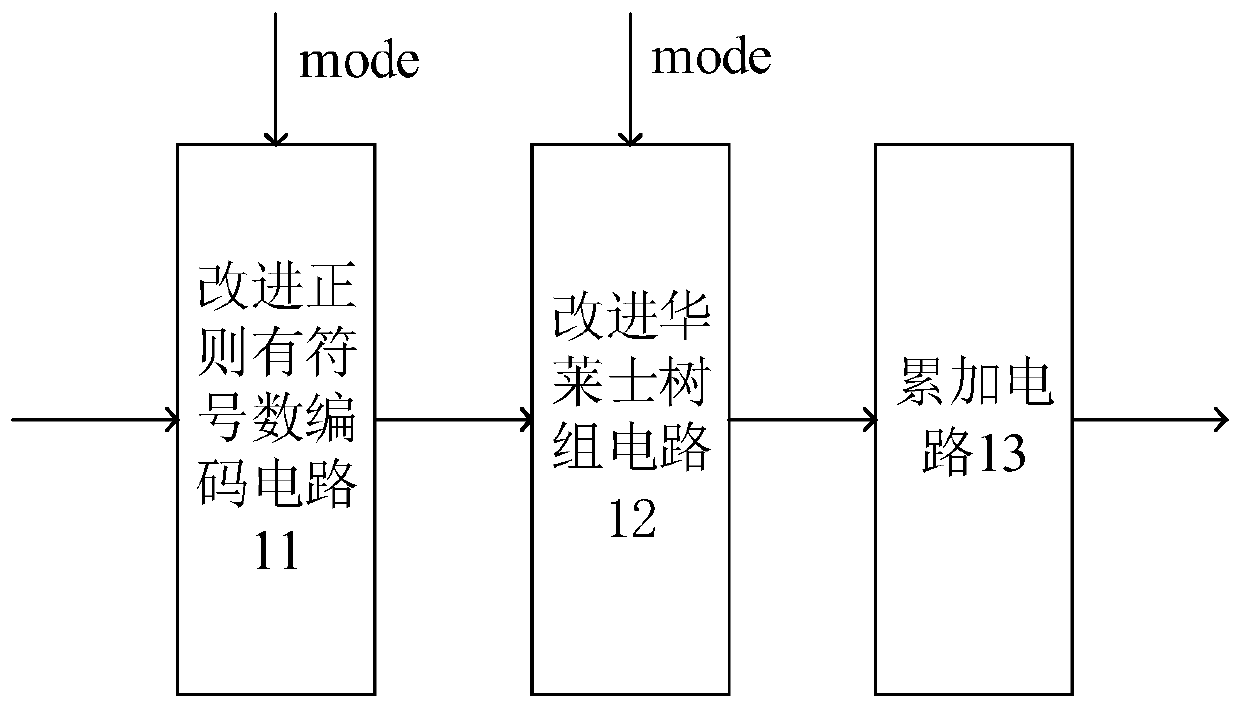

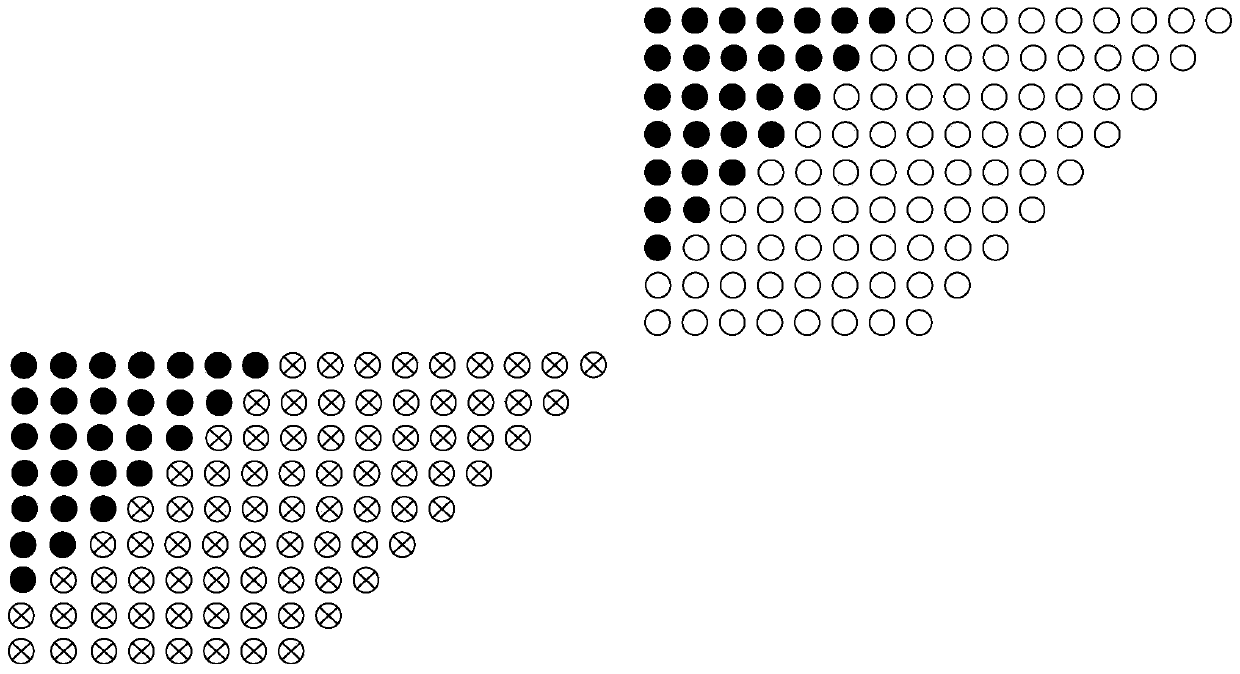

ActiveCN110673823AImprove versatilityReduce power consumptionDigital data processing detailsPhysical realisationWallace treeEngineering

The invention provides a multiplier, a data processing method and a chip. The multiplier comprises a correction Booth encoding circuit, a correction Wallace tree circuit and a correction accumulationcircuit, the output end of the correction Booth encoding circuit is connected with the input end of the correction Wallace tree circuit, and the output end of the correction Wallace tree circuit is connected with the input end of the correction accumulation circuit. The multiplier can carry out multiplication operation on various data with different bit widths, and the universality of the multiplier is improved.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

Mechanism for carryless multiplication that employs booth encoding

ActiveUS20120143934A1Avoid choiceDigital data processing detailsDigital computer detailsWallace treeBooth encoding

Owner:VIA TECH INC

FIR (finite impulse response) filter structure for low-power fault-tolerant circuit

ActiveCN103955585AReduce areaReduce power consumptionSpecial data processing applicationsDigital signal processingWallace tree

The invention belongs to the technical field of low-power integrated circuits, and particularly relates to an FIR (finite impulse response) filter structure for a low-power fault-tolerant circuit. The FIR filter structure mainly includes transcoding logical units, multiplier-accumulators (MACs), and a residual bit transmission chain, wherein the transcoding logical units are used for conversion between the two's complement and sign-magnitude binary numbers; each MAC mainly includes a sign processing unit, a Wallace tree, a last-stage accumulator and a magnitude computing logical unit; a residual bit is produced by each MAC and transmitted individually, and all the residual bits are added up at the last stage, so as to shorten the critical path. The FIR filter structure for the low-power fault-tolerant circuit has the characteristics of simple structure, small area overhead, low critical path activation probability and the like, and is particularly suitable for a low-power fault-tolerant digital signal processing system based on the VOS (voltage over-scaling) technology.

Owner:FUDAN UNIV

A multiplier based on memristor RRAM

PendingCN109445747AReduce the number of unitsPromote productionComputation using non-contact making devicesWallace treeBinary multiplier

The invention provides a multiplier based on a memristor RRAM. The multiplier of the voter logic is given based on the original adder, the structure of the Wallace tree is adopted for operation, the multiplication operation is converted into the corresponding addition operation, and by utilizing the Wallace tree structure, a plurality of n-Bit numbers are added up to 2n-Bit numbers, and each fulladdition operation can be performed simultaneously by using voter logic. The multiplier of the invention improves the overall running speed and reduces the area of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Fast binary counters based on symmetric stacking and methods for same

ActiveUS20200394017A1Increase speedSave powerComputation using non-contact making devicesNumber-of-one countersWallace treeBinary multiplier

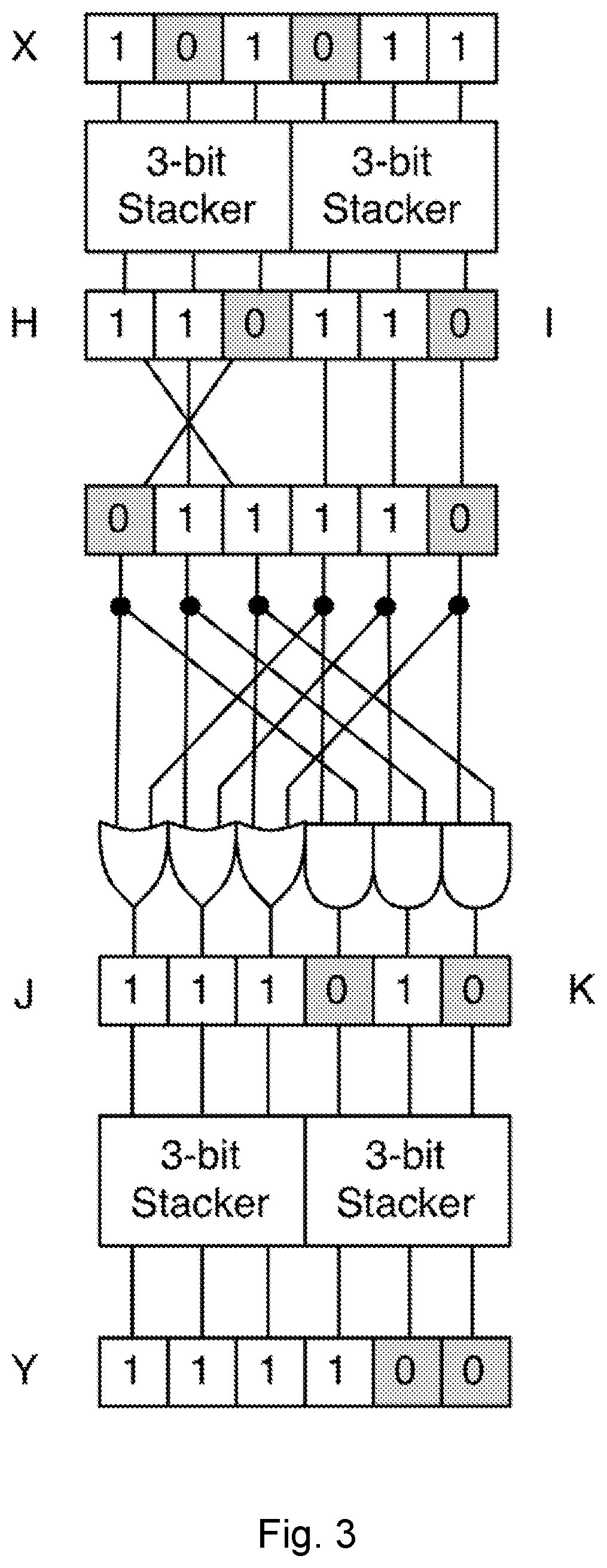

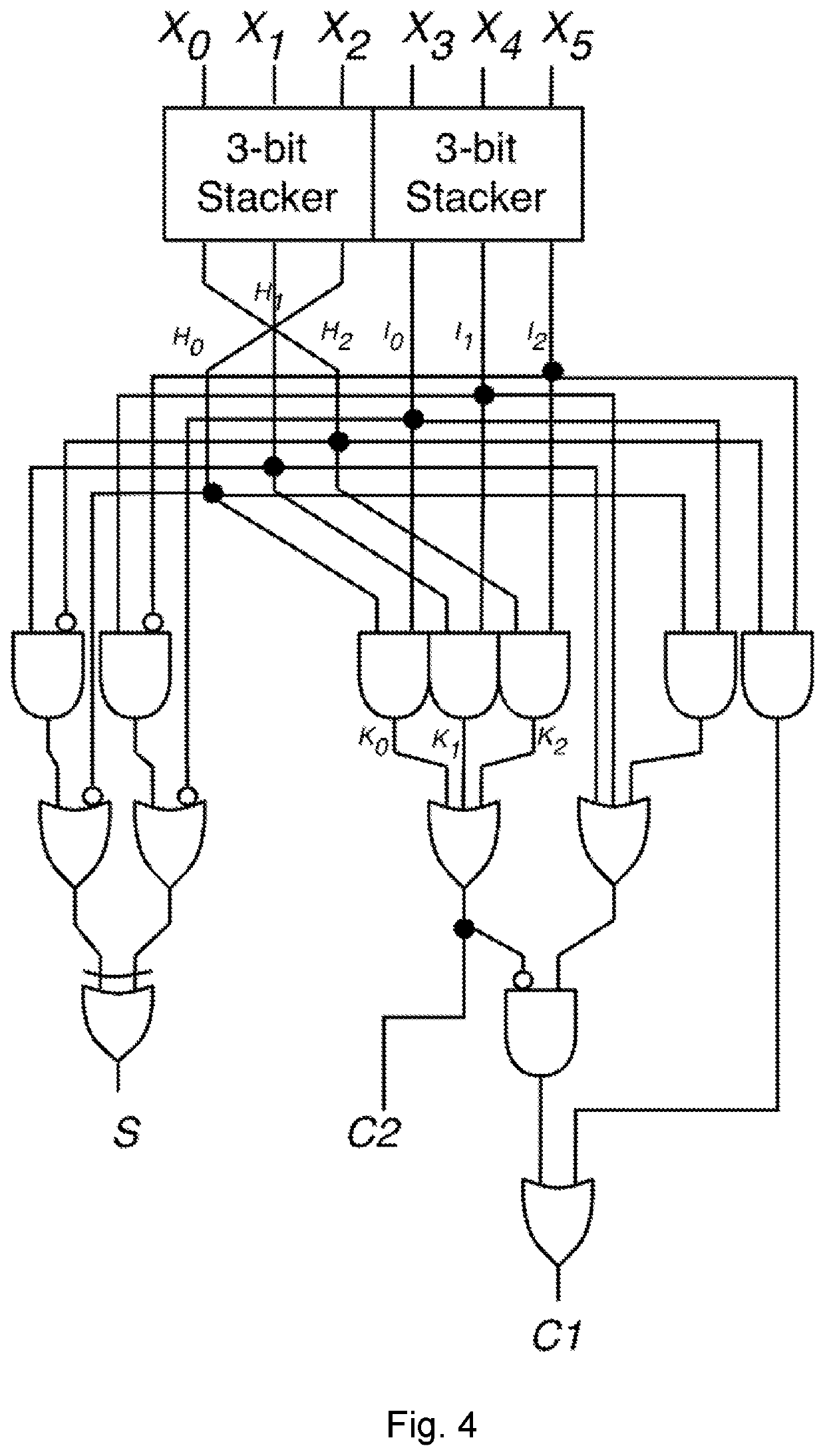

In this paper, binary stackers and counters are presented. In an embodiment, a counter uses 3-bit stacking circuits which group the T bits together, followed by a symmetric method to combine pairs of 3-bit stacks into 6-bit stacks. The bit stacks are then converted to binary counts, producing 6:3 and 7:3 Counter circuits with no XOR gates on the critical path. This avoidance of XOR gates results in faster designs with efficient power and area utilization. In VLSI simulations, the presently-disclosed counters were 30% faster and at consumed at least 20% less power than existing parallel counters. Additionally, using the presently-disclosed counter in existing Counter Based Wallace tree multiplier architectures reduces latency and improves efficiency in terms of power-delay product for 64-bit and 128-bit multipliers.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

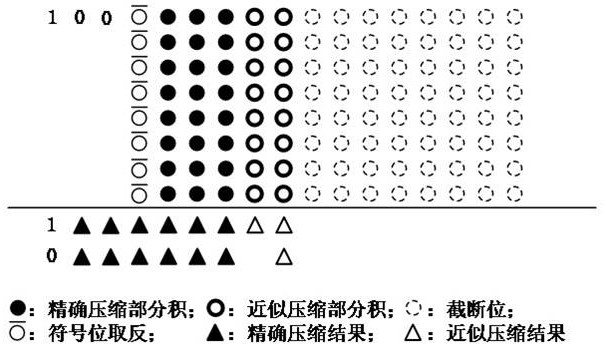

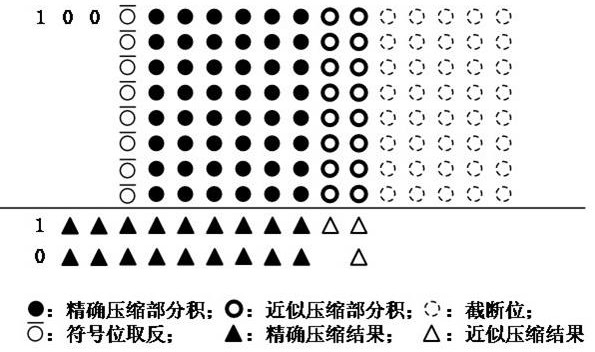

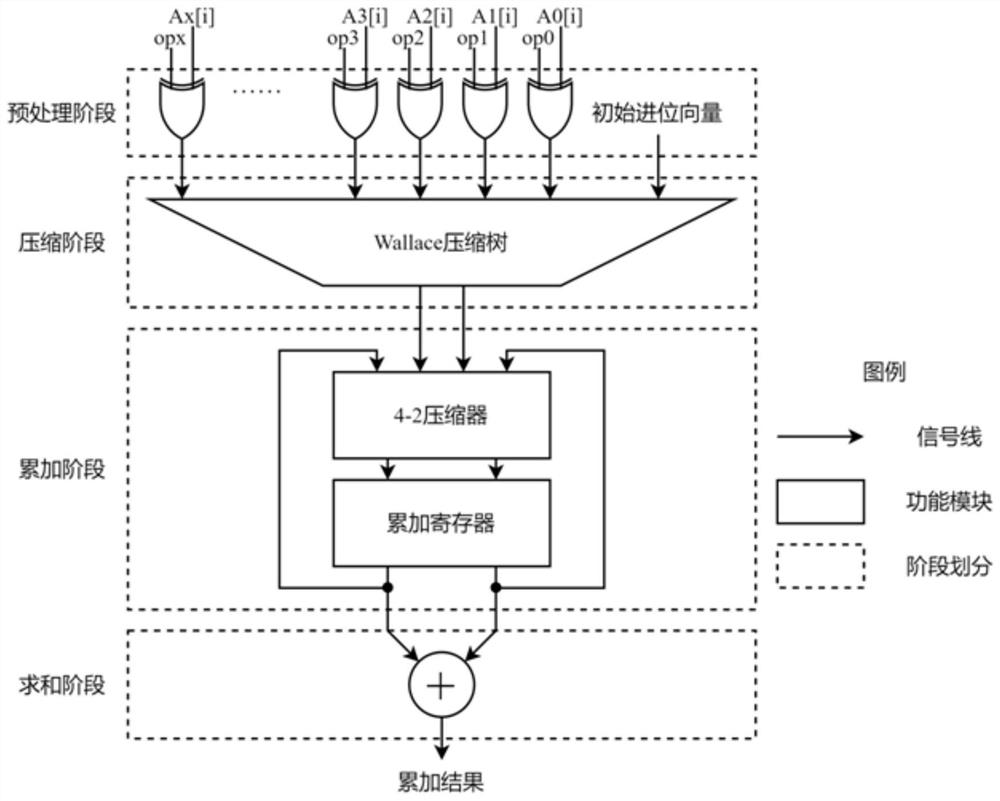

Low-energy-consumption high-precision approximate parallel fixed-width multiplication and accumulation device

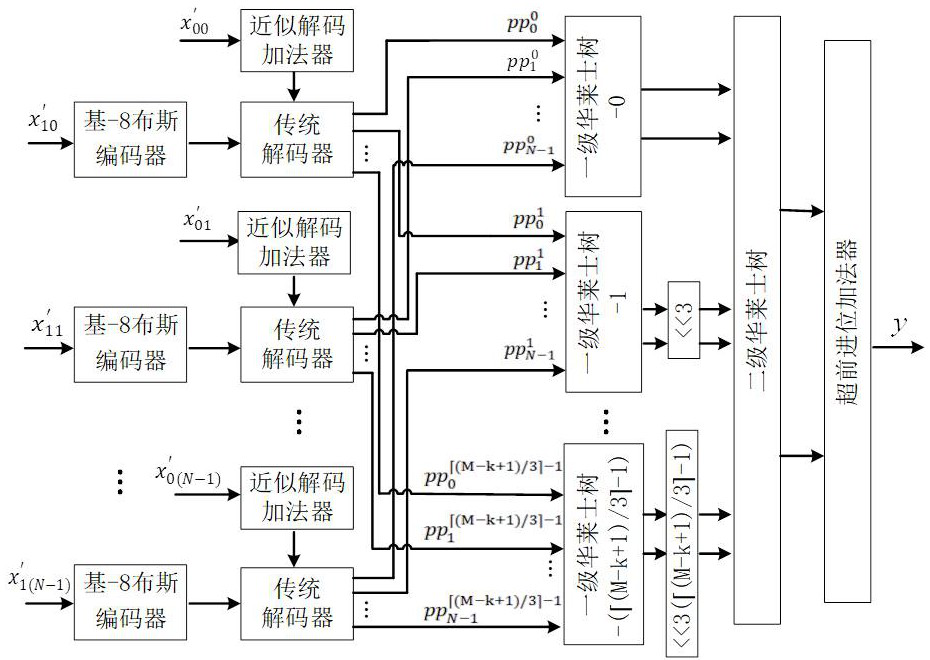

ActiveCN114647399AImprove parallelismImprove performanceDigital data processing detailsEnergy efficient computingWallace treeHemt circuits

The invention discloses a low-energy-consumption high-precision approximate parallel fixed-width multiplication and accumulation device which comprises an input truncation compensation circuit, a base-8 Booth encoder and decoder circuit, a first-stage partial product compression circuit, a second-stage partial product compression circuit and a carry lookahead adder circuit. Wherein in the first-stage partial product compression circuit, a Wallace tree with the weight is cut off at a low position, an approximate 42 compressor is used at a second low position, and an accurate compressor is used at a high position; the second-stage partial product compression circuit uses a precise compressor and comprises a probability constant compensation part which is used for compensating for first-stage partial product truncation, compensating for errors generated by using an approximate 42 compressor and compensating for second-stage partial product truncation. According to the method, power consumption is reduced by using truncation and approximation methods, hardware overhead is reduced, a probability constant compensation strategy is adopted for errors, and high precision is maintained.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

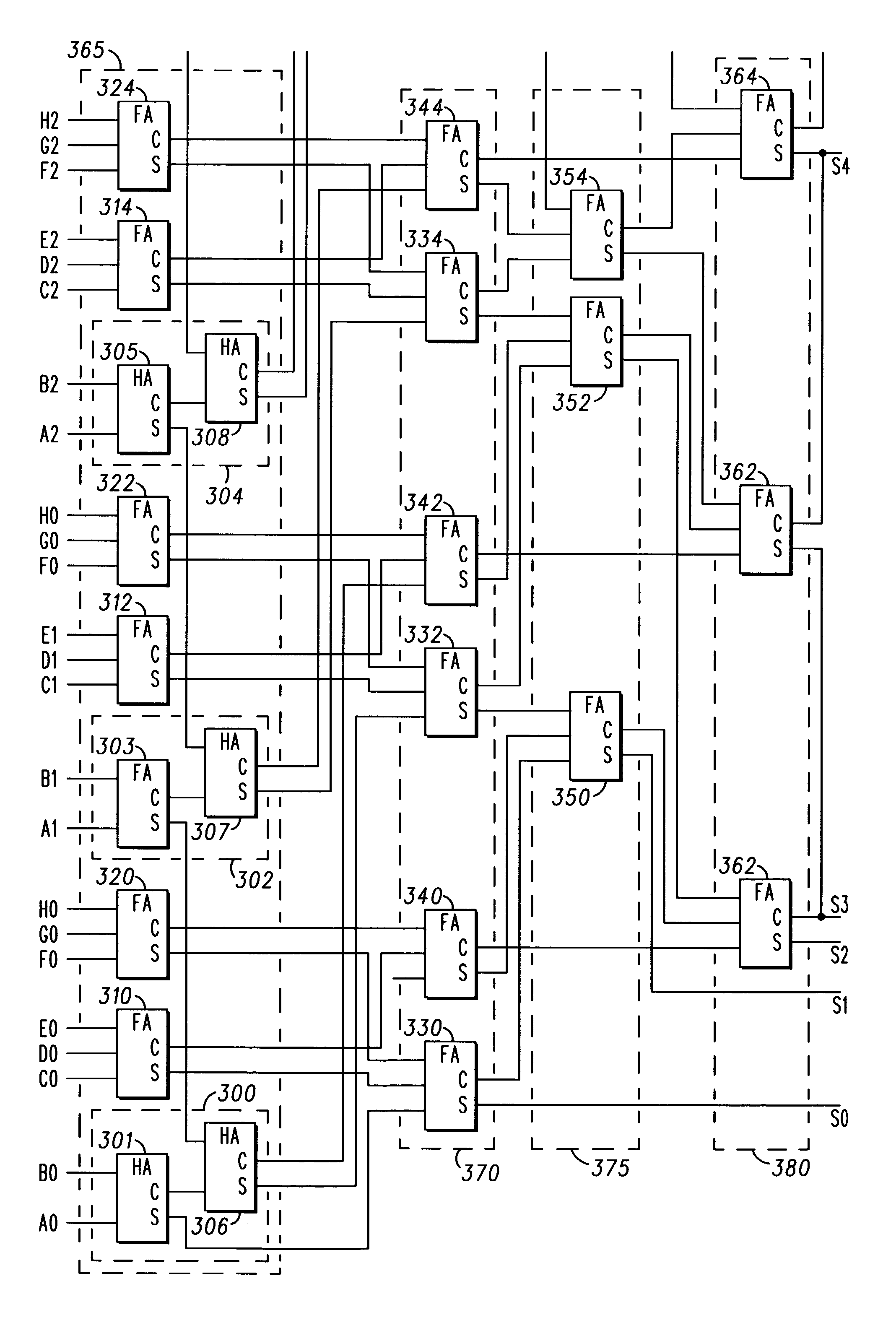

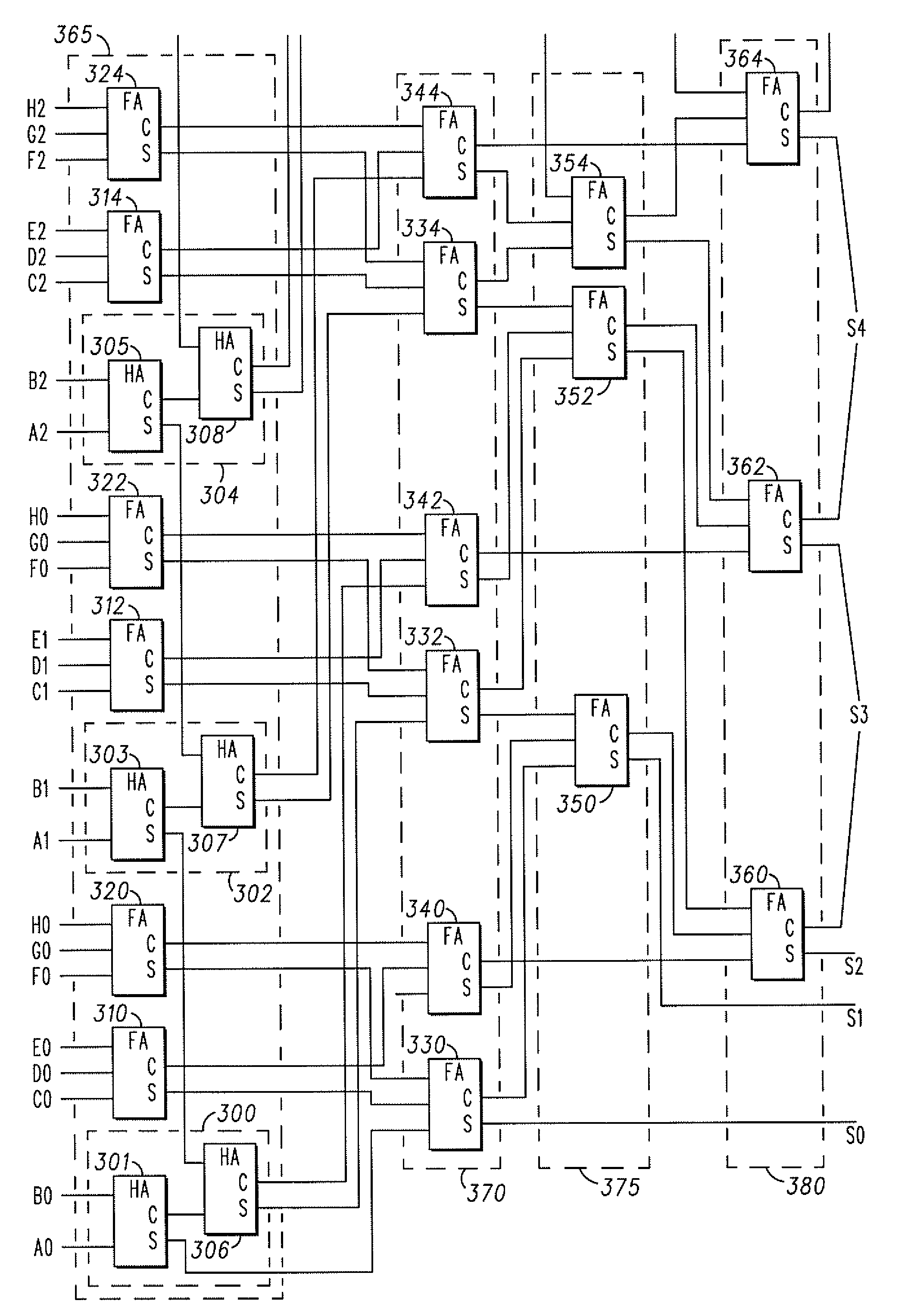

Adder tree structure DSP system and method

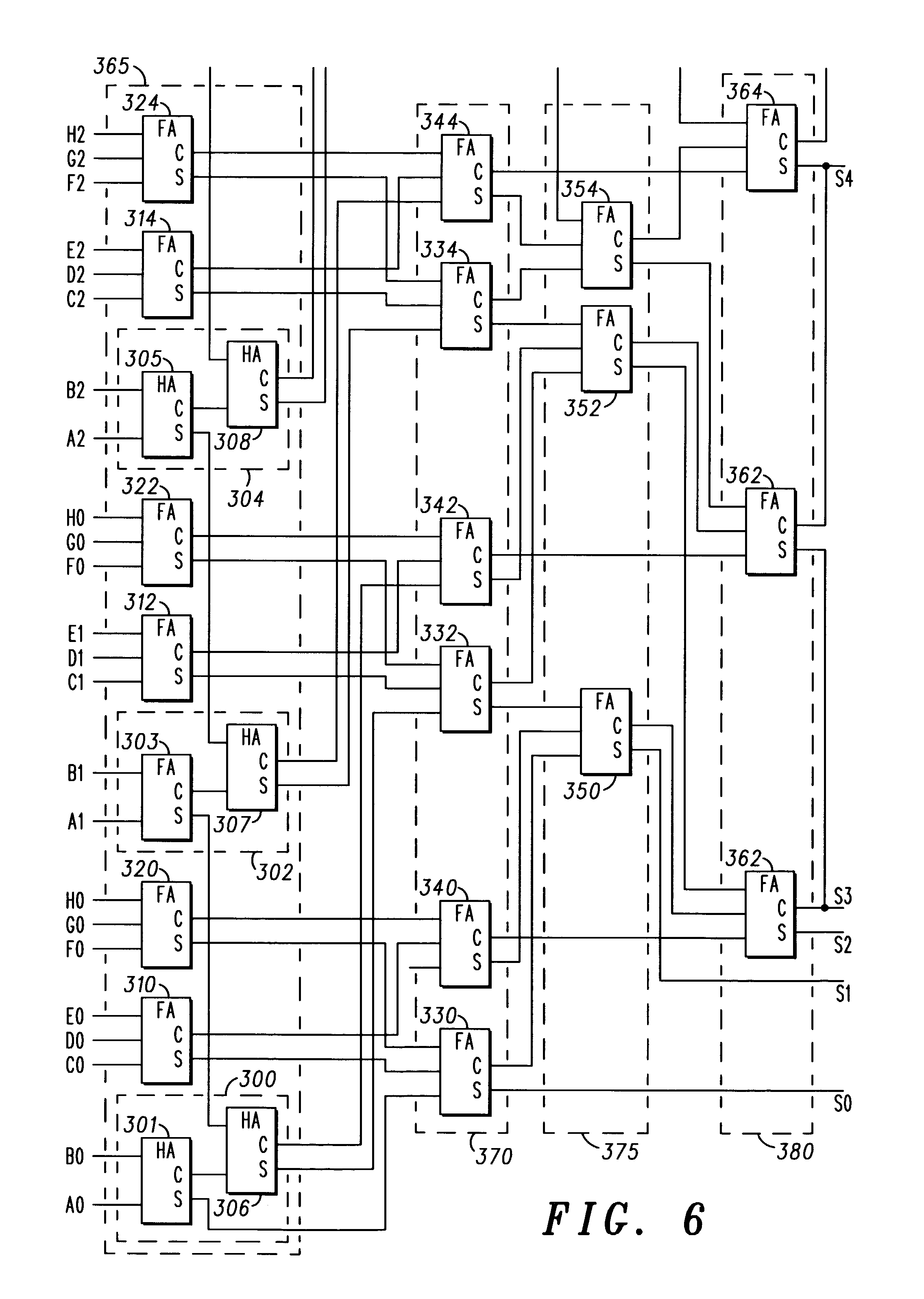

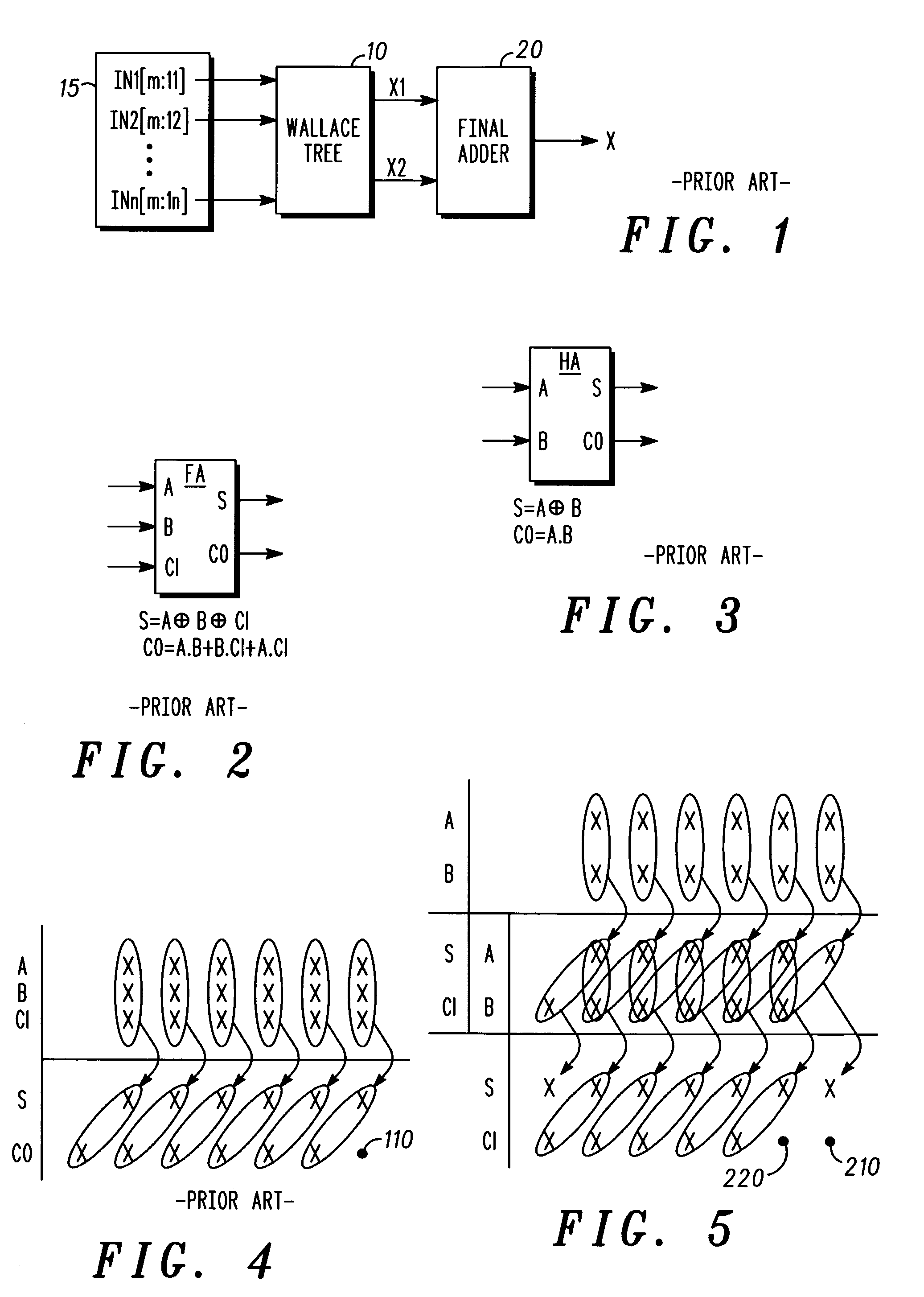

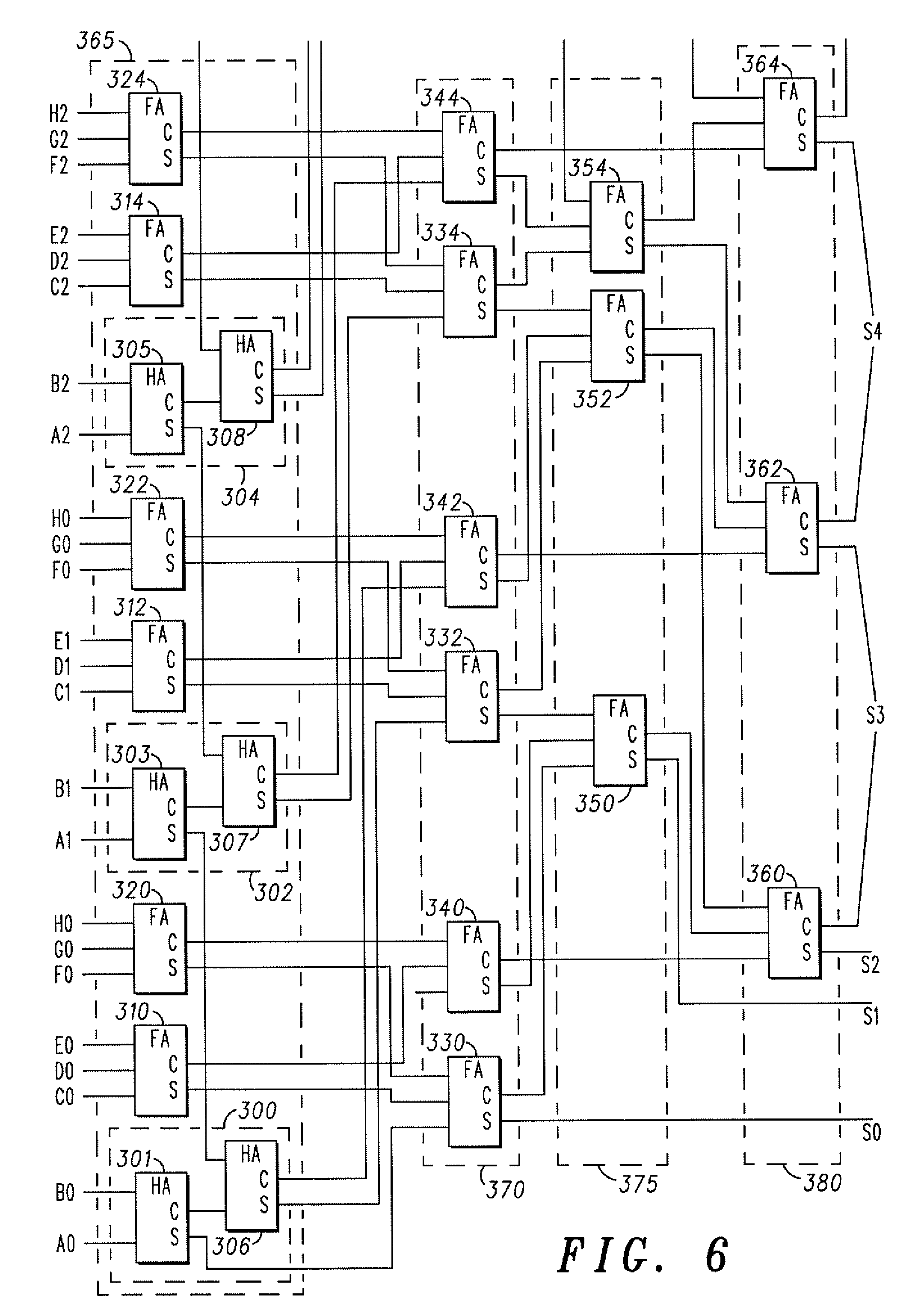

ActiveUS20030093454A1Reduce Propagation DelayAddressing slow performanceComputation using non-contact making devicesPropagation delayWallace tree

A Wallace tree structure such as that used in a DSP is arranged to sum vectors. The structure has a number of adder stages (365, 370, 375), each of which may have half adders (300) with two input nodes, and full adders (310) with three input nodes. The structure is designed with reference to the vectors to be summed. The number of full- and half-adders in each stage and the arrangement of vector inputs depends upon their characteristics. An algorithm calculates the possible tree structures and input arrangements, and selects an optimum design having a small final stage ripple adder (380), the design being based upon the characteristics of the vector inputs. This leads to reduced propagation delay and a reduced amount of semiconductor material for implementation of the DSP.

Owner:NXP USA INC

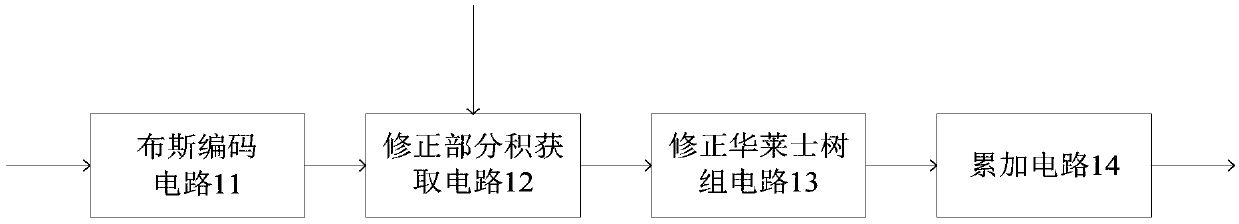

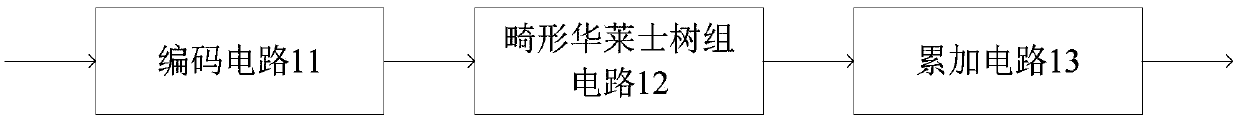

Multiplying device, data processing method, chip and electronic equipment

PendingCN110515587AComputation using non-contact making devicesPhysical realisationWallace treeBinary multiplier

The invention provides a multiplier, a data processing method, a chip and electronic equipment. The multiplier comprises: an improved regular signed number encoding circuit, an improved Wallace tree group circuit and an accumulation circuit. The output end of the improved regular signed number encoding circuit is connected with the input end of the improved Wallace tree group circuit; the output end of the improved Wallace tree group circuit is connected with the input end of the accumulation circuit, the multiplier can carry out regular signed number encoding on received data through the regular signed number encoding circuit, the number of obtained effective partial products is small, and therefore the complexity of multiplication operation achieved by the multiplier is reduced.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

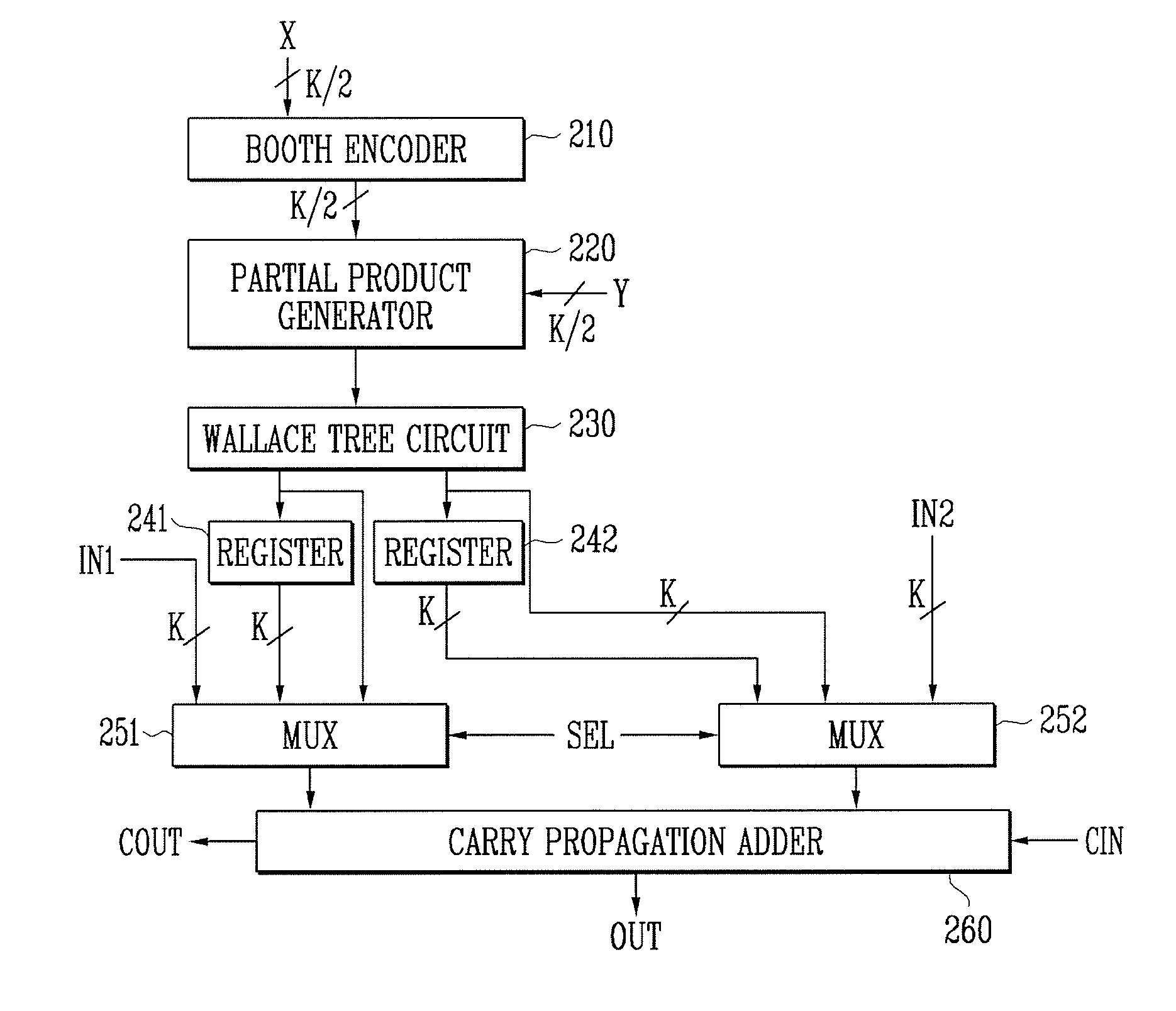

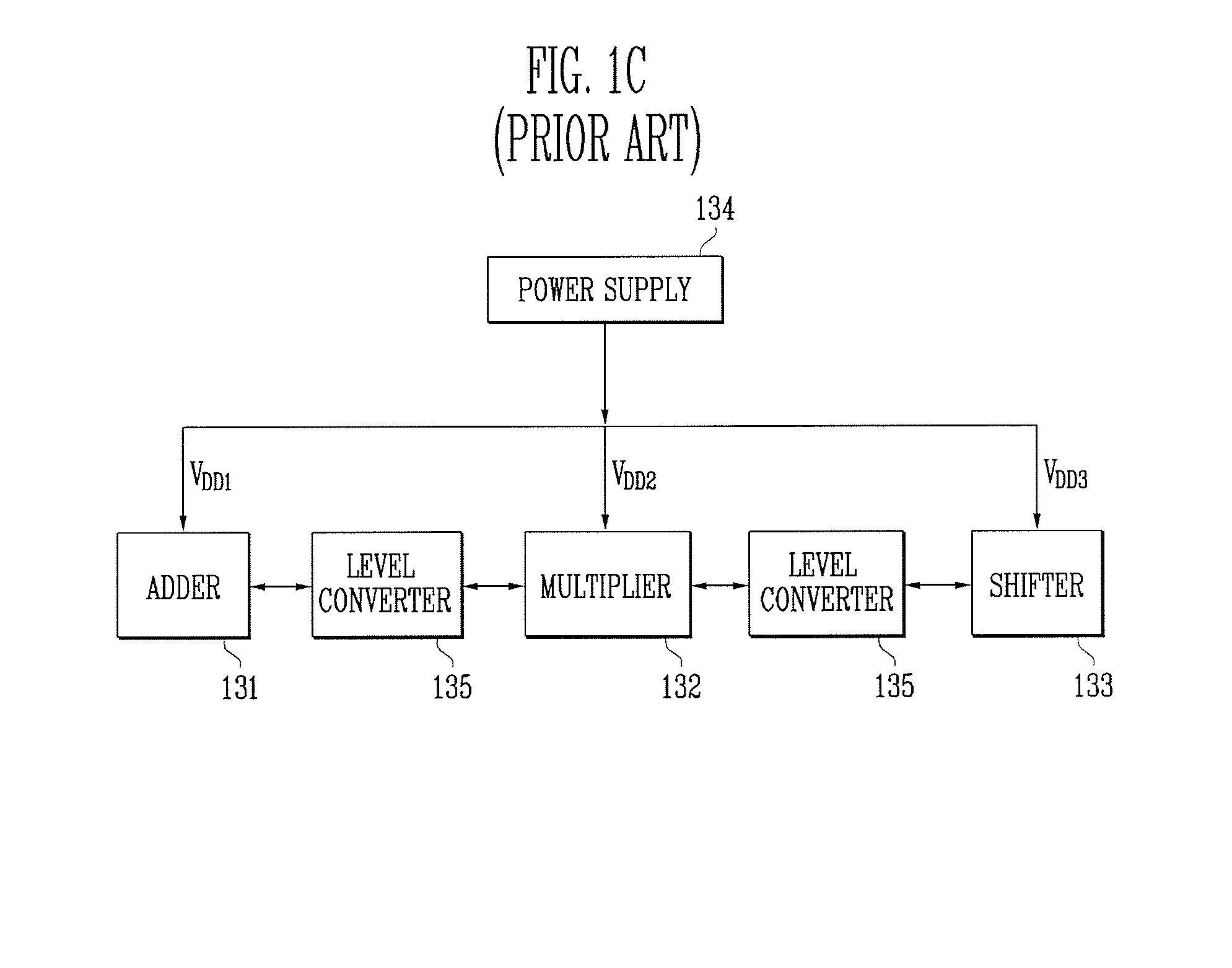

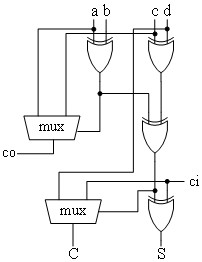

Reconfigurable arithmetic unit and high-efficiency processor having the same

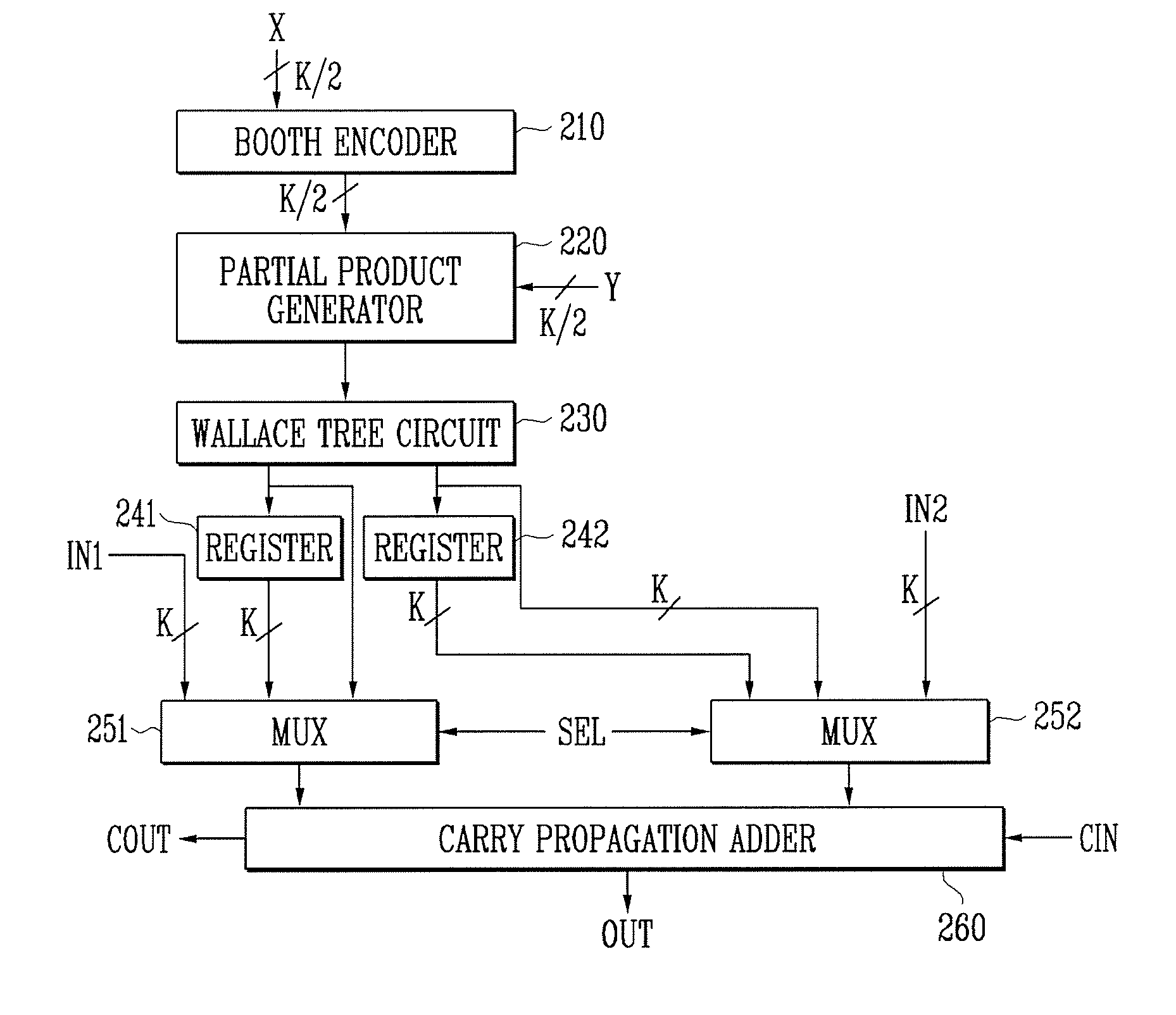

ActiveUS20090150471A1High degree of useImprove energy efficiencyComputation using non-contact making devicesComplex mathematical operationsWallace treeBinary multiplier

Provided are a reconfigurable arithmetic unit and a processor having the same. The reconfigurable arithmetic unit can perform an addition operation or a multiplication operation according to an instruction by sharing an adder. The reconfigurable arithmetic unit includes a booth encoder for encoding a multiplier, a partial product generator for generating a plurality of partial products using the encoded multiplier and a multiplicand, a Wallace tree circuit for compressing the partial products into a first partial product and a second partial product, a first Multiplexer (MUX) for selecting and outputting one of the first partial product and a first addition input according to a selection signal, a second MUX for selecting and outputting one of the second partial product and a second addition input according to the selection signal, and a Carry Propagation Adder (CPA) for adding an output of the first MUX and an output of the second MUX to output an operation result. The arithmetic unit can operate as an adder or a multiplier according to an instruction, and thus can increase the degree of use of entire hardware.

Owner:ELECTRONICS & TELECOMM RES INST

Adder tree structure digital signal processor system and method

ActiveUS7124162B2Reduce degradationAddressing slow performanceComputation using non-contact making devicesPropagation delayWallace tree

A Wallace tree structure such as that used in a digital signal processor (DSP) is arranged to sum vectors. The structure has a number of adder stages, each of which may have half adders with two input nodes, and full adders with three input nodes. The structure is designed with reference to the vectors to be summed. The number of full- and half-adders in each stage and the arrangement of vector inputs depends upon their characteristics. An algorithm calculates the possible tree structures and input arrangements, and selects an optimum design having a small final stage ripple adder after the last stage of the Wallace tree structure, the design being based upon the characteristics of the vector inputs. This leads to reduced propagation delay and a reduced amount of semiconductor material for implementation of the DSP.

Owner:NXP USA INC

Reconfigurable arithmetic unit and high-efficiency processor having the same

ActiveUS8150903B2High degree of useImprove energy efficiencyComputation using non-contact making devicesWallace treeBinary multiplier

Provided are a reconfigurable arithmetic unit and a processor having the same. The reconfigurable arithmetic unit can perform an addition operation or a multiplication operation according to an instruction by sharing an adder. The reconfigurable arithmetic unit includes a booth encoder for encoding a multiplier, a partial product generator for generating a plurality of partial products using the encoded multiplier and a multiplicand, a Wallace tree circuit for compressing the partial products into a first partial product and a second partial product, a first Multiplexer (MUX) for selecting and outputting one of the first partial product and a first addition input according to a selection signal, a second MUX for selecting and outputting one of the second partial product and a second addition input according to the selection signal, and a Carry Propagation Adder (CPA) for adding an output of the first MUX and an output of the second MUX to output an operation result. The arithmetic unit can operate as an adder or a multiplier according to an instruction, and thus can increase the degree of use of entire hardware.

Owner:ELECTRONICS & TELECOMM RES INST

Wallace tree compressor based on Xilinx FPGA primitive

ActiveCN113872608AReduce areaSmall delayLogic circuits characterised by logic functionComputation using non-contact making devicesWallace treeTree pattern

The invention provides a Wallace tree compressor based on a Xilinx FPGA primitive. The Wallace tree compressor is composed of a tree type compression structure and a final summation unit. The tree-shaped compression structure compresses a plurality of binary numbers to two or three outputs, and the summing module adds compression results and outputs a final result. The tree-shaped compression structure takes a 4: 2 compressor as a basic compression unit and is matched with a 3: 2 compressor when necessary. The bit level structure of the 4: 2 compressor comprises an LUT6-2 module, a first muxcy module and a first xorcy module which are used for original intonation of the Xilinx FPGA; the LUT6-2 module is configured to be two LUT5 which share input and independently output, and two independent binary functions can be realized; and the first muxcy module and the first xorcy module are special carry logic resources in the CLB and are configured into a 3: 2 compressor. A 3: 1 compressor is designed as a final summation unit of the Wallace tree according to the same thought. The method is used for achieving multi-operand addition and subtraction operation, the utilization rate of hardware resources is greatly improved, and the overall delay and power consumption of the Wallace tree are reduced.

Owner:NAVAL UNIV OF ENG PLA

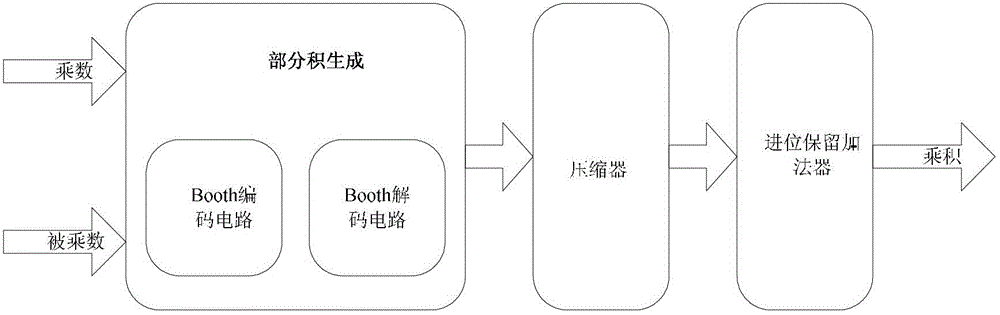

Booth multiplier

The invention discloses a Booth multiplier, which comprises a Booth coding circuit, a Booth decoding circuit, compressors and a carry save adder, wherein the Booth coding circuit is used for implementing Booth coding and coding a binary multiplying factor B to acquire signals X1, X2 and Neg; the Booth decoding circuit is used for combining the signals X1, X2 and Neg and a binary multiplicand A to generate partial product terms; the compressors are used for accumulating a plurality of partial product terms generated by the decoding circuit to acquire two accumulated values; and the carry save adder is used for implementing carry save adding operation on the two accumulated values acquired by accumulation of a plurality of partial product terms through the compressors to acquire a final product result. The operating rate is improved by adopting a hybrid Wallace-Tree structure and inserting a streamline. Compared with the prior art, the invention has the advantages that the Booth multiplier can achieve good effects on rate and area, and is low in energy consumption and accurate in calculation result at the same time.

Owner:SOUTH CHINA UNIV OF TECH

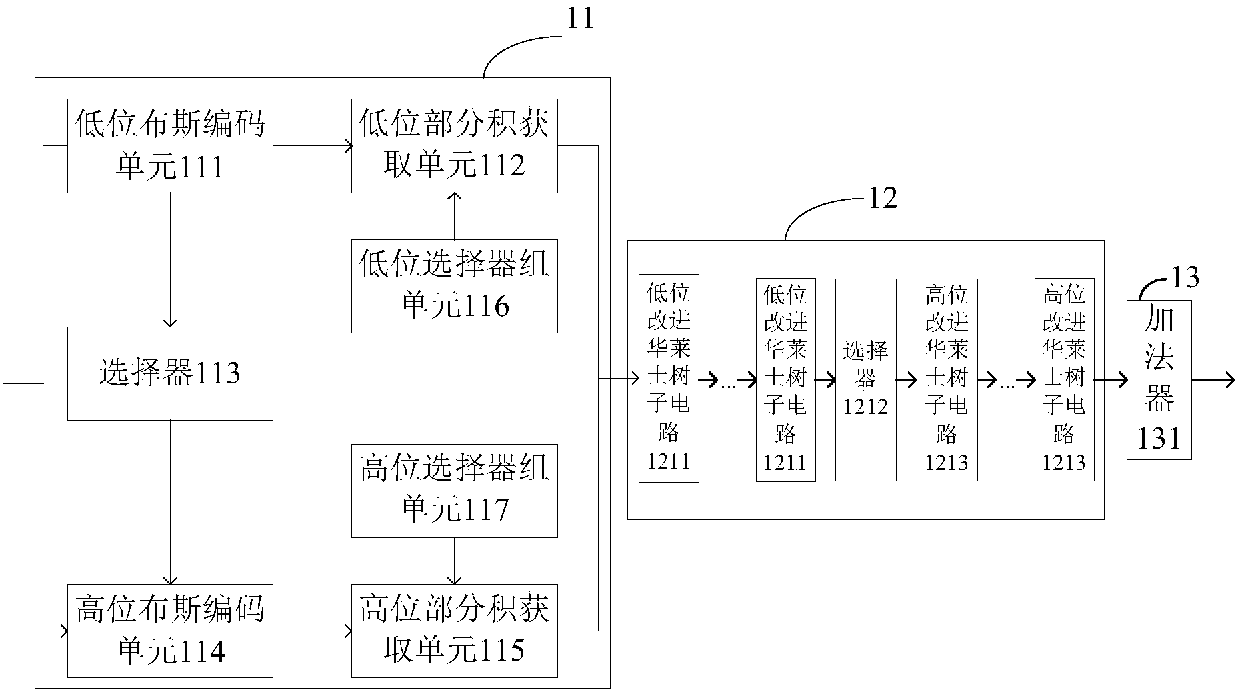

Multiplier, data processing method, chip and electronic equipment

ActiveCN111258633AReduce power consumptionReduce the area occupied by AI chipsPhysical realisationEnergy efficient computingComputer hardwareWallace tree

The invention provides a multiplier, a data processing method, a chip and electronic equipment. The multiplier comprises: an improved coding circuit, an improved Wallace tree group circuit and an accumulation circuit, the output end of the improved coding circuit is connected with the input end of the improved Wallace tree group circuit, the output end of the improved Wallace tree group circuit isconnected with the input end of the accumulation circuit, the multiplier can carry out multiplication operation on various data with different bit widths, and the area of an AI chip occupied by the multiplier is effectively reduced; and, in addition, the multiplier performs accumulation operation on the partial product of the target code by improving a Wallace tree group circuit, and the power consumption of the multiplier can be effectively reduced.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

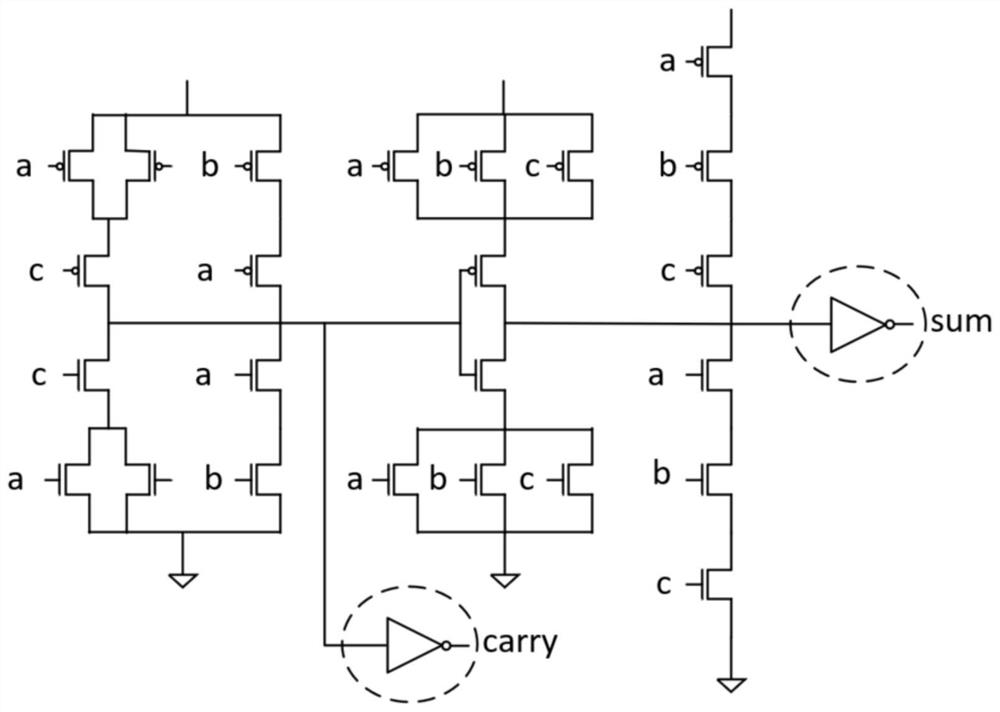

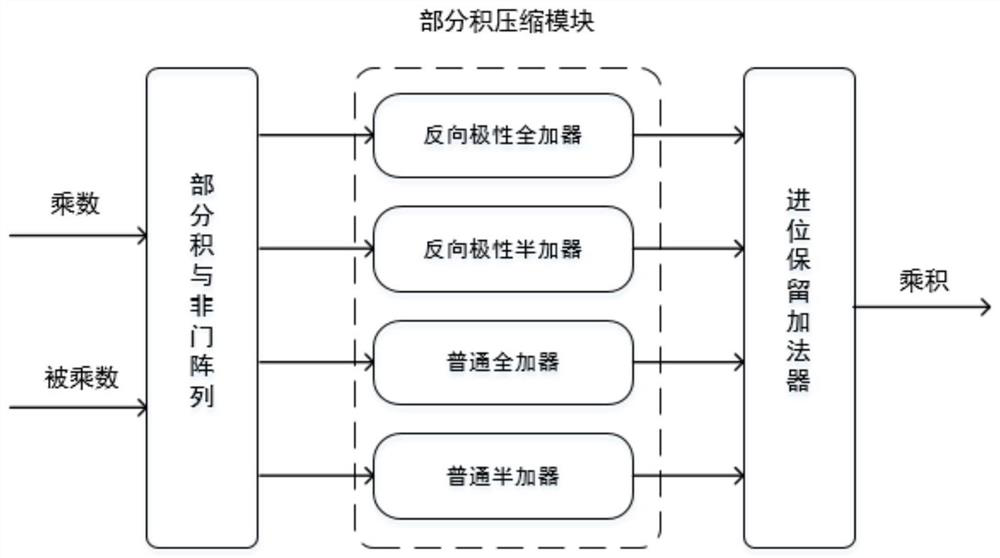

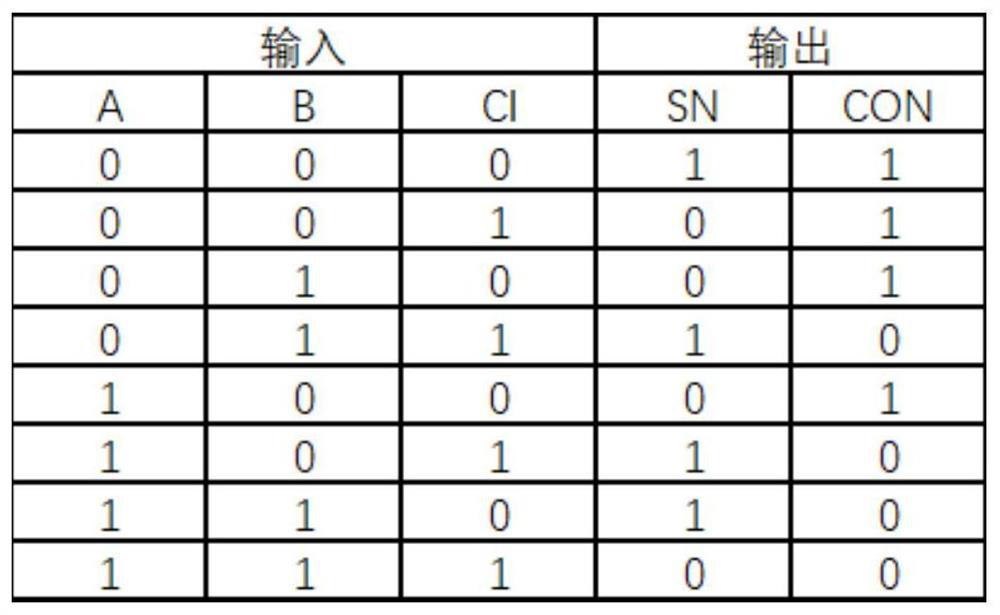

Multiplier based on reverse polarity technology and code generation method thereof

ActiveCN111897513AReduce power consumptionReduce areaDigital data processing detailsEnergy efficient computingWallace treeCode generation

The invention discloses a multiplier based on a reverse polarity technology and a code generation method thereof. The multiplier comprises a partial product generation module, a partial product compression module and a carry-save adder; the partial product generation module calculates the multiplier and the multiplicand to obtain a partial product; the partial product compression module compressesthe partial product to obtain a partial product compression tree; and the carry-save adder performs addition processing on the signals connected to the carry-save adder in the compression process, and an addition processing result is connected to the output end of the multiplier; the partial product generation module adopts an NAND gate array, the partial product compression module adopts a Wallace tree structure, the compressor mainly adopts a reverse polarity full adder and a reverse polarity half adder, and a common full adder and a common half adder are adopted under specific conditions.By adopting the reverse polarity full adder with small area and low power consumption, the power consumption of the multiplier is effectively reduced, codes of the multiplier can be automatically generated, and the time sequence of the multiplier can be integrally optimized.

Owner:上海芷锐电子科技有限公司

Multiply-accumulate modules and parallel multipliers and methods of designing multiply-accumulate modules and parallel multipliers

InactiveUS7315879B2Width of at least one transistor employedReduce the amount requiredComputation using non-contact making devicesDigital computer detailsWallace treeParallel computing

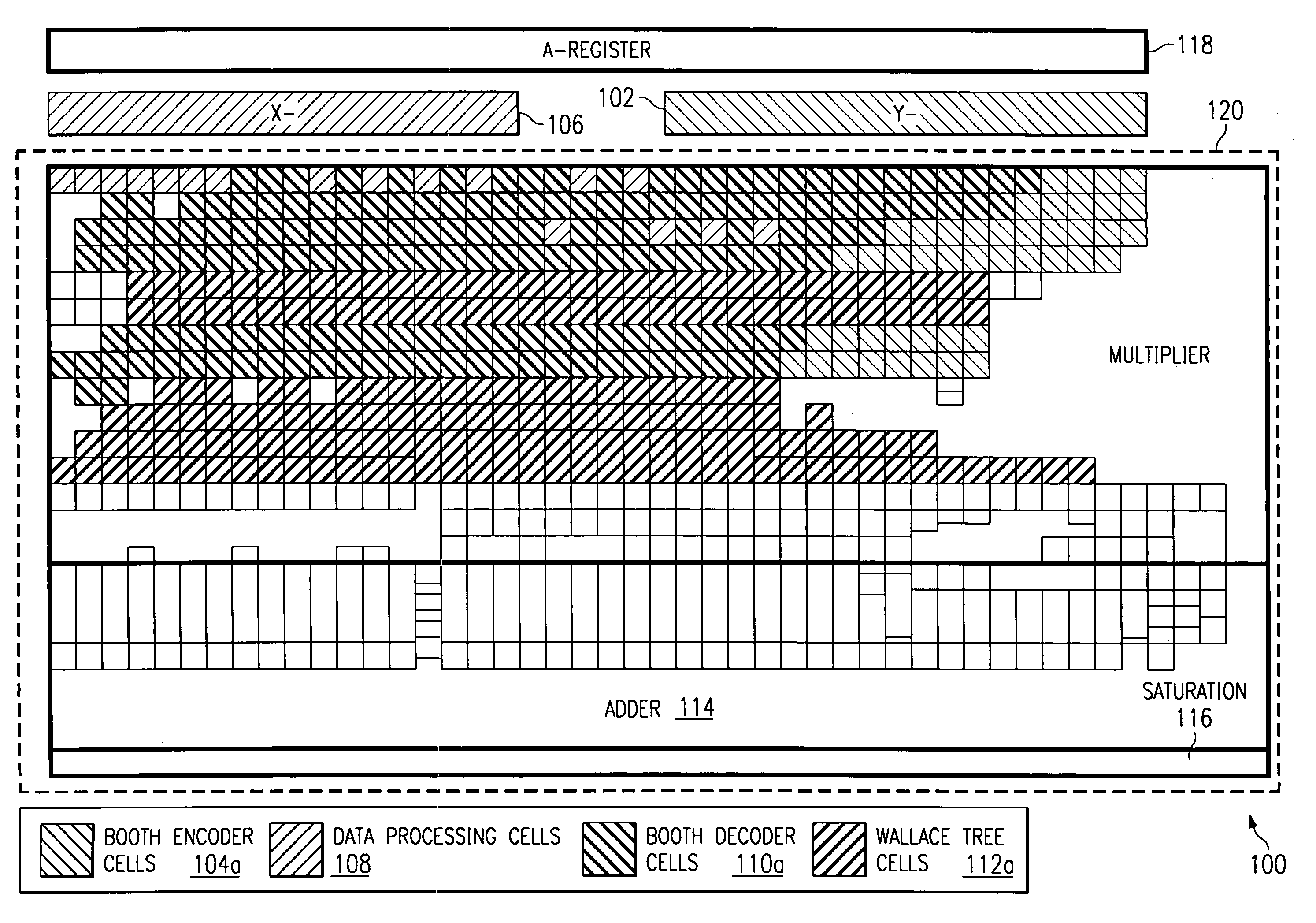

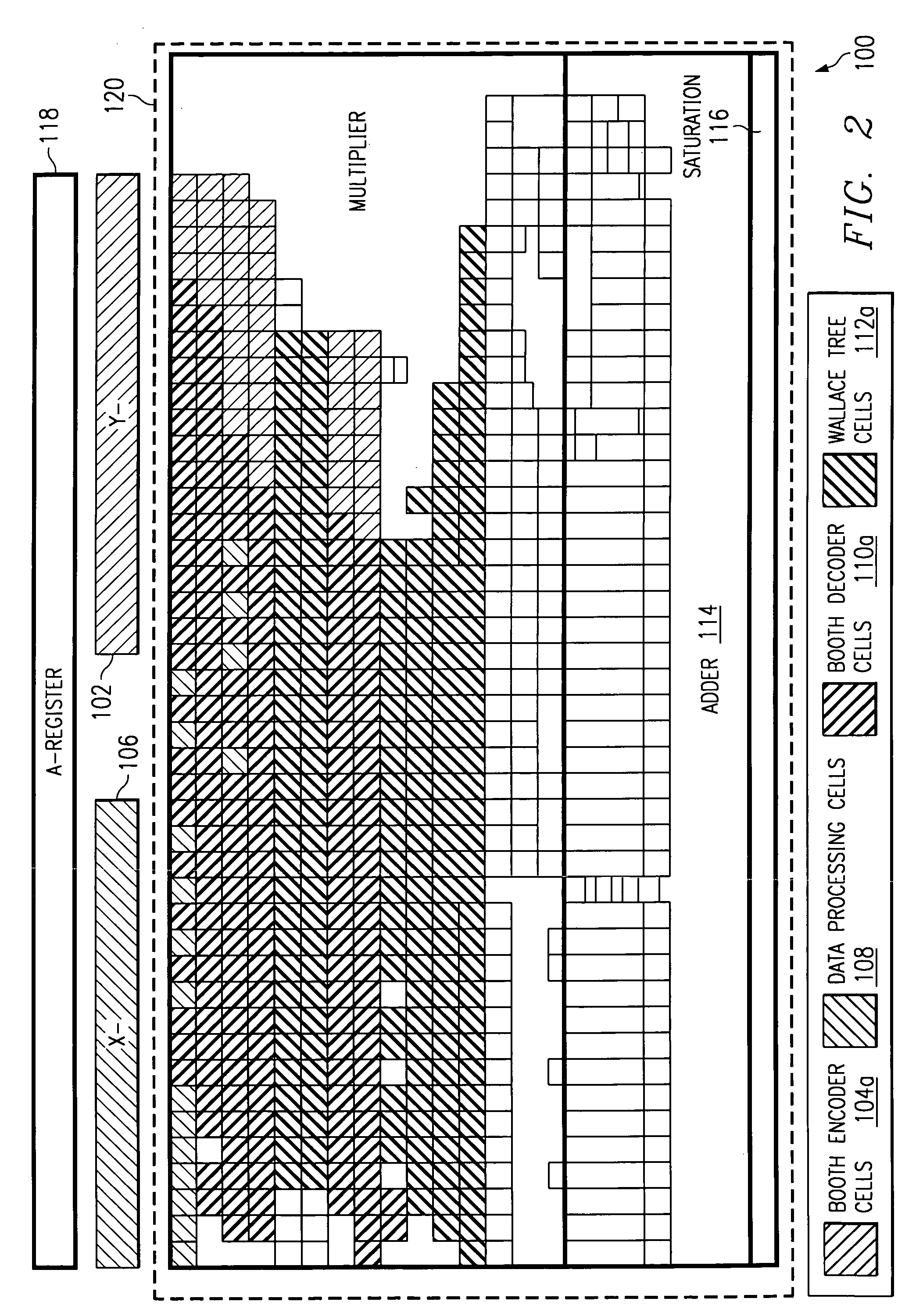

A multiply-accumulate module (100) includes a multiply-accumulate core (120), which includes a plurality of Booth encoder cells (104a). The multiply-accumulate core (120) also includes a plurality of Booth decoder cells (110a) connected to at least one of the Booth encoder cells (104a) and a plurality of Wallace tree cells (112a) connected to at least one of the Booth decoder cells (110a). Moreover, at least one first Wallace tree cell (112a1) or at least one first Booth decoder cell (110a1), or any combination thereof, includes a first plurality of transistors, and at least one second Wallace tree cell (112a2) or at least one second Booth decoder cell (110a2), or any combination thereof, includes a second plurality of transistors. In addition, at least one critical path of the multiply-accumulate module (100) includes the at least one first cell and a width of at least one of the first plurality of transistors is greater than a width of at least one of the second plurality of transistors.

Owner:TEXAS INSTR INC

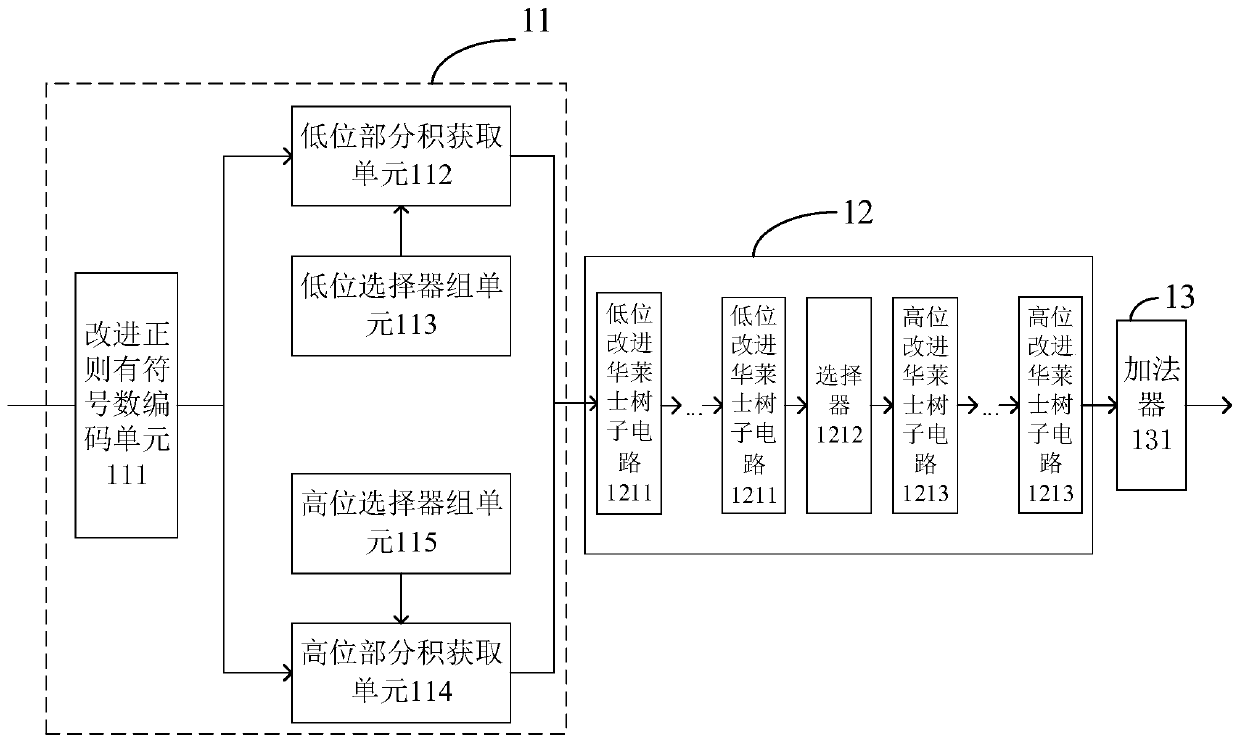

Multiplying device, data processing method, chip and electronic equipment

PendingCN110515588AReduce complexityReduce the numberComputation using non-contact making devicesPhysical realisationWallace treeBinary multiplier

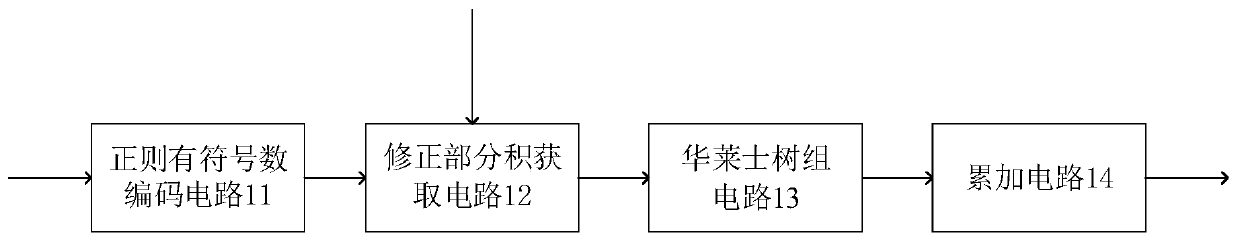

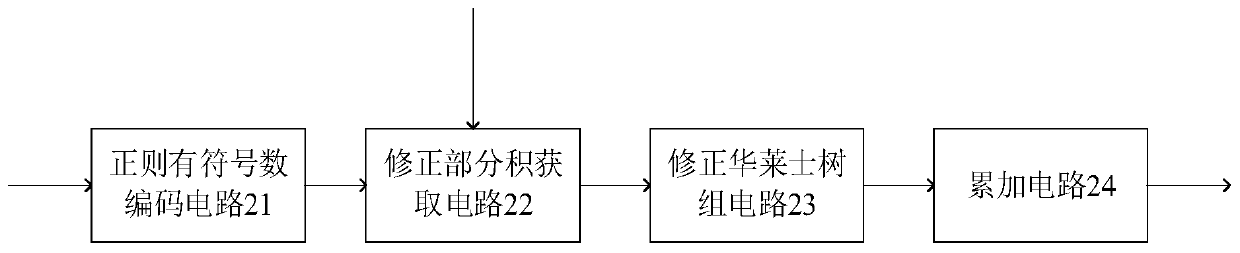

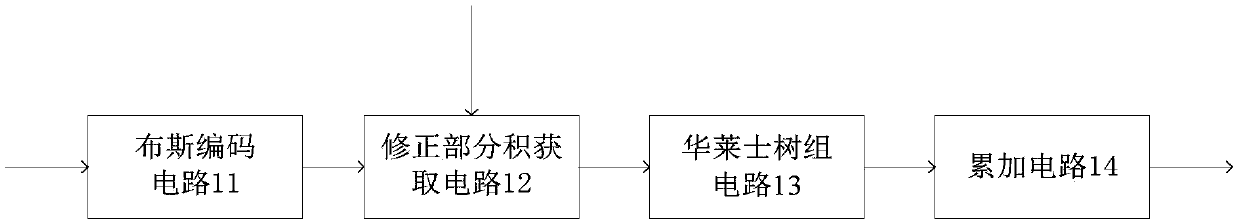

The invention provides a multiplier, a data processing method, a chip and electronic equipment. The multiplier comprises: a regular sign number coding circuit, a corrected partial product acquisitioncircuit, a correcting Wallace tree group circuit and an accumulation circuit; the output end of the regular signed number encoding circuit is connected with the input end of the correction partial product acquisition circuit; the output end of the correction partial product acquisition circuit is connected with the input end of the correction Wallace tree group circuit; according to the multiplier, regular signed number encoding can be carried out on received data through the regular signed number encoding circuit, the number of obtained effective partial products is small, and therefore the complexity of multiplication operation of the multiplier is lowered.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

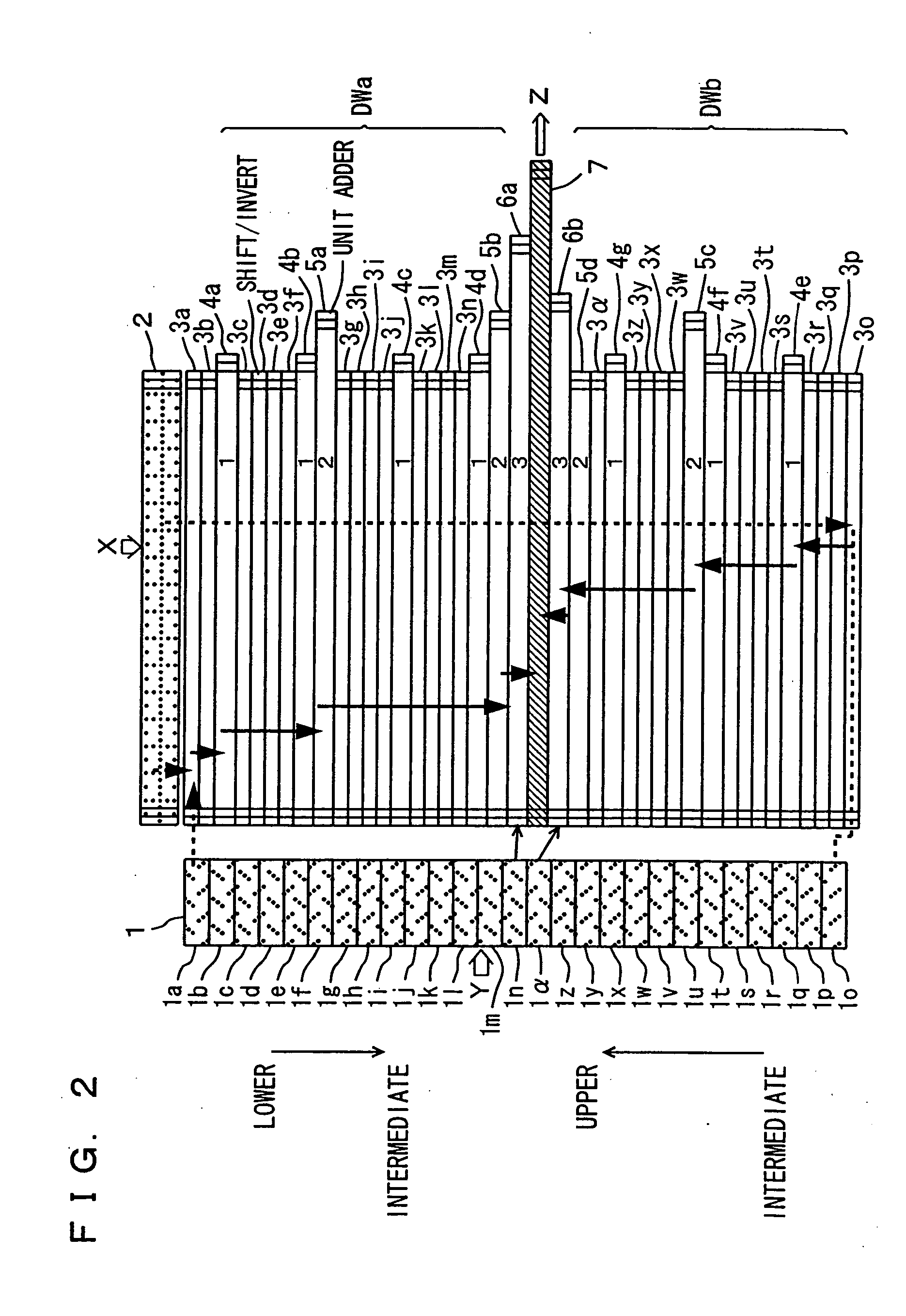

High speed multiplication apparatus of Wallace tree type with high area efficiency

InactiveUS20050246407A1High speed multiplicationGuaranteed high speed operationComputation using non-contact making devicesWallace treeTheoretical computer science

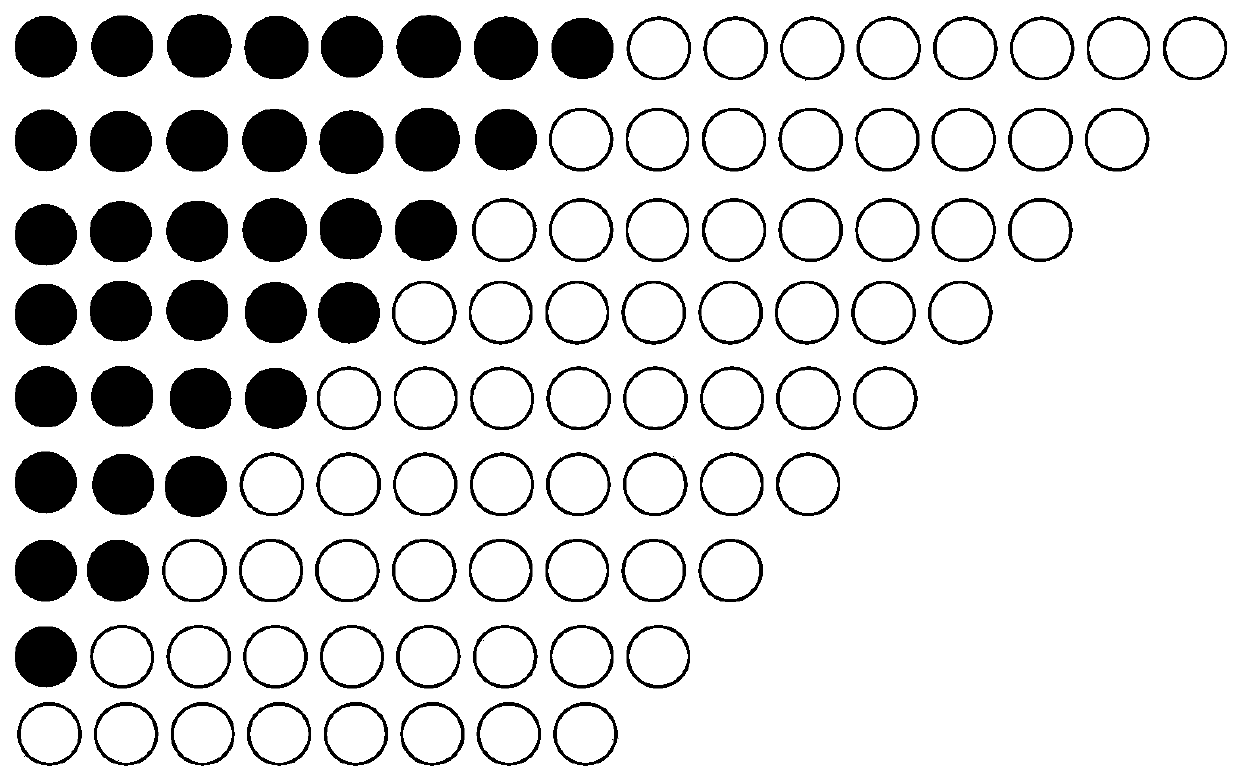

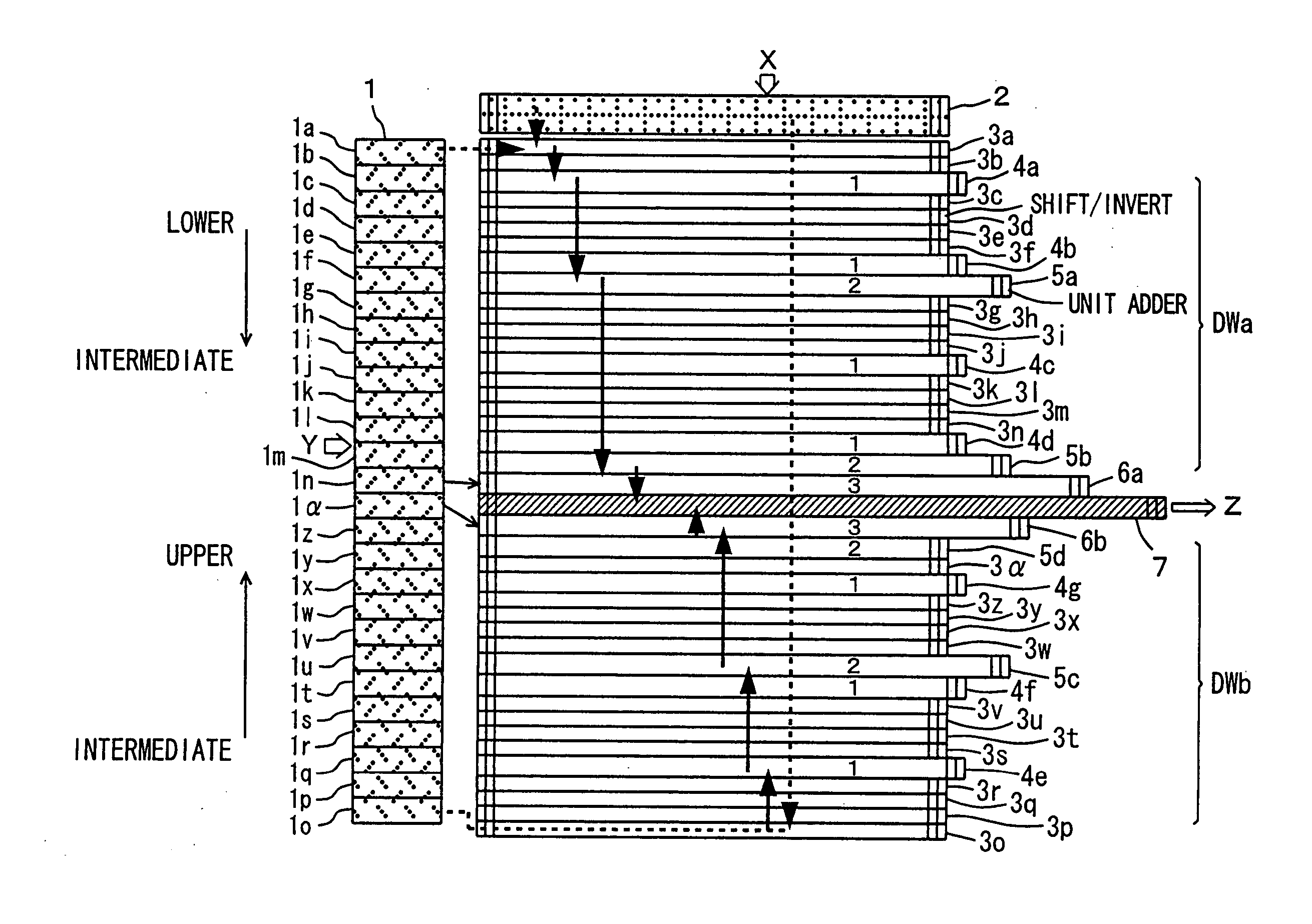

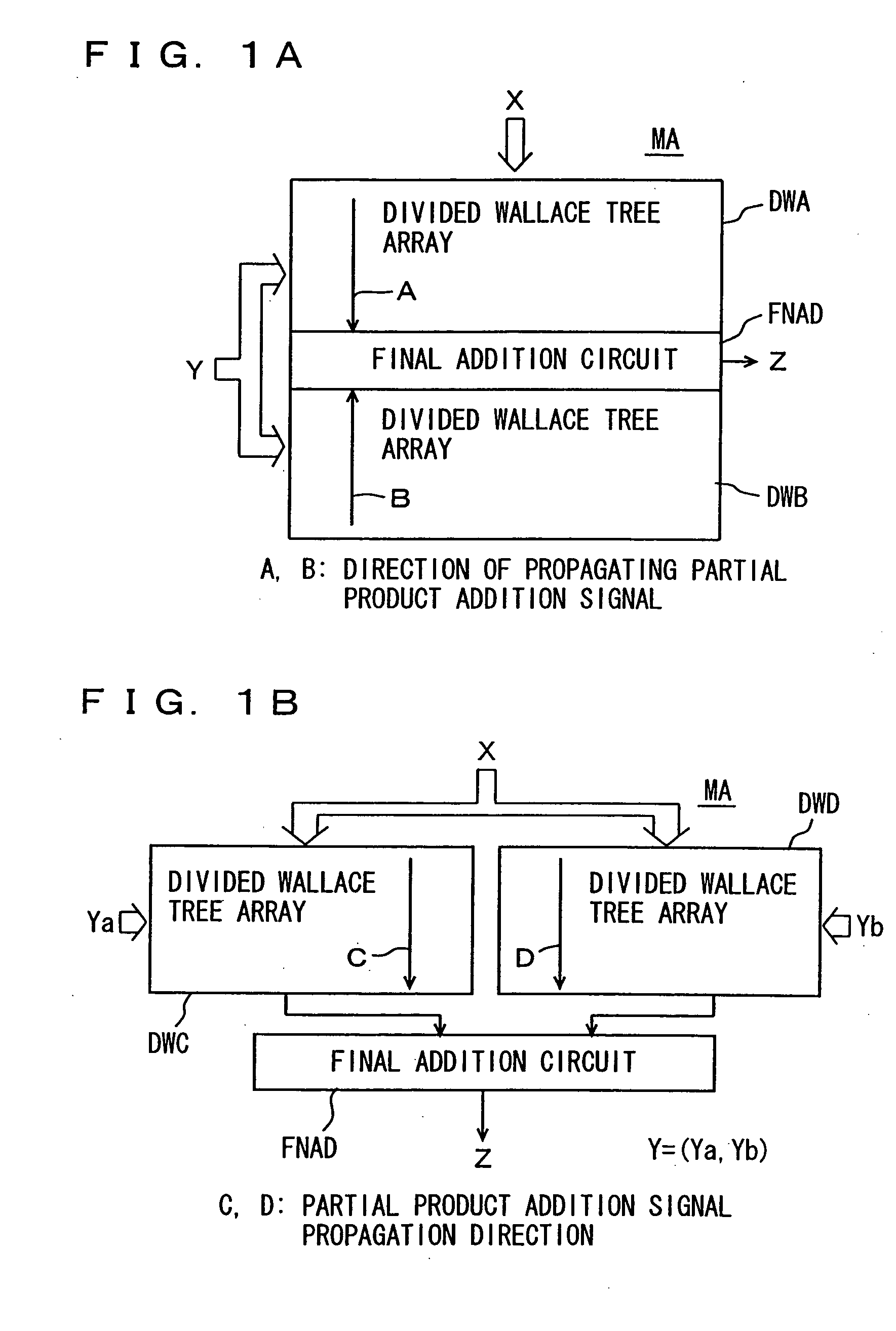

A multiplication array is divided into divided Wallace tree arrays each performing multiplication by addition in a tree-like form. An addition result is transmitted from the divided Wallace tree arrays to a final addition circuit. Thus, an interconnection line length of a critical path of a multiplication apparatus can be reduced.

Owner:RENESAS TECH CORP

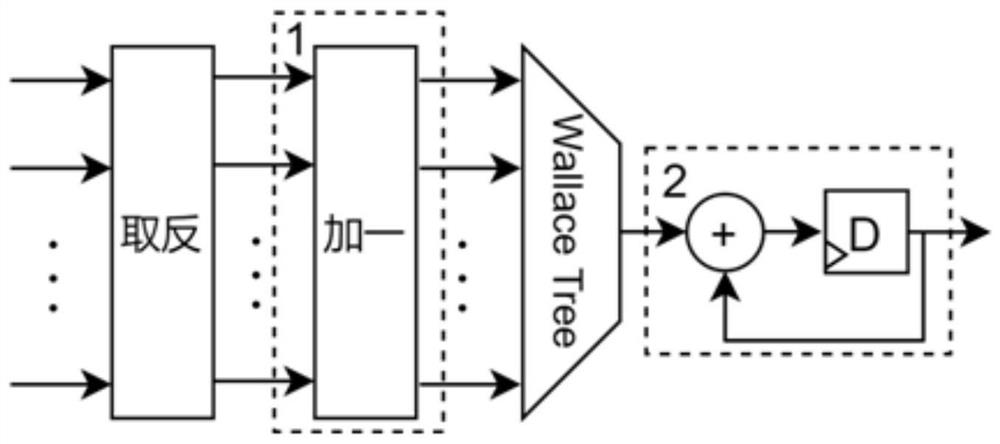

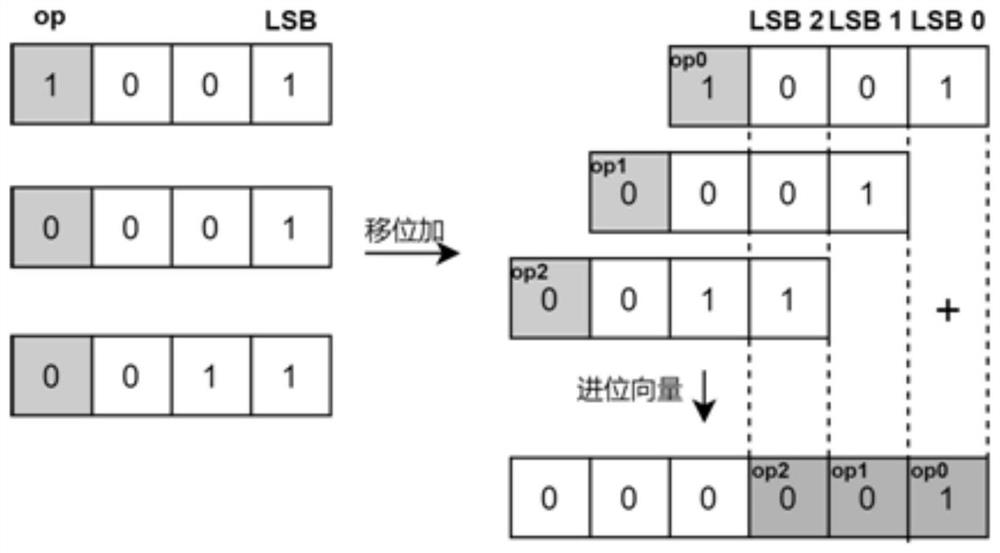

Multi-input shift summation accumulator based on Wallace tree

PendingCN114237550AReduce overheadSimple designComputation using non-contact making devicesConcurrent instruction executionMulti inputWallace tree

The invention belongs to the technical field of intelligent processors, and particularly provides a multiple-input shift summation accumulator based on a Wallace tree, which comprises an exclusive-OR gate array, an initial carry vector generation module, a Wallace compression tree, a 4-2 compressor, an accumulation register and an adder, through the exclusive-OR gate array and the initial carry vector generation module, the original code and subtraction operation are converted into complement addition at one time to be used for a Wallace tree, native support for multiple data formats and addition and subtraction is provided, and hardware overhead is saved; and then accumulation is realized based on a 4-2 compressor and an accumulation register, the 4-2 compressor compresses two output values of the Wallace tree and a storage value in the accumulation register to obtain two intermediate results, and the intermediate results are output to the accumulation register to update the storage value, so that the carry chain overhead for summation of the results of the Wallace tree is saved, and meanwhile, a full adder carry chain is removed before the accumulation register. The design of an assembly line is greatly facilitated, and the clock frequency and the accumulation efficiency can be improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Digital logic operation method and circuit and FPGA chip

ActiveCN108255463AReduce the maximum delayReduce latencyDigital data processing detailsWallace treeProcessor register

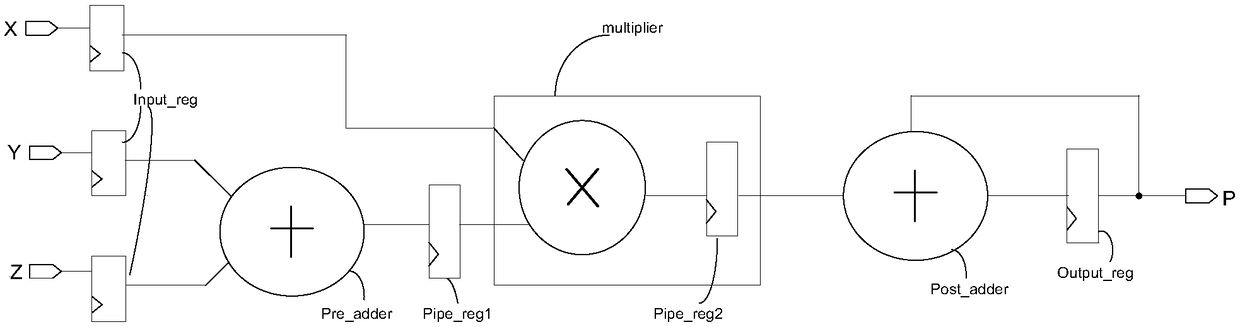

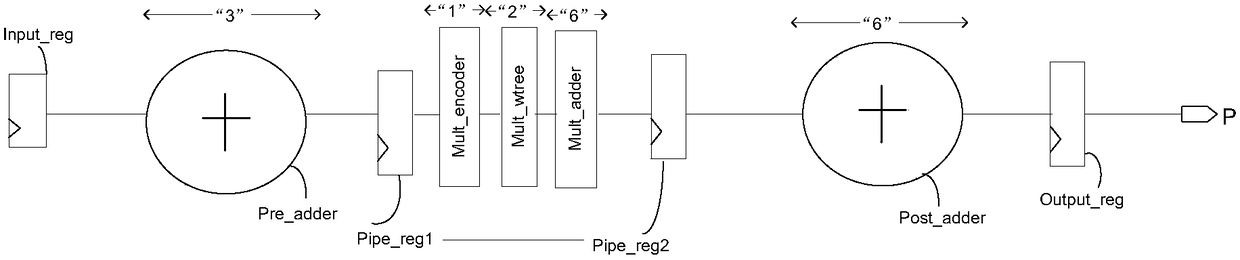

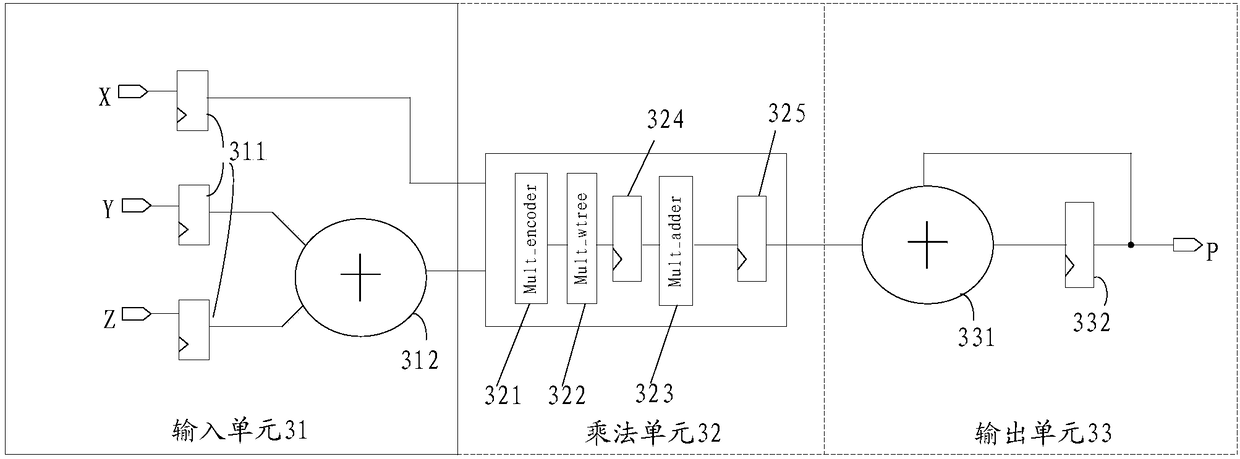

The invention provides a digital logic operation method and circuit and an FPGA chip. A first pipeline register is arranged in a multiplication unit to shorten the time delay between two registers; the circuit comprises an input unit, the multiplication unit and an output unit which are sequentially connected, the input unit includes multiple input registers for receiving input data separately, the multiplication unit includes an encoder, a Wallace tree structure module and an adder which are sequentially connected, the first pipeline register is arranged between any two devices in the multiplication unit, and a second pipeline register is arranged behind the adder; the output unit includes an accumulator and an output register which are connected sequentially, and the output of the accumulator and the output of the multiplication unit are used as the input of the accumulator. By means of the digital logic operation method and circuit and the FPGA chip, the time delay between the firstpipeline register and the second pipeline register is shortened, the maximum time delay of the overall digital logic operation circuit is shortened, the running period of a system is shortened accordingly, and the operation rate of the system is increased.

Owner:SHENZHEN PANGO MICROSYST CO LTD

Multiplier, data processing method, chip and electronic equipment

InactiveCN111258543AGuarantee the accuracy of calculationReduce power consumptionDigital data processing detailsWallace treeBooth encoding

The invention provides a multiplier, a data processing method, a chip and electronic equipment. The multiplier comprises: a Booth encoding circuit, a corrected partial product acquisition circuit, a Wallace tree group circuit and an accumulation circuit. The output end of the Booth encoding circuit is connected with the input end of the correction partial product acquisition circuit, the output end of the correction partial product acquisition circuit is connected with the input end of the Wallace tree group circuit, and the output end of the Wallace tree group circuit is connected with the input end of the accumulation circuit. According to the multiplier, on the premise that the operation accuracy of the multiplier can be completely guaranteed, when an original partial product is obtained due to a negative coded signal, carry forward transmission is possibly generated due to the fact that negation plus one operation needs to be conducted, and consequently multi-bit data signals are overturned is eliminated, and the power consumption of the multiplier is effectively reduced.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

A testing method for a second-order booth coded wallace tree multiplier circuit

ActiveCN111025133BIncrease coverageLow number of vectorsDigital circuit testingWallace treeBooth encoding

The present invention relates to a test method for a second-order Booth coded Wallace tree multiplier circuit: S1, obtaining the multiplier structure; S2, generating a test vector set for testing a partial product generation circuit; S3, generating a test vector set for a partial product compression circuit Test vector set: traverse all inputs of all compressor units in the partial product compression circuit to obtain a set of partial product array outputs; according to the topology of the multiplier, convert each partial product array output in the set of partial product array outputs into The original input of the multiplier, thereby obtains the test vector set that is used for testing partial product compression circuit; S4, compares the test vector used for partial product generation circuit and partial product compression circuit, removes repeated test vectors, obtains final test vector set input to the multiplier for test verification; S5, using a pseudo-random code test method to test the final summation circuit part. The present invention uses fewer test vectors to achieve higher test coverage.

Owner:BEIJING MXTRONICS CORP +1

Multiplier, data processing method, chip and electronic equipment

ActiveCN111258546AGuarantee the accuracy of calculationReduce power consumptionDigital data processing detailsEnergy efficient computingComputer hardwareWallace tree

The invention provides a multiplier, a data processing method, a chip and electronic equipment. The multiplier comprises: a coding circuit, a malformed Wallace tree group circuit and an accumulation circuit, the output end of the encoding circuit is connected with the input end of the malformed Wallace tree group circuit, the output end of the malformed Wallace tree group circuit is connected withthe input end of the accumulation circuit, and the multiplier can remove and process a numerical value of 0 on the premise of completely ensuring the operation accuracy of the multiplier, so that thepower consumption of the multiplier is effectively reduced.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com