Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

247results about How to "Increase in circuit size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

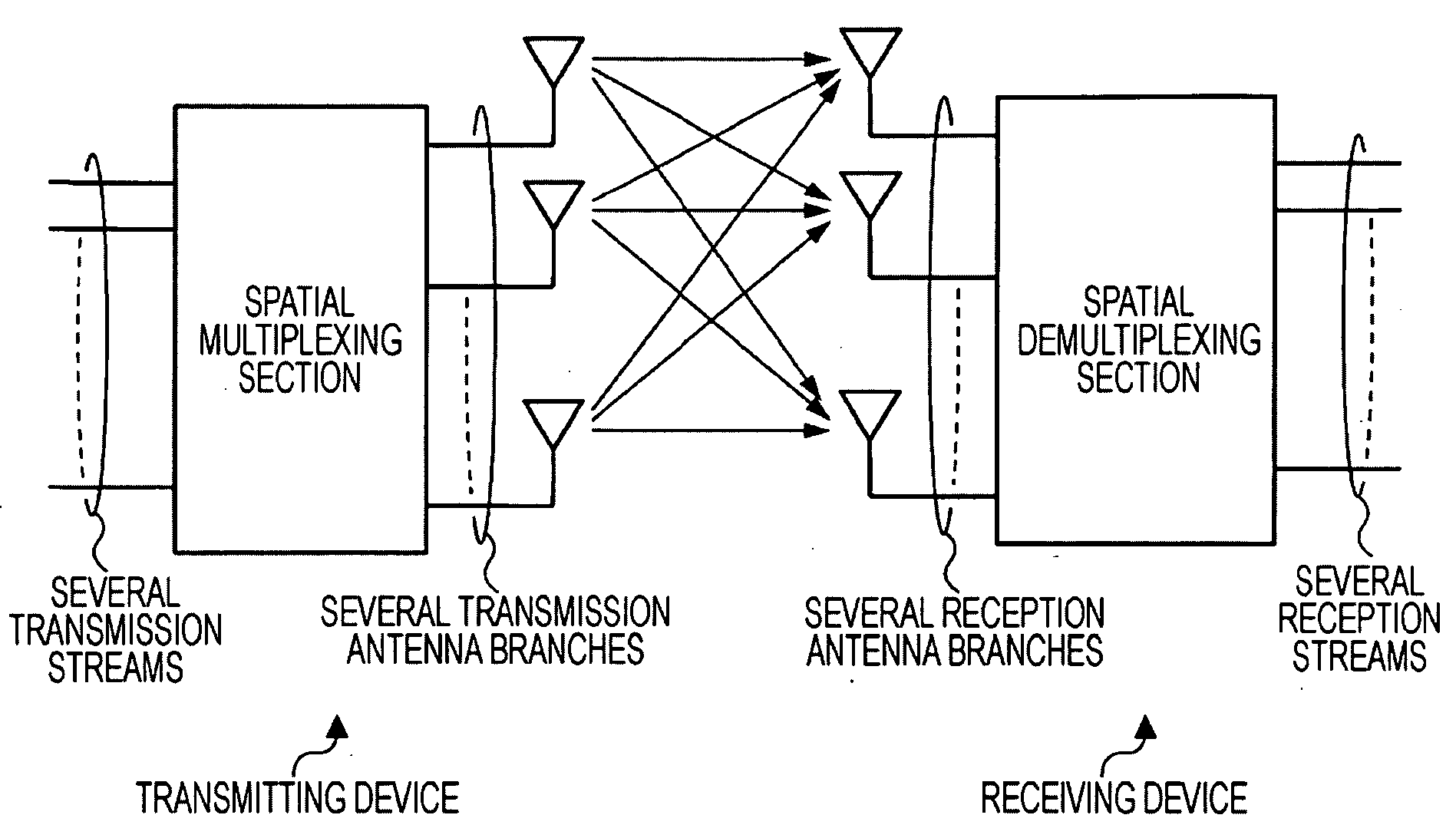

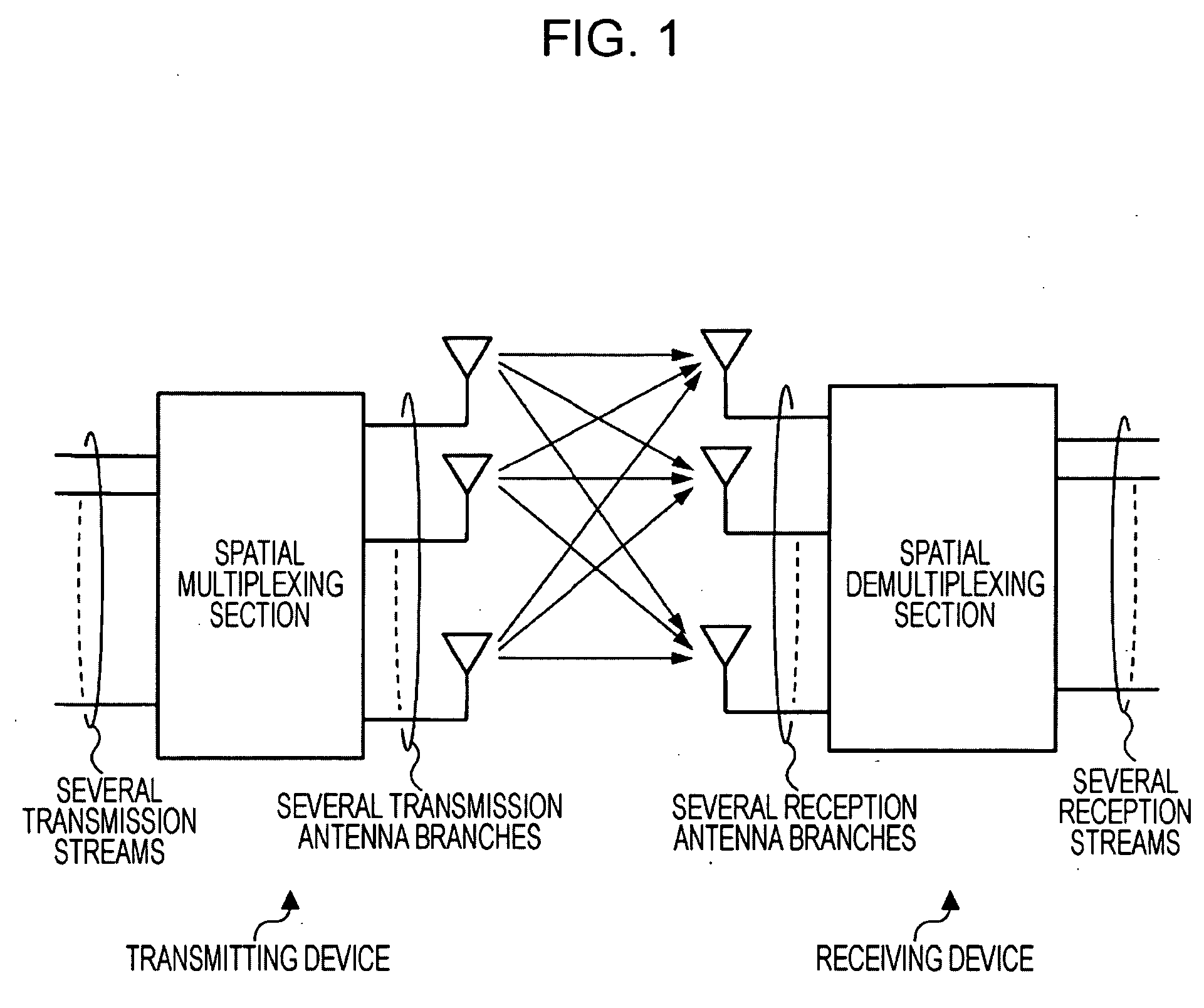

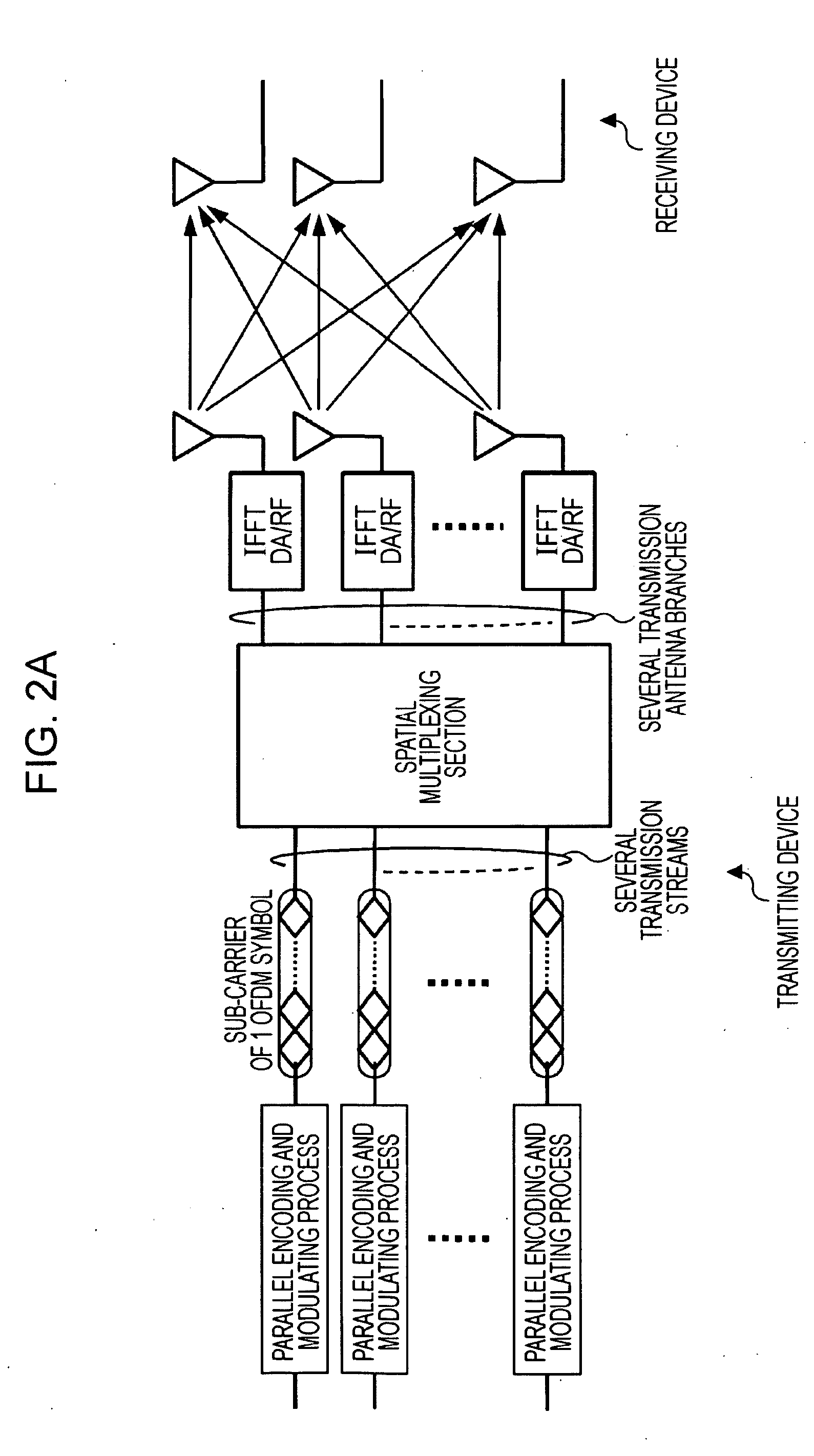

Wireless communication system, wireless communication device, and wireless communication method

ActiveUS20090052578A1Improve transmission performanceConvenient wireless communicationSpatial transmit diversityModulated-carrier systemsCommunications systemSpatial multiplexing

A wireless communication system includes a transmitting device and a receiving device each including a plurality of antennas. A plurality of streams are subjected to spatial multiplexing and are transmitted in a downlink in which packets are transmitted from the transmitting device to the receiving device. In the transmitting device, each of the plurality of transmission streams is divided into a plurality of bit-series groups having decoding characteristics to which priority levels are assigned, the bit-series groups are subjected to encoding processes and modulating processes in accordance with the priority levels and further subjected to weighting and synthesizing, and each of the plurality of transmission streams in which a plurality of bit series items are synthesized with one another is spatially multiplexed and transmitted.

Owner:PANTECH CORP

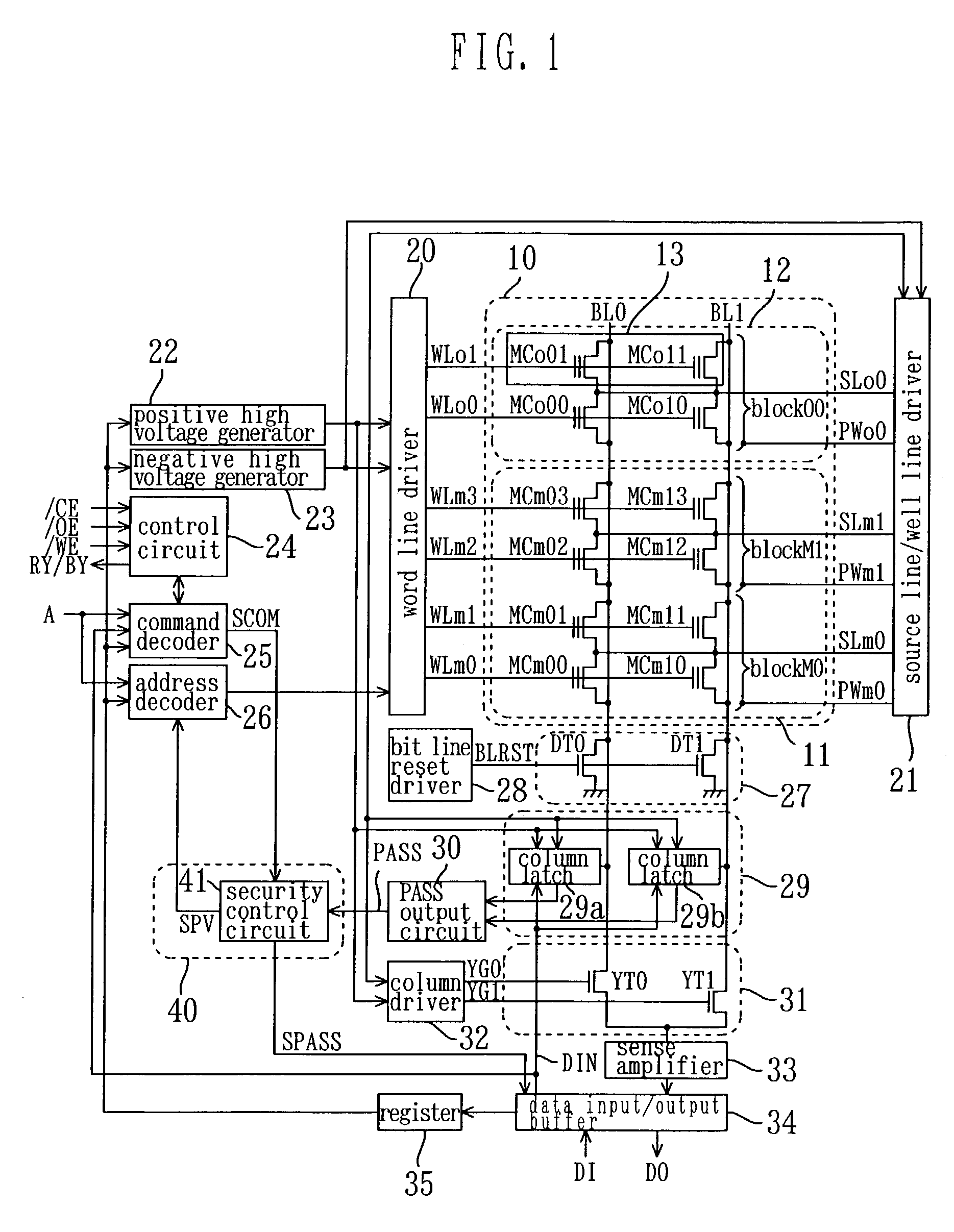

Nonvolatile semiconductor memory device and method for providing security for the same

InactiveUS6996692B2Easy to operateIncrease in circuit sizeRead-only memoriesUnauthorized memory use protectionPasswordExecution control

An inventive nonvolatile semiconductor memory device is provided, in advance, with a column latch circuit 29 for performing a batch write operation (page latching operation, page programming operation, and verifying operation), and the column latch circuit 29 is utilized to realize a security function. The inventive memory device is further provided with a security control circuit 41 for carrying out control so that a password for deactivating the security function is stored in the column latch circuit 29 and a verifying operation is performed to determine whether the password stored in the column latch circuit 29 is identical to a security function deactivation code stored in a deactivation code storage 13. If it is determined that the password and the security function deactivation code are identical as a result of the verifying operation, the security function is deactivated.

Owner:PANASONIC CORP

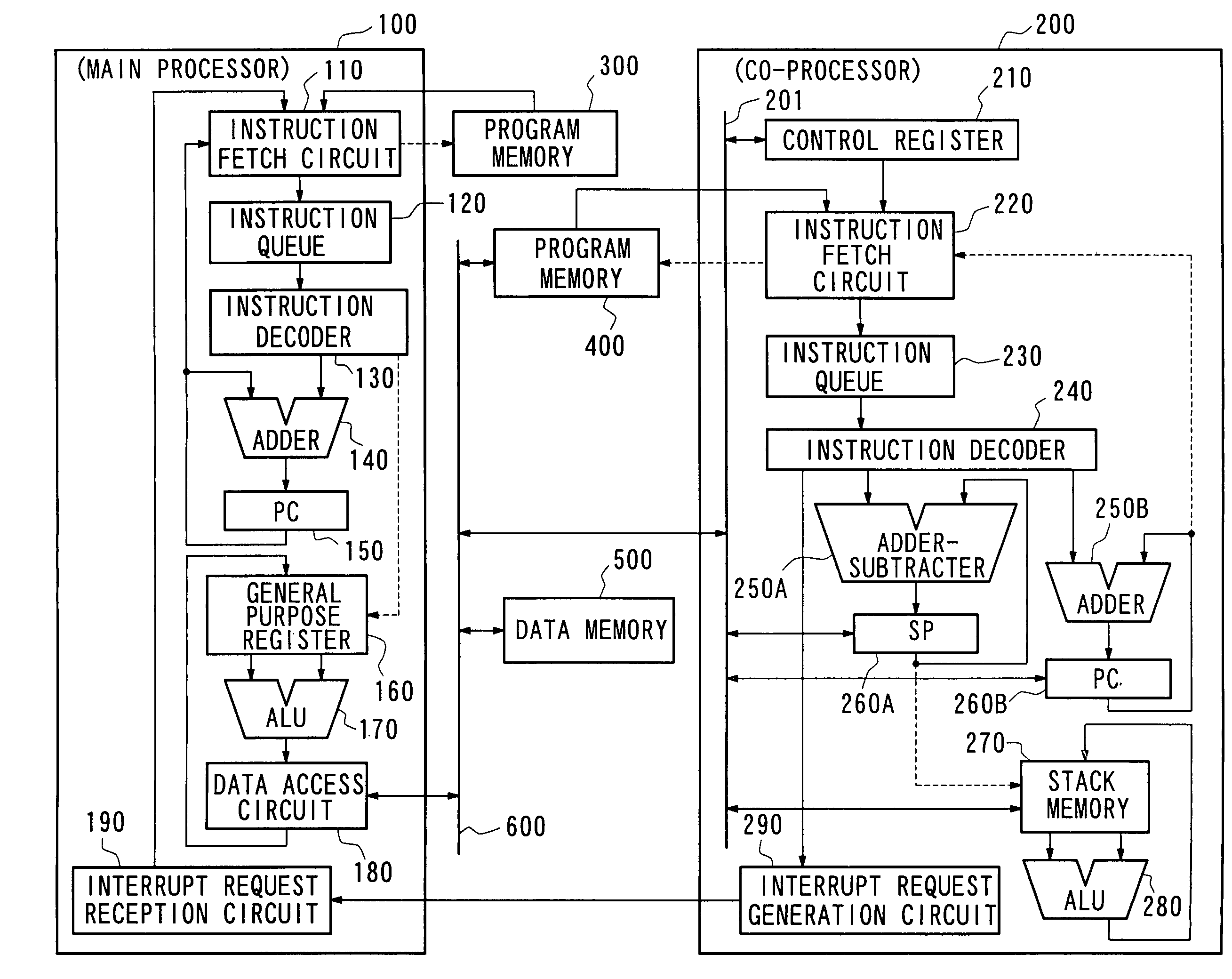

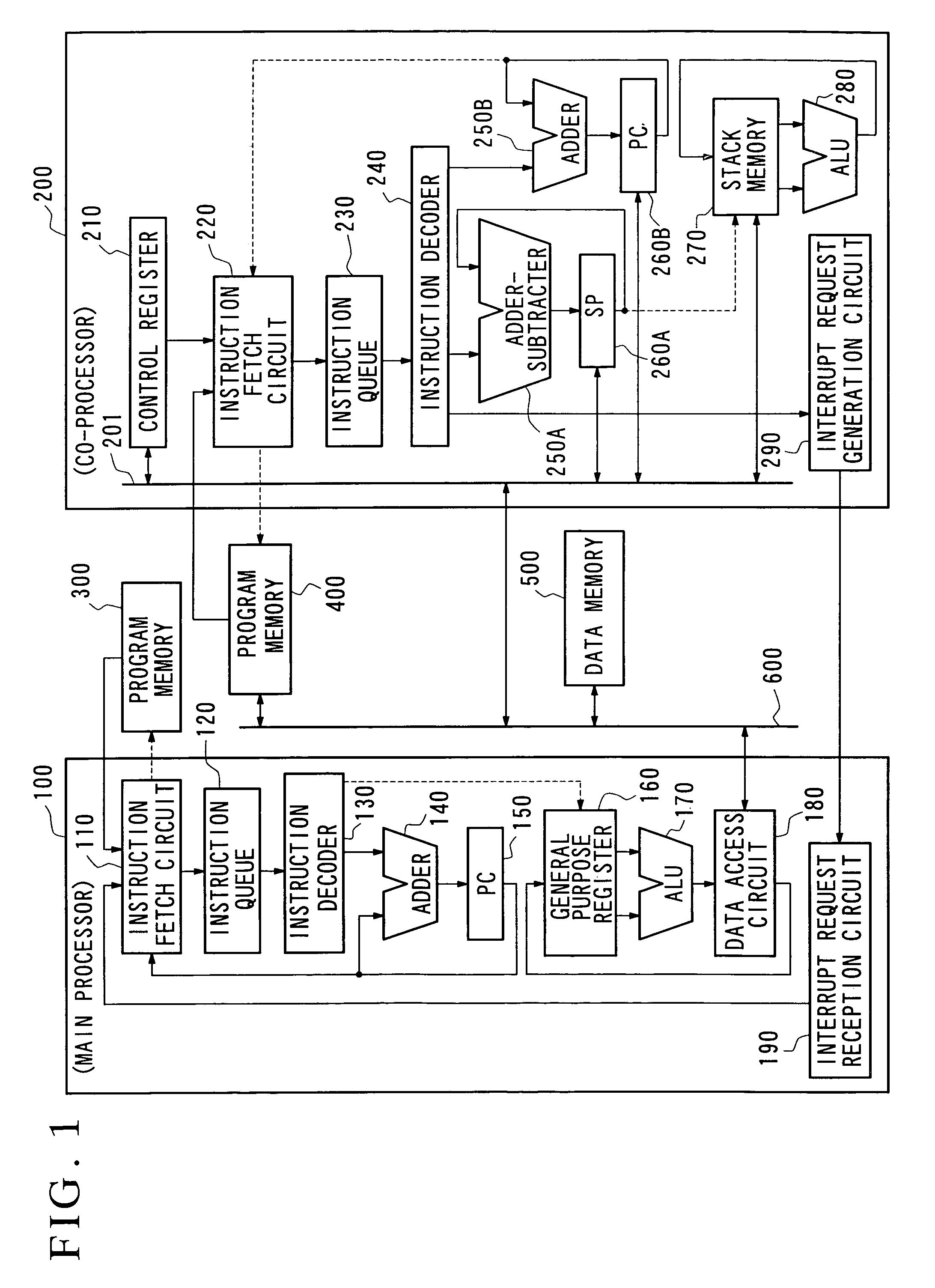

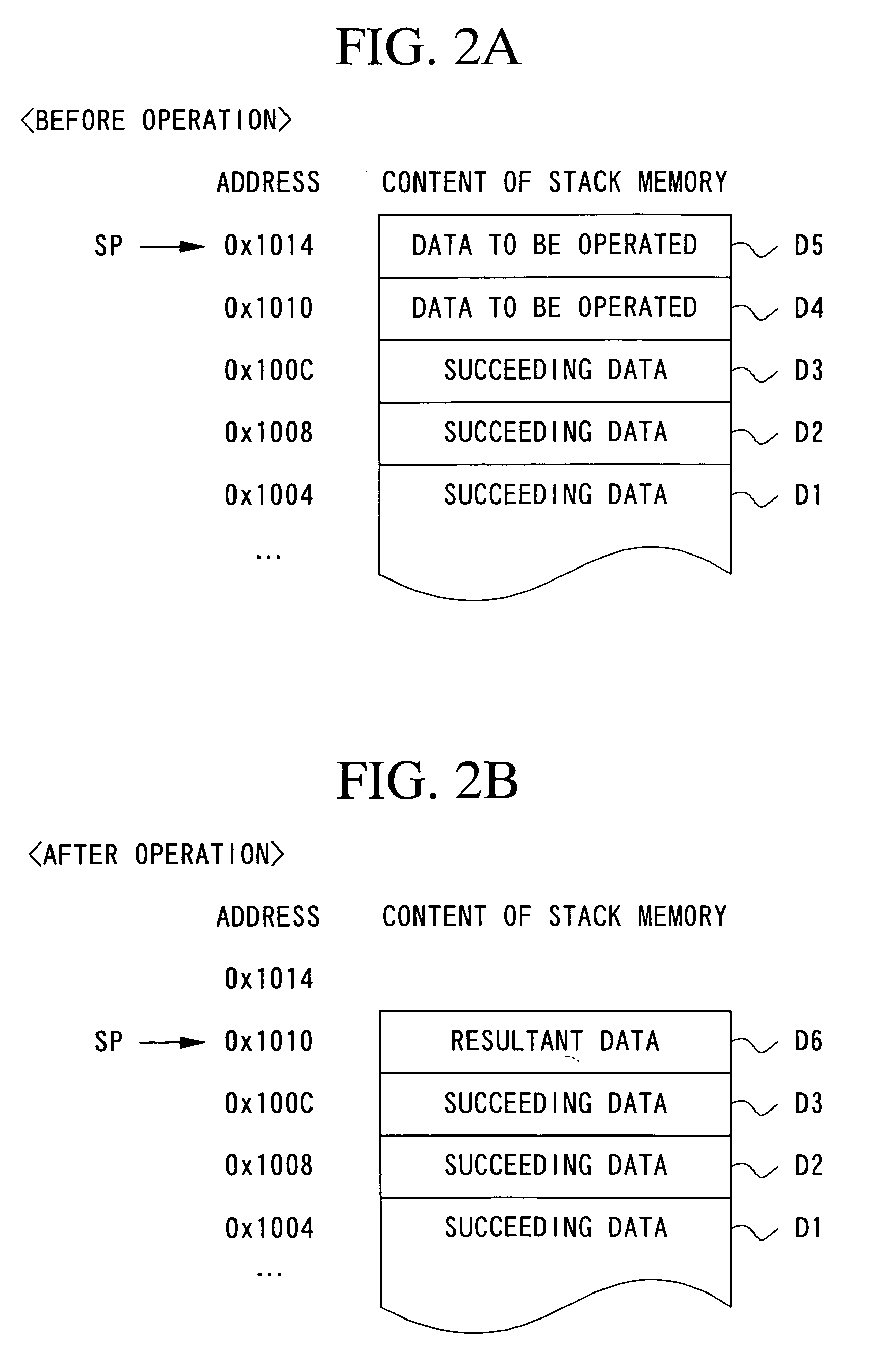

Microprocessor having main processor and co-processor

InactiveUS7200741B1Increase speedReduce loadConcurrent instruction executionMultiple digital computer combinationsMaster processorSoftware

There is provided a microprocessor system that can execute a specific set of instructions at a high speed while limiting the increase in size of the circuitry. The microprocessor system, which executes instructions described in a program, comprises a main processor which executes a first set of instructions by means of hardware and executes a second set of instructions by means of software and a co-processor which operates under the control of the main processor to execute the second set of instructions by means of hardware. When the co-processor encounters a specific instructions of the second set for which data under the control of the main processor needs to be operated, the co-processor issues a notification of this fact to the main processor to request it to execute the specific instruction. In this case, the co-processor updates its stack pointer and program counter by itself by means of hardware.

Owner:RENESAS ELECTRONICS CORP

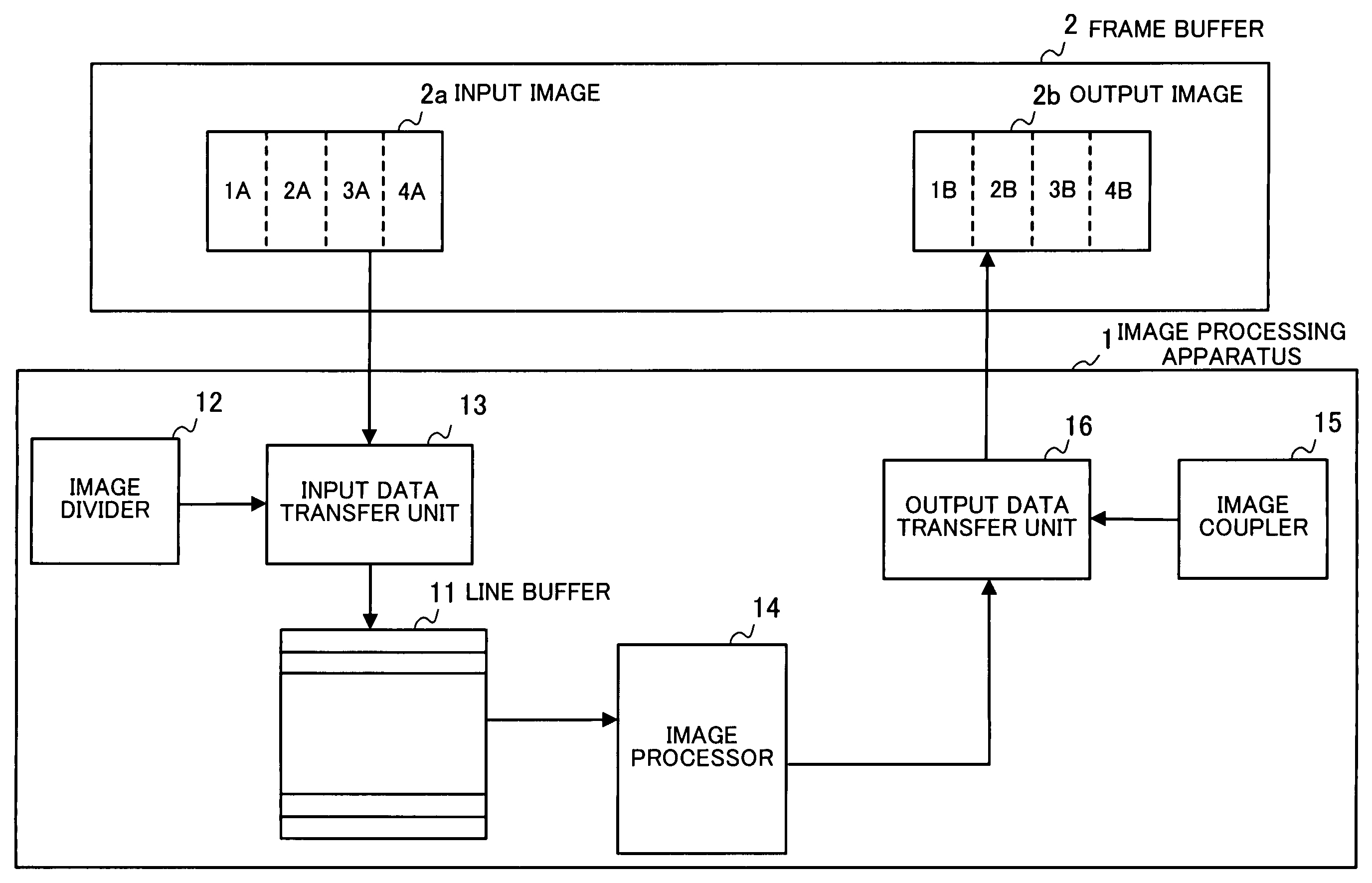

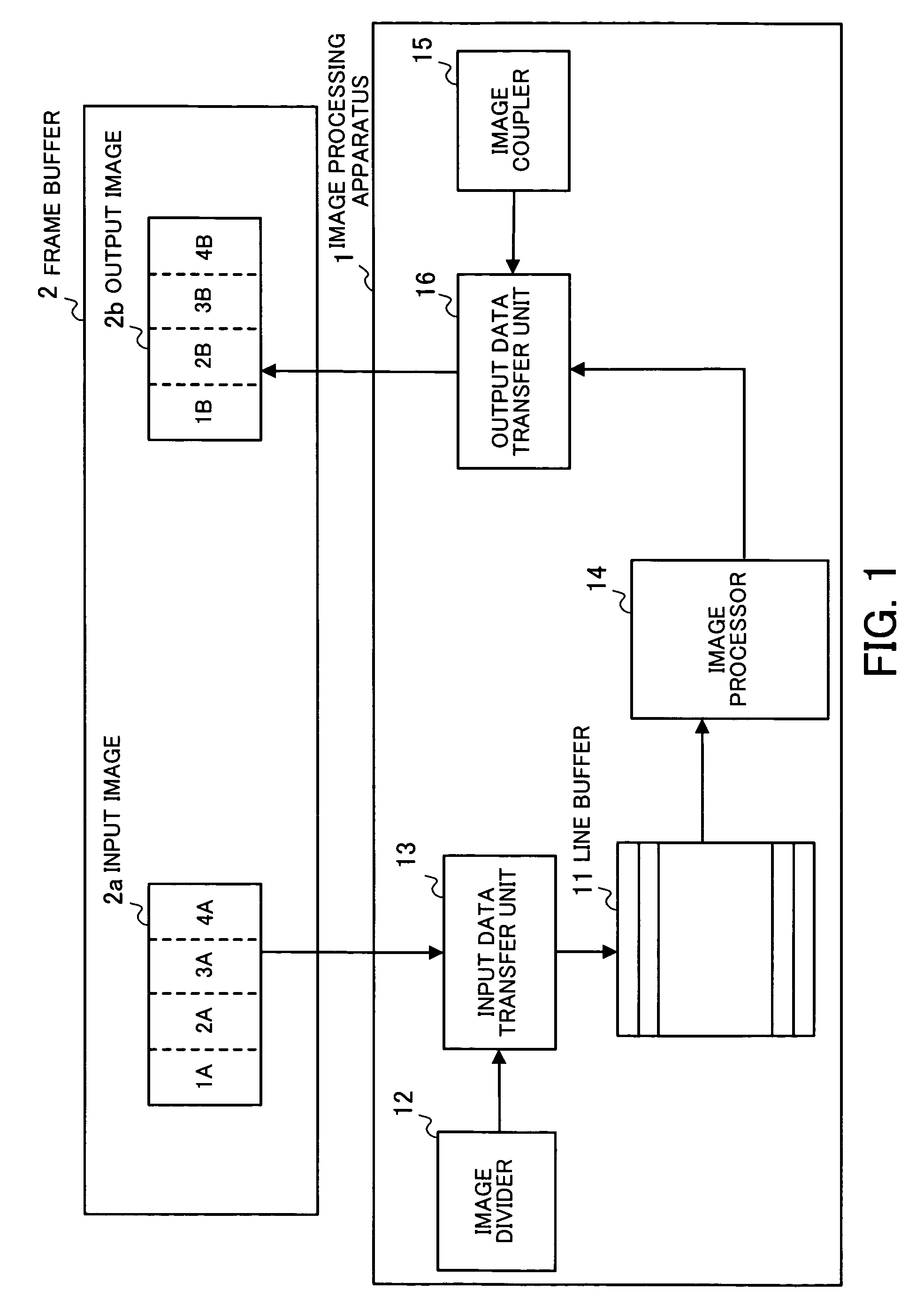

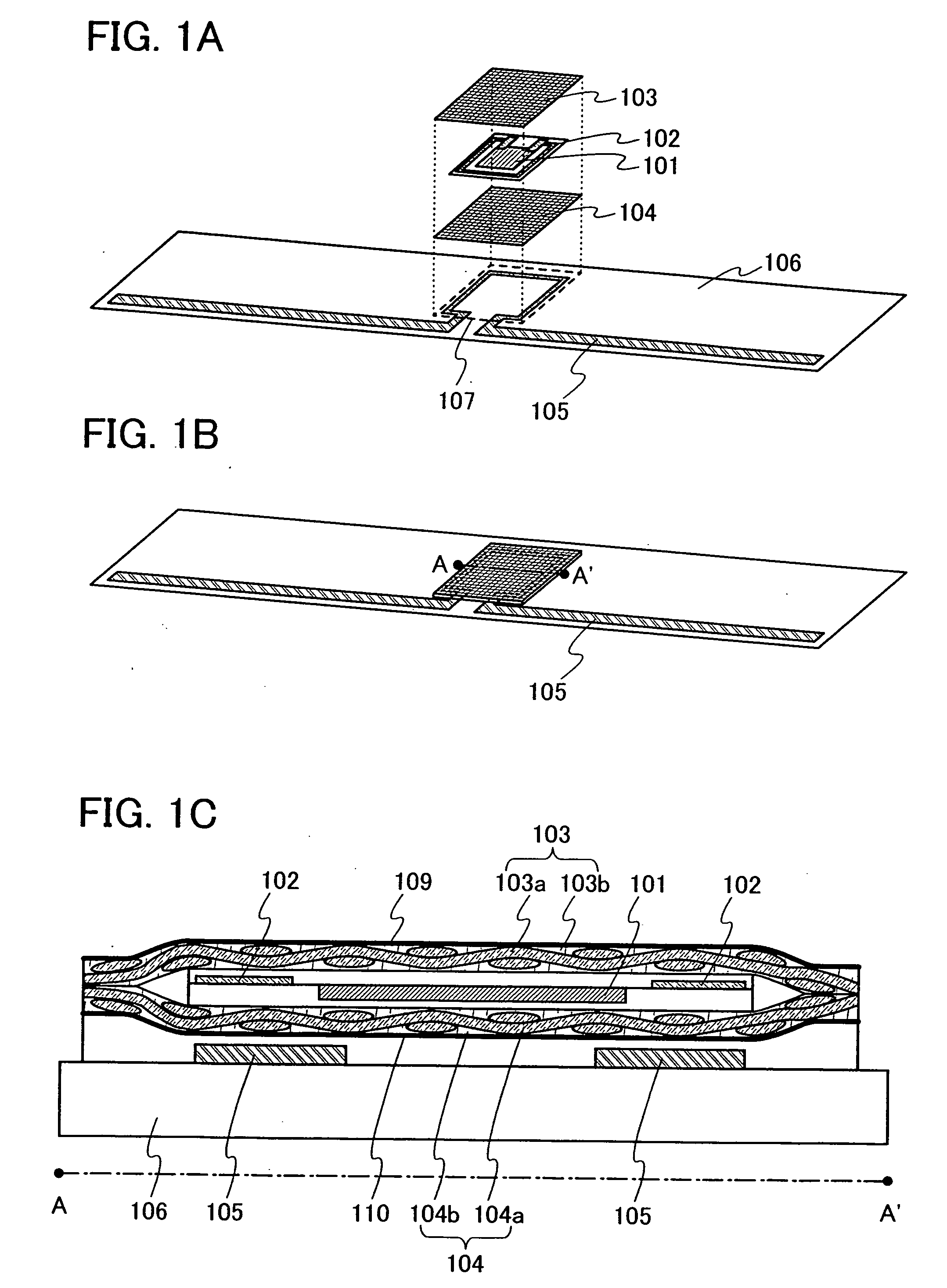

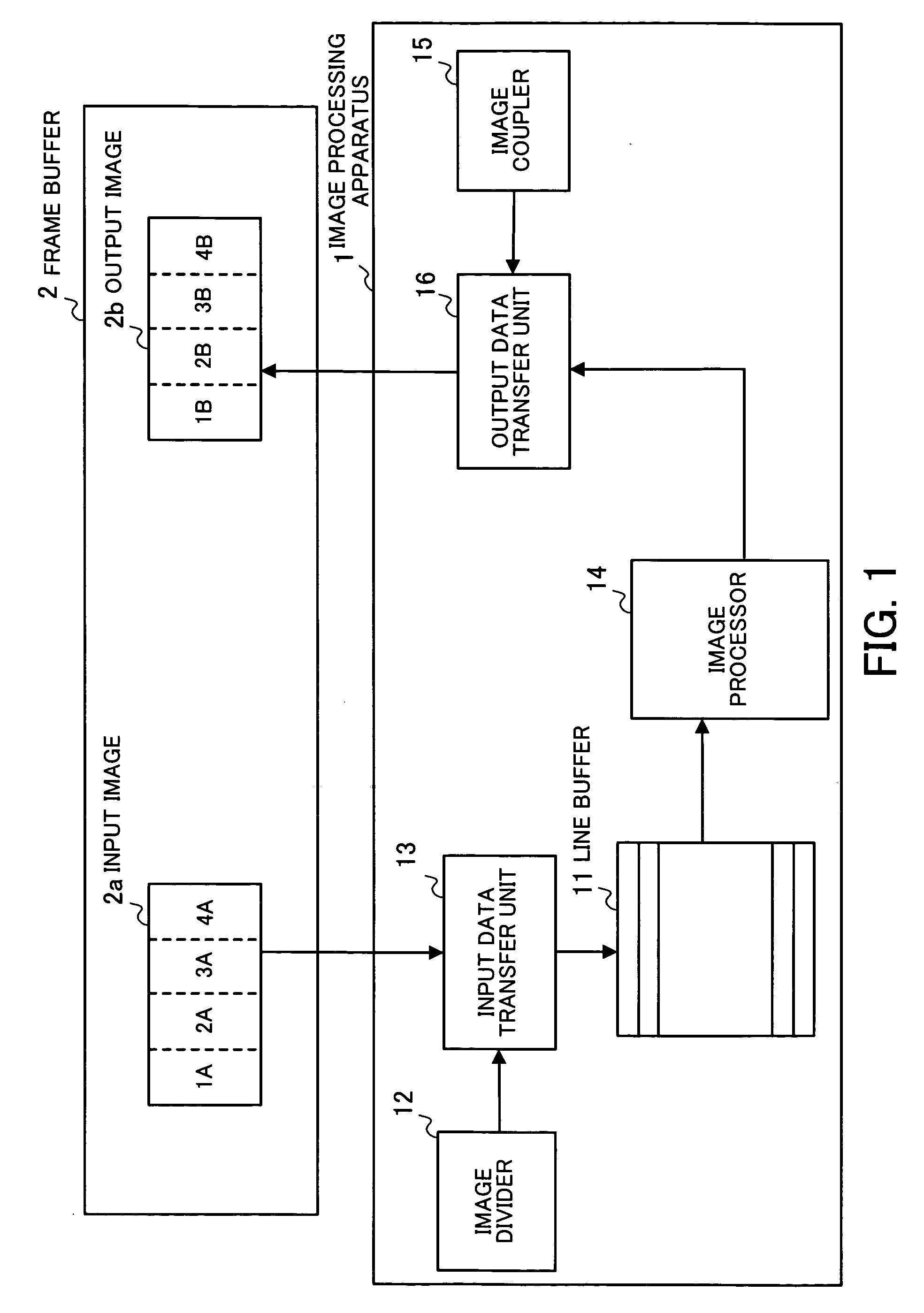

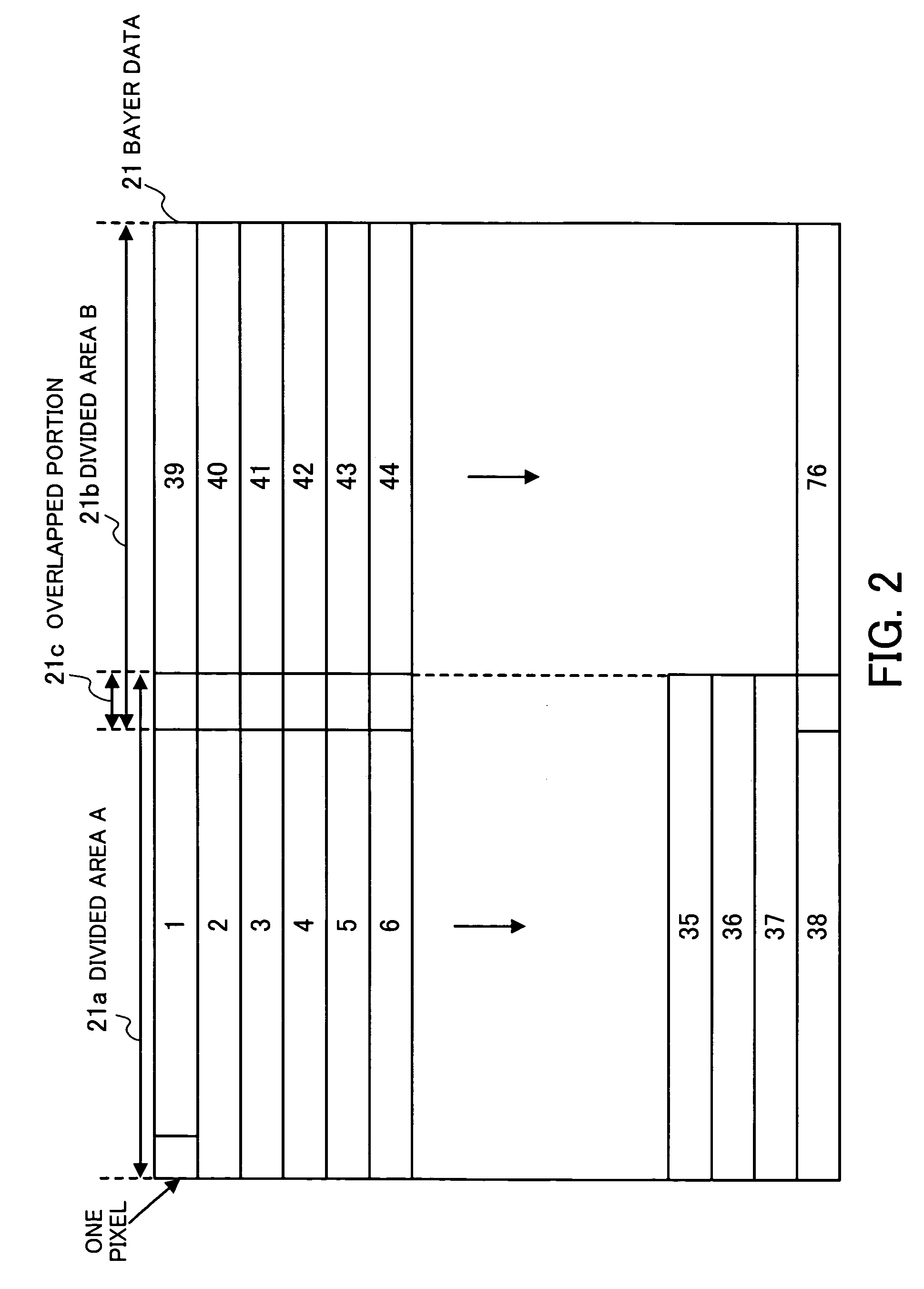

Apparatus and method for processing an image

InactiveUS7583851B2Increase in circuit sizeIncrease processing functionImage memory managementCharacter and pattern recognitionImaging processingComputer graphics (images)

An image processing apparatus is provided for enhancing the image processing function without having to increase the circuit scale. The image processing apparatus includes an image divider, a pixel processor, and an image coupler. If the number of horizontal pixels on the width of an input image is larger than a size of a line buffer, the image divider equally divides the input image in the vertical direction so that the resulting divided area is smaller than the number of horizontal pixels on the width of the line buffer. Then, the image divider controls an input data transfer circuit so that the pixel data of the input image may be sequentially transferred to the line buffer for each of the equally divided areas. The image processor sequentially processes the pixel data of the input image temporarily stored in the line buffer and then sends out the output pixel data. The image coupler controls the output data transfer circuit so that the output pixel data sequentially outputted for one divided area may be coupled with the output pixel for another divided area, for generating the output image.

Owner:SOCIONEXT INC

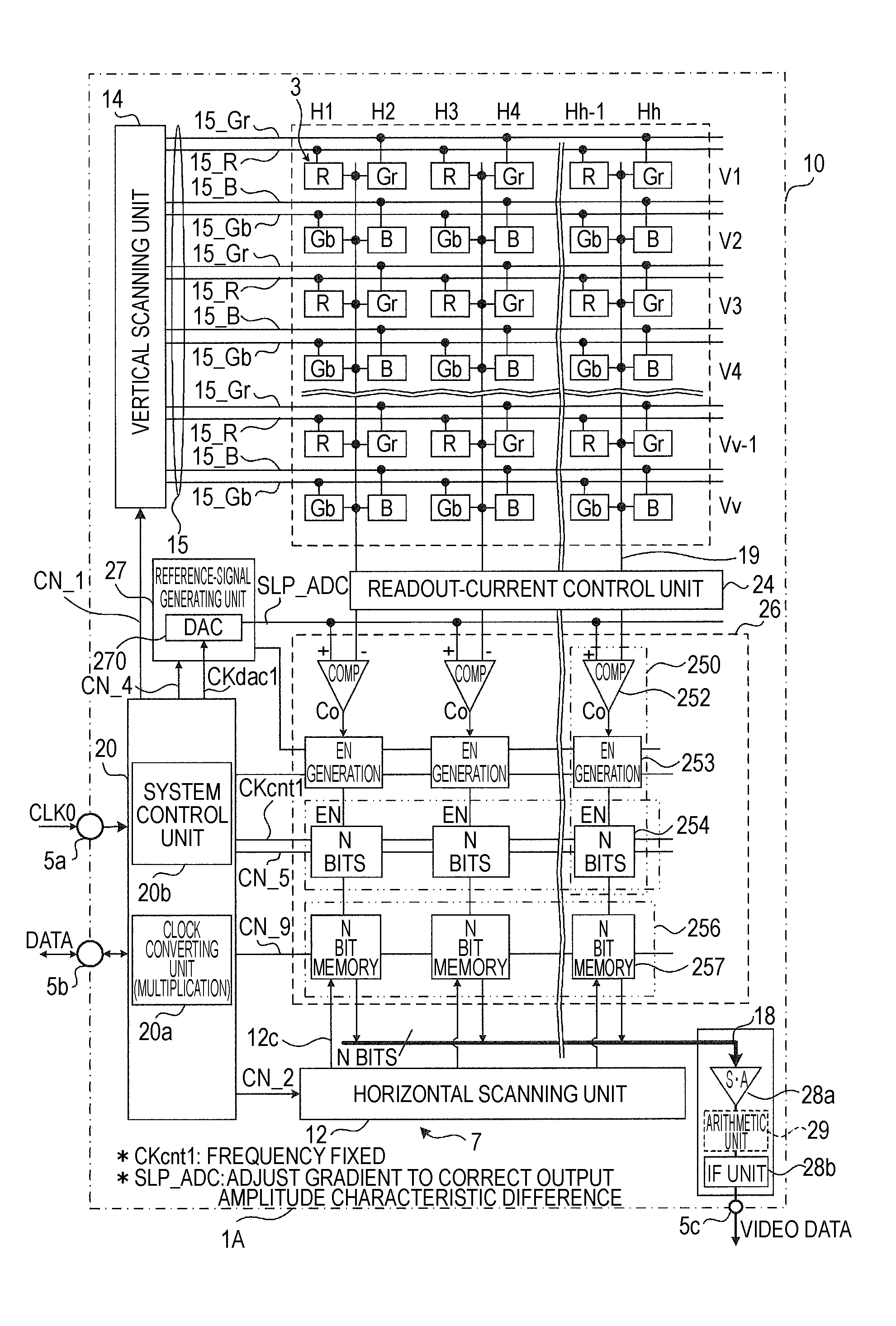

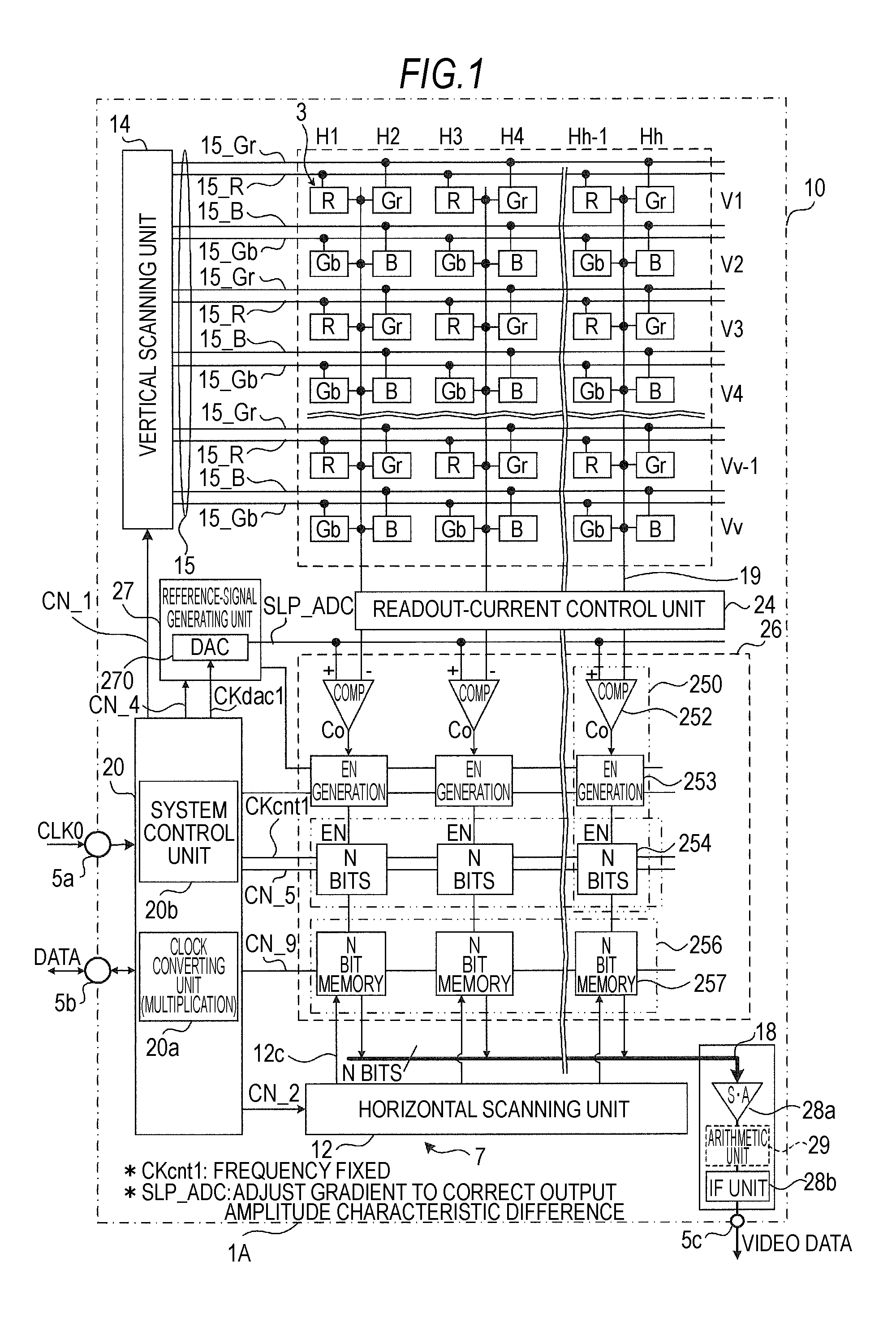

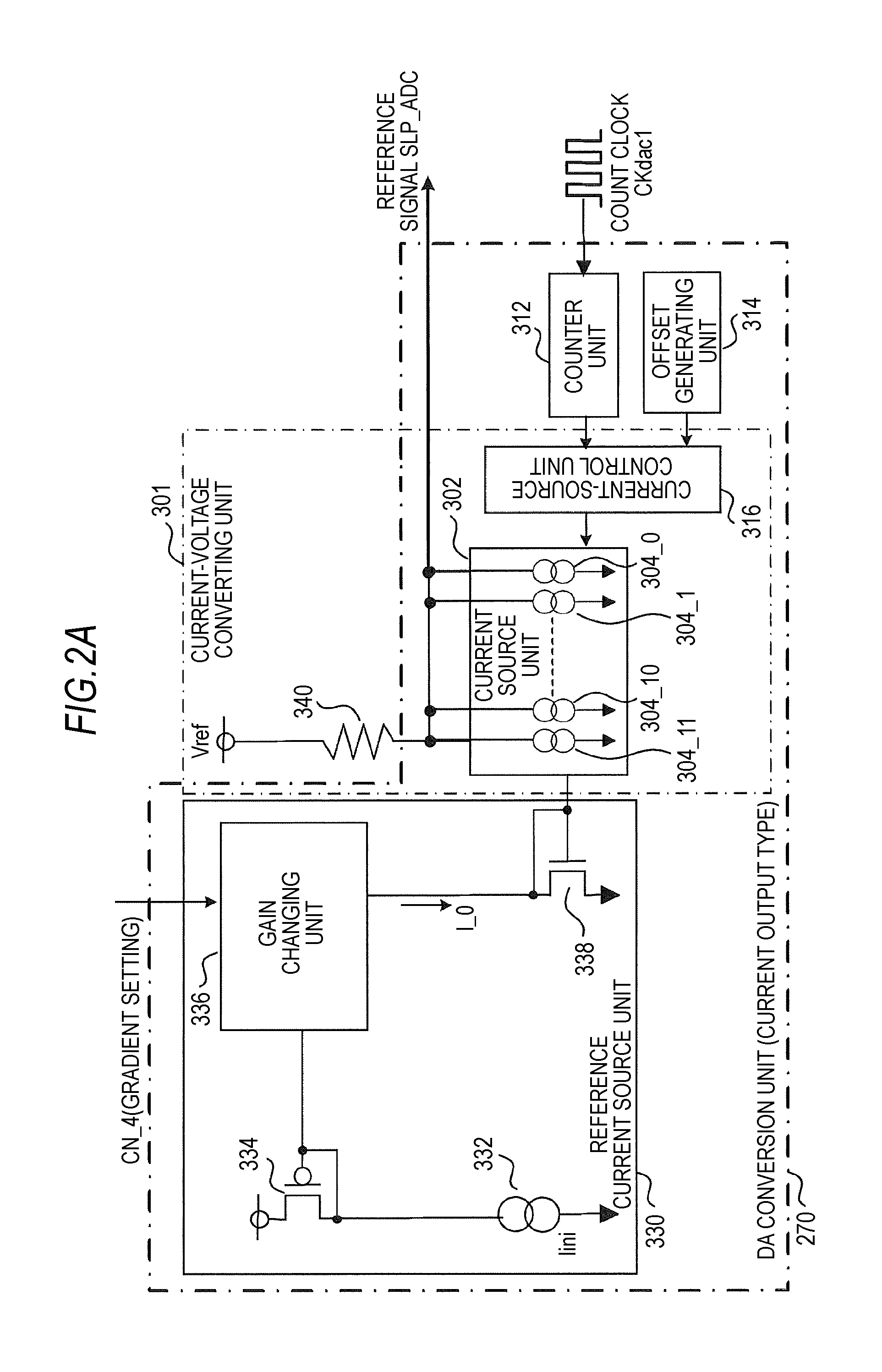

Solid-state imaging device, imaging apparatus, and ad conversion gain adjusting method

ActiveUS20100079611A1Reduce decreaseIncrease in circuit sizeTelevision system detailsTelevision system scanning detailsTarget signalExecution control

A solid-state imaging device includes: a pixel unit in which unit pixels outputting processing target signals are arranged in a horizontal direction and scanning lines are wired such that the processing target signals can be read out in order in a vertical direction within a repetition unit of an array of the unit pixels in the horizontal direction; an AD conversion unit including comparing units that compare a reference signal supplied from a reference-signal generating unit and the processing target signals, and counter units that perform count operation, the AD conversion unit performing AD conversion processing based on output data of the counter units; and a driving control unit that performs control to read out the processing target signals in order in the vertical direction and controls the reference-signal generating unit and the AD conversion unit such that AD conversion gains are individually adjusted in order to correct an output amplitude characteristic difference within the repetition unit during AD conversion processing.

Owner:SONY CORP

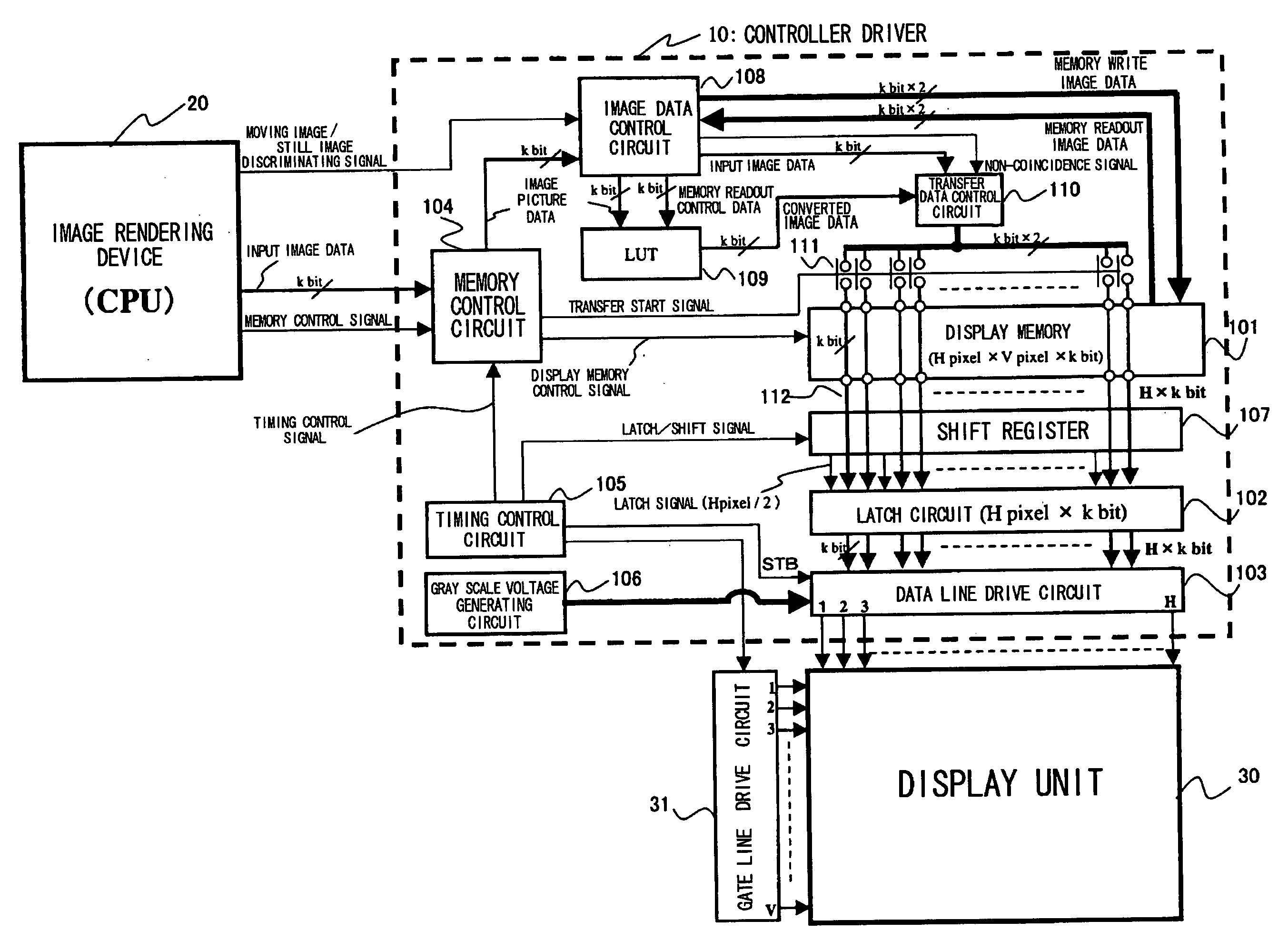

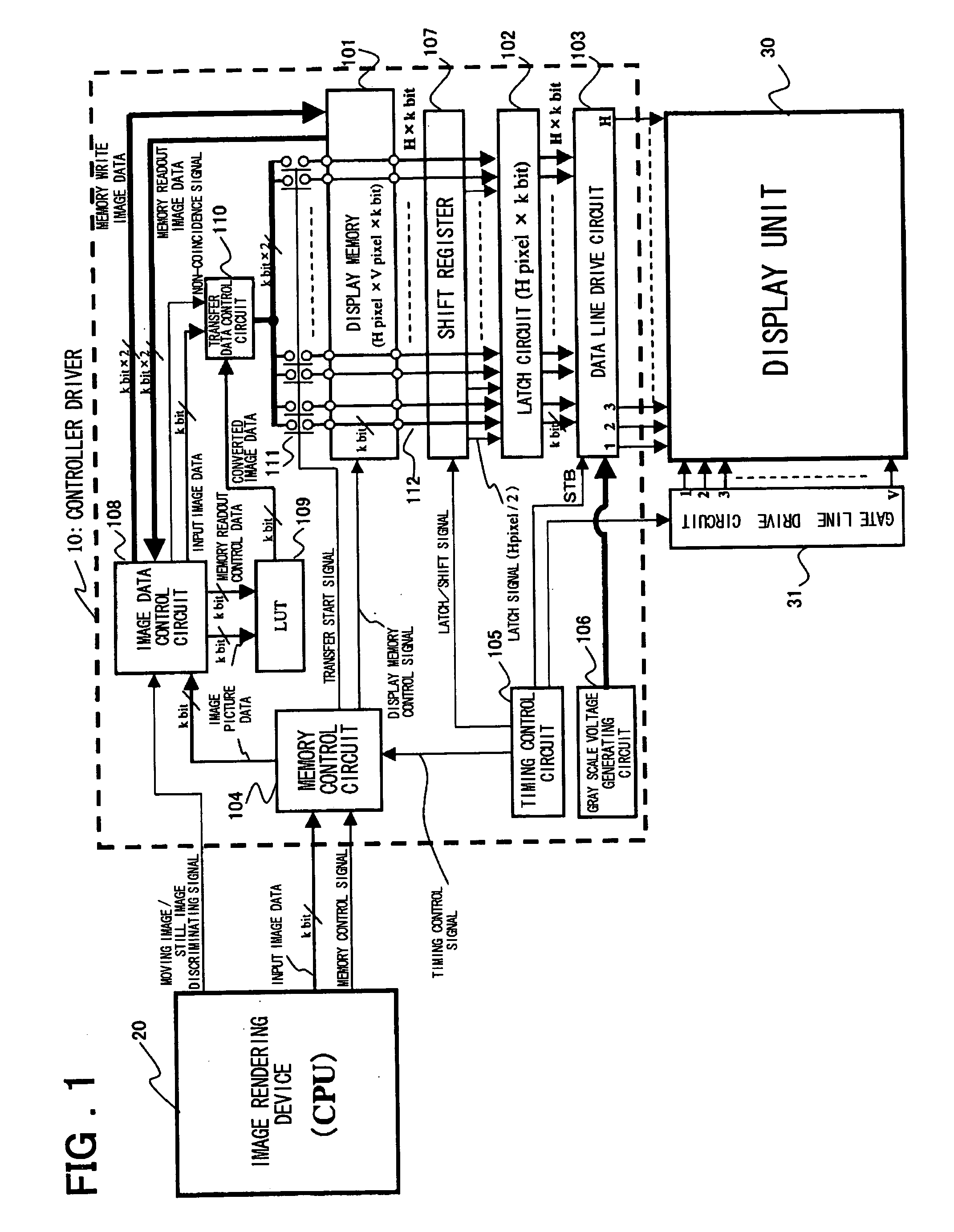

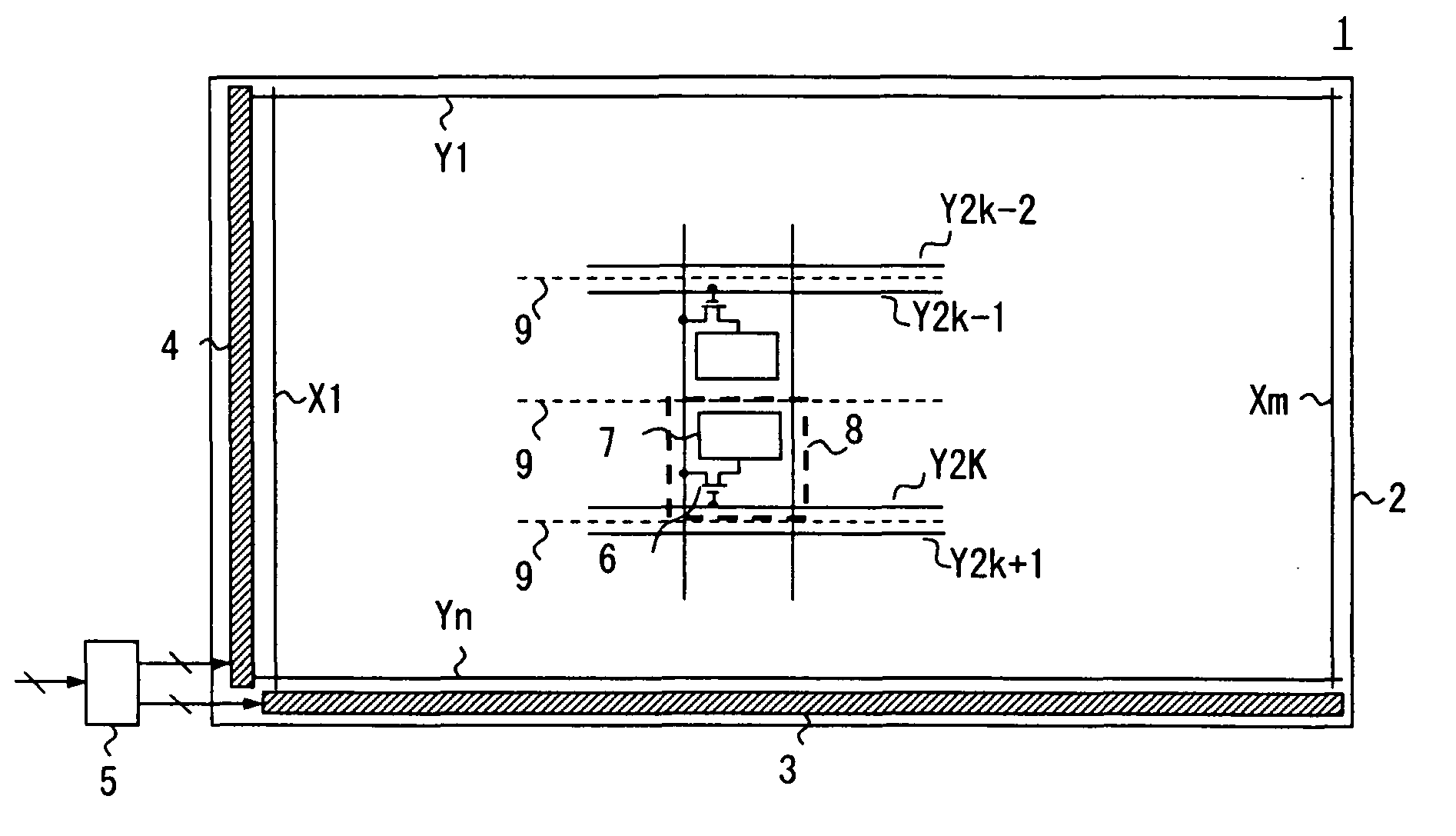

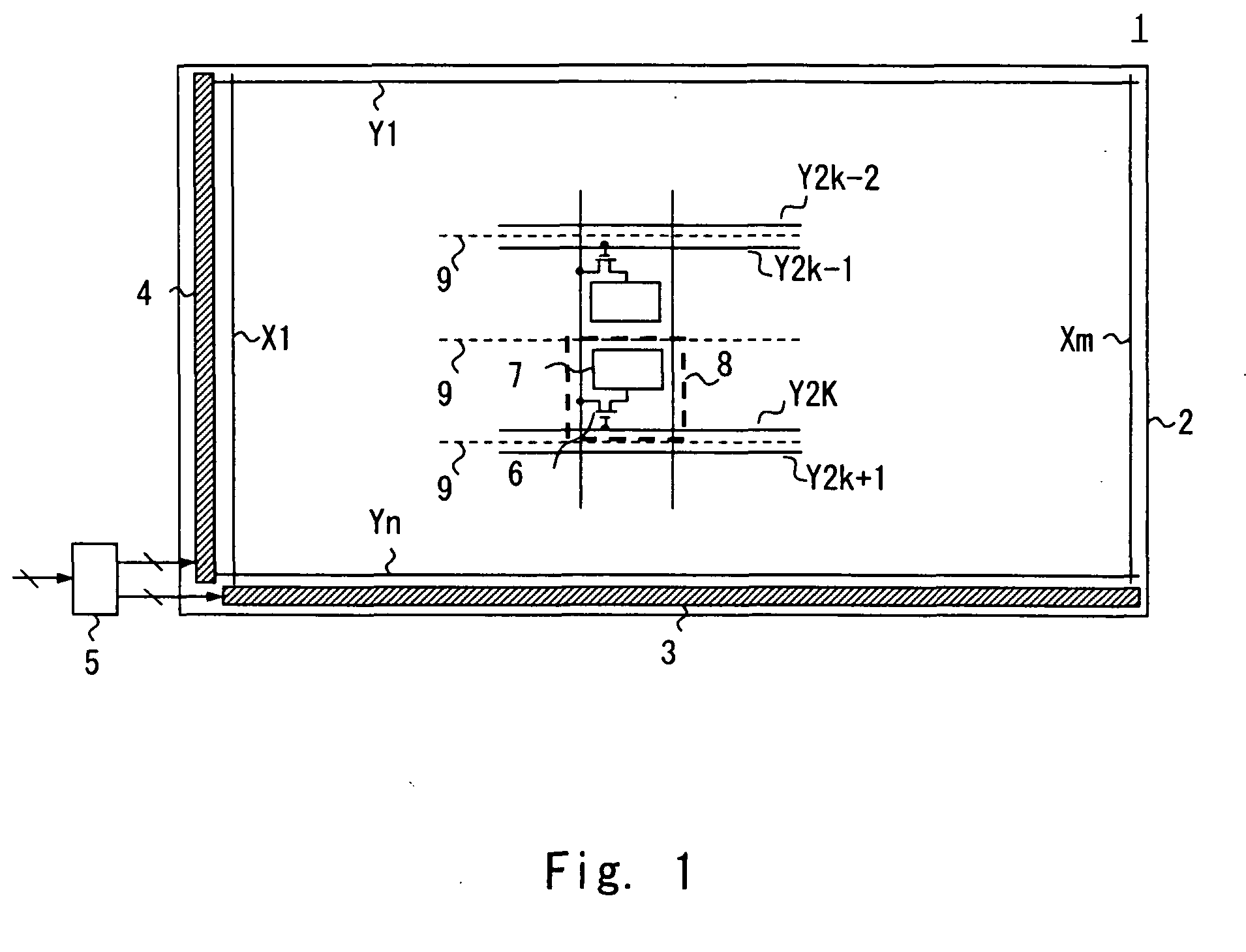

Controller driver and display apparatus

ActiveUS20050253833A1Increase in circuit sizeIncrease consumptionCathode-ray tube indicatorsInput/output processes for data processingData controlShift register

A driving apparatus for over-drive driving includes a display memory, a memory control circuit performing control for receiving input image data supplied from an image rendering device, reading out image data one frame before of the input image data from the display memory and for writing the input image data in the display memory as write image data for the display memory, and a image data control circuit for verifying whether or not the input image data from the memory control circuit coincides with the readout image data one frame before read out from the display memory. The apparatus also includes an LUT for outputting converted image data, a transfer data control circuit for selectively outputting the input image data or the converted image data, and latch circuits for latching image data of one horizontal line equivalent of pixels. A shift register circuit generates latch signal for image data.

Owner:RENESAS ELECTRONICS CORP

Display panel driving method, gate driver, and display apparatus

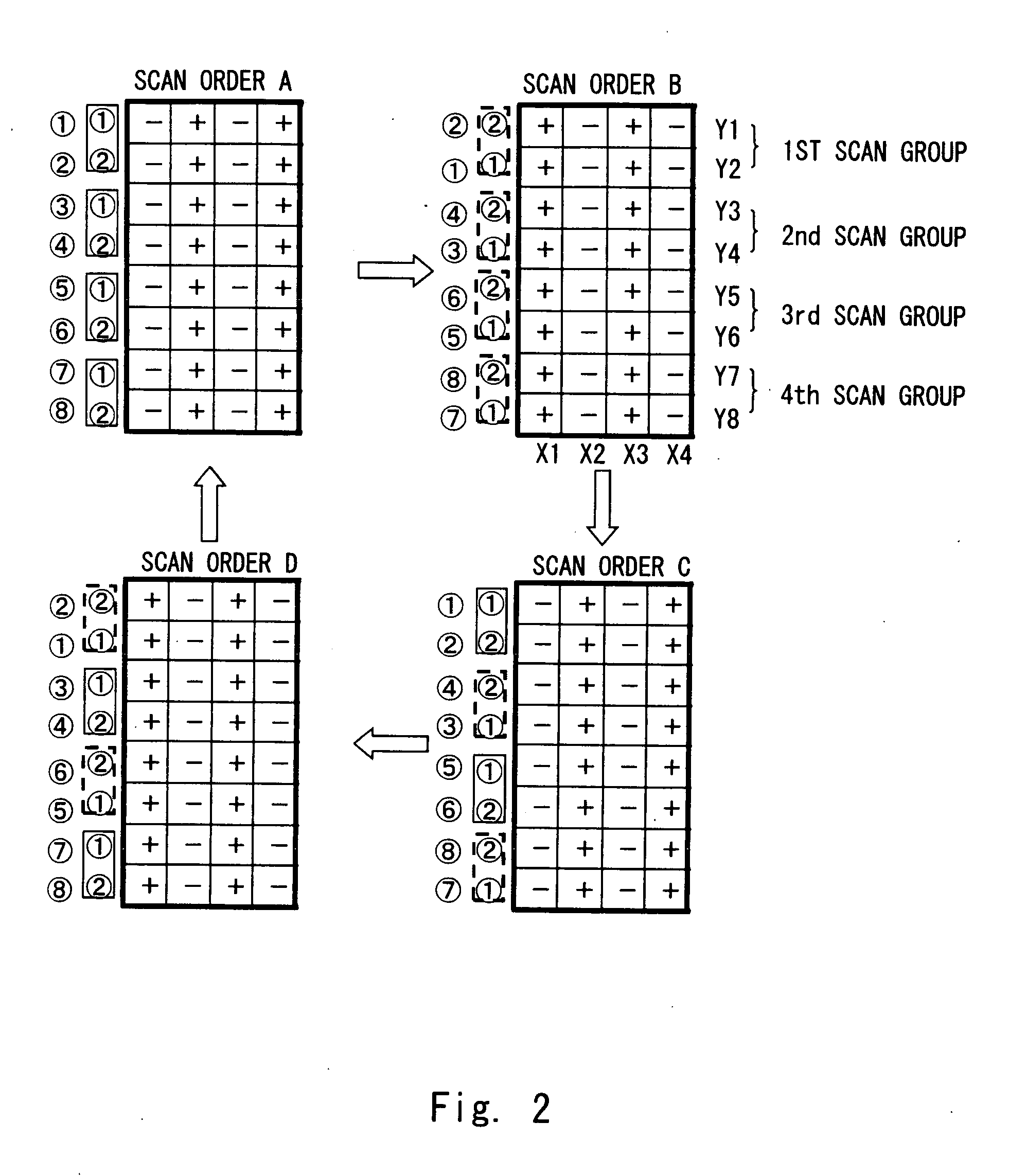

InactiveUS20100315402A1Reduce image qualityReduced drive capability requirementsCathode-ray tube indicatorsNon-linear opticsScan lineElectrical polarity

A method of driving a display panel in which a voltage polarity reverse cycle of a data signal is three or more scan periods, and multiple scan lines are driven by switching between a first and a second scan orders by a predetermined period. The method includes setting a display pattern as a first maximum current pattern, the display pattern in which the multiple scan lines are driven in the first scan order and a number of charge and discharge of the data signal becomes a maximum number, and specifying that the number of charge and discharge of the data signal when displaying the first maximum current pattern in the second scan order is to be ½ of that of the data signal when displaying the first maximum current pattern in the first scan order. Further, the voltage polarity reverse cycle for specifying the first and the second scan orders is one frame period.

Owner:RENESAS ELECTRONICS CORP

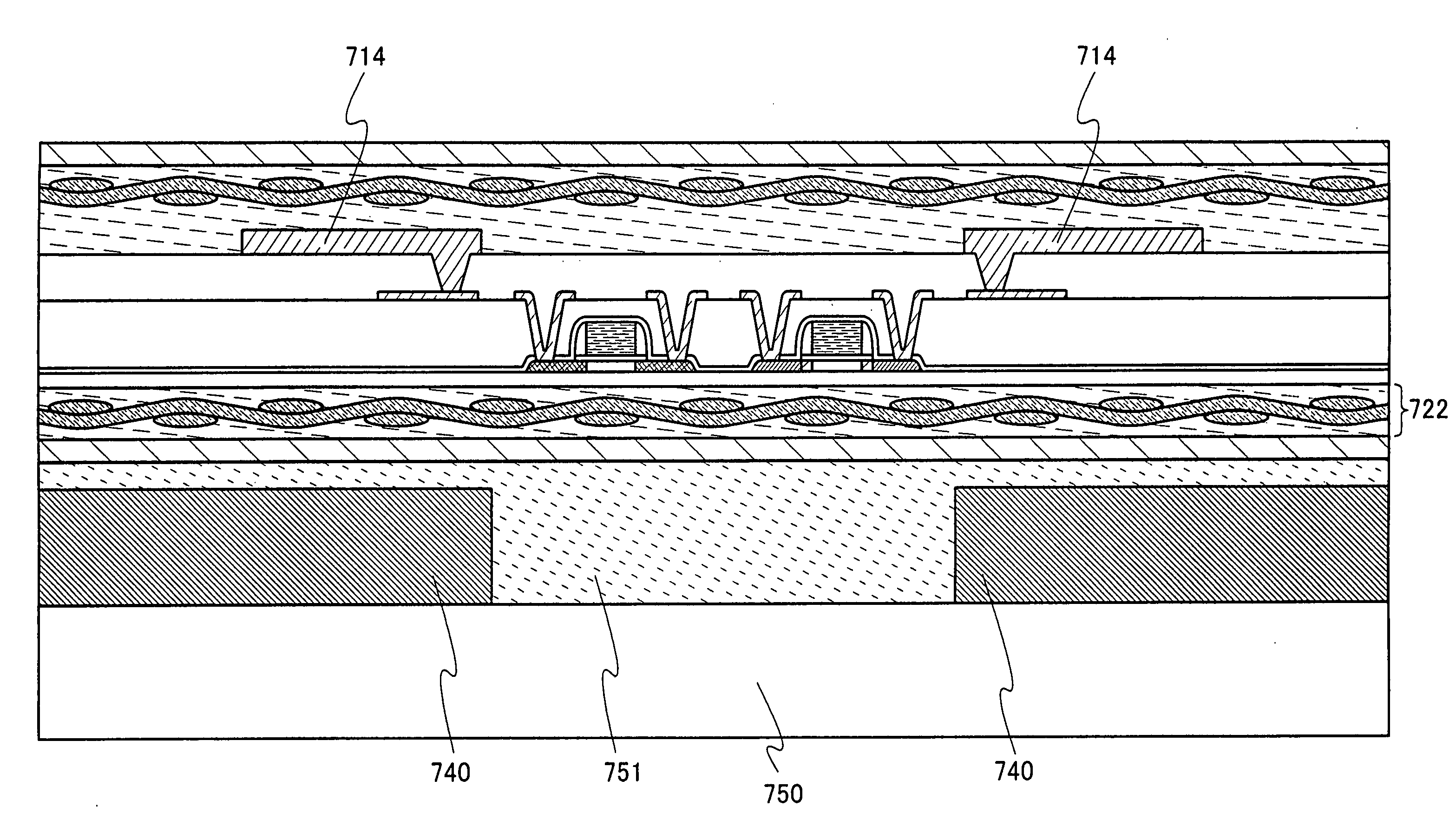

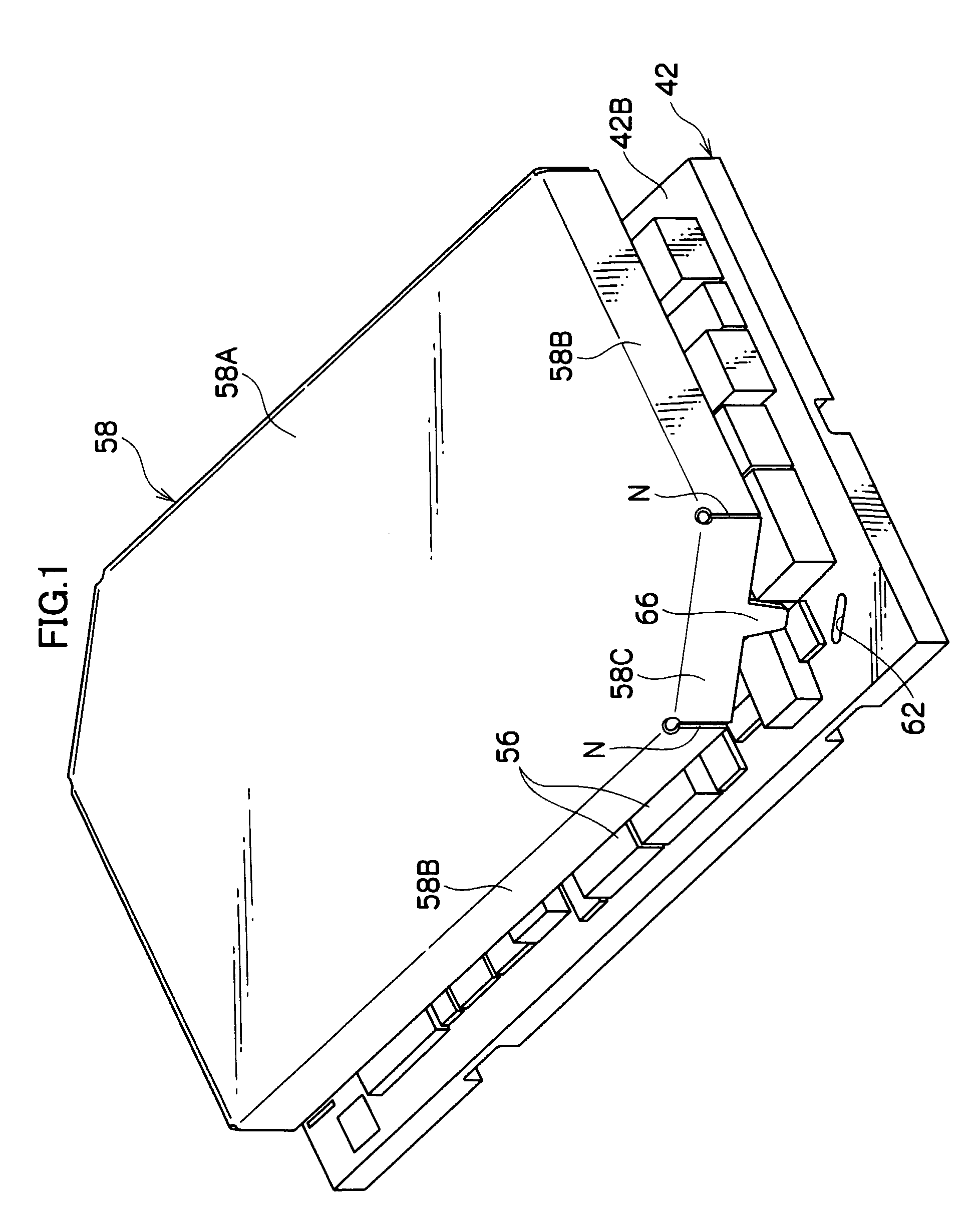

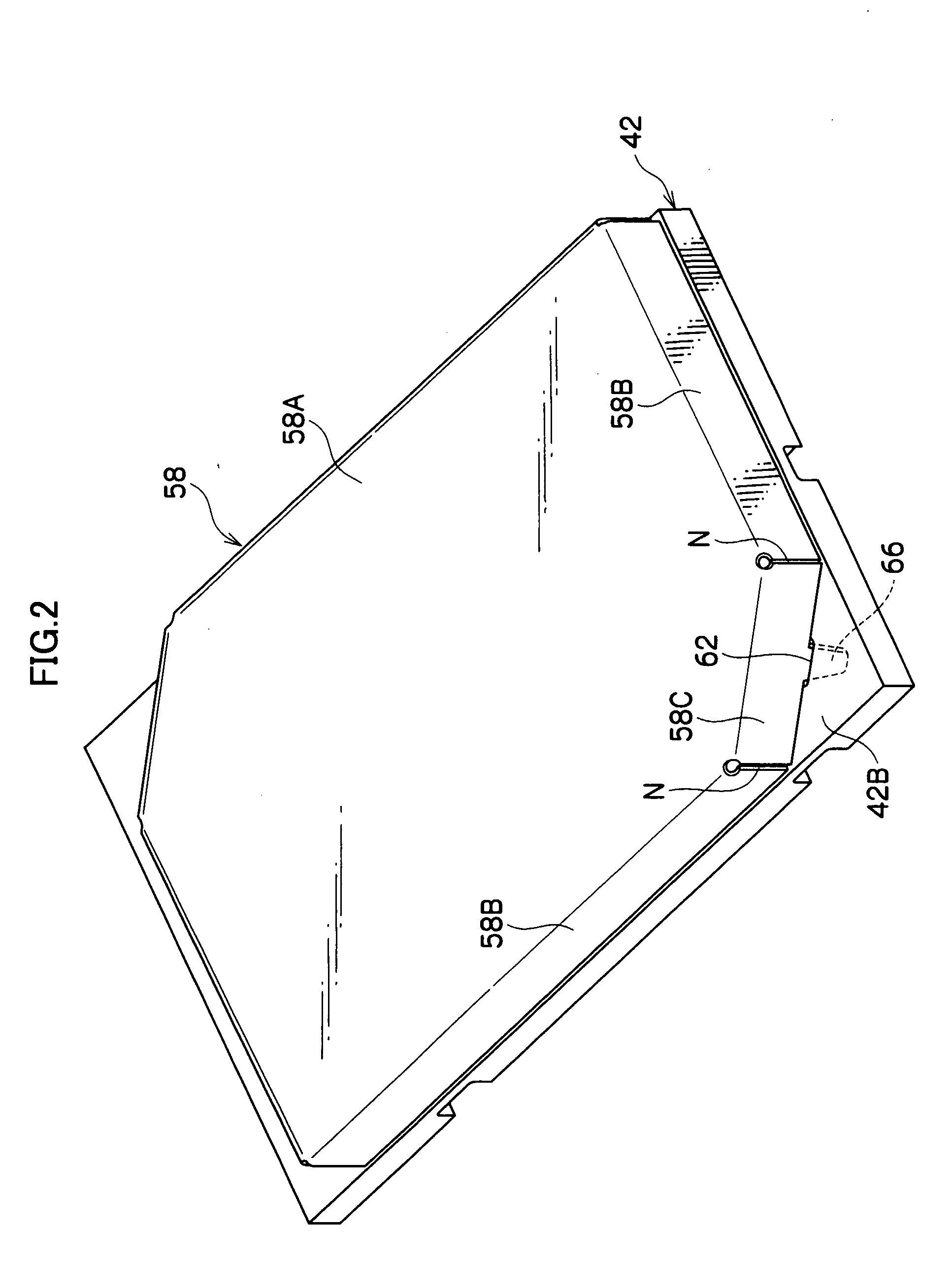

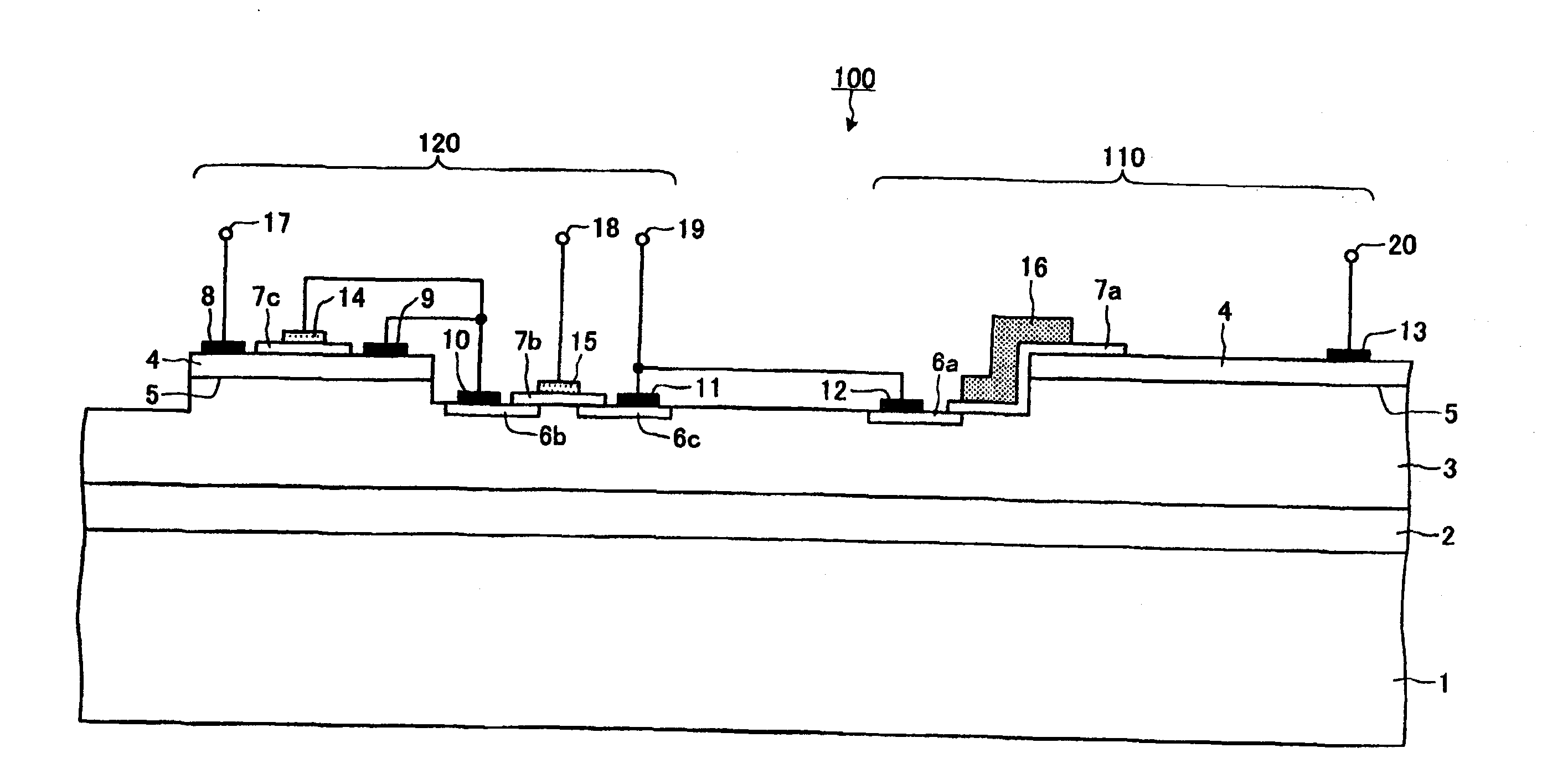

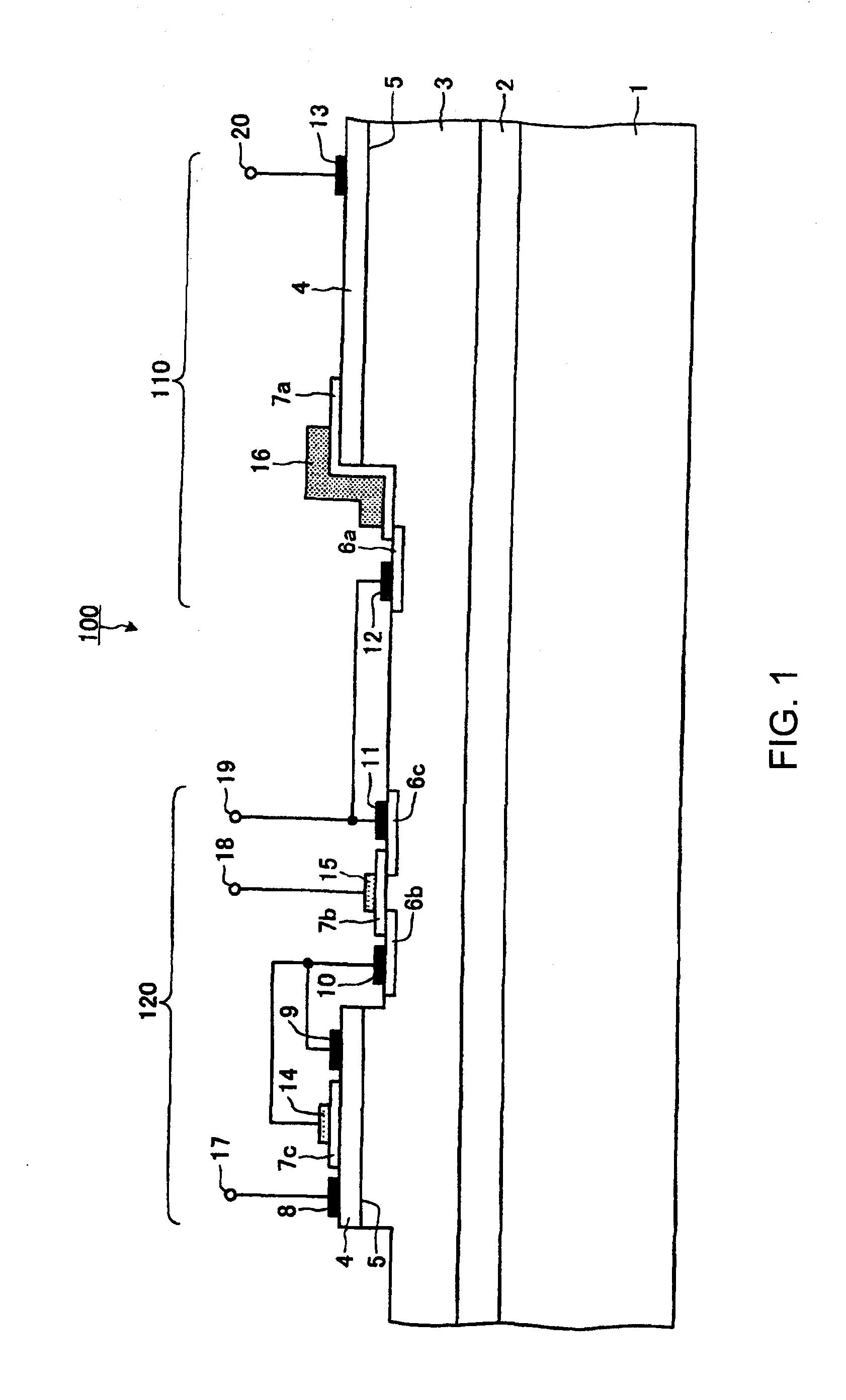

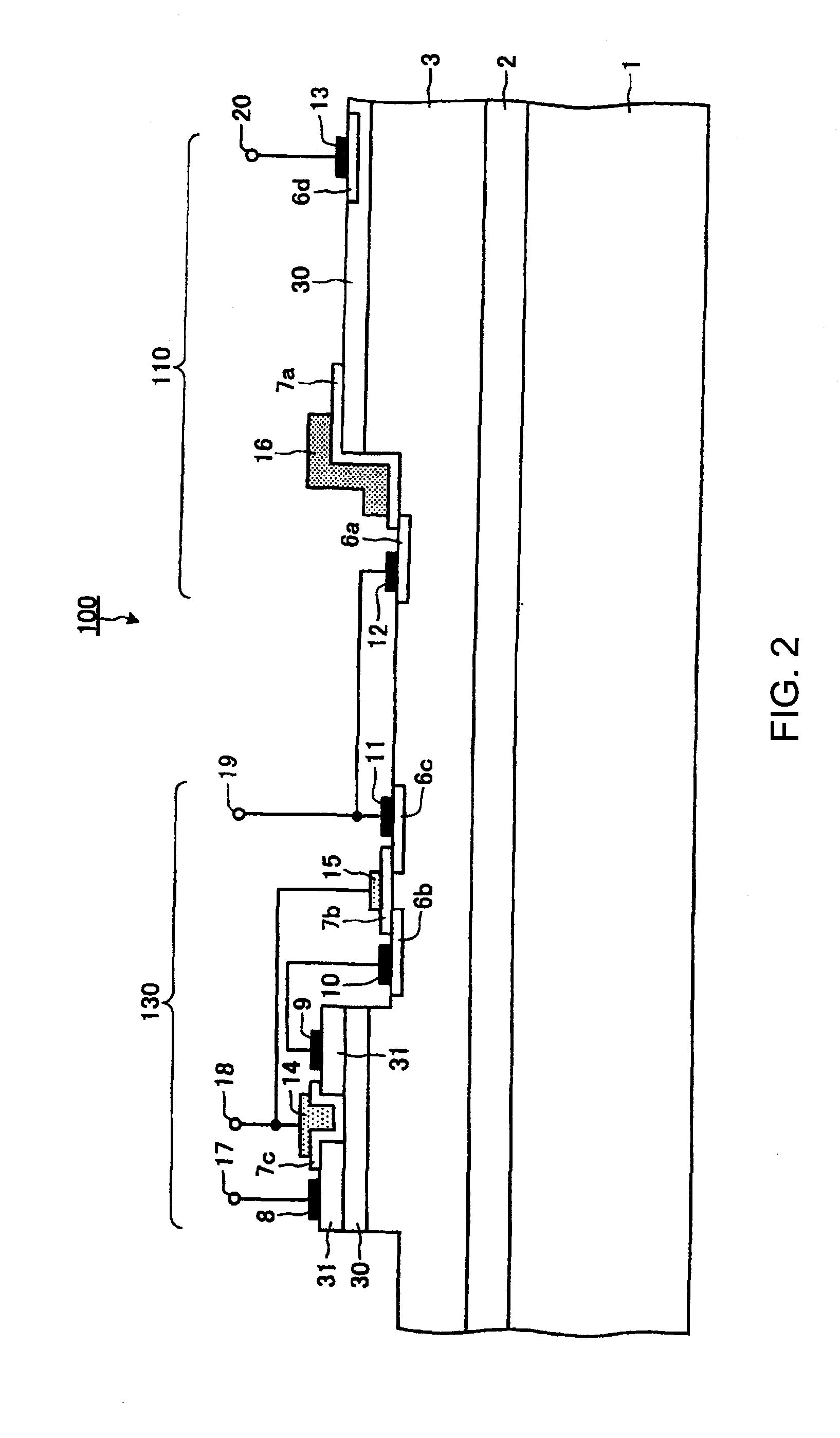

Semiconductor device and method for manufacturing the same

InactiveUS20090085182A1High modulusAvoid destructionResonant long antennasAntenna supports/mountingsFiberElectrical resistance and conductance

A semiconductor device capable of wireless communication, which has high reliability in terms of resistance to external force, in particular, pressing force and can prevent electrostatic discharge in an integrated circuit without preventing reception of an electric wave. The semiconductor device includes an on-chip antenna connected to the integrated circuit and a booster antenna which transmits a signal or power included in a received electric wave to the on-chip antenna without contact. In the semiconductor device, the integrated circuit and the on-chip antenna are interposed between a pair of structure bodies formed by impregnating a fiber body with a resin. One of the structure bodies is provided between the on-chip antenna and the booster antenna. A conductive film having a surface resistance value of approximately 106 to 1014 Ω / cm2 is formed on at least one surface of each structure body.

Owner:SEMICON ENERGY LAB CO LTD

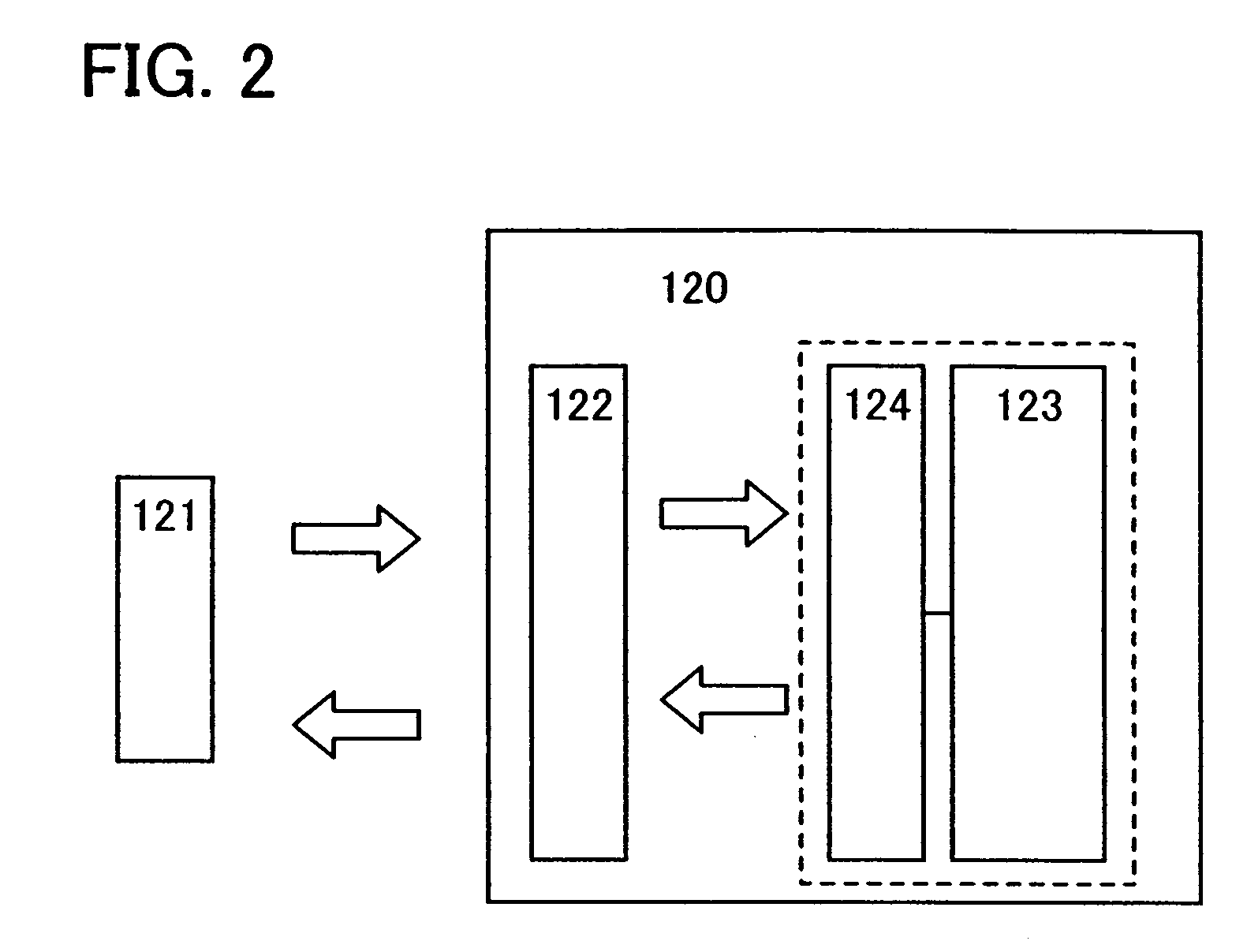

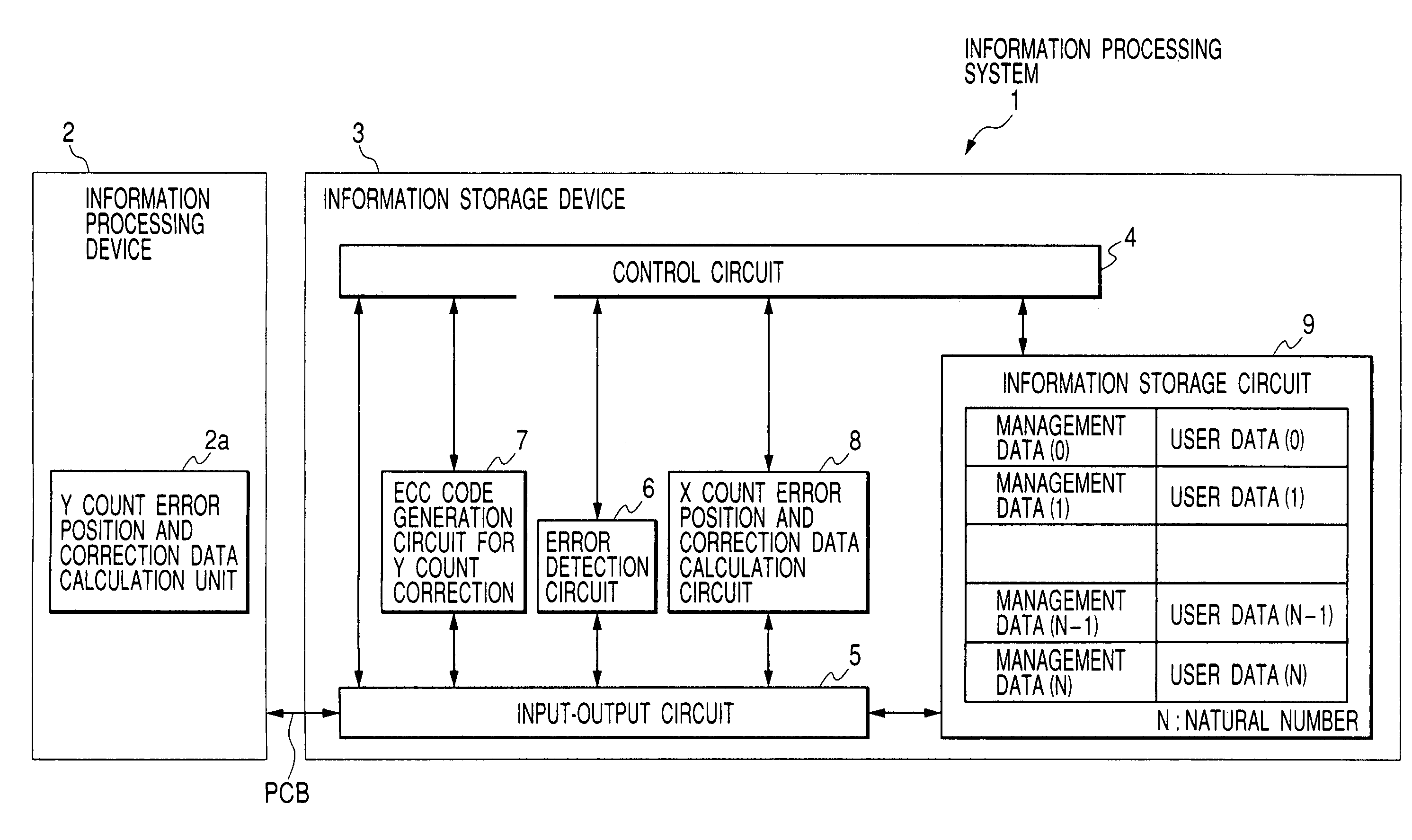

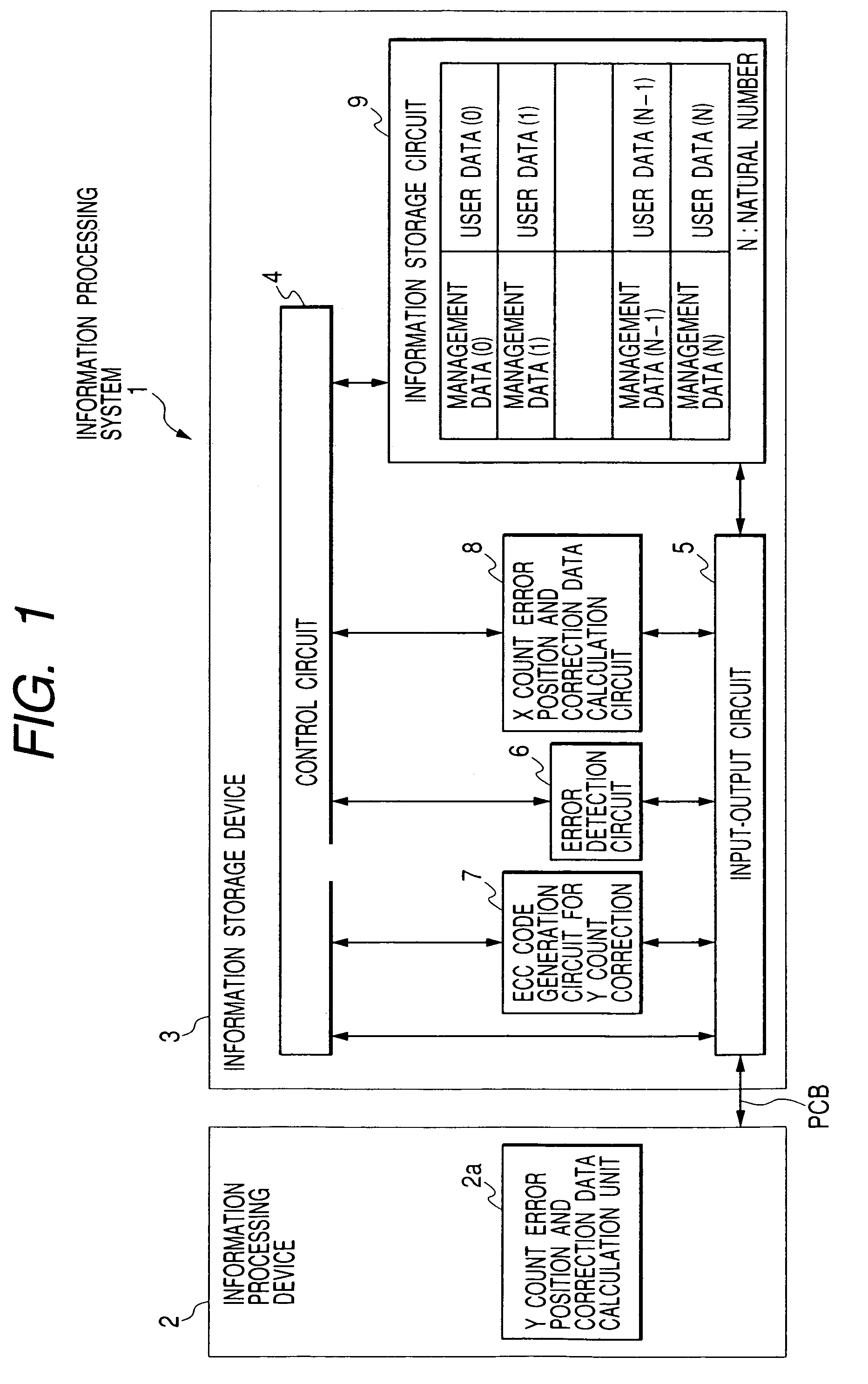

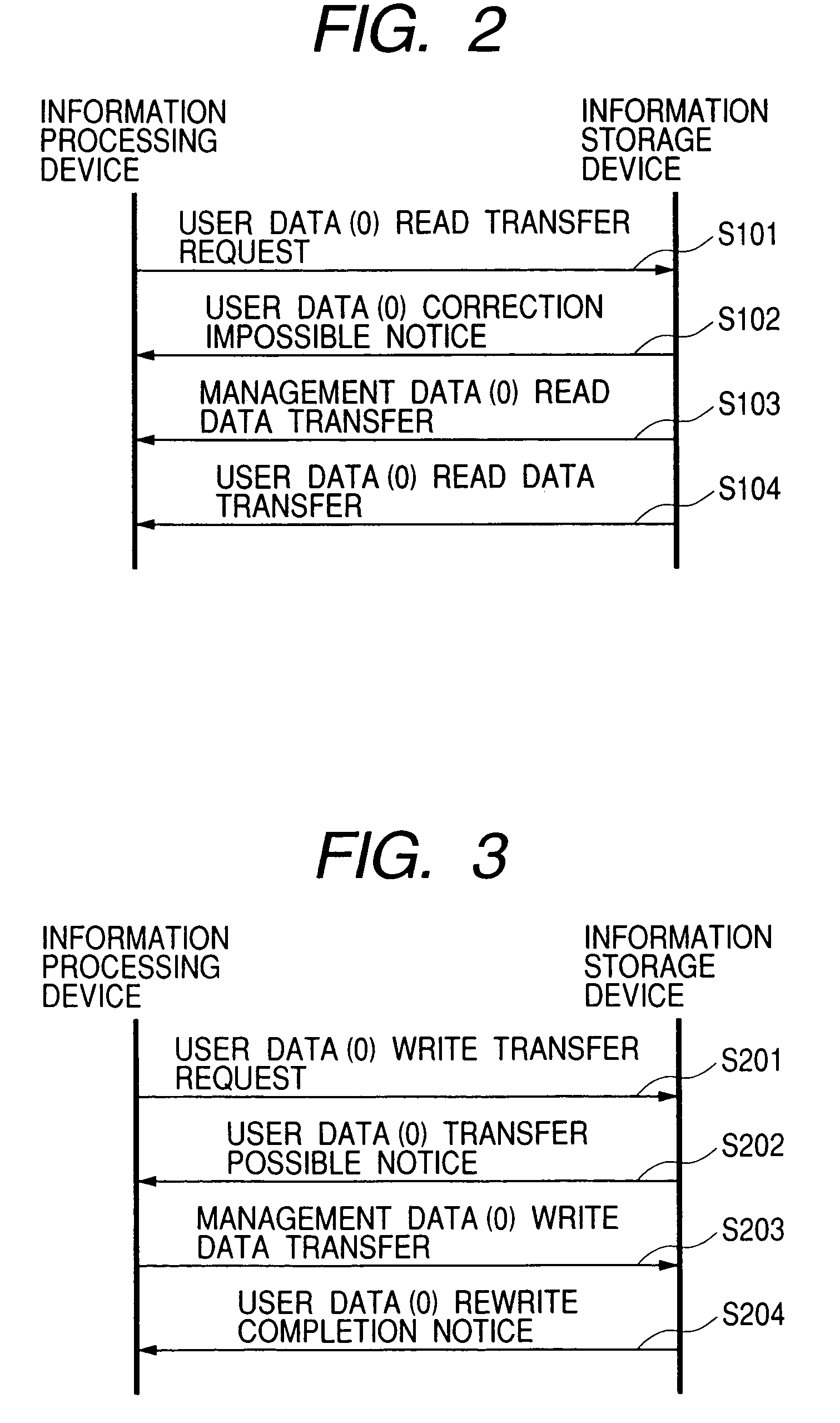

Nonvolatile memory apparatus and data processing system

InactiveUS7231580B2Increase costReduce processing performance requirementsInput/output to record carriersMemory loss protectionData processing systemInformation processing

The reliability of data is significantly increased without considerably increasing costs by performing minor data corrections within an information storage device and performing major error corrections in an information processing device. When a request to transfer user data for reading is issued from an information processing device, a control circuit transfers the user data and management data to an error detection circuit, which checks the user data for errors. If the user data contains no error, the control circuit notifies the information processing device that the user data can be transferred, and transfers it to the information processing device. If the user data contains errors, an X count error position and correction data calculation circuit uses the user data and the management data to calculate correction locations and correction data, and judges whether the correction locations are correctable. If uncorrectable (there are more correction locations than X locations), the control circuit notifies the information processing device that the user data is uncorrectable, and then transfers the user data and the management data to the information processing device.

Owner:RENESAS ELECTRONICS CORP

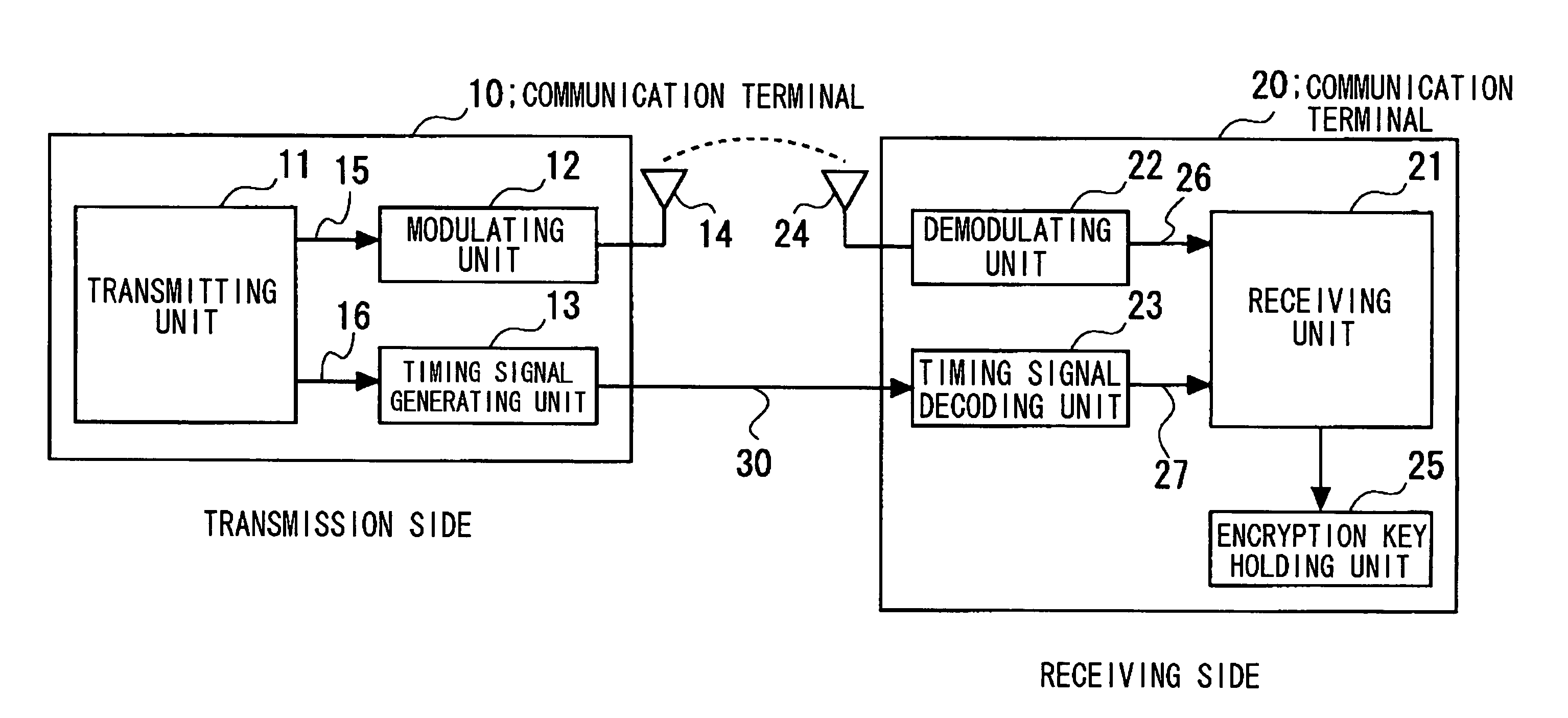

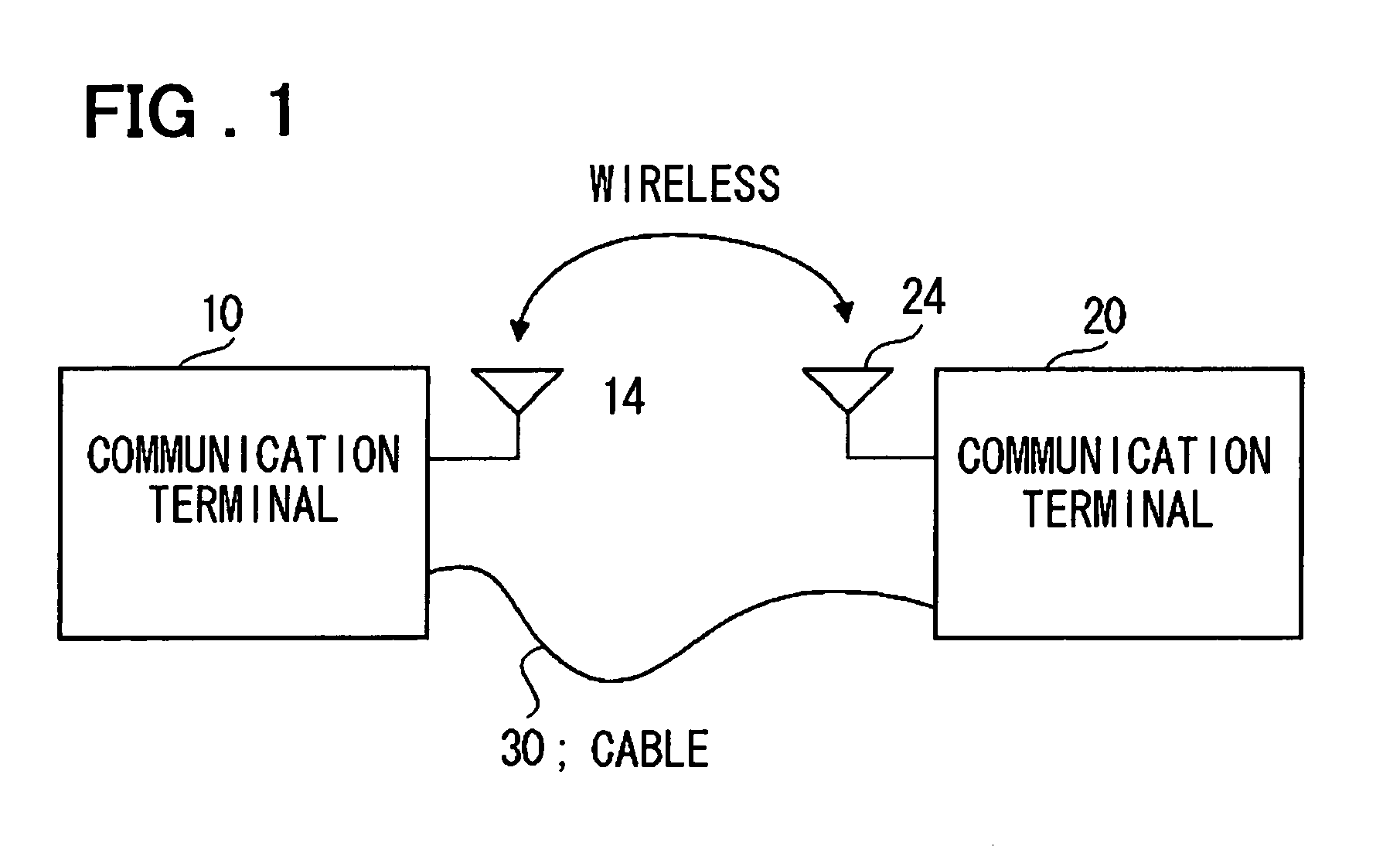

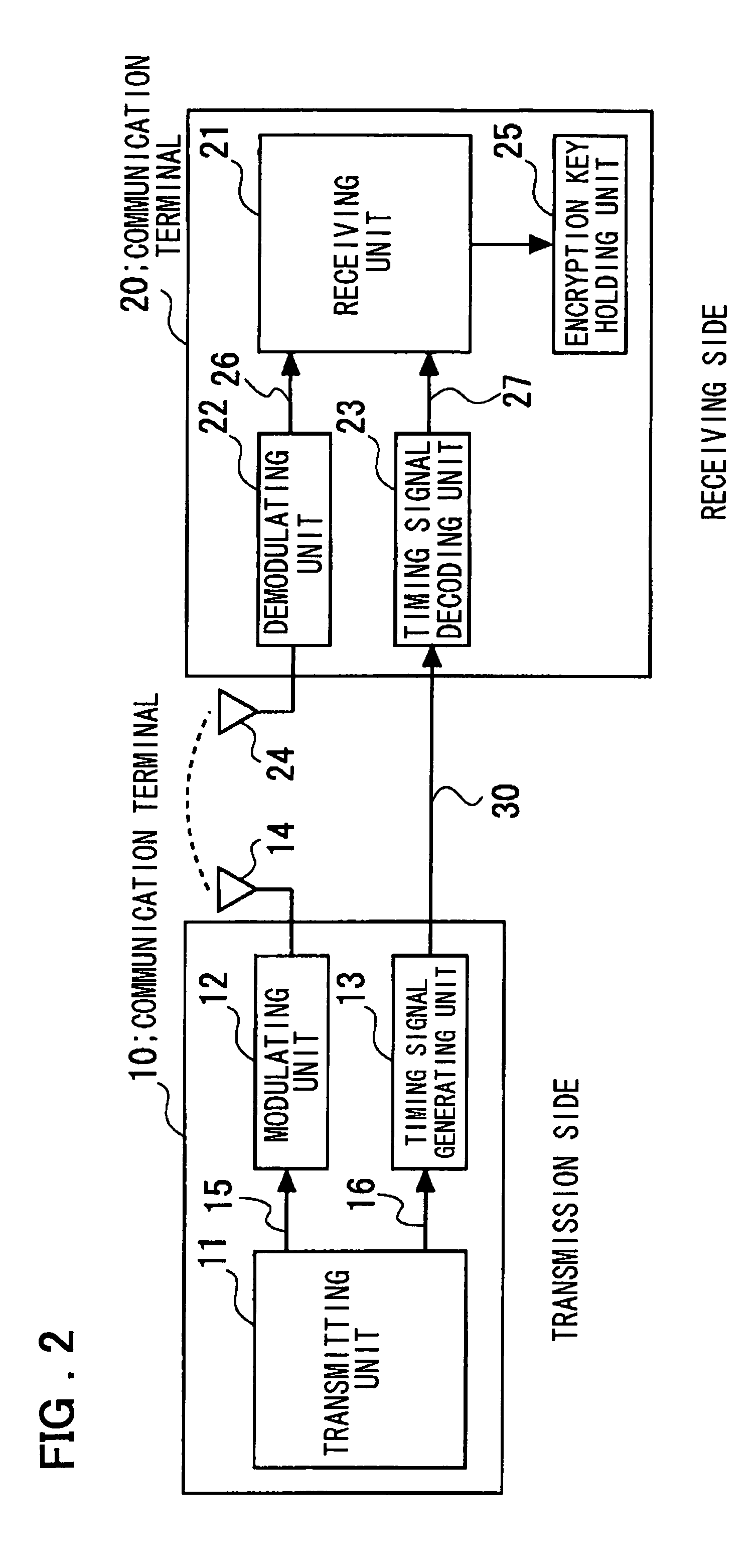

Communication system, communication device, and communication method

InactiveUS7548623B2Increase in circuit sizeIncreased power consumptionKey distribution for secure communicationUnauthorised/fraudulent call preventionComputer hardwareCommunications system

One and the other communication terminals for performing wireless communication are connected by a cable. The one communication terminal performs control so that an encryption key is transmitted from the one communication terminal to the other communication terminal by wireless during a period in which the potential of the cable is active. The other communication terminal stores the encryption key received from the one communication terminal within the period in which the potential of the cable is active, as a valid key, for use in subsequent encryption processing.

Owner:RENESAS ELECTRONICS CORP

Apparatus and method for processing an image

InactiveUS20060140498A1Improve image processing capabilitiesIncrease in circuit sizeImage memory managementElectric controllersImaging processingComputer graphics (images)

An image processing apparatus is provided for enhancing the image processing function without having to increase the circuit scale. The image processing apparatus includes an image divider, a pixel processor, and an image coupler. If the number of horizontal pixels on the width of an input image is larger than a size of a line buffer, the image divider equally divides the input image in the vertical direction so that the resulting divided area is smaller than the number of horizontal pixels on the width of the line buffer. Then, the image divider controls an input data transfer circuit so that the pixel data of the input image may be sequentially transferred to the line buffer for each of the equally divided areas. The image processor sequentially processes the pixel data of the input image temporarily stored in the line buffer and then sends out the output pixel data. The image coupler controls the output data transfer circuit so that the output pixel data sequentially outputted for one divided area may be coupled with the output pixel for another divided area, for generating the output image.

Owner:SOCIONEXT INC

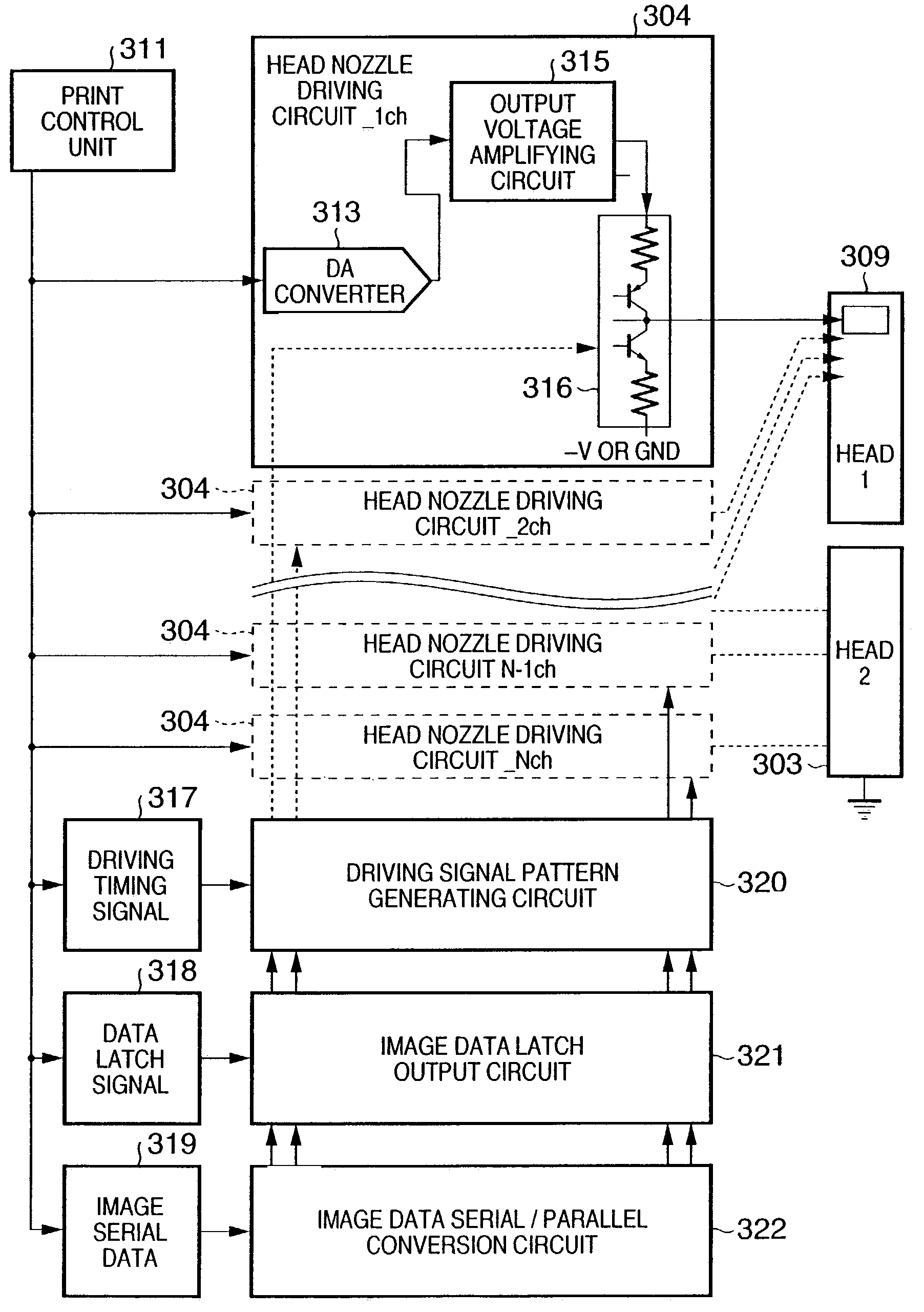

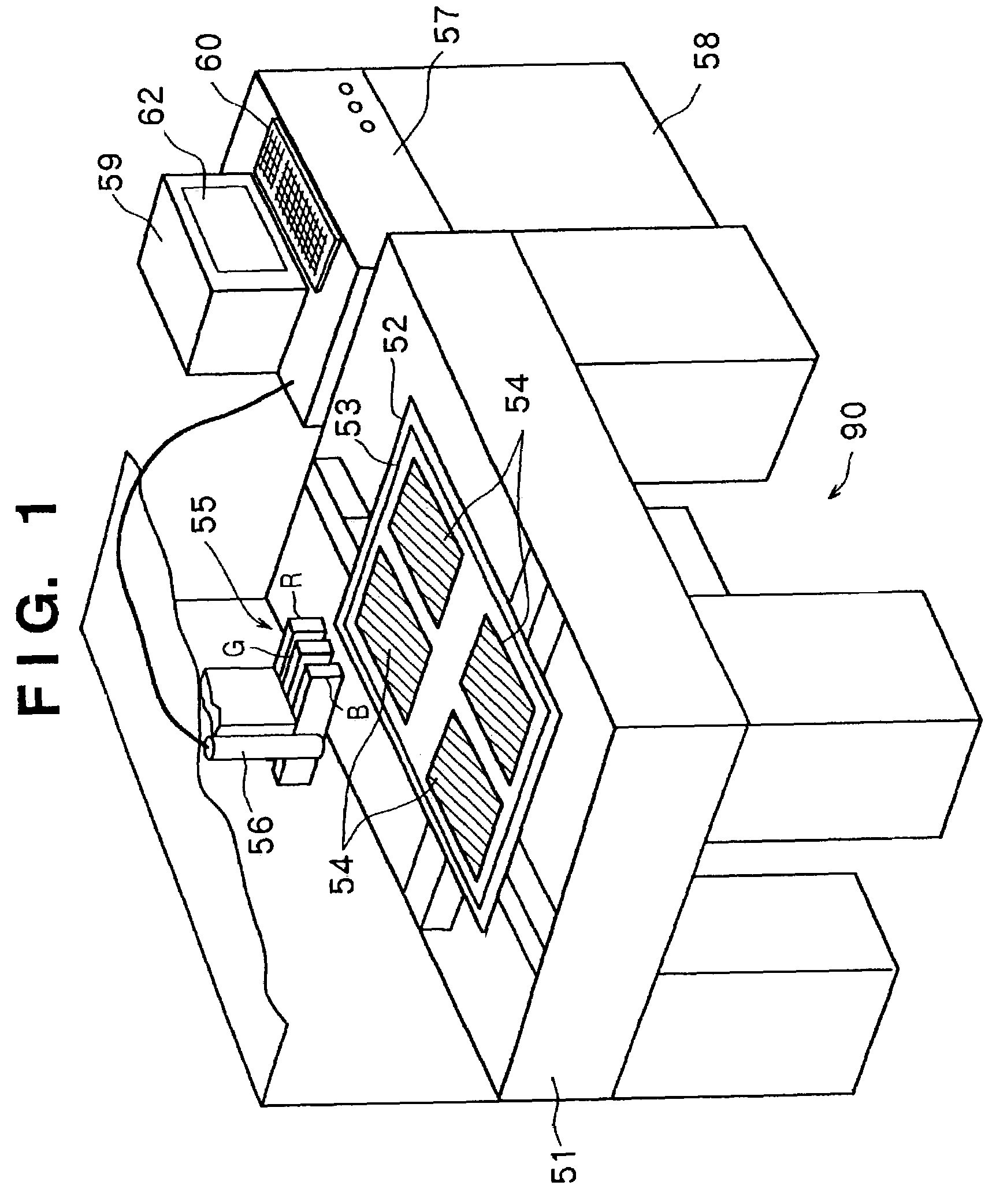

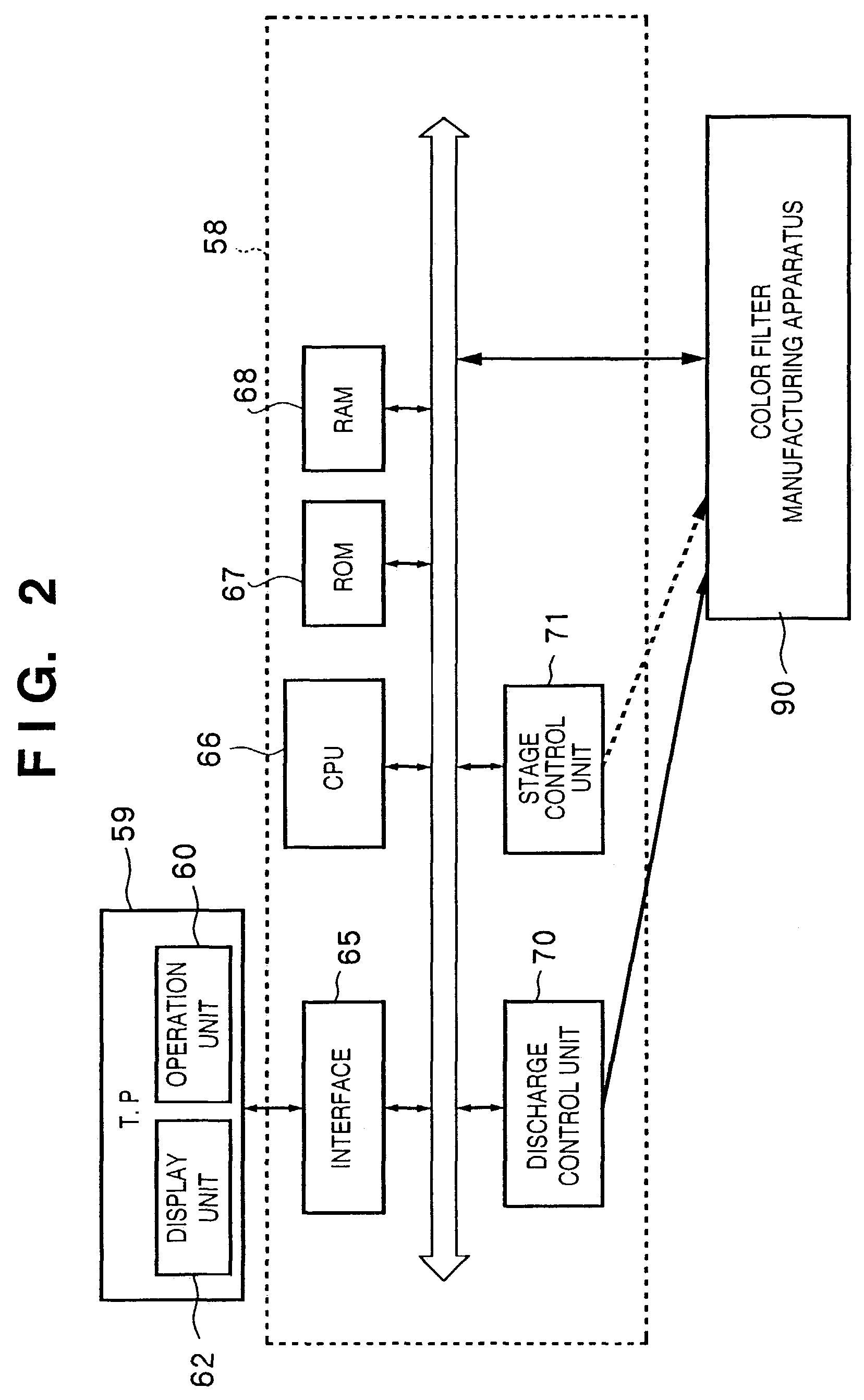

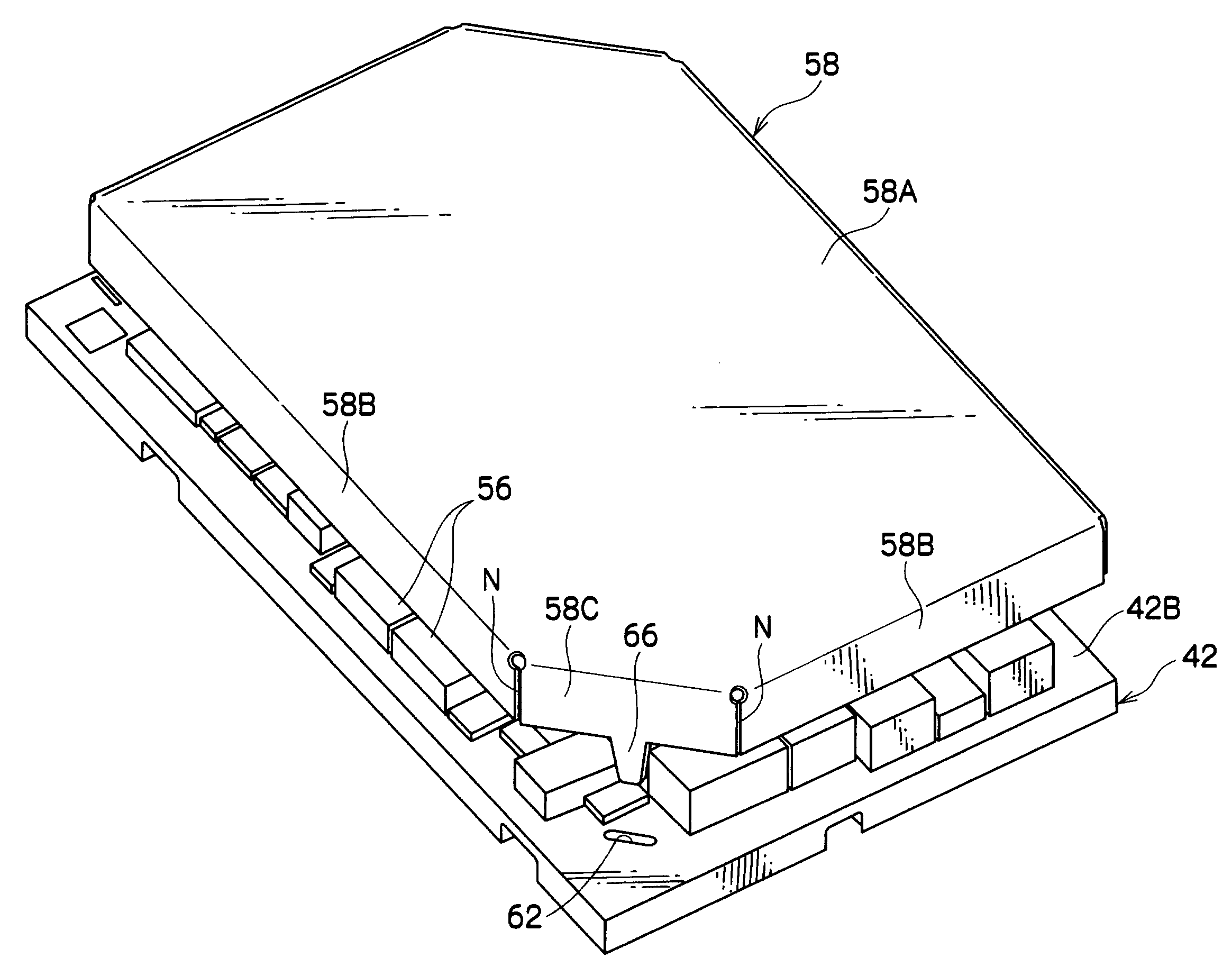

Liquid discharge method and apparatus using individually controllable nozzles

InactiveUS7188919B2Increase in circuit sizeSmall circuit sizeInking apparatusLiquid spraying apparatusEngineeringNozzle

The amounts of liquid discharged from a liquid discharge head to predetermined areas can be made uniform while suppressing an increase in circuit size. In order to achieve this object, there is provided a liquid discharge apparatus which discharges a liquid from a liquid discharge head having a plurality of nozzles for discharging the liquid, wherein the liquid discharge head includes a subset of nozzles capable of individually controlling liquid discharge amounts, among the plurality of nozzles. The subset of nozzles is smaller in number than the total number of the plurality of nozzles.

Owner:CANON KK

Structure And Method For Attaching Shield Case To Circuit Board, Electronic Component Module And Portable Telephone

InactiveUS20090016039A1Increase in circuit sizePrinted circuit assemblingMagnetic/electric field screeningSolder ballStructural engineering

A structure for attachment of a shield case to a circuit board. Electronic components are mounted at one face of the circuit board. The shield case is for covering the electronic components and blocking electromagnetic waves. The attachment structure includes toe portions, formed to protrude from the shield case, and holes formed in the circuit board, at which the toe portions can be inserted. The toe portions are fixed to the circuit board by being inserted into the holes and soldered to soldering lands at the other face of the circuit board. Thus, it is possible to prevent solder balls and solder flux entering the shield case, it is further possible to reserve space for soldering lands, with sizes that are required for fixing of the shield case, at a rear face of the circuit board, and it is possible to attach the shield case to the circuit board strongly.

Owner:FUJIFILM CORP

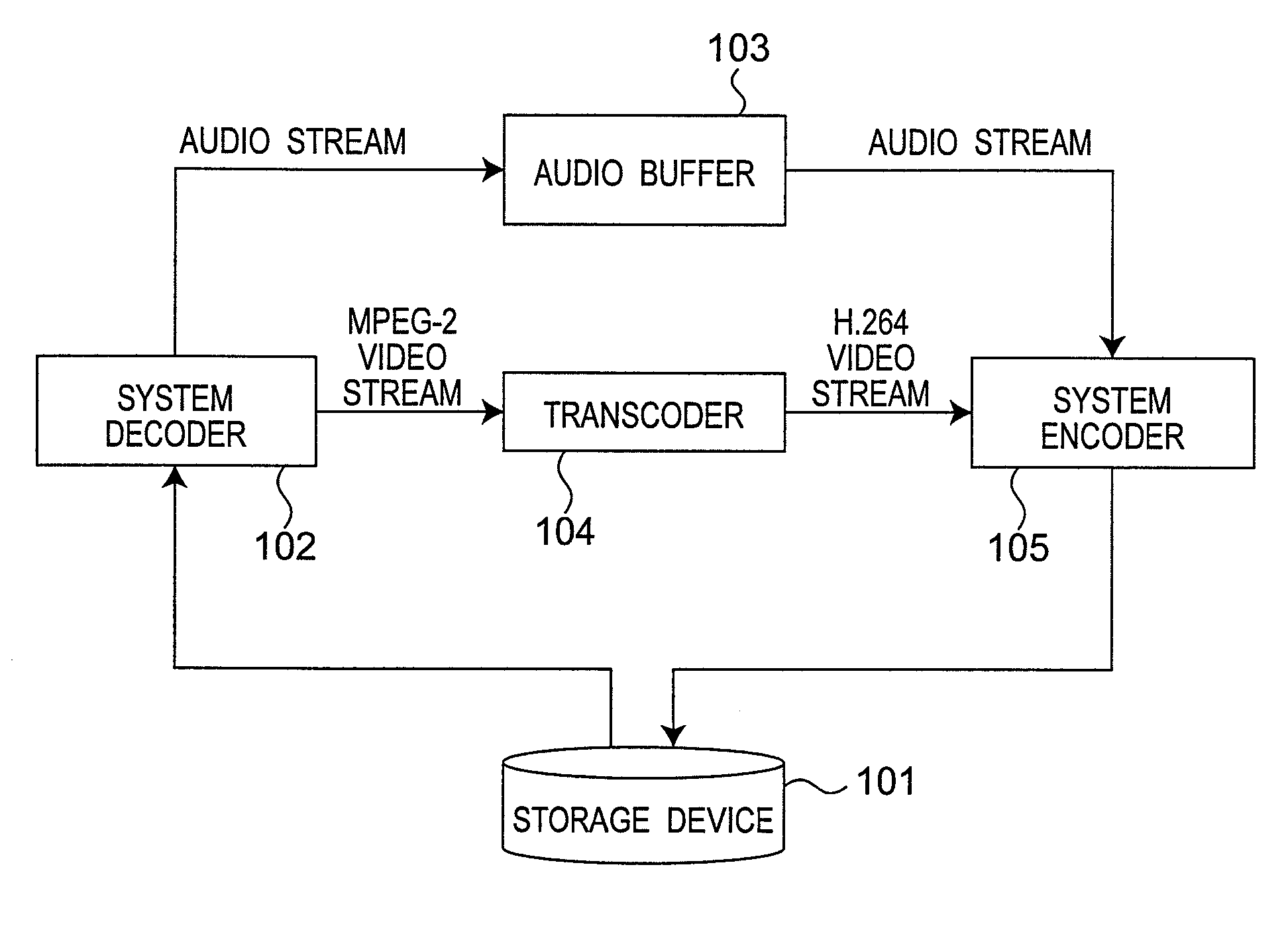

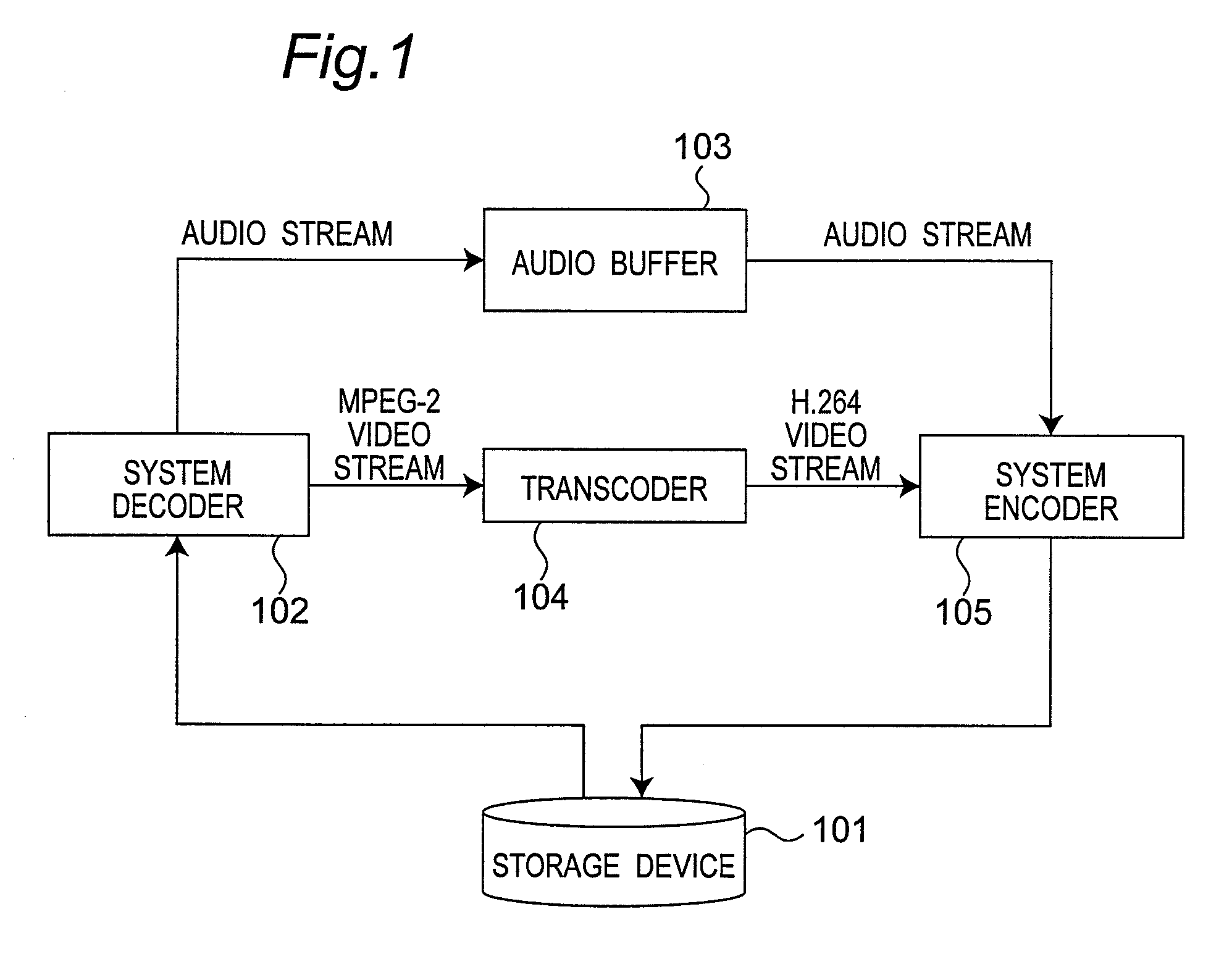

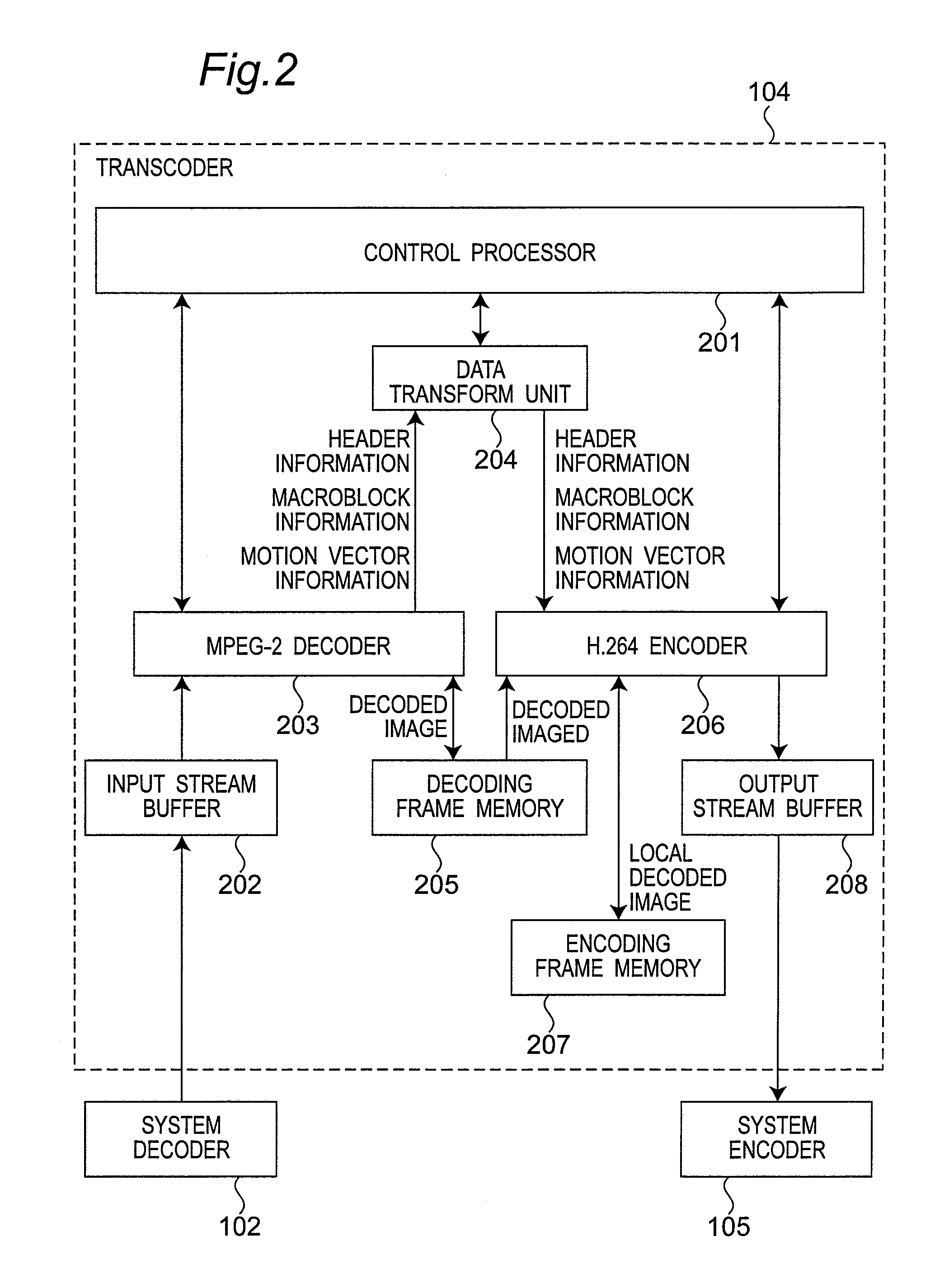

Transcoding apparatus and transcoding method

InactiveUS20080101473A1Reduce circuit sizePreventing Image Quality DeteriorationColor television with pulse code modulationColor television with bandwidth reductionComputer graphics (images)Imaging quality

A transcoding apparatus and a transcoding method convert MPEG-2 compressed video to H.264 compressed video without increasing the circuit size while also preventing loss of image quality. The transcoding apparatus has a transcoder. The transcoder has an MPEG-2 decoder for decoding an MPEG-2 video stream, a data transform unit, and a H.264 encoder. The data transform unit converts the header information, macroblock information, and motion vector information of the macroblocks in the decoded MPEG-2 video stream to the header information, macroblock information, and motion vector information of H.264 macroblocks. The H.264 encoder encodes the MPEG-2 video stream as an H.264 video stream based on the converted information.

Owner:PANASONIC CORP

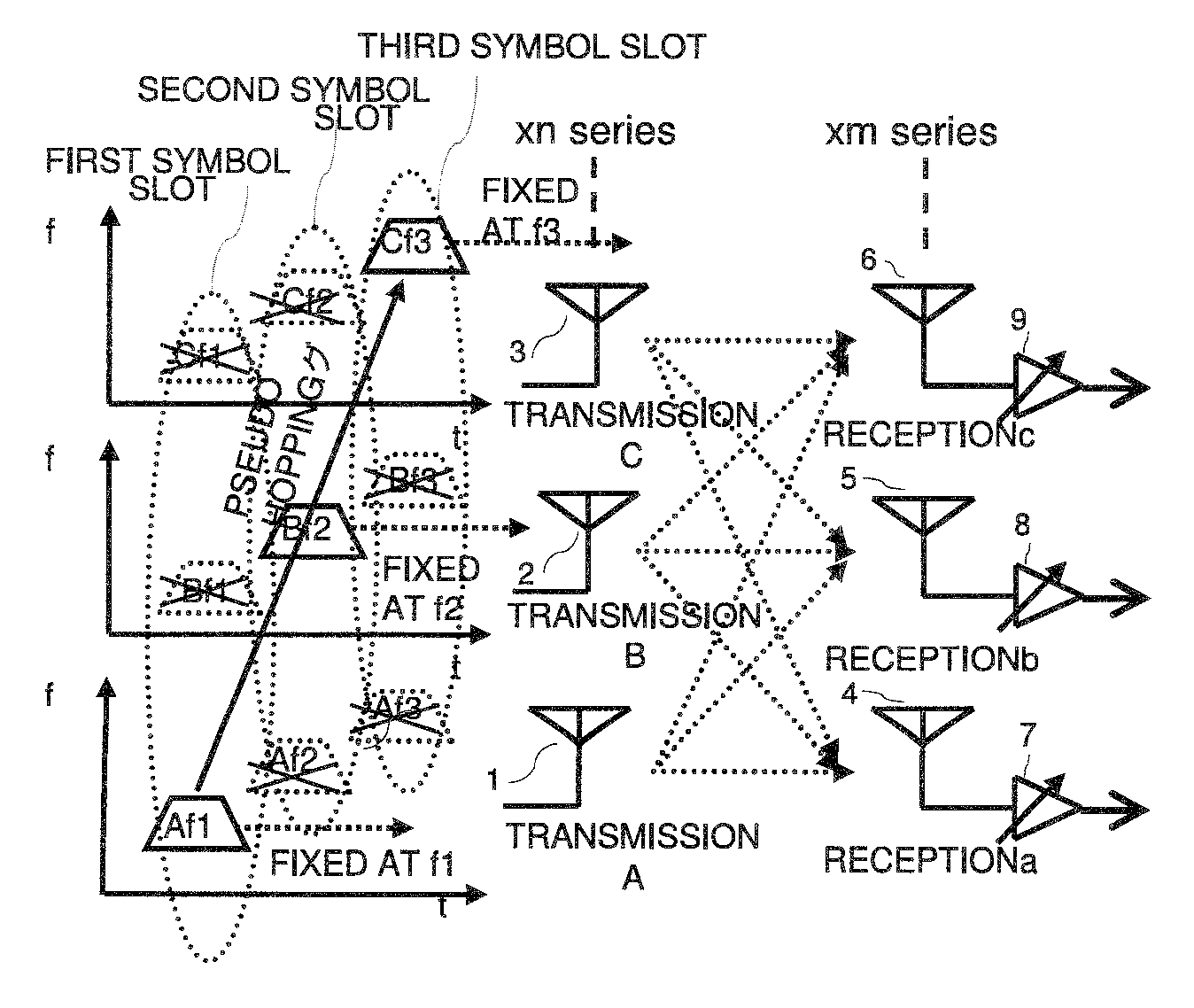

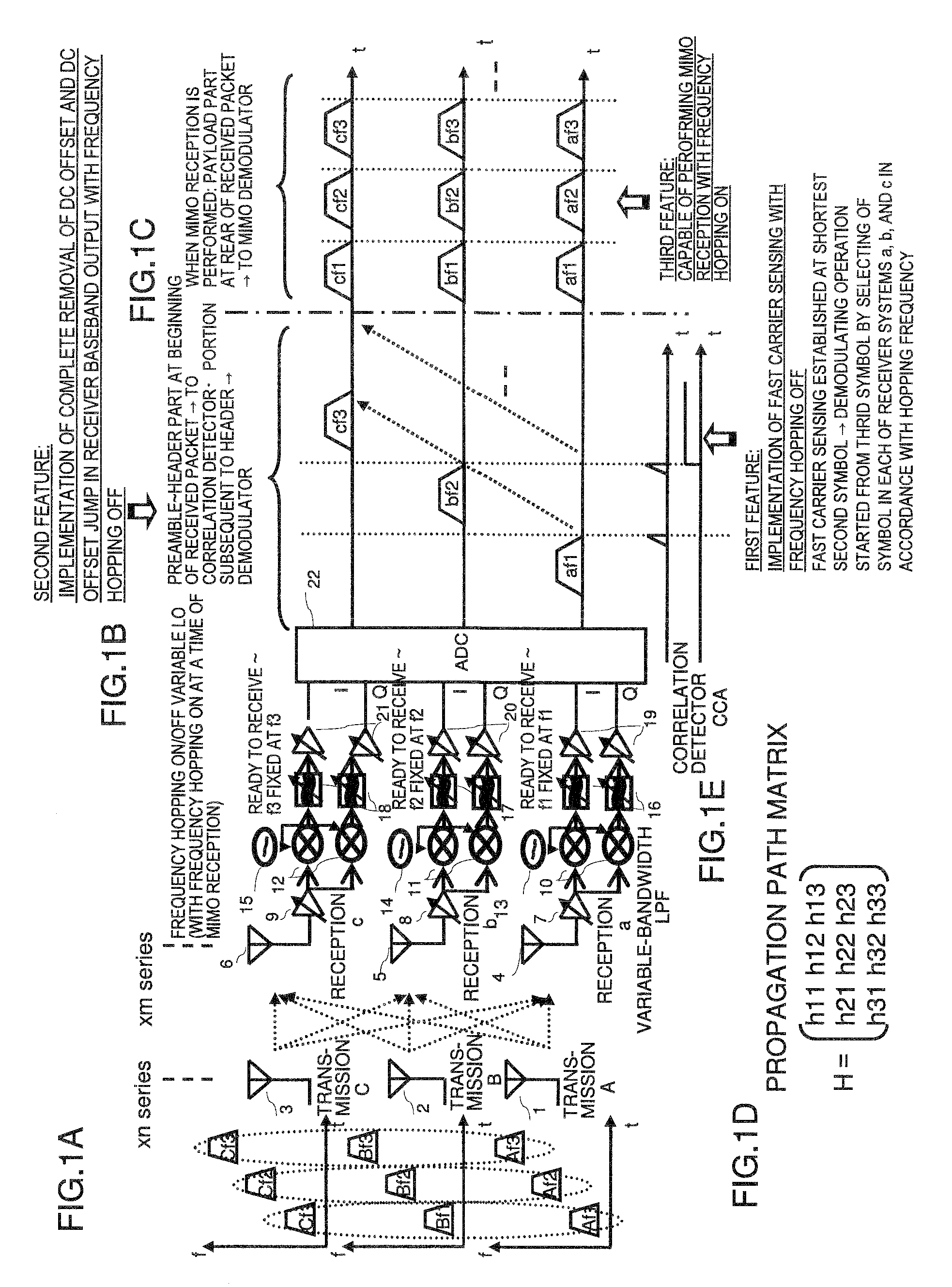

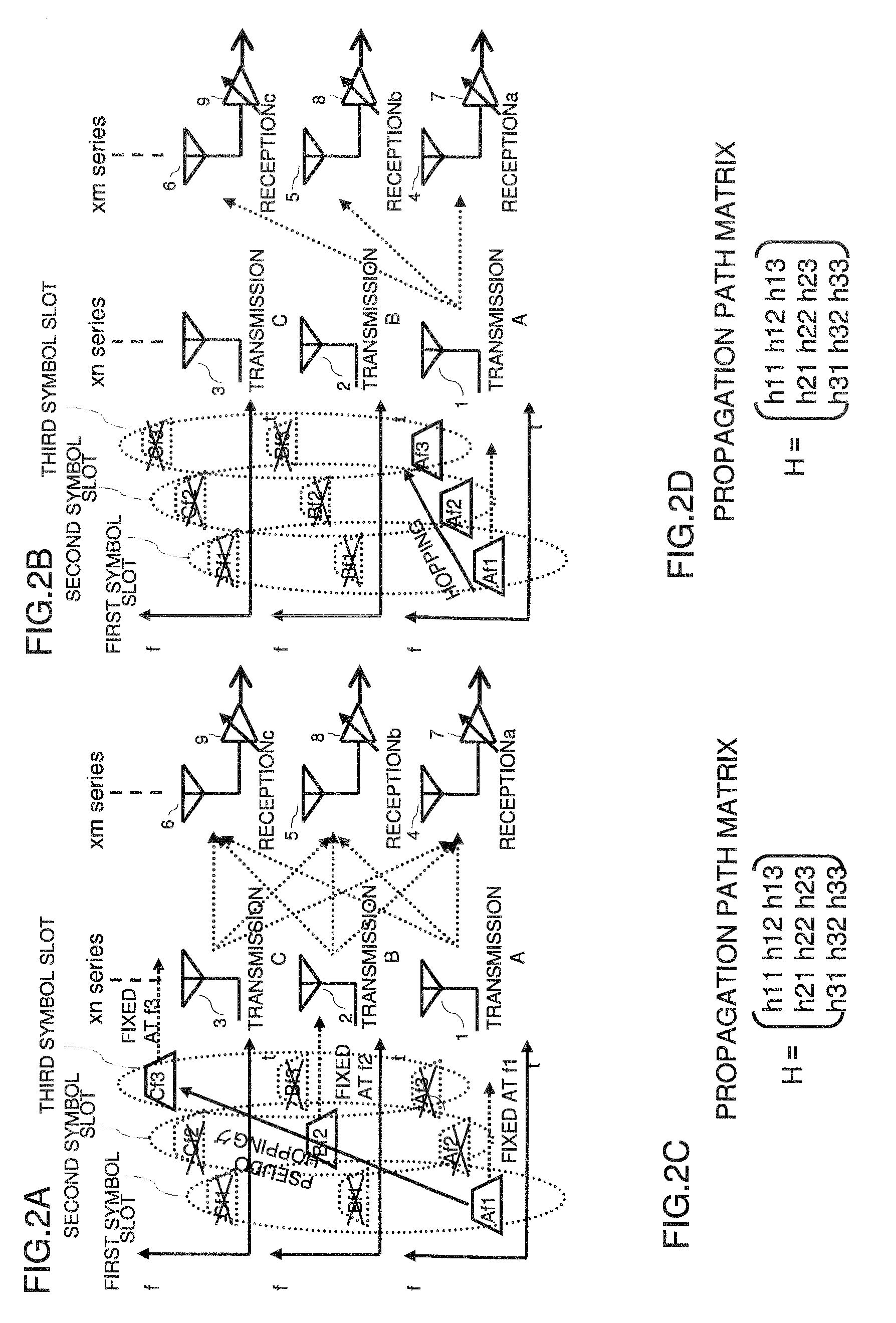

Wireless communication apparatus and a reception method involving frequency hopping

InactiveUS20090279588A1Solve the real problemIncrease speedSpatial transmit diversityModulated-carrier systemsBandpass filteringEngineering

Disclosed is a receiver of a direct conversion receiving scheme in which a packet is transmitted or received while performing frequency hopping for each symbol and demodulation is started by carrier sensing at the beginning of the packet, which performs demodulation without hopping frequencies of LOs of receiving systems to reliably execute fast carrier sensing and hopping synchronization at the beginning of the packet and remove the DC offset jump. At a time of demodulation of a payload part, the frequencies of LOs of the receiving system are hopped to allow a transition of MIMO. Further, by concurrently using complex bandpass filters while fixing all the LOs at a center LO frequency, complete removal of the DC offset jump over the entire length of the packet and MIMO can be simultaneously implemented.

Owner:RENESAS ELECTRONICS CORP

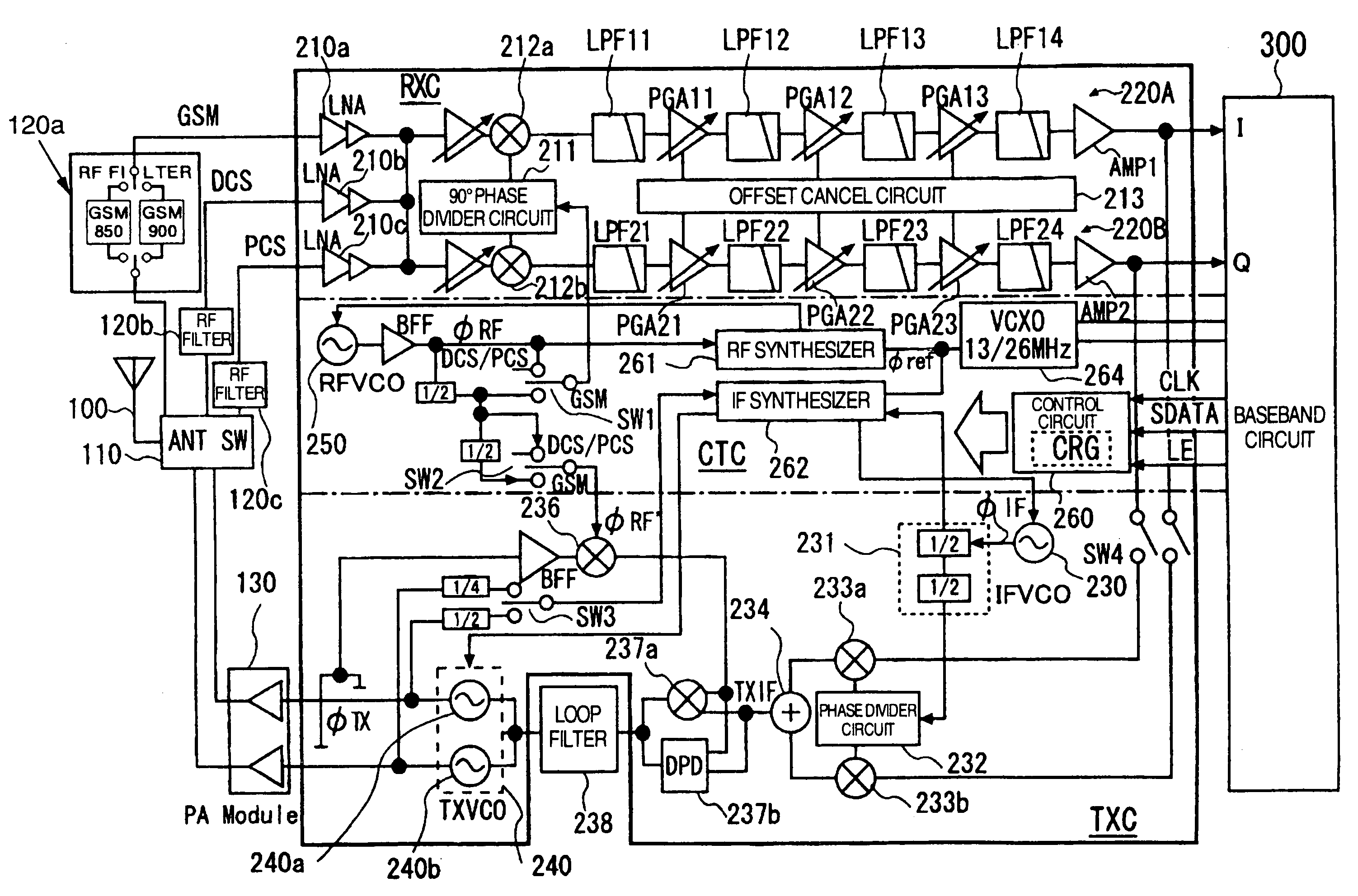

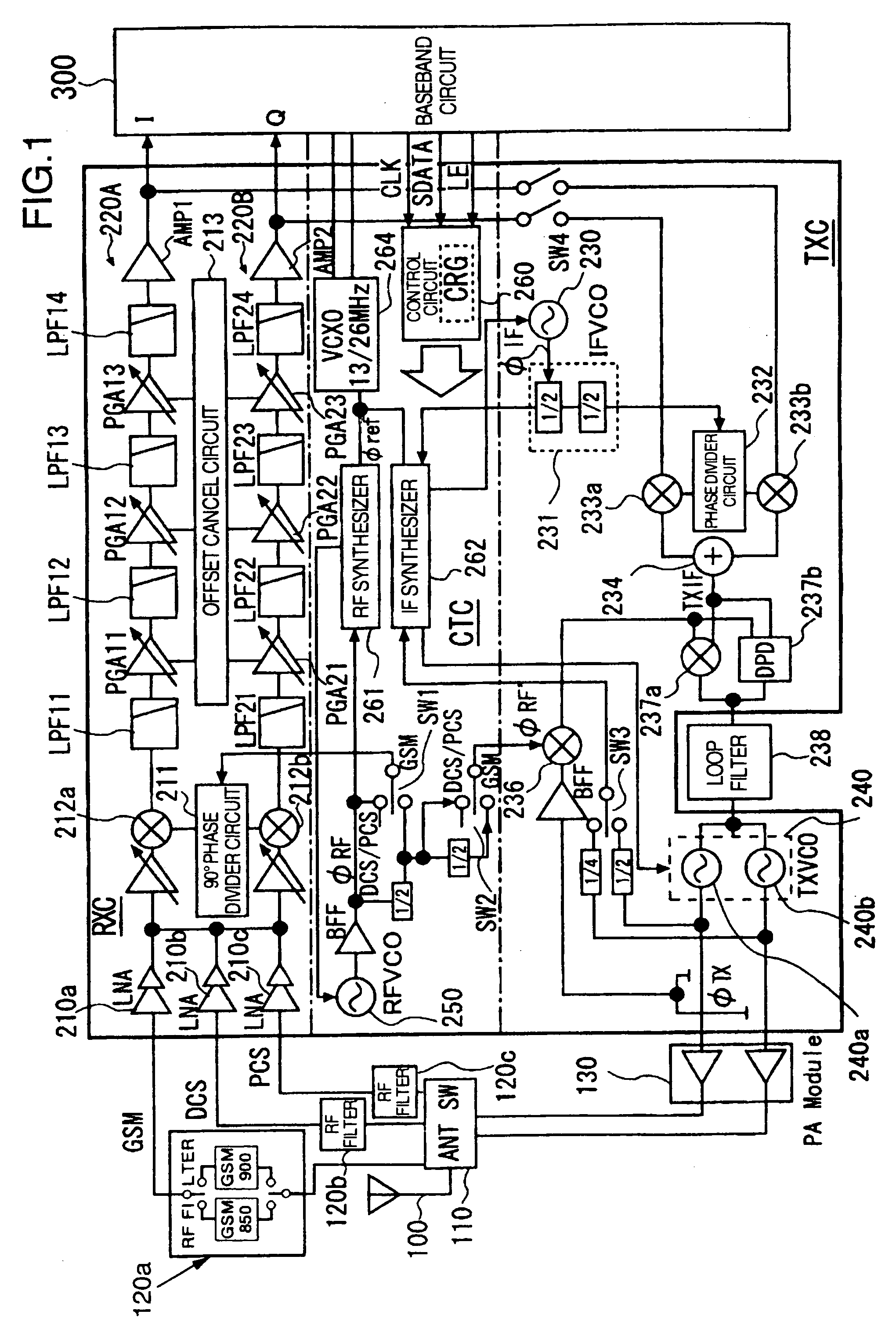

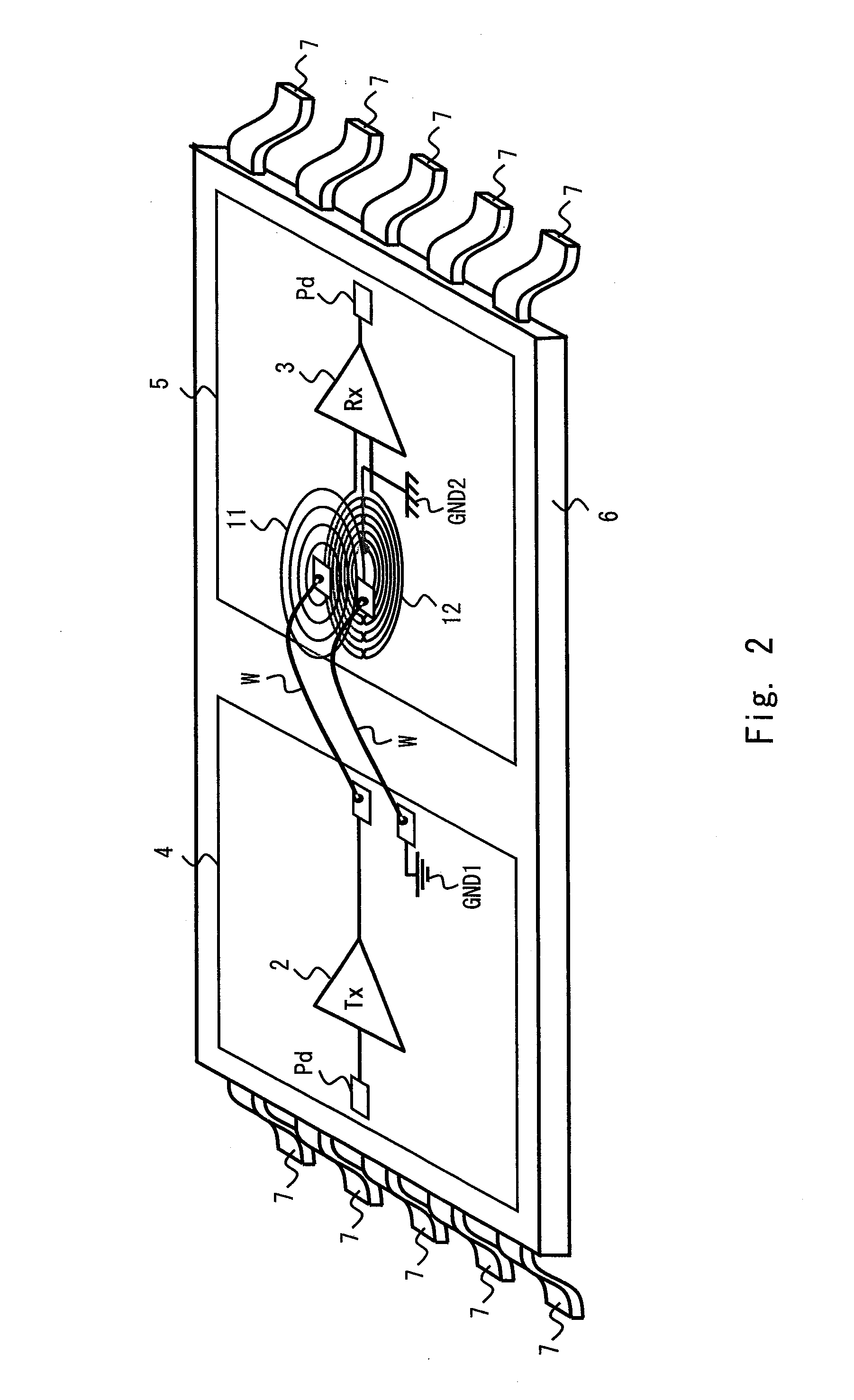

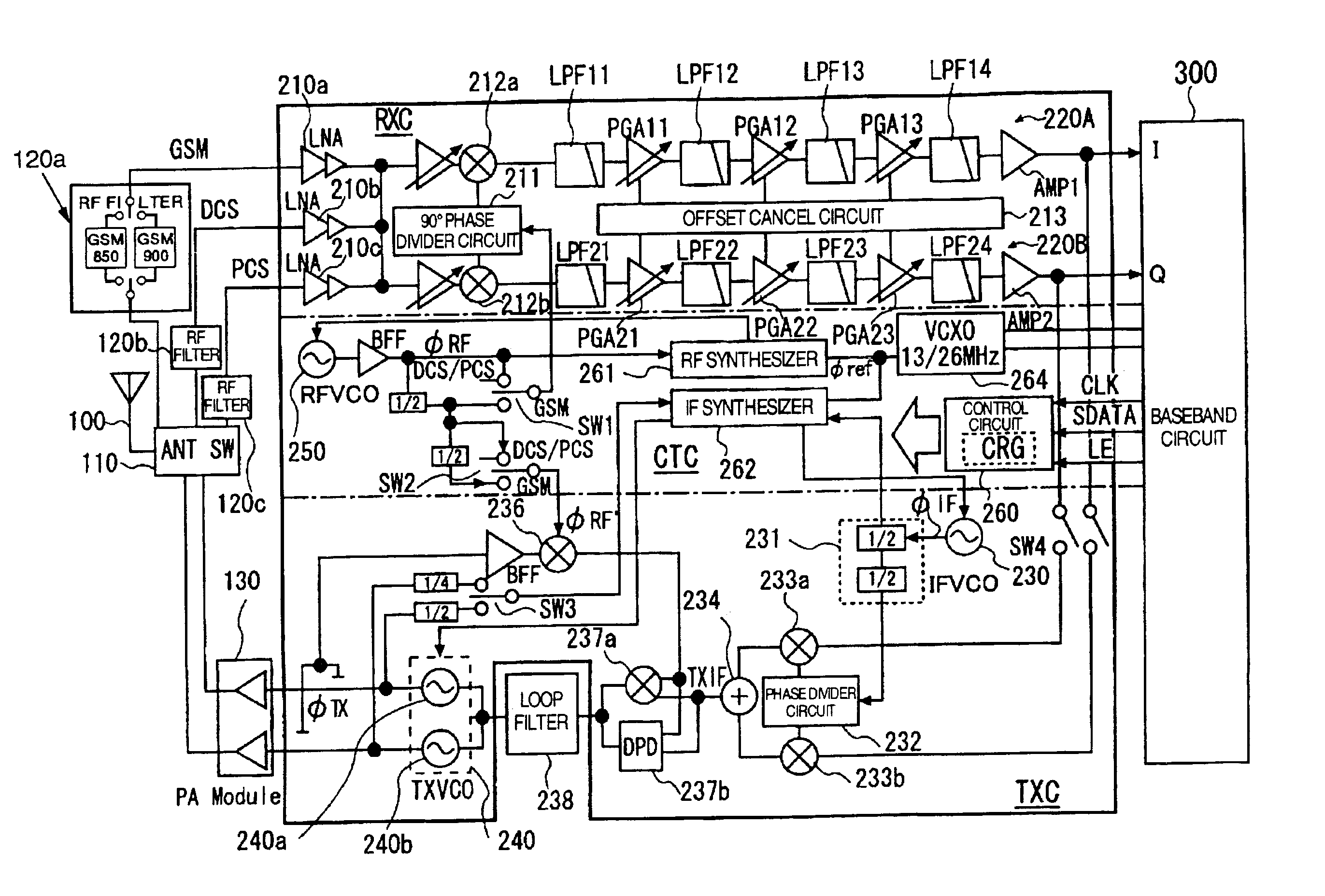

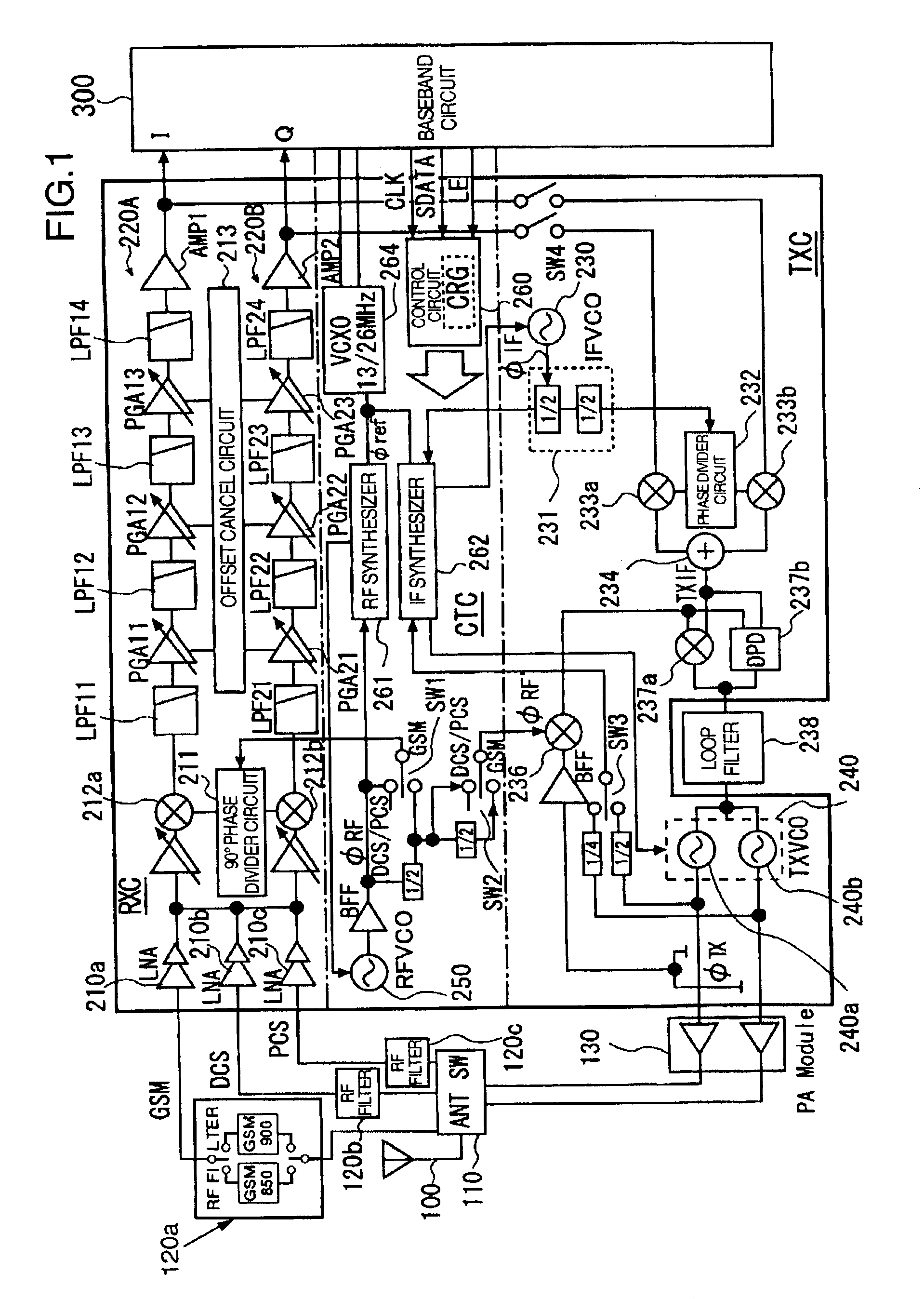

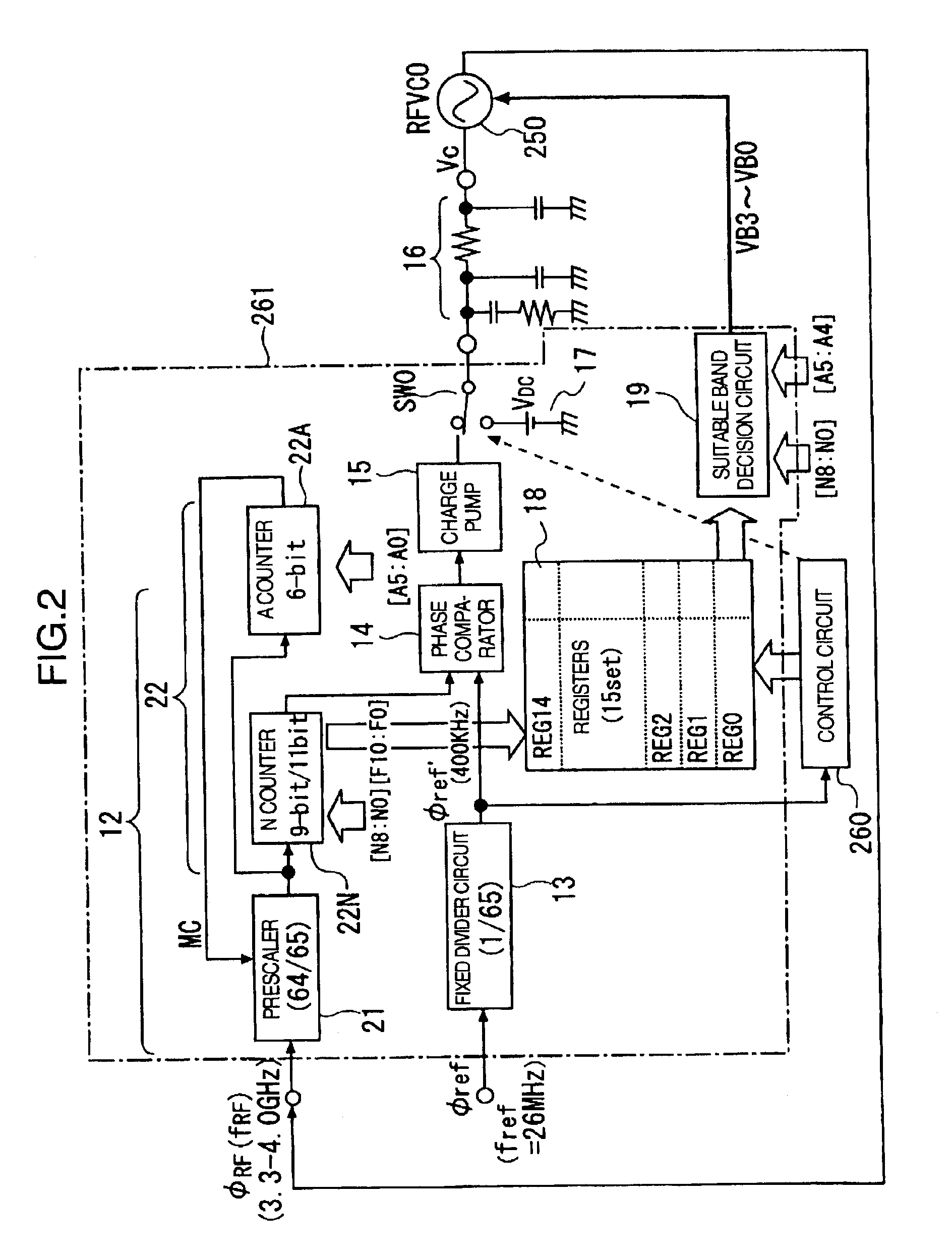

Communication semiconductor integrated circuit and radio communication system

InactiveUS20050239499A1Increase in circuit sizeWide frequency rangePulse automatic controlPulse generation by logic circuitsCommunications systemIntermediate frequency

A communication semiconductor integrated circuit has an oscillator circuit forming part of a transmission PLL circuit fabricated on a single semiconductor chip together with an oscillator circuit forming part of a reception PLL circuit and an oscillator circuit for an intermediate frequency. The oscillator circuit forming part of the transmission PLL circuit is configured to be operable in a plurality of bands. A circuit for measuring the oscillating frequency of the oscillator circuit forming part of the transmission PLL circuit is also used for measuring the oscillating frequency of the oscillator circuit forming part of the reception PLL circuit or for measuring the oscillating frequency of the oscillator circuit for the intermediate frequency.

Owner:RENESAS ELECTRONICS CORP +1

Display device and method for driving same

ActiveUS20160300534A1Increase in circuit sizeChange in measurementStatic indicating devicesComputational physicsDigital data

A display device that can compensate for degradation of circuit elements while suppressing an increase in circuit size is implemented.A data signal line (S(j)) is not only used as a signal line that transfers a signal for allowing an organic EL element (OLED) in each pixel circuit (11) to emit light at a desired luminance, but also used as a signal line for characteristic detection. In addition, a switch (334) is provided between the data signal line (S(j)) and an internal data line (Sin(j)). In such a configuration, during an AD conversion period during which analog data obtained for characteristic detection is converted into digital data, the switch (334) is brought into an off state and a potential of the data signal line (S(j)) obtained immediately before the AD conversion period is supplied from through a predetermined control line (CL) to the data signal line (S(j)).

Owner:SHARP KK

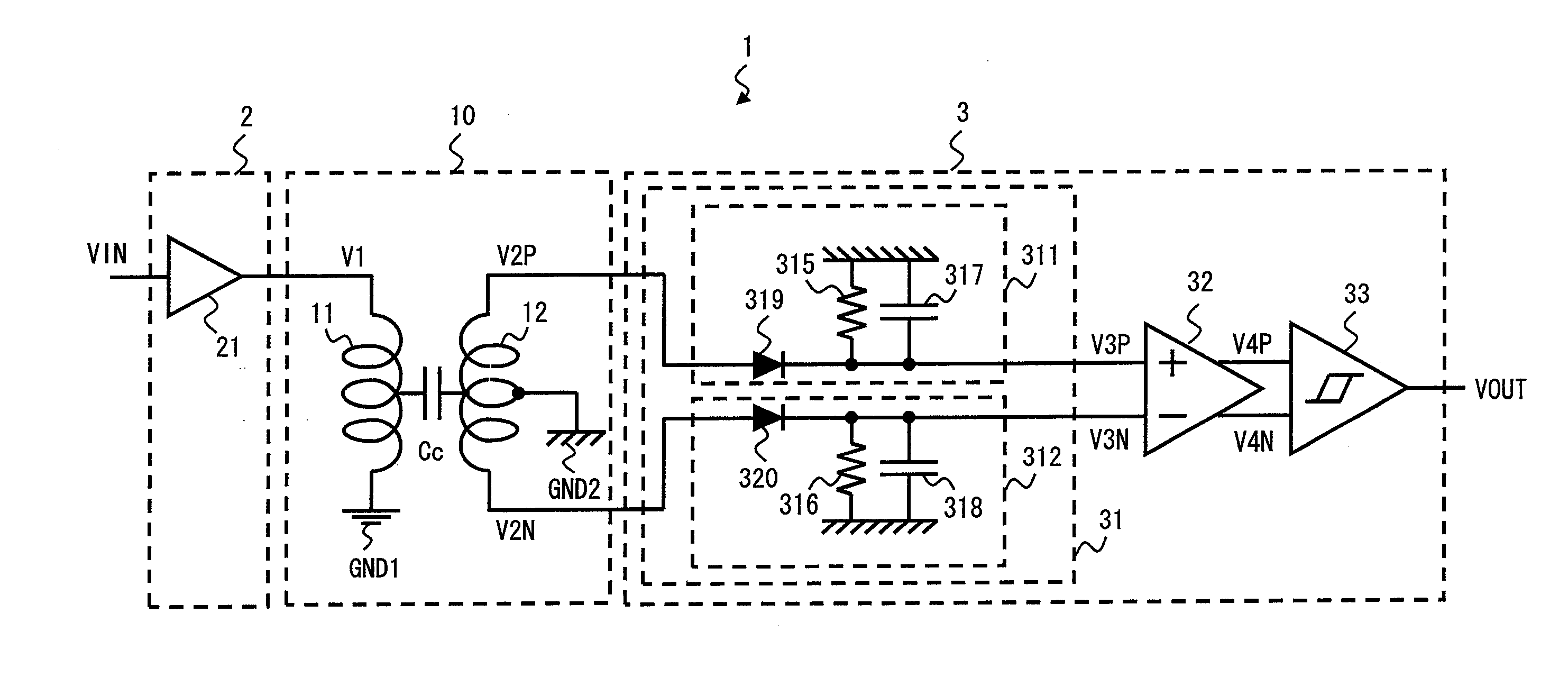

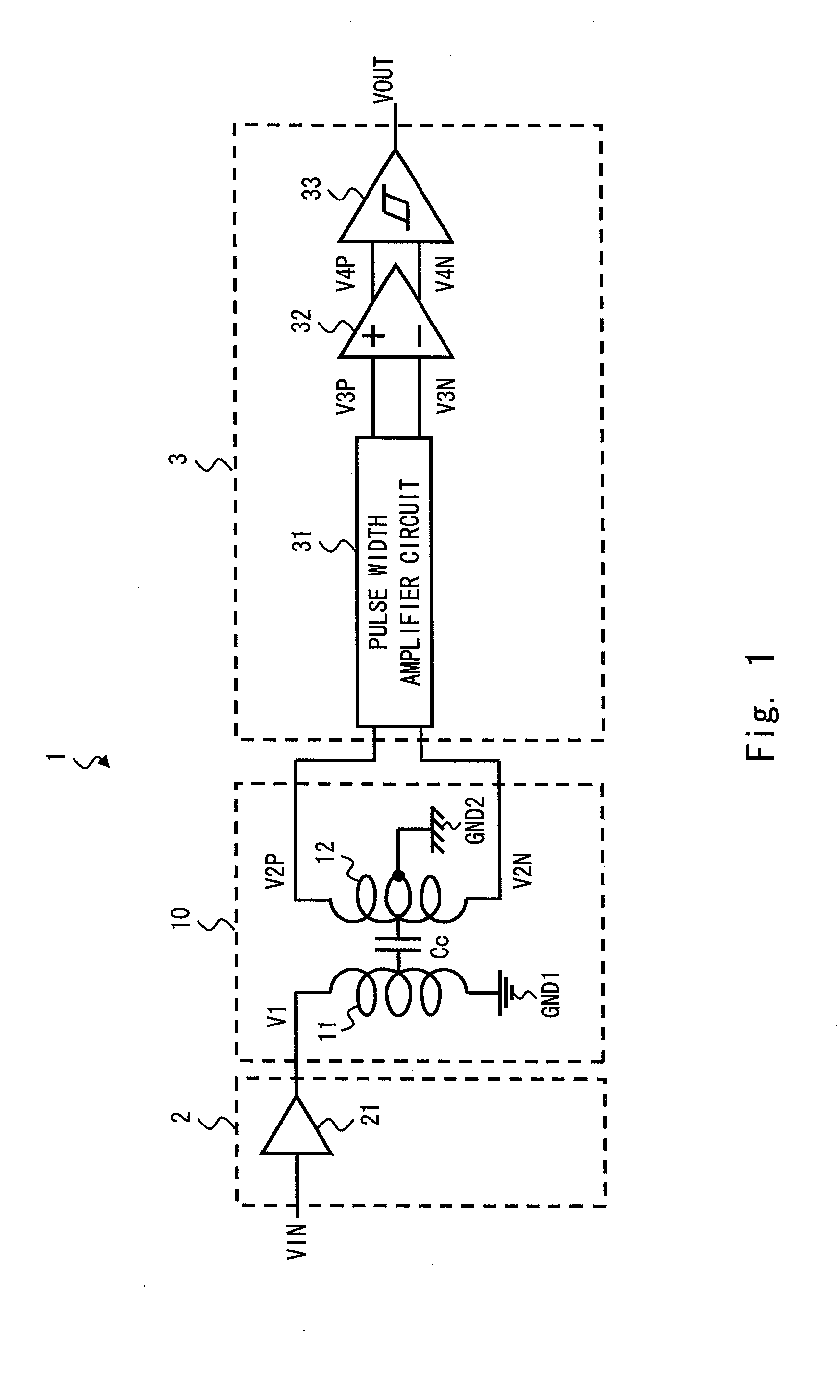

Receiving circuit and signal receiving method

InactiveUS20140085951A1Increase in circuit sizeAvoid signalingNear-field transmissionAc-dc conversion without reversalDifferential amplifierVIT signals

Provided is a receiving circuit that operates in a power supply system different from a transmitting circuit outputting a transmission signal and receives the transmission signal through an AC coupling device where a primary coil through which the transmission signal flows and a secondary coil having a center tap to which a specified voltage is supplied from an external terminal are magnetically coupled, which includes a pulse width amplifier circuit that holds pulse signals appearing at both ends of the secondary coil for a specified period of time and outputs them as hold signals, respectively, and a differential amplifier that compares a voltage of the hold signal and a voltage of the hold signal and outputs a comparison result.

Owner:RENESAS ELECTRONICS CORP

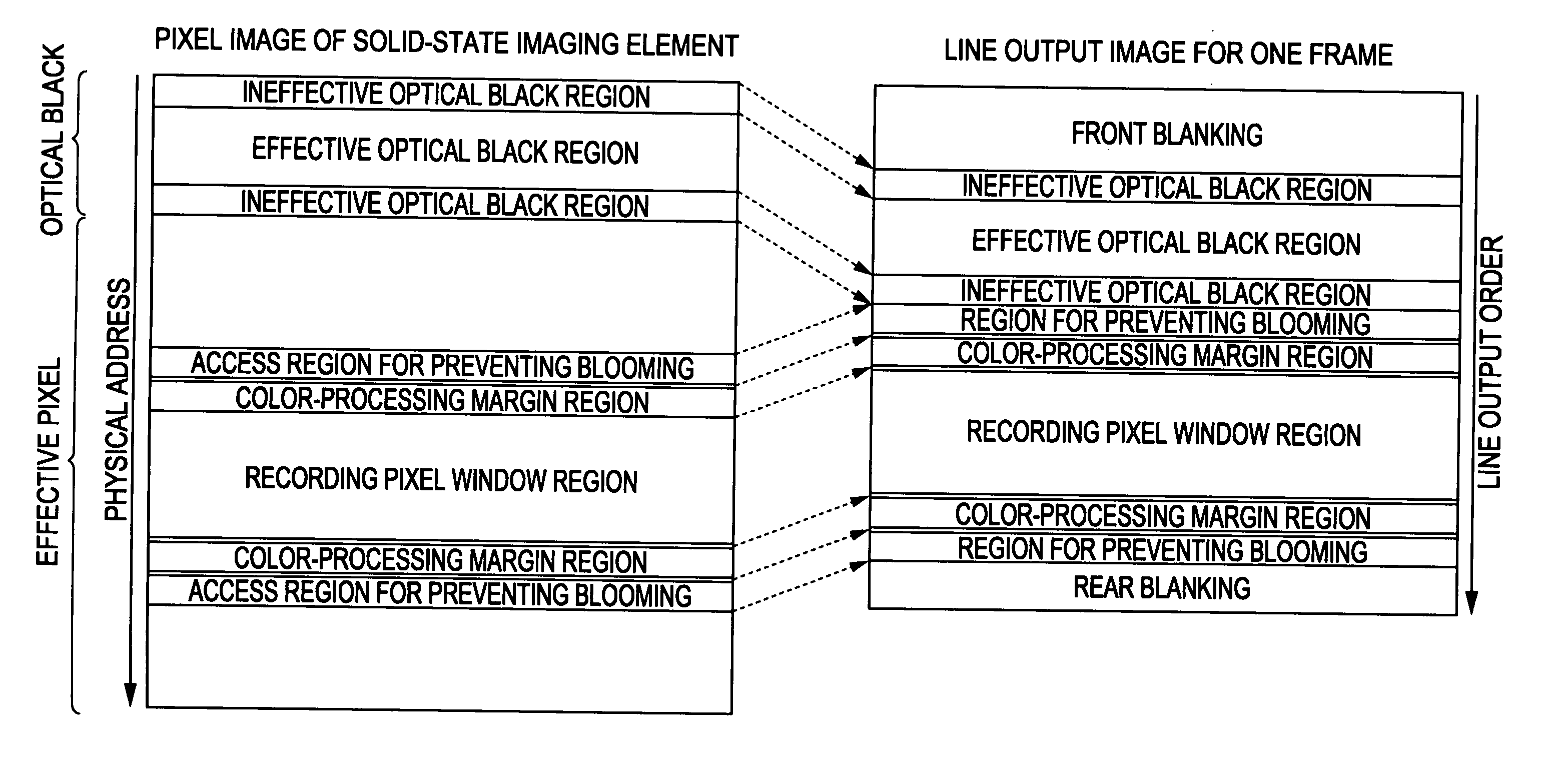

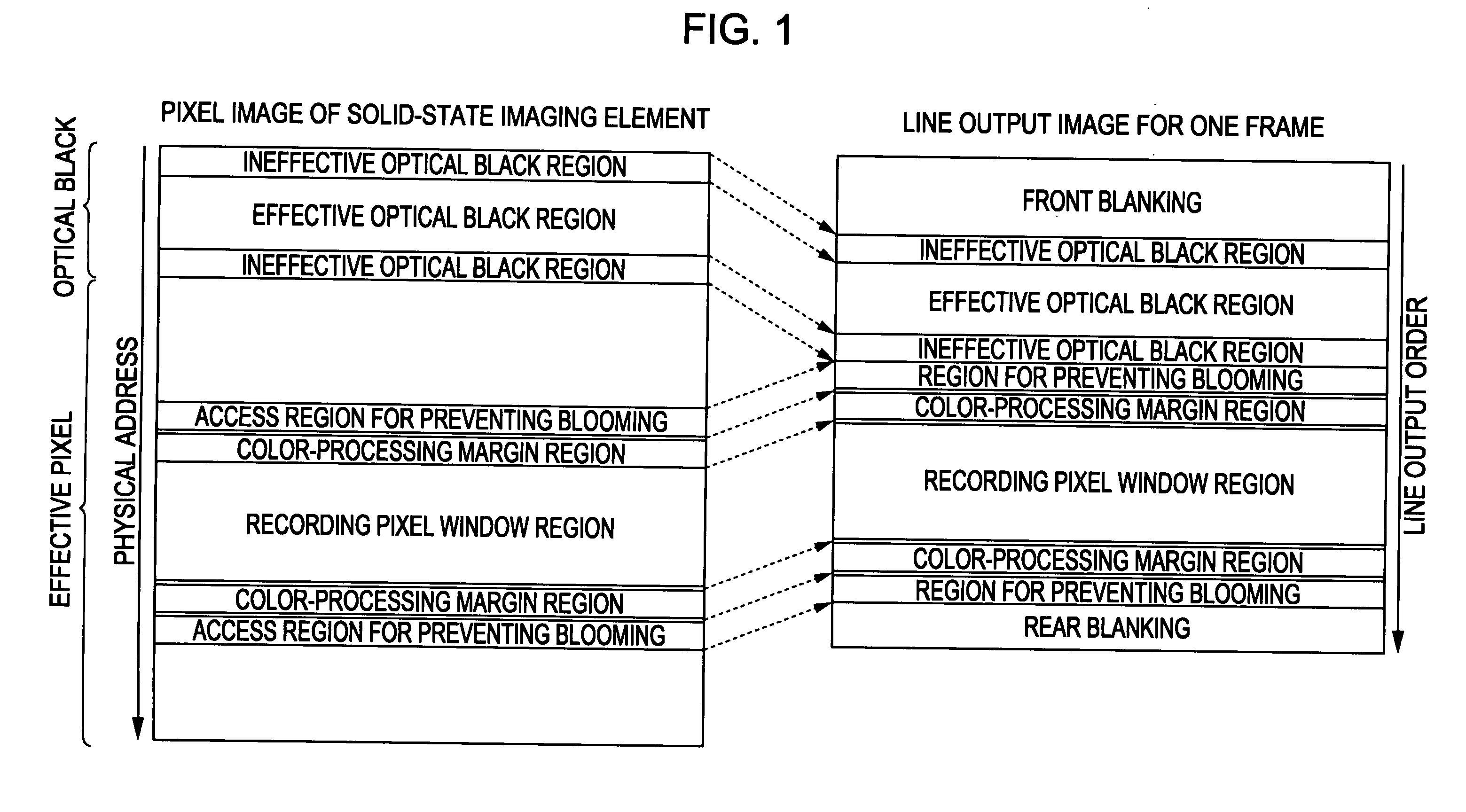

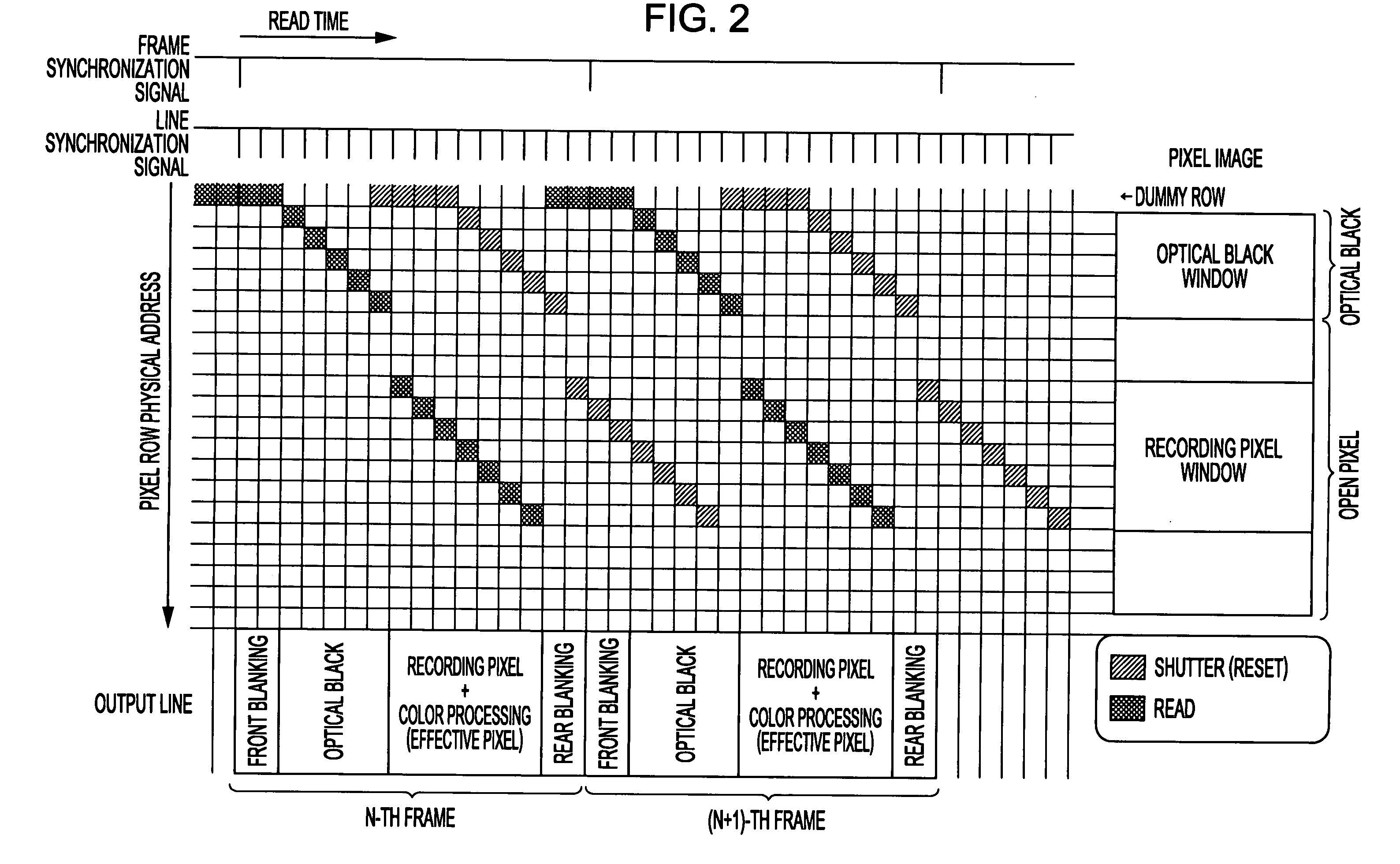

Solid-state imaging element, driving method therefor, and camera system

ActiveUS20100085458A1Increase in circuit sizeTelevision system detailsTelevision system scanning detailsPhotoelectric conversionEngineering

A solid-state imaging element includes a pixel array unit having pixels arranged in a matrix, each pixel including a photoelectric conversion element, and a pixel drive control unit capable of controlling driving of the pixel array unit so as to perform a read or reset access operation of the pixel array unit in accordance with specified address information. The pixel drive control unit is capable of setting a desired region in the pixel array unit as a window region to be accessed. The pixel drive control unit includes a function for performing, concurrently with access to the window region and output processing, read or reset access on at least one adjacent outer row that is adjacent to the window region.

Owner:SONY SEMICON SOLUTIONS CORP

Gallium nitride semiconductor device and method for producing the same

ActiveUS20100109015A1Increase in circuit sizeLowering of operating speed can be suppressedSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSurface layer

An insulating layer, an undoped first GaN layer and an AlGaN layer are laminated in this order on a surface of a semiconductor substrate. A surface barrier layer formed by a two-dimensional electron gas is provided in an interface between the first GaN layer and the AlGaN layer. A recess (first recess) which reaches the first GaN layer but does not pierce the first GaN layer is formed in a surface layer of the AlGaN layer. A first high withstand voltage transistor and a control circuit are formed integrally on the aforementioned semiconductor substrate. The first high withstand voltage transistor is formed in the first recess and on a surface of the AlGaN layer. The control circuit includes an n-channel MOSFET formed in part of the first recess, and a depression type n-channel MOSFET formed on a surface of the AlGaN layer. In this manner, there are provided a gallium nitride semiconductor device which can be used under a high temperature environment while reduction in total circuit size can be attained, and a method for producing the gallium nitride semiconductor device.

Owner:FUJI ELECTRIC CO LTD

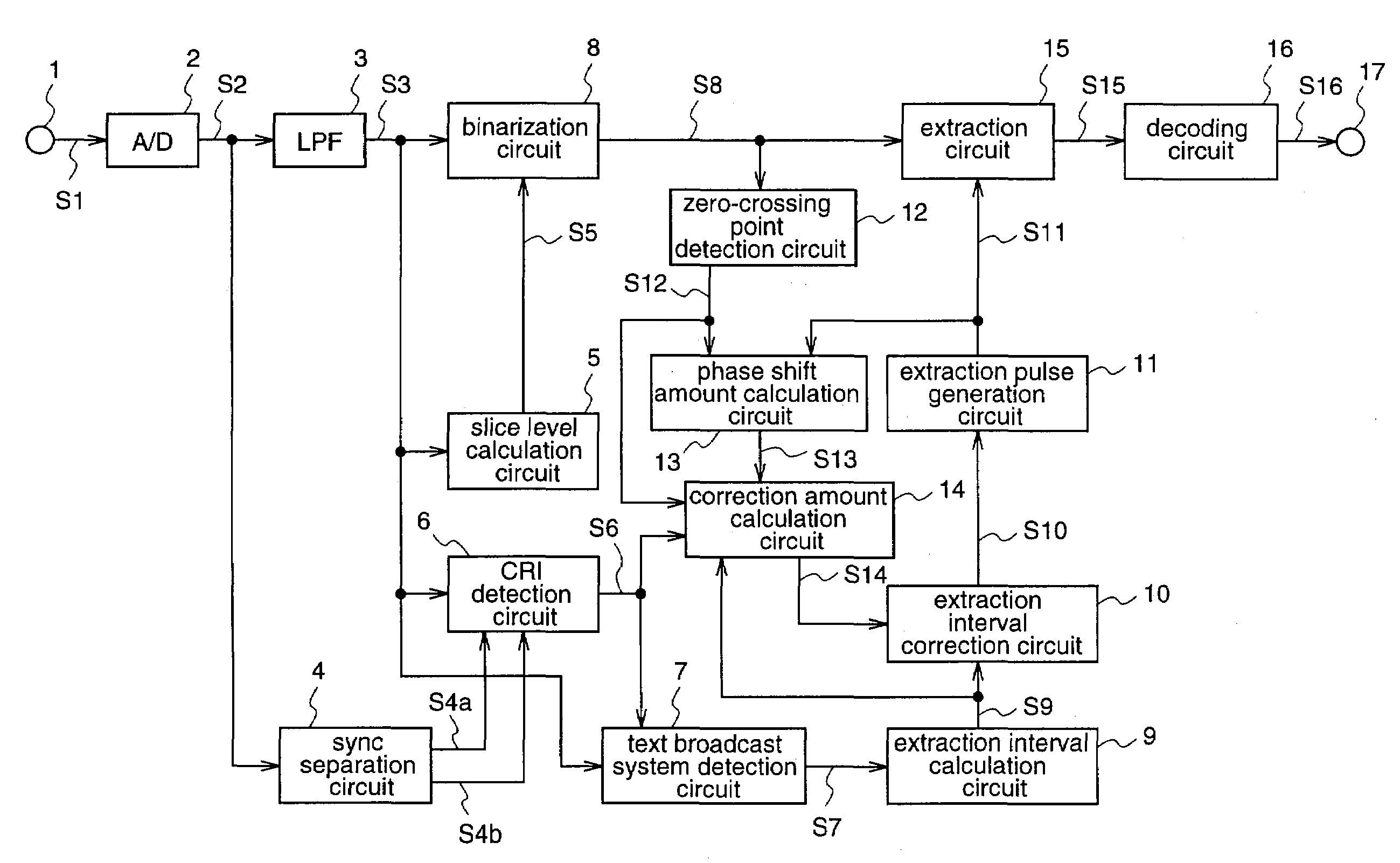

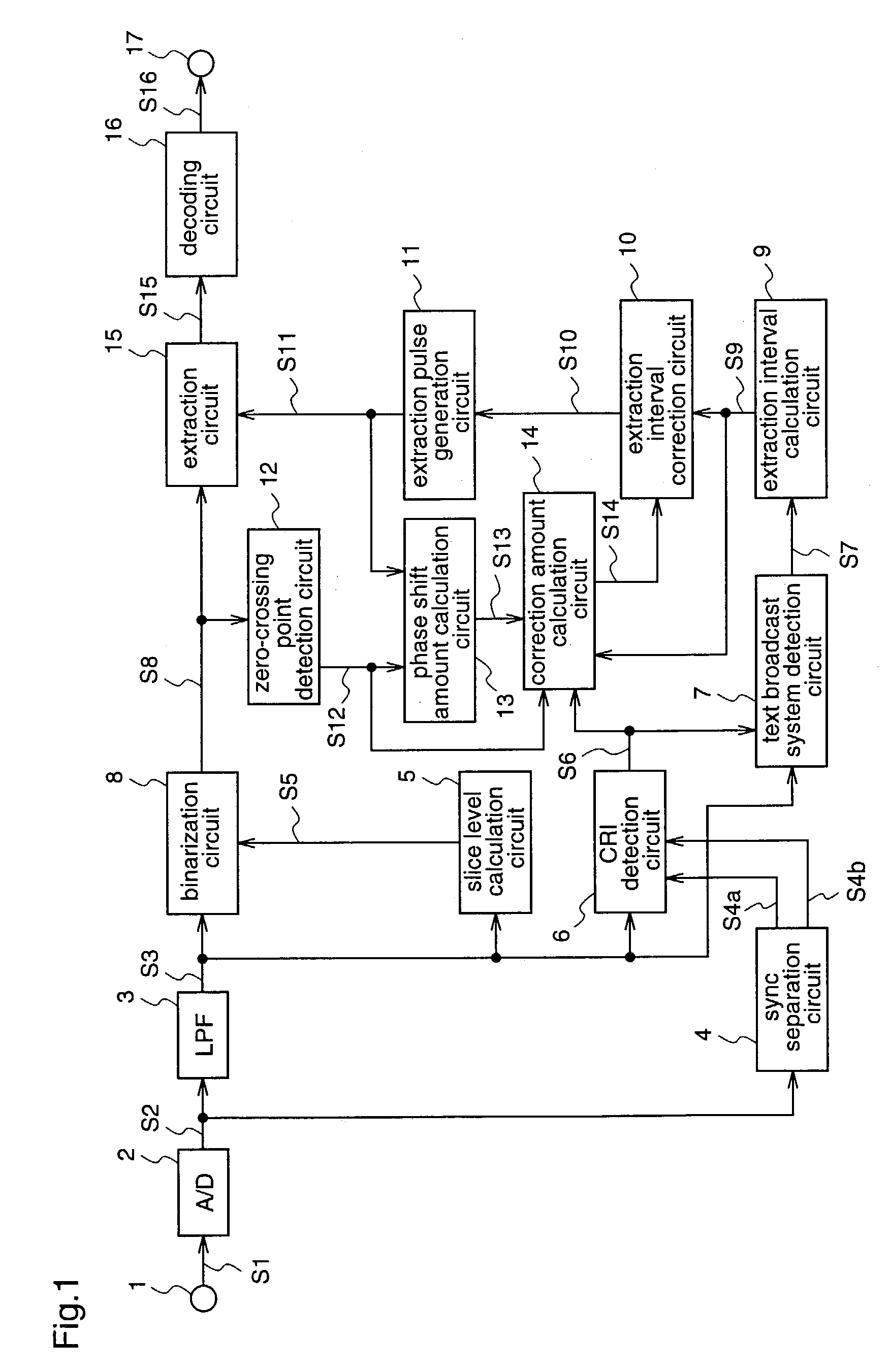

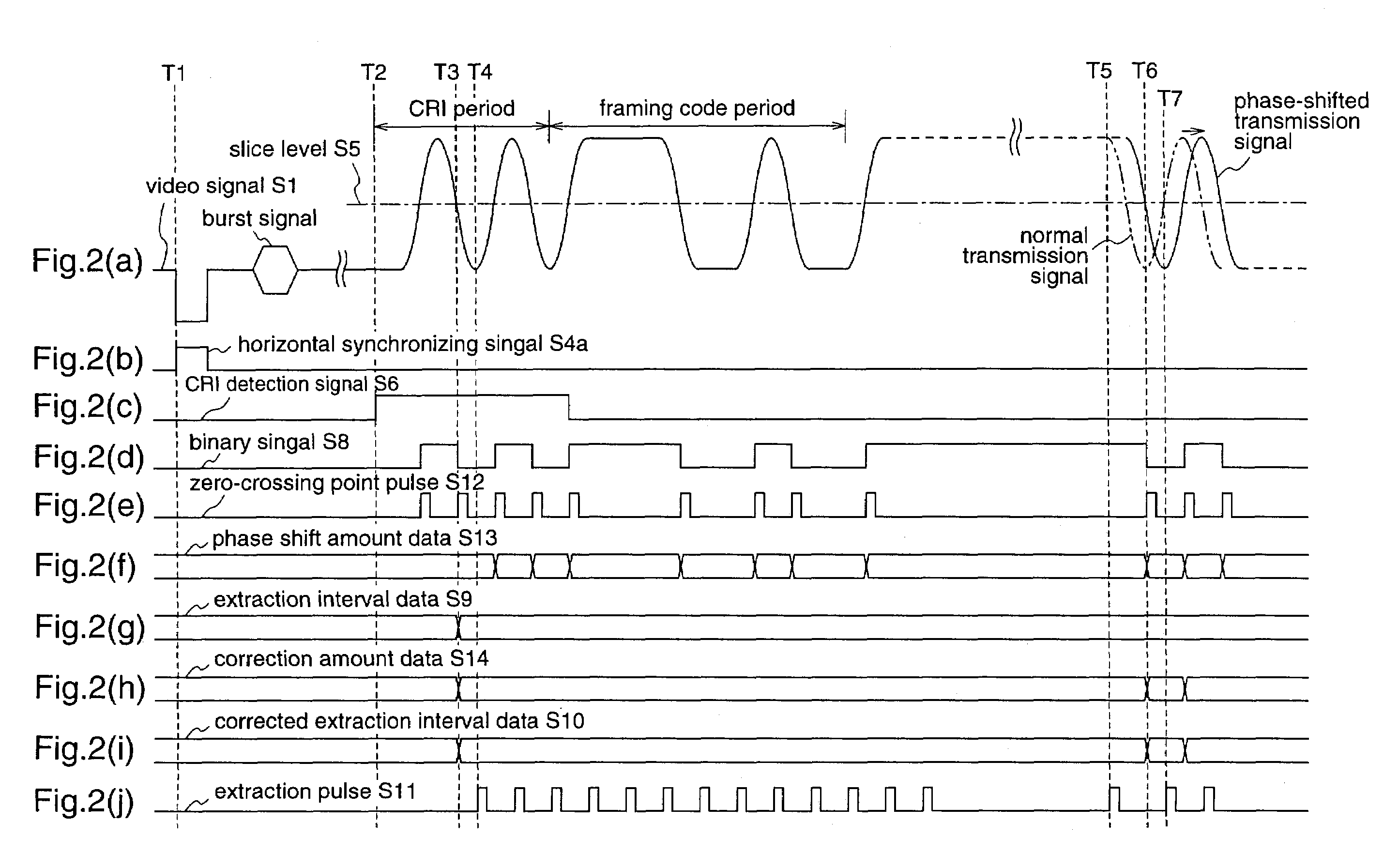

Data signal extraction apparatus

InactiveUS7046298B2Reduce circuit sizeImprove accuracyPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningPhase shiftedData signal

This invention provides a data signal extraction apparatus that accurately extracts data from a data signal that is serially transmitted even when phase shift or the like occurs. According to this apparatus, a phase shift amount calculation circuit 13 calculates a phase shift amount S13, then a correction amount calculation circuit 14 calculates a correction amount S14 on the basis of the phase shift amount S13, an extraction interval correction circuit 10 corrects an extraction interval value S9 on the basis of the correction amount, and an extraction pulse generation circuit 11 generates an extraction pulse S11 on the basis of a corrected extraction interval value S10, thereby extracting data from a binary signal S8 on the basis of the extraction pulse.

Owner:SOCIONEXT INC

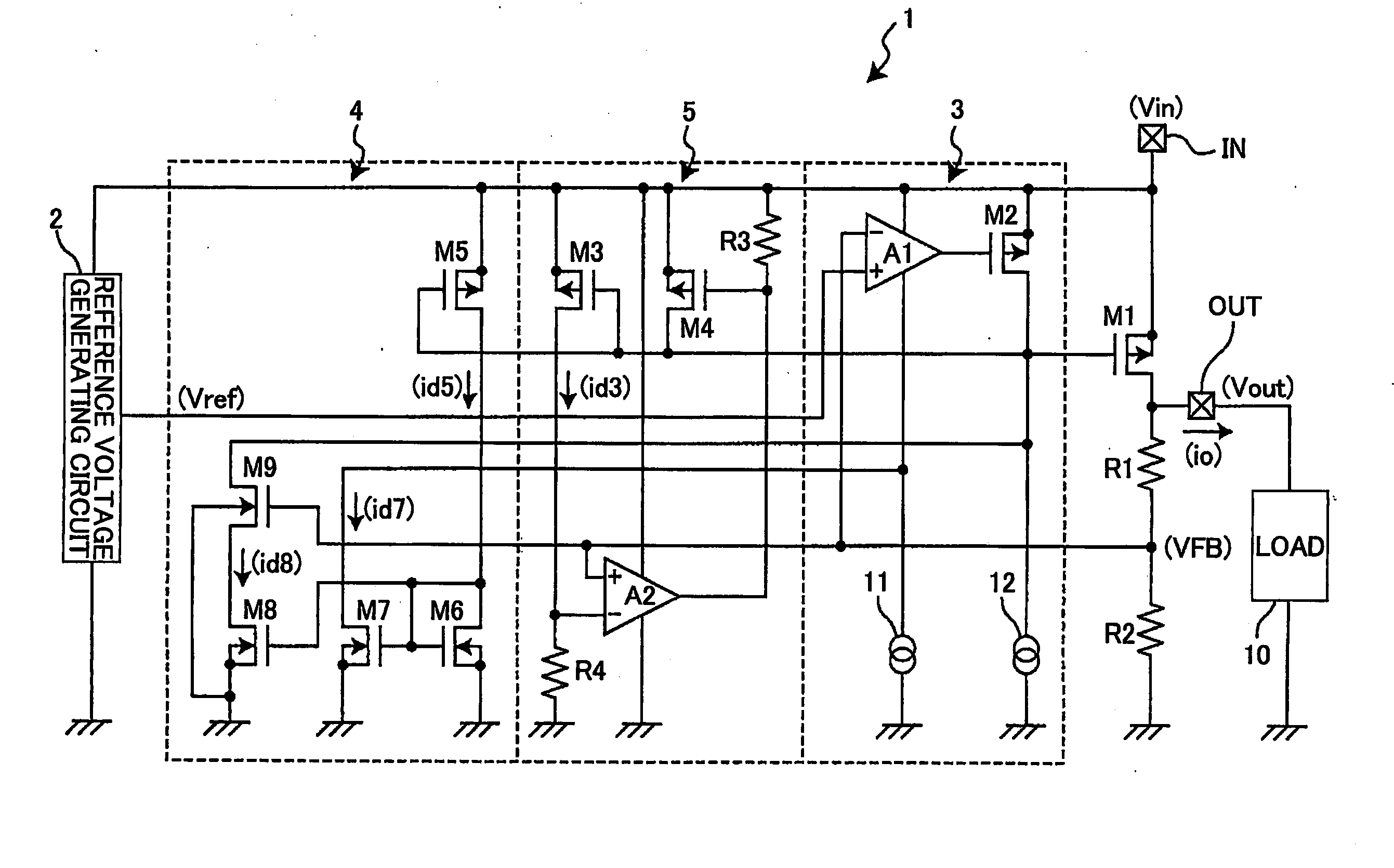

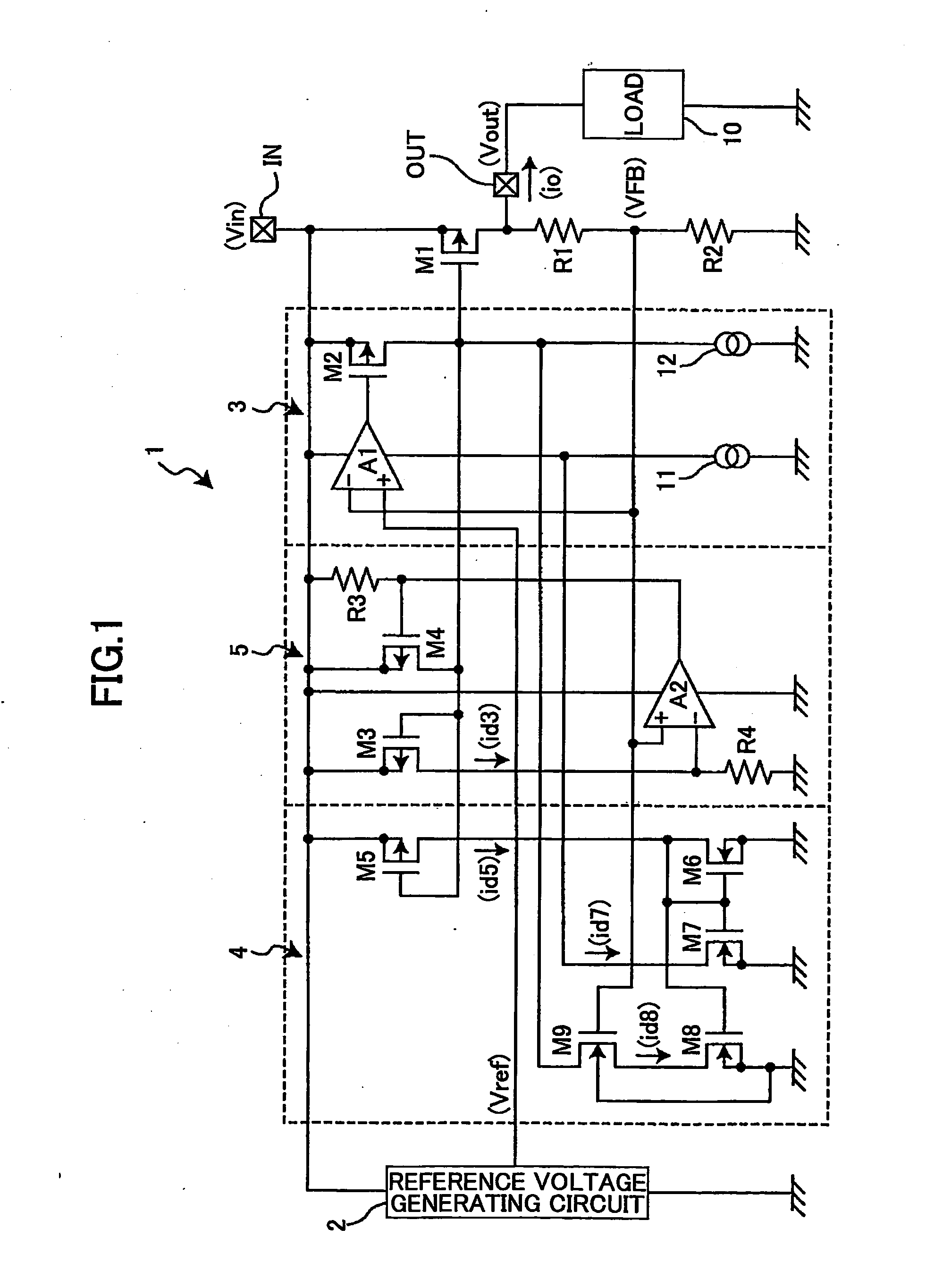

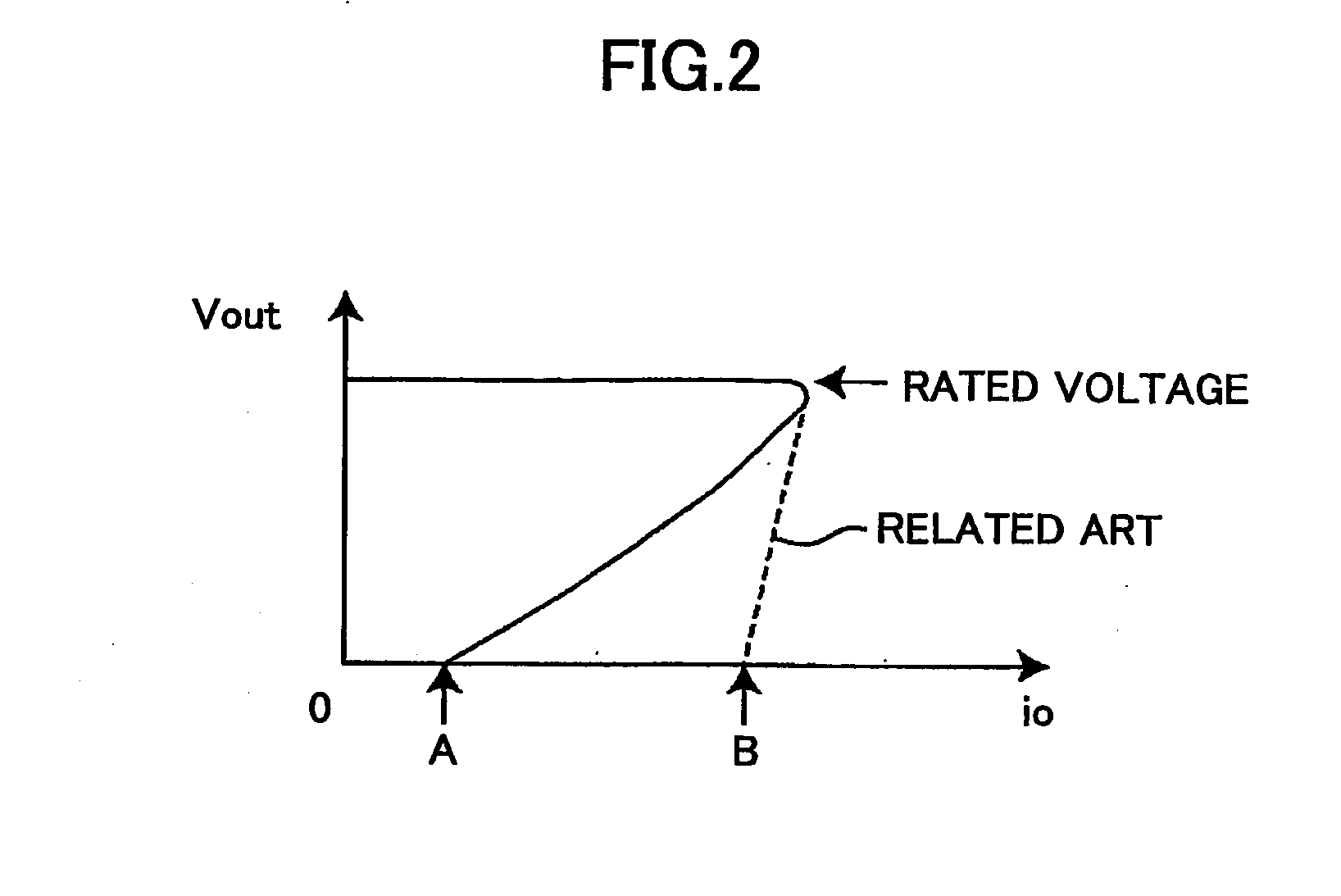

Constant-Voltage Power Supply Circuit with Fold-Back-Type Overcurrent Protection Circuit

InactiveUS20080278127A1Increase in circuit sizeWithout increasing the operating current of the overcurrent protection circuitArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentControl signalEngineering

A constant-voltage power supply circuit for converting an input voltage applied to an input terminal into a predetermined constant voltage for output from an output terminal includes an output transistor to supply from the input terminal to the output terminal an output current responsive to an applied control signal, an error amplifying circuit unit to receive a predetermined bias current to control an operation of the output transistor, and a bias current adjusting circuit unit to supply the error amplifying circuit unit with the bias current responsive to the output current output from the output transistor, wherein the bias current adjusting circuit unit is configured to suspend the supply of the bias current to the error amplifying circuit unit in response to lowering of the output voltage to a predetermined voltage.

Owner:RICOH ELECTRONIC DEVICES CO LTD

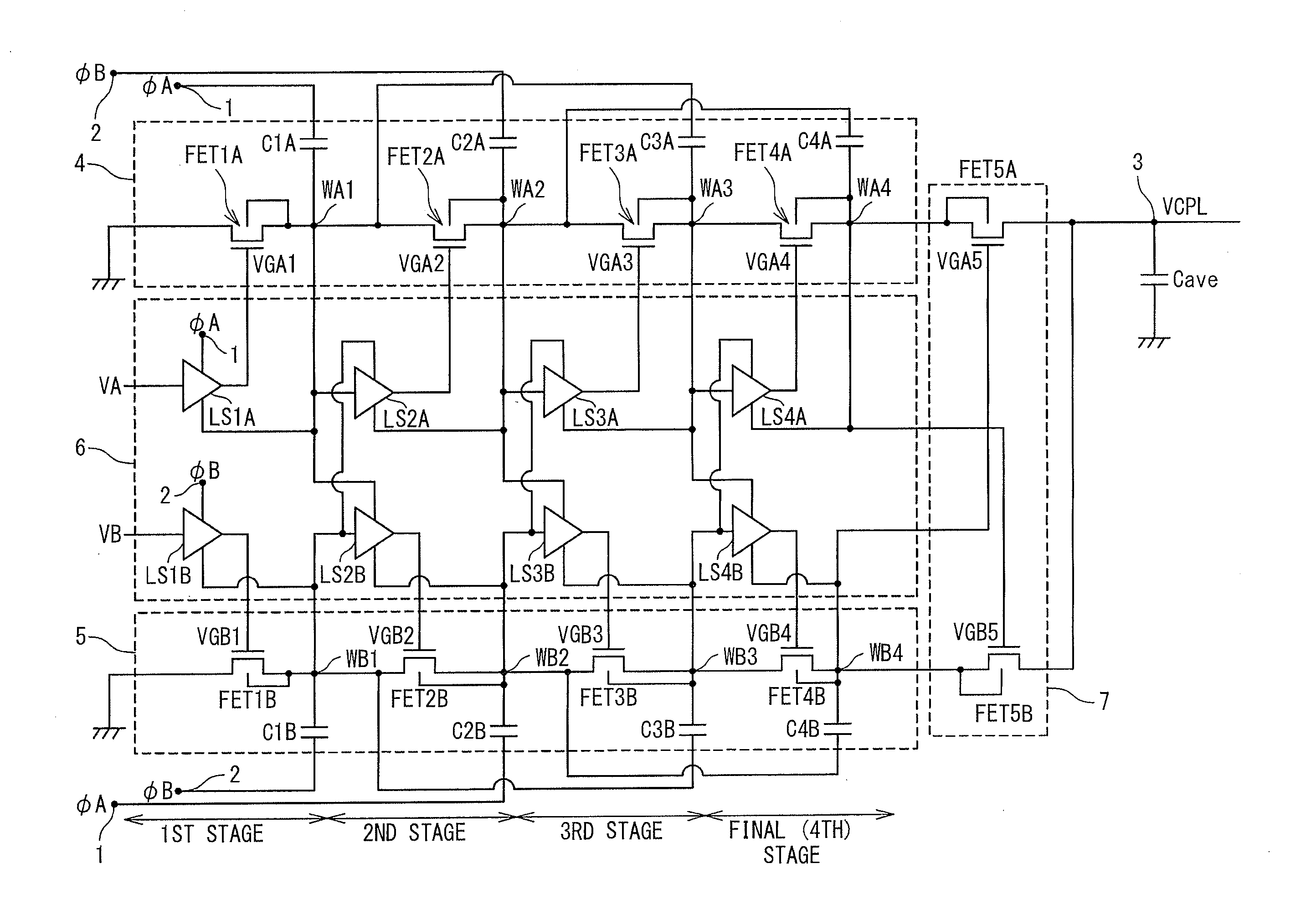

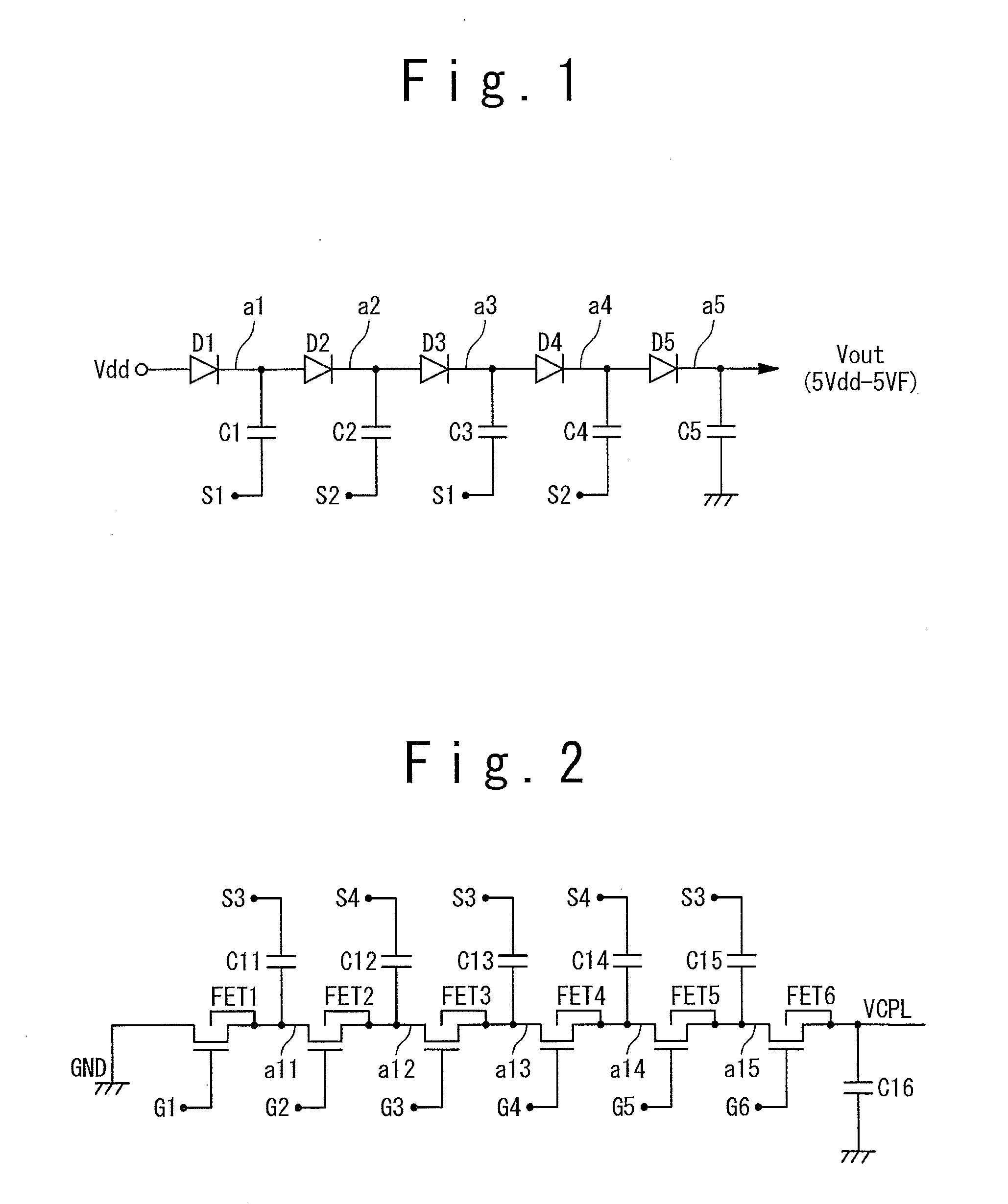

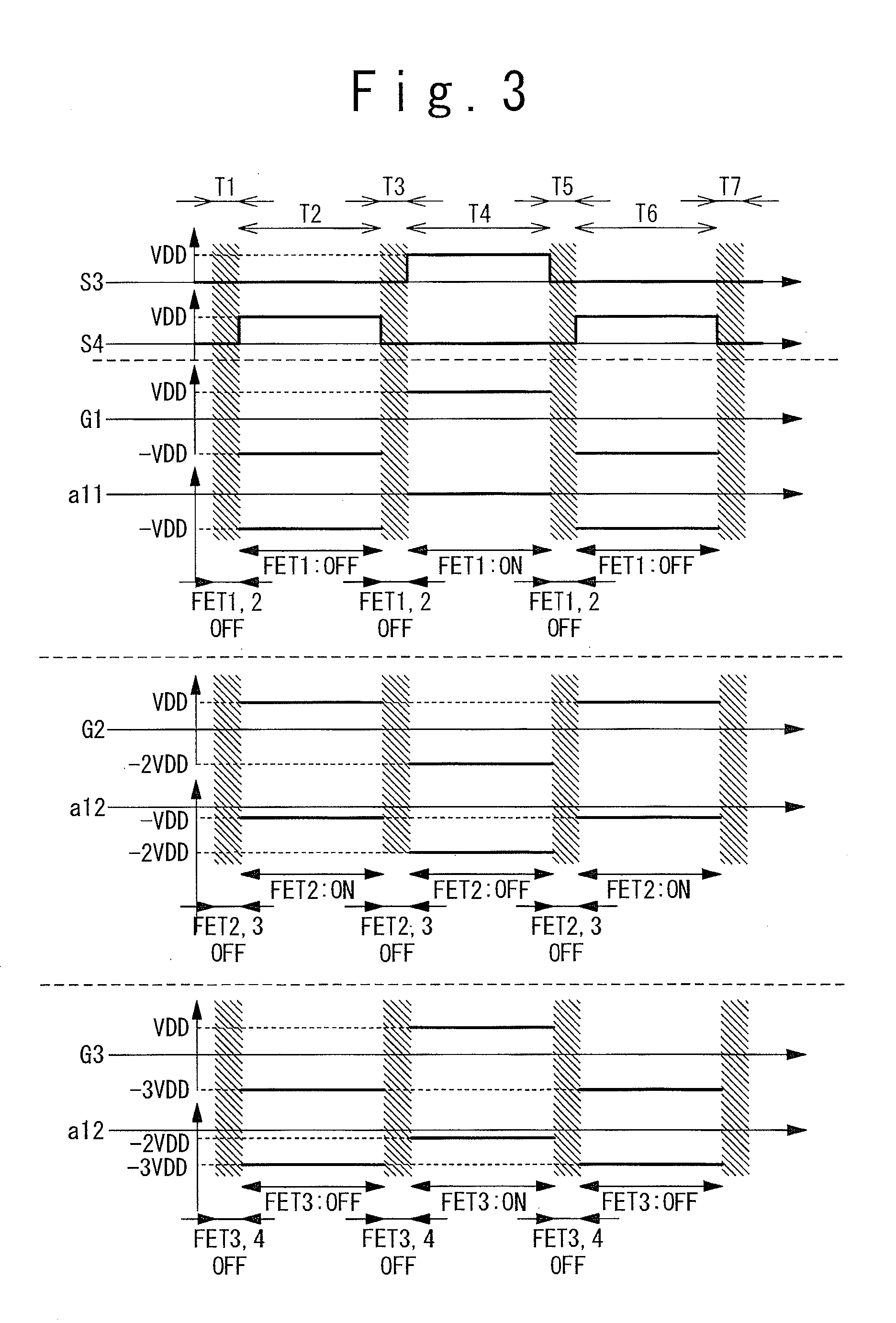

Charge pump circuit

InactiveUS20110133821A1Large output voltageElement breakdown voltage of be reduceDc-dc conversionElectric variable regulationPower inverterControl circuit

A charge pump circuit has: first and second charge pump circuits alternately performing boosting operations; and a control circuit. The first (second) charge pump circuit has: plural stages of first (second) switch transistors connected in series; plural stages of first (second) connection nodes respectively connected to sources of the first (second) switch transistors; and plural stages of first (second) capacitors respectively connected to the first (second) connection nodes. The control circuit has: plural stages of first inverters and plural stages of second inverters. The n-th-stage first (second) inverter is supplied with a positive-side power supply voltage from the (n−1)-th-stage second (first) connection node, is supplied with a negative-side power supply voltage from the n-th-stage first (second) connection node, is supplied with an input voltage from the (n−1)-th-stage first (second) connection node, and outputs an output voltage to a gate of the n-th-stage first (second) switch transistor.

Owner:RENESAS ELECTRONICS CORP

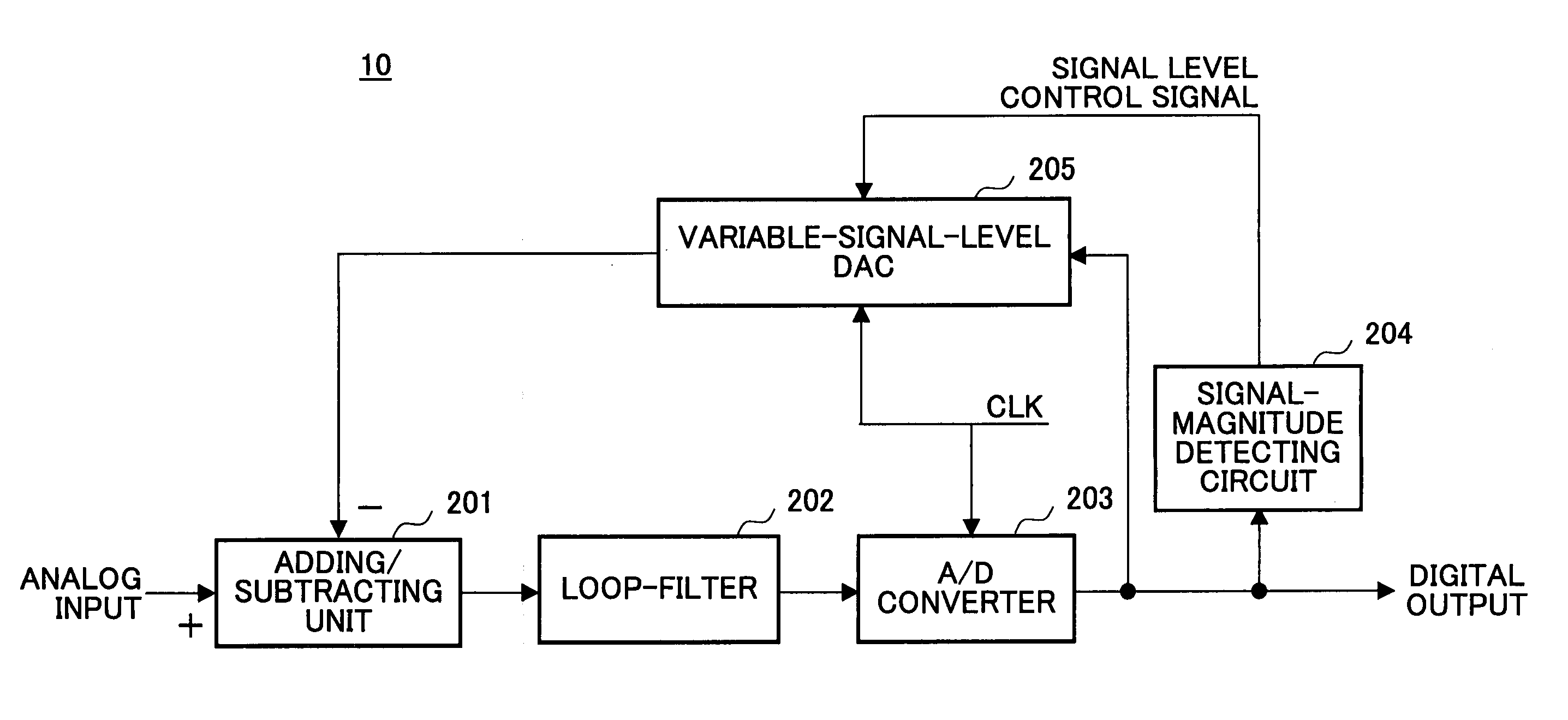

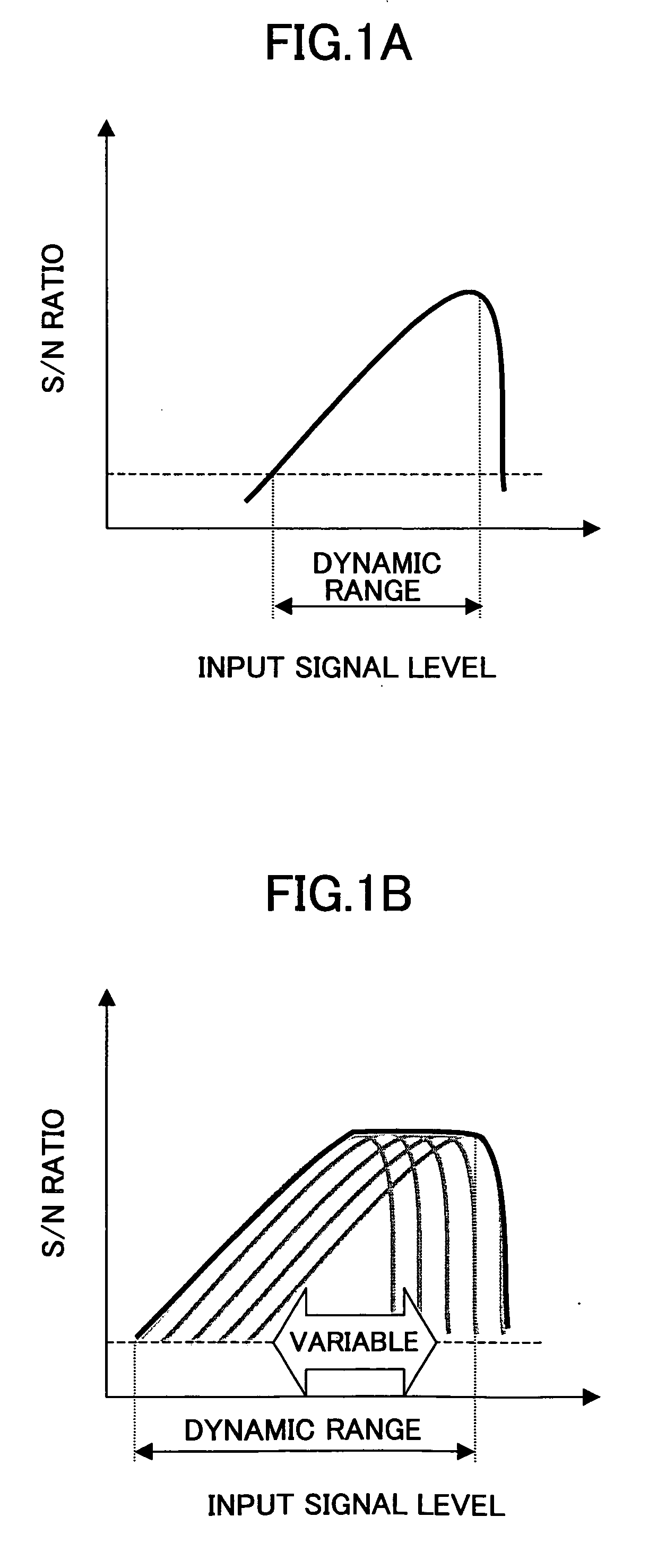

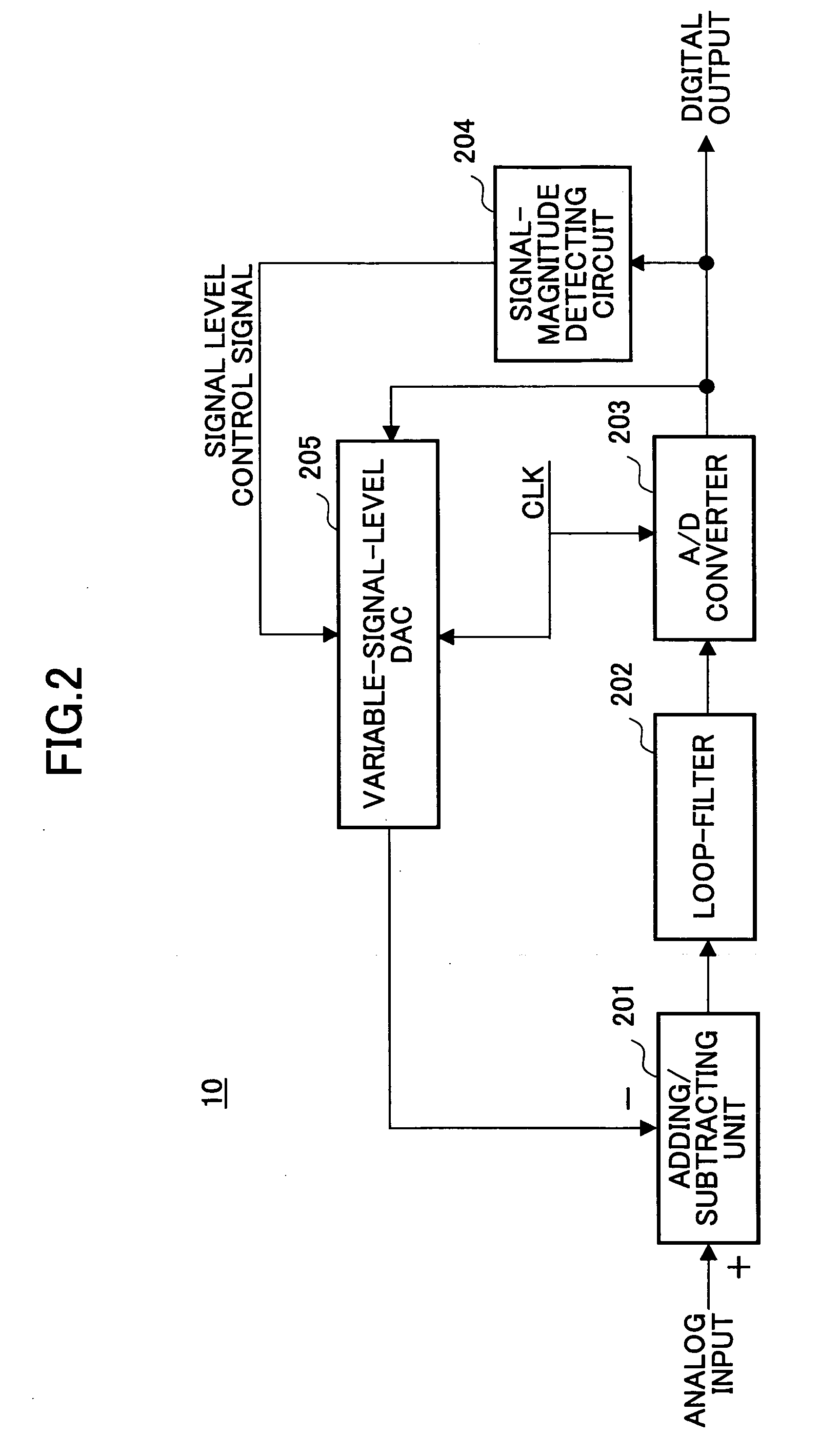

Adaptive-type sigma-delta a/d converter

InactiveUS20060097899A1Reduce power consumptionIncrease speedElectric signal transmission systemsAnalogue conversionCapacitanceControl signal

A sigma-delta A / D converter includes an A / D converter configured to output a digital signal, a signal-magnitude detecting circuit coupled to the output of the A / D converter to output a control signal responsive to a magnitude indicated by the digital signal, a D / A converter coupled to the output of the A / D converter and the output of the signal-magnitude detecting circuit to output an analog signal having a signal level responsive to the digital signal and the control signal, a differential circuit coupled to an external analog input and the output of the D / A converter to output a differential between the external analog input and the analog signal, and a filter circuit to couple between the output of the differential circuit and an input of the A / D converter, wherein the D / A converter is configured to control, in response to the control signal, a capacitance of a capacitor that discharges following charging of electric charge to supply an electric current of the analog signal.

Owner:FUJITSU LTD

Communication semiconductor integrated circuit and radio communication system

InactiveUS6900700B2Increase in circuit sizeWide frequency rangePulse automatic controlPulse generation by logic circuitsFrequency bandIntermediate frequency

A communication semiconductor integrated circuit has an oscillator circuit forming part of a transmission PLL circuit fabricated on a single semiconductor chip together with an oscillator circuit forming part of a reception PLL circuit and an oscillator circuit for an intermediate frequency. The oscillator circuit forming part of the transmission PLL circuit is configured to be operable in a plurality of bands. A circuit for measuring the oscillating frequency of the oscillator circuit forming part of the transmission PLL circuit is also used for measuring the oscillating frequency of the oscillator circuit forming part of the reception PLL circuit or for measuring the oscillating frequency of the oscillator circuit for the intermediate frequency.

Owner:RENESAS ELECTRONICS CORP +2

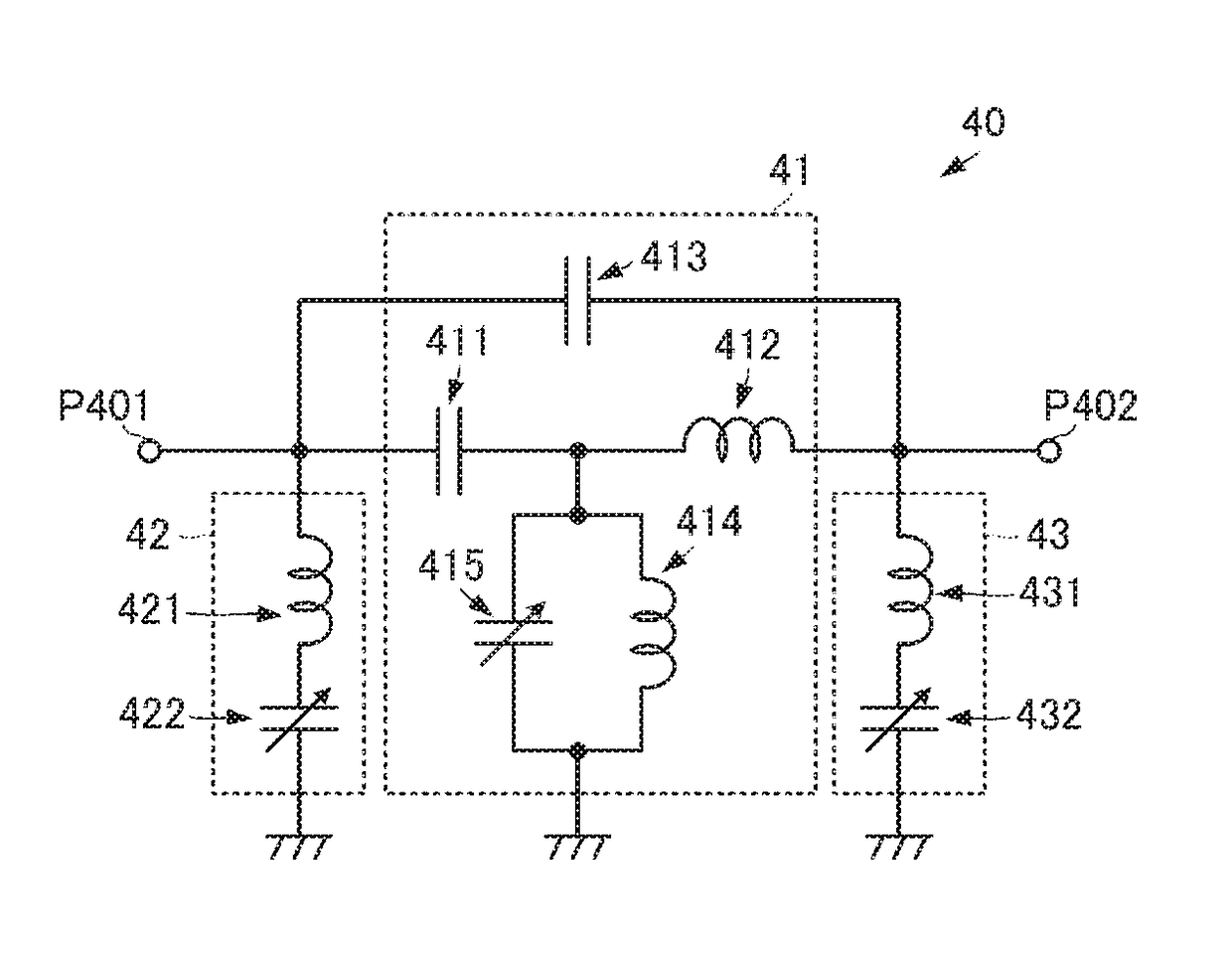

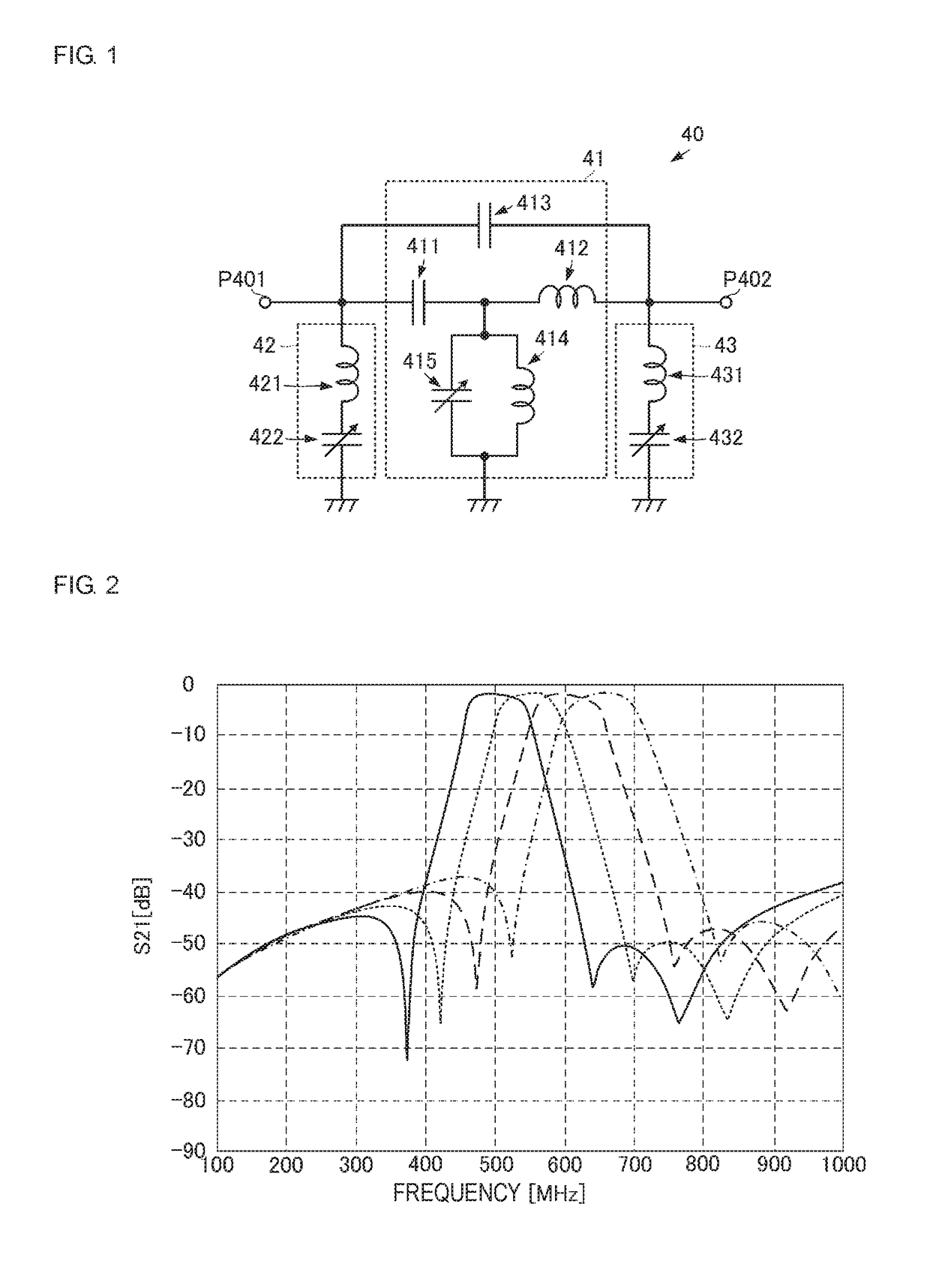

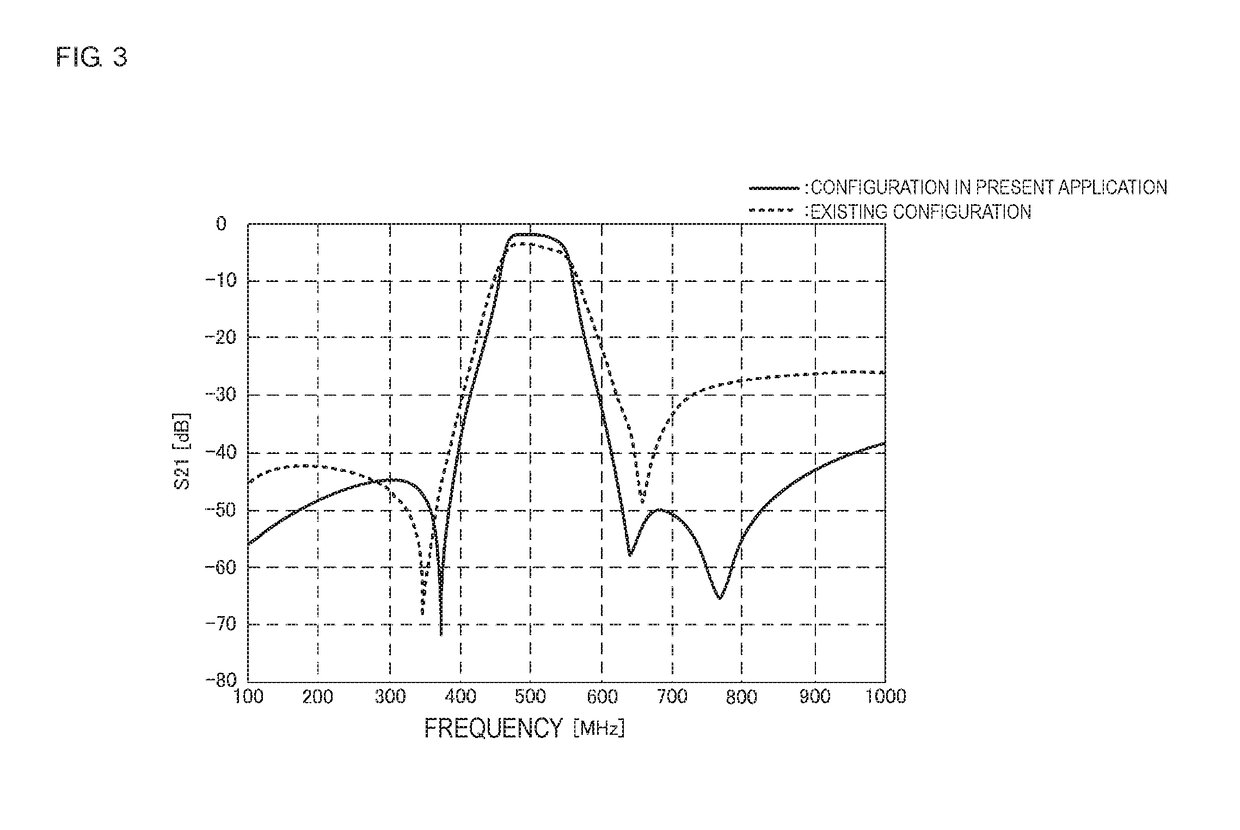

Frequency-variable lc filter and high-frequency front end circuit

ActiveUS20180198433A1Loss of characteristicSmall sizeMultiple-port networksTransmissionInductorElectrical and Electronics engineering

A first series arm LC filter circuit includes a capacitor and an inductor connected in series to provide a series circuit between a first connection terminal and a second connection terminal, a capacitor connected in parallel to the series circuit, and an inductor and a variable capacitor connected in parallel between a connection point of the capacitor and the inductor and a ground potential. A first parallel arm LC filter circuit is connected between the first connection terminal and the ground potential. A second parallel arm LC filter circuit is connected between the second connection terminal and the ground potential. The inductor is directly connected to the second connection terminal or is connected to the second connection terminal with another inductor interposed therebetween.

Owner:MURATA MFG CO LTD

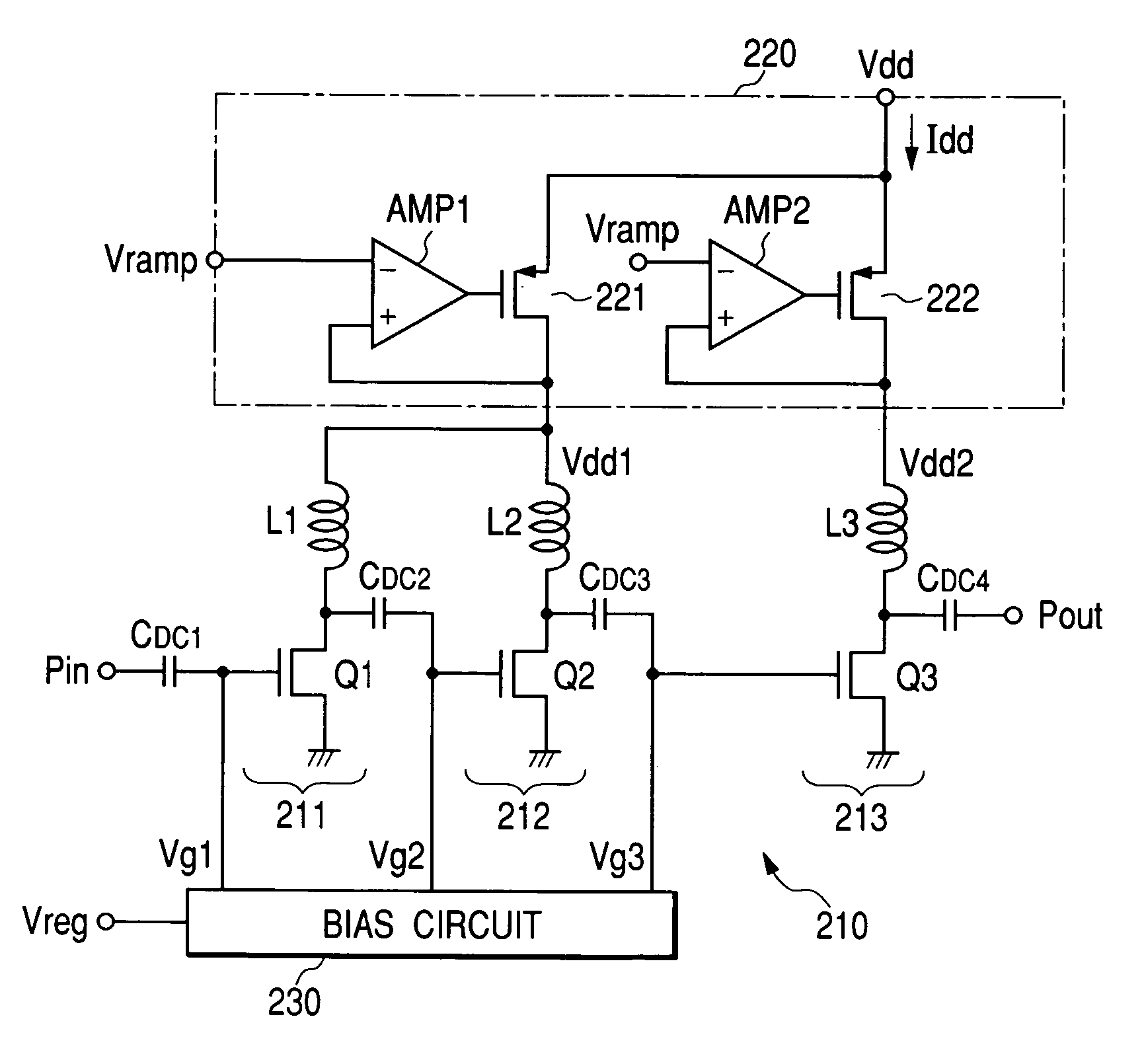

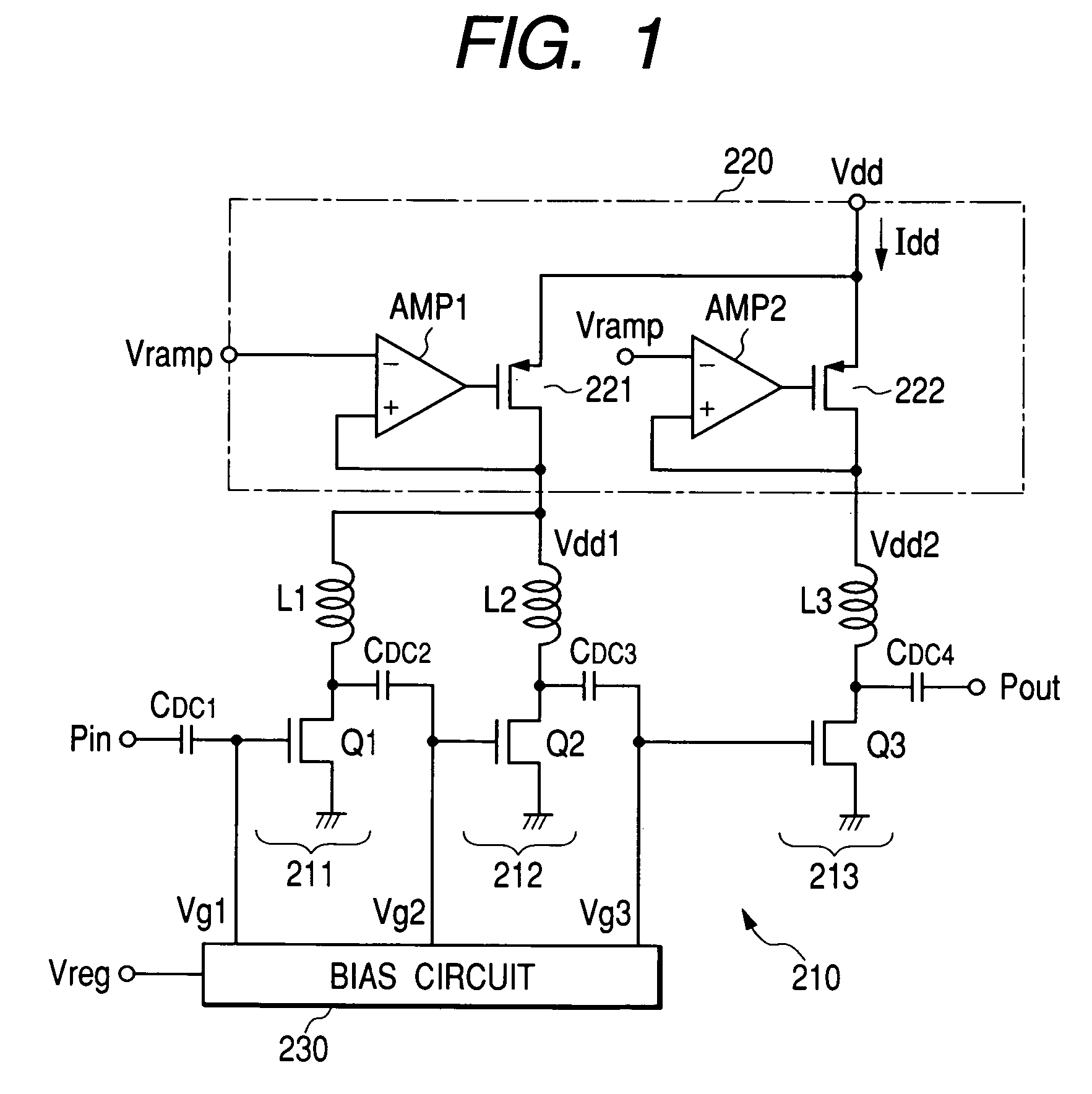

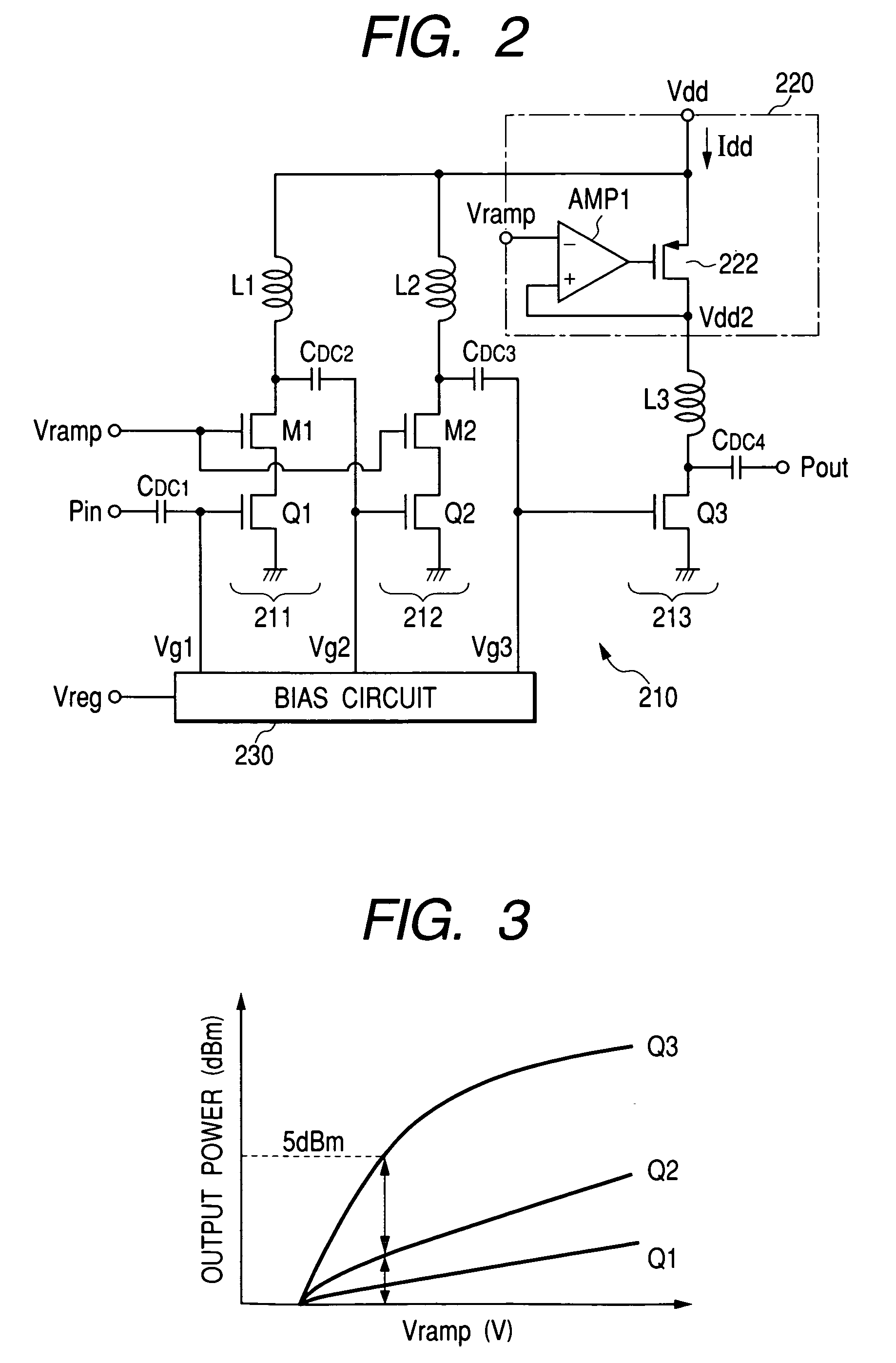

High frequency power amplifier circuit and radio communication system

InactiveUS7123094B2Power efficiency is satisfactoryIncrease in circuit sizeEnergy efficient ICTGain controlCommunications systemControl power

Providing a high frequency power amplifier circuit and a radio communication system which can control output power by a power voltage, produce sufficient output power in high regions of demanded output power and improve power efficiency in low regions of demanded output power. In a high frequency power amplifier circuit (RF power module) which comprises two or more cascaded FETs for amplification and controls output power by controlling power voltages of the FETs for amplification to gate terminals of which bias voltages of a predetermined level are applied, different transistors for power voltage control are provided for a last-stage FET for amplification and preceding-stage FETs for amplification. The transistors for power voltage control generate and apply the power voltage so that the preceding-stage FETs for amplification saturate when a demanded output level is relatively low.

Owner:RENESAS TECH CORP

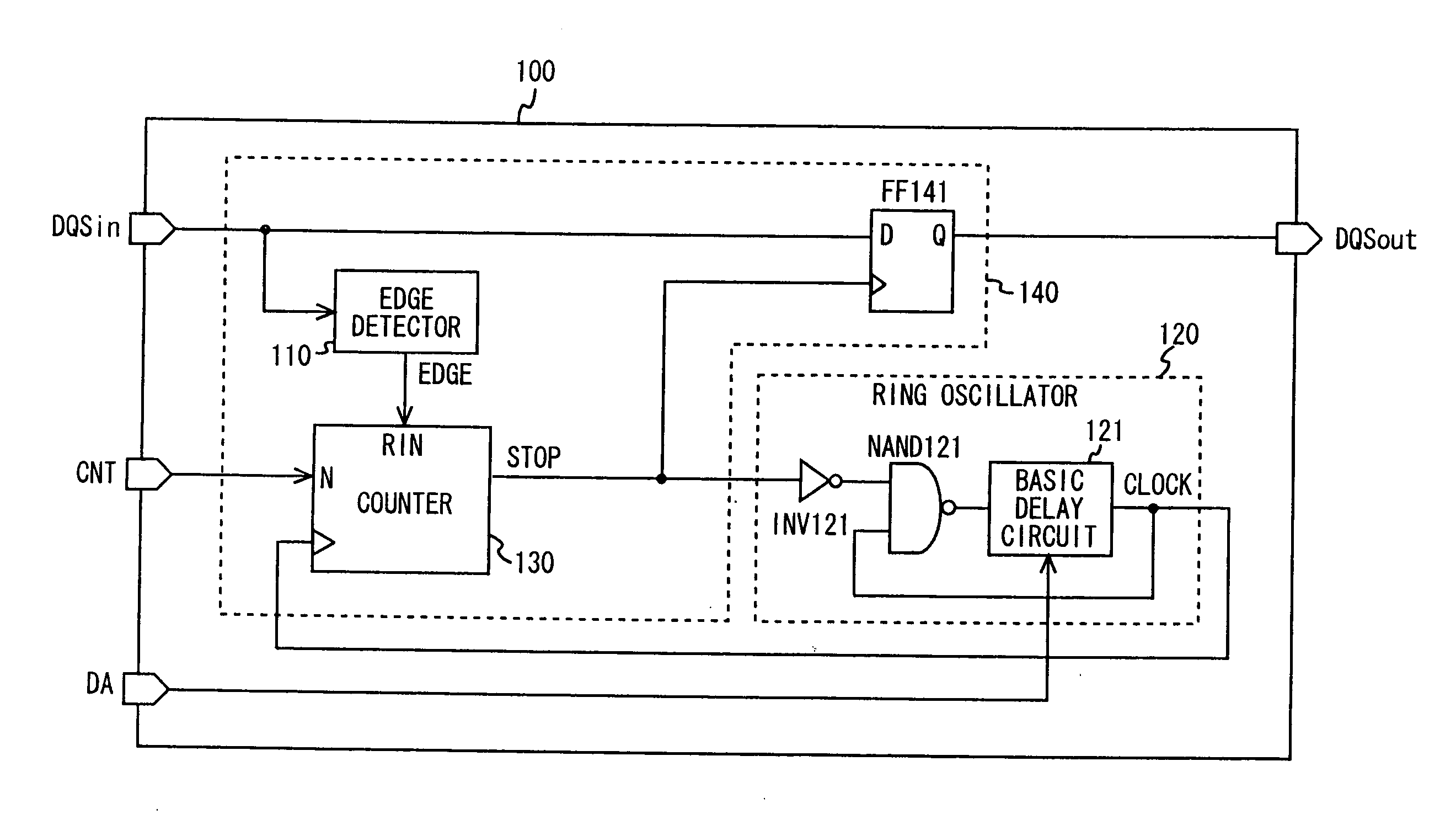

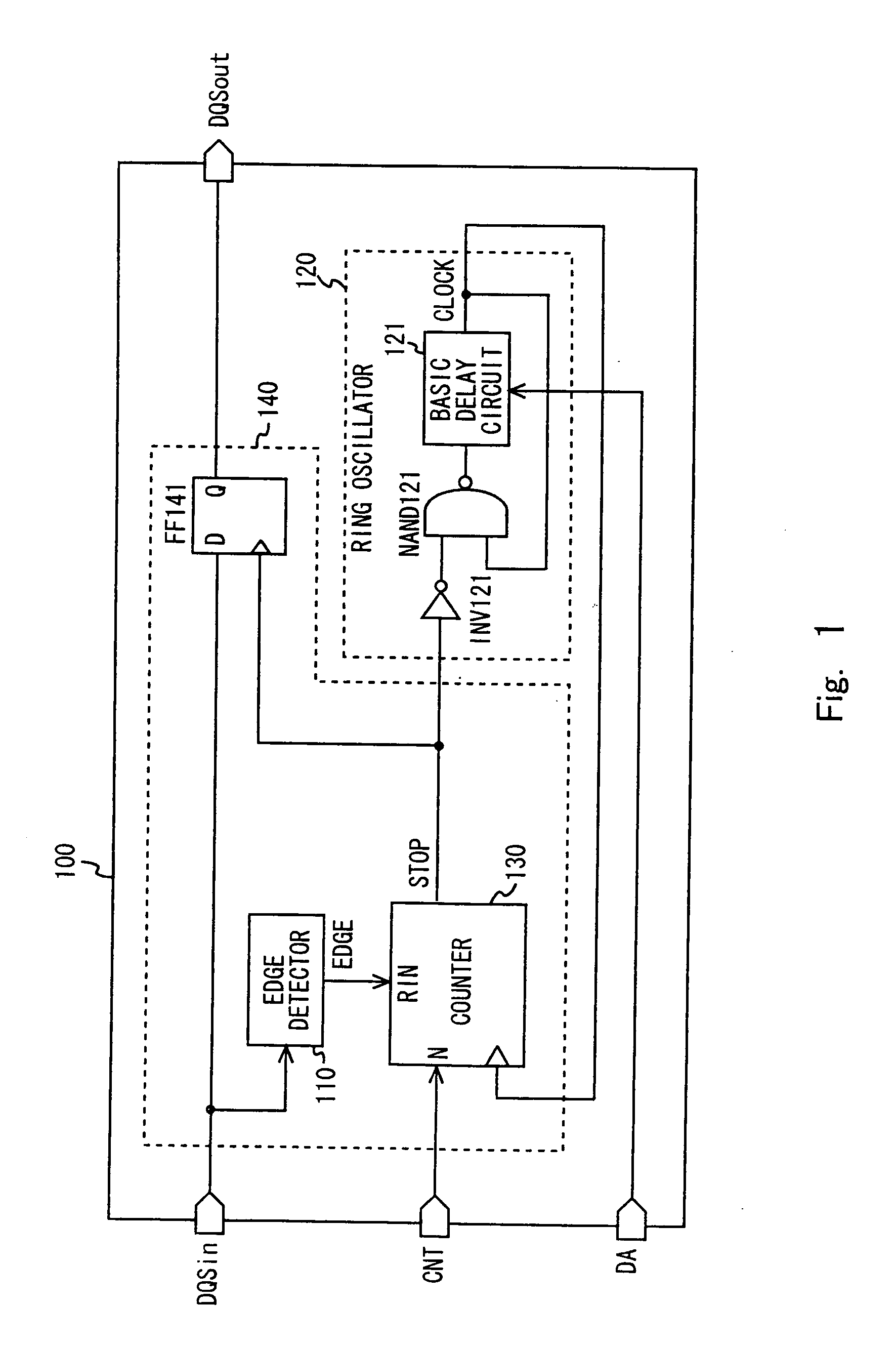

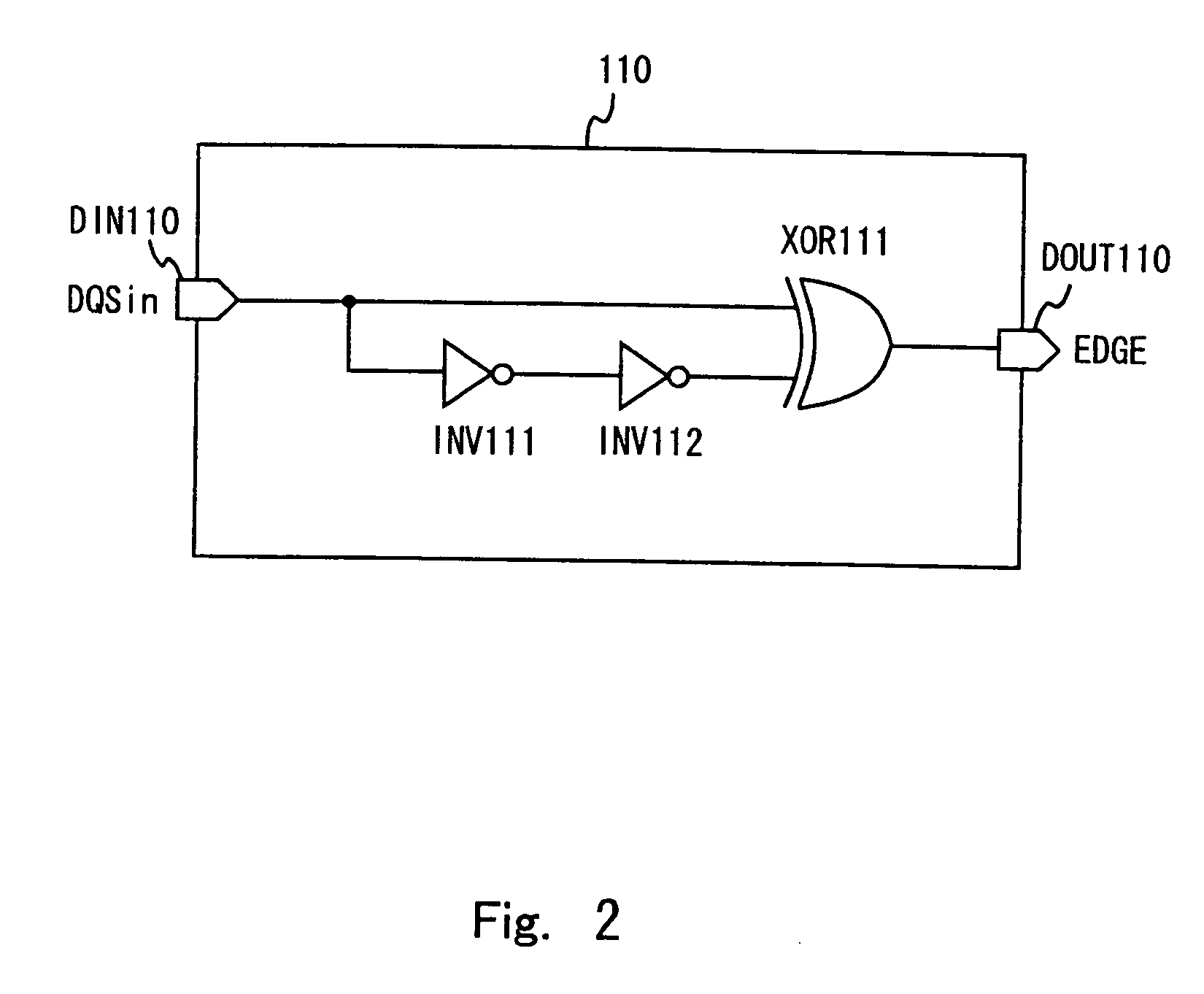

Delay Circuit

InactiveUS20100134169A1Prevent increase in scaleIncrease in sizeSingle output arrangementsDigital storageEdge detectorCounting Number

A delay circuit includes a ring oscillator and a control circuit. The control circuit includes an edge detector that outputs a first control signal in response to a rising edge or a falling edge of an input signal, and a counter that counts the number of pulses of an output pulse signal output from the ring oscillator and outputs a second control signal upon reaching a predetermined count number. The control circuit performs control to make the ring oscillator oscillate in response to the first control signal and to output the input signal in response to the second control signal.

Owner:RENESAS ELECTRONICS CORP

Radio Communication Terminal

InactiveUS20060053321A1Improve circuit efficiencyExtension of timeEnergy efficient ICTImpedence matching networksAudio power amplifierCell voltage

A radio communication terminal has a plurality of matching circuits that optimize the efficiency of a power amplifier for a range of different battery voltages. A first matching circuit optimizes the efficiency of the power amplifier for a battery voltage higher than a predetermined threshold value. A second matching circuit optimizes the efficiency of the power amplifier at a voltage lower than the threshold value. A control section compares a detection result of a battery voltage from a voltage monitor section with the threshold value, and performs switching between the plurality of matching circuits.

Owner:SONY MOBILE COMM INC

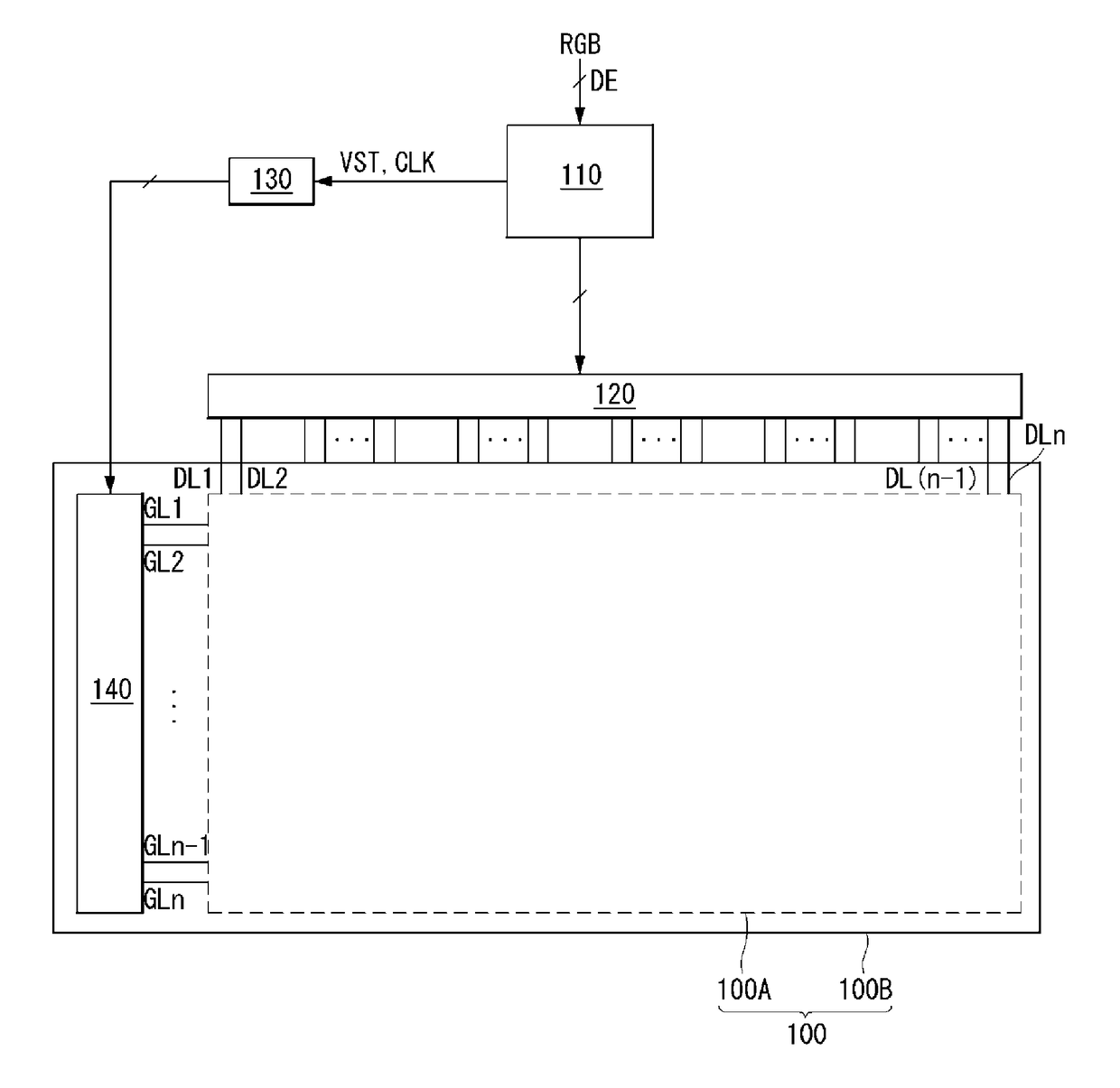

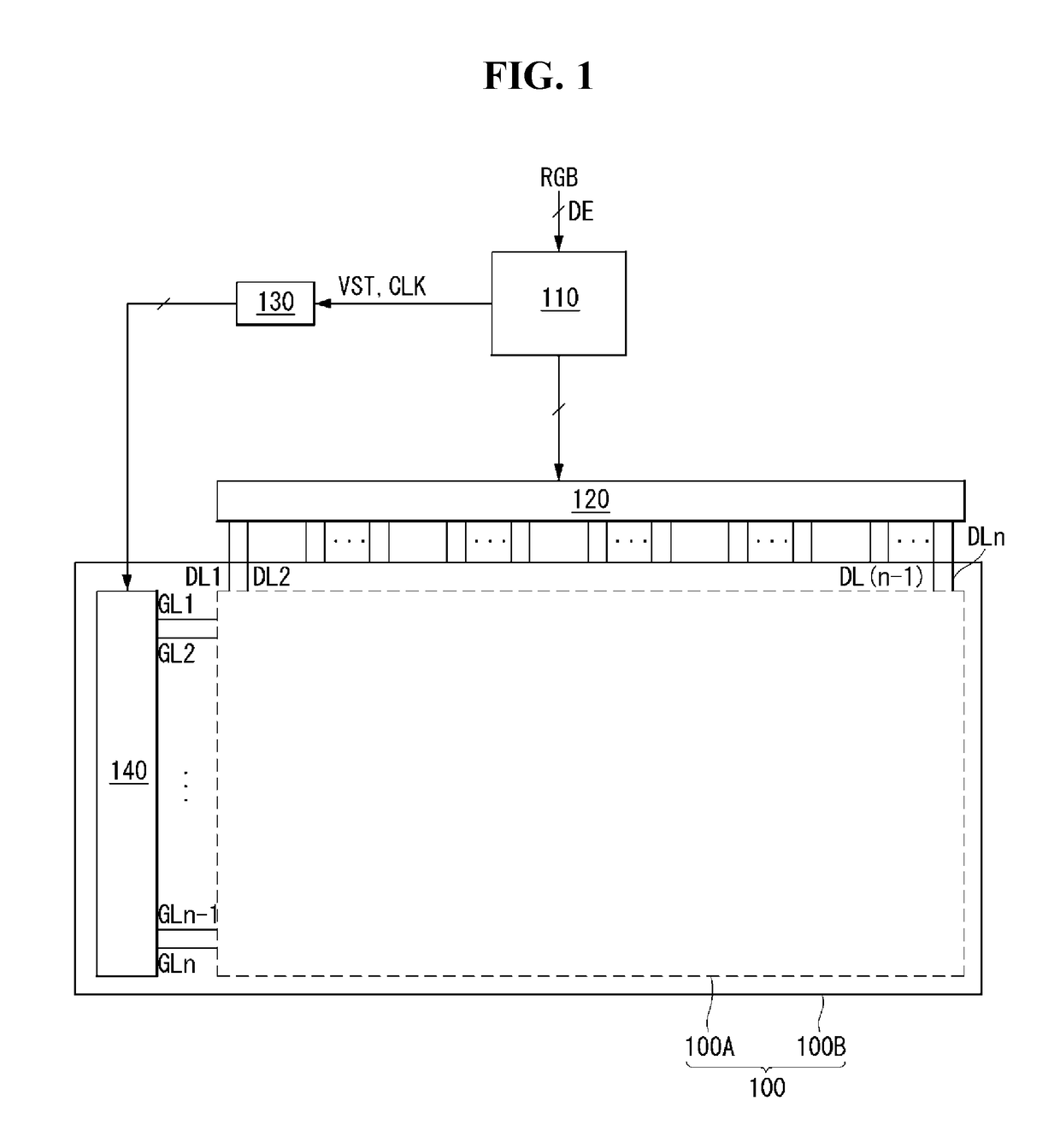

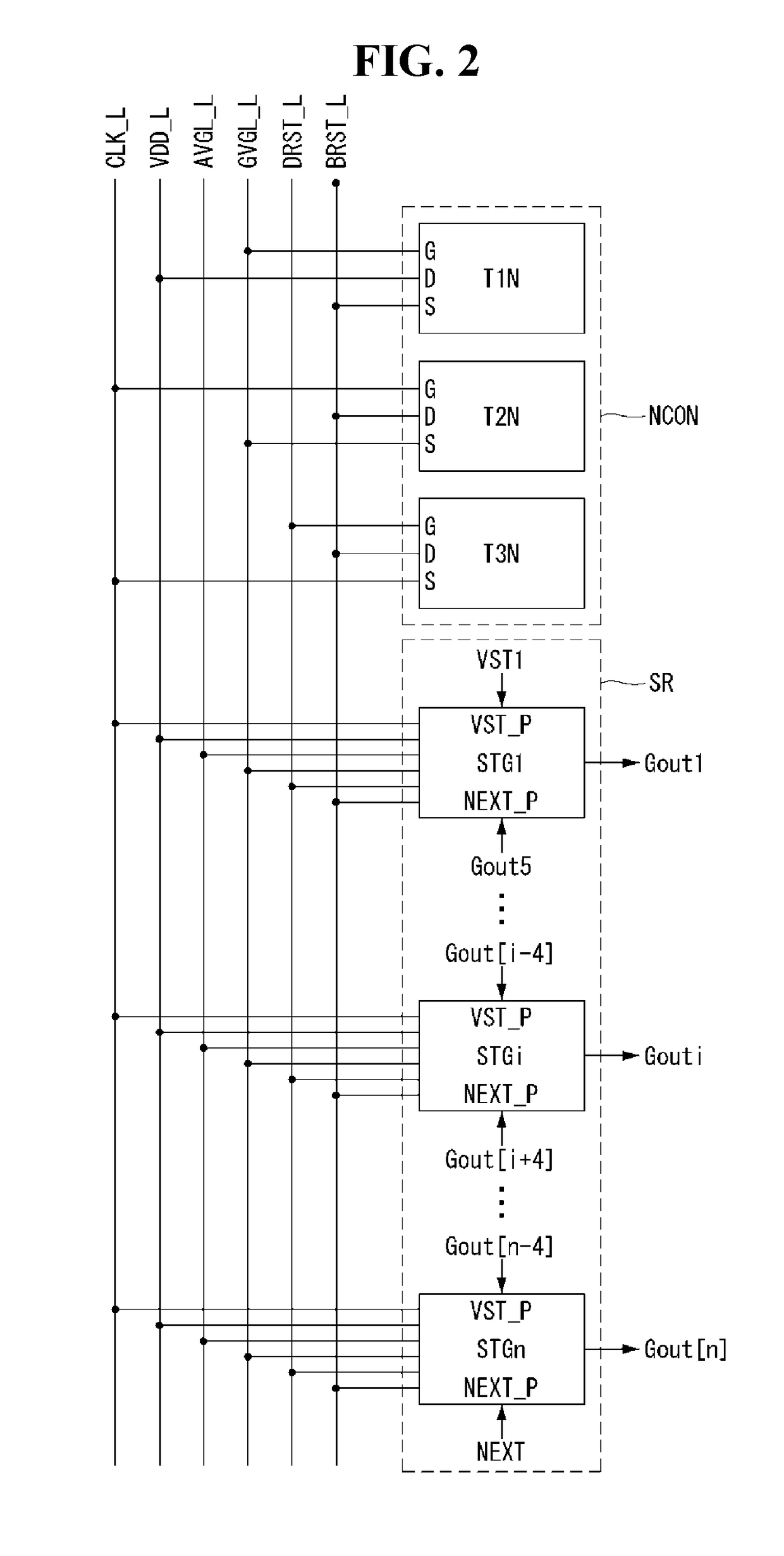

Display device and method of operating the same

ActiveUS20170372654A1Reduce manufacturing costIncrease in circuit sizeStatic indicating devicesShift registerLow voltage

A display device includes: a pixel array including pixels at intersections of data lines and gate lines, a shift register including stages connected as a cascade, the shift register sequentially supplying gate pulses to the gate lines, and a node controller controlling nodes in the shift register, a first stage including: a pull-up transistor charging the output based on a Q node for a first gate pulse, a pull-down transistor discharging the output to a gate-low voltage based on a QB node voltage, a start controller pre-charging the Q node, and a QB node discharge controller discharging the QB node to a first low-potential voltage based on a first reset signal input line (IL), the node controller including a first reset signal generator that, during a vertical blanking interval of each frame, charges the first reset signal IL in response to a turn-on voltage applied to a gate-low voltage IL.

Owner:LG DISPLAY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com