Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

414 results about "Display memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Display memory is the amount of RAM that is installed on your video board. If your computer has on-board video, part of your system RAM is allocated to. be used as video RAM.

Display apparatus and driving method thereof

InactiveUS20020075211A1Static indicating devicesNon-linear opticsAddress decoderLiquid-crystal display

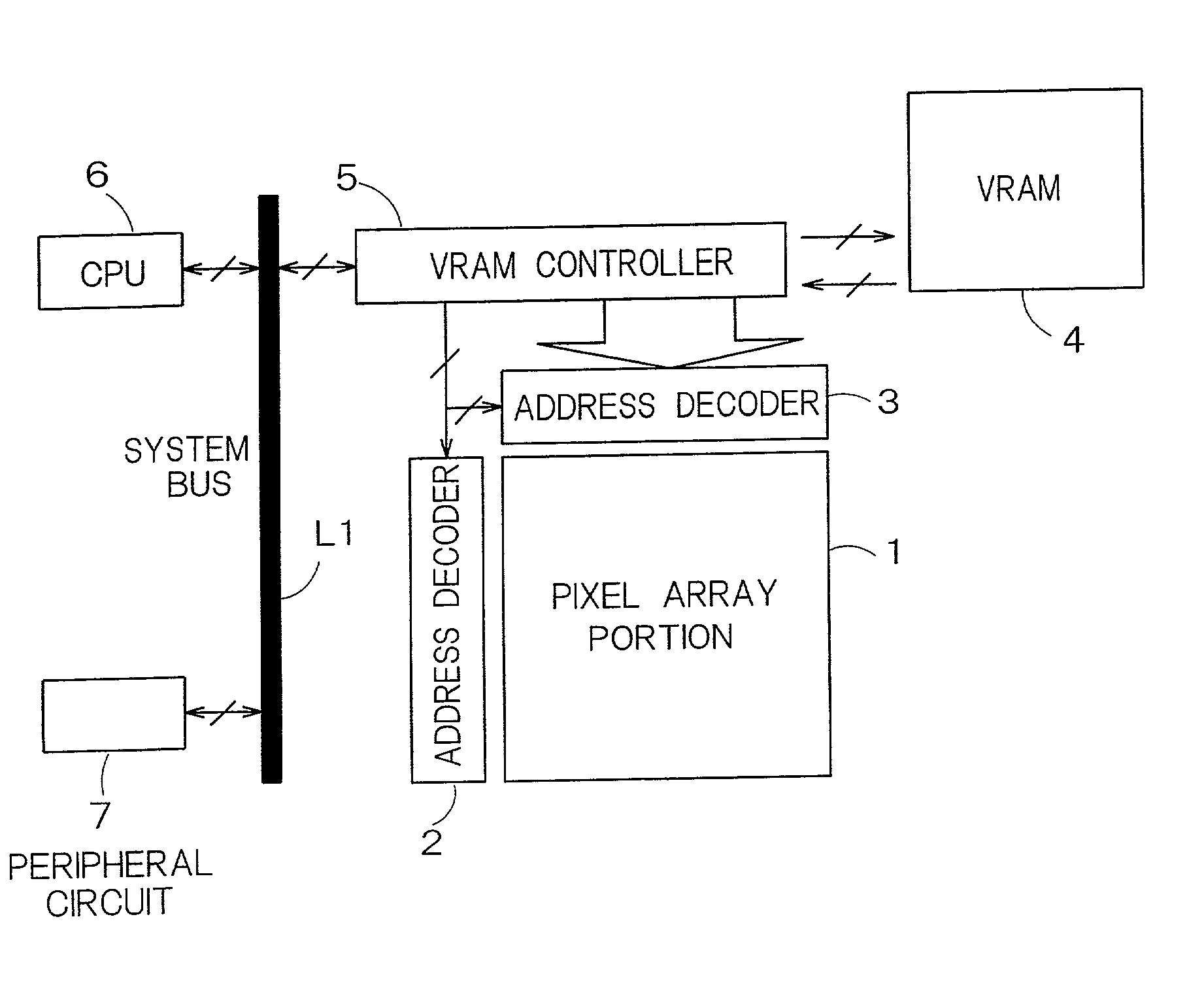

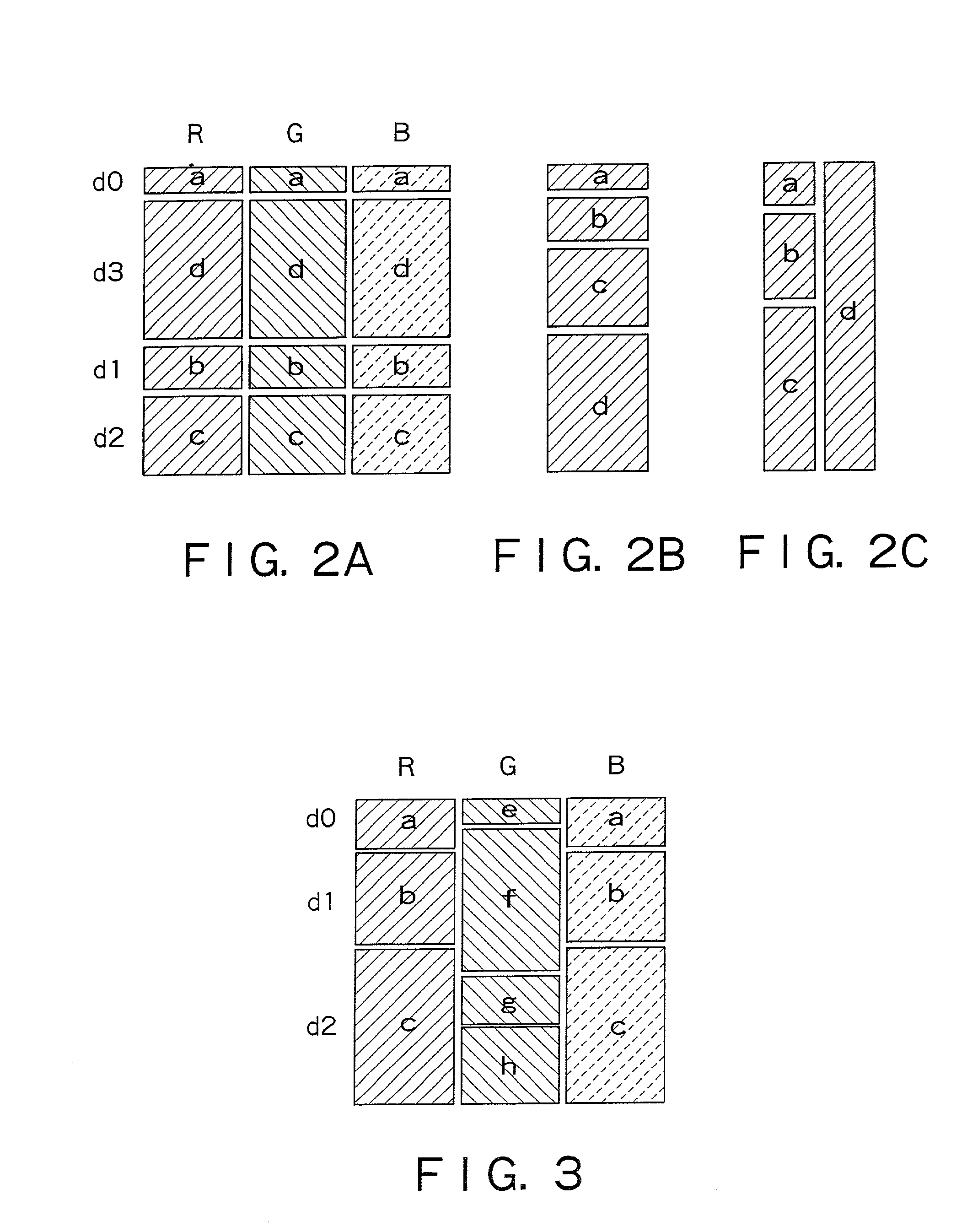

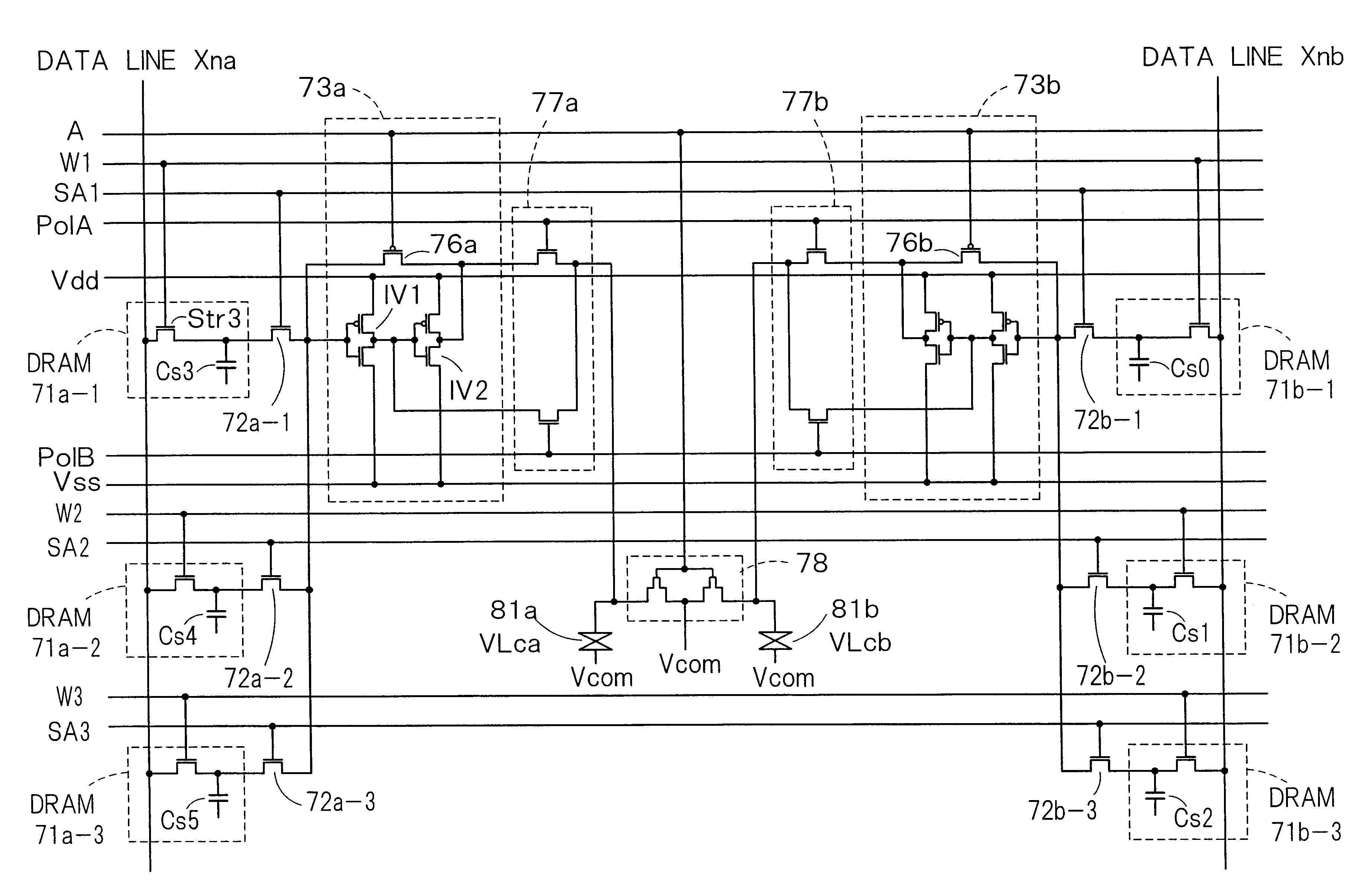

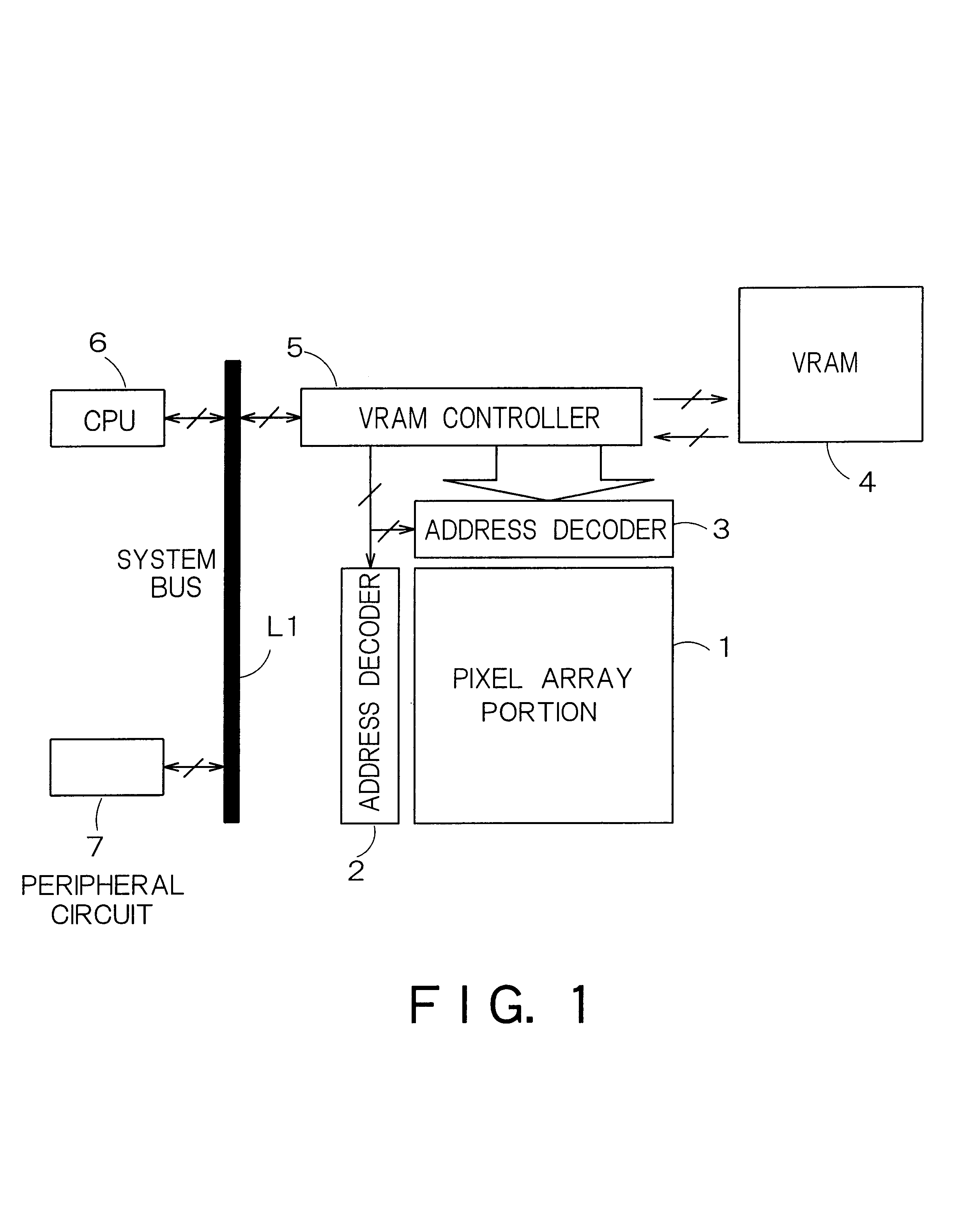

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:JAPAN DISPLAY CENTRAL CO LTD

Integrally formed light emitting diode light wire and uses thereof

ActiveUS20100164409A1Low costImprove artLighting heating/cooling arrangementsLighting elementsMicrocontrollerComputer module

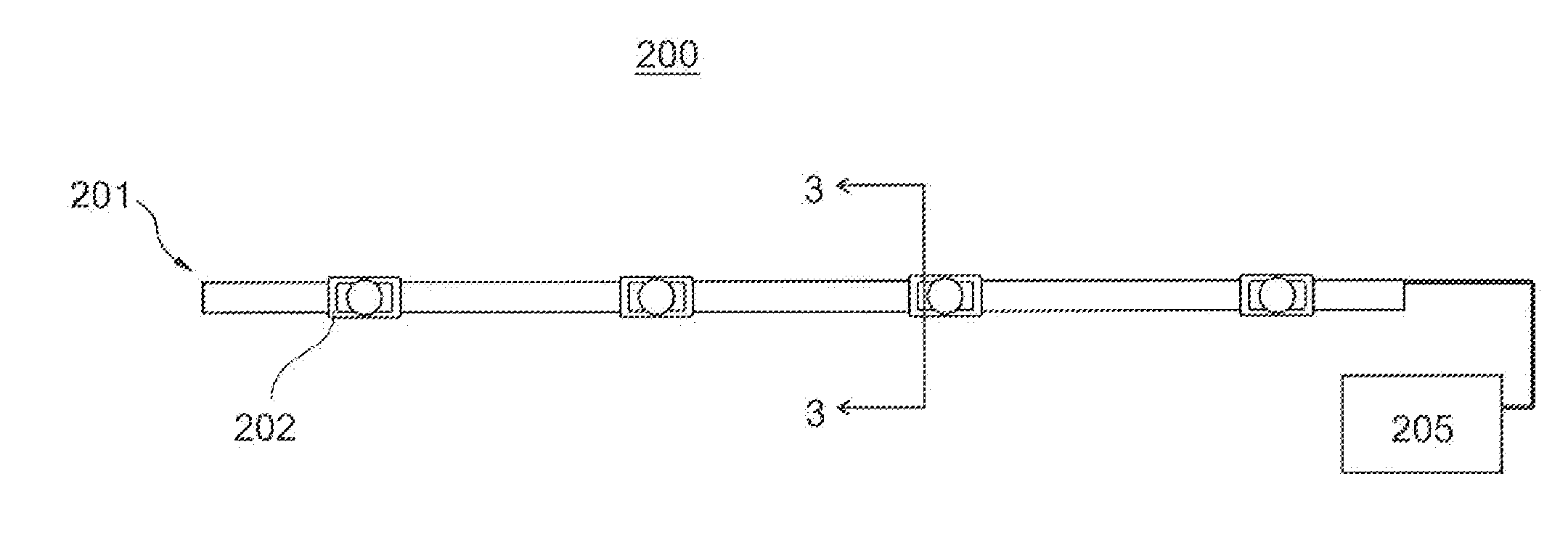

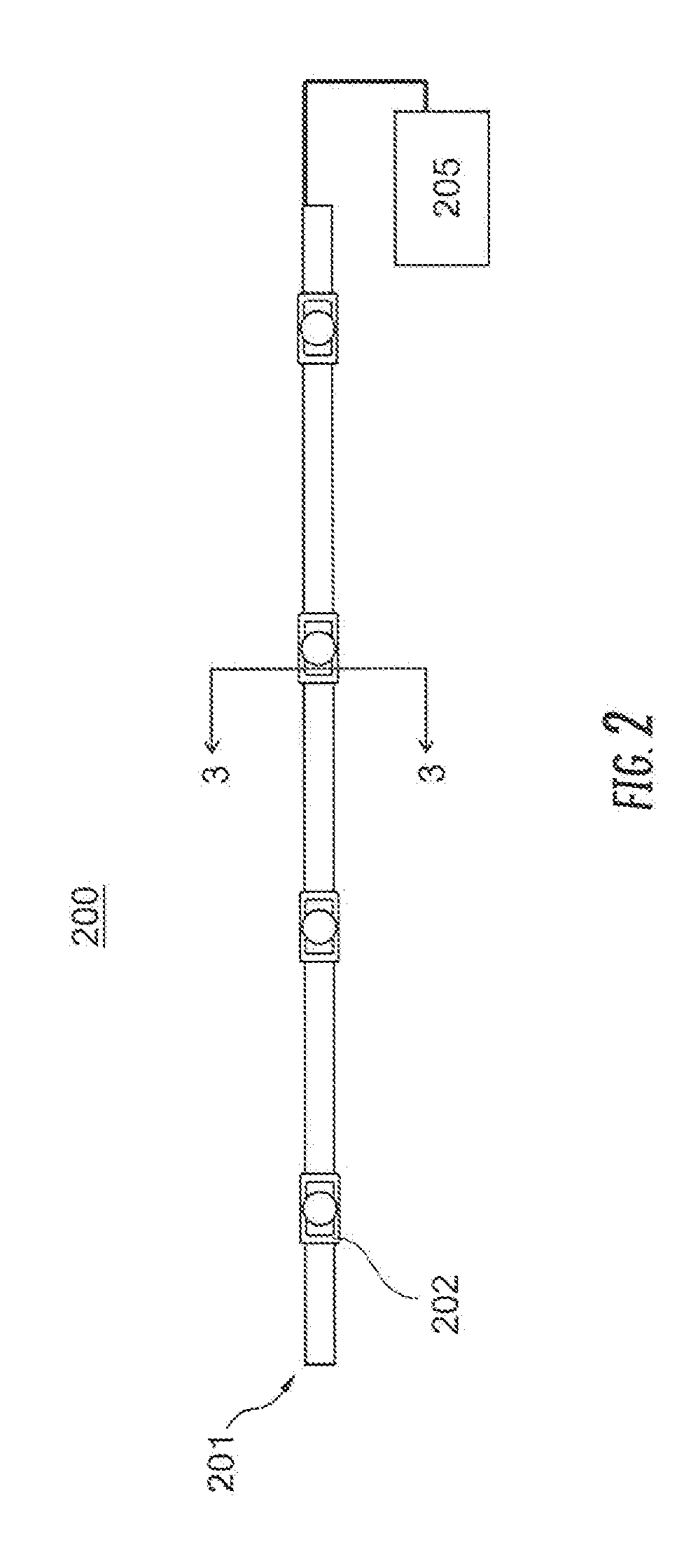

Integrally formed LED light wires are provided, comprising a plurality of dynamically addressible LED modules, each LED module comprising one or more LEDs; a microcontroller; and one or more ports, said microcontroller being configured to: check a status of at least one of said one or more ports; if the status of the port corresponds to a predetermined state: assign the LED module to which said microcontroller belongs to a first display address, and send signals to said microcontroller of a neighboring LED module, said signals assigning respective further display address to the neighboring LED module. Such LED light wires can also include a display memory which stores current display information associated with each of said LED modules in said LED light wire, and a display controller, said display controller being configured to update the current display information stored in said display memory.

Owner:HUIZHOU LIGHT ENGINE LTD

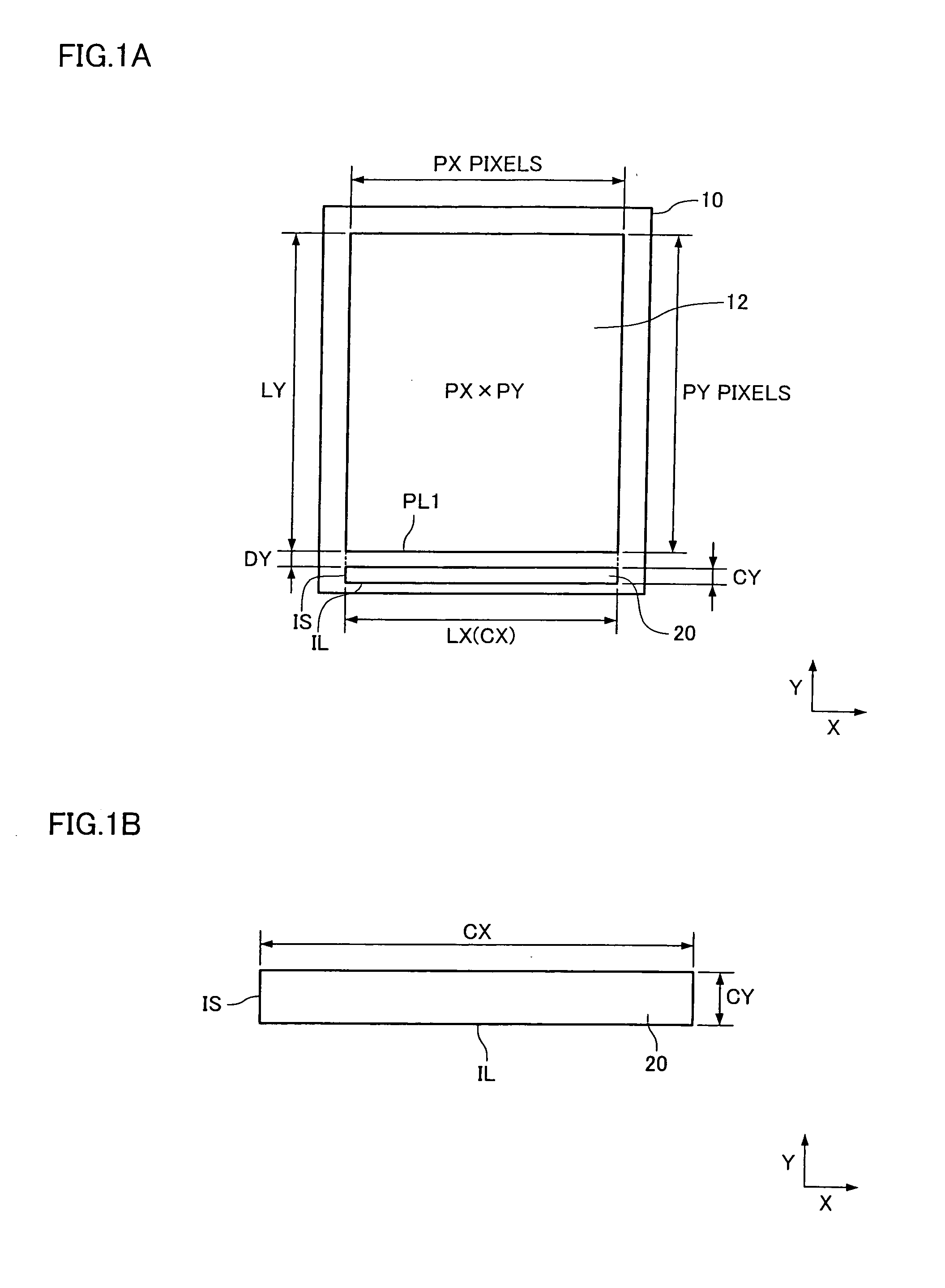

Display device and driving method thereof

InactiveUS6873320B2Reduce consumptionSmall sizeCathode-ray tube indicatorsNon-linear opticsAddress decoderLiquid-crystal display

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:KK TOSHIBA

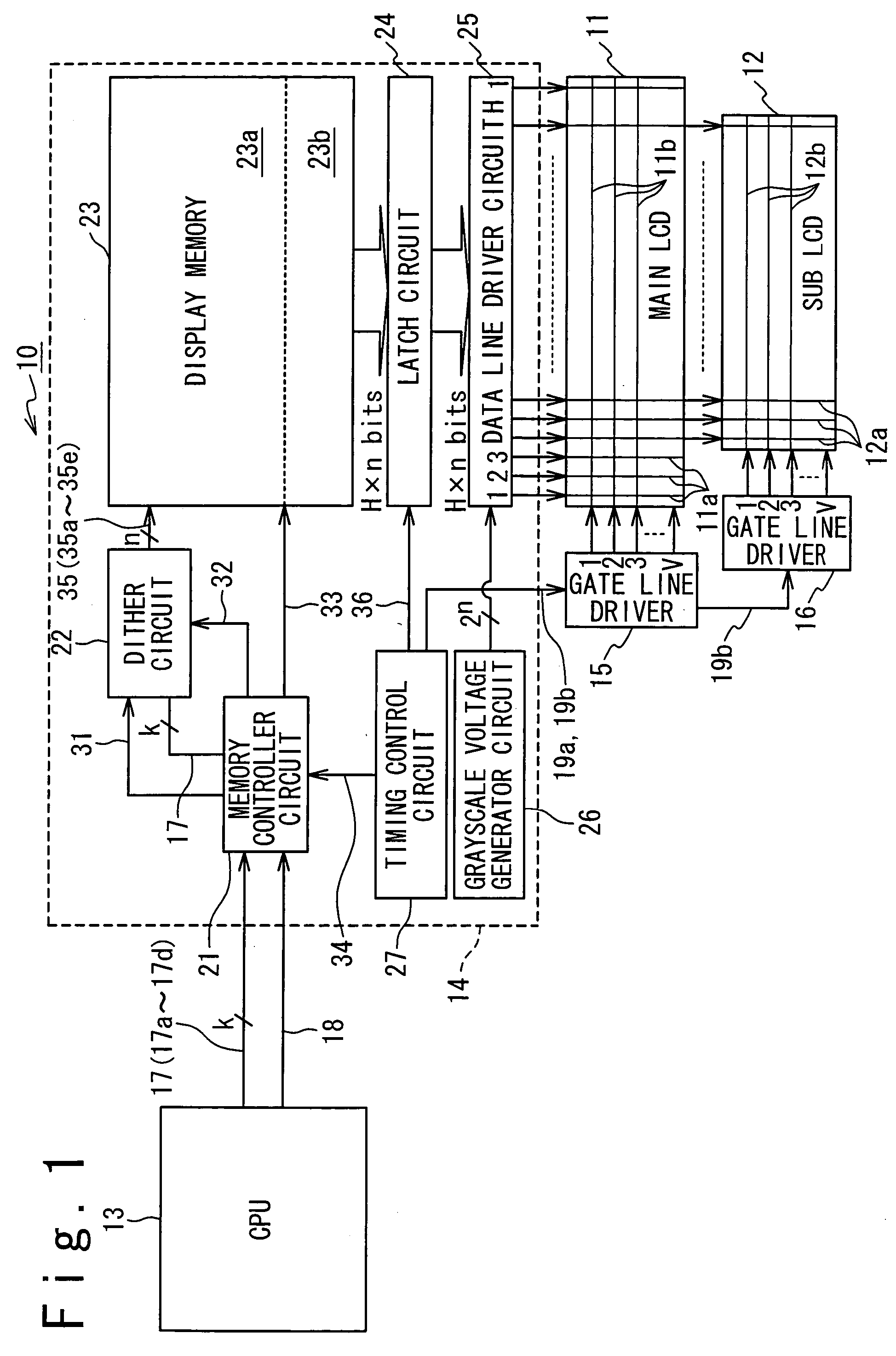

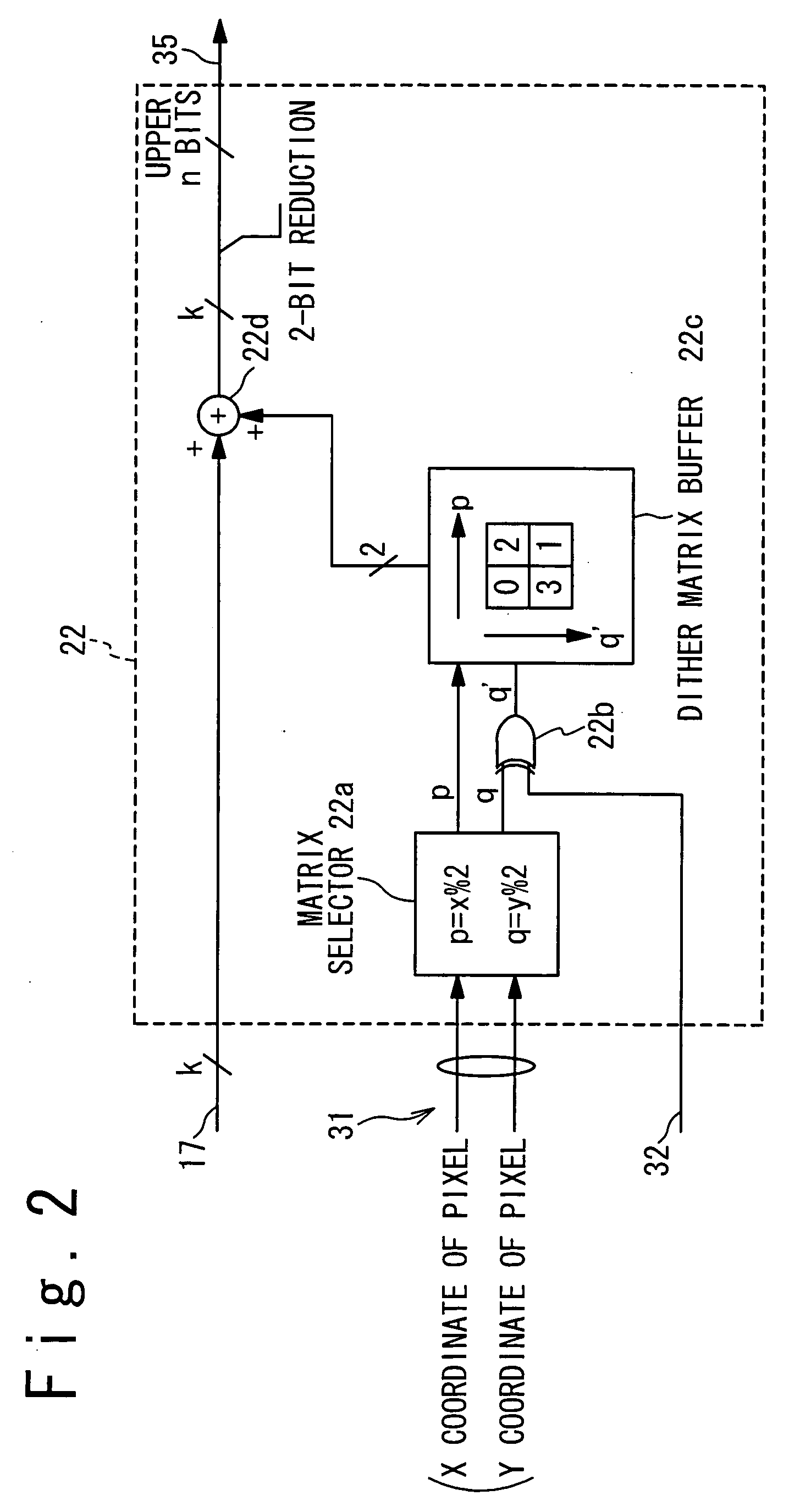

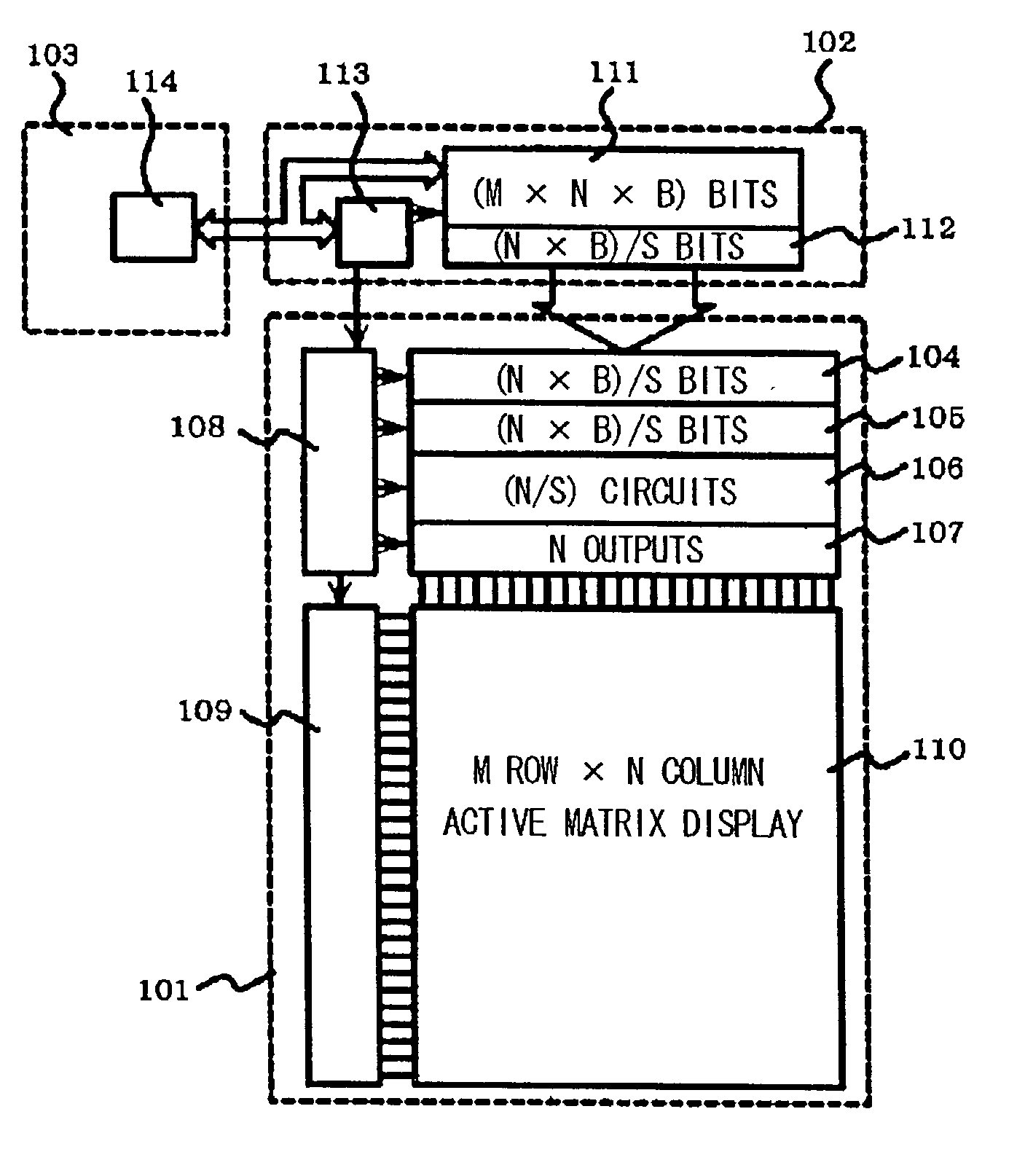

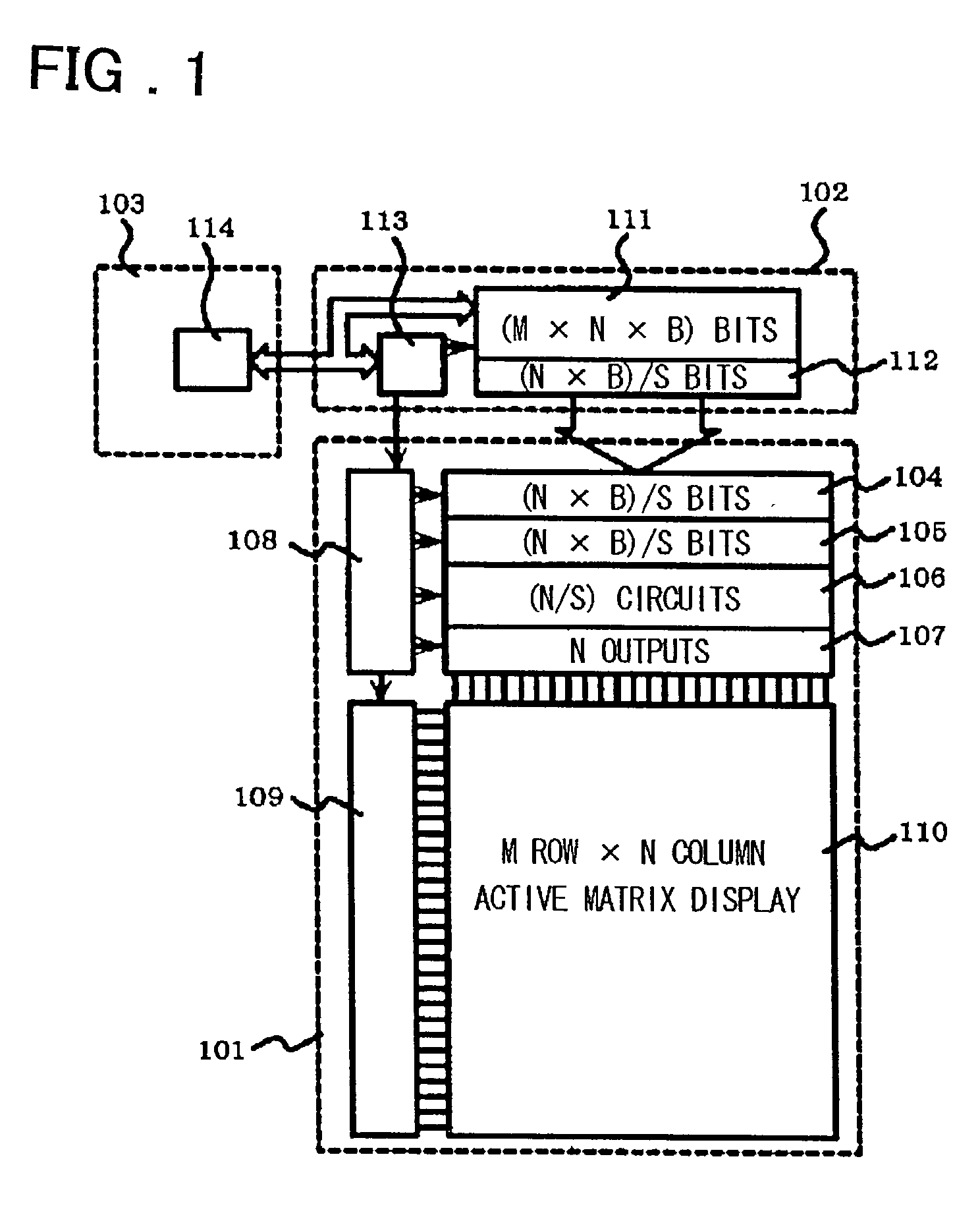

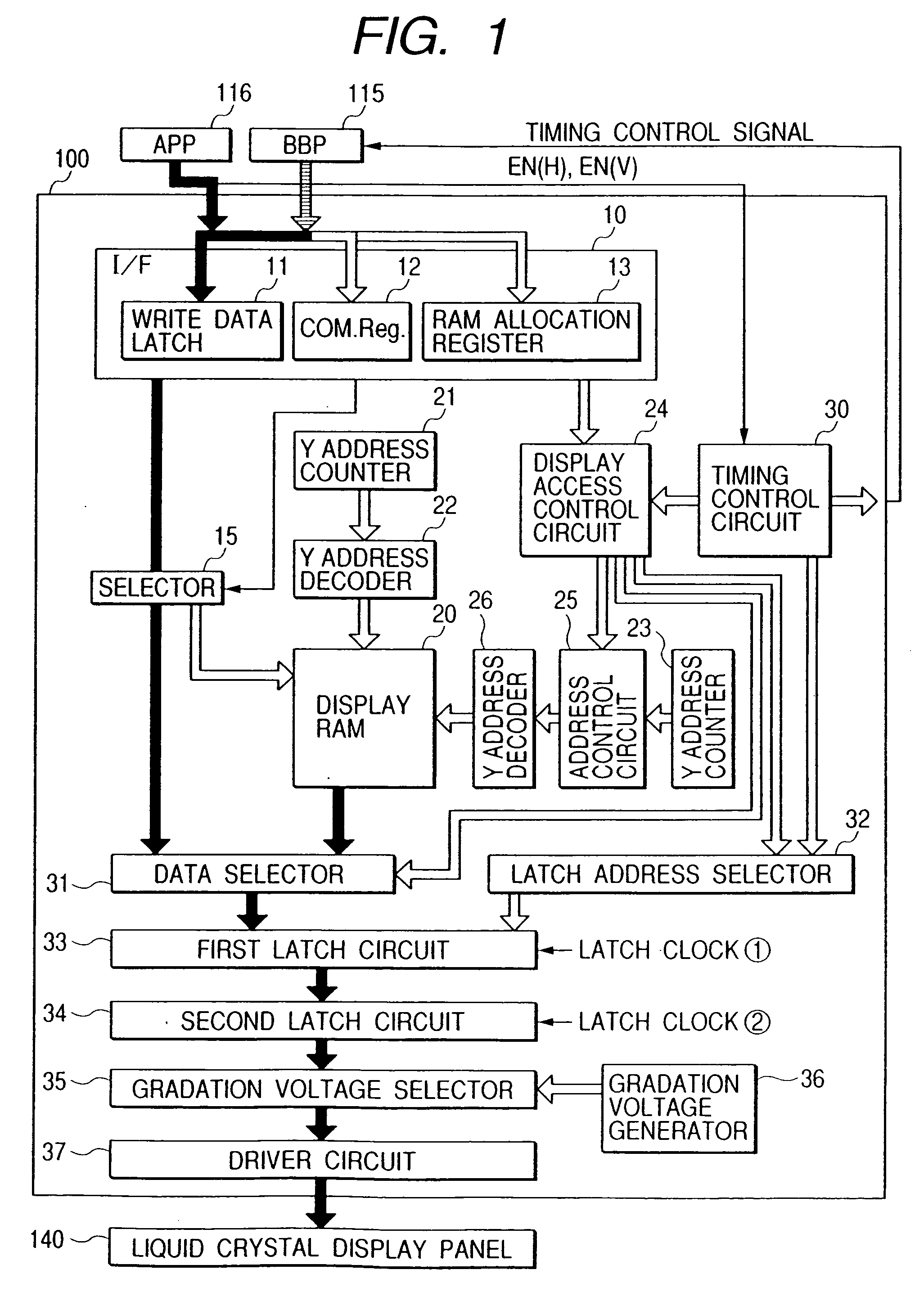

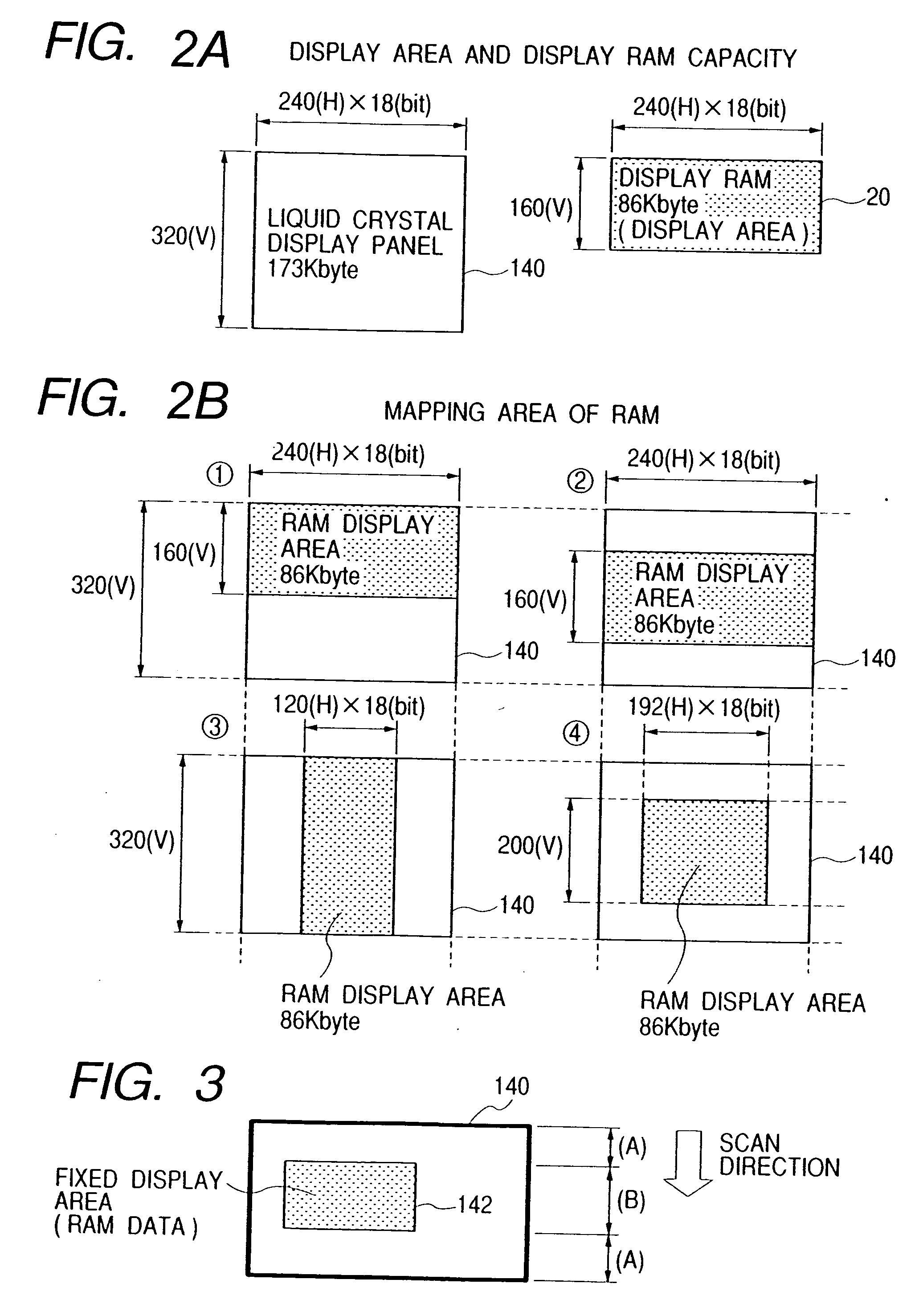

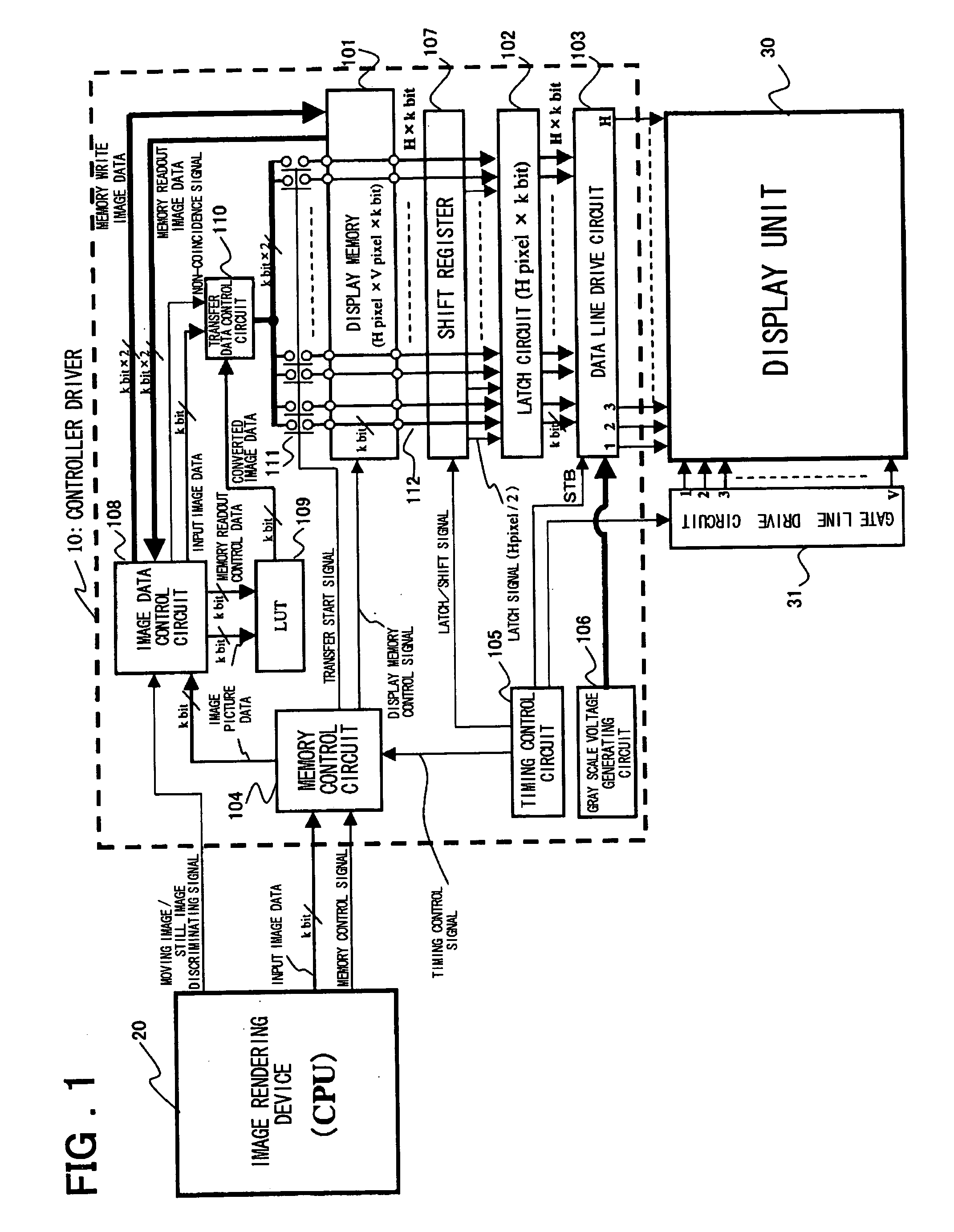

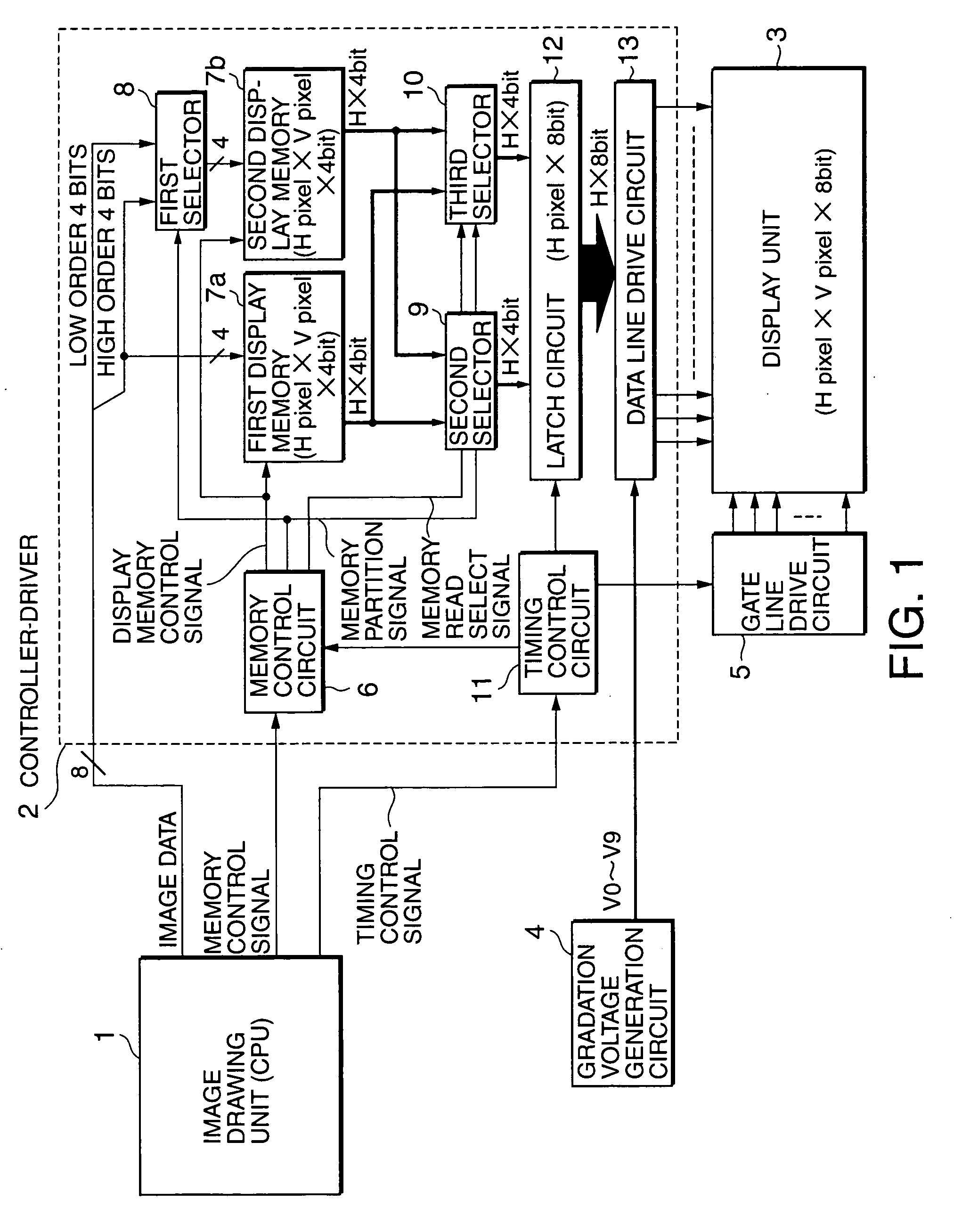

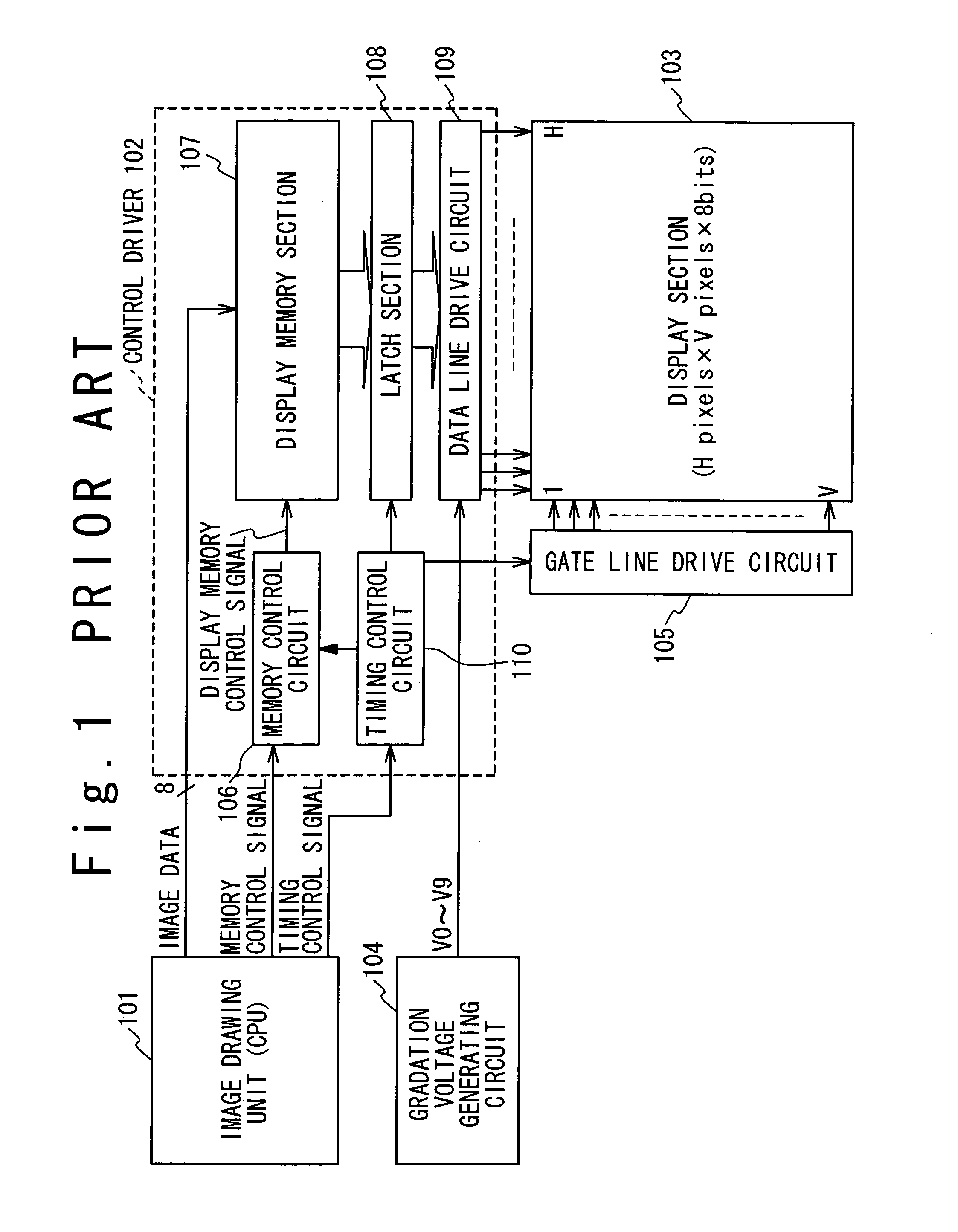

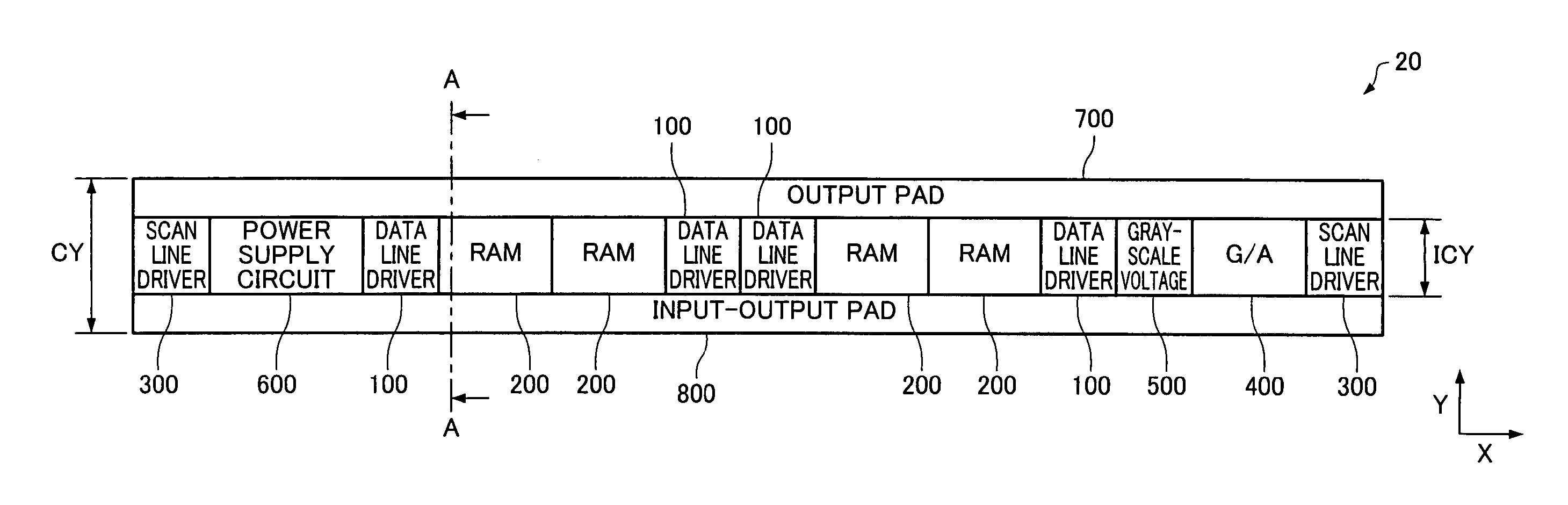

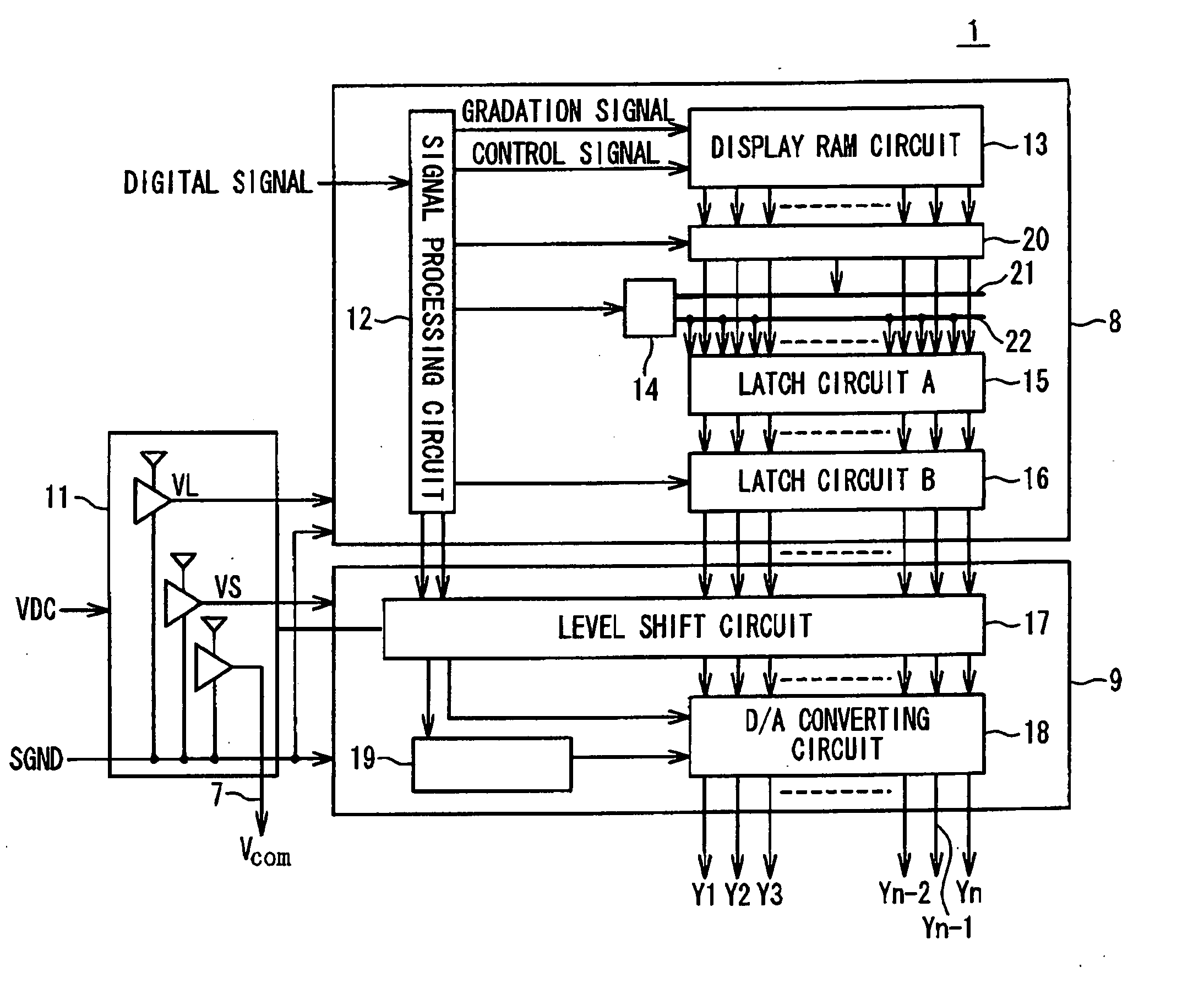

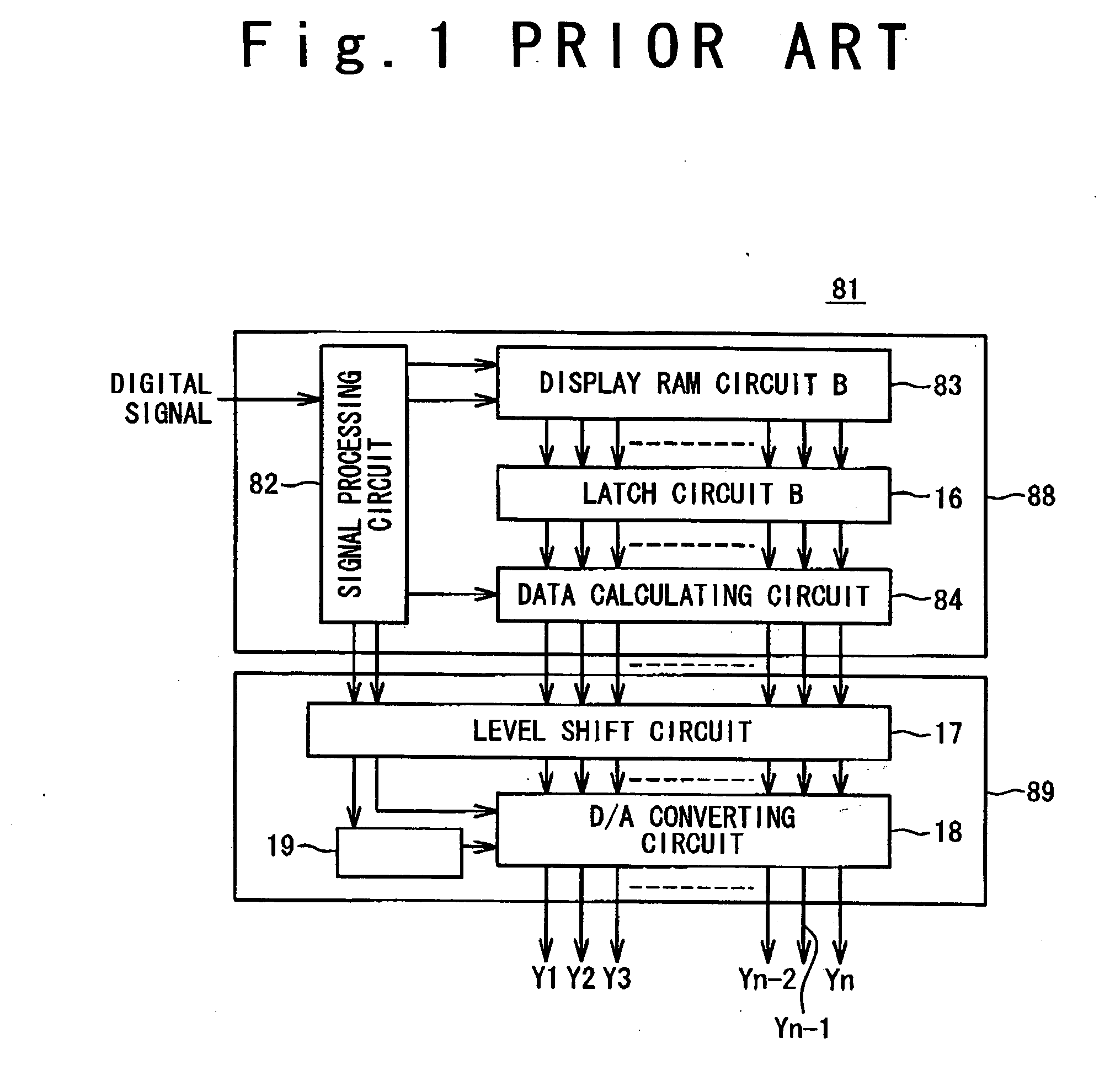

Controller/driver for driving display panel

ActiveUS20050073470A1Quality improvementReduce capacityCathode-ray tube indicatorsInput/output processes for data processingDriver circuitDisplay board

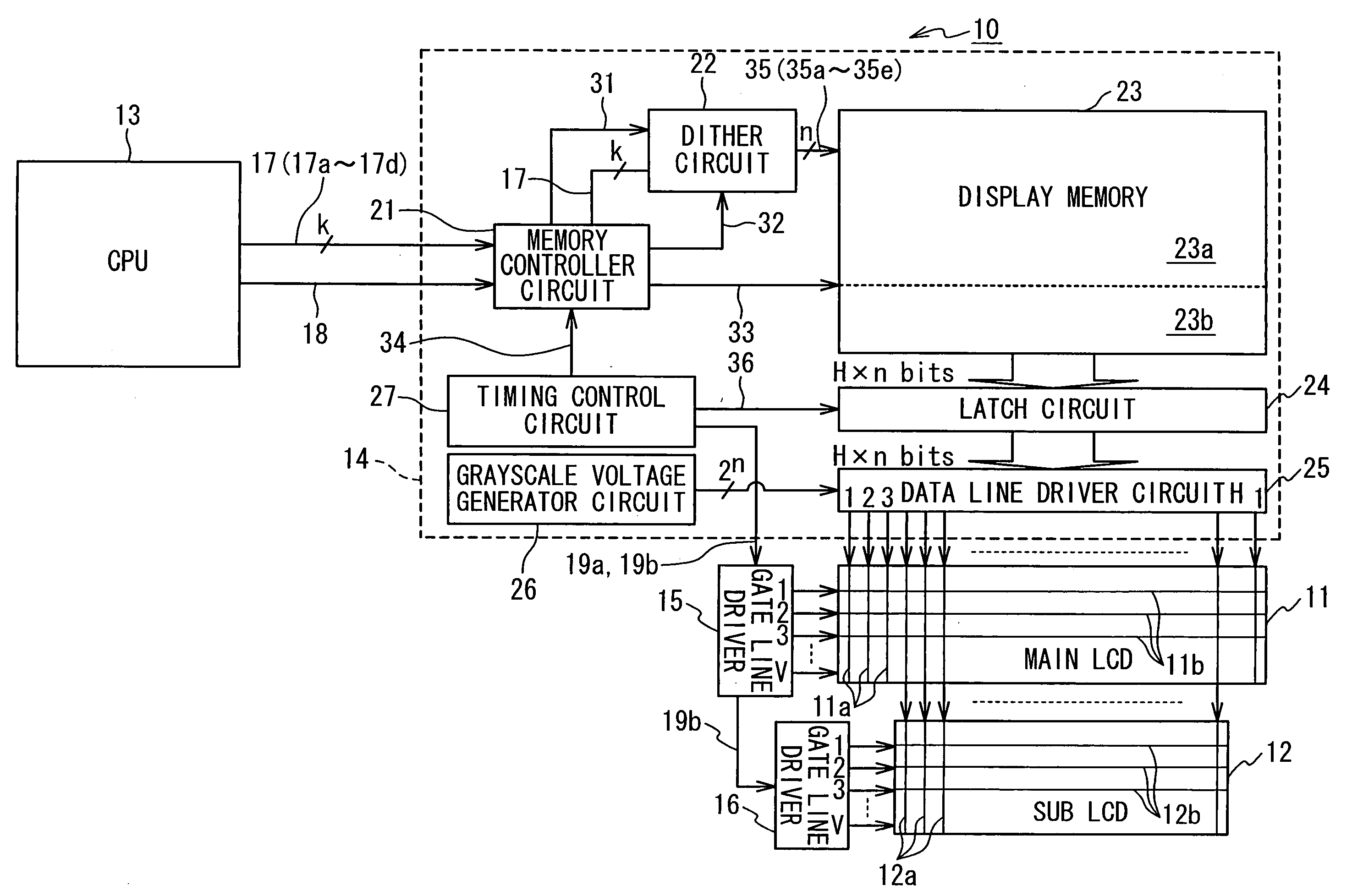

A controller / driver for driving main and sub display panels is composed of first and second memory sections, a color reduction circuit, and a data line driver circuit. The first and second memory sections are used as multipurpose display memories. When the controller / driver is placed in a first mode, the first and second memory sections store therein a pair of image data color-reduced under different conditions for achieving frame rate control. When the controller / driver is placed in a second mode, on the other hand, the first and second memory sections store sub and main image data respectively associated with images to be displayed on main and sub display panels.

Owner:RENESAS ELECTRONICS CORP

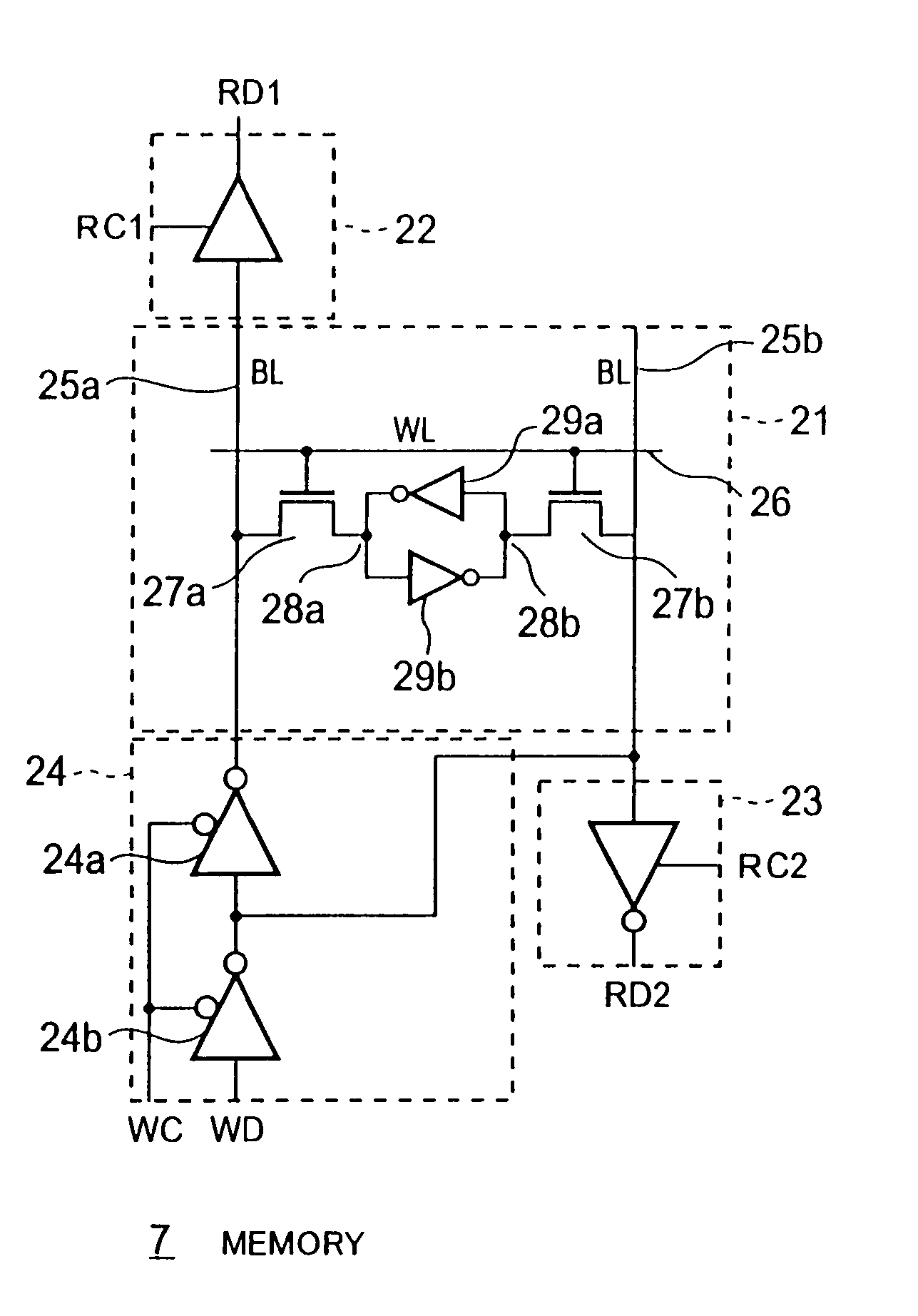

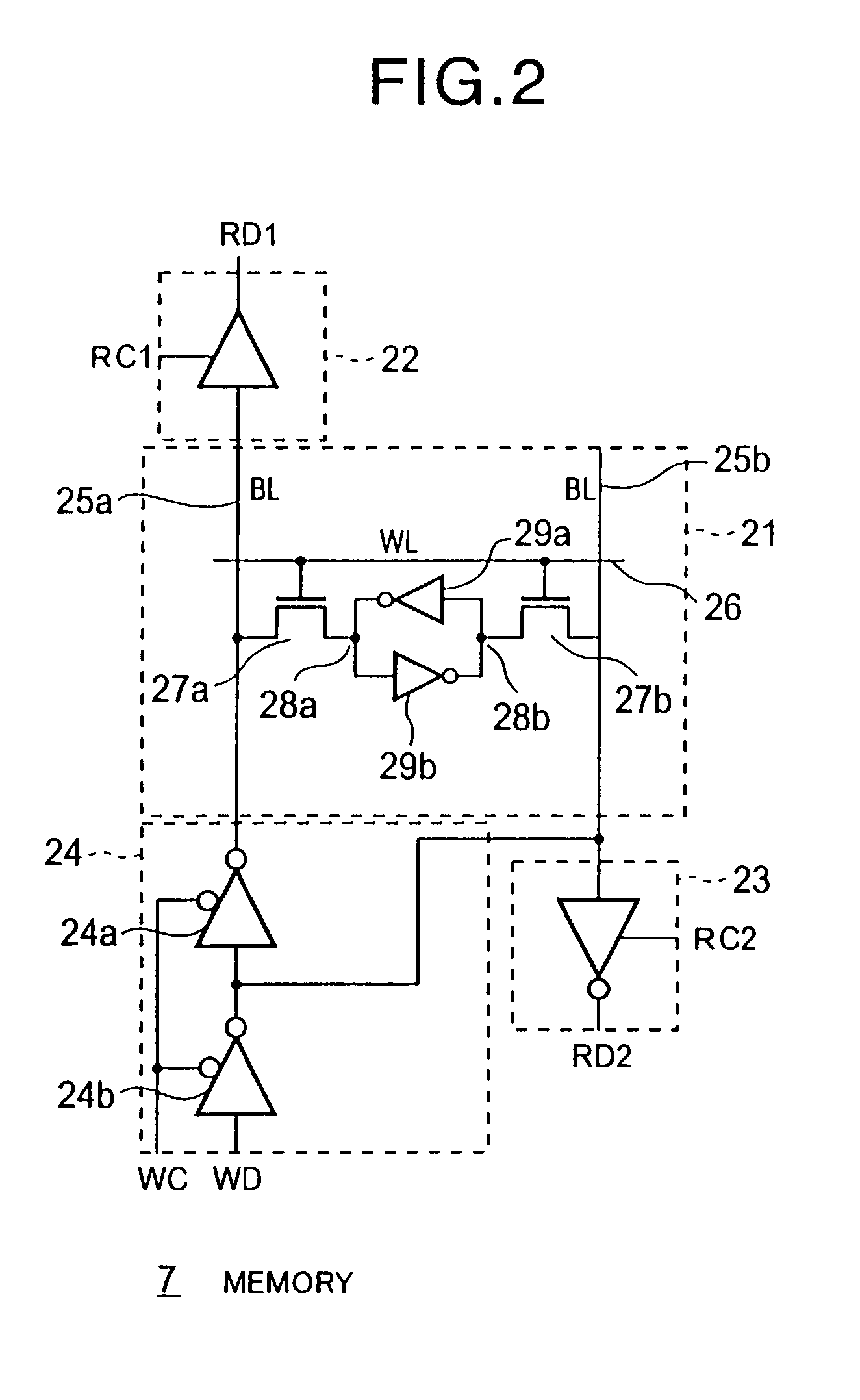

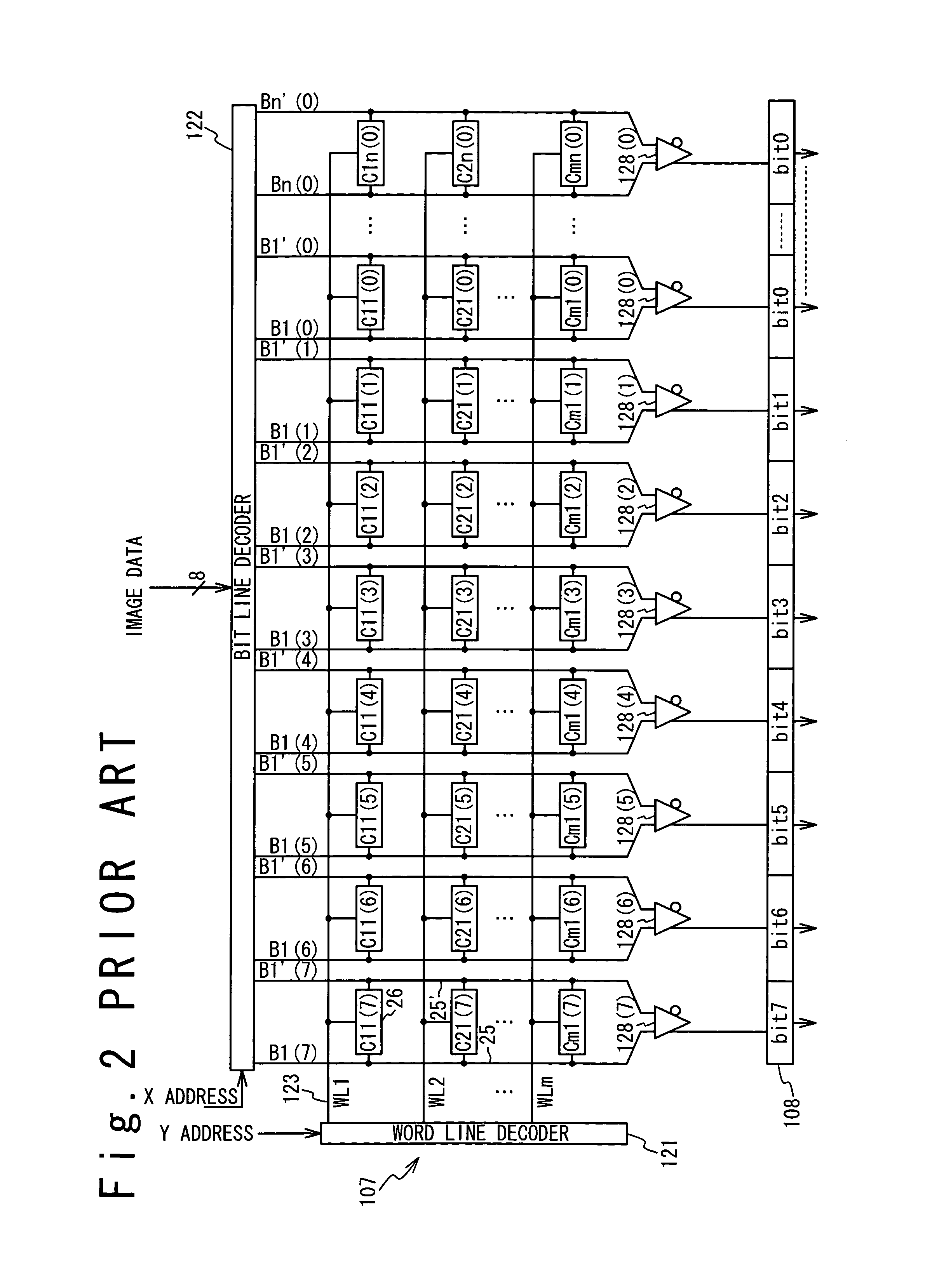

Display memory, driver circuit, display, and cellular information apparatus

InactiveUS7176864B2Reduce power consumptionIncrease speedCathode-ray tube indicatorsDigital storageBit lineDriver circuit

A display memory able to reduce power consumption, able to generate graphics at a high speed, and not needing memory mapping, a driver circuit, a display using the driver circuit, and a portable information apparatus, wherein a CPU read circuit is connected to one bit line of a display memory 7, a display read circuit is connected to the other bit line, a write circuit is connected to both bit lines, the CPU read circuit and write circuit are assigned to the access from the CPU, the display read circuit is assigned to the display screen display, and further the access from the CPU and the reading to the display screen are assigned to different two level periods of a clock signal of the memory and independently controlled. Further, a drive power supply of the display memory is divided and a drive power supply voltage is supplied to the display memory for every memory cell or for every plurality of memory cells.

Owner:SONY GRP CORP

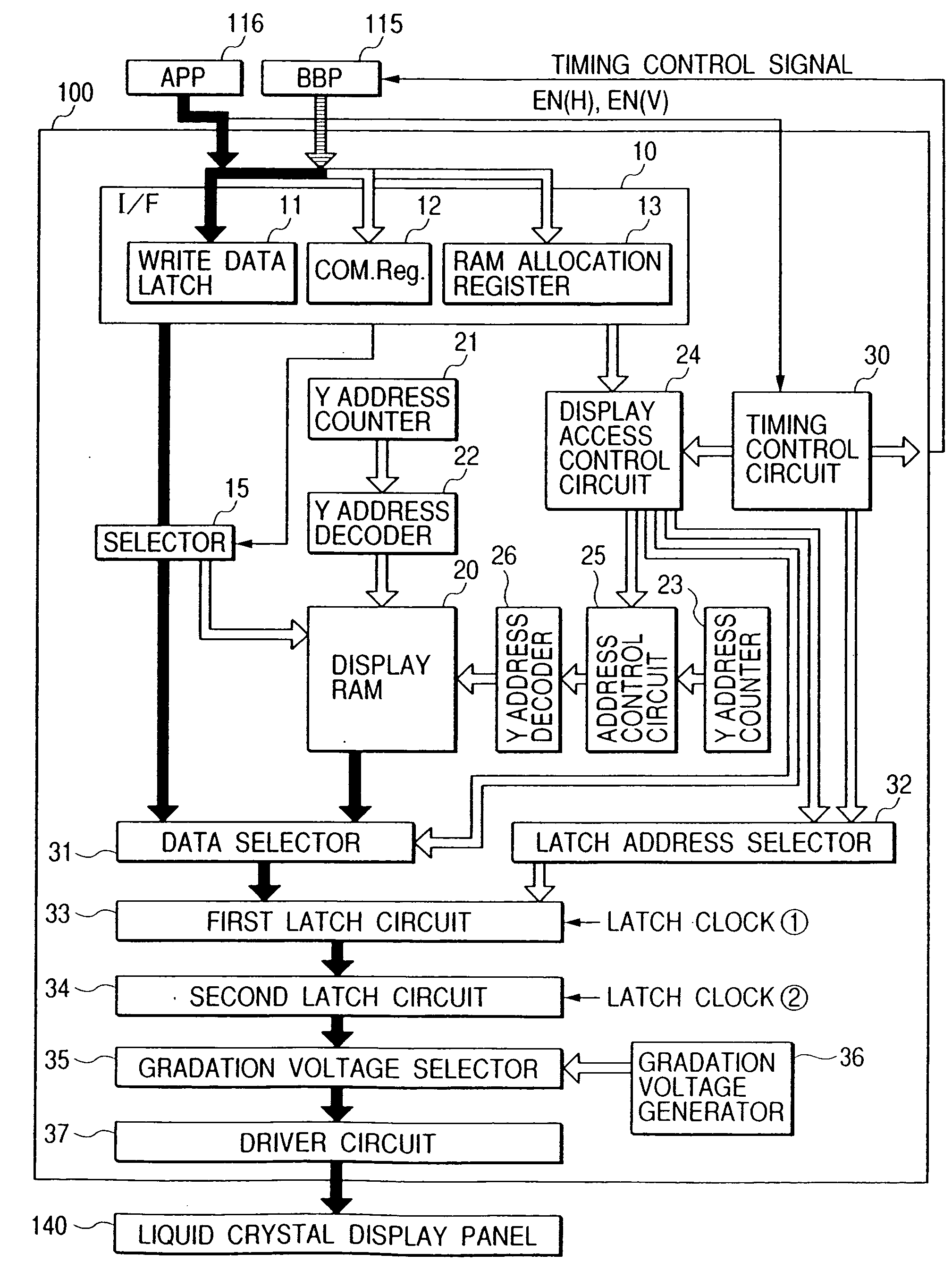

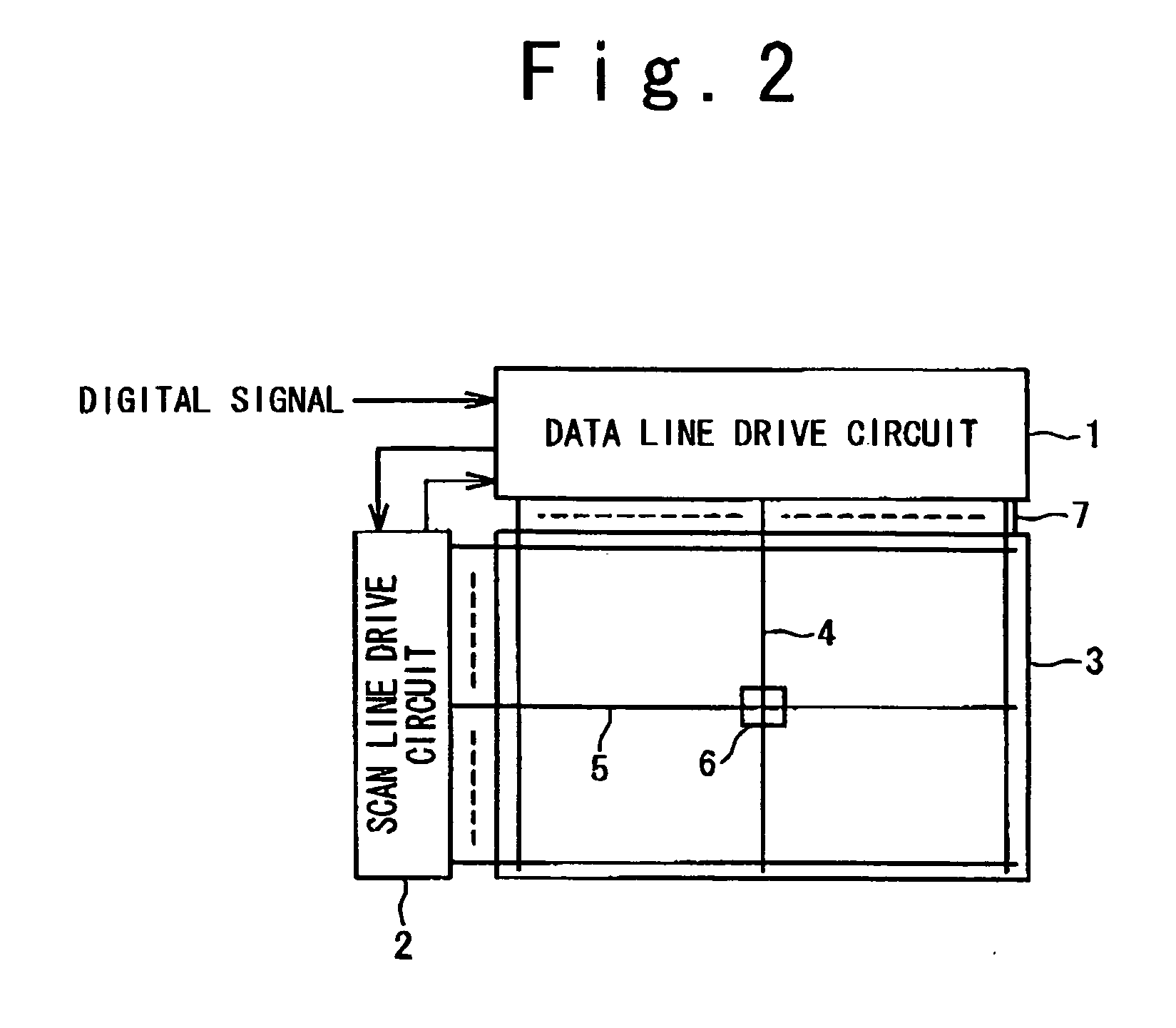

Display device and semiconductor device

InactiveUS20030067434A1High definitionIncrease the number of pixelsCathode-ray tube indicatorsInput/output processes for data processingEngineeringLine driver

A display device of high definition, multiple colors and low power consumption includes a display panel having a pixel section in which pixels are arrayed in the form of a matrix at the cross points of a plurality of data lines and a plurality of scanning lines, a scanning circuit for applying voltage sequentially to the plurality of scanning lines, and a data-line driver, which receives display data supplied by a host device, for applying signals corresponding to the display data to the plurality of data lines. Provided external to the display panel is a controller IC having a display memory for storing display data corresponding to the pixel section, an output buffer for reading data out of the display memory and outputting this data to the display panel, and a controller for controlling the display memory and output buffer and communication with the host device. The display panel is provided with a digital / analog converter, which forms part of the data-line driver, for converting display data represented by a digital signal to an analog signal. The width of a bus for data transfer between the controller IC and data-line driver of the display panel is such that data of a greater number of bits is transferred in parallel by a single transfer than is transferred by the bus between the controller and the host device. This allows the operating frequency of the data-line driver to be reduced.

Owner:HANNSTAR DISPLAY CORPORATION

Display driver control circuit and electronic equipment with display device

InactiveUS20070035503A1Large capacityNumber of display colors are more and more increasingCathode-ray tube indicatorsControl circuitComputer science

There is provided a display driver control circuit which is just suitable for display drive including display with a small amount of change and display with a large amount of change and can realize saving of chip area and reduction of power consumption and cost. In this display driver control circuit, memory capacity of an internal display memory is set smaller than amount of data of one display picture of a display panel as the drive object, and the display data can be transferred with the system in which externally inputted display data is once stored in the display memory and is then sent of a drive circuit to output a drive signal and with the system in which the display data is sent in direct to the drive circuit by way of no display memory to output a drive signal. Moreover, both transfer methods can be executed on the time division basis.

Owner:KUROKAWA YASUHITO +4

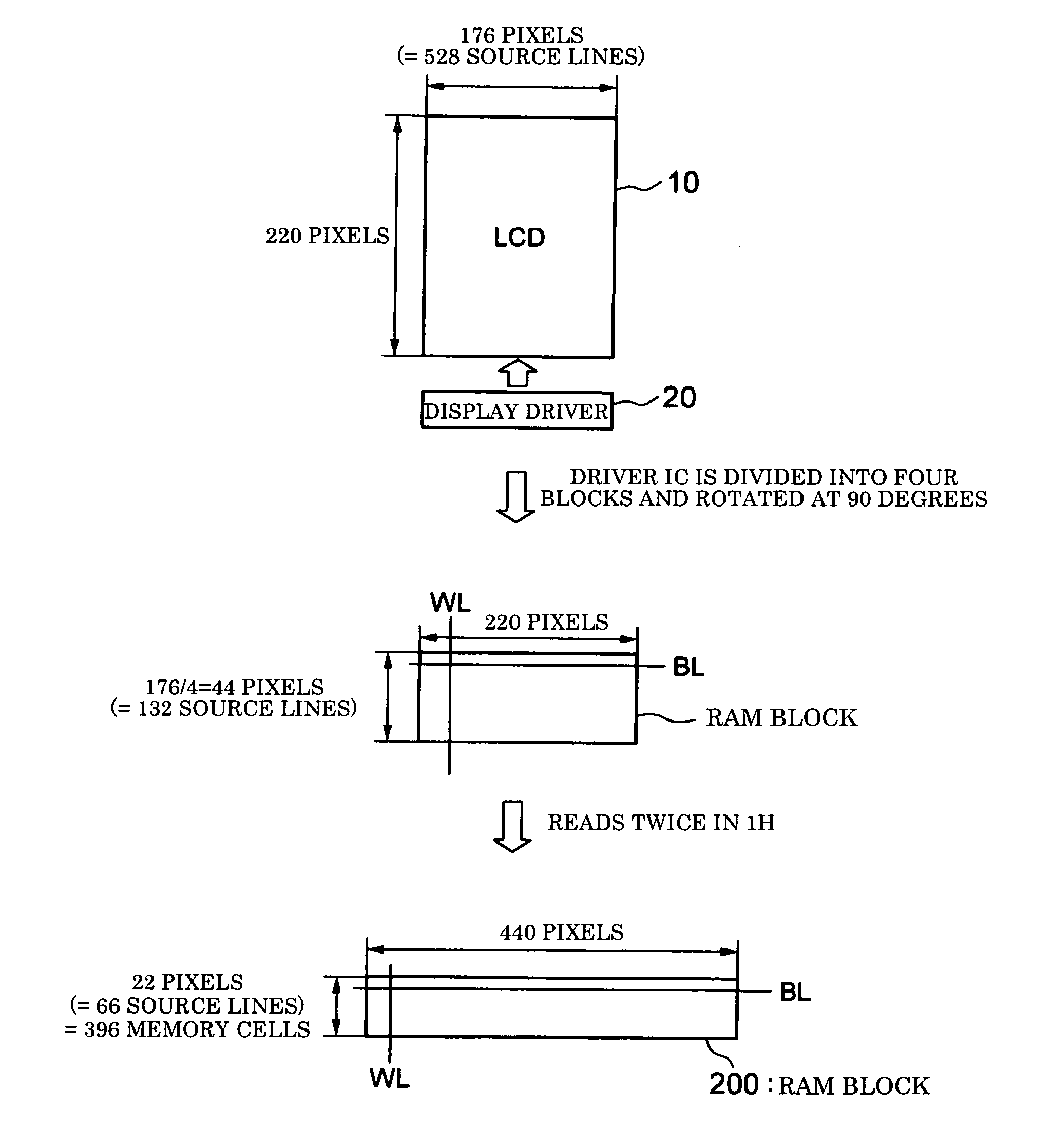

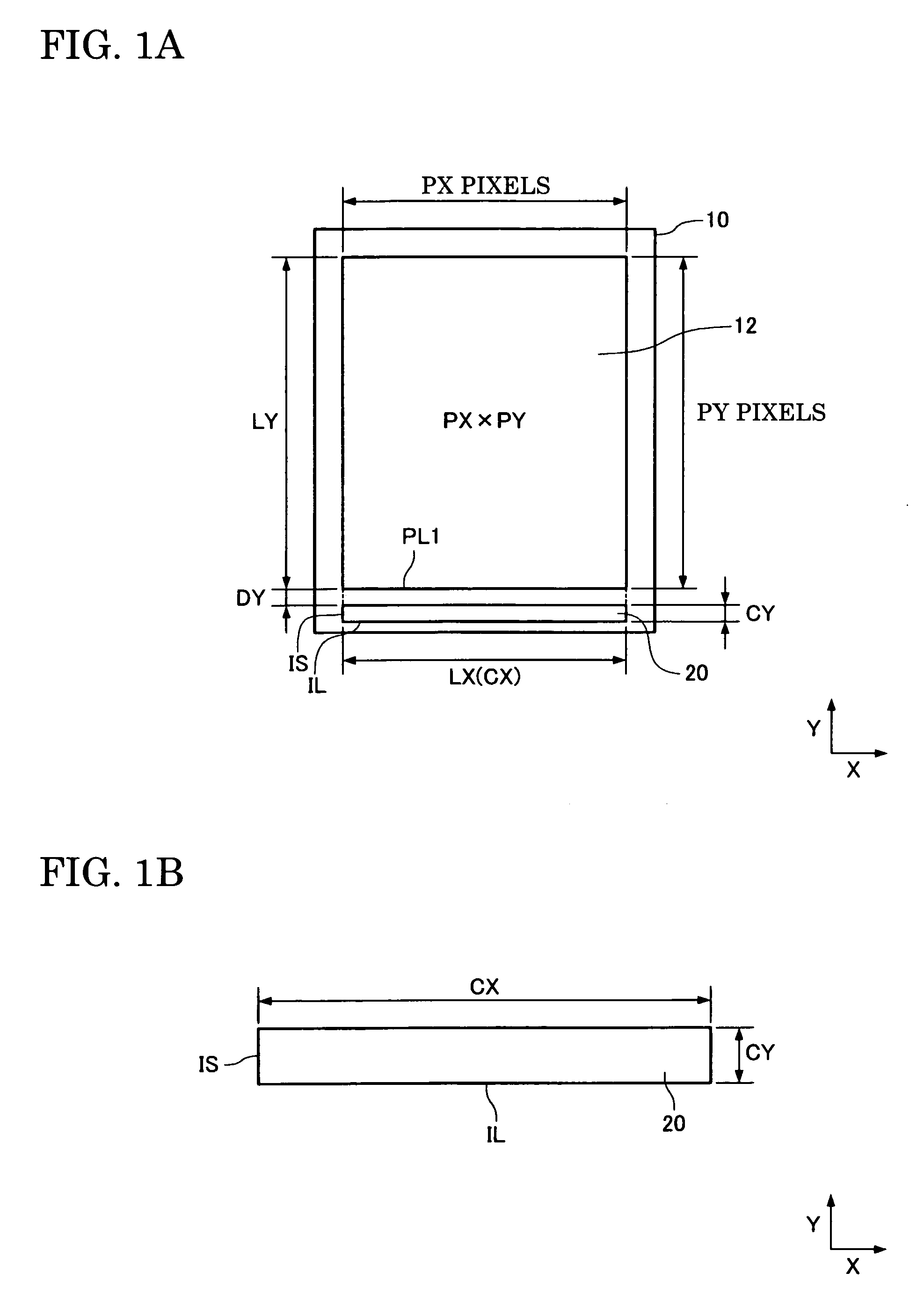

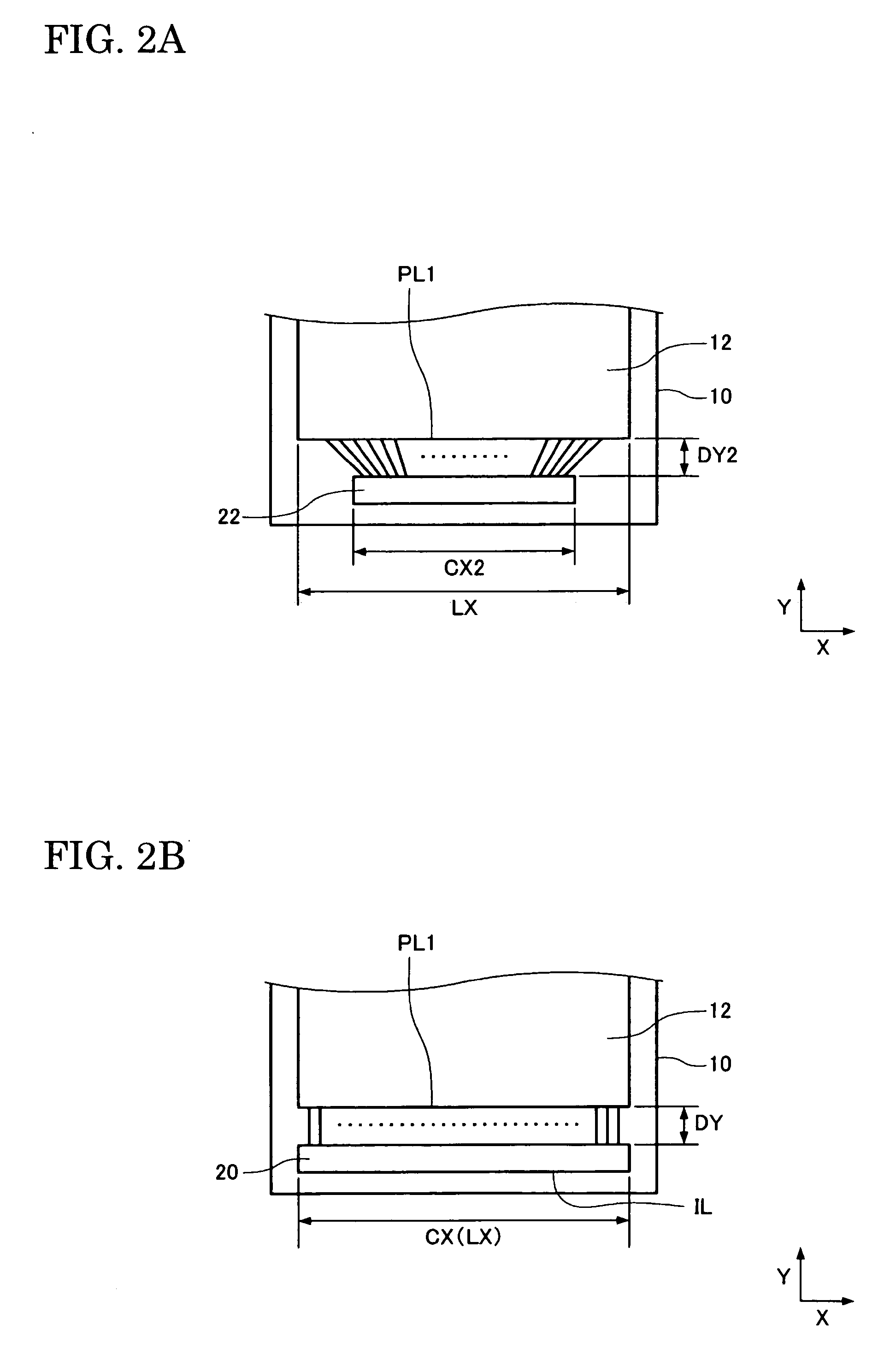

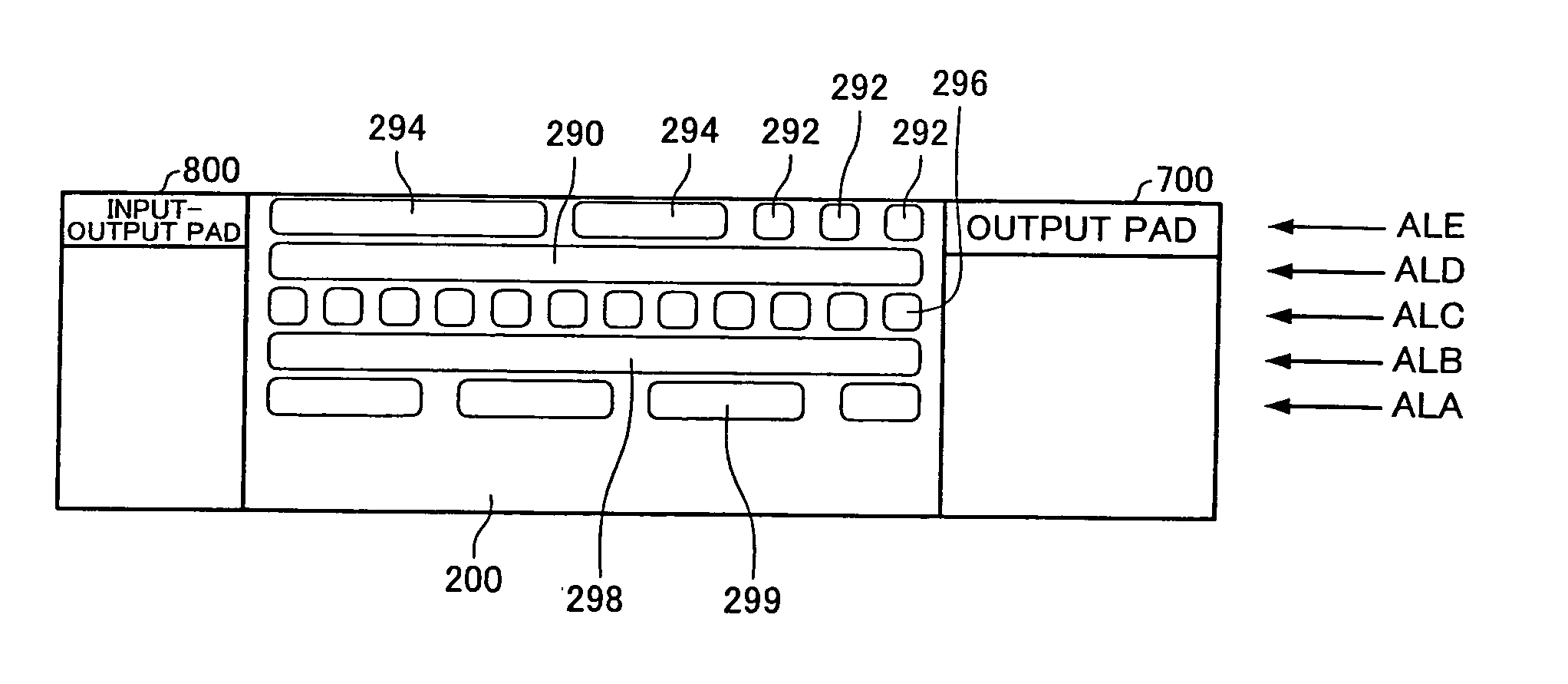

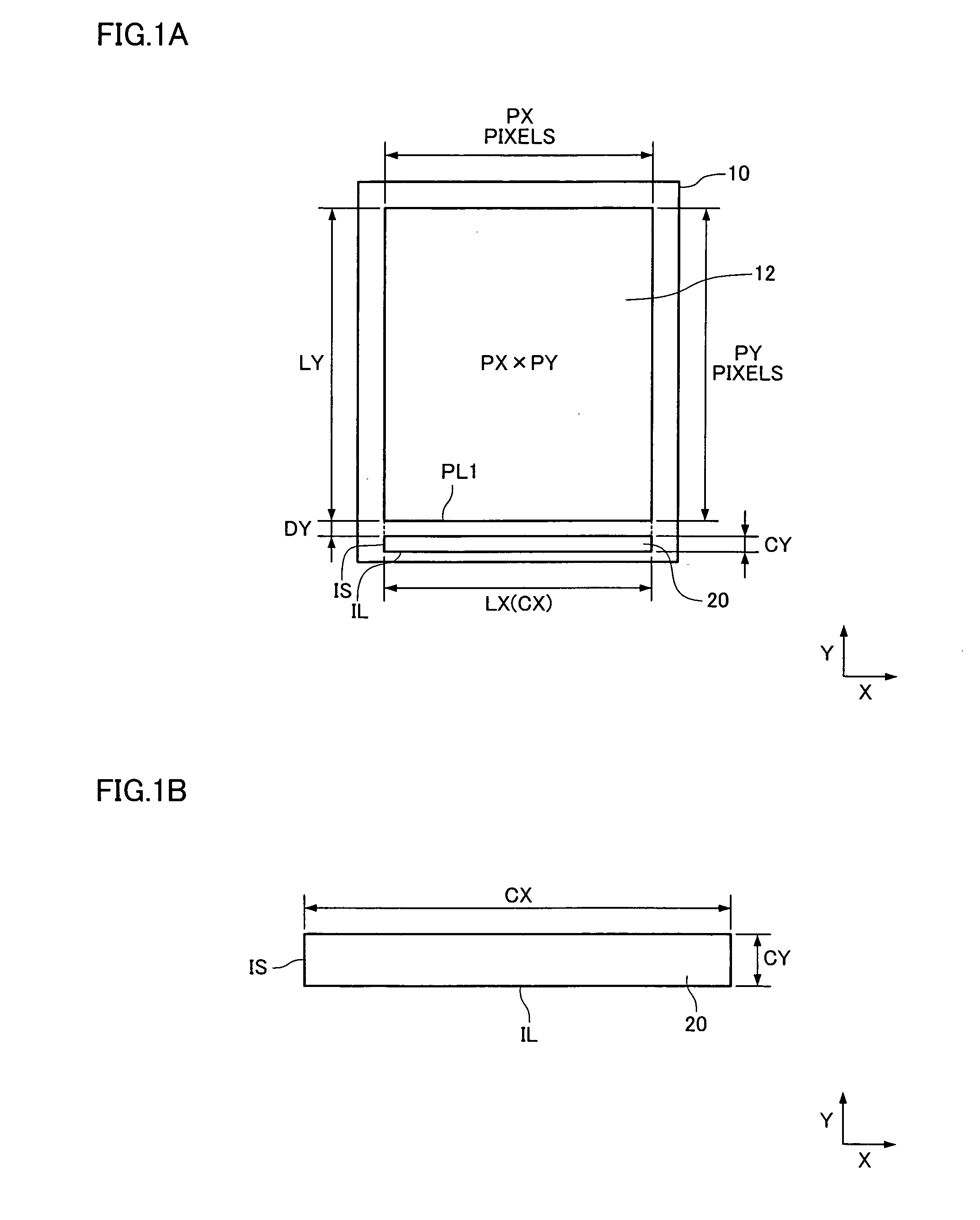

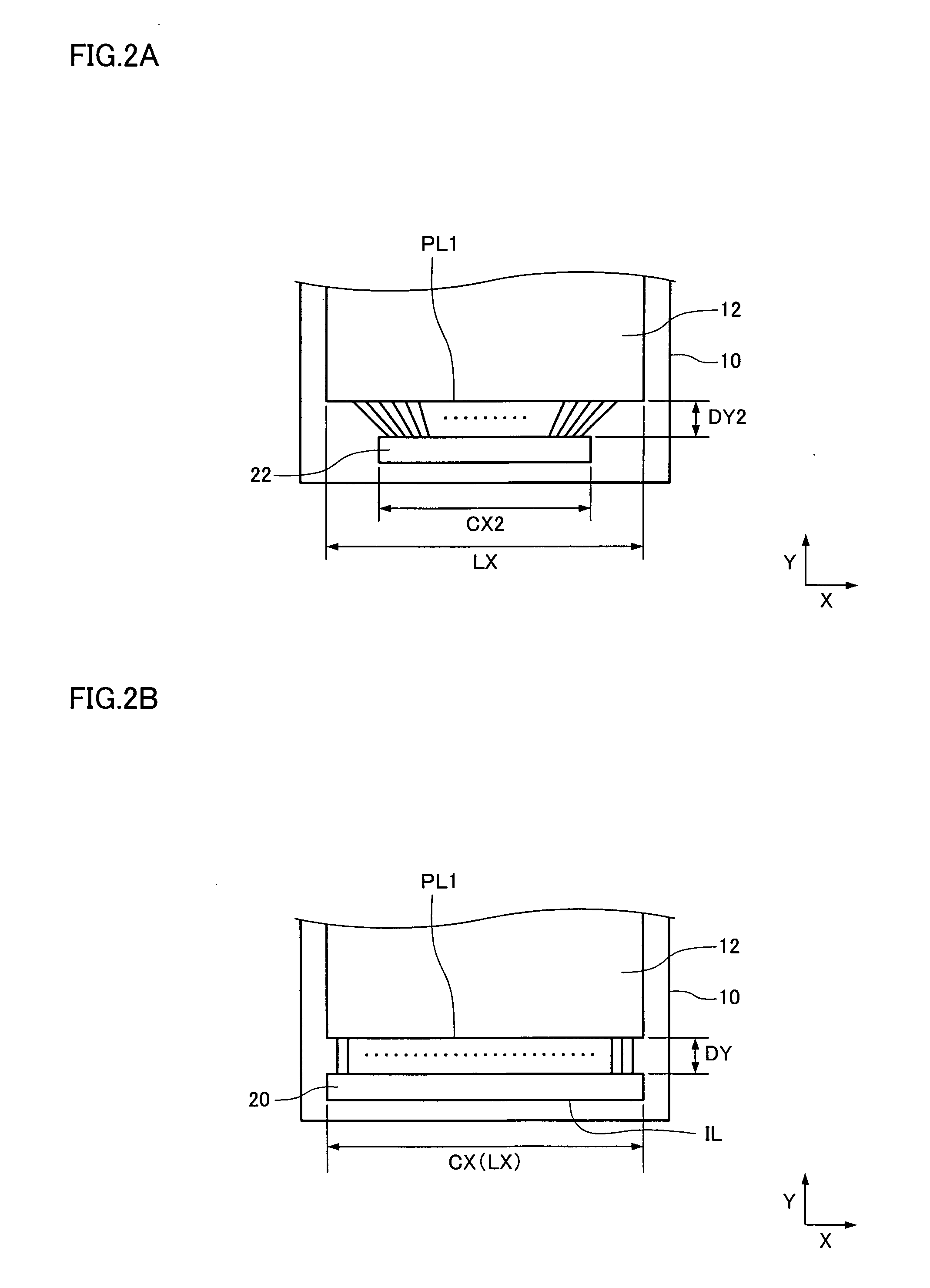

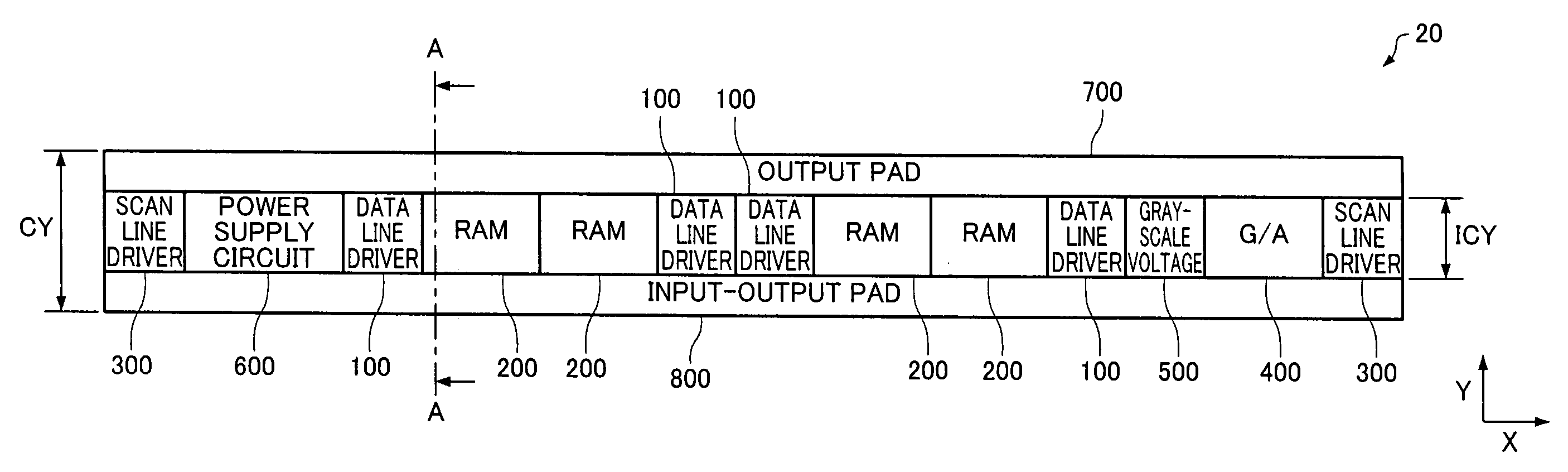

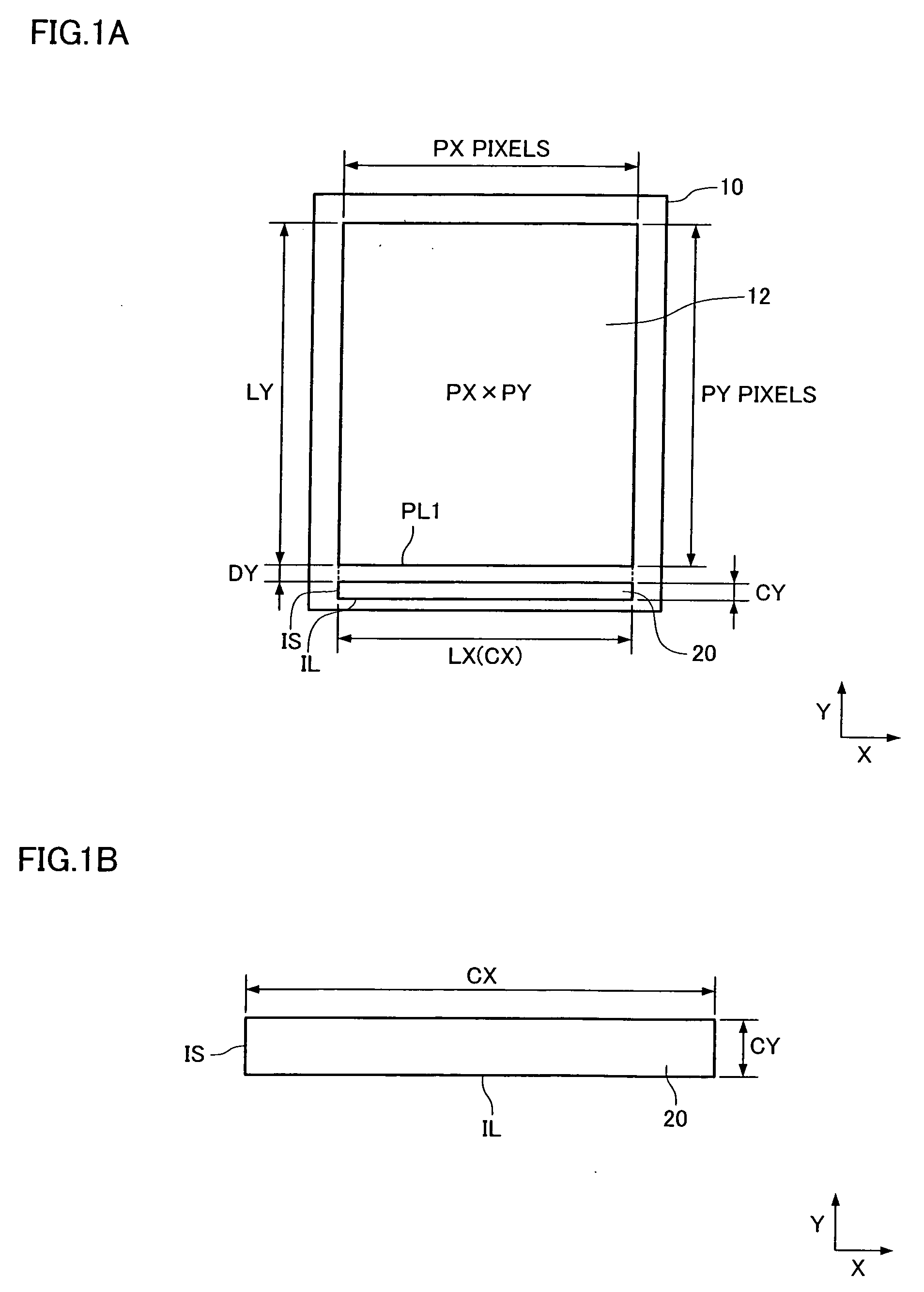

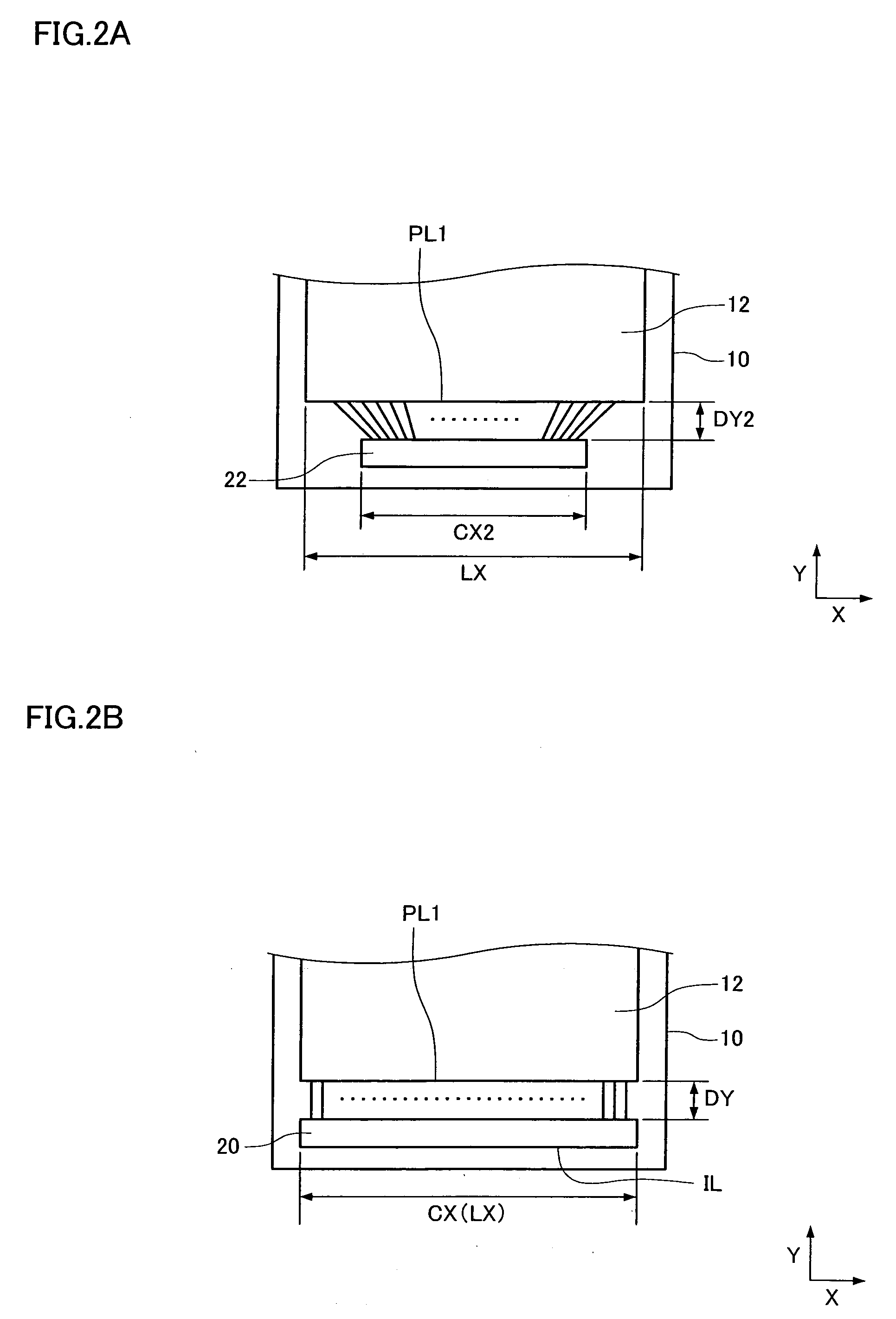

Integrated circuit device and electronic instrument

InactiveUS20070013706A1Memory adressing/allocation/relocationCathode-ray tube indicatorsAudio power amplifierElectronic instrument

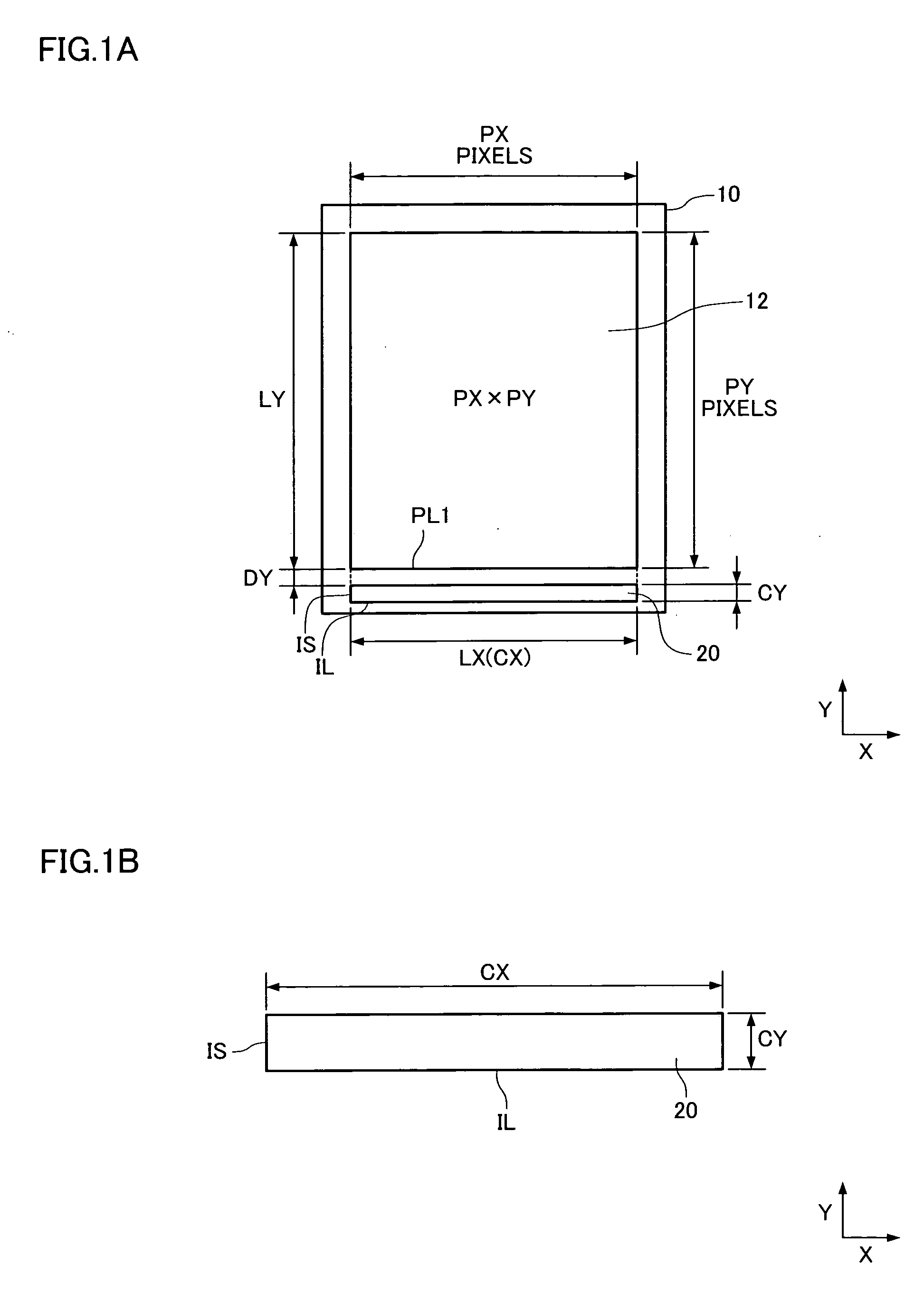

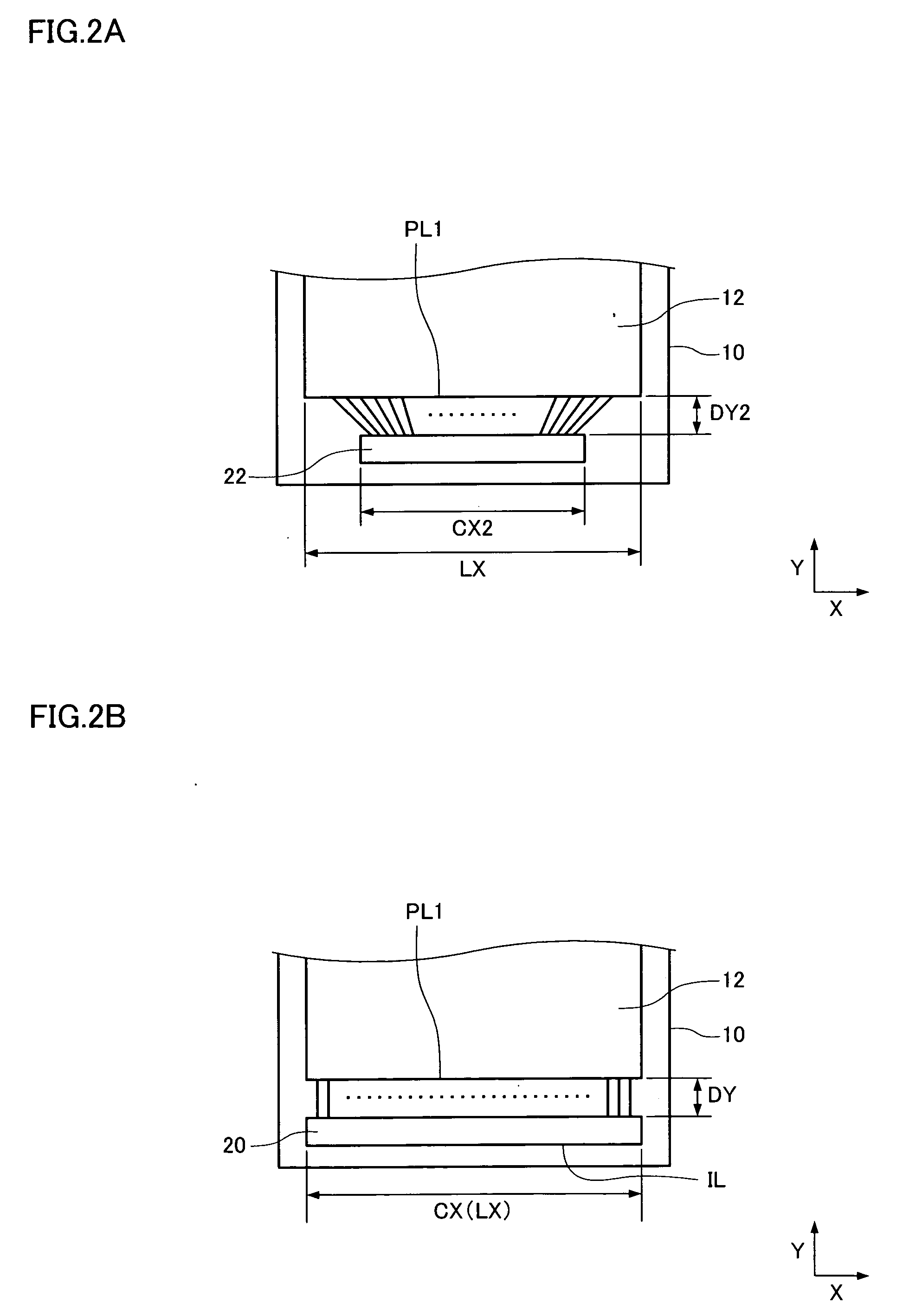

Each of RAM blocks provided in a display memory and disposed along a first direction in which bitlines extend includes a sense amplifier circuit which outputs M-bit data upon one wordline selection (M is an integer larger than 1). At least M memory cells are arranged in each of the RAM blocks along a second direction in which wordlines extend. M sense amplifier cells to which M-bit data read from the M memory cells is input are provided in the sense amplifier circuit. L sense amplifier cells of the M sense amplifier cells are disposed at a position corresponding to L memory cells adjacent in the second direction (L is an integer which satisfies 2≦L<M / 2). When the height of the memory cell in the second direction is denoted by MCY and the height of the sense amplifier cell in the second direction is denoted by SACY, “(L−1)×MCY<SACY≦L×MCY” is satisfied.

Owner:SEIKO EPSON CORP

Integrated circuit device and electronic instrument

An integrated circuit device includes a display memory and a data read control circuit. The data read control circuit controls data reading so that data of pixels corresponding to a plurality of signal lines is read out by N-time reading in one horizontal scan period of a display panel (N is an integer larger than 1). The display memory includes a plurality of sense amplifier cells respectively connected with a plurality of bitlines. L sense amplifier cells (L is an integer larger than 1) respectively connected with the bitlines of L memory cells adjacent in a first direction (wordline direction) in which wordlines extend are disposed along a second direction (bitline direction) in which the bitlines extend.

Owner:SEIKO EPSON CORP

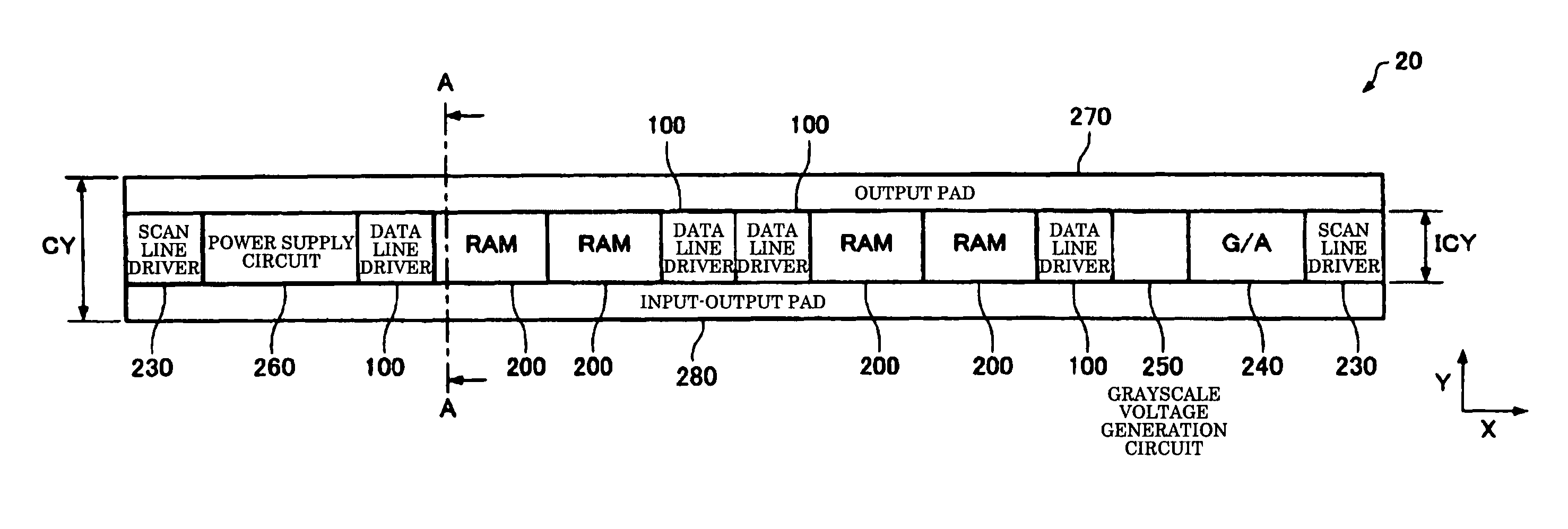

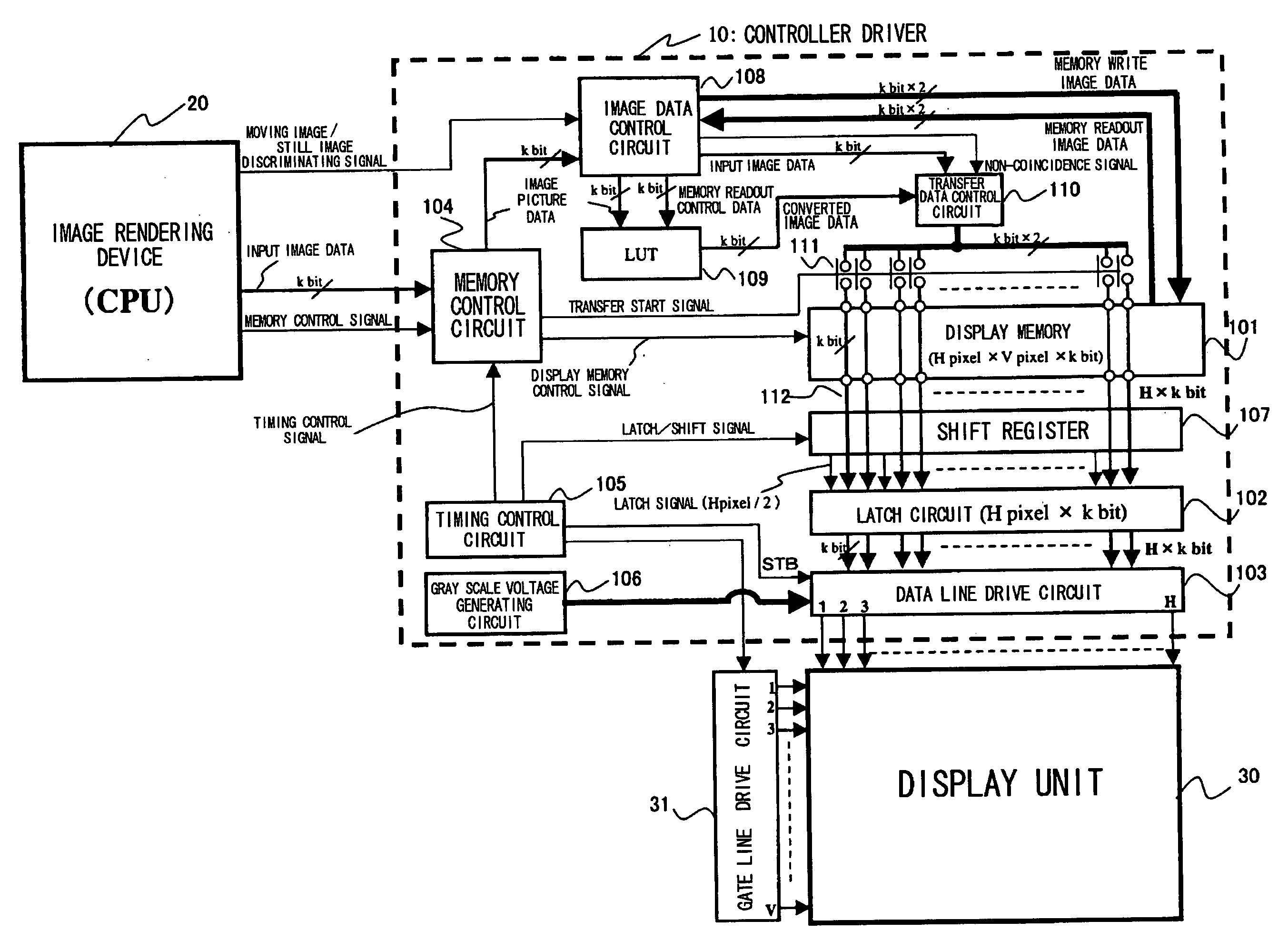

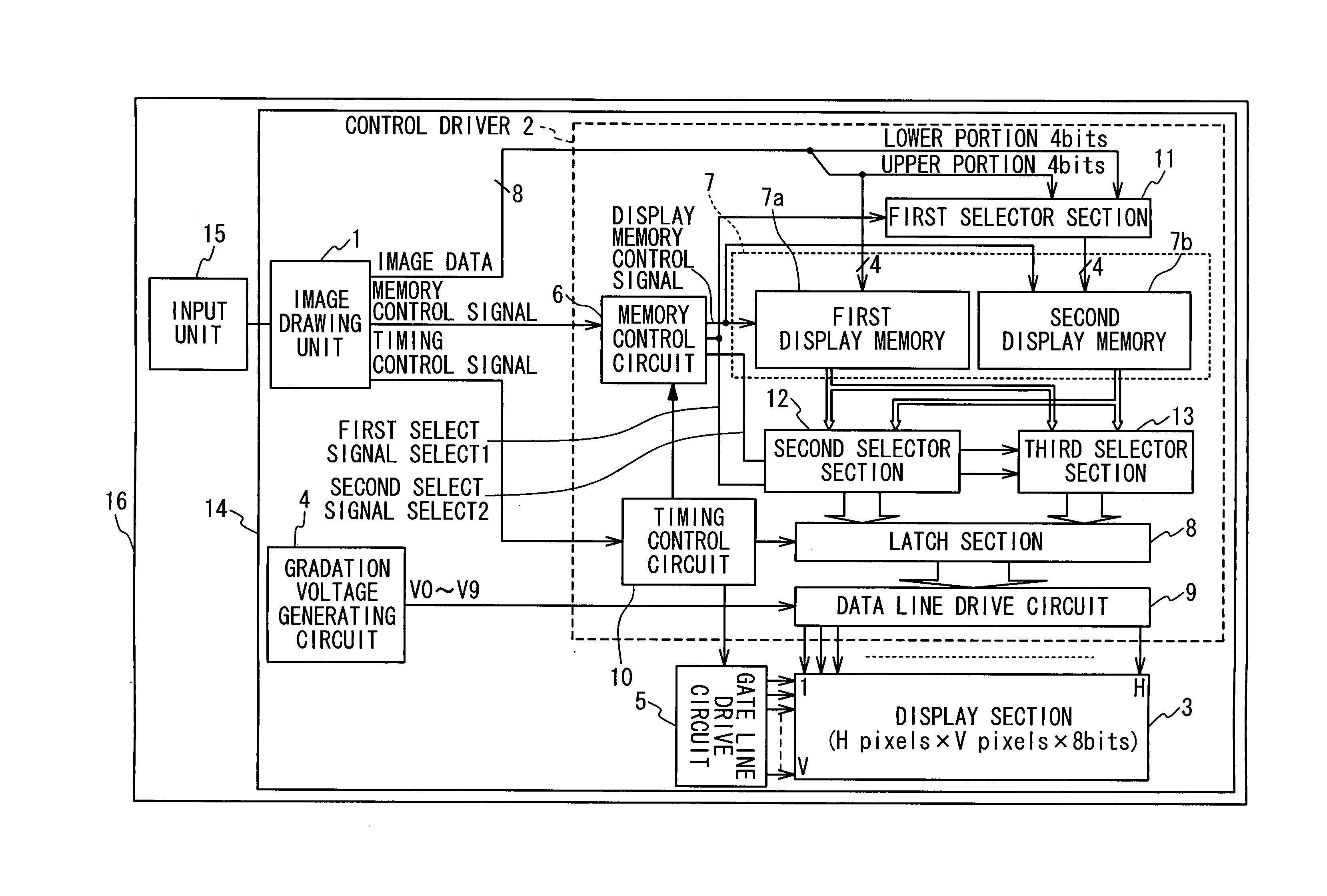

Controller driver and display apparatus

ActiveUS20050253833A1Increase in circuit sizeIncrease consumptionCathode-ray tube indicatorsInput/output processes for data processingData controlShift register

A driving apparatus for over-drive driving includes a display memory, a memory control circuit performing control for receiving input image data supplied from an image rendering device, reading out image data one frame before of the input image data from the display memory and for writing the input image data in the display memory as write image data for the display memory, and a image data control circuit for verifying whether or not the input image data from the memory control circuit coincides with the readout image data one frame before read out from the display memory. The apparatus also includes an LUT for outputting converted image data, a transfer data control circuit for selectively outputting the input image data or the converted image data, and latch circuits for latching image data of one horizontal line equivalent of pixels. A shift register circuit generates latch signal for image data.

Owner:RENESAS ELECTRONICS CORP

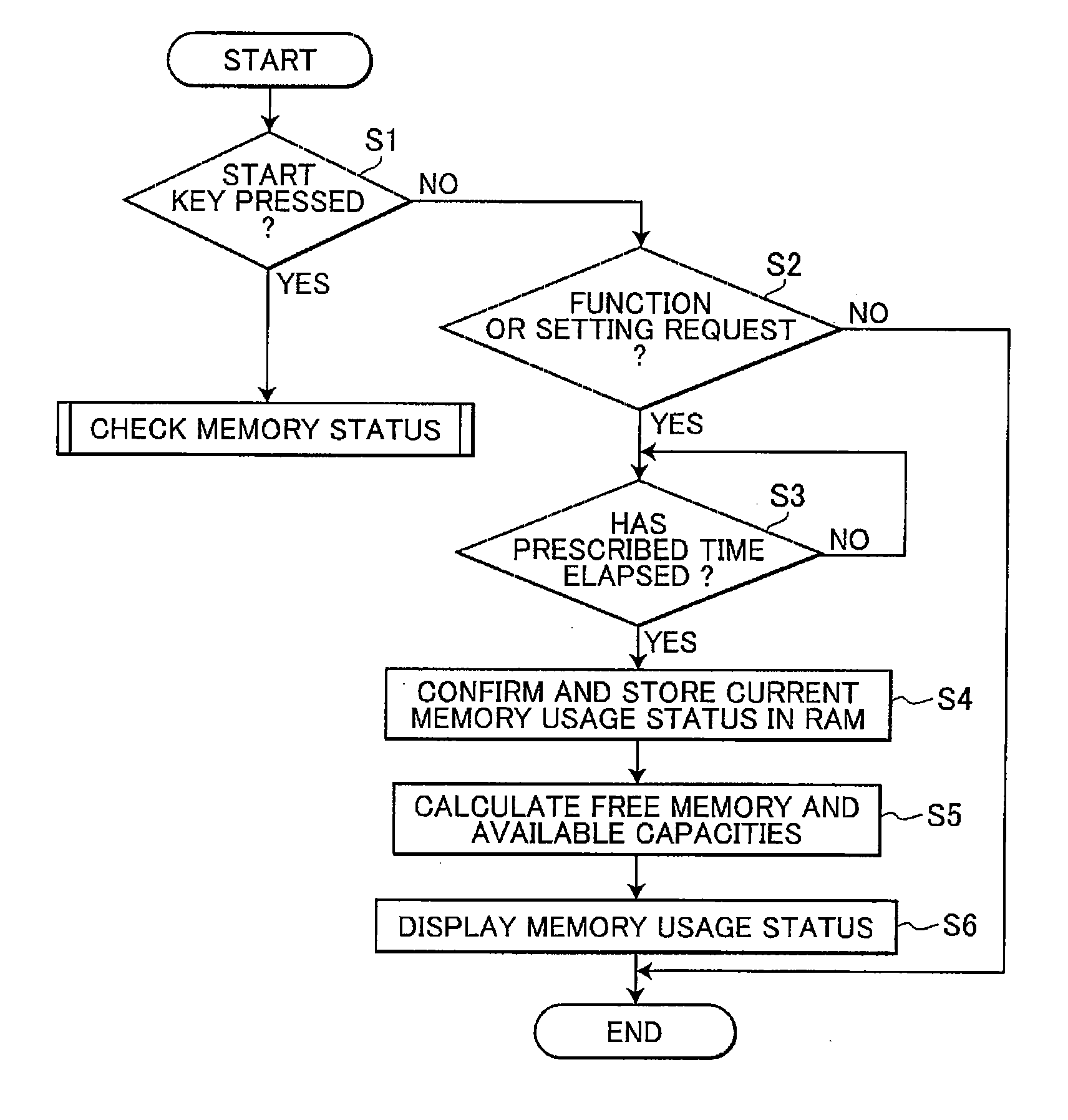

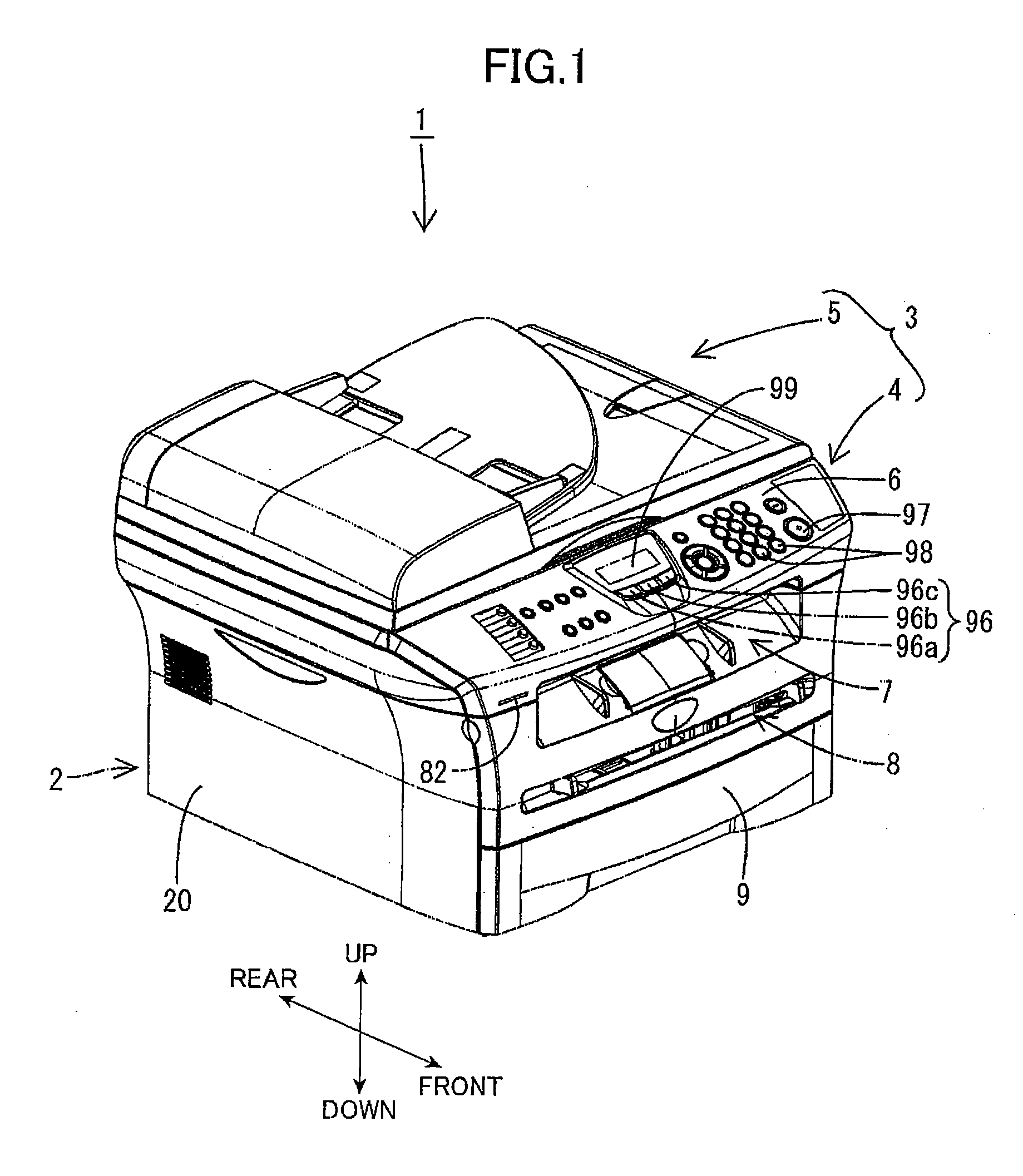

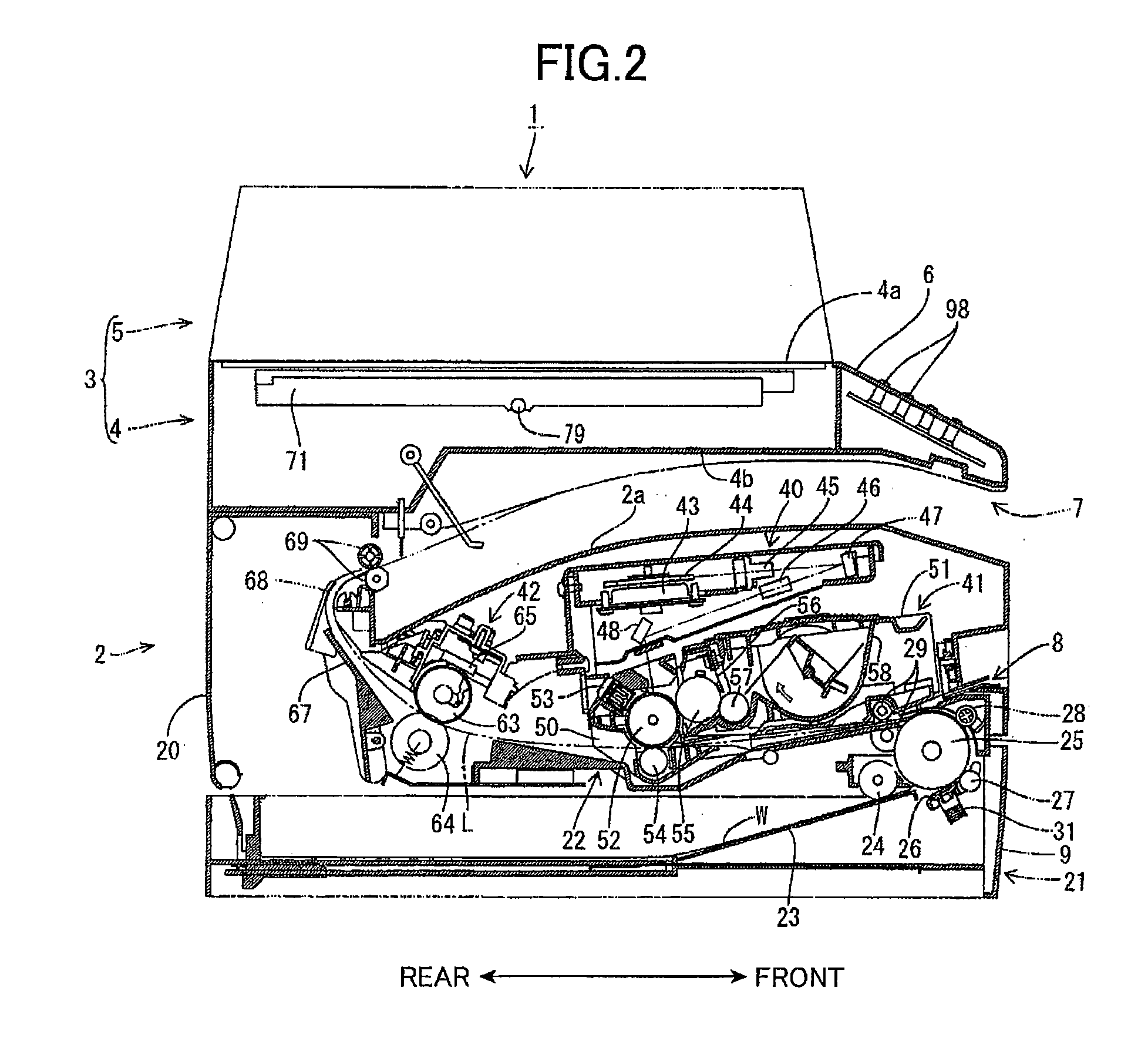

Image-Processing Device

An image-processing device performs a job related to an image processing, having a storage unit, a control unit, and a display unit. The storage unit stores data generated by the job. The storage unit having a storage memory capacity. The control unit determines whether the storage memory capacity is insufficient for processing a new job, while a current job is in process. The control unit restricts the new job if the storage memory capacity is insufficient for processing the new job. The display unit displays memory usage status of the storage unit and a memory requirement to process the new job.

Owner:BROTHER KOGYO KK

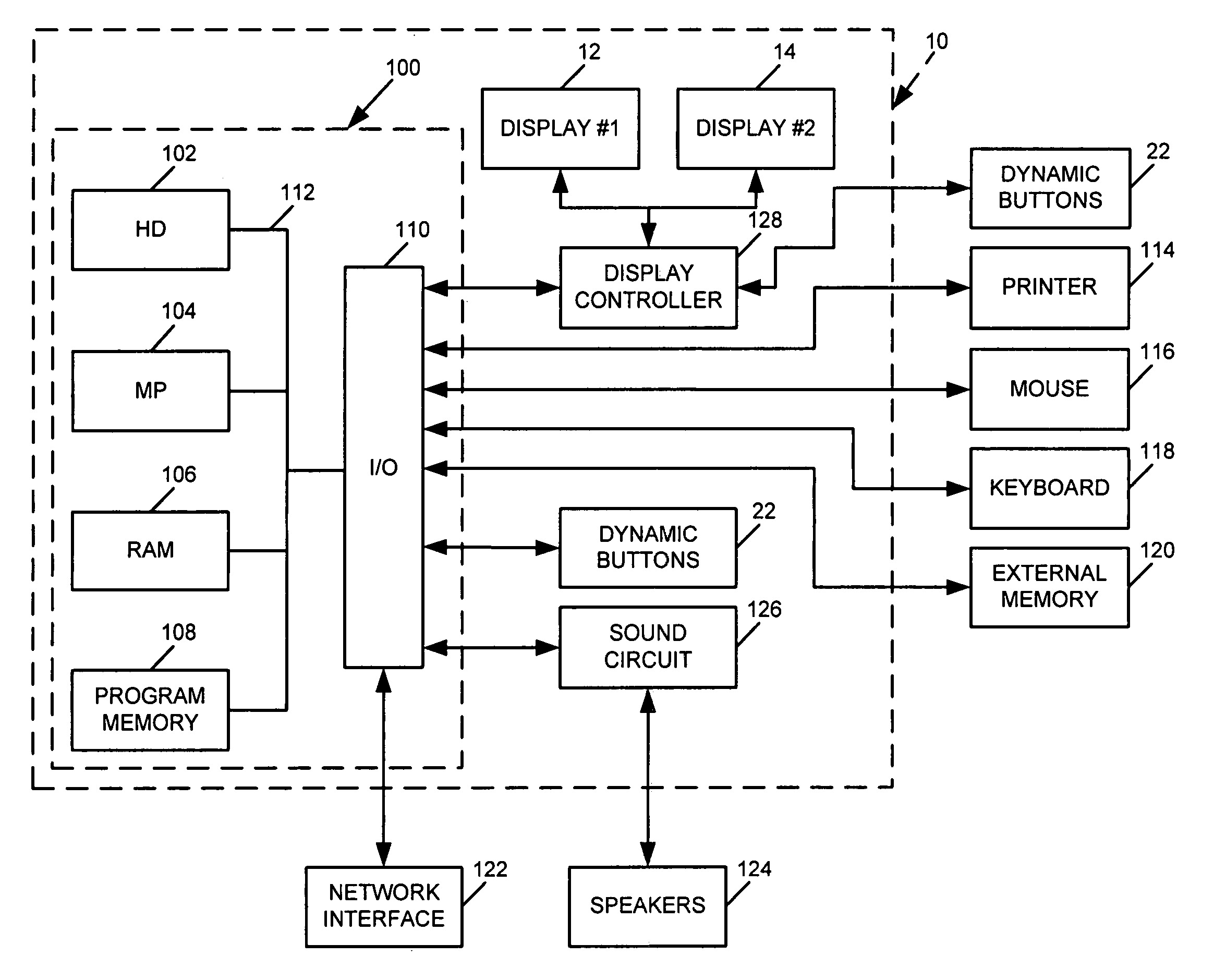

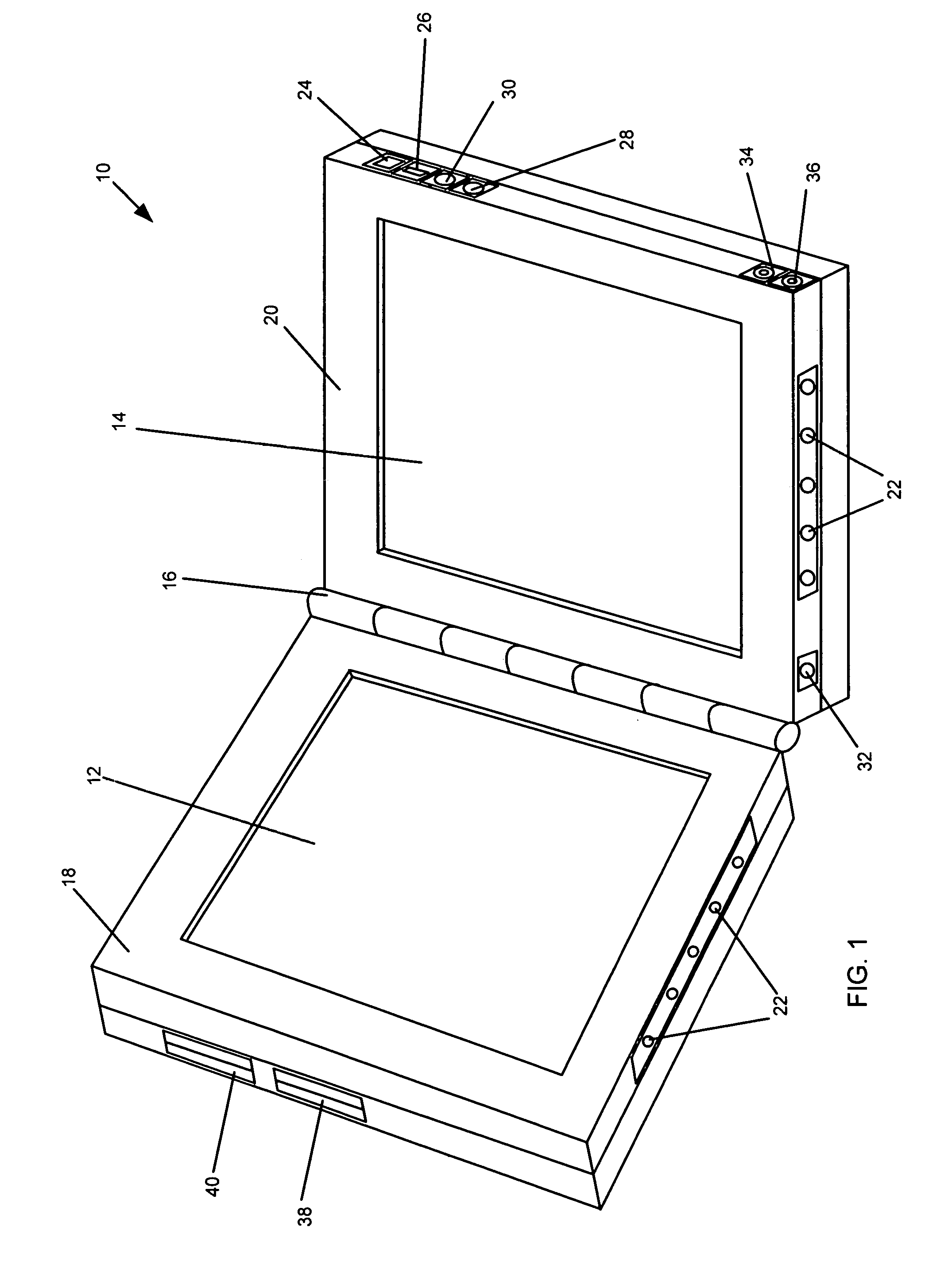

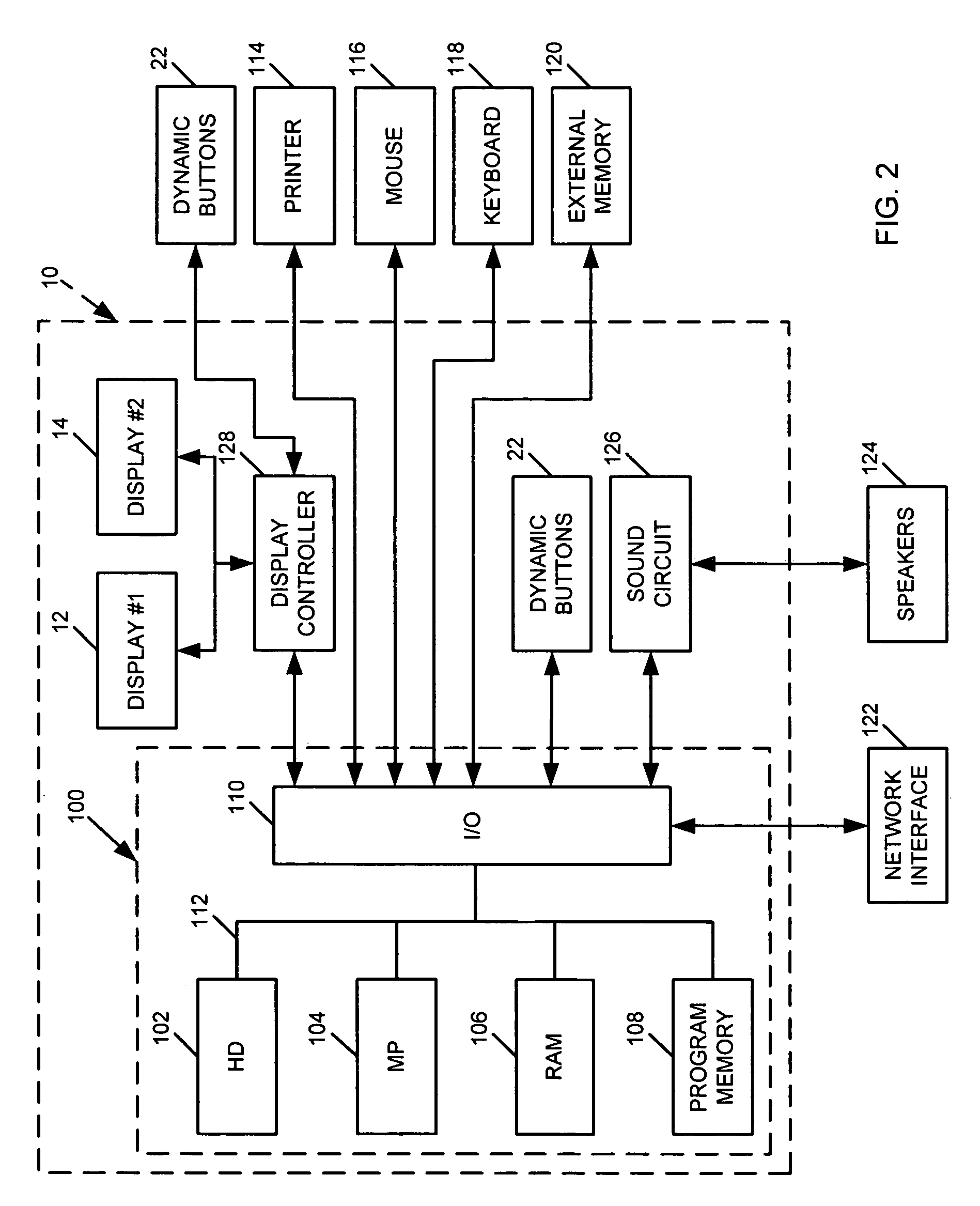

Computer display apparatus

A computer display apparatus includes first and second display units operatively coupled to a display controller. The display controller receives imaging instructions for images and display mode instructions for displaying the images, and causes the display units to independently generate images from the imaging instructions according to the display mode instructions. The display controller may include a display processor programmed to generate pixel data according to the imaging instructions, and first and second refresh outputs programmed to independently generate image displays from the manipulated pixel data on the first and second display units in first and second display modes, respectively. A display re-mapper may manipulate the pixel data according to display mode instructions. A display memory fetcher may manipulate pixel data according to display mode instructions in response to a request for pixel data from the first and second refresh outputs independently.

Owner:ZHENG CAPITAL

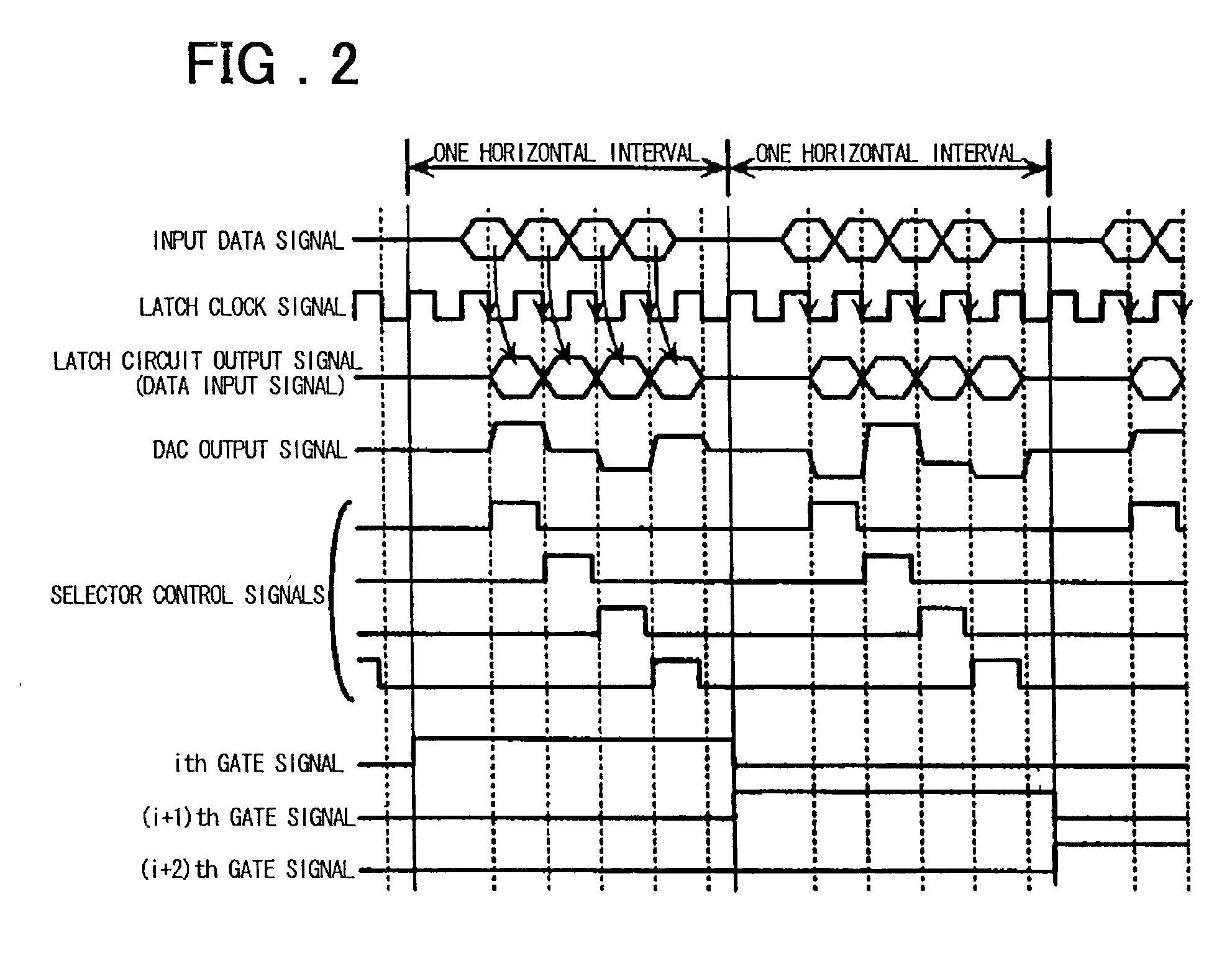

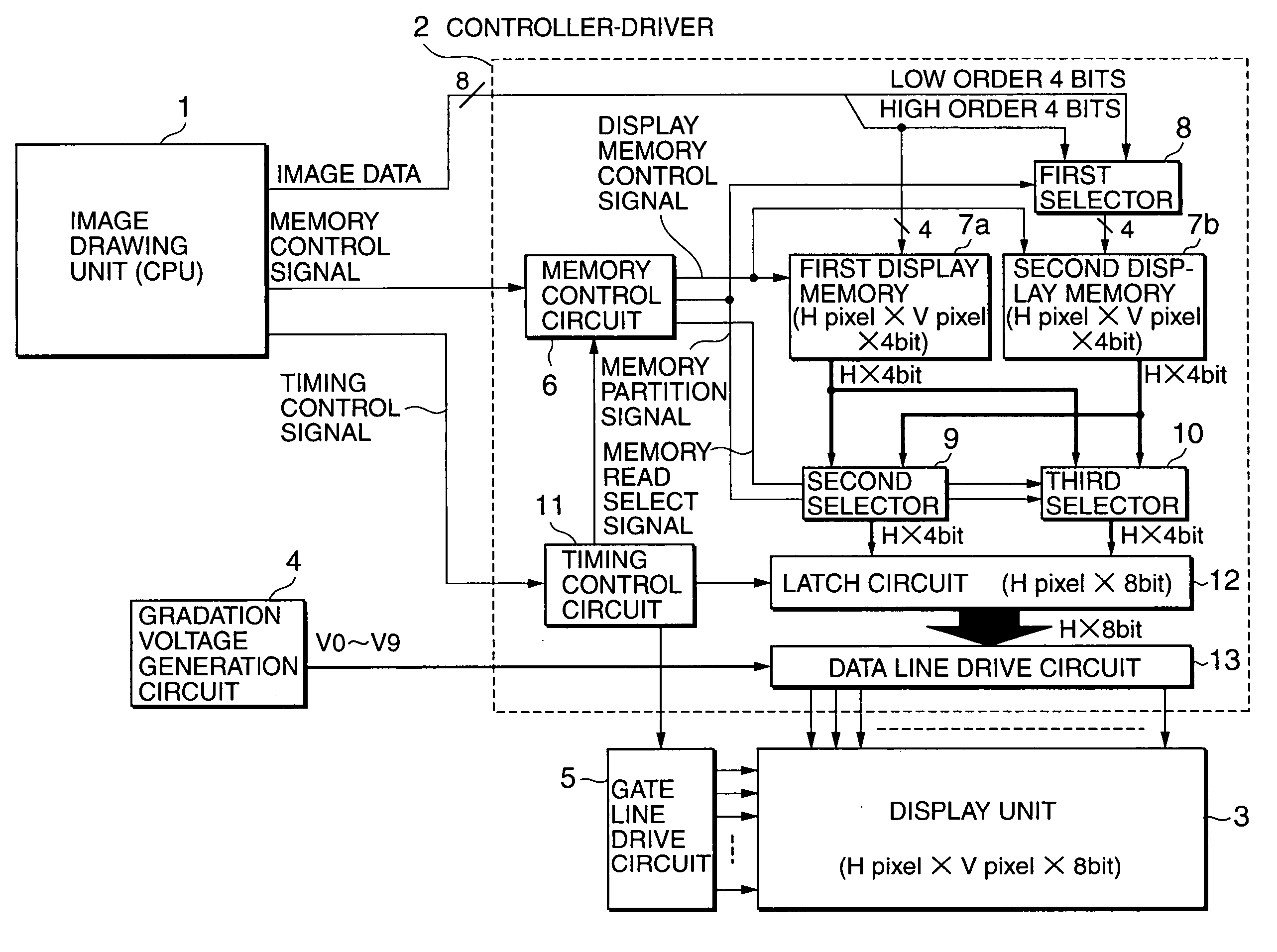

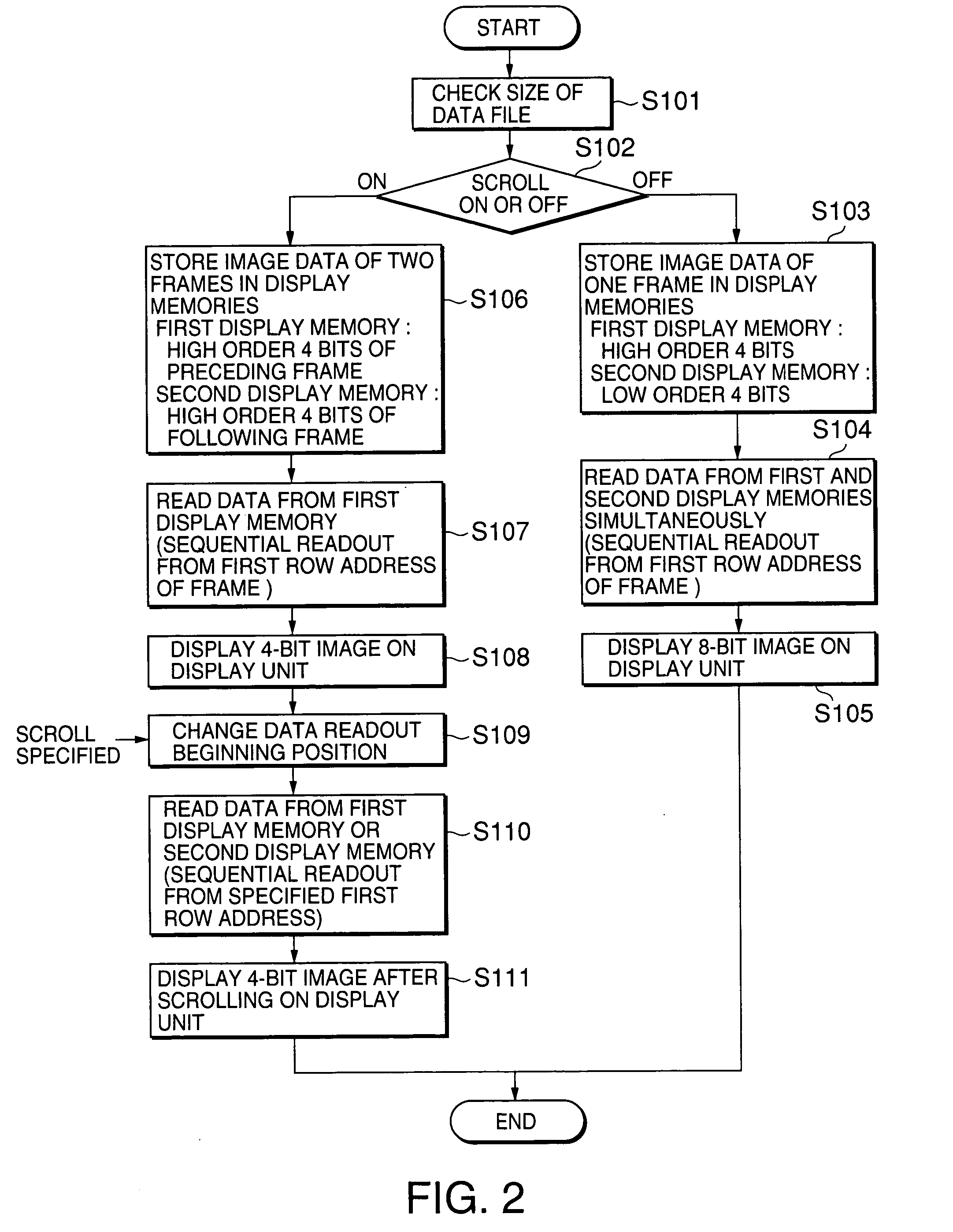

Controller-driver, display device, and display method

InactiveUS20040080521A1Memory adressing/allocation/relocationDigital computer detailsImage typeImaging data

A controller-driver, a method of driving the controller-driver, and a method of processing image data enabling scroll or other various functions without adding a storage capacity of a display memory nor increasing power consumption. A built-in display memory having a capacity of one frame (H pixelsxV pixelsxthe number of bits) is partitioned into a plurality of memories according to an image type. High order bits are then stored in a first display memory 7a and high order bits of the next frame or low order bits are stored in a second display memory 7b by using a first selector 8 to a third selector 10 controlled by a memory control circuit 6 before they are read out. Thereby, high-level image data of one frame can be displayed when the scroll function is not used and image data of a plurality of frames can be displayed without accessing an image drawing unit 1 when the scroll function is used, thereby reducing power consumption.

Owner:RENESAS ELECTRONICS CORP

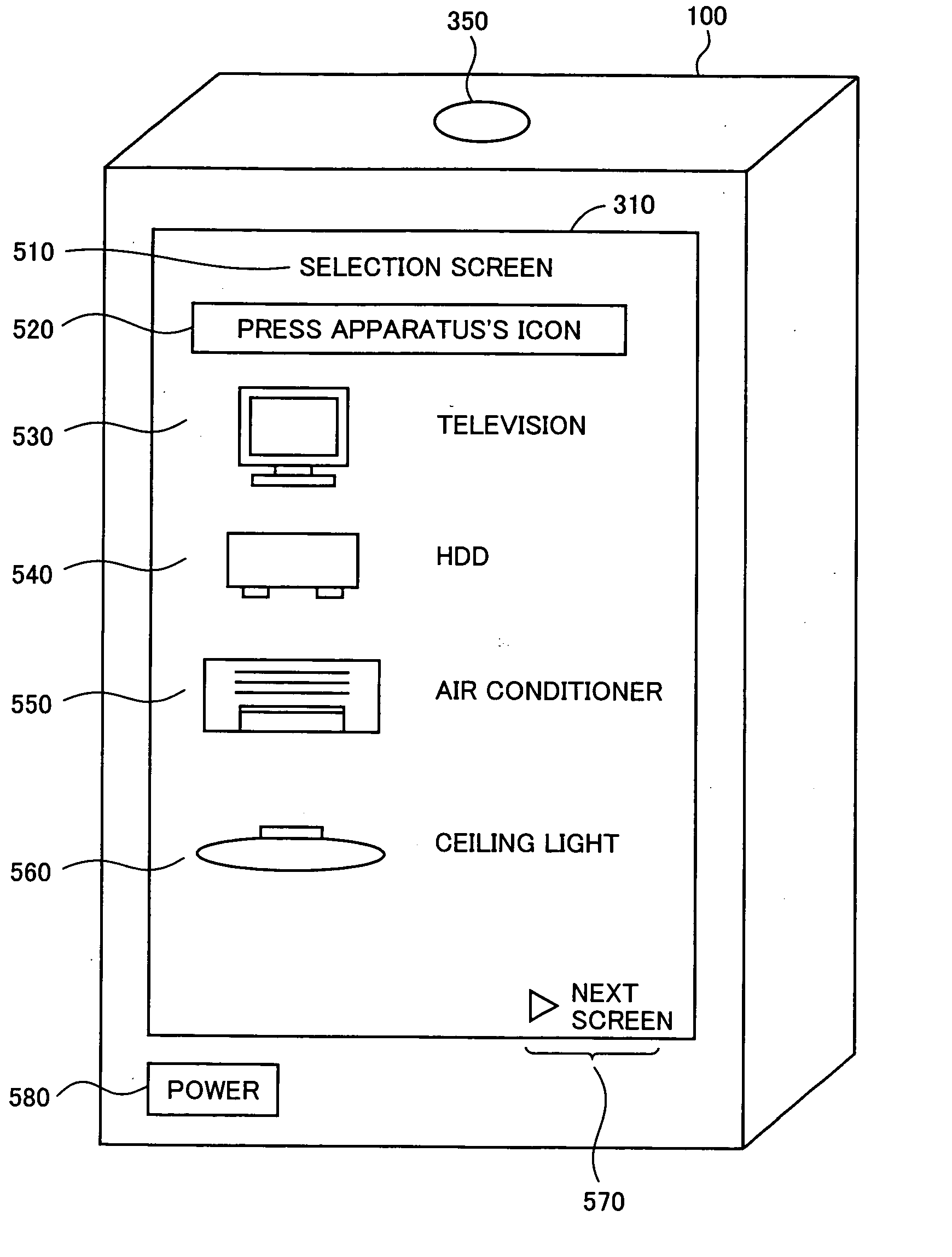

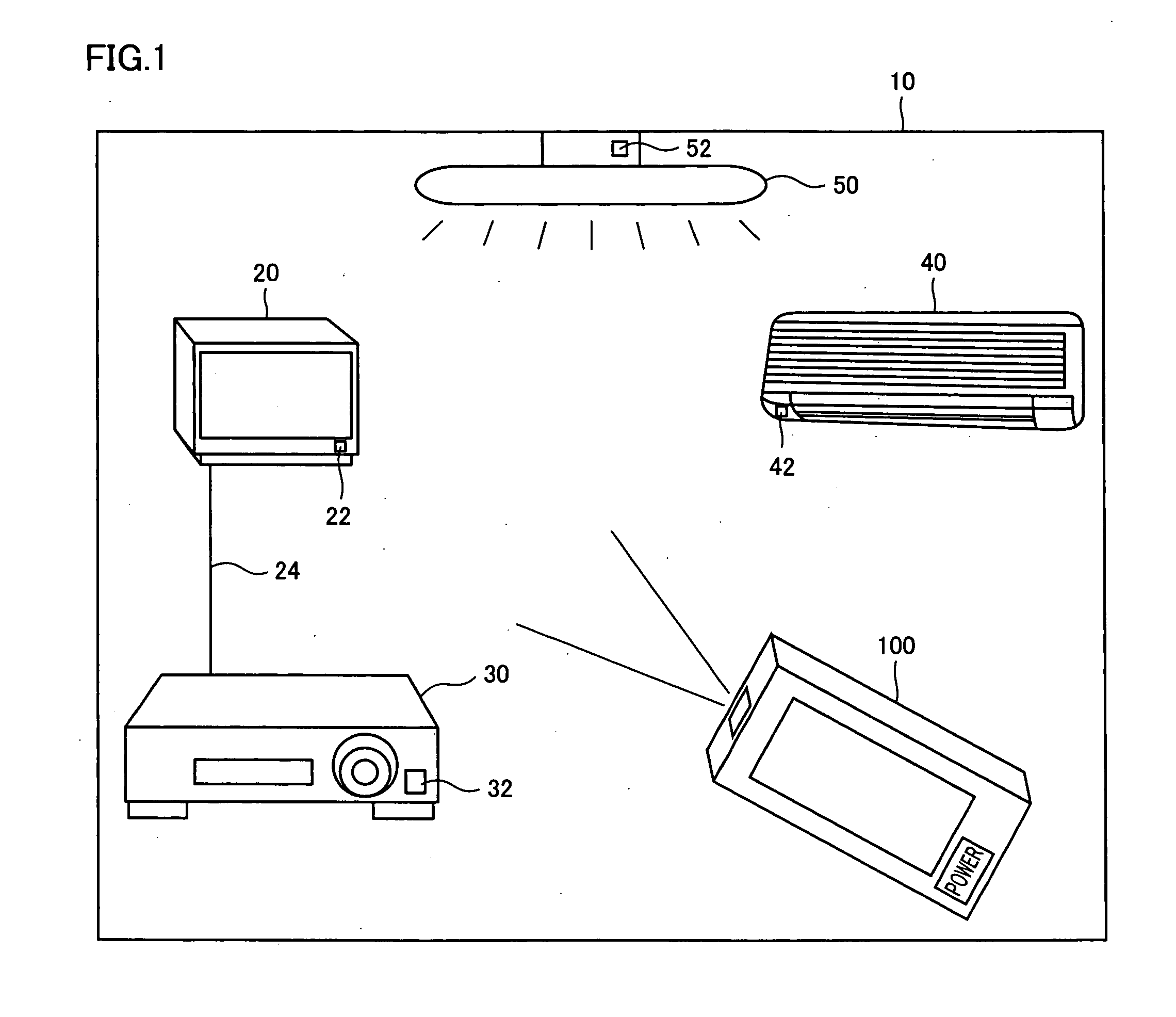

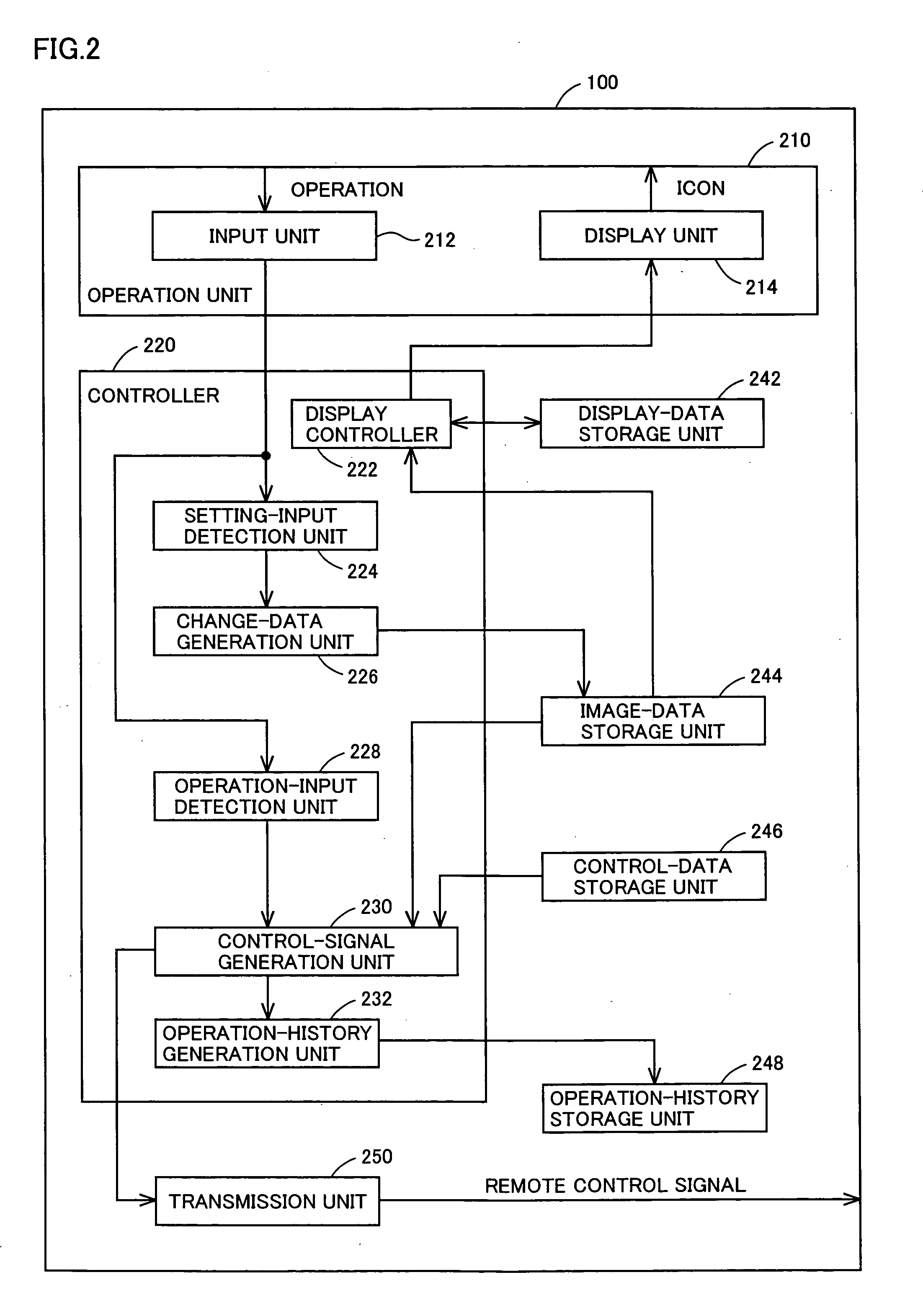

Remote controller

ActiveUS20070146160A1Easy to operateReduce stepsTelevision system detailsElectric signal transmission systemsControl signalElectrical battery

A remote controller allowing a user to change settings is provided. The remote controller includes a touch panel, a control circuit, a screen display memory, a setting data memory, a control data memory, an infrared transmission unit, and a battery. The control circuit includes a screen-display control circuit for displaying an image provided in advance for controlling the operation of a specific apparatus, a pressed-area detection circuit for detecting pressing in the display area of touch panel, an instructed-operation detection circuit for detecting the instruction of an operation, a display-data generation circuit for generating image data for displaying icons in the display area of touch panel, and a control-signal generation circuit for generating a signal for controlling the operation of the apparatus.

Owner:DISPLAY INNOVATIONS INC

GPU acceleration method of CT image reconstruction

InactiveCN101283913AReduce transmissionReduce transfer speedComputerised tomographsTomographyCt technologyReconstruction method

The invention relates to a CT image reconstruction method based on GPU hardware acceleration, which belongs to the field of X-ray CT technology. The software portion of the invention generally comprises a GPU-based CT data preprocessing module, a GPU-based CT data filter module, a GPU-based CT orthogonal protection module, and a GPU-based CT image reconstruction and back projection module. The method can achieve acceleration of CT image reconstruction algorithm by using GPU hardware, and the reconstructed portion and the data processing portion are achieved on GPU. The invention provides a segmentation processing method used for processing larger data, which aims to solve the prior problems of insufficient display memory of GPU and low data transmission speed from memory to the display memory. Different from prior methods, the segmentation processing method only needs a portion of projection data desired for each segment to be reconstructed, thus reducing data transmission and improving the entire reconstruction speed.

Owner:CAPITAL NORMAL UNIVERSITY

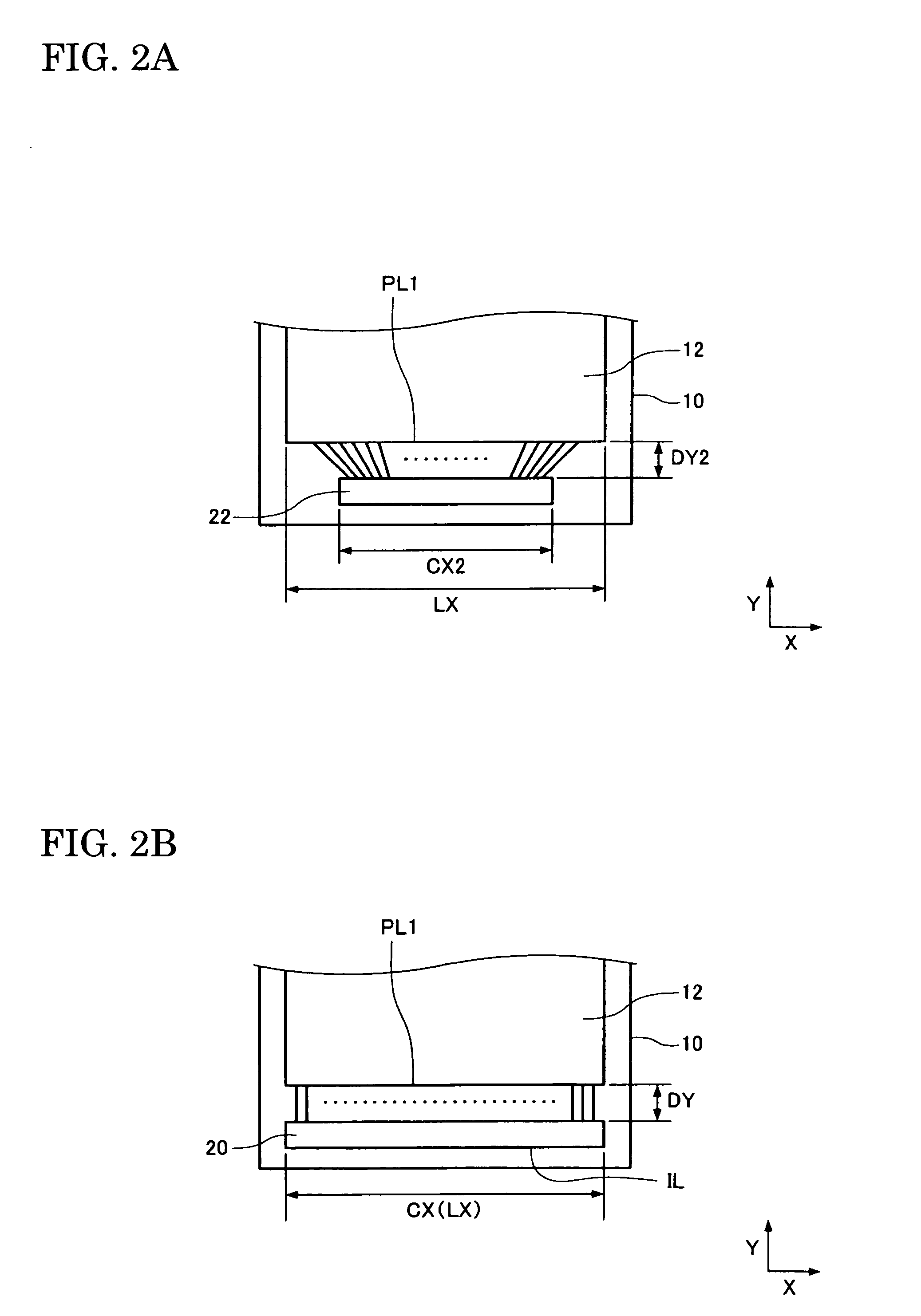

Integrated circuit device and electronic instrument

InactiveUS20070013074A1Static indicating devicesSemiconductor/solid-state device detailsMetal interconnectElectronic instrument

An integrated circuit device having a display memory, wherein a plurality of first power supply interconnects for supplying a first power supply voltage to a plurality of memory cells are provided in a metal interconnect layer in which a plurality of bitlines are formed; wherein a second power supply interconnect for supplying a second power supply voltage to the memory cells is provided in a metal interconnect layer in which a plurality of wordlines are formed, the second power supply voltage being higher than the first power supply voltage; wherein a plurality of bitline protection interconnects are formed in a layer above the bitlines, each of the bitline protection interconnects at least partially covering one of the bitlines in a plan view; and wherein a third power supply interconnect for supplying a third power supply voltage to circuits of the integrated circuit device other than the display memory is provided in a layer above the bitline protection interconnects, the third power supply voltage being higher than the second power supply voltage.

Owner:138 EAST LCD ADVANCEMENTS LTD

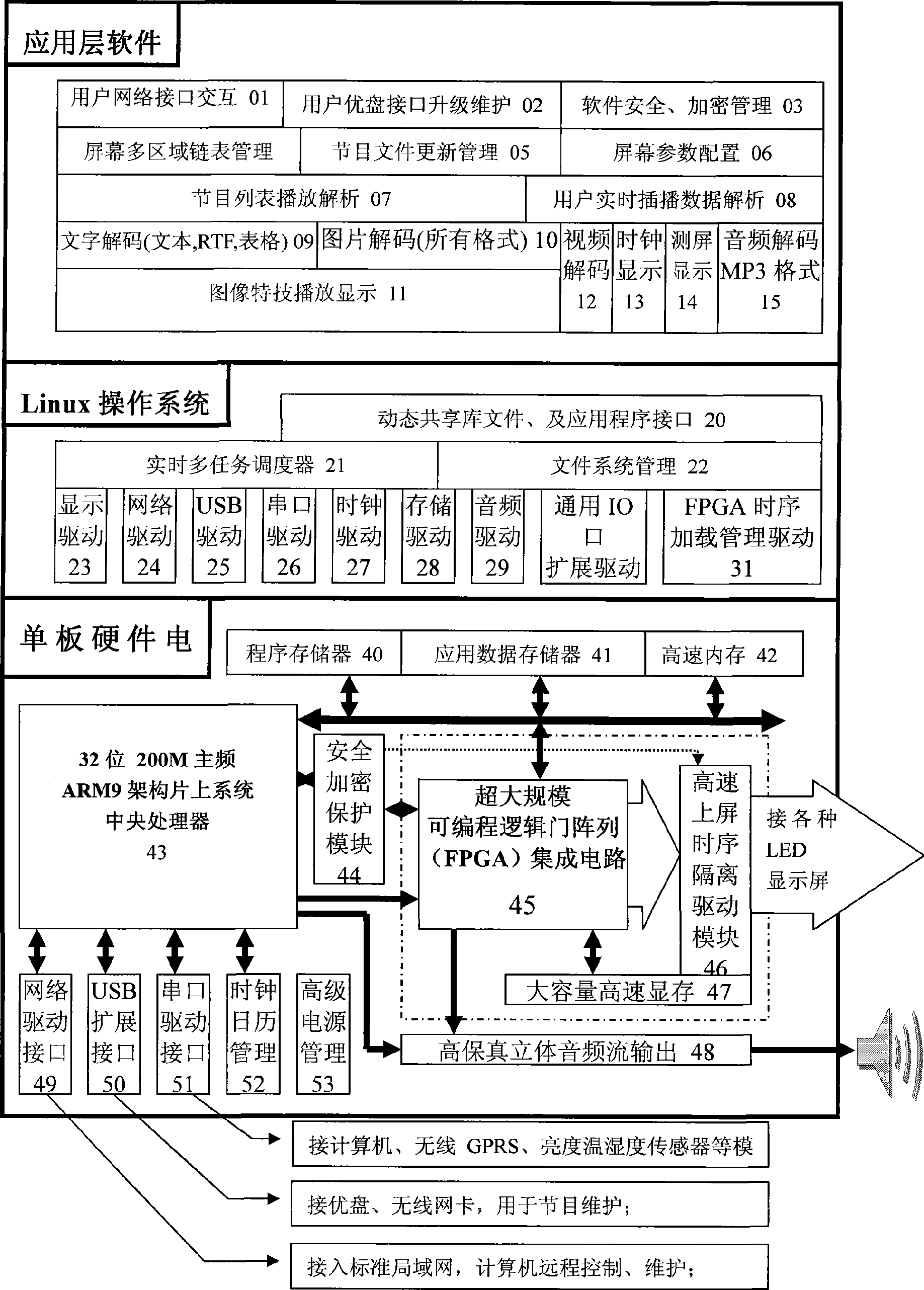

Embedded multimedia LED display screen control system

InactiveCN101447171ASuitable for a wide range of occasionsFreedom to adapt to the occasionCathode-ray tube indicatorsInput/output processes for data processingOperational systemHigh speed memory

The invention relates to an embedded multimedia LED display screen control system, comprising a single board hardware circuit which comprises a program memory, an application data memory, a high-speed memory, a CPU, a safety encrypting protection module, an ultra-large scale field programmable gate array (FPGA) integrated circuit, a high-speed upper screen time-sequence separation driving module, a large-capacity high-speed display memory, a high fidelity solid audio stream output module, a network driving interface, a USB extension interface, a serial driving interface, a clock calendar management module, and a high-class power management module. The embedded multimedia LED display screen control system employs mature and advanced 32-bit SOC (system on chip) high-speed processor and millions of ultra-large scale programmable integrated circuit FPGA as LED display scanning time-sequence signal generators, uses Linux real-time multi-task operation system with open sound code as for software to integrate electrons, software, memory, communication, graphs and images, audio / video decoding, and the like into a whole, and brings qualitative leap for the LED display system.

Owner:上海熙讯电子科技有限公司

Controller driver and display apparatus using the same

ActiveUS7292235B2Without increasing consumption powerIncrease display capacityTelevision system detailsColor signal processing circuitsDisplay memoryComputer graphics (images)

A control driver includes a display memory control section which generates a first process control signal when image data includes only first image data which has a pixel size equal to or smaller than that of a display section, and generates a second process control signal when the image data includes first image data and second image data and the first image data has a pixel size equal to that of the display section, and a display memory section which stores upper and lower portions of the first image data as first and second portions of display data in response to the first process control signal, and stores the upper portion of the first image data and an upper portion of the second image data as the first and second portions of the display data in response to the second process control signal. The display data is displayed on the display section.

Owner:RENESAS ELECTRONICS CORP

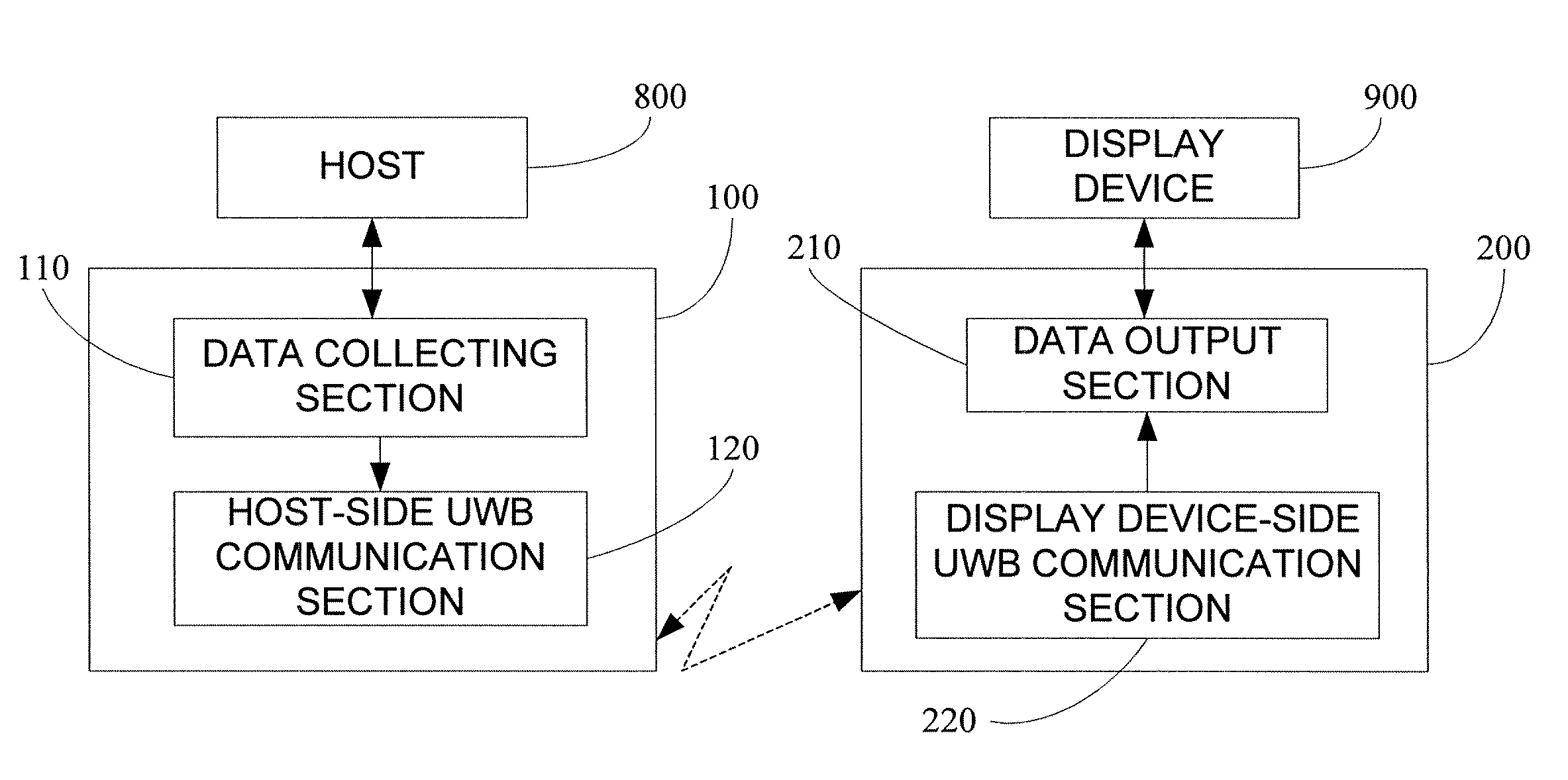

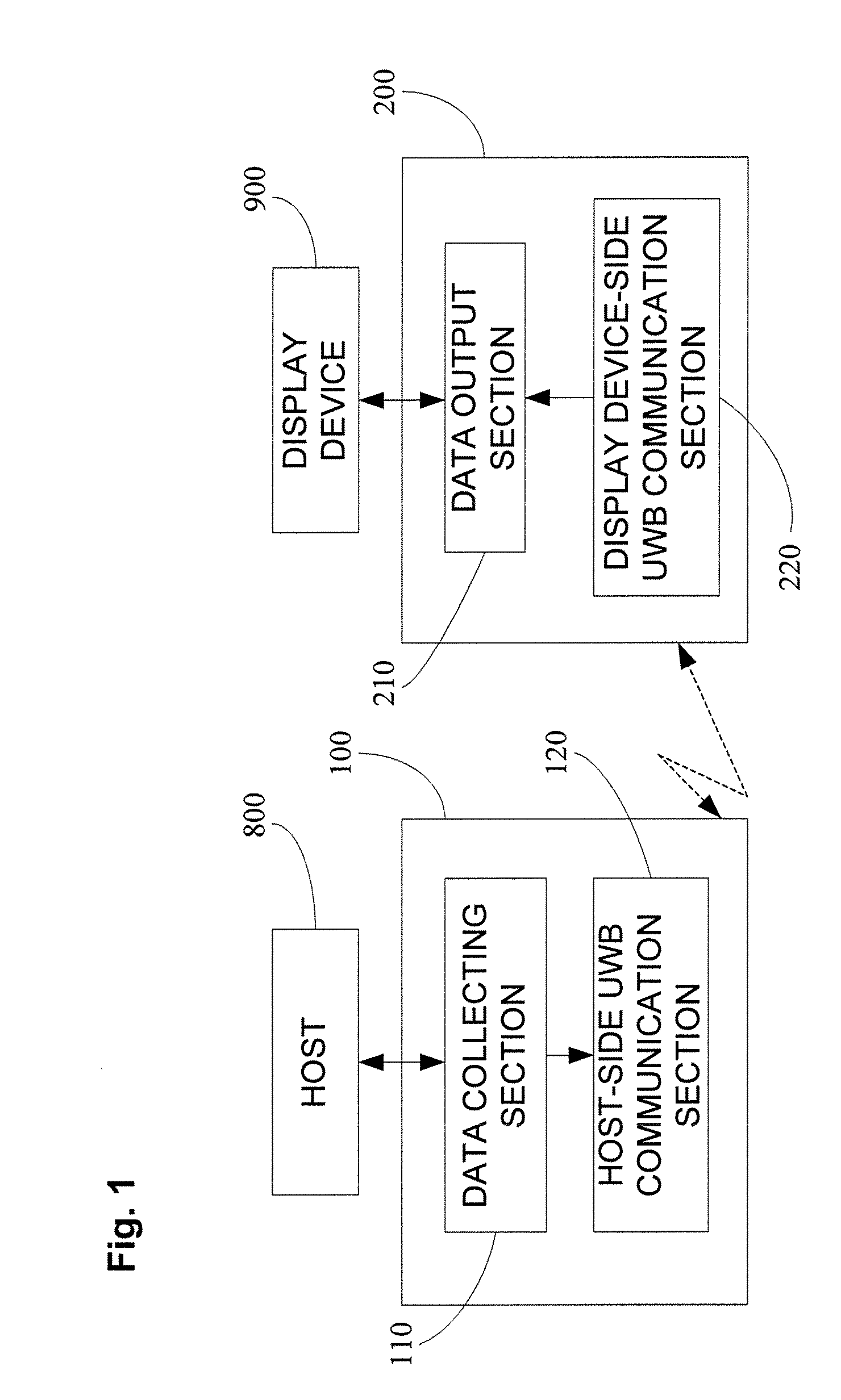

Wireless display system and method thereof

ActiveUS20090029647A1Reduce workloadCathode-ray tube indicatorsClosed circuit television systemsComputer hardwareWireless transmission

A wireless display system is disclosed comprising a host-side data communication apparatus connected to a host and configured to acquire media data containing at least display data from the hardware of said host, generate data message and transfer the data message wirelessly, and a display-device side data communication apparatus configured to receive the data message transferred wirelessly, interpret it into media data and then output to a display device. With the system of the present invention, CPU does not need to execute a screen-capturing program to acquire display information from a display memory unit and thus has a reduced work load, and transmission delay can also be reduced.

Owner:LENOVO (BEIJING) CO LTD

Integrated circuit device and electronic instrument

InactiveUS20070013685A1Cathode-ray tube indicatorsDigital storageMetal interconnectElectronic instrument

An integrated circuit device having a display memory, wherein a plurality of first power supply interconnects VSSL for supplying a first power supply voltage VSS to memory cells MC are formed in a metal interconnect layer in which a plurality of wordlines WL are formed; and wherein a plurality of second power supply interconnects VDDL for supplying a second power supply voltage VDD to the memory cells are formed in another metal interconnect layer in which a plurality of bitlines BL are formed, the second power supply voltage VDD being higher than the first power supply voltage VSS. A plurality of bitline protection interconnects SHD are formed in a layer above the bitlines BL, and each of the bitline protection interconnects SHD at least partially covers one of the bitlines BL in a plan view. A third power supply interconnect GL for supplying a third power supply voltage to circuits other than the display memory are formed in a layer above the bitline protection interconnects SHD, the third power supply voltage being higher than the second power supply voltage VDD.

Owner:138 EAST LCD ADVANCEMENTS LTD

Integrated circuit device and electronic instrument

An integrated circuit device having a display memory which stores data for at least one frame among the data displayed in a display panel which has a plurality of scan lines and a plurality of data lines. The display memory includes a plurality of wordlines, a plurality of bitlines, a plurality of memory cells, and a data read control circuit. The data read control circuit controls data reading so that data for pixels corresponding to a plurality of signal lines is read out by N times reading in one horizontal scan period of the display panel (N is an integer larger than 1).

Owner:SEIKO EPSON CORP

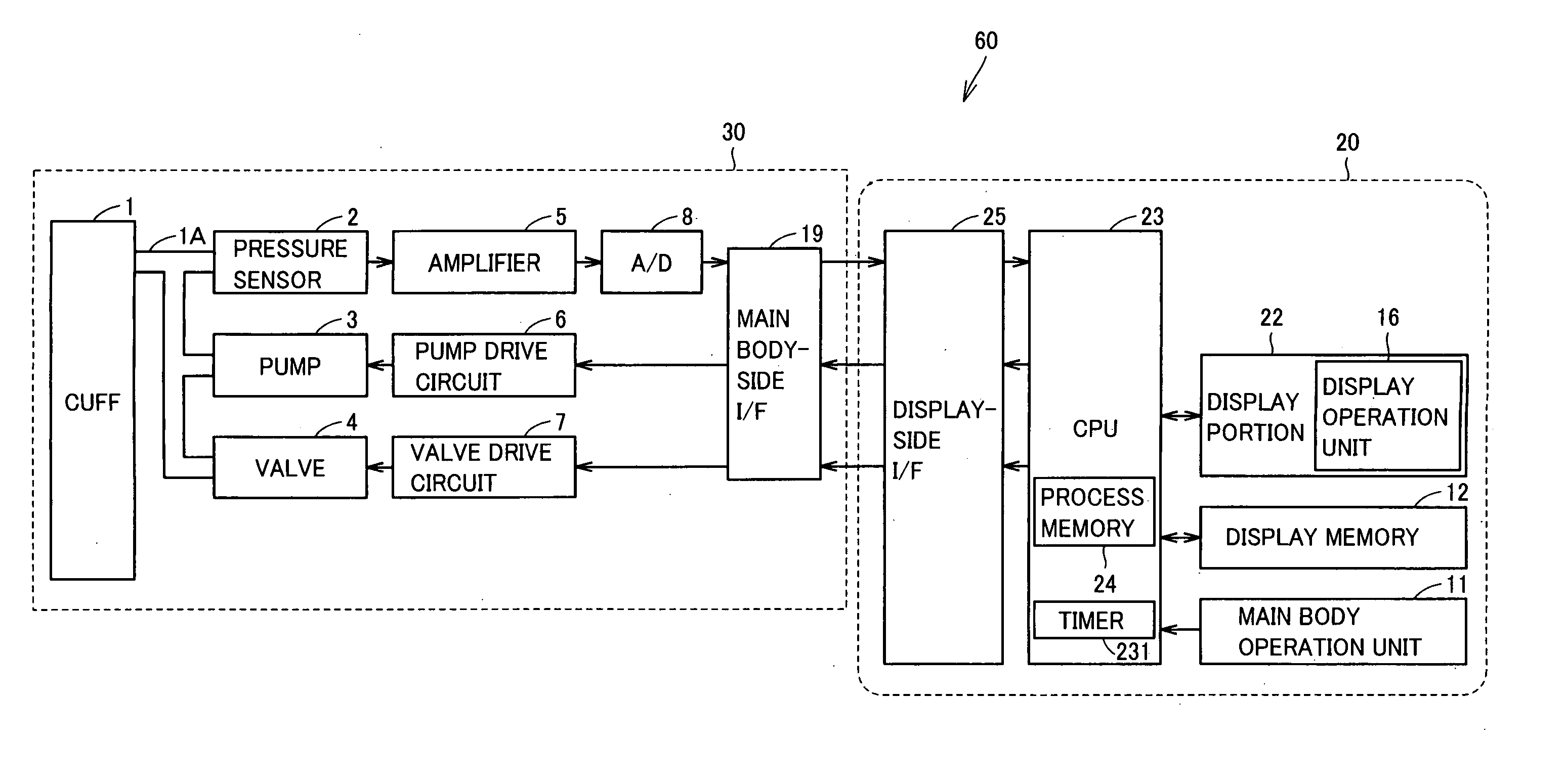

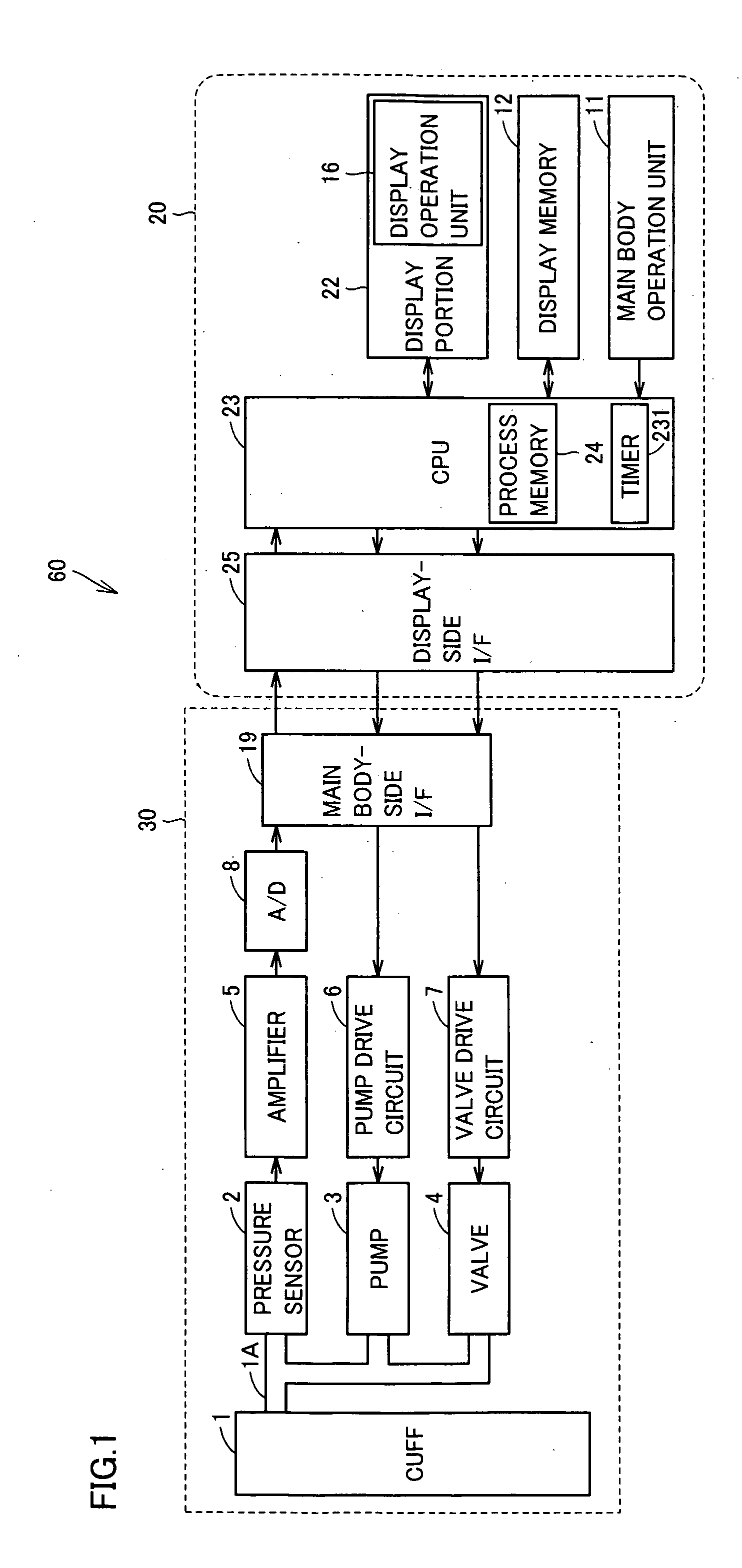

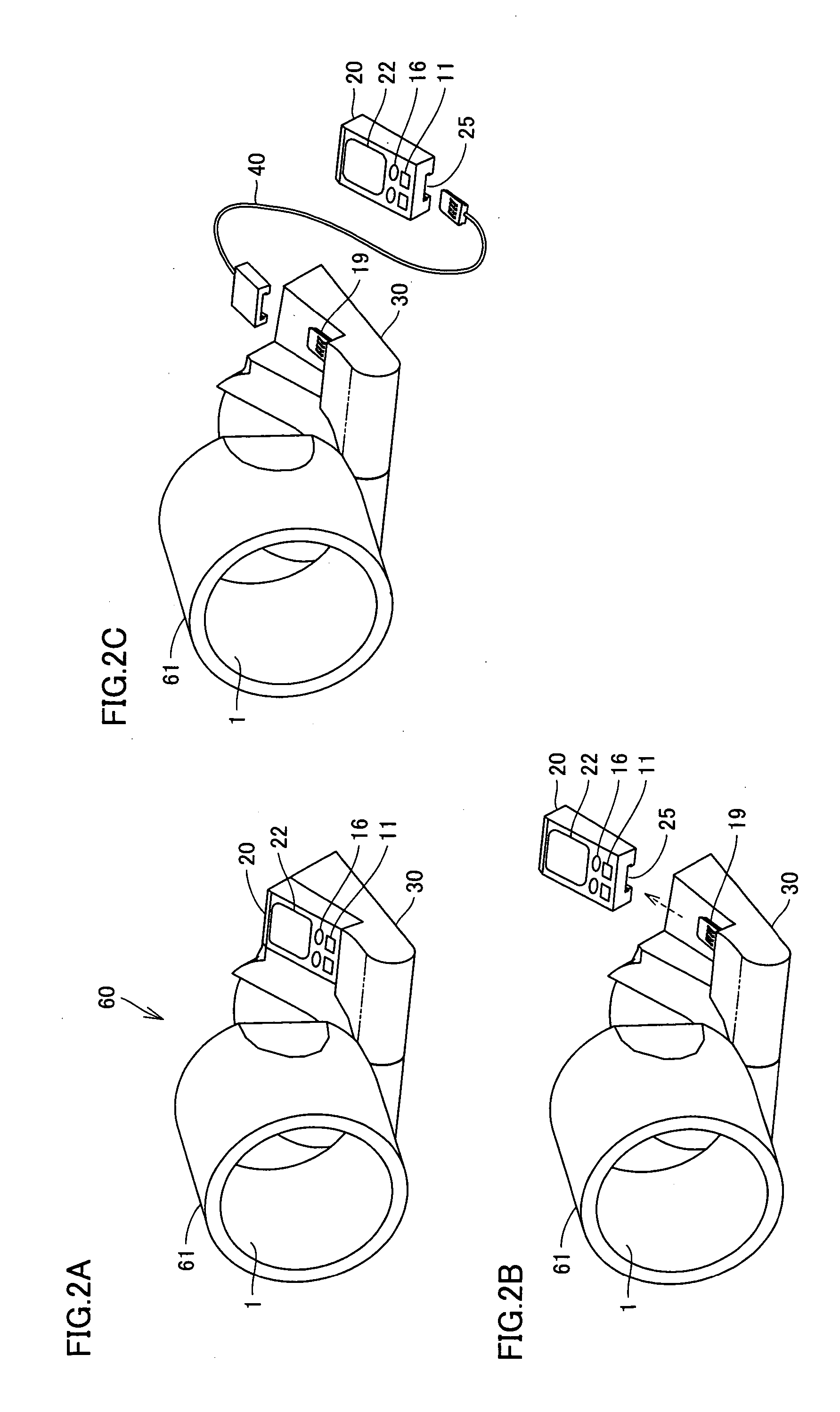

Blood pressure measurement device storing measurement data

InactiveUS20050187484A1Improve practicalitySmall and lightEvaluation of blood vesselsCatheterMeasurement deviceBlood pressure

A blood pressure measurement device includes a fixed main body unit and a removable display unit. The main body unit includes a cuff mounted on a region for measurement of a living body, a control unit including a CPU for measuring a blood pressure with adjusting a pressure of the cuff, and a main body operation unit operated by a subject to externally provide instructions for a measurement operation of the control unit. The display unit includes a display memory storing data of the measurement with the control unit, a display portion displaying measurement data in the display memory, and a display operation unit operated by a subject to externally provide instructions for a display operation of the display portion. A measurement result stored in the display memory of the removable display unit can be displayed on the display portion by operating the display operation unit when the display unit is removed from the main body unit.

Owner:OMRON HEALTHCARE CO LTD

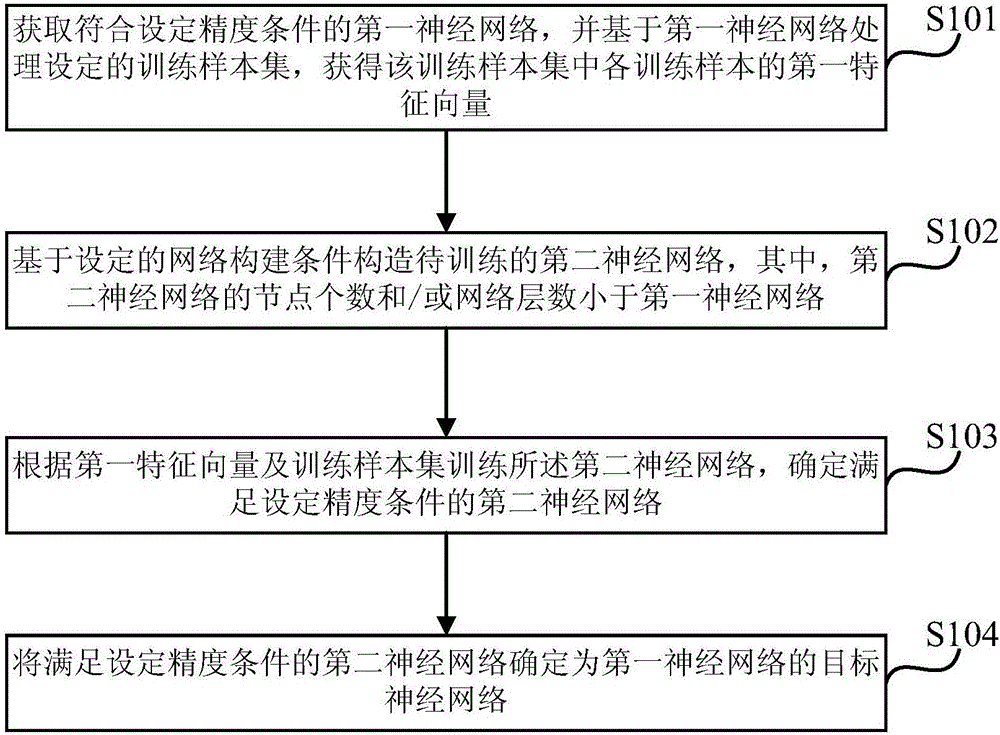

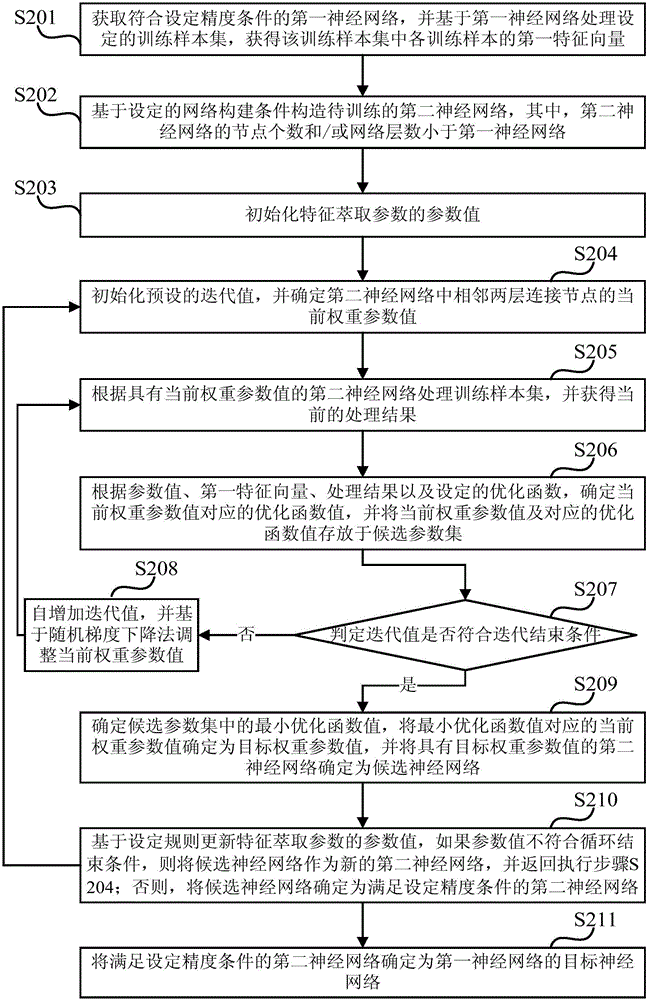

Optimization method and device for neural network

InactiveCN106709565AAchieve optimizationSpeed up recognition processingNeural architecturesNeural learning methodsDisplay memoryMachine learning

The embodiments of the invention disclose an optimization method and device for a neural network. The method comprises the steps of: acquiring a first neural network satisfying a set precision condition, and processing a training sample set based on the first neural network to obtain a first feature vector of each training sample in the training sample set; constructing second neural networks to be trained based on a set network construction condition; training the second neural networks according to the first feature vectors and the training sample set, and determining a second neural network satisfying the set precision condition; and determining the second neural network as a target neural network of the first neural network. By using the method, another newly-constructed small-scale neural network can be directly trained and learnt according to the optimization condition and then determined as a target optimization network of the neural network to be optimized, so that when feature recognition is performed based on the optimized neural network, the purposes of improving the recognition speed, shortening the recognition time and reducing the spatial occupation of a memory, a running memory, a display memory and the like can be fulfilled.

Owner:GUANGZHOU SHIYUAN ELECTRONICS CO LTD

Integrated circuit device and electronic instrument

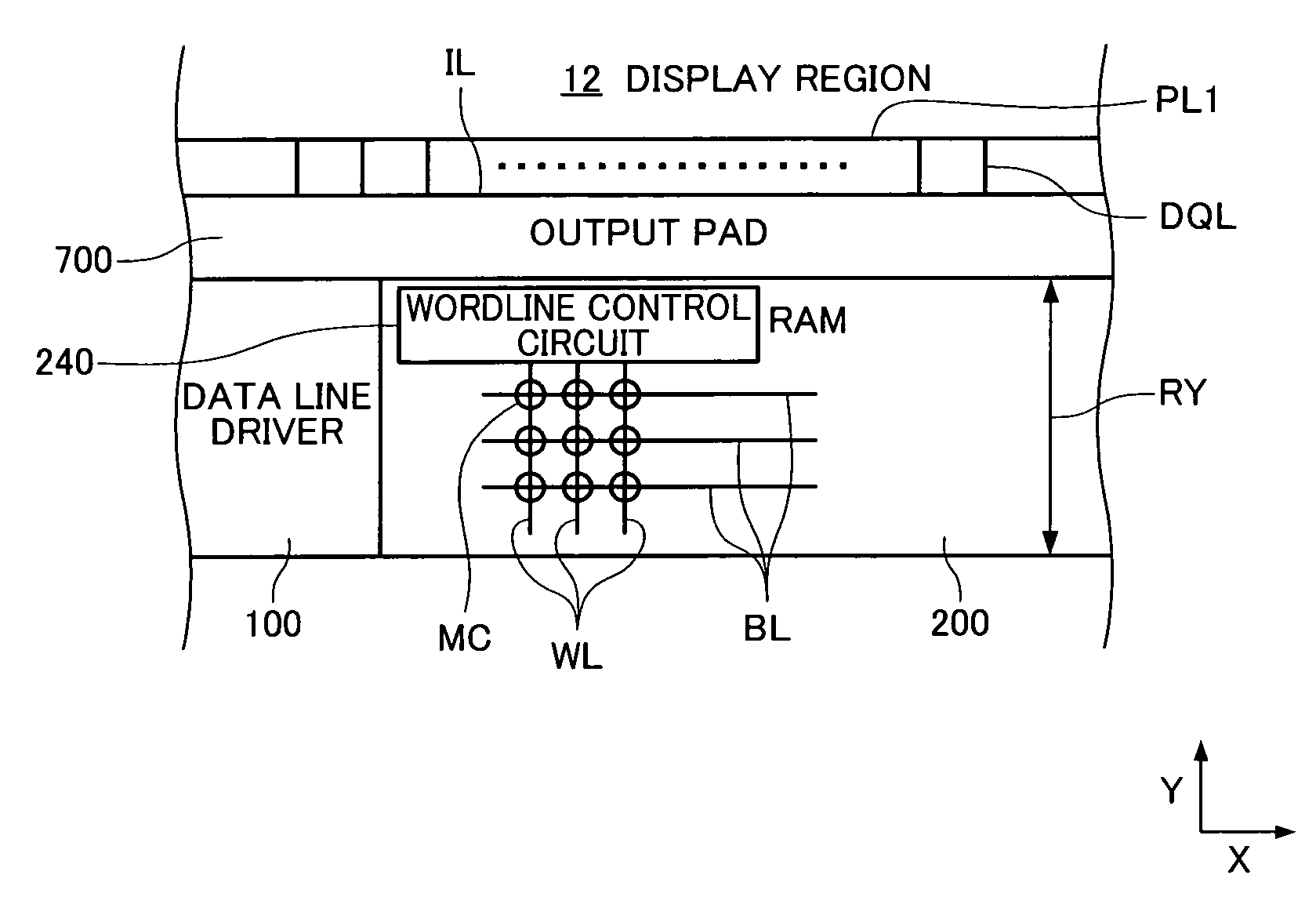

An integrated circuit device has a display memory which stores data for at least one frame displayed in a display panel which has a plurality of scan lines and a plurality of data lines, the display memory includes a plurality of RAM blocks, each of the RAM blocks including a plurality of wordlines, a plurality of bitlines, a plurality of memory cells, and a wordline control circuit, each of the RAM blocks is disposed along a first direction in which the bitlines extend, each of the memory cells has a short side and a long side, the bitlines are formed along a direction in which the long side of the memory cell extends, and the wordlines are formed along a direction in which the short side of the memory cell extends.

Owner:138 EAST LCD ADVANCEMENTS LTD

Drive circuit for display apparatus and driving method

InactiveUS20060262059A1Improve image qualityReduce noiseStatic indicating devicesSemiconductor chipLogical part

A drive circuit includes a logic section having a data bus and a display memory circuit and configured to read out a plurality of gradation data from the display memory circuit through the data bus and to collectively output the plurality of gradation data as display pixel data; and a drive section configured to drive a display unit based on analog gradation signals which are generated based on the display pixel data outputted from the logic section. The drive circuit further includes a power supply circuit configured to supply at least one of first and second power supply voltages to the logic section and the drive section. The logic section, the drive section and the power supply circuit may be formed in a same semiconductor chip.

Owner:RENESAS ELECTRONICS CORP

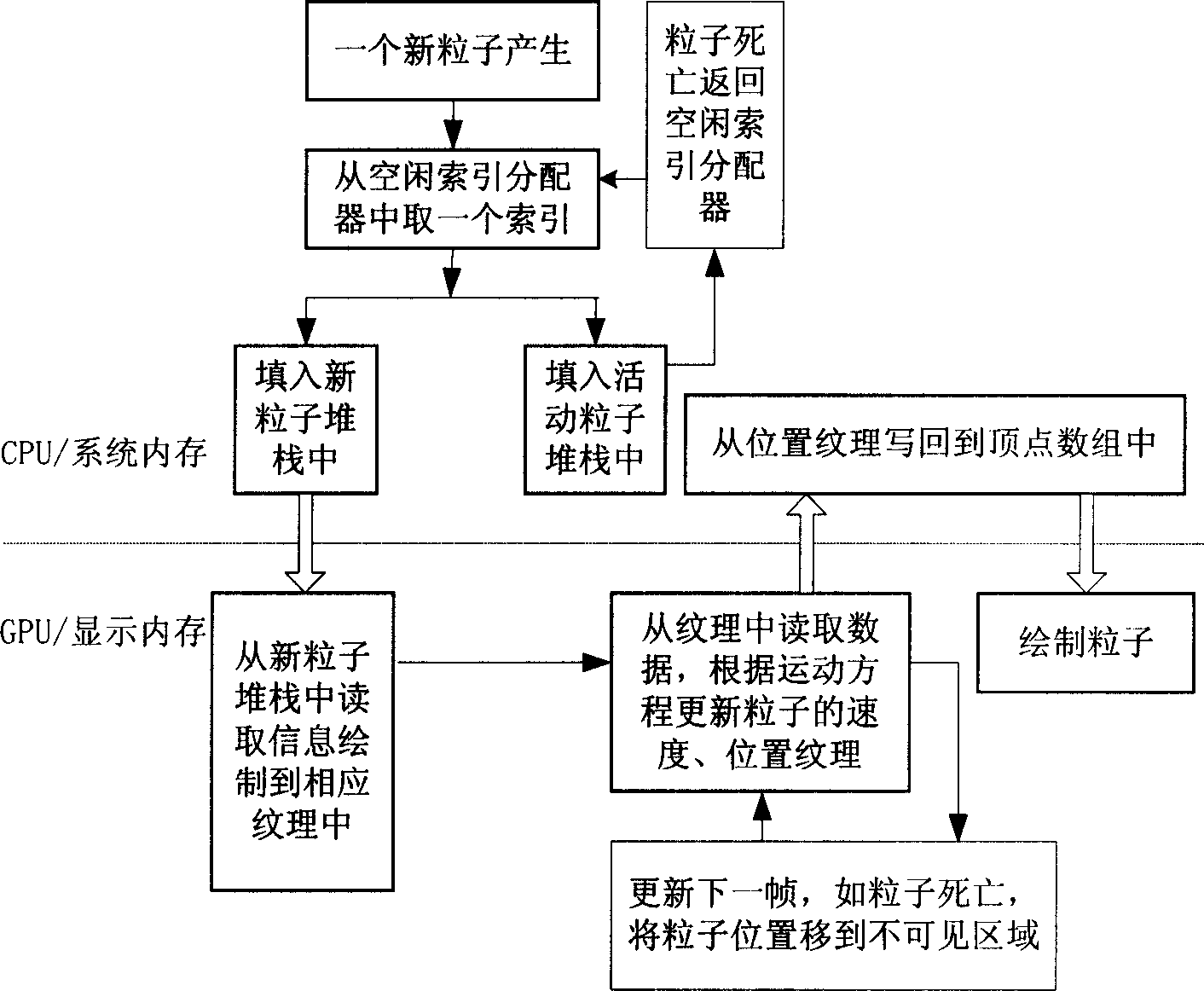

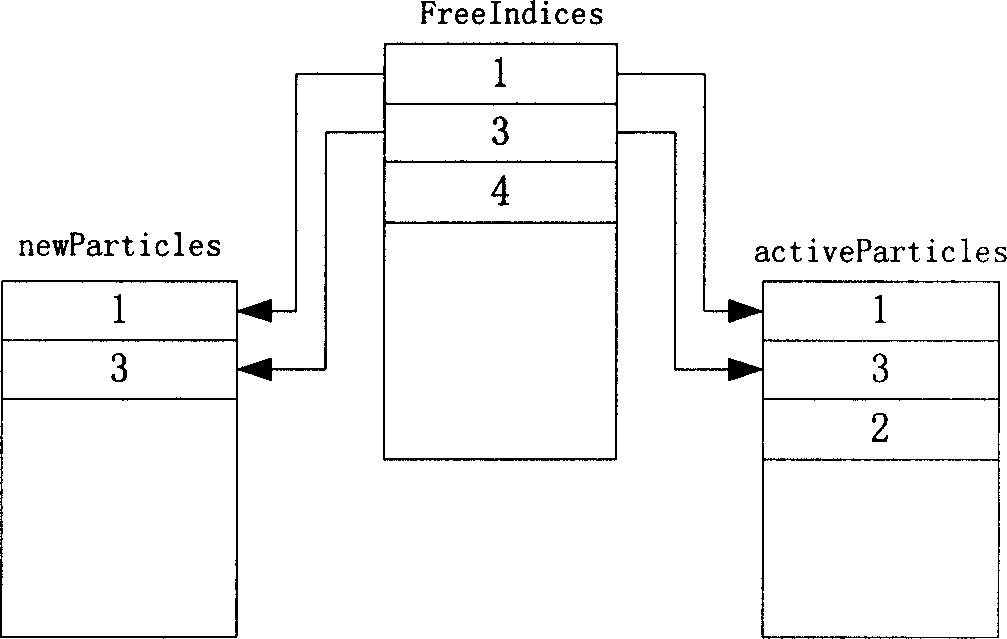

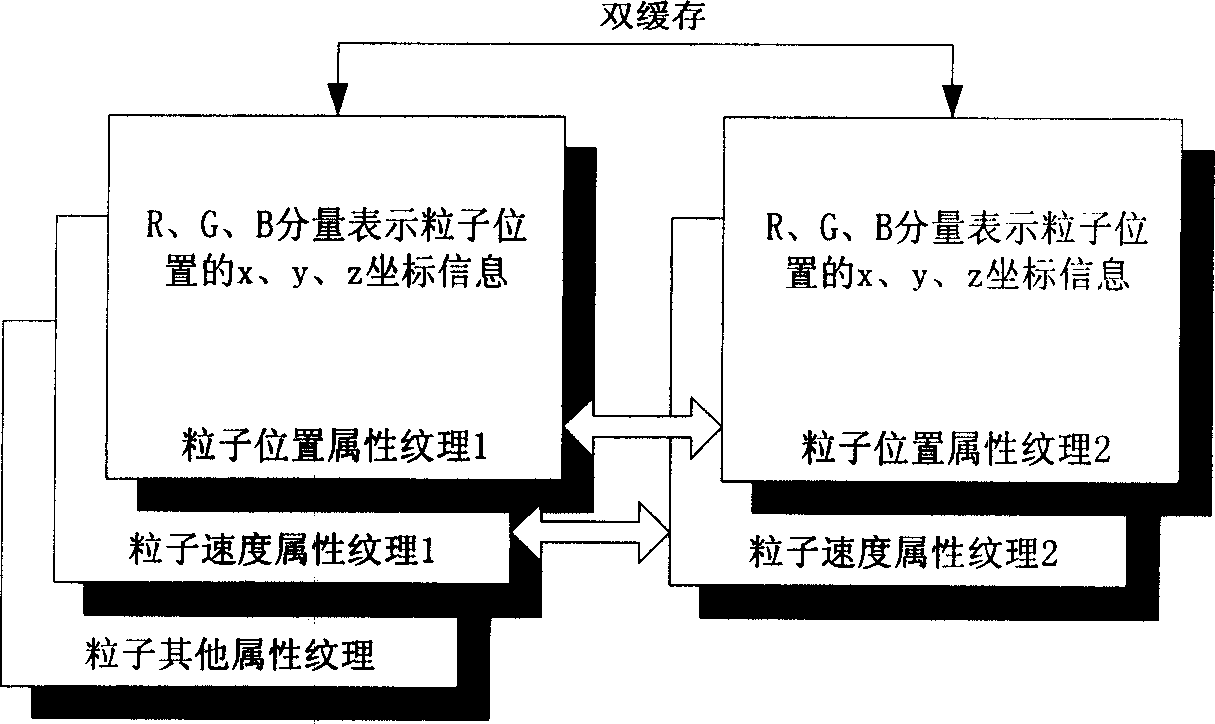

Particle system based on GPU

InactiveCN1753031AReduce data volumeImprove performanceImage data processing details3D-image renderingDisplay memoryEquations of motion

The invention is a GPU-based particle system, firstly allocating a block of memory area in the CPU of a system memory , where the memory area is divided into í‹idle indexesíŒ, í‹new particle stackíŒ, and í‹active particle stackíŒ, then reading an idle index from the í‹idle indexesíŒ, storing the idle index together with new produced particle index and particle attributes in the two stacks so as to produce new particle; then reading new particle information from the í‹new particle stackíŒ to store in a display memory, where the speed and position information of the particle is stored in the first-group grains, then updating the particle attributes; reading the particle information from a group of grains of the GPU of the display memory, calculating the next-time position and speed information of the particle according to motion equation and storing them into the second group of grains of the GPU, updating the particle information; writing back the updated particle attributes from the grains of the display memory to a vertex array of the CPU of the system memory; drawing the particle. The invention improves calculating ability and operating efficiency and at the same time, largely improves the real-time performance of the system.

Owner:BEIHANG UNIV

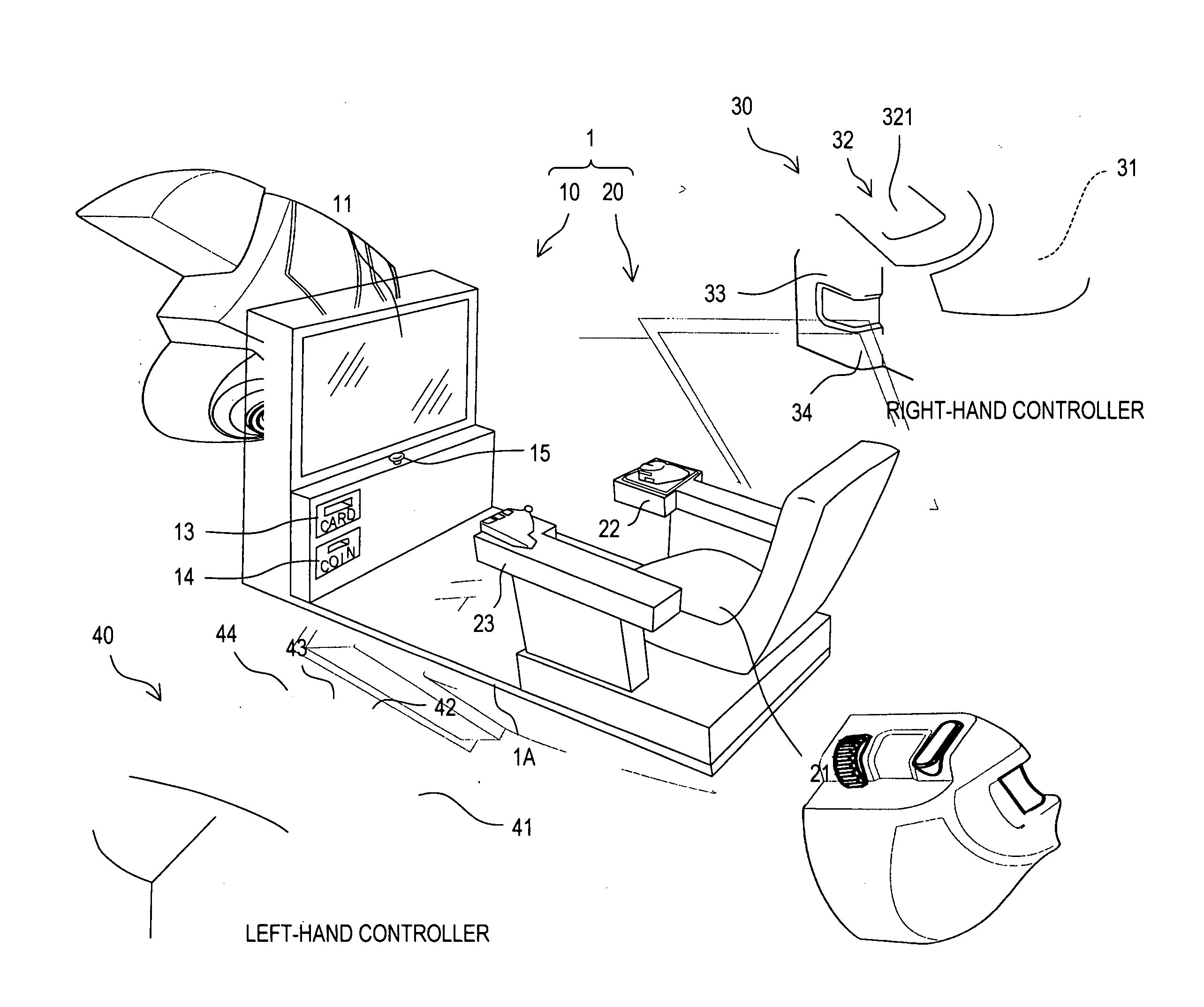

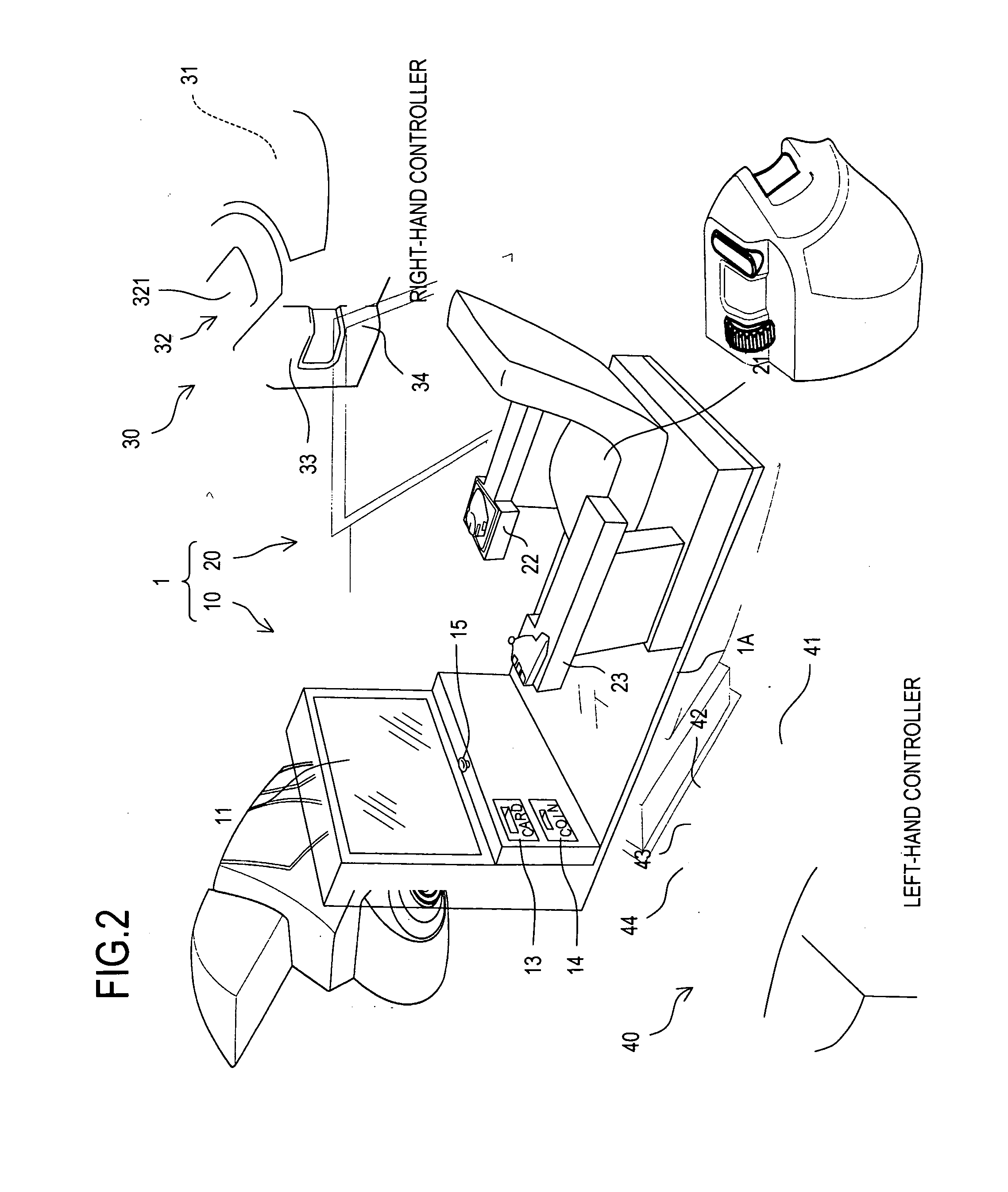

Video game machine, gaming image display method, gaming image dispaly program and network game system

InactiveUS20110018867A1Reduced D processing burdenReduce processing burdenCathode-ray tube indicatorsVideo gamesPleasant FeelingVirtual camera

A video game machine includes a monitor that permits three-dimensional viewing, a virtual camera controller for moving first and second virtual cameras while maintaining a positional relationship in which the two virtual cameras are separated from each other, an image display controller for synthesizing first and second image data acquired by the two virtual cameras upon leading the image data to a display memory, and reading out data content thereof, a game-related image storage block for storing panel images including objects and textures, and a specifier which issues a command for presenting a panel image. The image display controller maps a texture corresponding to an object read out in accordance with the command given from the specifier twice in two storage locations of the display memory that are offset from each other. A player is provided with a gaming image generated with a reduced 3D processing burden, yet creating compelling reality and enjoyable sensation in game playing.

Owner:KONAMI DIGITAL ENTERTAINMENT CO LTD

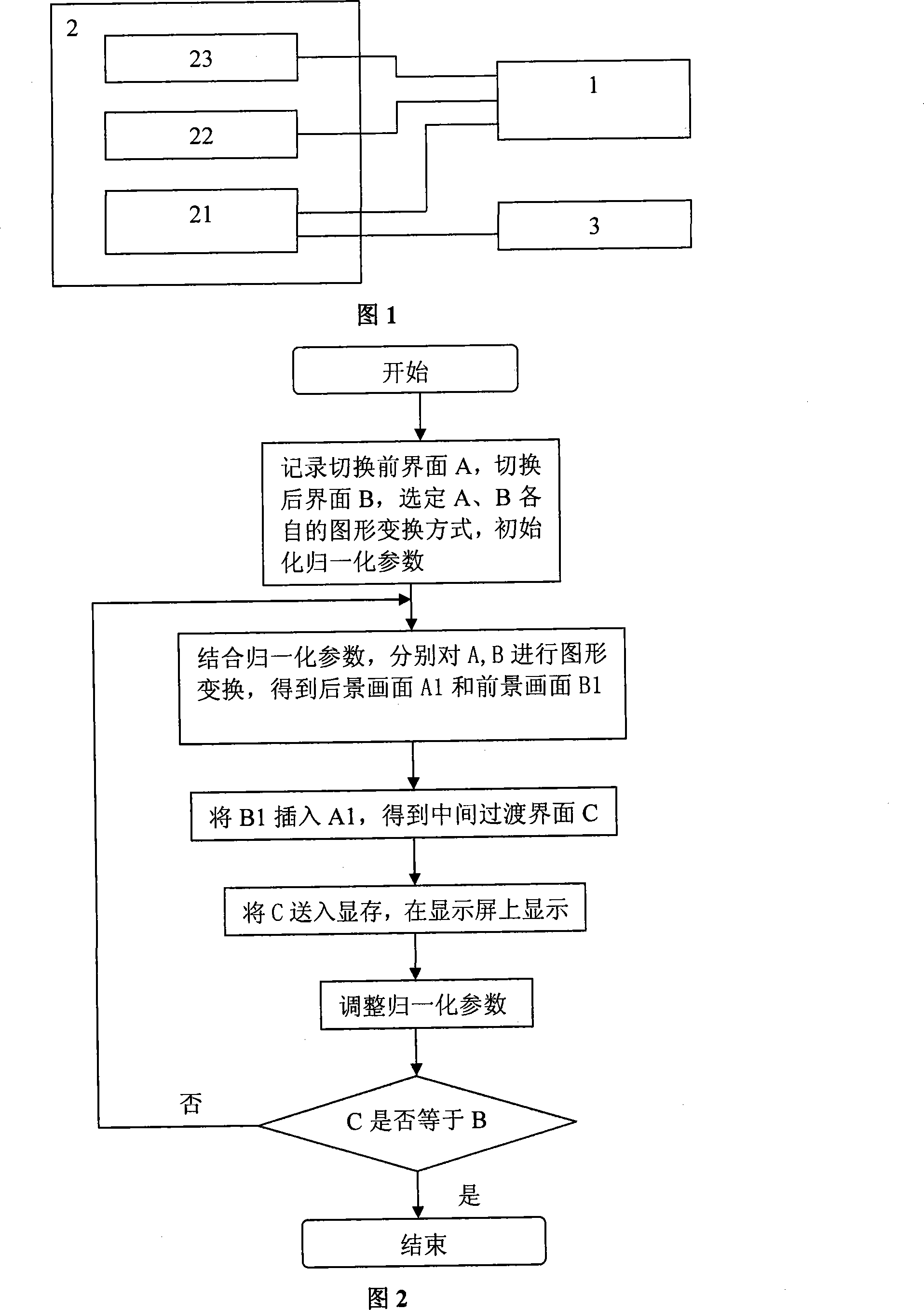

Mobile phone with dynamic switch interface and method of mobile phone interface dynamic switch

InactiveCN101227680AImprove the status of interface static switchingFriendly operating environmentRadio/inductive link selection arrangementsSpecific program execution arrangementsEmbedded systemDisplay memory

The invention relates to a cell phone and a process, in particular to cell phone with dynamic switching interface and the process of the dynamic switching cell phone interface. The cell phone comprises a CPU, an internal memory which has a display memory and a display screen, and is characterized in that an initial image buffer which stores the interface before switching and a target image buffer which stores the interface after switching are arranged in the internal memory, the CPU is connected with the initial image buffer, the target image buffer and the display memory, and the display memory is connected with the display screen. The dynamic switching of the interface comprises the following steps that conducting the image switching for the interfaces before and after the switching by the CPU combining with the normalized parameter to obtain the background pictures and the foreground pictures, then conducting the insertion connection to gain an intermediate transition interface and inputting to the display screen, continuously conducting of process of the calculation of the CPU and the display of the intermediate interface, and adjusting the asymptotic parameter during the process until the interface after switched is displayed on the display screen. The invention realizes the dynamic switching of the cell phone interface, changes the current condition that the cell phone only has the static switching, and provides more friendly operation environment for users.

Owner:WINGTECH COMM

Double-screen mobile phone

InactiveCN104486467APreserve high-definition displayFlexible operationTelephone set constructionsBoard structureHigh definition

The invention provides a double-screen mobile phone which at least comprises a shell, a first display screen, a second display screen and a main board structure, wherein the first display screen is arranged on the front side of the shell; the second display screen is arranged on the rear side of the shell; the main board structure is arranged inside the shell; the main board structure at least comprises a first display controller which is connected with the first display screen, a second display controller which is connected with the second display screen, a display memory which is connected with the first display controller and the second display controller, and a main processor which is connected with the display memory and is used for controlling the storage position of data to be displayed at present in the display memory so as to control switching display of the first display screen and the second display screen. The double-screen mobile phone both maintains the advantages of high definition display and flexible operation of an intelligent mobile phone and has the advantages of power conservation and sight protection of a conventional functional mobile phone as well.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com