Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4638results about "Image memory management" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

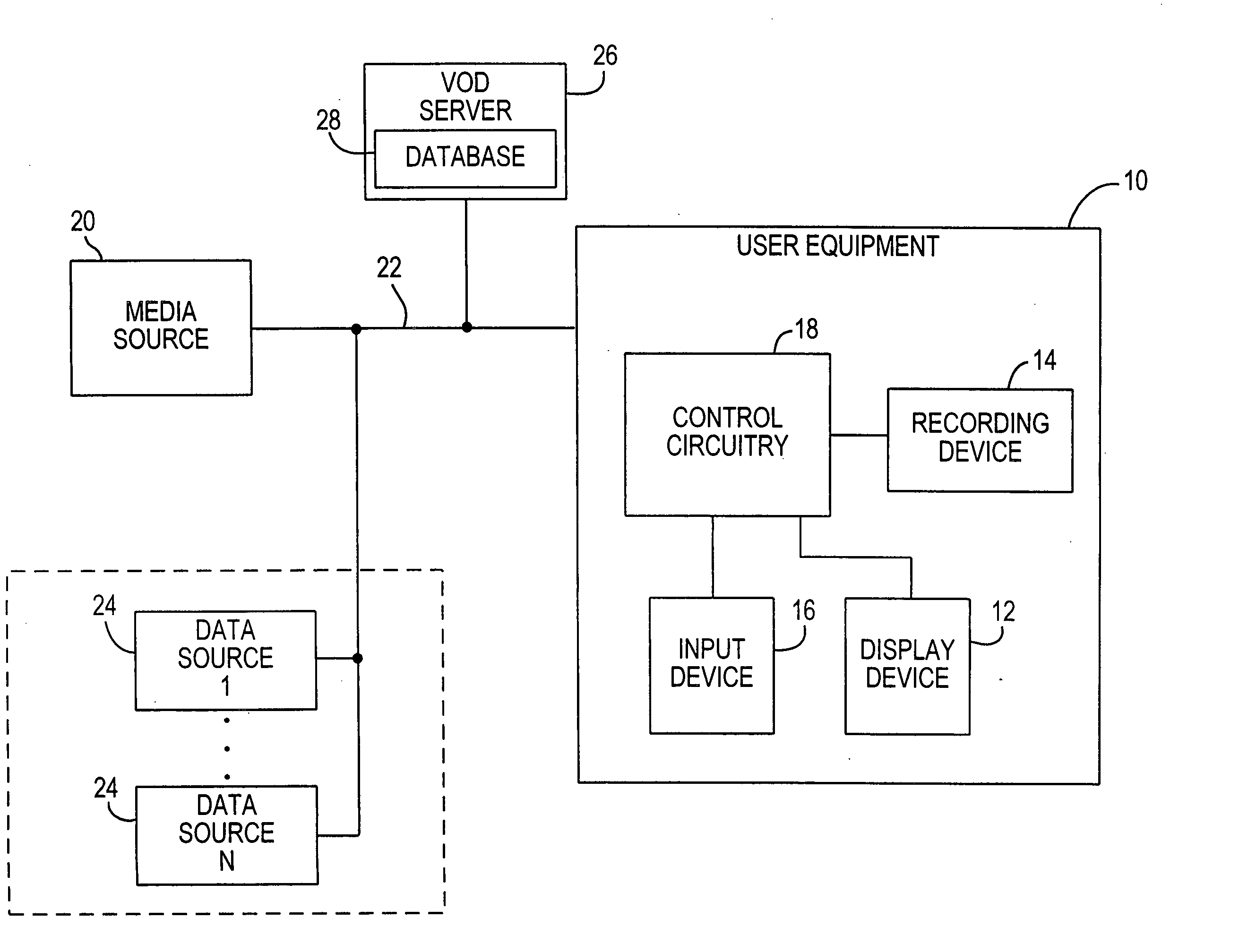

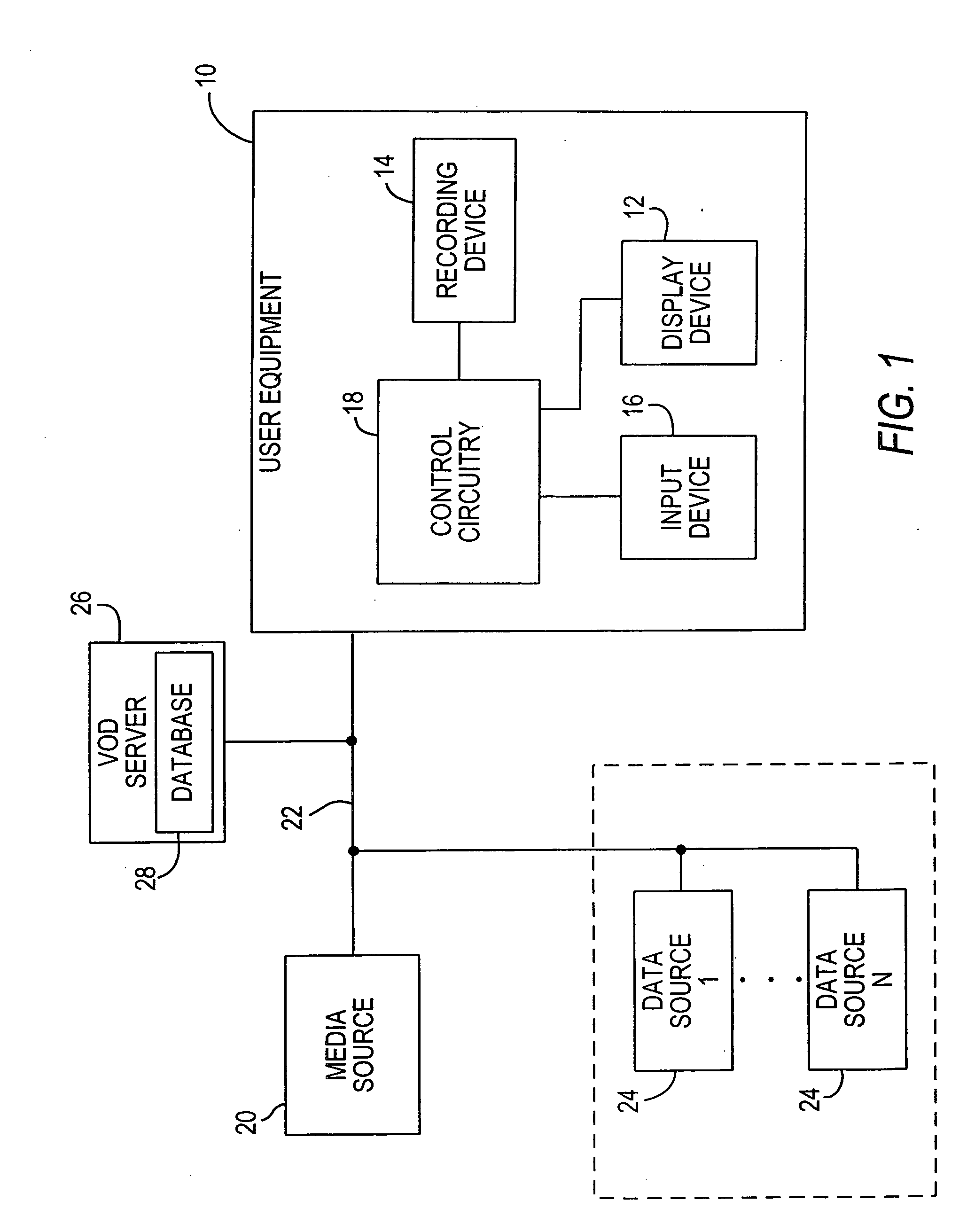

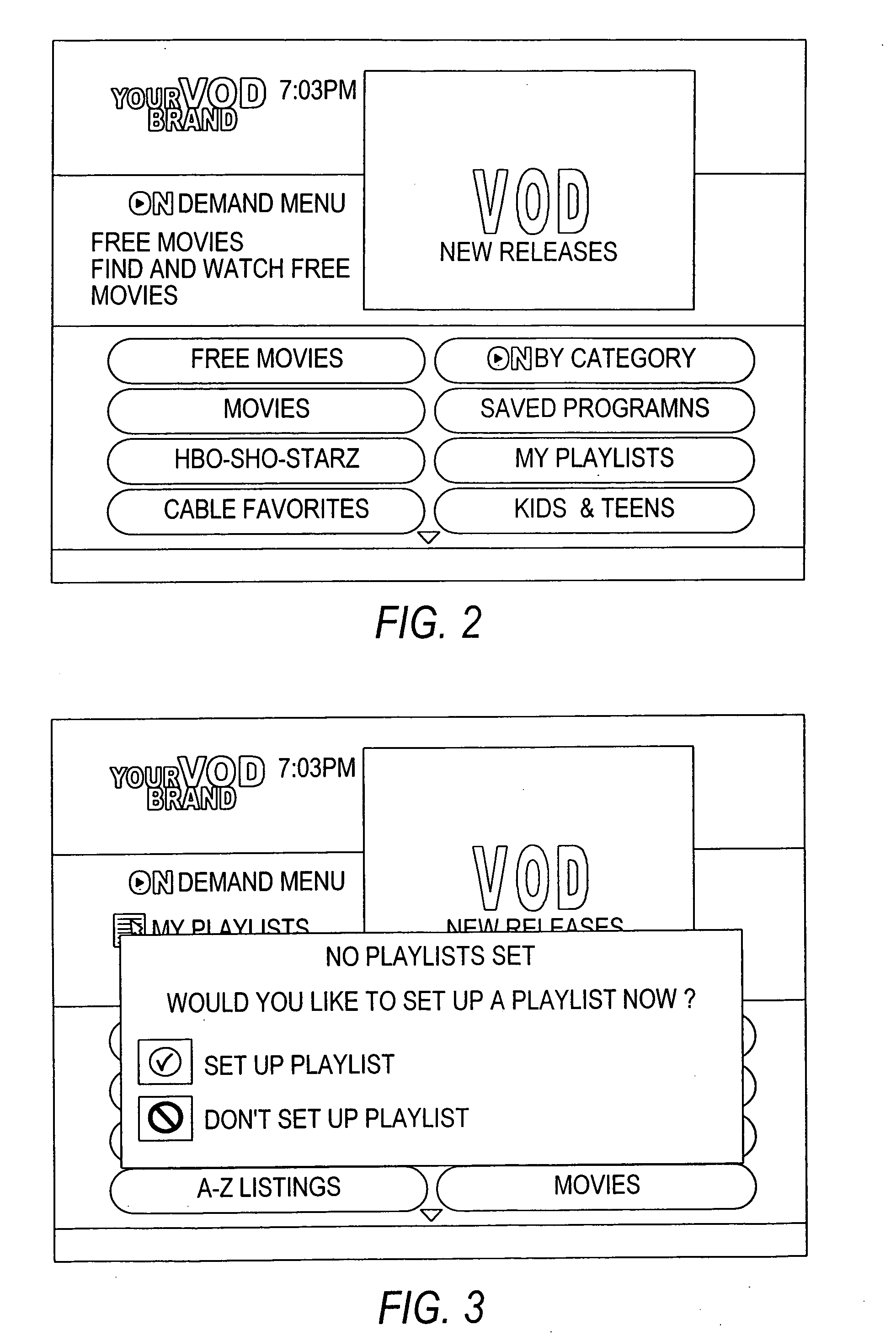

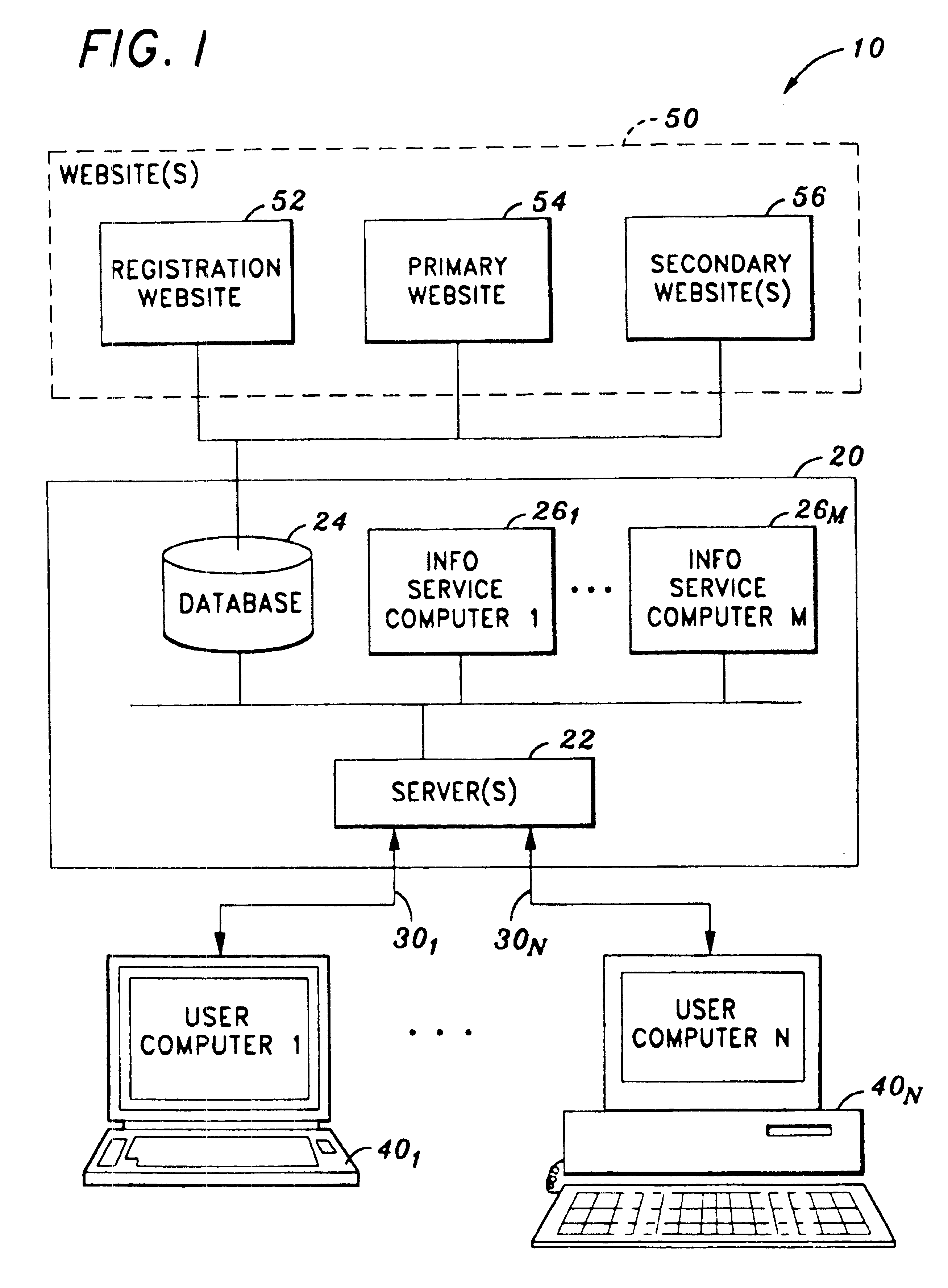

Playlists and bookmarks in an interactive media guidance application system

ActiveUS20060267995A1Amount of spaceTelevision system detailsMultimedia data retrievalGraphicsBookmarking

Systems and method are provided for providing a playlist transport bar. The playlist transport bar provides an overlay which graphically represents assets (e.g., programs) of a playlist in a manner that enables a user to simultaneously ascertain a playback position within the playlist and a particular asset. The playlist transport may include asset regions which each correspond to an asset in a playlist and a position indication region which may provide information relating to a playback position.

Owner:ROVI GUIDES INC

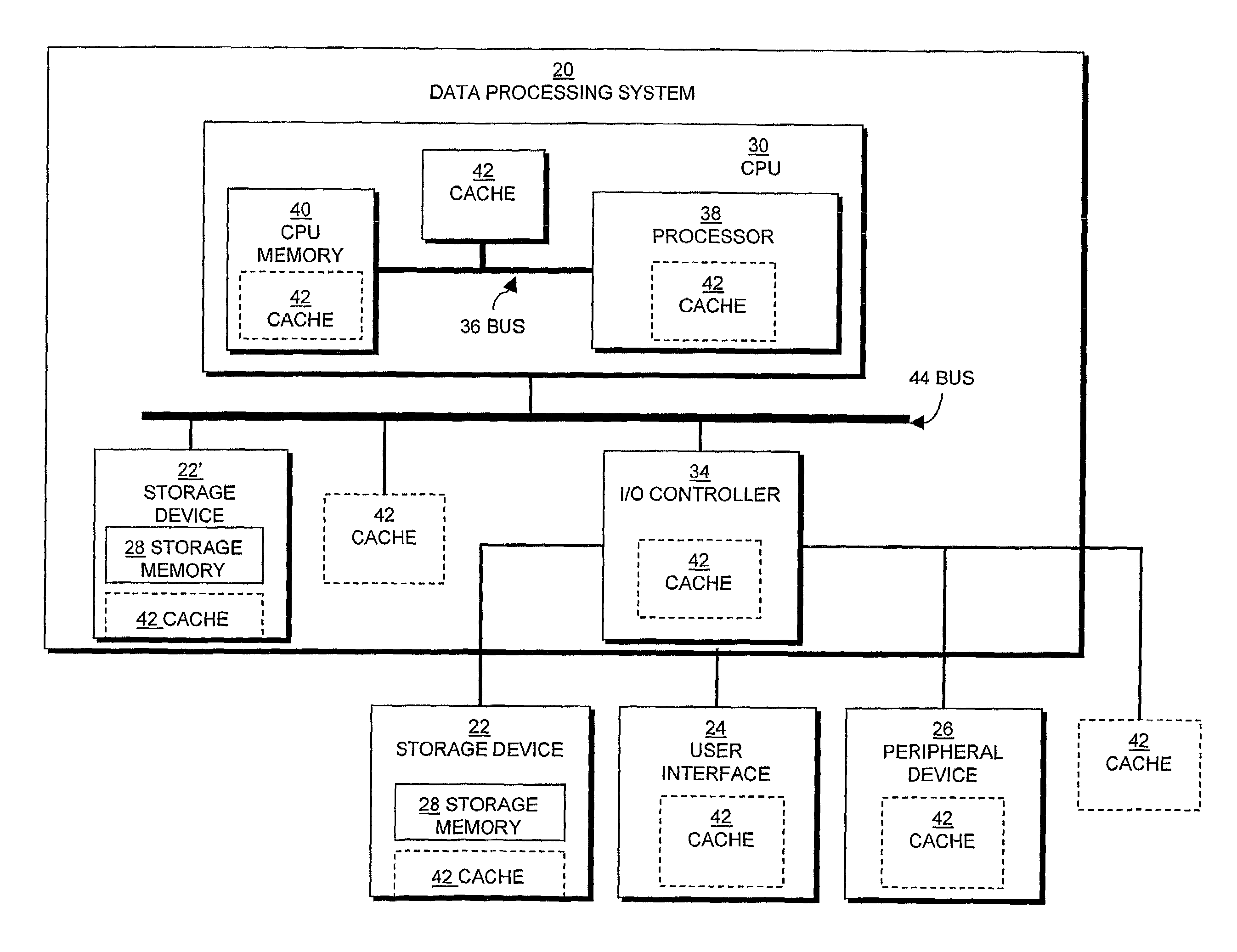

Cache system and method for generating uncached objects from cached and stored object components

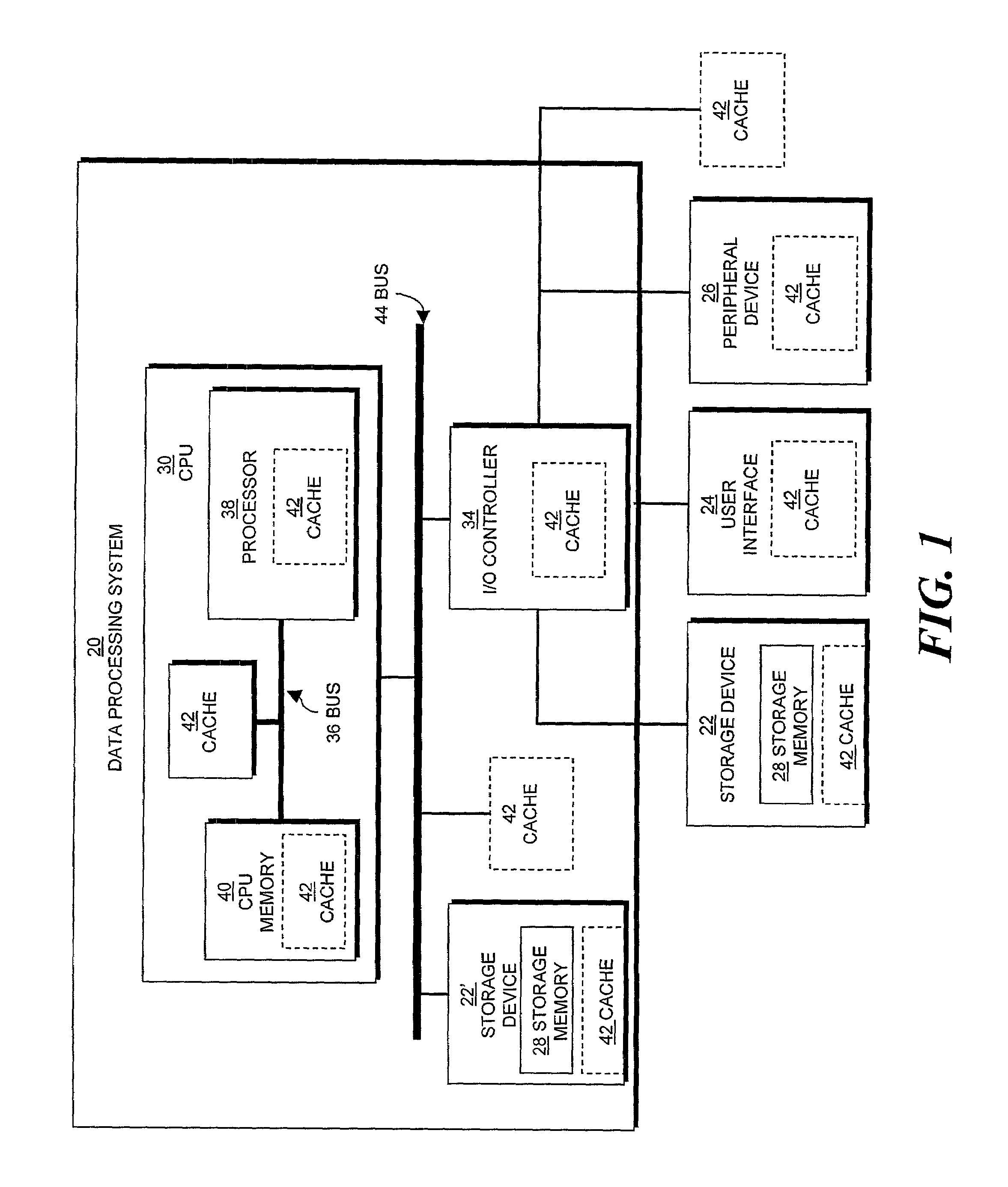

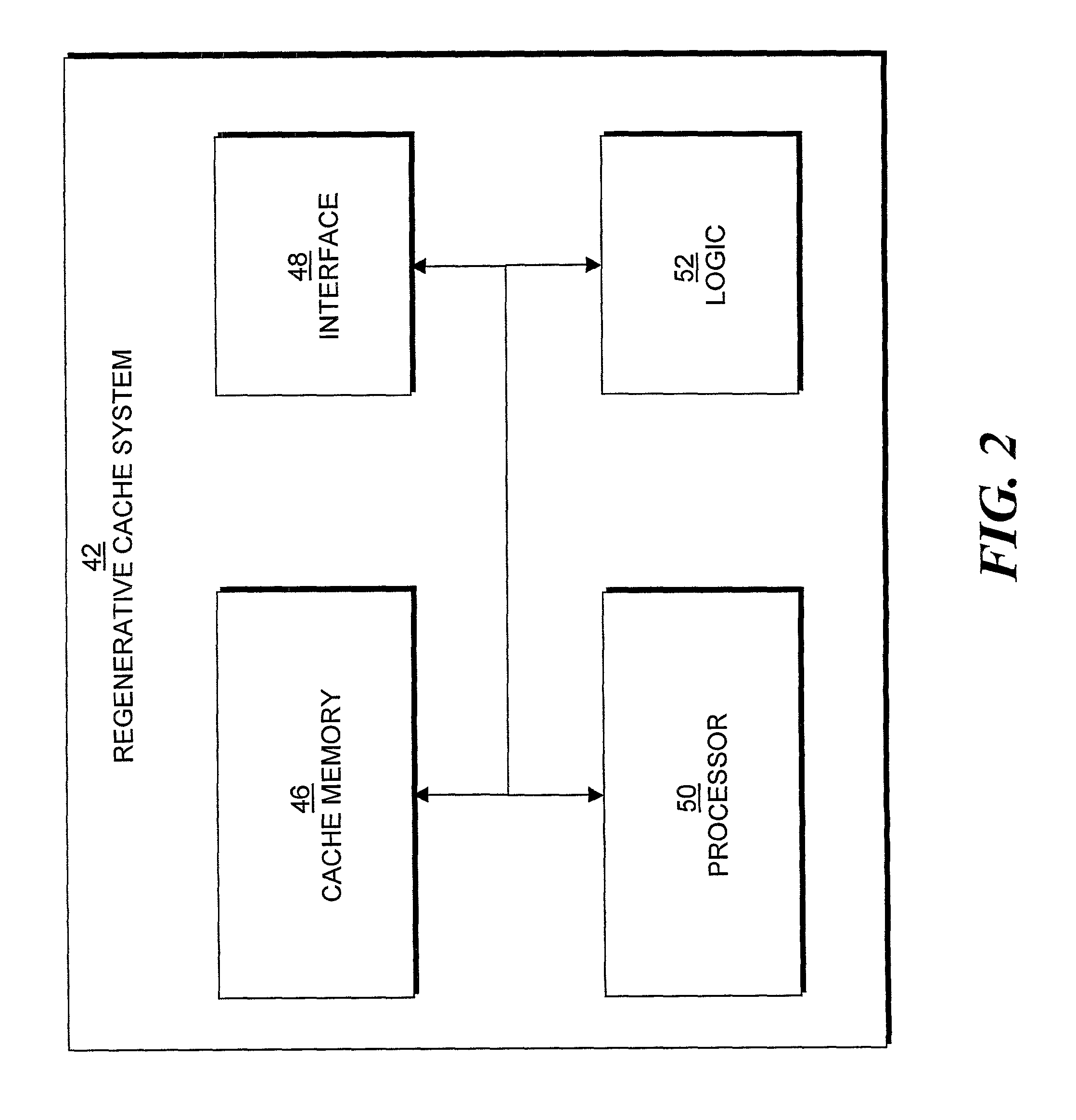

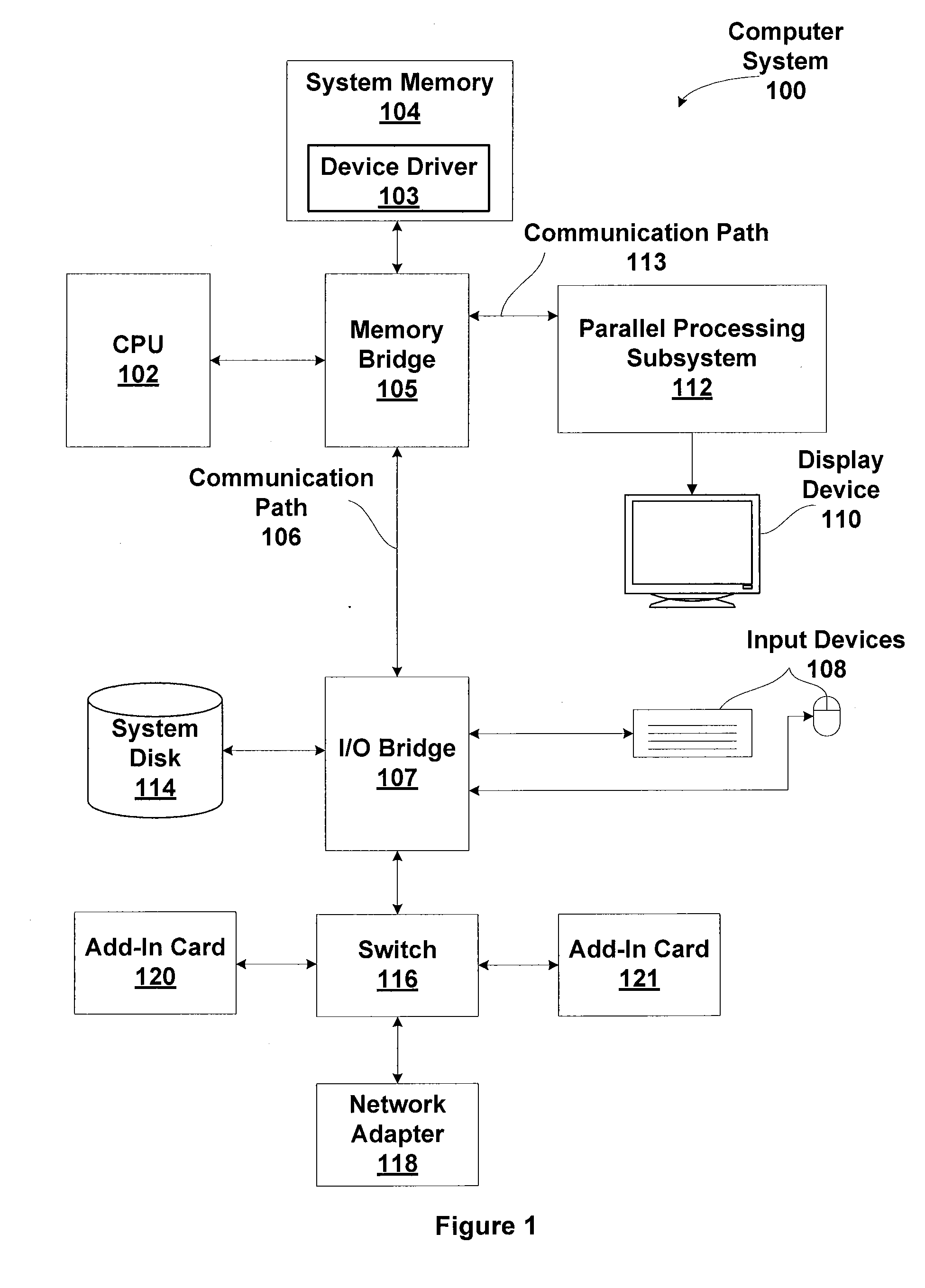

InactiveUS7006099B2Memory architecture accessing/allocationImage memory managementExternal storageParallel computing

Methods and apparatus for constructing objects within a cache system thereby allowing the cache system to respond to requested objects that are not initially available within the cache system. One embodiment of the invention caches image files, where the images are divided into components and stored in a format that allows identification and access to the components. The cache system determines that an object, such as an image file, is missing from the cache memory, locates sufficient components from the cache memory and / or external storage, and constructs the object from the located components.

Owner:AWARE INC

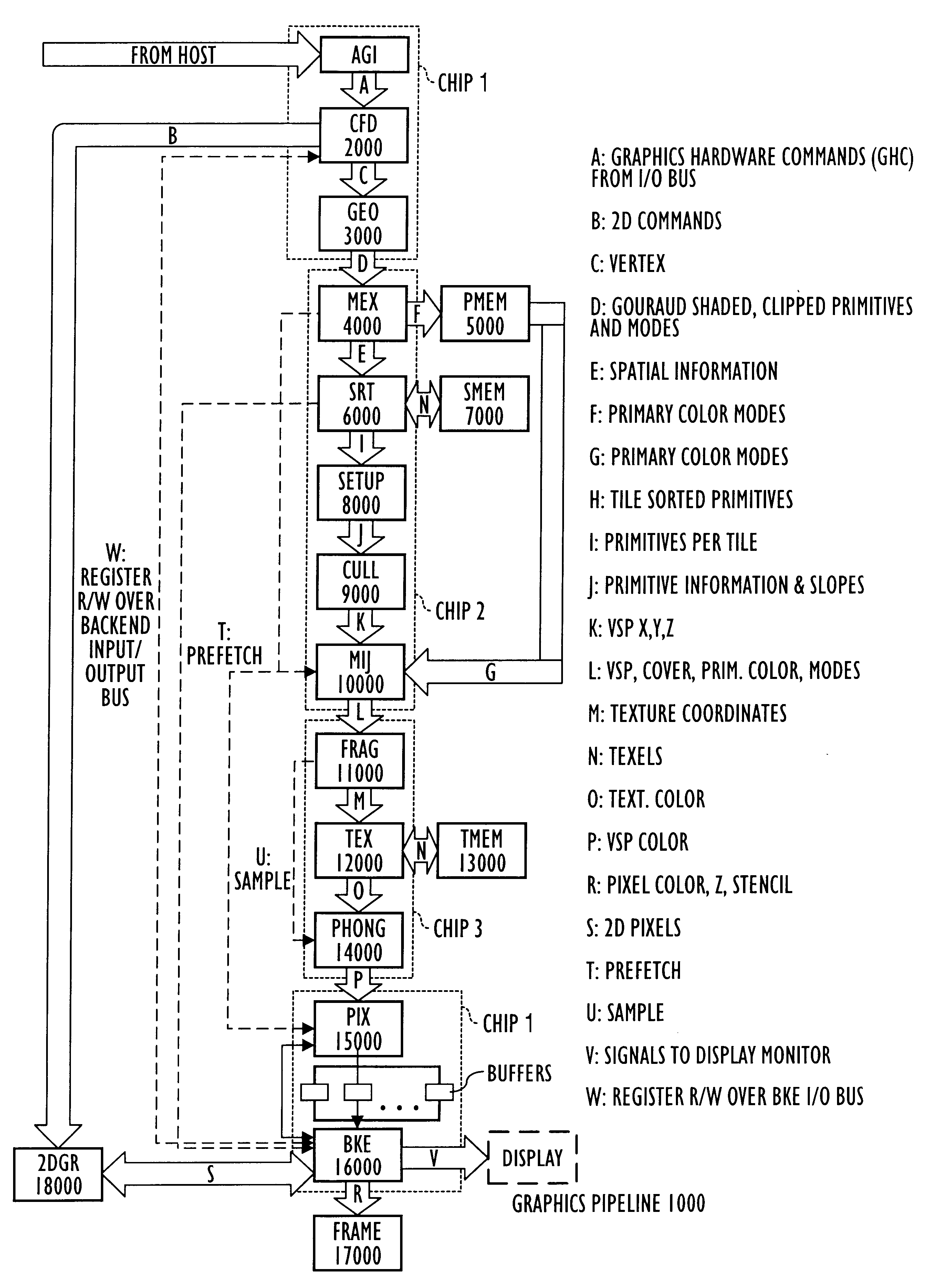

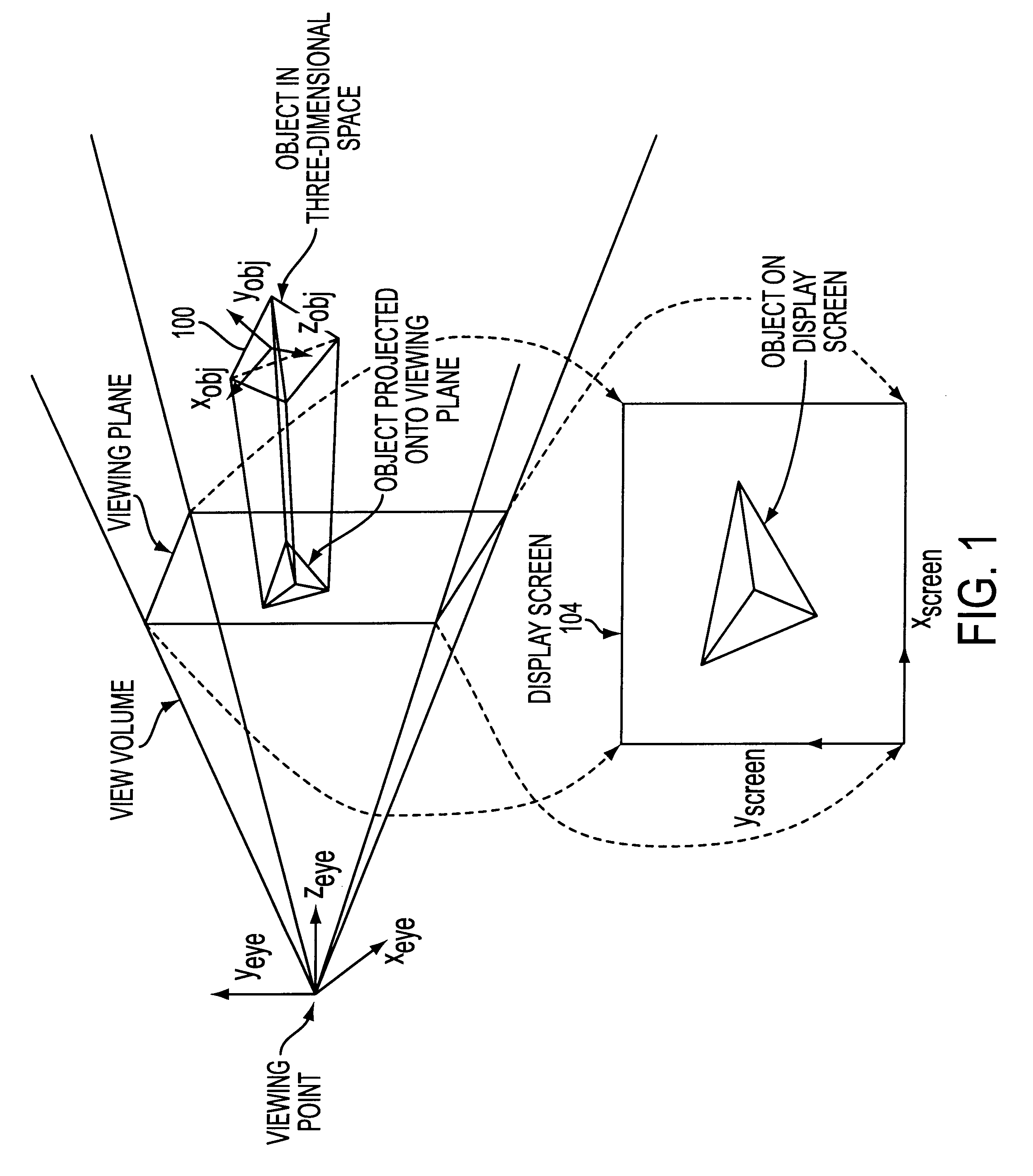

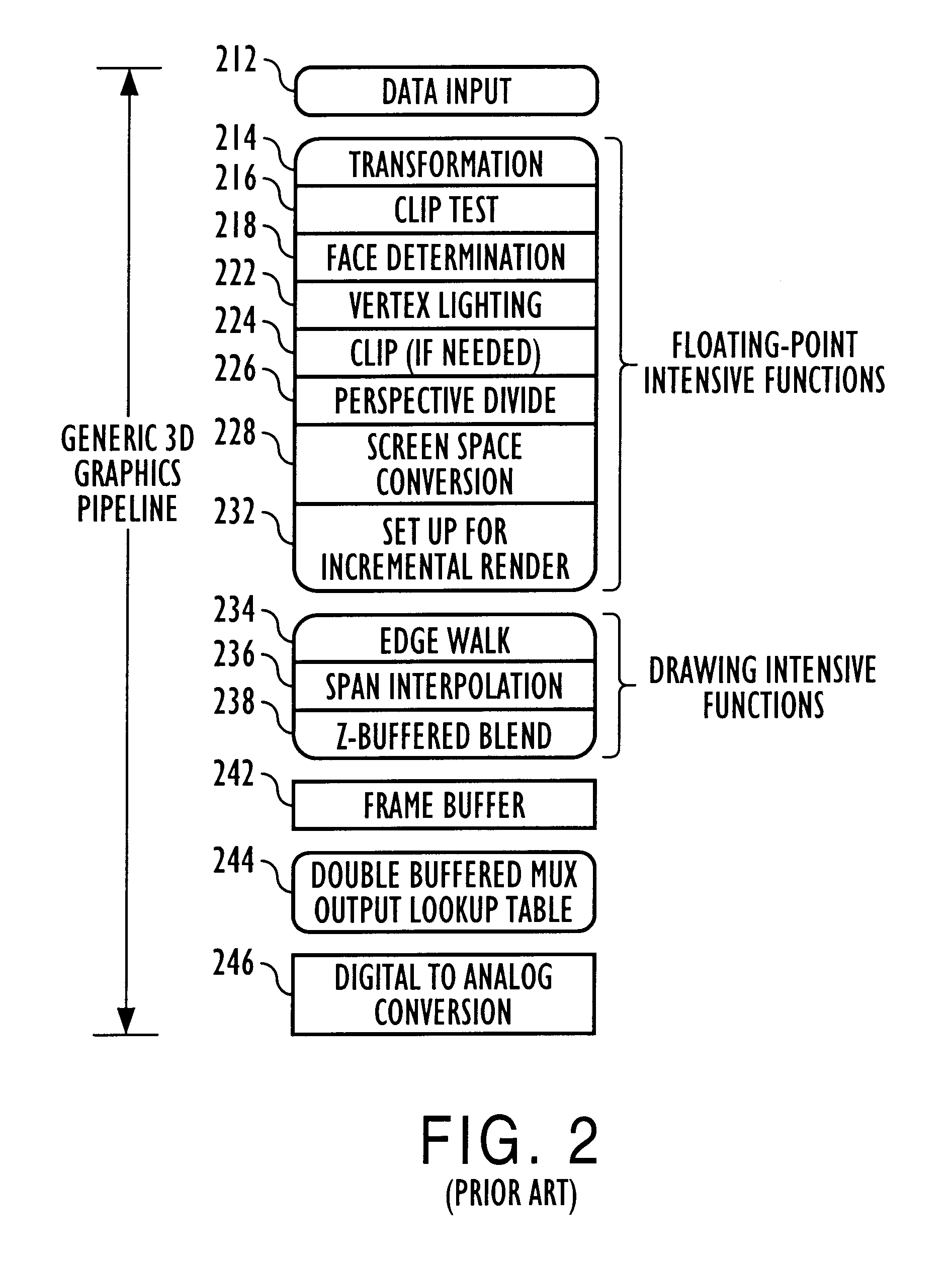

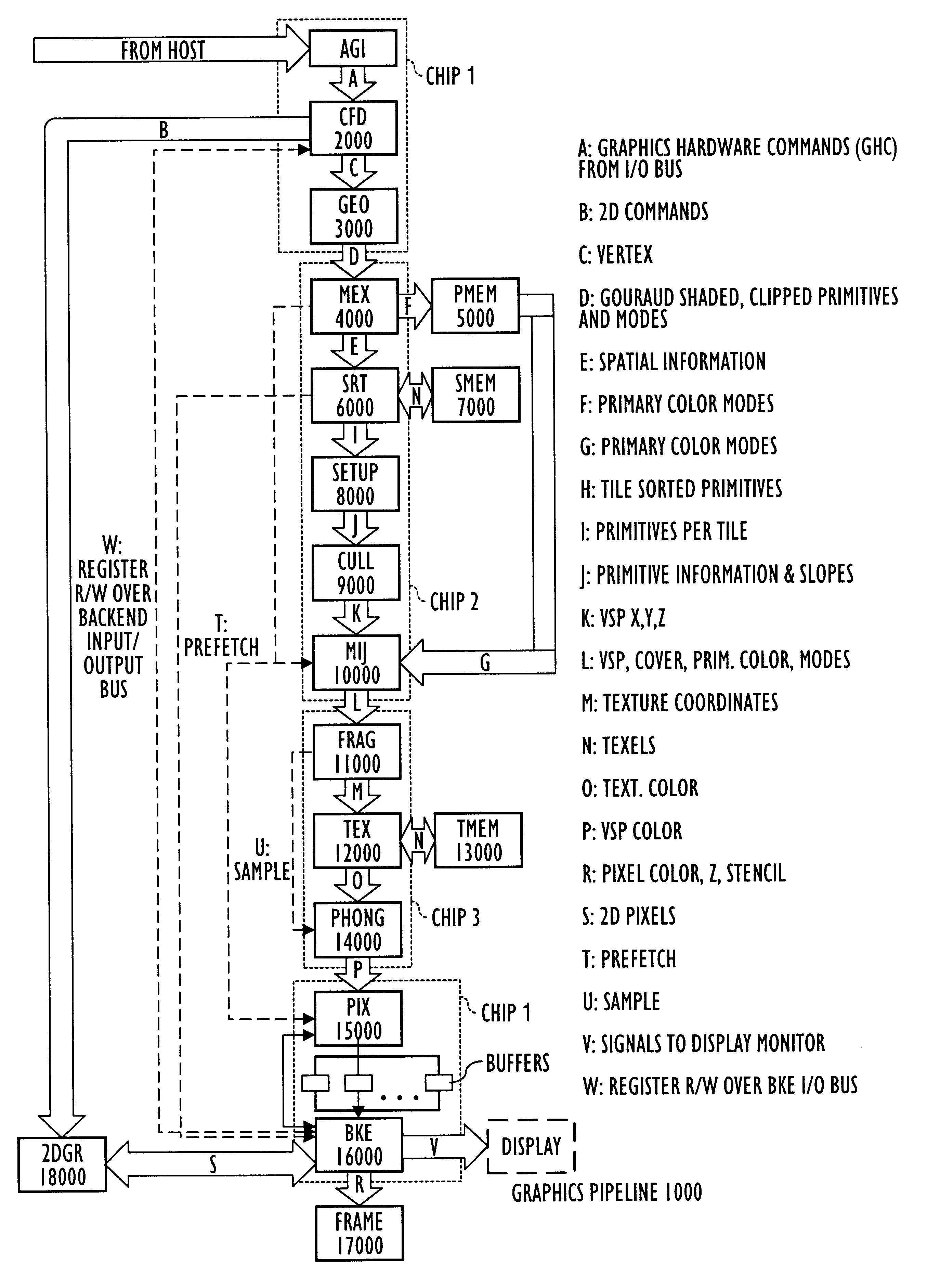

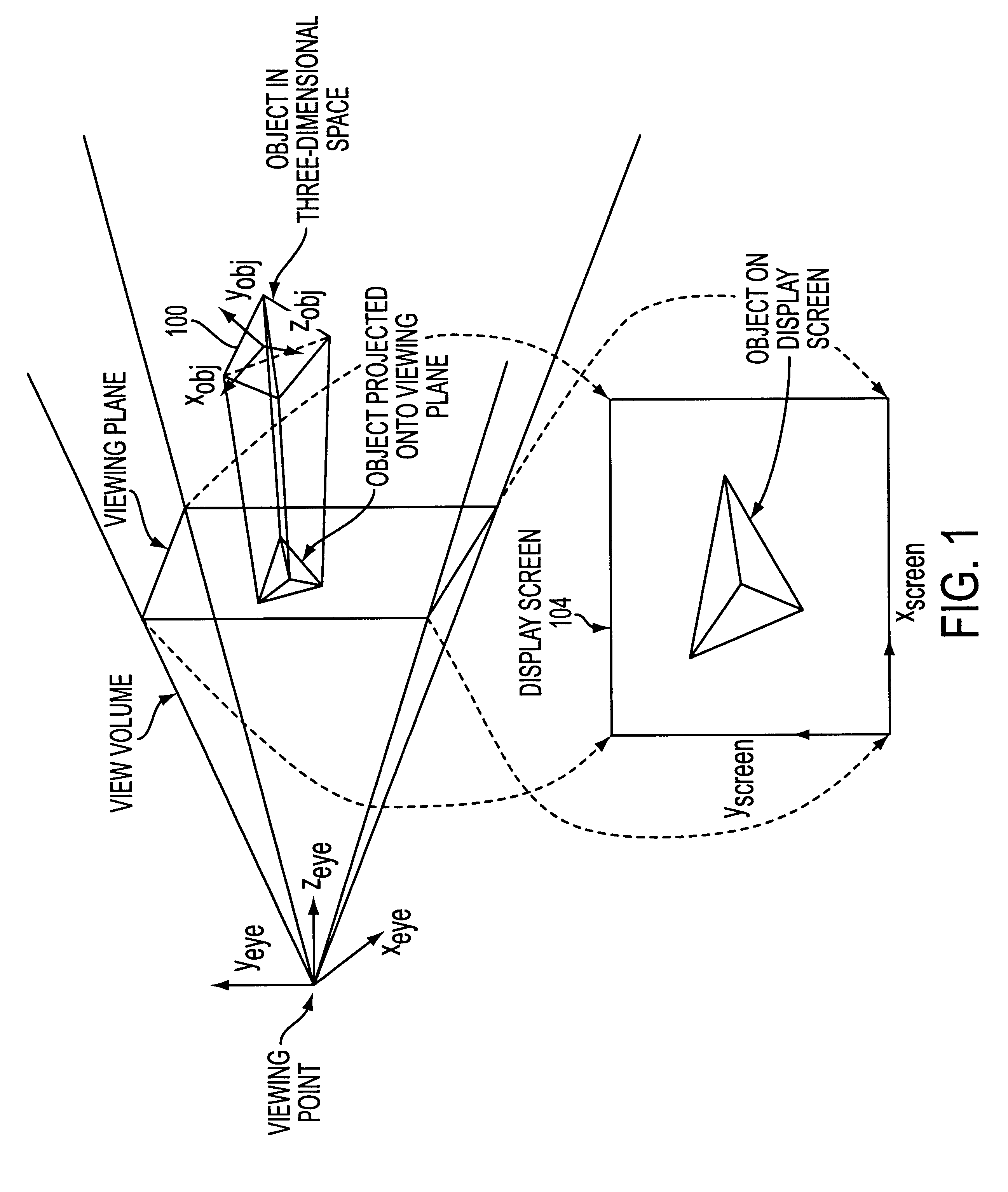

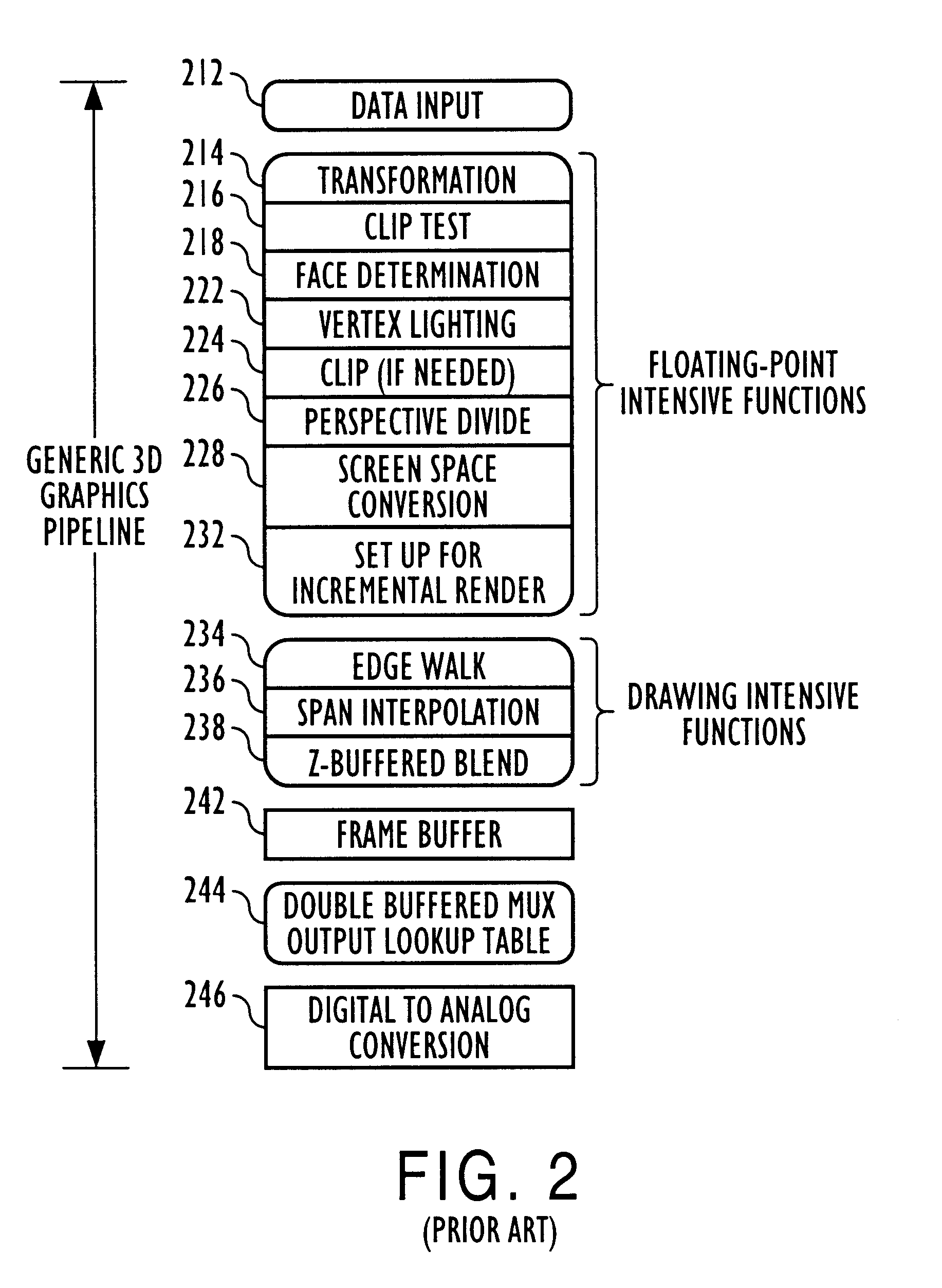

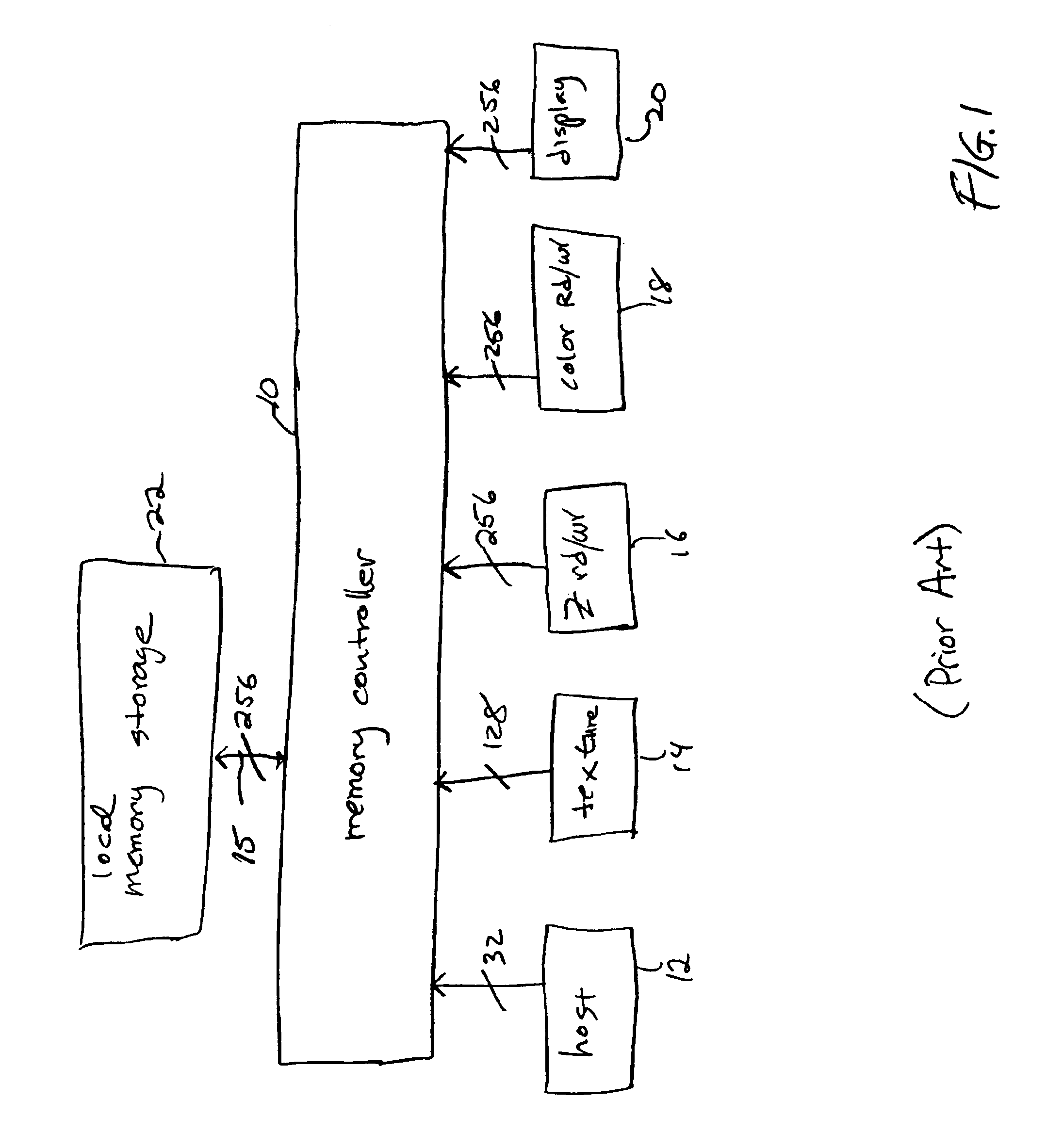

Deferred shading graphics pipeline processor

InactiveUS6229553B1Lower communication bandwidthAttenuation bandwidthTexturing/coloringImage memory managementPhong shadingDeferred shading

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

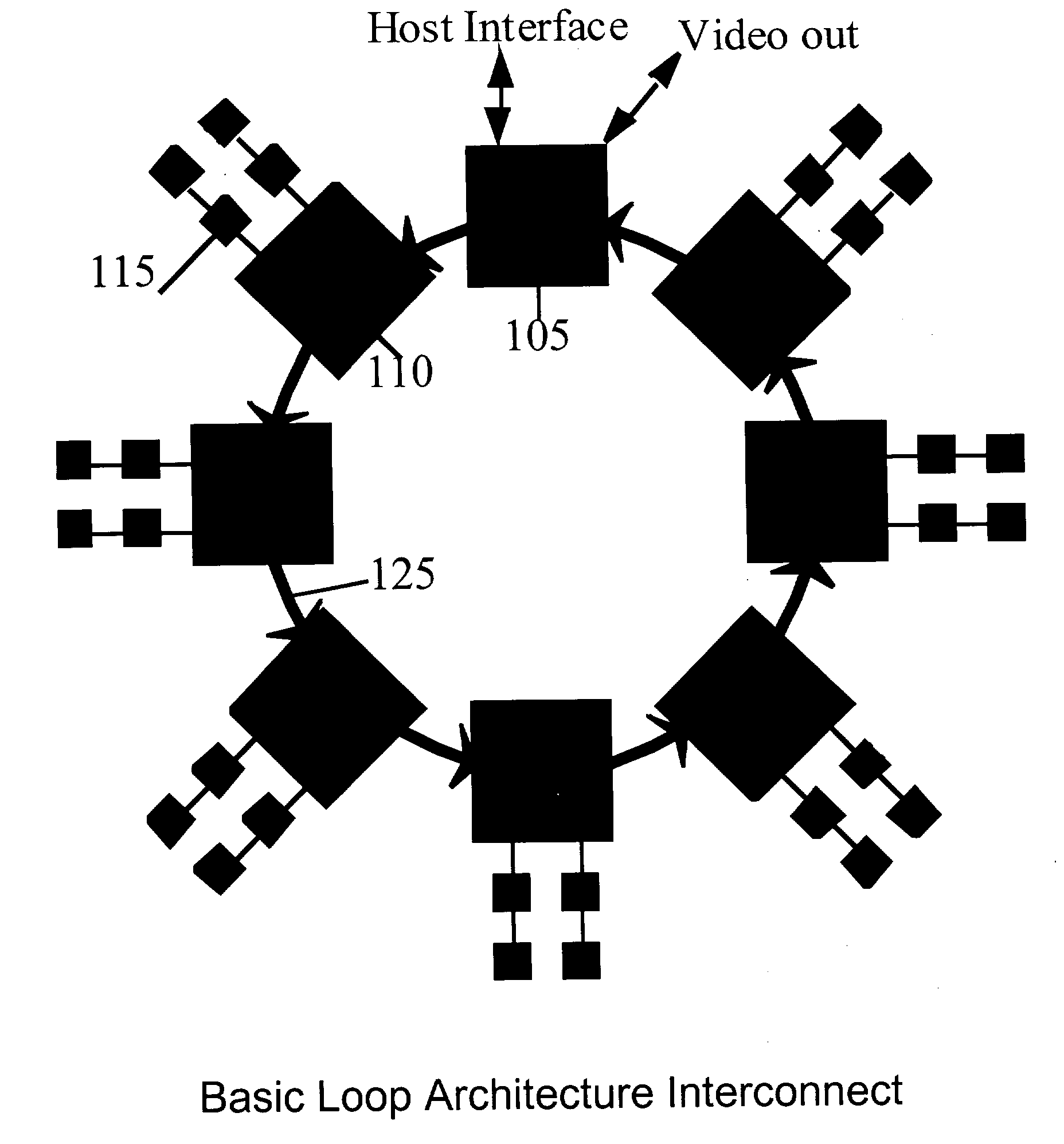

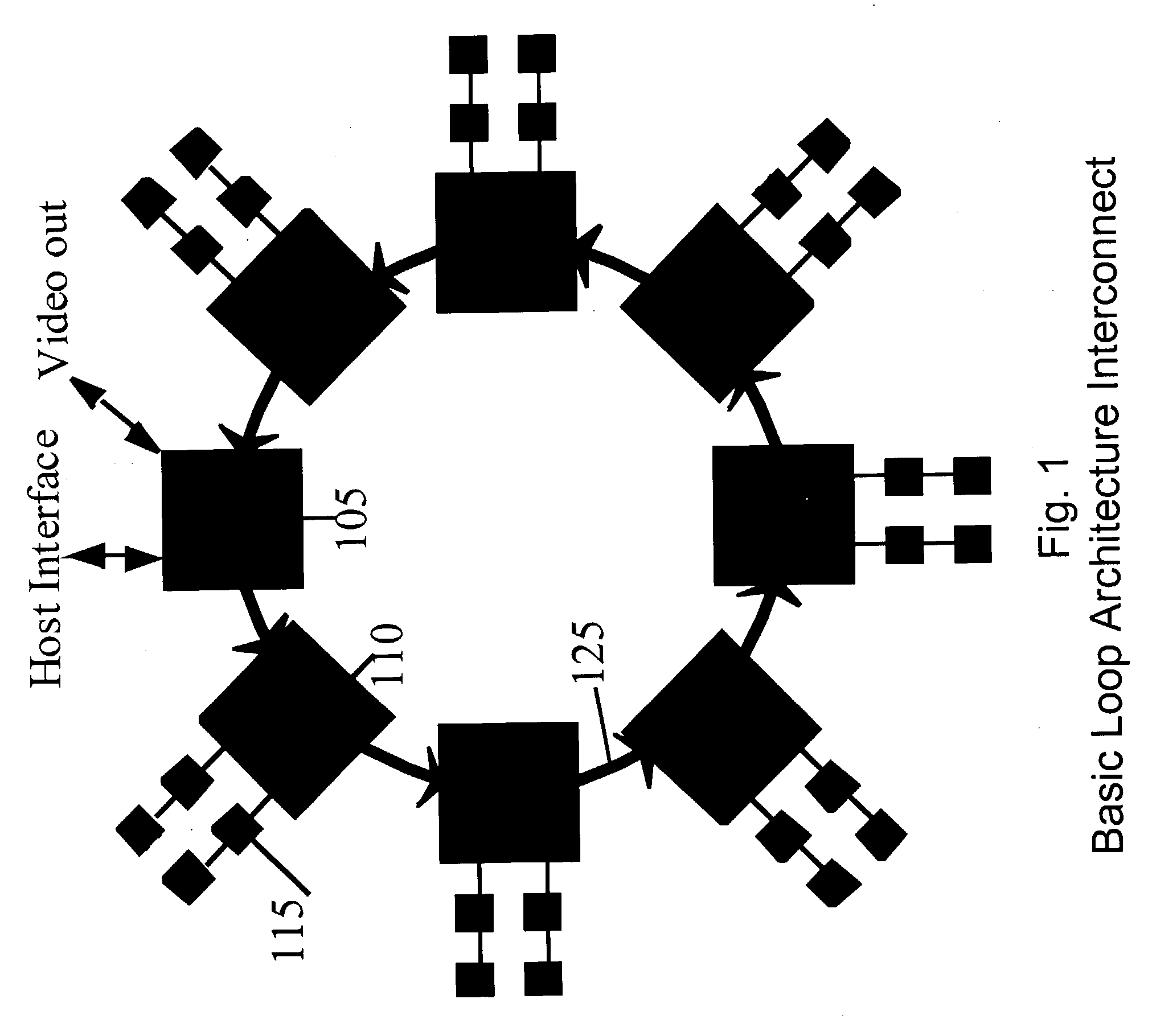

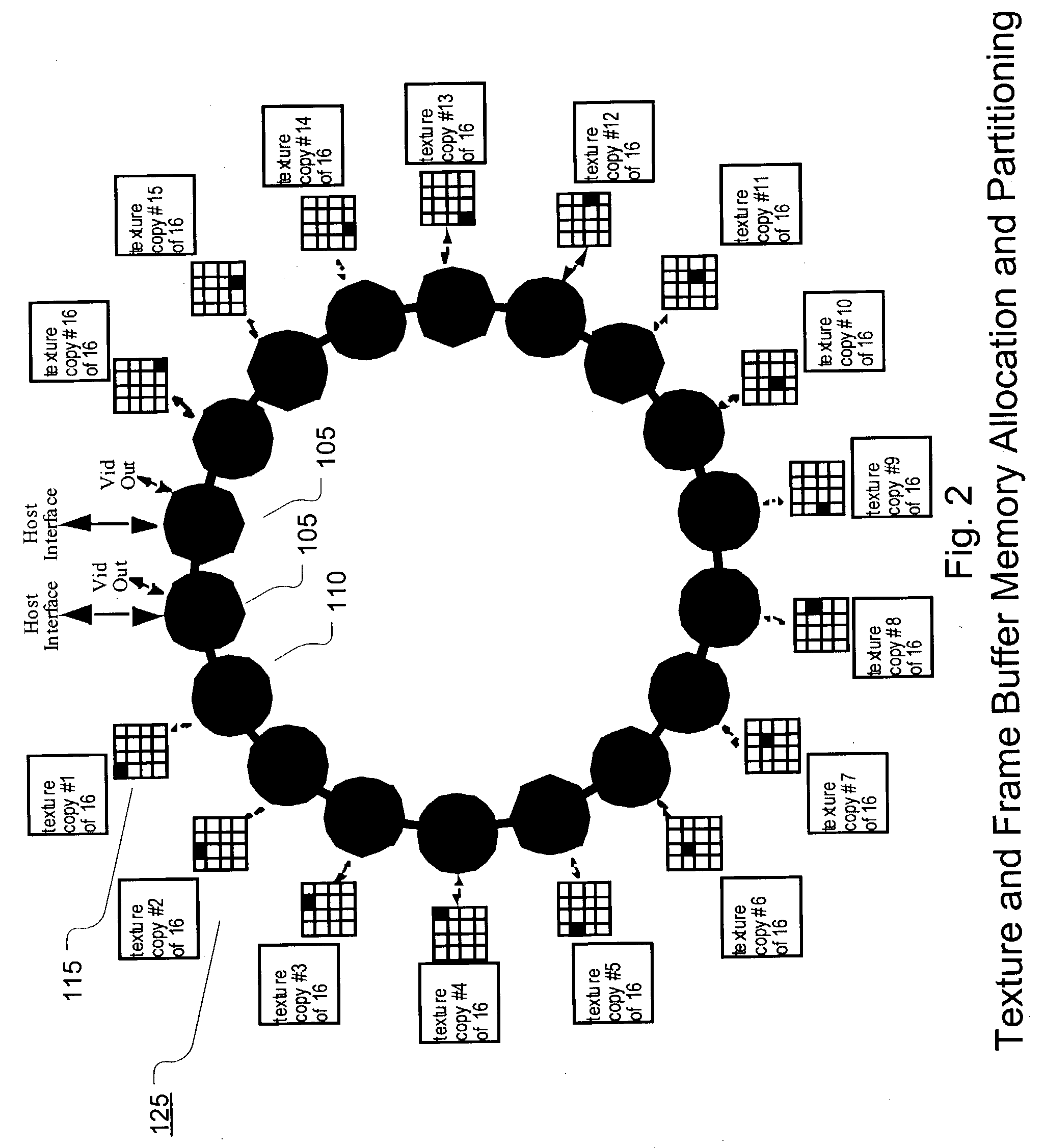

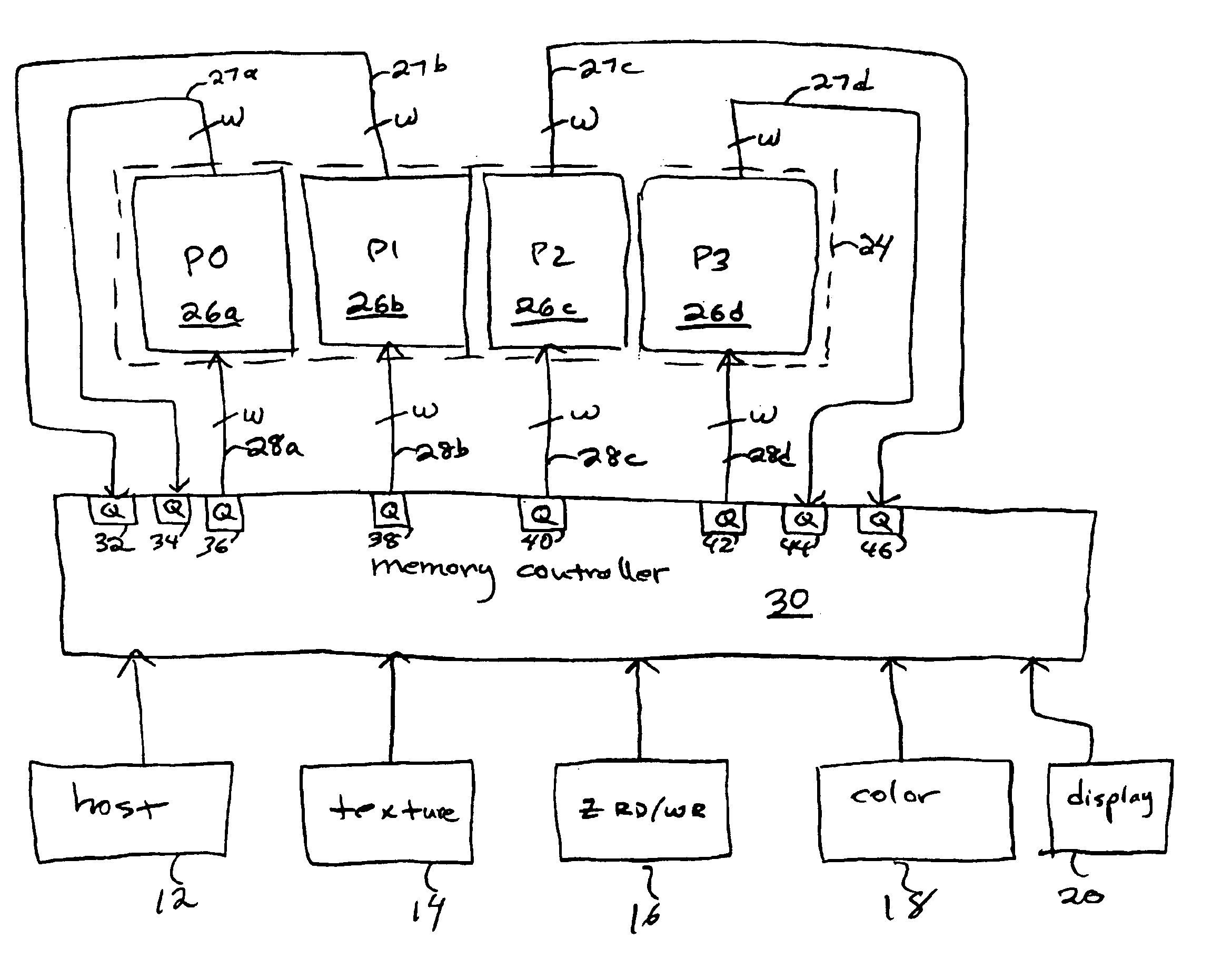

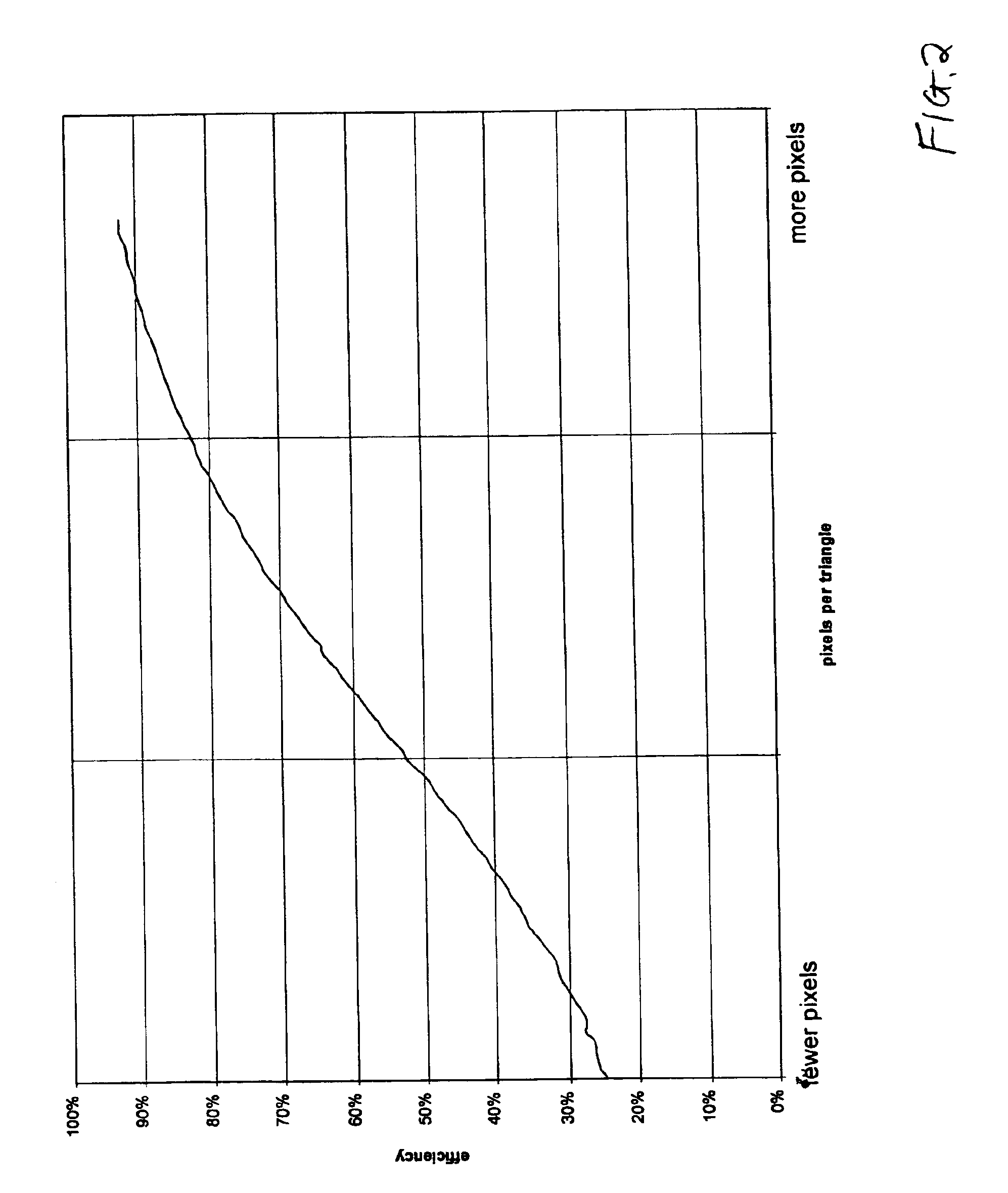

Scalable high performance 3d graphics

InactiveUS20040012600A1Minimizes cost and riskEasy to scaleImage enhancementImage memory managementGraphicsHigh bandwidth

A high-speed ring topology. In one embodiment, two base chip types are required: a "drawing" chip, LoopDraw, and an "interface" chip, LoopInterface. Each of these chips have a set of pins that supports an identical high speed point to point unidirectional input and output ring interconnect interface: the LoopLink. The LoopDraw chip uses additional pins to connect to several standard memories that form a high bandwidth local memory sub-system. The LoopInterface chip uses additional pins to support a high speed host computer host interface, at least one video output interface, and possibly also additional non-local interconnects to other LoopInterface chip(s).

Owner:DEERING MICHAEL F +2

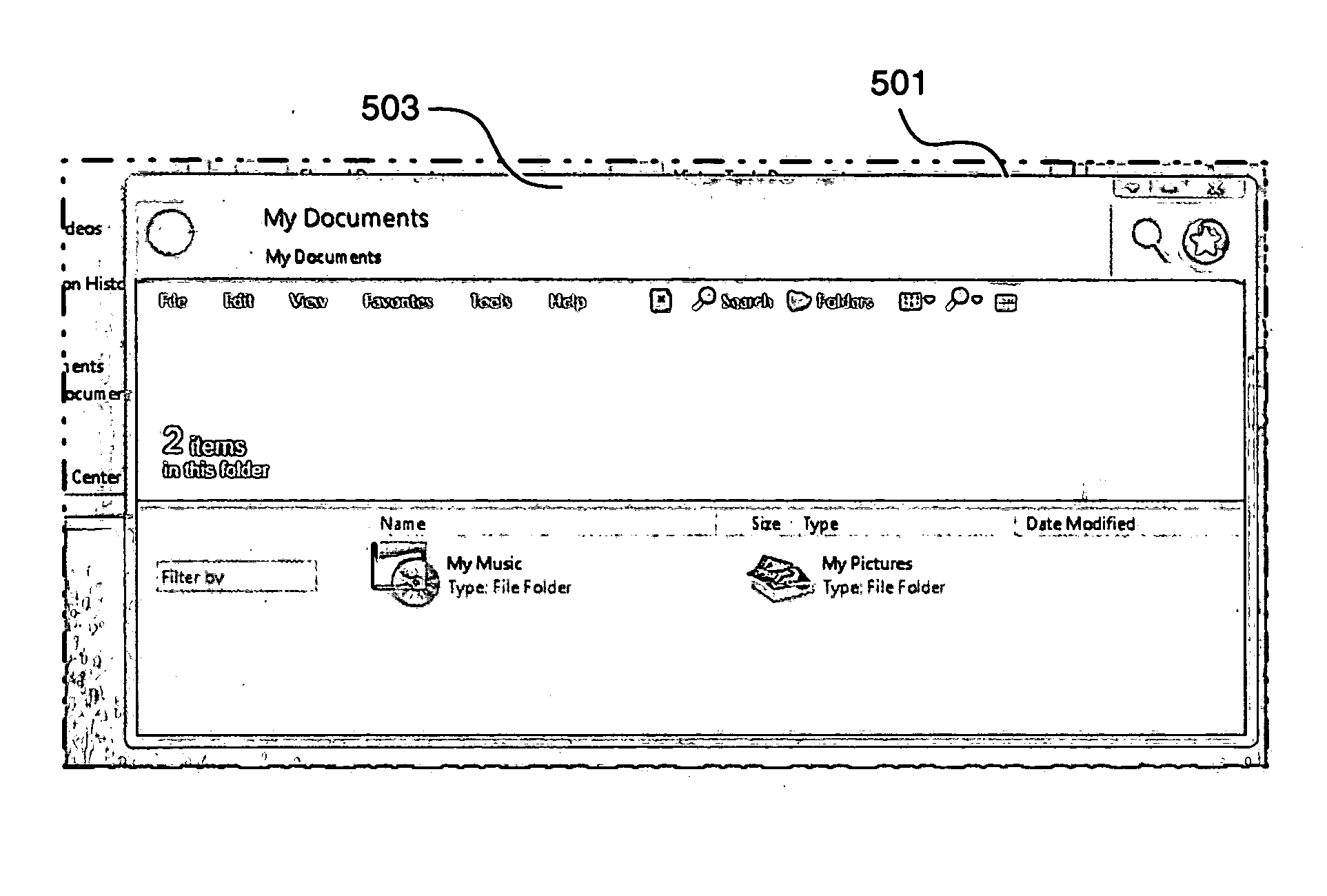

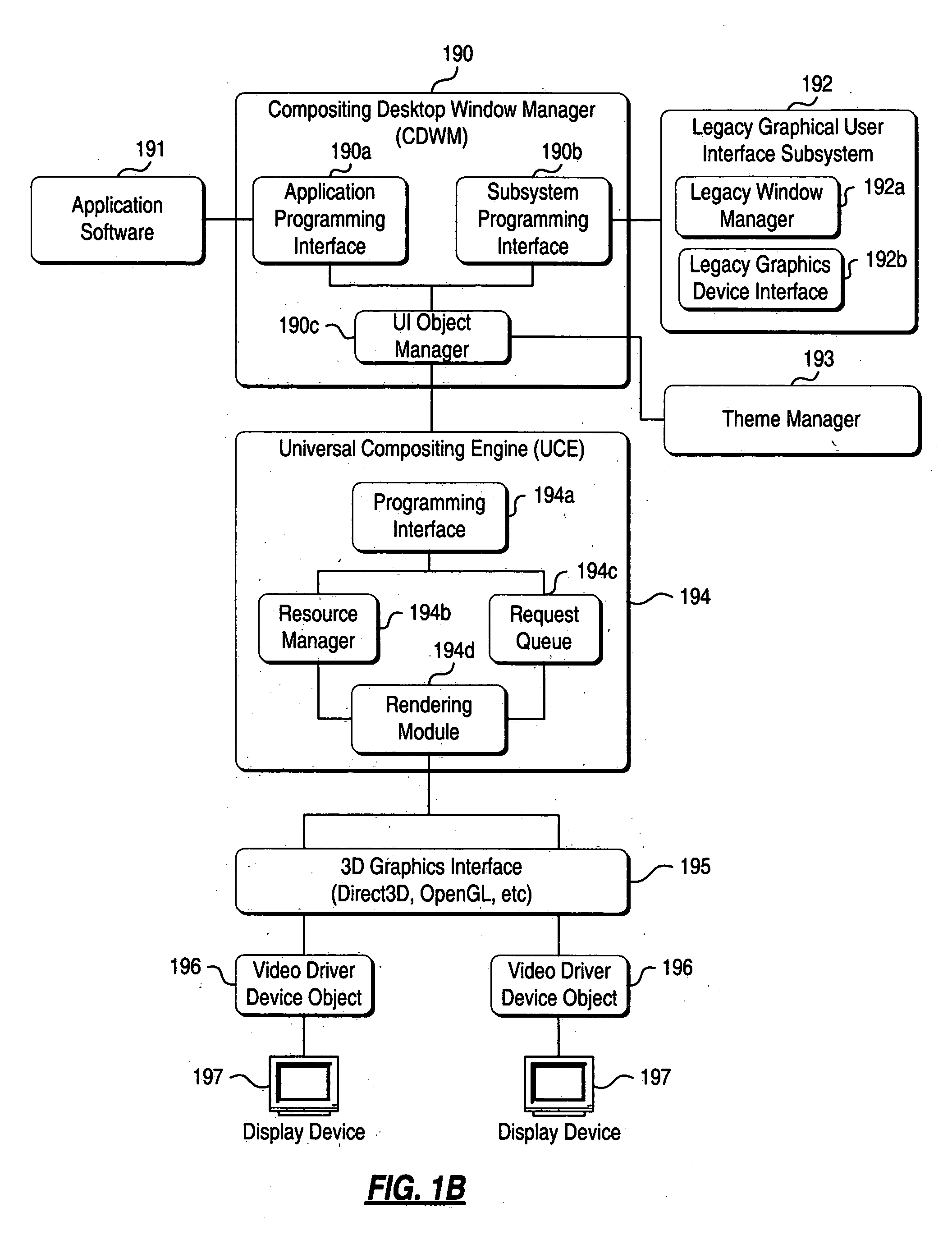

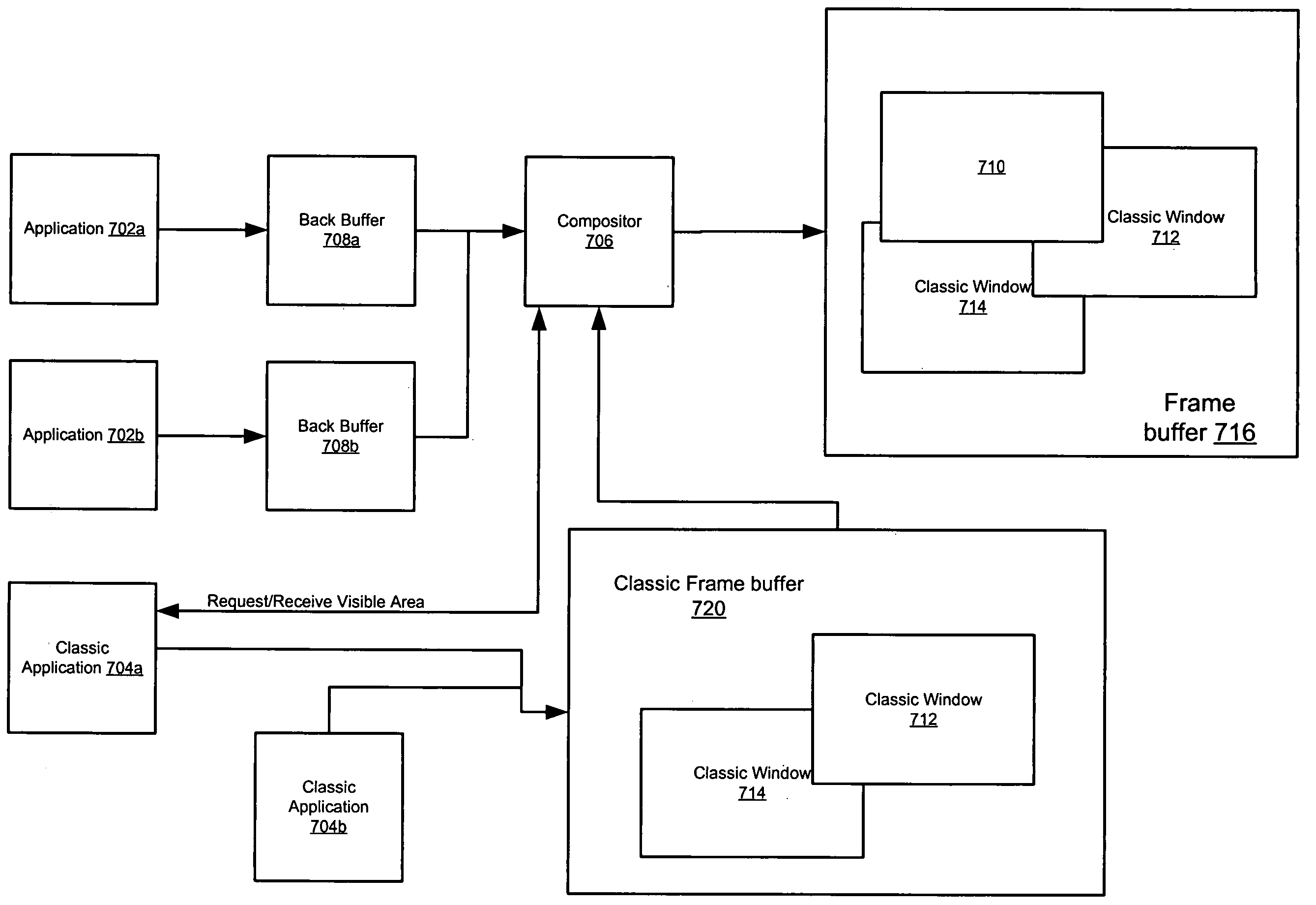

Compositing desktop window manager

InactiveUS20050088447A1Improve abilitiesMemory adressing/allocation/relocationDigital computer detailsWindow managerOperational system

A method and system for rendering a desktop on a computer using a composited desktop model operating system are disclosed. A composited desktop window manager, upon receiving content information from application programs, draws the window to a buffer memory for future reference, and takes advantage of advanced graphics hardware and visual effects to render windows based on content on which they are drawn. The windows may also be rendered based on environment variables including virtual light sources. The frame portion of each window may be generated by pixel shading a bitmap having the appearance of frosted glass based on the content of the desktop on top of which the frame is displayed. Legacy support is provided so that the operating system can draw and render windows generated by legacy applications to look consistent with non-legacy application windows.

Owner:MICROSOFT TECH LICENSING LLC

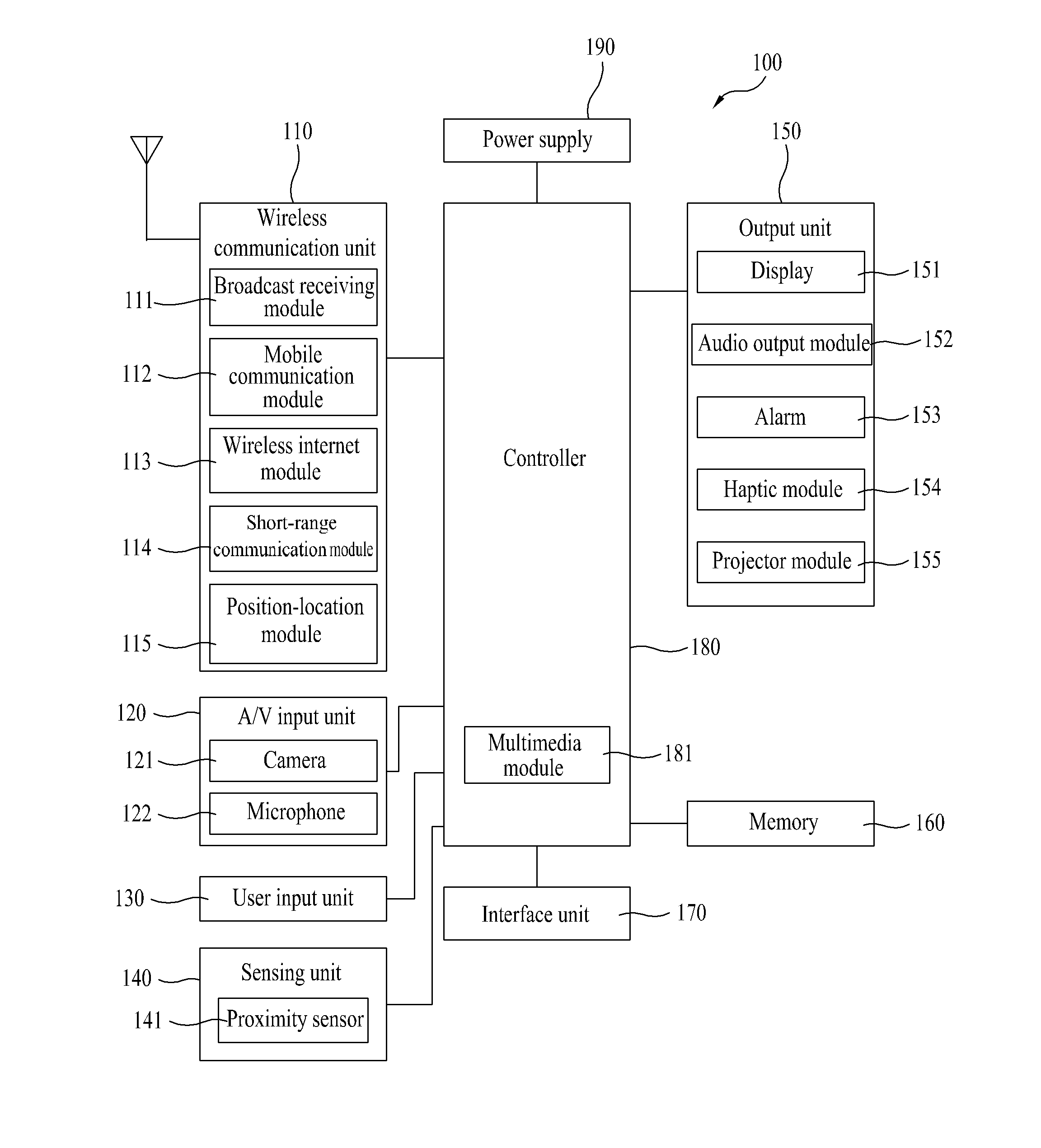

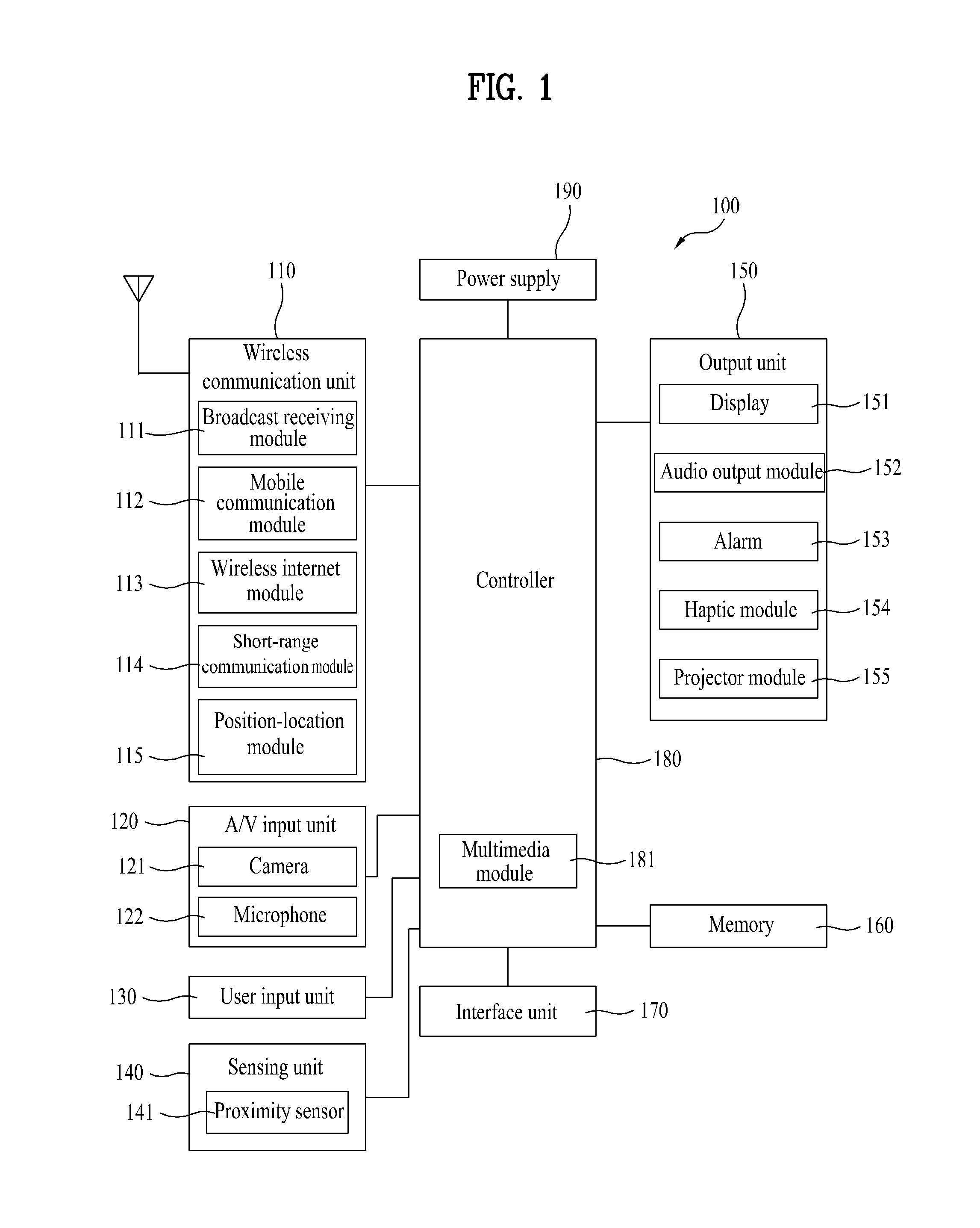

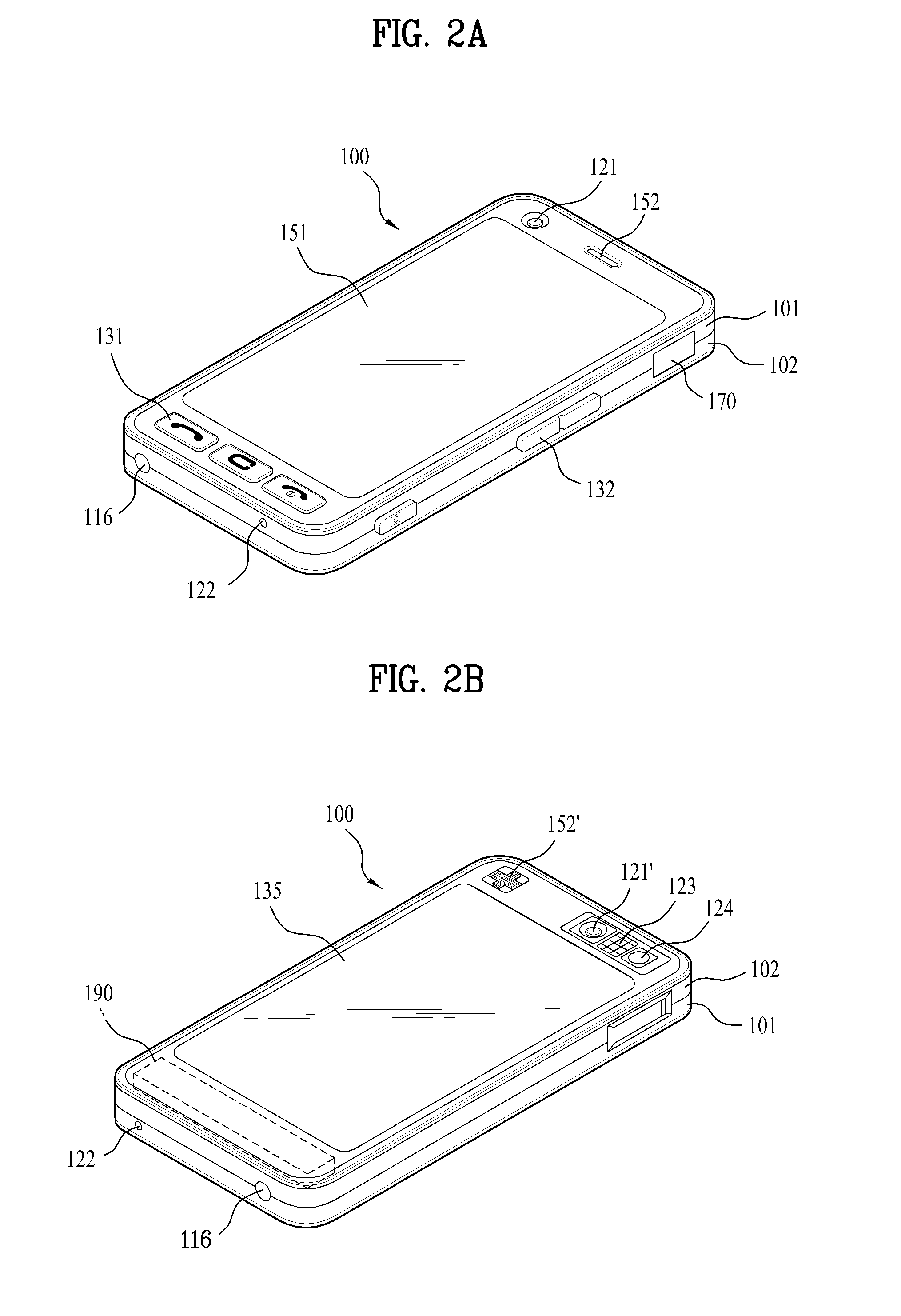

Mobile terminal and method of controlling a mode switching therein

InactiveUS20120154413A1Efficient executionReinforcing inter-mode data securityImage memory managementInternal/peripheral component protectionOperational systemCommunication unit

A mobile terminal including a communication unit configured to communicate with at least one external terminal; a memory configured to store at least a first and second operating system including at least first and second modes, respectively; and a controller configured to execute the first operating system and to activate the first mode corresponding to the first operating system, to display a first information screen on a display unit corresponding to the activated first mode, to receive a switching signal indicating the first mode is to be switched to the second mode, to perform an authentication procedure for authenticating that the first mode can be switched to the second mode, to activate the second mode and deactivate the first mode when the authentication procedure is validly performed, and to display a second information screen on the display unit corresponding to the second mode and that is different than the first information screen.

Owner:LG ELECTRONICS INC

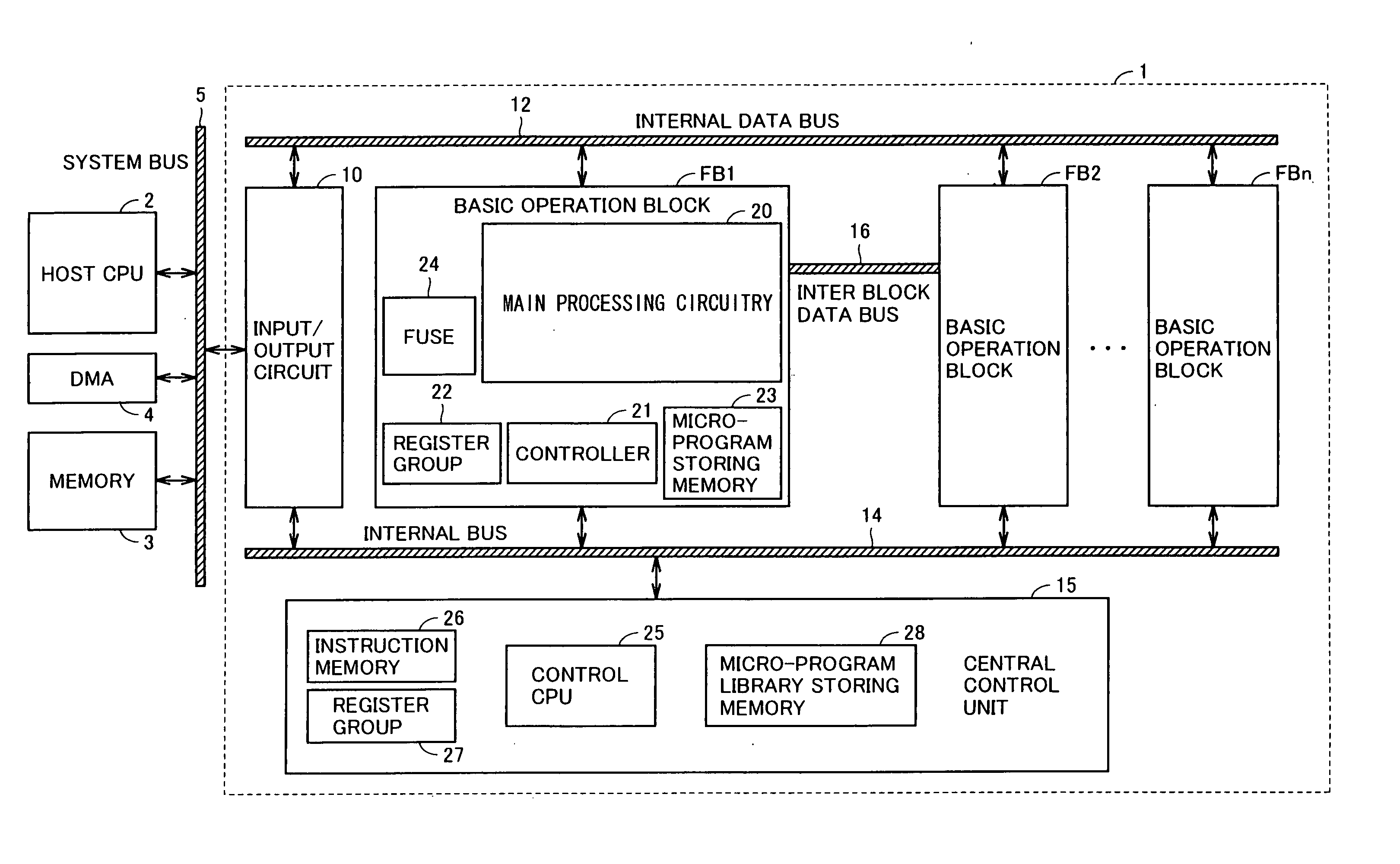

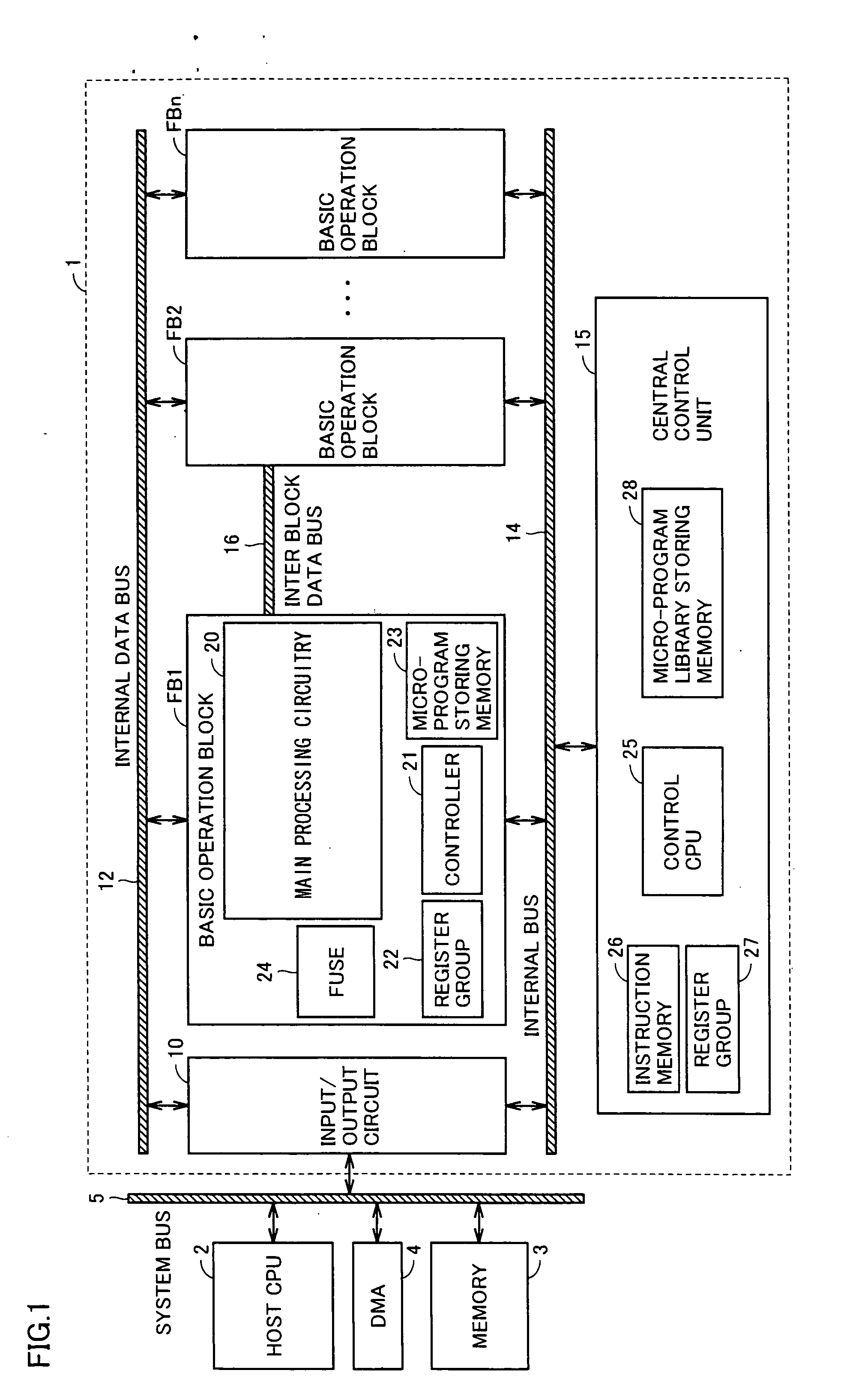

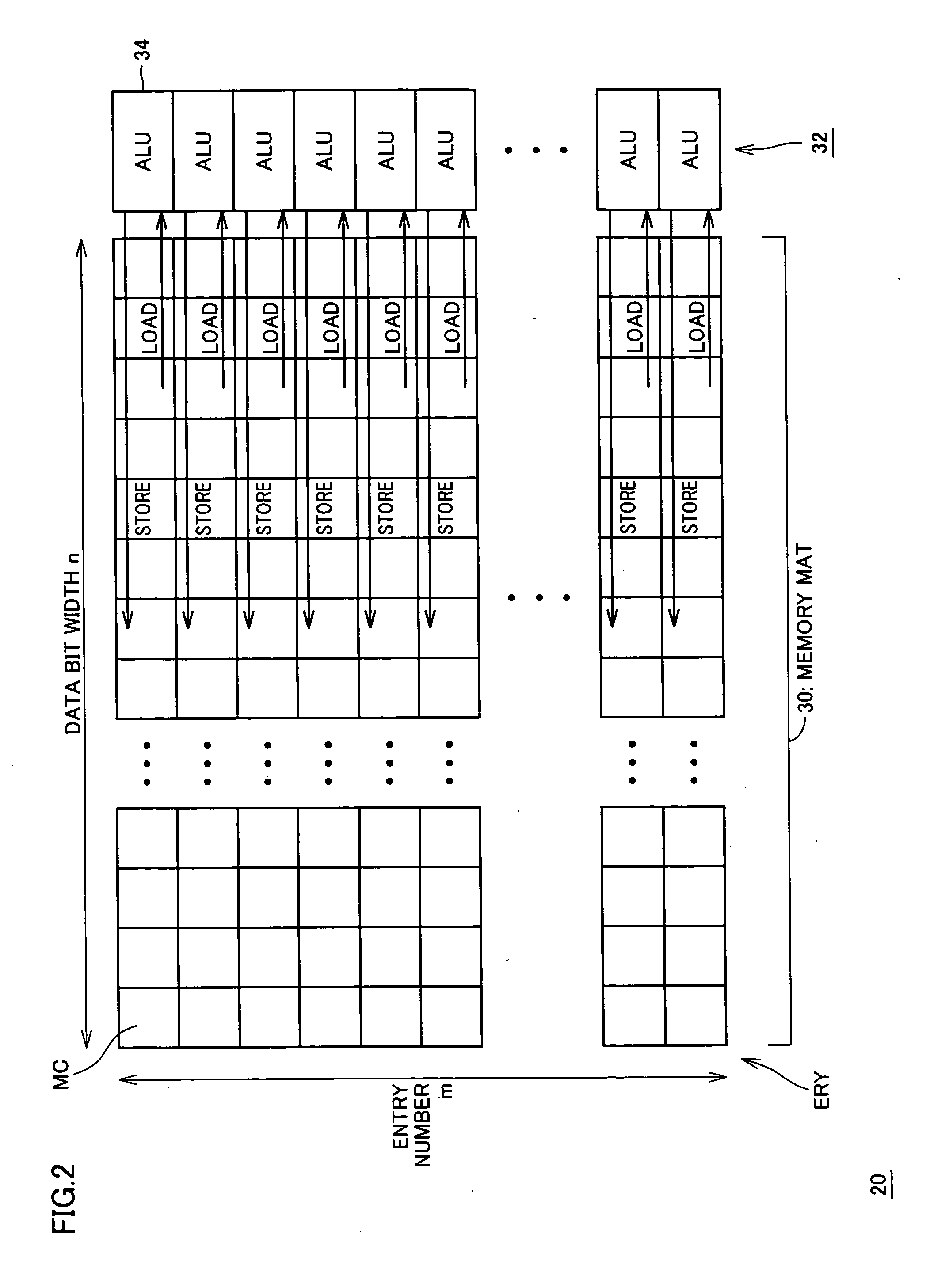

Semiconductor device and semiconductor signal processing apparatus

InactiveUS20050285862A1Operation control becomes easyEasy to processImage memory managementMultiple digital computer combinationsArithmetic logic unitDevice material

A memory cell mat is divided into a plurality of entries, and an arithmetic logic unit is arranged corresponding to each entry. Between the entries and the corresponding arithmetic logic units, arithmetic / logic operation is executed in bit-serial and entry-parallel manner. Where parallel operation is not very effective, data is transferred in entry-serial and bit-parallel manner to a group of processors provided at a lower portion of the memory mat. In this manner, a large amount of data can be processed at high speed regardless of the contents of operation or data bit width.

Owner:RENESAS ELECTRONICS CORP

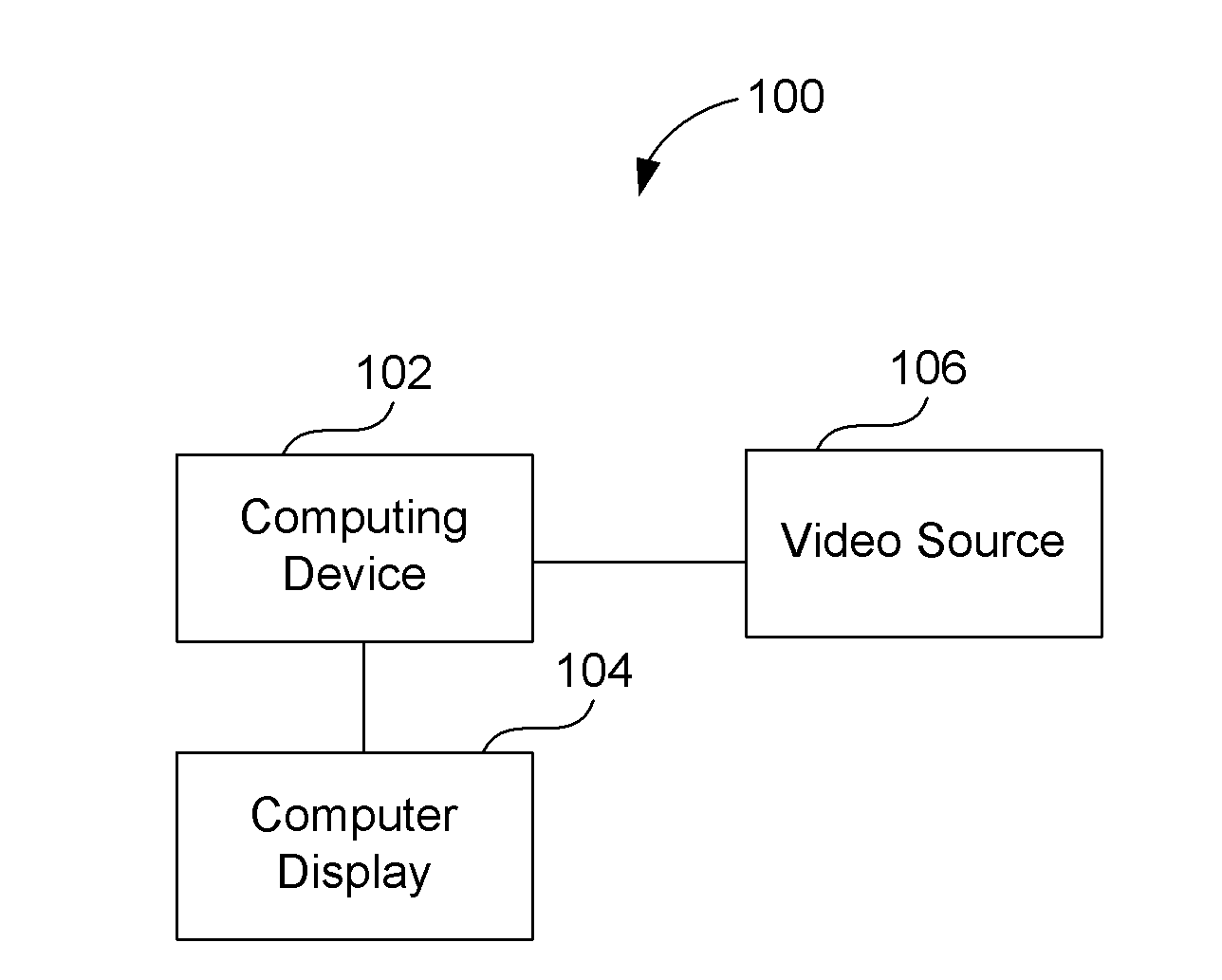

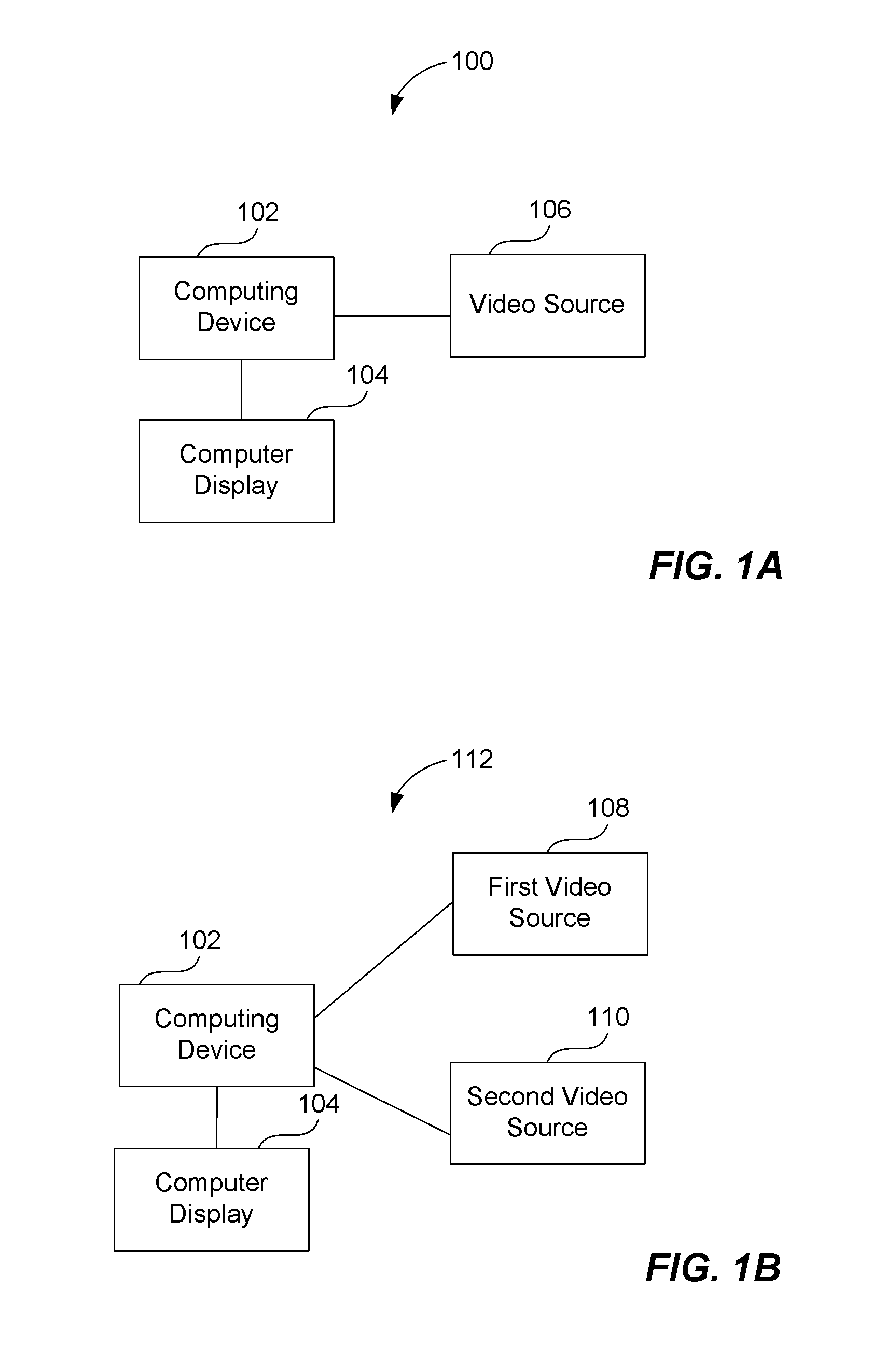

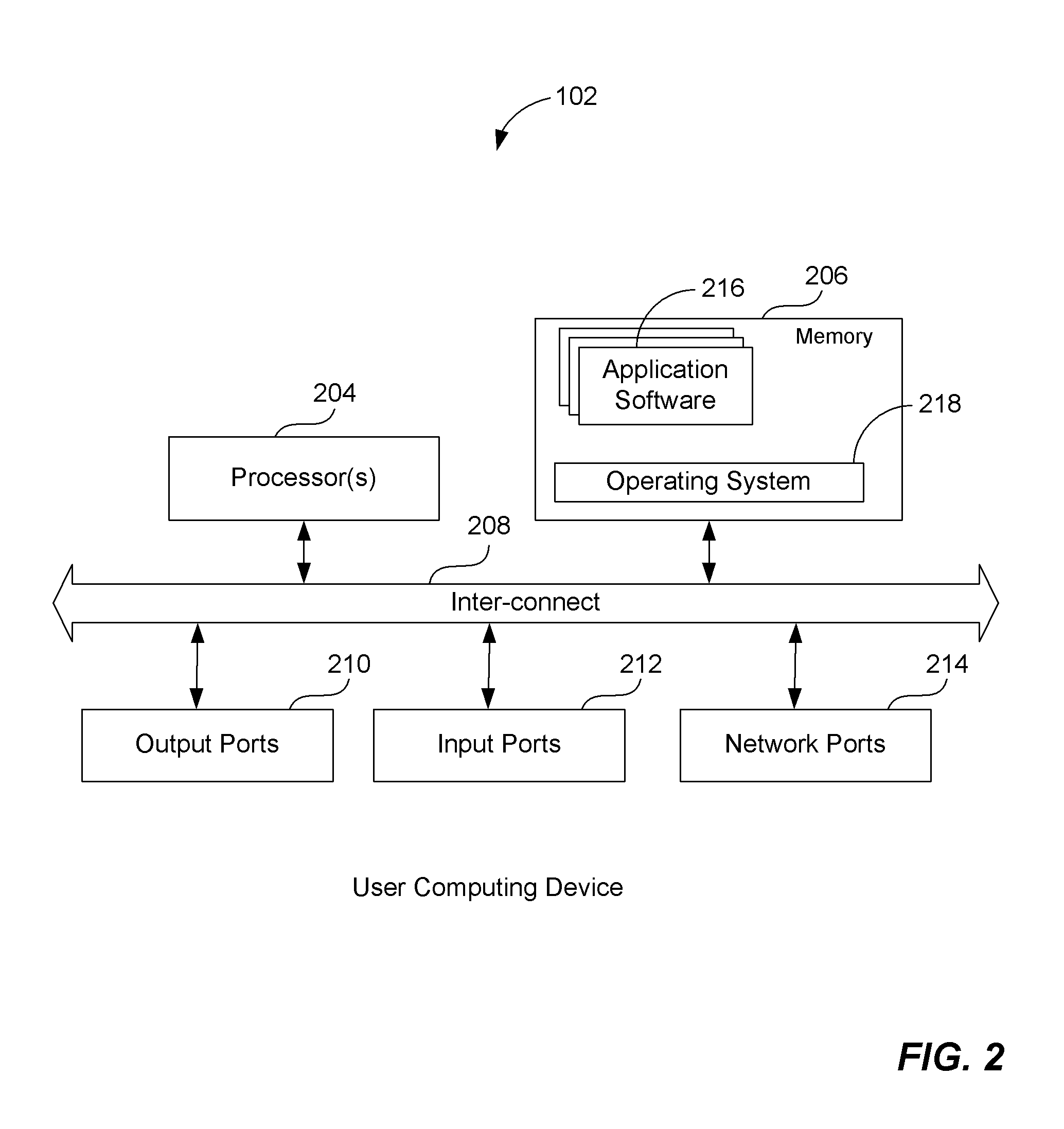

Method and system for presenting video

InactiveUS20080111822A1Television system detailsImage memory managementComputer graphics (images)Display device

Owner:OATH INC

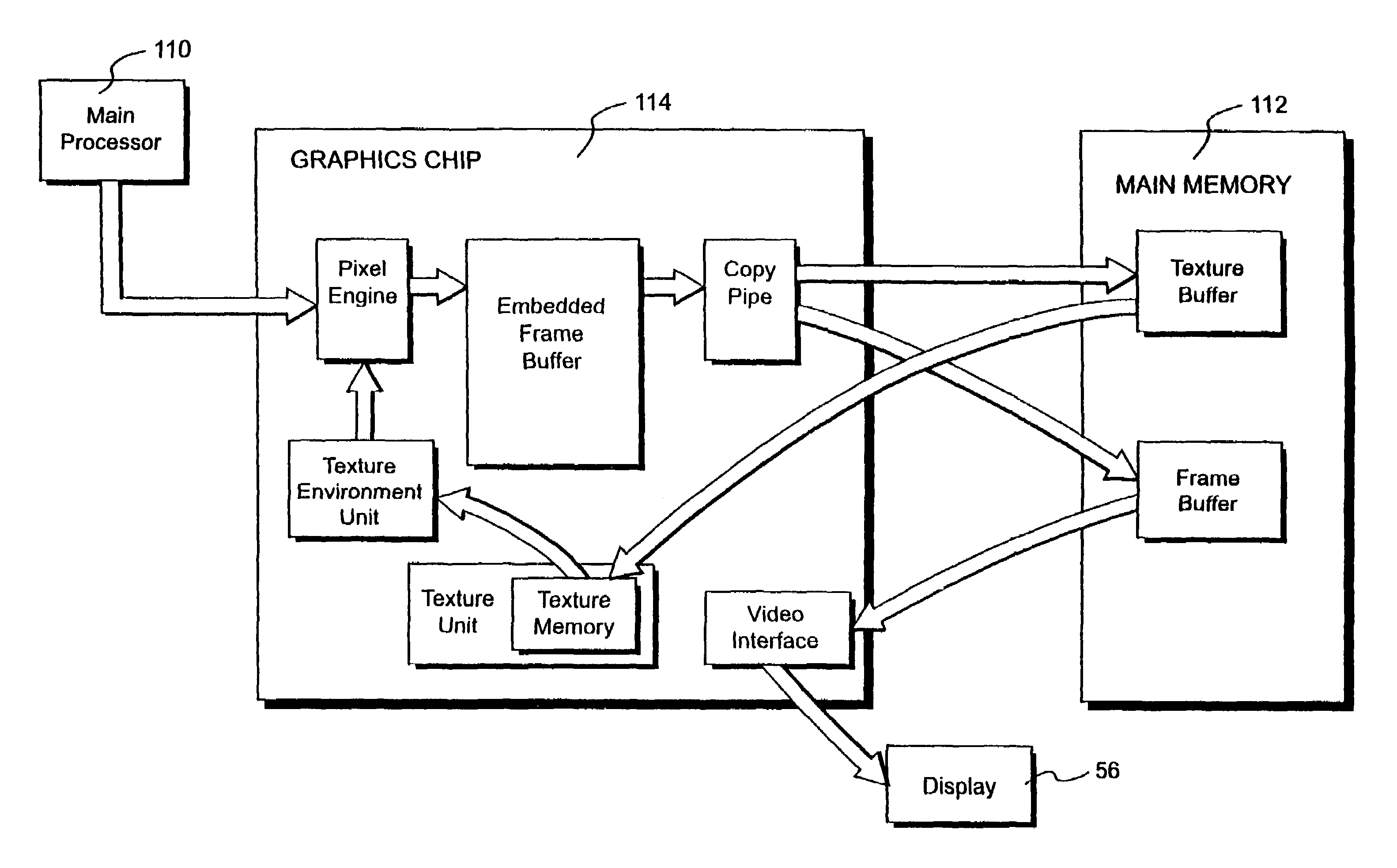

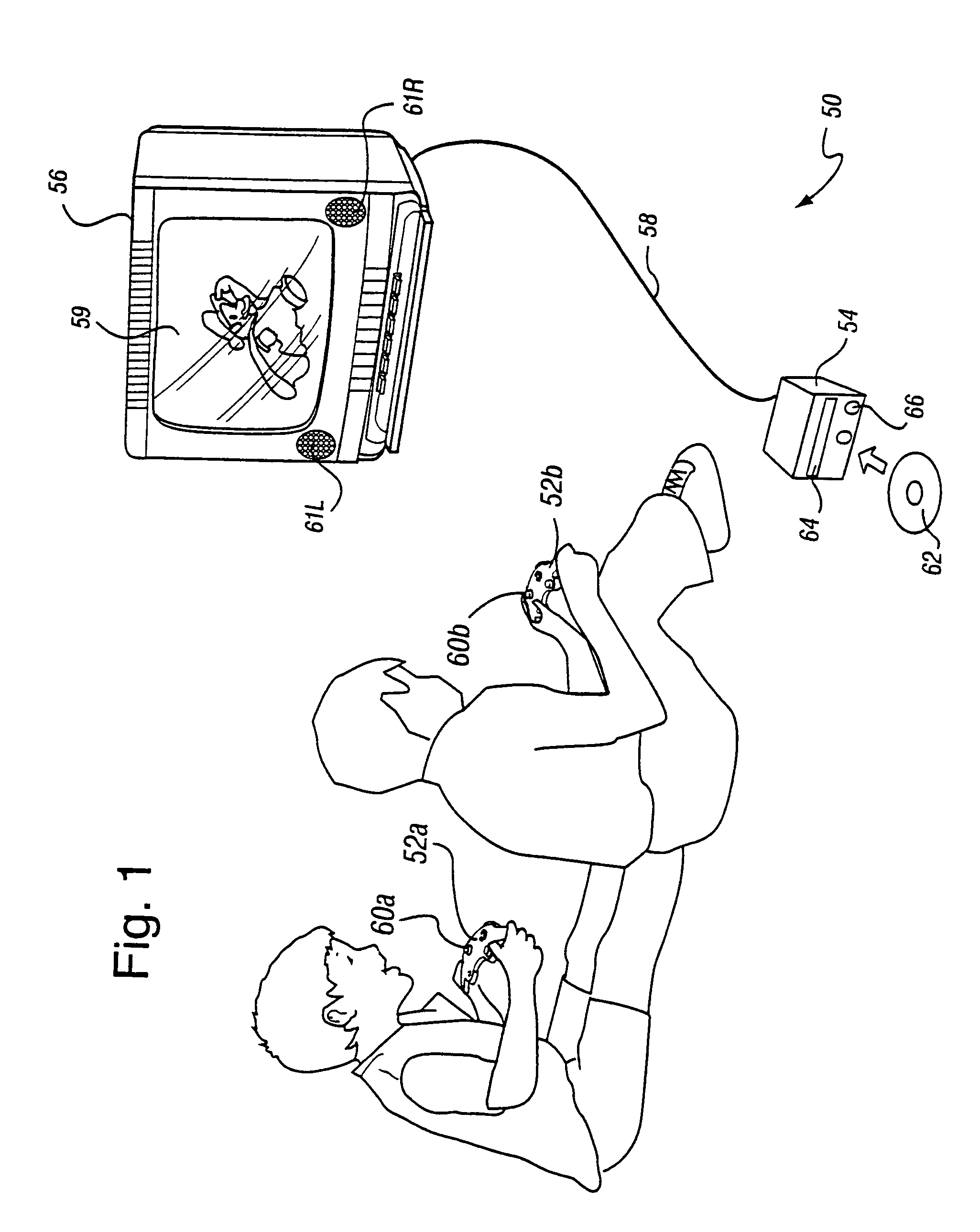

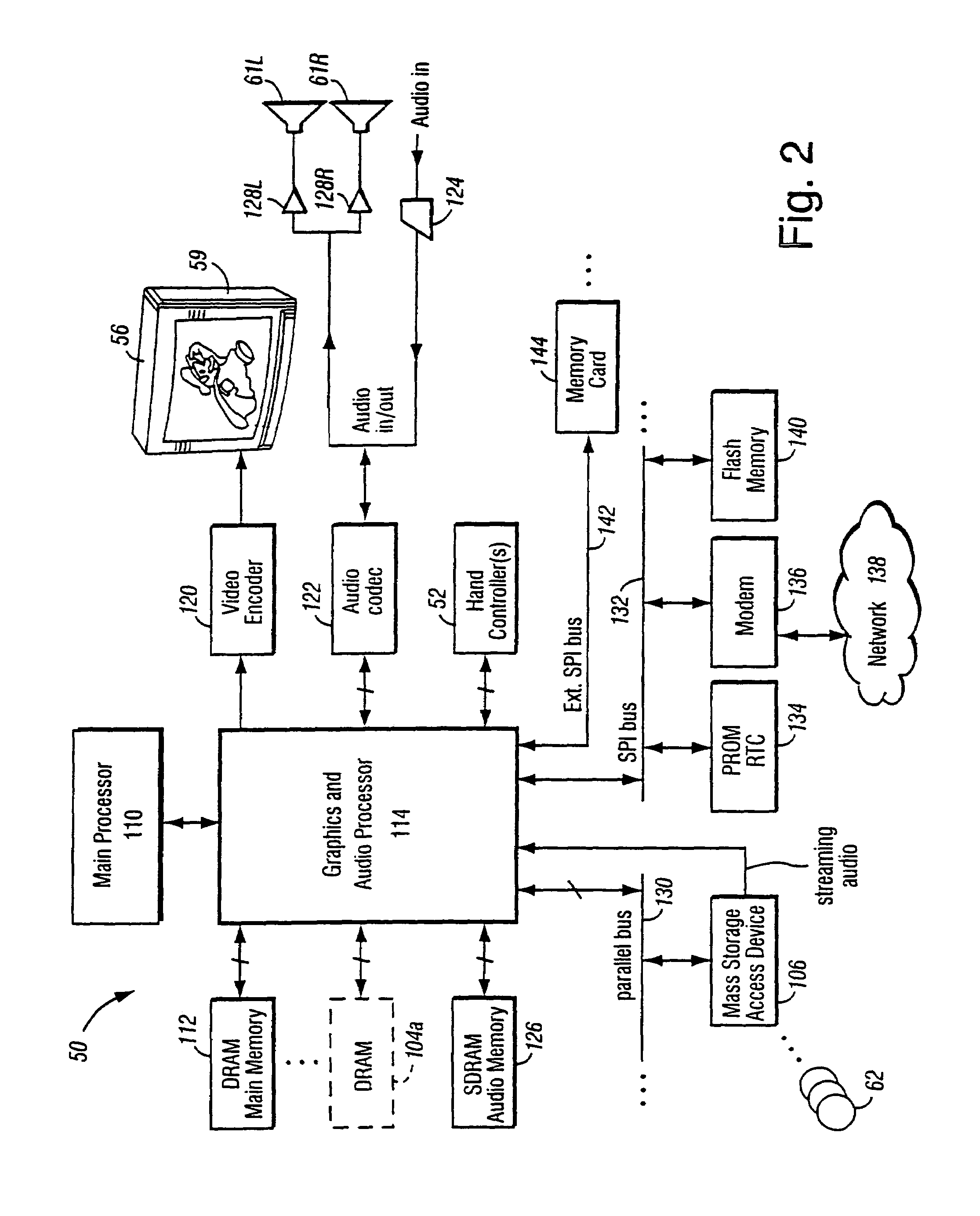

Graphics system with copy out conversions between embedded frame buffer and main memory

InactiveUS7184059B1Improve system flexibilityEasy to useImage memory managementCathode-ray tube indicatorsGraphic systemGraphics processing unit

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics processor includes an embedded frame buffer for storing frame data prior to sending the frame data to an external location, such as main memory. A copy pipeline is provided which converts the data from one format to another format prior to writing the data to the external location. The conversion may be from one RGB color format to another RGB color format, from one YUV format to another YUV format, from an RGB color format to a YUV color format, or from a YUV color format to an RGB color format. The formatted data is either transferred to a display buffer, for use by the video interface, or to a texture buffer, for use as a texture by the graphics pipeline in a subsequent rendering process.

Owner:NINTENDO CO LTD

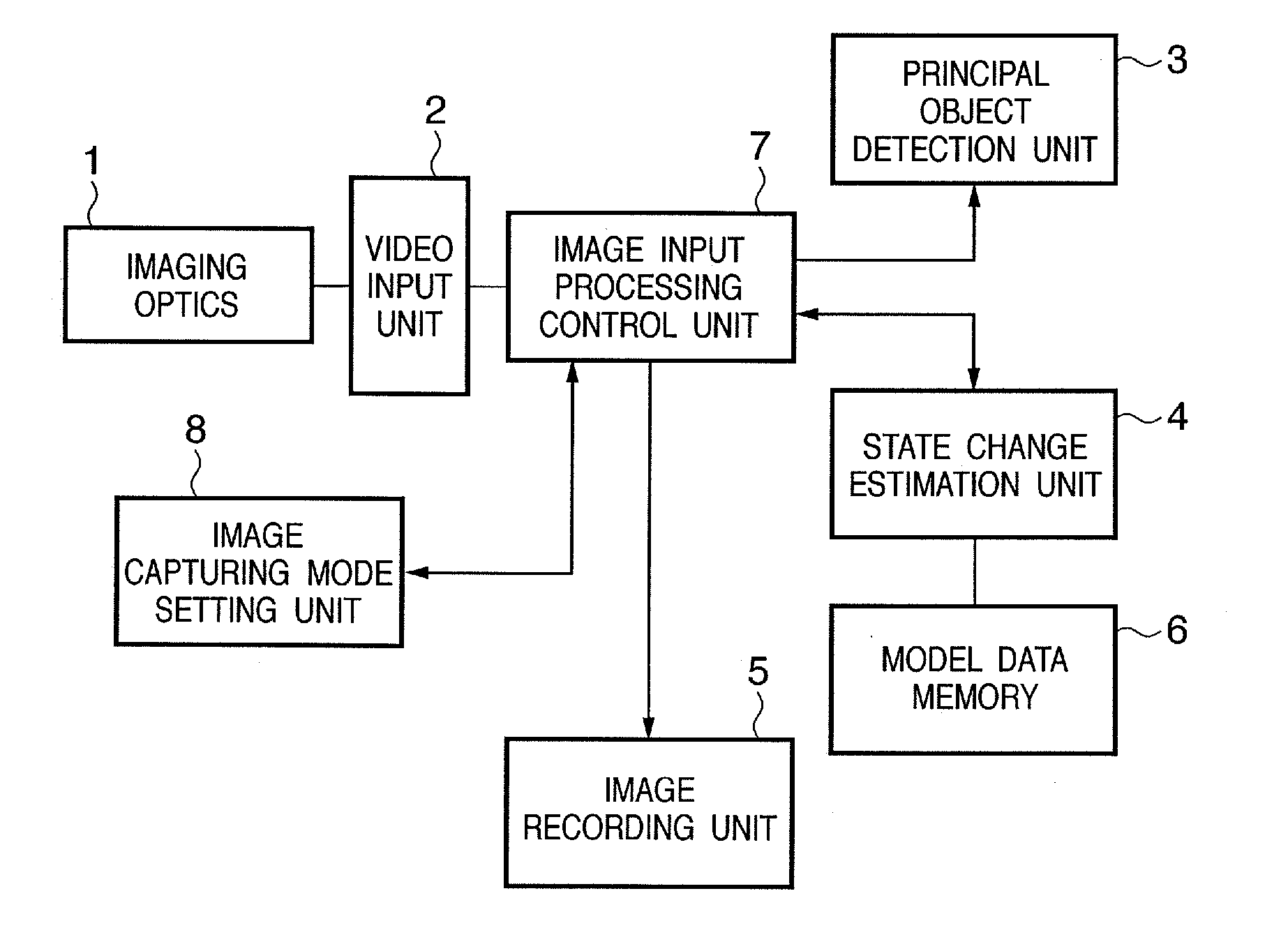

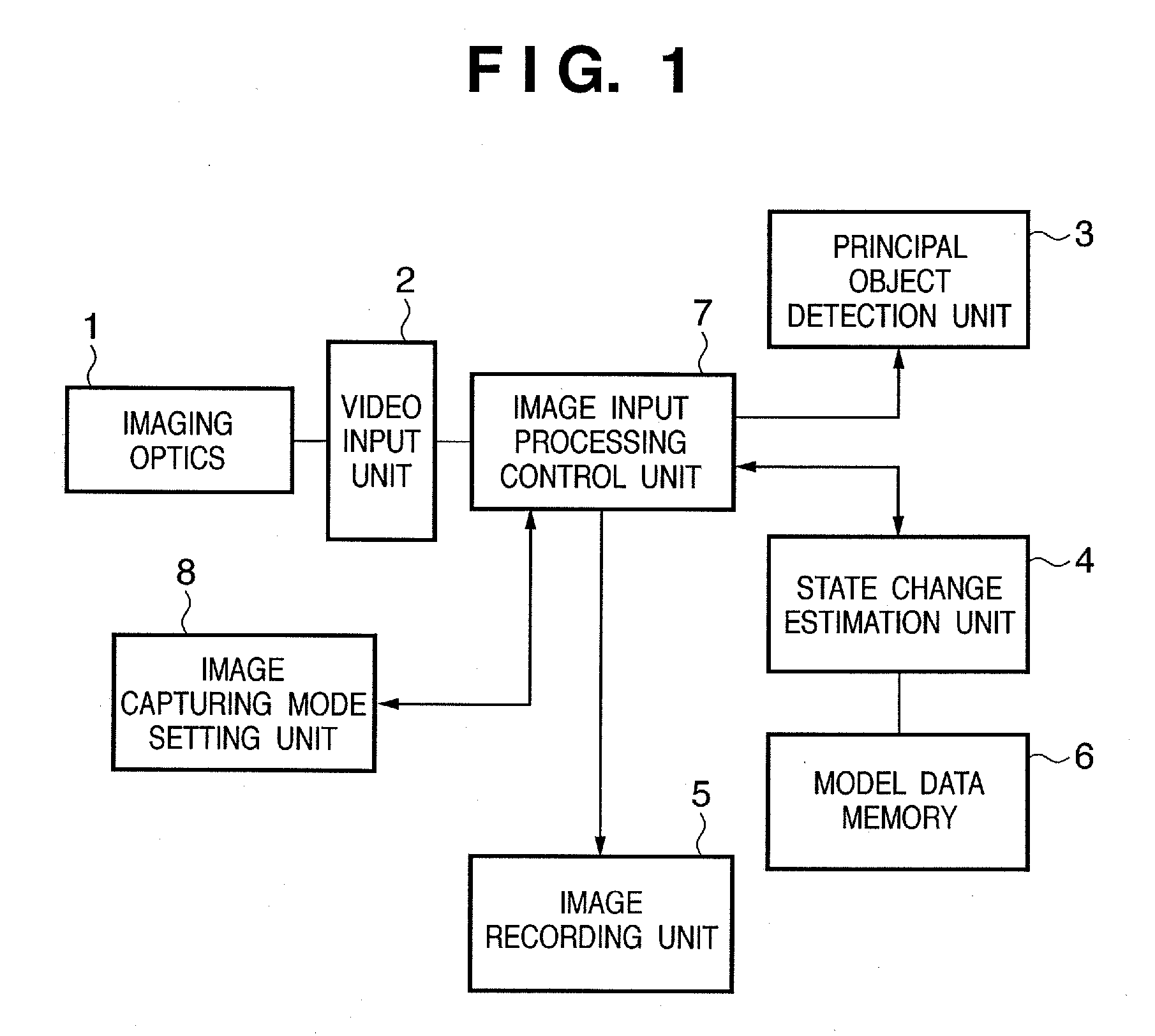

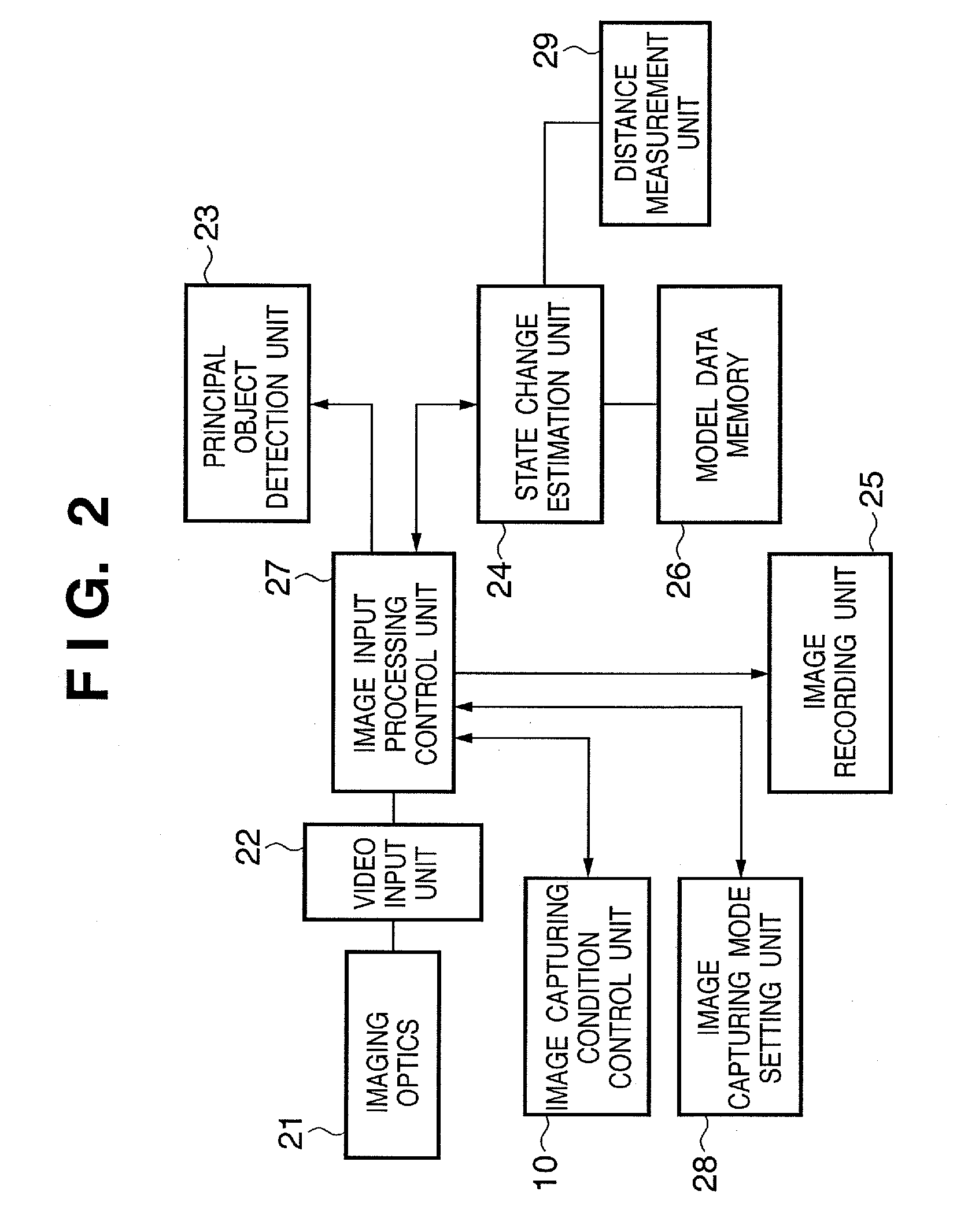

Image capturing apparatus and image capturing method

InactiveUS20070025722A1Photo opportunity can be missedTelevision system detailsImage analysisState variationImage recording

In an image capturing apparatus, a video input unit (2) captures the image of an object and sequentially acquires image data associated with the image capturing, a model data memory (6) stores model data associated with the first feature quantity calculated from a feature point of the object in a model image, a principal object detection unit (3) calculates the second feature quantity from a feature point of the object in the acquired image data, a state change estimation unit (4) estimates, on the basis of the second feature quantity and the model data, the timing when the object satisfies a predetermined condition, and an image input processing control unit (7) stores the image data corresponding to the estimated timing in an image recording unit (5). This configuration makes the image capturing apparatus acquire an image in a more proper state without large-capacity memory.

Owner:CANON KK

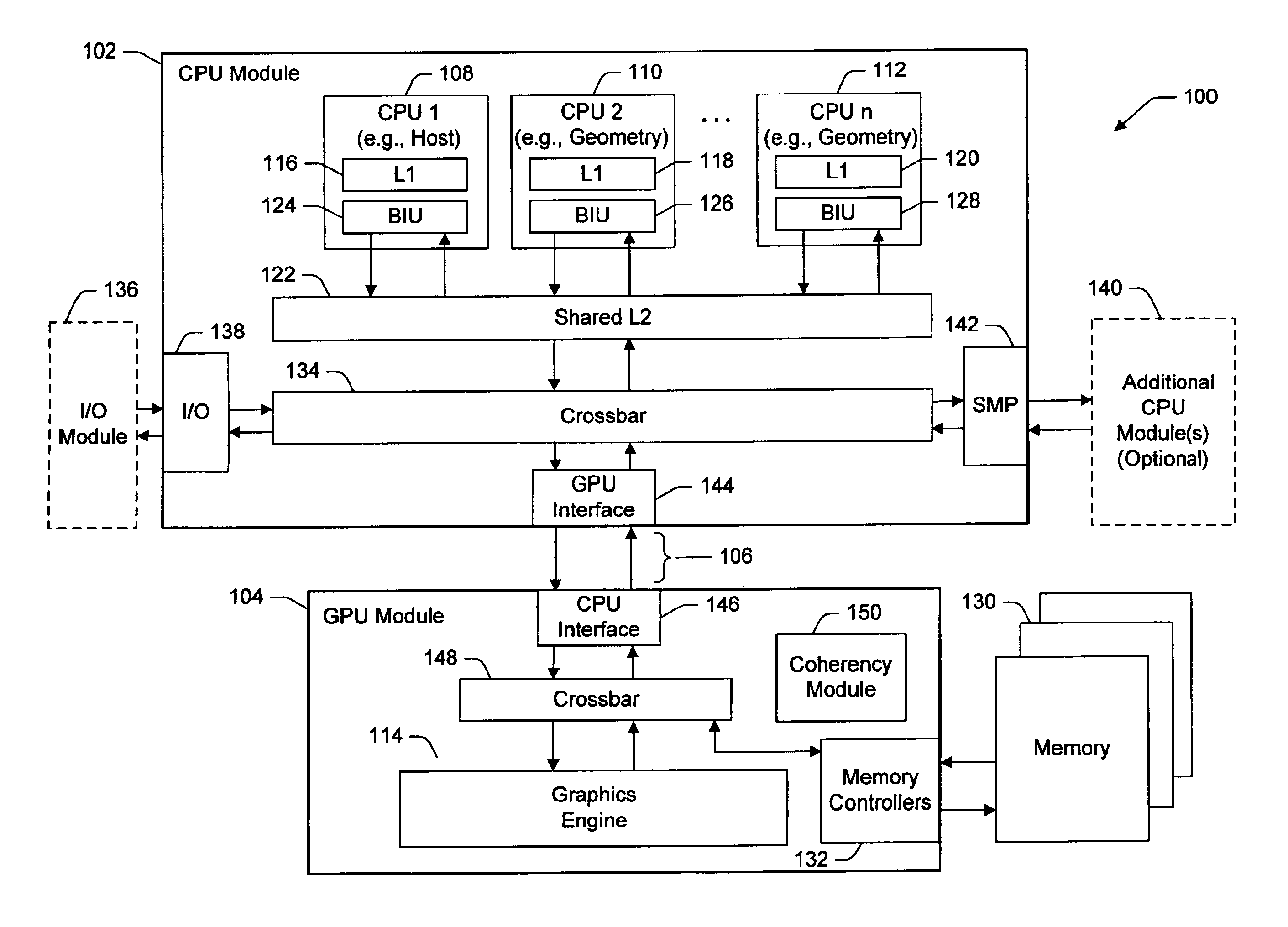

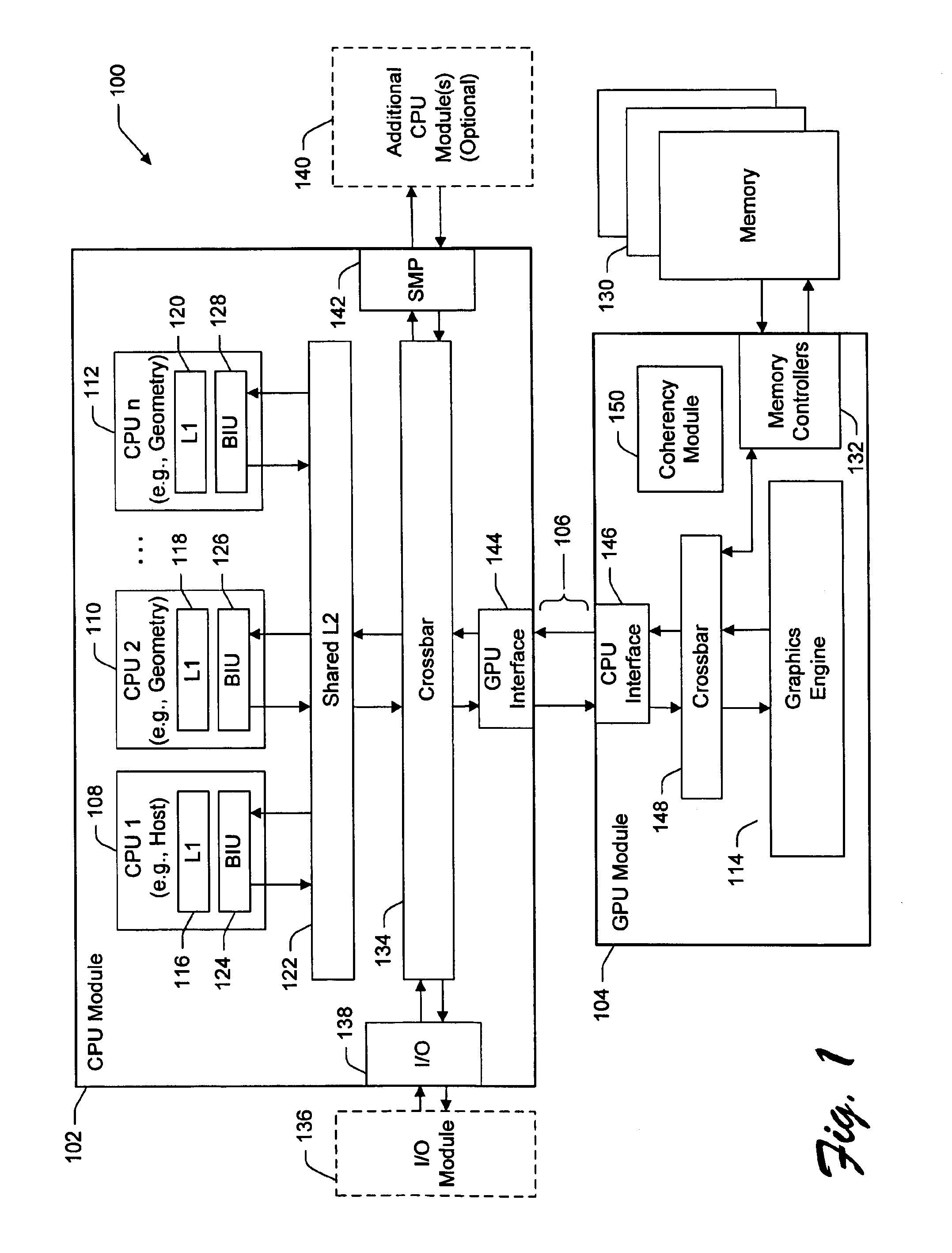

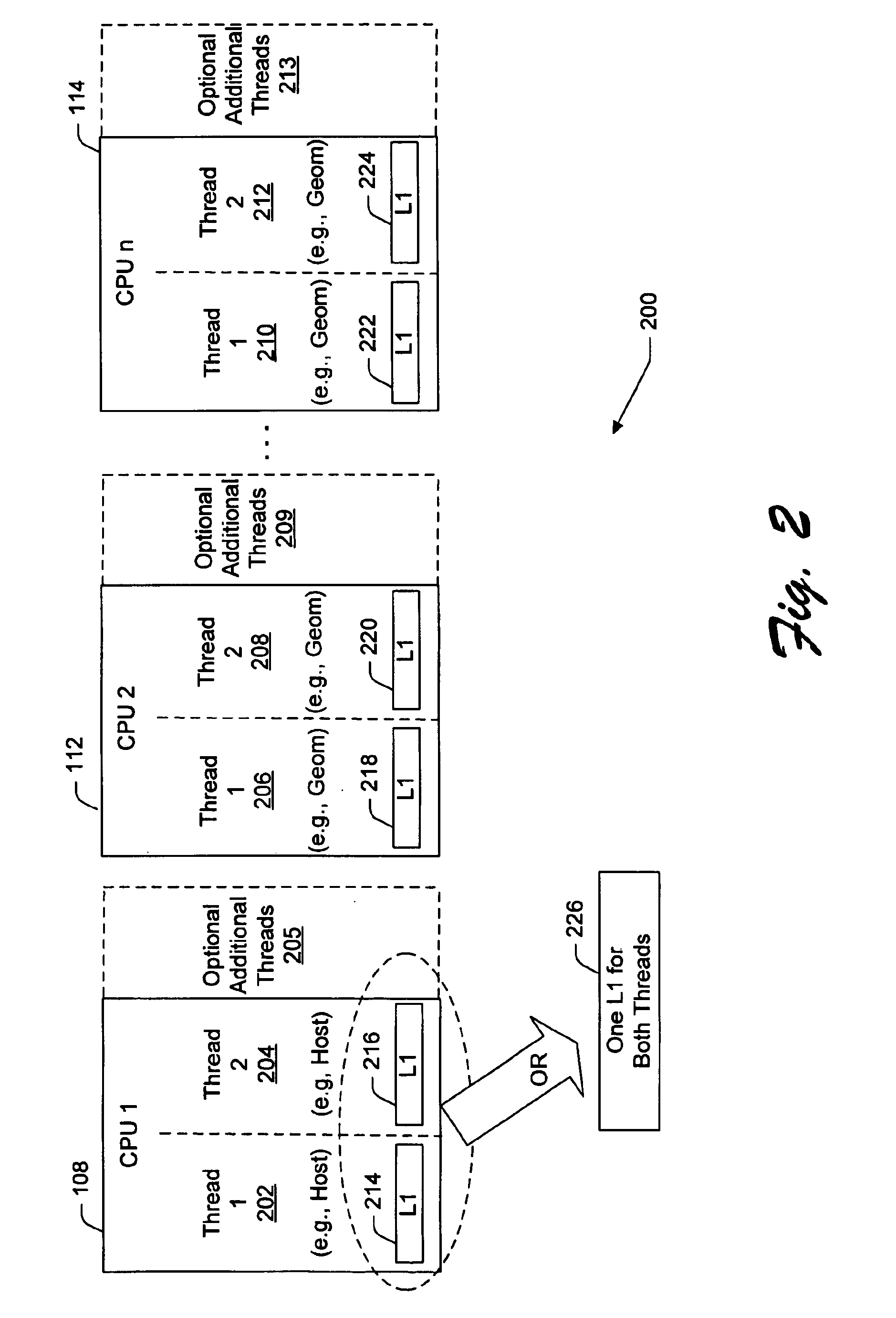

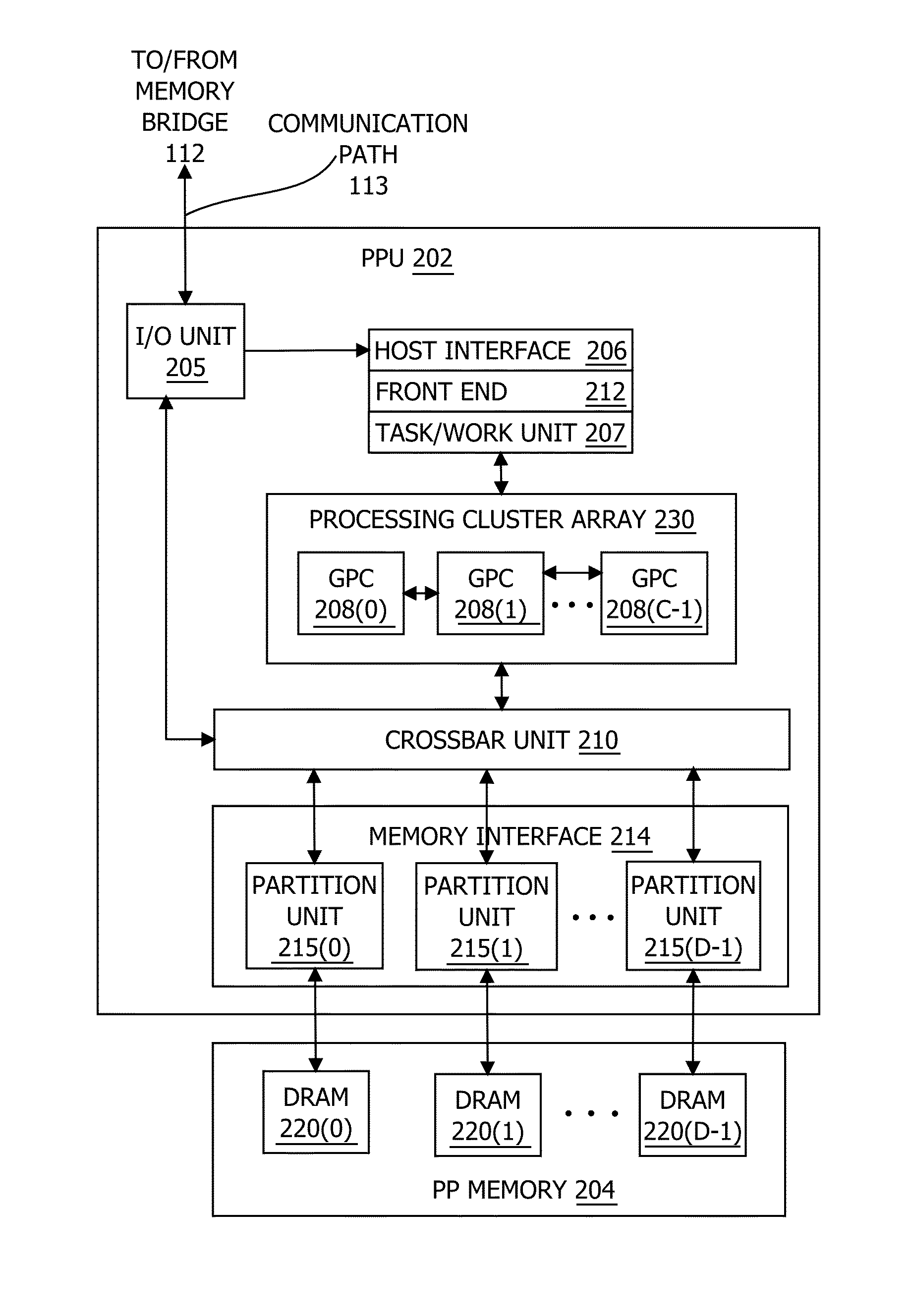

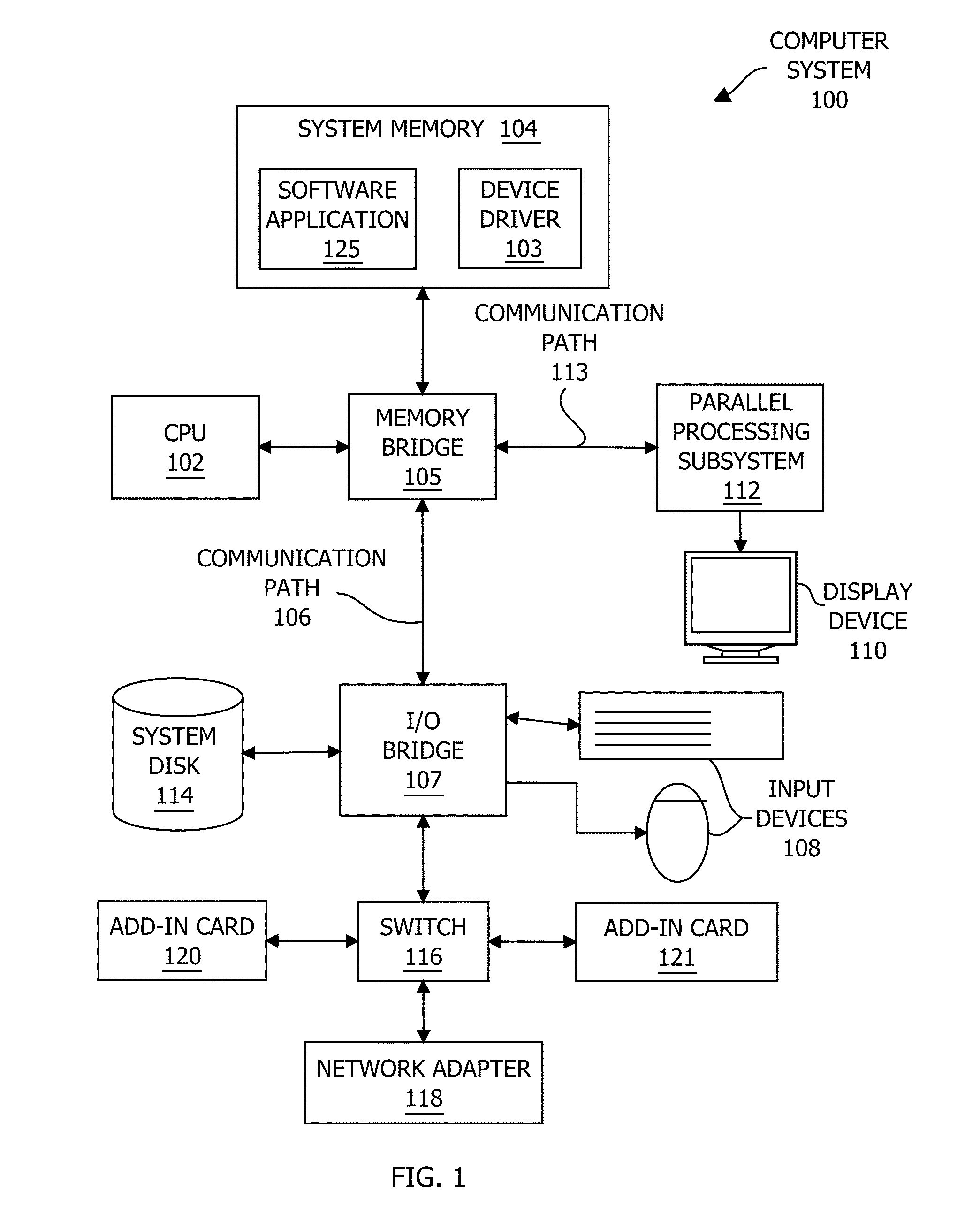

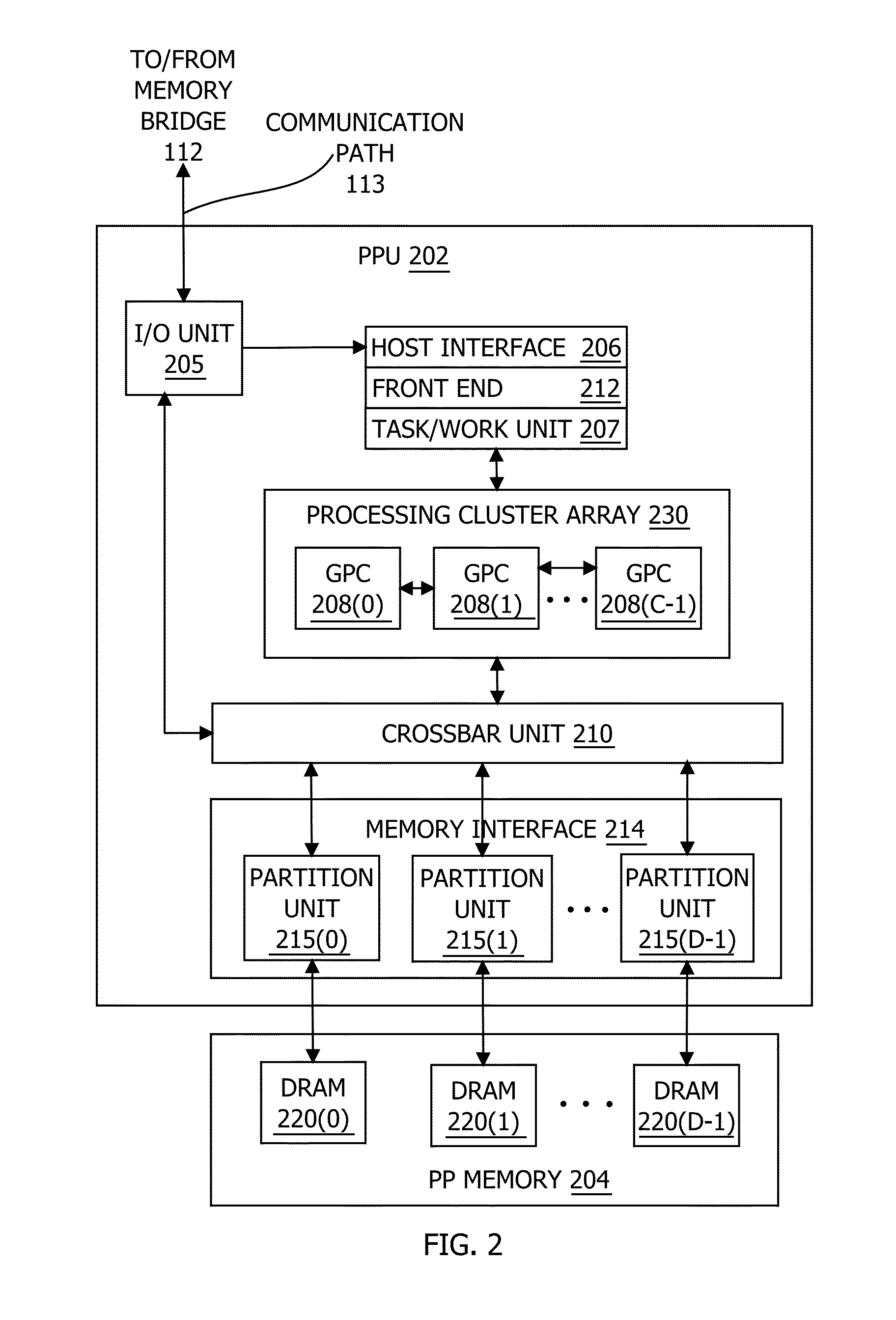

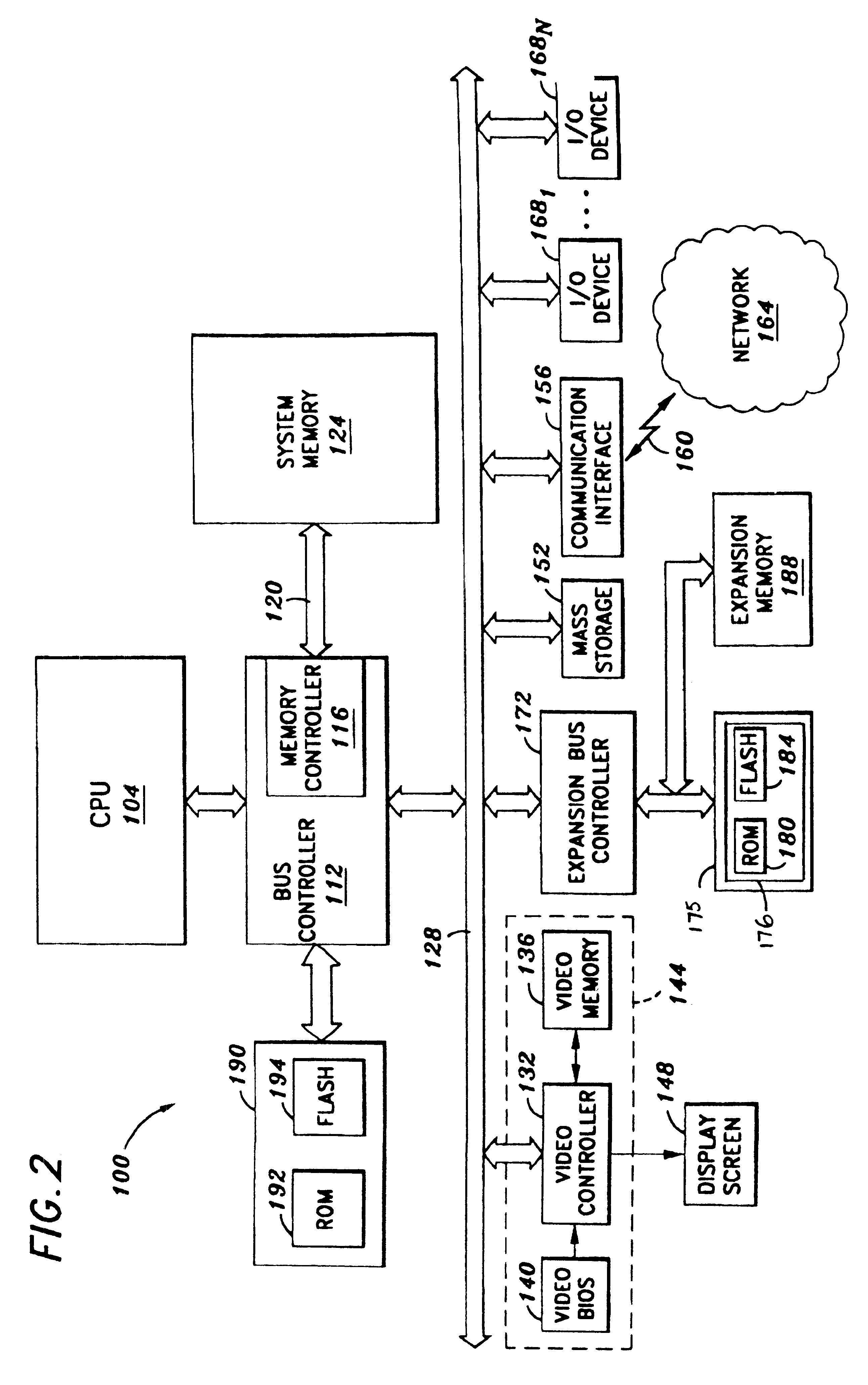

System and method for parallel execution of data generation tasks

InactiveUS6862027B2Reduce storage requirementsReduces deleterious bandwidth restrictionResource allocationMemory adressing/allocation/relocationGraphicsParallel computing

A CPU module includes a host element configured to perform a high-level host-related task, and one or more data-generating processing elements configured to perform a data-generating task associated with the high-level host-related task. Each data-generating processing element includes logic configured to receive input data, and logic configured to process the input data to produce output data. The amount of output data is greater than an amount of input data, and the ratio of the amount of input data to the amount of output data defines a decompression ratio. In one implementation, the high-level host-related task performed by the host element pertains to a high-level graphics processing task, and the data-generating task pertains to the generation of geometry data (such as triangle vertices) for use within the high-level graphics processing task. The CPU module can transfer the output data to a GPU module via at least one locked set of a cache memory. The GPU retrieves the output data from the locked set, and periodically forwards a tail pointer to a cacheable location within the data-generating elements that informs the data-generating elements of its progress in retrieving the output data.

Owner:MICROSOFT TECH LICENSING LLC

Composite graphics rendered using multiple frame buffers

Owner:APPLE INC

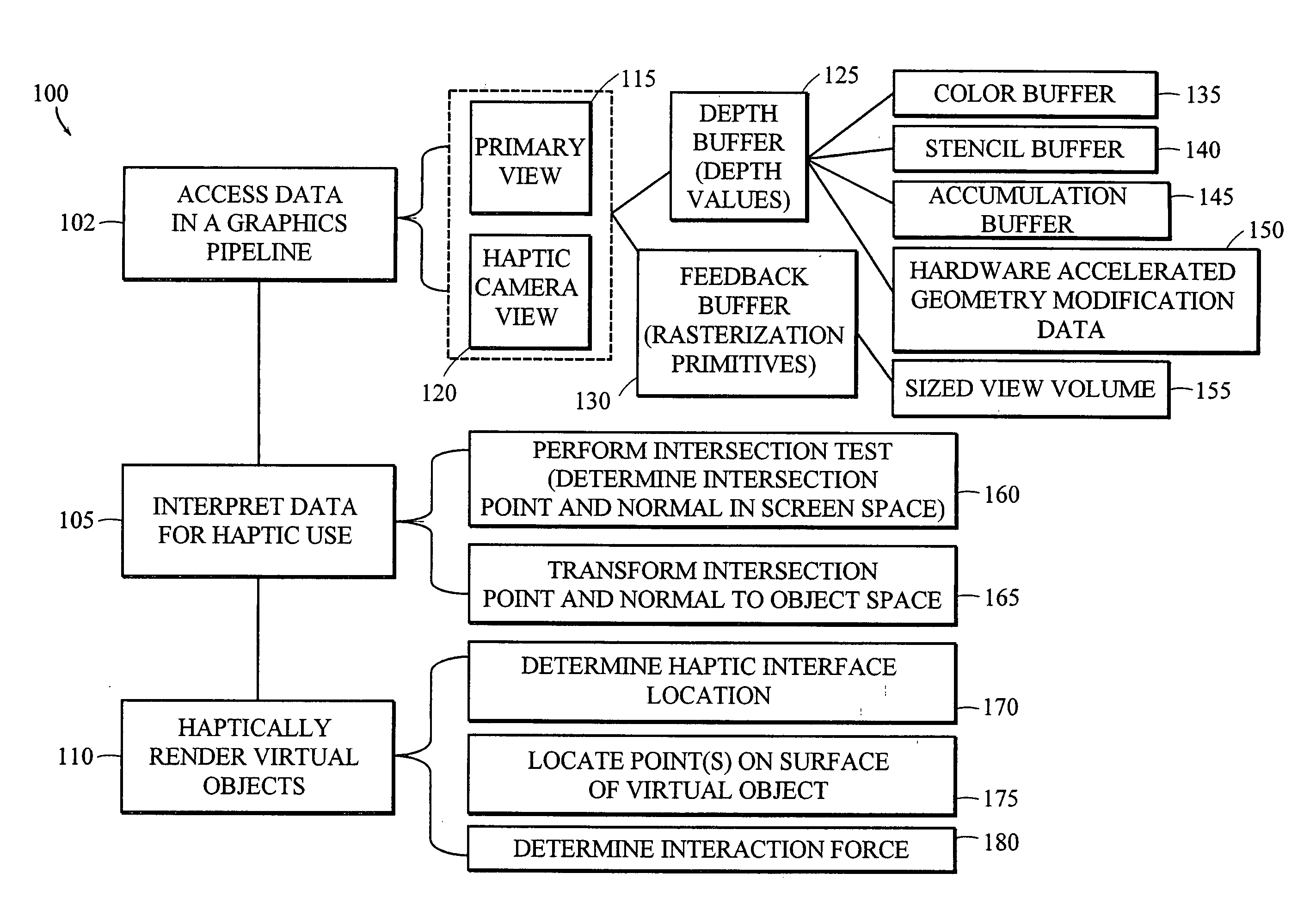

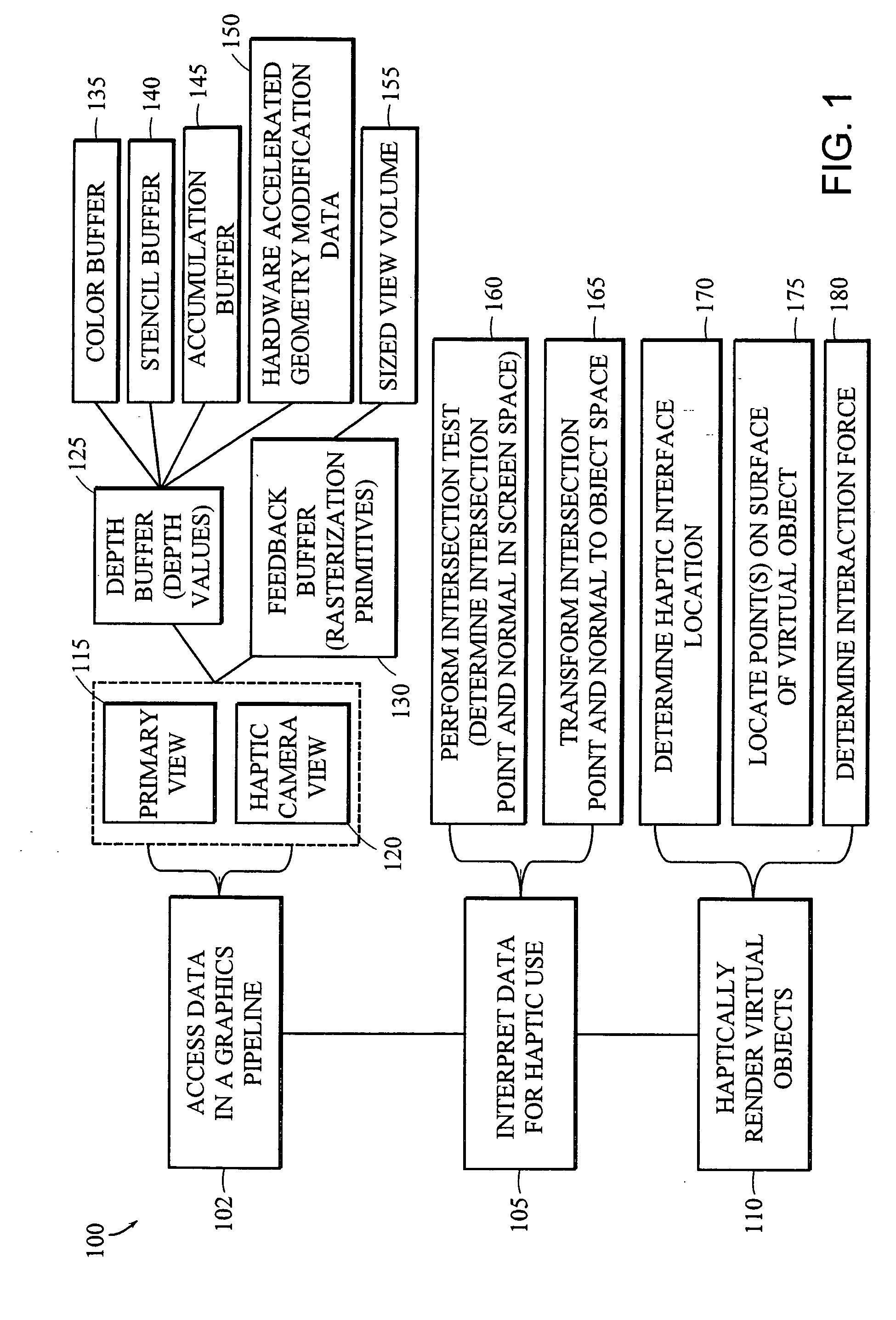

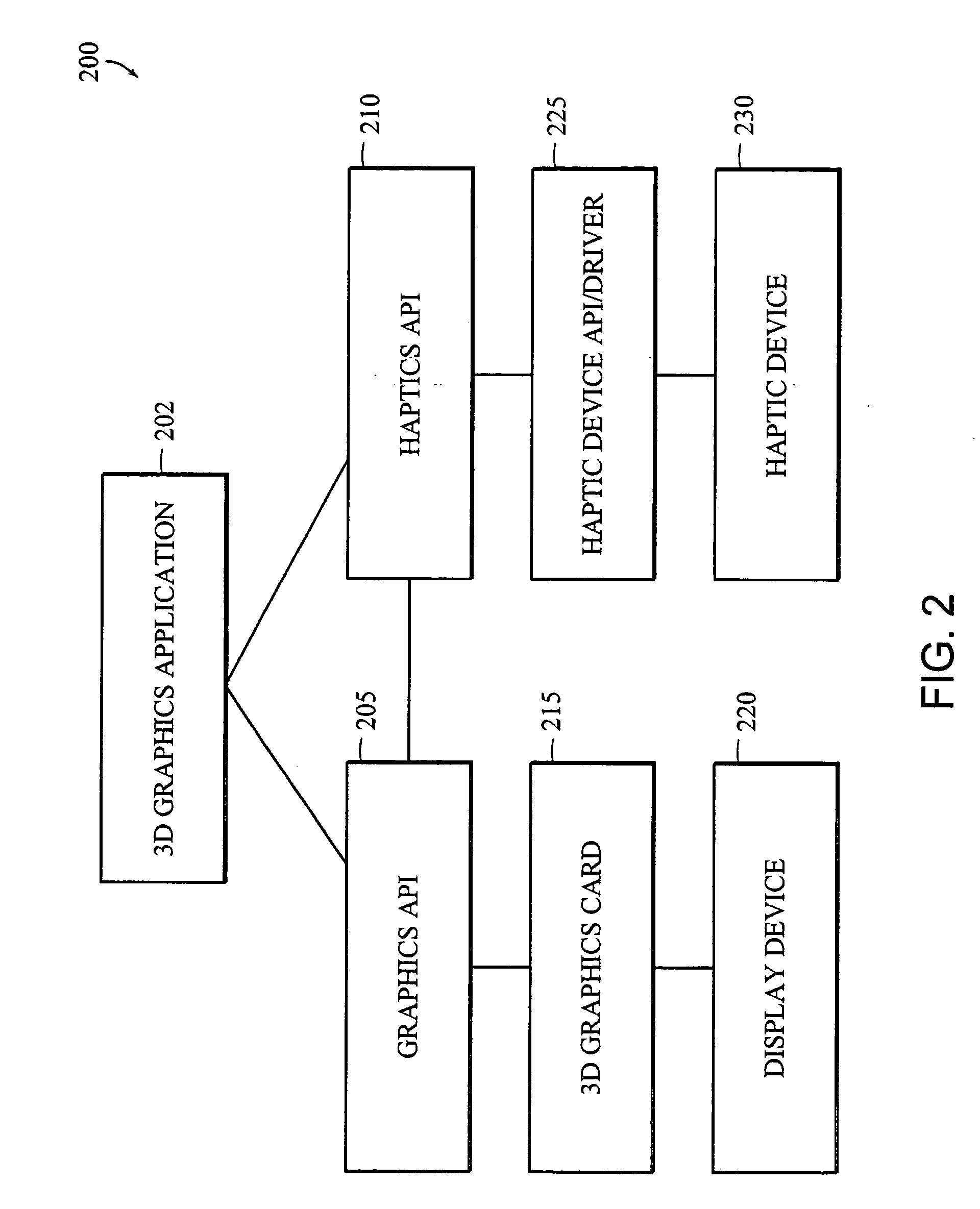

Apparatus and methods for haptic rendering using data in a graphics pipeline

ActiveUS20060109266A1Unleash processing performanceQuick fixGearworksMusical toysGraphicsLine tubing

The invention provides methods for leveraging data in the graphics pipeline of a 3D graphics application for use in a haptic rendering of a virtual environment. The invention provides methods for repurposing graphical information for haptic rendering. Thus, at least part of the work that would have been performed by a haptic rendering process to provide touch feedback to a user is obviated by work performed by the graphical rendering process.

Owner:3D SYST INC

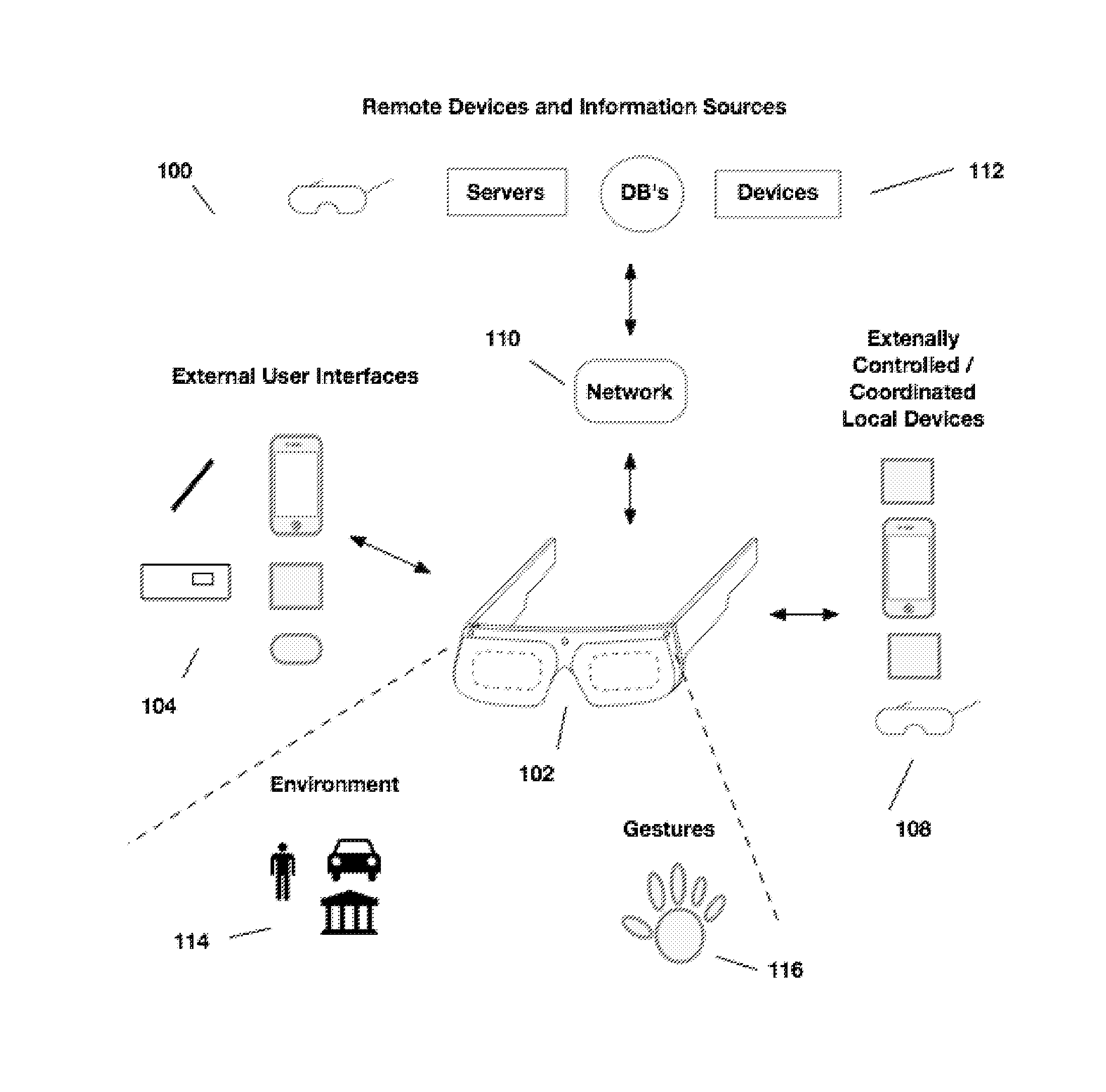

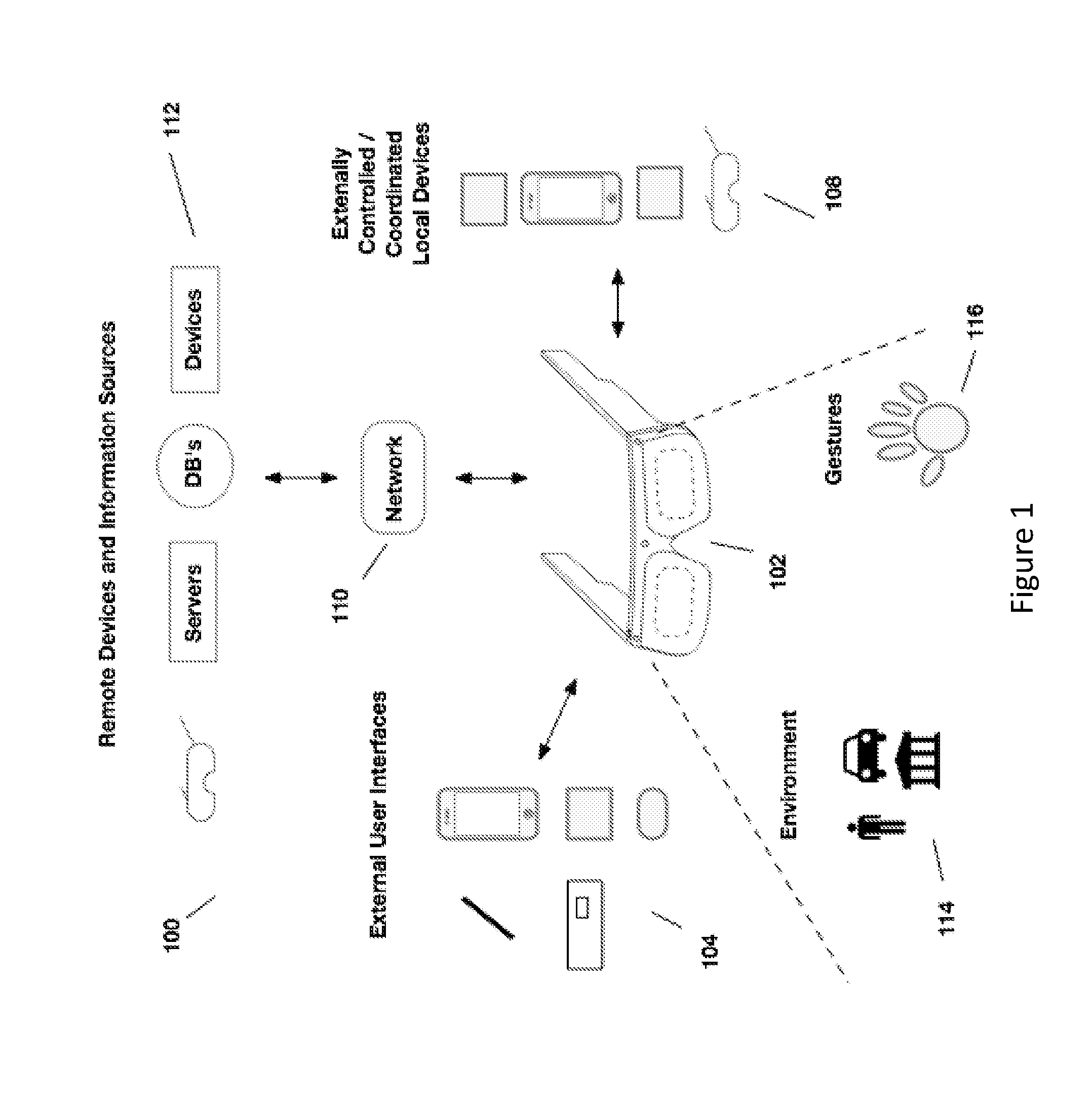

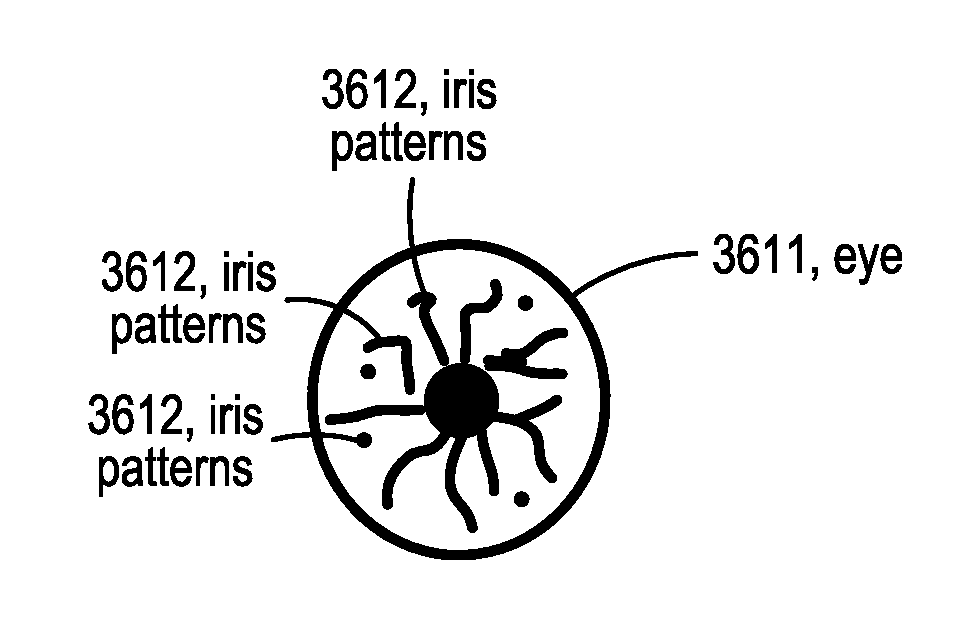

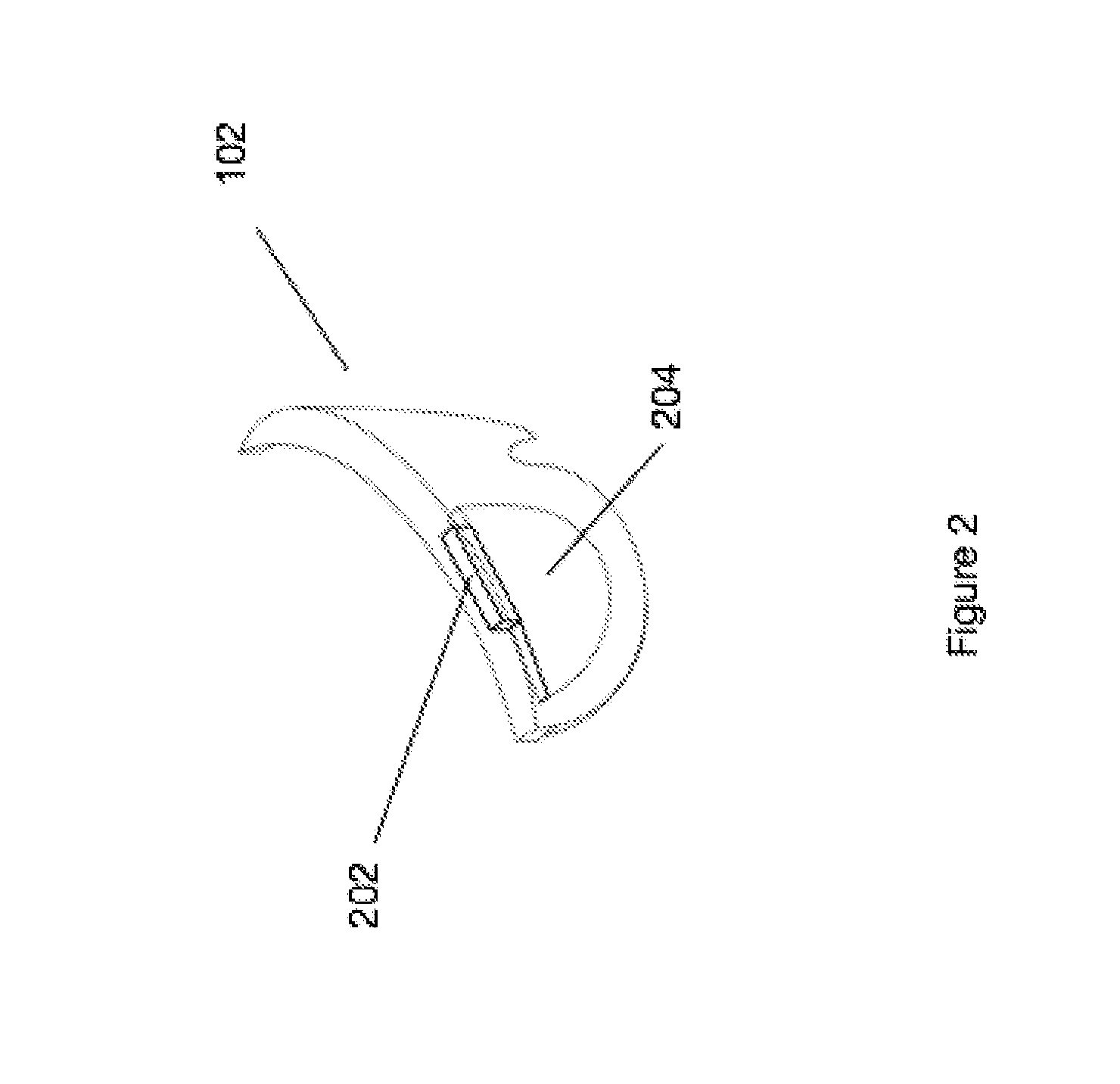

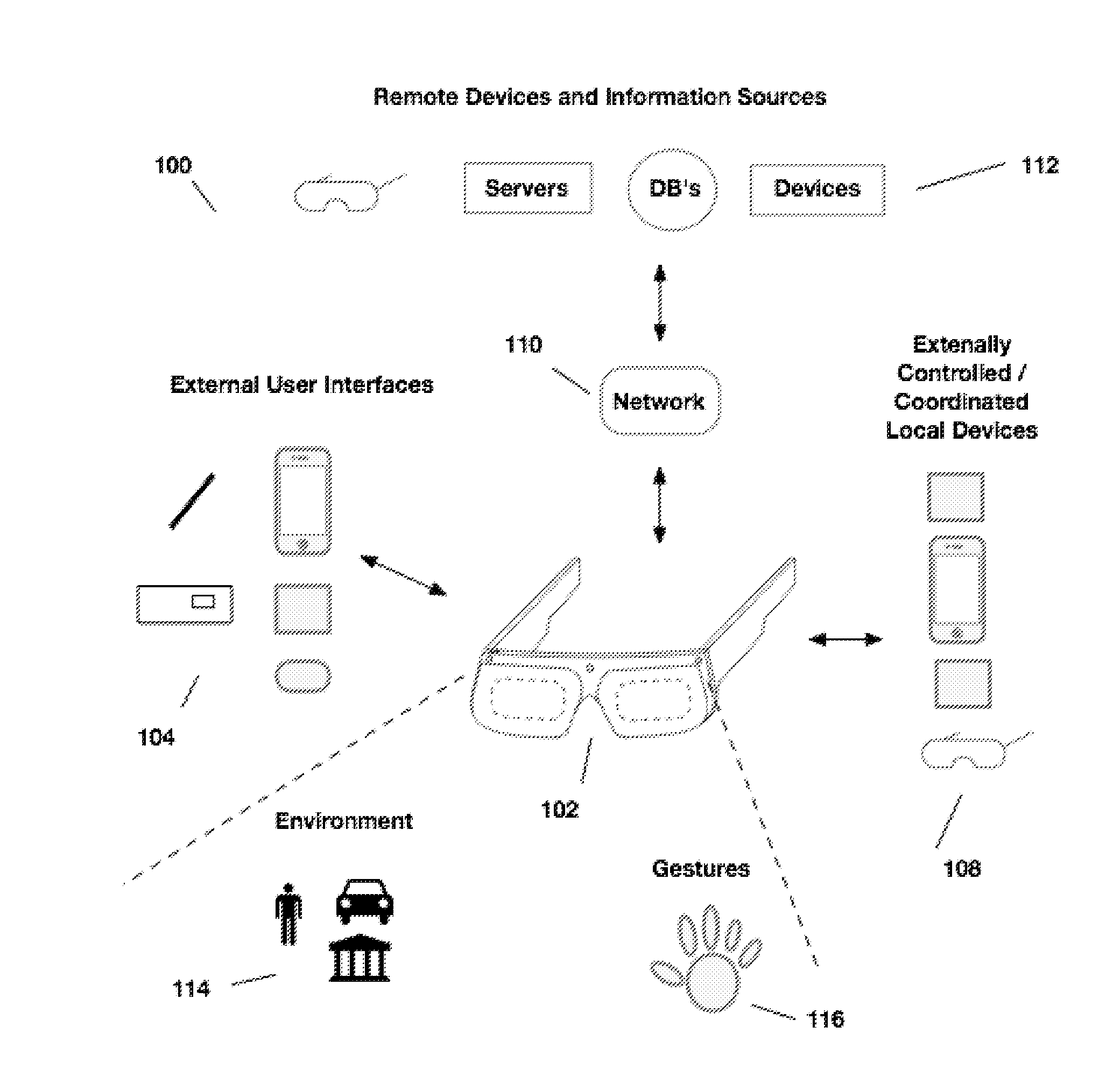

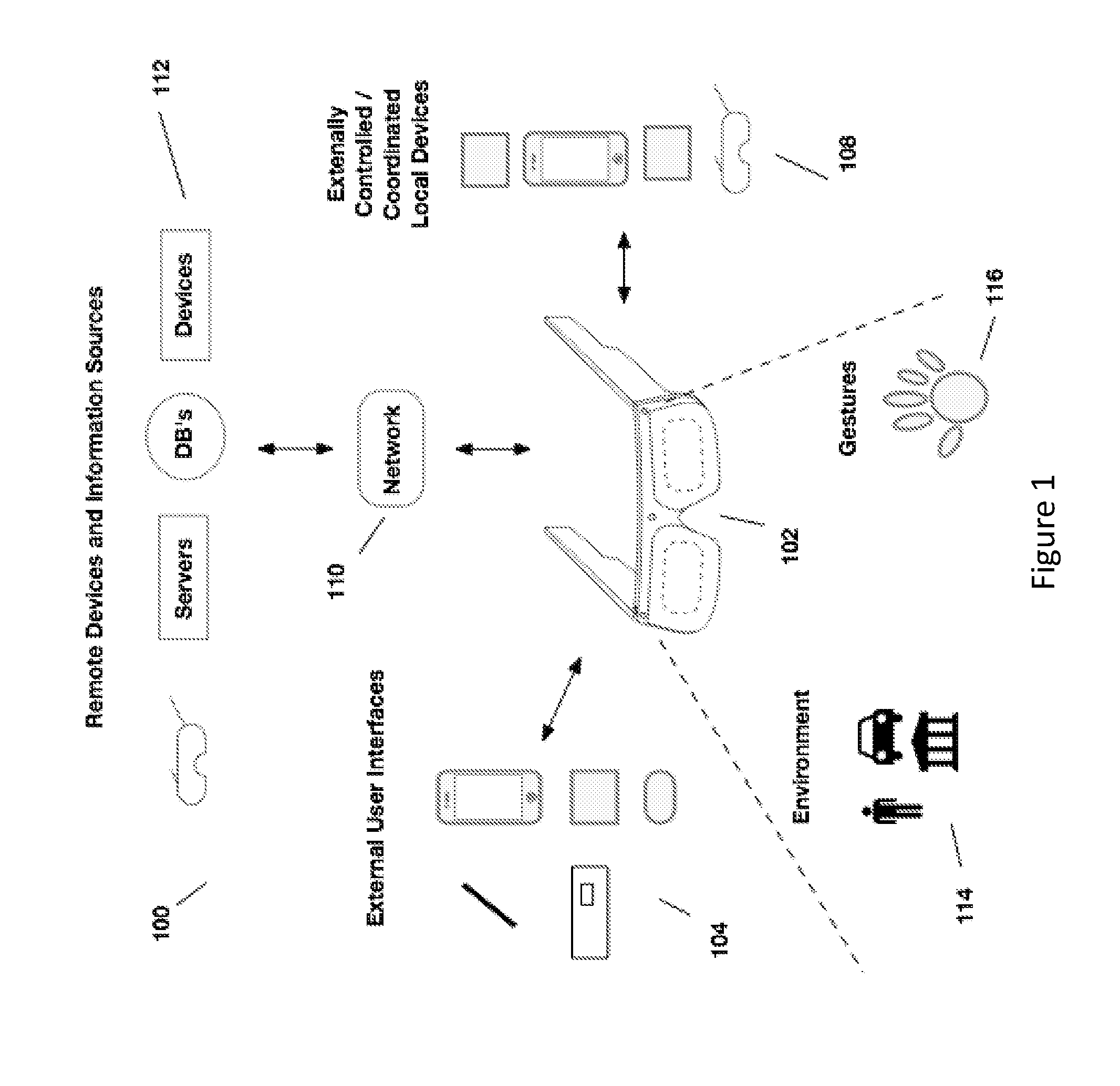

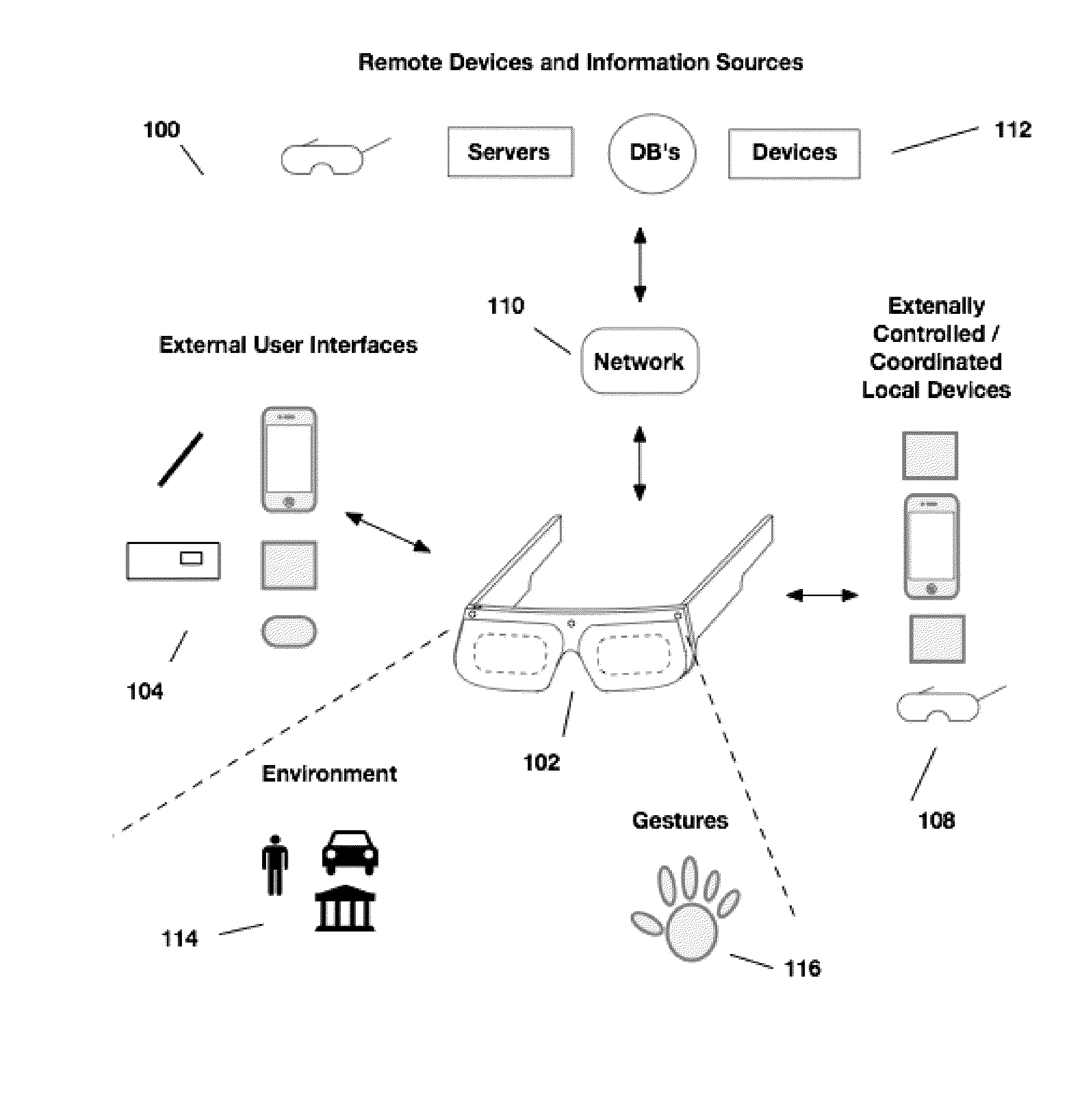

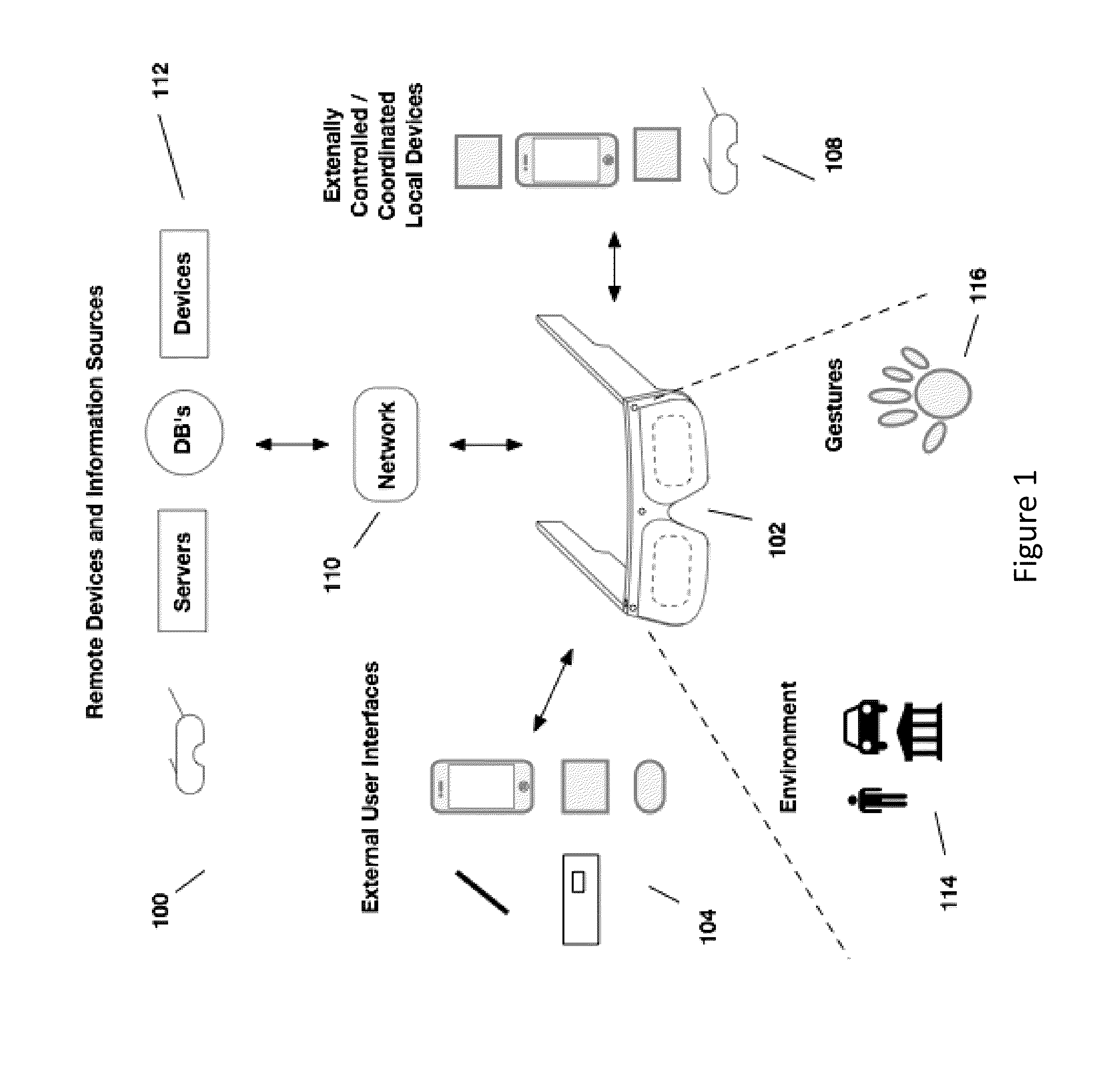

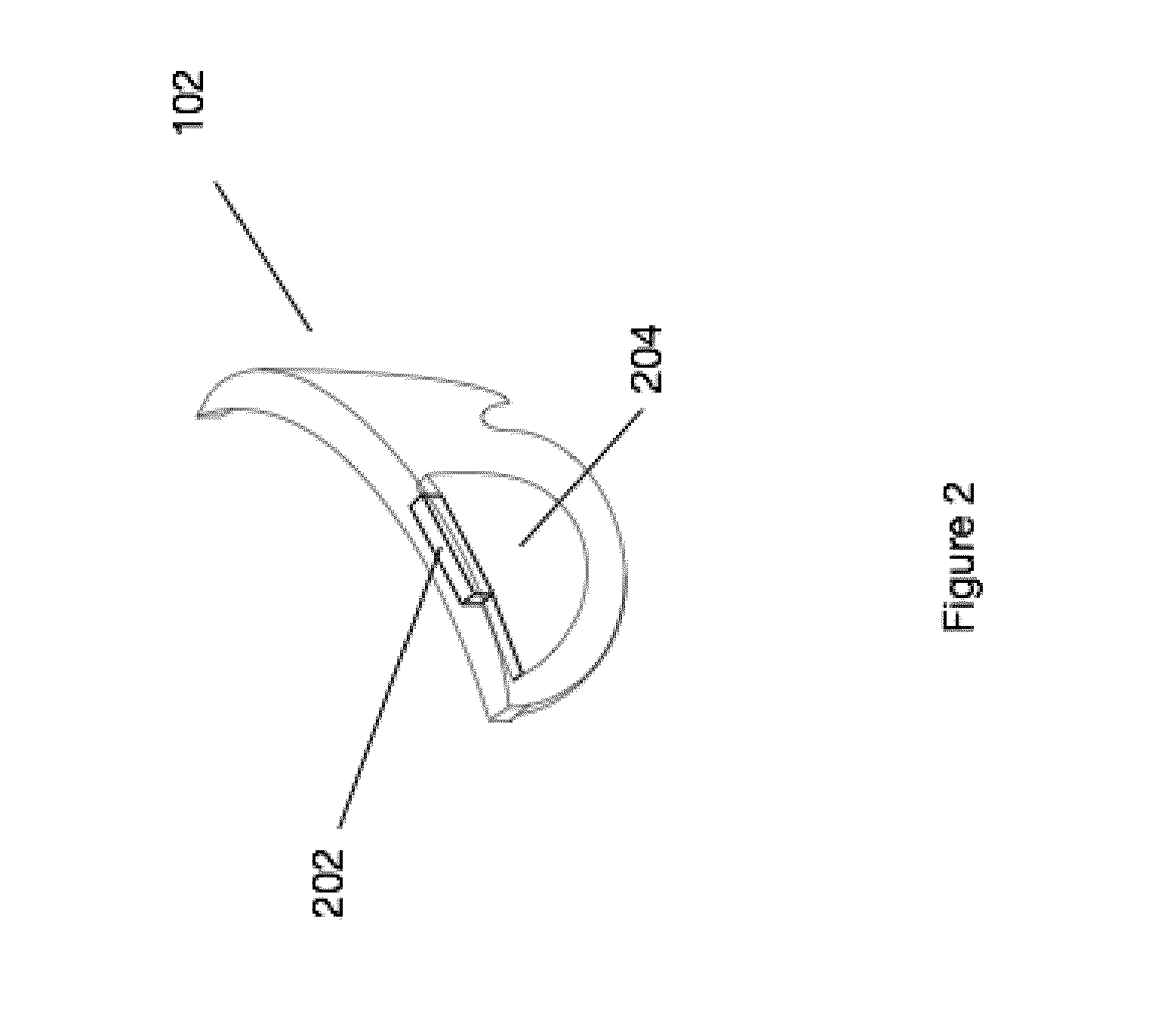

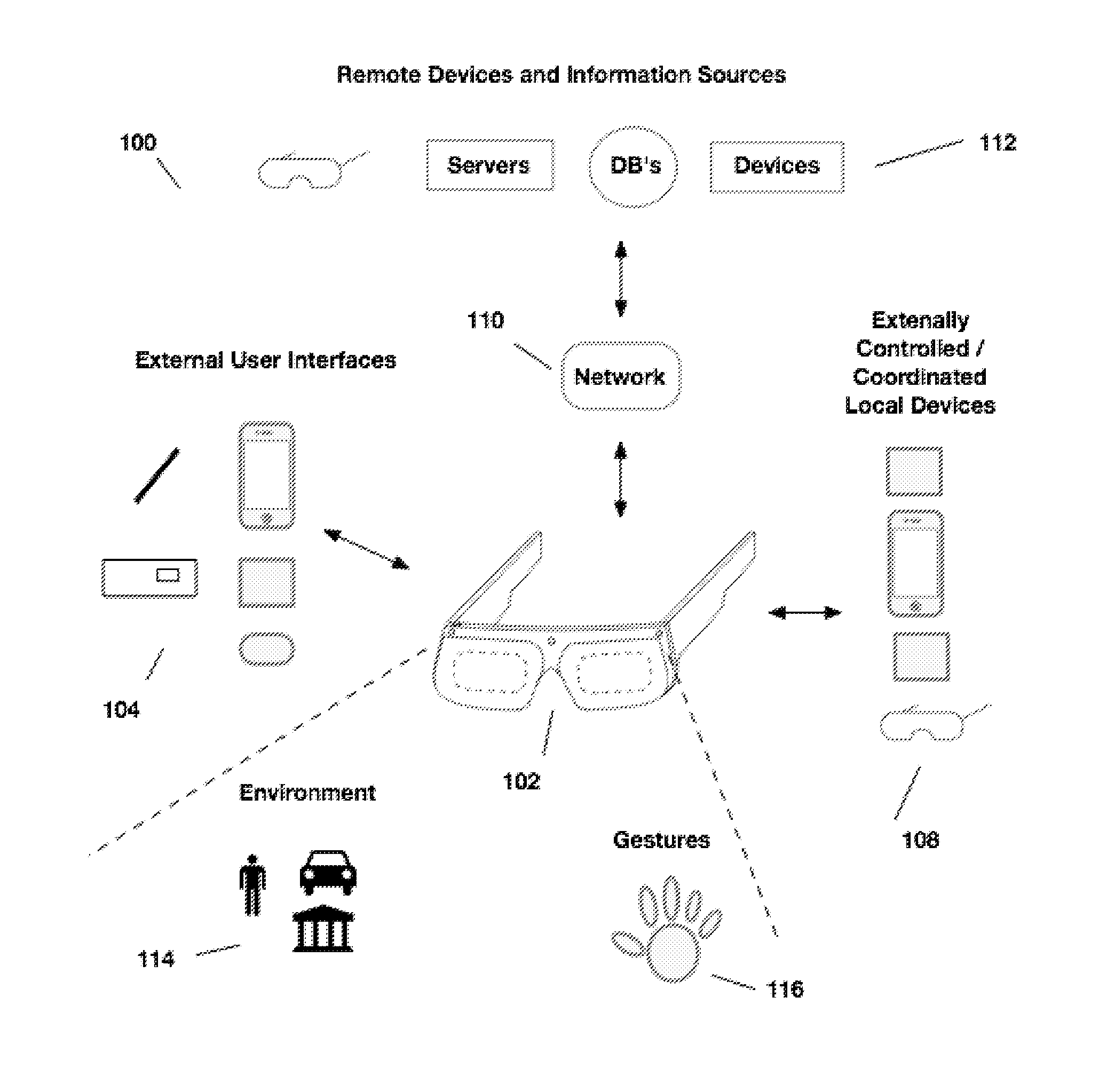

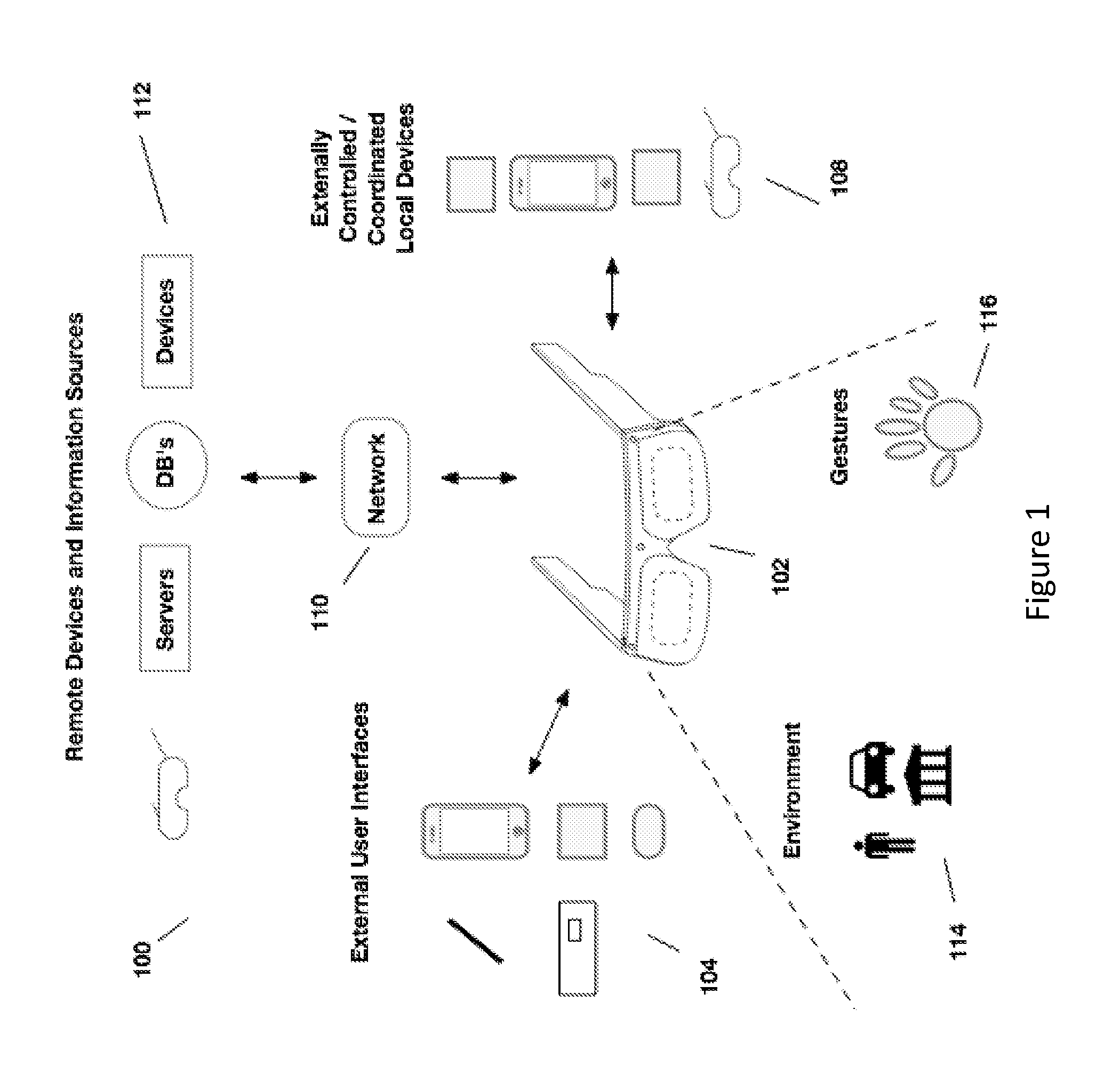

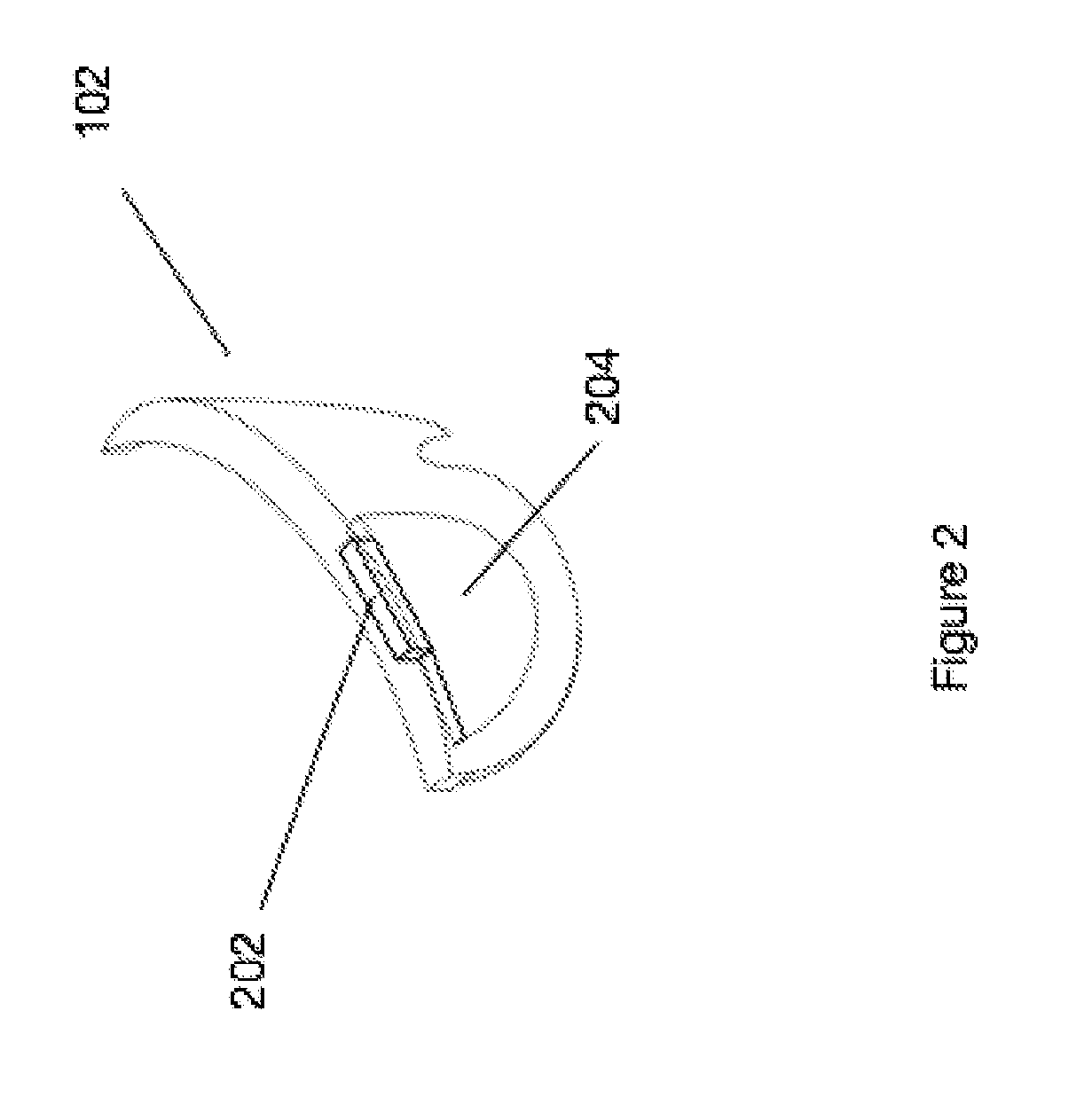

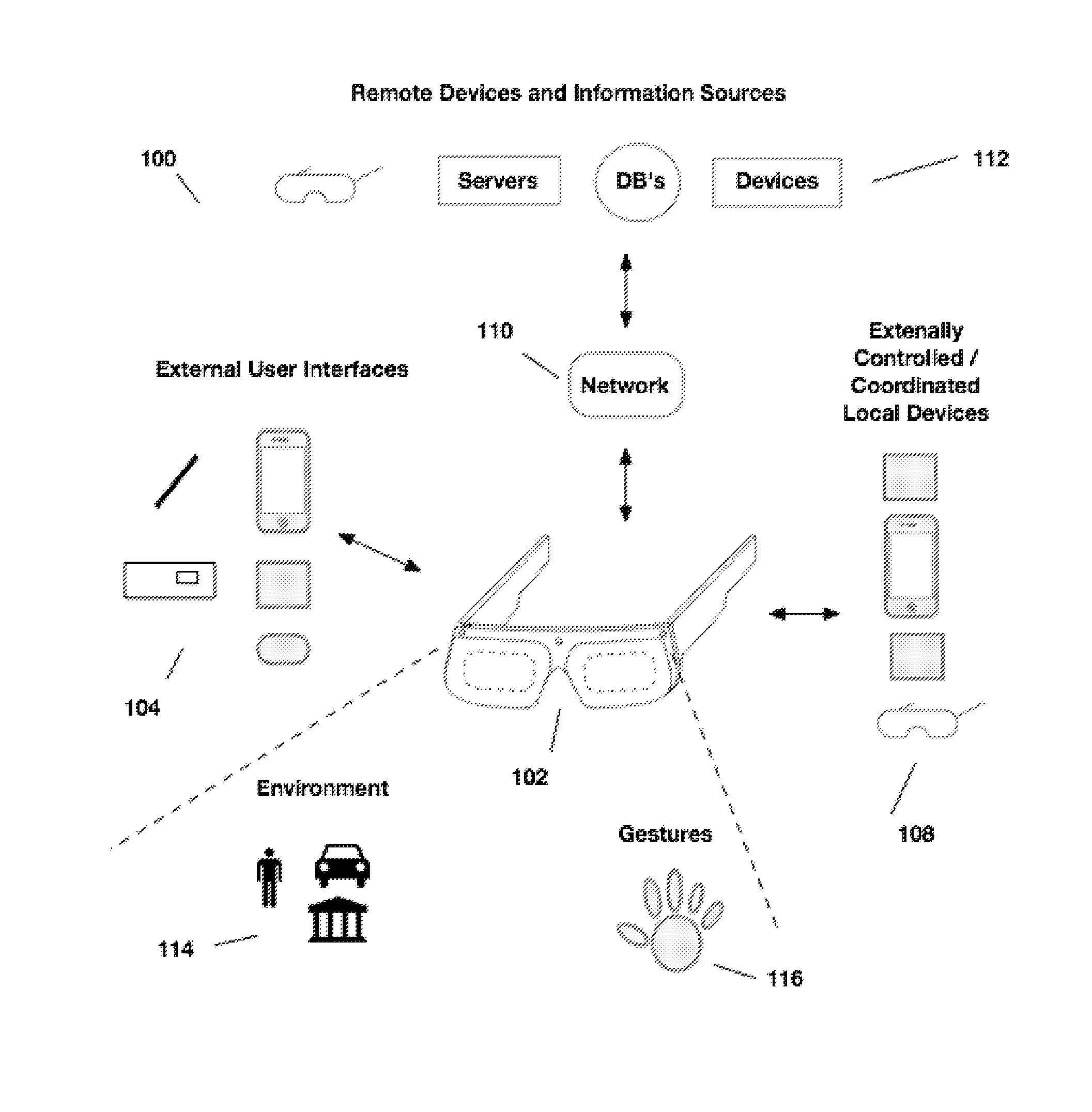

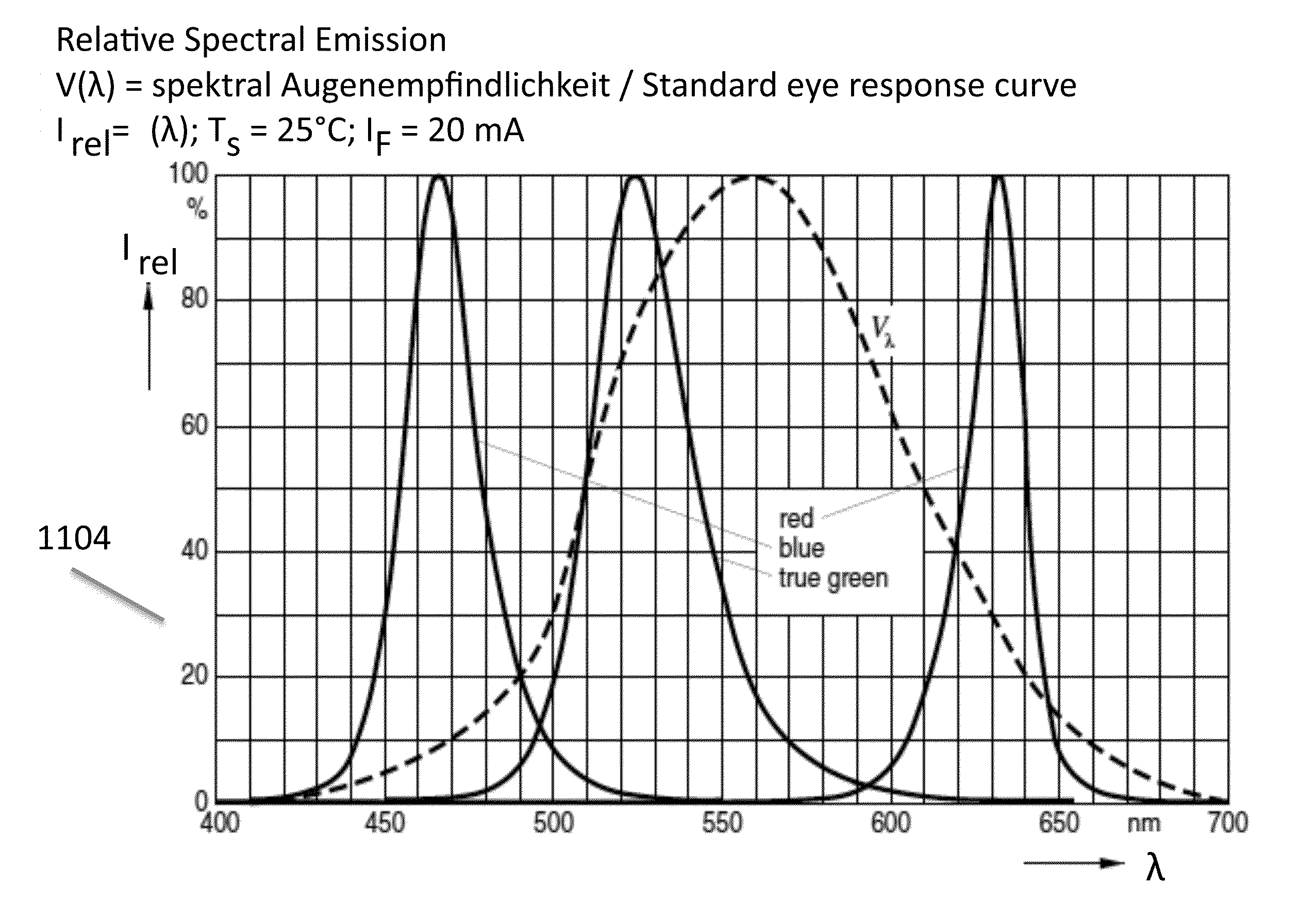

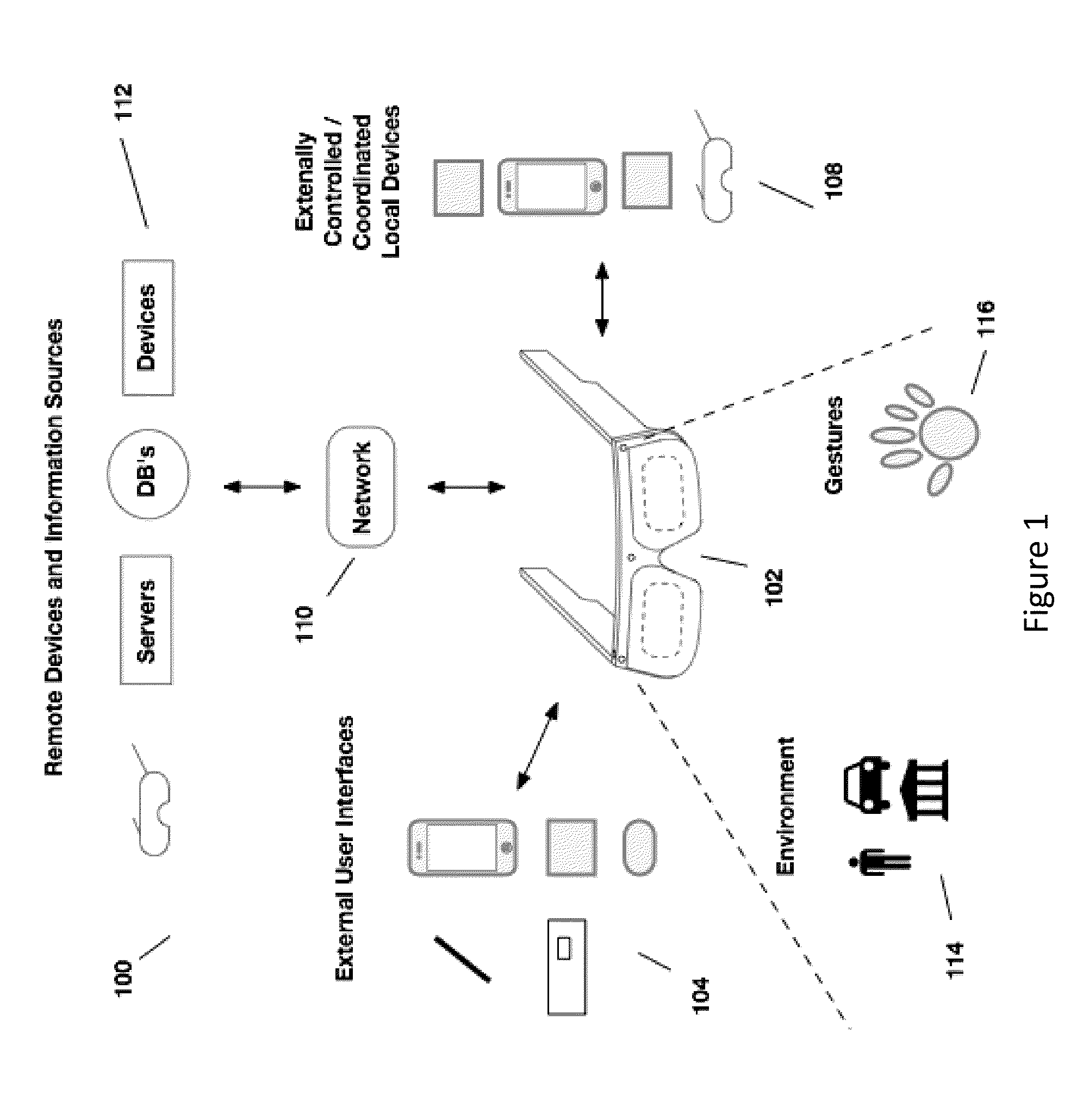

Sensor dependent content position in head worn computing

InactiveUS20150277113A1Input/output for user-computer interactionImage memory managementComputer vision

Owner:OSTERHOUT GROUP INC

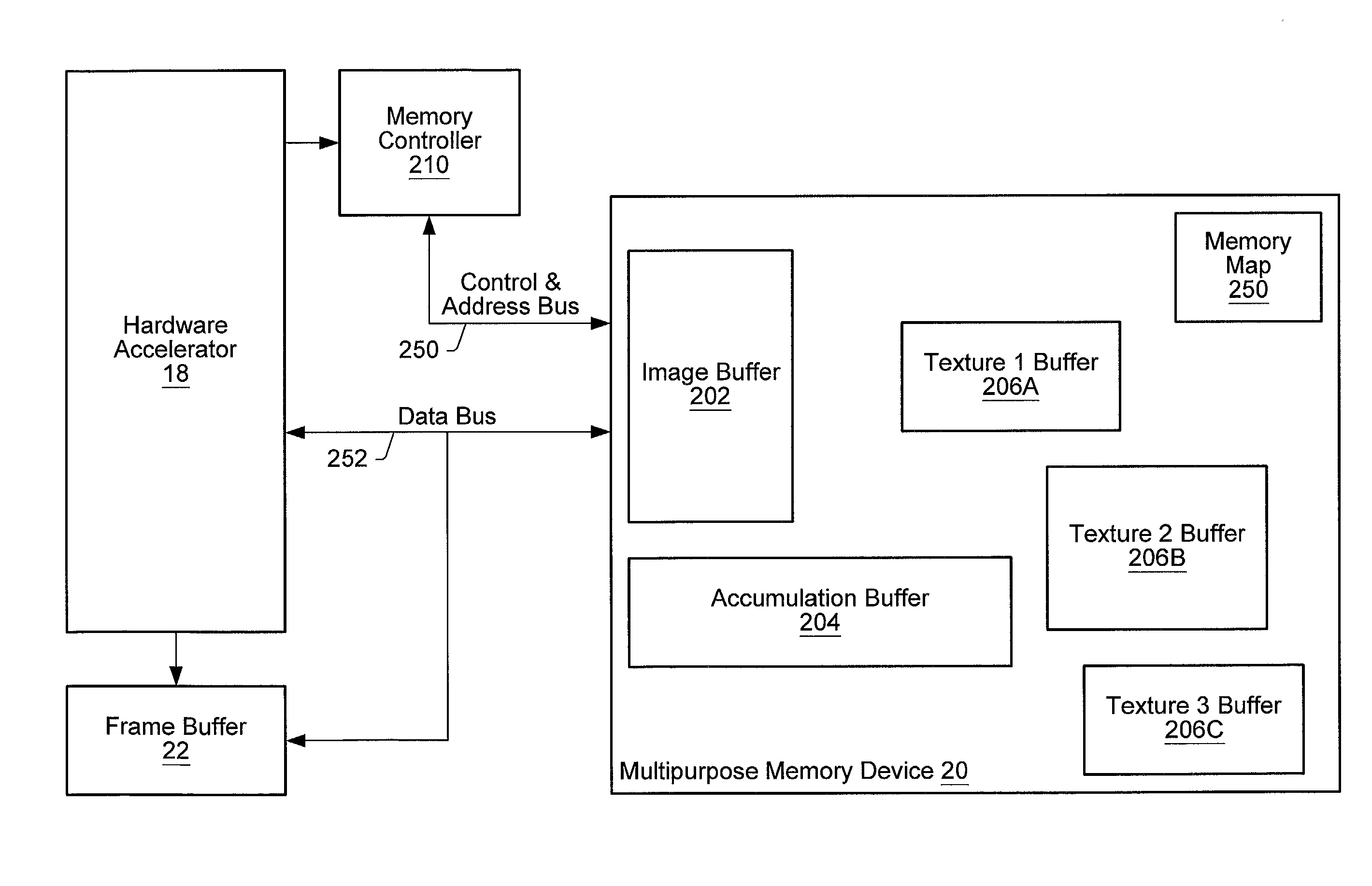

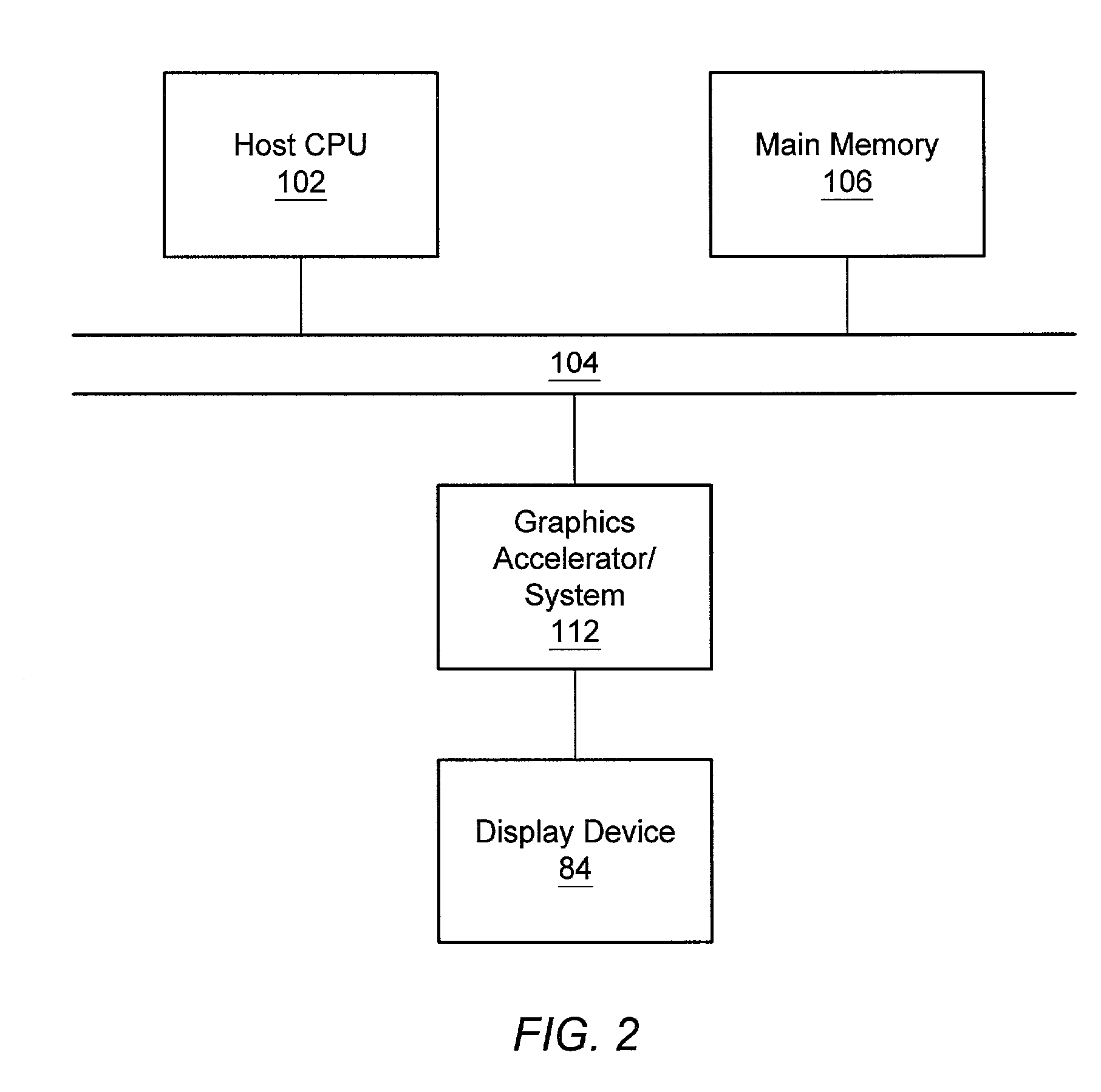

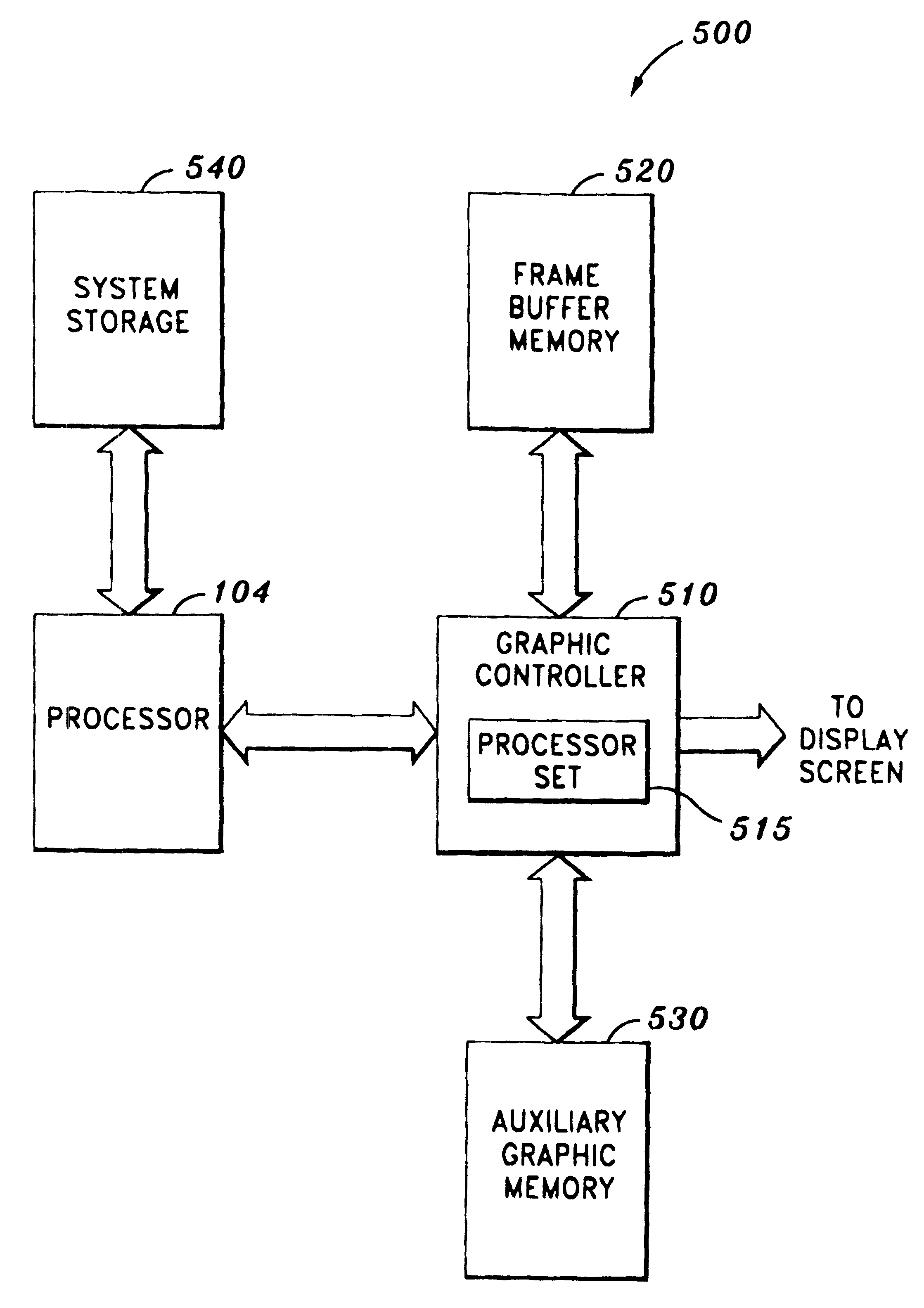

Multipurpose memory system for use in a graphics system

InactiveUS20030174136A1Memory adressing/allocation/relocationDigital computer detailsGraphicsGraphic system

A graphics system may include a frame buffer, a processing device coupled to output data, a multipurpose memory device that includes a plurality of storage locations and is coupled to store data output from the processing device, and a multipurpose memory controller coupled to the multipurpose memory device. The multipurpose memory controller may be configured to allocate a first plurality of the storage locations to a first image buffer configured to store image data, a second plurality of the storage locations to a first texture buffer configured to store texture data, and a third plurality of the storage locations to a first accumulation buffer configured to store accumulation buffer data. The multipurpose memory device may be configured to include a first image buffer, a first texture buffer, and a first accumulation buffer at the same time.

Owner:ORACLE INT CORP

Sensor dependent content position in head worn computing

Owner:OSTERHOUT GROUP INC

Rendering to multi-resolution hierarchies

ActiveUS20150049104A1Accurate explanationImage memory managementFilling planer surface with attributesState parameterComputer graphics (images)

One embodiment of the present invention includes techniques for processing a multi-resolution hierarchy, where an application configures a ROP unit to render all the levels included in the multi-resolution hierarchy to a single composite render target. The ROP unit renders memory pages to the composite render target in pitch order. In contrast, the texture unit accesses the composite render target with memory pages in pitch order for each level of the hierarchy. The application configures the MMU to ensure that the composite render target is correctly interpreted by the texture unit. Notably, the MMU translates ROP unit virtual addresses and texture unit virtual addresses using different mapping strategies to the same physical address space. One advantage of the disclosed embodiments is that rendering to the multi-resolution hierarchy does not require the CPU to execute the state parameter changes that are associated with rendering the different hierarchical levels using prior-art techniques.

Owner:NVIDIA CORP

Sensor dependent content position in head worn computing

InactiveUS20150277549A1Input/output for user-computer interactionImage memory managementComputer vision

Owner:OSTERHOUT GROUP INC

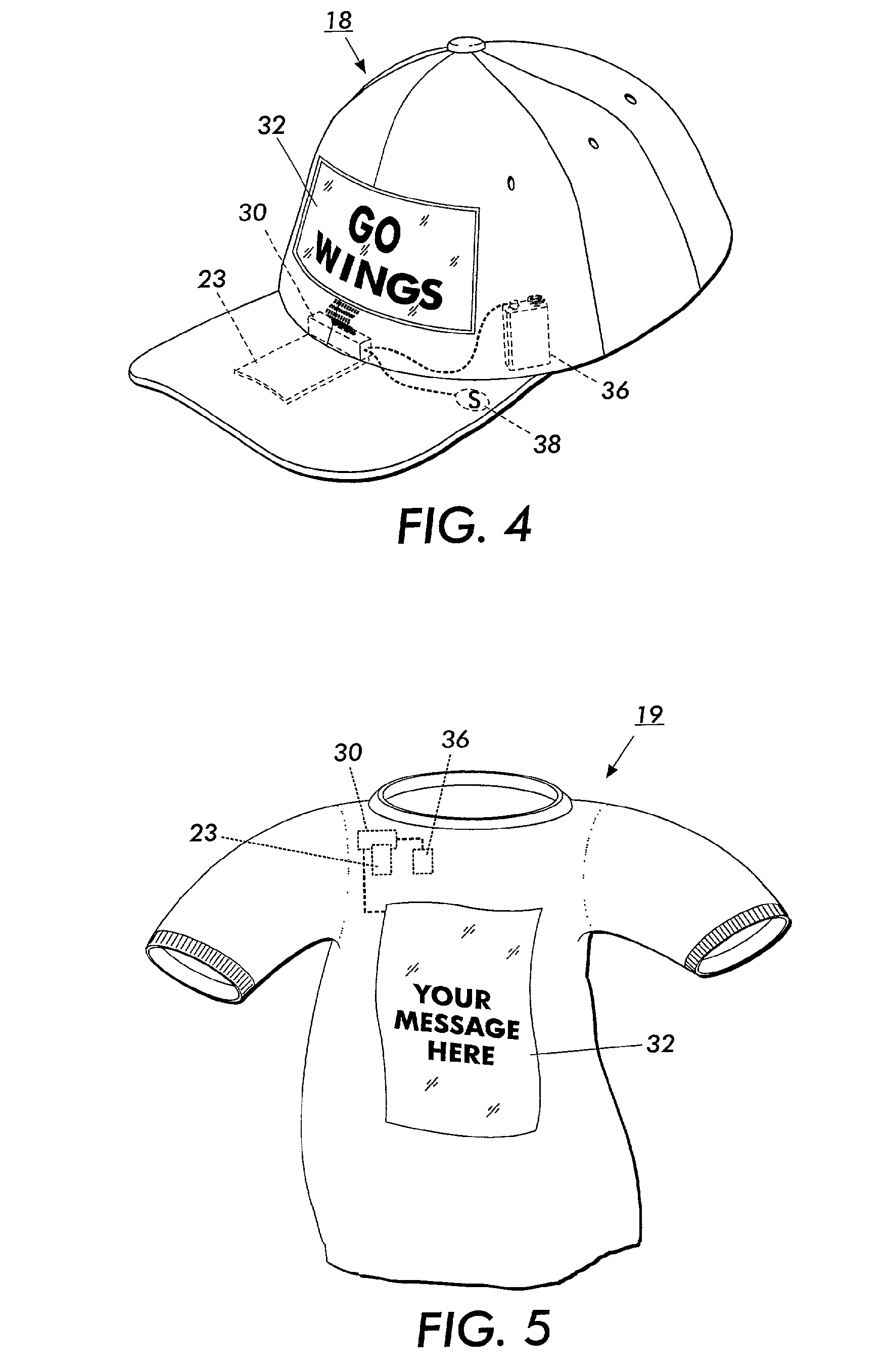

Apparatus for the display of embedded information

InactiveUS20090085900A1Easy for to accustomed to readingLow production costCo-operative working arrangementsImage memory managementDisplay deviceDigital recording

An apparatus for the electronic display of information, where the apparatus is a substrate incorporating a digital recording medium attached to or embedded within the substrate. The substrate further includes a flexible-substrate display located on an exposed surface of the substrate, where the display is a medium capable of selectively displaying one of at least two possible colors at each pixel location thereon in order to produce a substrate medium that may be modified in accordance with a user's selection.

Owner:EDGED DISPLAY MANAGEMENT LLC

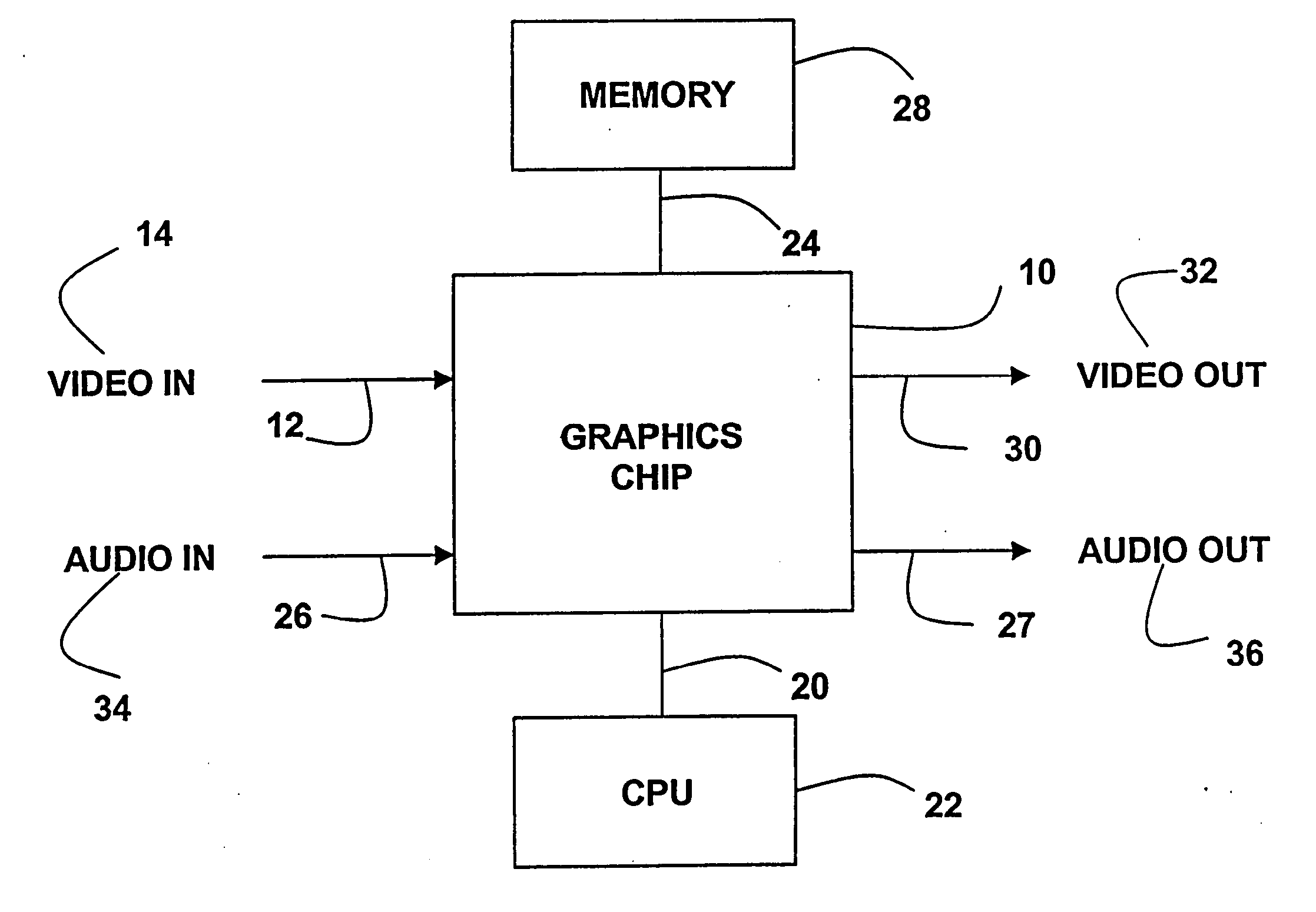

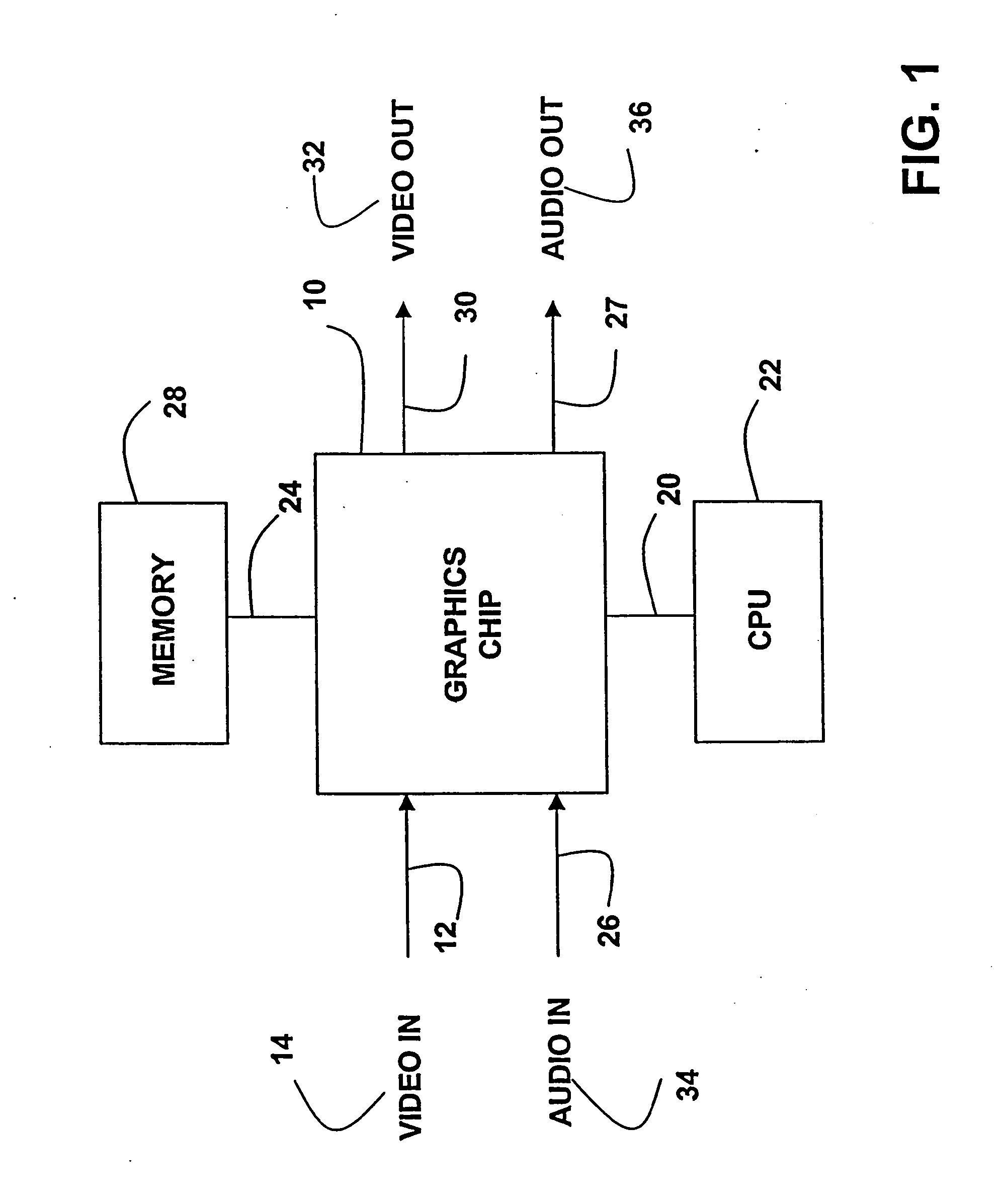

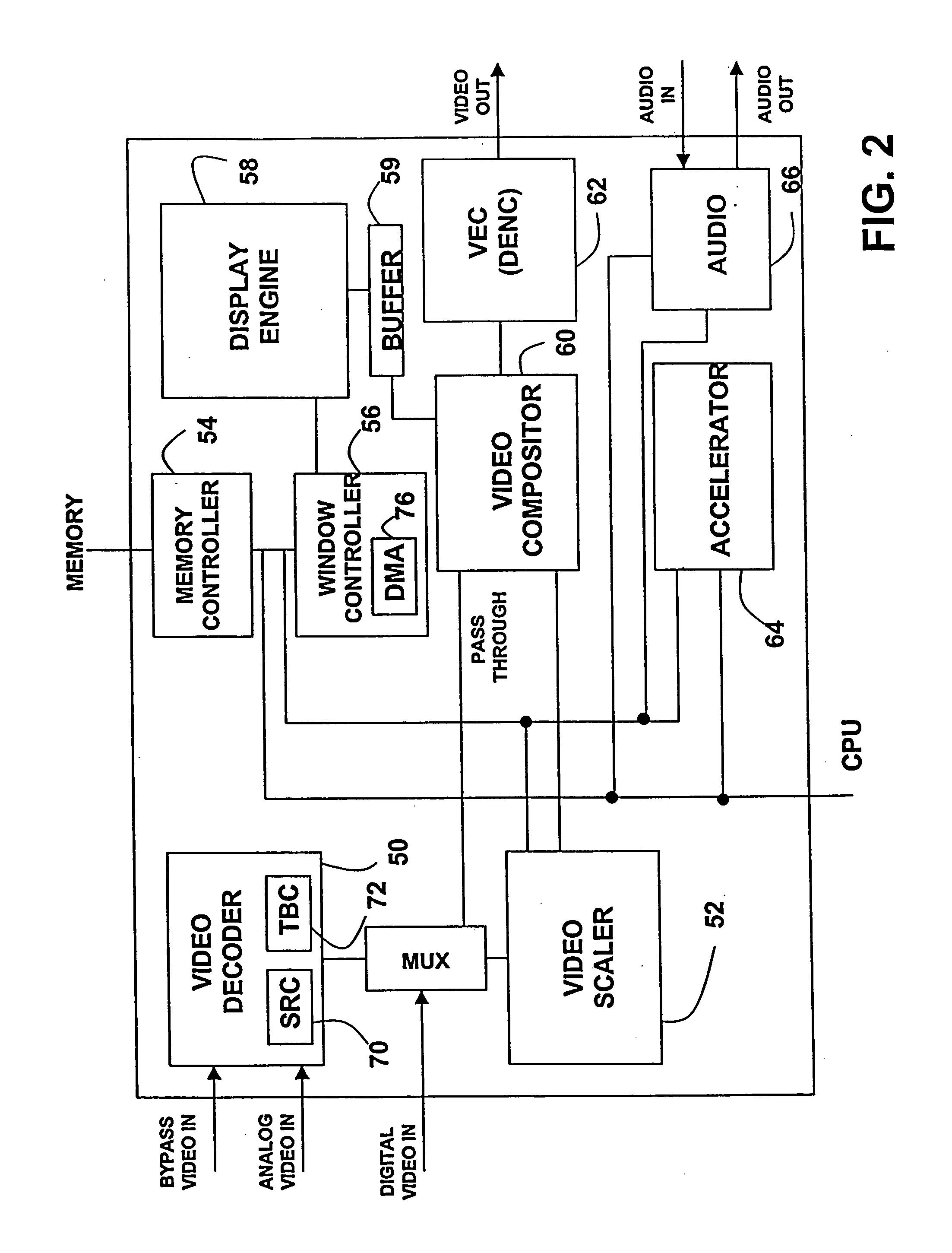

Video and Graphics System with Video Scaling

InactiveUS20110280307A1Television system detailsTelevision system scanning detailsVideocassette recorderGraphics

A video and graphics system has a reduced memory mode in which video images are reduced in half in horizontal direction during decoding. The video and graphics system includes a video decoder for decoding MPEG-2 video data. The video images may not be downscaled in the horizontal direction when no bi-directionally predicted pictures are used. The video and graphics system may output an HDTV video while converting the HDTV video and providing as another output having an SDTV format or another HDTV format. The output having an SDTV format may be recorded using a video cassette recorder (VCR) while the HDTV video is being displayed.

Owner:AVAGO TECH INT SALES PTE LTD

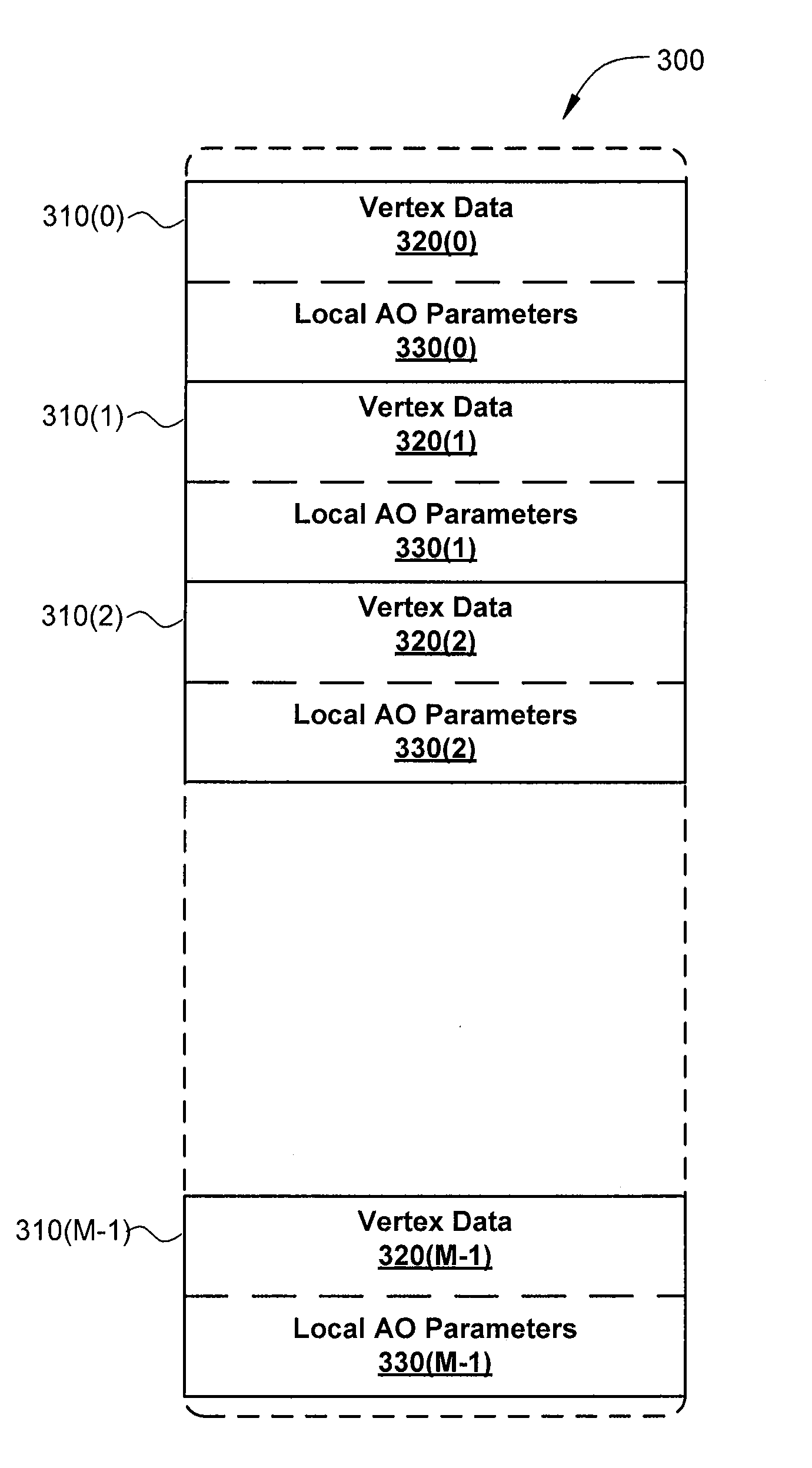

Technique for pre-computing ambient obscurance

ActiveUS20150187129A1Reduce memory spaceReduce artifactsImage memory management3D-image renderingShadowingsComputer graphics (images)

One embodiment of the present invention includes techniques for pre-computing ambient shadowing parameters for a computer-generated scene. A processing unit retrieves a reference object associated with the computer-generated scene and comprising a plurality of vertices. For each vertex in the plurality of vertices, the processing unit computes a local ambient shadowing parameter, and stores the local ambient shadowing parameter in a memory. For each instance of the reference object included in the computer-generated scene, the processing unit computes a first global ambient shadowing parameter based on the position of the instance within the computer-generated scene, and stores the first global ambient shadowing parameter in the memory. One advantage of the disclosed embodiments is that ambient obscurance is applied to instance objects in a scene in real time while reducing memory space dedicated to storing the AO parameters.

Owner:NVIDIA CORP

Sensor dependent content position in head worn computing

Owner:OSTERHOUT GROUP INC

Sensor dependent content position in head worn computing

InactiveUS20150277122A1Input/output for user-computer interactionImage memory managementComputer vision

Owner:OSTERHOUT GROUP INC

Re-generating a displayed image

Owner:KINGLITE HLDG INC

Sensor dependent content position in head worn computing

Owner:OSTERHOUT GROUP INC

Sensor dependent content position in head worn computing

InactiveUS20150277118A1Input/output for user-computer interactionImage memory managementComputer vision

Owner:OSTERHOUT GROUP INC

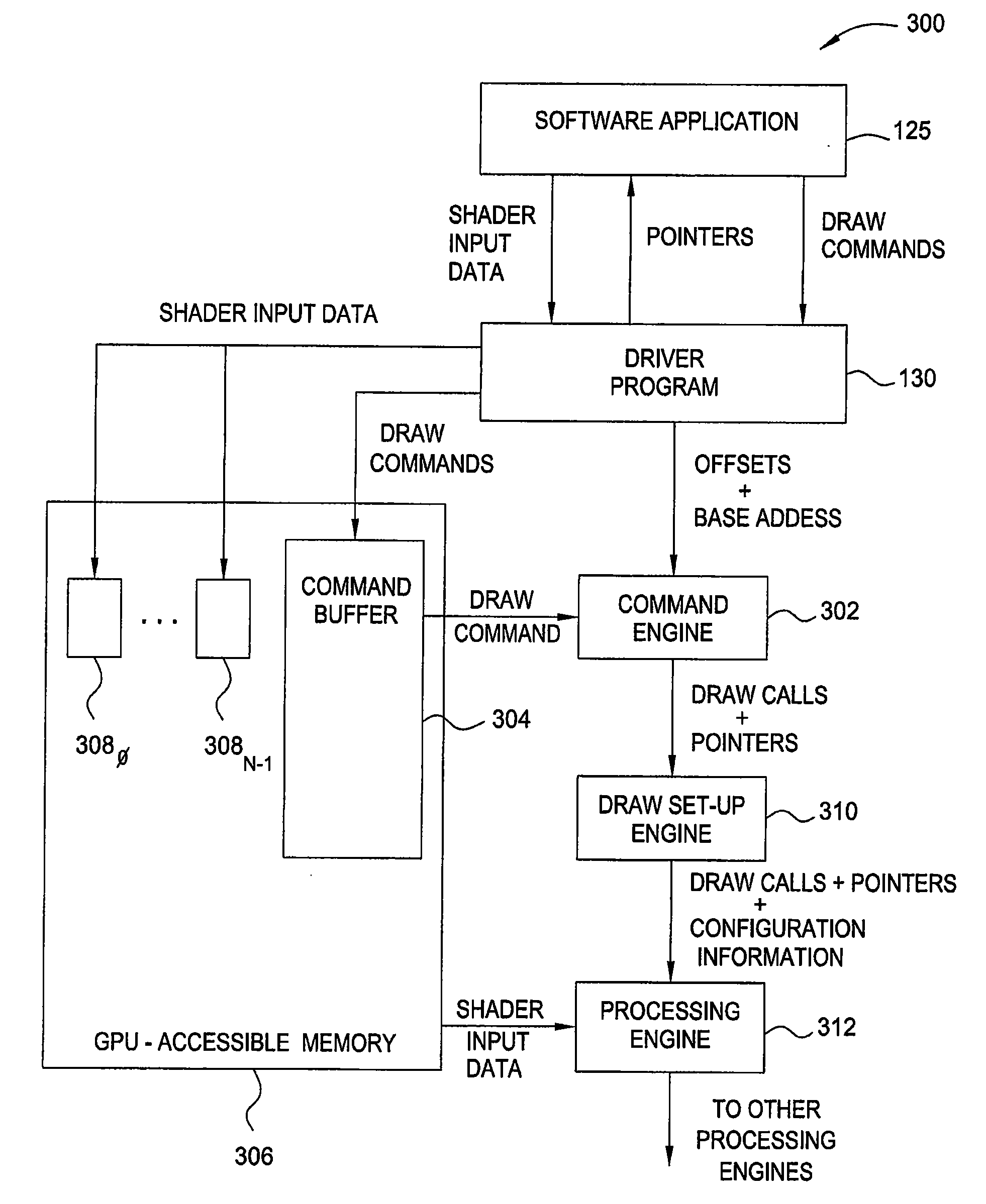

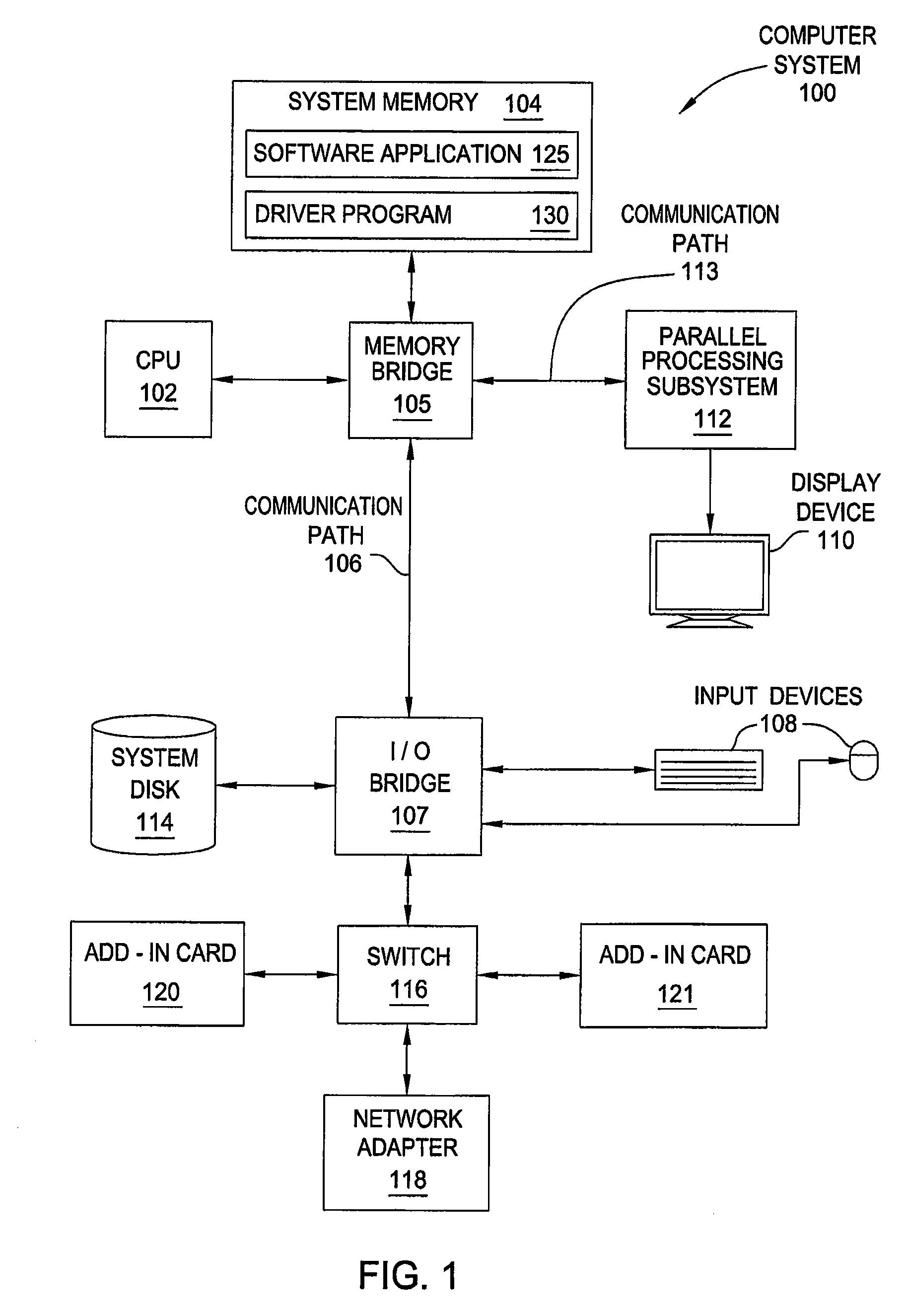

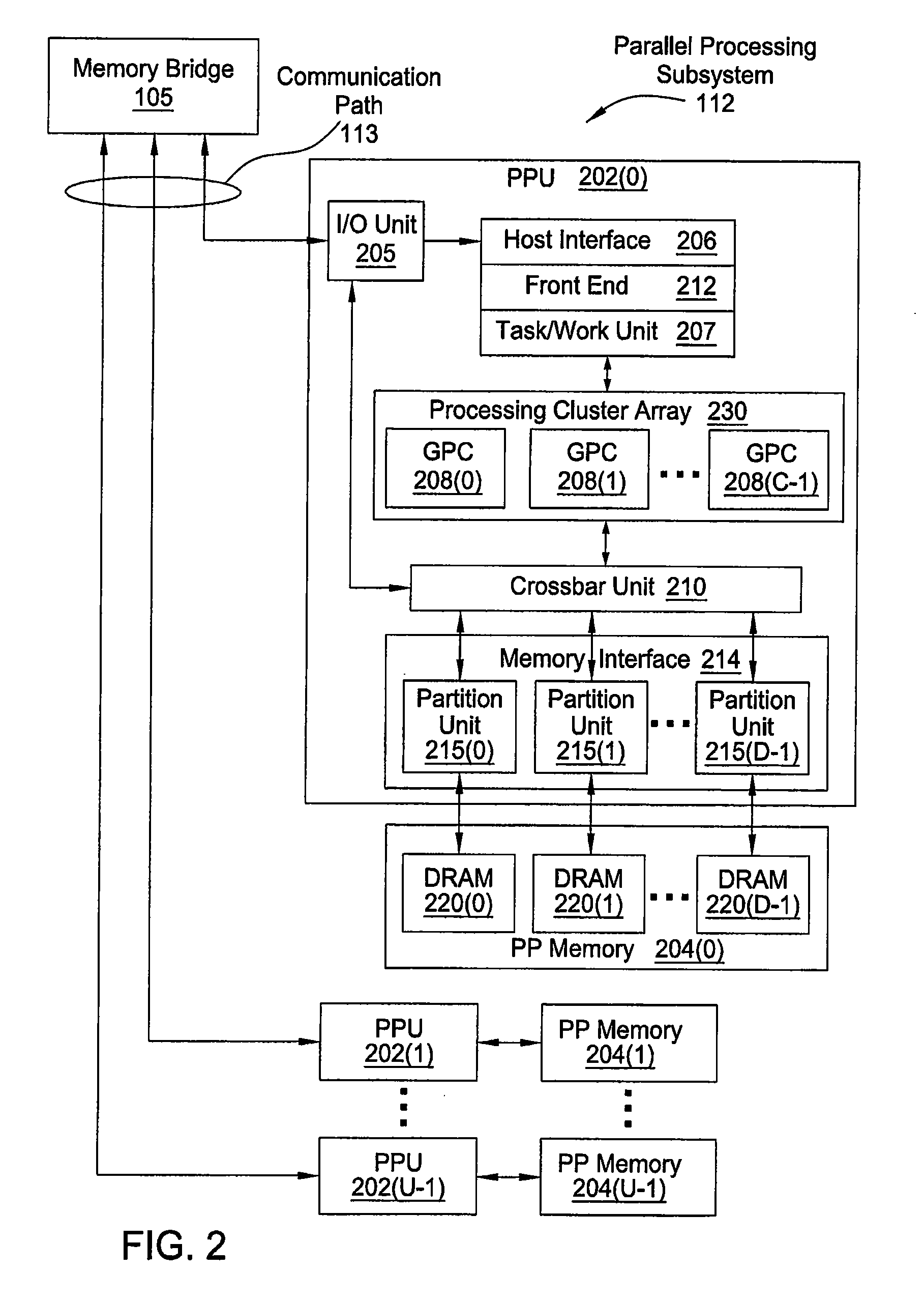

Techniques for setting up and executing draw calls

ActiveUS20140168242A1Improve processing efficiencyImage memory managementProgram controlComputational scienceApplication software

One embodiment sets forth a method for processing draw calls that includes setting up a plurality of shader input buffers in memory, receiving shader input data related to a graphics scene from a software application, storing the shader input data in the plurality of shader input buffers, computing a pointer to each shader input buffer included in the plurality of shader input buffers, and passing the pointers to the plurality of shader input buffers to the software application. By implementing the disclosed techniques, a shader program advantageously can access the shader input data associated with a graphics scene and stored in various shader input buffers without having to go through the central processing unit to have the shader input buffers binded to the shader program.

Owner:NVIDIA CORP

Deferred shading graphics pipeline processor

InactiveUS6268875B1Attenuation bandwidthTexturing/coloringImage memory managementPhong shadingComputer graphics (images)

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is a Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch & decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

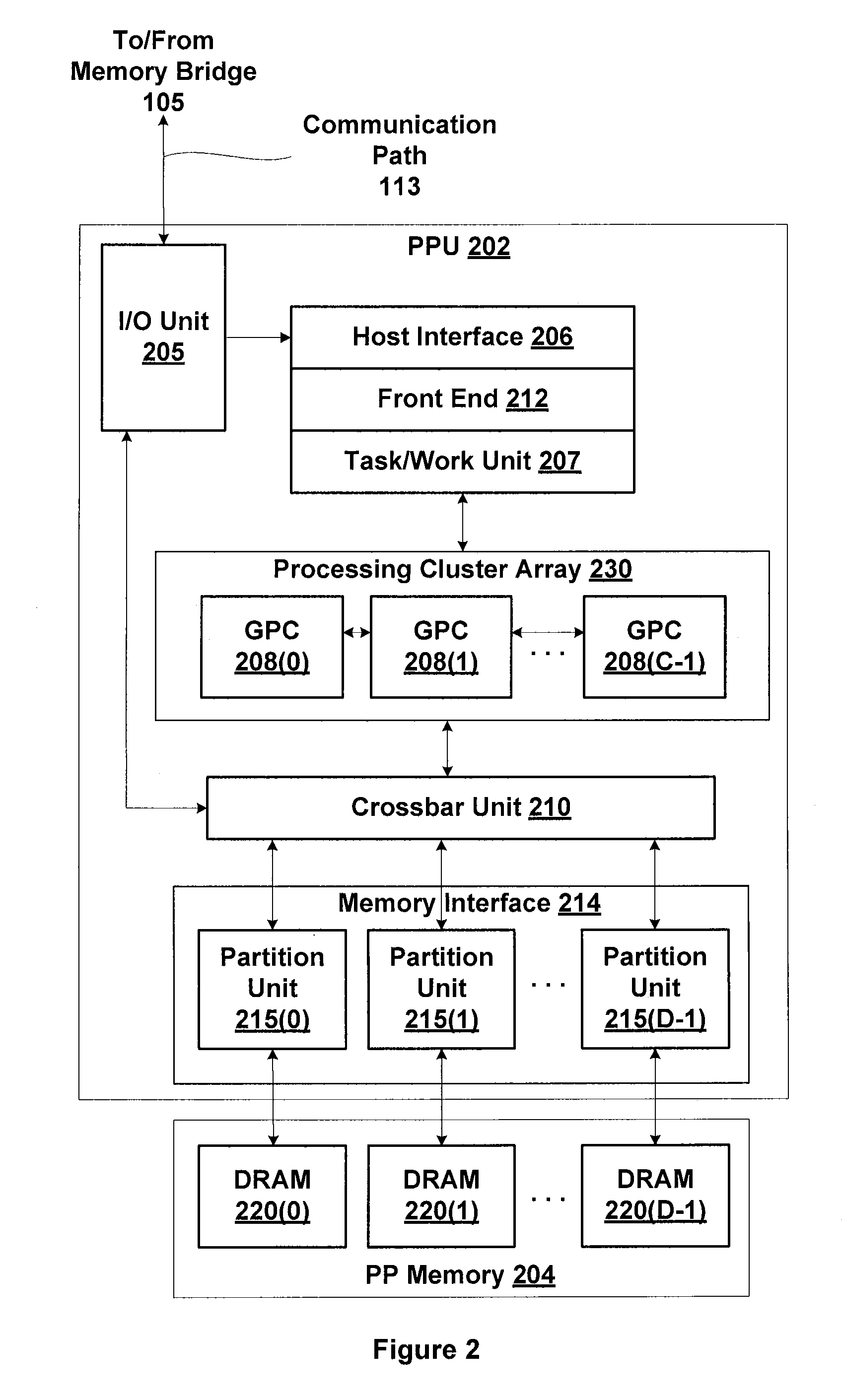

Controller for a memory system having multiple partitions

InactiveUS6853382B1Improving topologyExtend cycle timeMemory adressing/allocation/relocationImage memory managementLeast recently frequently usedClient-side

A memory system having a number of partitions each operative to independently service memory requests from a plurality of memory clients while maintaining the appearance to the memory client of a single partition memory subsystem. The memory request specifies a location in the memory system and a transfer size. A partition receives input from an arbiter circuit which, in turn, receives input from a number of client queues for the partition. The arbiter circuit selects a client queue based on a priority policy such as round robin or least recently used or a static or dynamic policy. A router receives a memory request, determines the one or more partitions needed to service the request and stores the request in the client queues for the servicing partitions. In one embodiment, an additional arbiter circuit selects memory requests from one of a subset of the memory clients and forwards the requests to a routing circuit, thereby providing a way for the subset of memory clients to share the client queues and routing circuit. Alternatively, a memory client can make requests directed to a particular partition in which case no routing circuit is required. For a read request that requires more than one partition to service, the memory system must collect the read data from read queues for the various partitions and deliver the collected data back to the proper client. Read queues can provide data in non-fifo order to satisfy an memory client that can receive data out-of-order.

Owner:NVIDIA CORP

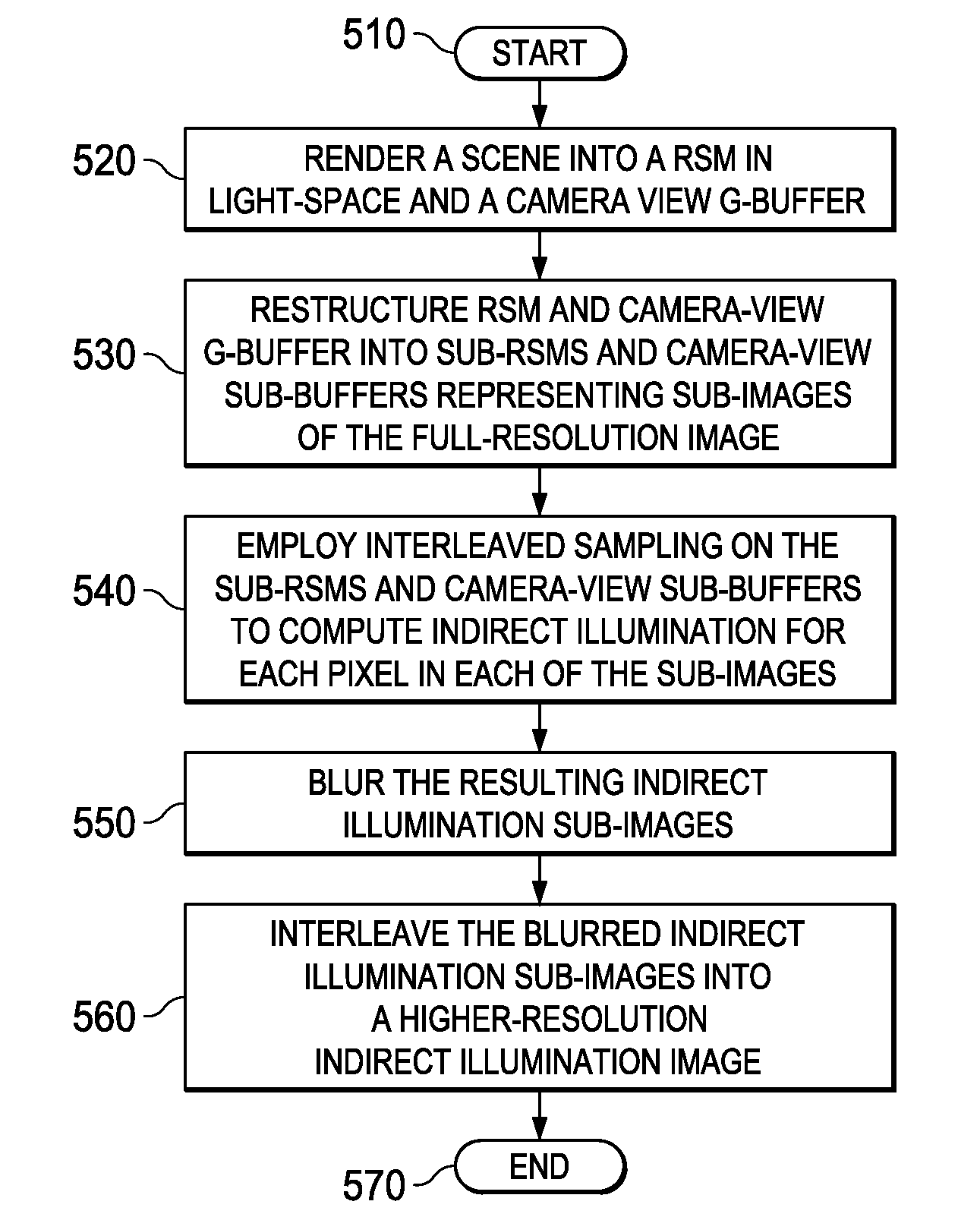

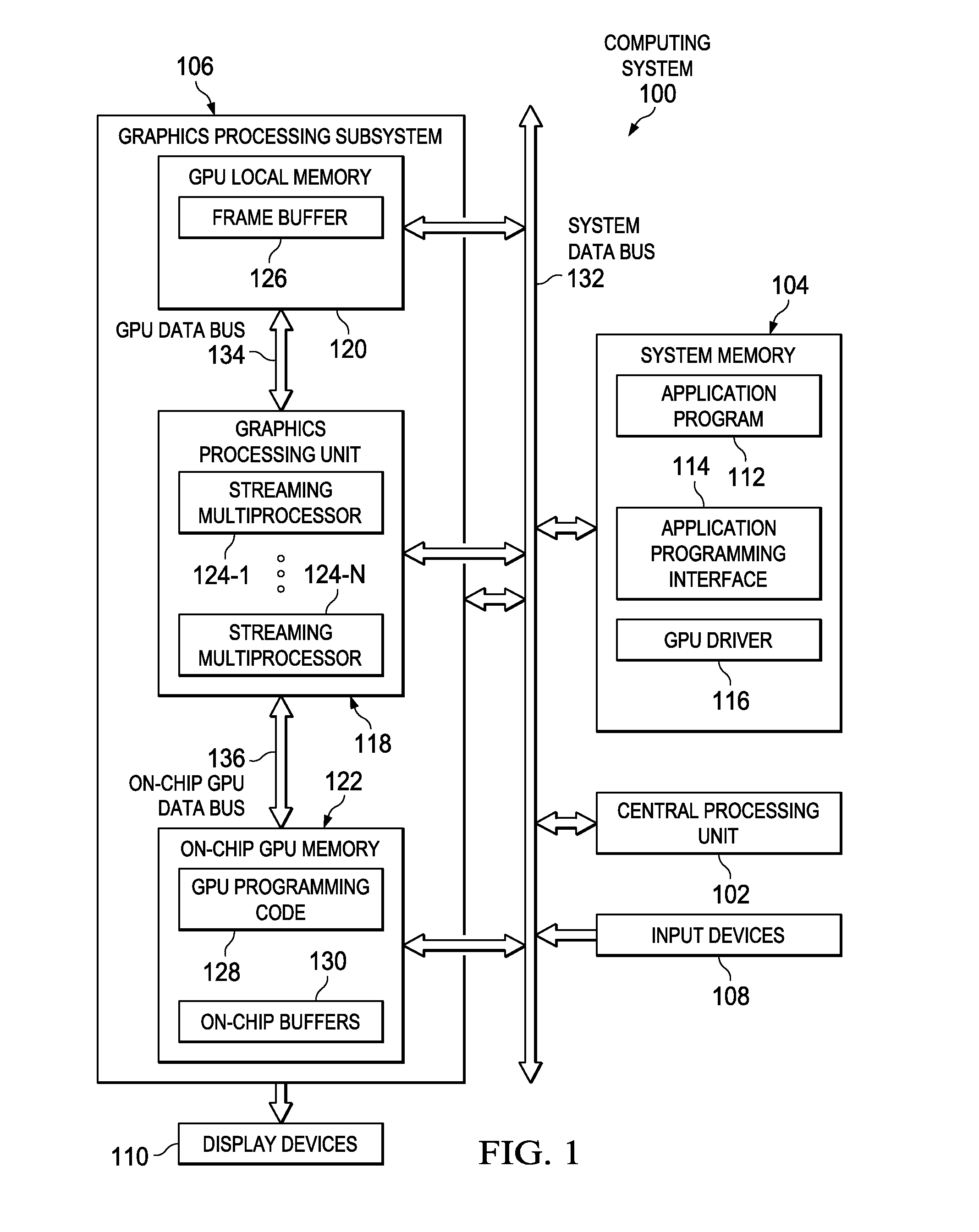

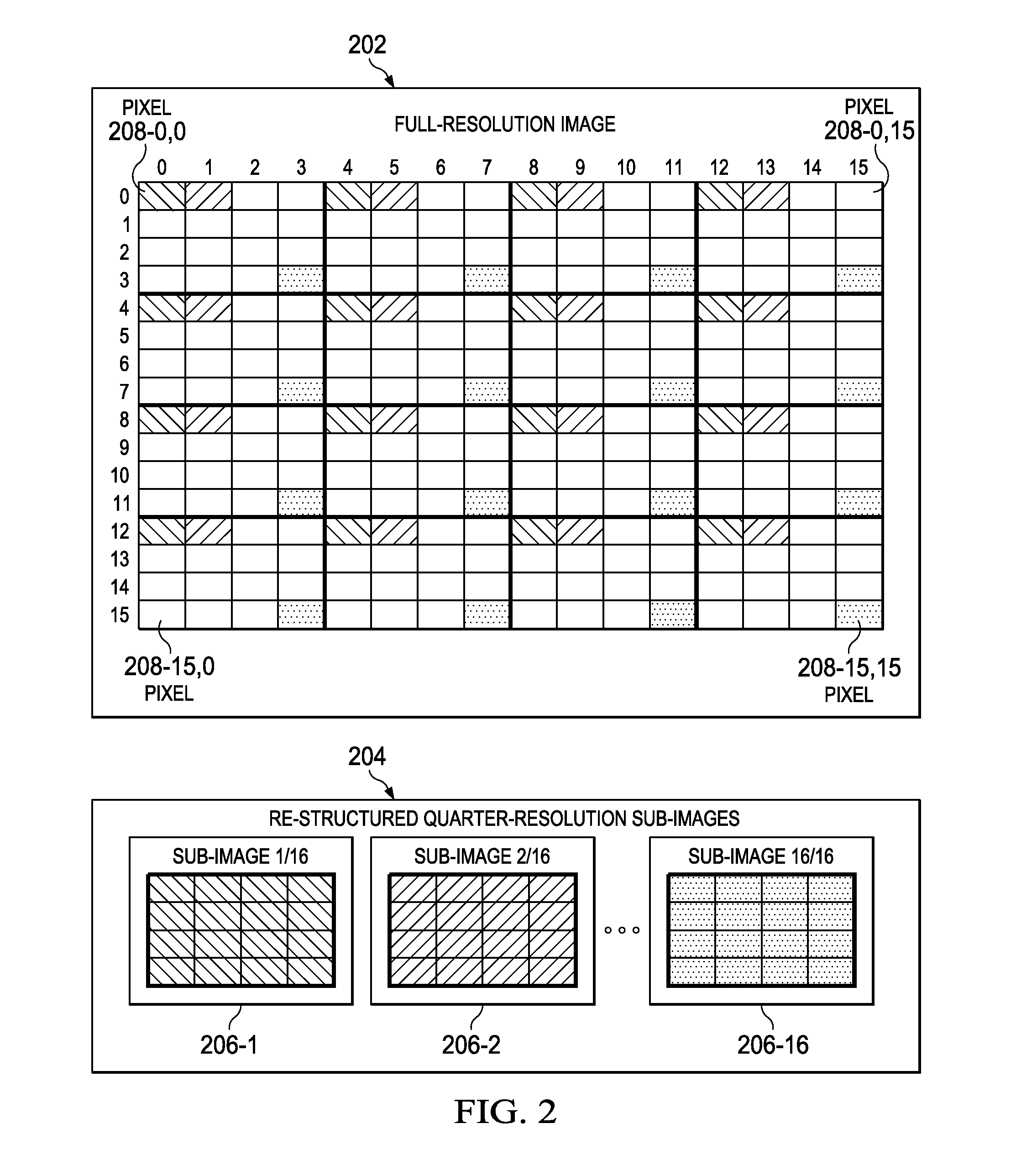

Cache-efficient processor and method of rendering indirect illumination using interleaving and sub-image blur

A cache-efficient processor and method for rendering indirect illumination using interleaving and sub-image blur. One embodiment of the processor is configured to render an indirect illumination image and includes: (1) a buffer restructurer configured to organize a reflective shadow map (RSM), rendered with respect to a reference point, into a plurality of unique sub-RSMs, each having sub-RSM pixels, (2) an indirect illumination computer configured to employ interleaved sampling on the plurality of unique sub-RSMs to generate a plurality of indirect illumination sub-images, and (3) a filter operable to smooth accumulated light values of the indirect illumination sub-images for subsequent interleaving into the indirect illumination image.

Owner:NVIDIA CORP

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com