Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

915 results about "Shader" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

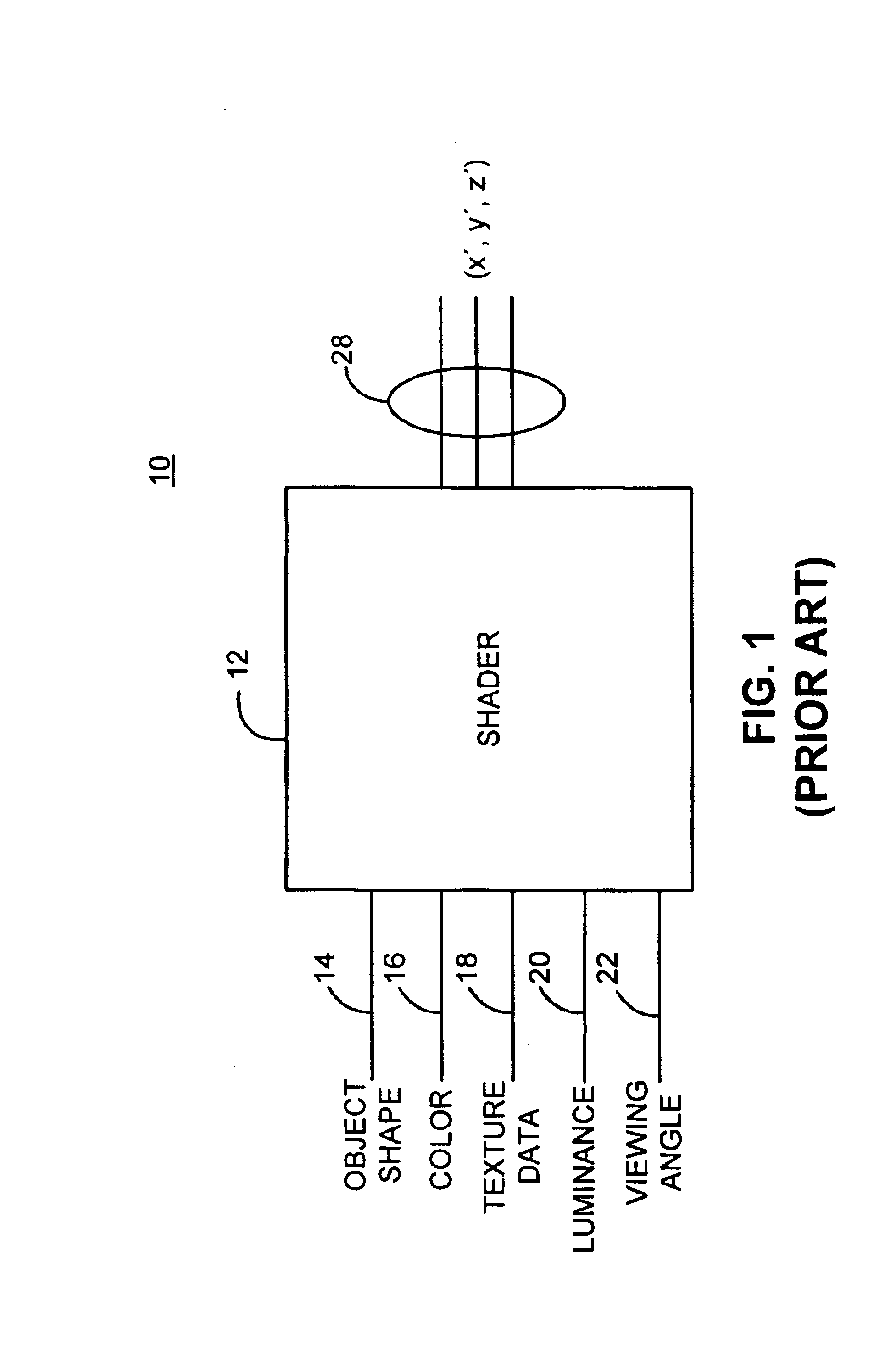

In computer graphics, a shader is a type of computer program that was originally used for shading (the production of appropriate levels of light, darkness, and color within an image), but which now performs a variety of specialized functions in various fields of computer graphics special effects, or does video post-processing unrelated to shading, or even performs functions unrelated to graphics at all.

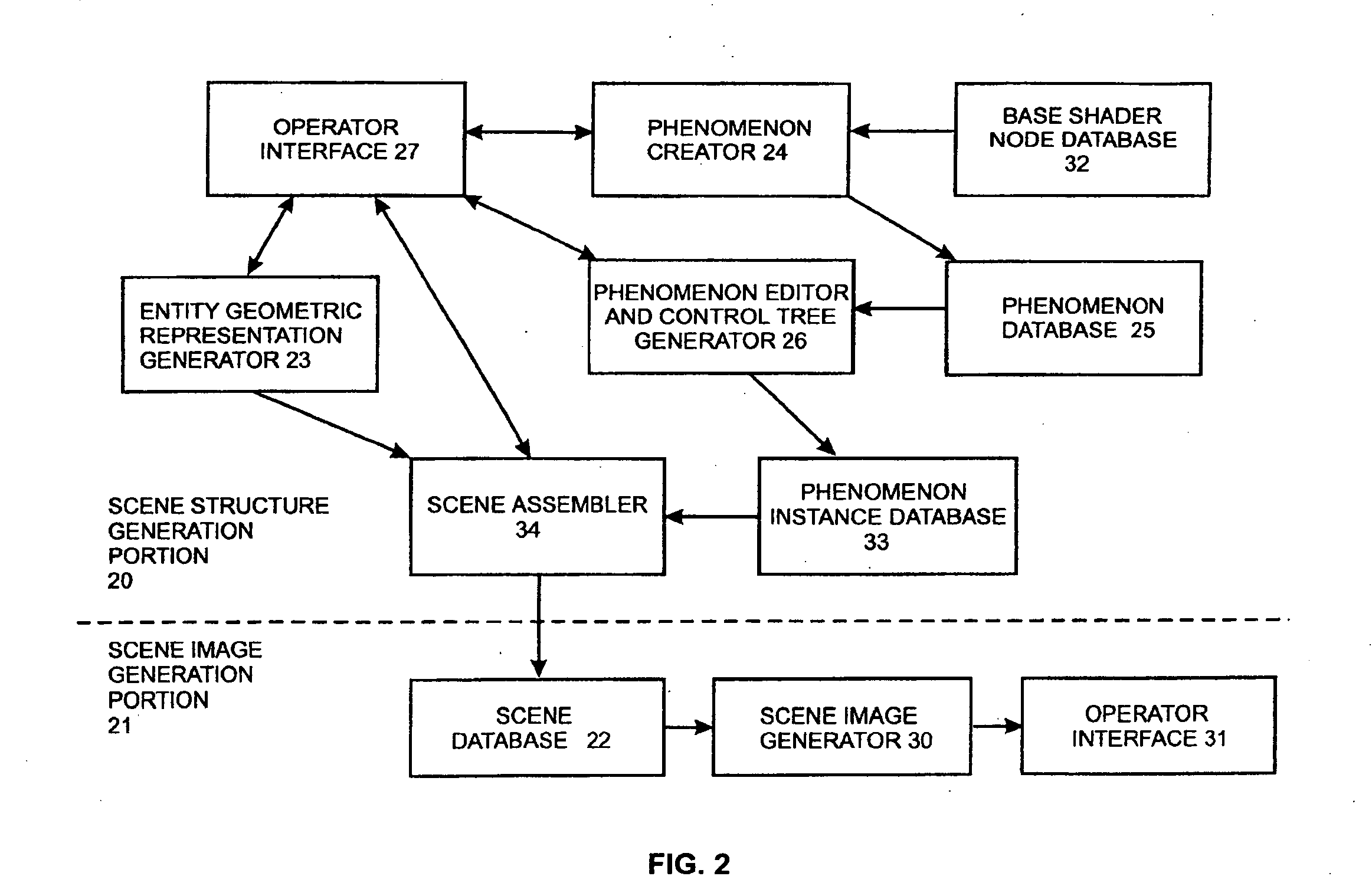

Efficient use of user-defined shaders to implement graphics operations

ActiveUS7015909B1Possible total numberGood orthogonalityProgram control3D-image renderingParallel computingRunning time

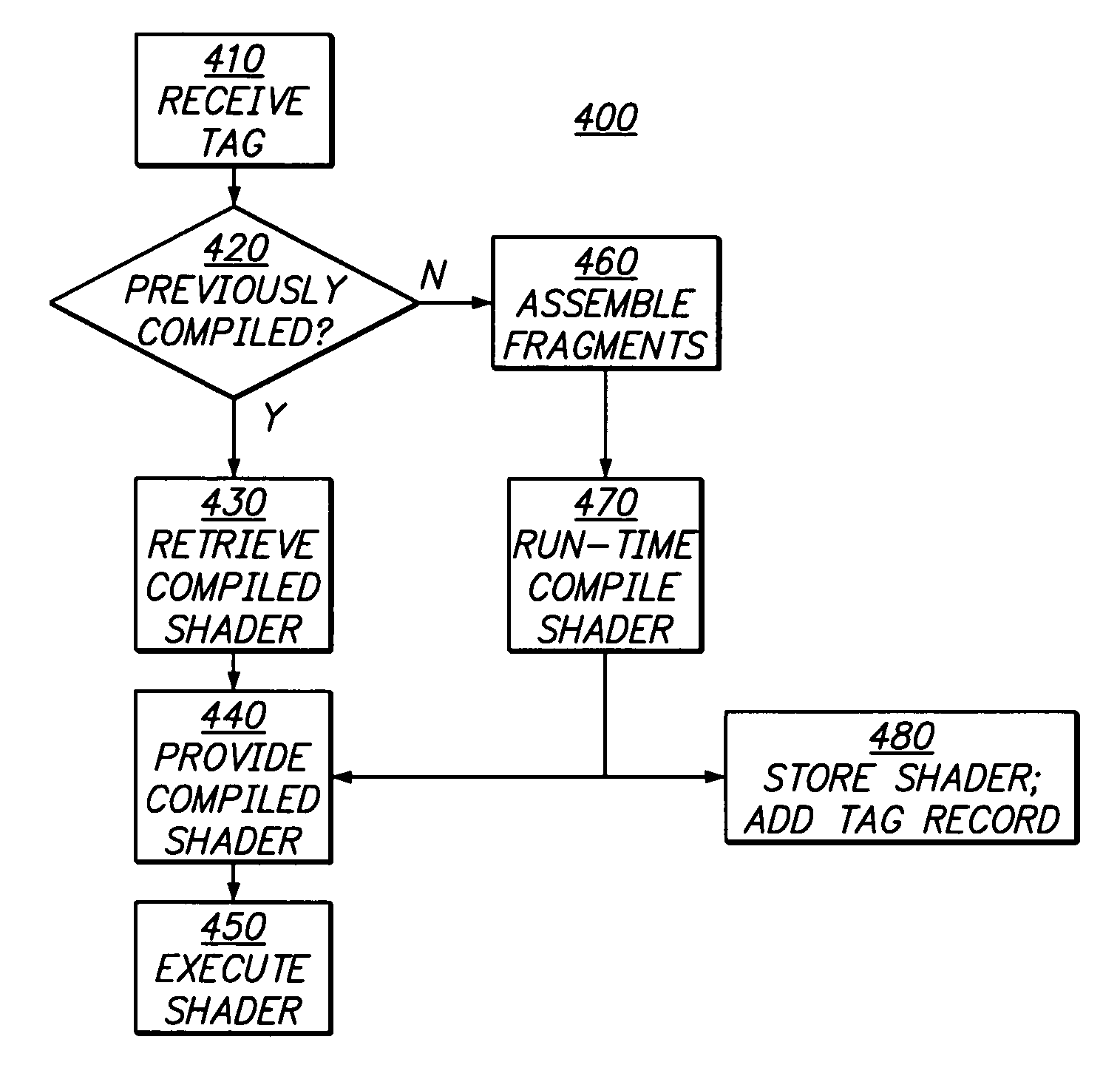

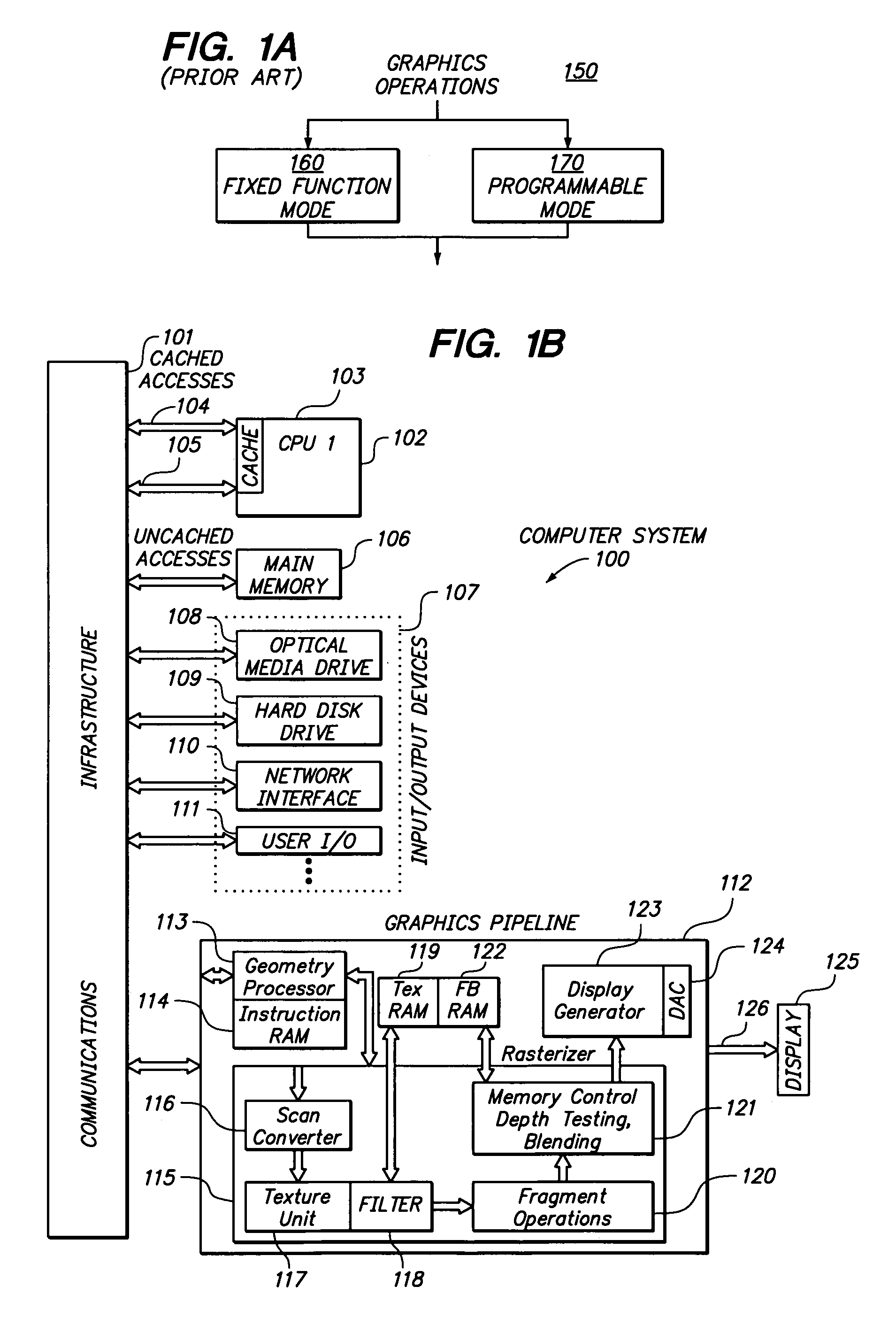

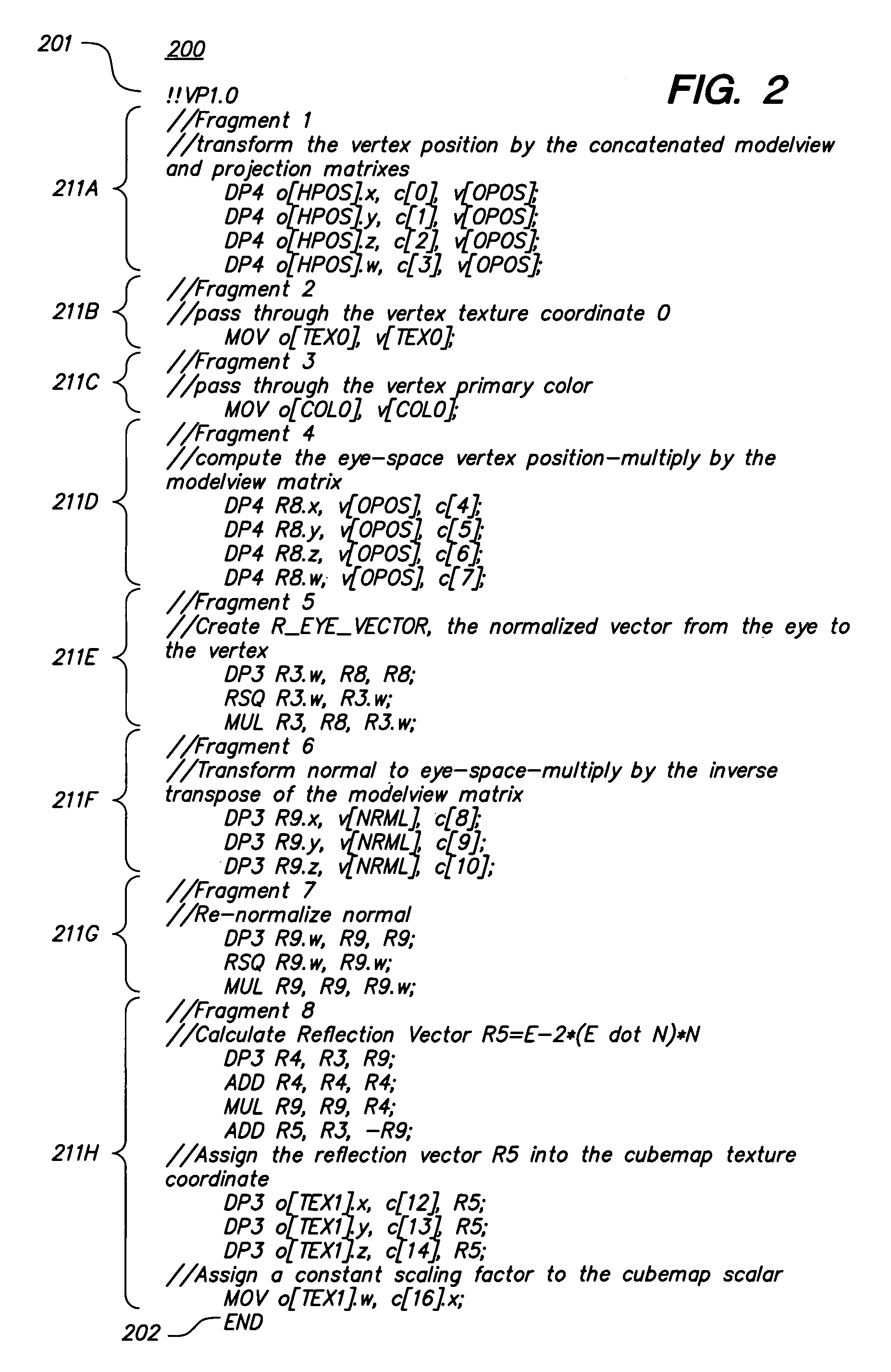

User-defined shaders are constructed from fragments. The shaders are identified by tags. At run-time, the tag is used to determine whether the user-defined shader has been previously compiled. If it has, the compiled version is executed. If it has not, the fragments are assembled to form the shader and the shader is run-time compiled. The compiled shader can be stored for subsequent reuse, with the tag serving as an index to the compiled version.

Owner:AECHELON TECH

Recirculating shade tree blender for a graphics system

InactiveUS7034828B1Good flexibilityReduce in quantityCathode-ray tube indicatorsProcessor architectures/configurationGraphic systemComputer science

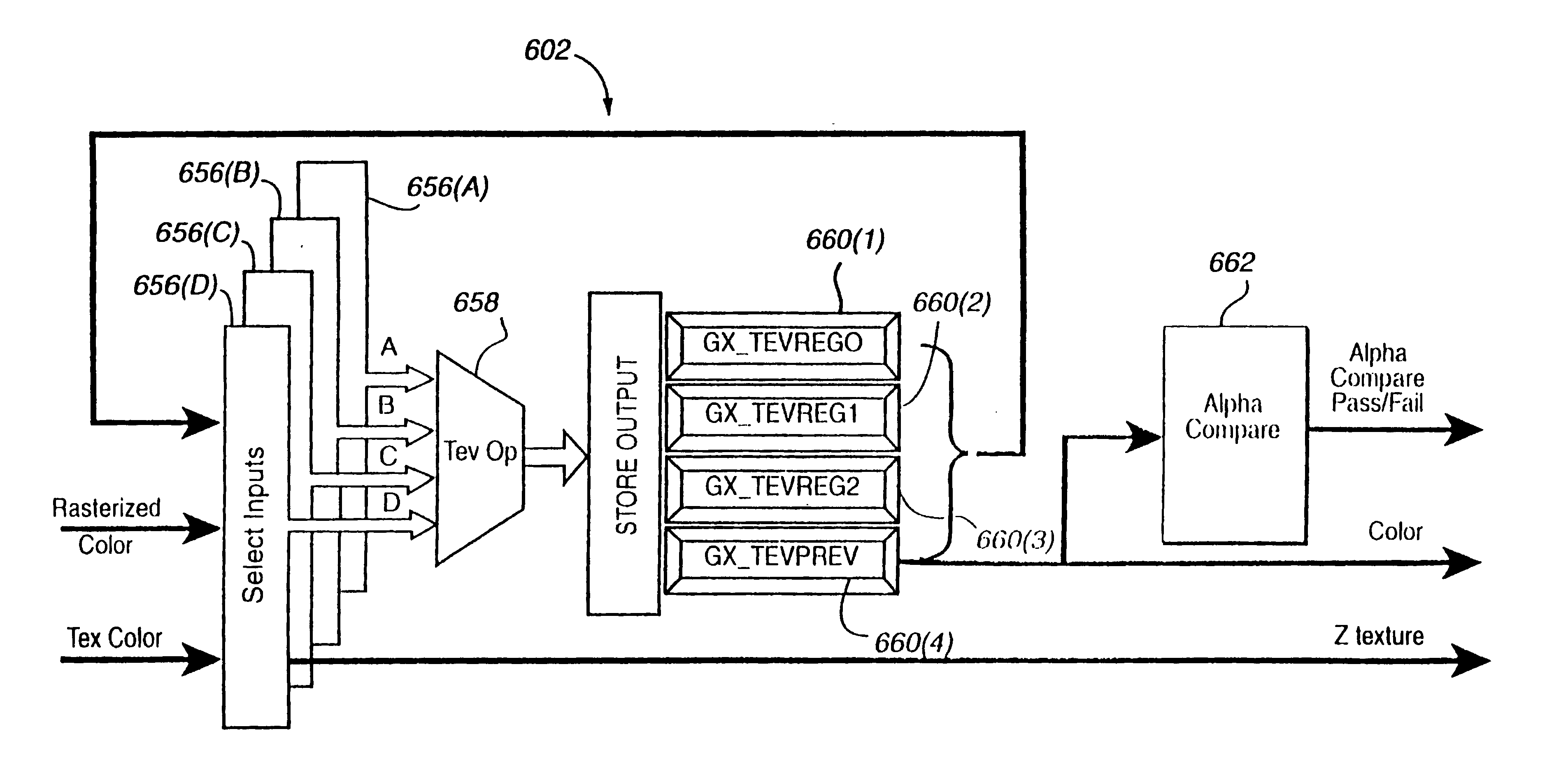

A hardware-accelerated recirculating programmable texture blender / shader arrangement circulates computed color and alpha data over multiple texture blending / shading cycles (stages) to provide multi-texturing and other effects. Up to sixteen independently programmable consecutive stages, forming a chain of blending operations, are supported for applying multiple textures to a single object in a single rendering pass.

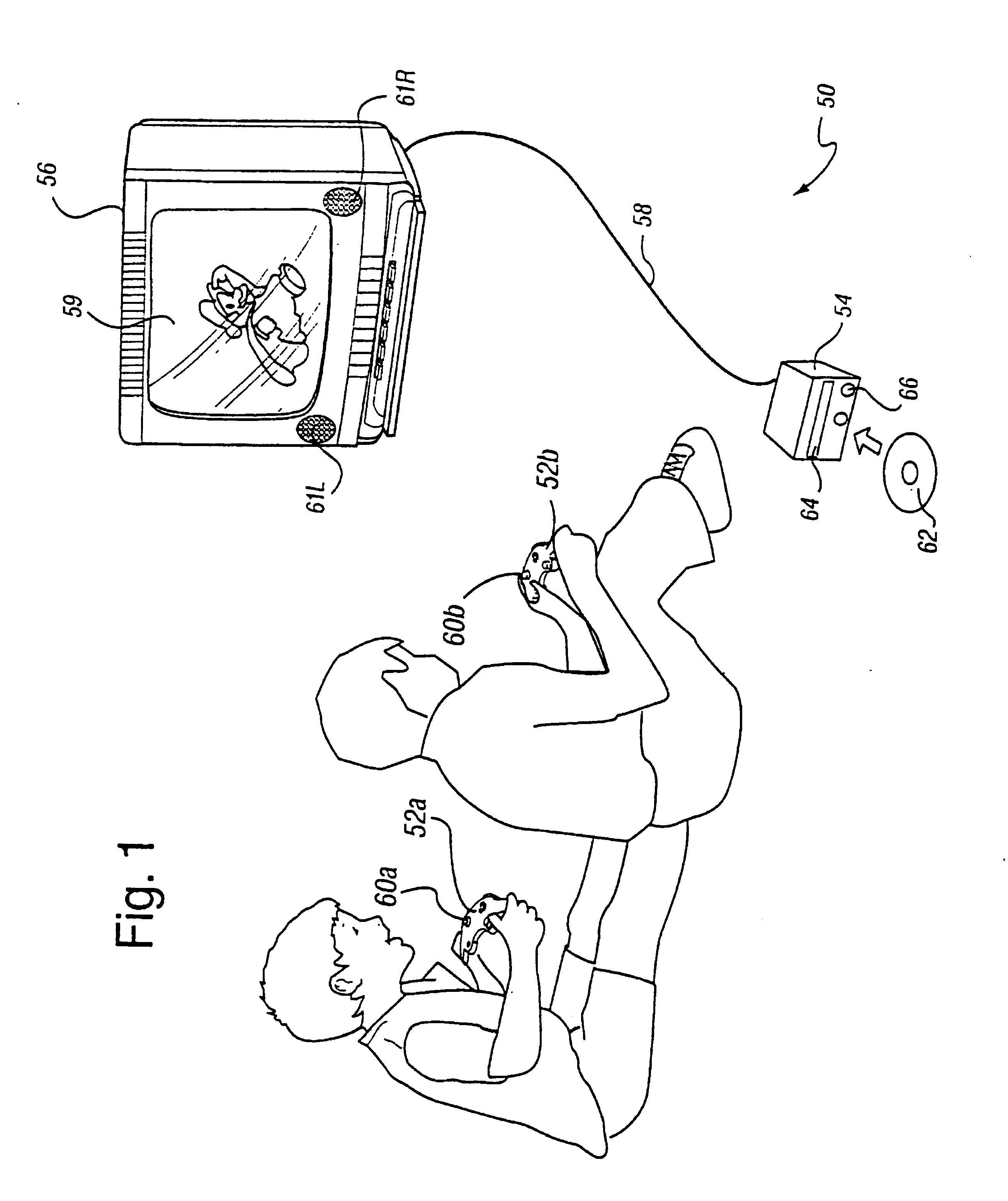

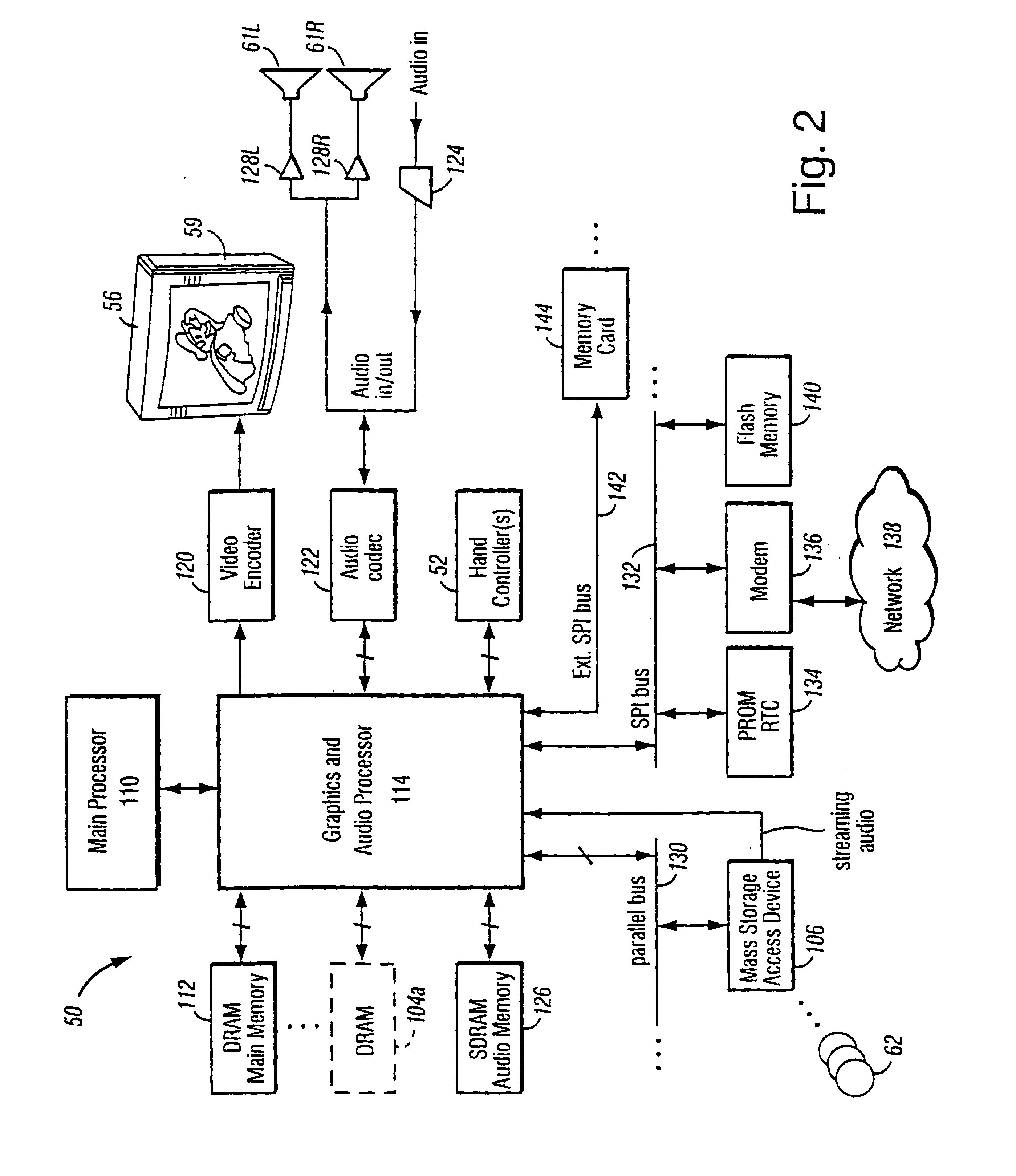

Owner:NINTENDO CO LTD

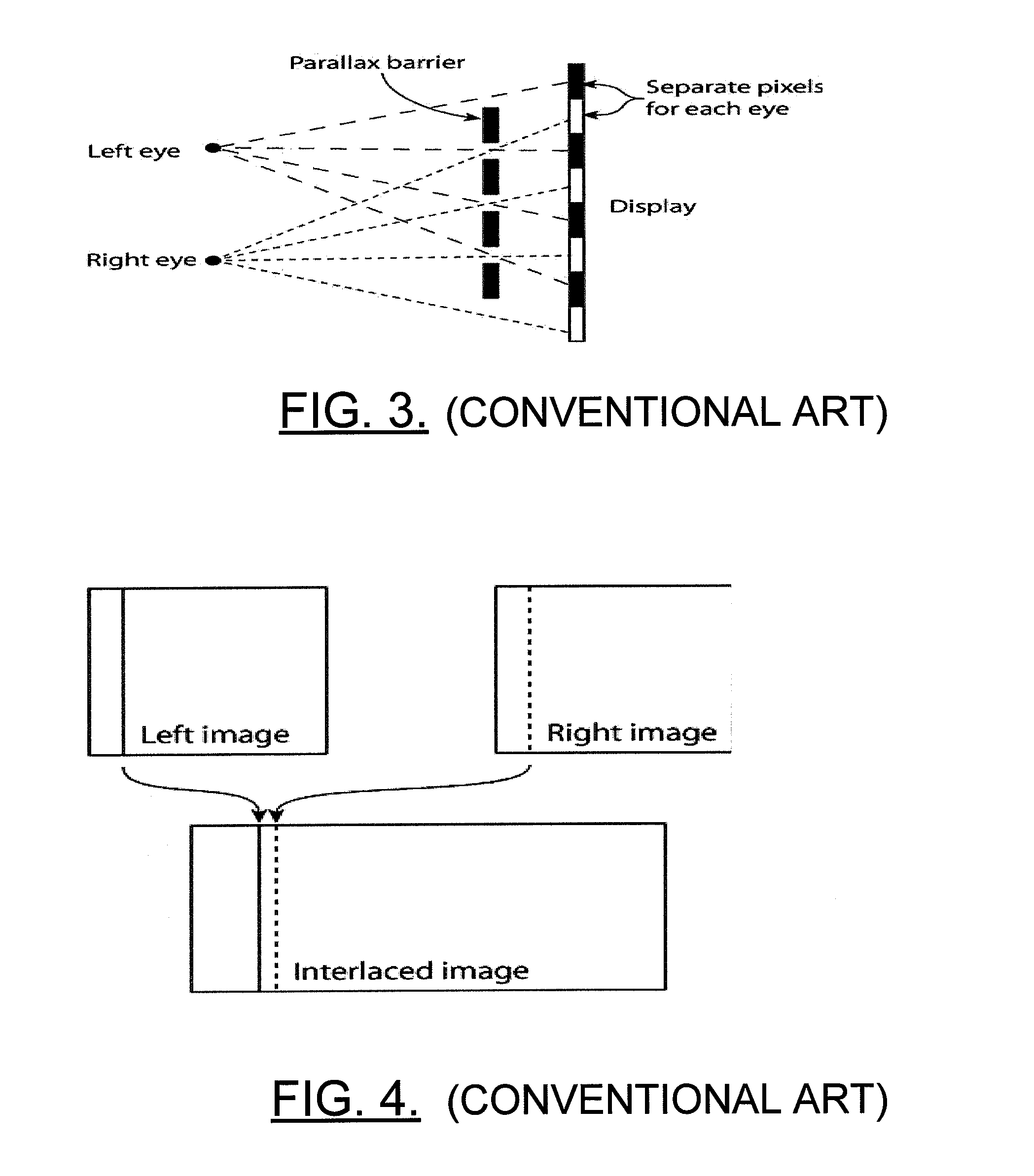

Apparatus, method and a computer program product for providing a unified graphics pipeline for stereoscopic rendering

InactiveUS20080007559A1Reduce computationReduce power consumptionDigital computer detailsImage data processing detailsDisplay deviceMultiple viewpoint

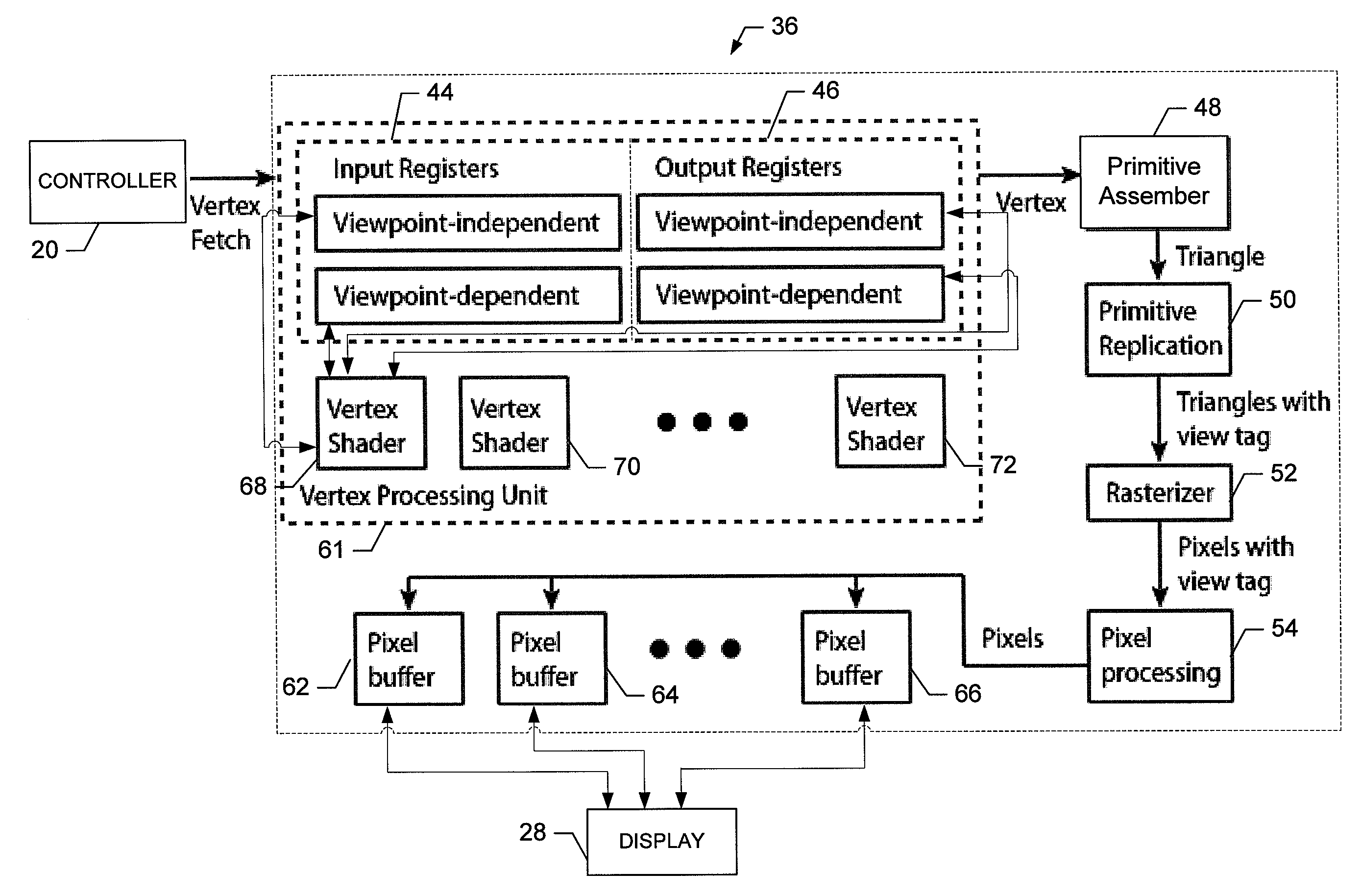

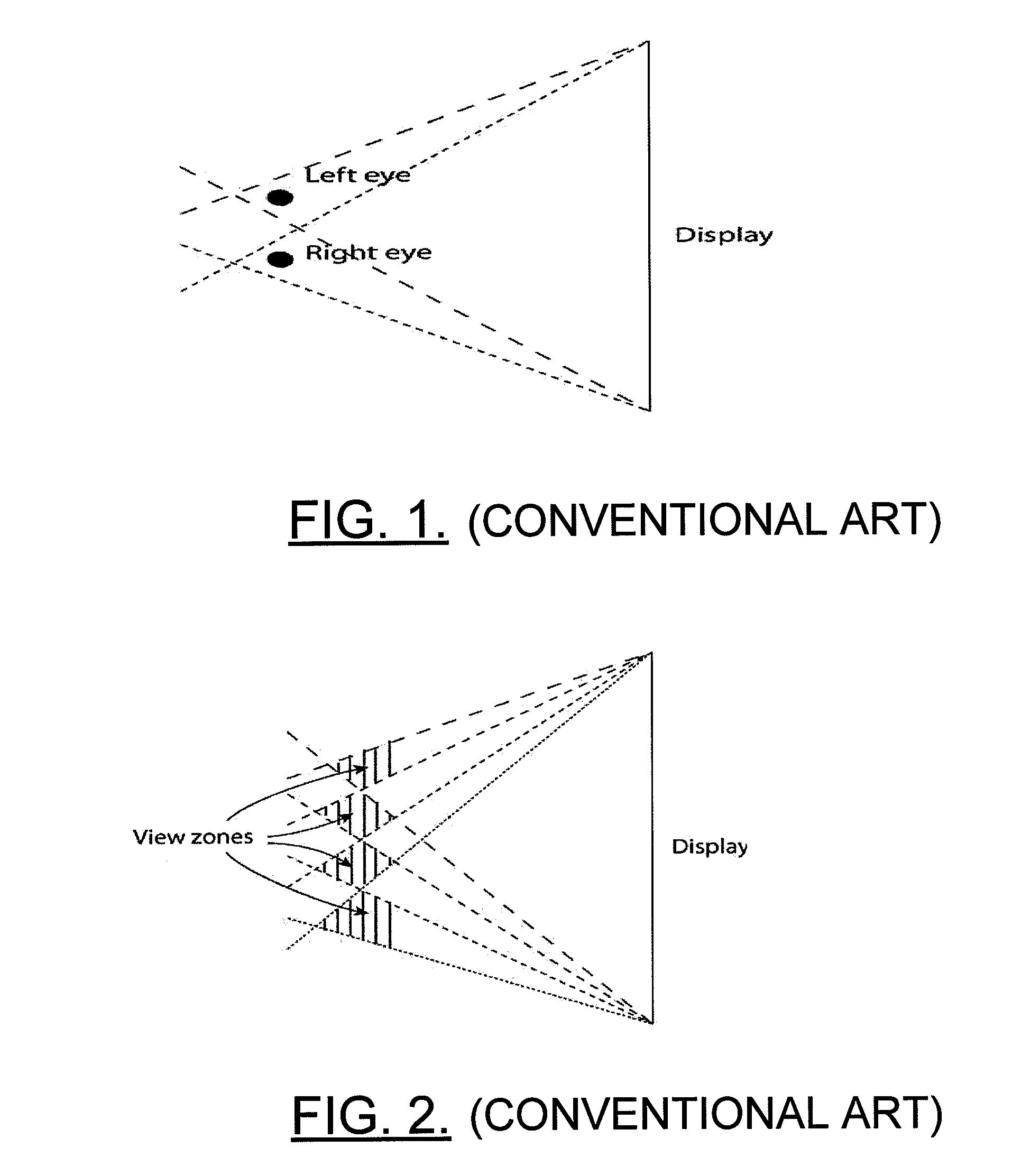

A device for rendering to multiple viewpoints of a stereoscopic display is provided. The device includes vertex shaders which receive vertices corresponding to primitives and process viewpoint dependent information. The device also includes a primitive replication unit which replicates primitives according to a number of viewpoints supported by the stereoscopic display. The primitive replication unit adds unique view tags to each of the primitives which identify the viewpoint that the respective primitive is destined for. Each replicated primitive is processed by a rasterizer and converted into pixels. The rasterizer adds a view tag to the rasterized pixels so that the pixels identify a respective primitive and identify a respective pixel buffer that the pixel is destined for. The pixels can then be processed by a pixel processing unit and written to a pixel buffer corresponding to a respective viewpoint. The pixels are subsequently output to the stereoscopic display.

Owner:WSOU INVESTMENTS LLC

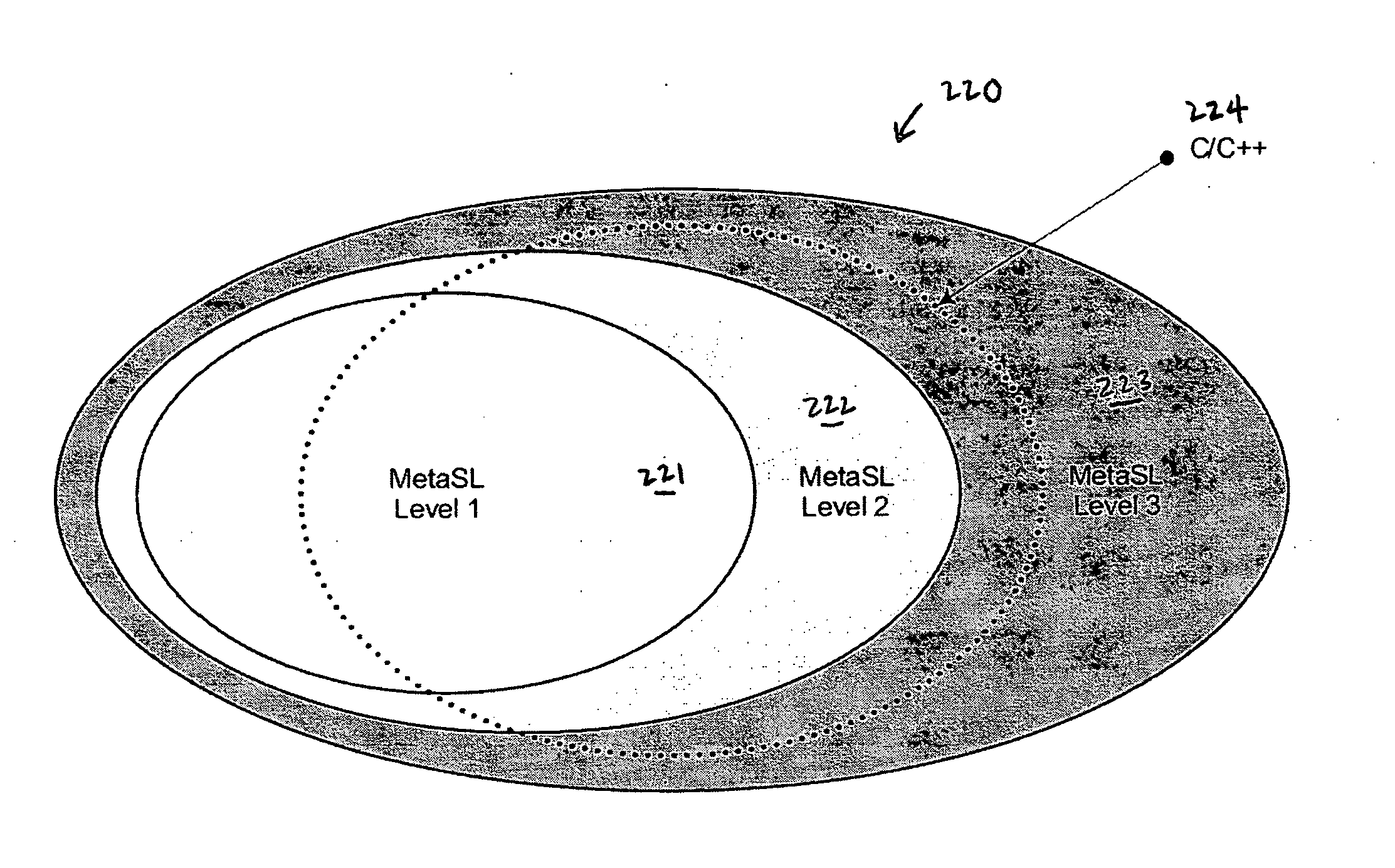

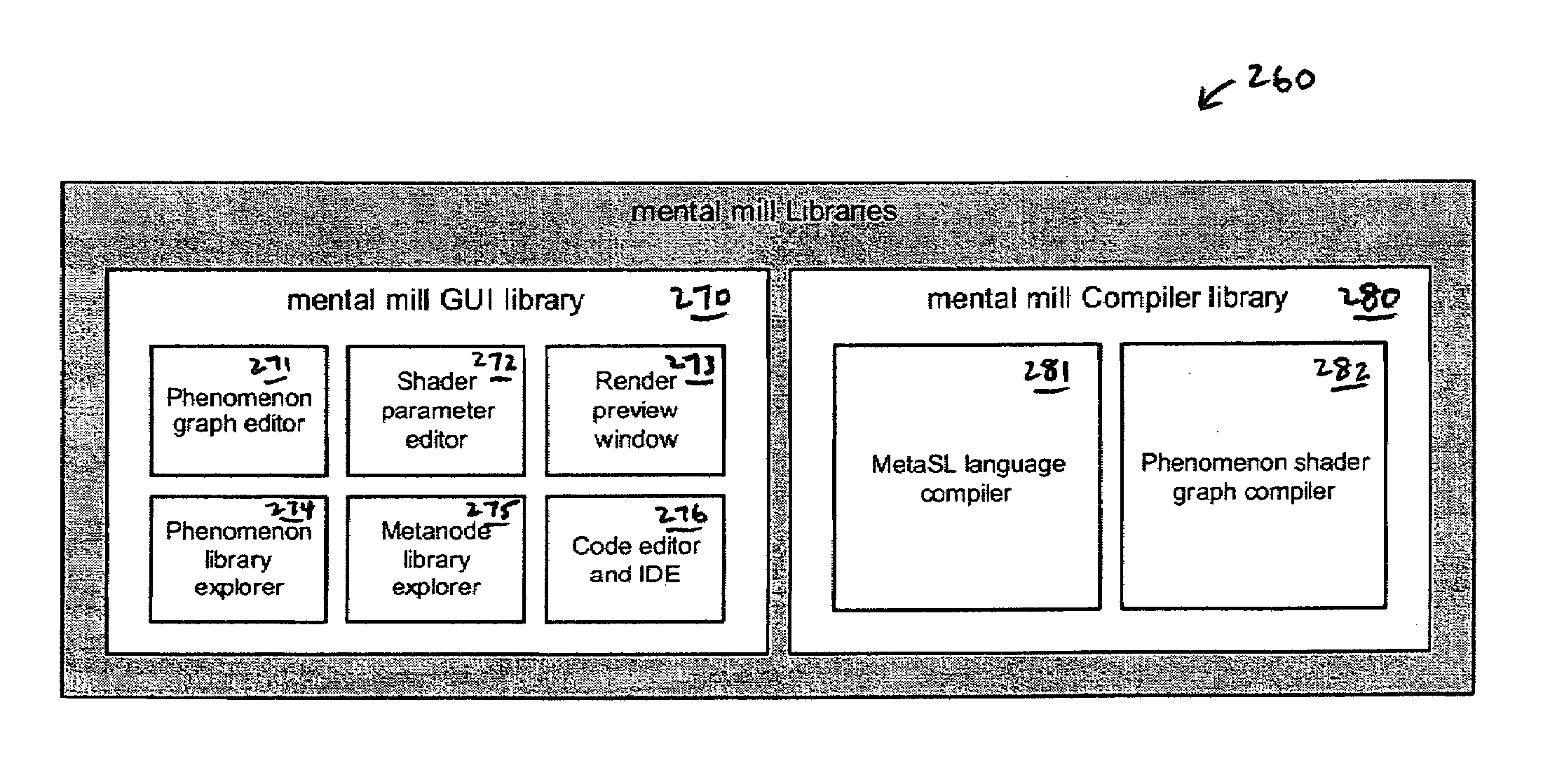

Computer graphics shader systems and methods

InactiveUS20070018980A1Simple re-useSimple re-purposingCathode-ray tube indicatorsMultiple digital computer combinationsComputer programmingHuman language

Methods and systems are described that unite various shading applications under a single language, enable the simple re-use and re-purposing of shaders, facilitate the design and construction of shaders without need for computer programming, and enable the graphical debugging of shaders.

Owner:MENTAL IMAGES

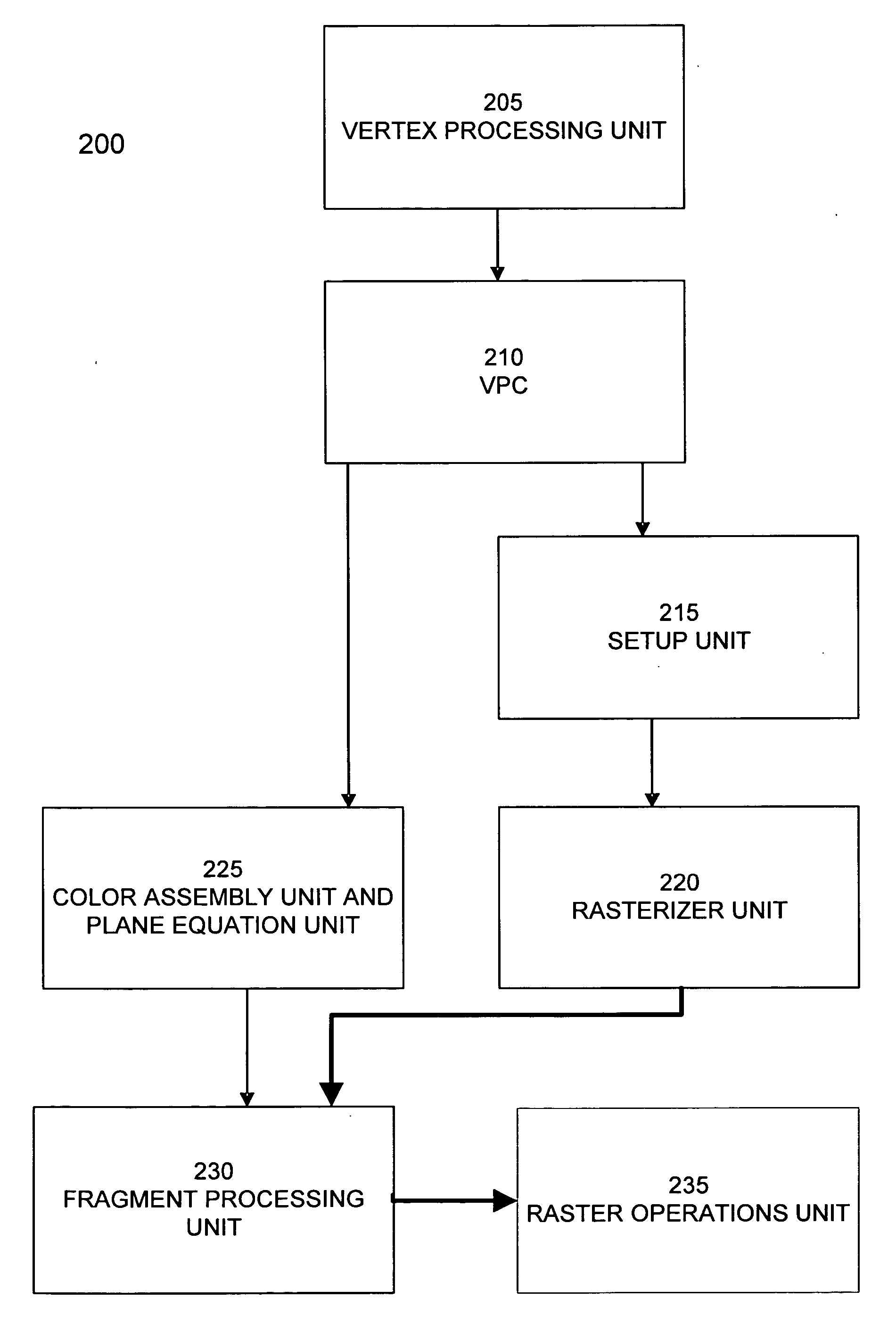

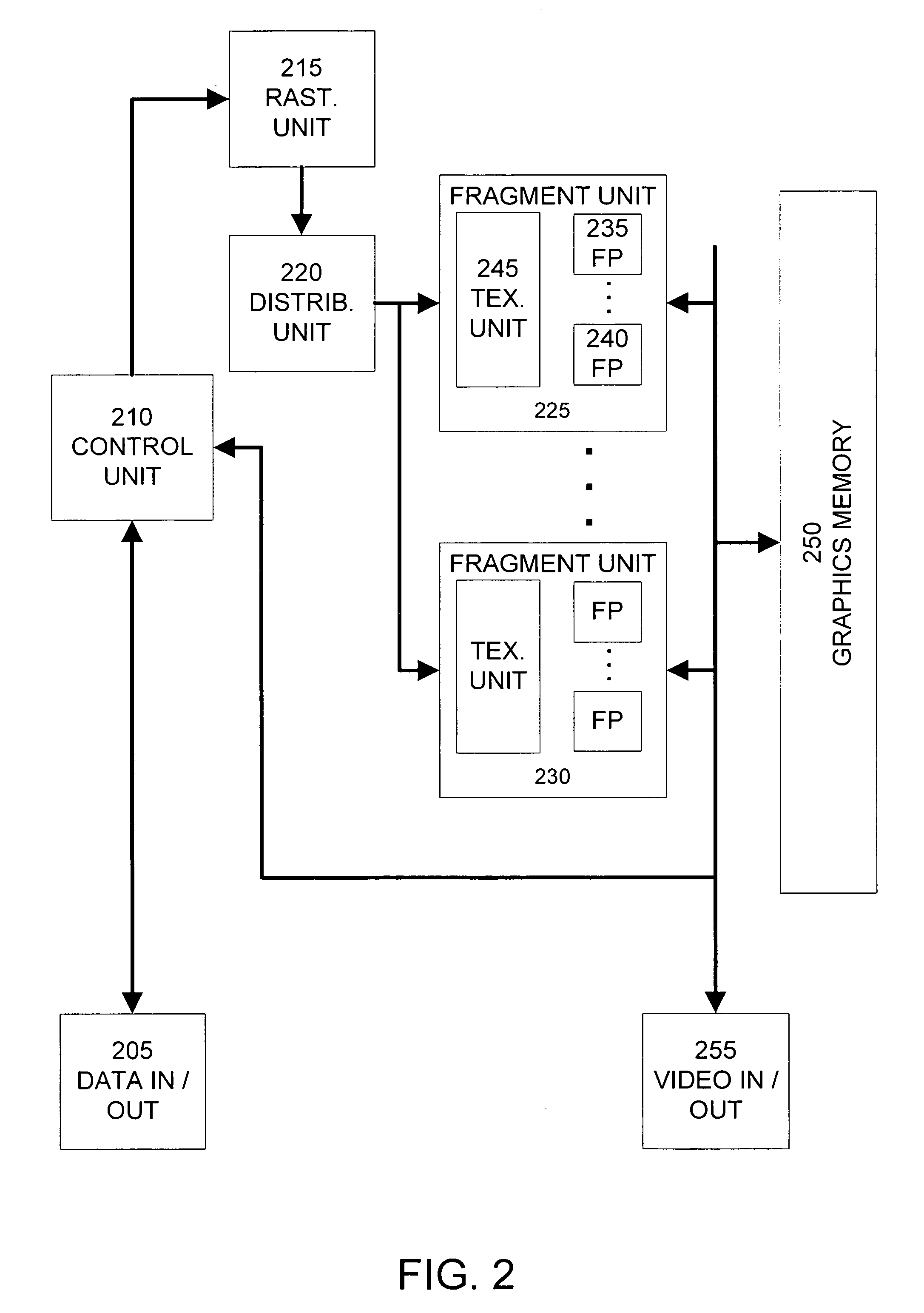

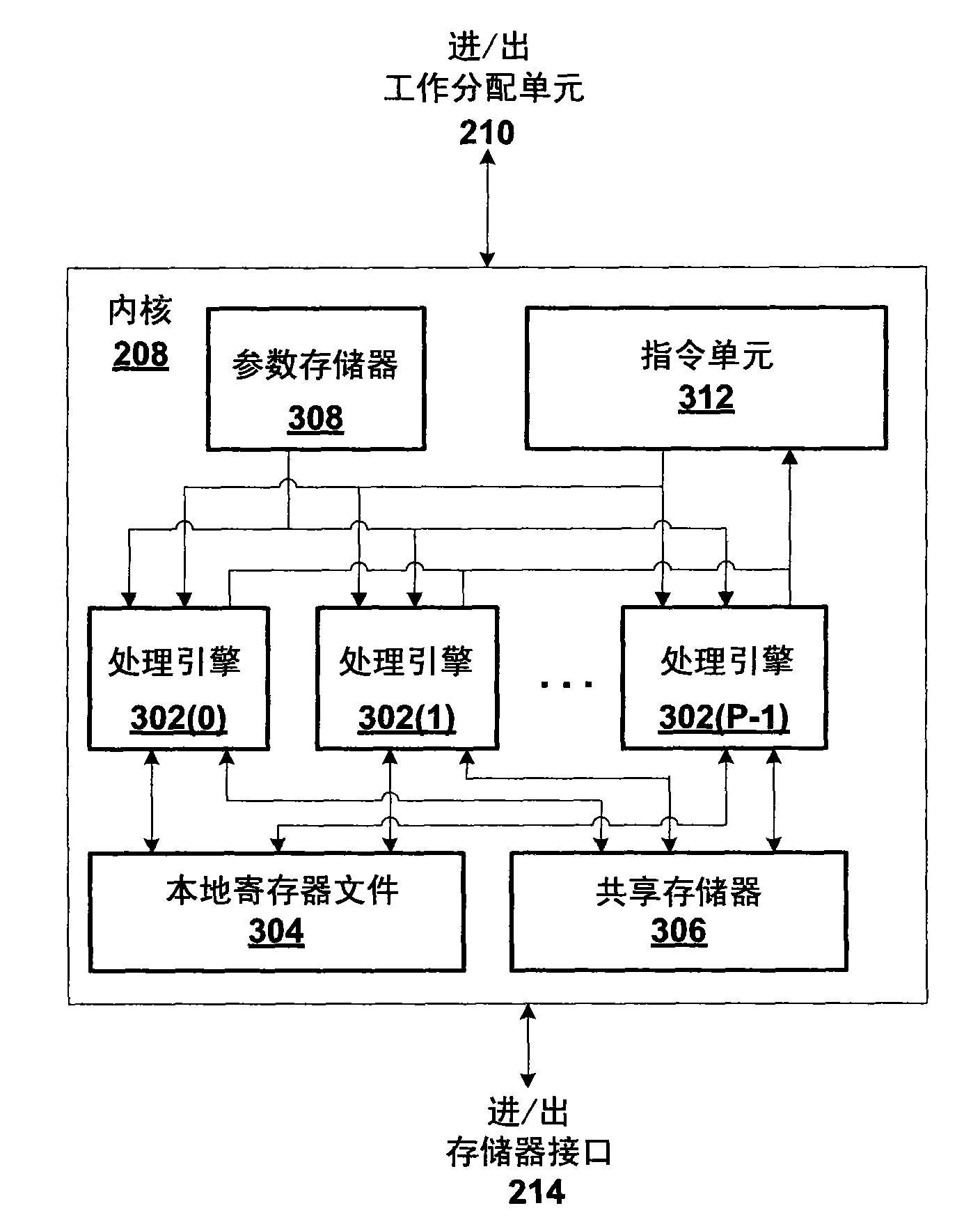

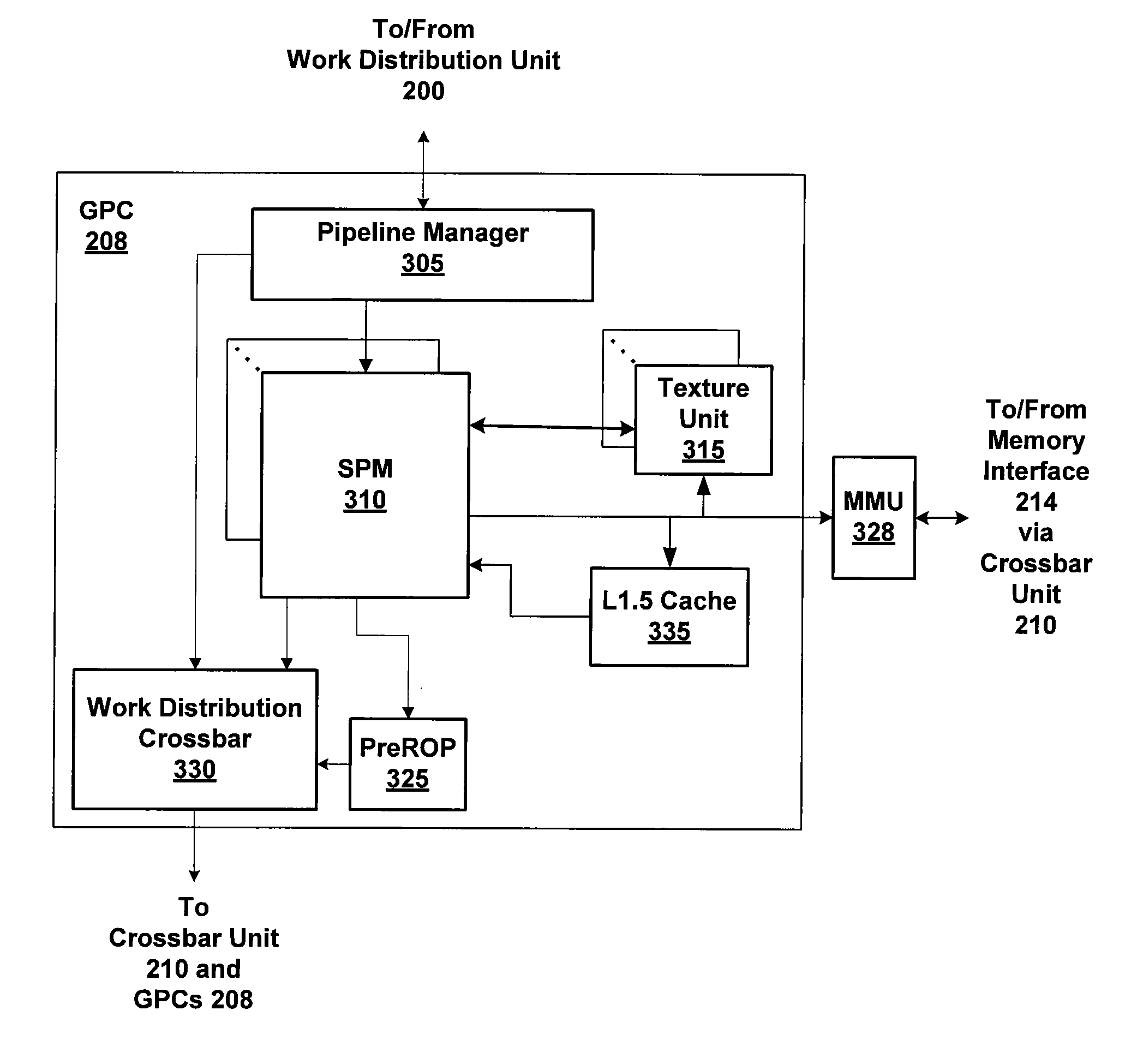

Increased scalability in the fragment shading pipeline

ActiveUS20060055695A1Drawing from basic elementsCathode-ray tube indicatorsComputational scienceDistributor

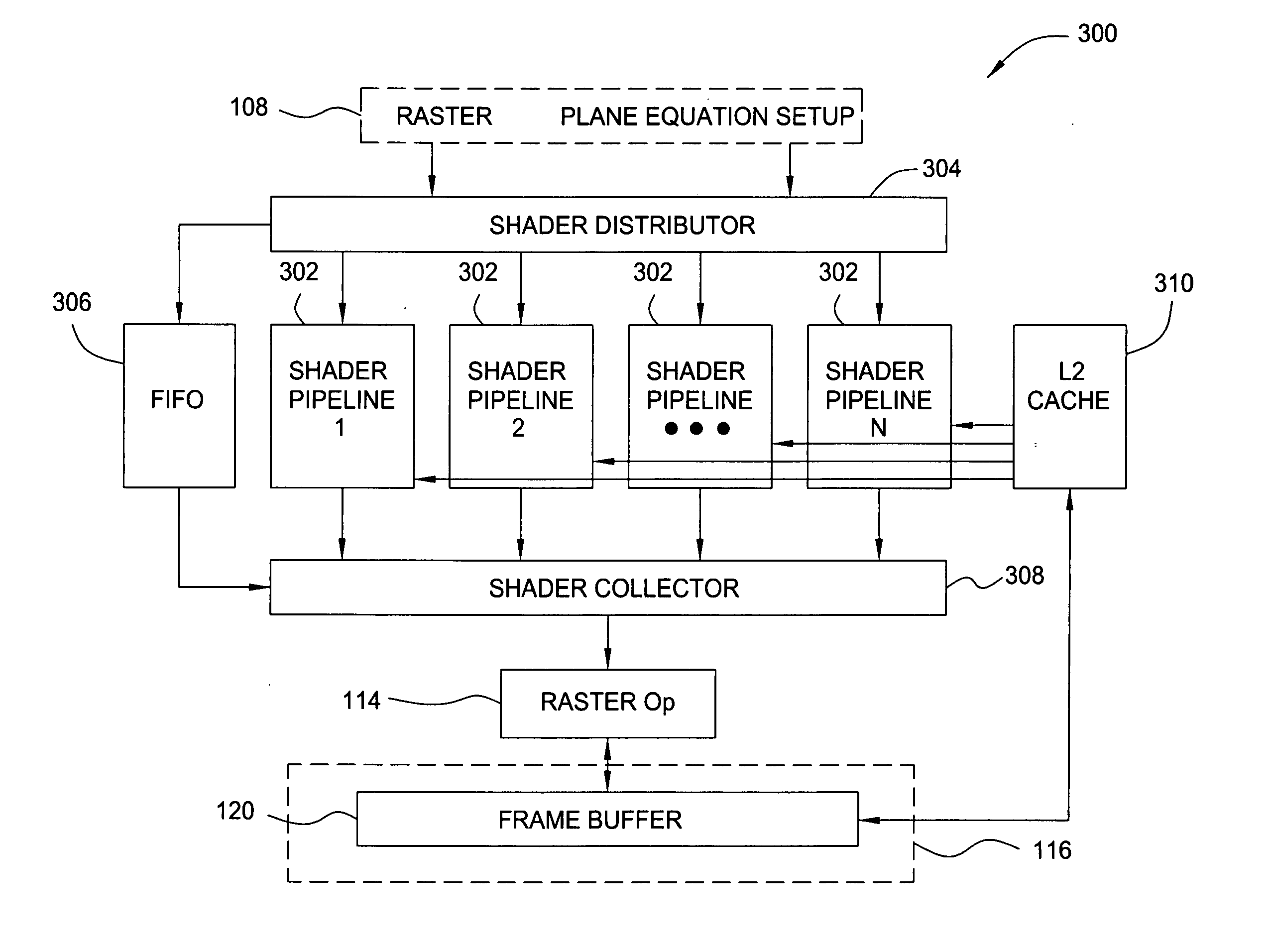

A fragment processor includes a fragment shader distributor, a fragment shader collector, and a plurality of fragment shader pipelines. Each fragment shader pipeline executes a fragment shader program on a segment of fragments. The plurality of fragment shader pipelines operate in parallel, executing the same or different fragment shader programs. The fragment shader distributor receives a stream of fragments from a rasterization unit and dispatches a portion of the stream of fragments to a selected fragment shader pipeline until the capacity of the selected fragment shader pipeline is reached. The fragment shader distributor then selects another fragment shader pipeline. The capacity of each of the fragment shader pipelines is limited by several different resources. As the fragment shader distributor dispatches fragments, it tracks the remaining available resources of the selected fragment shader pipeline. A fragment shader collector retrieves processed fragments from the plurality of fragment shader pipelines.

Owner:NVIDIA CORP

Techniques for locally modifying draw calls

ActiveUS20140292771A1Reduce the amount requiredAmount of data transferredDigital computer detailsProcessor architectures/configurationComputational scienceApplication software

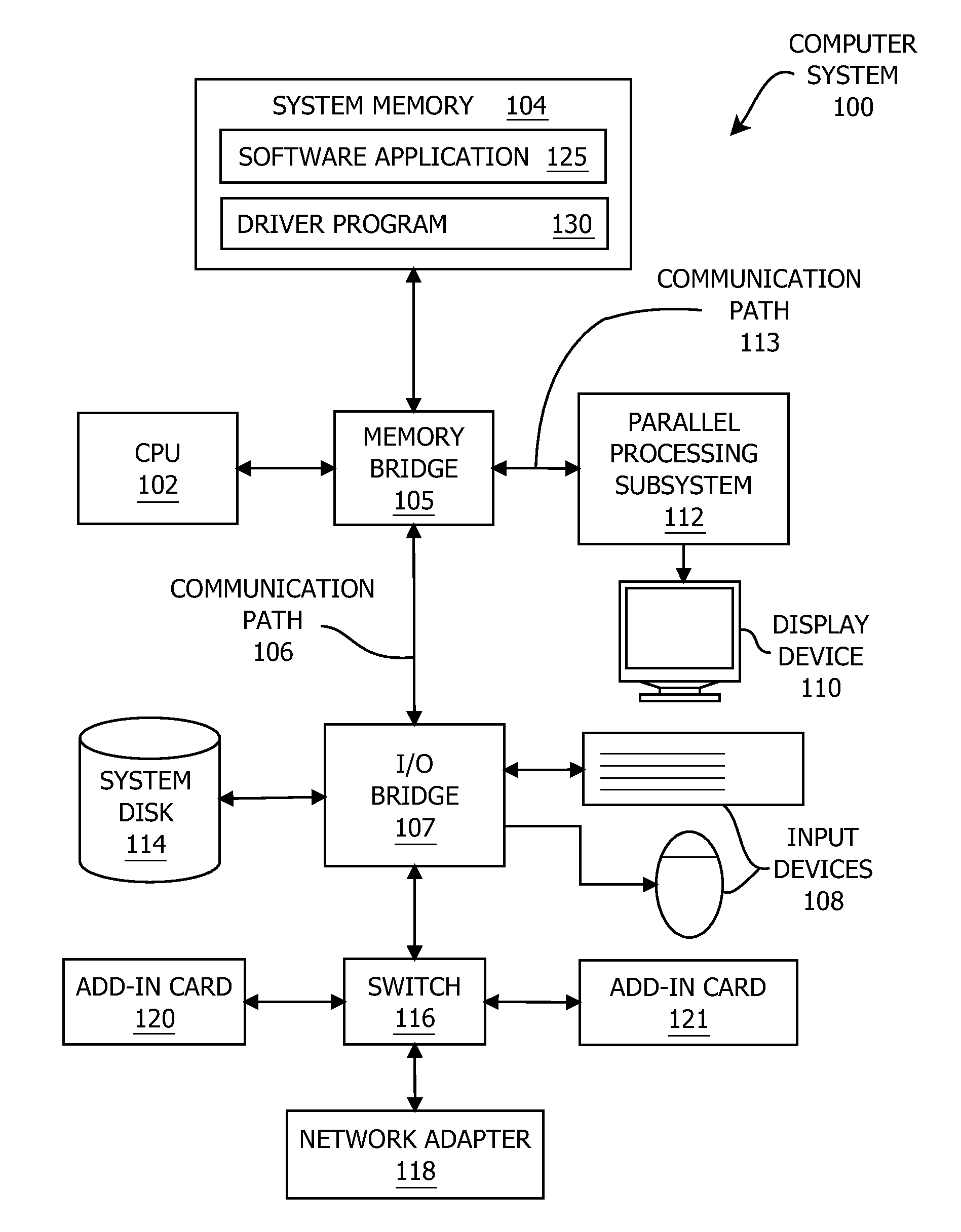

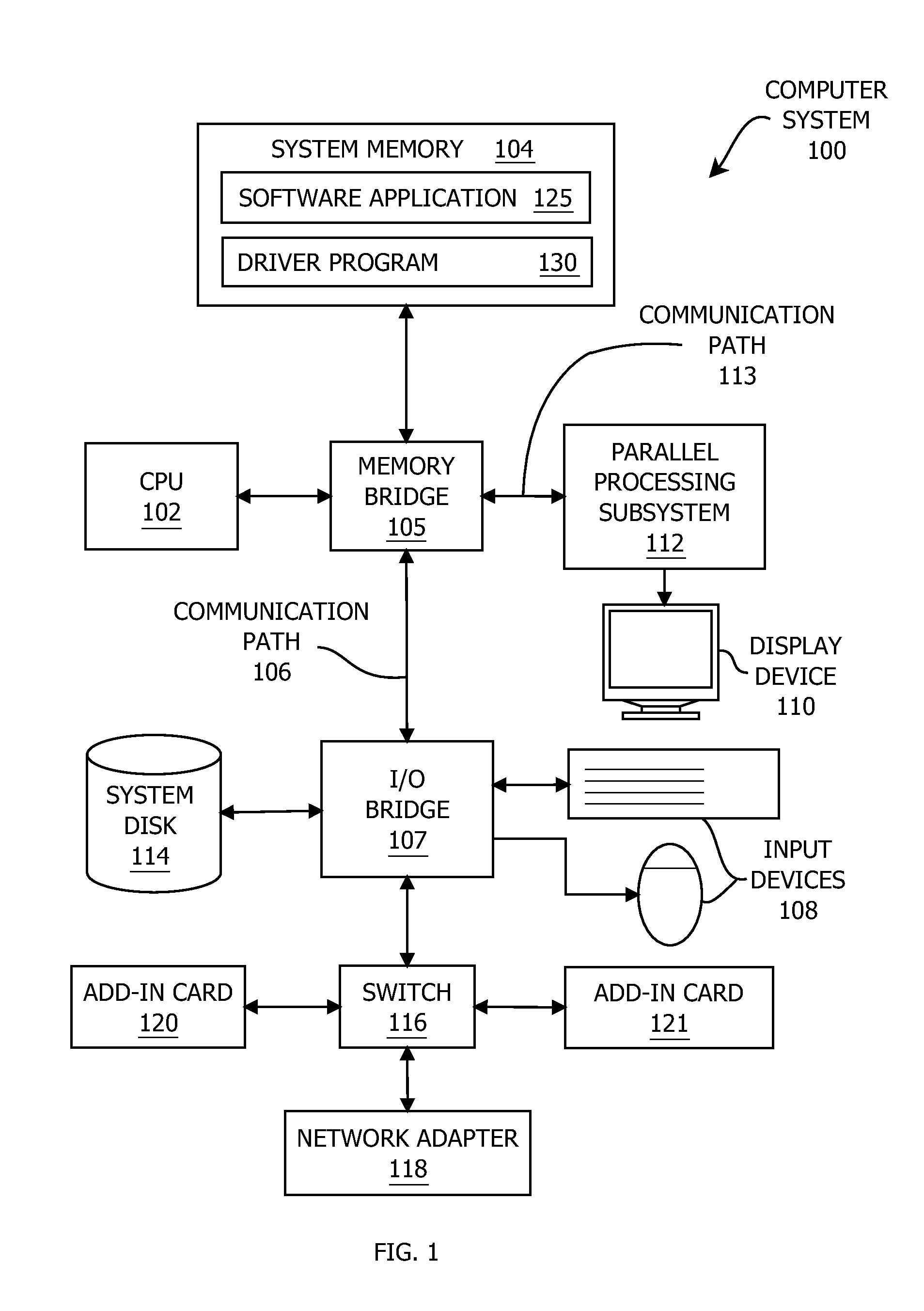

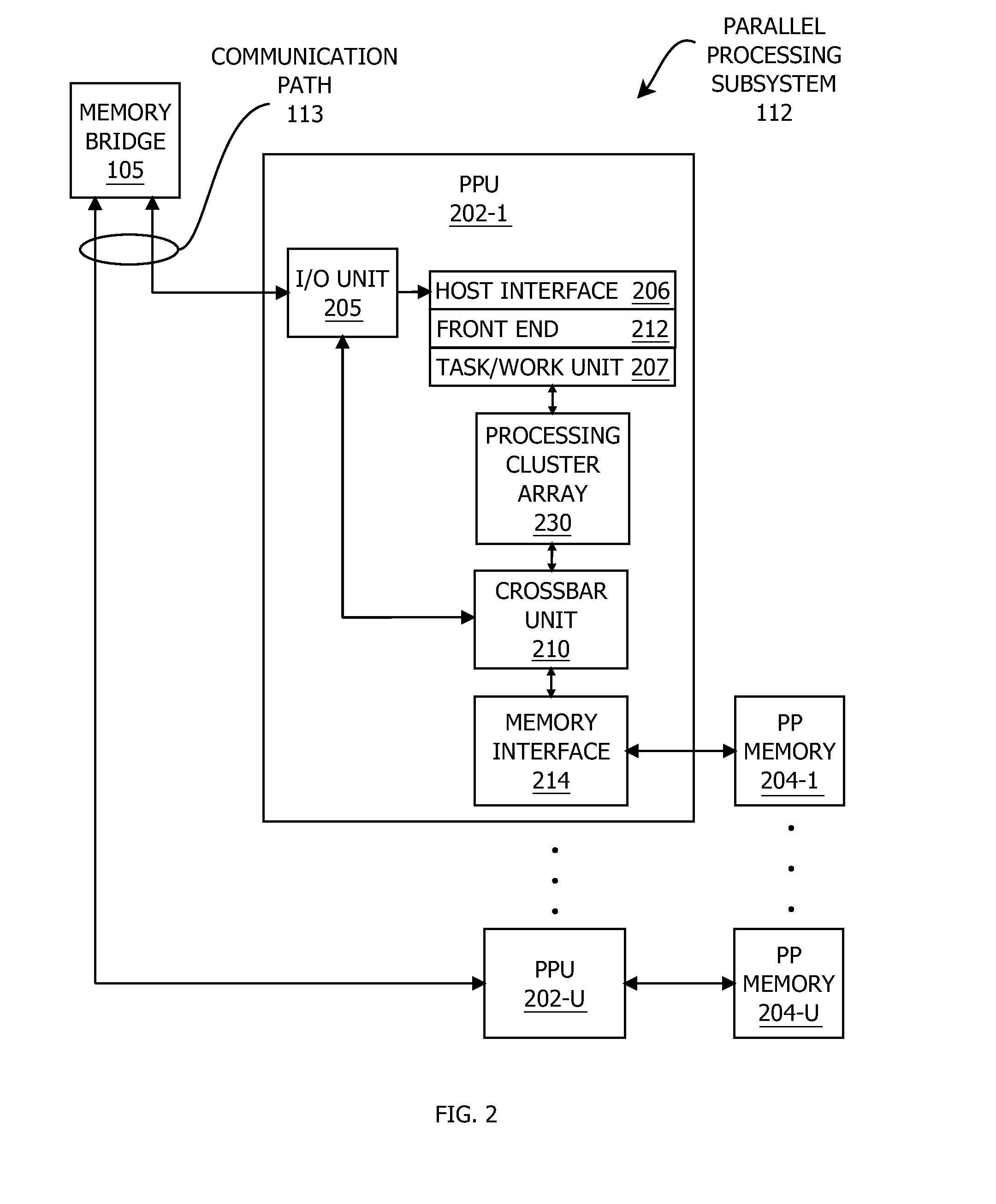

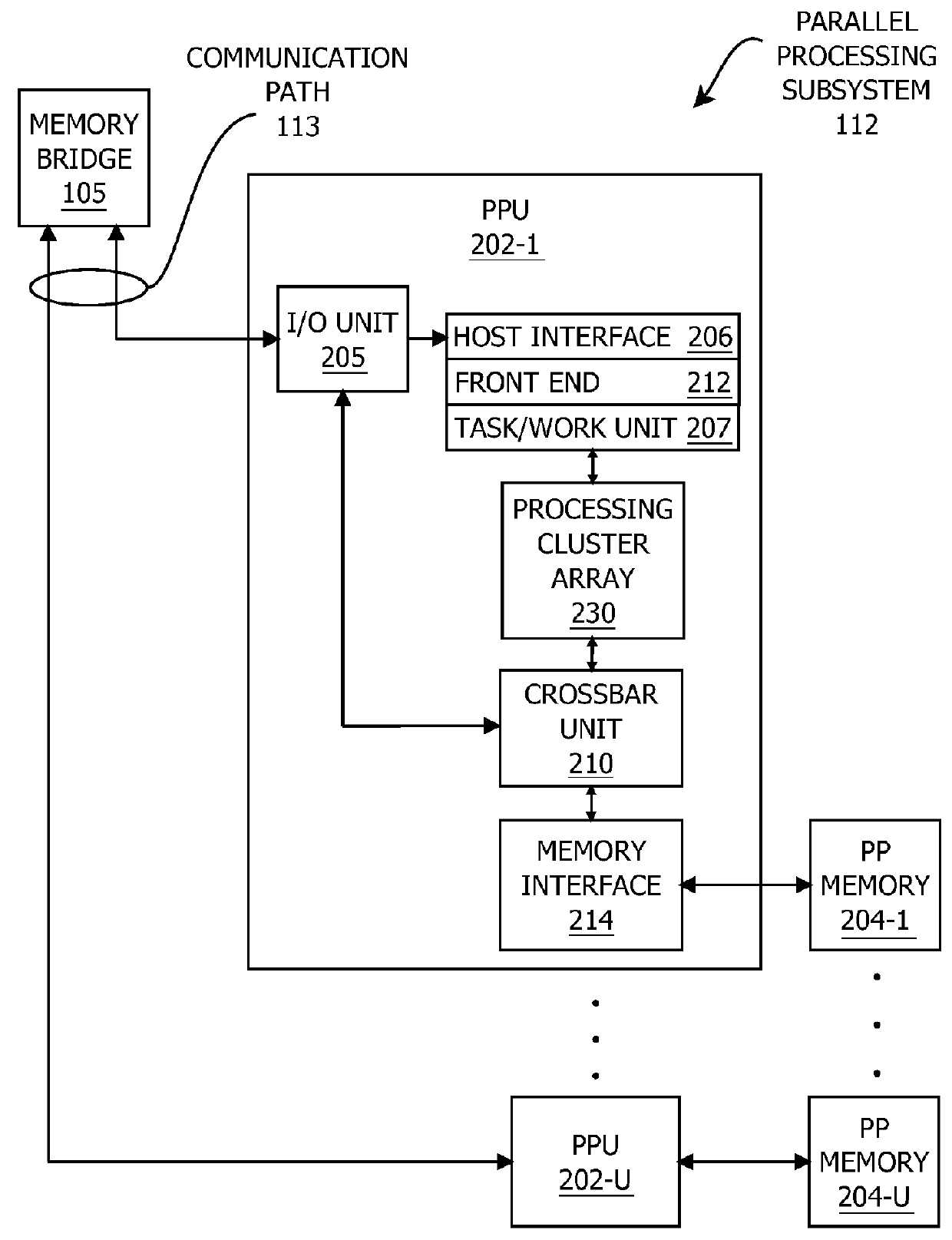

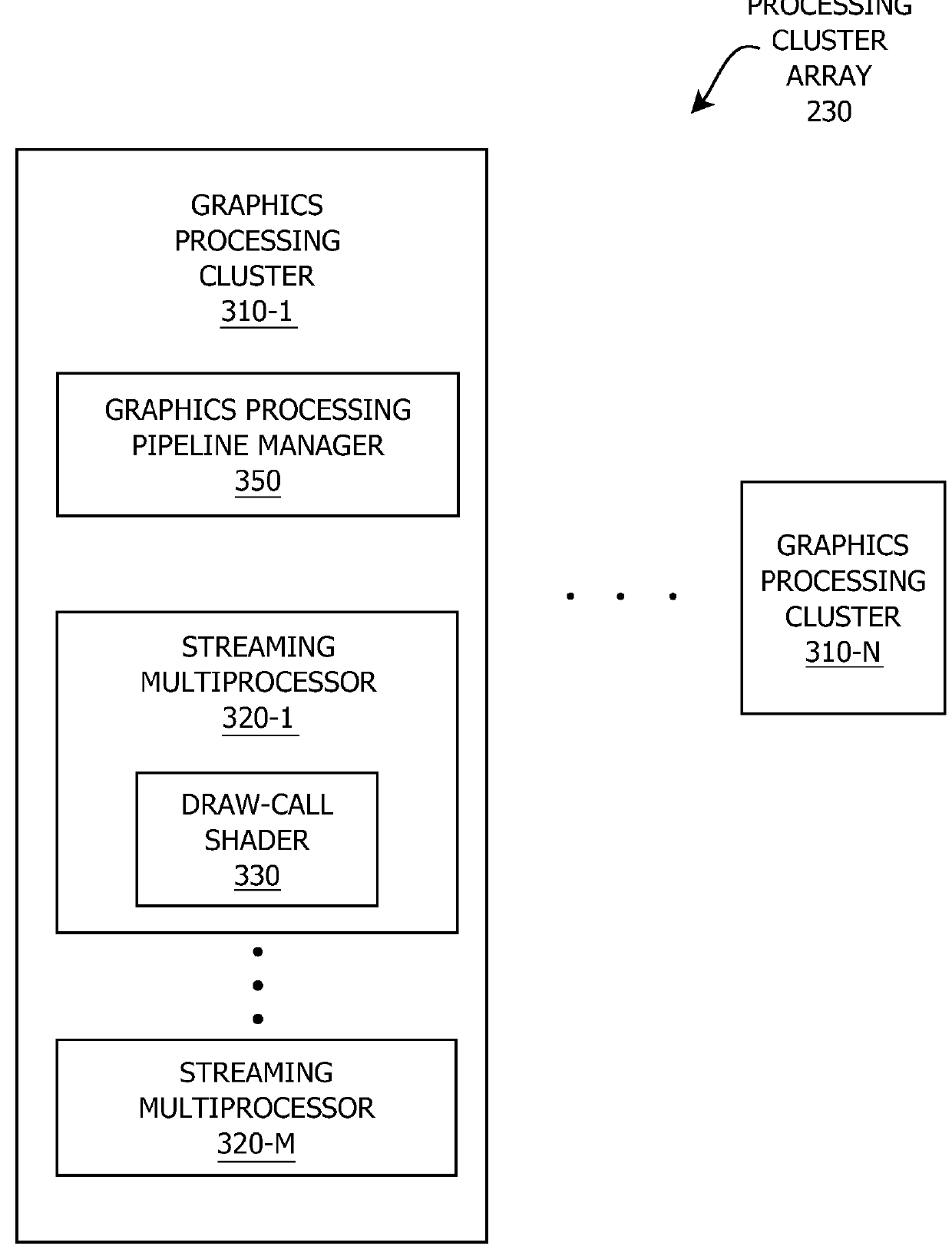

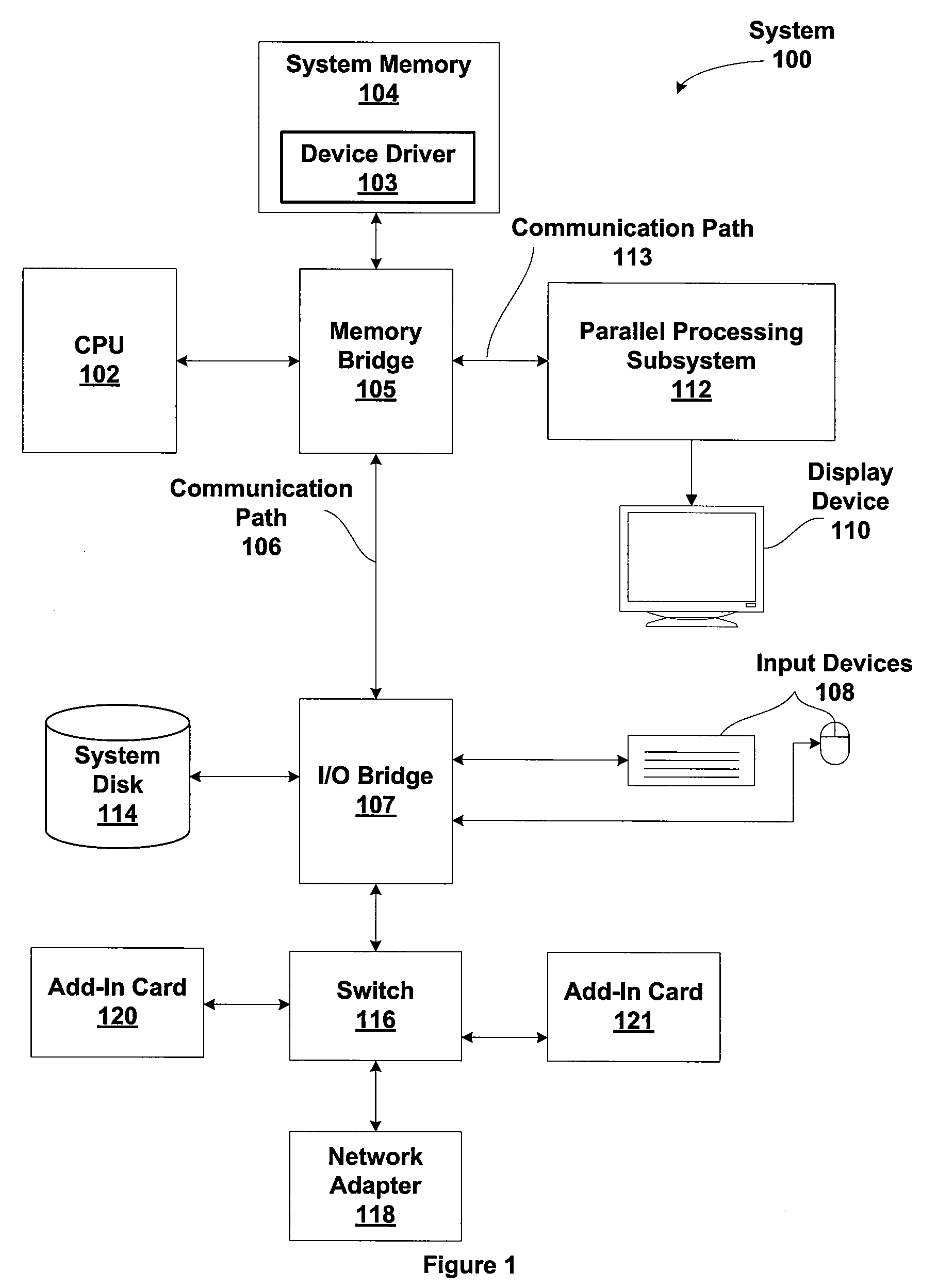

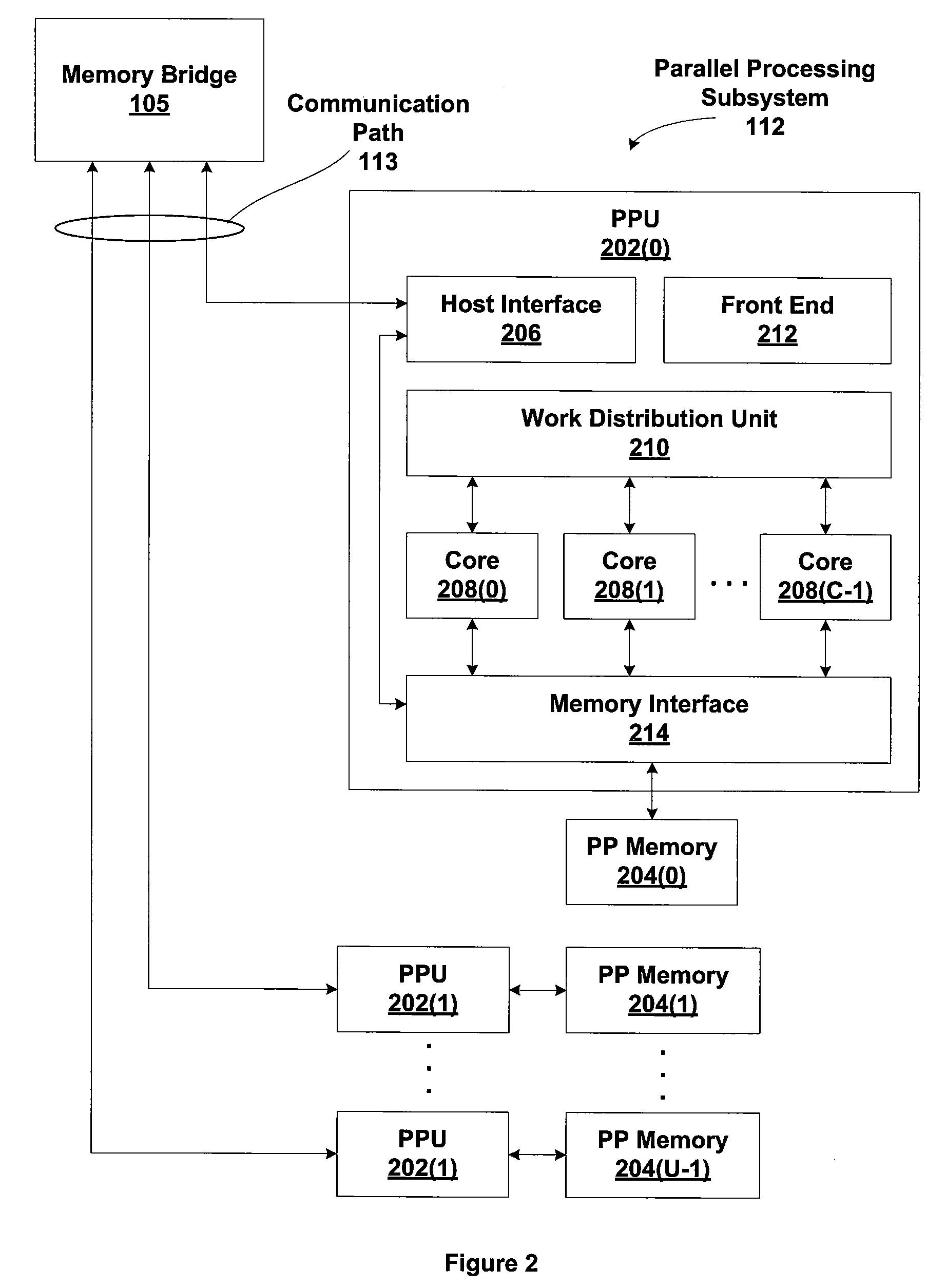

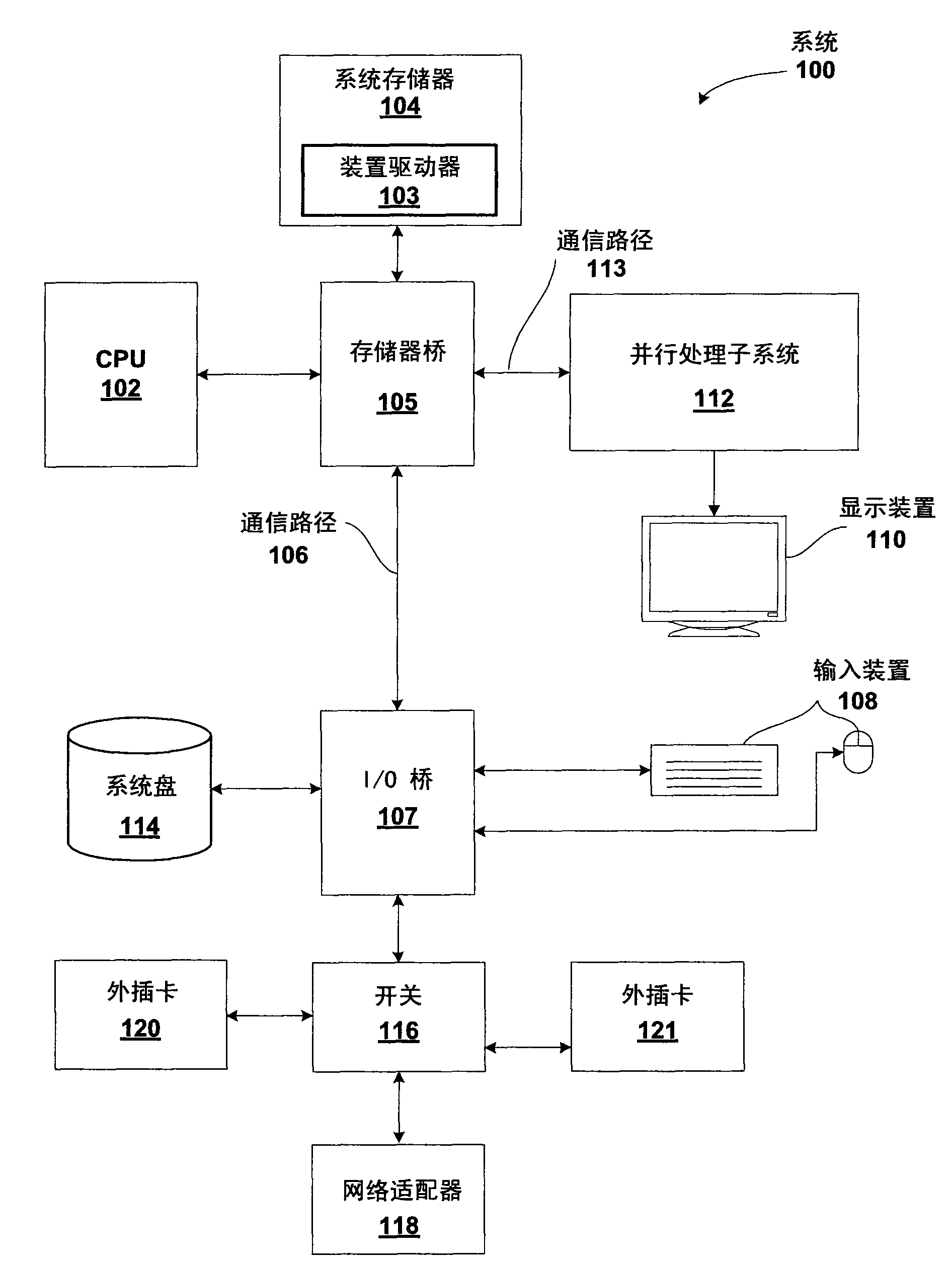

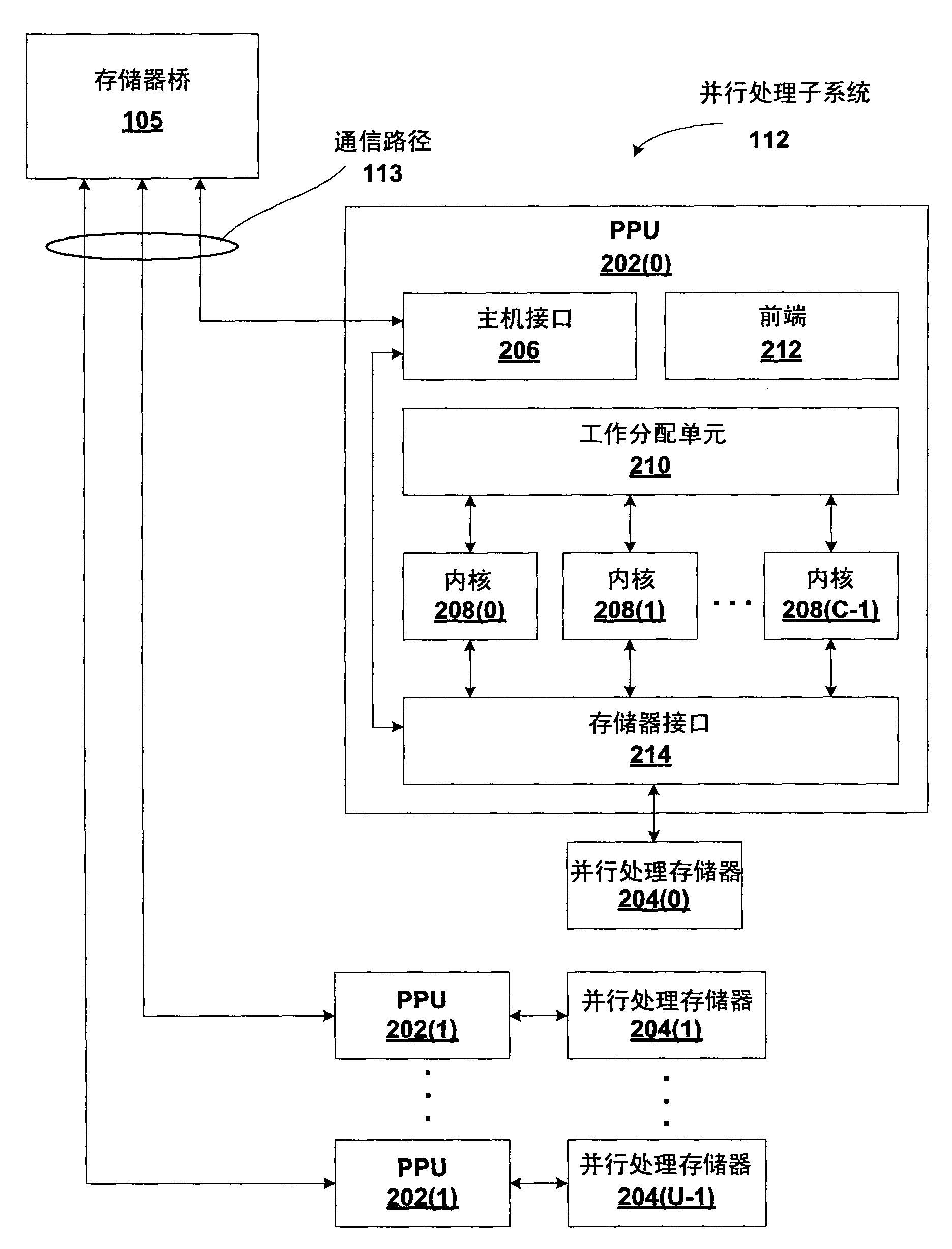

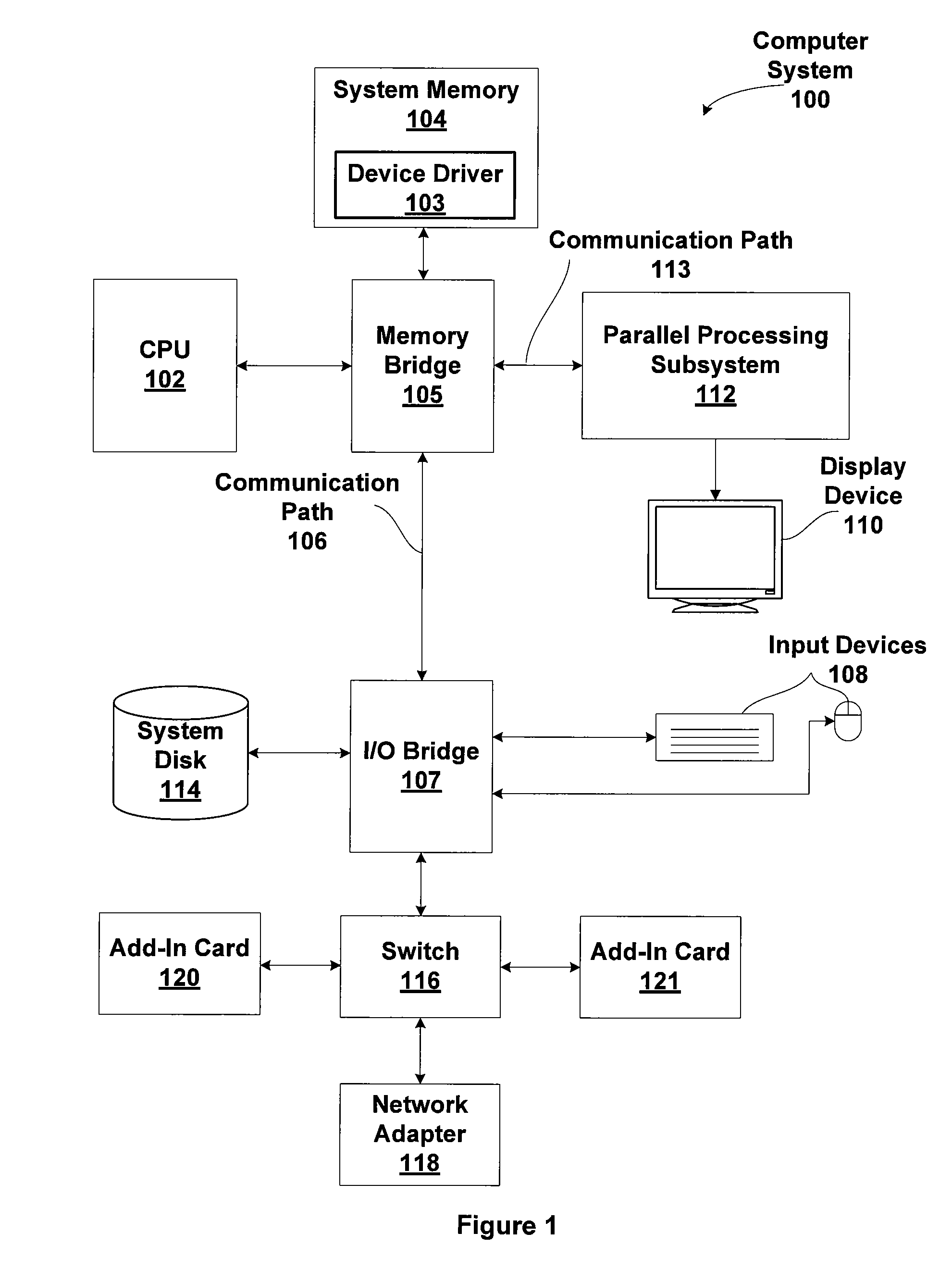

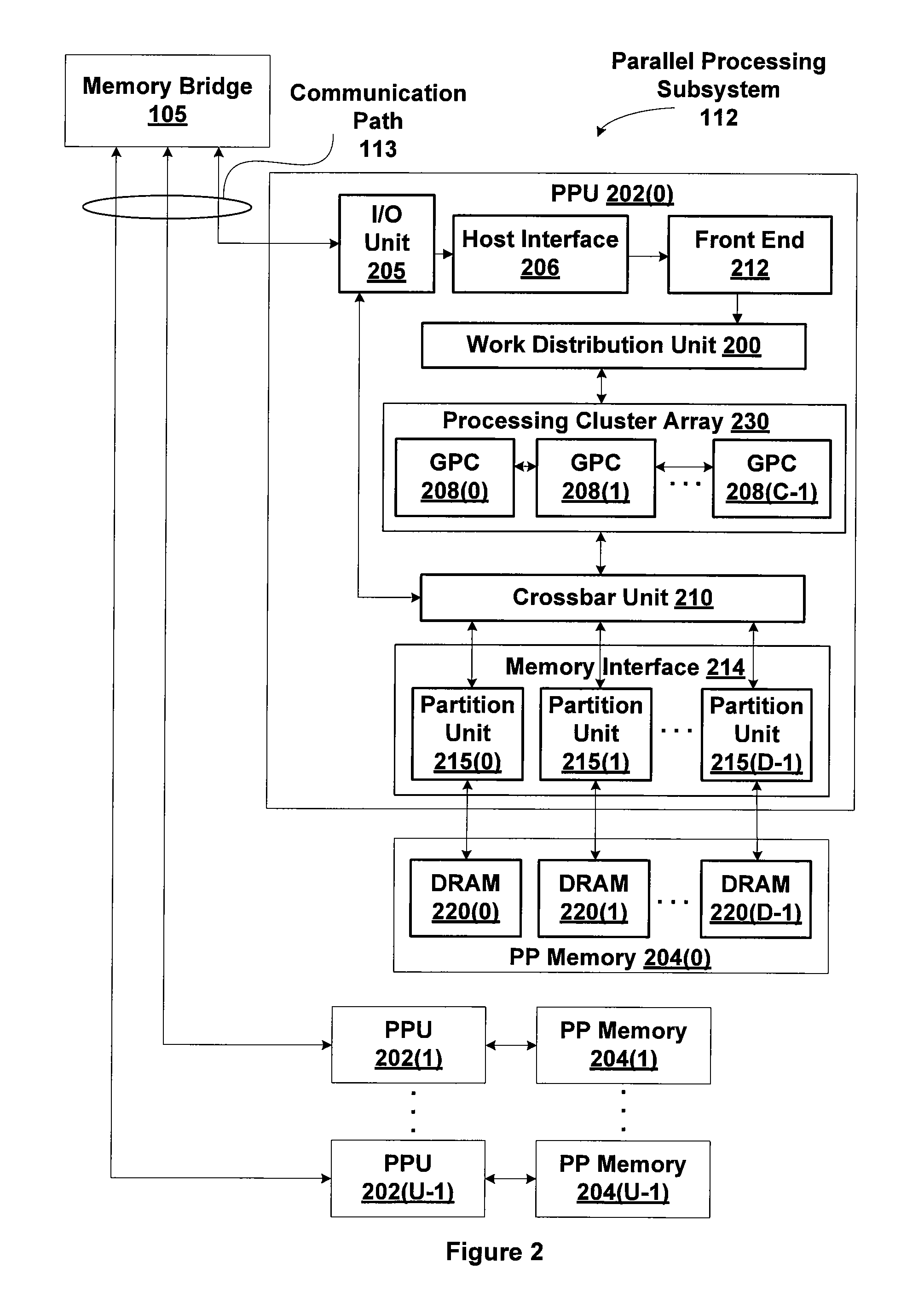

One embodiment sets forth a method for modifying draw calls using a draw-call shader program included in a processing subsystem configured to process draw calls. The draw call shader receives a draw call from a software application, evaluates graphics state information included in the draw call, generates modified graphics state information, and generates a modified draw call that includes the modified graphics state information. Subsequently, the draw-call shader causes the modified draw call to be executed within a graphics processing pipeline. By performing the computations associated with generating the modified draw call on-the-fly within the processing subsystem, the draw-call shader decreases the amount of system memory required to render graphics while increasing the overall processing efficiency of the graphics processing pipeline.

Owner:NVIDIA CORP

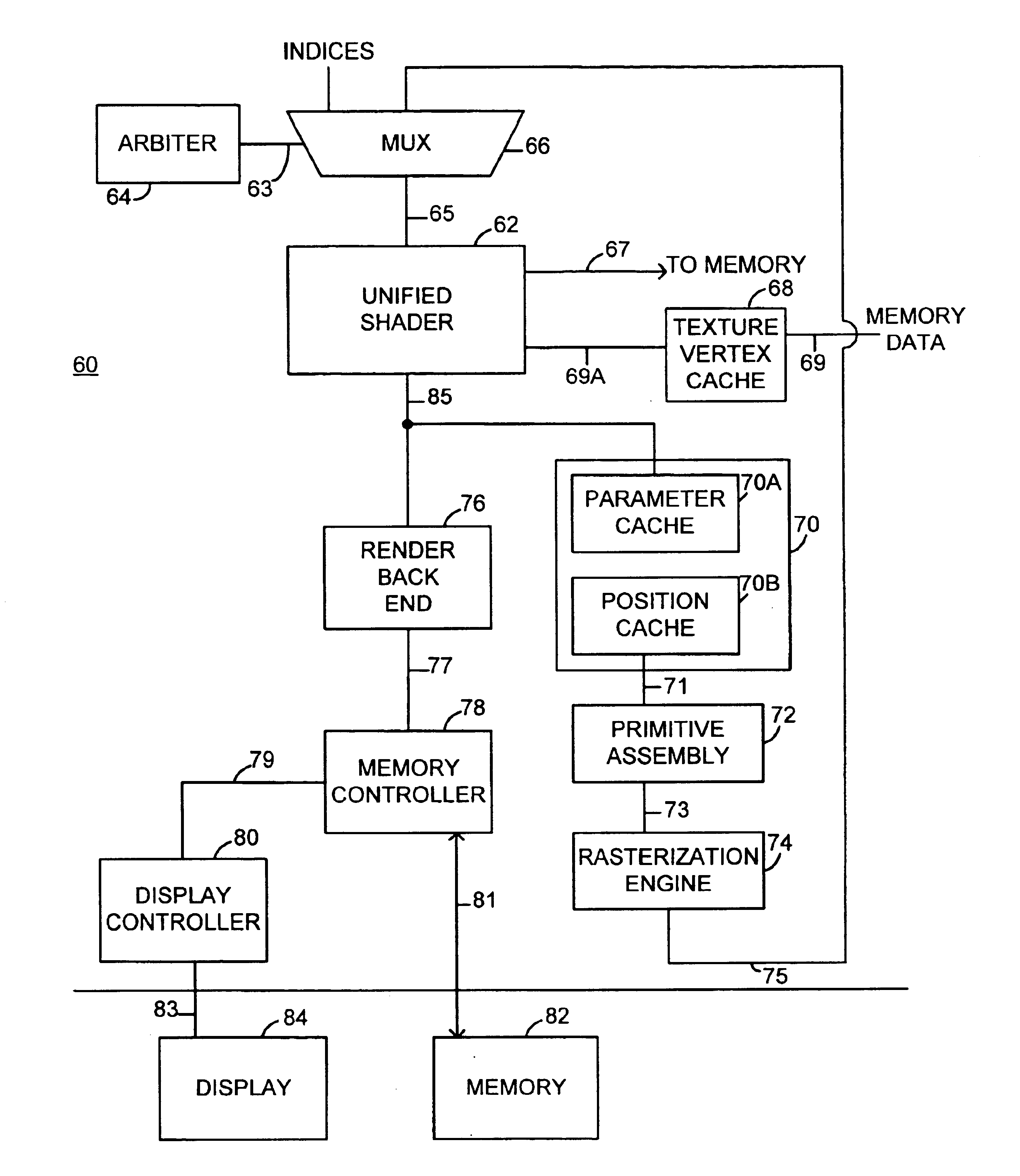

Graphics processing architecture employing a unified shader

ActiveUS6897871B1More computationally efficientFlexiblyDigital computer detailsCathode-ray tube indicatorsControl signalLogical operations

A graphics processing architecture employing a single shader is disclosed. The architecture includes a circuit operative to select one of a plurality of inputs in response to a control signal; and a shader, coupled to the arbiter, operative to process the selected one of the plurality of inputs, the shader including means for performing vertex operations and pixel operations, and wherein the shader performs one of the vertex operations or pixel operations based on the selected one of the plurality of inputs. The shader includes a register block which is used to store the plurality of selected inputs, a sequencer which maintains vertex manipulation and pixel manipulations instructions and a processor capable of executing both floating point arithmetic and logical operations on the selected inputs in response to the instructions maintained in the sequencer.

Owner:ATI TECH INC

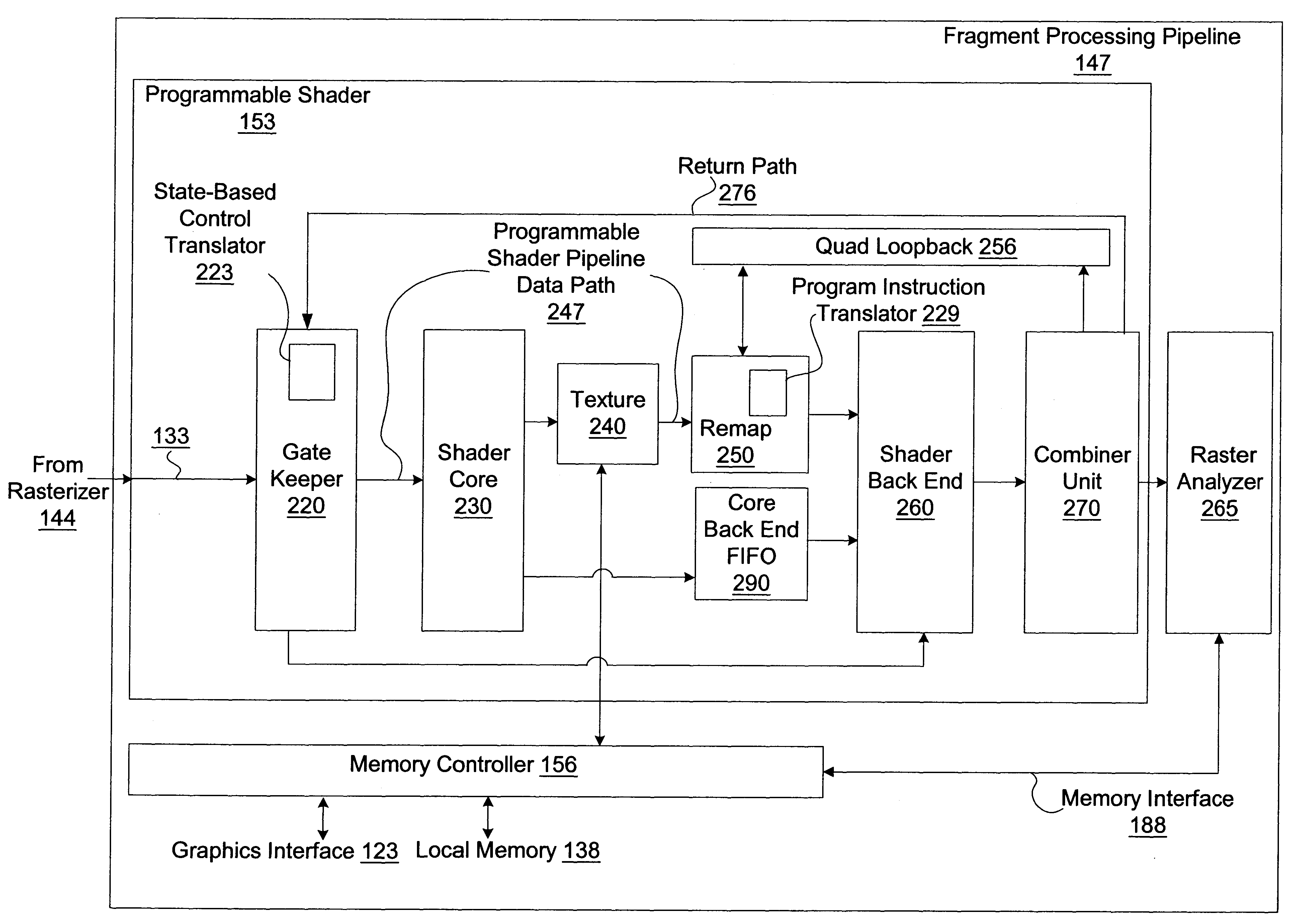

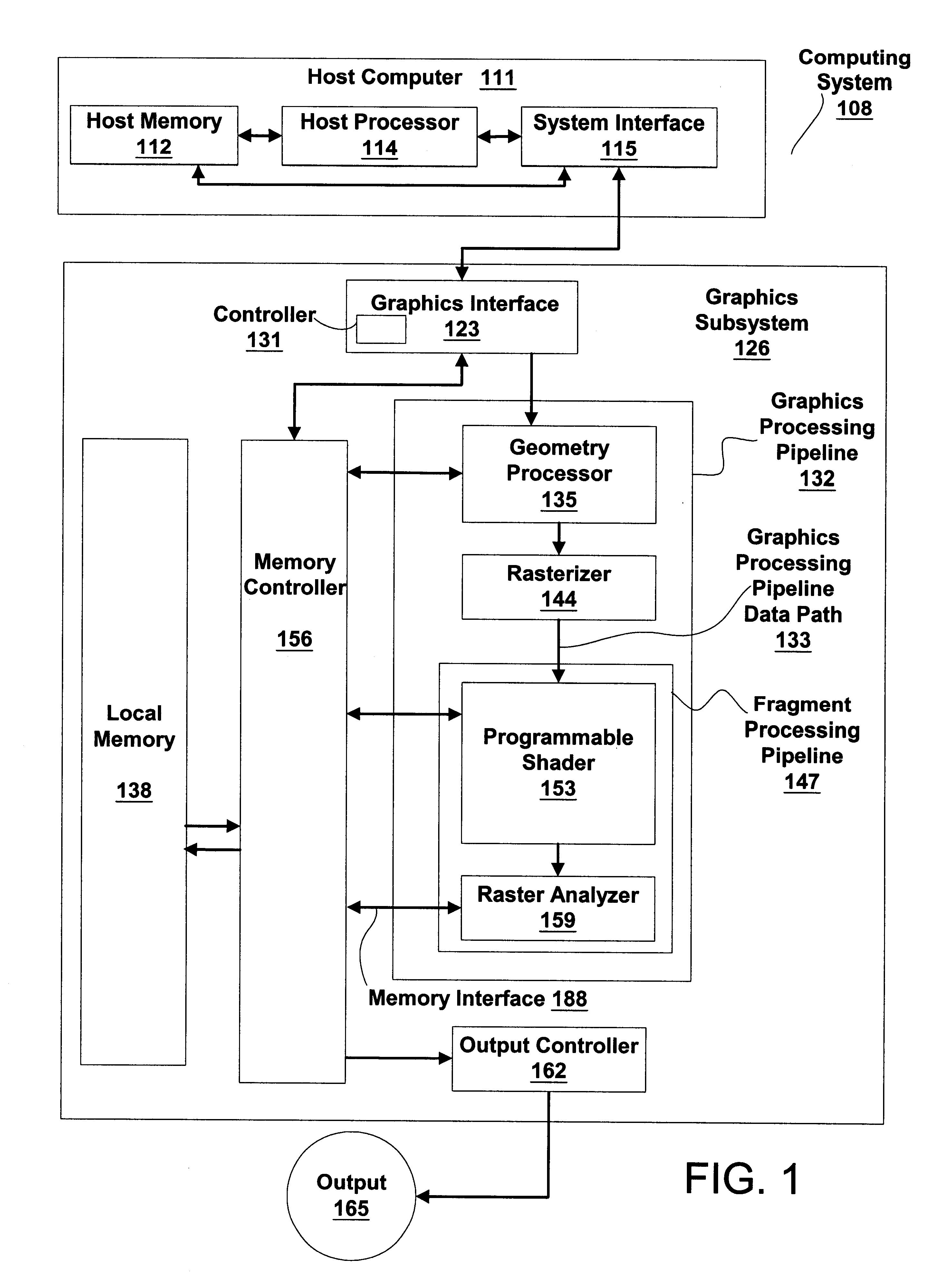

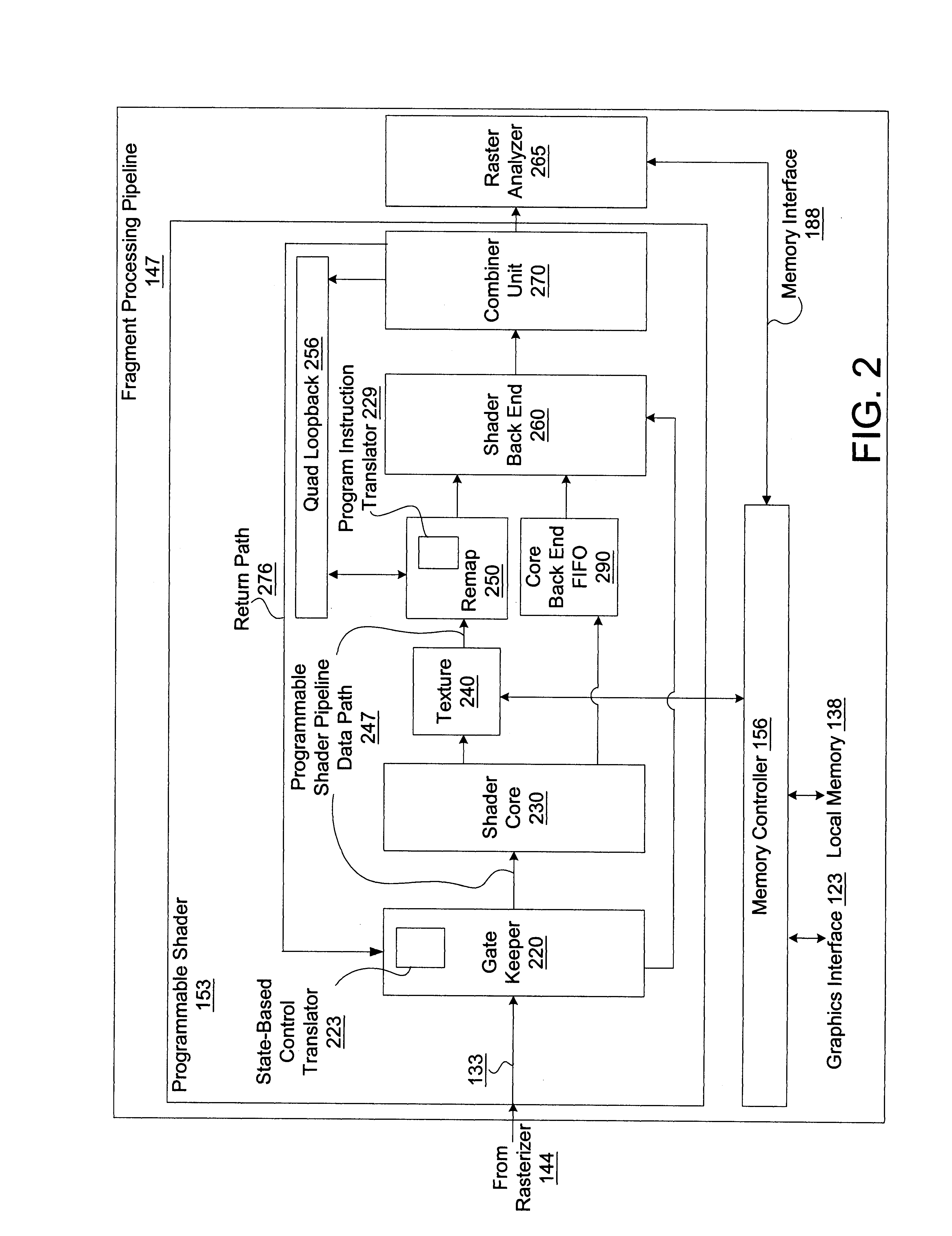

Method and apparatus for generation of programmable shader configuration information from state-based control information and program instructions

InactiveUS6809732B2Multiple digital computer combinationsProcessor architectures/configurationDirectXProgram instruction

Owner:NVIDIA CORP

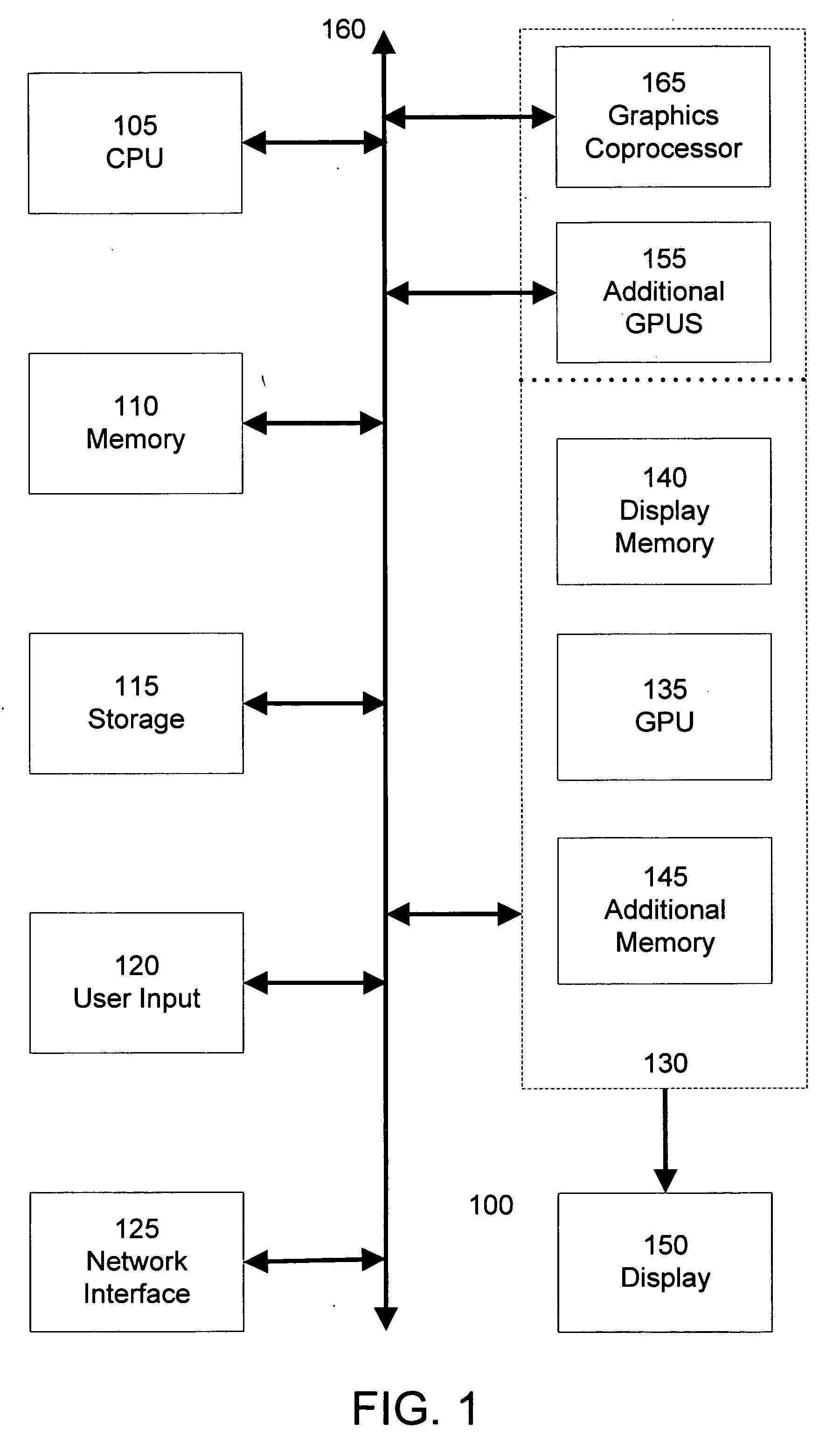

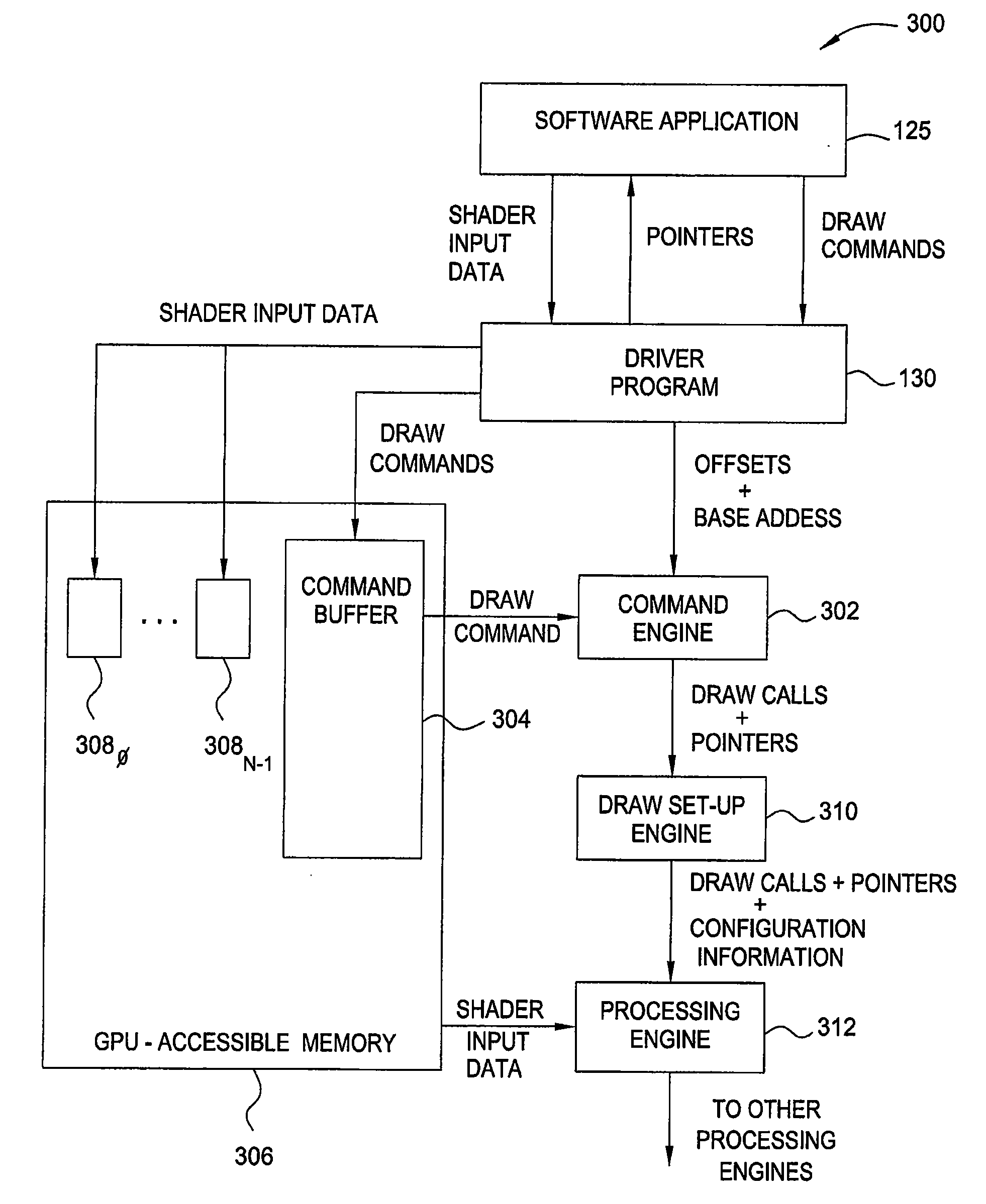

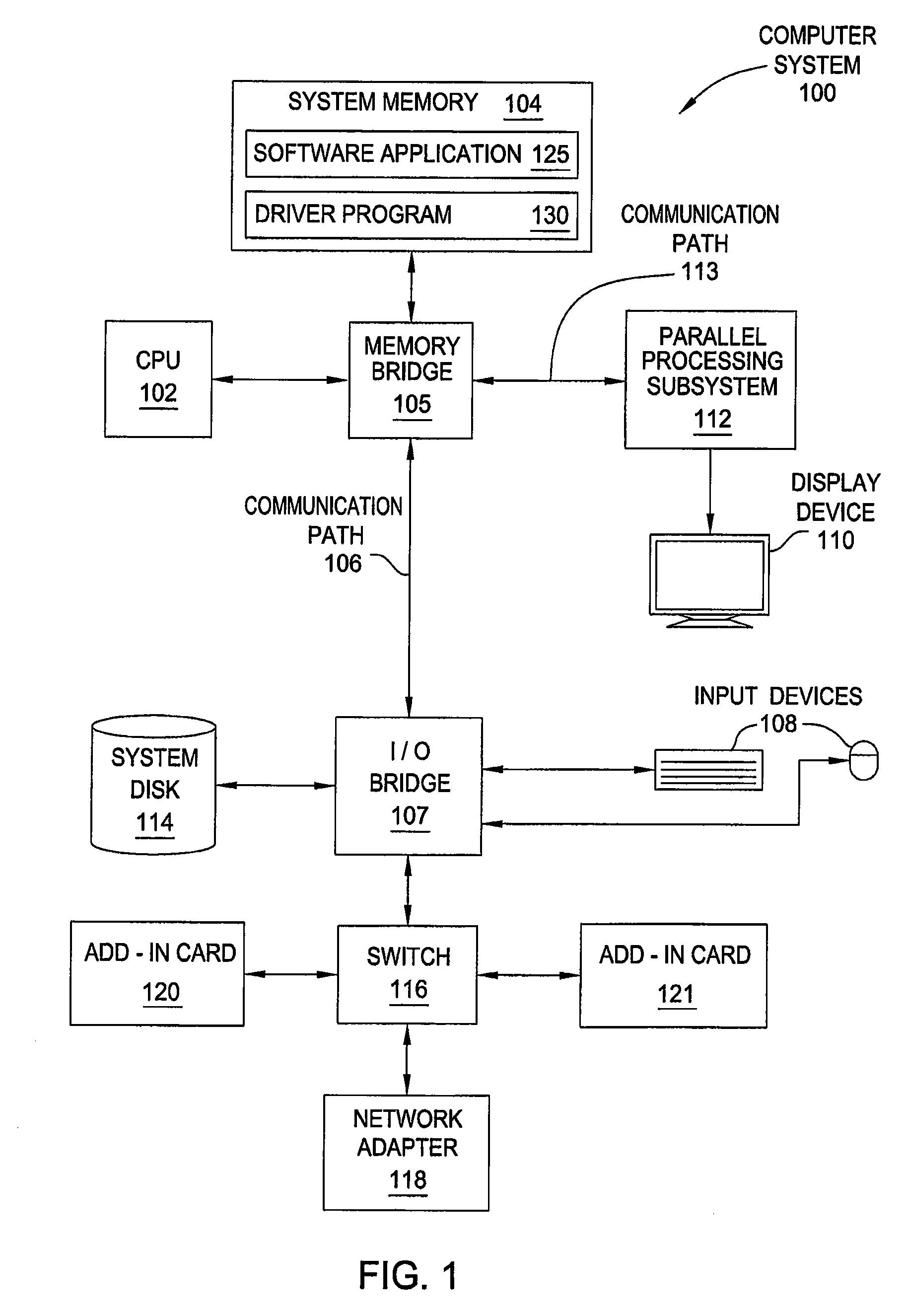

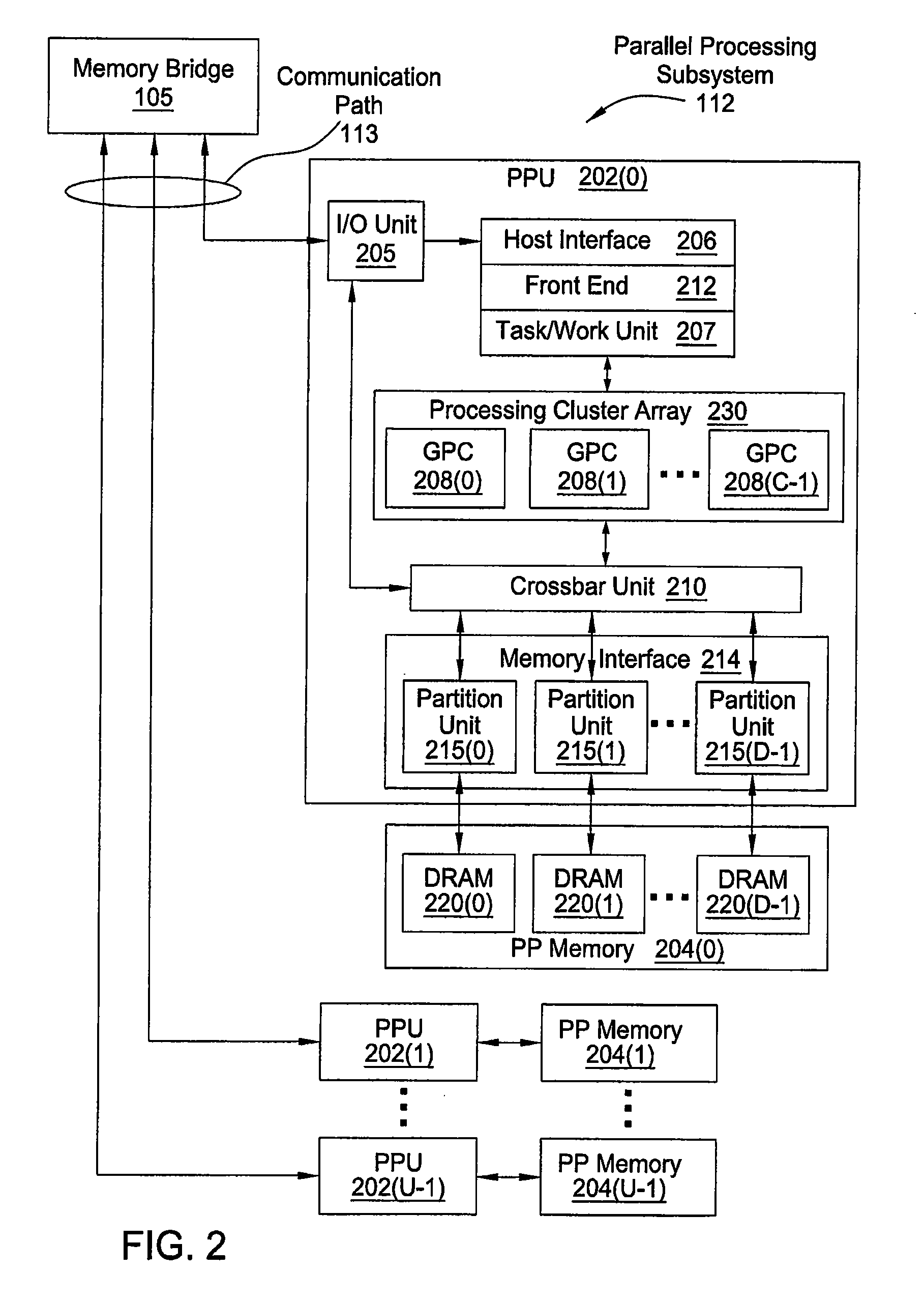

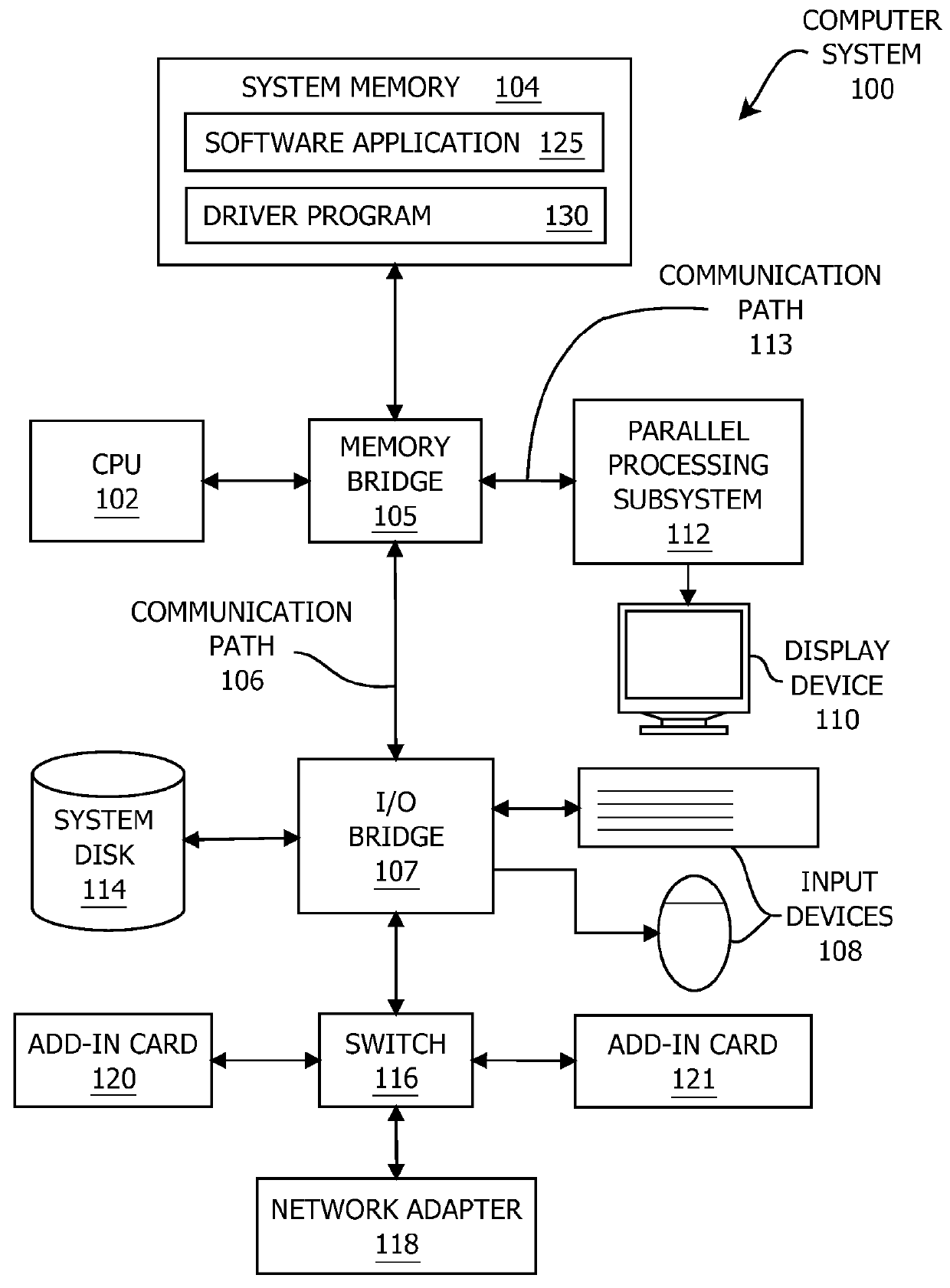

Techniques for setting up and executing draw calls

ActiveUS20140168242A1Improve processing efficiencyImage memory managementProgram controlComputational scienceApplication software

One embodiment sets forth a method for processing draw calls that includes setting up a plurality of shader input buffers in memory, receiving shader input data related to a graphics scene from a software application, storing the shader input data in the plurality of shader input buffers, computing a pointer to each shader input buffer included in the plurality of shader input buffers, and passing the pointers to the plurality of shader input buffers to the software application. By implementing the disclosed techniques, a shader program advantageously can access the shader input data associated with a graphics scene and stored in various shader input buffers without having to go through the central processing unit to have the shader input buffers binded to the shader program.

Owner:NVIDIA CORP

Techniques for locally modifying draw calls

ActiveUS9342857B2Reduce the amount requiredAmount of data transferredProcessor architectures/configurationComputational scienceSoftware

One embodiment sets forth a method for modifying draw calls using a draw-call shader program included in a processing subsystem configured to process draw calls. The draw call shader receives a draw call from a software application, evaluates graphics state information included in the draw call, generates modified graphics state information, and generates a modified draw call that includes the modified graphics state information. Subsequently, the draw-call shader causes the modified draw call to be executed within a graphics processing pipeline. By performing the computations associated with generating the modified draw call on-the-fly within the processing subsystem, the draw-call shader decreases the amount of system memory required to render graphics while increasing the overall processing efficiency of the graphics processing pipeline.

Owner:NVIDIA CORP

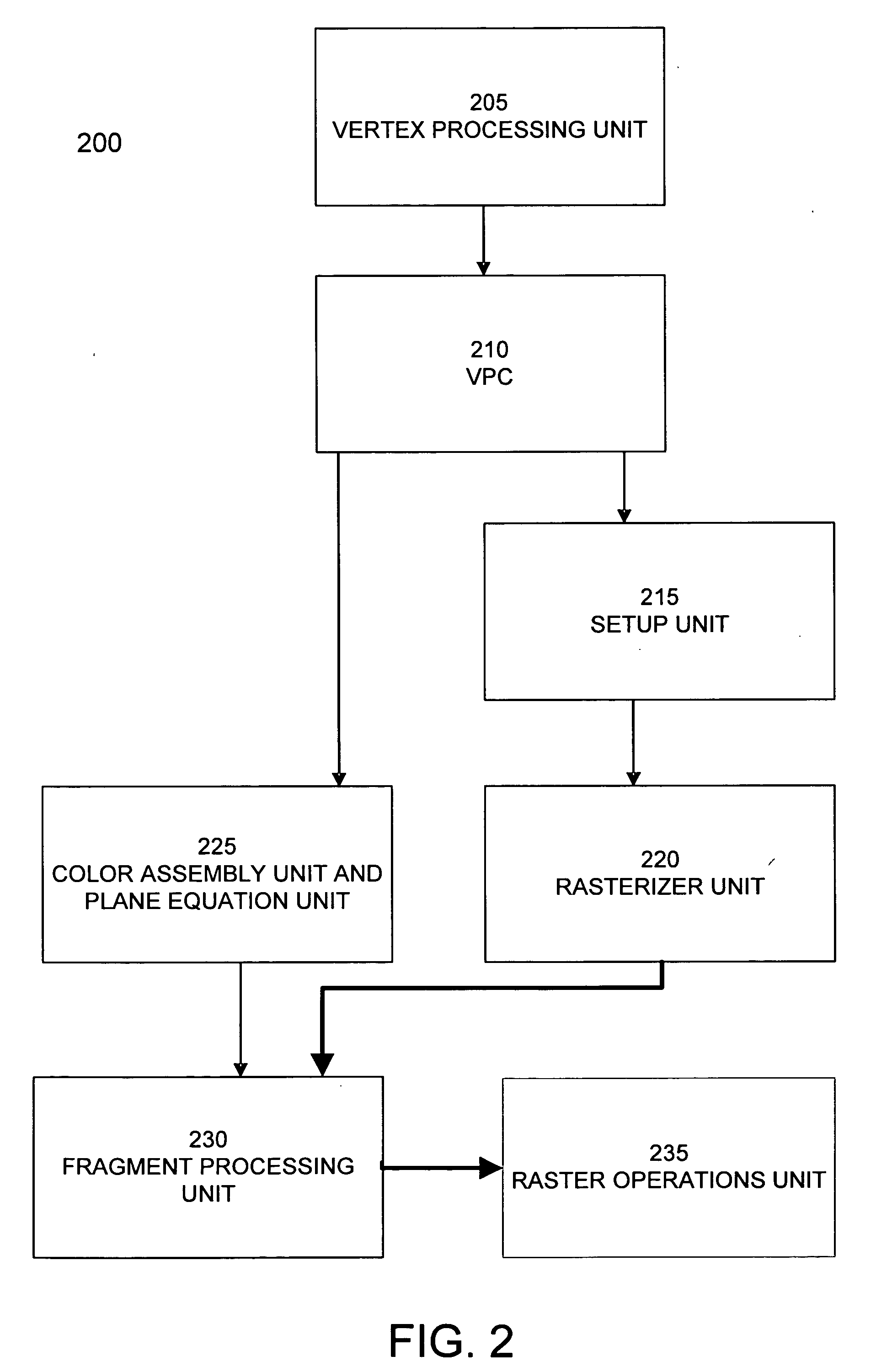

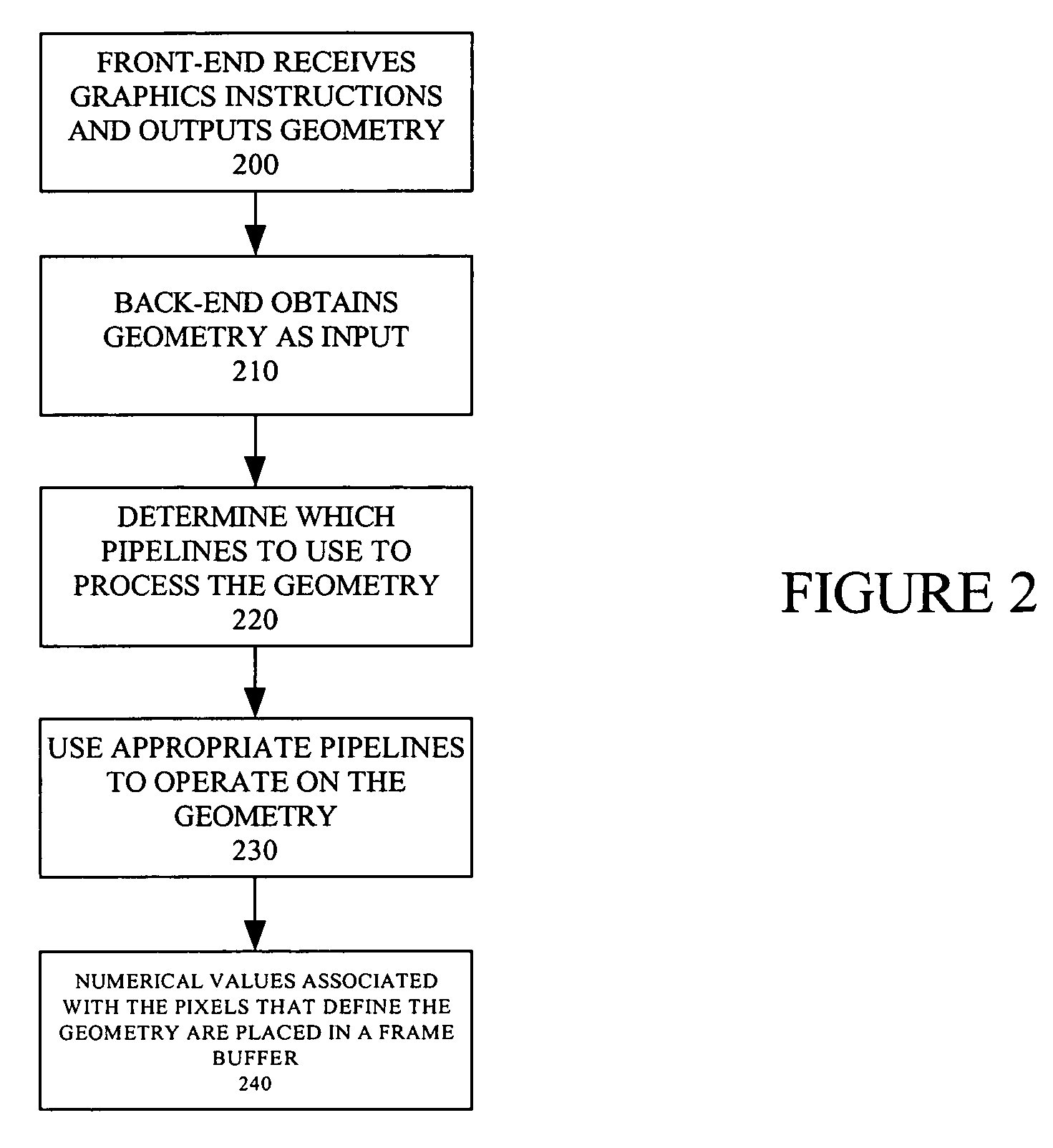

Parallel pipeline graphics system

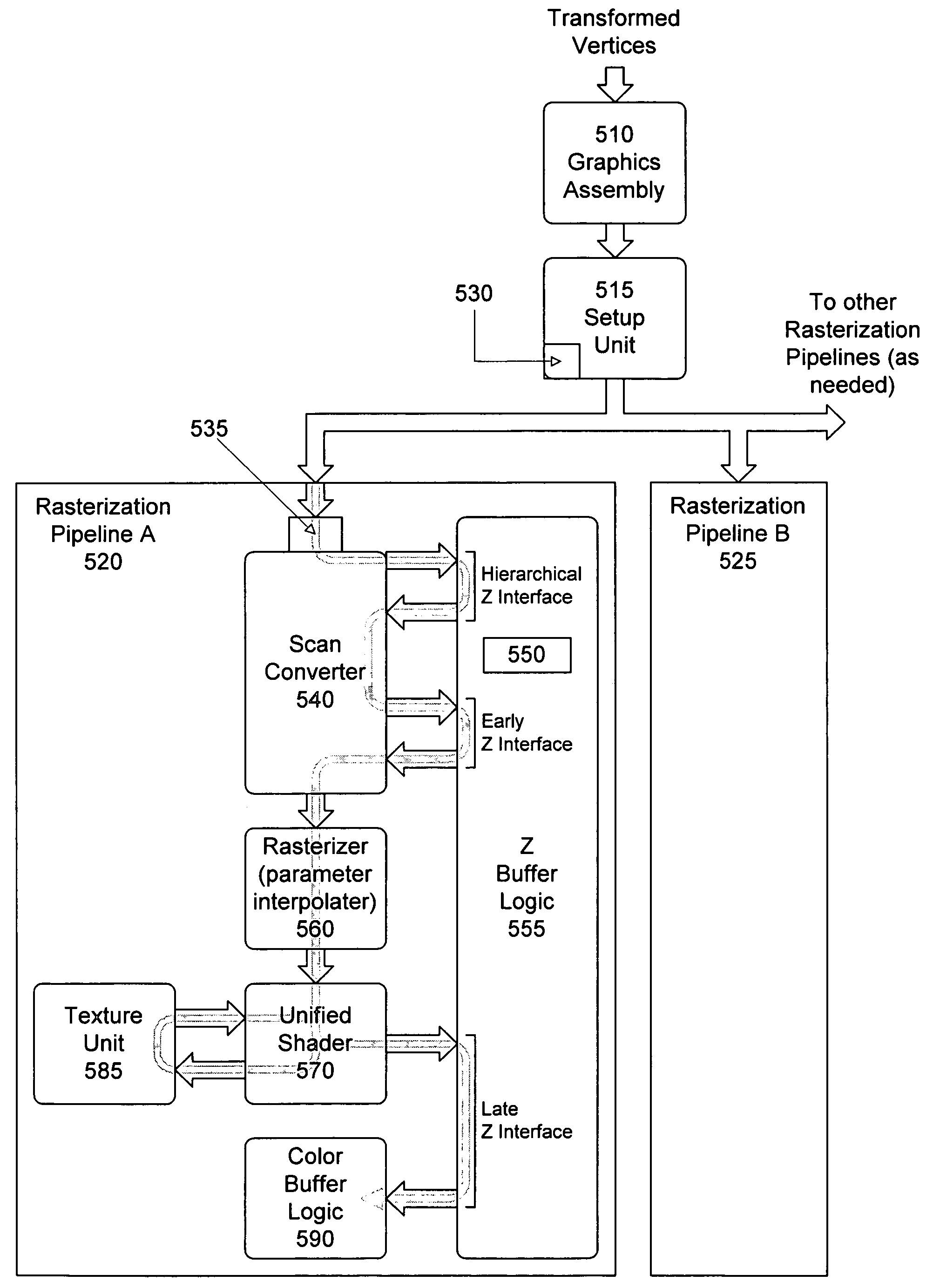

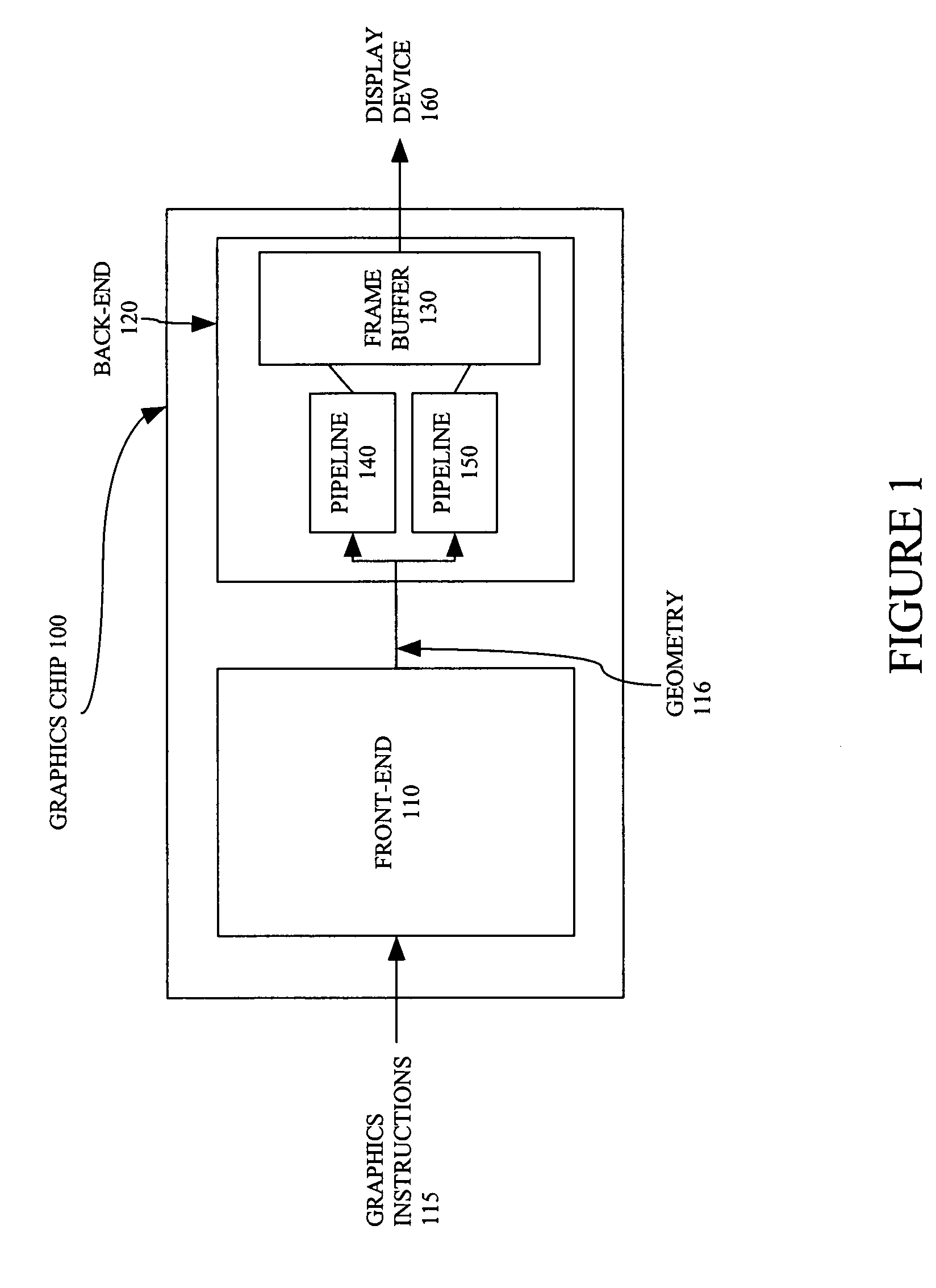

ActiveUS7633506B1Precise definitionCathode-ray tube indicatorsProcessor architectures/configurationComputational scienceScan conversion

The present invention relates to a parallel pipeline graphics system. The parallel pipeline graphics system includes a back-end configured to receive primitives and combinations of primitives (i.e., geometry) and process the geometry to produce values to place in a frame buffer for rendering on screen. Unlike prior single pipeline implementation, some embodiments use two or four parallel pipelines, though other configurations having 2^n pipelines may be used. When geometry data is sent to the back-end, it is divided up and provided to one of the parallel pipelines. Each pipeline is a component of a raster back-end, where the display screen is divided into tiles and a defined portion of the screen is sent through a pipeline that owns that portion of the screen's tiles. In one embodiment, each pipeline comprises a scan converter, a hierarchical-Z unit, a z buffer logic, a rasterizer, a shader, and a color buffer logic.

Owner:ATI TECH INC

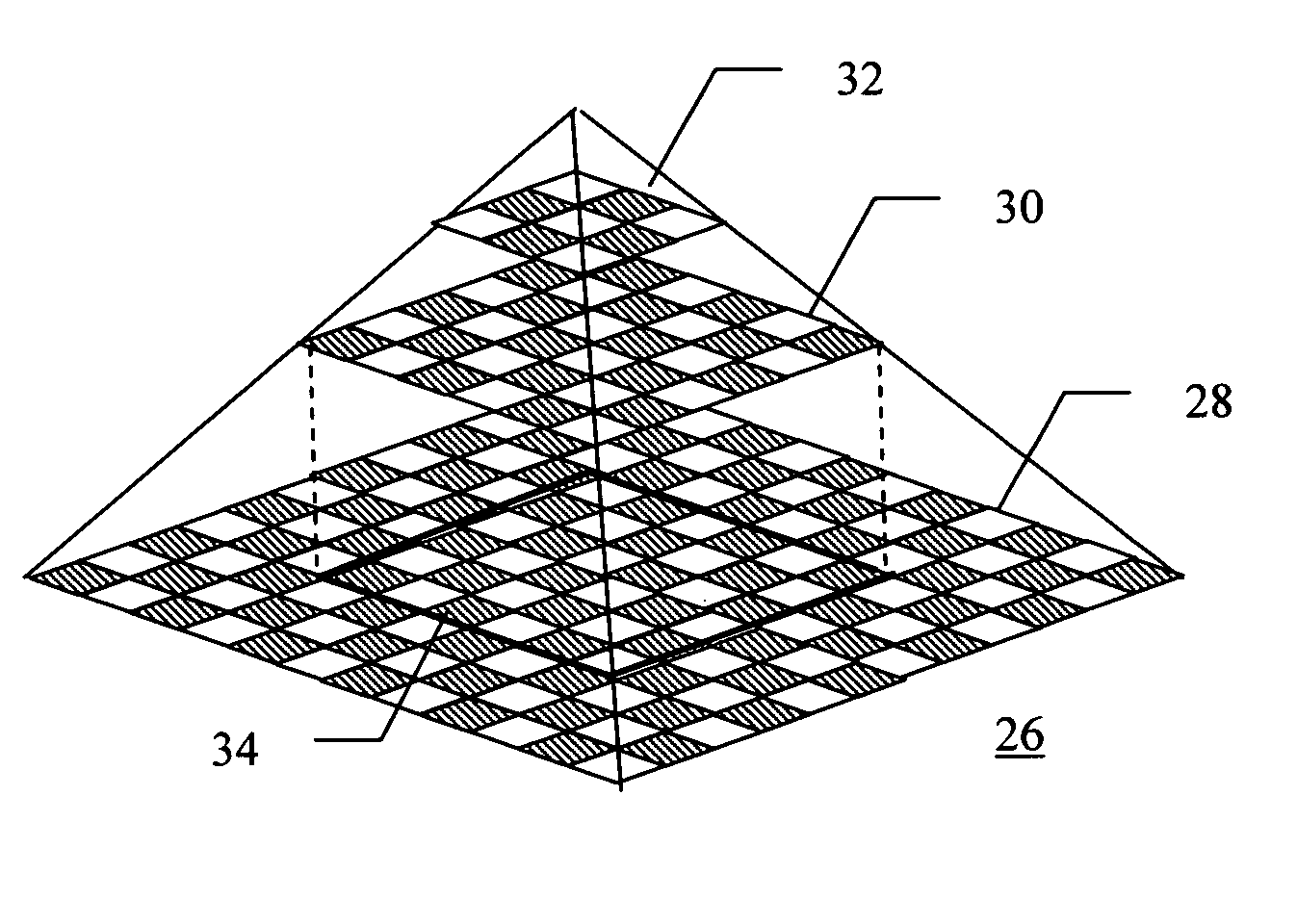

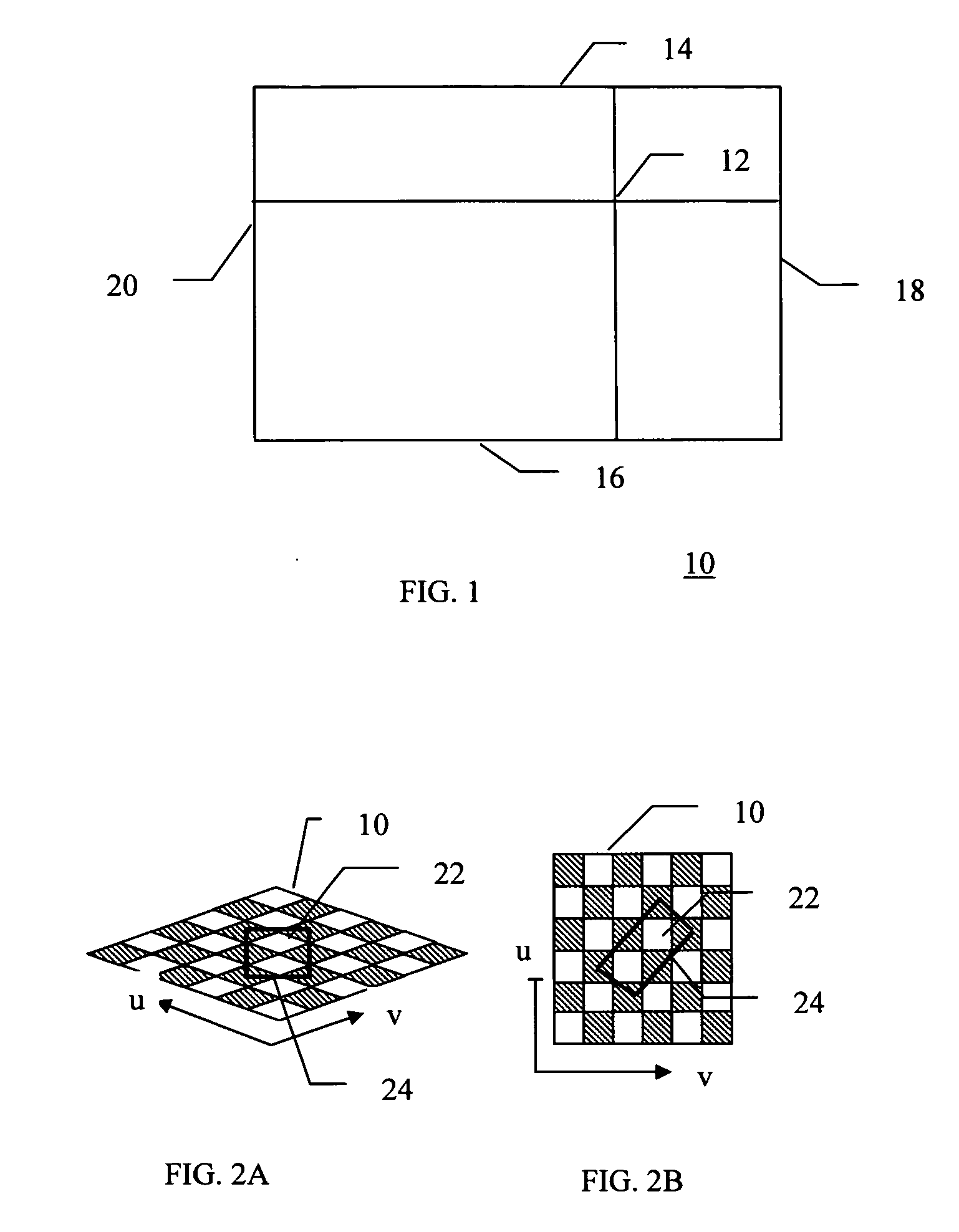

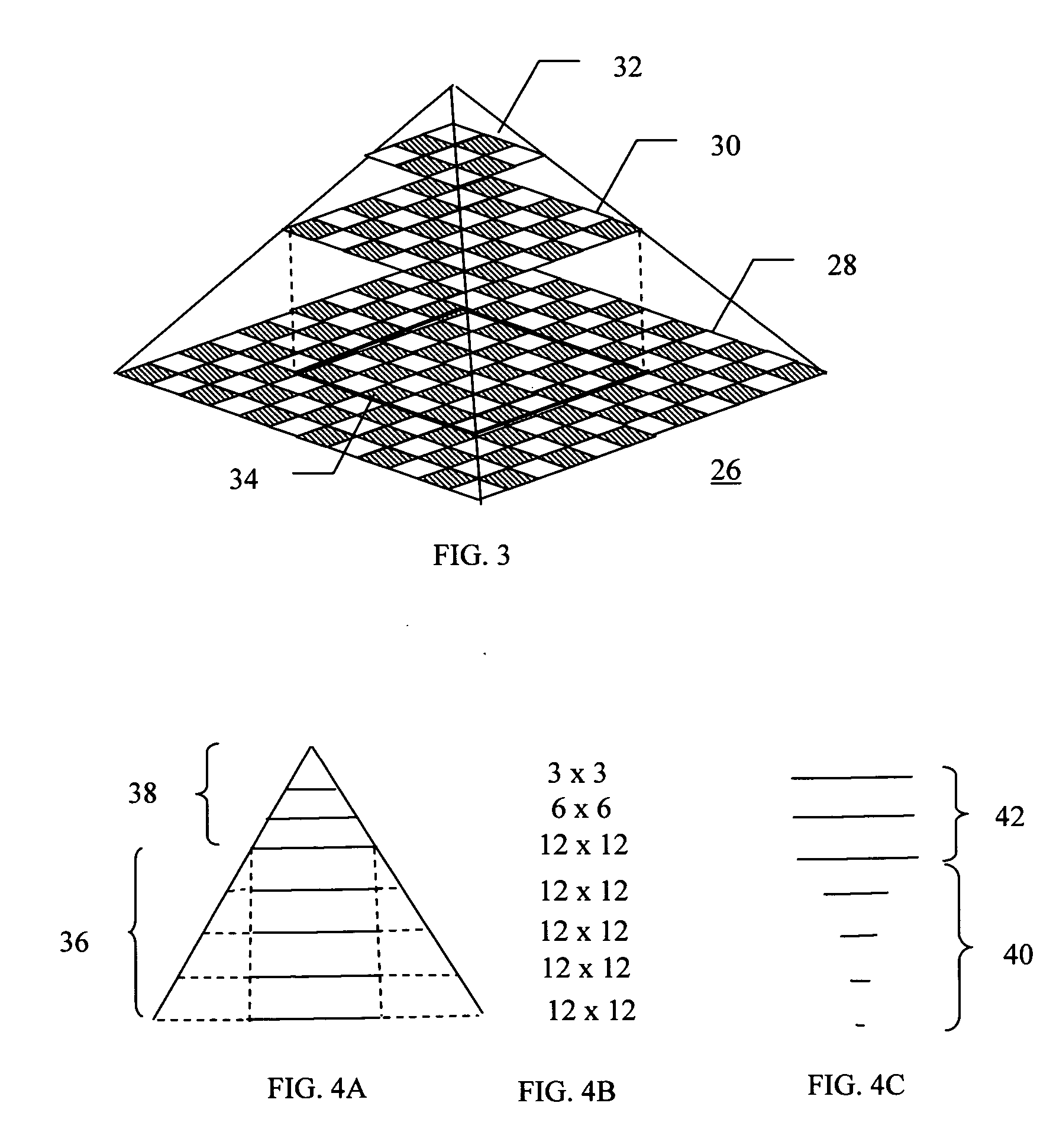

System and method for asynchronous continuous-level-of-detail texture mapping for large-scale terrain rendering

InactiveUS20070171234A1Character and pattern recognitionCathode-ray tube indicatorsLevel of detailMulti resolution

A multi-resolution texture mapping system suitable for large scale terrain rendering using commodity graphics processing units (GPU). The GPU vertex and fragment shaders are used to implement the clip-mapping functionality. The terrain texture is represented by a combination of a mip-map and a multi-level clip-map having independent origins and off-set values. The independent clip-map levels may be independently updated. The offset values allow the origins to be associated with a reference point in a scene to be rendered. The desired clip-map level to be used to render a particular fragment may be determined using the base 2 logarithm of the maximum screen-space derivative of the source texture required by the terrain geometry to be drawn. If the desired clip-map level is non-integer and lies between two clip-map levels, appropriate texel data is created by interpolating between the bounding clip-map levels. This interpolation allows a multi-resolution texture mapping to be displayed.

Owner:D& S CONSULTANTS

Efficient 2-d and 3-d graphics processing

ActiveUS20080198168A1Easy to useEffective supportDigital computer detailsCathode-ray tube indicatorsComputational scienceGraphics processing unit

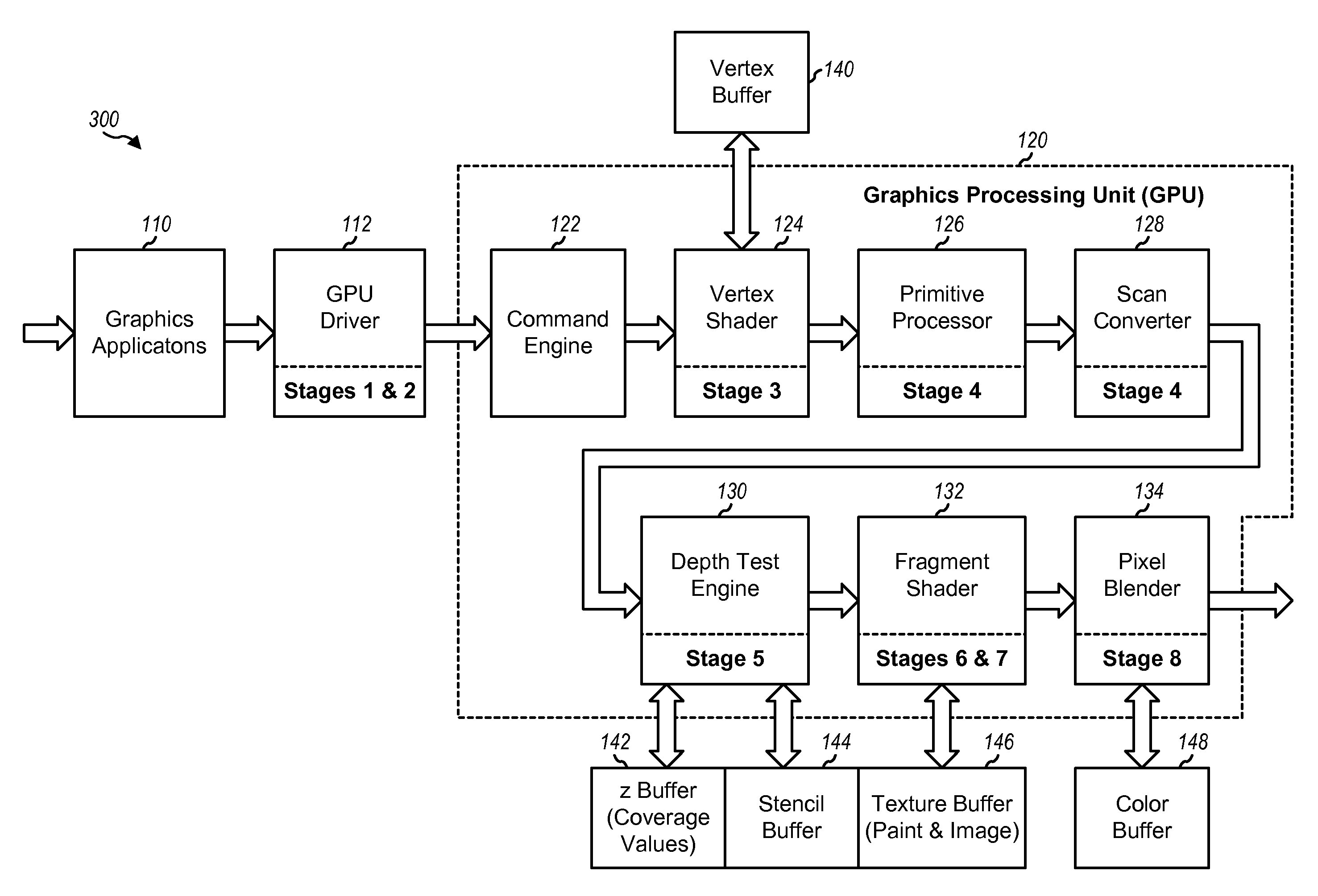

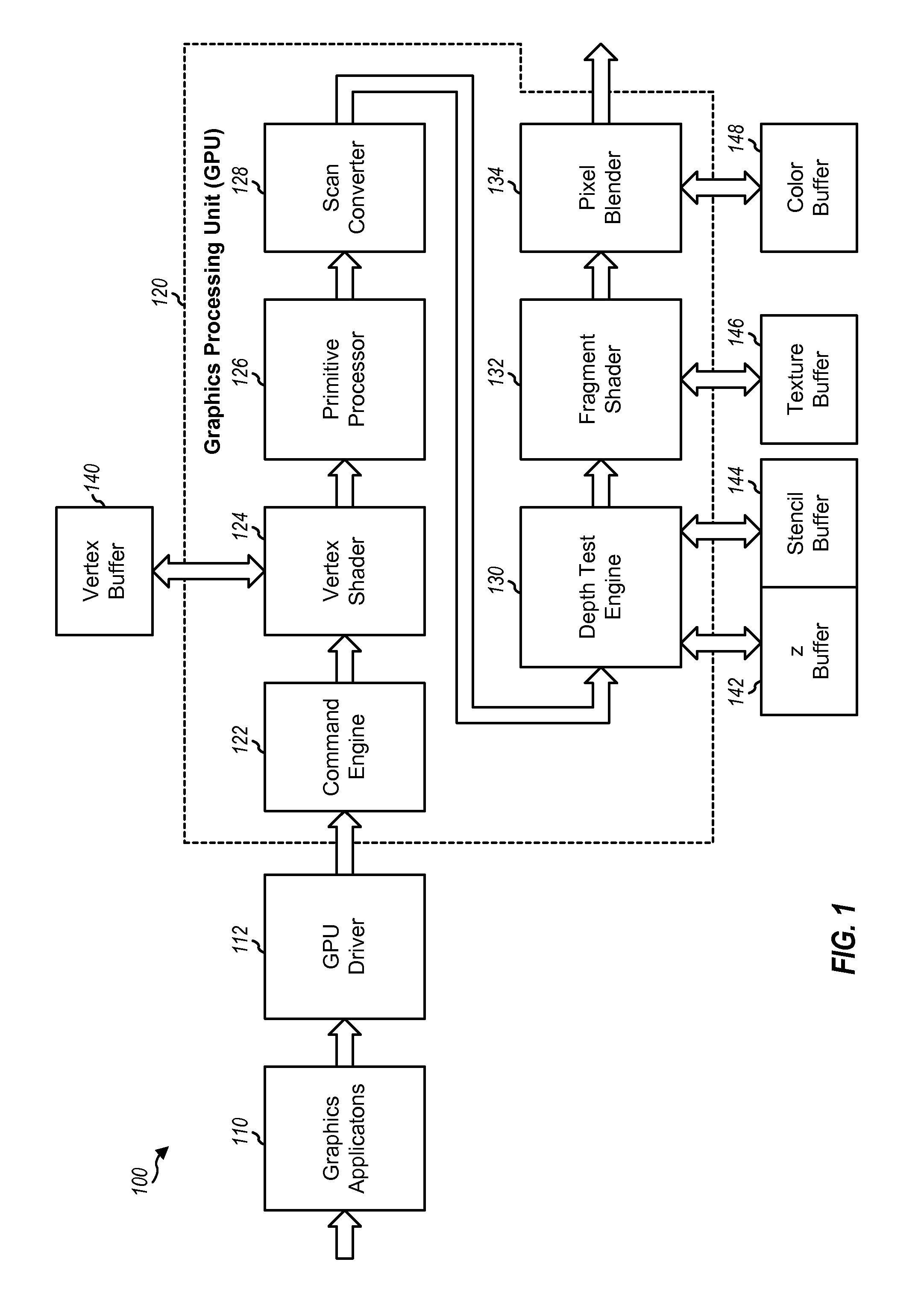

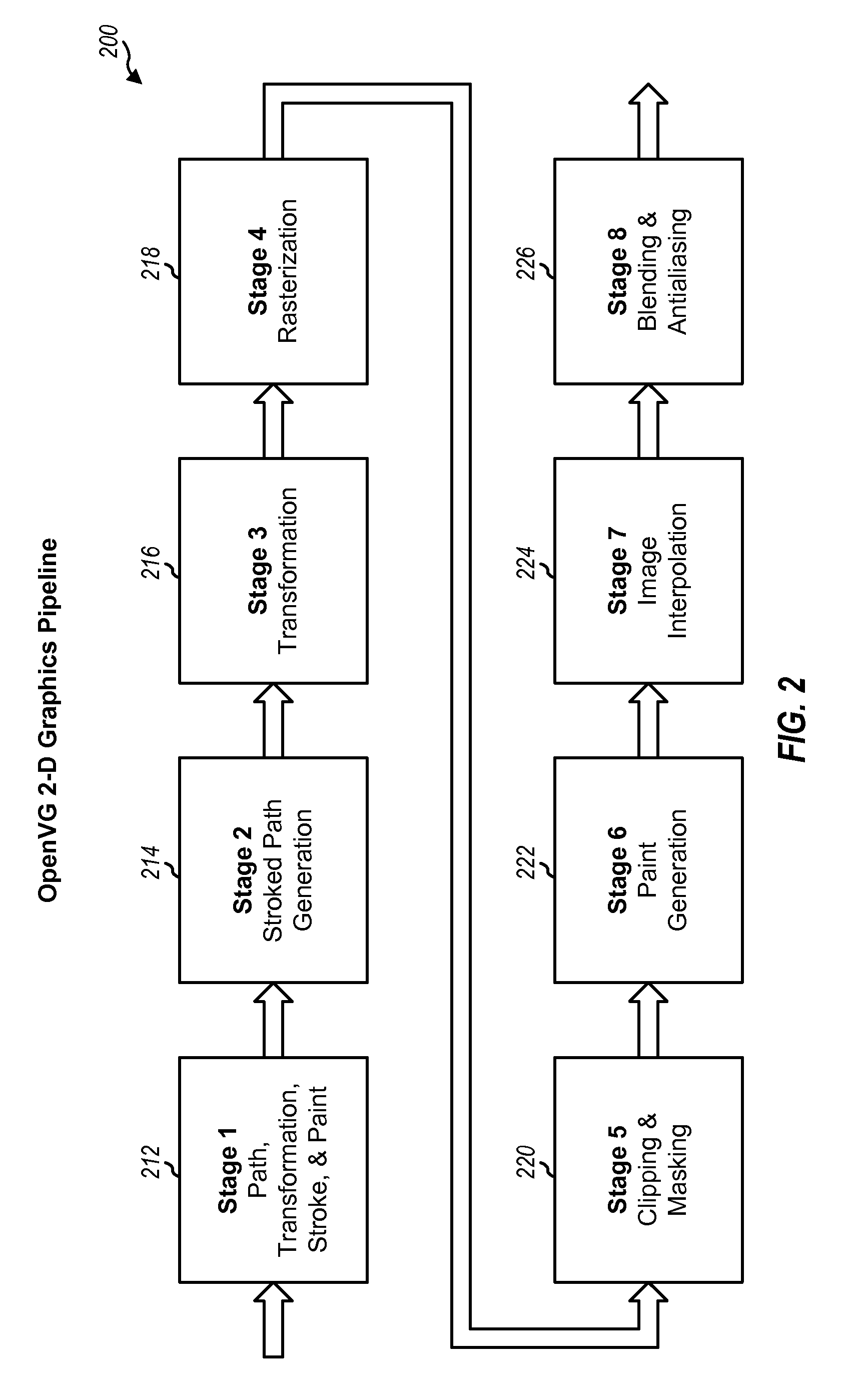

Techniques for supporting both 2-D and 3-D graphics are described. A graphics processing unit (GPU) may perform 3-D graphics processing in accordance with a 3-D graphics pipeline to render 3-D images and may also perform 2-D graphics processing in accordance with a 2-D graphics pipeline to render 2-D images. Each stage of the 2-D graphics pipeline may be mapped to at least one stage of the 3-D graphics pipeline. For example, a clipping, masking and scissoring stage in 2-D graphics may be mapped to a depth test stage in 3-D graphics. Coverage values for pixels within paths in 2-D graphics may be determined using rasterization and depth test stages in 3-D graphics. A paint generation stage and an image interpolation stage in 2-D graphics may be mapped to a fragment shader stage in 3-D graphics. A blending stage in 2-D graphics may be mapped to a blending stage in 3-D graphics.

Owner:QUALCOMM INC

Scalable shader architecture

ActiveUS20050225554A1Perform operationMultiple digital computer combinationsProcessor architectures/configurationComputational scienceProcessor scheduling

A scalable shader architecture is disclosed. In accord with that architecture, a shader includes multiple shader pipelines, each of which can perform processing operations on rasterized pixel data. Shader pipelines can be functionally removed as required, thus preventing a defective shader pipeline from causing a chip rejection. The shader includes a shader distributor that processes rasterized pixel data and then selectively distributes the processed rasterized pixel data to the various shader pipelines, beneficially in a manner that balances workloads. A shader collector formats the outputs of the various shader pipelines into proper order to form shaded pixel data. A shader instruction processor (scheduler) programs the individual shader pipelines to perform their intended tasks. Each shader pipeline has a shader gatekeeper that interacts with the shader distributor and with the shader instruction processor such that pixel data that passes through the shader pipelines is controlled and processed as required.

Owner:NVIDIA CORP

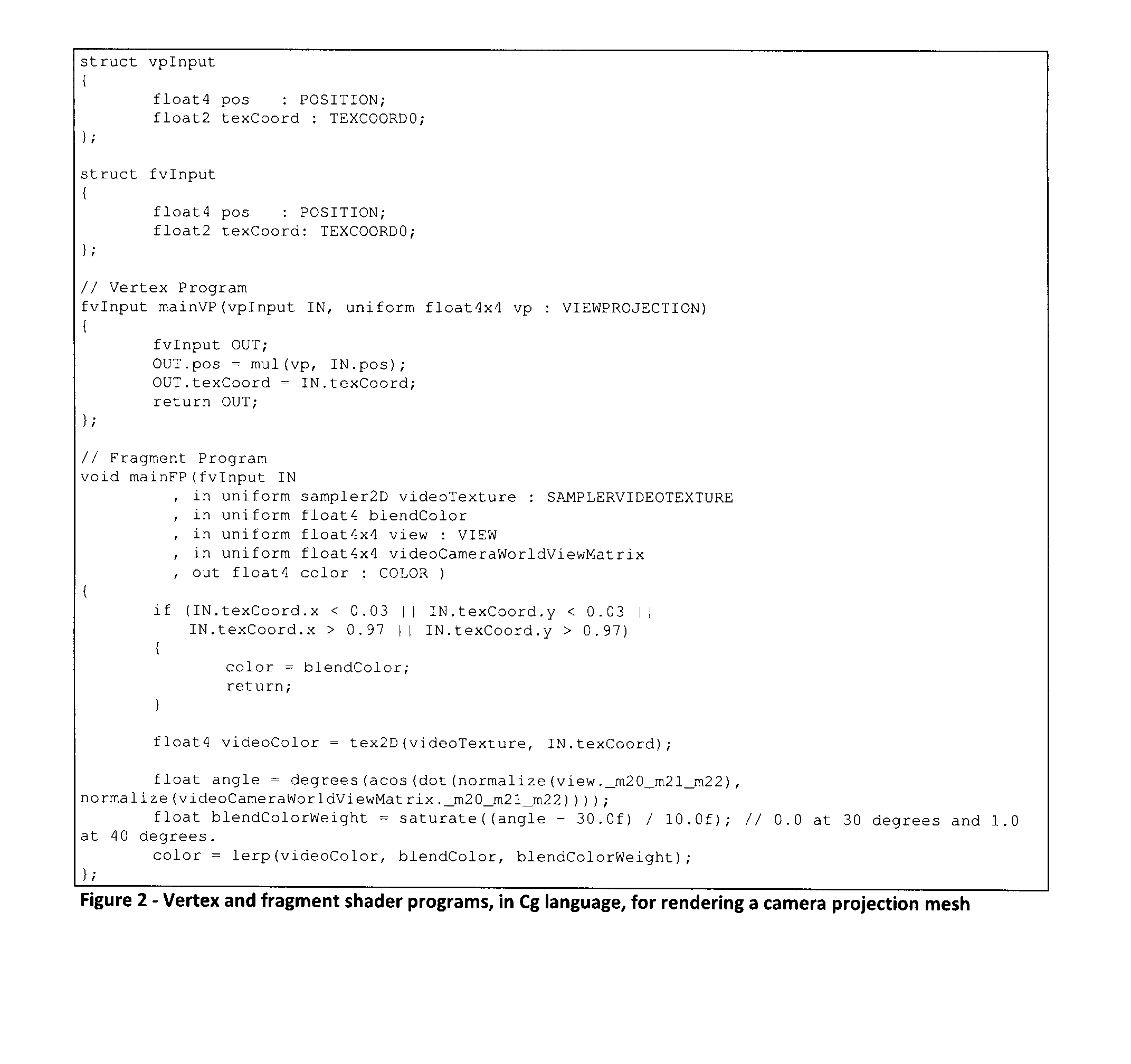

Camera Projection Meshes

InactiveUS20130021445A1Improve performanceLess complexSteroscopic systems3D-image renderingShadow mappingVideo sequence

A 3D rendering method is proposed to increase the performance when projecting and compositing multiple images or video sequences from real-world cameras on top of a precise 3D model of the real world. Unlike previous methods that relied on shadow-mapping and that were limited in performance due to the need to re-render the complex scene multiple times per frame, the proposed method uses, for each camera, one Camera Projection Mesh (“CPM”) of fixed and limited complexity per camera. The CPM that surrounds each camera is effectively molded over the surrounding 3D world surfaces or areas visible from the video camera. Rendering and compositing of the CPMs may be entirely performed on the Graphic Processing Unit (“GPU”) using custom shaders for optimal performance. The method also enables improved view-shed analysis and fast visualization of the coverage of multiple cameras.

Owner:FORTEM SOLUTIONS

Computer graphics shader systems and methods

InactiveUS7548238B2Simple re-useSimple re-purposingCathode-ray tube indicatorsMultiple digital computer combinationsTheoretical computer scienceComputer graphics

Methods and systems are described that unite various shading applications under a single language, enable the simple re-use and re-purposing of shaders, facilitate the design and construction of shaders without need for computer programming, and enable the graphical debugging of shaders.

Owner:MENTAL IMAGES

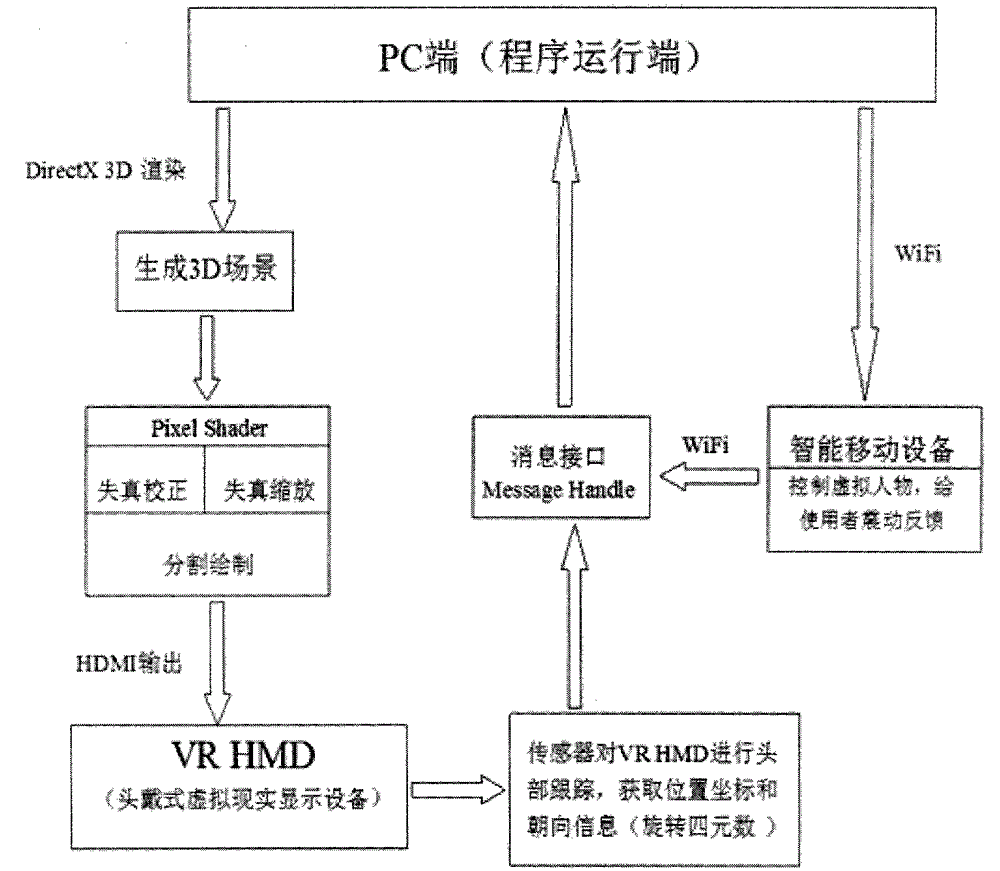

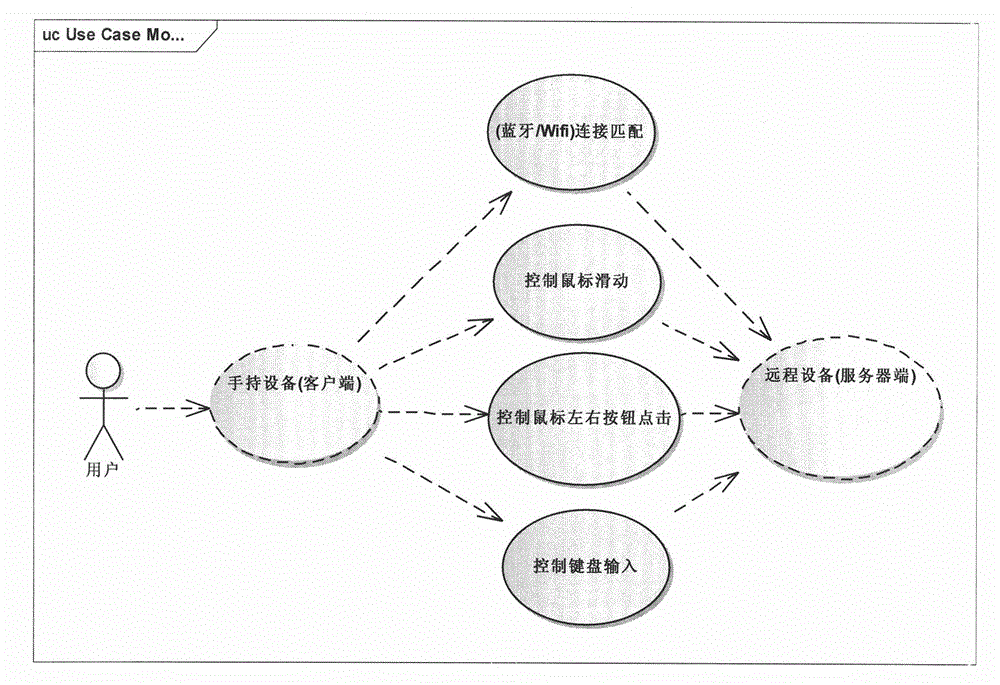

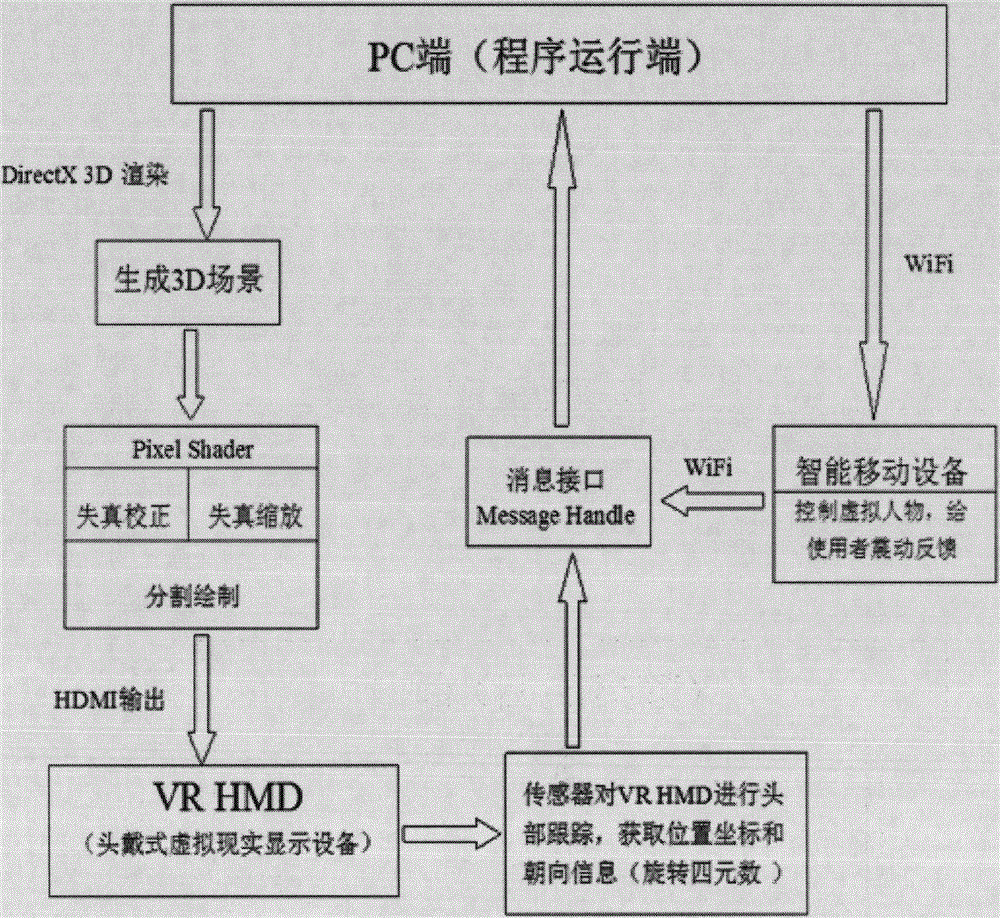

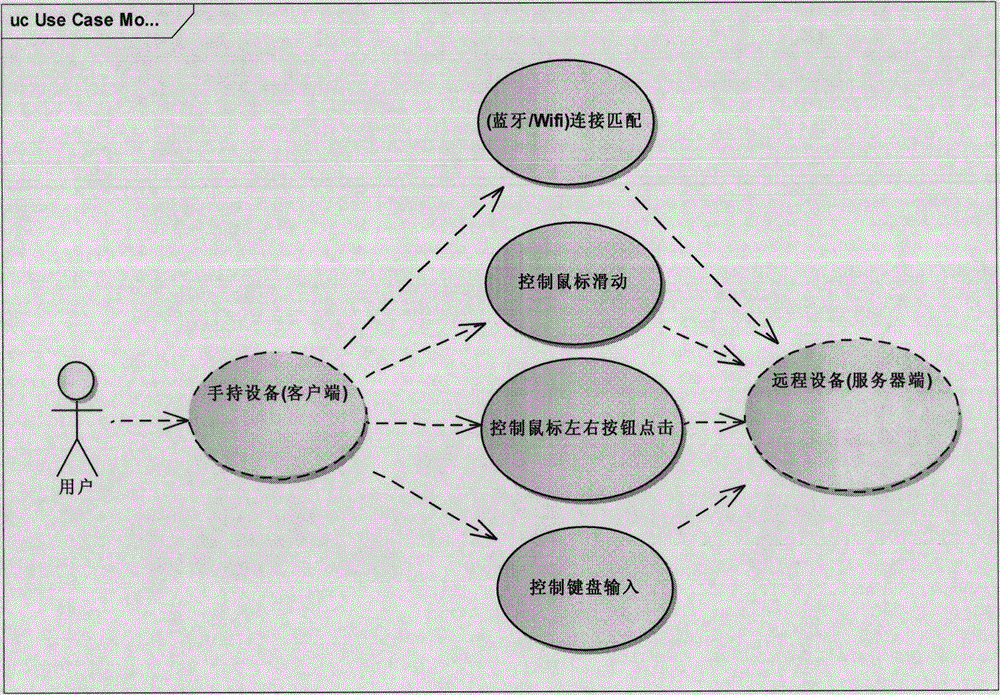

System capable of realizing immersive virtual reality across mobile platforms

InactiveCN104915979AAccurate placementAchieve interactionInput/output for user-computer interactionGraph readingQuaternionApplication software

The invention relates to a system capable of realizing immersive virtual reality across mobile platforms. A DirectX3D rendering technology is adopted to perform distortion correction and distortion scale on images rendered by virtual three-dimensional scenes via a Pixel Shader, the images are segmented and drawn on left-eye and right-eye screens of HMD equipment, and a refresh frequency of more than 60 frames per second is kept; position information and facing information of the HMD equipment are acquired from a sensor and used for head tracking, and coordinate and rotating quaternion information are fed back to an application program via a message interface; and interaction between a client end and a server end is realized by adopting a wireless communication technology. The system provided by the invention has the advantages that one product only needs to be developed for once, reality is enhanced, virtual objects not existing in the real environment are generated via a computer graphic technology and a visualization technology, the virtual objects are accurately 'placed' in the real environment via the sensing technology and are integrally mixed with the real environment by the aid of displaying equipment.

Owner:苏州天魂网络科技股份有限公司

System capable of realizing immersive virtual reality over mobile platforms

InactiveCN104035760AAccurate placementAchieve interactionTransmissionSpecific program execution arrangementsQuaternionVirtual reality

The invention relates to a system capable of realizing immersive virtual reality over mobile platforms. A DirectX3D rendering technique is adopted to perform distortion correction and distortion zooming on images rendered by virtual three-dimensional scenes via a Pixel Shader , the images are segmented and drawn on a left and right binoculus screen of HMD (helmet-mounted display) equipment, and an updating frequency of more than 60 frames per second is kept; position information and facing information of the HMD equipment are acquired from a sensor and used for head tracking, and coordinate and rotating quaternion information are fed back to an application program via a message port; interaction between a client end and a server end is realized via a wireless communication technology. The system has the advantages that one product only needs to be developed for once, reality is enhanced, virtual objects not existing in the real environment are generated via a computer graphic technology and a visualization technology, the virtual objects are accurately 'placed' in the real environment via the sensing technology and are integrally mixed with the real environment by the aid of displaying equipment.

Owner:苏州天魂网络科技股份有限公司

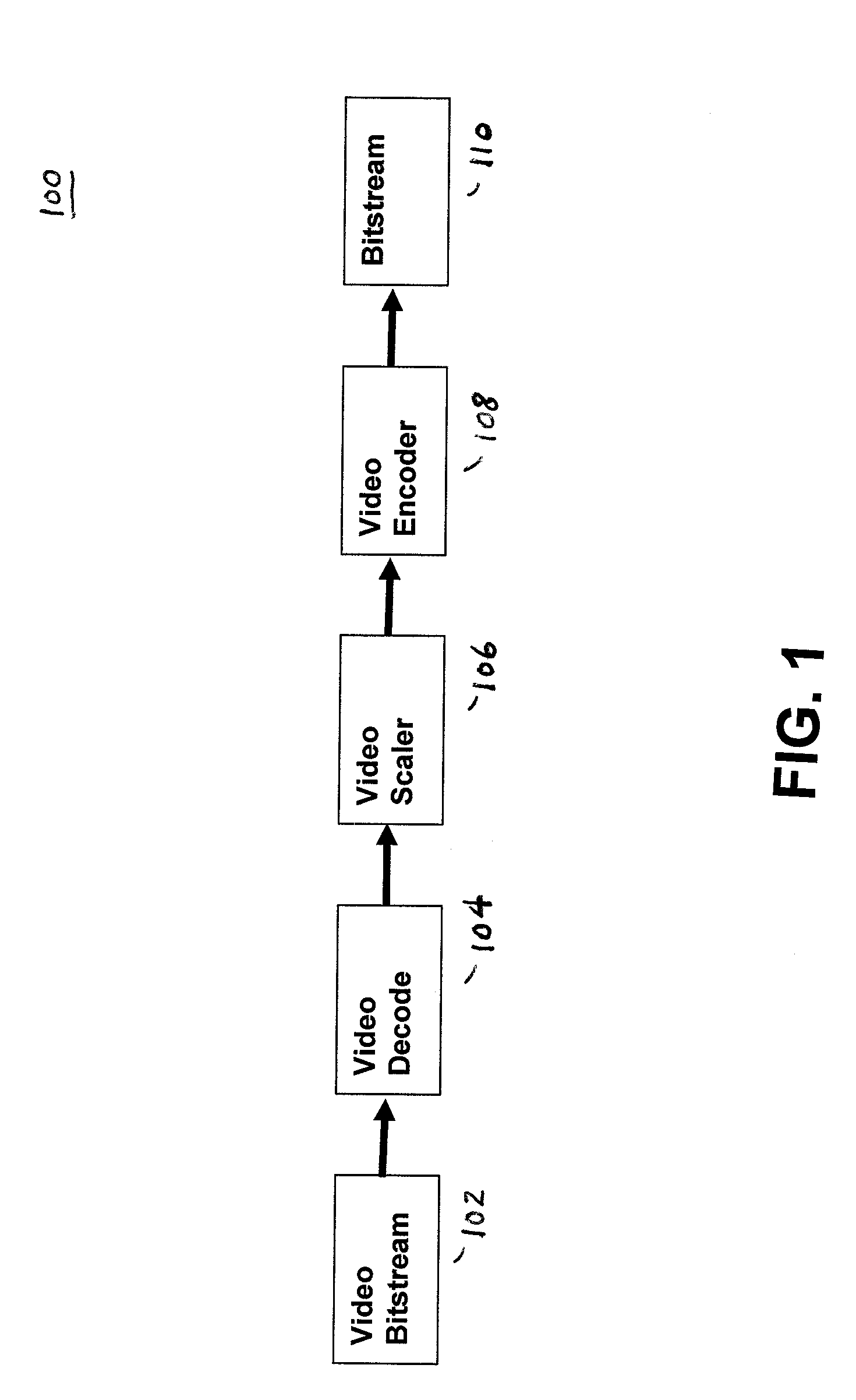

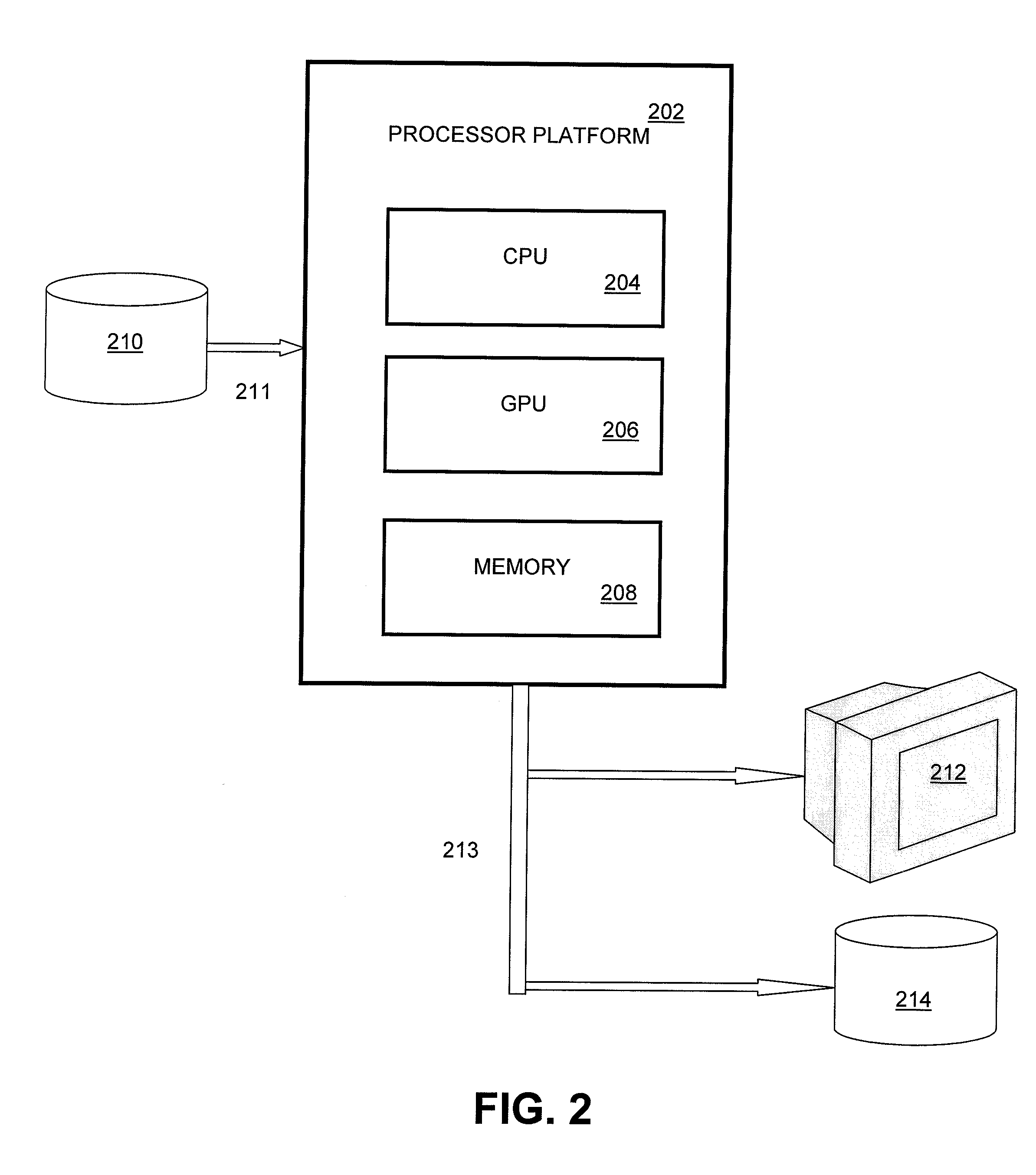

Software Video Transcoder with GPU Acceleration

ActiveUS20090060032A1Picture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningTranscodingWorkload

Embodiments of the invention as described herein provide a solution to the problems of conventional methods as stated above. In the following description, various examples are given for illustration, but none are intended to be limiting. Embodiments are directed to a transcoding system that shares the workload of video transcoding through the use of multiple central processing unit (CPU) cores and / or one or more graphical processing units (GPU), including the use of two components within the GPU: a dedicated hardcoded or programmable video decoder for the decode step and compute shaders for scaling and encoding. The system combines usage of an industry standard Microsoft DXVA method for using the GPU to accelerate video decode with a GPU encoding scheme, along with an intermediate step of scaling the video.

Owner:ADVANCED MICRO DEVICES INC

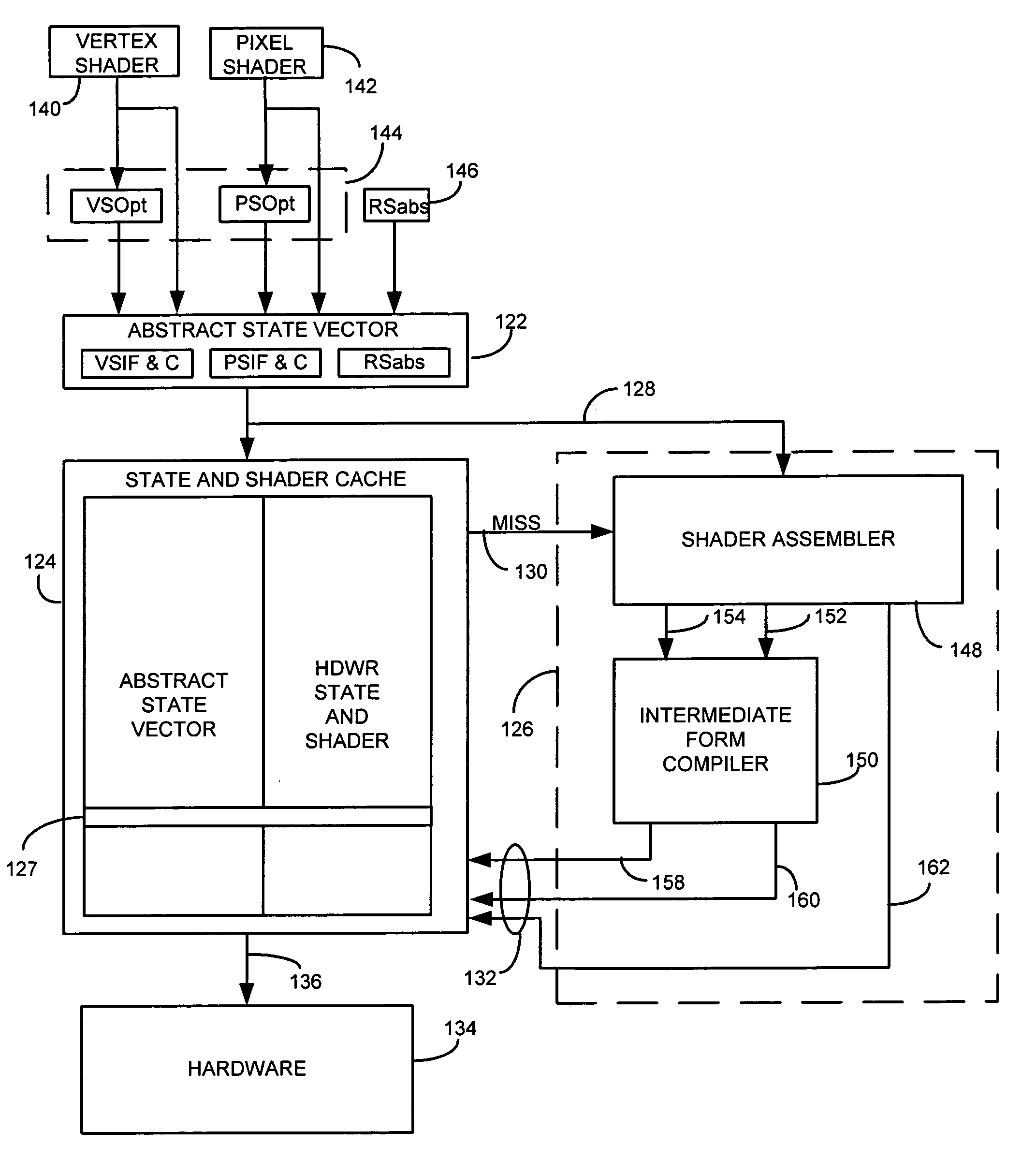

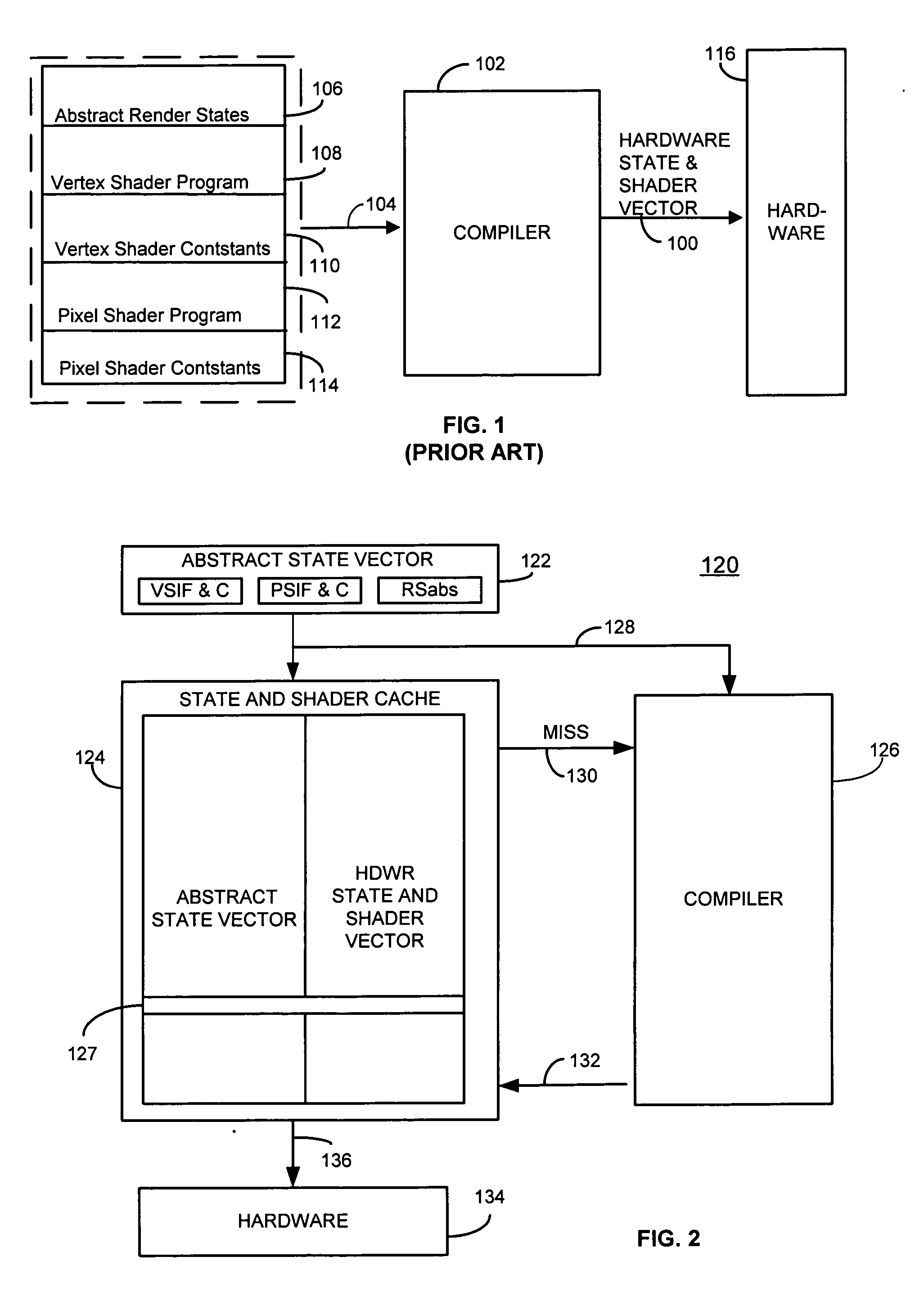

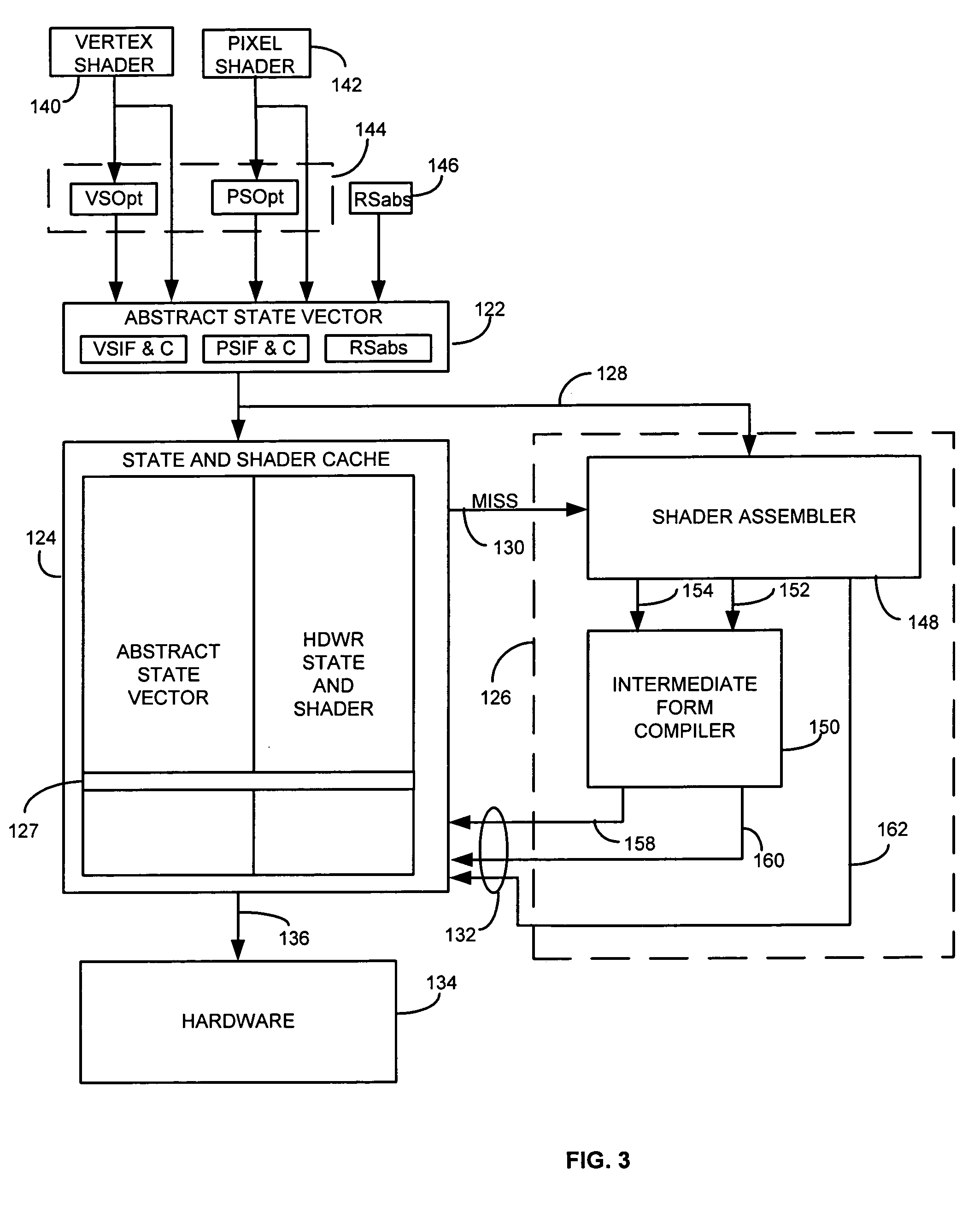

Method and apparatus for graphics processing using state and shader management

A method and apparatus for graphics processing using state and shader management includes at least one state and shader cache coupled to a compiler for compiling a hardware state and shader vector from an abstract state vector. Also included is an abstract state vector register containing the abstract state vector that is provided to the state and shader cache and the compiler. The state and shader cache receives the abstract state vector and determines whether a cache entry for that abstract state vector already exists. If the cache entry exists, the hardware state and shader vector is provided to hardware. If the entry does not exist, the state and shader cache provides a miss signal to the compiler, whereupon the compiler compiles the abstract state vector and generates a hardware state and shader vector. Thereupon the hardware state and shader vector is provided to the hardware.

Owner:ATI TECH INC

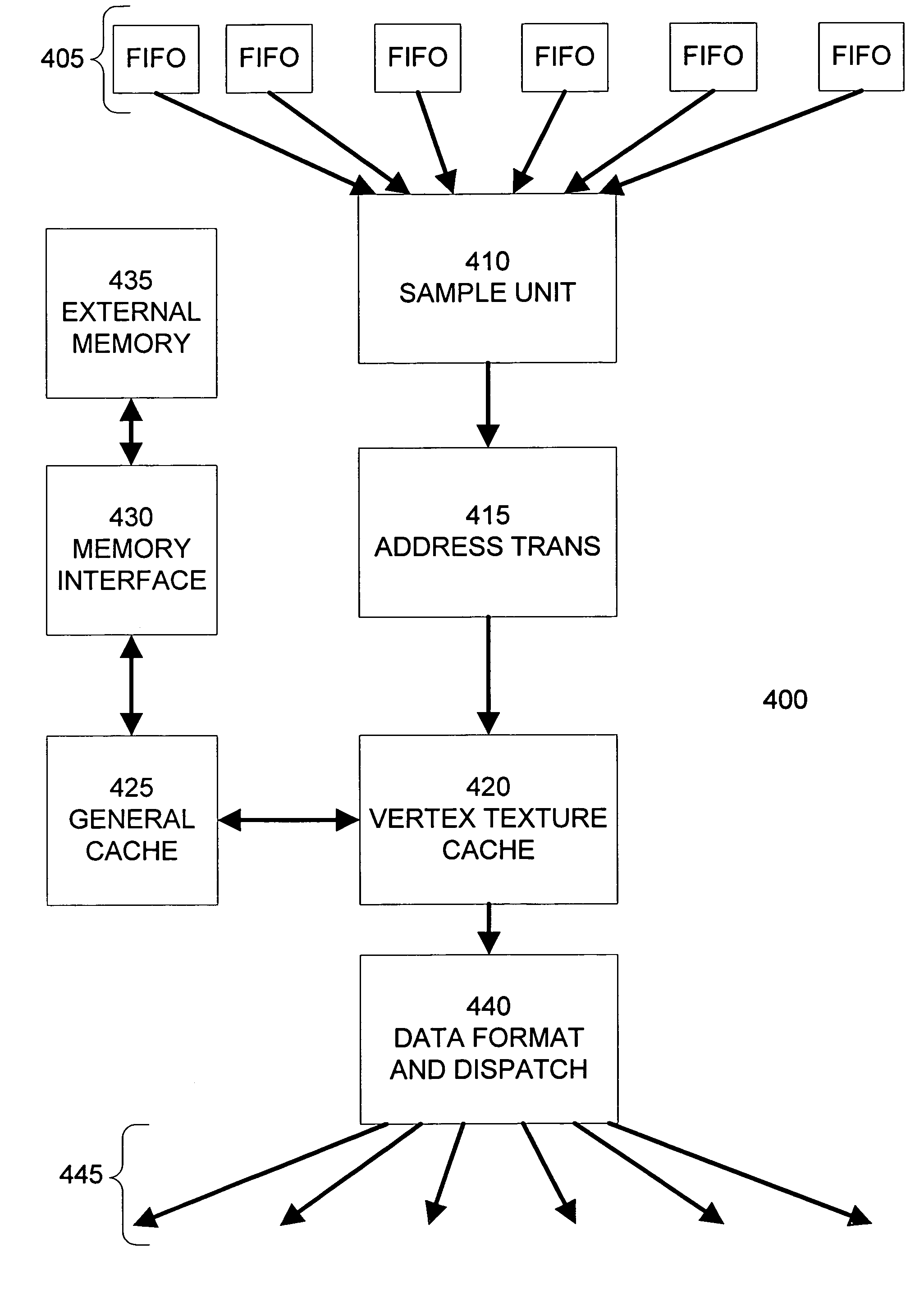

Vertex texture cache returning hits out of order

ActiveUS6972769B1Minimizing pipeline stallsCorrect formatCathode-ray tube indicatorsFilling planer surface with attributesComputer graphics (images)Computer science

A vertex texture cache unit enables vertex shader programs to arbitrarily access array data while minimizing pipeline stalls due to memory latency. The vertex texture cache unit receives vertex texture requests from multiple vertex processing engines, each executing multiple vertex shader programs. The vertex texture cache unit stores frequently accessed vertex texture map data in a cache memory. When a cache miss occurs, the vertex texture cache unit continues to process subsequent vertex texture requests while data is being retrieved from memory for the cache miss. Because the vertex texture cache unit may output vertex texture map data in a different order than the corresponding vertex texture requests are received, the vertex texture cache unit maintains the association between vertex texture map data and its set of attributes, so that the vertex texture map data is formatted correctly and returned to the appropriate vertex processing engine and vertex shader program.

Owner:NVIDIA CORP

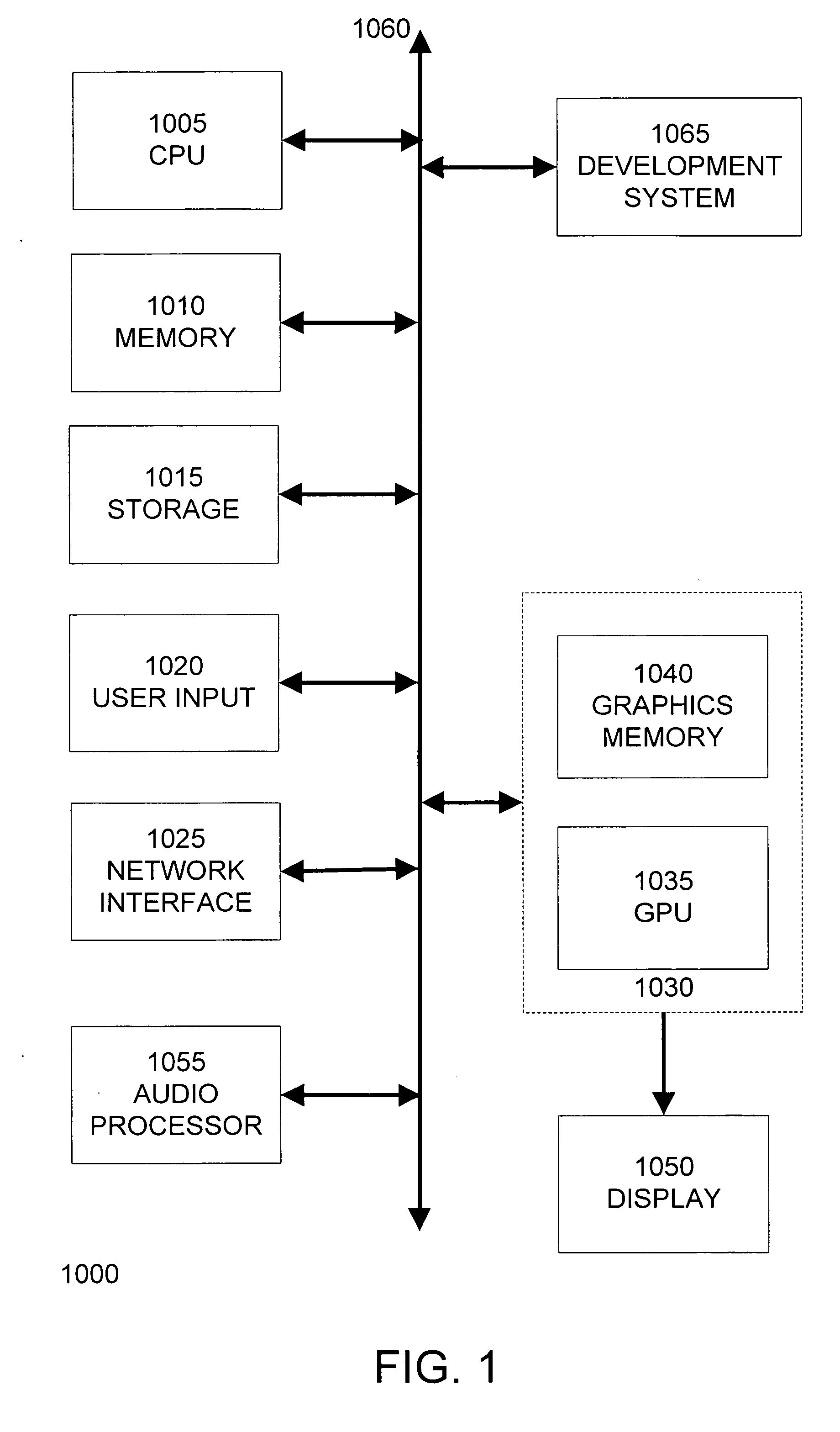

Interactive debugging and monitoring of shader programs executing on a graphics processor

ActiveUS20060152509A1Error detection/correctionMultiple digital computer combinationsComputerized systemExecution unit

A development application leverages the programmability of shader execution units in the graphics processing subsystem to make graphics processing subsystem state data accessible to applications executed outside the graphics processing subsystem. The development application modifies shaders to include state output instructions adapted to direct a shader execution unit to copy graphics processing subsystem state data to a location in the computer system that is accessible to applications executed outside of the graphics processing subsystem. Following the execution of the state output instructions, the shader execution unit can be halted or can continue executing the shader. The development application can modify the shader to include state restoration instructions adapted to direct the shader execution unit to set state data of the graphics processing subsystem to previous or new values. The development application can dynamically modify shaders with state output and restoration instructions to update state data of the graphics processing subsystem.

Owner:SONY COMPUTER ENTERTAINMENT INC

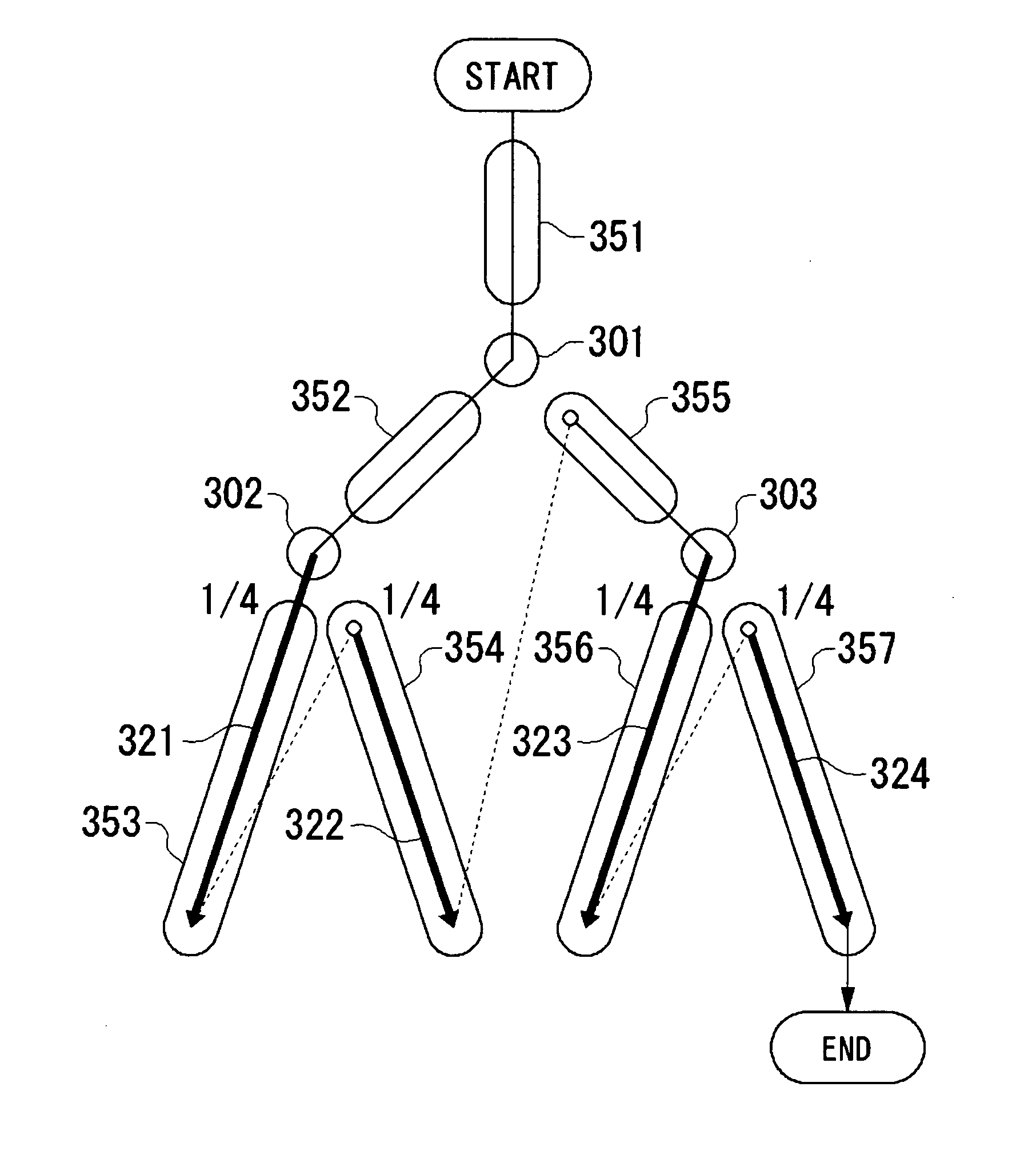

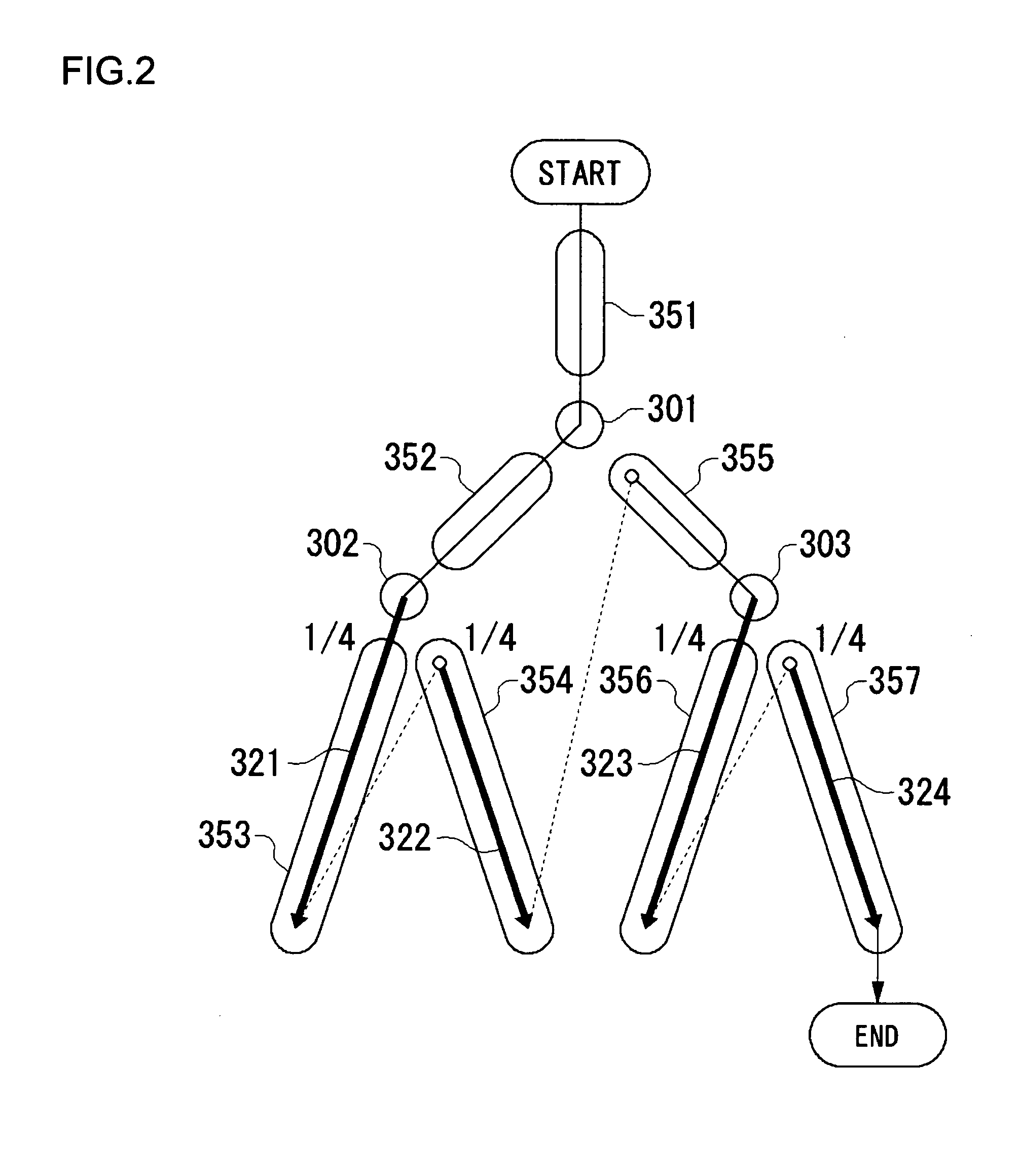

Drawing processing apparatus and drawing processing method for multipass rendering

ActiveUS20060267981A1Efficient executionMultiple digital computer combinationsProcessor architectures/configurationComputer graphics (images)Granularity

A drawing processing apparatus capable of executing a drawing processing program having conditional branches efficiently by multipass rendering. The drawing processing apparatus comprises arithmetic processing parts including an object input part, a primitive generating part, a raster part, a pixelation part, a distribution part, and a shader which constitute pipeline stages. The shader divides the program into and executes the same in a plurality of passes depending on conditional branches. The shader generates enable flags determining whether or not respective pixels satisfy branch conditions. The flag generating part generates bind enable flags which are the enable flags on the pixels bound into the processing granularities of the pipeline stages, and feeds back the same to the respective pipeline stages. The arithmetic processing parts in the individual pipeline stages refer to the bind enable flags and limit the submission of data not targeted for arithmetic processing in the branched passes.

Owner:SONY COMPUTER ENTERTAINMENT INC

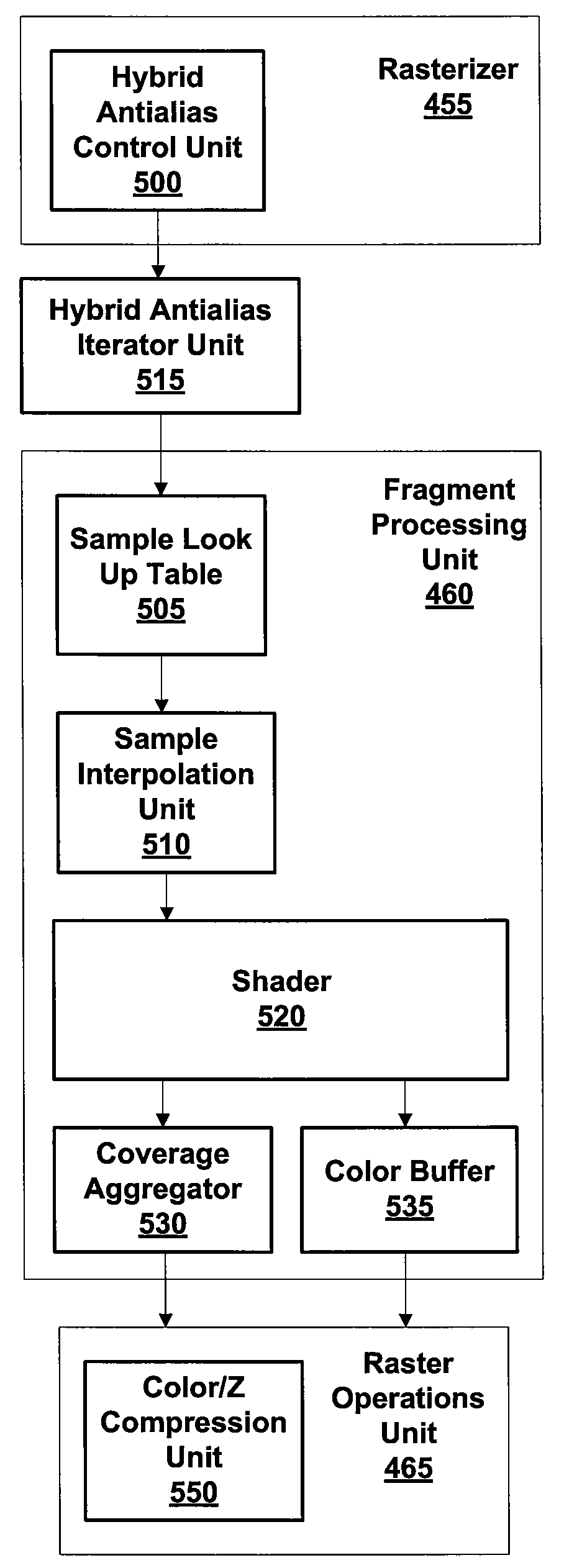

Hybrid Multisample/Supersample Antialiasing

ActiveUS20100002000A1Improve image qualityGood colorCathode-ray tube indicatorsDetails involving image processing hardwareImaging qualityComputer graphics (images)

A system and method for dynamically adjusting the pixel sampling rate during primitive shading can improve image quality or increase shading performance. Hybrid antialiasing is performed by selecting a number of shaded samples per pixel fragment. A combination of supersample and multisample antialiasing is used where a cluster of sub-pixel samples (multisamples) is processed for each pass through a fragment shader pipeline. The number of shader passes and multisamples in each cluster can be determined dynamically for each primitive based on rendering state.

Owner:NVIDIA CORP

Method for hybrid rasterization and raytracing with consistent programmable shading

ActiveUS20070035545A1Consistent imageAccurate evaluationImage data processing detailsSpecial data processing applicationsComputer imageVirtual camera

A method of generating a computer image wherein secondary raytrace vectors are calculated for the image after the image is rendered using rasterization. The secondary raytrace vectors are based on virtual camera angles that are stored during the rasterization process. The raytrace vectors can be calculated using the same processor as the rasterization, thereby providing greater consistency in the image. A metaprogrammed shader can also be applied to the generated image, wherein the shader uses the same processor as the raytrace and rasterization steps. The metaprogrammed shader allows the shader algorithm to be segmented for streamlined processing by the processor.

Owner:DASSAULT SYST 3DEXCITE +1

Hybrid multisample/supersample antialiasing

ActiveCN101620725AImage enhancementProcessor architectures/configurationImaging qualityImage quality

The present invention discloses a calculating device configured to shade graphical elements using hybrid antialiasing. A system and method for dynamically adjusting the pixel sampling rate during primitive shading can improve image quality or increase shading performance. Hybrid antialiasing is performed by selecting a number of shaded samples per pixel fragment. A combination of supersample and multisample antialiasing is used where a cluster of sub-pixel samples (multisamples) is processed for each pass through a fragment shader pipeline. The number of shader passes and multisamples in each cluster can be determined dynamically for each primitive based on rendering state.

Owner:NVIDIA CORP

Method and System For Tile Mode Renderer With Coordinate Shader

ActiveUS20110148901A1Cathode-ray tube indicatorsFilling planer surface with attributesComputer graphics (images)Shader

A method and system are provided in which one or more processors and / or circuits are operable to generate position information for a plurality of primitives utilizing a coordinate shader, one or more lists based on the generated position information, and rendering information for the plurality of primitives utilizing a vertex shader and the generated one or more lists. The generated one or more lists may comprise indices associated with one or more primitives from the plurality of primitives and with one or more tiles from a plurality of tiles in a screen plane. The position information and the one or more lists may be generated during a first rendering phase, and the rendering information may be generated during a second rendering phase different from the first rendering phase. The coordinate shader may perform a subset of the operations supported by the vertex shader.

Owner:AVAGO TECH INT SALES PTE LTD

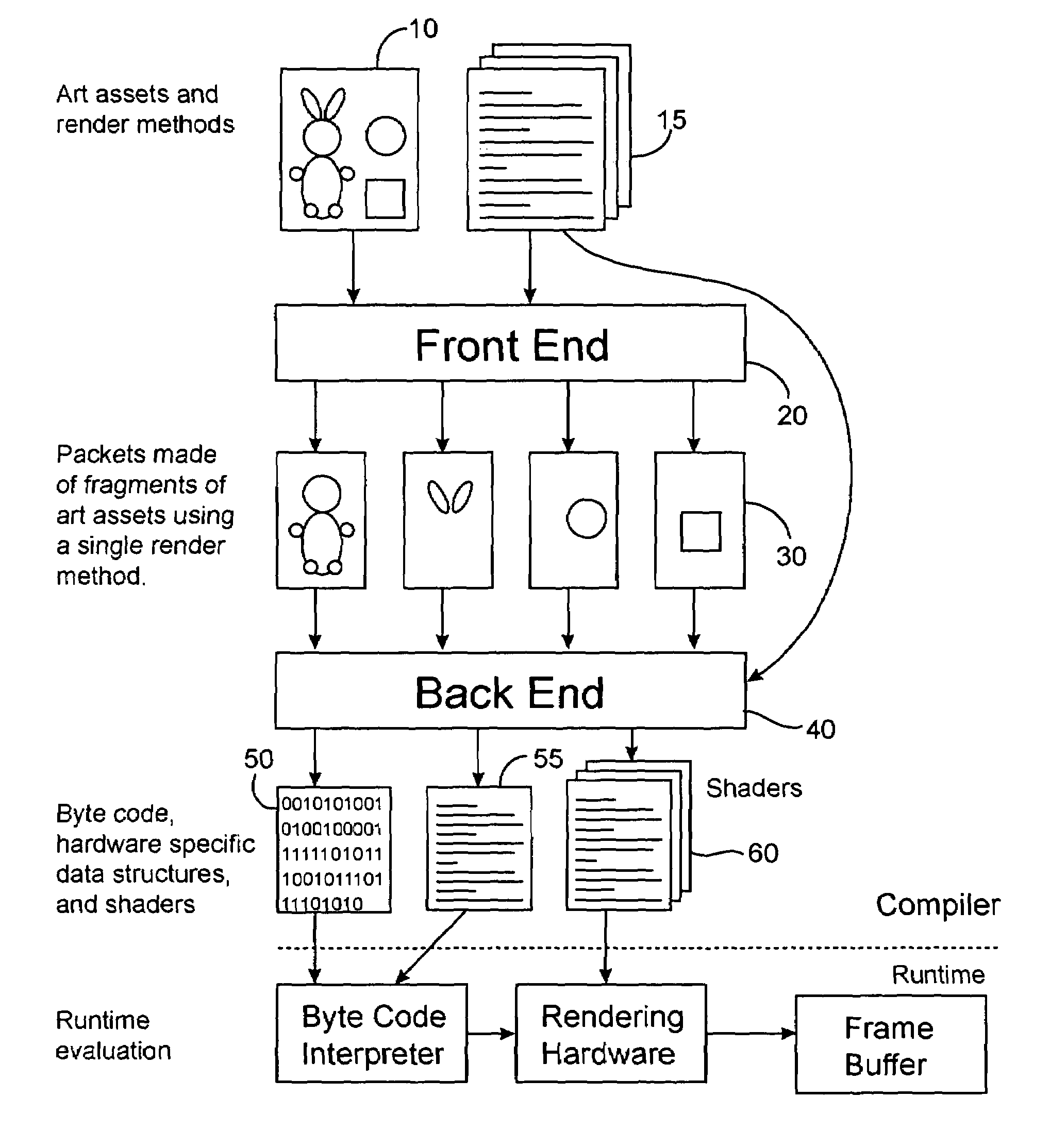

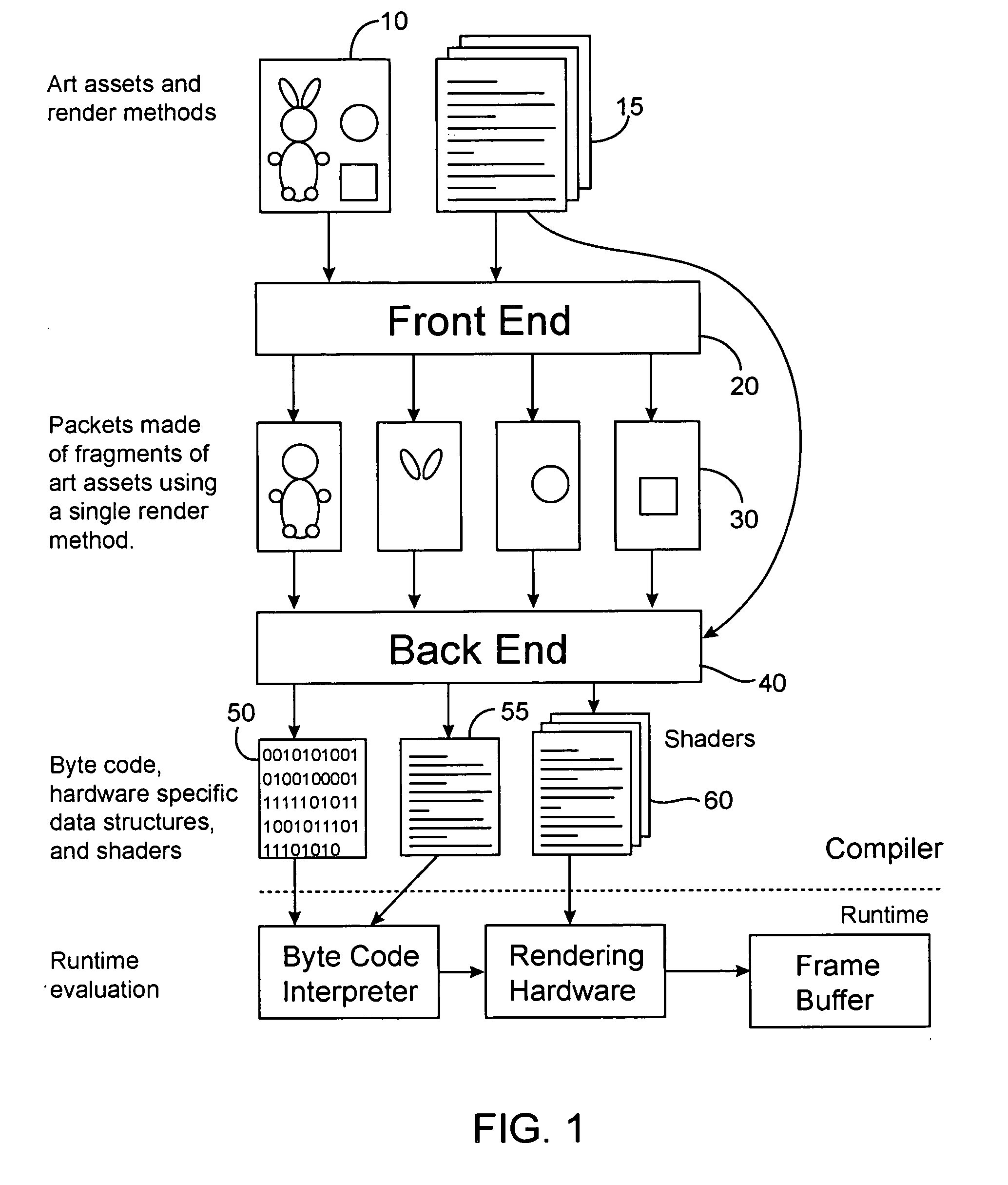

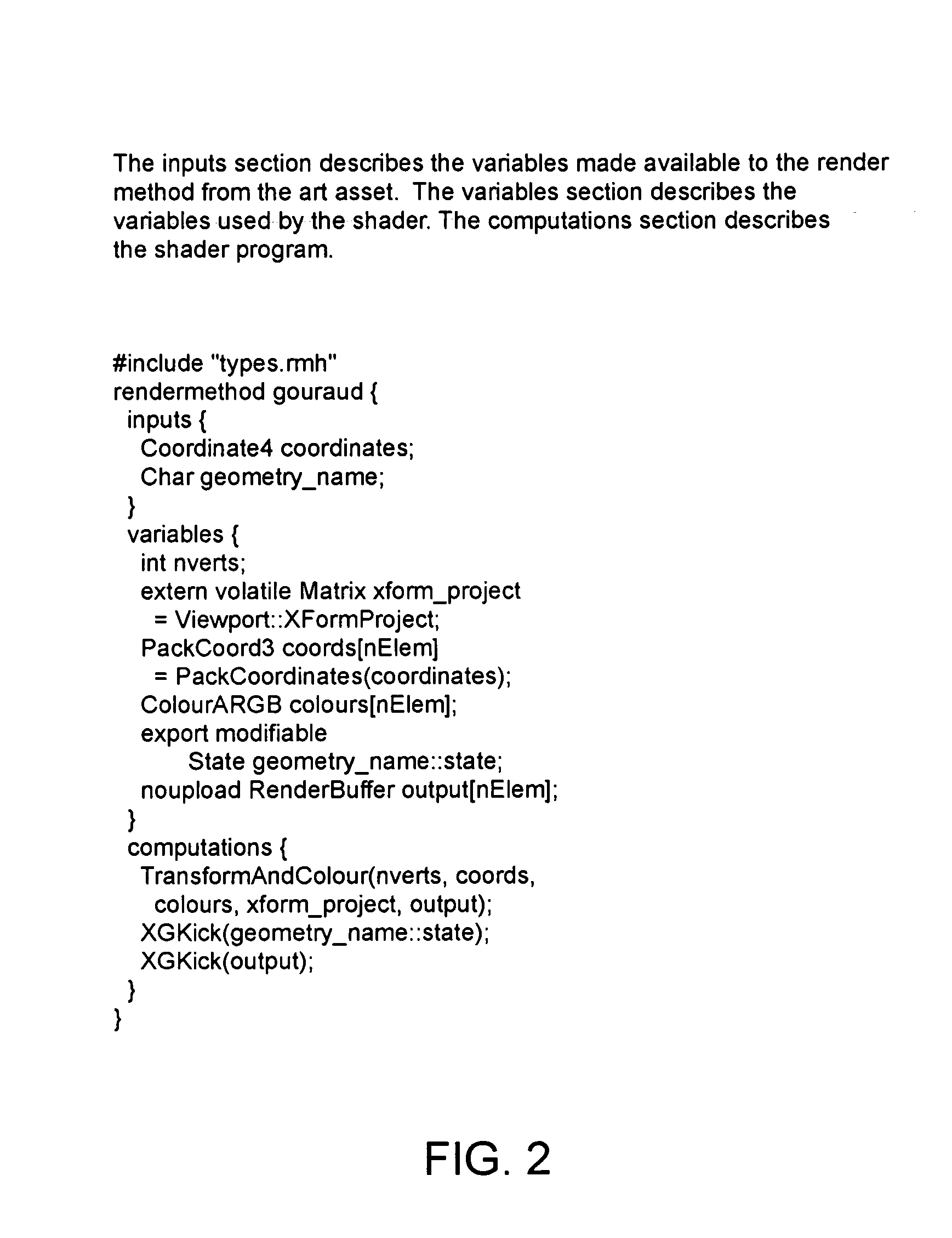

Systems and methods for implementing shader-driven compilation of rendering assets

ActiveUS7159212B2Fast iterationFlexible and fastSpecific program execution arrangementsMemory systemsComputer science3D modeling

Art asset rendering systems and methods in which pre-processing is performed in a compilation process. Geometric data are processed in the compilation process with knowledge of associated shading programs. The data are converted into data structures targeted directly to a target hardware platform, and a code stream is assembled that describes the manipulations required to render these data structures. The compiler includes a front end configured to read the geometric data and attributes (an art asset) output from a 3D modeling package and shaders in a platform independent form and perform platform-independent optimizations, and a back end configured to perform platform-specific optimizations and generate platform-targeted data structures and code streams.

Owner:ELECTRONICS ARTS INC

Providing pipeline state through constant buffers

ActiveUS20110087864A1Digital computer detailsConcurrent instruction executionParallel computingApplication software

One embodiment of the present invention sets forth a technique for providing state information to one or more shader engines within a processing pipeline. State information received from an application accessing the processing pipeline is stored in constant buffer memory accessible to each of the shader engines. The shader engines can then retrieve the state information during execution.

Owner:NVIDIA CORP

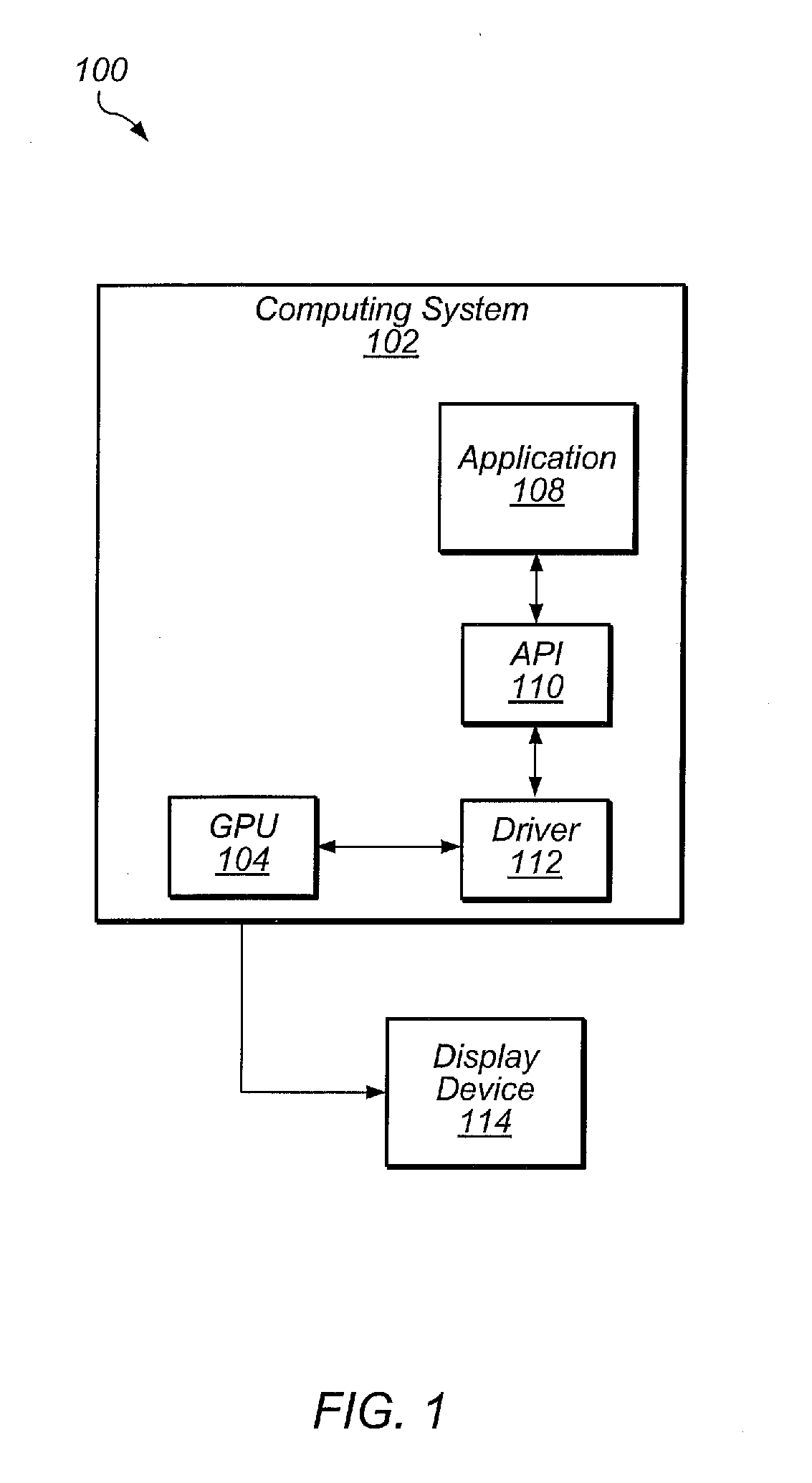

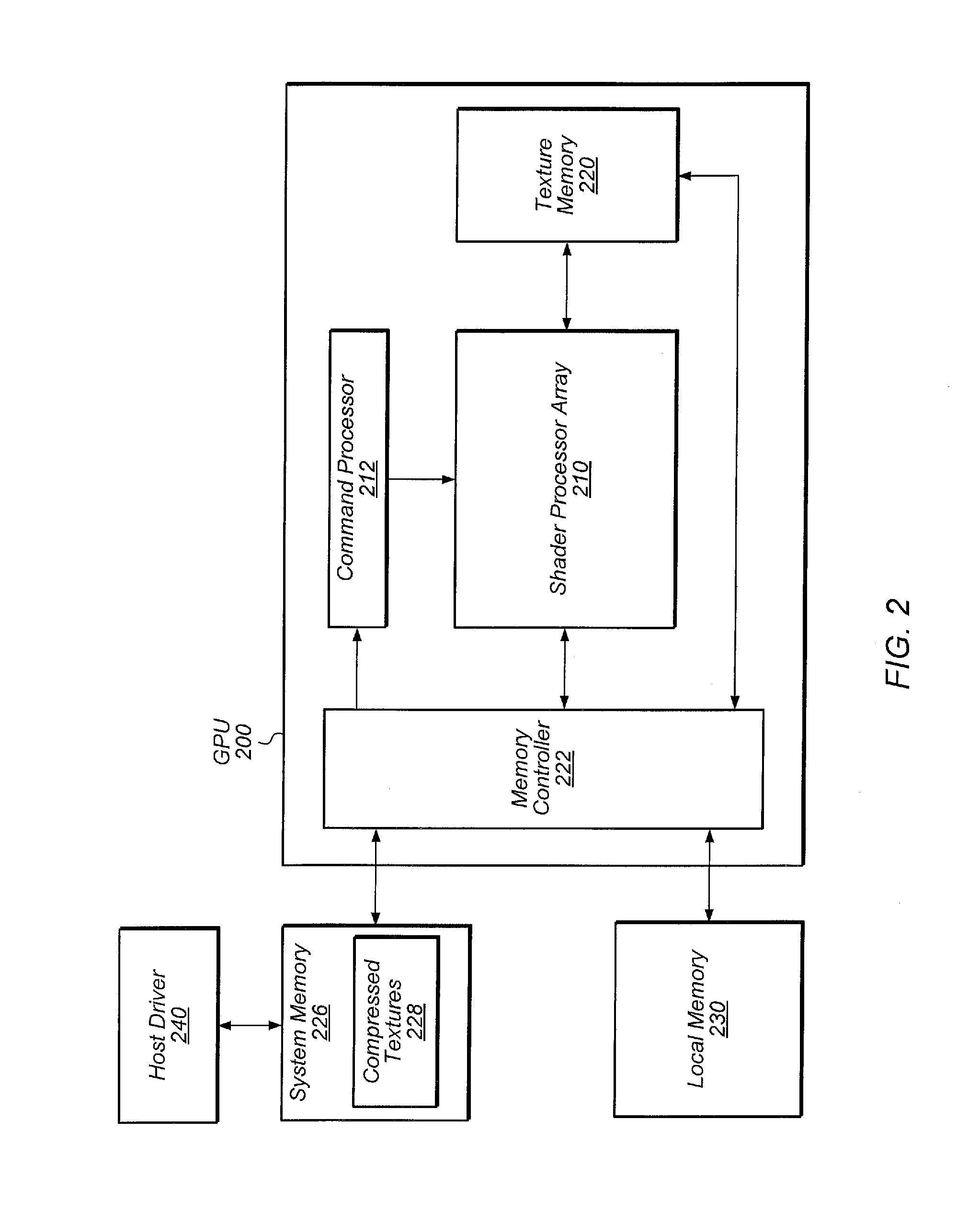

Real time on-chip texture decompression using shader processors

ActiveUS20120320067A1Low costMuch of quality of originalMemory architecture accessing/allocationDigital computer detailsComputational scienceJPEG

A processing unit, method, and medium for decompressing or generating textures within a graphics processing unit (GPU). The textures are compressed with a variable-rate compression scheme such as JPEG. The compressed textures are retrieved from system memory and transferred to local cache memory on the GPU without first being decompressed. A table is utilized by the cache to locate individual blocks within the compressed texture. A decompressing shader processor receives compressed blocks and then performs on-the-fly decompression of the blocks. The decompressed blocks are then processed as usual by a texture consuming shader processor of the GPU.

Owner:ADVANCED MICRO DEVICES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com