Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7296 results about "Memory controller" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

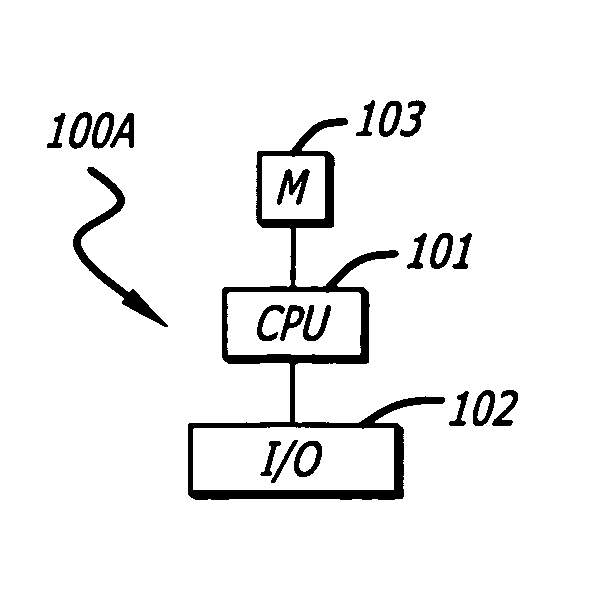

The memory controller is a digital circuit that manages the flow of data going to and from the computer's main memory. A memory controller can be a separate chip or integrated into another chip, such as being placed on the same die or as an integral part of a microprocessor; in the latter case, it is usually called an integrated memory controller (IMC). A memory controller is sometimes also called a memory chip controller (MCC) or a memory controller unit (MCU).

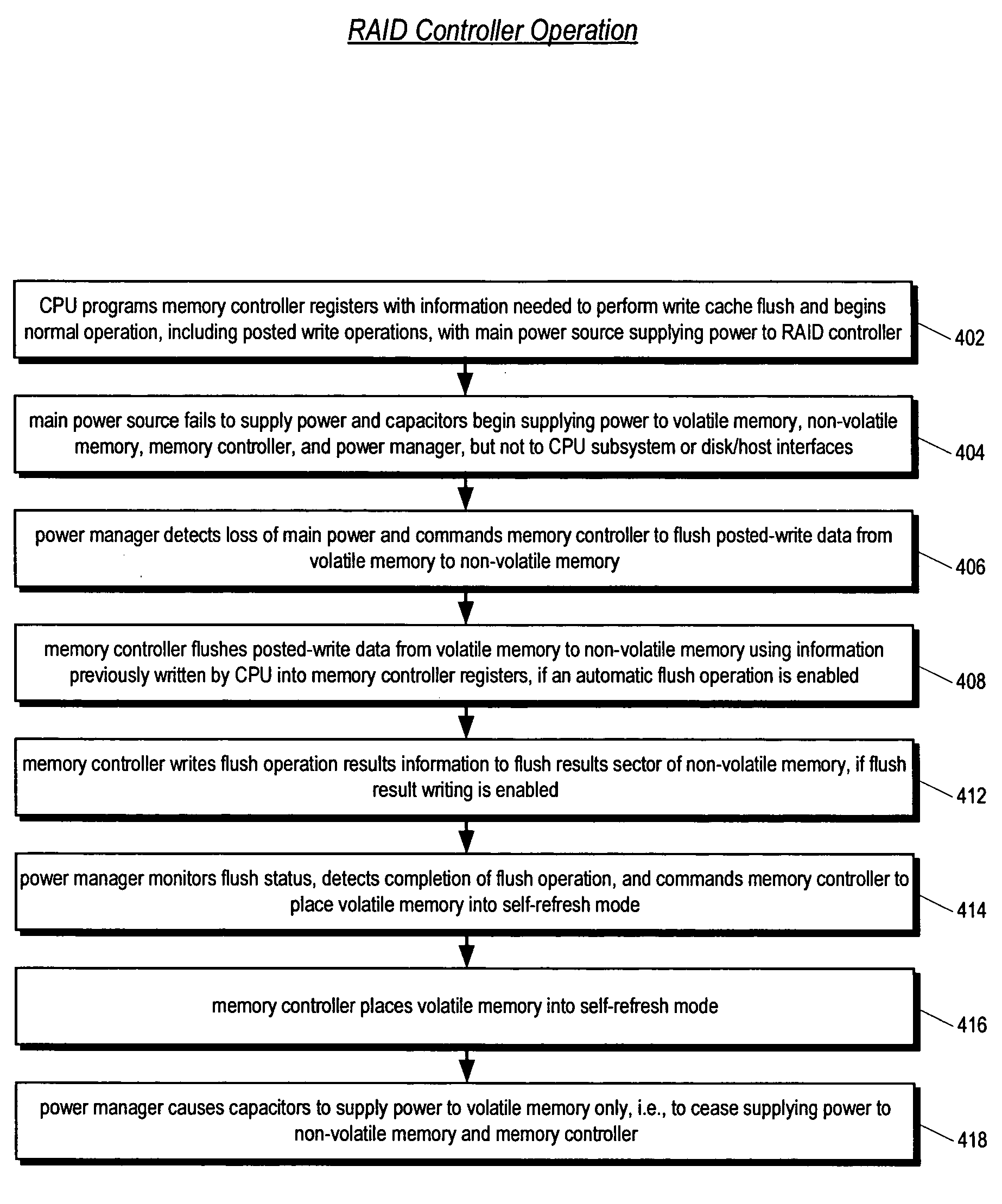

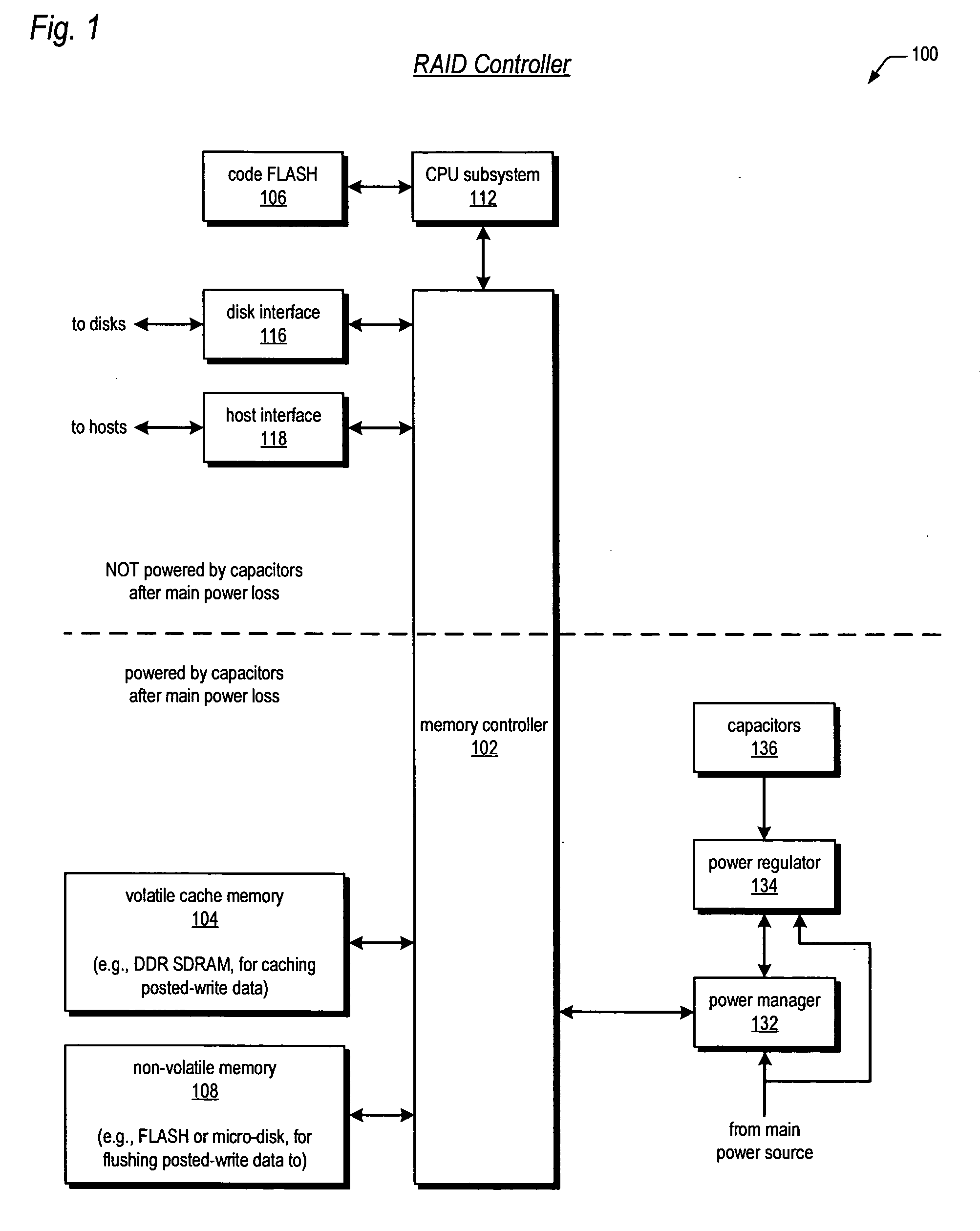

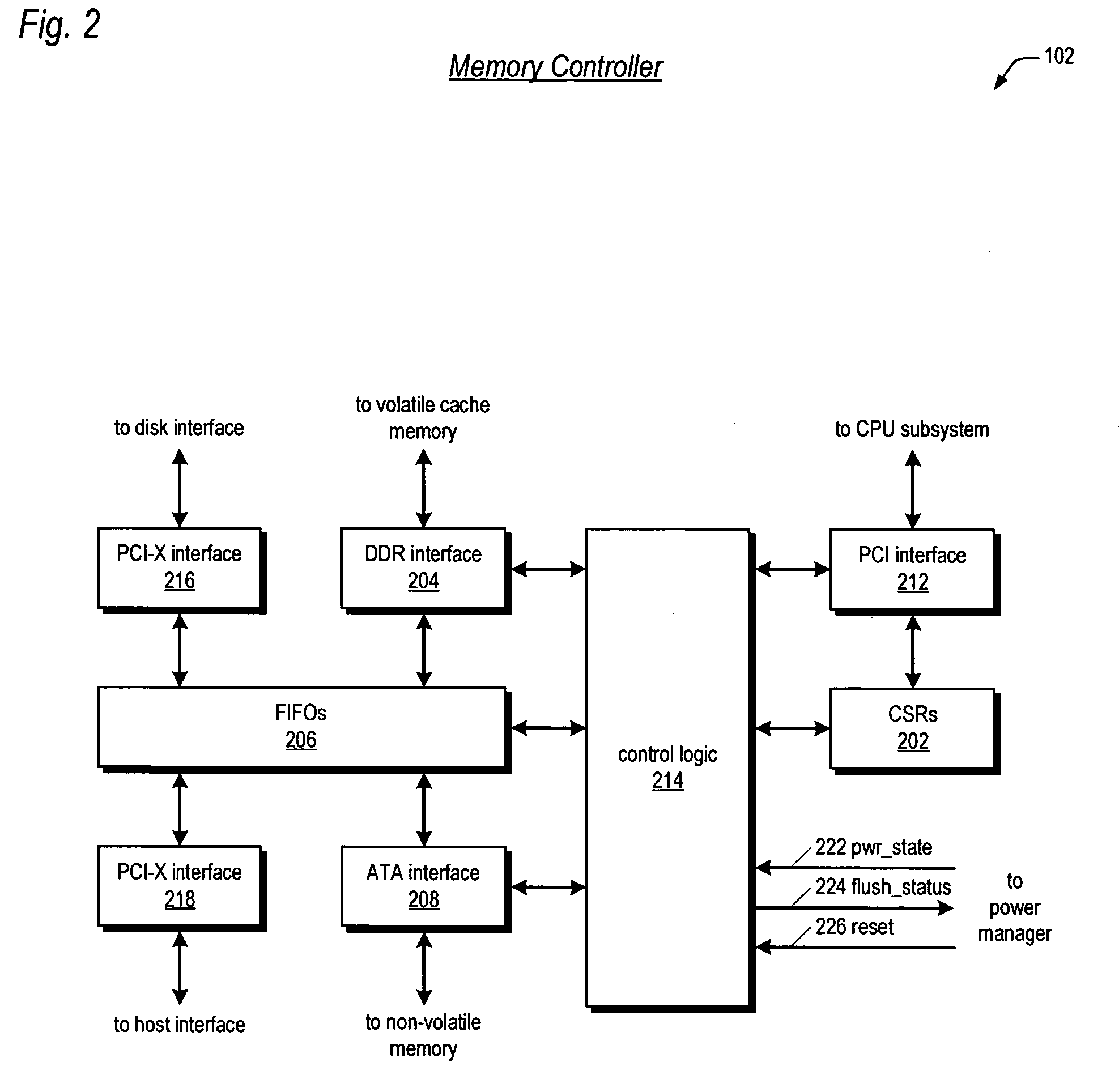

Raid controller using capacitor energy source to flush volatile cache data to non-volatile memory during main power outage

InactiveUS20060015683A1Reduces amount of energy storage capacity requirementLess expensiveEnergy efficient ICTMemory loss protectionRAIDStored energy

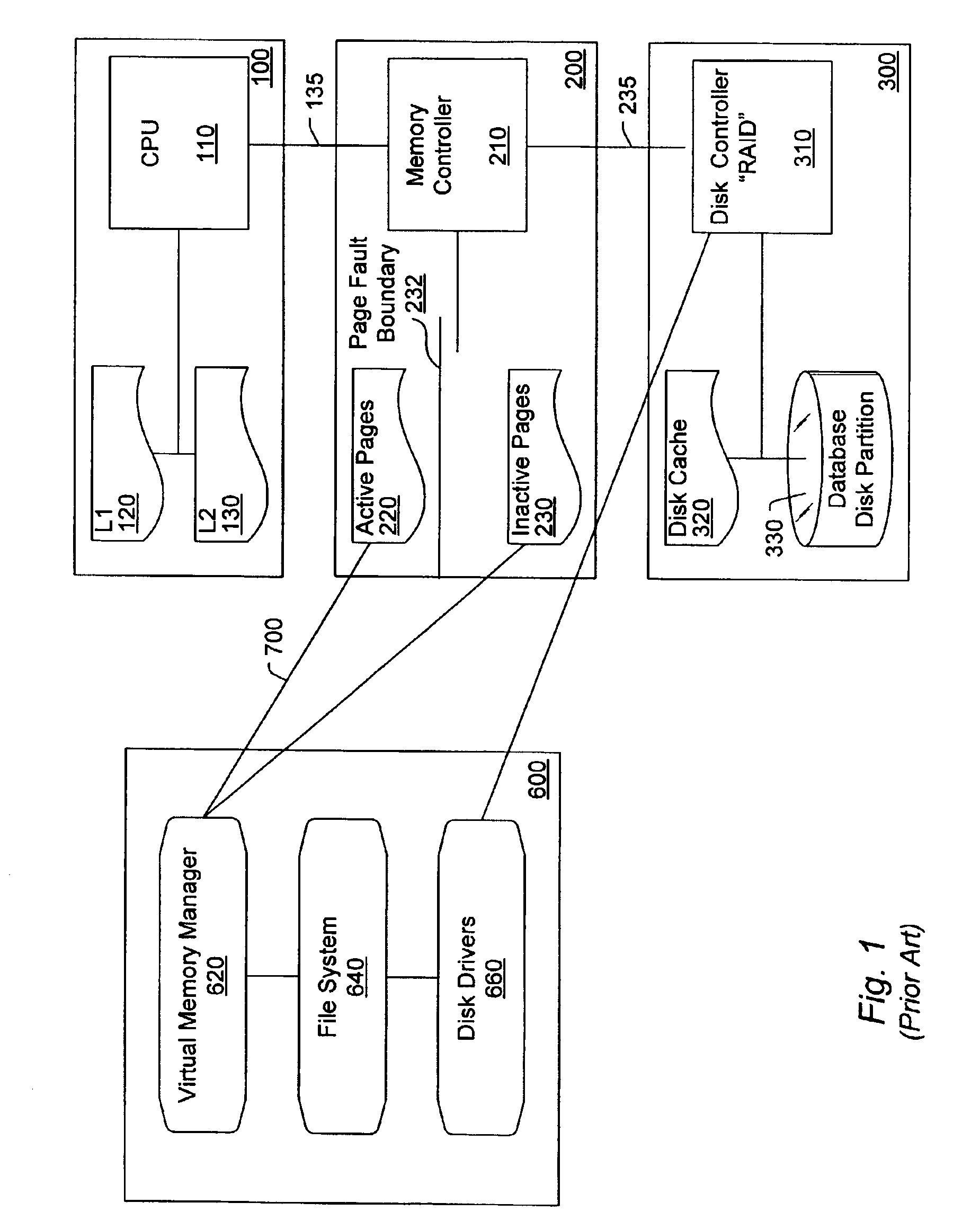

A write-caching RAID controller is disclosed. The controller includes a CPU that manages transfers of posted-write data from host computers to a volatile memory and transfers of the posted-write data from the volatile memory to storage devices when a main power source is supplying power to the RAID controller. A memory controller flushes the posted-write data from the volatile memory to the non-volatile memory when main power fails, during which time capacitors provide power to the memory controller, volatile memory, and non-volatile memory, but not to the CPU, in order to reduce the energy storage requirements of the capacitors. During main power provision, the CPU programs the memory controller with information needed to perform the flush operation, such as the location and size of the posted-write data in the volatile memory and various flush operation characteristics.

Owner:DOT HILL SYST

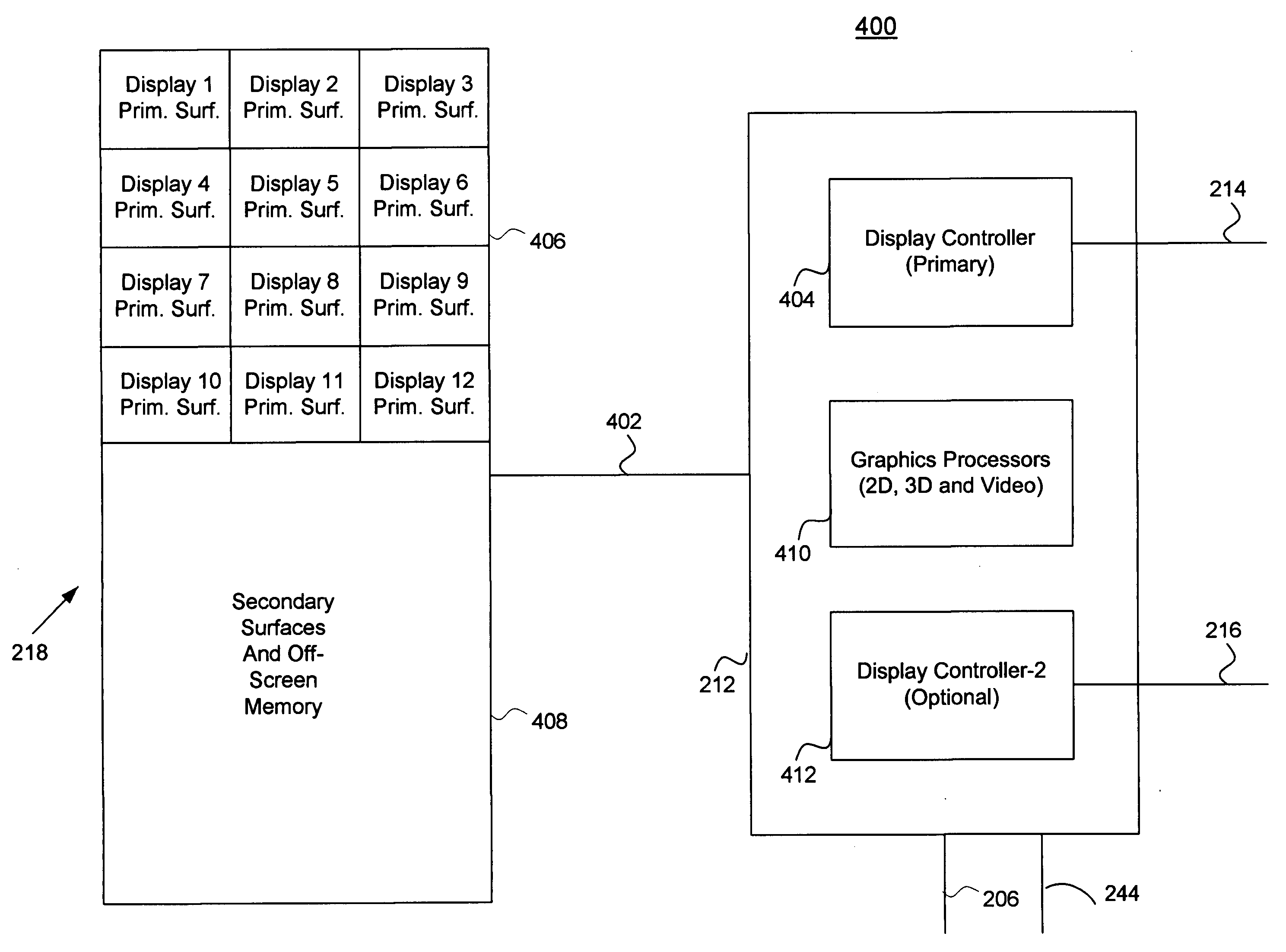

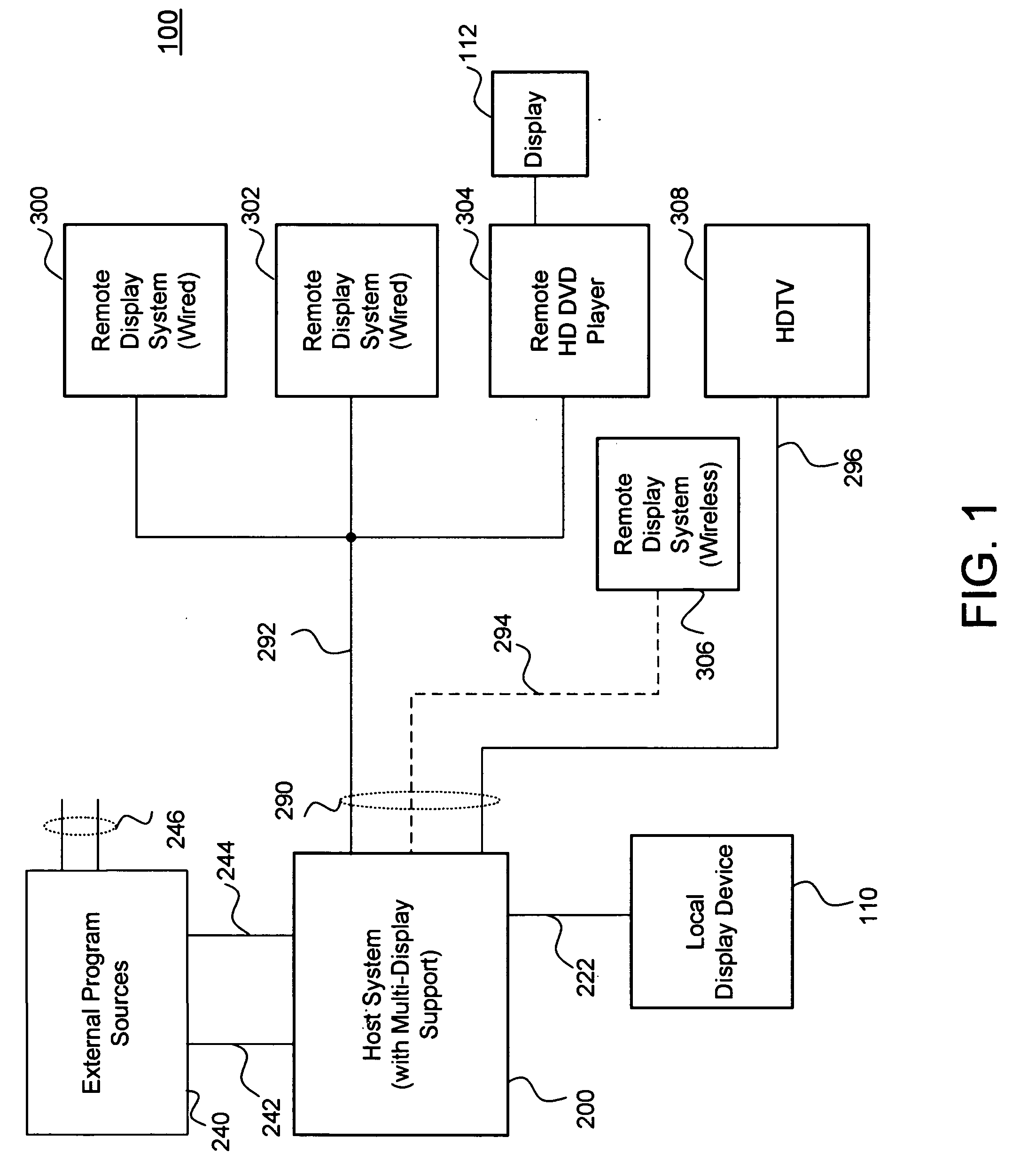

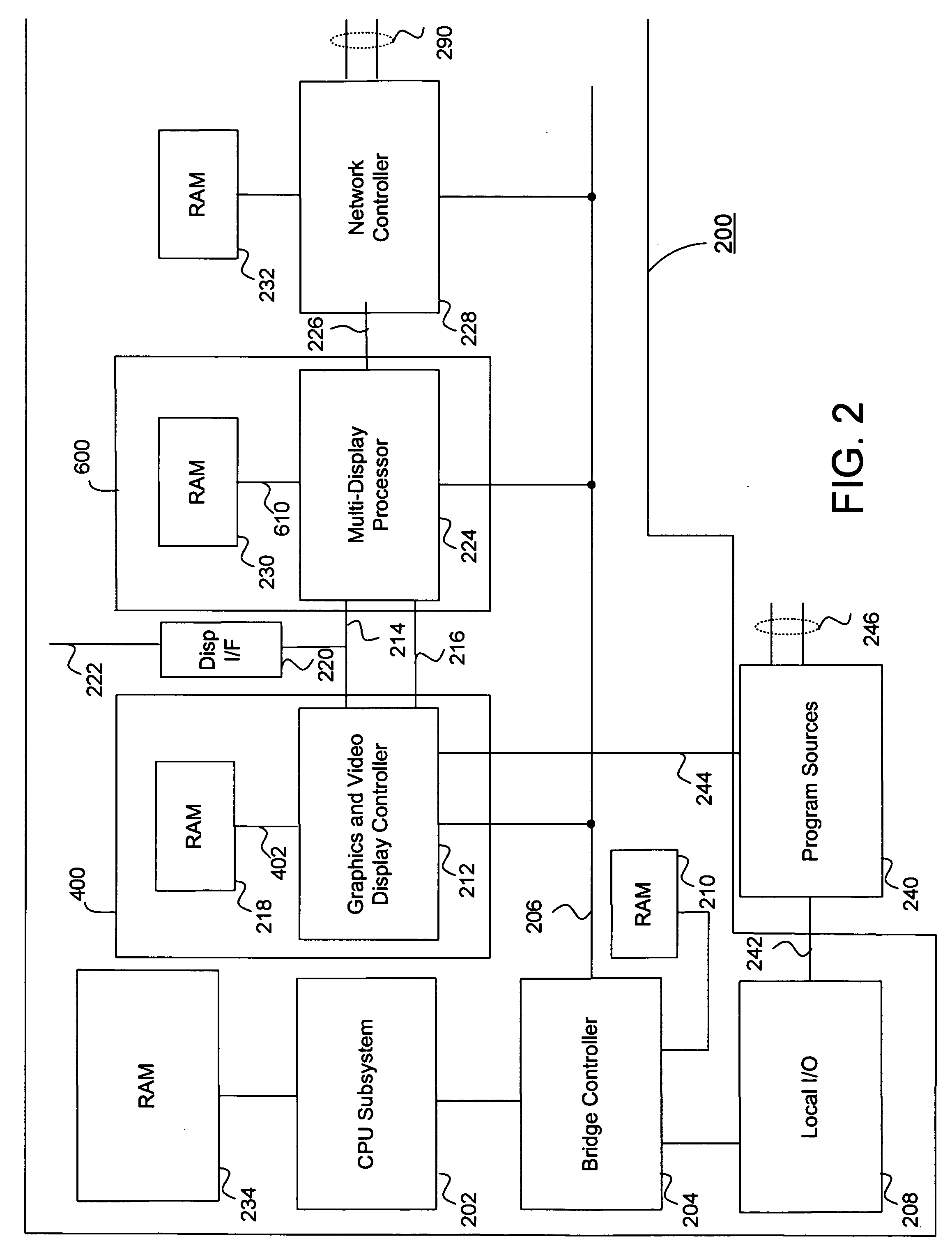

Multiple remote display system

InactiveUS20060282855A1Lower latencyGood frame rateTelevision system detailsColor television detailsGraphicsInternet traffic

A multi-display system includes a host system that supports both graphics and video based frames for multiple remote displays, multiple users or a combination of the two. For each display and for each frame, a multi-display processor responsively manages each necessary aspect of the remote display frame. The necessary portions of the remote display frame are further processed, encoded and where necessary, transmitted over a network to the remote display for each user. In some embodiments, the host system manages a remote desktop protocol and can still transmit encoded video or encoded frame information where the encoded video may be generated within the host system or provided from an external program source. Embodiments integrate the multi-display processor with either the video decoder unit, graphics processing unit, network controller, main memory controller, or any combination thereof The encoding process is optimized for network traffic and attention is paid to assure that all users have low latency interactive capabilities.

Owner:III HLDG 1

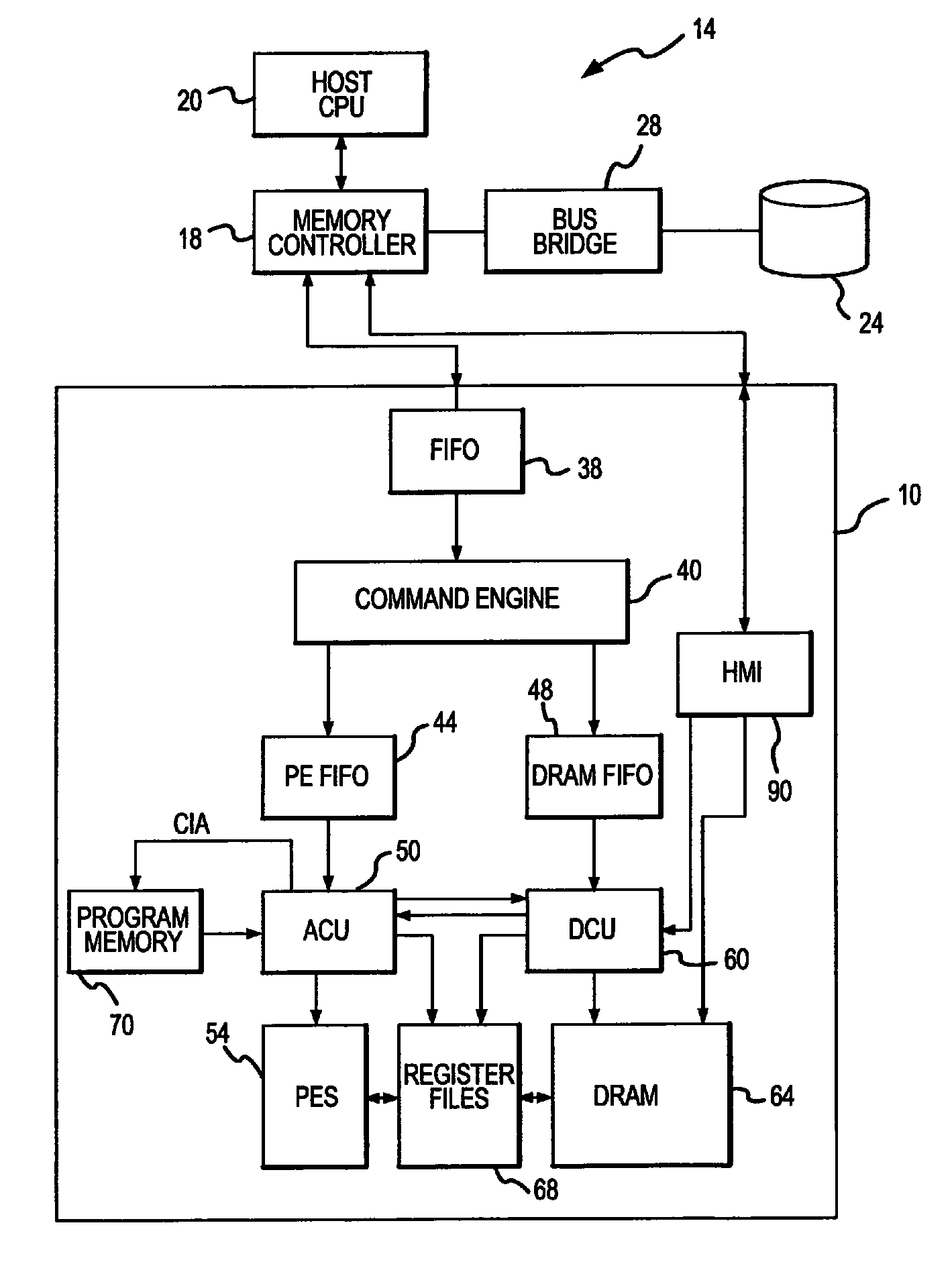

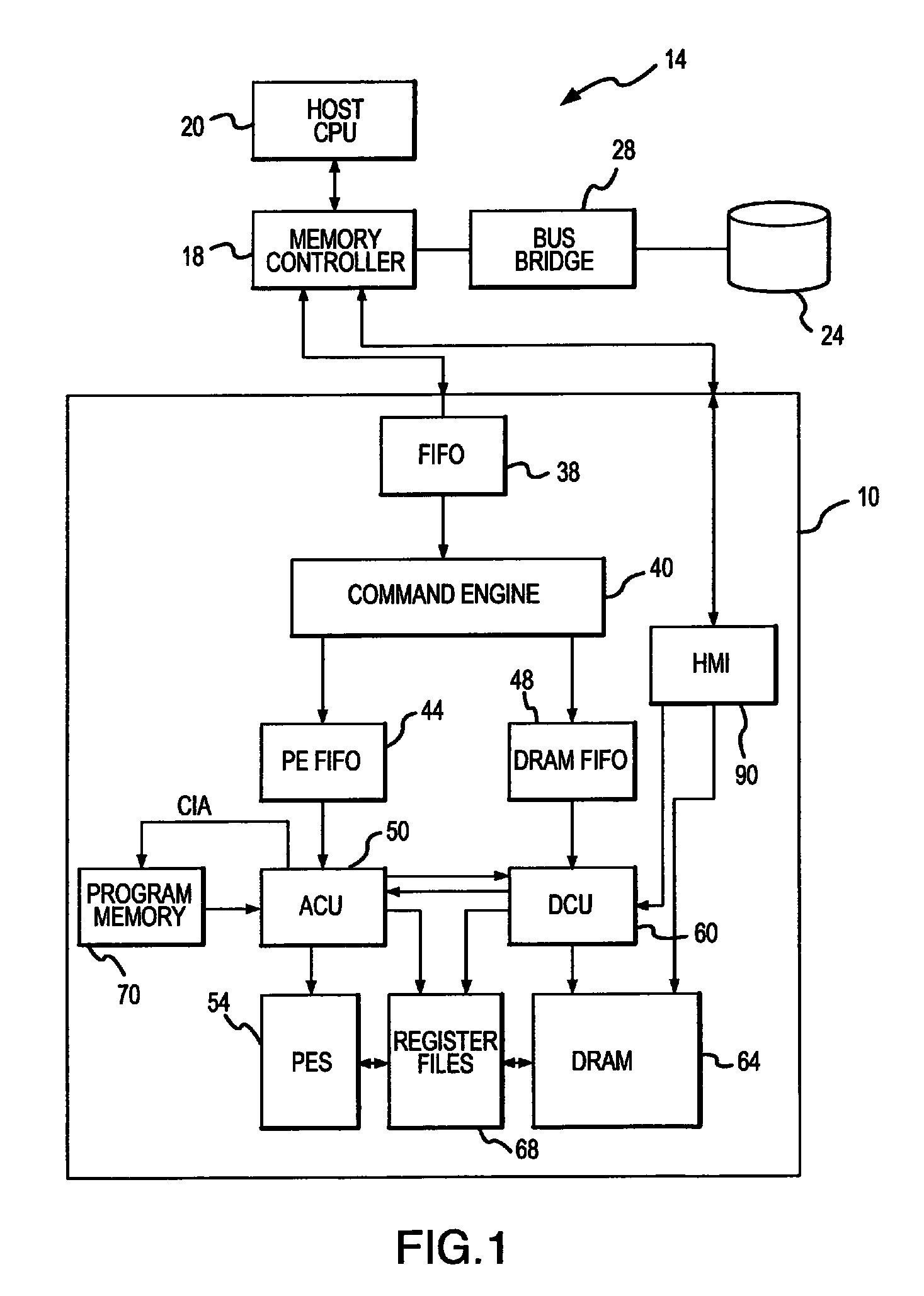

Active memory data compression system and method

ActiveUS9015390B2Concurrent instruction executionArchitecture with single central processing unitMass storageData compression

An integrated circuit active memory device receives task commands from a component in a host computer system that may include the active memory device. The host system includes a memory controller coupling the active memory device to a host CPU and a mass storage device. The active memory device includes a command engine issuing instructions responsive to the task commands to either an array control unit or a DRAM control unit. The instructions provided to the DRAM control unit cause data to be written to or read from a DRAM and coupled to or from either the processing elements or a host / memory interface. The processing elements execute instructions provided by the array control unit to decompress data written to the DRAM through the host / memory interface and compress data read from the DRAM through the host / memory interface.

Owner:MICRON TECH INC

Programmable logic device with ferroelectric configuration memories

InactiveUS6924663B2Increase the effective amountEfficient architectureDigital storageInternal/peripheral component protectionElectricityData stream

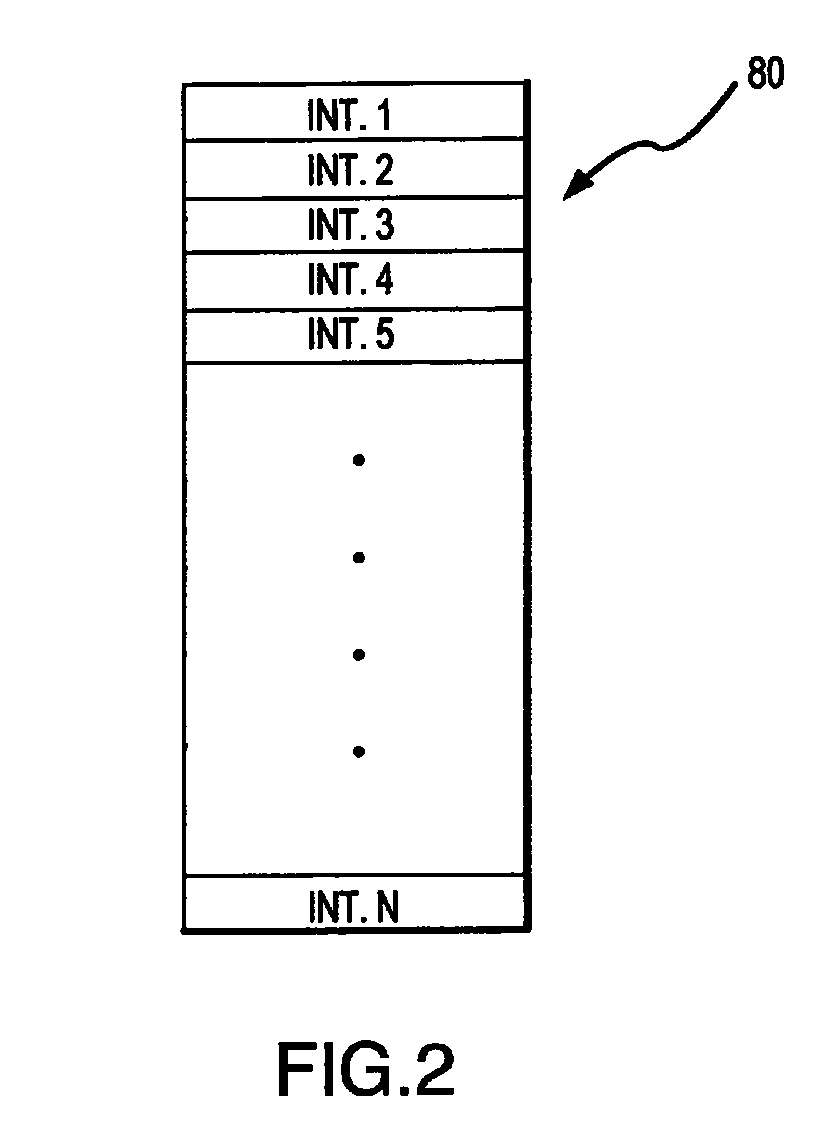

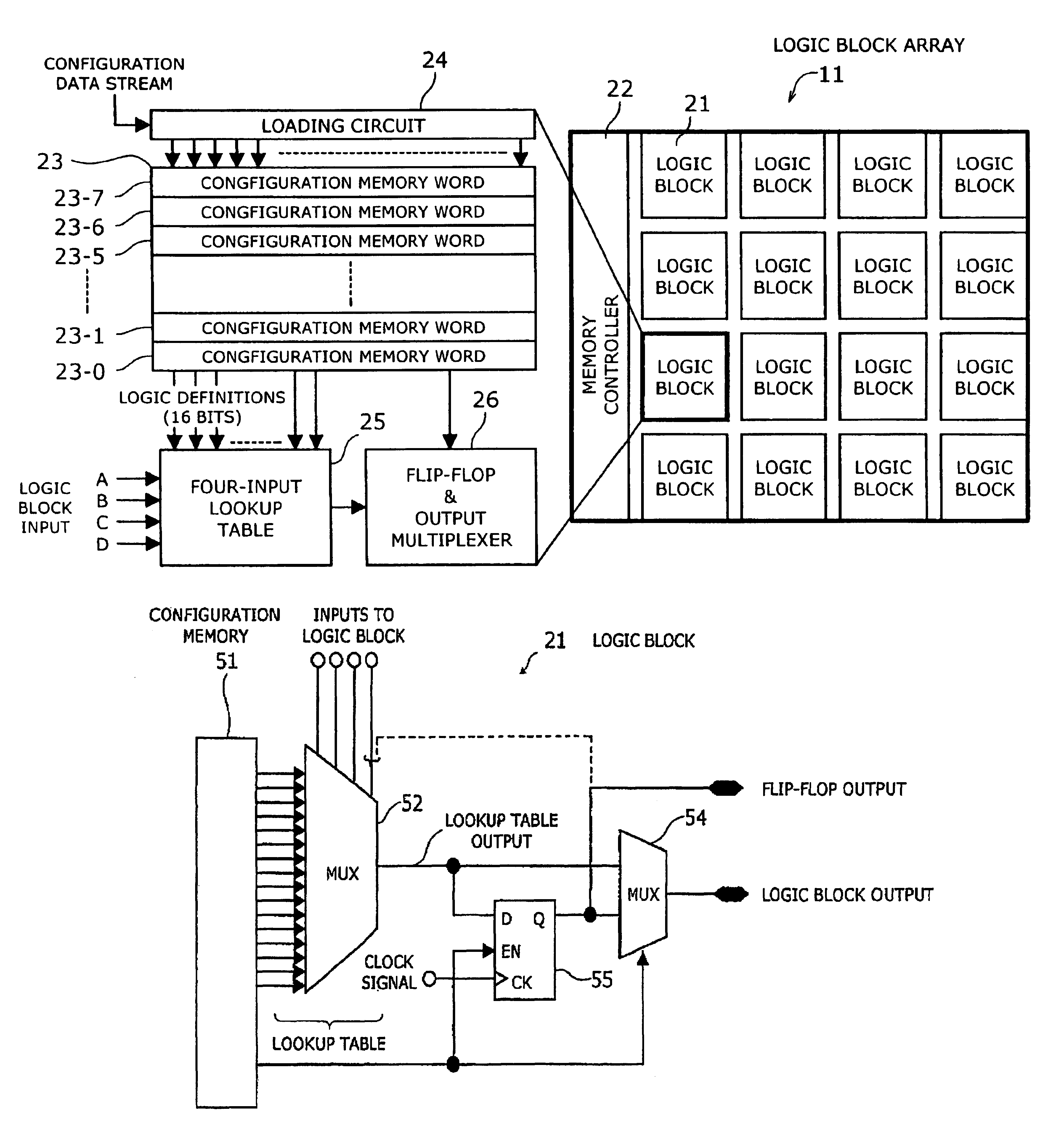

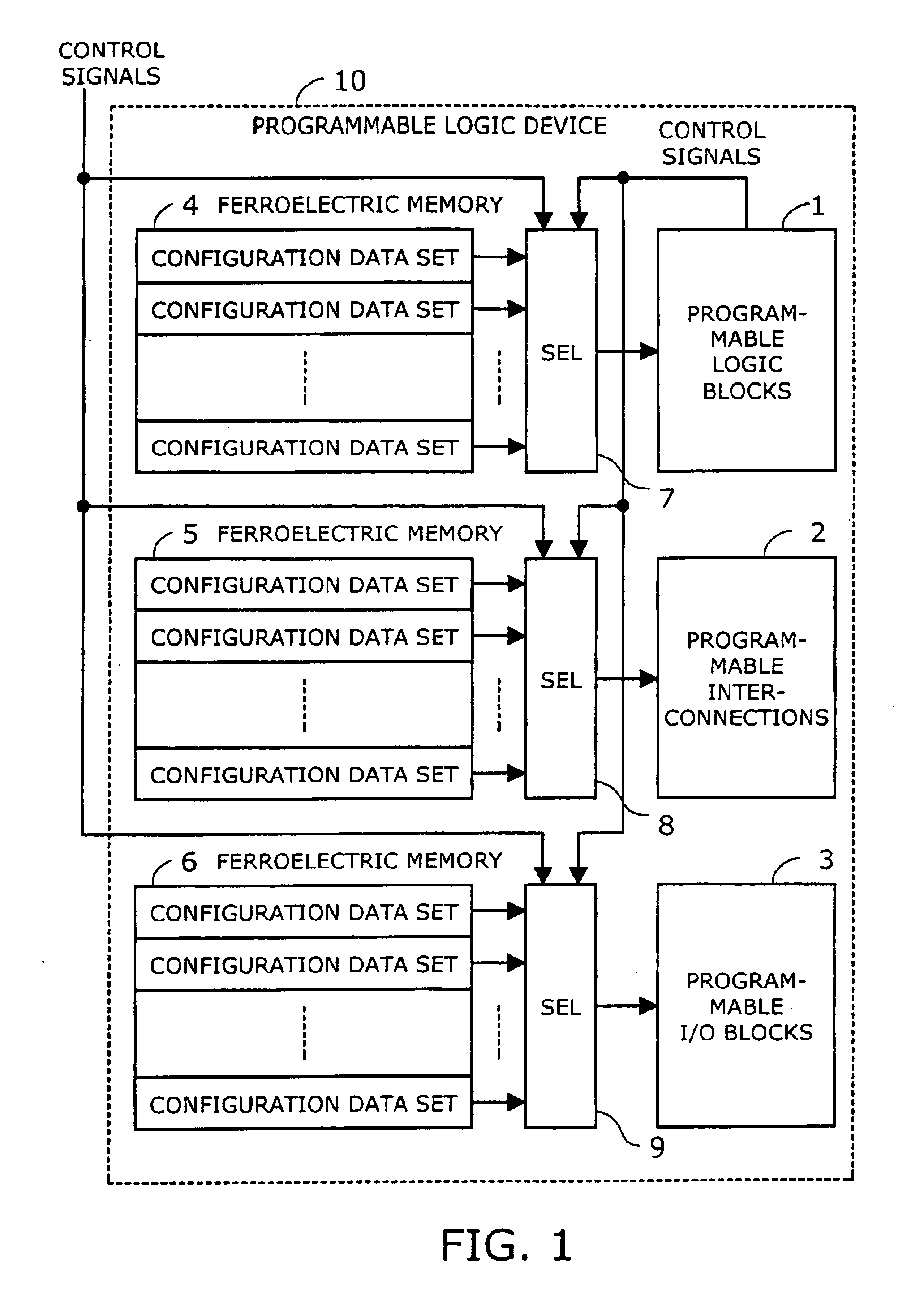

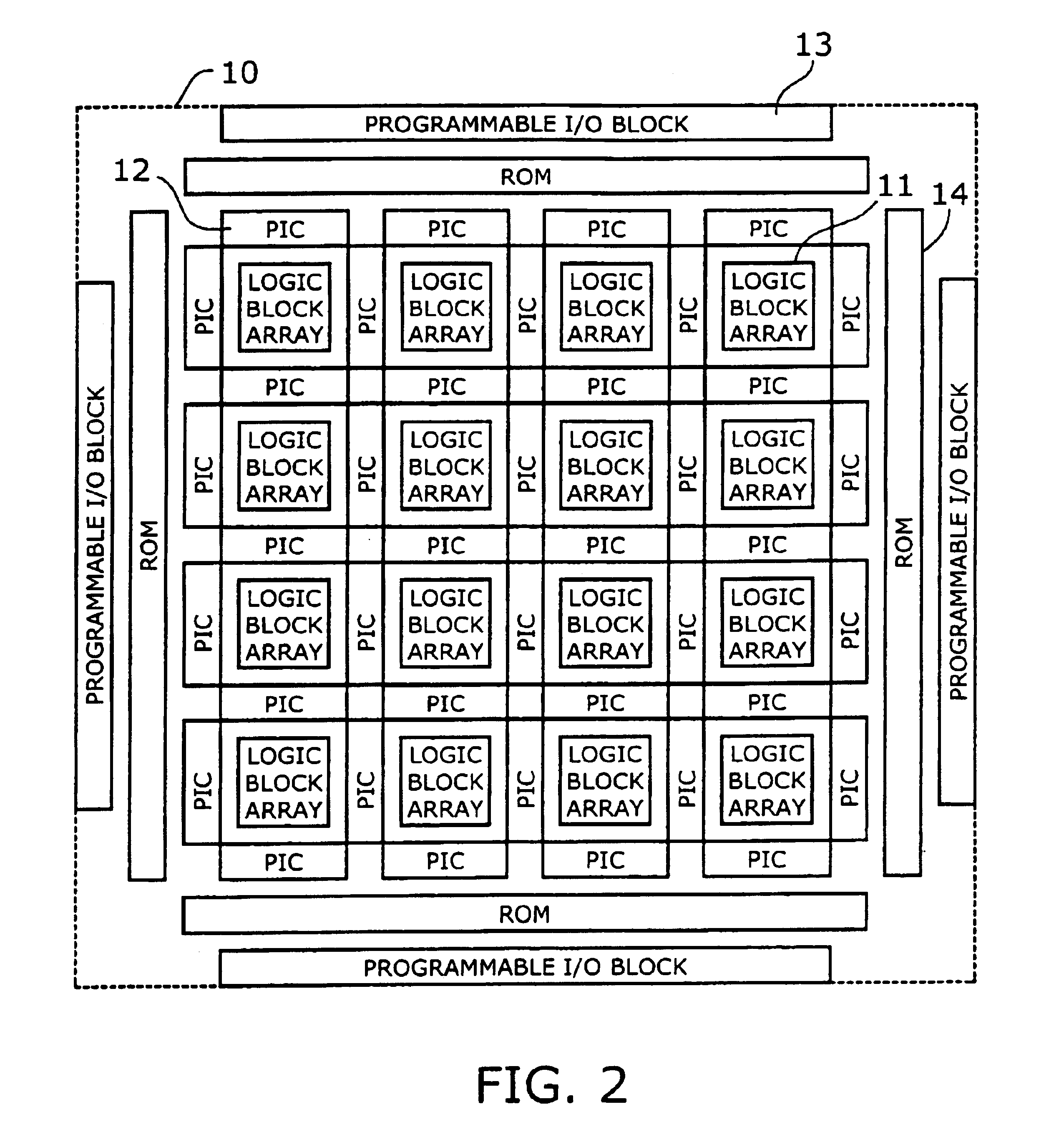

A programmable logic device with ferroelectric configuration memories storing multiple configuration data sets. The device has programmable logic blocks, interconnections, and I / O blocks to provide desired logic functions. Those building blocks can be dynamically reconfigured by changing the selection of configuration data stored in the device's integral configuration memories. The configuration memories are divided into groups, so that they can be loaded concurrently with multiple configuration data streams. To protect the content of configuration memories from unauthorized access, the device employs an authentication mechanism that uses security IDs stored in the configuration memories. The device has a memory controller to provide an appropriate power supply sequence for ferroelectric memory cells to ensure the reliable data retention when the device is powered up or shut down.

Owner:FUJITSU SEMICON LTD

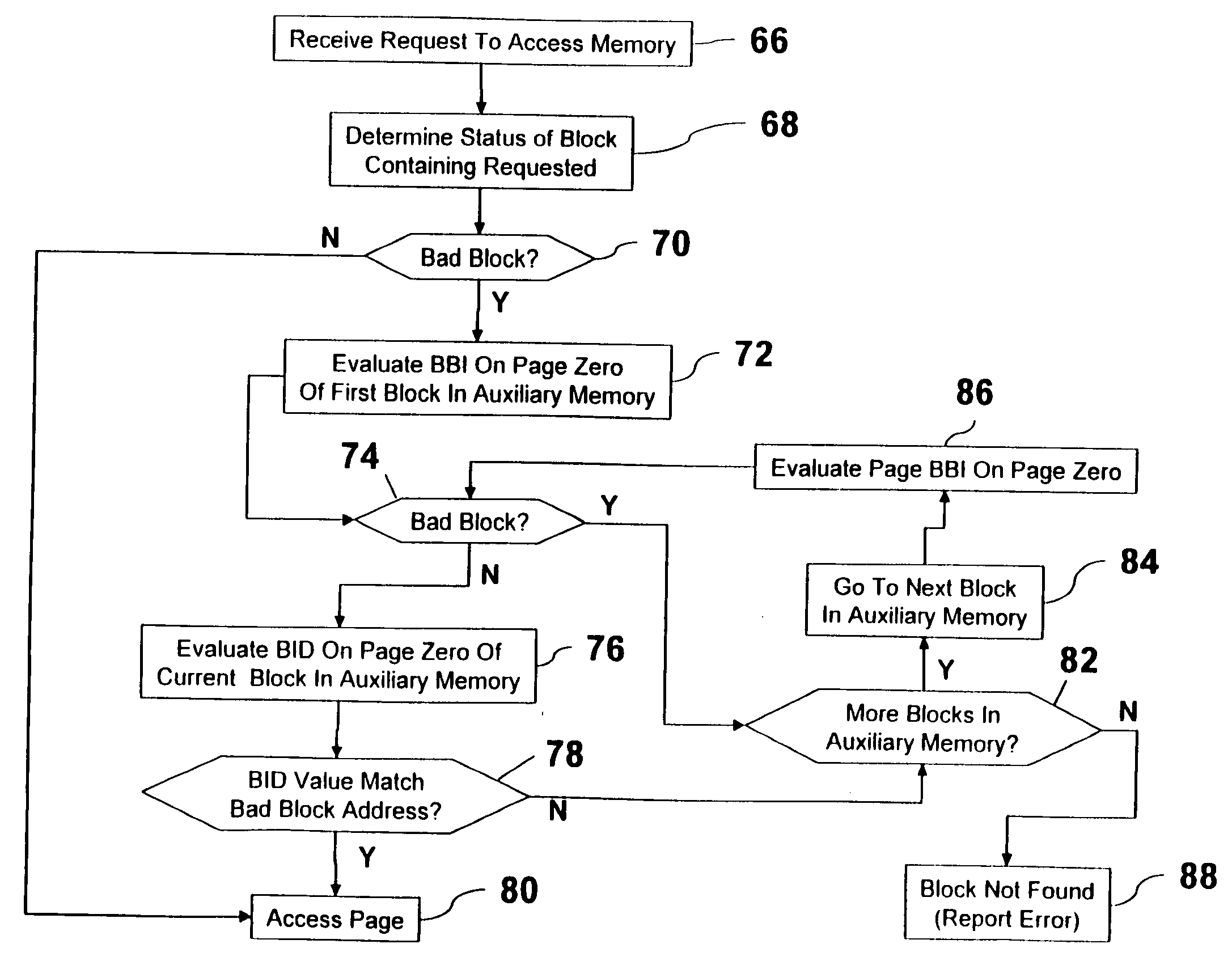

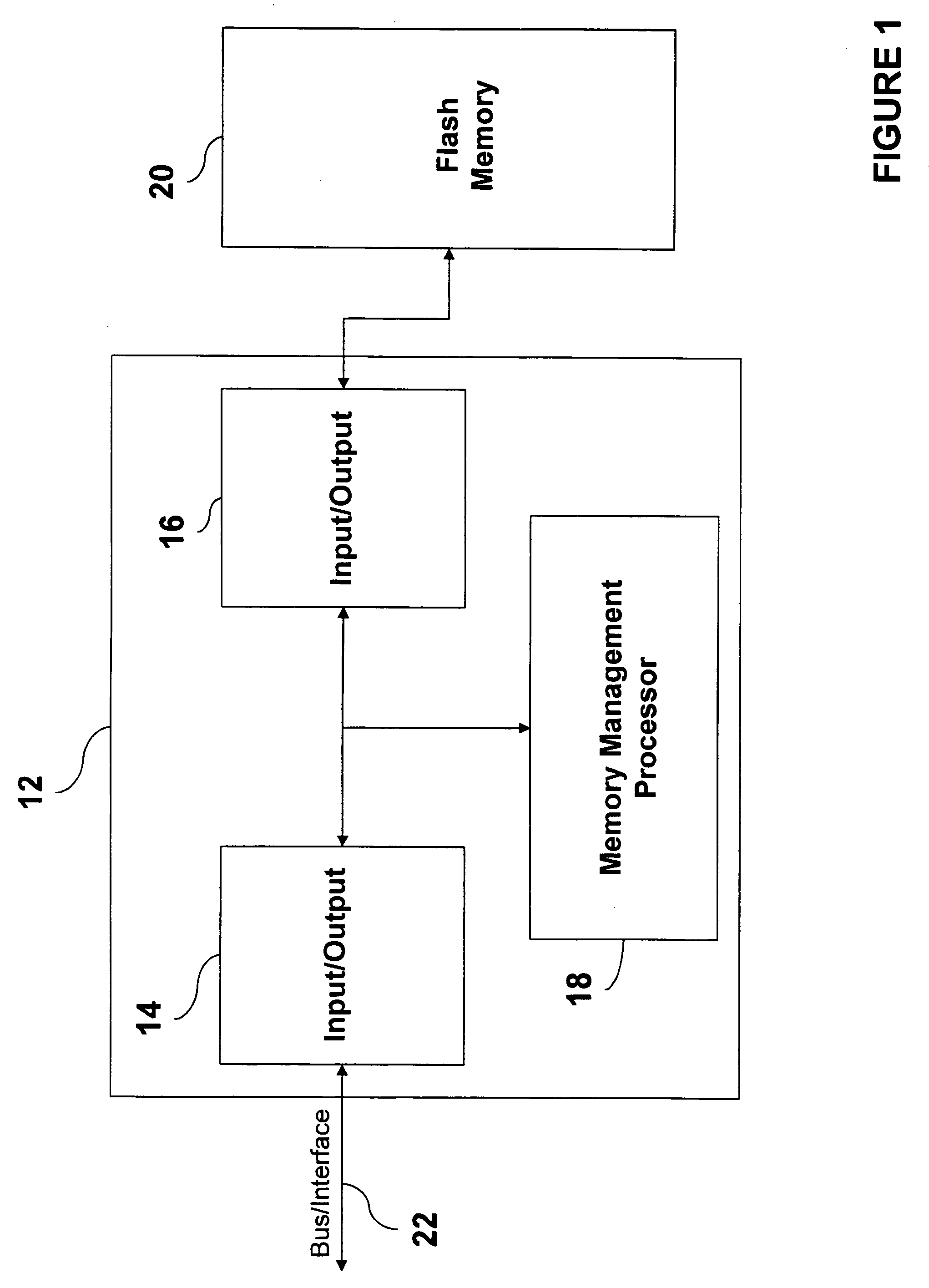

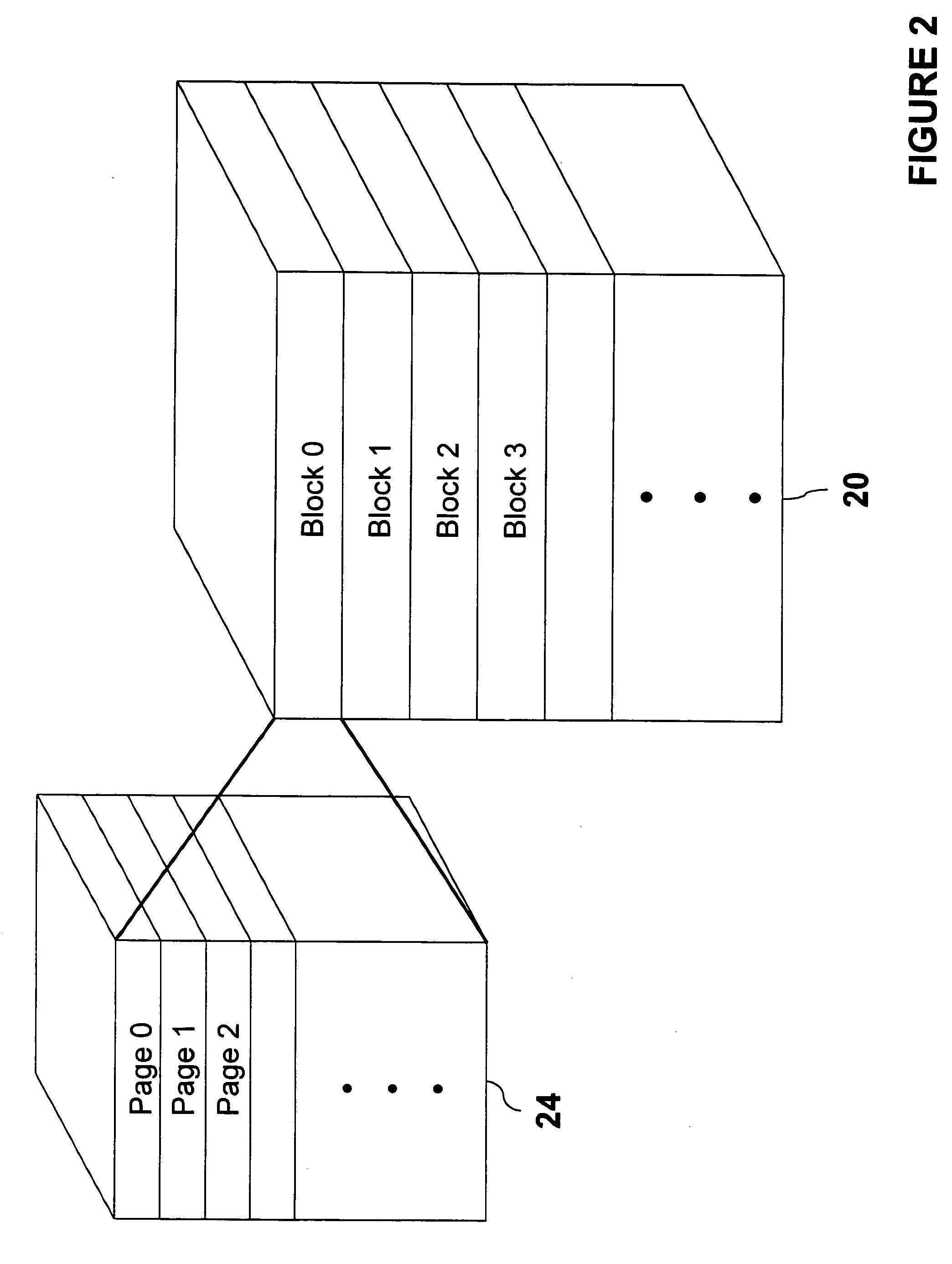

NAND flash memory management

A memory controller is utilized to overcome NAND flash memory's propensity for comprising bad blocks of memory. The memory controller utilizes minimal hardware and is essentially transparent to a device requesting access to the NAND memory. A NAND flash memory device is configured to comprise a set of main blocks of memory and a set of auxiliary blocks of memory. Each block is divided into pages of memory and each page includes metadata. The metadata includes a block status indicator, indicating whether a block is good or bad. When receiving a request to access a page in the NAND flash memory, if the block in which the page resides is good, that block is accessed. If the block is bad, auxiliary memory is searched until a block containing the address of the bad block in its metadata is found. The found block is accessed in lieu of the bad block.

Owner:MICROSOFT TECH LICENSING LLC

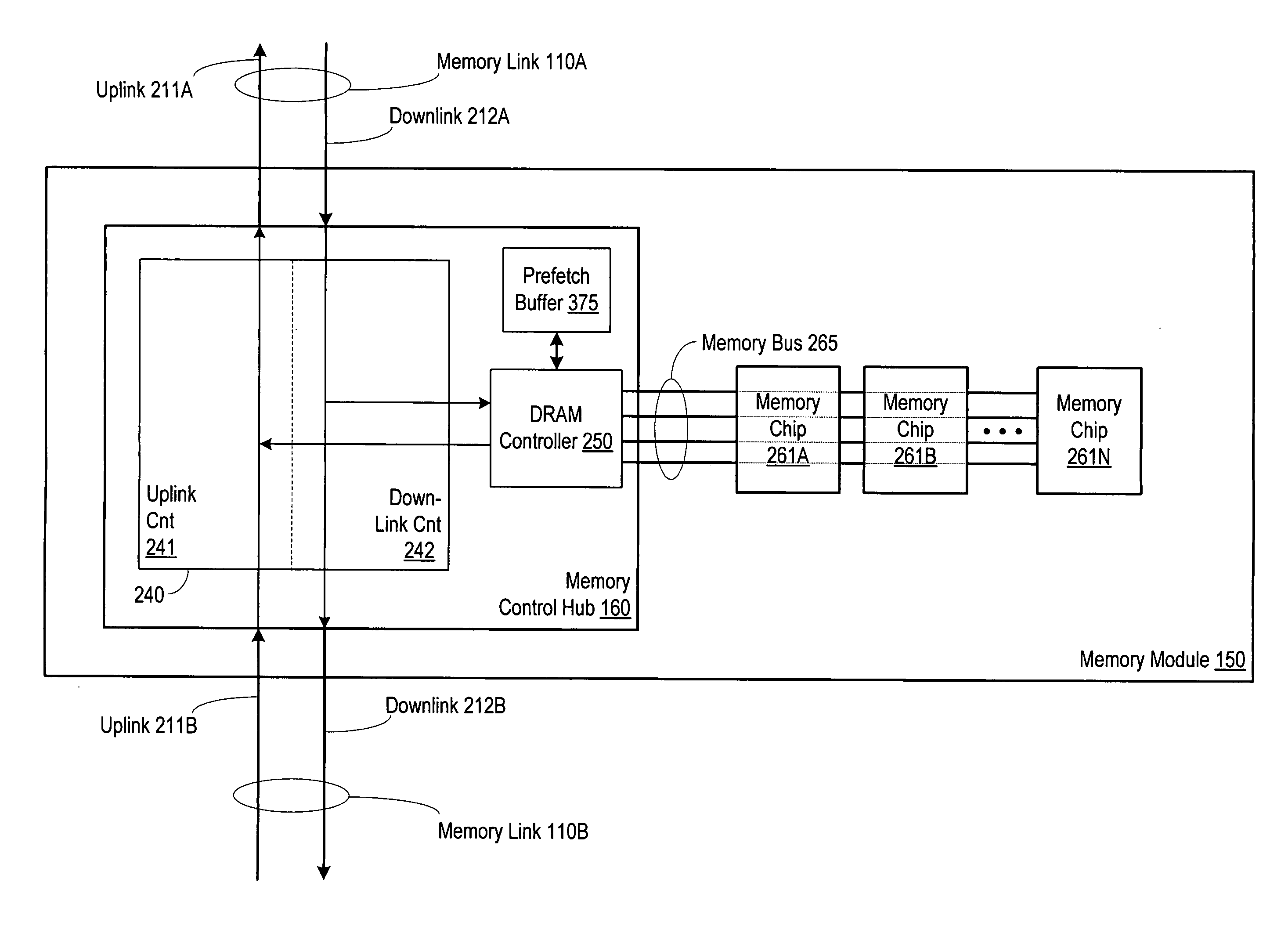

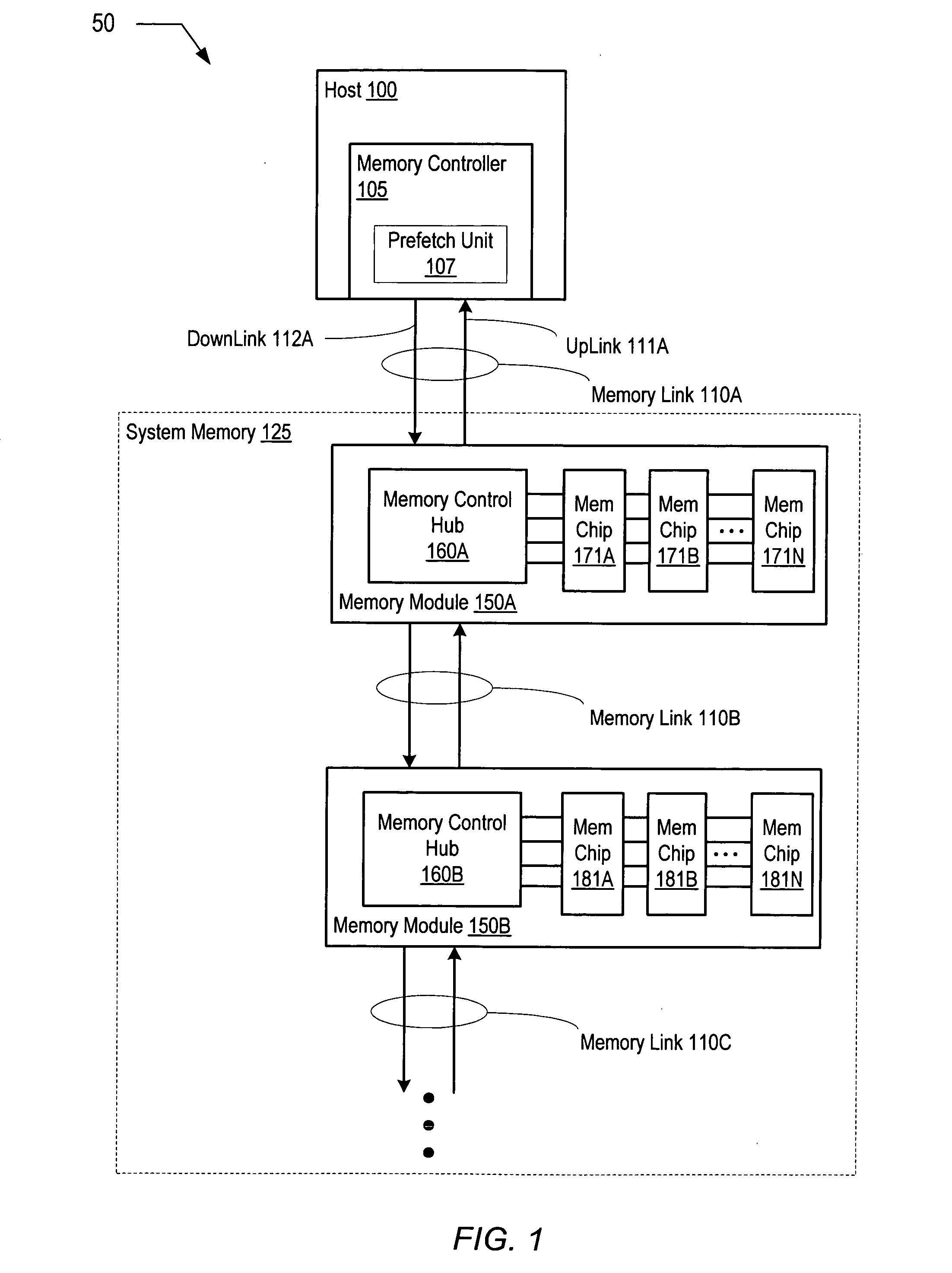

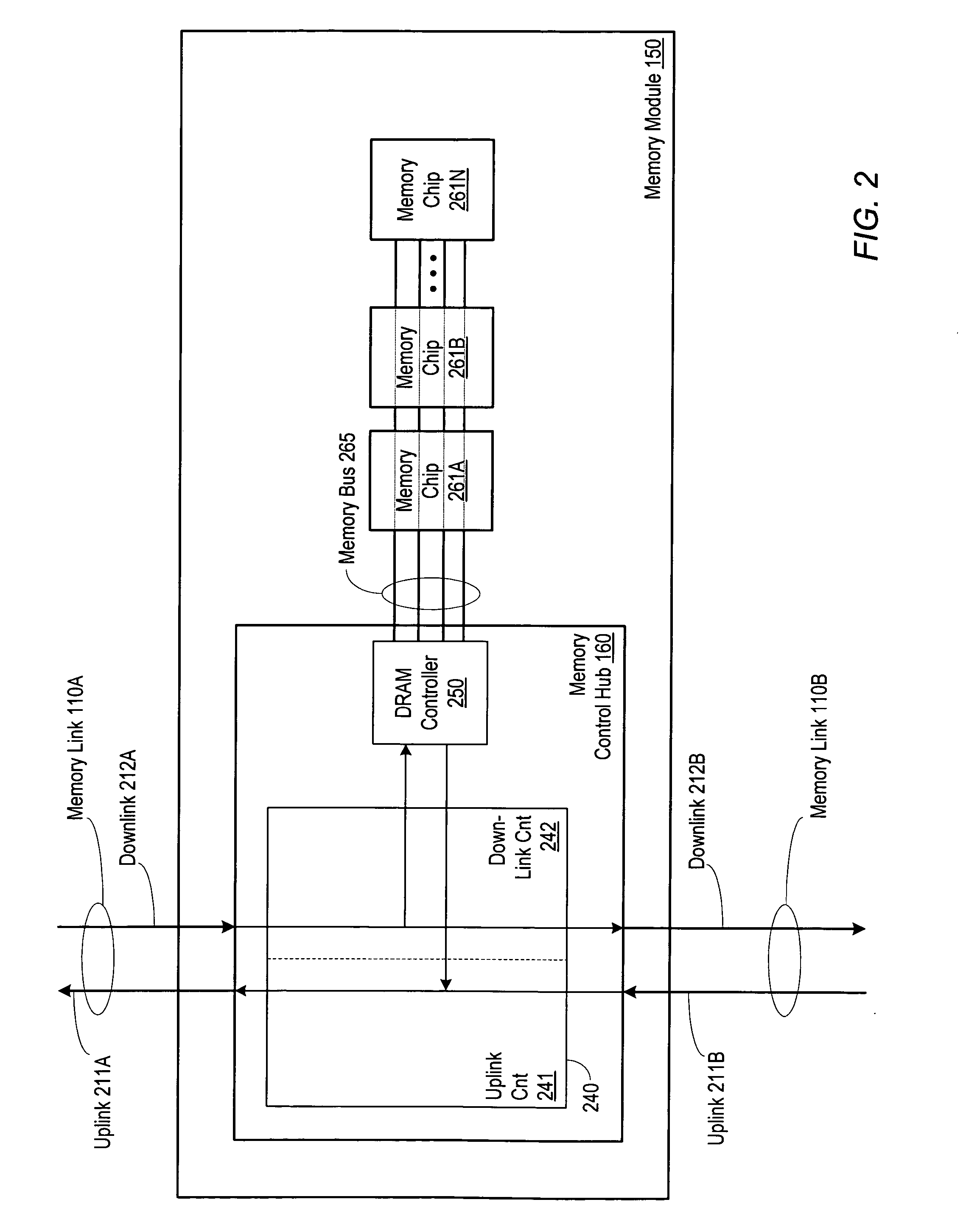

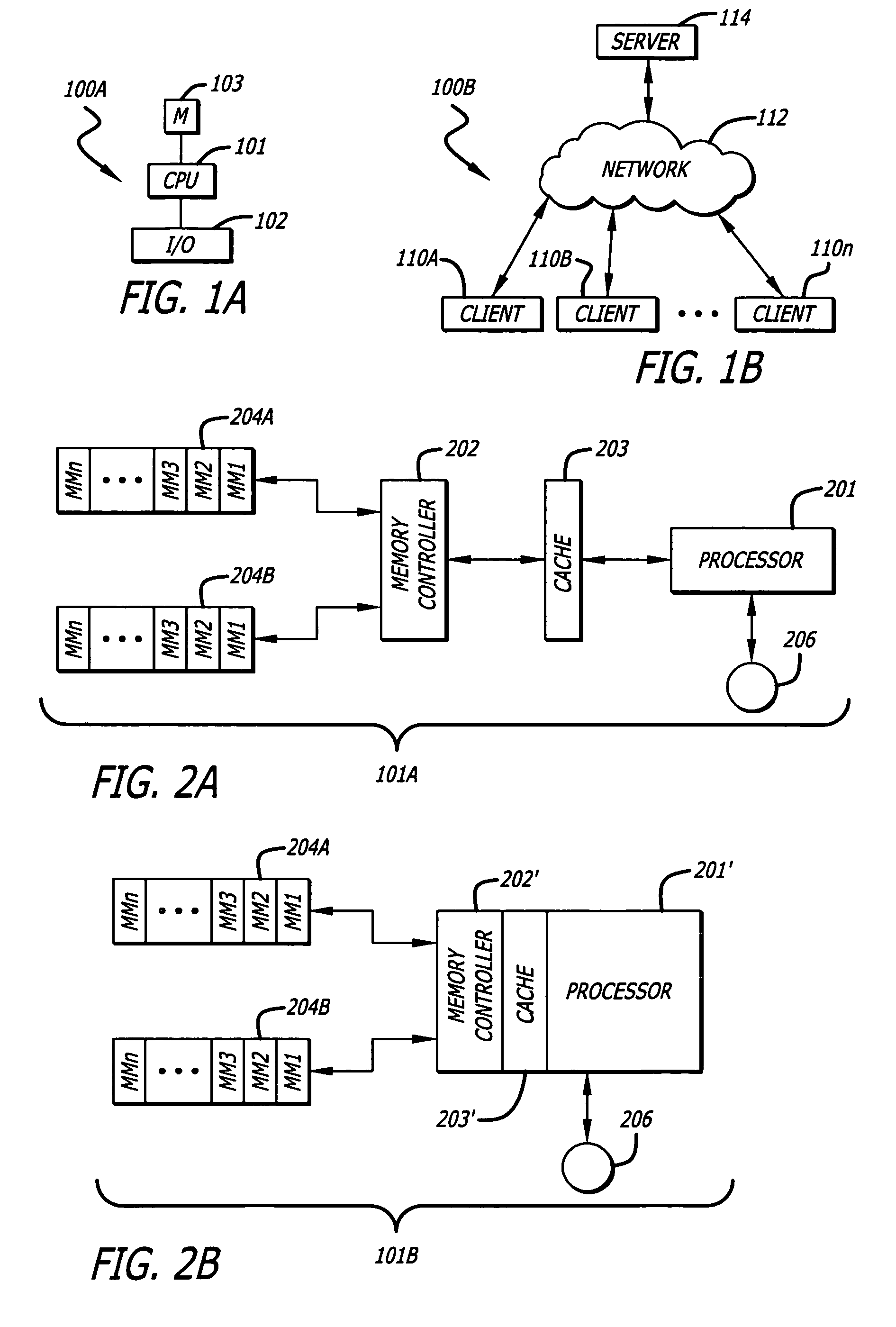

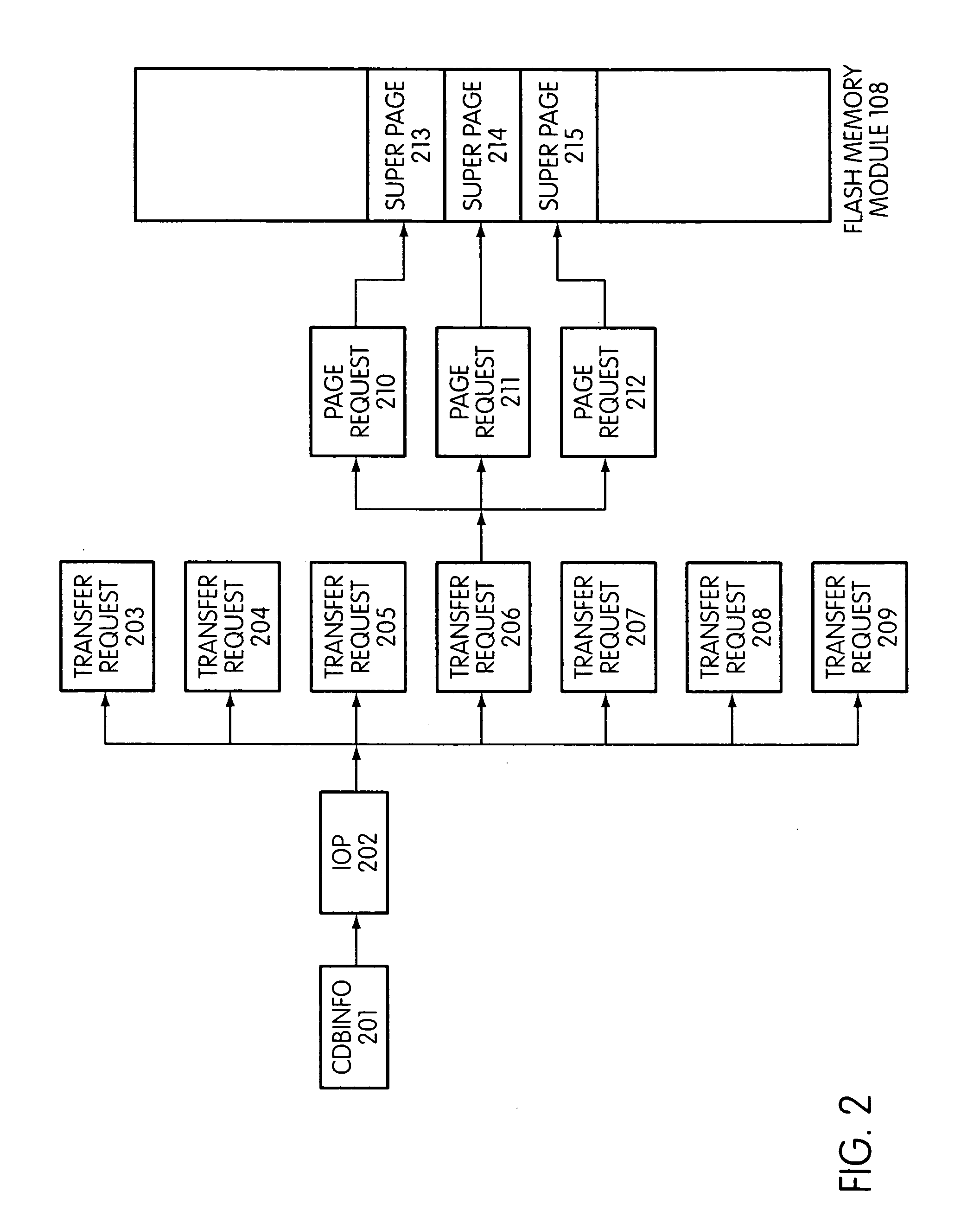

Prefetch mechanism for use in a system including a host connected to a plurality of memory modules via a serial memory interconnect

InactiveUS20050071542A1Memory architecture accessing/allocationStatic storageMemory controllerData storing

A system includes a host coupled to a serially connected chain of memory modules. In one embodiment, the host includes a memory controller that may be configured to issue a memory read request for data stored within the memory modules. The memory controller may further request that data be prefetched from the memory modules by encoding prefetch information within the memory read request. The memory controller may also be configured to issue a memory write request to write data to the memory modules and to selectively request that one or more pages of memory within a given one of the memory modules remain open by encoding the prefetch information within the memory write request.

Owner:ADVANCED MICRO DEVICES INC

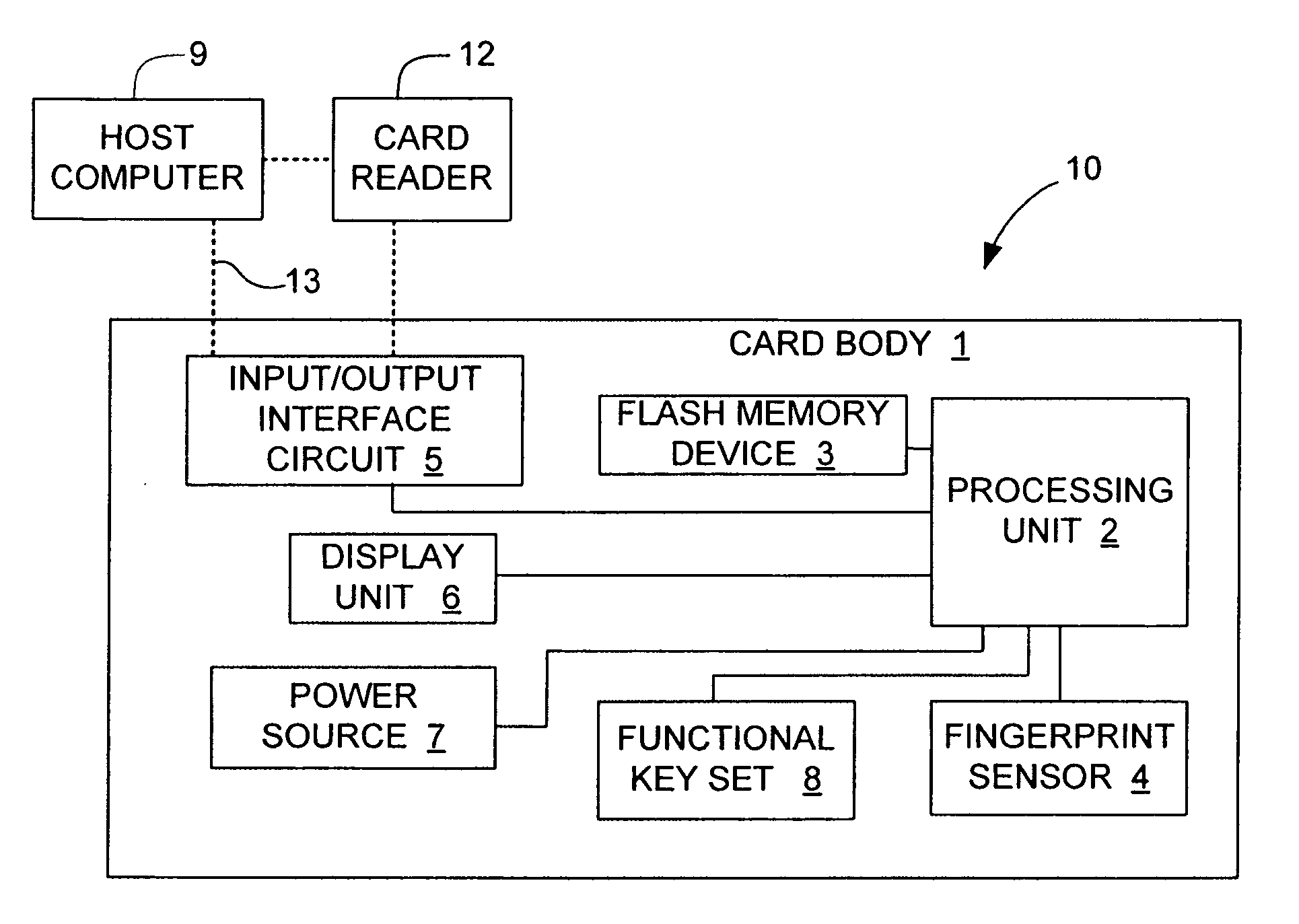

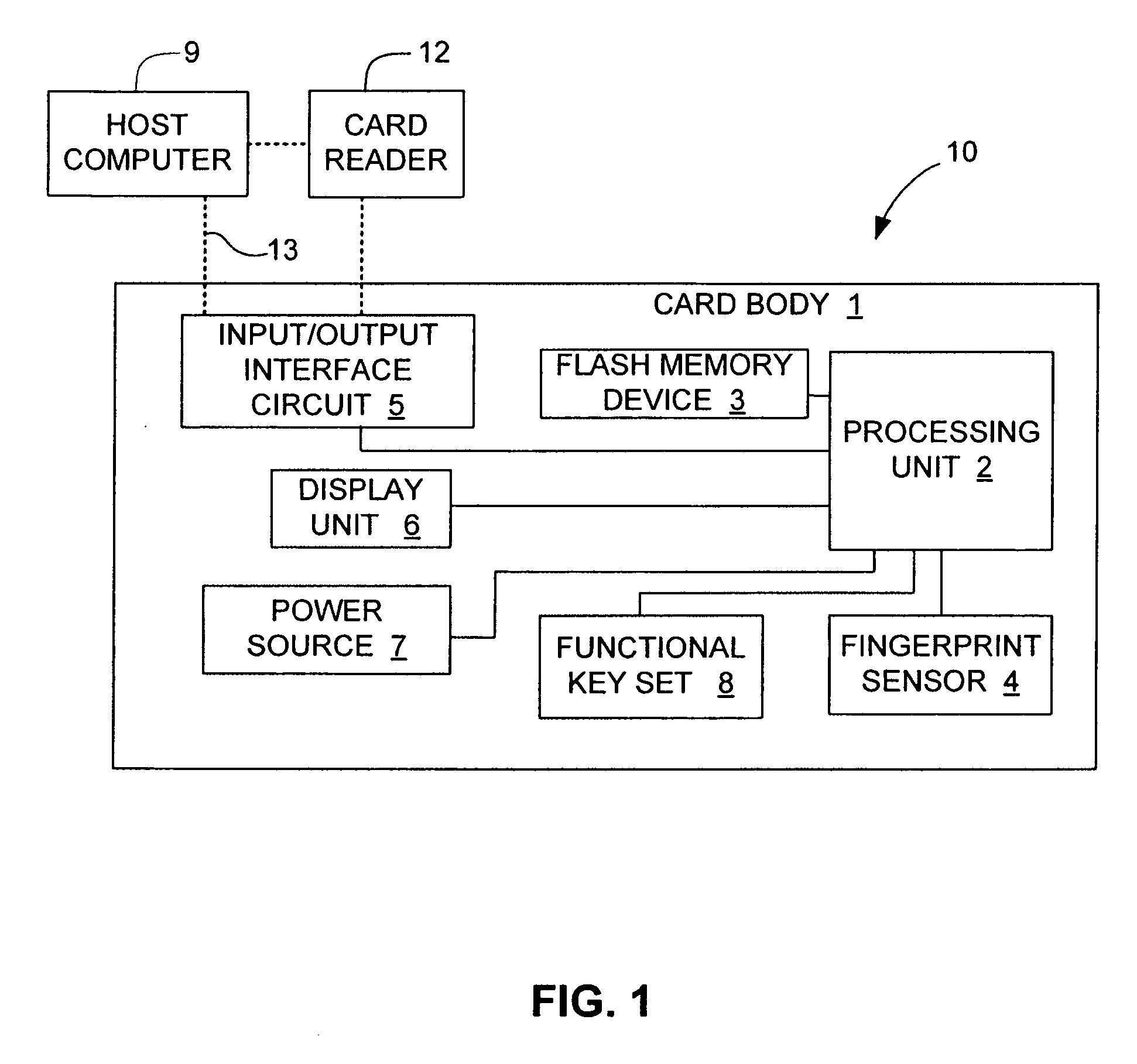

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

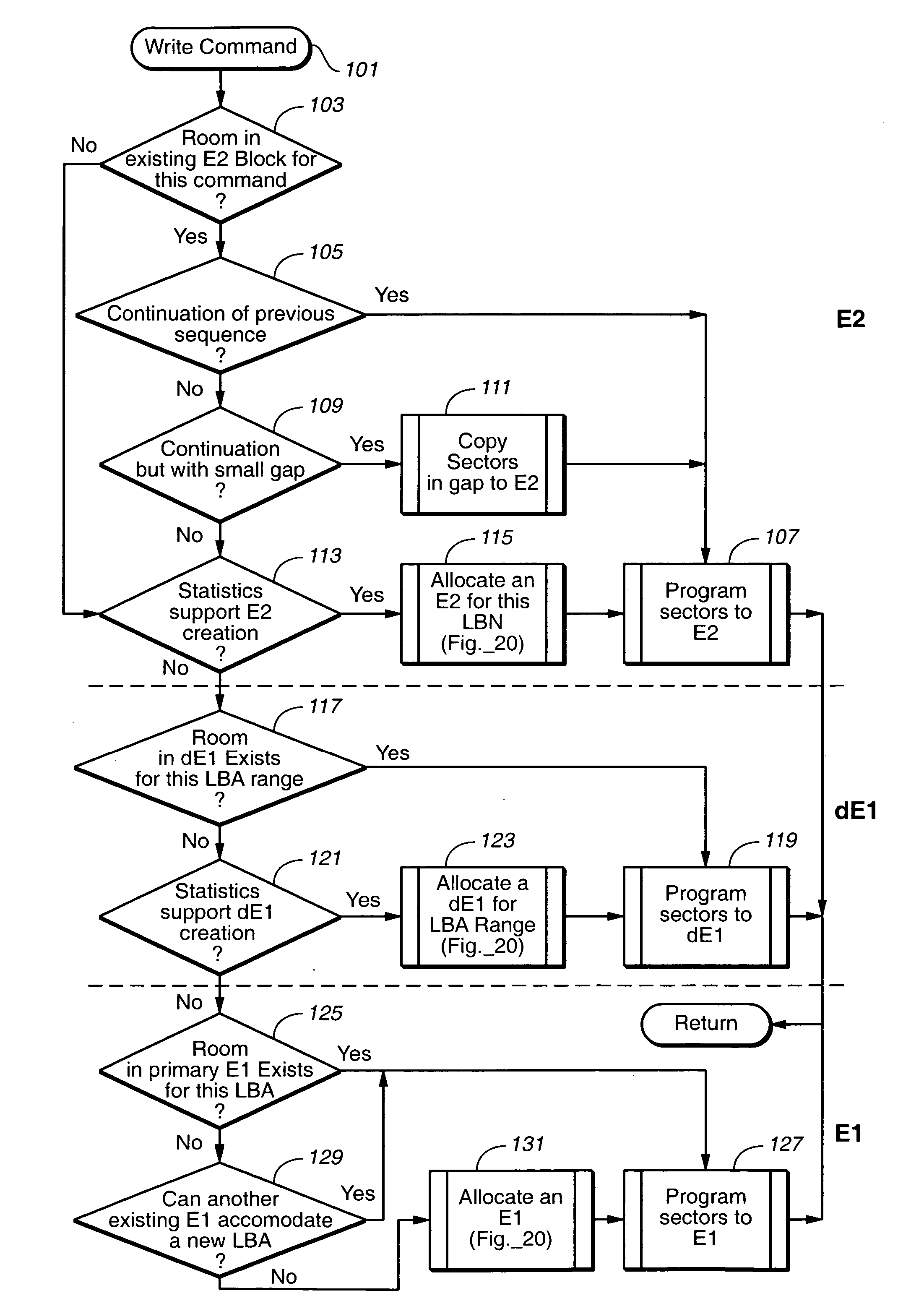

Management of non-volatile memory systems having large erase blocks

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

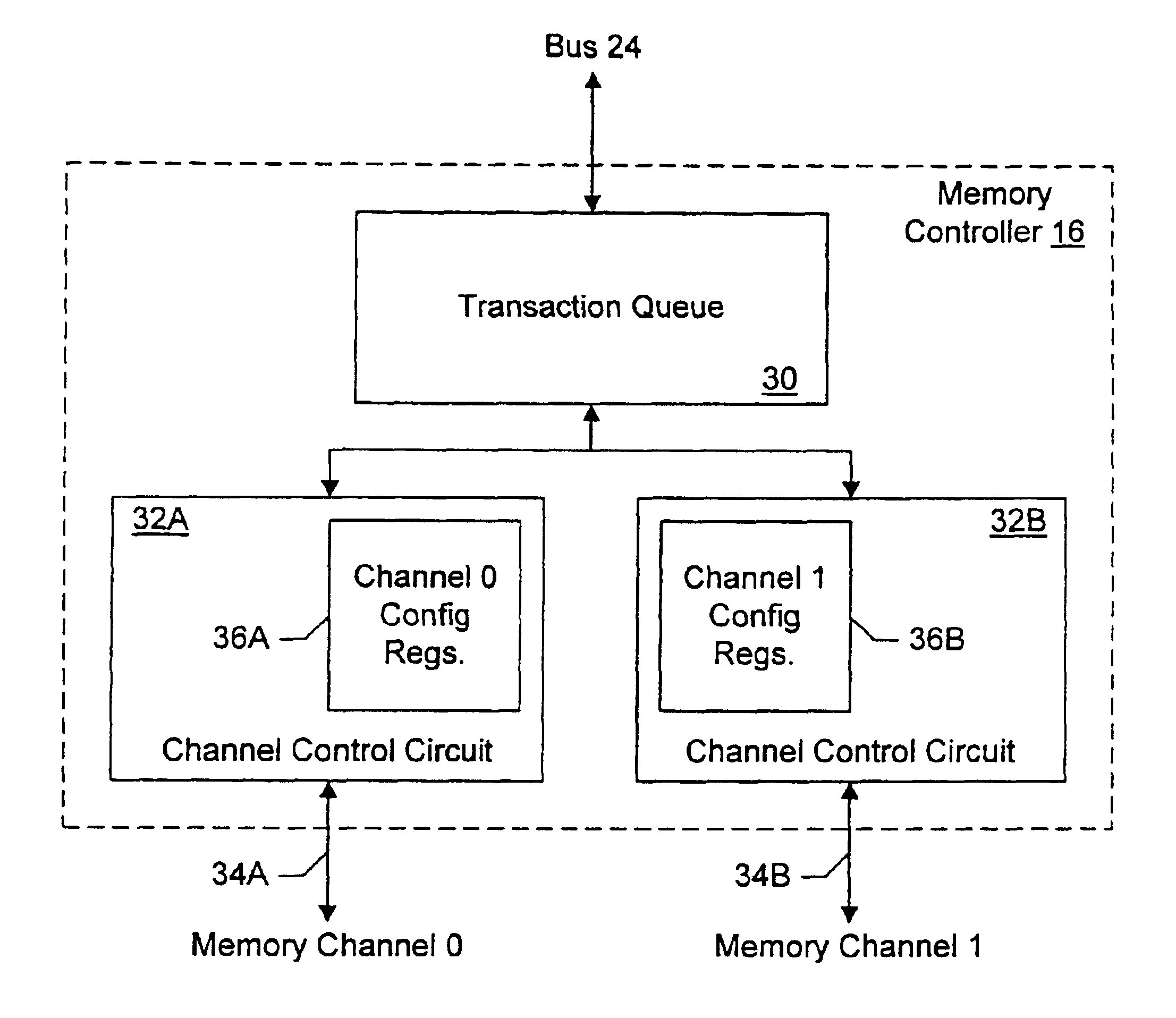

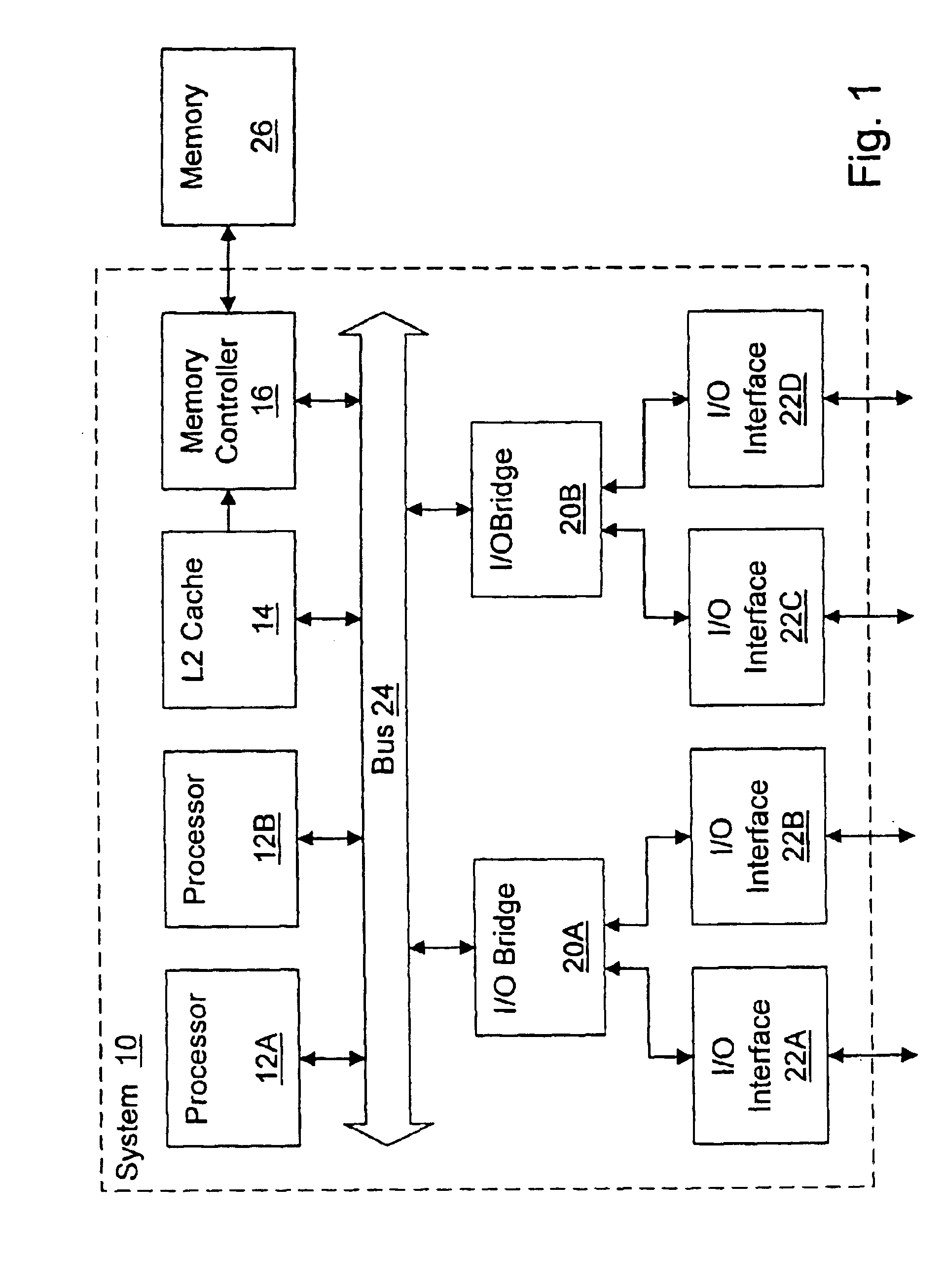

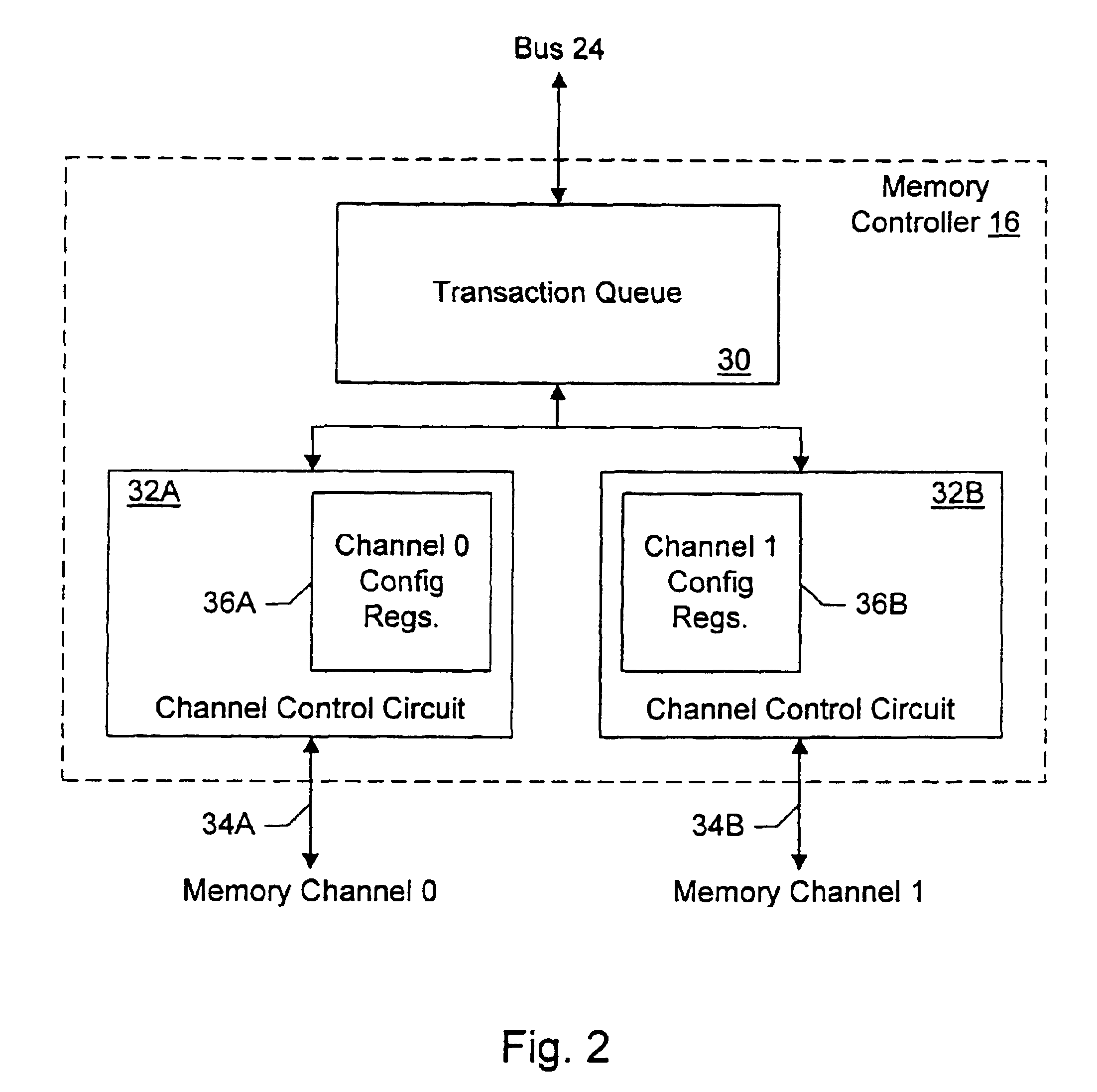

Memory controller with programmable configuration

InactiveUS6877076B1Flexible configurationOpen in timeMemory adressing/allocation/relocationMicro-instruction address formationProcessor registerParallel computing

Owner:AVAGO TECH INT SALES PTE LTD

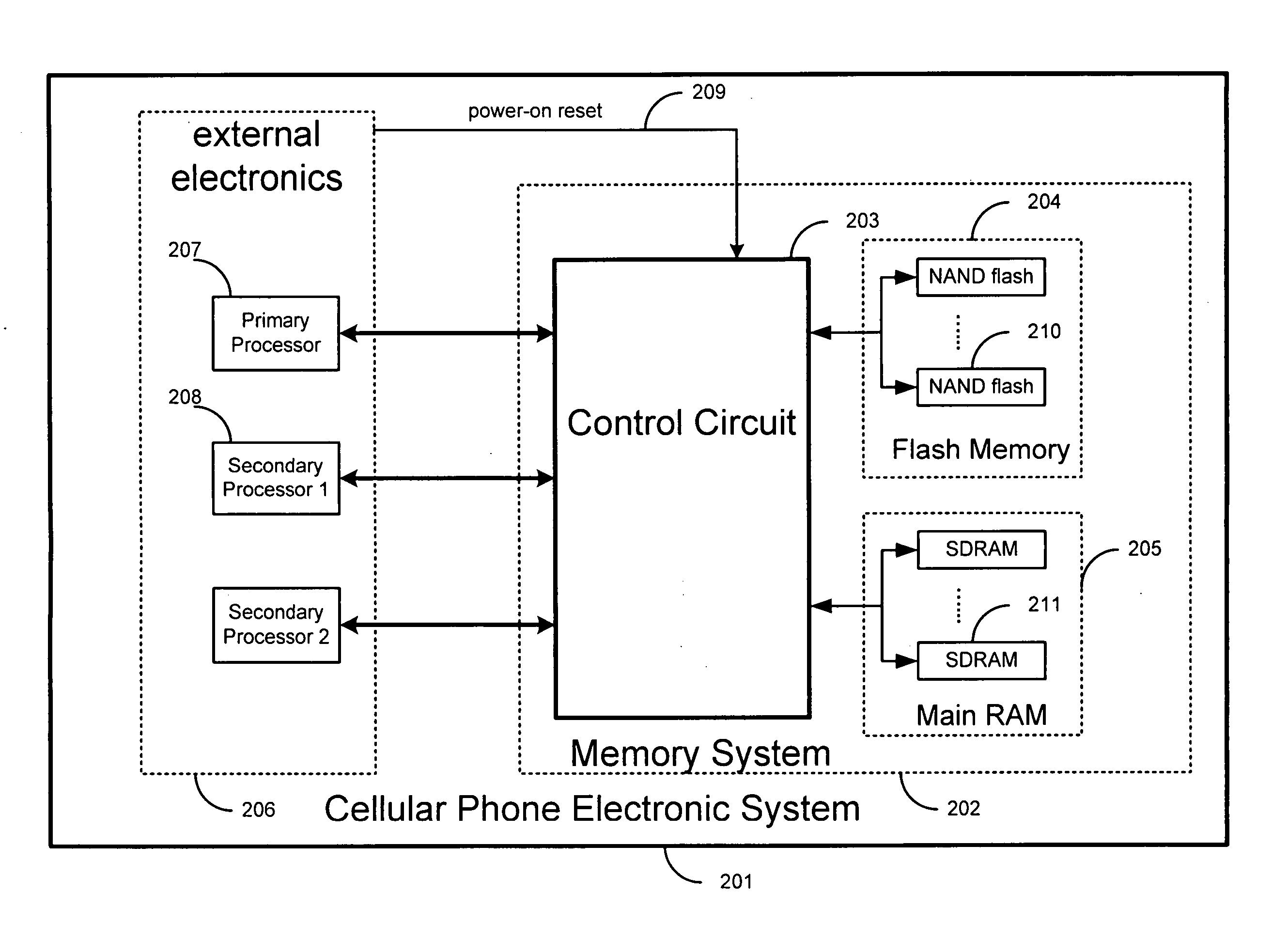

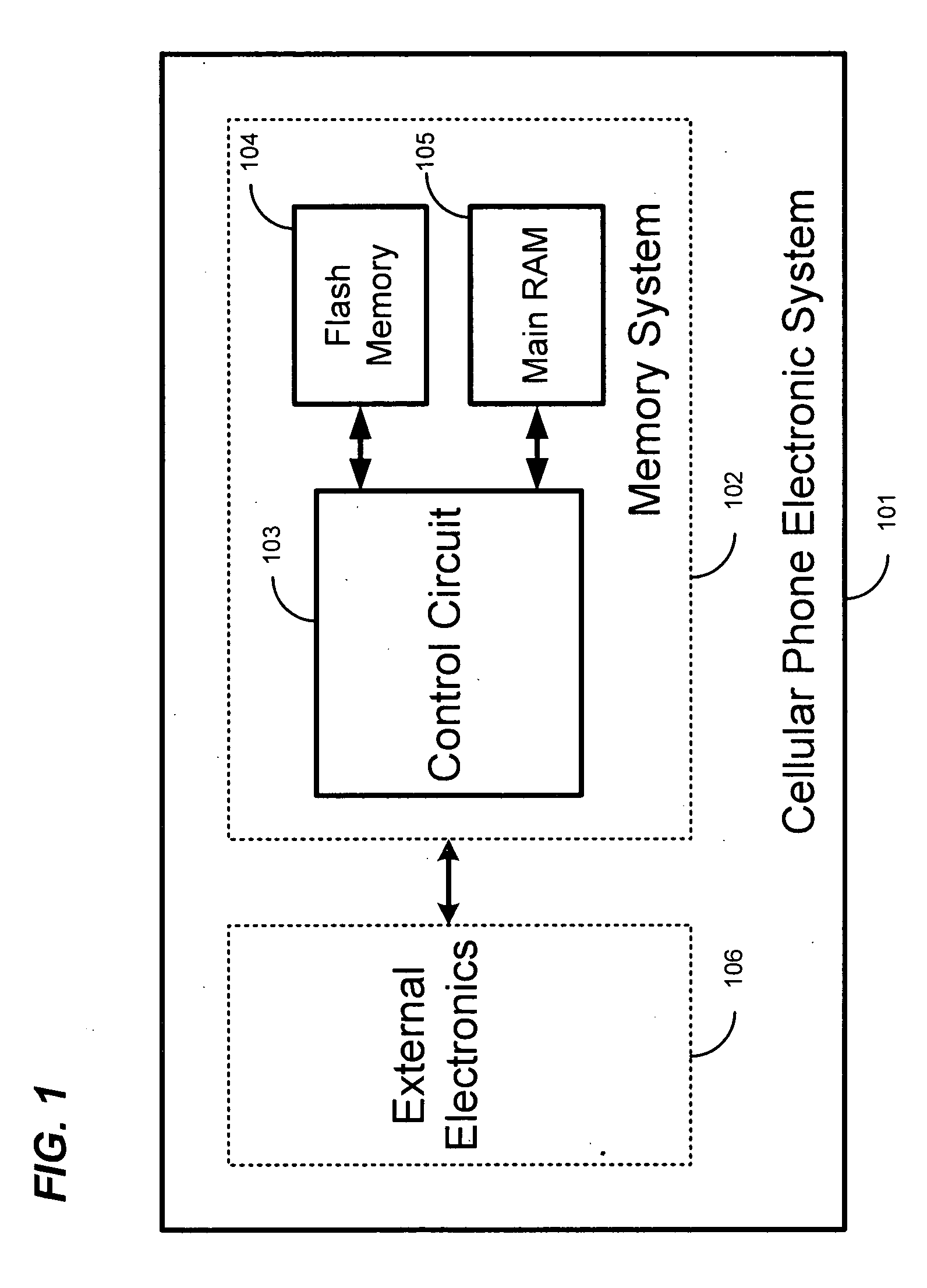

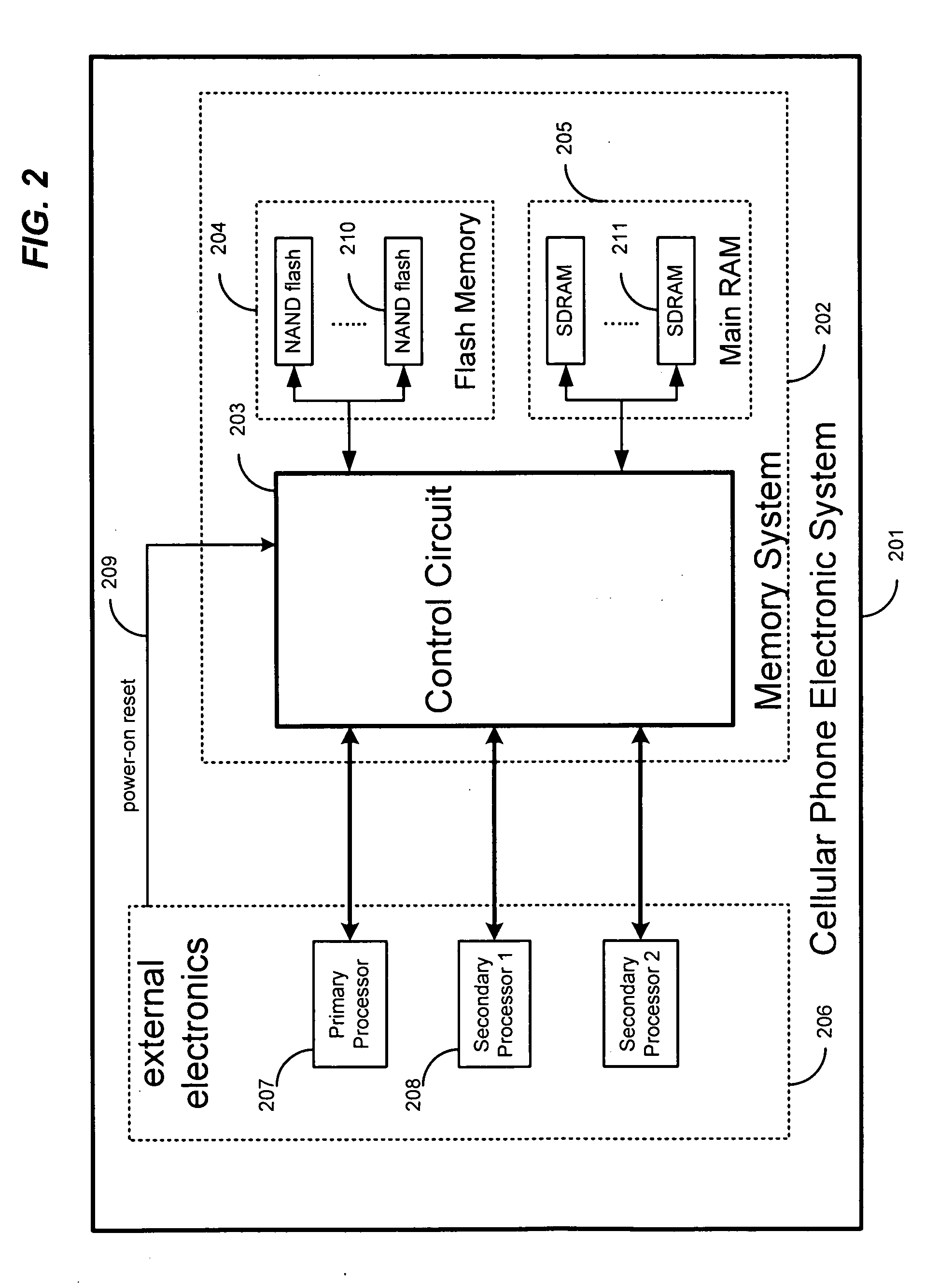

Systems and methods for providing nonvolatile memory management in wireless phones

ActiveUS20060053246A1Low costSmall sizeUnauthorized memory use protectionDigital storageMemory controllerInterface circuits

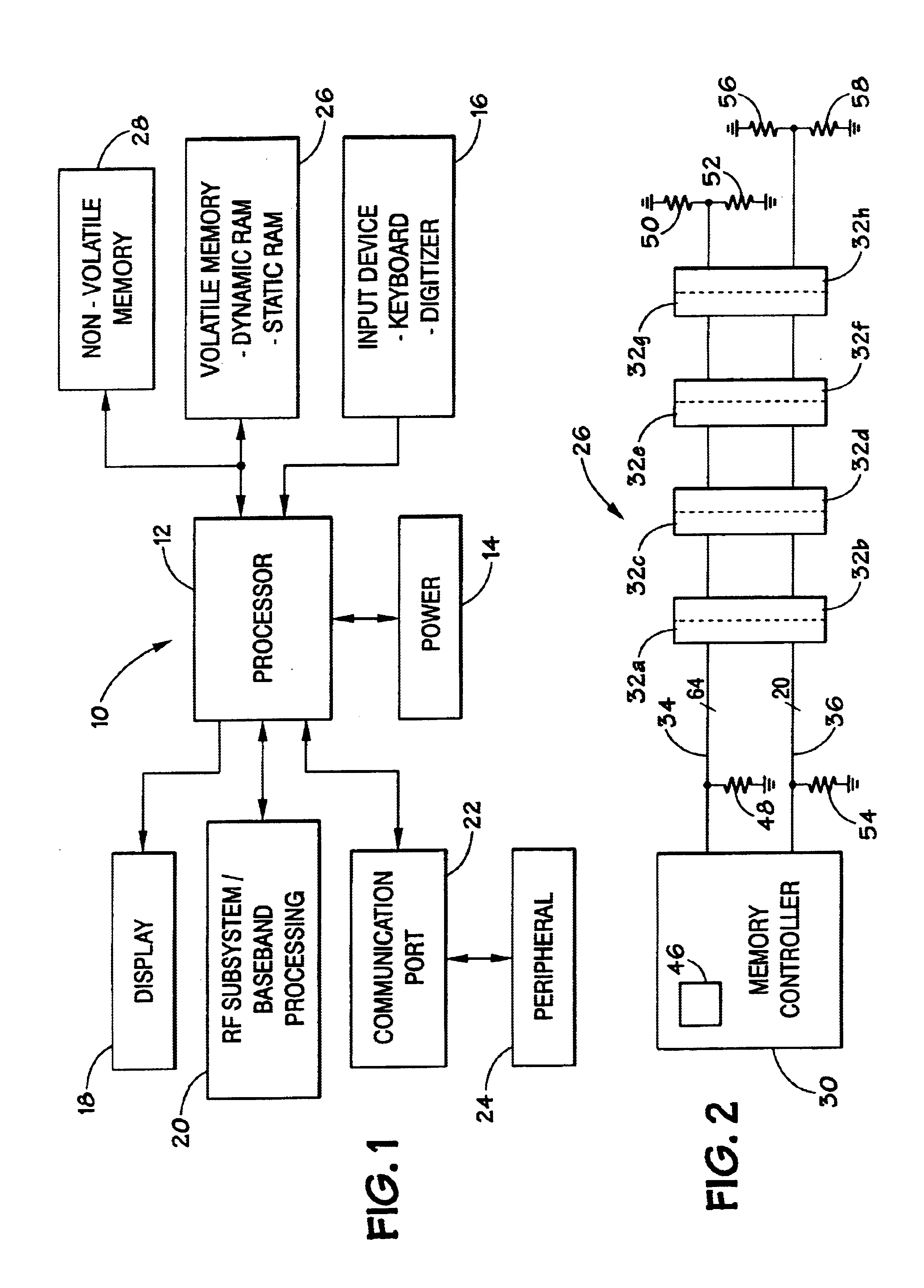

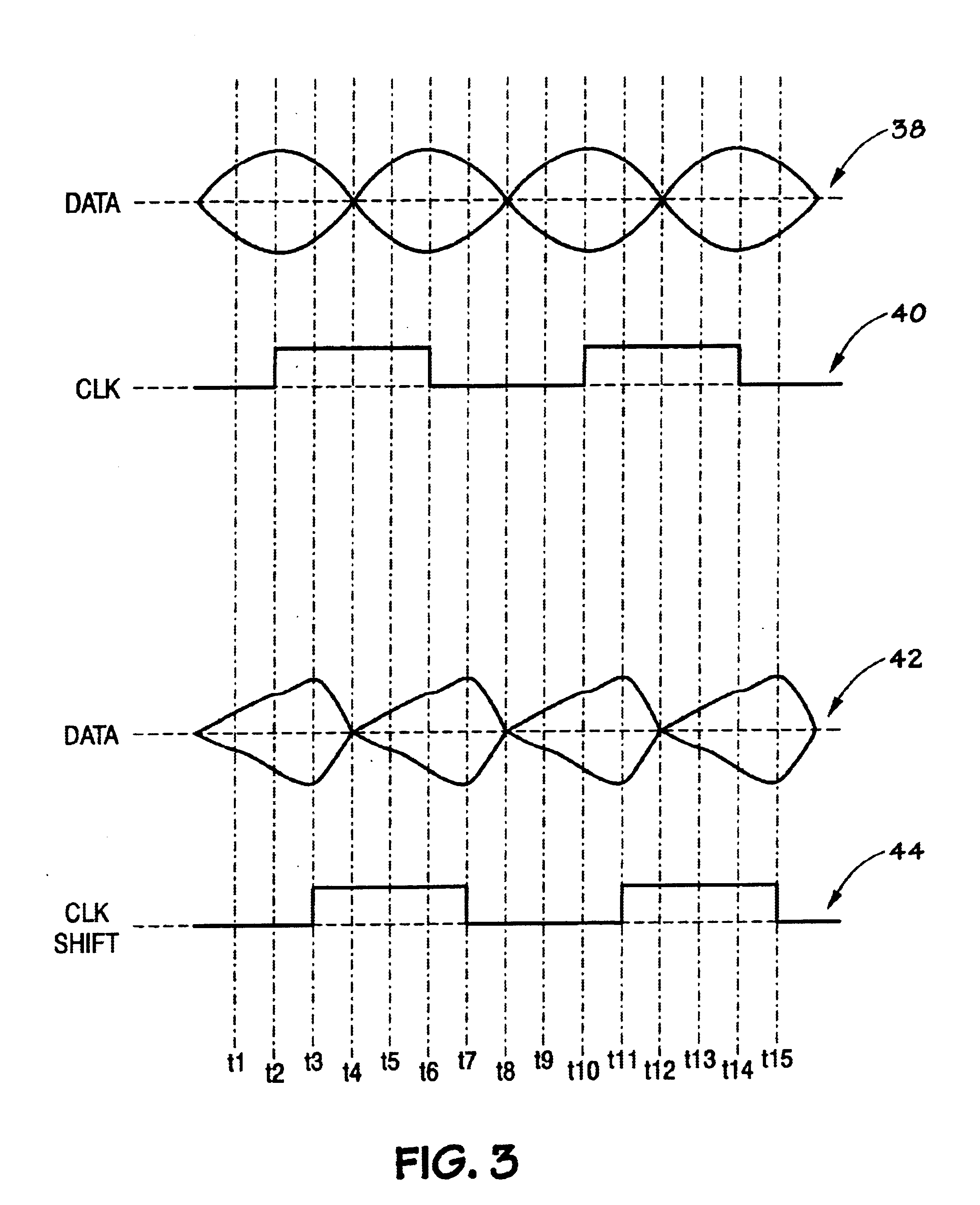

The present invention is related to memory management, and in particular, to methods and systems for accessing and managing nonvolatile, such as in a wireless phone. A wireless phone memory controller is disclosed that, comprises a first interface circuit configured to be coupled to wireless phone nonvolatile memory, a second interface circuit configured to be coupled to wireless phone volatile memory, a first processor interface configured to be coupled to a first wireless phone processor, wherein the first processor interface is configured to provide the first processor with access to the wireless phone volatile memory, a second processor interface configured to be coupled to a second wireless phone processor, and a controller circuit configured to copy at least a portion of wireless phone nonvolatile memory data to the wireless phone volatile memory.

Owner:GOOGLE LLC

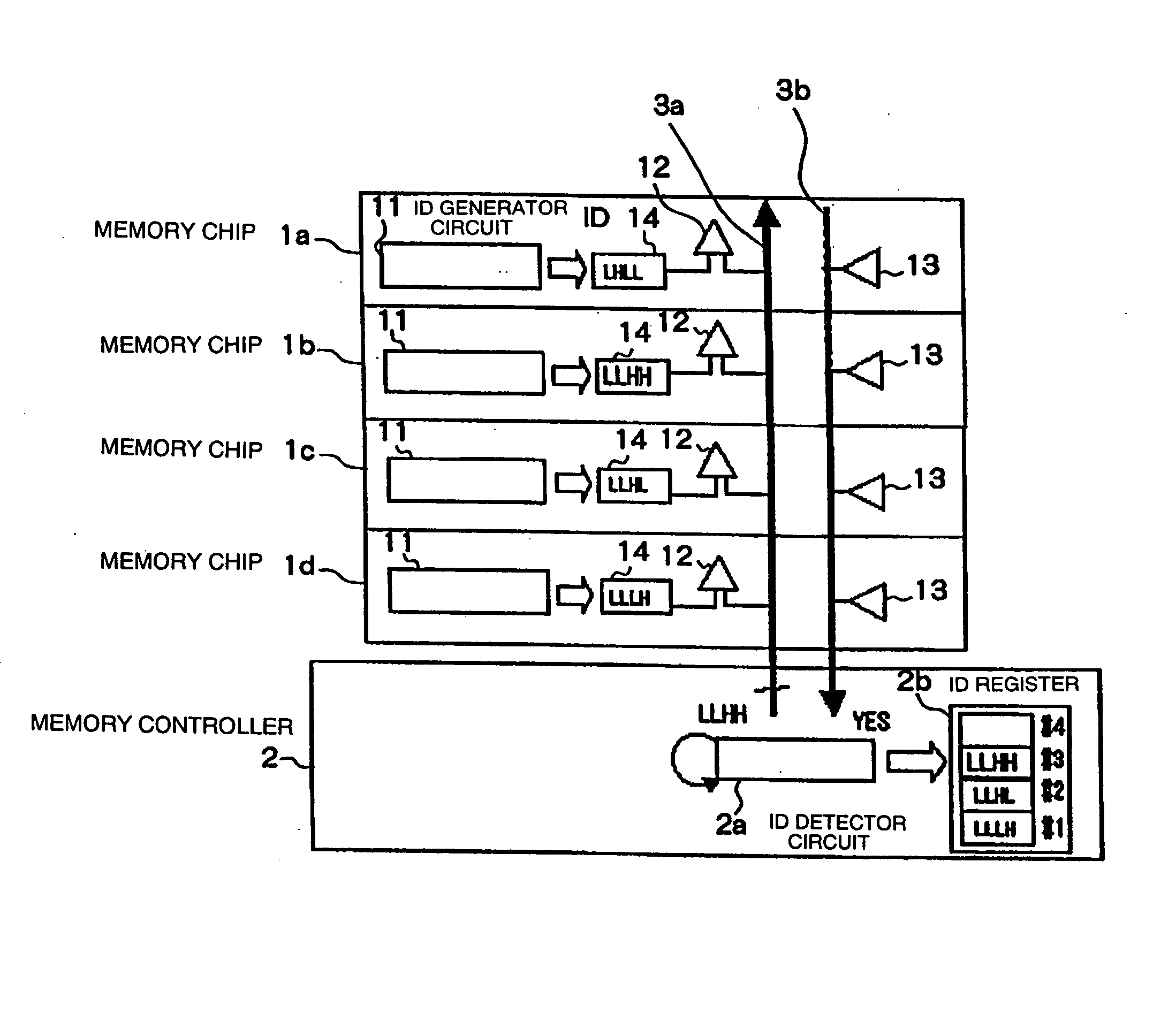

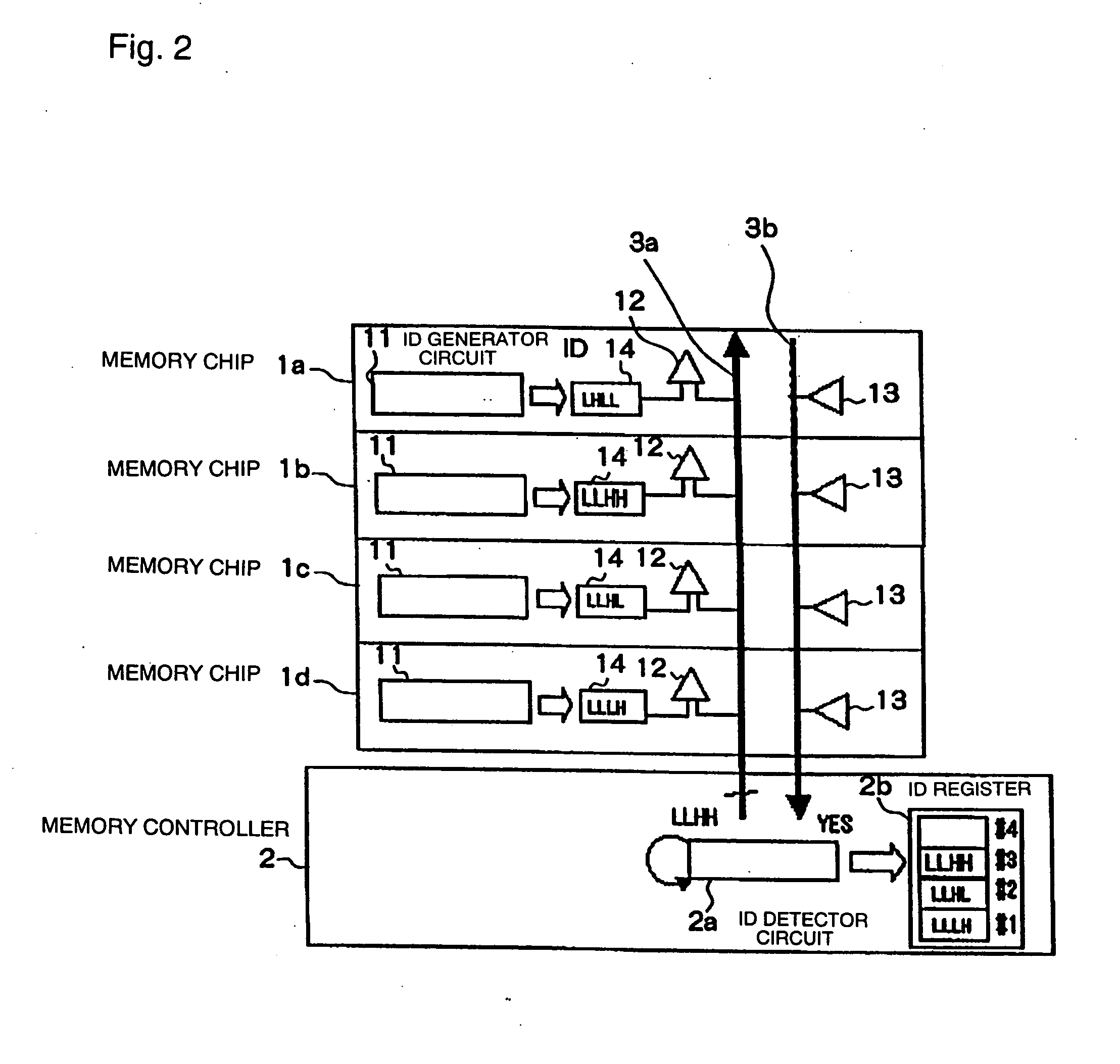

Stacked semiconductor device and semiconductor chip control method

InactiveUS20050082664A1Semiconductor/solid-state device detailsSolid-state devicesMemory chipDetector circuits

Each of stacked memory chips has an ID generator circuit for generating identification information in accordance with its manufacturing process. Since the memory chip manufacturing process implies process variations, the IDs generated by the respective ID generator circuits are different from one another even though the ID generator circuits are identical in design. A memory controller instructs an ID detector circuit to detect the IDs of the respective memory chips, and individually controls the respective memory chips based on the detected IDs.

Owner:ELPIDA MEMORY INC

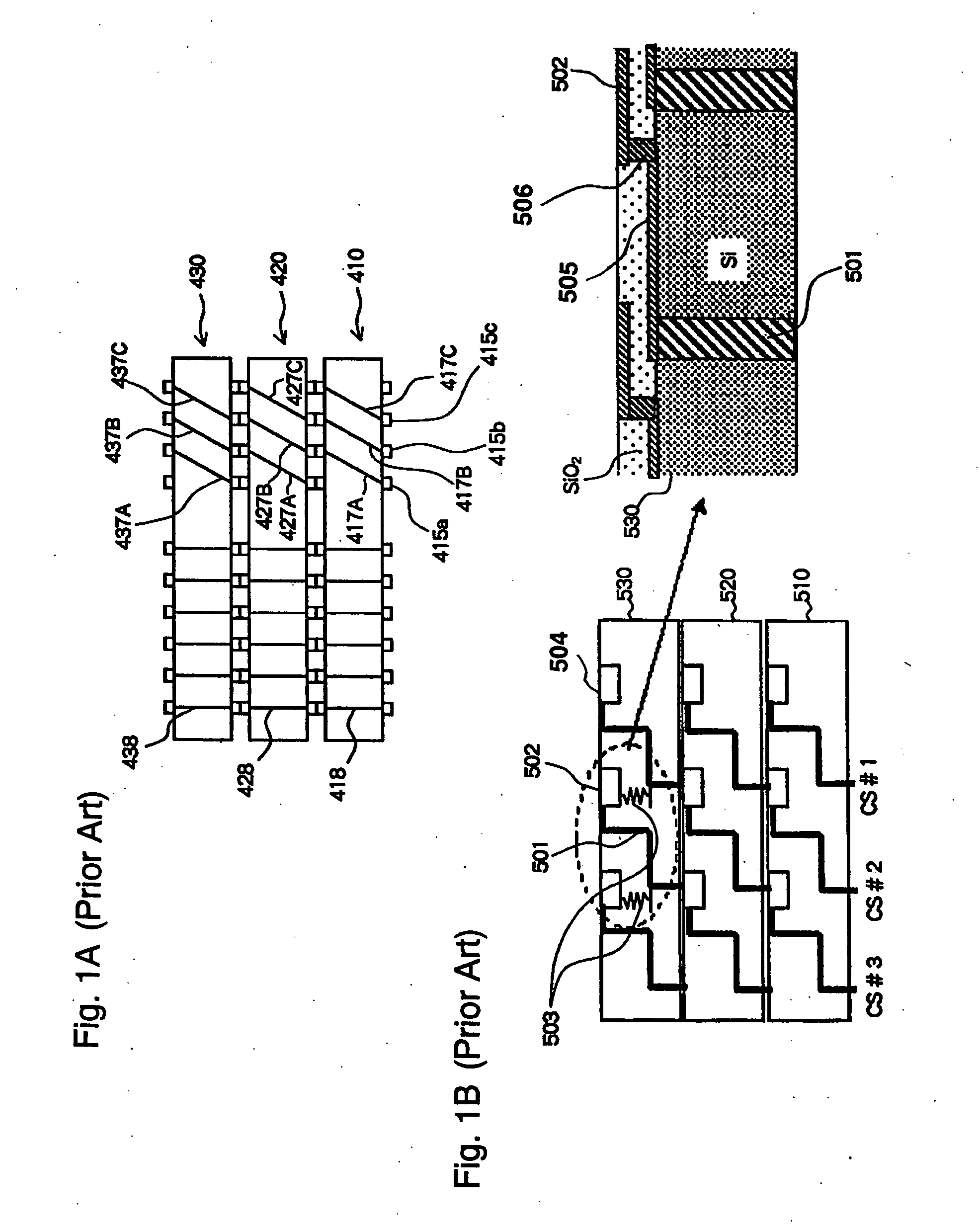

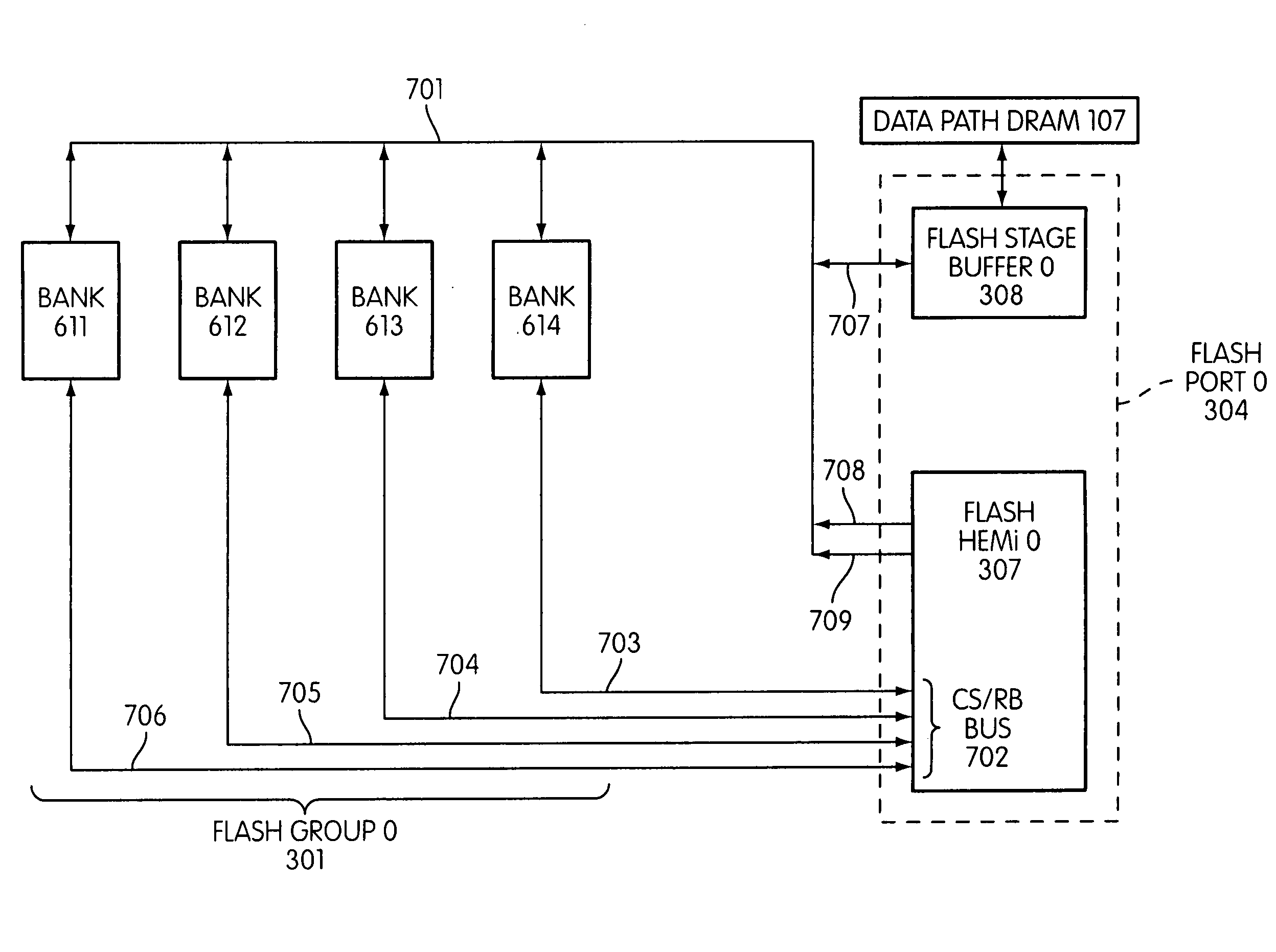

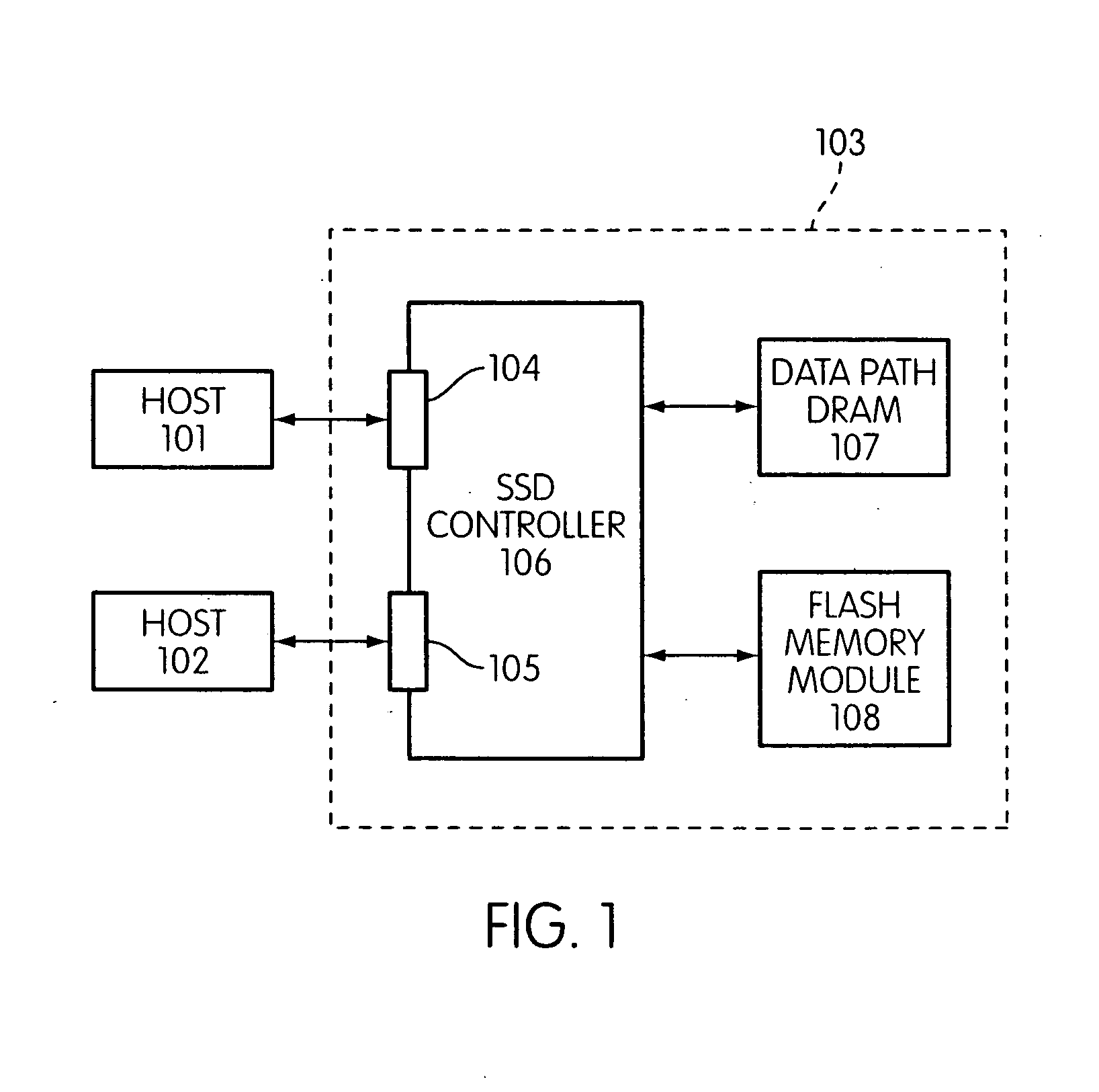

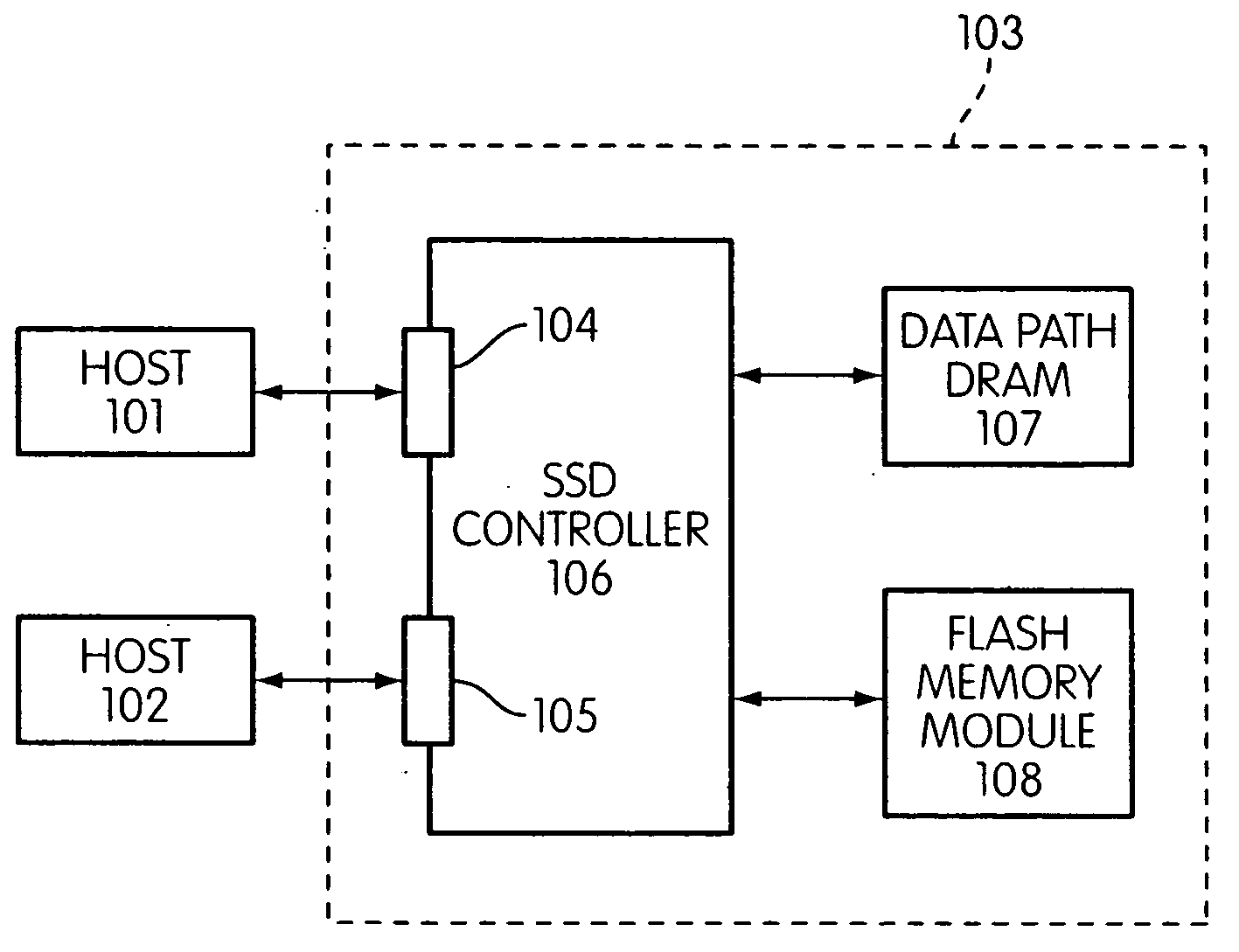

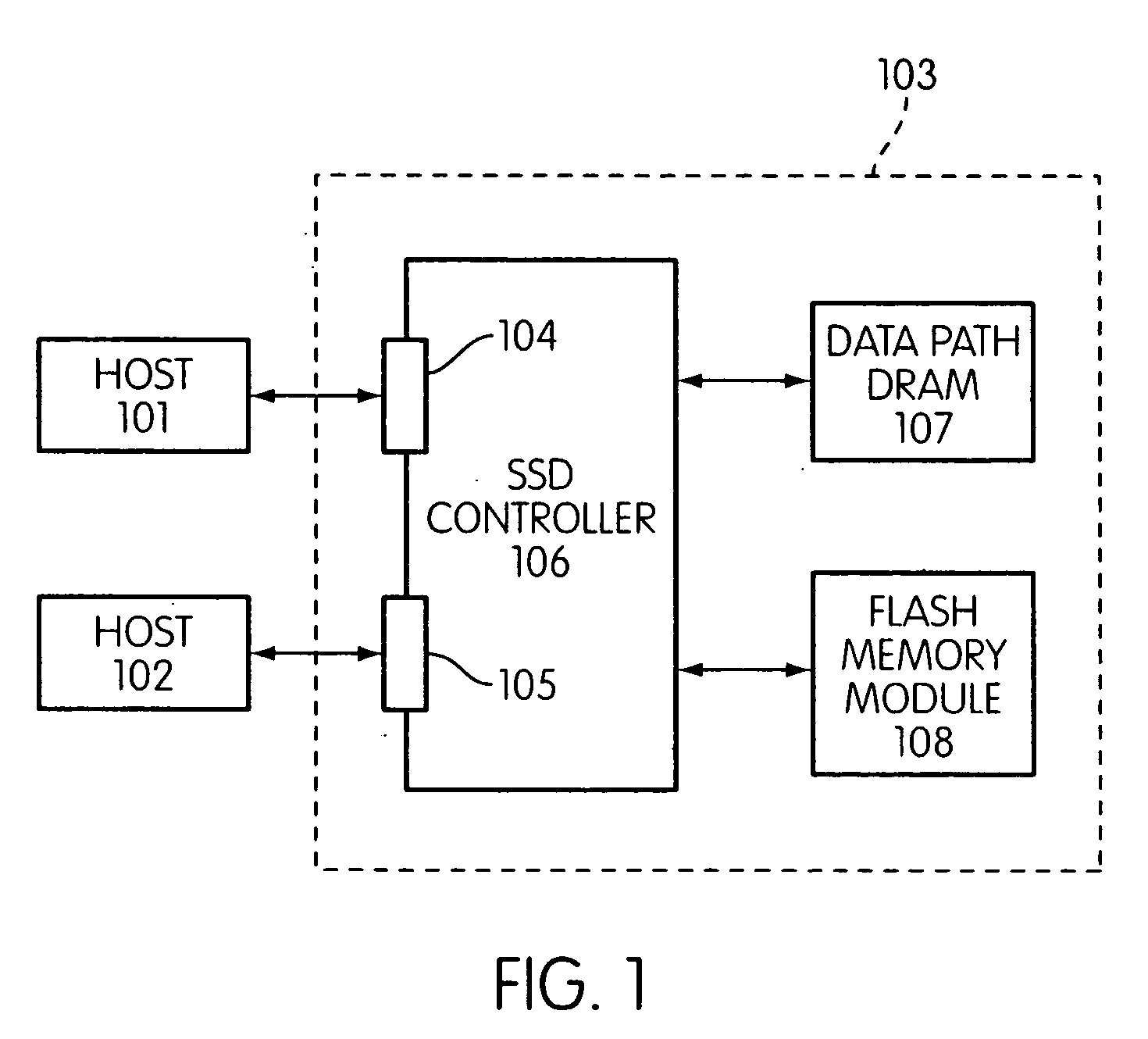

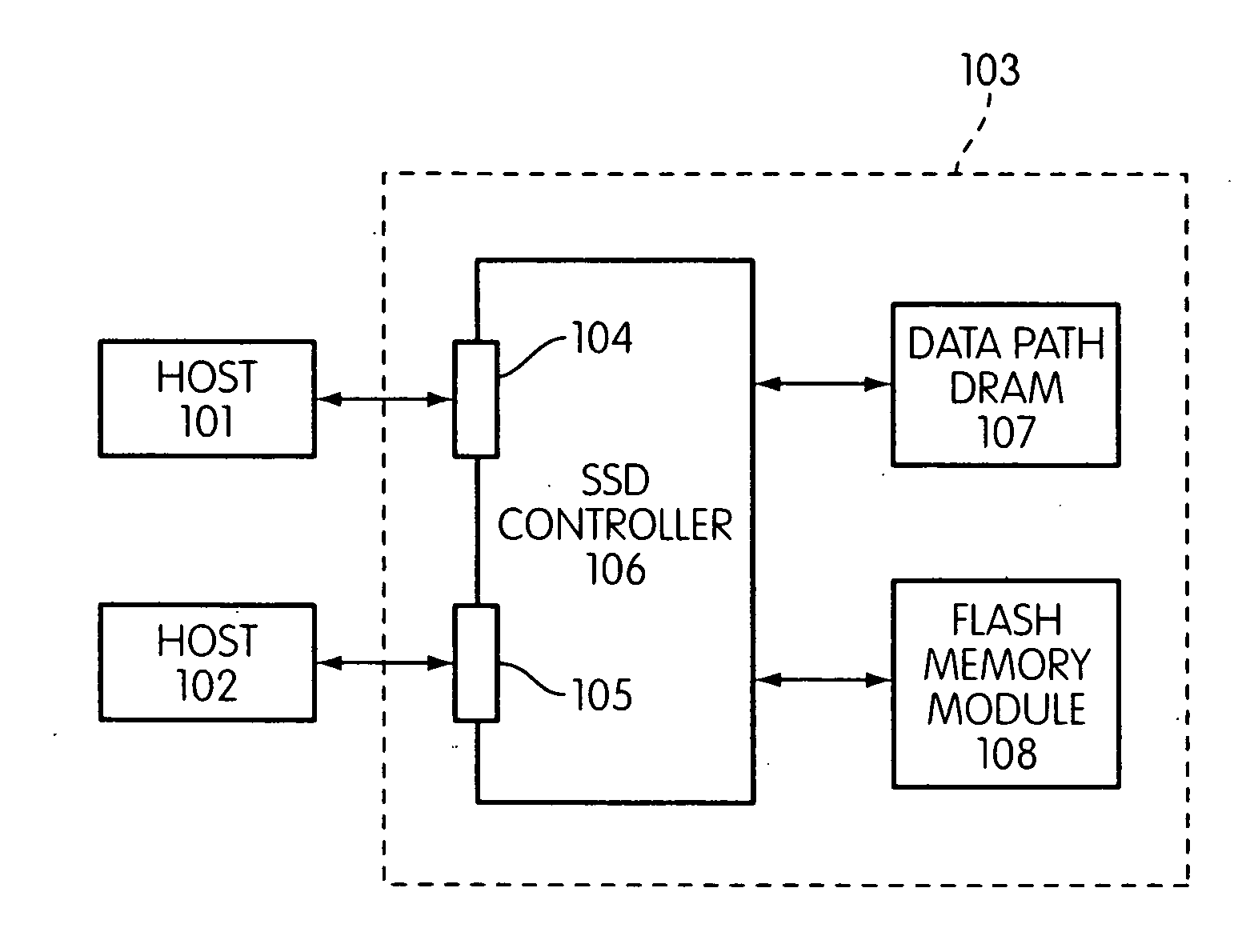

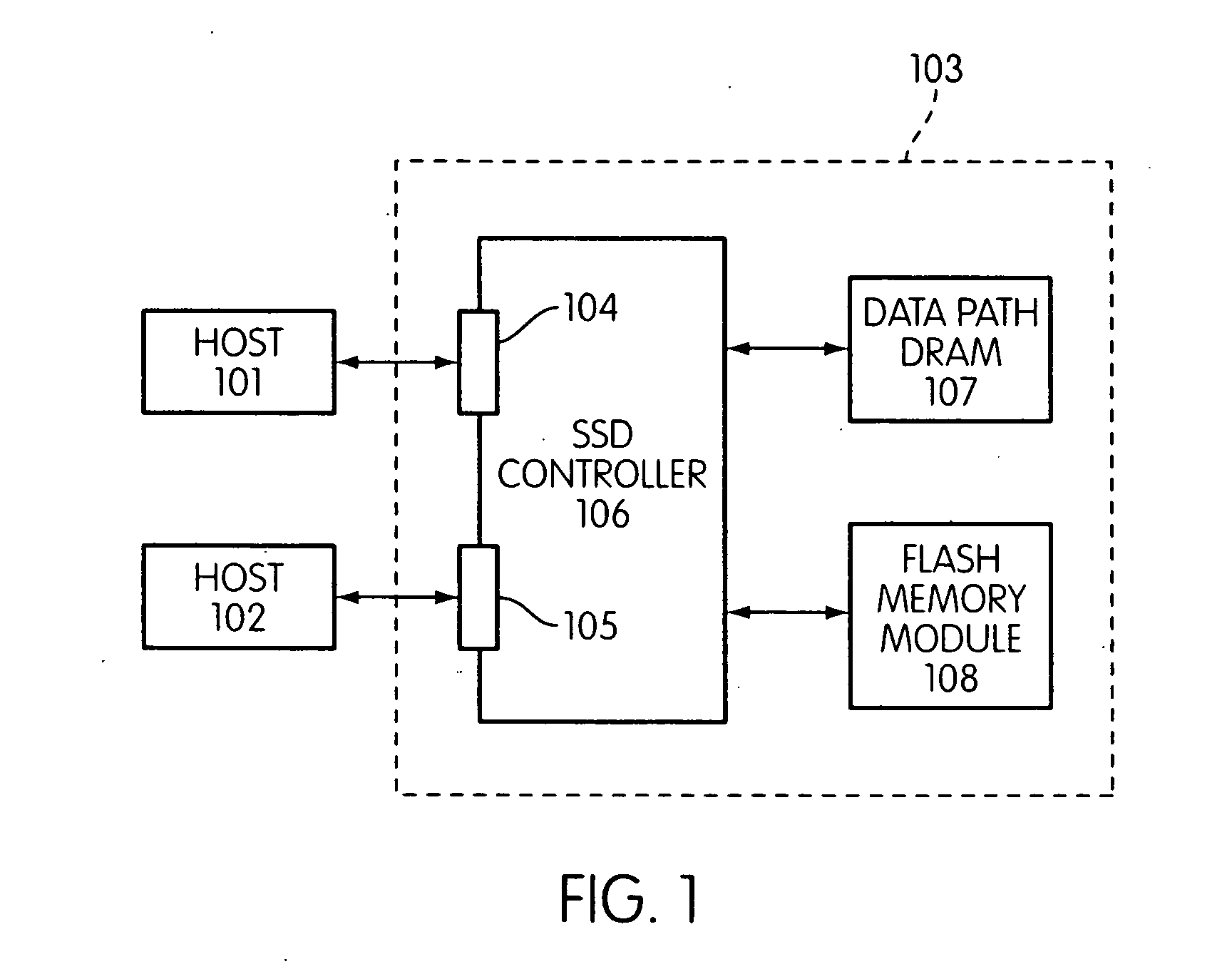

Flash memory controller having reduced pinout

InactiveUS20090168525A1Affect performanceMaximize useMemory architecture accessing/allocationMemory adressing/allocation/relocationChip selectFlash memory controller

Disclosed is a flash memory controller connected to a flash memory module. The pin-out of the flash memory controller combines ready-busy and chip-select signals. In one embodiment, the flash memory module is made up of a set of banks, each consisting of a plurality of devices, with each bank sharing a single chip-select / ready-busy connection to the controller.

Owner:SANDISK TECH LLC

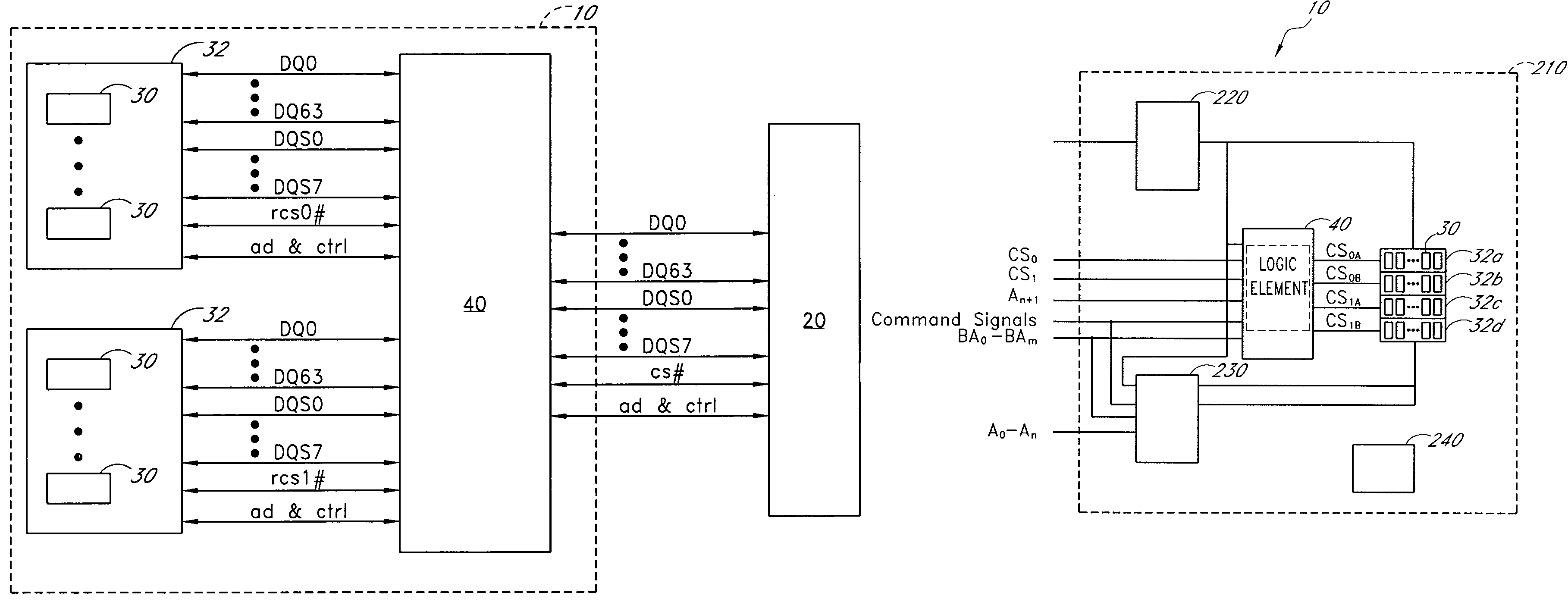

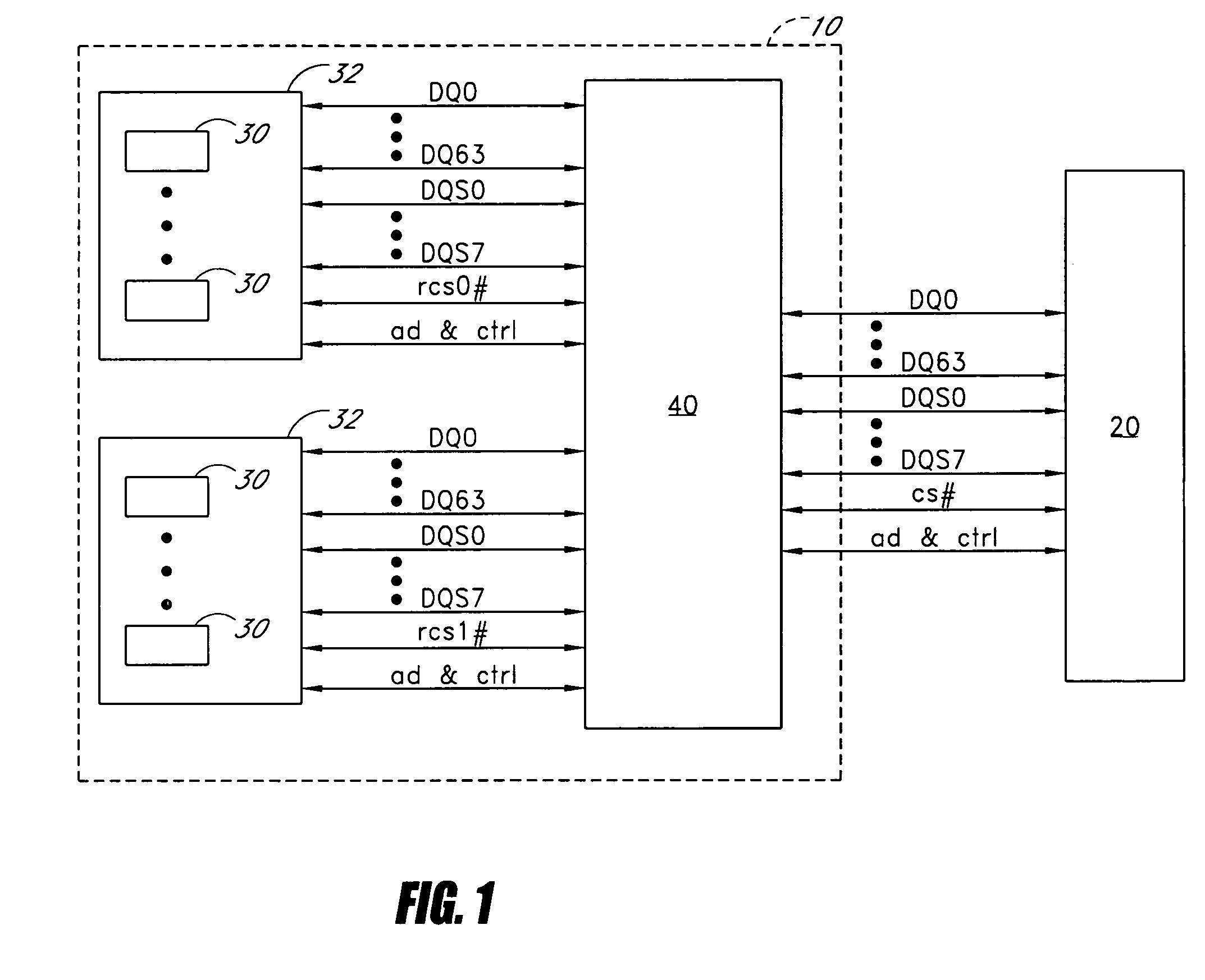

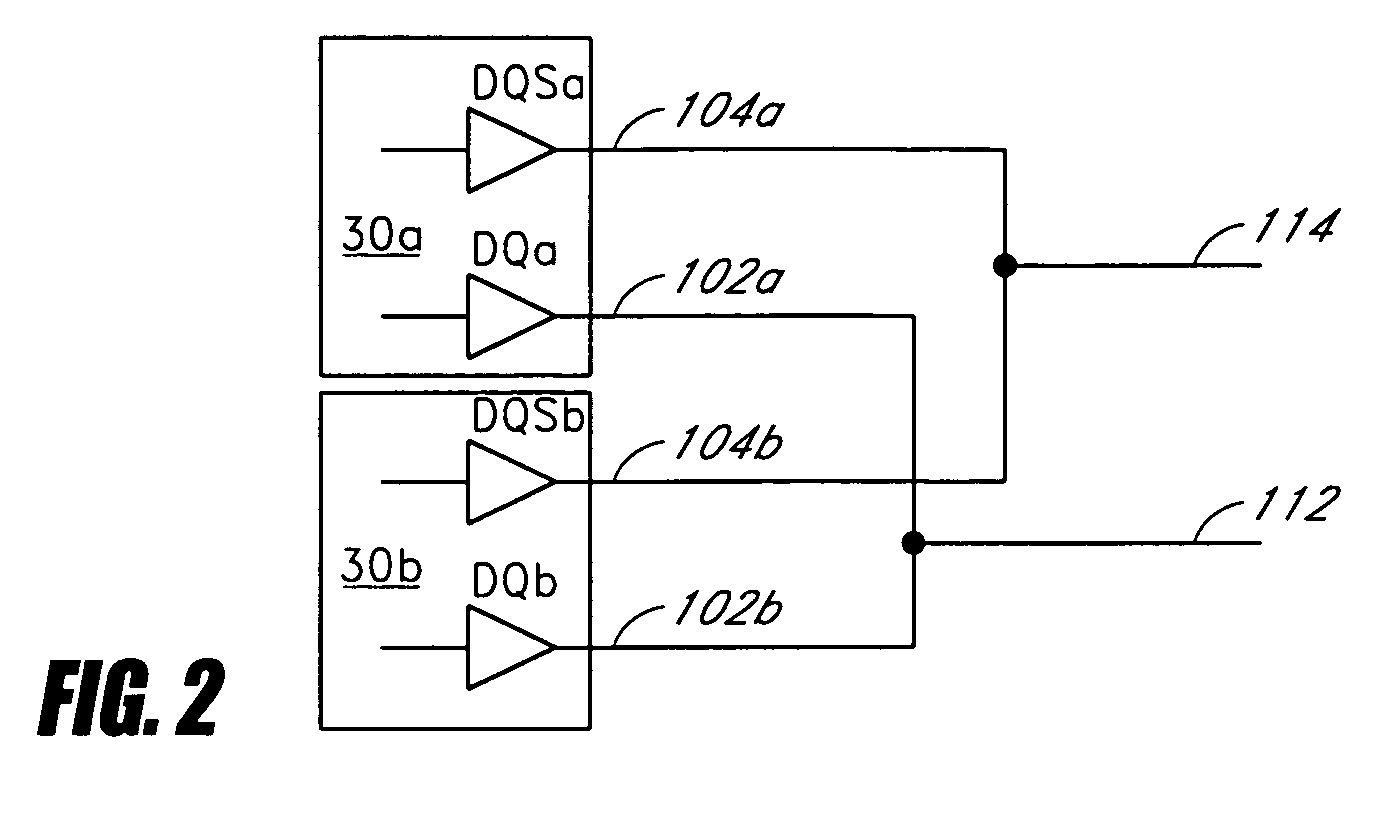

Memory module with a circuit providing load isolation and memory domain translation

A memory module includes a plurality of memory devices and a circuit. Each memory device has a corresponding load. The circuit is electrically coupled to the plurality of memory devices and is configured to be electrically coupled to a memory controller of a computer system. The circuit selectively isolates one or more of the loads of the memory devices from the computer system. The circuit comprises logic which translates between a system memory domain of the computer system and a physical memory domain of the memory module.

Owner:NETLIST INC

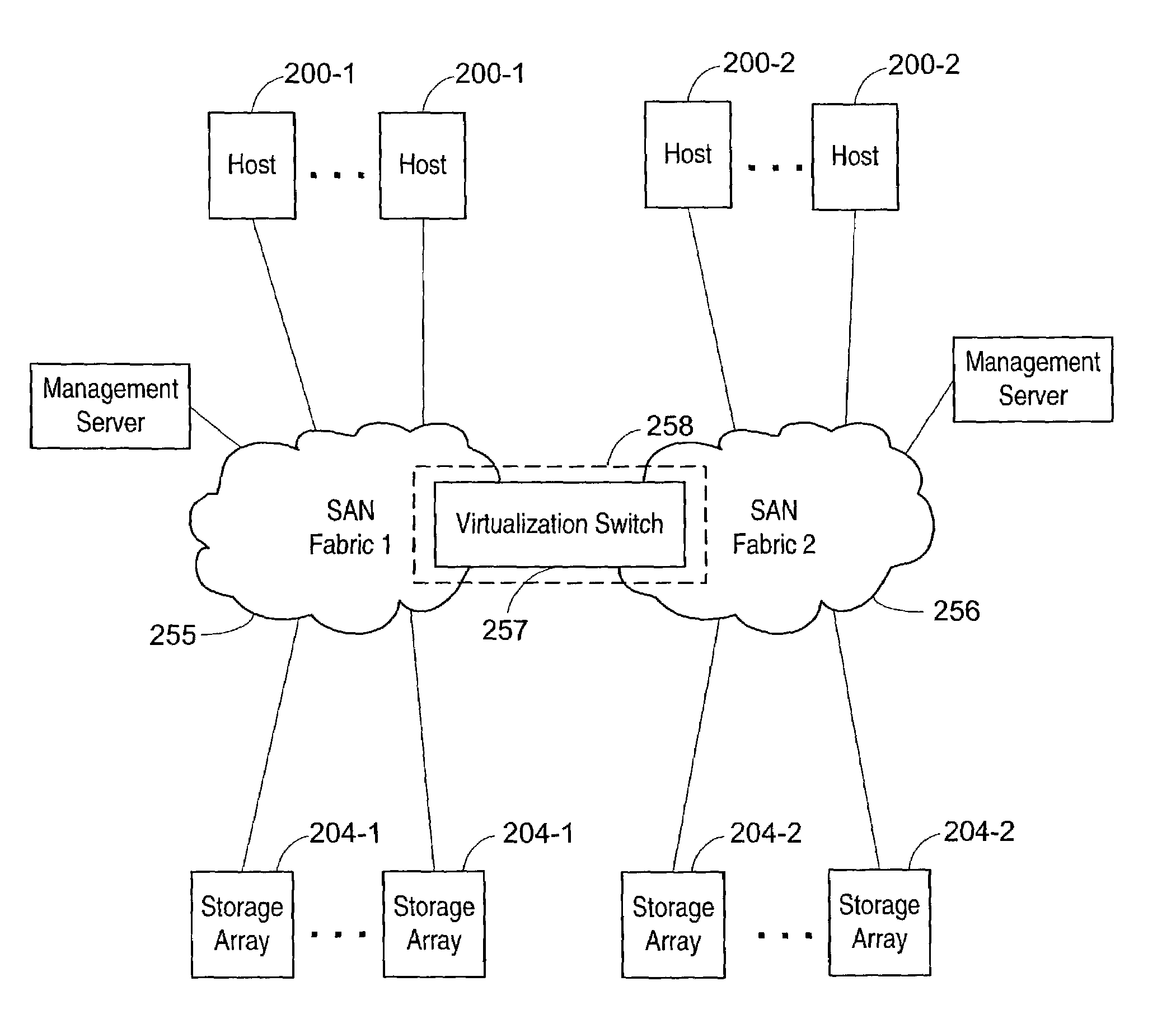

Hardware-based translating virtualization switch

InactiveUS7120728B2Improve throughputComprehensive performance is smallMultiplex system selection arrangementsInput/output to record carriersVirtualizationComputer hardware

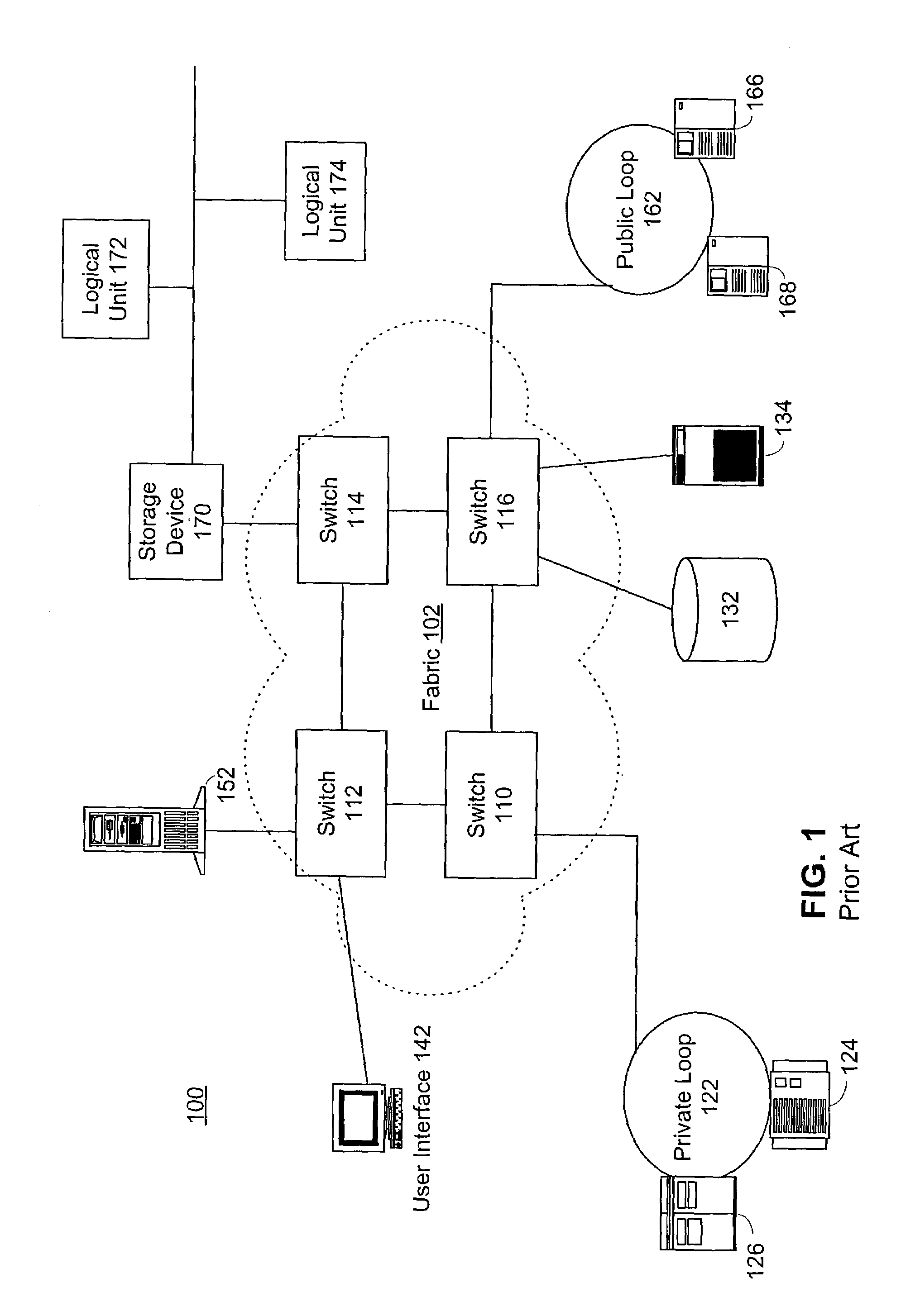

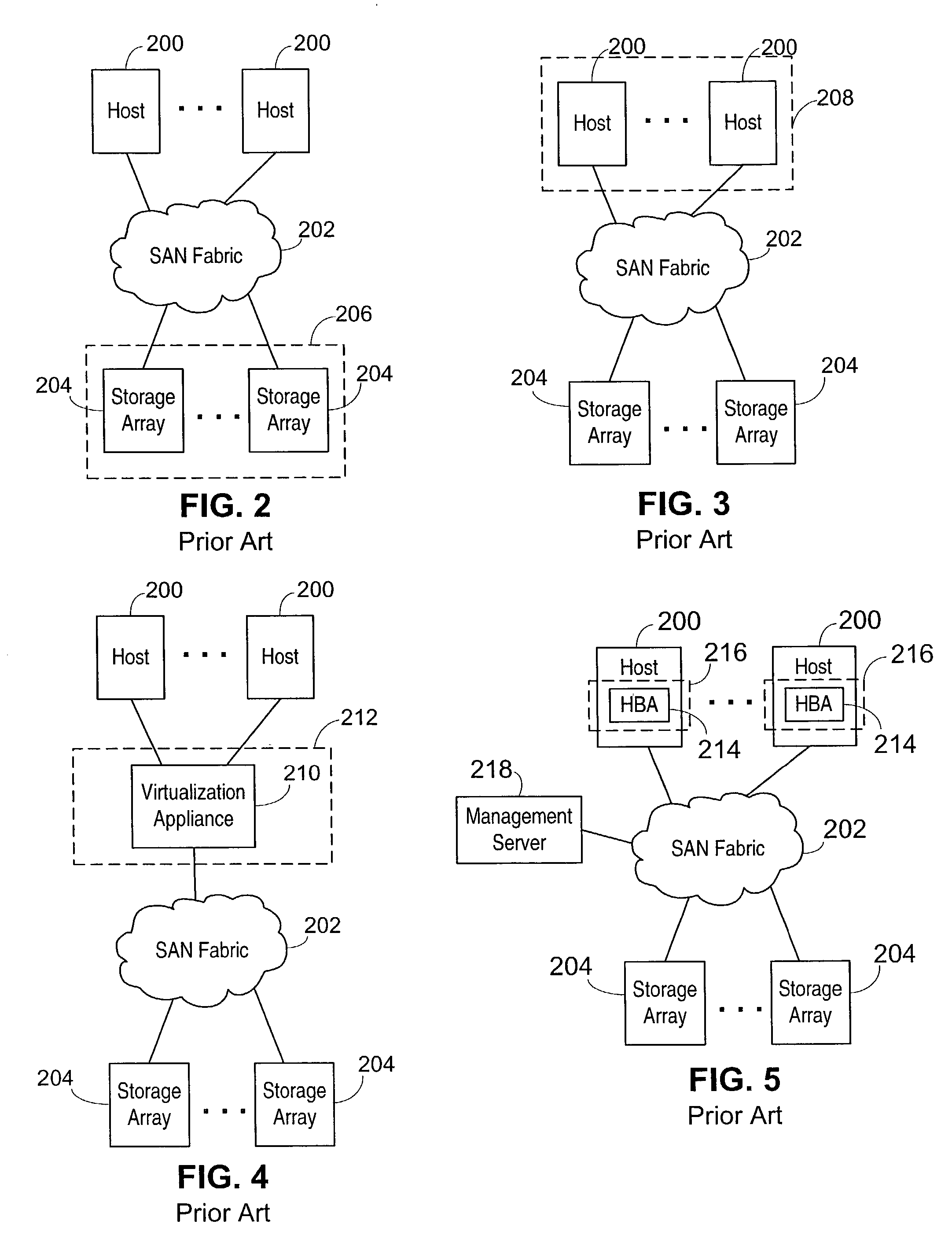

Placing virtualization agents in the switches which comprise the SAN fabric. Higher level virtualization management functions are provided in an external management server. Conventional HBAs can be utilized in the hosts and storage units. In a first embodiment, a series of HBAs are provided in the switch unit. The HBAs connect to bridge chips and memory controllers to place the frame information in dedicated memory. Routine translation of known destinations is done by the HBA, based on a virtualization table provided by a virtualization CPU. If a frame is not in the table, it is provided to the dedicated RAM. Analysis and manipulation of the frame headers is then done by the CPU, with a new entry being made in the HBA table and the modified frames then redirected by the HBA into the fabric. This can be done in either a standalone switch environment or in combination with other switching components located in a director level switch. In an alternative embodiment, specialized hardware scans incoming frames and detects the virtualized frames which need to be redirected. The redirection is then handled by translation of the frame header information by hardware table-based logic and the translated frames are then returned to the fabric. Handling of frames not in the table and setup of hardware tables is done by an onboard CPU.

Owner:AVAGO TECH INT SALES PTE LTD

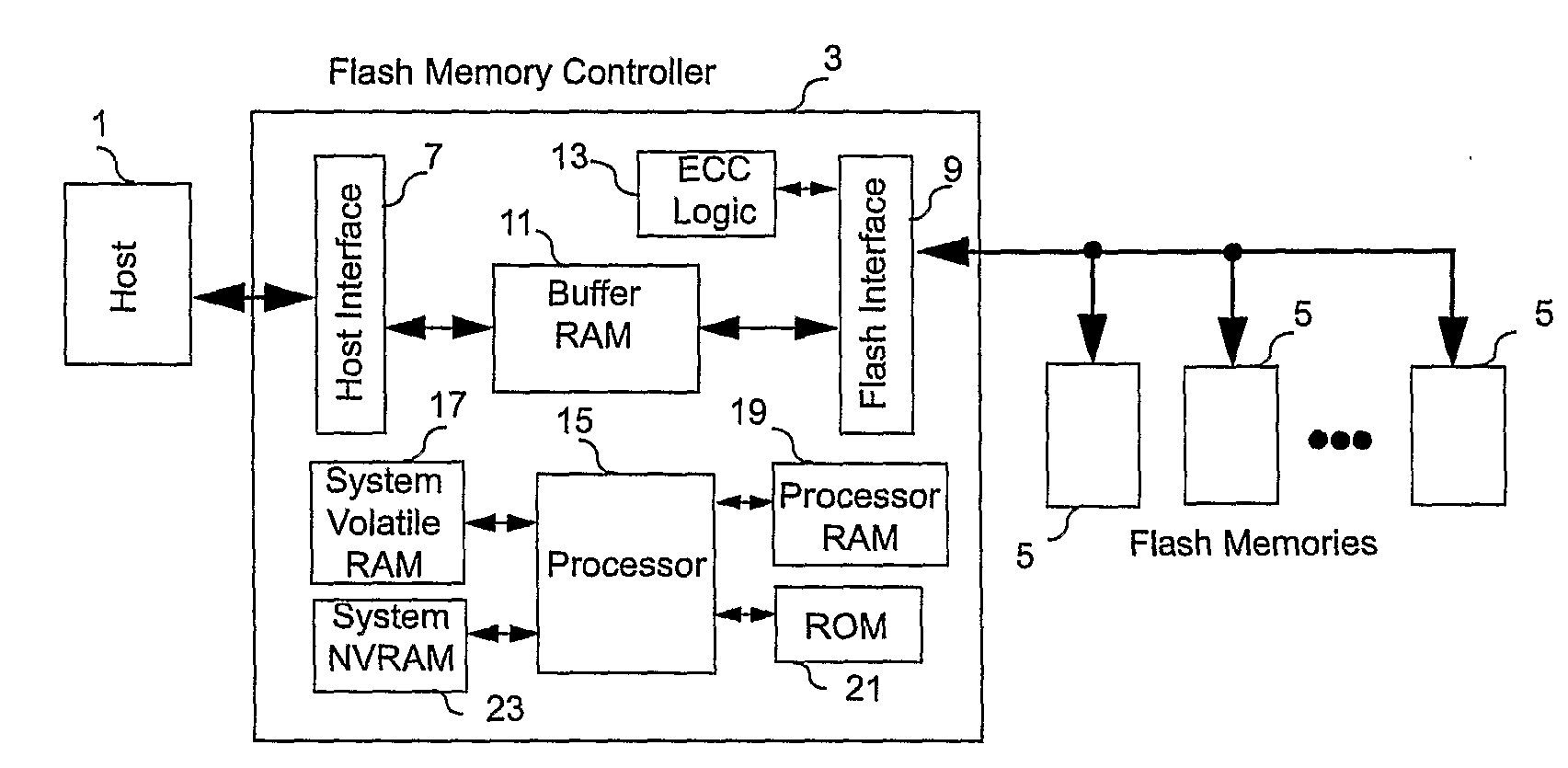

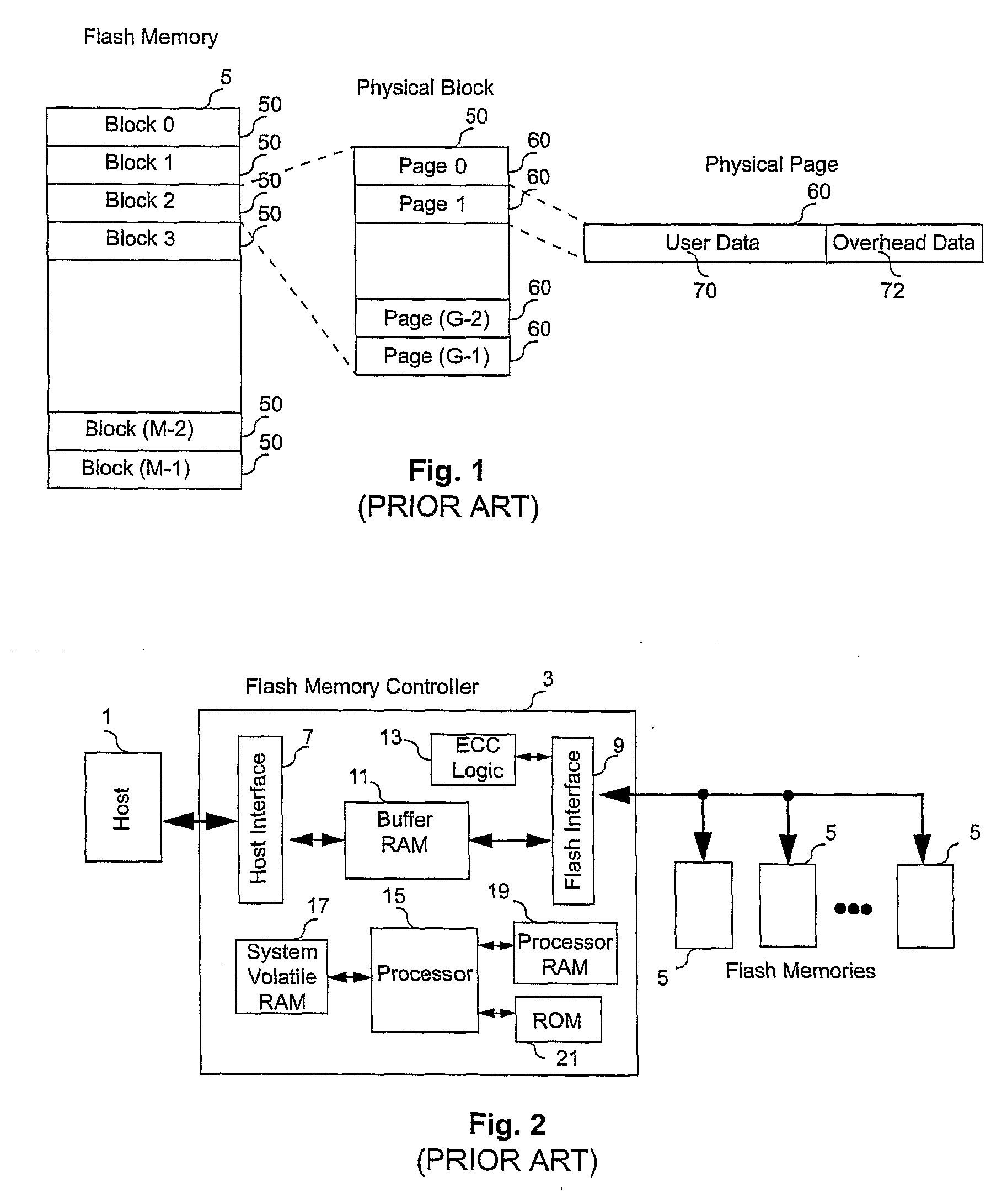

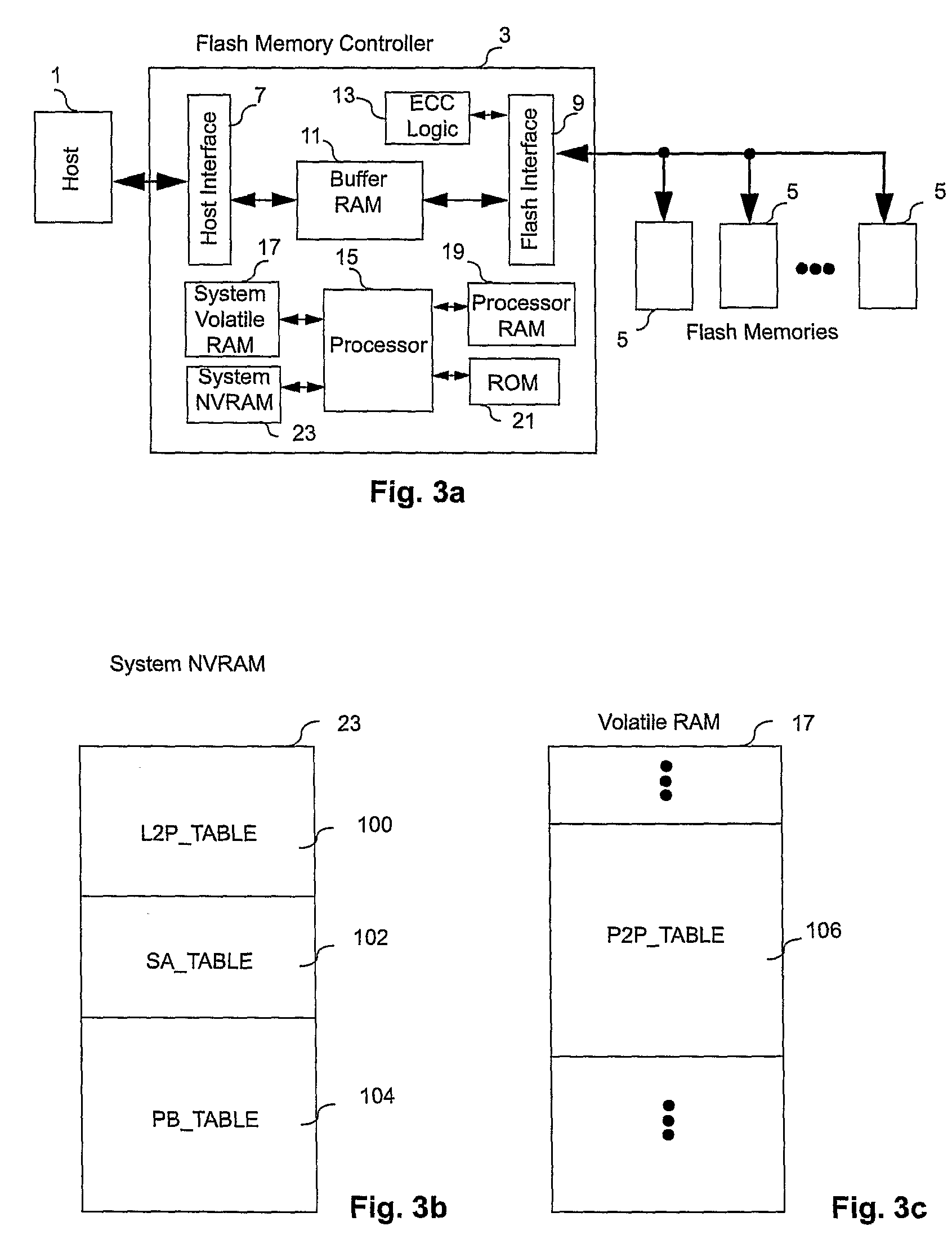

Controller for Non-Volatile Memories and Methods of Operating the Memory Controller

ActiveUS20080270680A1Improve system performanceReduce stepsMemory adressing/allocation/relocationRead-only memoriesMemory controllerByte

A non-volatile memory system (3) is proposed consisting of a first non-volatile flash memory (5) having a plurality of blocks, each block having a plurality of pages, each block being erasable and each page being programmable, and a second non-volatile random access memory (23) having a plurality of randomly accessible bytes. The second non-volatile memory (23) stores data for mapping logical blocks to physical blocks and status information of logical blocks. Each logical block has an associated physical page pointer stored in the second non-volatile memory (23) that identifies the next free physical page of the mapped physical block to be written. The page pointer is incremented after every page write to the physical block, allowing all physical pages to be fully utilized for page writes. Furthermore, a method of writing and reading data is disclosed whereby the most recently written physical page associated with a logical address is identifiable by the memory system without programming flags into superseded pages, or recording time stamp values in any physical page or block of the first non-volatile memory (5). Furthermore, a method is provided for a logical block to be mapped to two physical blocks instead of one to provide additional space for page writes, resulting in reduction in page copy operations, thereby increasing the performance of the system.

Owner:CHANG CHEE KENG

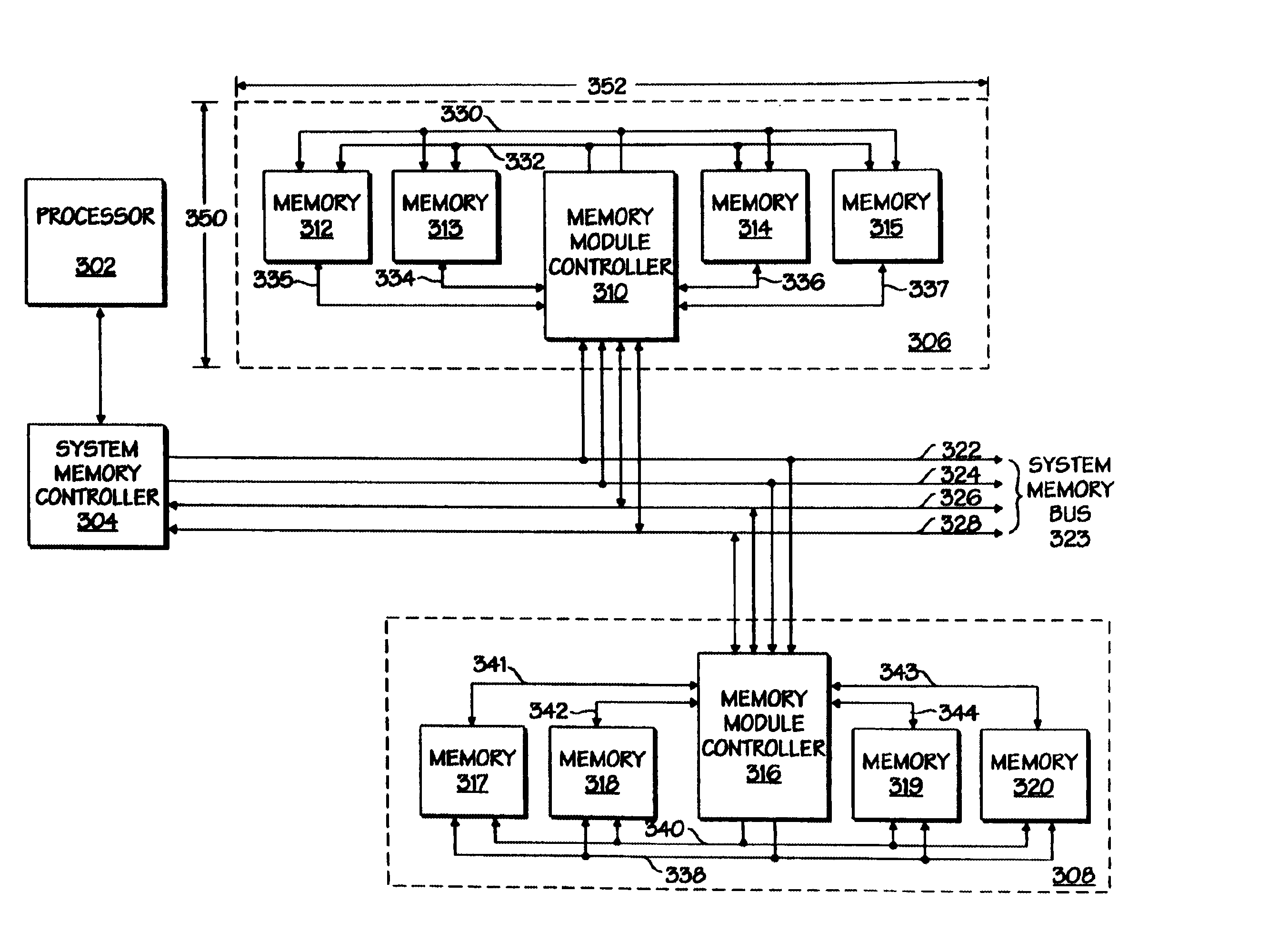

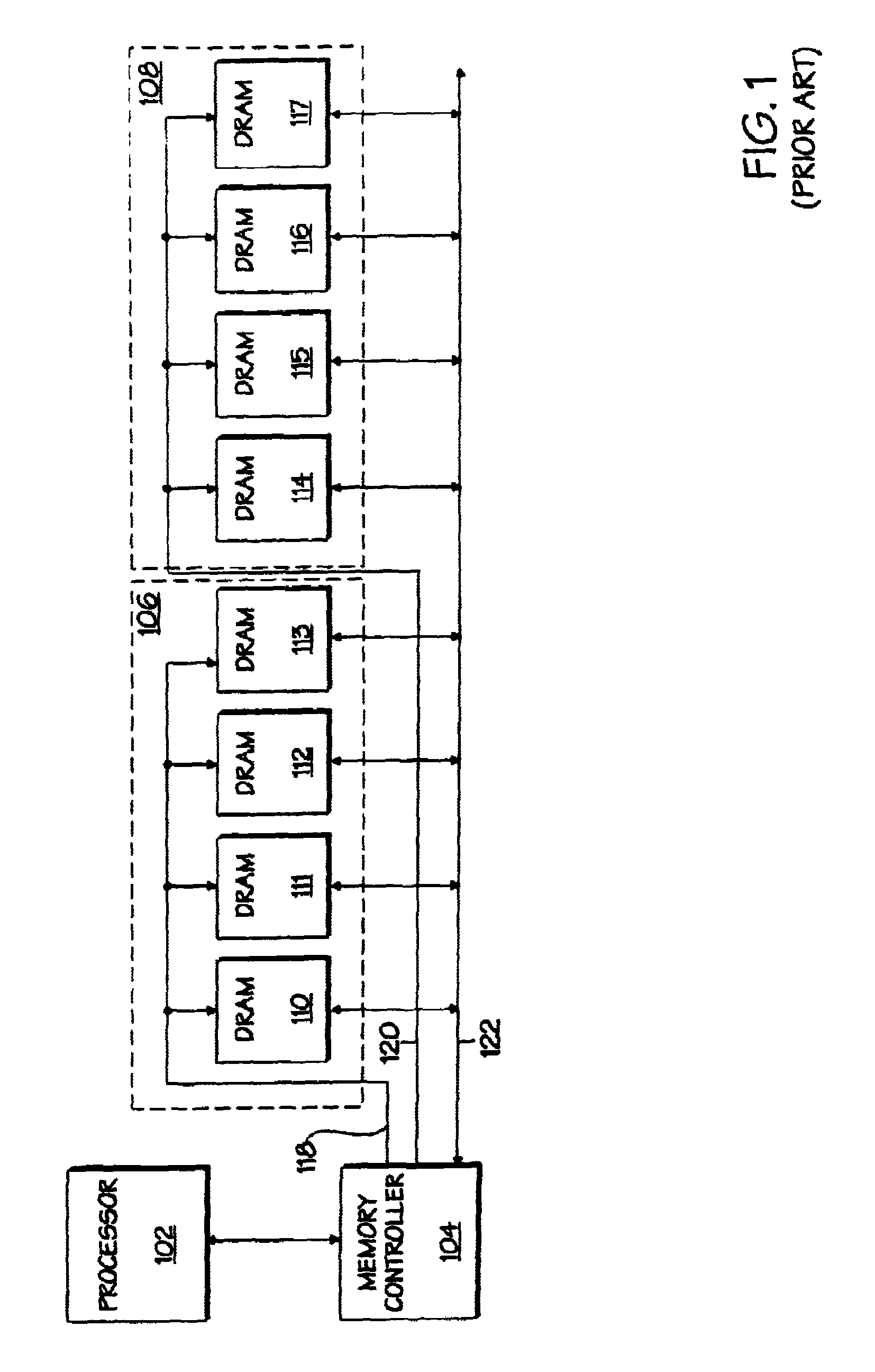

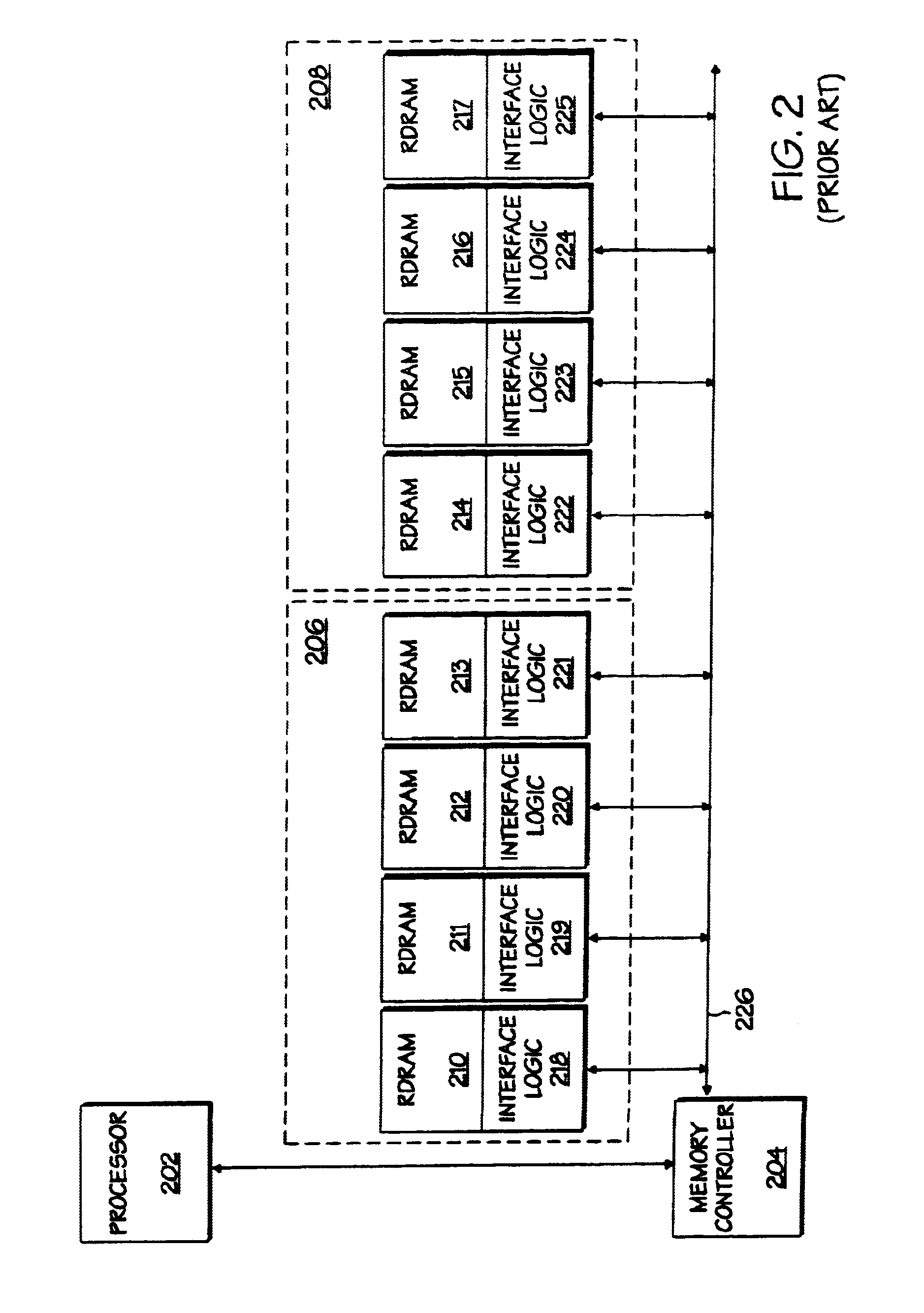

Memory module controller for providing an interface between a system memory controller and a plurality of memory devices on a memory module

A memory module controller for providing interface between a system memory controller and a plurality of memory devices on a memory module. The memory module includes first interface circuitry and control logic. The first interface circuitry is configured to receive from the system memory controller a first memory transaction in a first format. The control logic is coupled to the first interface circuitry and configured to convert the first memory transaction into a second memory transaction in a second format for the plurality of memory devices. The second format of the second memory transaction is different than the first format of the first memory transaction.

Owner:INTEL CORP

Write clock and data window tuning based on rank select

A configuration register used to adjust a clock or request signal with respect to the other. Specifically, a look-up table is provided in the memory controller. The look-up table is filled at bootup such that it contains test information from a master look-up table in the system BIOS, for instance. The look-up table in the memory controller stores current test data correlative to optimal sampling times for the current configuration. Adjustable delay elements or adjustable load elements may be used to change the relative sampling time of the request signal correlative to the values stored in the memory controller look-up table.

Owner:MICRON TECH INC

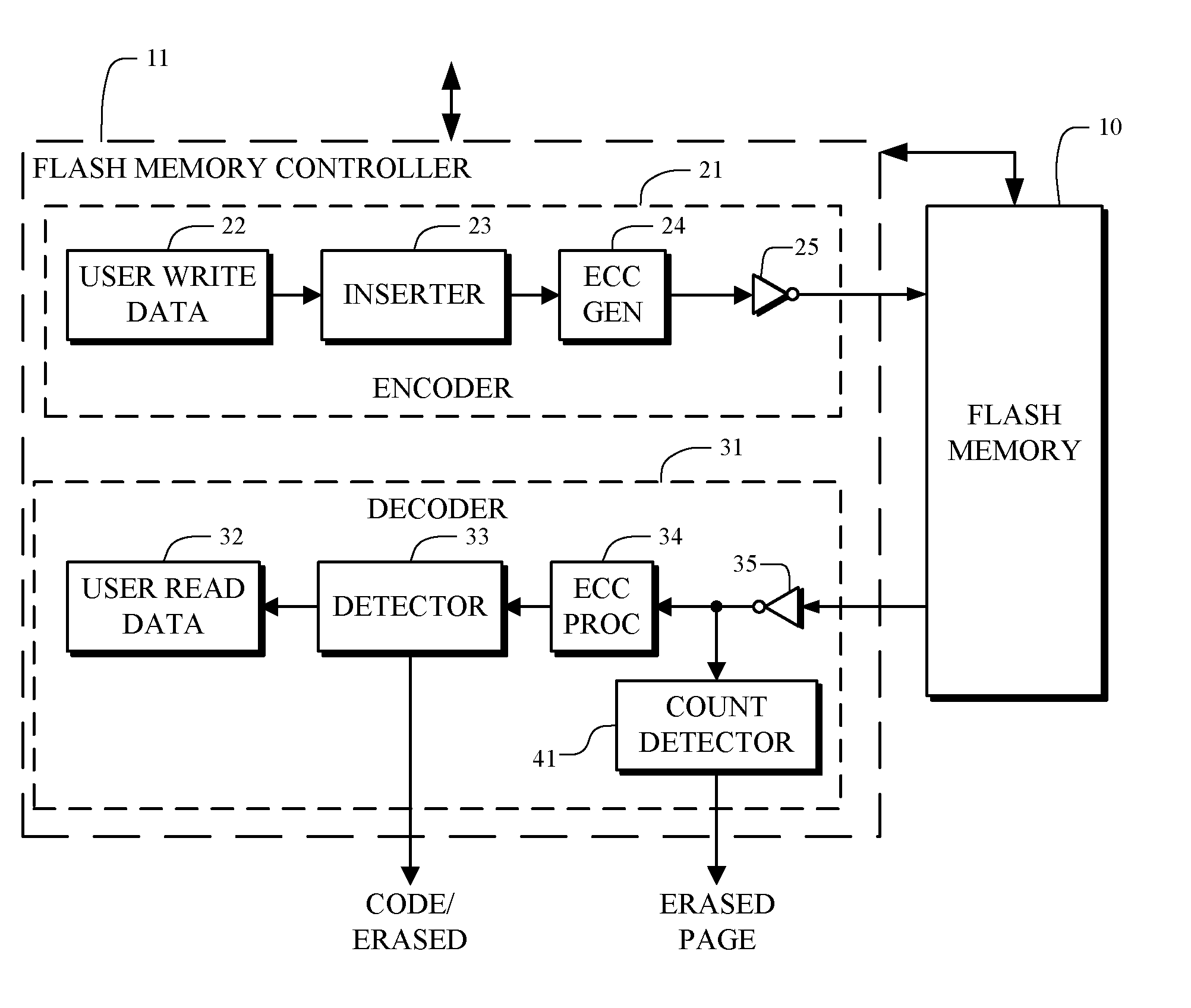

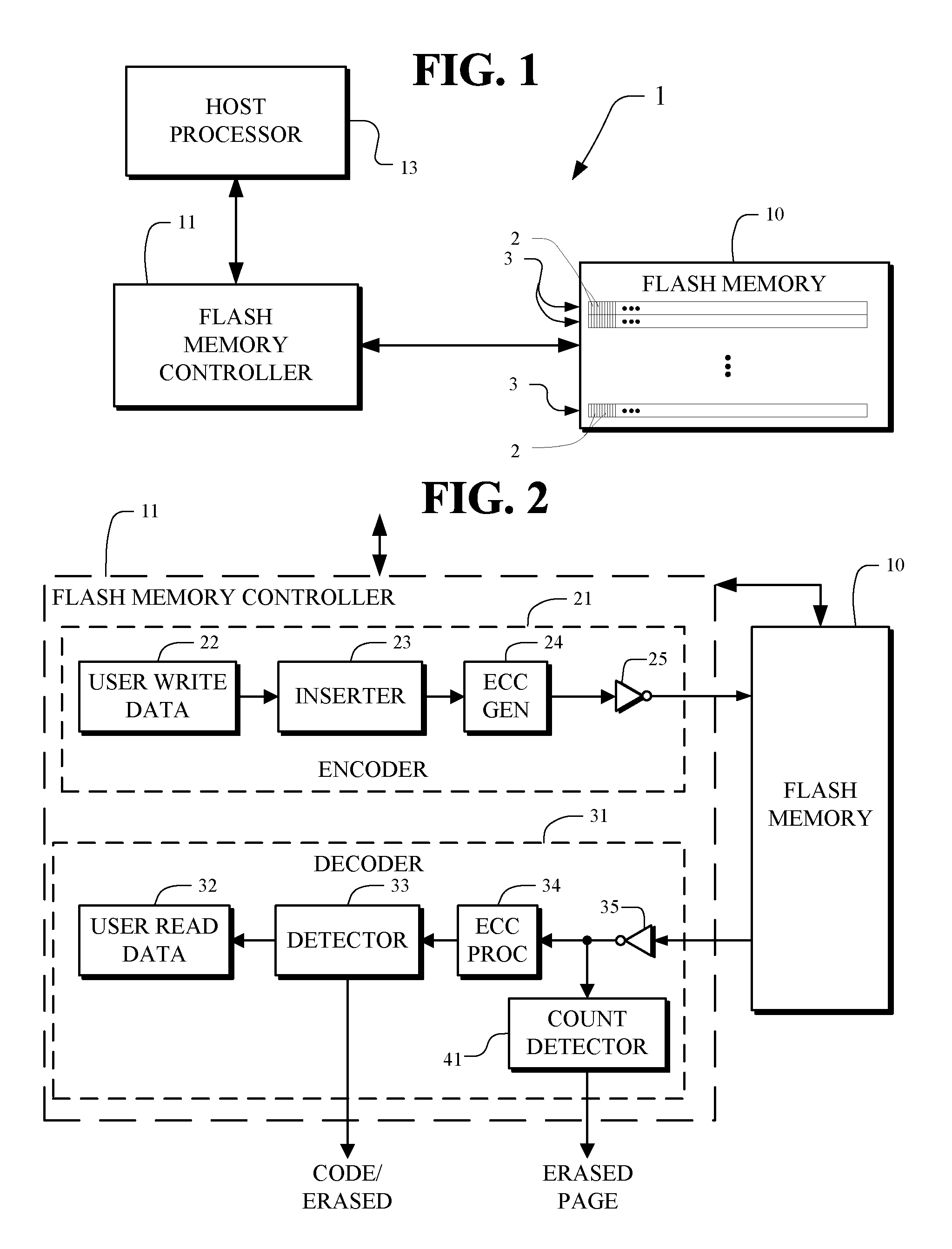

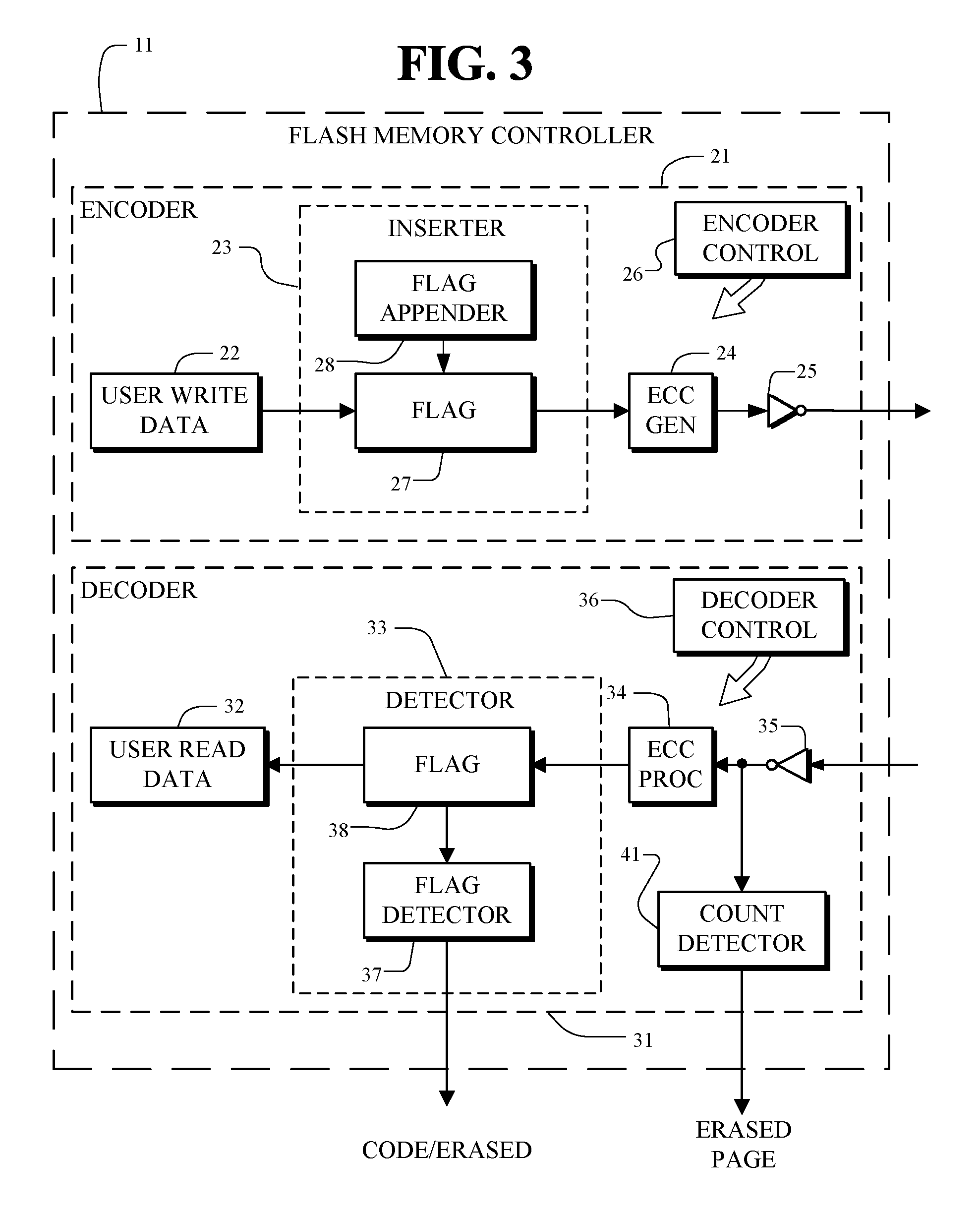

Erased page detection

A memory device and method, such as a flash memory device and method, includes a memory having a plurality of nonvolatile memory cells for storing stored values of user data. The memory device and method includes a memory controller for controlling the memory. The memory controller includes an encoder for encoding user write data for storage of code values as the stored values in the memory. The encoder includes an inserter for insertion of an indicator as part of the stored values for use in determining when the stored values are or are not in an erased state. The memory controller includes a decoder for reading the stored values from the memory to form user read data values when the stored values are not in the erased state.

Owner:MARVELL ASIA PTE LTD

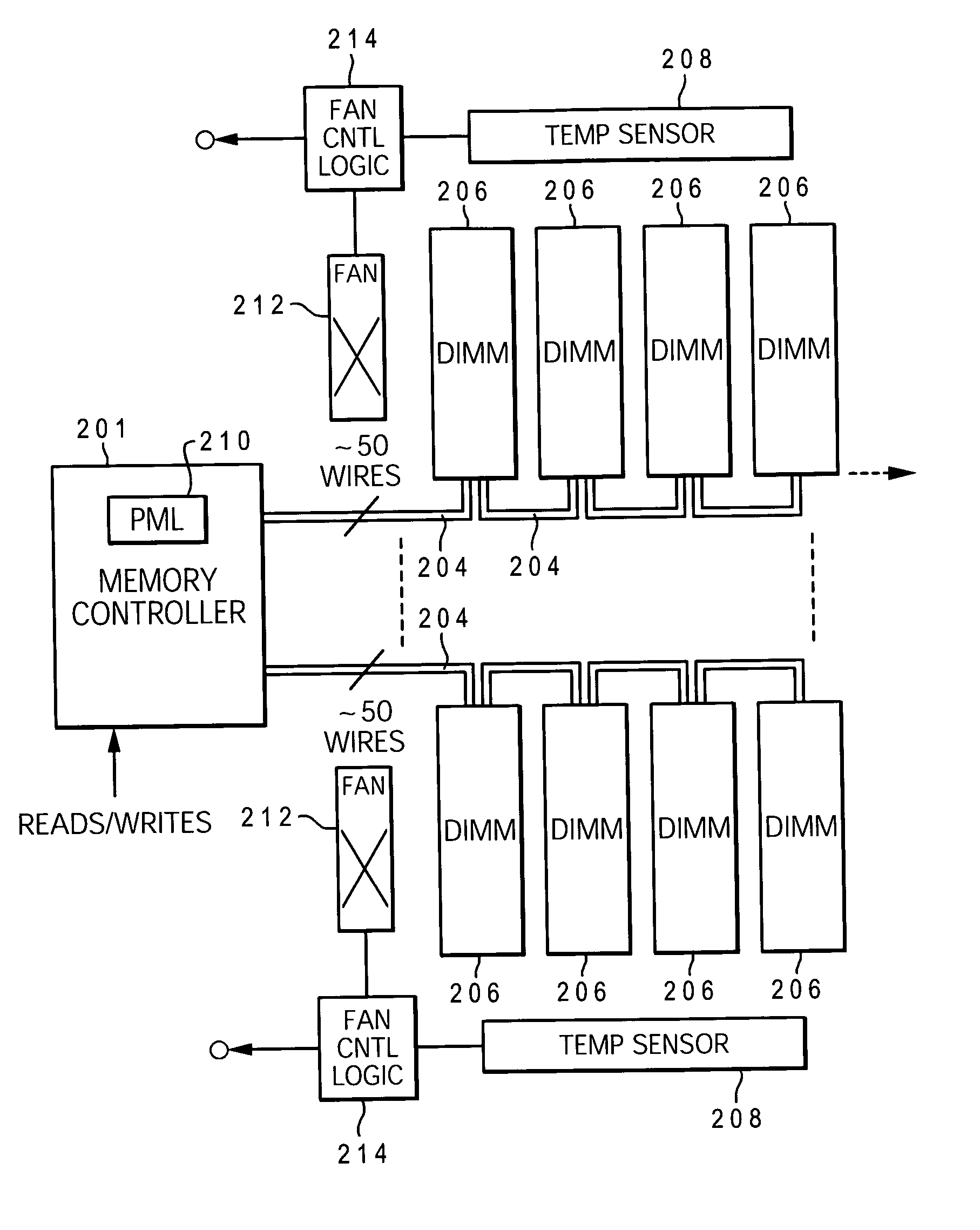

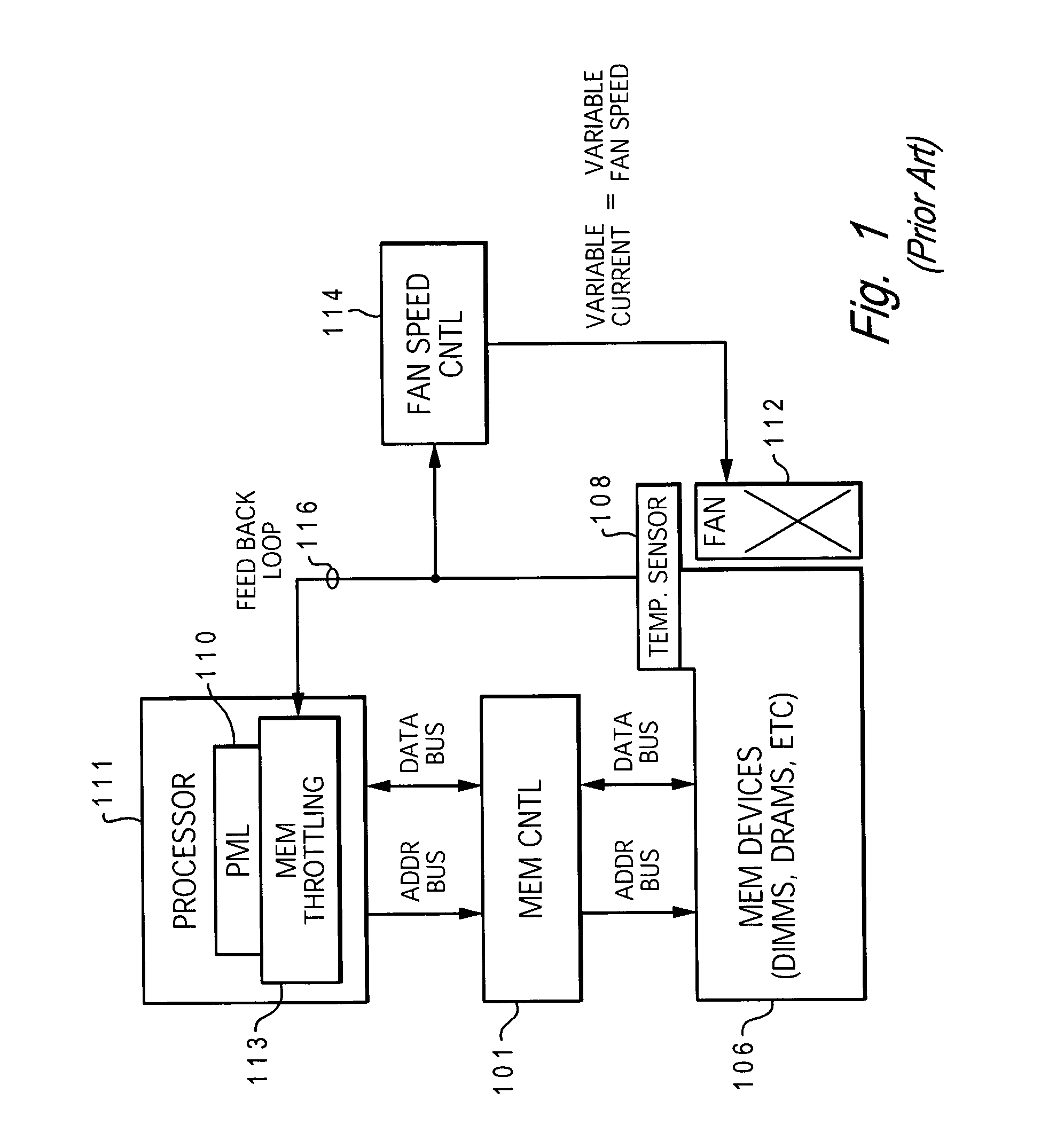

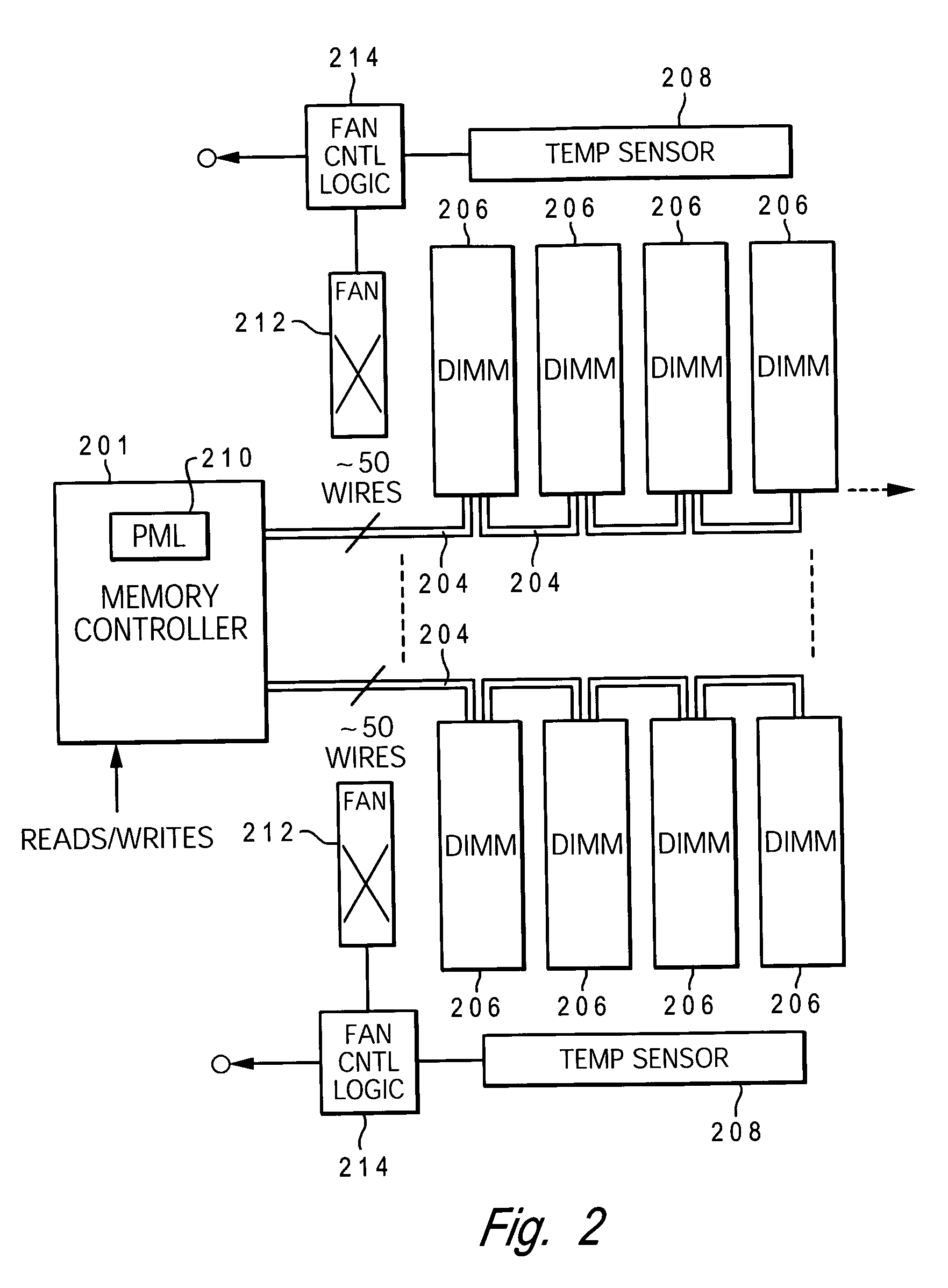

Dynamic power management via DIMM read operation limiter

InactiveUS20060179334A1Little or no usePower usageEnergy efficient ICTVolume/mass flow measurementDIMMDynamic power management

A method and system for enabling directed temperature / power management at the DIMM-level and / or DRAM-level utilizing intelligent scheduling of memory access operations received at the memory controller. Hot spots within the memory subsystem, caused by operating the DIMMs / DRAMs above predetermined / preset threshold power / temperature values for operating a DIMM and / or a DRAM, are avoided / controlled by logic within the memory controller. The memory controller logic throttles the number / frequency at which commands (read / write operations) are issued to the specific DIMM / DRAM based on feedback data received from the specific DIMM / DRAM reaching the preset threshold power usage value.

Owner:IBM CORP

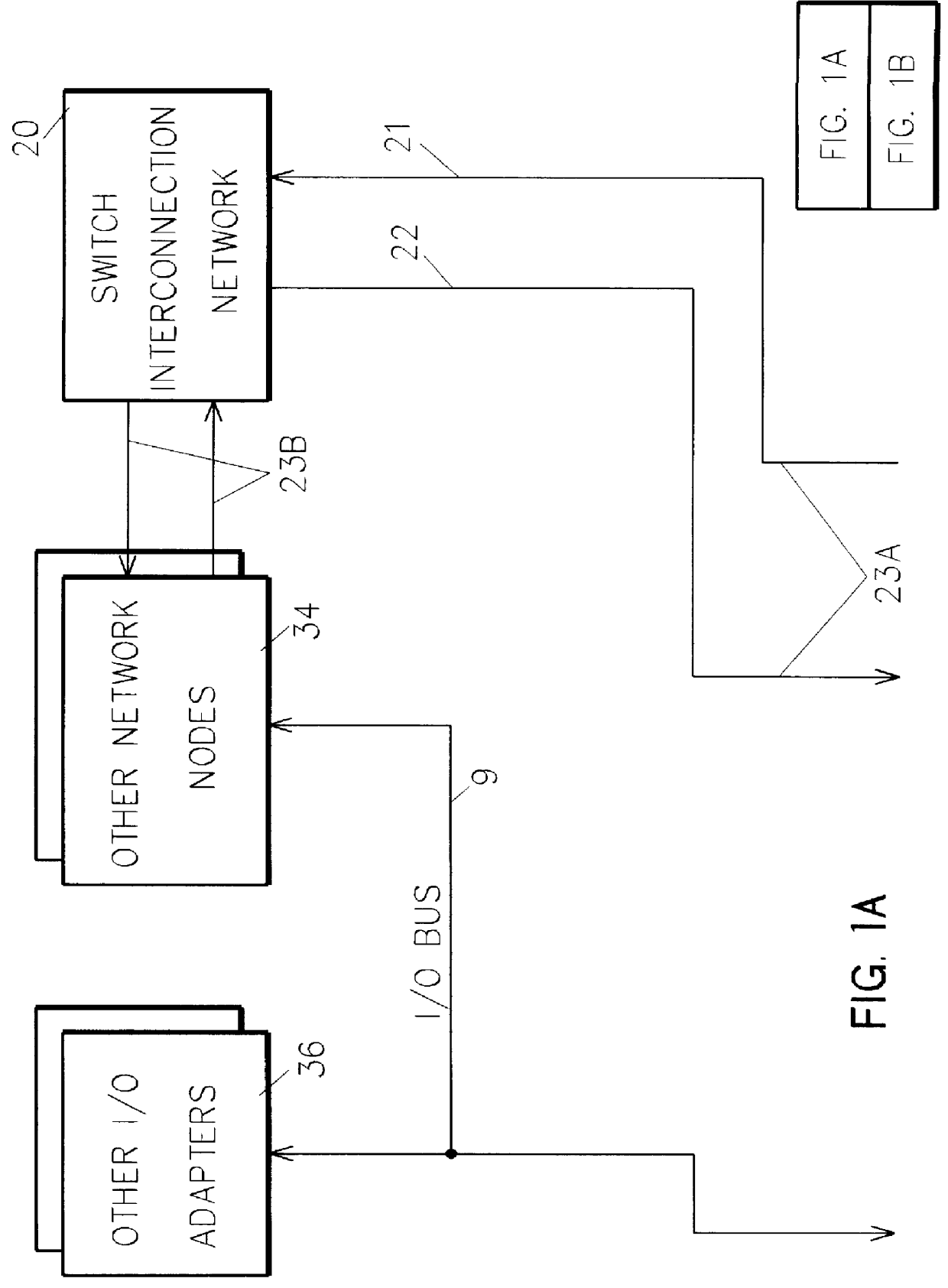

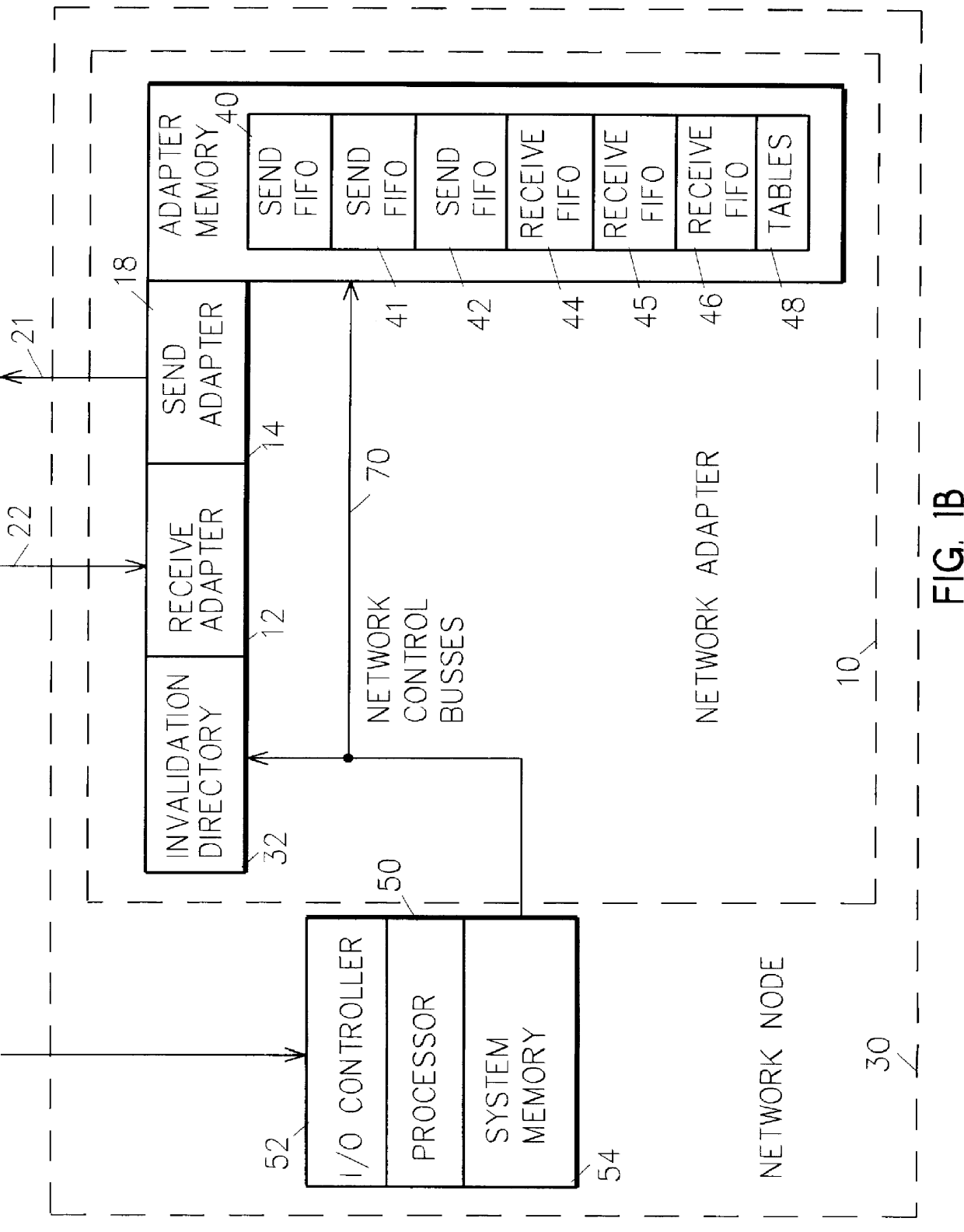

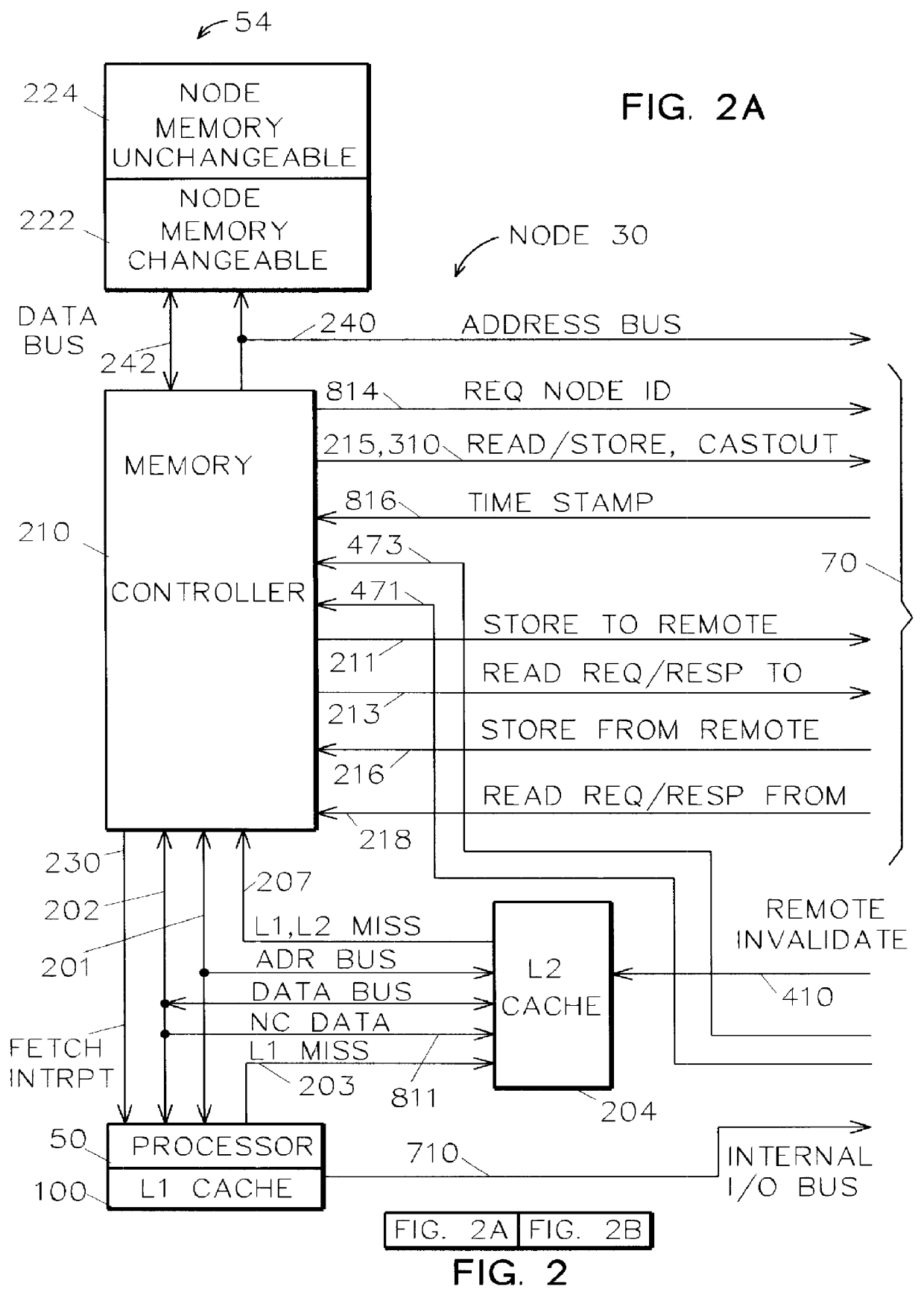

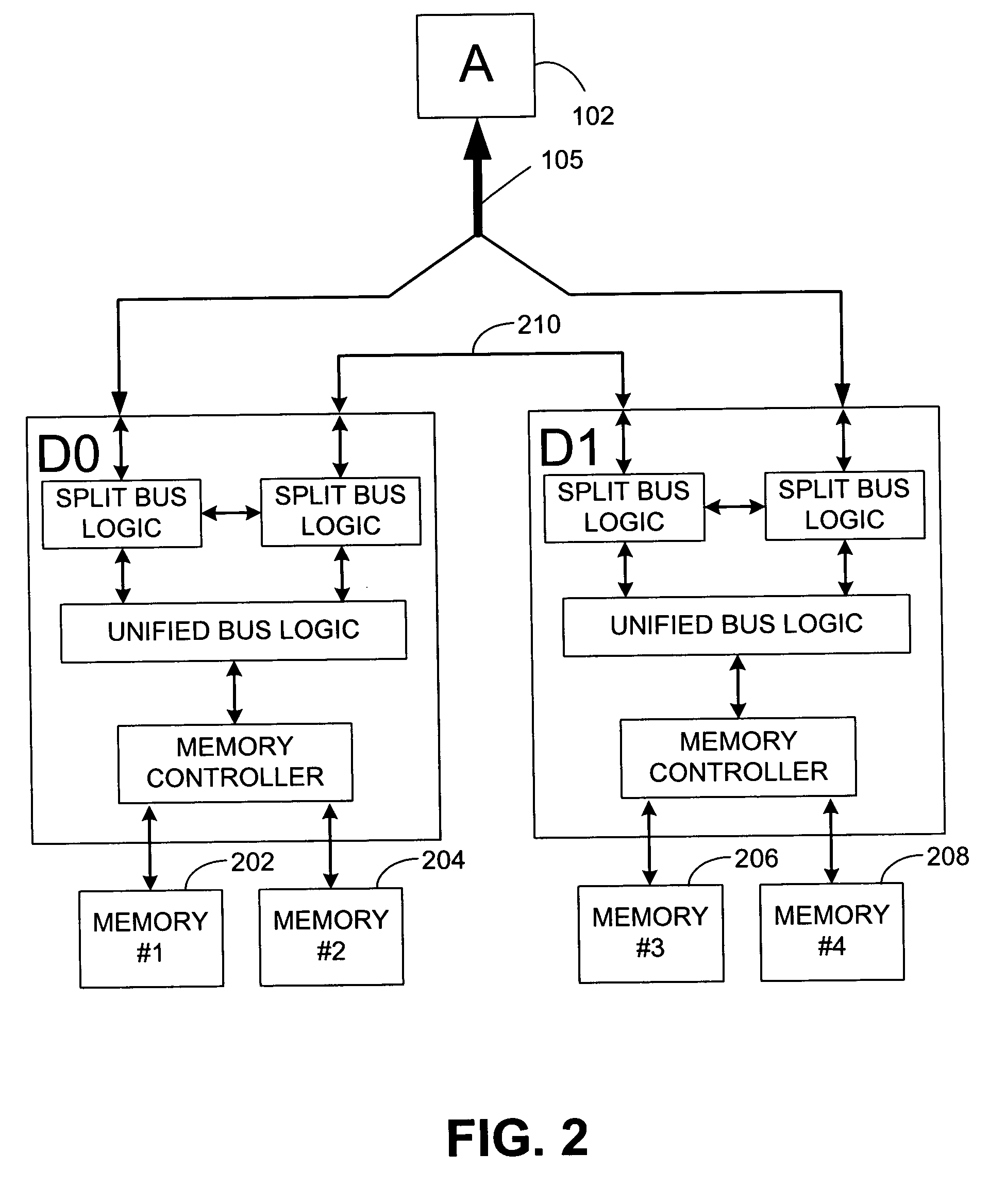

Memory controller for controlling memory accesses across networks in distributed shared memory processing systems

InactiveUS6044438AMore efficient cache coherent systemData processing applicationsMemory adressing/allocation/relocationRemote memory accessRemote direct memory access

A shared memory parallel processing system interconnected by a multi-stage network combines new system configuration techniques with special-purpose hardware to provide remote memory accesses across the network, while controlling cache coherency efficiently across the network. The system configuration techniques include a systematic method for partitioning and controlling the memory in relation to local verses remote accesses and changeable verses unchangeable data. Most of the special-purpose hardware is implemented in the memory controller and network adapter, which implements three send FIFOs and three receive FIFOs at each node to segregate and handle efficiently invalidate functions, remote stores, and remote accesses requiring cache coherency. The segregation of these three functions into different send and receive FIFOs greatly facilitates the cache coherency function over the network. In addition, the network itself is tailored to provide the best efficiency for remote accesses.

Owner:IBM CORP

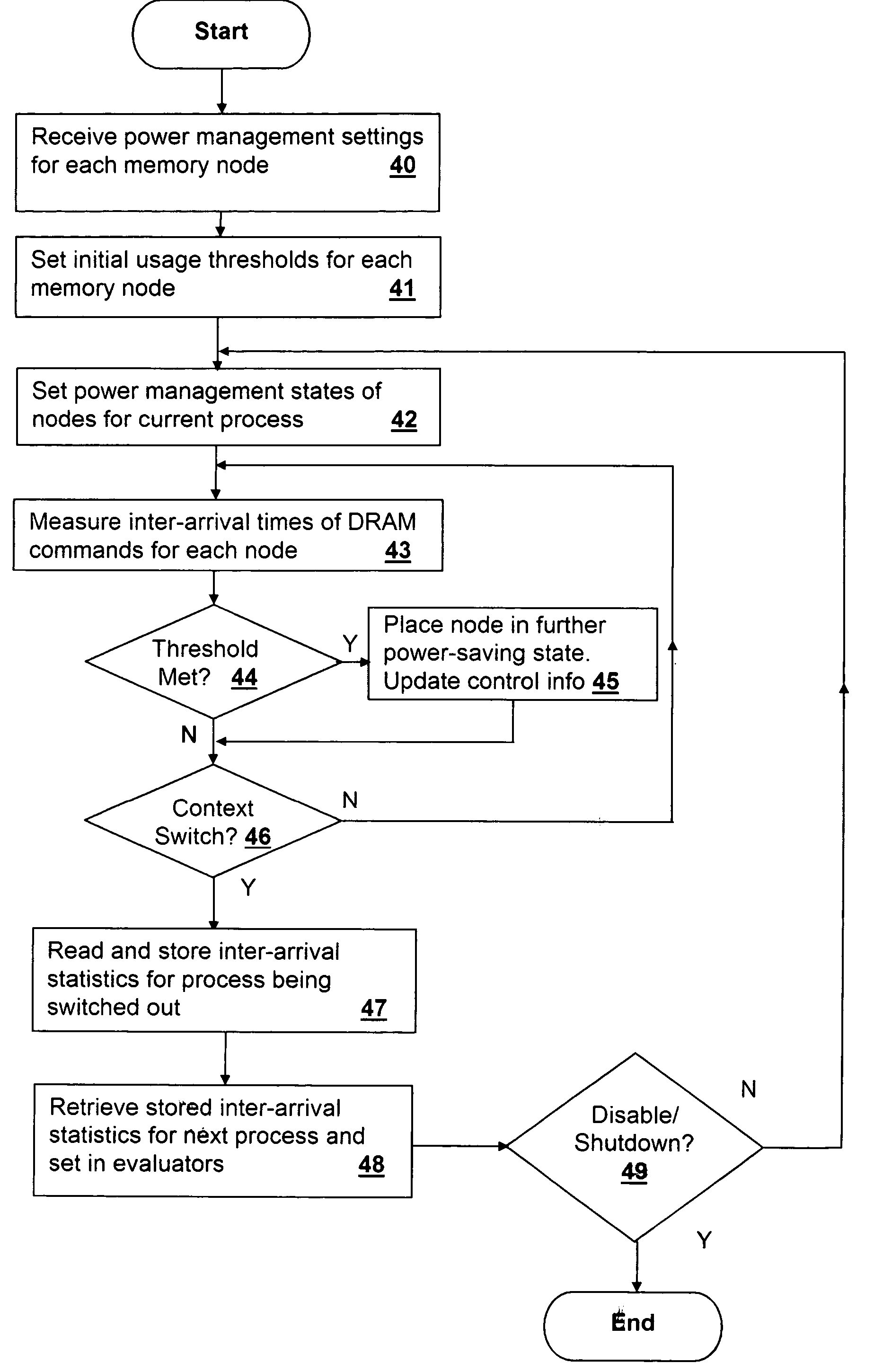

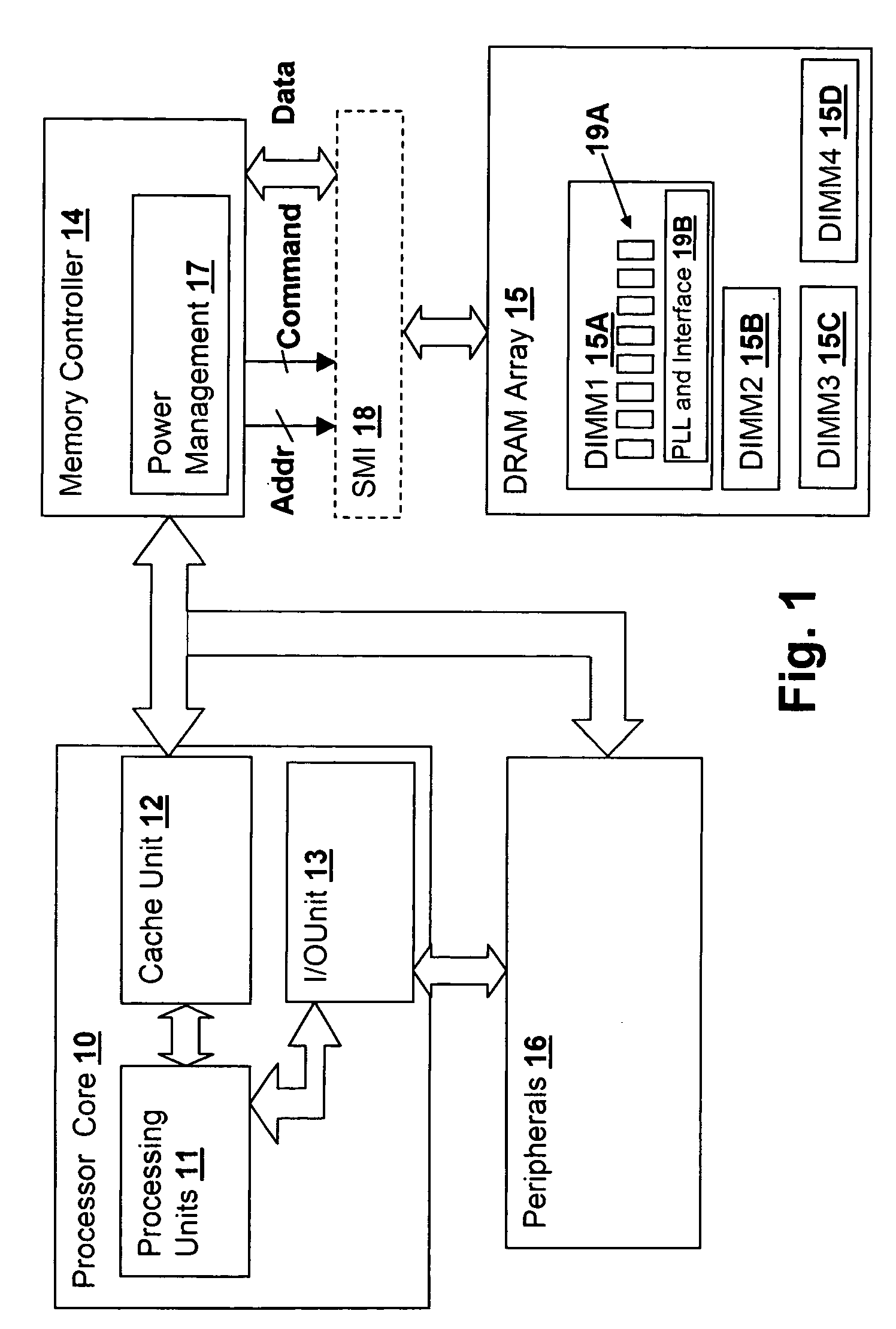

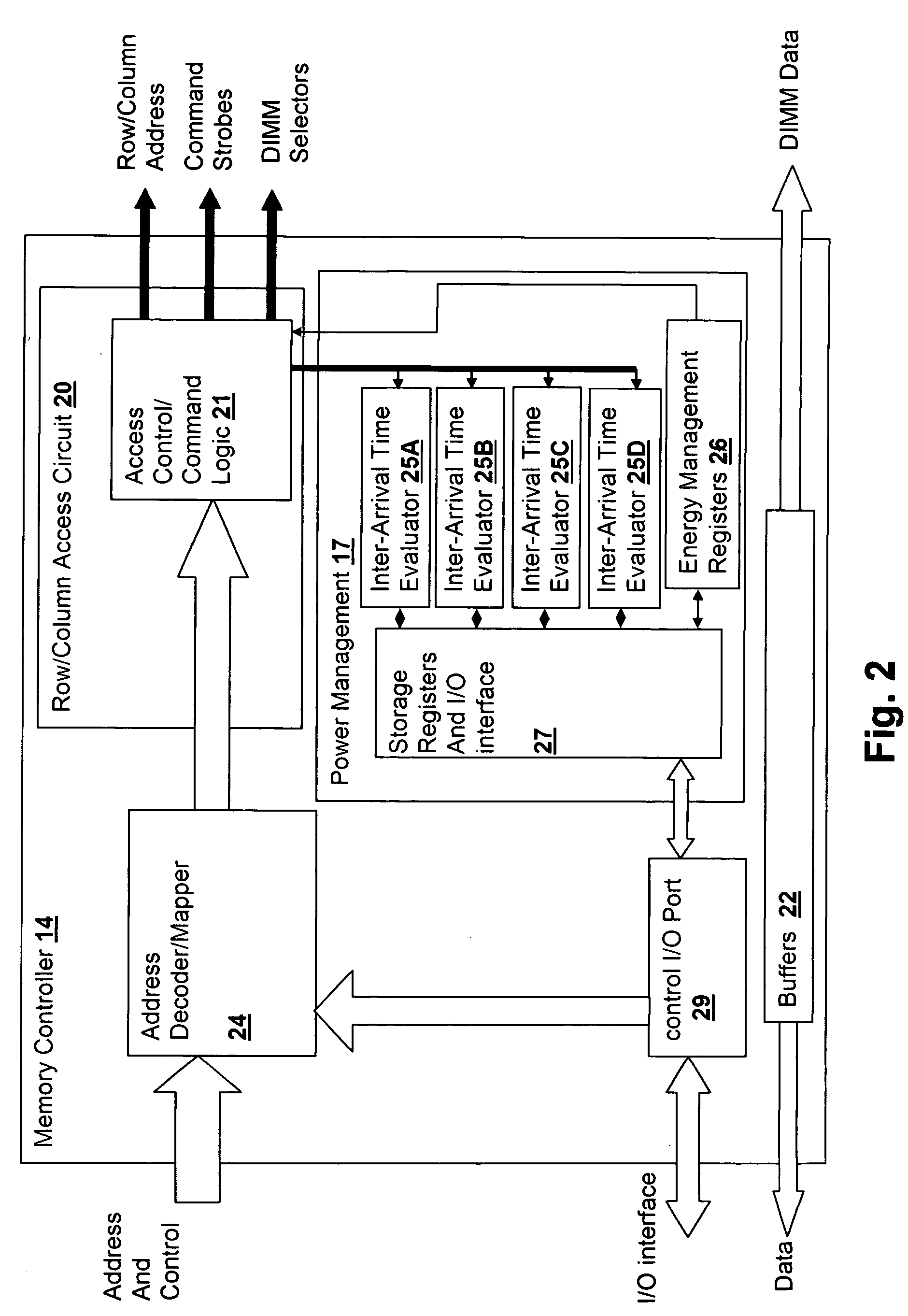

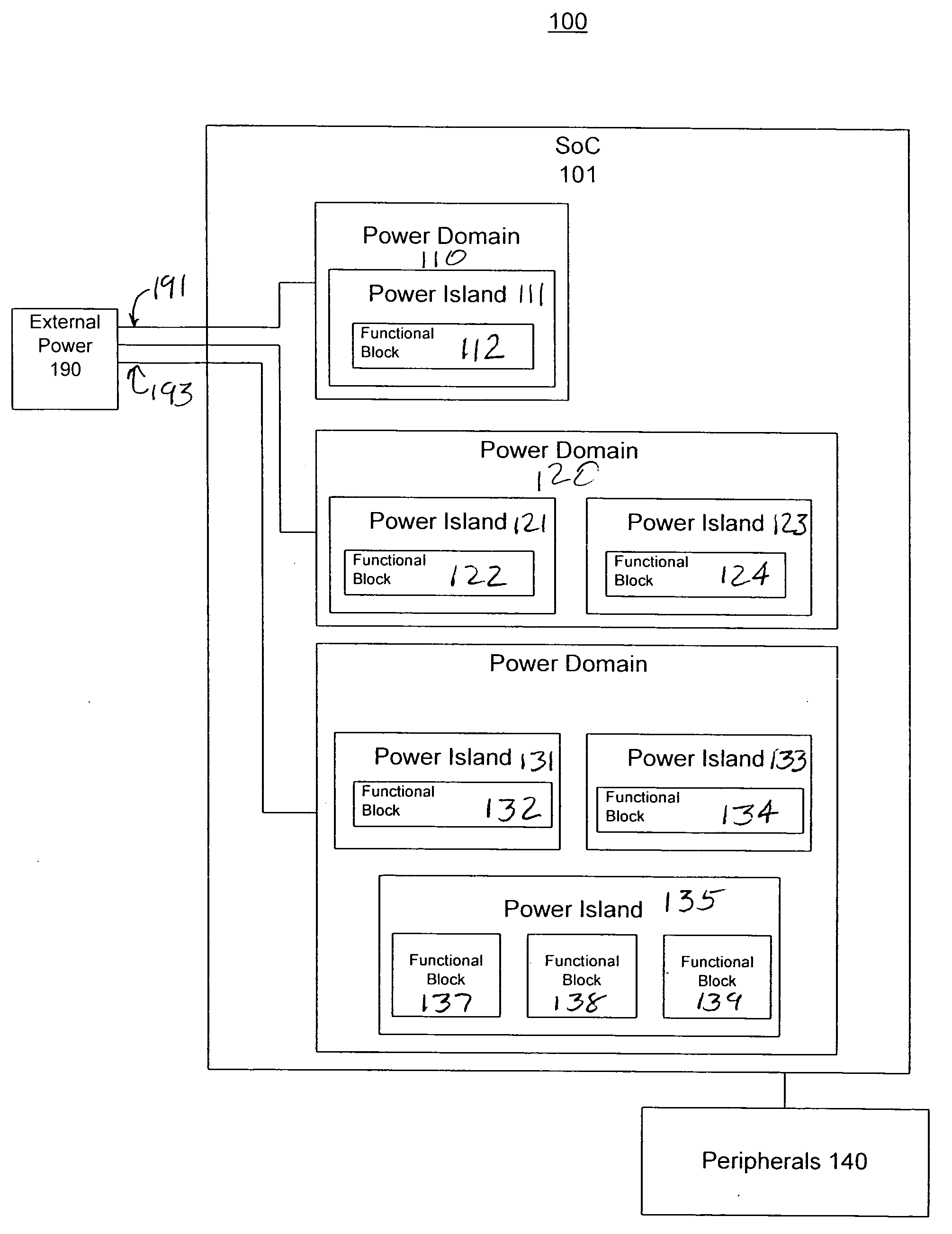

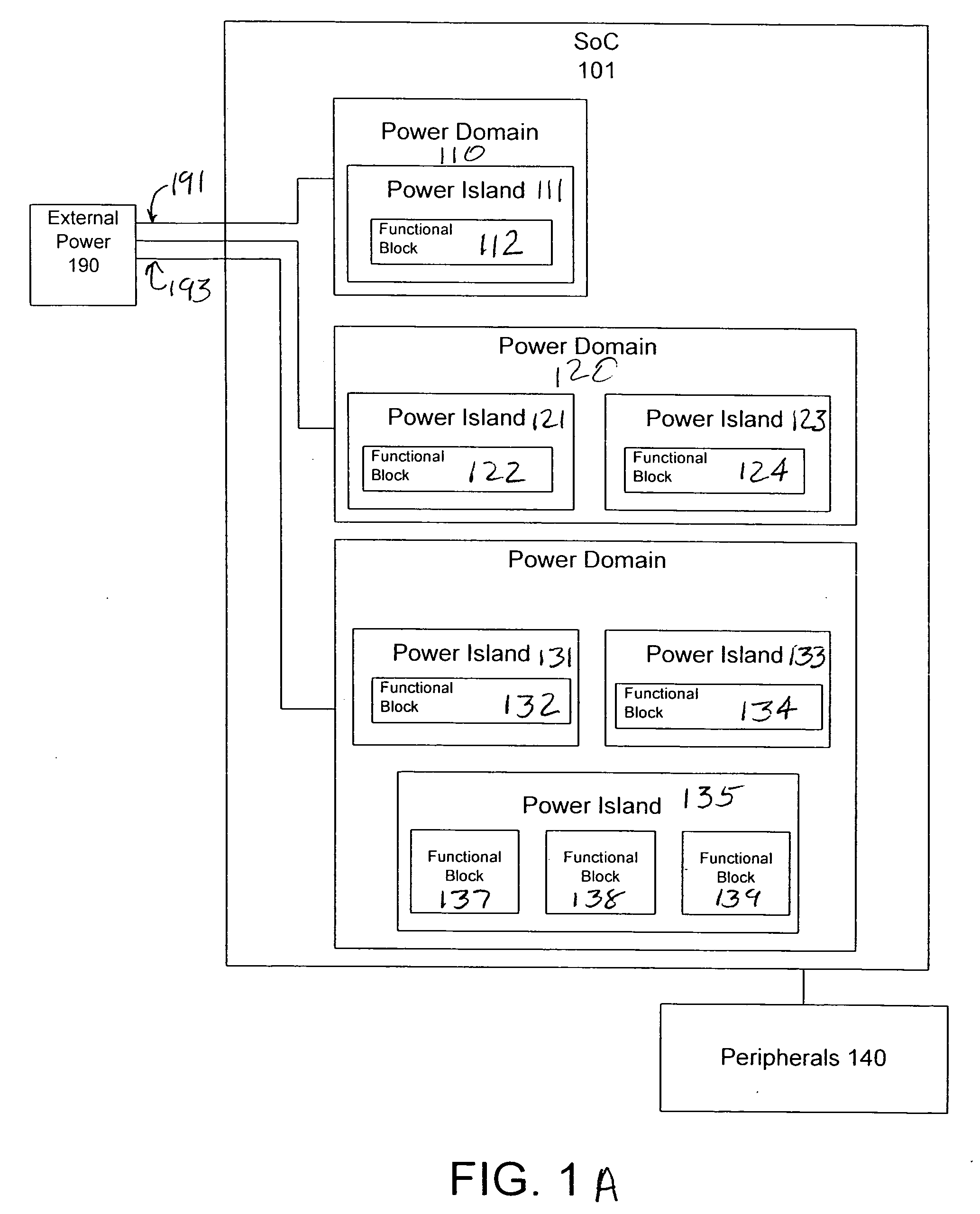

Method and system for power management including device controller-based device use evaluation and power-state control

InactiveUS20050125702A1Lower latencyReduce power consumptionEnergy efficient ICTVolume/mass flow measurementOperational systemDevice Usage

A method and system for power management including device controller-based device use evaluation and power-state control provides improved performance in a power-managed processing system. Per-device usage information is measured and evaluated during process execution and is retrieved from the device controller upon a context switch, so that upon reactivation of the process, the previous usage evaluation state can be restored. The device controller can then provide for per-process control of attached device power management states without intervention by the processor and without losing the historical evaluation state when a process is switched out. The device controller can control power-saving states of connected devices in conformity with the usage evaluation without processor intervention and across multiple process execution slices. The device controller may be a memory controller and the controlled devices memory modules or banks within modules if individual banks can be power-managed. Local thresholds provide the decision-making mechanism for each controlled device. The thresholds may be history-based, fixed or adaptive and are generally set initially by the operating system and may be updated by the memory controller adaptively or using historical collected usage evaluation counts or alternatively by the operating system via a system processor.

Owner:IBM CORP

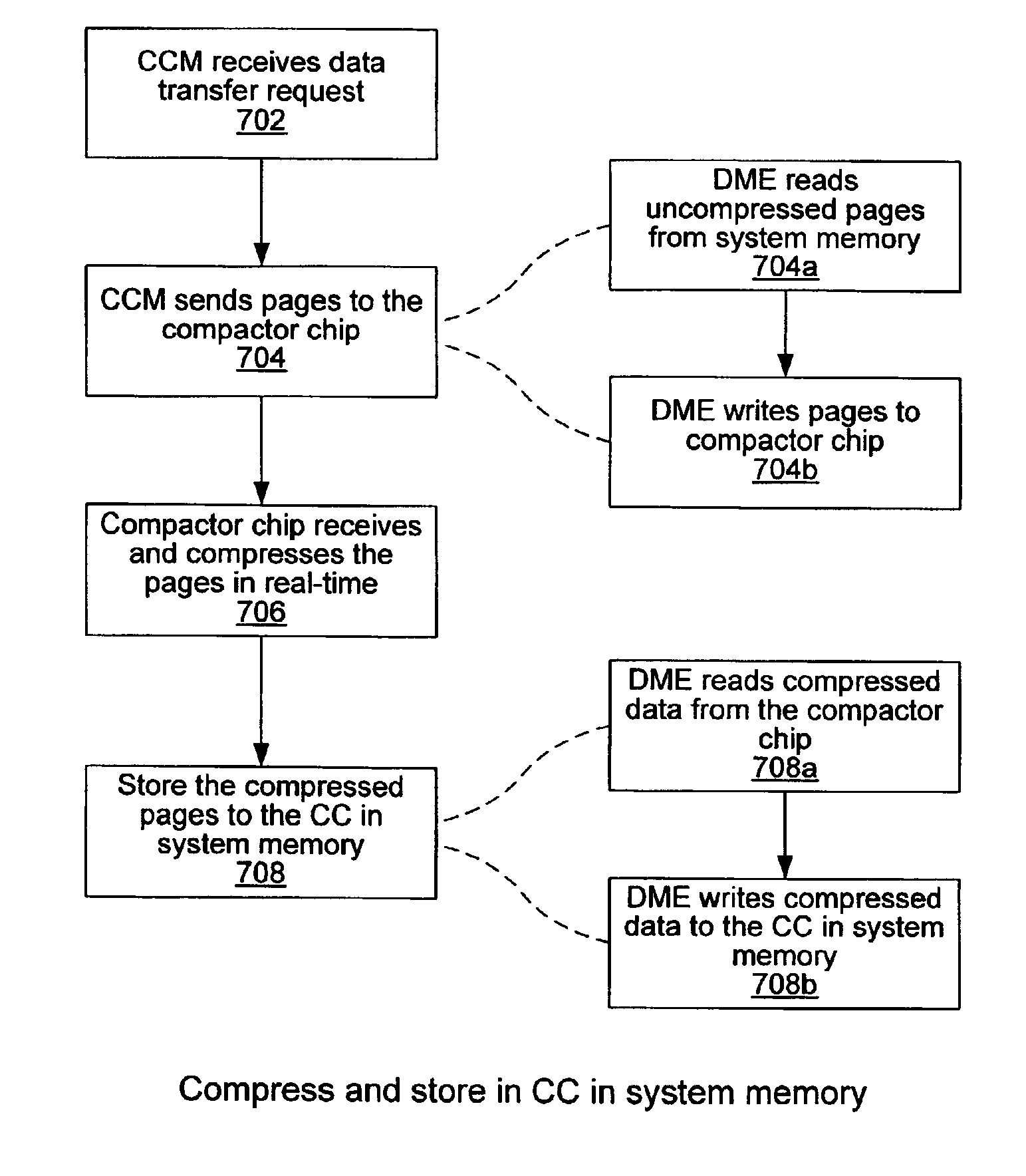

Managing a codec engine for memory compression/decompression operations using a data movement engine

InactiveUS7089391B2Memory architecture accessing/allocationMemory adressing/allocation/relocationComputerized systemMemory controller

A system and method for managing a functional unit in a system using a data movement engine. An exemplary system may comprise a CPU coupled to a memory controller. The memory controller may include or couple to a data movement engine (DME). The memory controller may in turn couple to a system memory or other device which includes at least one functional unit. The DME may operate to transfer data to / from the system memory and / or the functional unit, as described herein. In one embodiment, the DME may also include multiple DME channels or multiple DME contexts. The DME may operate to direct the functional unit to perform operations on data in the system memory. For example, the DME may read source data from the system memory, the DME may then write the source data to the functional unit, the functional unit may operate on the data to produce modified data, the DME may then read the modified data from the functional unit, and the DME may then write the modified data to a destination in the system memory. Thus the DME may direct the functional unit to perform an operation on data in system memory using four data movement operations. The DME may also perform various other data movement operations in the computer system, e.g., data movement operations that are not involved with operation of the functional unit.

Owner:INTELLECTUAL VENTURES I LLC

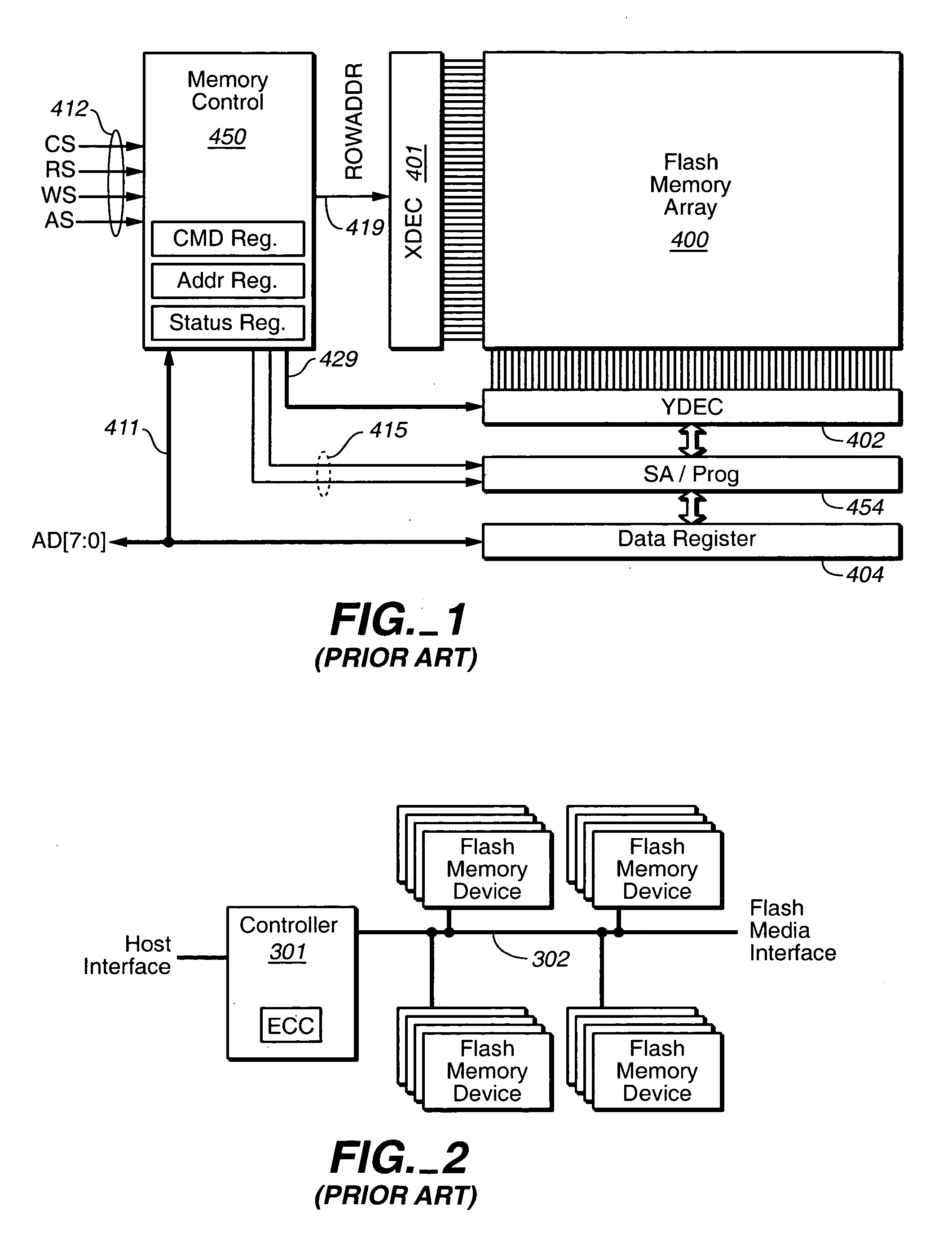

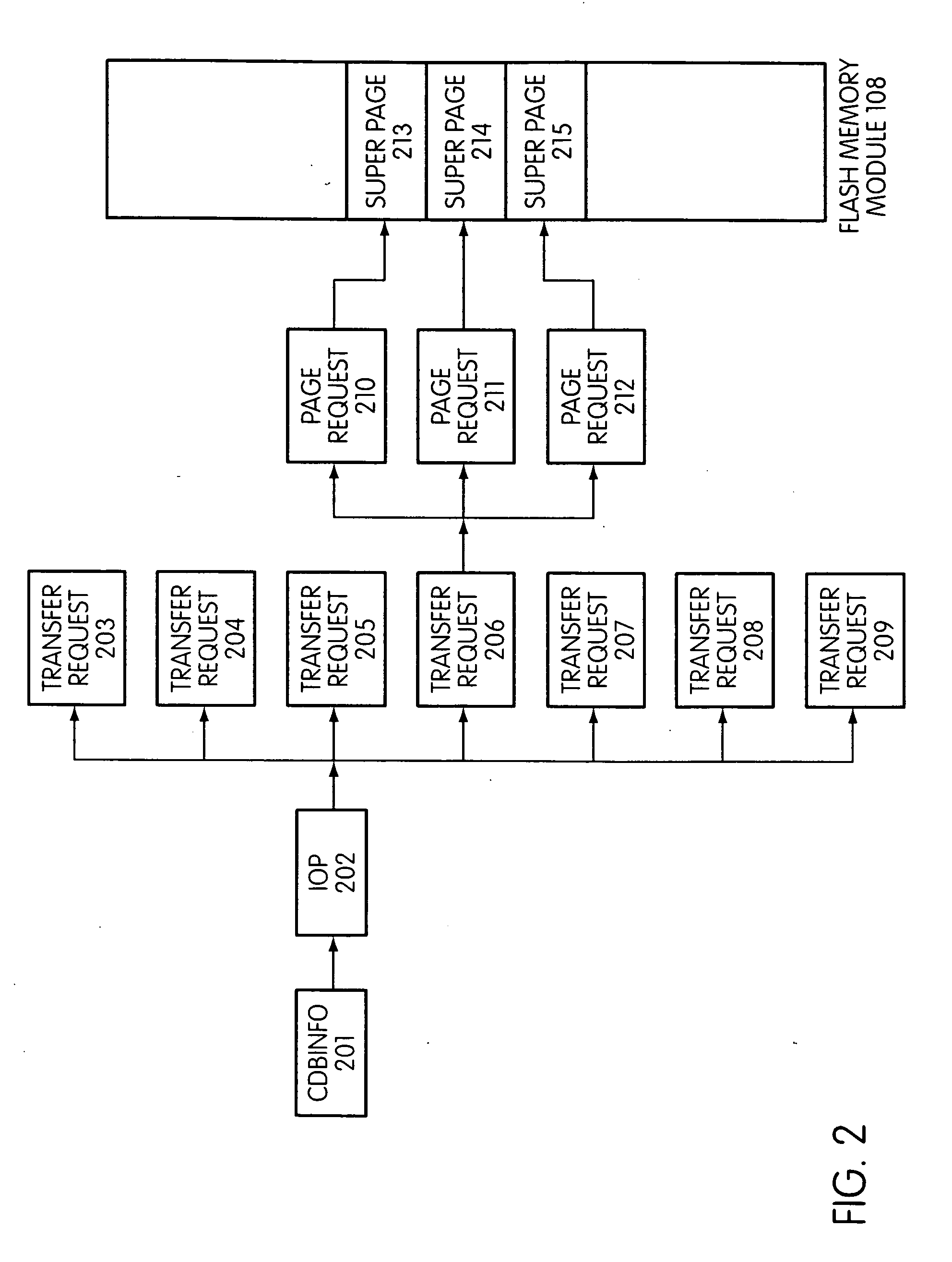

Storage system using flash memory modules logically grouped for wear-leveling and RAID

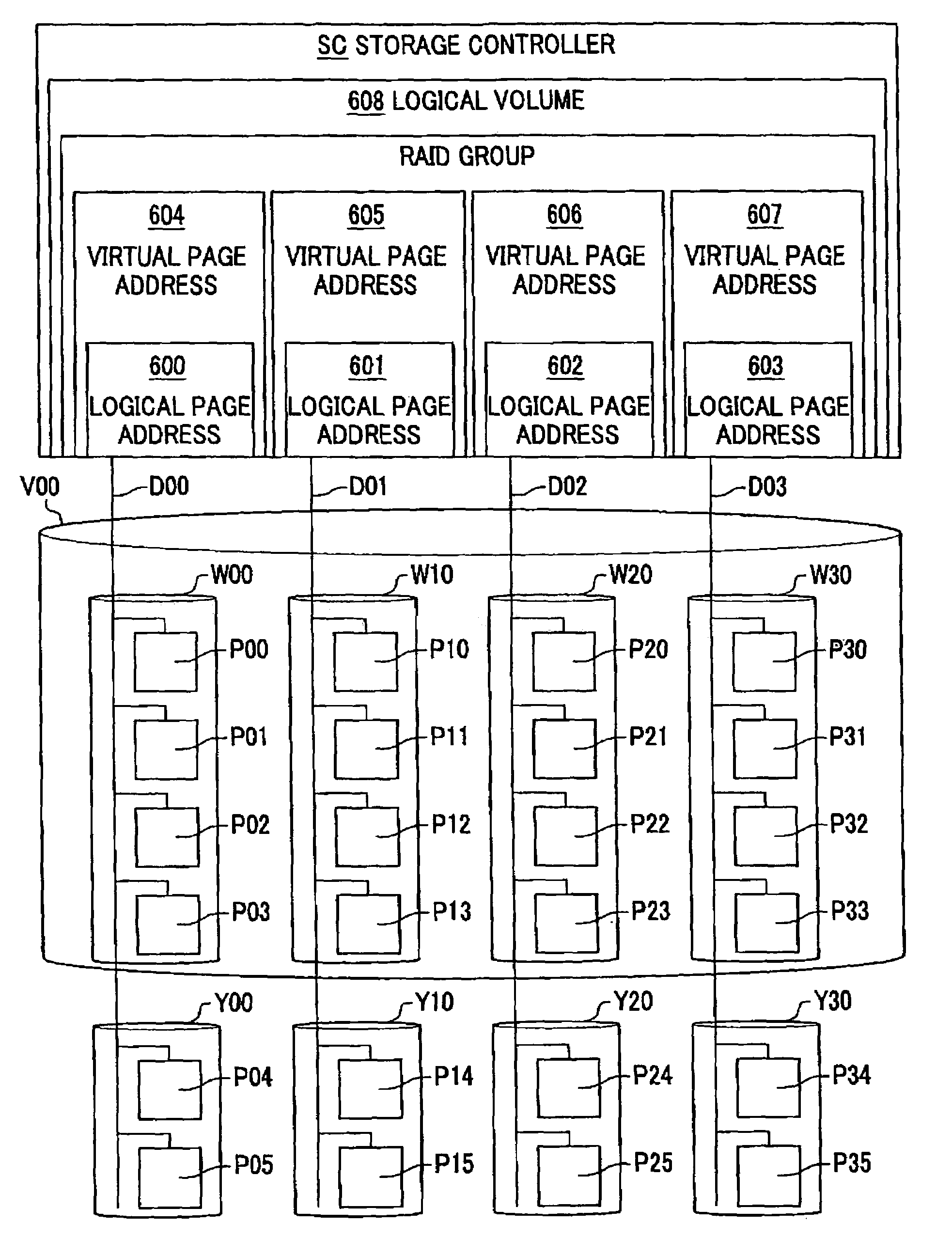

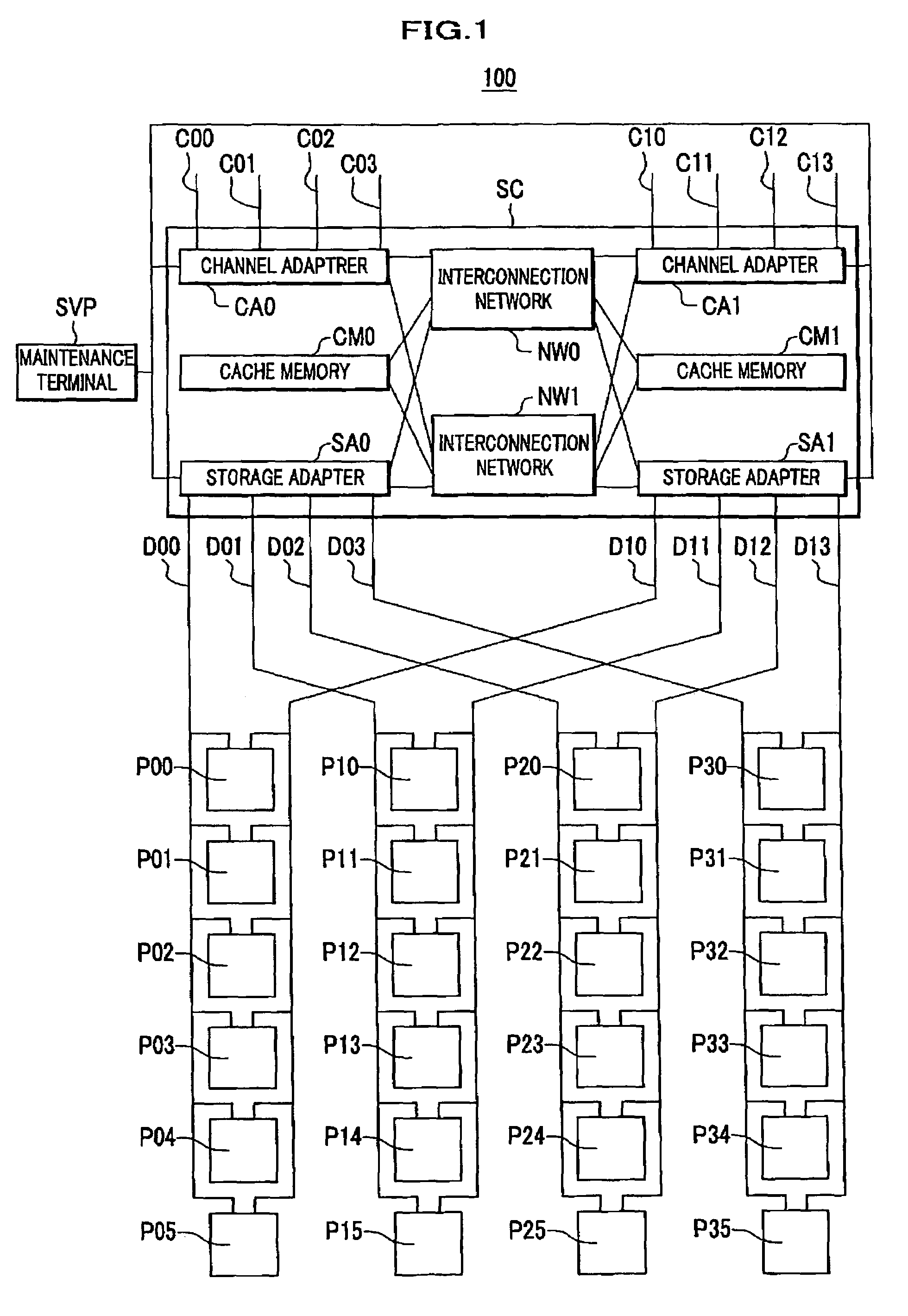

A storage system using flash memories includes a storage controller and plural flash memory modules as storage media. Each flash memory module includes at least one flash memory chip and a memory controller for leveling erase counts of blocks belonging to the flash memory chip. The storage controller combines the plural flash memory modules into a first logical group, translates a first address used for accessing the flash memory modules belonging to the first logical group to a second address used for handling the first address in the storage controller, and combines the plural first logical groups into a second logical group.

Owner:HITACHI LTD

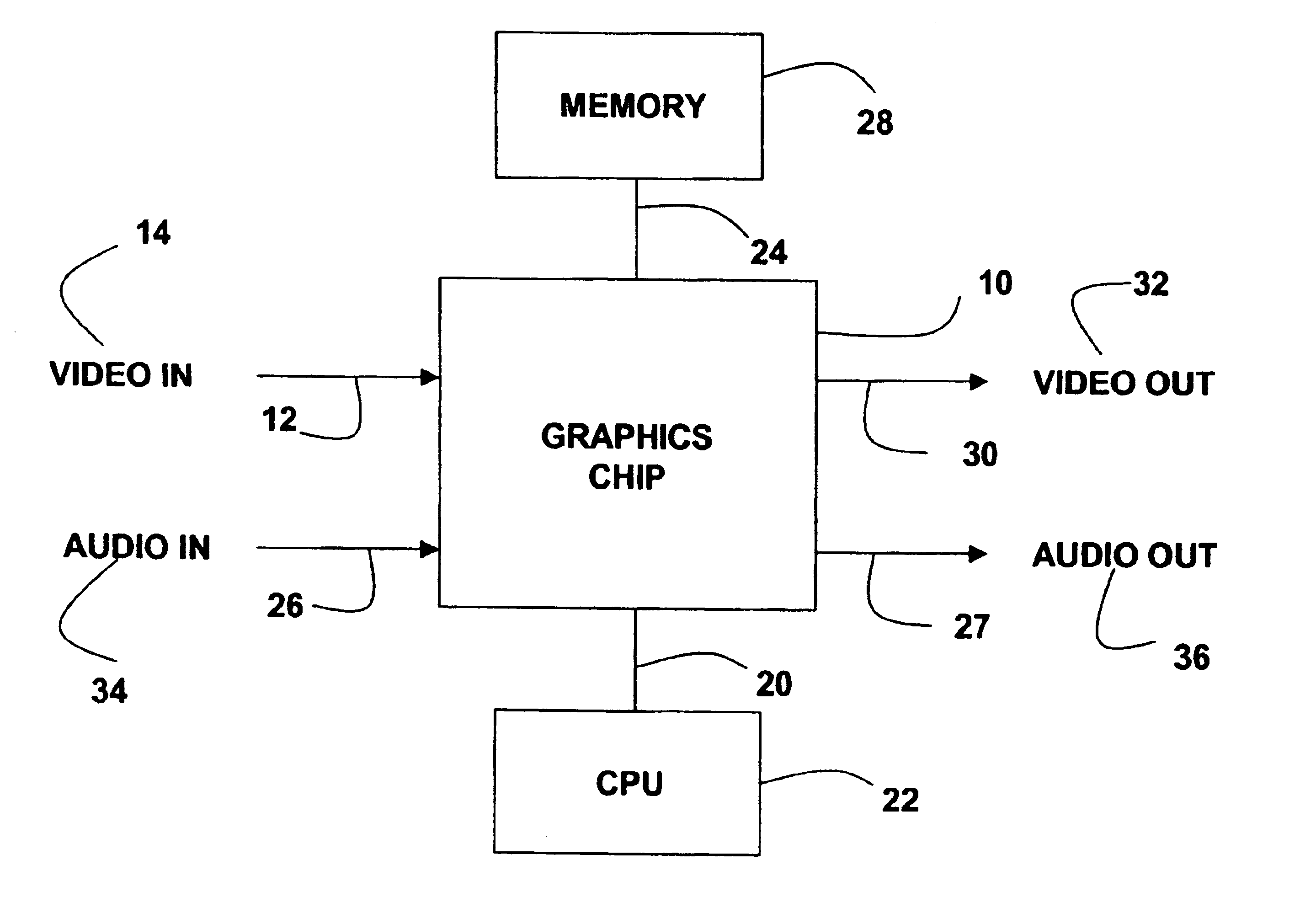

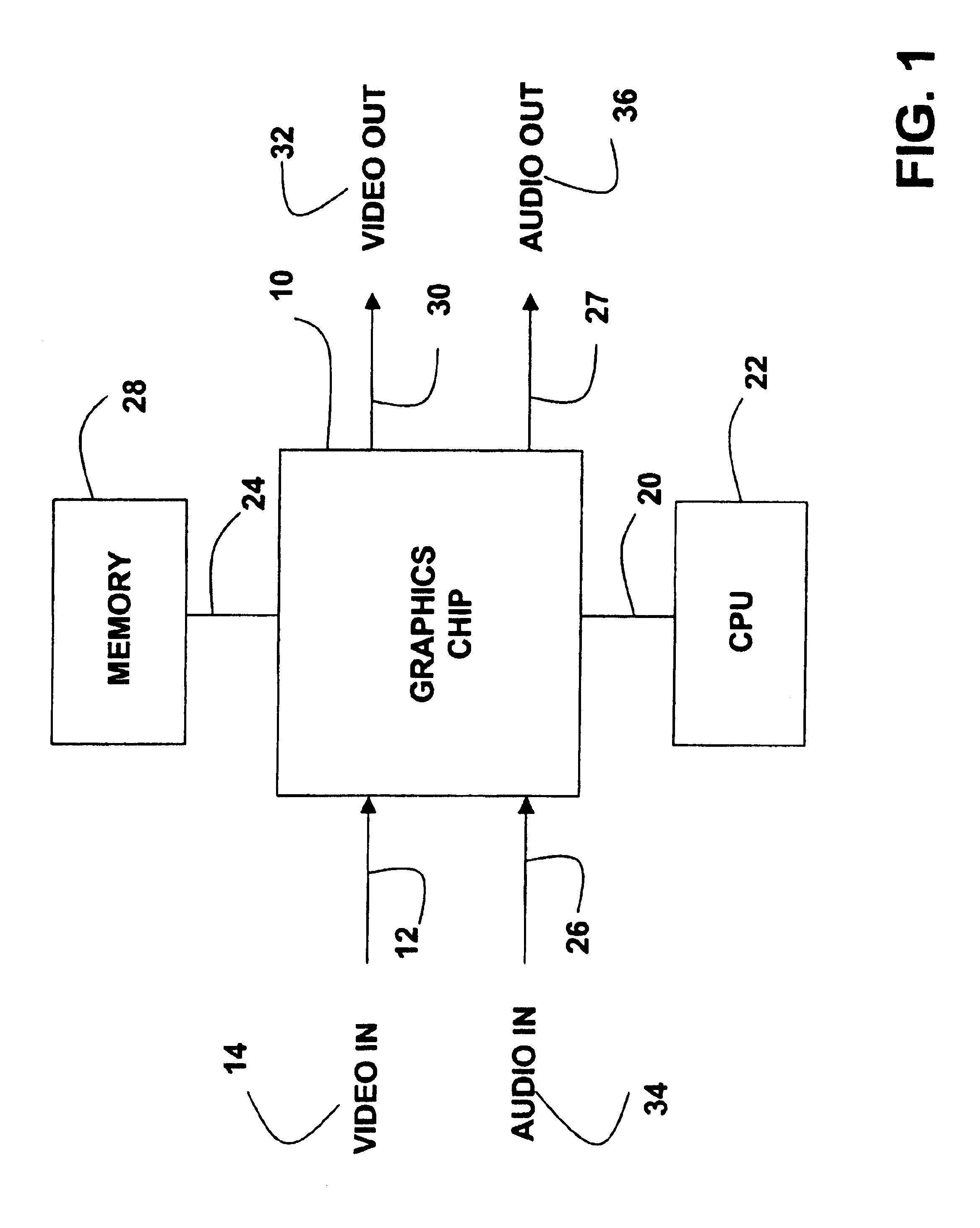

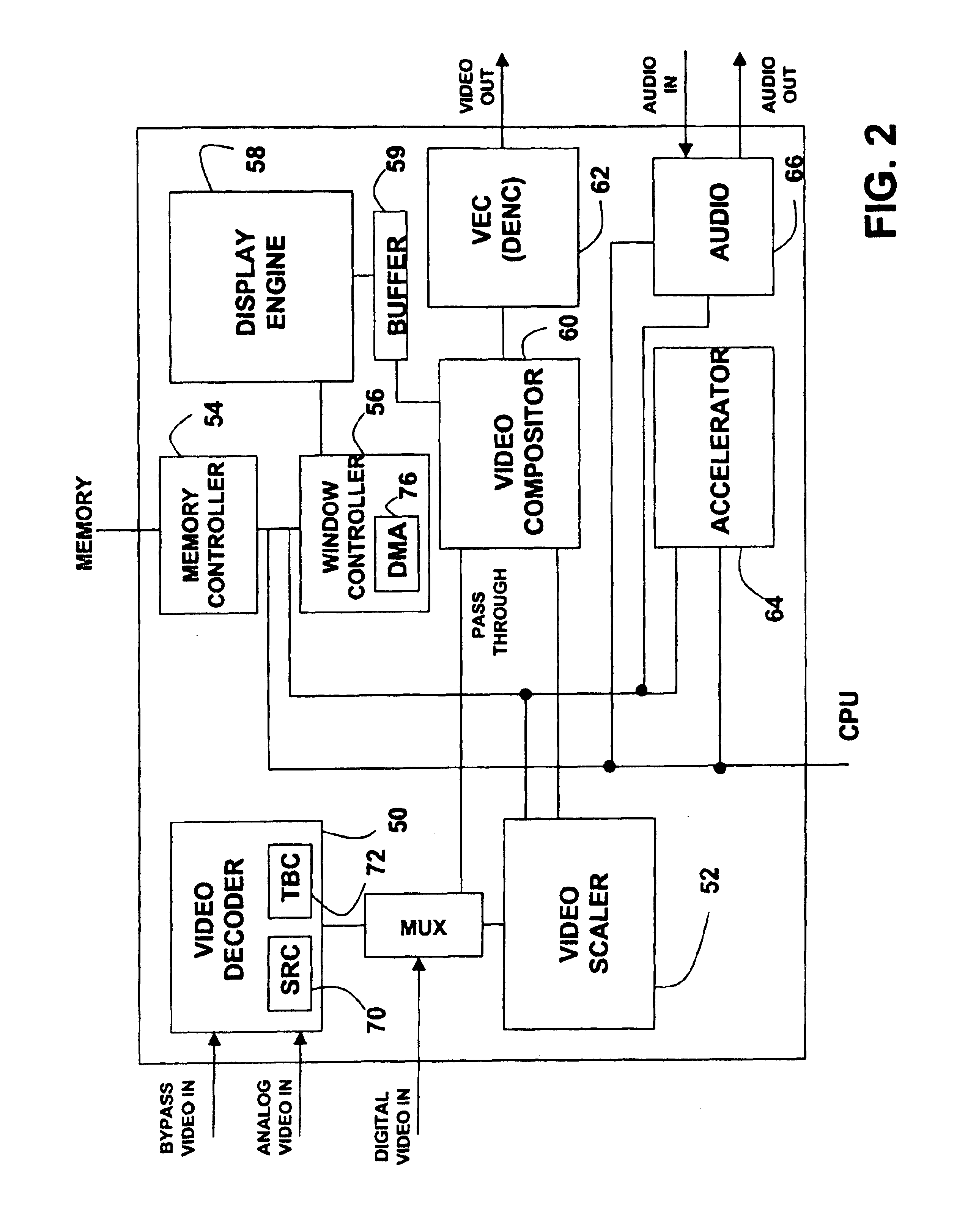

Video, audio and graphics decode, composite and display system

InactiveUS6853385B1Minimum total system costLow costTelevision system detailsTelevision system scanning detailsDigital videoDigital audio signals

A video, audio and graphics system uses multiple transport processors to receive in-band and out-of-band MPEG Transport streams, to perform PID and section filtering as well as DVB and DES decryption and to de-multiplex them. The system processes the PES into digital audio, MPEG video and message data. The system is capable of decoding multiple MPEG SLICEs concurrently. Graphics windows are blended in parallel, and blended with video using alpha blending. During graphics processing, a single-port SRAM is used equivalently as a dual-port SRAM. The video may include both analog video, e.g., NTSC / PAL / SECAM / S-video, and digital video, e.g., MPEG-2 video in SDTV or HDTV format. The system has a reduced memory mode in which video images are reduced in half in horizontal direction only during decoding. The system is capable of receiving and processing digital audio signals such as MPEG Layer 1 and Layer 2 audio and Dolby AC-3 audio, as well as PCM audio signals. The system includes a memory controller. The system includes a system bridge controller to interface a CPU with devices internal to the system as well as peripheral devices including PCI devices and I / O devices such as RAM, ROM and flash memory devices. The system is capable of displaying video and graphics in both the high definition (HD) mode and the standard definition (SD) mode. The system may output an HDTV video while converting the HDTV video and providing as another output having an SDTV format or another HDTV format.

Owner:AVAGO TECH INT SALES PTE LTD

Power control system and method

An efficient and effective power control system method are described with expedited recovery from a reduced power state. In one embodiment, a present invention power control system includes performing a reduced power detection process for detecting a reduced power state, wherein the reduced power state is associated with an expedited recovery; performing a reduced power state entry process; performing a recovery detection process for detecting a recover indication event; and performing an expedited recovery process in accordance with detection of a recovery indication event. The reduced power state entry process comprises saving an expedited recovery information in registers of an always on domain and putting an external memory in self refresh mode to preserve a system context while a chip is turned off. The expedited recovery process comprises determining whether to proceed with the expedited recovery process; initializing memory controller registers and directing memory controller to exit self refresh; validating system context recovered from memory using keys stored in an always on domain; jumping to recovery instructions in memory; restoring operating system information and returning to operating system control.

Owner:NVIDIA CORP

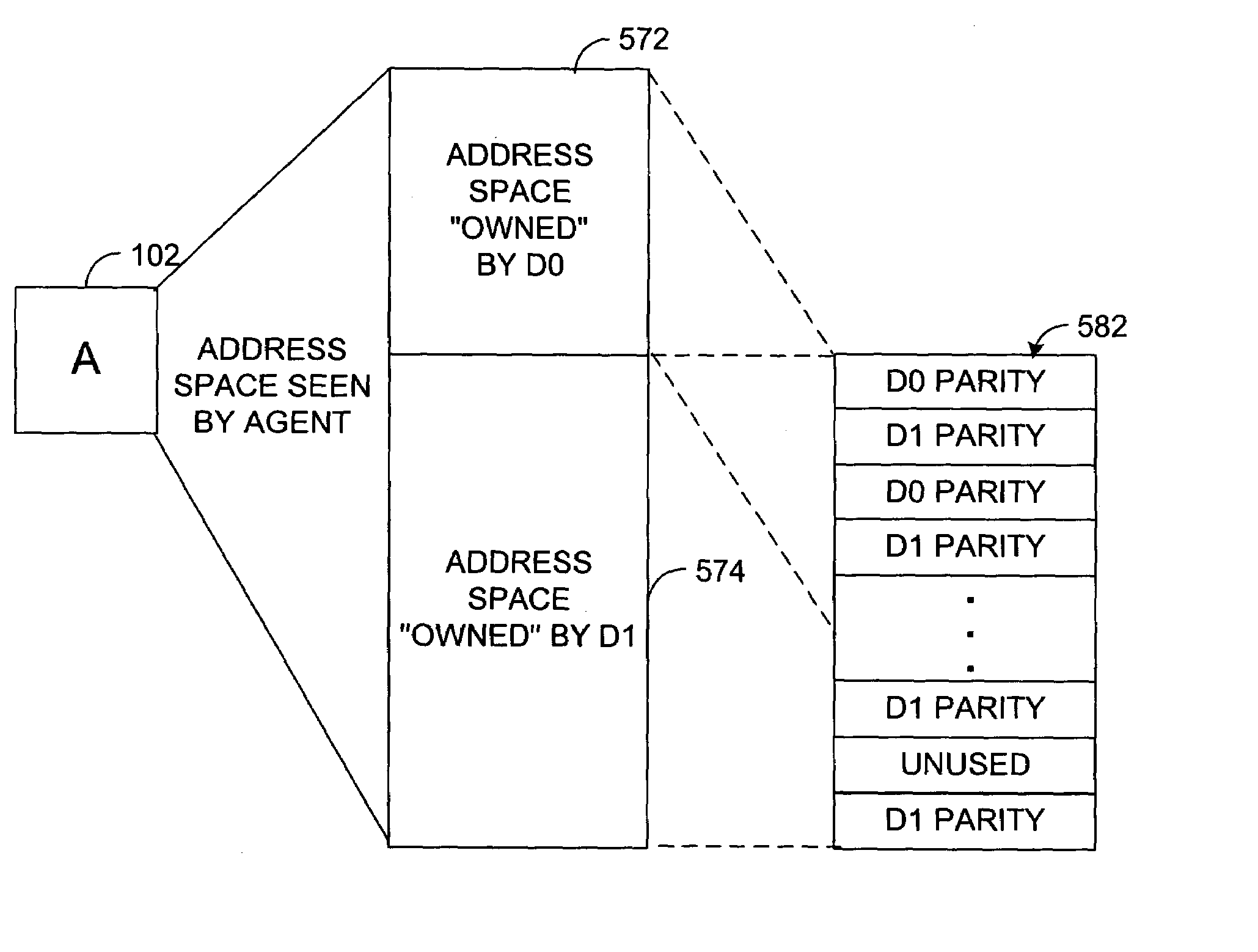

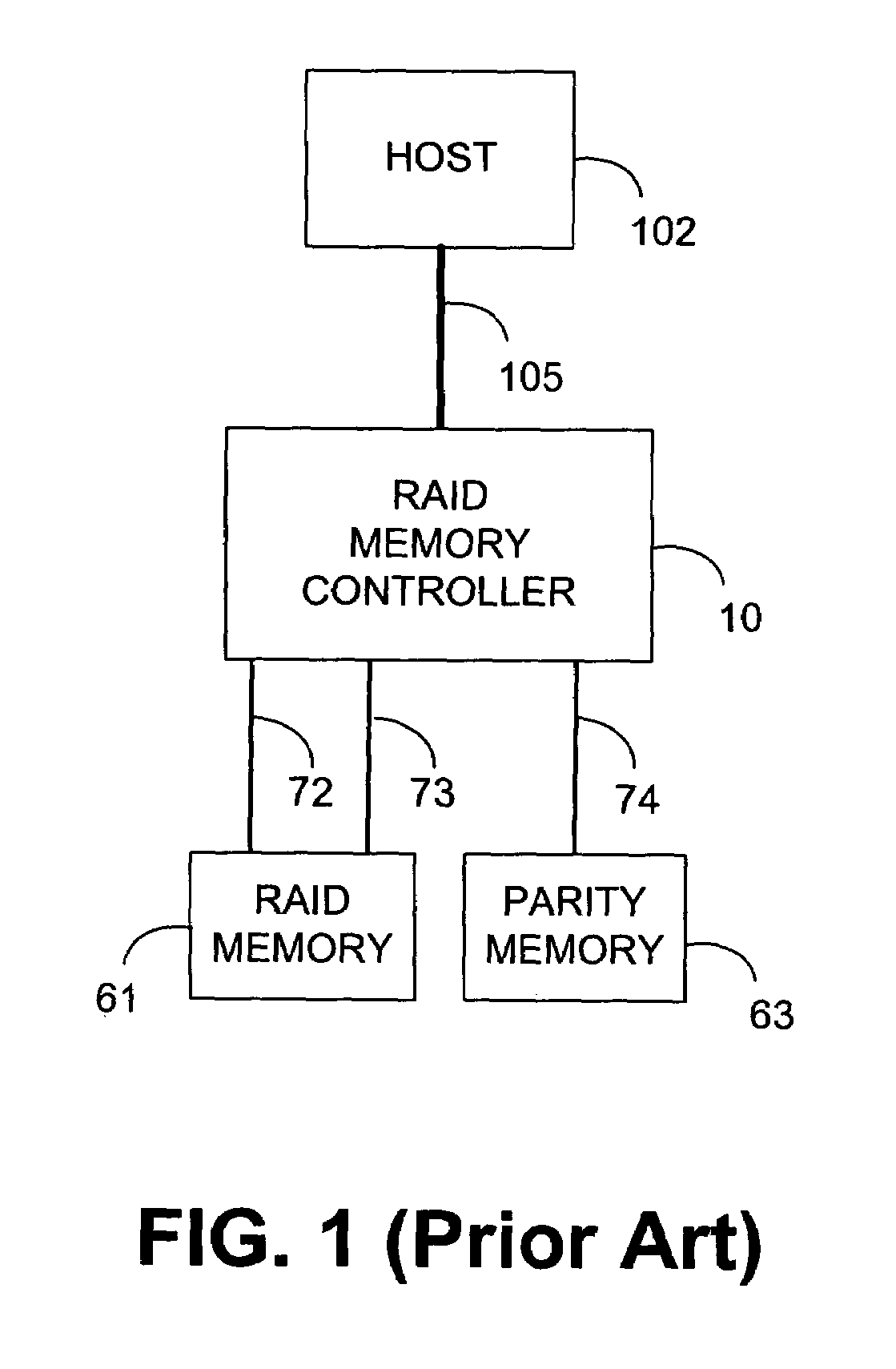

RAID memory system

Embodiments of the present invention are broadly directed to a memory system. In one embodiment, a first data memory is coupled to a first memory controller and a second data memory is coupled to a second memory controller. A parity memory is coupled to a parity controller, the parity controller being directly coupled to both the first memory controller and the second memory controller. Parity data control logic is configured to store and retrieve parity information associated with data stored in both the first data memory and the second data memory, the parity data control logic configured to interleave within the parity memory parity data associated with data stored in the first data memory with parity data associated with data stored in the second data memory.

Owner:HEWLETT PACKARD DEV CO LP

Metadata rebuild in a flash memory controller following a loss of power

ActiveUS20090172262A1Maximize useImprove performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationFlash memory controllerMemory controller

A method of rebuilding metadata in a flash memory controller following a loss of power. The method includes reading logical address information associated with an area of flash memory, and using time stamp information to determine if data stored in the flash memory area is valid.

Owner:SANDISK TECH LLC

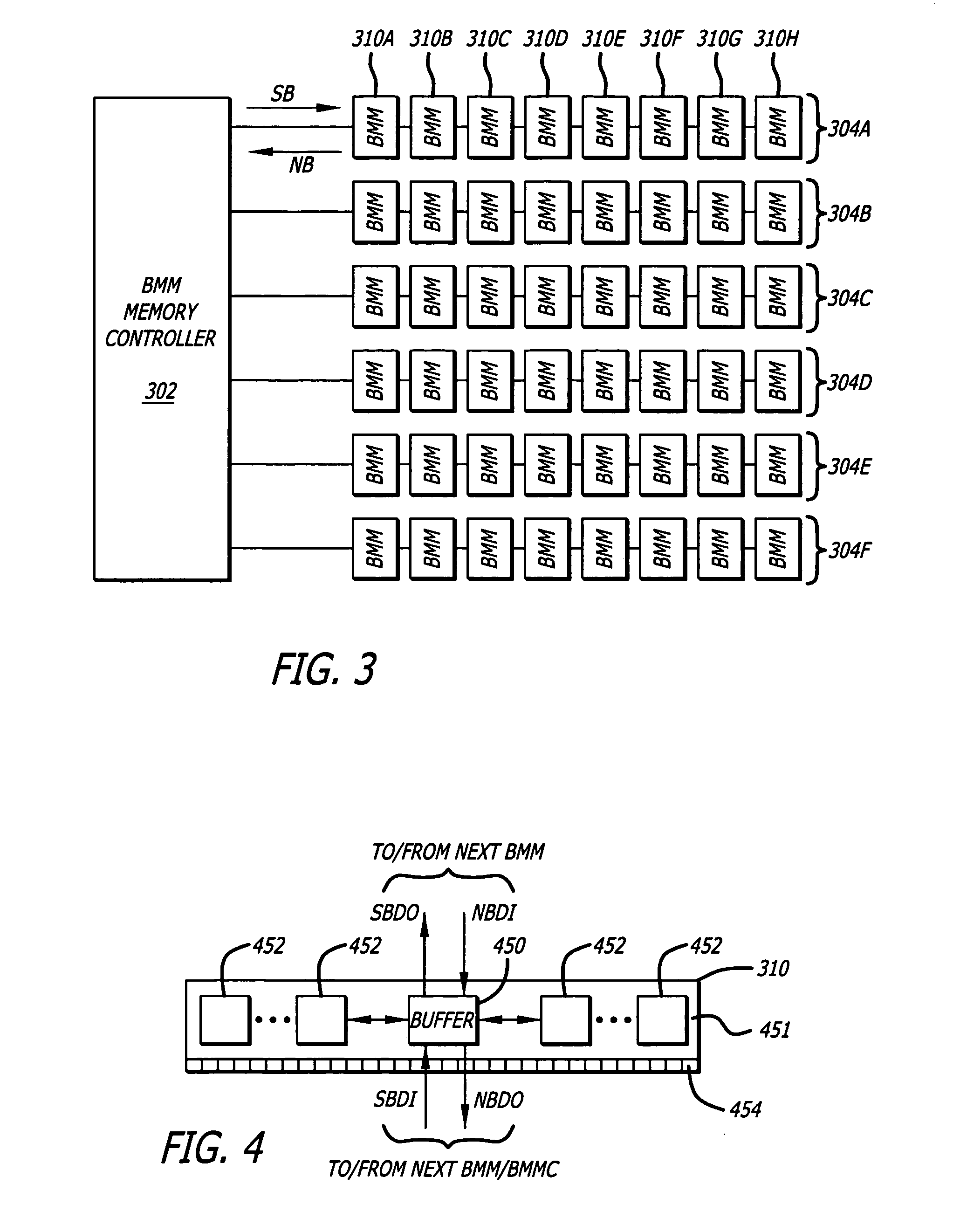

Memory buffers for merging local data from memory modules

InactiveUS20060195631A1Input/output for user-computer interactionDigital data processing detailsShift registerMultiplexing

An integrated circuit to serialize local data and selectively merge it with serialized feed-through data into a serial data stream output that includes a parallel-in-serial-out (PISO) shift register, a multiplexer, and a transmitter. The PISO shift register serializes parallel data on a local data bus into serialized local data. The multiplexer selectively merges serialized local data and feed-through data into a serial data stream. The transmitter drives the serial data stream onto a serial data link. In another embodiment of the invention, a method for a memory module includes receiving an input serial data stream; merging local frames of data and feed-through frames of data together into an output serial data stream in response to a merge enable signal; and transmitting the output serial data stream on a northbound data output to a next memory module or a memory controller. Other embodiments of the invention are disclosed and claimed.

Owner:INTEL CORP

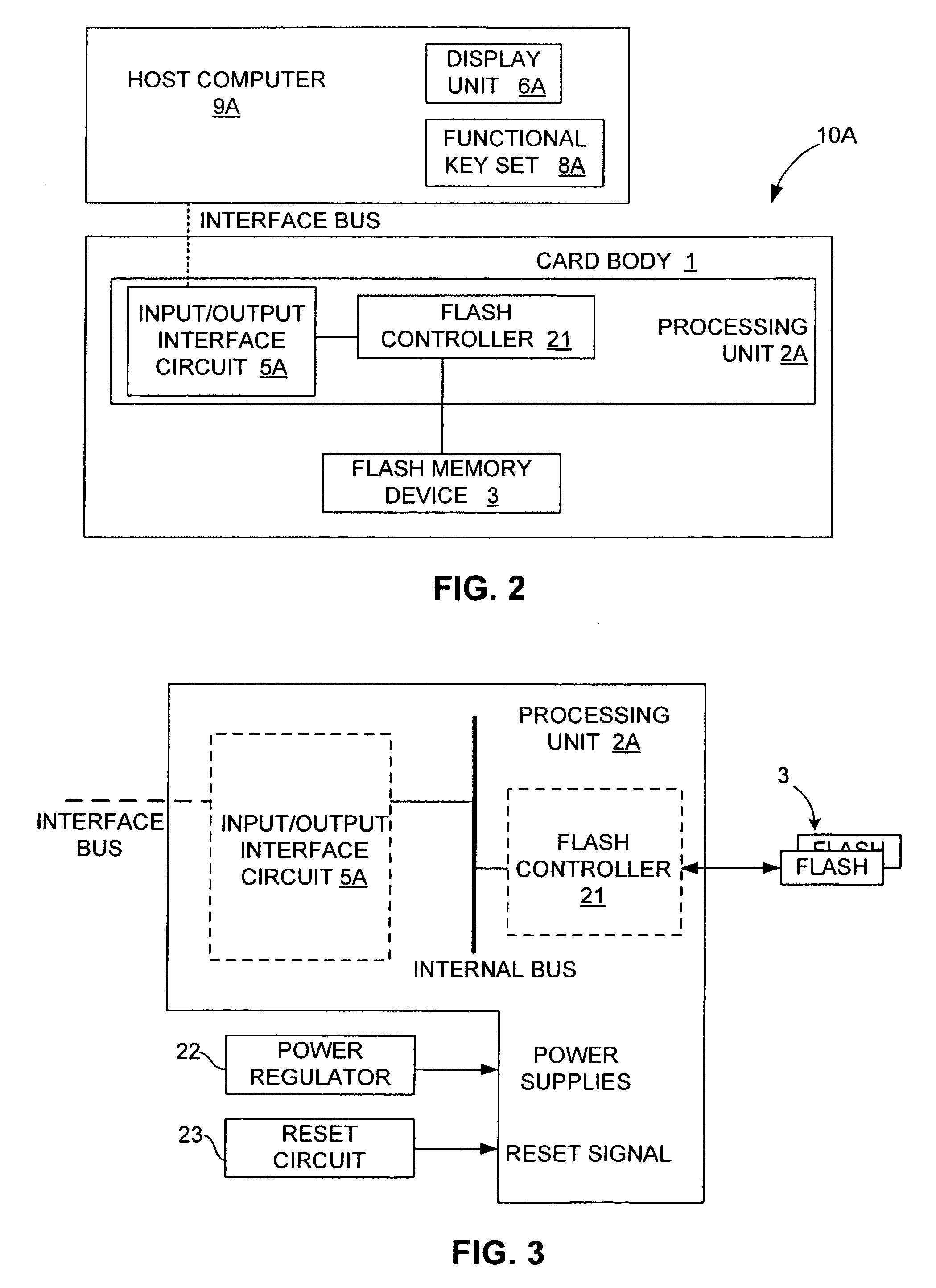

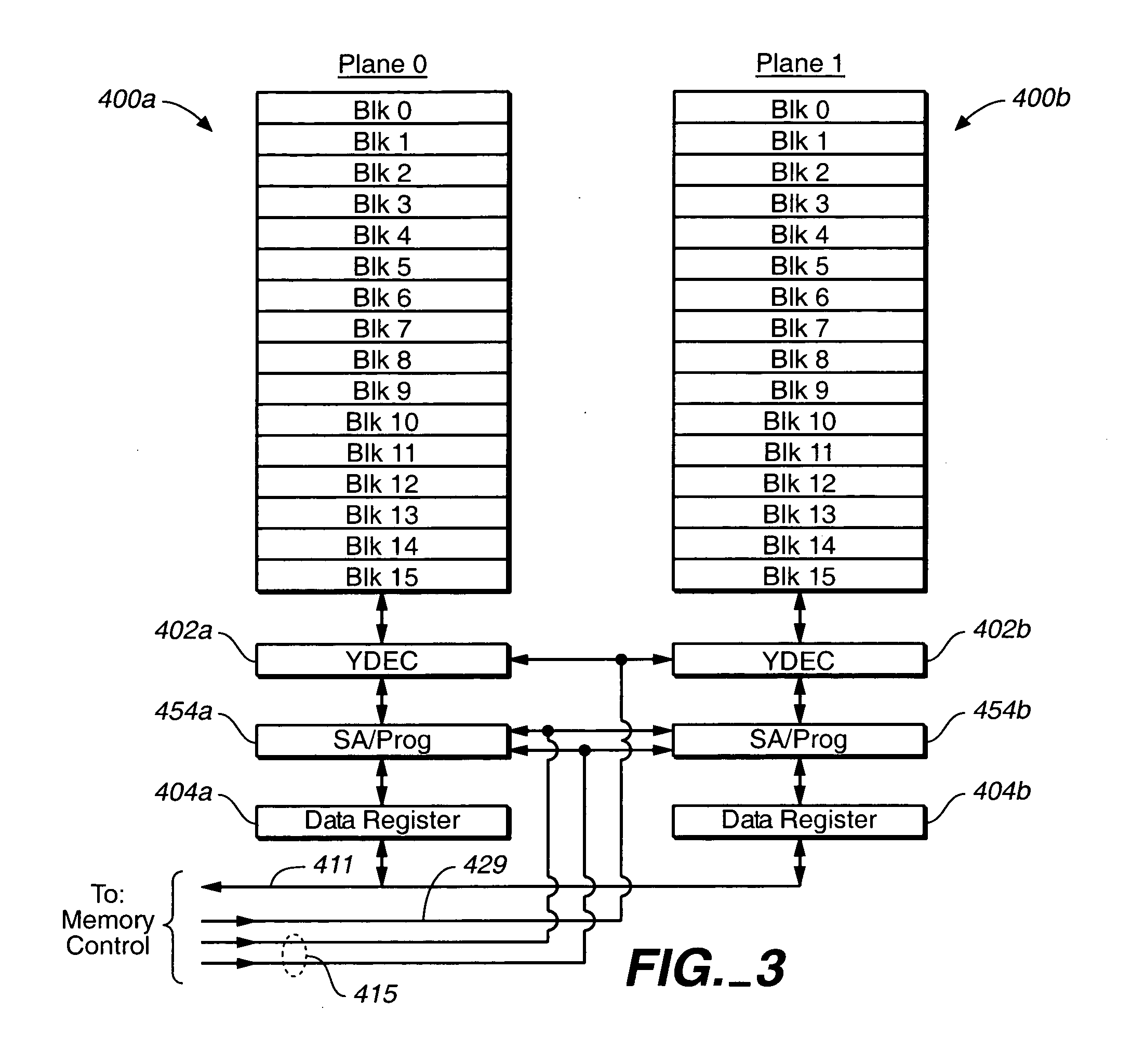

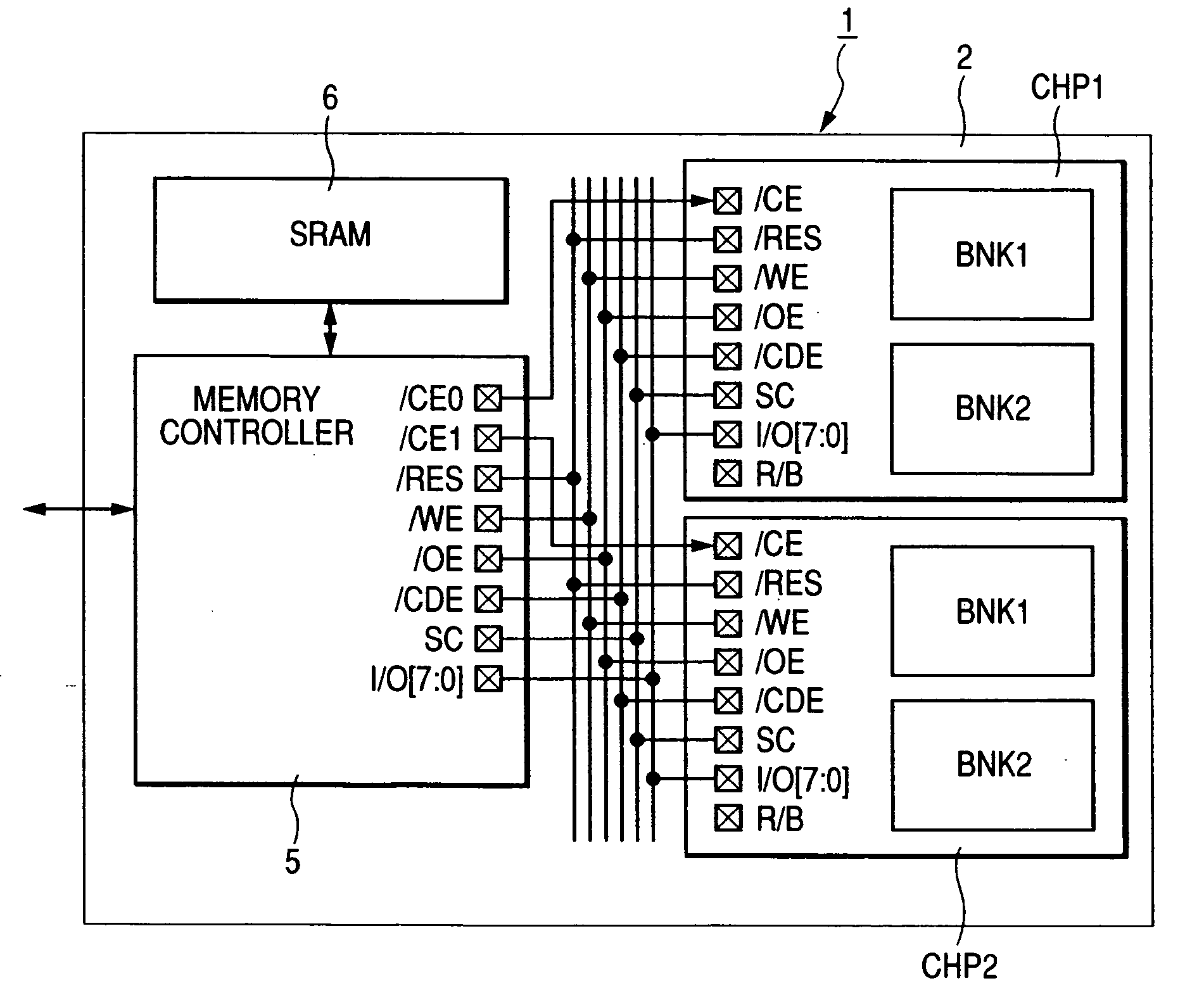

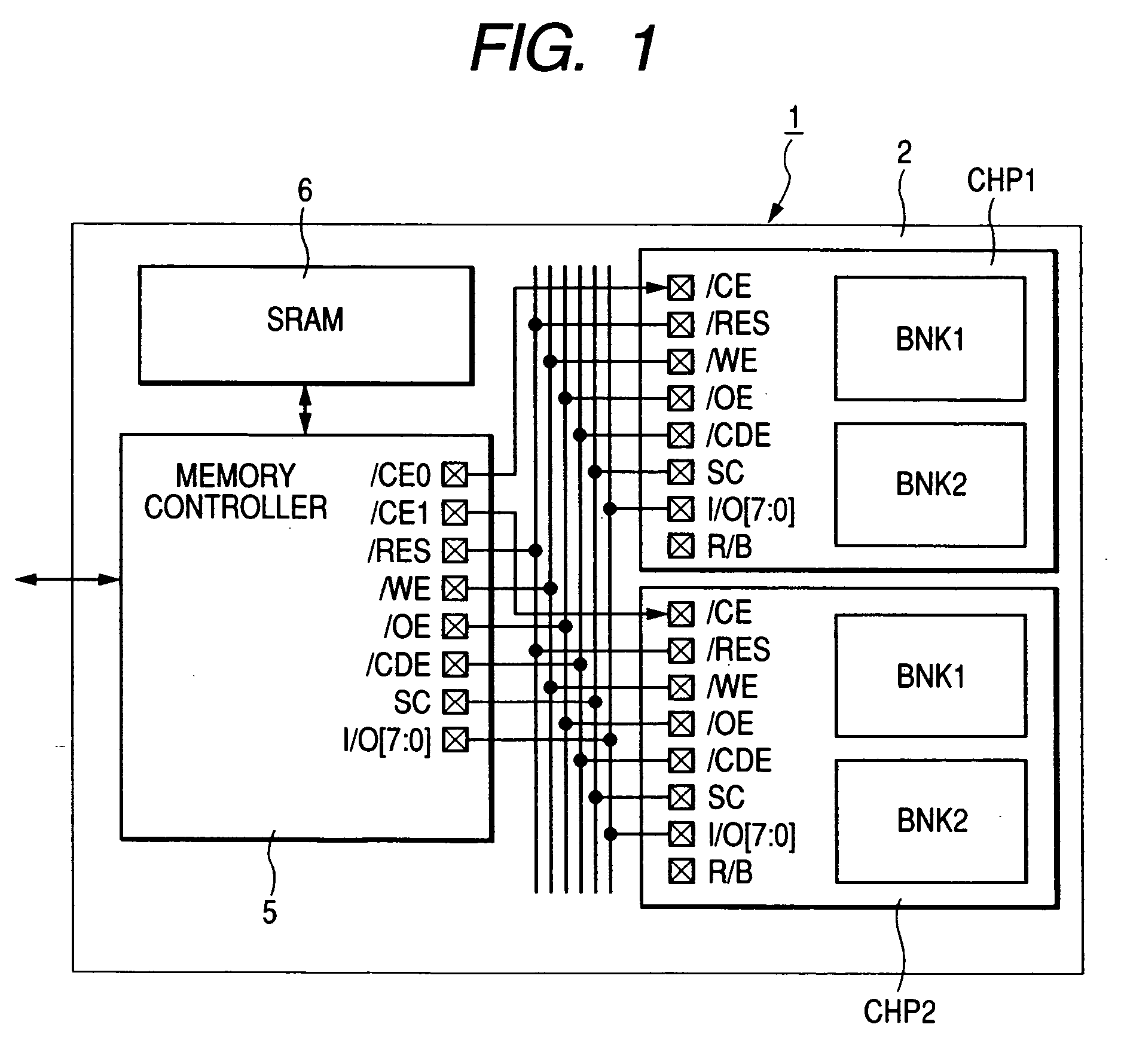

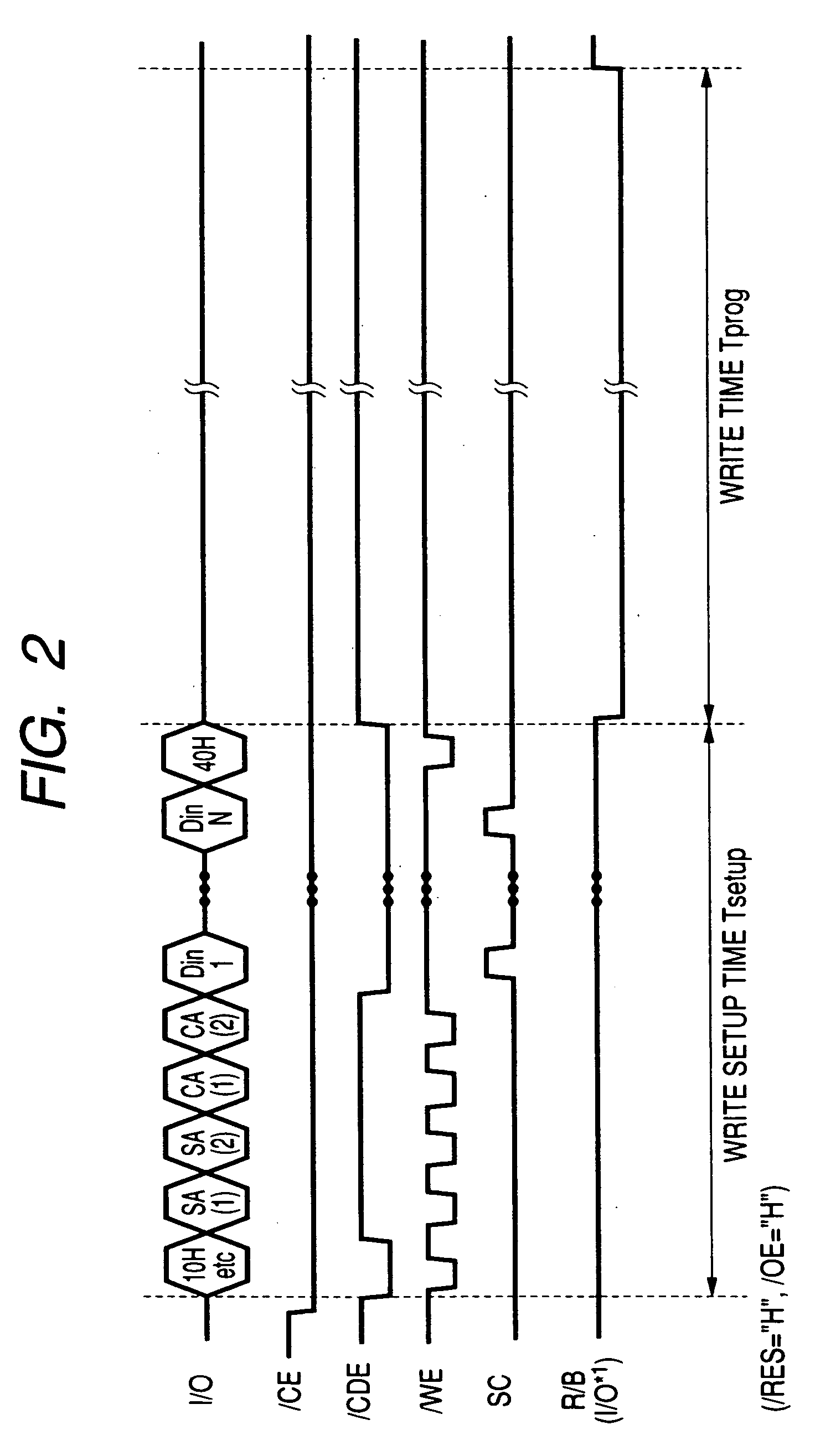

Memory system and memory card

InactiveUS20050015539A1Increase costIncrease speedMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:RENESAS ELECTRONICS CORP

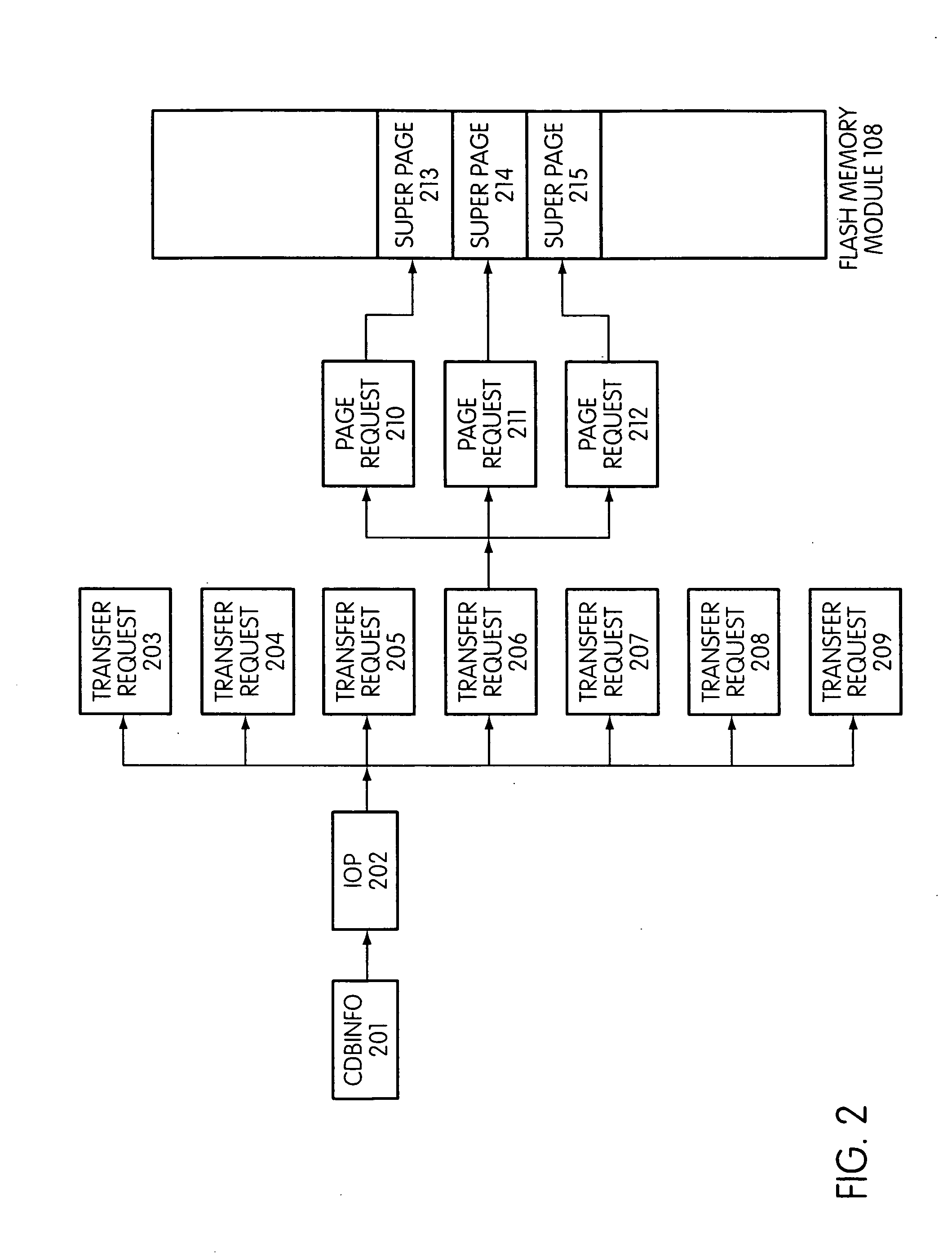

Flash memory controller garbage collection operations performed independently in multiple flash memory groups

ActiveUS20090172258A1Affect performanceMaximize useMemory architecture accessing/allocationRead-only memoriesWaste collectionFlash memory controller

A flash memory controller connected to multiple flash memory groups performs independent garbage collection operations in each group. For each group, the controller independently determines the amount of free space and performs garbage collection operations if the amount falls below a threshold.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com