Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2838 results about "Logical address" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, a logical address is the address at which an item (memory cell, storage element, network host) appears to reside from the perspective of an executing application program. A logical address may be different from the physical address due to the operation of an address translator or mapping function. Such mapping functions may be, in the case of a computer memory architecture, a memory management unit (MMU) between the CPU and the memory bus.

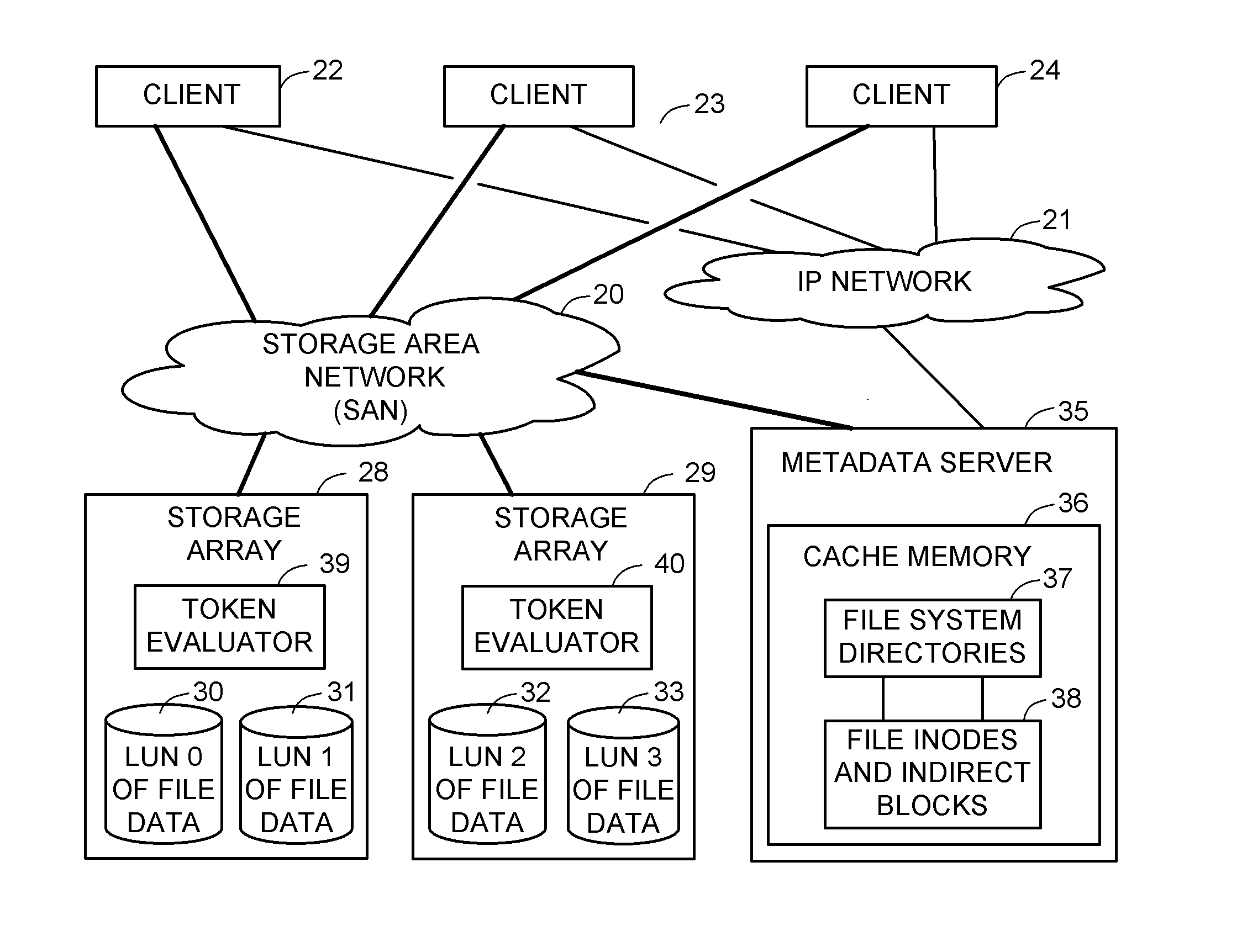

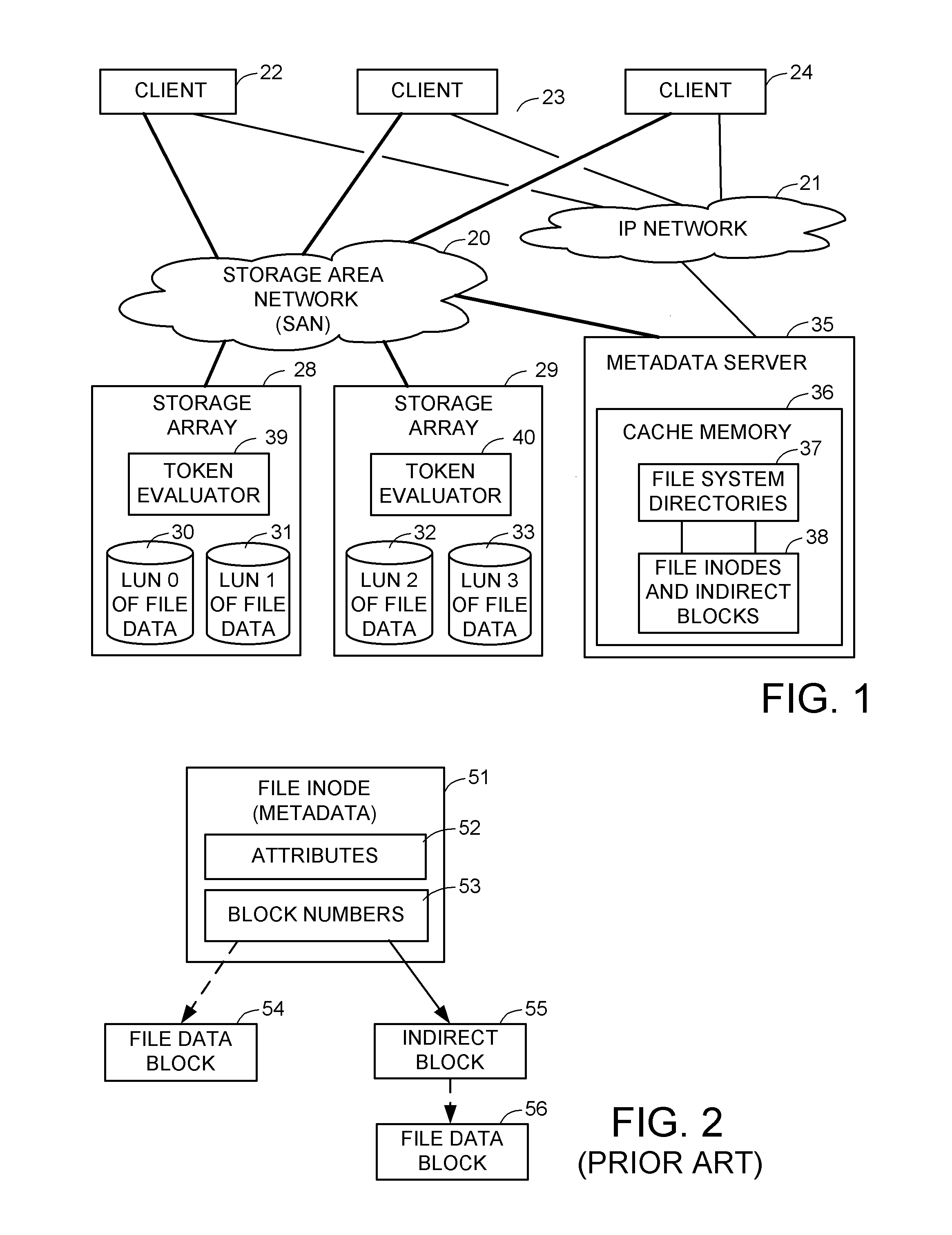

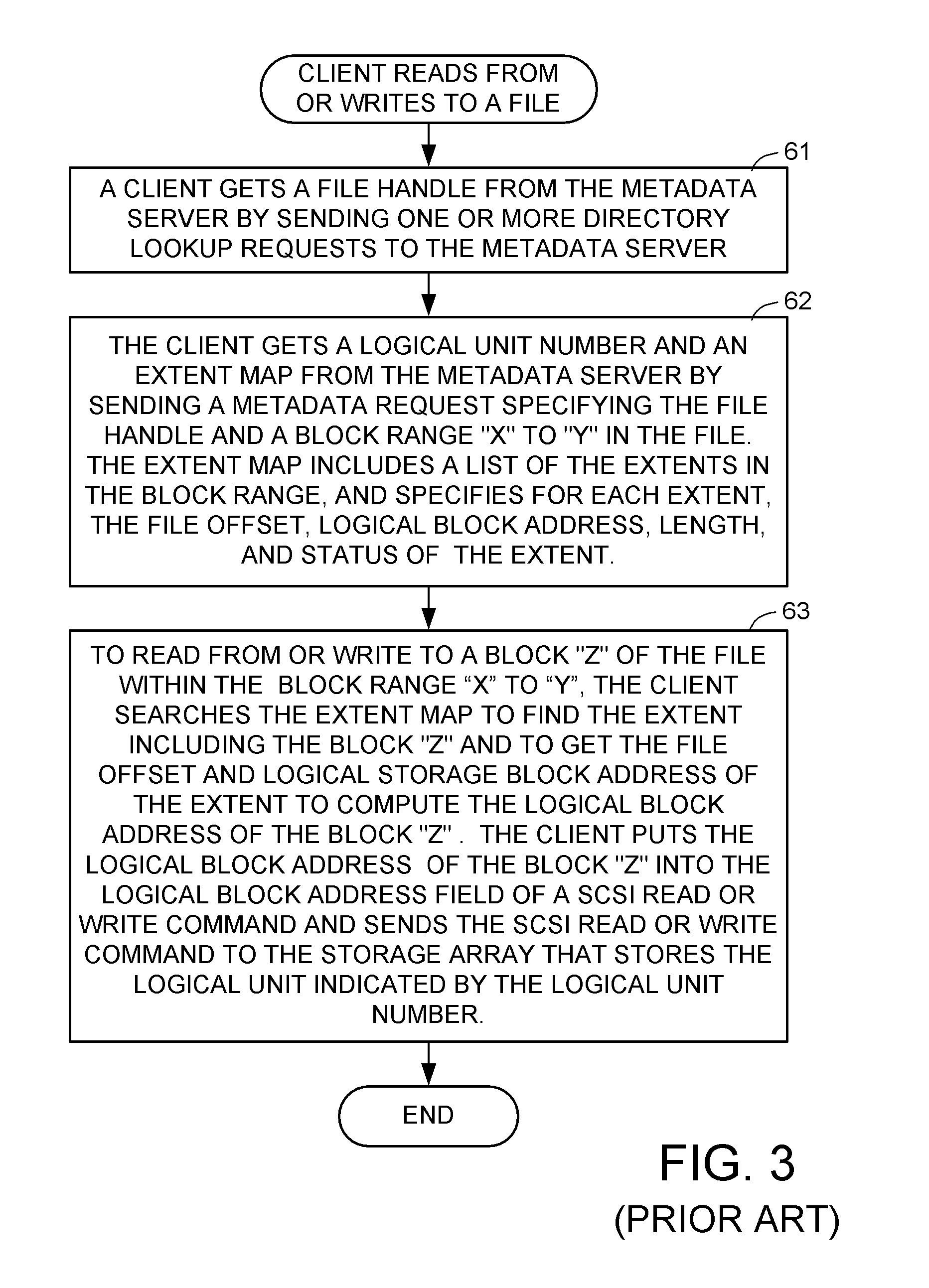

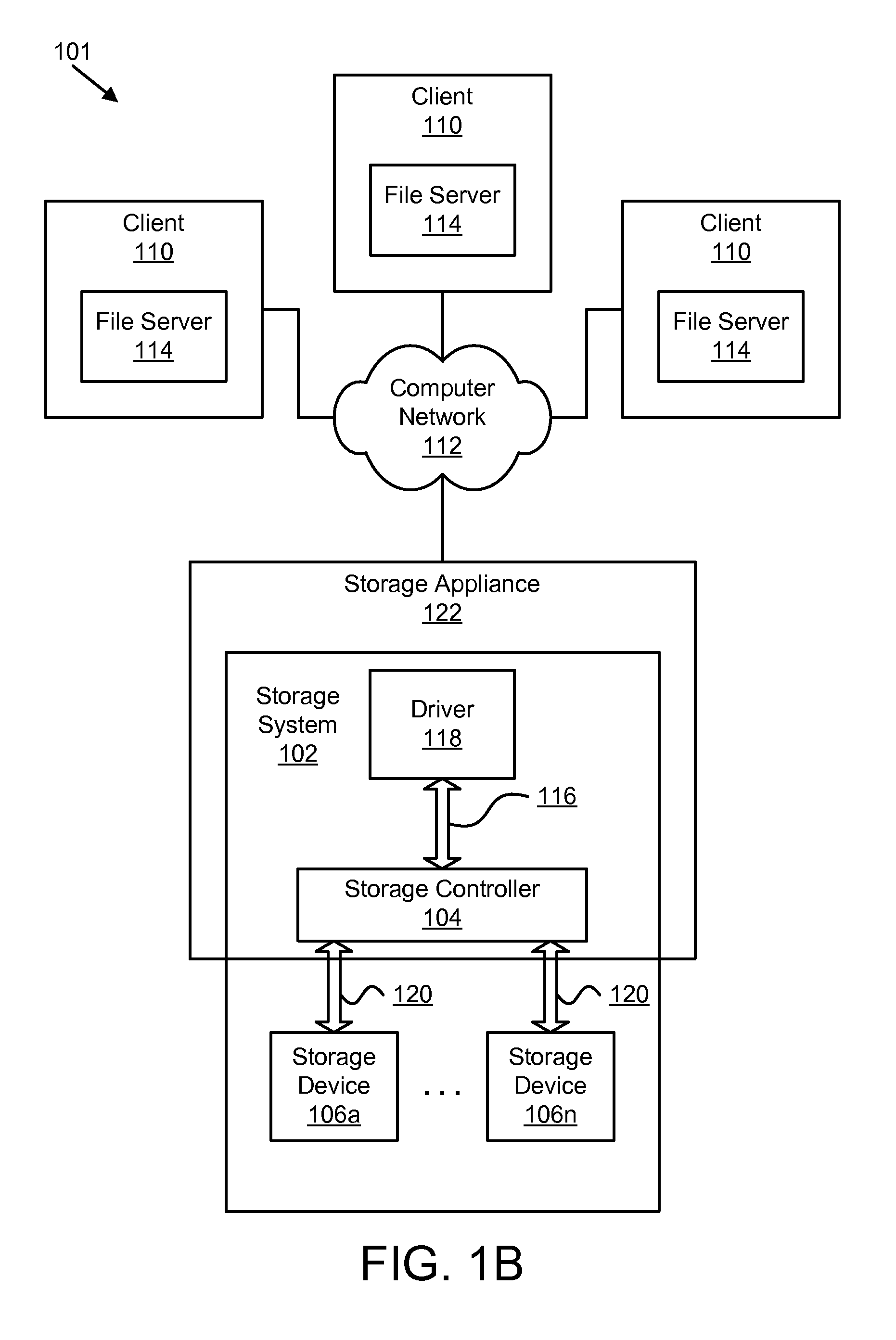

Access control to block storage devices for a shared disk based file system

ActiveUS8086585B1Improve securityChangeDigital data information retrievalDigital data processing detailsSCSILogical block addressing

For enhanced access control, a client includes a token in each read or write command sent to a block storage device. The block storage device evaluates the token to determine whether or not read or write access is permitted at a specified logical block address. For example, the token is included in the logical block address field of a SCSI read or write command. The client may compute the token as a function of the logical block address of a data block to be accessed, or a metadata server may include the token in each block address of each extent reported to the client in response to a metadata request. For enhanced security, the token also is a function of a client identifier, a logical unit number, and access rights of the client to a particular extent of file system data blocks.

Owner:EMC IP HLDG CO LLC

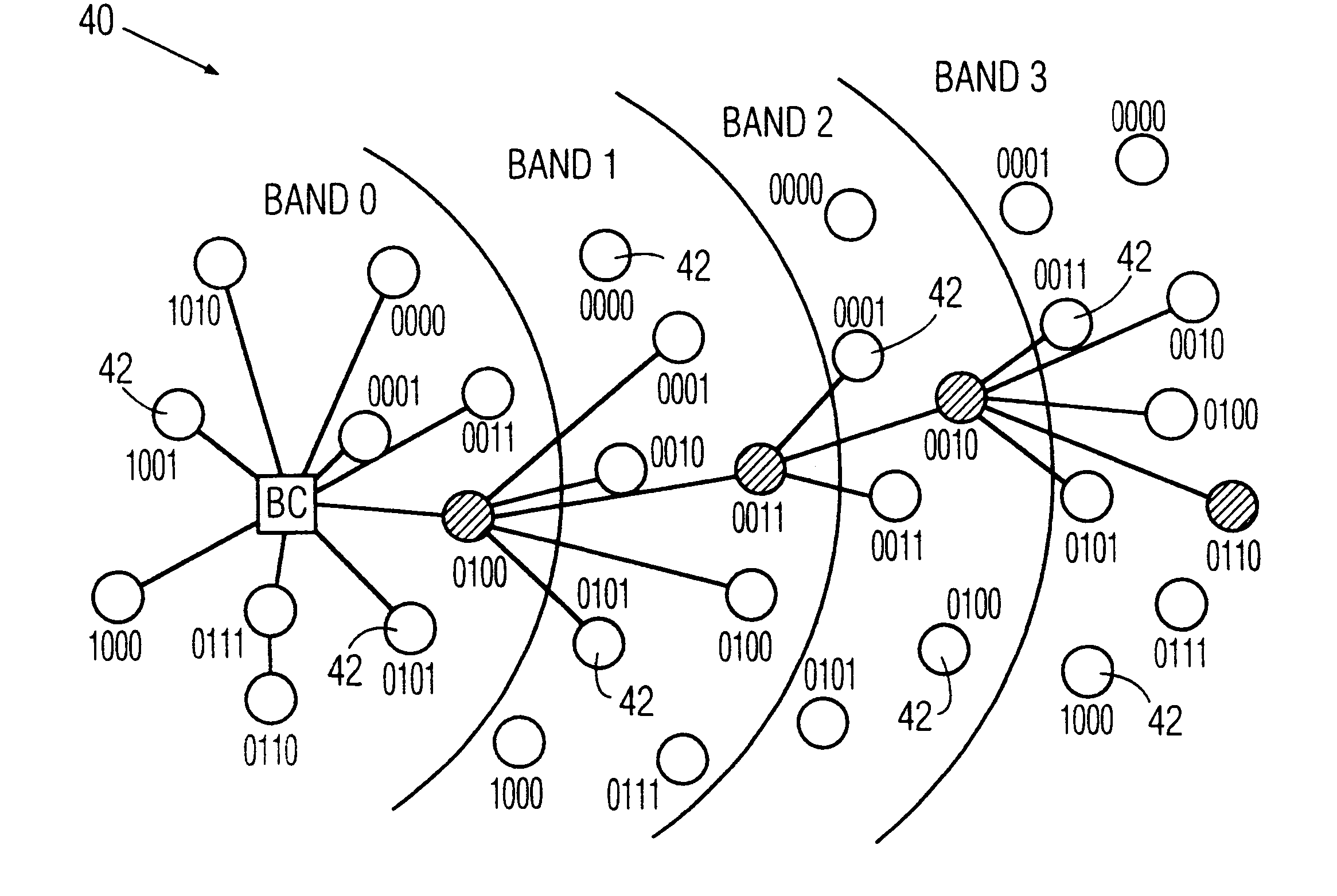

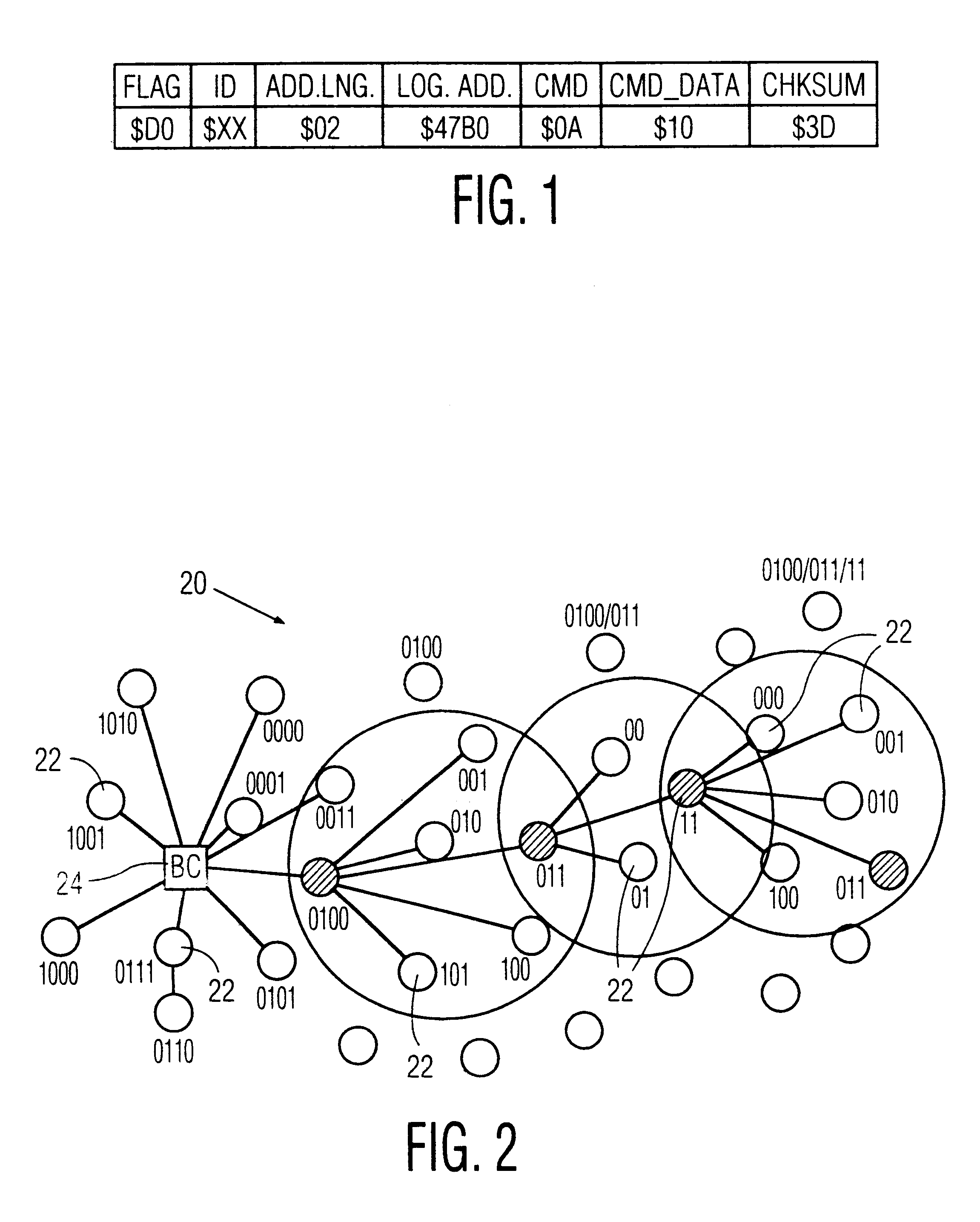

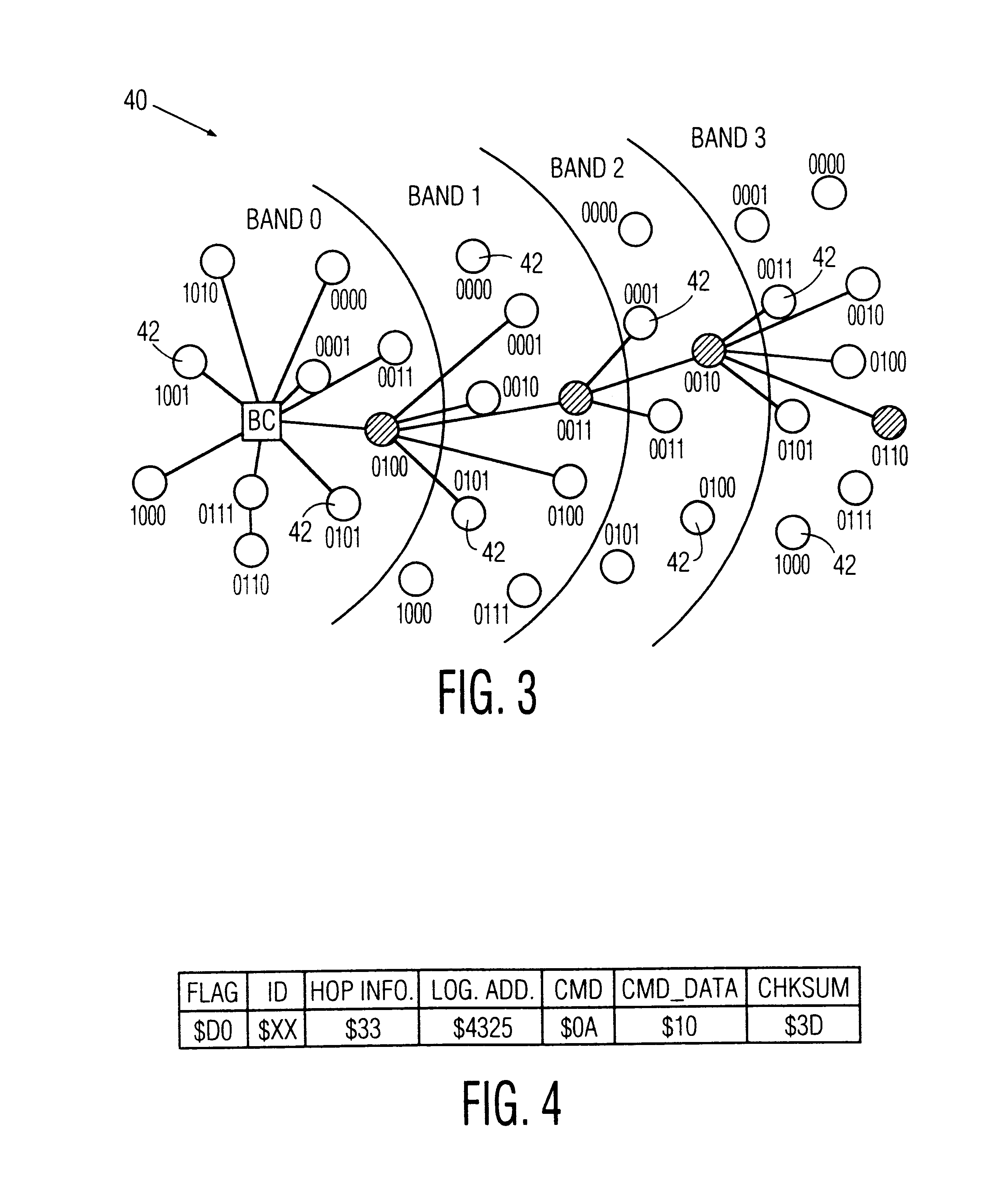

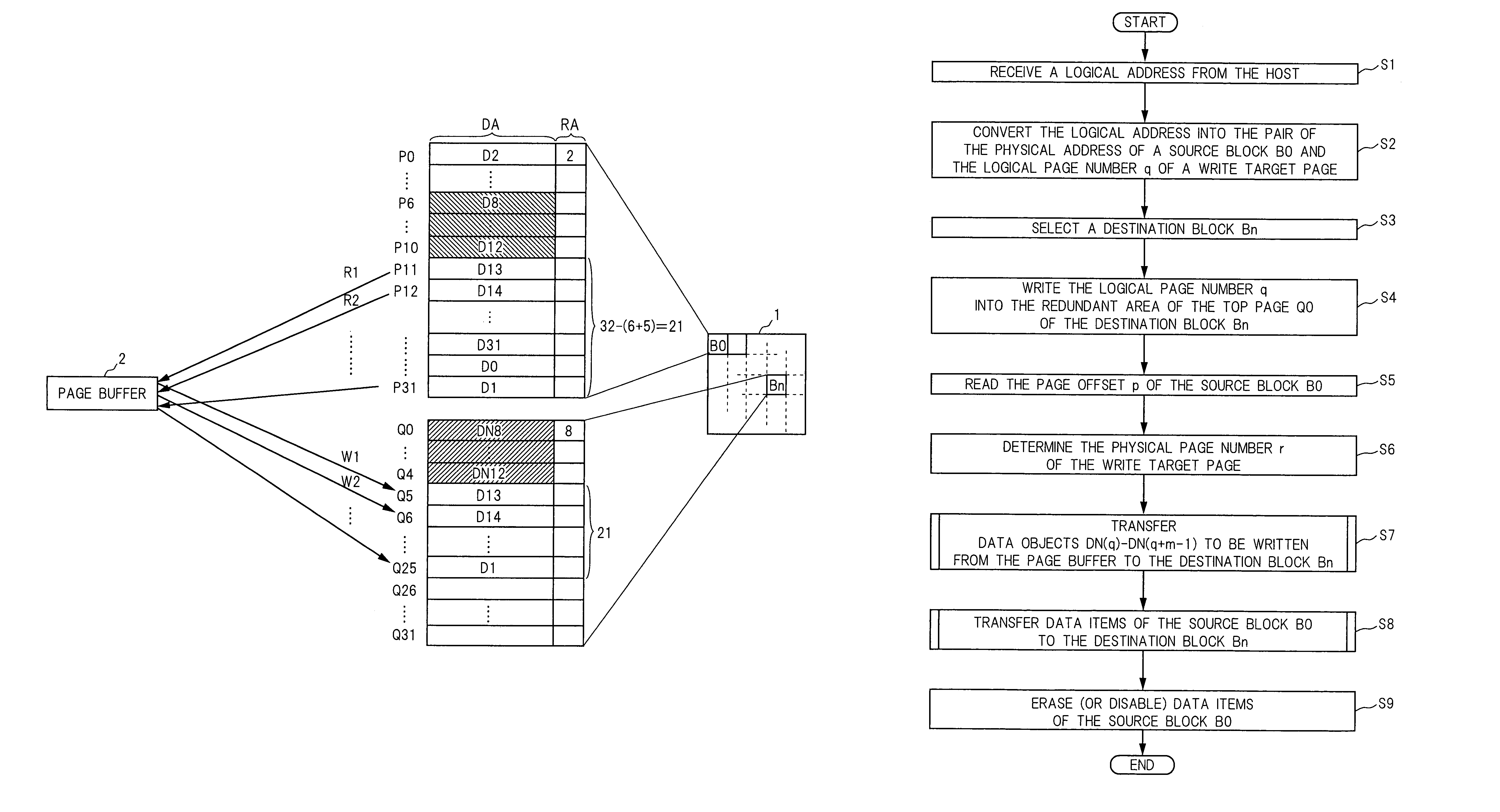

Method for configuring and routing data within a wireless multihop network and a wireless network for implementing the same

InactiveUS6842430B1Active radio relay systemsData switching by path configurationDistributed computingWireless network

A method for configuring a wireless network comprised of a control node and a multiplicity of individual nodes includes the steps of logically organizing the network into a plurality of bands Bi, wherein each of the bands Bi includes a plurality of the individual nodes and is located a number i of hops away from the control node, where i=0 through N, and N≧1, and then assigning a logical address to each of the individual nodes, and storing the assigned logical addresses in the respective individual nodes. The assigned logical address for each individual node includes a first address portion which indicates the band Bi in which that individual node is located, and a second address portion that identifies that node relative to all other individual nodes located in the same band. The network is preferably a packet-hopping wireless network in which data is communicated by transferring data packets from node-to-node over a common RF channel. Each of the individual nodes is preferably programmed to perform the step of comparing its own logical address to a routing logical address contained in each packet which it receives, and to either discard, re-transmit, or process the packet based upon the results of the comparison. The routing logical address contained in a received packet contains the full routing information required to route the packet from a sending node to a destination node along a communication path prescribed by the routing logical address. The control node is programmed to control the routing of packets by inserting the routing logical address into each packet which it transmit, detecting any unsuccessfully transmitted packets, detecting a faulty node in the communication path prescribed by the routing logical address in response to detecting an unsuccessfully transmitted packet, and changing the routing logical address of the unsuccessfully transmitted packet to a new routing logical address which prescribes a new communication path which does not include the detected faulty node. Also disclosed are a wireless network and a network node which are designed to implement the foregoing network configuration and / or routing methods.

Owner:SIGNIFY HLDG BV

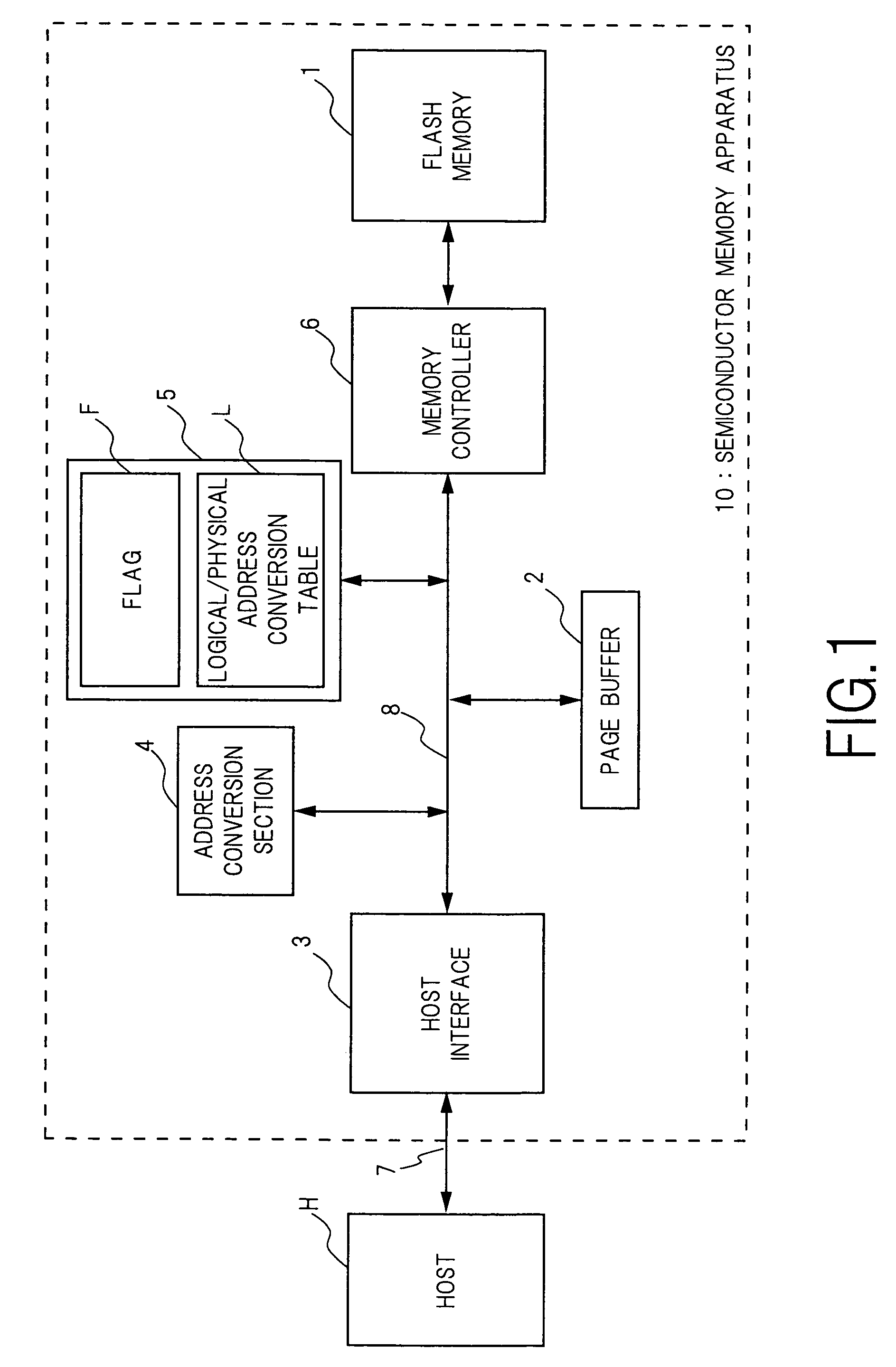

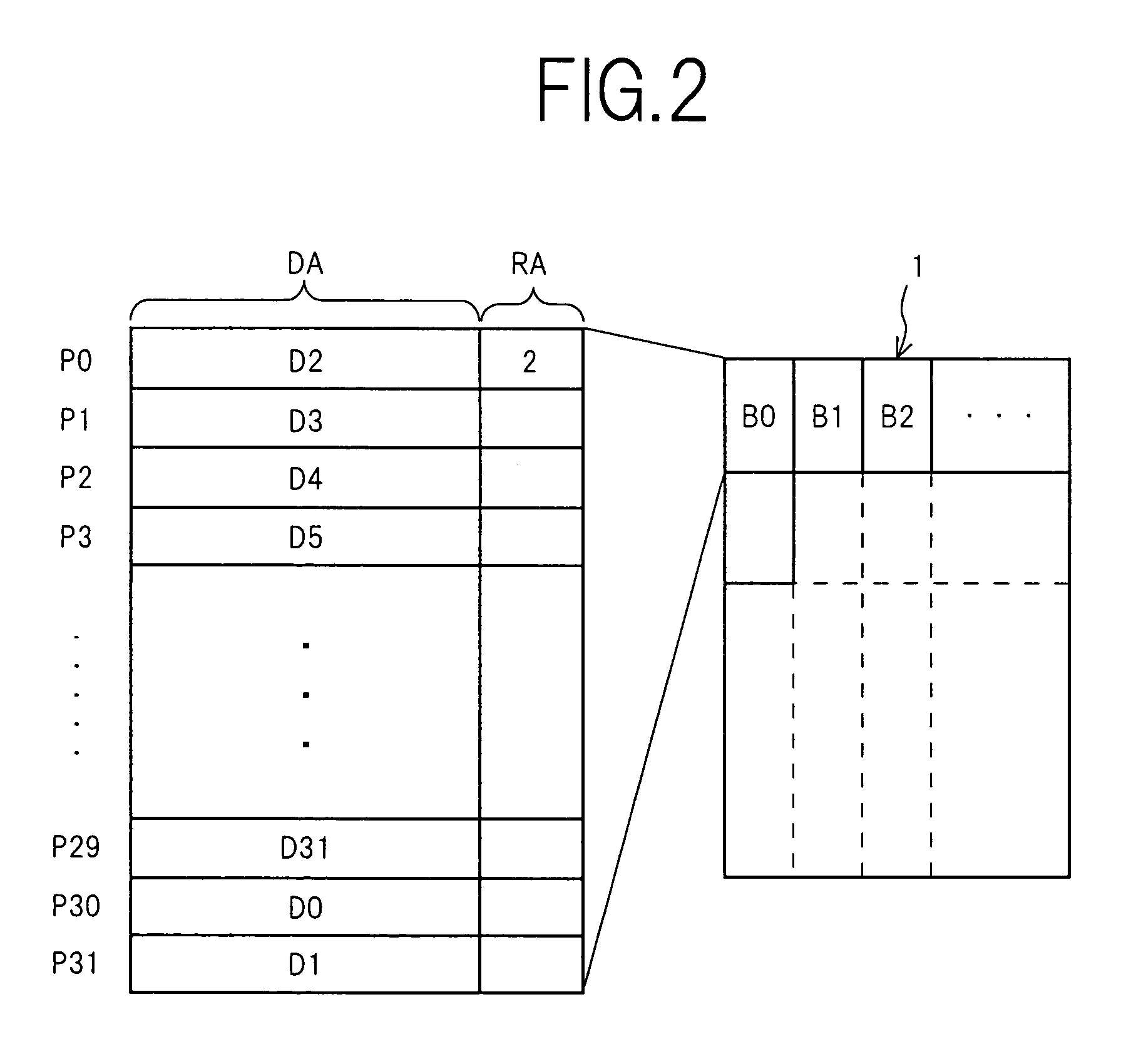

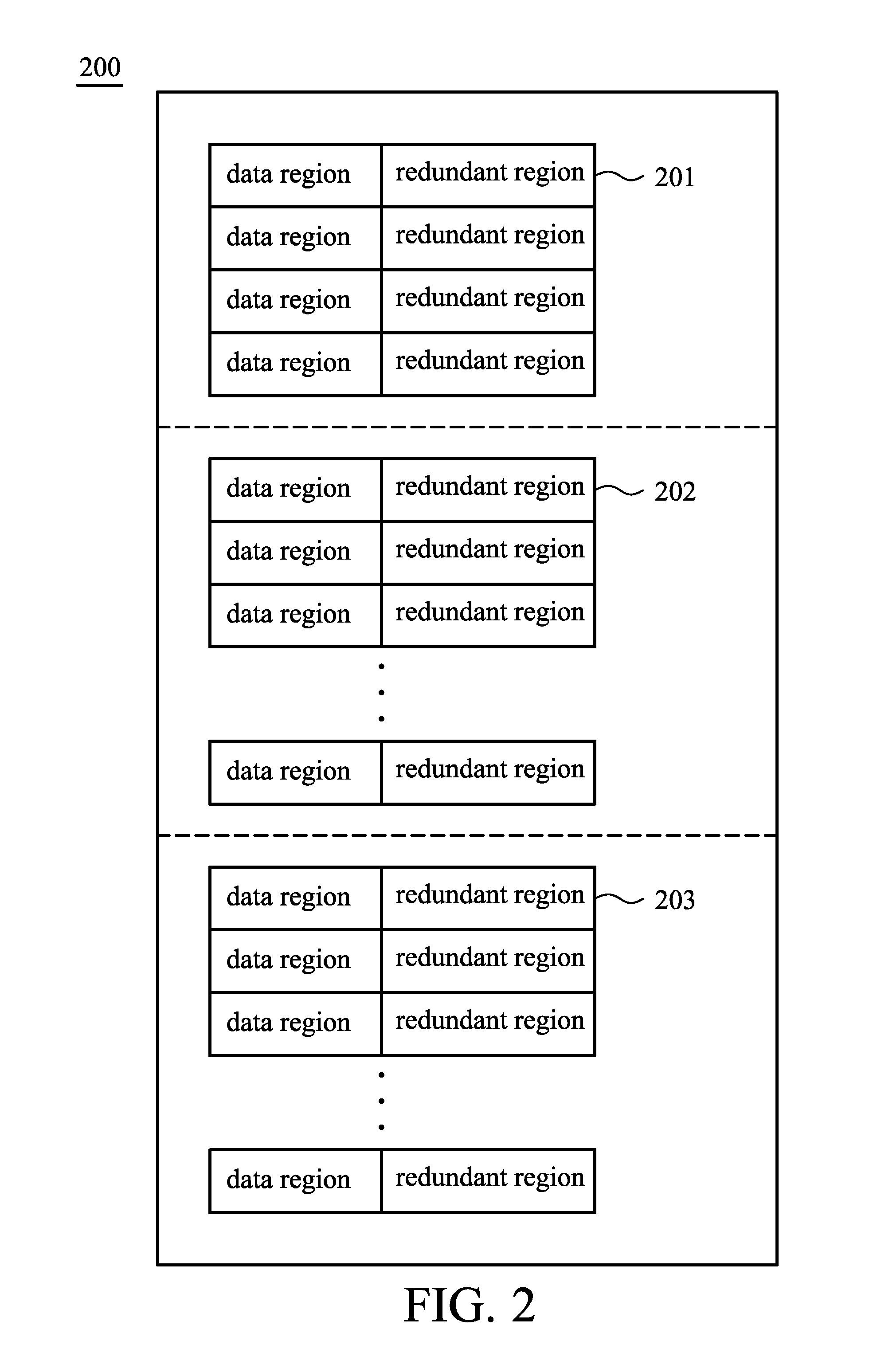

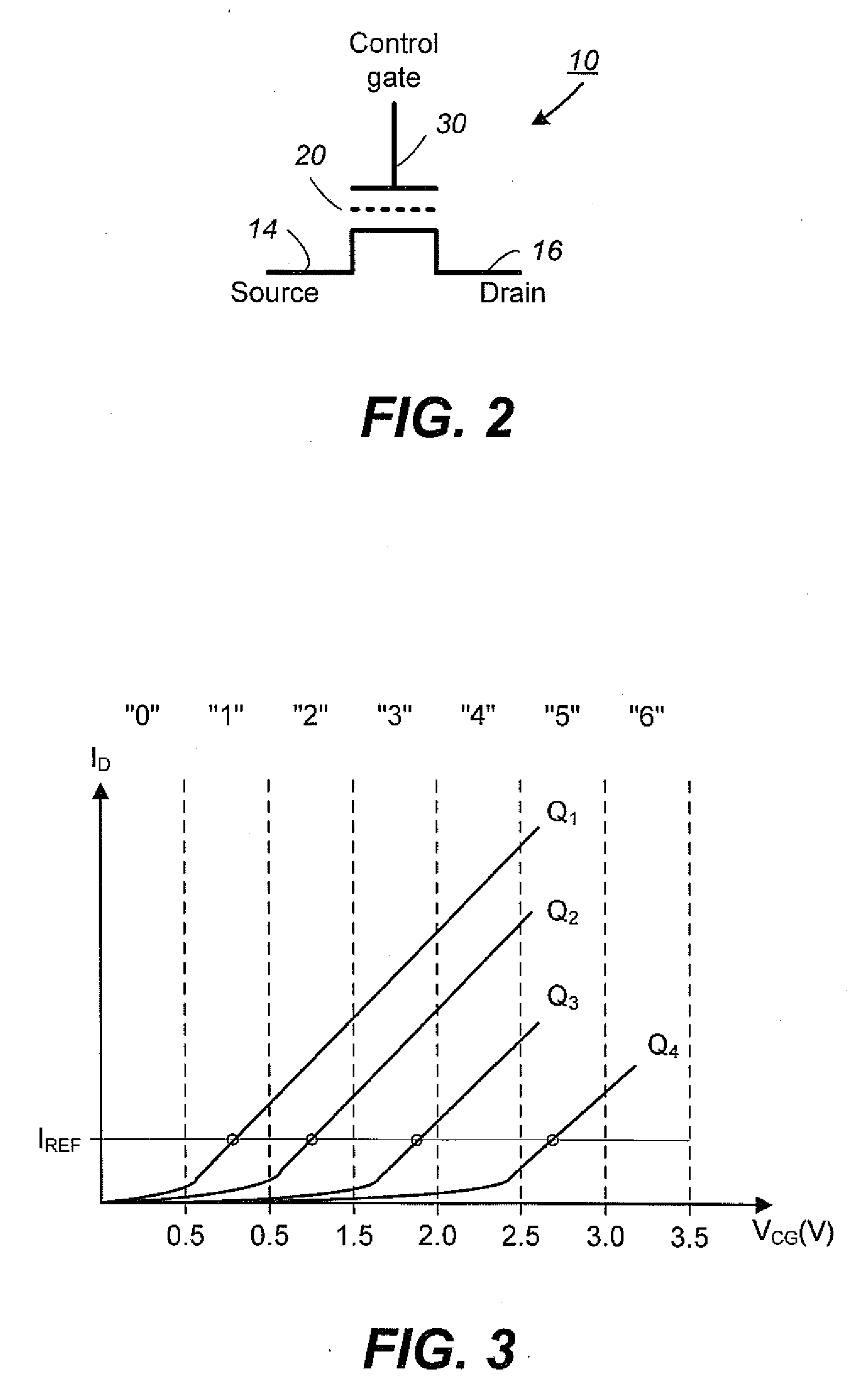

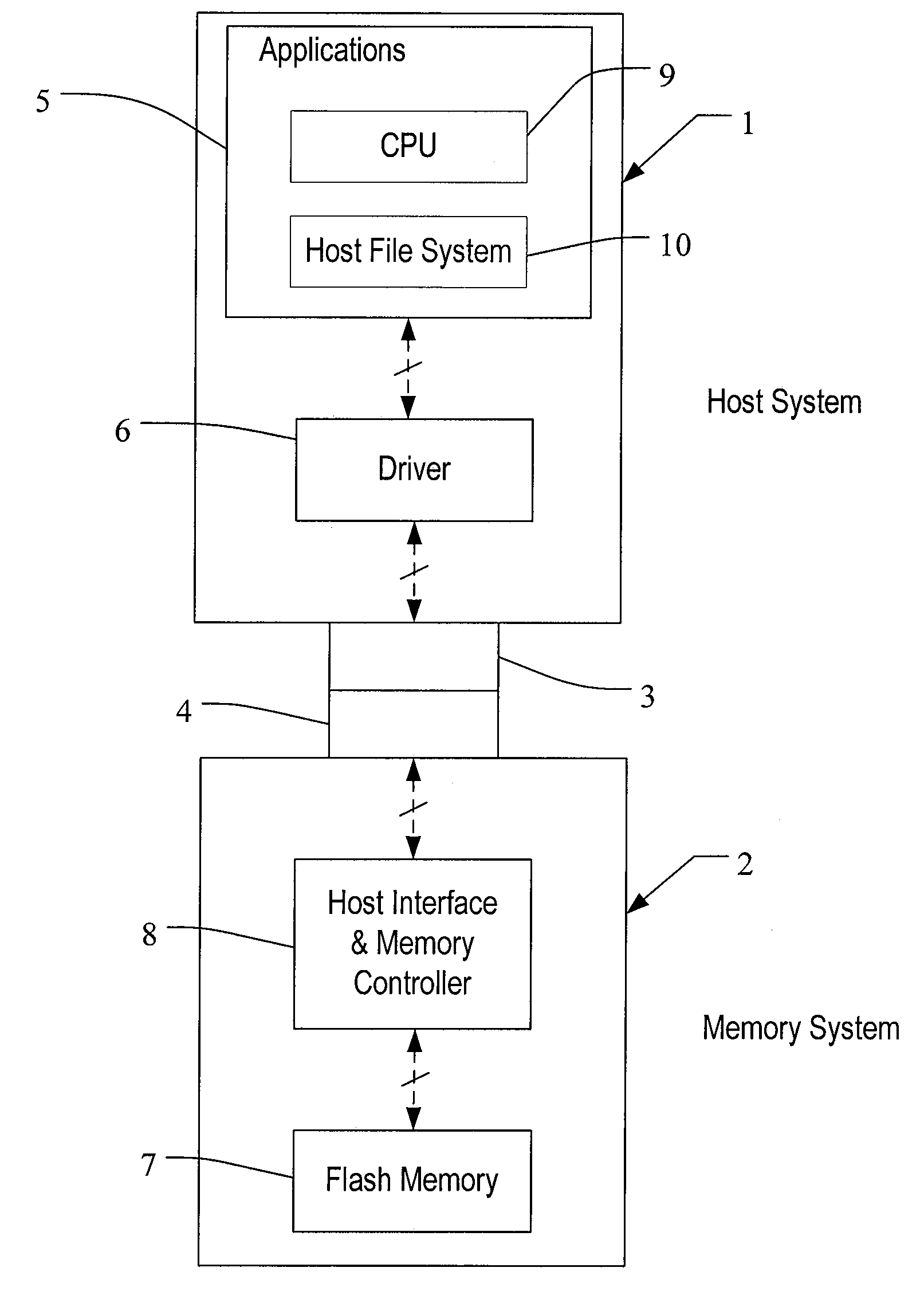

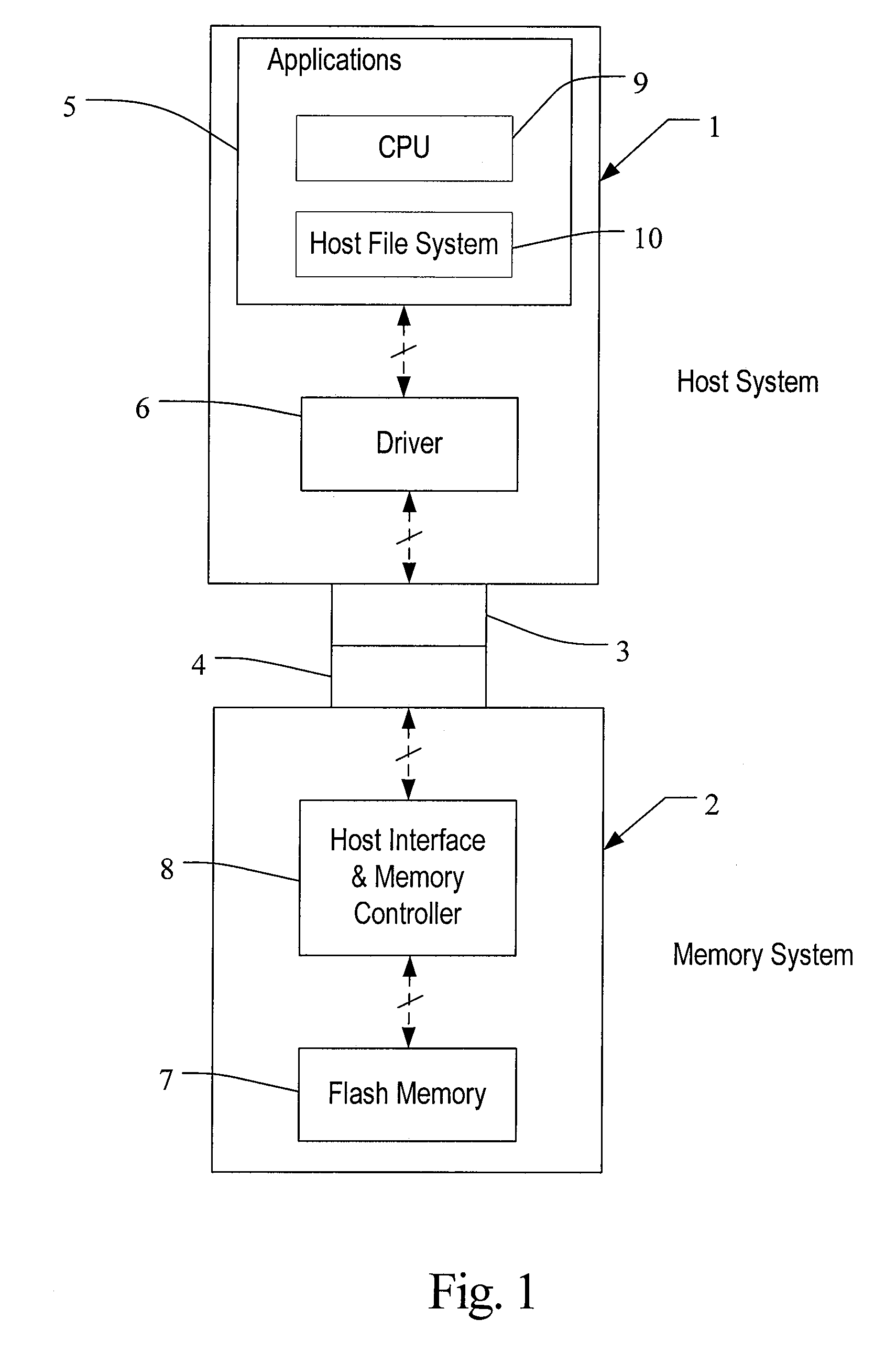

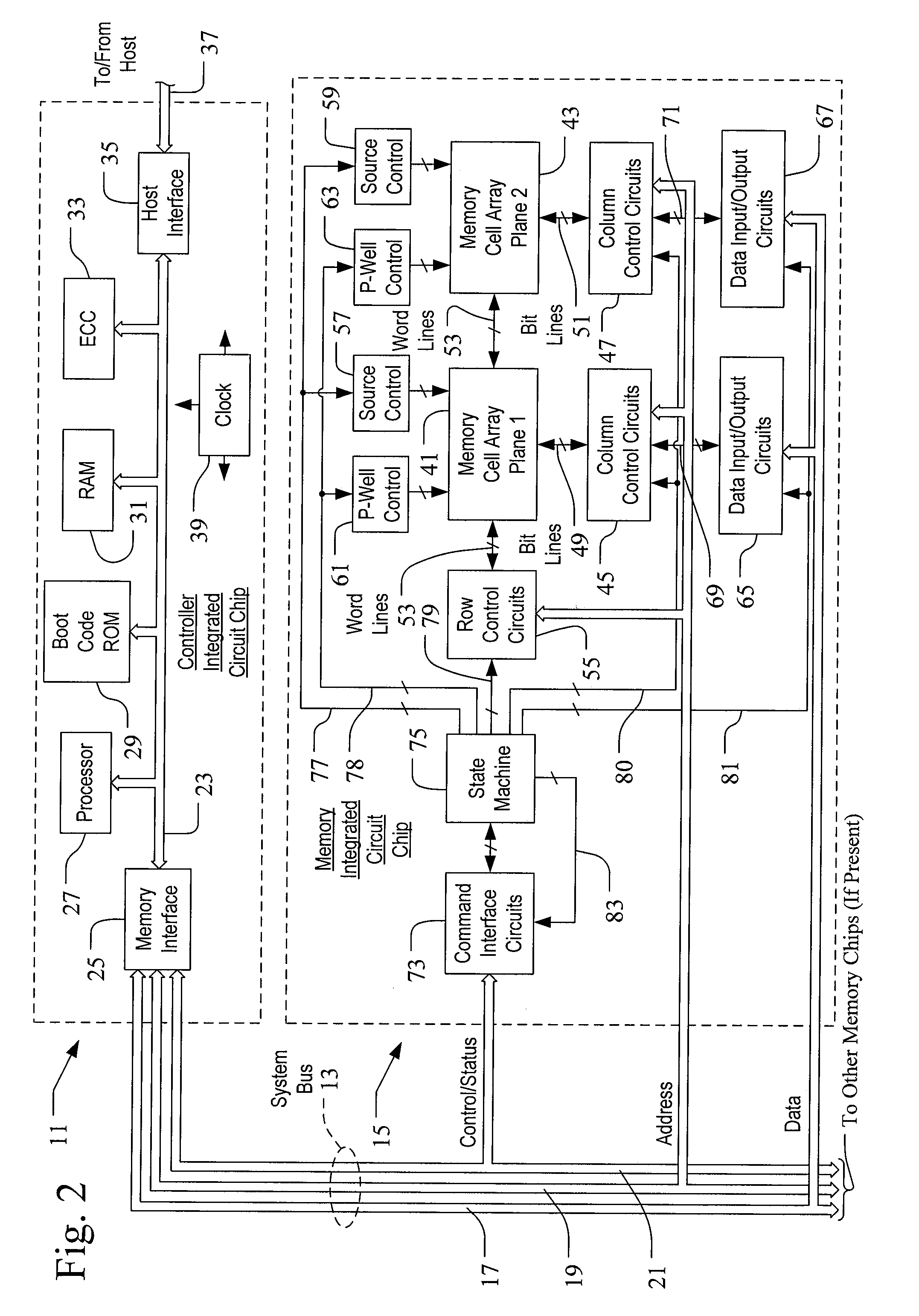

Semiconductor memory device and method for writing data into flash memory

ActiveUS7107389B2Small sizeReduce waiting timeMemory architecture accessing/allocationMemory adressing/allocation/relocationHome pageDatabase

A source block (B0) and the logical page number (“8”) of a write target page are identified from the logical address of the write target page. Data objects (DN8, DN9, . . . , DN12) to be written, which a host stores in a page buffer (2), are written into the data areas (DA) of the pages (Q0, Q1, . . . , Q4) of a destination block (Bn), starting from the top page (Q0) in sequence. The logical page number (“8”) of the write target page is written into the redundant area (RA) of the top page (Q0). The physical page number (“6=8−2”) of the write target page is identified, based on the logical page number (“8”) of the write target page and the page offset (“2”) of the source block (B0). When notified by the host of the end of the sending of the data objects (DN8, . . . , DN12), the data items (D13, . . . , D31, D0, D1, . . . , D7) in the source block (B0) are transferred to the pages (Q5, Q6, . . . , Q31) in the destination block (Bn) via the page buffer (2) sequentially and cyclically, starting from the page (P11) situated cyclically behind the write target page (P6) by the number (“5”) of pages of the data objects (DN8, . . . , DN12).

Owner:PANASONIC CORP

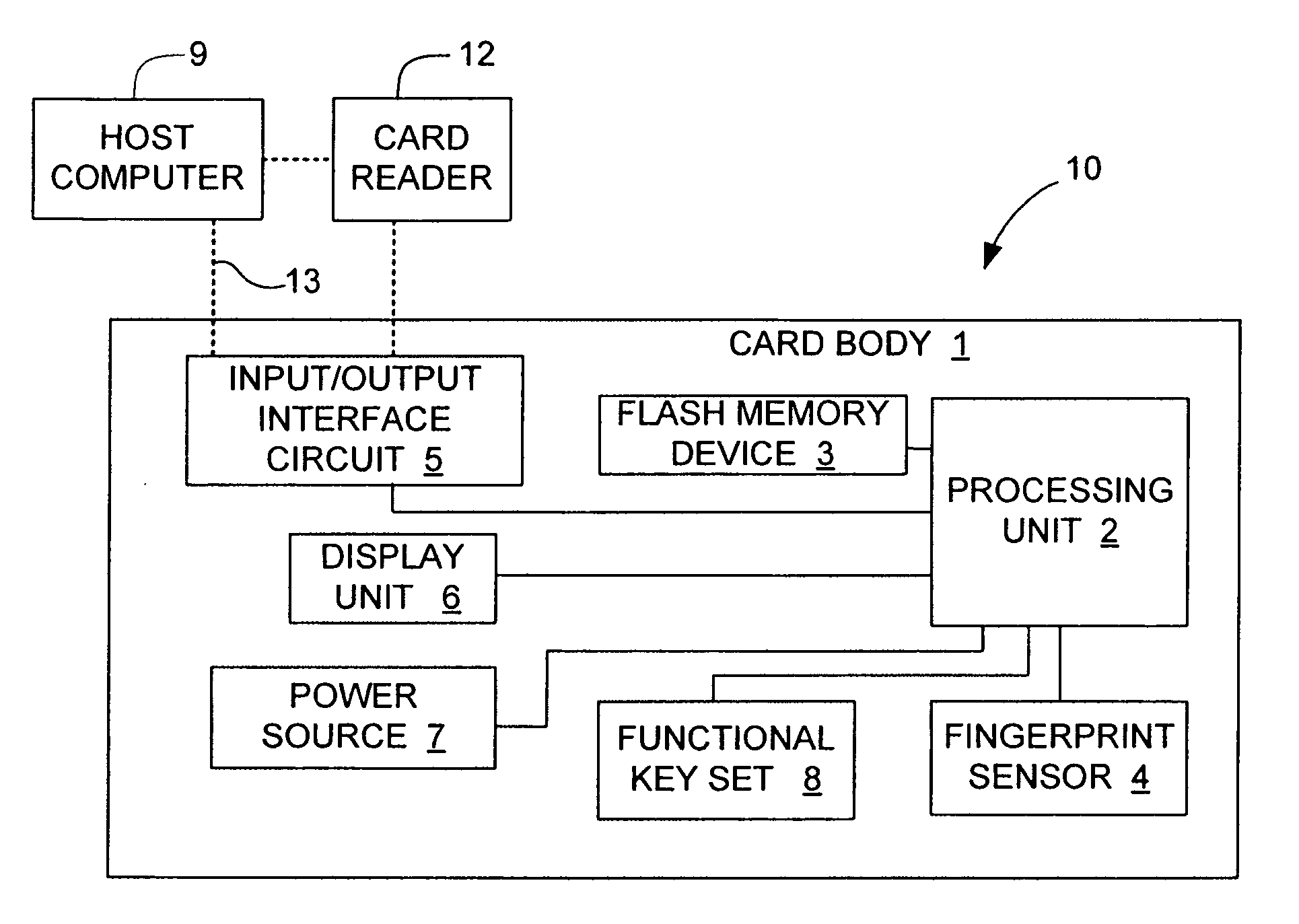

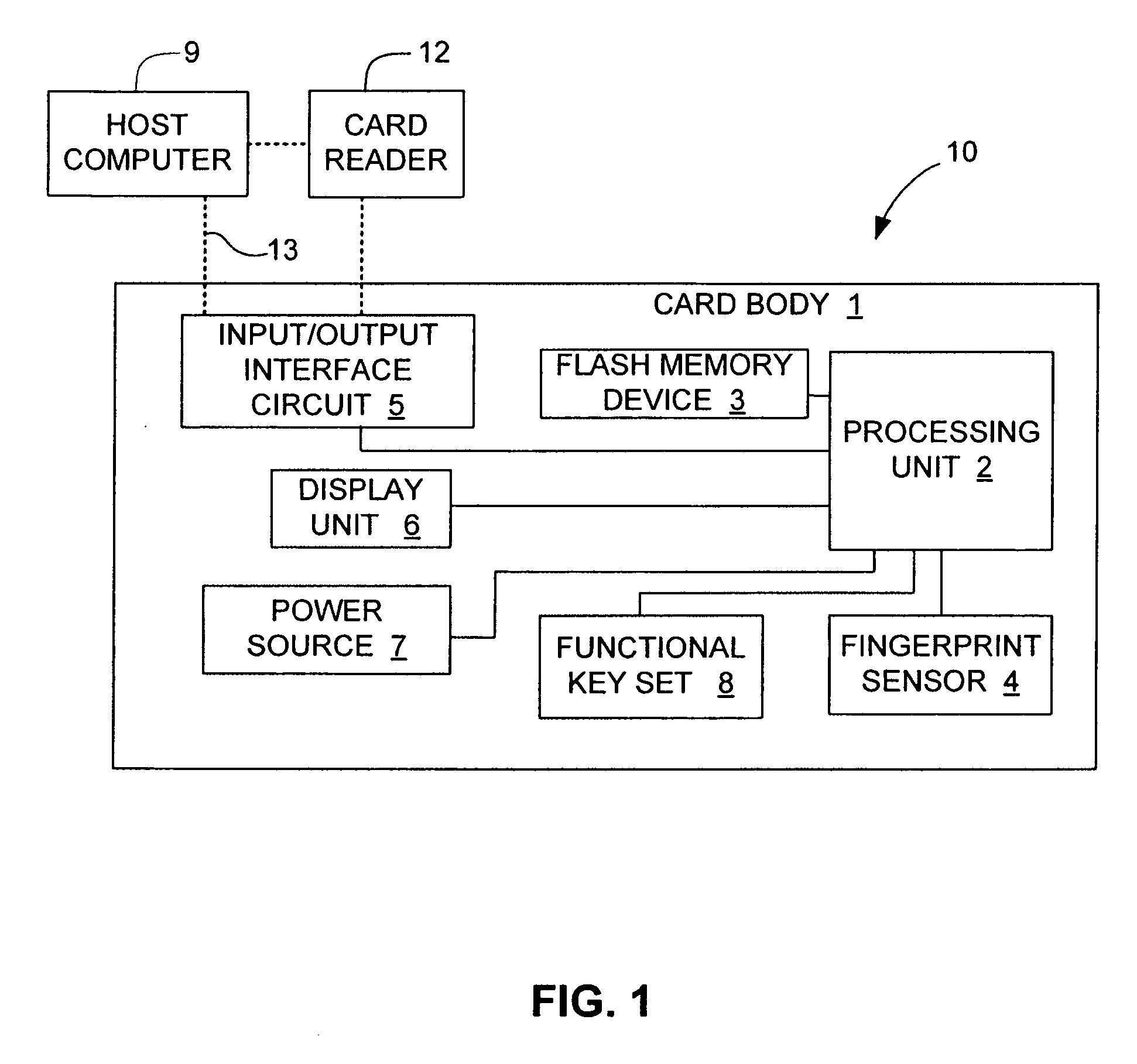

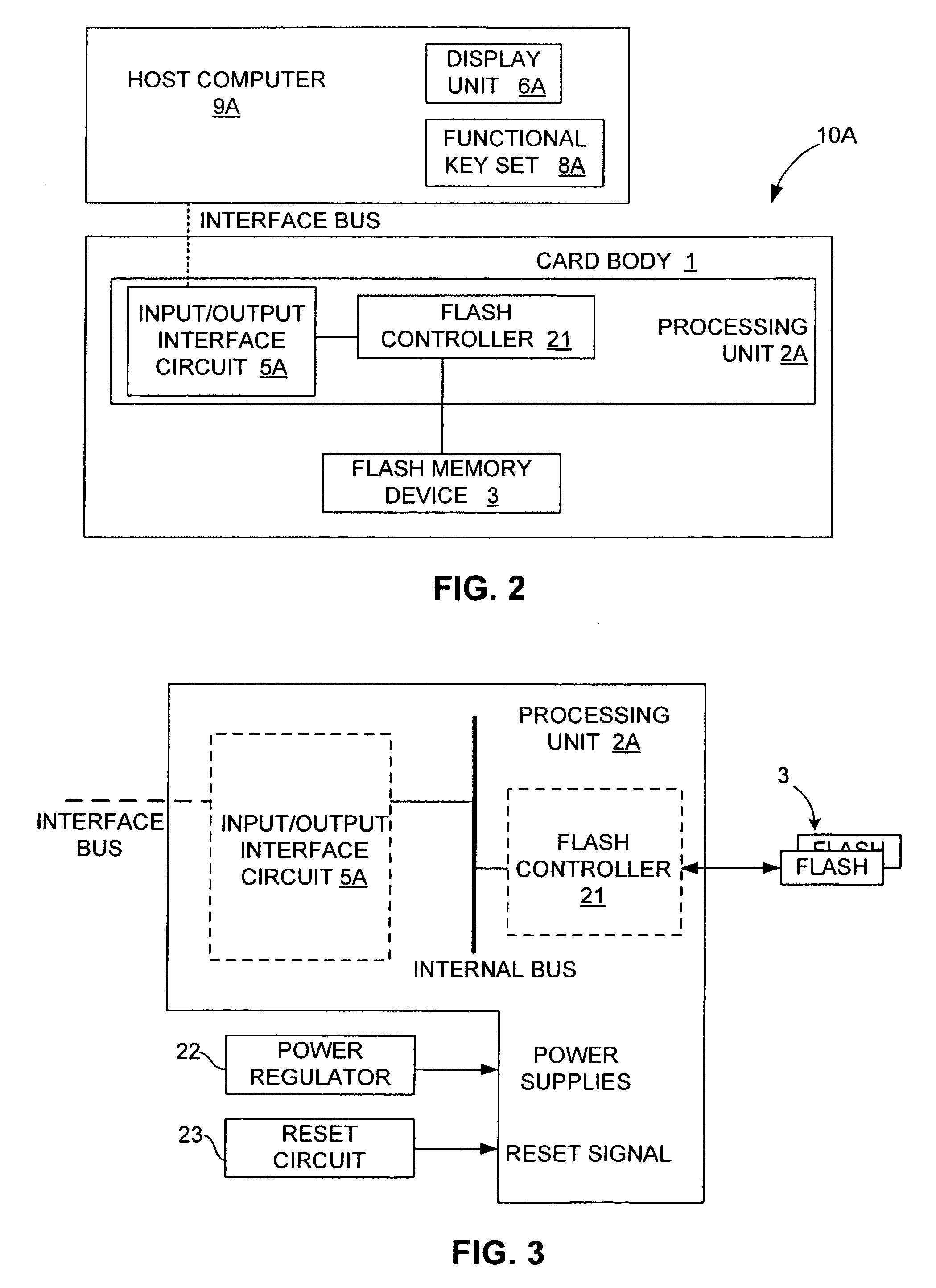

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

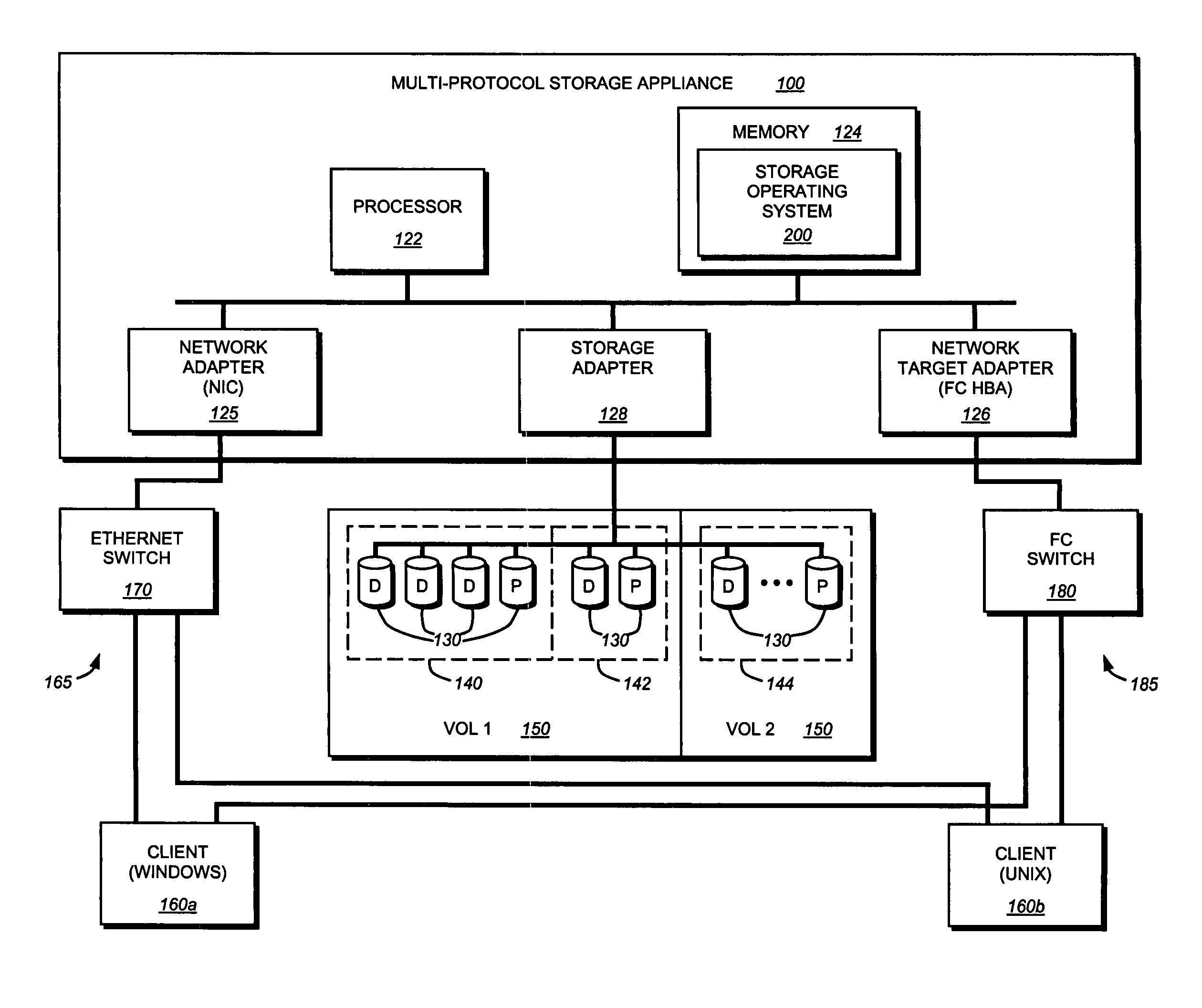

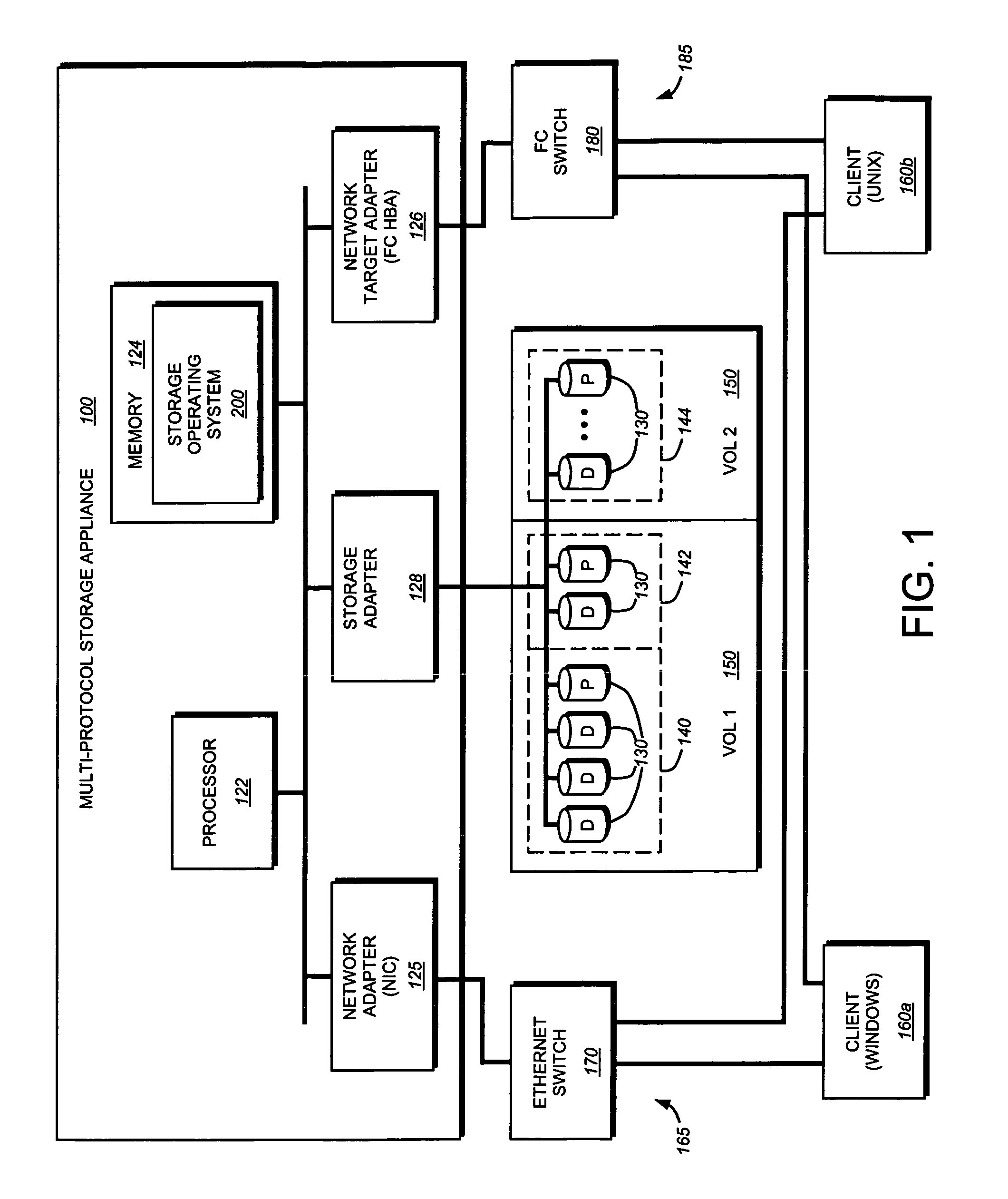

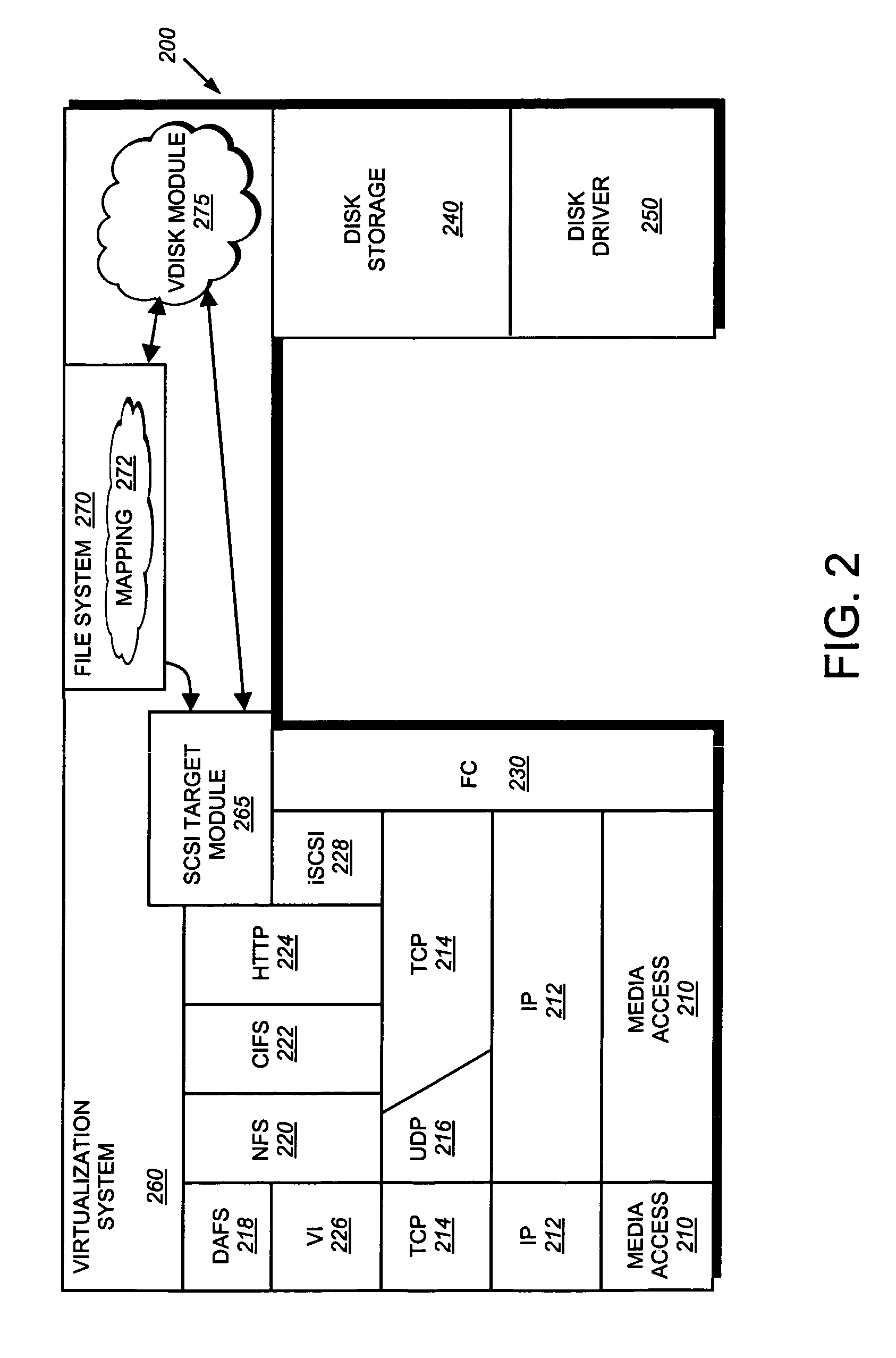

System and method for mapping file block numbers to logical block addresses

ActiveUS7437530B1Improve performanceRaise transfer toMultiple digital computer combinationsTransmissionOperational systemLogical block addressing

A system and method for mapping file block numbers (FBNs) to logical block addresses (LBAs) is provided. The system and method performs the mapping of FBNs to LBAs in a file system layer of a storage operating system, thereby enabling the use of clients in a storage environment that have not been modified to incorporate mapping tables. As a result, a client may send data access requests to the storage system utilizing FBNs and have the storage system perform the appropriate mapping to LBAs.

Owner:NETWORK APPLIANCE INC

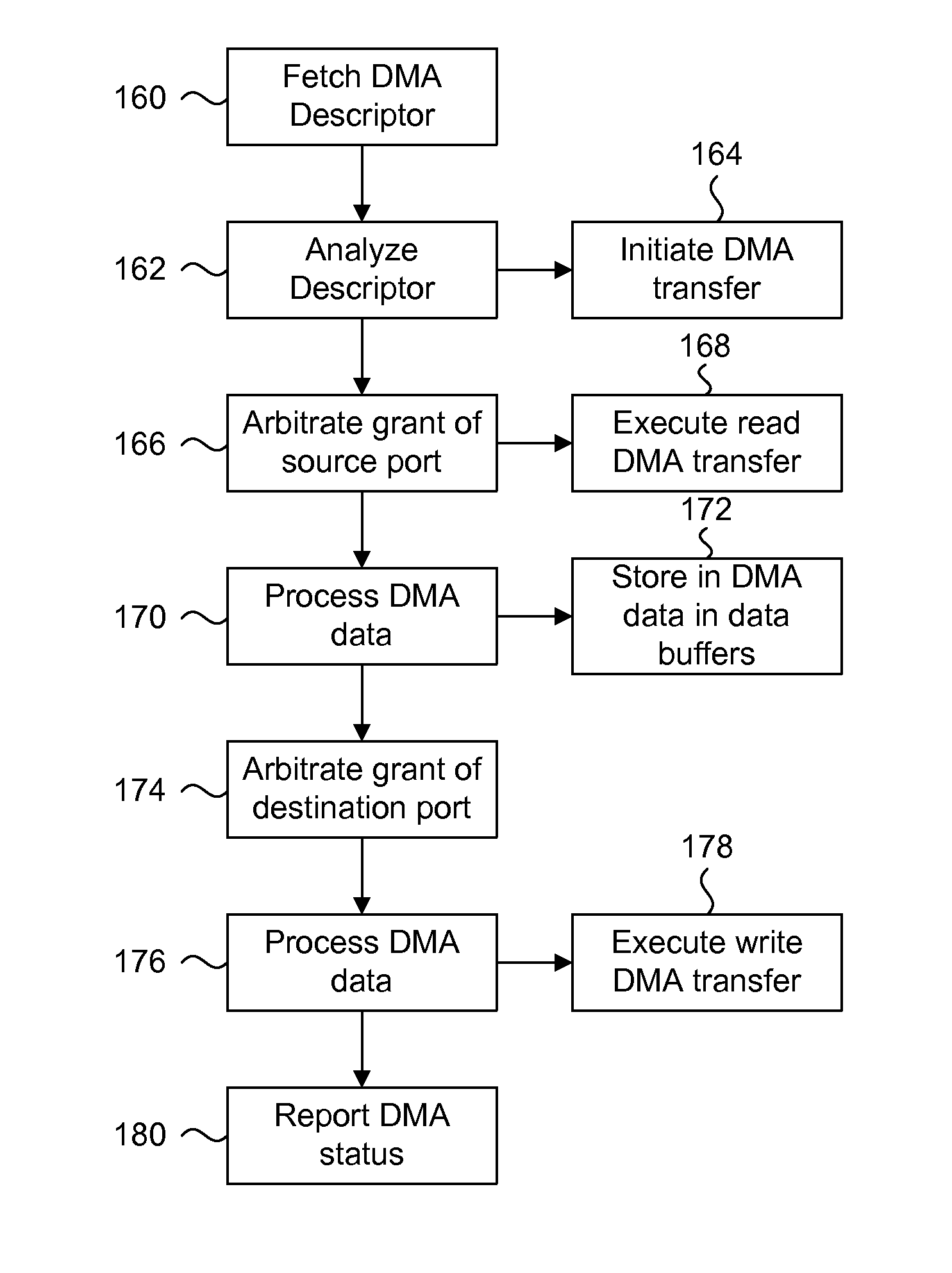

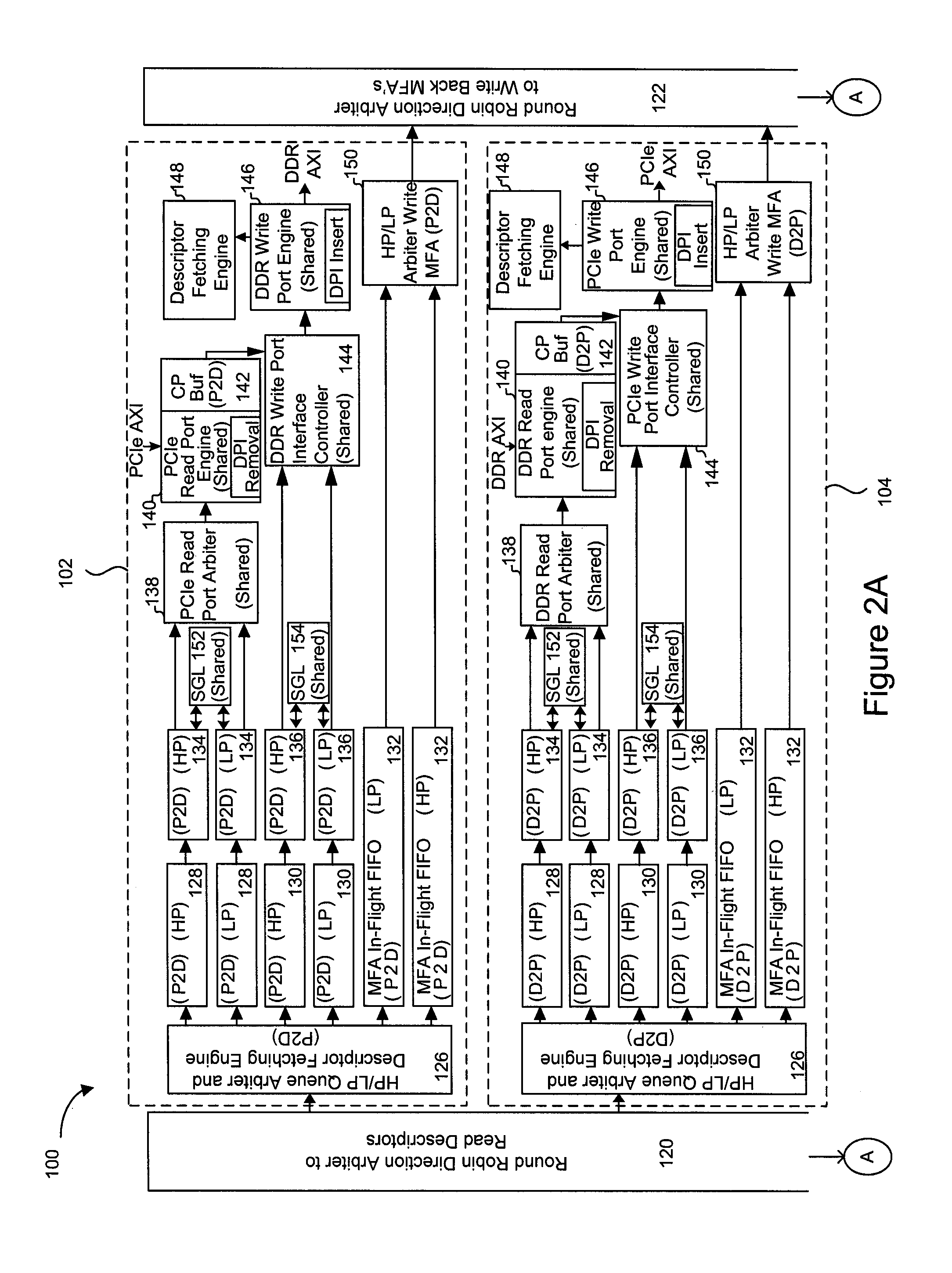

Logical address direct memory access with multiple concurrent physical ports and internal switching

A DMA engine is provided that is suitable for higher performance System On a Chip (SOC) devices that have multiple concurrent on-chip / off-chip memory spaces. The DMA engine operates either on logical addressing method or physical addressing method and provides random and sequential mapping function from logical address to physical address while supporting frequent context switching among a large number of logical address spaces. Embodiments of the present invention utilize per direction (source-destination) queuing and an internal switch to support non-blocking concurrent transfer of data on multiple directions. A caching technique can be incorporated to reduce the overhead of address translation.

Owner:MICROSEMI SOLUTIONS (US) INC

Method and system for storage address re-mapping for a multi-bank memory device

InactiveUS20090271562A1Improved memory managementMemory architecture accessing/allocationMemory adressing/allocation/relocationAddress spaceLogical address

A method and system for storage address re-mapping in a multi-bank memory is disclosed. The method includes allocating logical addresses in blocks of clusters and re-mapping logical addresses into storage address space, where short runs of host data dispersed in logical address space are mapped in a contiguous manner into megablocks in storage address space. Independently in each bank, valid data is flushed within each respective bank from blocks having both valid and obsolete data to make new blocks available for receiving data in each bank of the multi-bank memory when an available number of new blocks falls below a desired threshold within a particular bank.

Owner:SANDISK TECH LLC

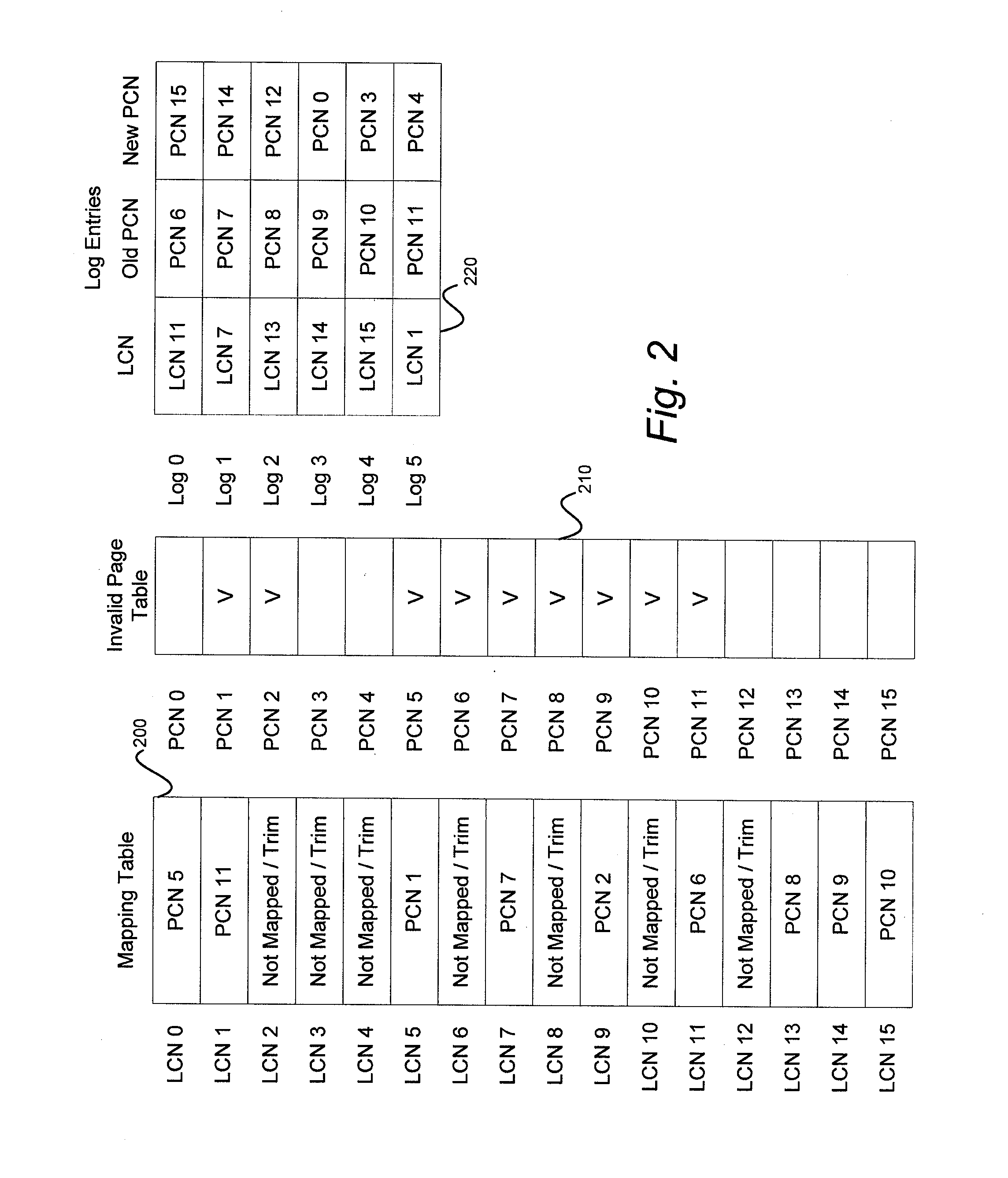

Spare Block Management of Non-Volatile Memories

ActiveUS20100172179A1Improve staminaMemory architecture accessing/allocationRead-only memoriesNon-volatile memoryLogical address

Techniques for the management of spare blocks in re-programmable non-volatile memory system, such as a flash EEPROM system, are presented. In one set of techniques, for a memory partitioned into two sections (for example a binary section and a multi-state section), where blocks of one section are more prone to error, spare blocks can be transferred from the more error prone partition to the less error prone partition. In another set of techniques for a memory partitioned into two sections, blocks which fail in the more error prone partition are transferred to serve as spare blocks in the other partition. In a complementary set of techniques, a 1-bit time stamp is maintained for free blocks to determine whether the block has been written recently. Other techniques allow for spare blocks to be managed by way of a logical to physical conversion table by assigning them logical addresses that exceed the logical address space of which a host is aware.

Owner:SANDISK TECH LLC

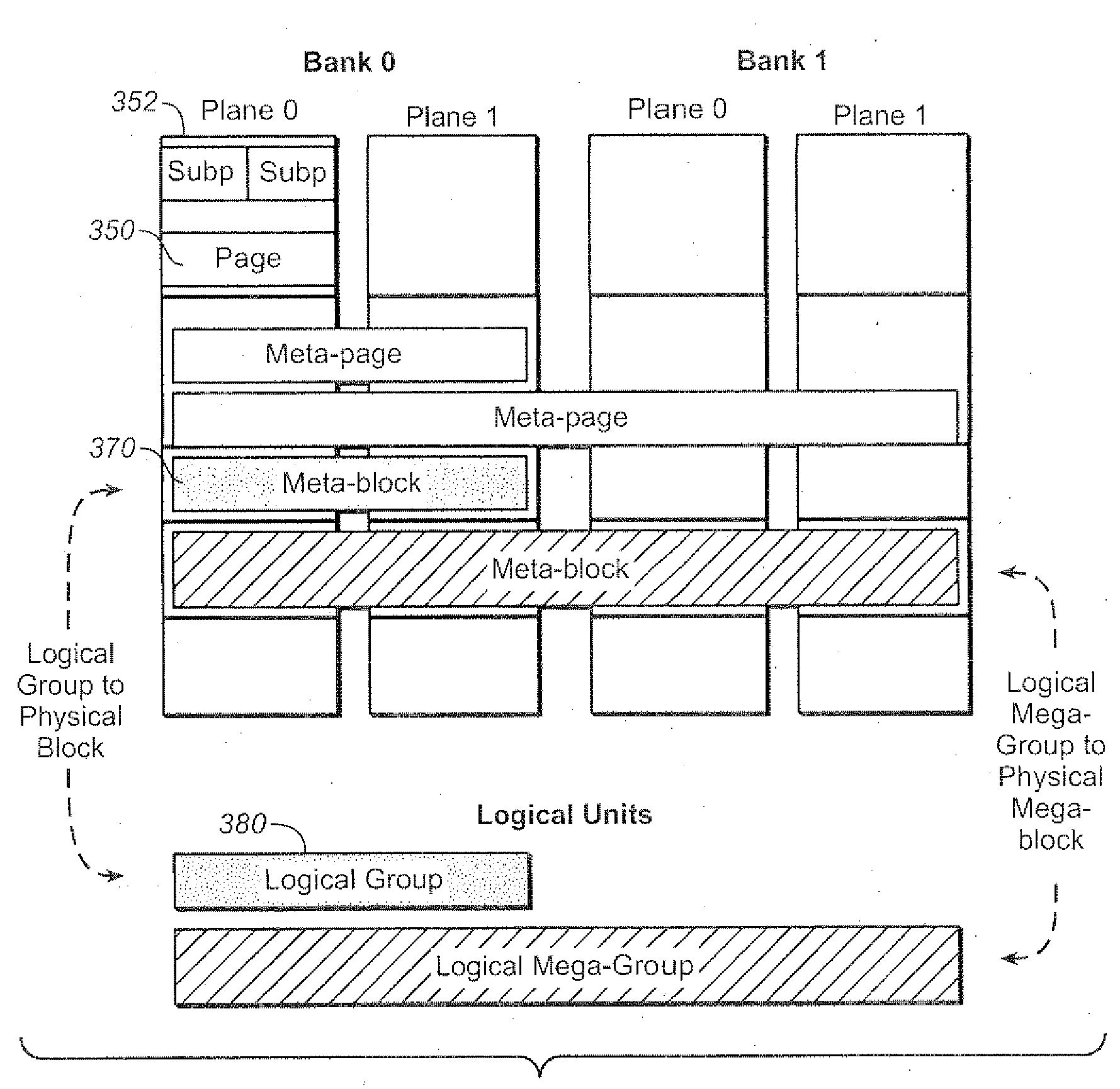

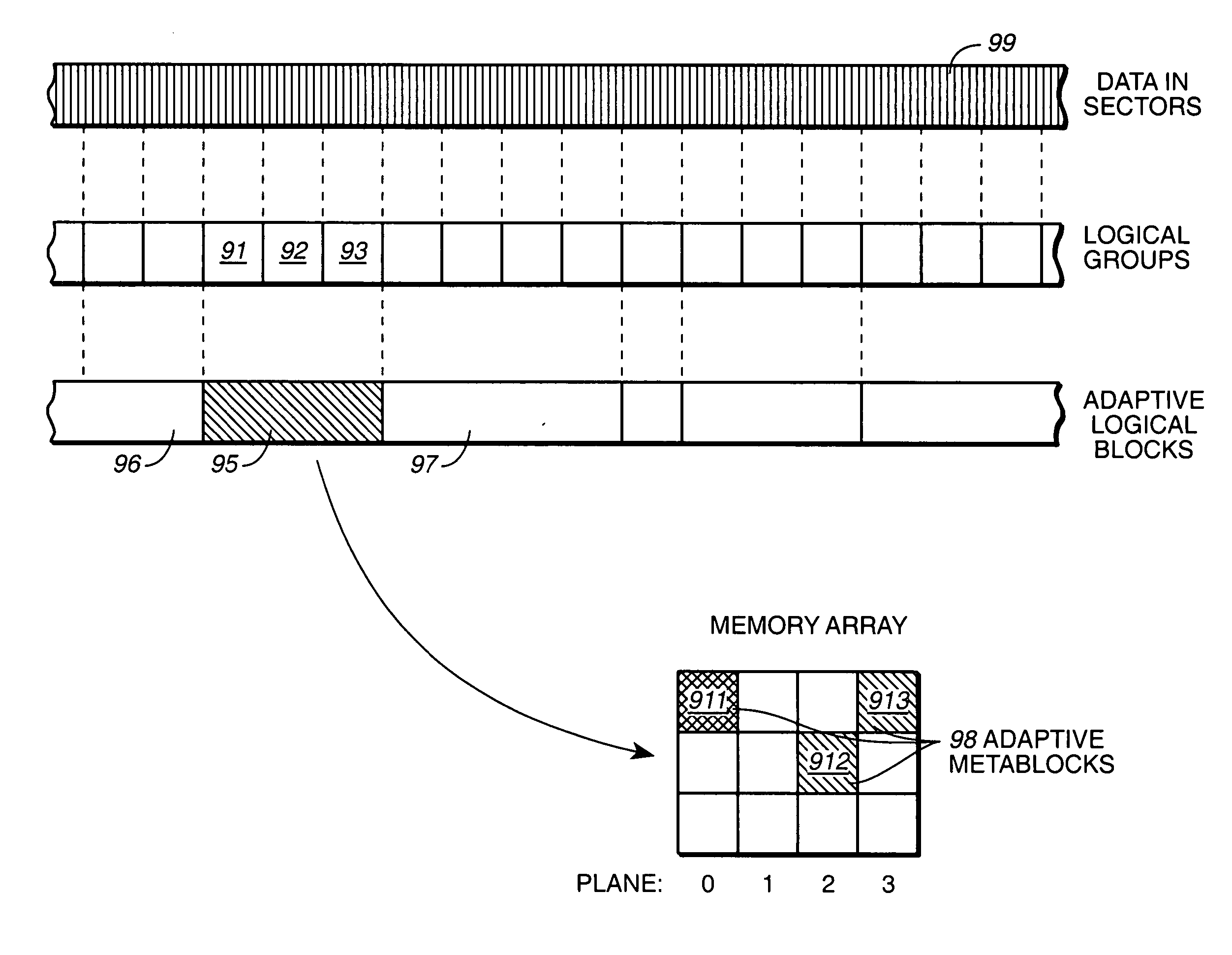

Adaptive metablocks

ActiveUS20050144357A1Reduce the impactEfficient updateMemory architecture accessing/allocationMemory adressing/allocation/relocationData selectionTheoretical computer science

In a memory system having multiple erase blocks in multiple planes, a selected number of erase blocks are programmed together as an adaptive metablock. The number of erase blocks in an adaptive metablock is chosen according to the data to be programmed. Logical address space is divided into logical groups, a logical group having the same size as one erase block. Adaptive logical blocks are formed from logical groups. One adaptive logical block is stored in one adaptive metablock.

Owner:SANDISK TECH LLC

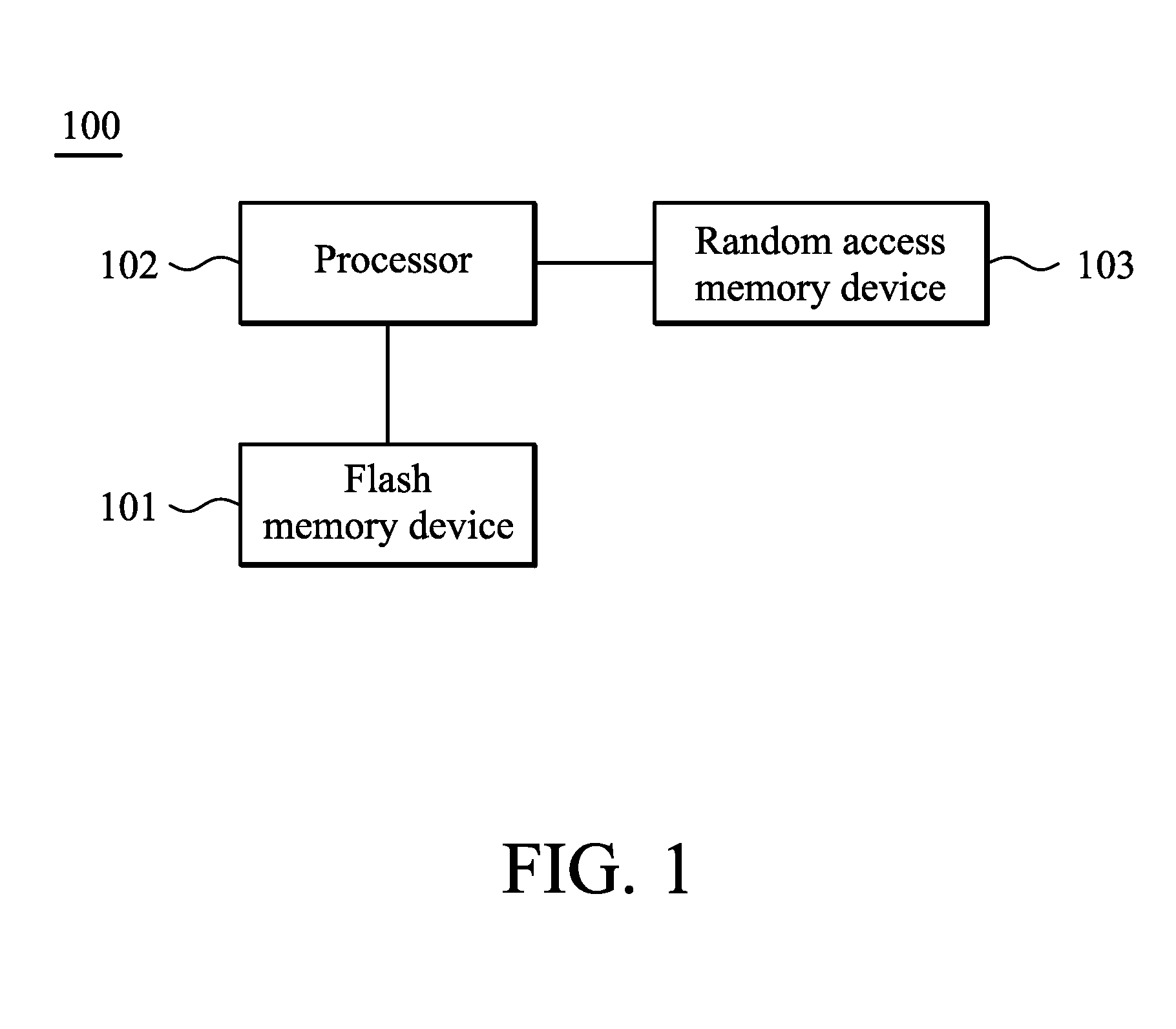

Computing systems and methods for managing flash memory device

InactiveUS20100287327A1Memory architecture accessing/allocationMemory adressing/allocation/relocationRandom access memoryData field

A computing system is provided. A flash memory device includes at least one mapping block, at least one modification block and at least one cache block. A processor is configured to perform: receiving a write command with a write logical address and predetermined data, loading content of a cache page from the cache block corresponding to the modification block according to the write logical address to a random access memory device in response to that a page of the mapping block corresponding to the write logical address has been used, the processor, reading orderly the content of the cache page stored in the random access memory device to obtain location information of an empty page of the modification block, and writing the predetermined data to the empty page according to the location information. Each cache page includes data fields to store location information corresponding to the data has been written in the pages of the modification block in order.

Owner:INTEL CORP

Non-Volatile Memory and Method With Write Cache Partition Management Methods

InactiveUS20100174847A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationMemory adressing/allocation/relocationGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. The cache memory has a capacity dynamically increased by allocation of blocks from the main memory in response to a demand to increase the capacity. Preferably, a block with an endurance count higher than average is allocated. The logical addresses of data are partitioned into zones to limit the size of the indices for the cache.

Owner:SANDISK TECH LLC

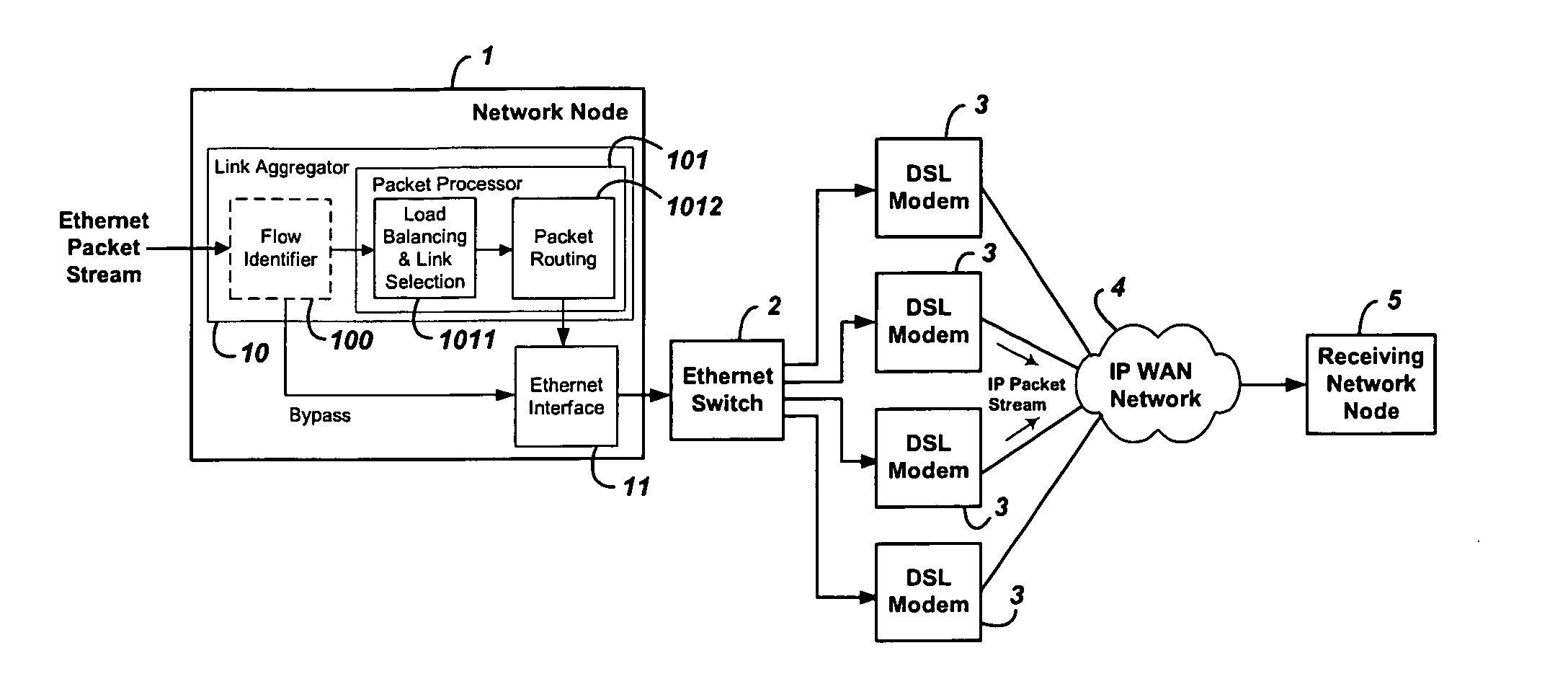

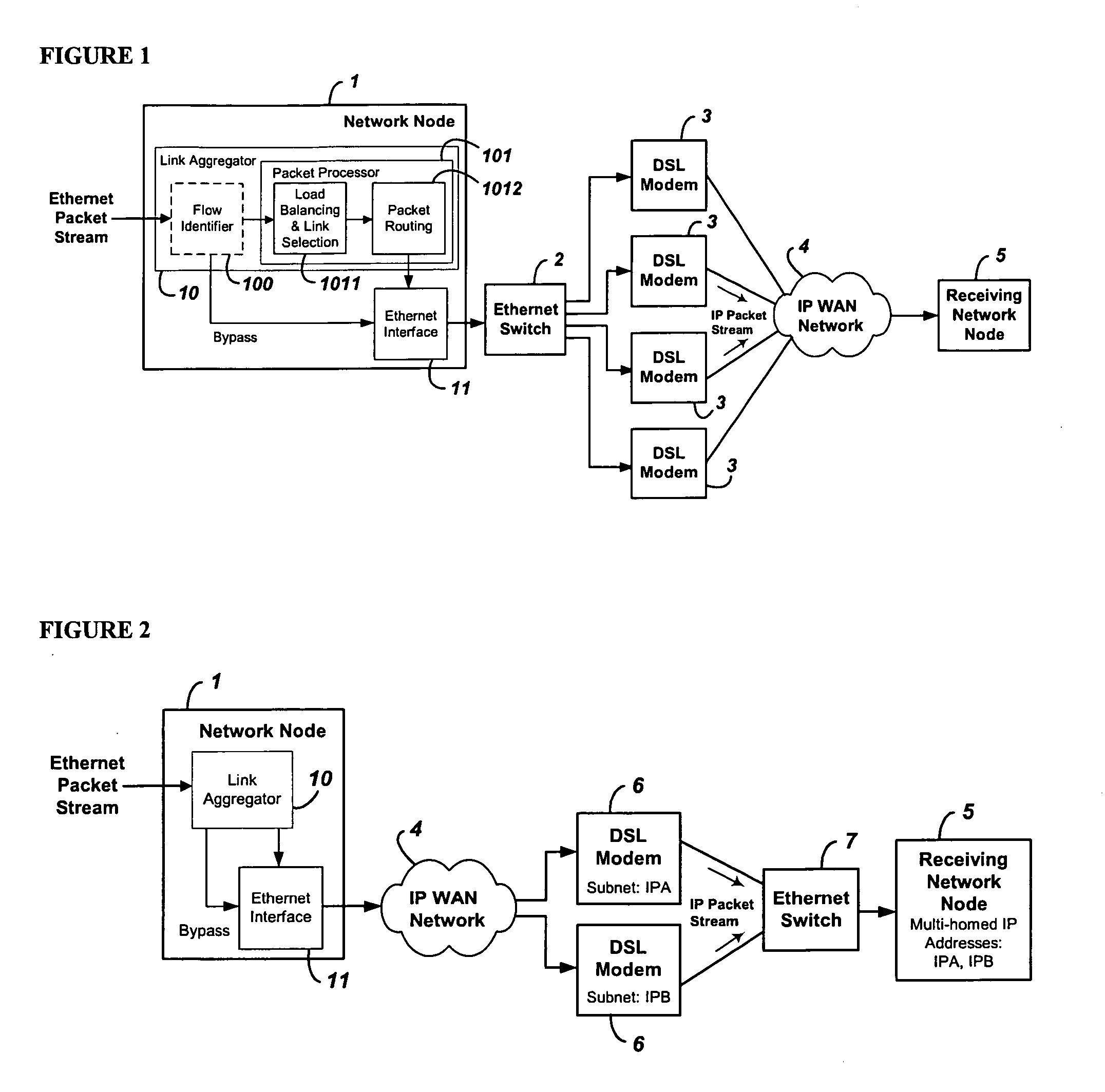

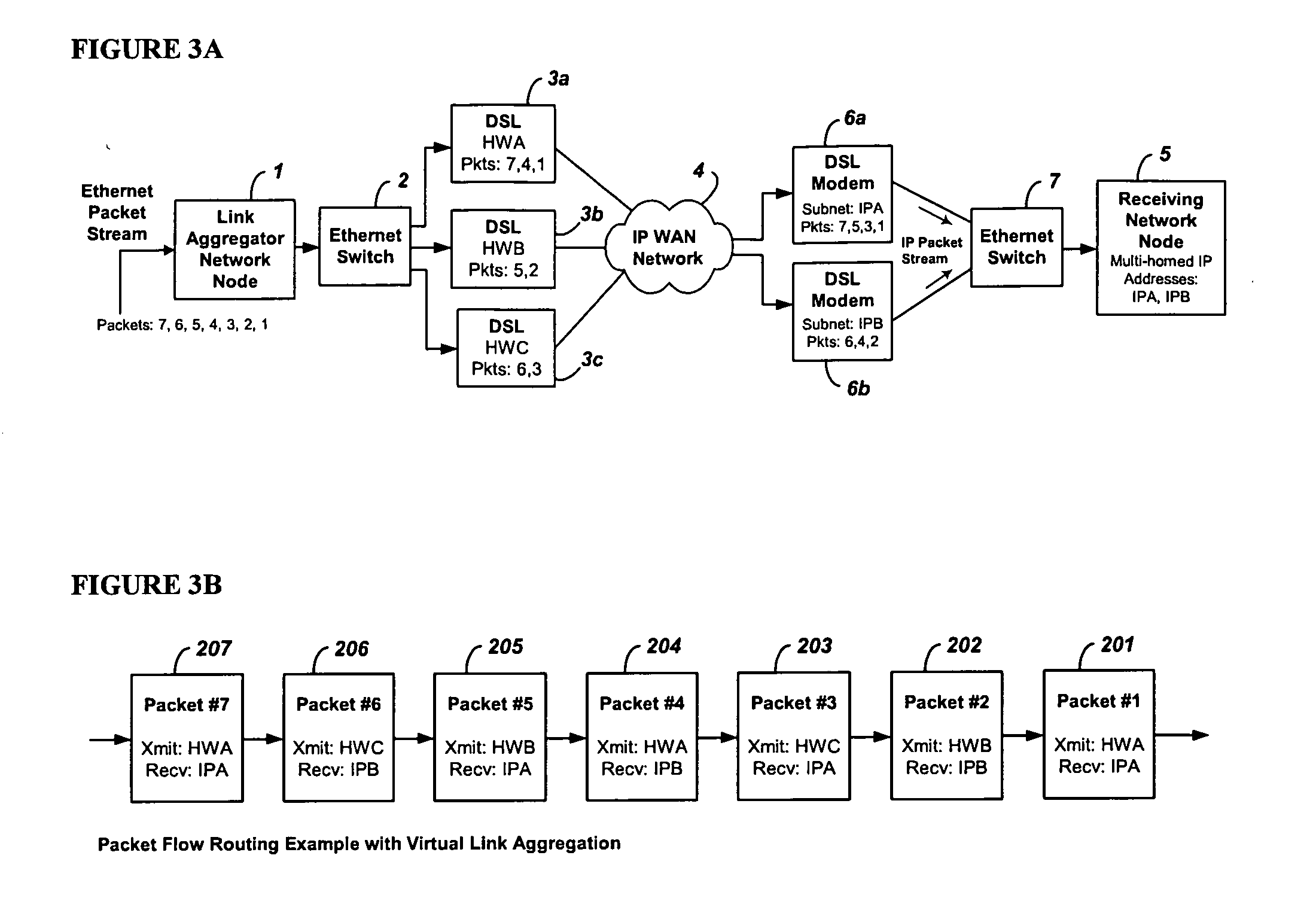

System and method for the virtual aggregation of network links

InactiveUS20060098573A1Improve throughputImprove reliabilityEnergy efficient ICTError preventionNetwork linkRewriting

A system and method for virtual link aggregation for combining network links of various types and speeds to increase throughput and reliability for packetized transport. In contrast with physical port trunking, the system does not require direct control over ports or network interfaces. Instead, the system rewrites packet addresses and works through existing networking equipment, without requiring any new or special protocols, processing, or equipment within the network. The system works through low-level rerouting by rewriting hardware addresses and / or high-level routing by rewriting logical addresses. Thus packets are redirected through multiple routes to a common destination via alternate gateways and links. Different algorithms may be employed to balance the load on each link and determine an optimal route for each packet. Embodiments may also employ packet flow or stream identification and thereby only provide link aggregation for a specified set of packet flows.

Owner:QVIDIUM TECH

Apparatus, system, and method for allocating storage

ActiveUS20110060887A1Memory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwareLogical address

An apparatus, system, and method are disclosed for allocating non-volatile storage. The storage device may present a logical address, which may exceed a physical storage capacity of the device. The storage device may allocate logical capacity in the logical address space. An allocation request may be allowed when there is sufficient unassigned and / or unallocated logical capacity to satisfy the request. Data may be stored on the non-volatile storage device by requesting physical storage capacity. A physical storage request, such as a storage request or physical storage reservation, when there is sufficient available physical storage capacity to satisfy the request. The device may maintain an index to associate logical identifiers (LIDs) in the logical address space with storage locations on the storage device. This index may be used to make logical capacity allocations and / or to manage physical storage space.

Owner:SANDISK TECH LLC

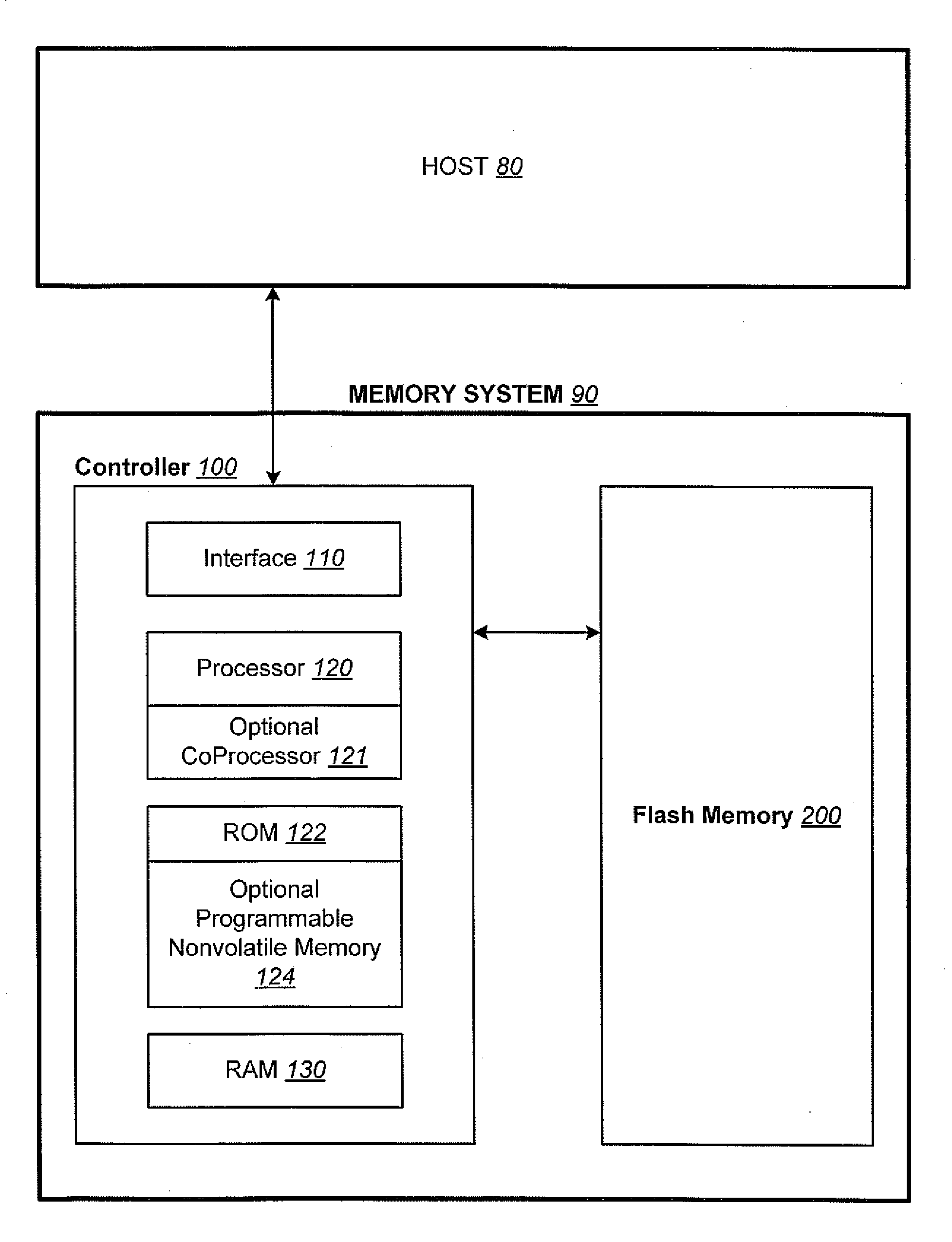

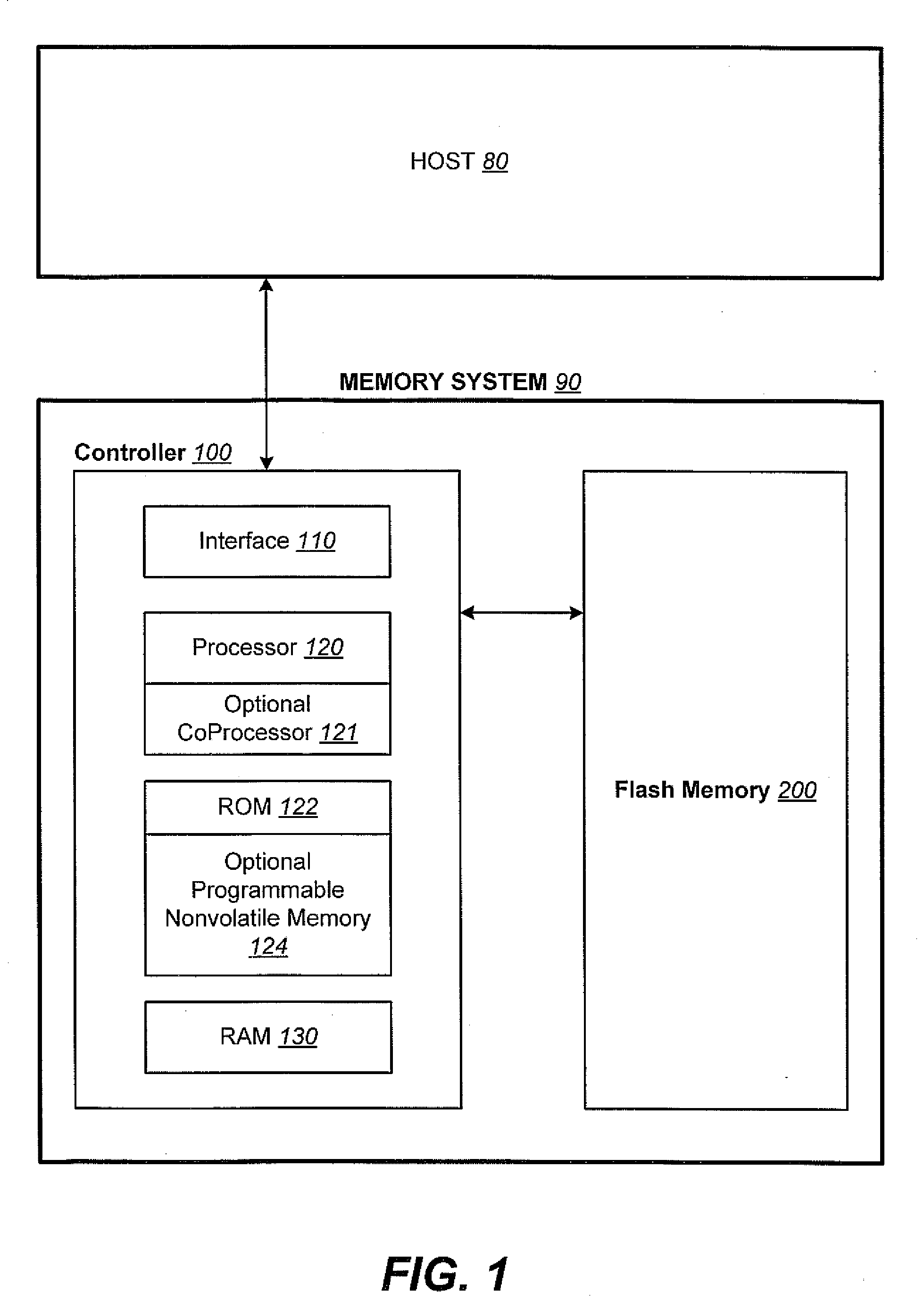

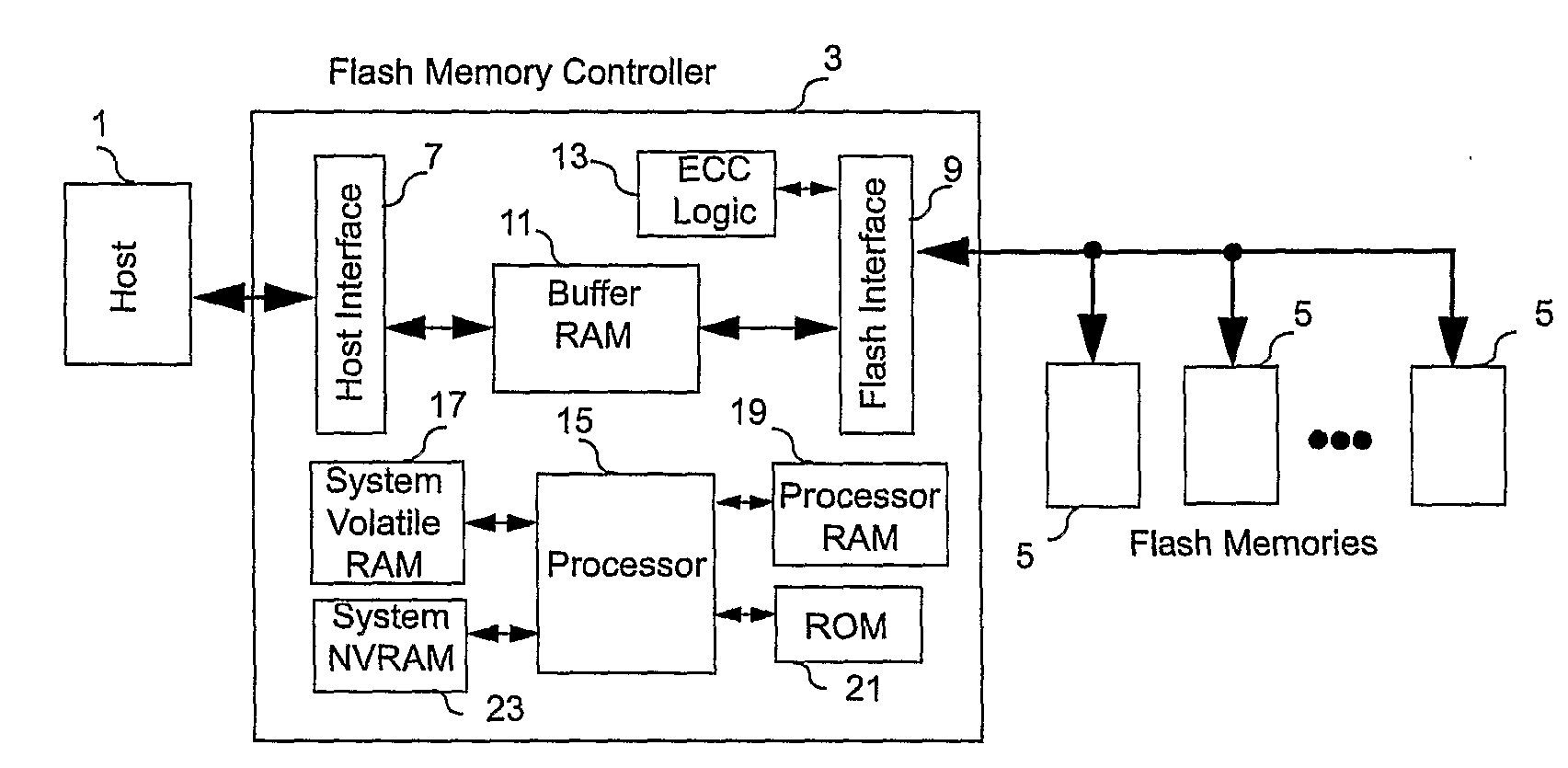

Controller for Non-Volatile Memories and Methods of Operating the Memory Controller

ActiveUS20080270680A1Improve system performanceReduce stepsMemory adressing/allocation/relocationRead-only memoriesMemory controllerByte

A non-volatile memory system (3) is proposed consisting of a first non-volatile flash memory (5) having a plurality of blocks, each block having a plurality of pages, each block being erasable and each page being programmable, and a second non-volatile random access memory (23) having a plurality of randomly accessible bytes. The second non-volatile memory (23) stores data for mapping logical blocks to physical blocks and status information of logical blocks. Each logical block has an associated physical page pointer stored in the second non-volatile memory (23) that identifies the next free physical page of the mapped physical block to be written. The page pointer is incremented after every page write to the physical block, allowing all physical pages to be fully utilized for page writes. Furthermore, a method of writing and reading data is disclosed whereby the most recently written physical page associated with a logical address is identifiable by the memory system without programming flags into superseded pages, or recording time stamp values in any physical page or block of the first non-volatile memory (5). Furthermore, a method is provided for a logical block to be mapped to two physical blocks instead of one to provide additional space for page writes, resulting in reduction in page copy operations, thereby increasing the performance of the system.

Owner:CHANG CHEE KENG

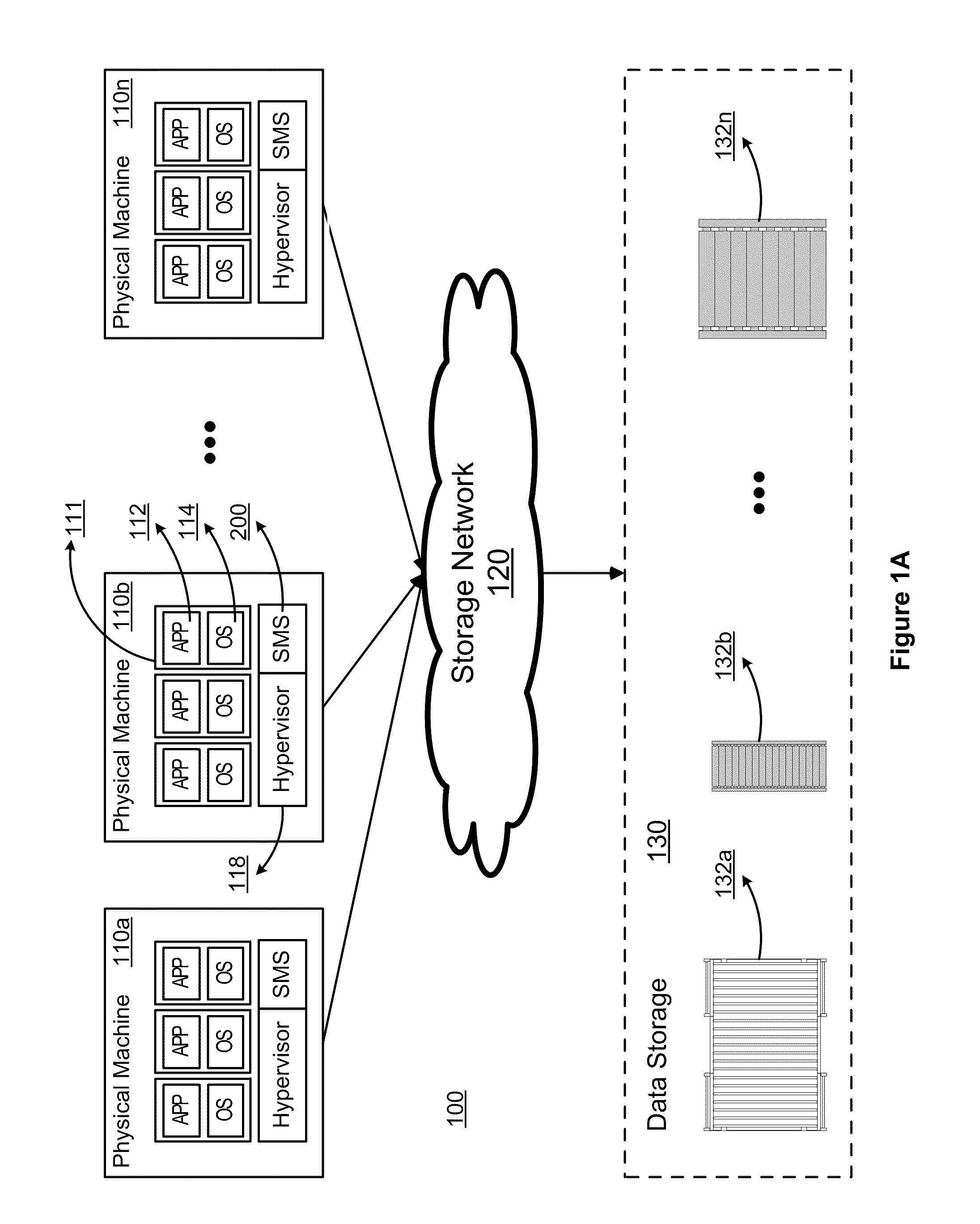

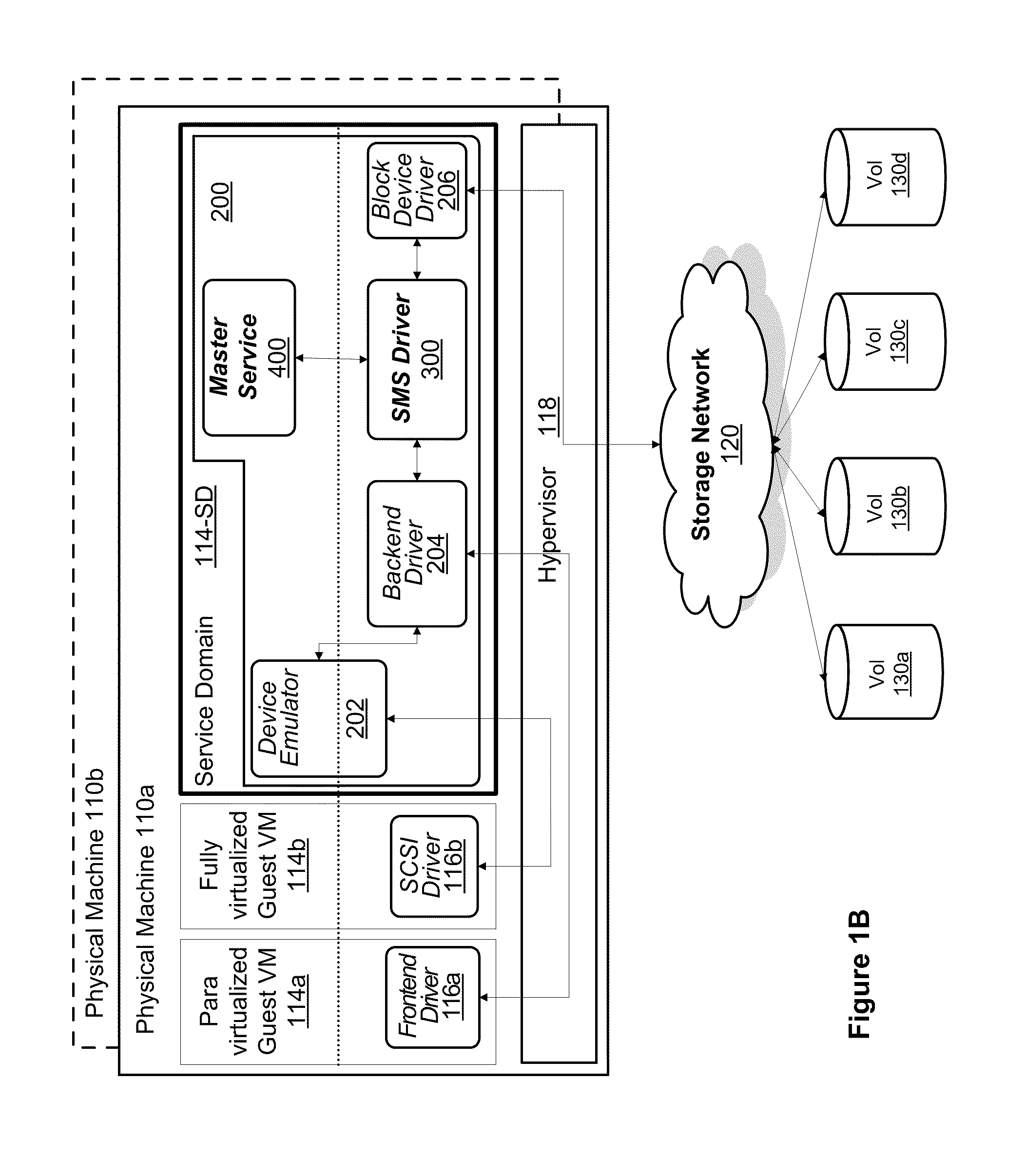

Storage management system for virtual machines

ActiveUS20100153617A1Overcome limitationsMemory adressing/allocation/relocationComputer security arrangementsVirtualizationData center

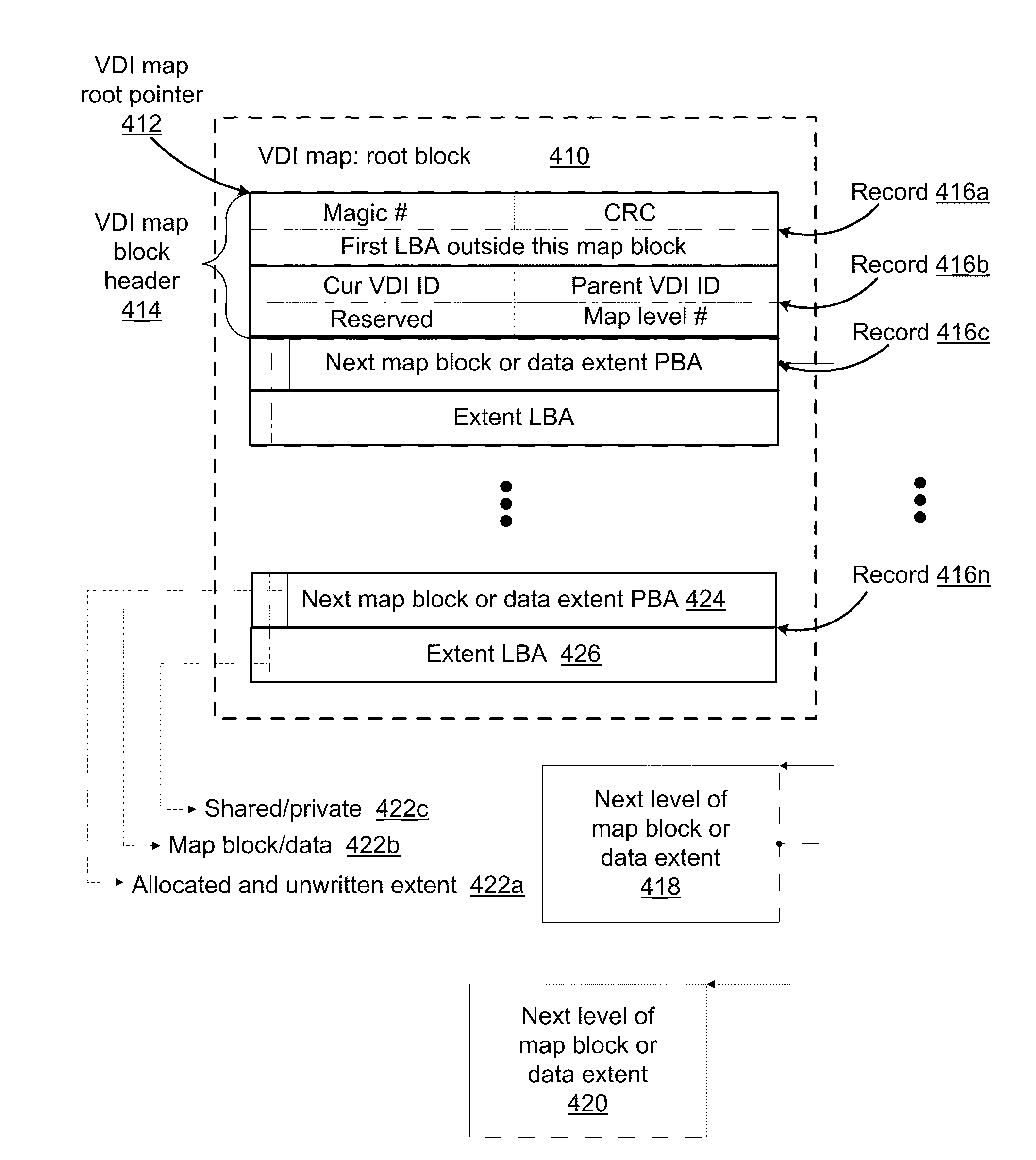

A computer system (a method) for providing storage management solution that enables server virtualization in data centers is disclosed. The system comprises a plurality of storage devices for storing data and a plurality of storage management drivers configured to provide an abstraction of the plurality of the storage devices to one or more virtual machines of the data center. A storage management driver is configured to represent a live disk or a snapshot of a live disk in a virtual disk image to the virtual machine associated with the driver. The driver is further configured to translate a logical address for a data block to one or more physical addresses of the data block through the virtual disk image. The system further comprises a master server configured to manage the abstraction of the plurality of the storage devices and to allocate storage space to one or more virtual disk images.

Owner:VMWARE INC

Method And System For Storage Address Re-Mapping For A Memory Device

ActiveUS20080307192A1Improve performanceImprove system performanceMemory architecture accessing/allocationMemory systemsFile systemAddress space

A method and system for storage address re-mapping is disclosed. The method includes allocating logical addresses in blocks of clusters and re-mapping logical addresses into storage address space, where short runs of data dispersed in logical address space are mapped in a contiguous manner into blocks in storage address space. Valid data is flushed from blocks having both valid and obsolete data to make new blocks available for receiving data when an available number of new blocks falls below a desired threshold. The system includes a host file system, processor executable instructions residing on a host separately from the host file system or residing on a flash memory device such as an embedded solid state disk, or a backend memory manager of the flash memory device that is configured to map data from a logical address space to complete blocks in storage address space in a contiguous manner.

Owner:SANDISK TECH LLC

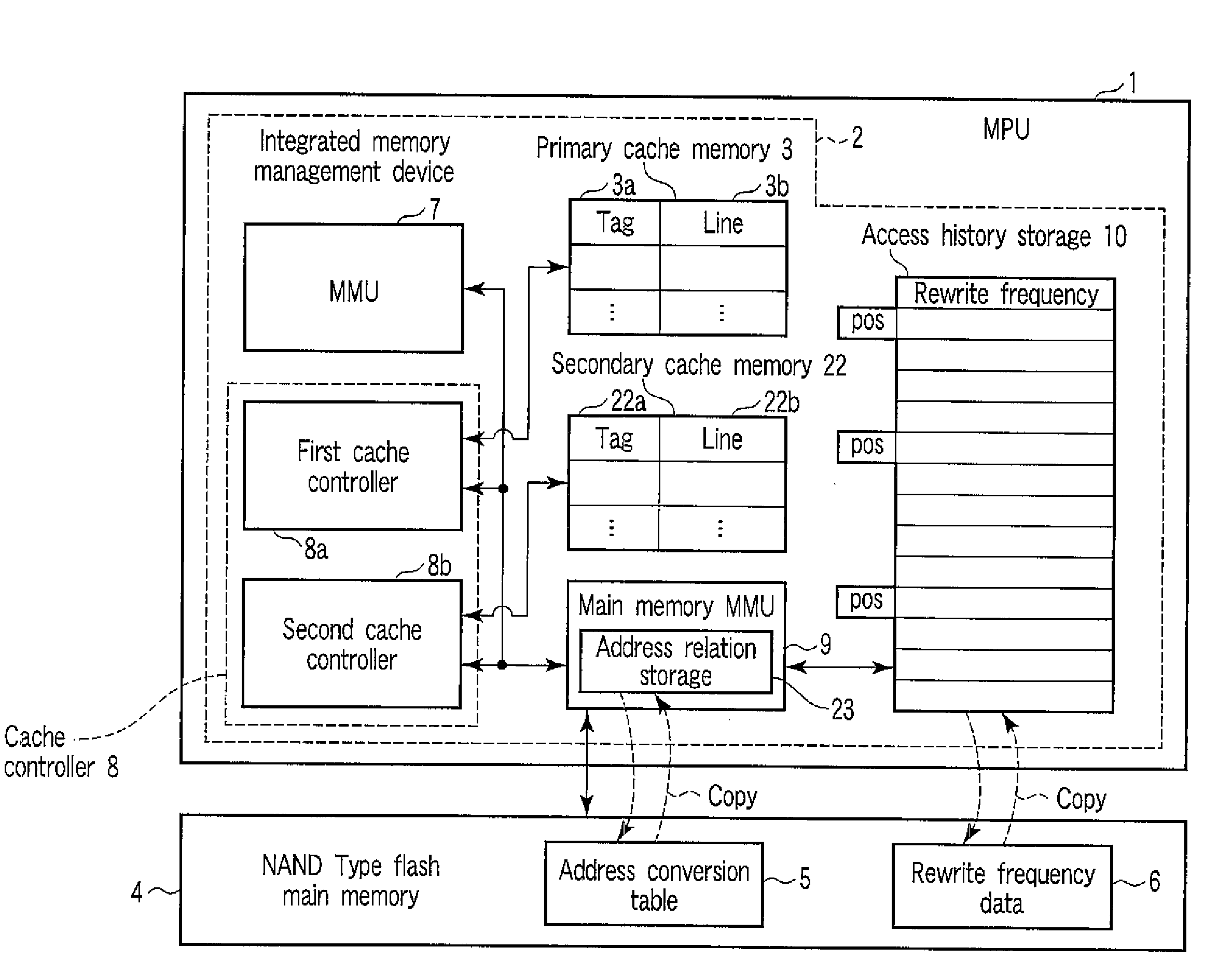

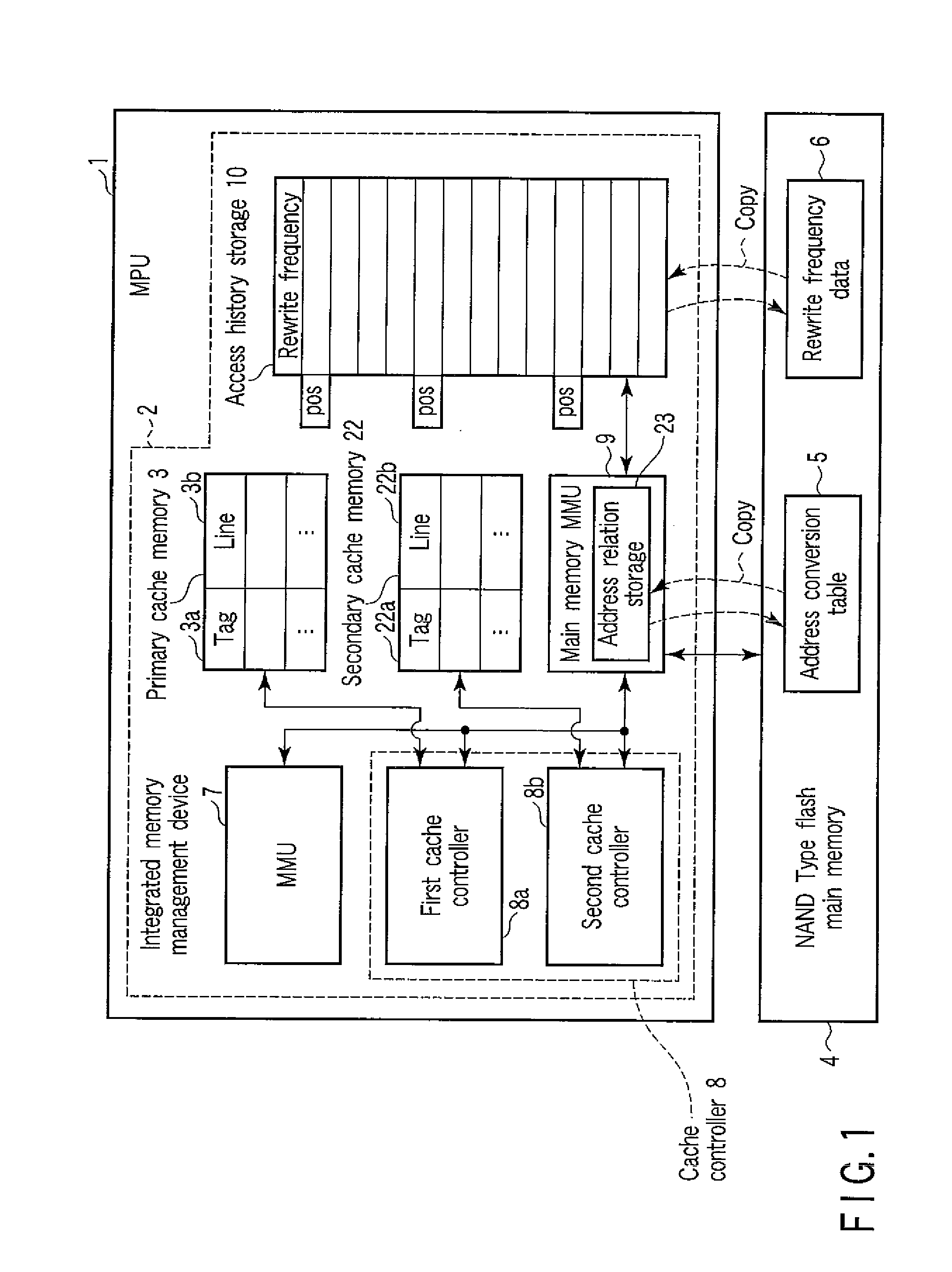

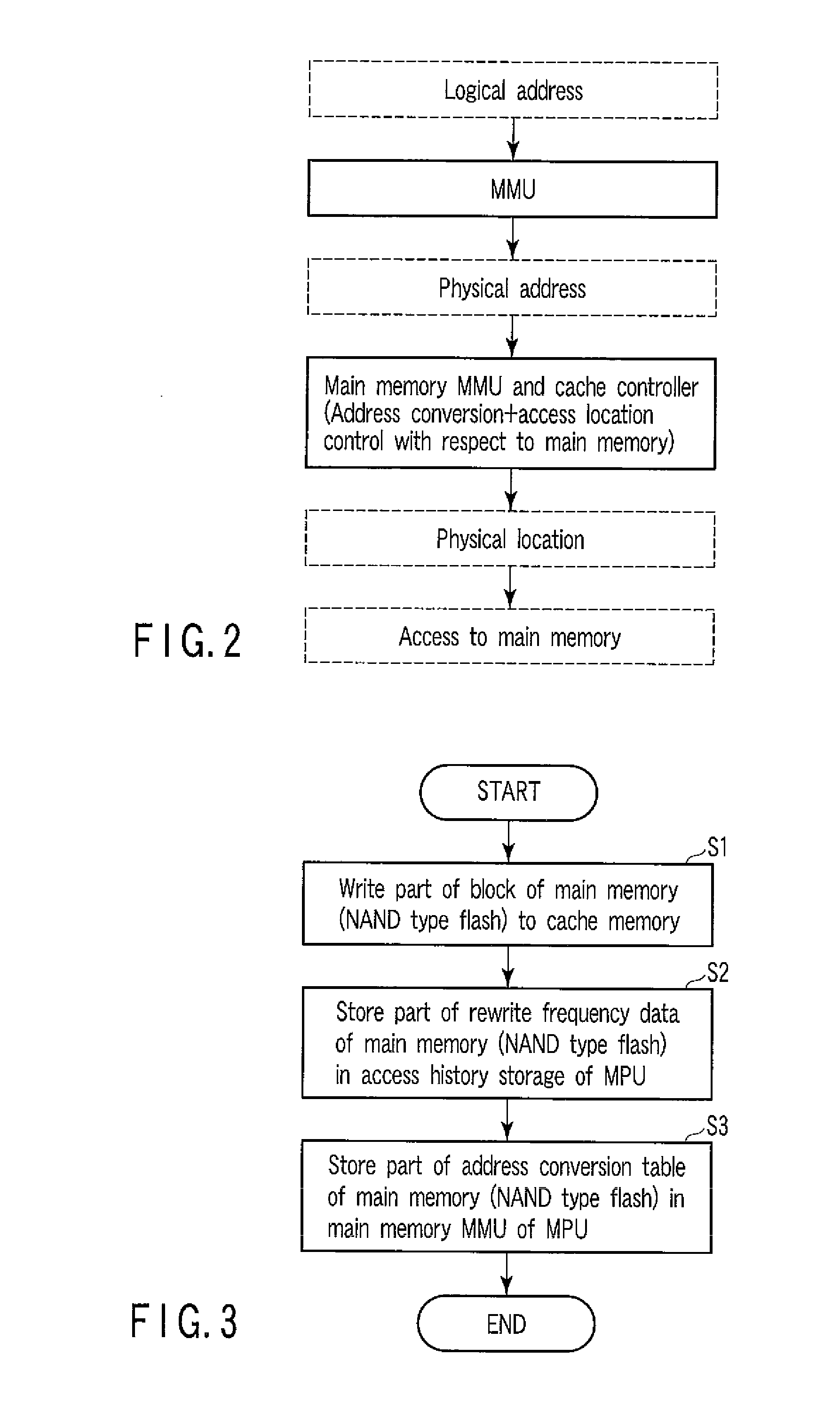

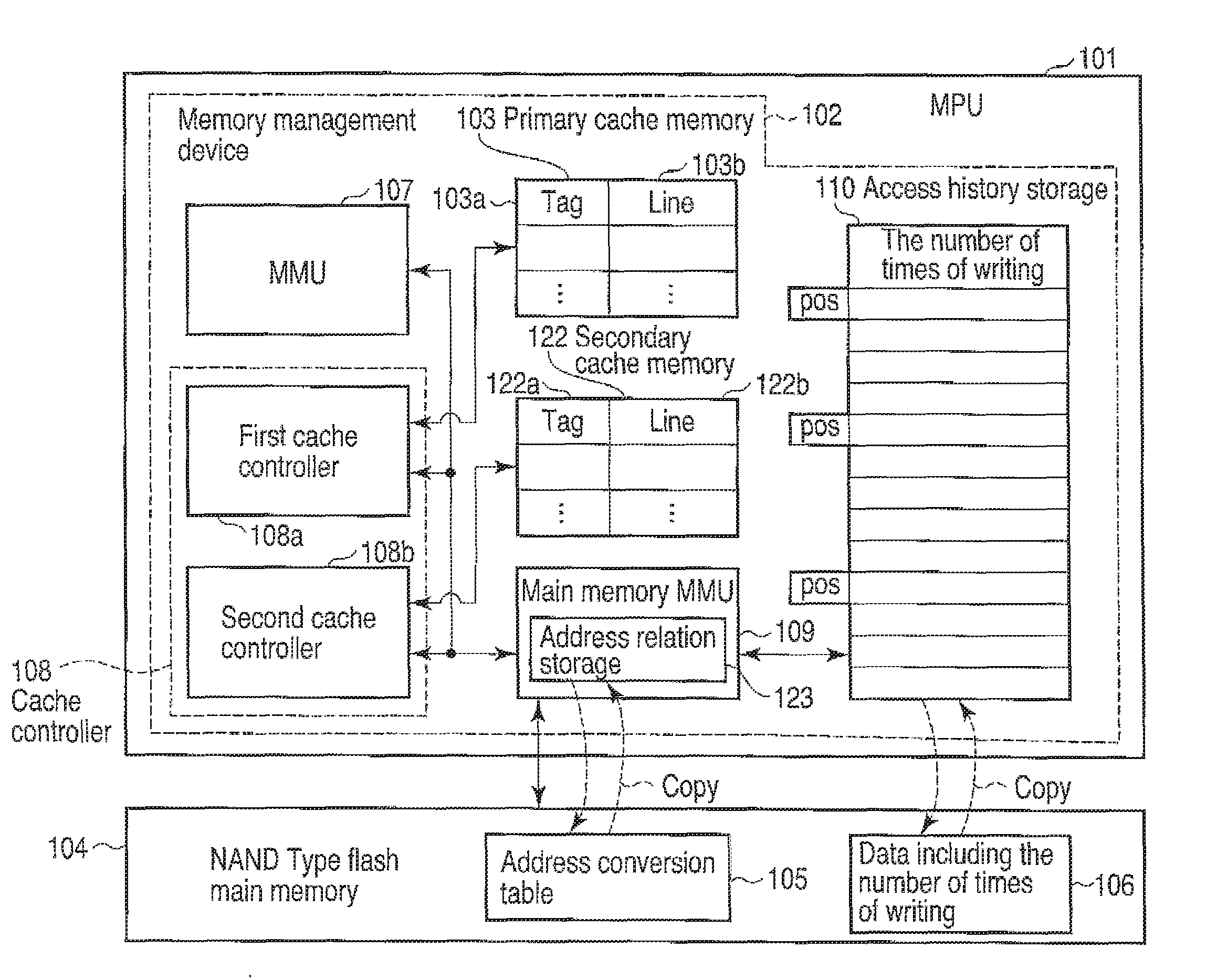

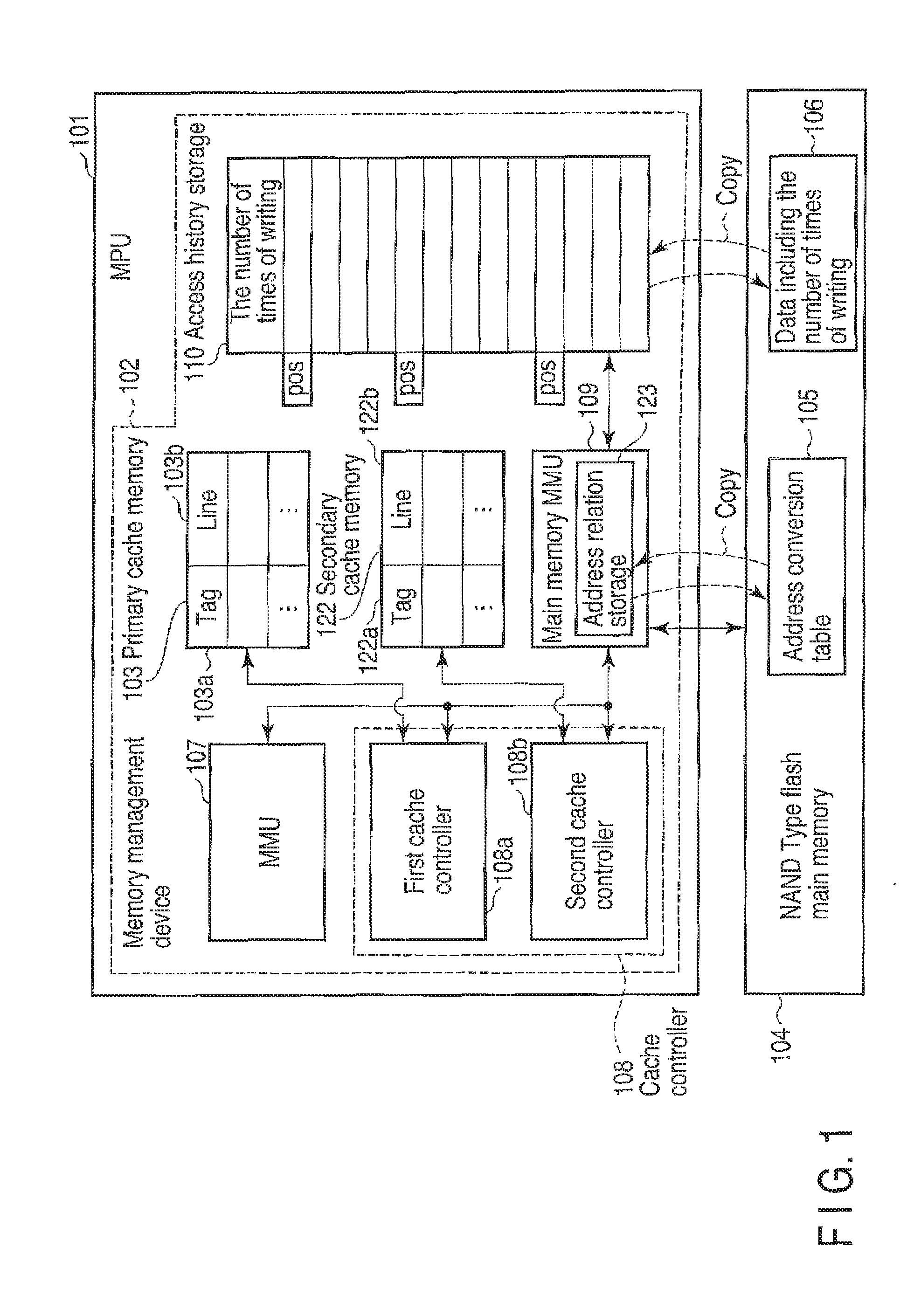

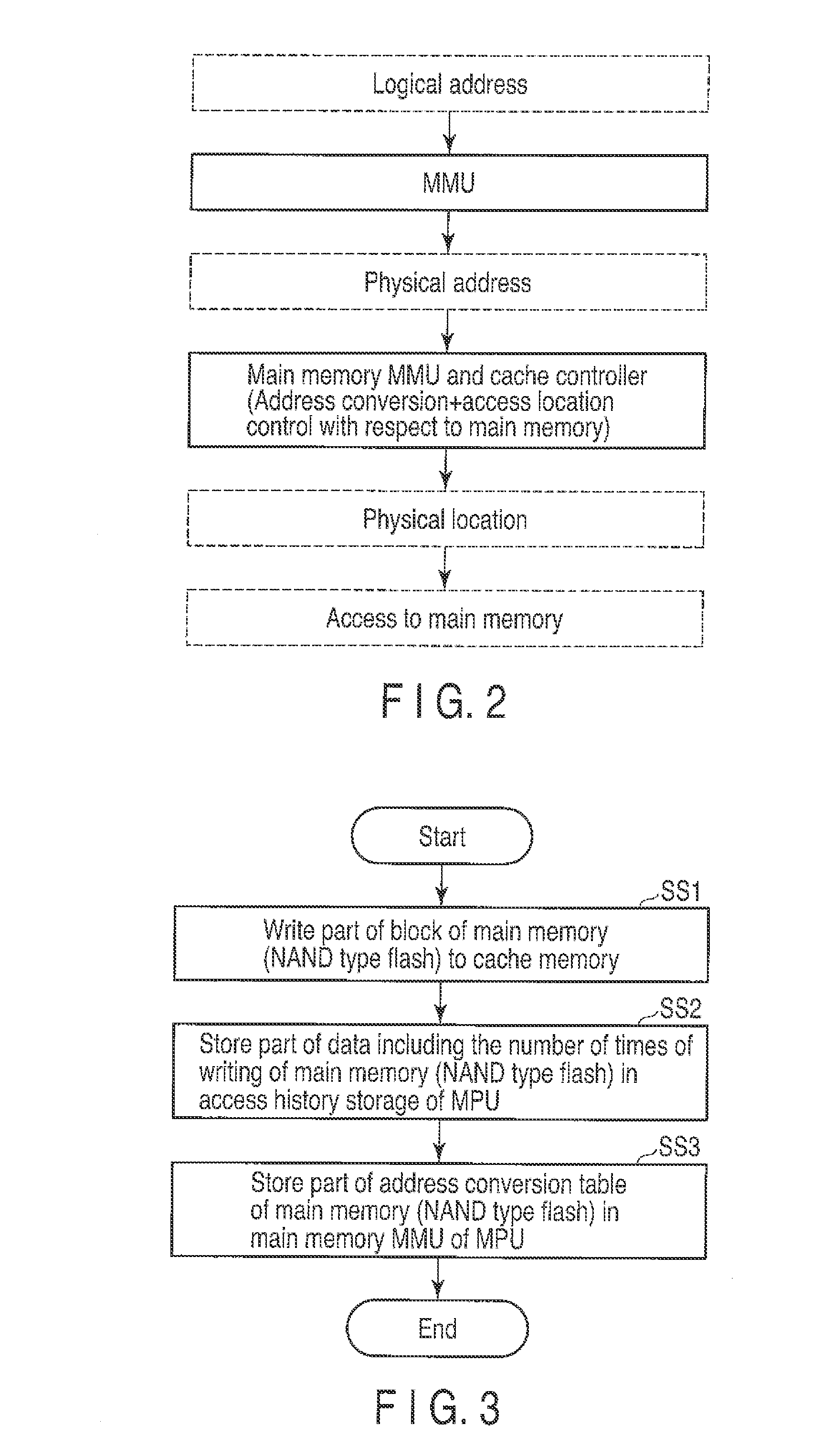

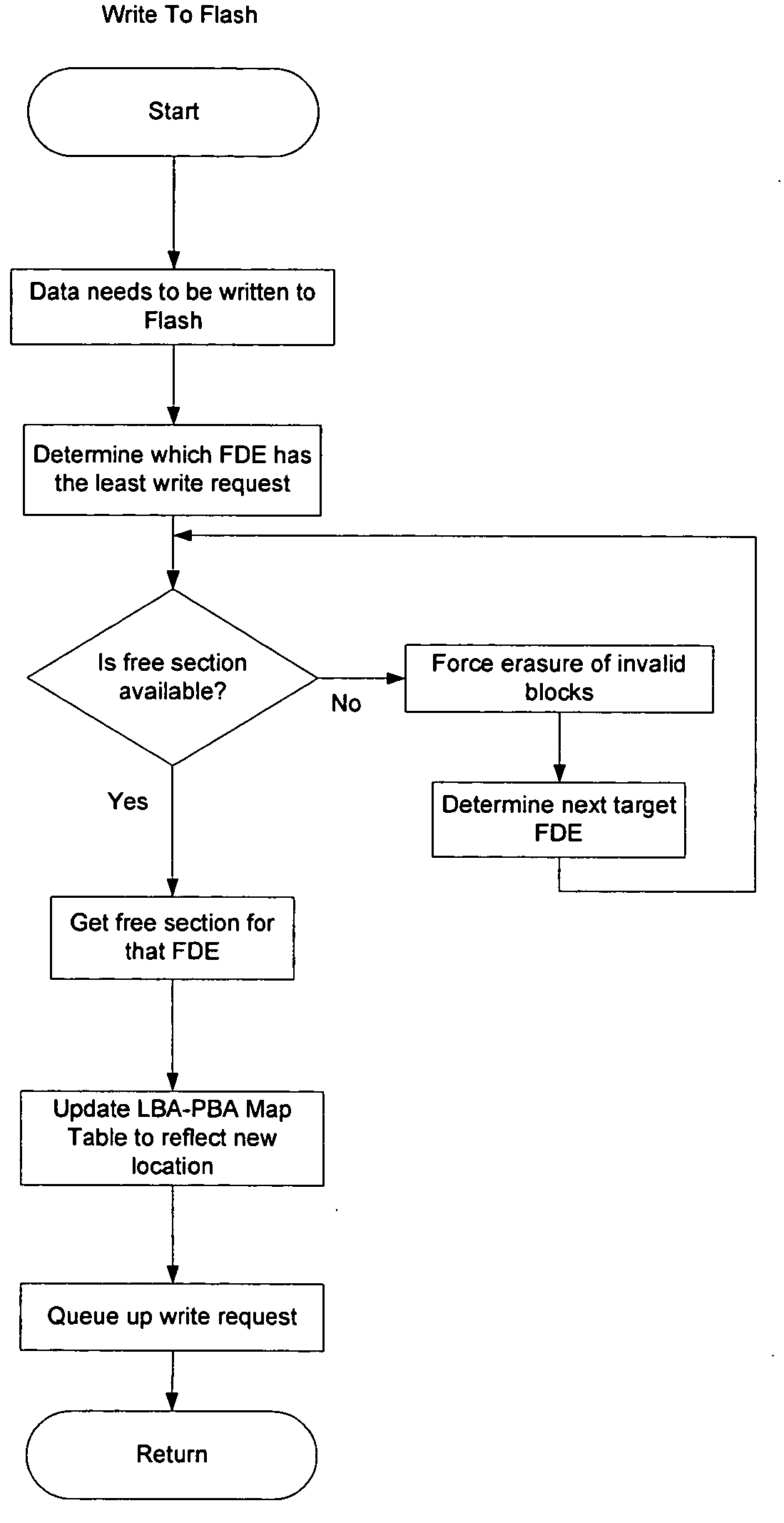

Integrated memory management and memory management method

ActiveUS20090083478A1Memory architecture accessing/allocationMemory adressing/allocation/relocationData transmissionMemory management unit

An integrated memory management device according to an example of the invention comprises an acquiring unit acquiring a read destination logical address from a processor, an address conversion unit converting the read destination logical address into a read destination physical address of a non-volatile main memory, an access unit reading, from the non-volatile main memory, data that corresponds to the read destination physical address and has a size that is equal to a block size or an integer multiple of the page size of the non-volatile main memory, and transmission unit transferring the read data to a cache memory of the processor having a cache size that depends on the block size or the integer multiple of the page size of the non-volatile main memory.

Owner:KIOXIA CORP

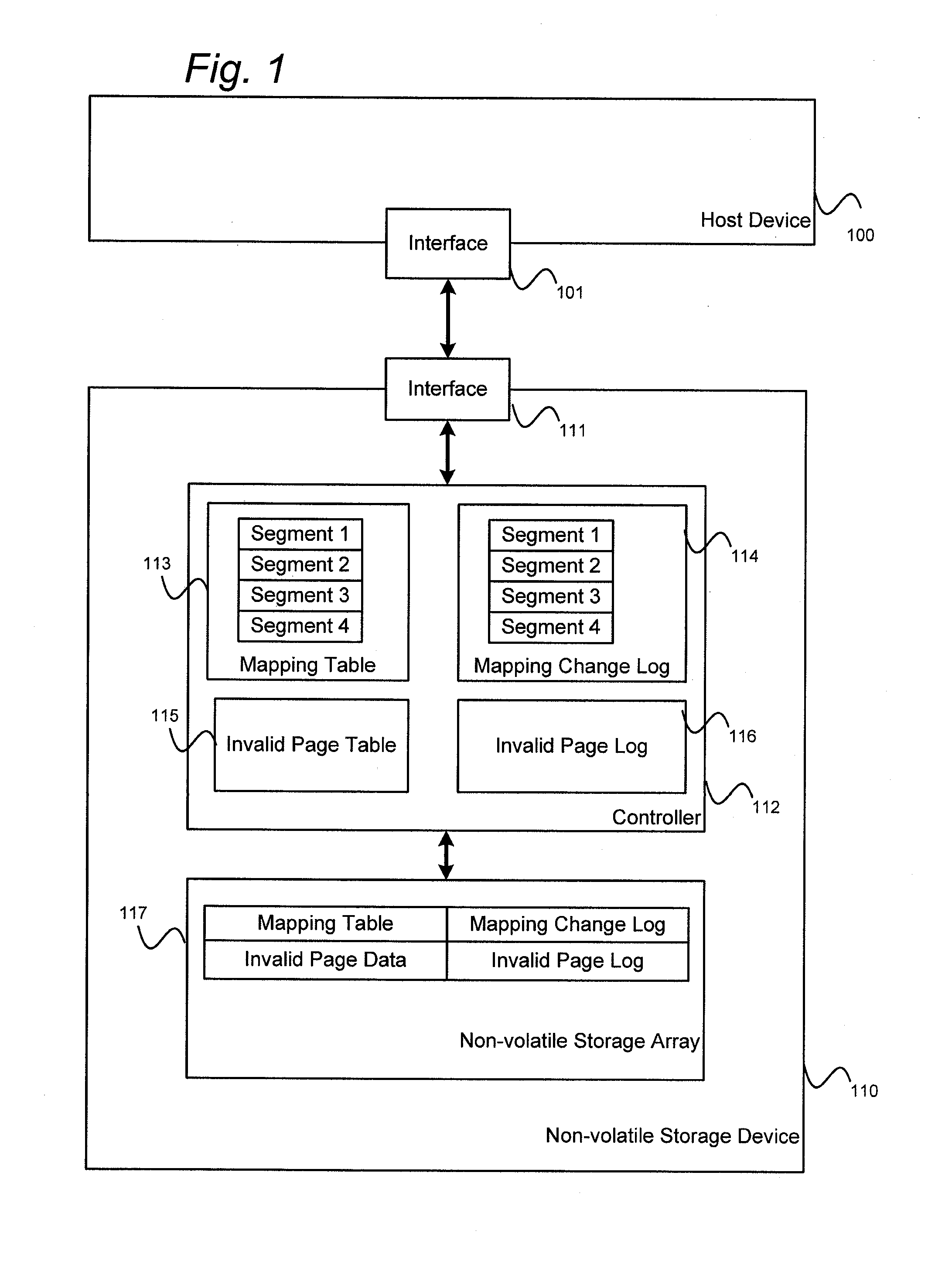

Metadata rebuild in a flash memory controller following a loss of power

ActiveUS20090172262A1Maximize useImprove performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationFlash memory controllerMemory controller

A method of rebuilding metadata in a flash memory controller following a loss of power. The method includes reading logical address information associated with an area of flash memory, and using time stamp information to determine if data stored in the flash memory area is valid.

Owner:SANDISK TECH LLC

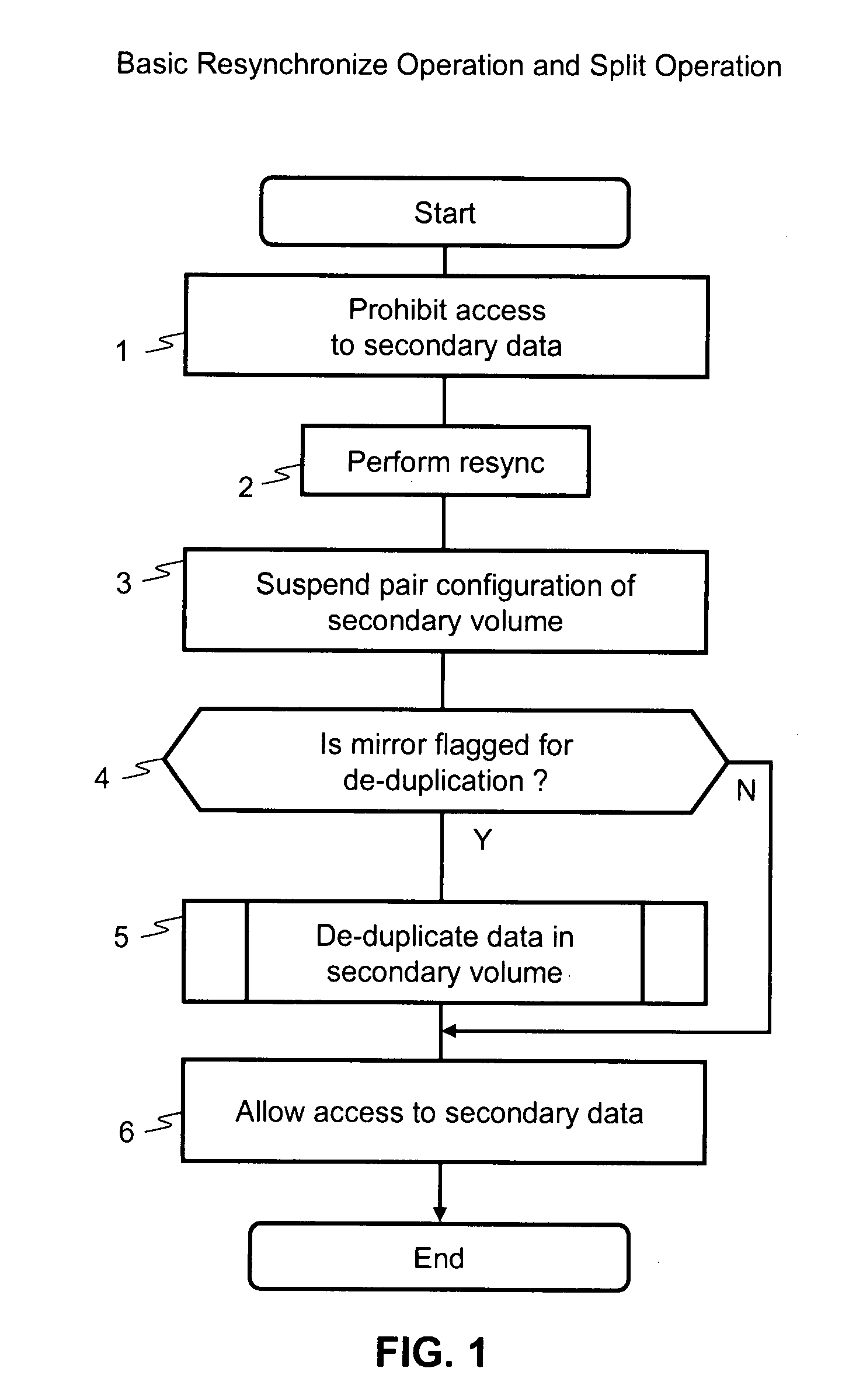

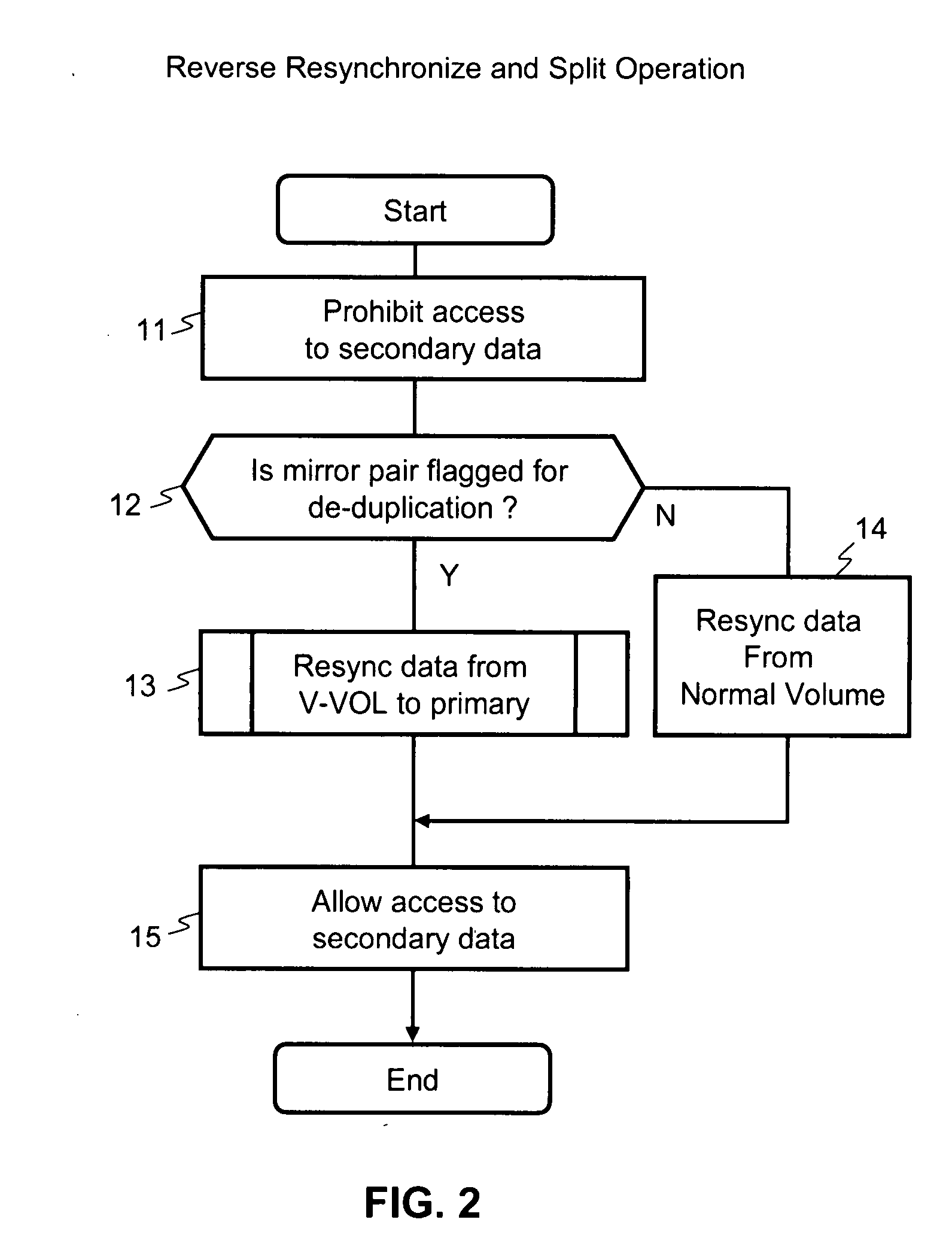

Method and apparatus for de-duplication after mirror operation

InactiveUS20080244172A1Digital data information retrievalError detection/correctionData storingData store

An amount of storage capacity used during mirroring operations is reduced by applying de-duplication operations to the mirror volumes. Data stored to a first volume is mirrored to a second volume. The second volume is a virtual volume having a plurality of logical addresses, such that segments of physical storage capacity are allocated for a specified logical address as needed when data is stored to the specified logical address. A de-duplication operation is carried out on the second volume following a split from the first volume. A particular segment of the second volume is identified as having data that is the same as another segment in the second volume or in the same consistency group. A link is created from the particular segment to the other segment and the particular segment is released from the second volume so that physical storage capacity required for the second volume is reduced.

Owner:HITACHI LTD

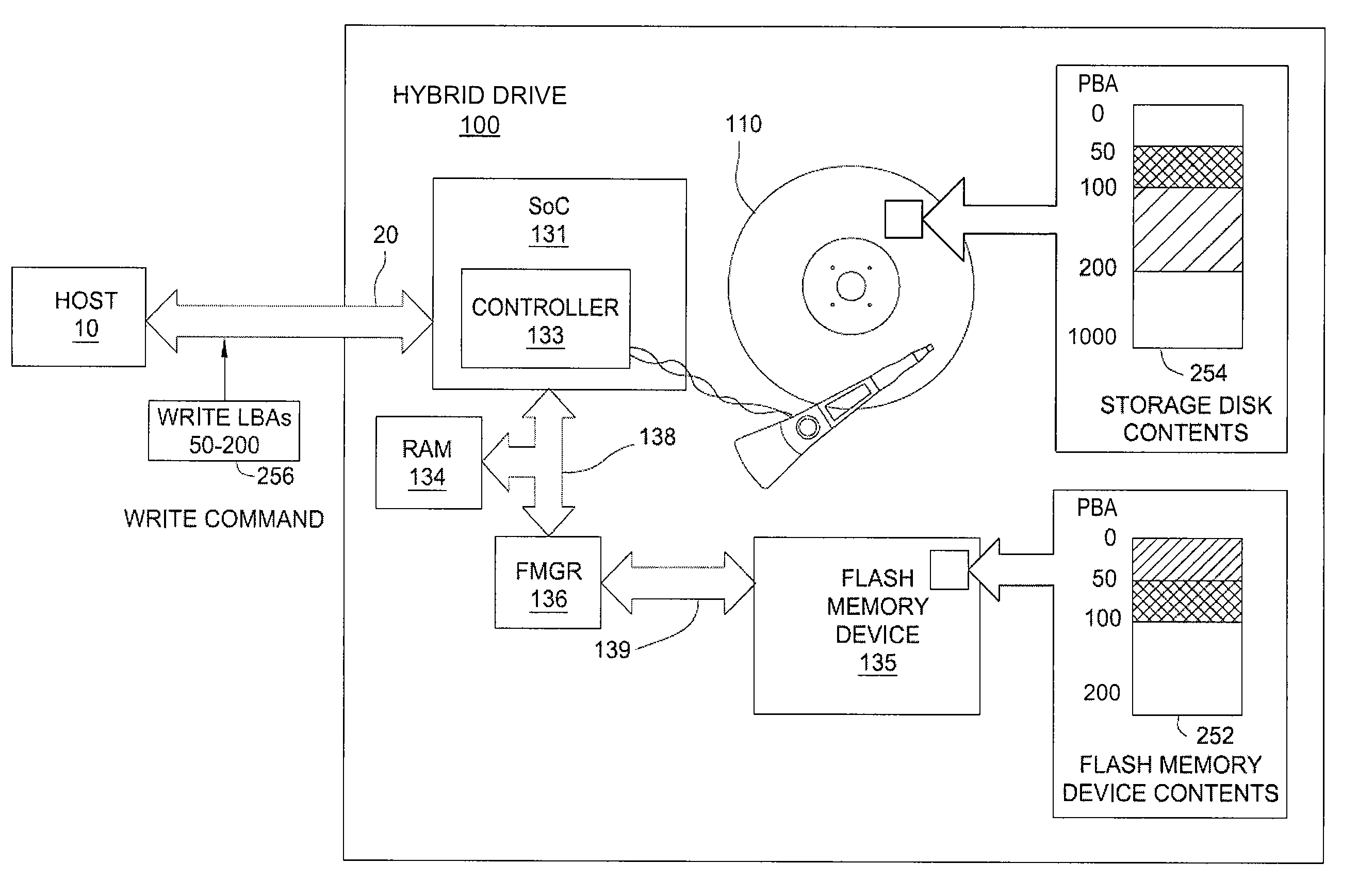

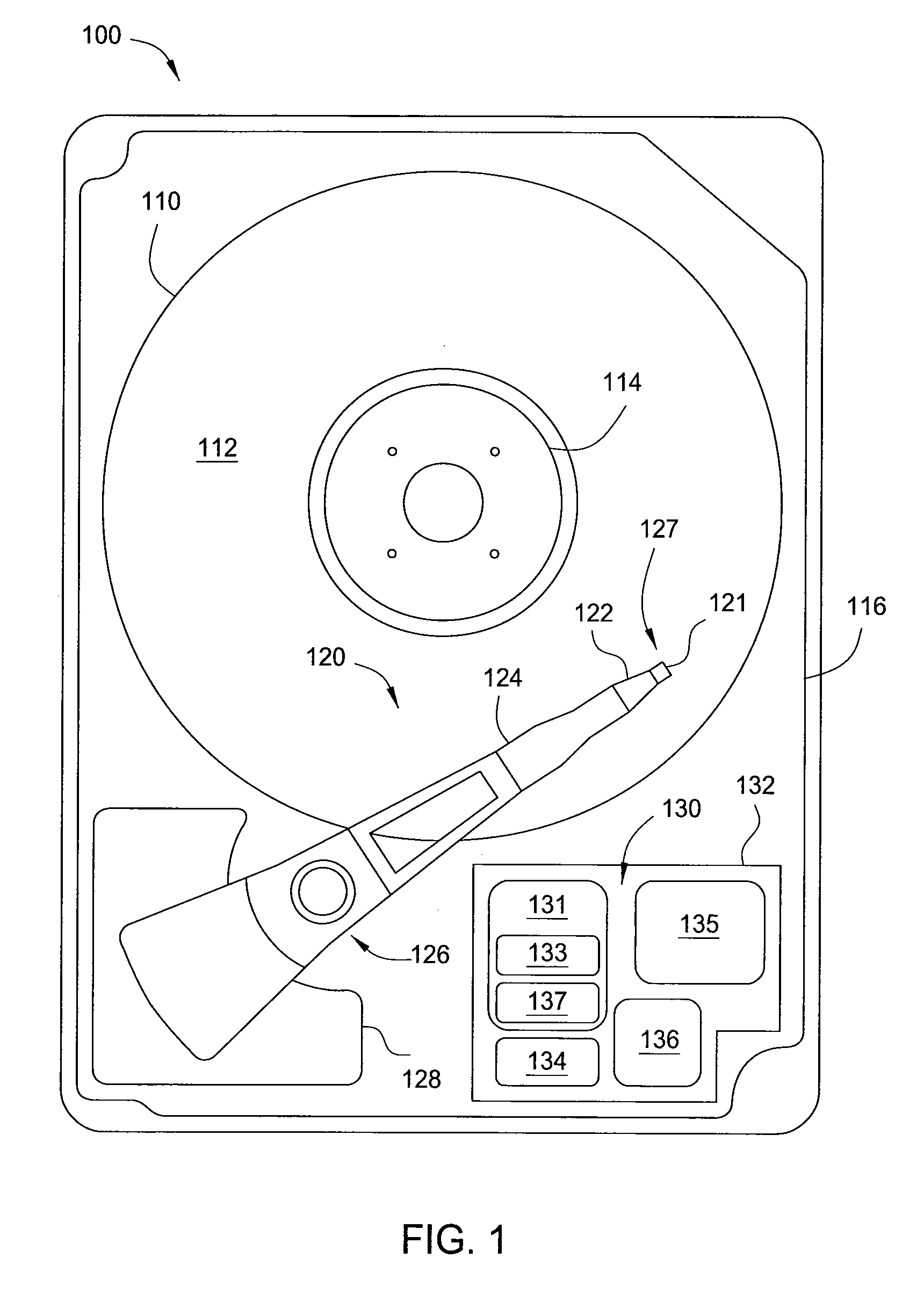

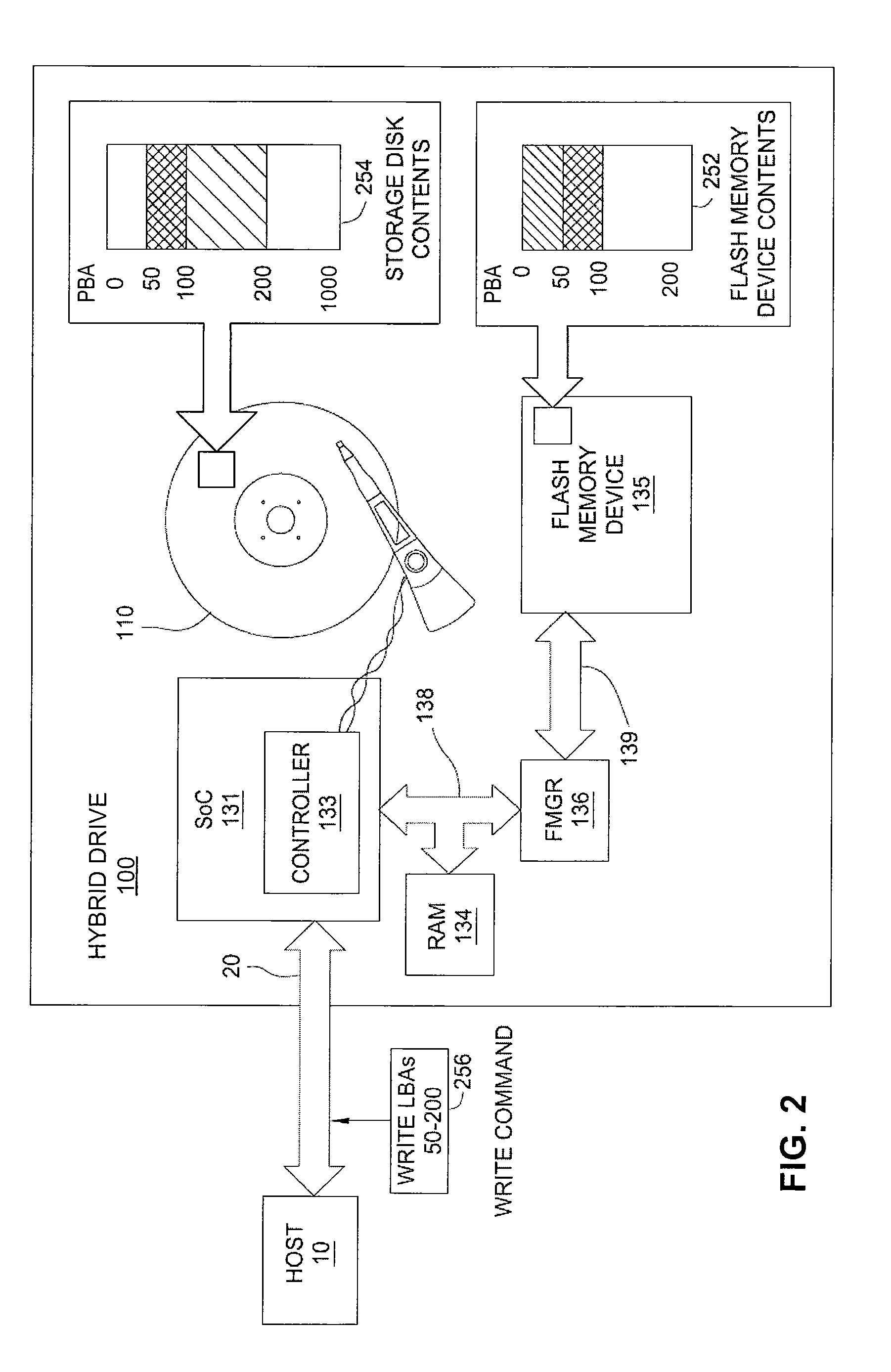

Hybrid drive that implements a deferred trim list

InactiveUS20140237164A1Prevent leakageMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer scienceLogical address

A hybrid drive controller maintains a deferred trim list that holds a subset of logical addresses of writes performed on magnetic disks. For example, if a write command is issued to an LBA space that overlaps a portion stored in flash memory and the write is to be performed on the magnetic disks, the trimming of the overlapping portion in the flash memory will be deferred. Instead of trimming, the logical addresses associated with the overlapping portion will be added to the deferred trim list and trimming of the logical addresses in the deferred trim list will be carried out at a later time, asynchronous to the write that caused them to be added to the list.

Owner:KK TOSHIBA

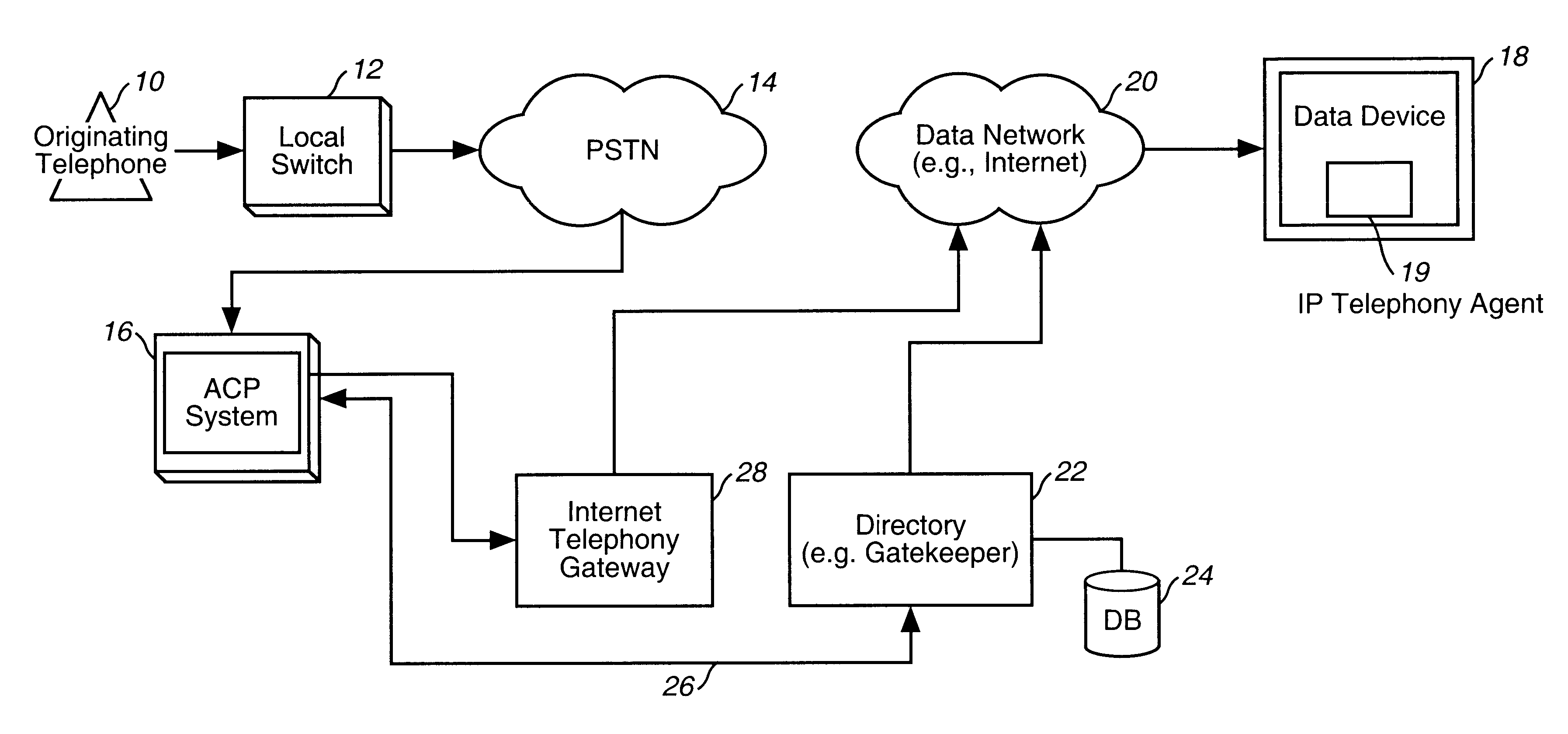

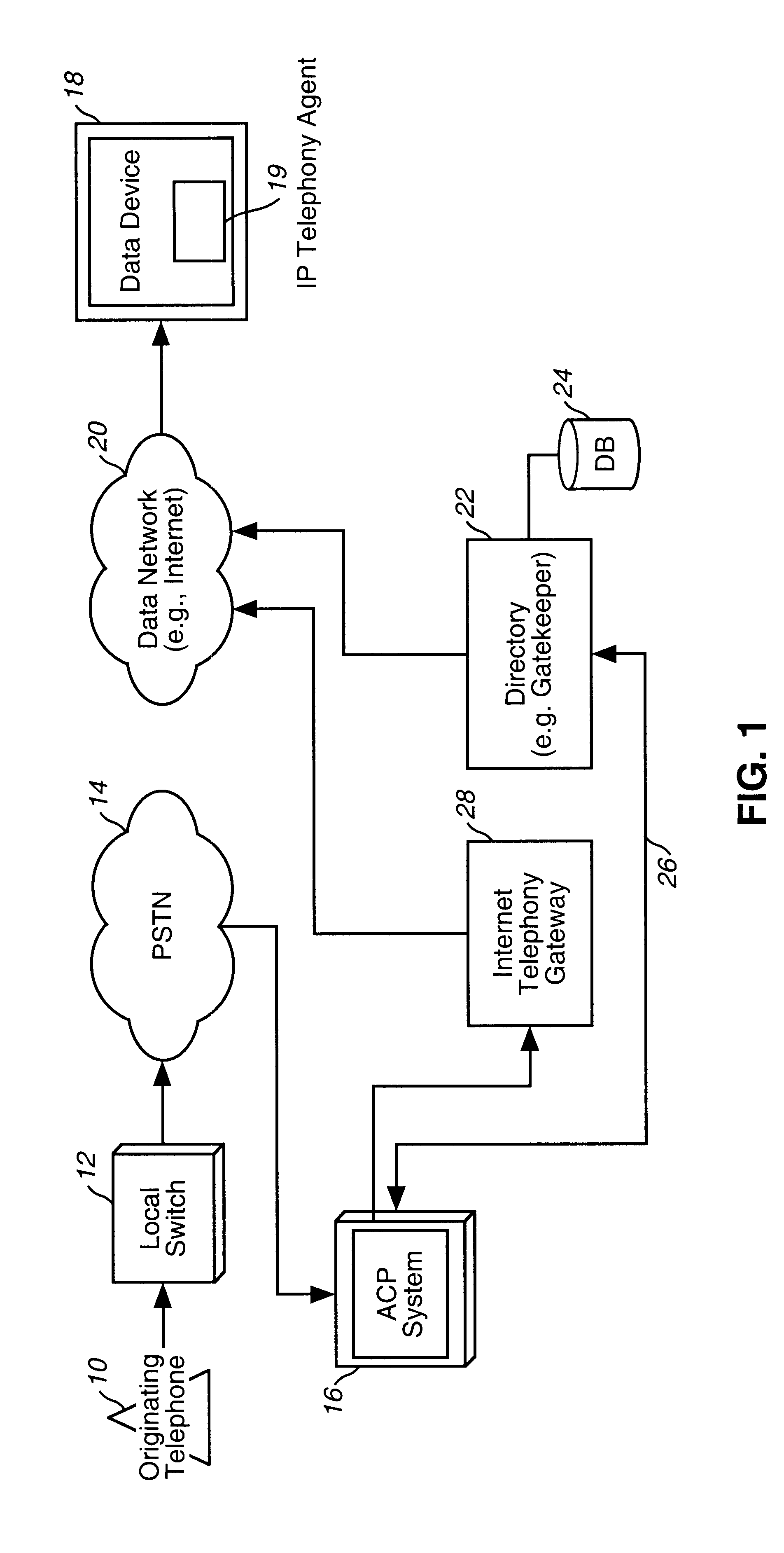

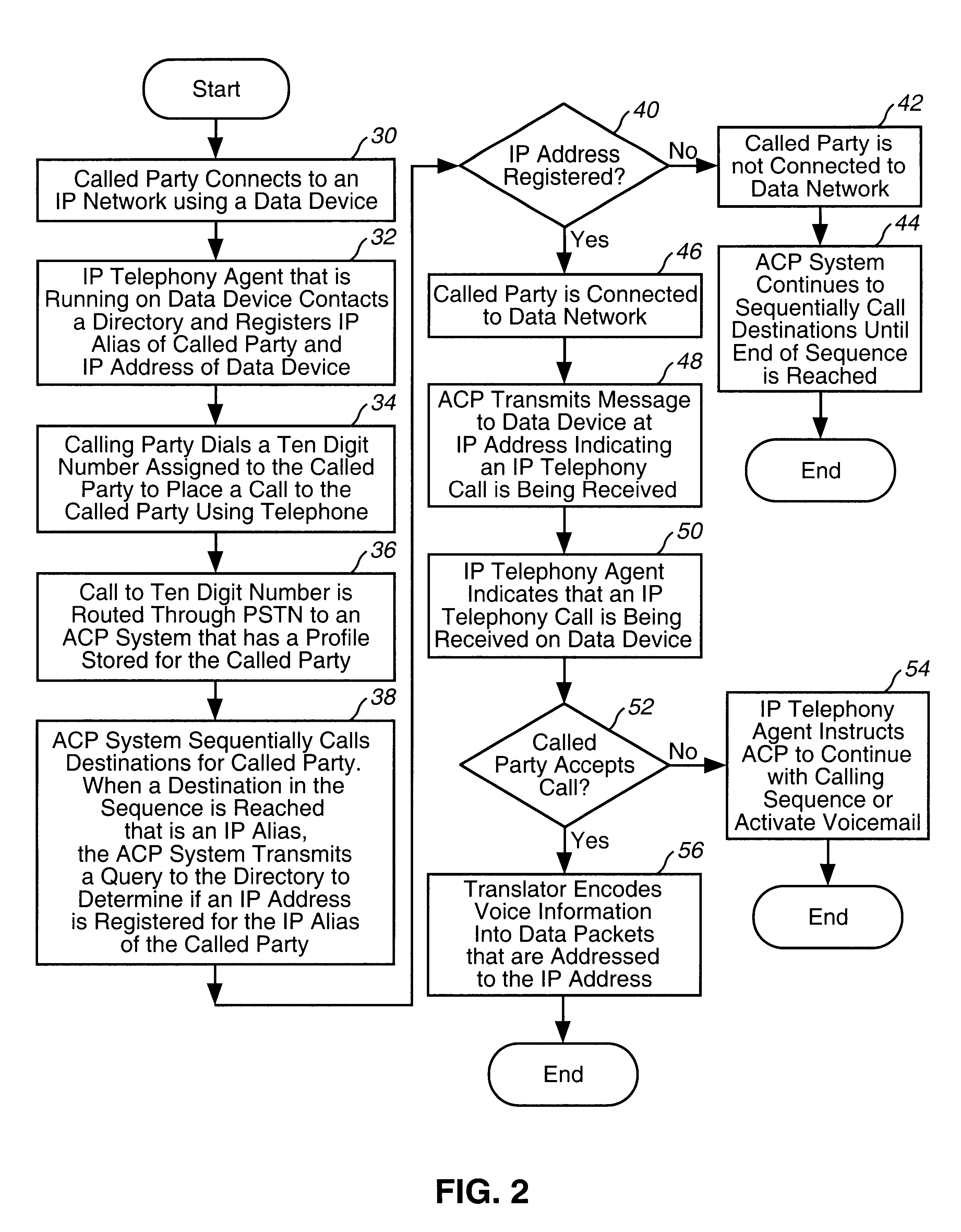

Virtual second line hybrid network communication system

InactiveUS6351464B1Reduce cost and inconvenienceReduce spreadInterconnection arrangementsSpecial service for subscribersMix networkIp address

A system and method for routing a telephone call on a PSTN network to a data device. The present invention utilizes an automatic call processing system that has a one number location service. A called party provides a calling profile that is stored in the automatic call processing (ACP) system. When a call is placed to a telephone number that is assigned to the called party, the call is routed to the ACP system. The ACP system calls each of the numbers of the calling profile for that called party until that party is reached. At least one of the destinations in the calling profile is a logical address for a data network. The automatic call processing system recognizes the logical address and queries a directory to determine if an IP address has been registered in the directory for the logical address of the called party. If the called party is using a data device that is logged on the Internet, an IP telephony agent, such as an IP telephony client running on the data device, registers the IP address of the data device together with the logical address of the caller. If the ACP system determines if an IP address is registered with the directory, the ACP system will direct the call to an Internet telephony gateway. The Internet telephony gateway encodes and packetizes the voice information for transmission over the data network to the data device.

Owner:VERIZON PATENT & LICENSING INC

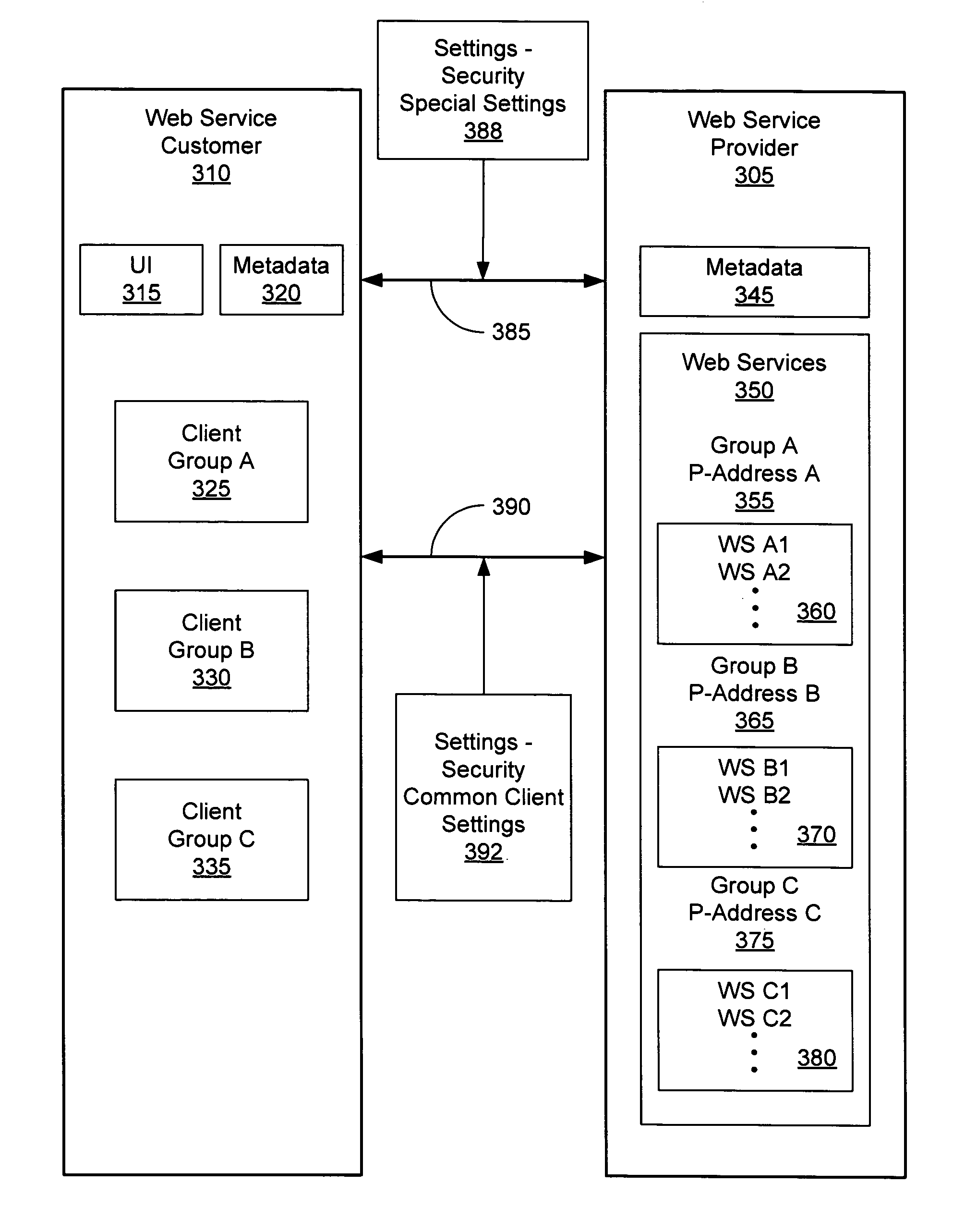

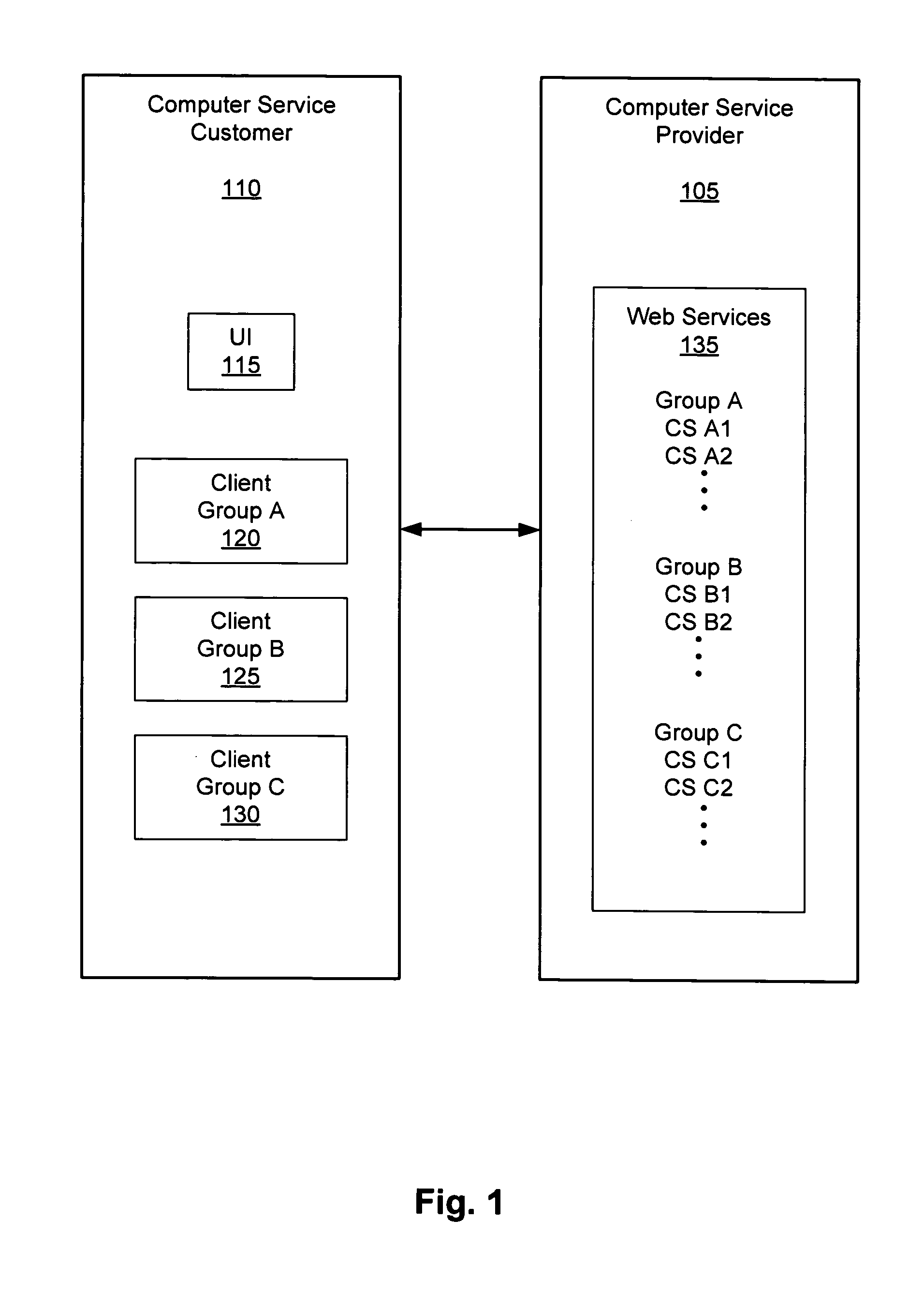

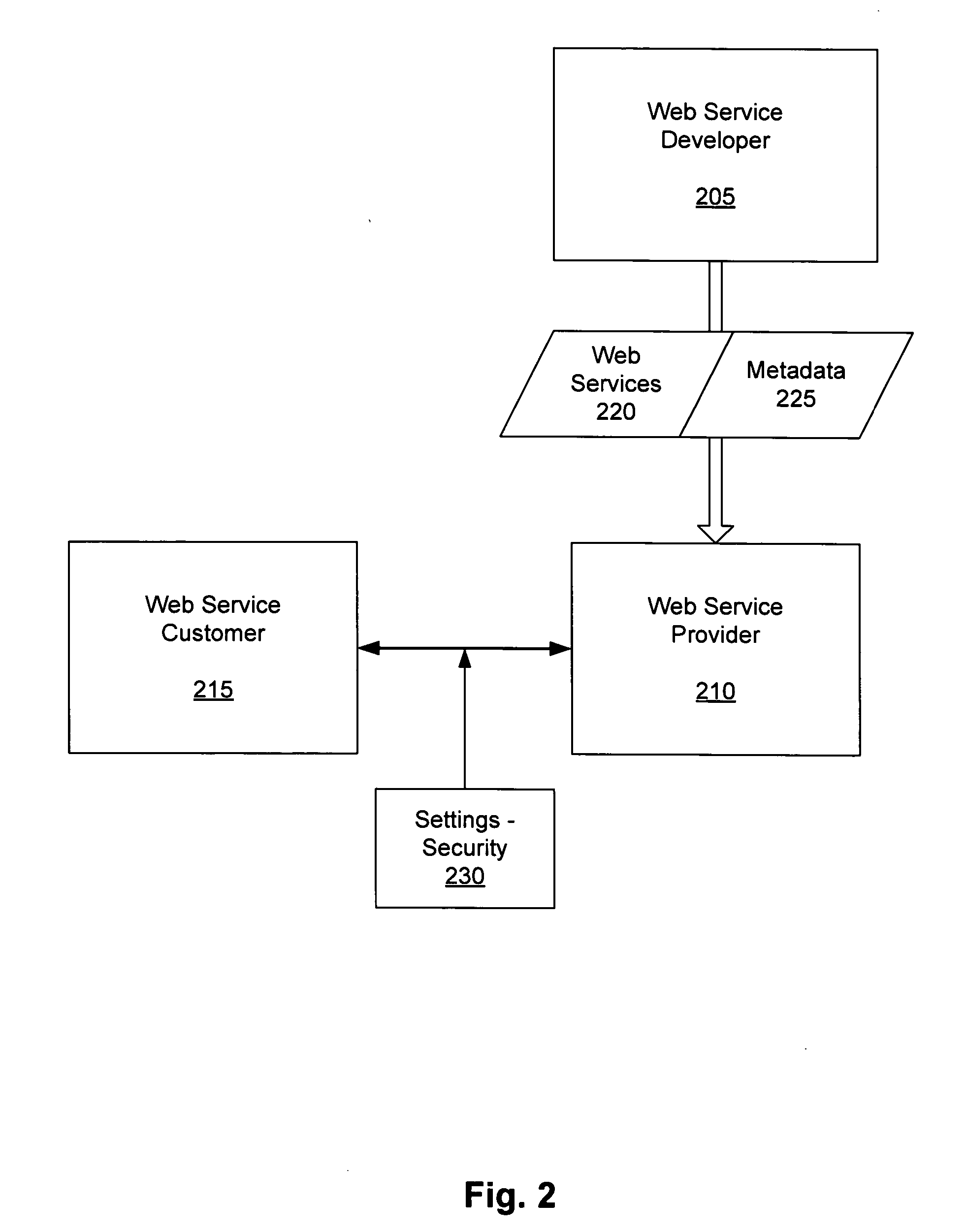

Configuration of clients for multiple computer services

A method and apparatus for configuration of clients for multiple computer services. An embodiment of a method includes receiving multiple computer services, the computer services including a group of computer services, with the group of computer services having a logical address. A client is configured for the group of computer services, with the configuration of the client including resolving the logical address of the group of computer services to a physical address. The method includes receiving a request from the client for a first computer service in the group of computer services, where the request includes the logical address of the group and an identification of the requested computer service. A physical address for the requested computer service is resolved based on the request.

Owner:SAP AG

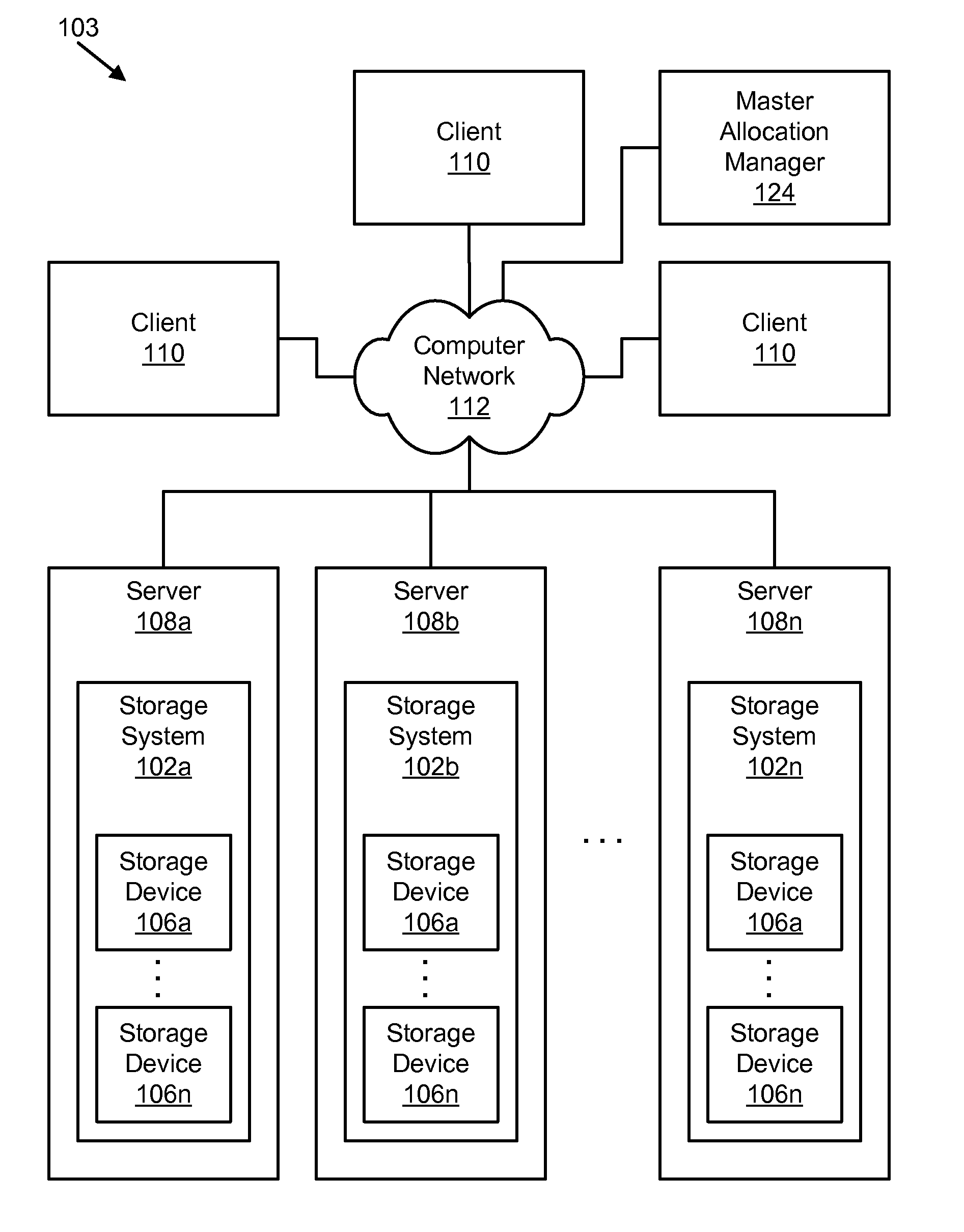

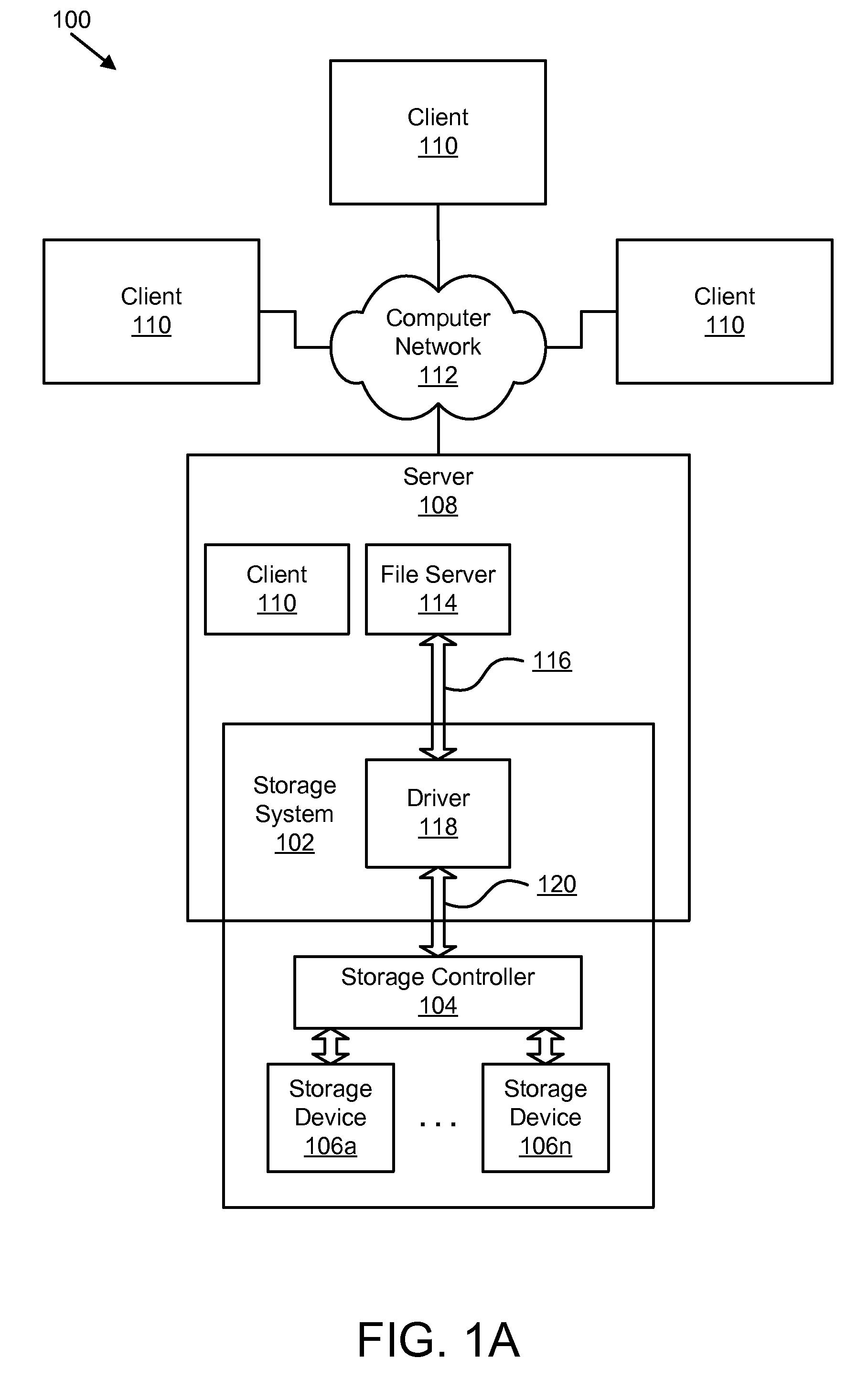

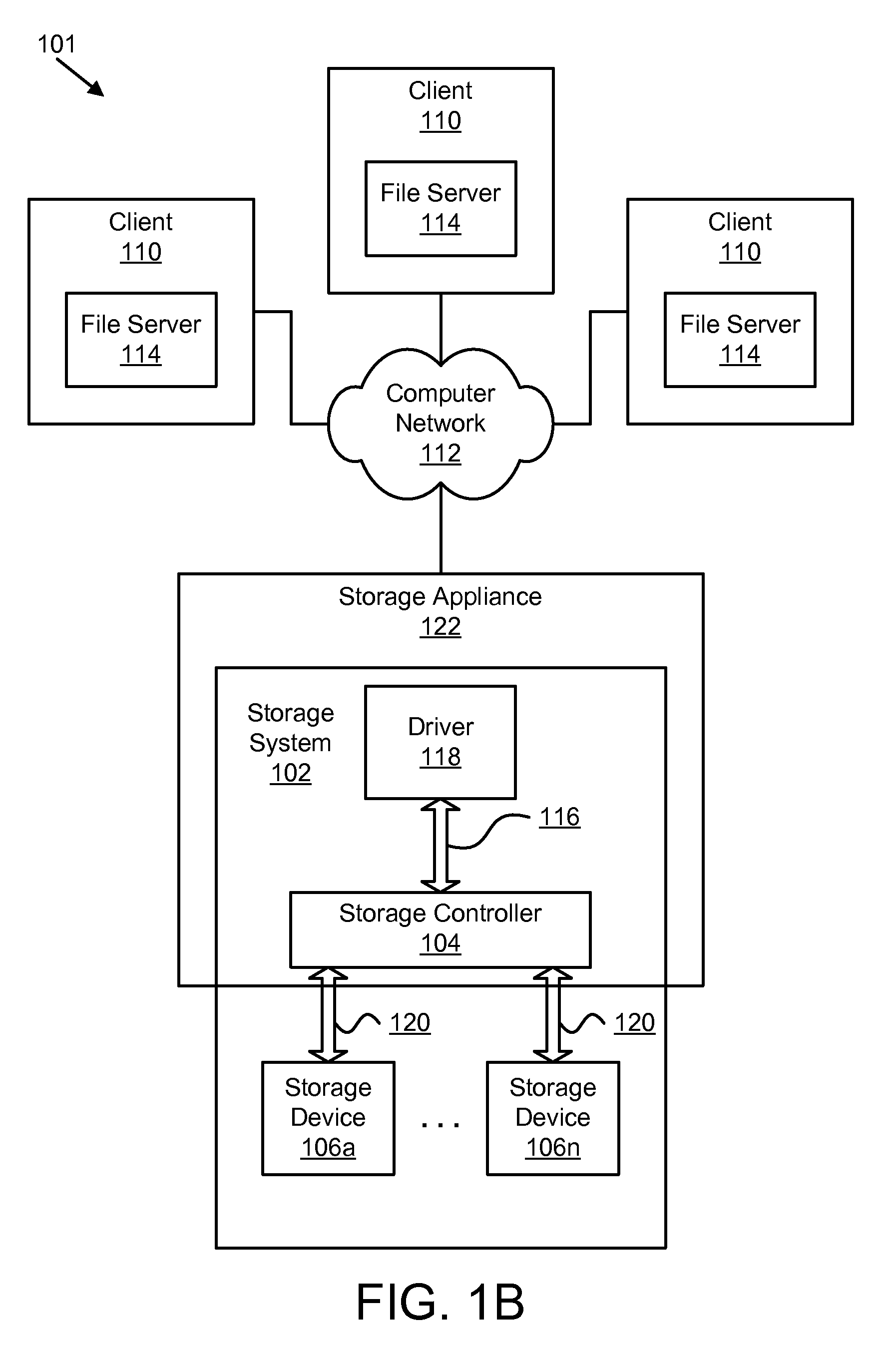

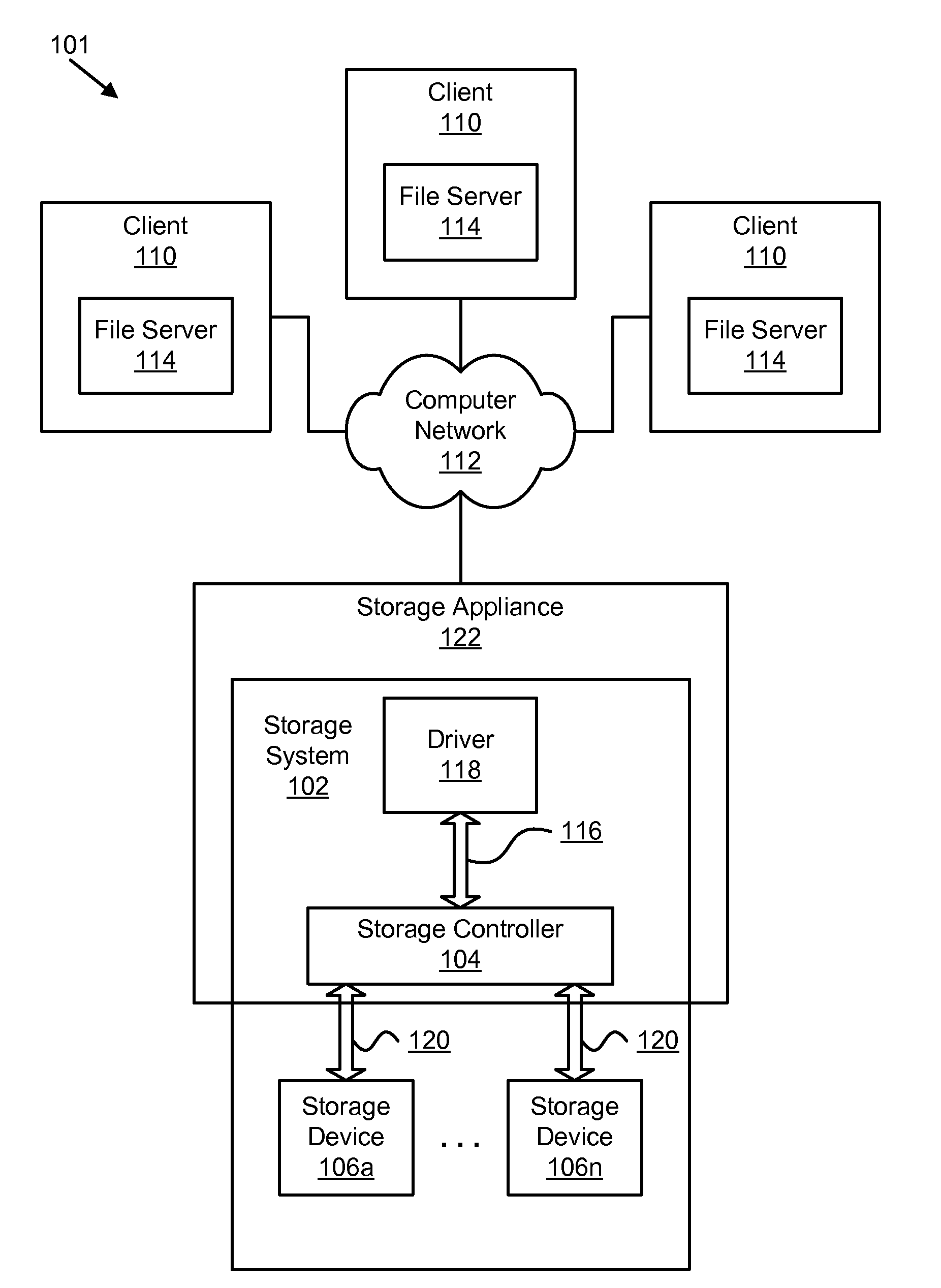

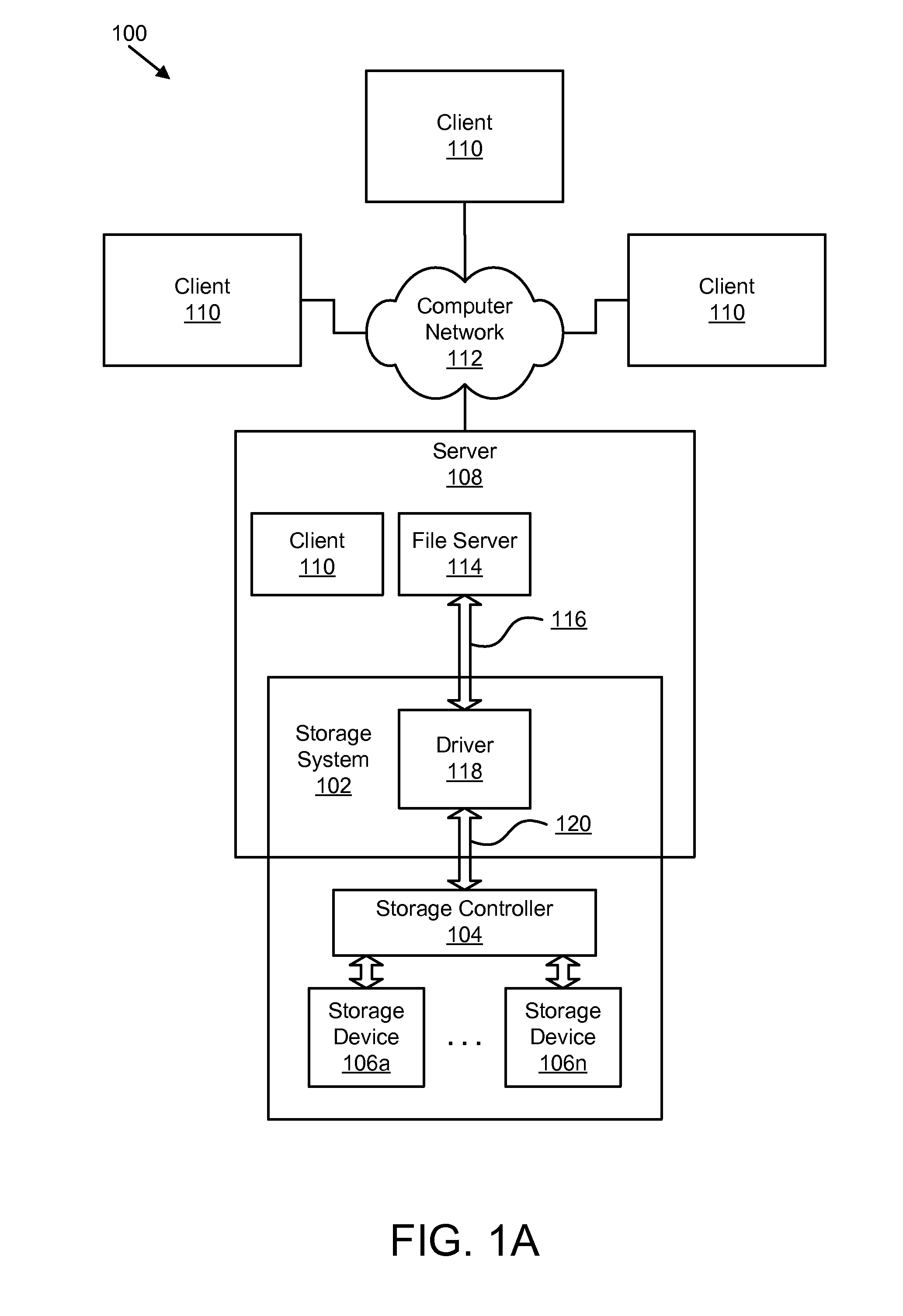

Apparatus, System, and Method for a Virtual Storage Layer

InactiveUS20120011340A1Memory architecture accessing/allocationMemory adressing/allocation/relocationFile systemData library

A virtual storage layer (VSL) for a non-volatile storage device presents a large, logical address space having a logical capacity that may exceed the storage capacity of the non-volatile storage device. The VSL implements persistent storage operations within the logical address space; storage operations performed within the logical address space may be persisted on the non-volatile storage device. The VSL maintains storage metadata to allocate ranges of the logical address space to storage entities. The VSL provides for allocation of contiguous logical address ranges, which may be implemented by segmenting logical identifiers into a first portion referencing storage entities, and a second portion referencing storage entity offsets. The VSL persists data on the non-volatile storage device in a sequential, log-based format. Accordingly, storage clients, such as file systems, databases, and other applications, may delegate logical allocations, physical storage bindings, and / or crash-recovery to the VSL.

Owner:SANDISK TECH LLC

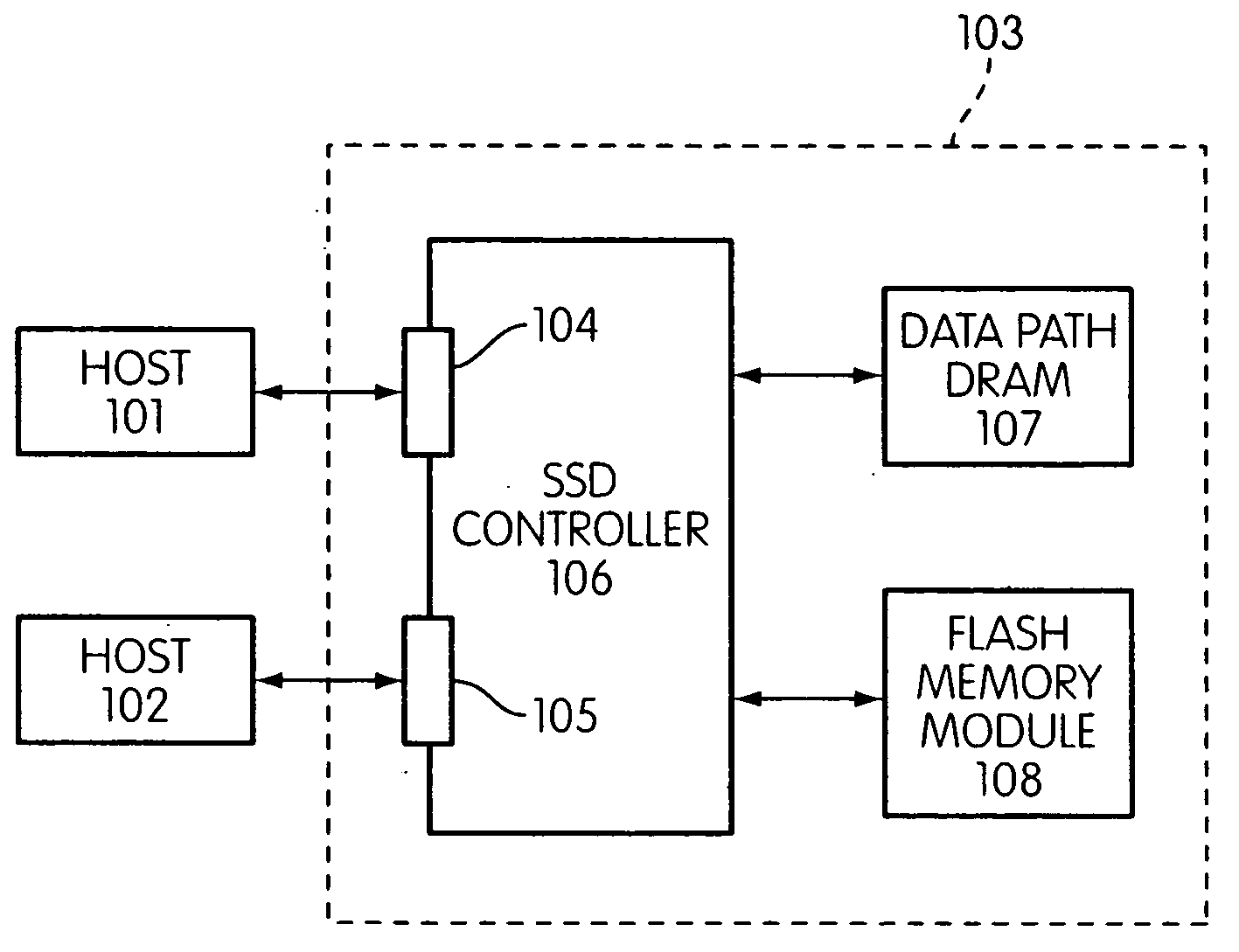

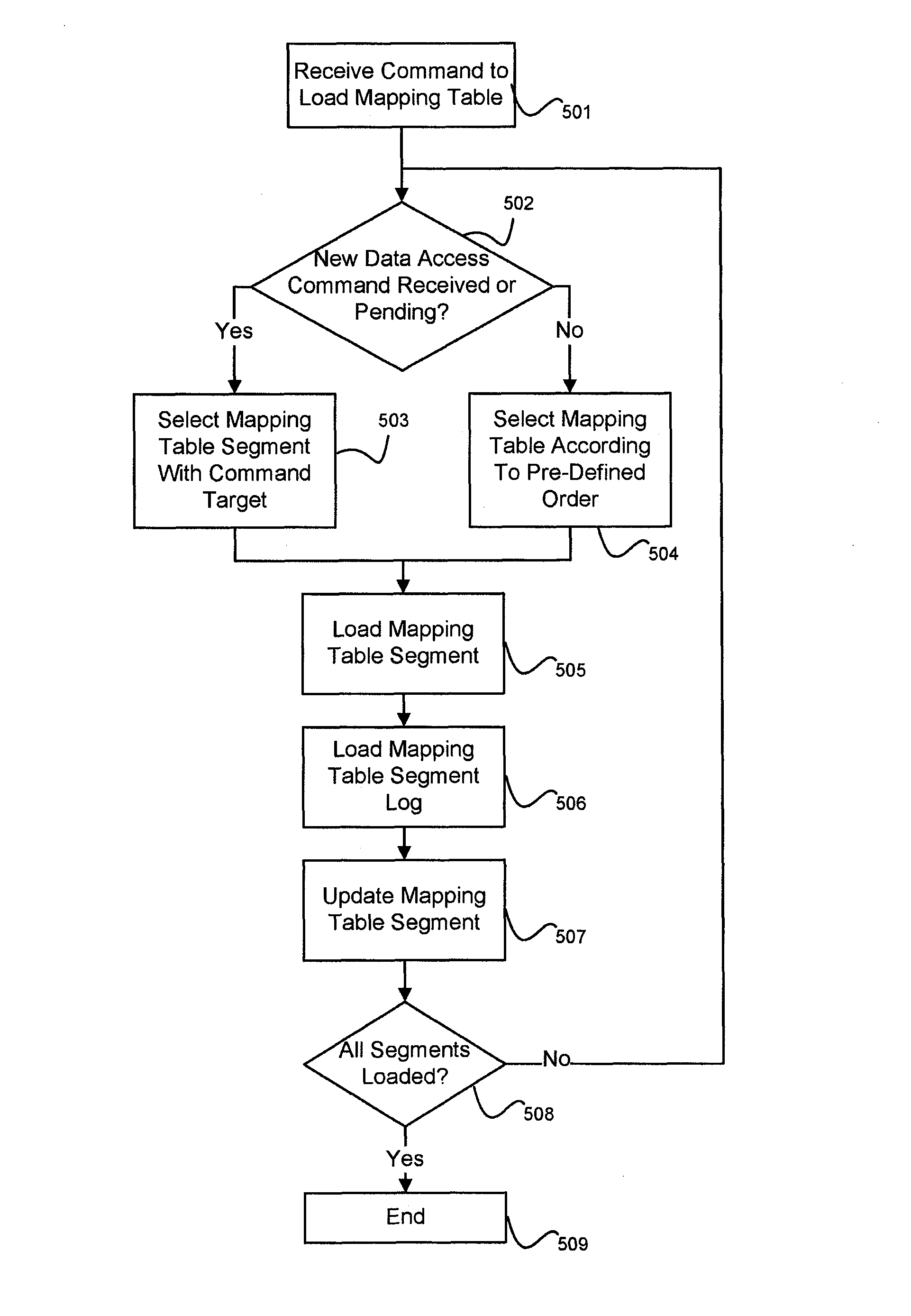

Solid-state drive with reduced power up time

ActiveUS8793429B1Reduce delaysMemory architecture accessing/allocationEnergy efficient ICTSolid-state driveComputer science

A non-volatile storage system is provided with reduced delays associated with loading and updating a logical-to-physical mapping table from non-volatile memory. The mapping table is stored in a plurality of segments, so that each segment can be loaded individually. The segmented mapping table allows memory access to logical addresses associated with the loaded segment when the segment is loaded, rather than delaying accesses until the entire mapping table is loaded. When loading mapping segments, segments can be loaded according to whether there is a pending command or by an order according to various algorithms.

Owner:WESTERN DIGITAL TECH INC

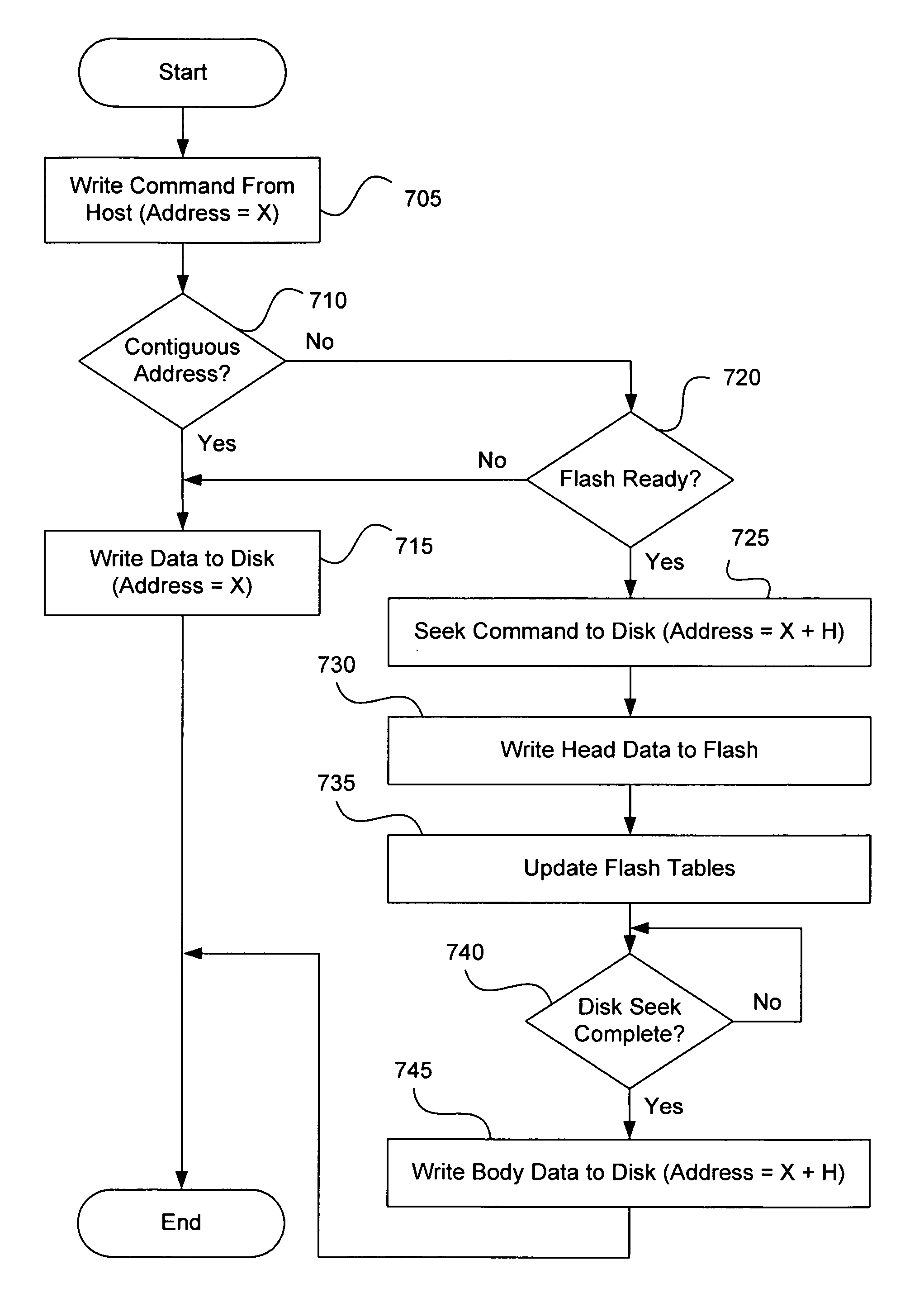

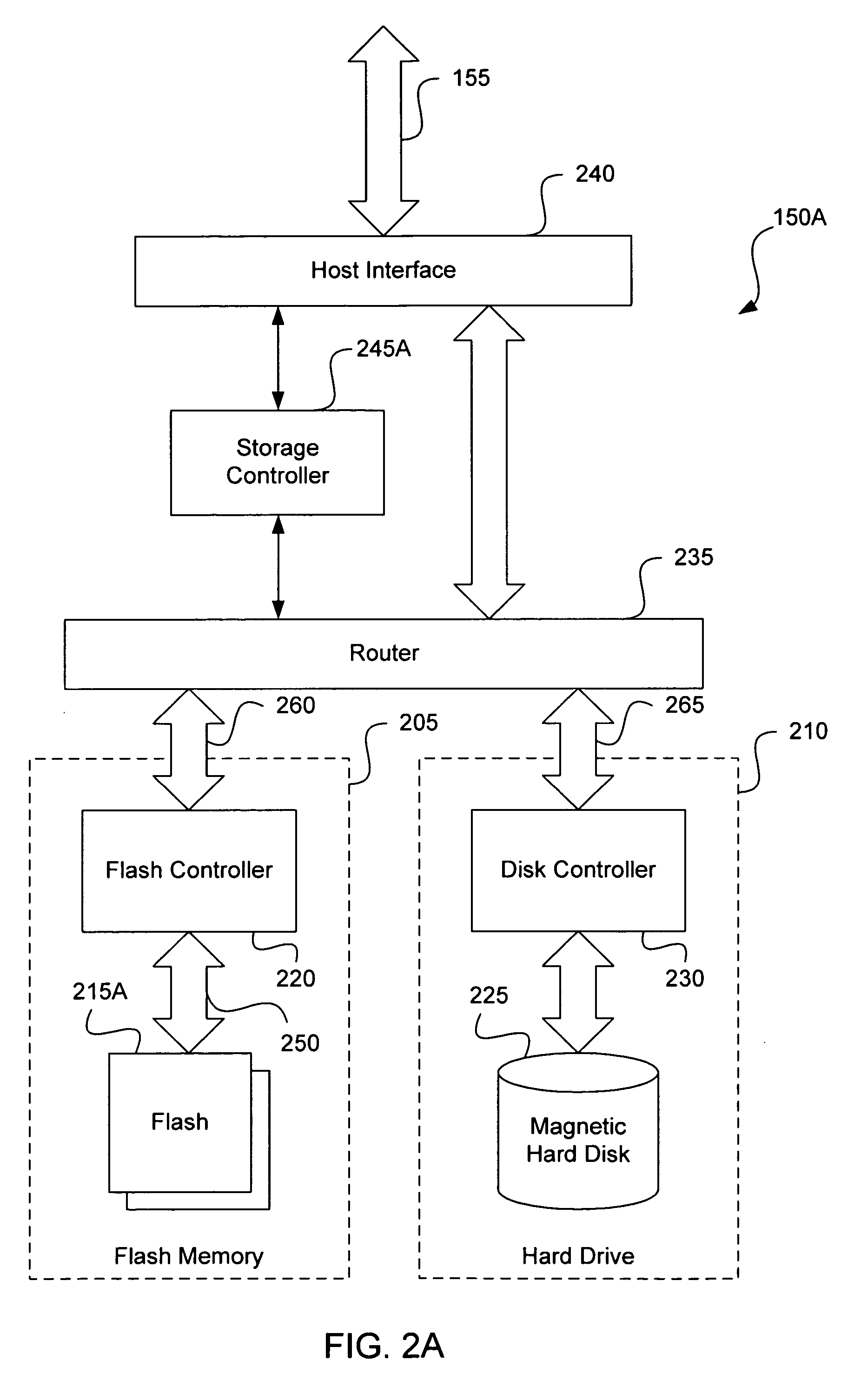

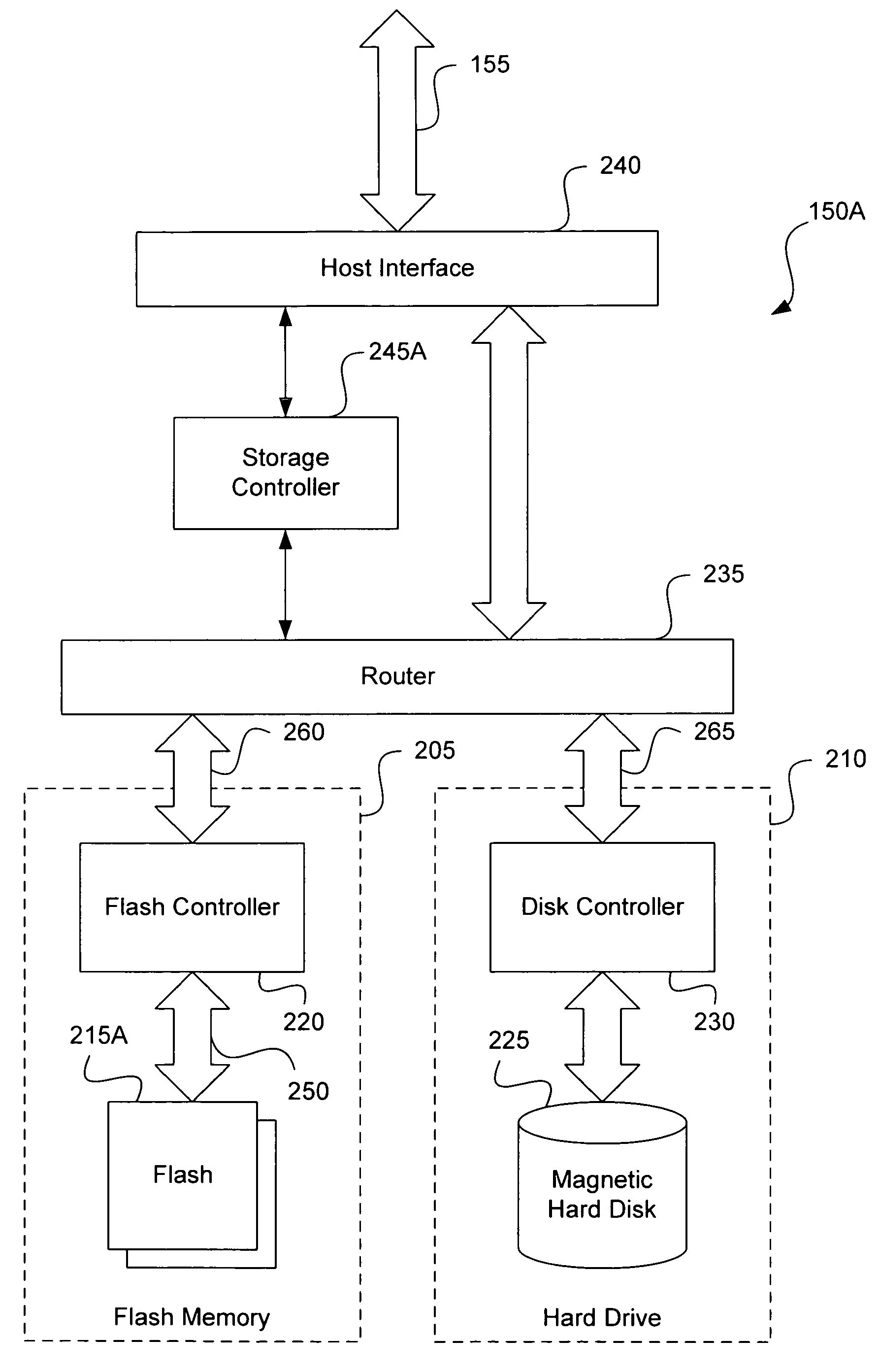

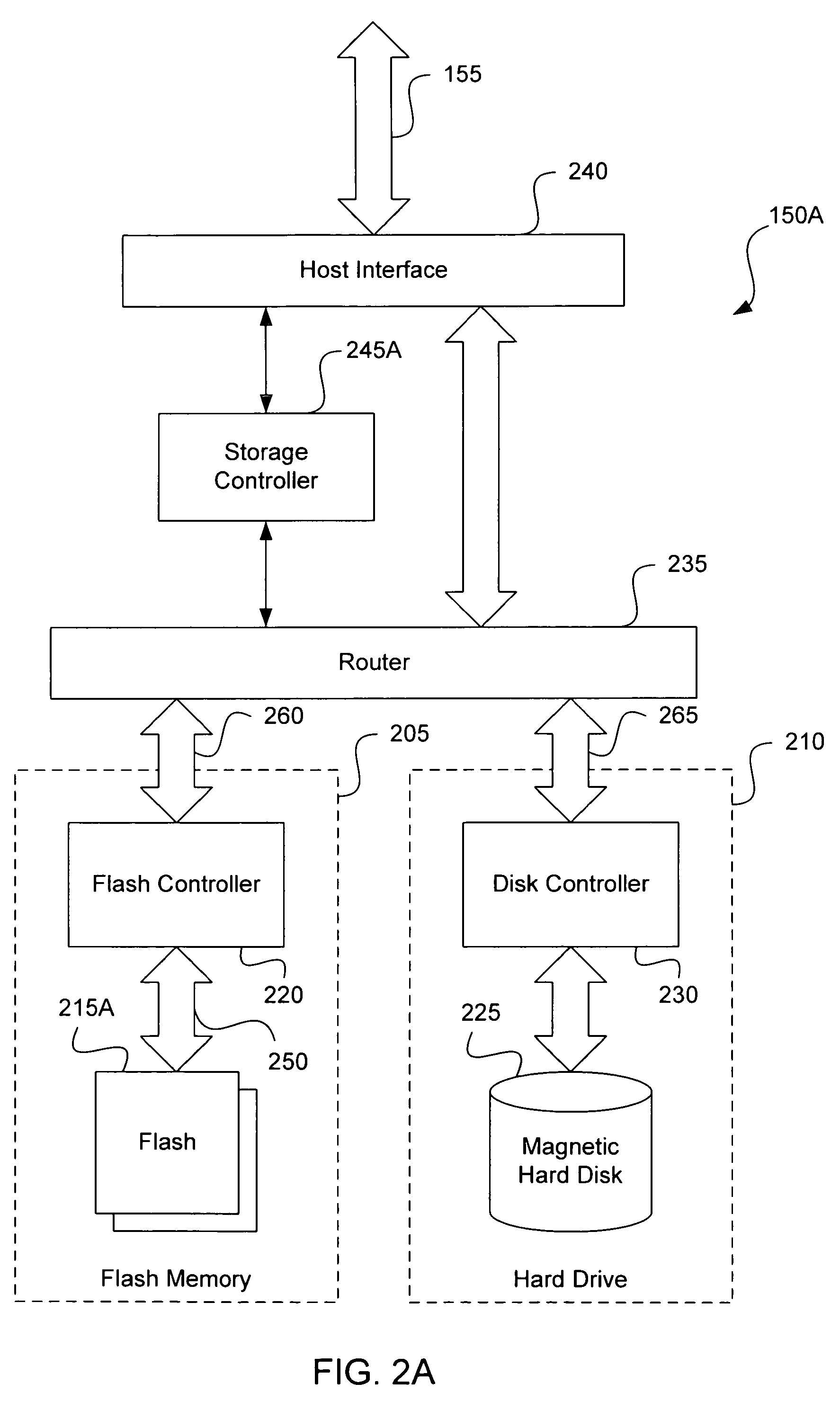

Mass storage accelerator

A data storage device is provided. A disk device is combined with a non-volatile memory device to provide much shorter write access time and much higher data write speed than can be achieved with a disk device alone. Interleaving bursts of sector writes between the two storage devices can effectively eliminate the effect of the seek time of the disk device. Following a non-contiguous logical address transition from a host system, the storage controller can perform a look-ahead seek operation on the disk device, while writing current data to the non-volatile memory device. Such a system can exploit the inherently faster write access characteristics of a non-volatile memory device, eliminating the dead time normally caused by the disk seek time.

Owner:SANDISK TECH LLC

Information processing device including memory management device managing access from processor to memory and memory management method

ActiveUS20100064111A1Memory architecture accessing/allocationMemory loss protectionInformation processingMemory management unit

A device according to an example of the invention comprises a section which accepts a write destination logical address and write target data from a processor, the write destination logical address indicating a write position to write the write target data into a composite memory which includes a first memory and a nonvolatile second memory, a section which determines a write destination physical address corresponding to the write destination logical address so that the number of times of access to the second memory is smaller than the number of times of access to the first memory, a section which stores, in a storage section, address conversion data associating the write destination logical address with the write destination physical address, and a section which writes the write target data into a position in the composite memory indicated by the write destination physical address.

Owner:KIOXIA CORP

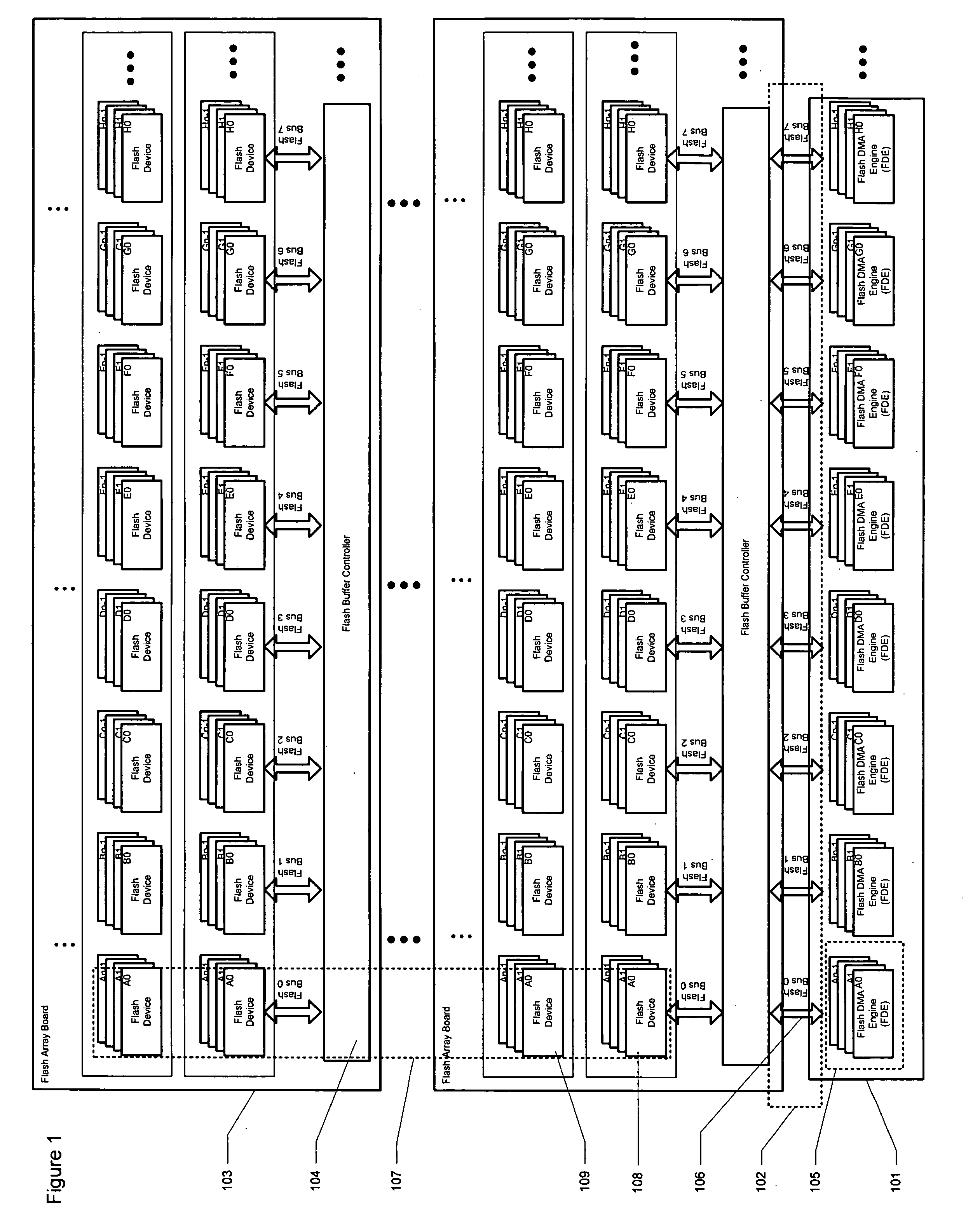

Optimized placement policy for solid state storage devices

InactiveUS20070288686A1Evenly loadedGuarantee efficiencyMemory architecture accessing/allocationMemory systemsSolid-state storageCurrent load

A data storage system is provided comprising several flash arrays in a board and stacking these boards to attain a high-capacity solid state hard drive. A remap table is used to map all logical addresses from a host system to the actual physical addresses where data are stored. The assignments of these physical locations are done in such a way that the load of the system is evenly distributed to its available resources. This would ensure that the storage system will run at its utmost efficiency utilizing its resources properly. To achieve this, the system would make sure that the physical location of data be evenly distributed according to the current load of the system.

Owner:BITMICRO LLC

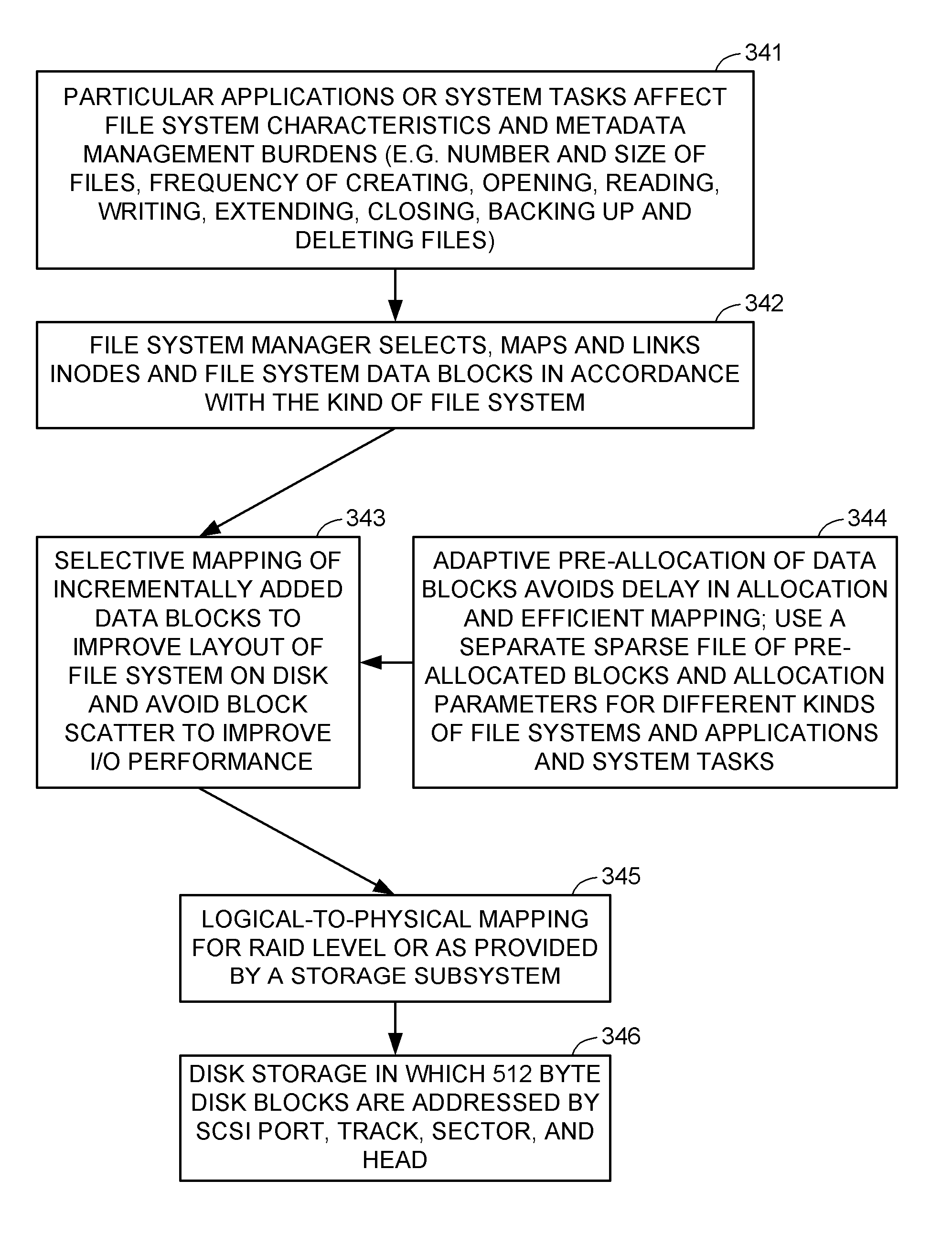

Pre-allocation and hierarchical mapping of data blocks distributed from a first processor to a second processor for use in a file system

ActiveUS20070260842A1Improve I/O performanceReduce block scatter on diskMemory systemsInput/output processes for data processingData processing systemFile system

In a data processing system, a first processor pre-allocates data blocks for use in a file system at a later time when a second processor needs data blocks for extending the file system. The second processor selectively maps the logical addresses of the pre-allocated blocks so that when the pre-allocated blocks are used in the file system, the layout of the file system on disk is improved to avoid block scatter and enhance I / O performance. The selected mapping can be done at a program layer between a conventional file system manager and a conventional logical volume layer so that there is no need to modify the data block mapping mechanism of the file system manager or the logical volume layer. The data blocks can be pre-allocated adaptively in accordance with the allocation history of the file system.

Owner:EMC IP HLDG CO LLC

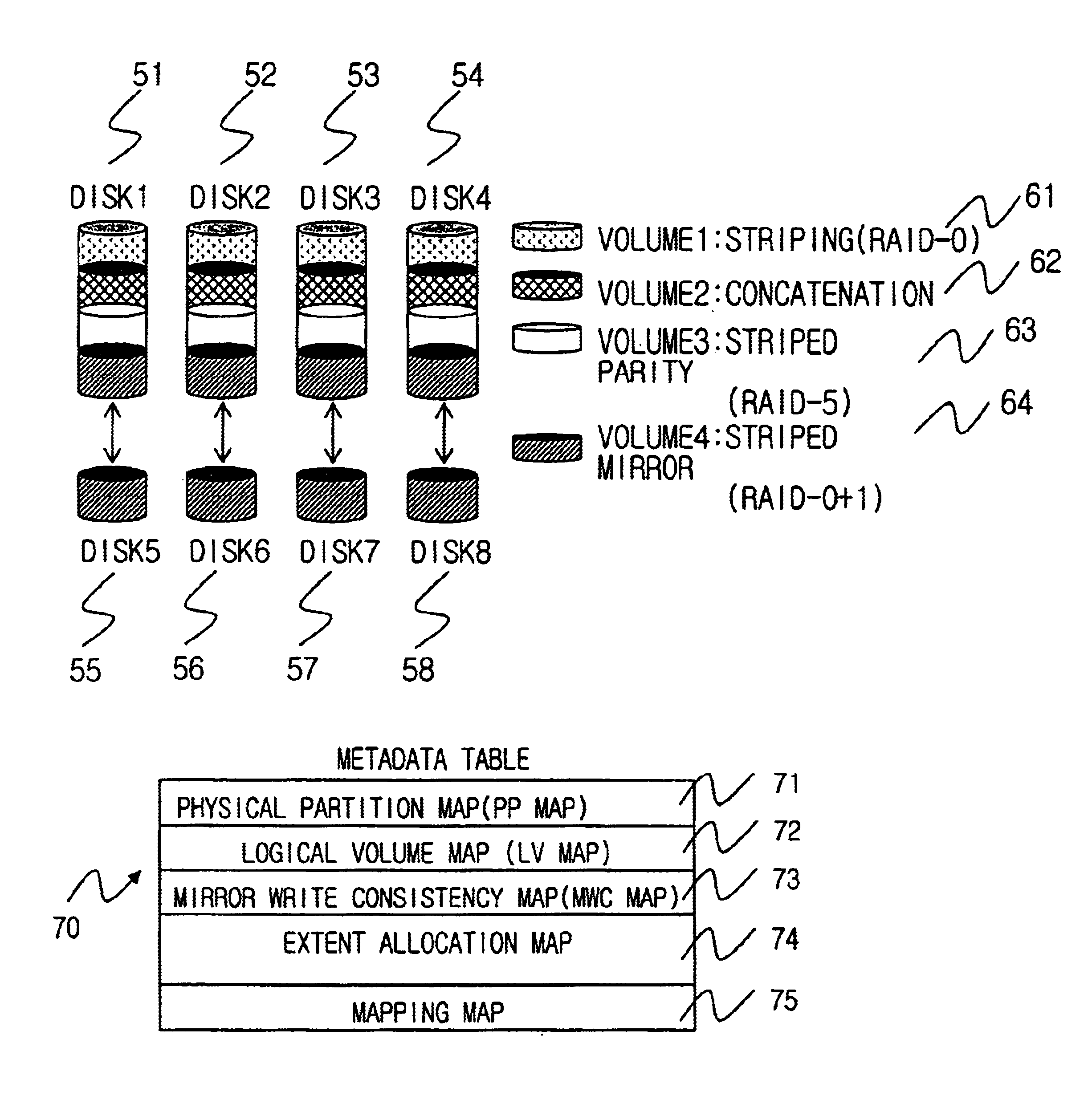

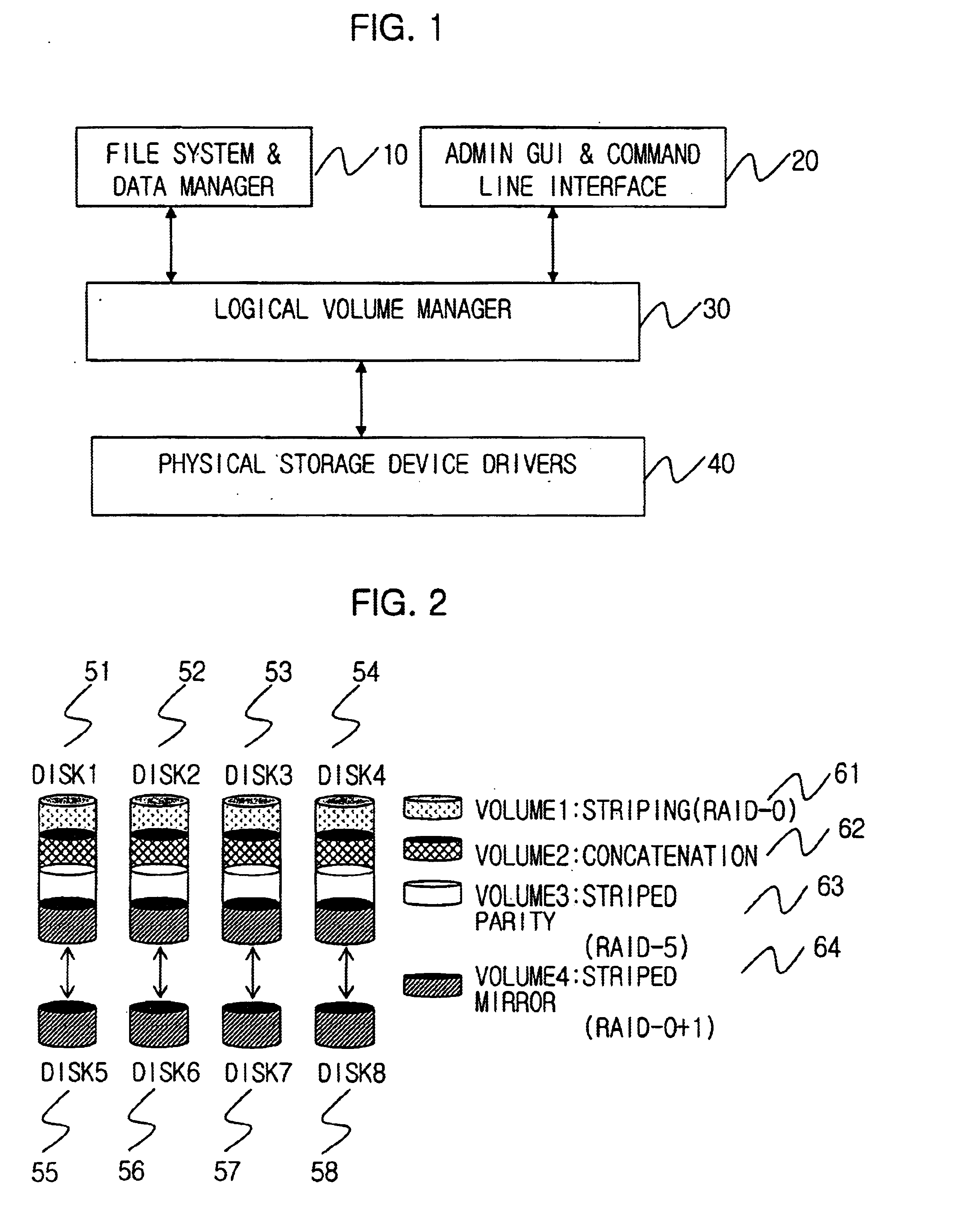

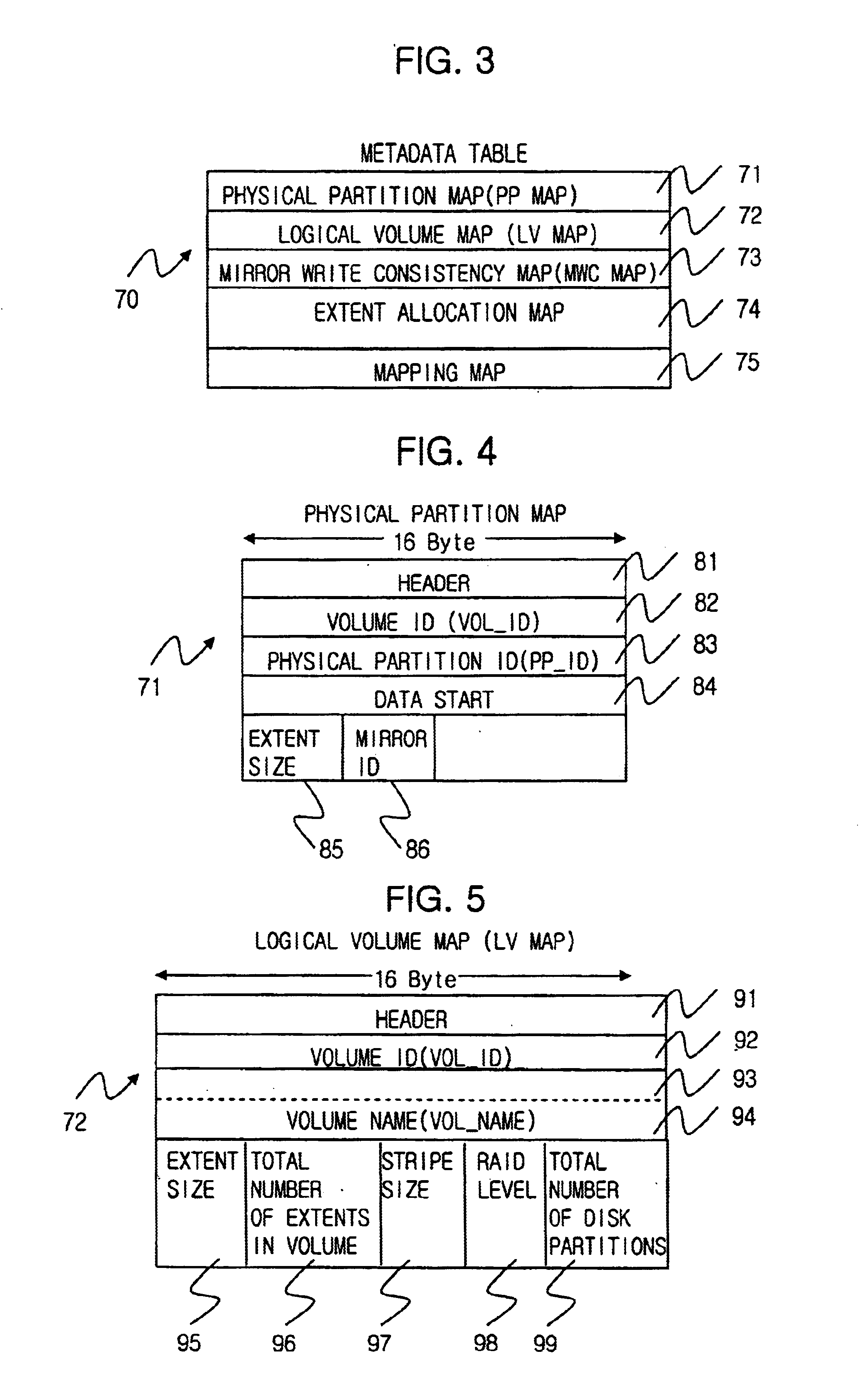

Method for managing logical volume in order to support dynamic online resizing and software raid and to minimize metadata and computer readable medium storing the same

InactiveUS6718436B2Increase or decrease sizeIncrease spaceInput/output to record carriersMemory adressing/allocation/relocationRAIDVolume table

A method for managing a logical volume for minimizing a size of metadata and supporting dynamic online resizing and software redundant array of independent disks (RAID), and a computer-readable recording medium storing instructions for embodying the method, are disclosed. The method includes the metadata having a disk partition table containing information of a disk partition in which the metadata is stored; a logical volume table for maintaining the information of the logical volume by storing duplicated information of the logical volume onto all disk partitions of the logical volume; an extent allocation table for indicating whether each extent in the disk partitions is used or not; and a mapping table for maintaining a mapping information for a physical address space corresponding to a logical address space which is a continuous address space equal in size of storage space of whole logical volume.

Owner:ELECTRONICS & TELECOMM RES INST

Mass storage accelerator

ActiveUS20050172067A1Slow access timeLarge capacityInput/output to record carriersMemory systemsMass storageDead time

A data storage device is provided. A disk device is combined with a non-volatile memory device to provide much shorter write access time and much higher data write speed than can be achieved with a disk device alone. Interleaving bursts of sector writes between the two storage devices can effectively eliminate the effect of the seek time of the disk device. Following a non-contiguous logical address transition from a host system, the storage controller can perform a look-ahead seek operation on the disk device, while writing current data to the non-volatile memory device. Such a system can exploit the inherently faster write access characteristics of a non-volatile memory device, eliminating the dead time normally caused by the disk seek time.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com