Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

524 results about "Wear leveling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Wear leveling (also written as wear levelling) is a technique for prolonging the service life of some kinds of erasable computer storage media, such as flash memory, which is used in solid-state drives (SSDs) and USB flash drives, and phase-change memory. There are several wear leveling mechanisms that provide varying levels of longevity enhancement in such memory systems.

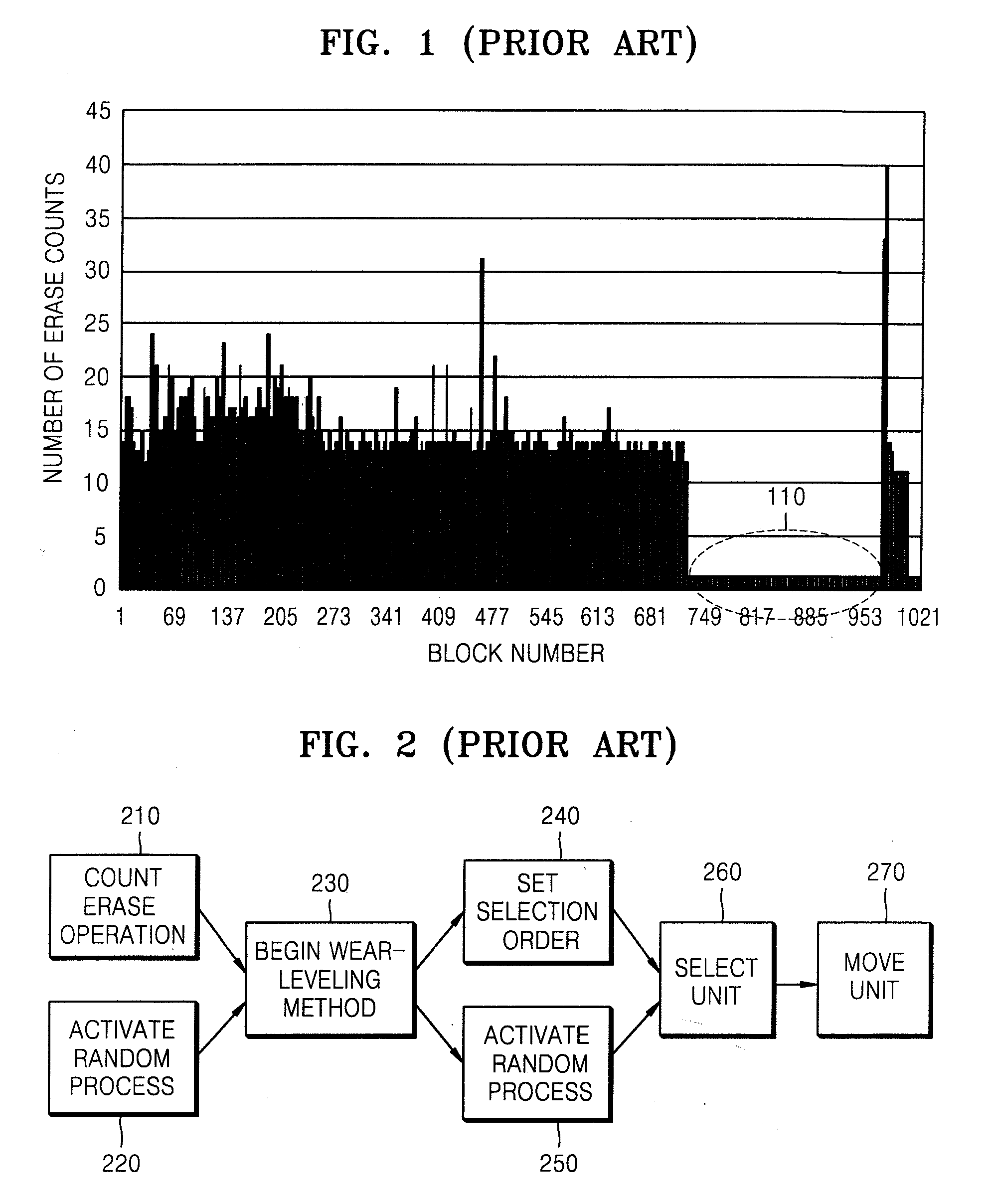

Wear leveling techniques for flash EEPROM systems

InactiveUS6850443B2Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

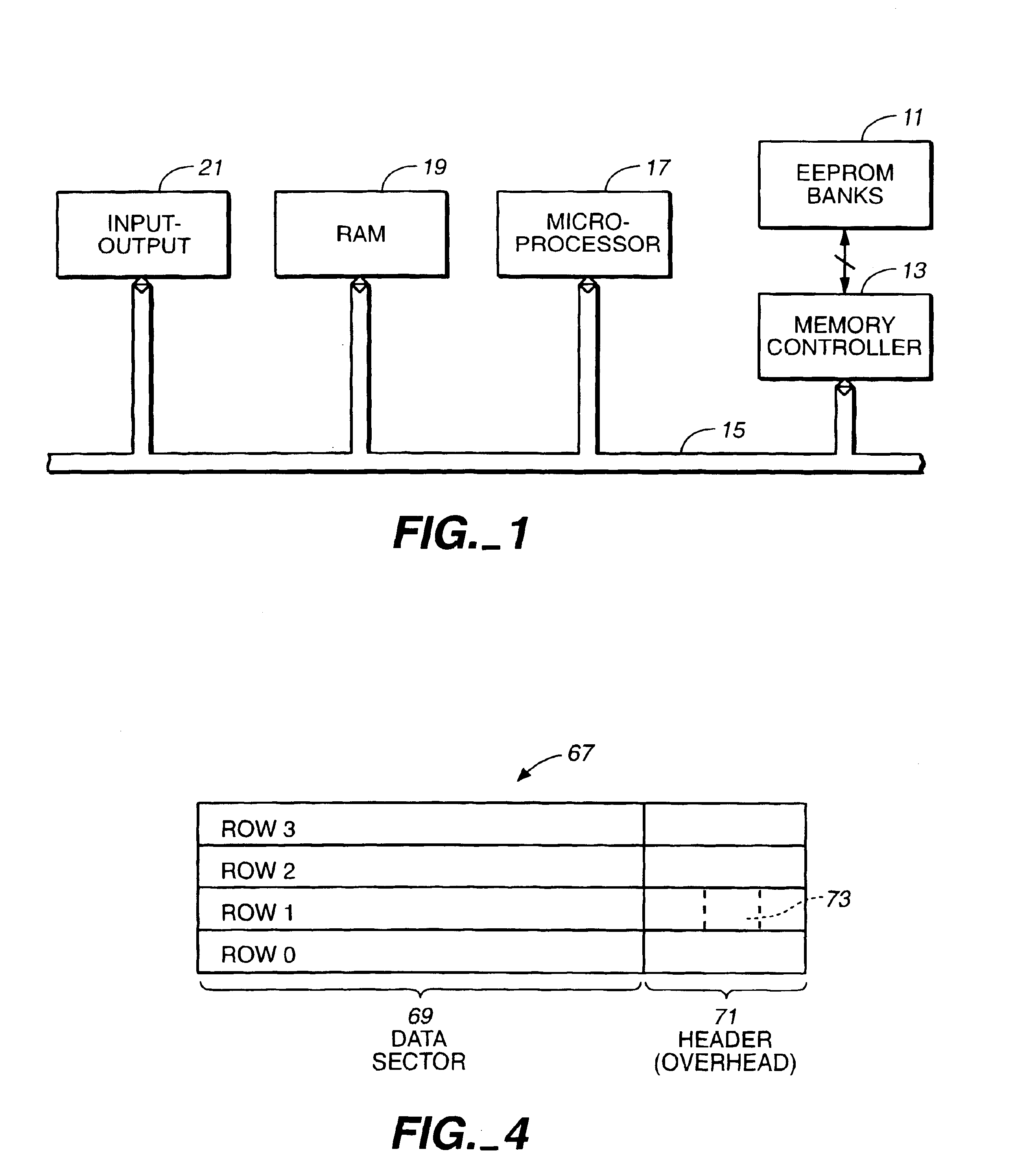

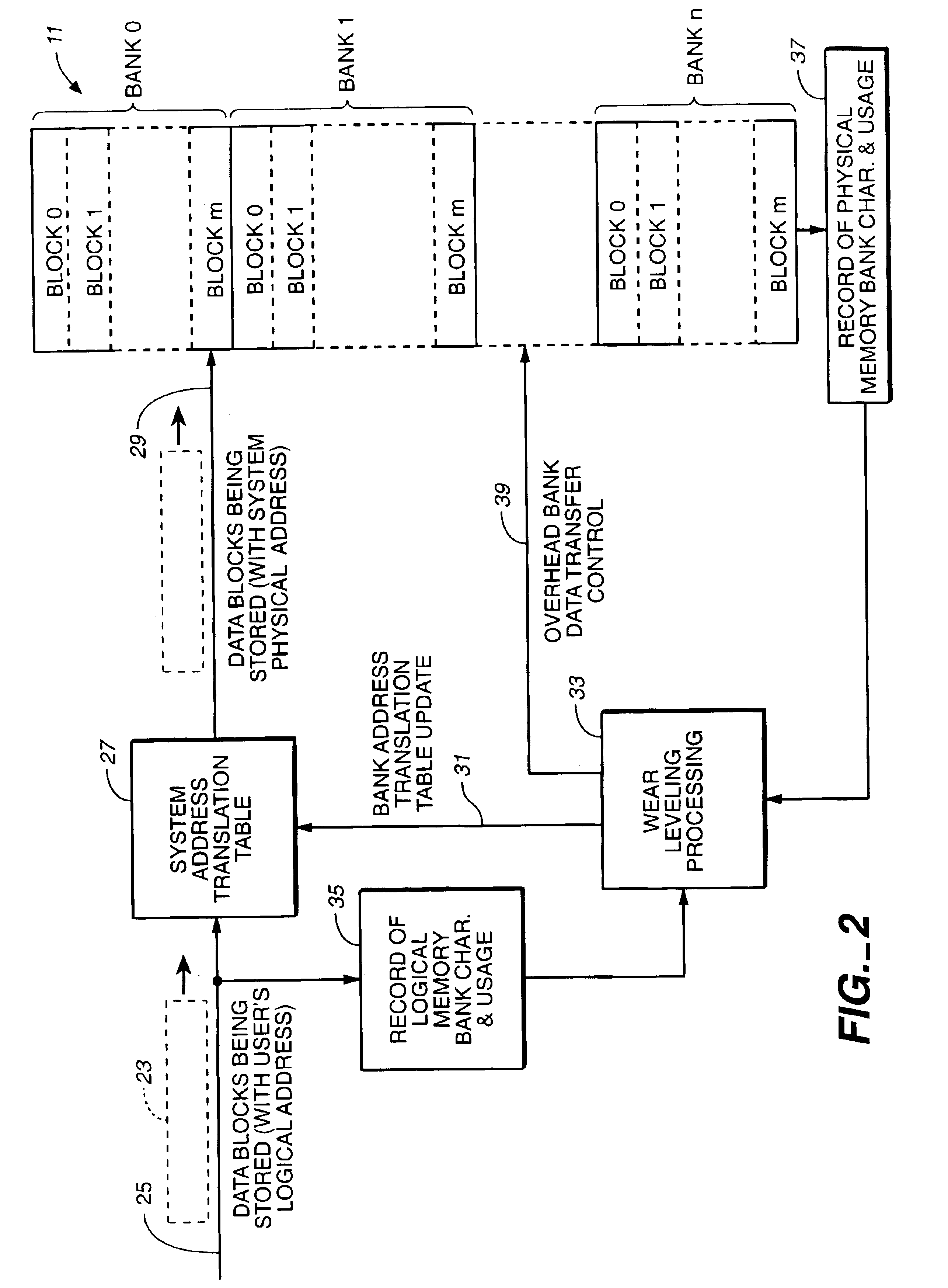

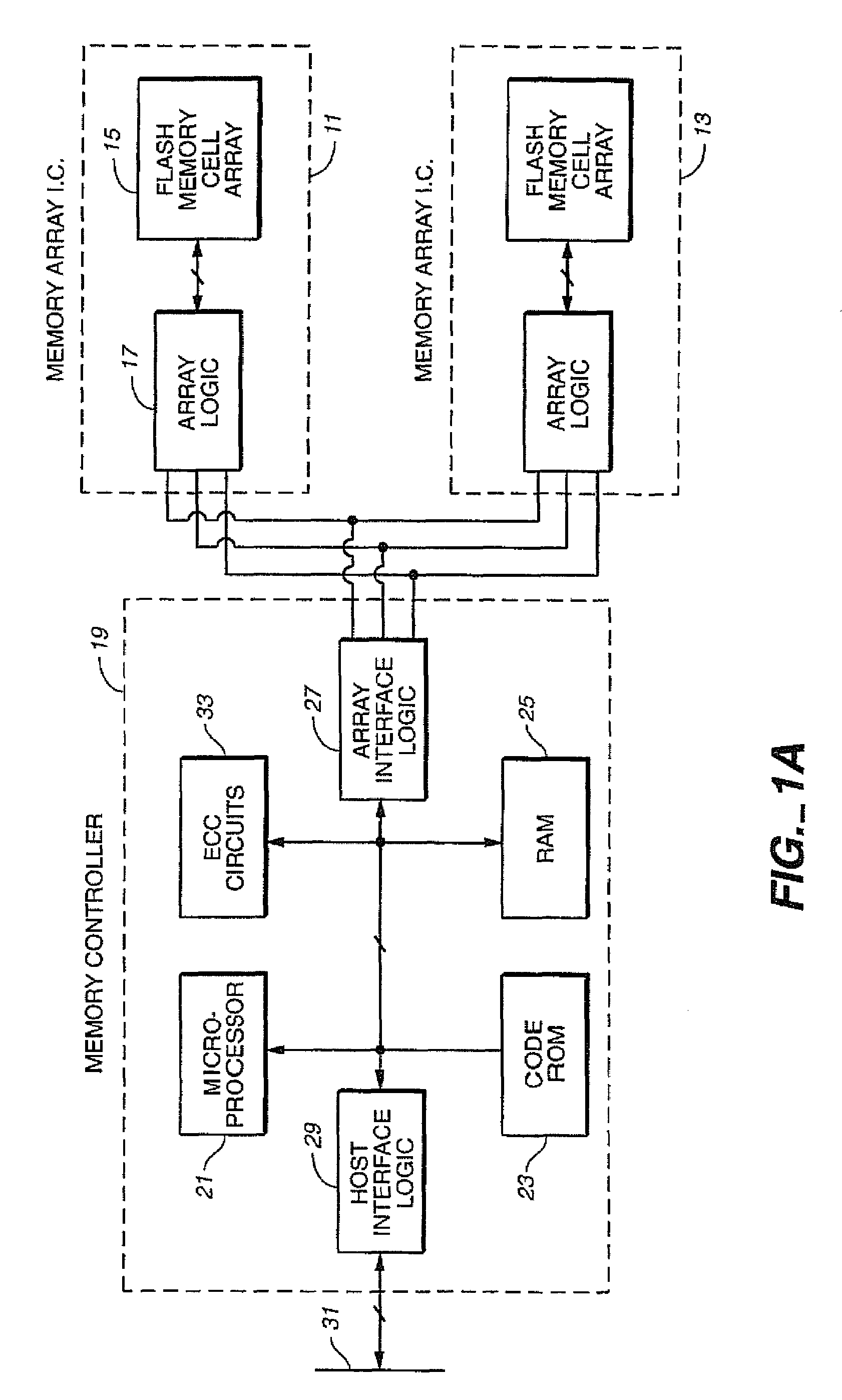

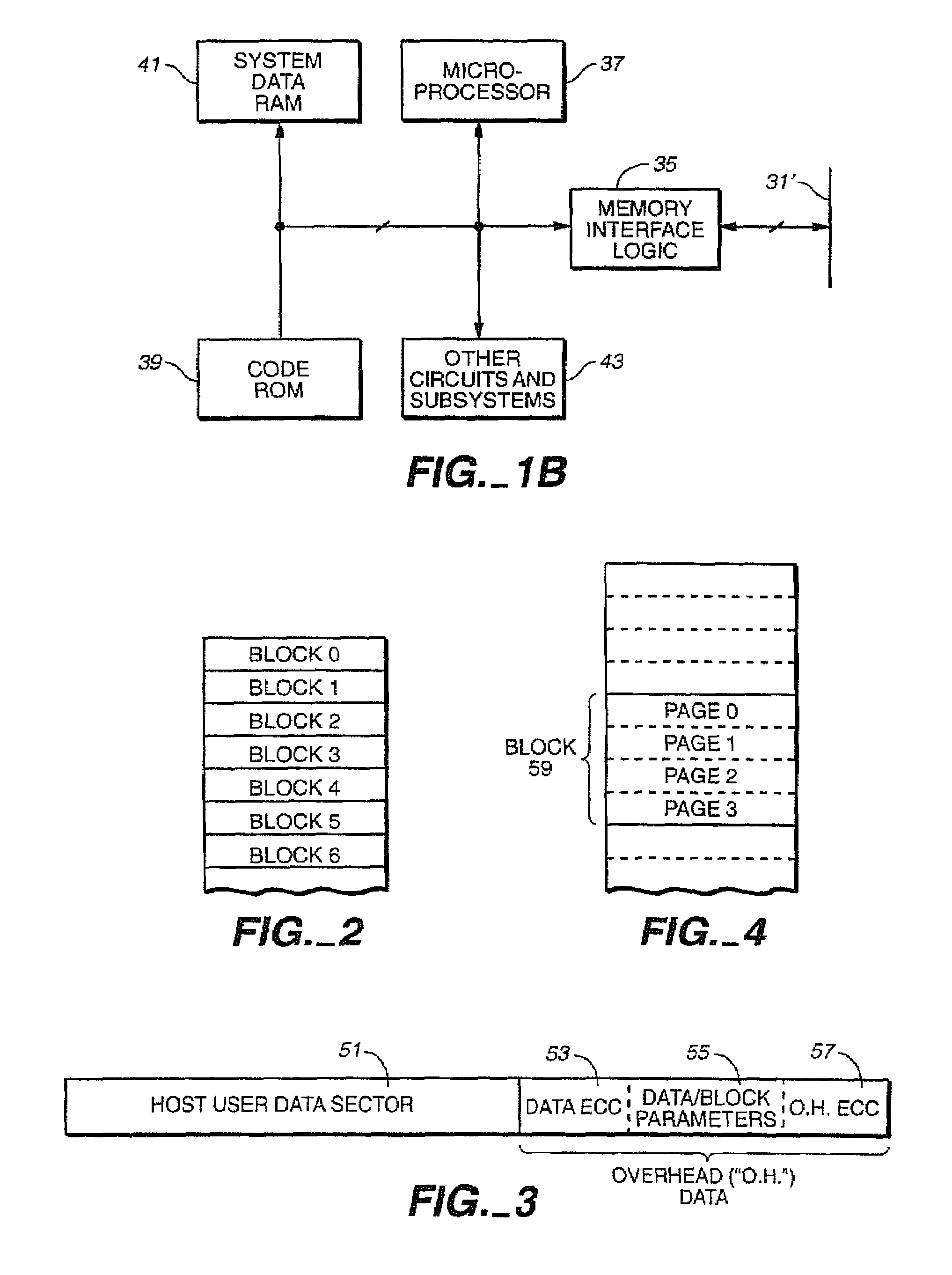

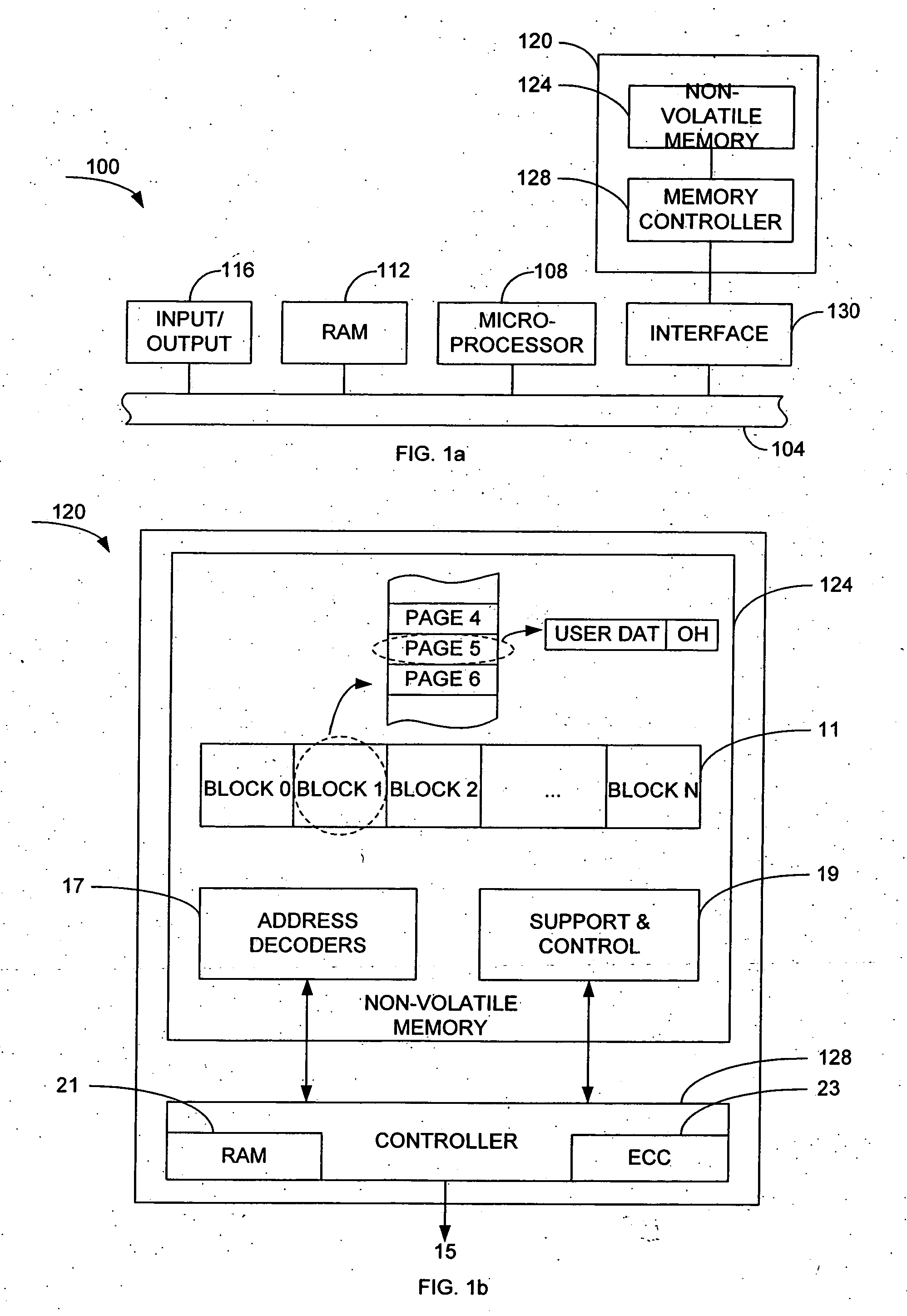

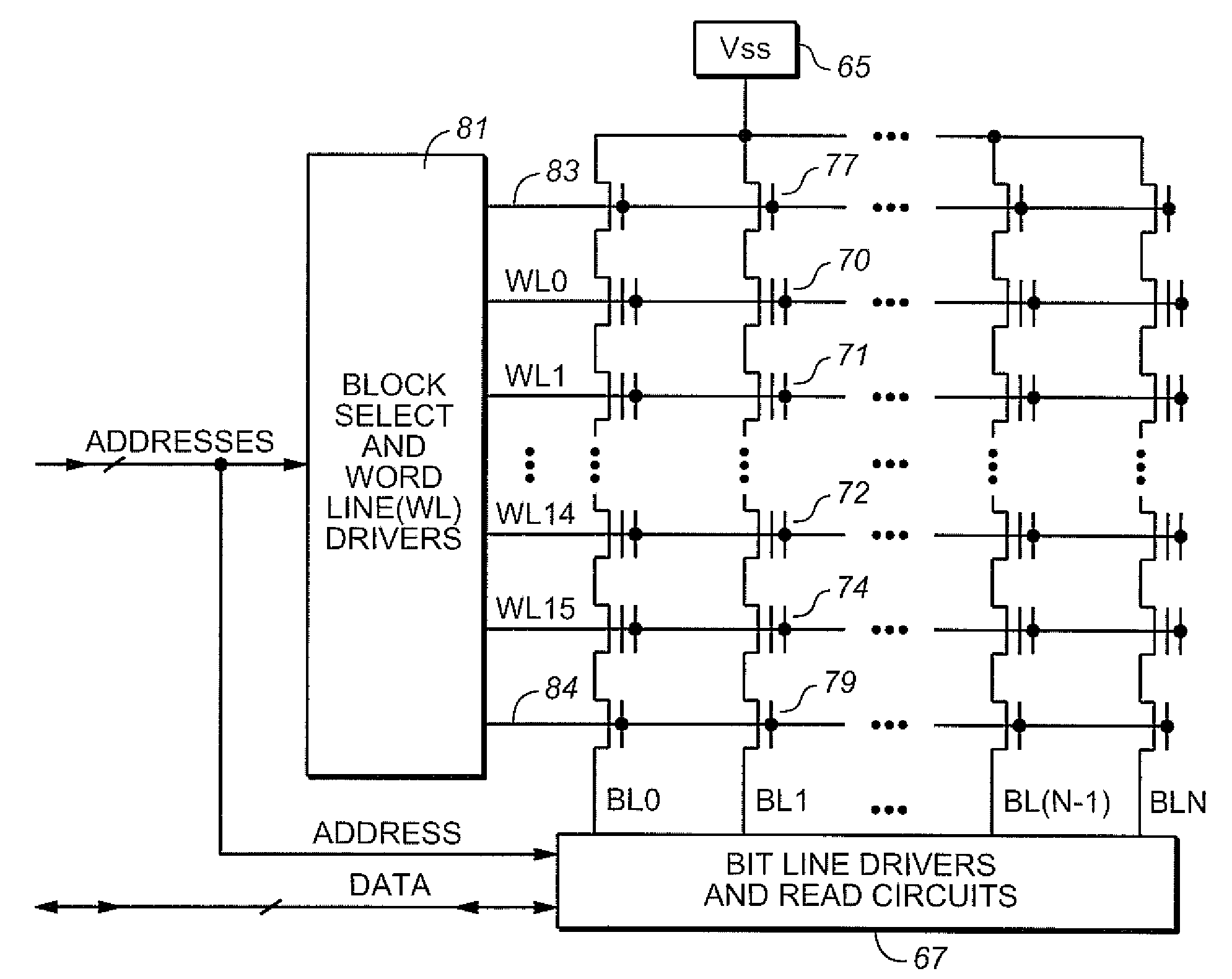

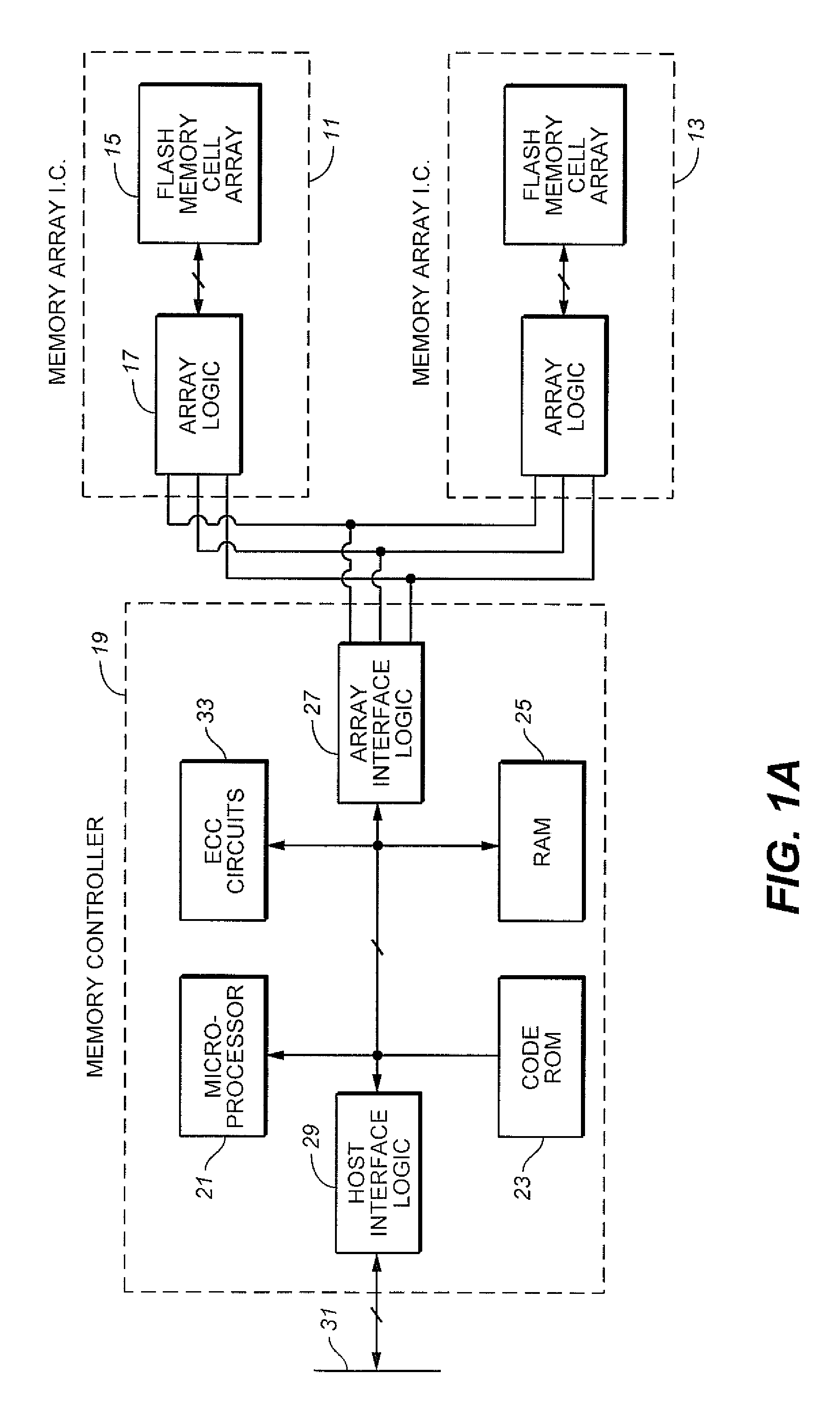

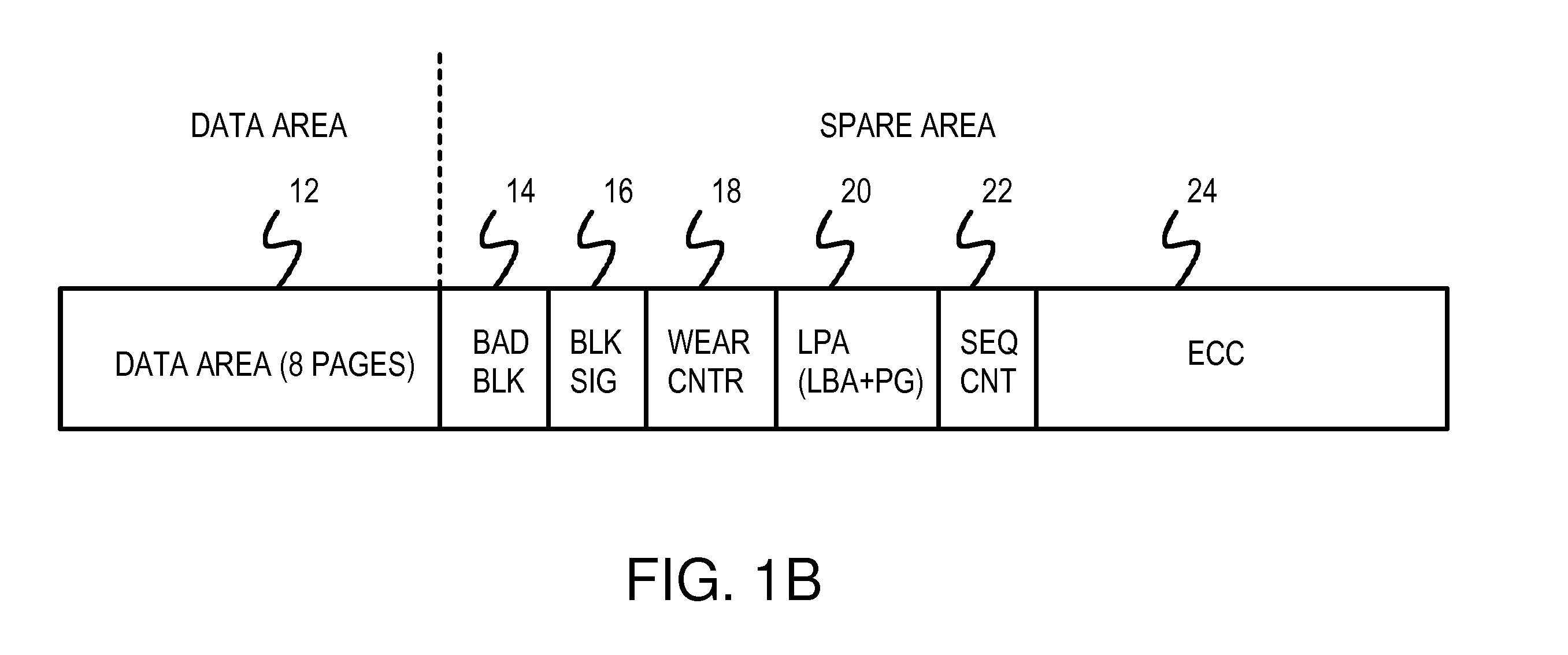

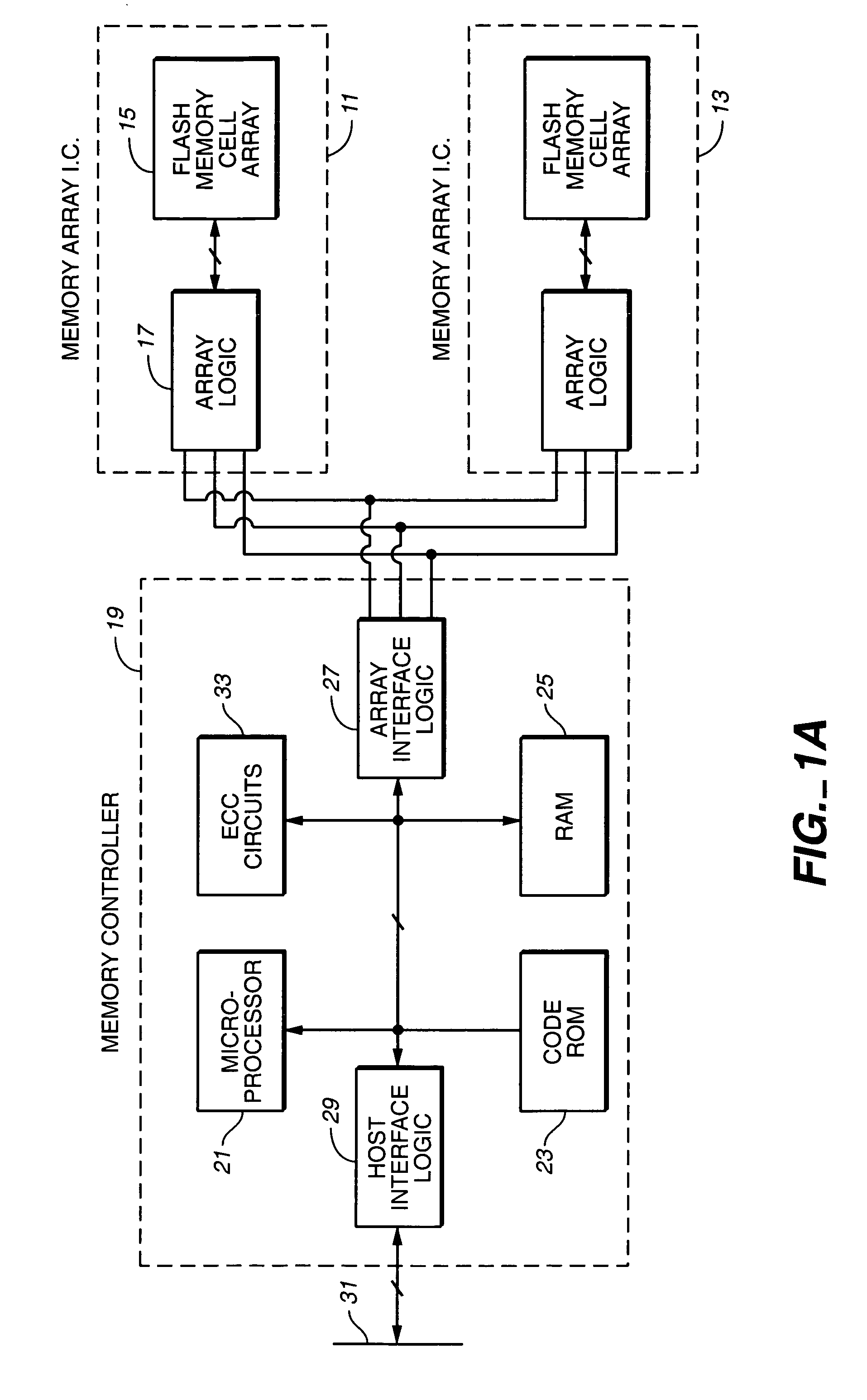

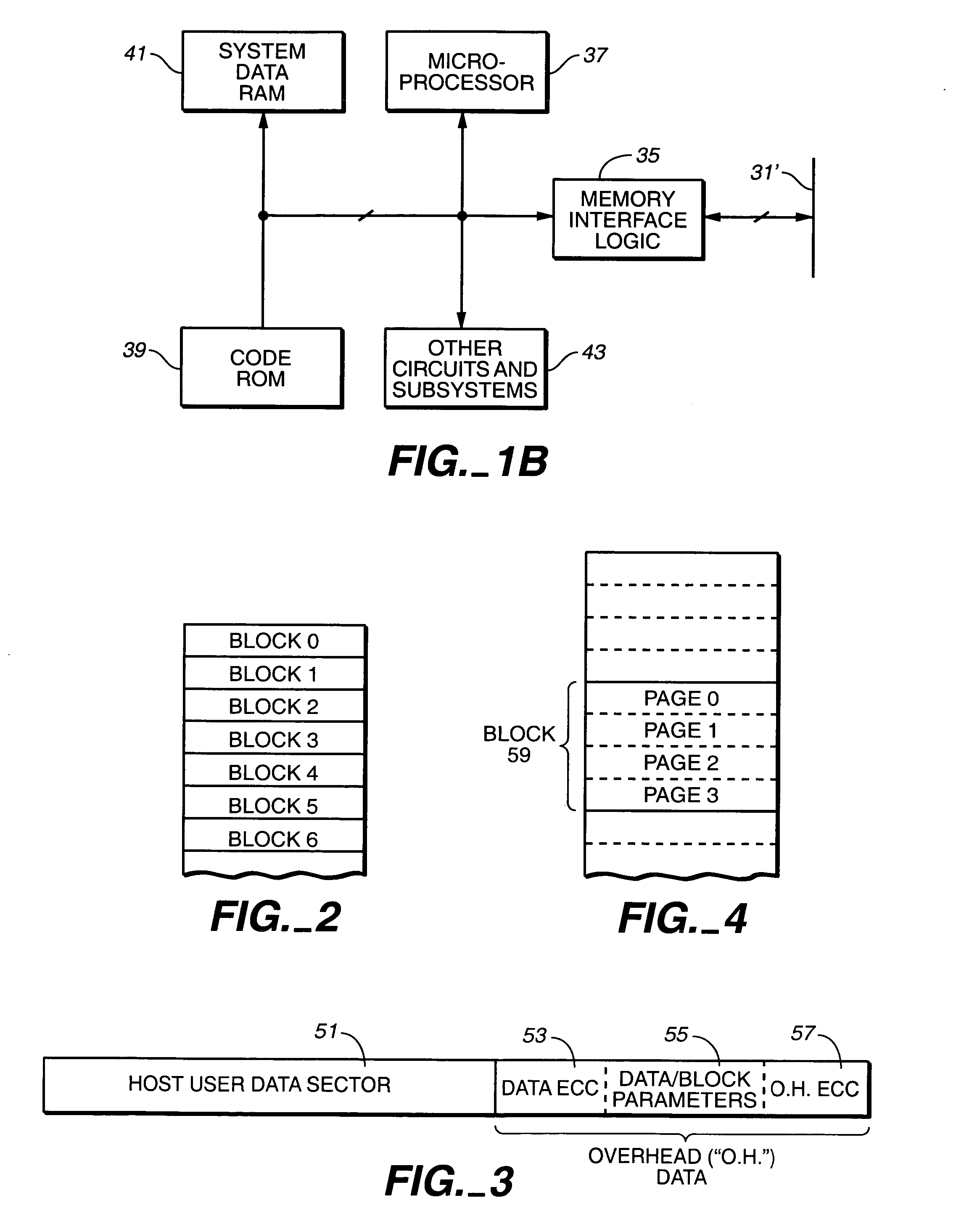

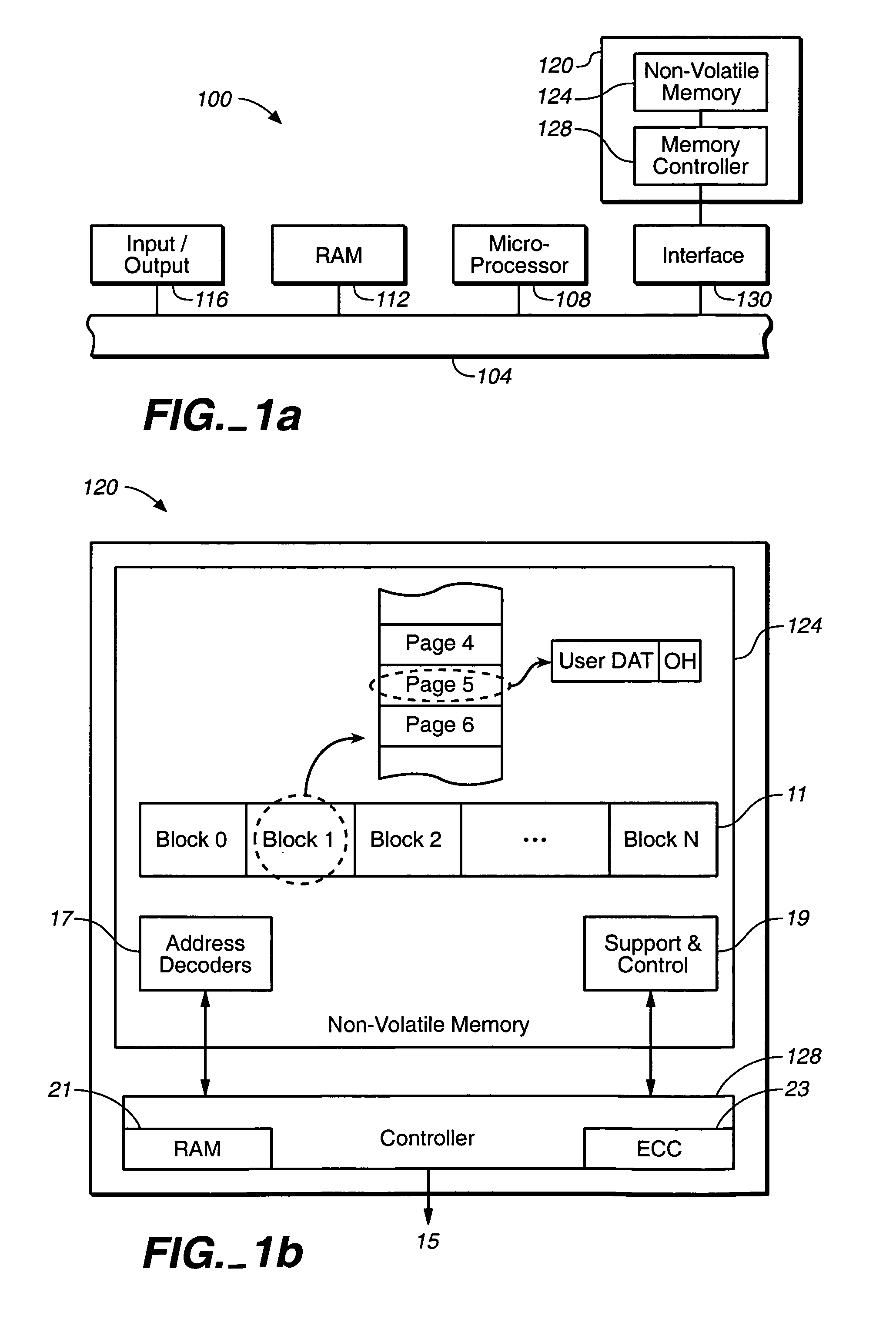

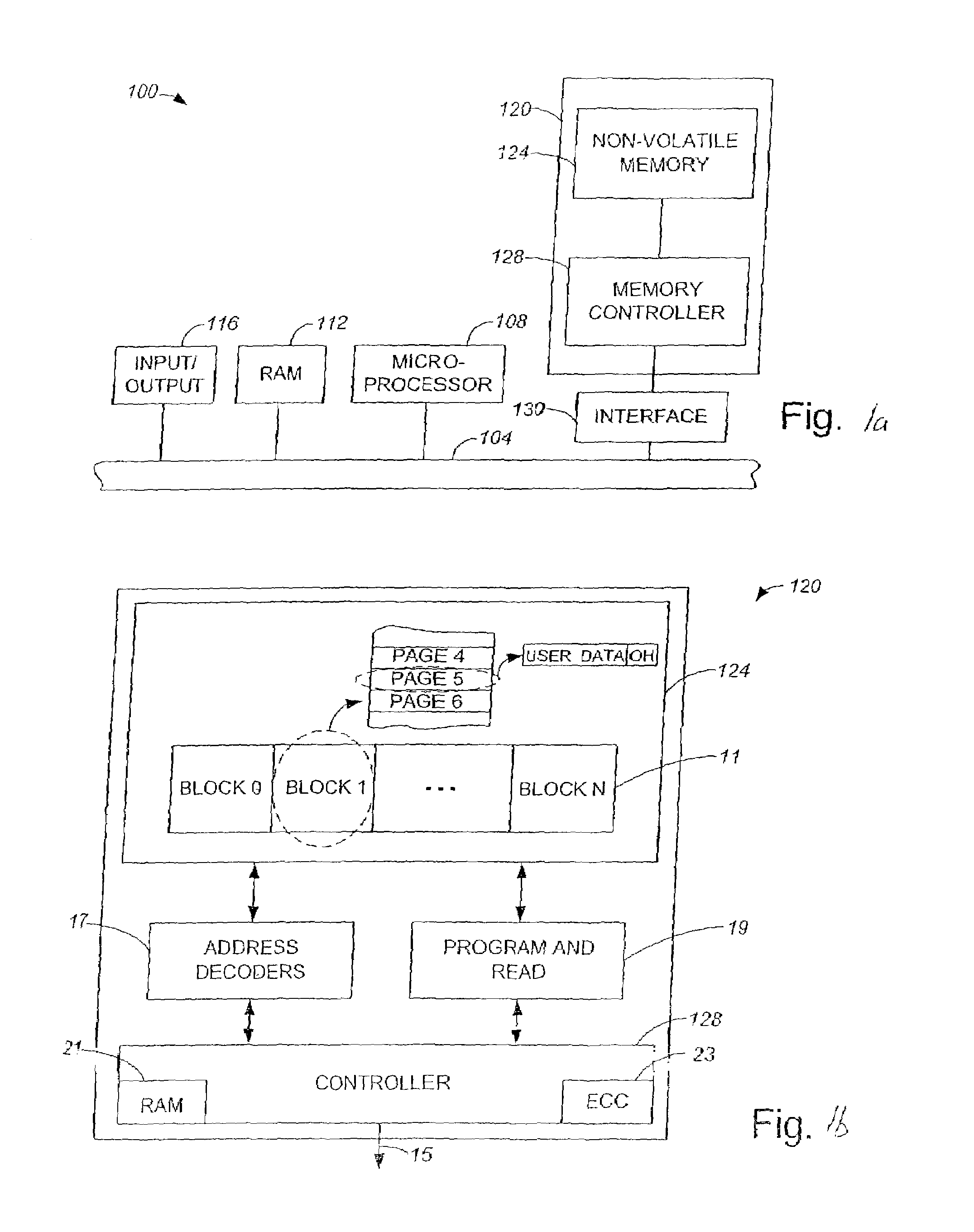

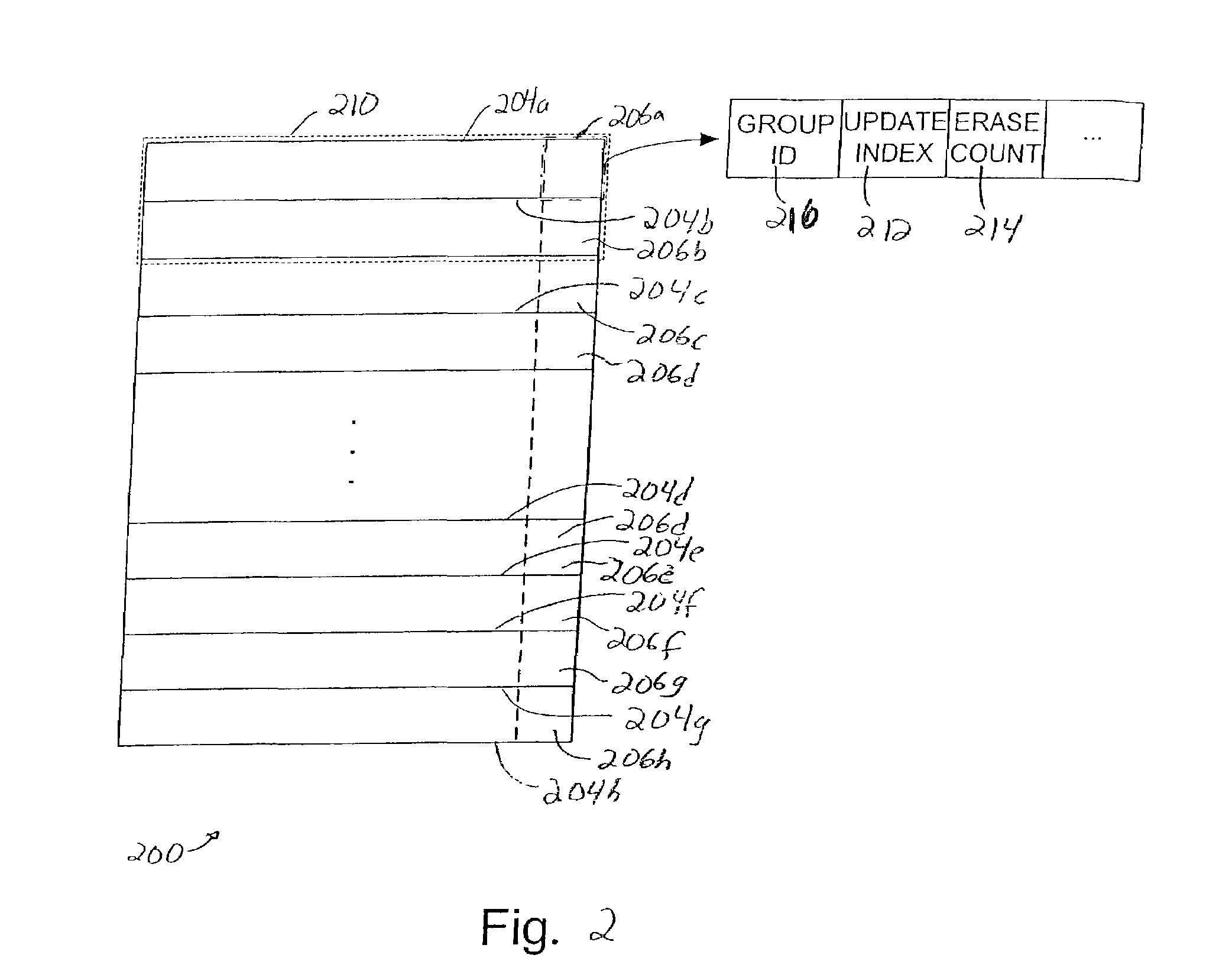

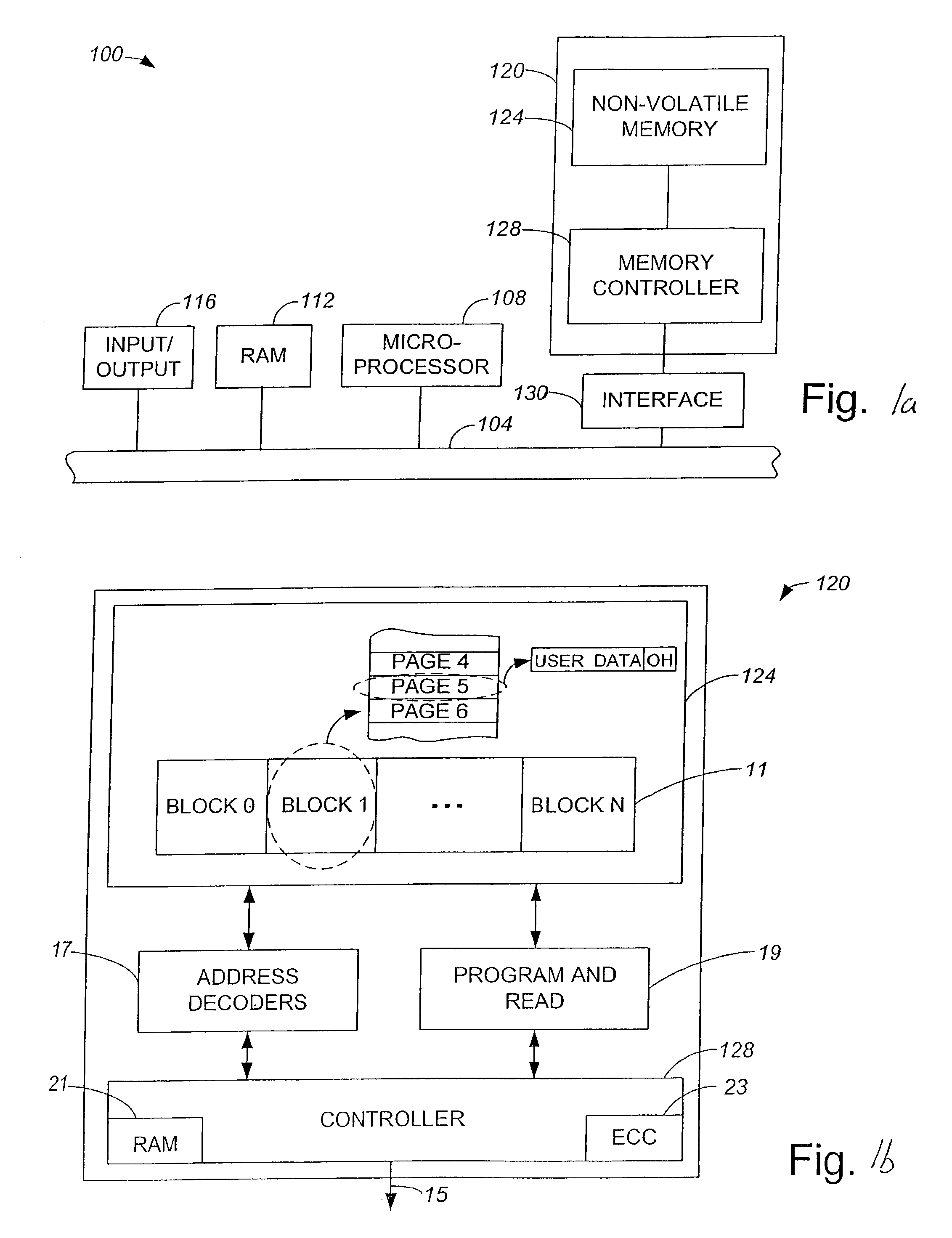

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

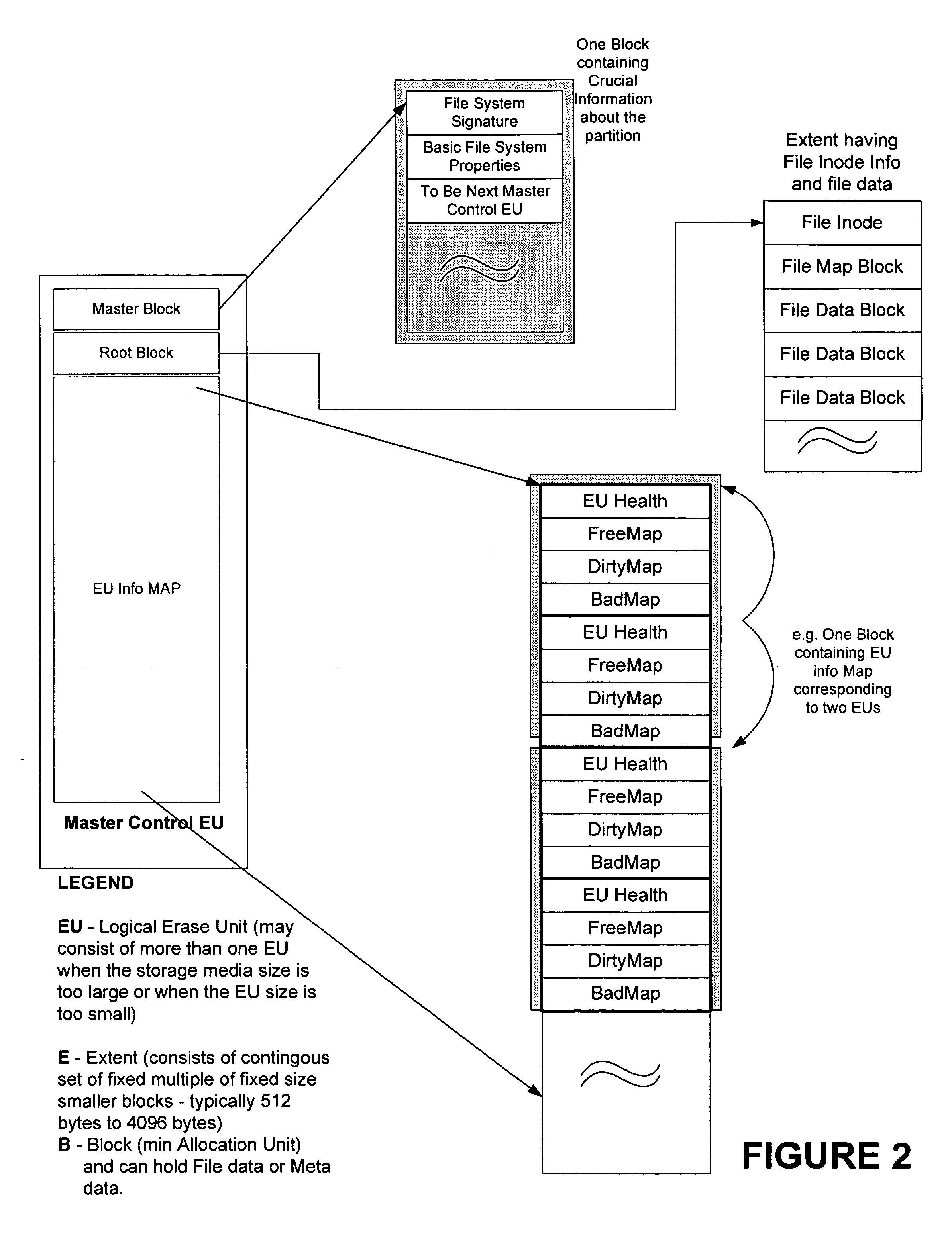

Effective wear-leveling and concurrent reclamation method for embedded linear flash file systems

InactiveUS20070150689A1Memory architecture accessing/allocationComputer security arrangementsRecovery methodFlash file system

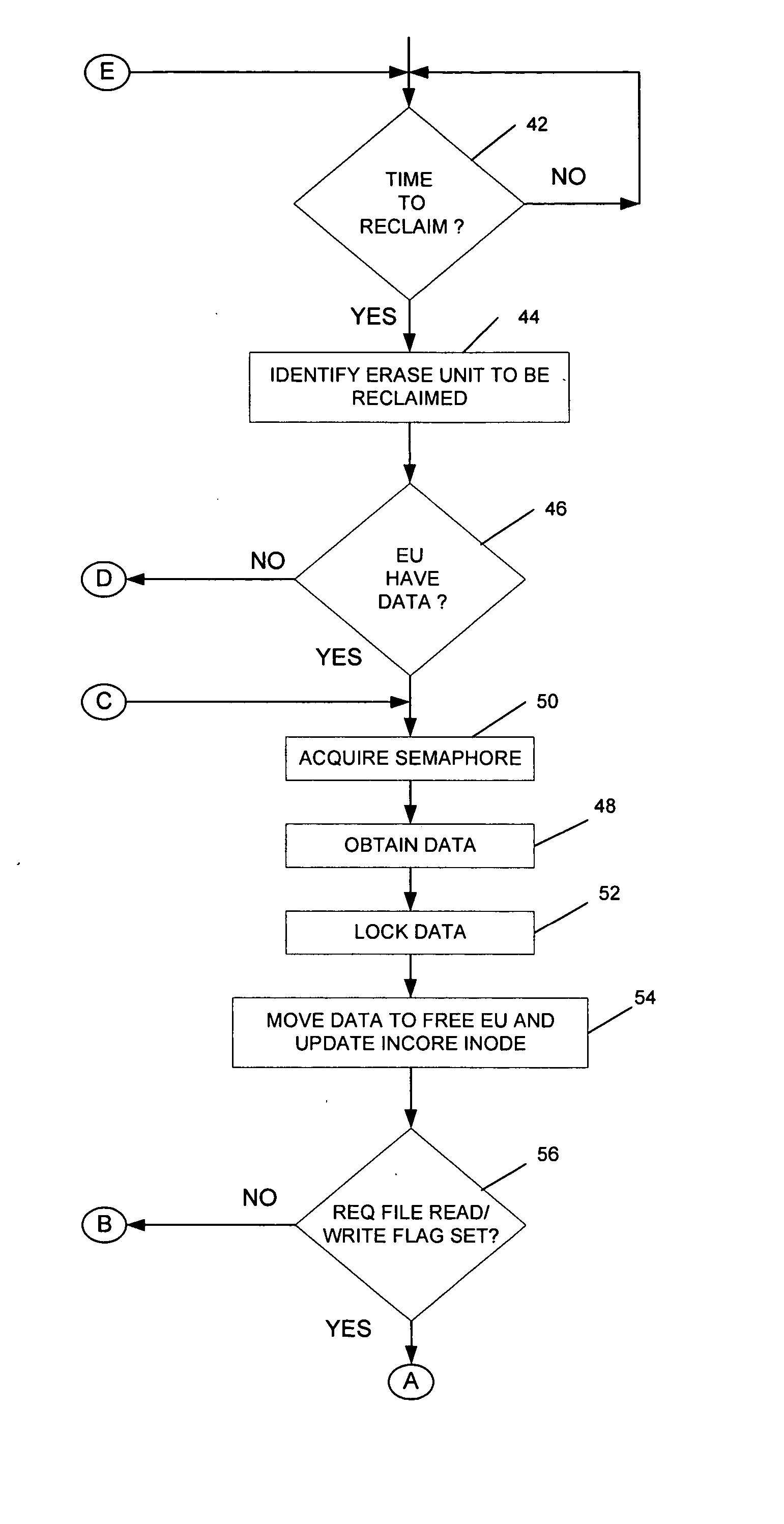

Reclamation of an Erase Unit of a flash memory is performed concurrently with a file operation on the flash memory by initiating a reclamation operation on the individually erasable portion of the memory, by suspending the reclamation operation for the file operation, by performing the file operation, and by resuming the reclamation operation.

Owner:HONEYWELL INT INC

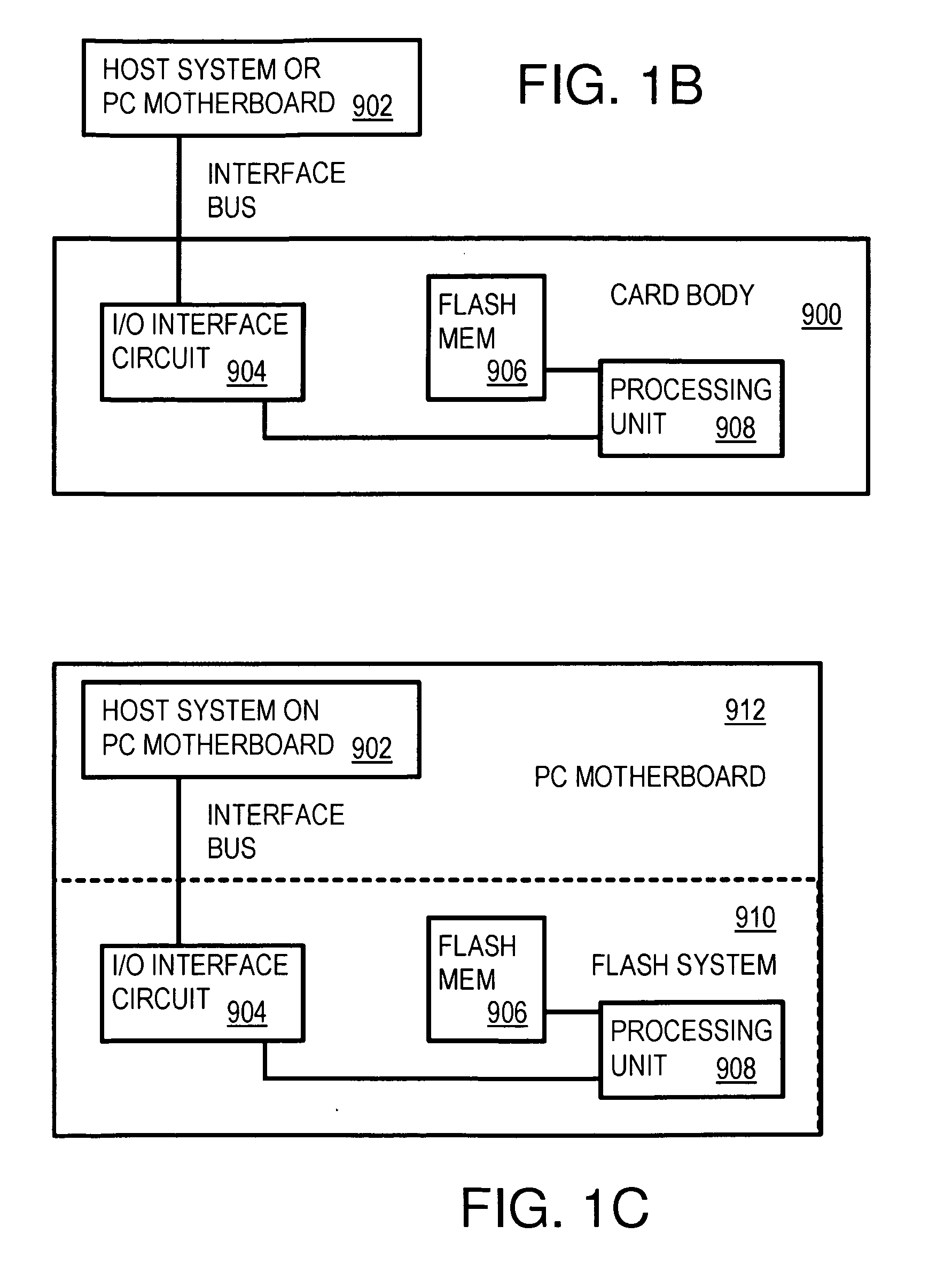

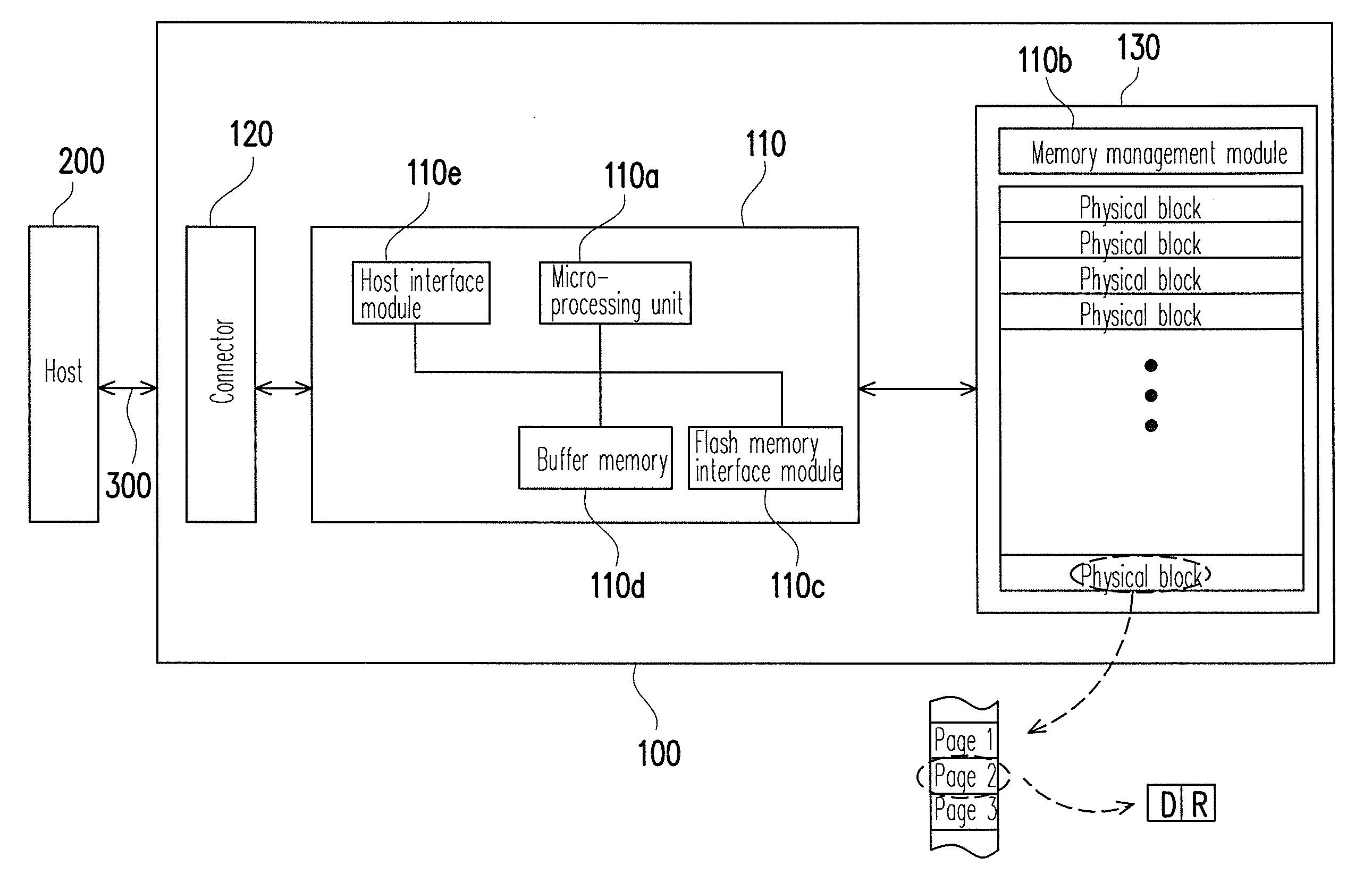

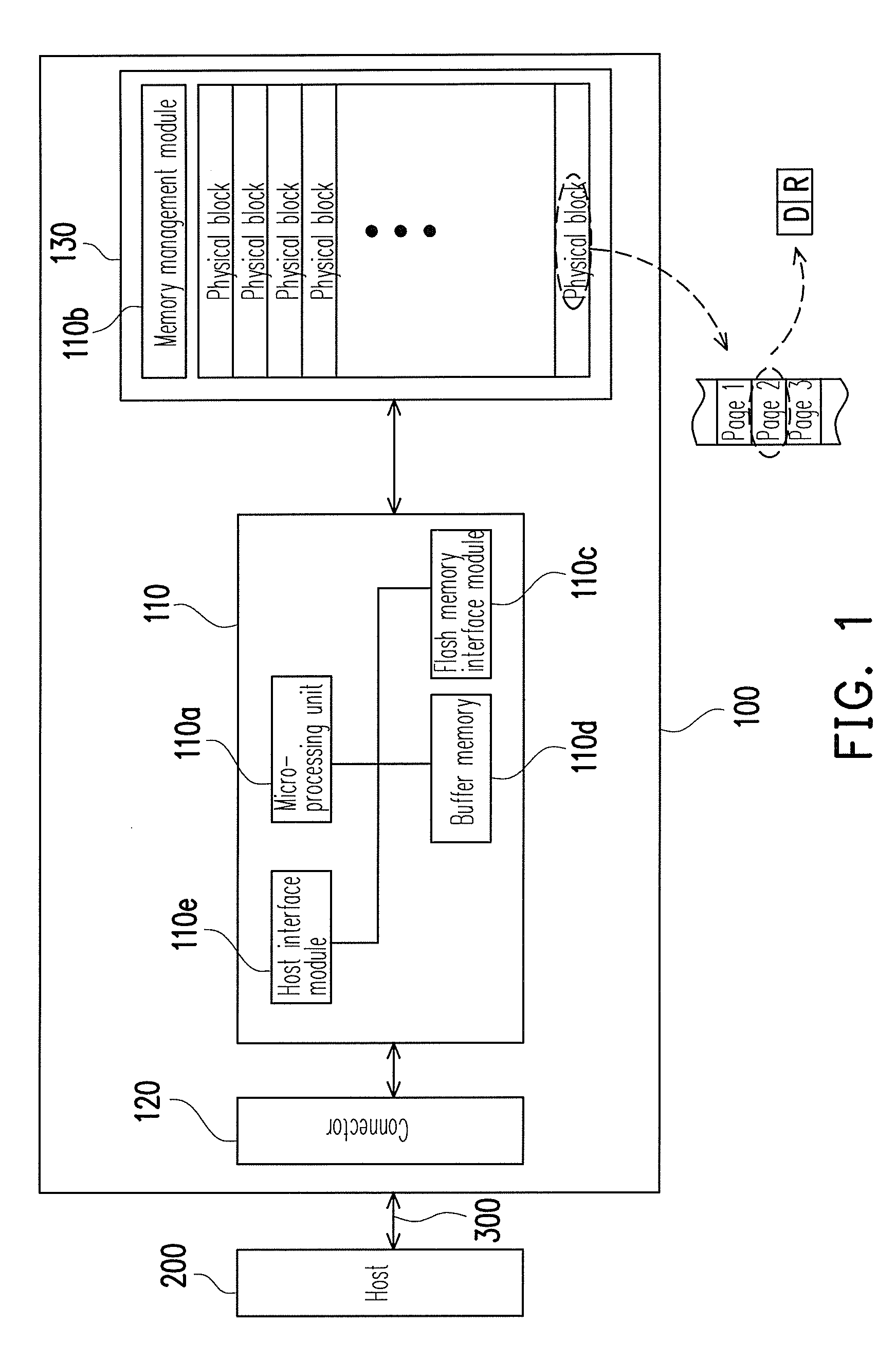

Flash memory storage system and method

ActiveUS20070061502A1Overcome disadvantagesEqually distributedMemory architecture accessing/allocationRead-only memoriesParallel computingStorage cell

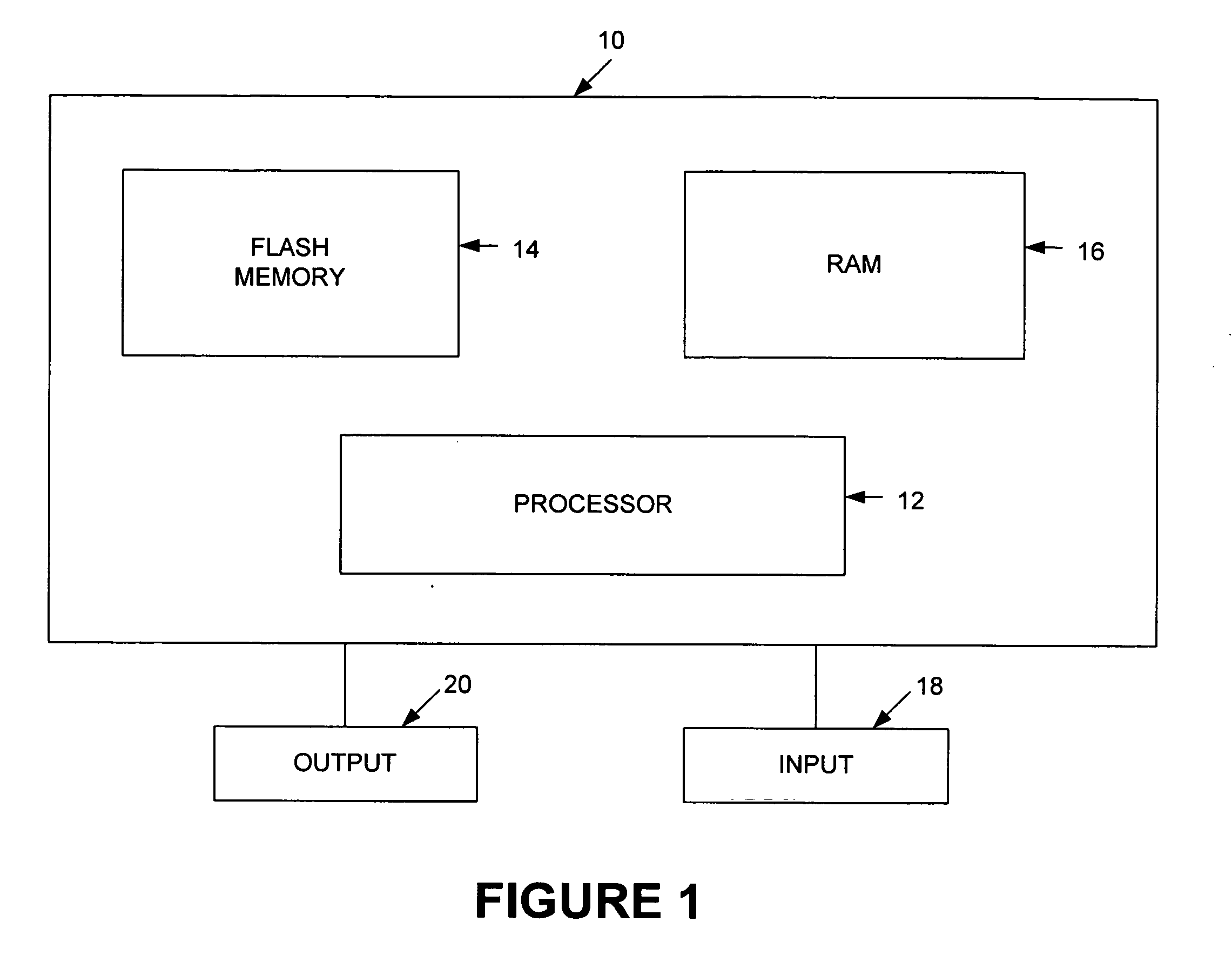

A flash memory storage system includes a memory array containing a plurality of memory cells and a controller for controlling the flash memory array. The controller dedicates a first group of memory cells to operate with a first number of bits per cell and a second, separate group of memory cells to operate with a second number of bits per cell. A mechanism is provided to apply wear leveling techniques separately to the two groups of cells to evenly wear out the memory cells.

Owner:WESTERN DIGITAL ISRAEL LTD

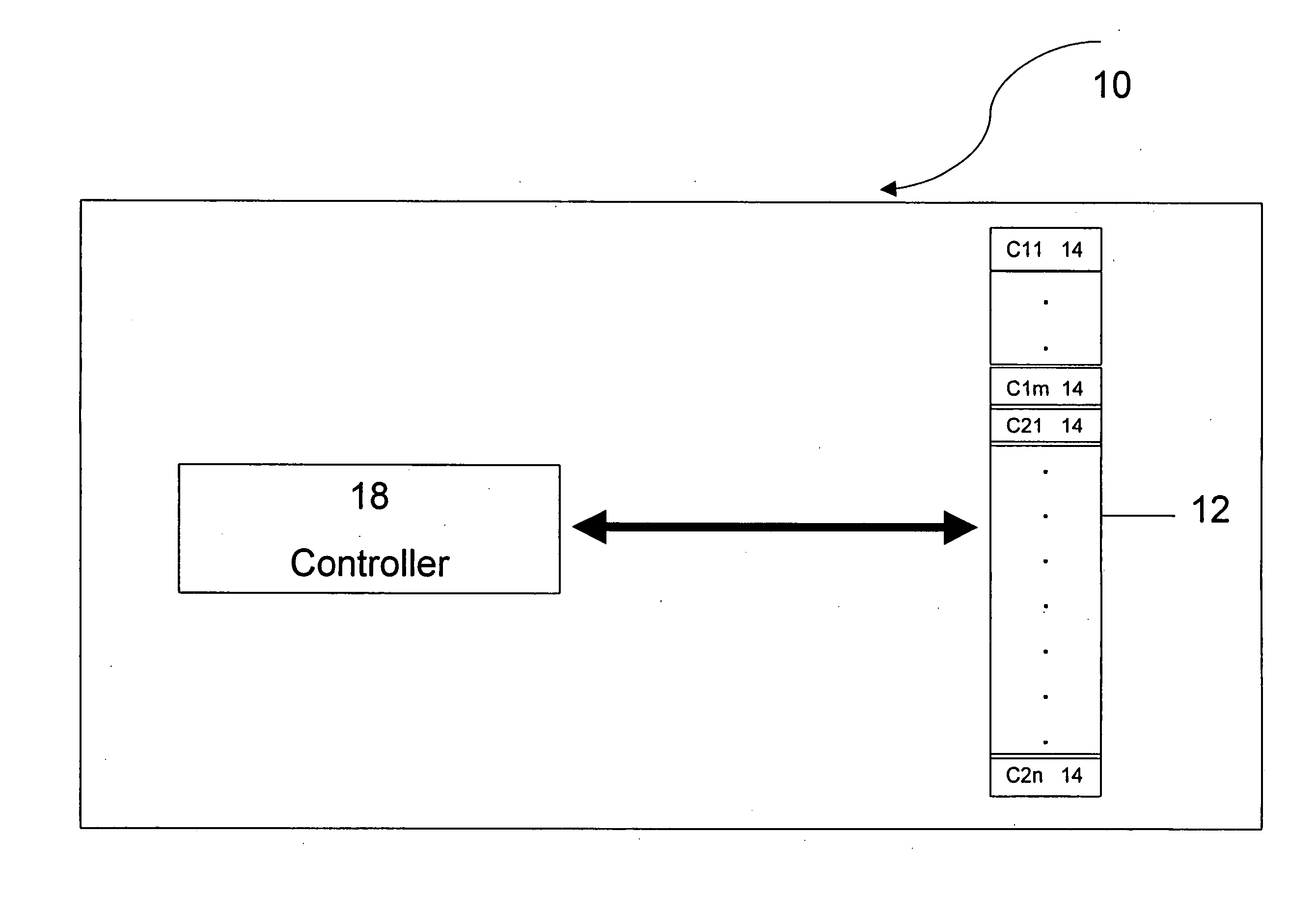

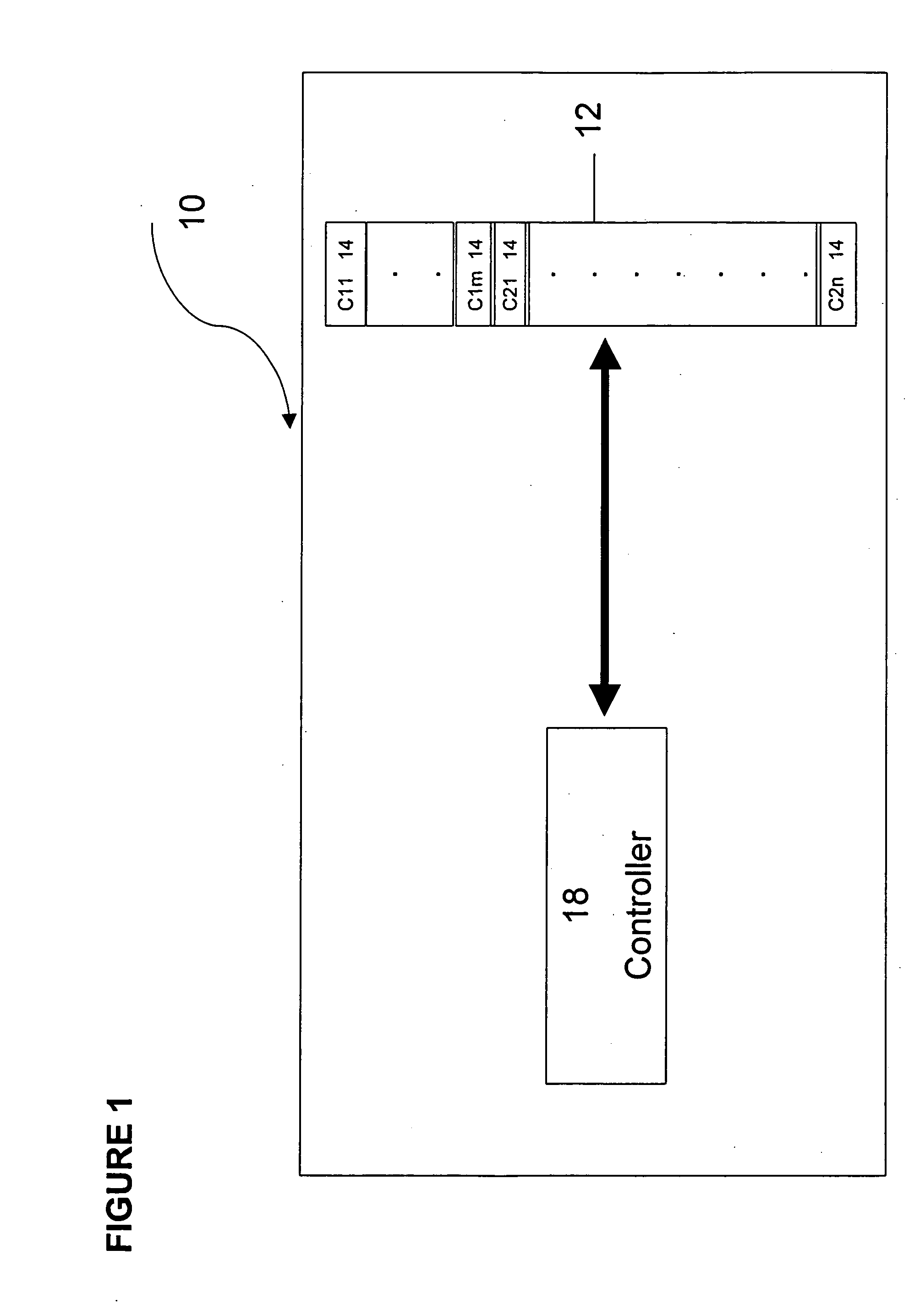

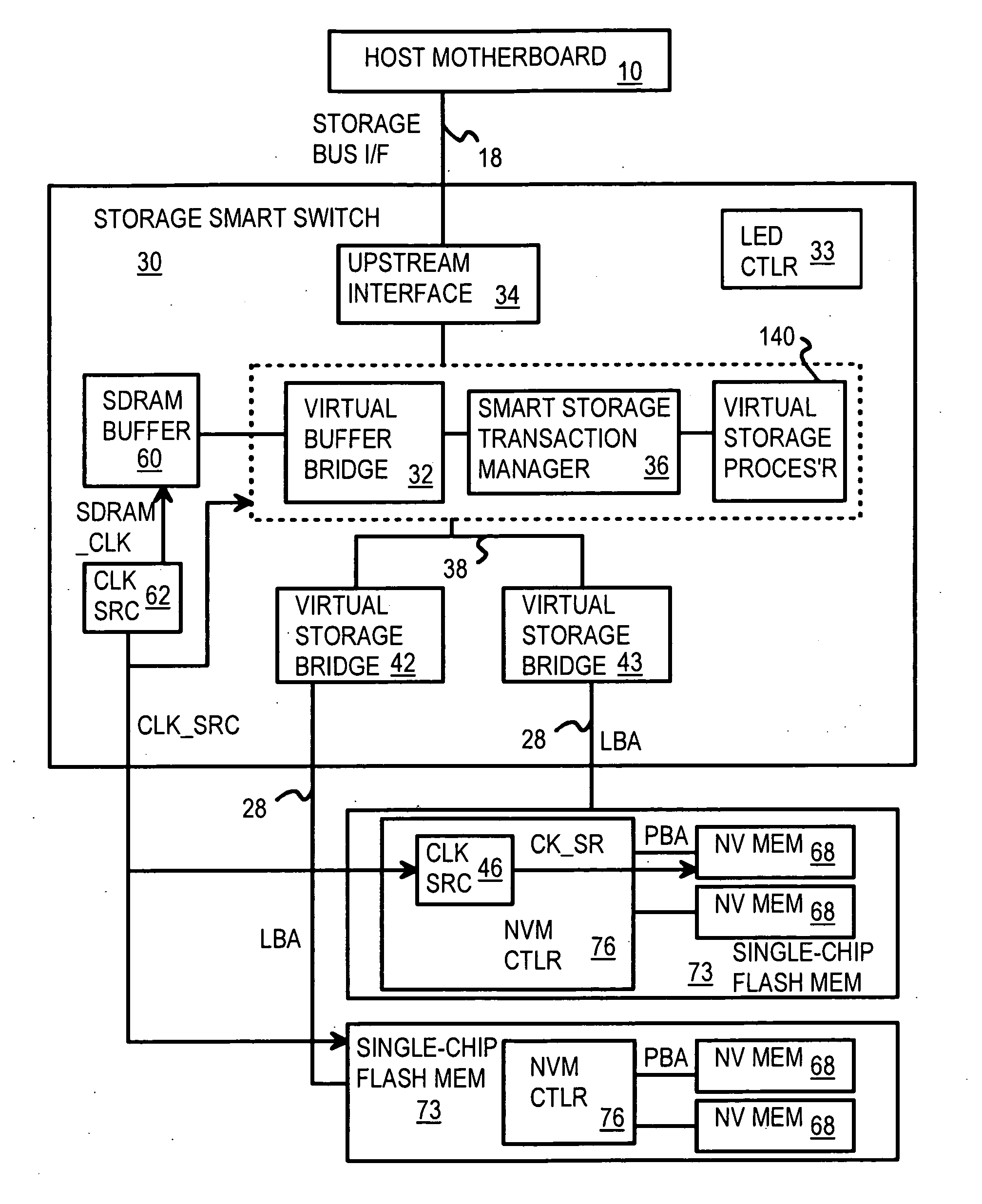

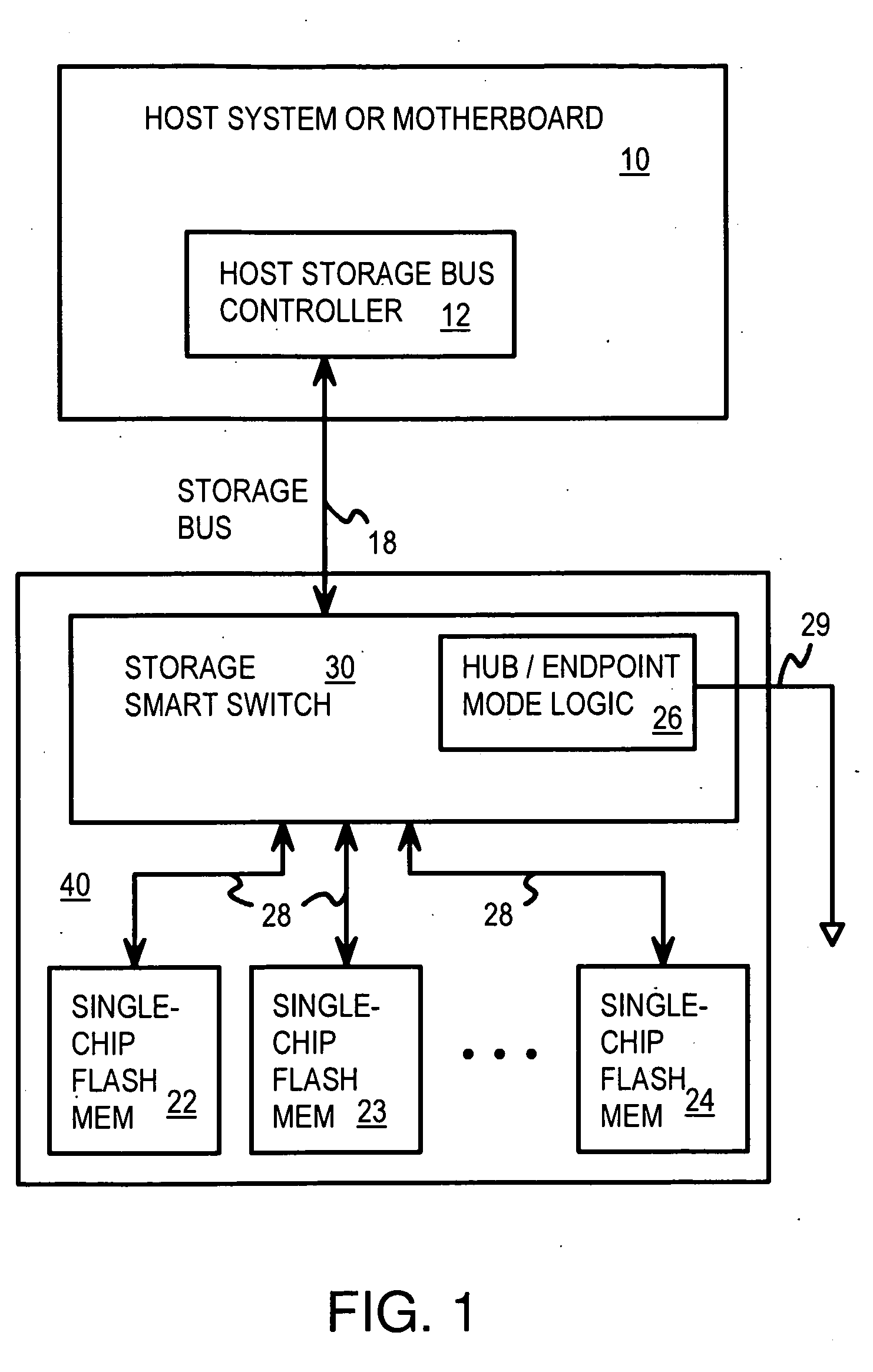

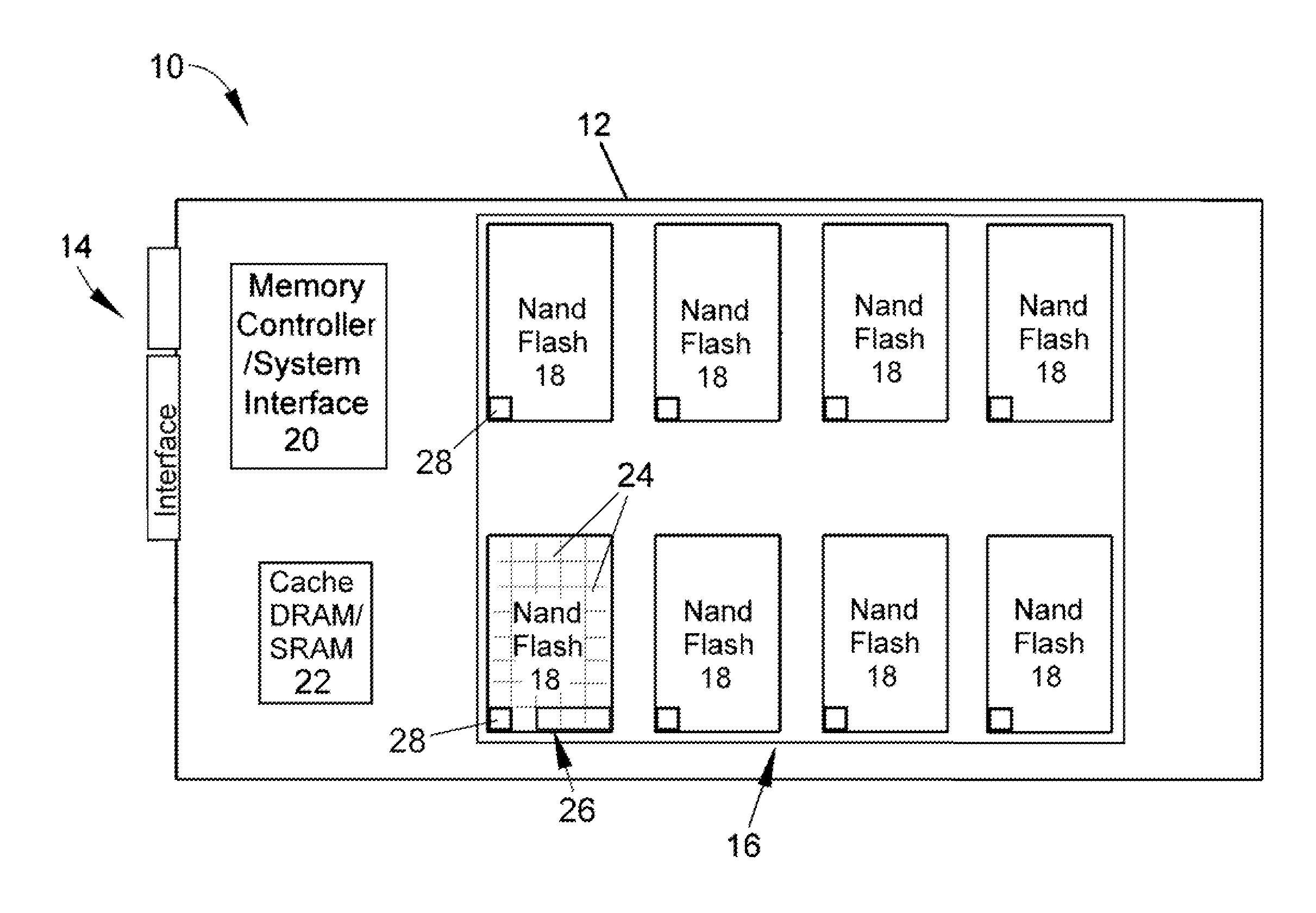

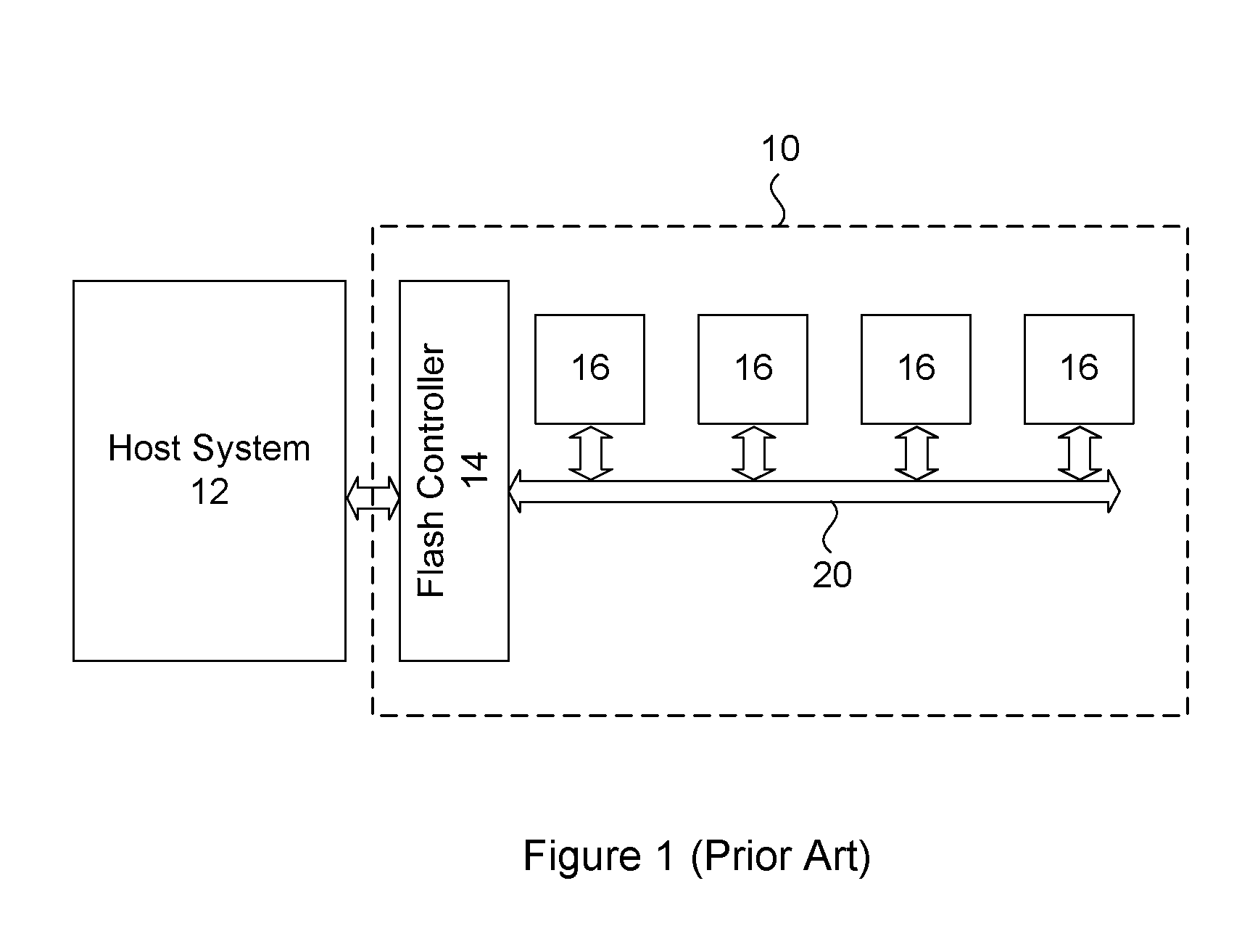

Multi-Level Controller with Smart Storage Transfer Manager for Interleaving Multiple Single-Chip Flash Memory Devices

InactiveUS20080320214A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingSolid-state drive

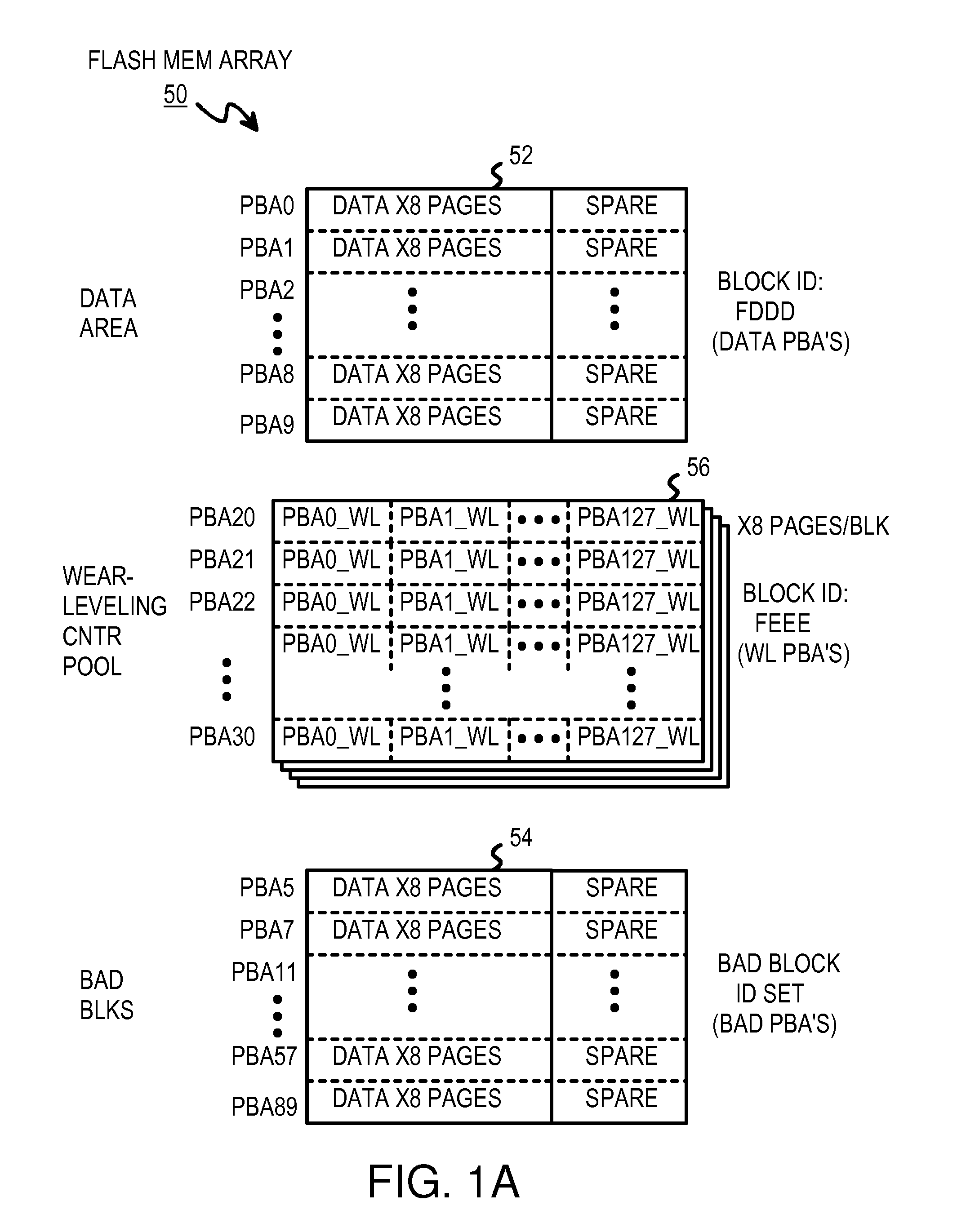

A solid-state disk (SSD) has a smart storage switch with a smart storage transaction manager that re-orders host commands for accessing downstream single-chip flash-memory devices. Each single-chip flash-memory device has a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory blocks in the single-chip flash-memory device. Wear-leveling and bad block remapping are preformed by each single-chip flash-memory device, and at a higher level by a virtual storage processor in the smart storage switch. Virtual storage bridges between the smart storage transaction manager and the single-chip flash-memory devices bridge LBA transactions over LBA buses to the single-chip flash-memory devices. Data striping and interleaving among multiple channels of the single-chip flash-memory device is controlled at a high level by the smart storage transaction manager, while further interleaving and remapping may be performed within each single-chip flash-memory device.

Owner:SUPER TALENT TECH CORP

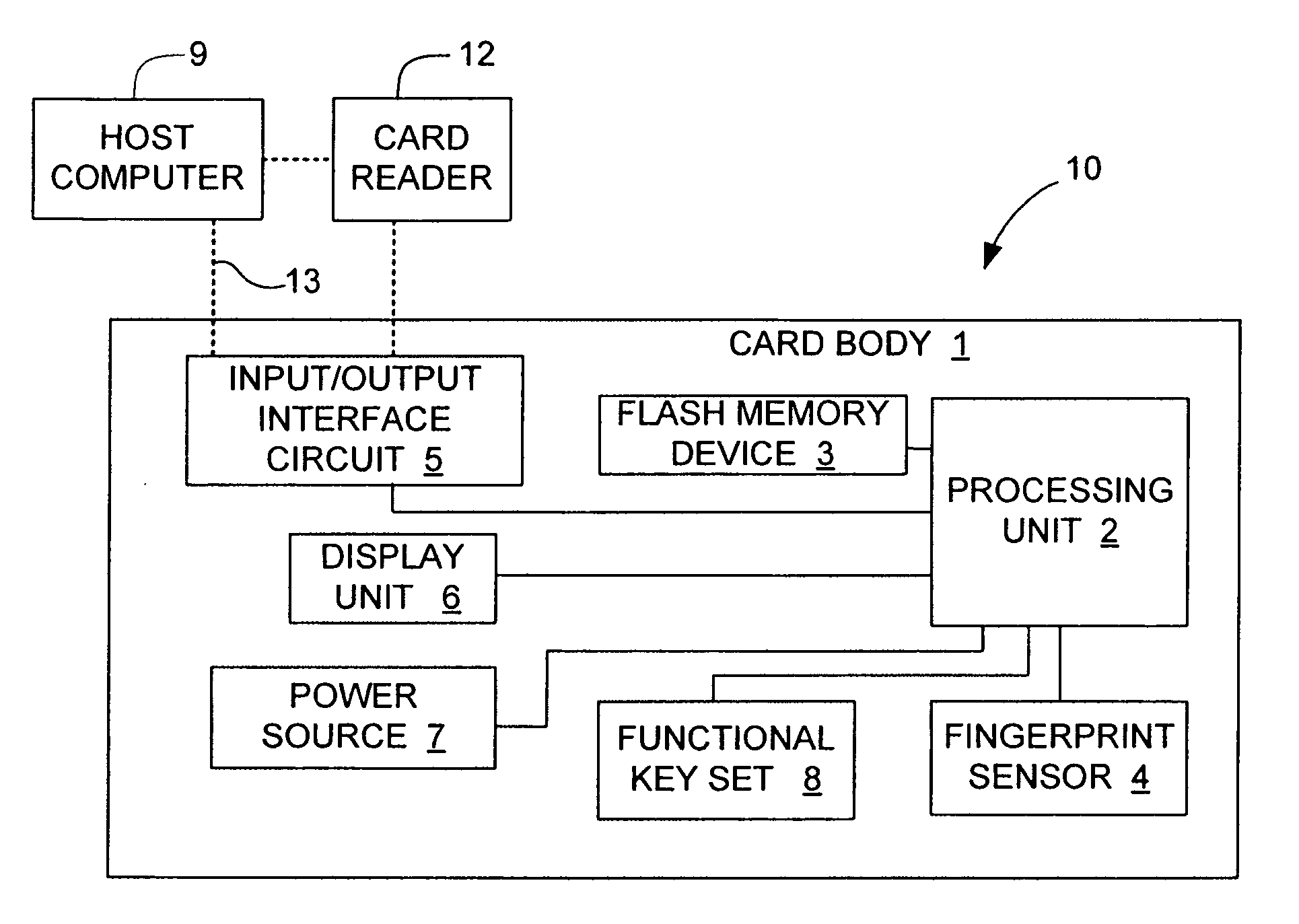

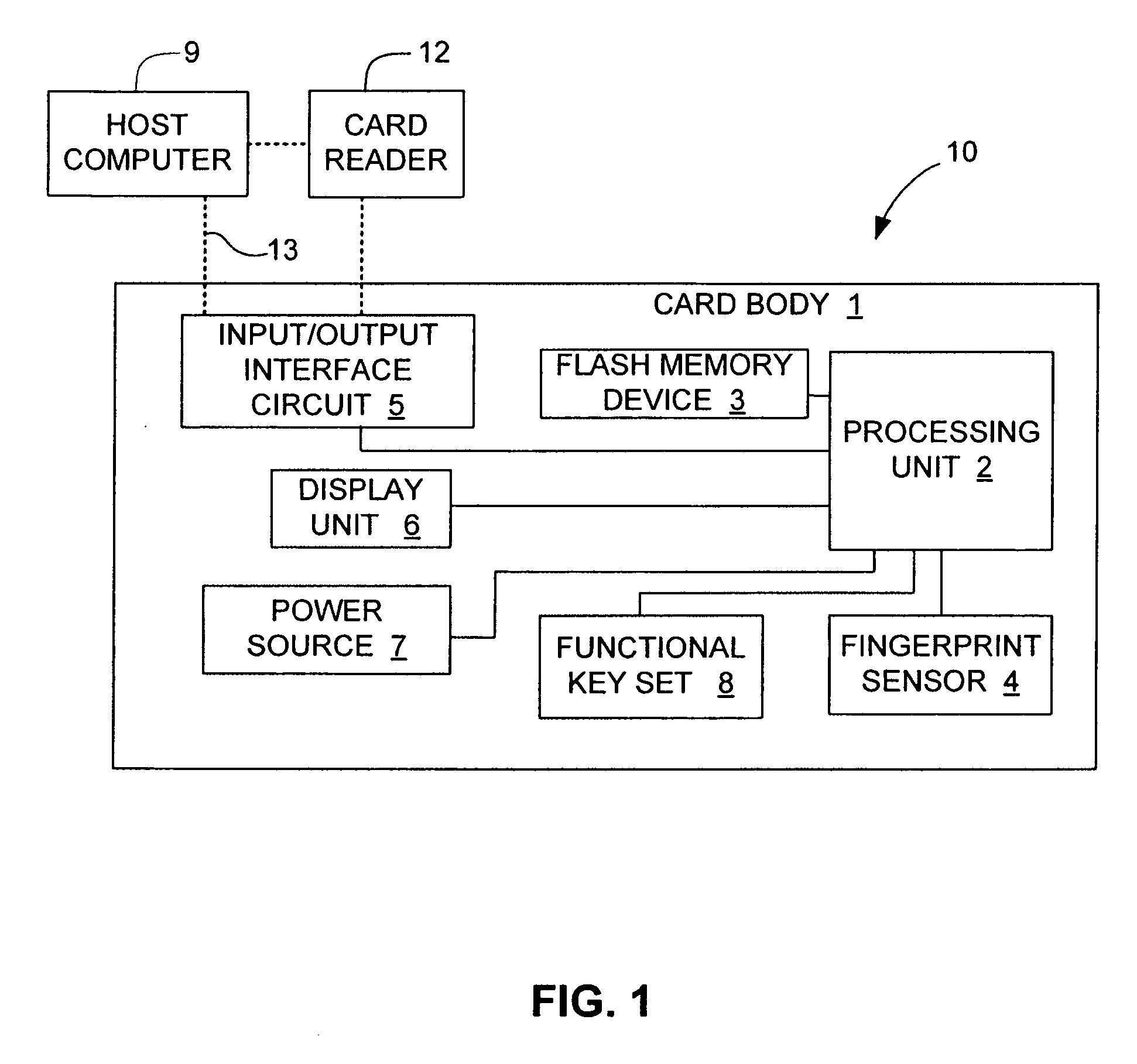

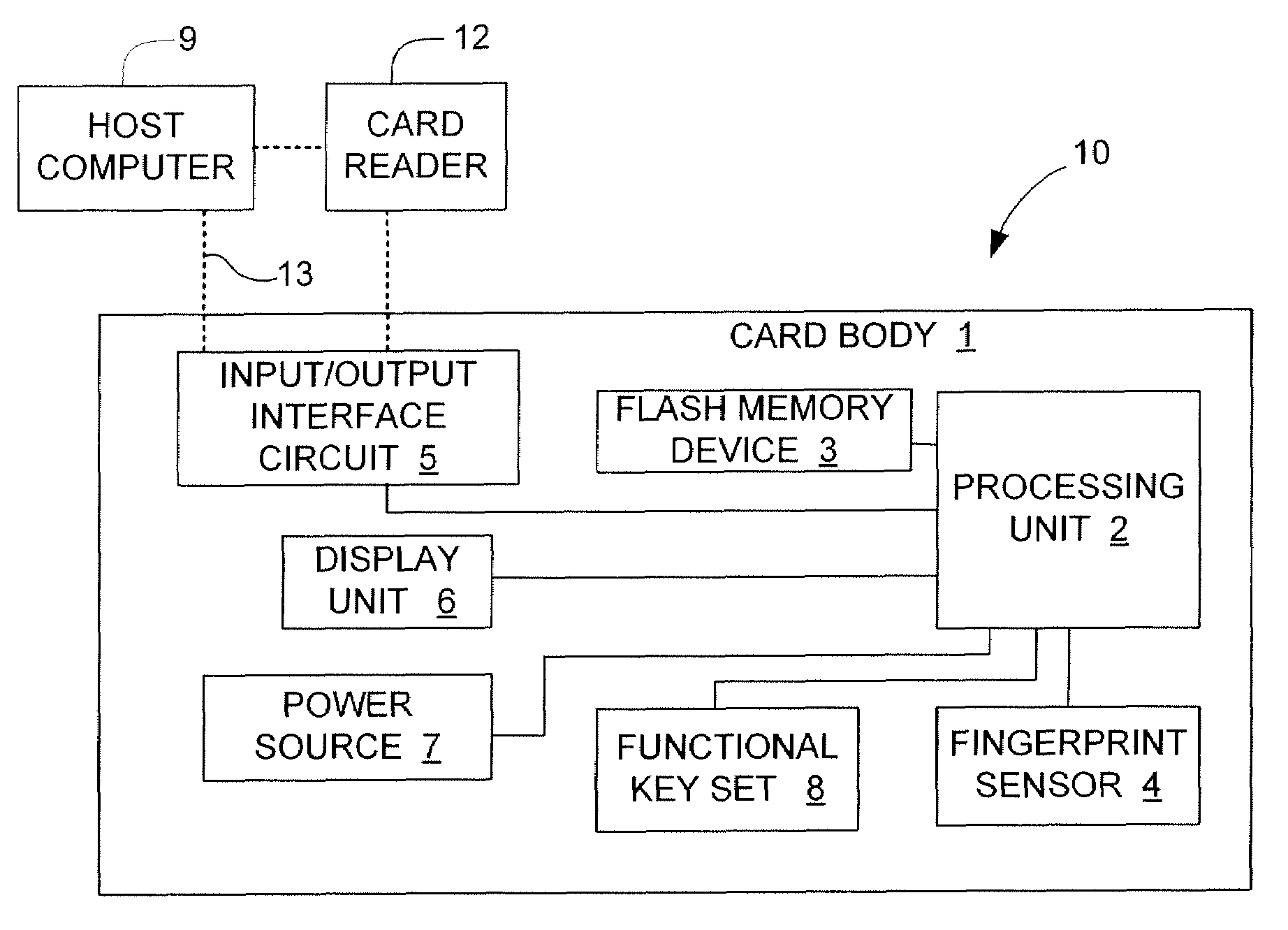

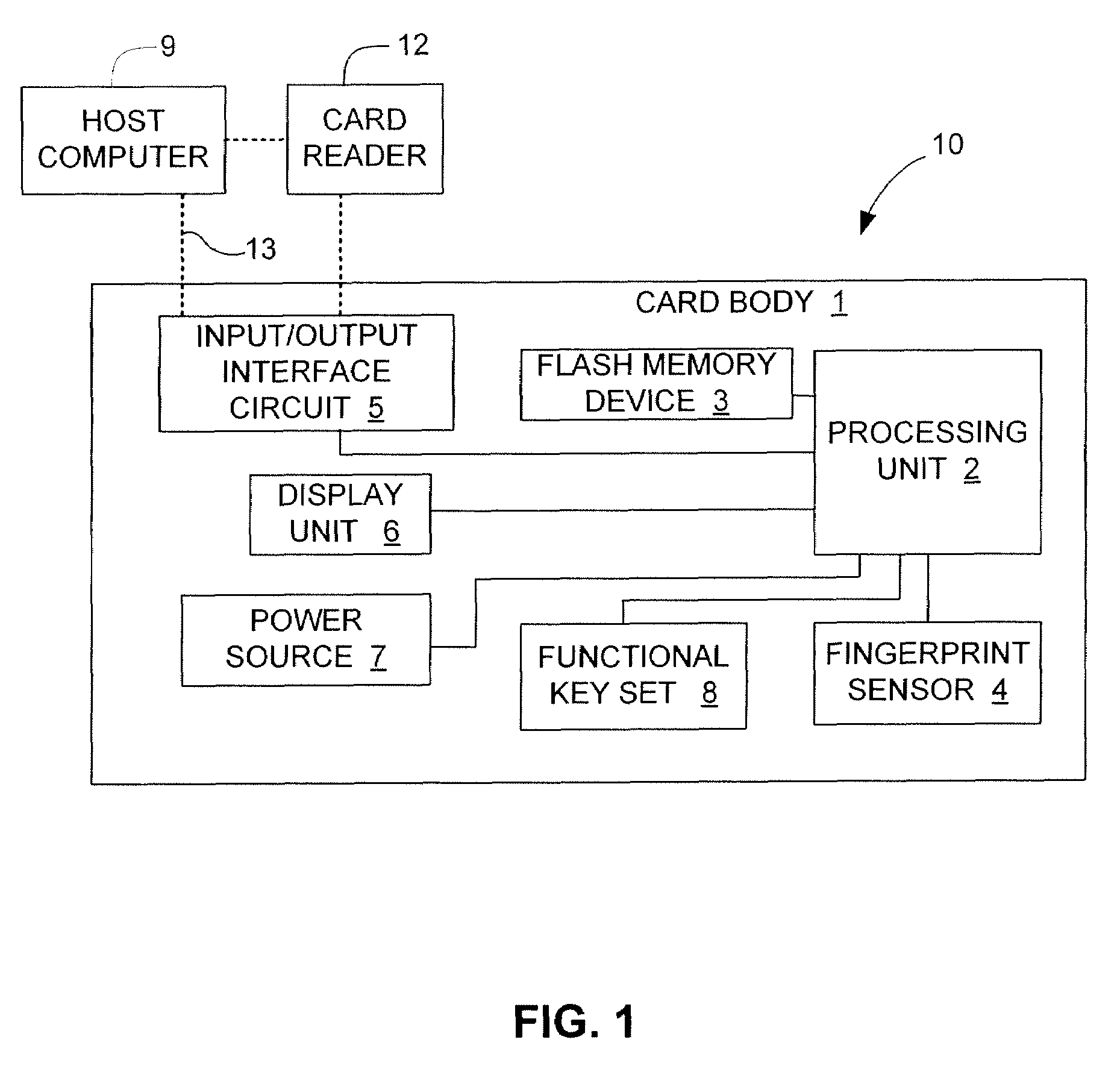

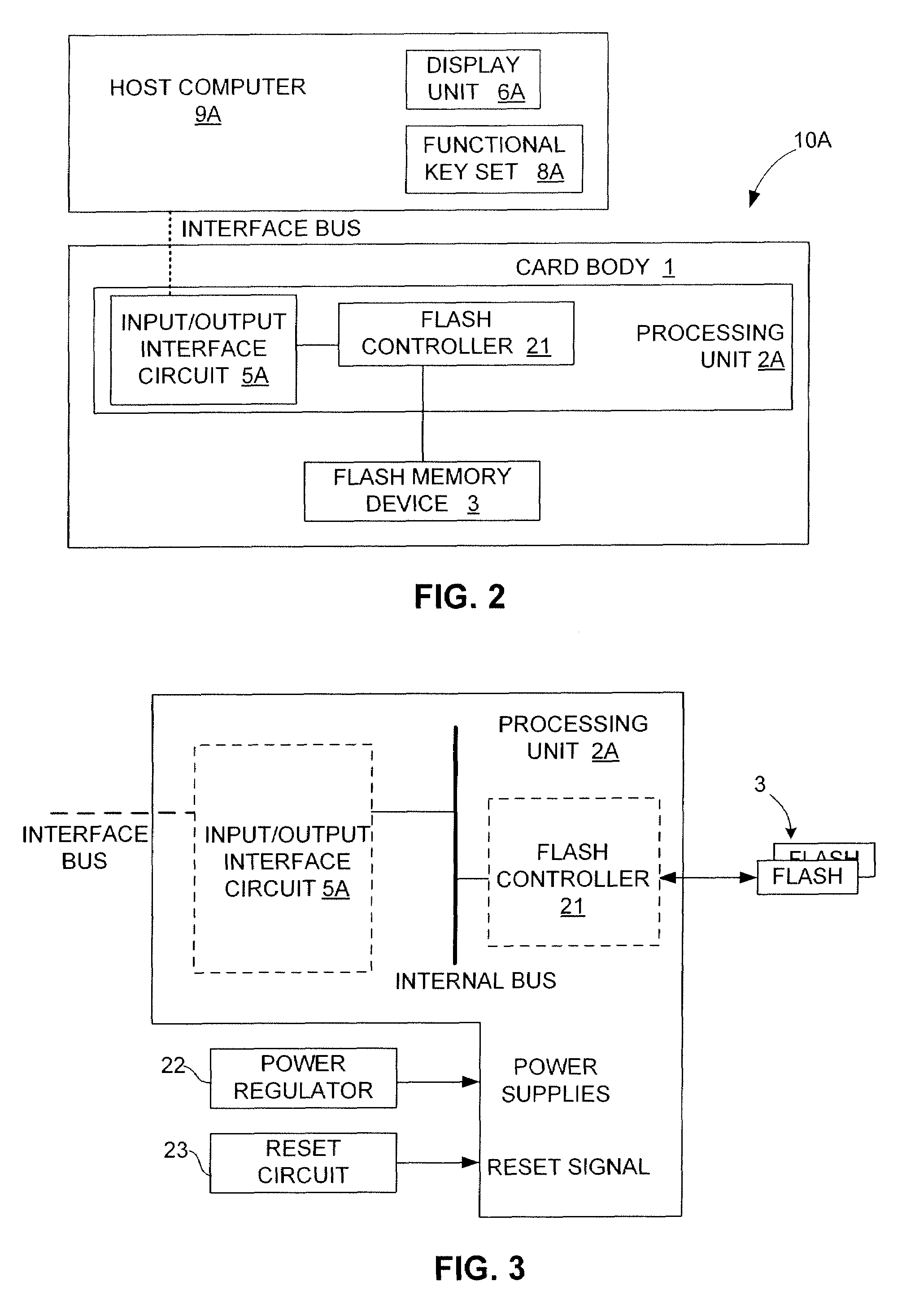

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

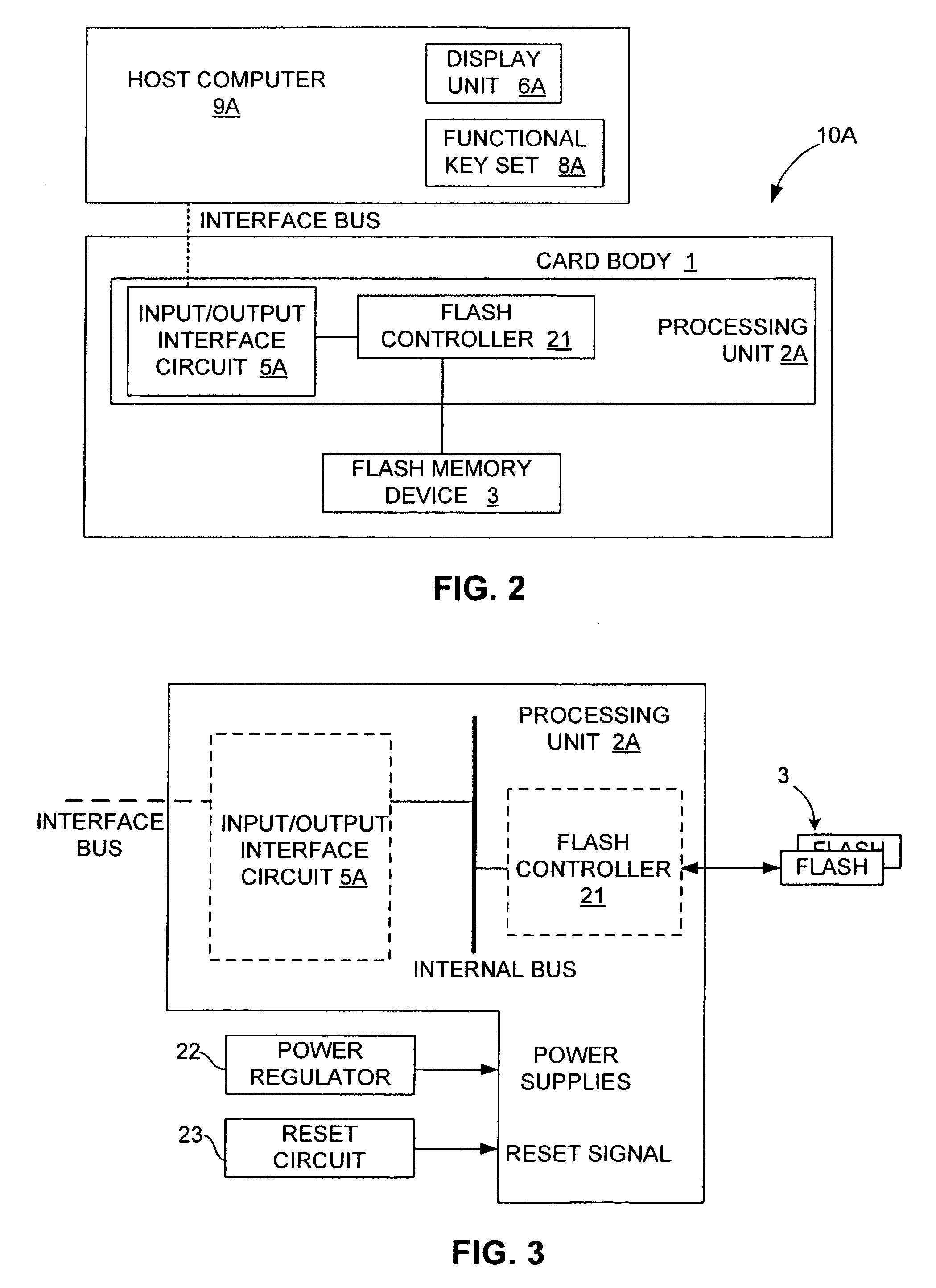

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

Cyclic flash memory wear leveling

InactiveUS7441067B2Speed up the processShorten the counting processMemory architecture accessing/allocationRead-only memoriesNon-volatile memoryWear leveling

Owner:SANDISK TECH LLC

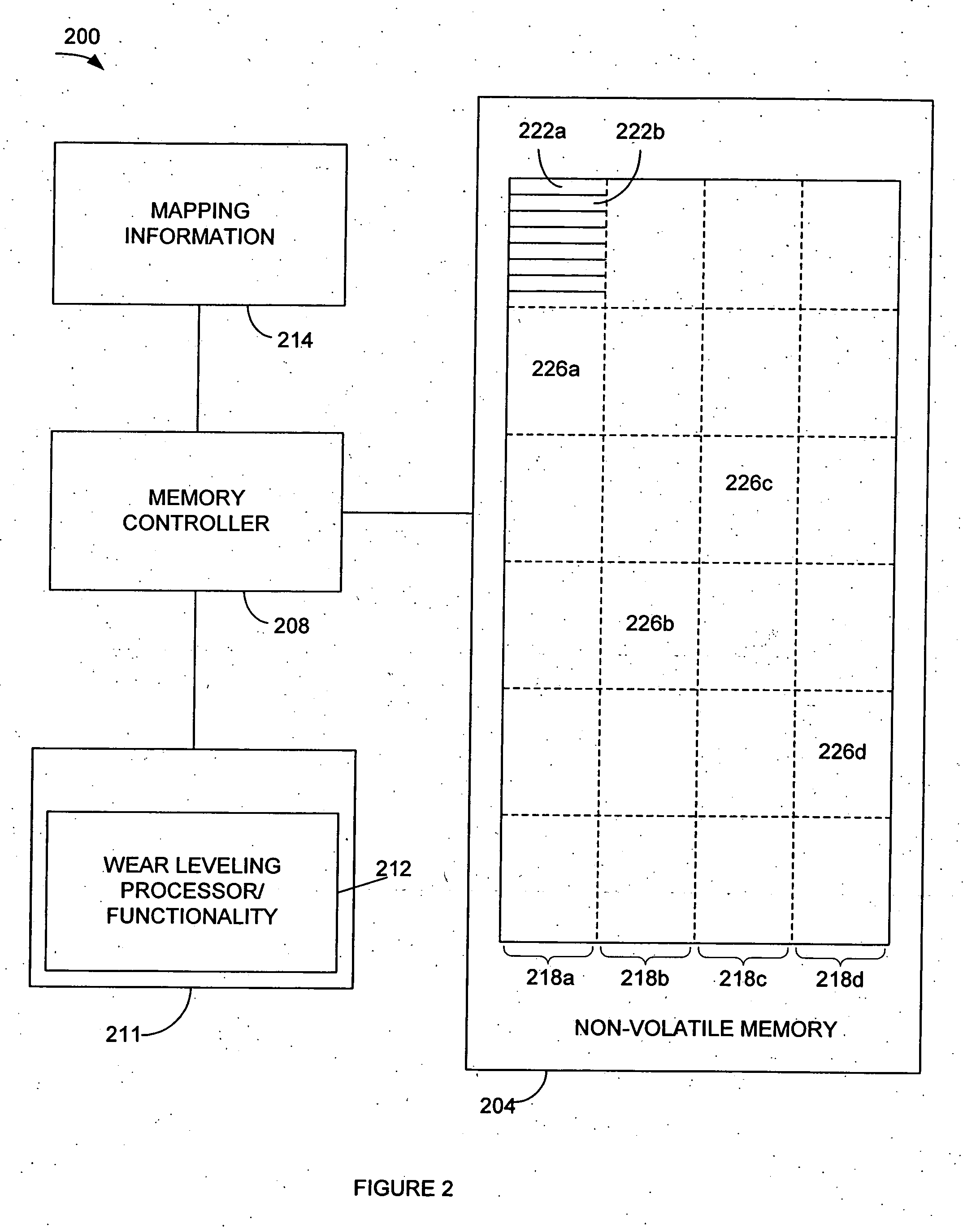

Automated wear leveling in non-volatile storage systems

ActiveUS20040083335A1Precise positioningMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingNon-volatile memory

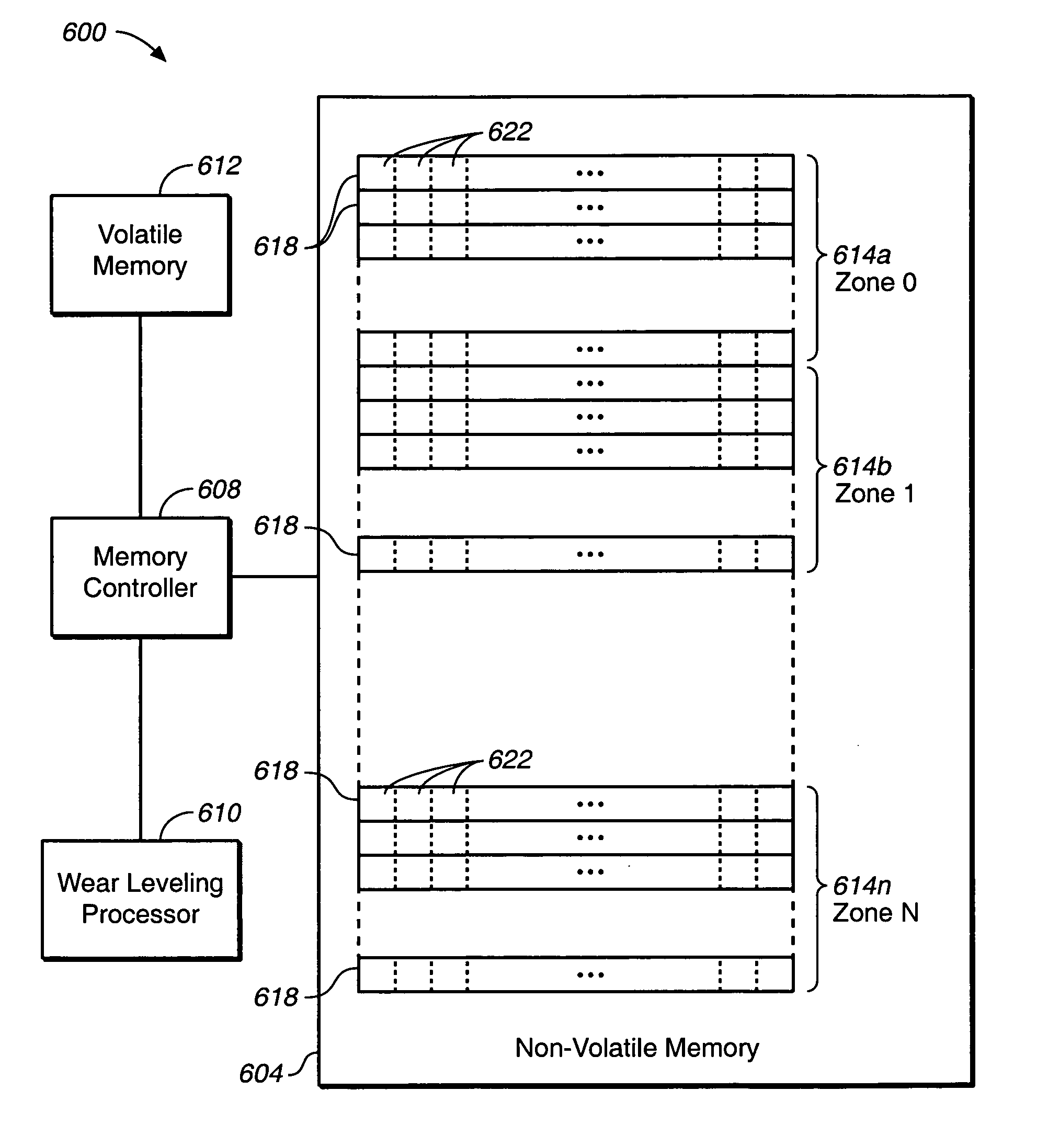

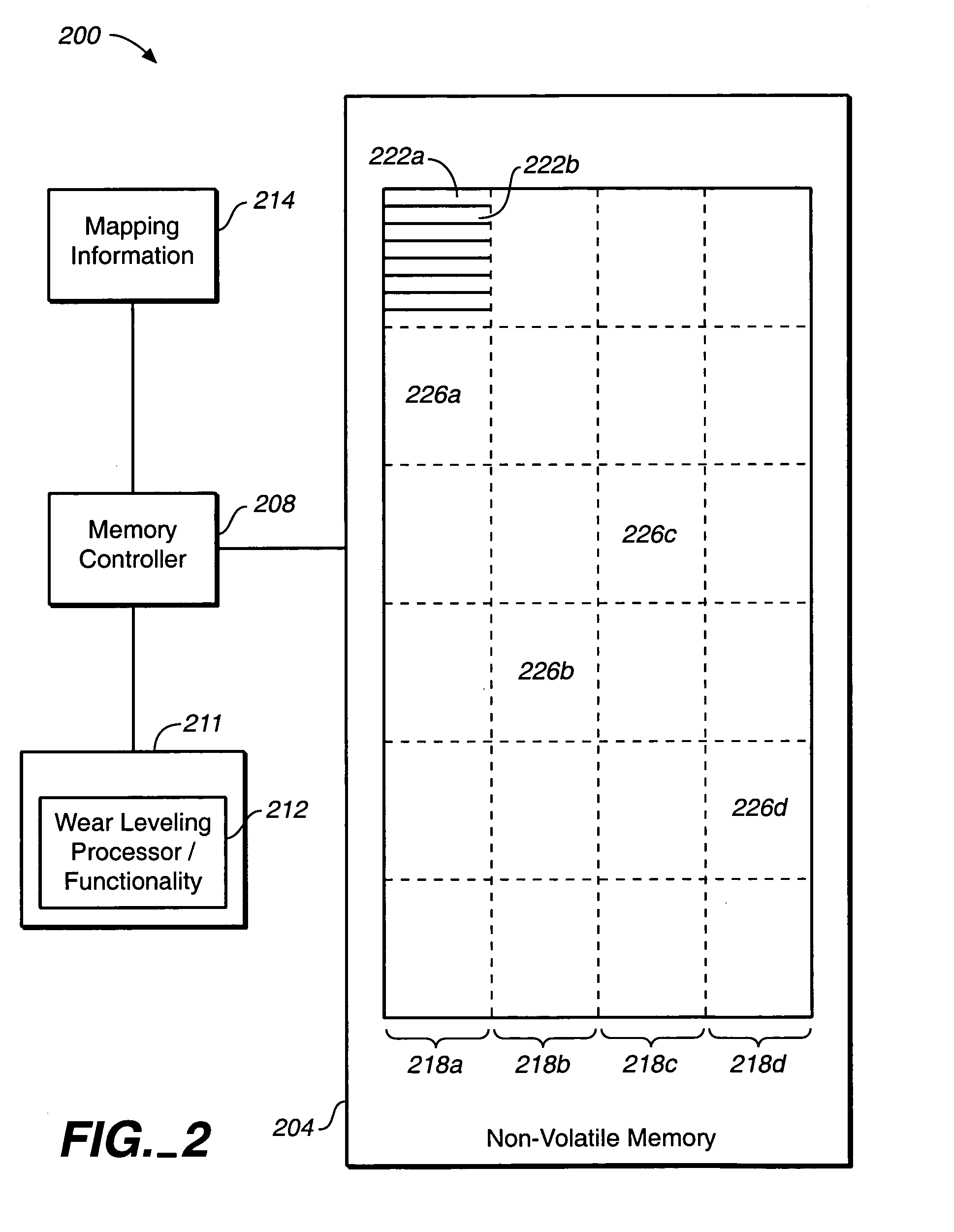

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. Included is a method for performing wear leveling in a memory system that includes a first zone, which has a first memory element that includes contents, and a second zone includes identifying the first memory element and associating the contents of the first memory element with the second zone while disassociating the contents of the first memory element from the first zone. In one embodiment, associating the contents of the first memory element with the second involves moving contents of a second memory element into a third memory element, then copying the contents of the first memory element into the second memory element.

Owner:SANDISK TECH LLC

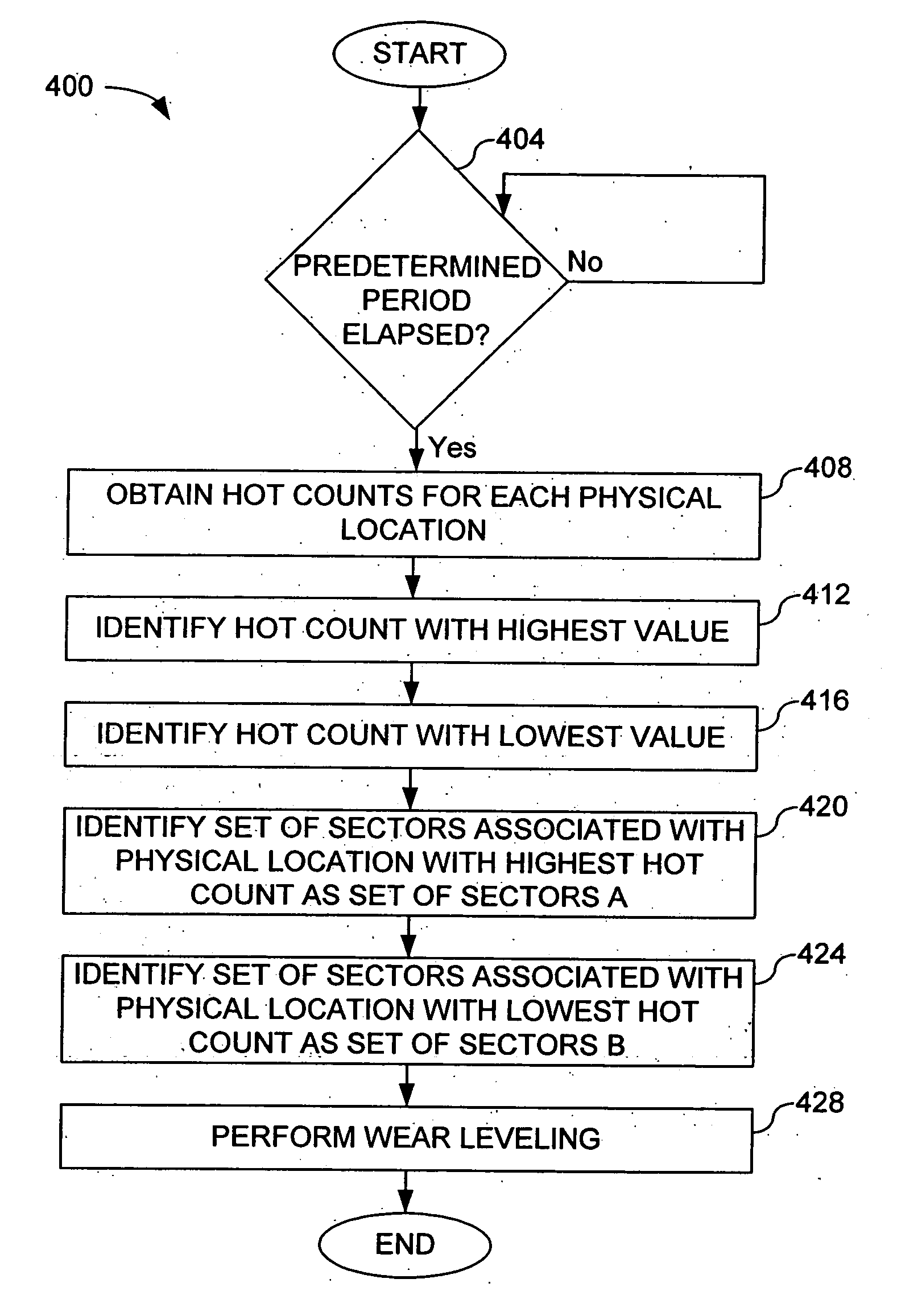

Wear Leveling for Non-Volatile Memories: Maintenance of Experience Count and Passive Techniques

InactiveUS20100174845A1Shorten the counting processMemory architecture accessing/allocationMemory adressing/allocation/relocationData managementCounting sort

Wear leveling techniques for re-programmable non-volatile memory systems, such as a flash EEPROM system, are described. One set of techniques uses “passive” arrangements, where, when a blocks are selected for writing, blocks with relatively low experience count are selected. This can be done by ordering the list of available free blocks based on experience count, with the “coldest” blocks placed at the front of the list, or by searching the free blocks to find a block that is “cold enough”. In another, complementary set of techniques, usable for more standard wear leveling operations as well as for “passive” techniques and other applications where the experience count is needed, the experience count of a block or meta-block is maintained as a block's attribute along its address in the data management structures, such as address tables.

Owner:SANDISK TECH LLC

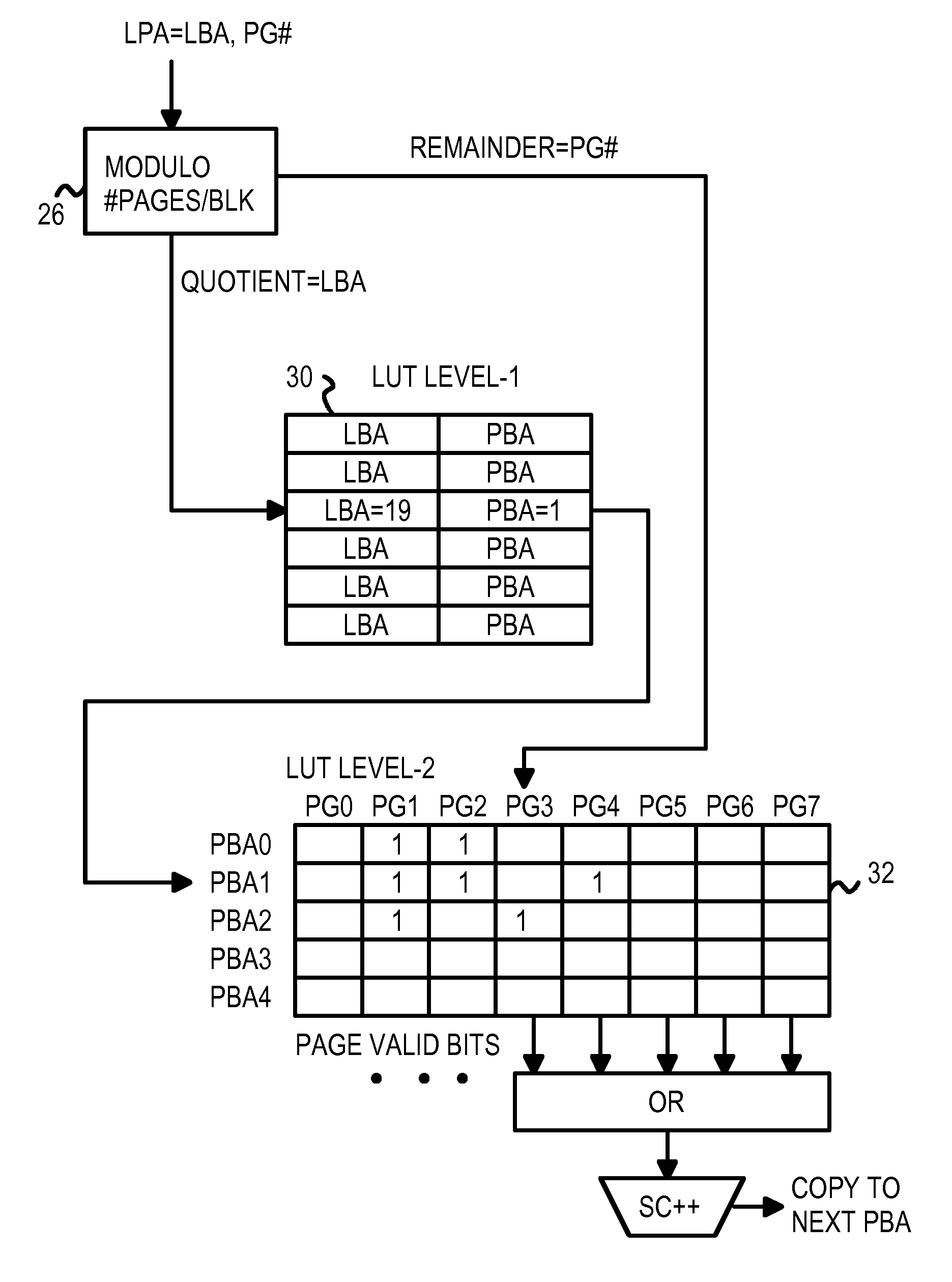

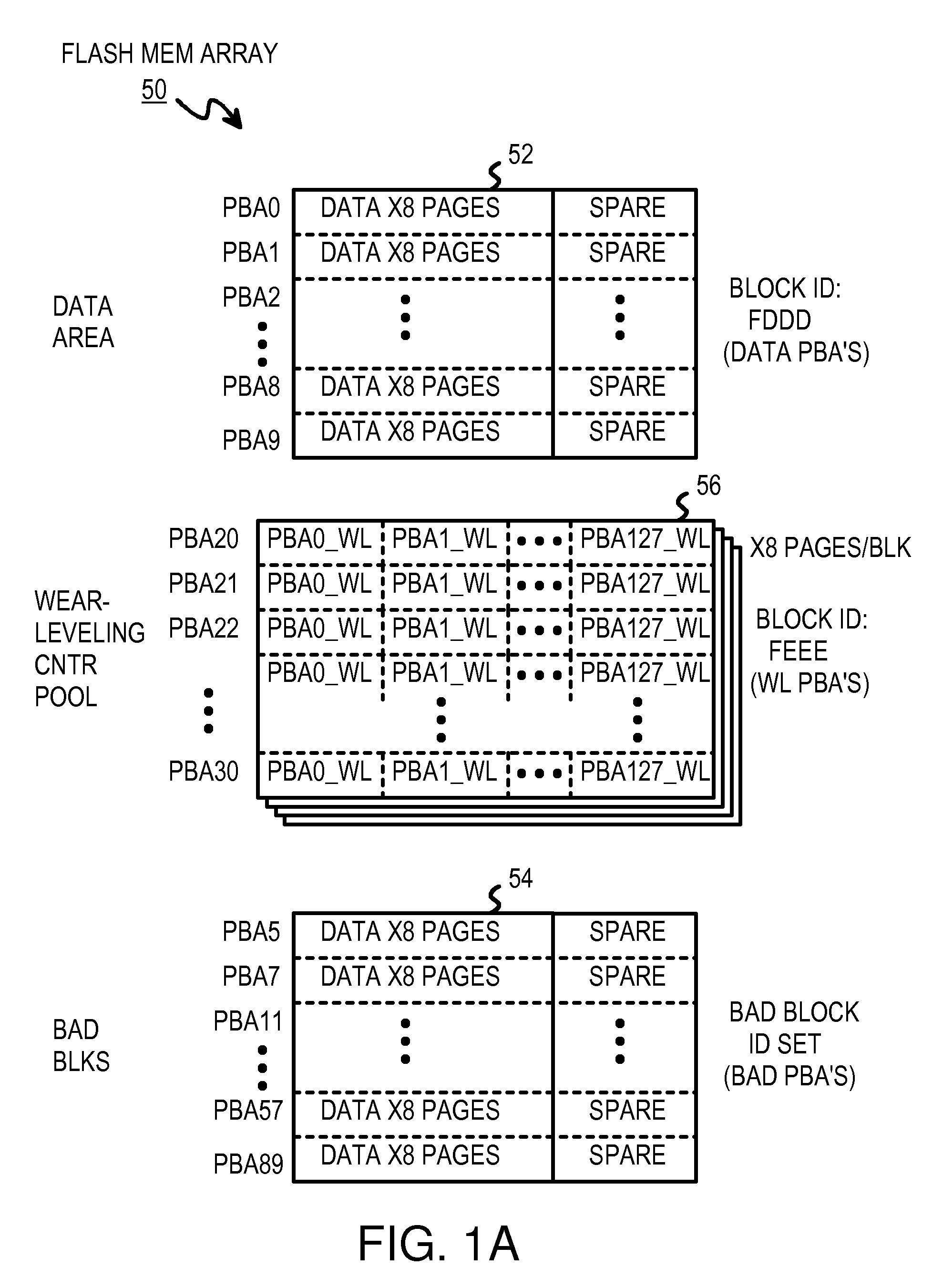

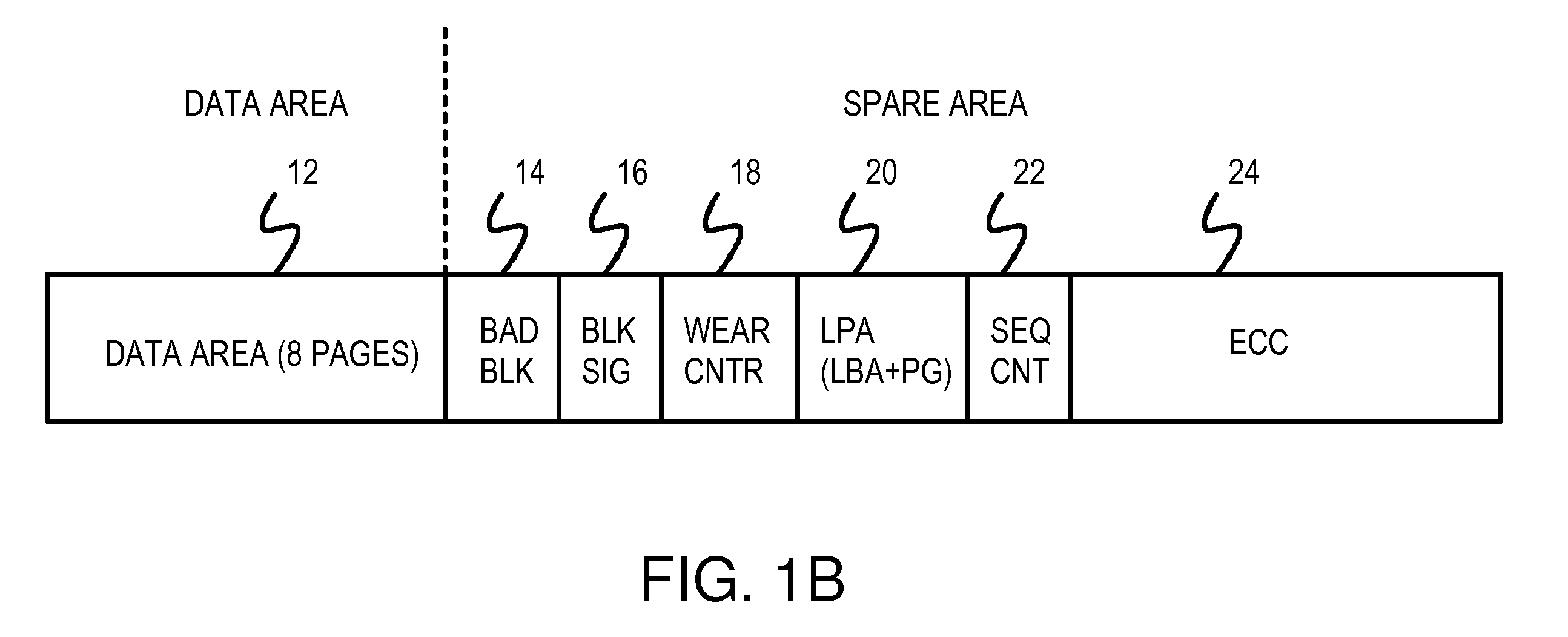

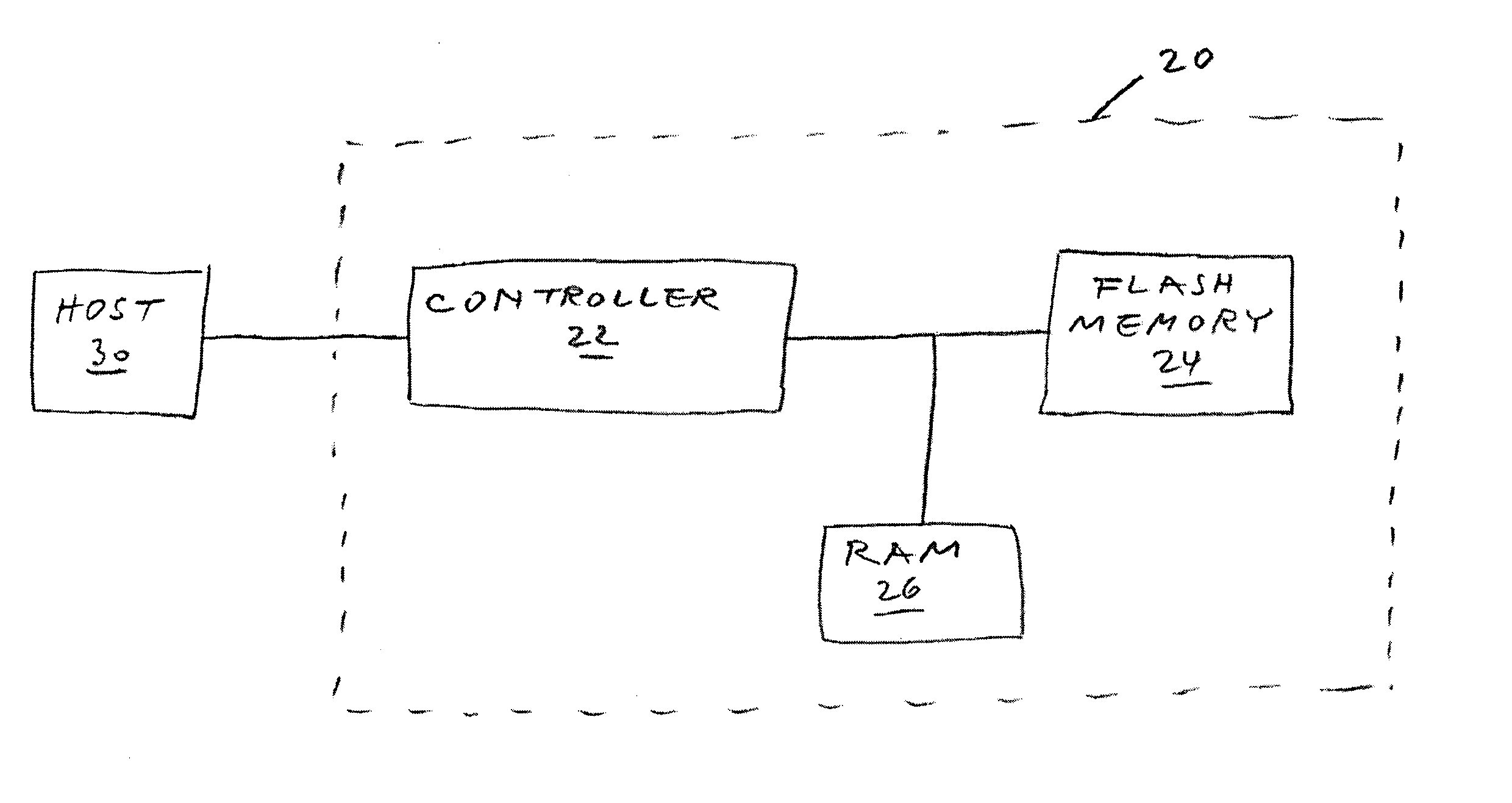

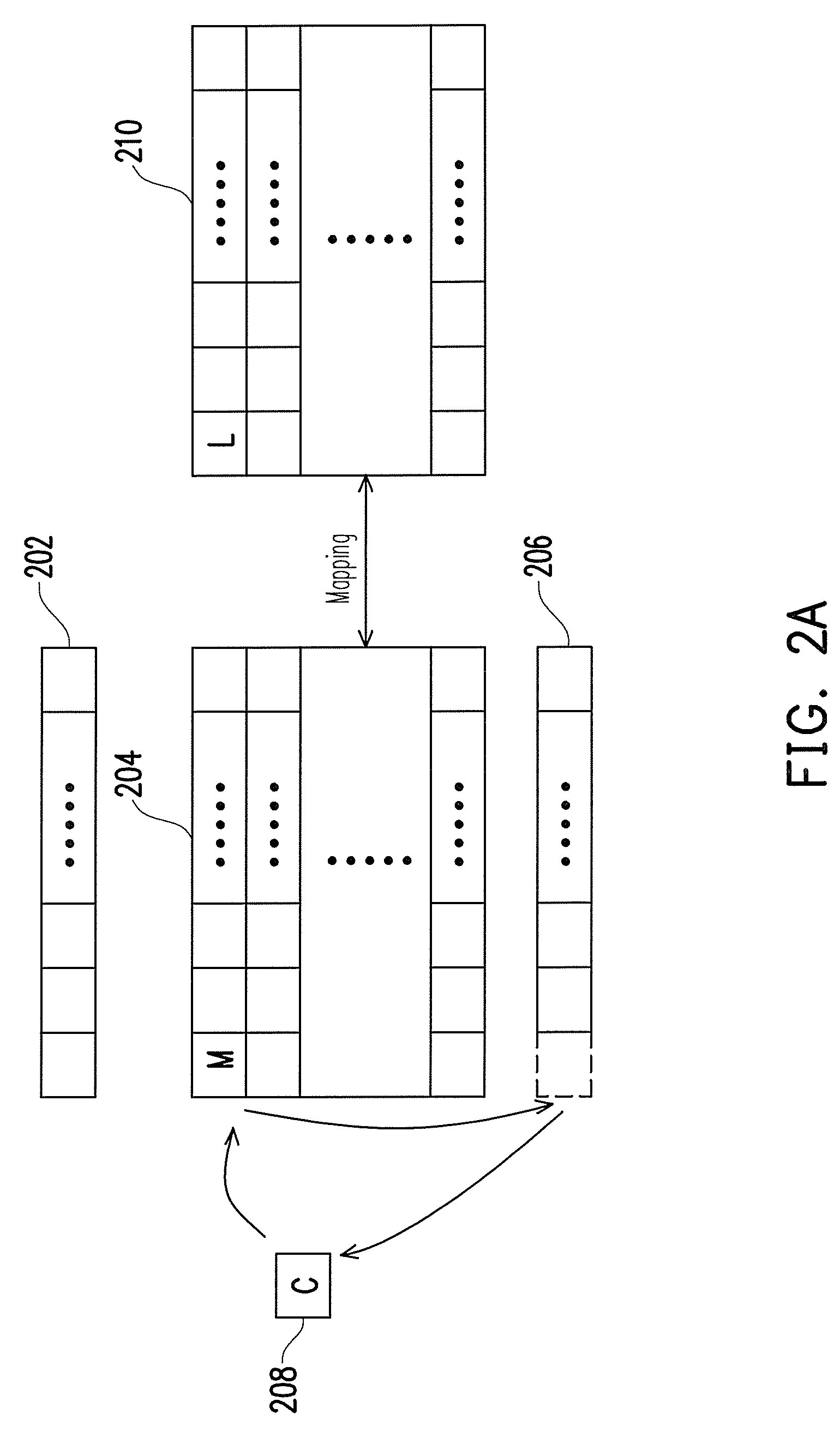

Two-Level RAM Lookup Table for Block and Page Allocation and Wear-Leveling in Limited-Write Flash-Memories

InactiveUS20070204128A1Memory architecture accessing/allocationRead-only memoriesRandom access memoryLogical block addressing

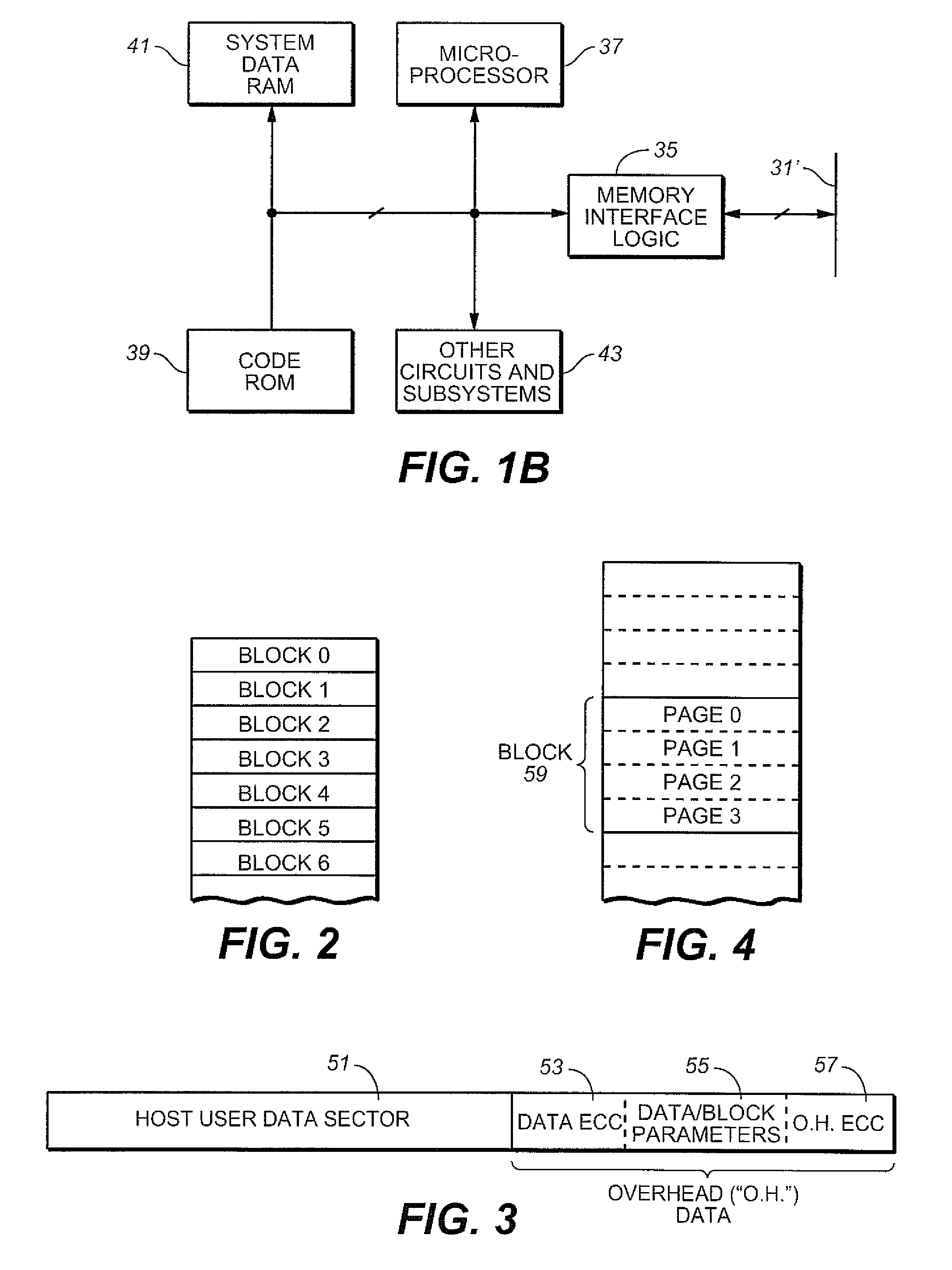

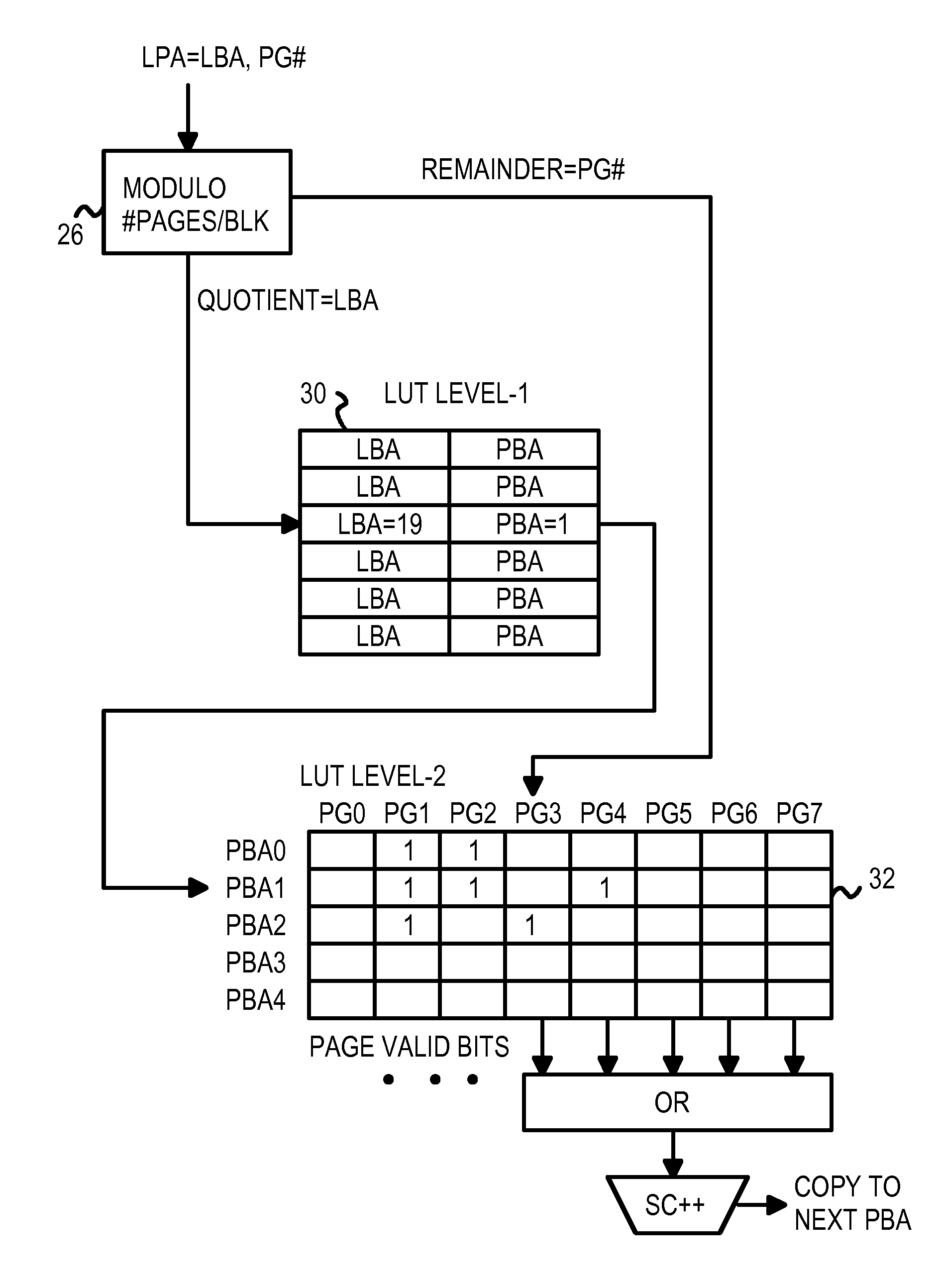

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

Cyclic flash memory wear leveling

InactiveUS20060106972A1Enhance wear leveling processShorten the counting processMemory architecture accessing/allocationRead-only memoriesStorage cellNon-volatile memory

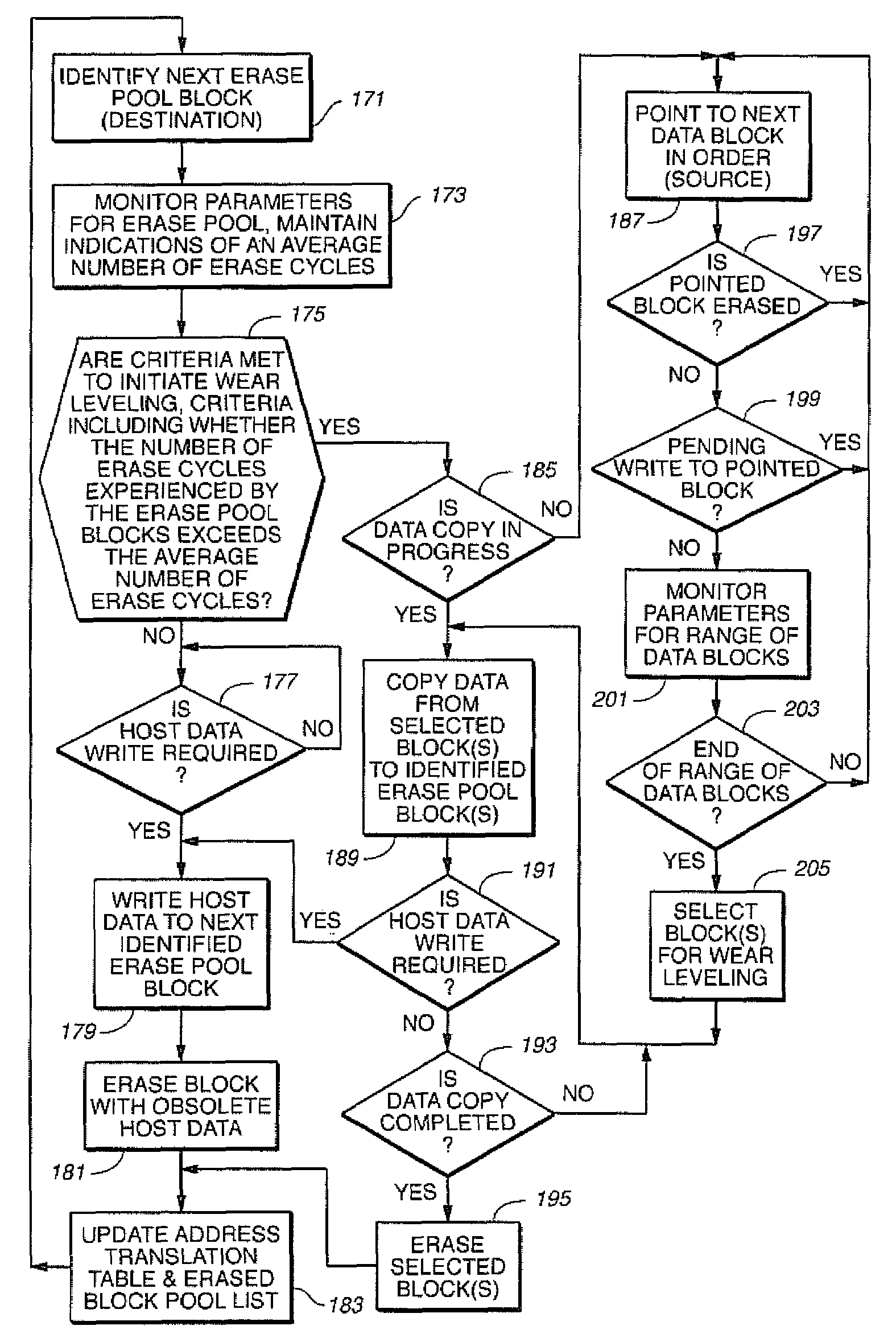

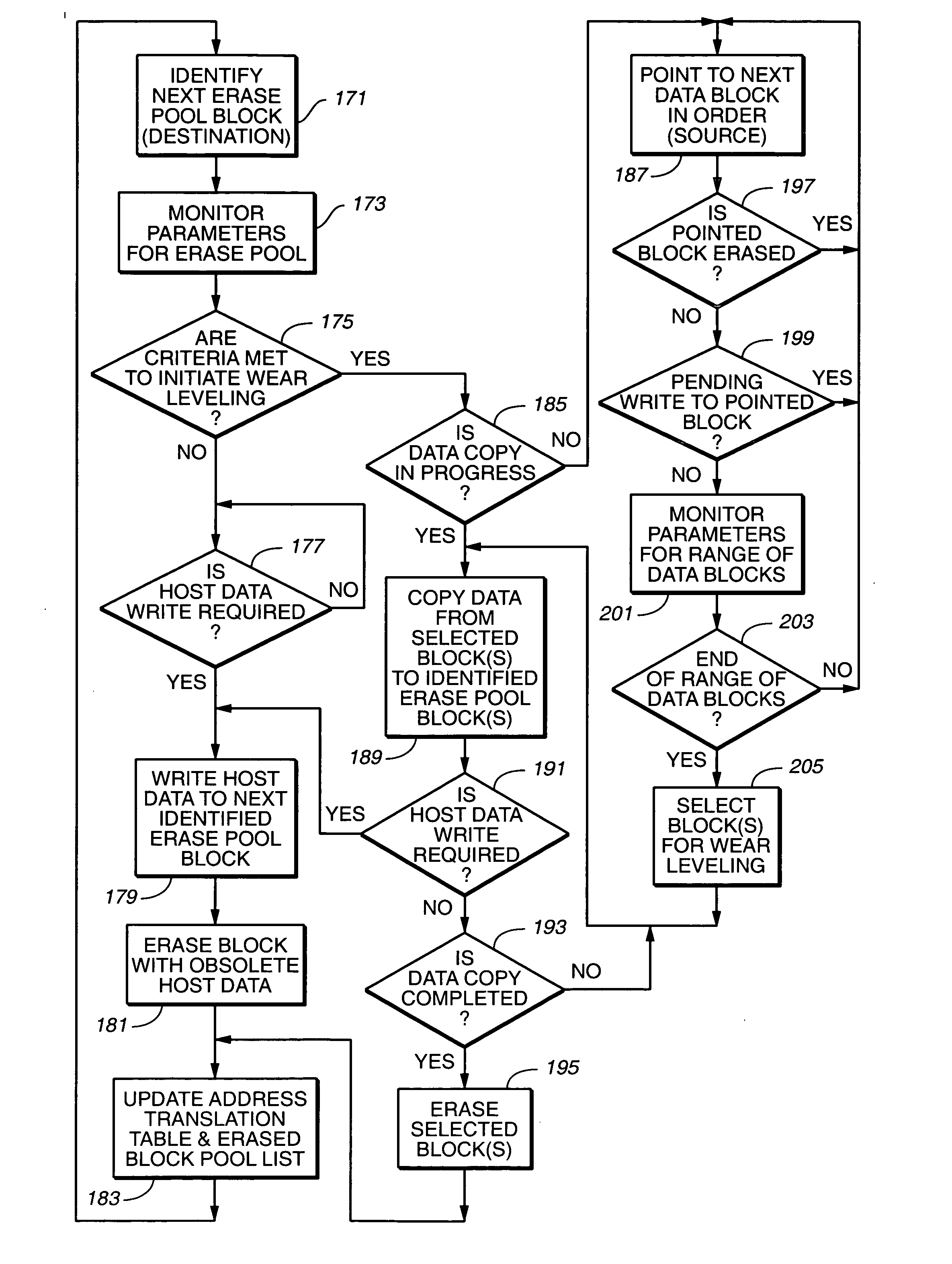

A re-programmable non-volatile memory system, such as a flash EEPROM system, having its memory cells grouped into blocks of cells that are simultaneously erasable is operated in a manner to level out the wear of the individual blocks through repetitive erasing and re-programming. This may be accomplished without use of counts of the number of times the individual blocks experience erase and re-programming but such counts can optionally aid in carrying out the wear leveling process. Individual active physical blocks are chosen to be exchanged with those of an erased block pool in a predefined order.

Owner:SANDISK TECH LLC

Automated wear leveling in non-volatile storage systems

ActiveUS7120729B2Lower Level RequirementsAvoid uneven wearMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingMemory systems

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. Included is a method for performing wear leveling in a memory system that includes a first zone, which has a first memory element that includes contents, and a second zone includes identifying the first memory element and associating the contents of the first memory element with the second zone while disassociating the contents of the first memory element from the first zone. In one embodiment, associating the contents of the first memory element with the second involves moving contents of a second memory element into a third memory element, then copying the contents of the first memory element into the second memory element.

Owner:SANDISK TECH LLC

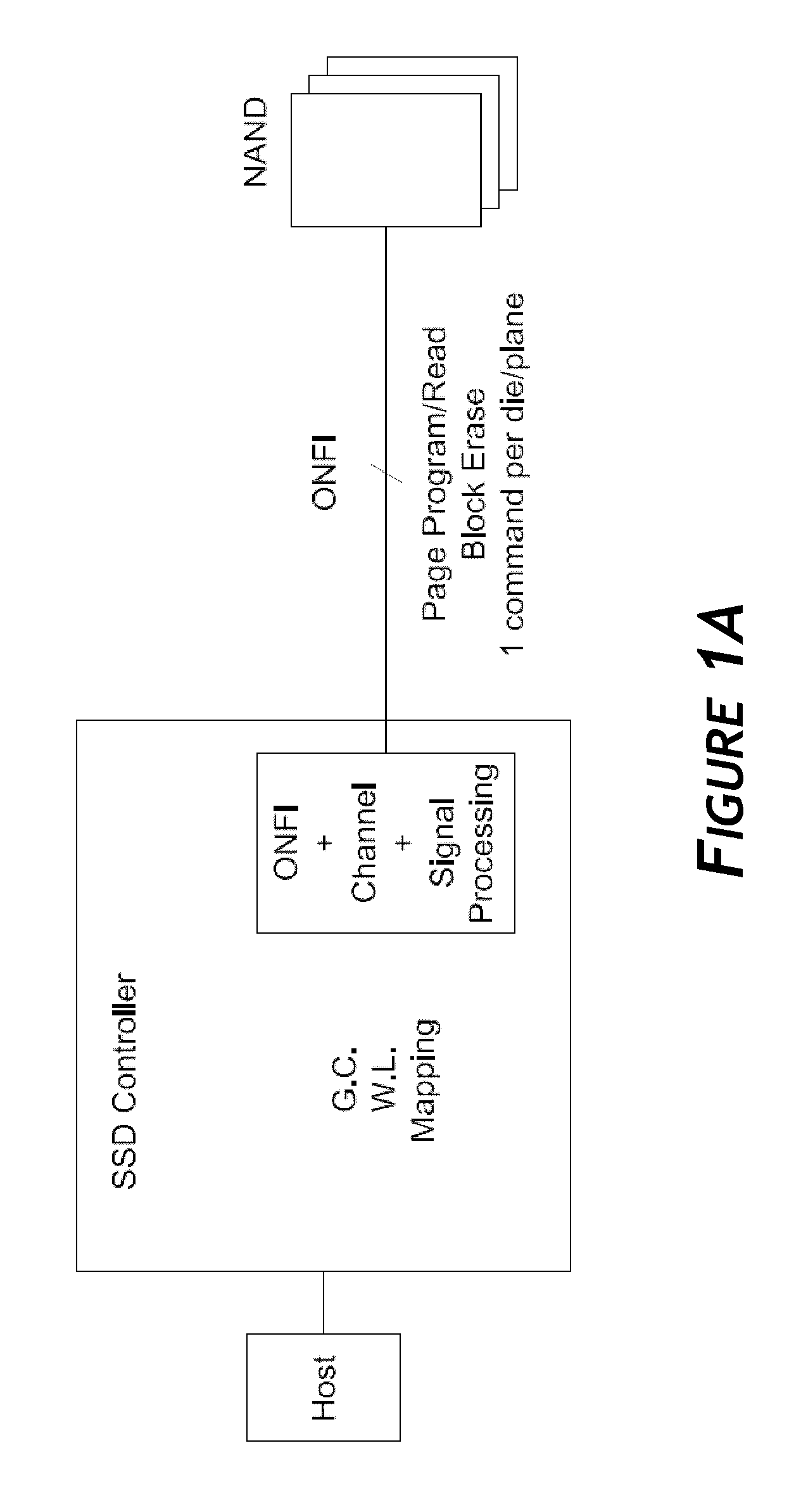

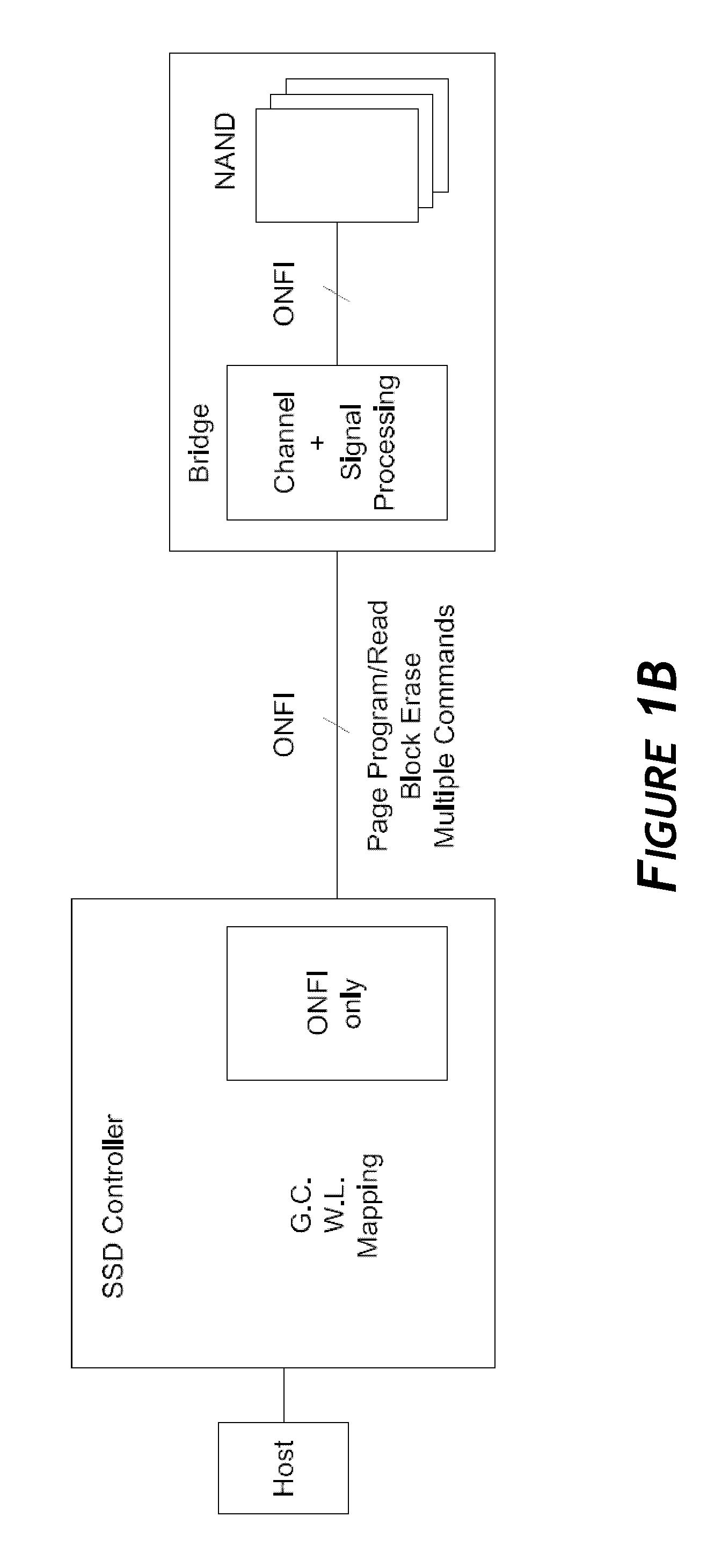

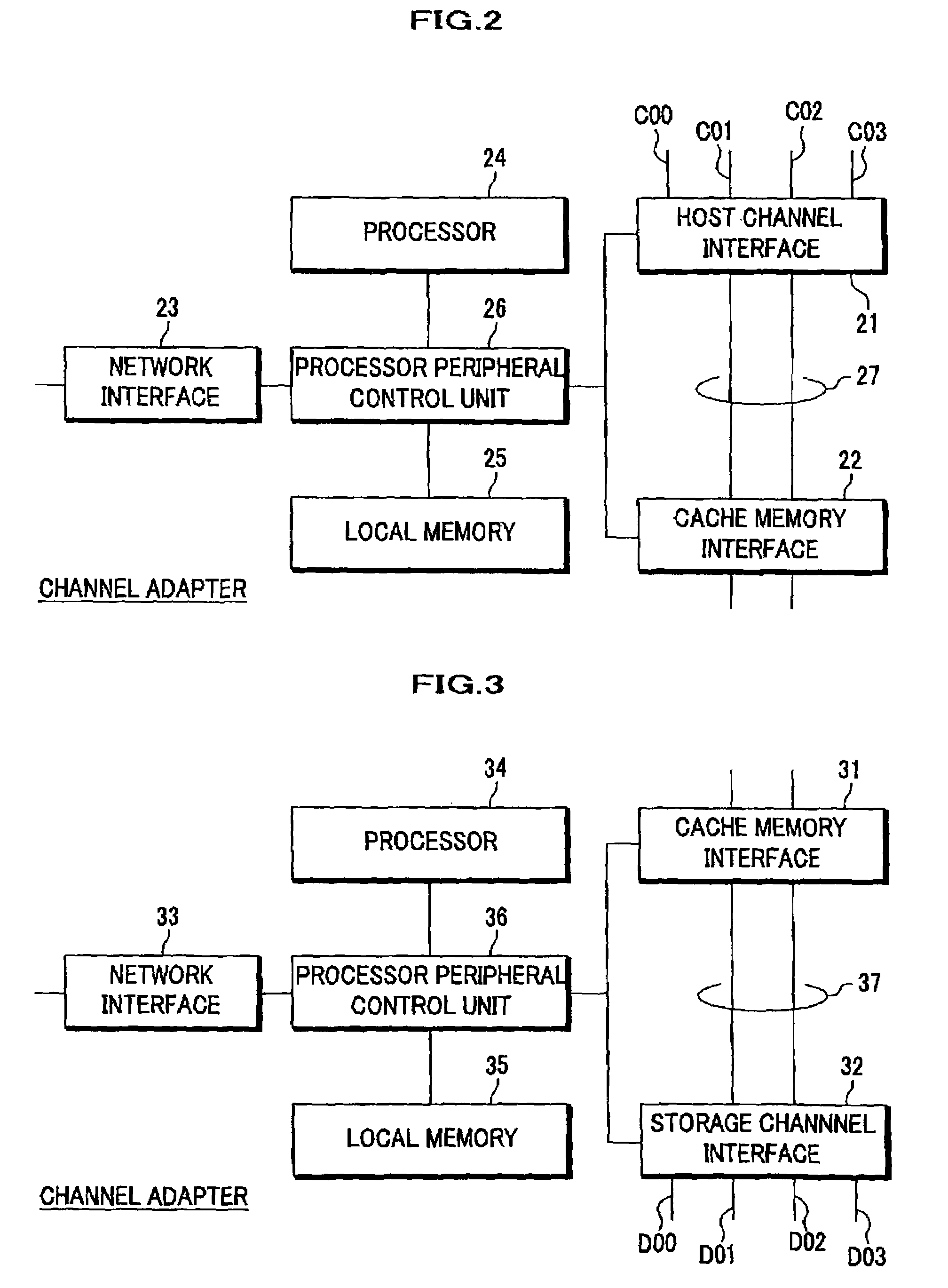

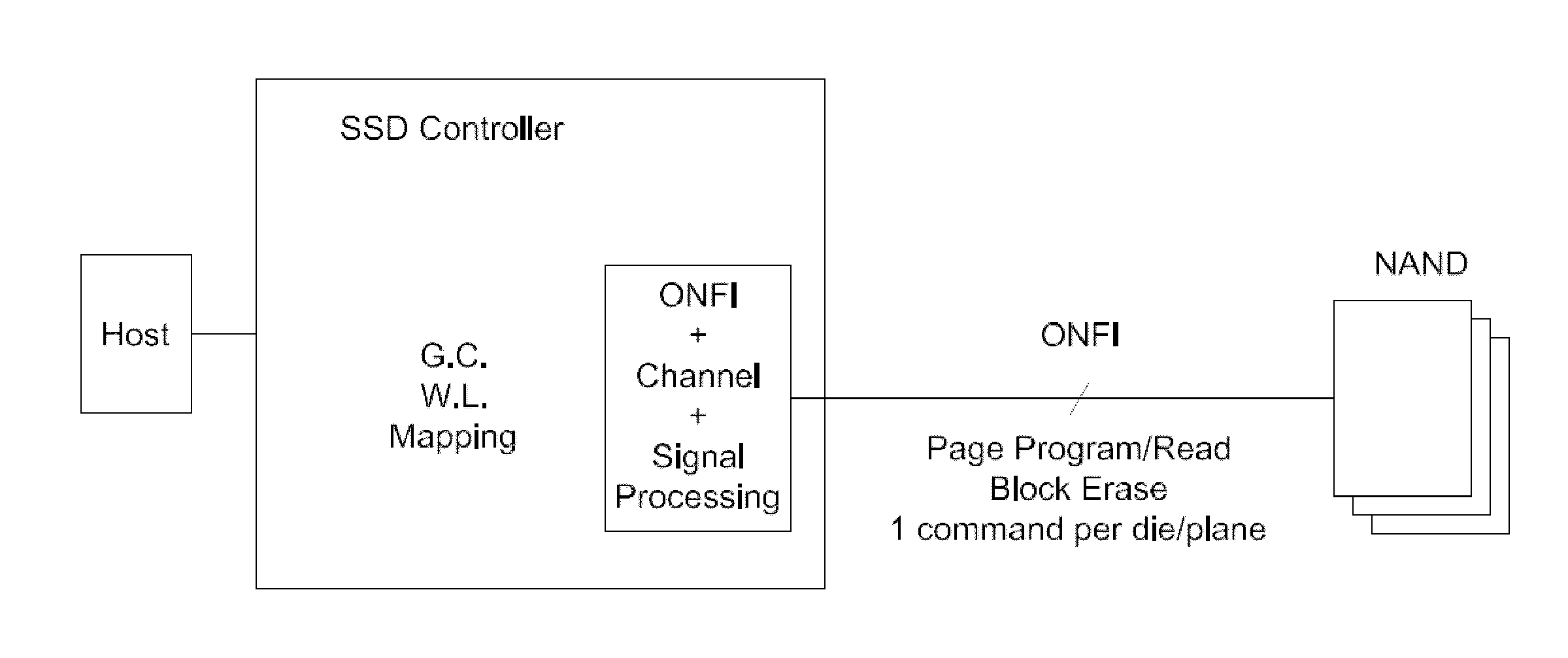

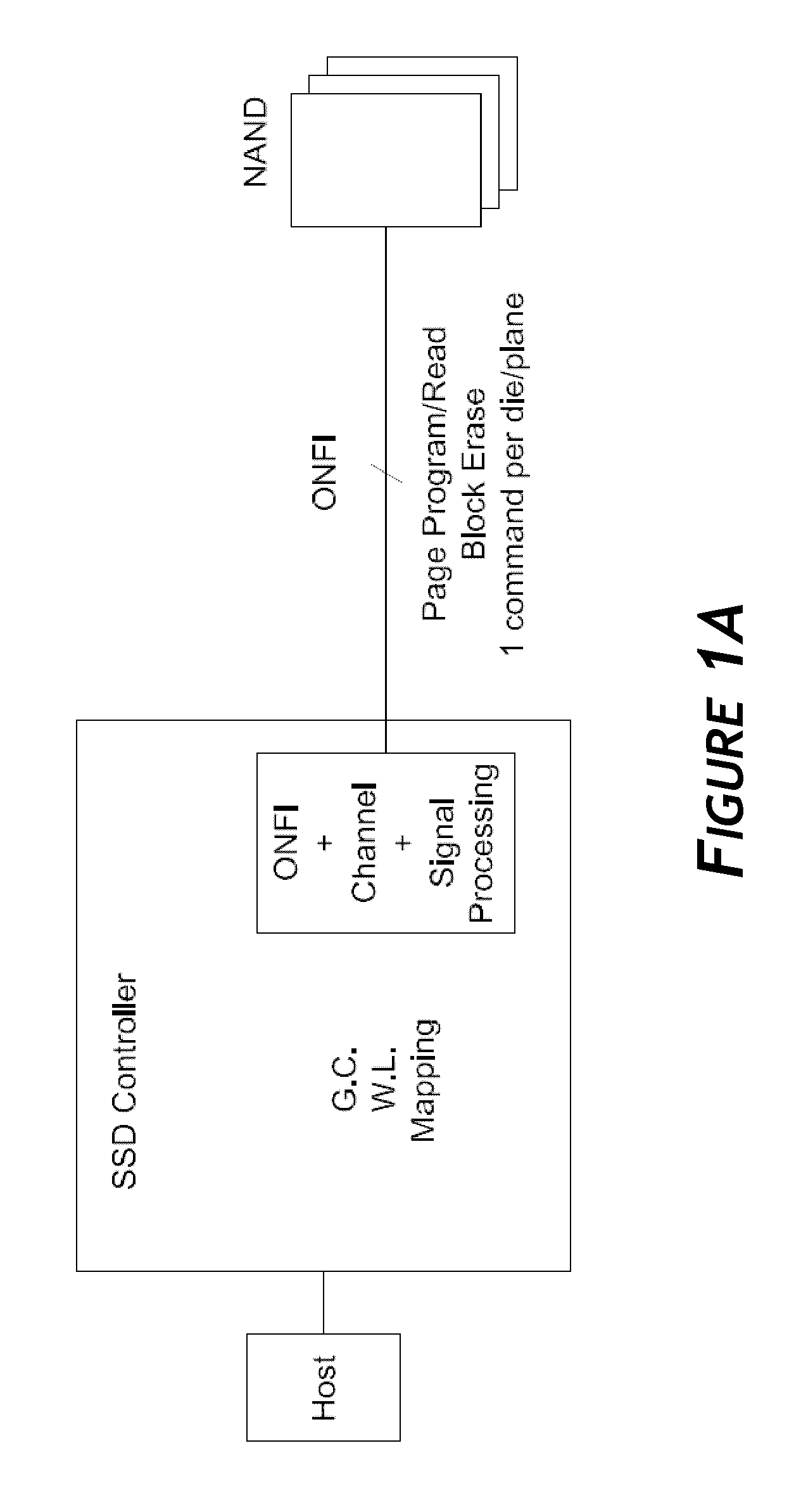

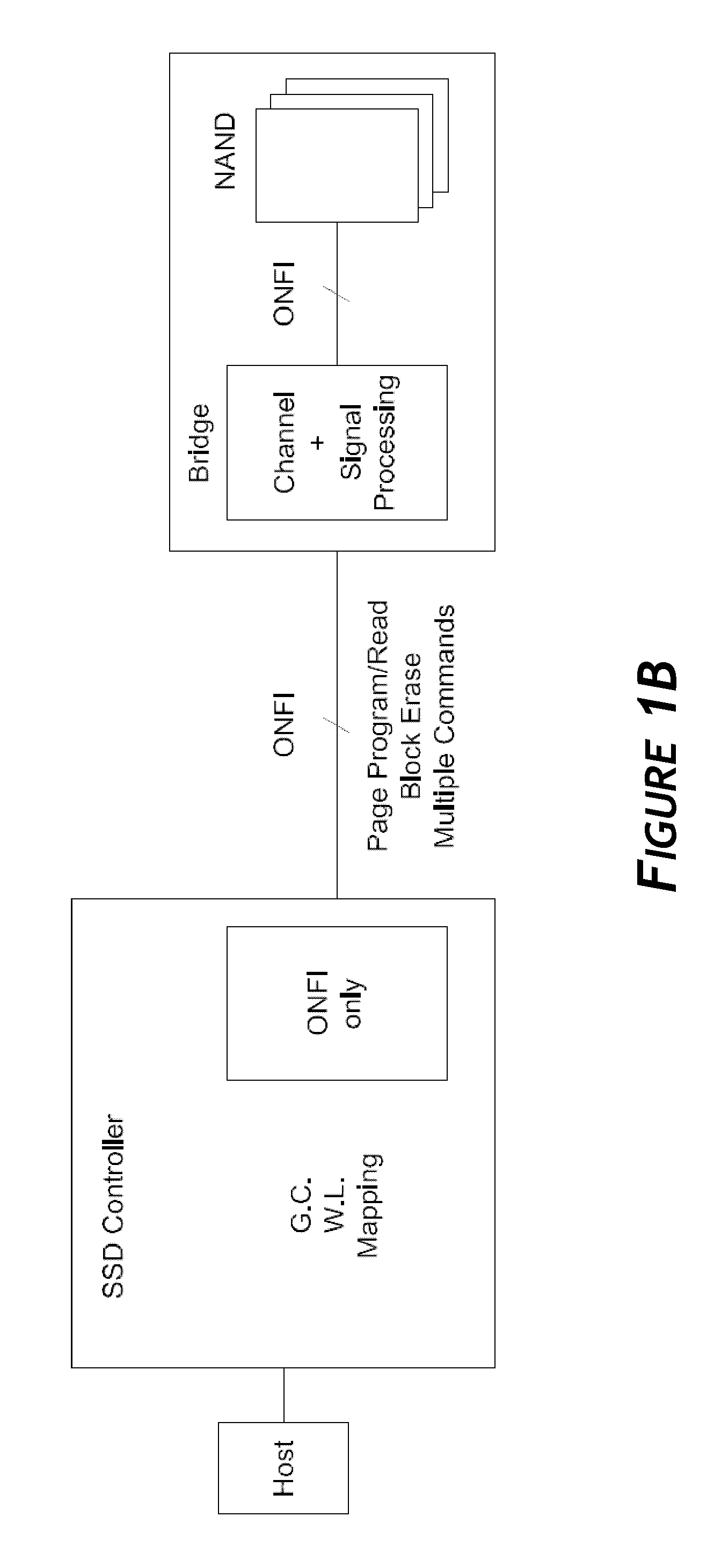

Systems and methods for an enhanced controller architecture in data storage systems

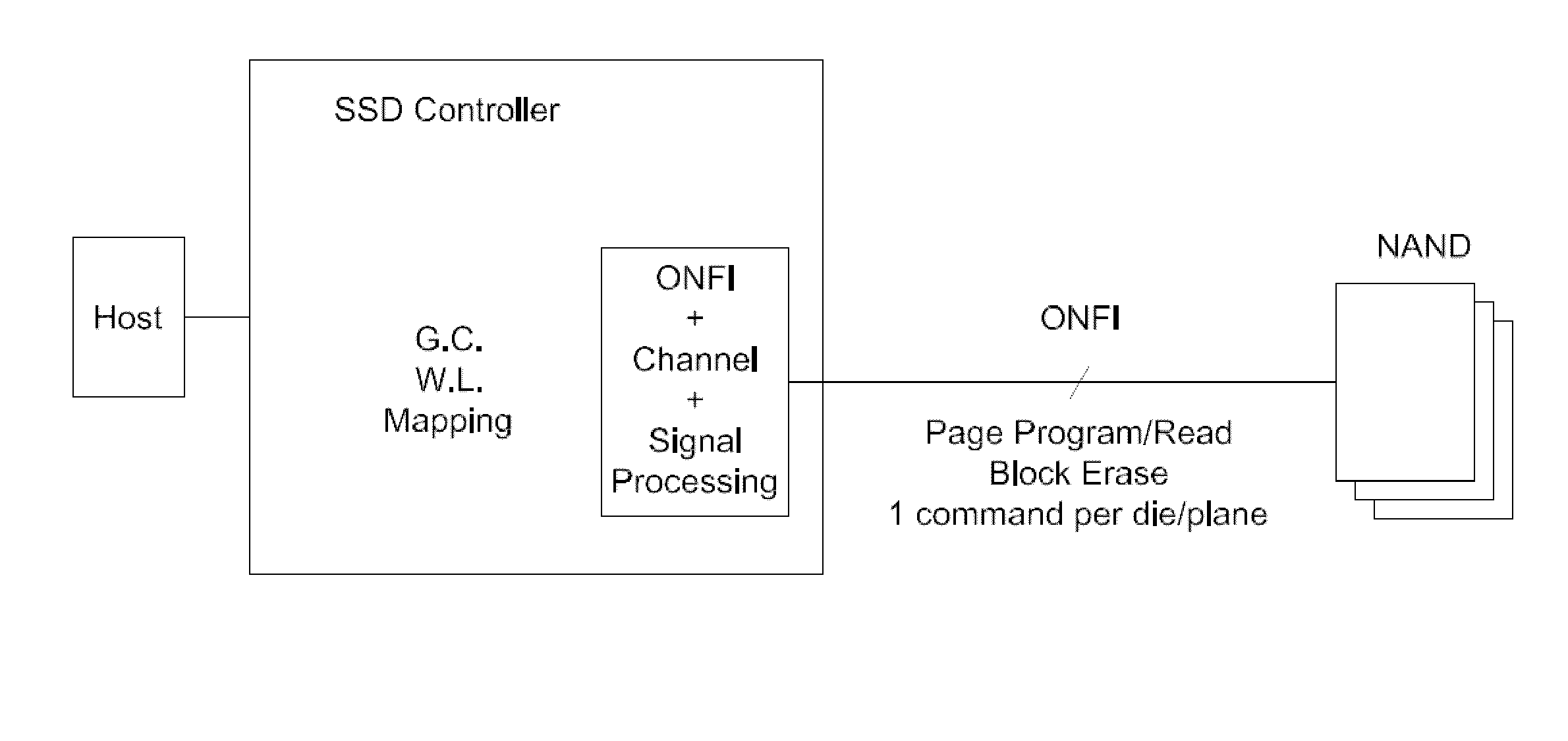

Disclosed herein is a controller architecture that pairs a controller with a NVM (non-volatile memory) storage system over a high-level, high speed interface such as PCIe. In one embodiment, the NVM storage system includes a bridge that communicates with the controller via the high-level interface, and controls the NVM via an interface (e.g., ONFI). The controller is provided a rich set of physical level of controls over individual elements of the NVM. In one embodiment, the controller is implemented in a higher powered processor that supports advanced functions such as mapping, garbage collection, wear leveling, etc. In one embodiment, the bridge is implemented in a lower powered processor and performs basic signal processing, channel management, basic error correction functions, etc. This labor division provides the controller physical control of the NVM over a fast, high-level interface, resulting in the controller managing the NVM at both the page and block level.

Owner:WESTERN DIGITAL TECH INC

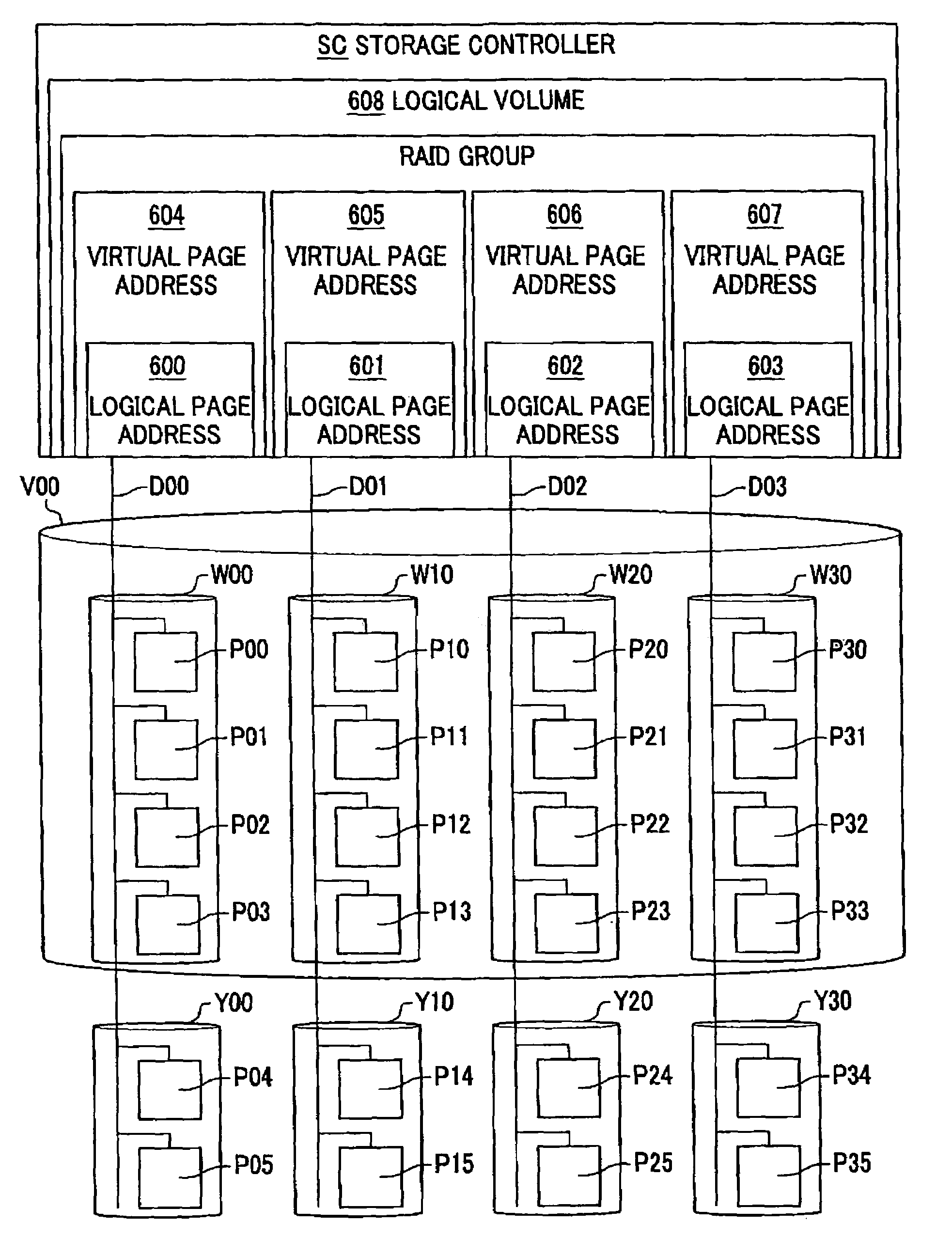

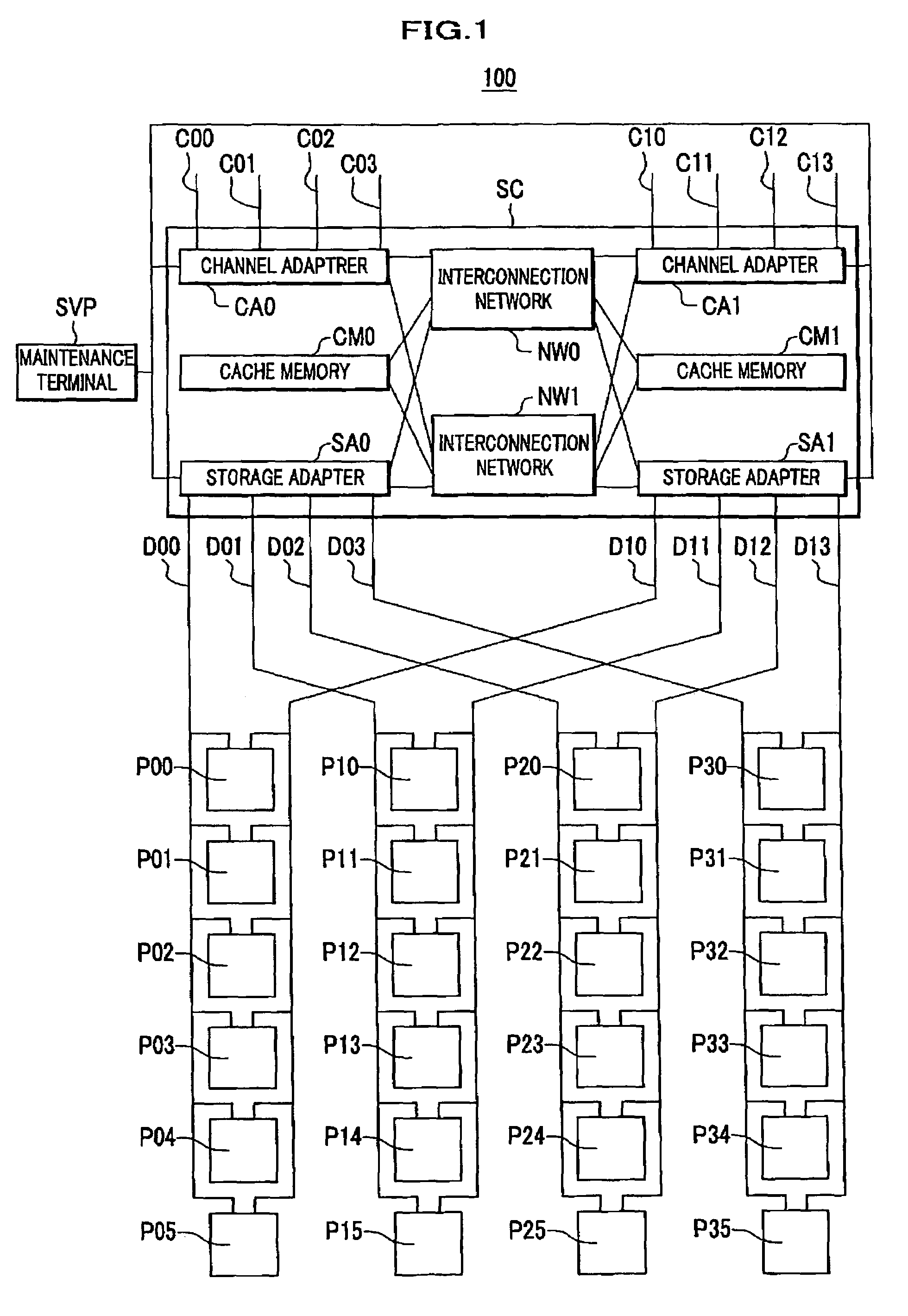

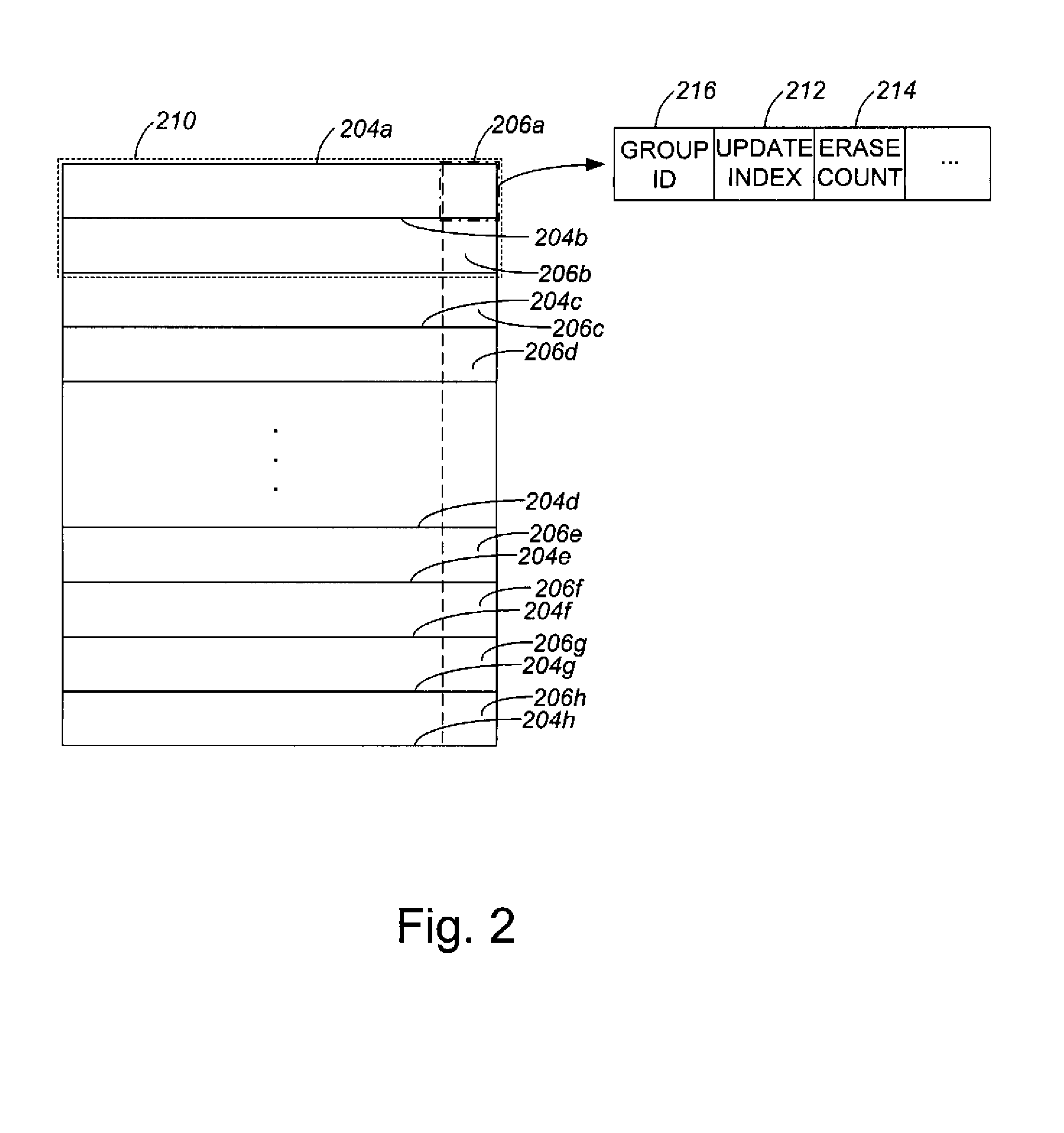

Storage system using flash memory modules logically grouped for wear-leveling and RAID

A storage system using flash memories includes a storage controller and plural flash memory modules as storage media. Each flash memory module includes at least one flash memory chip and a memory controller for leveling erase counts of blocks belonging to the flash memory chip. The storage controller combines the plural flash memory modules into a first logical group, translates a first address used for accessing the flash memory modules belonging to the first logical group to a second address used for handling the first address in the storage controller, and combines the plural first logical groups into a second logical group.

Owner:HITACHI LTD

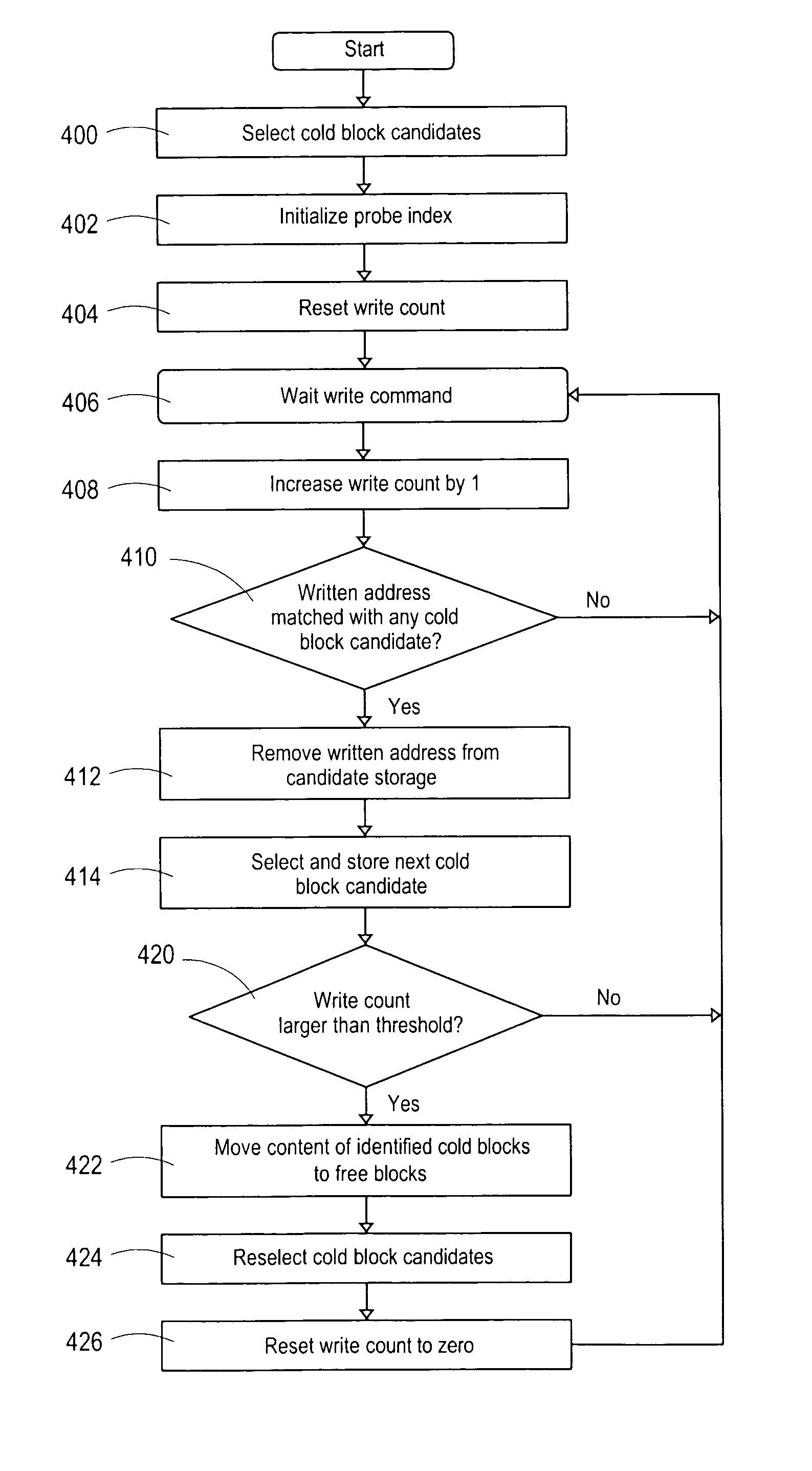

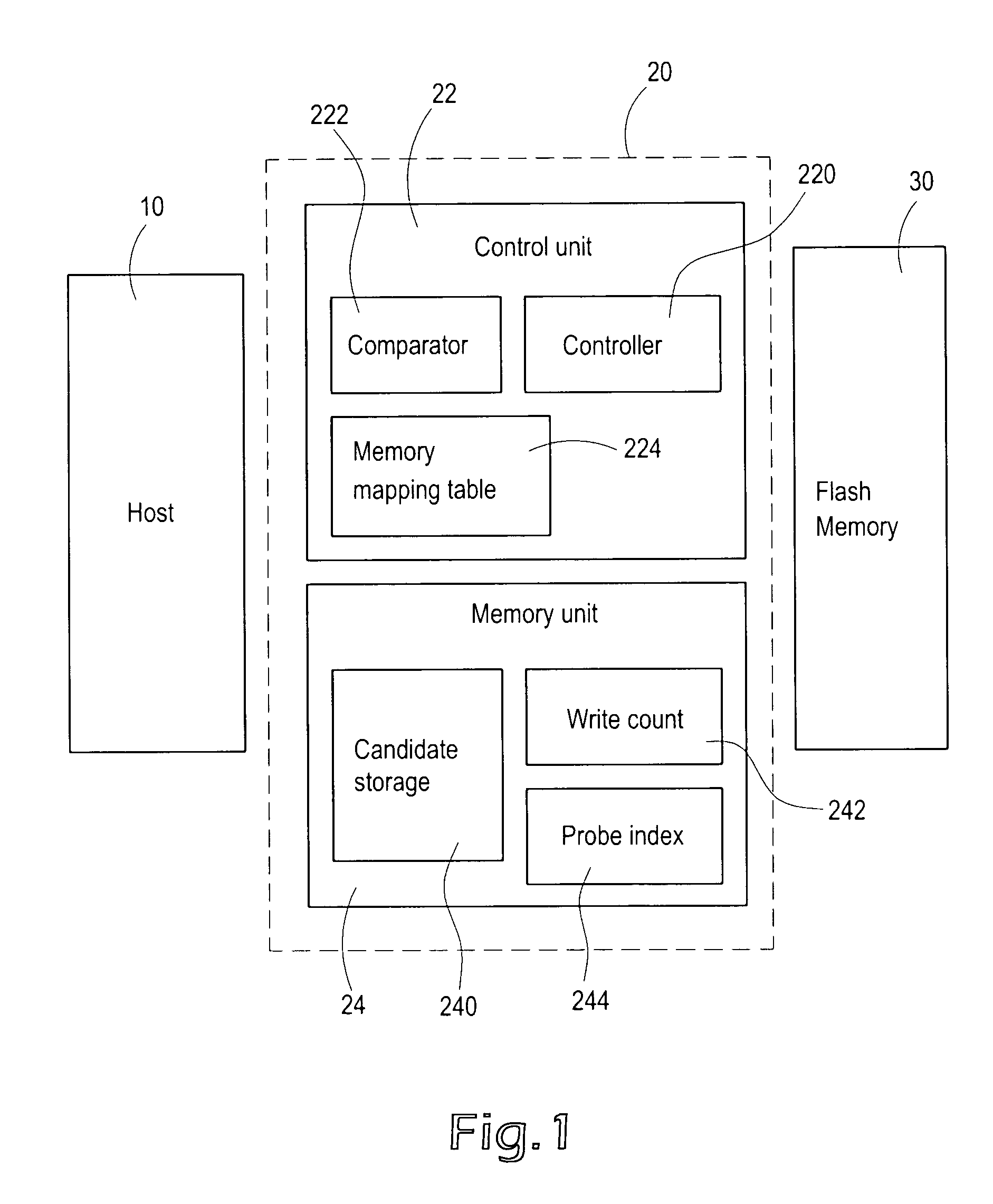

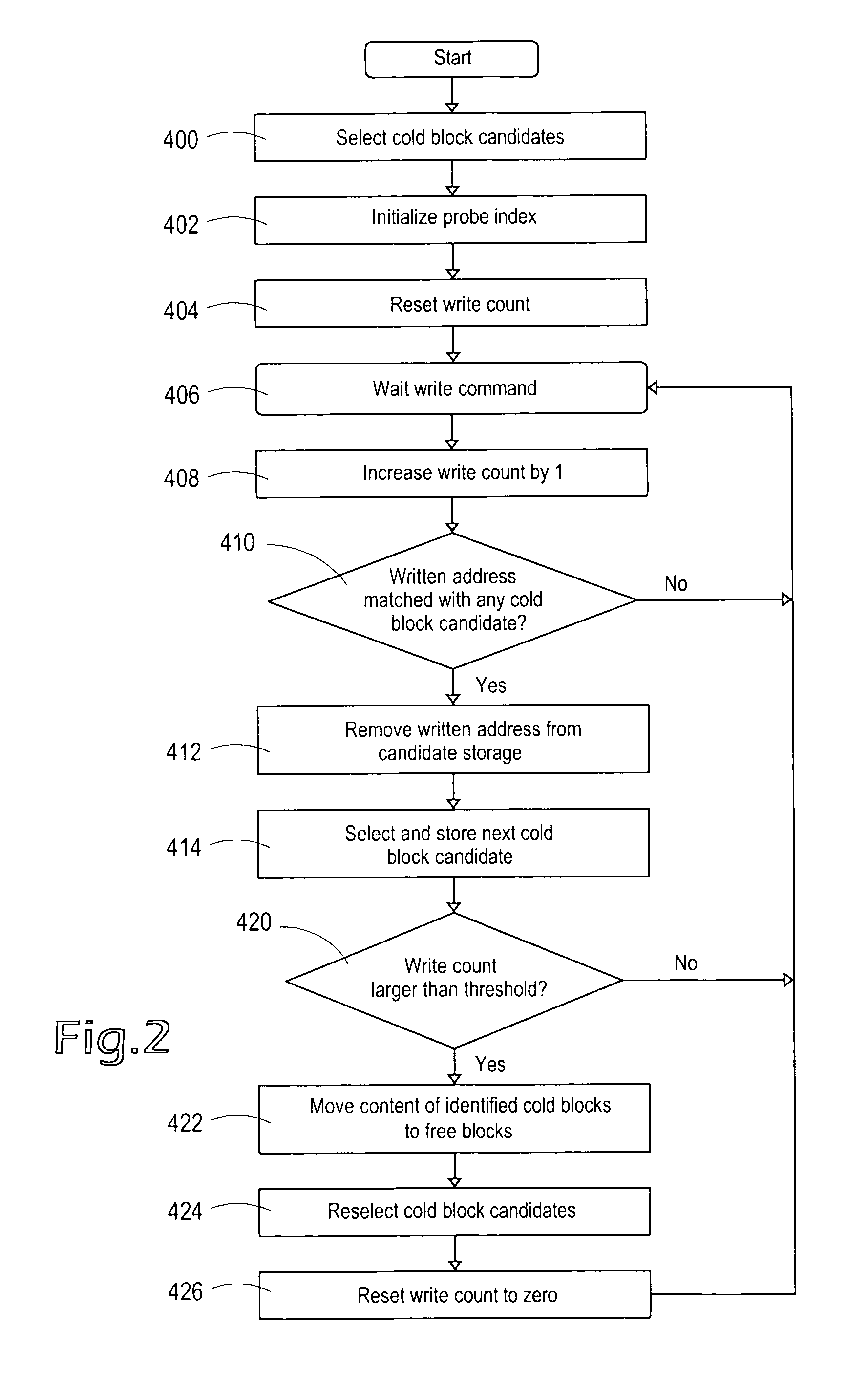

Wear leveling method and apparatus for nonvolatile memory

PendingUS20070208904A1Uniform wearImprove efficiencyMemory architecture accessing/allocationRead-only memoriesStorage cellControl unit

A wear leveling apparatus uniformly distributes wear over a nonvolatile memory containing a plurality of memory blocks. The wear leveling apparatus includes a memory unit for storing a record of cold block candidates in the nonvolatile memory and a control unit configured to update the memory unit and release the cold block candidates under a threshold condition. The control unit selects a new memory block to replace one cold block candidate in the memory unit when the cold block candidate is matched with a written address in a write command for the nonvolatile memory. The cold block candidates remained in the memory unit are identified as cold blocks when the nonvolatile memory has been written more than a predetermined write count threshold. The memory blocks with infrequent erasure can be identified and released to uniformly distribute wear over the nonvolatile memory.

Owner:SUNPLUS TECH CO LTD

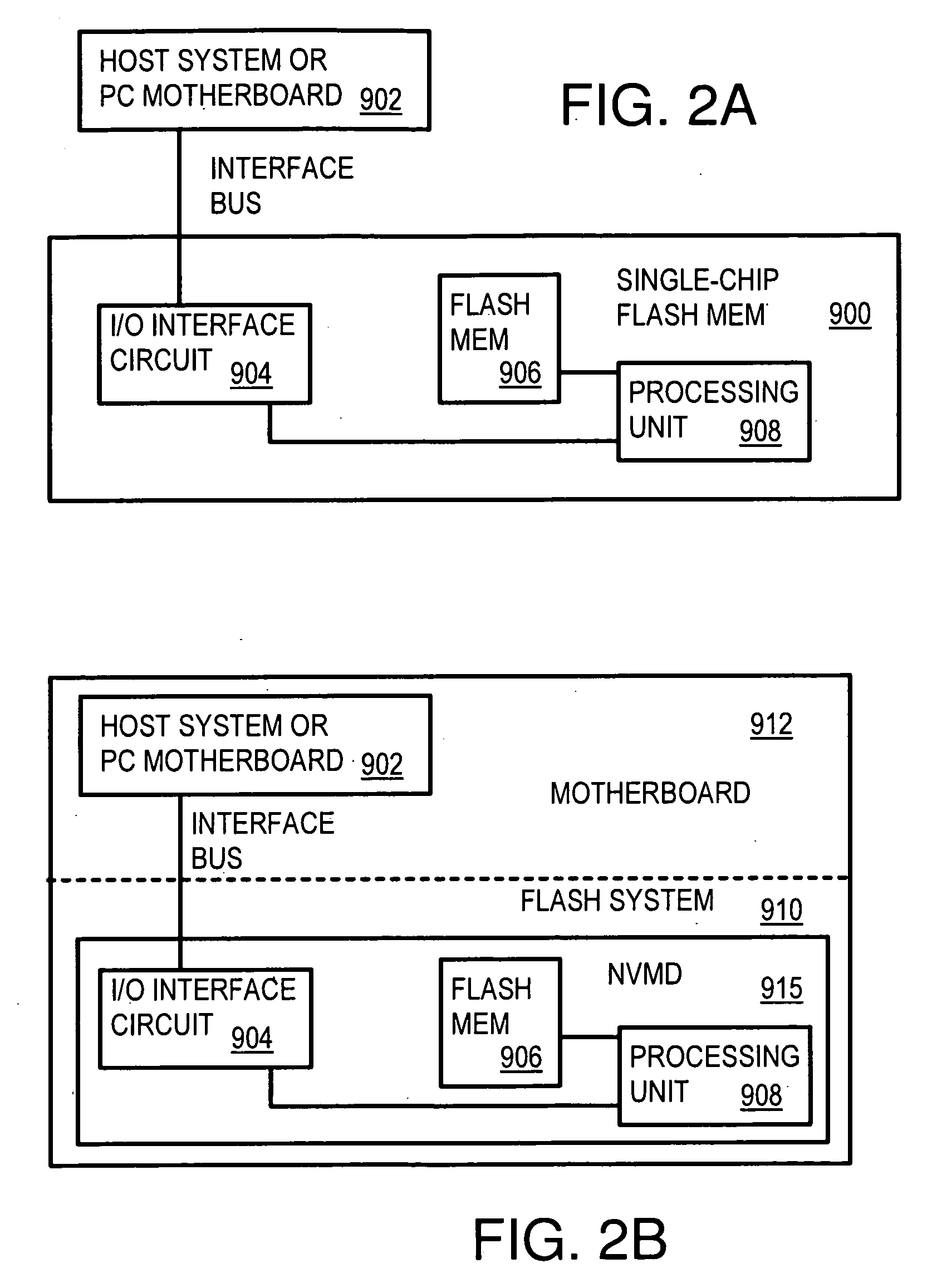

Intelligent Solid-State Non-Volatile Memory Device (NVMD) System With Multi-Level Caching of Multiple Channels

InactiveUS20080235443A1Memory architecture accessing/allocationEnergy efficient ICTPower controllerLogical block addressing

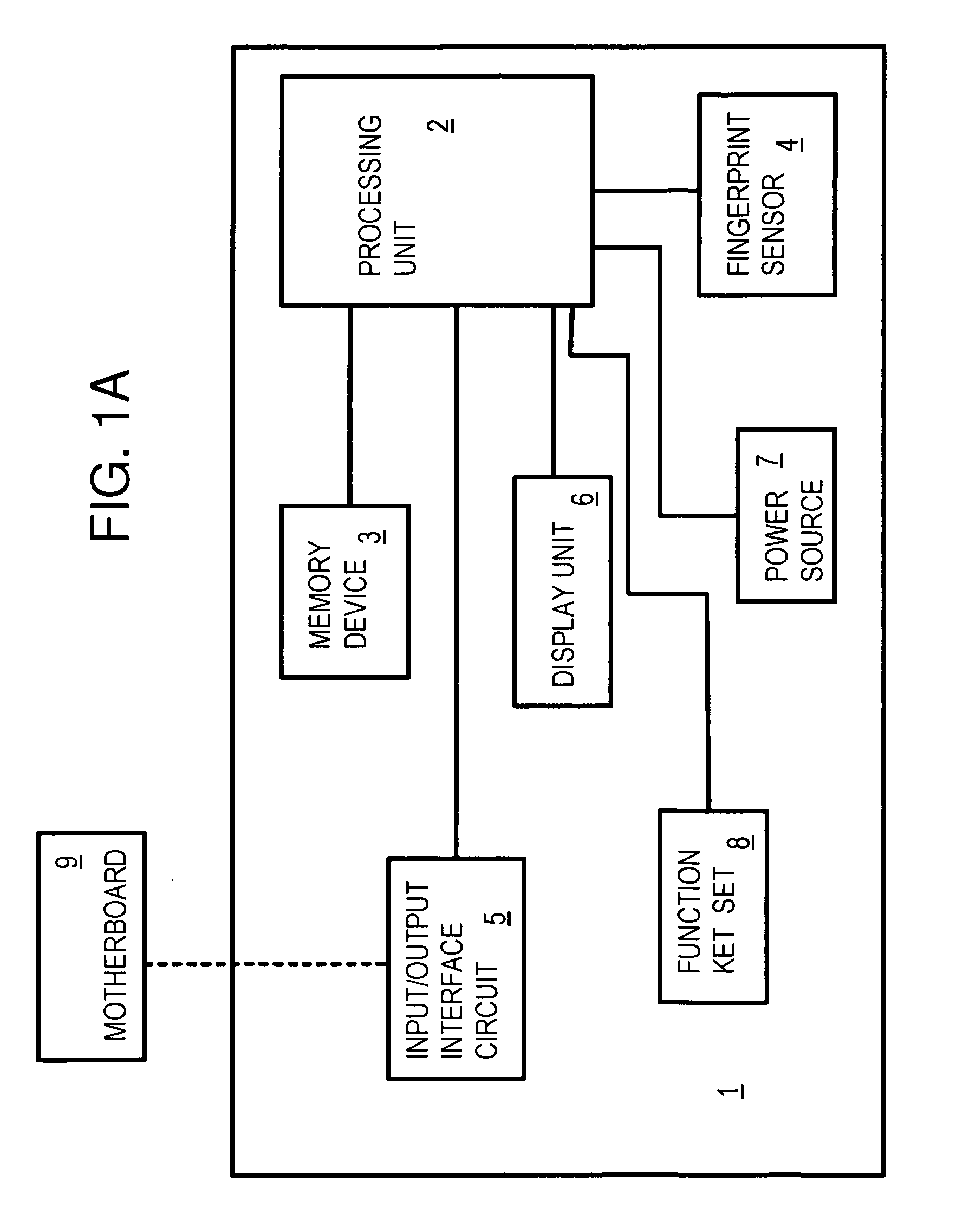

A flash memory system stores blocks of data in Non-Volatile Memory Devices (NVMD) that are addressed by a logical block address (LBA). The LBA is remapped for wear-leveling and bad-block relocation by the NVMD. The NVMD are interleaved in channels that are accessed by a NVMD controller. The NVMD controller has a controller cache that caches blocks stored in NVMD in that channel, while the NVMD also contain high-speed cache. The multiple levels of caching reduce access latency. Power is managed in multiple levels by a power controller in the NVMD controller that sets power policies for power managers inside the NVMD. Multiple NVMD controllers in the flash system may each controller many channels of NVMD. The flash system with NVMD may include a fingerprint reader for security.

Owner:SUPER TALENT TECH CORP

Wear-leveling in non-volatile storage systems

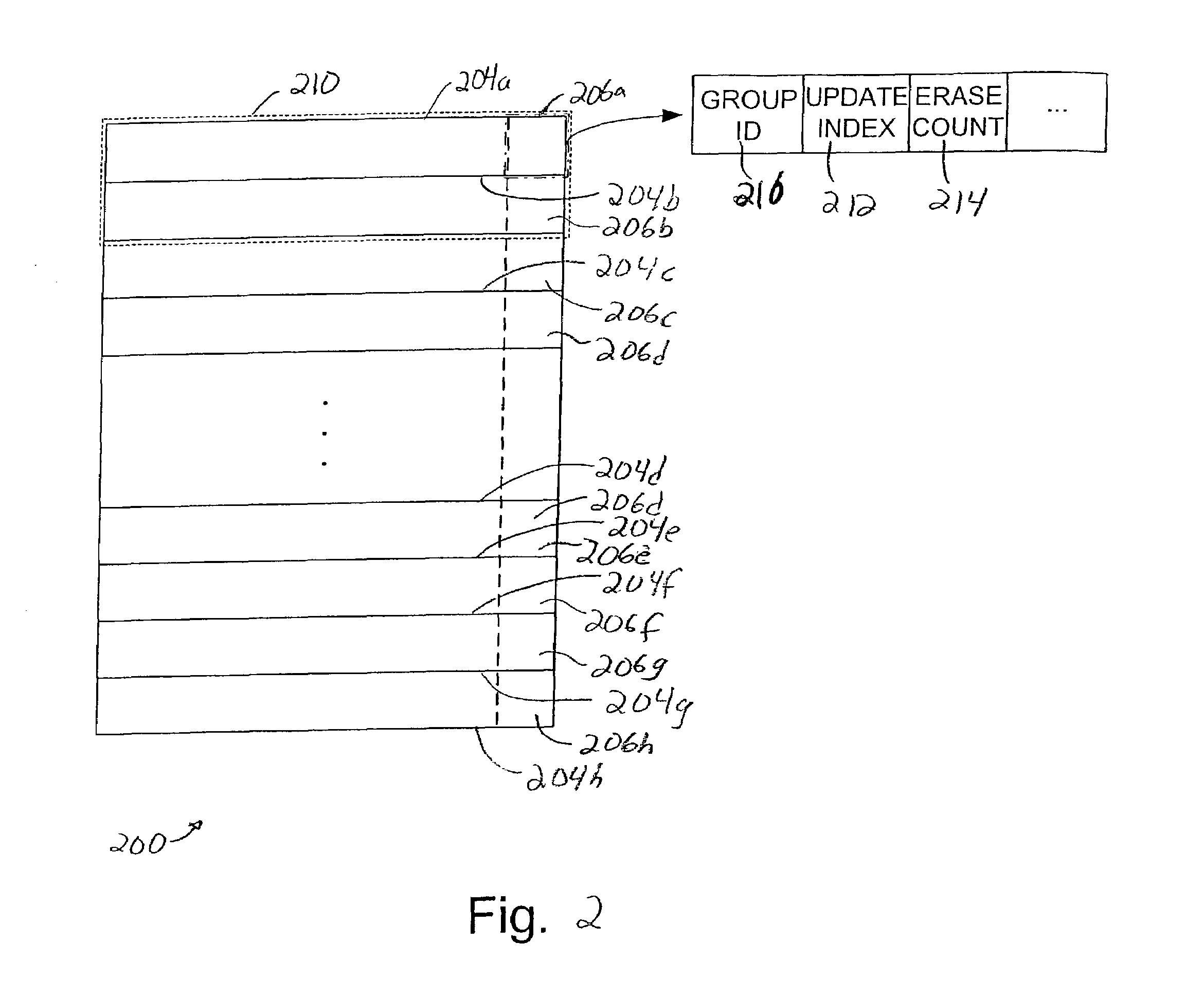

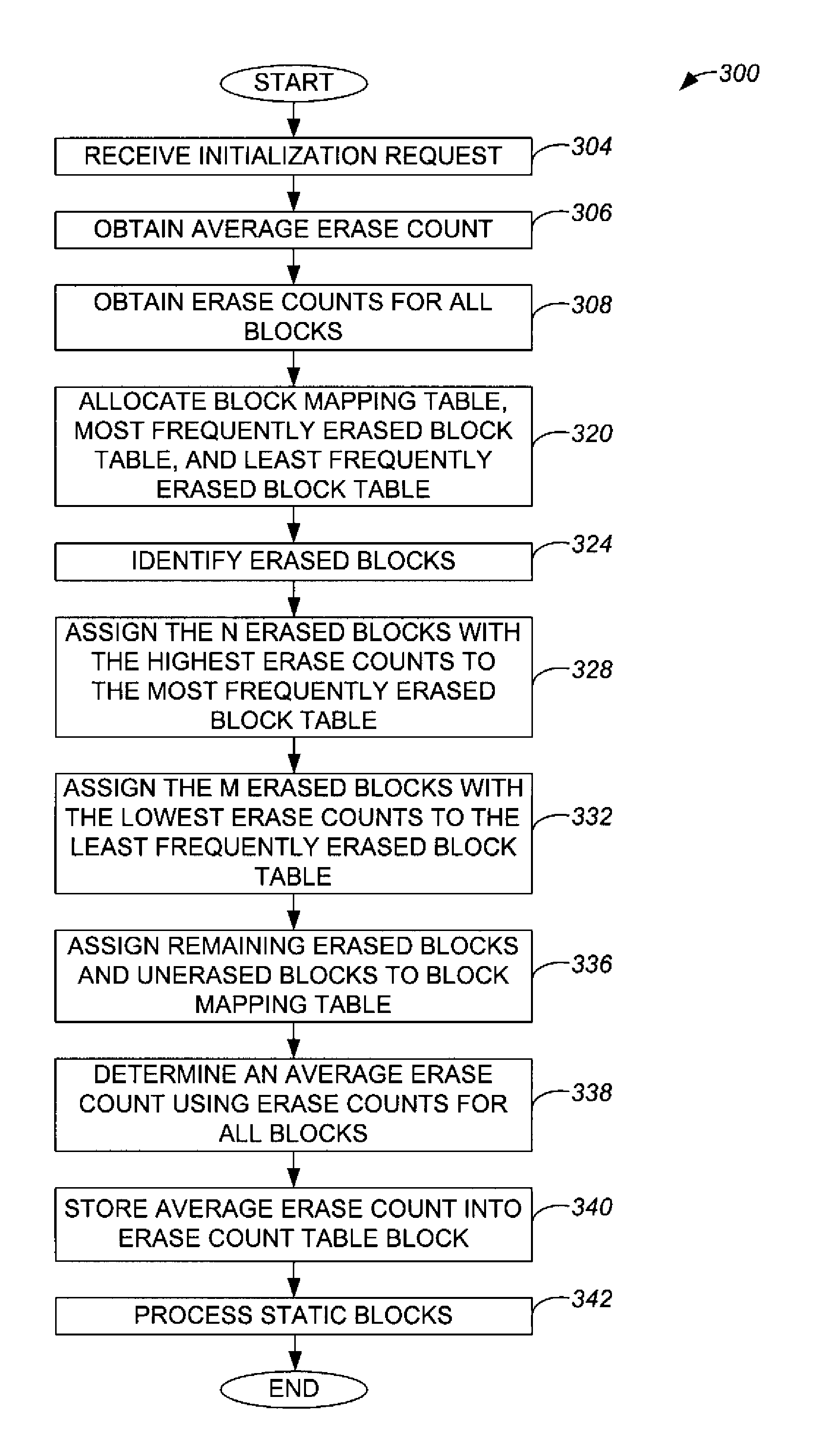

ActiveUS6985992B1Effective wearExtended service lifeMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer scienceNon-volatile memory

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. According to one aspect of the present invention, a method for allocating non-volatile memory that is divided into elements includes grouping the elements into a first group, a second group, and a third group. The first group includes erased elements with relatively low wear and the second group includes erased elements with relatively high wear. The method also includes determining when a first element included in the third group is to be replaced by a second element included in the first group. Contents of the first element are copied into the second element obtained from the first group. The contents are then erased from the first element, and the second element is associated with the third group. Associating the second element with the third group includes substantially disassociating the second element from the first group.

Owner:SANDISK TECH LLC

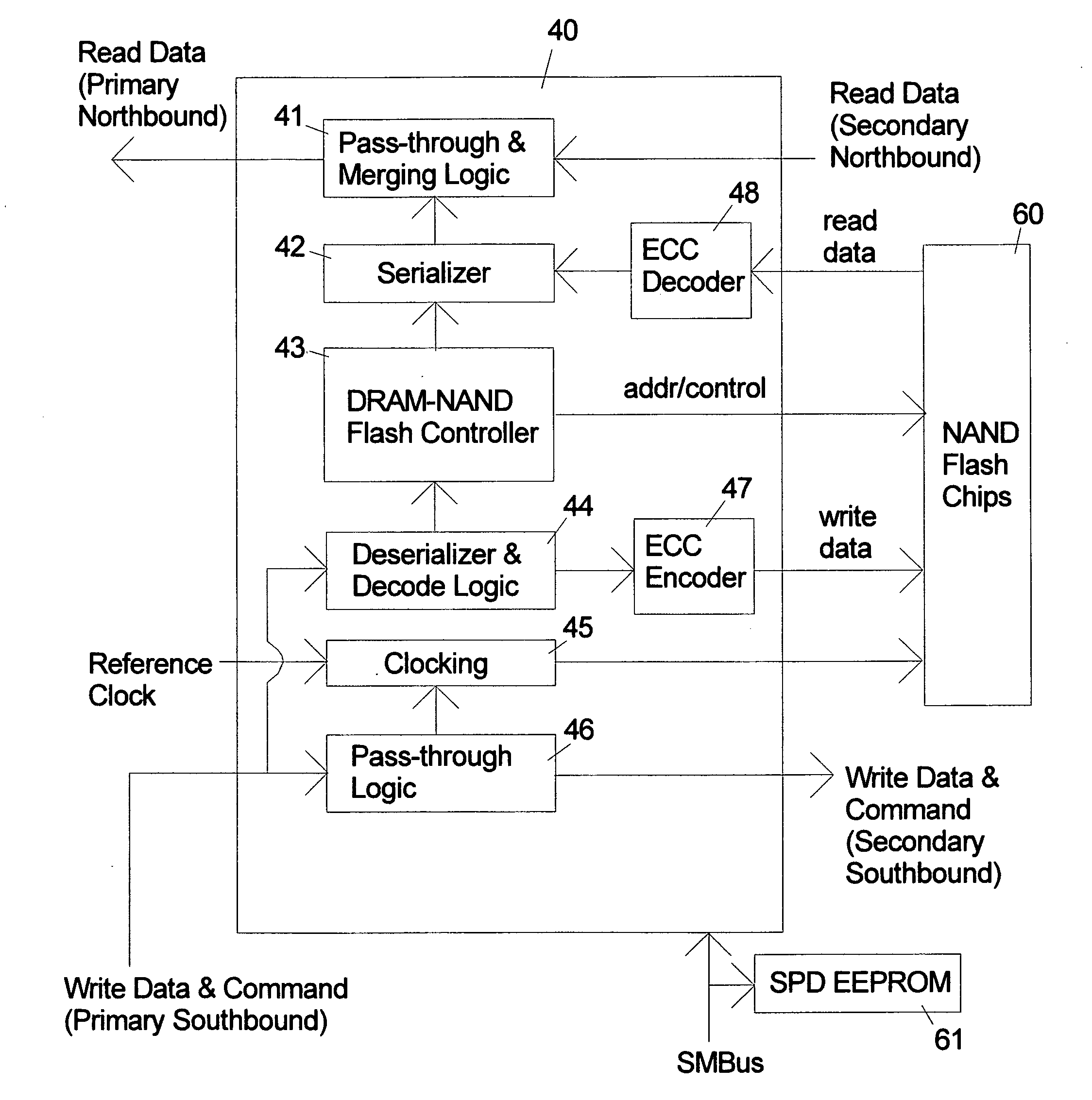

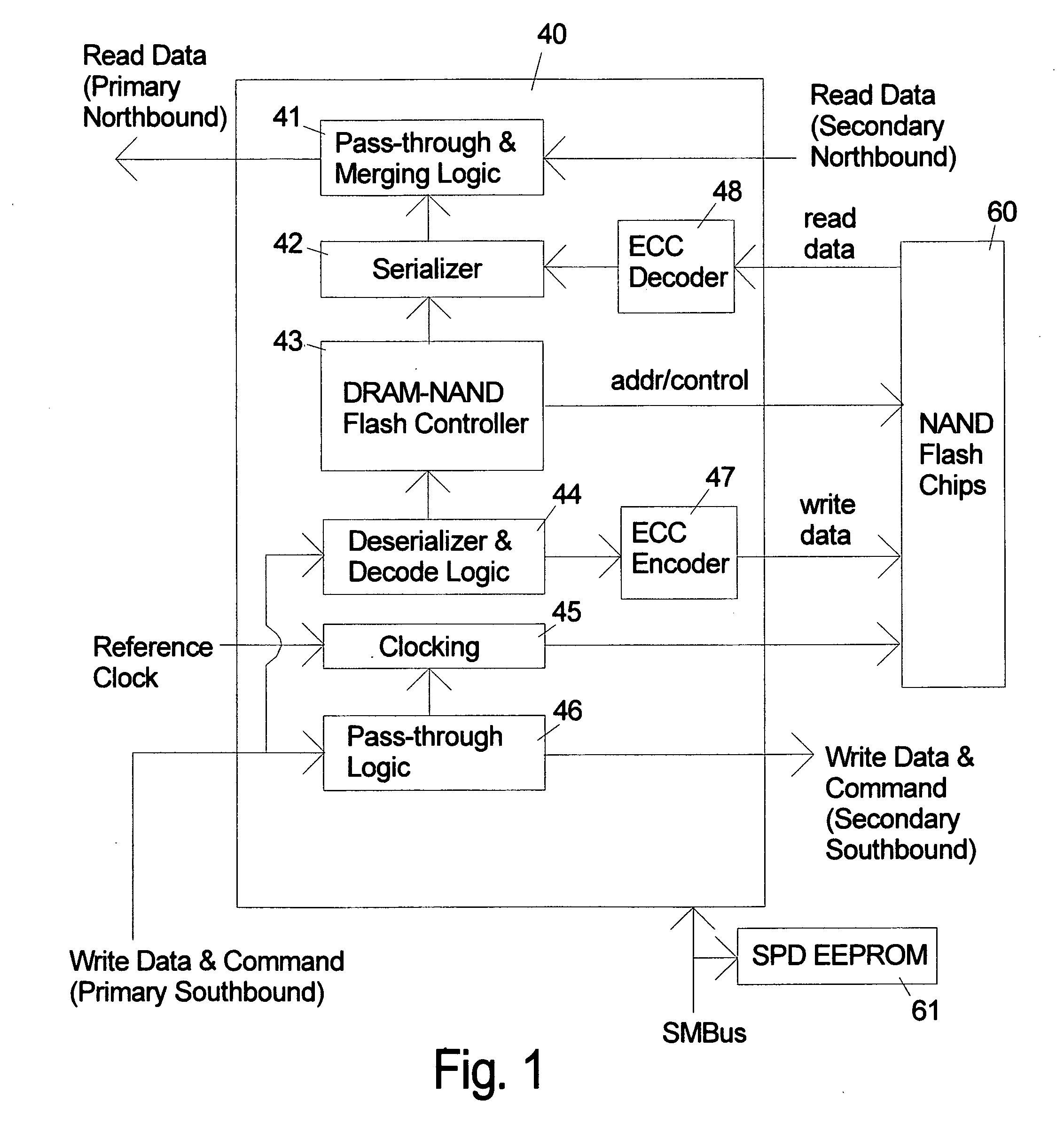

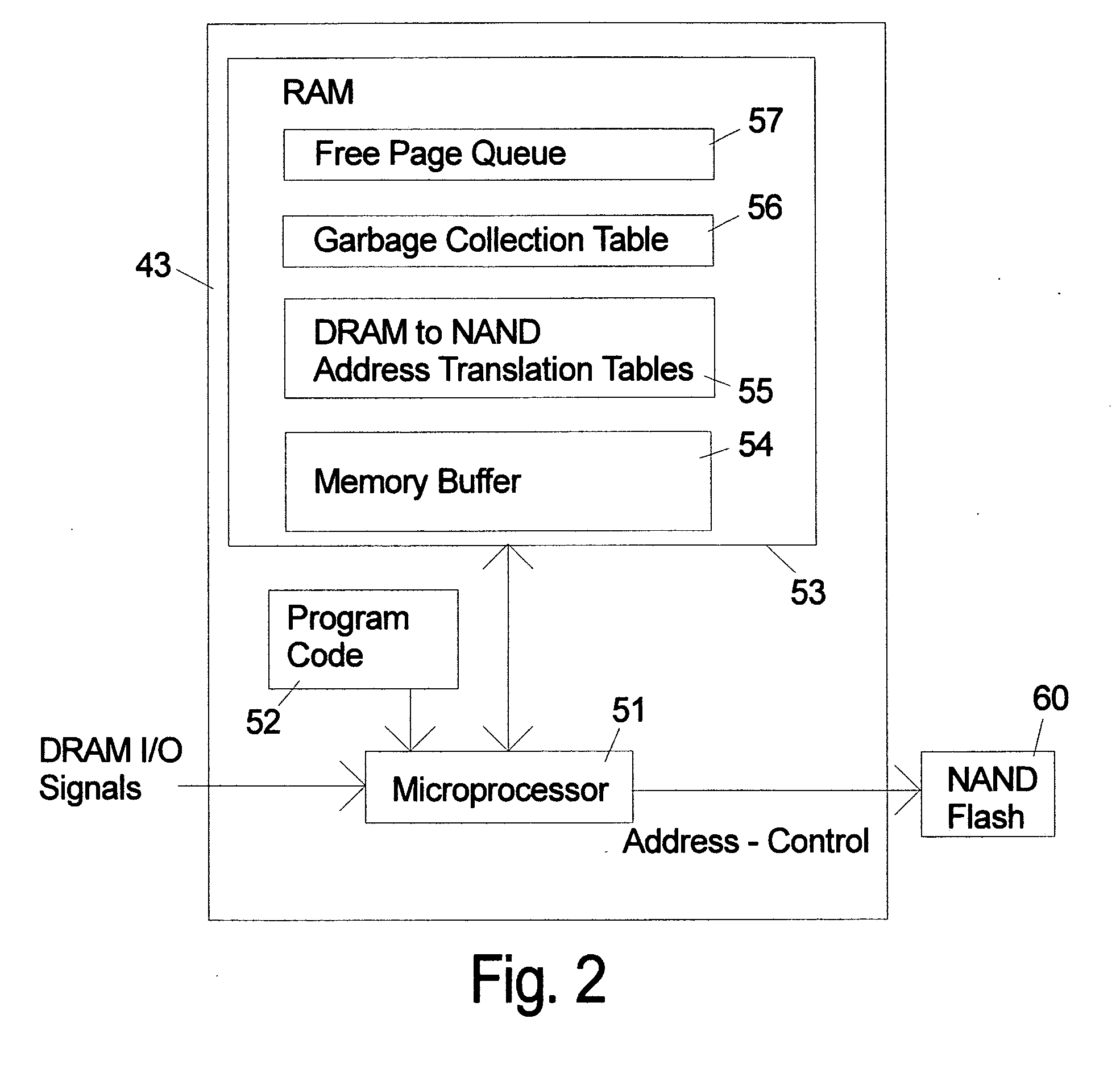

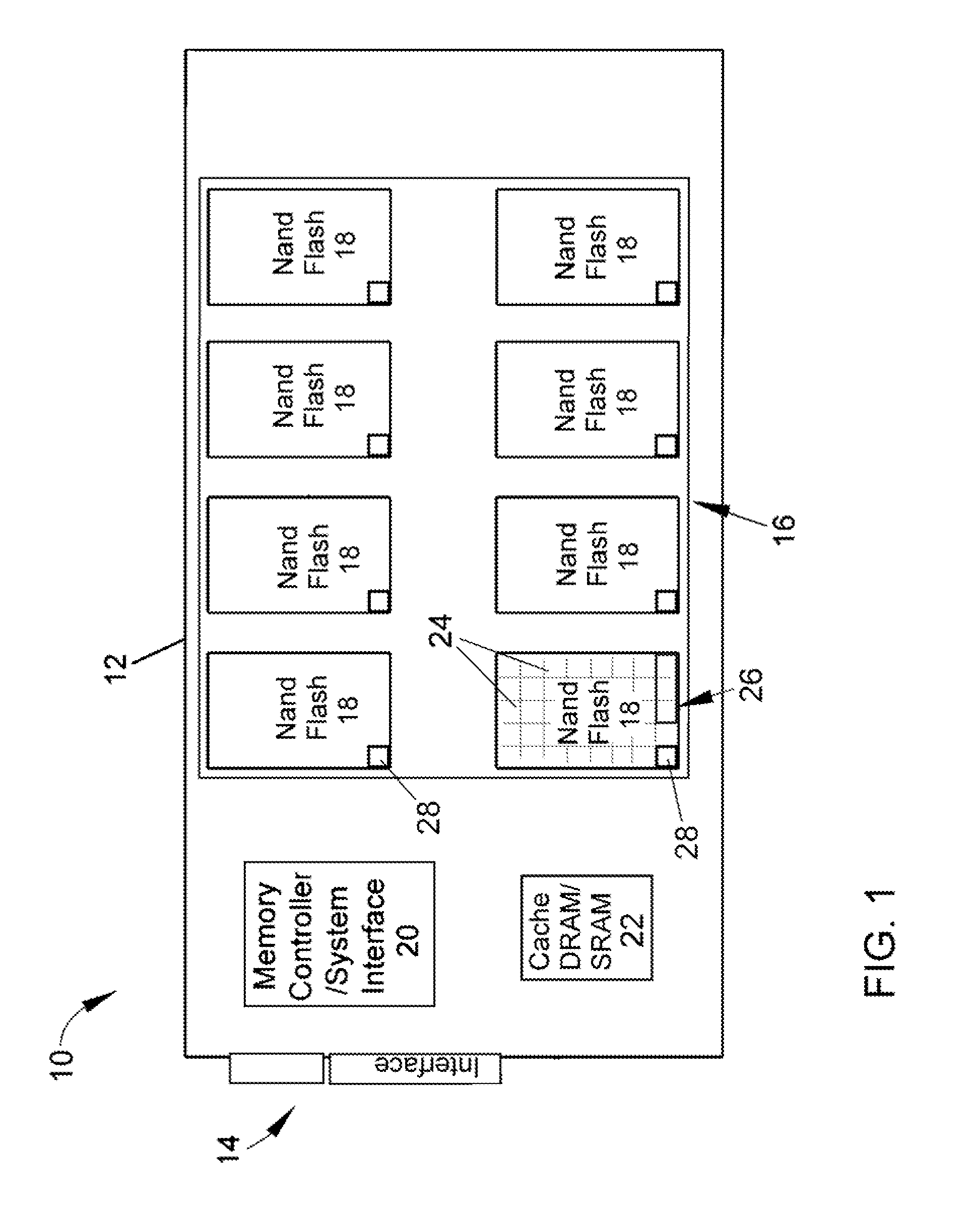

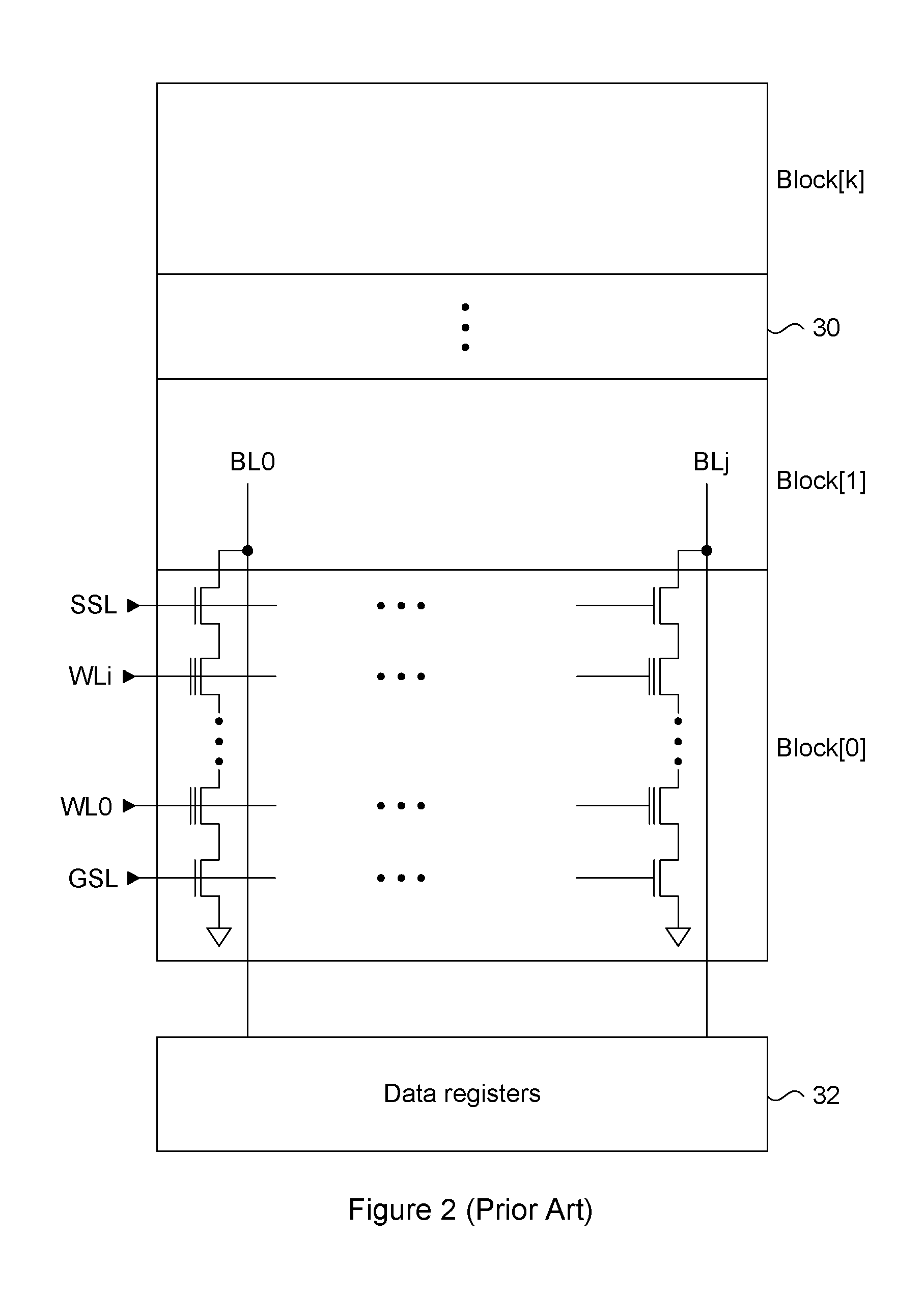

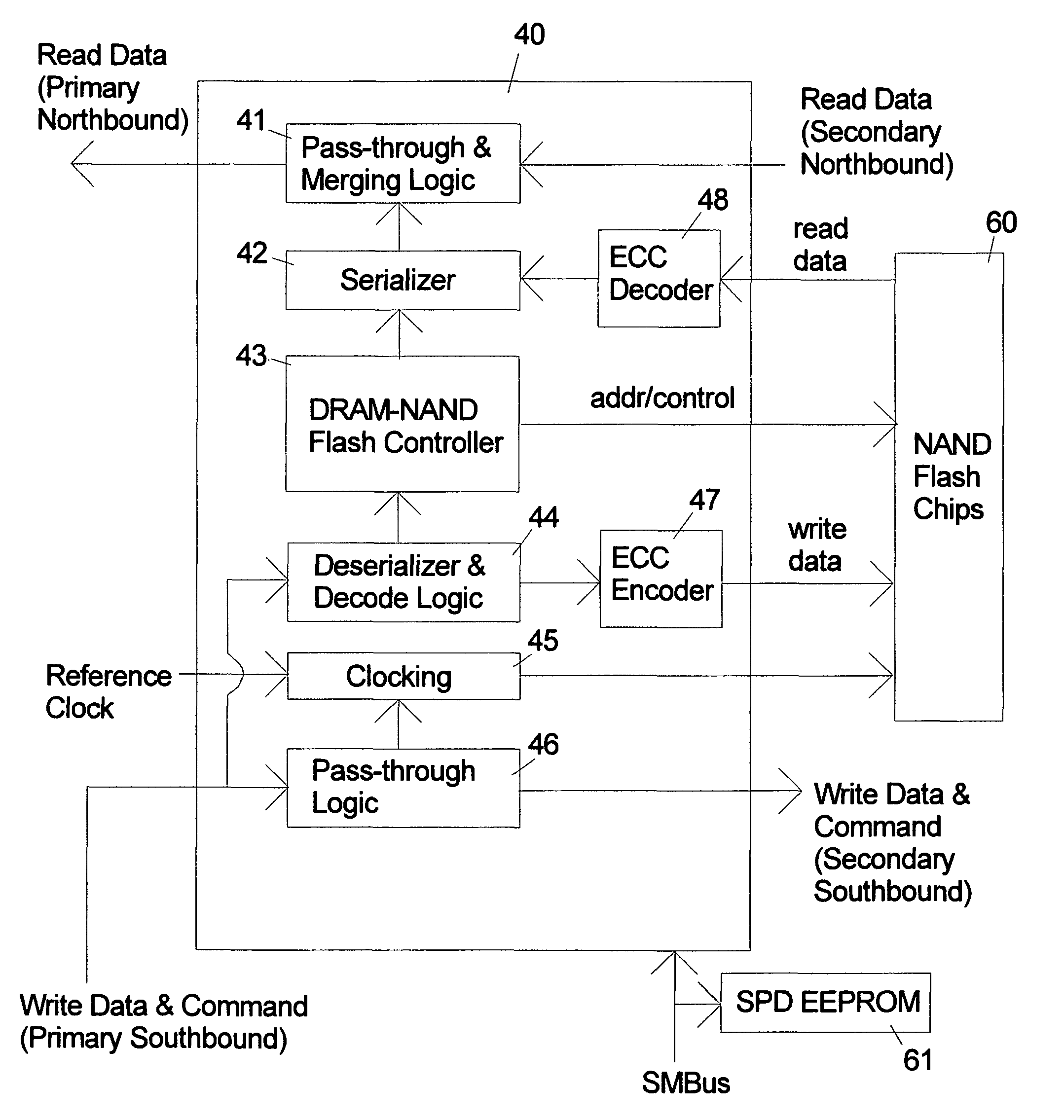

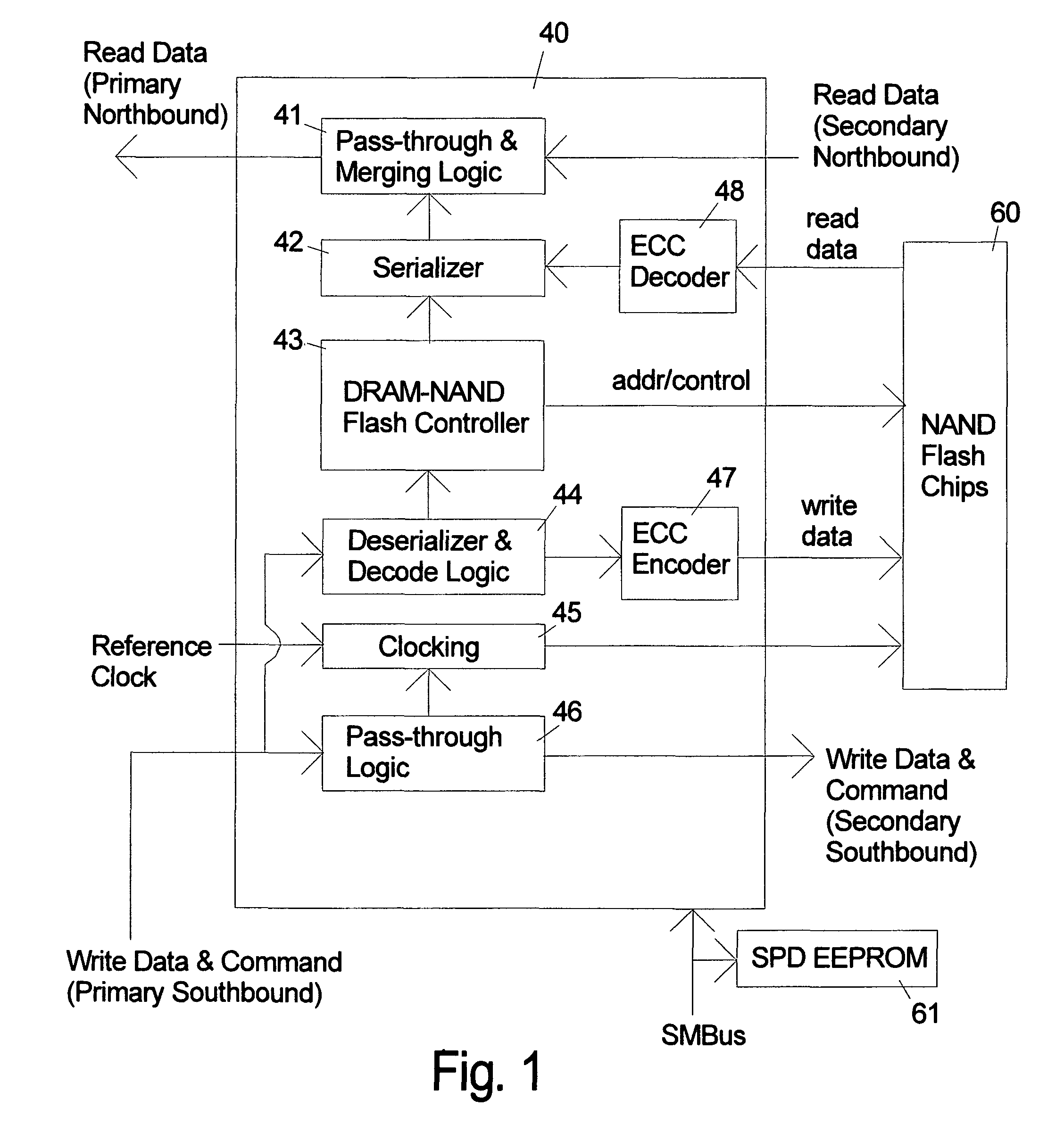

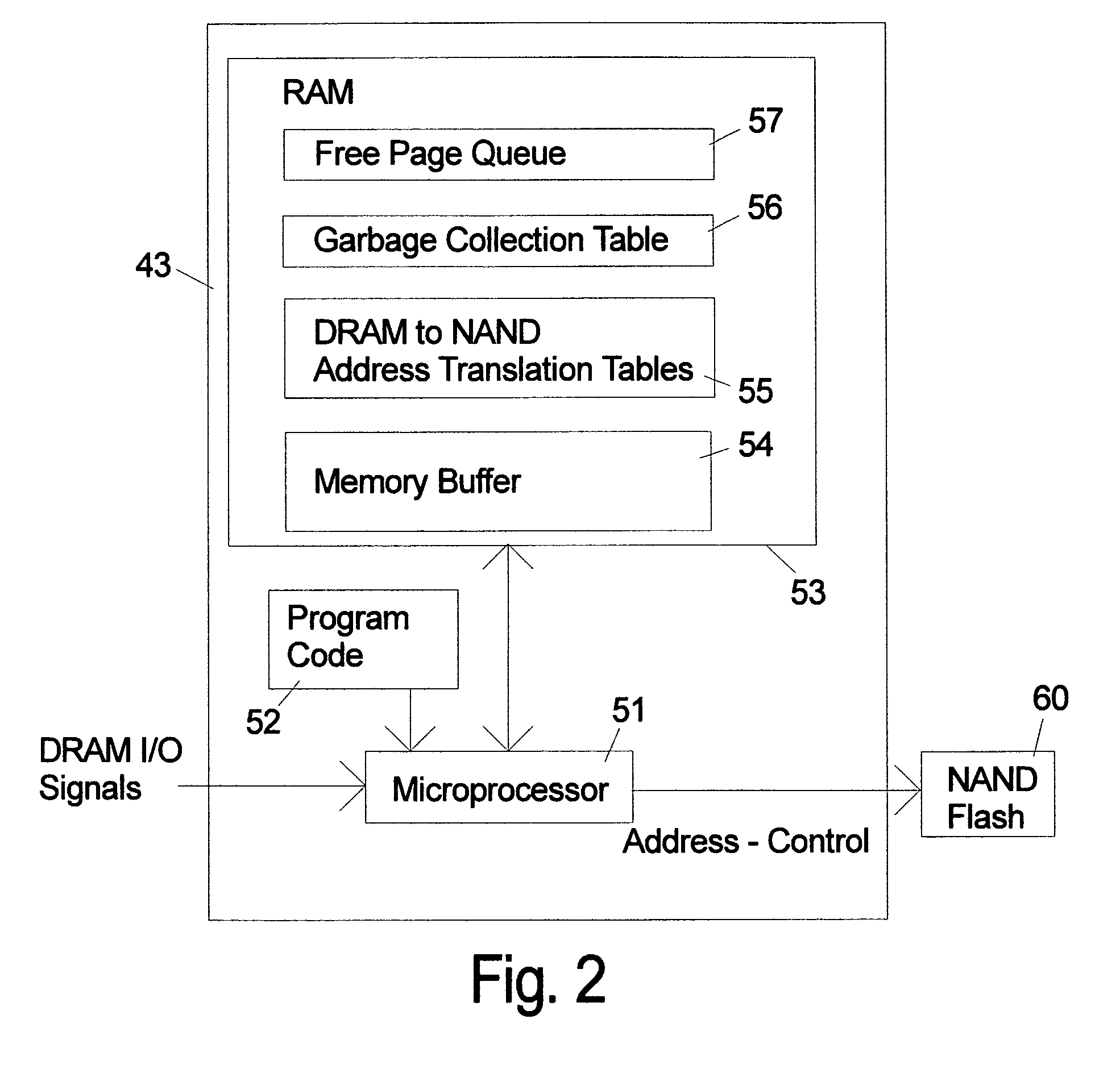

NAND flash module replacement for DRAM module

ActiveUS20090157950A1Most efficientAddressing slow performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationControl signalFlash memory controller

An electronic memory module according to the invention provides non-volatile memory that can be used in place of a DRAM module without battery backup. An embodiment of the invention includes an embedded microprocessor with microcode that translates the FB-DIMM address and control signals from the system into appropriate address and control signals for NAND flash memory. Wear-leveling, bad block management, garbage collection are preferably implemented by microcode executed by the microprocessor. The microprocessor, additional logic, and embedded memory provides the functions of a flash memory controller. The microprocessor memory preferably contains address mapping tables, free page queue, and garbage collection information.

Owner:WESTERN DIGITAL TECH INC

Flash drive fast wear leveling

ActiveUS20070050536A1Memory architecture accessing/allocationMemory adressing/allocation/relocationComputer scienceNon-volatile memory

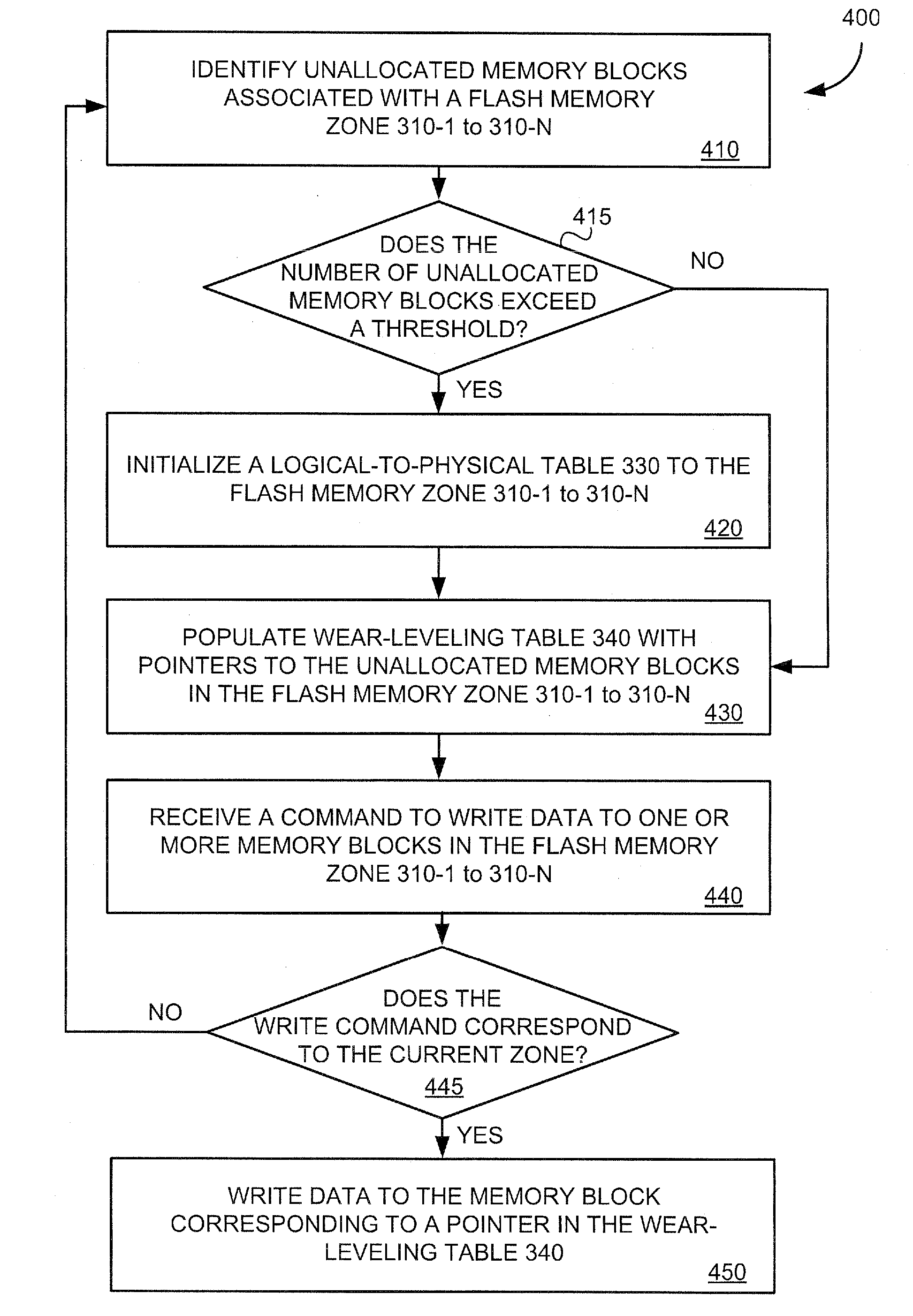

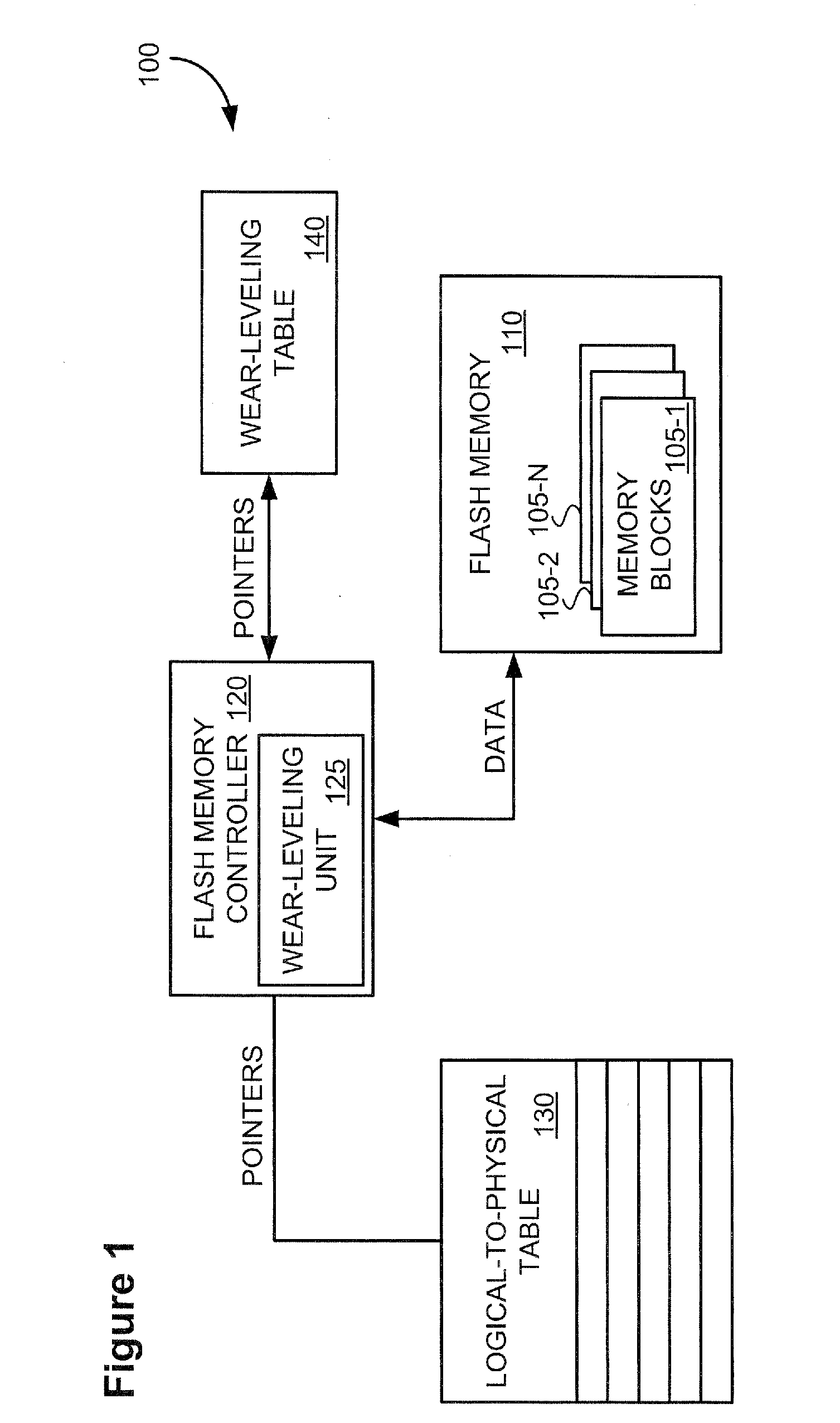

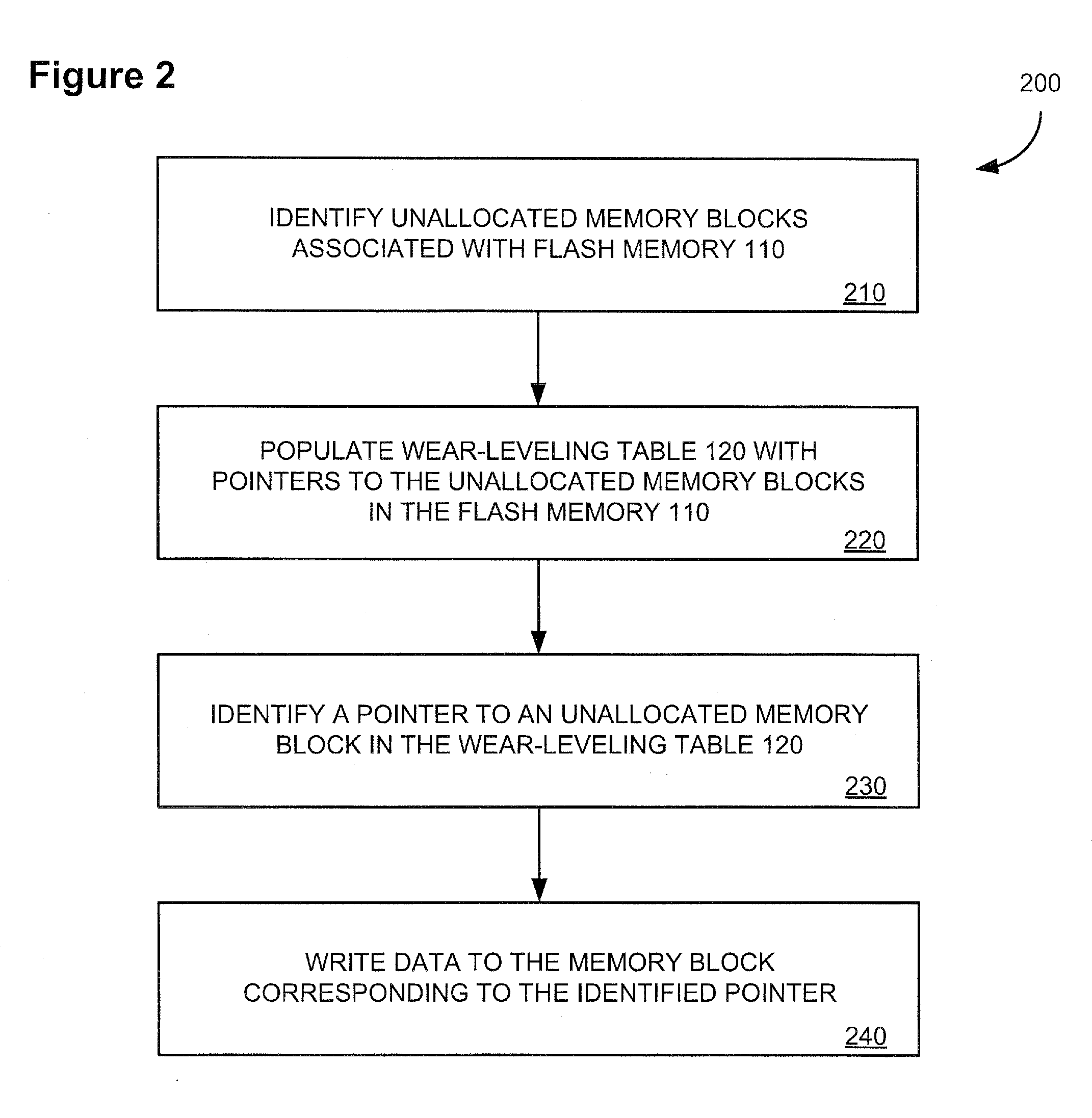

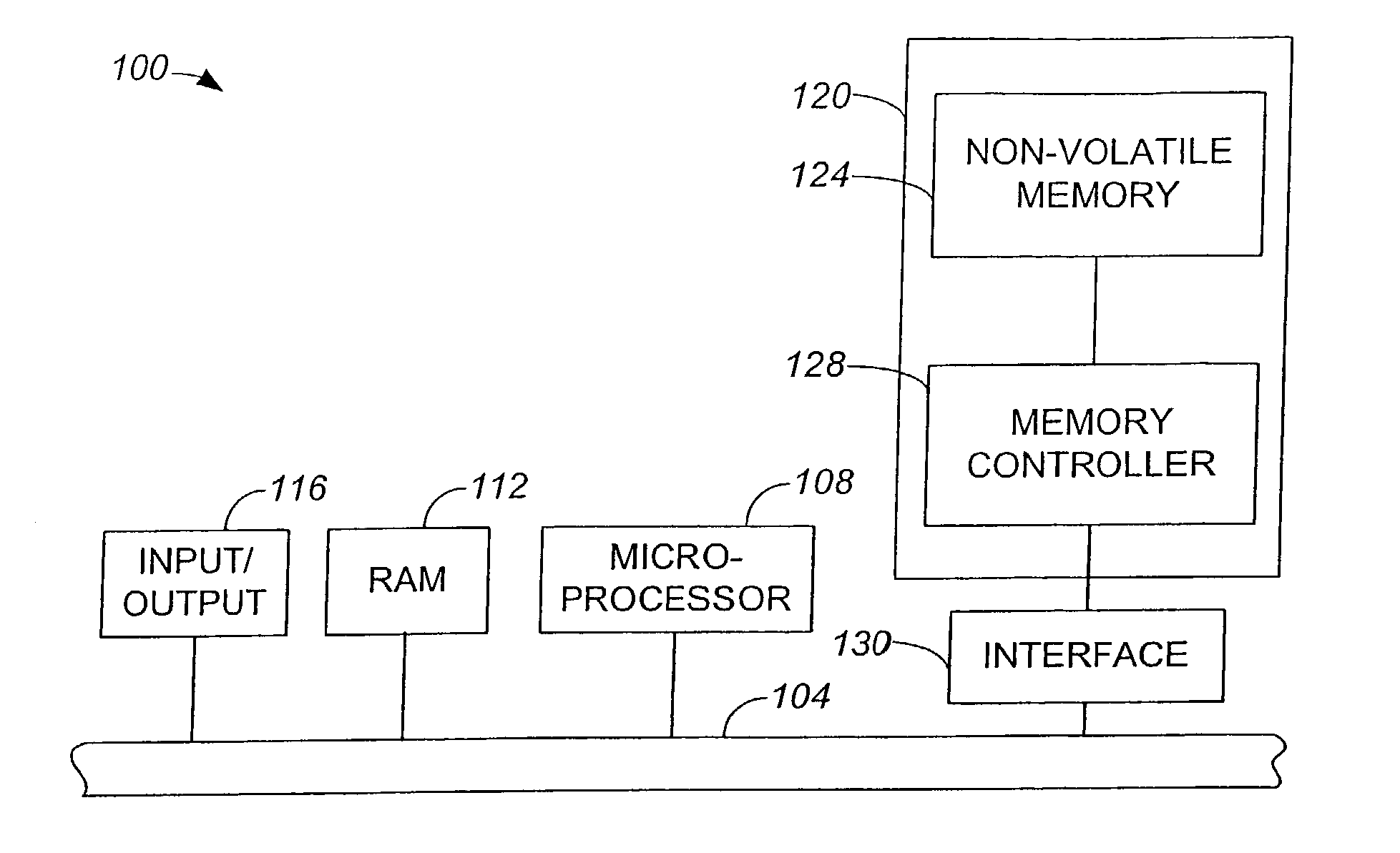

A system and method comprising a non-volatile memory including one or more memory blocks to store data, a controller to allocate one or more of the memory blocks to store data, and a wear-leveling table populated with pointers to unallocated memory blocks in the non-volatile memory, the controller to identify one or more pointers in the wear-leveling table and to allocate the unallocated memory blocks associated with the identified pointers for the storage of data.

Owner:MONTEREY RES LLC

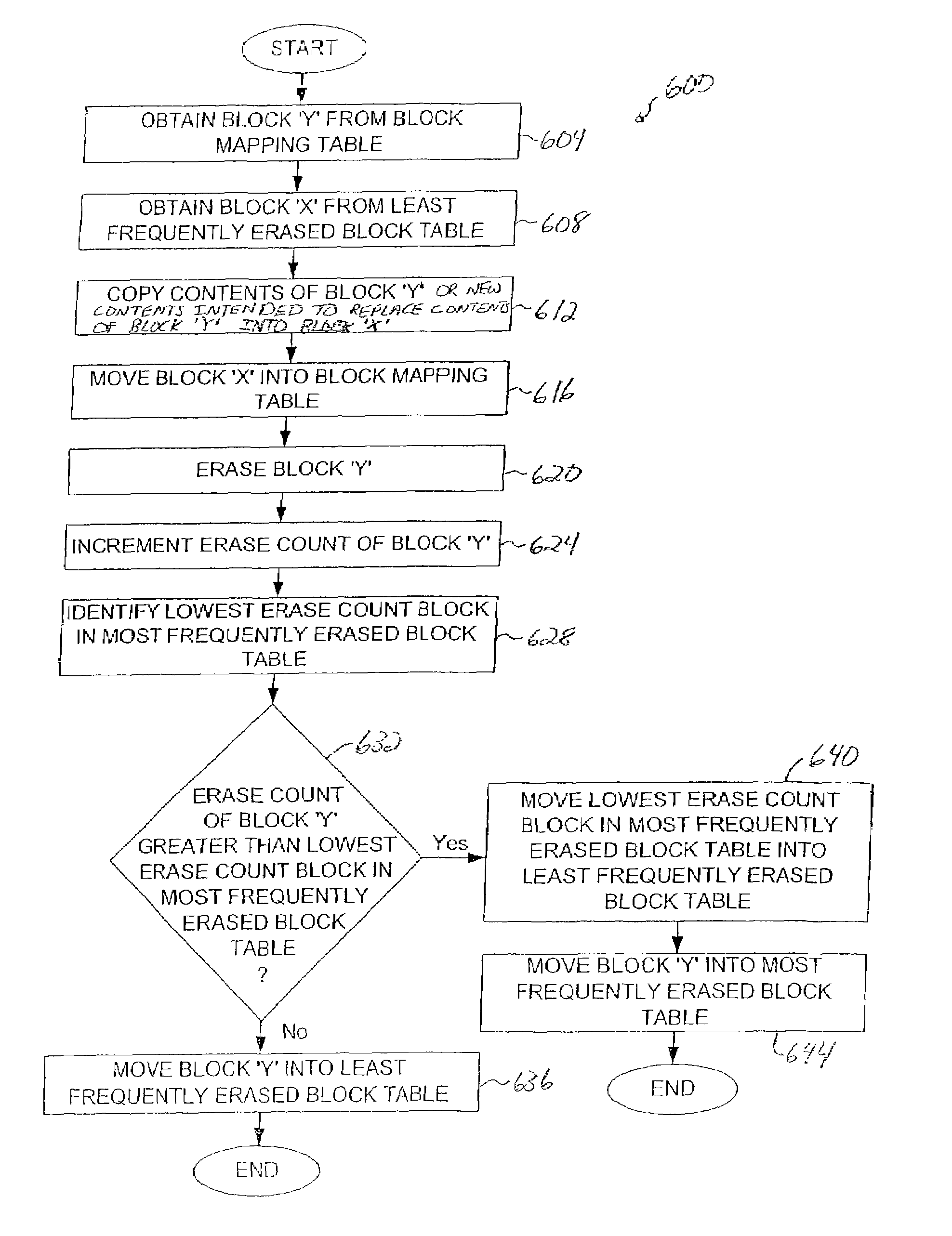

Tracking the most frequently erased blocks in non-volatile memory systems

InactiveUS6973531B1Raise countProlong lifeMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingProcessing element

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. According to one aspect of the present invention, a method for processing elements included in a non-volatile memory of a memory system includes obtaining erase counts associated with a plurality of erased elements. Each element included in the plurality of elements has an associated erase count that indicates a number of times the element has been erased. The method also includes grouping a number of erased elements included in the plurality of elements into a first set, and storing the erase counts associated with the first set in a memory component of the memory system. Grouping the number of elements into the first set typically includes selecting erased elements included in the plurality of elements which have the highest associated erase counts of the erase counts associated with the plurality of elements.

Owner:SANDISK TECH LLC

Tracking the least frequently erased blocks in non-volatile memory systems

InactiveUS7096313B1Optimize allocationProlong lifeMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingProcessing element

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. According to one aspect of the present invention, one method for processing elements included in a non-volatile memory of a memory system includes obtaining erase counts associated with elements and grouping a number of the elements into a first set. Each element has an associated erase count that substantially indicates a number of times the element has been erased. Grouping the number of elements into the first set includes selecting elements included in the plurality of elements which have the lowest associated erase counts of the erase counts associated with the plurality of elements. The method also includes storing the erase counts associated with the first set in a memory component substantially within a table.

Owner:SANDISK TECH LLC

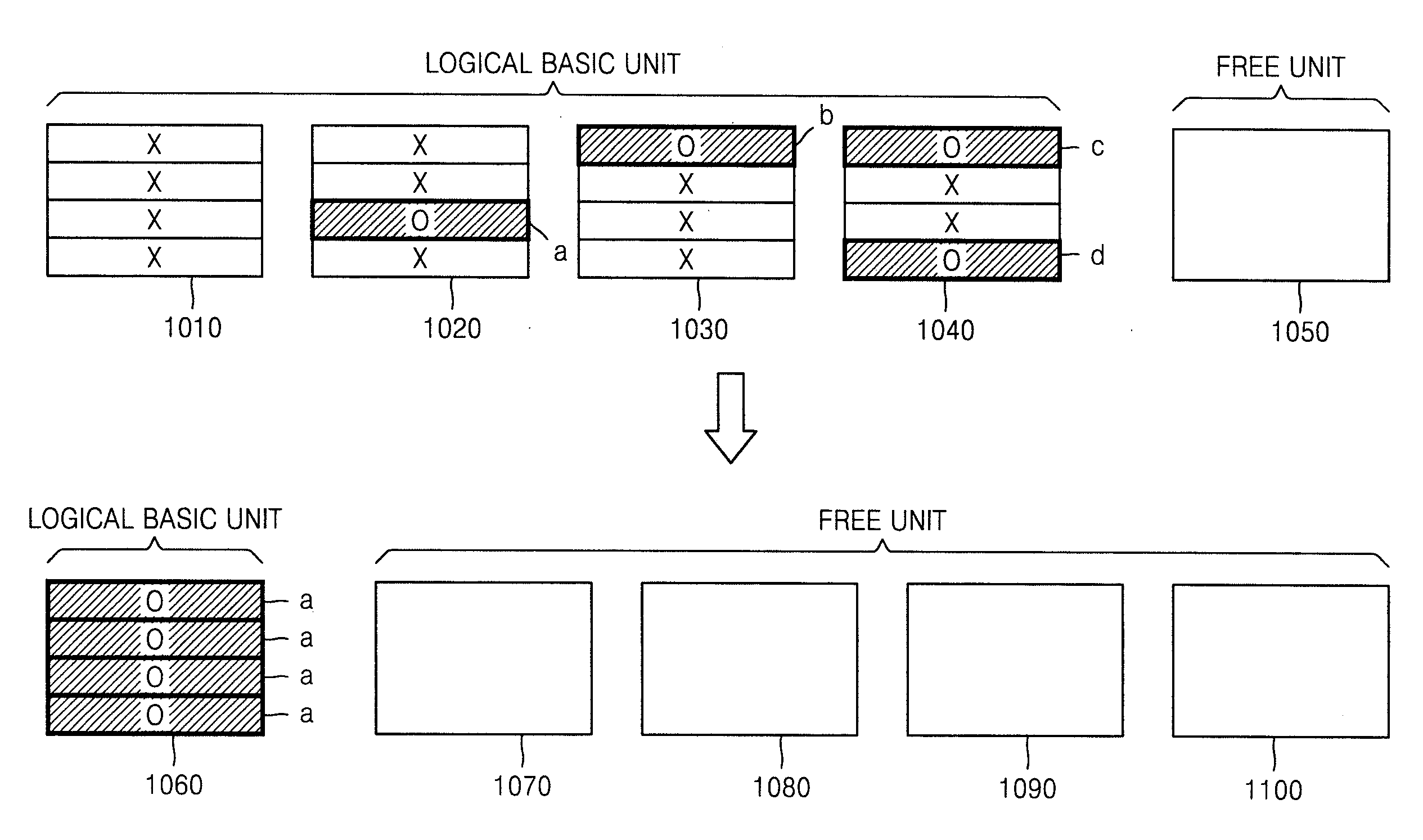

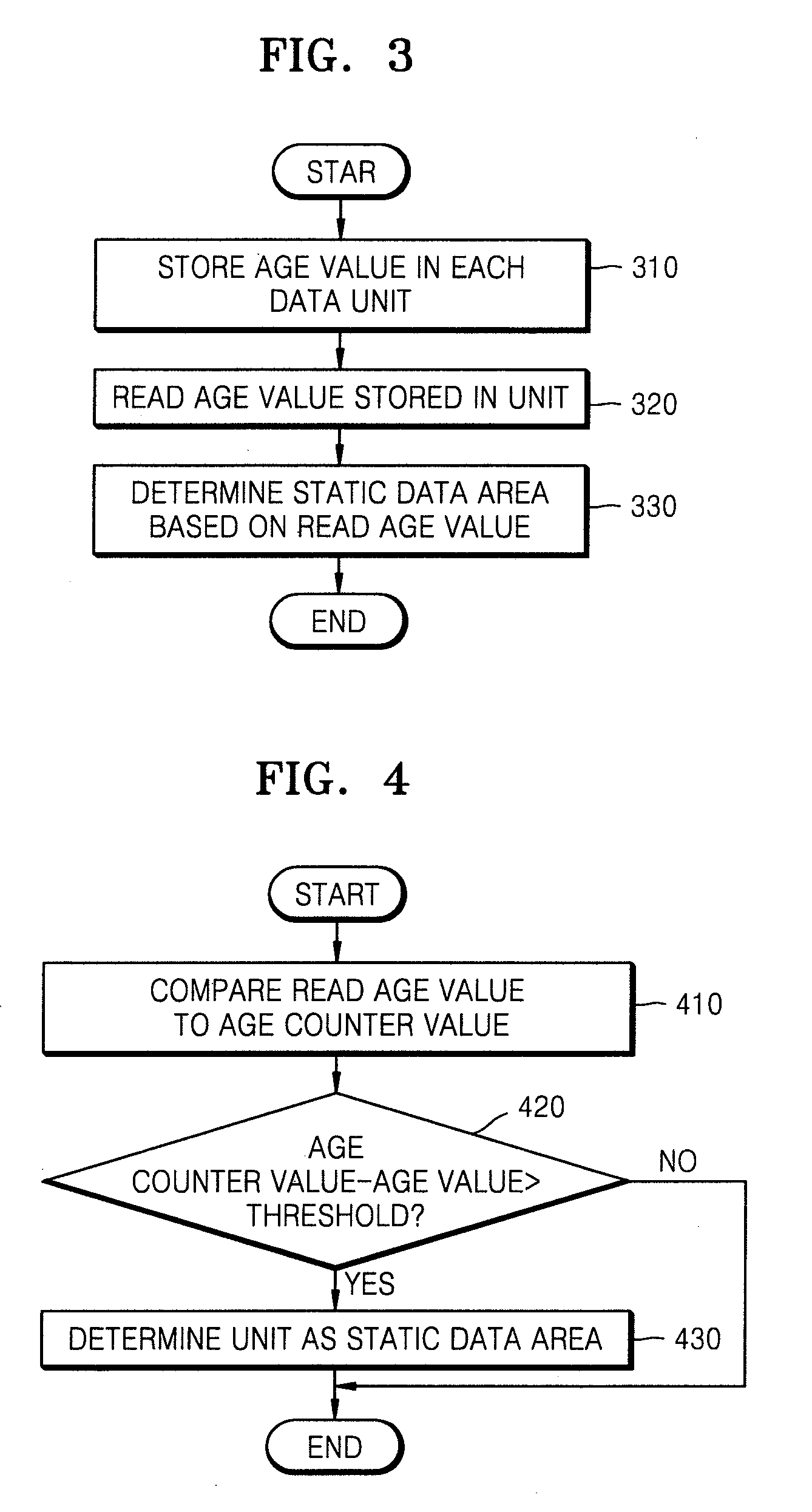

Method and apparatus for detecting static data area, wear-leveling, and merging data units in nonvolatile data storage device

ActiveUS20080147998A1Wear-leveling effectAccurate areaMemory architecture accessing/allocationRead-only memoriesLeveling effectAge values

Provided are a method and apparatus for wear-leveling of a nonvolatile data storage device, whereby a wear-leveling effect is maximized by storing an age value indicating a write time in each data unit of the nonvolatile data storage device and detecting a static data area based on age values. The method includes storing an age value indicating a write time in each unit assigned to write data therein, reading an age value stored in a unit, and determining a static data area based on the read age value. Accordingly, a static data area can be correctly detected without additional overhead, and a wear-leveling effect of the entire storage device can be increased by moving data to and from the static data area, thereby extending the lifespan of the storage device.

Owner:SAMSUNG ELECTRONICS CO LTD

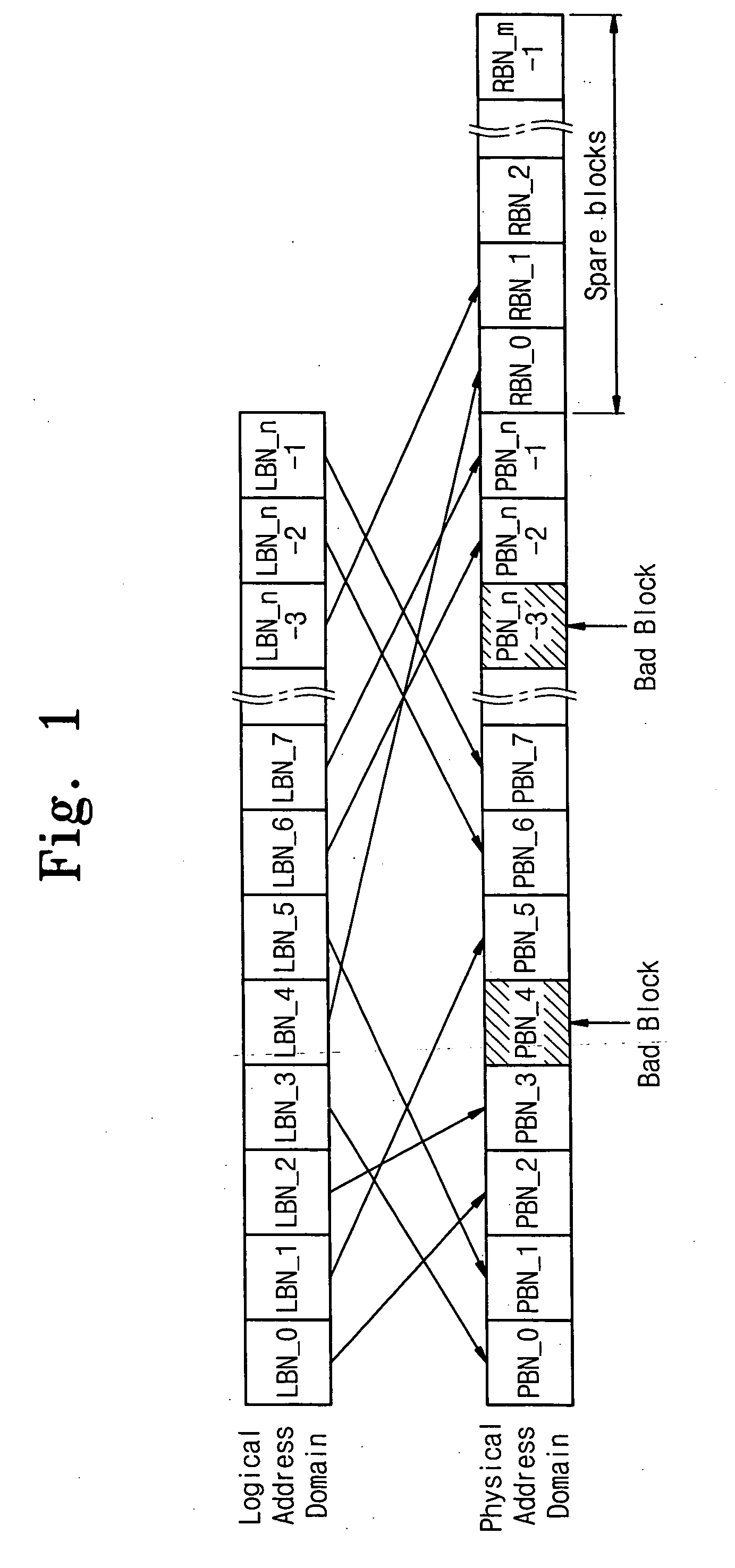

Managing Bad Blocks In Flash Memory For Electronic Data Flash Card

InactiveUS20070283428A1Reduce search timeAvoid congestionDigital data processing detailsUser identity/authority verificationLogical block addressingComputer access

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT TECH CORP

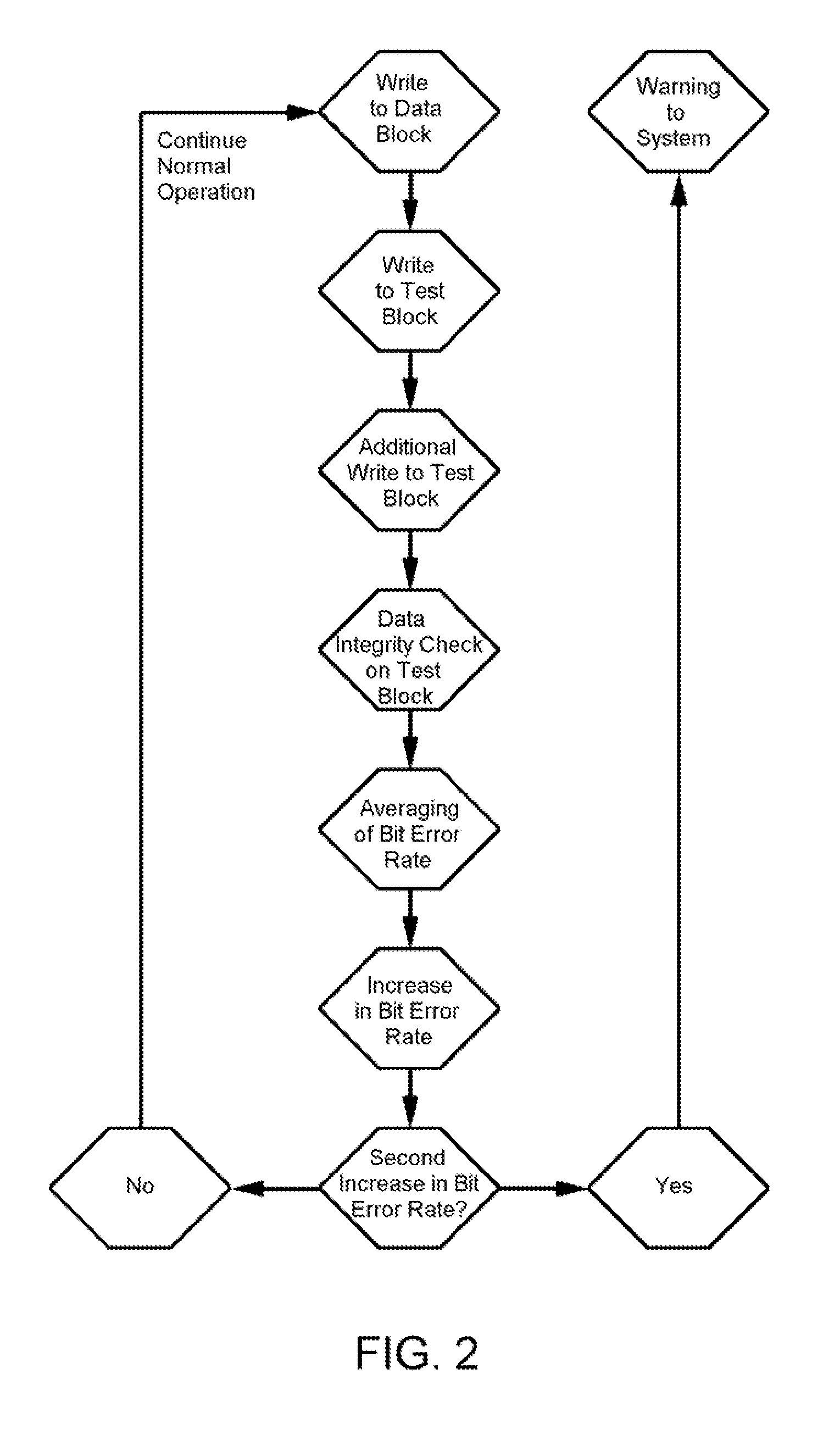

Computer system with backup function and method therefor

ActiveUS20110173378A1Avoid lostIncrease chanceMemory loss protectionMemory adressing/allocation/relocationMass storageDevice failure

A solid-state mass storage device and method of anticipating a failure of the mass storage device resulting from a memory device of the mass storage device reaching a write endurance limit. A procedure is then initiated to back up data to a second mass storage device prior to failure. The method includes assigning at least a first memory block of the memory device as a wear indicator, using other memory blocks of the memory device as data blocks for data storage, performing program / erase (P / E) cycles and wear leveling on the data blocks, subjecting the wear indicator to more P / E cycles than the data blocks, performing integrity checks and monitoring the bit error rate of the wear indicator, and taking corrective action if the bit error rate increases, including the initiation of the backup procedure and generating a request to replace the device.

Owner:KIOXIA CORP

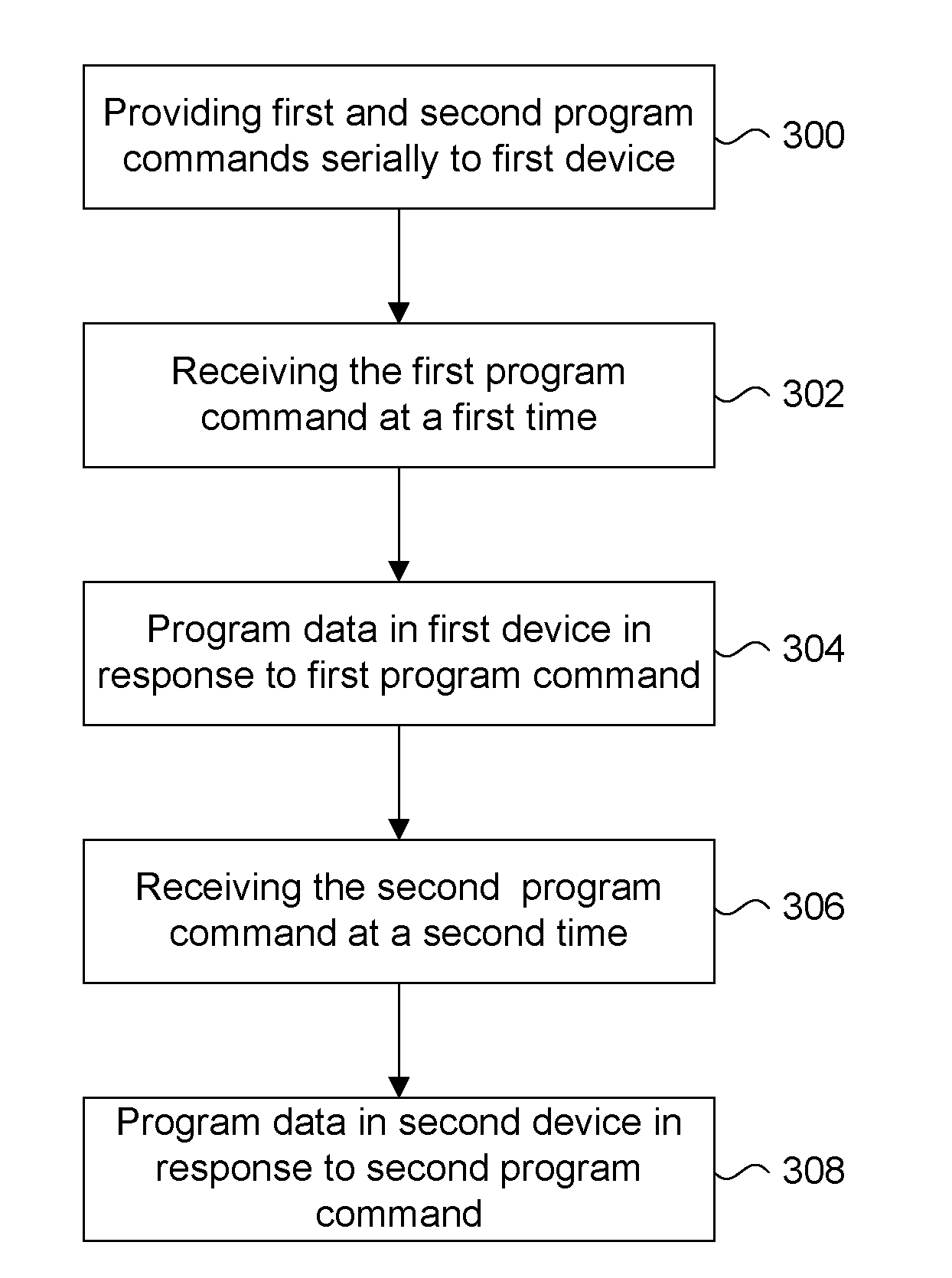

Flash memory system control scheme

ActiveUS20070233939A1Improve Flash memory system programming throughputImprove throughputMemory architecture accessing/allocationRead-only memoriesSequential programmingMemory controller

A Flash memory system architecture having serially connected Flash memory devices to achieve high speed programming of data. High speed programming of data is achieved by interleaving pages of the data to be programmed amongst the memory devices in the system, such that different pages of data are stored in different memory devices. A memory controller issues program commands for each memory device. As each memory device receives a program command, it either begins a programming operation or passes the command to the next memory device. Therefore, the memory devices in the Flash system sequentially program pages of data one after the other, thereby minimizing delay in programming each page of data into the Flash memory system. The memory controller can execute a wear leveling algorithm to maximize the endurance of each memory device, or to optimize programming performance and endurance for data of any size.

Owner:MOSAID TECH

NAND flash module replacement for DRAM module

ActiveUS8185685B2Reduce speedMost efficientMemory architecture accessing/allocationMemory adressing/allocation/relocationProcess memoryControl signal

An electronic memory module according to the invention provides non-volatile memory that can be used in place of a DRAM module without battery backup. An embodiment of the invention includes an embedded microprocessor with microcode that translates the FB-DIMM address and control signals from the system into appropriate address and control signals for NAND flash memory. Wear-leveling, bad block management, garbage collection are preferably implemented by microcode executed by the microprocessor. The microprocessor, additional logic, and embedded memory provides the functions of a flash memory controller. The microprocessor memory preferably contains address mapping tables, free page queue, and garbage collection information.

Owner:WESTERN DIGITAL TECH INC

Two-level RAM lookup table for block and page allocation and wear-leveling in limited-write flash-memories

InactiveUS7660941B2Memory architecture accessing/allocationRead-only memoriesLogical block addressingRandom access memory

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

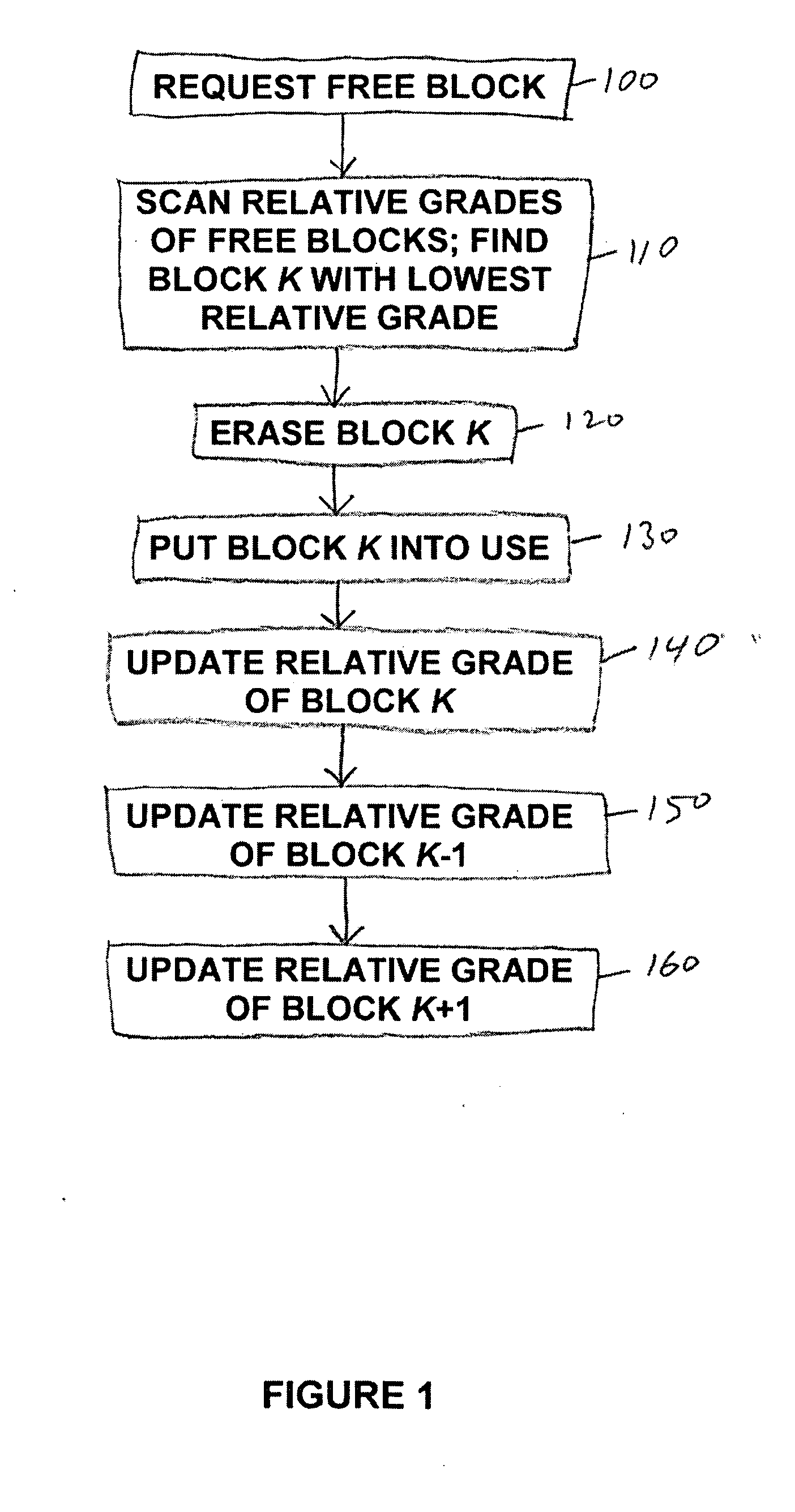

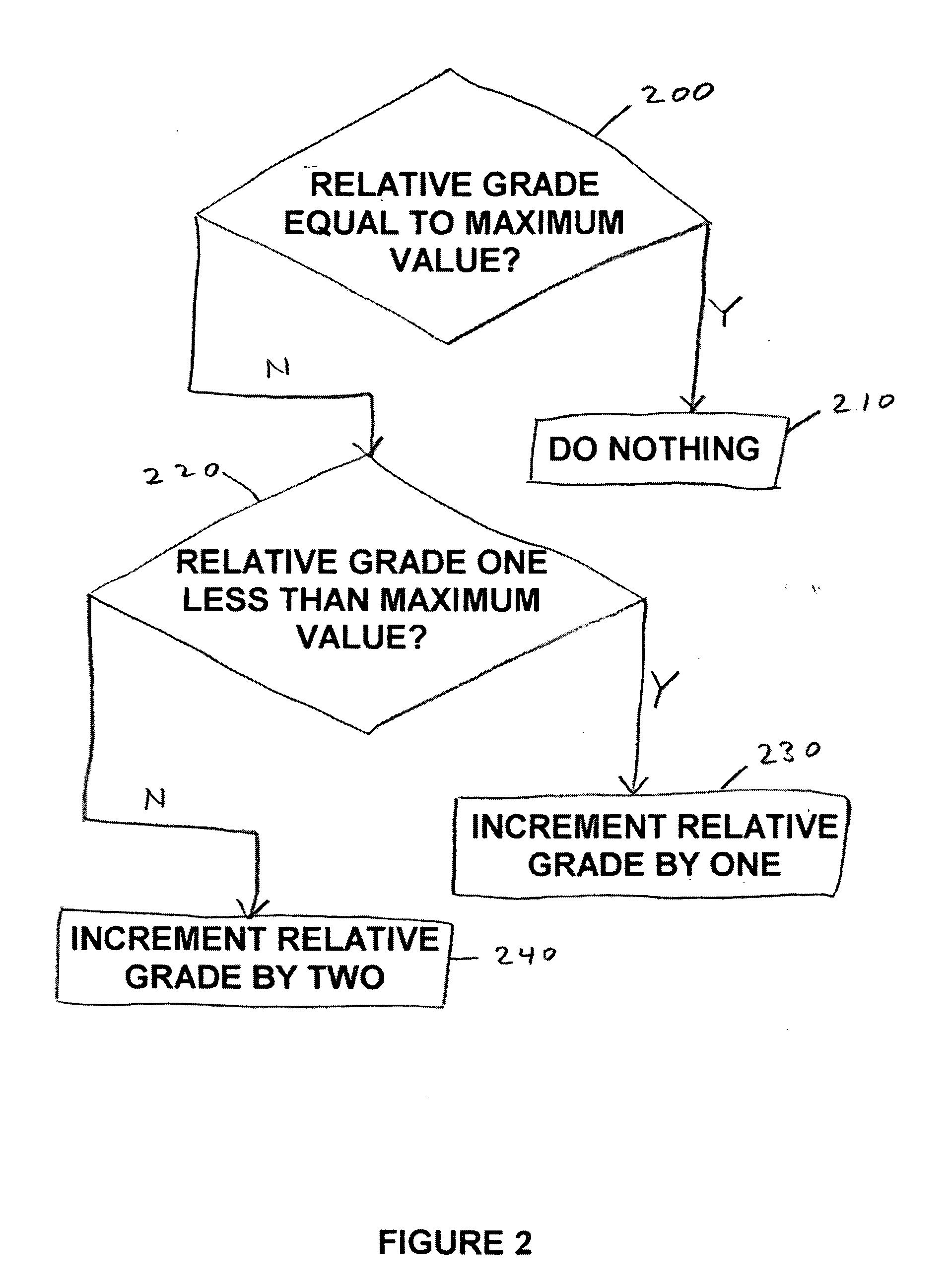

Method of achieving wear leveling in flash memory using relative grades

ActiveUS20060203546A1Memory architecture accessing/allocationRead-only memoriesS functionWear leveling

For each block of a memory, a number is calculated that is a function of how many times the block has been erased and of how many times at least one other block has been erased. The numbers are stored in the memory device that includes the memory. The numbers are updated as needed when blocks are erased. Blocks are selected to be erased in accordance with their numbers. Preferably, each block's function is the block's relative grade.

Owner:WESTERN DIGITAL ISRAEL LTD

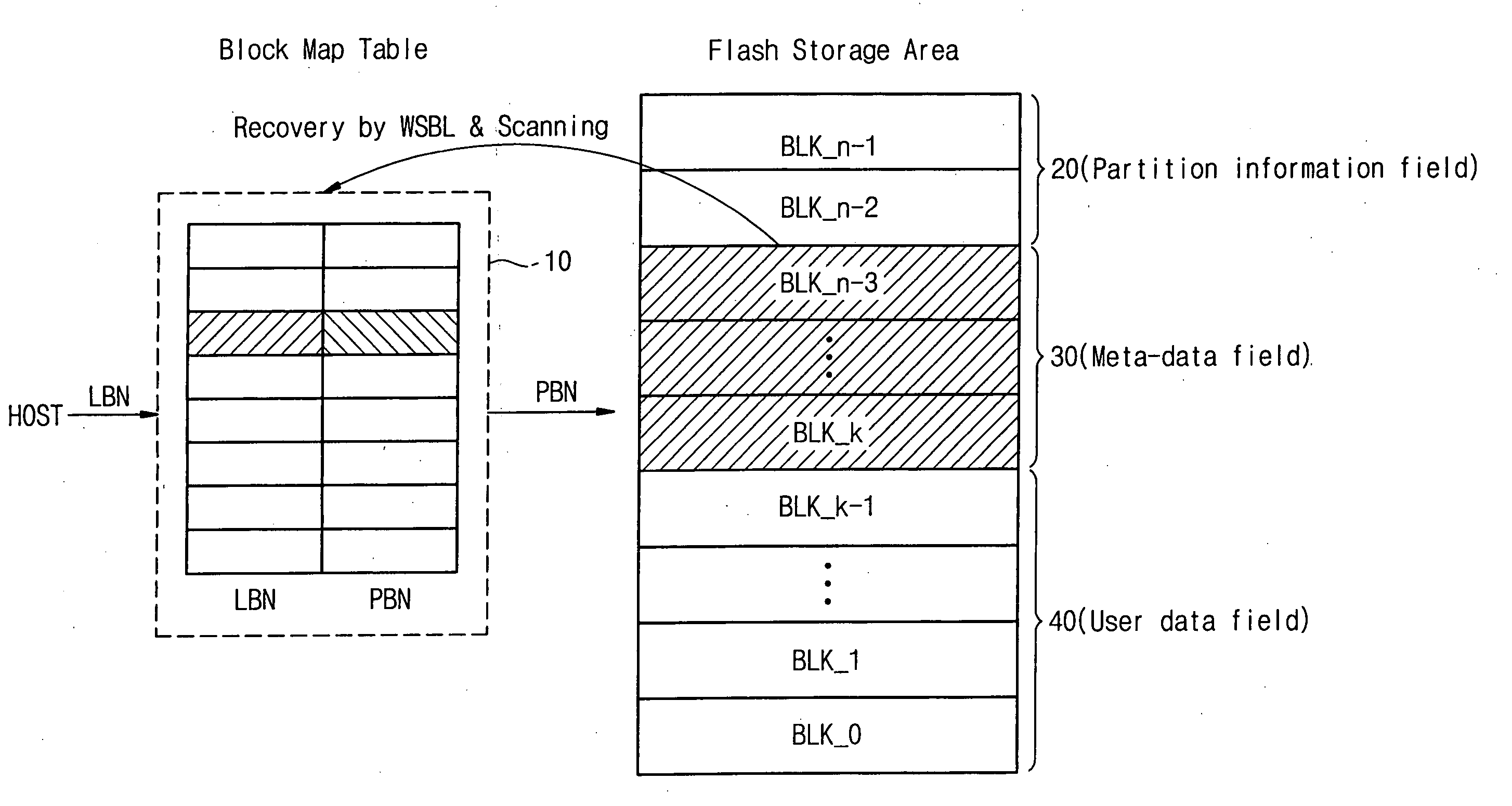

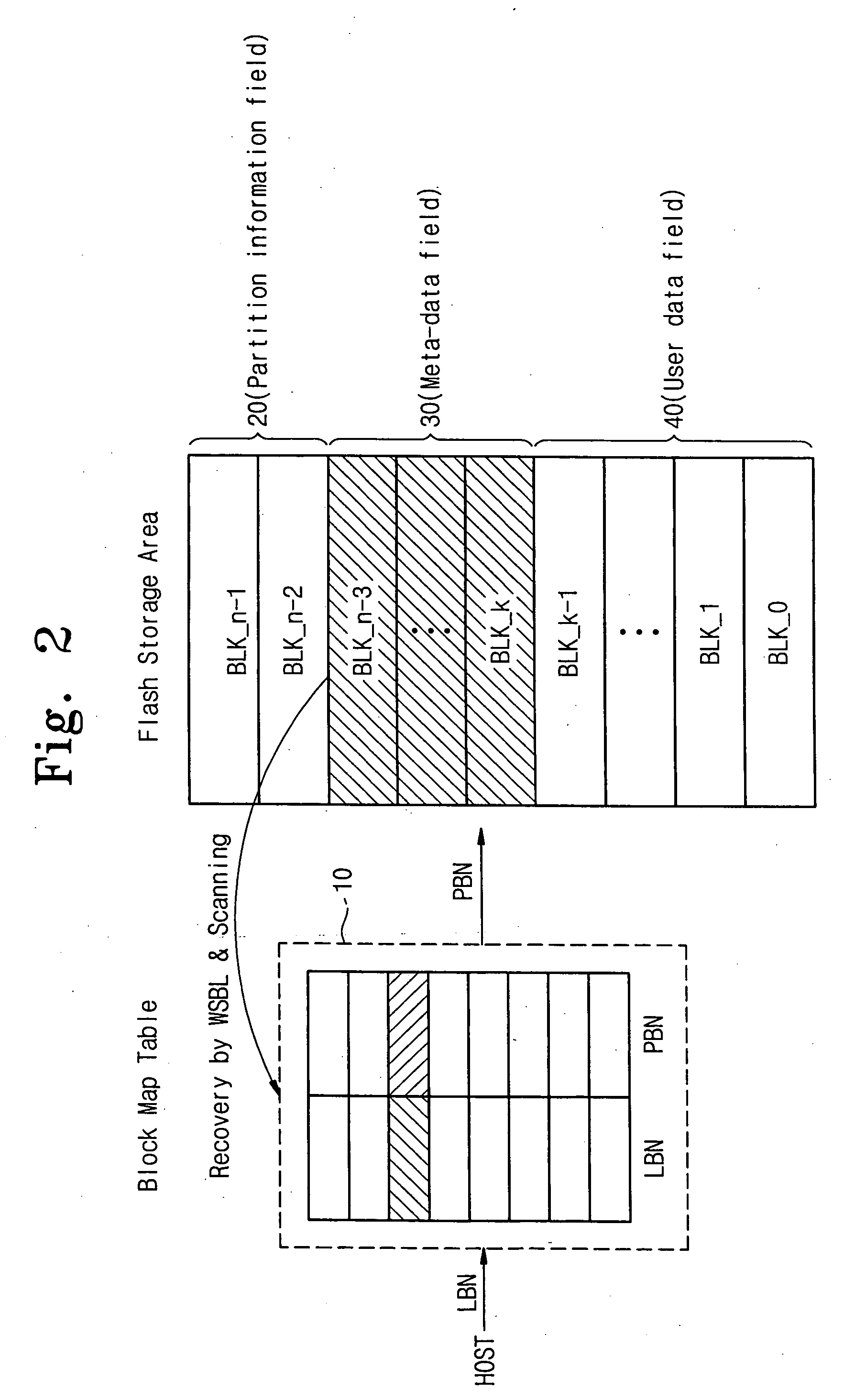

System with flash memory device and data recovery method thereof

ActiveUS20080104308A1Memory architecture accessing/allocationEnergy efficient ICTRecovery methodAddress mapping

A method is for recovering a block mapping table in a system including a flash memory device, where the block mapping table utilizes address mapping in accordance with a wear-leveling scheme. The method includes reading block arrangement information from the flash memory device for the wear-leveling scheme, restoring the block mapping table with reference to allocation block information included in the block arrangement information and scanning address allocation information included in spare regions of erased blocks of the flash memory device with reference to erased block information included in the block arrangement information and updating the block mapping table in accordance with the scanned address allocation information.

Owner:SAMSUNG ELECTRONICS CO LTD

Systems and methods for an enhanced controller architecture in data storage systems

ActiveUS20130060981A1Memory adressing/allocation/relocationDigital computer detailsController architectureEngineering

Disclosed herein is a controller architecture that pairs a controller with a NVM (non-volatile memory) storage system over a high-level, high speed interface such as PCIe. In one embodiment, the NVM storage system includes a bridge that communicates with the controller via the high-level interface, and controls the NVM via an interface (e.g., ONFI). The controller is provided a rich set of physical level of controls over individual elements of the NVM. In one embodiment, the controller is implemented in a higher powered processor that supports advanced functions such as mapping, garbage collection, wear leveling, etc. In one embodiment, the bridge is implemented in a lower powered processor and performs basic signal processing, channel management, basic error correction functions, etc. This labor division provides the controller physical control of the NVM over a fast, high-level interface, resulting in the controller managing the NVM at both the page and block level.

Owner:WESTERN DIGITAL TECH INC

Wear leveling method, and storage system and controller using the same

ActiveUS20100023675A1Effectively level wearingExtend your lifeMemory architecture accessing/allocationMemory adressing/allocation/relocationWear levelingBlock group

A wear leveling method for a flash is provided, wherein the flash memory includes a plurality of physical blocks grouped into at least a data area and a spare area. The method includes setting a first predetermined threshold value as a wear-leveling start value and randomly generating a random number as a memory erased count, wherein the random number is smaller than the wear-leveling start value. The method also includes counting the memory erased count each time when the physical blocks are erased and determining whether the memory erased count is smaller than the wear-leveling start value, wherein a physical blocks switching is performed between the data area and the spare area when the memory erased count is not smaller then the wear-leveling start value. Accordingly, it is possible to uniformly use the physical blocks, so as to effectively prolong a lifetime of the store system.

Owner:PHISON ELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com