Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

274 results about "Microcode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Microcode is a computer hardware technique that interposes a layer of organisation between the CPU hardware and the programmer-visible instruction set architecture of the computer. As such, the microcode is a layer of hardware-level instructions that implement higher-level machine code instructions or internal state machine sequencing in many digital processing elements. Microcode is used in general-purpose central processing units, although in current desktop CPUs it is only a fallback path for cases that the faster hardwired control unit cannot handle.

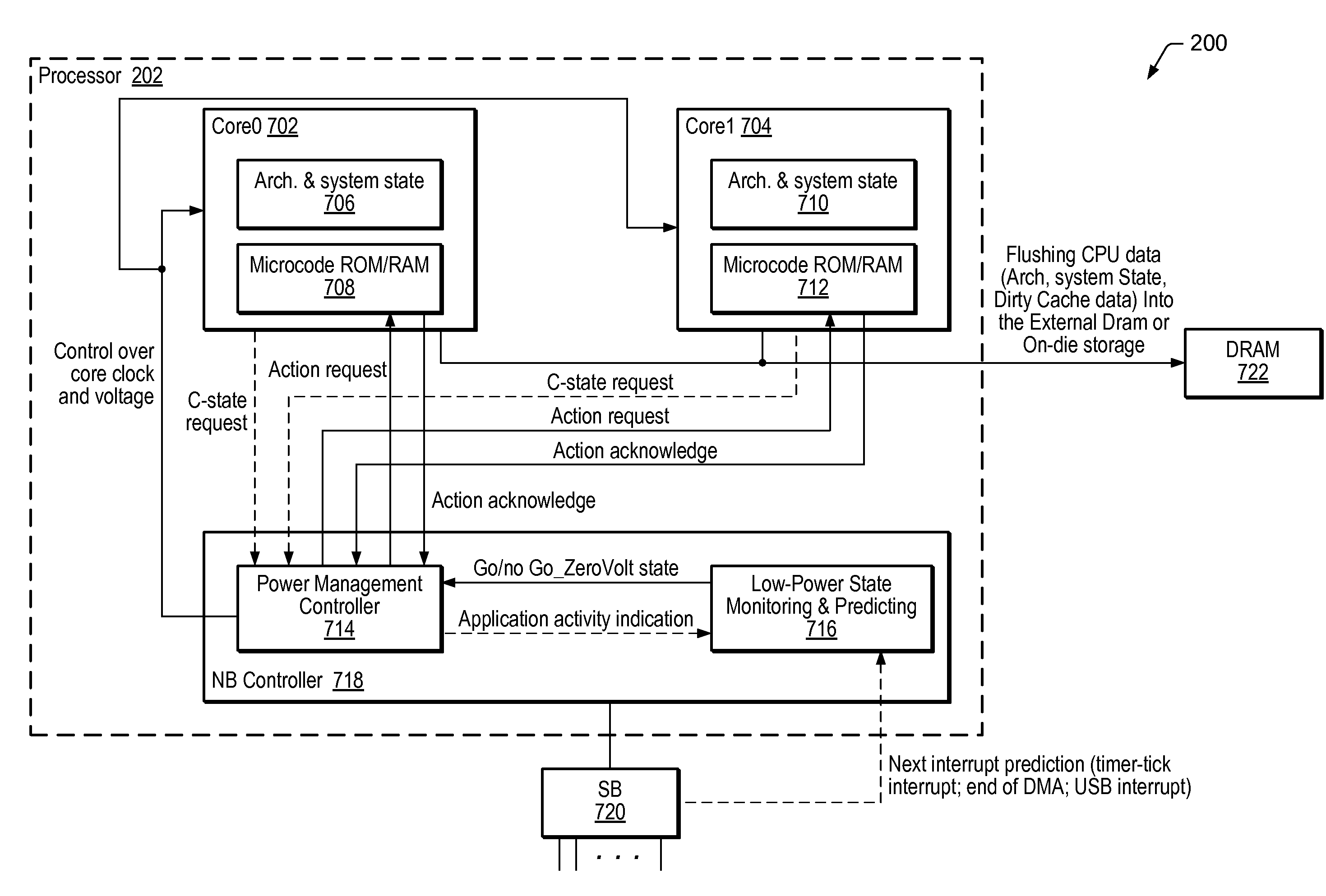

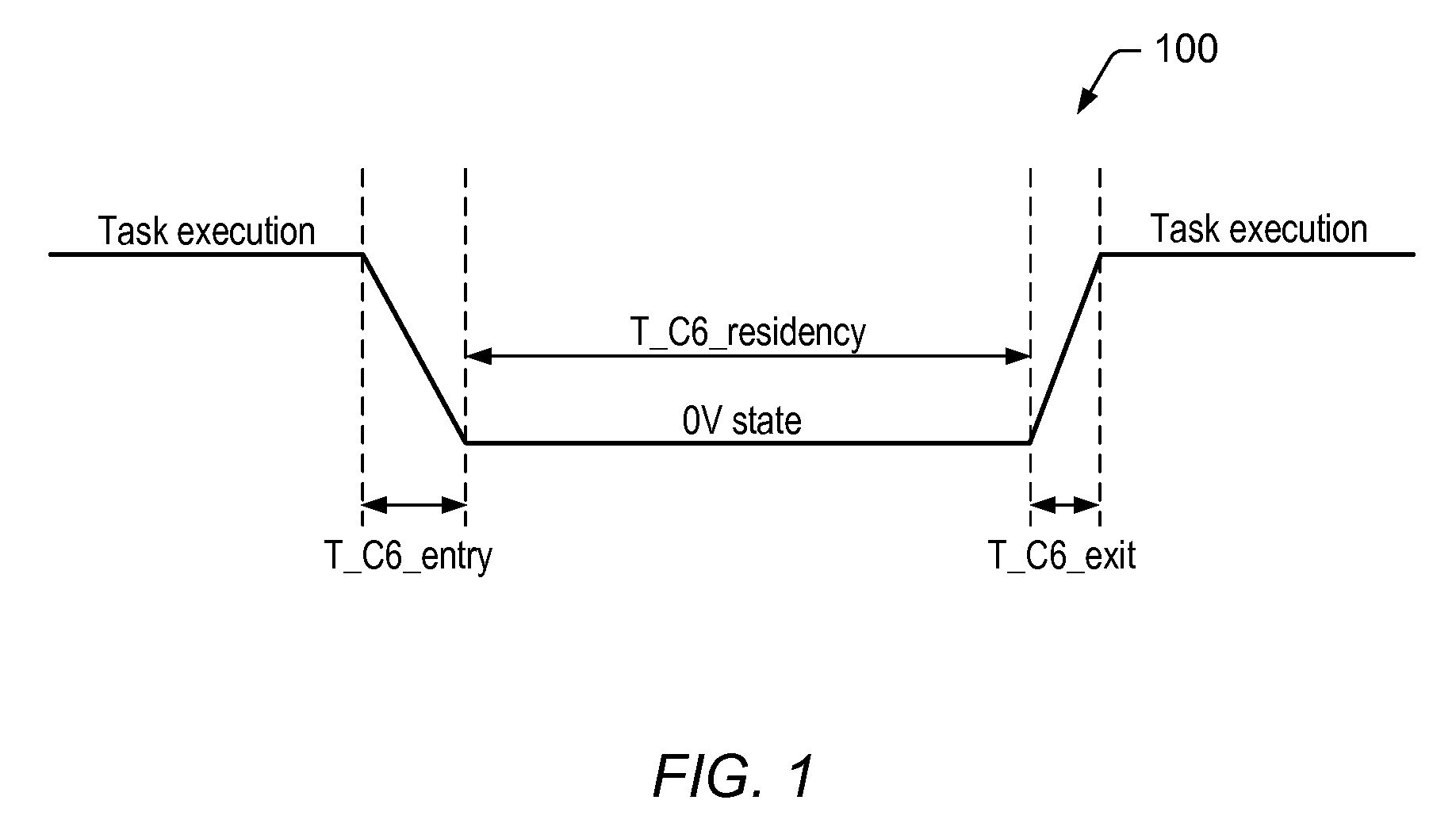

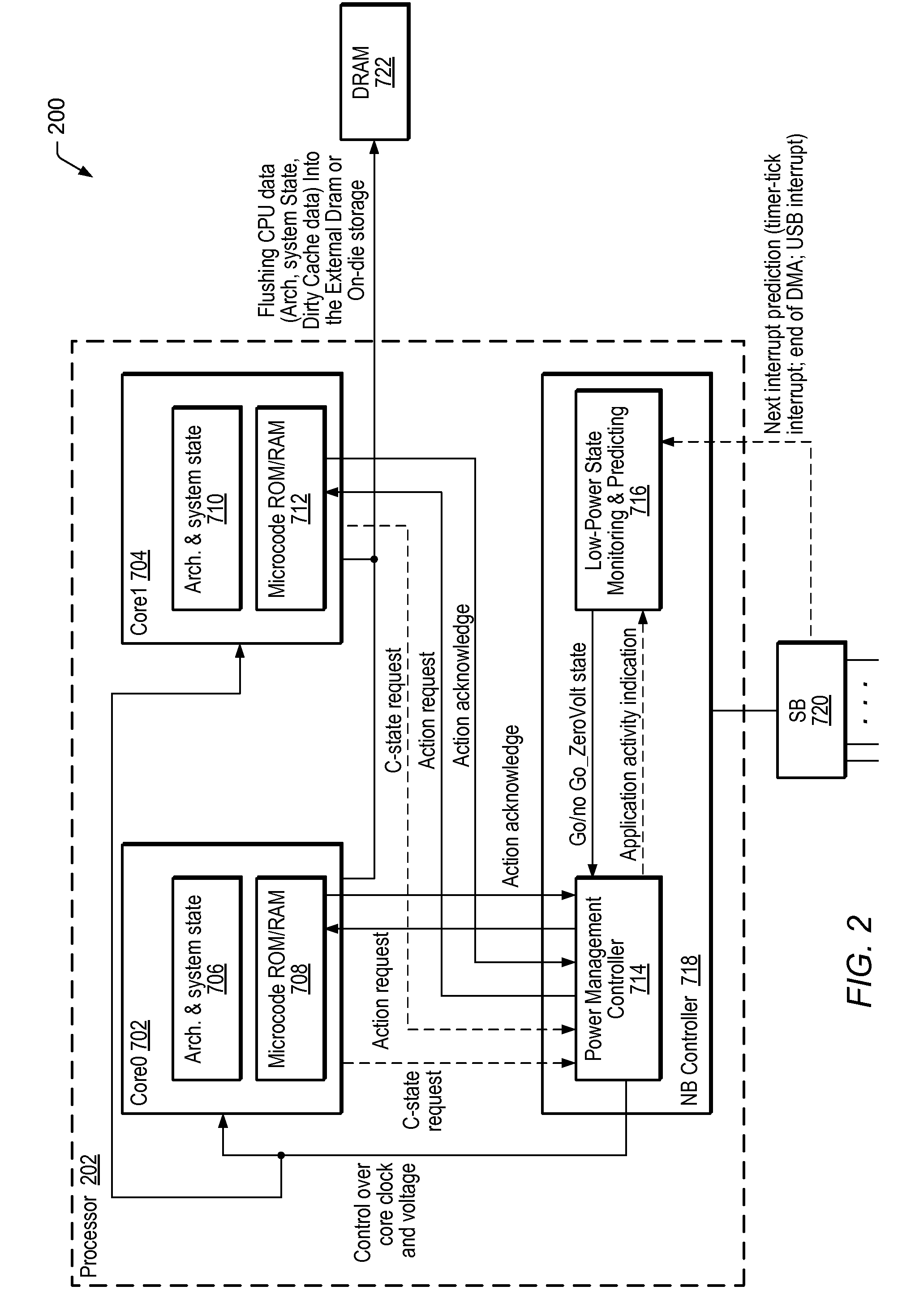

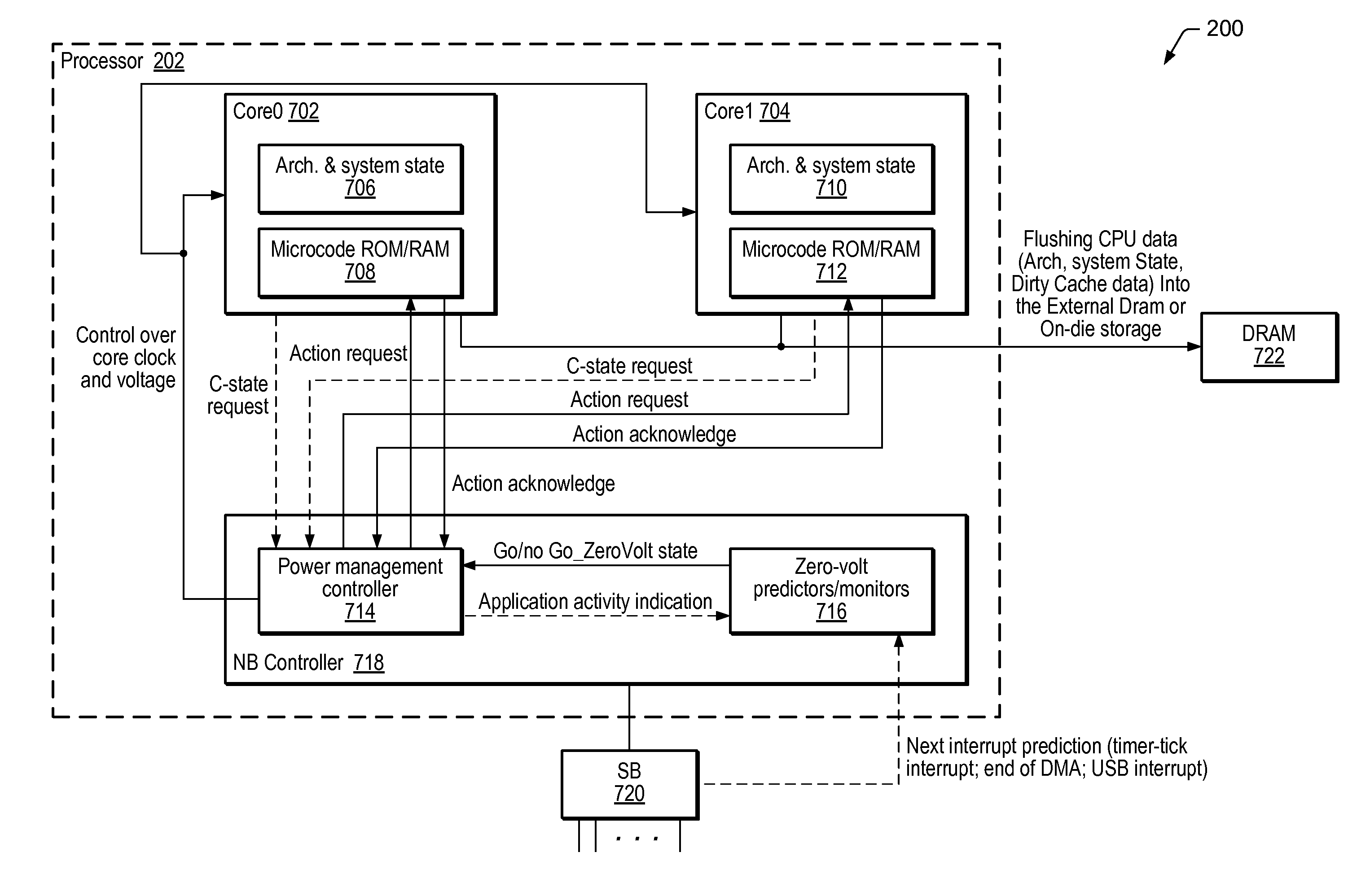

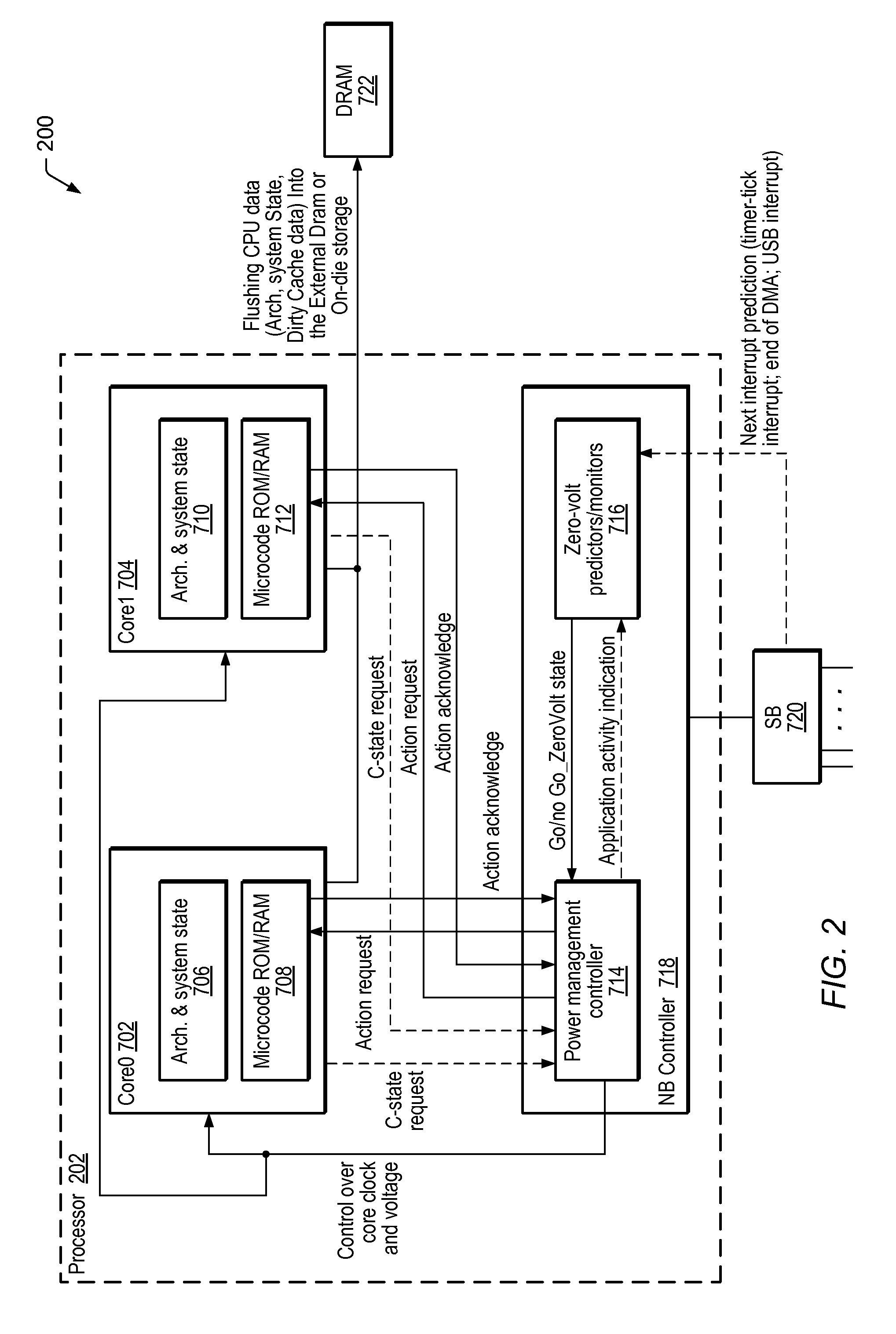

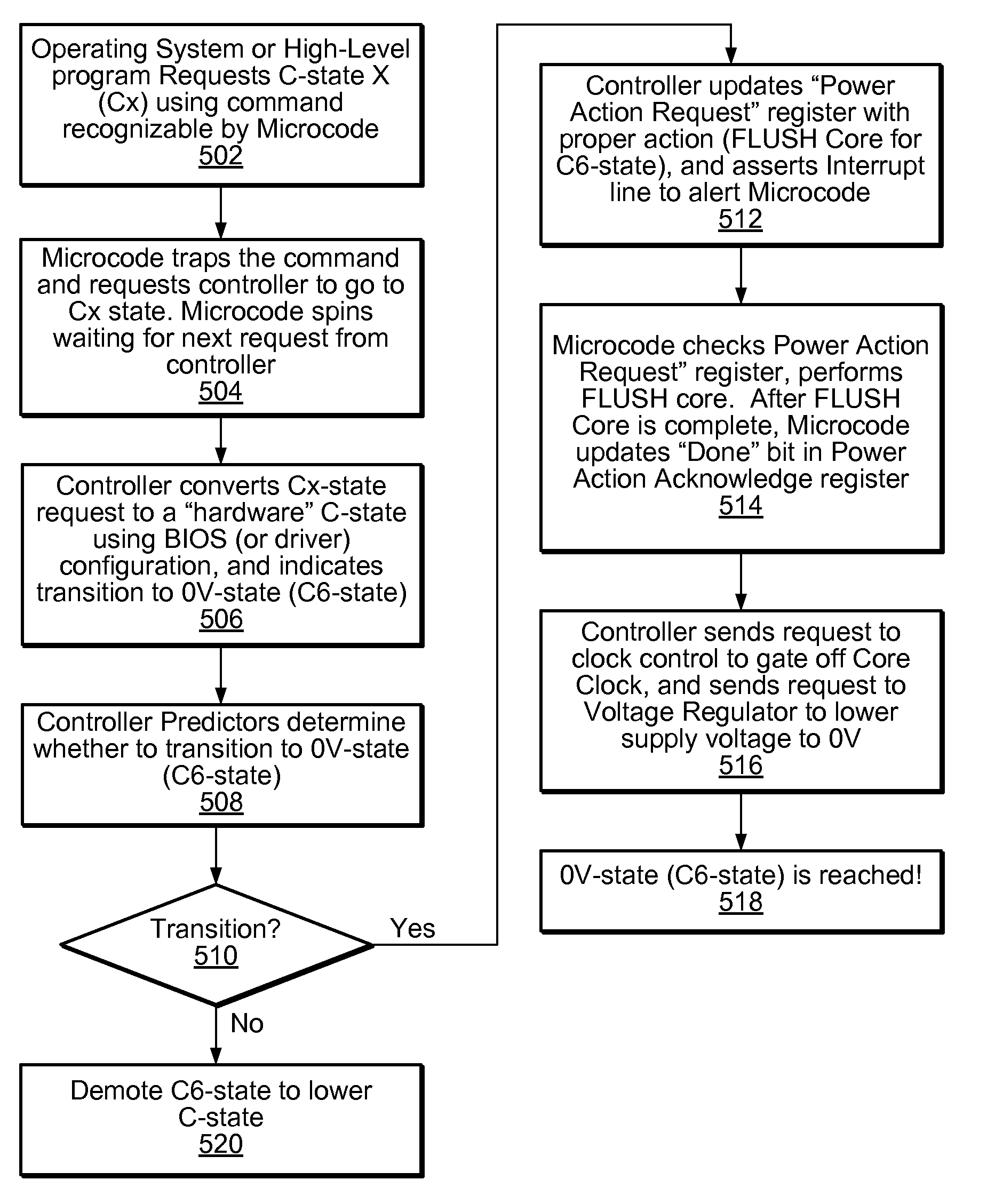

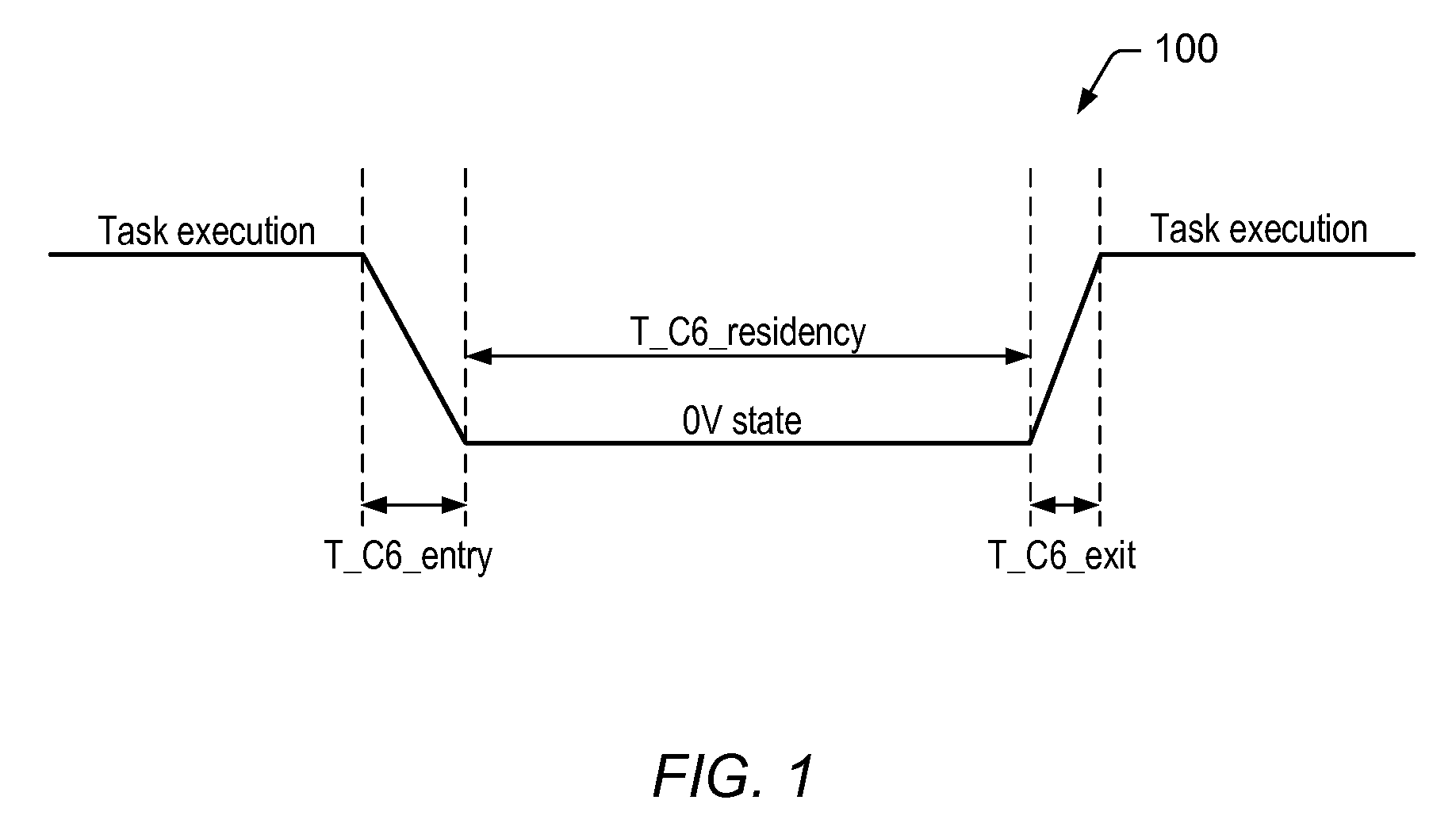

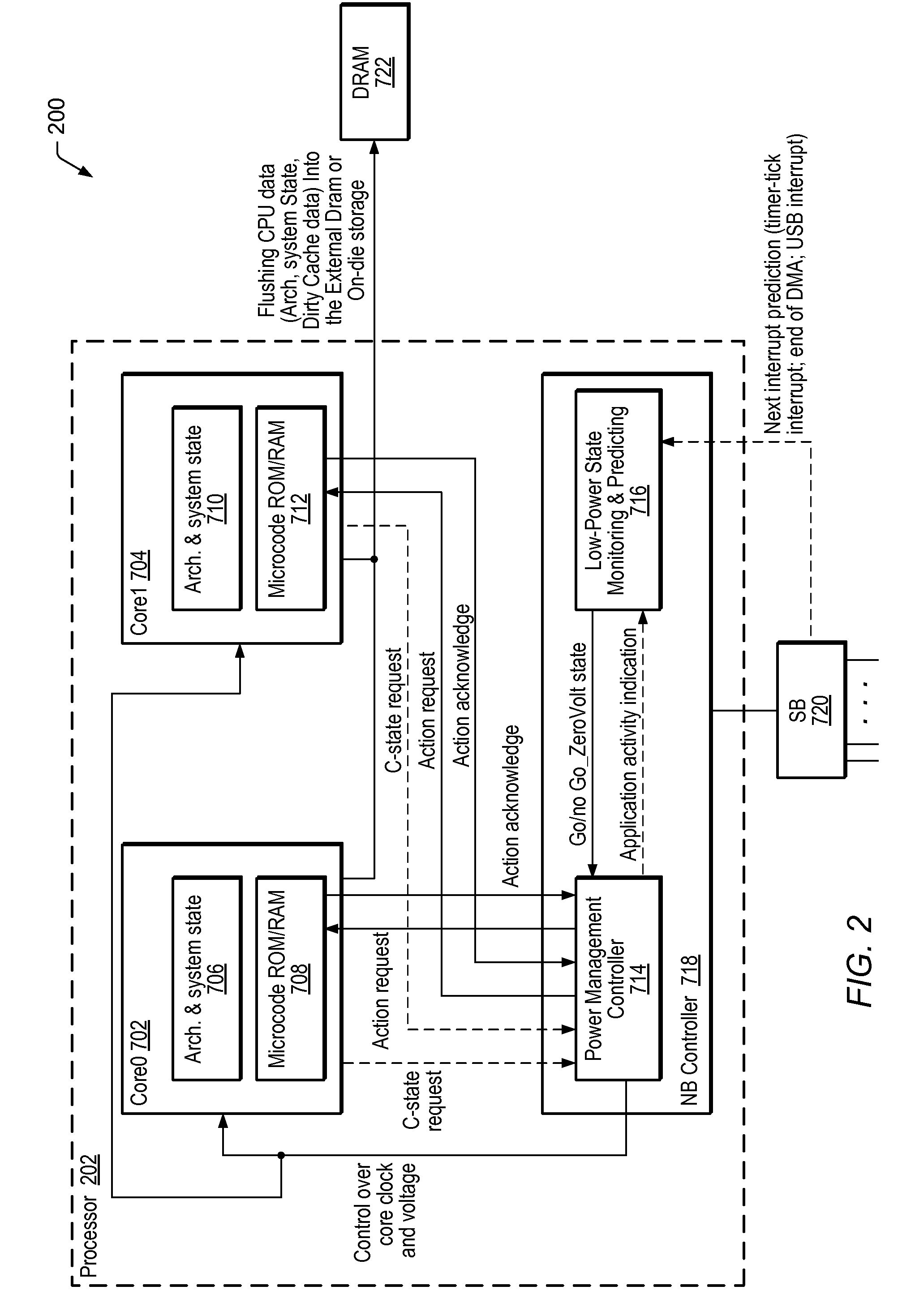

Hardware Monitoring and Decision Making for Transitioning In and Out of Low-Power State

ActiveUS20090235105A1Improve balanceMore efficiencyEnergy efficient ICTVolume/mass flow measurementDirect memory accessTimer

A power management controller (PMC) that interfaces with a processor comprising one or more cores. The PMC may be configured to communicate with each respective core, such that microcode executed by the respective processor core may recognize when a request is made to transition the respective core to a target power-state. For each respective core, the state monitor may monitor active-state residency, non-active-state residency, Direct Memory Access (DMA) transfer activity associated with the respective core, Input / Output (I / O) processes associated with the respective core, and the value of a timer-tick (TT) interval associated with the respective core. The status monitor may derive respective status information for the respective core based on the monitoring and indicate whether the respective core should be allowed to transition to the corresponding target power-state. The PMC may transition the respective processor core to the corresponding target power-state accordingly.

Owner:MEDIATEK INC

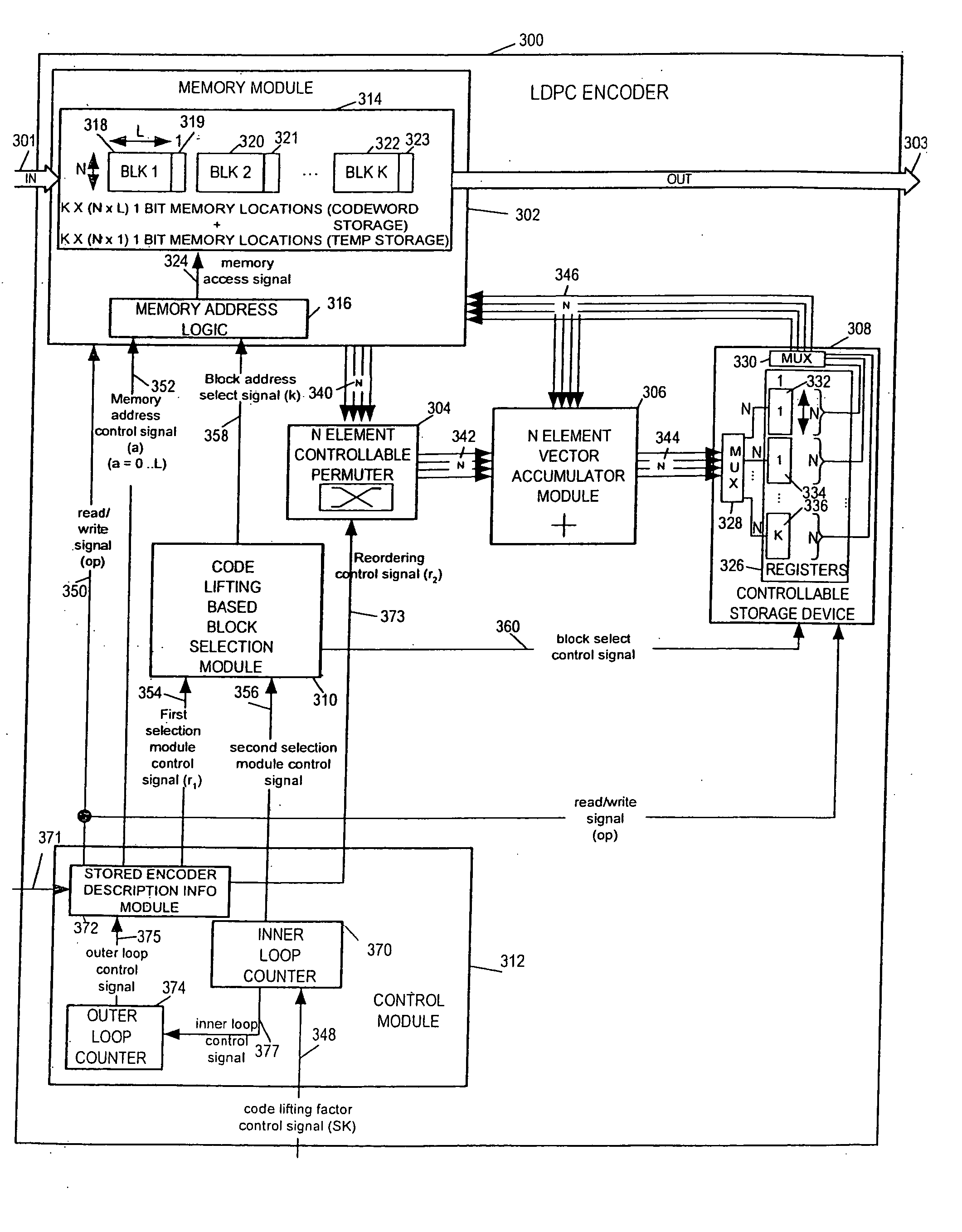

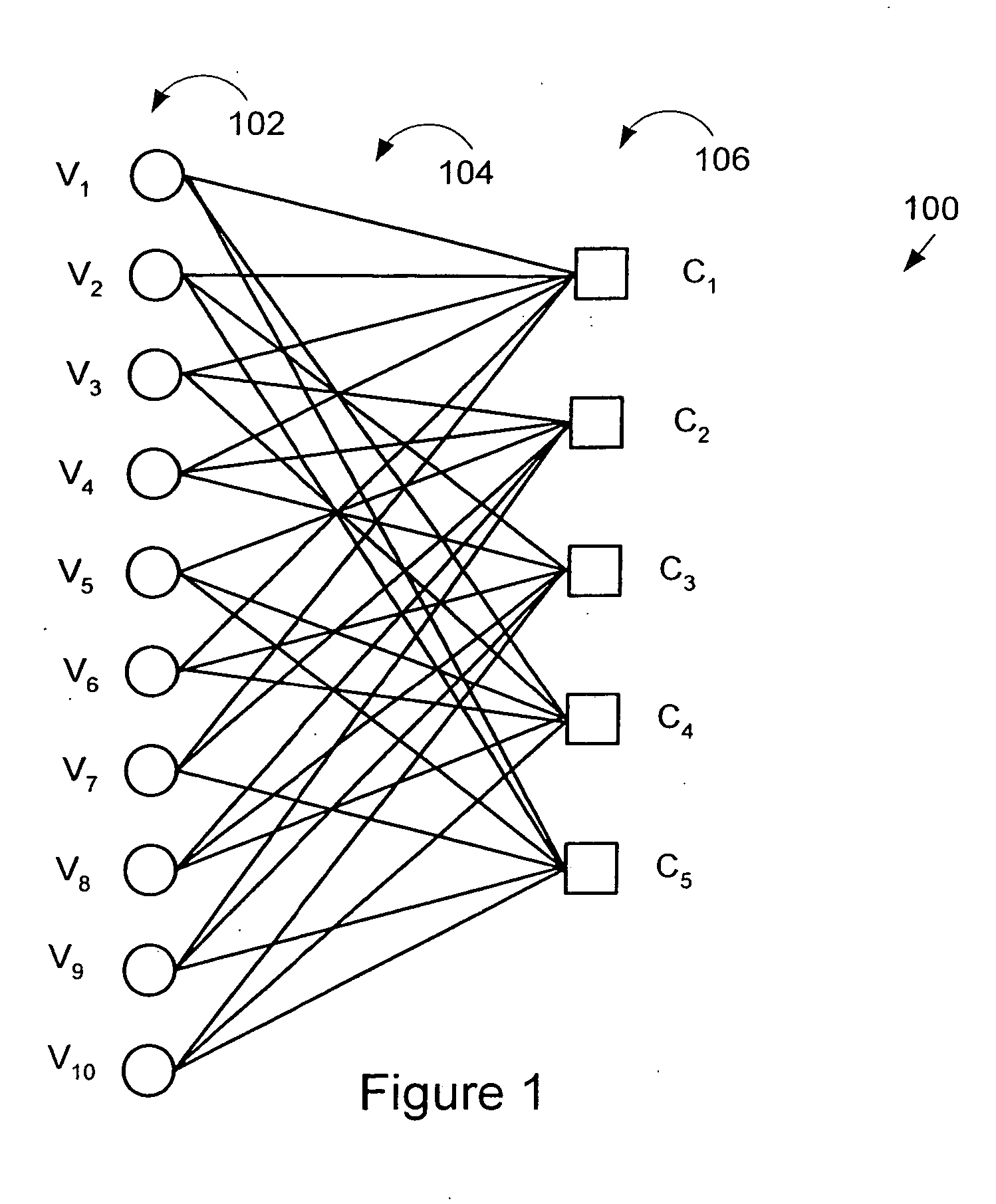

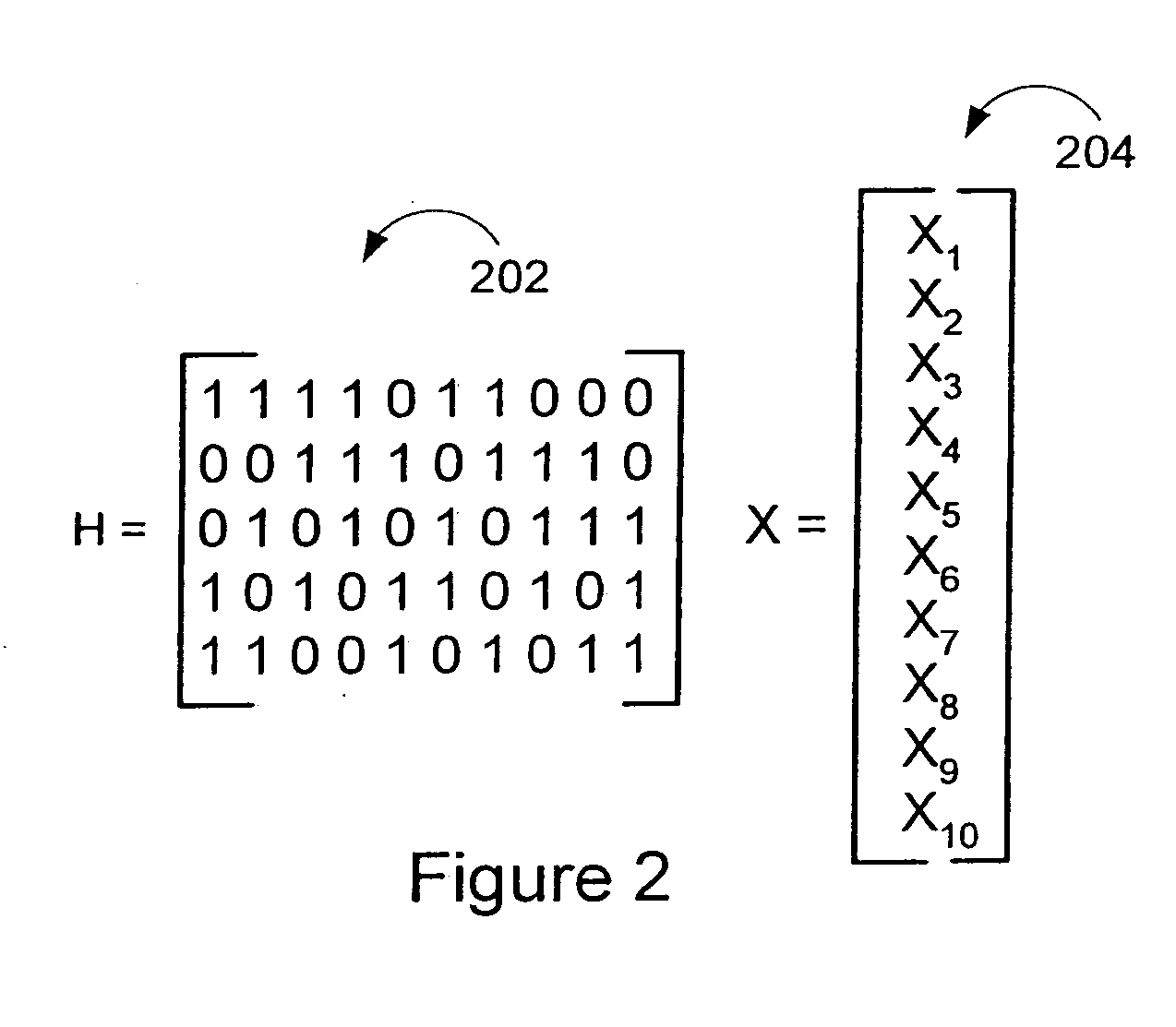

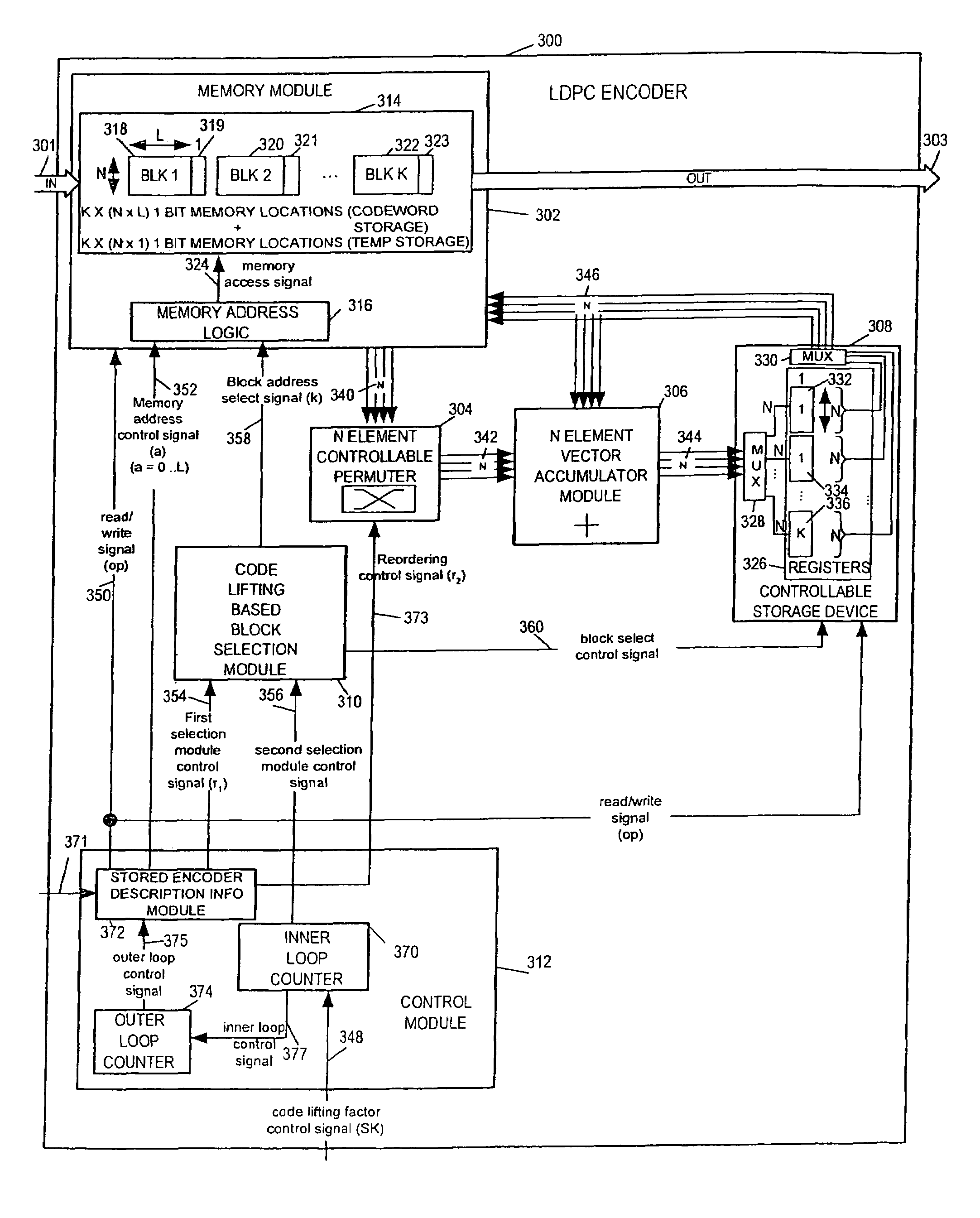

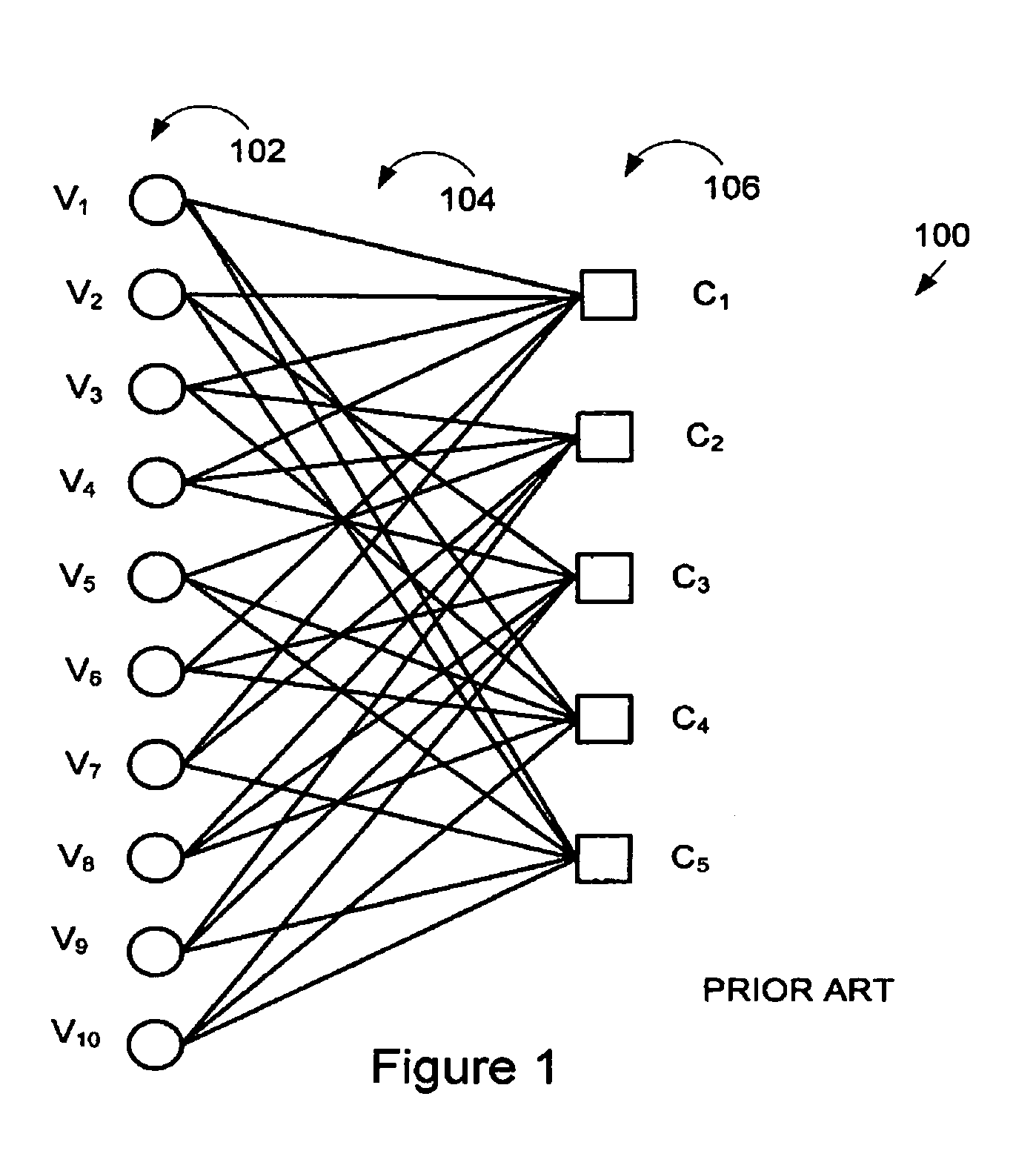

LDPC encoding methods and apparatus

ActiveUS20060020872A1Simple microcodeEasy to modifyError correction/detection using multiple parity bitsCode conversionDegree of parallelismInstruction set

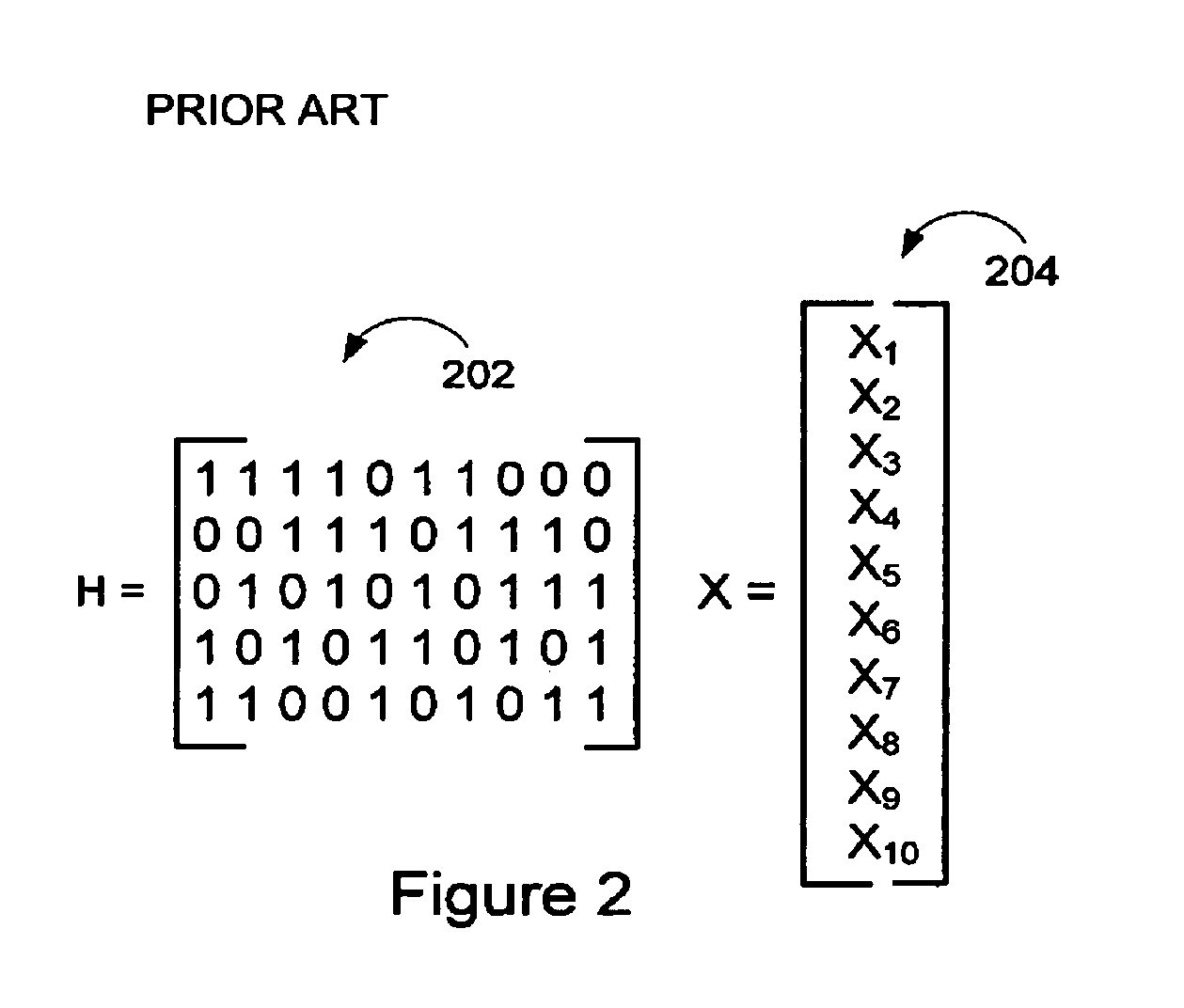

A flexible and relatively hardware efficient LDPC encoder is described. The encoder can be implemented with a level of parallelism which is less than the full parallelism of the code structure used to control the encoding process. Each command of a relatively simple microcode used to describe the code structure can be stored and executed multiple times to complete the encoding of a codeword. Different codeword lengths can be supported using the same set of microcode instructions but with the code being implemented a different number of times depending on the lifting factor selected to be used. The LDPC encoder can switch between encoding codewords of different lengths, without the need to change the stored code description information, by simply changing a code lifting factor used to control the encoding processes. When coding codewords shorter than the maximum supported codeword length some block storage locations and / or registers may go unused.

Owner:QUALCOMM INC

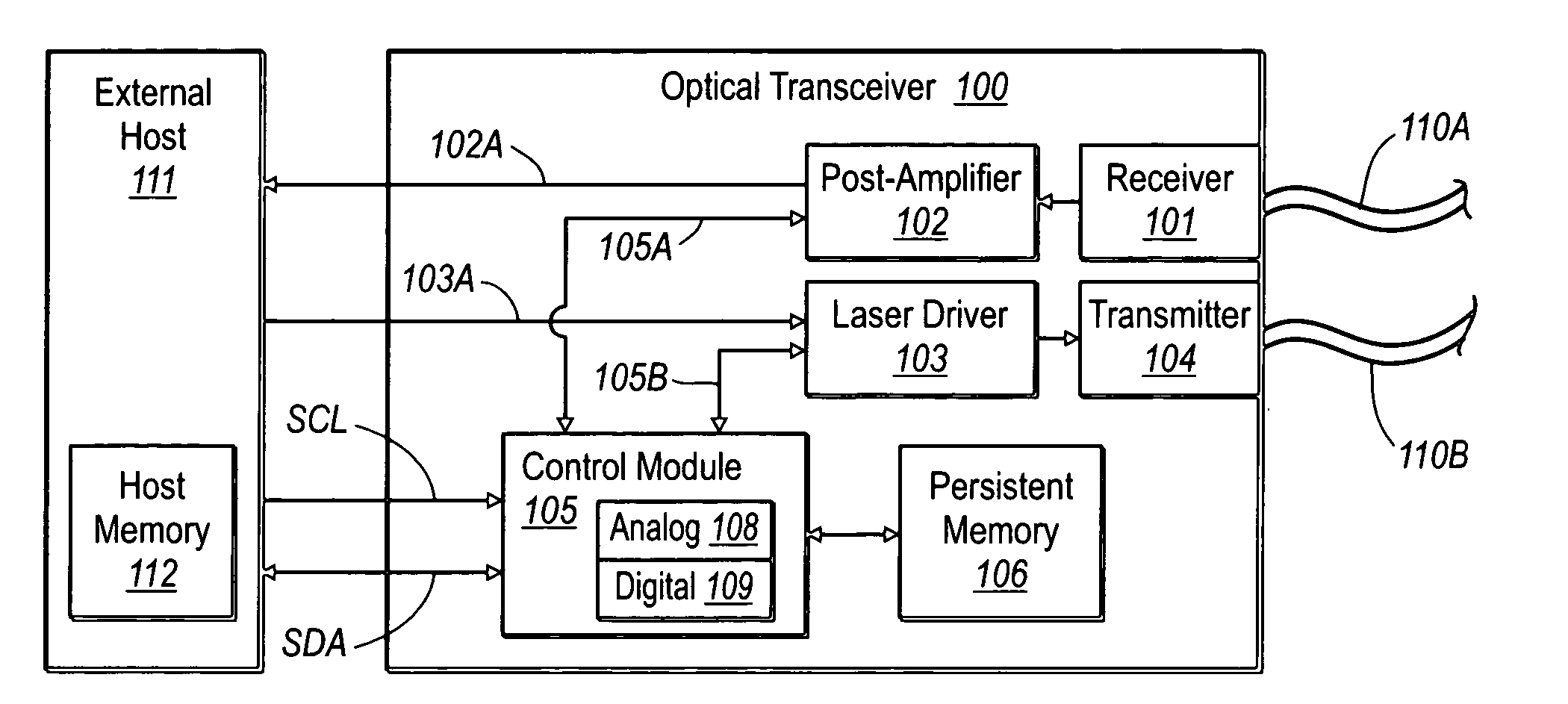

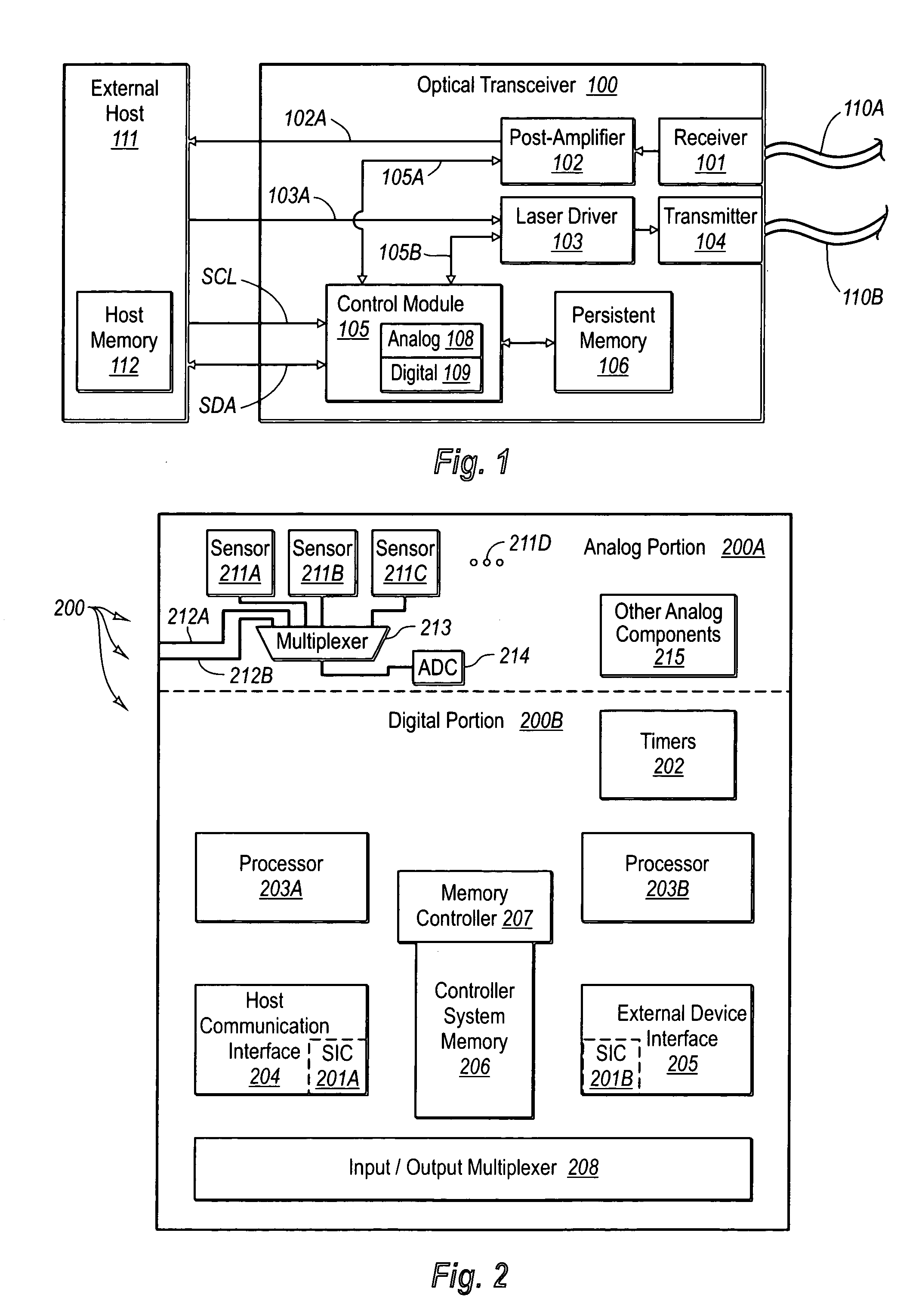

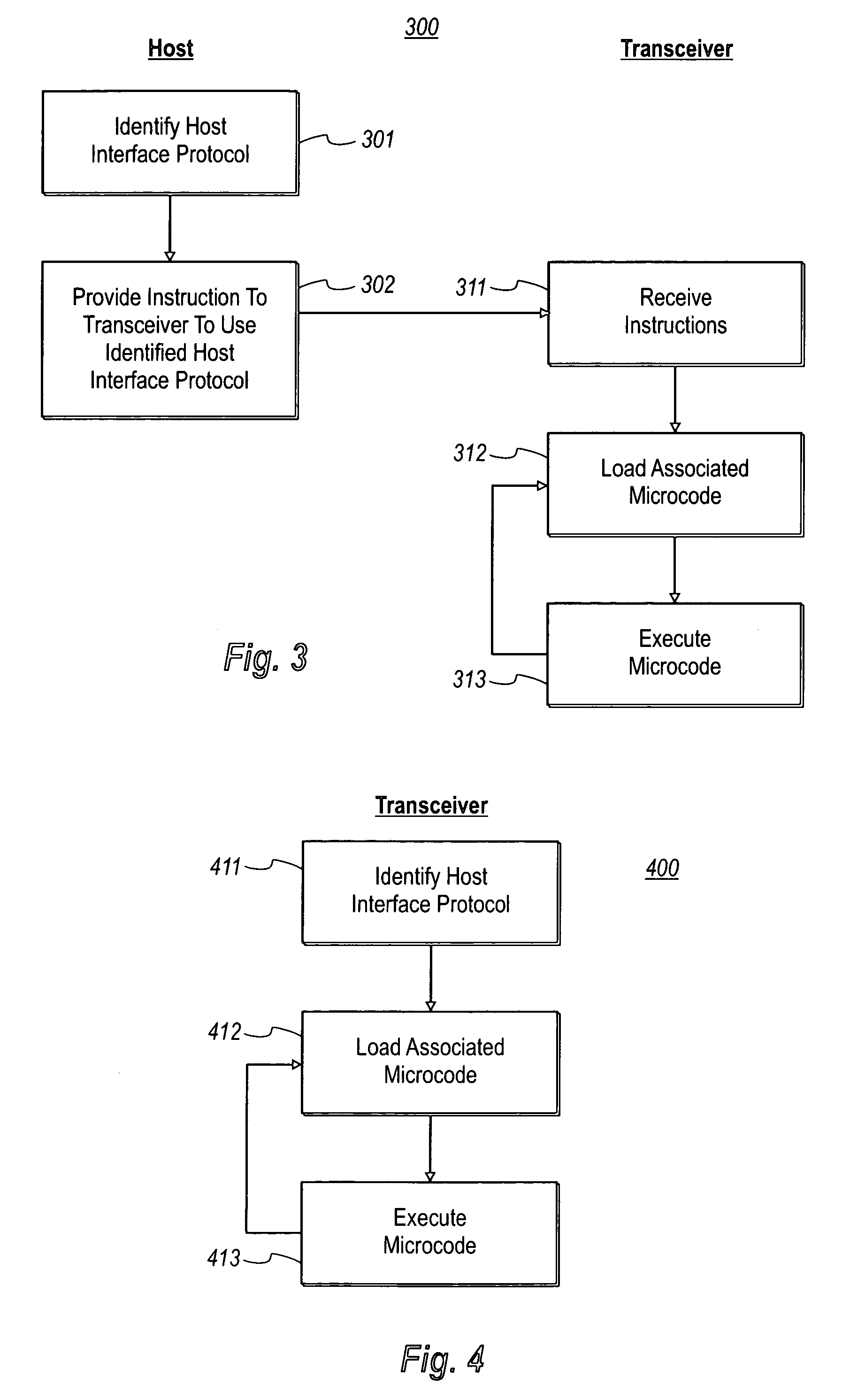

Selectable host-transceiver interface protocol

An optical transceiver, including a memory and a processor, which is capable of supporting different host interface protocols for communication between the optical transceiver and a host computing system. Each of the host interface protocols may be implemented by selecting microcode that corresponds to a particular host interface protocol and loading the microcode into the memory. The processor may later execute the microcode and cause the transceiver and the host to communicate using the specified interface protocol. The host interface protocols may also be implemented by hardware contained in the optical transceiver.

Owner:II VI DELAWARE INC

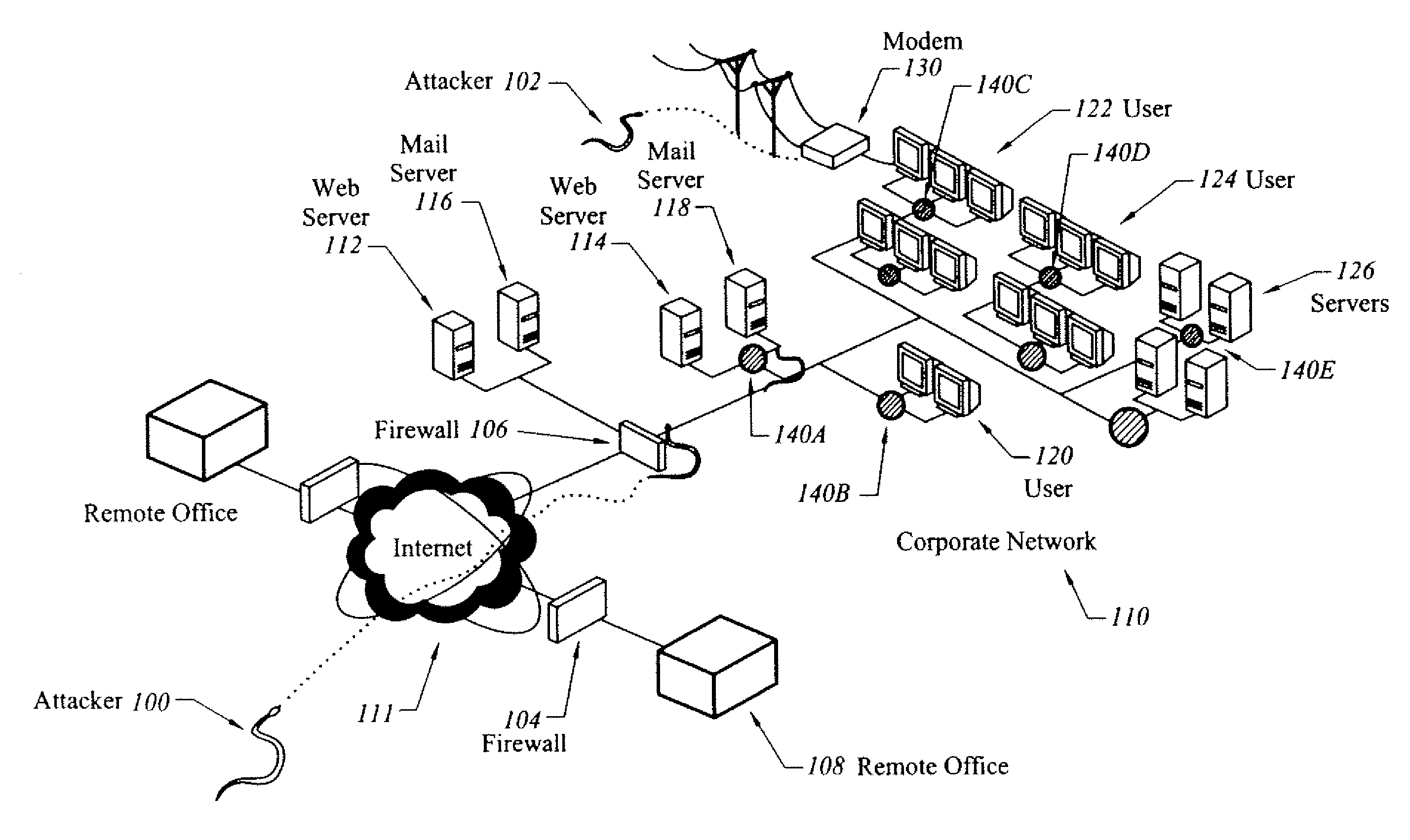

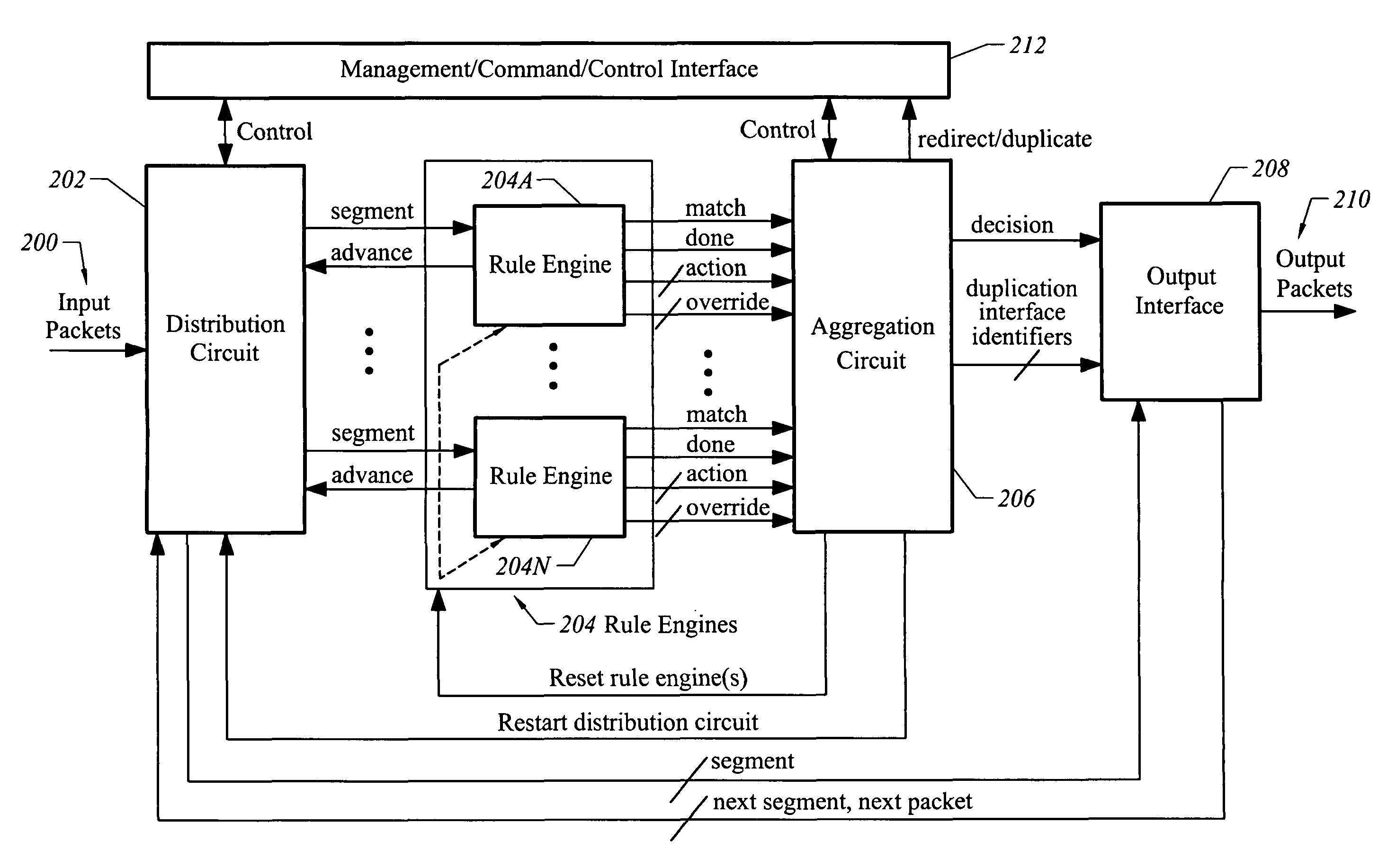

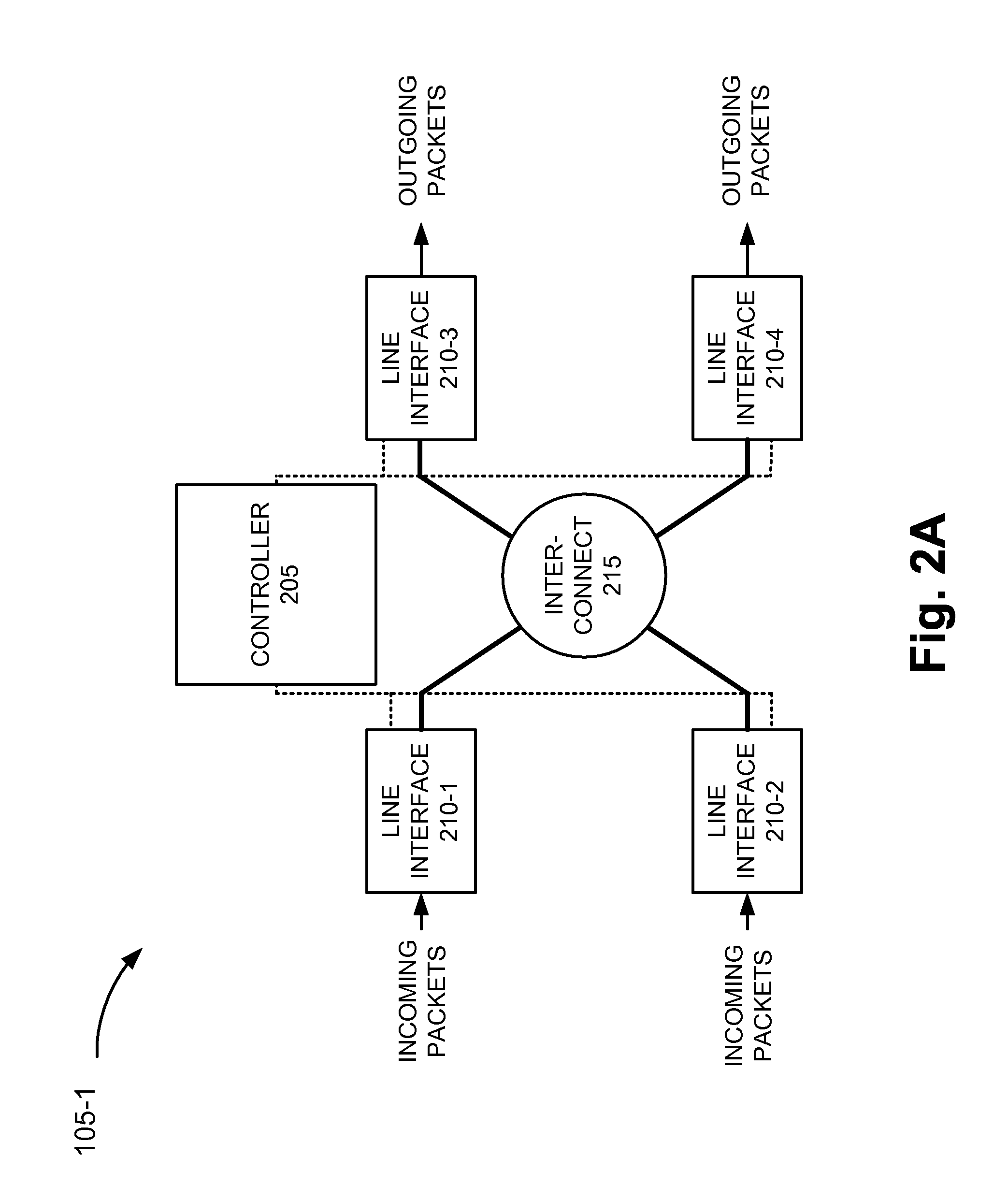

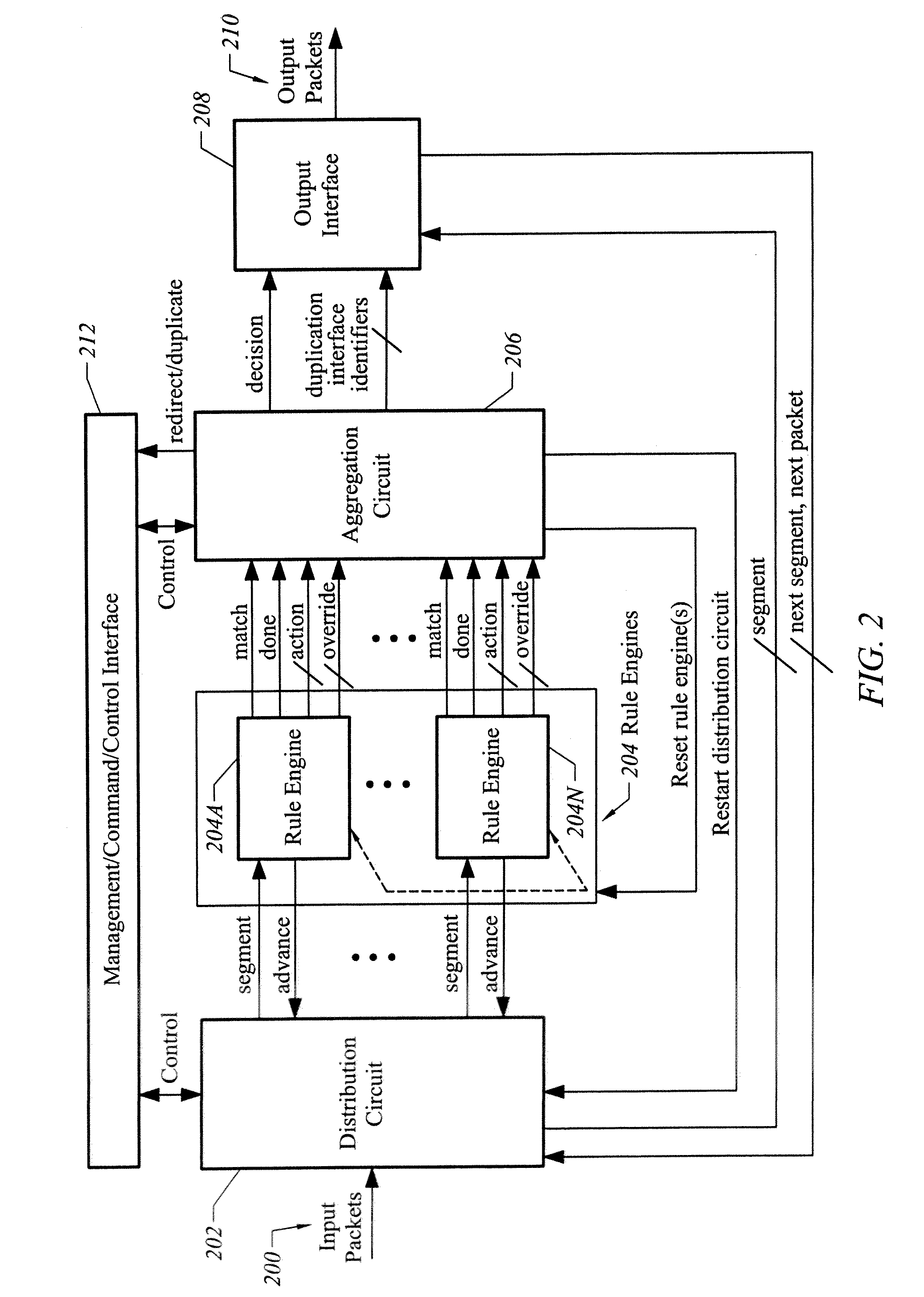

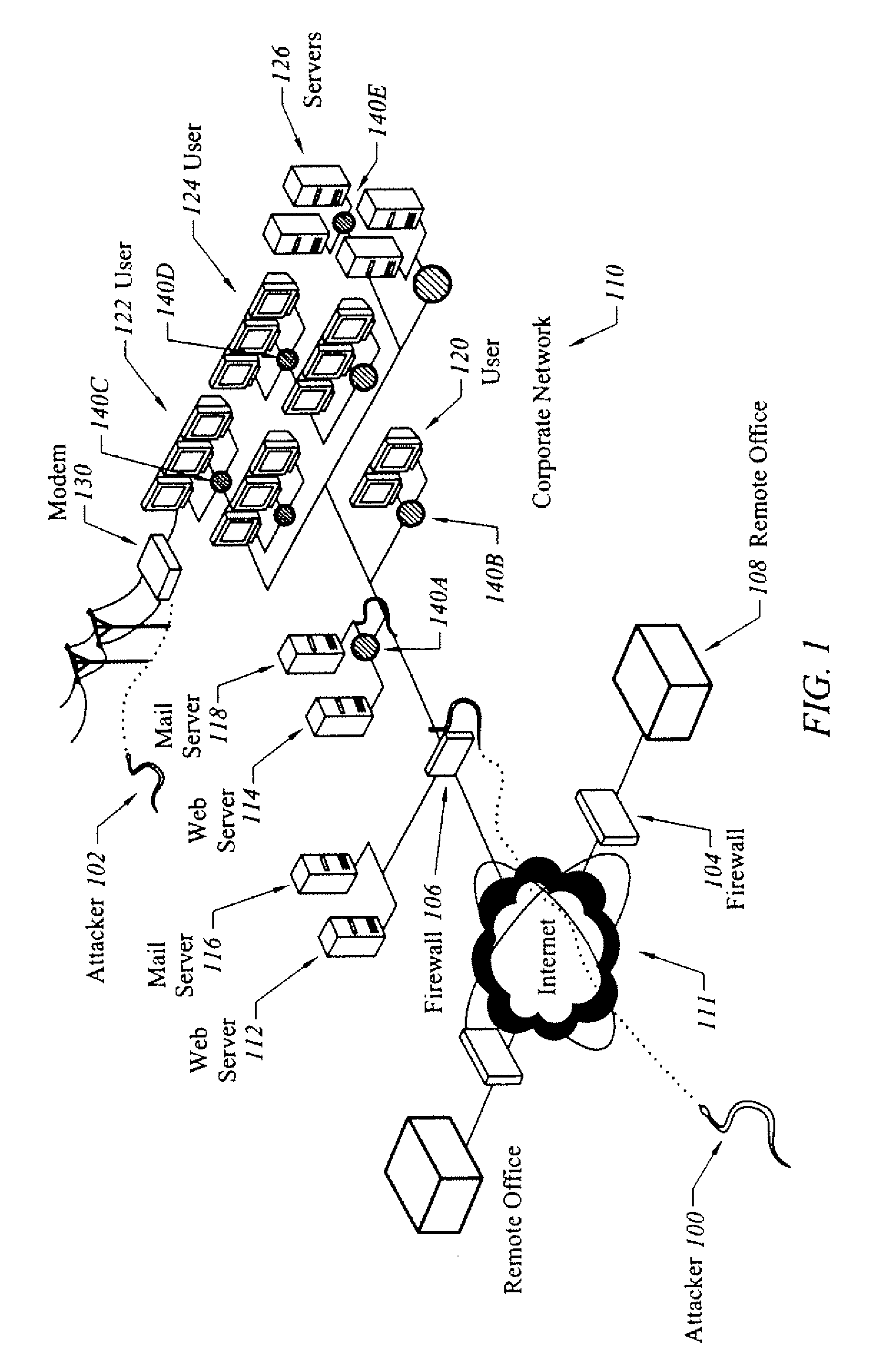

Apparatus and method for associating categorization information with network traffic to facilitate application level processing

ActiveUS20100011434A1Facilitate application level processingLow costError preventionFrequency-division multiplex detailsTraffic capacityHash function

An apparatus is described that associates categorization information with network traffic to facilitate application level processing through processing of network traffic in accordance with provisioned rules and policies. The apparatus includes a plurality of microcode controlled state machines, wherein at least one microcode state machine processes at least one input data field using a hash function to generate a hash identifier. This embodiment further includes a distribution circuit that routes input data to the plurality of microcode controlled state machines, such that at least one individual microcode controlled state machine applies a rule to the input data to produce the at least one input data field, and to produce modification instructions based on the hash identifier. This embodiment further includes a first circuit that appends the hash identifier to the input data to produce modified input data based on the modification instructions, and that routes the modified input data in accordance with an output routing strategy. Advantageously, the apparatus provides an architectural framework well suited to a low cost, high speed, robust implementation of flexible, advanced network security and monitoring features and network traffic analysis.

Owner:CPACKET NETWORKS

Protocol for Transitioning In and Out of Zero-Power State

A processor may comprise one or more cores, where each respective core may comprise one or more state registers, and non-volatile memory configured to store microcode instructions executed by the respective processor core. The processor may further comprise a power management controller (PMC) interfacing with each respective core, and a state monitor (SM) interfacing with the PMC. The PMC may be configured to communicate with each respective core, such that microcode executed by the respective processor core may recognize when a request is made to transition the respective core to a low-power state. The microcode may communicate the request to the PMC, which may in turn determine if the request is for the respective core to transition to a zero-power state. If it is, the PMC may communicate with the SM to determine whether to transition the respective processor core to the zero-power state, and initiate transition to the zero-power state if a determination to transition to the zero-power state is made.

Owner:MEDIATEK INC

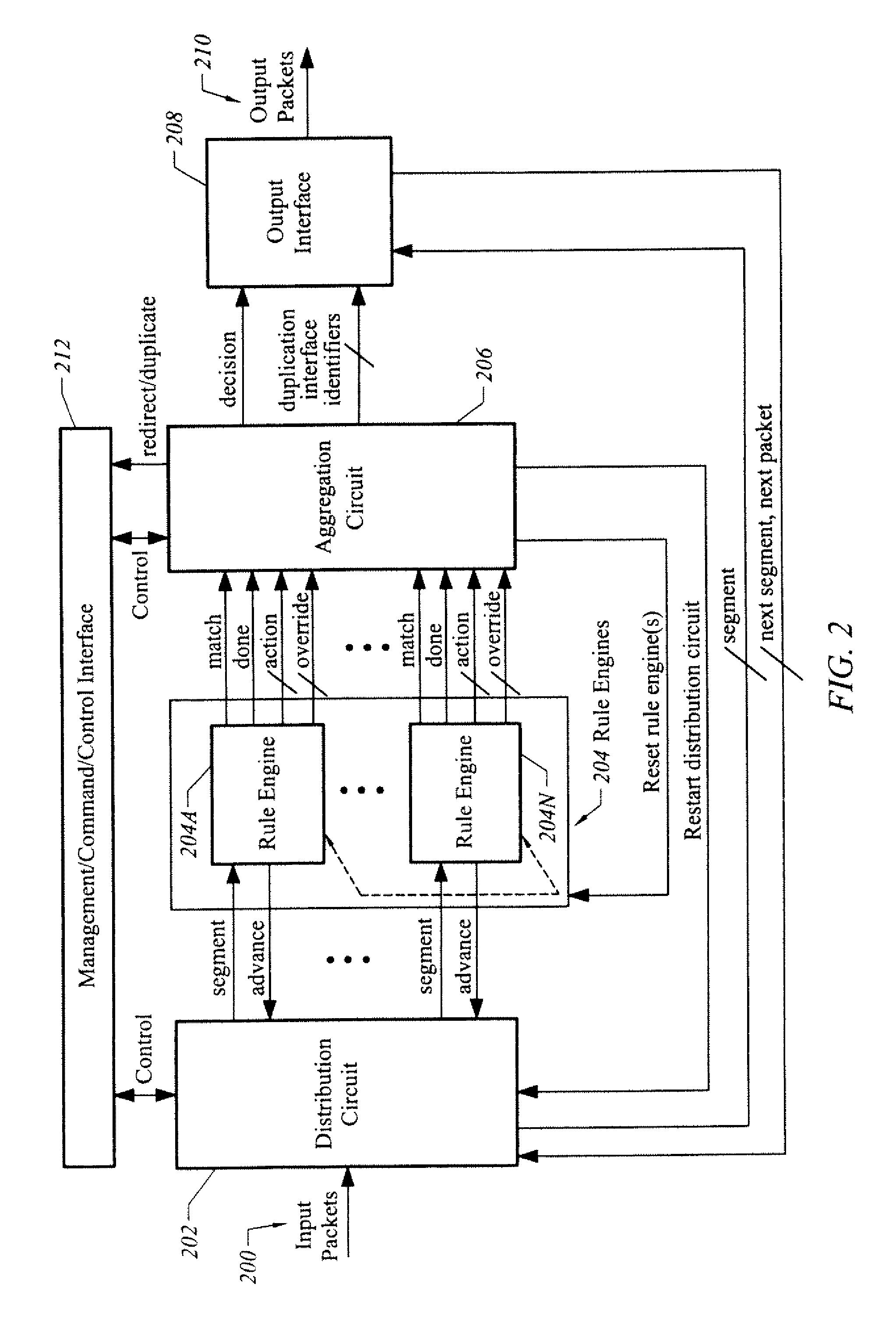

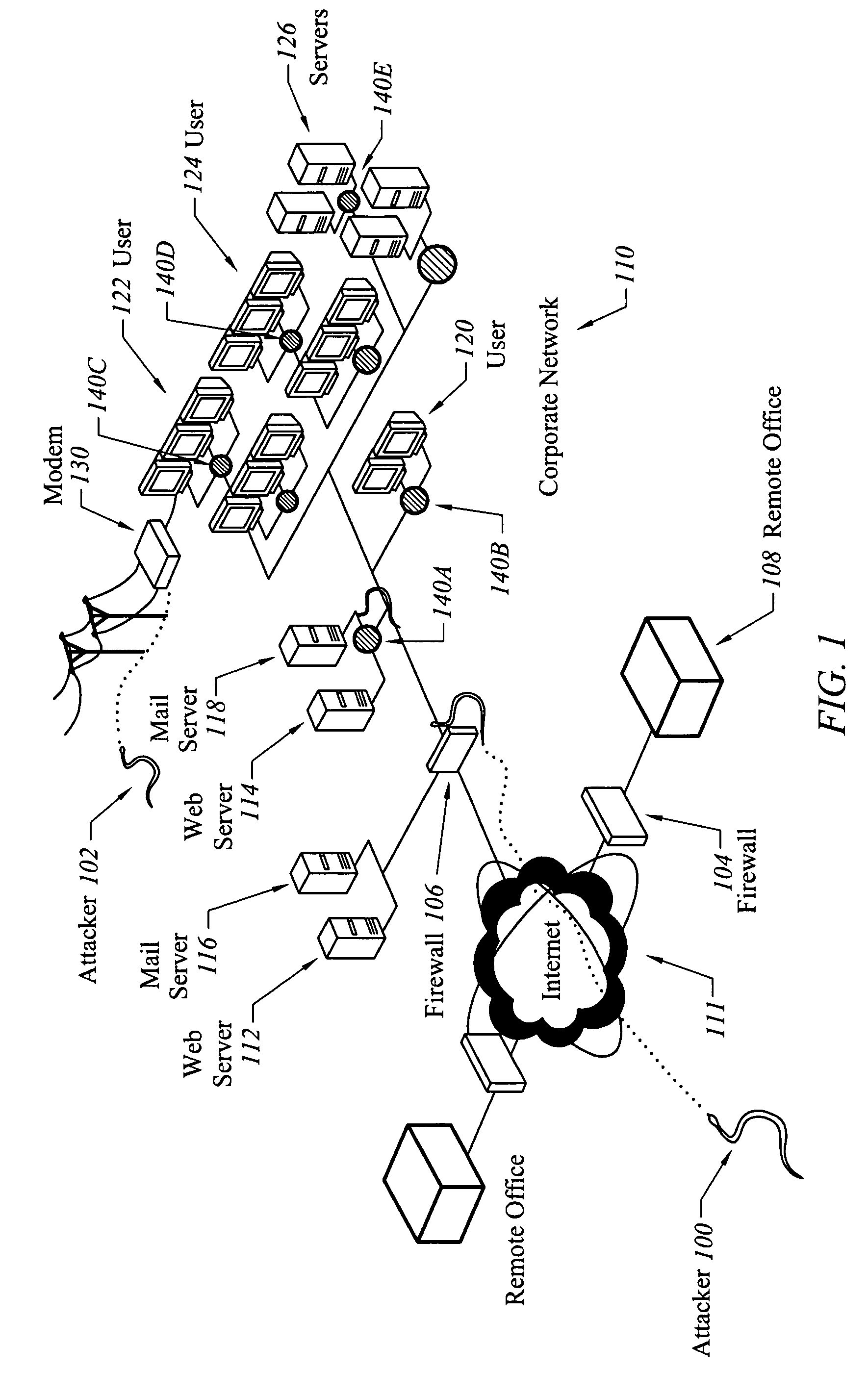

Apparatus and method for facilitating network security

ActiveUS7937756B2Easy networkingImprove securityError preventionFrequency-division multiplex detailsTraffic capacityLogical combination

An embodiment of an apparatus that facilitates network security and traffic monitoring for input network traffic includes a plurality of microcode controlled state machines, each of which includes a computation kernel. A plurality of rules applied to a network traffic segment are distributed across the computation kernels. Each of the computation kernels includes condition logic configured by microcode stored in an associated control store to evaluate a unique configured rule in the microcode to produce an associated output. A distribution circuit routes the network traffic segment to each of the plurality of microcode controlled state machines. An aggregation circuit generates a decision on which forwarding of the network traffic segment is based, where the decision is a logical combination of the associated output of each of the computation kernels.

Owner:CPACKET NETWORKS

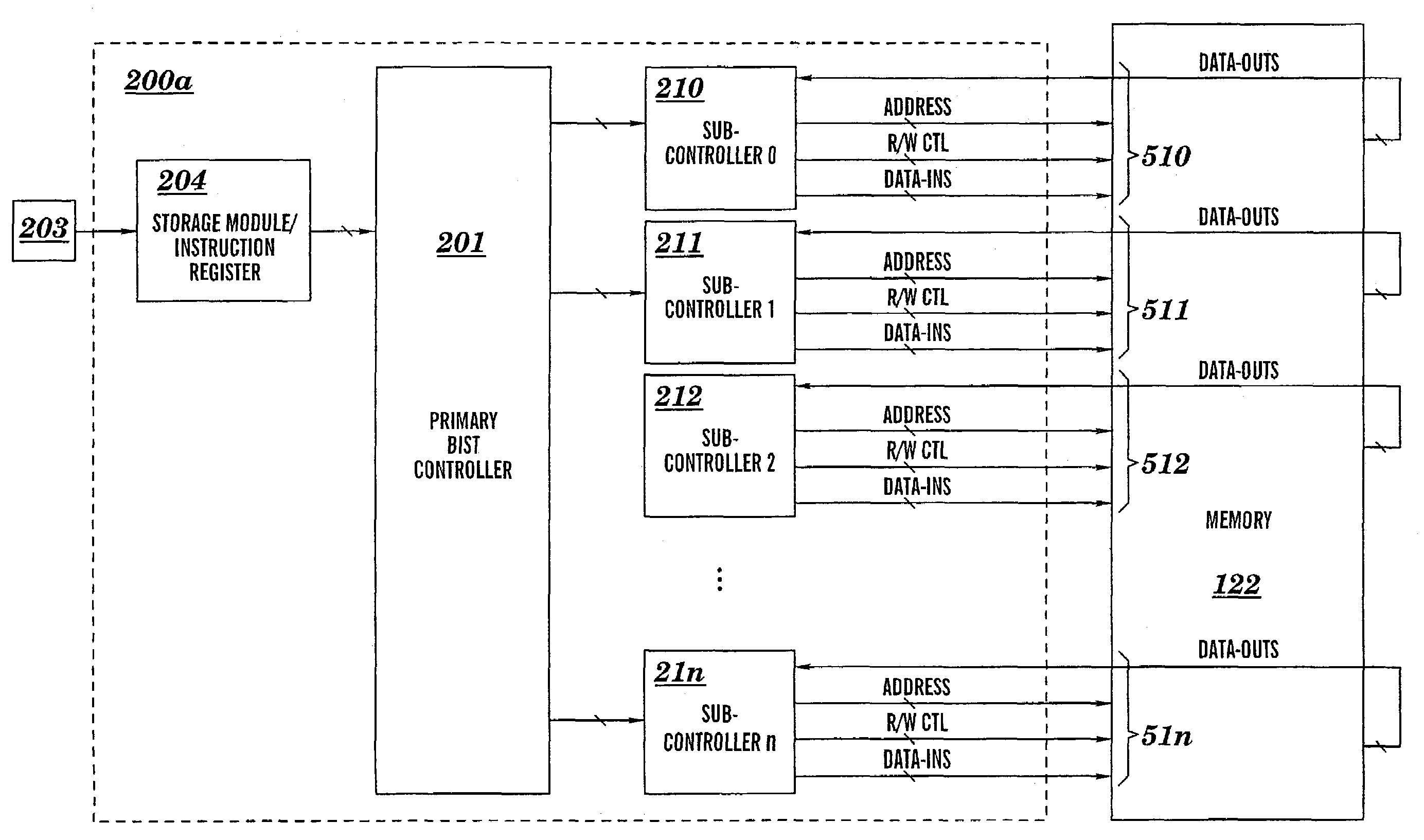

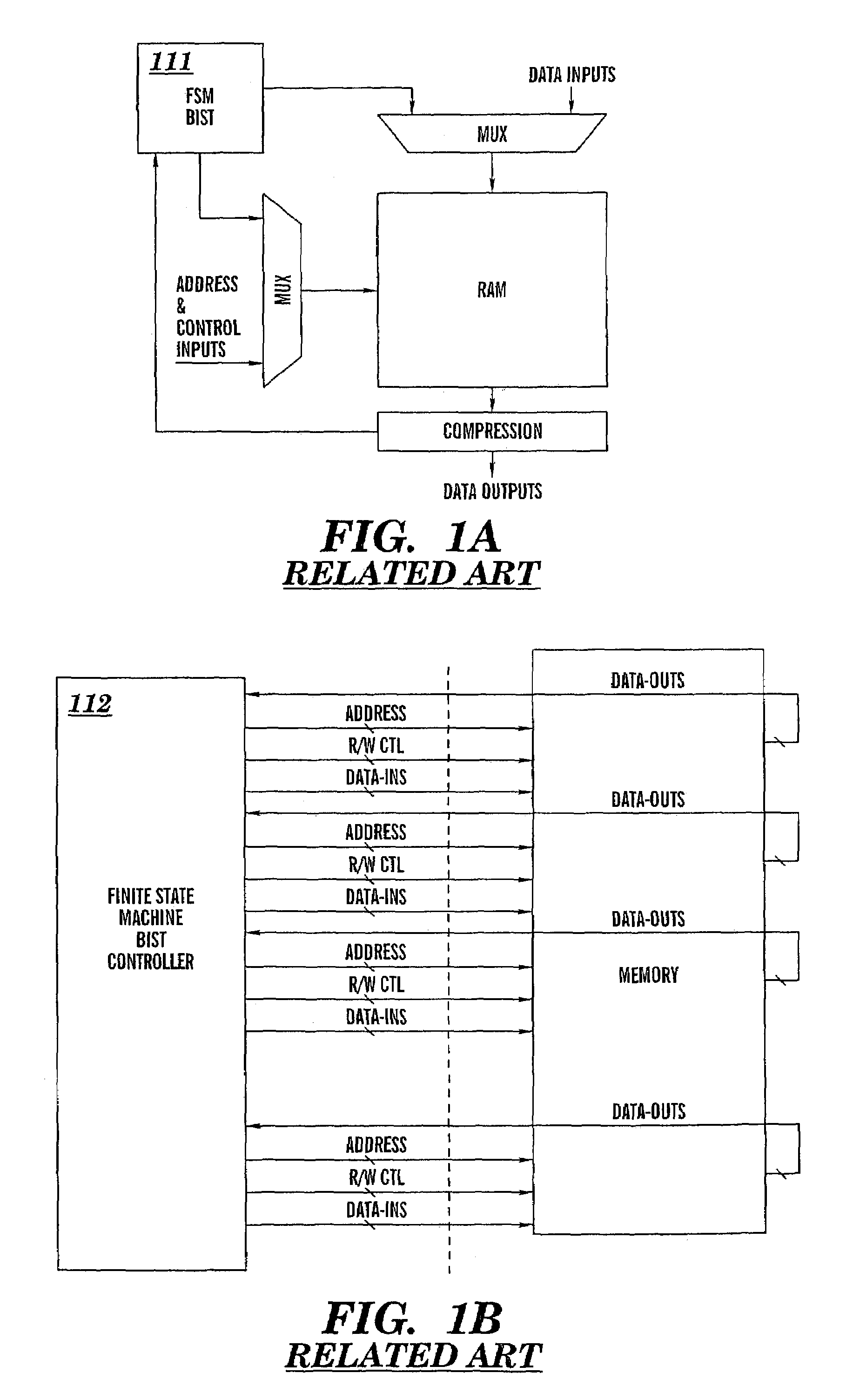

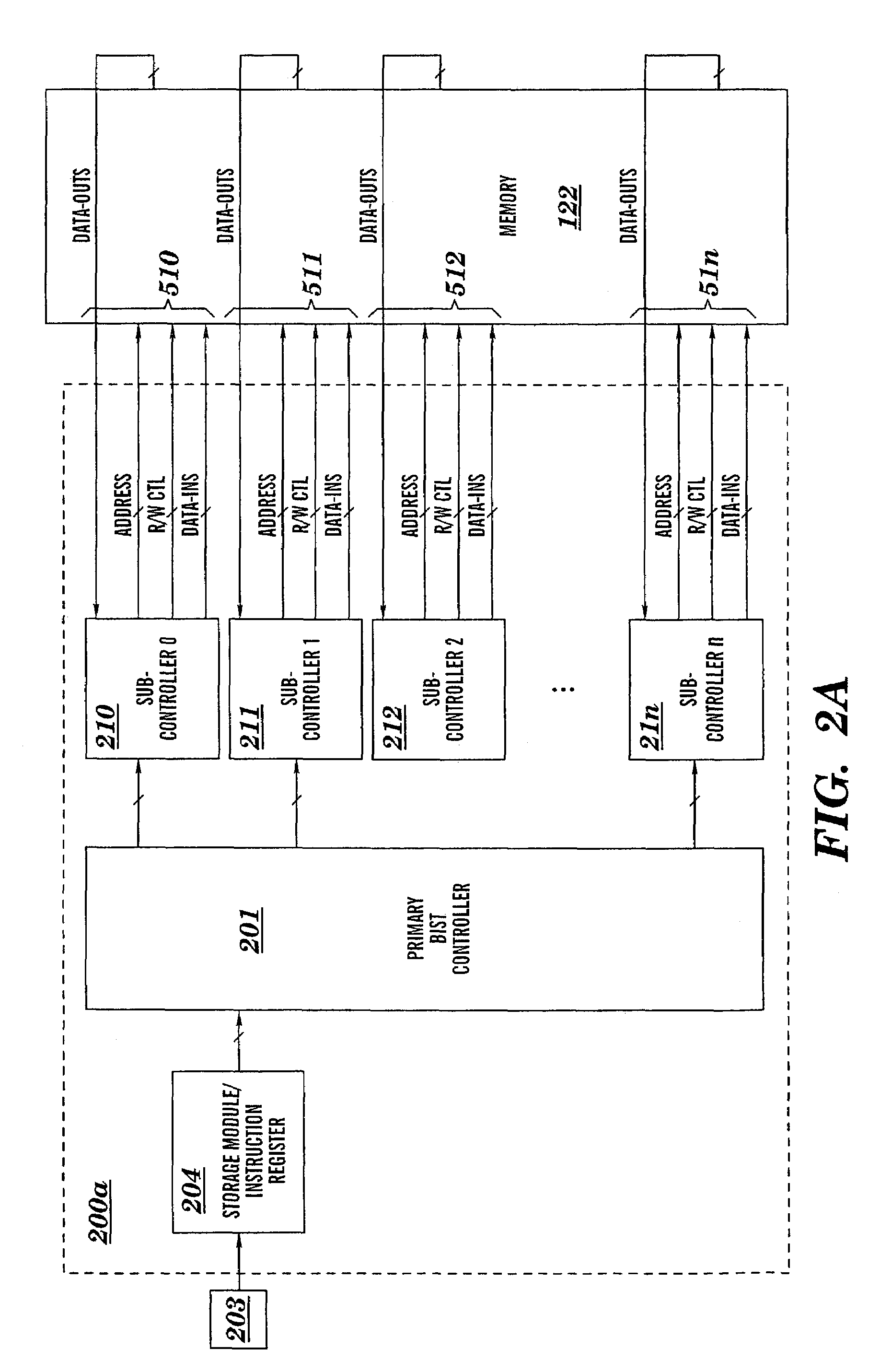

Programable multi-port memory BIST with compact microcode

InactiveUS7168005B2Easy to testIncrease flexibilityElectronic circuit testingFunctional testingAs DirectedMaster controller

A microcode programmable built-in-self-test (BIST) circuit and method for testing a multiported memory via multiple ports, either simultaneously or sequentially, as directed by a microcode instruction word. The microcode instruction word contains a plurality of executable subinstructions and one bit of information that controls whether the test operations prescribed in the plurality of subinstructions shall be executed in parallel or in series. The executable subinstructions are dispatched by a primary controller to subcontrollers which perform test operations at each port according to the subinstructions. The microcode programable BIST architecture flexibly facilitates the testing of multiple devices, multiported devices, including multiported memory structures and complex dependent multiported memory structures. The BIST supports in-situ testing of the functionality of the memory at wafer, module, and burn-in, as well as system-level testing.

Owner:CADENCE DESIGN SYST INC

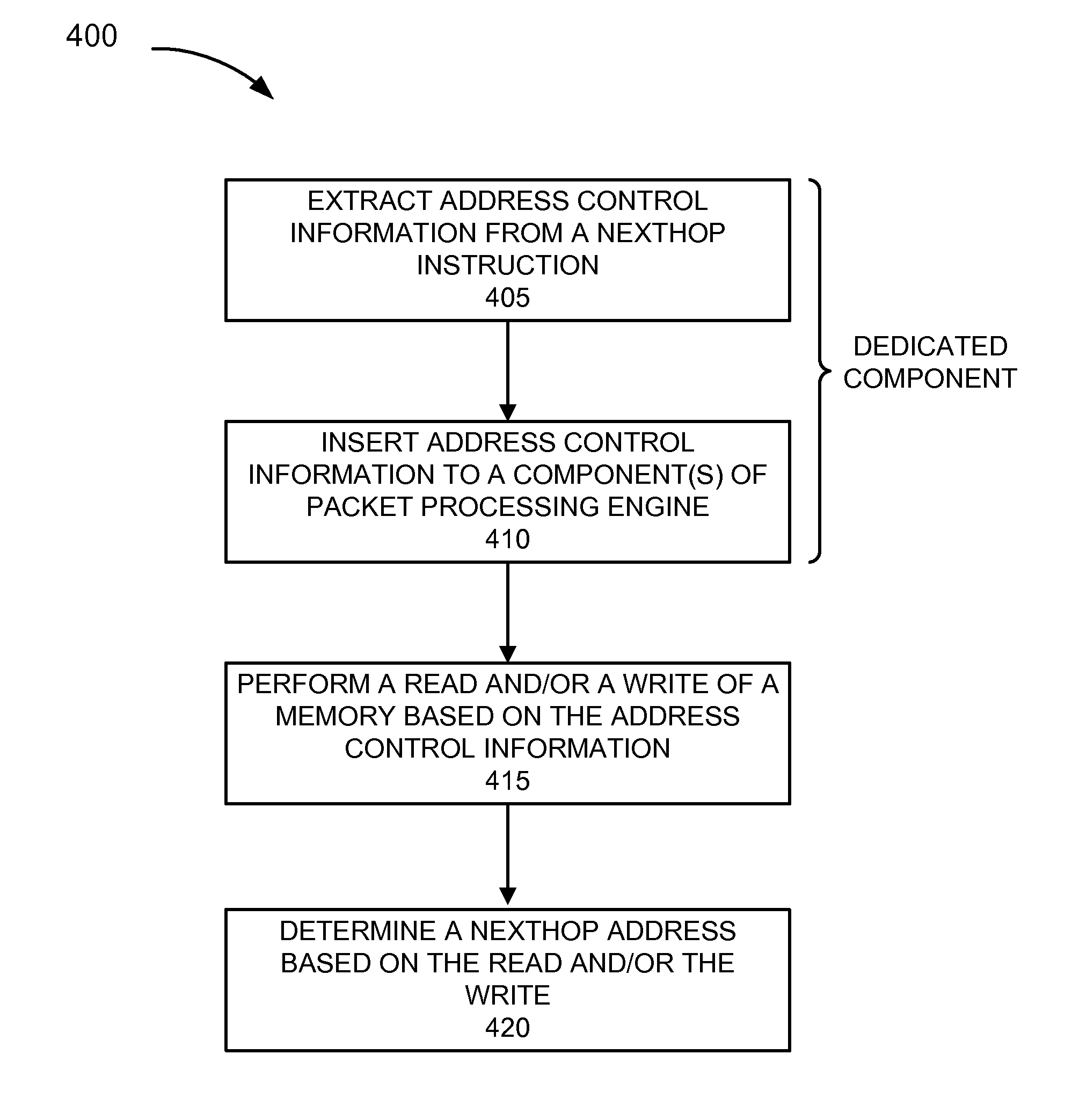

Hardware support for instruction set emulation

ActiveUS8069023B1Instruction analysisAnalogue computers for electric apparatusBit fieldNetwork addressing

A method for emulating a nexthop instruction in microcode with the assistance of dedicated hardware to extract read and write addressing from the nexthop instruction instead of performing this operation in microcode. A method for emulating a nexthop instruction in microcode with the assistance of dedicated hardware to compare a nexthop read address to a special value and to indicate whether the nexthop read address matches the special value, instead of performing this operation in microcode. A method for determining a network address by performing a single extraction of bit fields of a tree instruction to allow multiple tree search processes to be performed.

Owner:JUMIPER NETWORKS INC

Hardware monitoring and decision making for transitioning in and out of low-power state

ActiveUS8156362B2More efficiencyImprove balanceEnergy efficient ICTDigital data processing detailsDirect memory accessActive state

A power management controller (PMC) that interfaces with a processor comprising one or more cores. The PMC may be configured to communicate with each respective core, such that microcode executed by the respective processor core may recognize when a request is made to transition the respective core to a target power-state. For each respective core, the state monitor may monitor active-state residency, non-active-state residency, Direct Memory Access (DMA) transfer activity associated with the respective core, Input / Output (I / O) processes associated with the respective core, and the value of a timer-tick (TT) interval associated with the respective core. The status monitor may derive respective status information for the respective core based on the monitoring and indicate whether the respective core should be allowed to transition to the corresponding target power-state. The PMC may transition the respective processor core to the corresponding target power-state accordingly.

Owner:MEDIATEK INC

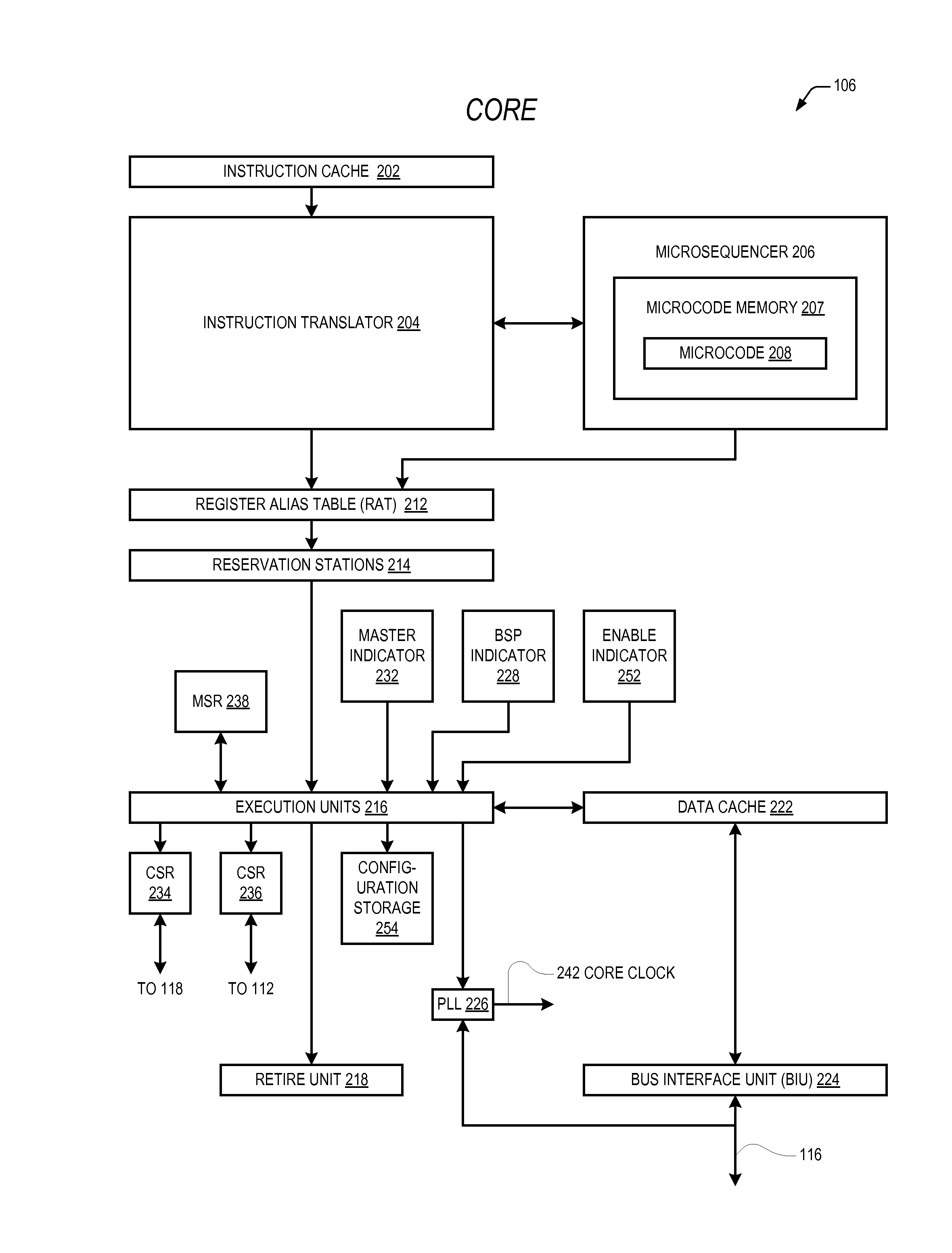

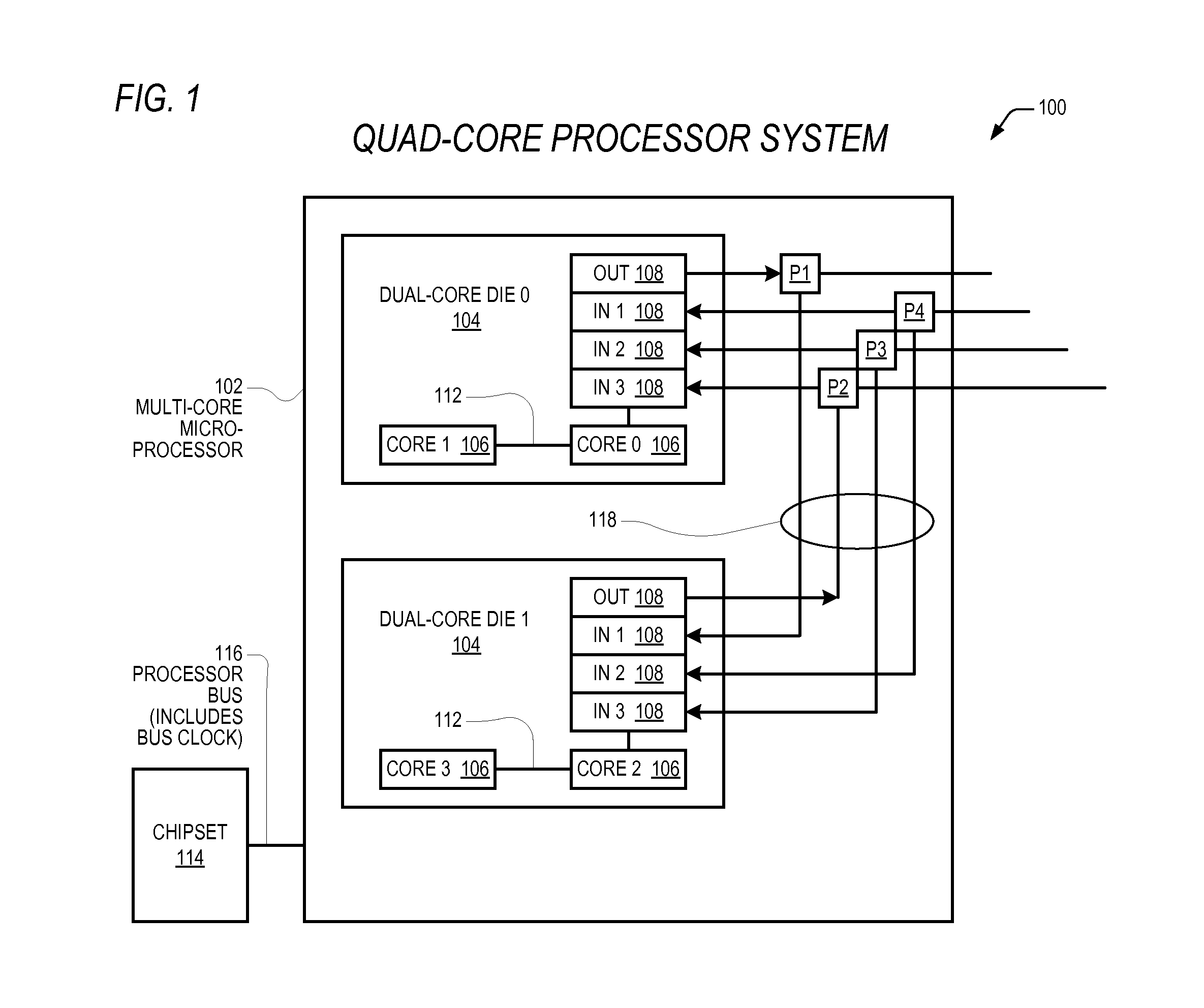

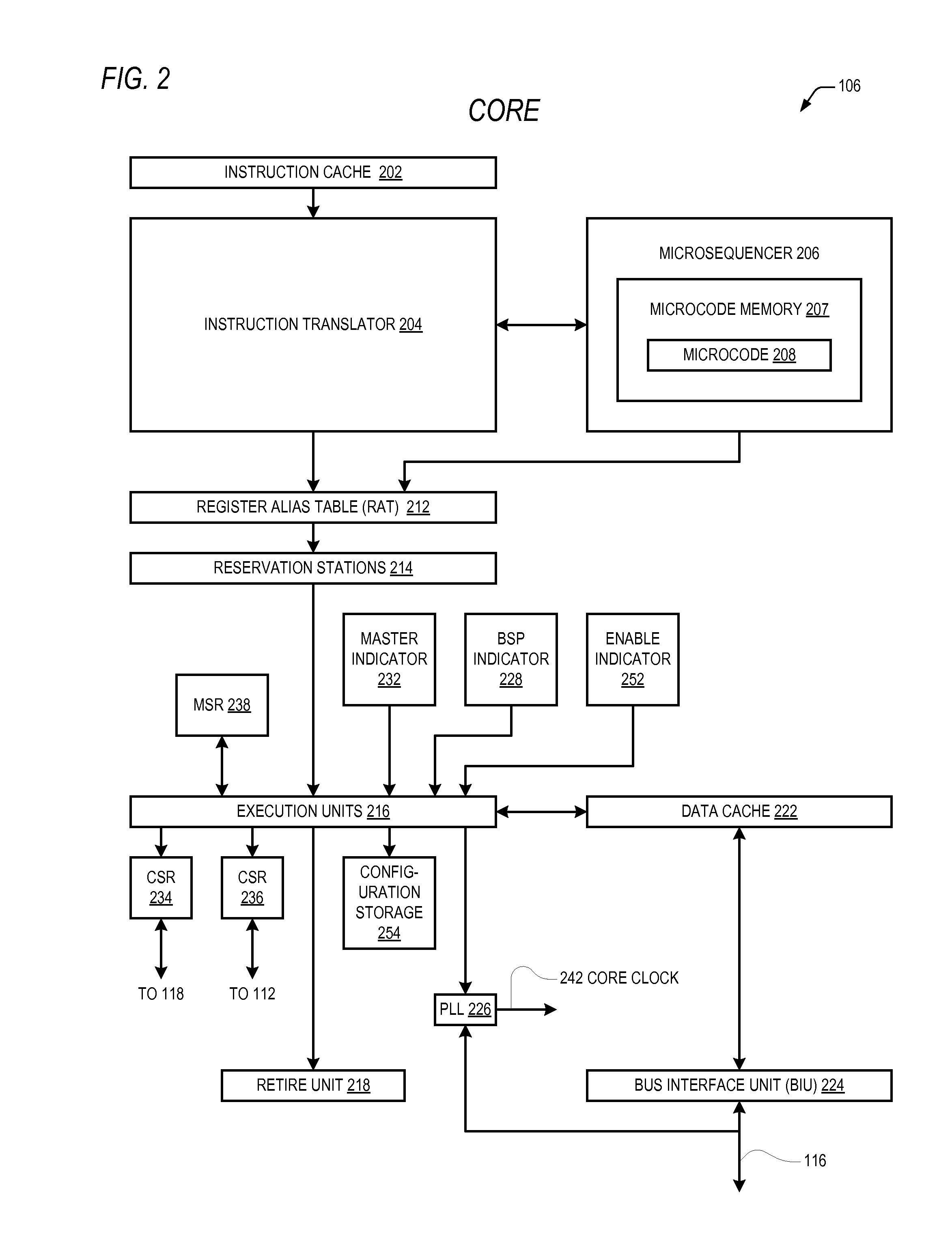

Dynamic multi-core microprocessor configuration discovery

ActiveUS20120166763A1Digital data processing detailsGeneral purpose stored program computerState managementVoltage source

A core configuration discovery method and corresponding microprocessor are provided that does not rely on off-core logic or queries by system BIOS. Reset microcode is provided in the microprocessor's cores. Upon reset, the microcode queries and / or receives from other cores configuration-revealing information and collects the configuration-revealing information to determine a composite core configuration for the microprocessor. The composite core configuration may reveal the number of enabled cores, identify the enabled cores, reveal a hierarchical coordination system of the multi-core processor, such as a nodal map of the cores for certain inter-core communication processes or restricted activities, identify various domains and domain masters within such a system, and / or identify resources, such as voltage sources, clock sources, and caches, shared by various domains of the microprocessor. The composite core configuration may be used for power state management, reconfiguration, and other purposes.

Owner:VIA TECH INC

Apparatus and method for facilitating network security with granular traffic modifications

ActiveUS20070056030A1Easy to optimizeLow costError preventionFrequency-division multiplex detailsInternet trafficControl store

An apparatus is described that facilitates network security and network traffic monitoring through processing of network traffic in accordance with provisioned rules and policies. The apparatus includes a set of microcode controlled state machines, each of which includes a computation kernel operating in accordance with microcode stored in a control store. A distribution circuit routes individual network traffic segments derived from input network traffic to the set of microcode controlled state machines, so that at least one of the microcode controlled state machines applies a rule encoded in the microcode to the individual network traffic segments to produce modification instructions. A circuit performs a modification of the input network traffic based on the modification instructions from the at least one microcode controlled state machine to produce output network traffic. Advantageously, the apparatus provides an architectural framework well suited to a low cost, high speed, robust implementation of flexible, advanced network security and monitoring features, traffic management, and integration of devices within a system.

Owner:CPACKET NETWORKS

Method and apparatus for predication using micro-operations

InactiveUS20050081017A1Instruction analysisRuntime instruction translationTemporary variableMicro-operation

Disclosed are an apparatus, system, and method for implementing predicated instructions using micro-operations. A micro-code engine receives an instruction, decomposes the instruction, and generates a plurality of micro-operations to implement the instruction. Each of the decomposed micro-operations indicates a single destination register. For predicated instructions, the decomposed micro-operations include “conditional move” micro-operations to select between two potential output values. Except in the case that one of the potential output values is a constant, the decomposed micro-operations for a predicated instruction also include an append instruction that saves the incoming value of a destination register in a temporary variable. For at least one embodiment, the qualifying predicate for a predicated instruction is appended to the incoming value stored in the temporary register.

Owner:INTEL CORP

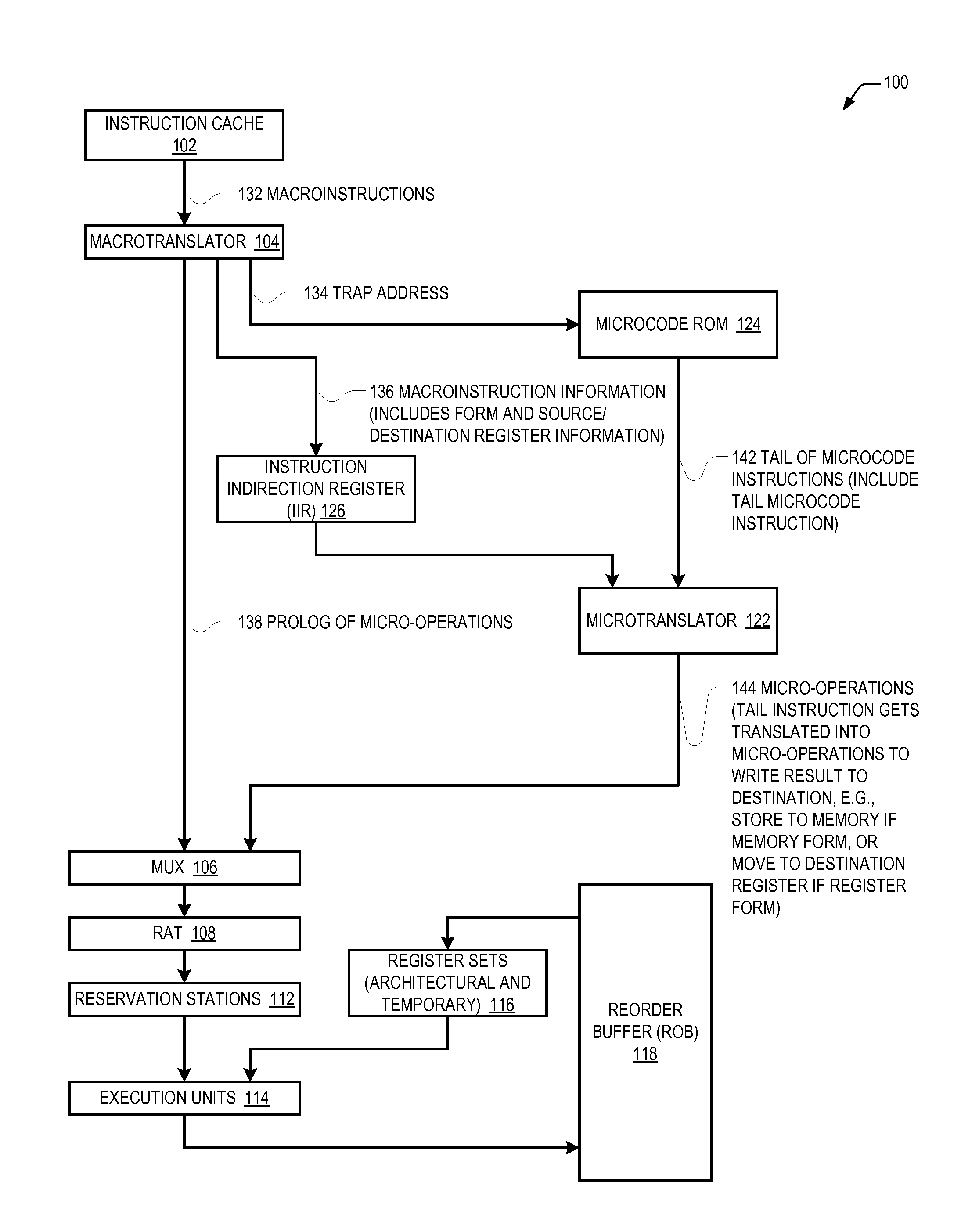

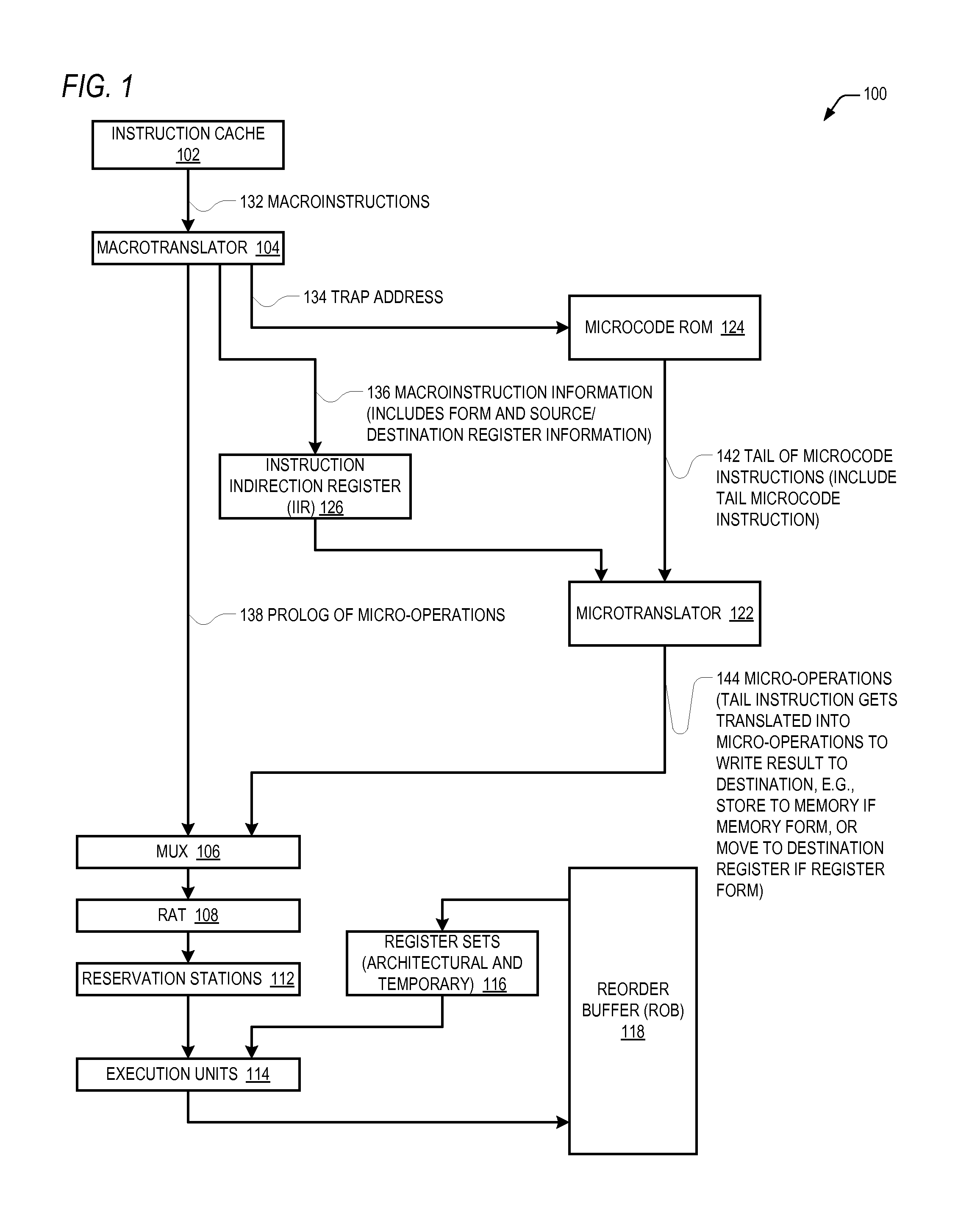

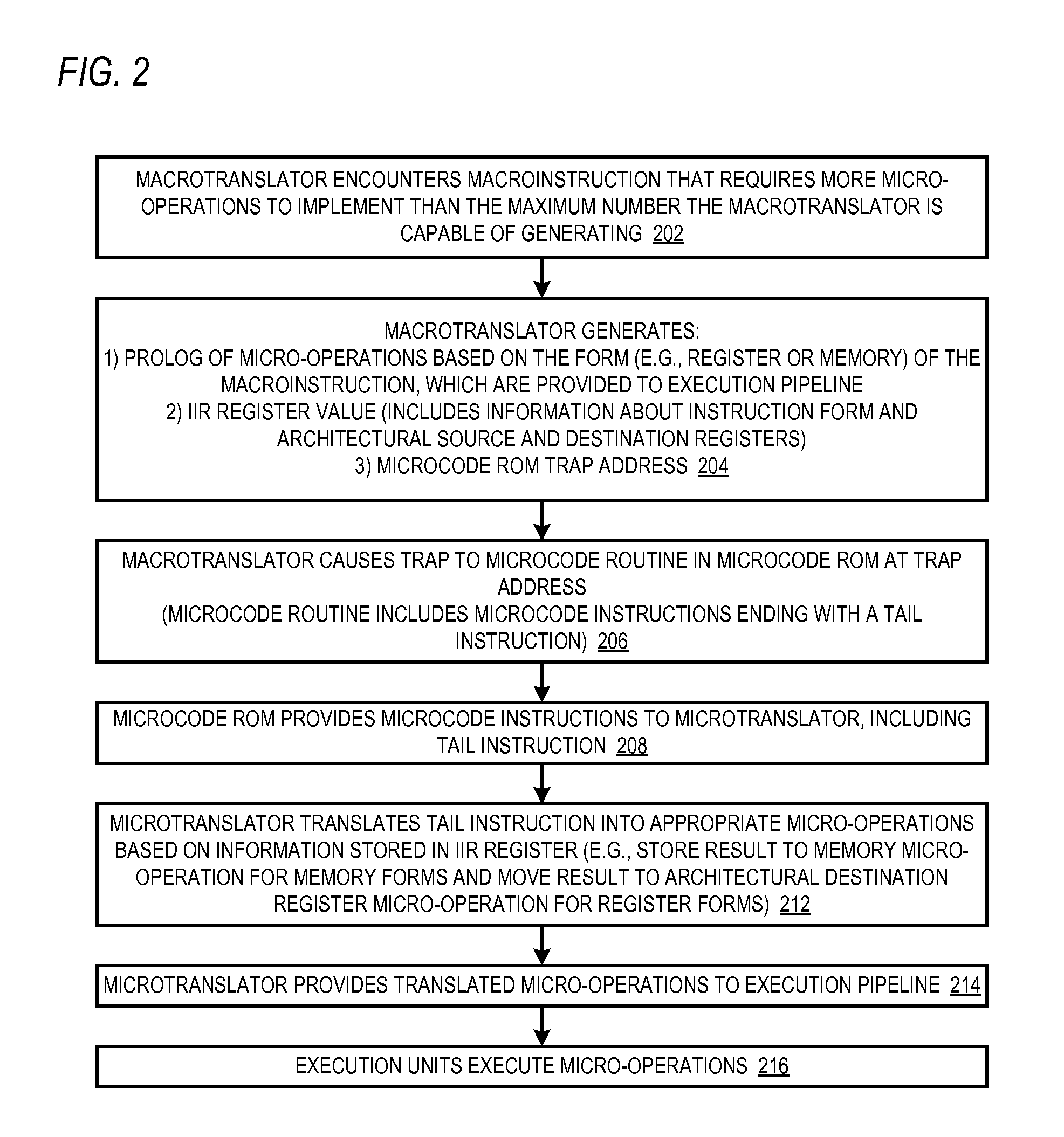

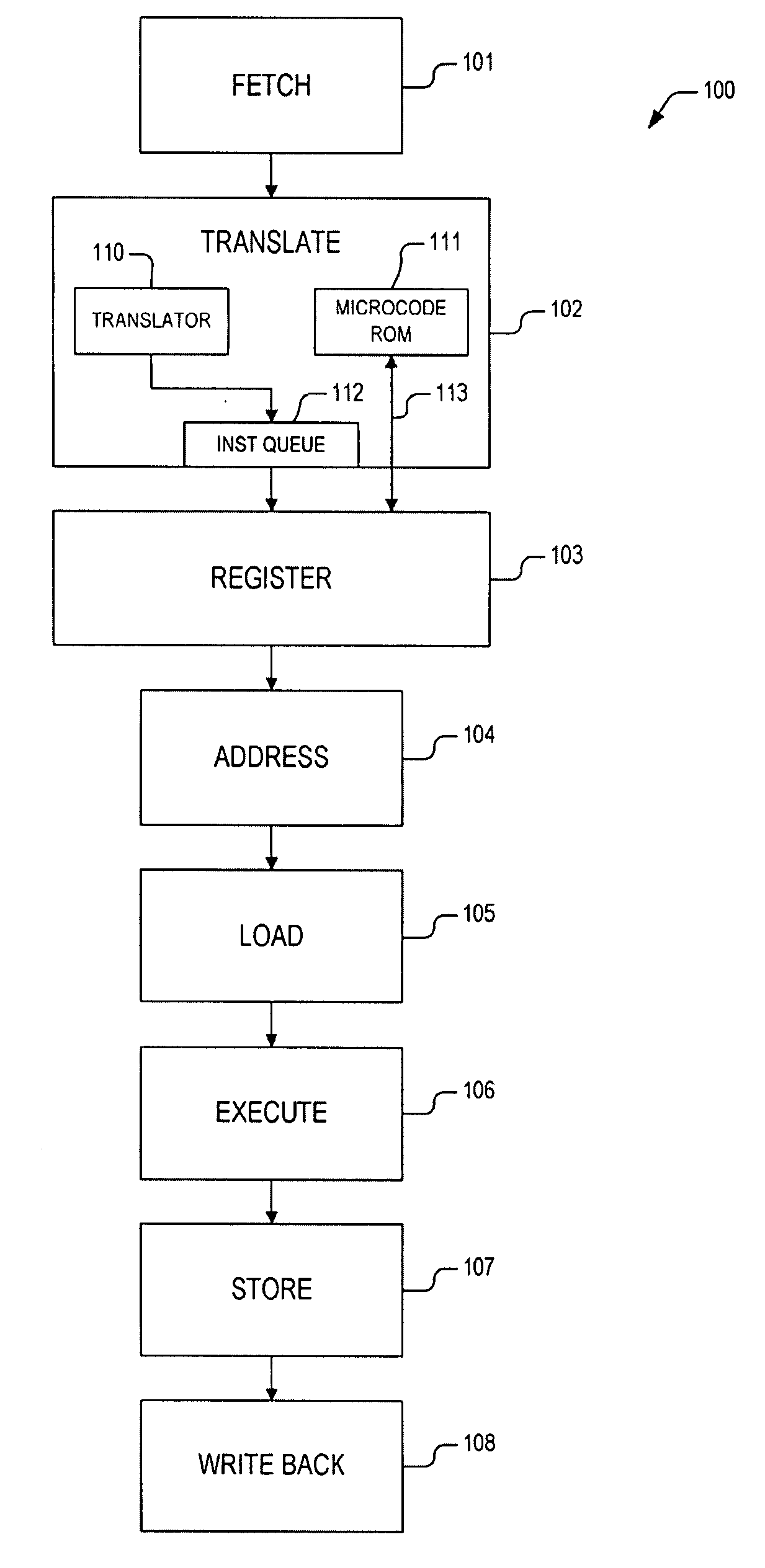

Microprocessor with microtranslator and tail microcode instruction for fast execution of complex macroinstructions having both memory and register forms

A microprocessor includes a first instruction translator that translates an instruction of an instruction set architecture of a microprocessor. The instruction may specify a first form that writes its result to a destination register or a second form that writes its result to memory. The first instruction translator generates, in response to encountering an instance of the instruction, an indication of whether the instance is of the first form or the second form. A microcode memory stores a tail instruction as part of a microcode routine invoked in response to encountering the instance of the instruction. A second instruction translator receives the tail instruction from the microcode memory and the indication and responsively generates a first micro-operation that writes the result to the destination register if the indication specifies the first form or a second micro-operation that completes a write of the result to memory if the indication specifies the second form.

Owner:VIA TECH INC

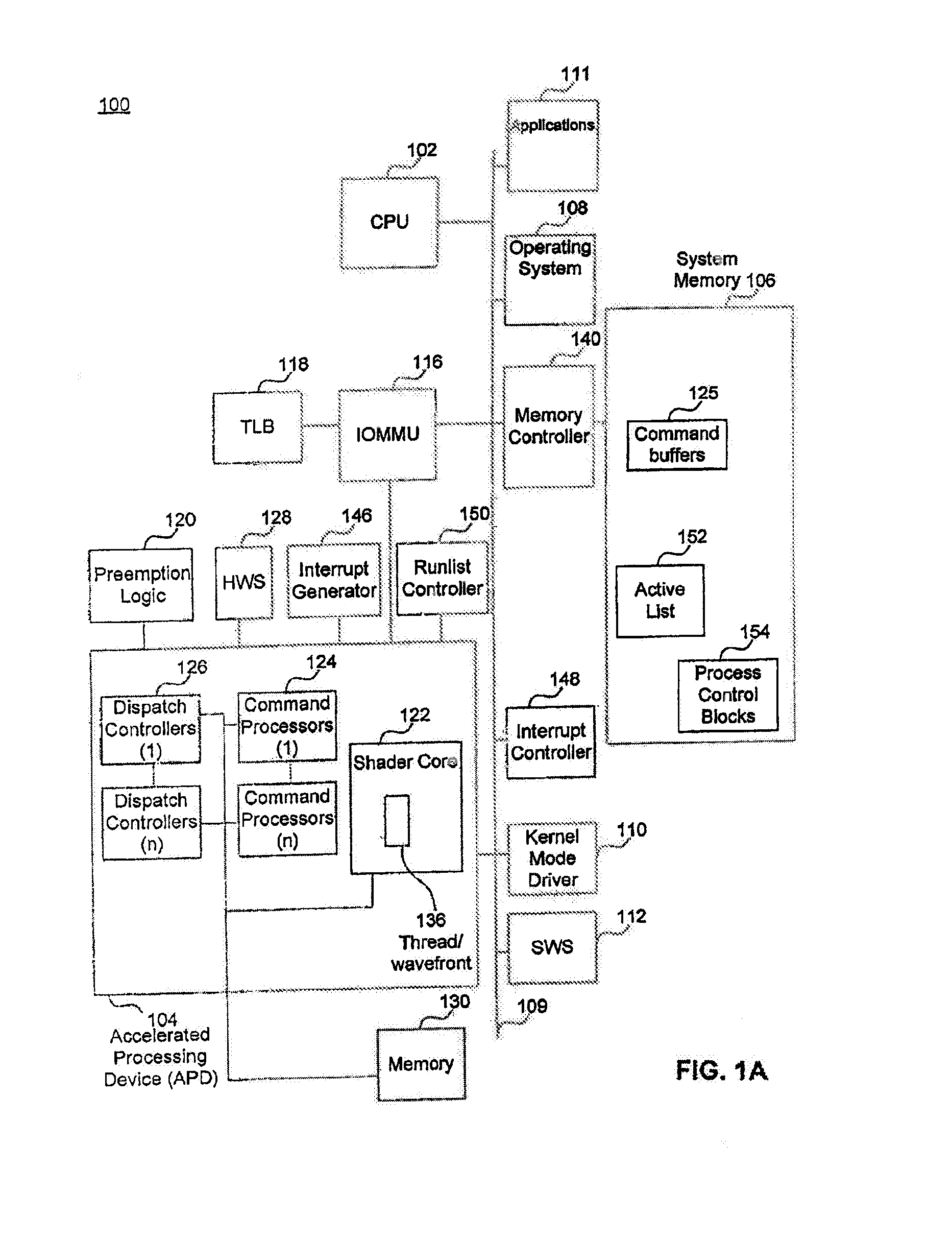

Infrastructure Support for Accelerated Processing Device Memory Paging Without Operating System Integration

ActiveUS20130159664A1Enabling useMemory architecture accessing/allocationMemory adressing/allocation/relocationSystem integrationOperational system

In a CPU of the combined CPU / APD architecture system, the CPU having multiple CPU cores, each core having a first machine specific register for receiving a physical page table / page directory base address, a second machine specific register for receiving a physical address pointing to a location controlled by an IOMMUv2 that is communicatively coupled to an APD, and microcode which when executed causes a write notification to be issued to the physical address contained in the second machine specific register; receiving in the first machine specific register of a CPU core, a physical page table / page directory base address, receiving in the second machine specific register of the CPU core, a physical address pointing to a location controlled by the IOMMUv2, determining that a control register of the CPU core has been updated, and responsive to the determination that the control register has been updated, executing microcode in the CPU core that causes a write notification to be issued to the physical address contained in the second machine specific register, wherein the physical address is able to receive writes that affect IOMMUv2 page table invalidations.

Owner:ATI TECH INC +1

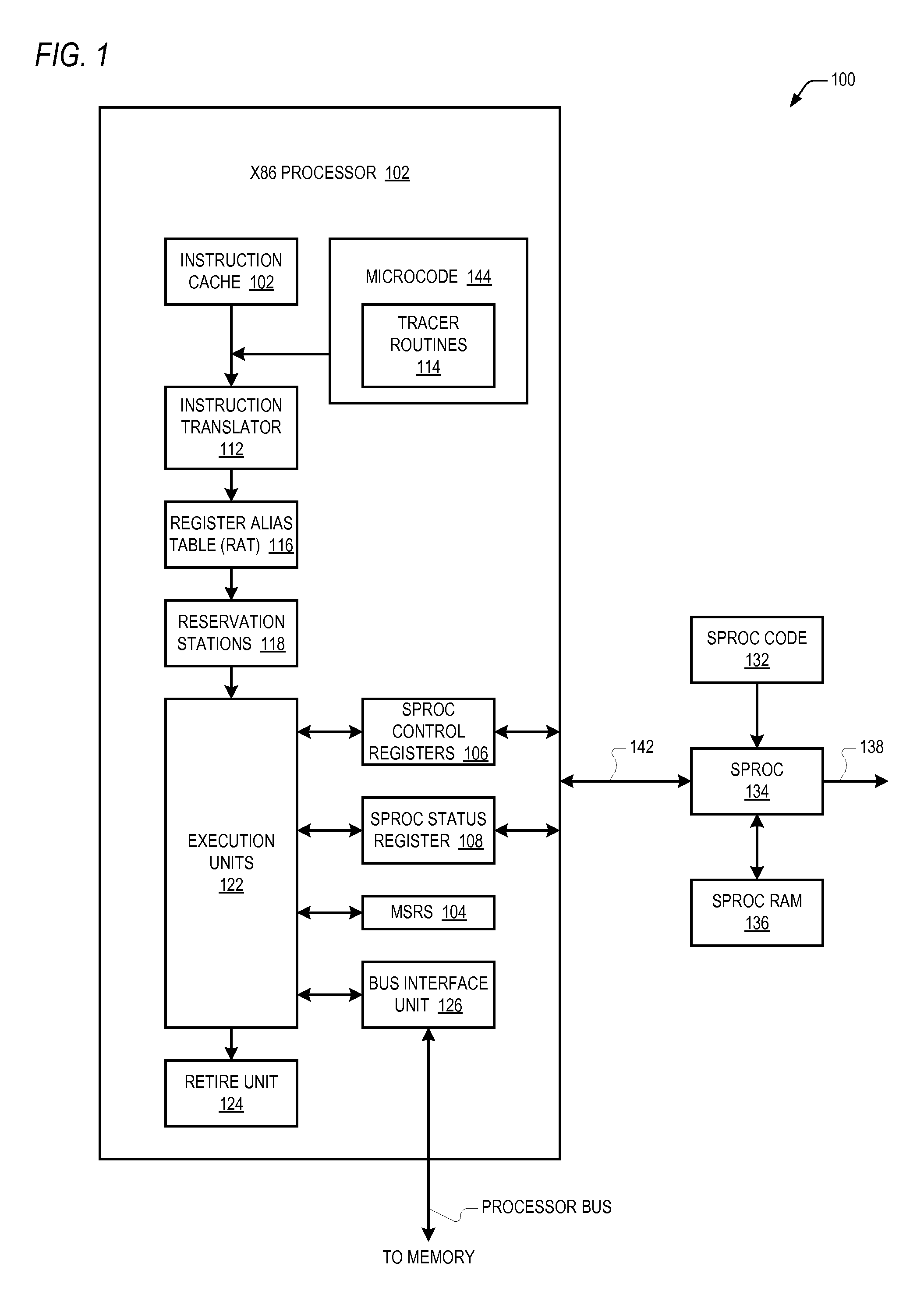

Debuggable microprocessor

A microprocessor integrated circuit includes first and second processors. The first processor is configured to detect that the second processor has not retired an instruction for a predetermined amount of clock cycles and to responsively reset the second processor. The microprocessor integrated circuit also includes microcode. The second processor is configured to execute the microcode in response to a reset of the second processor. The microcode is configured to read debug information within the microprocessor integrated circuit and to output the debug information external to the microprocessor integrated circuit in response to determining that the reset was performed by the first processor.

Owner:VIA TECH INC

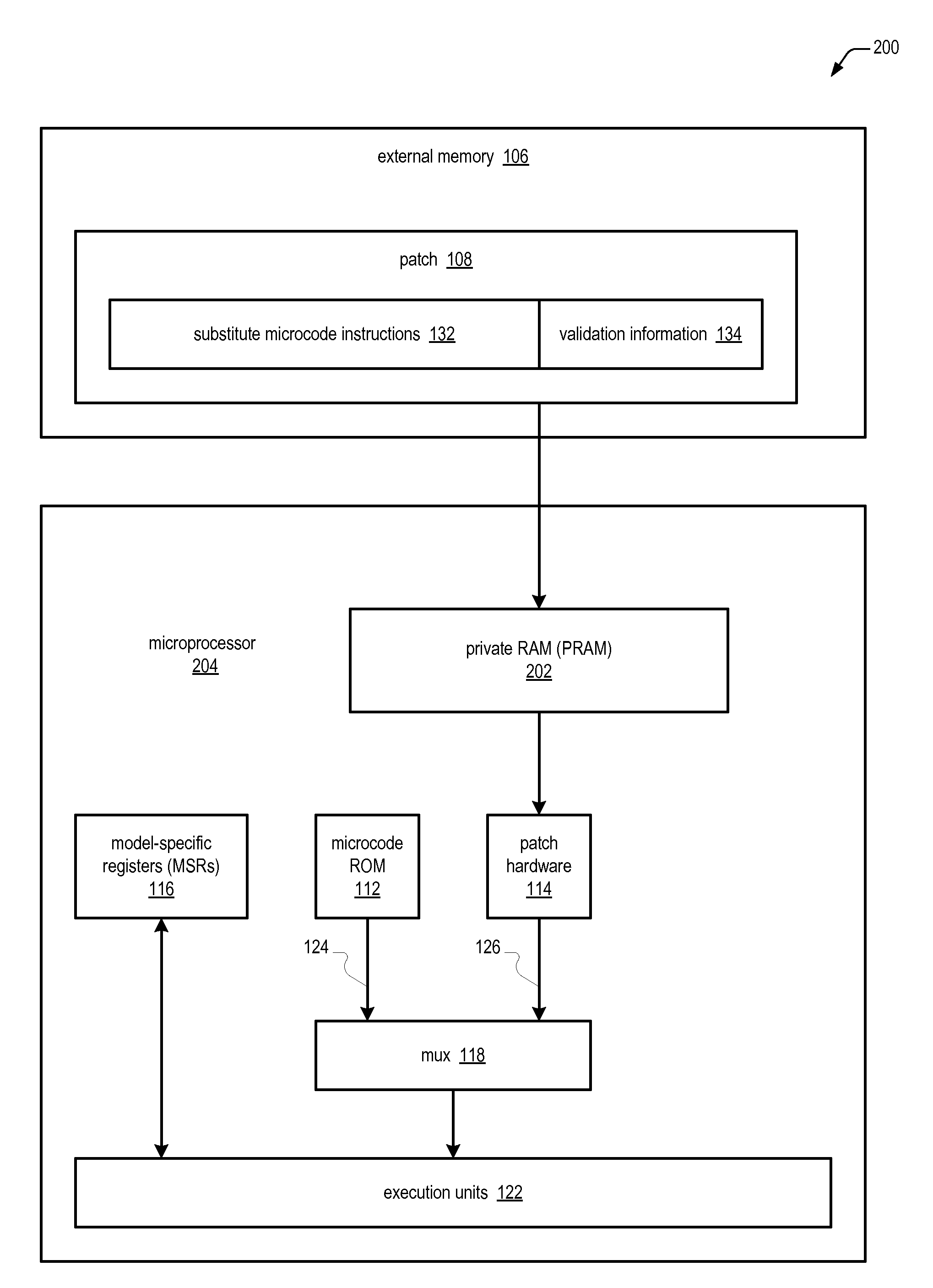

Apparatus and method for patching microcode in a microprocessor using private ram of the microprocessor

InactiveUS20100180104A1Reduce the possibilityDigital computer detailsNext instruction address formationExternal storageProgram instruction

A microprocessor has a microcode memory for storing original microcode instructions to implement user program instructions, and an interface to an external memory for storing a microcode patch. The microcode patch includes substitute microcode instructions and validation information. The microprocessor includes a private random access memory (PRAM), addressable by the original and substitute microcode instructions but not addressable by user program instructions. The microprocessor also includes patch hardware, which conditionally receives the substitute microcode instructions. The microprocessor executes the substitute microcode instructions when applied to the patch hardware instead of corresponding original microcode instructions. The microprocessor is configured to load the microcode patch from external memory into PRAM, determine whether the microcode patch is valid, apply substitute microcode instructions from PRAM to the patch hardware if the microcode patch is valid, and refrain from applying the substitute microcode instructions to the patch hardware, if the microcode patch is invalid.

Owner:VIA TECH INC

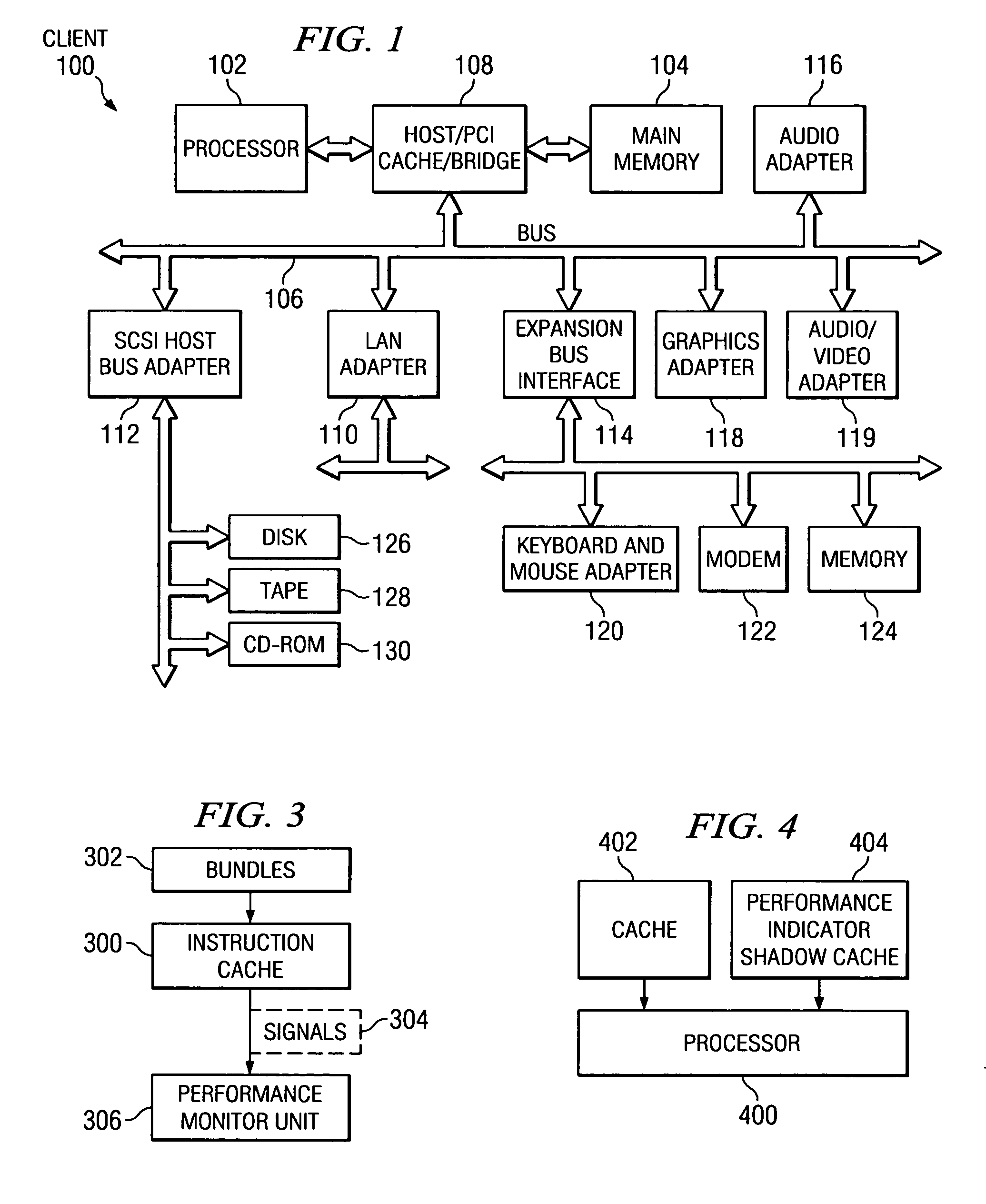

Method and apparatus for generating interrupts based on arithmetic combinations of performance counter values

InactiveUS20050155018A1Improve performanceError detection/correctionSpecific program execution arrangementsProcessing InstructionData processing system

A method, apparatus, and computer instructions in a data processing system for processing instructions are provided. Instructions are received at a processor in the data processing system. If a selected indicator is associated with the instruction, counting of each event associated with the execution of the instruction is enabled. In some embodiments of the present invention, arithmetic combinations of counter values generated based on the encountering of performance indicators may be generated and compared to threshold values to determine whether to generate interrupts to the monitoring application. In such embodiments, the microcode of the processor is programmed to check the counter values of counters specified by the monitoring application, combine the counter values in a manner specified by the monitoring application, and then compare the combined value to a threshold value supplied by the performance monitoring application. In this way, more complex conditioning of interrupts may be provided within the hardware of the processor.

Owner:IBM CORP

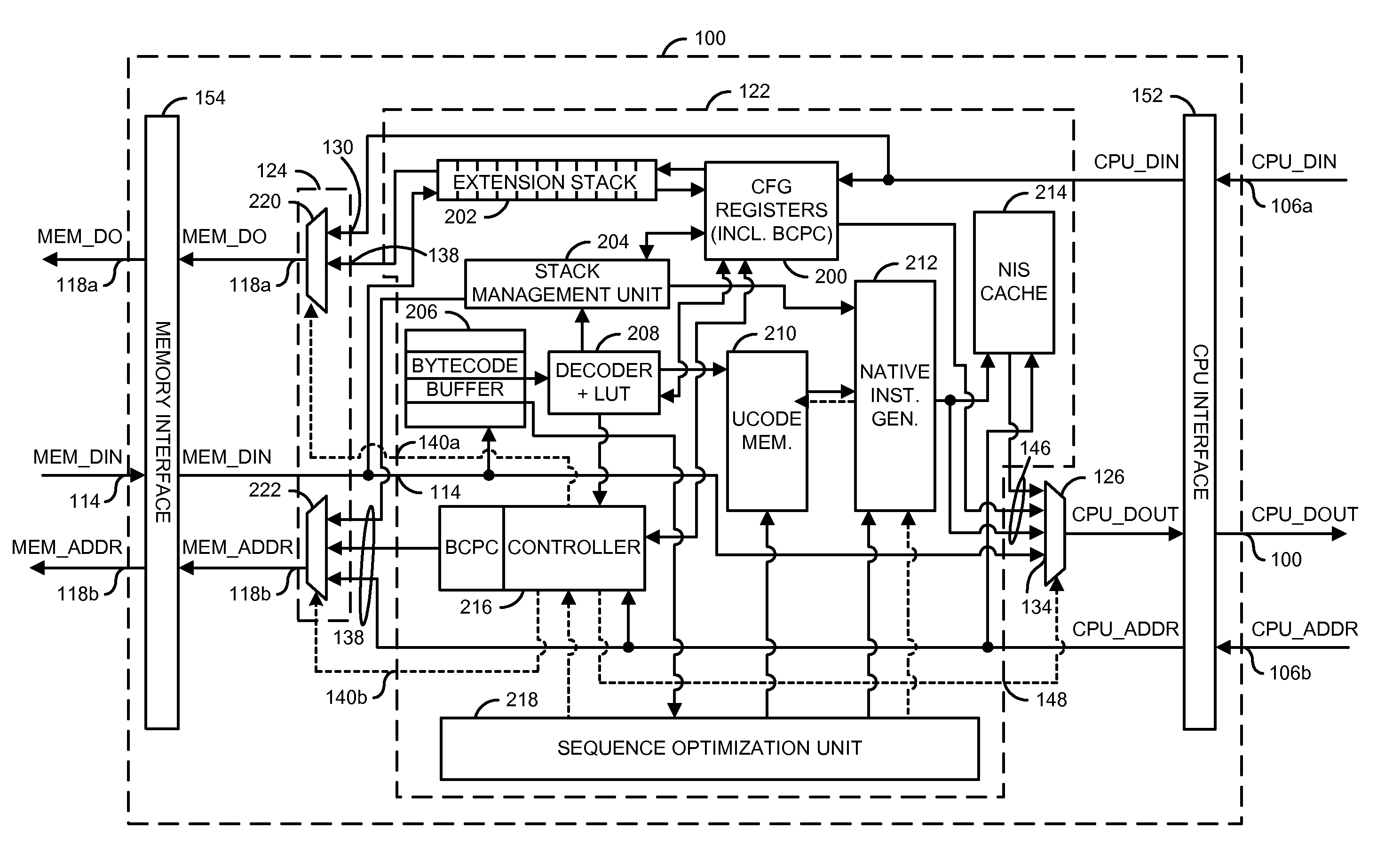

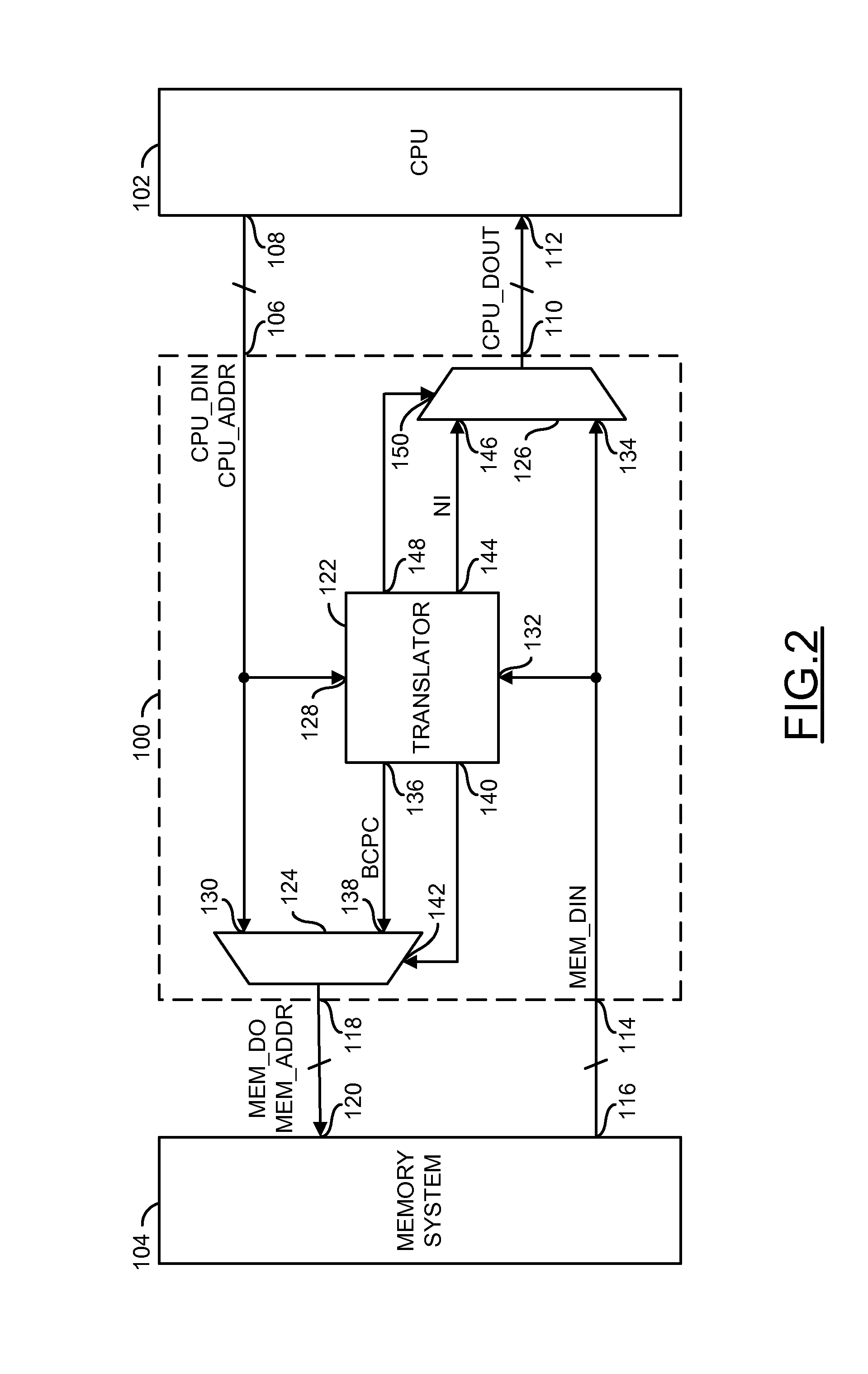

Microcode based hardware translator to support a multitude of processors

InactiveUS7873814B1Fast executionRuntime instruction translationDigital computer detailsMicrocodeInstruction set

An apparatus comprising a circuit configured to translate instruction codes of a first instruction set into sequences of instruction codes of a second instruction set that emulate a functionality of the instruction codes of the first instruction set.

Owner:AVAGO TECH INT SALES PTE LTD

Microprocessor with system-robust self-reset capability

A microprocessor includes a bus interface unit that interfaces the microprocessor to a bus that includes a signal that, when asserted, instructs all bus agents to refrain from initiating bus transactions. Microcode causes the bus interface unit to assert the signal in response to detecting an event and resets the microprocessor, but does not reset a portion of the bus interface unit that asserts the signal on the bus. After the reset, the microcode causes the bus interface unit to deassert the signal on the bus. Additionally, the microcode sets a flag and saves the microprocessor state to memory before resetting itself, but does not reset the interrupt controller. After the reset, the microcode reloads the state of the microprocessor from the memory. However, if the microcode determines that the flag is set, it forgoes reloading the state of the interrupt controller.

Owner:VIA TECH INC

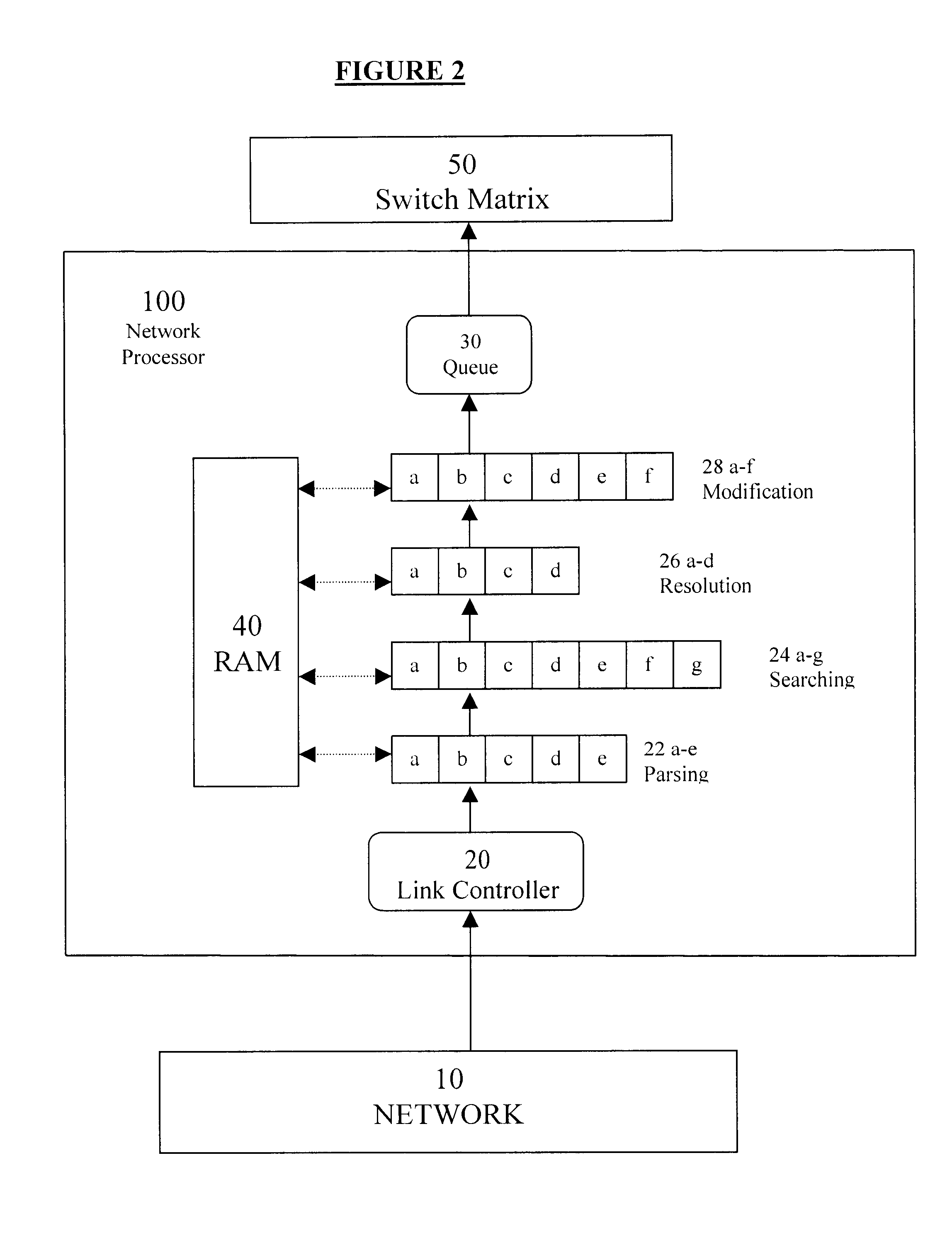

High-performance network processor

InactiveUS6778534B1Time-division multiplexData switching by path configurationImage resolutionHigh performance network

A high-speed system for processing a packet and routing the packet to a packet destination port, the system comprising: (a) a memory block for storing tabulated entries, (b) a parsing subsystem containing at least one microcode machine for parsing the packet, thereby obtaining at least one search key, (c) a searching subsystem containing at least one microcode machine for searching for a match between said at least one search key and said tabulated entries, (d) a resolution subsystem containing at least one microcode machine for resolving the packet destination port, and (e) a modification subsystem containing at least one microcode machine for making requisite modifications to the packet; wherein at least one of said microcode machines is a customized microcode machine.

Owner:MELLANOX TECHNOLOGIES LTD

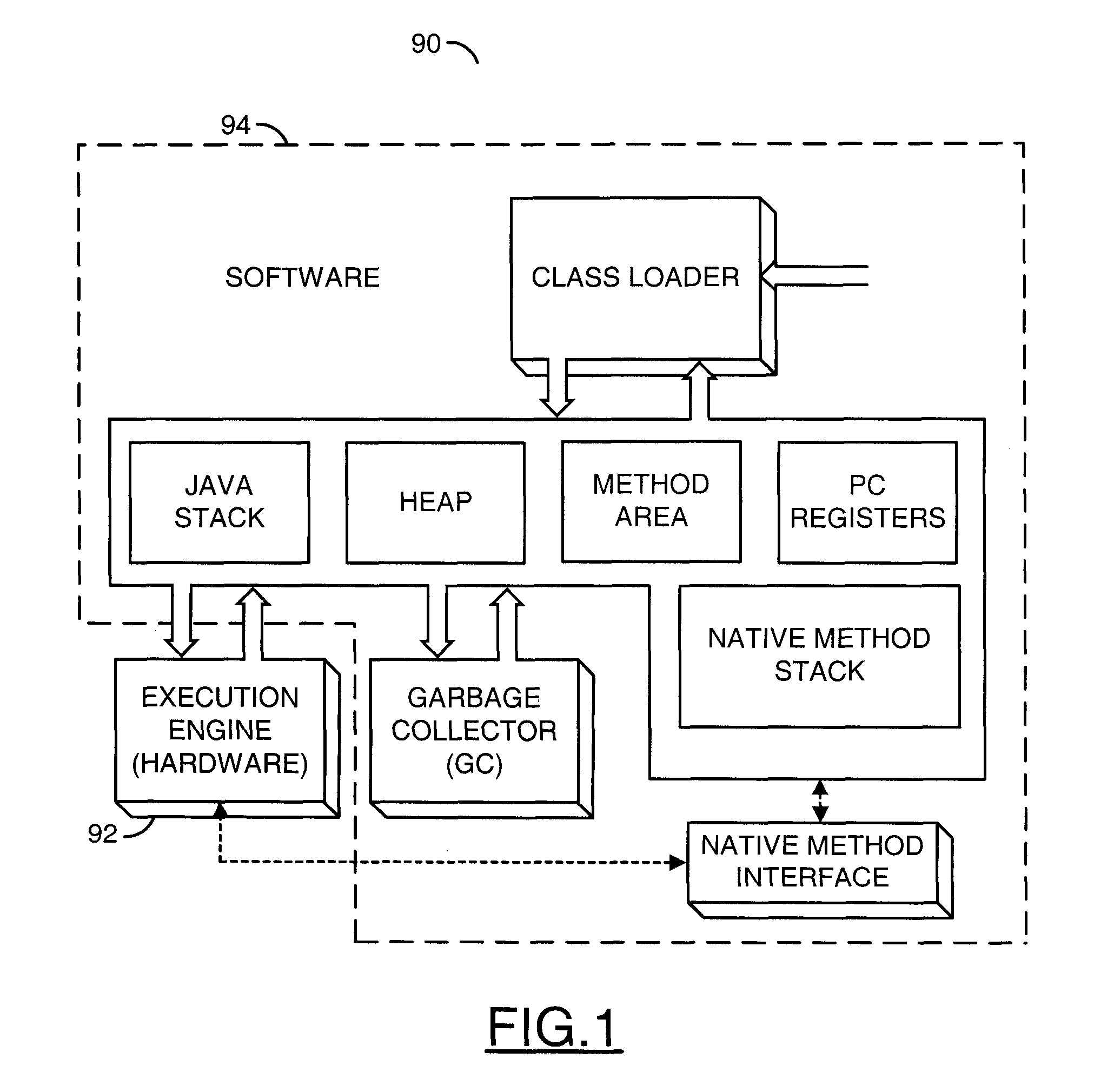

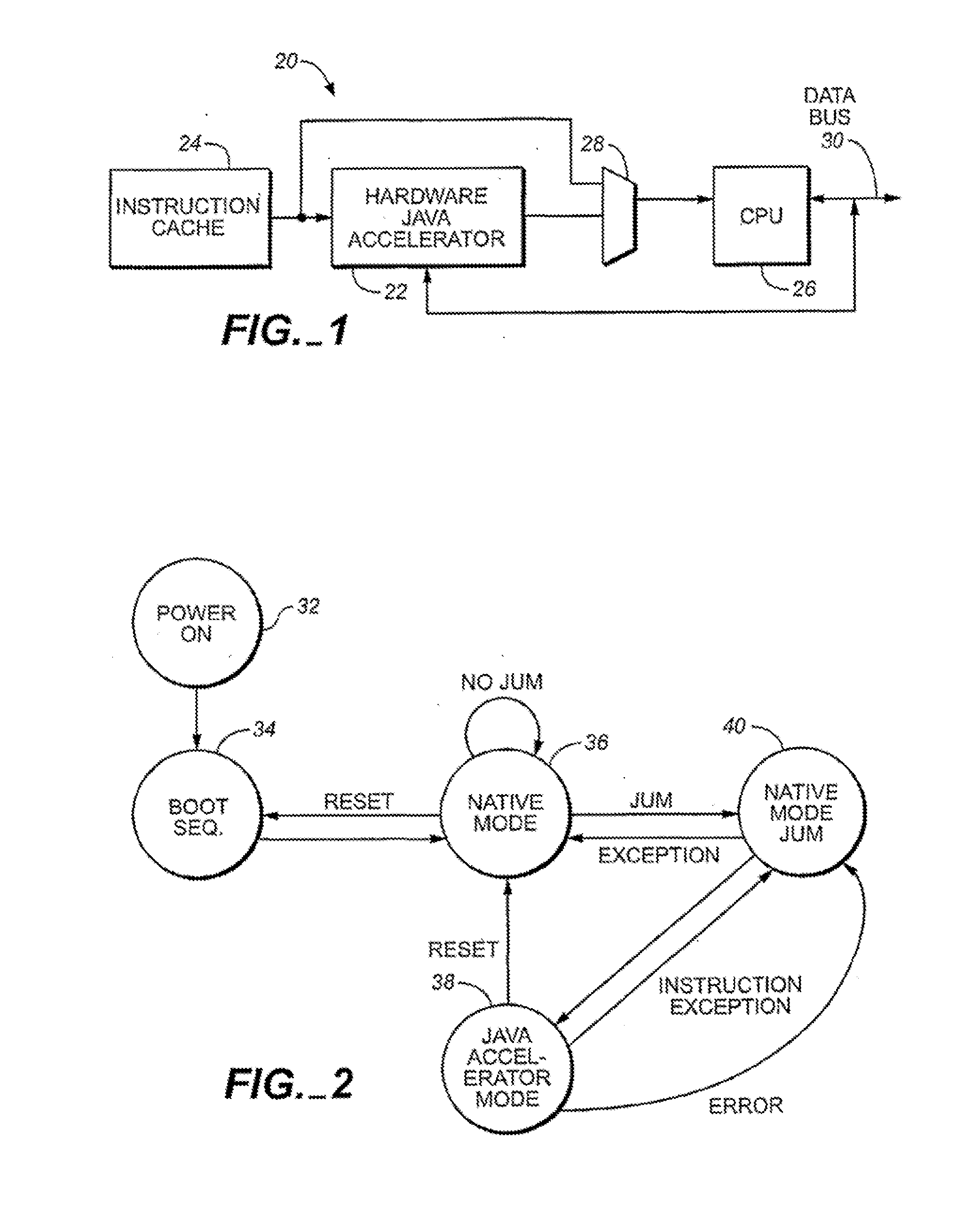

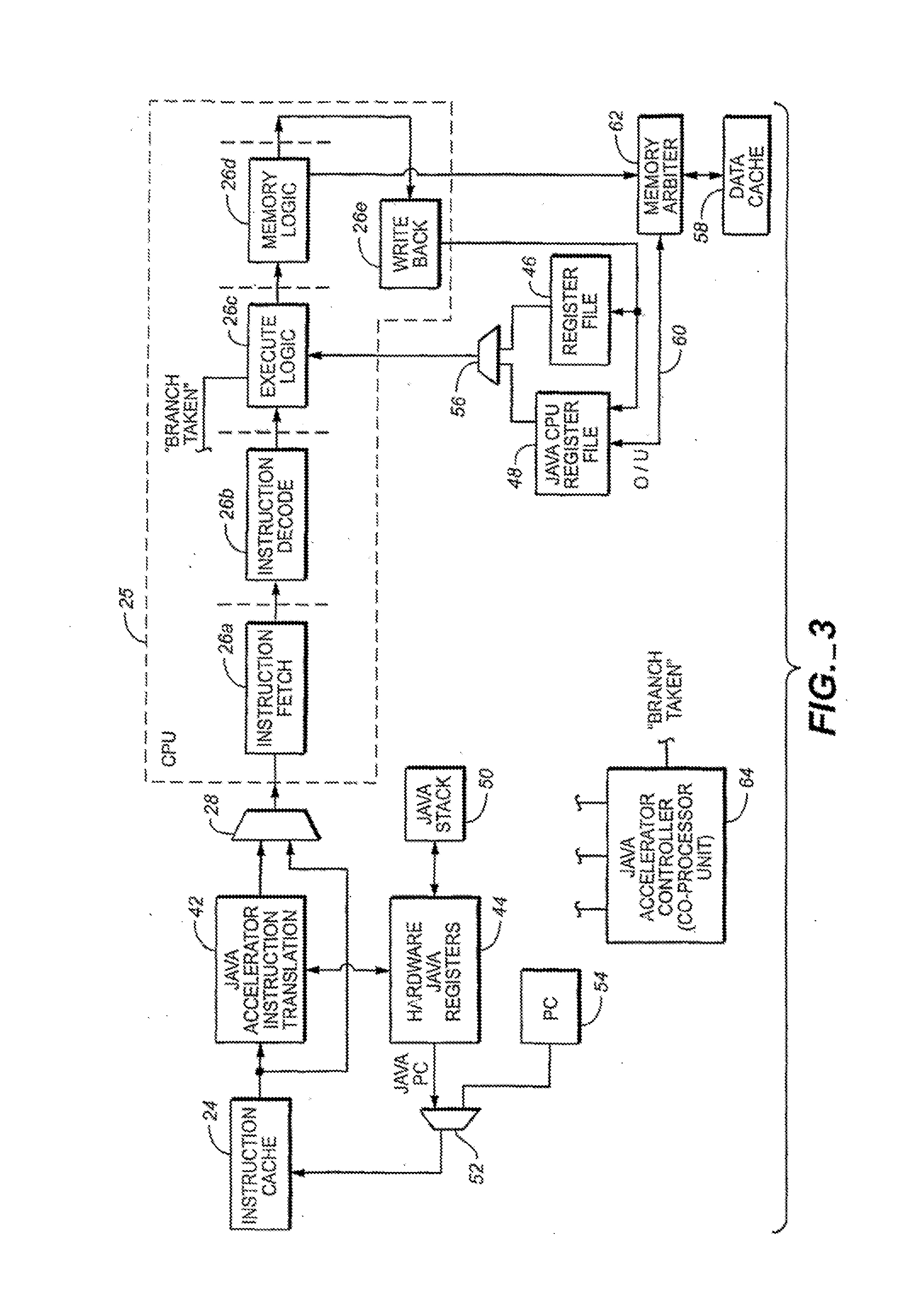

JAVA hardware accelerator using microcode engine

InactiveUS20070118724A1Easy to handleOperational speed enhancementTransformation of program codeJava bytecodeHardware acceleration

A hardware Java accelerator is comprised of a decode stage and a microcode stage. Separating into the decode and microcode stage allows the decode stage to implement instruction level parallelism while the microcode stage allows the conversion of a single Java bytecode into multiple native instructions. A reissue buffer is provided which stores the converted instructions and reissues them when the system returns from an interrupt. In this manner, the hardware accelerator need not be flushed upon an interrupt. A native PC monitor is also used. While the native PC is within a specific range, the hardware accelerator is enabled to convert the Java bytecodes into native instructions. When the native PC is outside the range, the hardware accelerator is disabled and the CPU operates on native instructions obtained from the memory.

Owner:NAZOMI COMM

Secure game download

ActiveUS20070150937A1Apparatus for meter-controlled dispensingPlatform integrity maintainanceOperational systemCode signing

A method for gaming terminals, gaming kiosks and lottery terminals to ensure that the code-signing verification process of downloaded game software can be trusted. Drivers independently developed from the operating system supplier are embedded within the operating system kernel to verify that the micro-coded hardware components, the BIOS, the operating system components and the downloaded game software can be trusted.

Owner:IGT

Apparatus and method for enhancing forwarding and classification of network traffic with prioritized matching and categorization

ActiveUS8665868B2Low costIncrease speedData switching by path configurationMultiple digital computer combinationsTraffic capacityEngineering

An apparatus is described that performs prioritized matching through processing of network traffic in accordance with provisioned rules and policies. The apparatus includes a plurality of microcode controlled state machines, and a distribution circuit that routes input data to the plurality of microcode controlled state machines, such that the plurality of microcode controlled state machines apply rules to the input data to determine matches and produce priority indicators, wherein each match has an associated priority indicator. At least one of the matches is selected based on the priority indicators. Advantageously, the apparatus provides an architectural framework well suited to a low cost, high speed, robust implementation of flexible, advanced network security and monitoring features and network traffic analysis.

Owner:CPACKET NETWORKS

LDPC encoding methods and apparatus

ActiveUS7346832B2Simple microcodeEasy to modifyError correction/detection using multiple parity bitsCode conversionProcessor registerDegree of parallelism

A flexible and relatively hardware efficient LDPC encoder is described. The encoder can be implemented with a level of parallelism which is less than the full parallelism of the code structure used to control the encoding process. Each command of a relatively simple microcode used to describe the code structure can be stored and executed multiple times to complete the encoding of a codeword. Different codeword lengths can be supported using the same set of microcode instructions but with the code being implemented a different number of times depending on the lifting factor selected to be used. The LDPC encoder can switch between encoding codewords of different lengths, without the need to change the stored code description information, by simply changing a code lifting factor used to control the encoding processes. When coding codewords shorter than the maximum supported codeword length some block storage locations and / or registers may go unused.

Owner:QUALCOMM INC

Processing core with programmable microcode unit

A method and circuit arrangement utilize a programmable microcode unit that is capable of being programmed via software to modify the instruction sequences output by the microcode unit in response to microcode instructions issued to the microcode unit. Among other benefits, a programmable microcode unit consistent with the invention enables customization of a processor design to handle specific applications or tasks, as well as to support specific hardware configurations such as specific execution units. In addition, a programmable microcode unit may be updatable, e.g., to correct bugs or faults found in previous instruction sequences supported by the unit.

Owner:IBM CORP

Asymmetric Cryptographic Device With Local Private Key Generation and Method Therefor

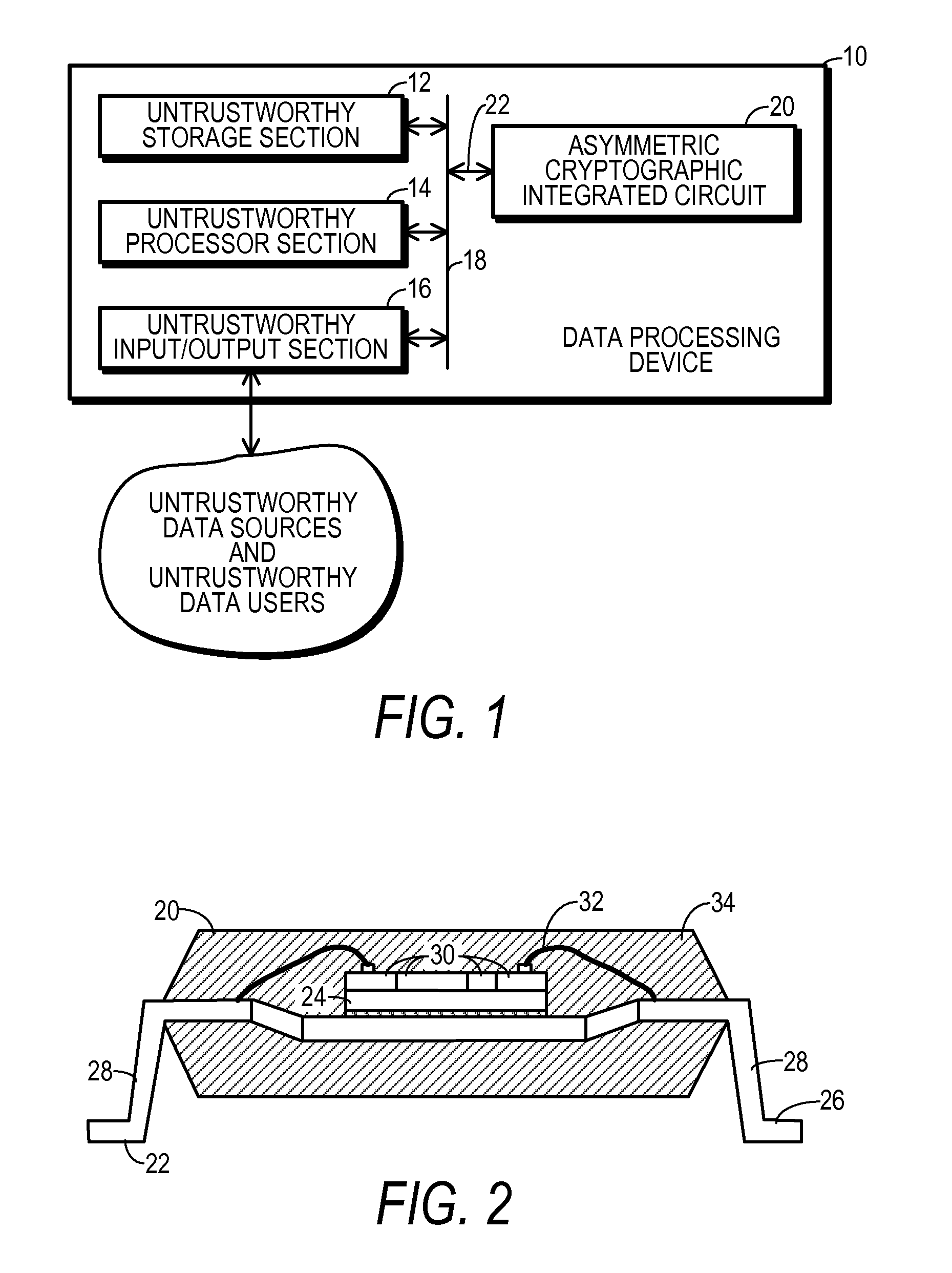

ActiveUS20100027788A1Random number generatorsMultiple keys/algorithms usageData treatmentNumber generator

An asymmetric cryptographic integrated circuit 20 and a data processing device 10 in which the integrated circuit 20 is used are disclosed. A security boundary 44 is confined to the interior of integrated circuit 20. A random number generator 50 with a hardware entropy source 54 and an arithmetic unit 62 programmed through microcode 38″ to perform a variety of cryptographically useful functions are included within security boundary 44. One of these functions is a primality tester 72. A controller 36 for integrated circuit 20 may cause cryptographically sensitive data, such as large random prime numbers and a clear private key to be generated within the confines of security boundary 44. A symmetric key encryption engine 56 is included within security boundary 44 and used to encrypt the clear private key so that a resulting encrypted private key may be stored outside security boundary 44 in a non-volatile memory 12.

Owner:NXP USA INC

Early access to microcode ROM

An apparatus and method are provide for precluding stalls in a microprocessor pipeline due to microcode ROM access delay. The apparatus includes a micro instruction queue and early access logic. The micro instruction queue provides a plurality of queue entries to register logic. Each of tile plurality of queue entries includes first micro instructions and a microcode entry point. All of the first micro instructions correspond to an instruction. The microcode entry point is coupled to the first micro instructions. The microcode entry point is configured to point to second micro instructions stored within a microcode ROM. The early access logic is coupled to the micro instruction queue. The early access logic employs the microcode entry point to access the microcode ROM prior to when the each of the plurality of queue entries is provided to the register logic, whereby a first one of the second micro instructions is provided to the register logic when the first one of the second micro instructions is required by the register logic.

Owner:IP FIRST

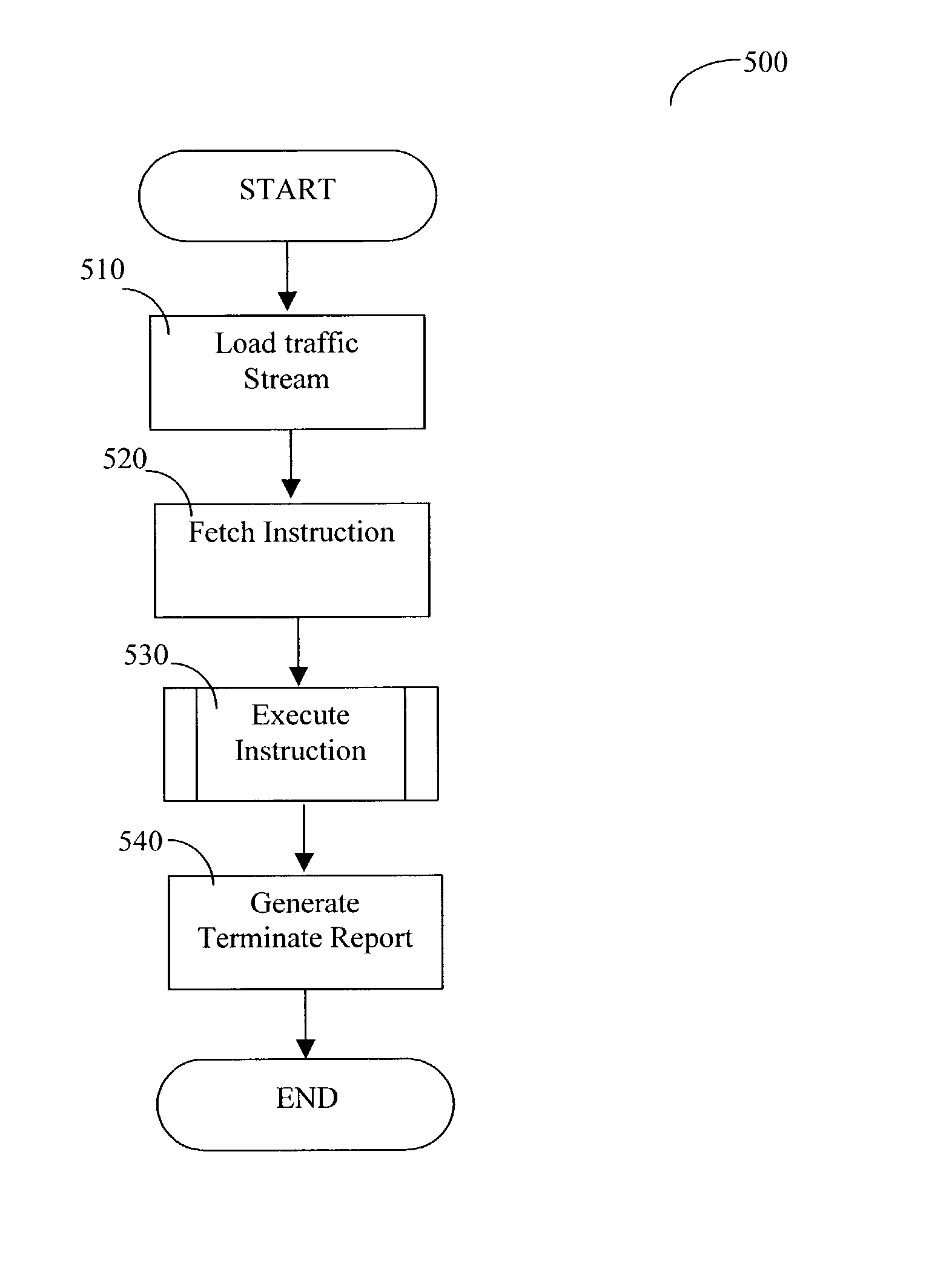

Apparatus and method for pattern matching in text based protocol

InactiveUS20030204584A1Data processing applicationsDigital data information retrievalText-based protocolText mode

A search engine for matching textual patterns in a traffic stream. The search engine comprises a traffic control unit, a micro-code memory, a comparator and a report memory. The traffic control unit is capable of managing the traffic stream. The micro-code memory is capable of storing and retrieving micro-code instructions. The comparator is capable of executing said micro-code instructions to match the textual patterns. The report memory is capable of storing and retrieving reports generated said comparator.

Owner:CISCO SYST ISRAEL

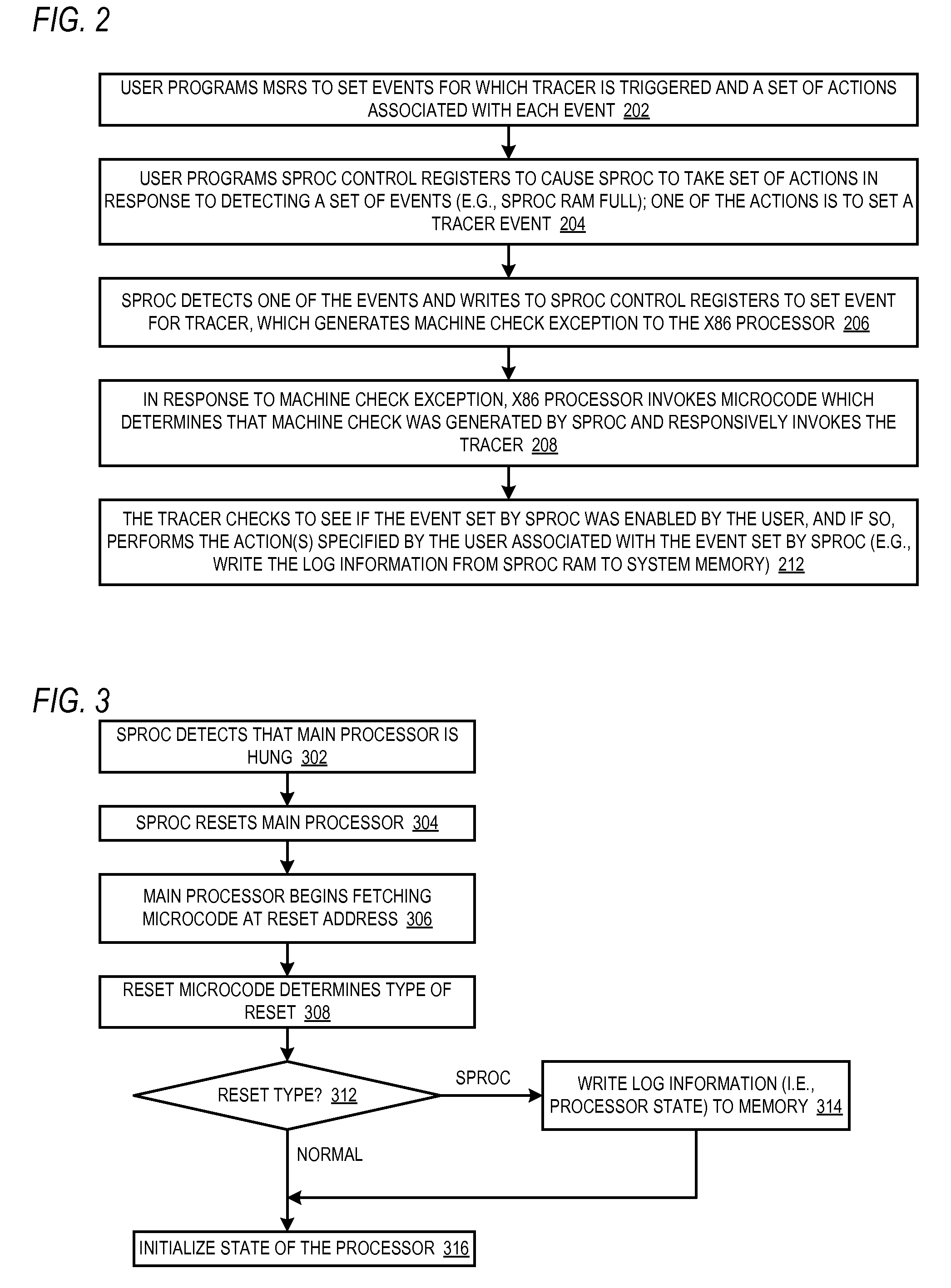

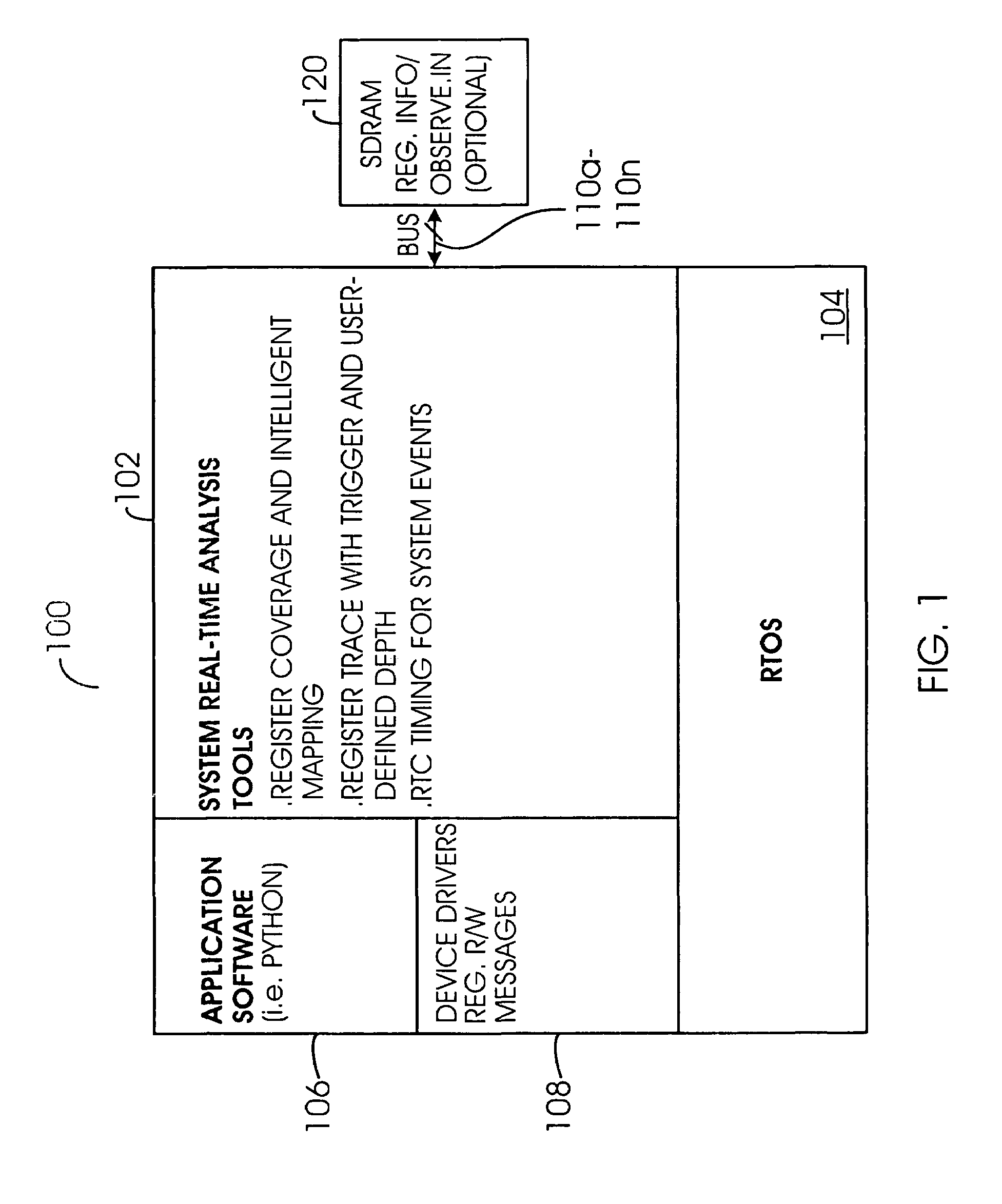

System real-time analysis tool

InactiveUS7043718B1Error detection/correctionSpecific program execution arrangementsSystem monitorReal time analysis

Owner:BELL SEMICON LLC

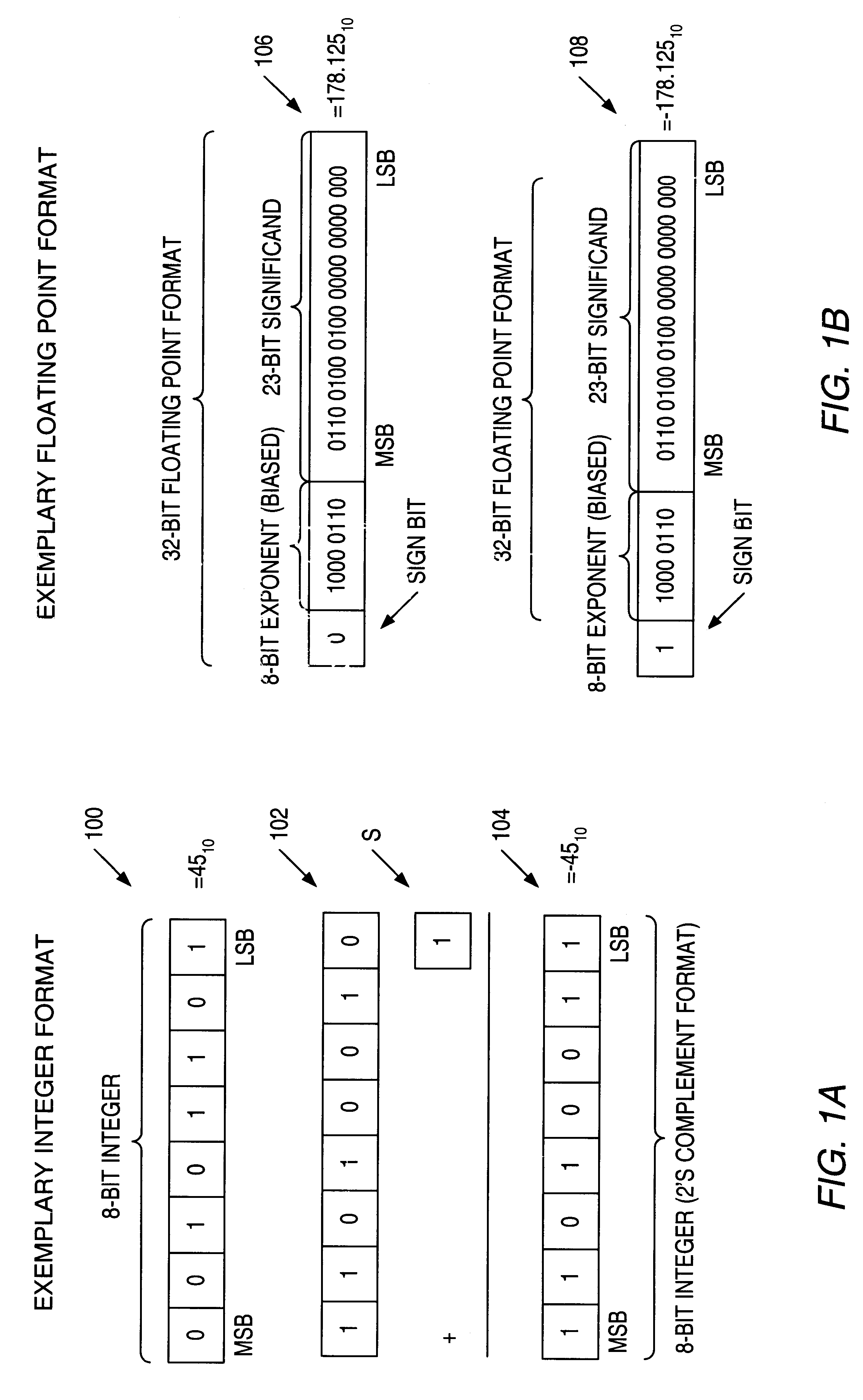

Apparatus and method for using checking instructions in a floating-point execution unit

InactiveUS6247117B1Digital computer detailsSpecific program execution arrangementsExecution unitOperand

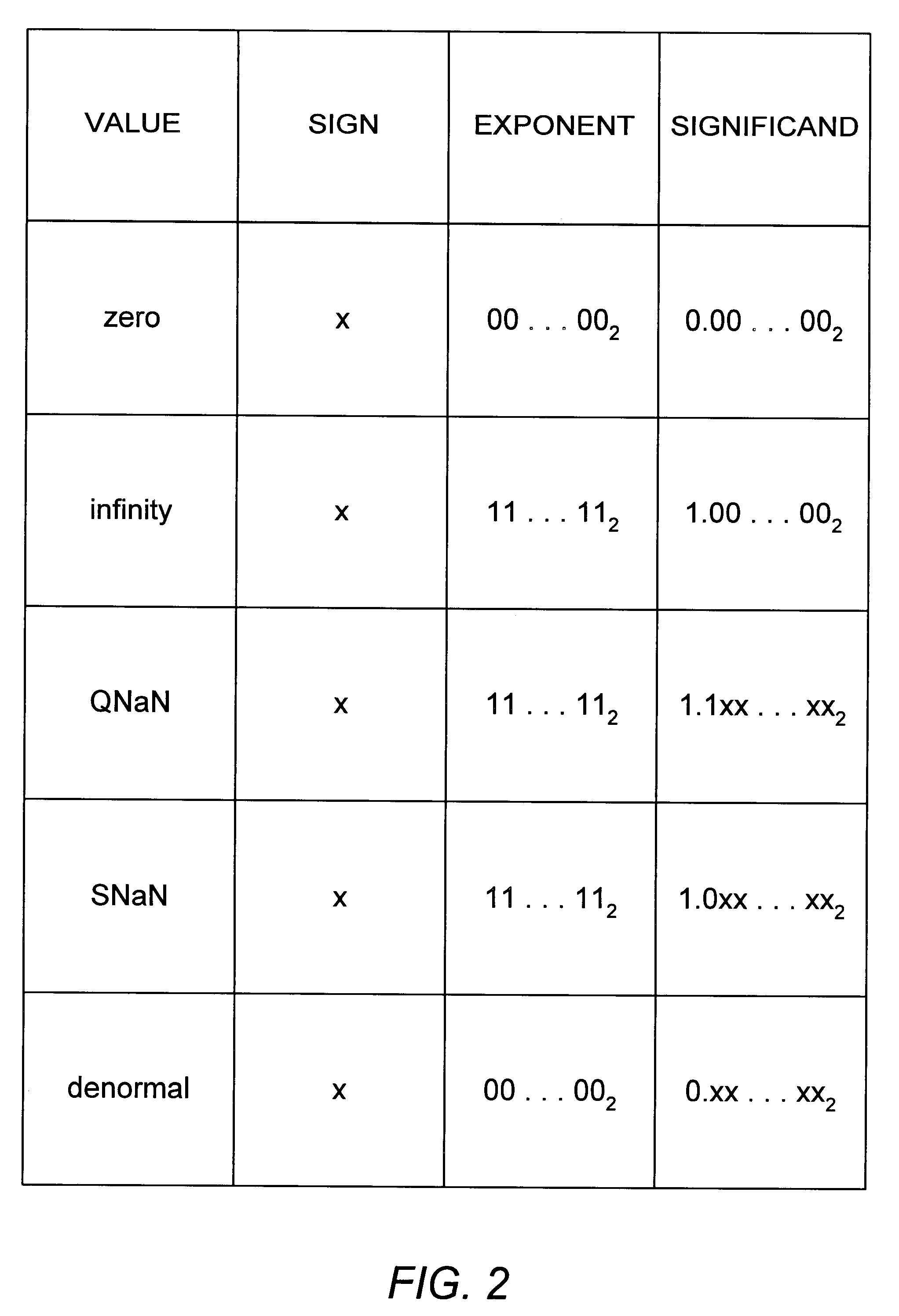

The use of checking instructions to detect special and exceptional cases of a defined data format in a microprocessor is disclosed. Generally speaking, a checking instruction is included with the microcode of floating-point instructions to detect special and exceptional cases of operand values for the floating-point instructions. A checking instruction is configured to set one or more flags in a flags register if it detects a special or exceptional case for an operand value. A checking instruction may also set the result or results of a floating-point instruction to a result value if a special or exceptional case is detected. In addition, a checking instruction may be configured to set one or more bits in status register if a special or exceptional case is detected. After a checking instruction completes execution, a subsequent microcode instruction can be executed to determine if one or more flags were set by the checking instruction. If one or more flags have been set by the checking instruction, the subsequent microcode instruction can branch to a non-sequential microcode instruction to handle the special or exceptional case detected by the checking instruction.

Owner:ADVANCED MICRO DEVICES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com