Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

357 results about "Micro-operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer central processing units, micro-operations (also known as a micro-ops or μops) are detailed low-level instructions used in some designs to implement complex machine instructions (sometimes termed macro-instructions in this context).

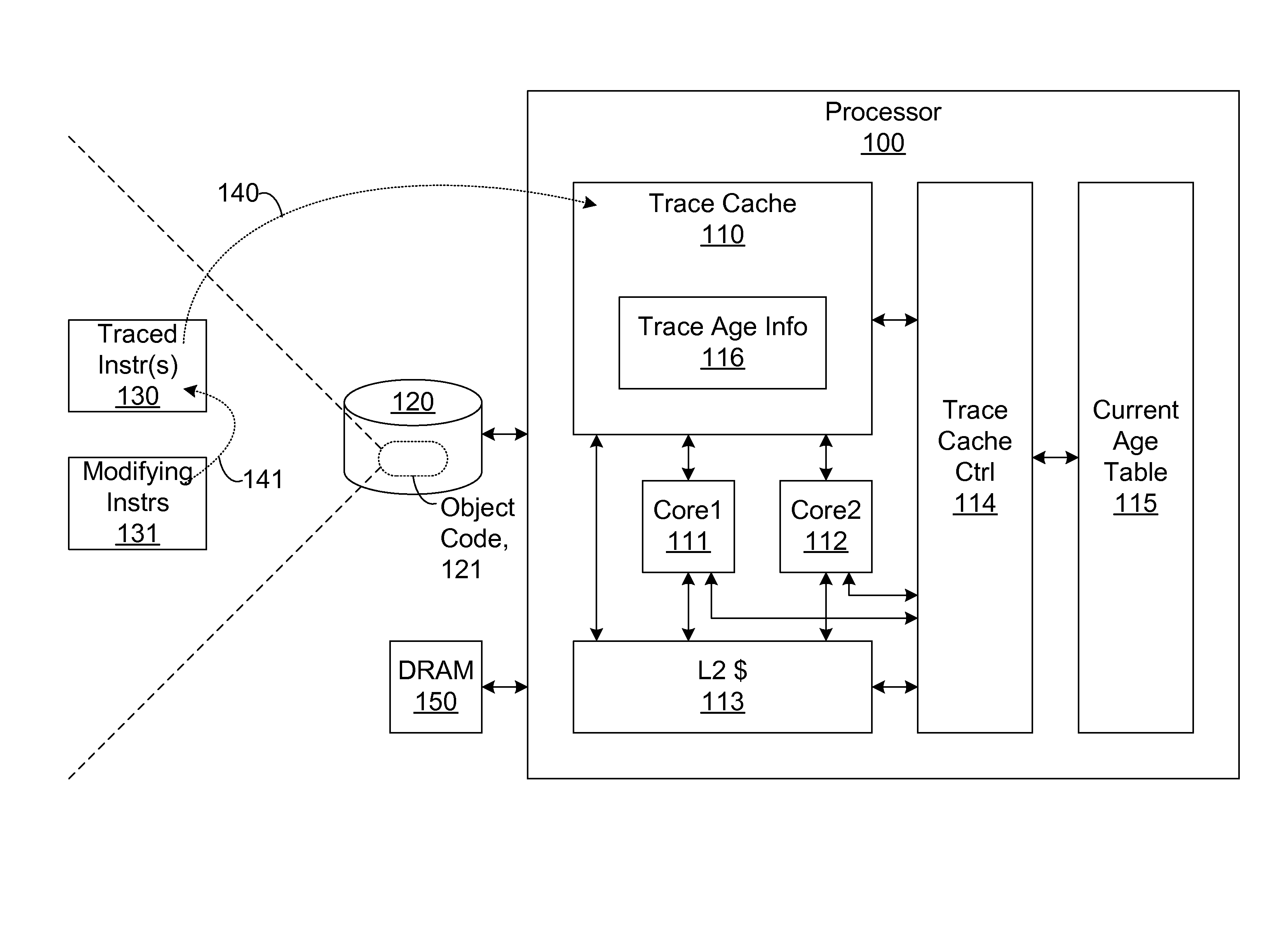

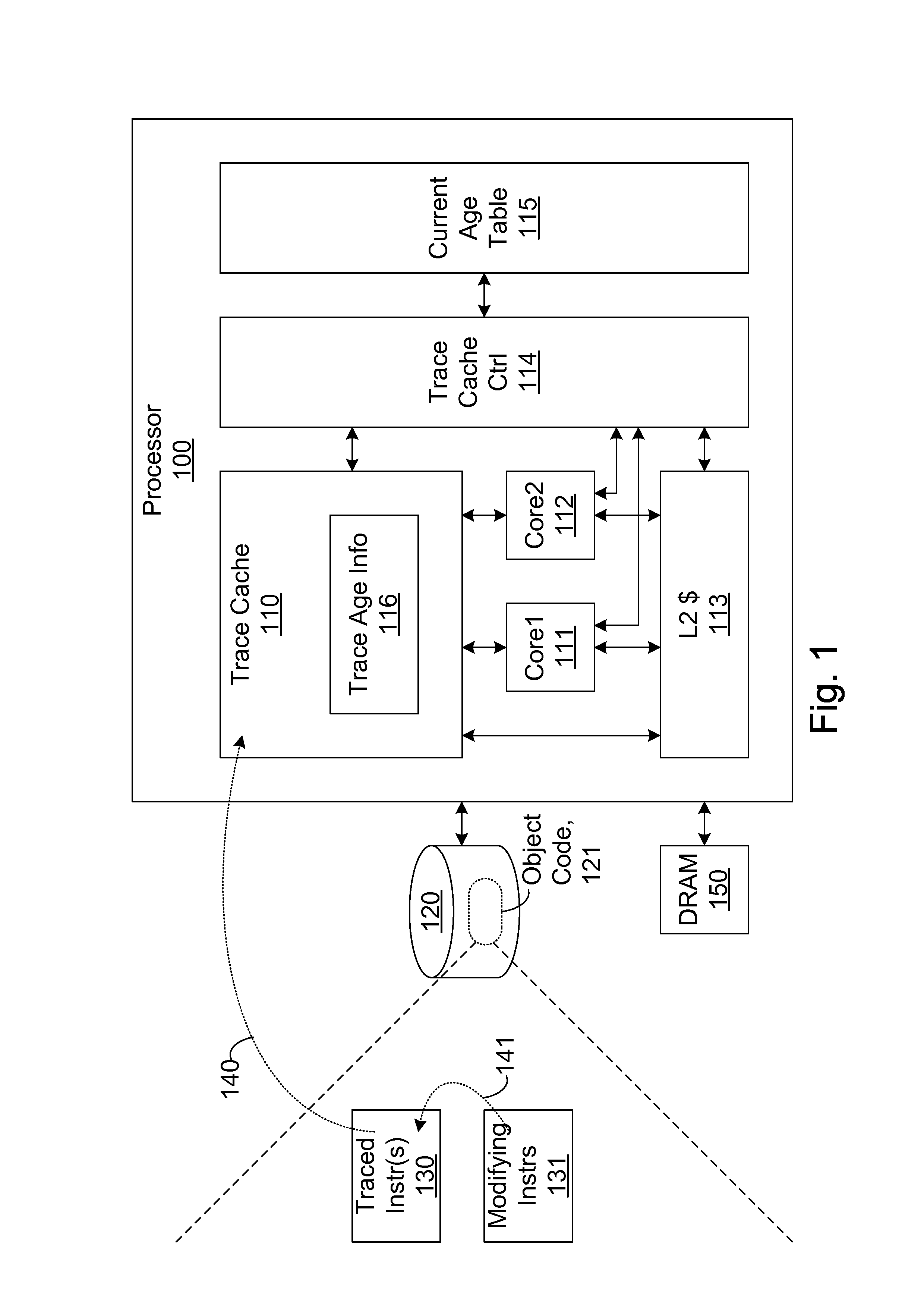

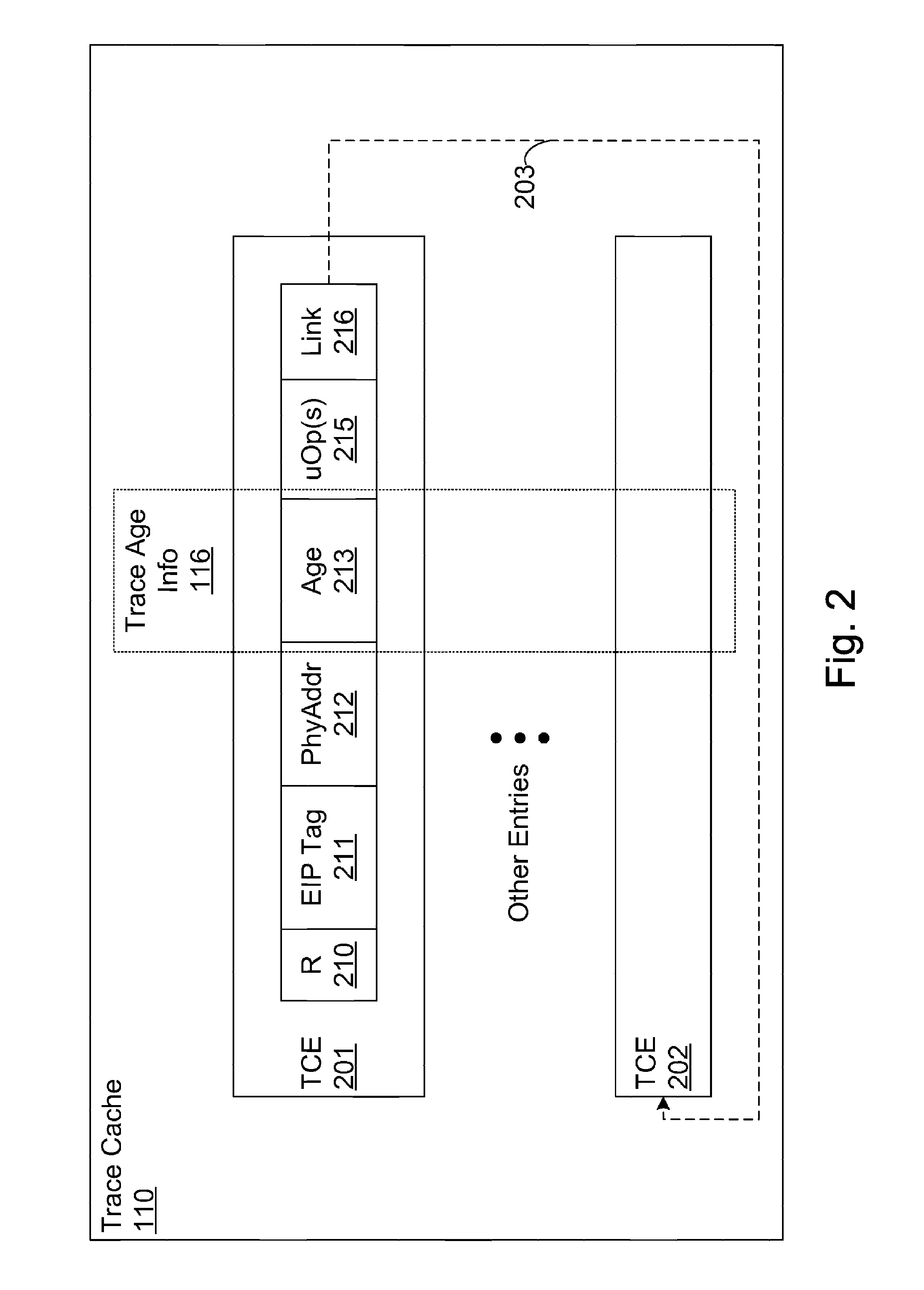

Efficient trace cache management during self-modifying code processing

ActiveUS7546420B1Process less-efficientMore hardwareEnergy efficient ICTProgram controlSelf-modifying codeMicro-operation

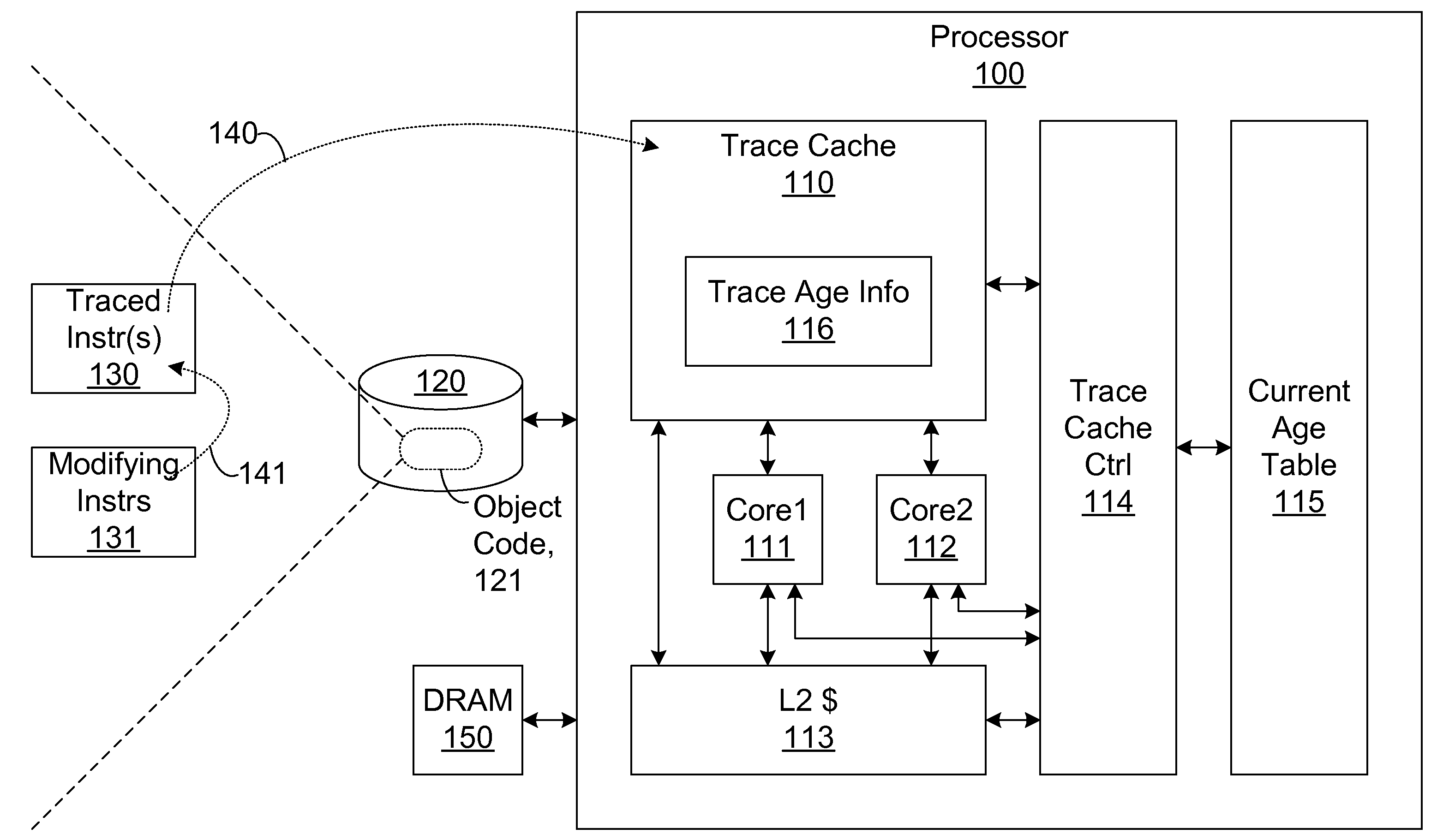

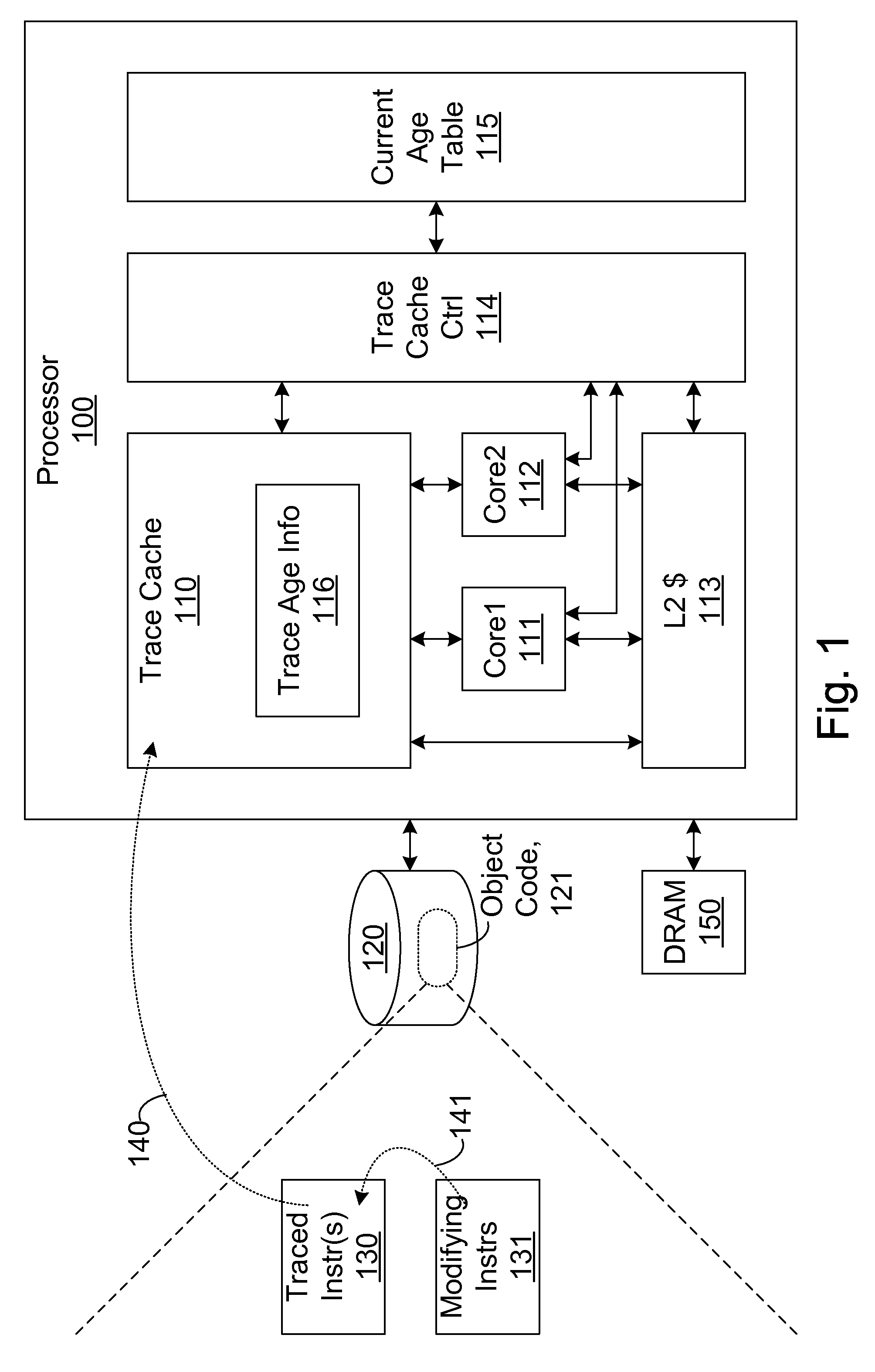

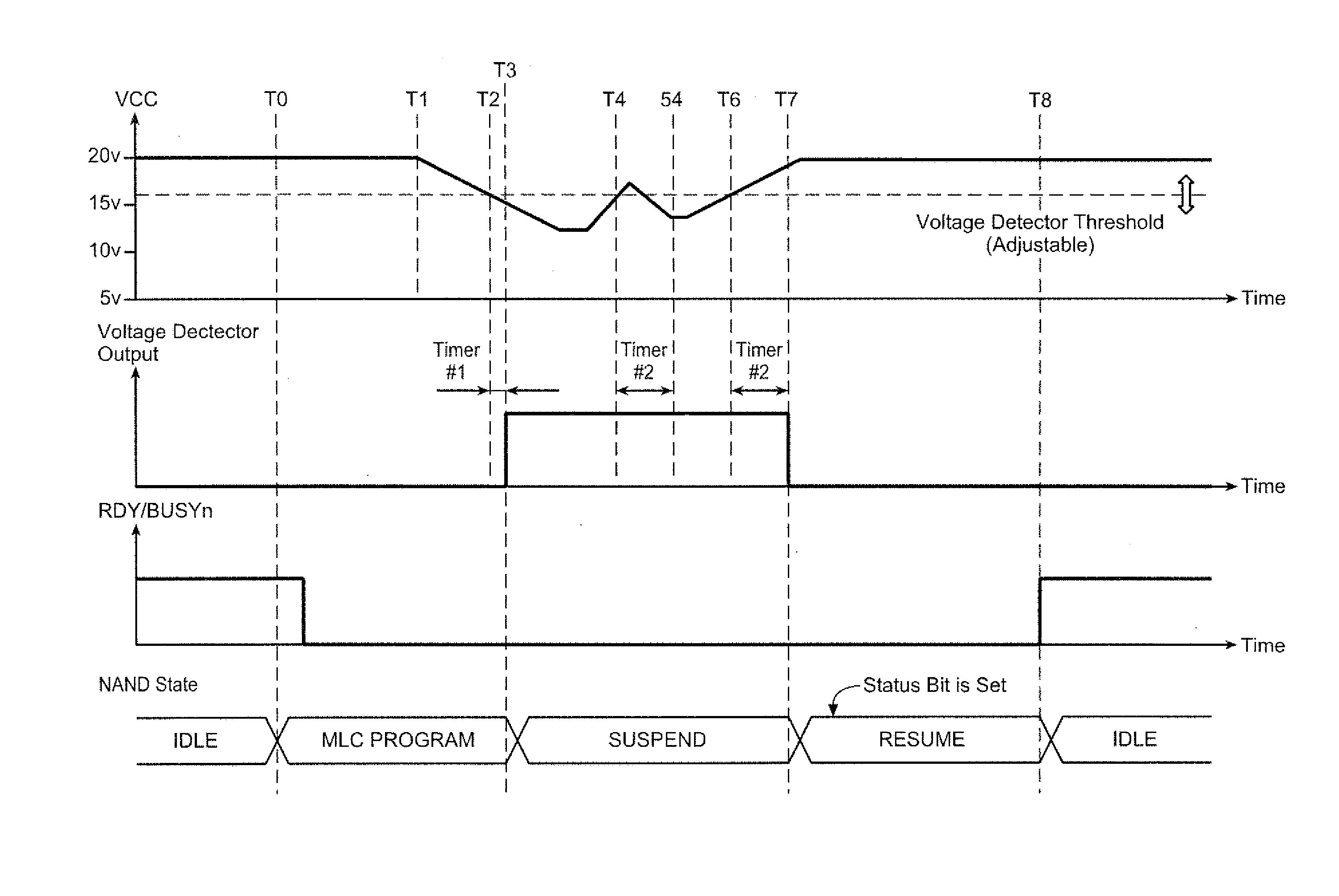

Efficient trace cache management during self-modifying code processing enables selective invalidation of entries of the trace cache, advantageously retaining some of the entries in the trace cache even during self-modifying code events. Instructions underlying trace cache entries are monitored for modification in groups, enabling advantageously reduced hardware. One or more translation ages are associated with each trace cache entry, and are determined when the entry is built by sampling current ages of memory blocks underlying the entry. When the entry is accessed and micro-operations therein are processed, the translation ages of the accessed entry are compared with the current ages of the memory blocks underlying the accessed entry. If any of the age comparisons fail, then the micro-operations are aborted and the entry is invalidated. When any portion of a memory block is modified, the current age of the modified memory block is incremented.

Owner:ORACLE INT CORP

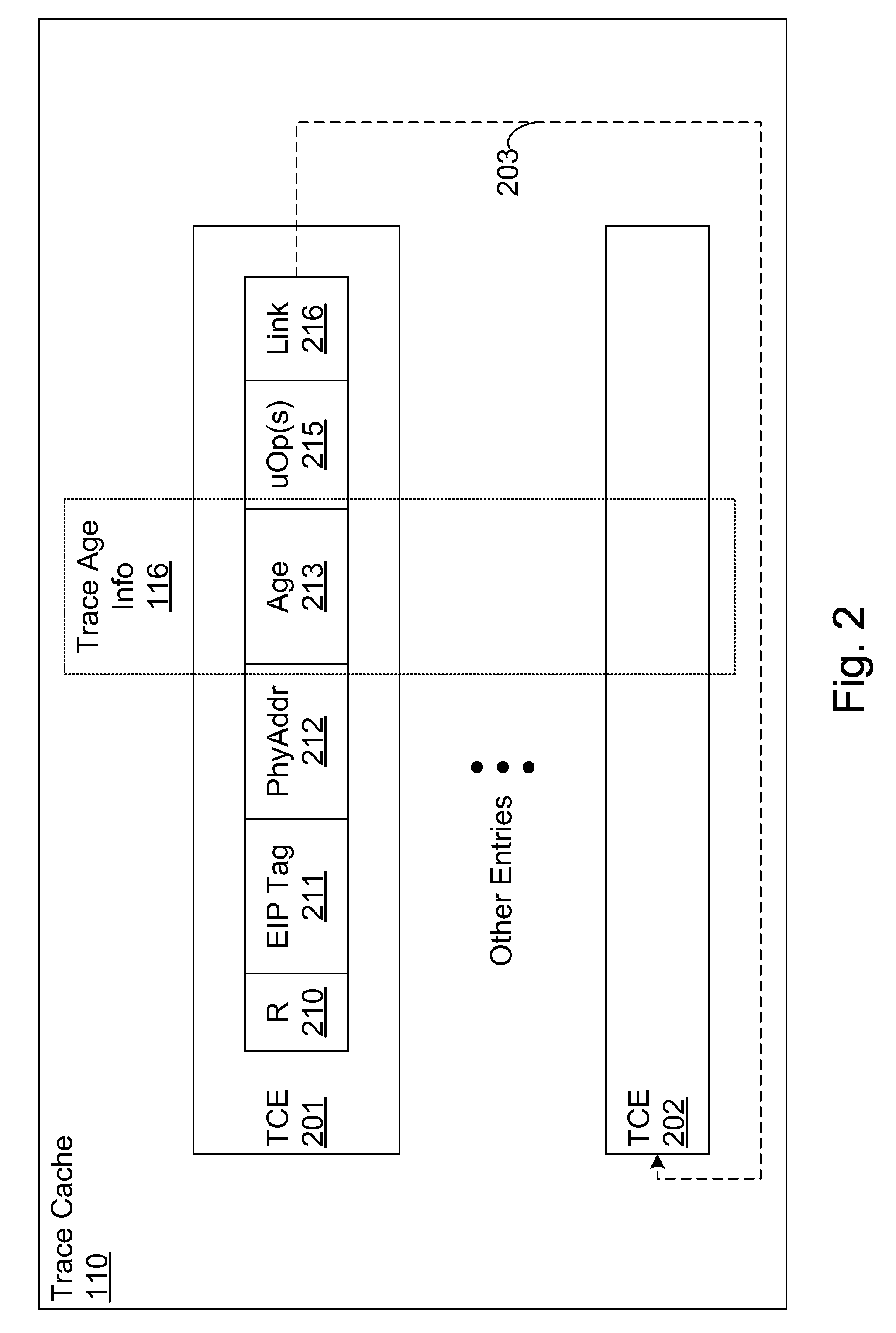

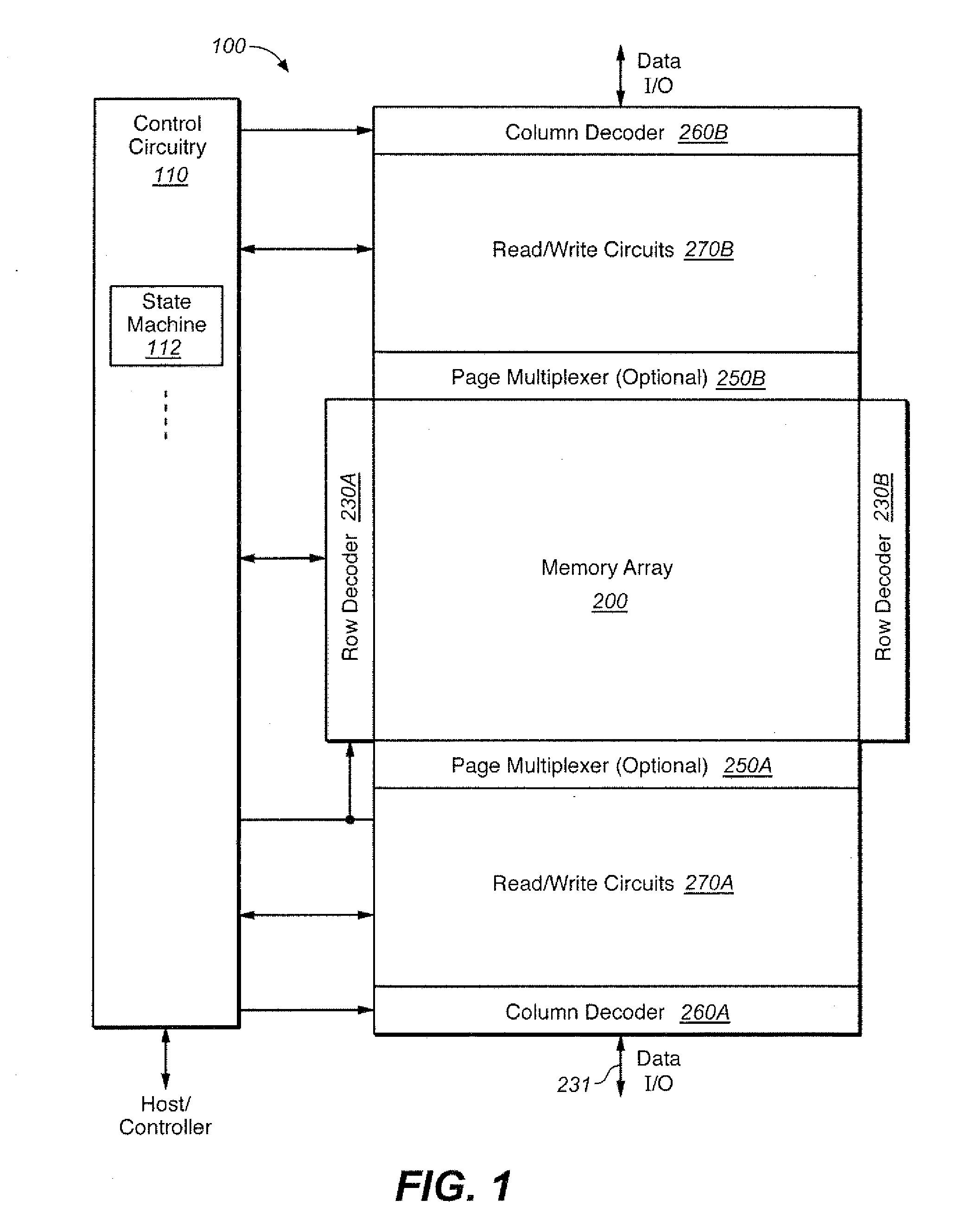

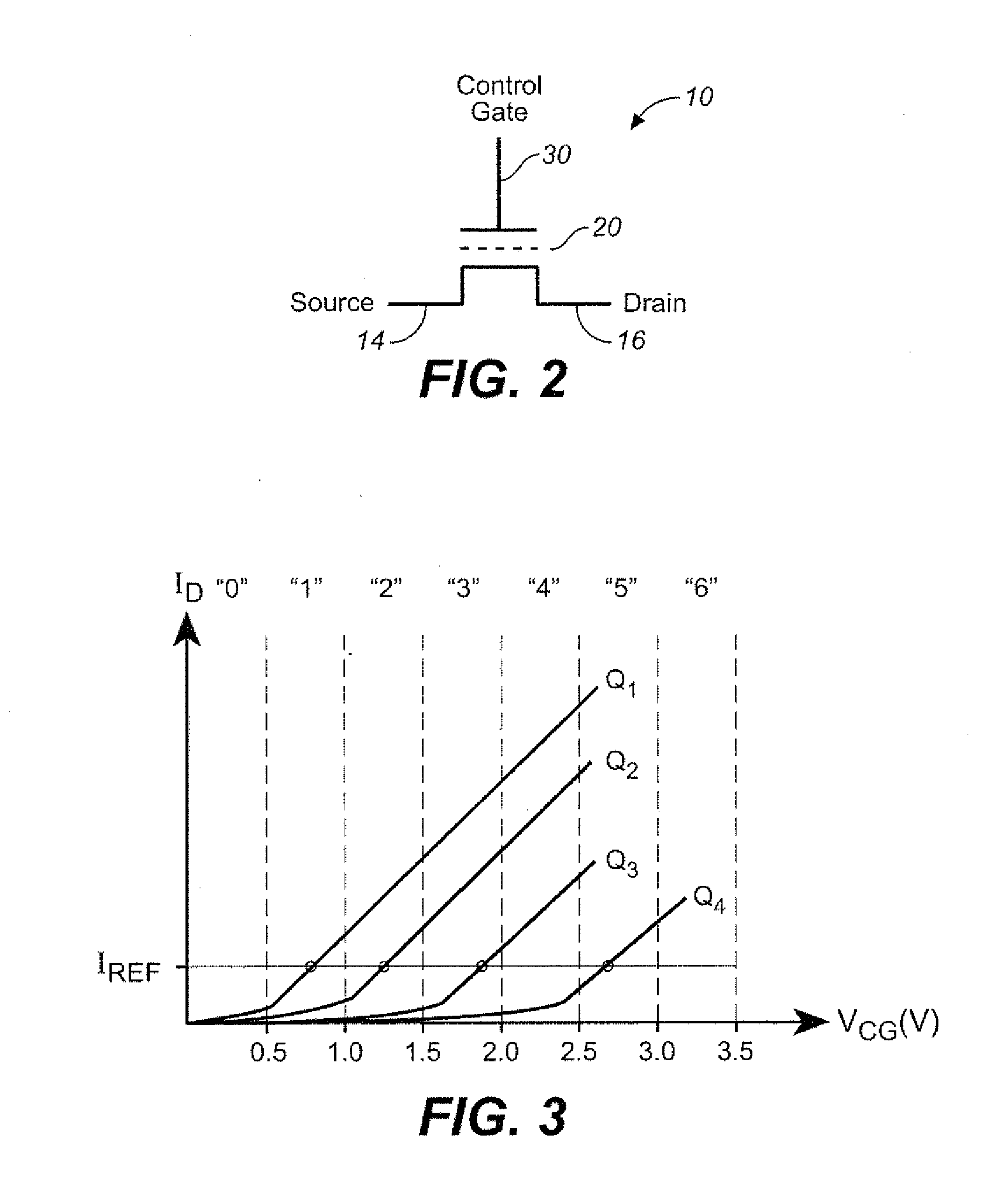

Immunity Against Temporary and Short Power Drops in Non-Volatile Memory: Pausing Techninques

A mechanism is presented memory circuits, such a NAND-type flash memories, to autonomously protect themselves from temporary and short power drops. A detection mechanism looks for the supply voltage to drop below a function voltage for a period of time. When such an event occurs, a suspend mechanism is activated, and after completing the last micro-operation (such as a program pulse) the memory freezes. When power is again stable at an operational level, the suspended operation is resumed. The memory controller can then be notified upon occurrence of such voltage drop by polling a special status bit. Examples of how the pausing can be implemented include altering of clock signals and suspending sub-phases of larger operations.

Owner:SANDISK TECH LLC

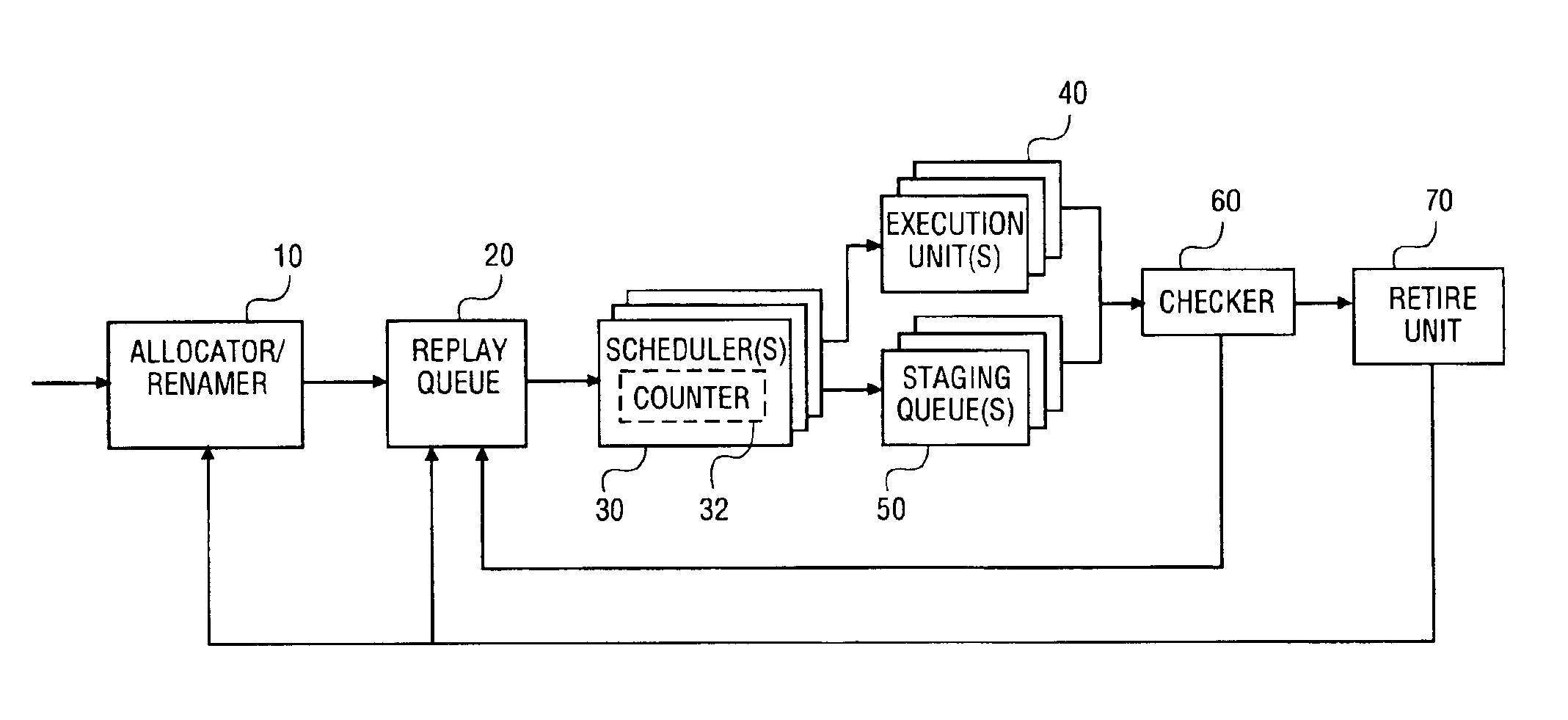

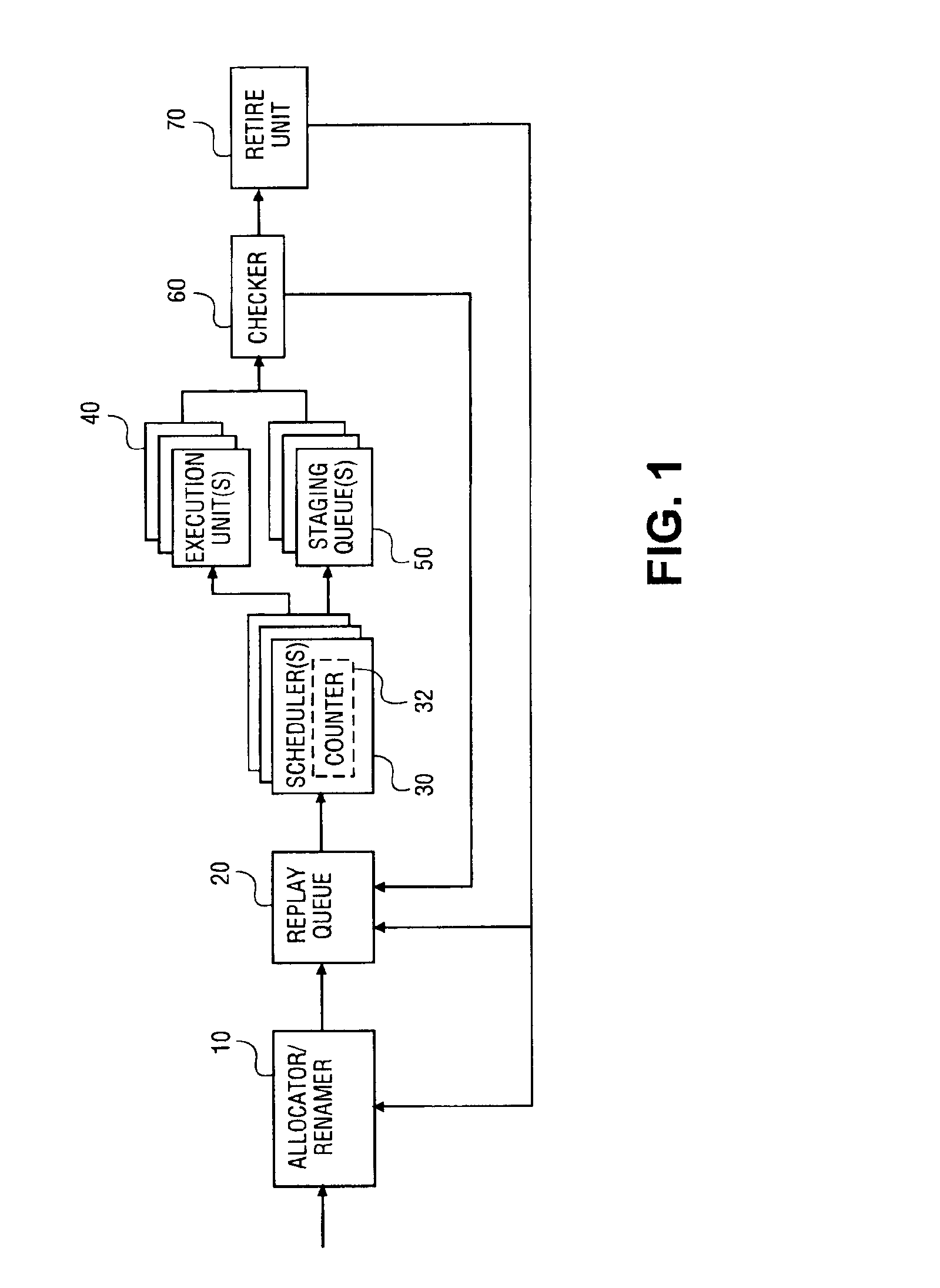

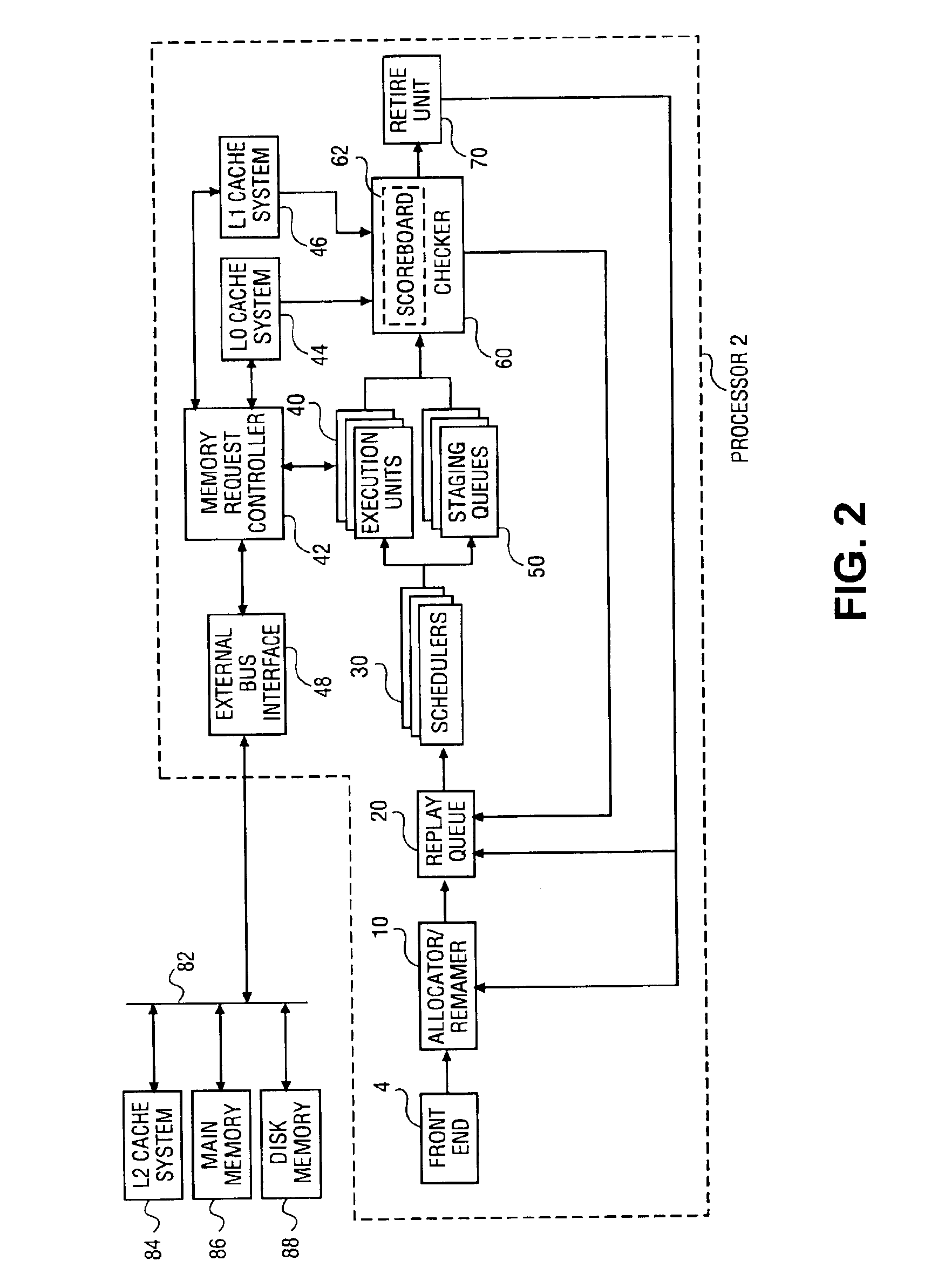

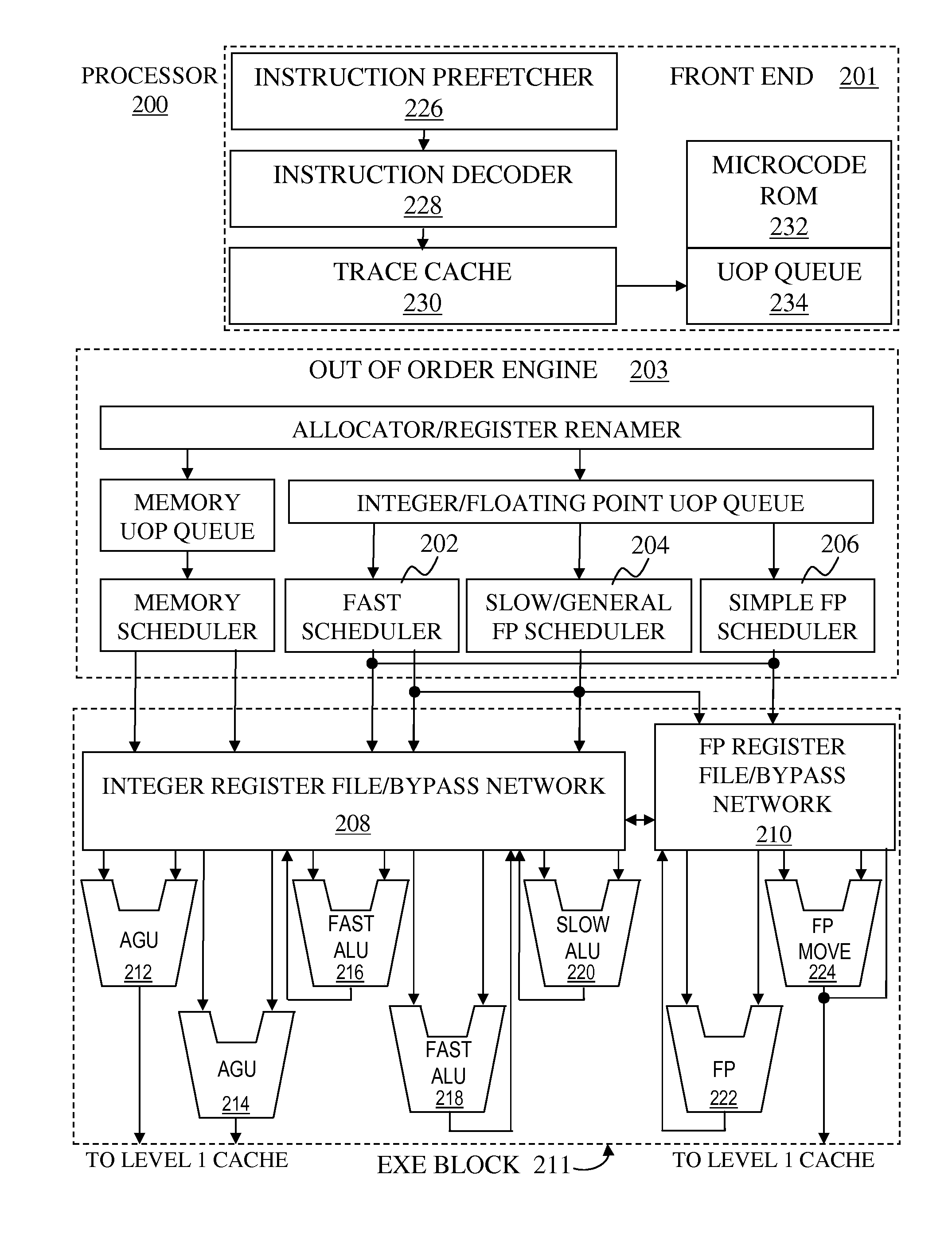

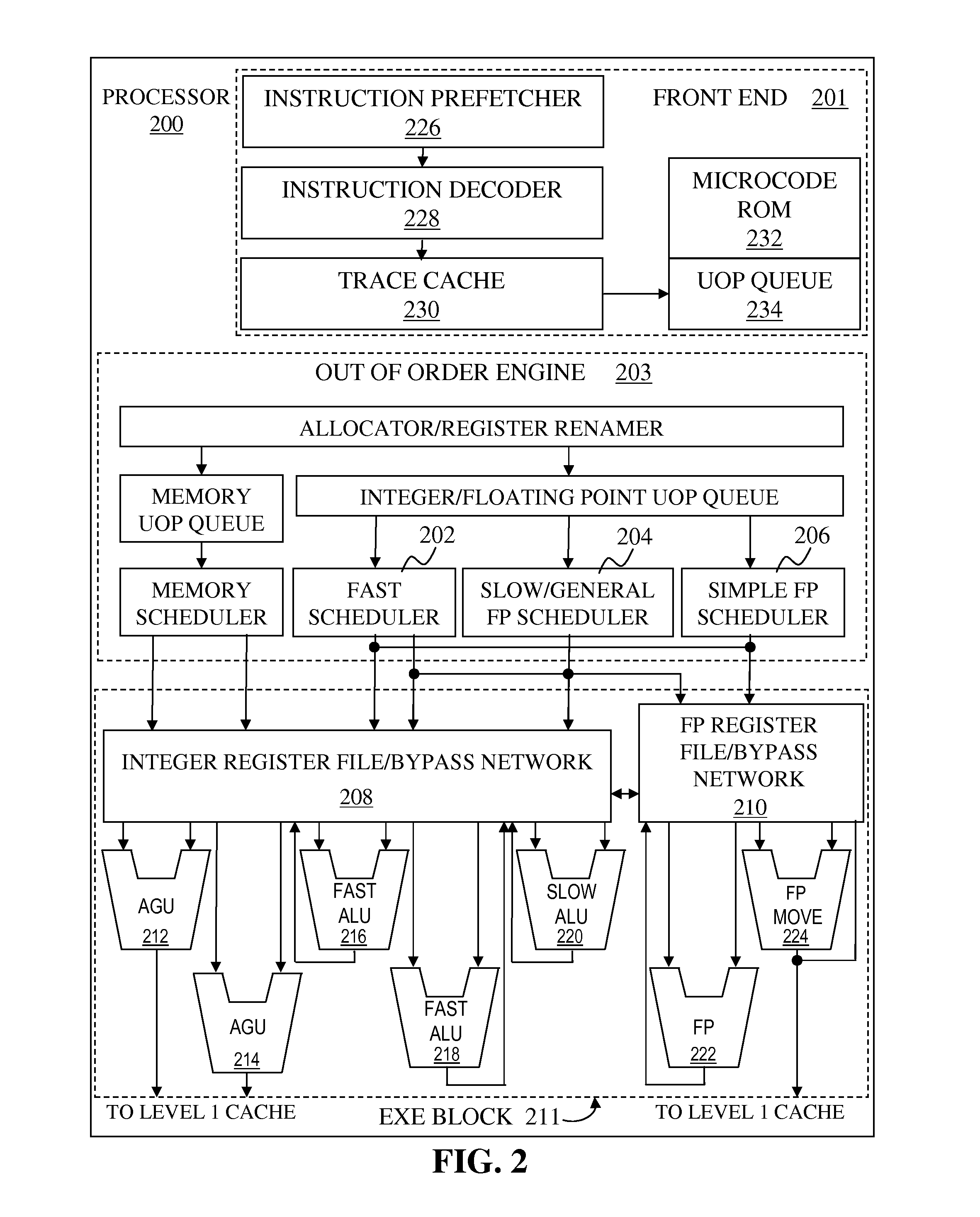

Method and apparatus for rescheduling multiple micro-operations in a processor using a replay queue and a counter

InactiveUS6877086B1Digital computer detailsConcurrent instruction executionMicro-operationParallel computing

Rescheduling multiple micro-operations in a processor using a replay queue. The processor comprises a replay queue to receive a plurality of instructions and an execution unit to execute the plurality of instructions. A scheduler is coupled between the replay queue and the execution unit. The scheduler speculatively schedules instructions for execution and dispatches each instruction to the execution unit. A checker is coupled to the execution unit to determine whether each instruction has executed successfully. The checker is also coupled to the replay queue to communicate to the replay queue each instruction that has not executed successfully.

Owner:INTEL CORP

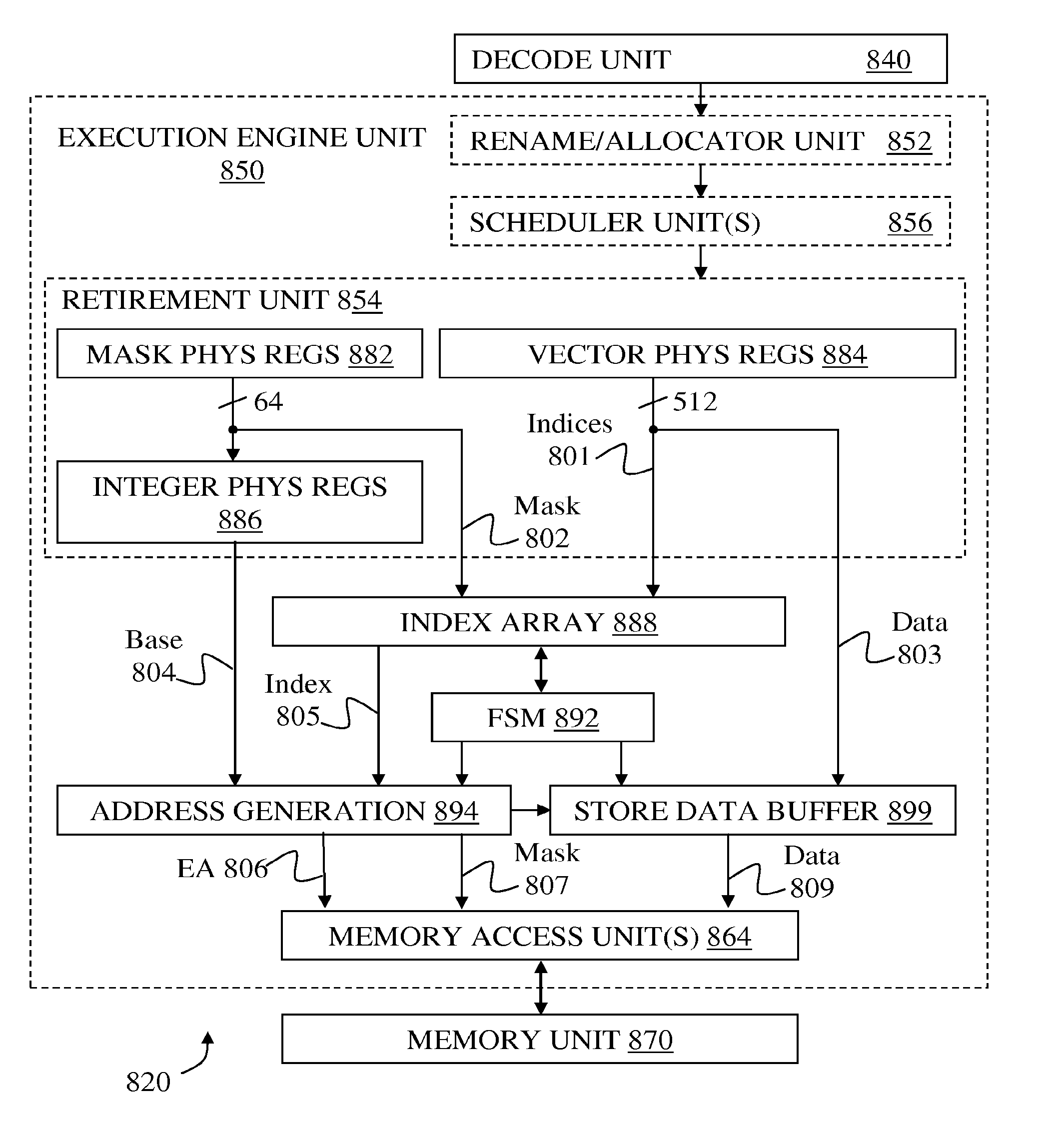

Gather using index array and finite state machine

ActiveUS20130326160A1Single instruction multiple data multiprocessorsInstruction analysisMicro-operationTheoretical computer science

Methods and apparatus are disclosed for using an index array and finite state machine for scatter / gather operations. Embodiment of apparatus may comprise: decode logic to decode a scatter / gather instruction and generate a set of micro-operations, and an index array to hold a set of indices and a corresponding set of mask elements. A finite state machine facilitates the gather operation. Address generation logic generates an address from an index of the set of indices for at least each of the corresponding mask elements having a first value. An address is accessed to load a corresponding data element if the mask element had the first value. The data element is written at an in-register position in a destination vector register according to a respective in-register position the index. Values of corresponding mask elements are changed from the first value to a second value responsive to completion of their respective loads.

Owner:INTEL CORP

Method and apparatus for predication using micro-operations

InactiveUS20050081017A1Instruction analysisRuntime instruction translationTemporary variableMicro-operation

Disclosed are an apparatus, system, and method for implementing predicated instructions using micro-operations. A micro-code engine receives an instruction, decomposes the instruction, and generates a plurality of micro-operations to implement the instruction. Each of the decomposed micro-operations indicates a single destination register. For predicated instructions, the decomposed micro-operations include “conditional move” micro-operations to select between two potential output values. Except in the case that one of the potential output values is a constant, the decomposed micro-operations for a predicated instruction also include an append instruction that saves the incoming value of a destination register in a temporary variable. For at least one embodiment, the qualifying predicate for a predicated instruction is appended to the incoming value stored in the temporary register.

Owner:INTEL CORP

Paired execution scheduling of dependent micro-operations

InactiveUS20120023314A1Lower latencySimple logicDigital computer detailsConcurrent instruction executionMicro-operationData dependence

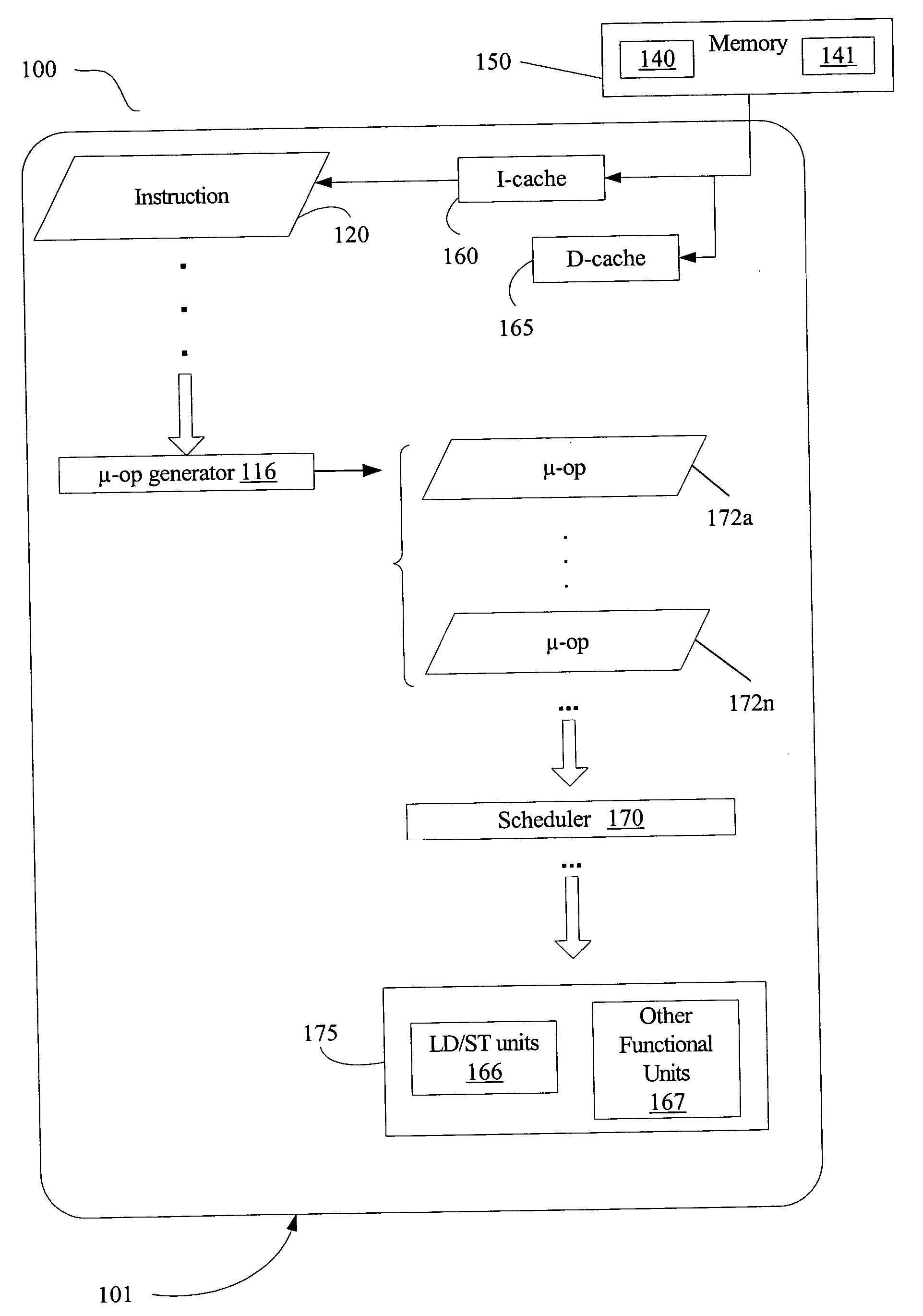

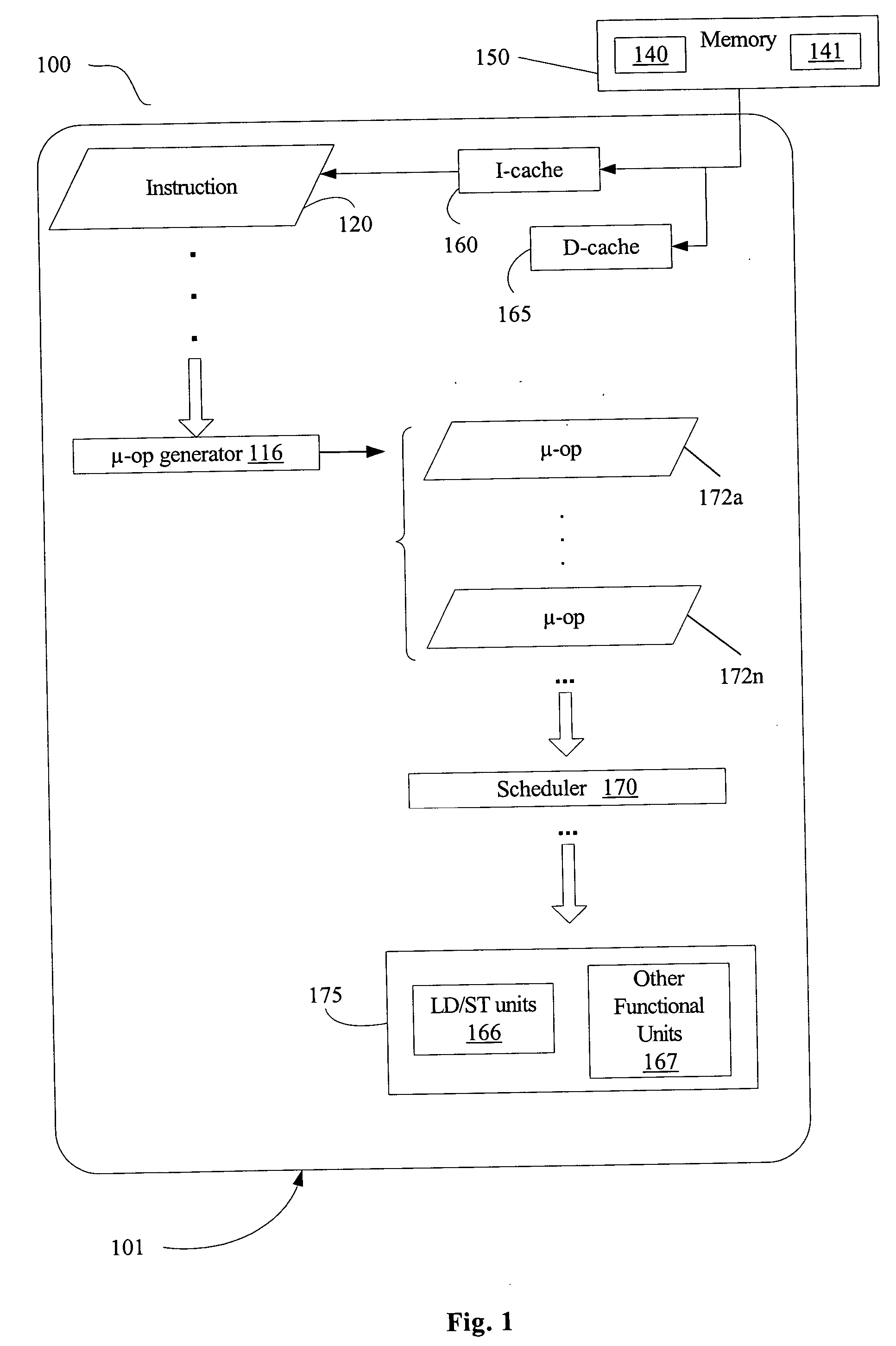

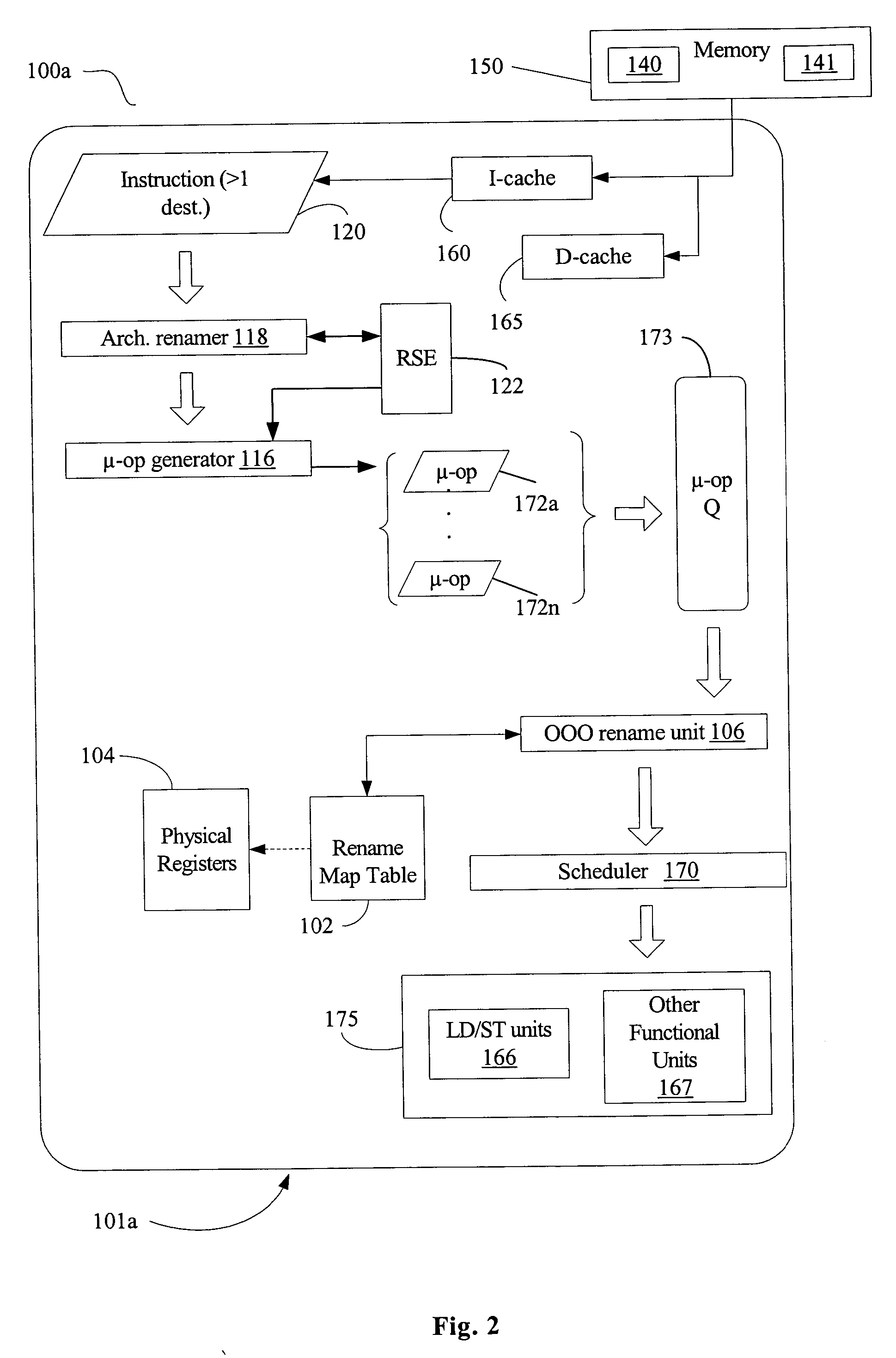

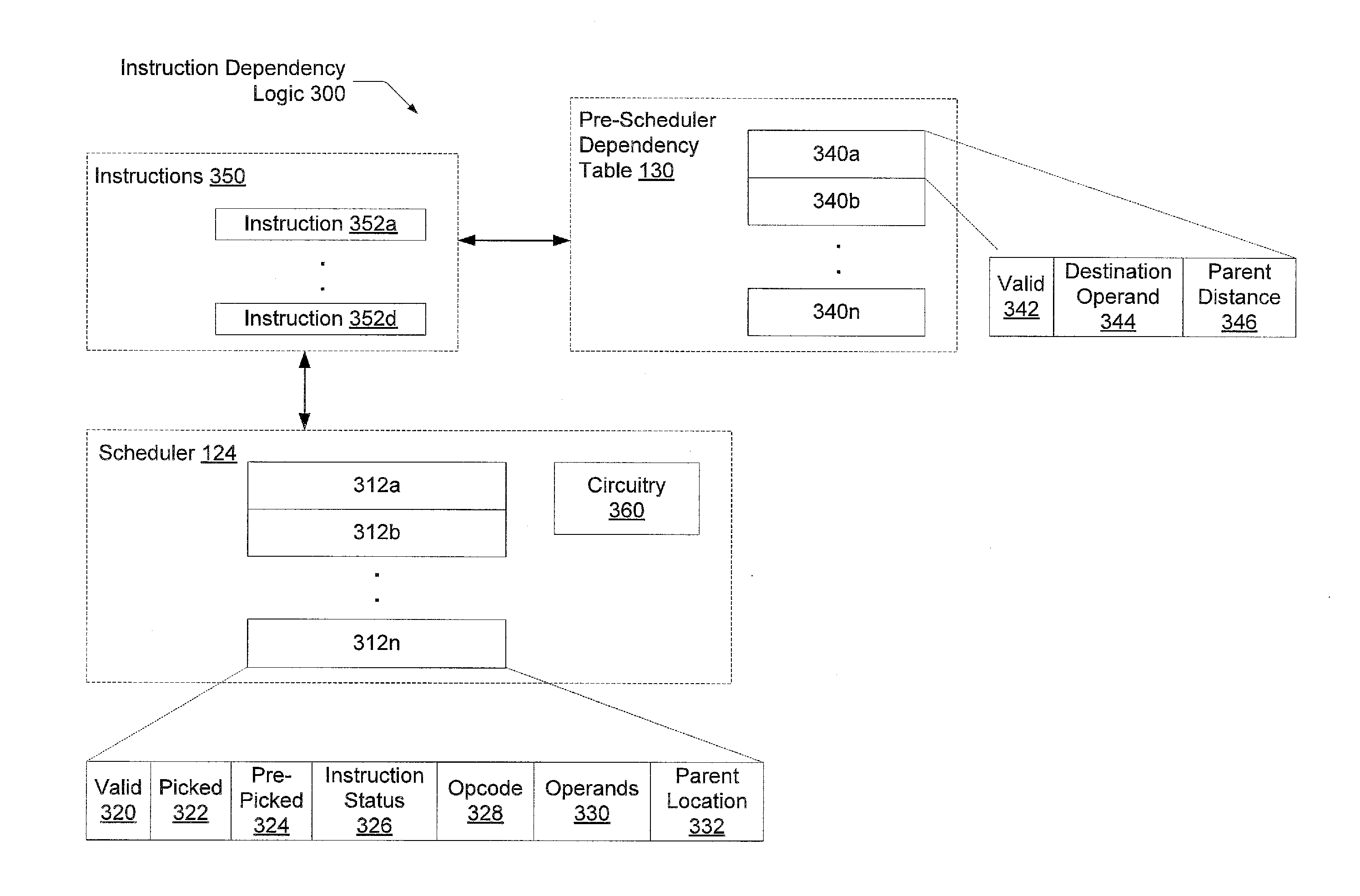

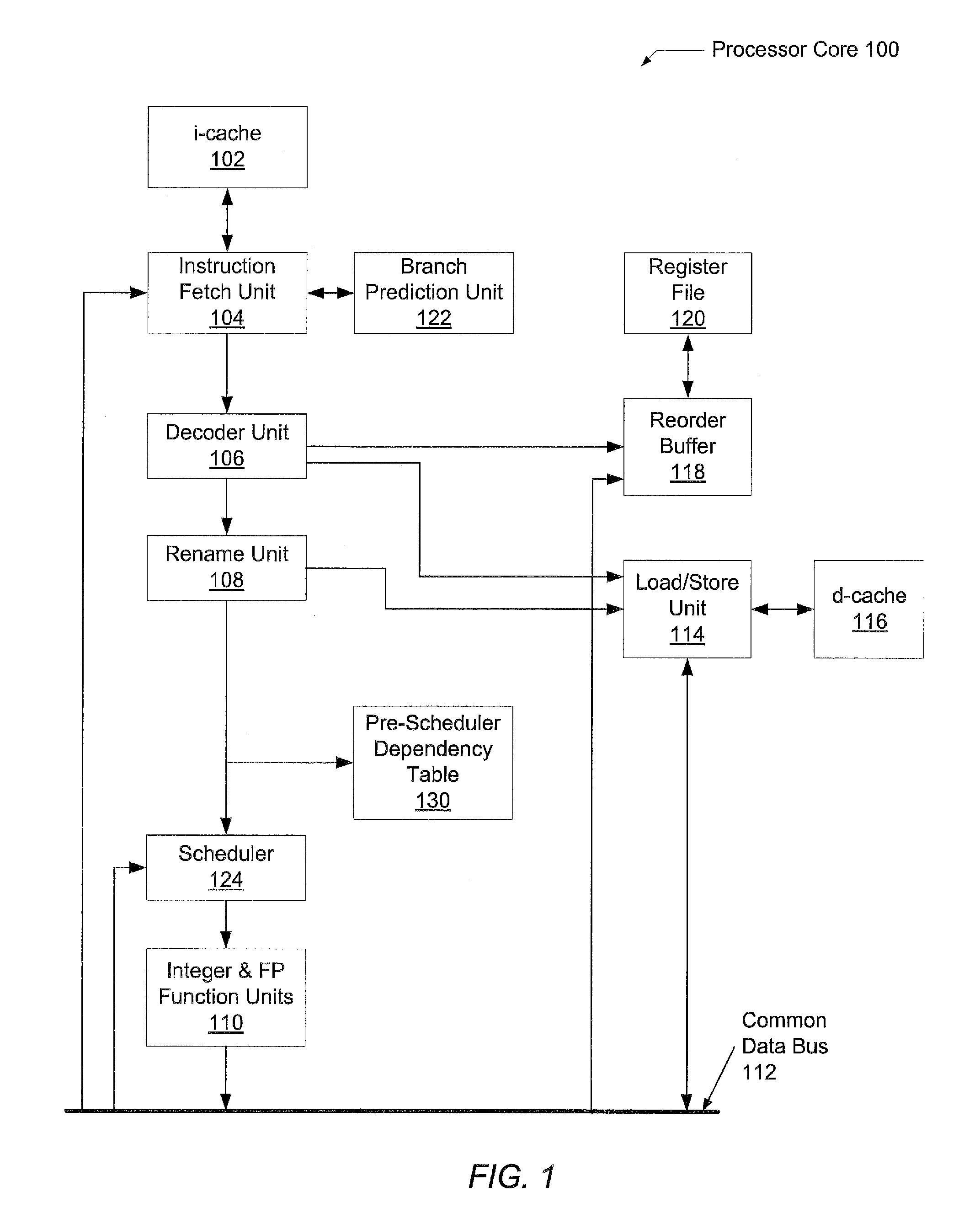

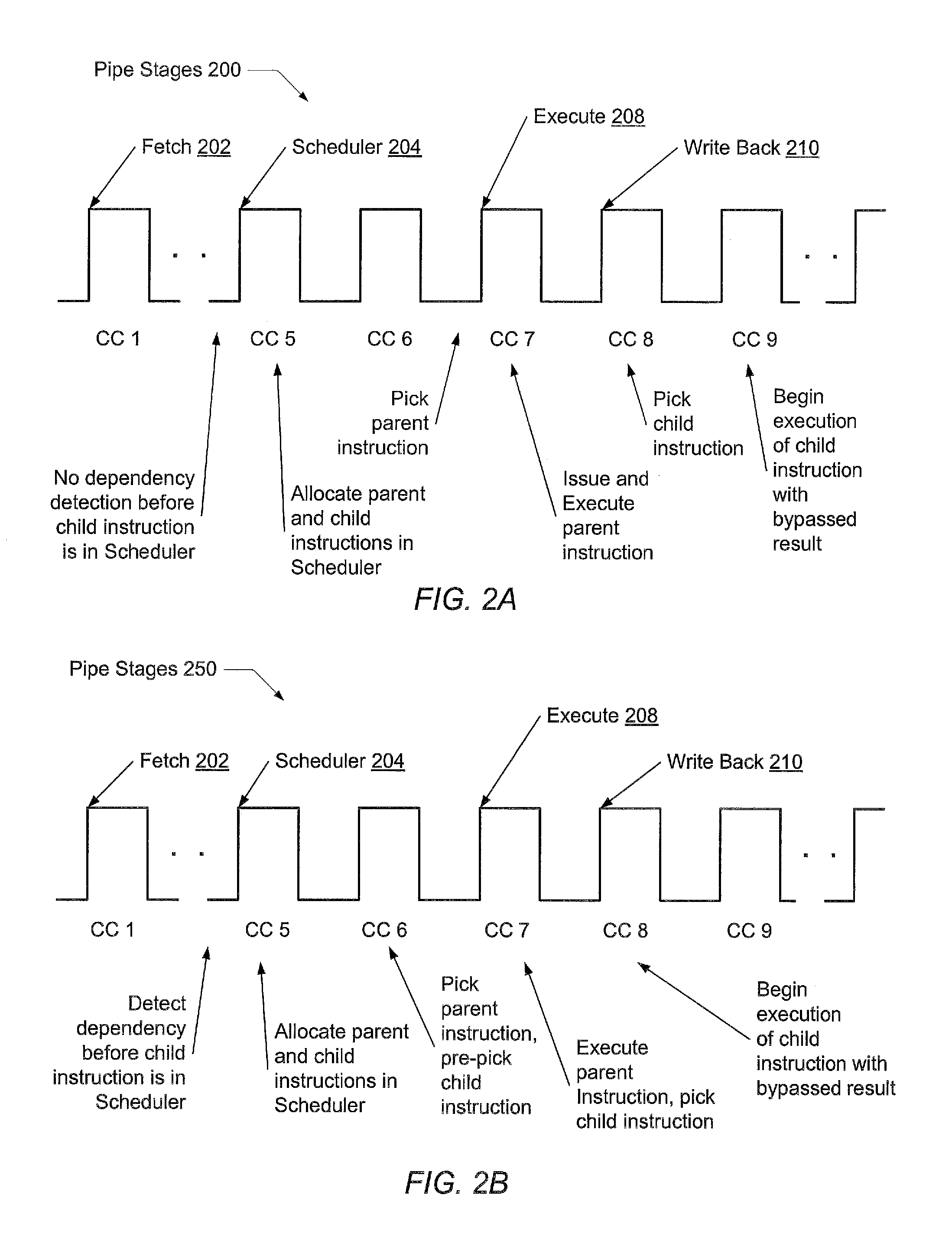

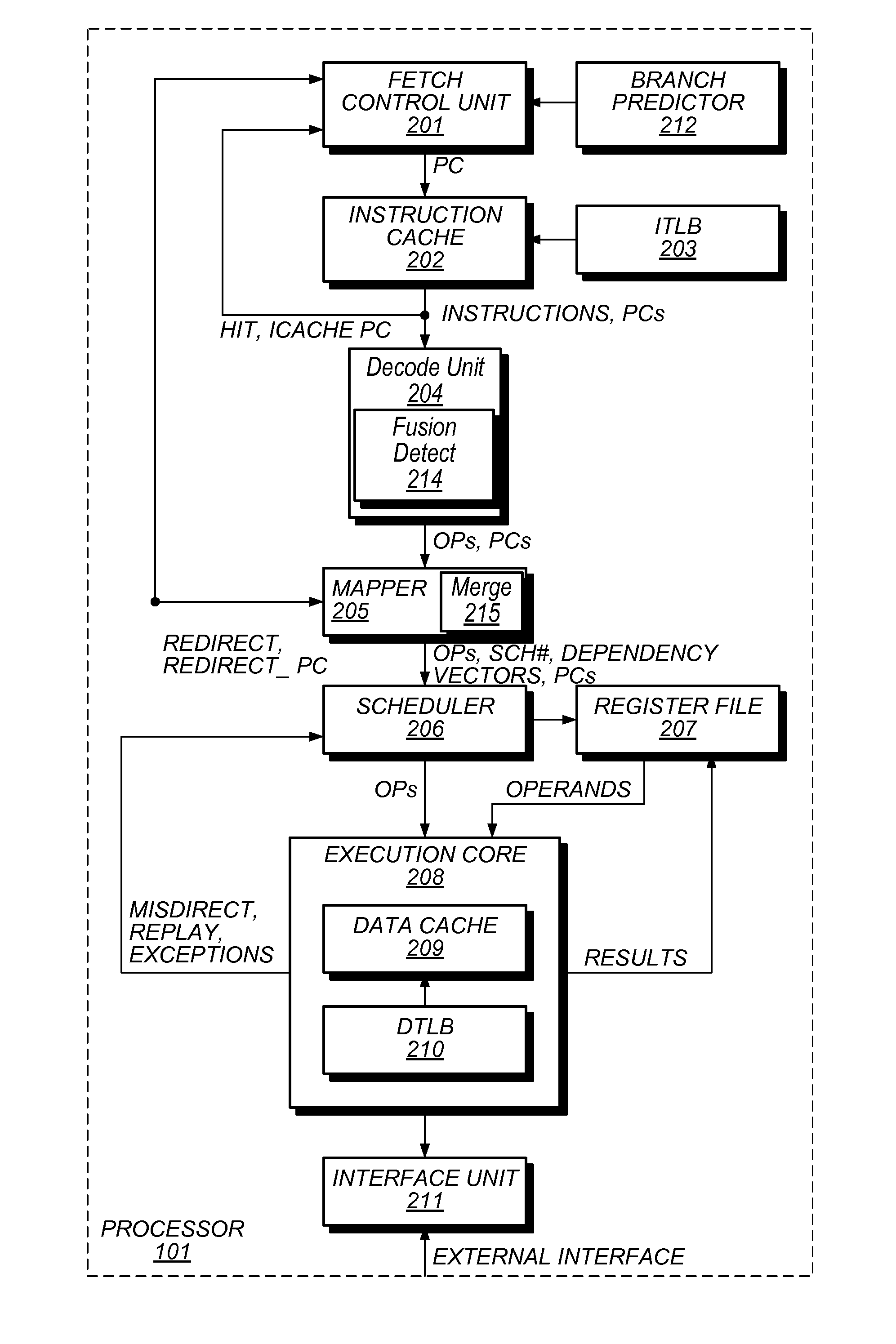

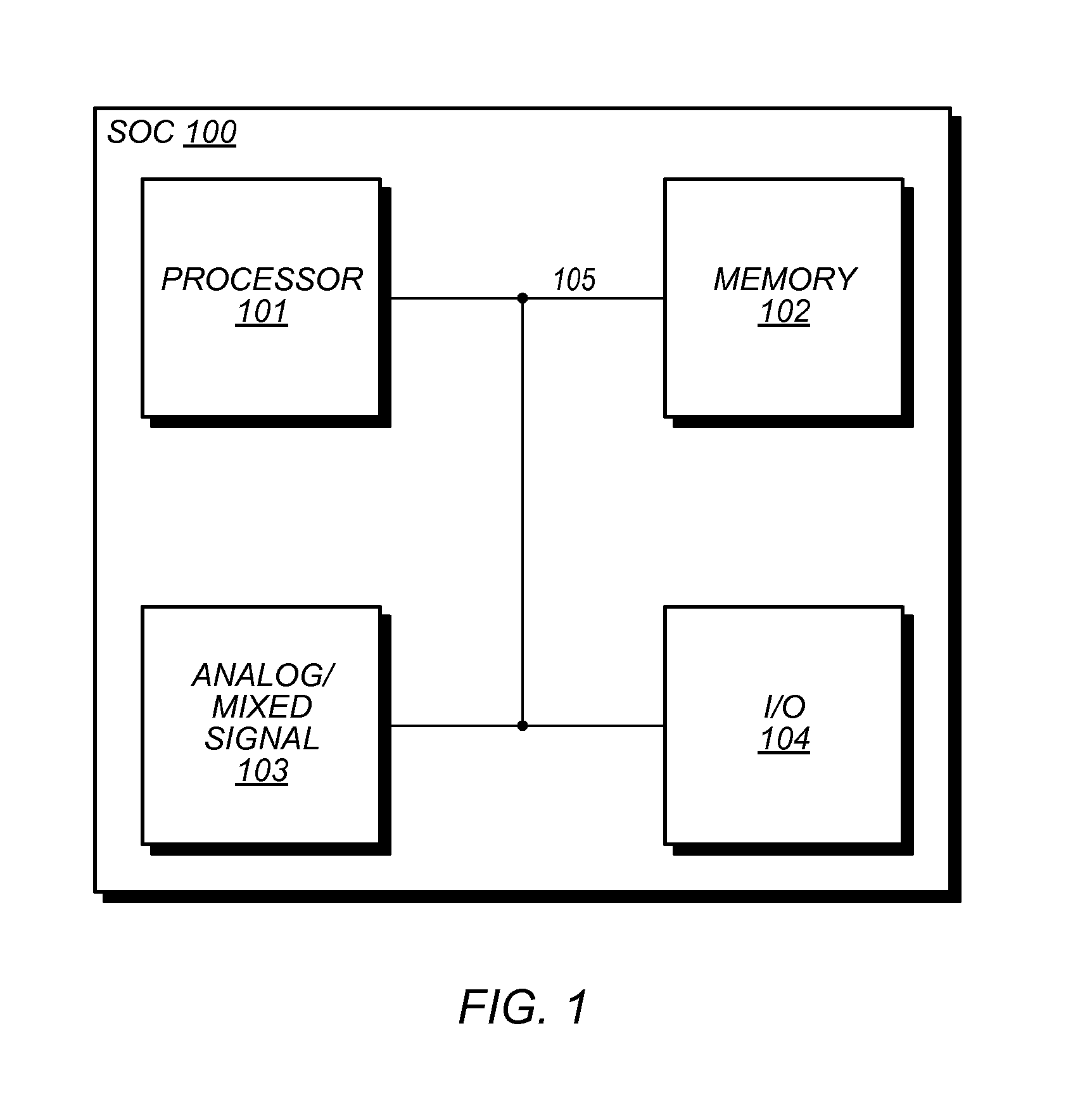

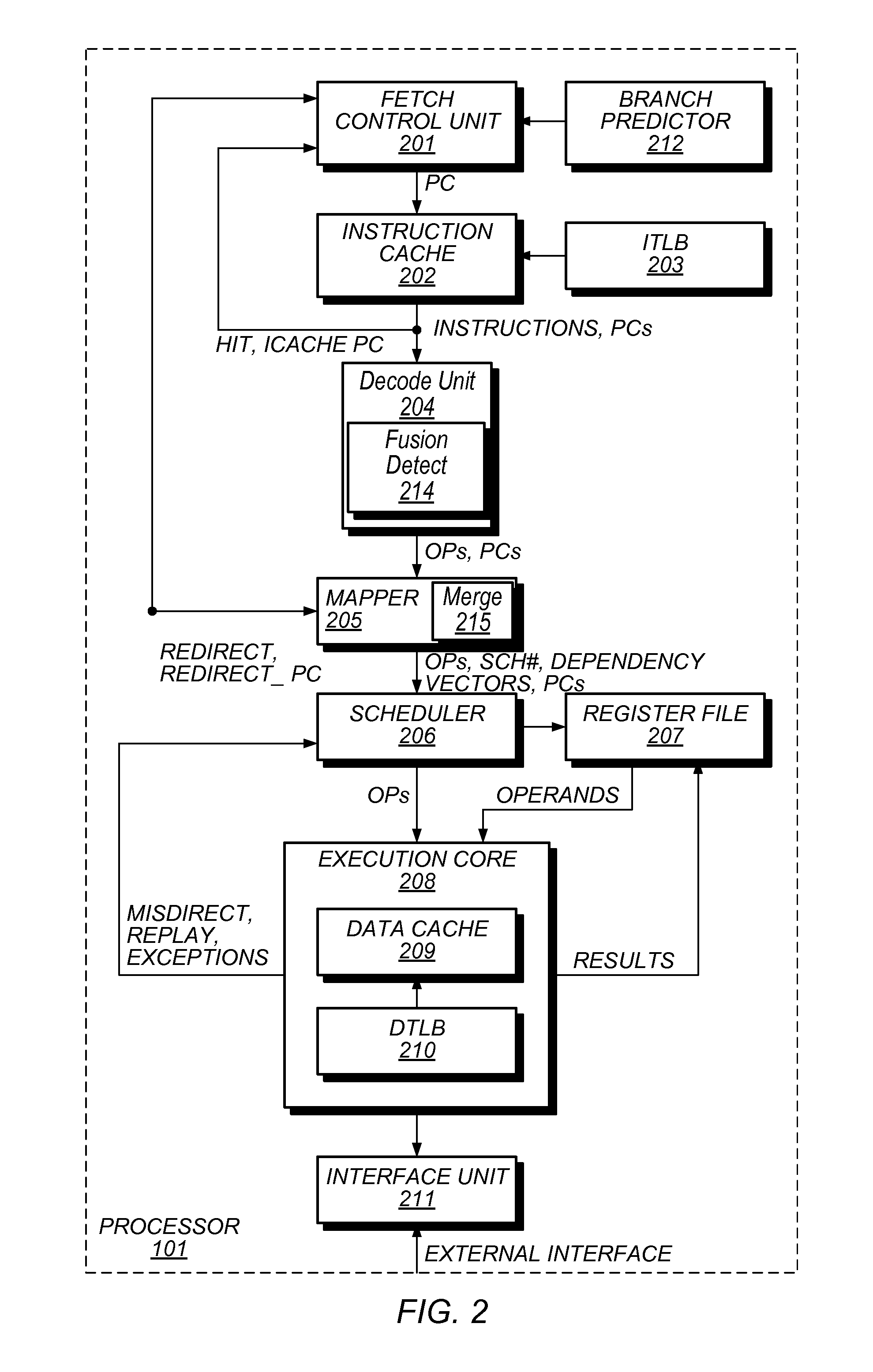

A method and mechanism for reducing latency of a multi-cycle scheduler within a processor. A processor comprises a front end pipeline that determines data dependencies between instructions prior to a scheduling pipe stage. For each data dependency, a distance value is determined based on a number of instructions a younger dependent instruction is located from a corresponding older (in program order) instruction. When the younger dependent instruction is allocated an entry in a multi-cycle scheduler, this distance value may be used to locate an entry storing the older instruction in the scheduler. When the older instruction is picked for issue, the younger dependent instruction is marked as pre-picked. In an immediately subsequent clock cycle, the younger dependent instruction may be picked for issue, thereby reducing the latency of the multi-cycle scheduler.

Owner:ADVANCED MICRO DEVICES INC

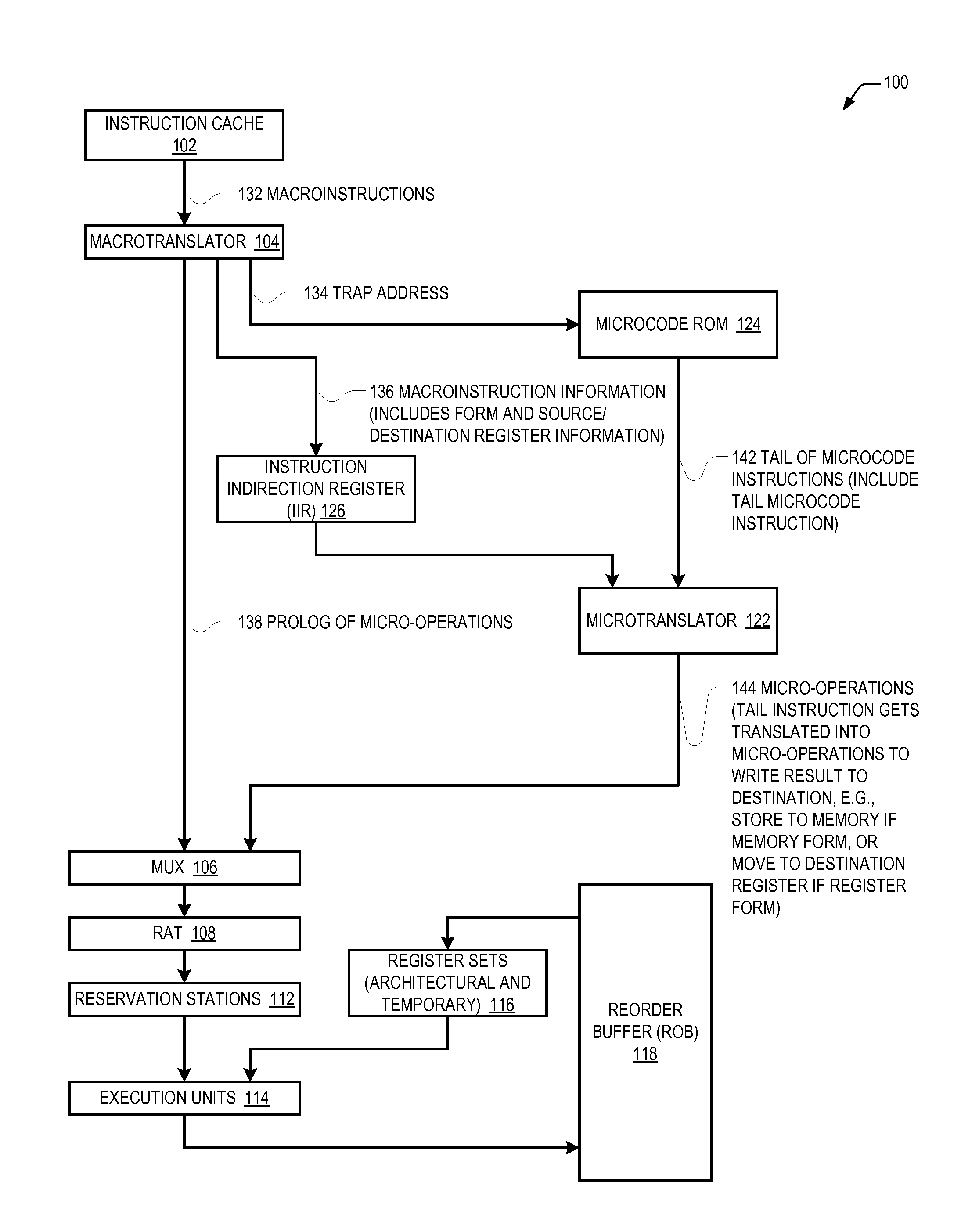

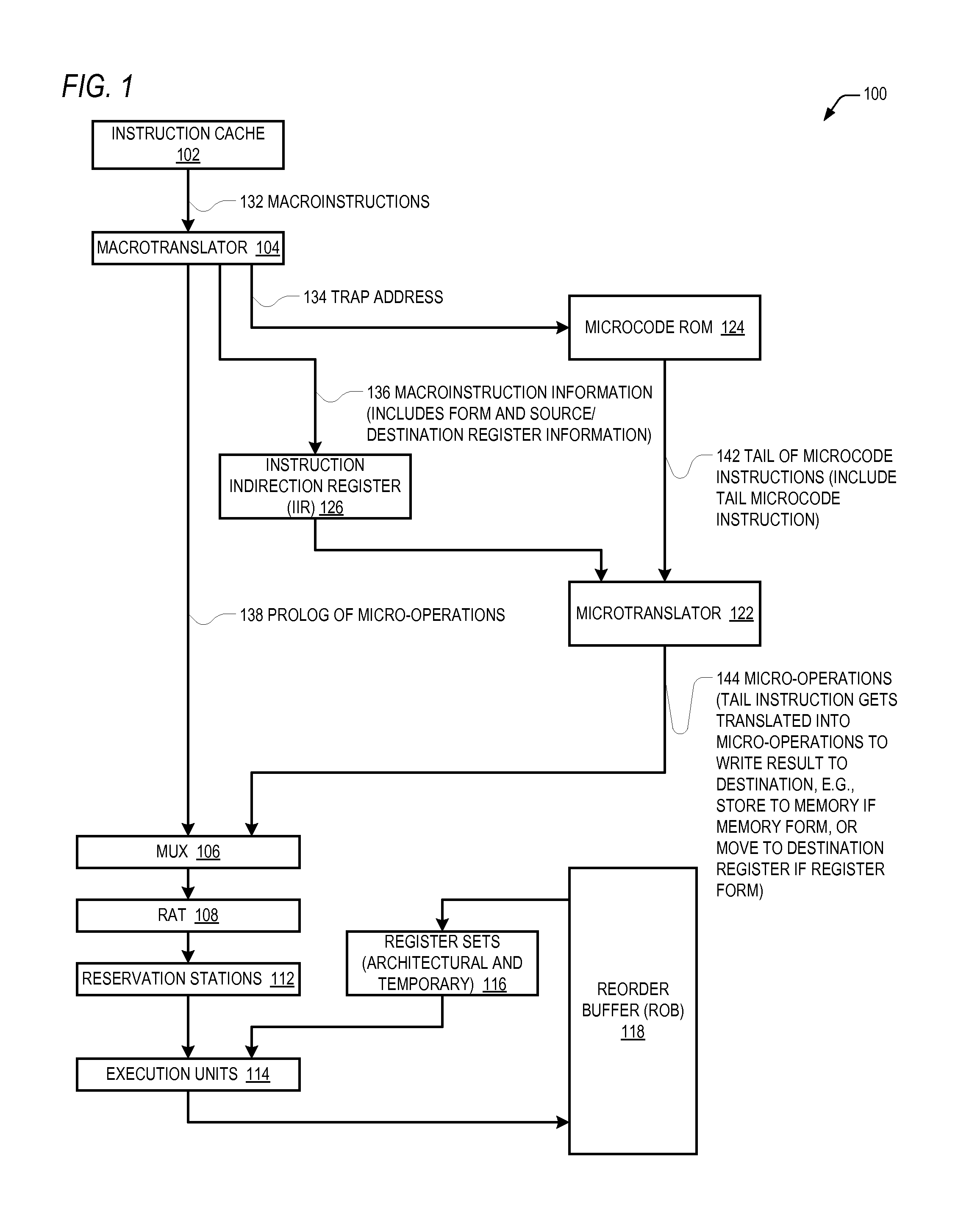

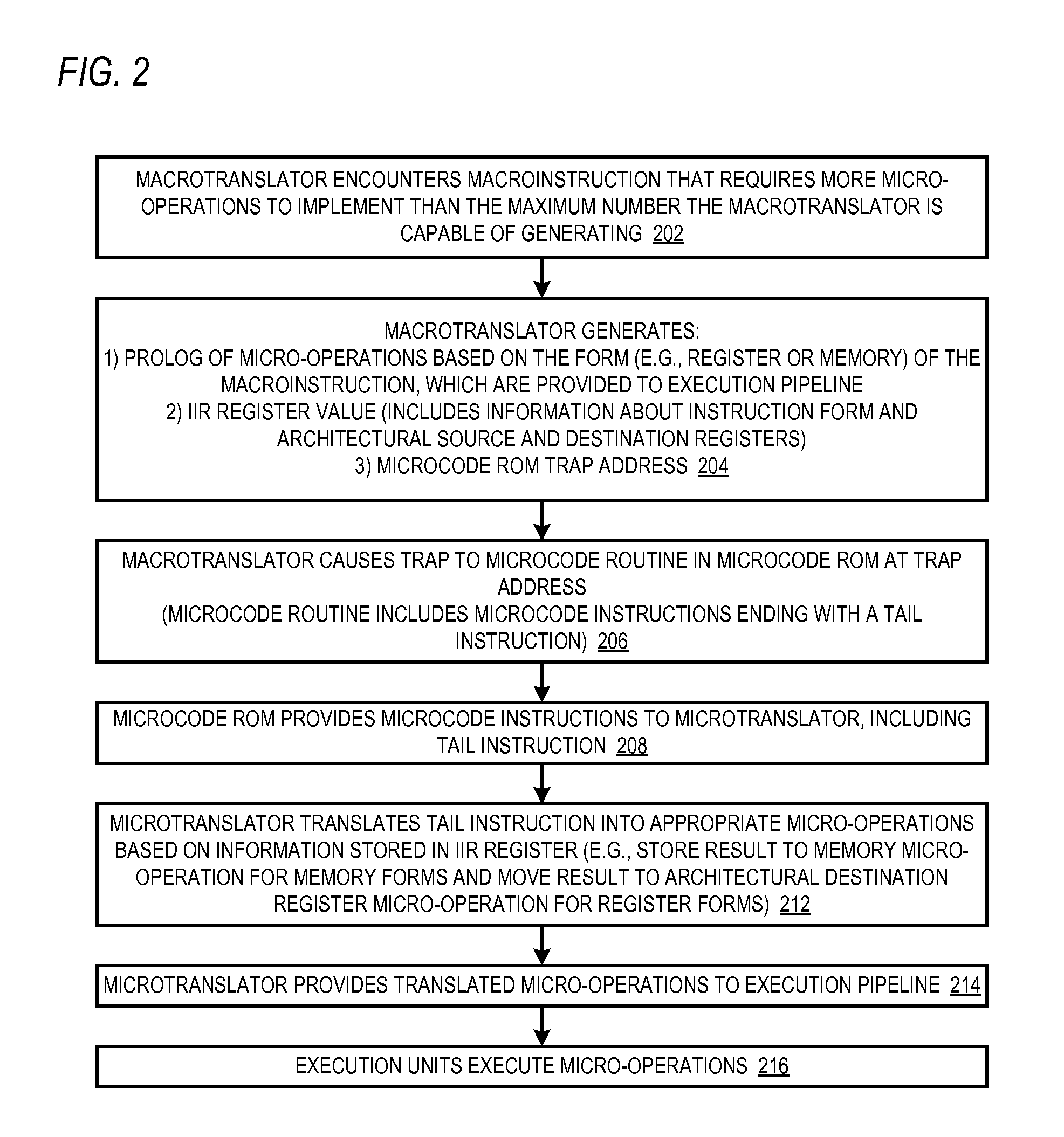

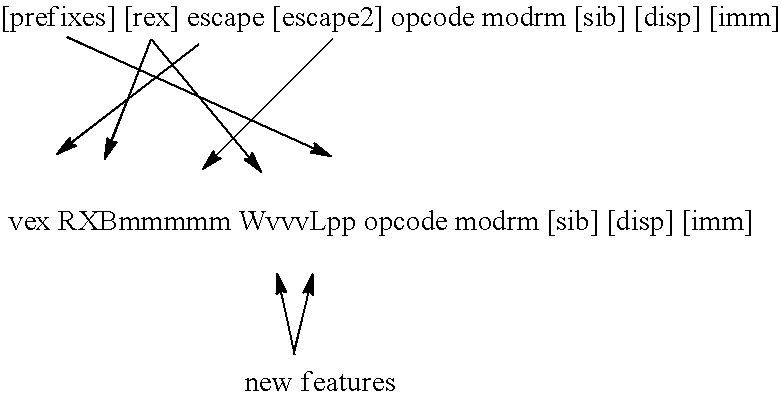

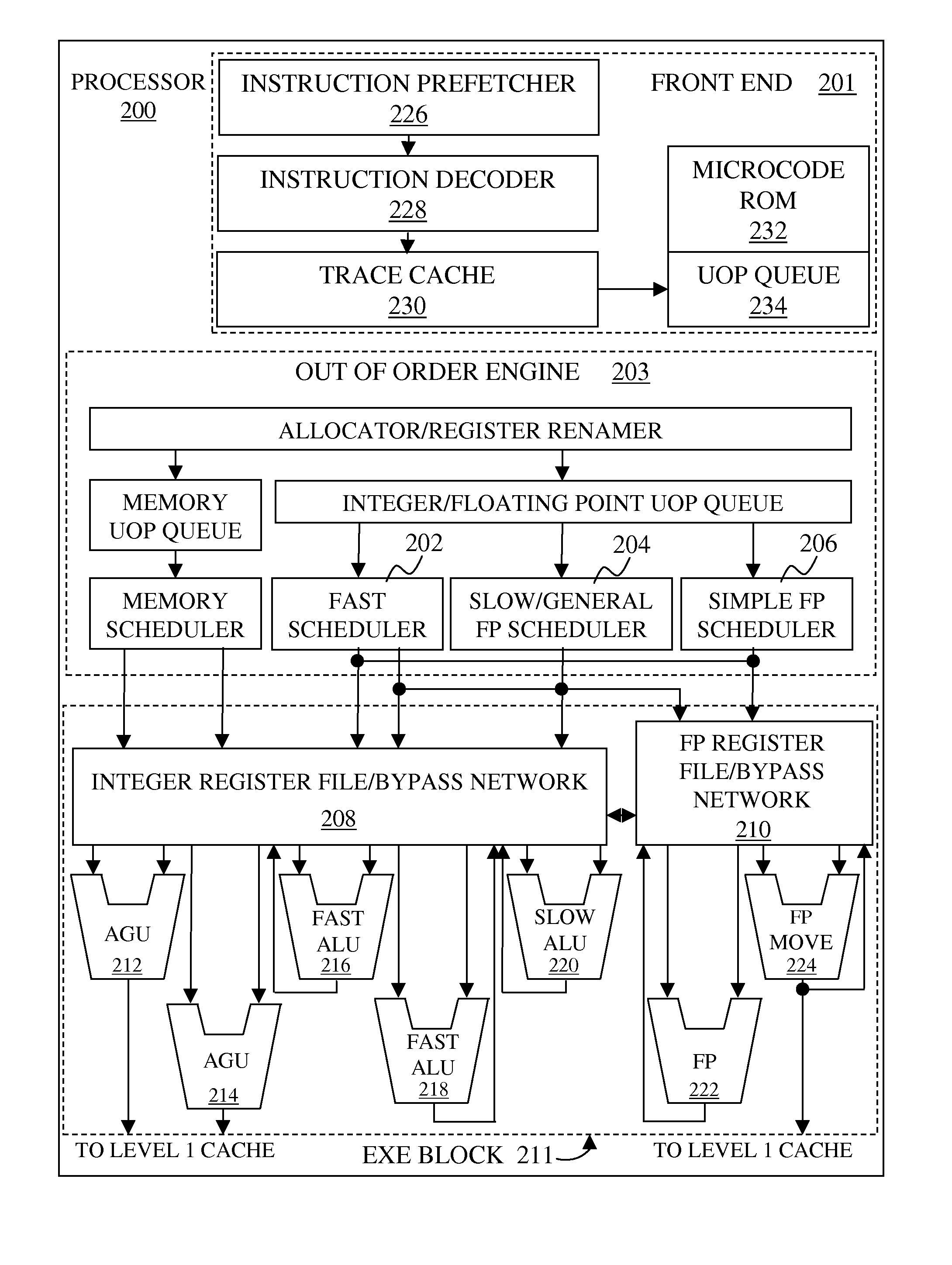

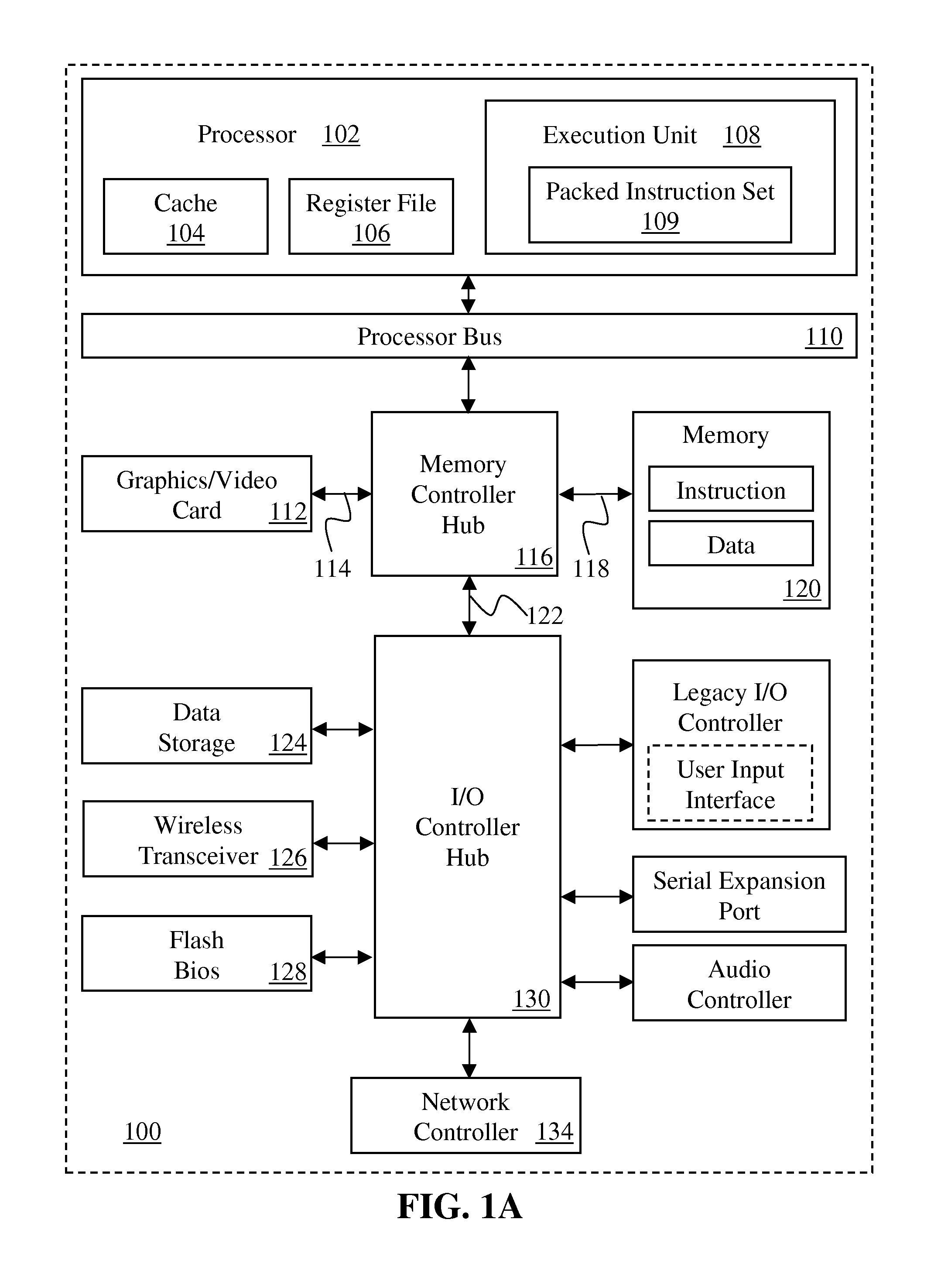

Microprocessor with microtranslator and tail microcode instruction for fast execution of complex macroinstructions having both memory and register forms

A microprocessor includes a first instruction translator that translates an instruction of an instruction set architecture of a microprocessor. The instruction may specify a first form that writes its result to a destination register or a second form that writes its result to memory. The first instruction translator generates, in response to encountering an instance of the instruction, an indication of whether the instance is of the first form or the second form. A microcode memory stores a tail instruction as part of a microcode routine invoked in response to encountering the instance of the instruction. A second instruction translator receives the tail instruction from the microcode memory and the indication and responsively generates a first micro-operation that writes the result to the destination register if the indication specifies the first form or a second micro-operation that completes a write of the result to memory if the indication specifies the second form.

Owner:VIA TECH INC

Methods and apparatus for fusing instructions to provide or-test and and-test functionality on multiple test sources

ActiveUS20140281389A1Binary to binaryConditional code generationJust-in-time compilationMicro-operation

Methods and apparatus are disclosed for fusing instructions to provide OR-test and AND-test functionality on multiple test sources. Some embodiments include fetching instructions, said instructions including a first instruction specifying a first operand destination, a second instruction specifying a second operand source, and a third instruction specifying a branch condition. A portion of the plurality of instructions are fused into a single micro-operation, the portion including both the first and second instructions if said first operand destination and said second operand source are the same, and said branch condition is dependent upon the second instruction. Some embodiments generate a novel test instruction dynamically by fusing one logical instruction with a prior-art test instruction. Other embodiments generate the novel test instruction through a just-in-time compiler. Some embodiments also fuse the novel test instruction with a subsequent conditional branch instruction, and perform a branch according to how the condition flag is set.

Owner:INTEL CORP

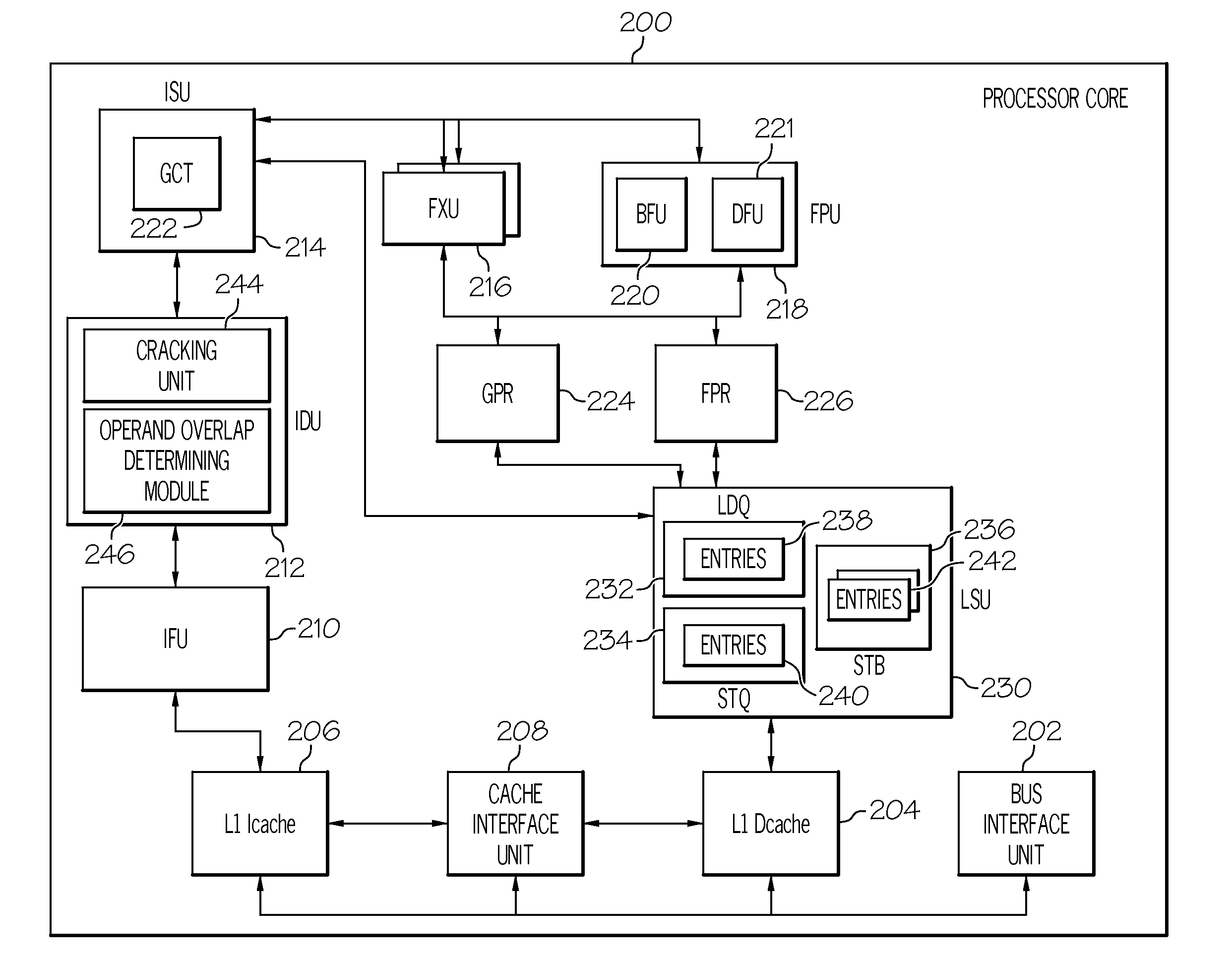

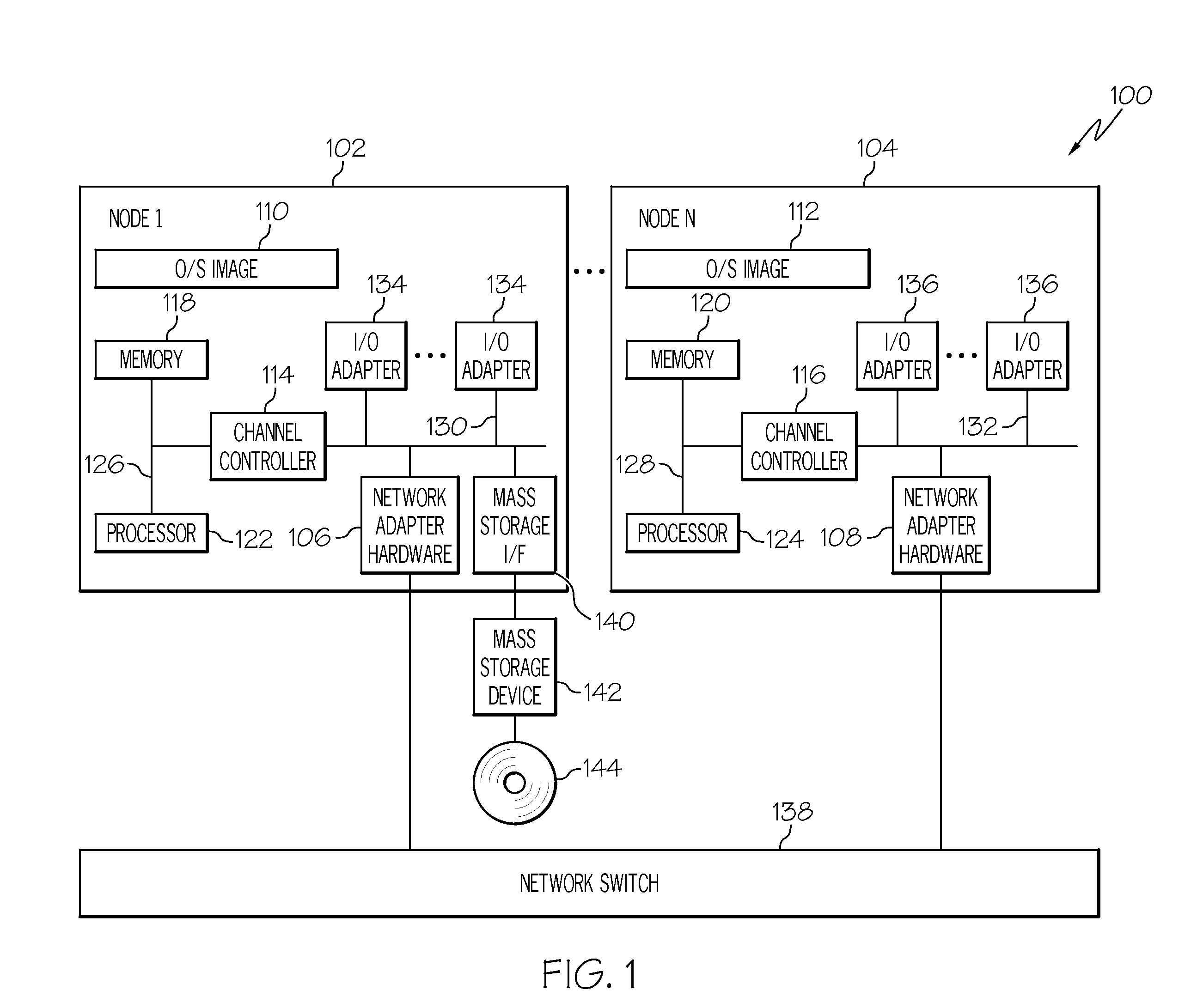

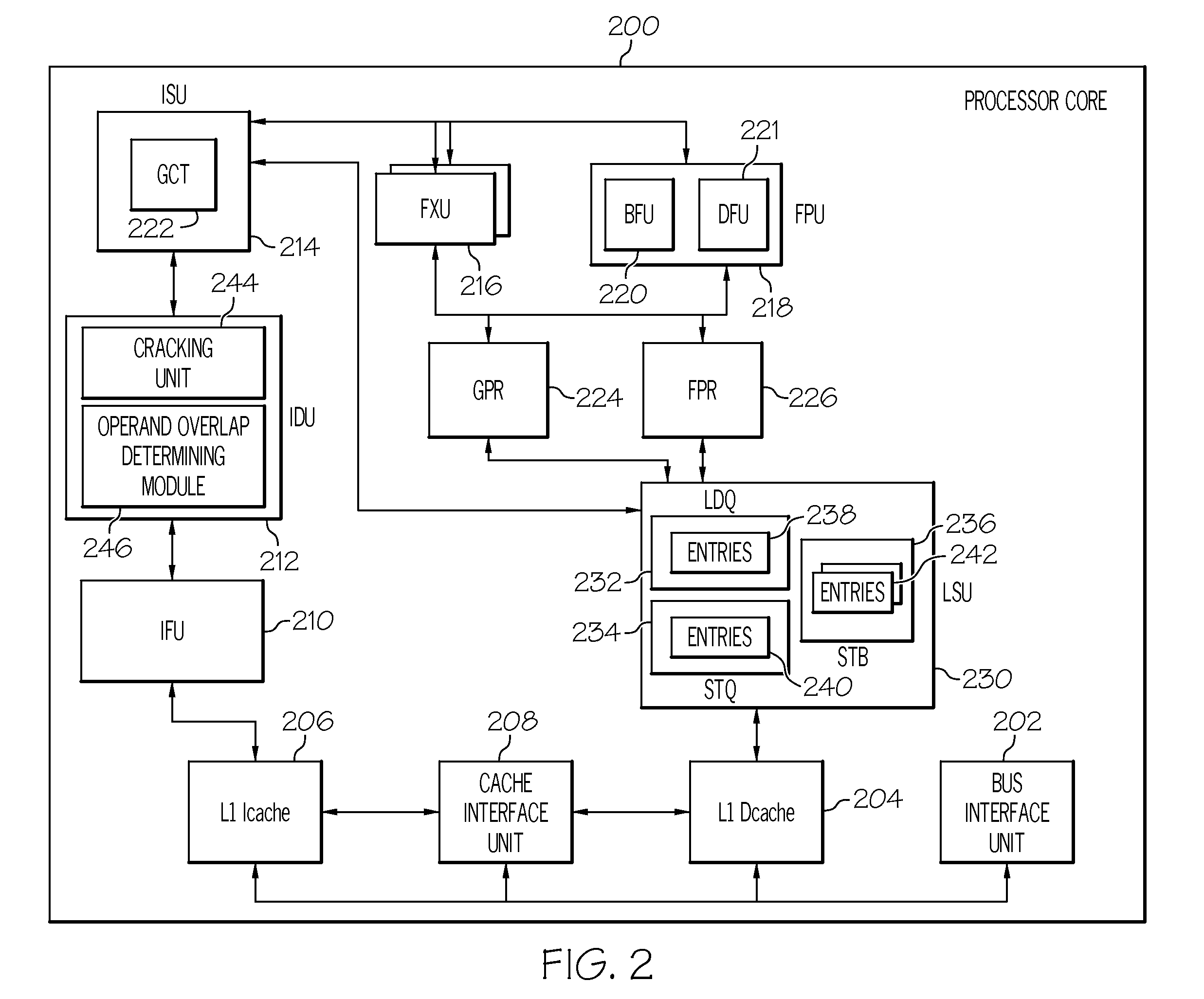

Cracking destructively overlapping operands in variable length instructions

ActiveUS20110276764A1Instruction analysisMemory adressing/allocation/relocationInformation processingMachine instruction

A method, information processing system, and computer program product manage computer executable instructions. At least one machine instruction for execution is received. The at least one machine instruction is analyzed. The machine instruction is identified as a predefined instruction for storing a variable length first operand in a memory location. Responsive to this identification and based on fields of the machine instruction, a relative location of a variable length second operand of the instruction with location of the first operand is determined. Responsive to the relative location having the predefined relationship, a first cracking operation is performed. The first cracking operation cracks the instruction into a first set of micro-ops (Uops) to be executed in parallel. The second set of Uops is for storing a first plurality of first blocks in the first operand. Each of said first block to be stored are identical. The first set Uops are executed.

Owner:IBM CORP

Scatter using index array and finite state machine

ActiveUS20150074373A1Instruction analysisArchitecture with single central processing unitMicro-operationFinite-state machine

Methods and apparatus are disclosed using an index array and finite state machine for scatter / gather operations. Embodiment of apparatus may comprise: decode logic to decode scatter / gather instructions and generate micro-operations. An index array holds a set of indices and a corresponding set of mask elements. A finite state machine facilitates the scatter operation. Address generation logic generates an address from an index of the set of indices for at least each of the corresponding mask elements having a first value. Storage is allocated in a buffer for each of the set of addresses being generated. Data elements corresponding to the set of addresses being generated are copied to the buffer. Addresses from the set are accessed to store data elements if a corresponding mask element has said first value and the mask element is changed to a second value responsive to completion of their respective stores.

Owner:INTEL CORP

Remapping source Registers to aid instruction scheduling within a processor

ActiveUS20100332805A1Rapidly dealEfficient mechanismInstruction analysisRuntime instruction translationProgram instructionMicro-operation

An out-of-order renaming processor is provided with a register file within which aliasing between registers of different sizes may occur. In this way a program instruction having a source register of a double precision size may alias with two single precision registers being used as destinations of one or more preceding program instructions. In order to track this data dependency the double precision register may be remapped into a micro-operation specifying two single precision registers as its source register. In this way, scheduling circuitry may use its existing hazard detection and management mechanisms to handle potential data hazards and dependencies. Not all program instructions having such data hazards between registers of different sizes are handled by this source register remapping. For these other program instructions a slower mechanism for dealing with the data dependency hazard is provided. This slower mechanism may, for example, be to drain all the preceding micro-operations from the execution pipelines before issuing the micro-operation having the data hazard.

Owner:ARM LTD

Decoding conditional program instructions

InactiveUS20120124346A1Improve versatilityIncrease overheadInstruction analysisRuntime instruction translationProgram instructionMicro-operation

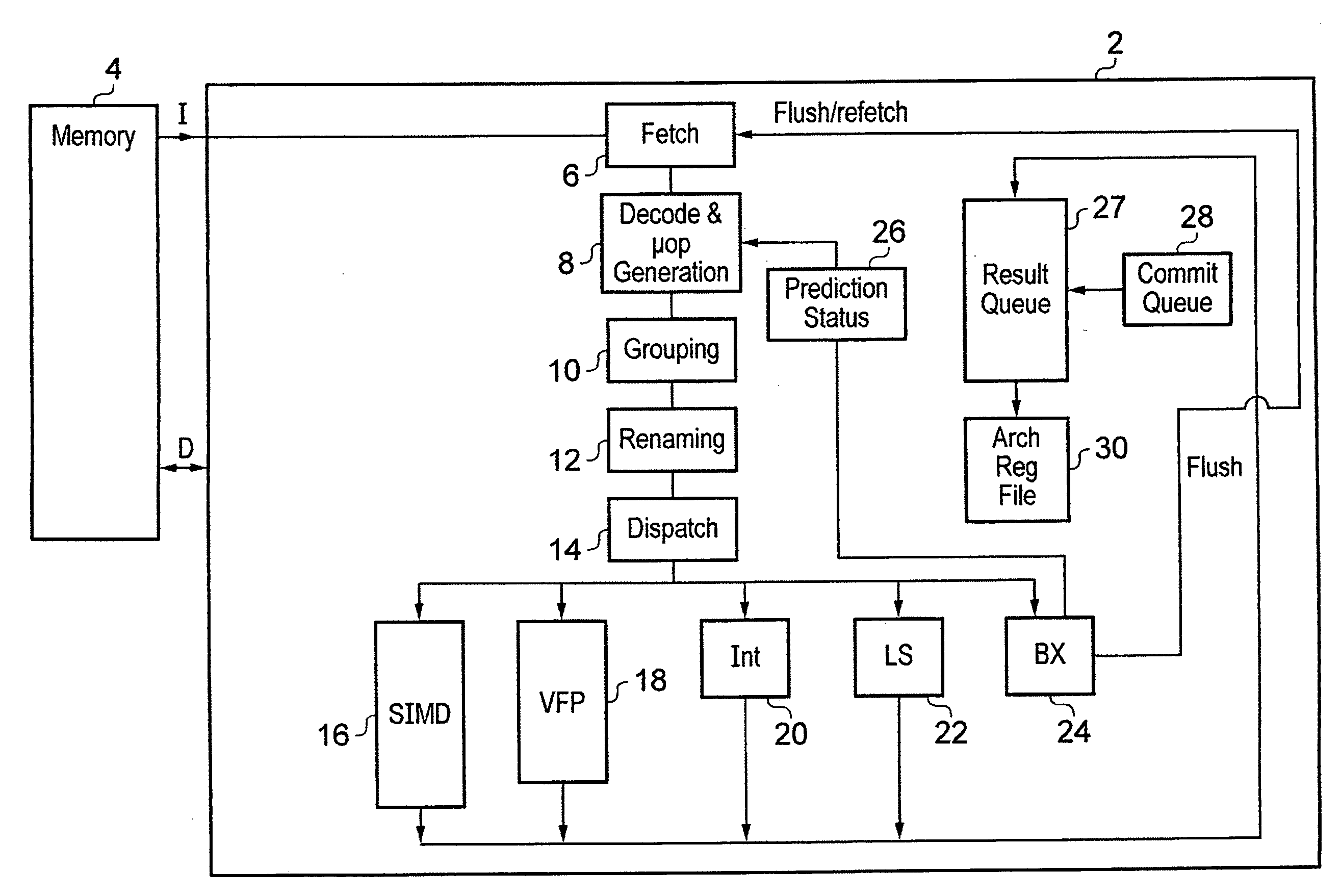

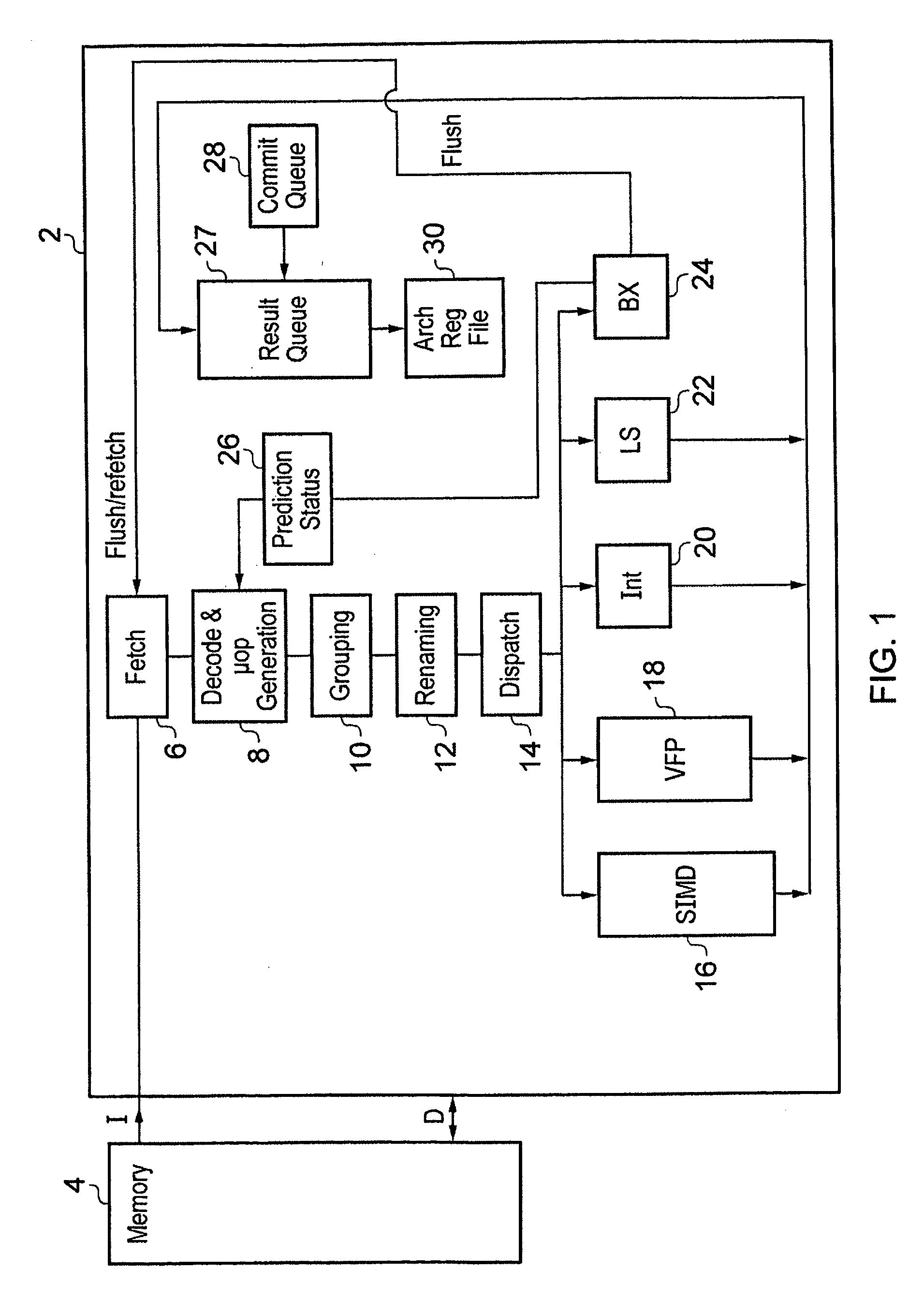

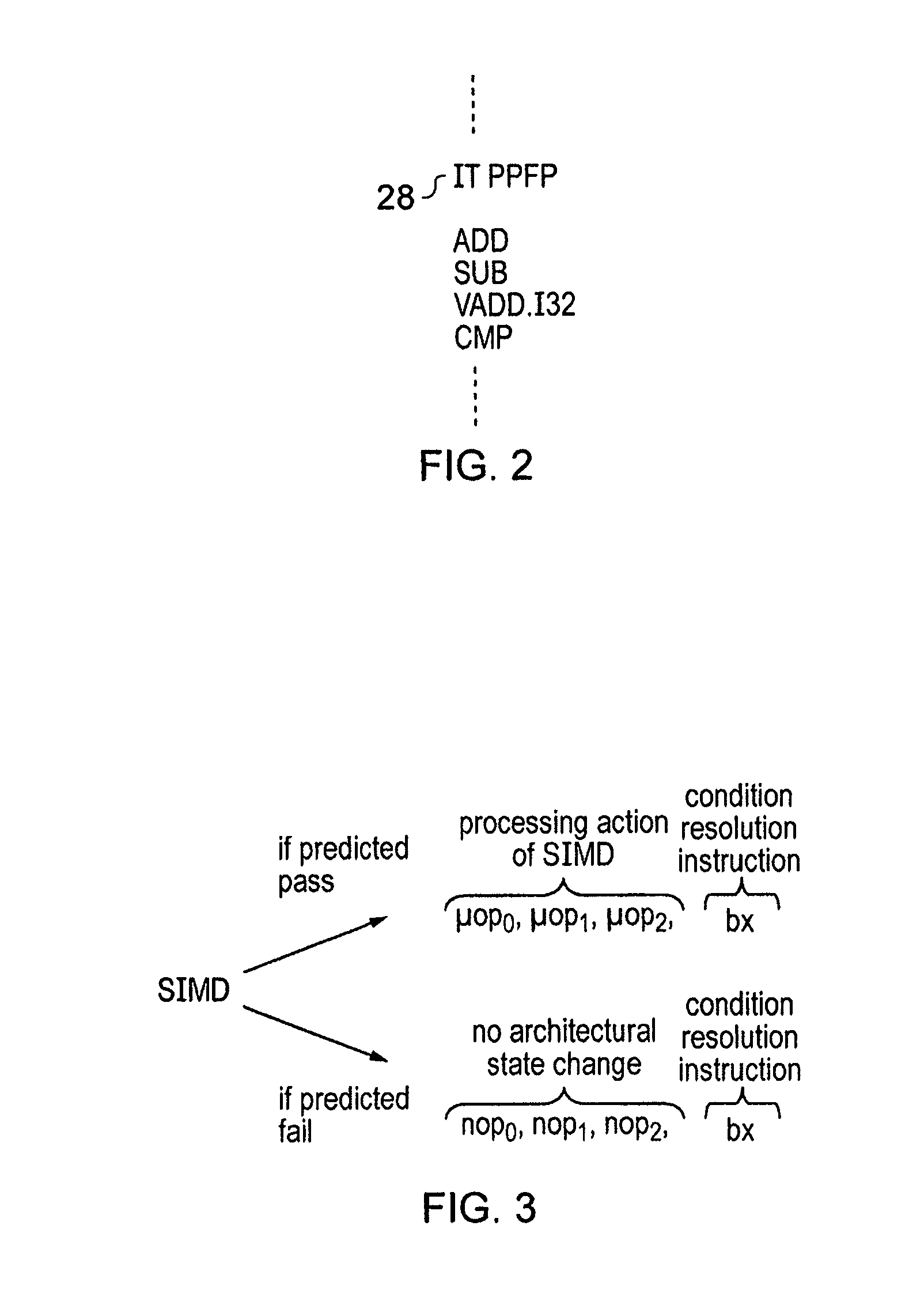

A processor 2 includes instruction decoding circuitry 8 and processing circuitry 16, 18, 20, 22, 24. The instruction decoding circuitry decodes at least one conditional program instruction in accordance with a conditional prediction as one of, in accordance with the condition prediction being a condition pass, one or more micro-operation instructions that control the processing circuitry to perform the processing action together with a condition resolution micro-operation instruction, or in accordance with the condition prediction being a condition fail, at least a condition resolution micro-operation instruction. Condition resolution circuitry 24 responds to the condition resolution micro-operation instruction to determine if the condition prediction is incorrect. If the condition prediction is incorrect, then the condition resolution circuitry flushes any micro-operation instructions associated with the conditional program instruction from the processing circuitry, changes the condition prediction to a new prediction and triggers the redecoding of the conditional program instruction in accordance with the new condition prediction.

Owner:ARM LTD

Arithmetic Branch Fusion

ActiveUS20140208073A1Conditional code generationInstruction analysisMicro-operationParallel computing

A processor and method for fusing together an arithmetic instruction and a branch instruction. The processor includes an instruction fetch unit configured to fetch instructions. The processor may also include an instruction decode unit that may be configured to decode the fetched instructions into micro-operations for execution by an execution unit. The decode unit may be configured to detect an occurrence of an arithmetic instruction followed by a branch instruction in program order, wherein the branch instruction, upon execution, changes a program flow of control dependent upon a result of execution of the arithmetic instruction. In addition, the processor may further be configured to fuse together the arithmetic instruction and the branch instruction such that a single micro-operation is formed. The single micro-operation includes execution information based upon both the arithmetic instruction and the branch instruction.

Owner:APPLE INC

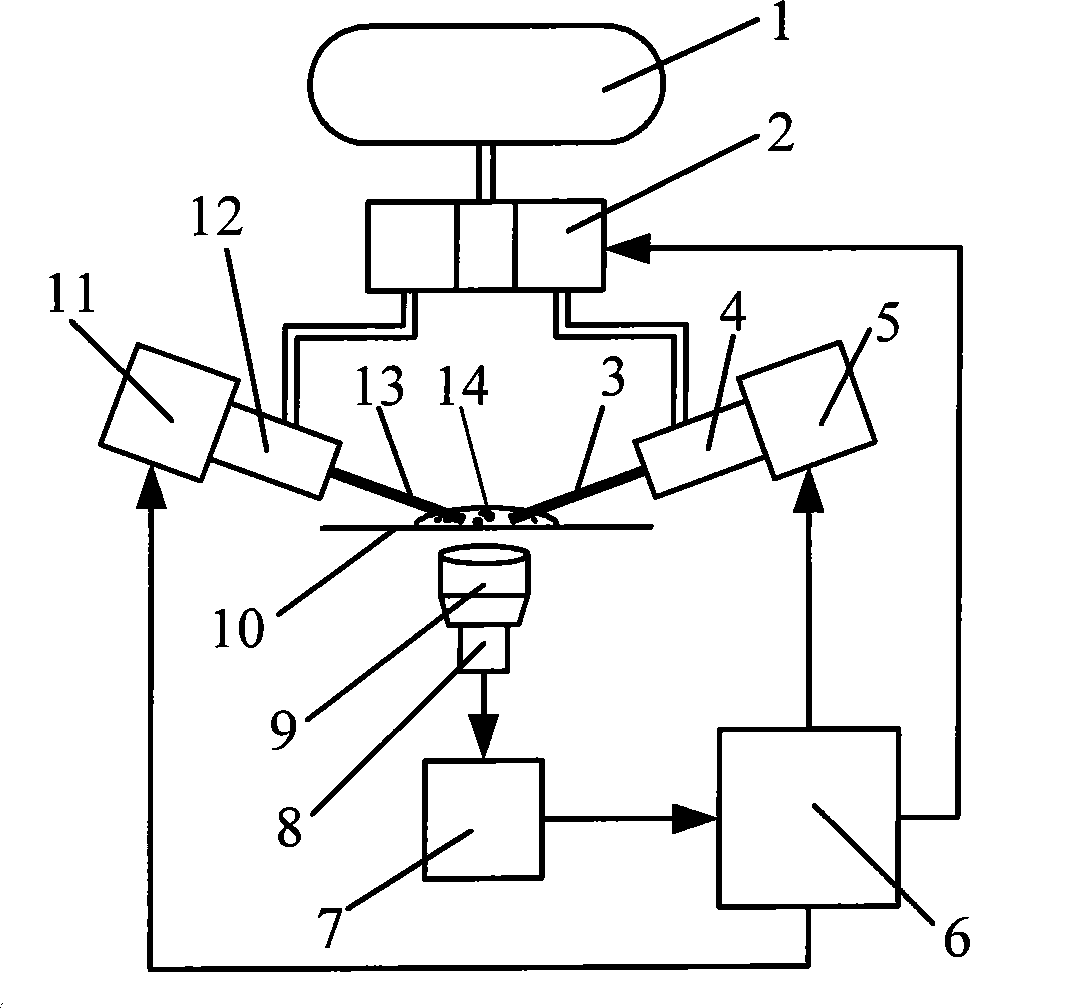

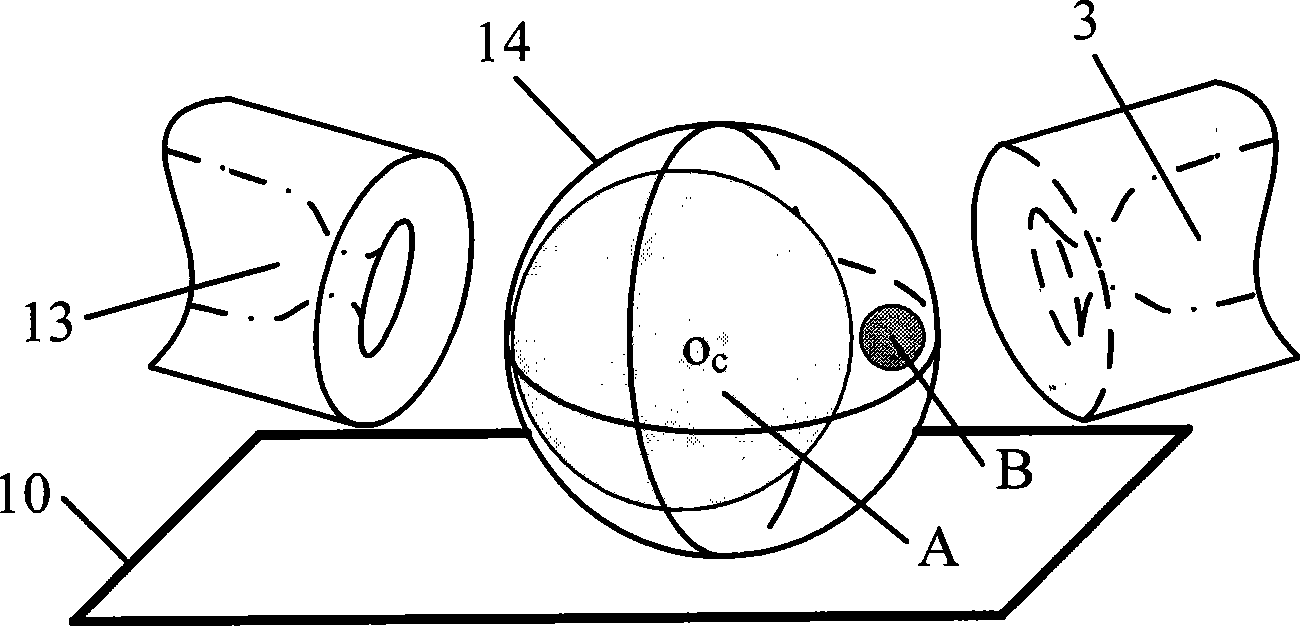

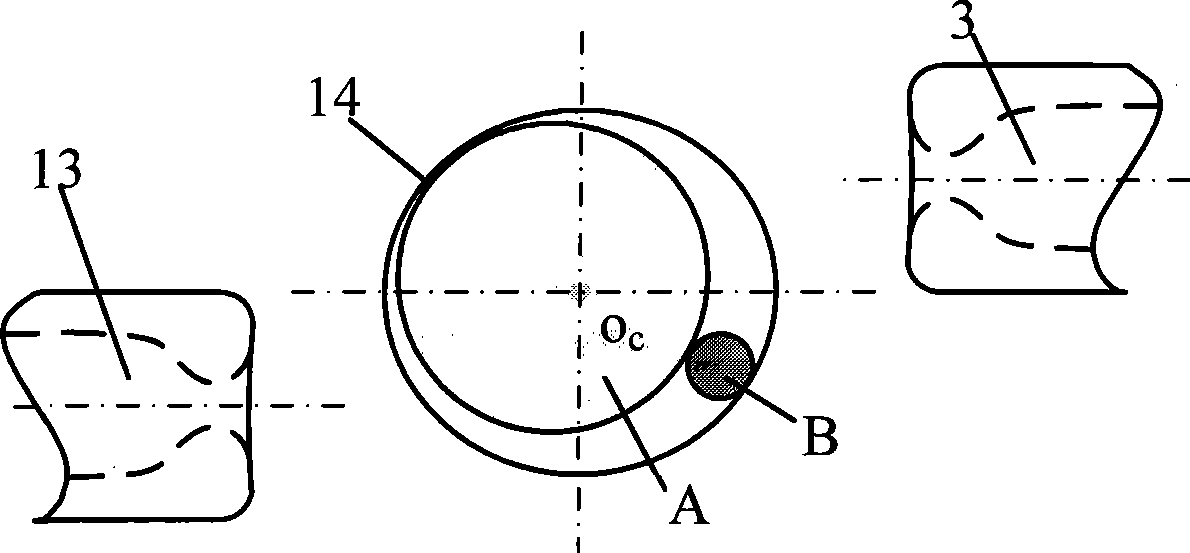

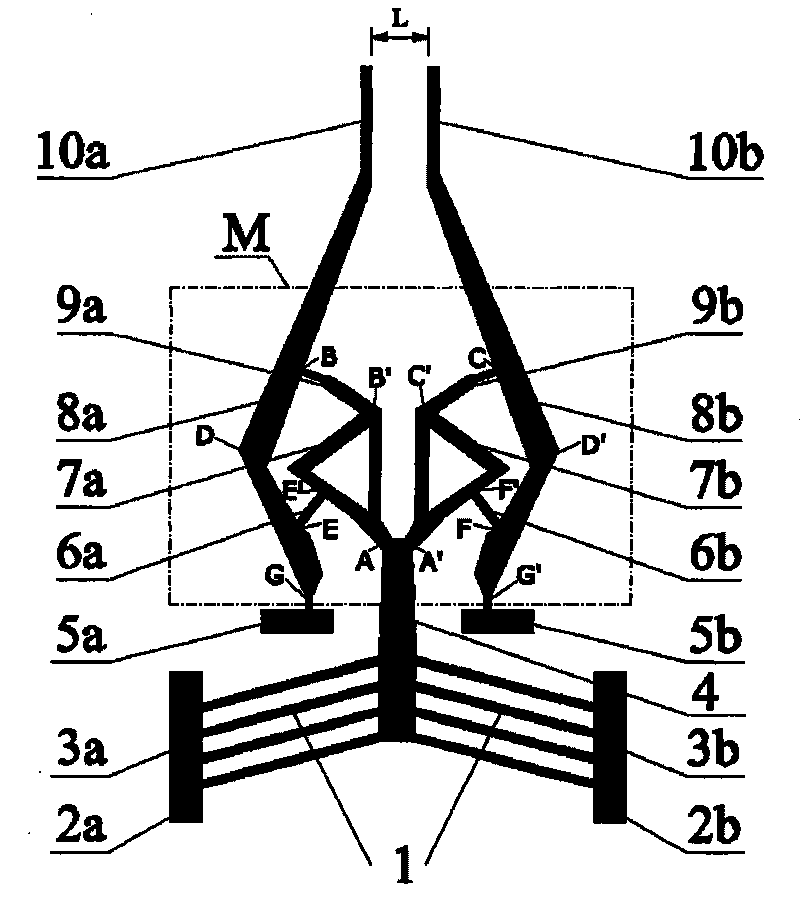

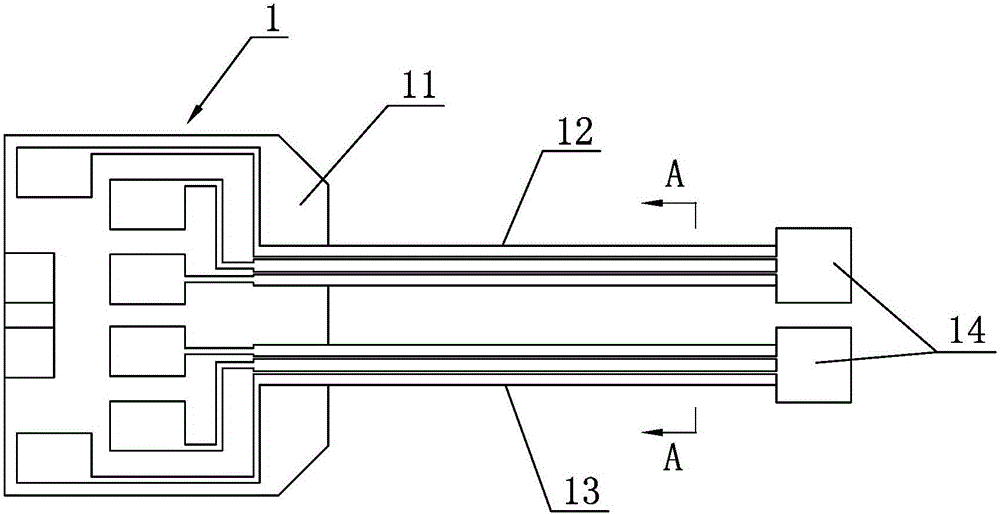

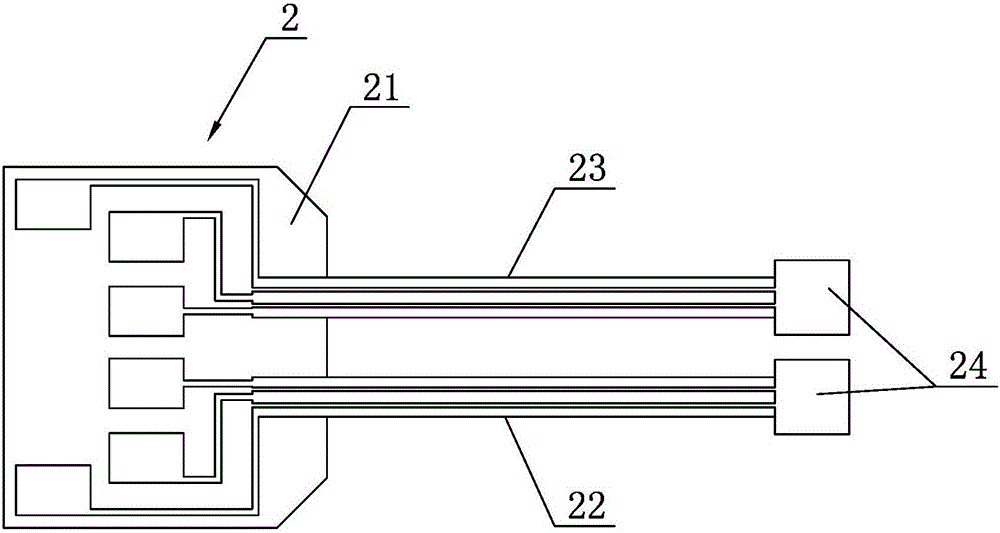

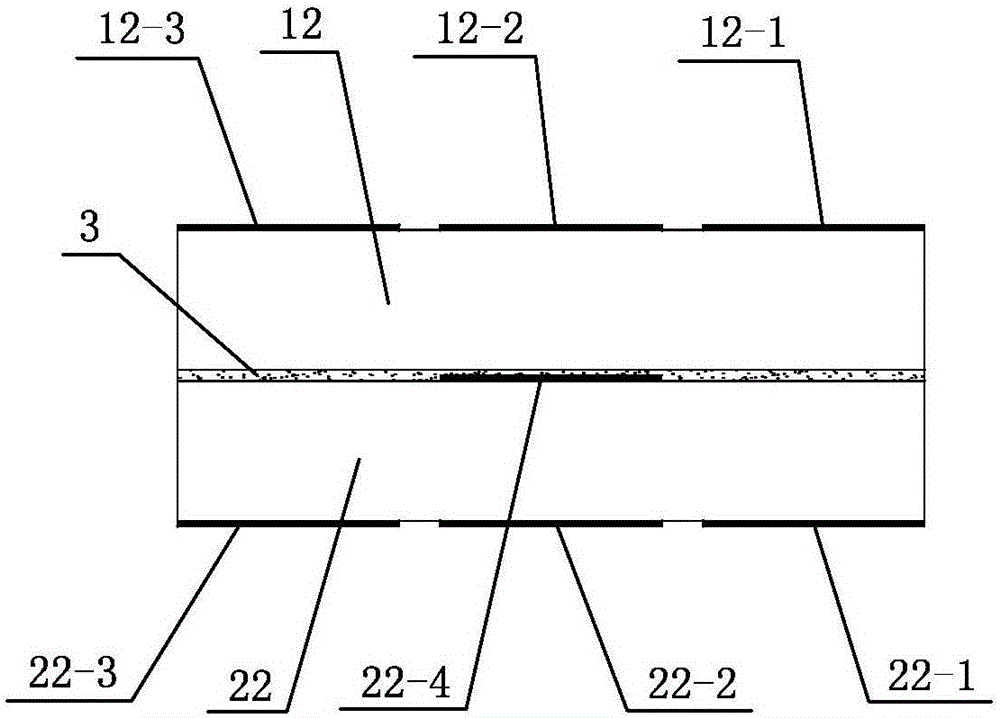

Single cell microoperation apparatus for microscopic injection

InactiveCN101481653ASimple structureBare microBioreactor/fermenter combinationsBiological substance pretreatmentsMicro-operationThree degrees of freedom

The invention discloses a unicellular micro-operation device used for microinjection. An air supply and a pressure control valve of the device and a left and a right end effectors form a sealed air course through a passage in a holder; the left and the right end effectors are respectively connected with a left and a right three dimensional micromotion stages through the holders; the left and the right three dimensional micromotion stages are symmetrically arranged on the left side and the right side of an inverted microscope worktable; the left and the right end effectors form a unicellular micro-operation flow field with controllable flow rate distribution on the inverted microscope worktable; and a computer collects signals of an image detecting and processing unit to respectively control the pressure control valve and the left and the right three dimensional micromotion stages. The micro-operation device effectively controls the operation environmental flow field of cells, and forms a stable unicellular micro-operation flow field with controllable flow rate distribution to drive the cells to move. Through the invention, the cellular angle in the three dimensional orthogonalized plane can be randomly adjusted, so that the three degrees of freedom (DOF) attitude of the cells can be accurately controlled; and the three dimensional spatial location of the cells is adjusted to realize the accurate positioning of the location and attitude of the cells.

Owner:NANJING UNIV OF SCI & TECH

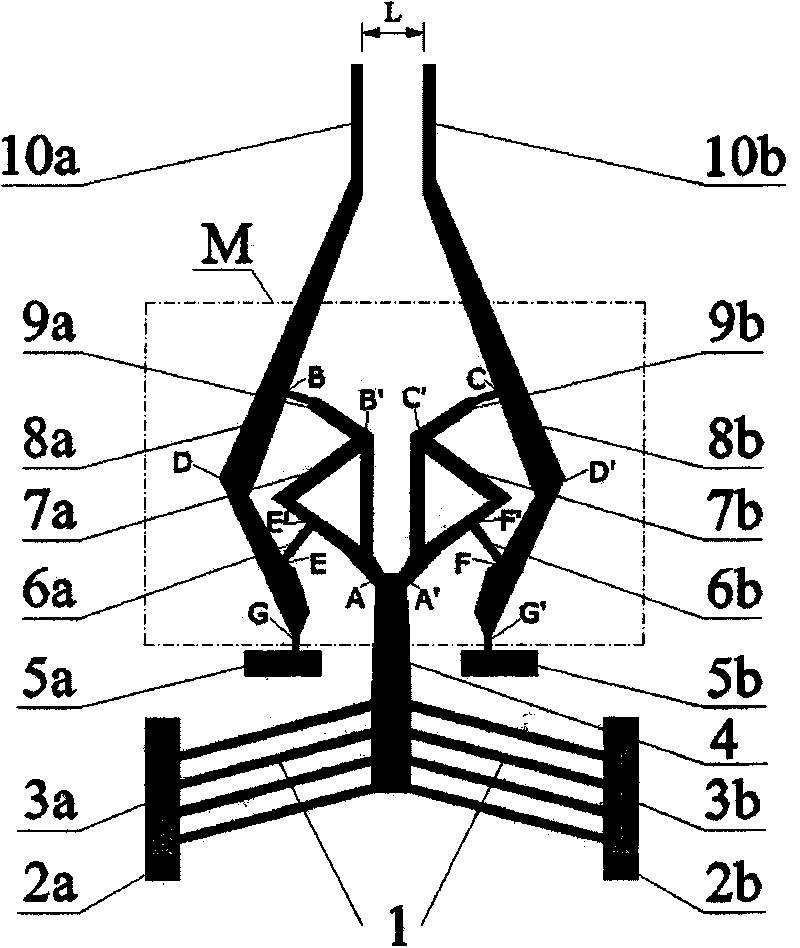

Flexible microgripper through topological optimization

InactiveCN101717063ALarge output displacementNovel structure typeMicromanipulatorPiezoelectric/electrostriction/magnetostriction machinesShaped beamMicro-operation

The invention relates to a flexible microgripper through topological optimization, which belongs to a microactuators in the technical field of the micro electro mechanical systems and is a flexible electrothermally driven microgripper. The flexible microgripper consists of a shift amplifying section and a driving section and is an integral structure with the eudipleural gripper body. The shift amplifying section M is designed by using the topological optimization method and comprises left and right triangular components and a flexible rod, wherein the left and right triangular components randomly hollow triangle structures. The driving section comprises a V-shaped beam array, left and right driving fixed rods and left and right electrodes. The microgripper has the advantages of unique and novel structure, large output shift, rapid response, simple control, convenient integration and is effective and energy-saving without applying drive in the process of gripping objects, thereby the microgripper is quite suitable for gripping minute objects for micro-assembly, micro-operation and the like.

Owner:DALIAN UNIV OF TECH

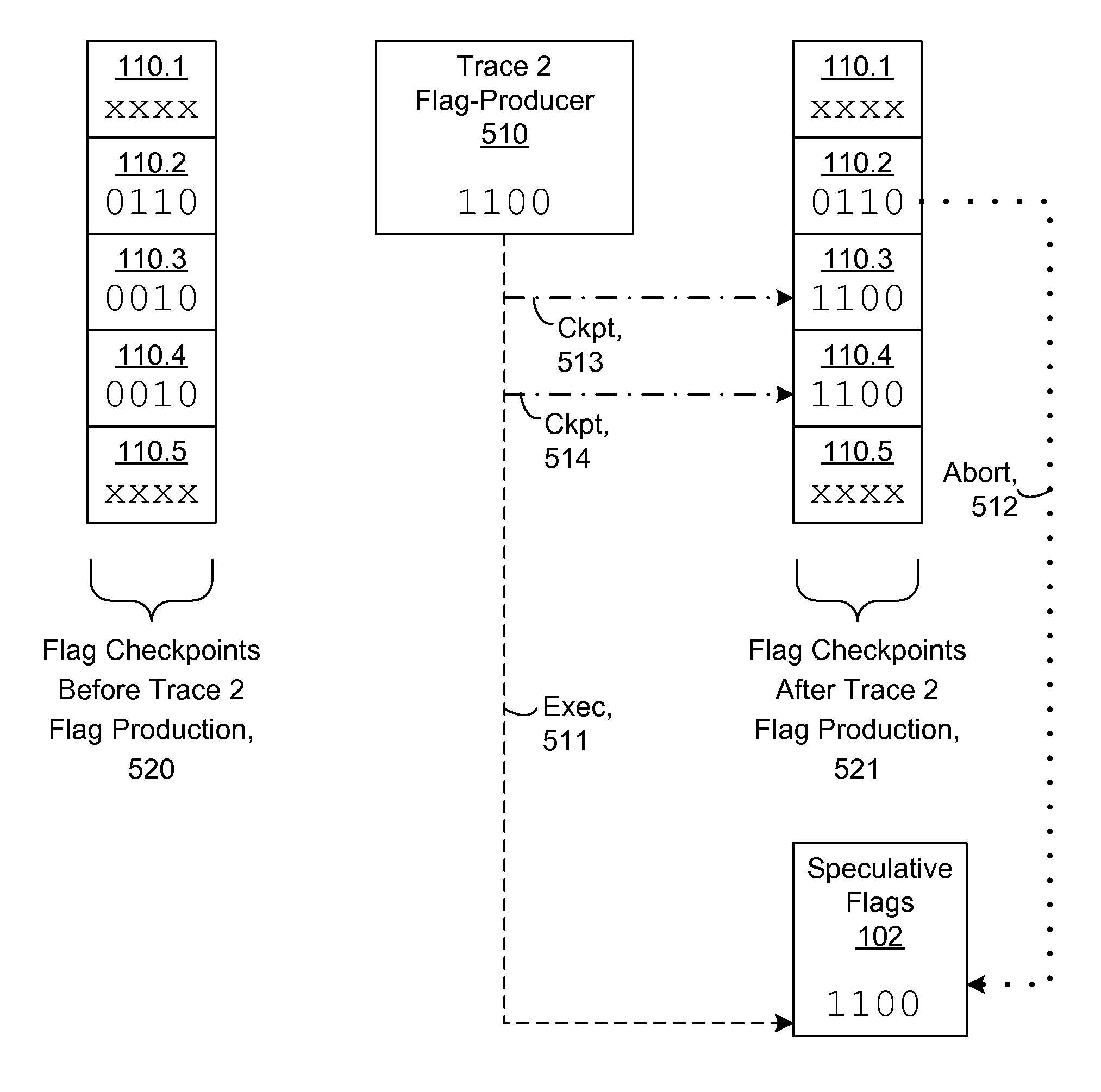

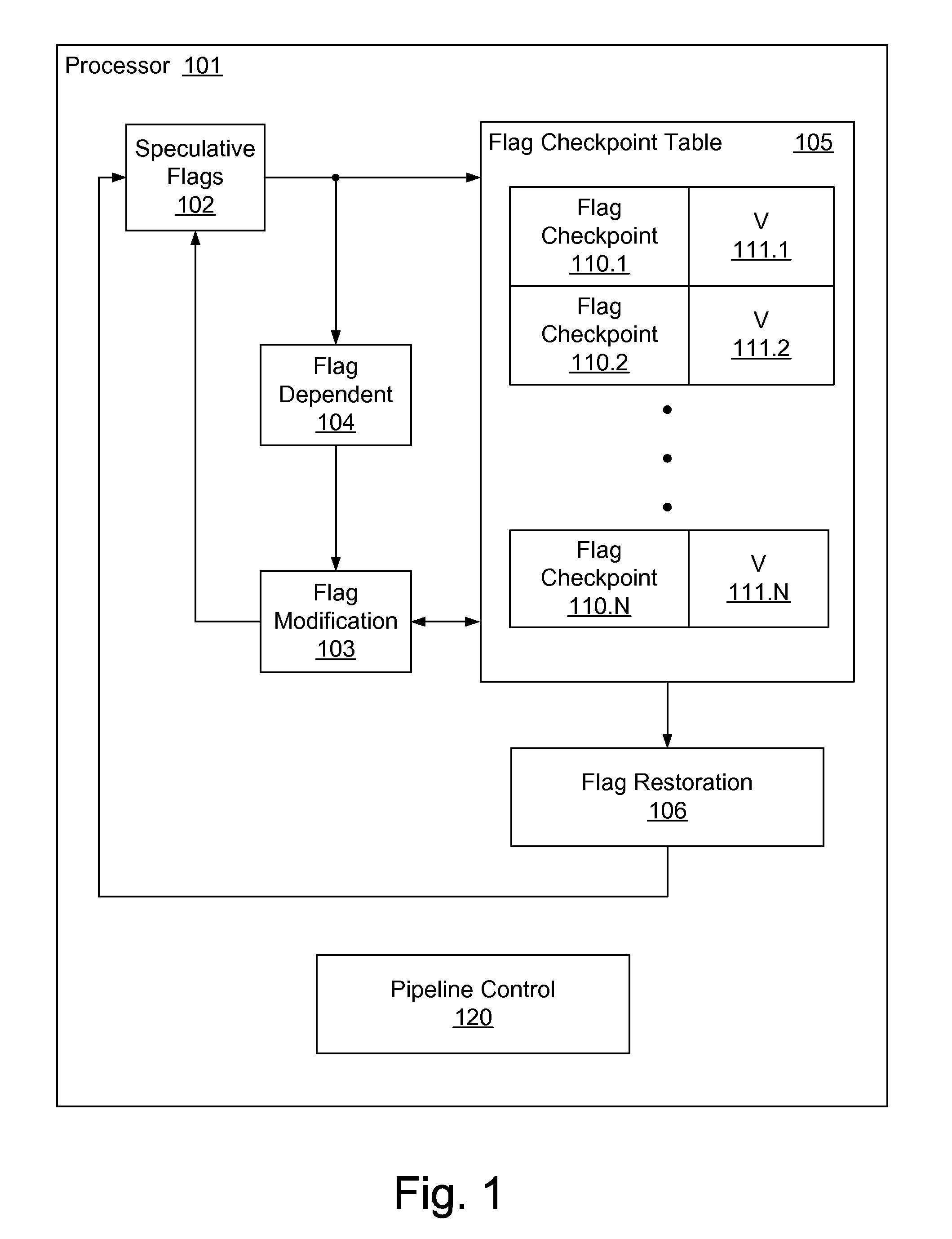

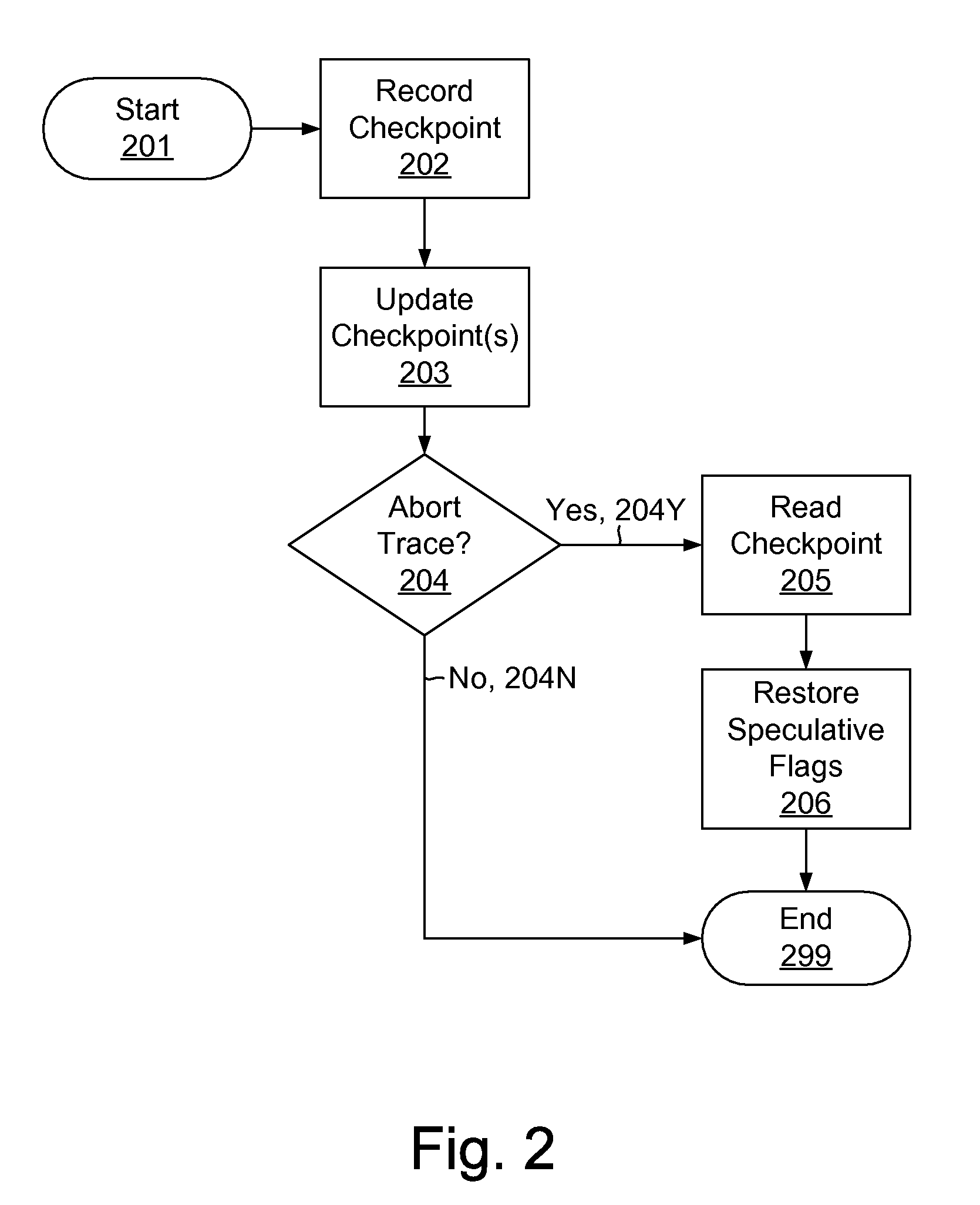

Flag management in processors enabled for speculative execution of micro-operation traces

ActiveUS7568089B1Conditional code generationDigital computer detailsSpeculative executionMicro-operation

Managing speculative execution via groups of actions corresponding to atomic traces enables efficient processing of flag-related actions, as atomic traces advantageously enable single checkpoints of flags at trace boundaries. Flag restoration from checkpoints for trace aborts uses a flag checkpoint table to store flag checkpoints, each corresponding to an atomic trace. The table is accessed for flag restoration in response to a trace abort. In a first technique, a corresponding flag checkpoint is stored in response to trace renaming, and the flag checkpoints are updated as flags are modified. Flags are restored from the flag checkpoint corresponding to an aborted atomic trace. In a second technique, a corresponding flag checkpoint is allocated to an invalid state in response to trace renaming, and initialized on-demand when flags are first modified in accordance with the atomic trace. Flags are restored from the oldest flag checkpoint starting from an aborted atomic trace.

Owner:SUN MICROSYSTEMS INC

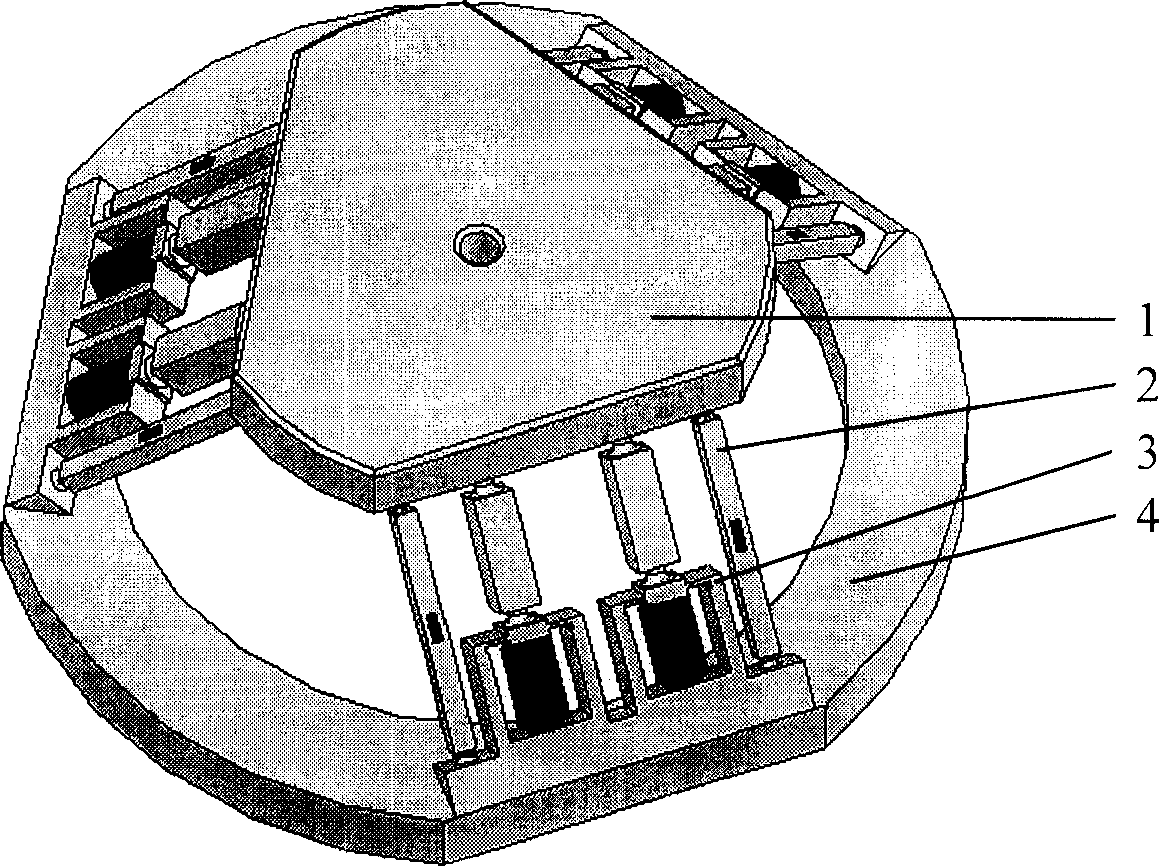

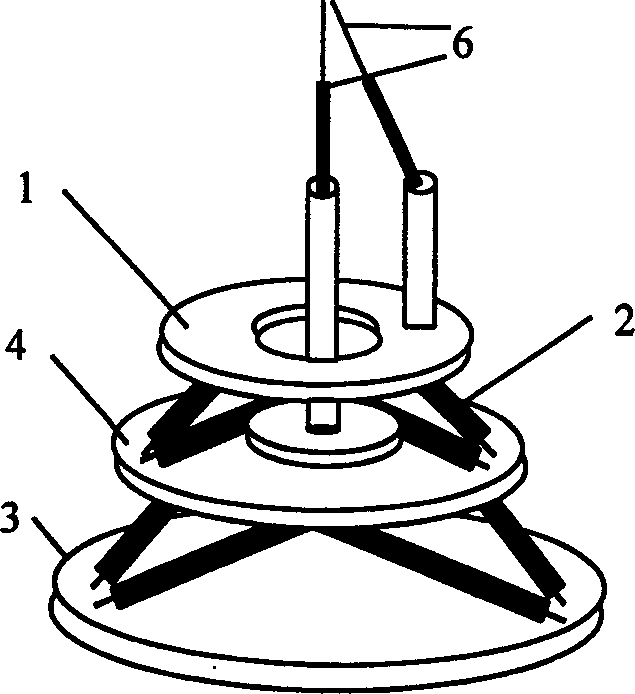

Six-freedom micro operation robot with complete position and posture feedback

InactiveCN1846948ARealize full closed-loop controlProgramme-controlled manipulatorMicro-operationParallel plate

The six-freedom micro operation robot with complete position a posture feedback features that the bench and the pedestal are connected through 12 kinematic link branches, including 6 feedback branches comprising a feedback branch pillar with flexible hinges on two ends and a strain gauge each, and 6 driving branches comprising a driving branch pillar with flexible hinges on two ends, parallel plate elastic shift pair and piezoelectric ceramic displacement unit each. The 12 kinematic link branches are separated into 3 groups including 2 feedback branches and 2 driving branches each. The main body of the six-freedom micro operation robot is one integral part machined through once machining. The present invention has simple structure, small size, low manufacture cost and other advantages, can realize micro complete closed-loop control with no friction, no interval and high resolution, and may be used widely.

Owner:YANSHAN UNIV

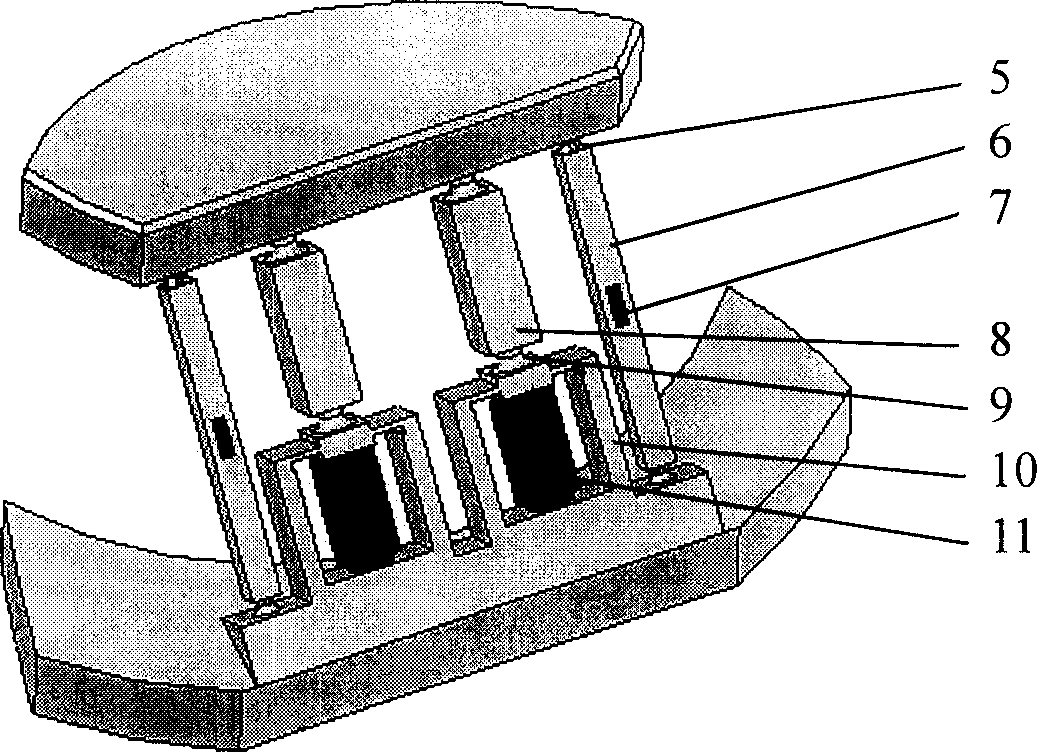

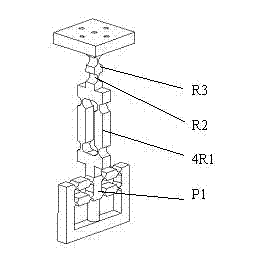

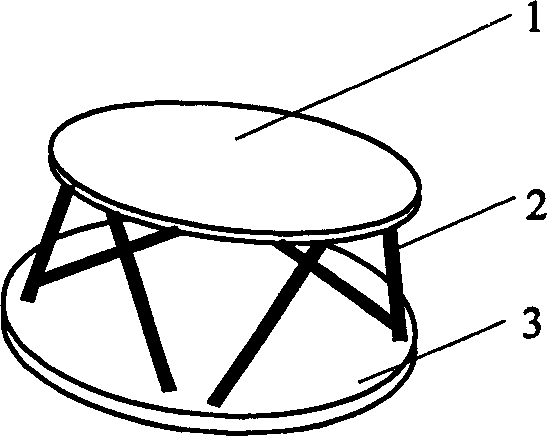

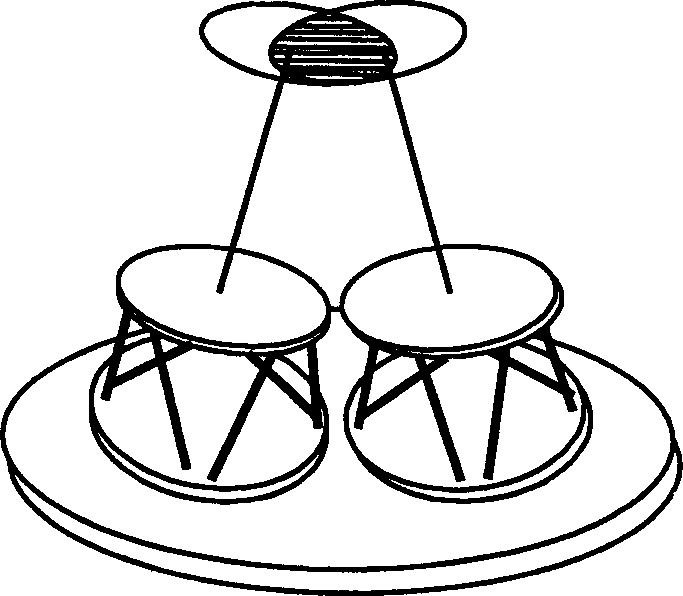

Three-degree-of-freedom microoperation orthogonal parallel operating platform used for ultraprecise location

The invention discloses a three-degree-of-freedom microoperation orthogonal parallel operating platform used for ultraprecise location, which realizes space three-dimensional translation ultraprecise location. The three-degree-of-freedom microoperation orthogonal parallel operating platform is provided with a static platform and a movable platform, wherein a piezoelectric ceramic driver is fixedly vertically arranged on each panel of the static platform, a drive of each piezoelectric ceramic driver is connected with the top end of a branched chain, the tail end of each branched chain is vertically connected with the movable platform, three branched chains are formed by sequentially serially connecting a flexible movable pair, a parallelogram structure, a first rotating pair and a second rotating pair according to position relationships of vertical, vertical and parallel among axial lines, the top end of each branched chain is a movable pair, the tail end of each branched chain is a second rotating pair, the three movable pairs are mutually orthogonal, and the three second rotating pairs are mutually orthogonal. According to the invention, the advantages of a parallel mechanism and a flexible movement pair are combined, a movement is generated by depending self elastic deformation, and output reaches high precision of micro level even nano level.

Owner:JIANGSU UNIV

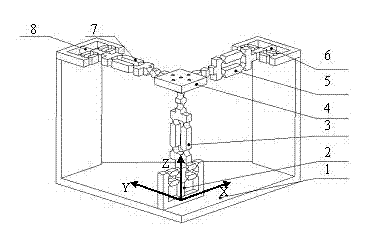

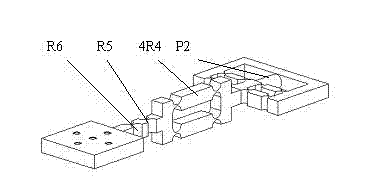

Series-parallel micro operation parallel-connection robot mechanical apparatus

InactiveCN1454753AReduce volumeGreat effortProgramme-controlled manipulatorComputer control systemMicro-operation

Disclosed is a parallel robot set to assemble diminutive machine. The robot comprises two same three-dimensional parallel frames which are in series. The parallel frame has three active links that comprise two Huke gemels and a micro displacement amplifier. The computer control system drives the displacement output of the piezoelectricity equipment. The undersides of the three active links are connected with the middle plate, and another side is connected with the work plate in a parallel frame group.In another group, the undersides of the three active links are connected with the underpan, and another side is connected with the middle plate. The middle plate is hung under the underpan. The two fingers of the robot are set on the work plate and the middle plate, which can work just like the human fingers.

Owner:BEIJING UNIV OF TECH

Dynamic online optimizer

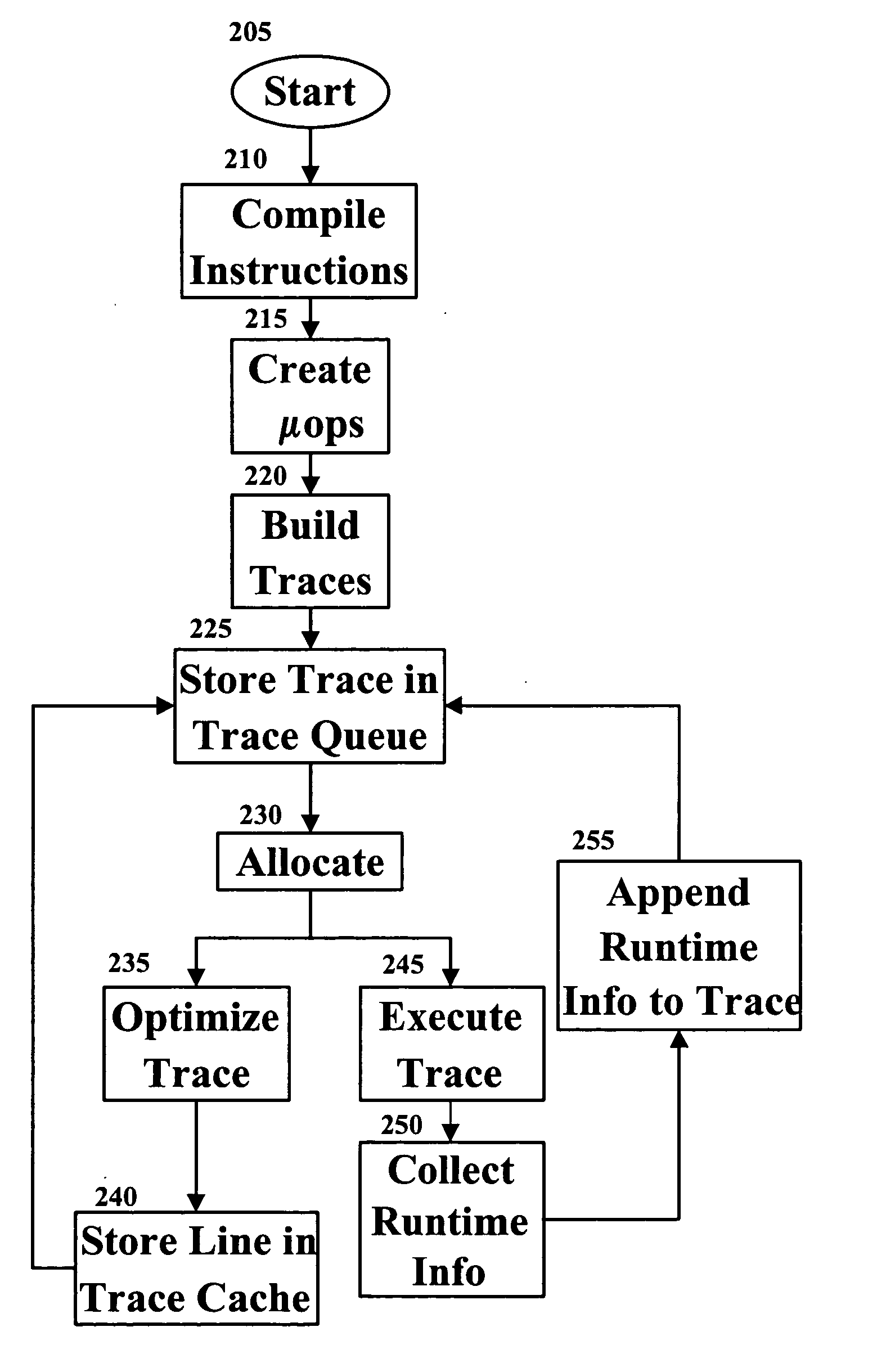

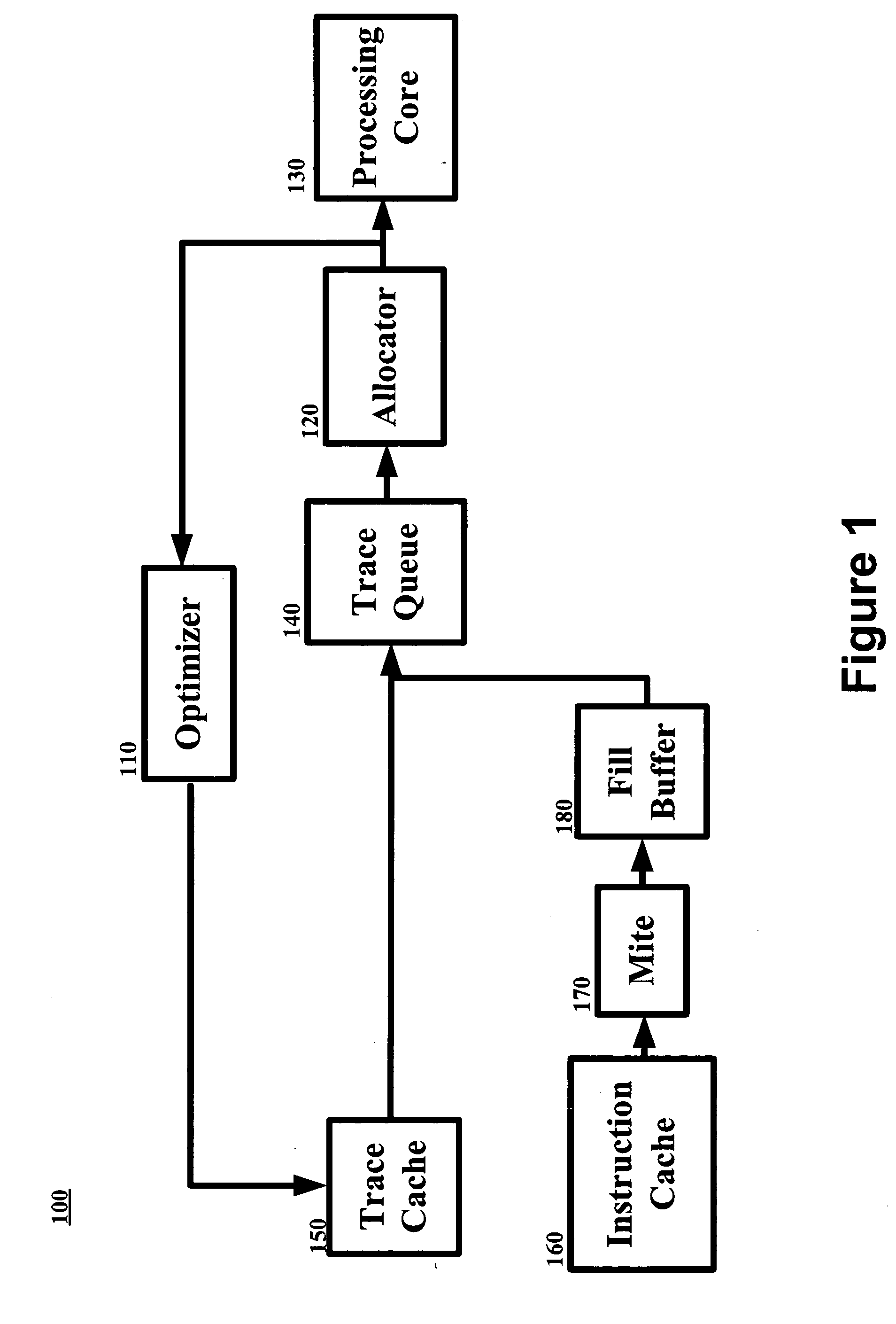

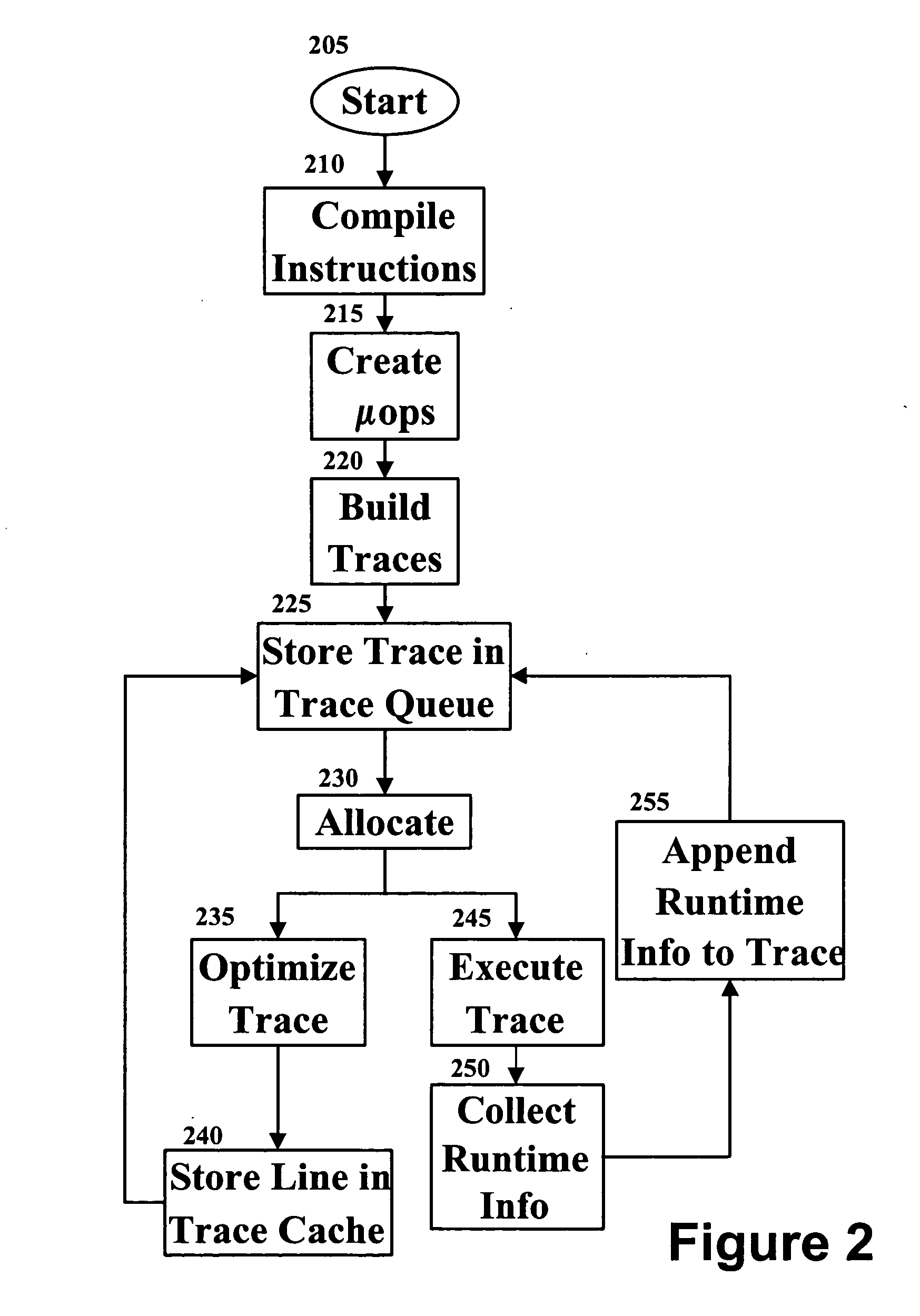

InactiveUS20050149912A1Better optimize the micro-operations of the lines of the traceImprove efficiencySoftware engineeringConcurrent instruction executionProcessing coreMicro-operation

A system and method for optimizing a series of traces to be executed by a processing core is disclosed. The lines of a trace are sent to an optimizer each time they are sent to a processing core to be executed. Runtime information may be collected on a line of a trace each time that trace is executed by a processing core. The runtime information may be used by the optimizer to better optimize the micro-operations of the lines of the trace. The optimizer optimizes a trace each time the trace is executed to improve the efficiency of future iterations of the trace. Most of the optimizations result in a reduction of the number of μops within the trace. The optimizer may optimize two or more lines at a time in order to find more opportunities to remove μops and shorten the trace. The two lines may be alternately offset so that each line has the maximum allowed number of micro-operations.

Owner:INTEL CORP

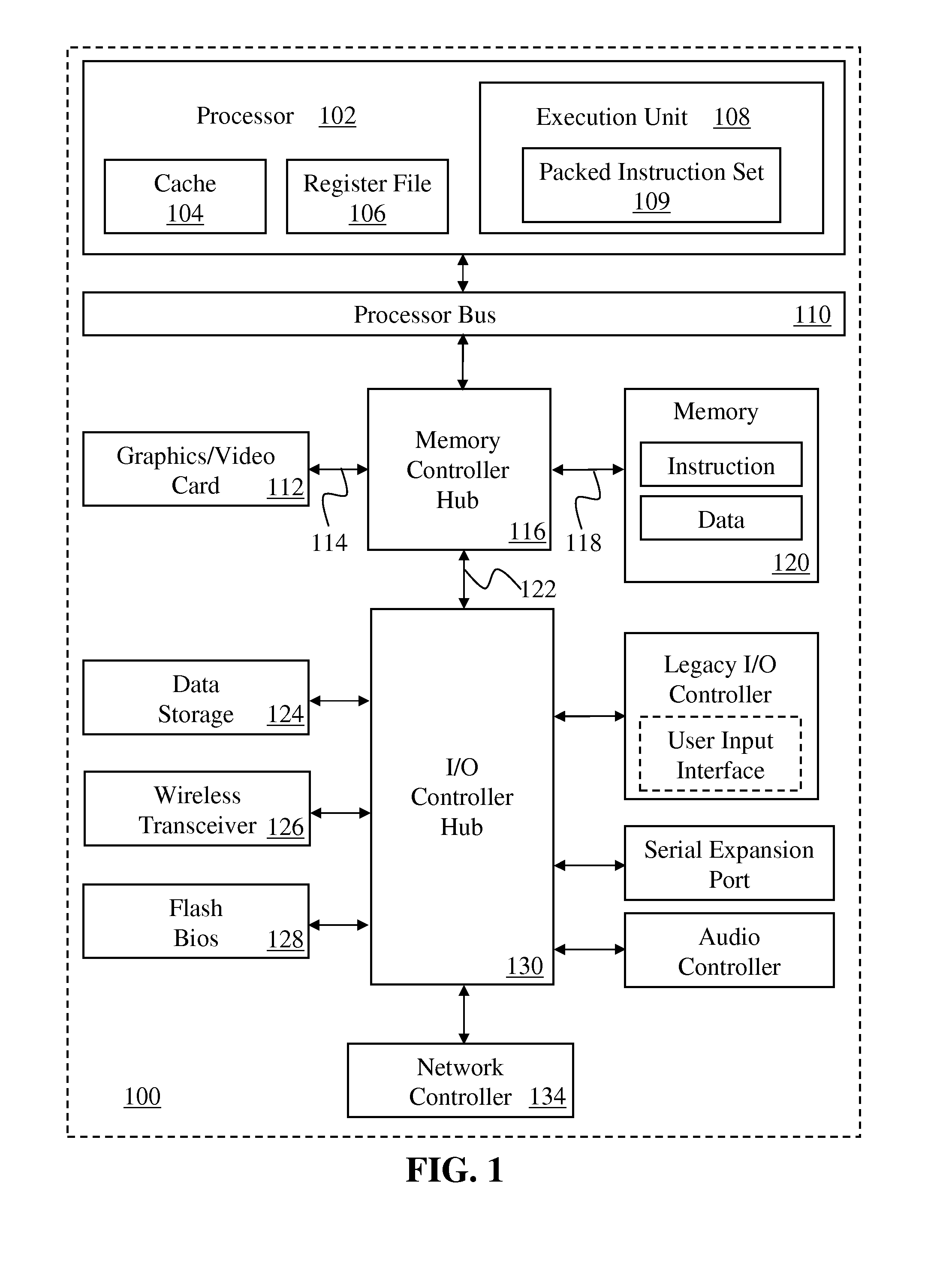

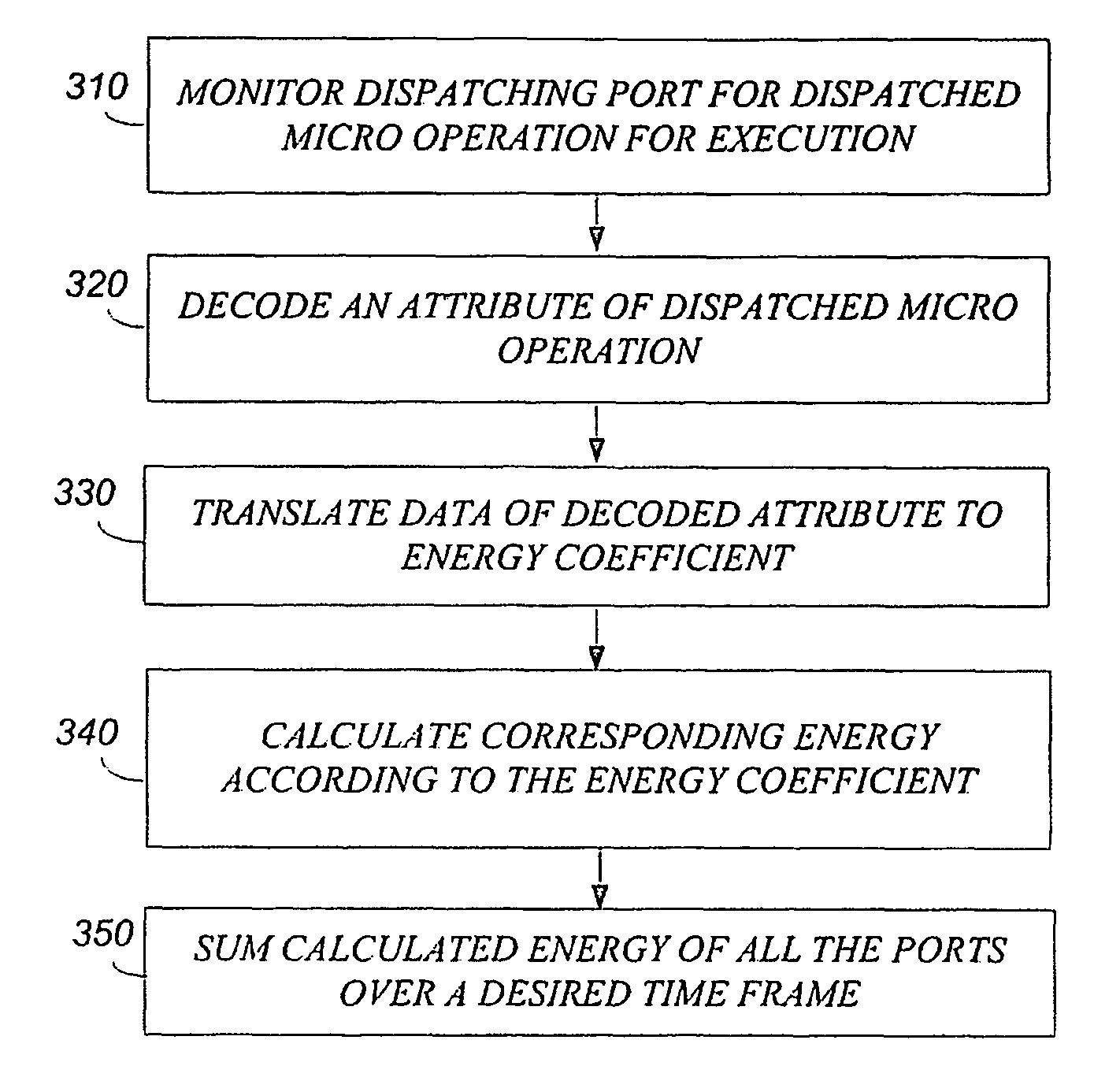

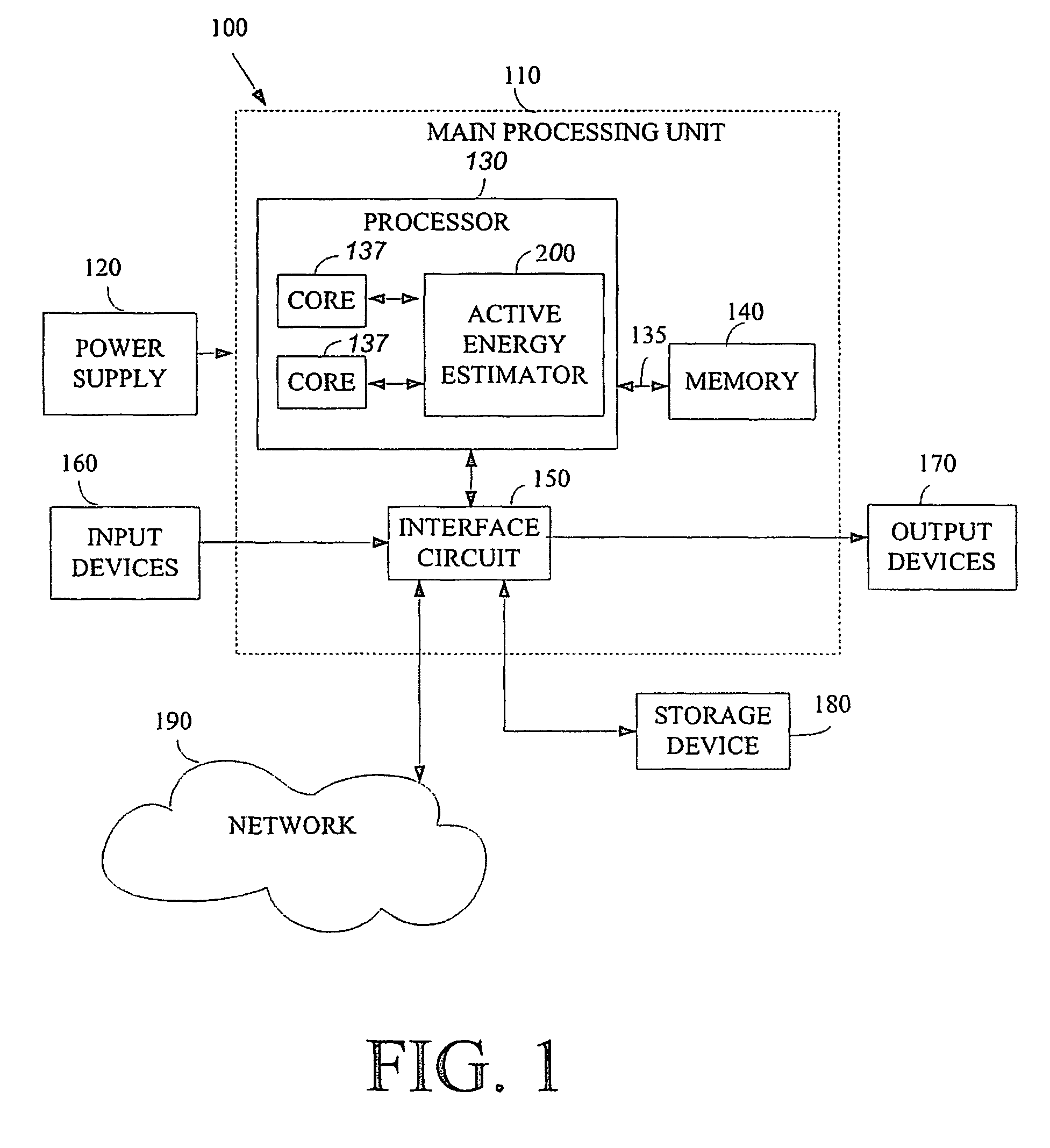

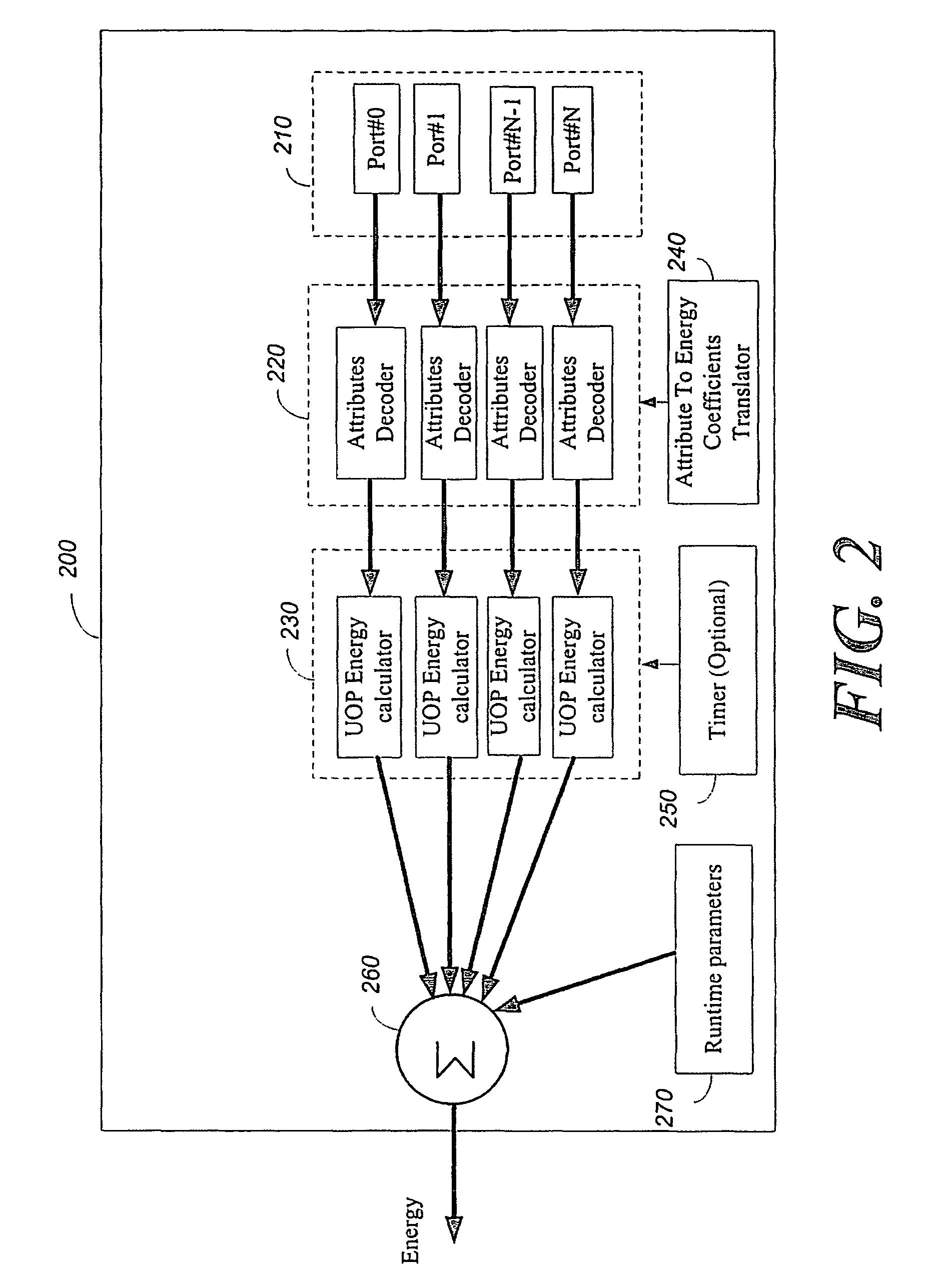

Method and apparatus to estimate energy consumed by central processing unit core

InactiveUS7757103B2Energy efficient ICTVolume/mass flow measurementMicro-operationParallel computing

Briefly, a processor and a method of estimating an active energy consumption of two or more cores of a processor based on dispatching micro operations to one or more execution units of the processor.

Owner:INTEL CORP

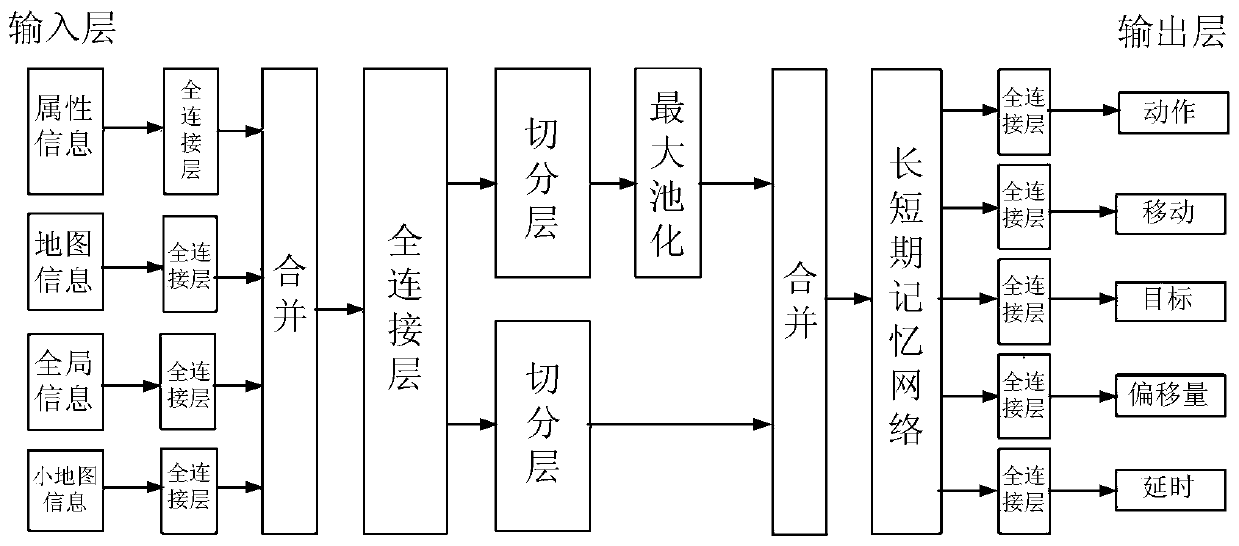

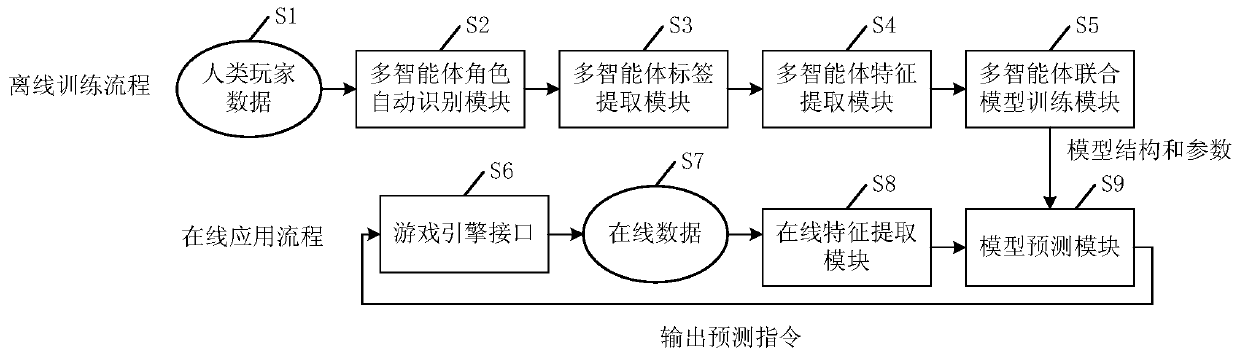

Operation information prediction method, model training method and related device

ActiveCN109893857AImprove rationalityImprove predictive performanceNeural architecturesVideo gamesMicro-operationFeature set

The invention discloses an operation information prediction method. The operation information prediction method comprises the following steps: acquiring image data to be predicted; determining N characters to be predicted in a first character set according to image data to be predicted; acquiring a feature set to be predicted of each role to be predicted in the image data to be predicted; and acquiring first operation information corresponding to each role to be predicted through a target joint model, wherein the target joint model is used for generating second operation information accordingto the feature set to be predicted, the target joint model is also used for generating first operation information according to the second operation information, the first operation information represents information related to operation contents, and the second operation information represents information related to the operation intention. The invention also discloses a model training method anda related device. According to the invention, the cooperative capability of the micro-operation level and the macro-operation level can be obtained simultaneously by utilizing the target joint model,so that the prediction capability of the model is enhanced, and the rationality of information prediction is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Trace cache for efficient self-modifying code processing

A trace cache for efficient self-modifying code processing enables selective invalidation of entries of the trace cache, advantageously retaining some of the entries in the trace cache even during self-modifying code events. Instructions underlying trace cache entries are monitored for modification in groups, enabling advantageously reduced hardware. Associated with trace cache entries are one or more translation ages, determined when the entry is built by sampling current ages of memory blocks underlying the entry. When the entry is accessed and micro-operations therein are processed, each of the translation ages of the accessed entry are compared with the current ages of the memory blocks underlying the accessed entry. If any of the age comparisons fail, then the micro-operations are aborted and the entry is invalidated. When any portion of a memory block is modified, the current age of the modified memory block is incremented.

Owner:SUN MICROSYSTEMS INC

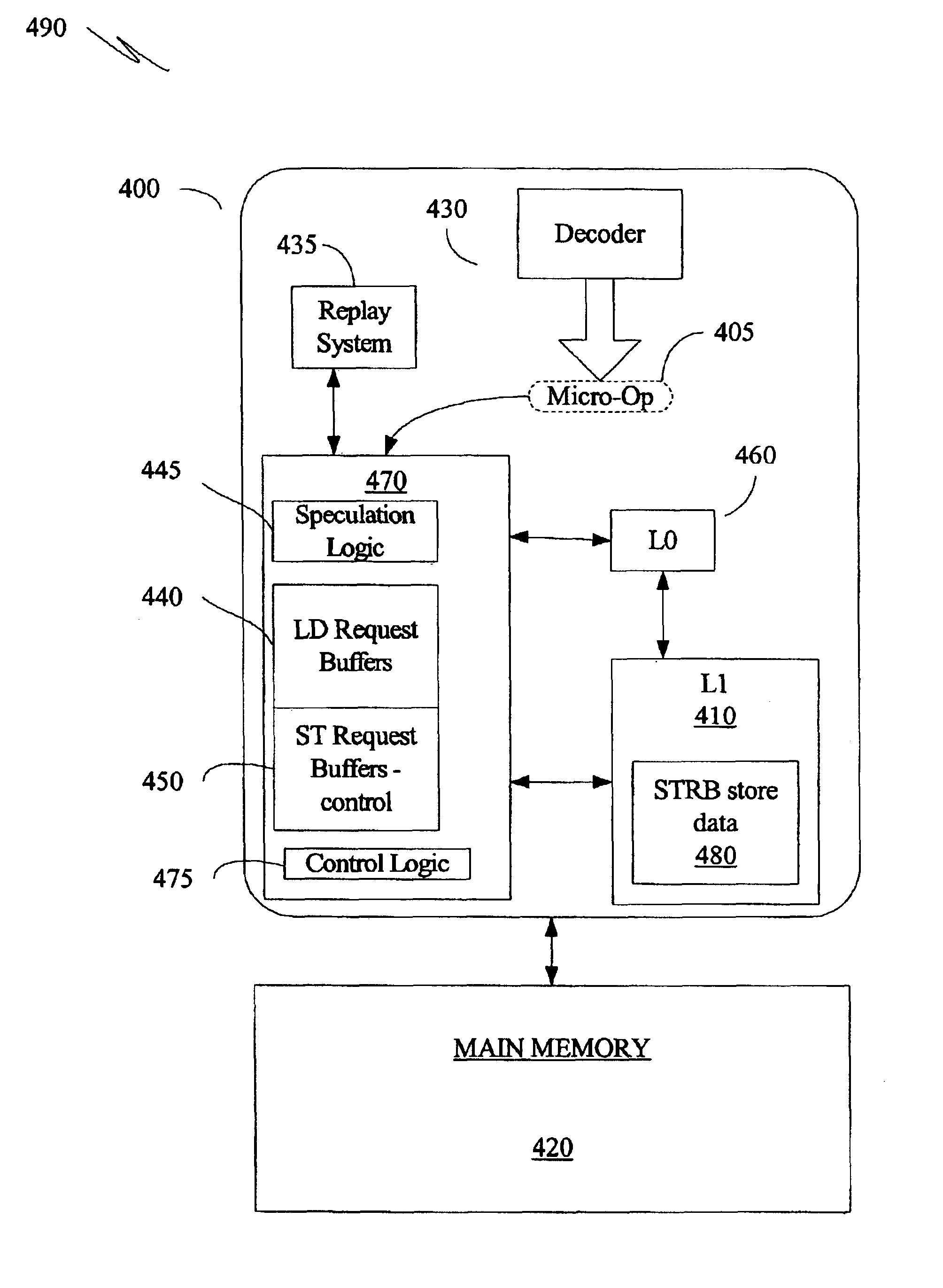

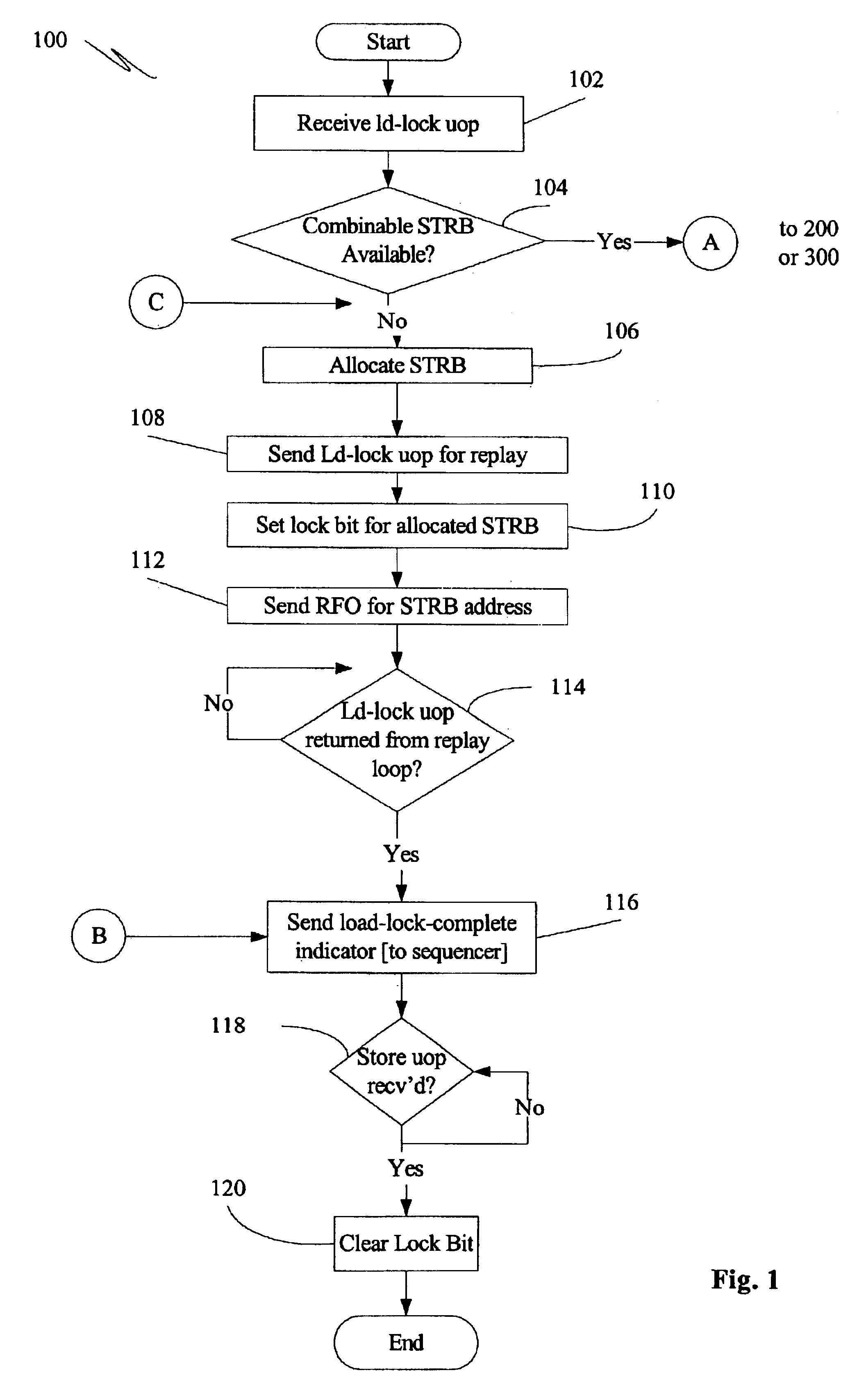

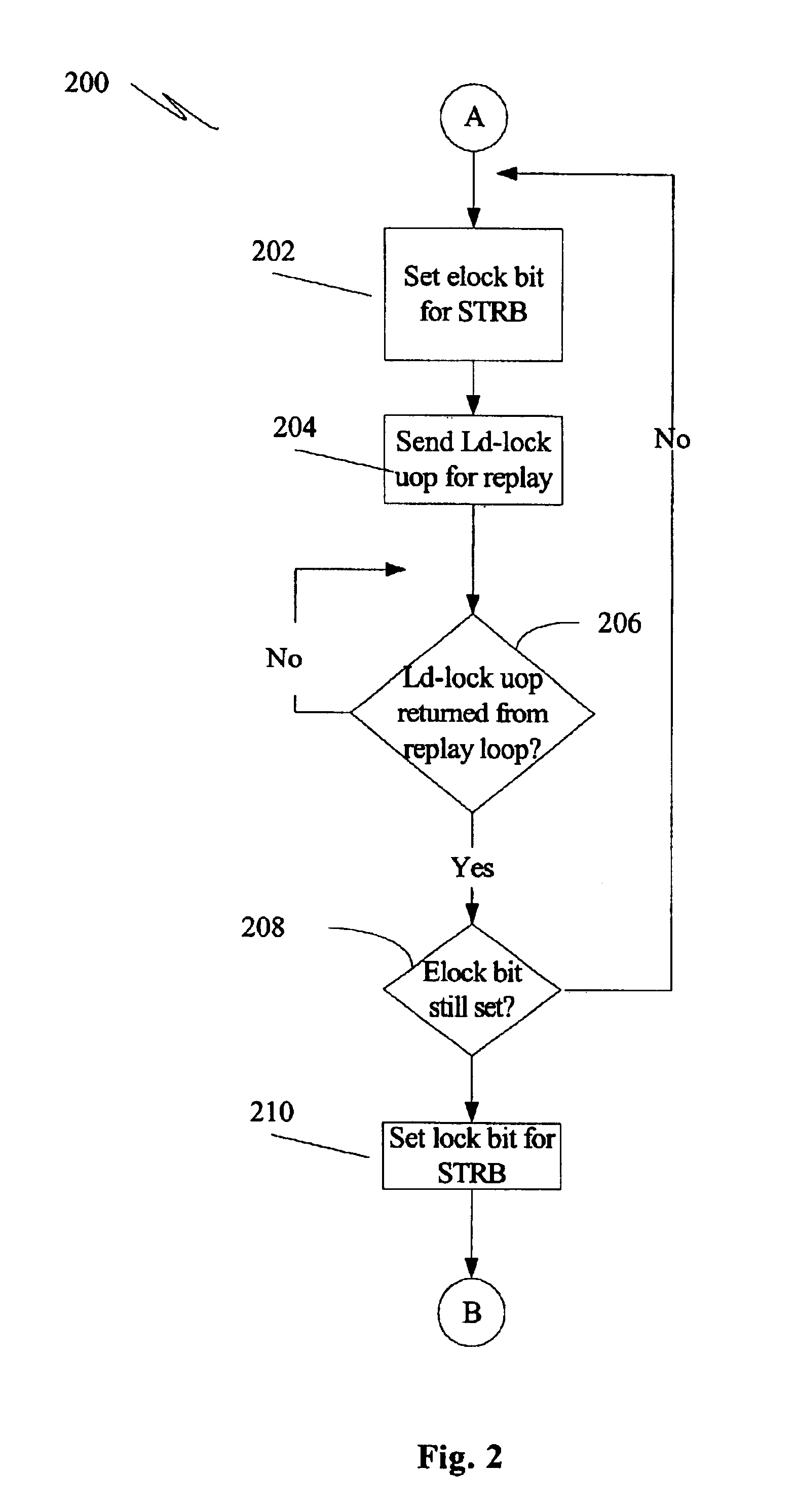

Cache lock mechanism with speculative allocation

InactiveUS6986010B2Memory adressing/allocation/relocationUnauthorized memory use protectionMicro-operationLocking mechanism

A method and apparatus to speculatively allocate a combinable store request buffer for a cache lock operation by setting an extended lock indicator. The store request buffer is speculatively allocated and the load-lock micro-operation associated with the cache lock operation is sent to a replay loop. During the replay window, conflict detection processing is completed. When the load-lock micro-operation returns from replay, the store buffer is de-allocated if a conflict has been detected during the replay window.

Owner:INTEL CORP

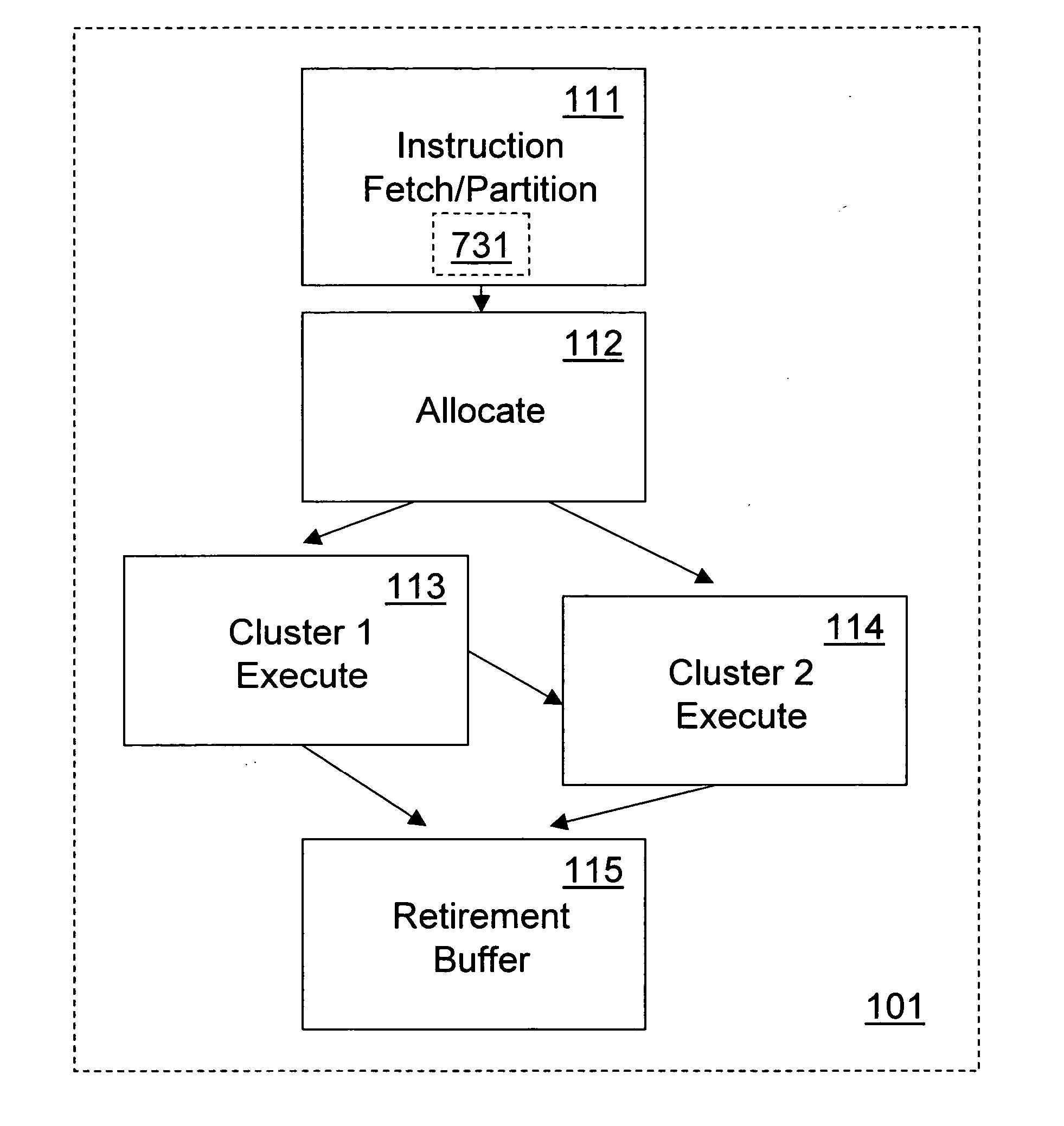

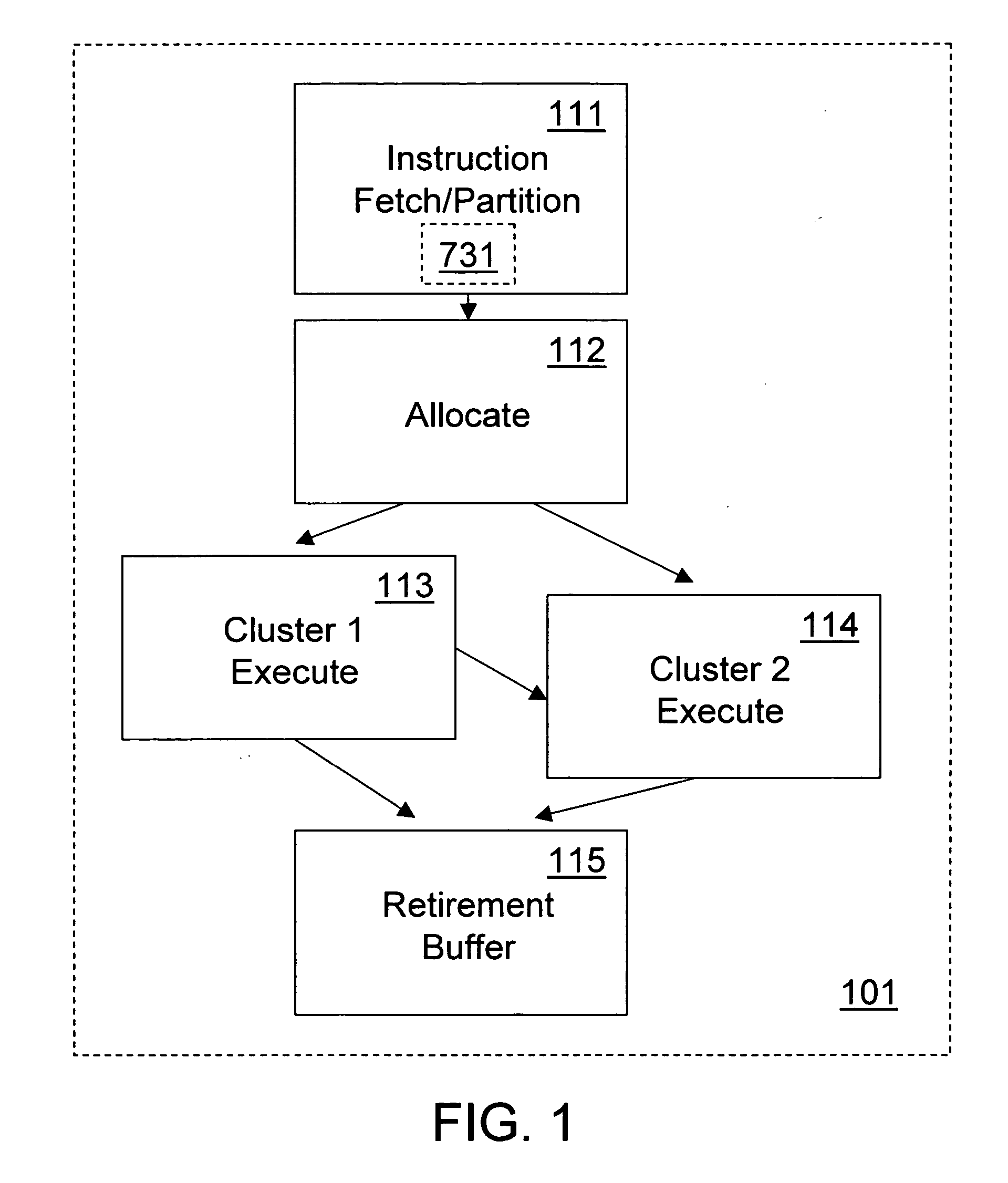

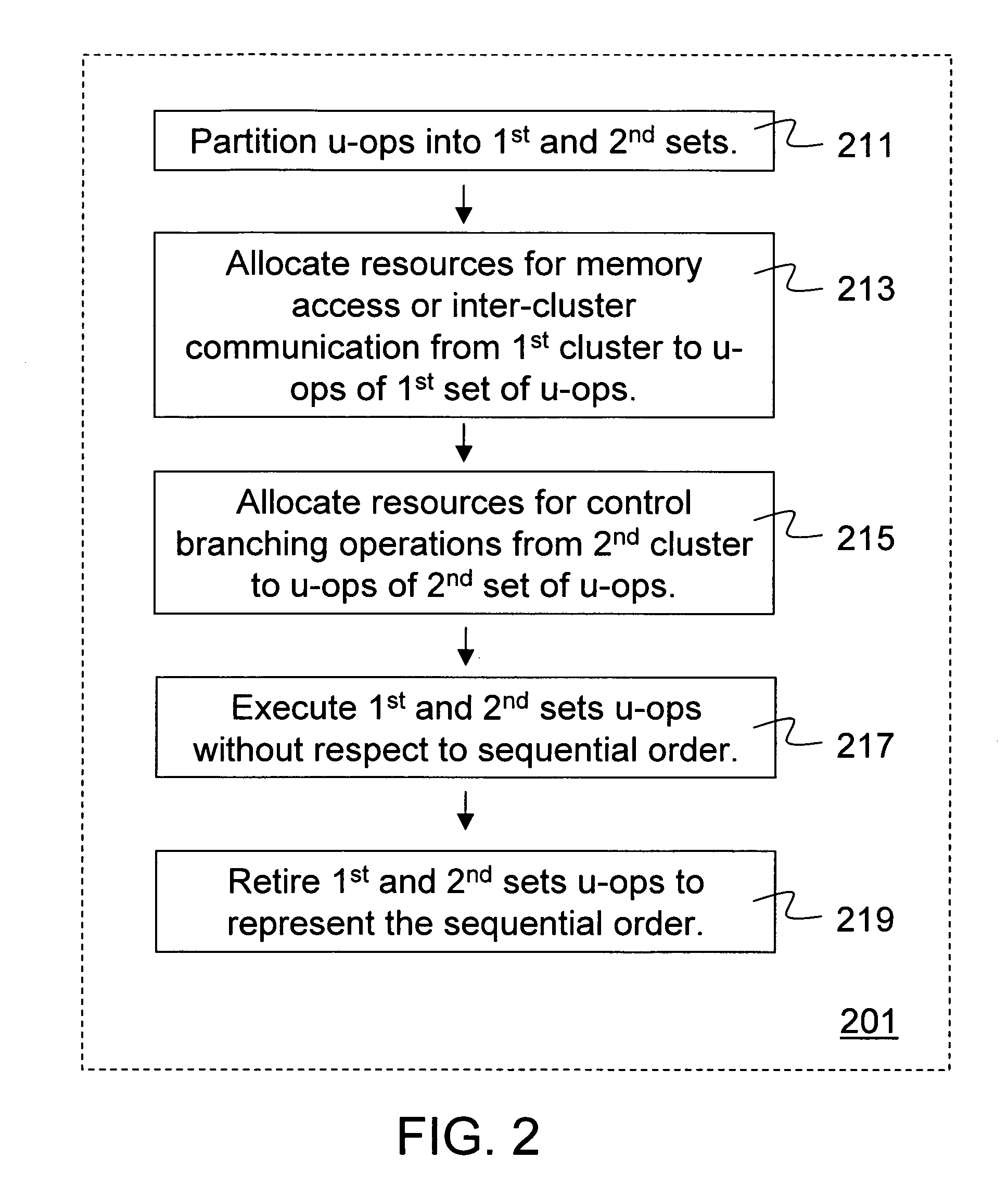

Method and apparatus for microarchitecture partitioning of execution clusters

ActiveUS20070157006A1Register arrangementsDigital computer detailsMicro-operationResource allocation

Microarchitecture policies and structures partition execution resource clusters. In disclosed microarchitecture embodiments, micro-operations representing a sequential instruction ordering are partitioned into a two sets. To one set of micro-operations execution resources are allocated from a cluster of execution resources that can perform memory access operations but not branching operations. To the other set of micro-operations execution resources are allocated from a cluster of execution resources that can perform branching operations but not memory access operations. The first and second sets of micro-operations may be executed out of sequential order but are retired to represent their sequential instruction ordering.

Owner:INTEL CORP

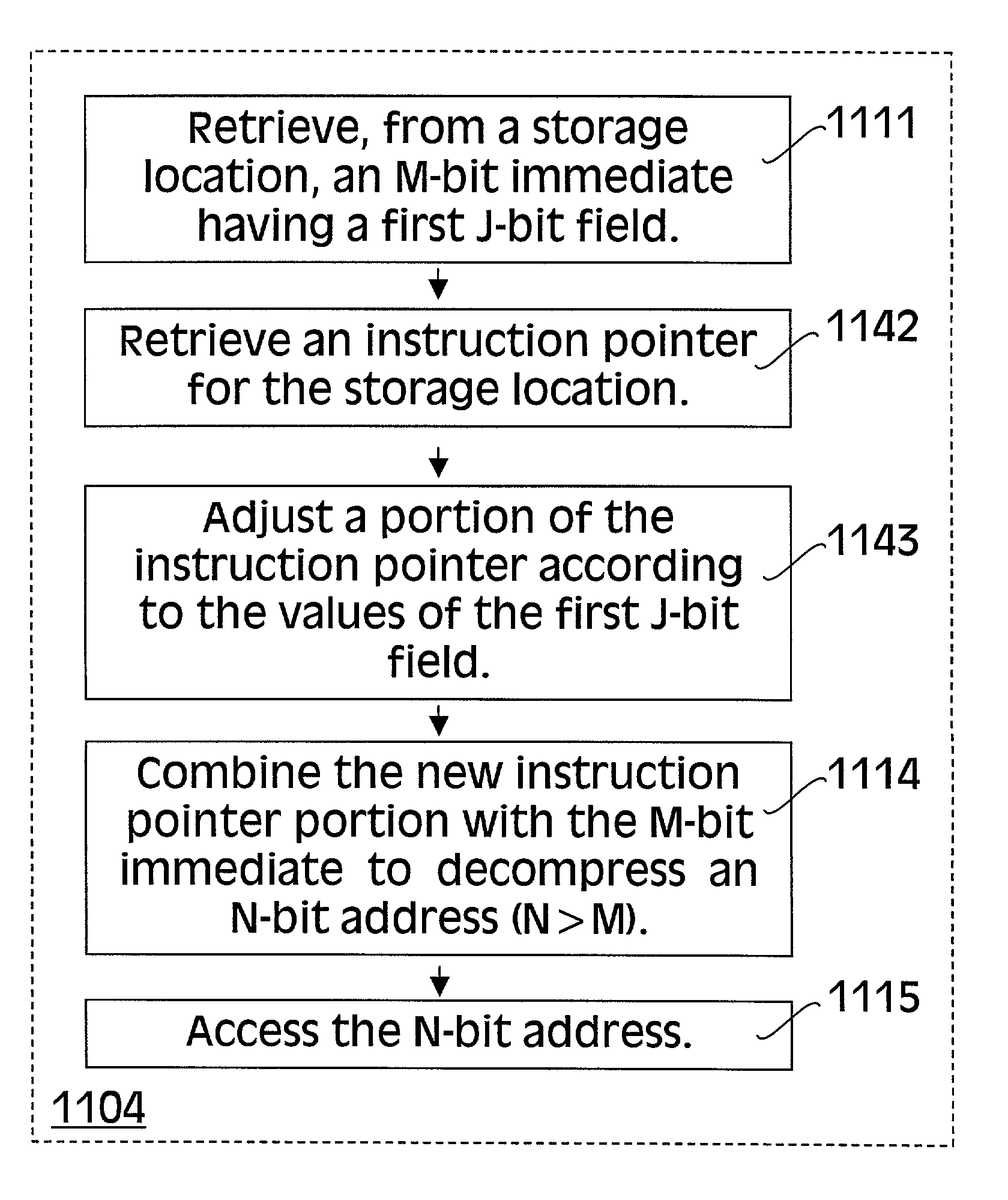

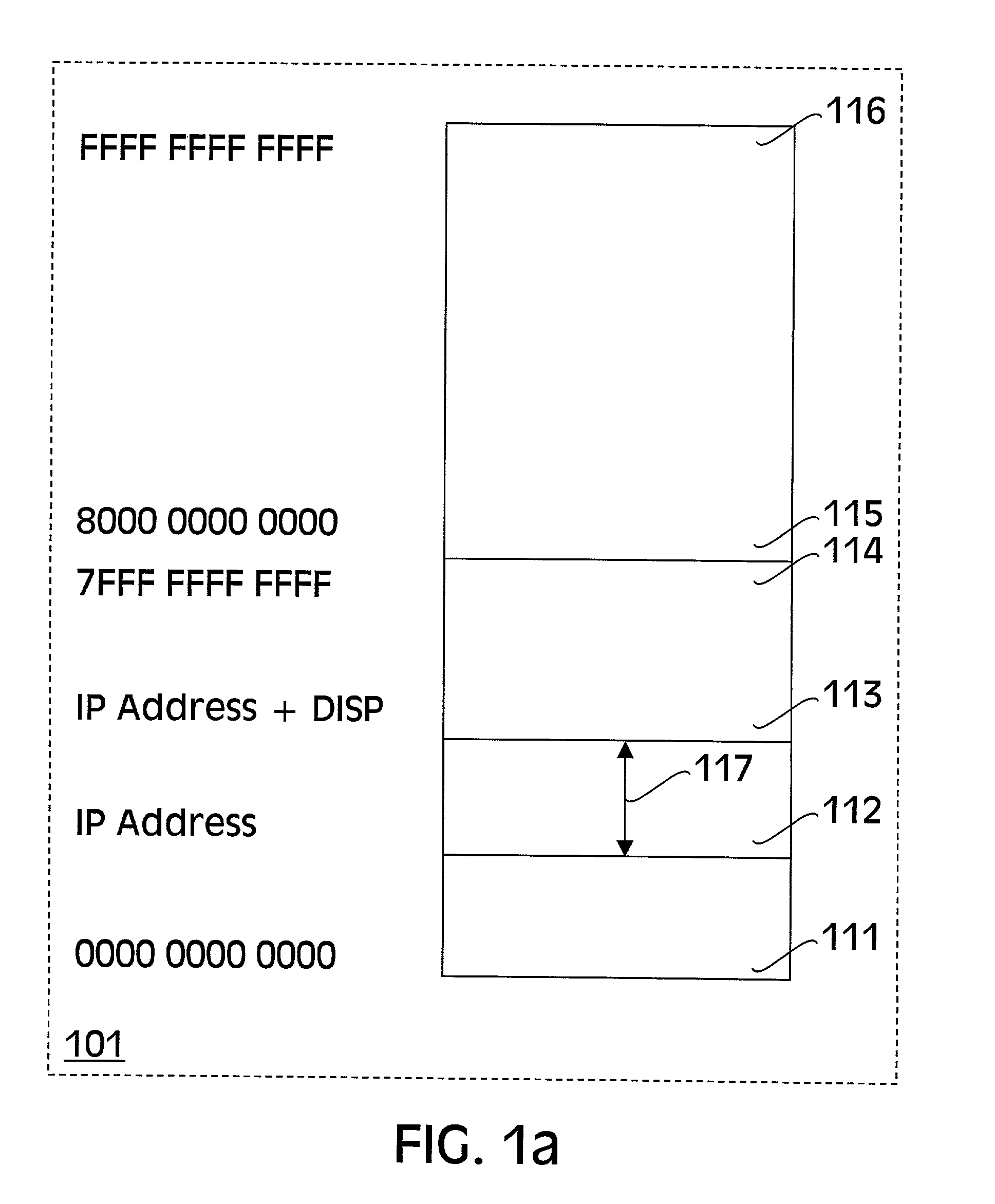

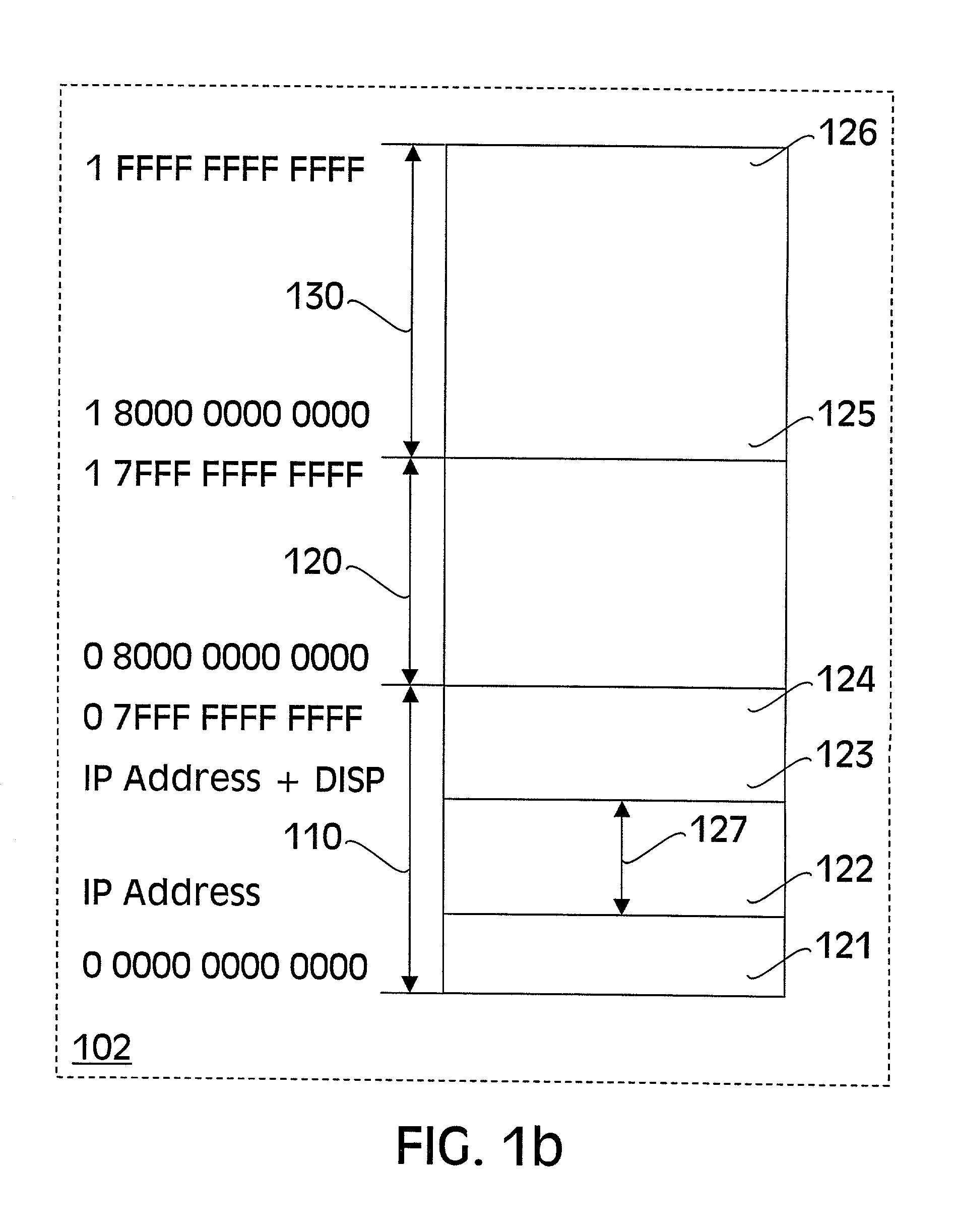

Method and apparatus for decompressing relative addresses

A method and apparatus for decompressing relative addresses. A compressed relative address is retrieved from one or more micro-operation entries of a micro-operation storage and an uncompressed relative address is reconstructed from the compressed relative address and an instruction pointer (IP) address associated with the head of the micro-operation storage line in which the compressed relative address was stored. IP-relative addresses may be computed in a manner similar to relative branch targets, then compressed and stored in one or more micro-operation entries of a micro-operation storage line to be reconstructed later according to an IP address associated with the respective micro-operation storage line in which their compressed counterpart was stored.

Owner:INTEL CORP

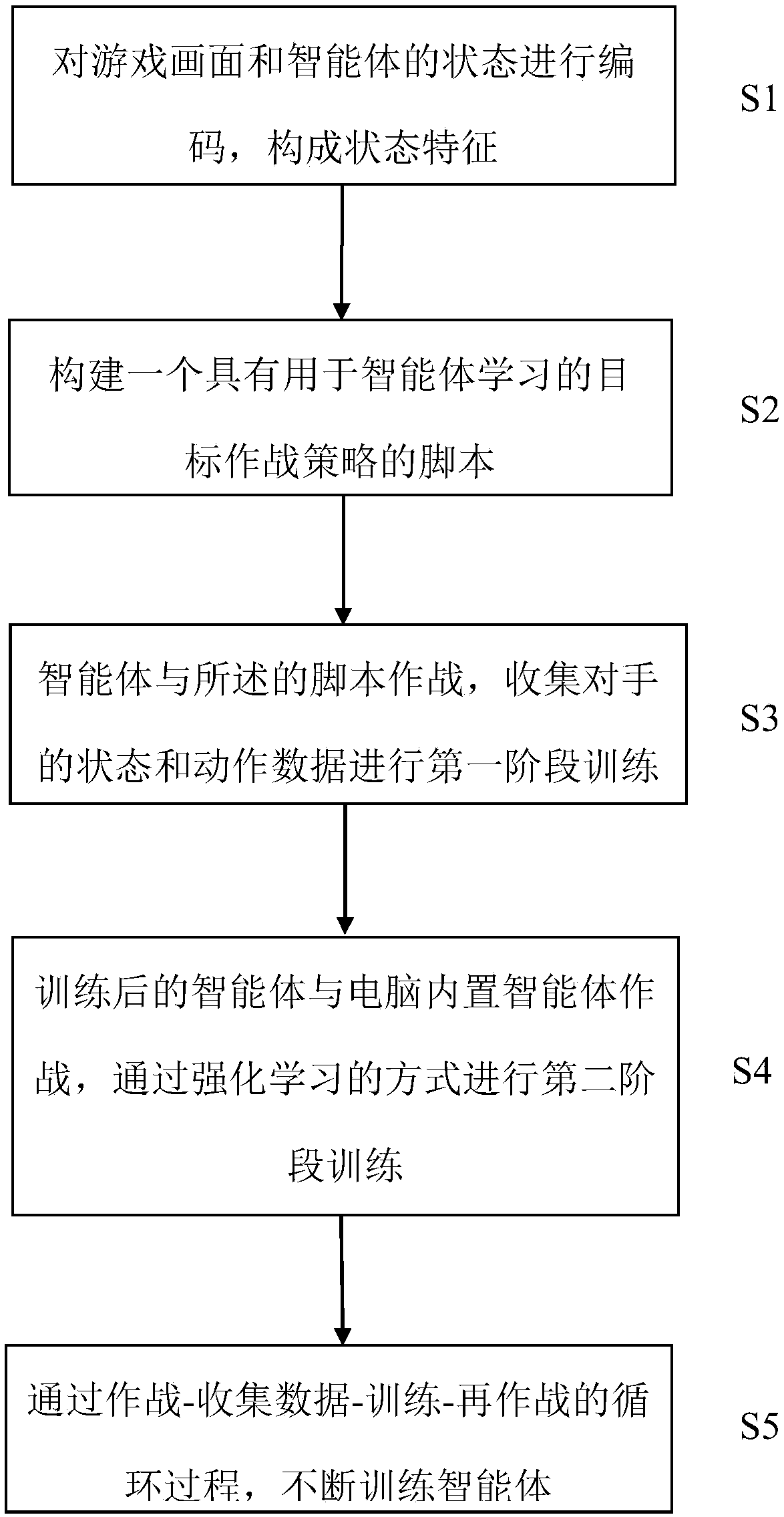

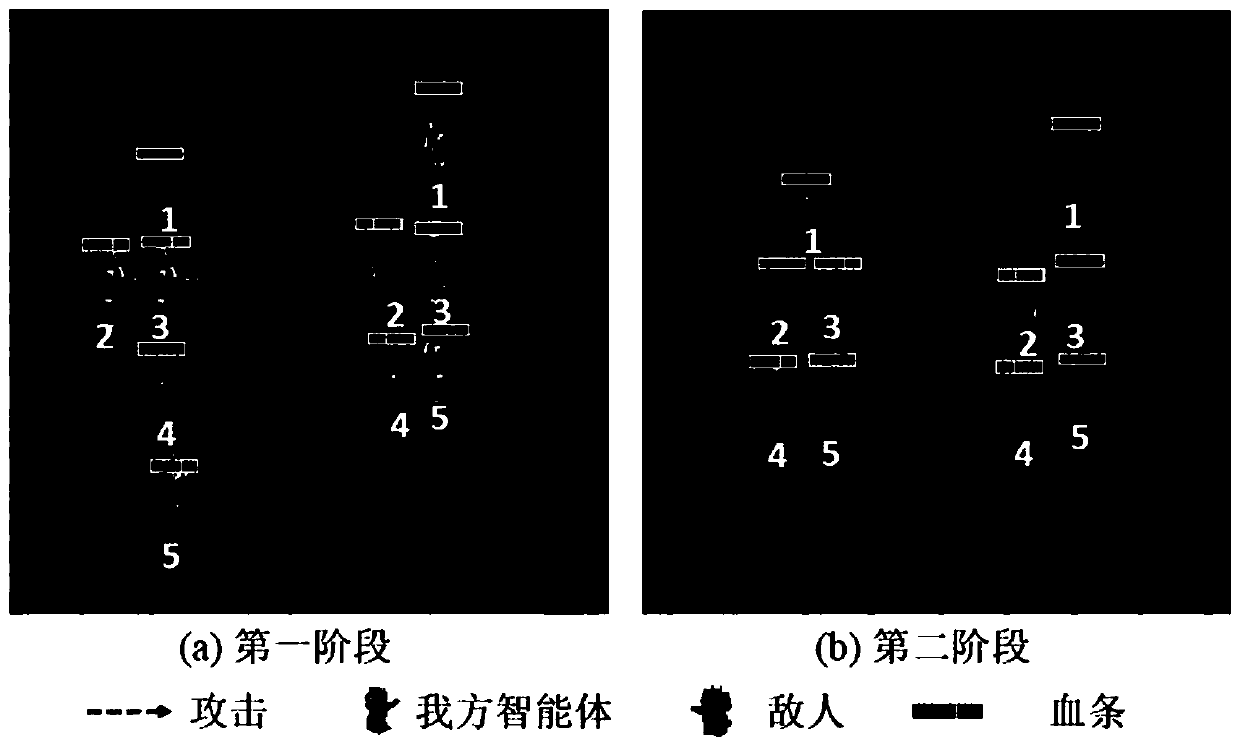

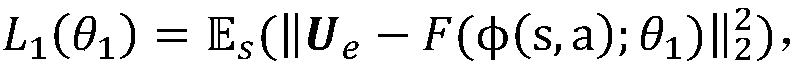

Agent learning method based on knowledge guidance-tactical perception

ActiveCN108629422AReduce training timeGood initial modelComputing modelsVideo gamesMicro-operationPhacus

The invention discloses an agent learning method based on knowledge guidance-tactical perception. In the environment of a two-party fight game, human knowledge is used to train an agent which fights with a specific tactical strategy through two stages of training. The method comprises the steps that 1) a game screen and the state of the agent are encoded to form a state feature; 2) a script with aspecific fight strategy is constructed by manually writing a script; 3) the agent fights with the script to collect the state and motion data of an opponent to carry out training in the first stage;4) the trained agent fights with a computer built-in AI, and training in the second stage is carried out through reinforcement learning; and 5) the learning framework is used to train the agent to participate in fight with specific tactics. The method provided by the invention is applicable to agent training in a two-party fight mode in a micro-operation environment, and acquires a good winning rate in the face of various micro-operation fight scenes.

Owner:ZHEJIANG UNIV

Four-degree-of freedom piezoelectric micro-clamp

ActiveCN105058366AReduce design difficultyReduce Design ComplexityMicromanipulatorPrecision positioning equipmentElectricityMicro-operation

The invention discloses a four-degree-of-freedom piezoelectric micro-clamp. The four-degree-of-freedom piezoelectric micro-clamp has the following advantages: the piezoelectric micro-clamp can enable each clamp finger to realize actions in a clamping direction and a direction perpendicular to the clamping direction, that is, each clamp finger has degrees of freedom in two directions; and the whole piezoelectric micro-clamp has four degrees of freedom, so that part front end execution mechanisms of micro-assembly and micro-operation systems can be saved, the design difficulty and complexity of the system are reduced, the mass and the volume of the system are decreased, and the system cost is reduced.

Owner:NINGBO UNIV

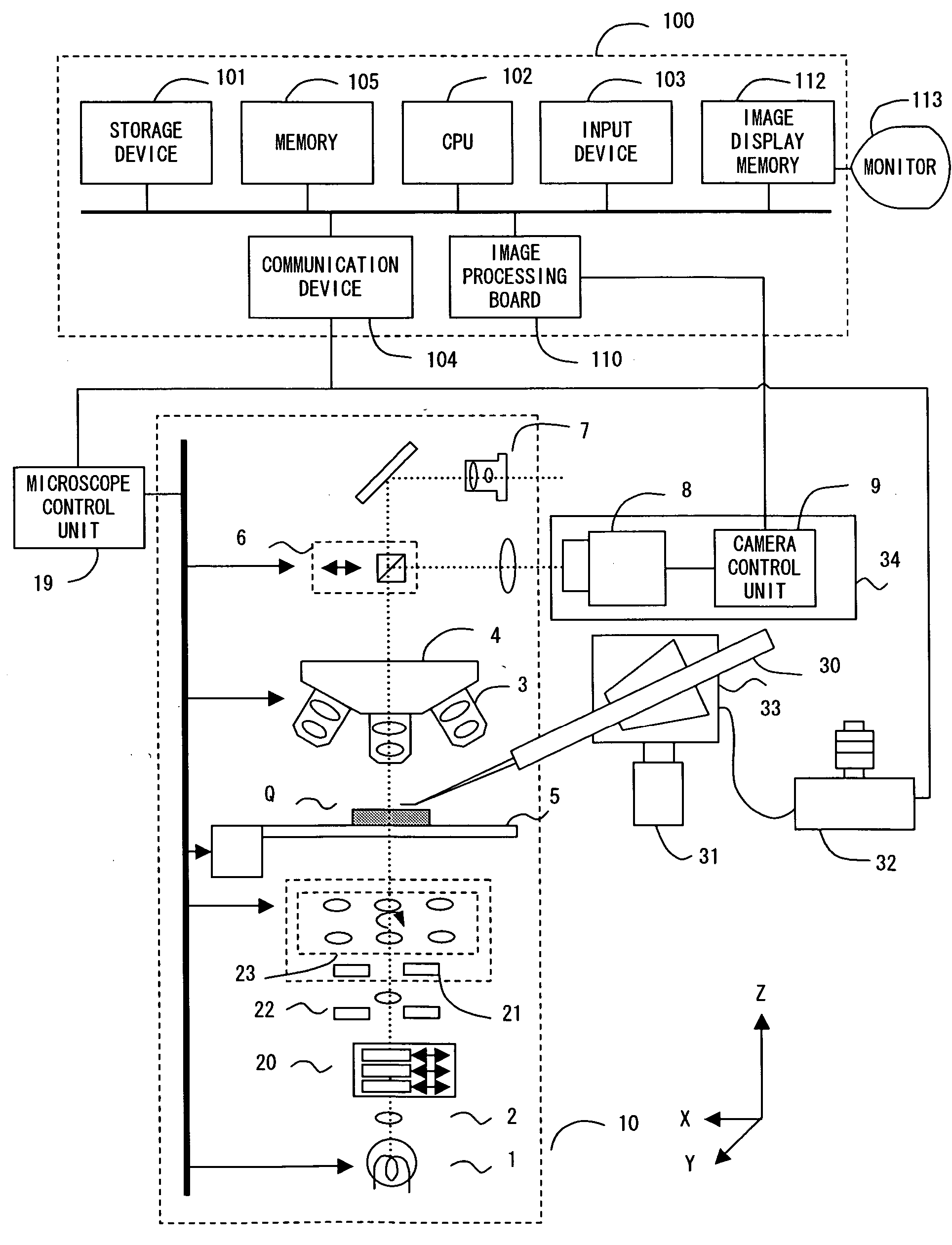

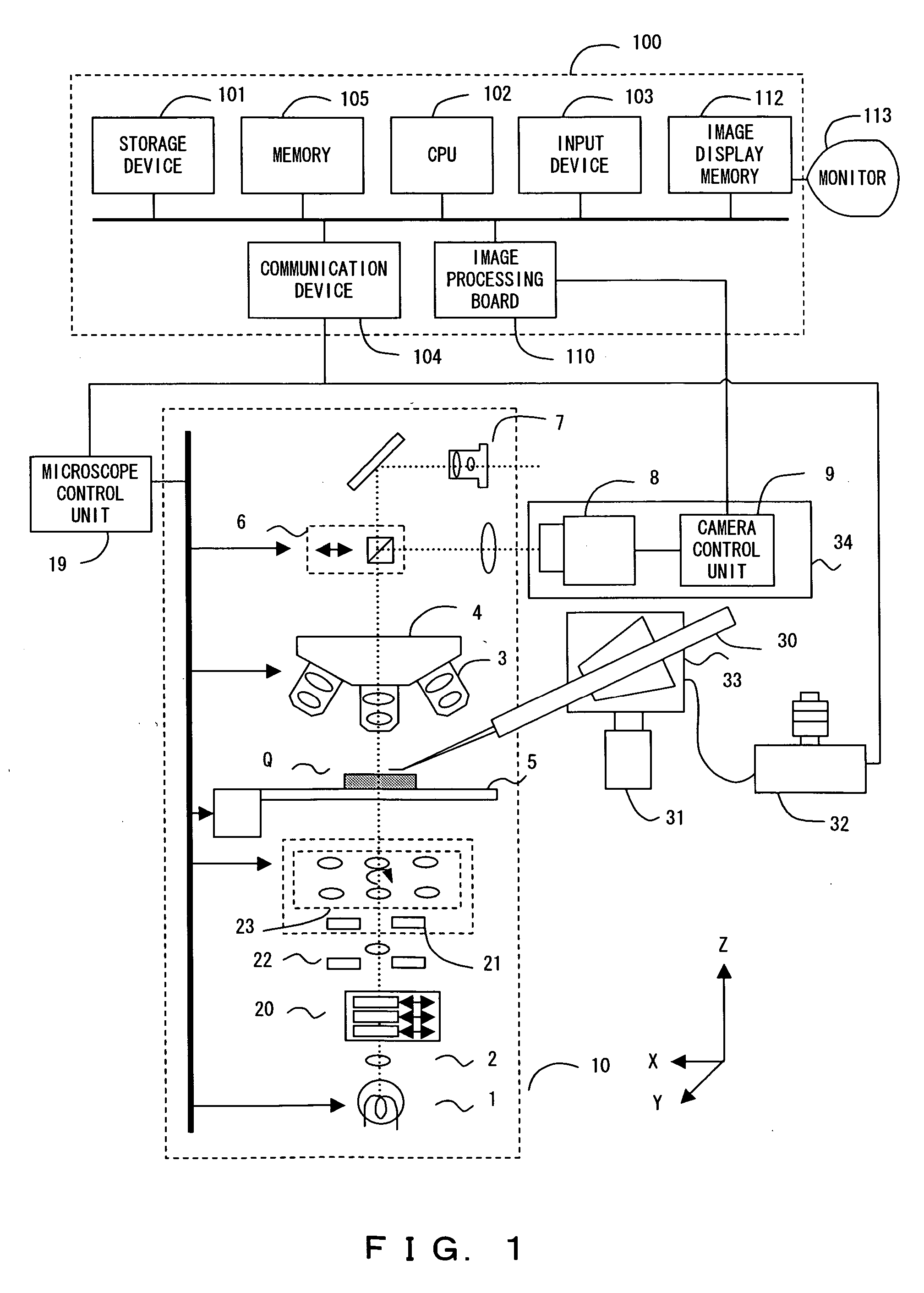

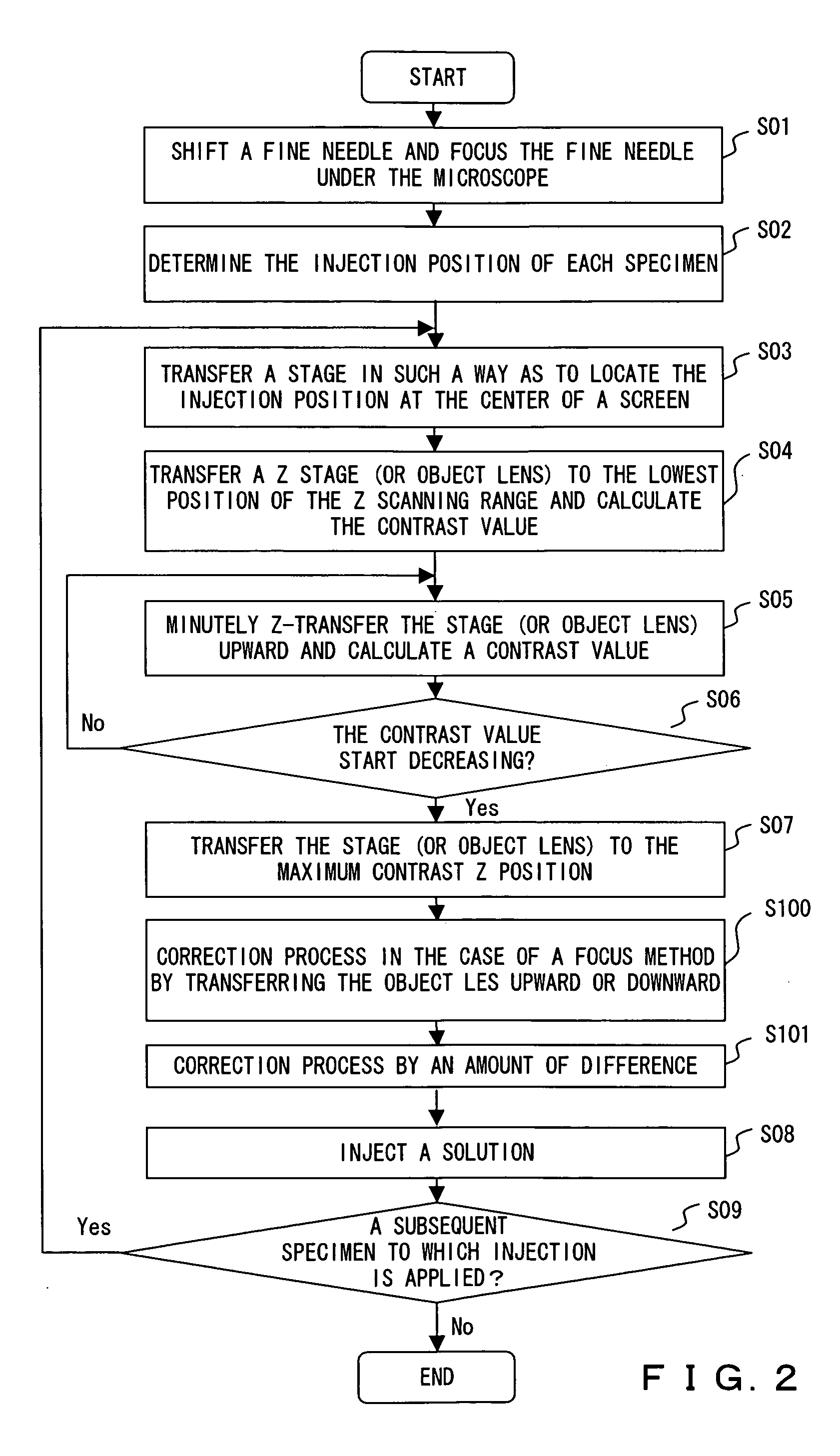

Micromanipulation system

A micromanipulation system for applying a micro manipulation to an object within the view of a microscope, using a fine needle, comprising: a manipulator driving unit for transferring the fine needle at least along the optic axis direction of the microscope, a micro manipulation starting position determining unit for determining a micro manipulation starting position as a reference position, an object transfer unit for relatively transferring the respective positions of the object and object lens, a focus position detecting unit for detecting a focus position indicating the focus of the object in the object lens, in accordance with the relative transfer of the object, an object transfer control unit for controlling a movement of the object transfer unit, based on the detection result, and a micro manipulation control unit for performing the micro manipulation.

Owner:OLYMPUS CORP

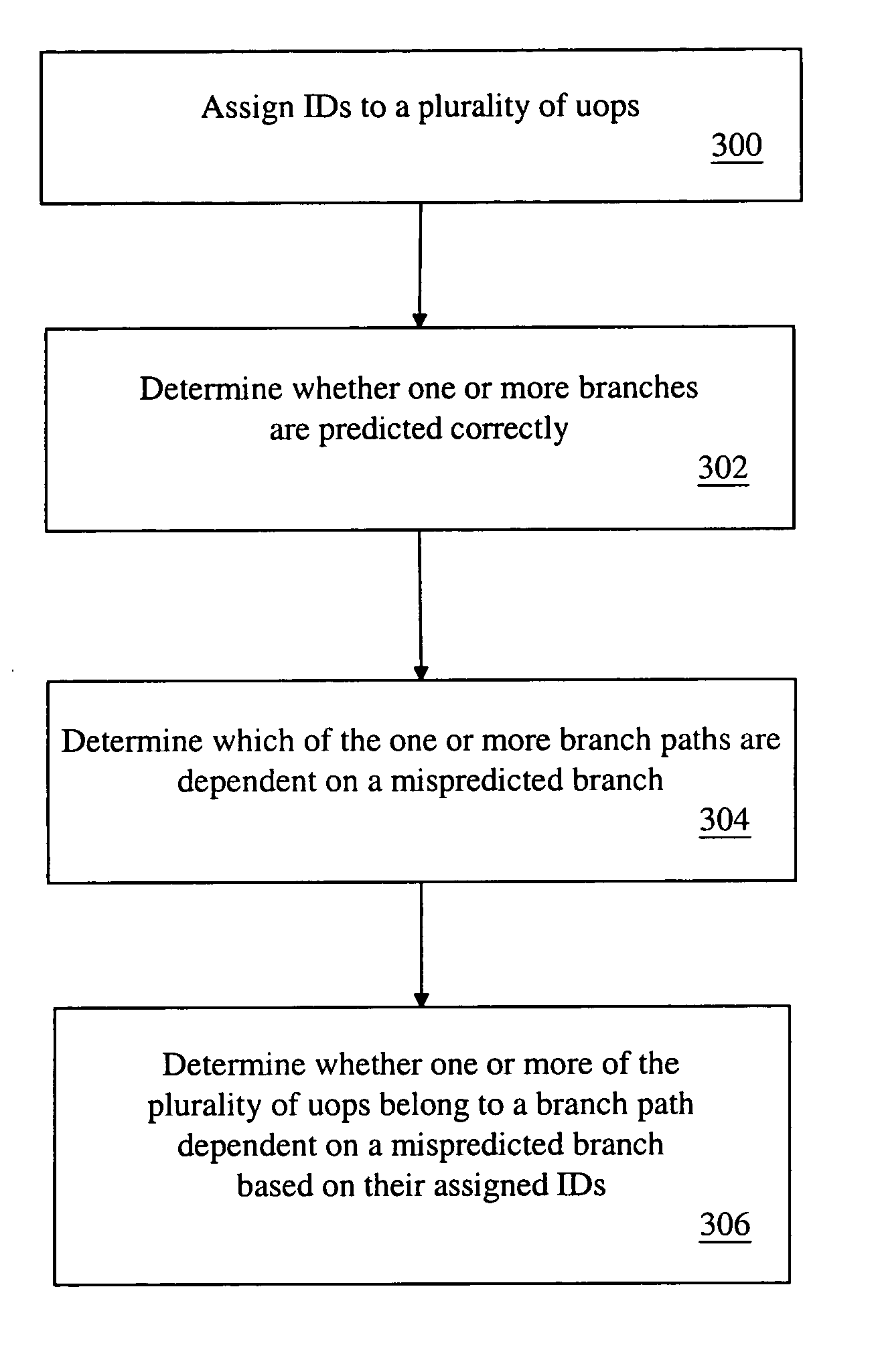

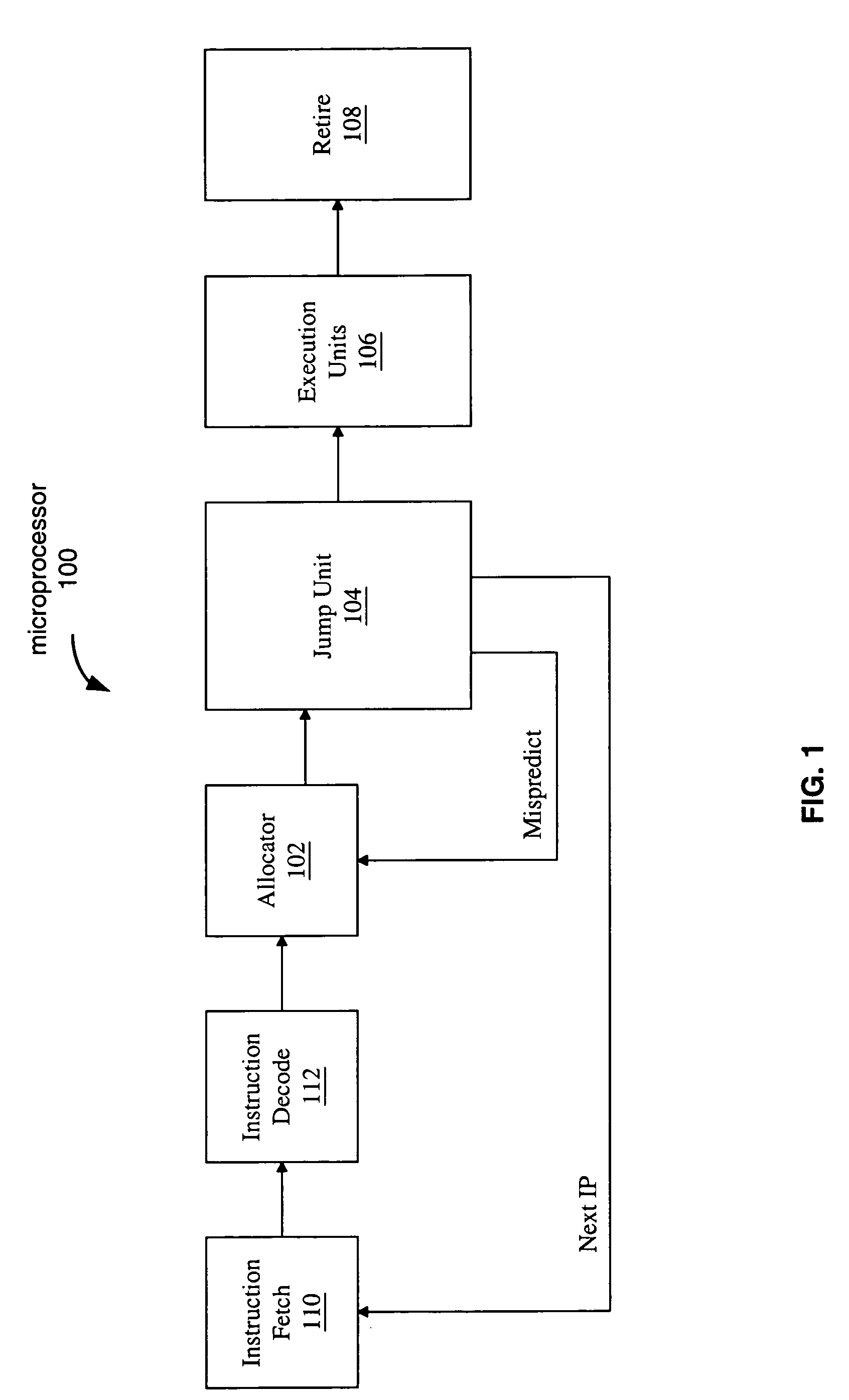

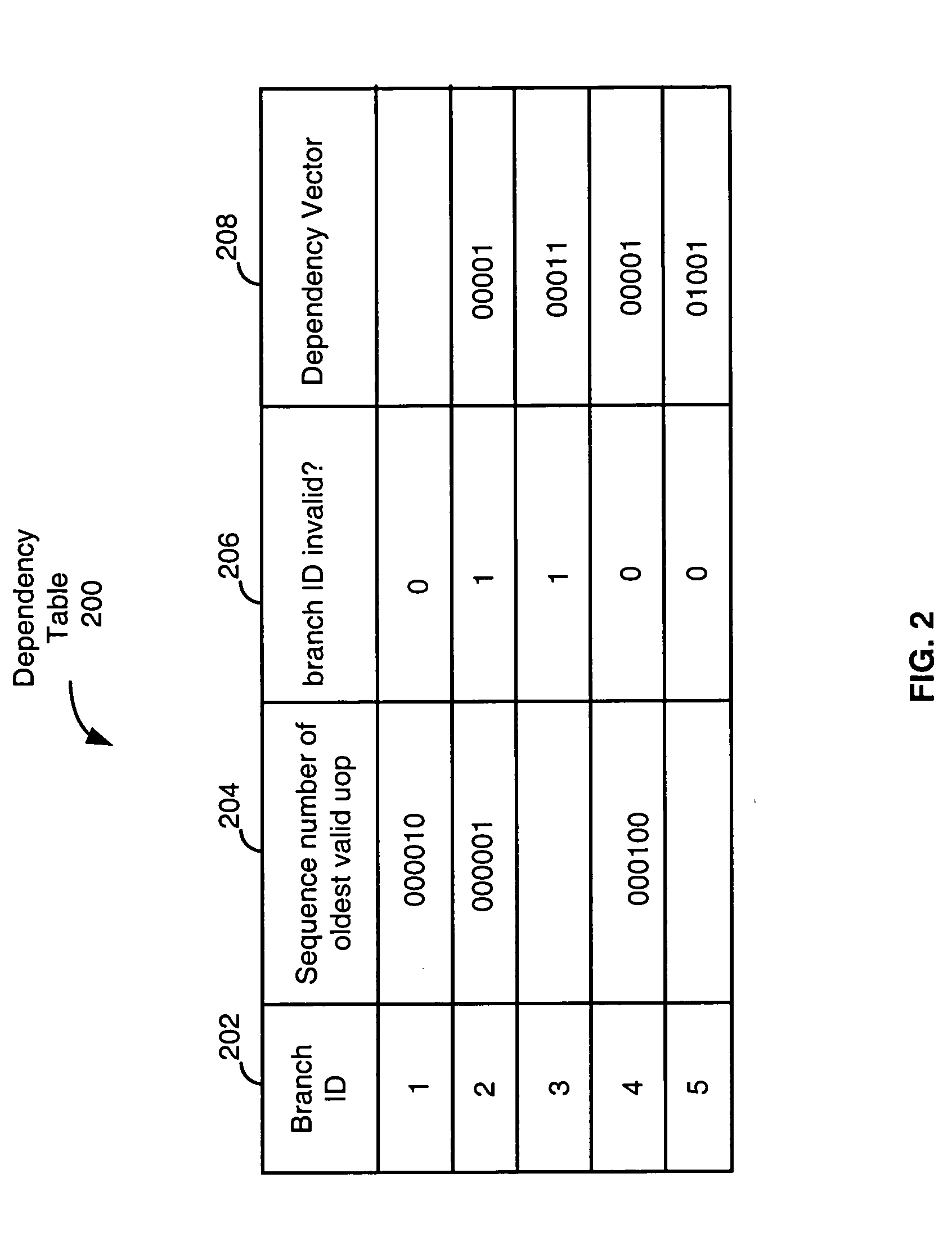

Method and system for multiple branch paths in a microprocessor

InactiveUS20050071614A1Runtime instruction translationDigital computer detailsMicro-operationParallel computing

A method and system for multiple branch paths in a microprocessor is described. The method includes assigning an identification number (ID) to each of a plurality of micro-operations (uops) to identify a branch path to which the uop belongs, determining whether one or more branches are predicted correctly, determining which of the one or more branch paths are dependent on a mispredicted branch, and determining whether one or more of the plurality of uops belong to a branch path that is dependent on a mispredicted branch based on their assigned IDs.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com