Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1284 results about "Host interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In the context of this document, the term "host interface" refers to interfaces that can be used by software running on a computer system to access the Redfish Service that is used to manage that computer system.

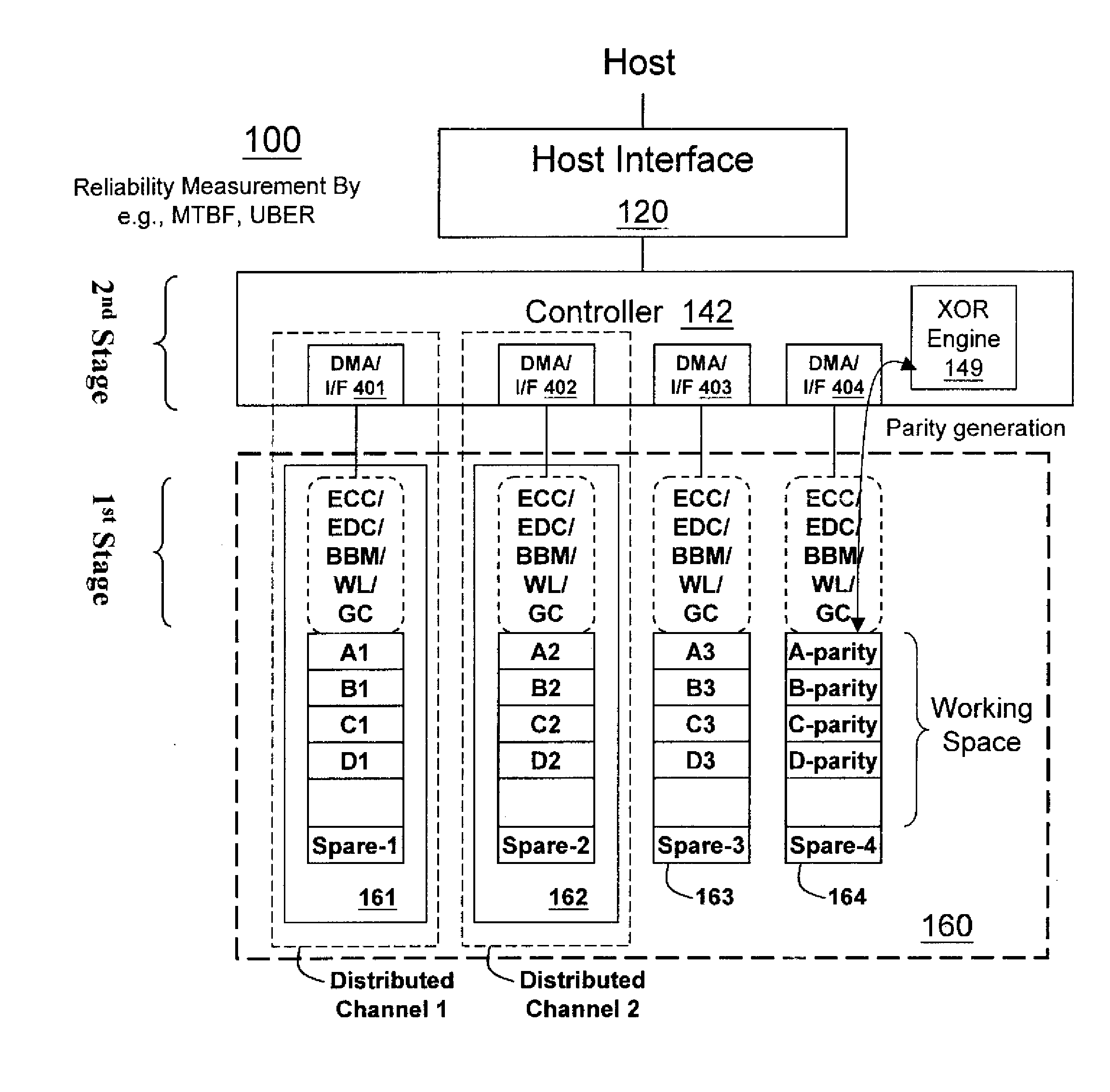

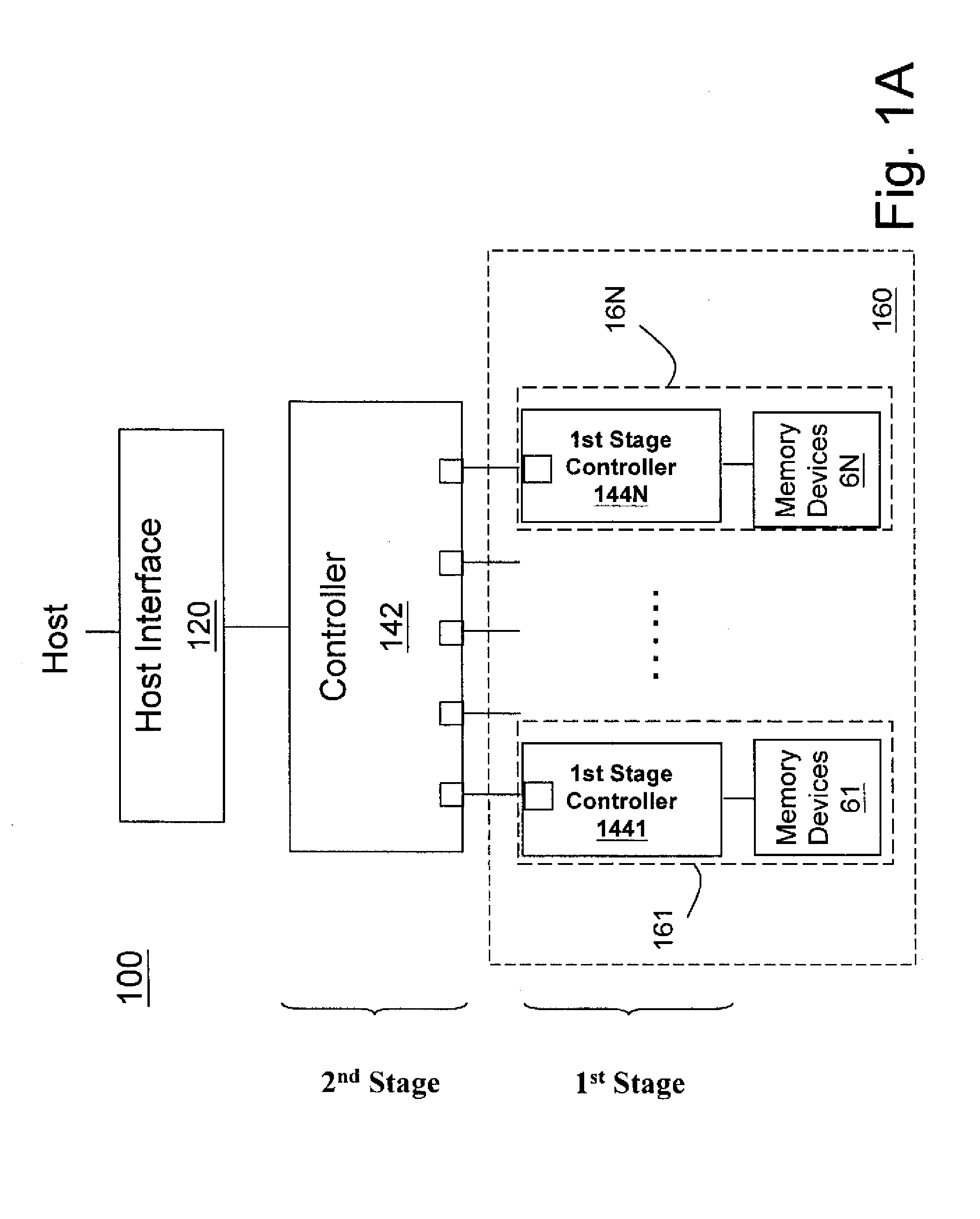

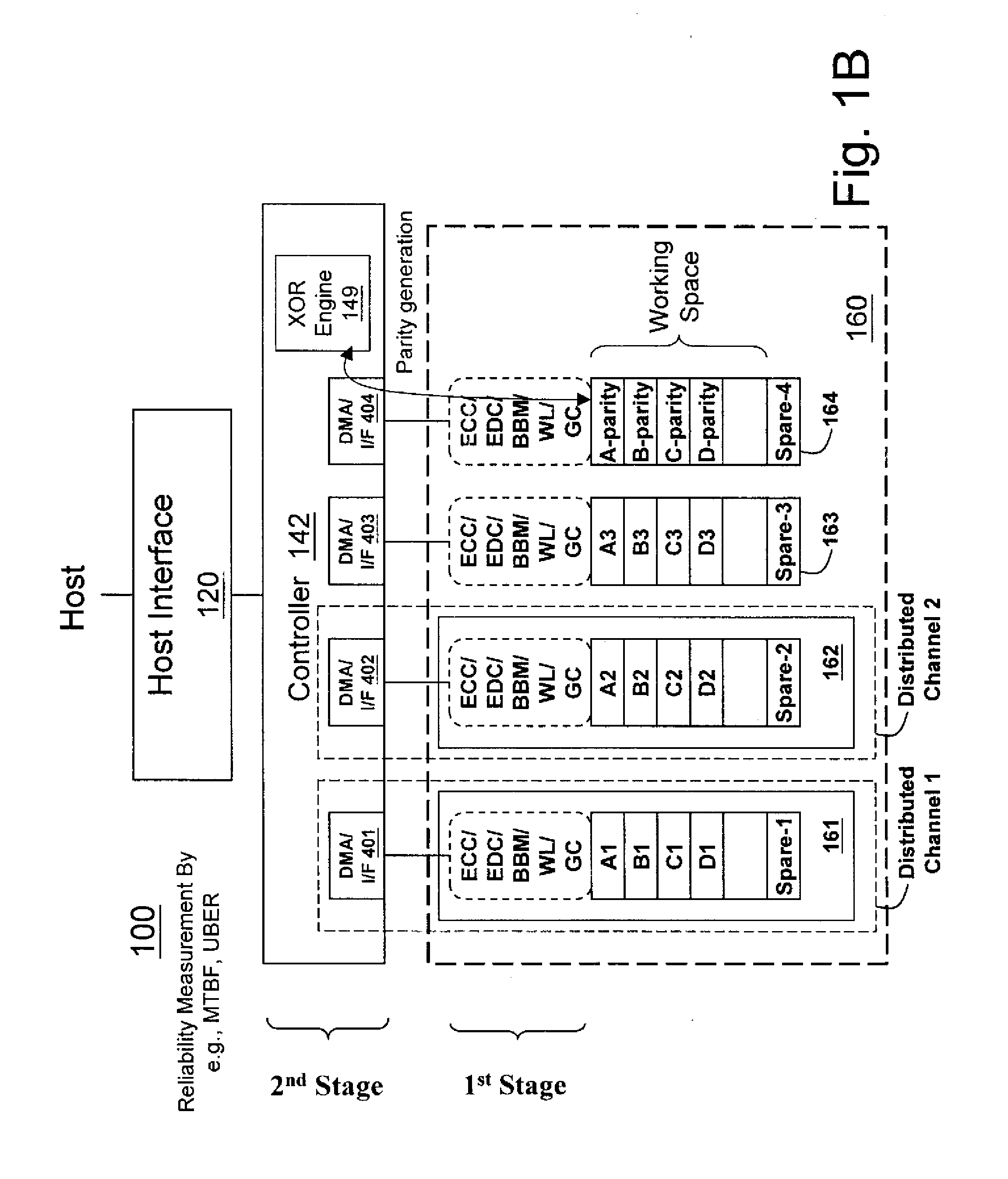

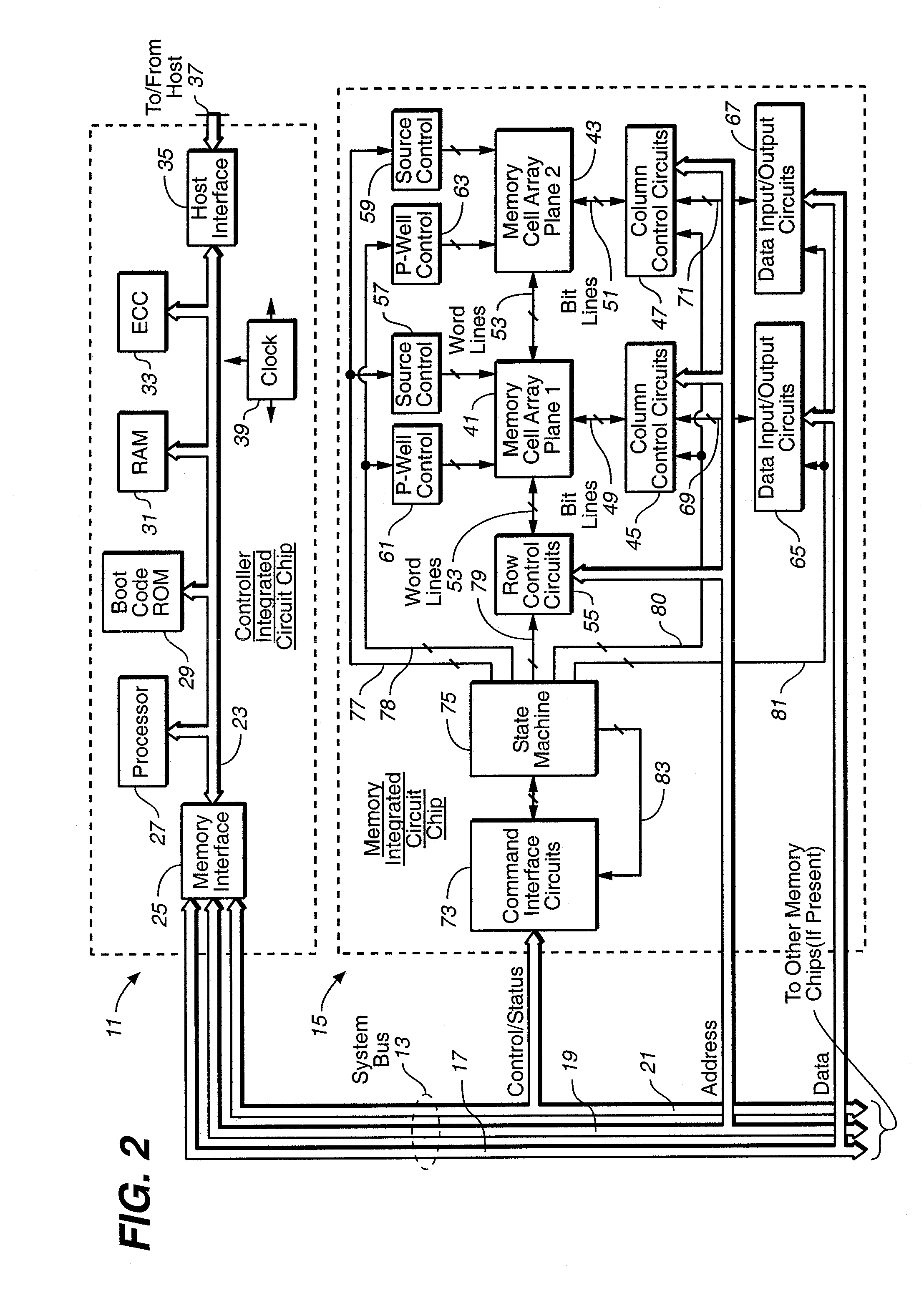

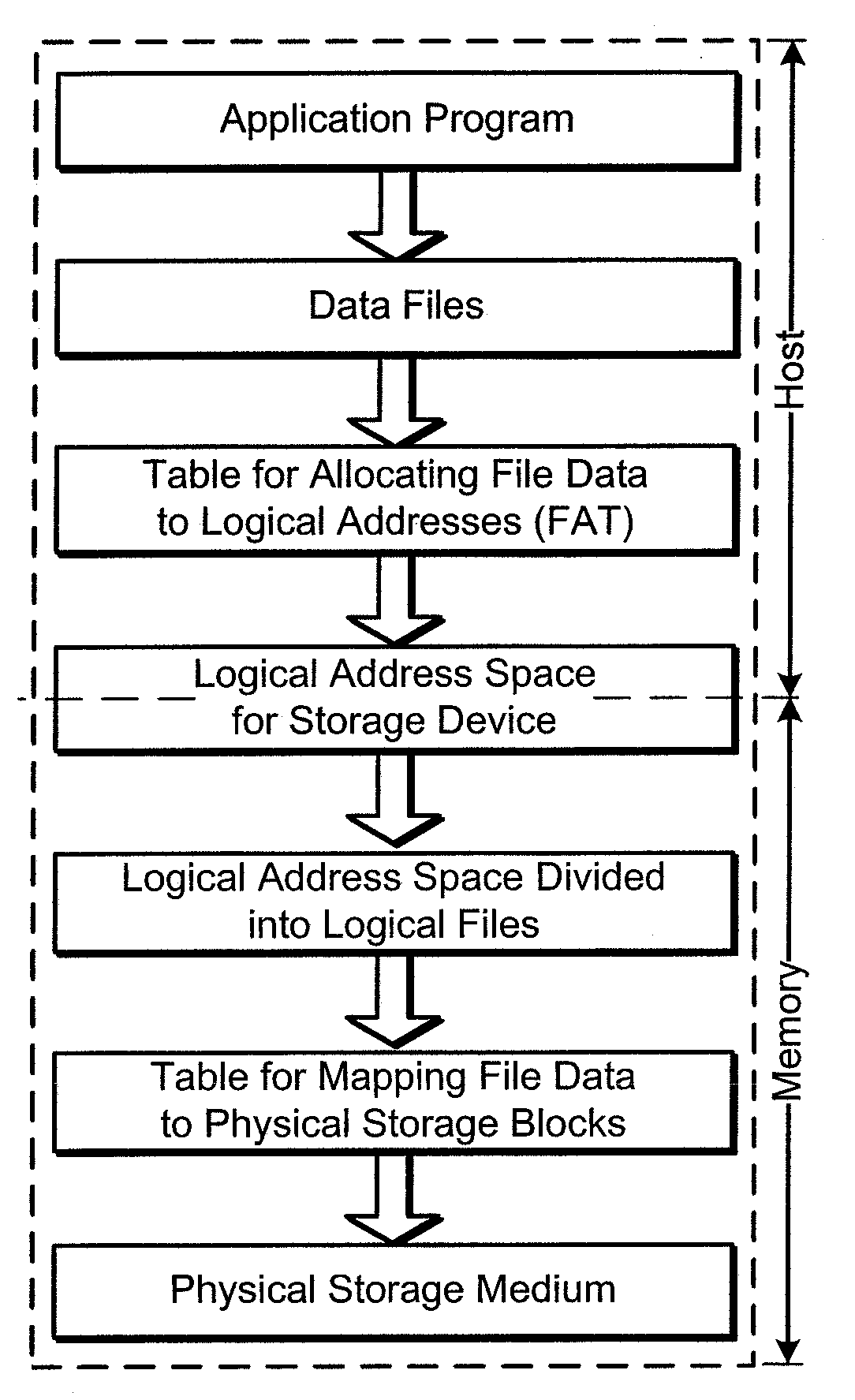

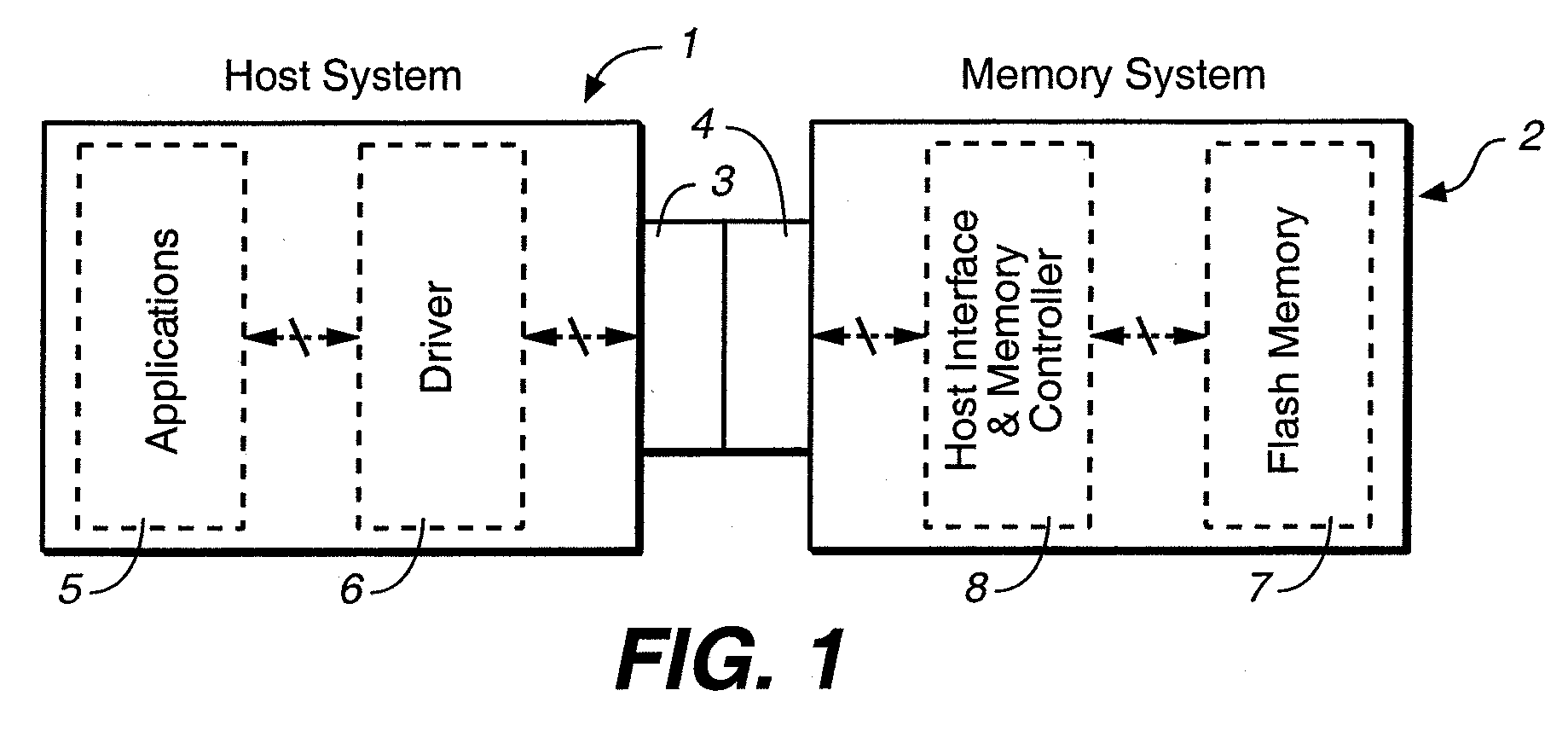

Non-volatile memory data storage system with reliability management

InactiveUS20100017650A1Improve reliabilityReliable managementMemory loss protectionMemory adressing/allocation/relocationRAIDData recovery

A non-volatile memory data storage system, comprising: a host interface for communicating with an external host; a main storage including a first plurality of flash memory devices, wherein each memory device includes a second plurality of memory blocks, and a third plurality of first stage controllers coupled to the first plurality of flash memory devices; and a second stage controller coupled to the host interface and the third plurality of first stage controller through an internal interface, the second stage controller being configured to perform RAID operation for data recovery according to at least one parity.

Owner:NANOSTAR CORP

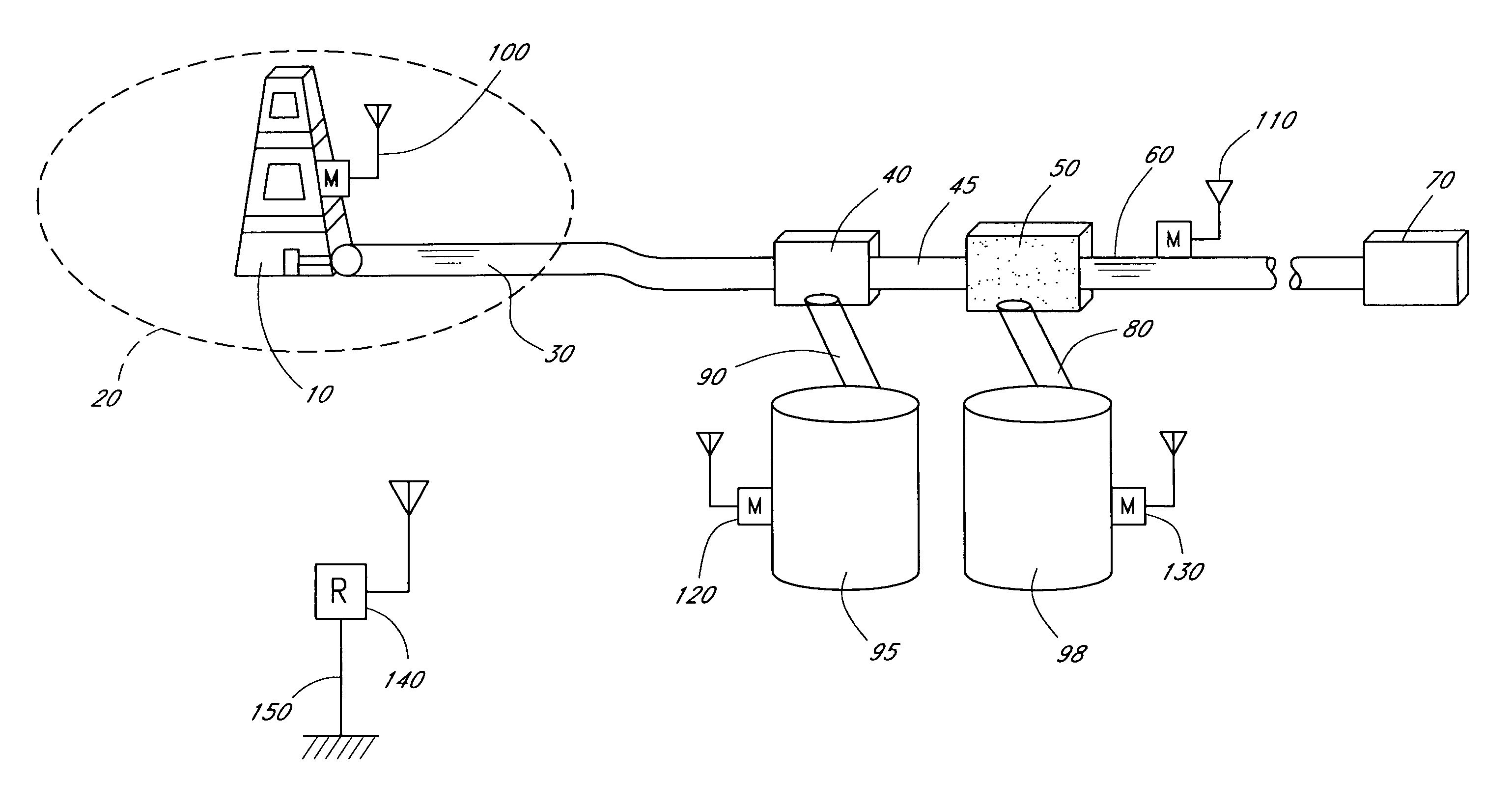

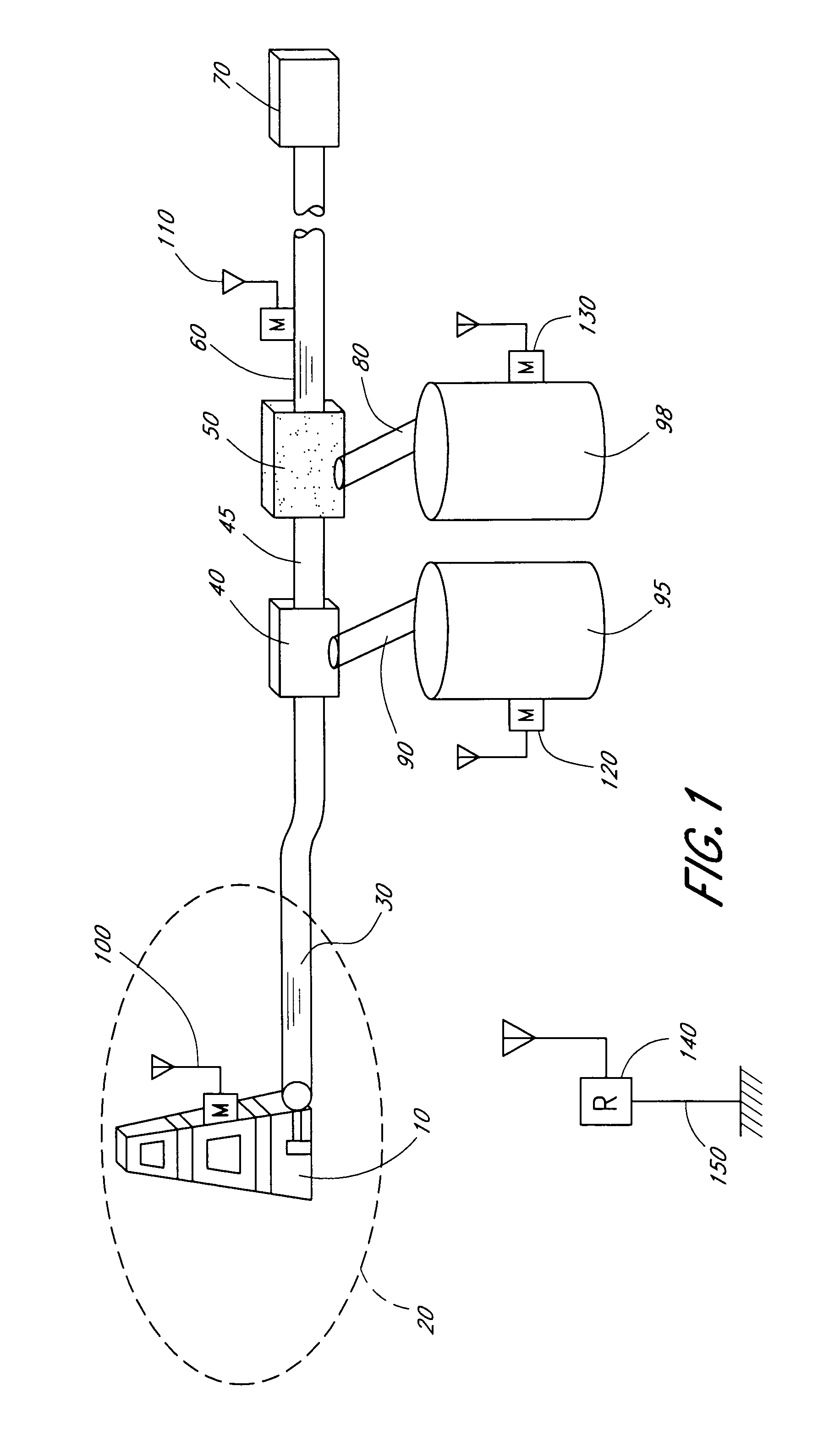

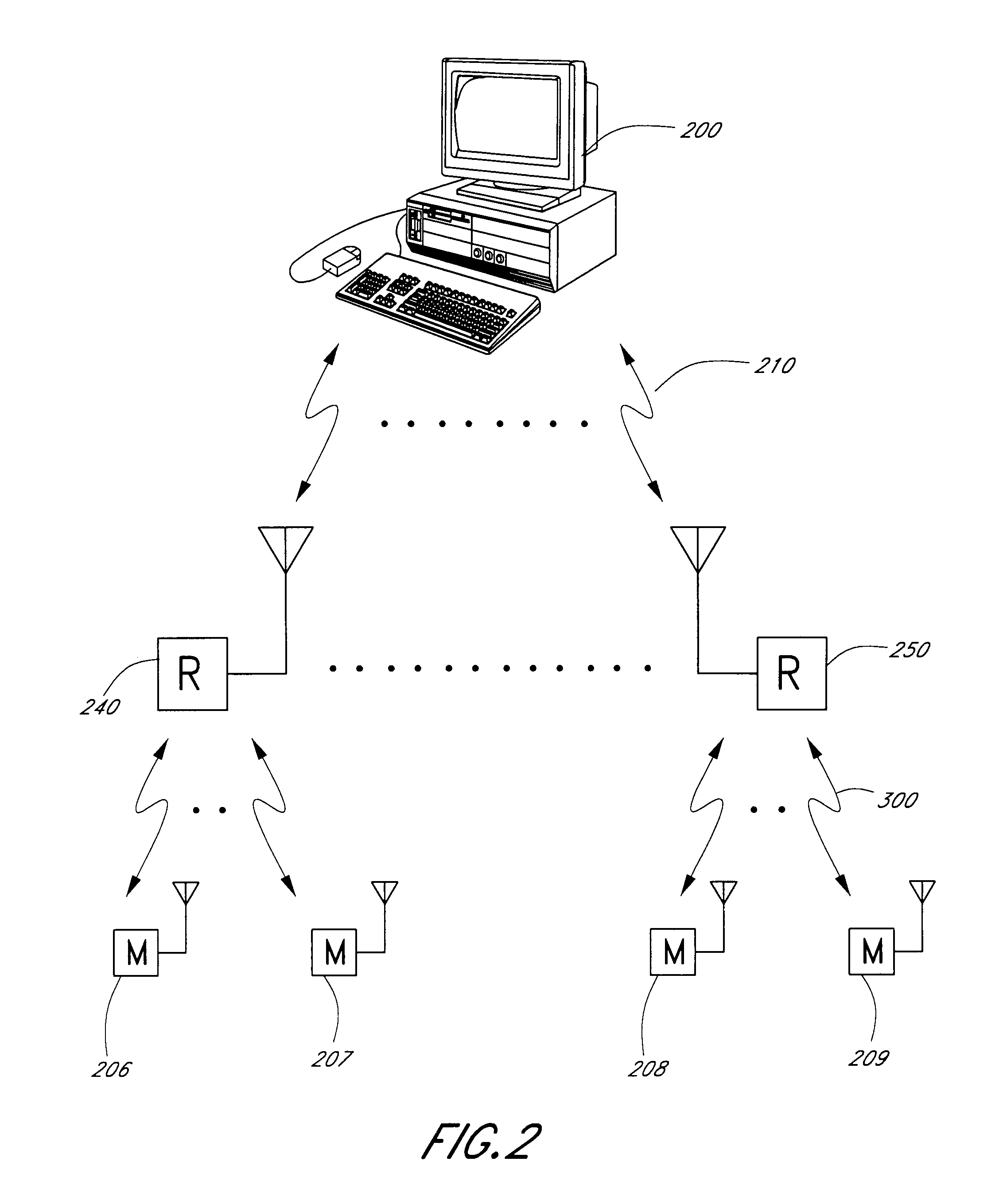

Gas/oil well monitoring system

A system for monitoring a gas / oil well is provided with a monitoring unit, a relay unit and a host interface. A monitoring unit collects data regarding the status of the gas / oil well and wirelessly transmits that data to a relay unit. The relay unit, in turn, connects to a host interface using cellular communications and transmits the data. The monitoring unit can transmit information on demand or after an alarm condition is sensed. In either case, the monitoring unit is normally in a sleep mode. The relay unit can request information from the monitoring unit or respond to a wake up transmission sent to it from either the host interface or monitoring unit. The host interface receives data from the relay unit and then informs an end user of that data.

Owner:OLEUMTECH CORP

Performance of a storage system

InactiveUS7979613B2Error detection/correctionMultiprogramming arrangementsReal-time computingHost interface

A method for operating a storage system, including storing data redundantly in the system and measuring respective queue lengths of input / output requests to operational elements of the system. The queue lengths are compared to an average queue length to determine respective performances of the operational elements of the storage system. In response to the average queue lengths and a permitted deviation from the average an under-performing operational element among the operational elements is identified. An indication of the under-performing operational element is provided to host interfaces in the storage system. One of the host interfaces receives requests for specified items of the data directed to the under-performing element, and in response to the indication, some of the requests are diverted from the under-performing operational element to one or more other operational elements of the storage system that are configured to provide the specified items of the data.

Owner:IBM CORP

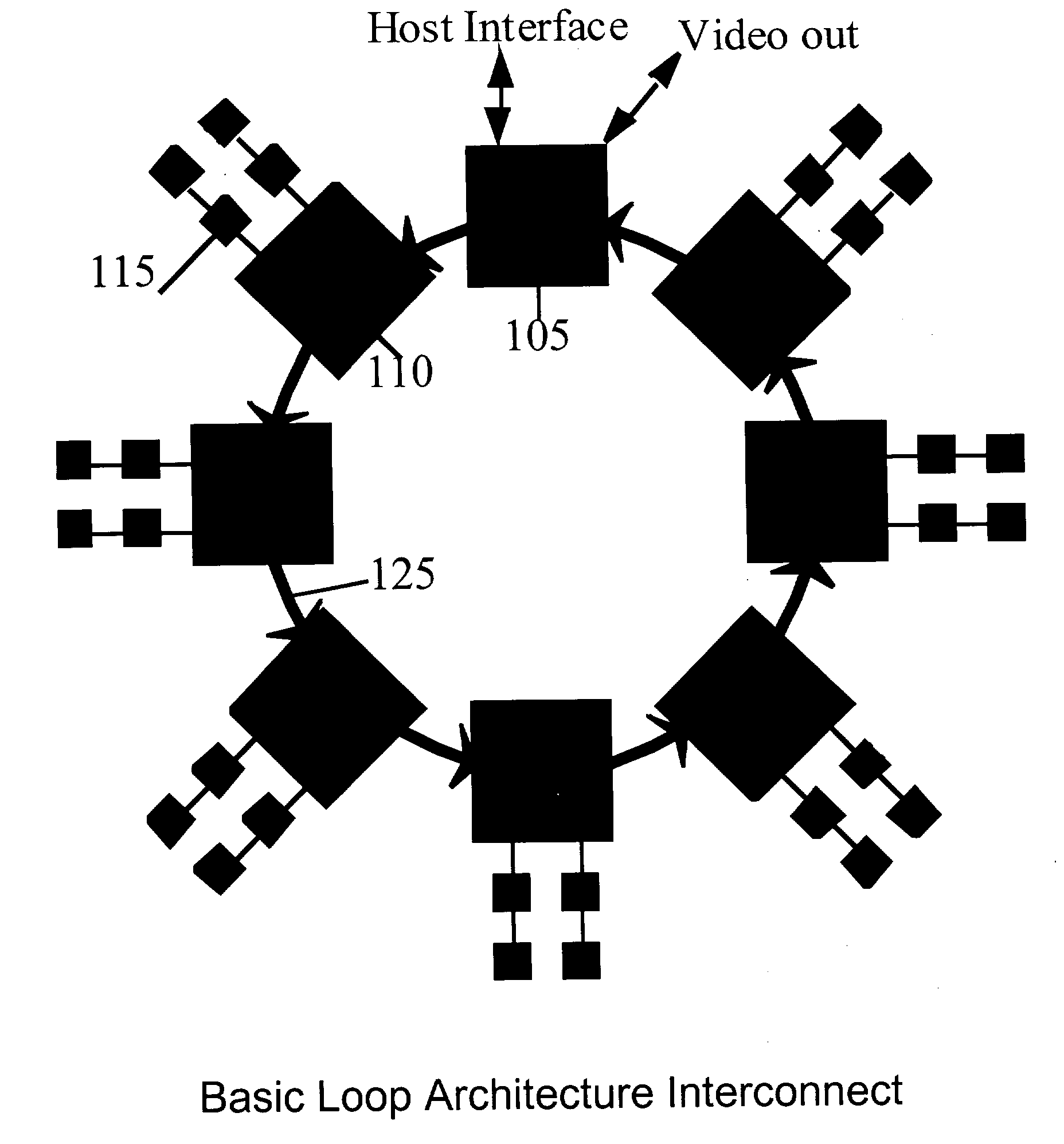

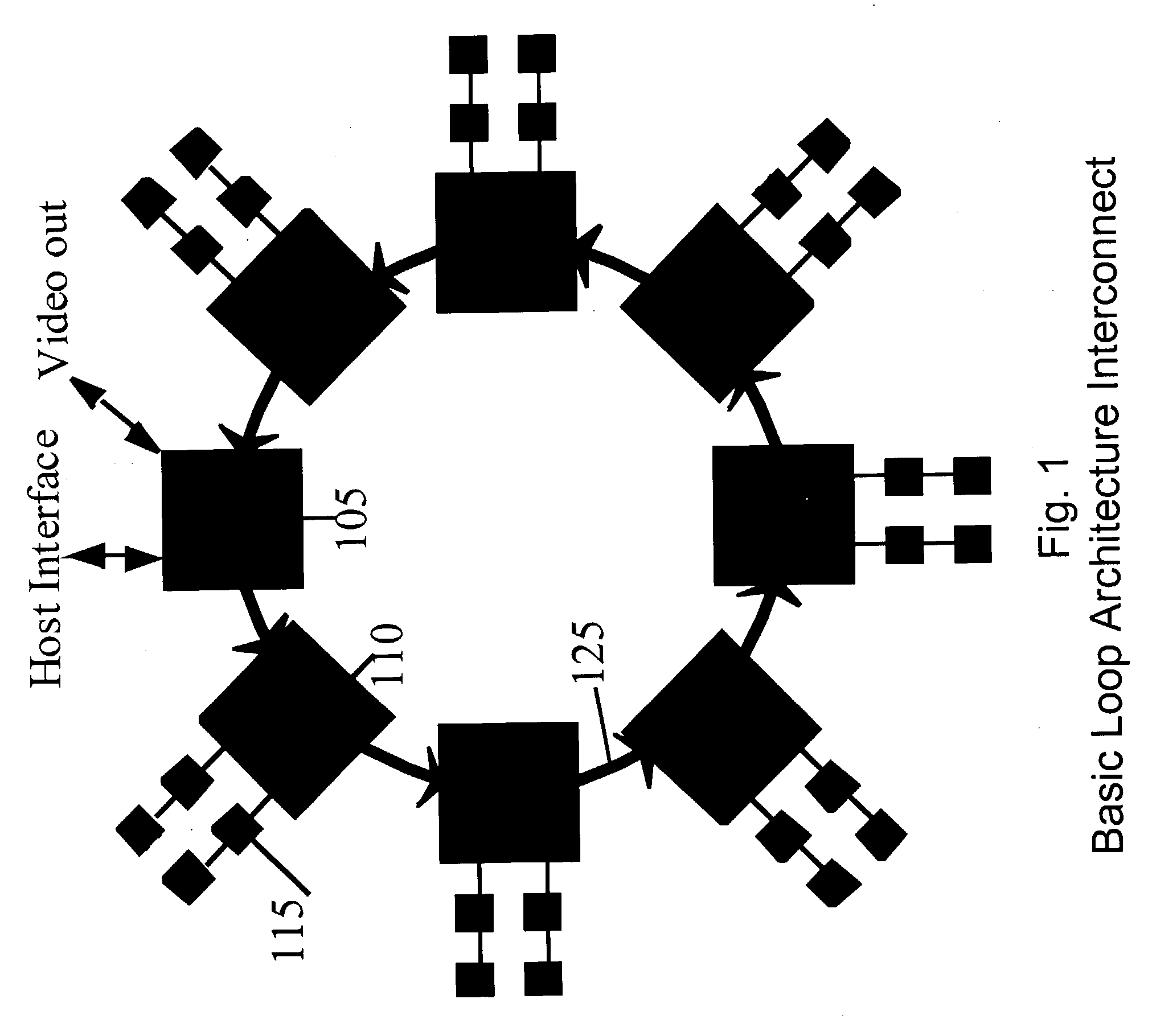

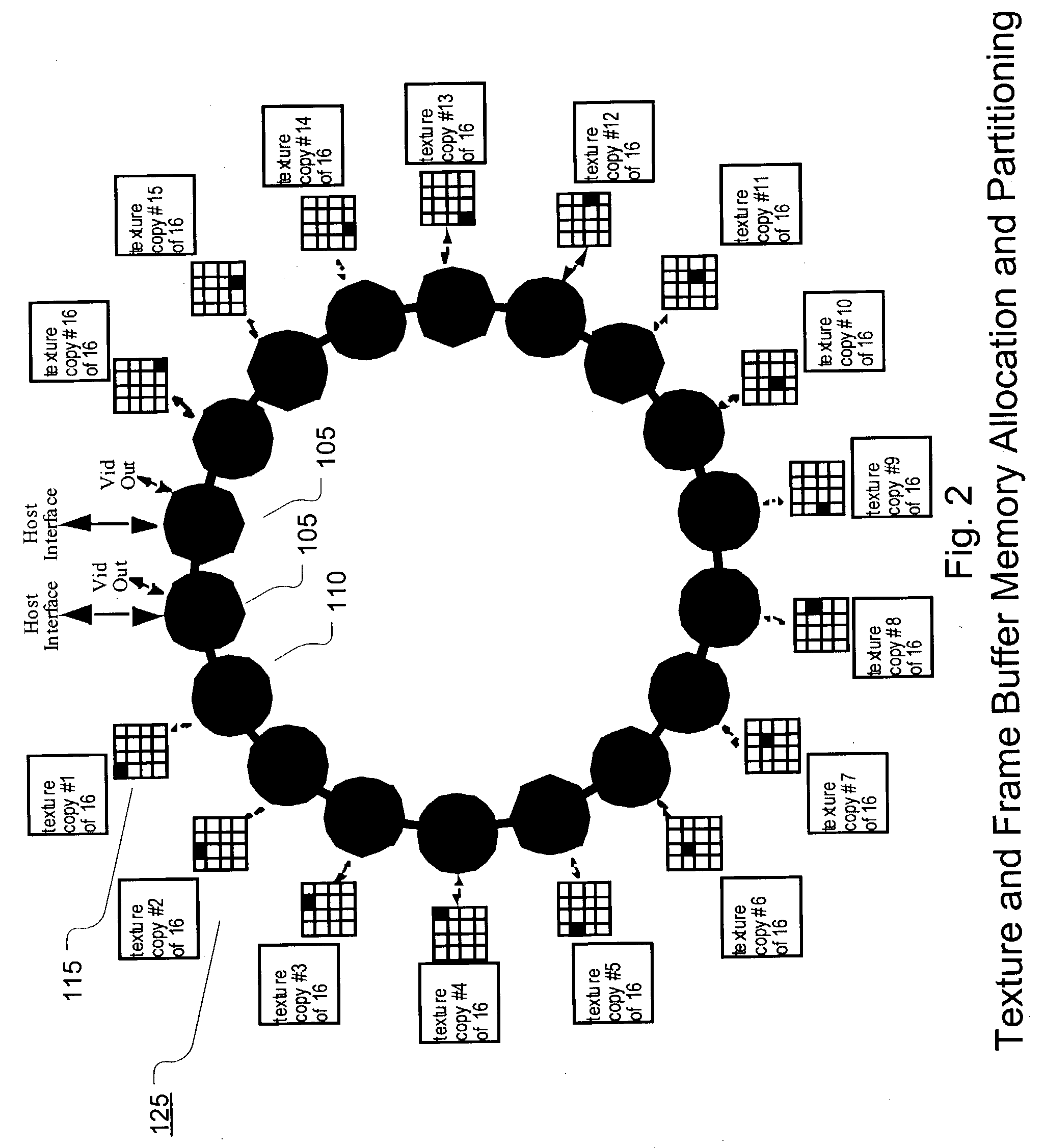

Scalable high performance 3d graphics

InactiveUS20040012600A1Minimizes cost and riskEasy to scaleImage enhancementImage memory managementGraphicsHigh bandwidth

A high-speed ring topology. In one embodiment, two base chip types are required: a "drawing" chip, LoopDraw, and an "interface" chip, LoopInterface. Each of these chips have a set of pins that supports an identical high speed point to point unidirectional input and output ring interconnect interface: the LoopLink. The LoopDraw chip uses additional pins to connect to several standard memories that form a high bandwidth local memory sub-system. The LoopInterface chip uses additional pins to support a high speed host computer host interface, at least one video output interface, and possibly also additional non-local interconnects to other LoopInterface chip(s).

Owner:DEERING MICHAEL F +2

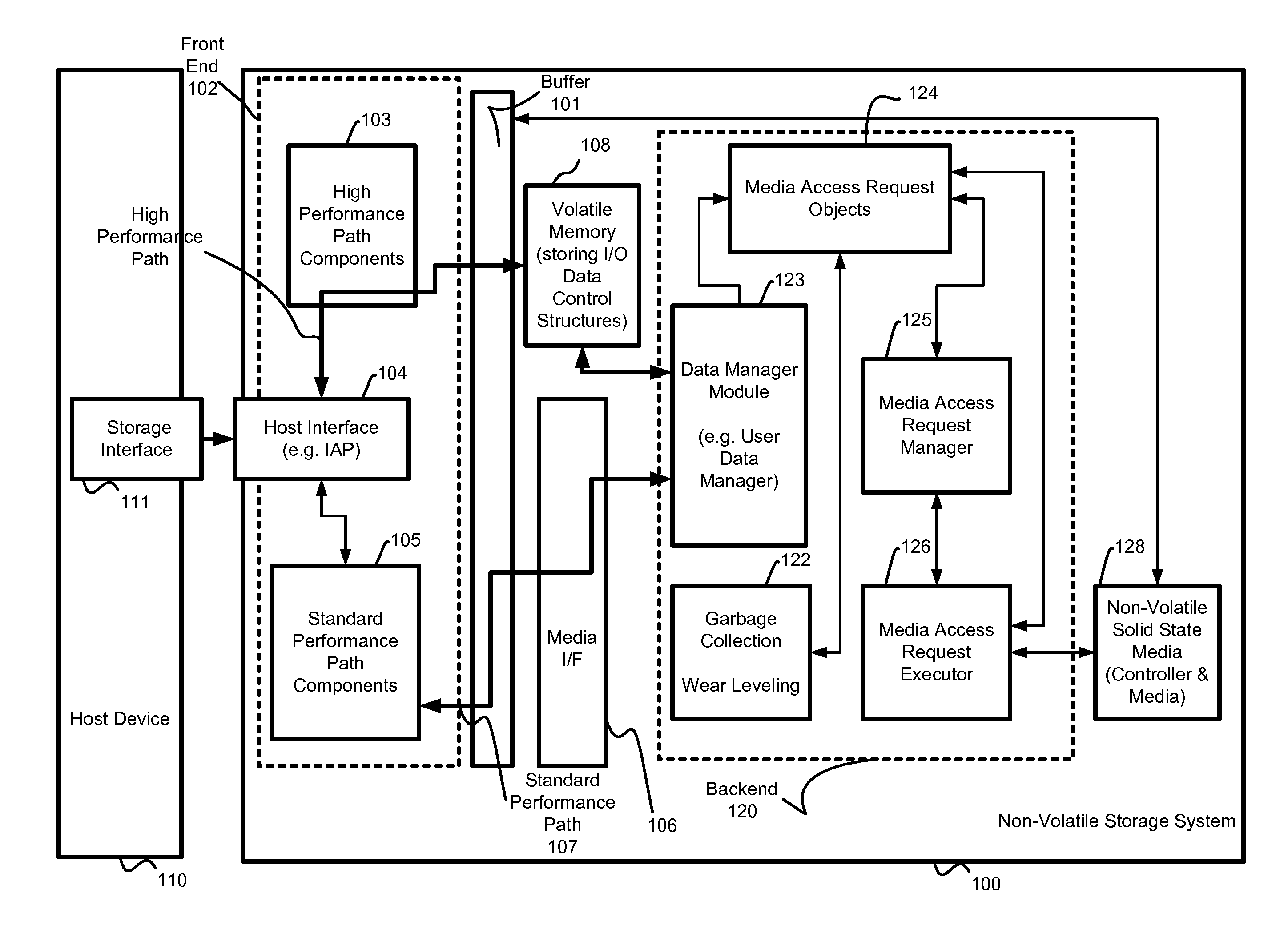

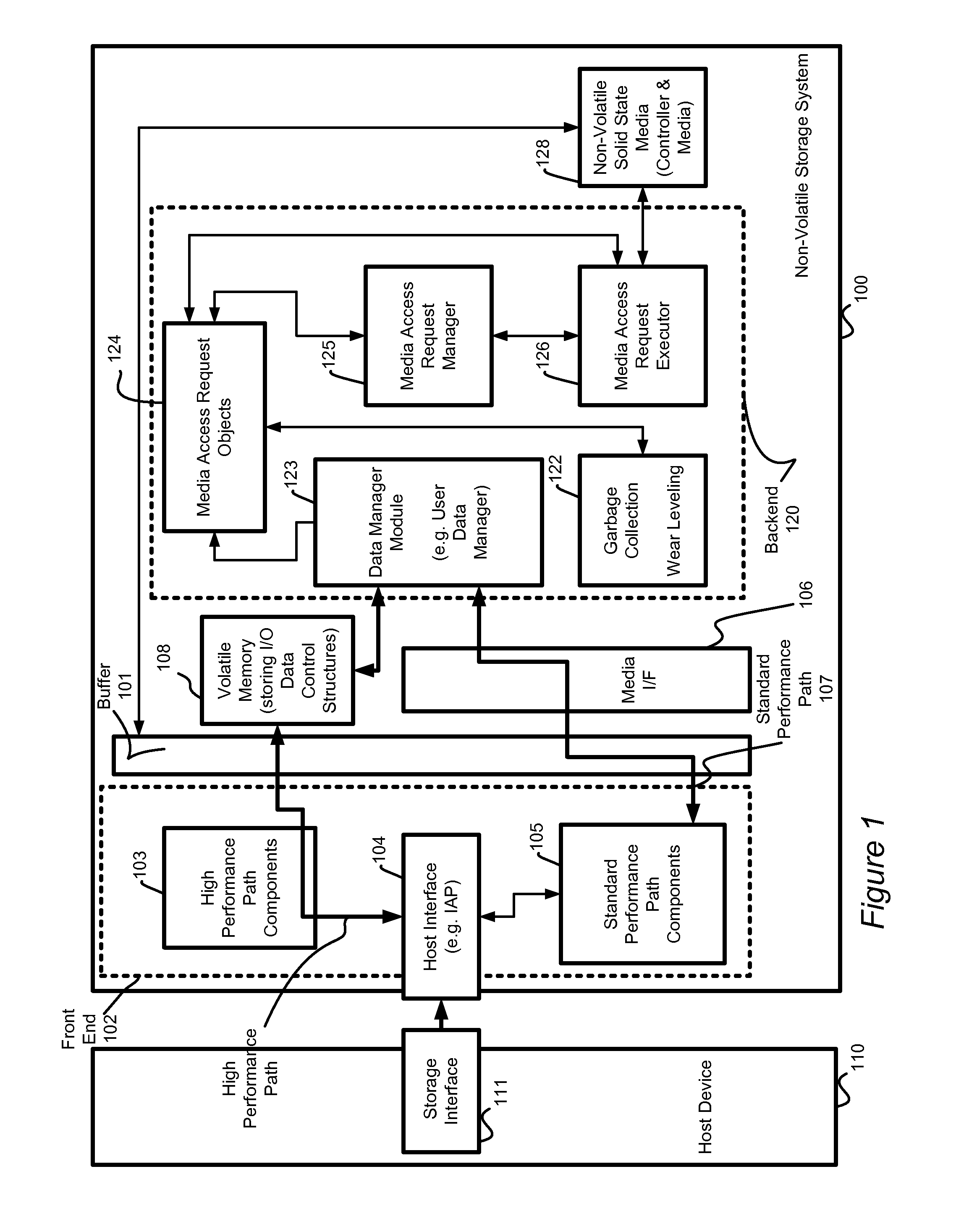

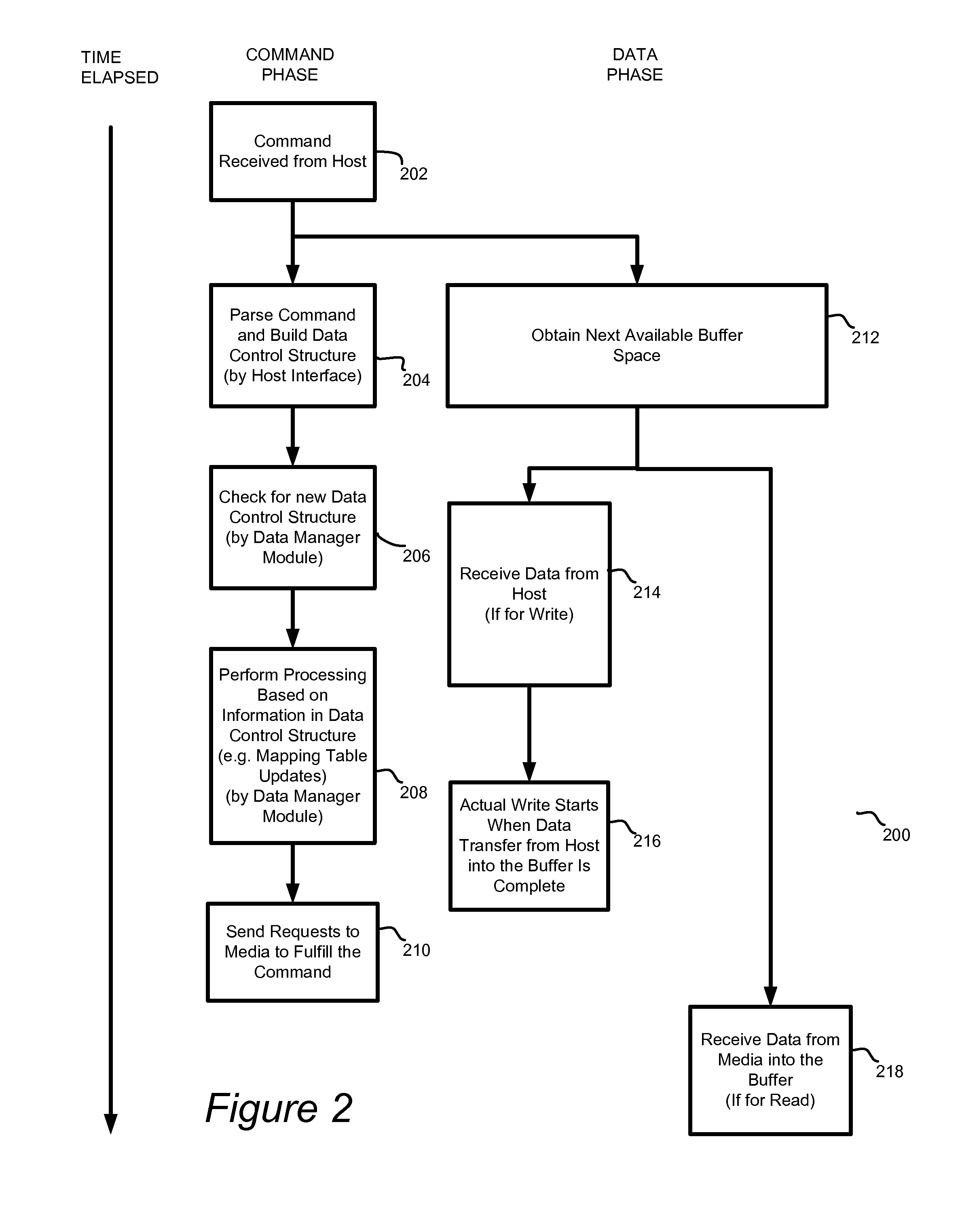

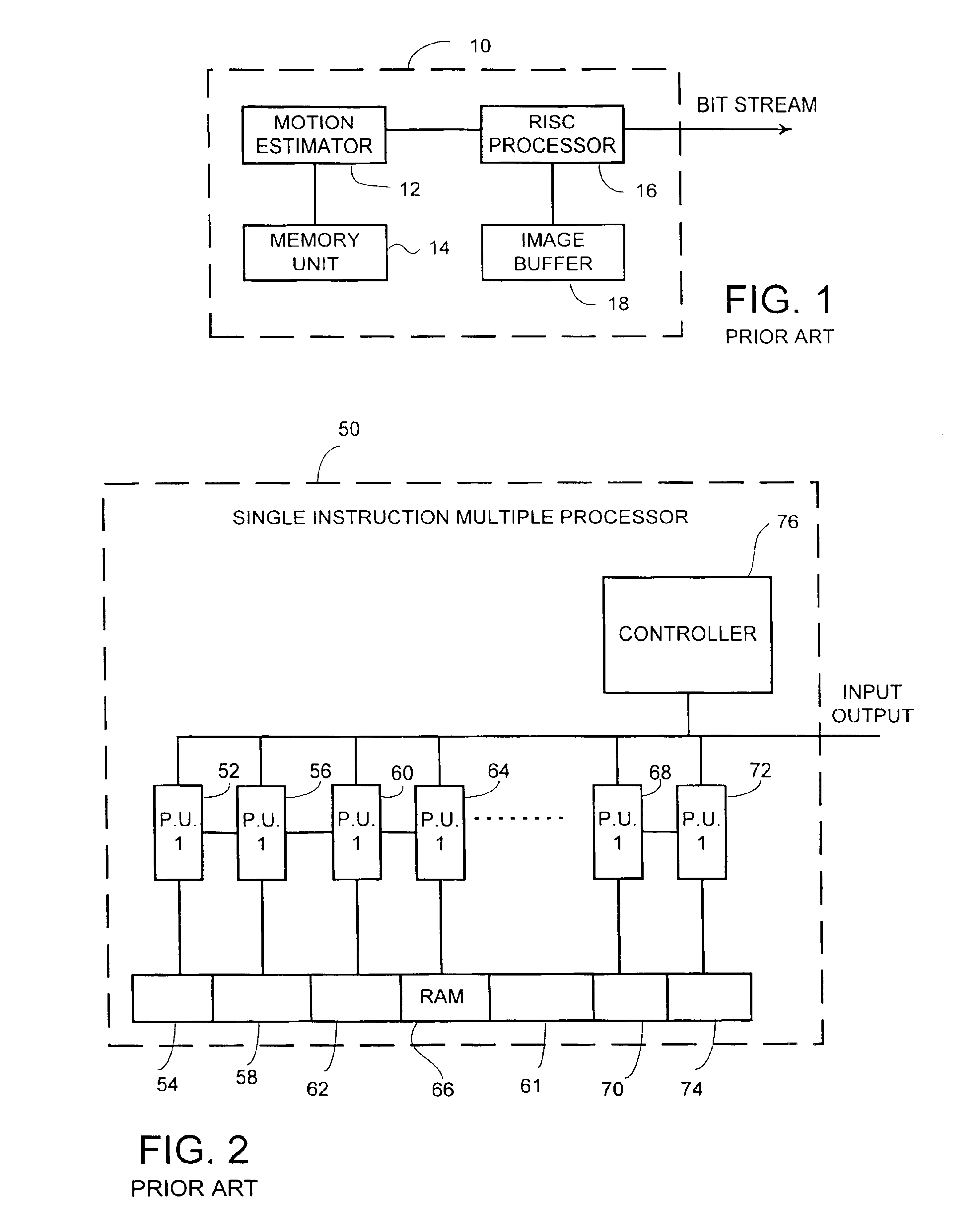

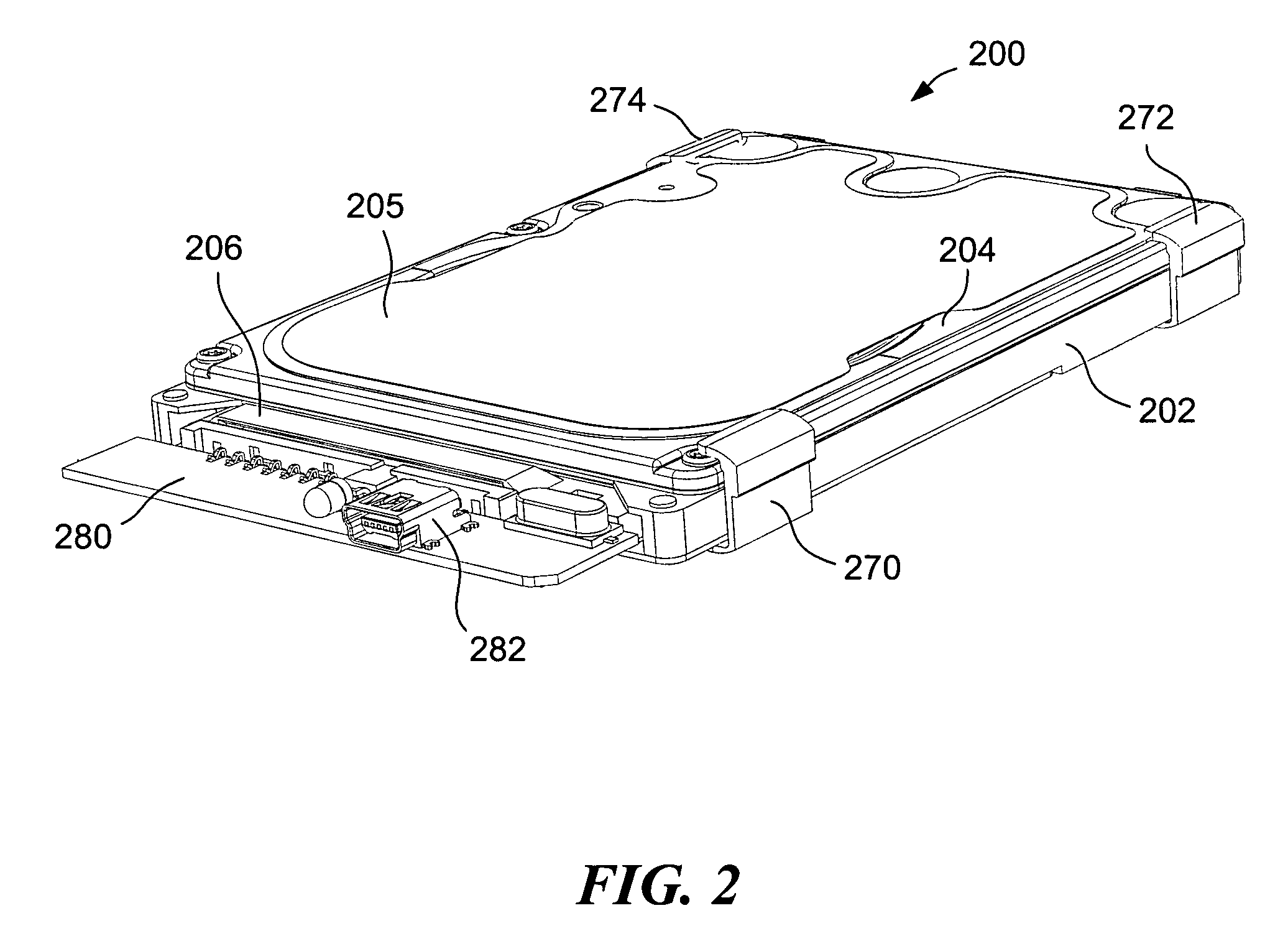

System and method for high performance command processing in solid state drives

ActiveUS8423722B1Improve performanceHigh bandwidthMemory architecture accessing/allocationMemory systemsHard disc driveHigh bandwidth

Solid State Drives (SSD) can yield very high performance if it is designed properly. A SSD typically includes both a front end that interfaces with the host and a back end that interfaces with the flash media. Typically SSDs include flash media that is designed with a high degree of parallelism that can support a very high bandwidth on input / output (I / O). A SSD front end designed according to a traditional hard disk drive (HDD) model will not be able to take advantage of the high performance offered by the typical flash media. Embodiments of the invention provide improved management of multiple I / O threads that take advantage of the high performing and concurrent nature of the back end media, so the resulting storage system can achieve a very high performance.

Owner:WESTERN DIGITAL TECH INC

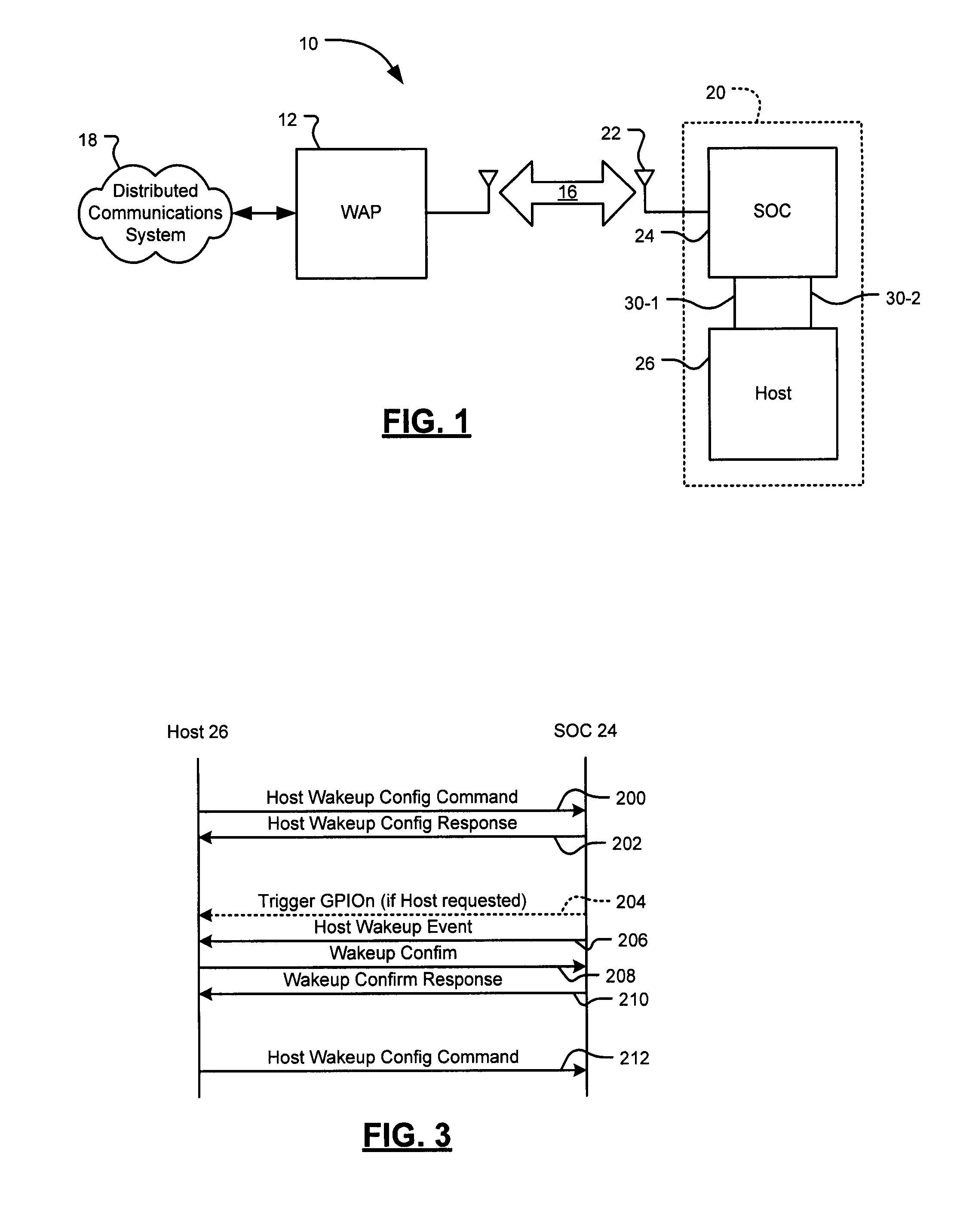

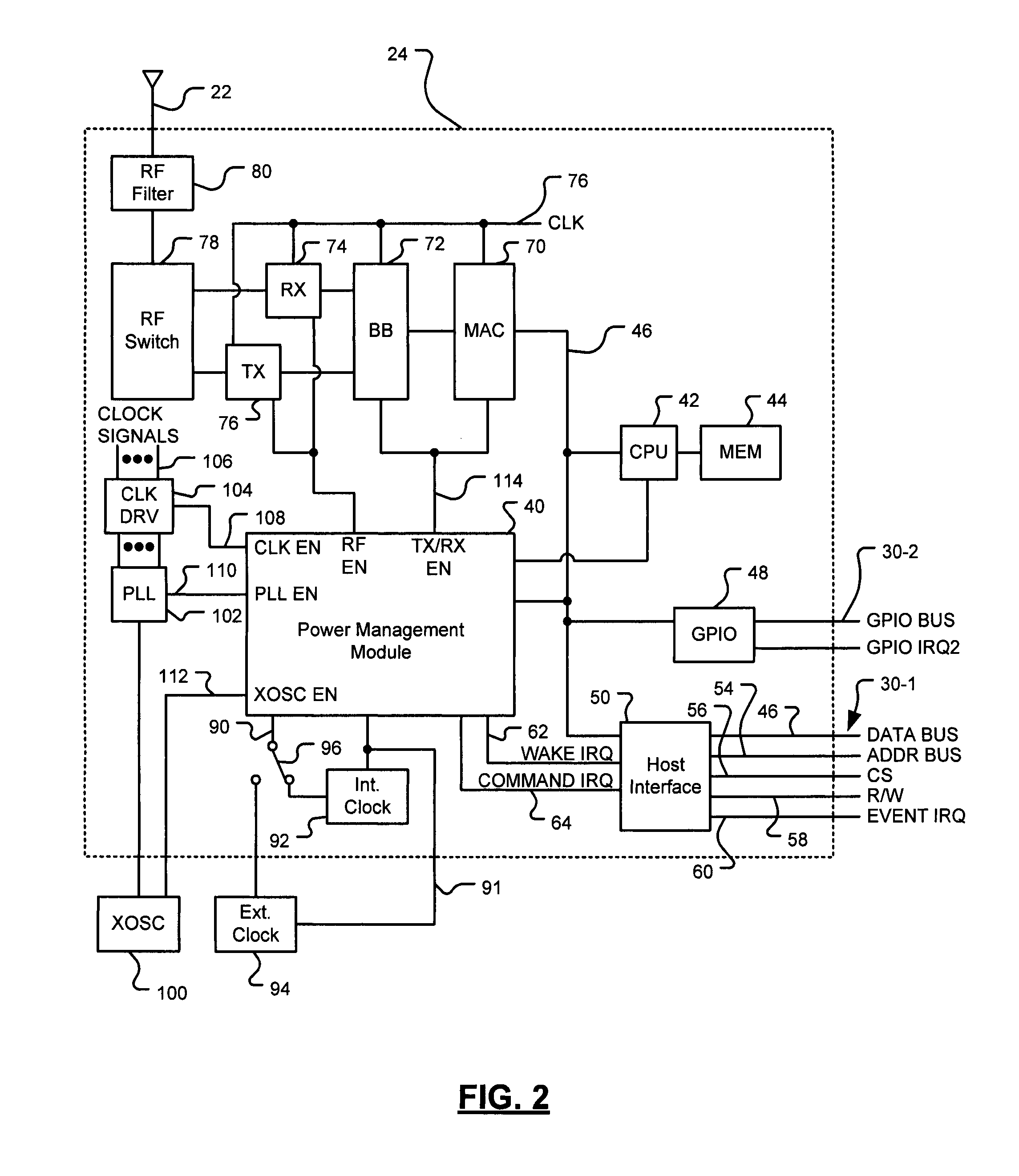

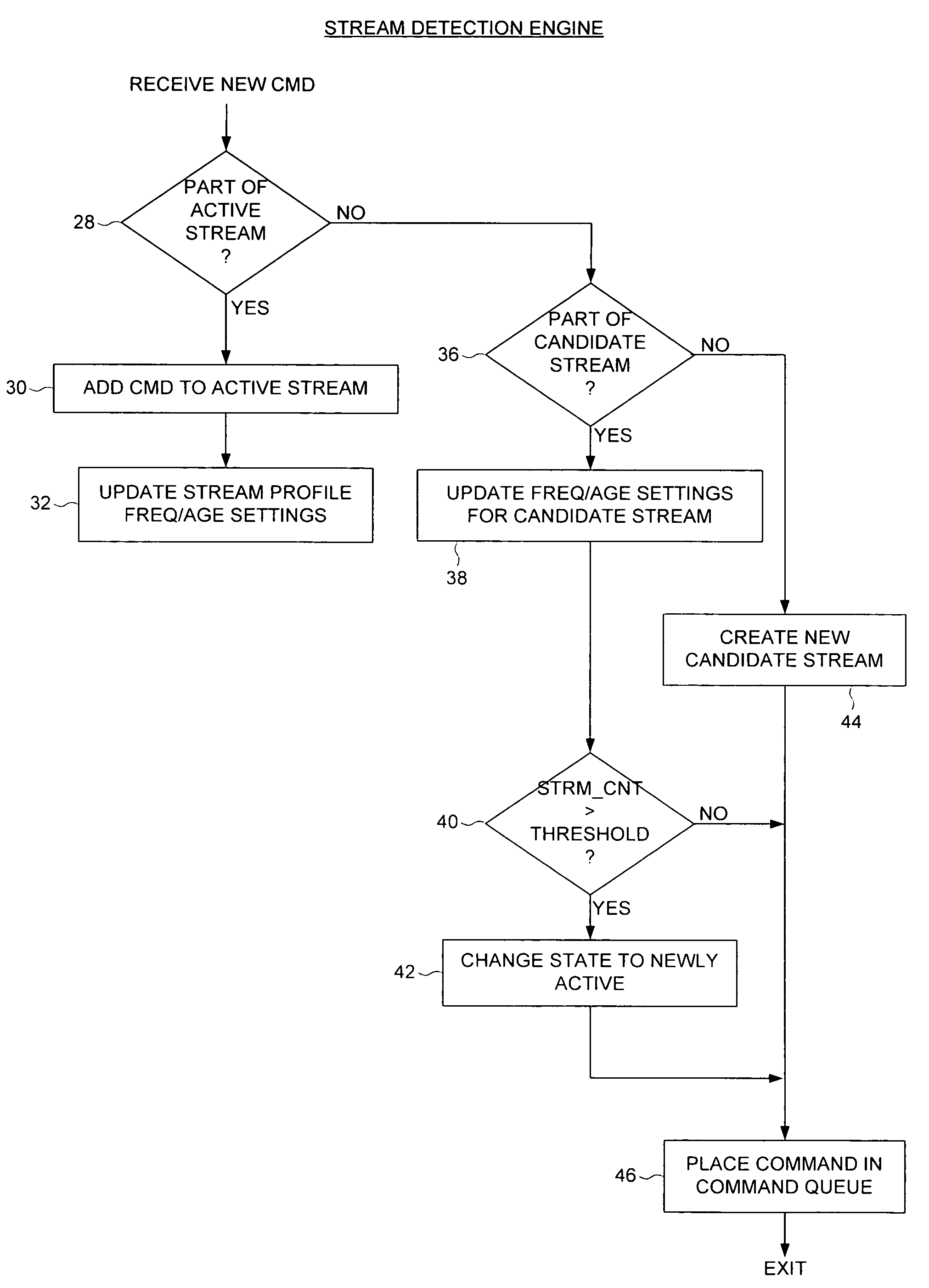

Wake on wireless LAN schemes

A system includes a host interface module and a power management module. The host interface module is configured to receive configuration information from a host processor of a wireless device. The configuration information indicates that the host processor is to (i) operate in a power save mode, and (ii) in response to the wireless device receiving data of a predetermined category from a wireless network, transition from the power save mode to an active mode. The power management module is configured to generate a first signal in response to the wireless device receiving data of the predetermined category from the wireless network. The first signal transitions the host processor from the power save mode to the active mode in which the host processor processes the data of the predetermined category.

Owner:NXP USA INC

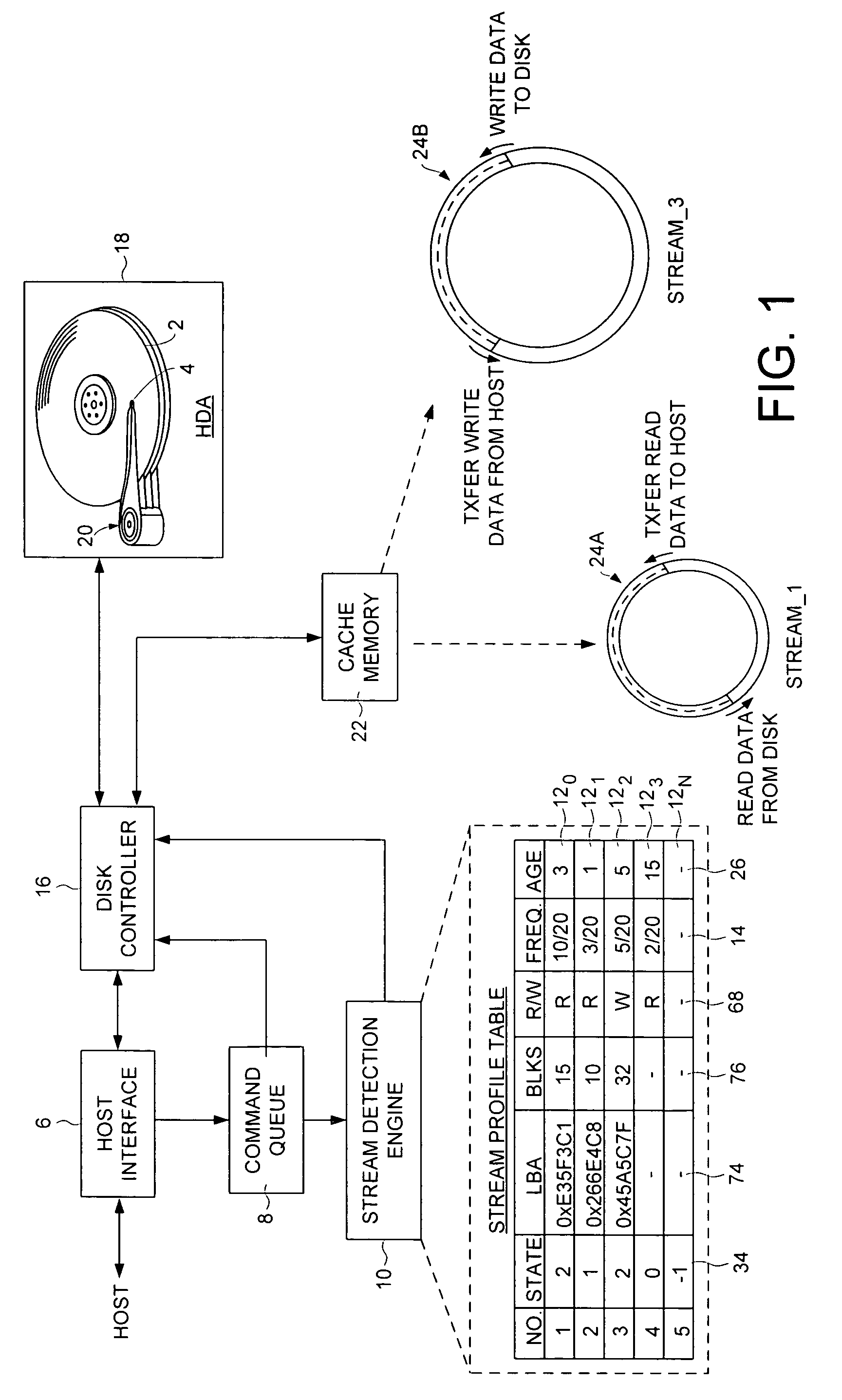

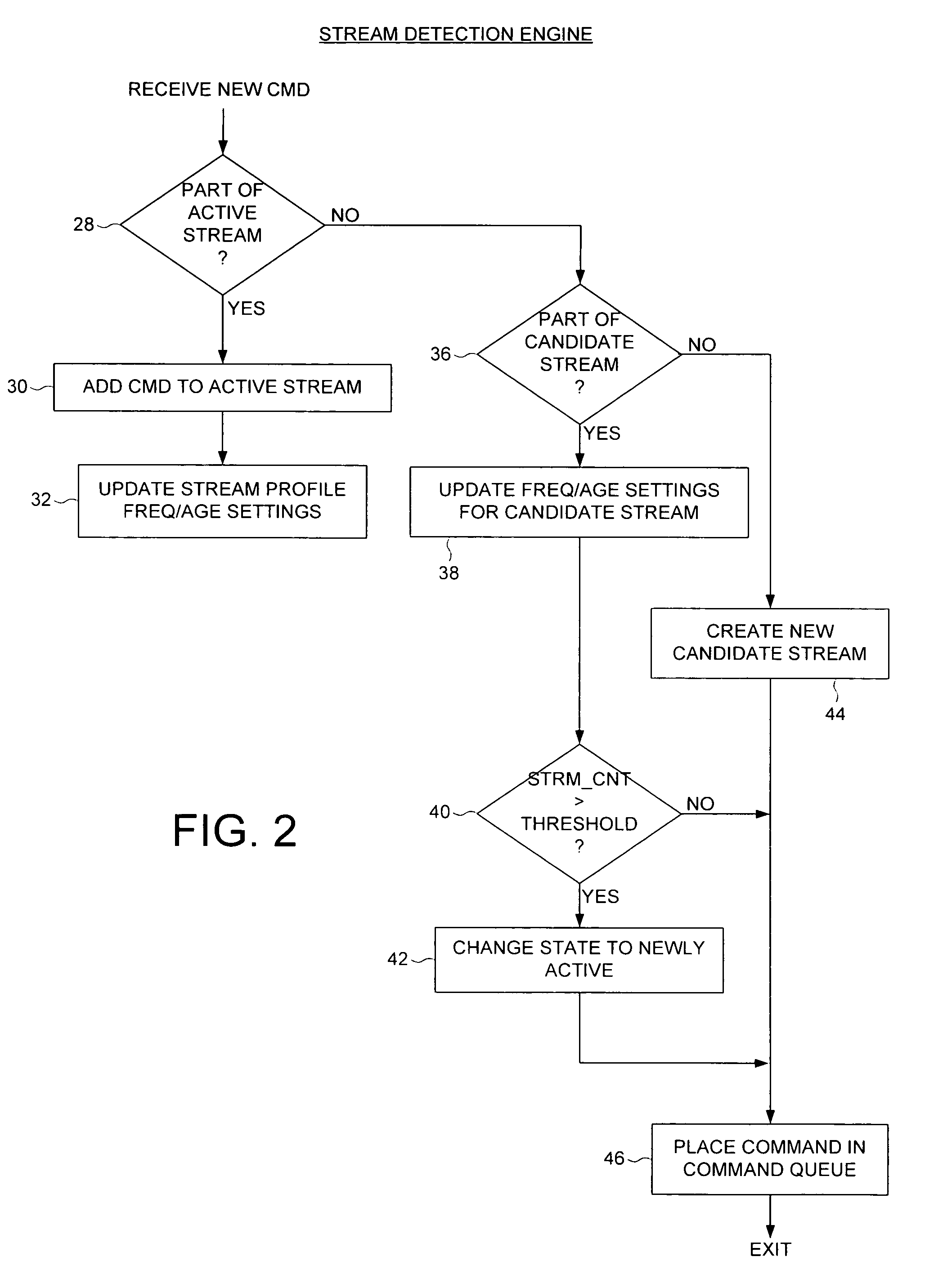

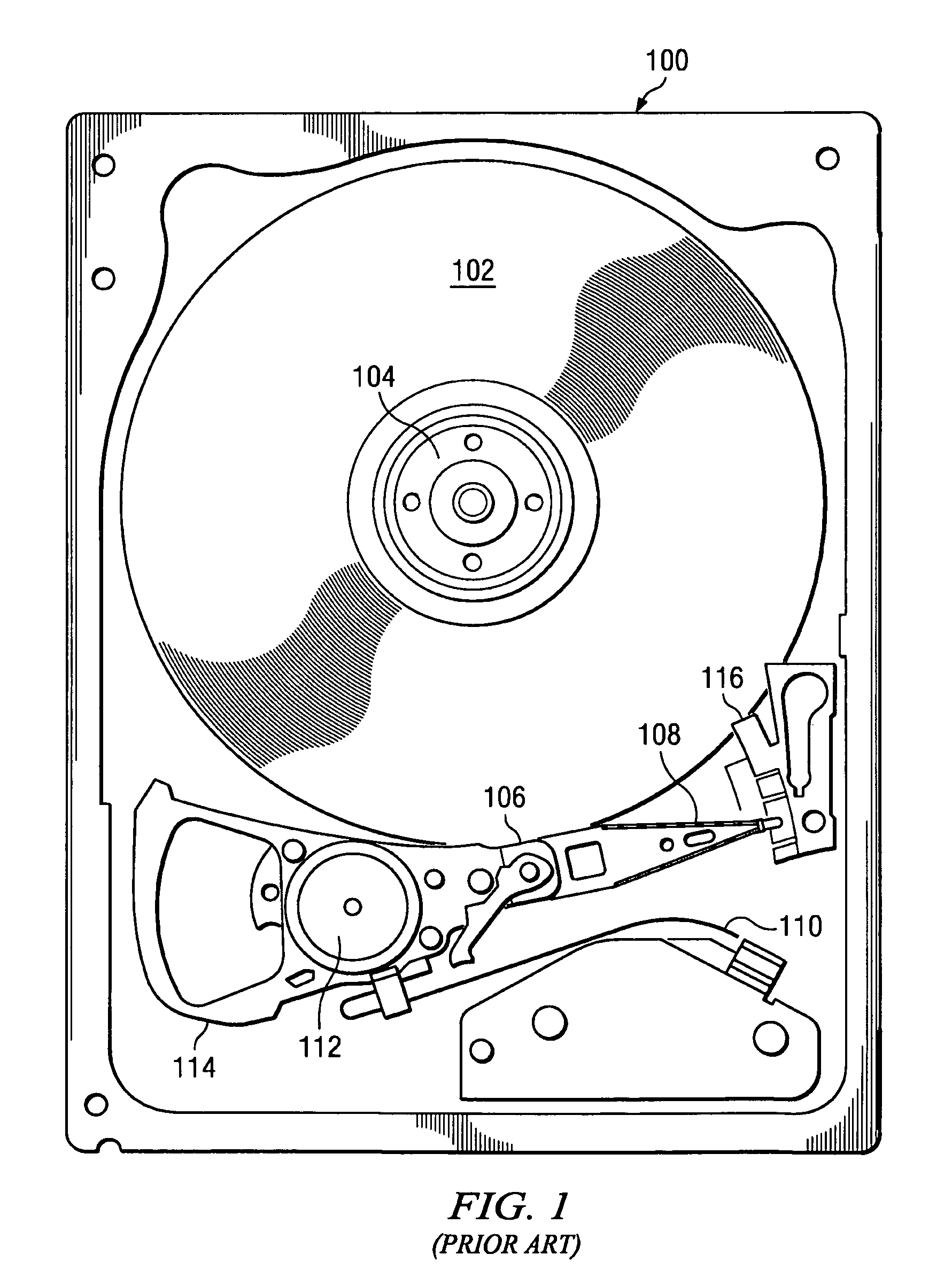

Disk drive employing stream detection engine to enhance cache management policy

A disk drive is disclosed comprising a disk, a head actuated over the disk, a host interface for receiving disk access commands from a host, a command queue for queuing the disk access commands, and a stream detection engine for evaluating the disk access commands to detect a plurality of streams accessed by the host. The stream detection engine maintains a stream data structure for each detected stream, wherein the stream data structure comprises a frequency counter for tracking a number of disk access commands associated with the stream out of a predetermined number of consecutive disk access commands received from the host. A disk controller selects one of the streams for servicing in response to the frequency counters.

Owner:WESTERN DIGITAL TECH INC

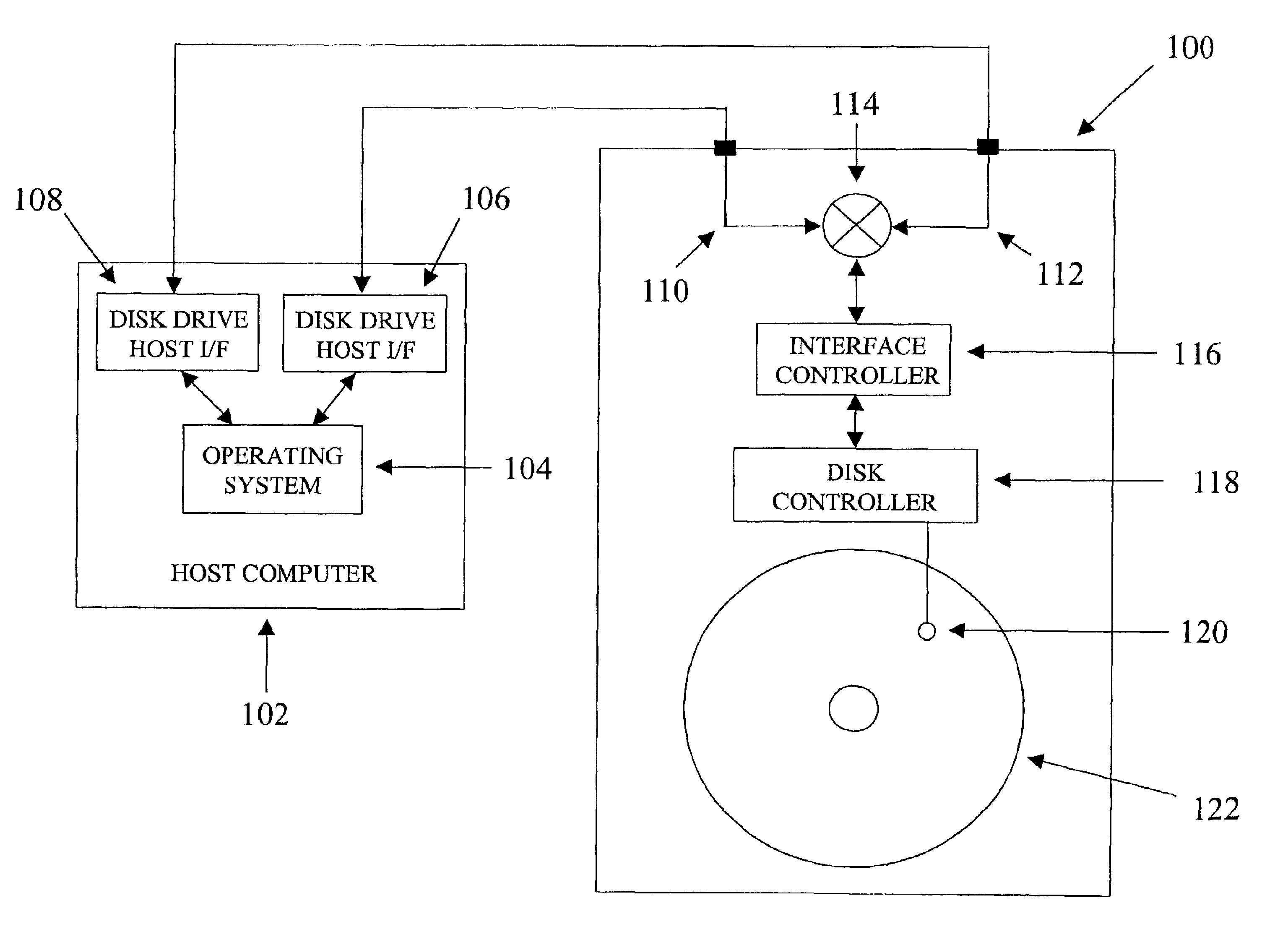

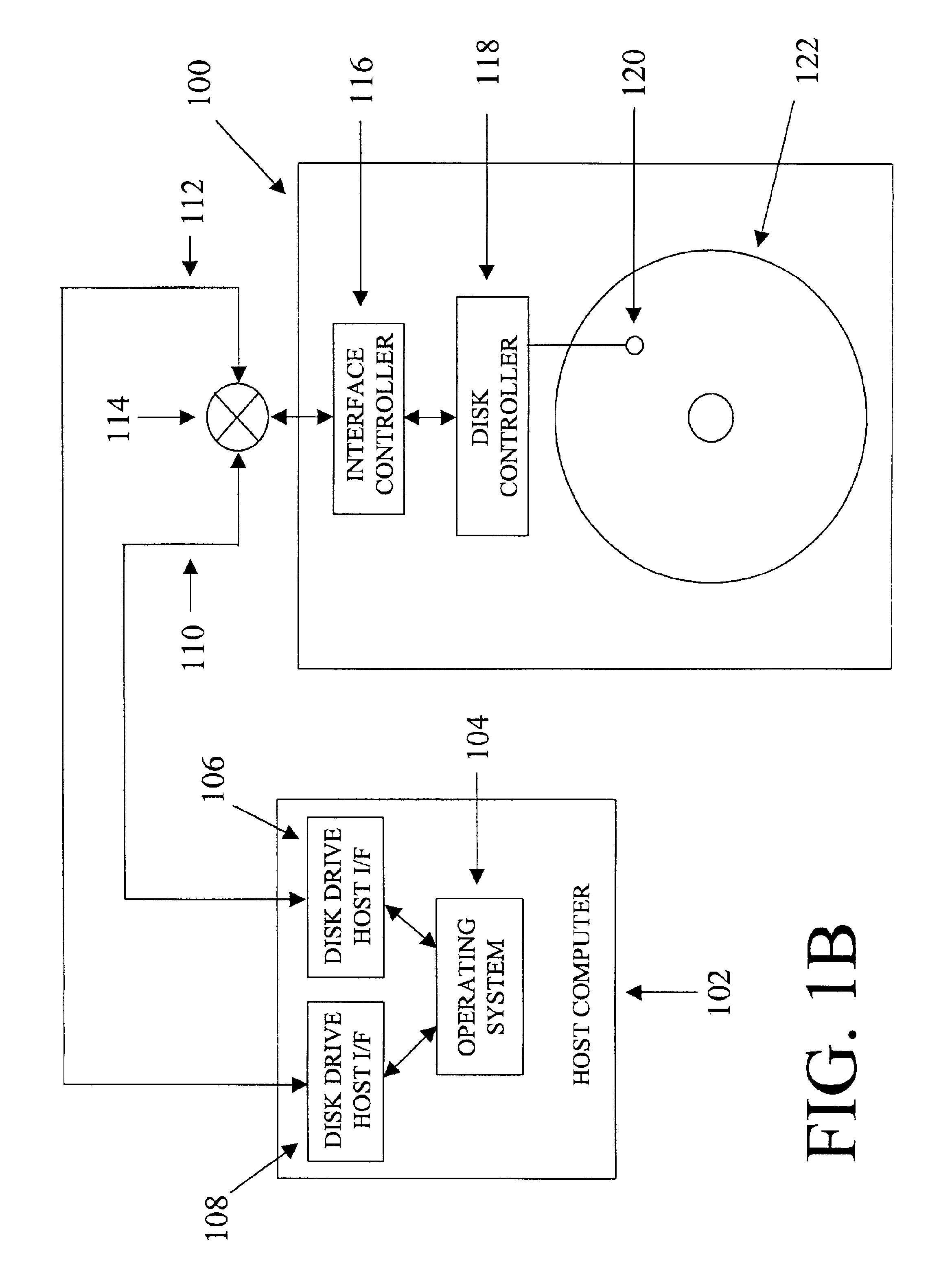

System and method for fail-over switching in a disk storage medium

A disk drive is disclosed that is configured to be accessible in fail-over via buses associated with plural host interfaces. In accordance with exemplary embodiments of the present invention, the disk drive comprises a disk storage medium, a first bus connection, and a second bus connection. The disk drive comprises a switch for selectively connecting the disk storage medium to at least one of the first and second bus connections. The disk drive also comprises an interface controller for detecting whether at least one of the first and second bus connections is active and for controlling the switch in response.

Owner:WESTERN DIGITAL TECH INC

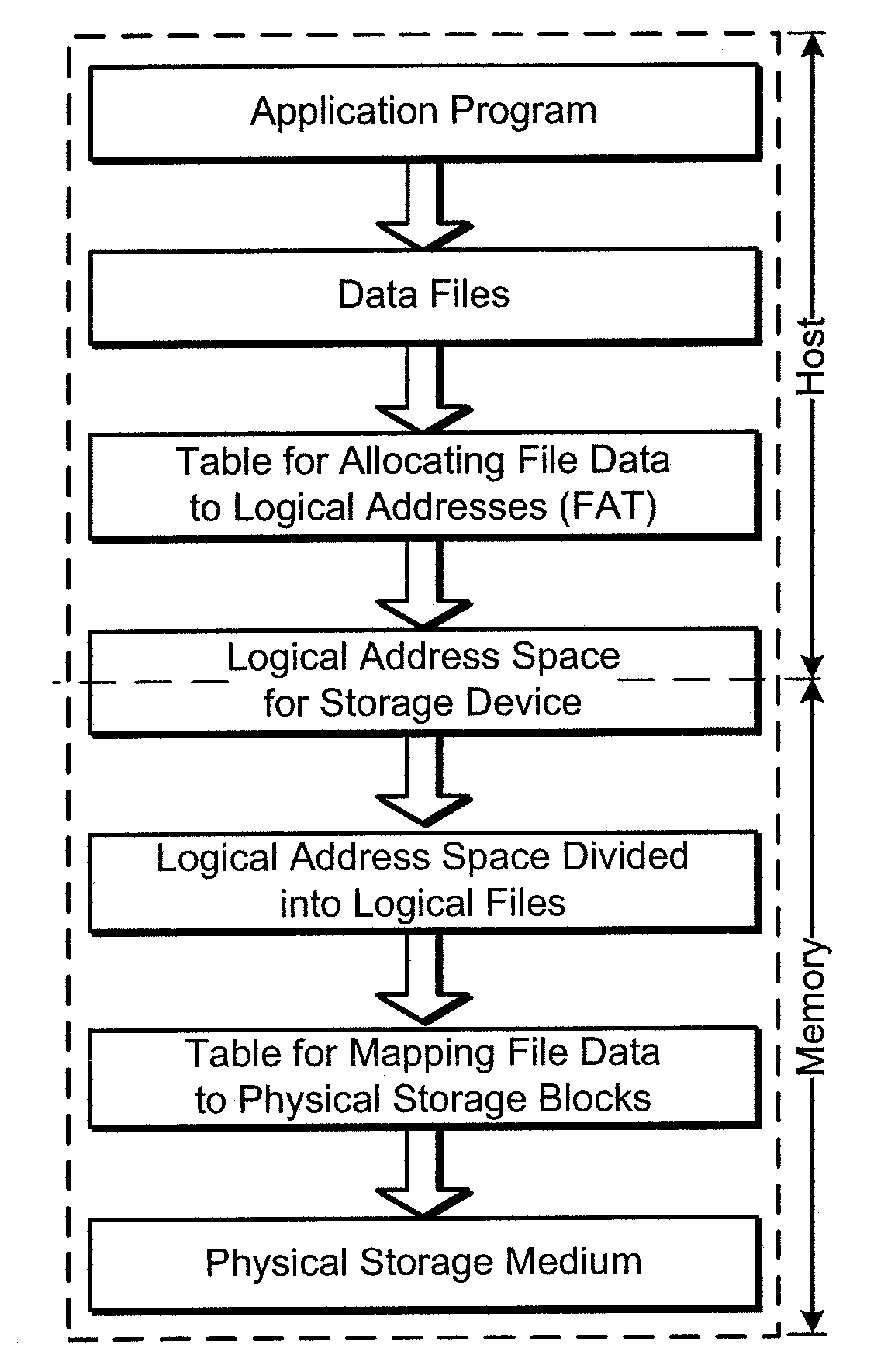

Enhanced host interfacing methods

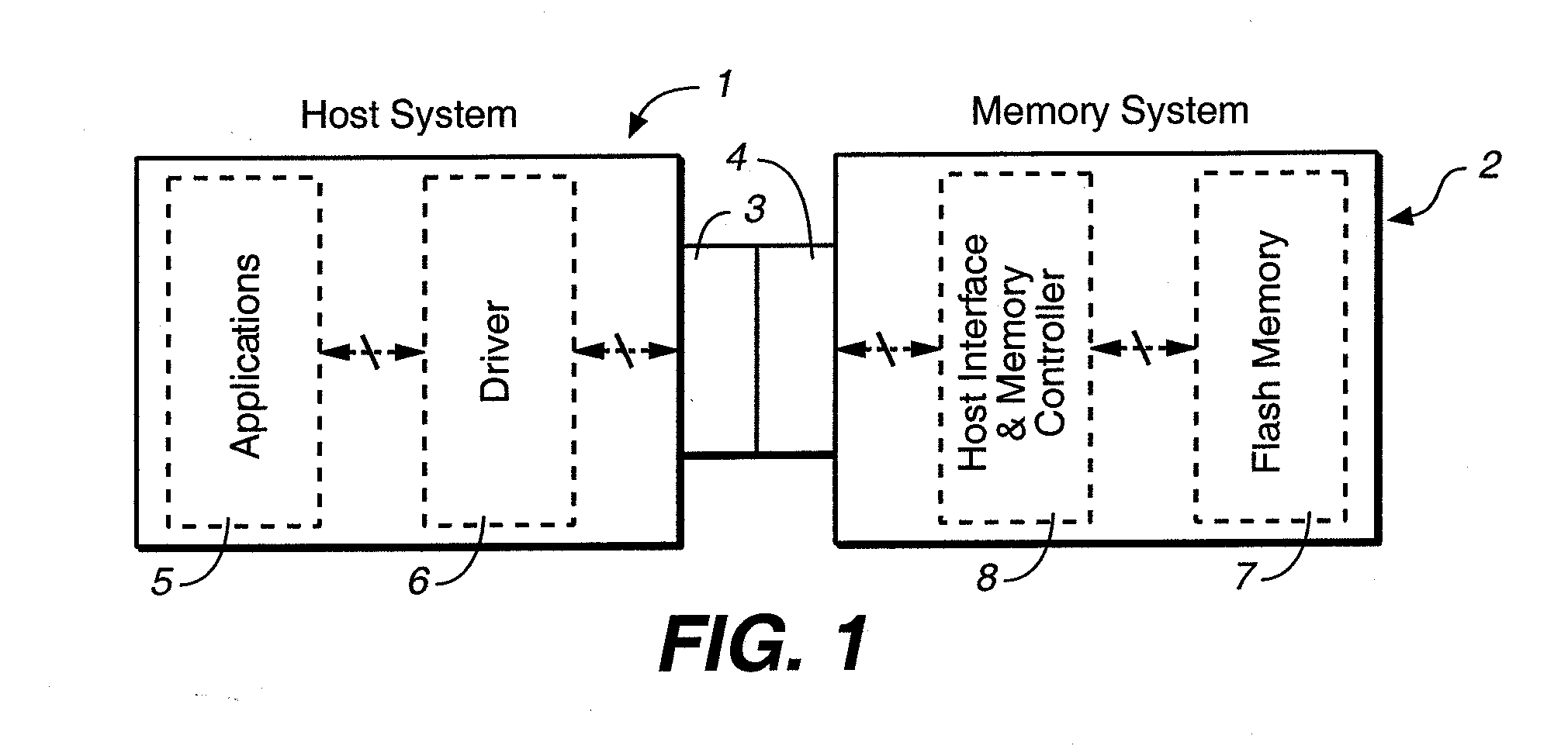

InactiveUS20070033326A1Efficient storageEfficient managementMemory architecture accessing/allocationDigital data information retrievalOperating systemMemory systems

A memory system that is compatible with hosts using different protocols includes protocol adapters for the different protocols. Protocol adapters allow a common backend system to be used for data that is provided in different formats. A protocol adapter generates responses to a host and generates commands for a backend as appropriate.

Owner:SANDISK TECH LLC

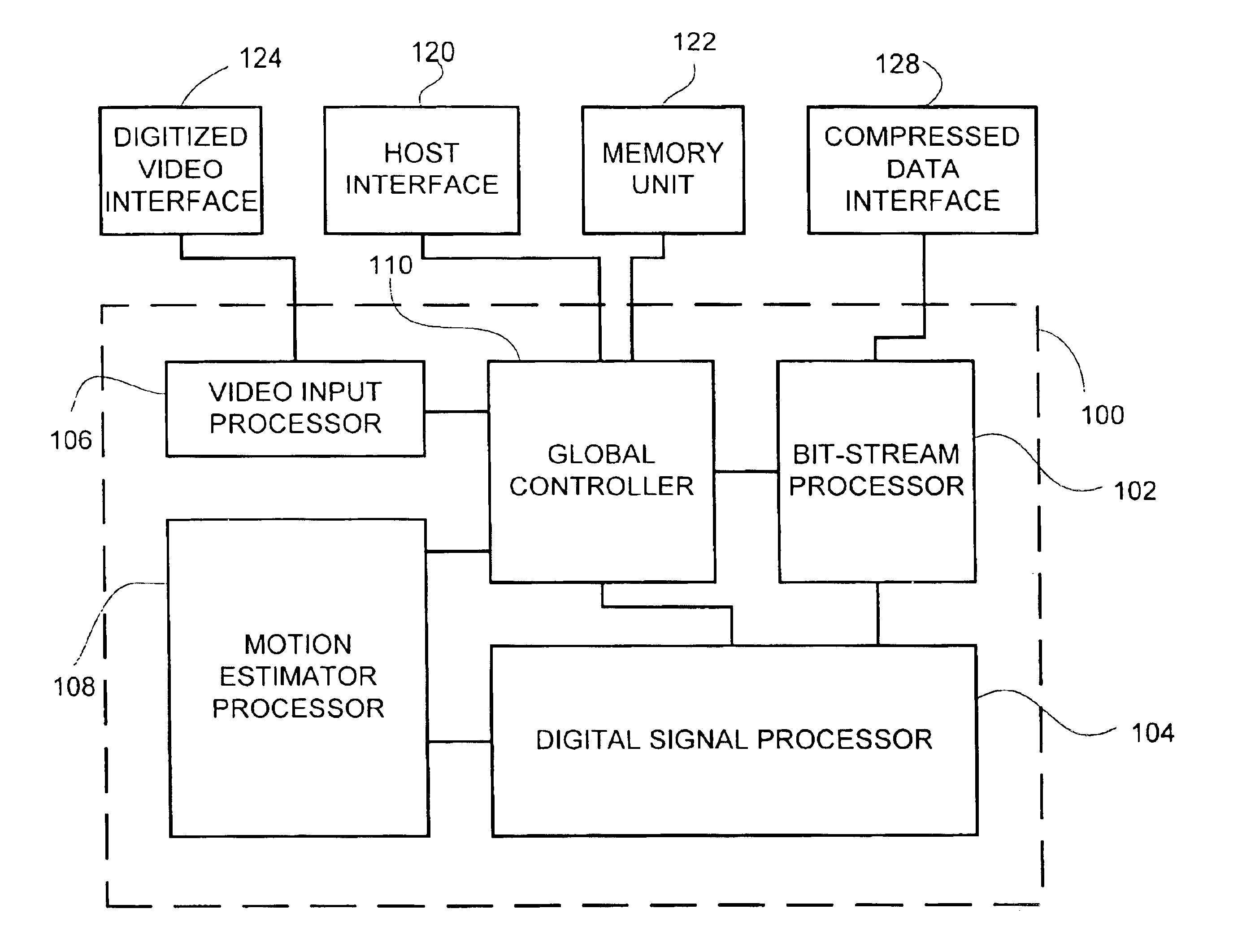

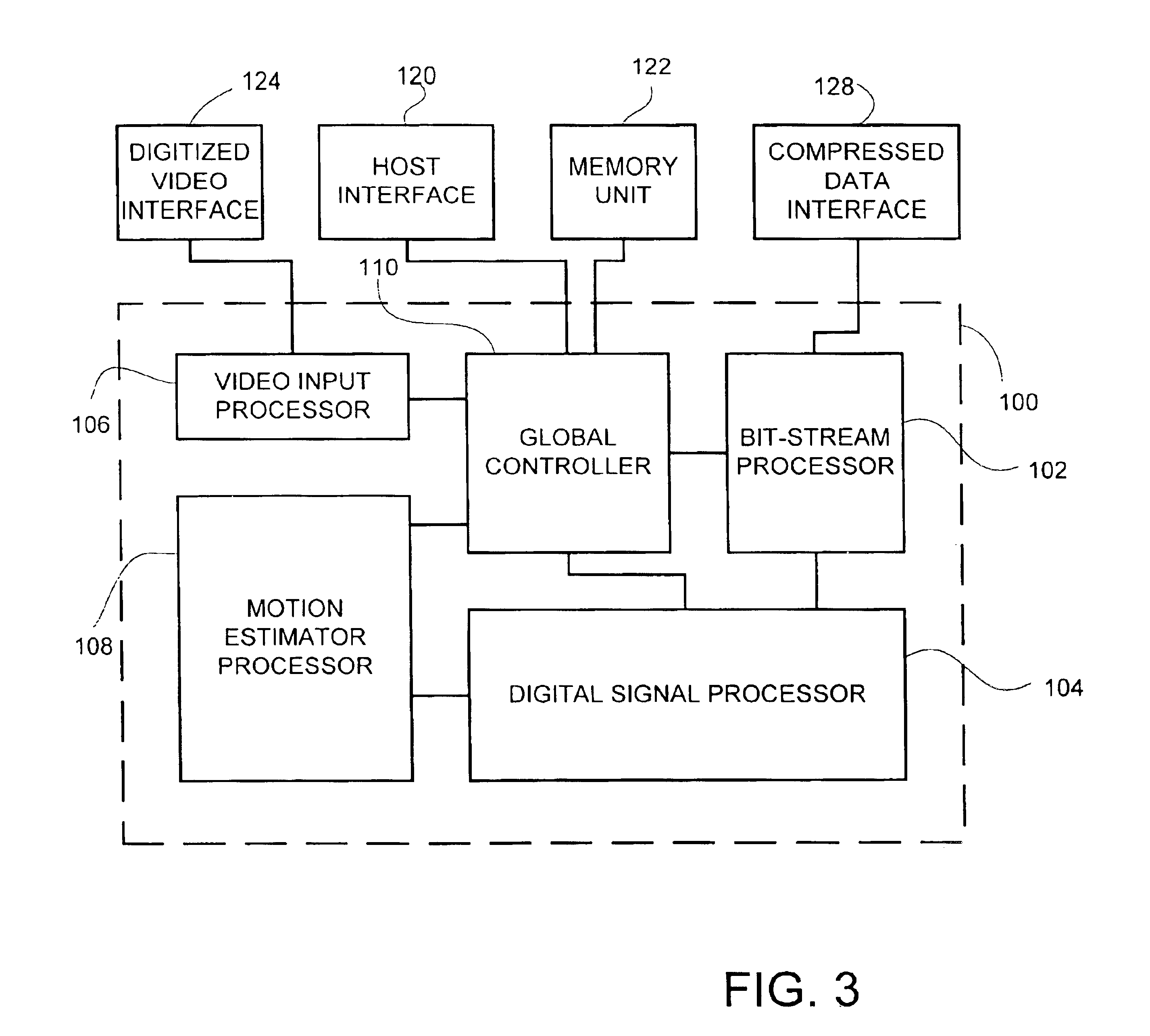

Video encoding device

InactiveUS6847686B2Reduce selection requirementsIncrease choiceColor television with pulse code modulationColor television with bandwidth reductionExternal storageVideo encoding

Video encoding device including a video input processor, for receiving said video signal, a global controller, for controlling the global operation of the video encoding device, a motion estimation processor, a digital signal processor and a bit-stream processor, wherein the global controller stores encodes commands received from a host interface thereby programming the video input processor, the motion estimation processor, the digital signal processor and the bit-stream processor, the video input processor receives and stores the video signal in an external memory unit, the motion estimation processor retrieves the video signal from the memory unit, generates motion analysis of the video signal, stores the motion analysis in the memory unit and provides the motion analysis to the digital signal processor, the digital signal processor processes the video signal according to the motion analysis, thereby producing an encoding commands sequence and encoded data, the bit-stream processor produces an encoded video signal according to the encoding command sequence and the encoded data.

Owner:AVAGO TECH INT SALES PTE LTD

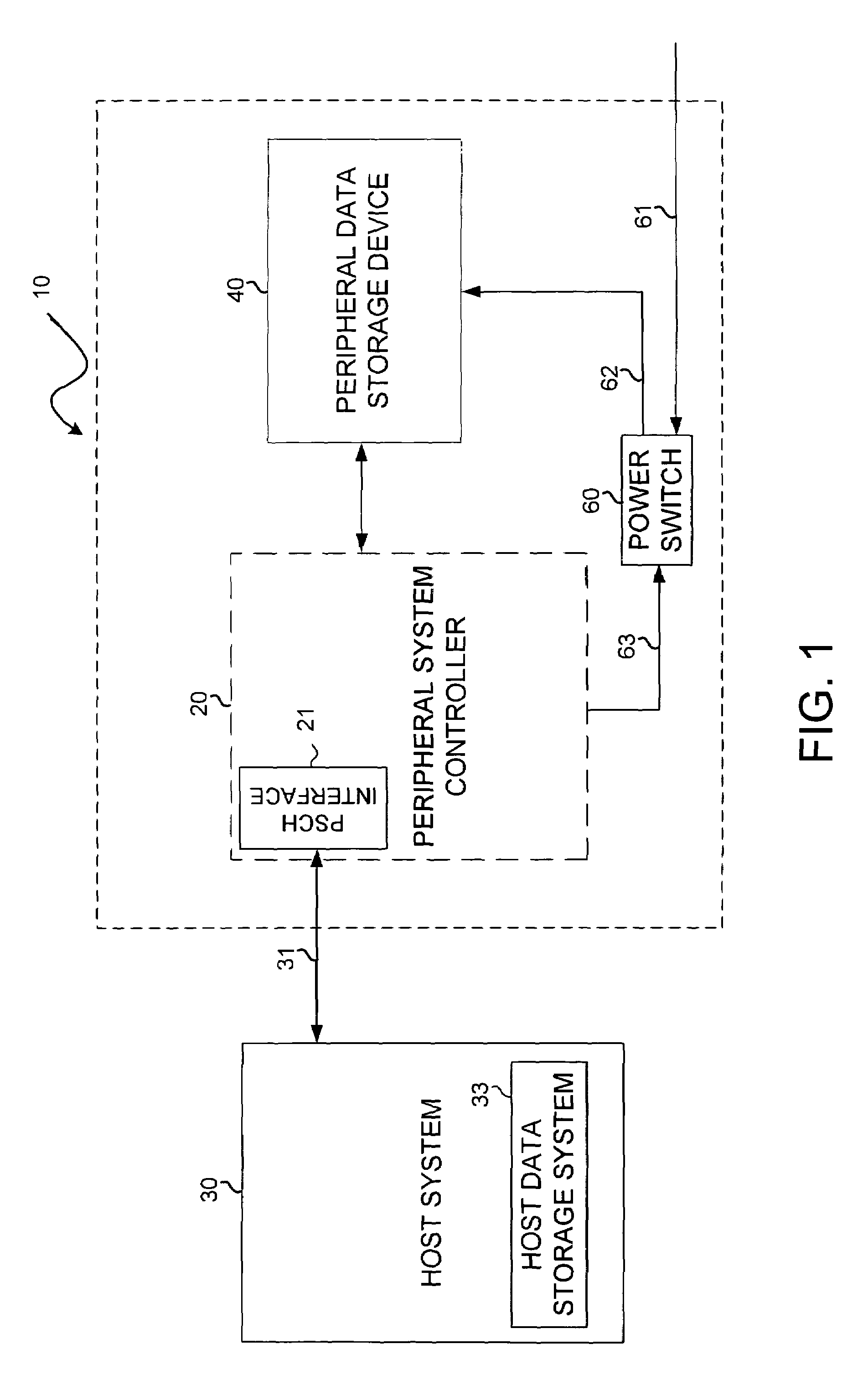

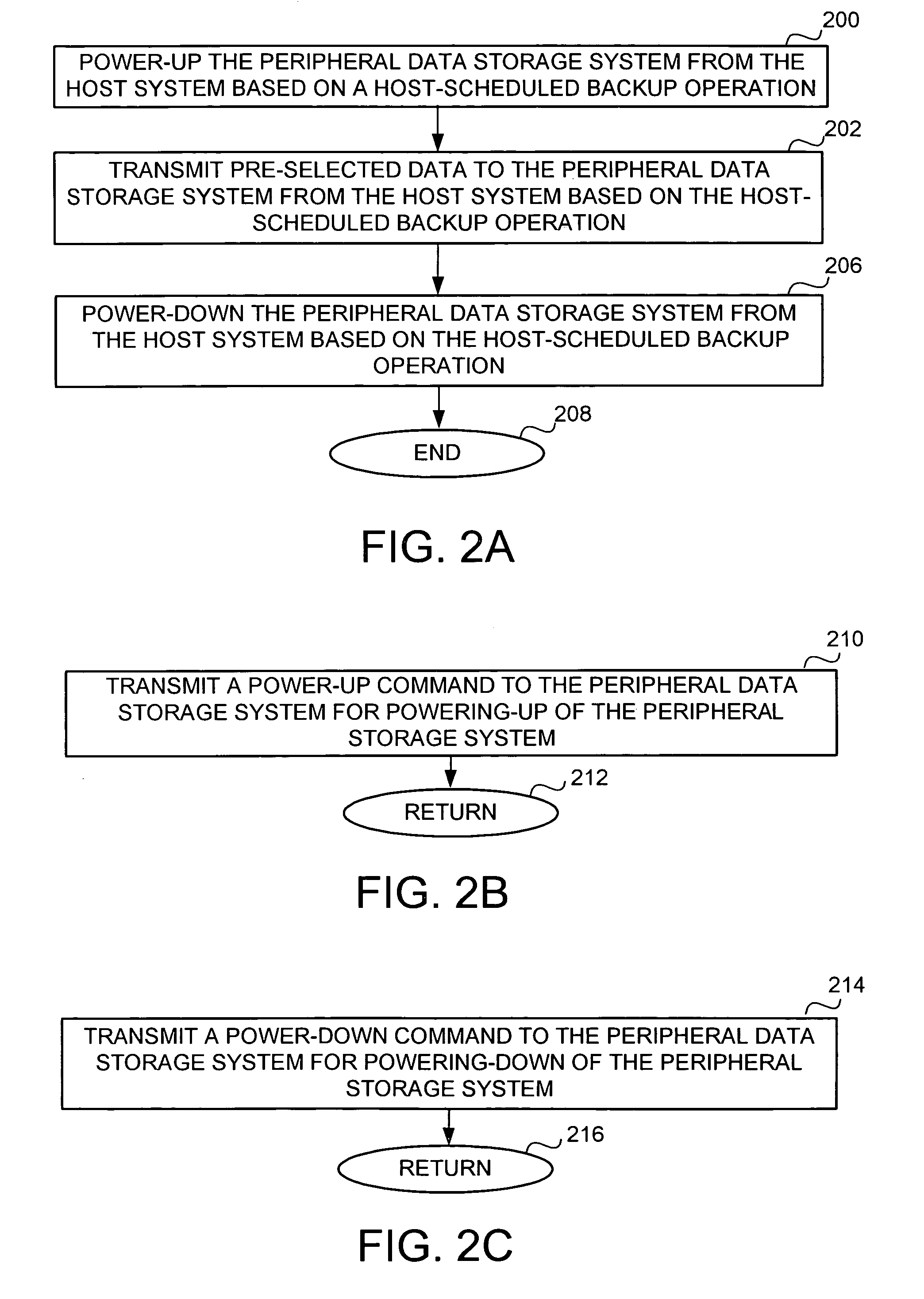

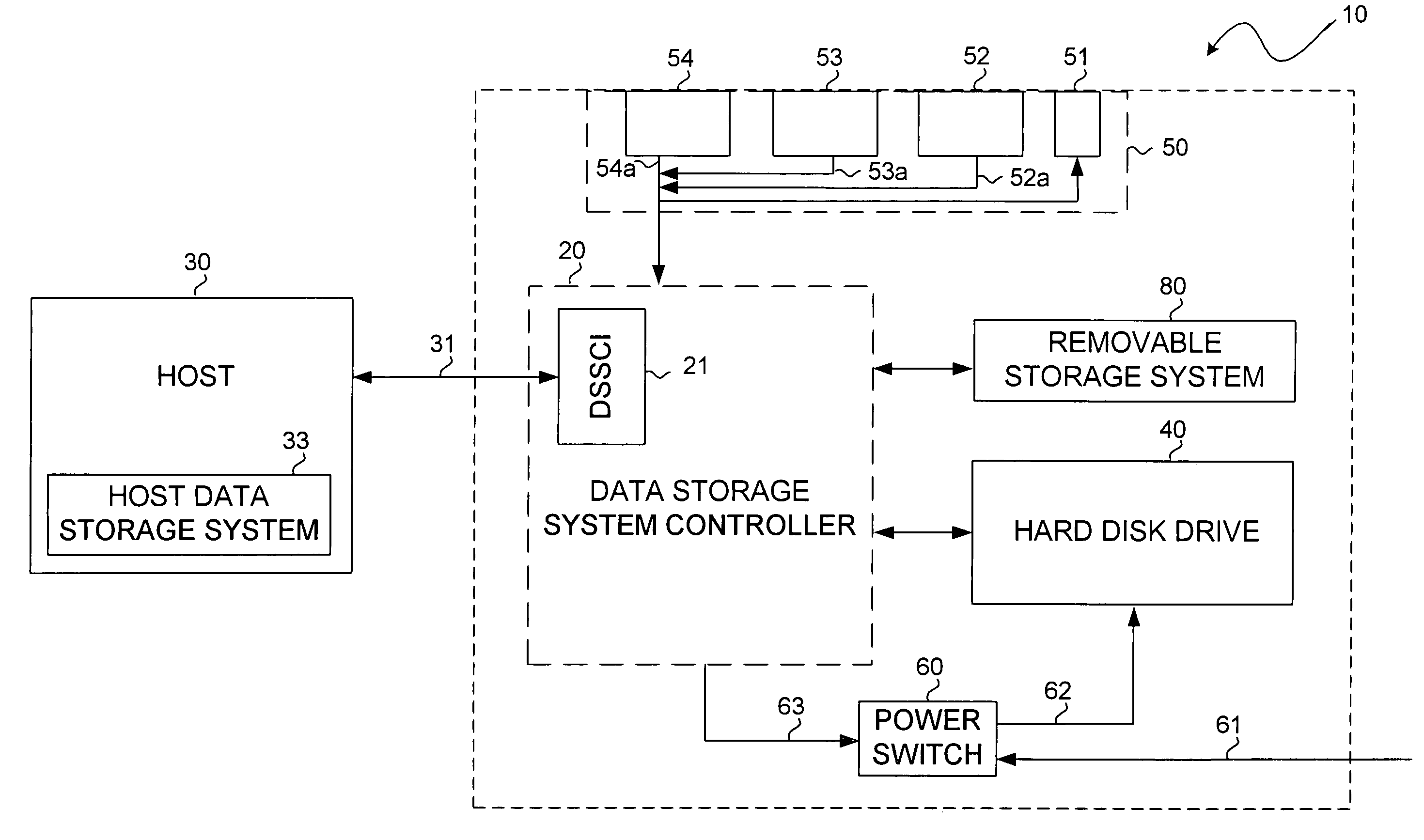

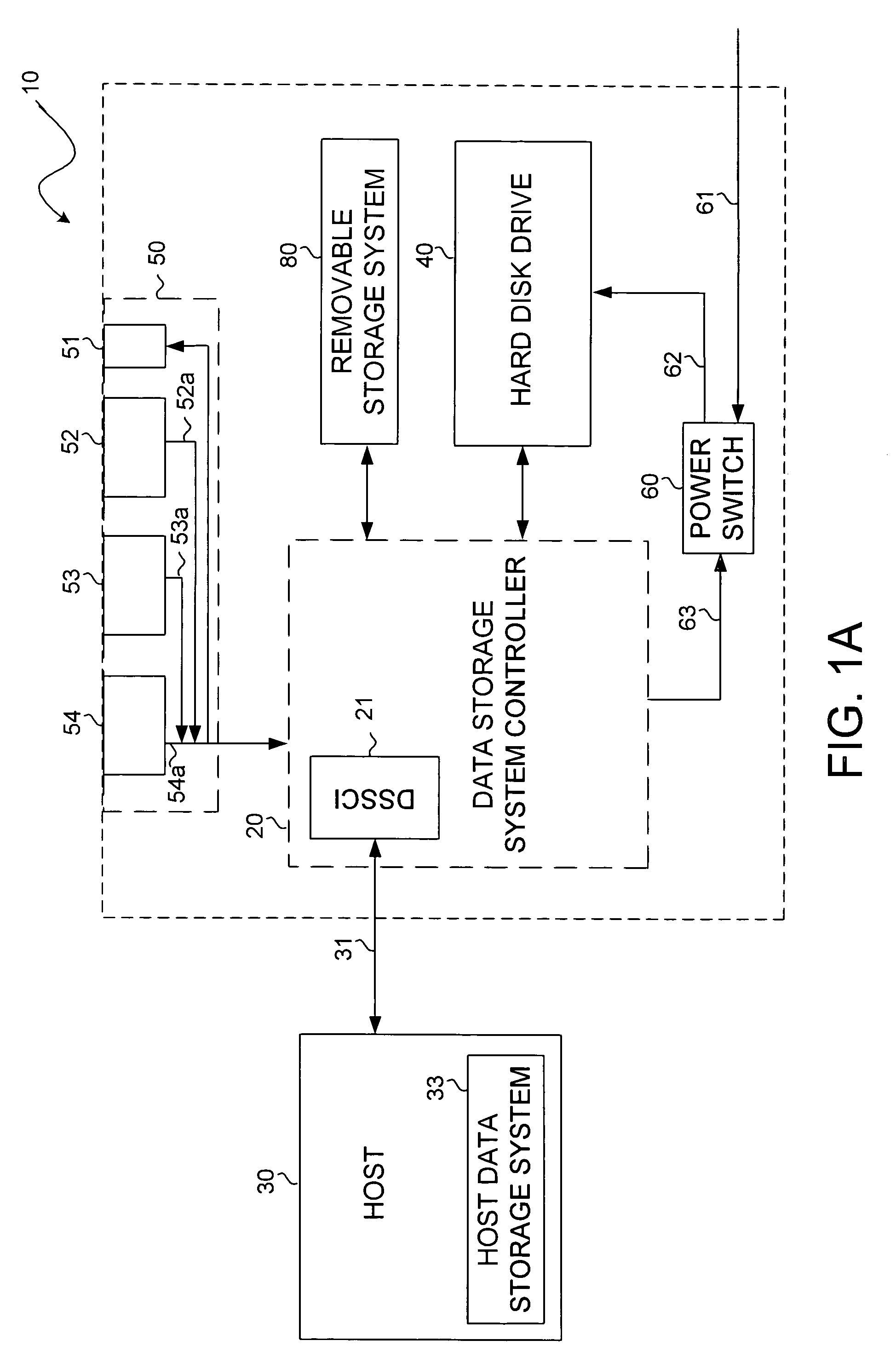

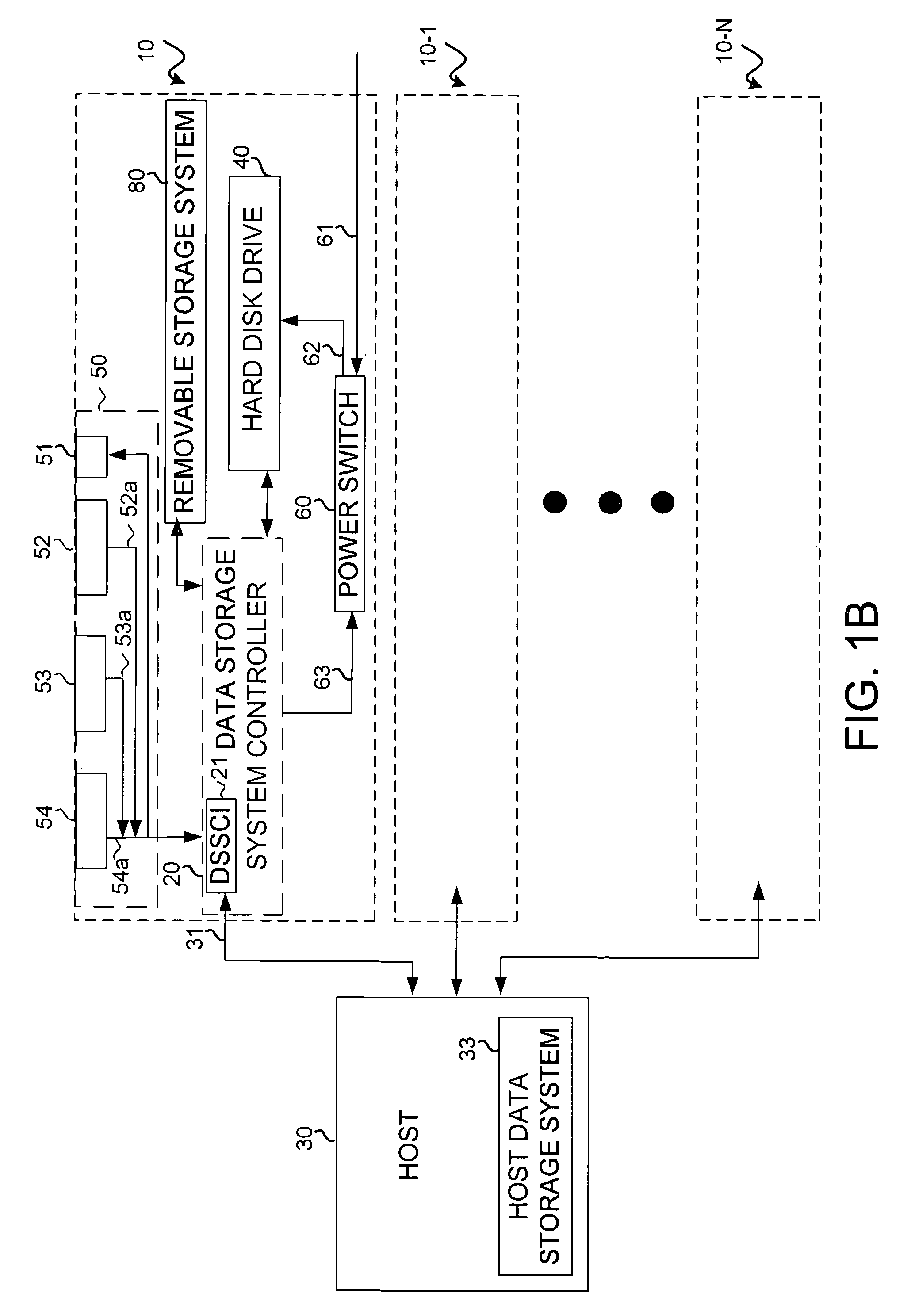

Remote power cycling of peripheral data storage system

A method for remotely power cycling a peripheral data storage system (PDSS) from a host system. The method comprises powering-up the PDSS from the host system based on a host-scheduled backup operation; transmitting pre-selected data to the PDSS from the host system based on the host-scheduled backup operation; and powering-down the PDSS from the host system based on the host-scheduled backup operation. Another method is for operating a PDSS for use with a host system configured to perform scheduled backup operations to the PDSS, the PDSS comprising a peripheral data storage device, a PDSS controller, and a peripheral data storage controller host interface adapted for communication with the host system. The method comprises powering-up the PDSS based on a host-scheduled backup operation; receiving data from the host system for storing in the peripheral data storage device; and powering-down the PDSS based on the host-scheduled backup operation.

Owner:WESTERN DIGITAL TECH INC

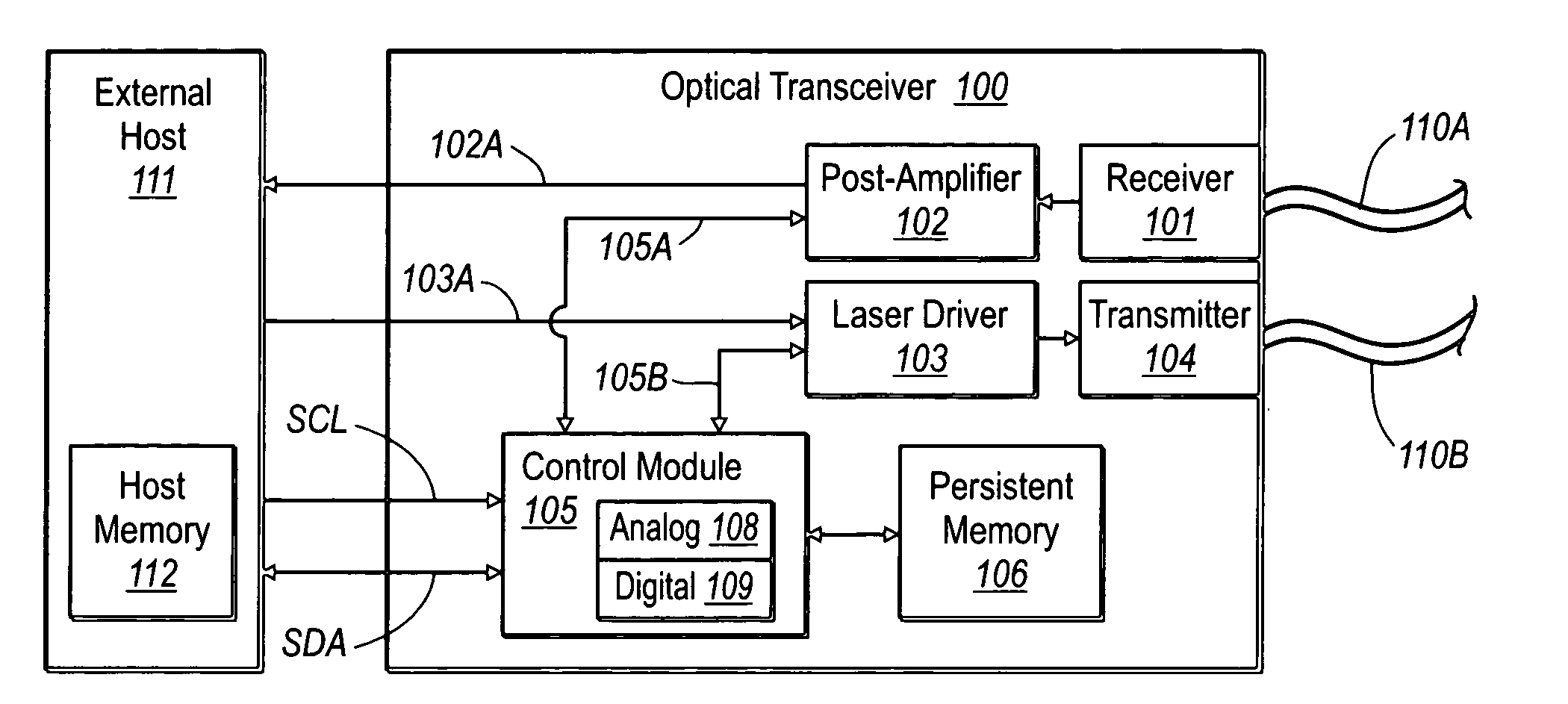

Selectable host-transceiver interface protocol

An optical transceiver, including a memory and a processor, which is capable of supporting different host interface protocols for communication between the optical transceiver and a host computing system. Each of the host interface protocols may be implemented by selecting microcode that corresponds to a particular host interface protocol and loading the microcode into the memory. The processor may later execute the microcode and cause the transceiver and the host to communicate using the specified interface protocol. The host interface protocols may also be implemented by hardware contained in the optical transceiver.

Owner:II VI DELAWARE INC

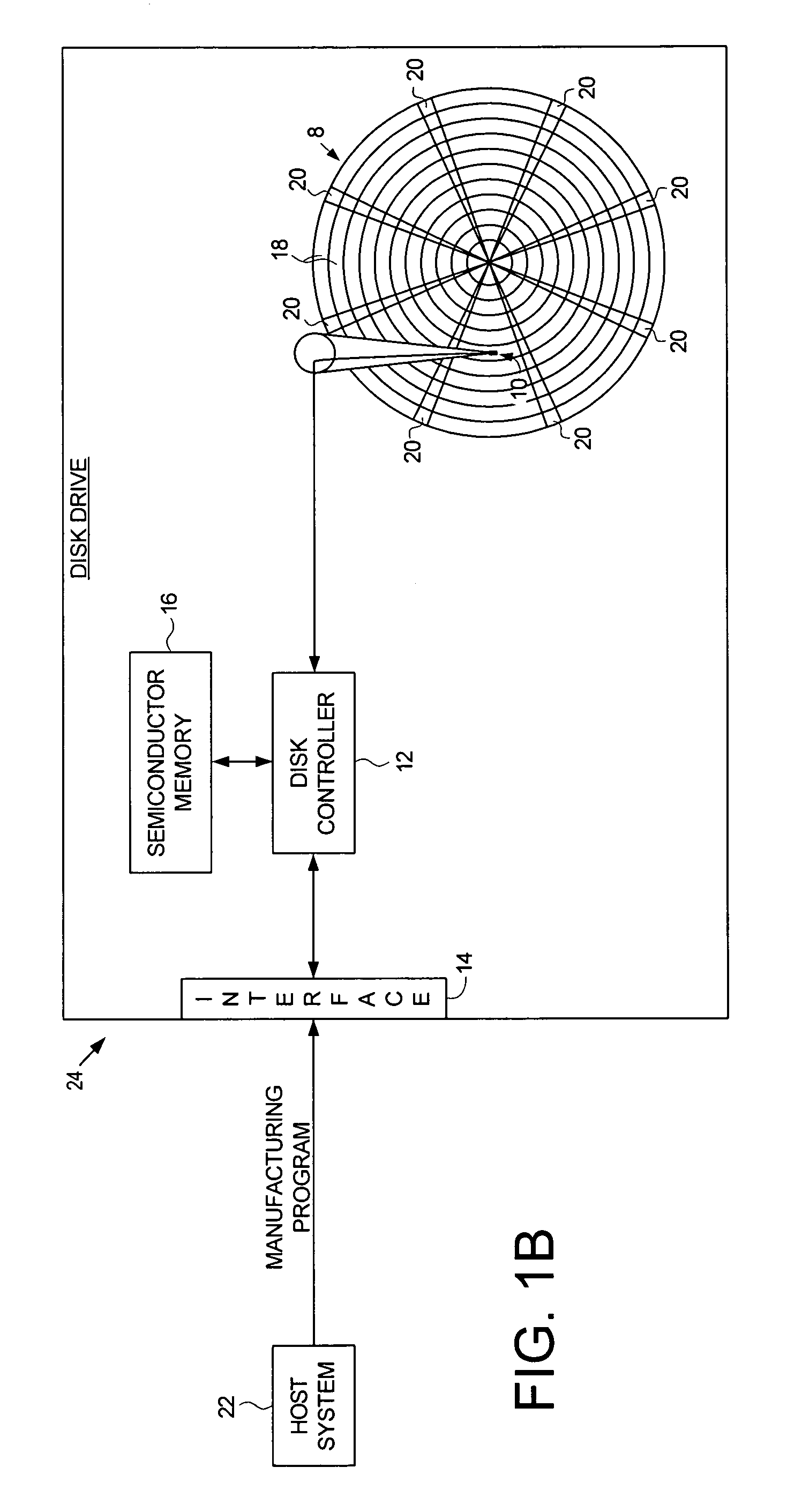

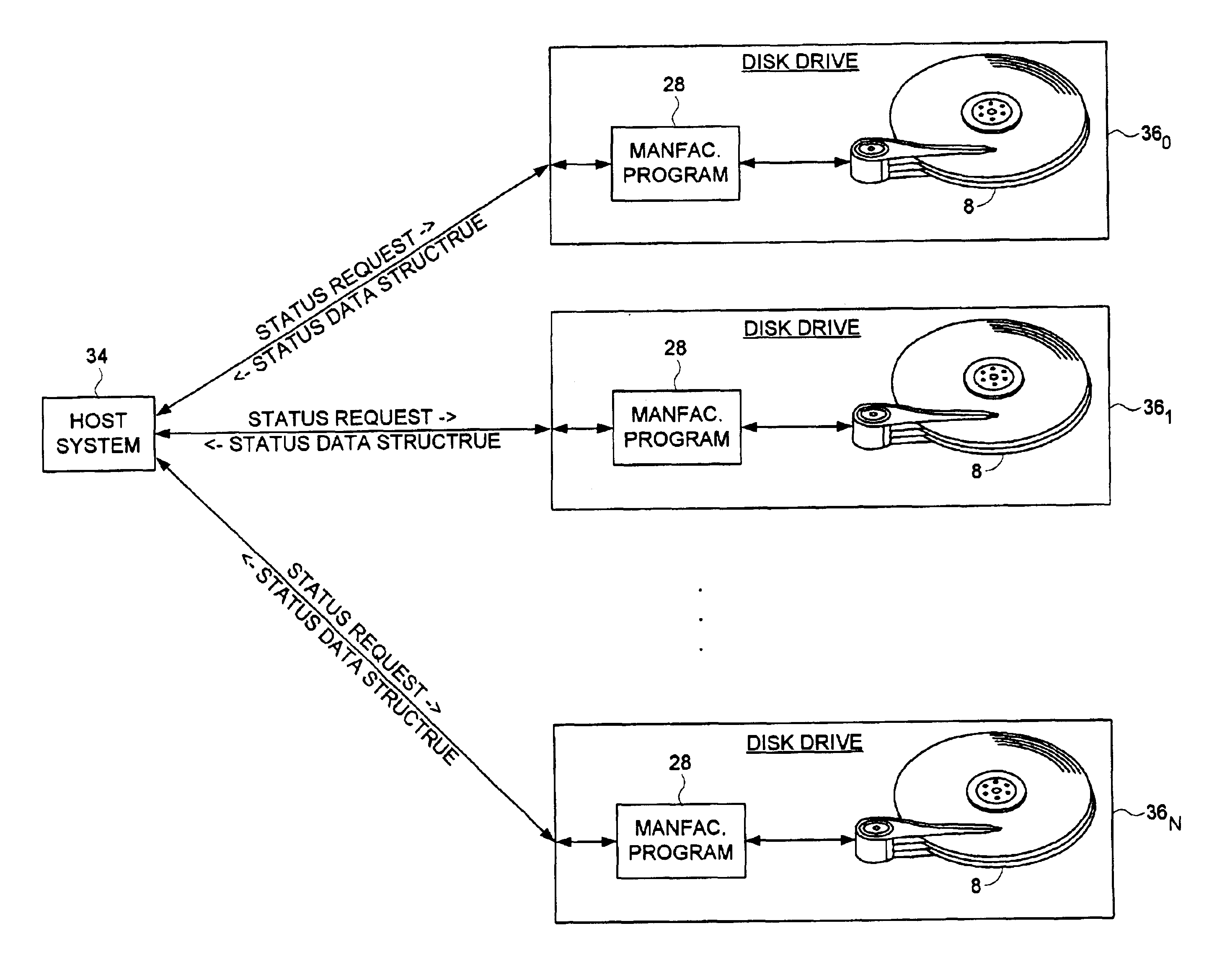

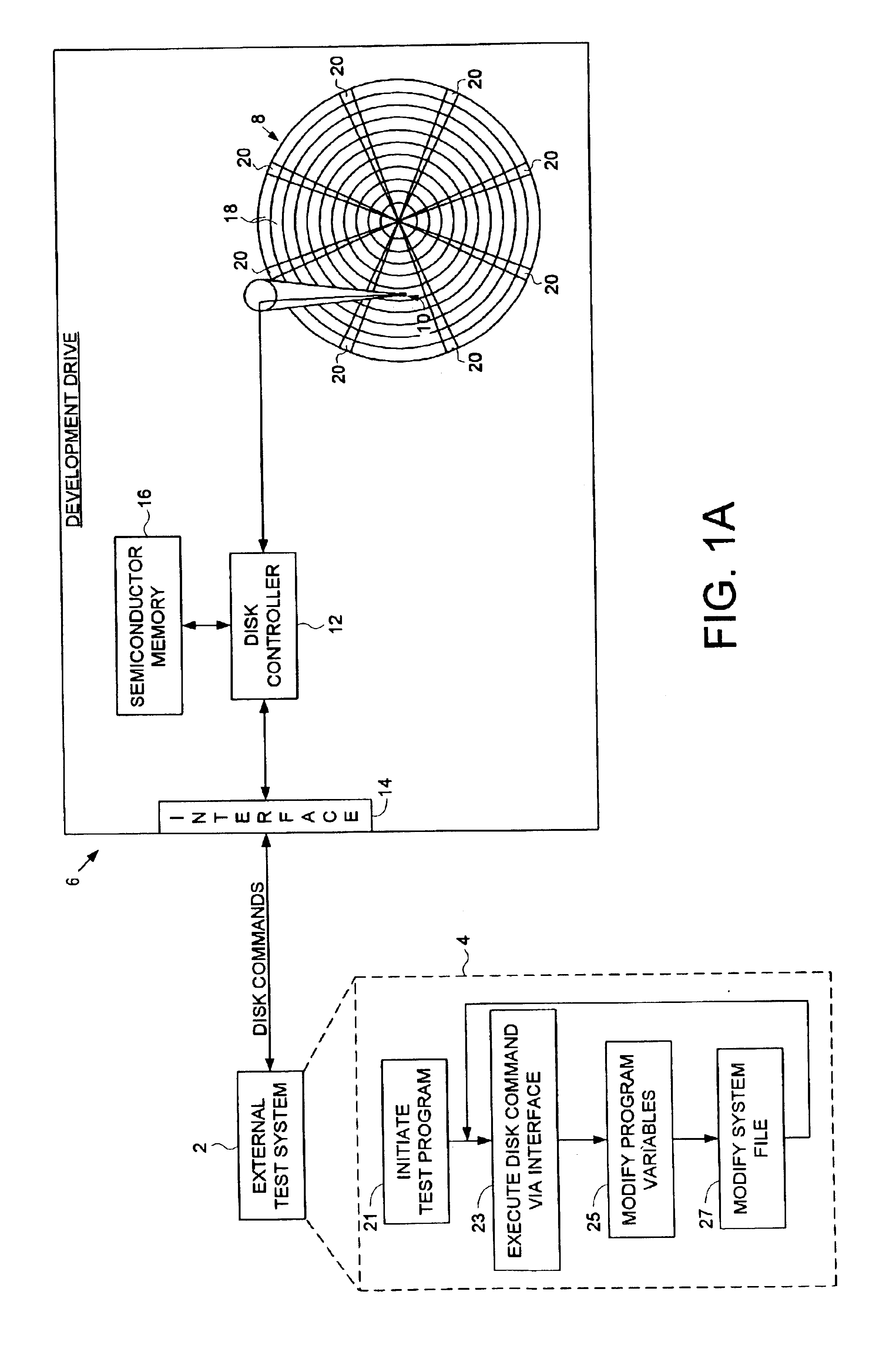

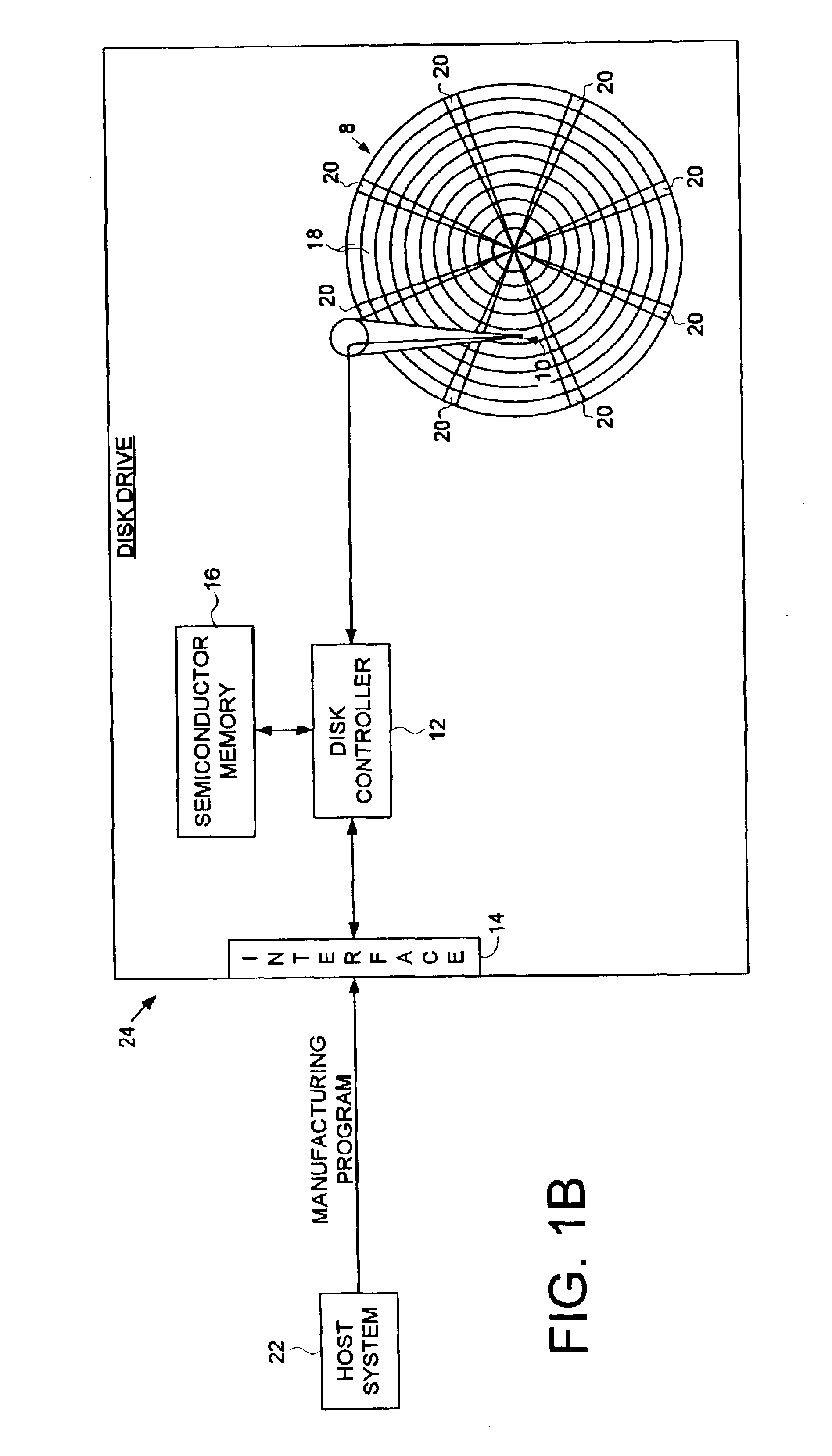

Developing a disk drive manufacturing program by executing the manufacturing program on an external test system

A method of manufacturing a disk drive is disclosed. The disk drive comprising a disk, a head actuated radially over the disk, a host interface for receiving disk commands from a host system, and a semiconductor memory for storing a drive operating program and a manufacturing program. The drive operating program comprising a disk access procedure for processing disk commands and a disk access vector for calling the disk access procedure. During a development stage, the manufacturing program is executed by an external test system that sends disk commands to a development drive. During a manufacturing stage, the manufacturing program is executed internally on each disk drive being manufactured by calling the disk access procedure of the drive operating program through the disk access vector.

Owner:WESTERN DIGITAL TECH INC

Disk drive executing a manufacturing program internally by executing disk commands through a vector

A disk drive is disclosed for executing a drive operating program and a manufacturing program during a manufacturing process. An external test system executes a test program comprising platform independent executable code segments and host interface executable code segments. The external test system for executing the host interface executable code segments to send disk commands to a development drive. The manufacturing program comprises the platform independent executable code segments of the test program and disk access executable code segments. The drive operating program comprises a disk access procedure for processing disk commands and a disk access vector for calling the disk access procedure. The disk access executable code segments of the manufacturing program execute disk commands by calling the disk access procedure of the drive operating program through the disk access vector.

Owner:WESTERN DIGITAL TECH INC

Performing backup operations to peripheral data storage systems

A method of operating a peripheral data storage system(PDSS) for use with a host system configured to perform scheduled backup operations to PDSS comprising a user-actuated backup signaling subsystem(UBSS), a user-notifying device comprising first and second notifying states, and a host interface adapted for communication with the host system. The method comprises receiving a first signal from UBSS; communicating first signal to host system via host interface; receiving an acknowledgement signal from host system in response to communicating; and switching user-notifying device between first notifying state and second notifying state in response to received acknowledgement signal. Another method comprises receiving in host system a first request from PDSS for performing a task corresponding to a host-scheduled backup operation for a scheduled backing up of data to PDSS; completing the task by host system based on received first request; and notifying PDSS of completion of the task by host system.

Owner:WESTERN DIGITAL TECH INC

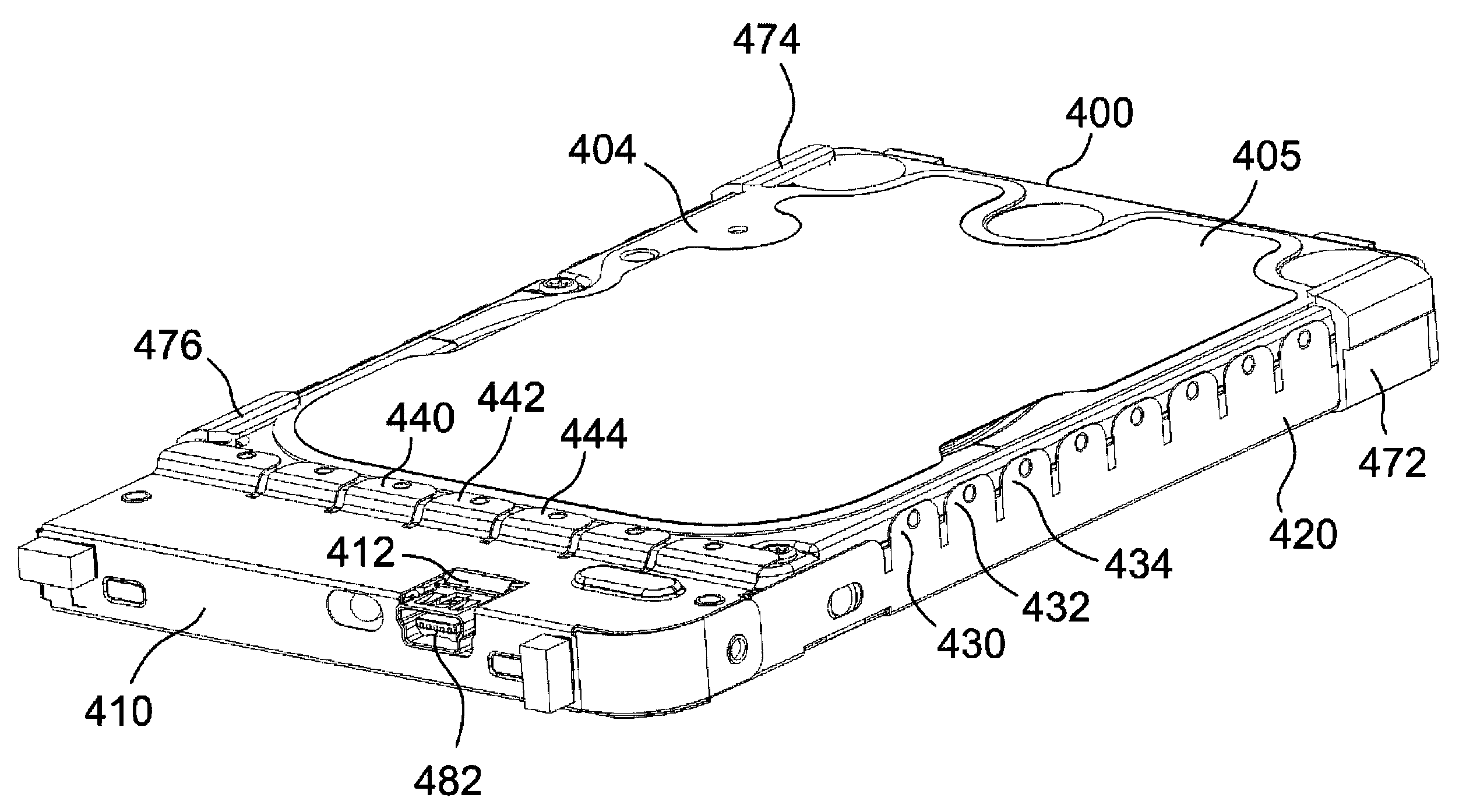

Information storage device having a disk drive and a bridge controller PCB within a monolithic conductive nest

InactiveUS7940491B2Apparatus modification to store record carriersDigital data processing detailsControl theoryPrinted circuit board

Owner:WESTERN DIGITAL TECH INC

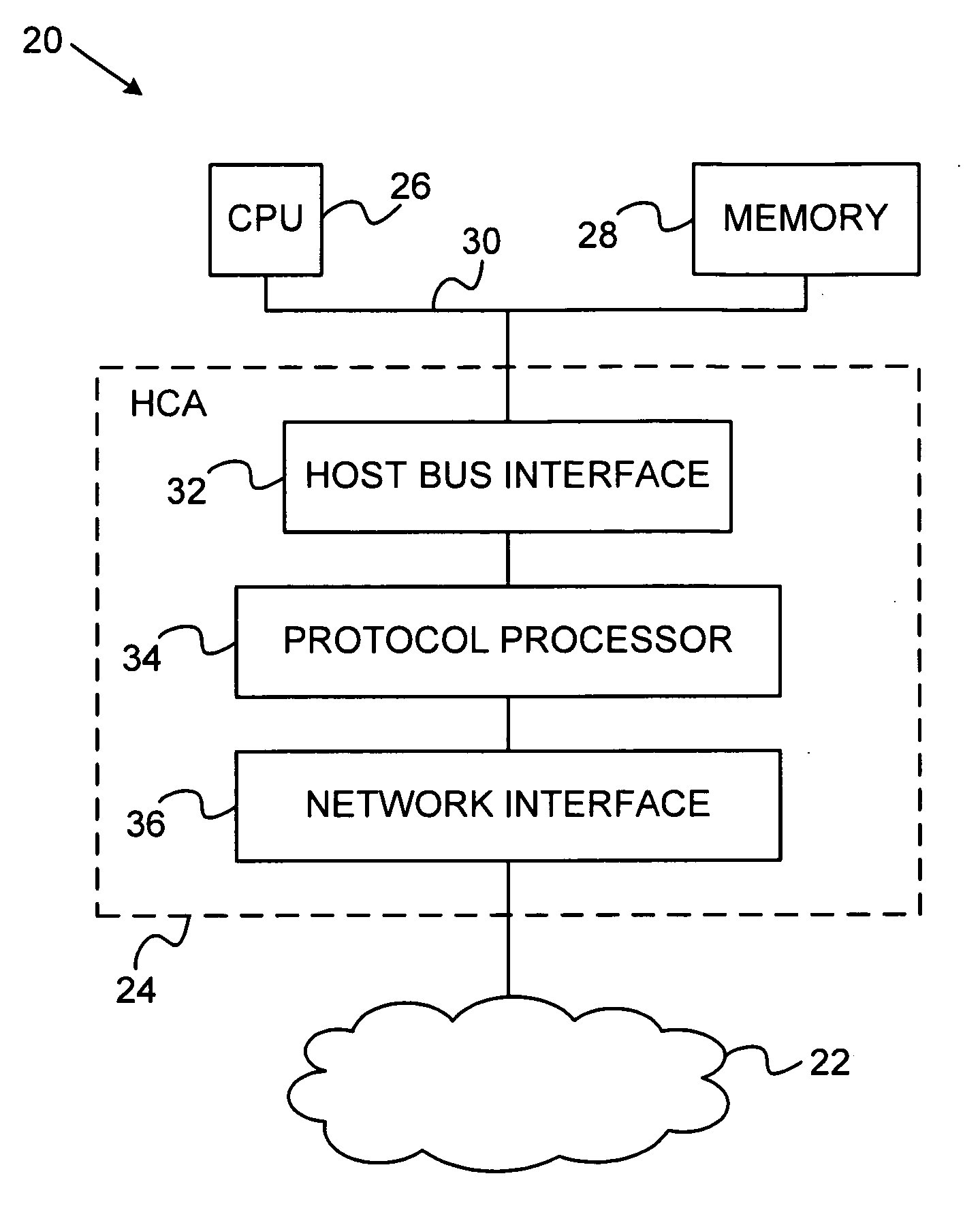

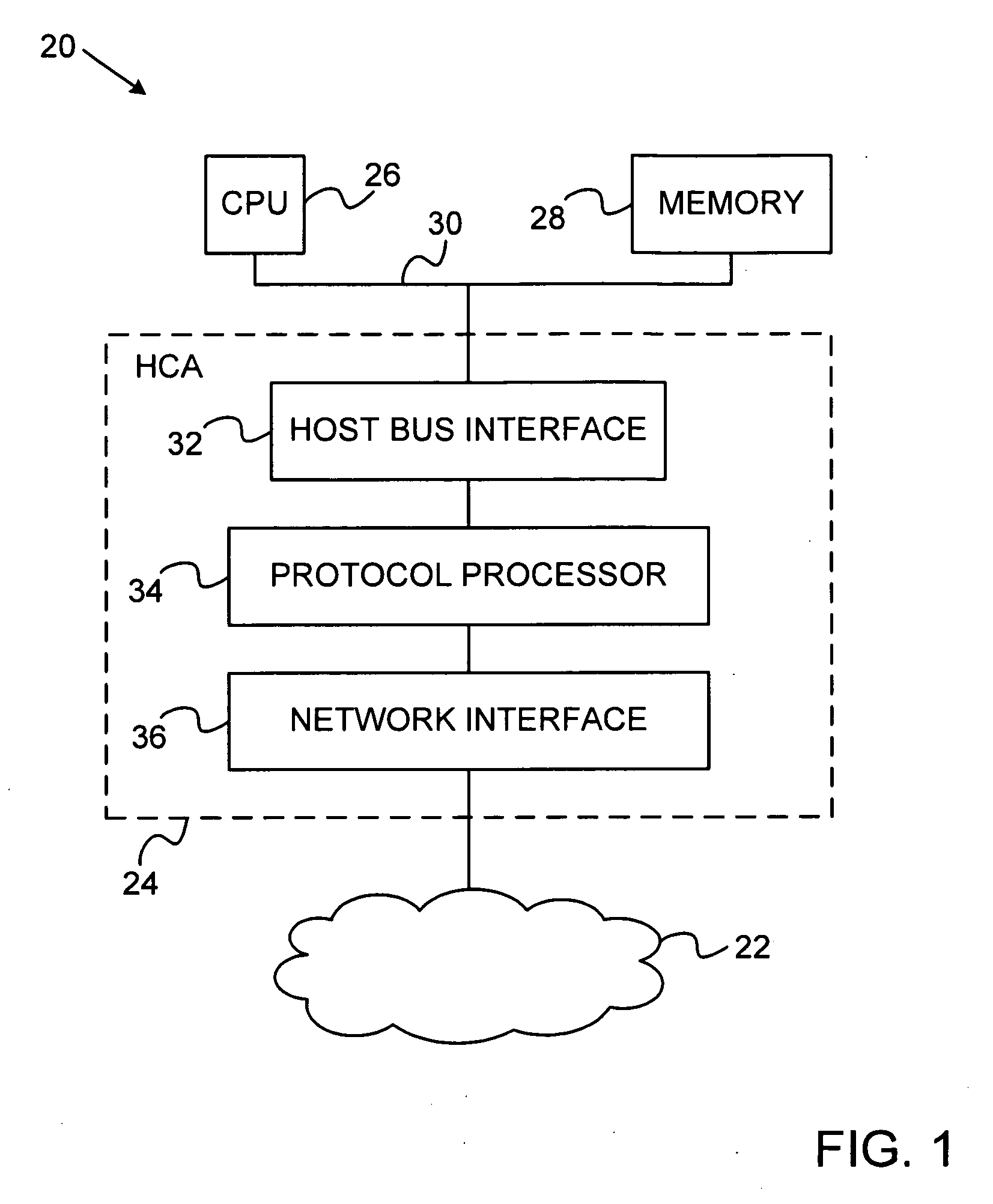

Network interface device with memory management capabilities

ActiveUS20100274876A1Multiple digital computer combinationsMemory systemsNetwork interface devicePhysical address

An input / output (I / O) device includes a host interface for connection to a host device having a memory and a network interface, which is configured to receive, over a network, data packets associated with I / O operations directed to specified virtual addresses in the memory. Packet processing hardware is configured to translate the virtual addresses into physical addresses and to perform the I / O operations using the physical addresses, and upon an occurrence of a page fault in translating one of the virtual addresses, to transmit a response packet over the network to a source of the data packets so as to cause the source to refrain from transmitting further data packets while the page fault is serviced.

Owner:MELLANOX TECHNOLOGIES LTD

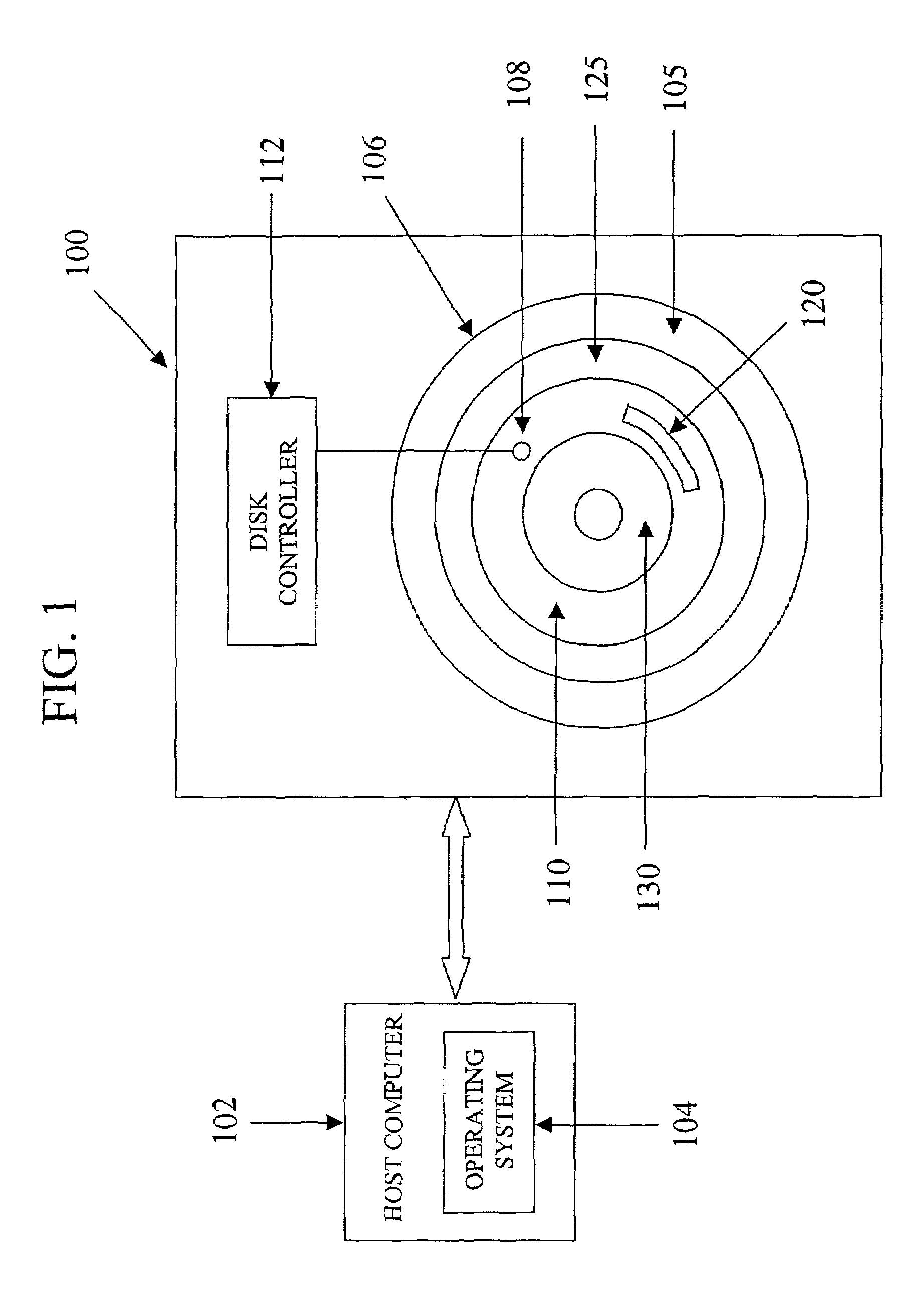

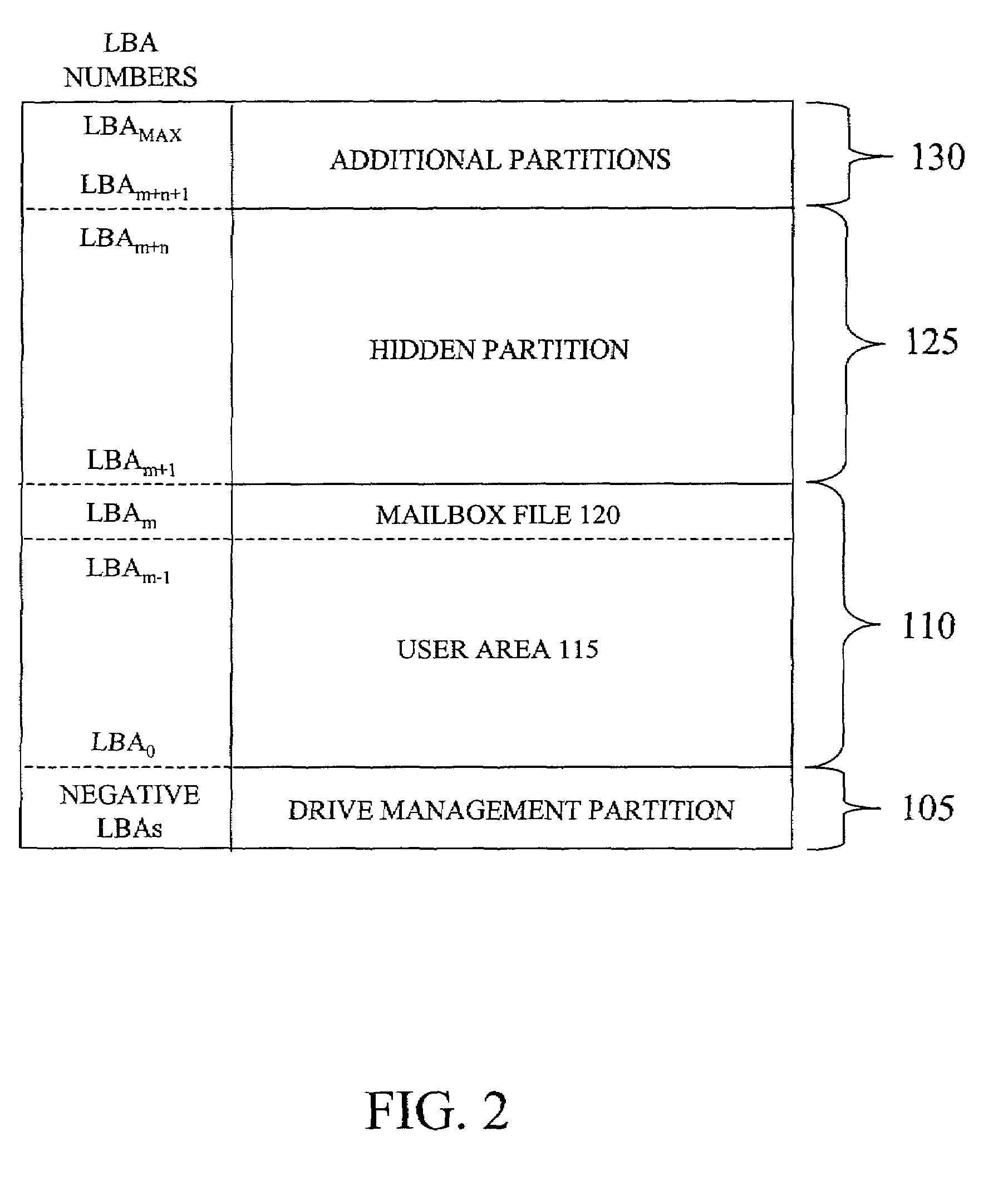

Method for installing a mailbox file associated with a disk storage medium

InactiveUS7543117B1Record information storageUsing detectable carrier informationComputerized systemComputer science

A method is disclosed for installing a mailbox file associated with a disk storage medium of a disk drive. In accordance with exemplary embodiments of the present invention, a computer system includes a host computer, a disk drive host interface and a disk drive having a disk storage medium with a first range of disk drive host interface addressable locations. A disk drive access key is obtained from an access key server, the access key being generated by the access key server as a function of an identifying characteristic of the disk drive. A mailbox file is created in the first range of addressable locations using the access key obtained from the access key server. The disk drive is notified of a location of the mailbox file in the first range of addressable locations such that the disk drive can perform a function characterized by contents of the mailbox file.

Owner:WESTERN DIGITAL VENTURES

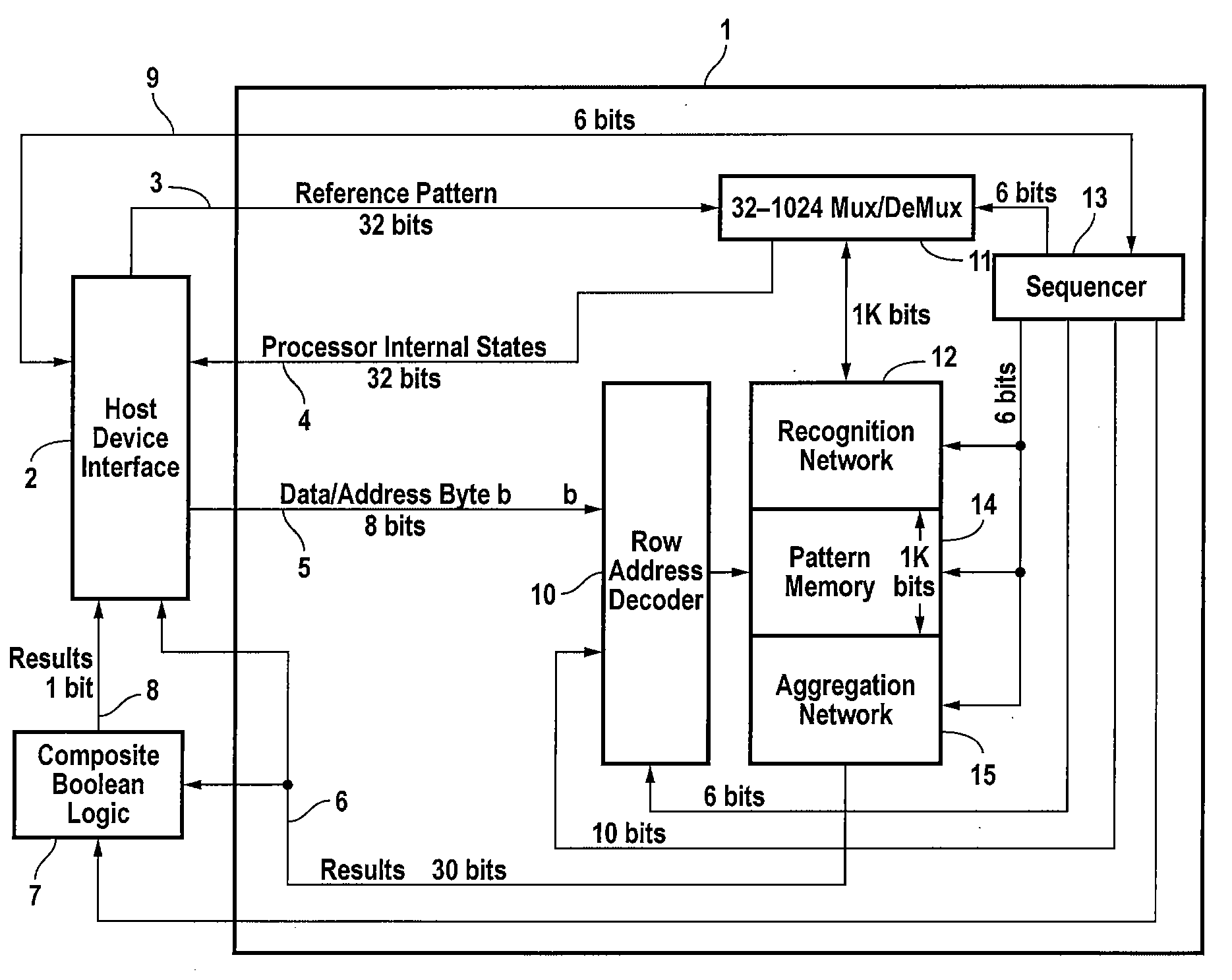

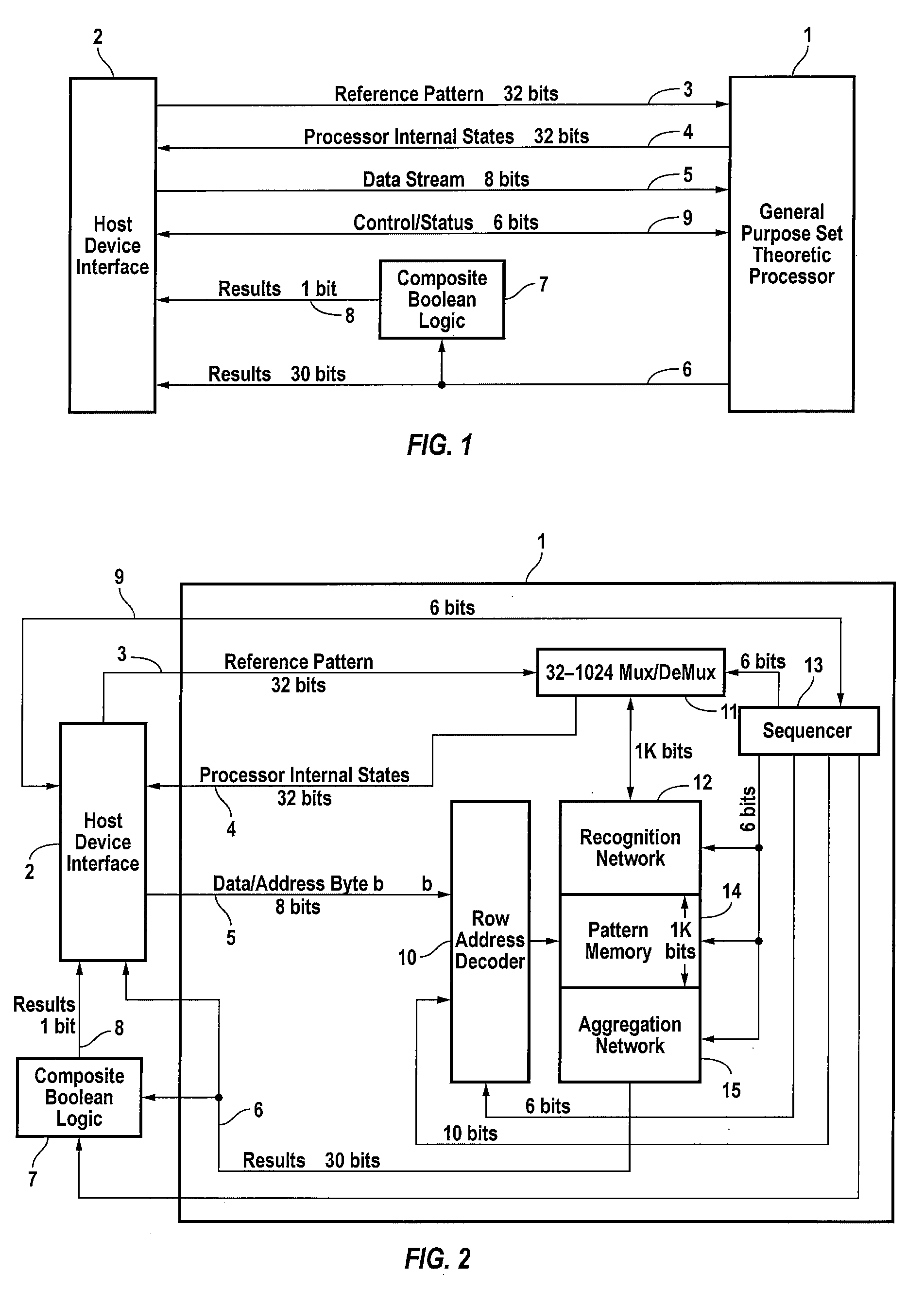

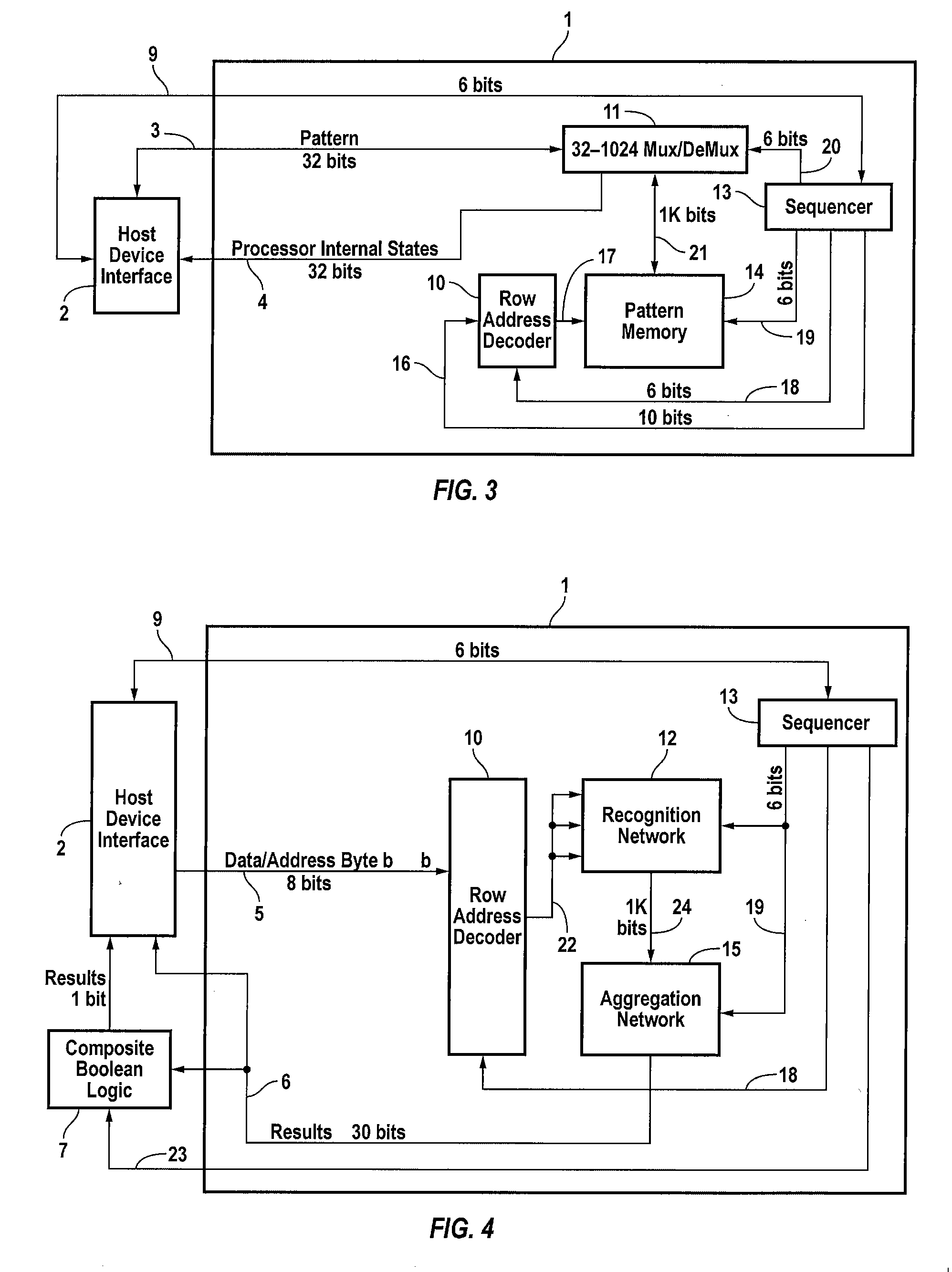

General Purpose Set Theoretic Processor

ActiveUS20070127482A1Low costLow of configurabilityDigital computer detailsCharacter and pattern recognitionGeneral purposeData stream

A general purpose processor architecture (methods and apparatuses) that can discern all subsets of a serial data stream which fulfill an arbitrarily complex reference pattern. The invention comprises an ordered set of Detection Cells conditionally interconnected according to the reference pattern and operationally controlling one another's states through the network. The invention preferably includes a Host Interface to enable reporting of Results from a search session as well as the input and control of reference patterns and source data.

Owner:HARRIS CURTIS L

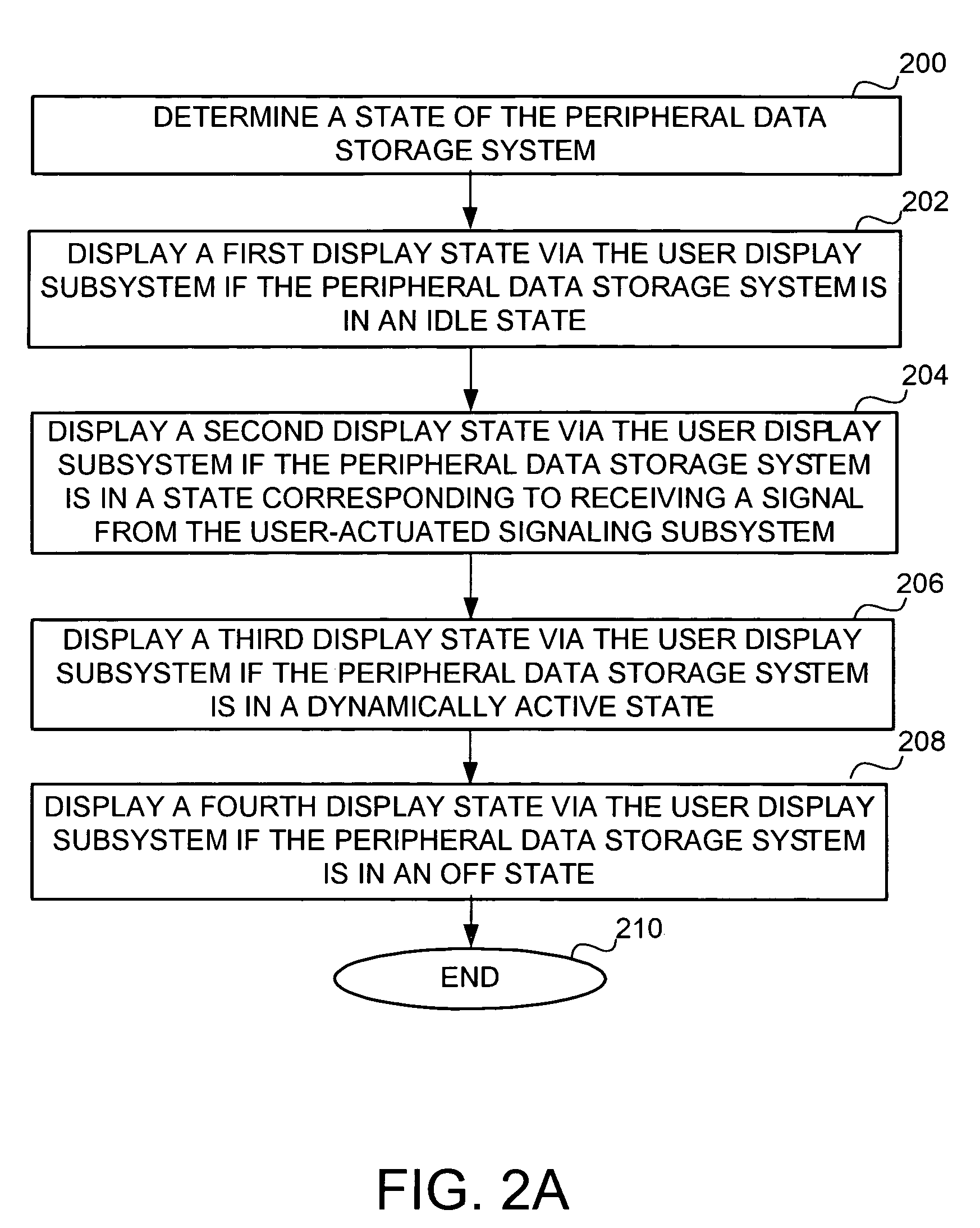

Peripheral data storage system with multi-state user display

InactiveUS7302501B1Error detection/correctionInput/output processes for data processingComputer hardwareActive state

A method of displaying states of a peripheral data storage system (PDSS) comprising a data storage device, a data storage system controller, a user-actuated signaling subsystem, a user display subsystem adapted to display the states, and a peripheral data storage controller host interface adapted for communication with a host system. The method includes determining a state of the PDSS; displaying a first display state via the user display subsystem if the PDSS is in an idle state; displaying a second display state via the user display subsystem if the PDSS is in a state corresponding to receiving a signal from the user-actuated signaling subsystem; displaying a third display state via the user display subsystem if the PDSS is in a dynamically active state; and displaying a fourth display state via the user display subsystem if the PDSS is in an off state.

Owner:WESTERN DIGITAL TECH INC

System and method for providing a host console for use with an electronic card game

InactiveUS20060287103A1Apparatus for meter-controlled dispensingVideo gamesComputer hardwareDisplay device

A host console and method for use with an electronic card table is disclosed. The electronic card table has plurality of electronic player interaction areas located around a periphery of the table and a game computer. The game computer administers the electronic card table and is coupled to the plurality of electronic player interaction areas. The host console is connected to the game computer. The host console includes a host display, a host interface, and a host controller. The host controller is coupled to the host display and the host interface and allows the host to display information related to the card game and reset the connection between the game computer and one or more of the electronic player interaction areas and / or restart software on one or more of the electronic player interaction areas and / or reboot one or more of the electronic player interaction areas.

Owner:POKERTEK

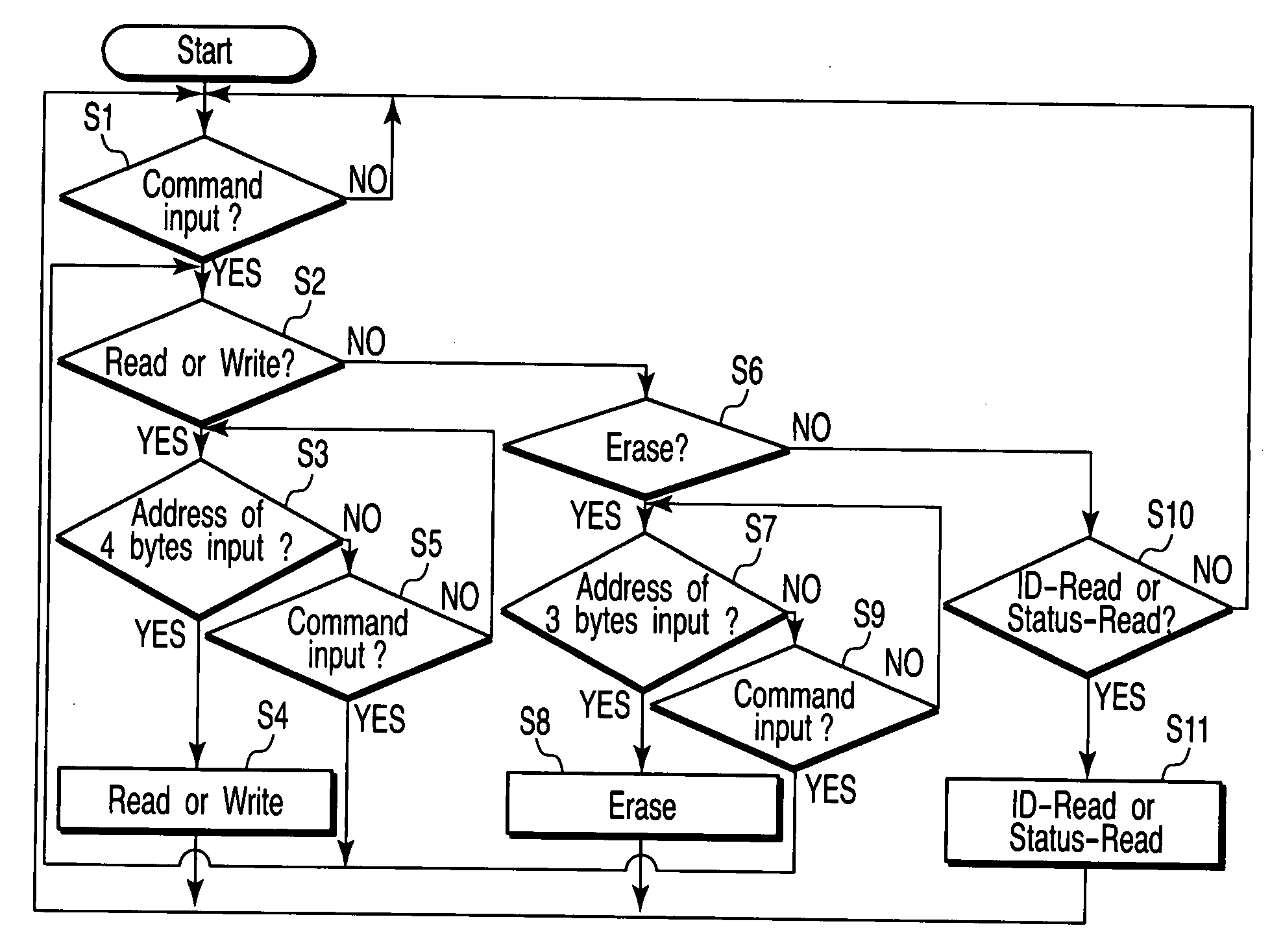

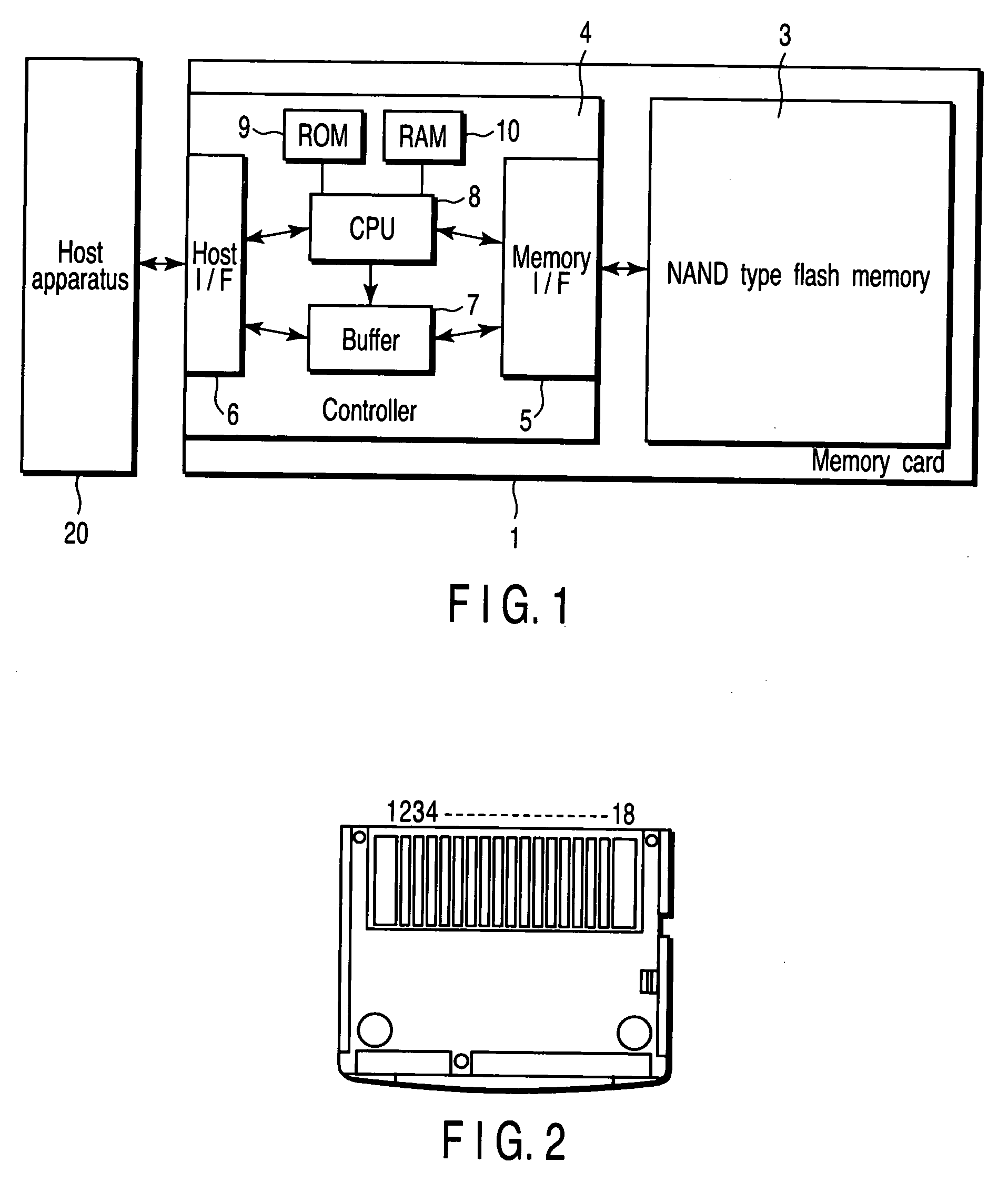

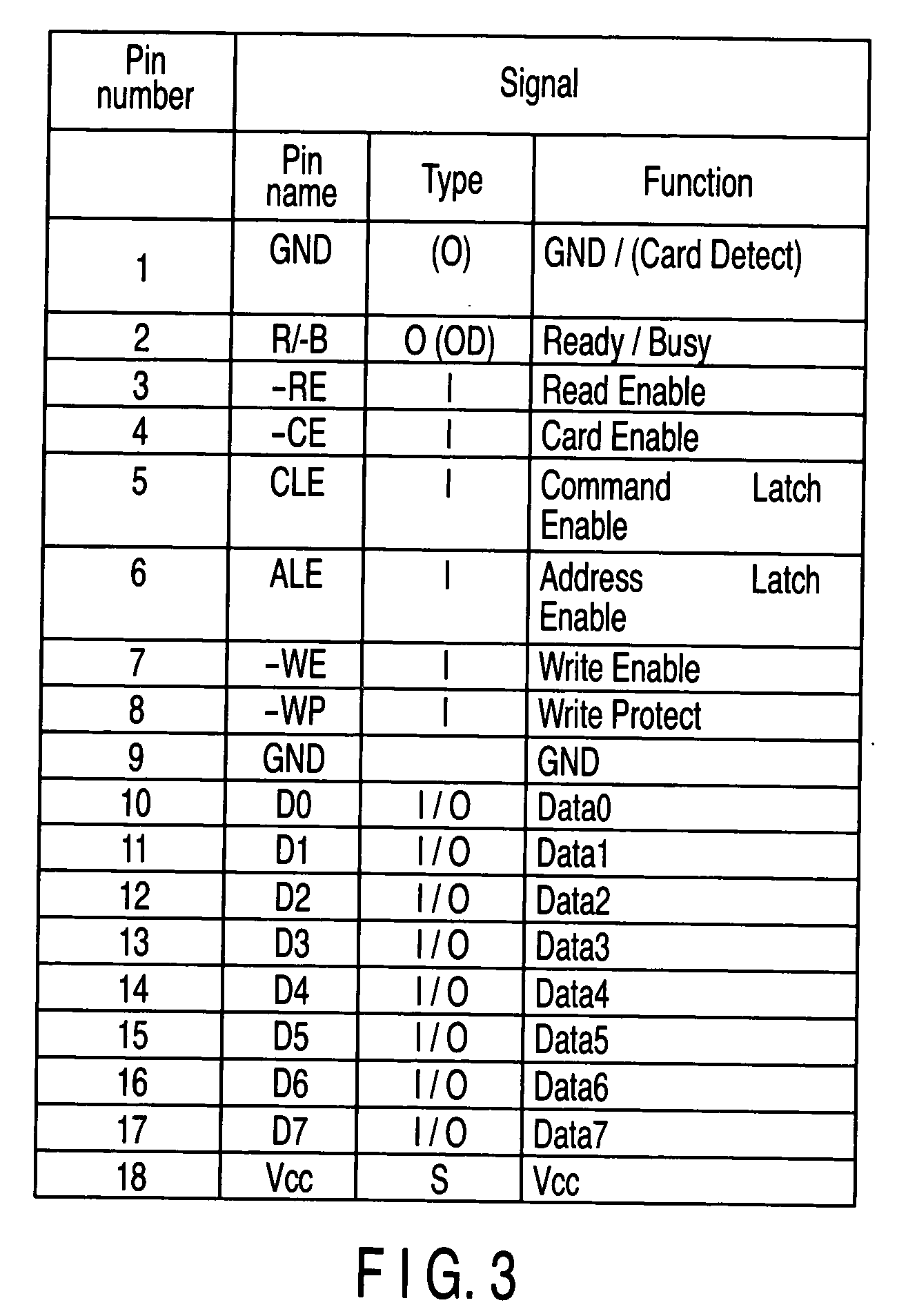

Memory card having a storage cell and method of controlling the same

A controller comprises a host interface section and a processing circuit. The host interface section receives a command sequence outputted from a host apparatus to a first nonvolatile semiconductor memory. The processing circuit processes the command sequence outputted from the host apparatus to the first nonvolatile semiconductor memory, and controls writing, reading and erase of data to a second nonvolatile semiconductor memory, according to the command sequence.

Owner:KIOXIA CORP

System and method for providing a host console for use with an electronic card game

InactiveUS20060264252A1Apparatus for meter-controlled dispensingVideo gamesDisplay deviceHuman–computer interaction

A host console and method for use with an electronic card table is disclosed. The electronic card table has plurality of electronic player interaction areas located around a periphery of the table and a game computer. The game computer administers the electronic card table and is coupled to the plurality of electronic player interaction areas. The host console is connected to the game computer. The host console includes a host display, a host interface, and a host controller. The host controller is coupled to the host display and the host interface and allows the host to display information related to the card game and to pause and / or stop the game, to reserve seats at a table and to penalize players.

Owner:POKERTEK

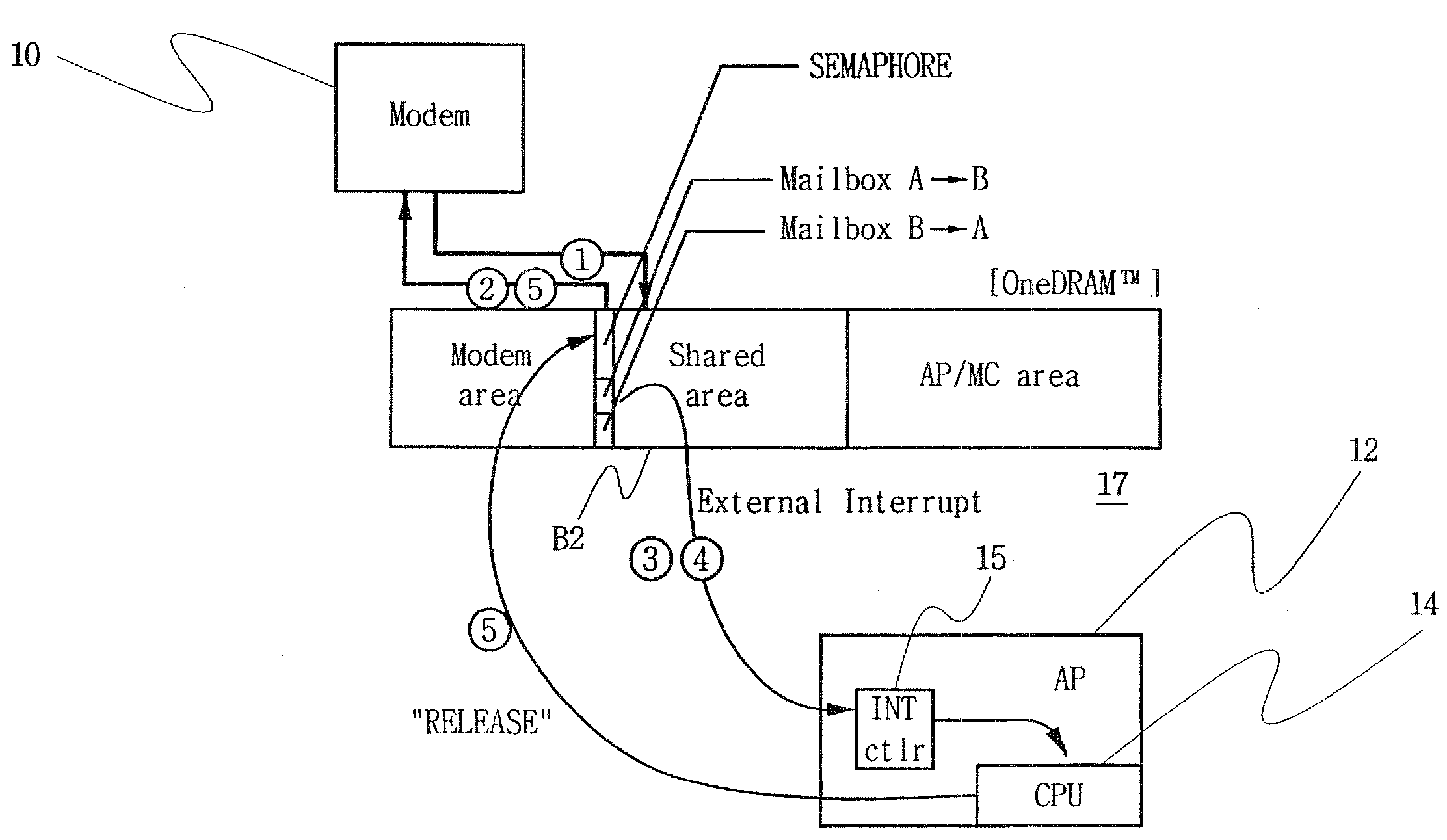

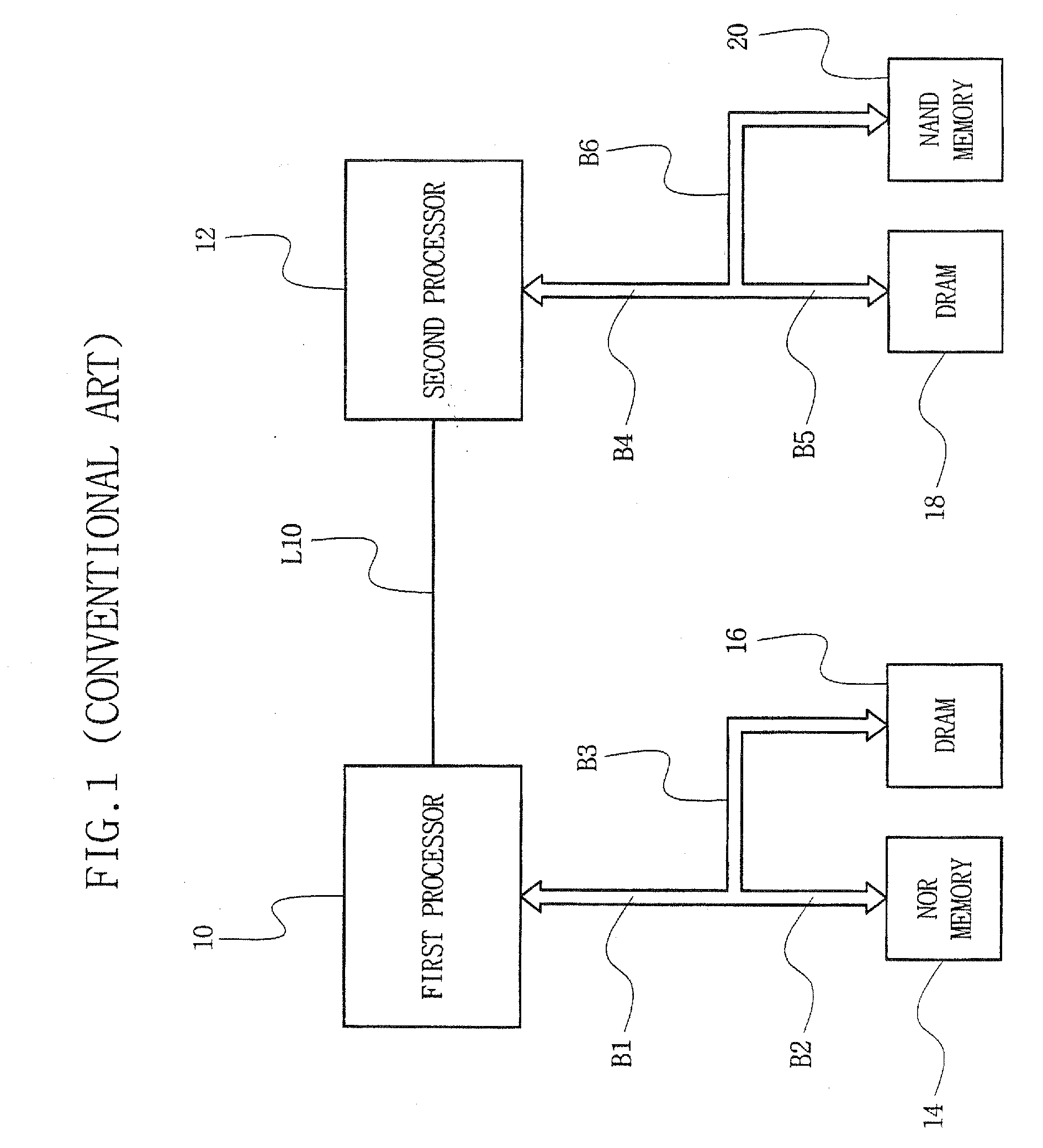

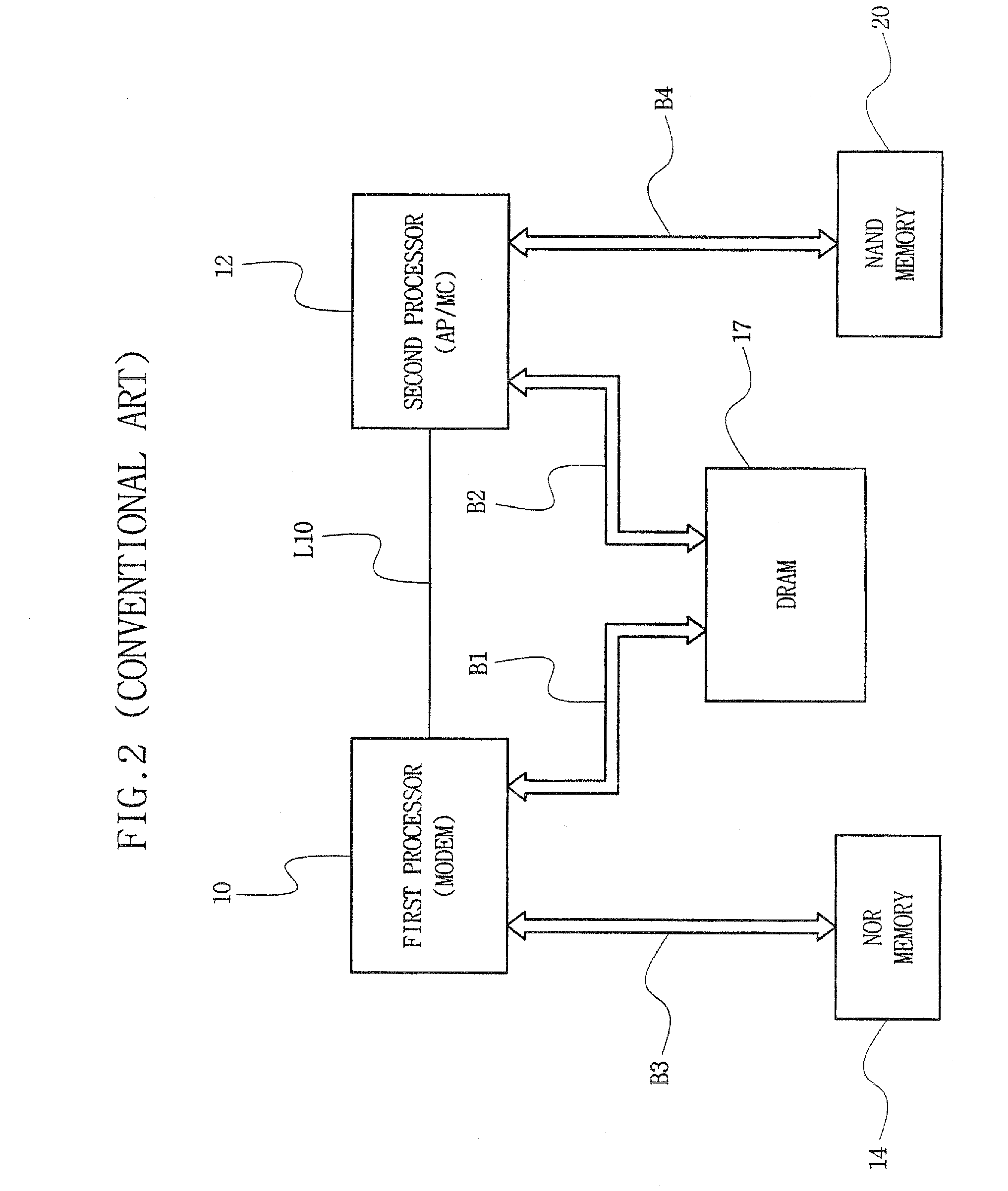

Multipath accessible semiconductor memory device with host interface between processors

ActiveUS20080077937A1Low costIncrease speedGeneral purpose stored program computerDigital storageMulti processorData access

A multipath accessible semiconductor memory device provides an interface function between processors. The memory device may include a memory cell array having a shared memory area operationally coupled to two or more ports that are independently accessible by two or more processors, an access path forming unit to form a data access path between one of the ports and the shared memory area in response to external signals applied by the processors, and an interface unit having a semaphore area and mailbox areas accessible in the shared memory area by the two or more processors to provide an interface function for communication between the two or more processors.

Owner:SAMSUNG ELECTRONICS CO LTD

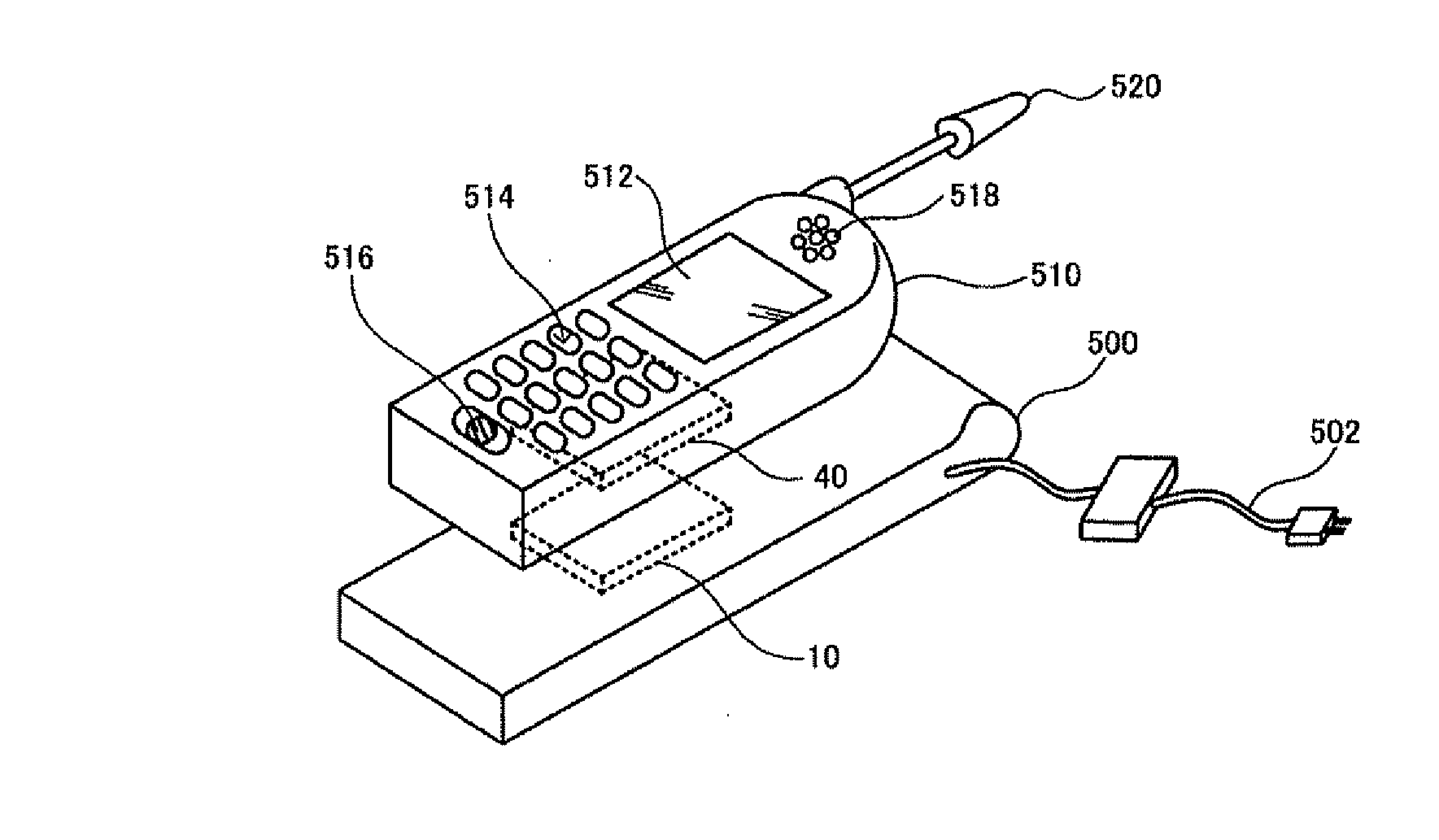

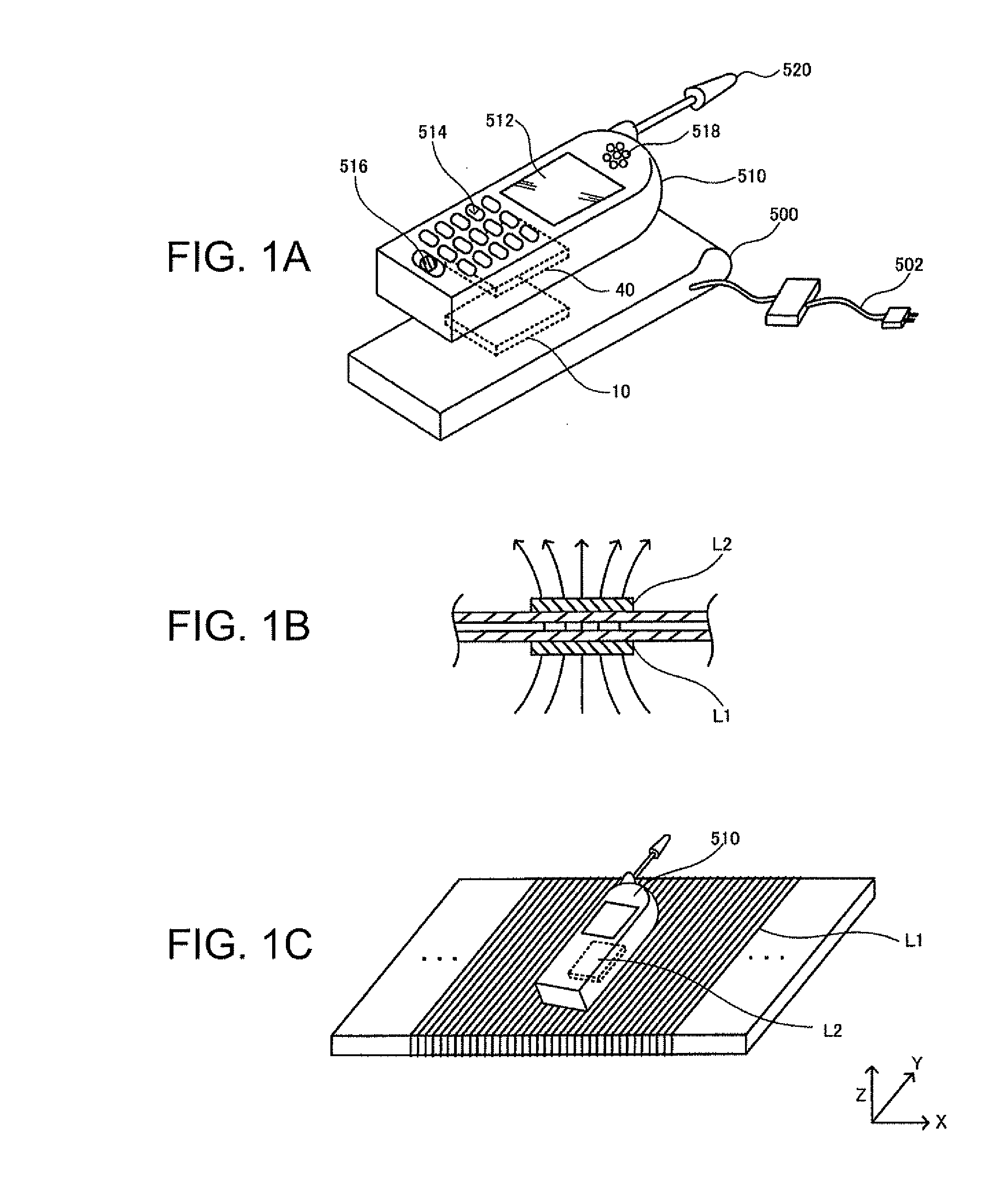

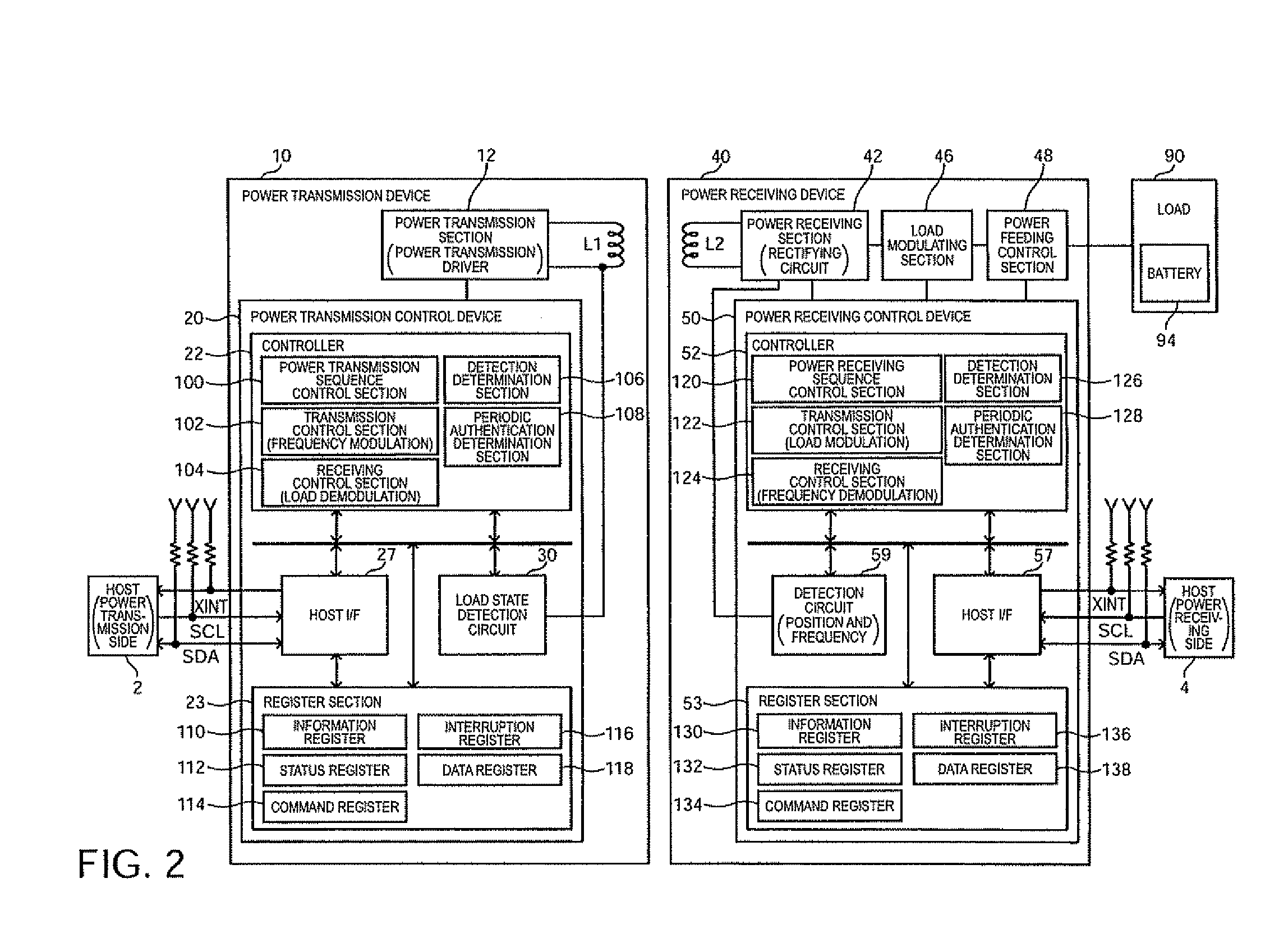

Power transmission control device, power transmission device, power receiving control device, power receiving device, and electronic apparatus

ActiveUS20100013319A1Efficient use ofReduce electricity loadVariable inductances/transformersSubstation equipmentElectricityElectric power transmission

There is provided a power transmission control device included in a power transmission device in a contactless power transmission system that transmits power from the power transmission device to a power receiving device by electromagnetically coupling a primary coil to a secondary coil to supply the power to a load of the power receiving device. The power transmission control device includes a controller controlling the power transmission control device, a host interface communicating with a power transmission-side host, and a register section accessible from the power transmission-side host via the host interface. The controller shifts into a communication mode that executes communication between the power transmission-side host and a power receiving-side host, when the power transmission-side host writes, via the host interface, a communication request command that requests the communication between the hosts in the register section. Then, the controller transmits the communication request command to the power receiving device.

Owner:138 EAST LCD ADVANCEMENTS LTD

Enhanced host interface

ActiveUS20070033327A1Efficient storageEfficient managementMemory architecture accessing/allocationDigital data information retrievalOperating systemMemory systems

A memory system that is compatible with hosts using different protocols includes protocol adapters for the different protocols. Protocol adapters allow a common backend system to be used for data that is provided in different formats. A protocol adapter generates responses to a host and generates commands for a backend as appropriate.

Owner:SANDISK TECH LLC

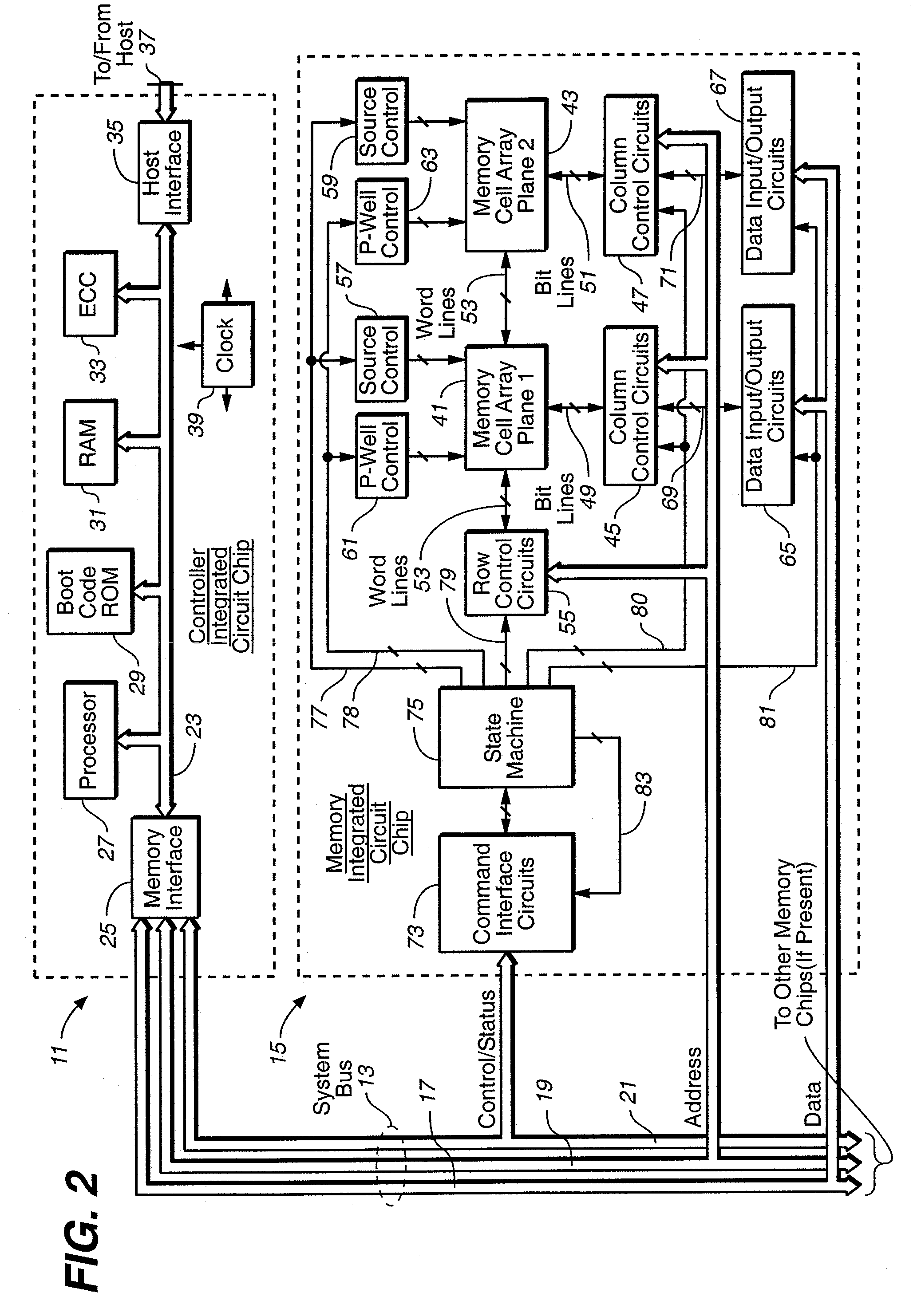

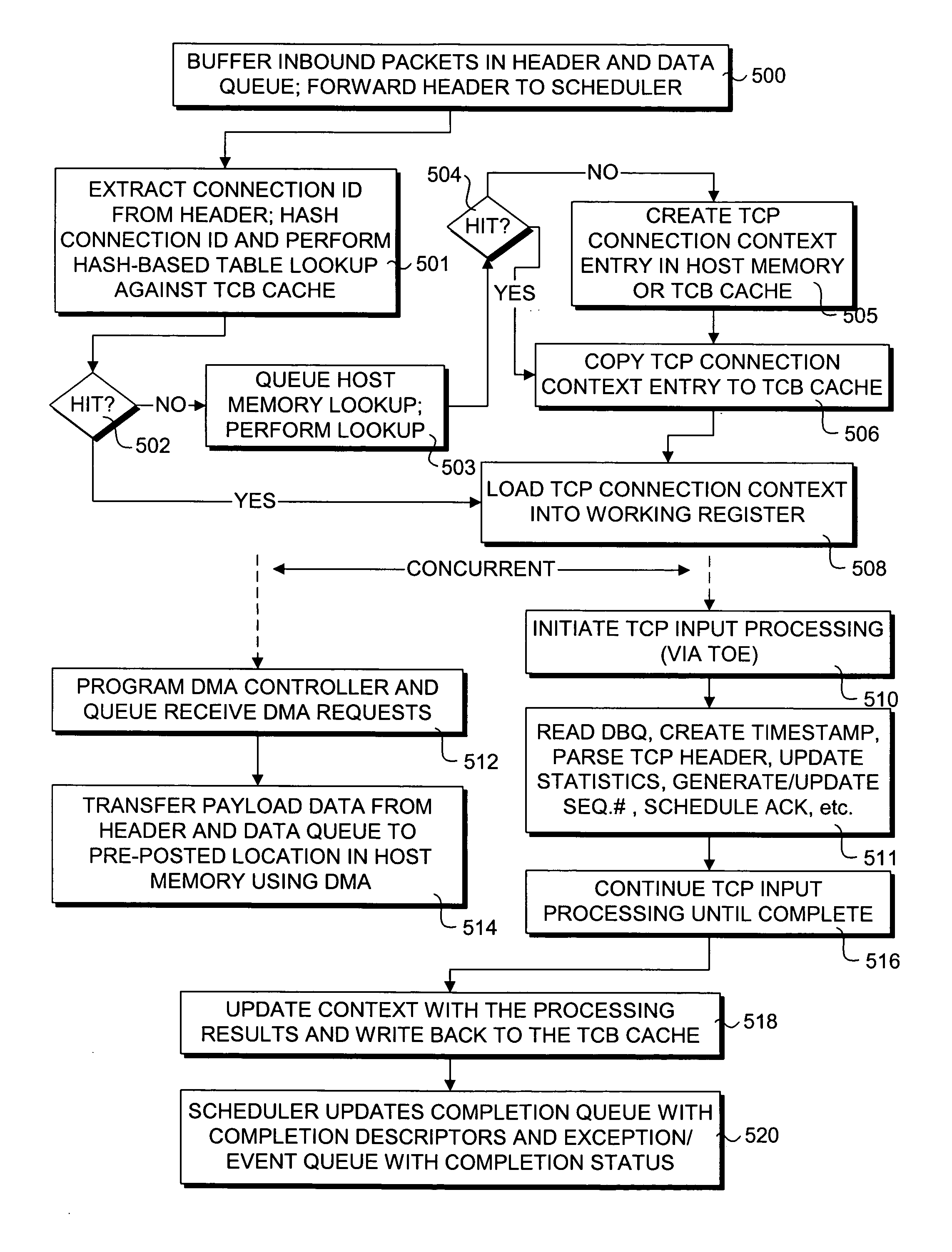

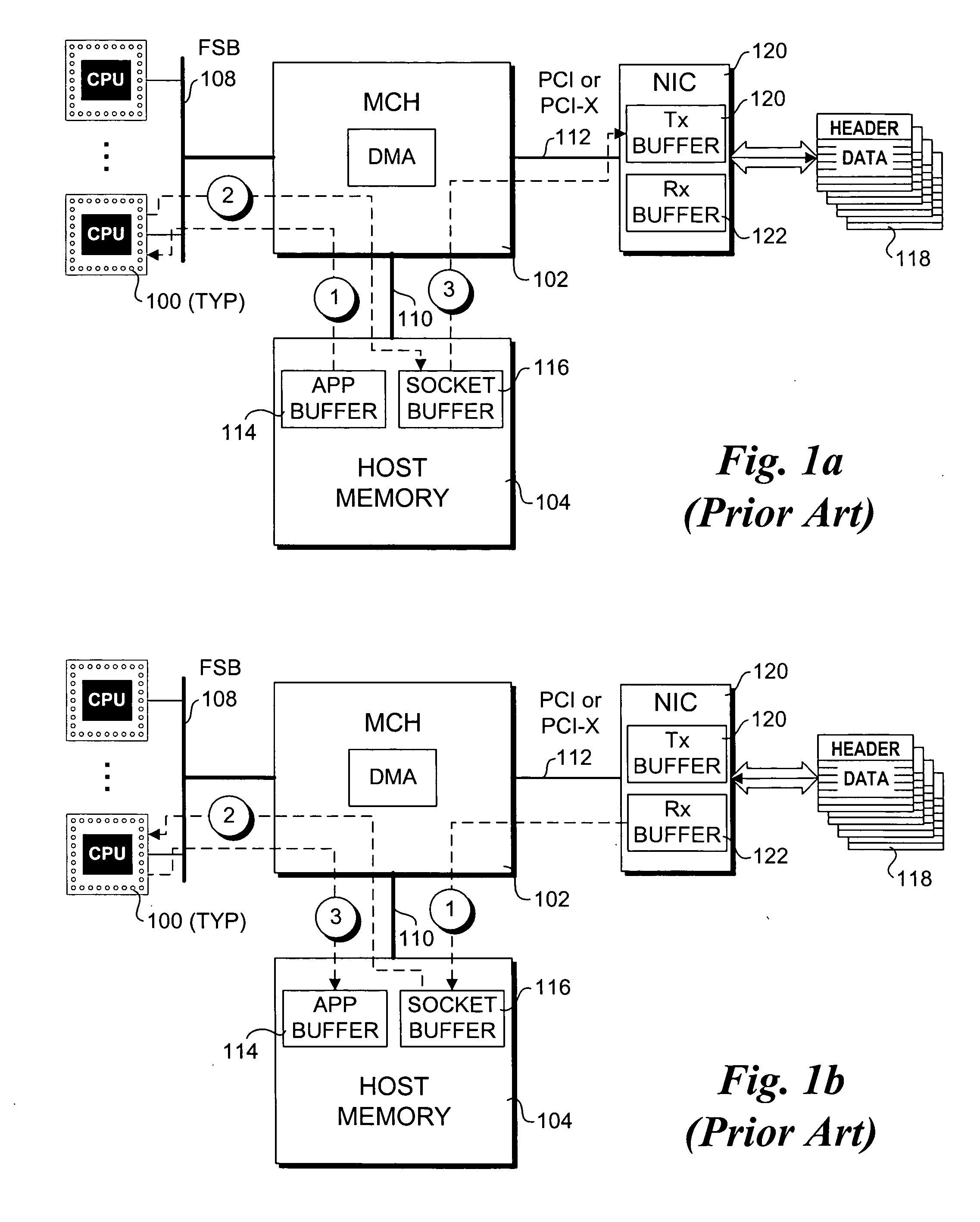

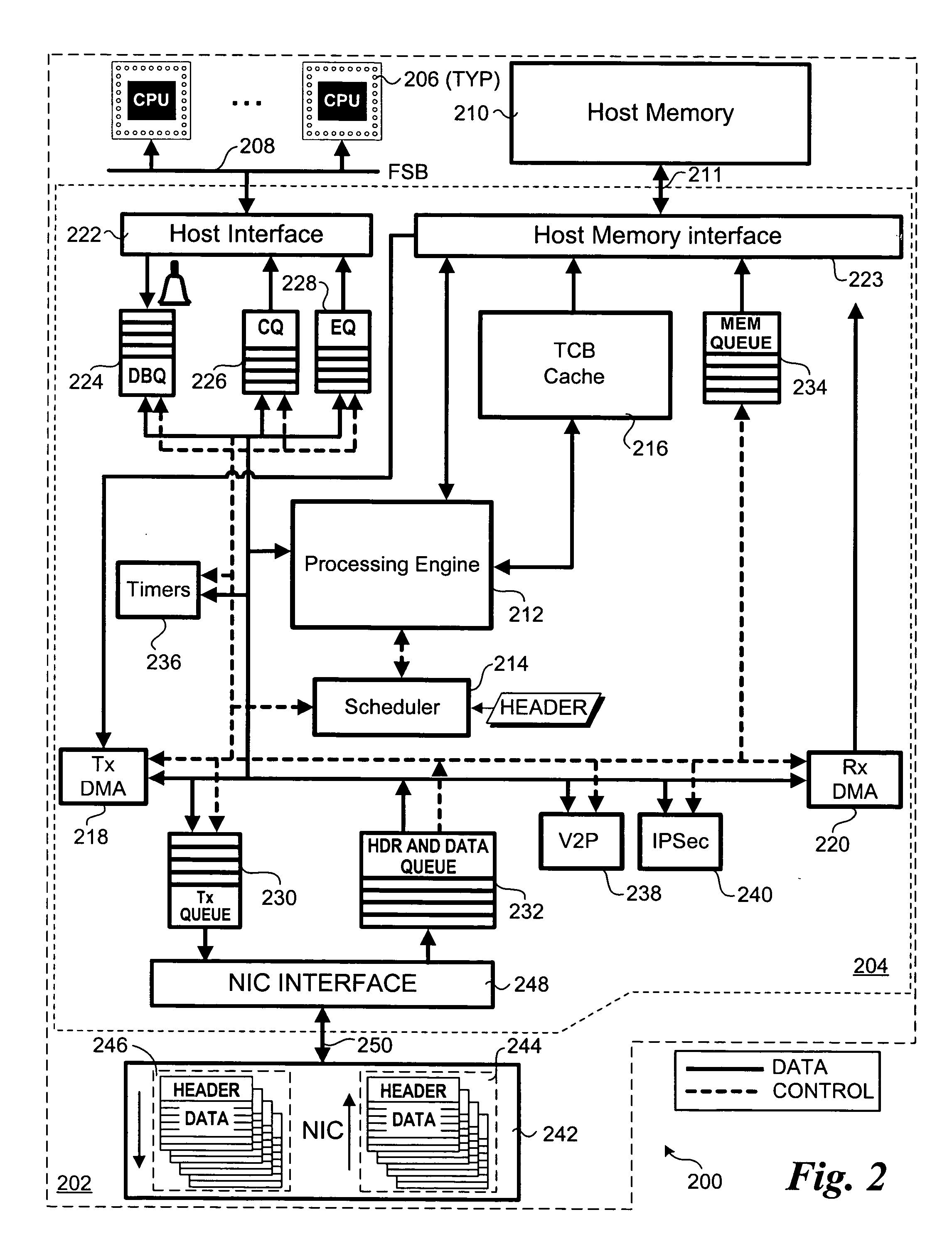

Hardware-based multi-threading for packet processing

Methods and apparatus for processing transmission control protocol (TCP) packets using hardware-based multi-threading techniques. Inbound and outbound TCP packet are processed using a multi-threaded TCP offload engine (TOE). The TOE includes an execution core comprising a processing engine, a scheduler, an on-chip cache, a host memory interface, a host interface, and a network interface controller (NIC) interface. In one embodiment, the TOE is embodied as a memory controller hub (MCH) component of a platform chipset. The TOE may further include an integrated direct memory access (DMA) controller, or the DMA controller may be embodied as separate circuitry on the MCH. In one embodiment, inbound packets are queued in an input buffer, the headers are provided to the scheduler, and the scheduler arbitrates thread execution on the processing engine. Concurrently, DMA payload data transfers are queued and asynchronously performed in a manner that hides memory latencies. In one embodiment, the technique can process typical-size TCP packets at 10 Gbps or greater line speeds.

Owner:TAHOE RES LTD

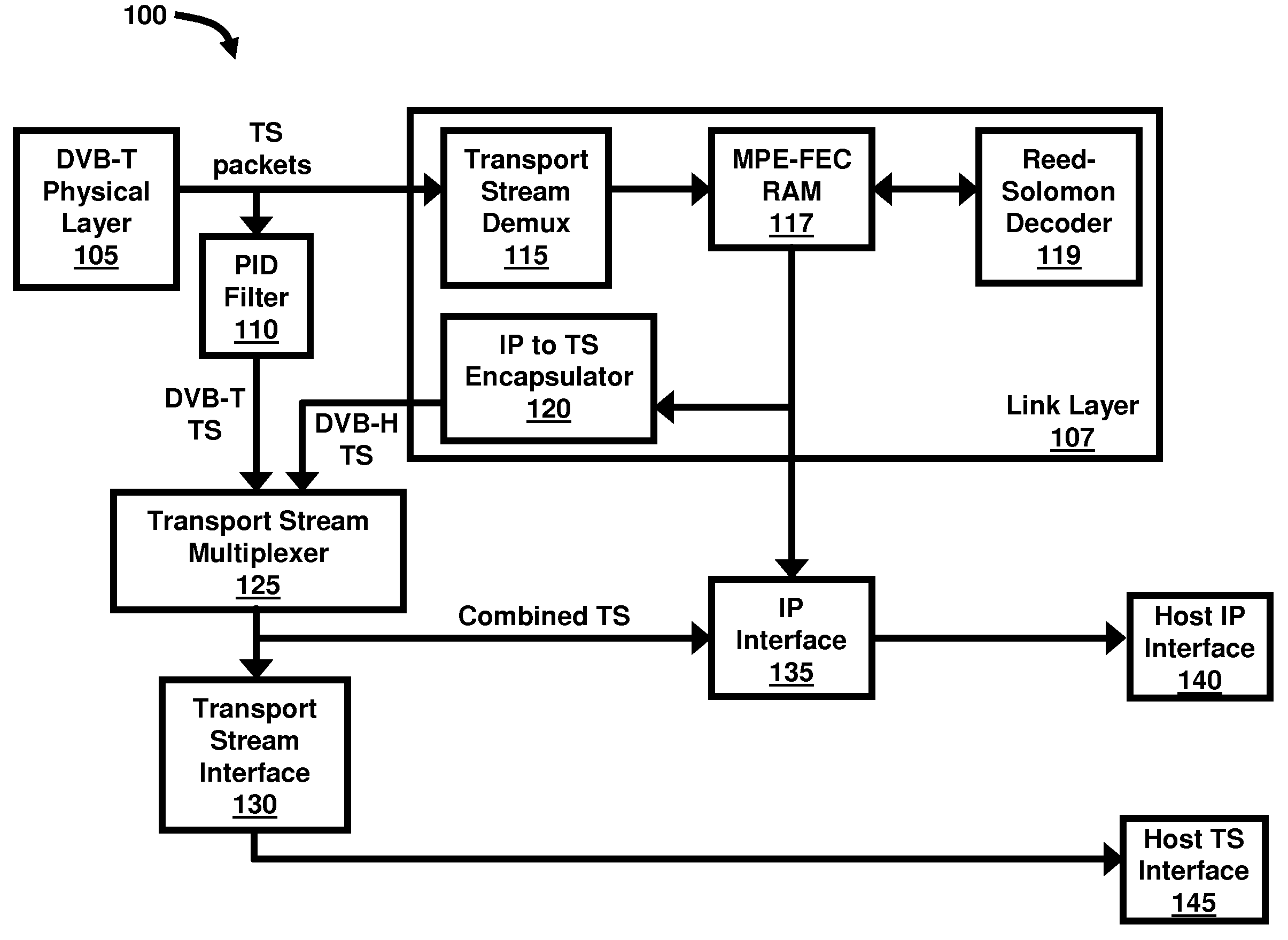

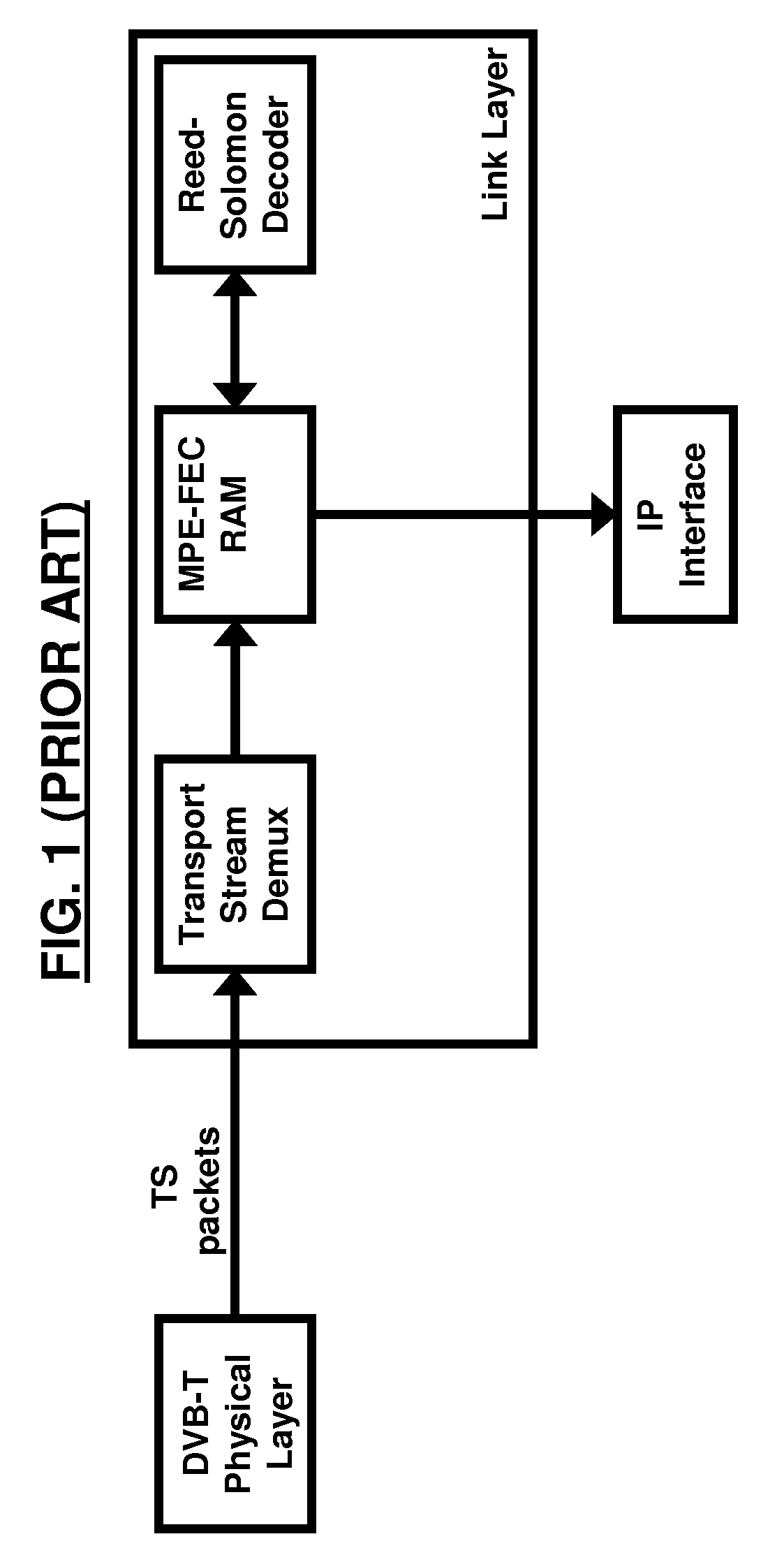

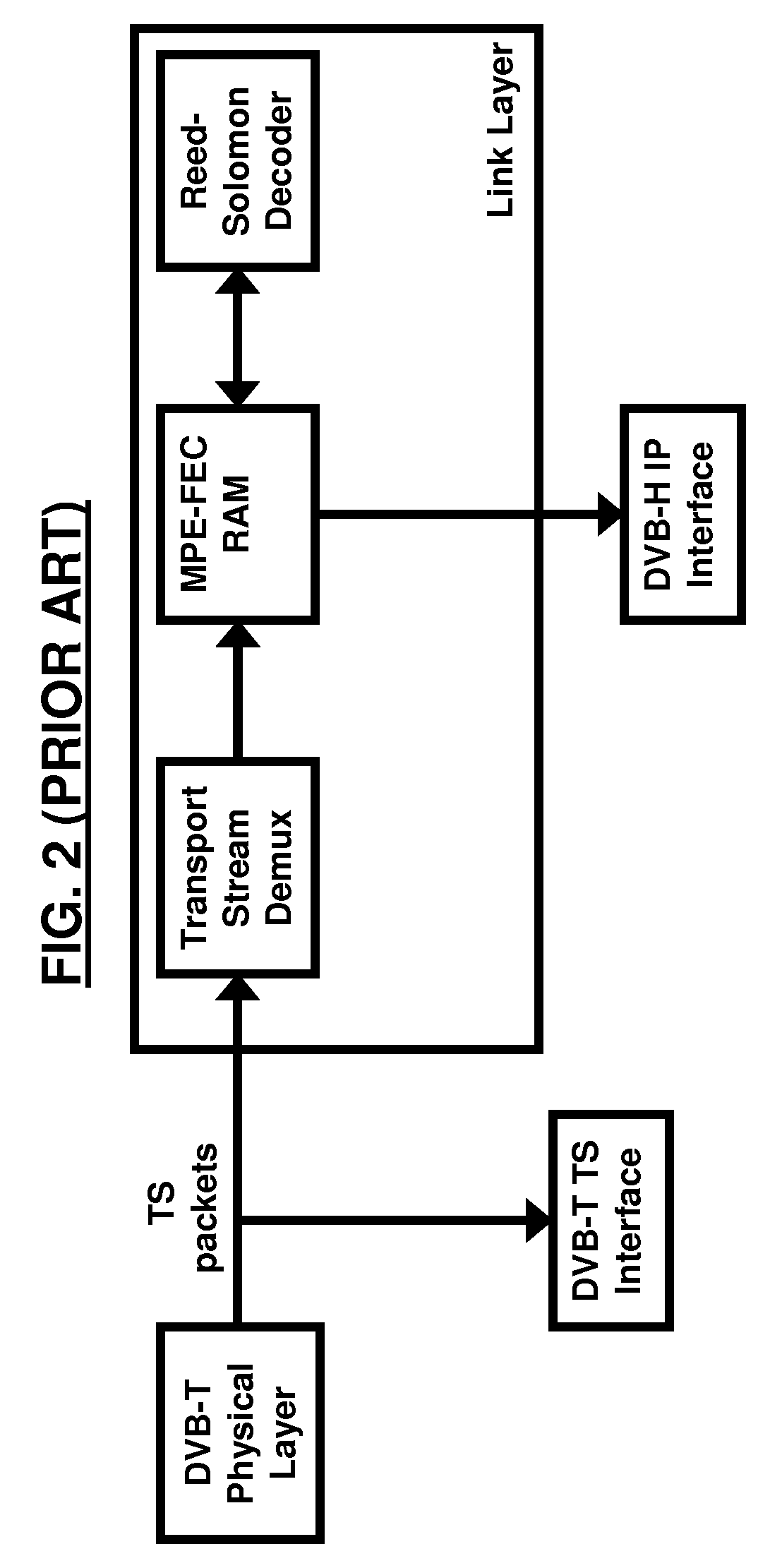

Unified interfacing for dvb-t/h mobile TV applications

InactiveUS20080159279A1Correction errorError preventionBroadcast information characterisationDigital videoComputer network

Transmitting data in a digital video broadcasting for handheld (DVB-H) receiver comprises a transport stream (TS) demultiplexer adapted to extract internet protocol (IP) datagrams from TS data packets; a packet identifier (PID) filter adapted to extract the TS data packets based on the PIDs of the TS data packets; a Multi Protocol Encapsulation-Forward Error Correction (MPE-FEC) random access memory (RAM) unit operatively connected to the TS demultiplexer; a Reed-Solomon decoder operatively connected to the MPE-FEC RAM unit; an IP to TS encapsulator operatively connected to the MPE-FEC RAM unit; a TS multiplexer operatively connected to each of the PID filter and the IP to TS encapsulator, wherein the TS multiplexer is adapted to combine both DVB-Terrestrial (DVB-T) and DVB-H TS data packets into a single combined TS data packet; and a host interface operatively connected to the TS multiplexer.

Owner:ATMEL CORP

Processing system with millimeter wave host interface and method for use therewith

InactiveUS20090037628A1Network topologiesElectric digital data processingModem deviceMillimetre wave

A processing system includes a plurality of first circuit modules and a wired data bus, connected to the plurality of first circuit modules. A plurality of second circuit modules are coupled to an RF data bus via a millimeter wave communication path. A millimeter wave modem receives first data from at least one of the plurality of first circuit modules via the wired data bus, and transmits the first data over the RF data bus to at least one of the plurality of second circuit modules.

Owner:AVAGO TECH INT SALES PTE LTD

Apparatus and method for in-line insertion and removal of markers

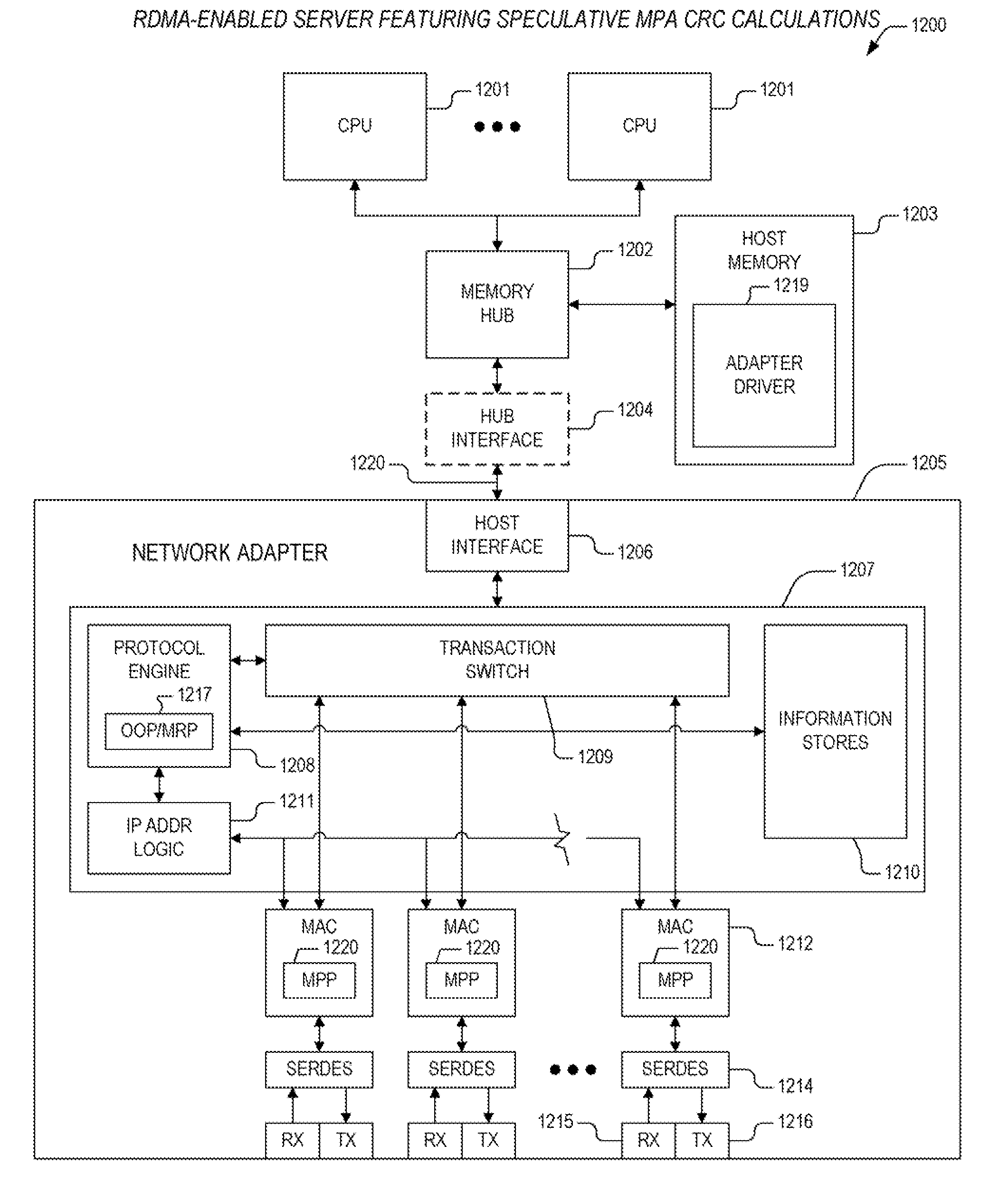

ActiveUS20080043750A1Efficient and effective insertion/removalData switching by path configurationDirect memory accessHost memory

An apparatus is provided, for performing a direct memory access (DMA) operation between a host memory in a first server and a network adapter. The apparatus includes a host frame parser and a protocol engine. The host frame parser is configured to receive data corresponding to the DMA operation from a host interface, and is configured to insert markers on-the-fly into the data at a prescribed interval and to provide marked data for transmission to a second server over a network fabric. The protocol engine is coupled to the host frame parser. The protocol engine is configured to direct the host frame parser to insert the markers, and is configured to specify a first marker value and an offset value, whereby the host frame parser is enabled to locate and insert a first marker into the data.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com