Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1015 results about "Disk controller" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

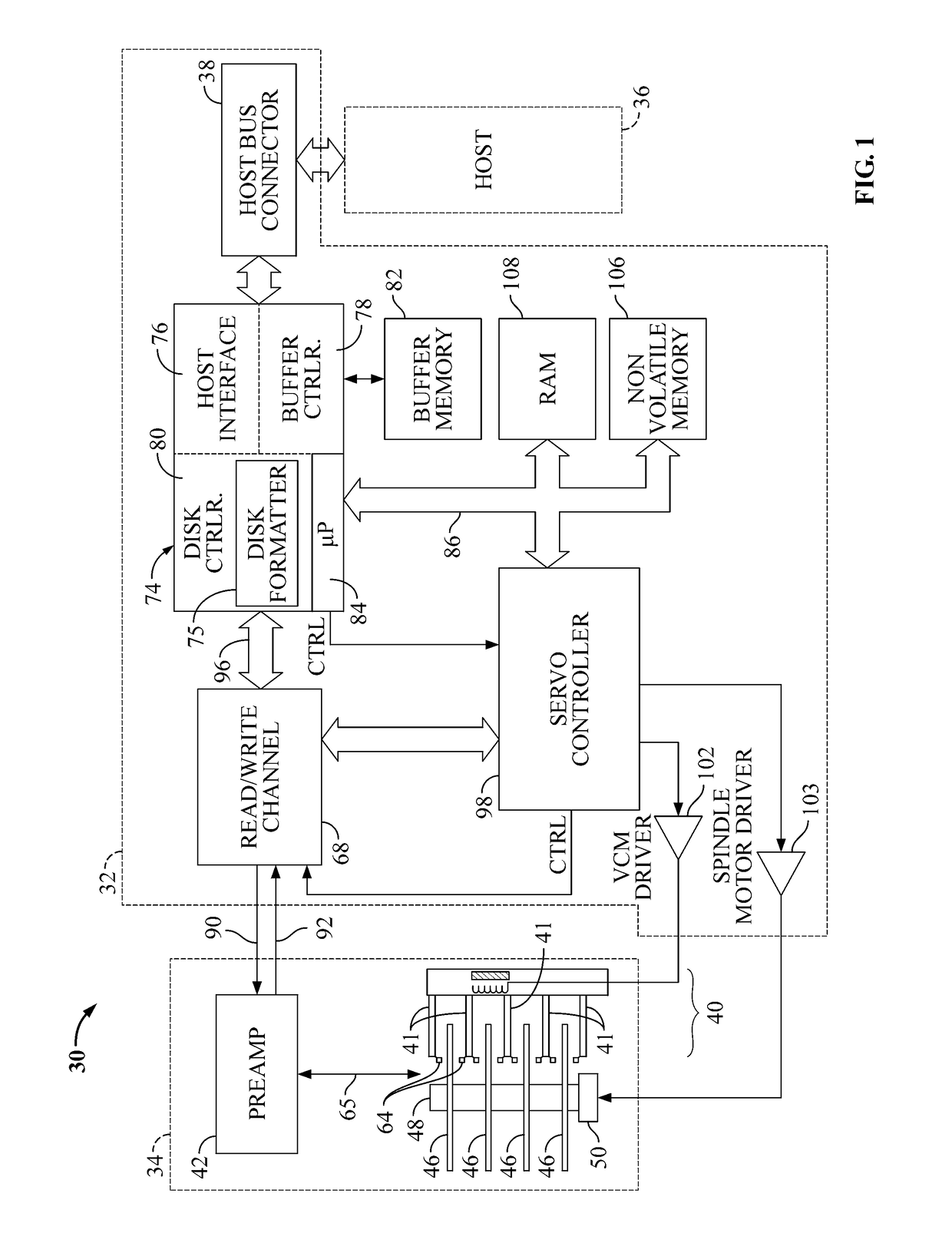

The disk controller is the controller circuit which enables the CPU to communicate with a hard disk, floppy disk or other kind of disk drive. Also it provides an interface between the disk drive and the bus connecting it to the rest of the system.

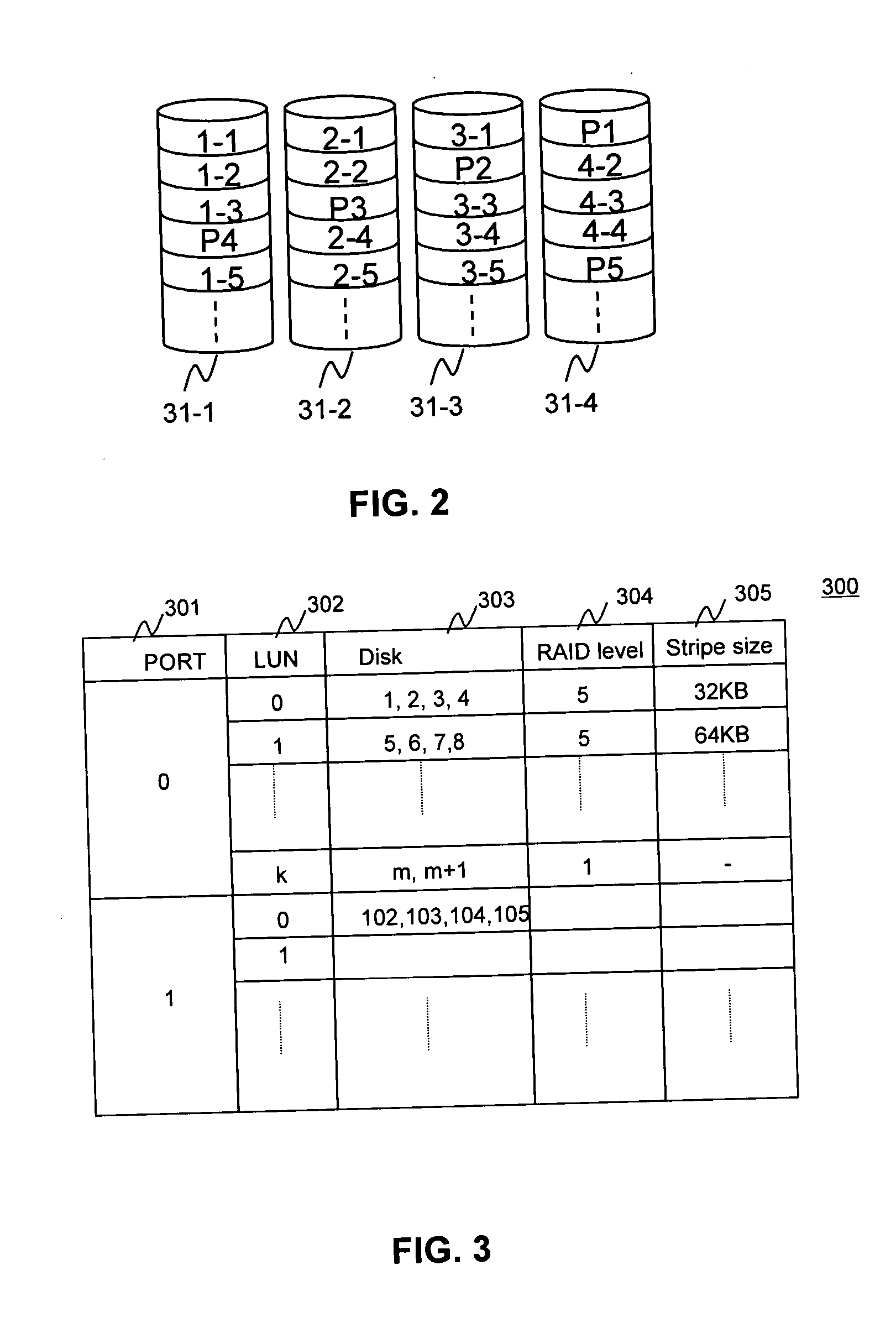

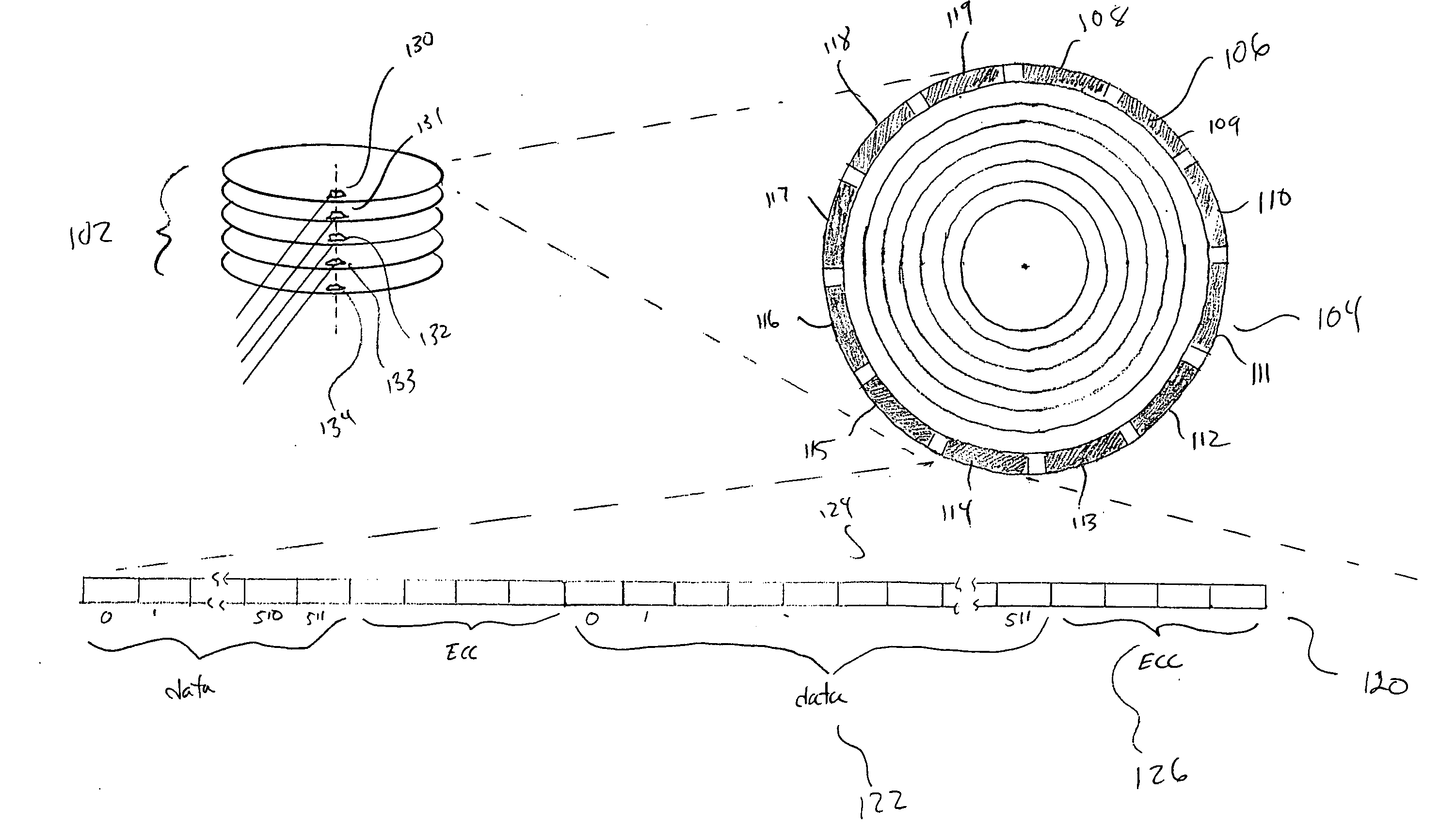

Method and apparatus for reconstructing data in object-based storage arrays

A method and apparatus for placing objects on a storage device of a storage system and reconstructing data of objects in the storage device. The storage system stores data as objects and implements a RAID architecture including a plurality of the storage devices, and a disk controller for processing Object-based Storage Device (OSD) commands. Each object includes data and attribute. Parity data is calculated for reconstructing an object upon occurrence of a storage device failure. Each storage device includes plural stripes each having a predetermined length. Each object is stored in a stripe wherein an attribute is stored in the head of the stripe and data is stored after the attribute. When the object size exceeds the stripe length, the remainder of the object is stored in the next stripe, and when another object is to be stored, an attribute is stored at a head of a further next stripe and data is stored just after the attribute.

Owner:GOOGLE LLC

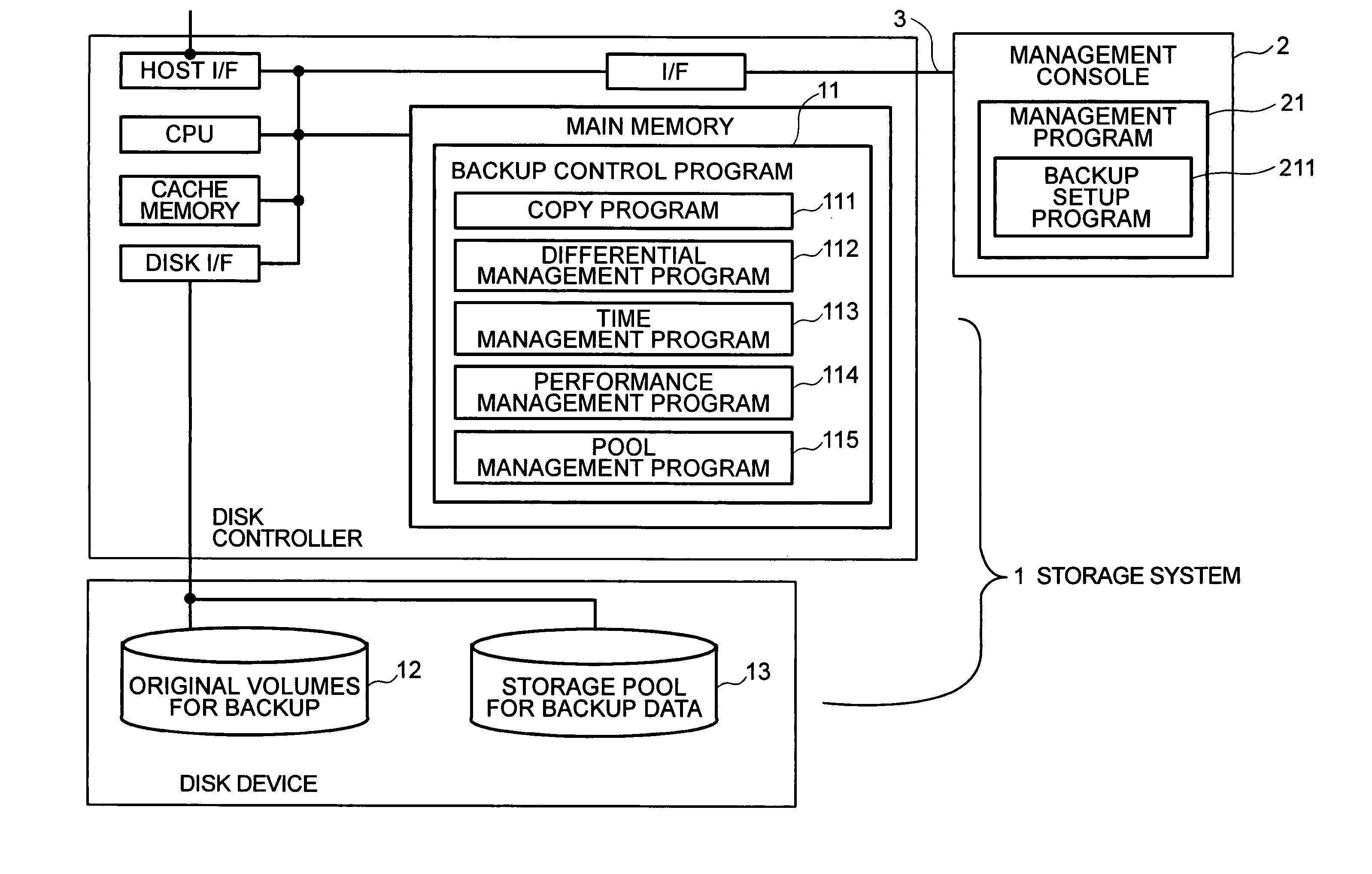

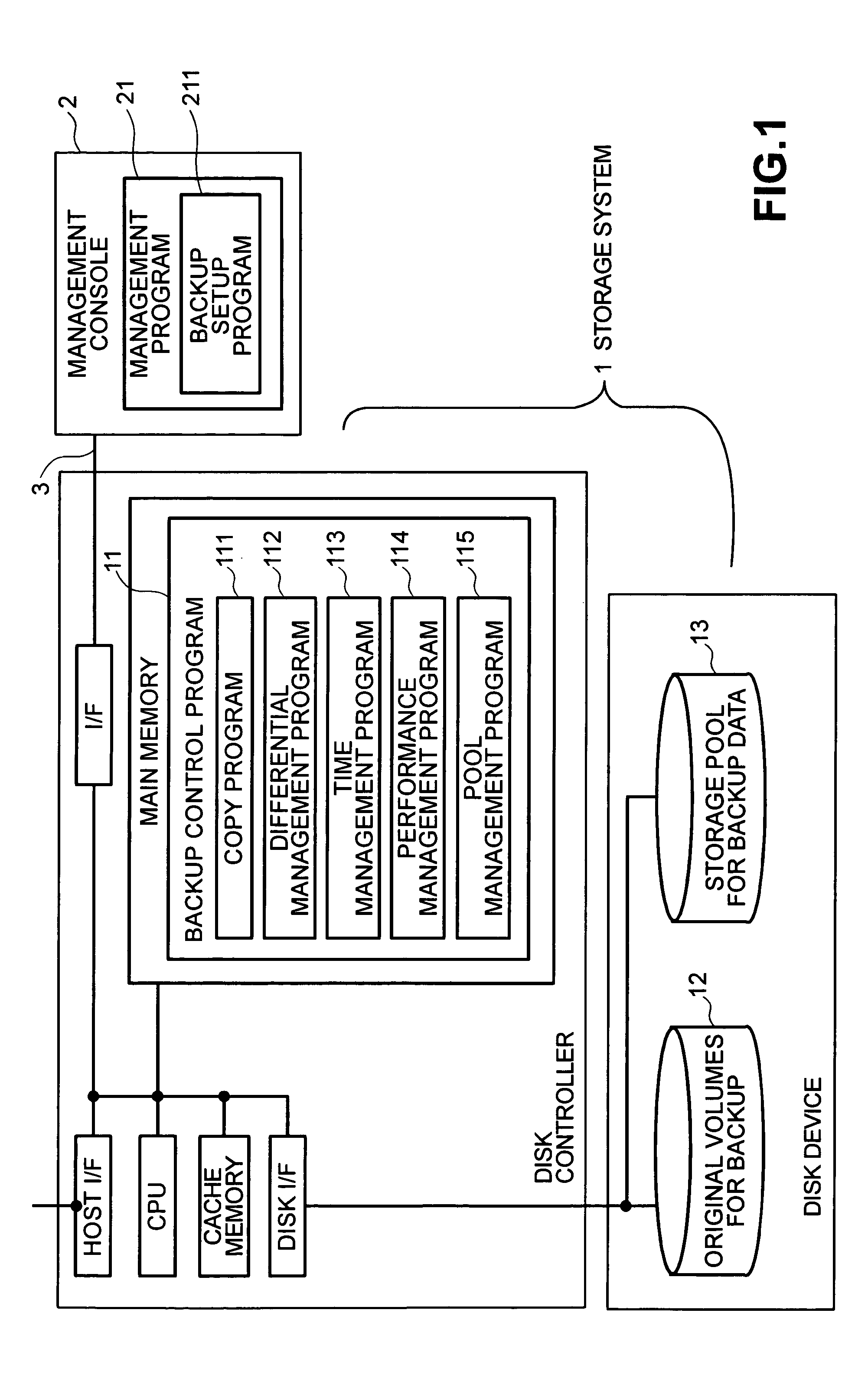

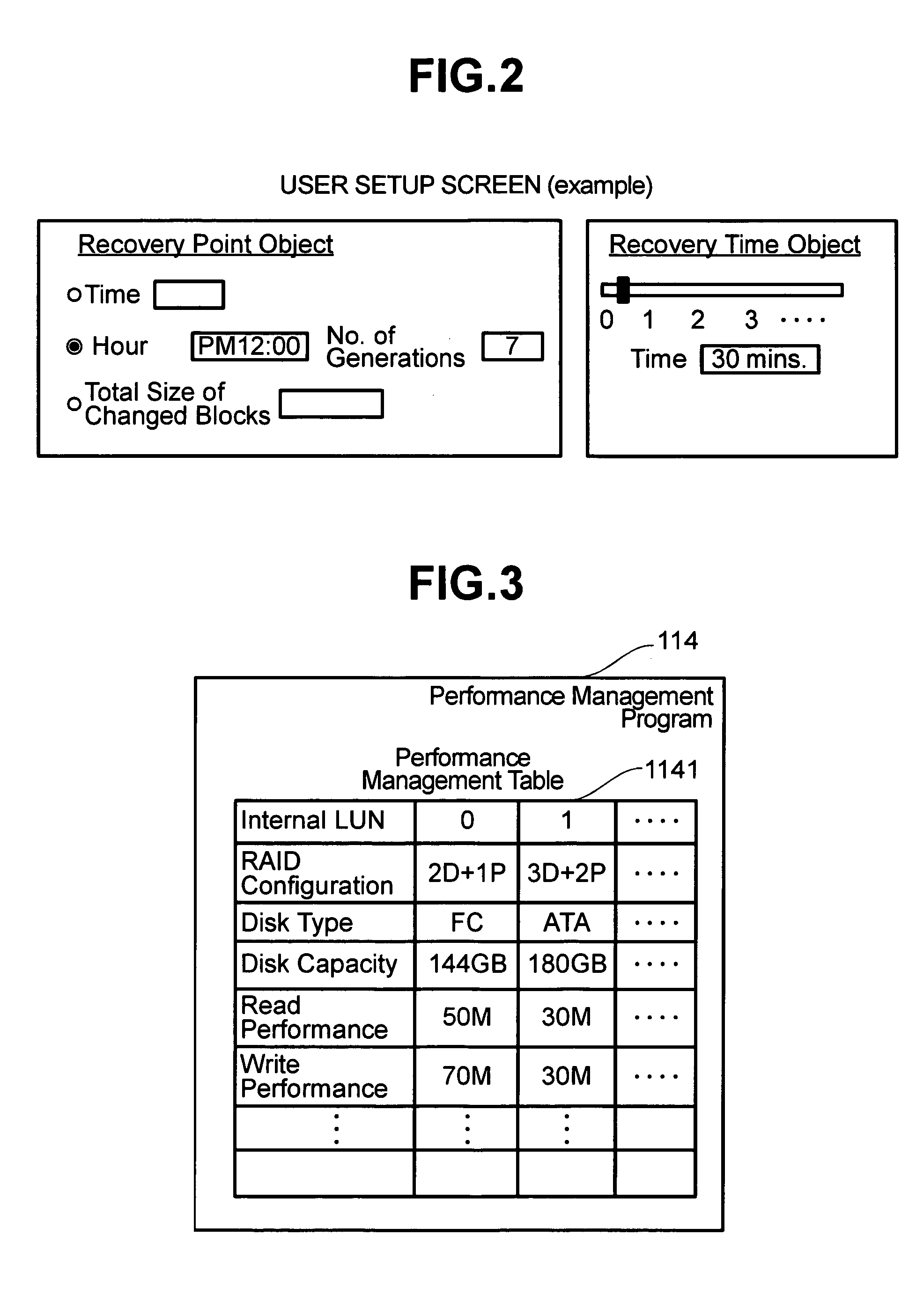

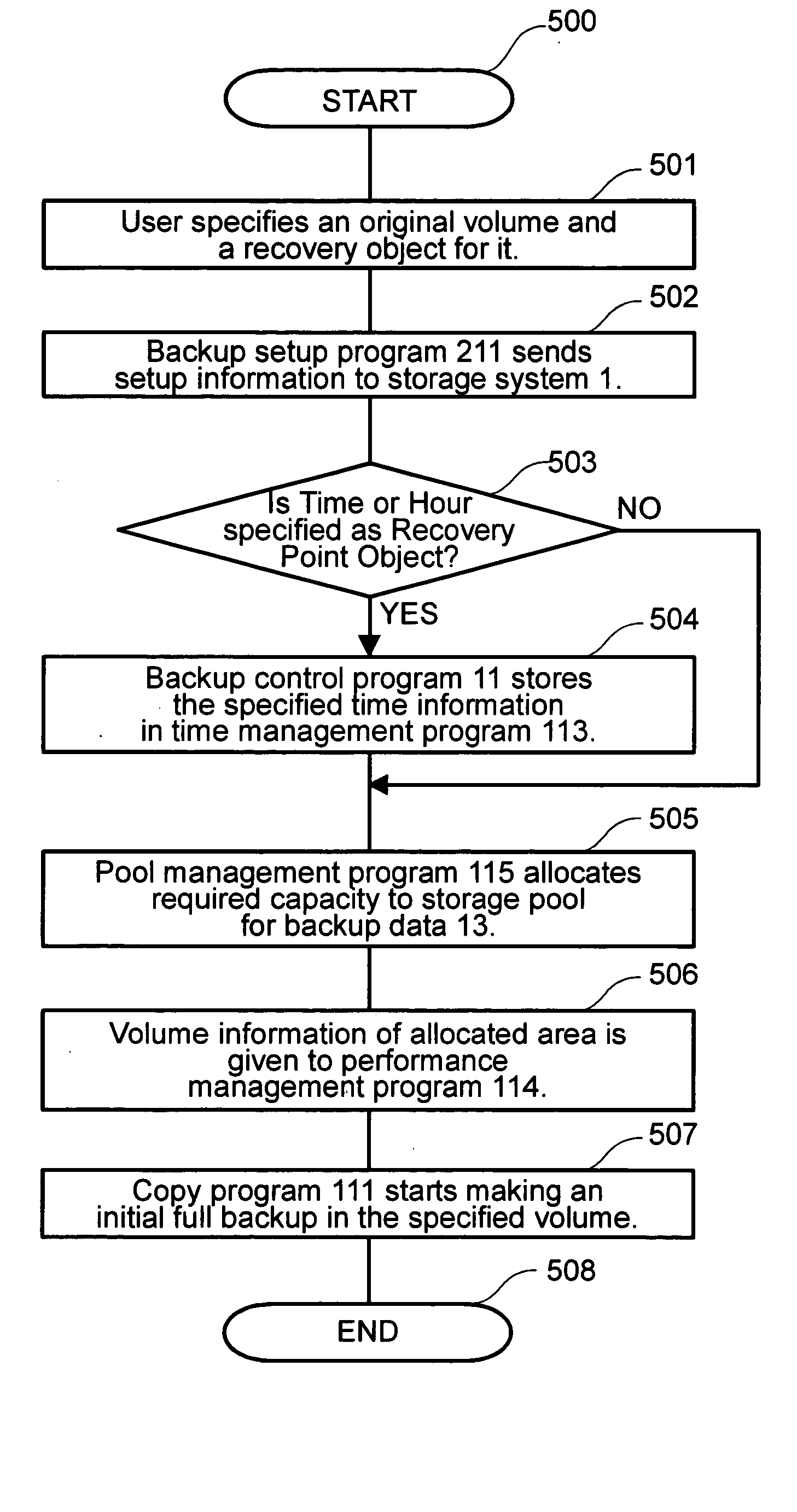

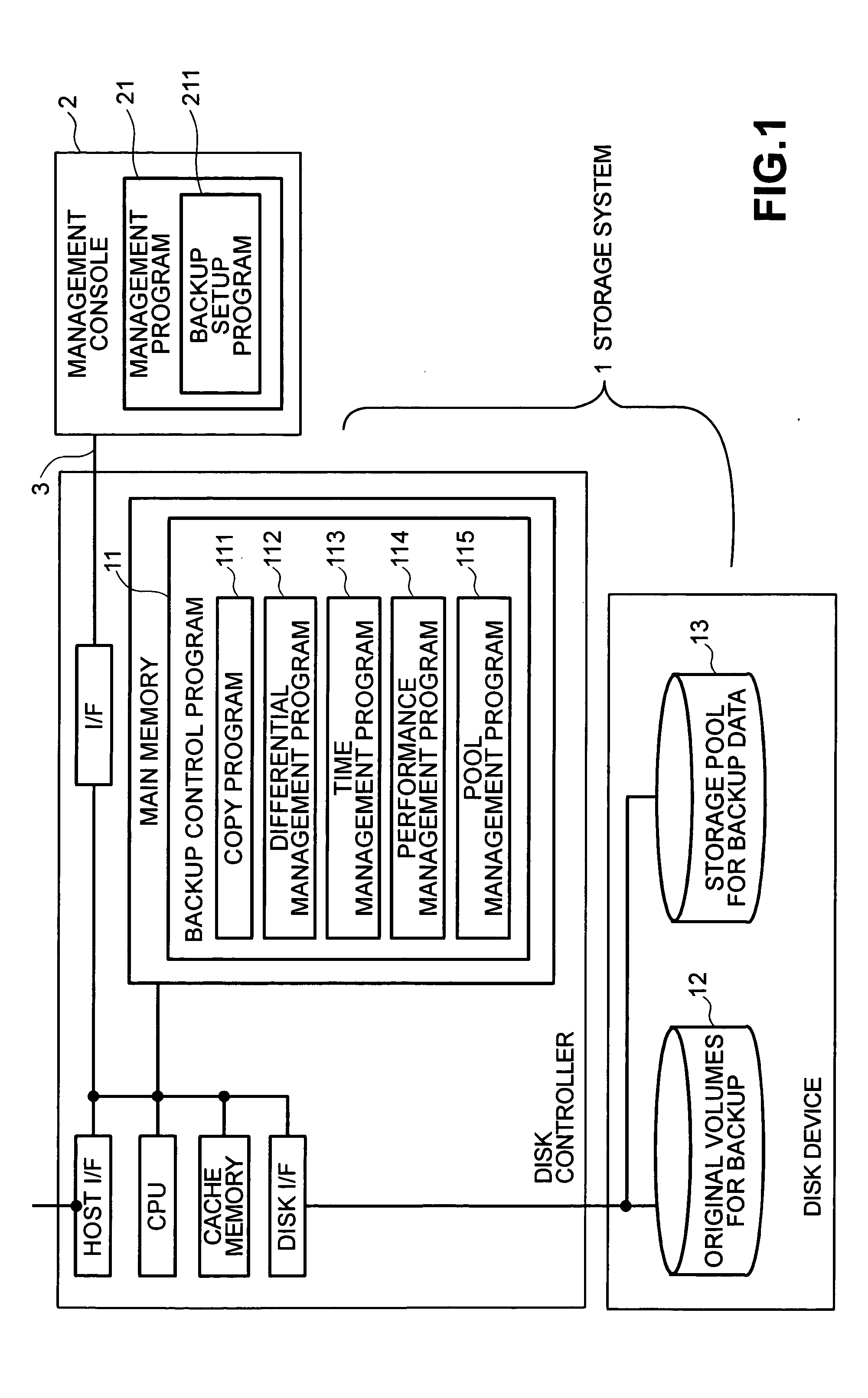

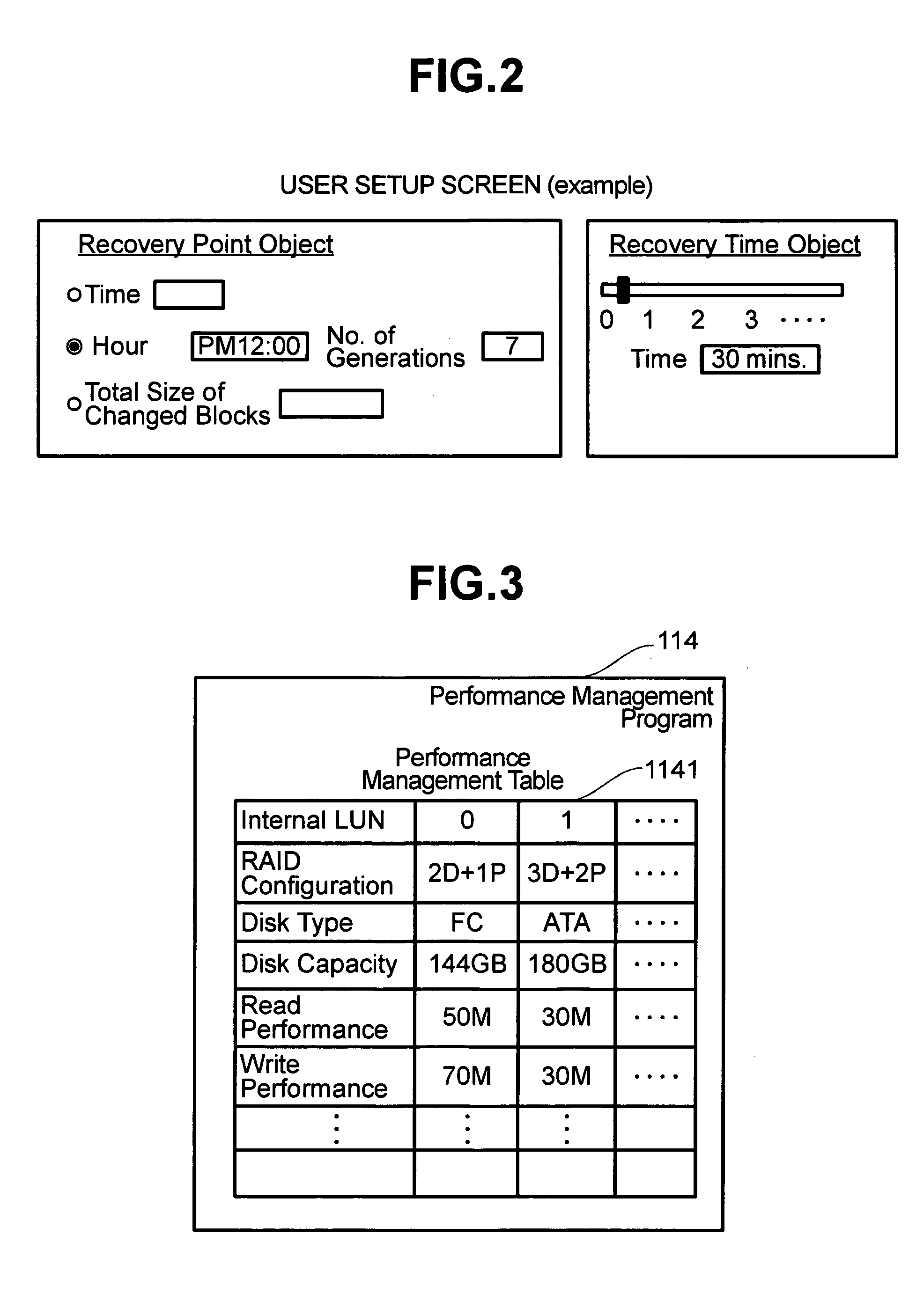

Storage system and method for backup

InactiveUS7085904B2Easy to getReduce the burden onData processing applicationsInput/output to record carriersDisk controllerStorage pool

A storage system includes a disk controller and a disk device having original volumes for backup and a storage pool for backup data. It incorporates a differential management program which checks whether the original volumes for backup are updated or not; a pool management program which allocates a disk area to the storage pool for backup data; a performance management program which manages the performance of each volume; and a backup control program which performs total backup control. A backup method by which recovery within a user-specified recovery object time is possible is selected according to the restore performance calculated by the performance management program and the total size of changed blocks after backup acquisition as counted by the differential management program.

Owner:HITACHI LTD

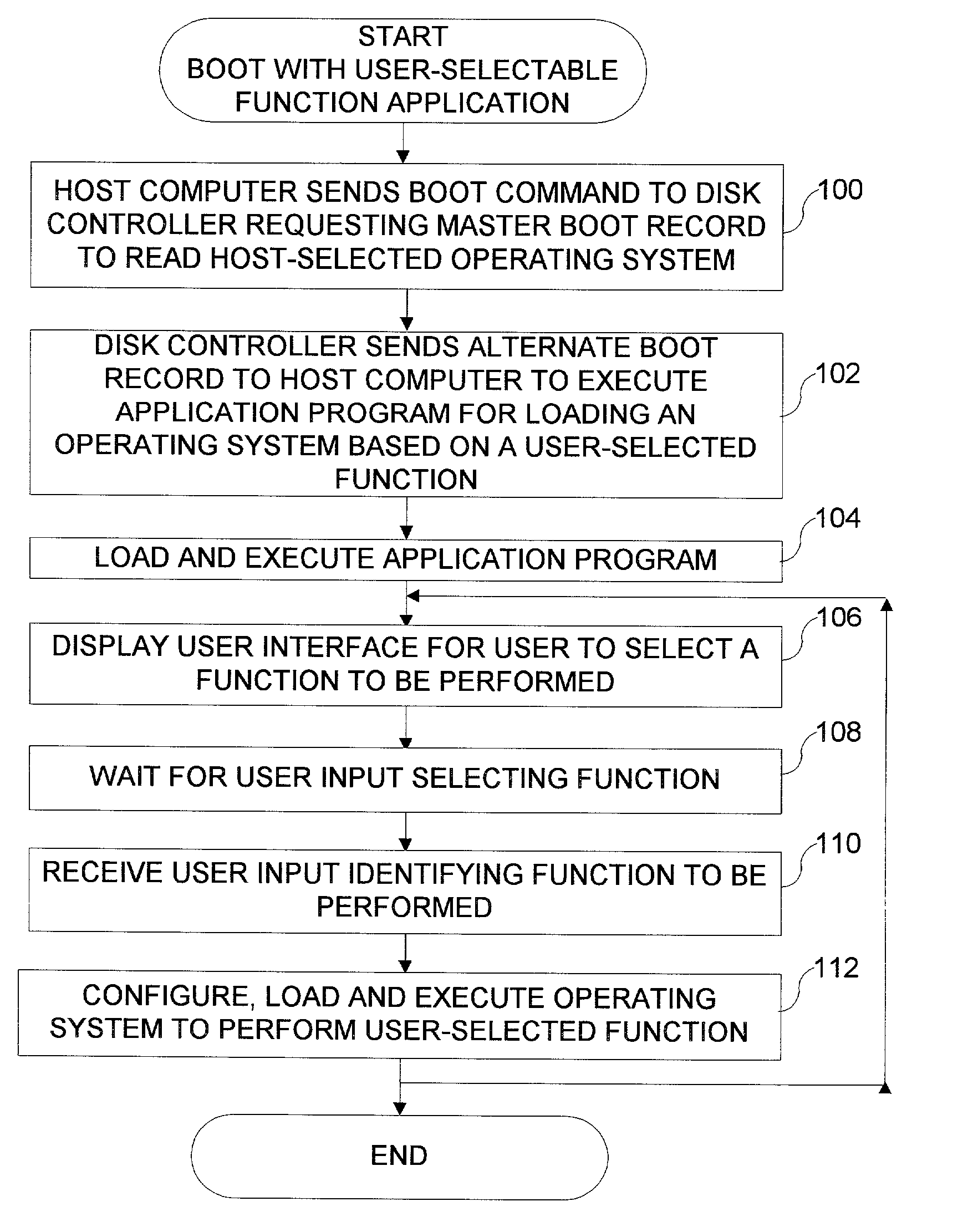

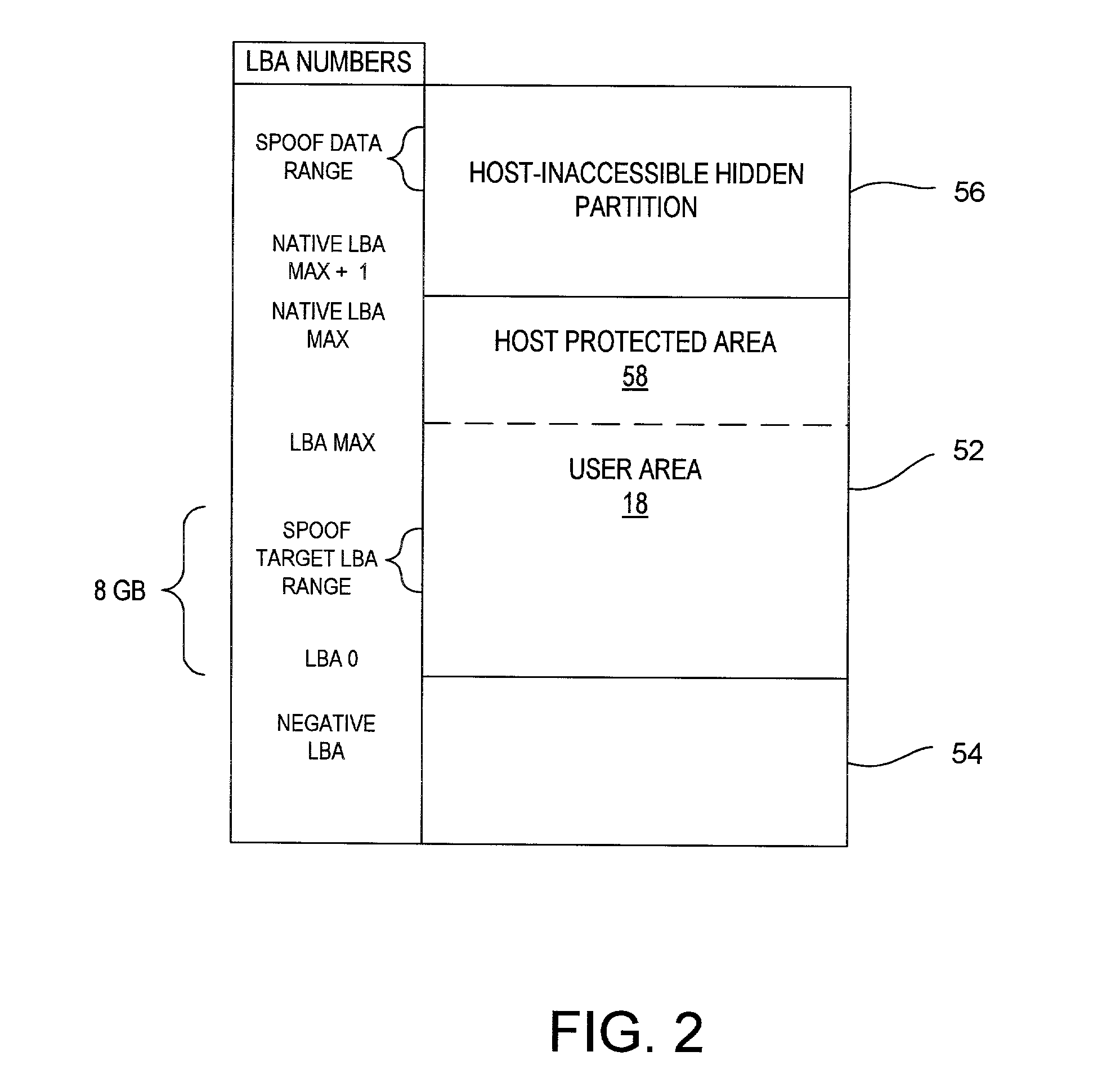

Disk drive having a protected partition configured to load an operating system for performing a user-selected function

A system for configuring, loading and executing an operating system for performing a user-selected function is disclosed. The system includes a disk drive including: a host-accessible user partition; a host-inaccessible hidden partition independent of the host-accessible user partition; and a disk controller. The user partition includes: a user partition address range; a host-selected operating system; and a host-selected master boot record. The host-inaccessible hidden partition includes: a hidden partition address range outside the user partition address range; an application program for allowing a user to select a function to perform and configuring, loading and executing an operating system to perform the selected function; and a drive-selected boot record for loading and executing the application program that allows the user to select a function and configures, loads and executes an operating system for performing the function.

Owner:WESTERN DIGITAL TECH INC

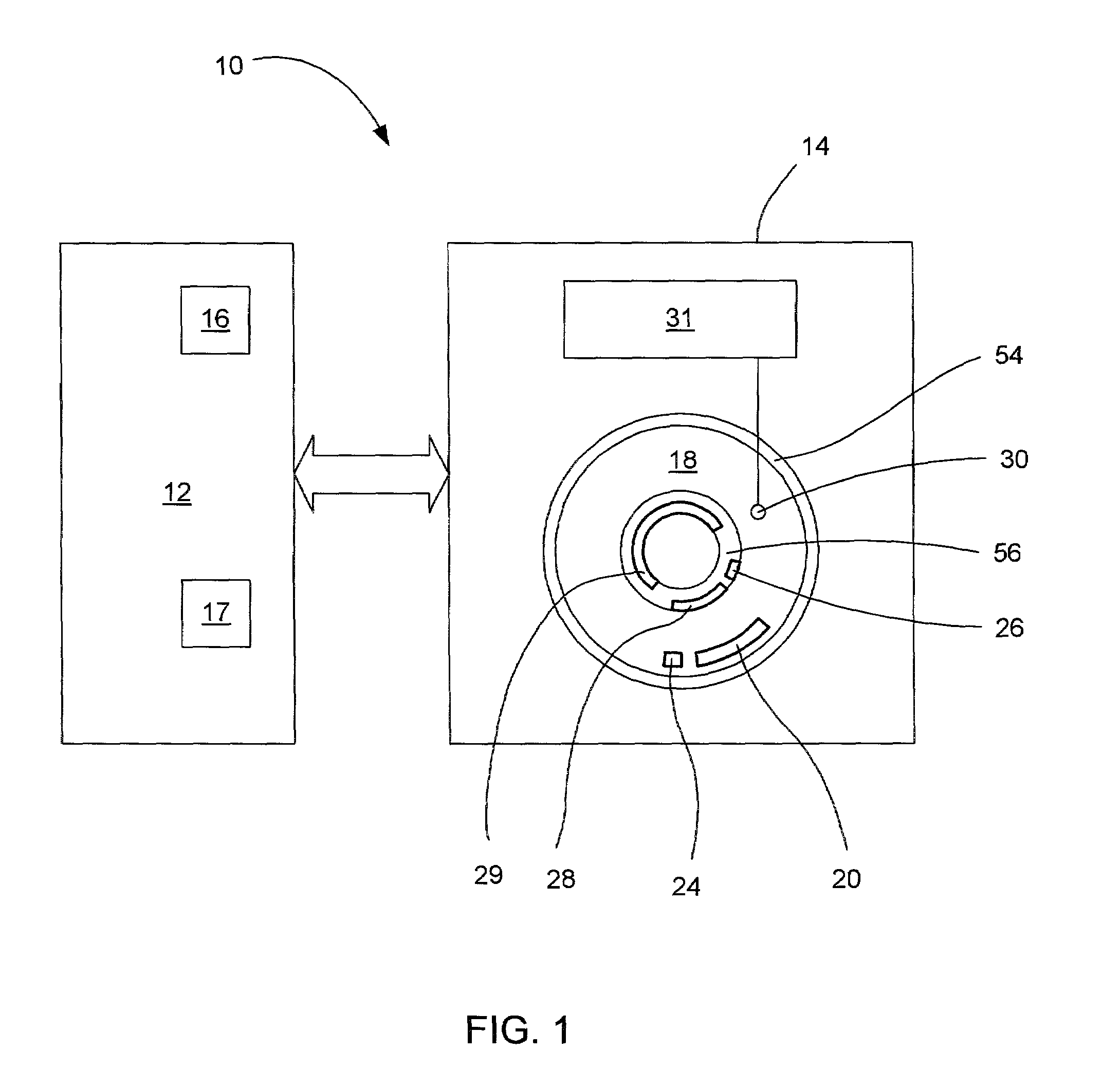

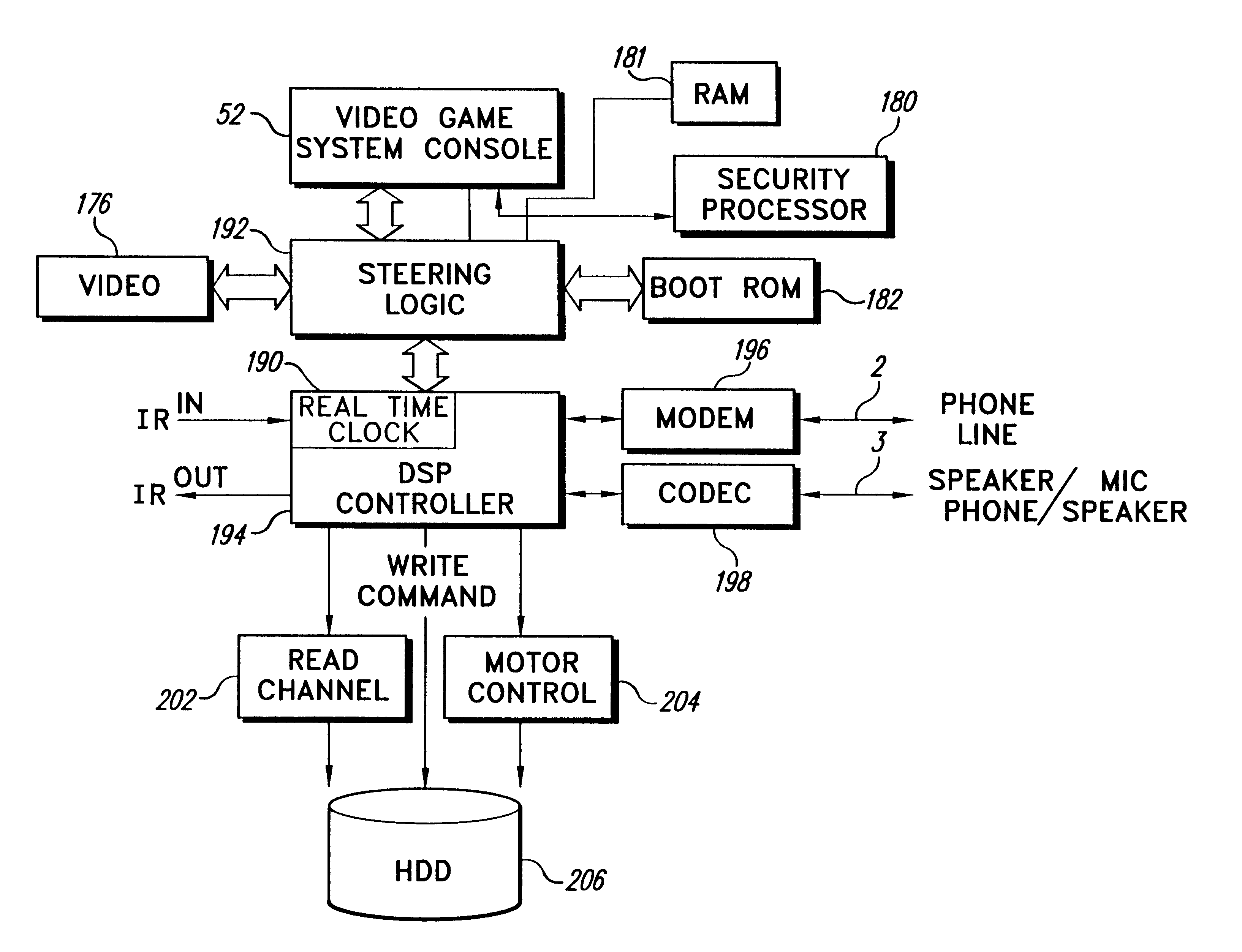

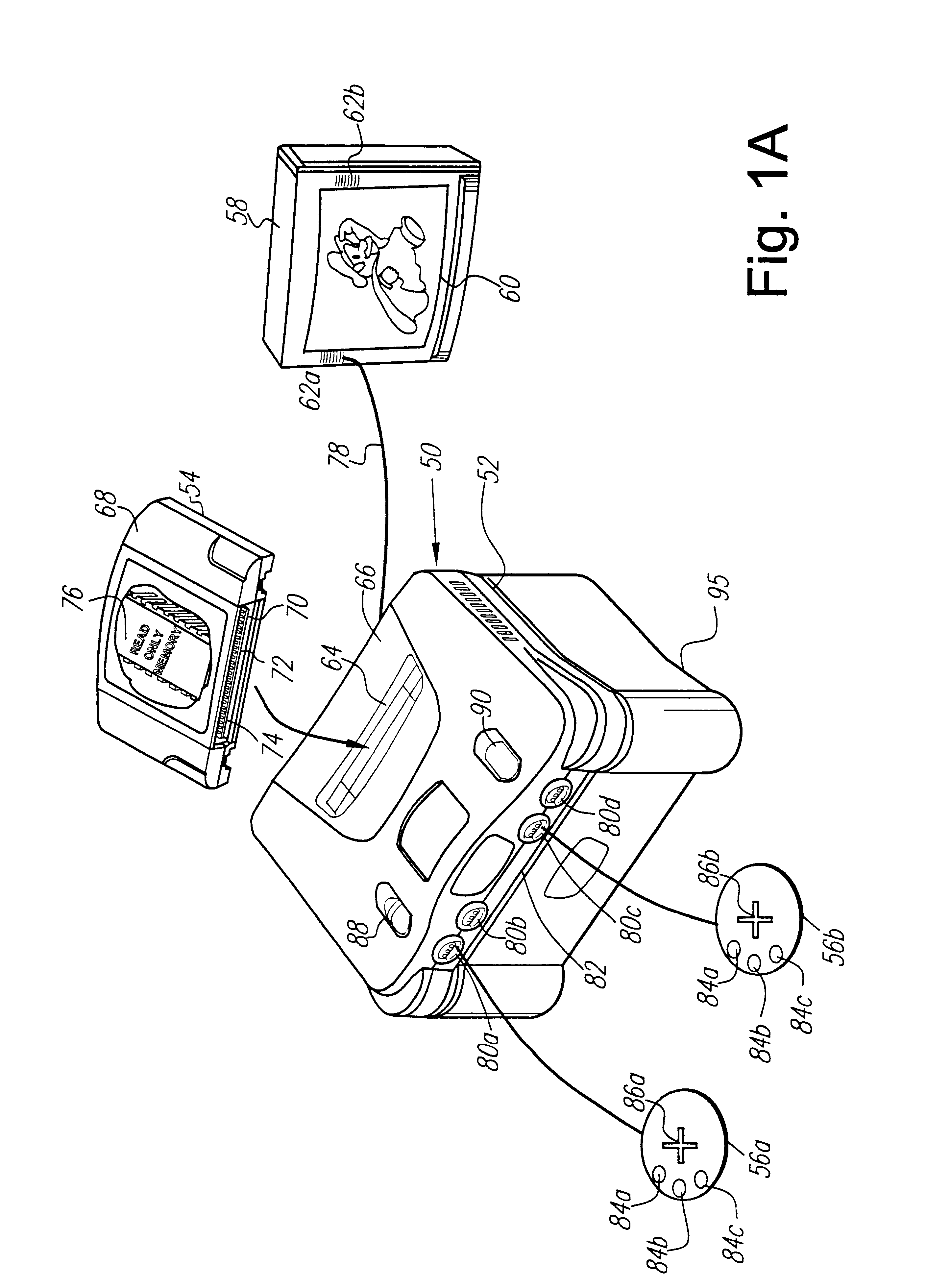

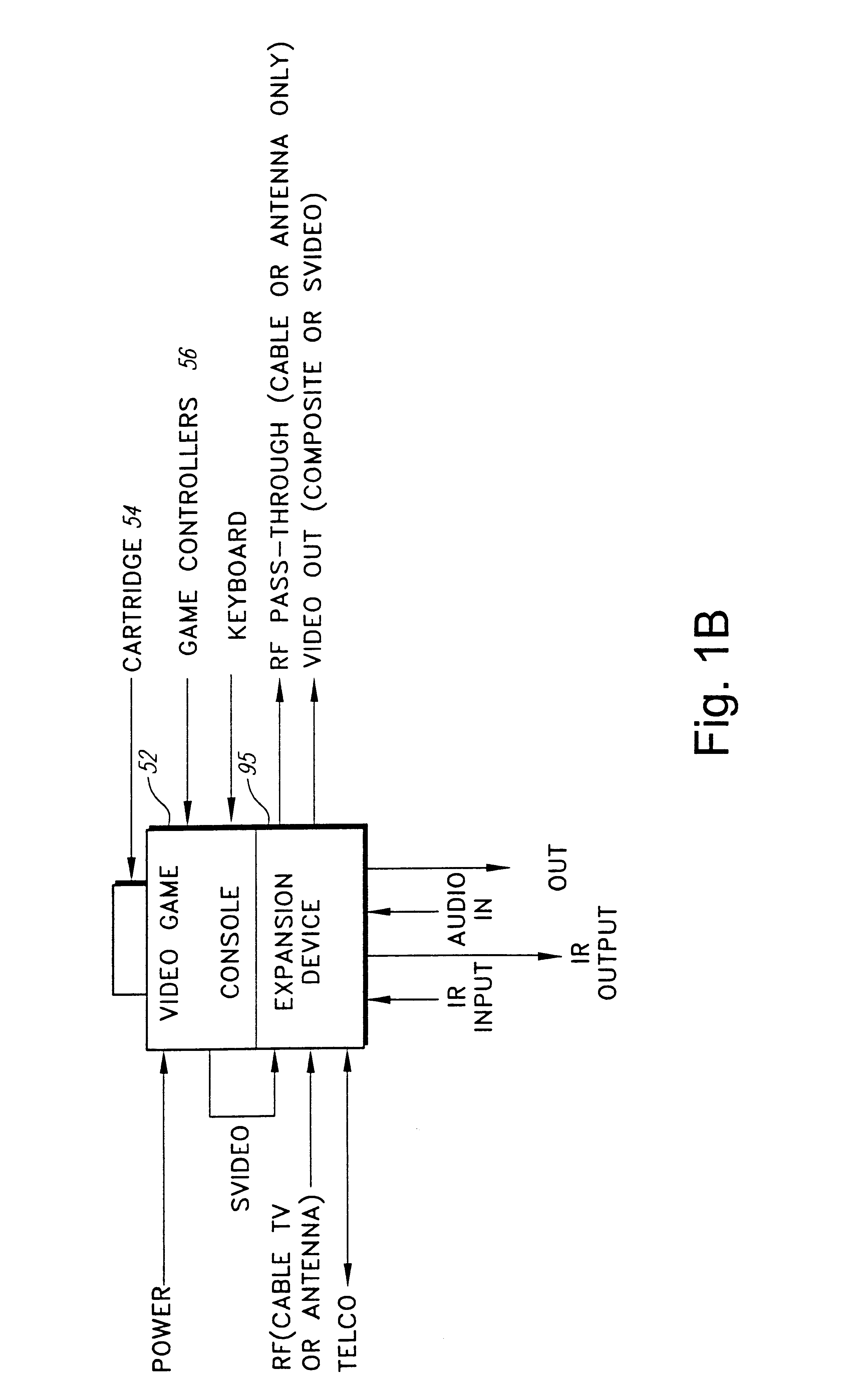

Security system for video game system with hard disk drive and internet access capability

An existing video game system is modified to include additional communication and storage capability via a modem and hard disk drive. In accordance with one embodiment of the present invention, the primary system security features are incorporated into a video game system expansion device having a hard disk drive. The security system does not rely on the relatively insecure video game system. The present exemplary embodiment focuses security control in a disk drive / mass media controlling engine which is physically disposed within the expansion device housing as close as possible to the hard disk drive and the downloaded video games and other data it is designed to protect. Security features are incorporated into, for example, a disk drive controlling processing engine to provide security features which extend far beyond simplistic password systems which have heretofore been utilized in conjunction with disk drive controllers. In accordance with an exemplary embodiment of the present invention, the disk controller also incorporates an encrypting engine which encrypts in accordance with a highly secure encrypting algorithm. A further level of security is provided in the illustrative embodiments by partitioning the hard drive into various partitions whose security / accessibility is tightly controlled. Each application program, e.g., a video game, has a predetermined number of private partitions, including a read only encrypted partition.

Owner:NINTENDO OF AMERICA

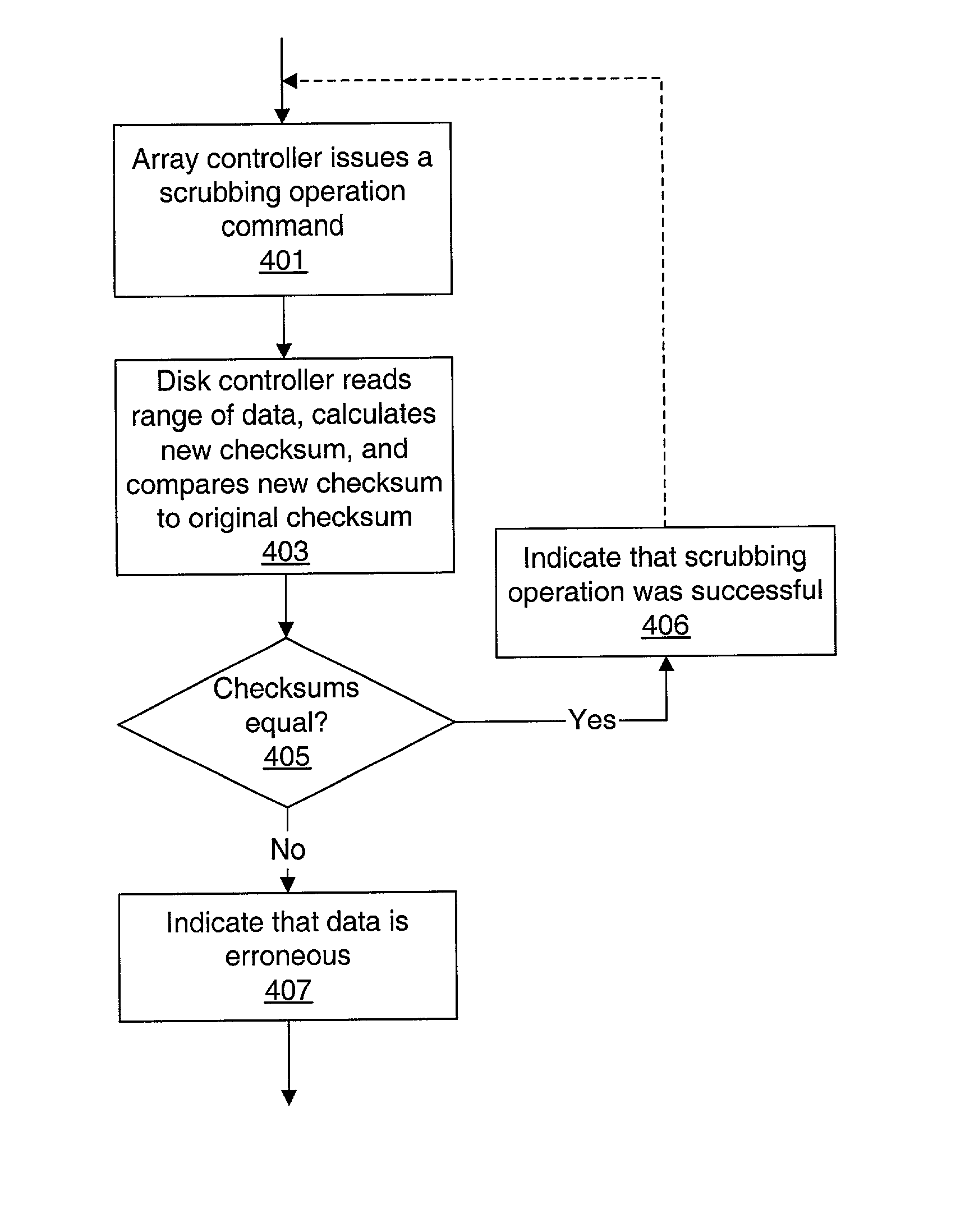

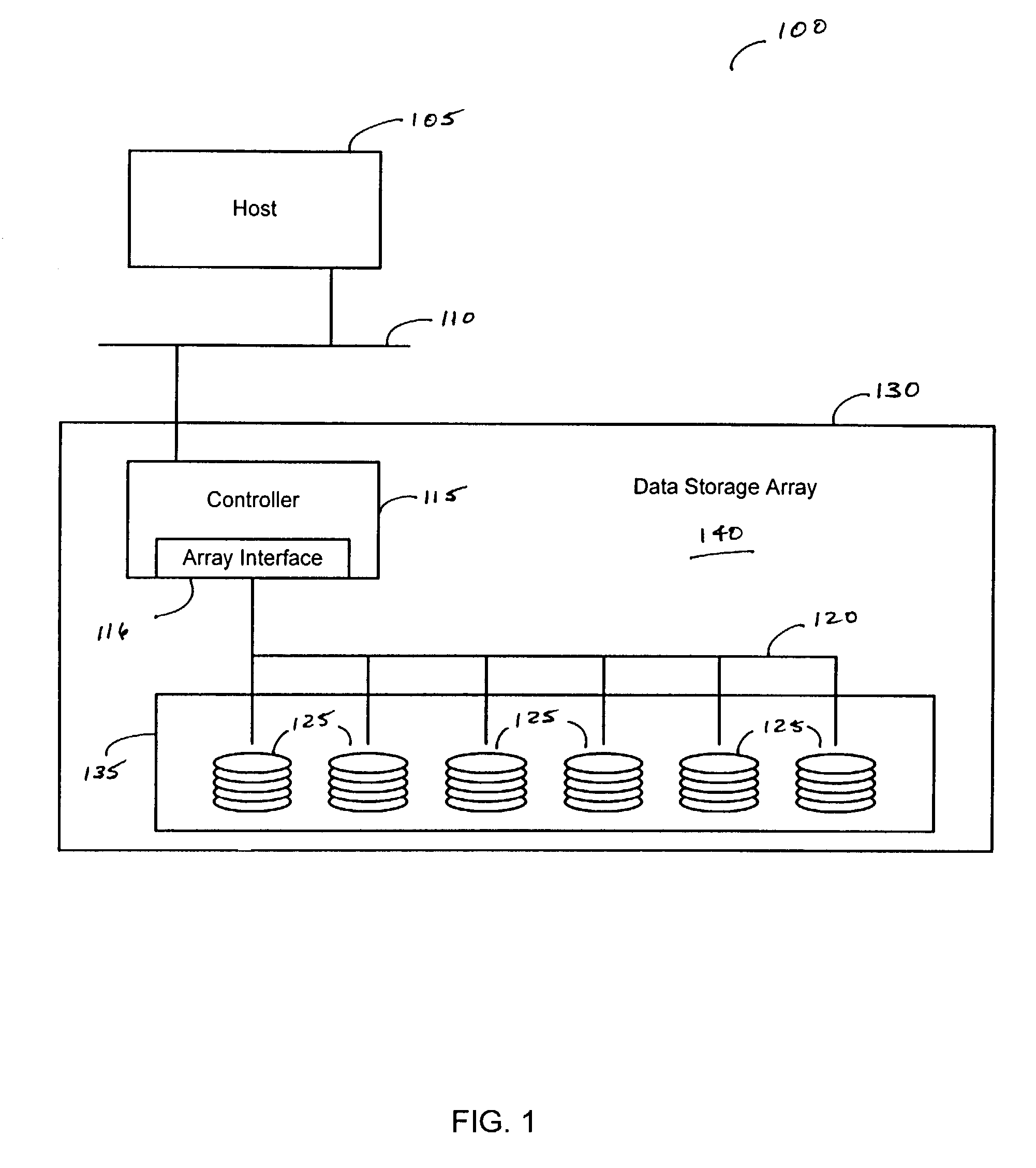

Storage array employing scrubbing operations at the disk-controller level

A storage system comprises a storage array controller and a storage array, which includes multiple disk drives and disk drive controllers. The storage array controller issues scrubbing operation commands to one or more of the disk drive controllers. In response, each disk drive controller that receives a scrubbing operation command reads data from within a data range from at least one of the disk drives, calculates a new checksum for the data, and compares the new checksum to a preexisting checksum for the data. If the new checksum doesn't equal the preexisting checksum, the data within the data range is determined to be erroneous.

Owner:ORACLE INT CORP

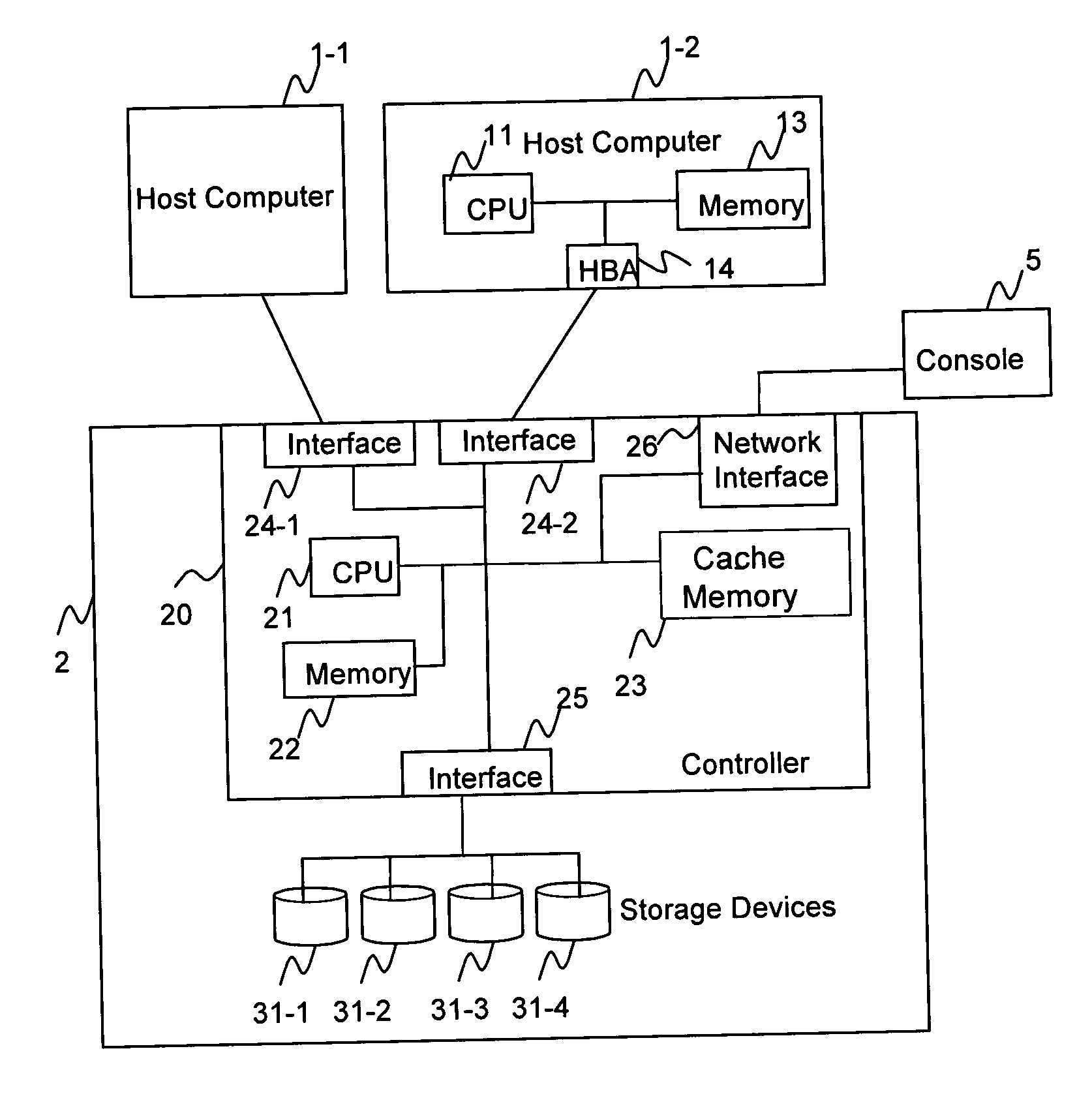

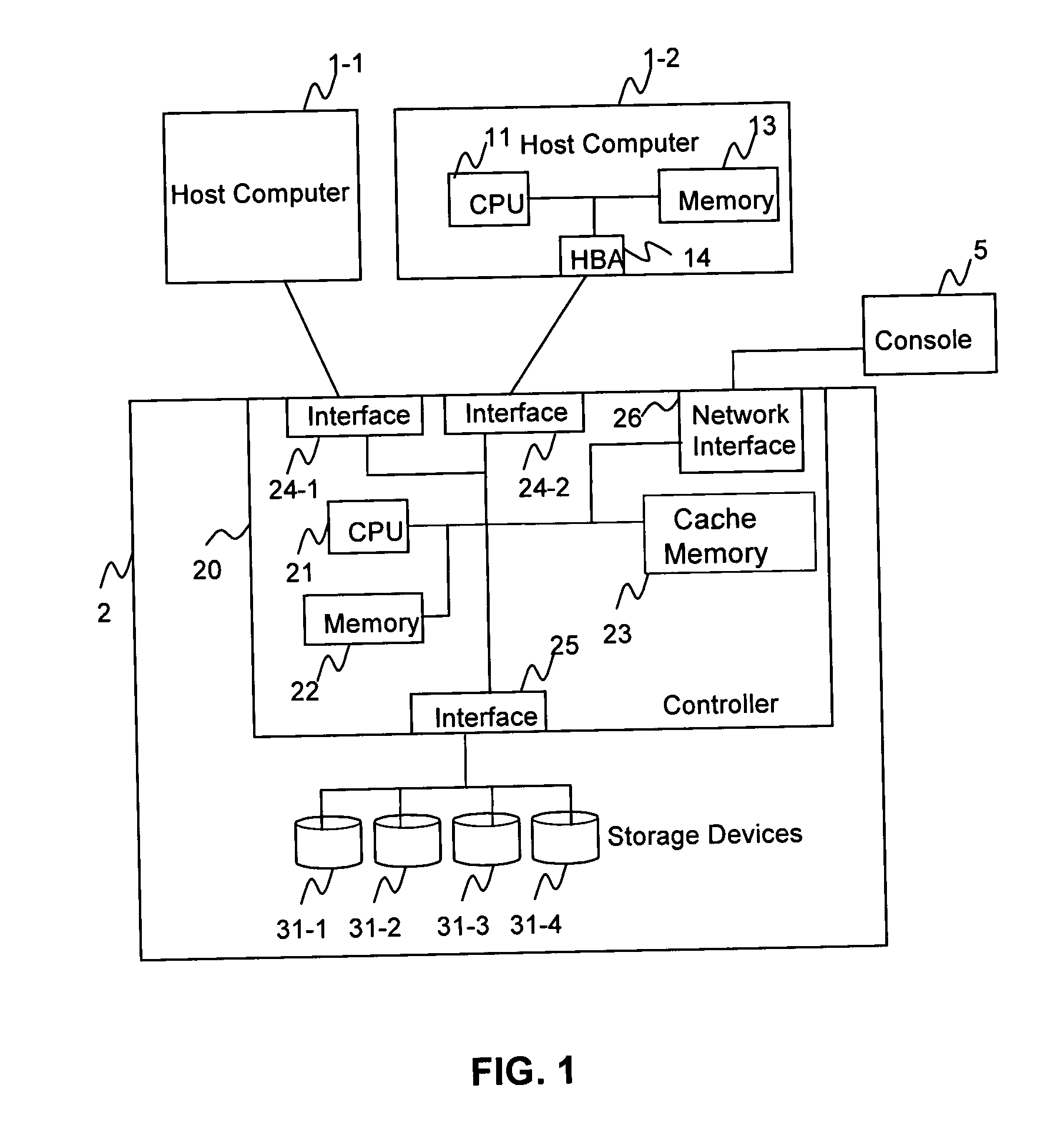

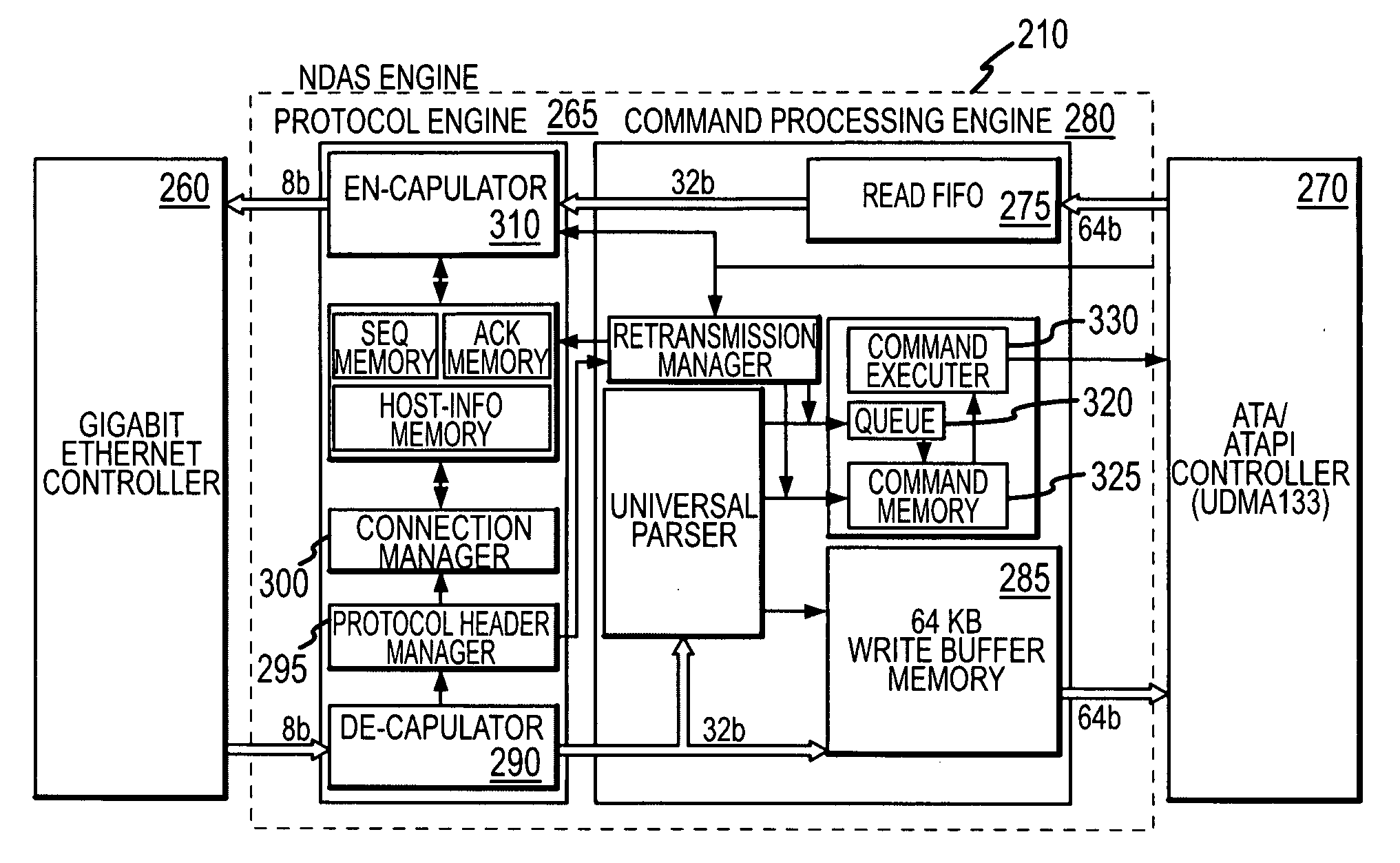

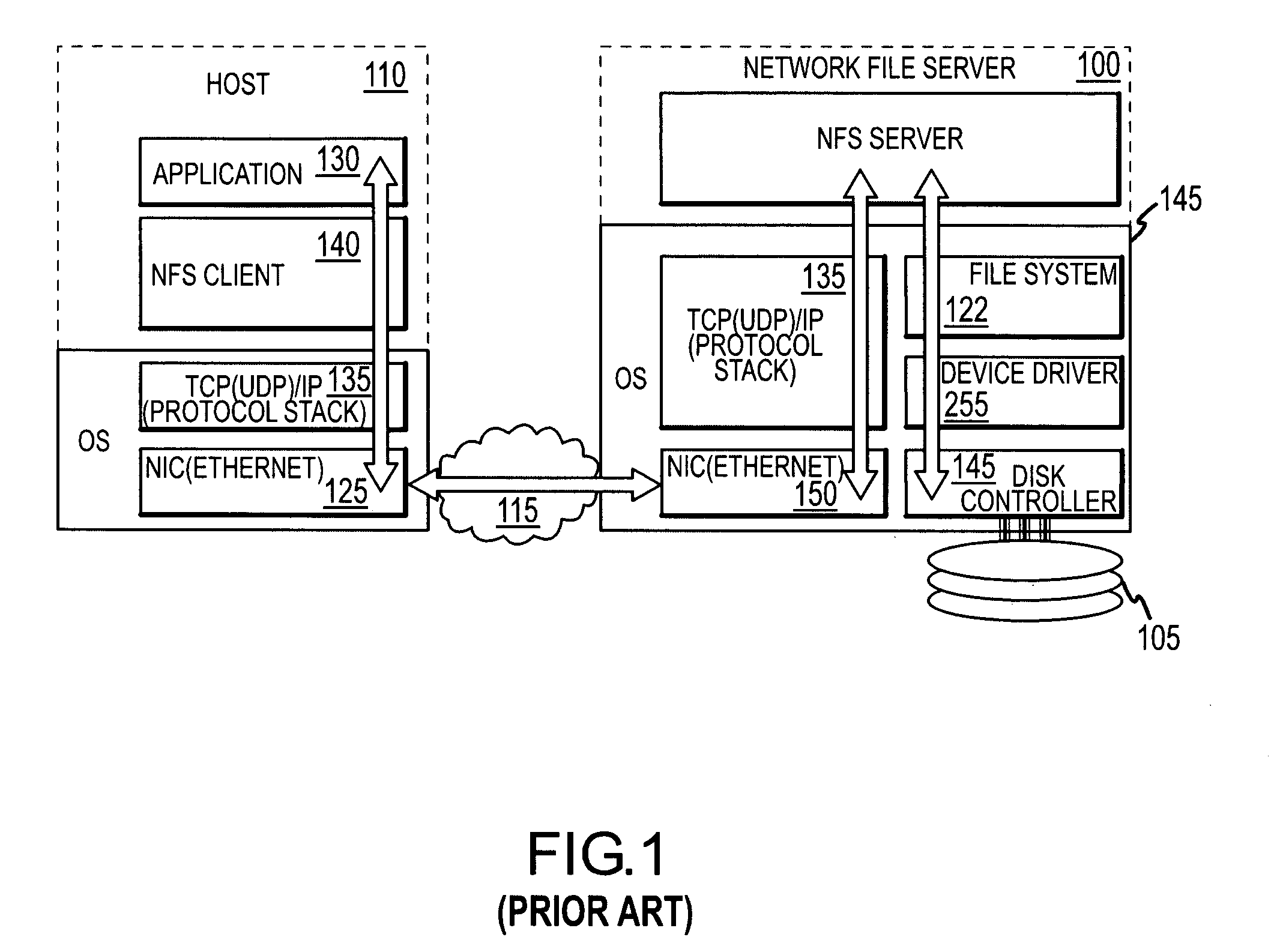

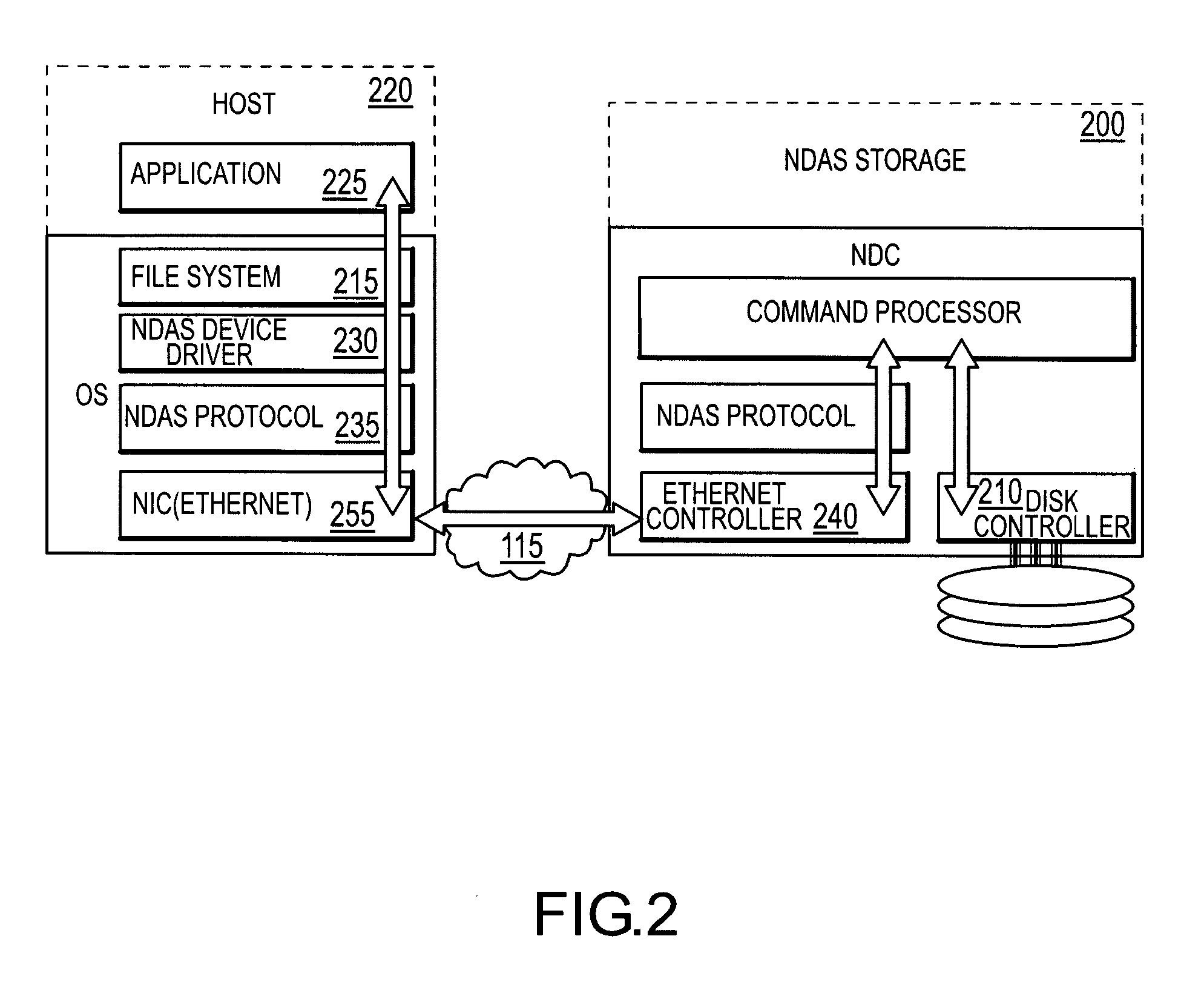

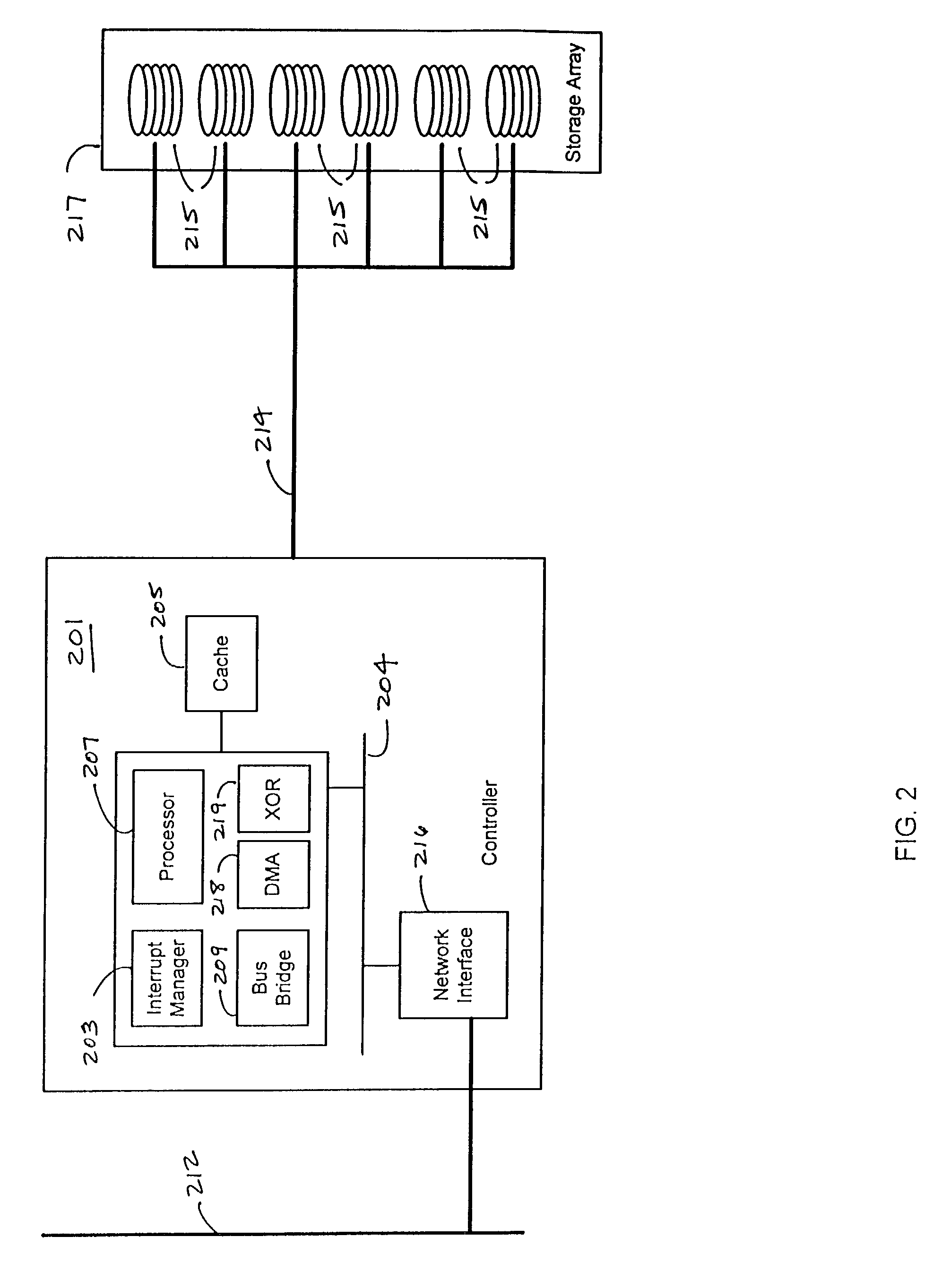

Method and apparatus for network direct attached storage

An apparatus and method for providing a storage medium accessible across a network to a host. The storage medium's operation is generally controlled by a network disk controller. The network disk controller may receive a packet from a remote host, decapsulate the packet, and act on the packet to either transmit data from a storage medium or write data to a storage medium. Generally, the network disk controller does not execute any file system. Rather, the file system for communication between the host and controller is executed by the host. The performance of the network disk controller generally matches that of a local (i.e., non-network) disk controller in terms of data access and writing.

Owner:LEE HEON SU

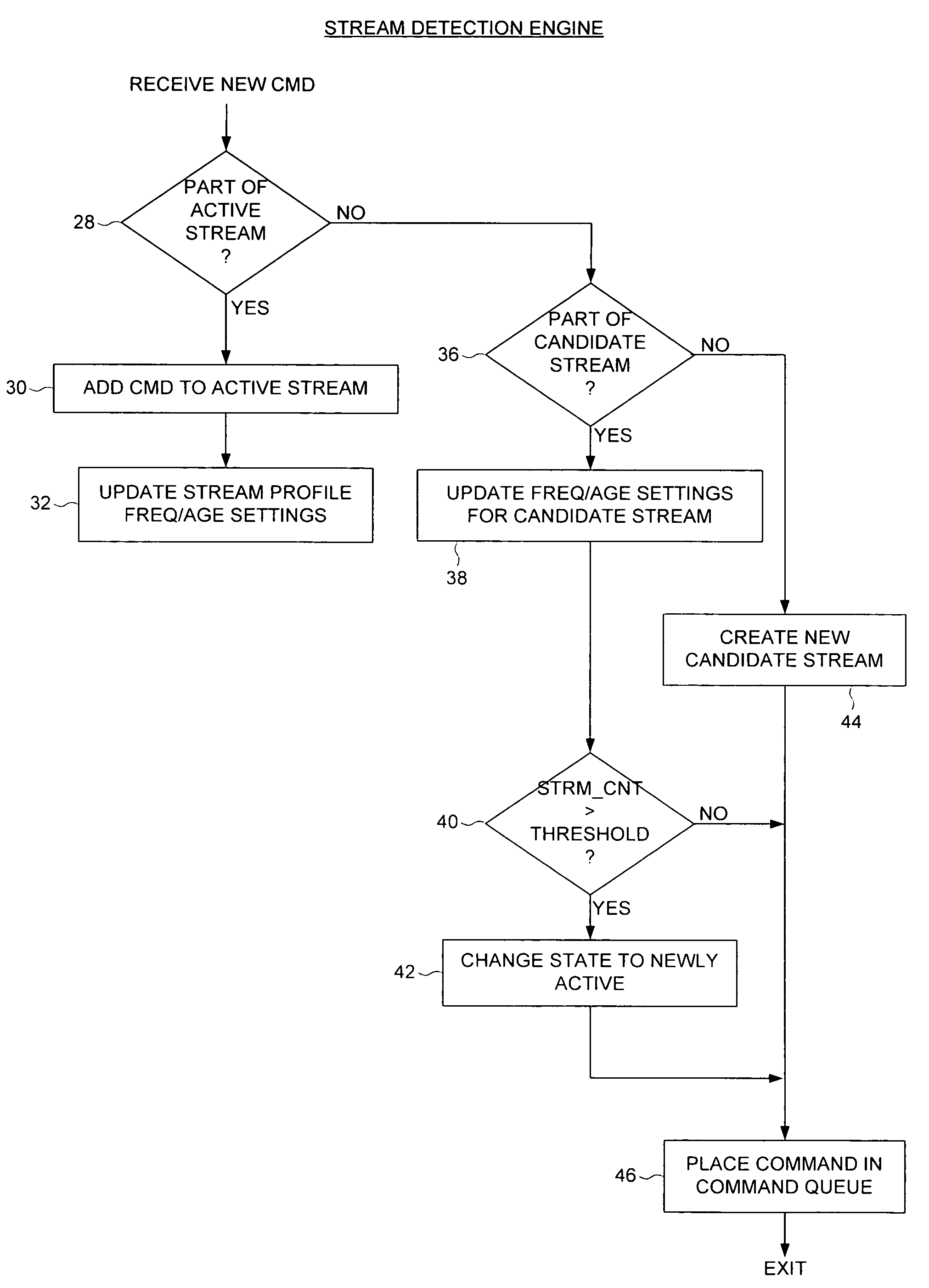

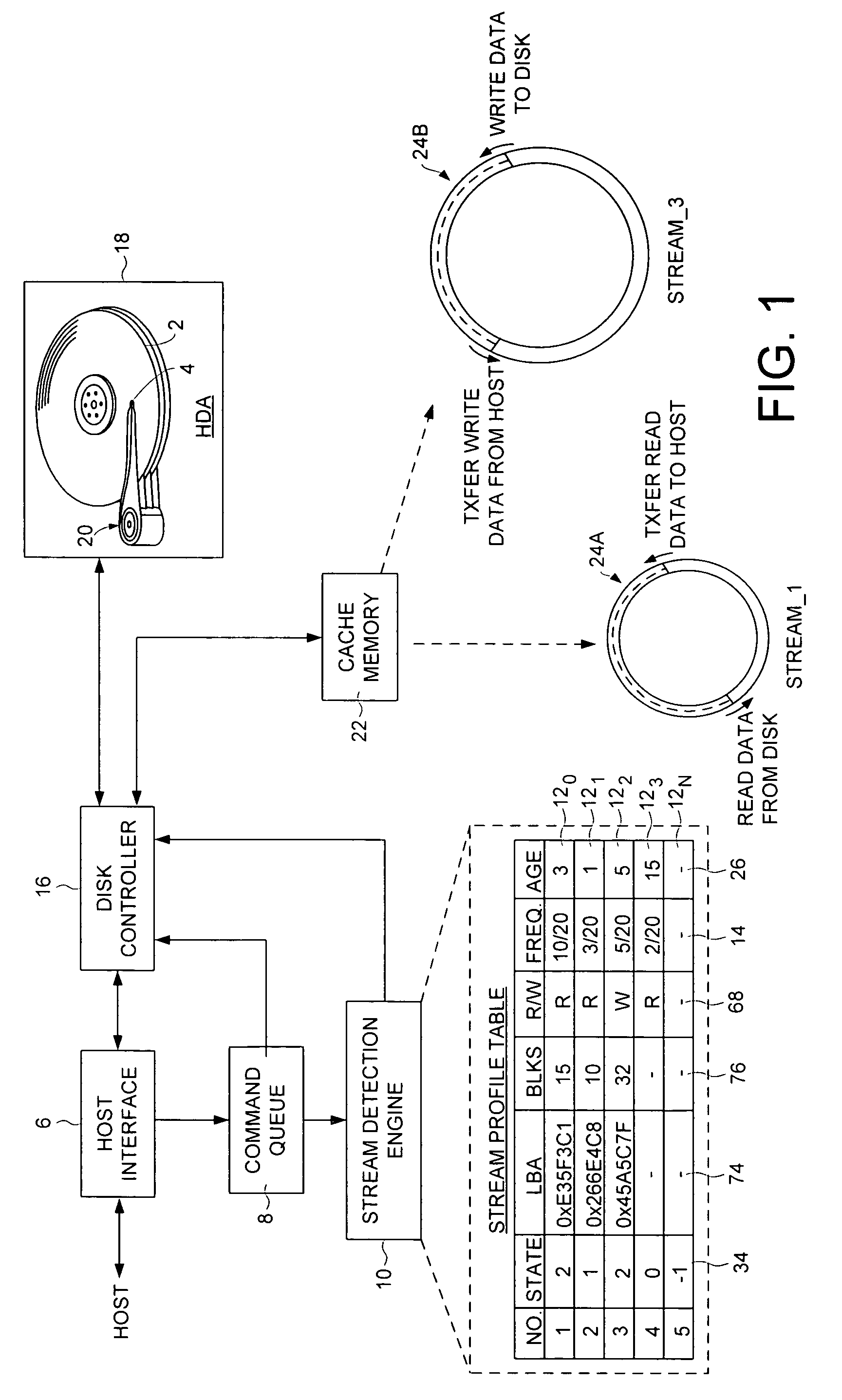

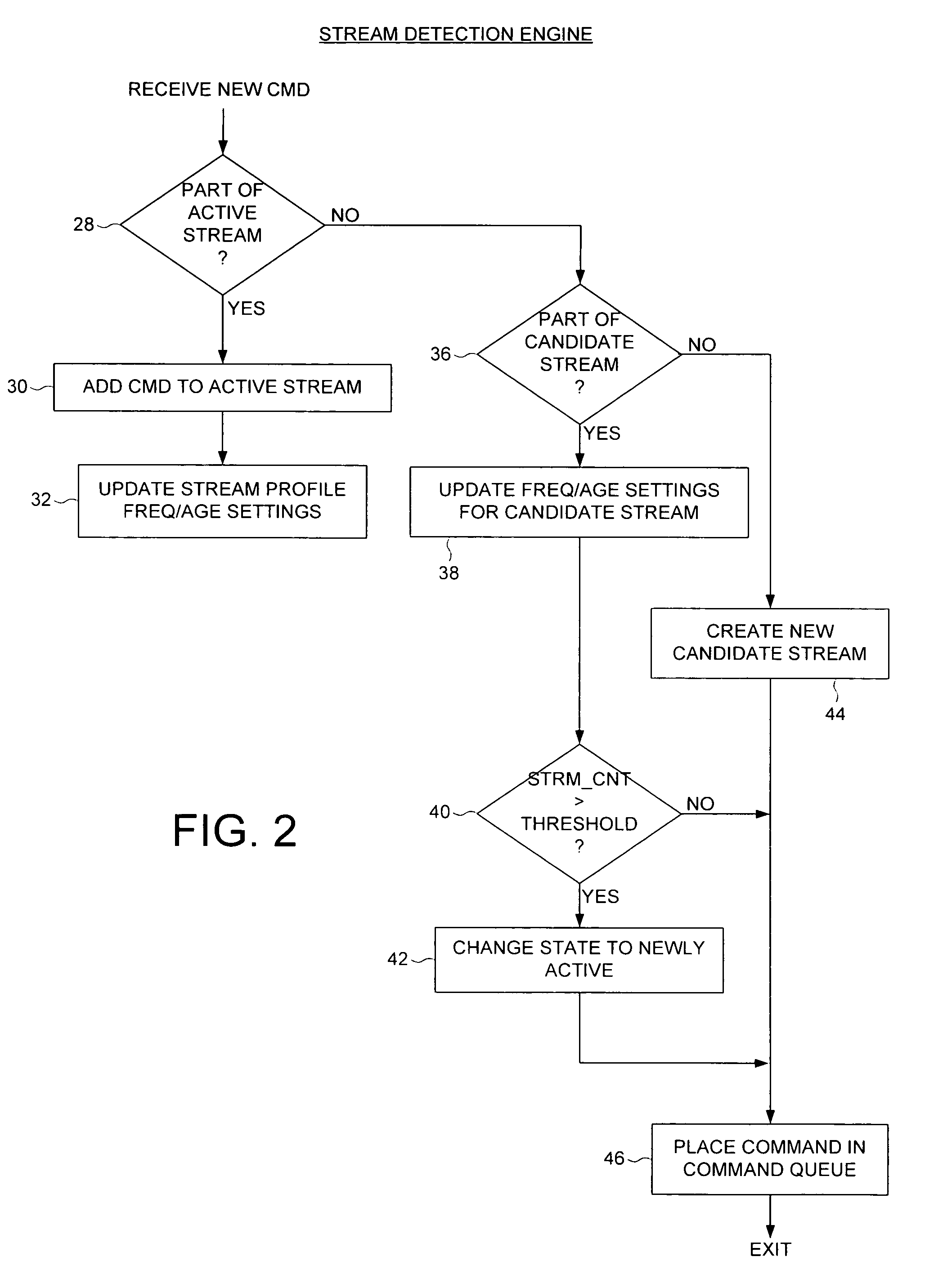

Disk drive employing stream detection engine to enhance cache management policy

A disk drive is disclosed comprising a disk, a head actuated over the disk, a host interface for receiving disk access commands from a host, a command queue for queuing the disk access commands, and a stream detection engine for evaluating the disk access commands to detect a plurality of streams accessed by the host. The stream detection engine maintains a stream data structure for each detected stream, wherein the stream data structure comprises a frequency counter for tracking a number of disk access commands associated with the stream out of a predetermined number of consecutive disk access commands received from the host. A disk controller selects one of the streams for servicing in response to the frequency counters.

Owner:WESTERN DIGITAL TECH INC

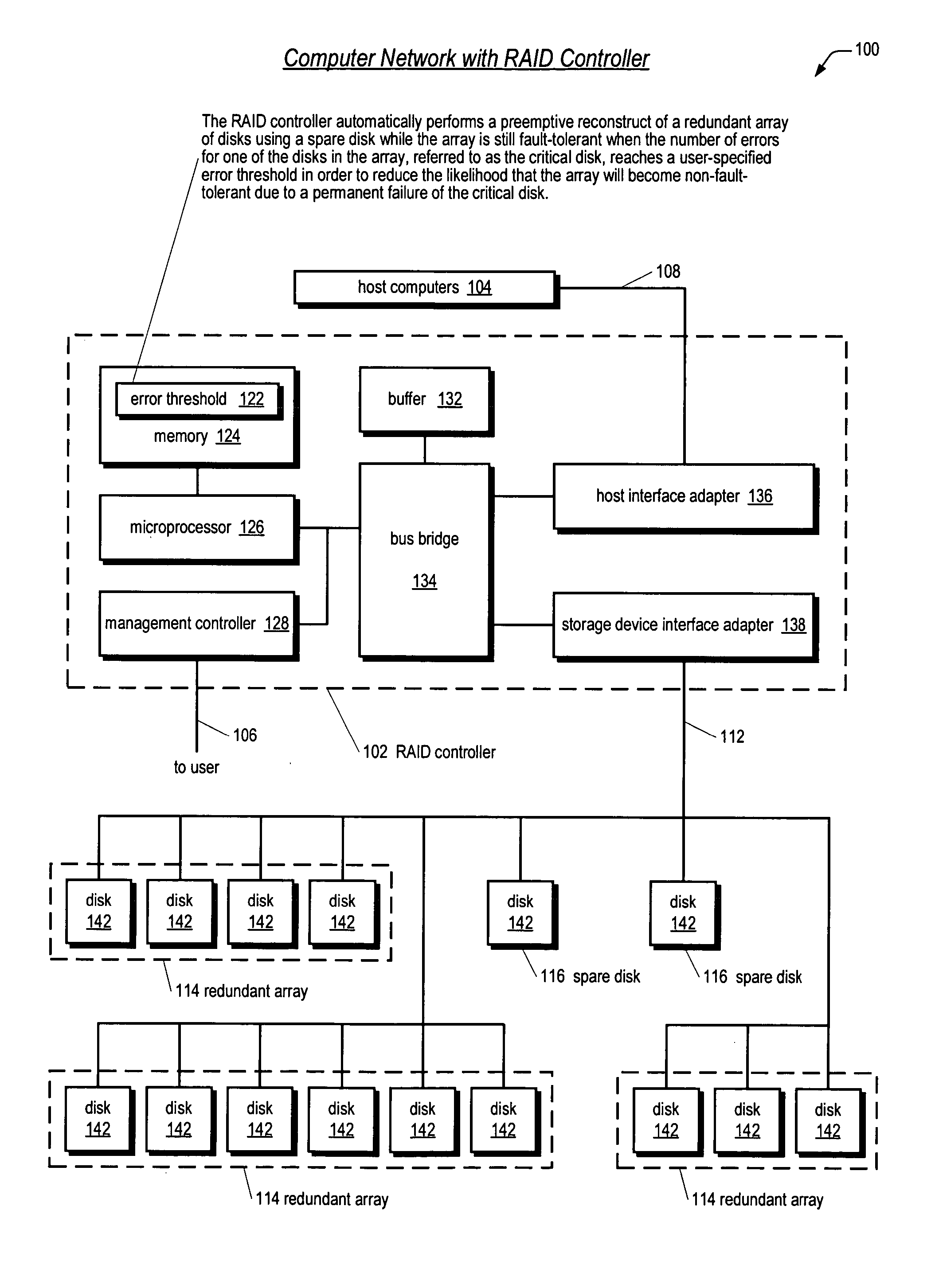

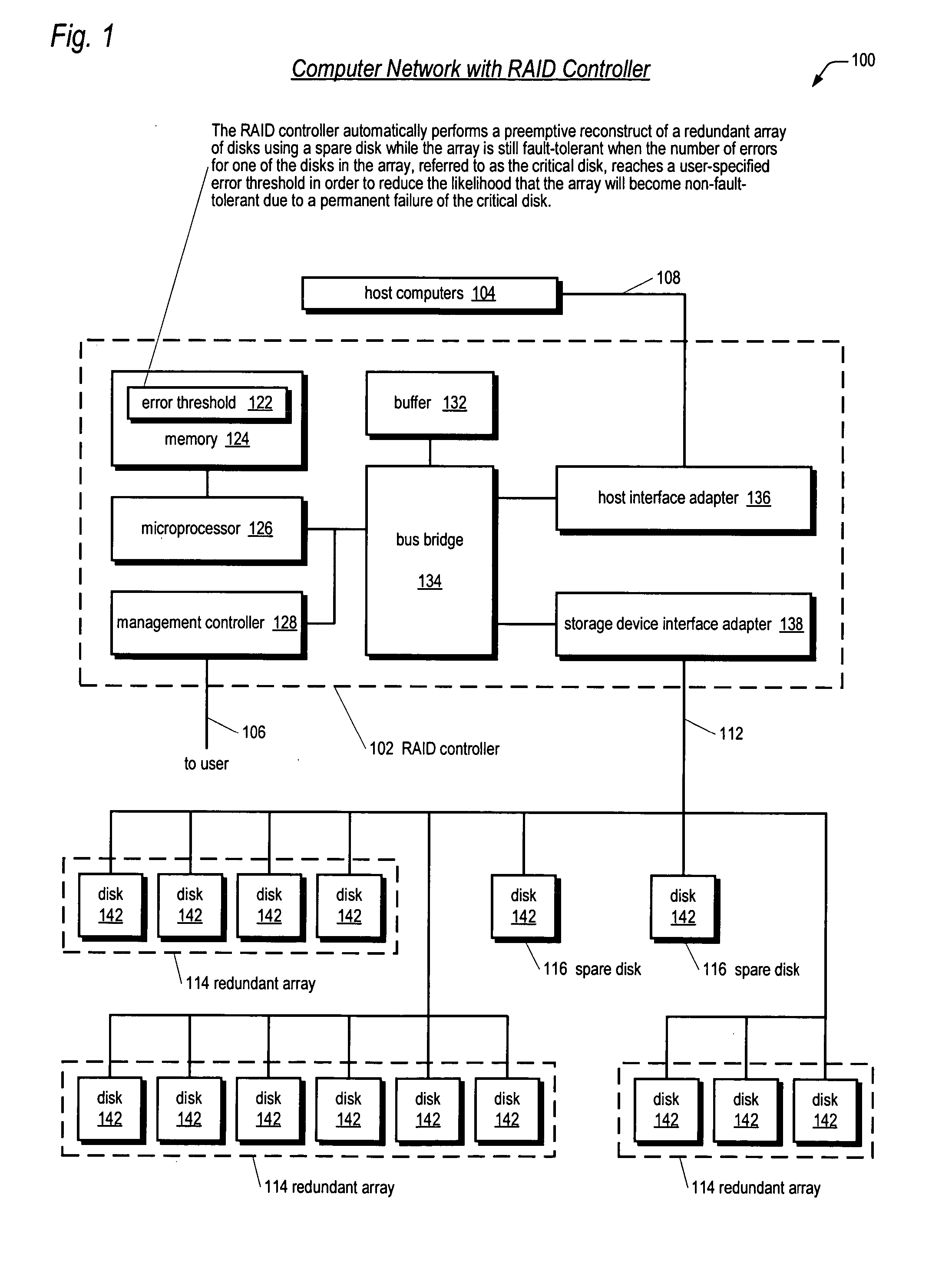

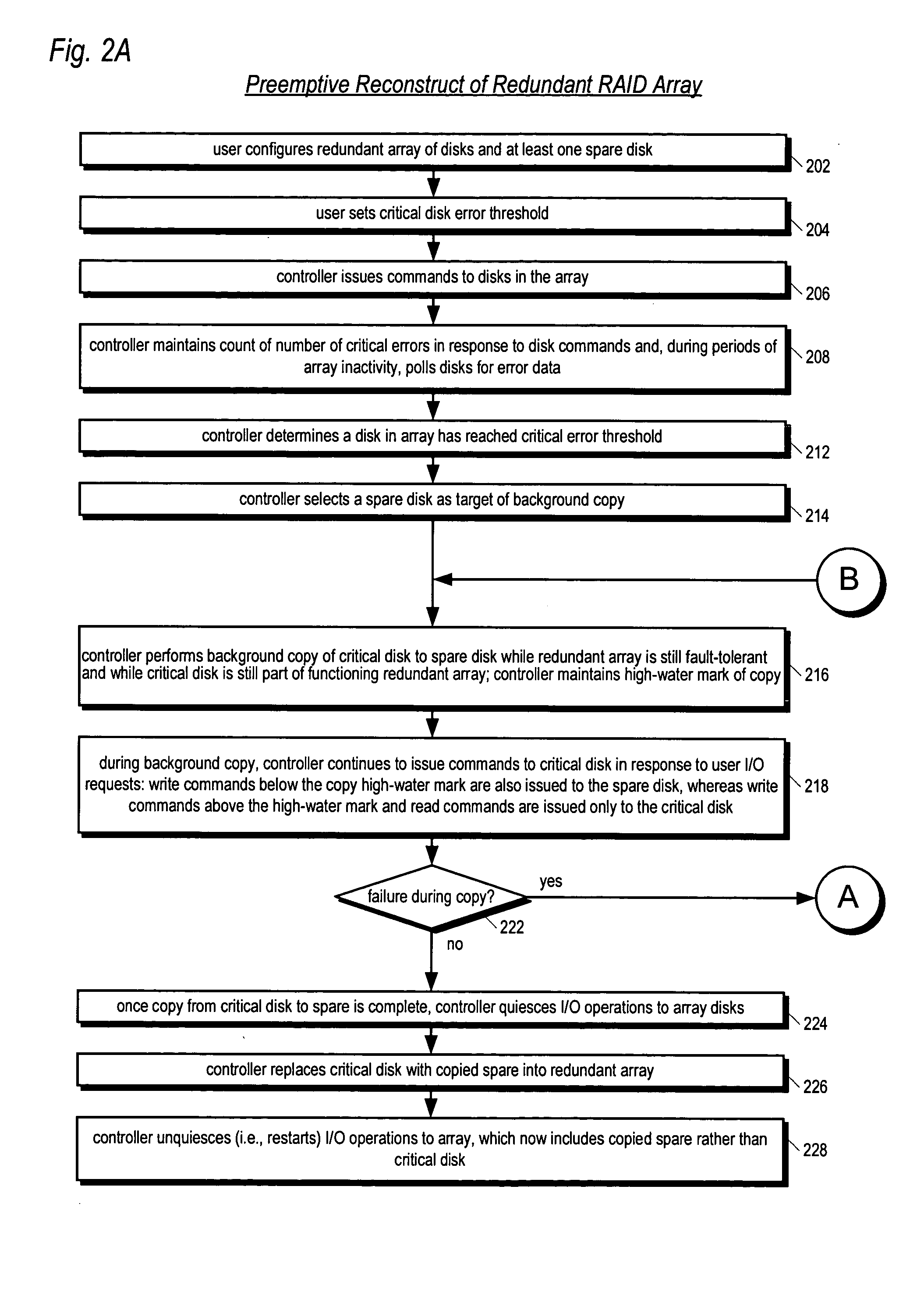

Apparatus and method for performing a preemptive reconstruct of a fault-tolerand raid array

ActiveUS20050283655A1Reduce the possibilityLess timeReliability/availability analysisError avoidanceRAIDUser input

A RAID controller performing a preemptive reconstruct of a redundant array of disks while the array is still fault-tolerant is disclosed. The controller receives user input specifying an error threshold. When a disk in the array (critical disk) exceeds the error threshold, the controller copies the critical disk data to a spare disk. After the copy completes, the controller replaces the critical disk with the spare disk in the array. The controller keeps the critical disk as part of the redundant array during the copy, i.e., continues to read and write the critical disk in response to user I / O requests. Hence, the array remains fault-tolerant during the preemptive reconstruct. In one embodiment, the controller automatically performs the reconstruct without user intervention. If the critical disk fails during the copy, the controller performs a conventional reconstruct to the spare disk starting where the copy left off.

Owner:DOT HILL SYST

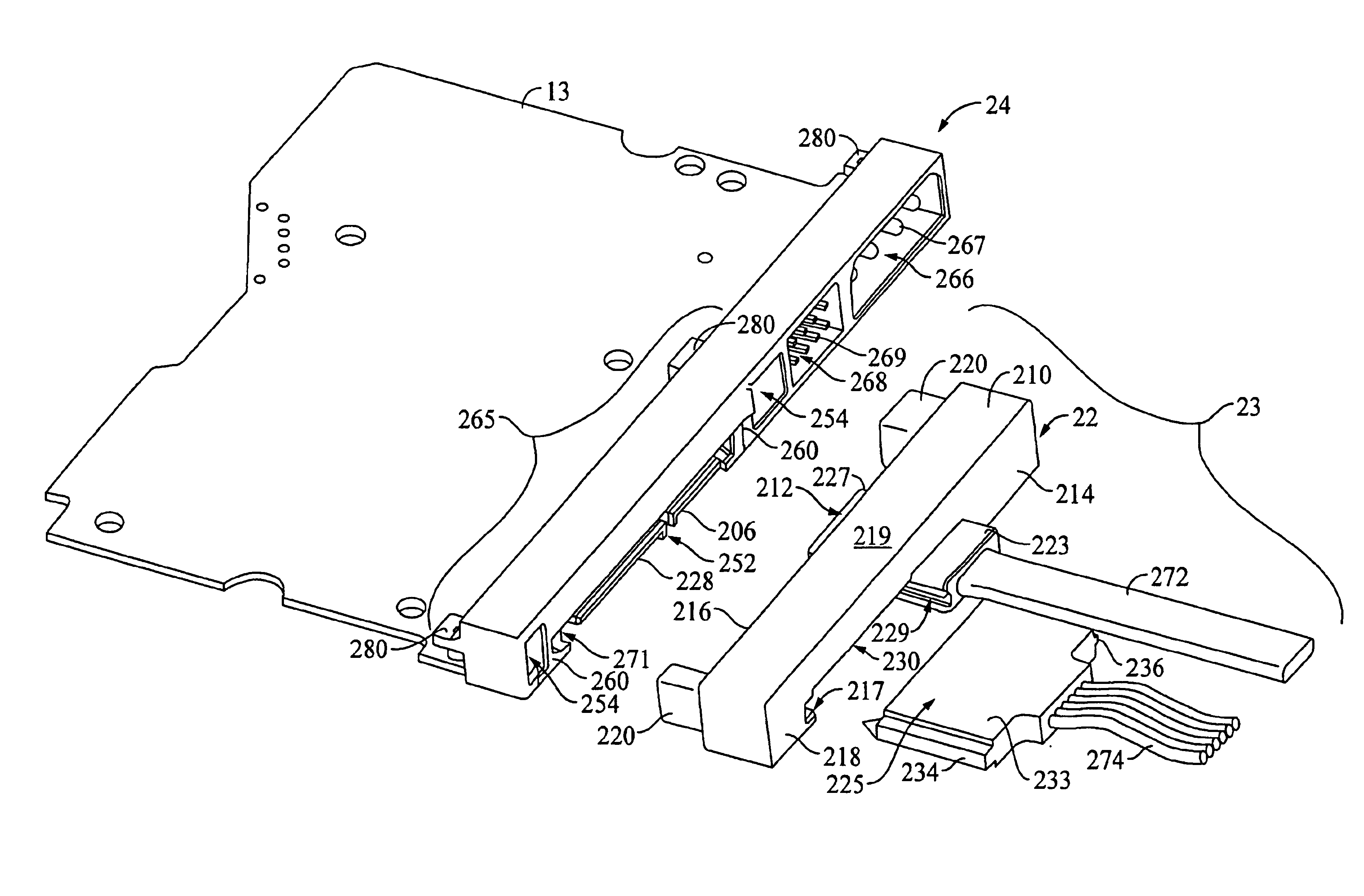

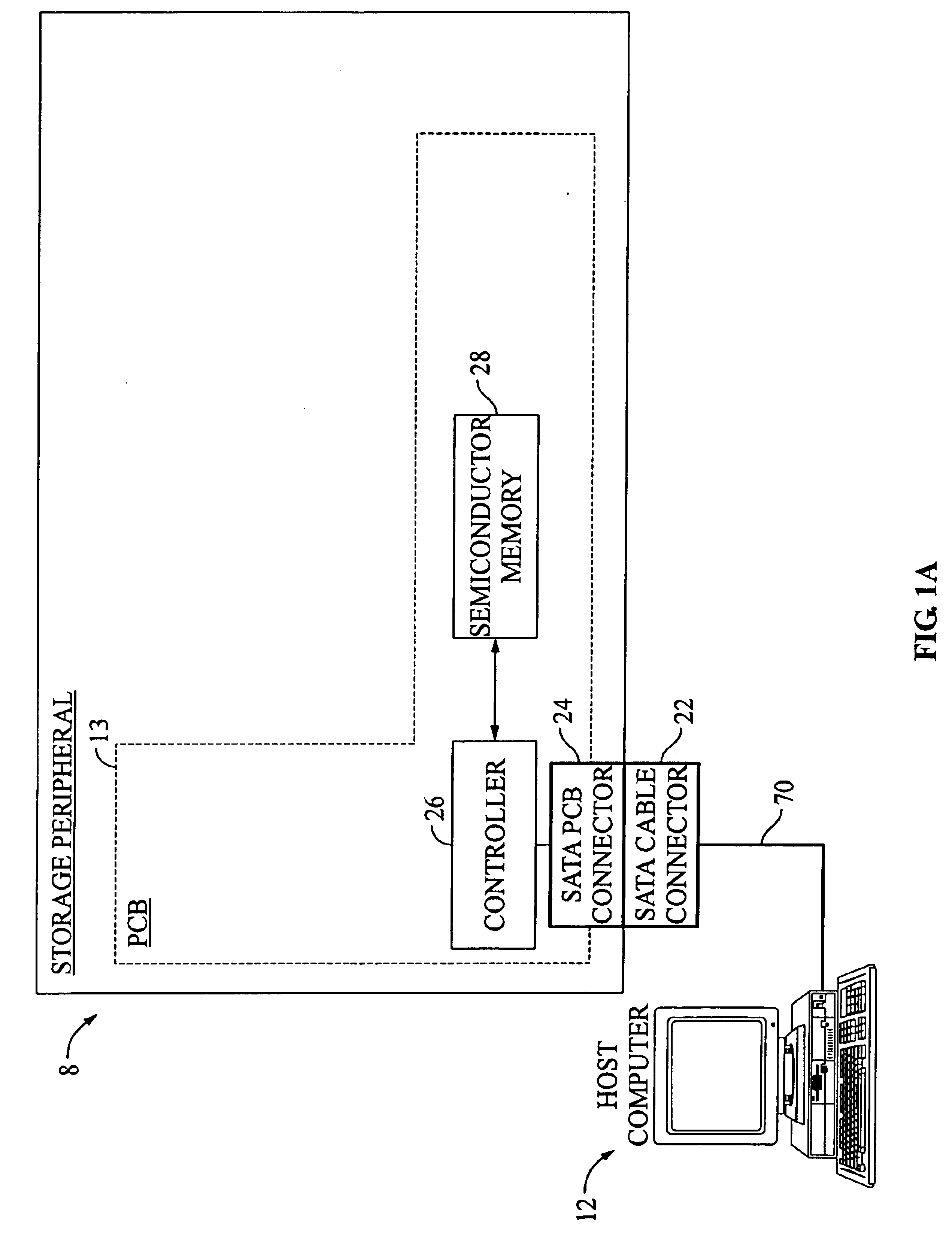

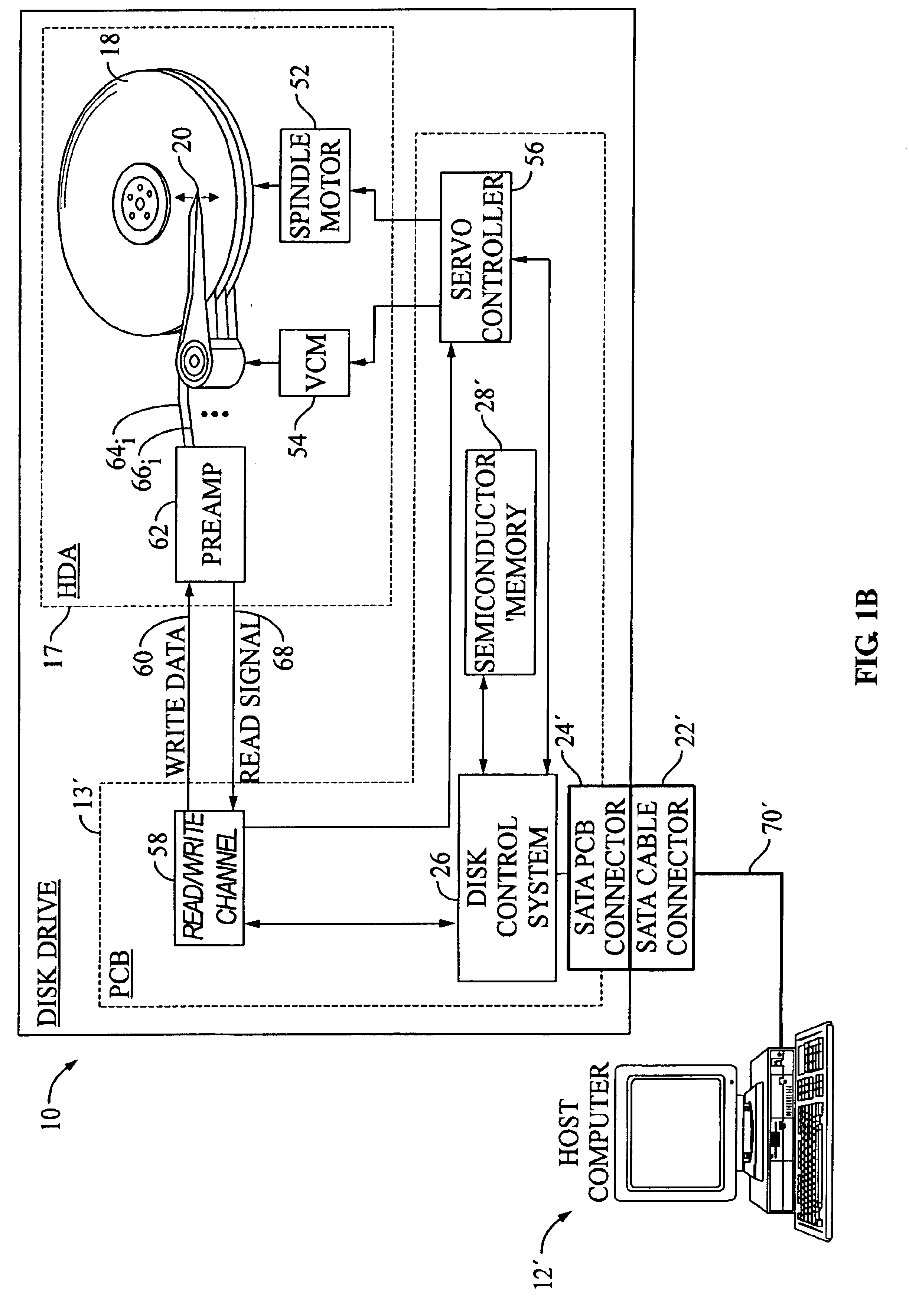

Storage peripheral having a robust serial advanced technology attachment (SATA) PCB connector

InactiveUS6908330B2Carrier constructional parts dispositionIncorrect coupling preventionDisk controllerSerial advanced technology attachment

A storage peripheral, such as disk drive, having a robust PCB connector configured in accordance with a SATA standard. The disk drive has a disk, a disk controller system, and a PCB for mounting the disk controller system, and a housing attached to the PCB. A first electrical contact arrangement in accordance with a SATA standard is connected to the PCB and is supported by a first blade connector. Both the first blade connector and the first electrical contact arrangement are enclosed by the housing. The housing further defines a cable connector receiving area around the first blade connector for the receipt of a cable connector. A pair of laterally-opposed guide arm receiving cavities are integrally formed with the housing and are disposed outside of the cable connector receiving area. The guide arm receiving cavities are adapted for the receipt of guide arms from a mating cable connector.

Owner:WESTERN DIGITAL TECH INC

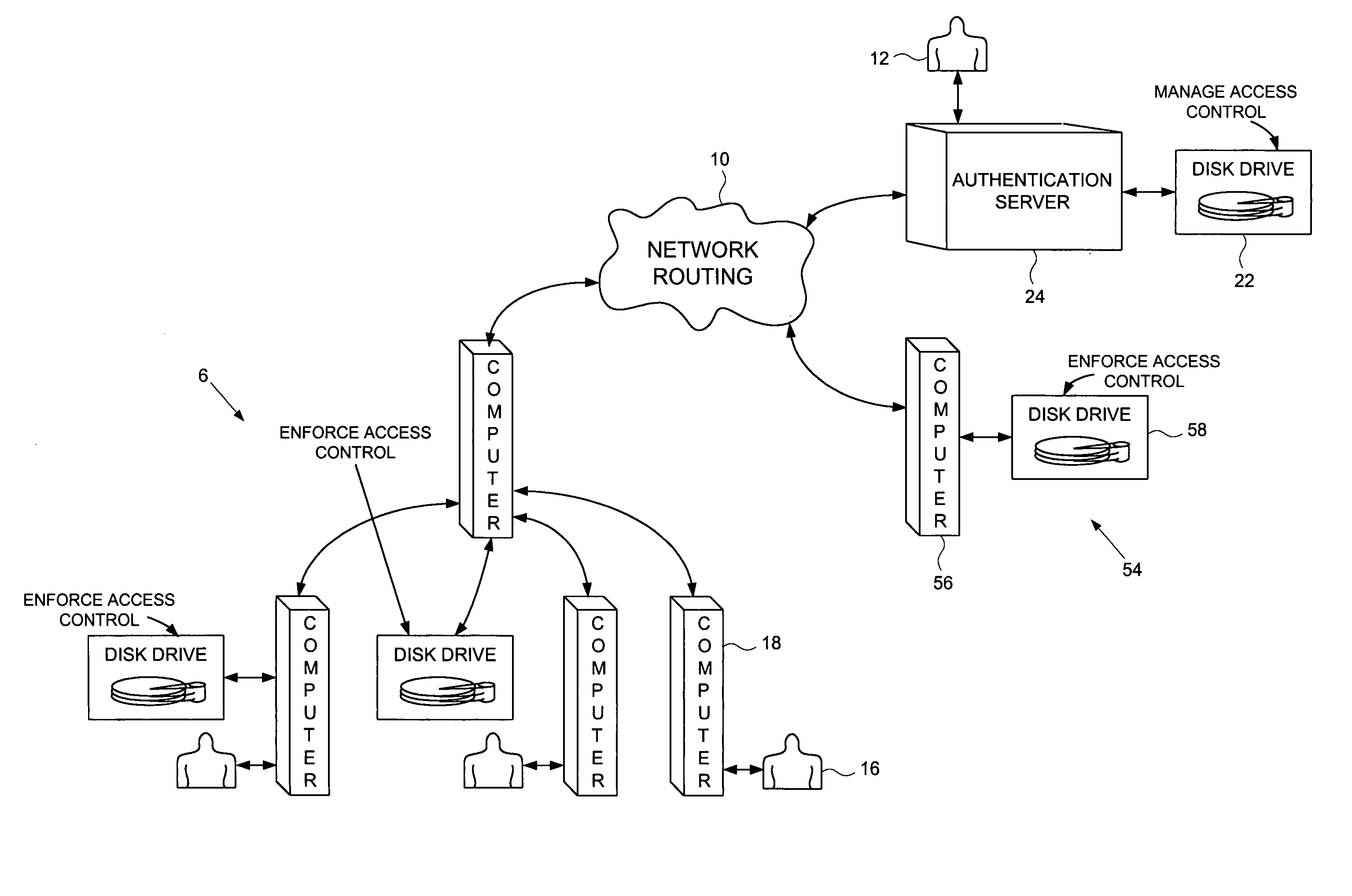

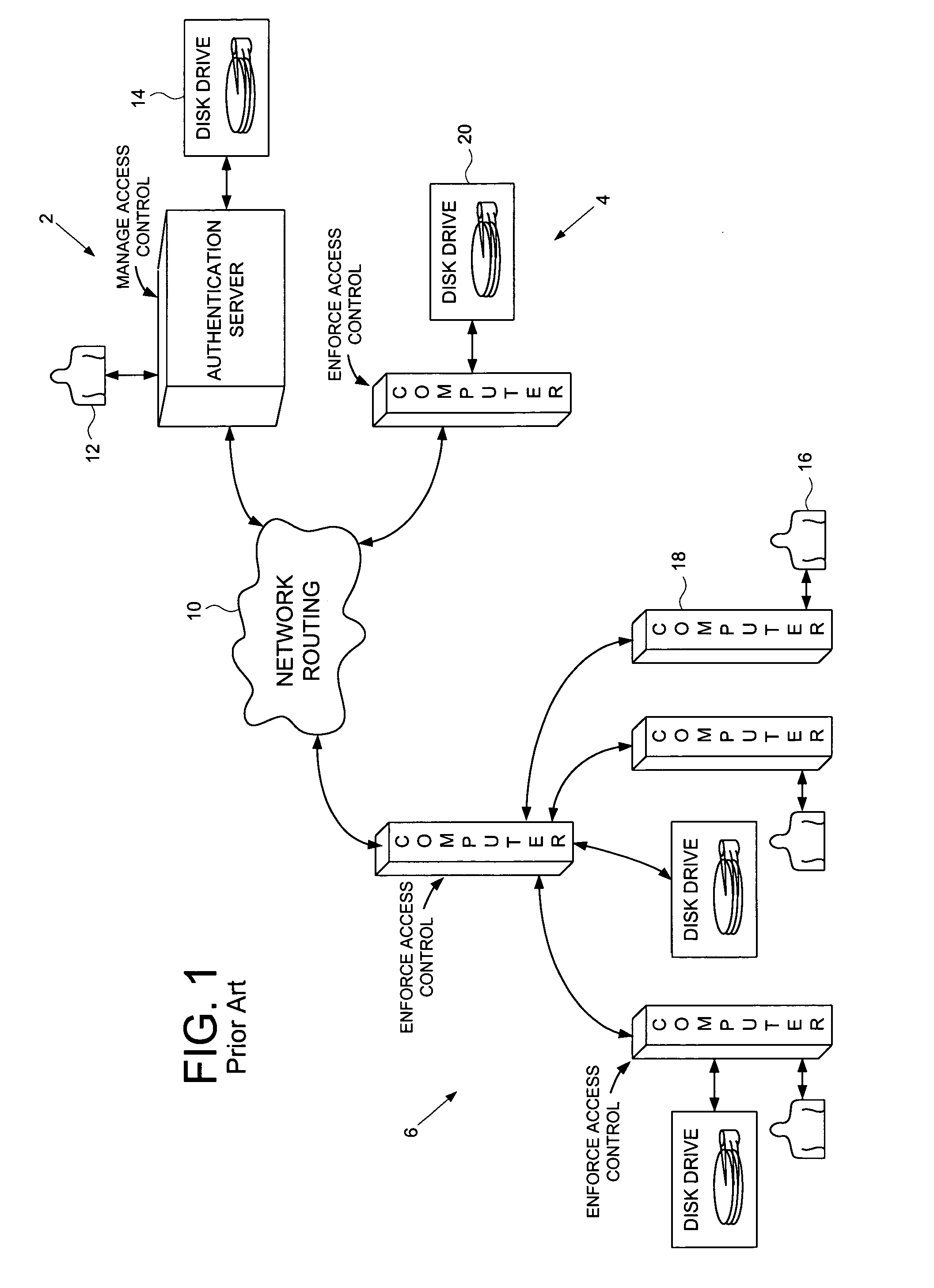

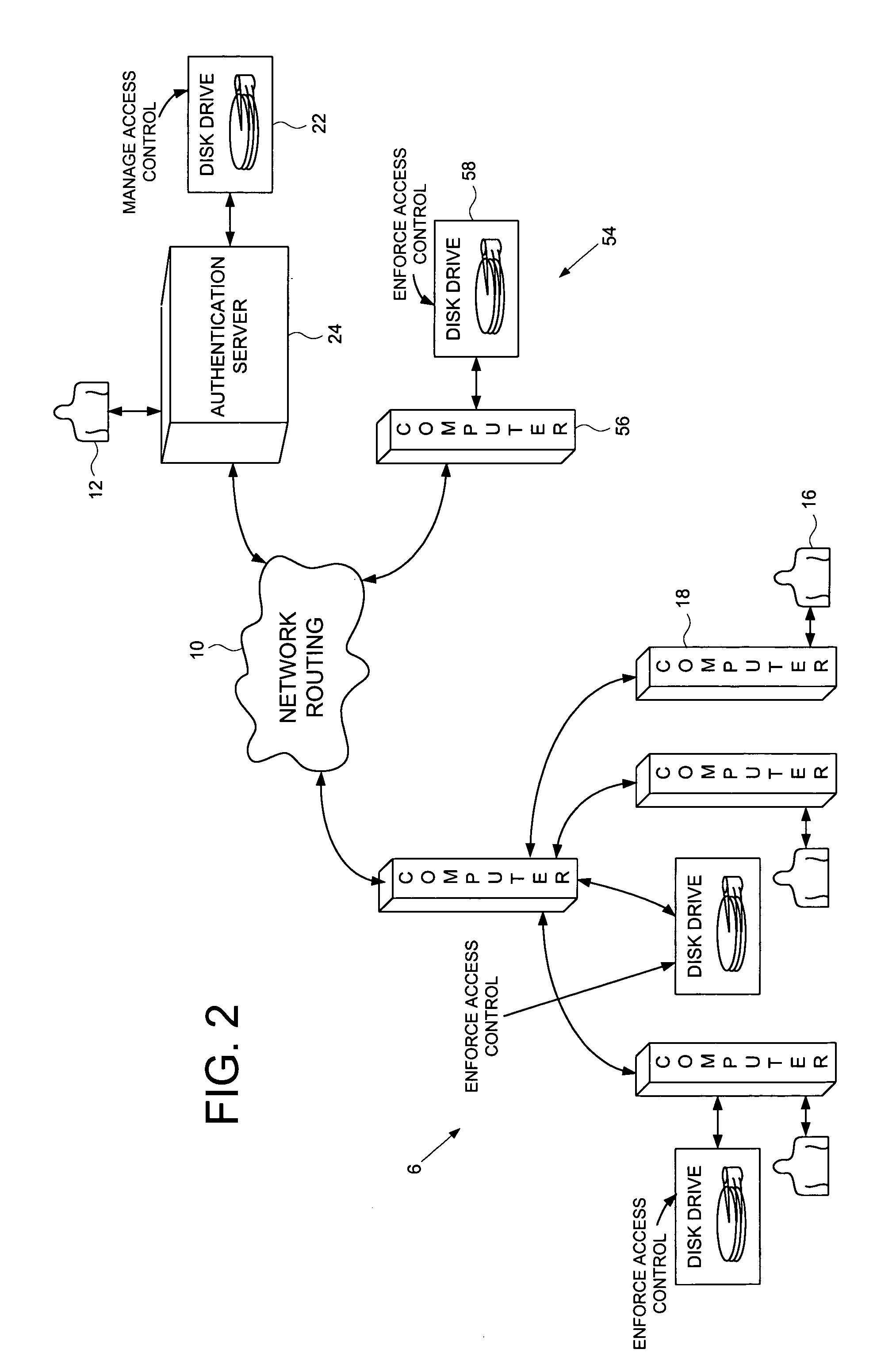

Computer network comprising network authentication facilities implemented in a disk drive

InactiveUS7155616B1Digital data processing detailsUser identity/authority verificationDisk controllerAuthentication server

A computer network is disclosed comprising a plurality of interconnected network devices including a plurality of client computers, an authentication server computer operated by a system administrator, and a disk drive connected to the authentication server computer. The disk drive comprises an interface for receiving the personal authentication data and user access data from the system administrator, a disk for storing data, and a disk controller for controlling access to the disk. An authenticator within the disk drive, responsive to the personal authentication data, enables the disk controller, and cryptographic circuitry encrypts the user access data received from the system administrator into encrypted data stored on the disk.

Owner:WESTERN DIGITAL TECH INC

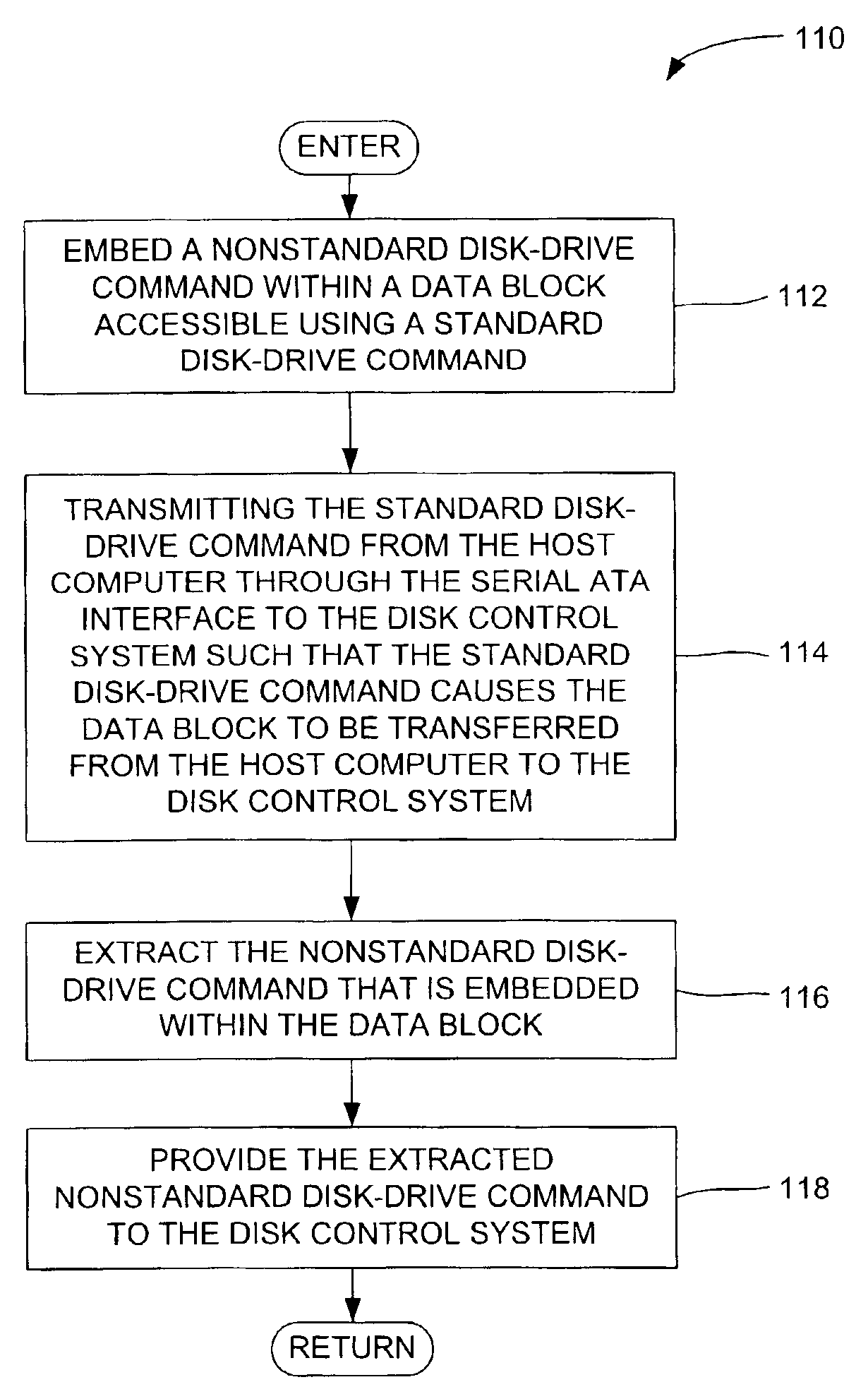

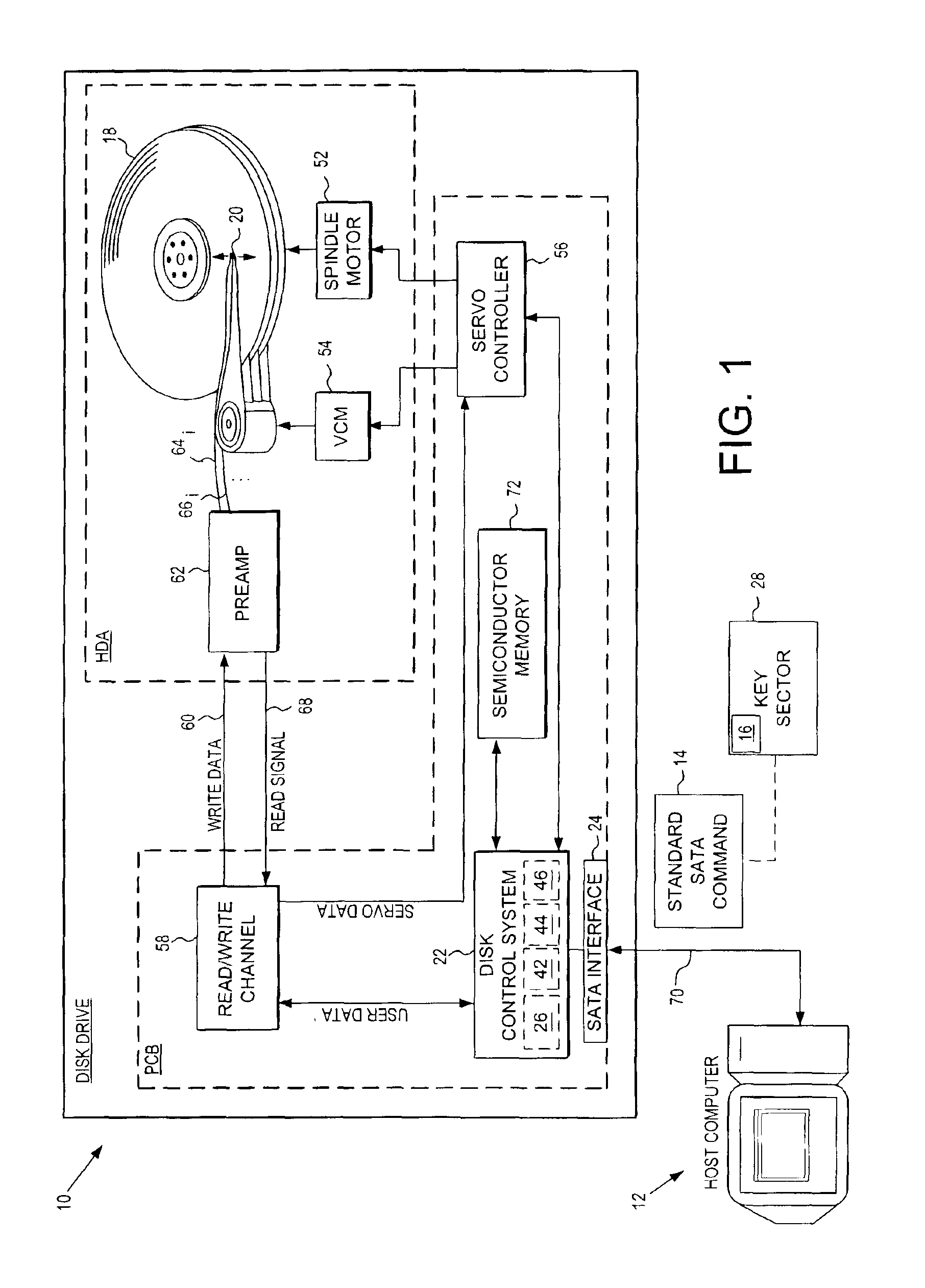

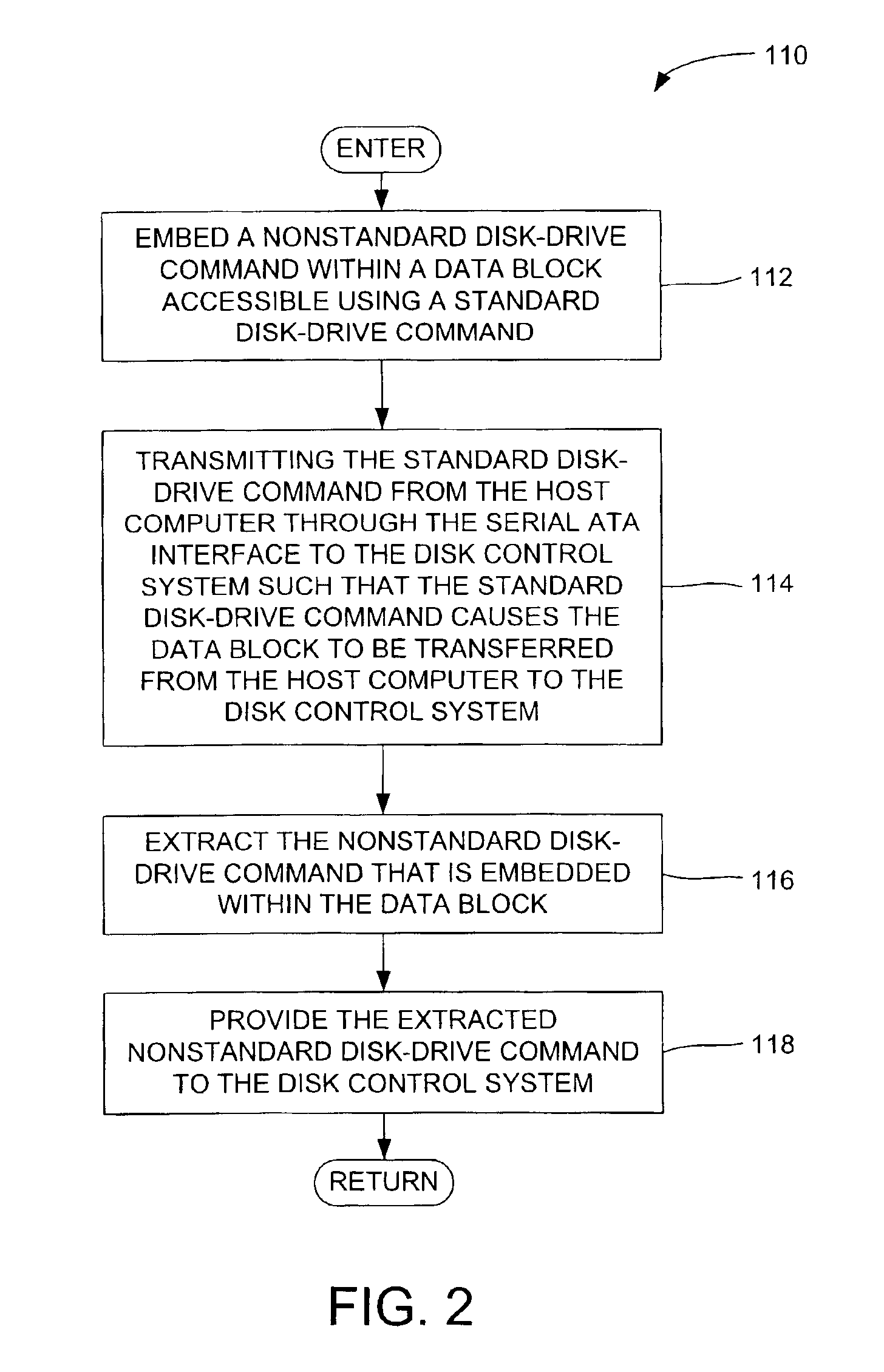

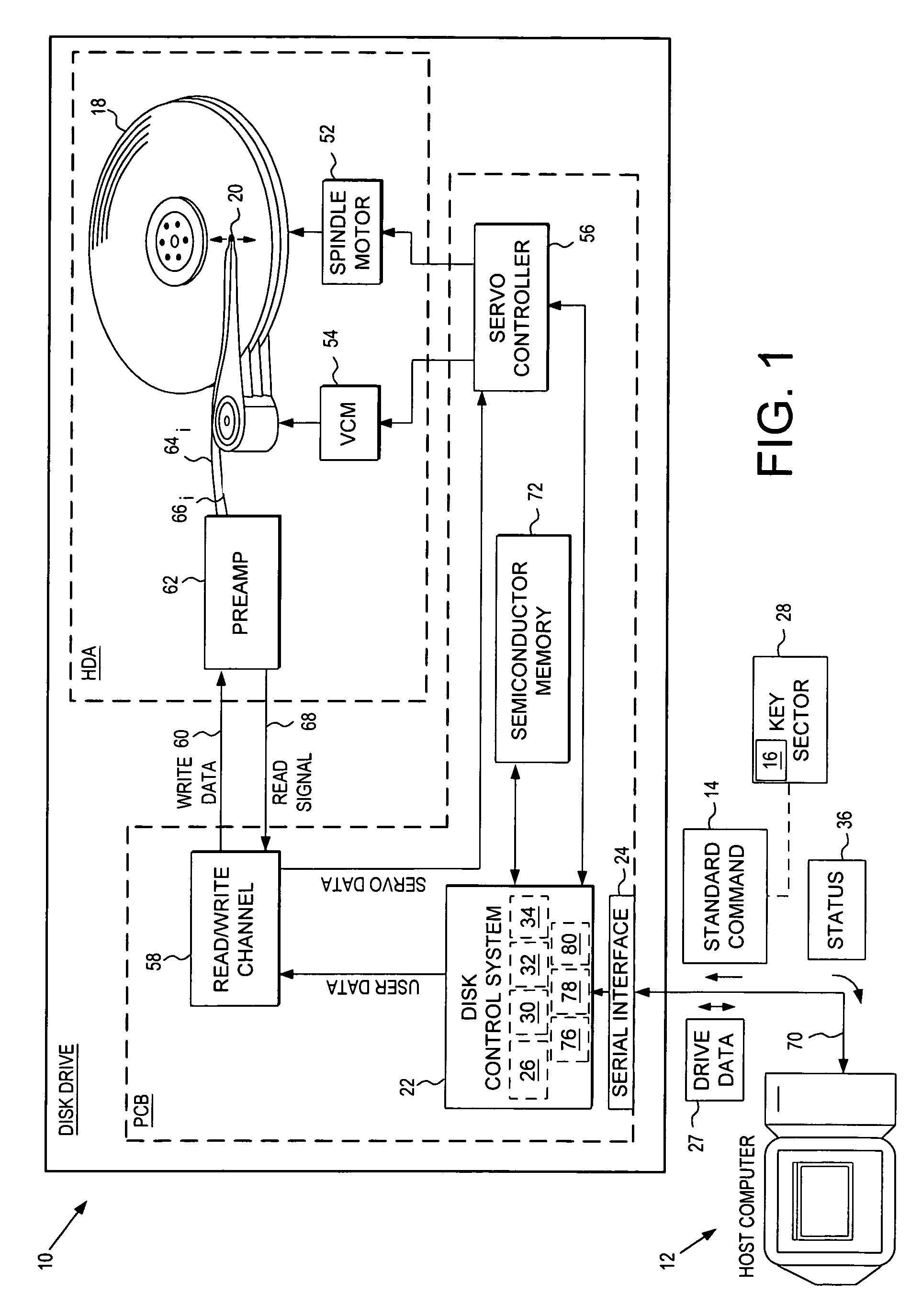

Disk drive and method for implementing nonstandard disk-drive commands on a serial ATA interface that only supports standard ATA disk-drive commands

A disk drive is disclosed that is responsive to standard disk-drive commands associated with disk-drive operations and to nonstandard disk-drive commands required for disk drive manufacture and quality testing. The disk drive includes a disk, a head actuated radially over the disk, and a disk control system. The disk control system responds to disk-drive commands and accesses data storage locations on the disk through the head. A serial ATA interface couples the disk control system to a host computer. The serial ATA interface is configured to transfer standard disk-drive commands from the host computer to the disk control system and is configured to not transfer nonstandard disk-drive commands from the host computer to the disk control system. The extracting means extracts a nonstandard disk-drive command that is embedded within a data block accessed using a standard disk-drive command and provides the extracted nonstandard disk-drive command to the disk control system.

Owner:WESTERN DIGITAL TECH INC

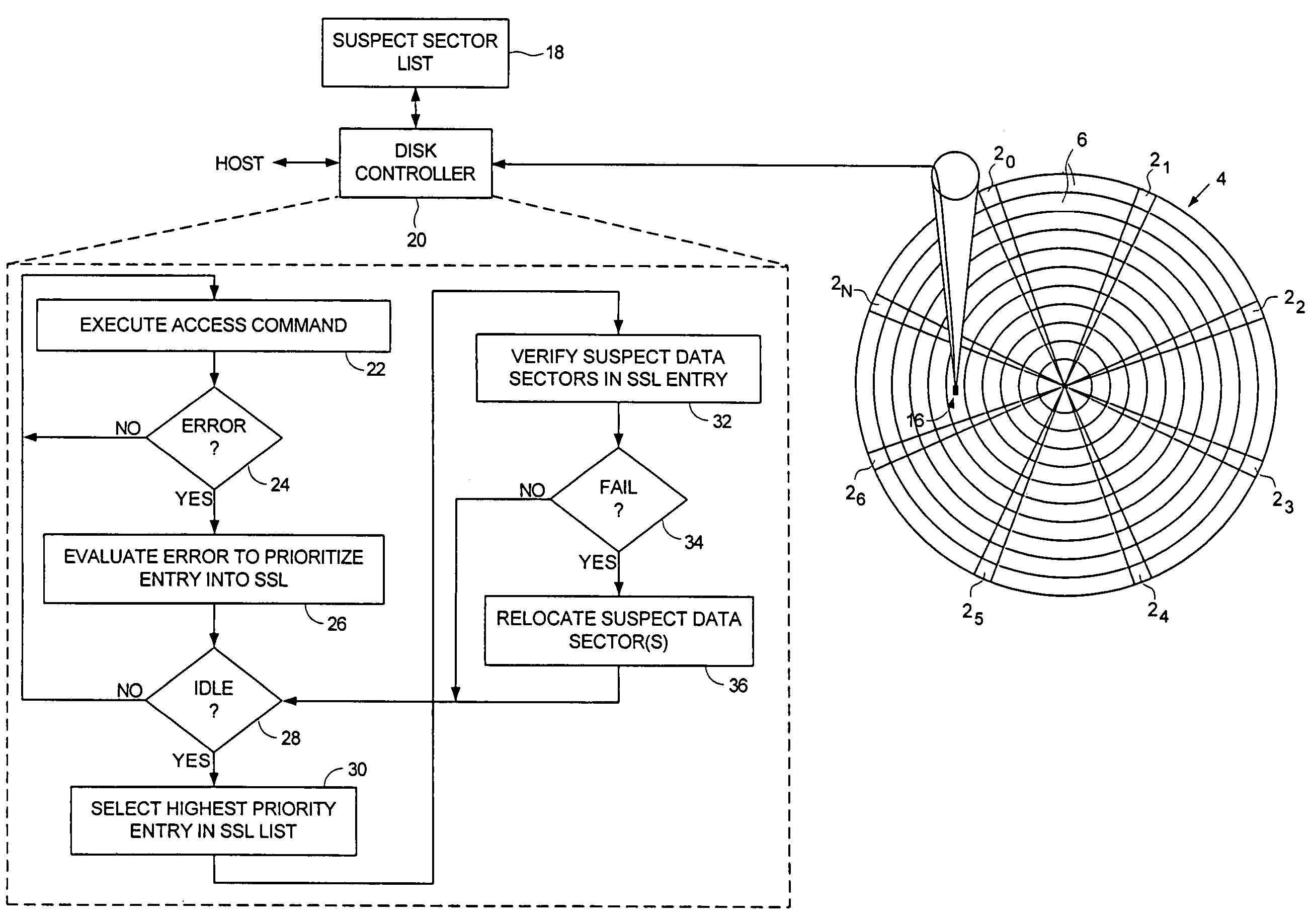

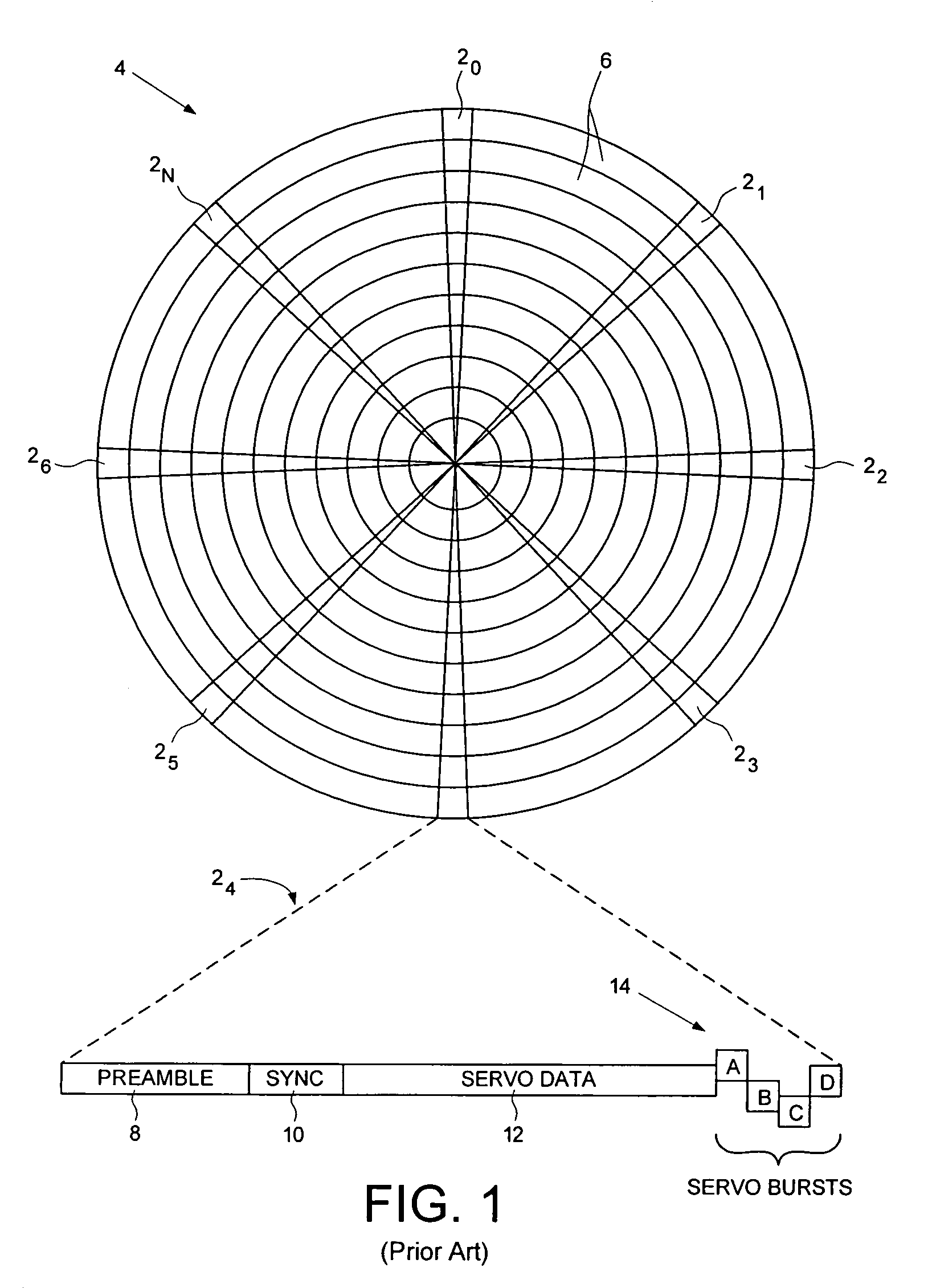

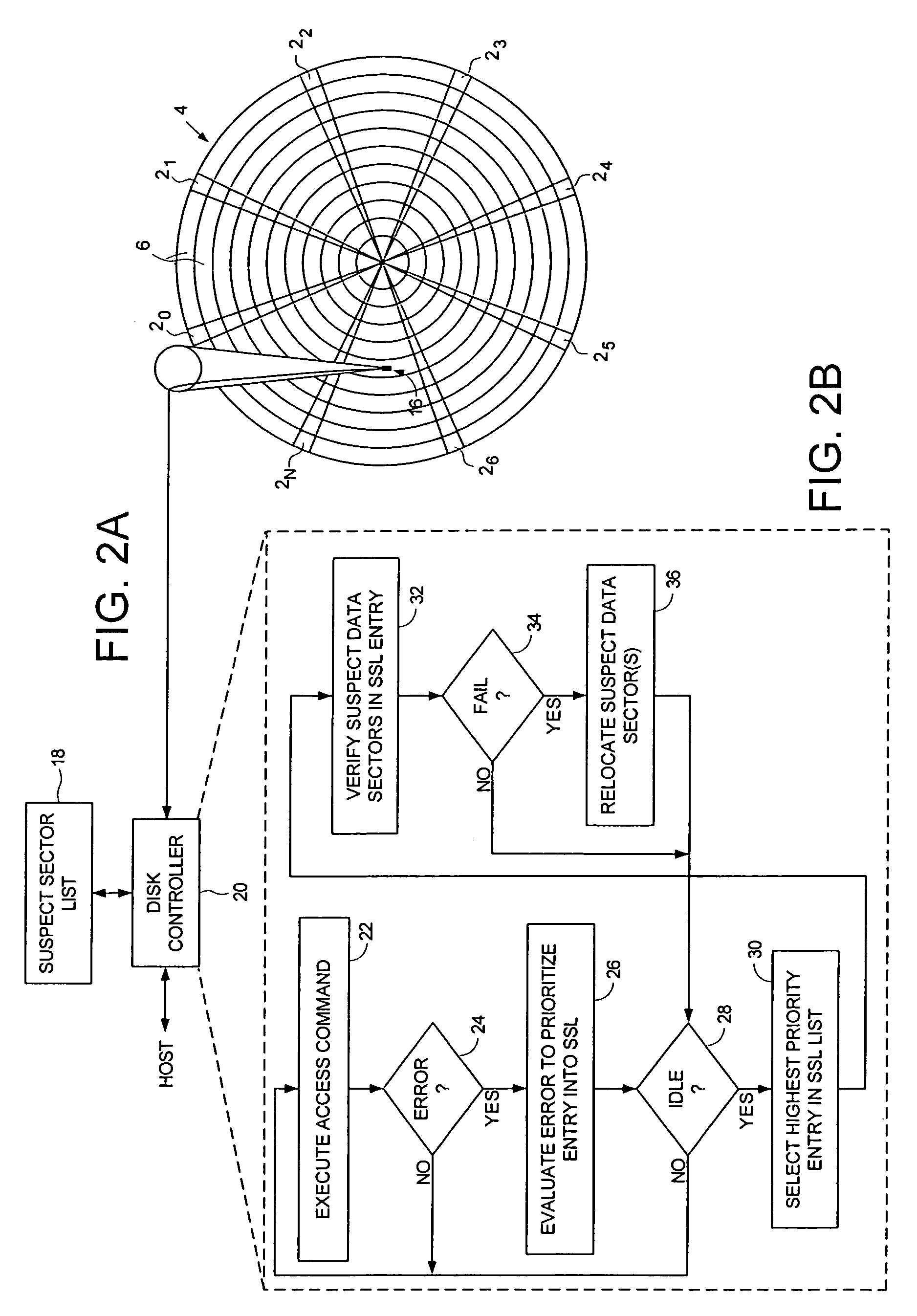

Disk drive performing multi-level prioritization of entries in a suspect sector list to identify and relocate defective data sectors

InactiveUS7274639B1Delay minimizationCombination recordingFilamentary/web record carriersDisk controllerOperating system

A disk drive is disclosed comprising a disk having a plurality of data tracks, wherein each data track comprises a plurality of data sectors, and a head is actuated over the disk. A suspect sector list (SSL) stores a plurality of SSL entries, wherein each SSL entry identifies at least one suspect data sector. The disk drive further comprises a disk controller for executing an access command received from a host computer to access at least one of the data sectors. If an error is detected while executing the access command, the disk controller generates an SSL entry having a priority level selected from at least three priority levels and adds the SSL entry to the SSL. A verification operation is executed for each suspect data sector identified by each SSL entry, wherein the SSL entries are processed relative to the priority level assigned to each SSL entry.

Owner:WESTERN DIGITAL TECH INC

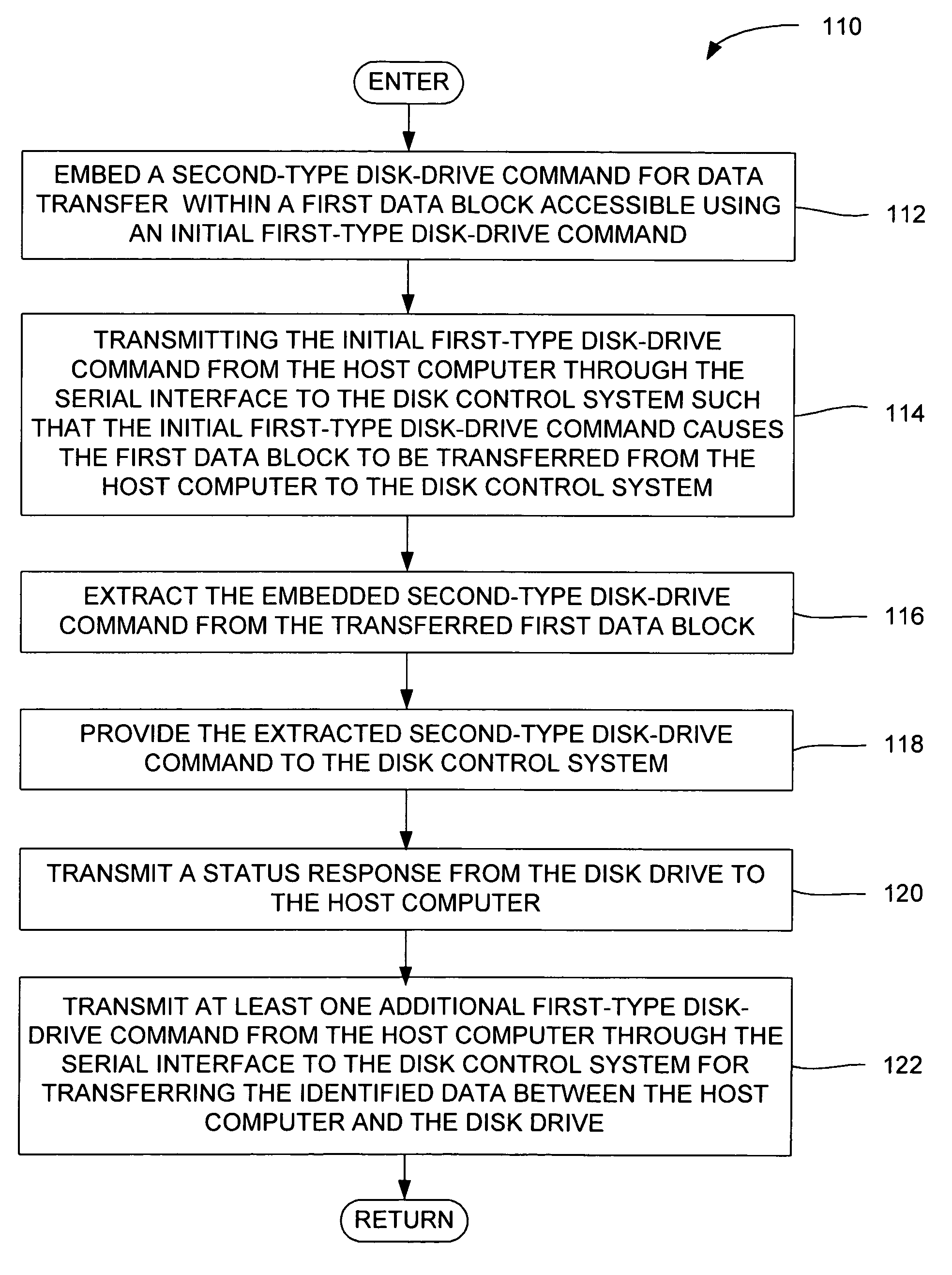

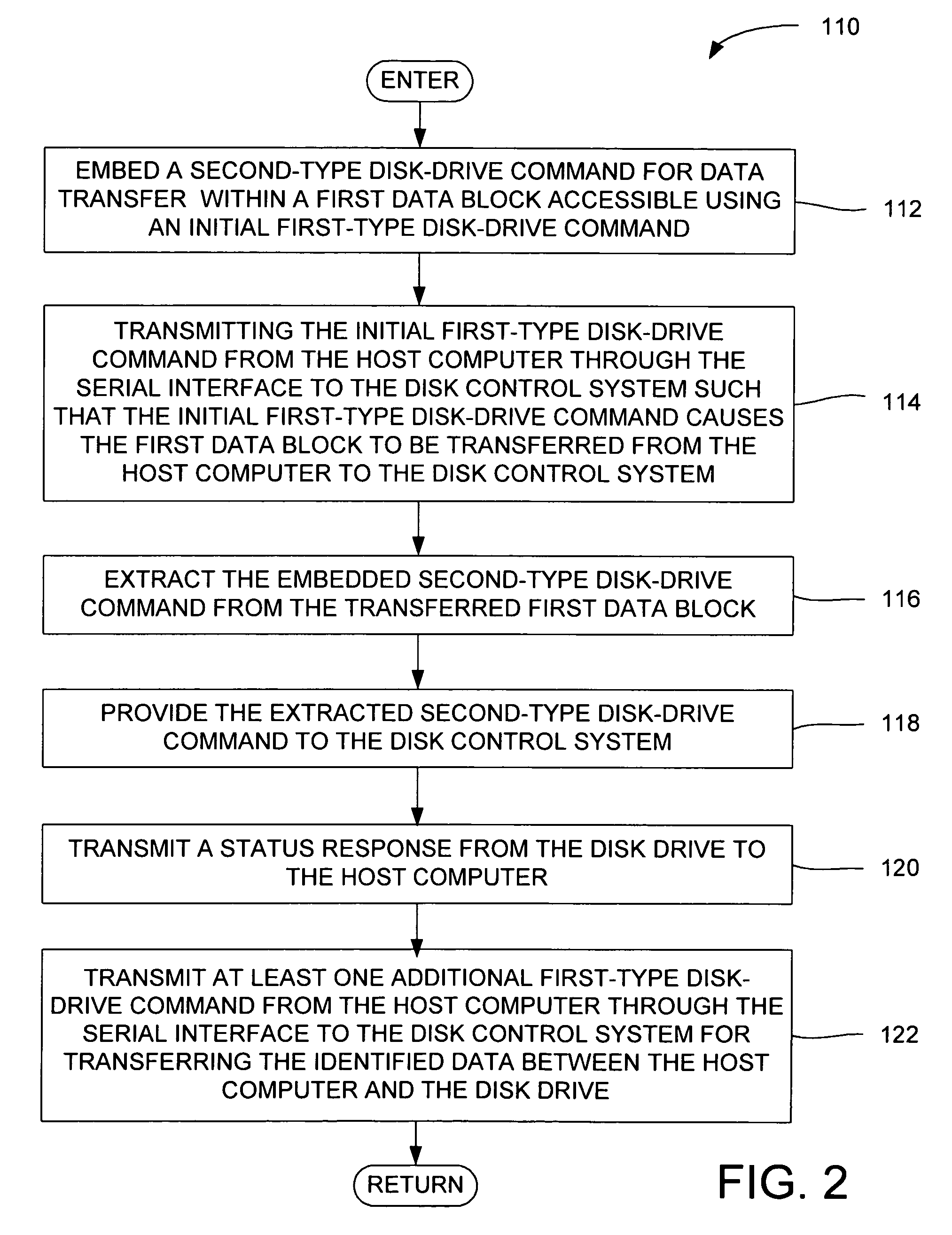

Disk drive and method for data transfer initiated by optional disk-drive commands on a serial interface that only supports standard disk-drive commands

A disk drive and method are disclosed for data transfer initiated by nonstandard disk-drive commands on a serial interface that only supports standard disk-drive commands. In the method, a nonstandard disk-drive command for data transfer is embedded within a first data block accessible using a first standard disk-drive command. The first standard disk-drive command is transmitted through the serial interface causing the first data block to be transferred from the host computer to the disk control system. The embedded command is extracted from the transferred first data block and provided to the disk control system. A status response is transmitted to the host computer based on the extracted command. At least one additional standard disk-drive command is transmitted through the serial interface to the disk control system for transferring the identified data between the host computer and the disk drive.

Owner:WESTERN DIGITAL TECH INC

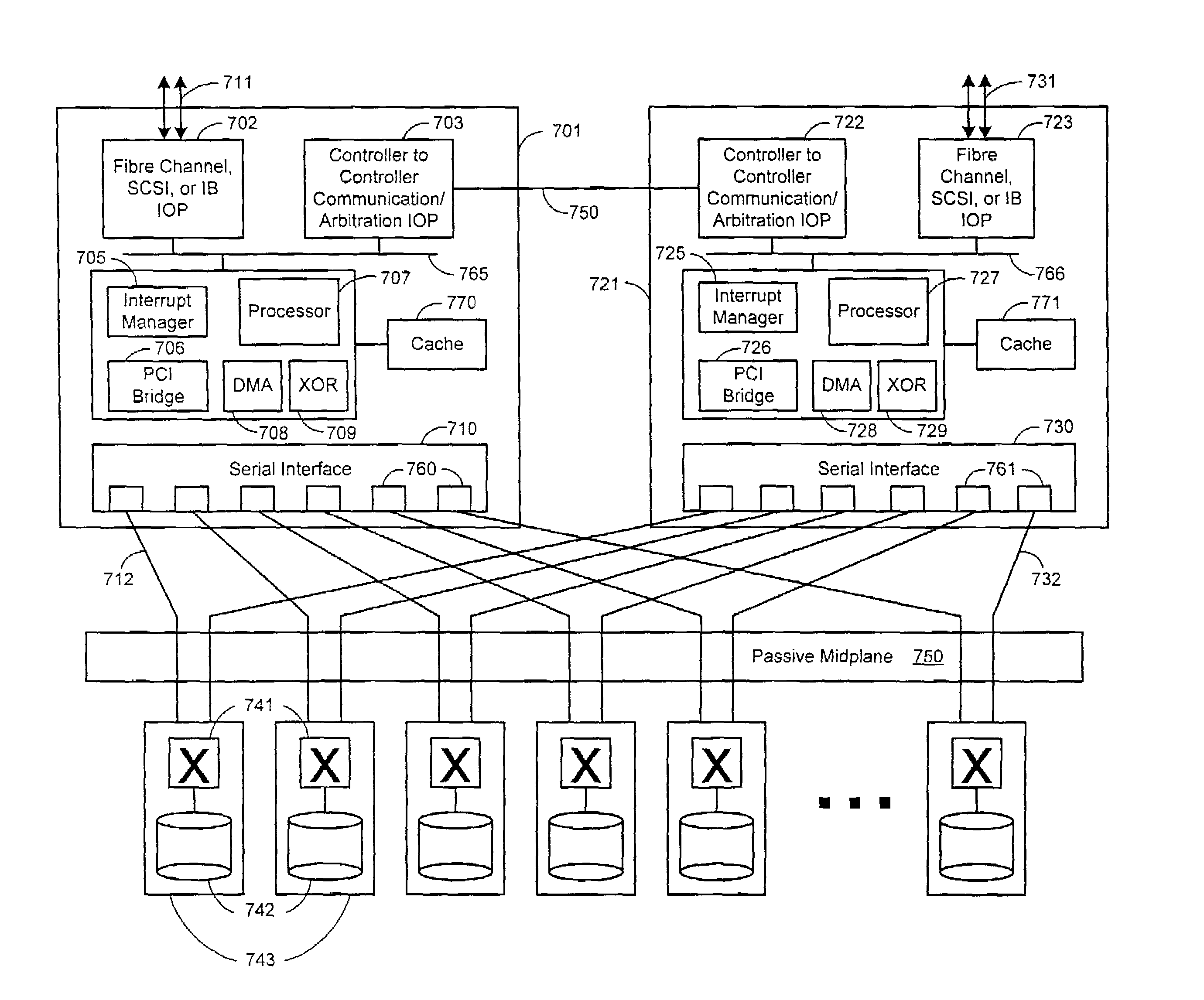

Serial interface for a data storage array

InactiveUS7073022B2Input/output to record carriersMemory systemsSerial digital interfaceDisk controller

The present invention describes a method and system for interfacing a plurality of device controllers to an array of data storage devices by serial connection. The device controllers are coupled to a serial interface by a bus and the devices of the storage array are coupled to the serial interface by a serial connection. The serial interface receives controller signals through the bus and multiplexes the signals onto the serial connections of the storage array. Arbitration between the various device controllers seeking access to the storage array is resolved through bus protocol and through drive based reserve / release registers in the serial interface processor.

Owner:IBM CORP

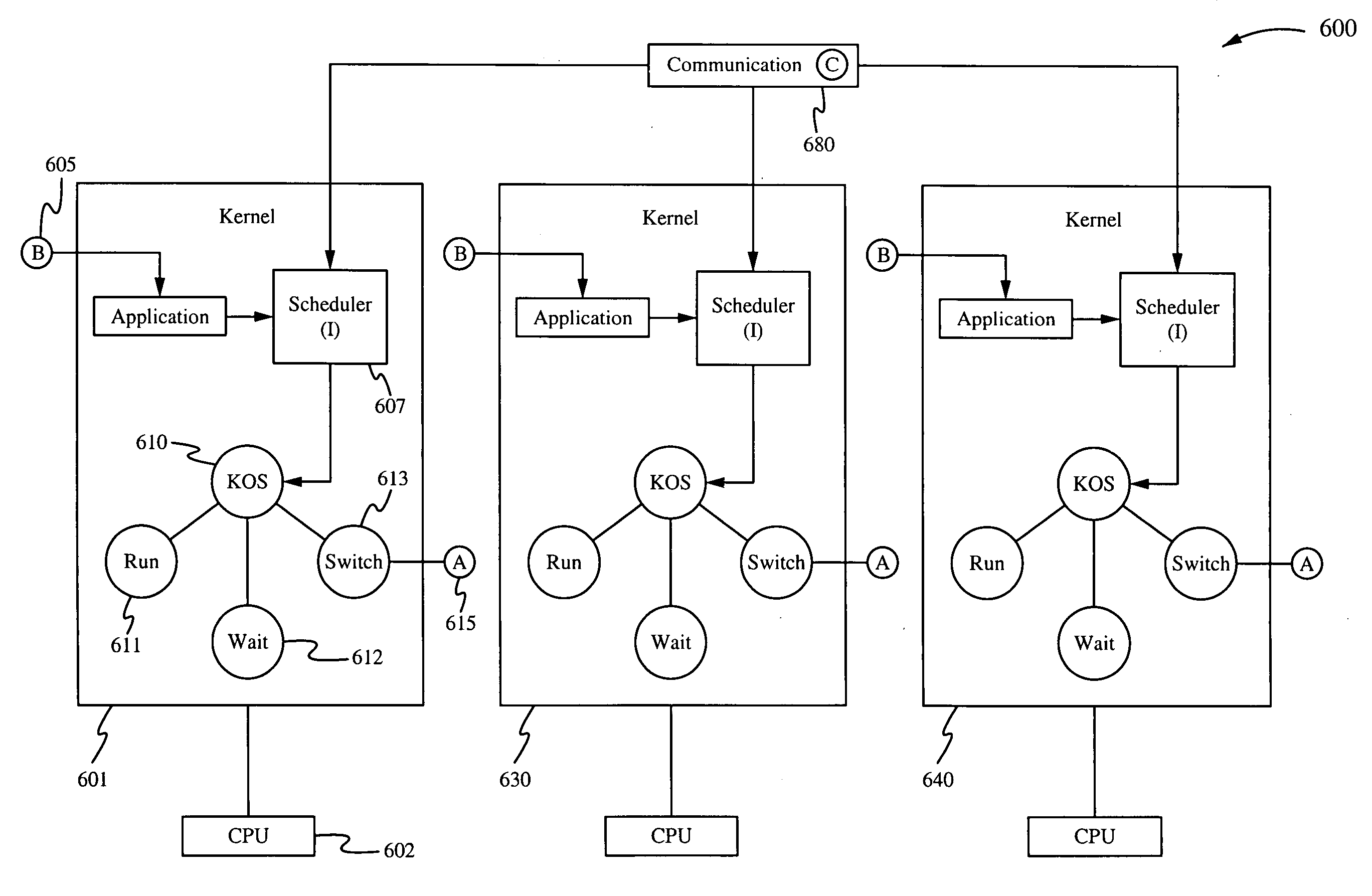

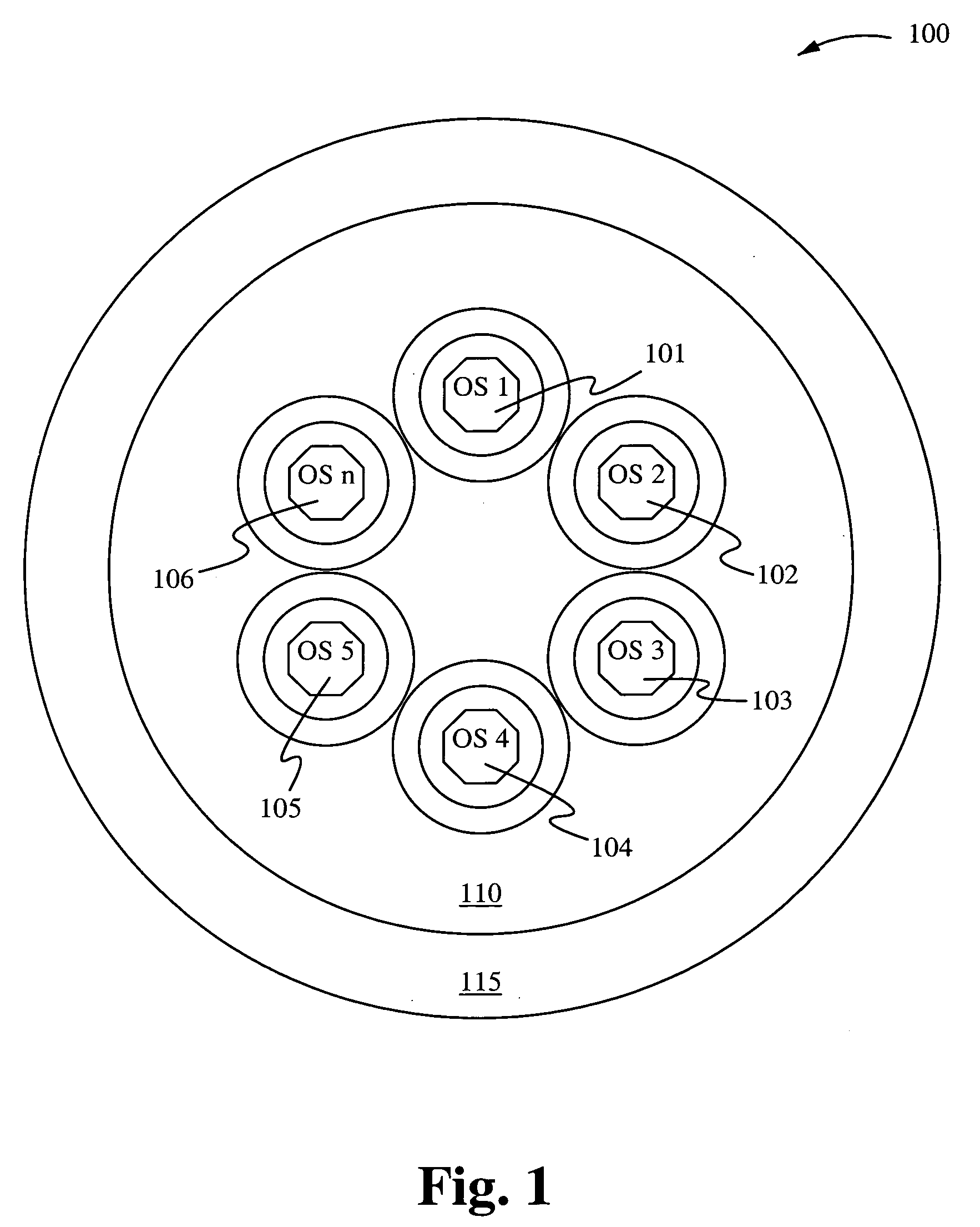

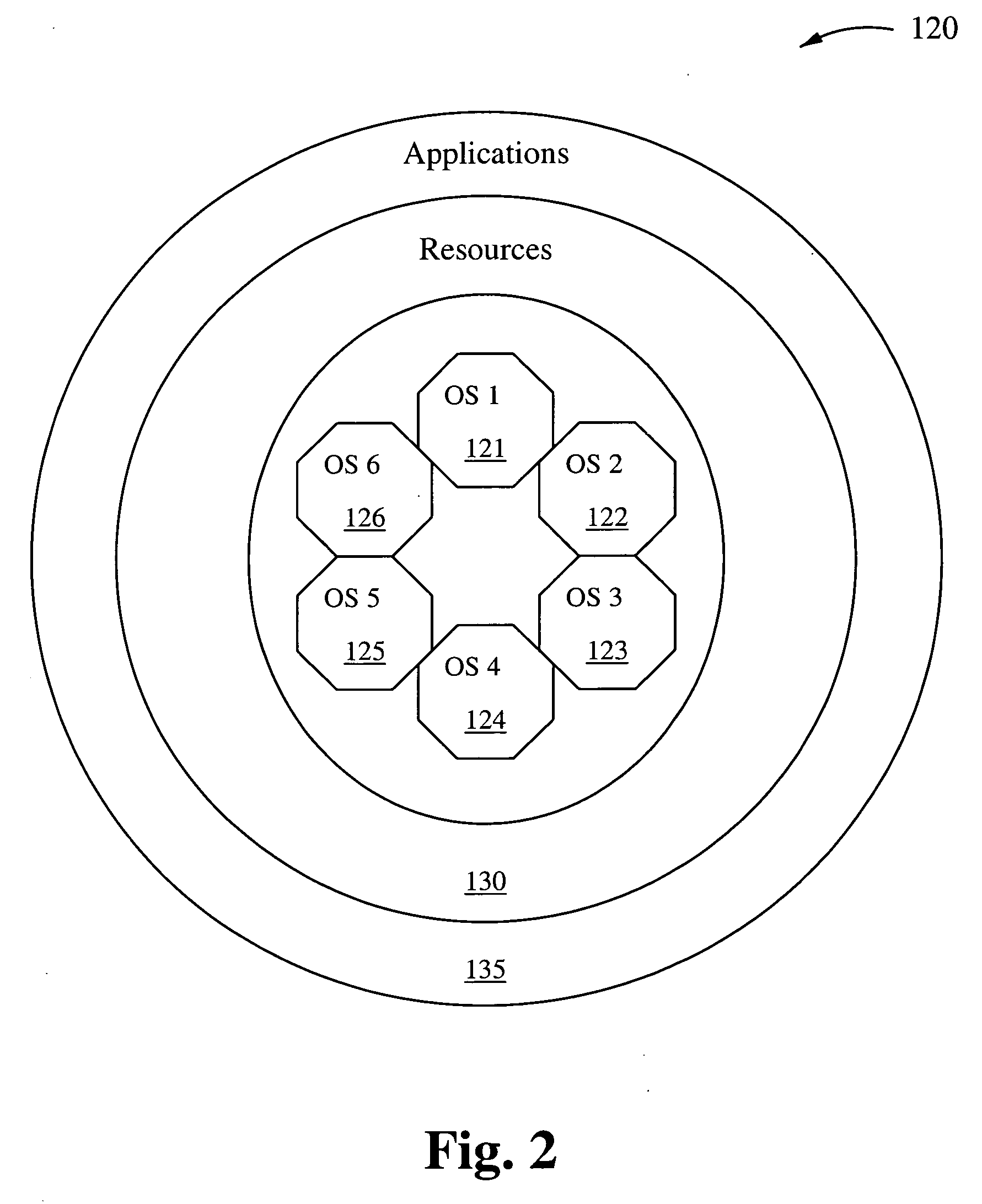

System for and method of uniform synchronization between multiple kernels running on single computer systems with multiple CPUs installed

InactiveUS20090158299A1Multiprogramming arrangementsMemory systemsLimited resourcesOperational system

The present invention allocates resources in a multi-operating system computing system, thereby avoiding bottlenecks and other degradations that result from competition for limited resources. In one embodiment, a computer system includes resources and multiple processors executing multiple operating systems that provide access to the resources. The resources include printers, disk controllers, memory, network controllers, and other often-accessed resources. Each operating system contains a kernel scheduler. Together, the multiple kernel schedulers are configured to coordinate allocating the resources to processes executing on the computer system.

Owner:EXIT CUBE HONG KONG

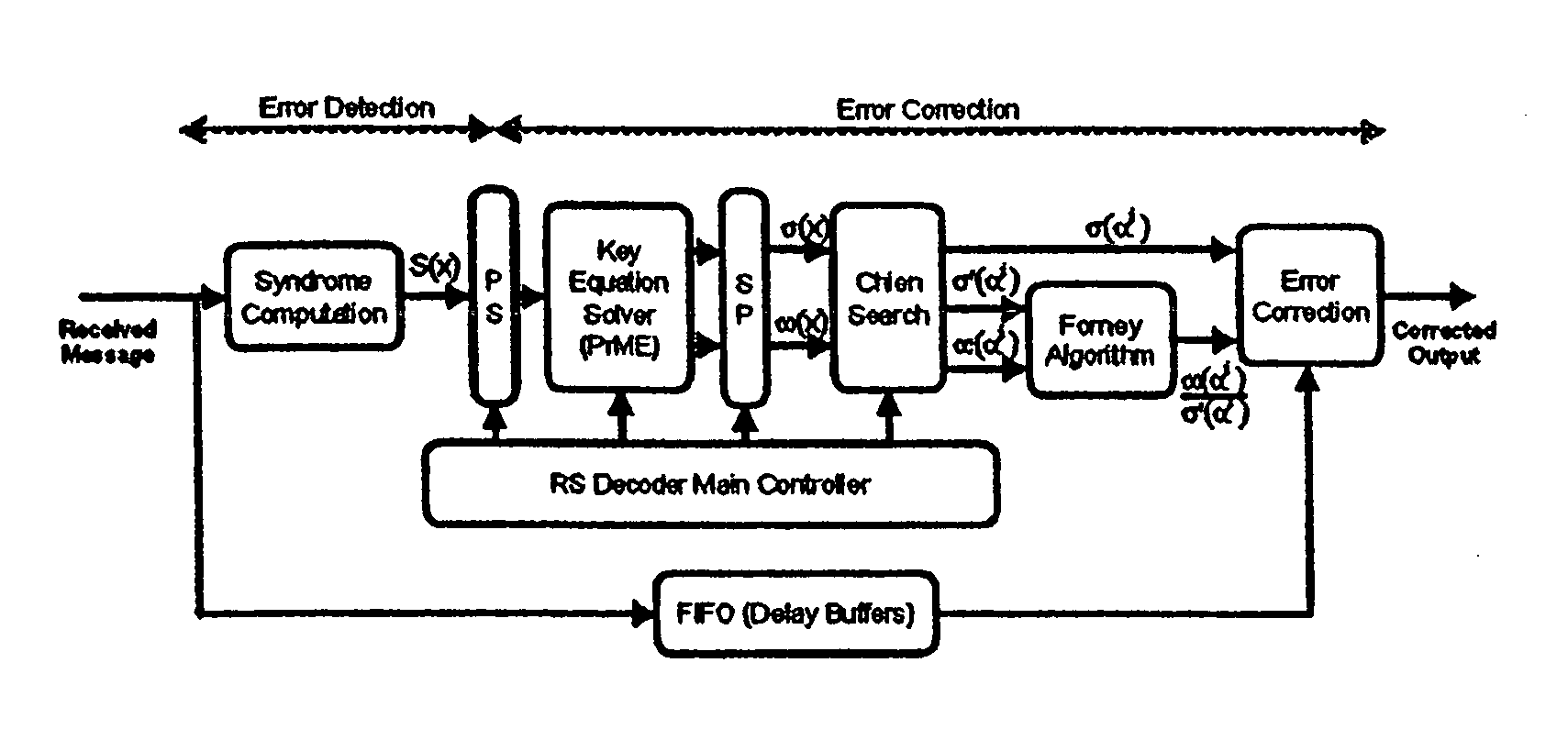

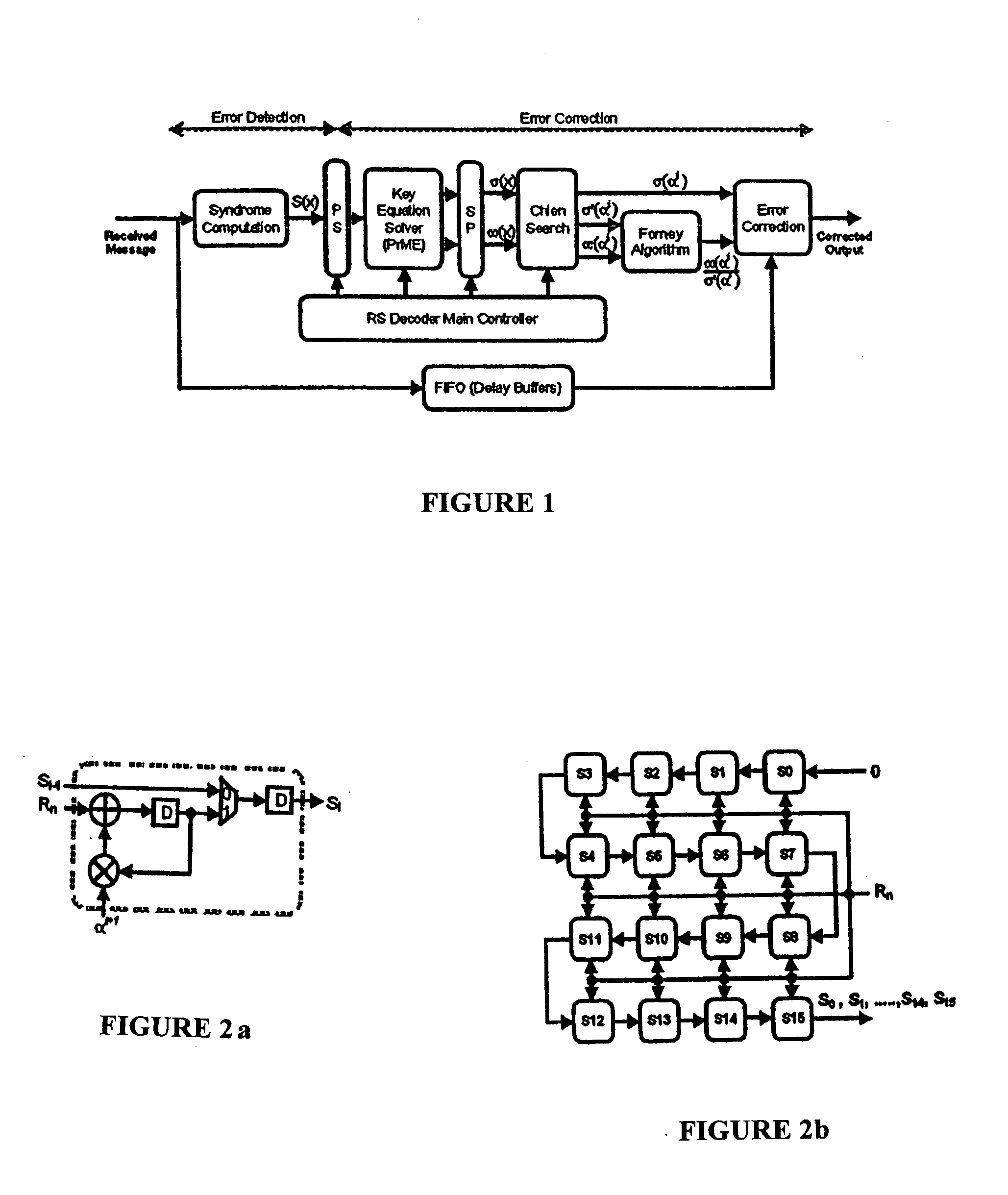

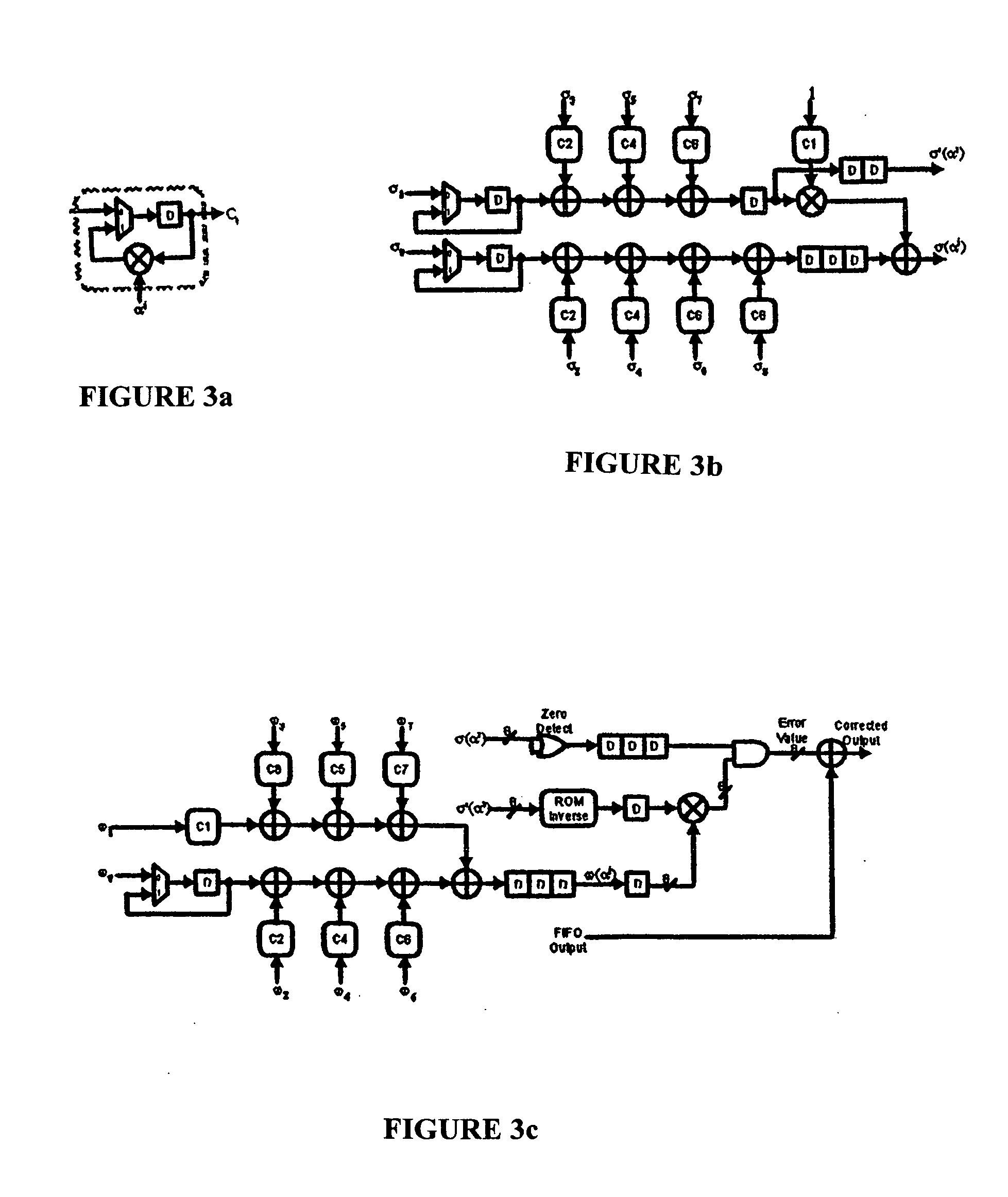

Reed-solomon decoder systems for high speed communication and data storage applications

InactiveUS20060059409A1Effective and reliable error correction functionalityReduce complexityCode conversionCoding detailsModem deviceHigh rate

A high-speed, low-complexity Reed-Solomon (RS) decoder architecture using a novel pipelined recursive Modified Euclidean (PrME) algorithm block for very high-speed optical communications is provided. The RS decoder features a low-complexity Key Equation Solver using a PrME algorithm block. The recursive structure enables the low-complexity PrME algorithm block to be implemented. Pipelining and parallelizing allow the inputs to be received at very high fiber optic rates, and outputs to be delivered at correspondingly high rates with minimum delay. An 80-Gb / s RS decoder architecture using 0.13-μm CMOS technology in a supply voltage of 1.2 V is disclosed that features a core gate count of 393 K and operates at a clock rate of 625 MHz. The RS decoder has a wide range of applications, including fiber optic telecommunication applications, hard drive or disk controller applications, computational storage system applications, CD or DVD controller applications, fiber optic systems, router systems, wireless communication systems, cellular telephone systems, microwave link systems, satellite communication systems, digital television systems, networking systems, high-speed modems and the like.

Owner:UNIV OF CONNECTICUT

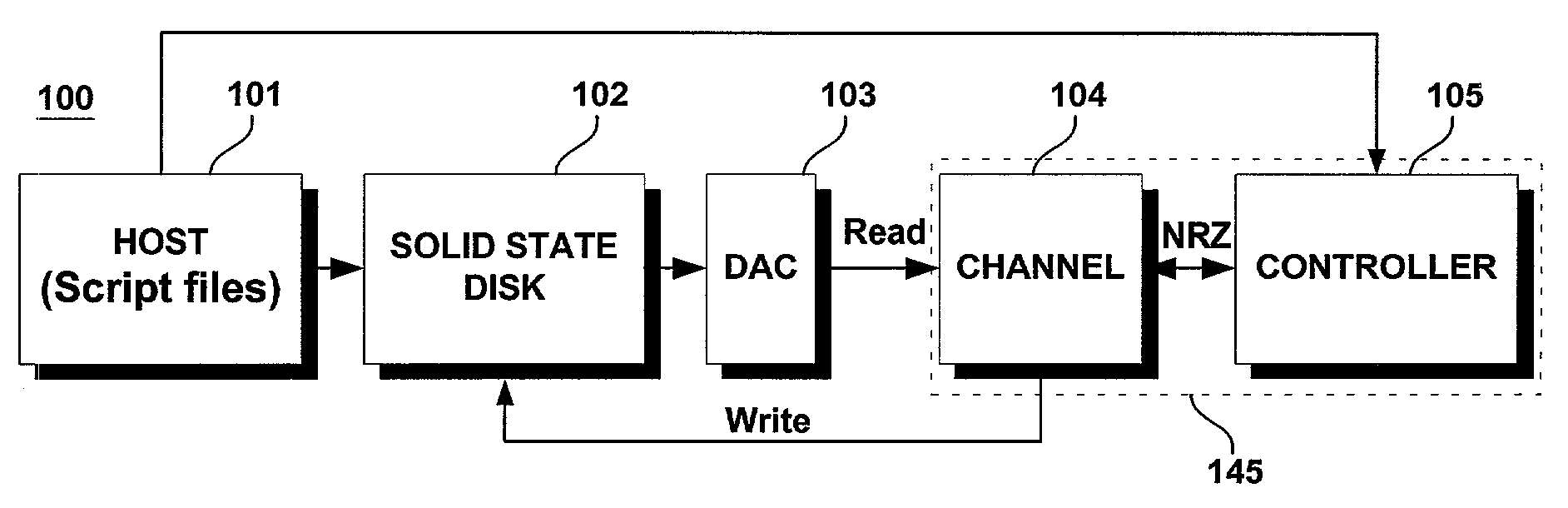

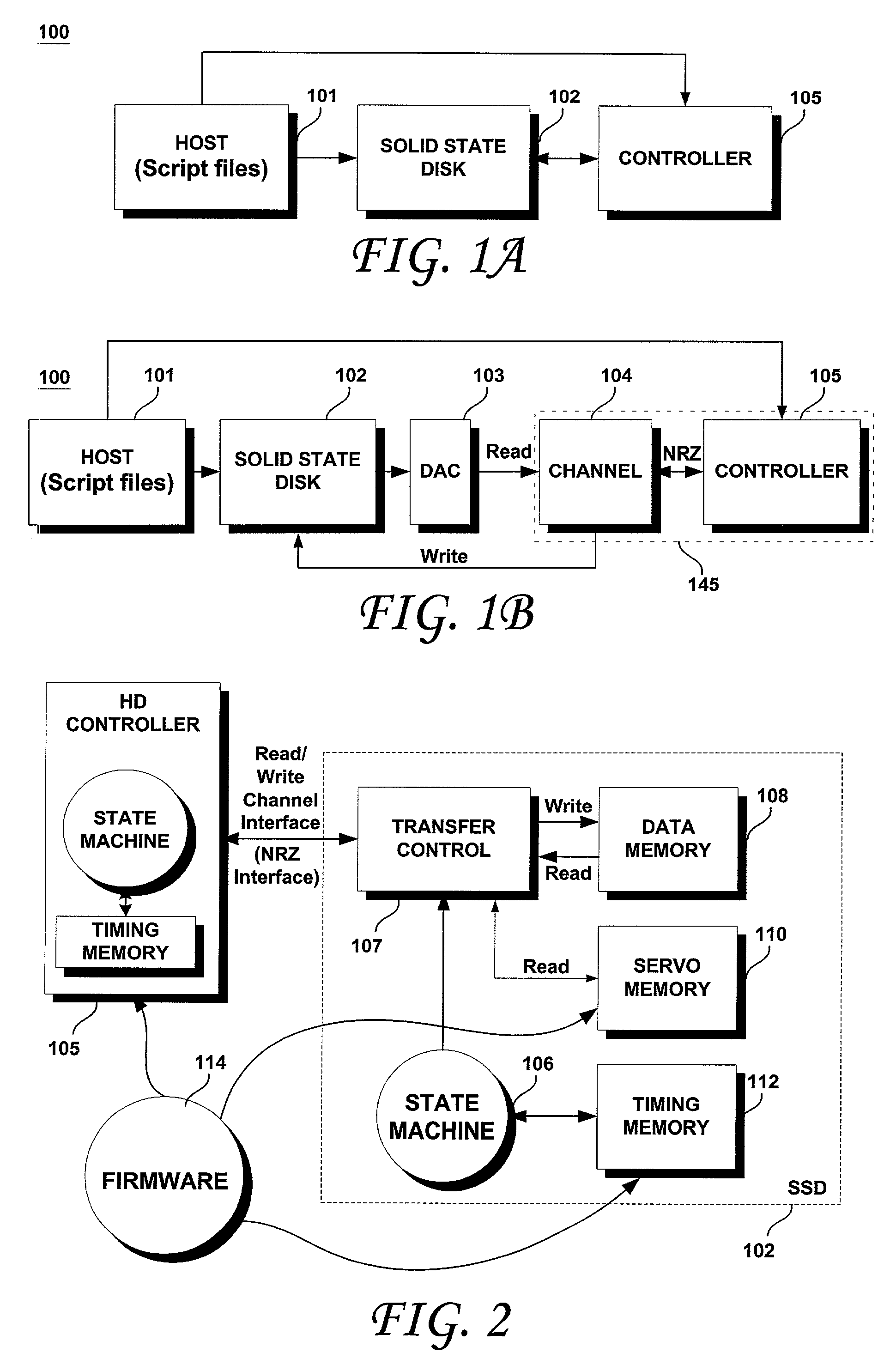

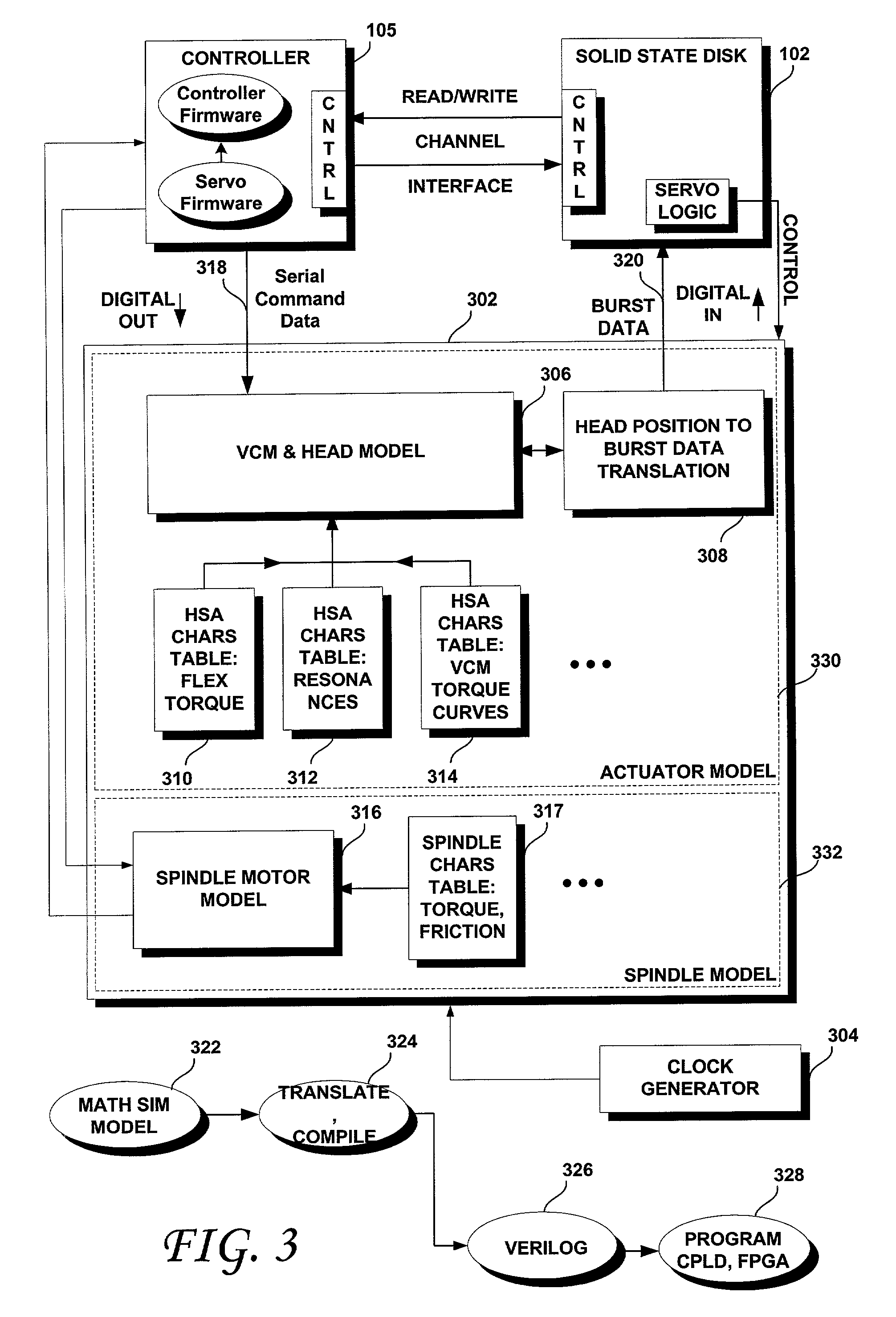

Presilicon disk model for design, development and validation

InactiveUS7031902B1Accurate relative time relationshipDesign optimisation/simulationSoftware simulation/interpretation/emulationDisk controllerActuator

A method for verifying the design of a disk controller circuit to be incorporated into a targeted hard disk drive system having a read / write channel and a head actuator may include steps of emulating reading and writing of data in the read / write channel based upon a model of the read / write channel, emulating a behavior of the head actuator during track seek and track following operations based upon an electromechanical model of the head actuator, providing a disk controller design base for defining integrated circuit elements comprising the disk controller circuit and providing a controller environment to support execution and debug of firmware for operating the disk controller circuit. A plurality of disk functions may be carried out at a time-scaled rate according to a script. The plurality of disk functions includes interaction of at least the read / write model, the electromechanical model, the disk controller design base and the controller environment.

Owner:WESTERN DIGITAL TECH INC

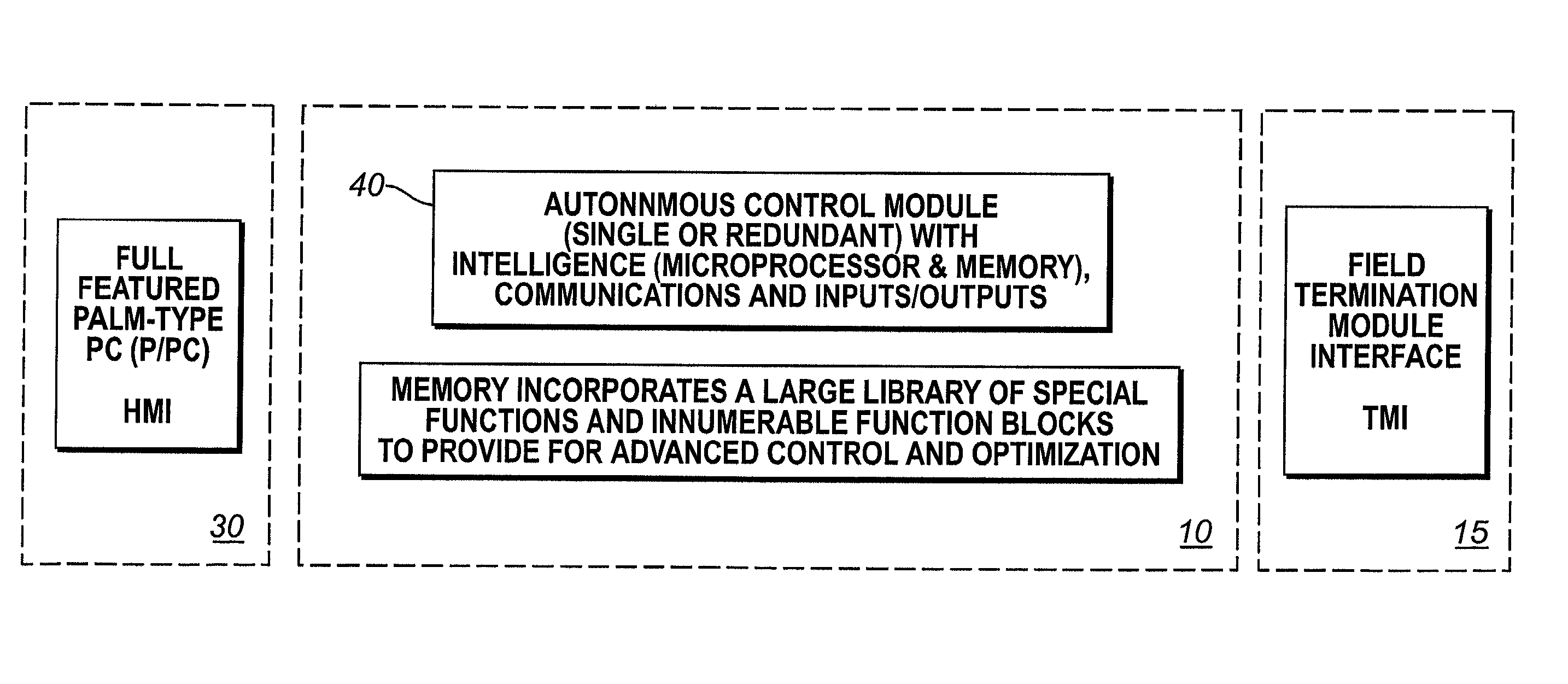

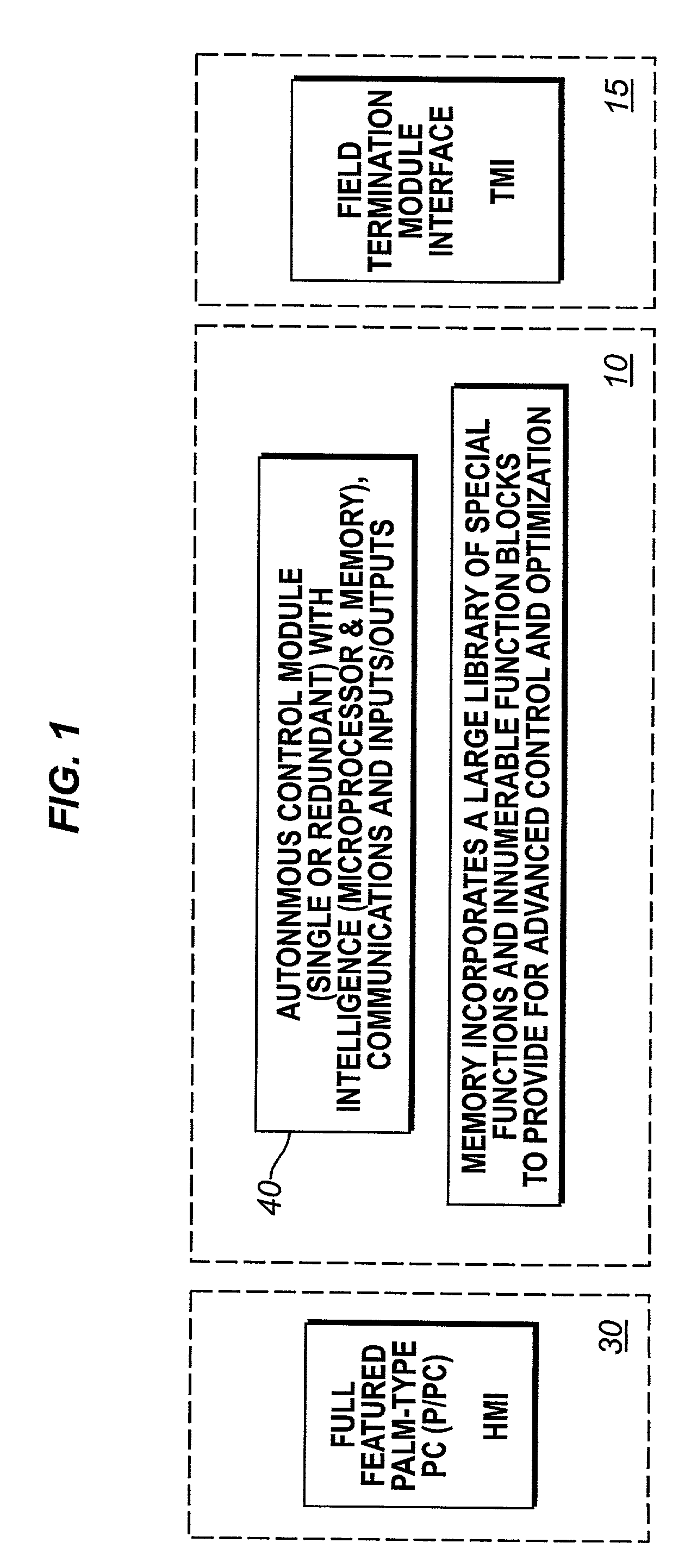

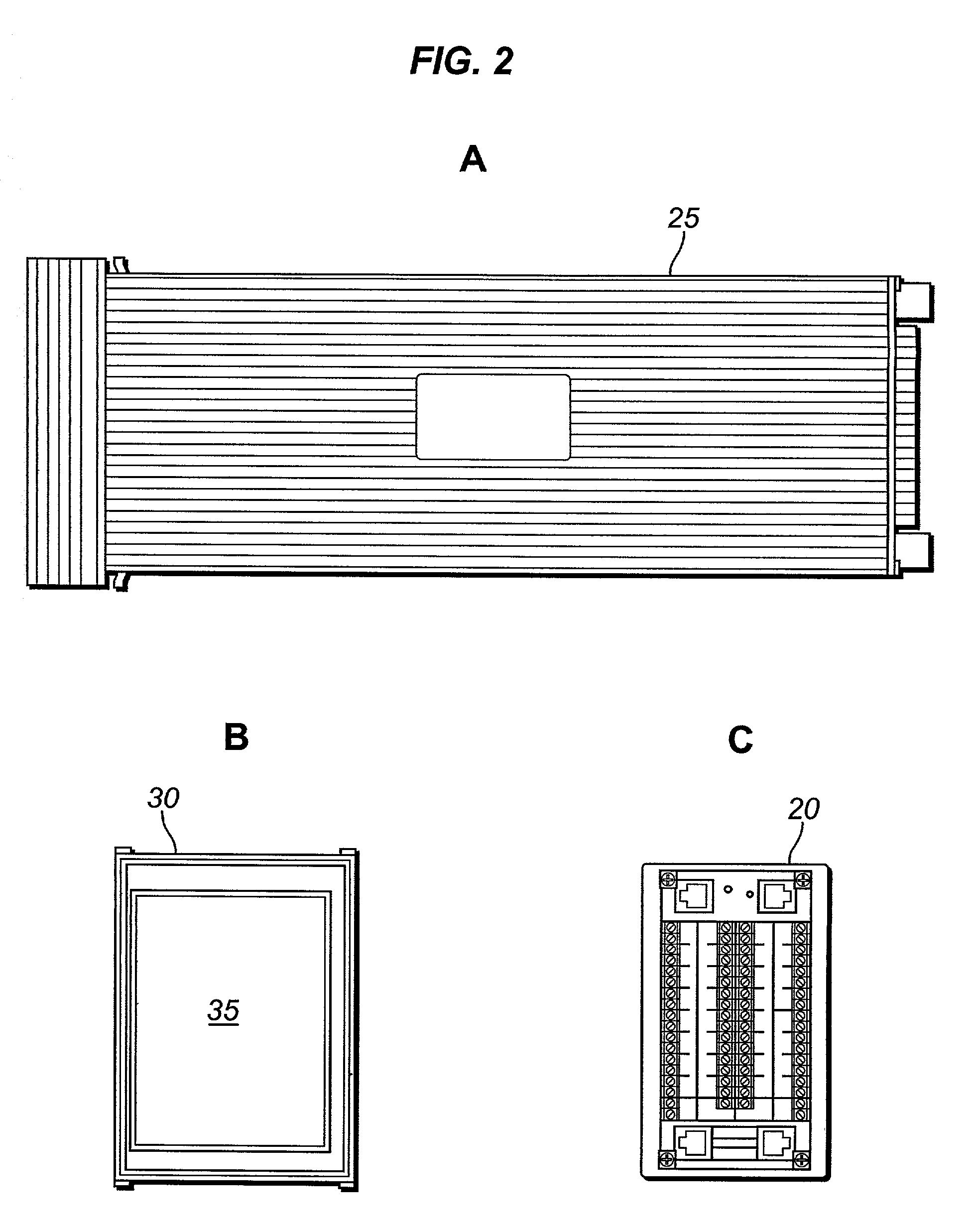

Unit controller with integral full-featured human-machine interface

An integrated unit controller / human-machine interface is disclosed which incorporates high-speed redundant control, sequence of events, supervisory control and data acquisition, alarm handling, trending & historian, process graphics and "open" communications in a compact form factor enclosure (the front panel less than 5x6 inches). The unit controller is composed of two primary hardware elements: the controller module (single or redundant) and the palm type computers (P / PC)-based human-machine interface (HMI) with touch screen. The controller covers a wide span of applications, from single process unit control to networked multi-unit management.

Owner:ICS TRIPLEX TECH

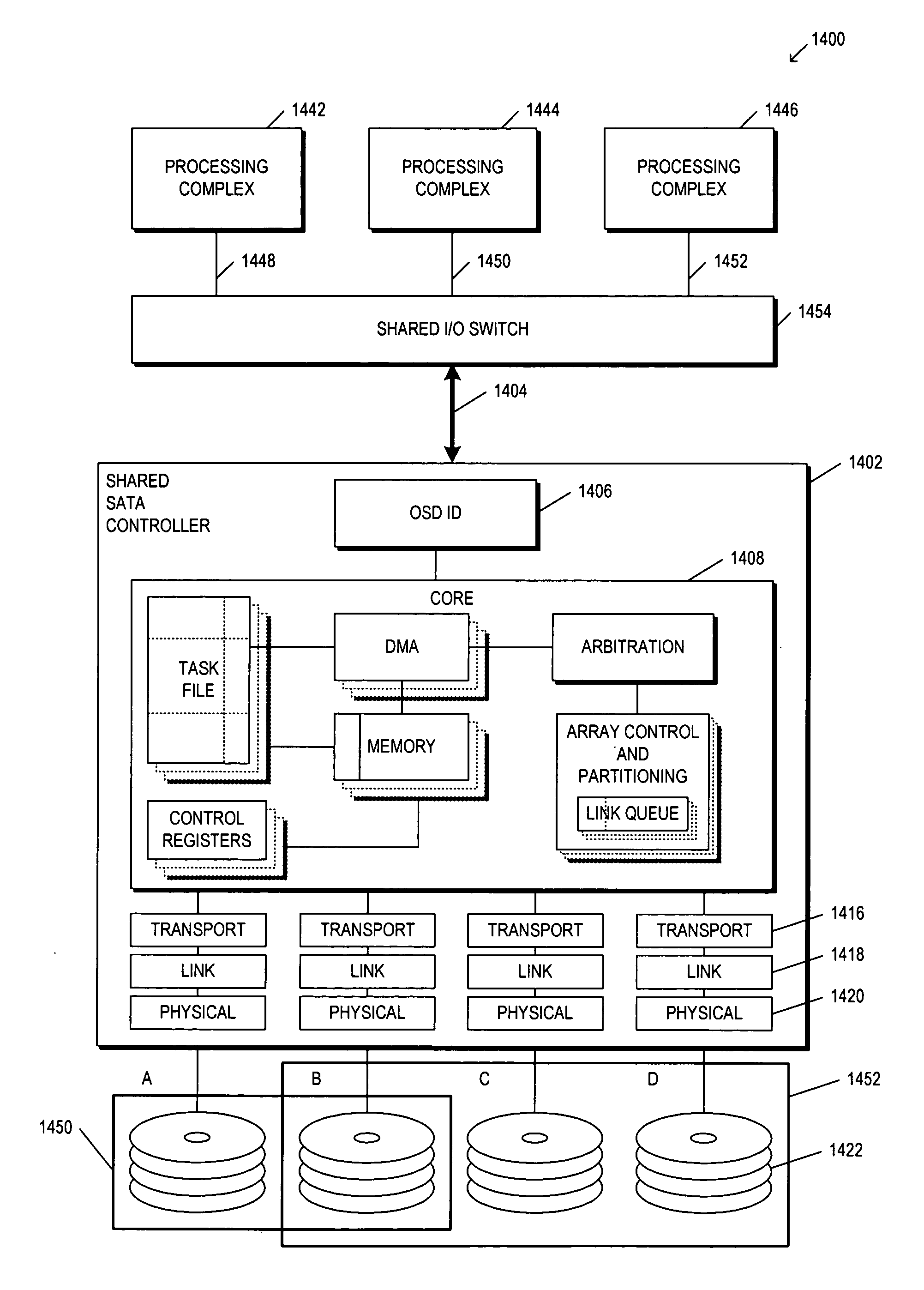

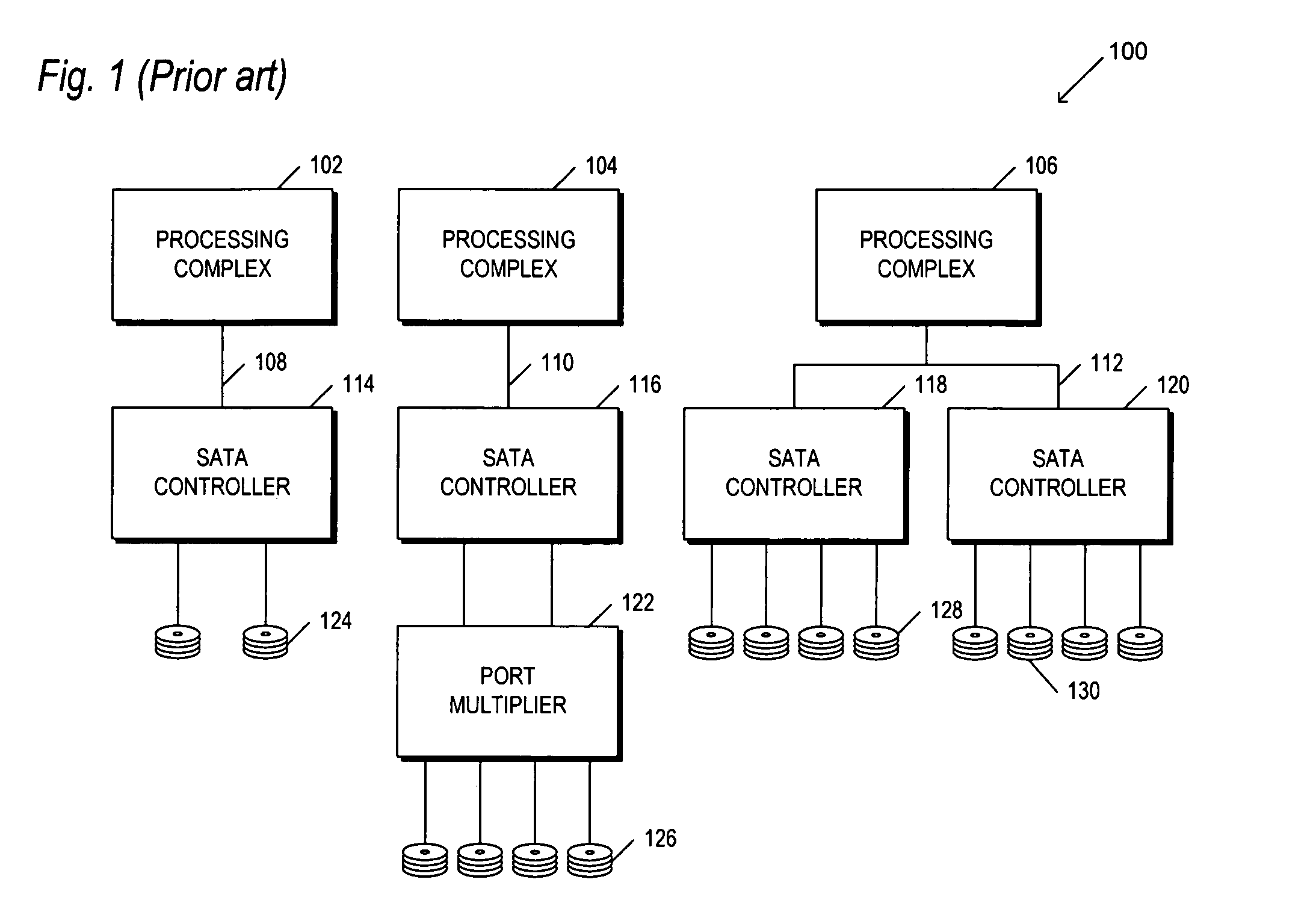

Method and apparatus for a shared I/O serial ATA controller

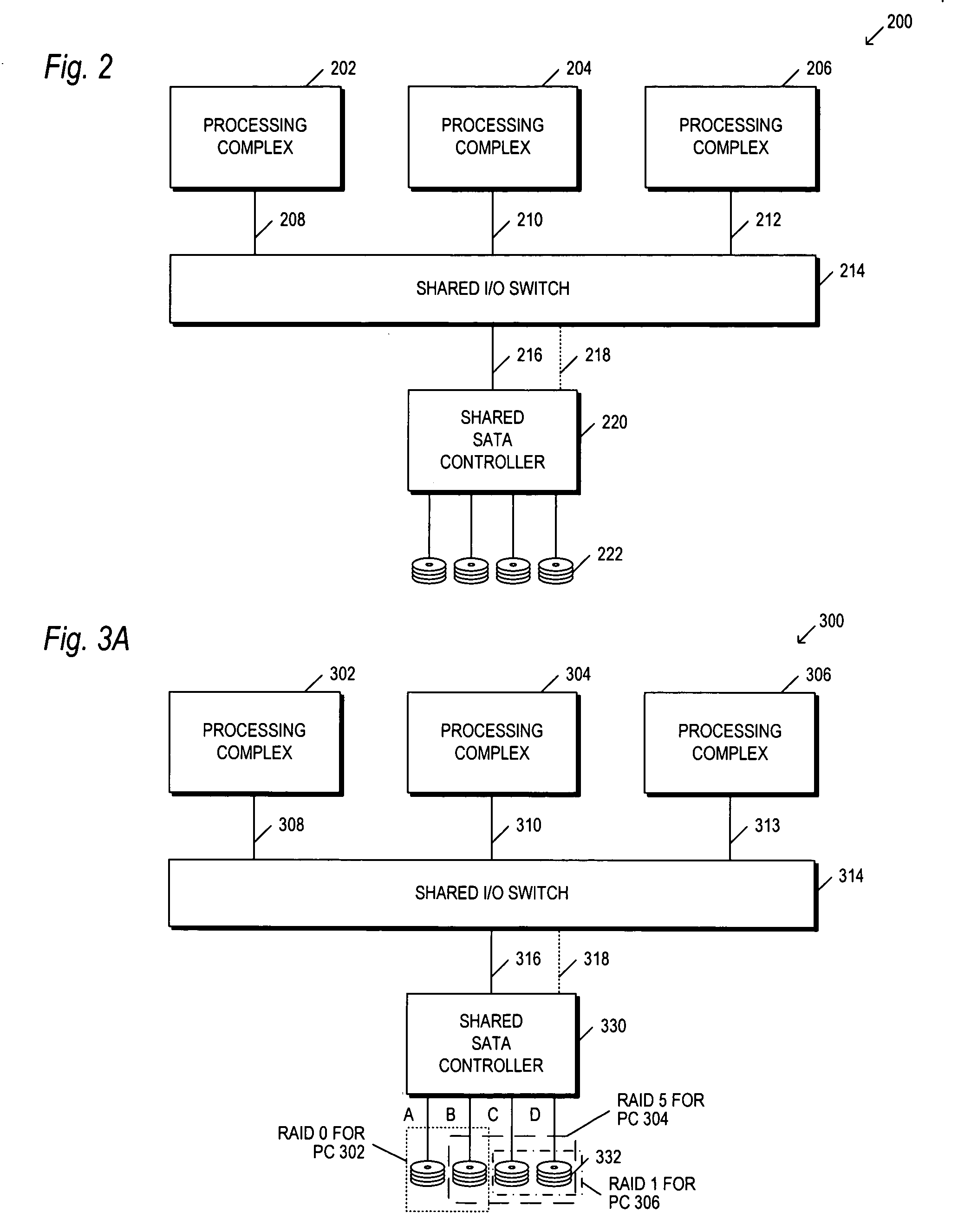

An apparatus and method is provided for allowing one or more processing complexes to share a disk controller, particularly a serial ATA (SATA) controller. Each processing complex utilizes its own load-store domain to couple to the shared SATA controller, either directly, or indirectly through a shared I / O switch. Ultimately, requests from the processing complexes are presented to the switch with operating system domain header (OSD header) information so that the shared SATA controller can determine which request came from which processing complex, and allocate resources accordingly. Upstream responses from the shared SATA controller include the OSD header so that the shared I / O switch can accurately route the responses to their respective processing complexes. The shared SATA controller includes OSD ID logic to determine the source / result of packets, one or more task files to support multiple processing complexes, and one or more DMA engines to improve performance for requests from multiple processing complexes.

Owner:MELLANOX TECHNOLOGIES LTD

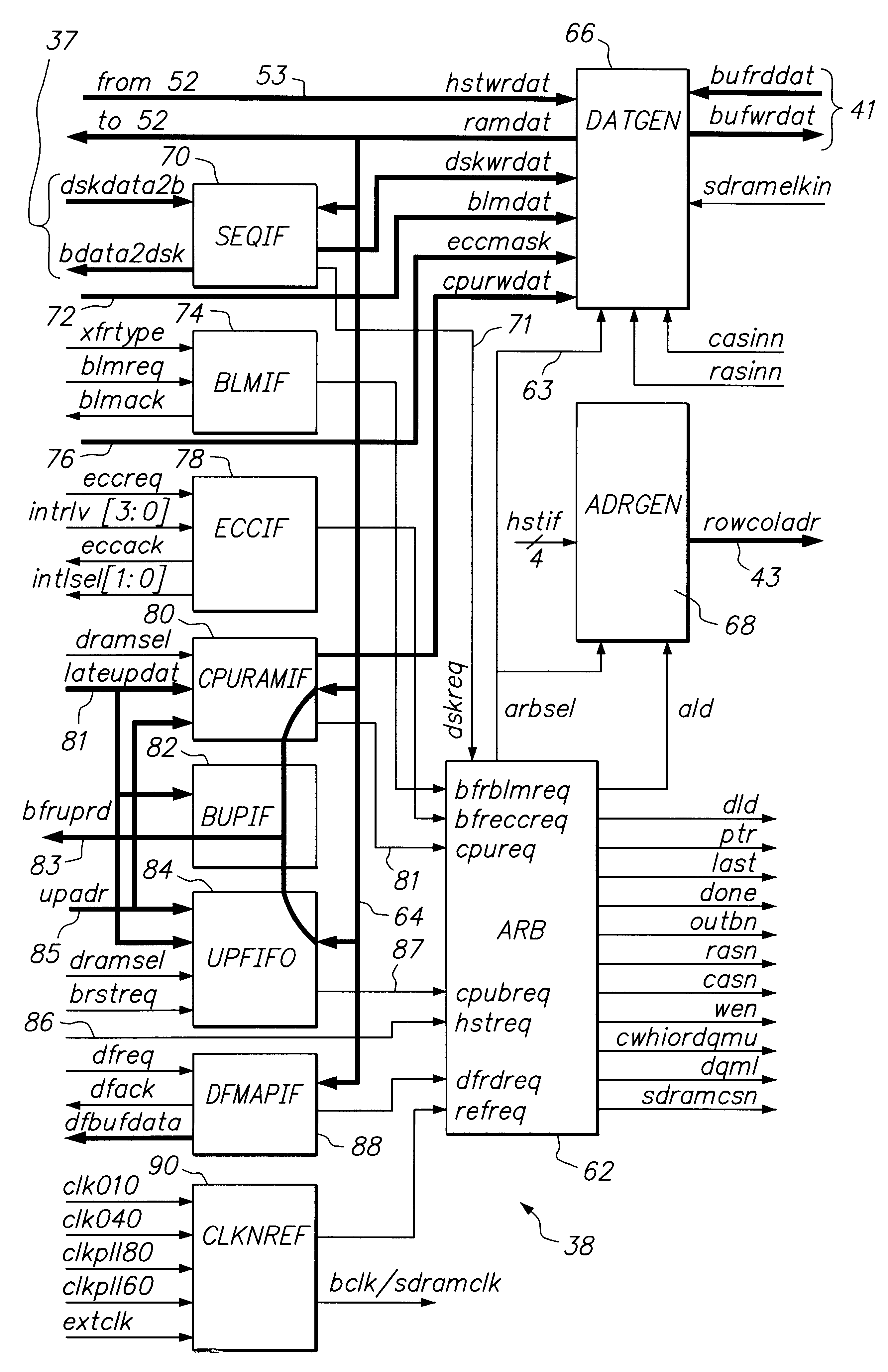

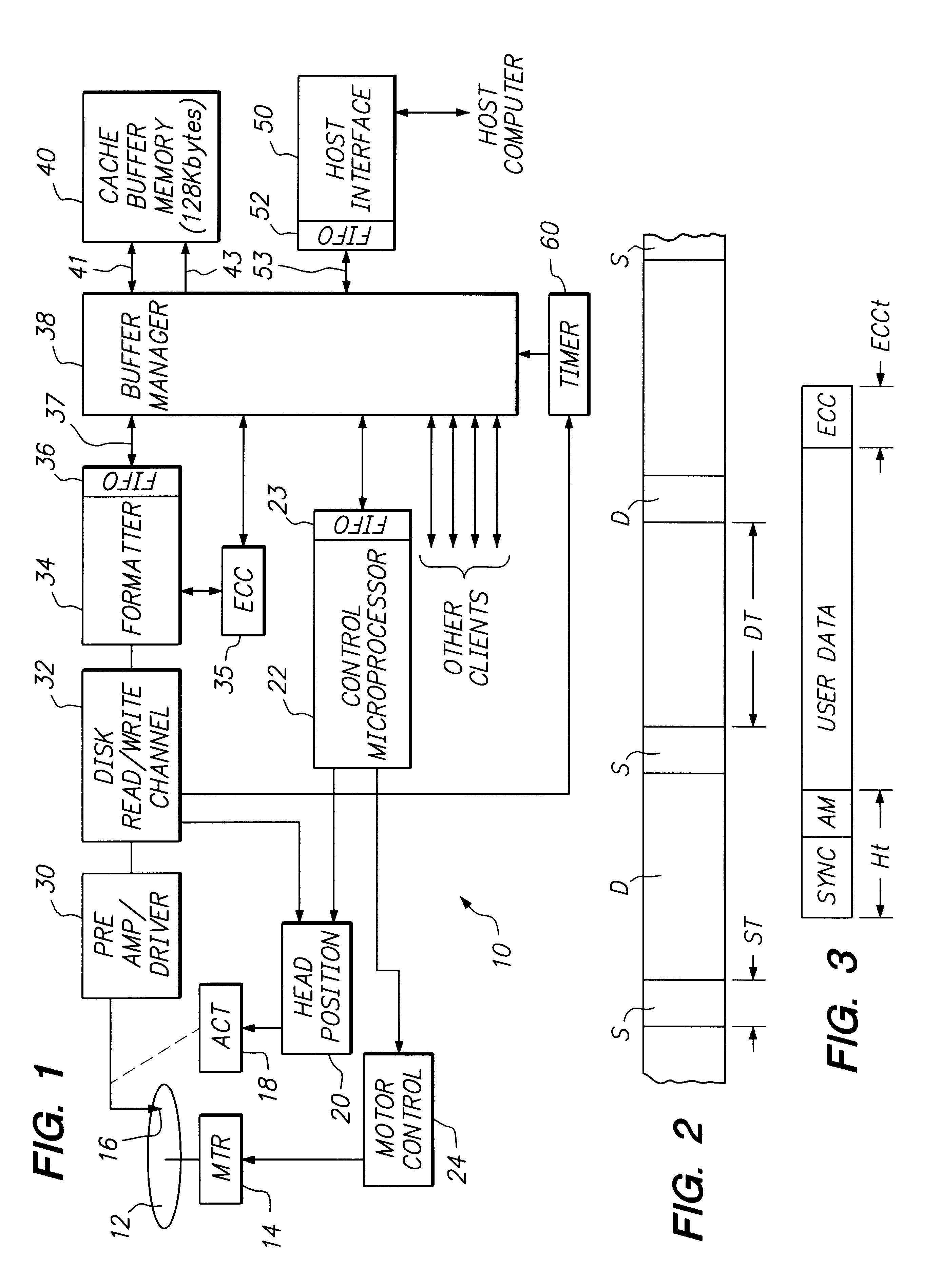

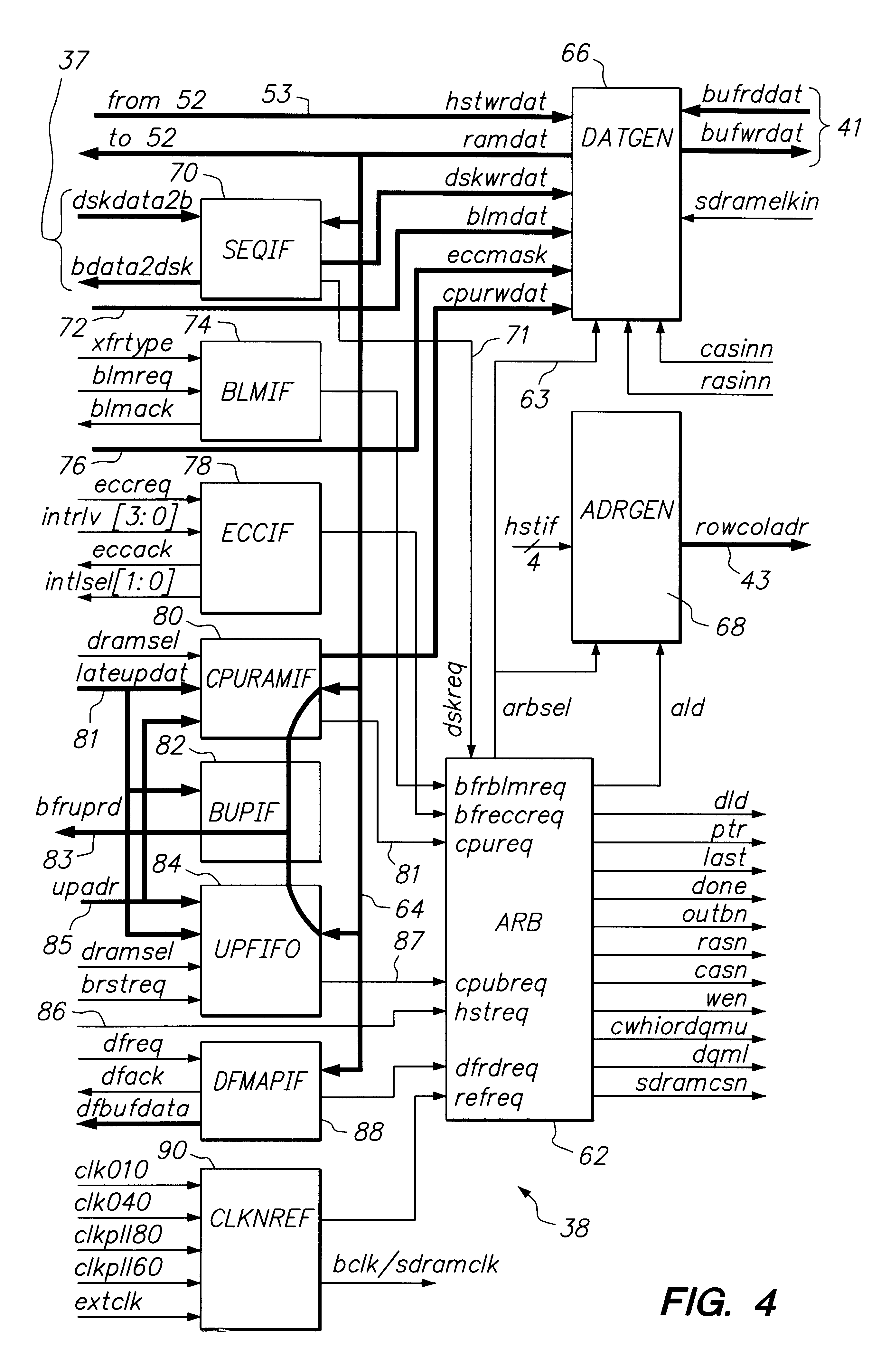

Time allocation shared memory arbitration for disk drive controller

InactiveUS6178486B1Efficient and effective arbitrationInput/output to record carriersMemory systemsDisk controllerShared memory

A method and apparatus for arbitrating requests for access to a single buffer memory embedded within a disk drive in which a disk data channel is assigned a highest priority for buffer access within a queue. An arbitration cycle progressively services access requests pending within the queue, beginning with providing buffer access to the disk data channel and following with accesses to other channels during an arbitration cycle completion interval in accordance with a round-robin circular priority arrangement providing orderly access to all channels contending for memory access. At the end of completion interval, buffer access returns to the disk data channel, and thereafter, the arbitration cycle is repeated.

Owner:MAXTOR

Storage system and method for backup

InactiveUS20050086443A1Easy to getReduce the burden onData processing applicationsInput/output to record carriersDisk controllerStorage pool

A storage system which comprise includes a disk controller and a disk device having original volumes for backup and a storage pool for backup data. It incorporates a differential management program which checks whether the original volumes for backup are updated or not; a pool management program which allocates a disk area to the storage pool for backup data; a performance management program which manages the performance of each volume; and a backup control program which performs total backup control. A backup method by which recovery within a user-specified recovery object time is possible is selected according to the restore performance calculated by the performance management program and the total size of changed blocks after backup acquisition as counted by the differential management program.

Owner:HITACHI LTD

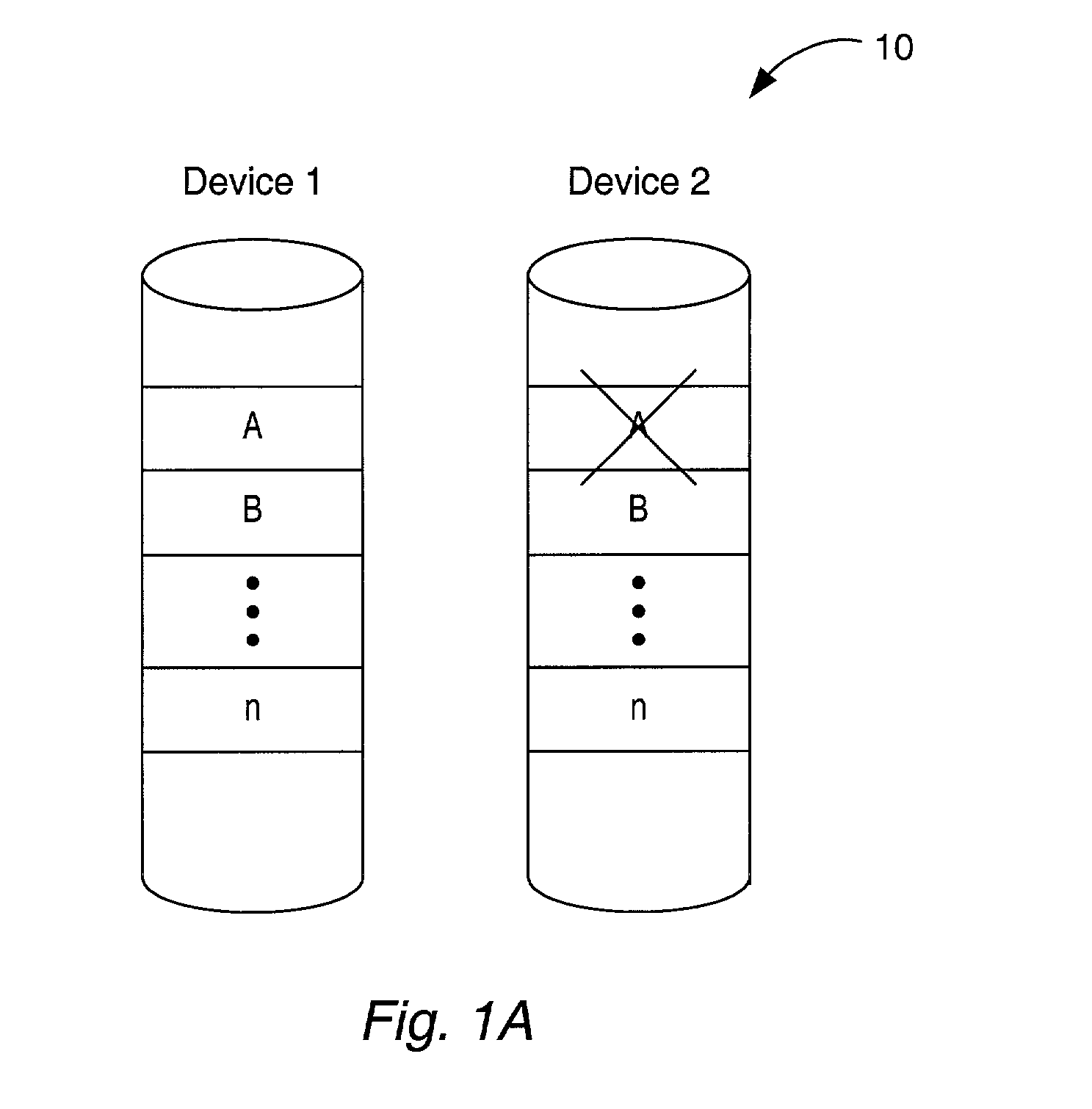

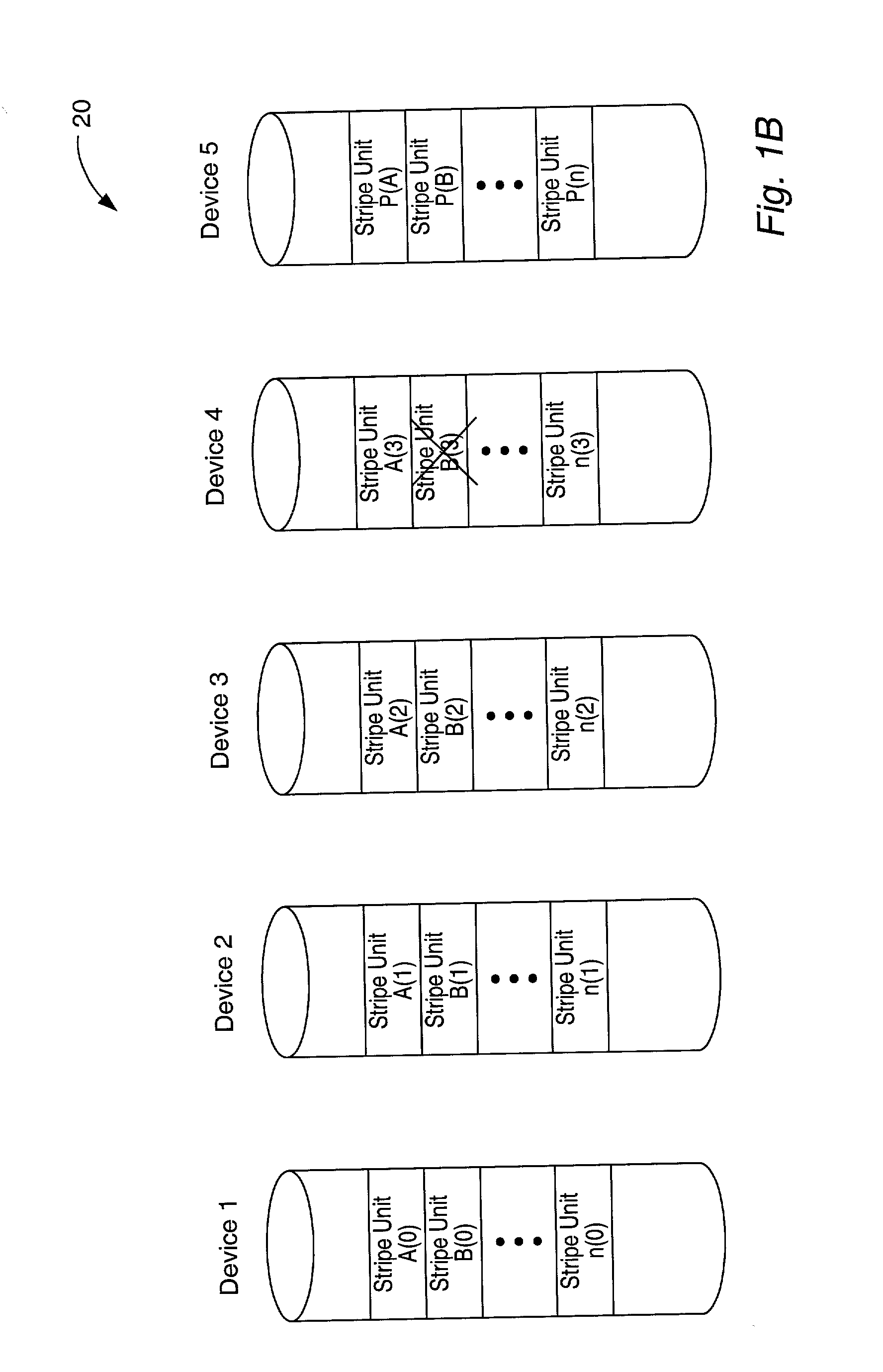

Detection and correction of block-level data corruption in fault-tolerant data-storage systems

ActiveUS20080115017A1Eliminate needEfficient detectionStatic storageRedundant data error correctionRAIDDisk controller

Various embodiments of the present invention provide fault-tolerant, redundancy-based data-storage systems that rely on disk-controller-implemented error detection and error correction, at the disk-block level, and RAID-controller-implemented data-redundancy methods, at the disk and disk-stripe level, in order to provide comprehensive, efficient, and system-wide error detection and error correction. Embodiments of the present invention use disk-level and stripe-level data redundancy to provide error detection and error correction for stored data objects, obviating the need for certain costly, intermediate levels of error detection and error correction commonly employed in currently available fault-tolerant, redundancy-based data-storage systems.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Disk drive including a delay circuit to provide a delayed reset signal

InactiveUS7907364B2Driving/moving recording headsRecord information storageDisk controllerCircuit delay

A disk drive including a delay circuit to provide a delayed reset signal is disclosed. The disk drive includes a head to perform write and read operations to and from a disk and a disk controller that is coupled to the head to control the write and read operations performed by the head. The disk drive further includes: a power loss detection circuit to detect a power loss and to generate a reset signal in response to the power loss; a reset power line coupled to the disk controller and the power loss detection circuit to provide a non-delayed reset signal to the disk controller; and a delay circuit coupled to the reset power line wherein the delay circuit delays the reset signal to provide a delayed reset signal.

Owner:WESTERN DIGITAL TECH INC

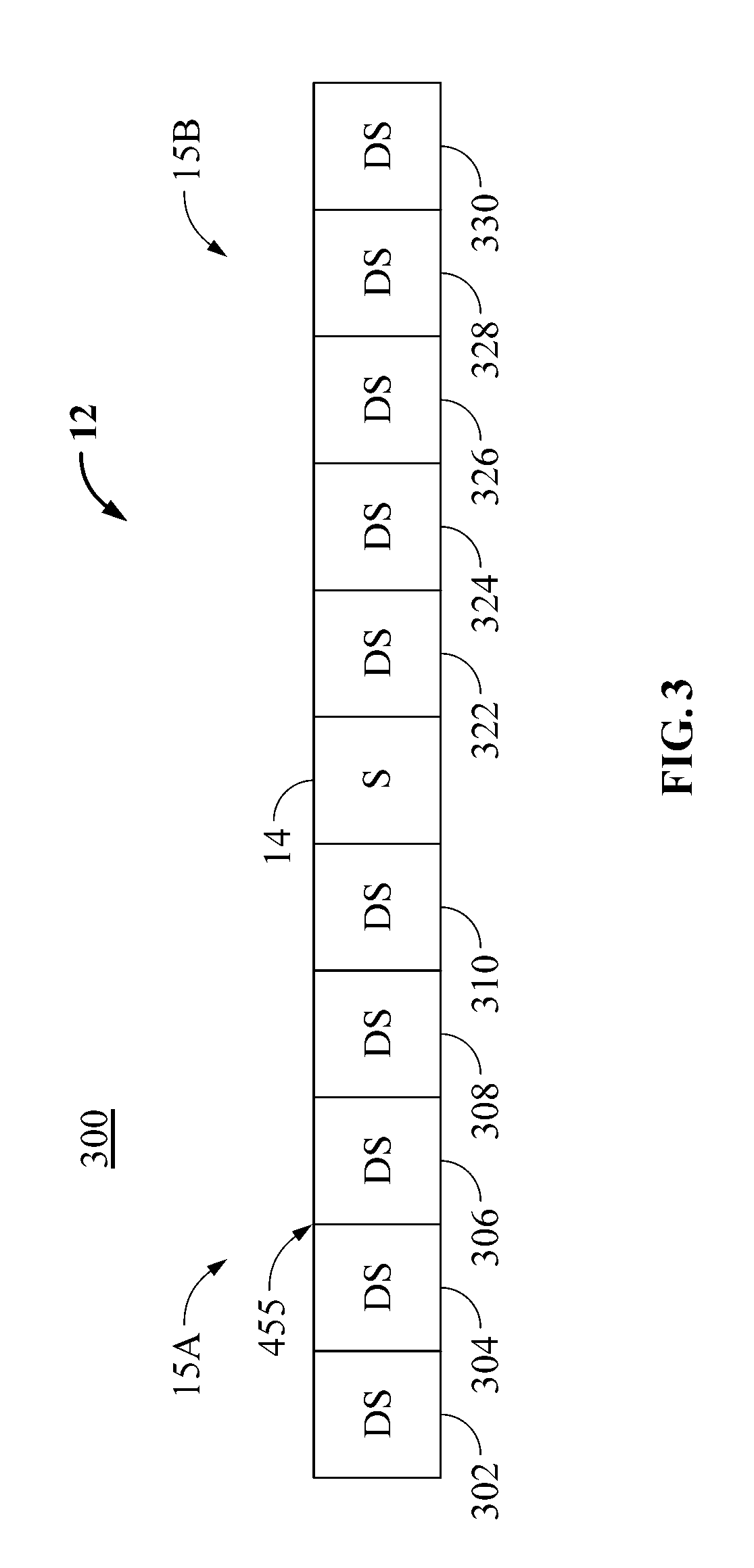

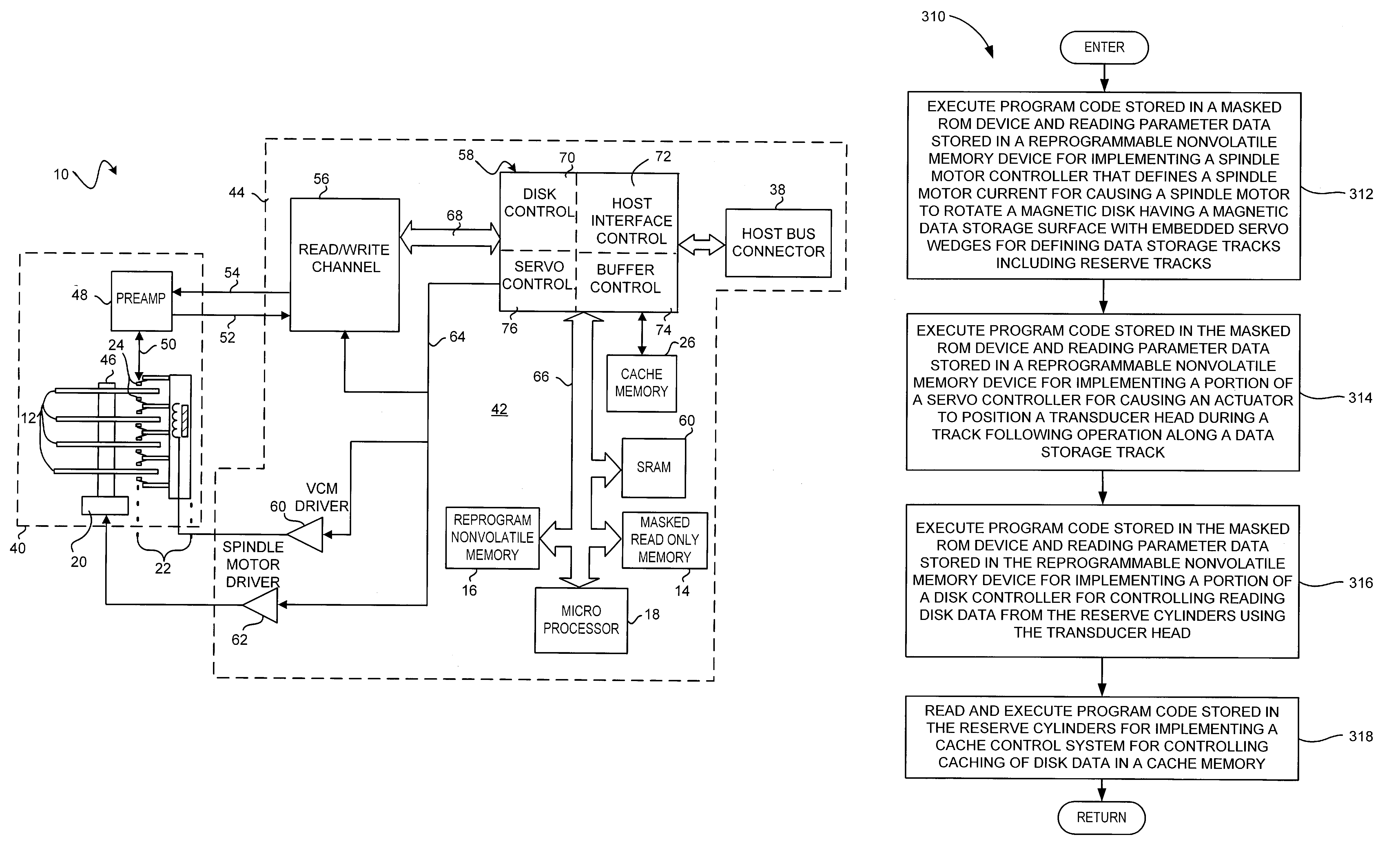

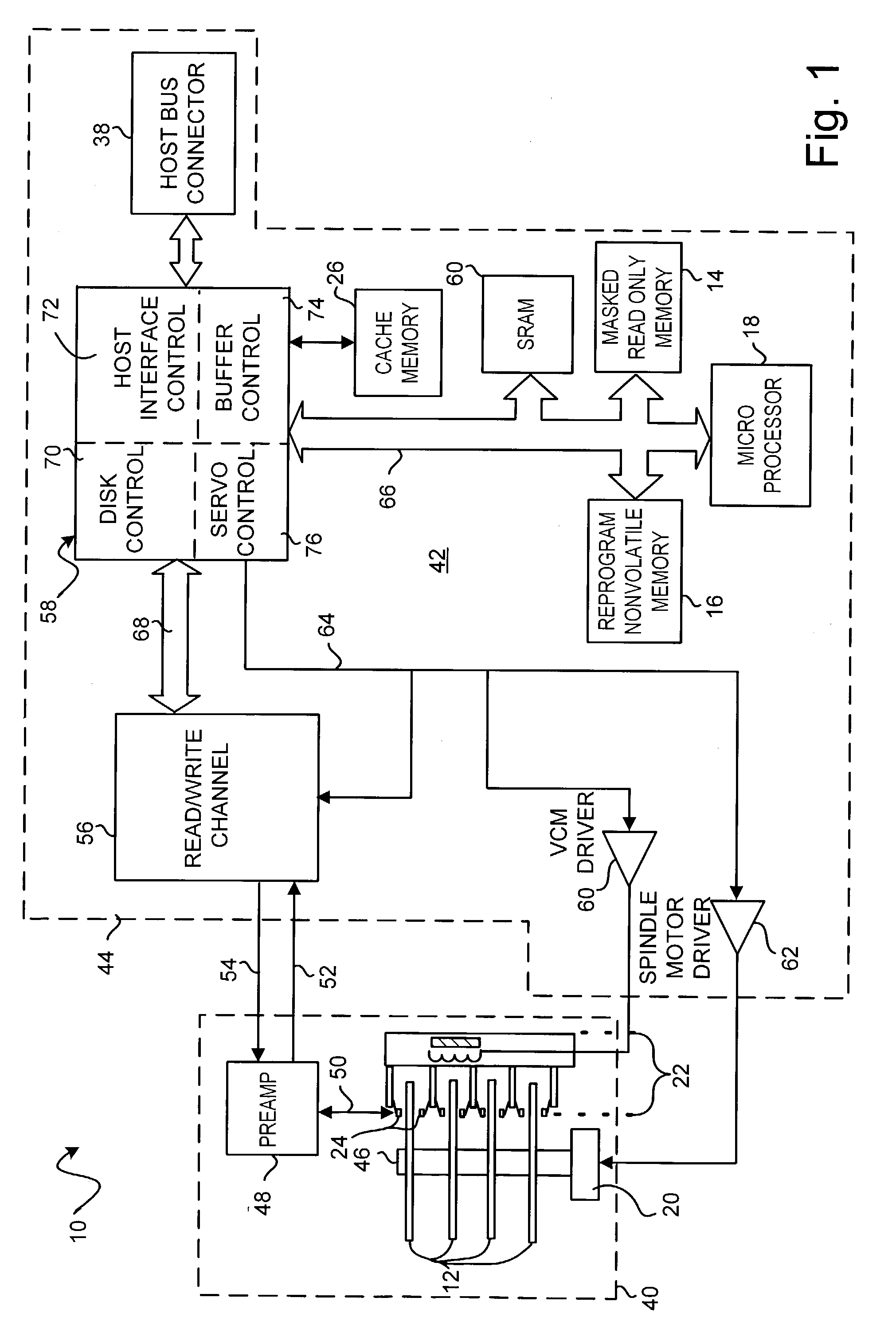

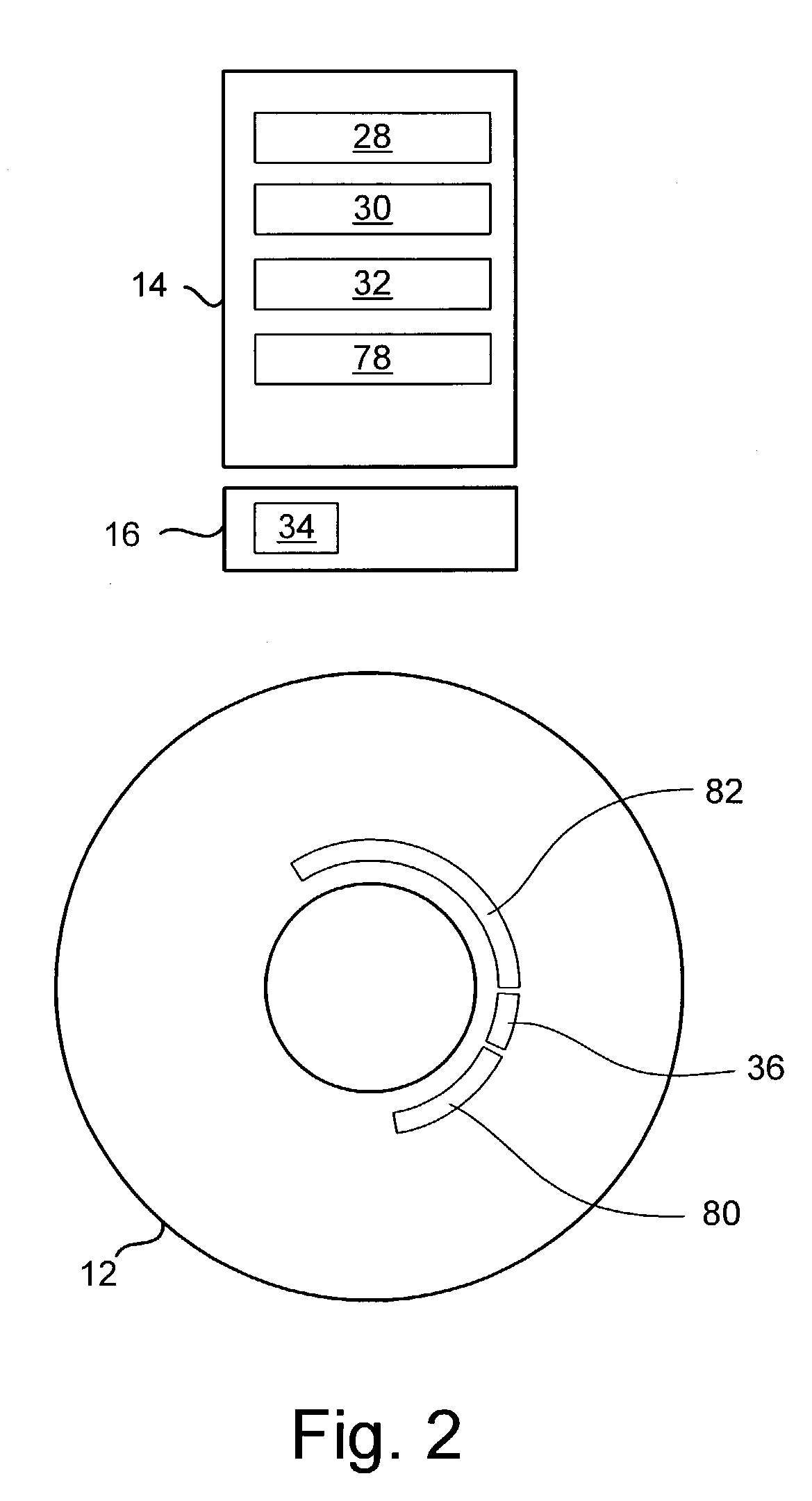

Disk drive and method having cost-effective storage of the disk drive's internal program code

InactiveUS7440214B1Improve data storage performanceFilamentary/web record carriersRecord information storageDisk controllerControl system

Disclosed is a disk drive having a disk, a masked read-only memory (ROM) device, a reprogrammable nonvolatile memory device, and a microprocessor for executing program code. The disk has a magnetic data storage surface with embedded servo wedges for defining data storage tracks including reserve tracks. The masked ROM device stores program code for implementing a spindle motor controller, program code for implementing a portion of a servo controller for track following along a data storage track, and program code for implementing a portion of a disk controller for controlling writing disk data to and reading disk data from the reserve tracks. The reprogrammable nonvolatile memory device stores data parameters relating to the disk drive's configuration. The reserve tracks store program code for implementing a cache control system for controlling caching of disk data in a cache memory.

Owner:WESTERN DIGITAL TECH INC

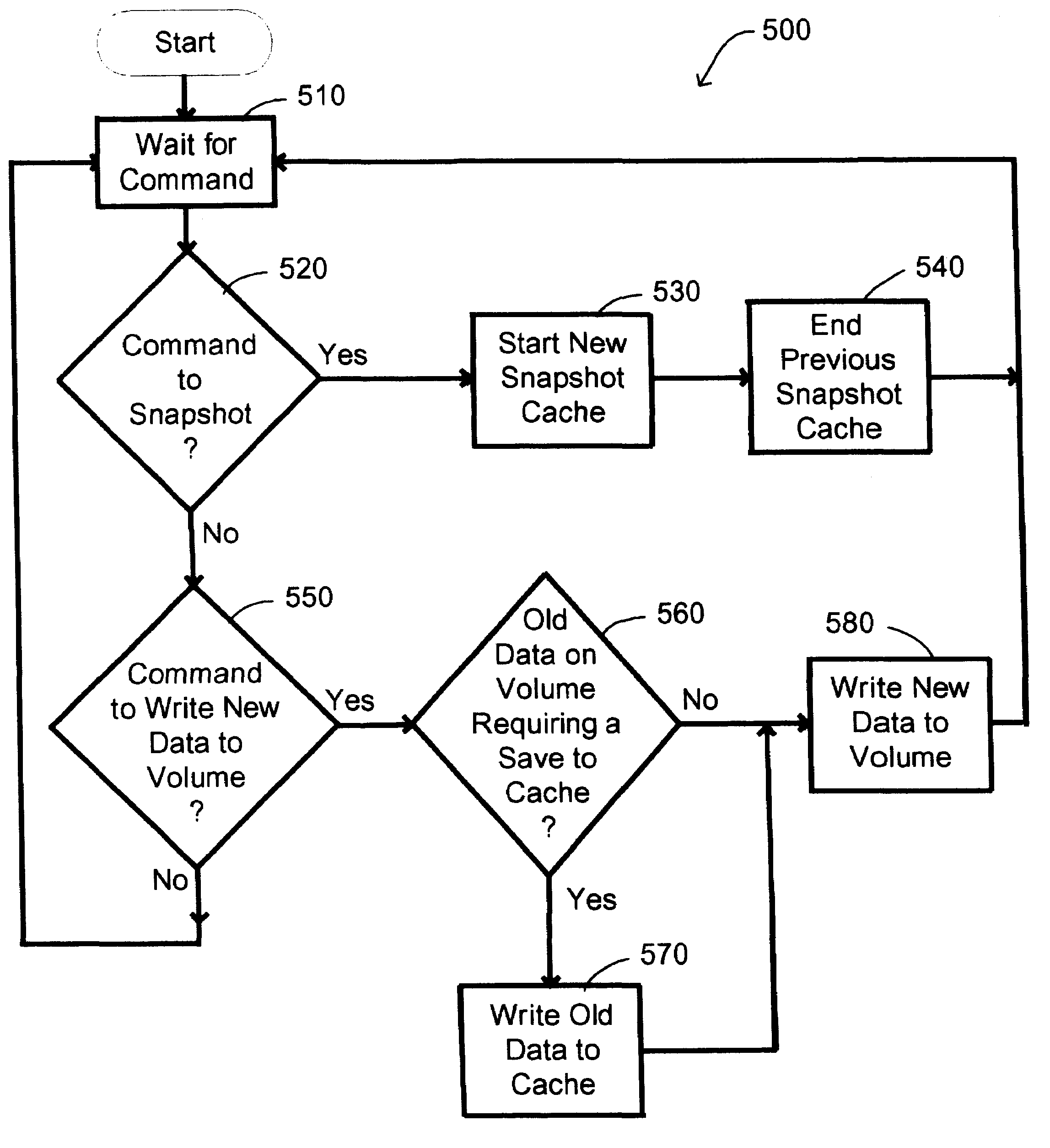

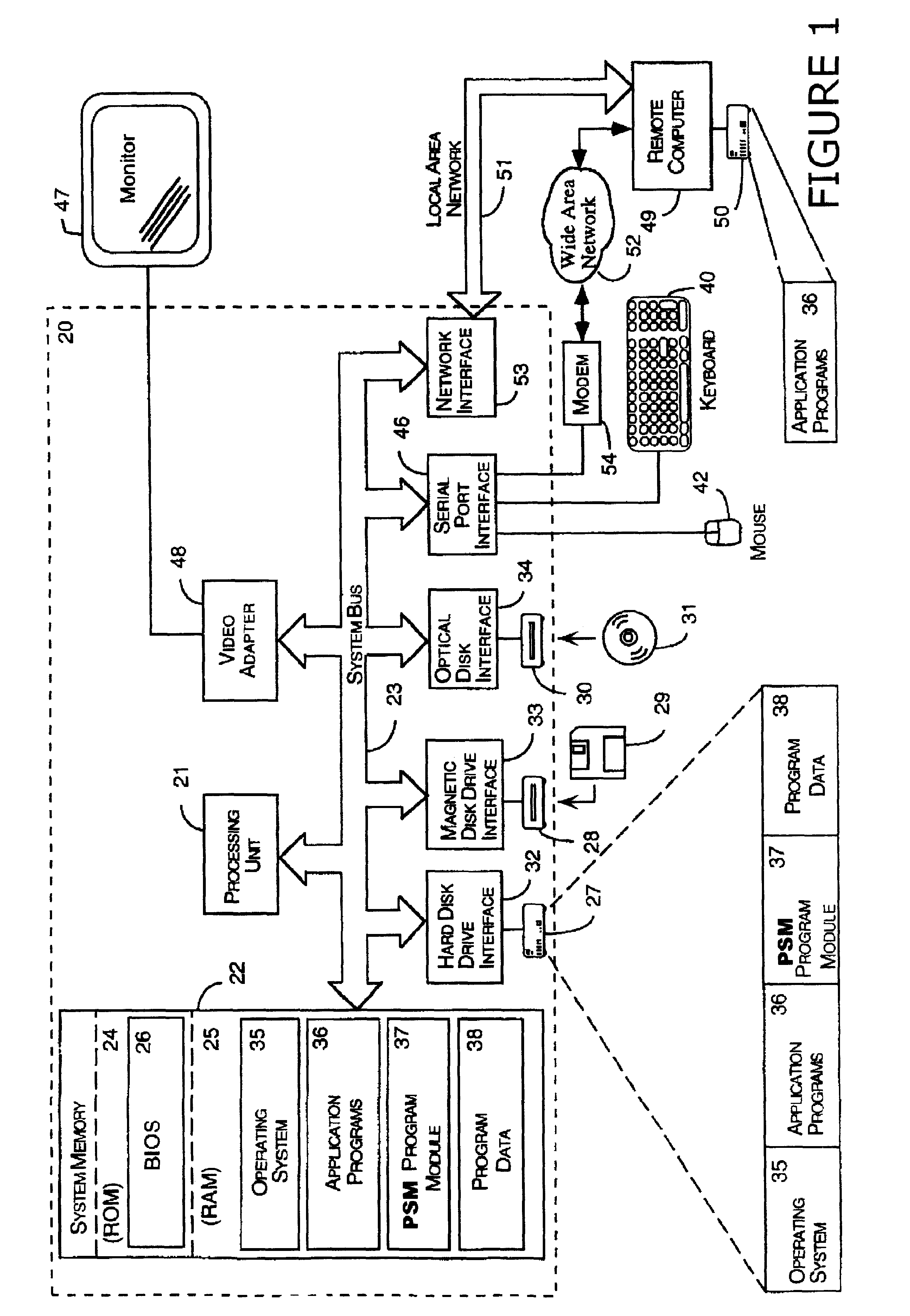

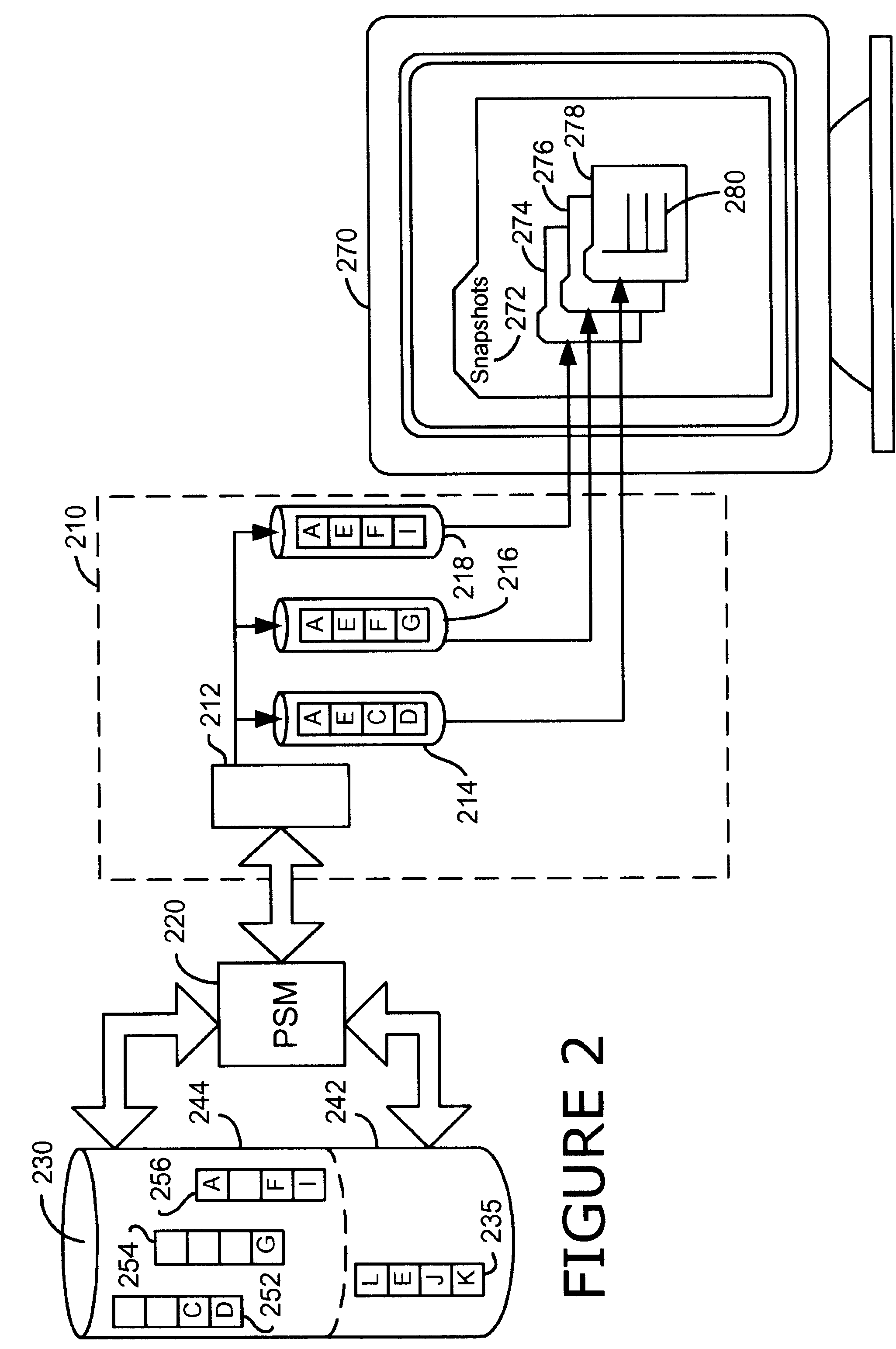

Persistent snapshot methods

A persistent snapshot is taken and maintained in accordance with a novel method and system for extended periods of time using only a portion of a computer readable medium of which the snapshot is taken. Multiple snapshots can be taken in succession at periodic intervals and maintained practically indefinitely. The snapshots are maintained even after powering down and rebooting of the computer system. The state of the object of the snapshot for each snapshot preferably is accessible via a folder on volume of the snapshot. A restore of a file or folder may be accomplished by merely copying that file or folder from the snapshot folder to a current directory of the volume. Alternatively, the entire computer system may be restored to a previous snapshot state thereof. Snapshots that occurred after the state to which the computer is restored are not lost in the restore operation. Different rule sets and scenarios can be applied to each snapshot. Furthermore, each snapshot can be written to within the context of the snapshot and later restored to its pristine condition. Software for implementing the systems and methods of snapshots in accordance with the present invention may comprise firmware of a hard disk drive controller or a disk controller board or within the HDD casing itself. The present invention further comprises novel systems and methods in which the systems and methods of taking and maintaining snapshots are utilized in creating and managing temporal data stores, including temporal database management systems. The implications for data mining and exploration, data analysis, intelligence gathering, and artificial intelligence (just to name a few areas) are profound.

Owner:COLUMBIA DATA PRODUCTS

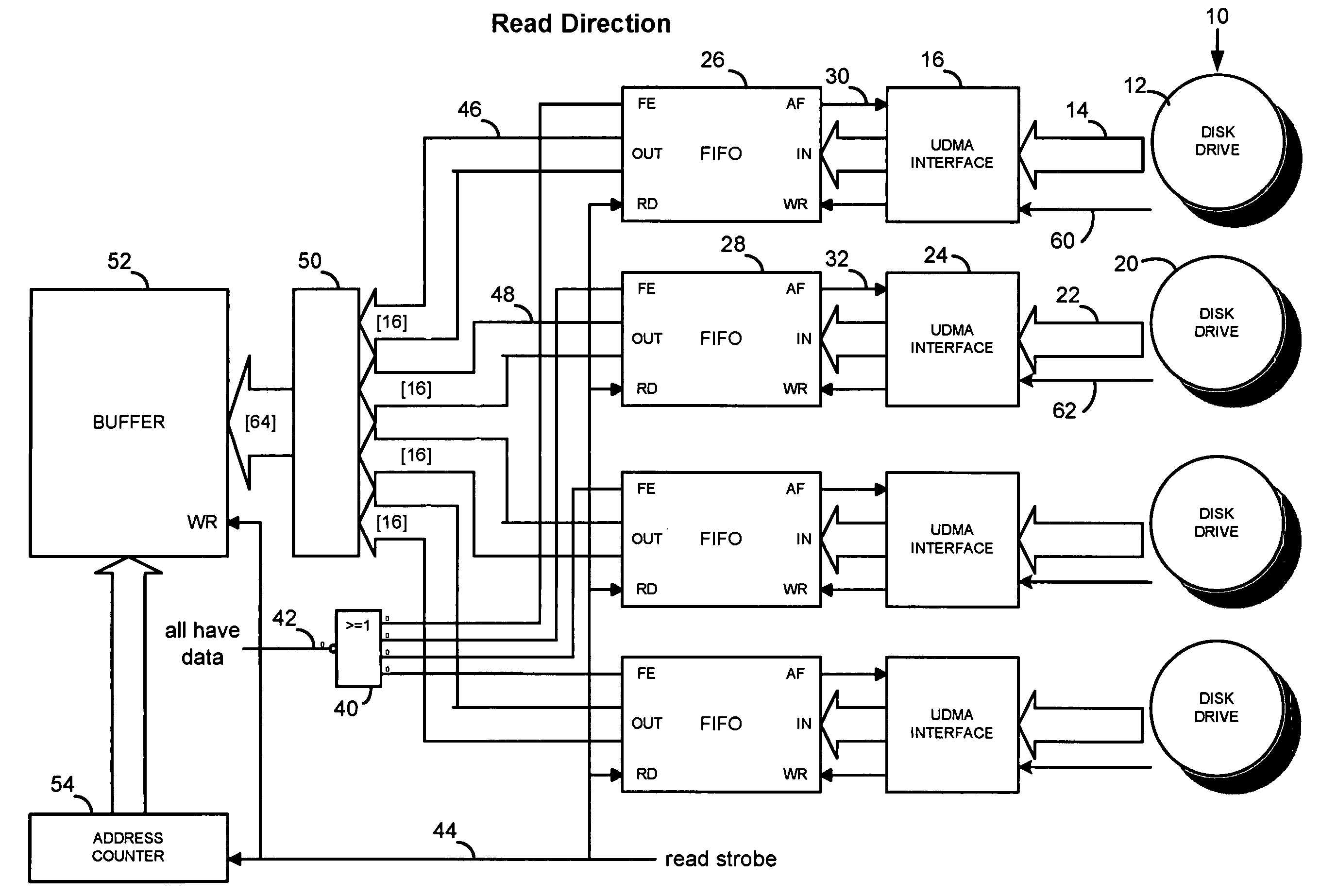

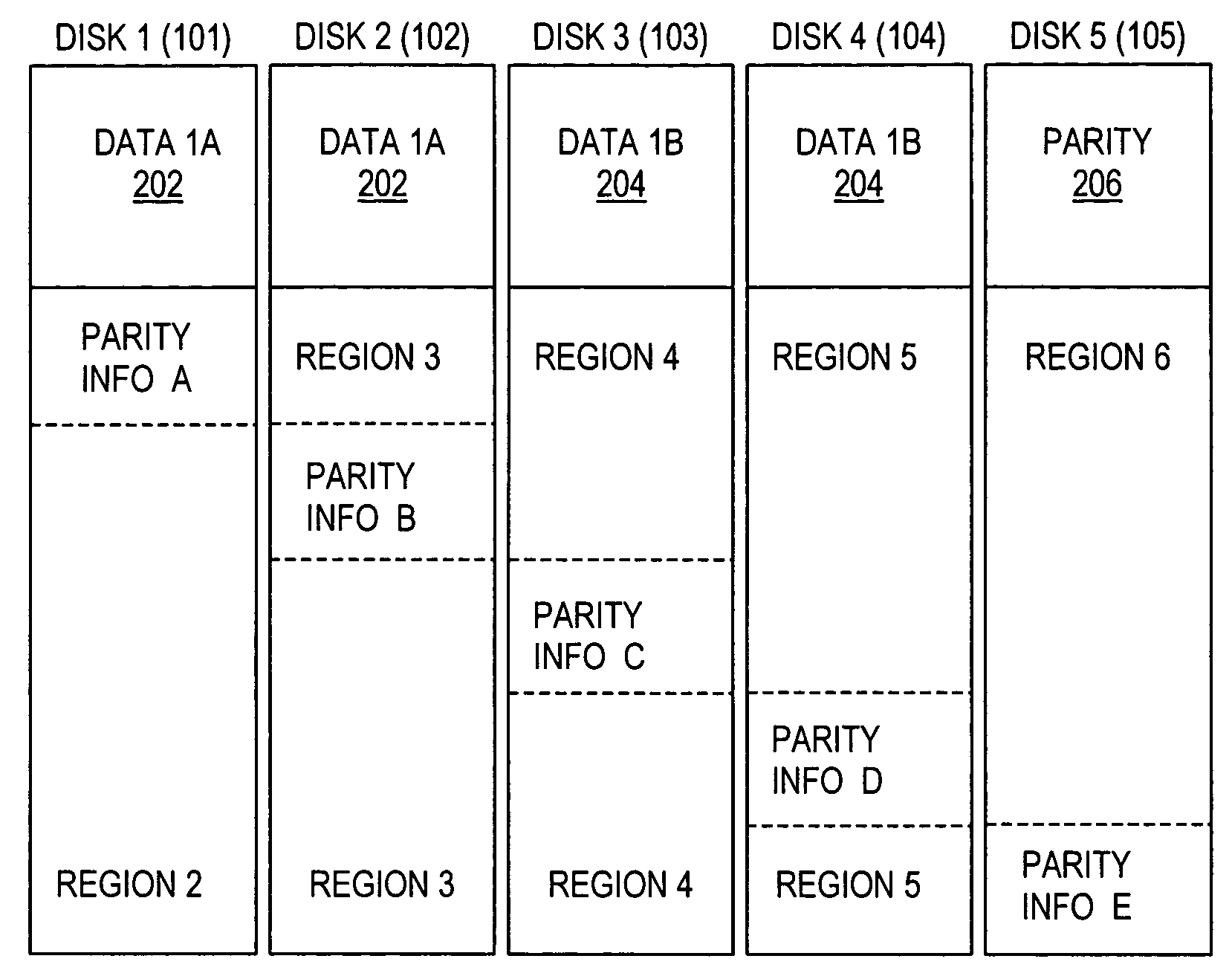

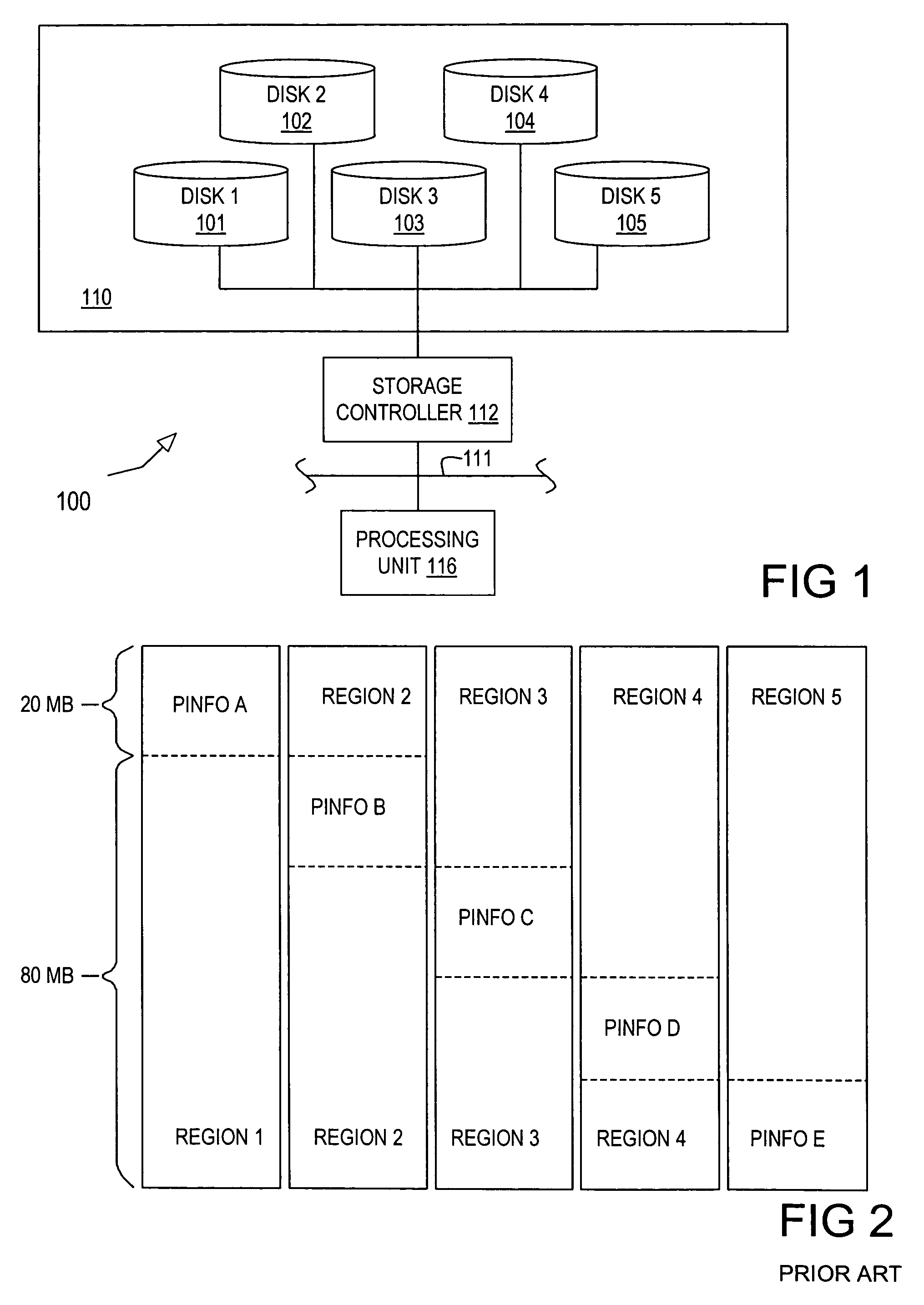

Disk controller methods and apparatus with improved striping, redundancy operations and interfaces

ActiveUS20050223269A1Improve performanceReduce hardware complexityStatic storageRedundant data error correctionRAIDTransport layer

A RAID disk drive controller (FIG. 33) implements disk storage operations, including striping and redundancy operations with multiple disk drives connected via respective SATA ports (520). Configurable data path switch logic (460) provides dynamic configuration of two or more attached drives into one or more arrays. Data transfers are synchronized locally by leveraging the SATA port transport layer FIFO (530). Synchronous transfers allow on-the-fly redundancy (XOR) operations (FIG. 36) for improved performance and reduced hardware complexity. XOR accumulator hardware (FIG. 42-FIG. 43) reduces buffer requirements for multiple DMA channels otherwise required for synchronization, and various narrow and wide striping modes are supported.

Owner:NVIDIA CORP

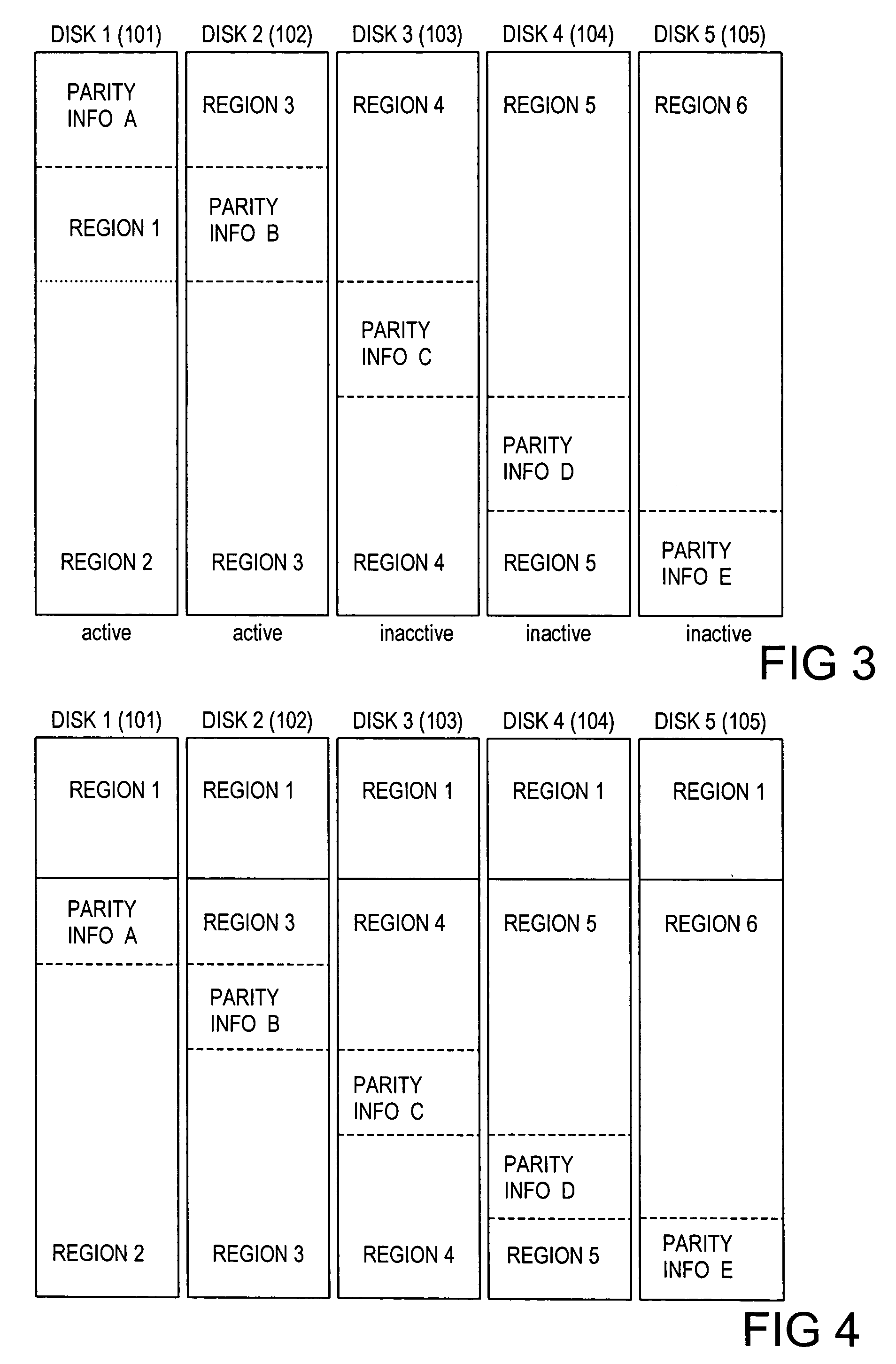

Multiple disk data storage system for reducing power consumption

InactiveUS7234074B2Digital data processing detailsError detection/correctionDisk controllerSystem maintenance

A data storage system in which each of a set of disks has a first portion for either popular data or error correction information (parity or Reed-Solomon code symbols) associated with the popular data, and a second portion used for other data. A disk controller connected to the set of disks maintains a first popular data block in the first portion of a first of the set of disks and a second popular data block in the first portion of a second of the set of disks. The system maintains at least two of the disks in an active state. The active disks are selected to insure that any data in the popular data blocks can be determined from data stored in the active disks. An additional disk is maintained in an active state if write access is permitted or if there is an additional popular data block.

Owner:IBM CORP

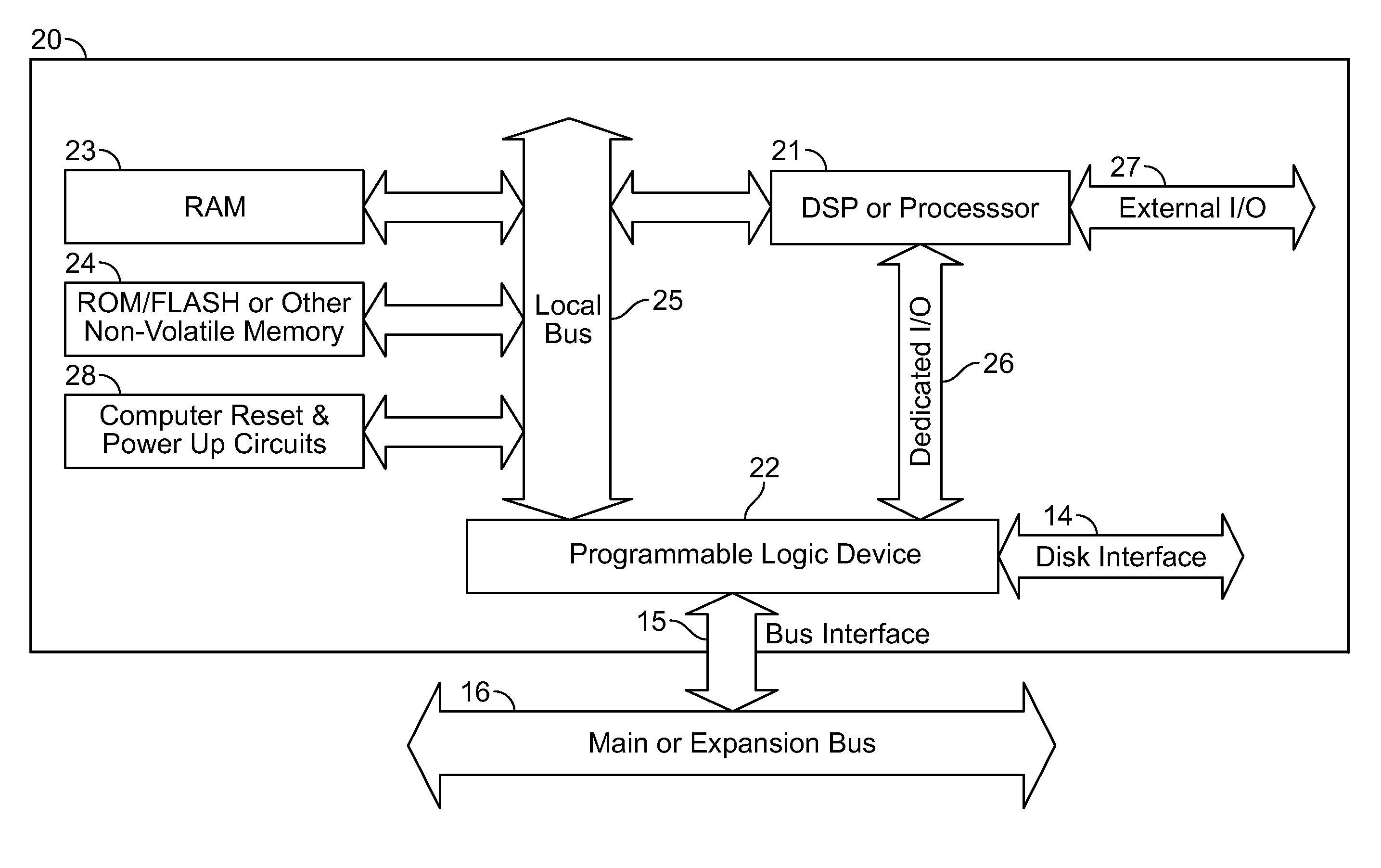

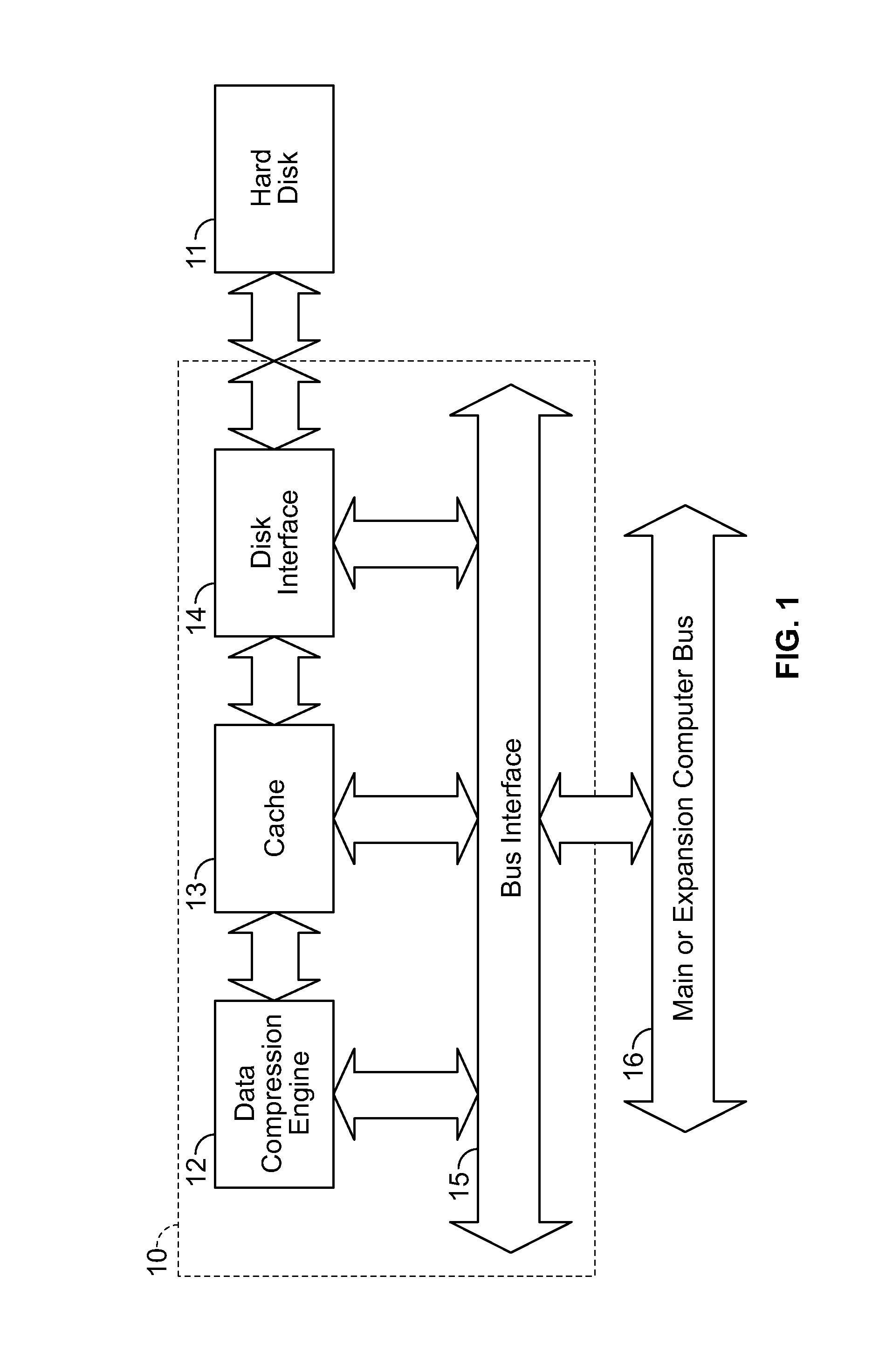

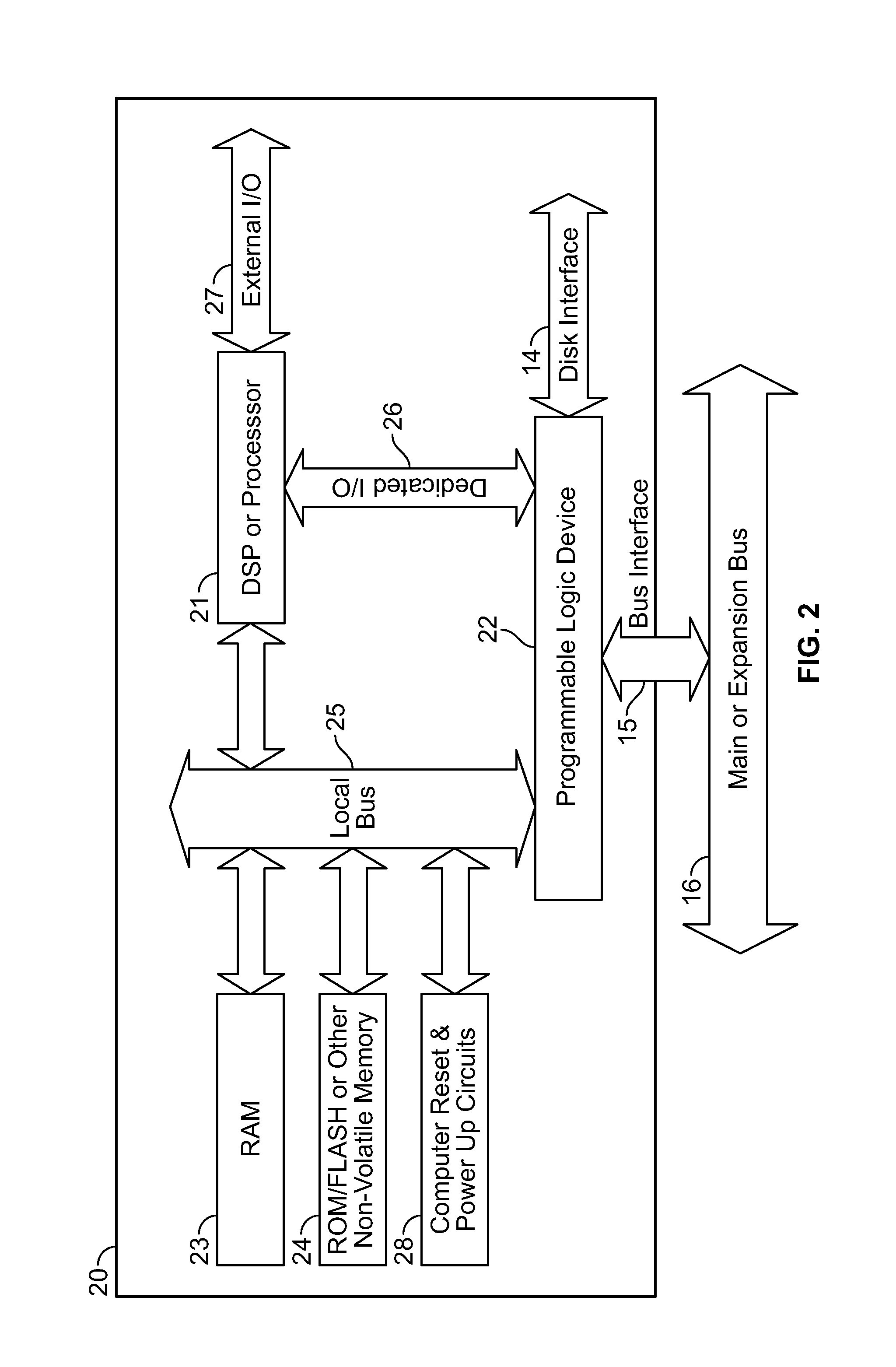

Data storewidth accelerator

InactiveUS7376772B2Improve processing speedHigh bandwidthCode conversionBootstrappingData compressionDisk controller

Data storage controllers and data storage devices employing lossless or lossy data compression and decompression to provide accelerated data storage and retrieval bandwidth. In one embodiment of the invention, a composite disk controller provides data storage and retrieval acceleration using multiple caches for data pipelining and increased throughput. In another embodiment of the invention, the disk controller with acceleration is embedded in the storage device and utilized for data storage and retrieval acceleration.

Owner:REALTIME DATA

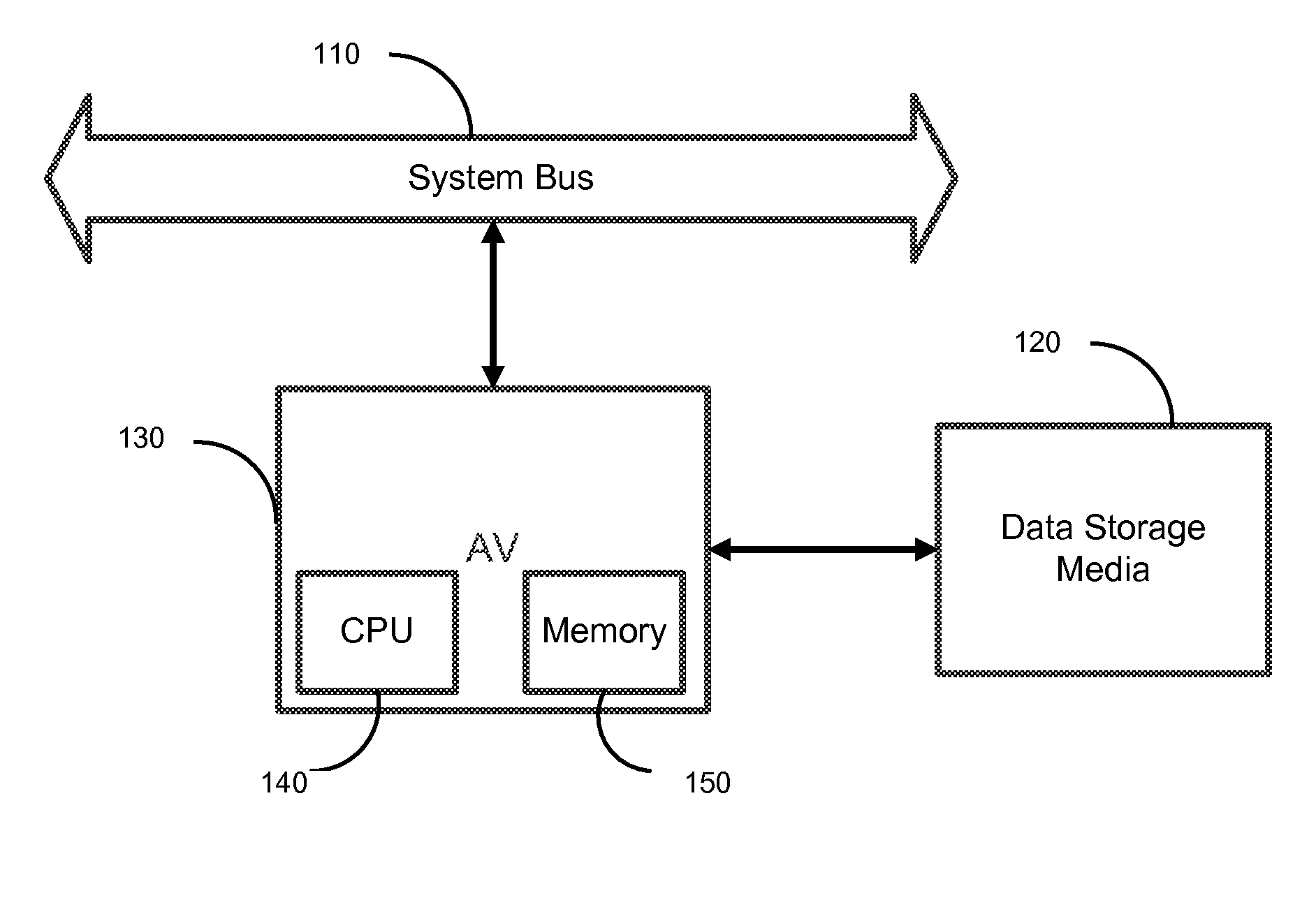

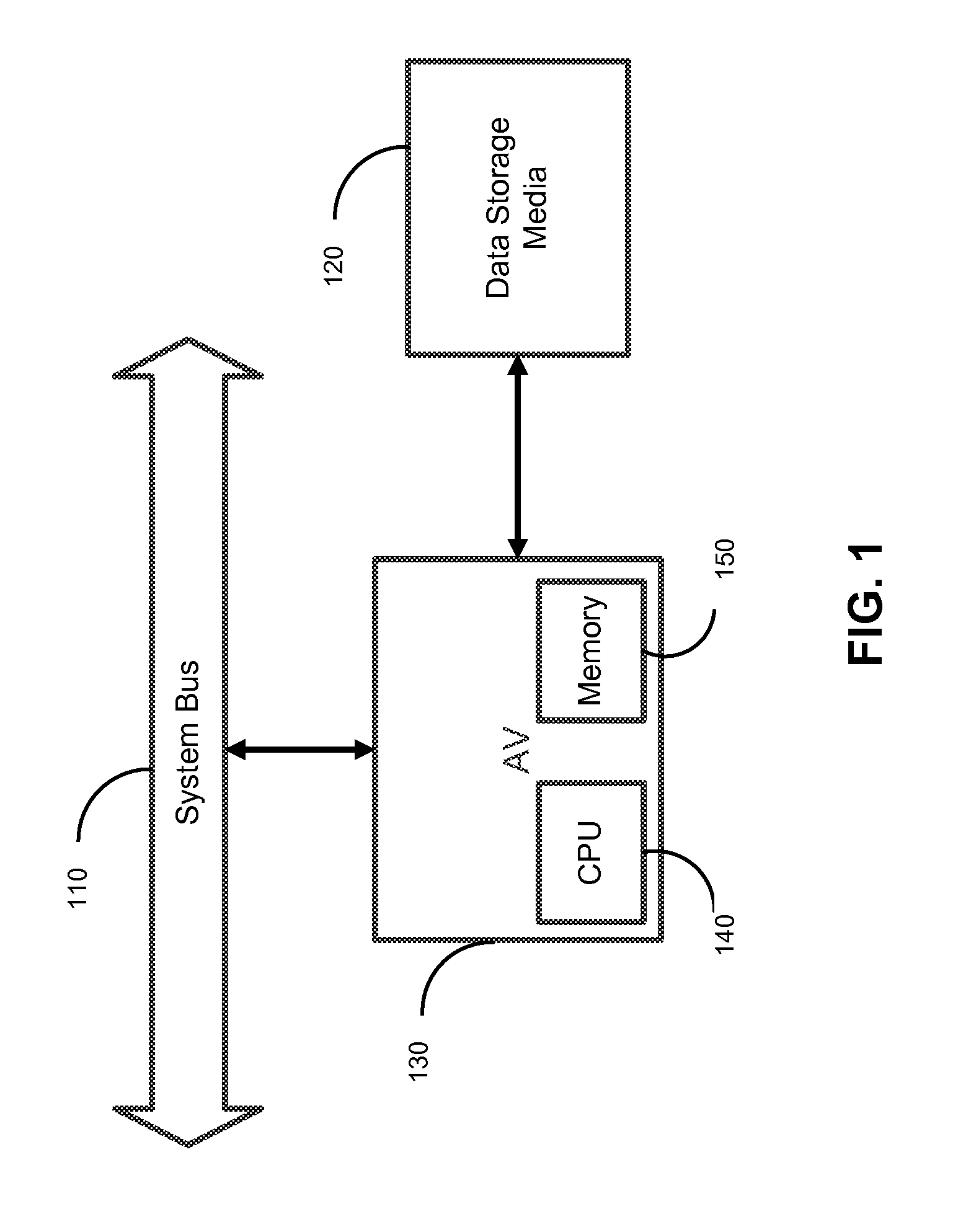

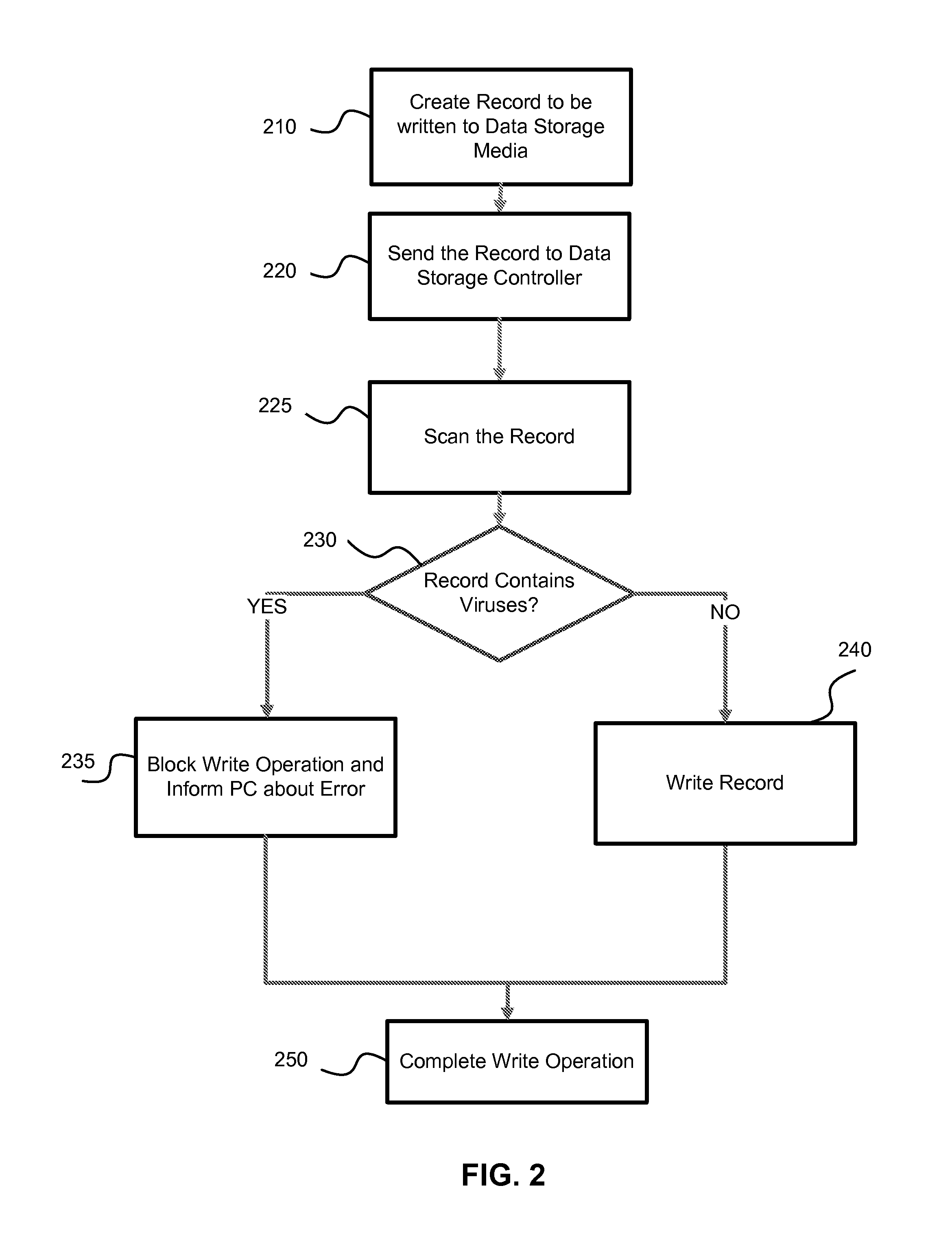

Hardware-based anti-virus system

An anti-virus (AV) system based on a hardware-implemented AV module for curing infected computer systems and a method for updating AV databases for effective curing of the computer system. The hardware-based AV system is located between a PC and a disk device. The hardware-based AV system can be implemented as a separate device or it can be integrated into a disk controller. An update method of the AV databases uses a two-phase approach. First, the updates are transferred to from a trusted utility to an update sector of the AV system. Then, the updates are verified within the AV system and the AV databases are updated. The AV system has its own CPU and memory and can be used in combination with AV application.

Owner:AO KASPERSKY LAB

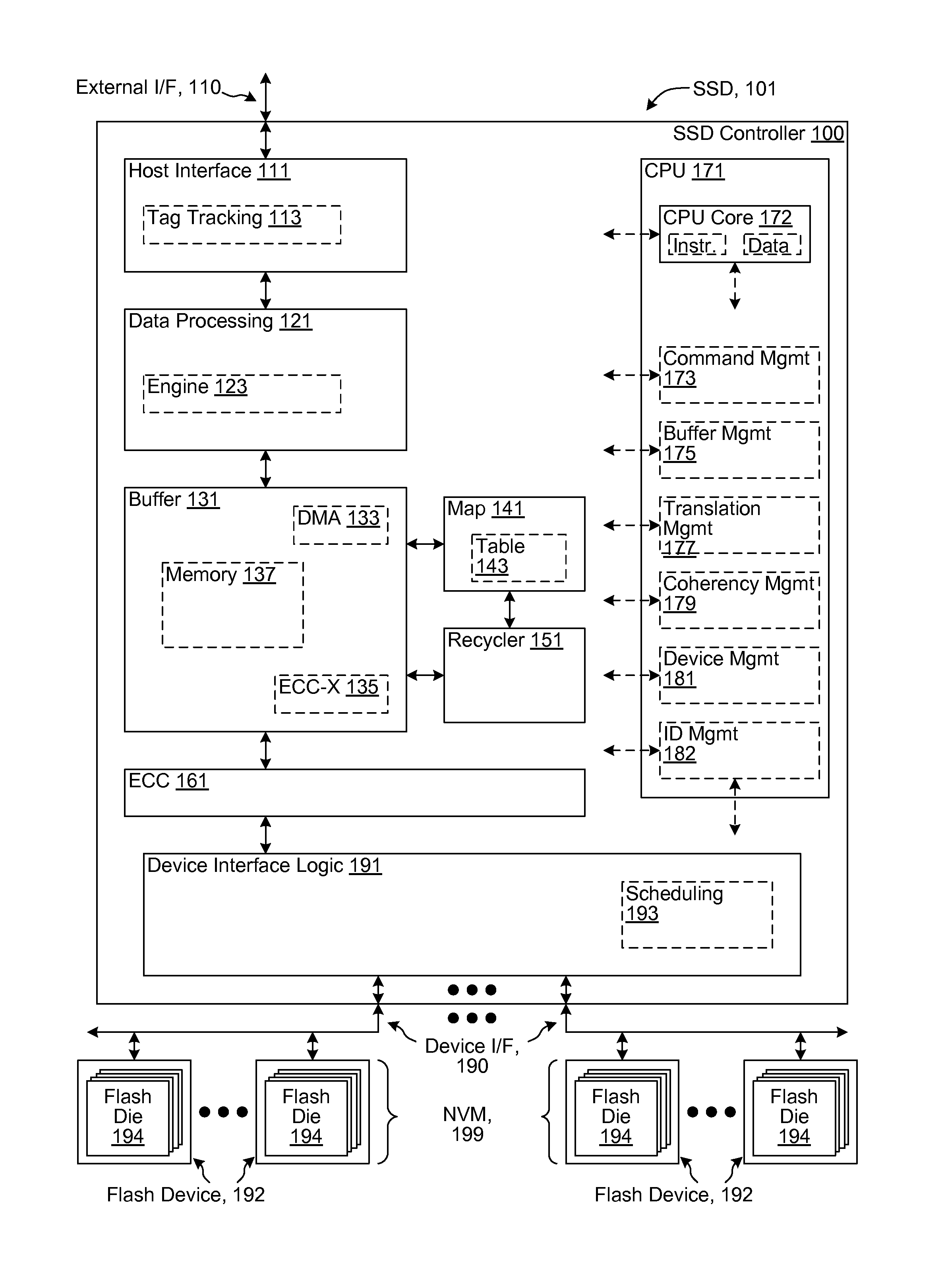

Zero-one balance management in a solid-state disk controller

An SSD controller maintains a zero count and a one count, and / or in some embodiments a zero / one disparity count, for each read unit read from an SLC NVM (or the lower pages of an MLC). In an event that the read unit is uncorrectable in part due to a shift in the threshold voltage distributions away from their nominal distributions, the maintained counts enable a determination of a direction and / or a magnitude to adjust a read threshold to track the threshold voltage shift and restore the read data zero / one balance. In various embodiments, the adjusted read threshold is determined in a variety of described ways (counts, percentages) that are based on a number of described factors (determined threshold voltage distributions, known stored values, past NVM operating events). Extensions of the forgoing techniques are described for MLC memories.

Owner:SEAGATE TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com