Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

564 results about "Hardware complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

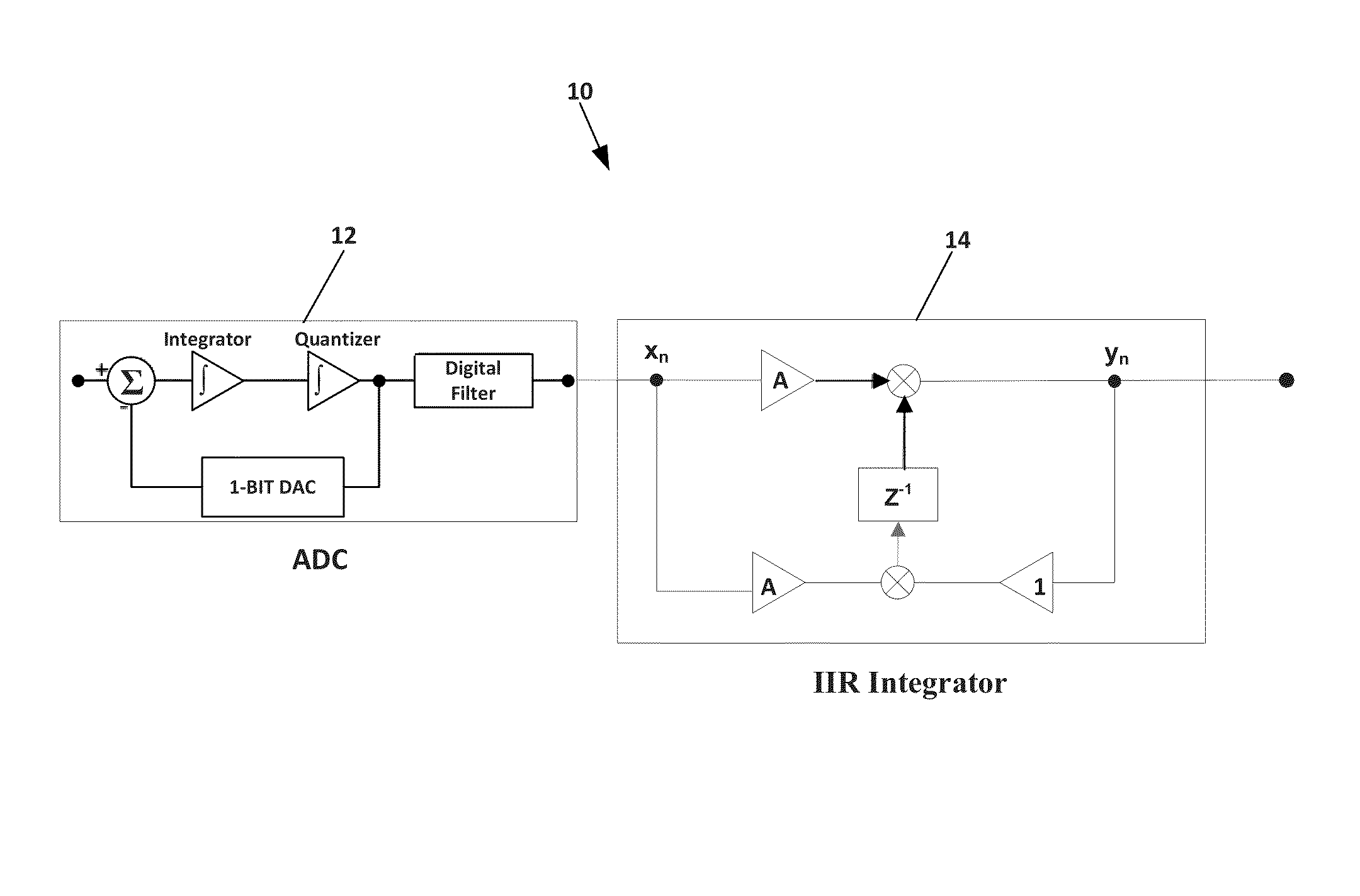

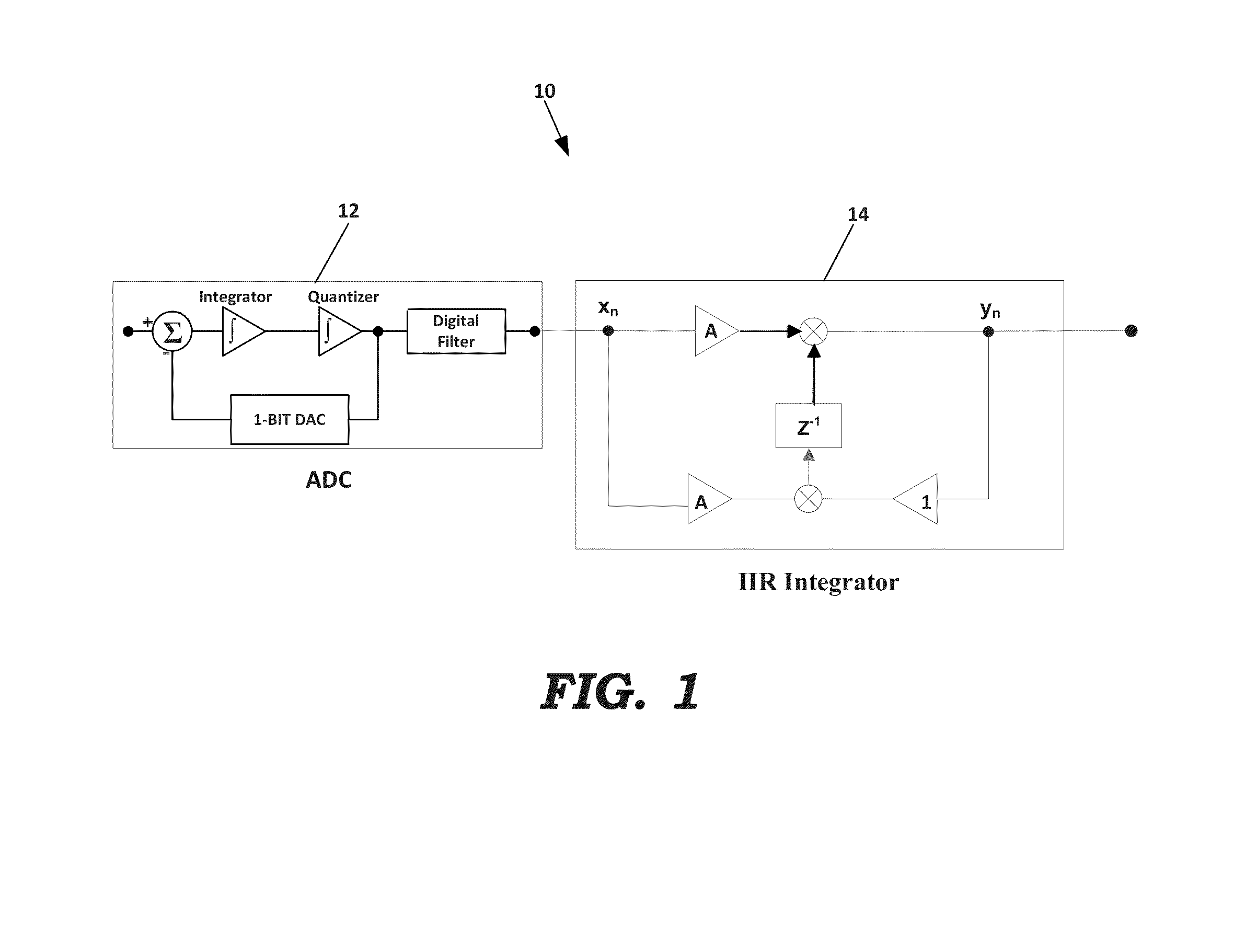

Integrated vibration measurement and analysis system

ActiveUS20140067289A1Reduce hardware complexityReduces data storage requirementVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesVibration measurementData rate

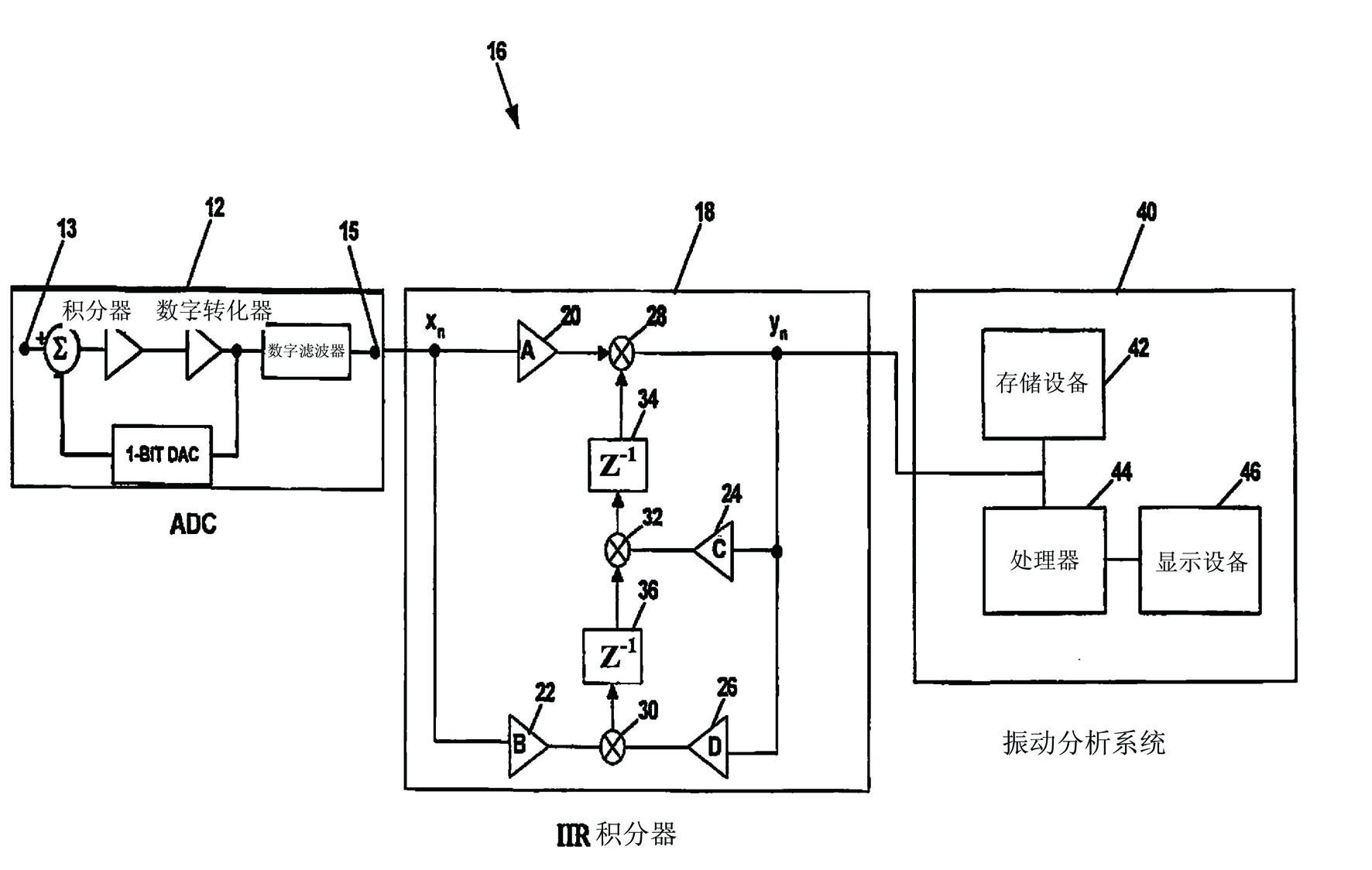

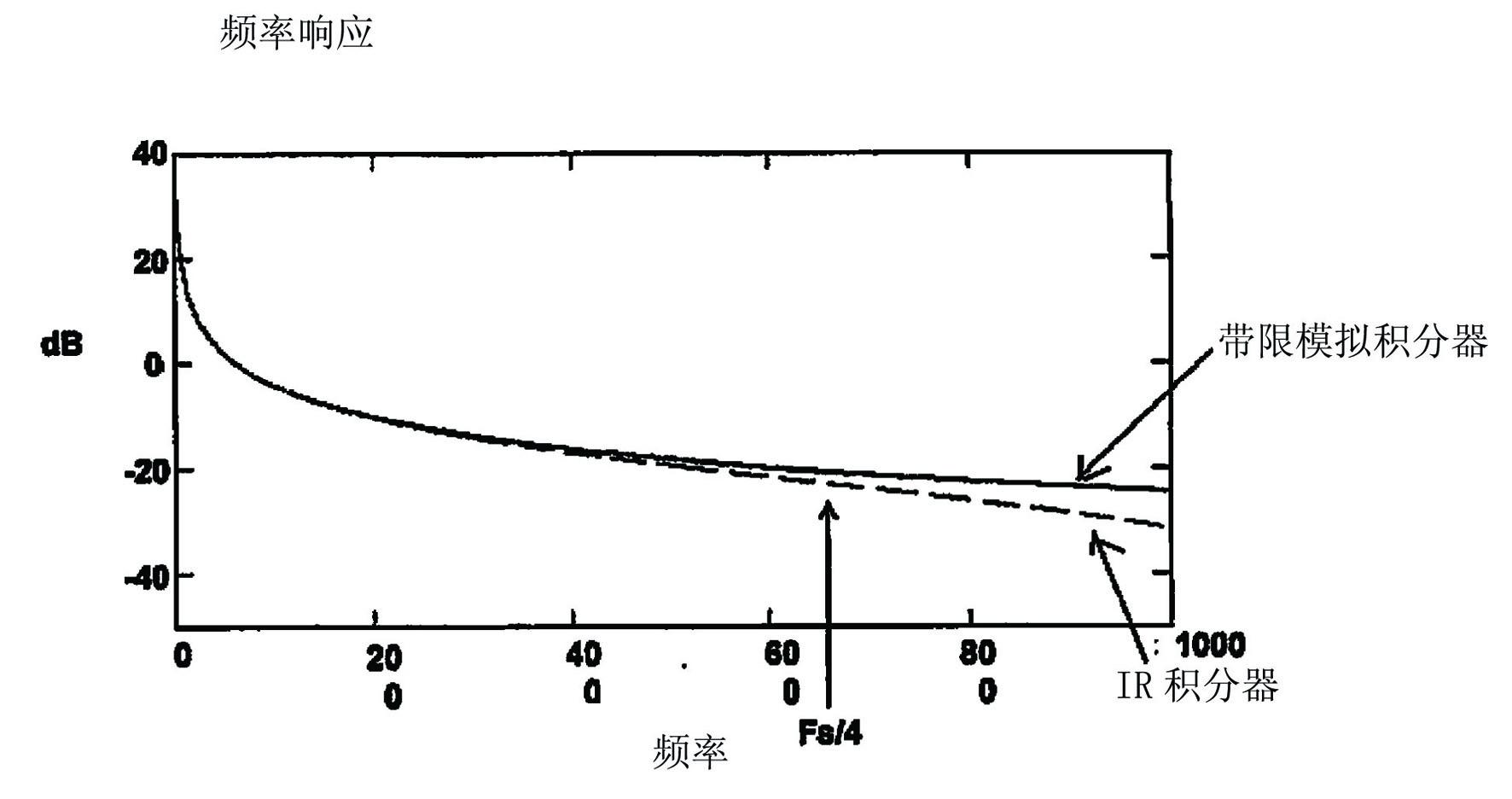

A vibration data collection system performs an integration or differentiation process on incoming digitized vibration data in real time. The system uses a digital Infinite Impulse Response (IIR) filter running at the input data rate to provide the integration or differentiation function. With this approach, the system reduces hardware complexity and data storage requirements. Also, the system provides the ability to directly integrate or differentiate stored time waveforms without resorting to FFT processing methods.

Owner:COMPUTATIONAL SYST

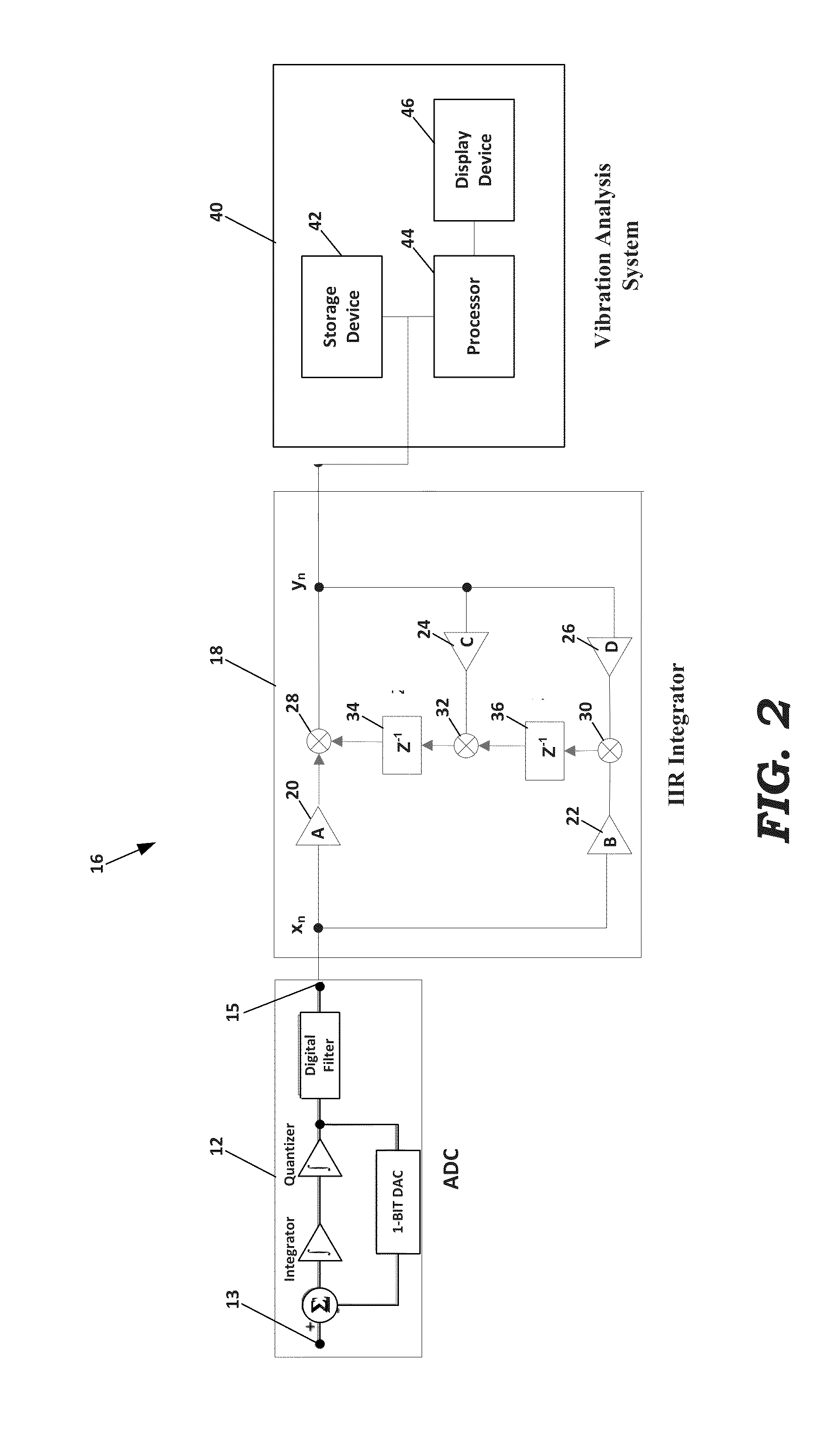

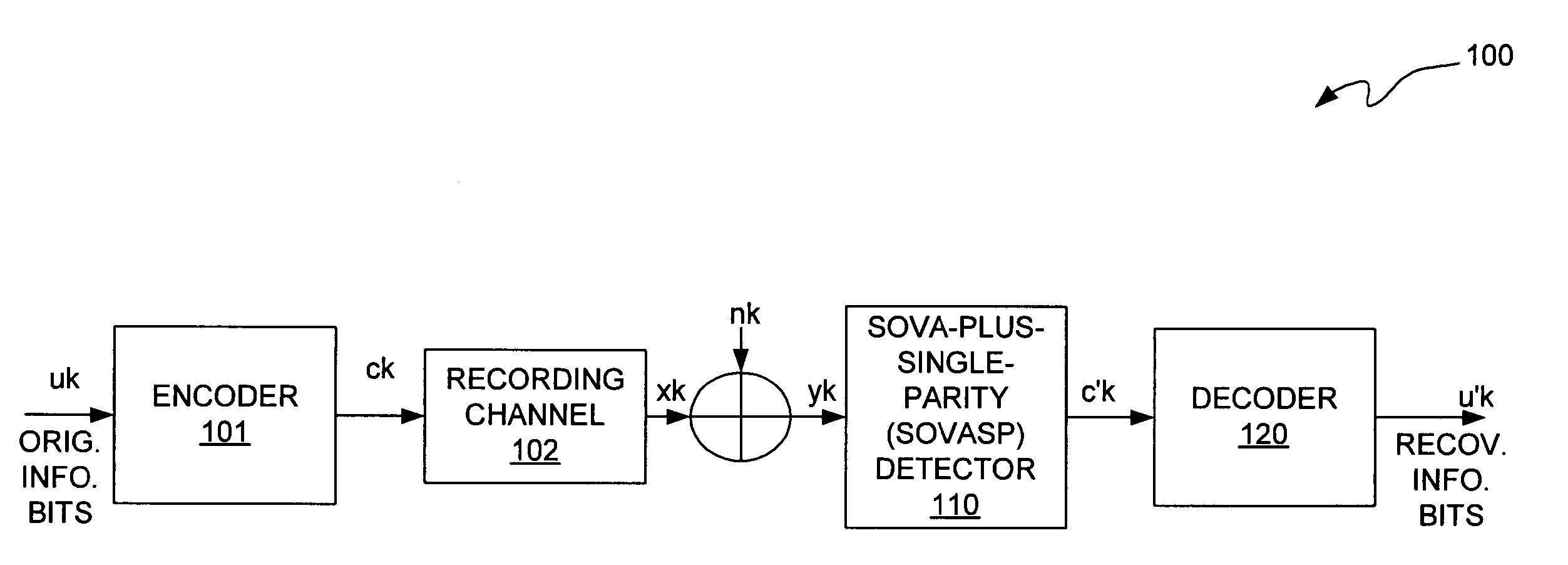

Data detection and decoding system and method

ActiveUS20060168493A1Data representation error detection/correctionOther decoding techniquesSingle parity checkAlgorithm

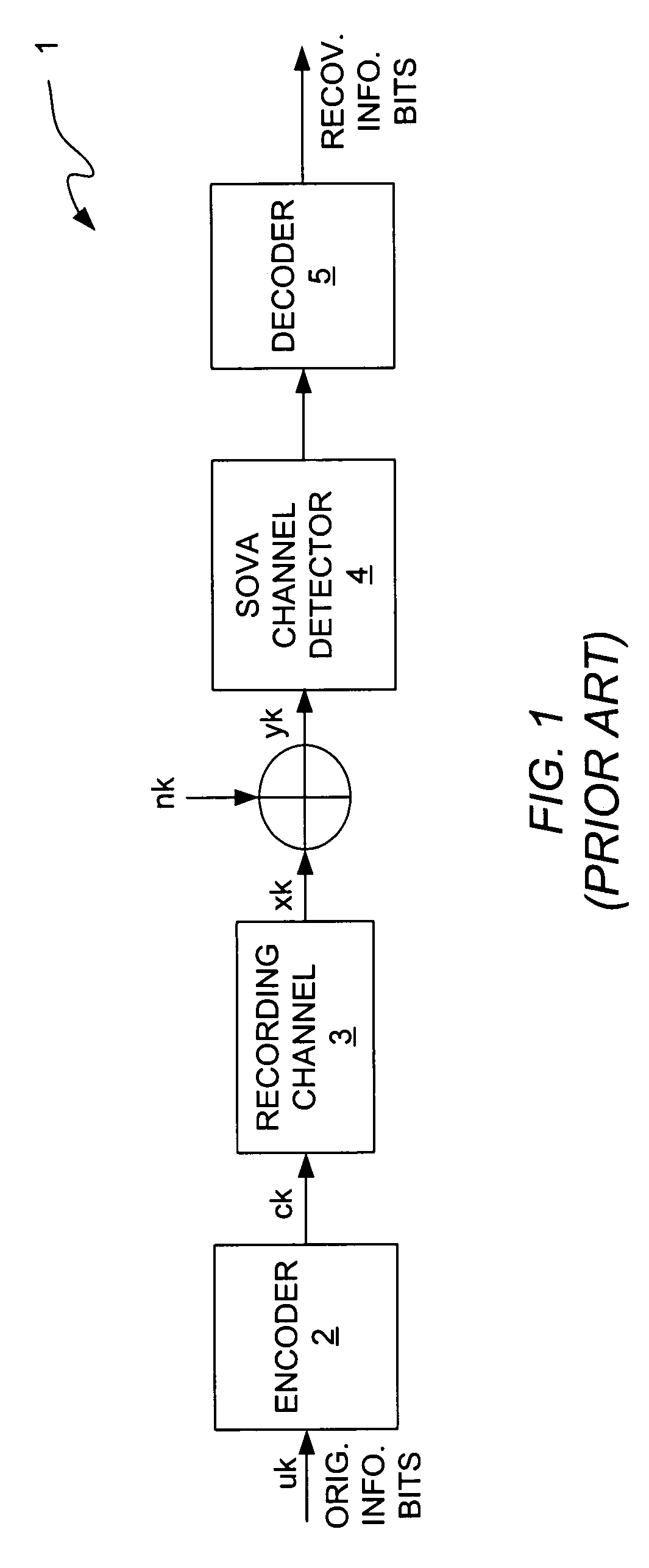

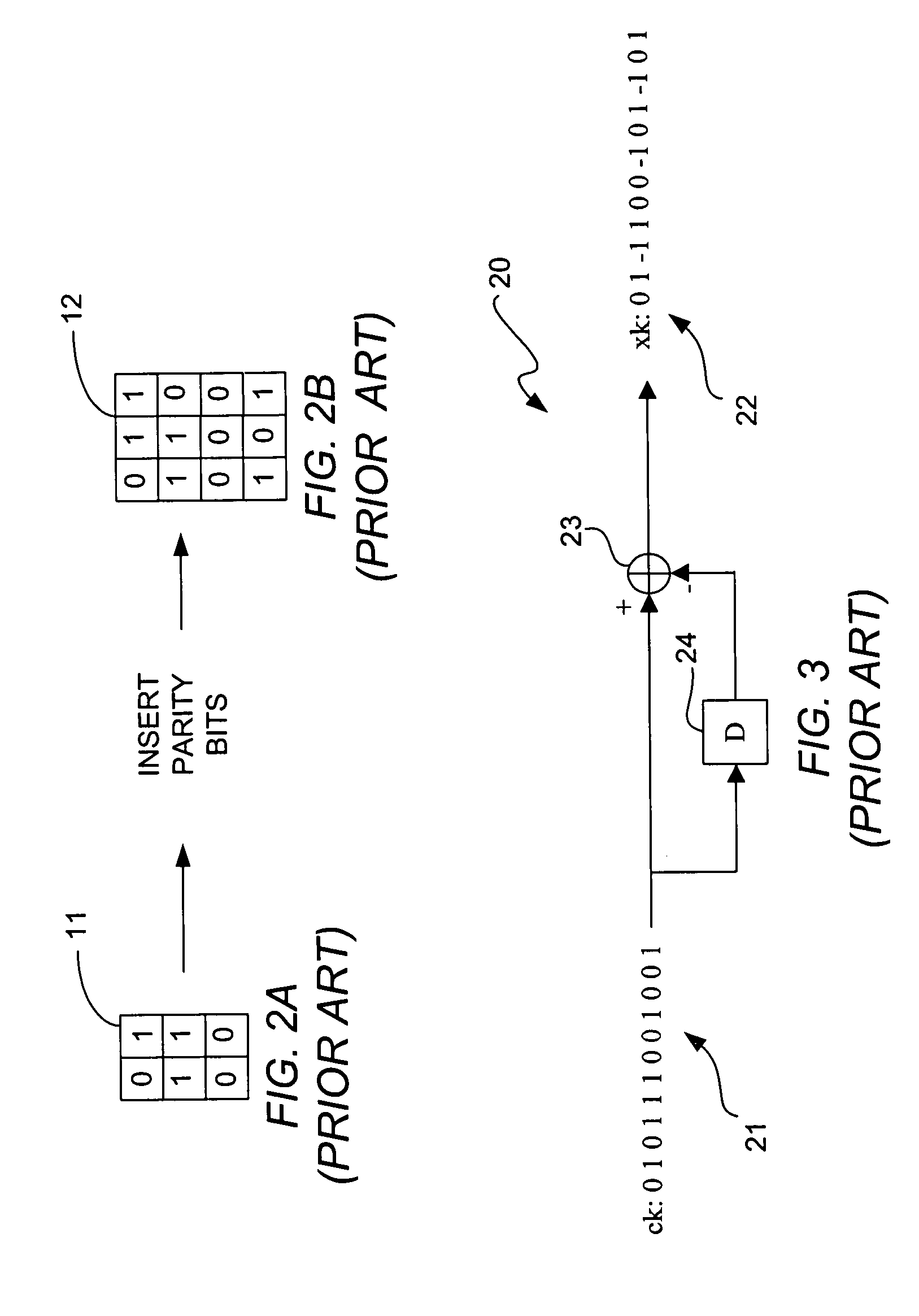

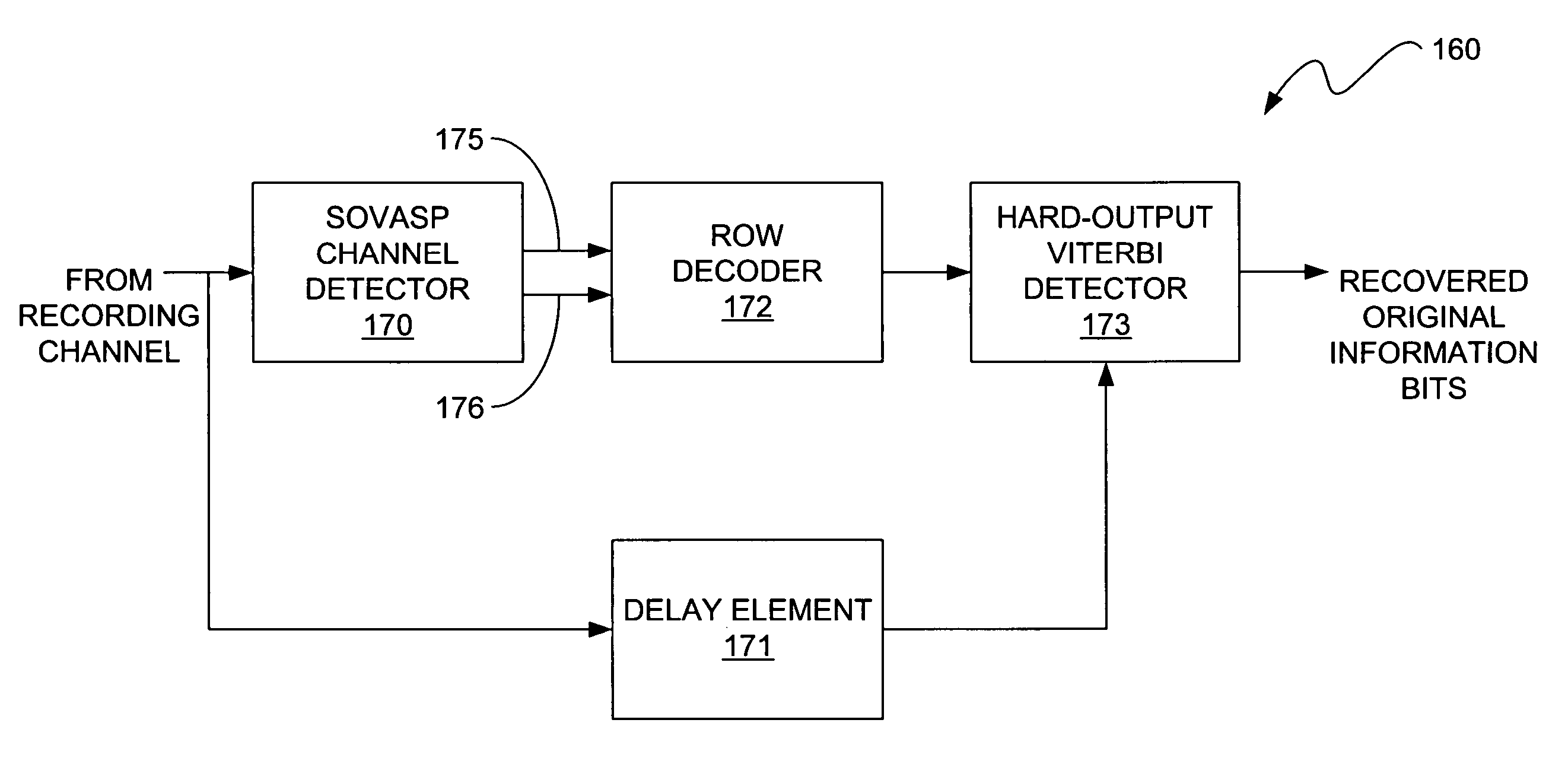

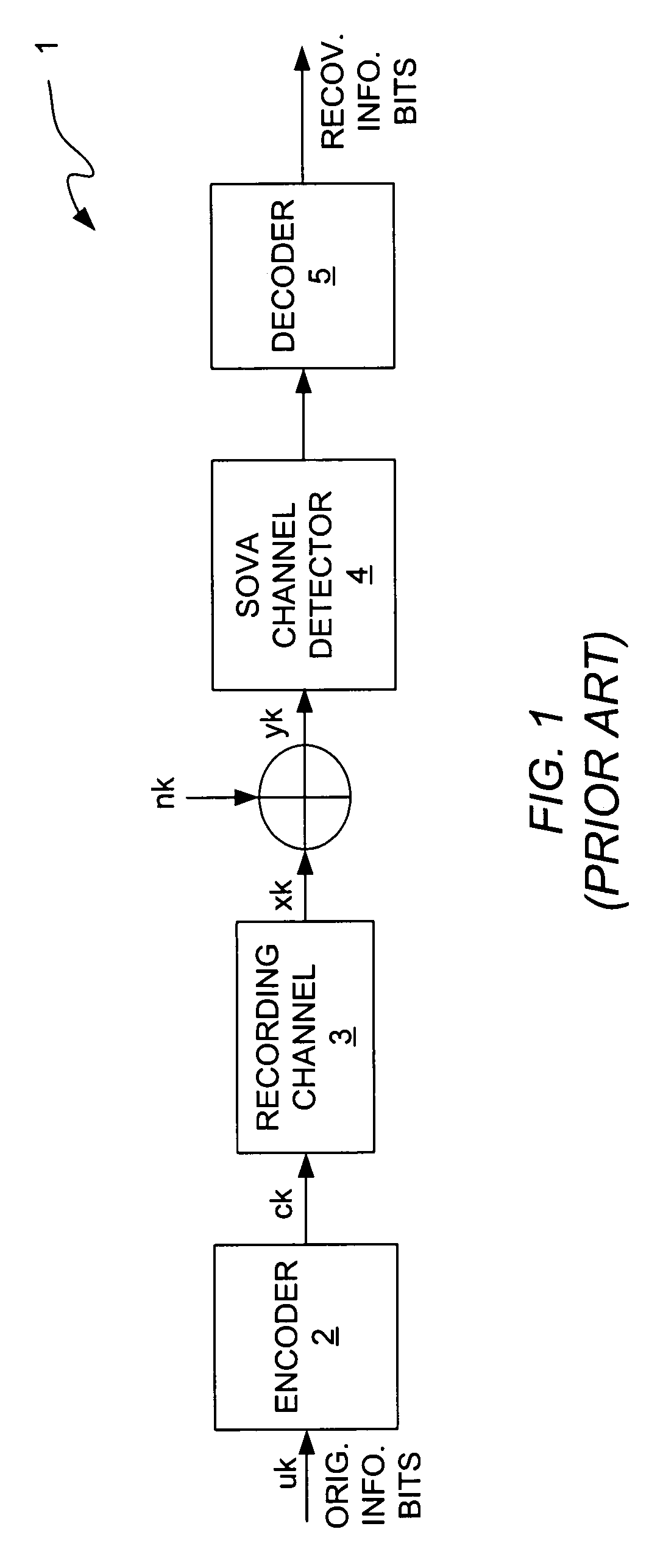

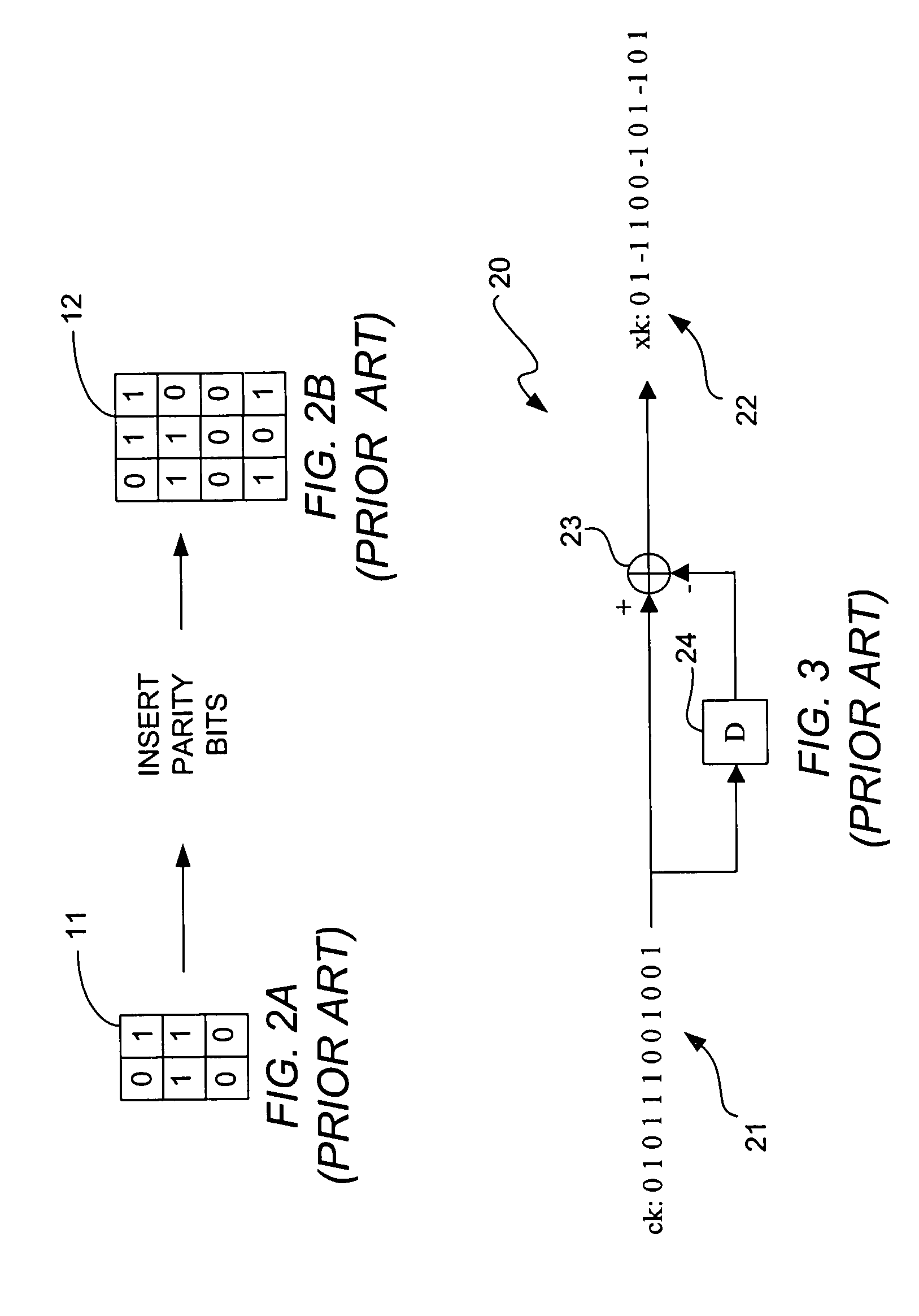

A data detection and decoding system includes a SOVA channel detector that uses single parity (SOVASP) to improve the accuracy with which the detector estimates bits. Each column or row read back from the read channel constitutes a code word and each code word is encoded to satisfy single parity. Because the SOVASP channel detector detects whether each code word satisfies single parity, it is unnecessary to use both a column decoder and a row decoder in the channel decoder. Either the row decoder or the column decoder can be eliminated depending on whether bits are read back on a column-by-column basis or on a row-by-row basis. This reduction in components reduces hardware complexity and improves system performance. The output of the row or column decoder is received by a second detector that processes the output received from the decoder to recover the original information bits.

Owner:AVAGO TECH INT SALES PTE LTD

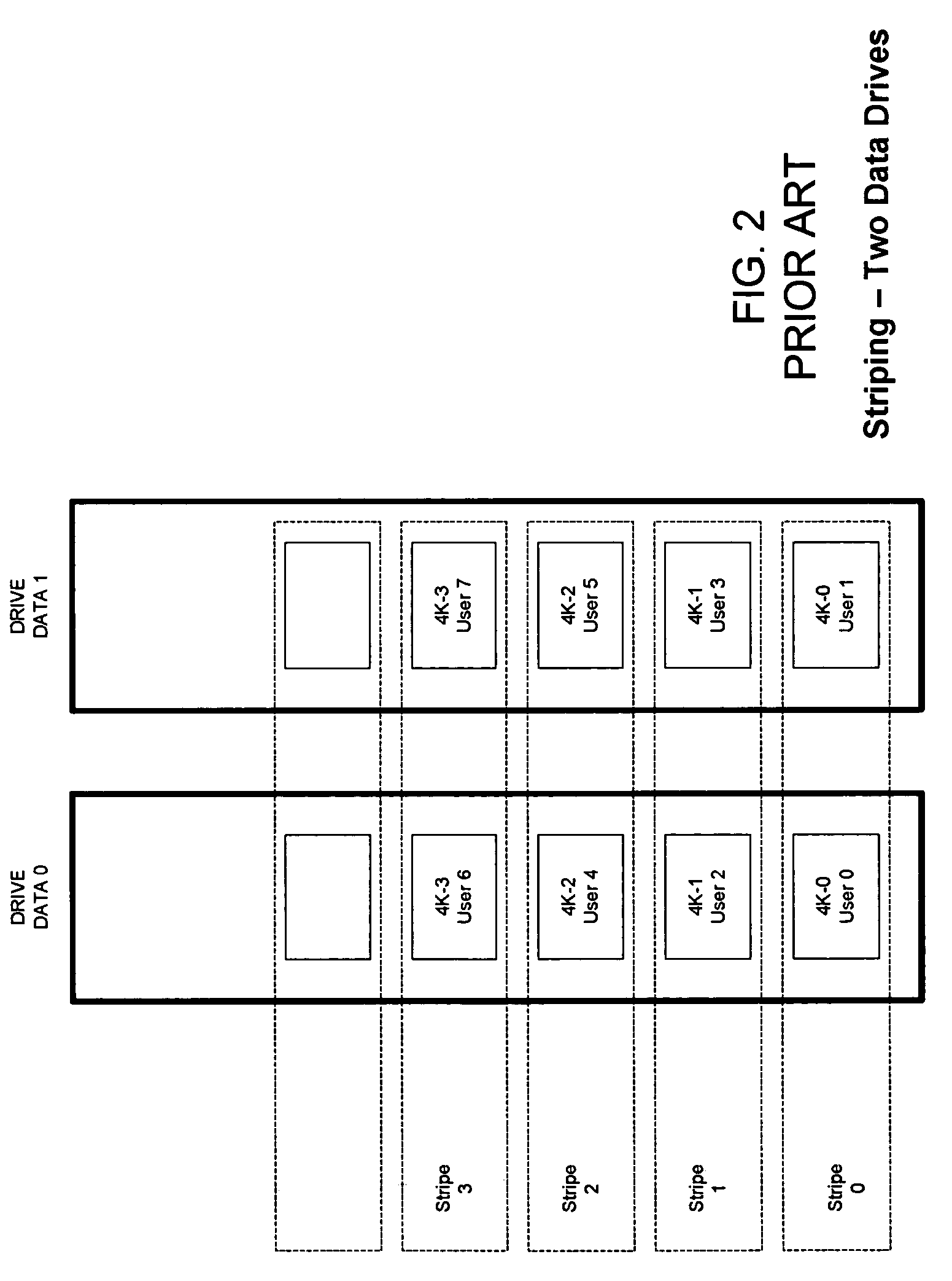

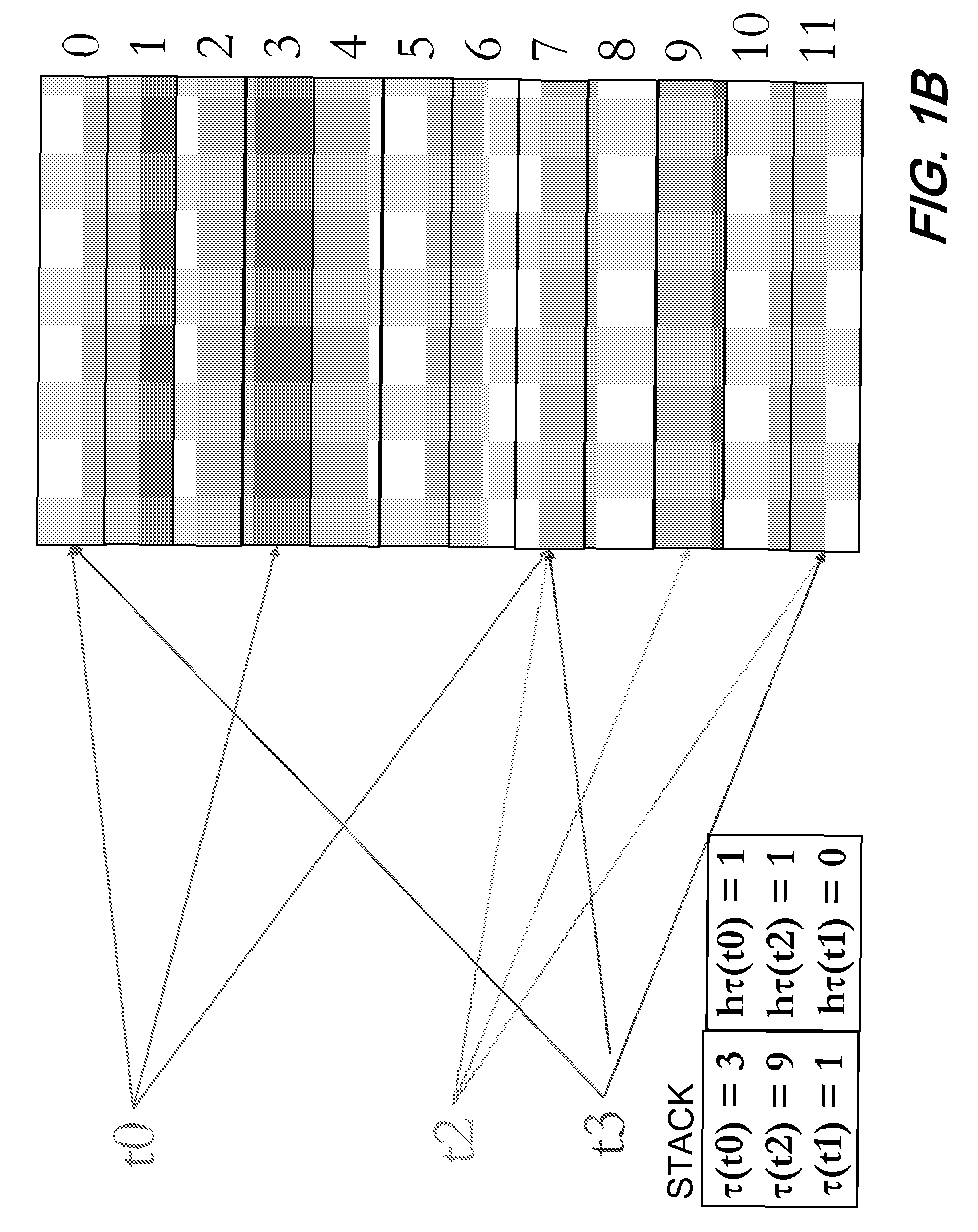

Disk controller methods and apparatus with improved striping, redundancy operations and interfaces

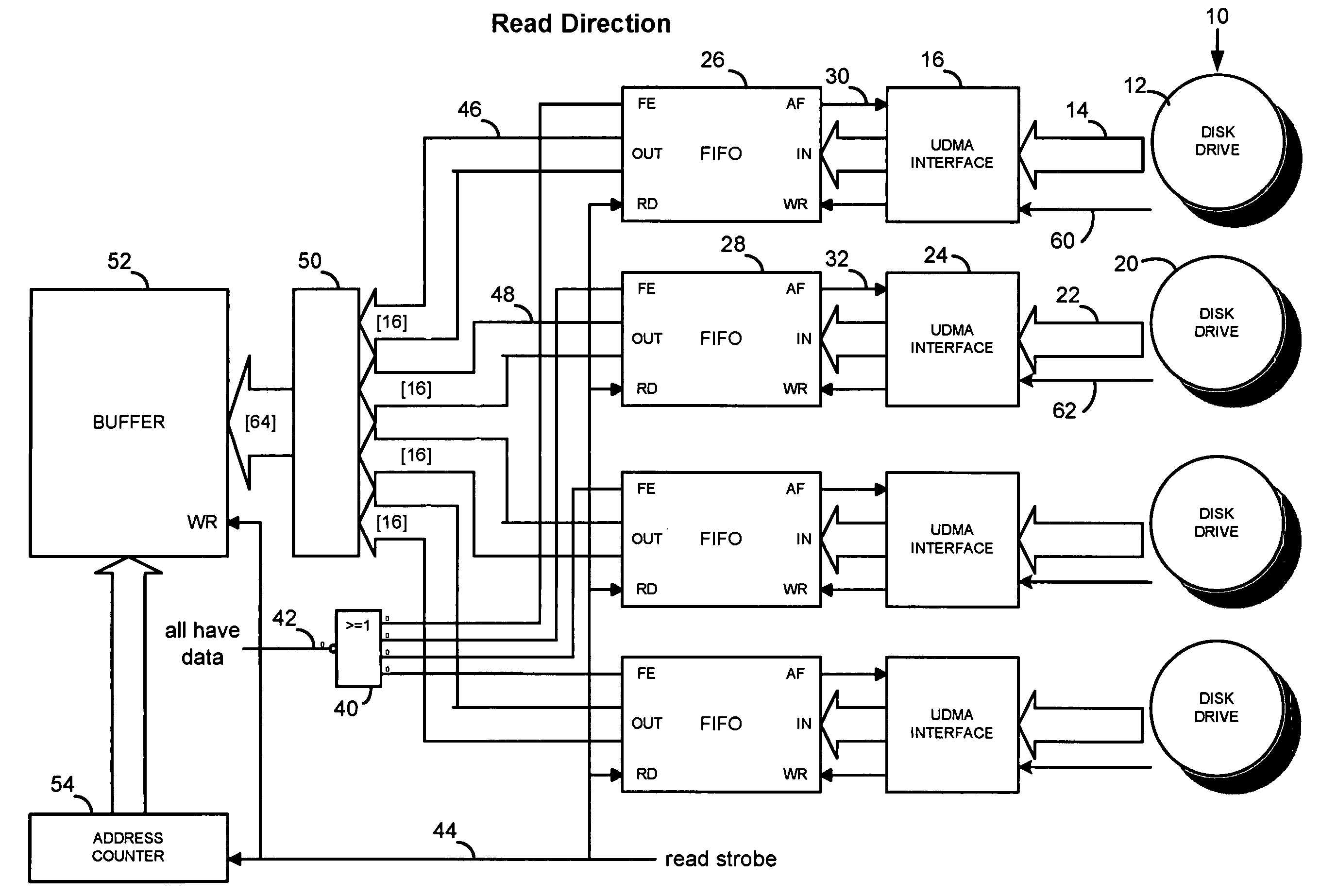

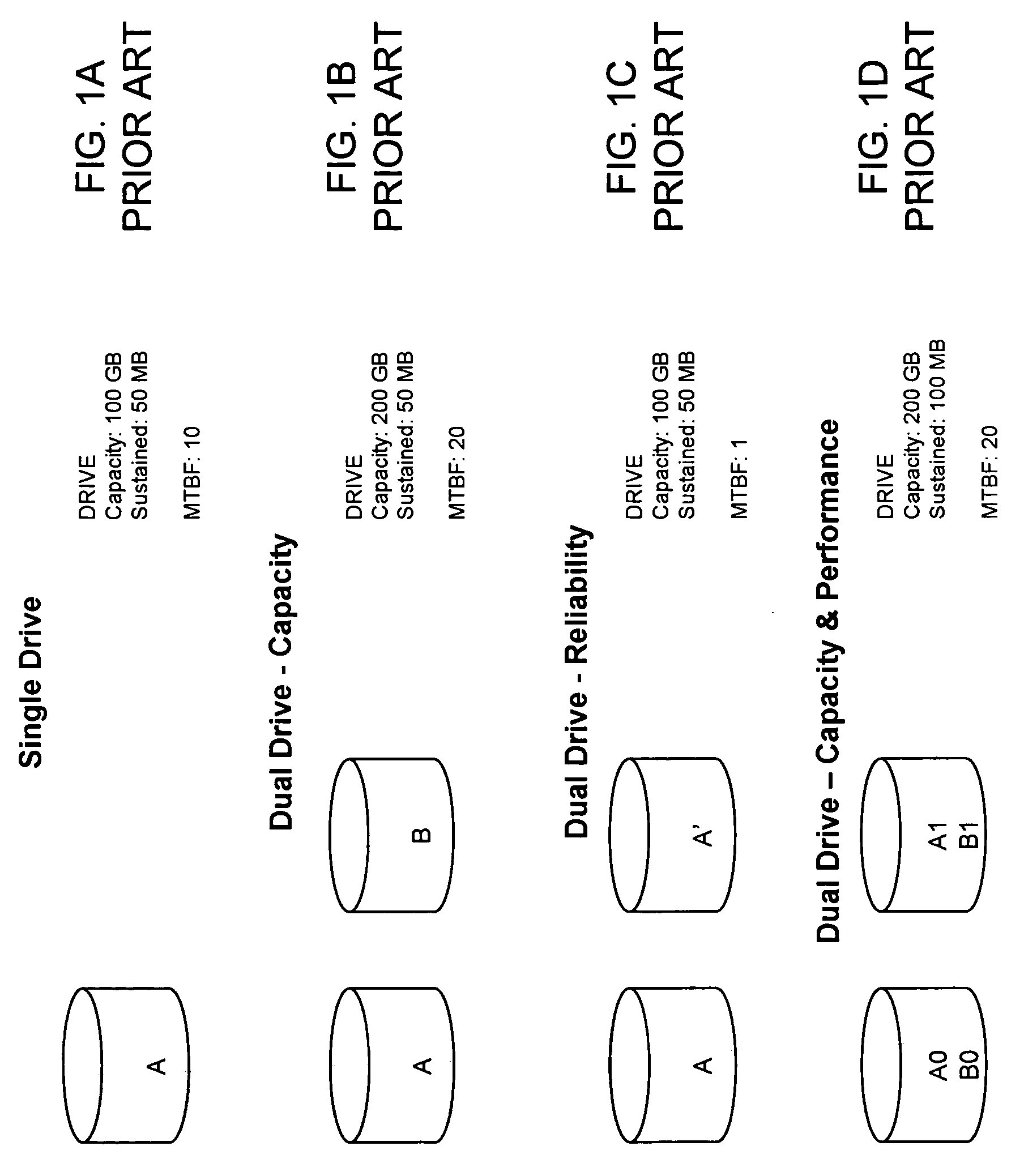

ActiveUS20050223269A1Improve performanceReduce hardware complexityStatic storageRedundant data error correctionRAIDTransport layer

A RAID disk drive controller (FIG. 33) implements disk storage operations, including striping and redundancy operations with multiple disk drives connected via respective SATA ports (520). Configurable data path switch logic (460) provides dynamic configuration of two or more attached drives into one or more arrays. Data transfers are synchronized locally by leveraging the SATA port transport layer FIFO (530). Synchronous transfers allow on-the-fly redundancy (XOR) operations (FIG. 36) for improved performance and reduced hardware complexity. XOR accumulator hardware (FIG. 42-FIG. 43) reduces buffer requirements for multiple DMA channels otherwise required for synchronization, and various narrow and wide striping modes are supported.

Owner:NVIDIA CORP

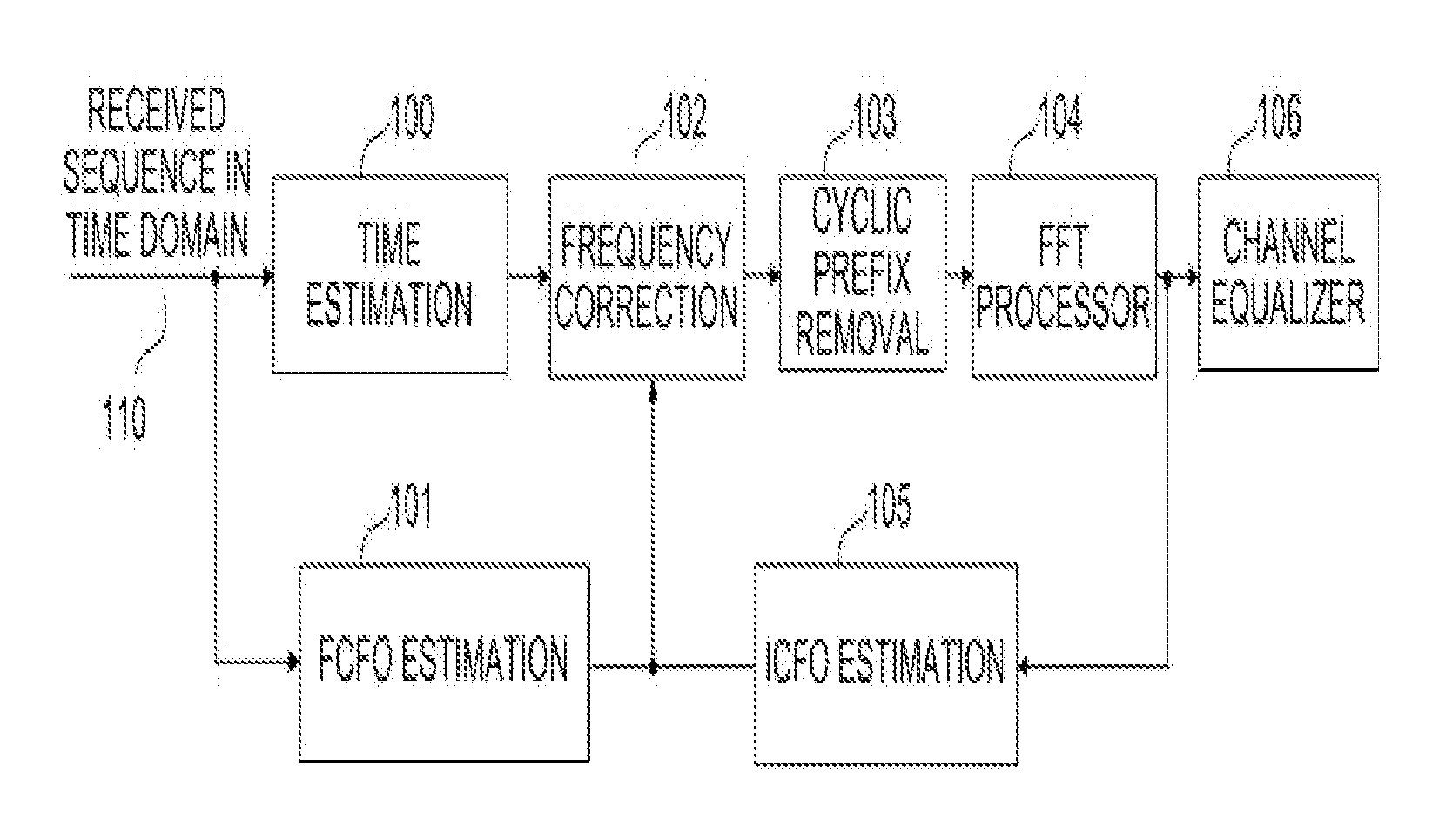

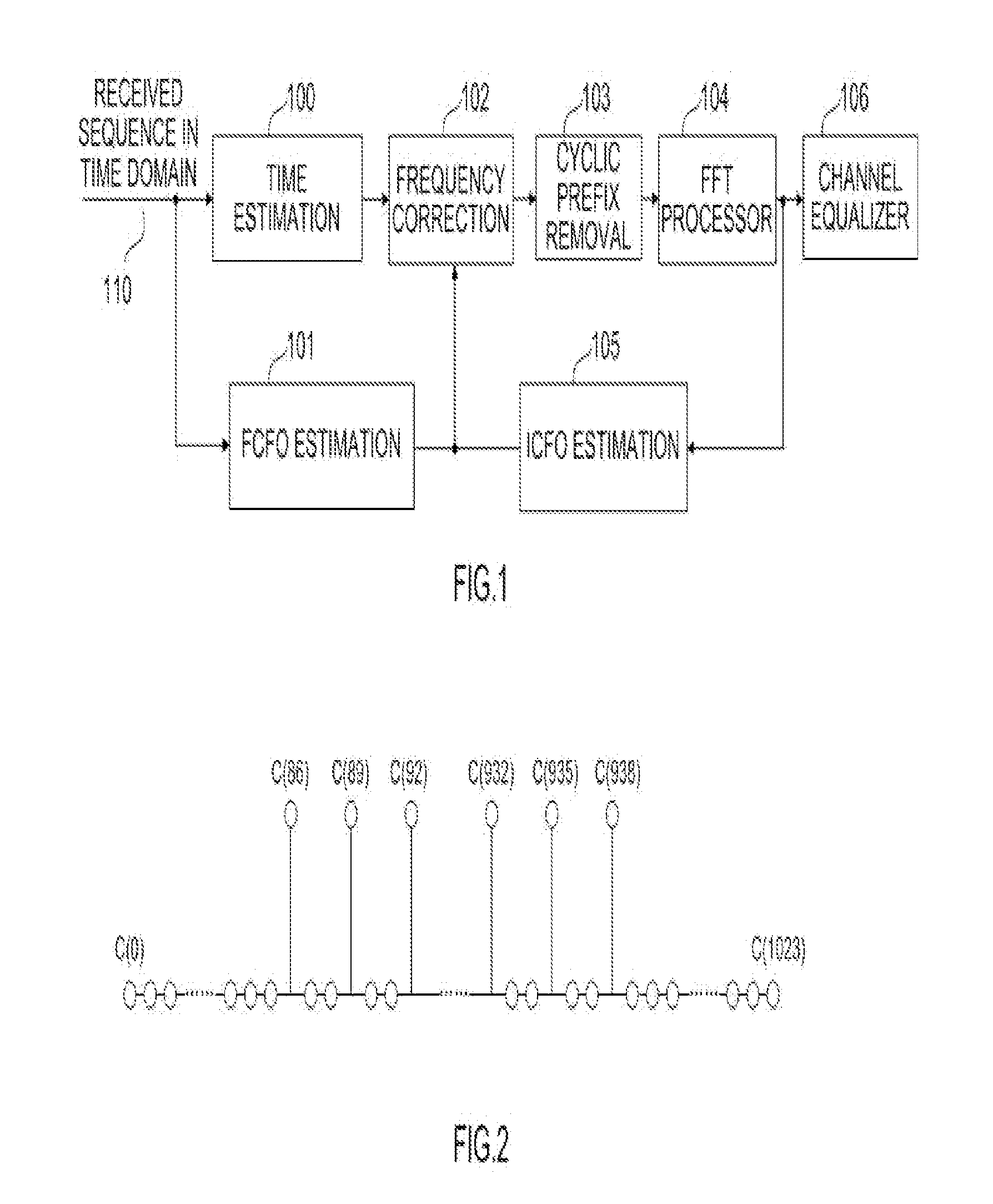

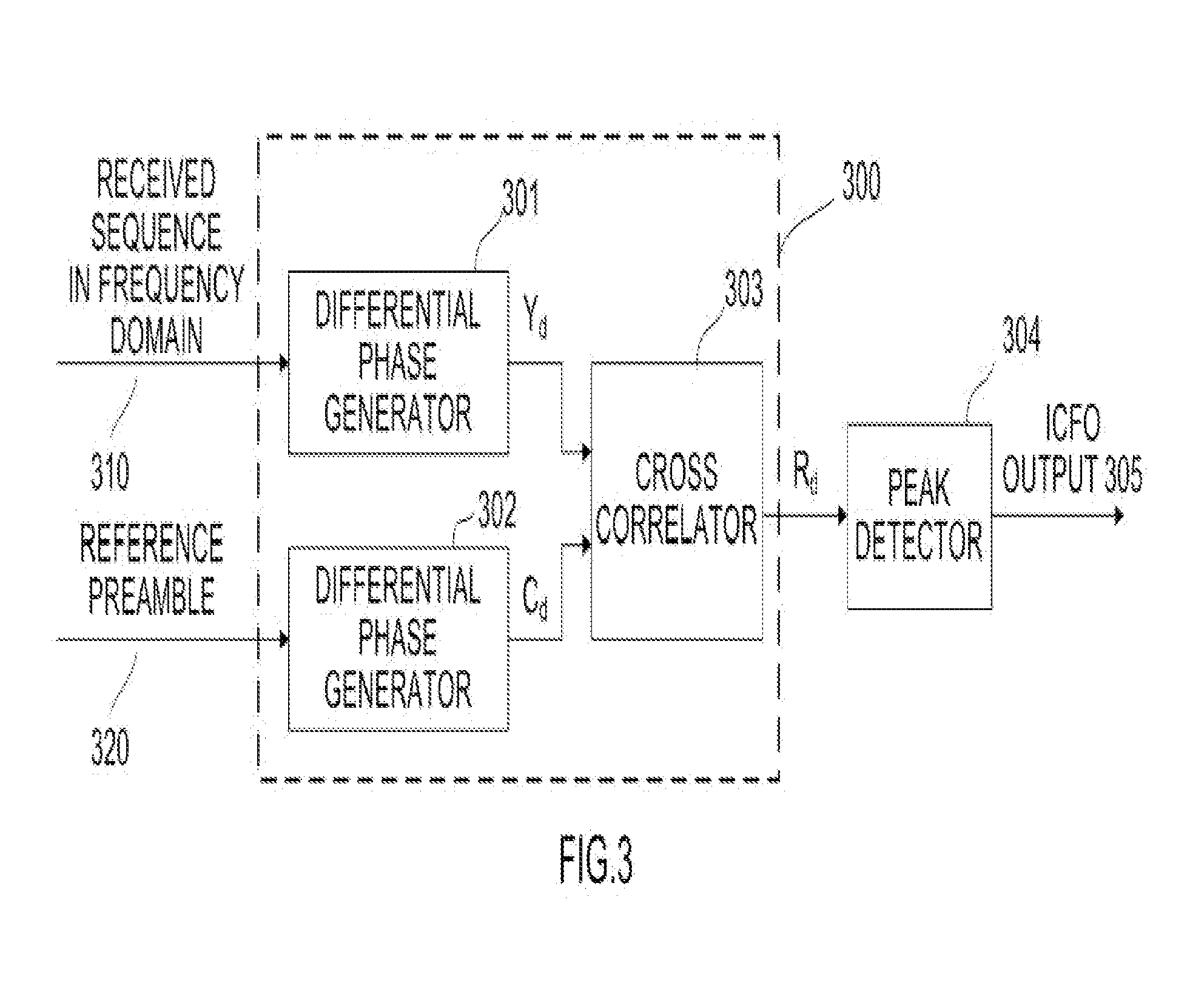

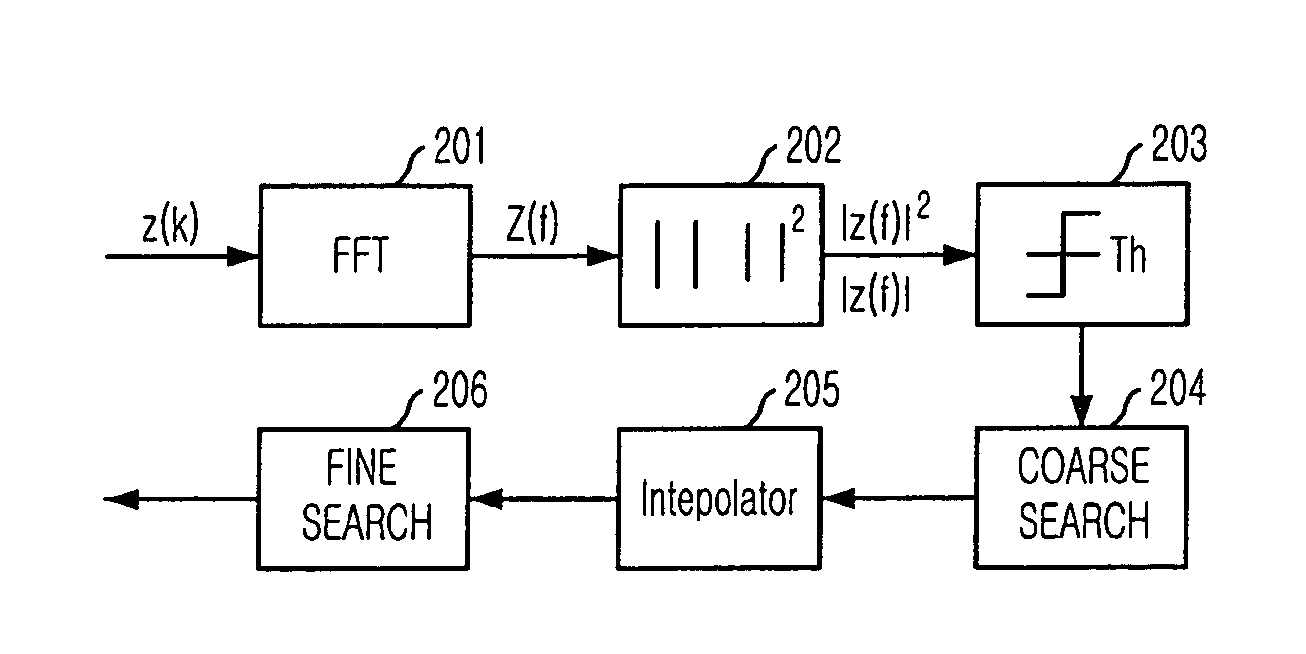

Method and apparatus for integer frequency offset estimation in wireless communication system

ActiveUS20130021977A1Facilitate ICFO detectionReduce hardware complexityModulated-carrier systemsWireless commuication servicesDifferential phaseCommunications system

A method and apparatus for performing time synchronization and an OFDMA receiver thereof are provided. The method preferably includes performing a differential phase correlation in a frequency domain based on one received sequence and one reference preamble and detecting an integer frequency offset based on a result of the differential phase correlation. The method and apparatus advantageously enable the use of one OFDM symbol to estimate ICFO and the use of a simple method to facilitate ICFO detection. Moreover, the performance of the integer frequency offset estimation becomes more robust in high noise and time-variant fading channels, with reduced hardware complexity.

Owner:MURATA MFG CO LTD

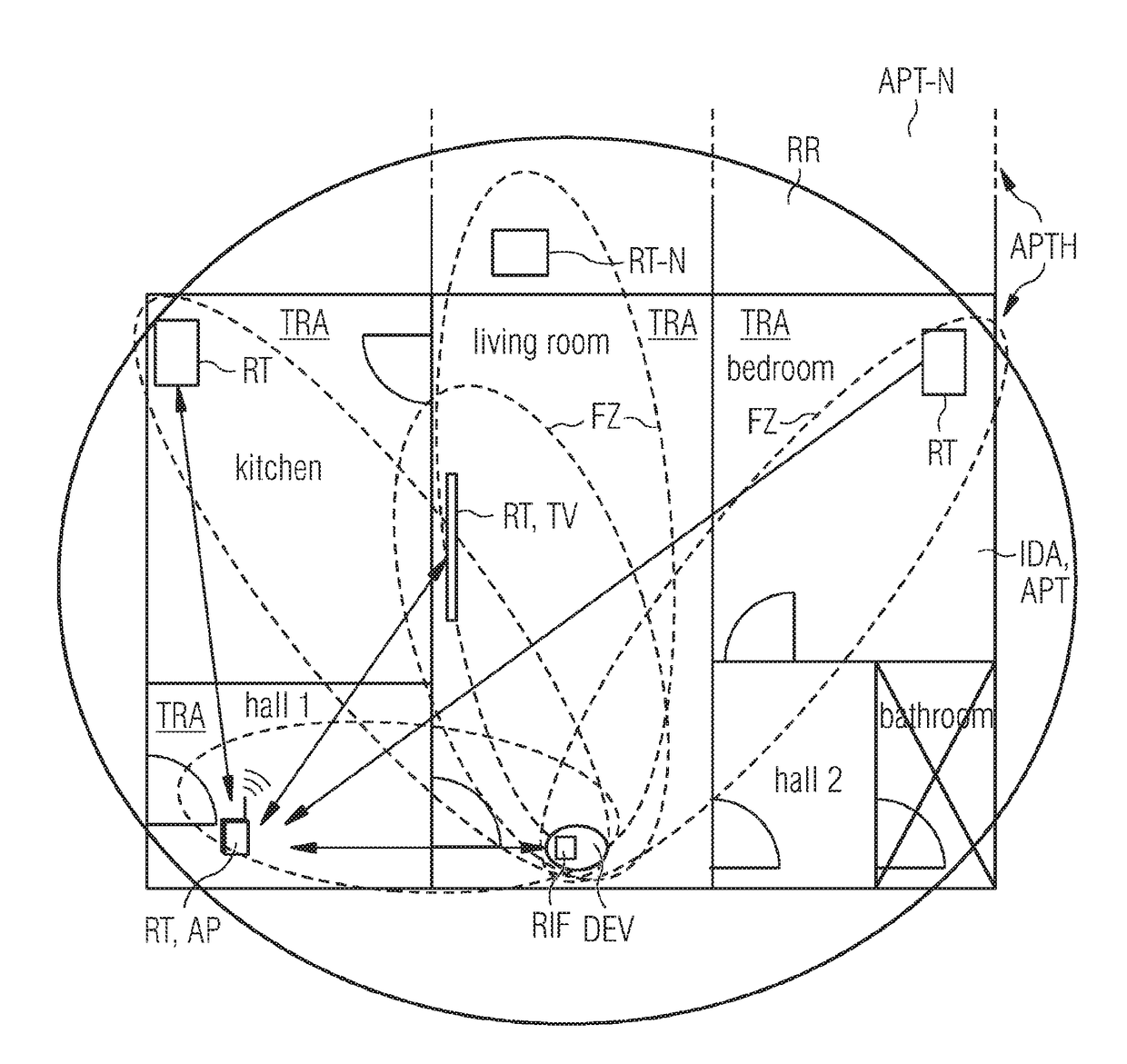

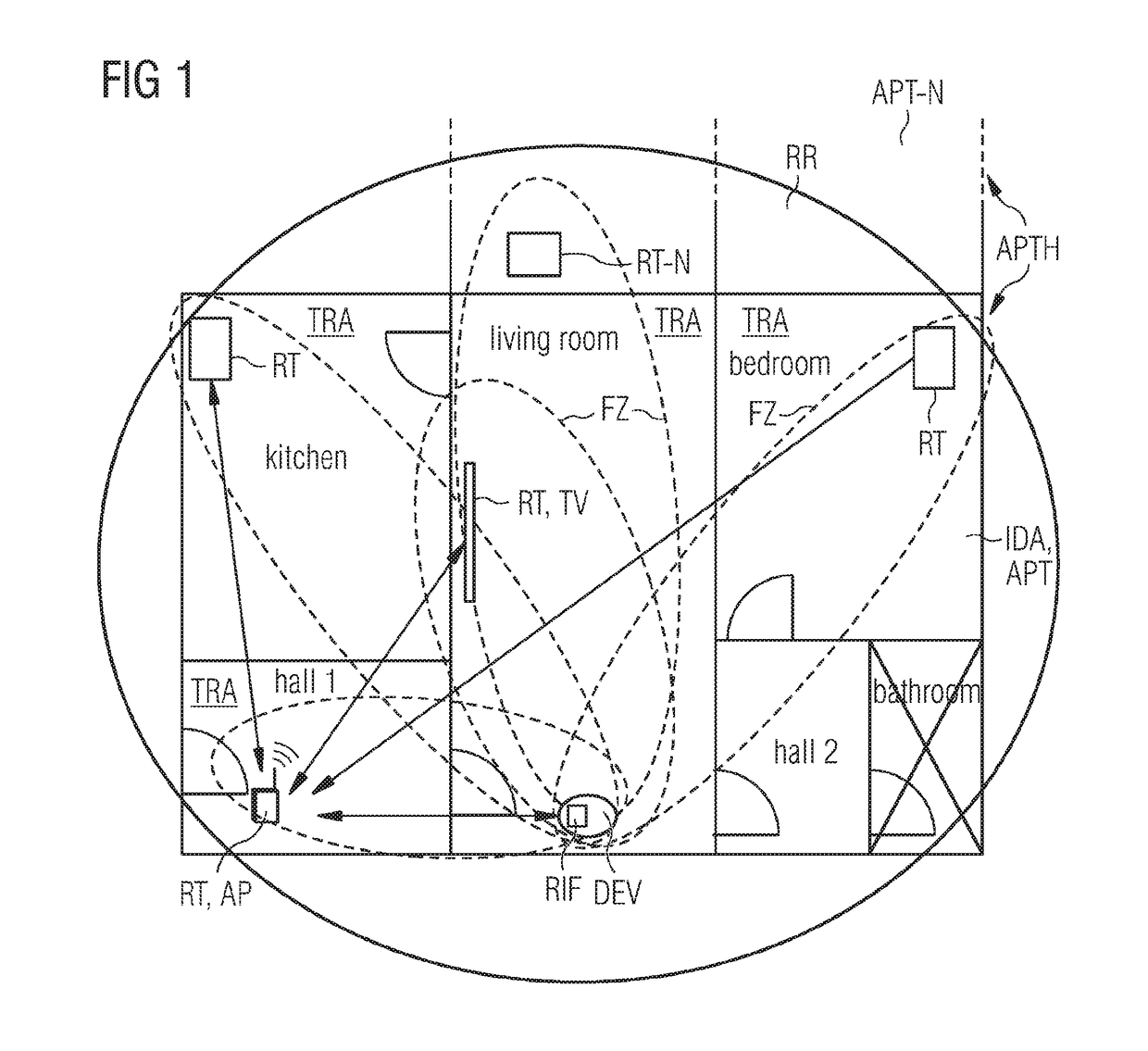

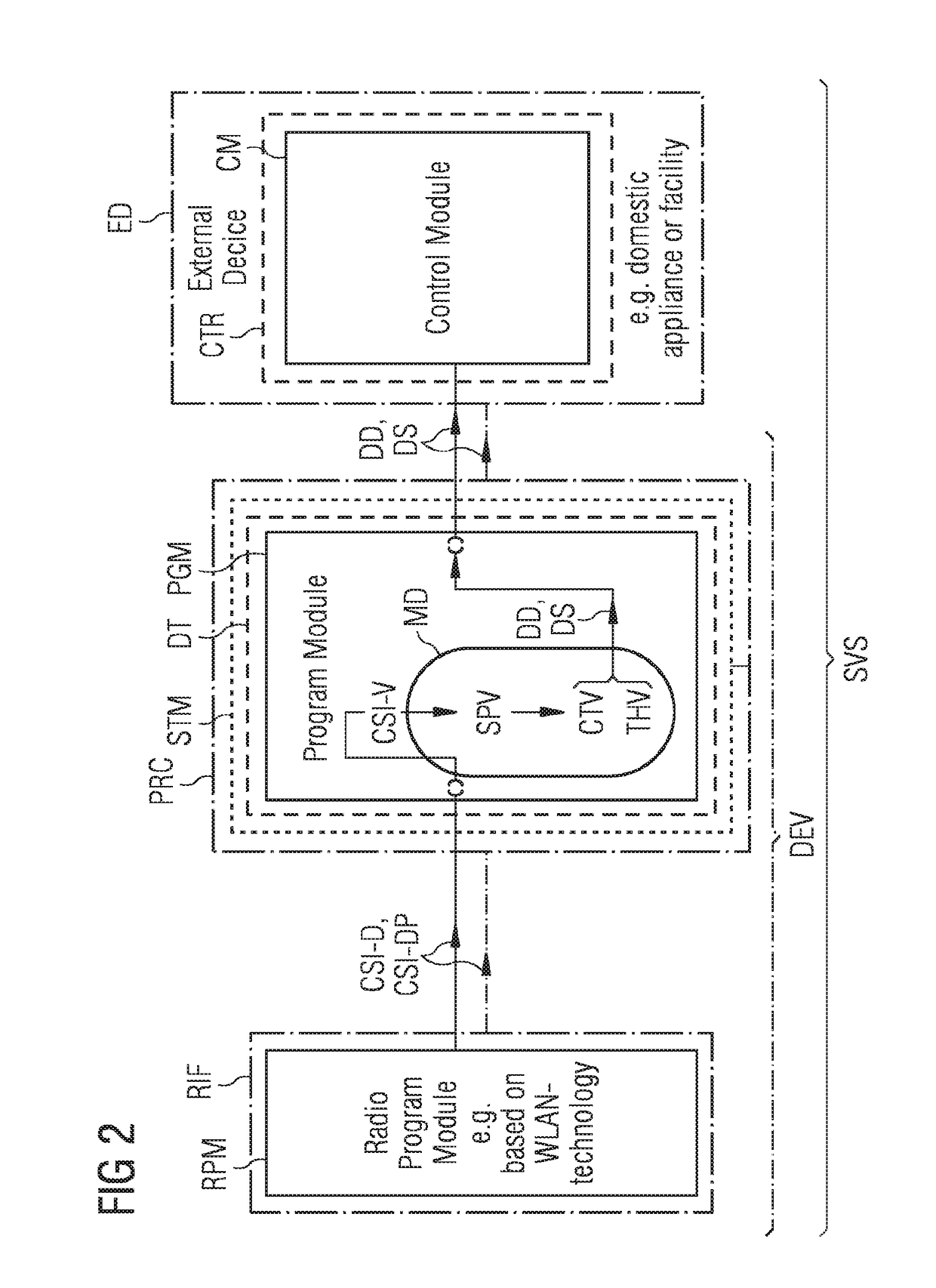

Method, digital tool, device and system for detecting movements of objects and/or living beings in a radio range, in particular of an indoor area

ActiveUS20170343658A1Low costGreat advantageTransmission systemsBurglar alarm electric actuationRadio equipmentChannel state information

In order to detect movements of objects and / or living beings in a radio range, which enables easily with a minimum of hardware complexity an automated movement detection based on a Single-Sensor, it is proposed to: Collect as input data for the movement detection based on received radio signals of an intended or unintended communication between a transmitting radio terminal being mobile or fixed and a receiving local fixed radio device in the radio range a set of “Channel State Information”-values, determine a change in the received radio signals, which are derived from the facts that the movement influences the transmitted radio signal in the radio range based on the collected CSI-values by the indication of a statistical parameter value, and assess on the basis of the statistical parameter value a “chaos index” value until the “chaos index” value in accordance with a threshold check provides a reliable statement.

Owner:SIEMENS AG

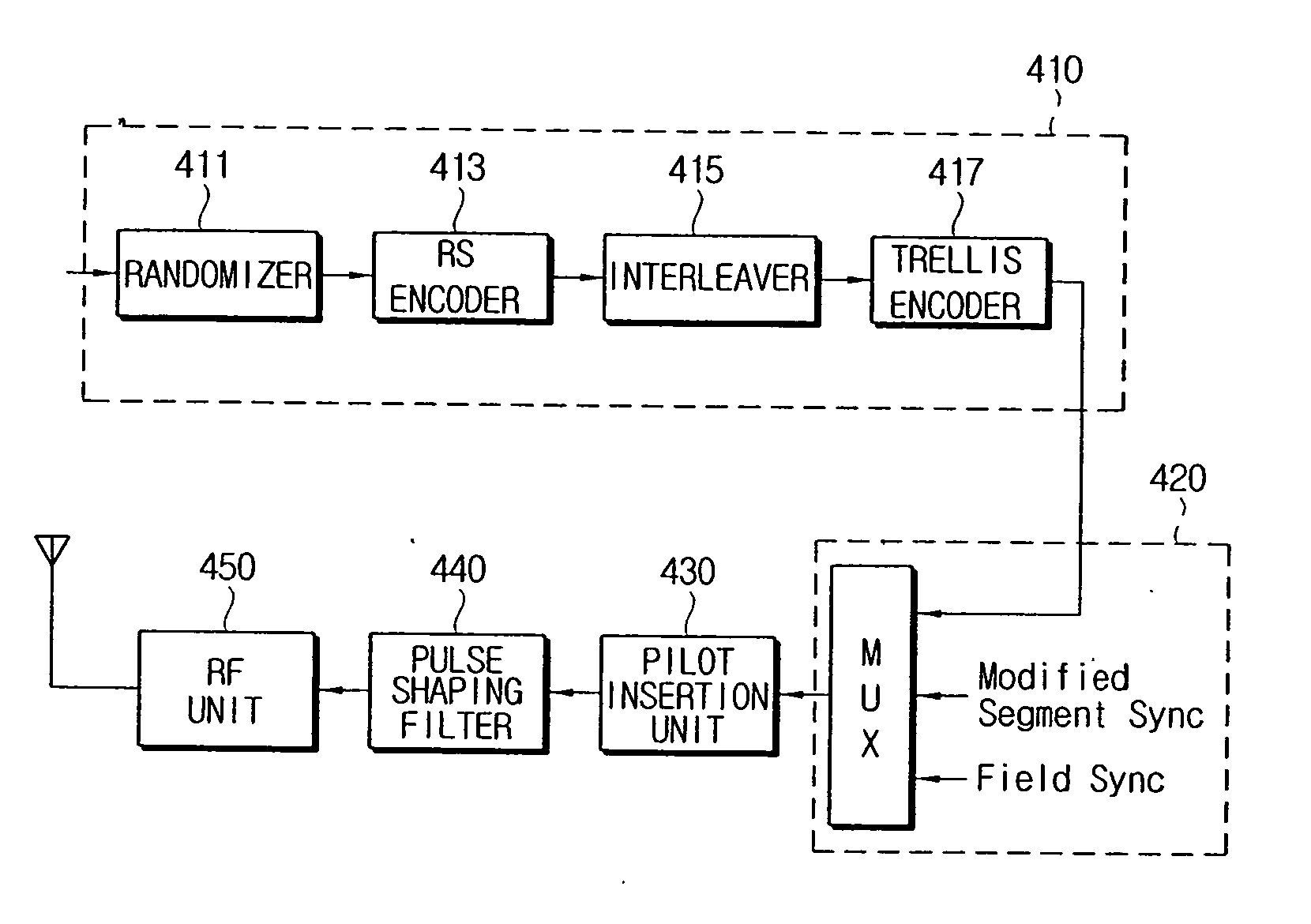

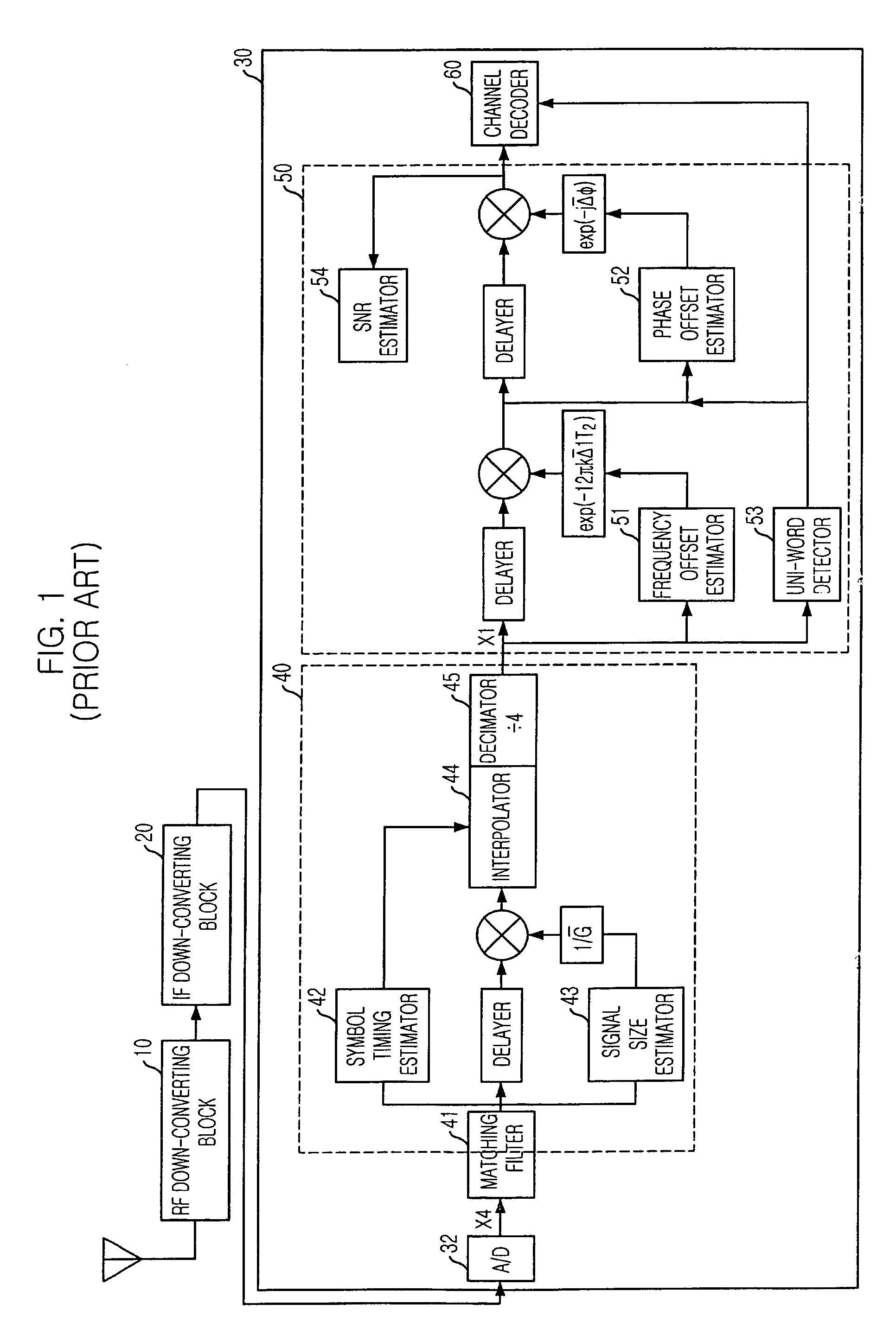

Digital broadcasting transmission/reception capable of improving a receiving performance and a signal processing method thereof

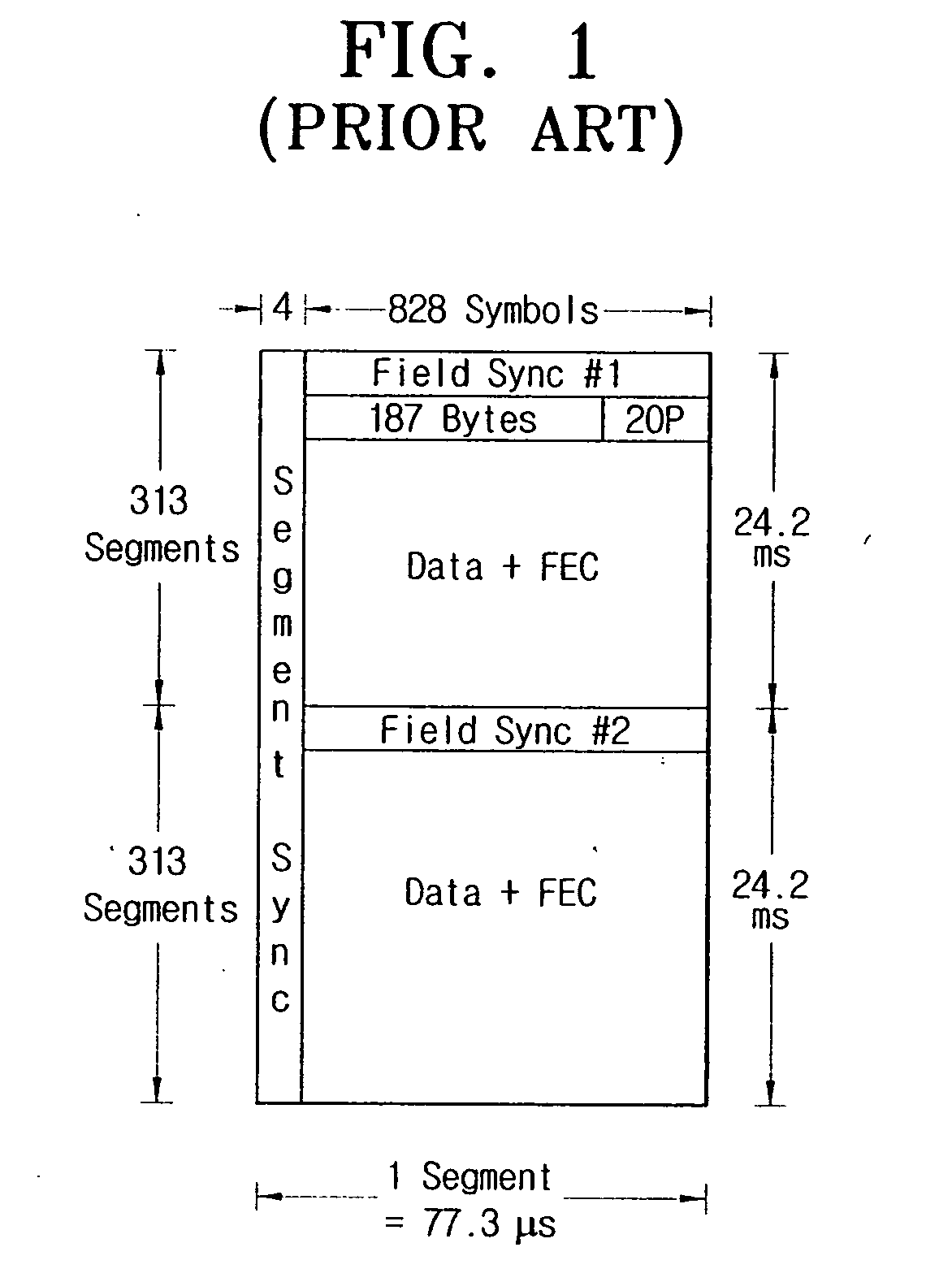

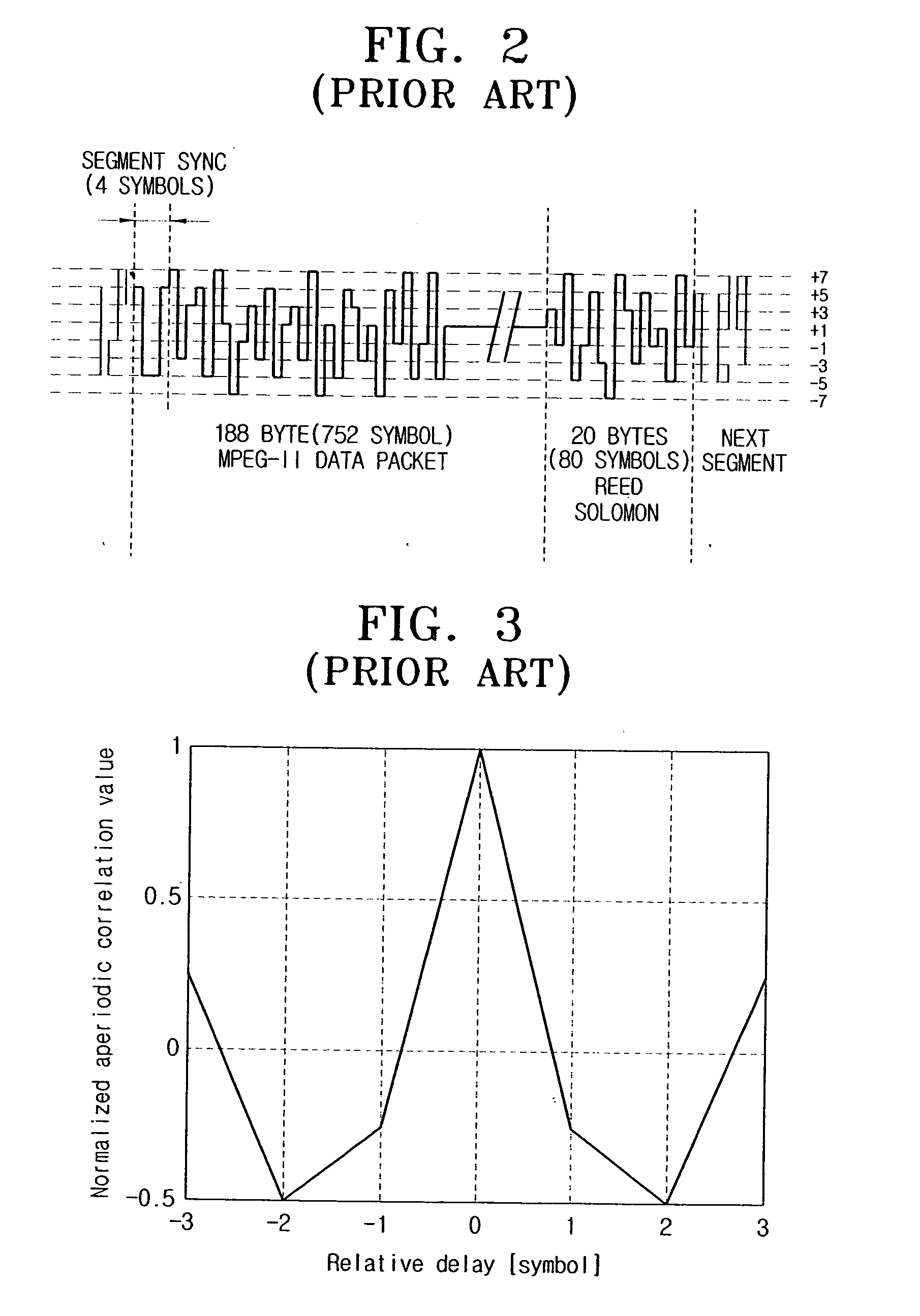

InactiveUS20050013380A1Improve reception performanceImprove compatibilityPulse modulation television signal transmissionError preventionTransmission channelEngineering

Digital broadcasting transmission / reception systems capable of improving the synchronization acquisition and the equalization performance, and signal processing methods thereof. The digital broadcasting transmission / reception systems include a FEC encoder encoding an incoming signal according to a FEC scheme, a sync signal insertion unit inserting into the encoded signal a segment sync signal including modified segment syncs, a pilot insertion unit inserting a pilot signal into the sync-inserted signal, a pulse shaping filter pulse-shaping the pilot-inserted signal with a roll-off factor, and a RF unit transmitting the pulse-shaped signal through a transmission channel band. The modified segment sync includes a predetermined number of sync signals, and an average of correlation values with respect to the predetermined number of the sync signals has an auto-correlation property. The transmission scheme utilizing the modified segment syncs promotes compatibility with the conventional reception system, minimizes hardware complexity, and enhances synchronization acquisition and equalization performance.

Owner:SAMSUNG ELECTRONICS CO LTD

Data detection and decoding system and method

ActiveUS7779325B2Data representation error detection/correctionOther decoding techniquesAlgorithmChannel decoder

A data detection and decoding system includes a SOVA channel detector that uses single parity (SOVASP) to improve the accuracy with which the detector estimates bits. Each column or row read back from the read channel constitutes a code word and each code word is encoded to satisfy single parity. Because the SOVASP channel detector detects whether each code word satisfies single parity, it is unnecessary to use both a column decoder and a row decoder in the channel decoder. Either the row decoder or the column decoder can be eliminated depending on whether bits are read back on a column-by-column basis or on a row-by-row basis. This reduction in components reduces hardware complexity and improves system performance. The output of the row or column decoder is received by a second detector that processes the output received from the decoder to recover the original information bits.

Owner:AVAGO TECH INT SALES PTE LTD

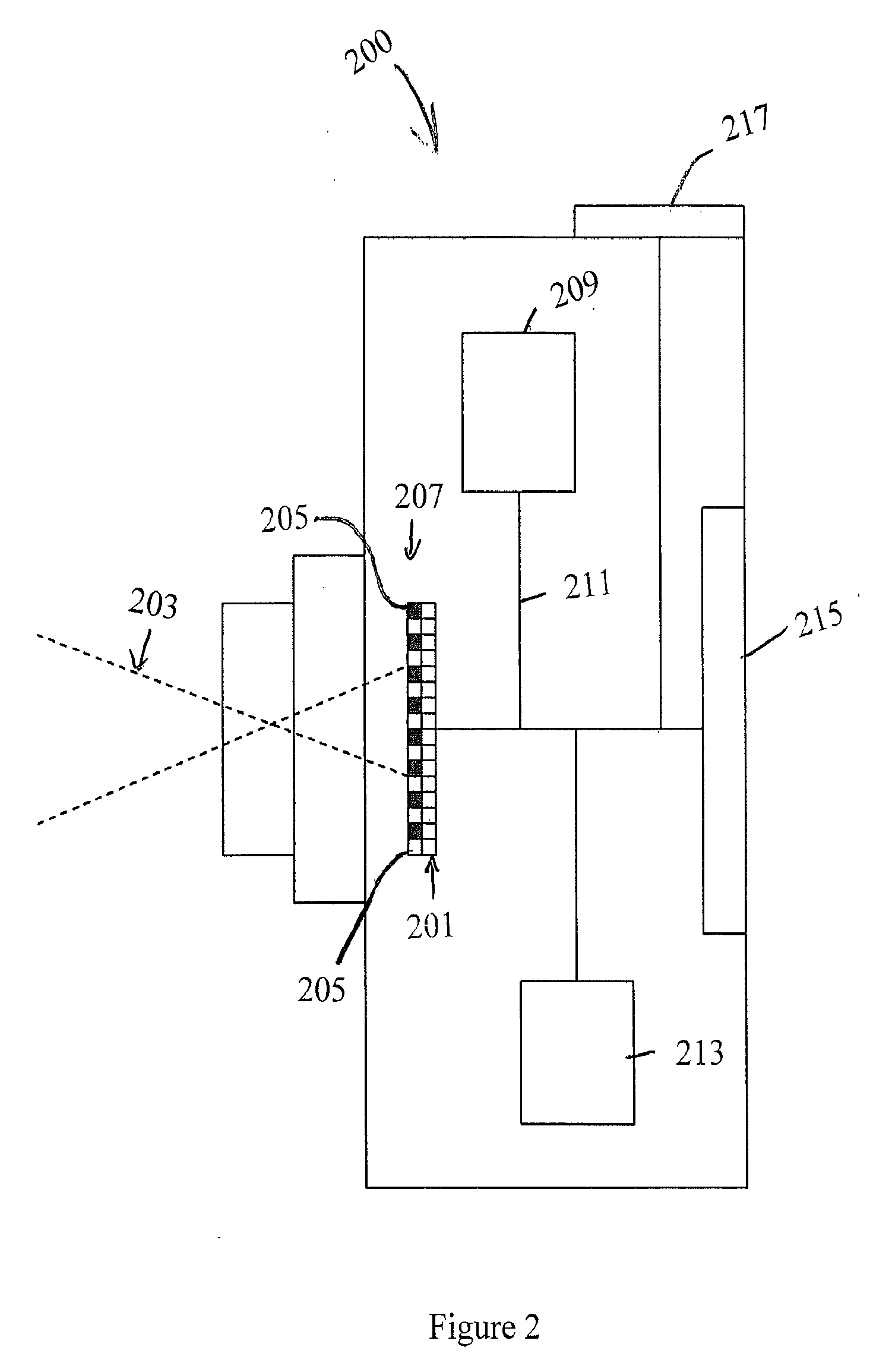

Apparatus and method for phased subarray imaging

InactiveUS7972271B2Ultrasonic/sonic/infrasonic diagnosticsInfrasonic diagnostics3d imageImaging quality

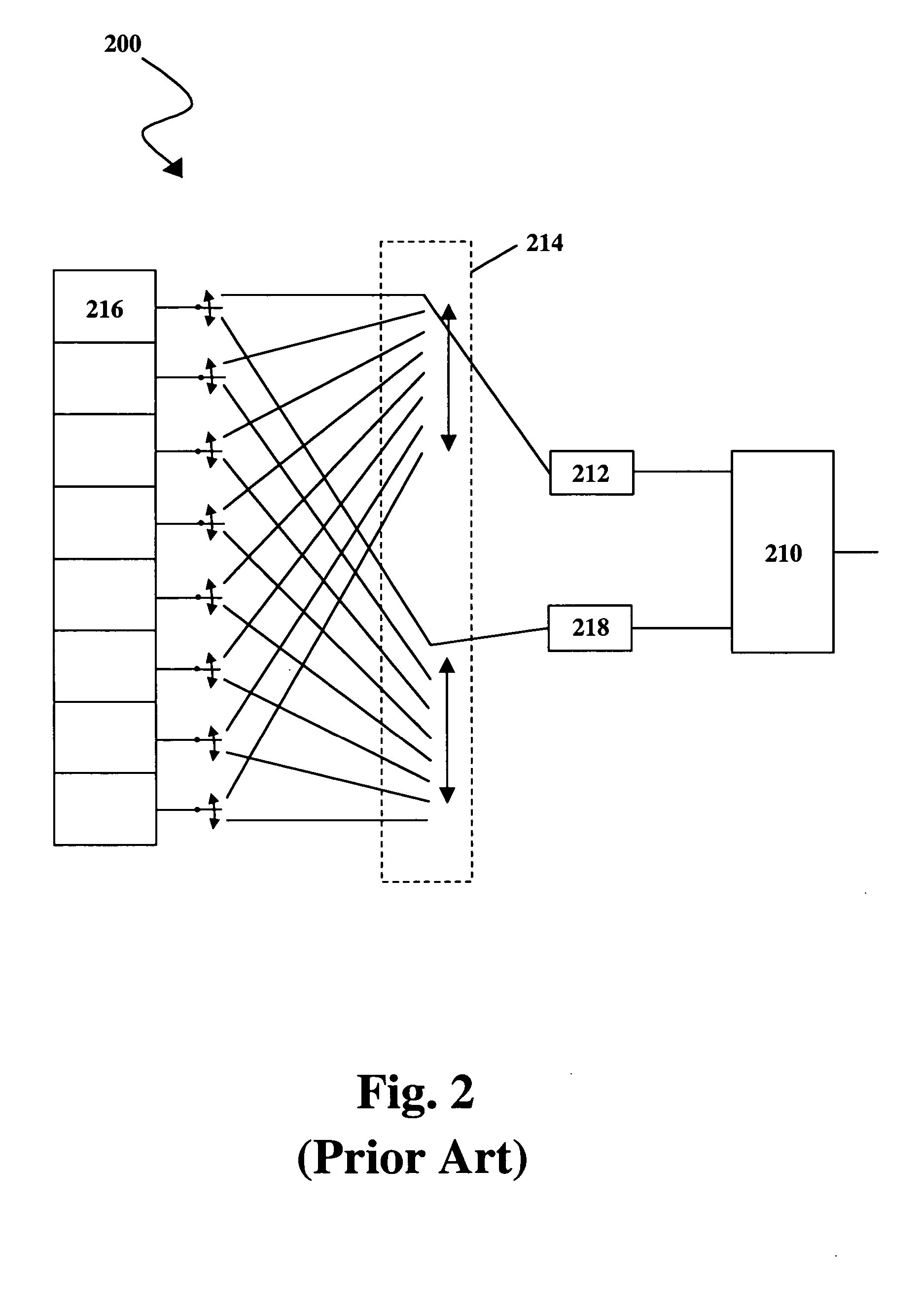

An invention for coherent array image formation and restoration is taught. The invention is applicable for both 2D and 3D imaging using either 1D or 2D arrays, respectively. A transducer array is subdivided into subarrays, each subarray having a number of adjacent array elements. All elements of each subarray transmit and receive in parallel. The signals received from each subarray are delayed and summed to form scan lines, or beams. The low-beam-rate beams formed from each subarray are upsampled and interpolated prior to forming high-beam-rate images. Depending on the subarray geometry, a subarray-dependent restoration filter is also applied to the subarray beams. The restored beams from each subarray are combined to form the final high-beam-rate image. The invention significantly reduces the front-end hardware complexity compared to conventional methods such as full phased array imaging with comparable image quality.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Apparatus and method for phased subarray imaging

InactiveUS20050101867A1Reduction front-end electronic complexityLow beam rateUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsImaging quality3d image

An invention for coherent array image formation and restoration is taught. The invention is applicable for both 2D and 3D imaging using either ID or 2D arrays, respectively. A transducer array is subdivided into subarrays, each subarray having a number of adjacent array elements. All elements of each subarray transmit and receive in parallel. The signals received from each subarray are delayed and summed to form scan lines, or beams. The low-beam-rate beams formed from each subarray are upsampled and interpolated prior to forming high-beam-rate images. Depending on the subarray geometry, a subarray-dependent restoration filter is also applied to the subarray beams. The restored beams from each subarray are combined to form the final high-beam-rate image. The invention significantly reduces the front-end hardware complexity compared to conventional methods such as full phased array imaging with comparable image quality.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Frequency offset estimating method and receiver employing the same

InactiveUS7616710B2Carrier regulationFrequency-modulated carrier systemsCarrier signalHardware complexity

Owner:ELECTRONICS & TELECOMM RES INST

Method and apparatus for signal acquisition in OFDM receivers

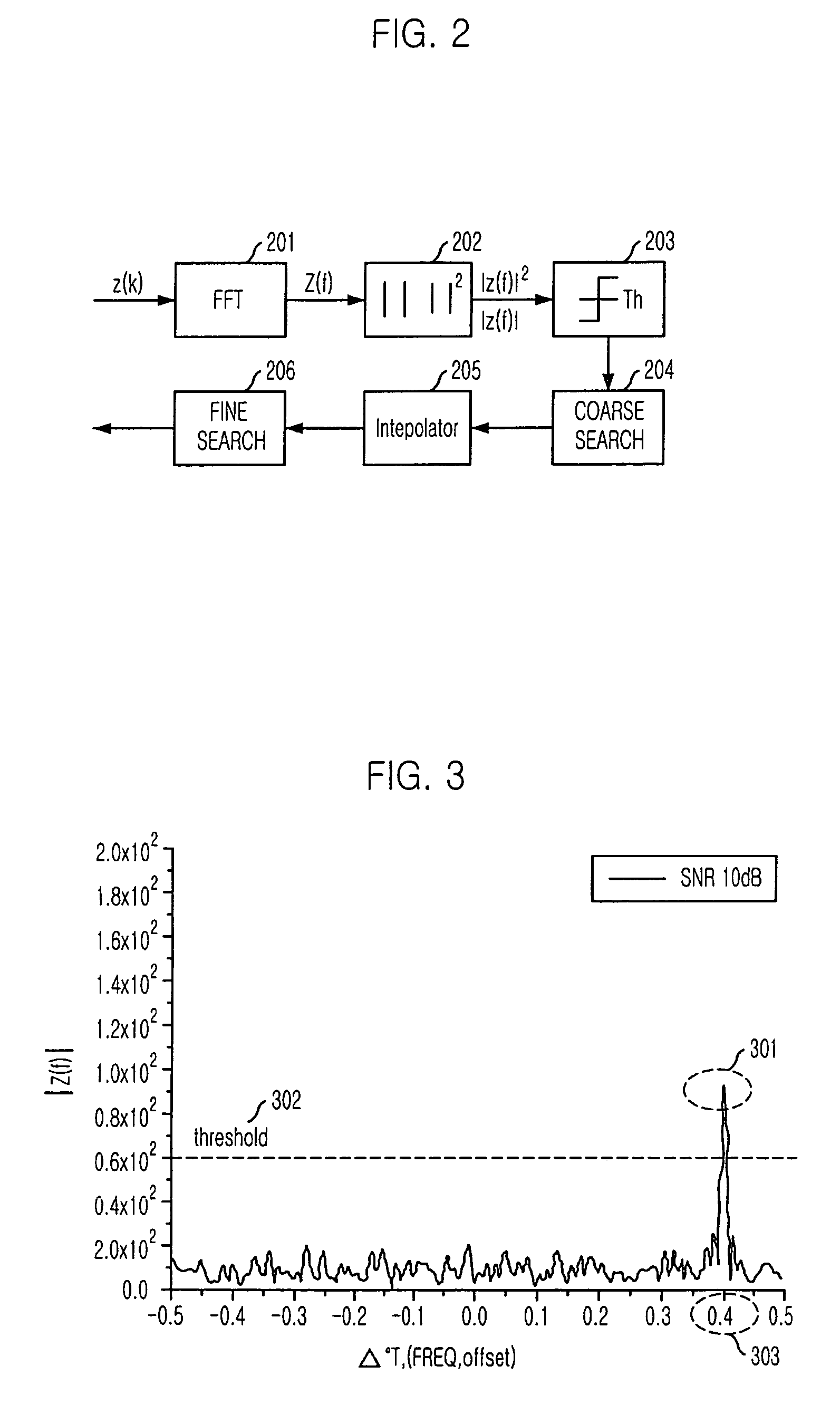

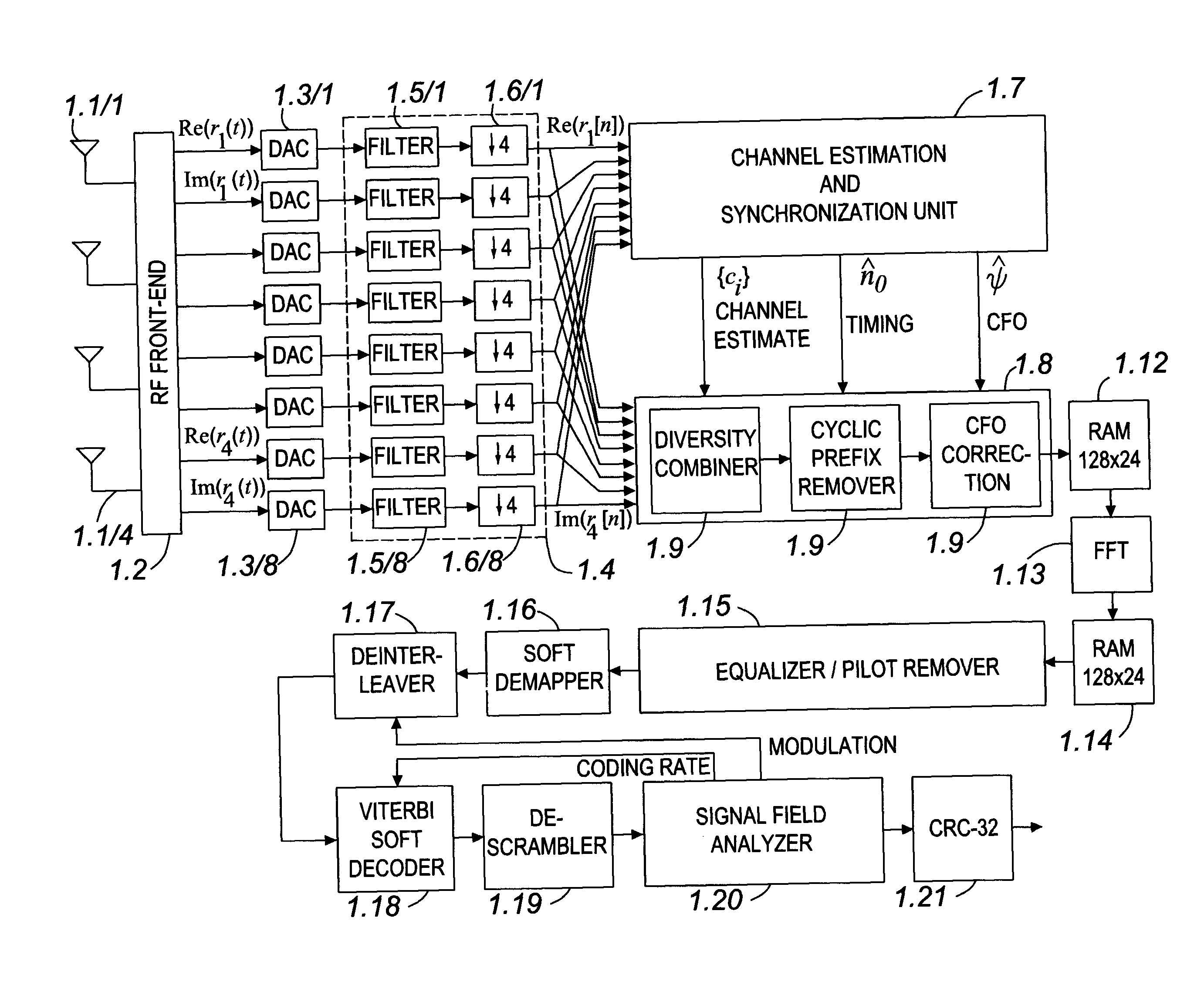

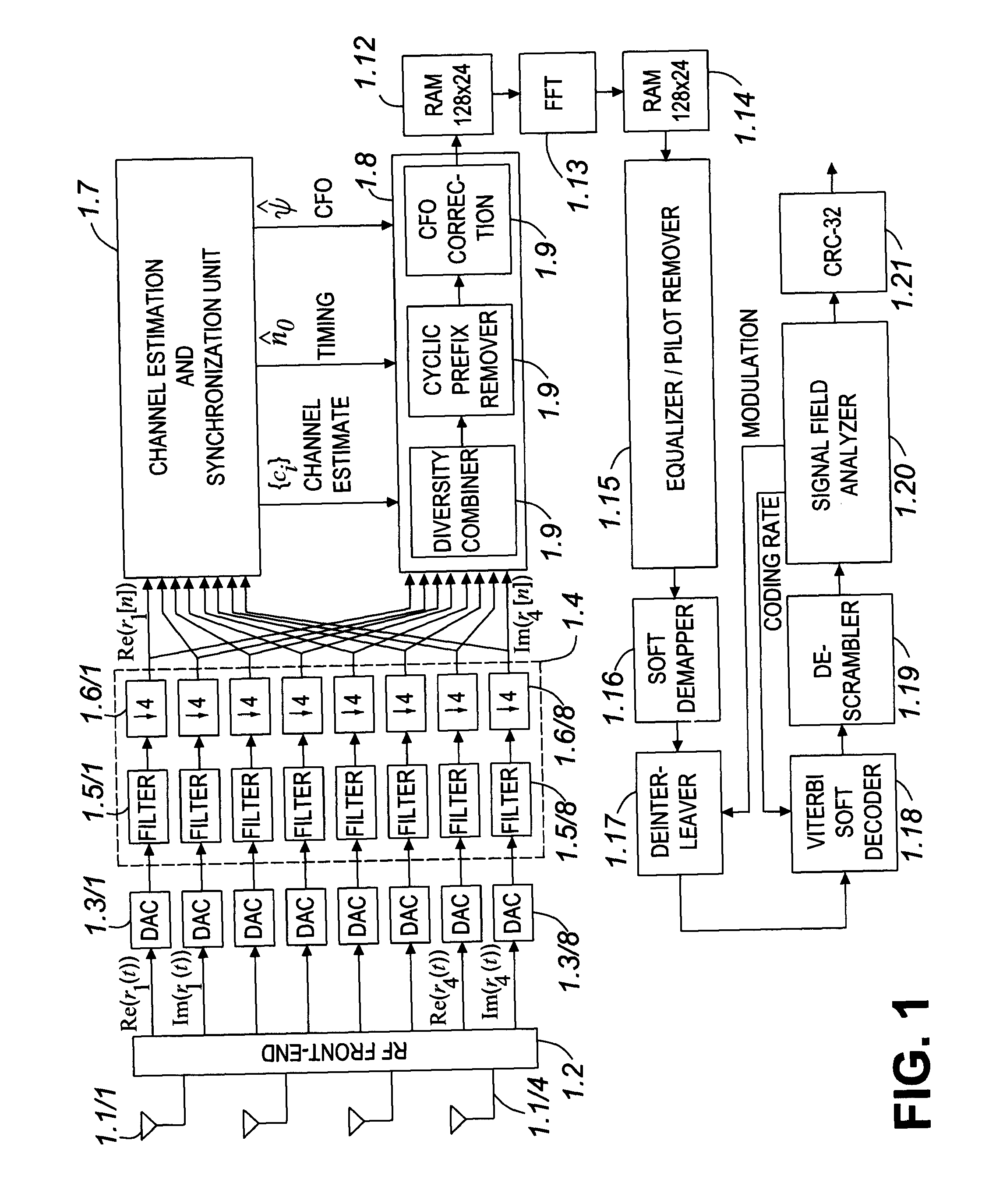

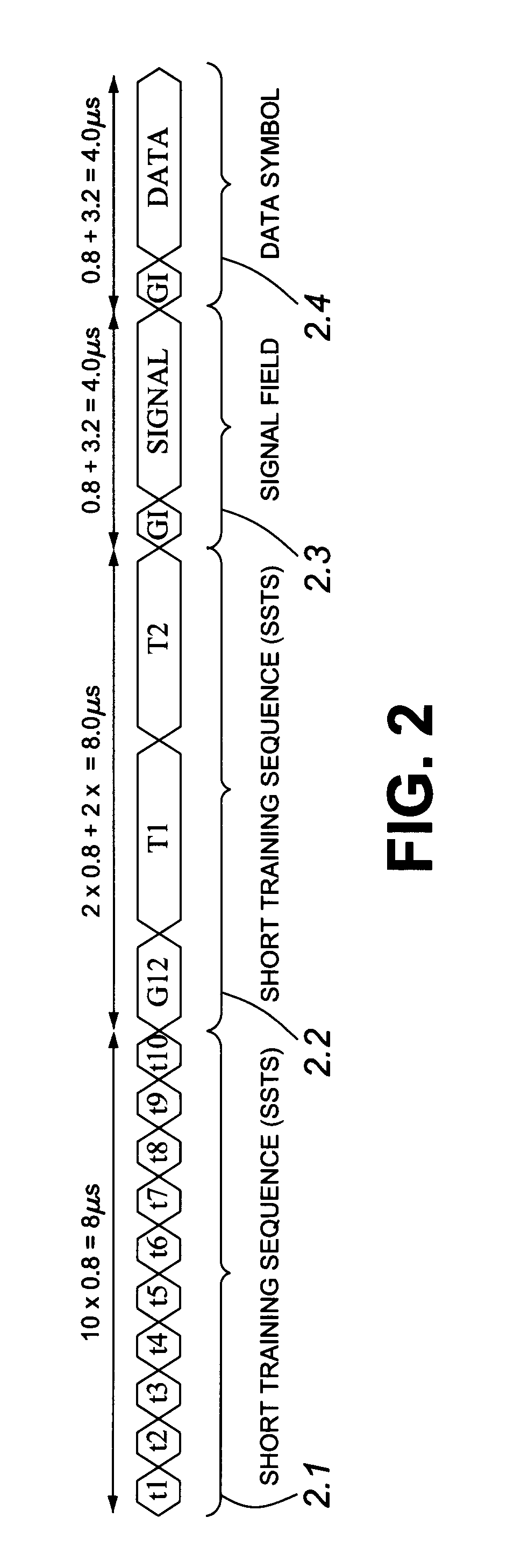

InactiveUS20110293040A1Electric signal transmission systemsAdaptive networkCarrier frequency offsetEngineering

A method and apparatus for signal acquisition in an OFDM receiver relies on a preamble training sequence to synchronize the receiver in time (e.g. determining the start of a frame) and in frequency (carrier frequency offset compensation). The preamble training sequence has a periodic structure and the method and apparatus perform a cross-correlation technique using a matched filter to achieve time synchronization and / or frequency synchronization and / or channel estimation, the latter being especially useful in multi-antenna receivers for diversity combining purposes. Many advantages derive from performing at least two and preferably all three operations jointly, in terms of latency, hardware complexity, and length of training sequence required to achieve satisfactory convergence on all counts. The periodicity of the training sequence is exploited to reduce considerably the main filter complexity and optionally dynamically adjust carrier offset compensation throughout the filtering process, thus improving the quality of all final estimates (carrier frequency offset, time synchronization, and channel).

Owner:DUPONT LOUIS +1

New spatio-spectral sampling paradigm for imaging and a novel color filter array design

InactiveUS20100085452A1Minimize overlapMinimize luminance deviationTelevision system detailsTelevision system scanning detailsColor imageDisplay device

One aspect of the present invention relates to a new alternative to the Bayer pattern for spatial subsampling in color imaging applications. One aspect of the present invention relates to a new design paradigm for spatio-spectral sampling, which is also described. The proposed scheme offers the potential to significantly reduce hardware complexity in a wide variety of applications, while at the same time improving output color image quality. According to another aspect, it is realized that conventional processing techniques are subject to diminishing returns, and with the exception of the most sophisticated processing techniques generate imperfections perceptible to a practiced eye. According to one aspect, a framework for CFA design in presented. In one embodiment the physical characteristics of the CFA are generated so that the spectral radii of luminance and chrominance channels are maximized. In another embodiment, the CFA designed to subject to the conditions of perfect reconstruction. In one aspect, the physical characteristics of CFA design are constrained to require physically realizable CFA(s). Alternatively, certain physical characteristics can be emphasized to generate easier to manufacture CFA(s). According to another aspect, conventional methods and systems are evaluated, confirming shortcomings regarding aliasing in imaging and bandwidth, against which certain embodiments are benchmarked, showing improved performance under at least some embodiments of proposed designs and methods. According to another aspect, a display device CFA is evaluated in terms of throughput of stimuli as limited by aliasing. It is shown the spectral replicas of the chrominance signals induced by existing CFA patterns are centered around frequencies that are not sufficiently far from the DC, consequently overlapping with the luminance signal spectrum and reducing the throughput of the stimuli. By reinterpreting the interactions between the stimuli, display CFA, and CSF in terms of amplitude modulation, an alternative CFA coding scheme that modulates the chrominance signals to a higher frequency relative to common schemes is provided in some embodiments.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

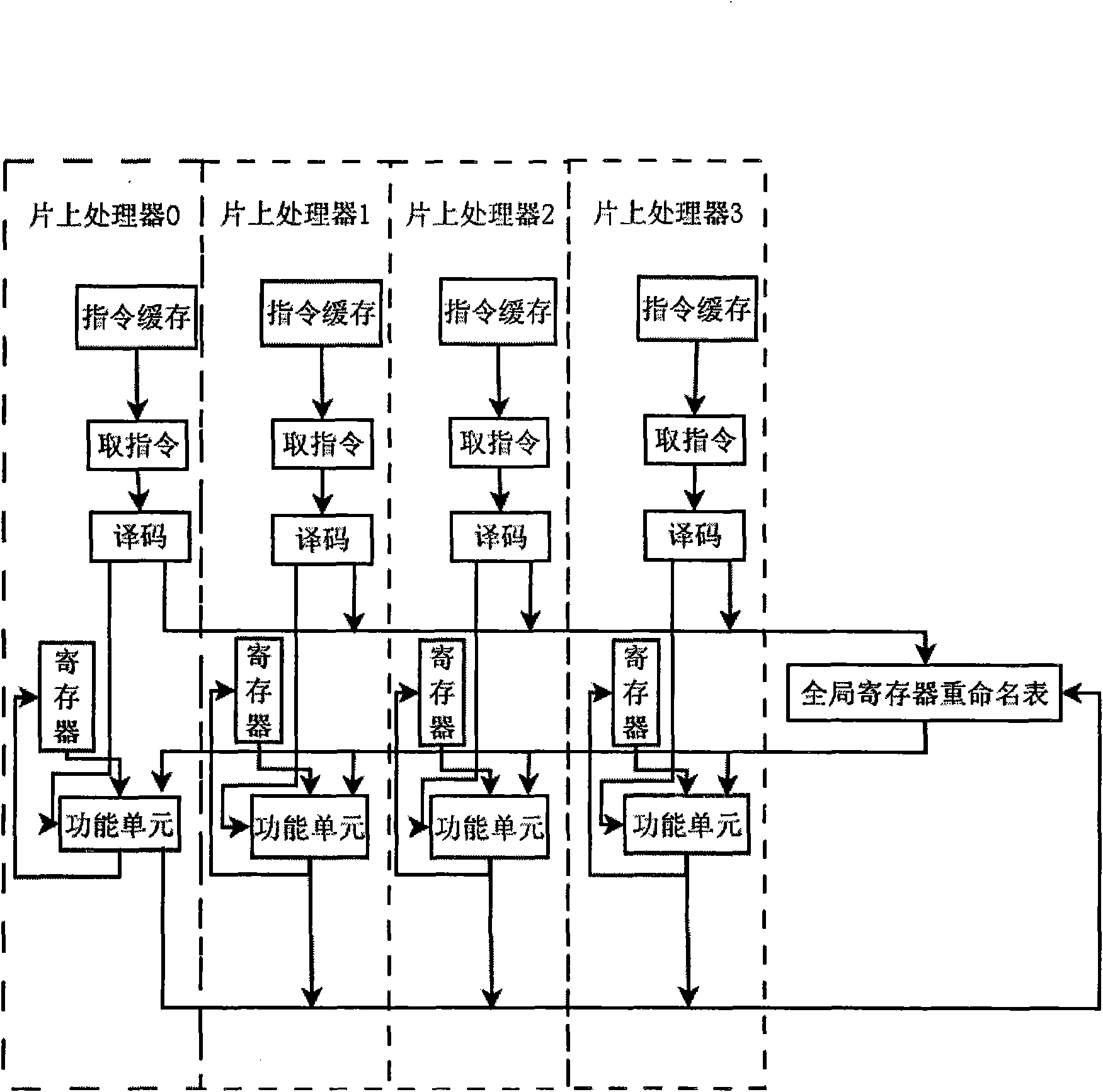

Implementation method of rename table of global register under on-chip multi-processor system framework

InactiveCN101582025AResolve dependenciesReduce trafficConcurrent instruction executionHardware structureProcessing Instruction

The invention relates to the technical field of on-chip multi-processor system structure, aiming at providing an implementation method of a rename table of a global register under on-chip multi-processor system framework. The method comprises the steps: designing the rename table of the global register; processing the dependency relationship 'writing-after-writing' of command; processing the dependency relationship 'writing-after-reading' of command; acquiring operand; writing back results; and submitting the command. As the rename table of the global register is used by the method, the dependency relationship of the commands of different processors can be recorded, and the dependency of 'writing-after-reading' and 'writing-after-writing' can be solved; the operand of the commands of the different processors can be maintained and transmitted through the rename table of the global register, so that the internuclear communication volume can be reduced; as hardware configuration used by the rename table of the global register is a logical table, the structure is simple, the complexity of hardware is low, the area of the rename table of the global register is only 1% of that of one on-chip processor, and tiny area cost is caused.

Owner:ZHEJIANG UNIV

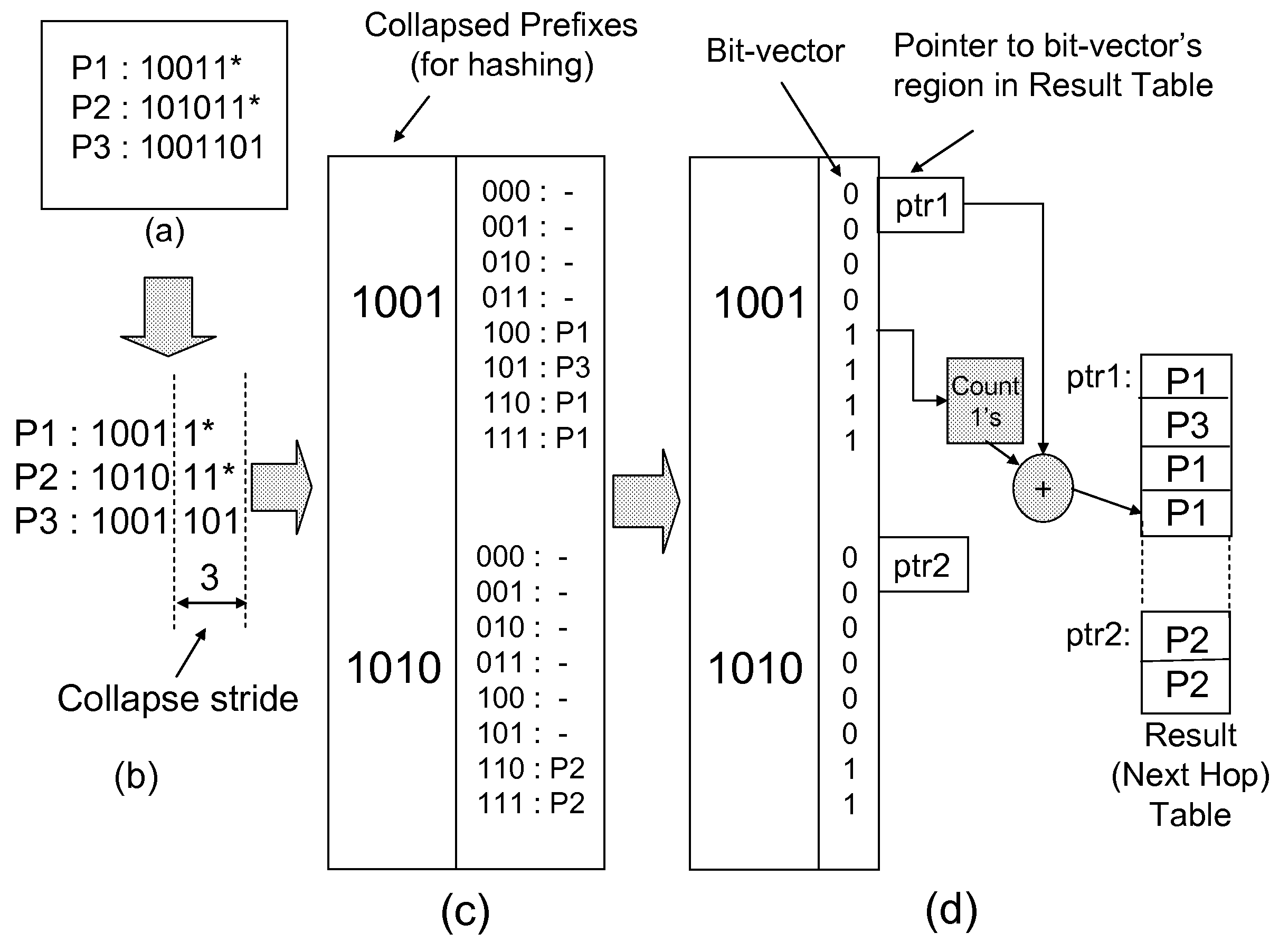

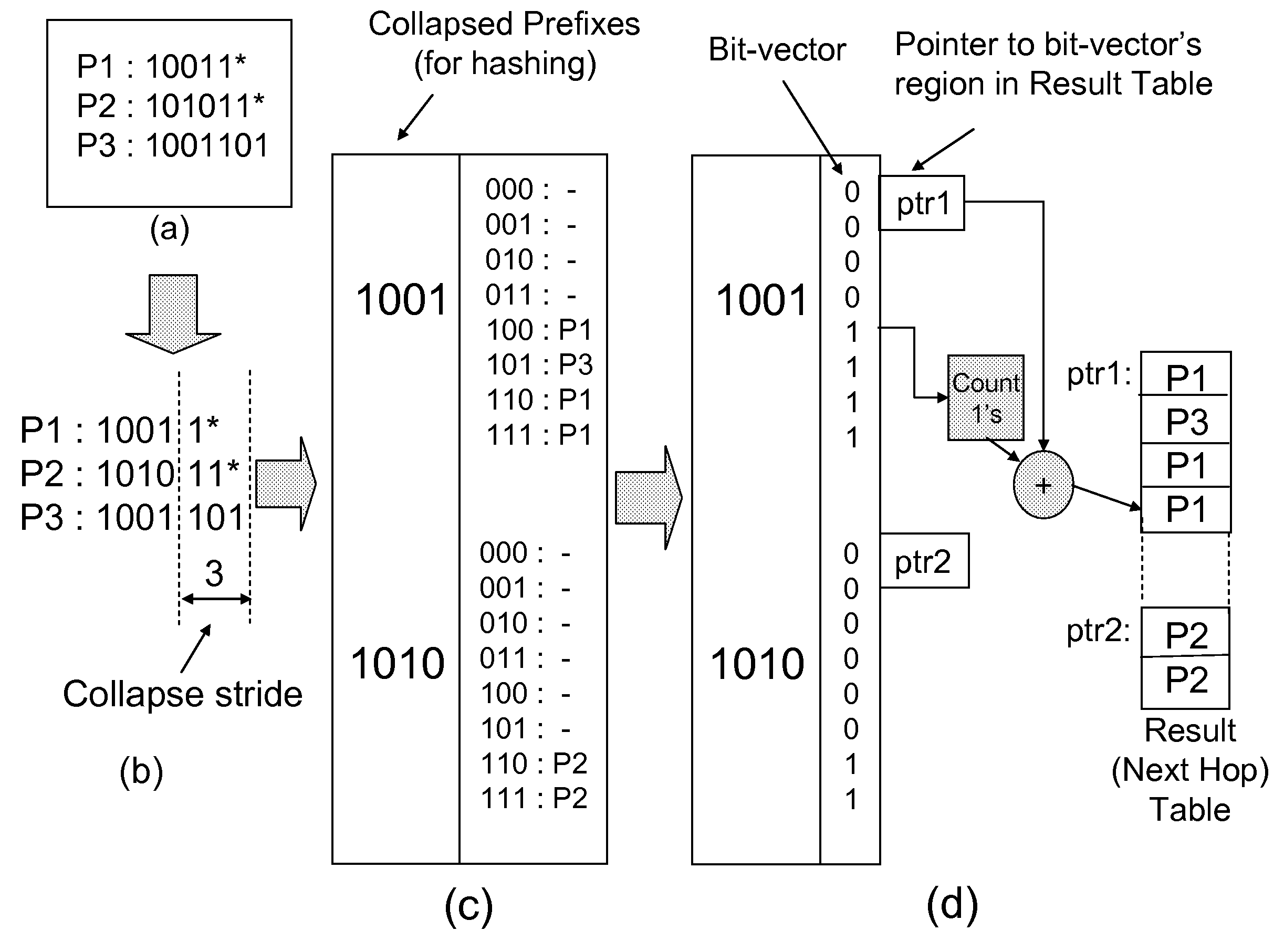

Storage-efficient and collision-free hash-based packet processing architecture and method

InactiveUS20070136331A1Eliminating false positivesLess storageData processing applicationsDigital data information retrievalHardware complexityWildcard character

An architecture and method for data storage and retrieval which also addresses a number of key problems associated with systems employing hash-based techniques. The architecture and method employs a collision-free hashing scheme called Bloomier filter while eliminates its false positives in a storage efficient way. Wildcard support is added through the use of a scheme called prefix collapsing, while introducing only a small additional storage requirement and reduced hardware complexity. Real update traces indicate that both fast and incremental updates are provided—features generally not available in prior-art collision-free hashing schemes.

Owner:NEC CORP

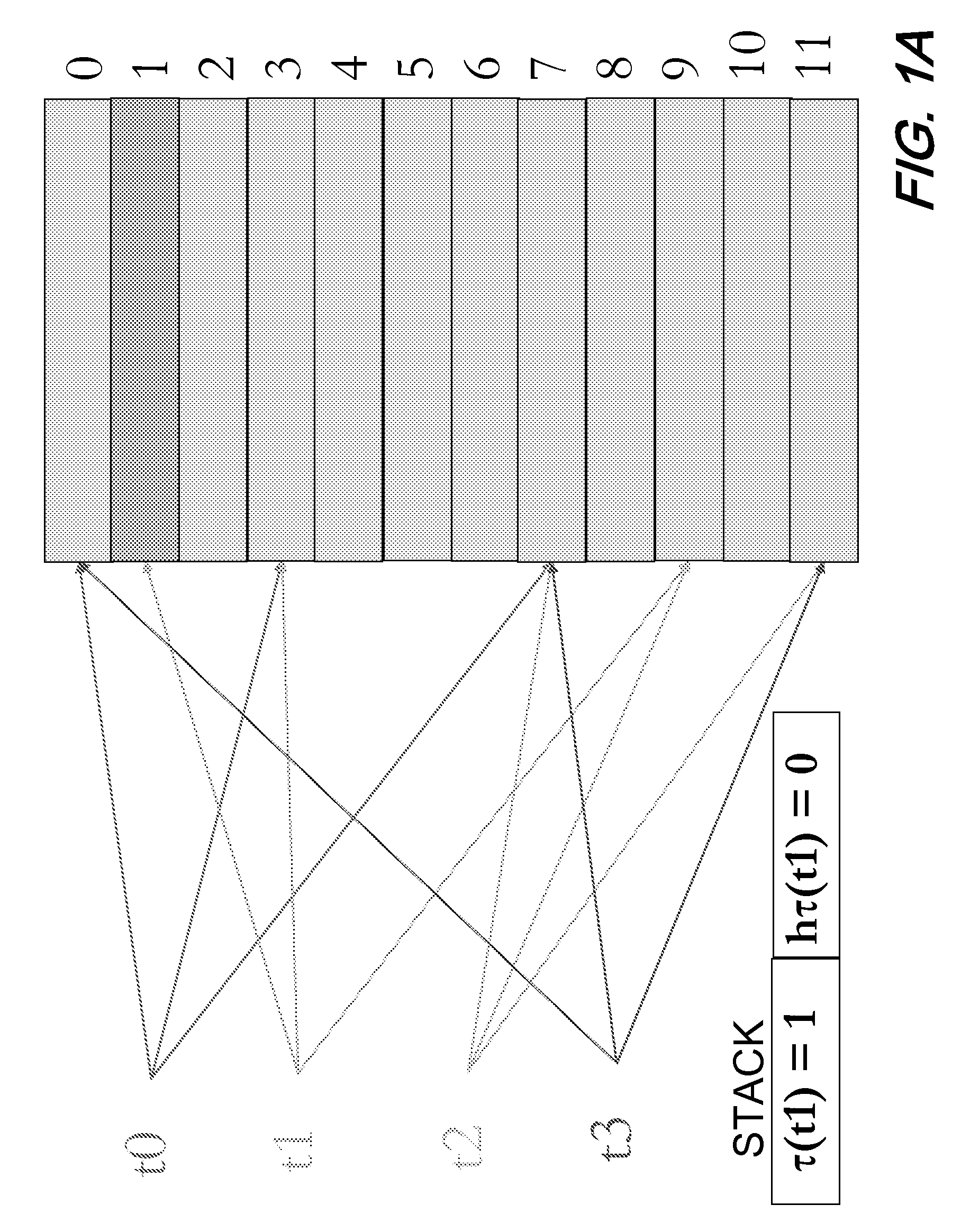

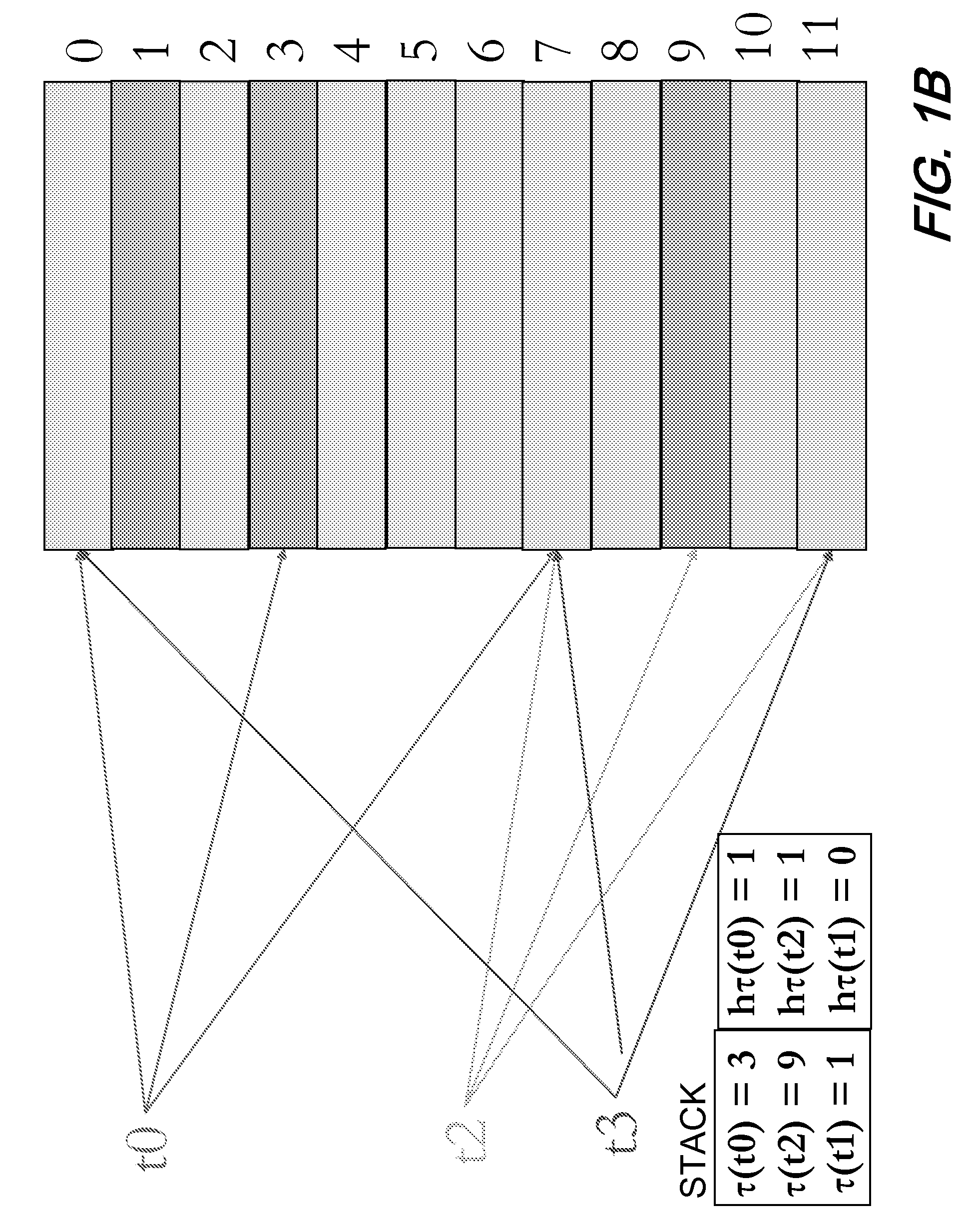

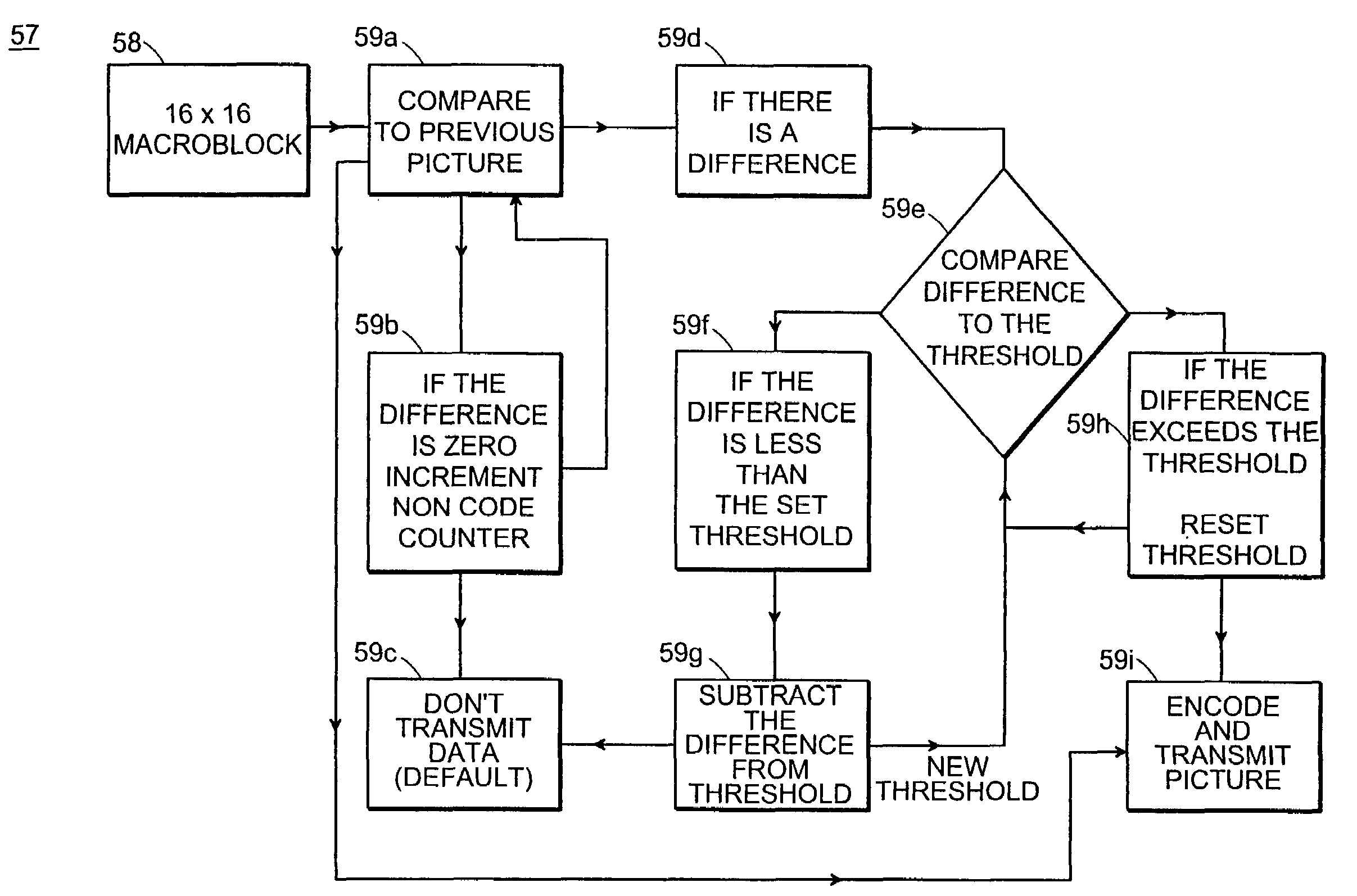

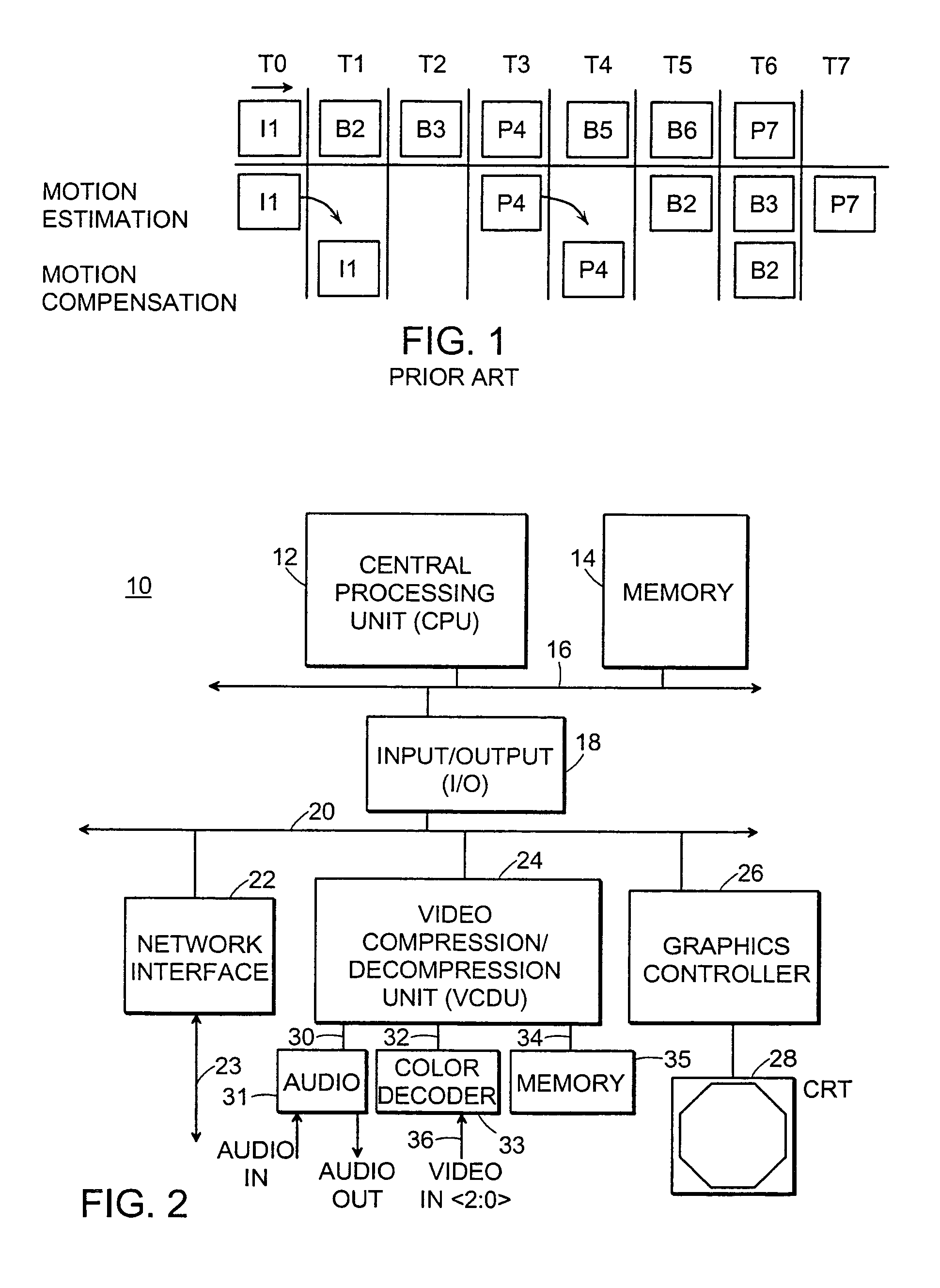

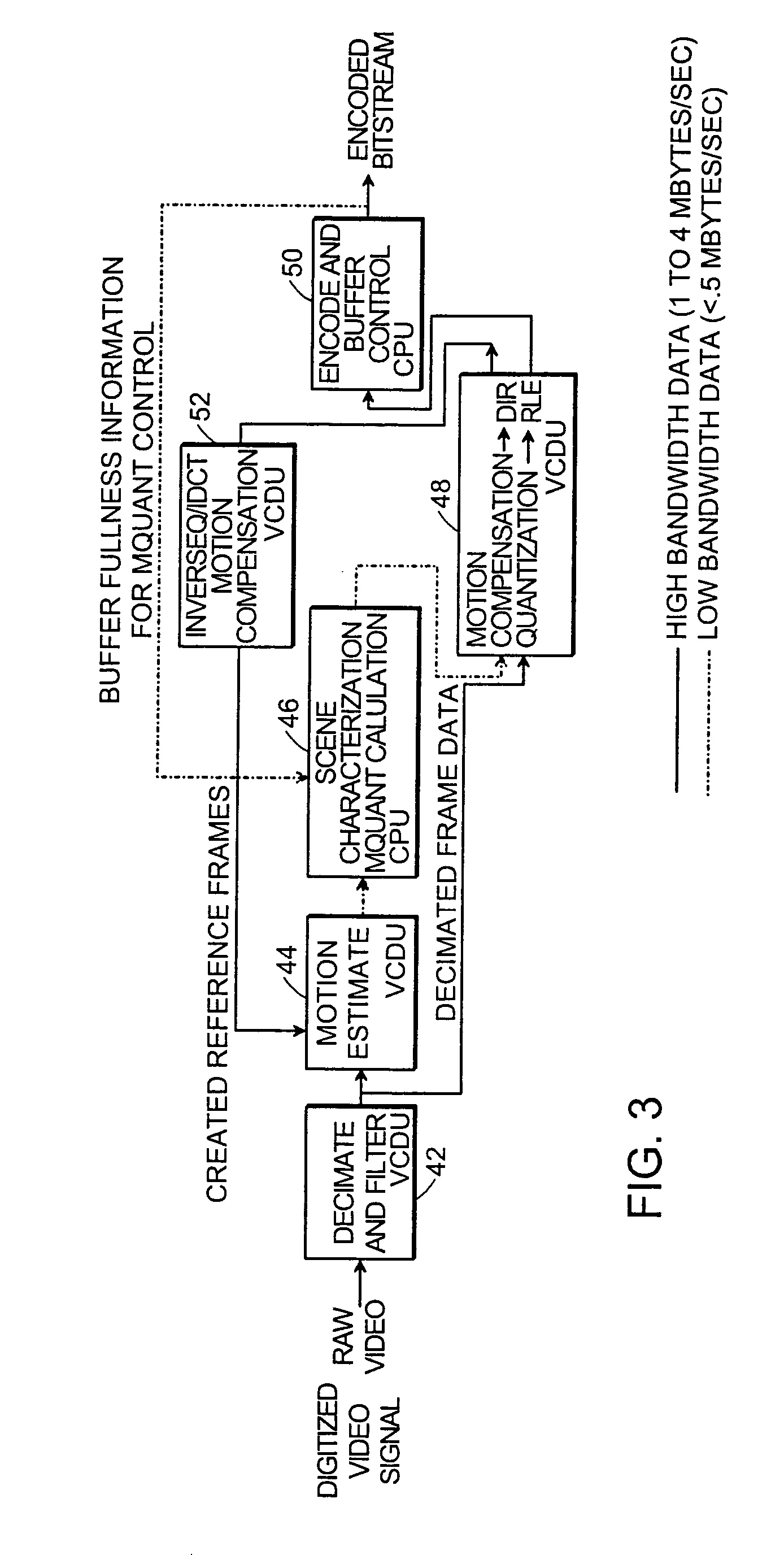

Method and apparatus for compressing a video image

InactiveUS7006698B2Quality improvementMore bitPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningHardware complexityDecision taking

An apparatus and method for performing two-pass real time video compression is provided. Tactical decisions such as encoding and quantification values are determined in software, whereas functional execution steps are performed in hardware. By appropriately apportioning the tasks between software and hardware, the benefits of each type of processing are exploited, while minimizing both hardware complexity and data transfer requirements. One key concept that allows the compression unit to operate in real time is that the architecture and pipe lining both allow for B frames to be executed out of order. By buffering B frames, two-pass motion estimation techniques can be performed to tailor bit usage to the requirements of the frame, and therefore provide a more appealing output image.

Owner:HEWLETT PACKARD DEV CO LP

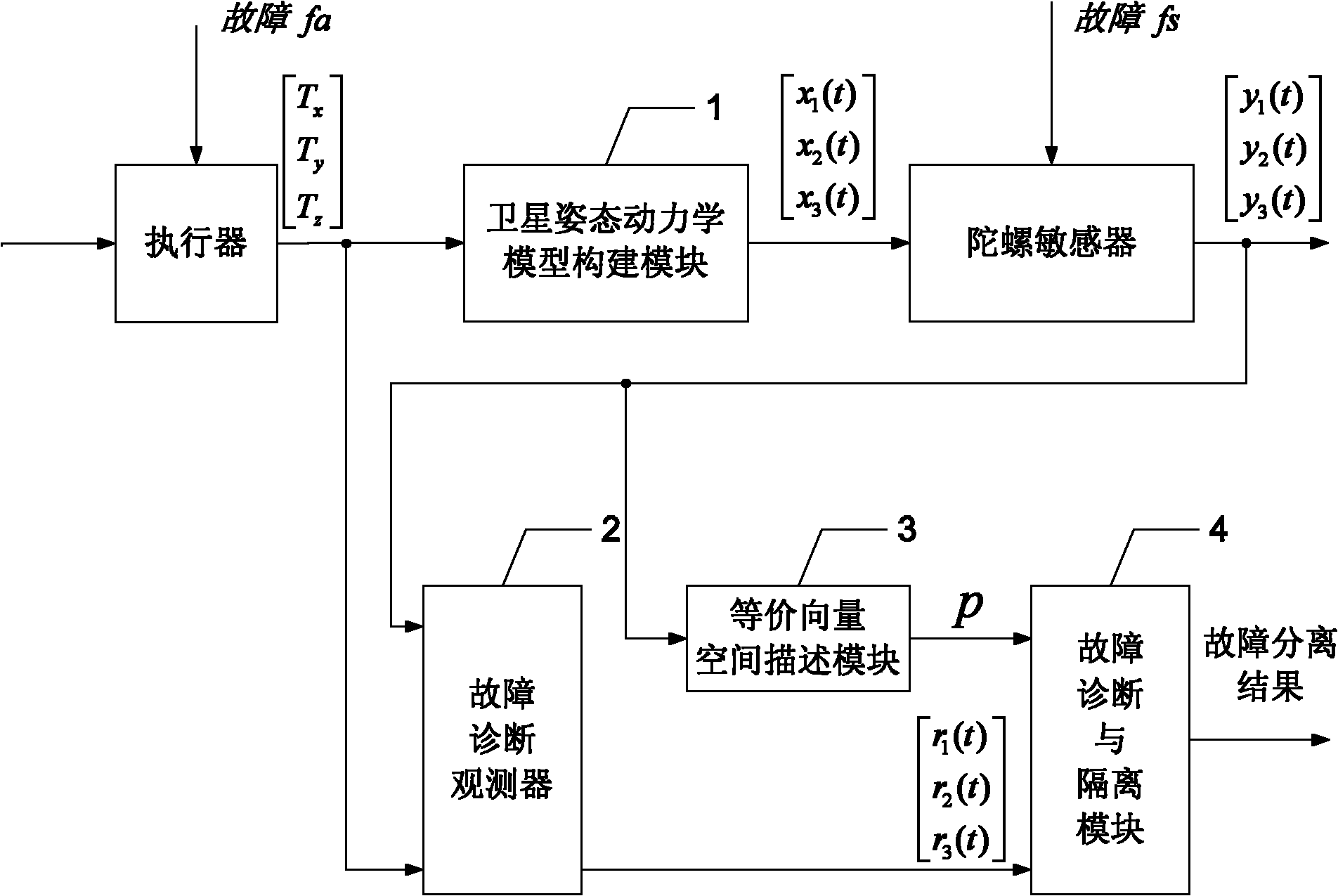

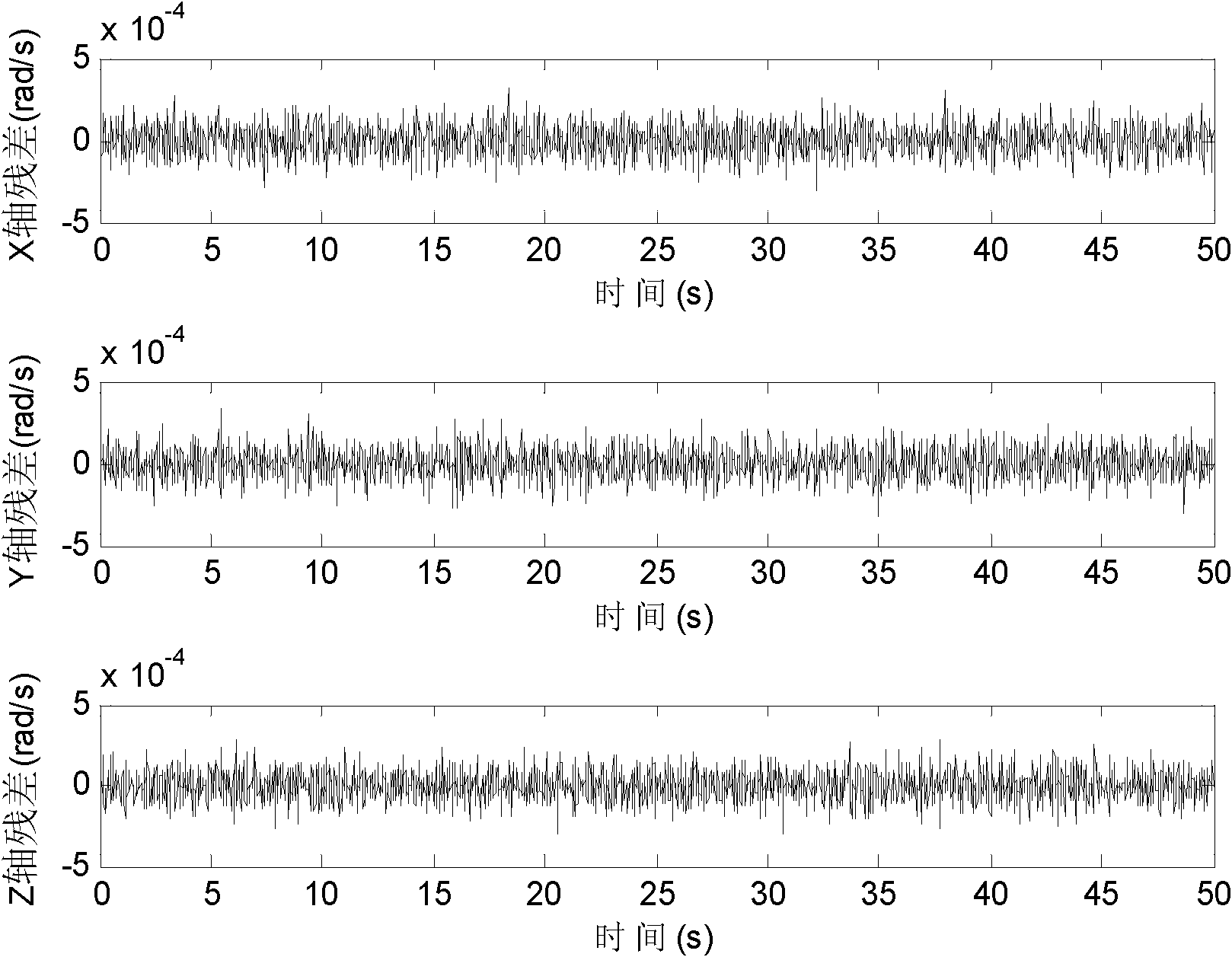

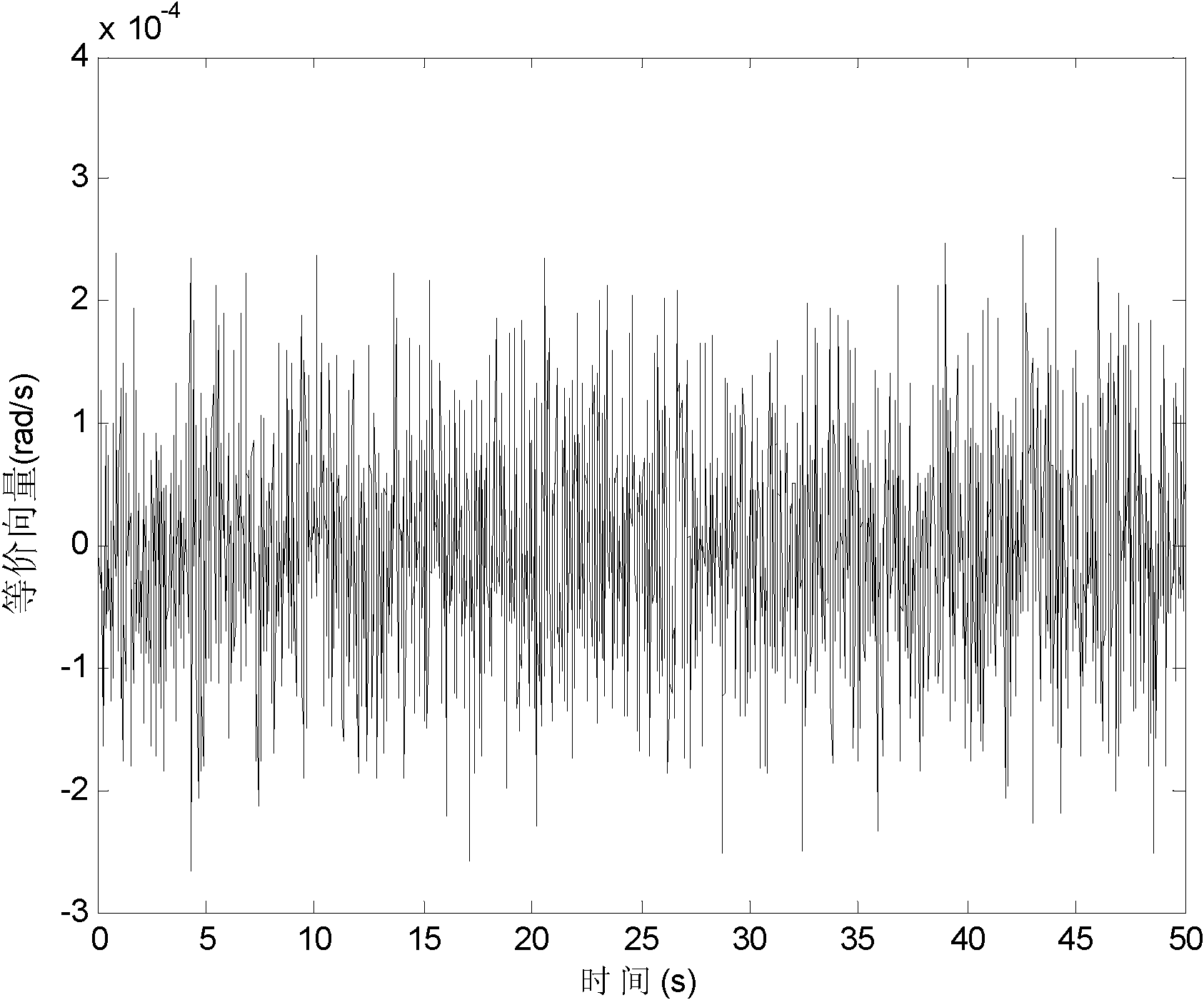

Satellite attitude control system failure diagnosis device and method based on state observer and equivalent space

ActiveCN102176159AImprove effectivenessImplement fault diagnosisElectric testing/monitoringState observerHardware complexity

The invention discloses a satellite attitude control system failure diagnosis device based on a state observer and an equivalent space and a satellite attitude control system failure diagnosis method based on the state observer and the equivalent space, which belong to the field of aerospace and aim to solve the problems of high hardware complexity, low control accuracy and low failure diagnosis algorithm effectiveness of the conventional failure diagnosis method. The method provided by the invention comprises the following steps that: 1, a failure diagnosis observer outputs a satellite triaxial angular rate residual according to output signals of an actuator and a gyro sensor; 2, an equivalent vector space description module constructs equivalent space descriptions of the gyro sensor according to the output signal of the gyro sensor, wherein an output equivalent vector p is used for judging whether the gyro sensor fails or not; and 3, a failure diagnosis and isolation module outputs a failure separation result indicating that the actuator or the gyro sensor fails according to the satellite triaxial angular rate residual obtained by the step 1 and the equivalent vector p obtained by the step 2, and further judges which axis of the failing part fails.

Owner:HARBIN INST OF TECH

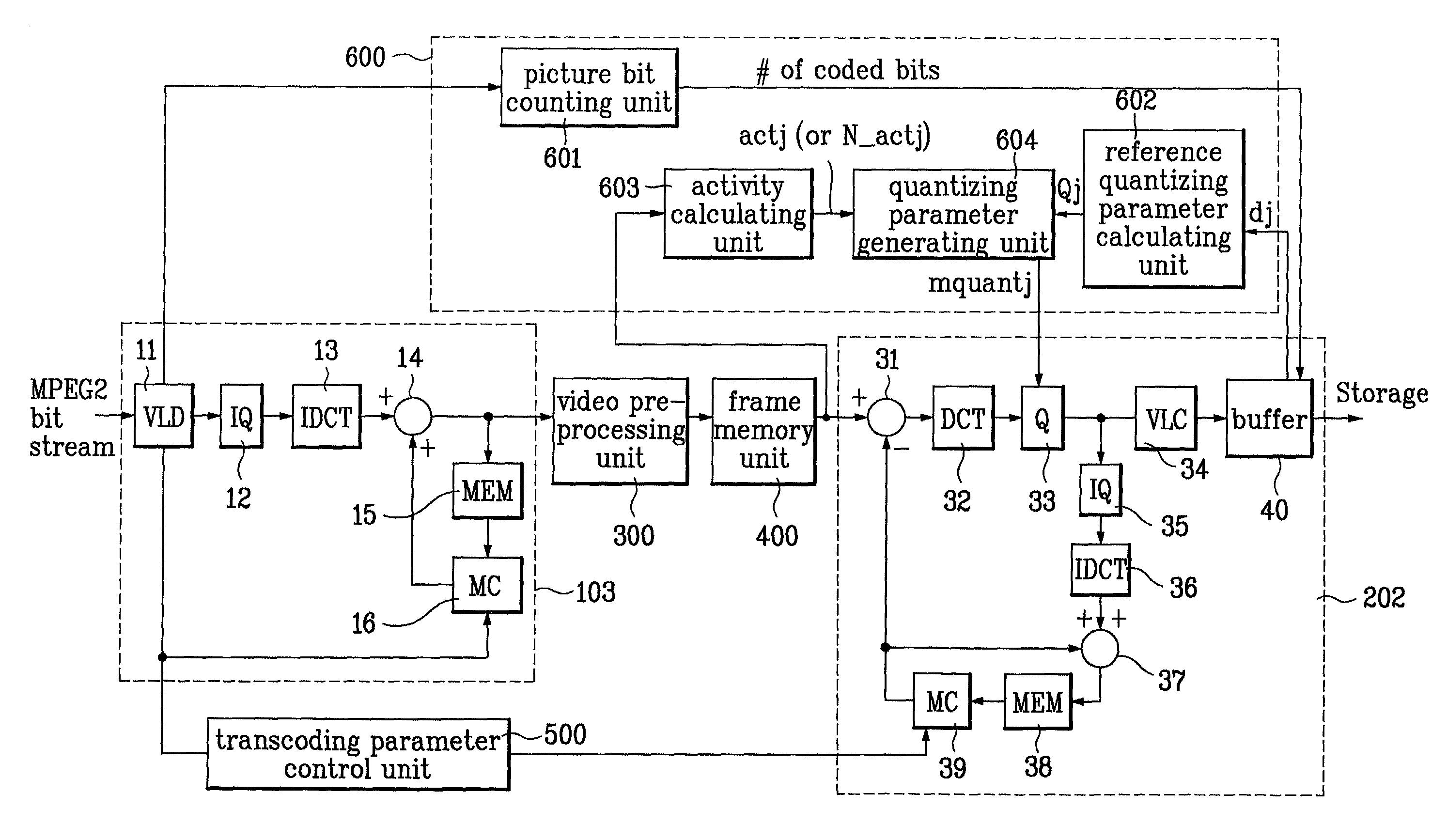

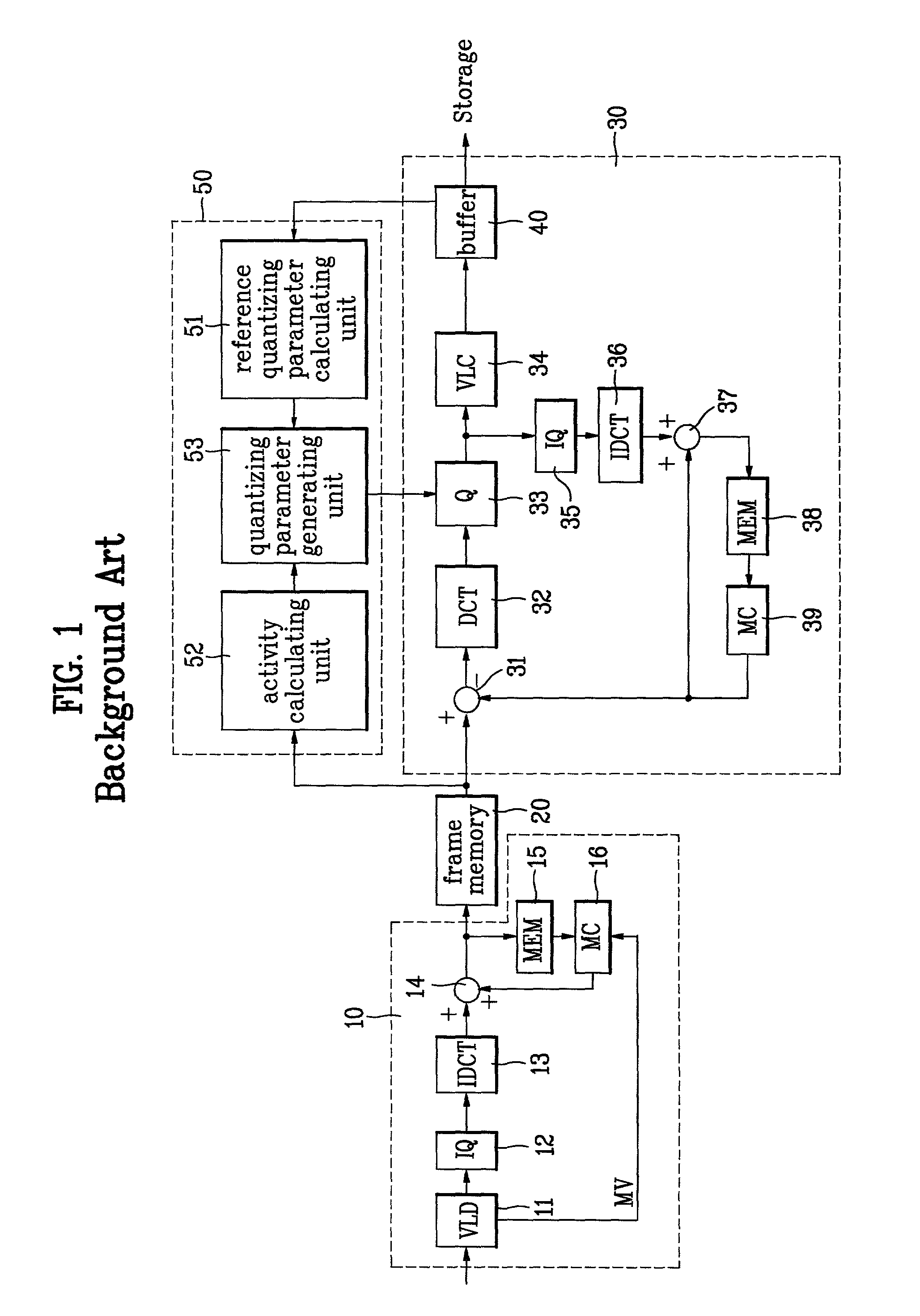

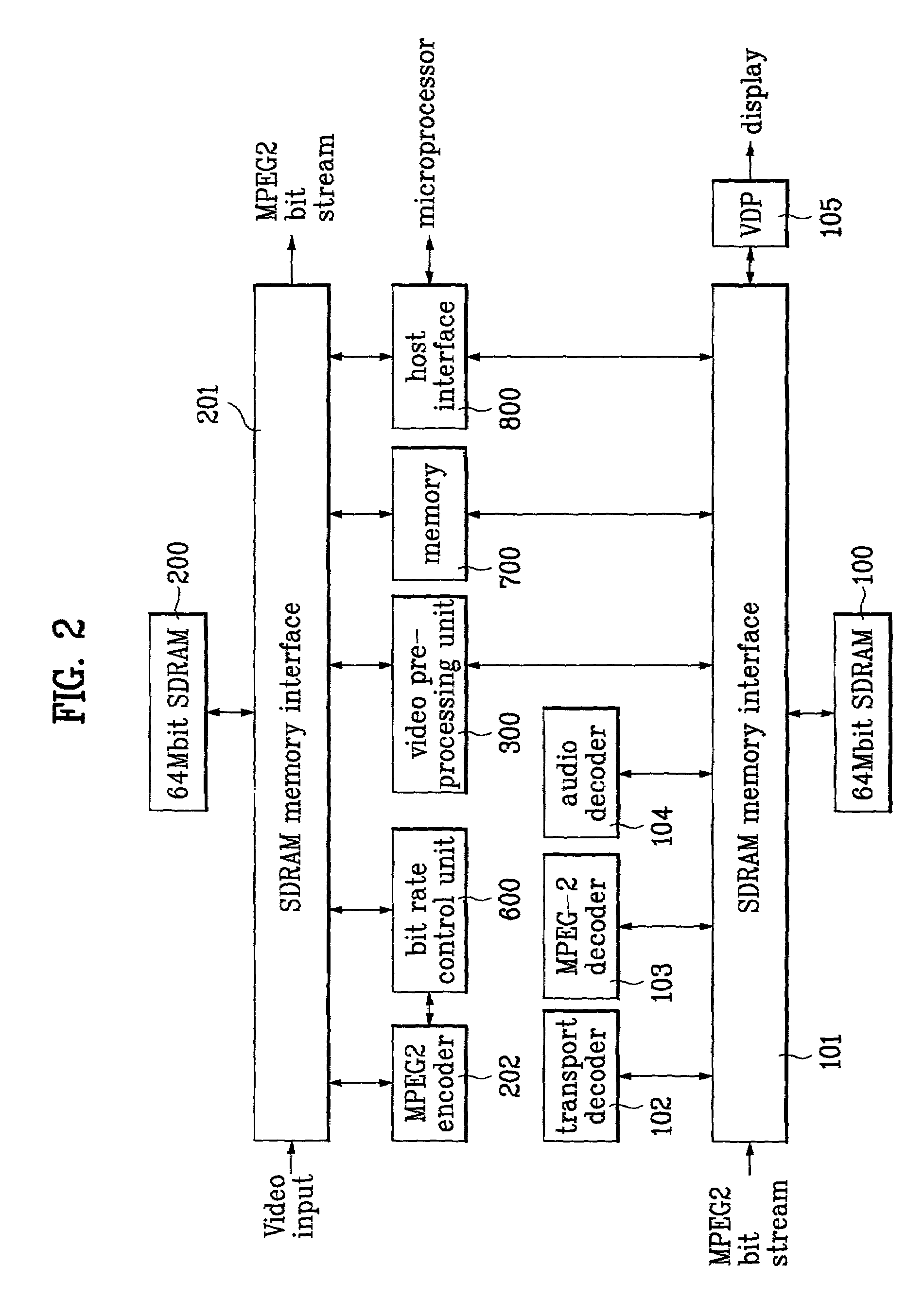

Video transcoding apparatus

InactiveUS7266148B2Reduce lossesReduce resolutionPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningBit allocationTranscoding

Disclosed is a video transcoding apparatus converting a specific bit rate of an MPEG (moving pictures experts group) bit stream into a different rate thereof for transportation. The present invention includes a video pre-processing unit having a predetermined matrix structure and down-sampling a macro block decoded by the video decoder by transforming the macro block into a corresponding picture structure to the compressed video bit stream, a transcoding parameter control unit detecting information about a picture from a previous bit stream variable-length-decoded by the video decoder and setting up an encoding mode for a transcoding in accordance with the detected information, etc. Therefore, the present invention does not need the motion estimation unit of encoder and reduce the complexity of the bit allocation unit. When changing HD-rated MPEG sequence over 10 Mbps into NTSC-rated MPEG sequence below 6 Mbps, the present invention reduces calculation time and complexity of hardware.

Owner:LG ELECTRONICS INC

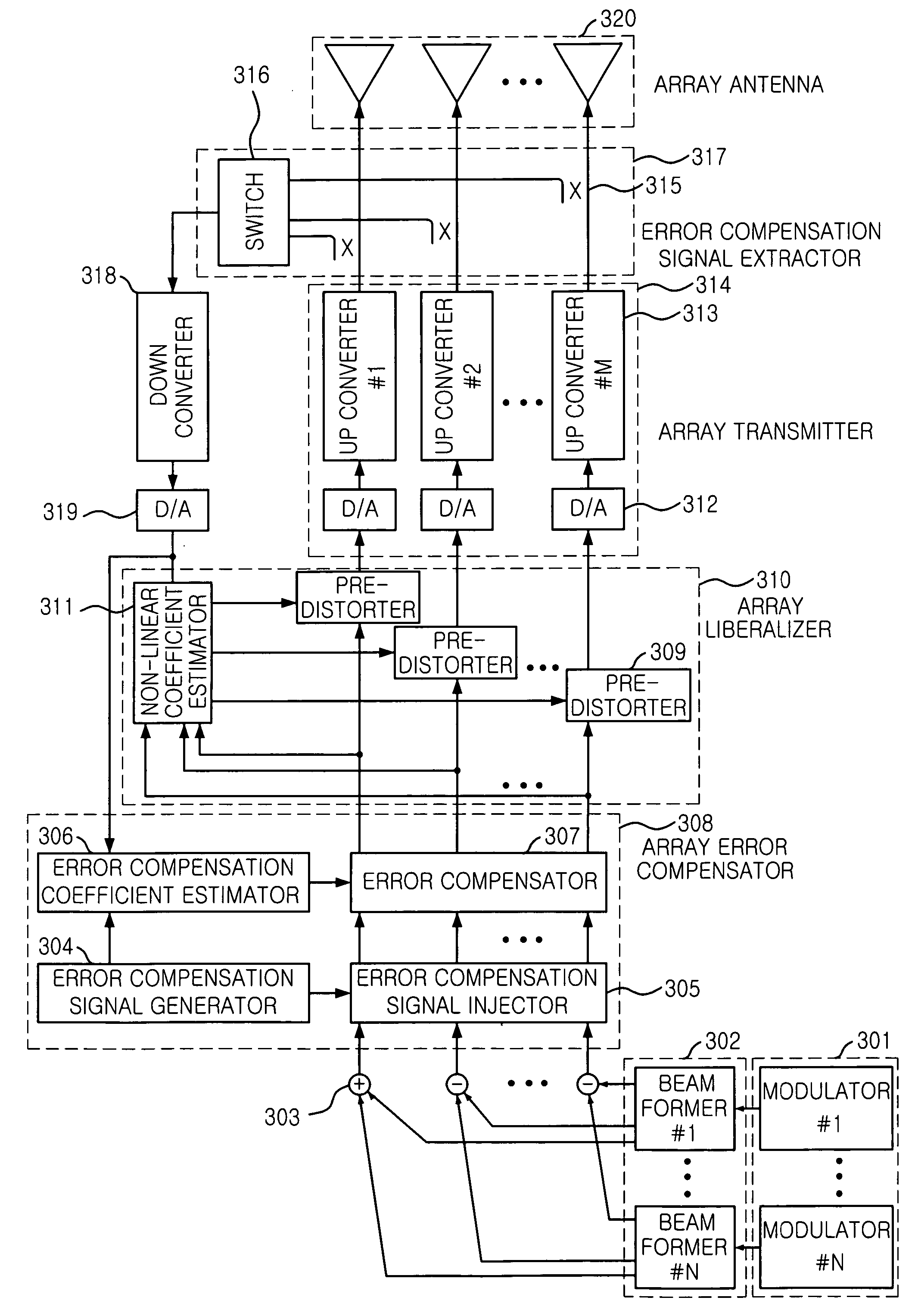

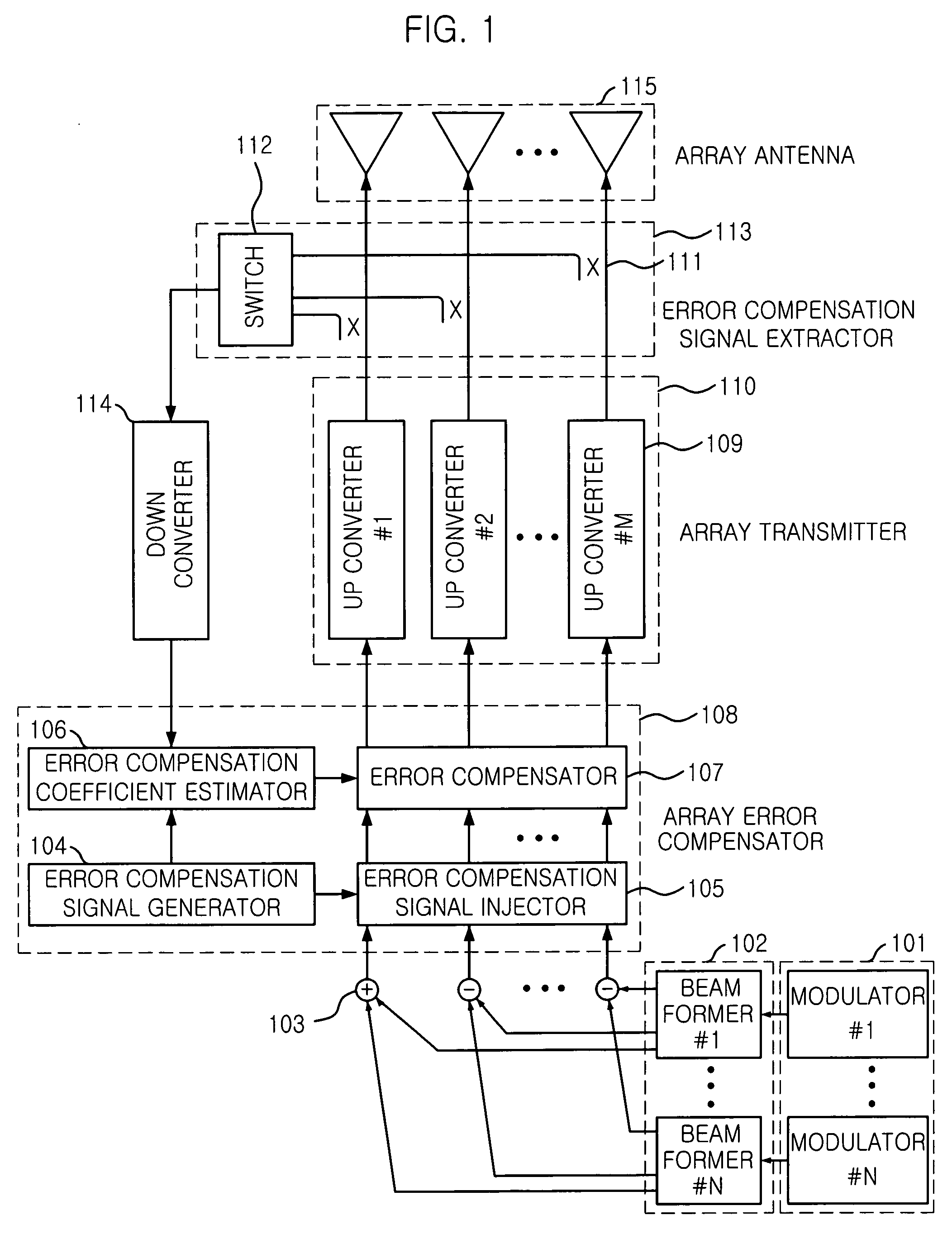

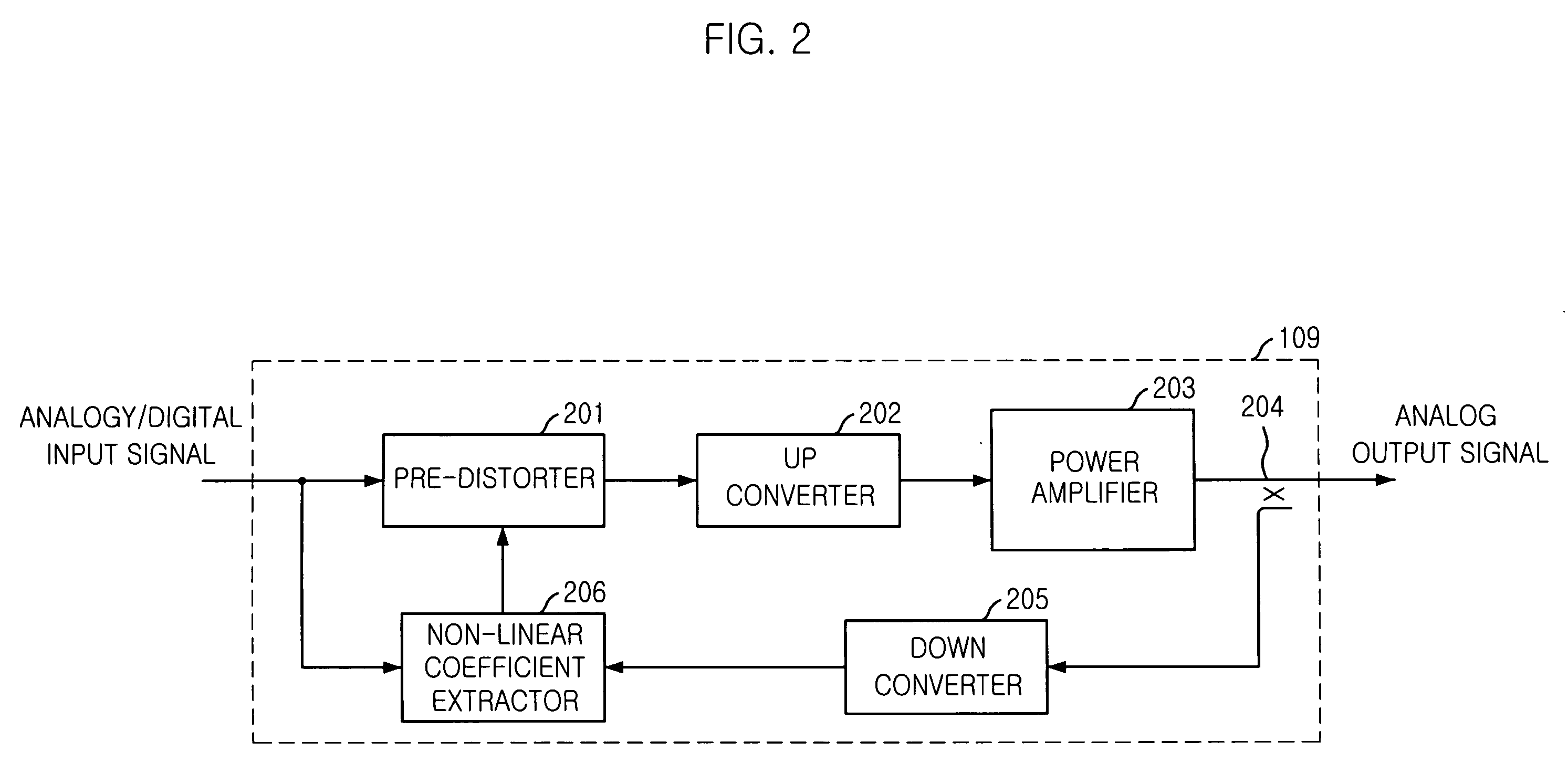

Apparatus and method for linearizing adaptive array antenna system

InactiveUS20060133535A1Reduce hardware complexitySpatial transmit diversityAntenna arraysTransmission channelEngineering

Disclosed is an apparatus and method for linearizing an adaptive array antenna system. The apparatus and method for linearizing an adaptive array antenna system uses an identical feedback path as feedback path for estimation of a transfer function and a feedback path for linearization of each transmission channel in a multi-channel transmitter, thereby reducing hardware complexity of an adaptive array transmitter.

Owner:ELECTRONICS & TELECOMM RES INST

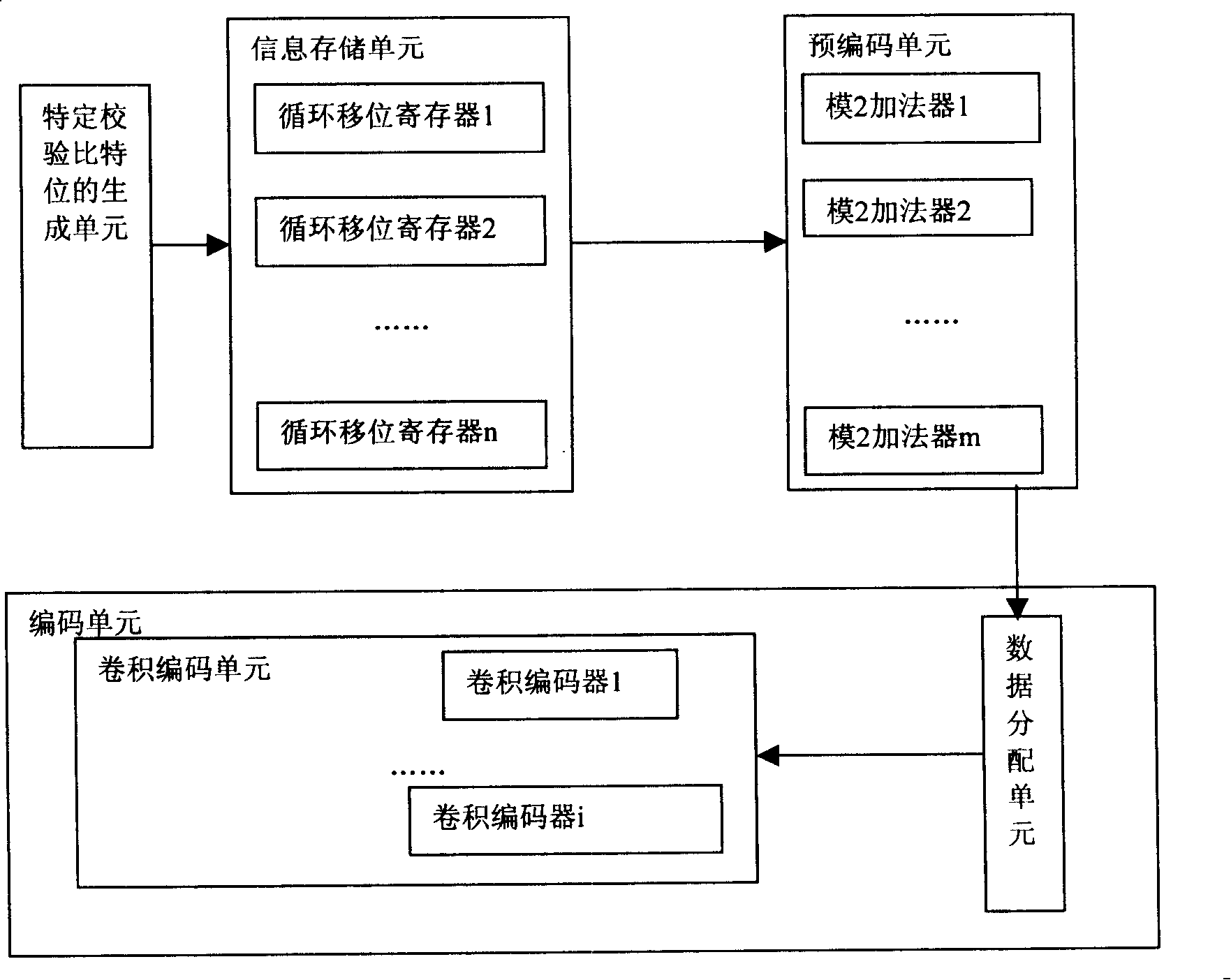

A device and method for low-density checksum LDPC parallel coding

InactiveCN101192833AReduce complexityImprove scalabilityError preventionError correction/detection using multiple parity bitsShift registerParallel encoding

The invention relates to the communications field and provides parallel encoding device and a method for a low density parity-check code (LDPC). By adopting the practice of step-by-step encoding combined with the serial-parallel approach, a concatenated encoding scheme with linear complexity combining with pre-encoding and parallel convolution coding structures is provided thereby. The encoding device for realizing the encoding scheme mainly comprises an information storage unit, a pre-encoding unit and an encoding unit (comprising a data distribution unit and a convolution coding unit) as well as a v (0) verification bit generating unit. The encoding device of the invention adopts a circular shift register and a model 2 adder, which is easy to realize and avoid multiplication operation of vector and matrix. Complexity of the encoding device is reduced. The encoding device provided by the invention features good expansibility. A plurality of basic encoders are used for parallel encoding so that encoding efficiency can be improved by many times compared with the single basic encoding device. Therefore, when hardware complexity permits, parallel structures can be applied as much as possible, which greatly improves encoding efficiency.

Owner:HUAWEI TECH CO LTD +1

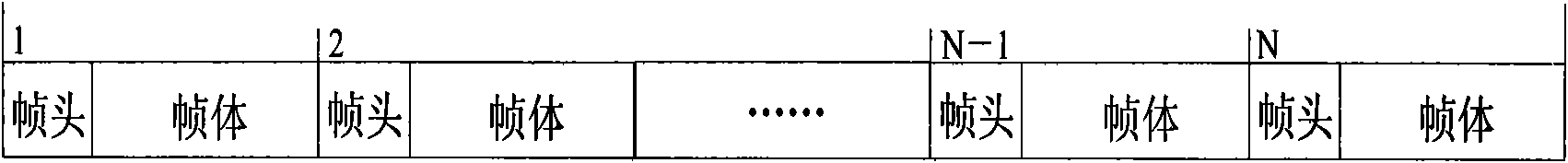

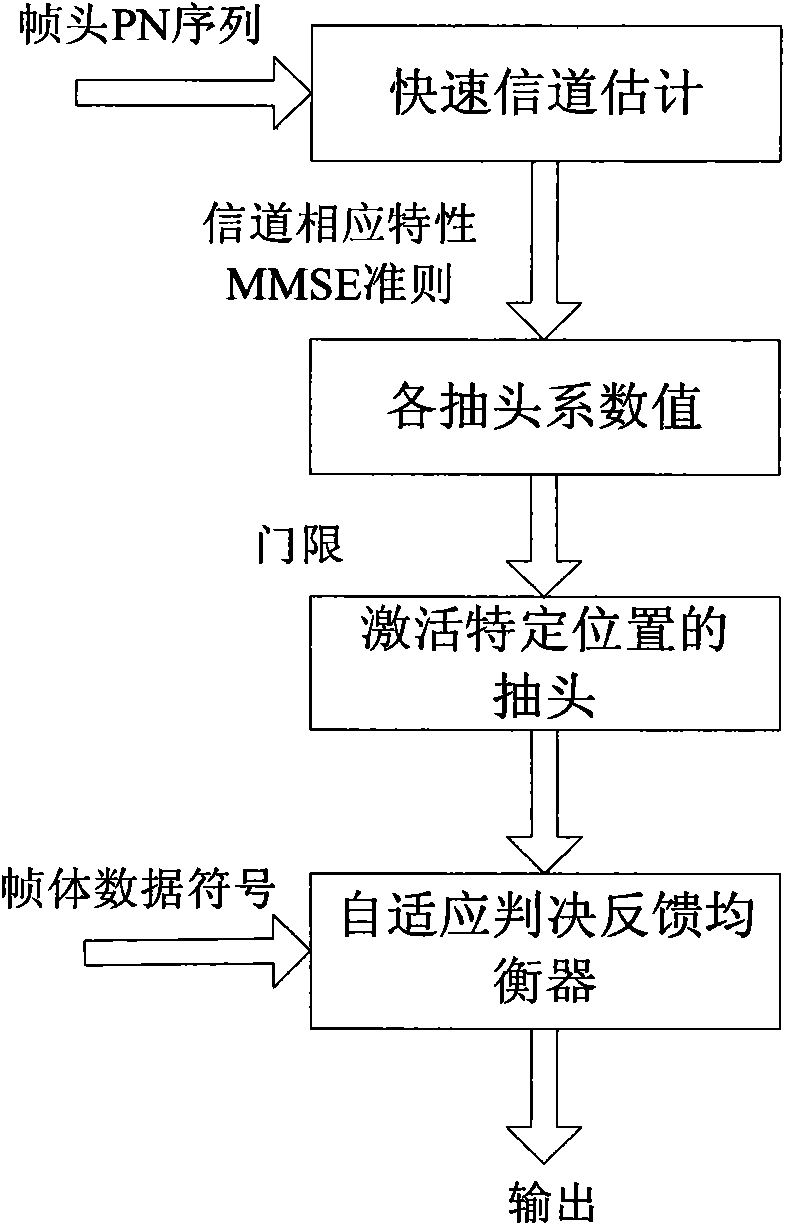

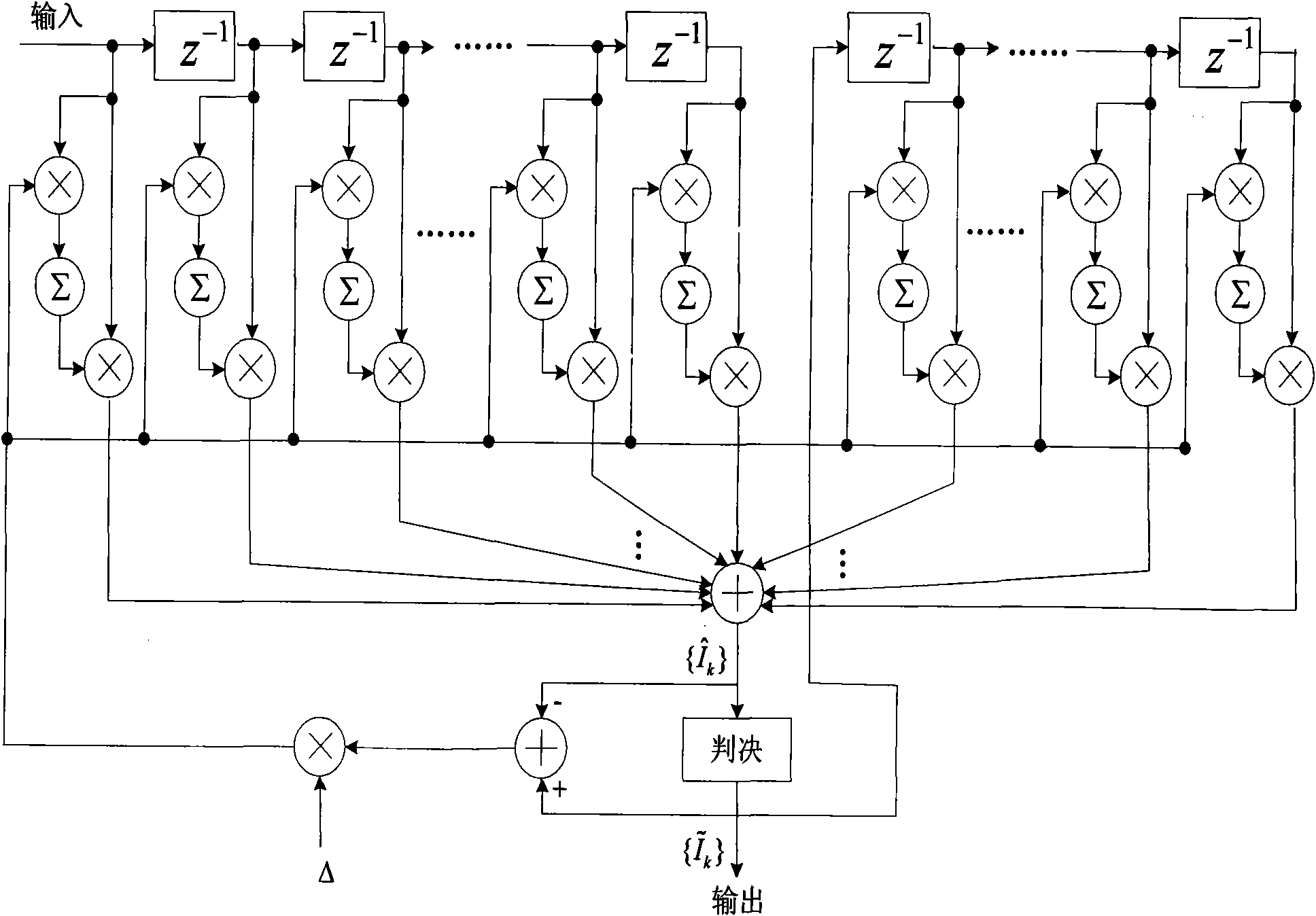

Indirect self-adaptive balancing method of shallow-sea underwater acoustic communication system

InactiveCN101567863ASimple structureGood estimateTransmitter/receiver shaping networksCommunications systemShallow sea

The invention discloses an indirect self-adaptive equalization method of a shallow-sea underwater acoustic communication system to eliminate transmission intersymbol interference brought by a shallow-sea underwater acoustic channel with the time-varying and multi-diameter characteristics. The method comprises the following steps: designing a signal frame structure suitable for transmission in the shallow-sea underwater acoustic channel at a sending terminal; utilizing a frame head PN sequence to carry out rapid channel estimation and the initialization of equalizer tap coefficients at a receiving terminal; selecting a corresponding threshold according to the practical transmission environment to realize the decentralization of equalizer taps; and adopting an LMS algorithm with a variable step size to further reduce errors so as to better equalize frame body data. The invention enables an equalizer in the shallow-sea underwater acoustic communication system to have rapid convergence and lower hardware complexity, has good equalization effect on a sending signal after high-level modulation and can be effectively applied to the shallow-sea high-speed digital communication system.

Owner:魏昕

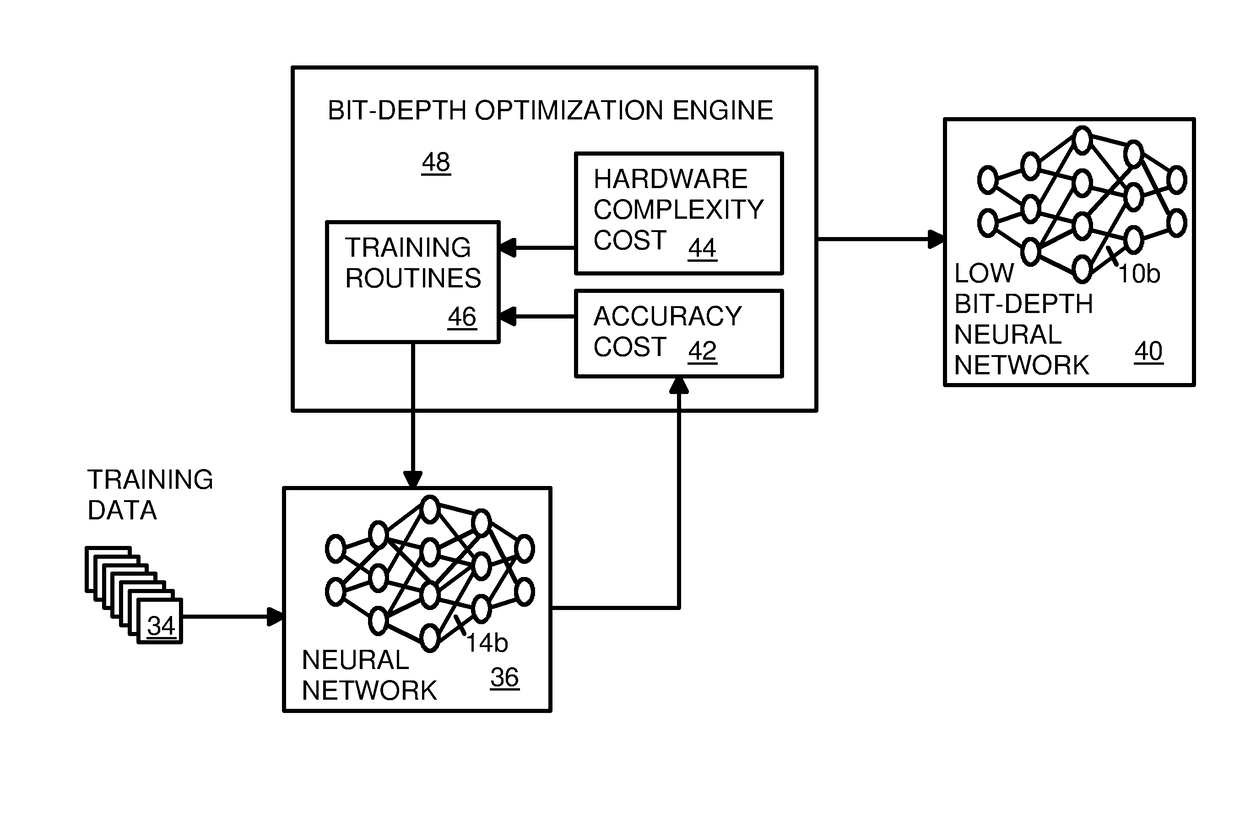

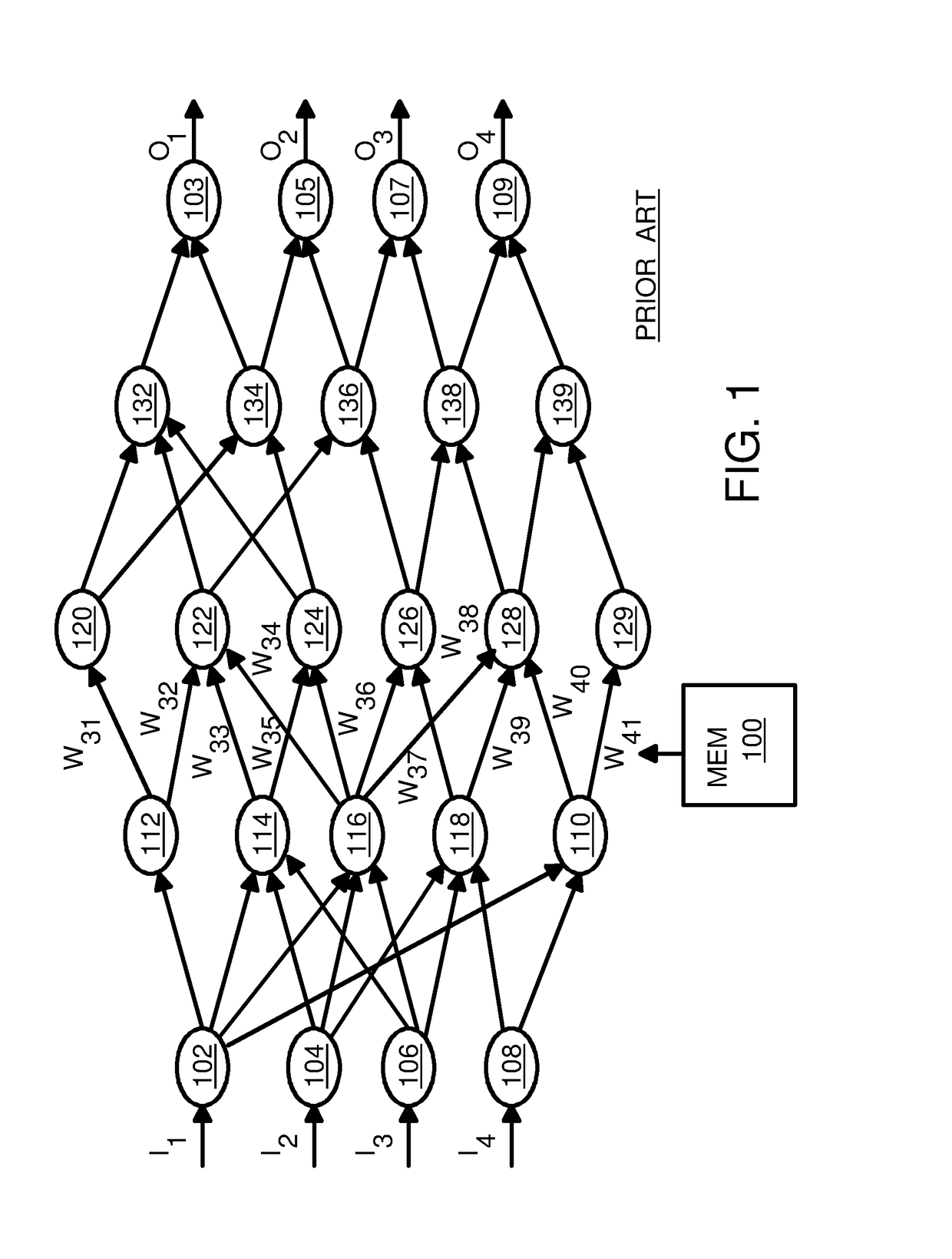

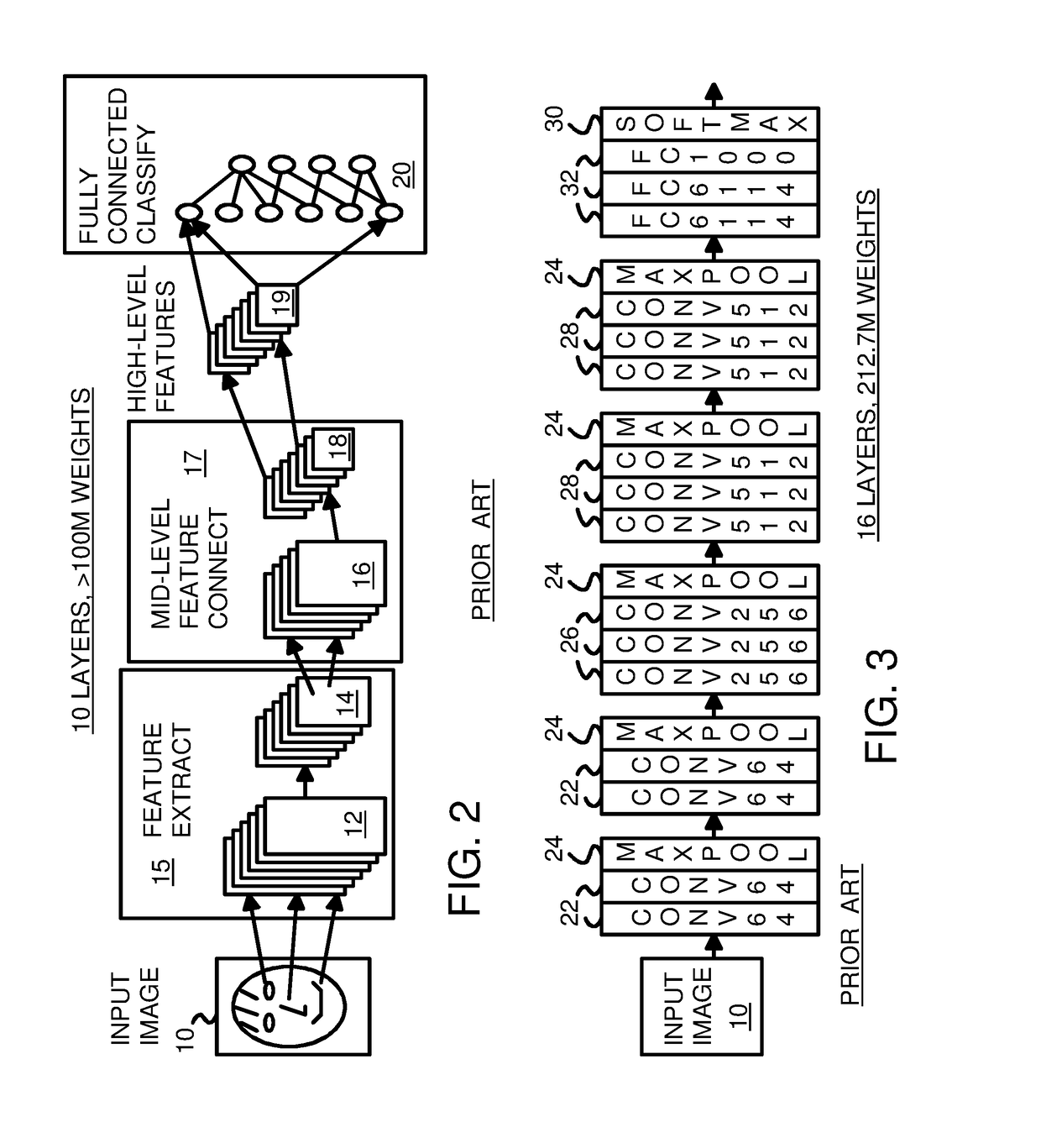

Method and System for Bit-Depth Reduction in Artificial Neural Networks

A bit-depth optimization engine reduces the hardware cost of a neural network. When training data is applied to a neural network during training routines, accuracy cost and hardware costs are generated. A hardware complexity cost generator generates costs for weights near bit-depth steps where the number of binary bits required to represent a weight decreases, such as from 2N to 2N−1, where one less binary bit is required. Gradients are generated from costs for each weight, and weights near bit-depth steps are easily selected since they have a large gradient, while weights far away from a bit-depth step have near-zero gradients. The selected weights are reduced during optimization. Over many cycles of optimization, a low-bit-depth neural network is generated that uses fewer binary bits per weight, resulting in lower hardware costs when the low-bit-depth neural network is manufactured on an Application-Specific Integrated Circuit (ASIC).

Owner:HONG KONG APPLIED SCI & TECH RES INST

Storage-efficient and collision-free hash-based packet processing architecture and method

InactiveUS7653670B2Eliminating false positivesLess storageData processing applicationsDigital data information retrievalComputer architectureHardware complexity

Owner:NEC CORP

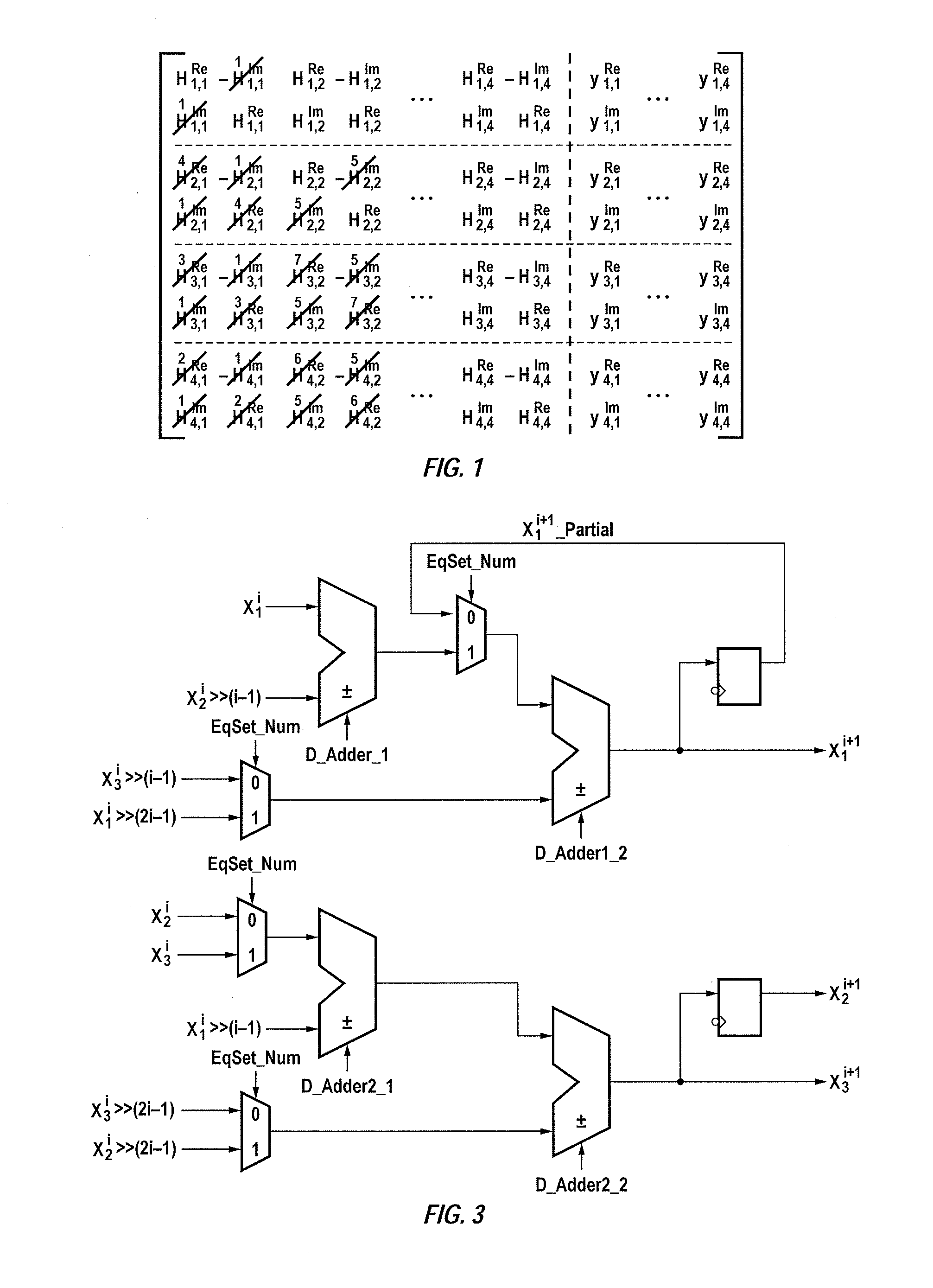

Signal processing block for a receiver in wireless communication

ActiveUS20110264721A1Digital computer detailsIndependent non-interacting antenna combinationsResource utilizationParallel computing

A QRD processor for computing input signals in a receiver for wireless communication relies upon a combination of multi-dimensional Givens Rotations, Householder Reflections and conventional two-dimensional (2D) Givens Rotations, for computing the QRD of matrices. The proposed technique integrates the benefits of multi-dimensional annihilation capability of Householder reflections plus the low-complexity nature of the conventional 2D Givens rotations. Such integration increases throughput and reduces the hardware complexity, by first decreasing the number of rotation operations required and then by enabling their parallel execution. A pipelined architecture is presented (290) that uses un-rolled pipelined CORDIC processors (245a to 245d) iteratively to improve throughput and resource utilization, while reducing the gate count.

Owner:MAXLINEAR INC

Soft grid connection method of grid-connected converter

ActiveCN102916437AIncrease the maximum precharge voltageImprove synchronous closed-loop control accuracySingle network parallel feeding arrangementsCapacitanceLoop control

The invention provides a soft grid connection method of a grid-connected converter. The method is characterized in that the closed-loop control of the filtering capacitance and the filtering voltage is carried out synchronously; the current inter-loop control is added; and DC pre-charging return circuits are separated and boosted. According to the invention, the non-impact grid connection is realized without increasing great hardware complexity, thereby overcoming the defects of the traditional grid-connected method and improving the reliability of the grid-connected converter.

Owner:XJ ELECTRIC +1

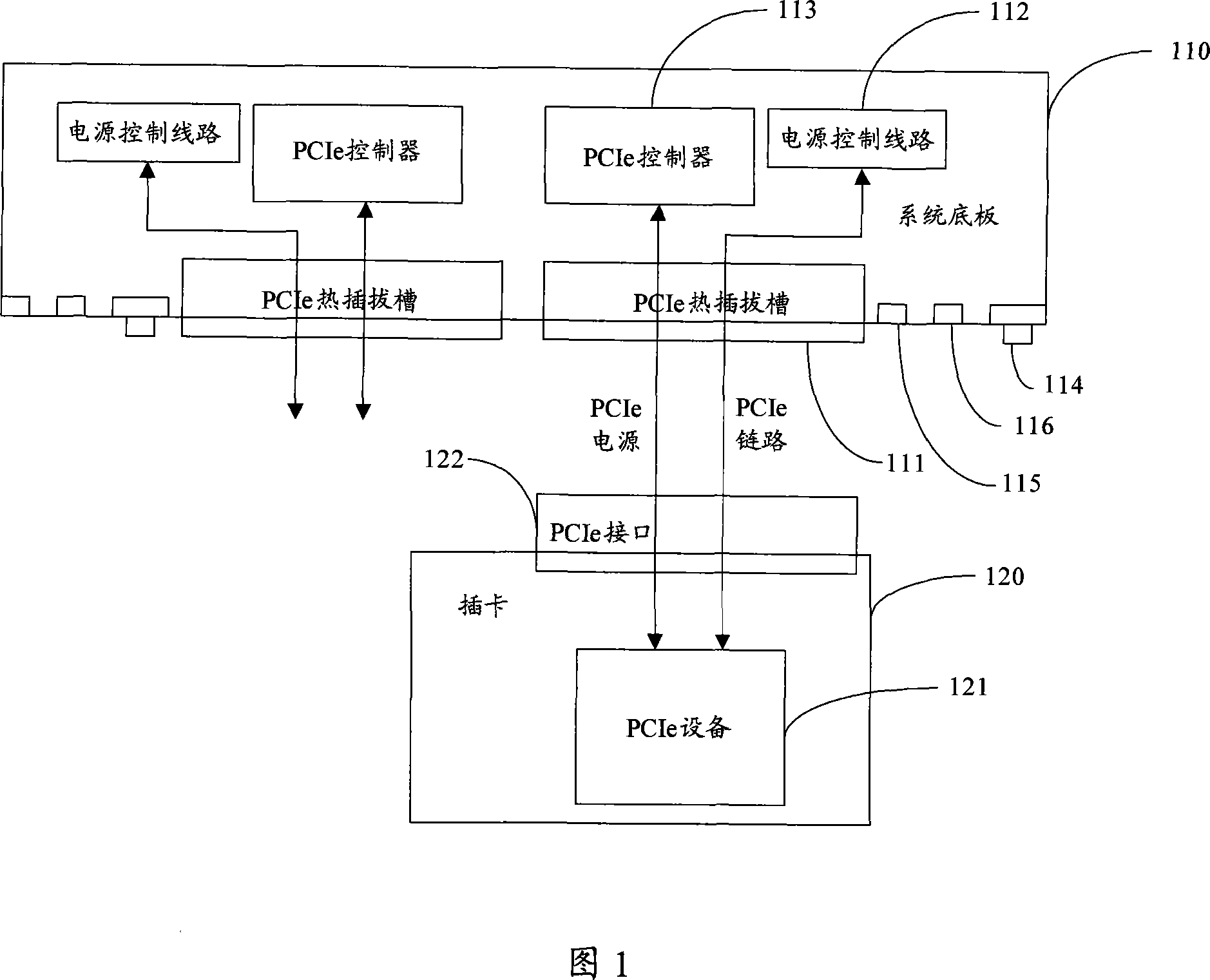

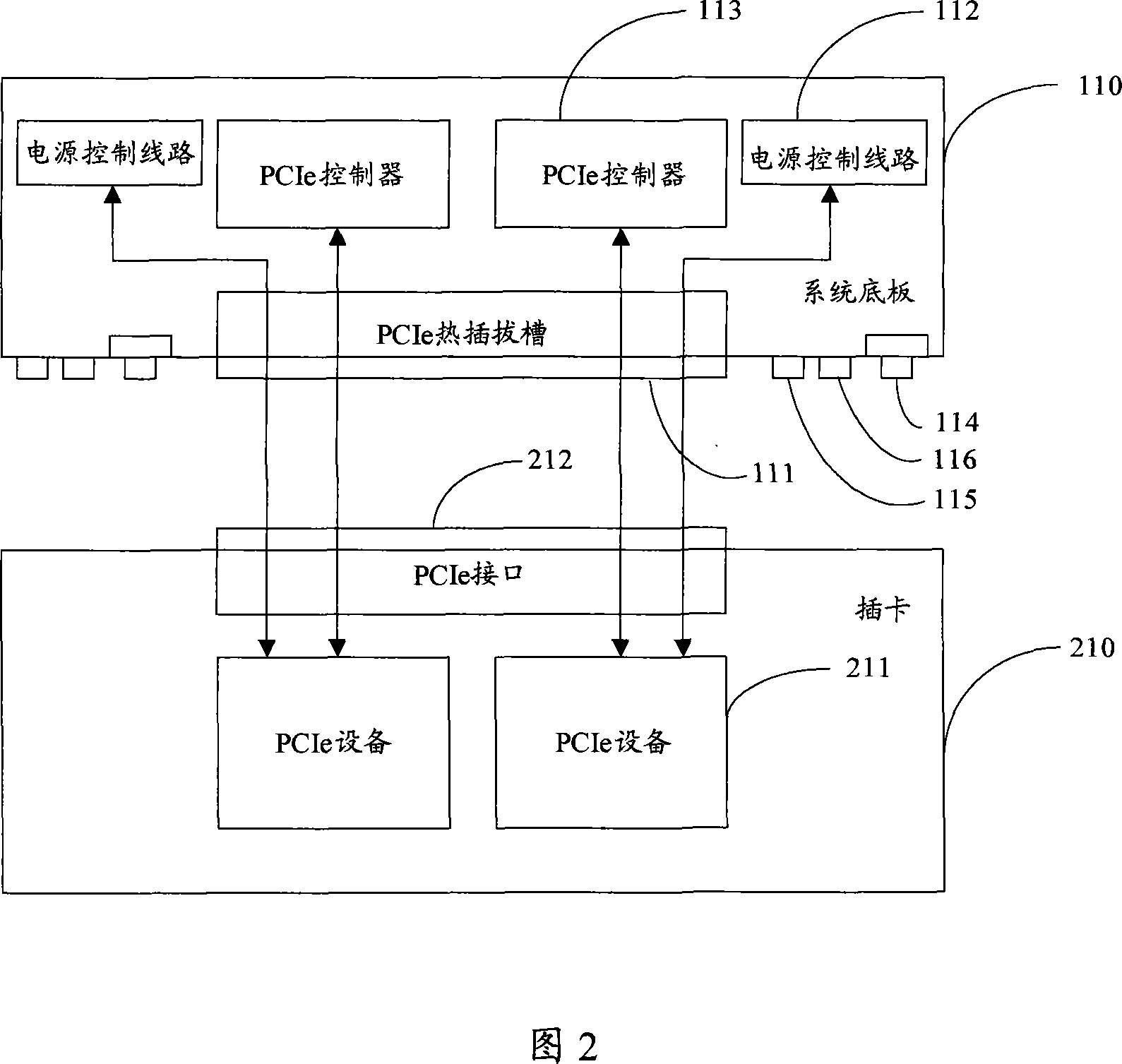

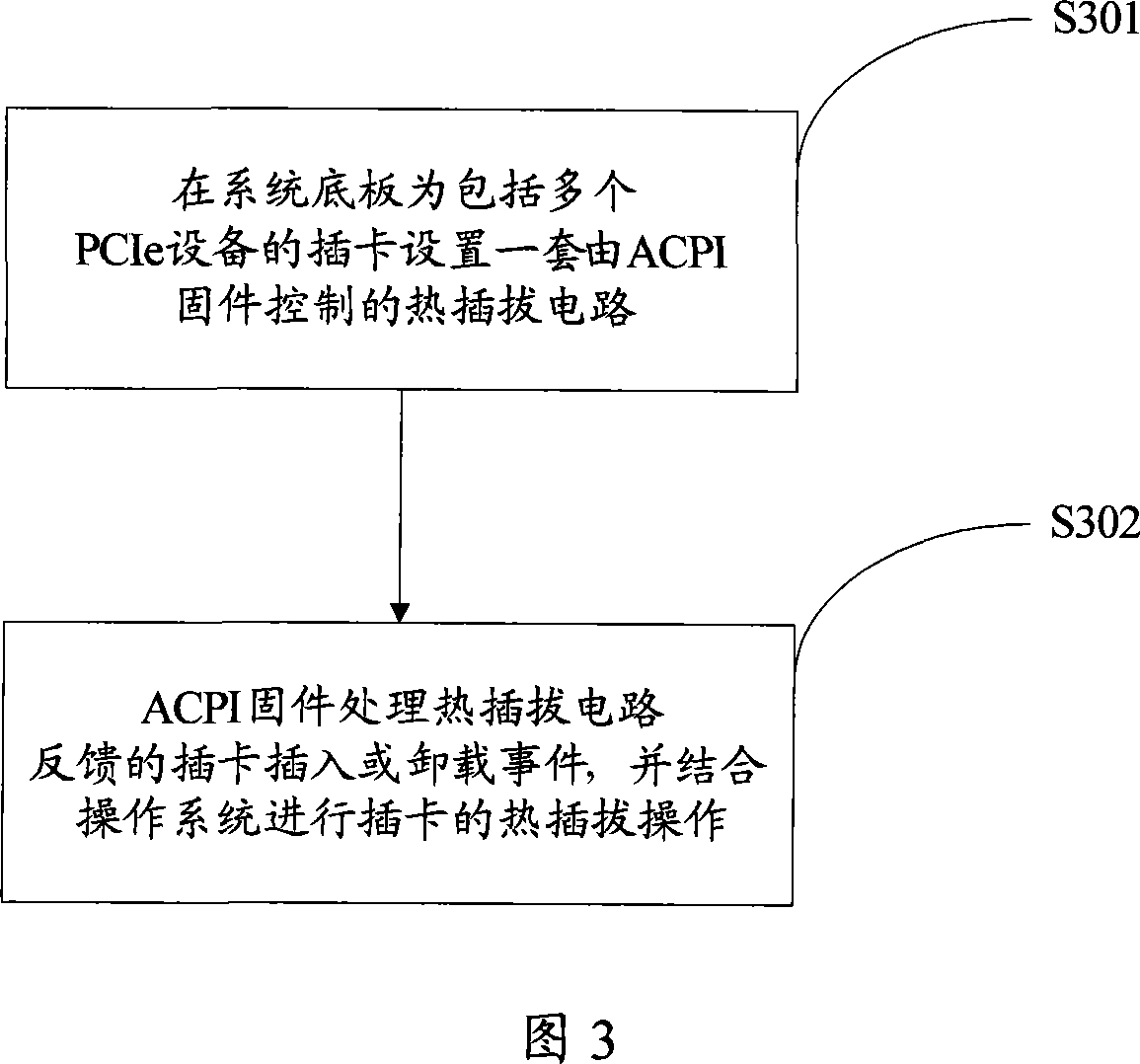

Method and device for implementing peripheral element interface accelerate bus inserted card hot-plug

ActiveCN101034380AReduce in quantityReduce complexityElectric digital data processingOperational systemHardware complexity

The invention publishes a method which realizes a PCIe card hot swap of bus accelerated of the peripheral device interface, including: First, the bottom of the system includes multiple PCIe card- installed equipment, a set of hot swap circuit controlled by the senior configuration and power management ACPI firmware; Then ACPI firmware handling the matter that the card is inserted or removed fed back by hot-circuit, and combining the card operating system to run a hot swap operation. The present invention also opens a system backplane of PCIe hot swap. The method and the implementation of this invention can realize the card's overall hot swap of a number of PCIe equipment cards through modifying the support-detail of the hot swap support of ACPI firmware, while reducing the number of hot-line support in the system, can reduce hardware complexity, reduce costs and streamline operational steps.

Owner:NEW H3C TECH CO LTD

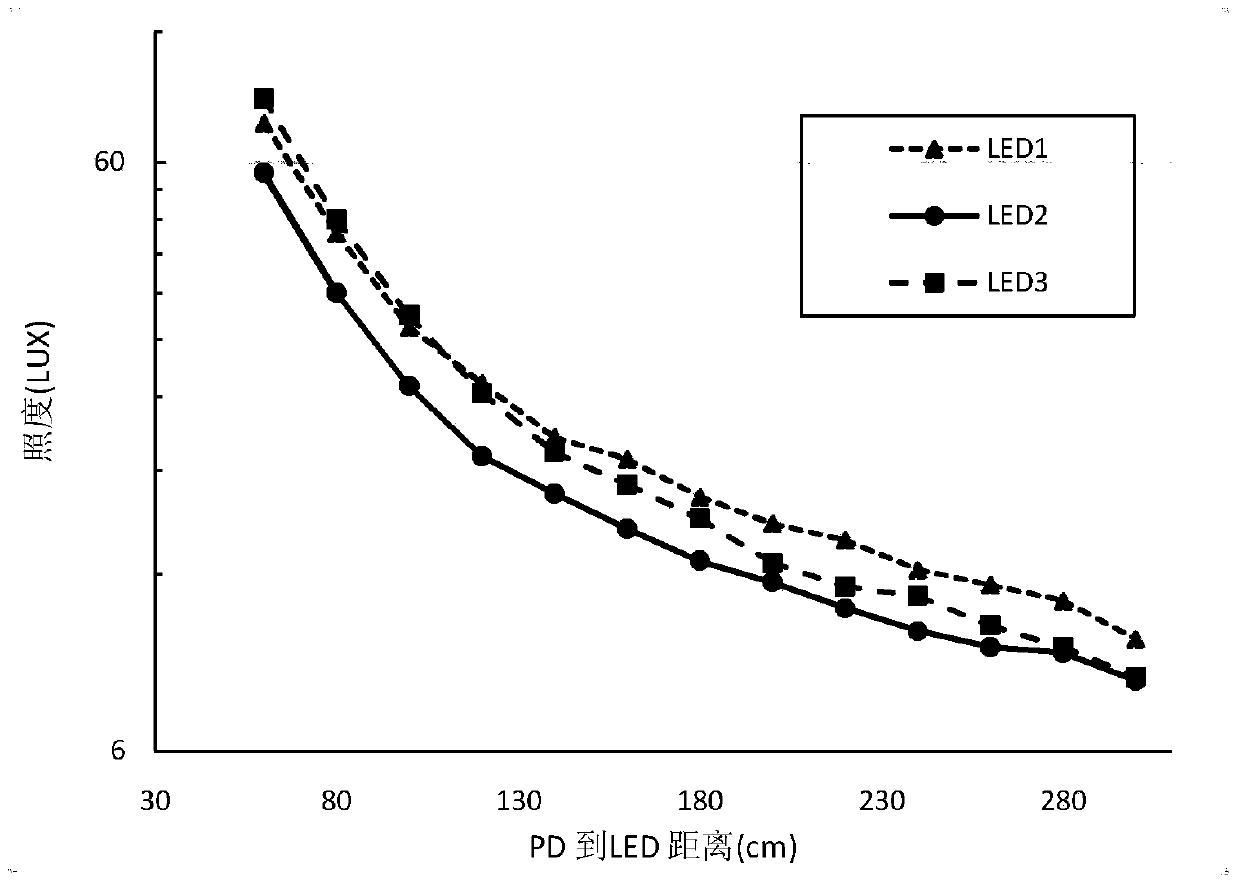

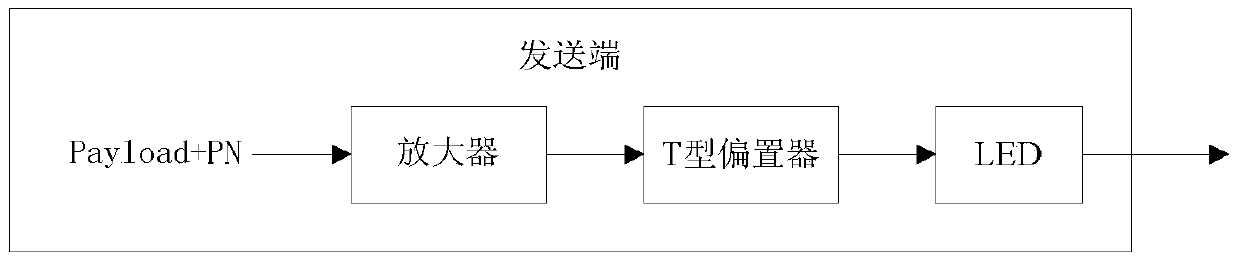

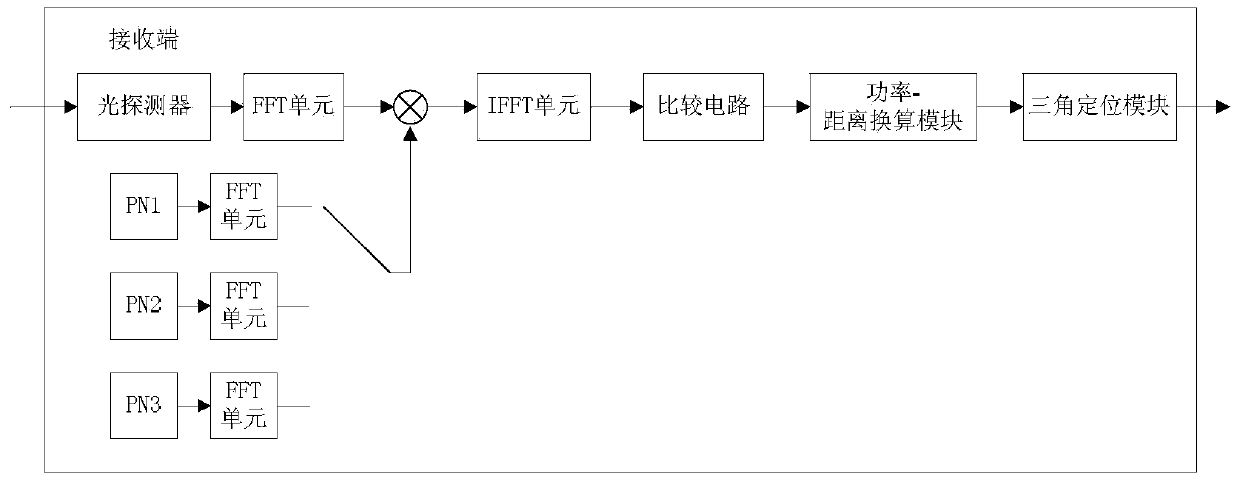

RSS-based LED positioning system and method

InactiveCN104181503AReduce hardware complexitySave bandwidthPosition fixationClose-range type systemsTime domainComputer module

The invention discloses an RSS-based LED positioning system and method, and relates to the field of LED communication and indoor positioning application. The RSS-based LED positioning system comprises at least three sending ends and one receiving end. Each sending end comprises a T-shaped bias device and an LED. The sending ends add PN code sequences before data to be transmitted, and the sequences are converted to visible light for emitting through the T-shaped bias devices and the LEDs; a photo-detector at the receiving end detects visible light signals and converts the visible light signals into electric signals, one FFT unit performs FFT transformation on the electric signals, other FFT units are used for FFT transformation of each PN code, a multiplier performs convolution multiplying on a result and an FFT operation result of each PN code, each product carries out IFFT transformation, a comparison circuit is used for finding out a peak value of time domain signals, and a power-distance conversion module estimates the value of a distance between the receiving end and each LED and outputting the value. According to the invention, multiple orthogonal PN codes are sent for distinguishing different LED sources, such that the hardware complexity of the sending ends is reduced, and the LED bandwidth is decreased.

Owner:WUHAN POST & TELECOMM RES INST CO LTD

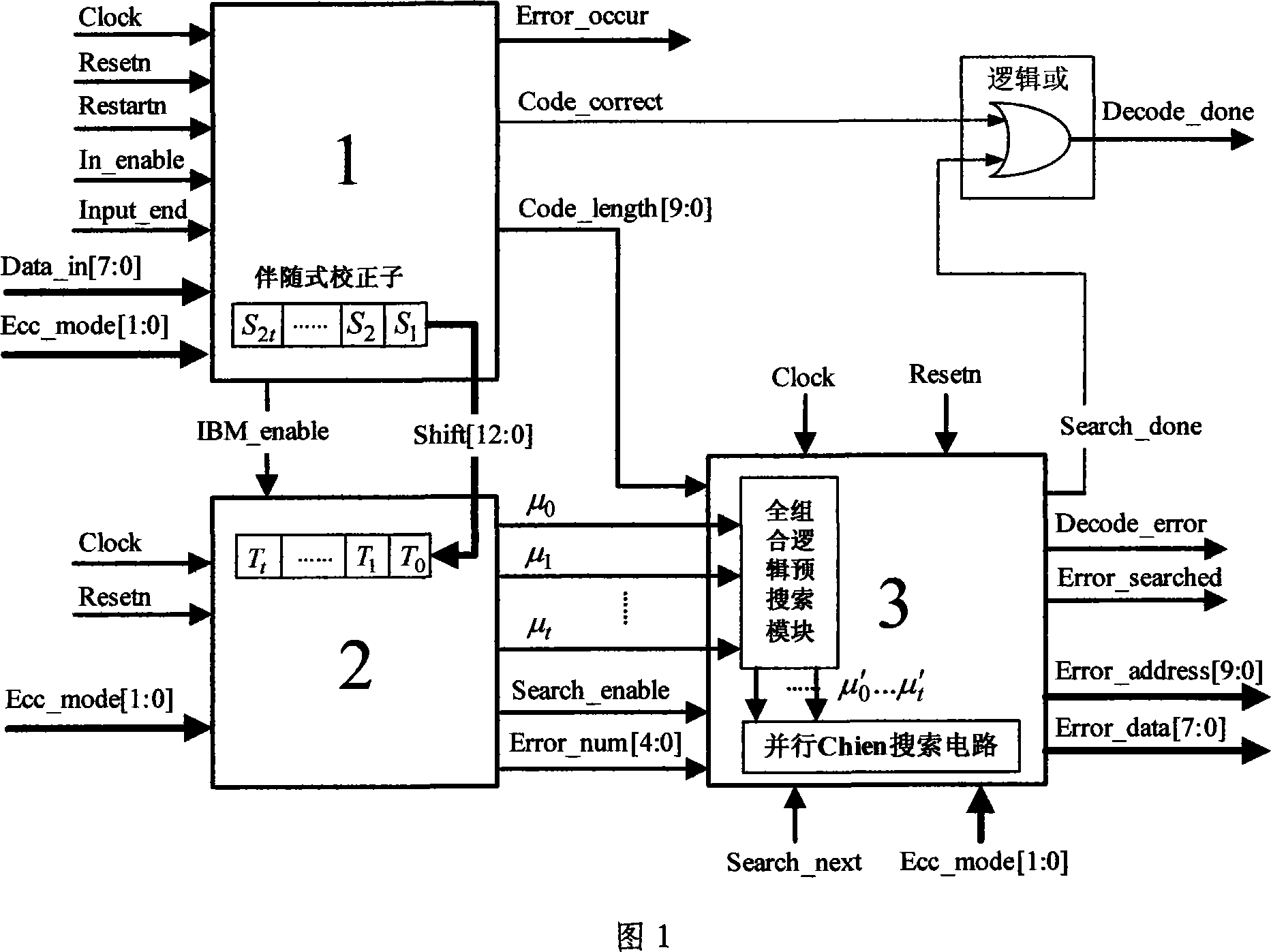

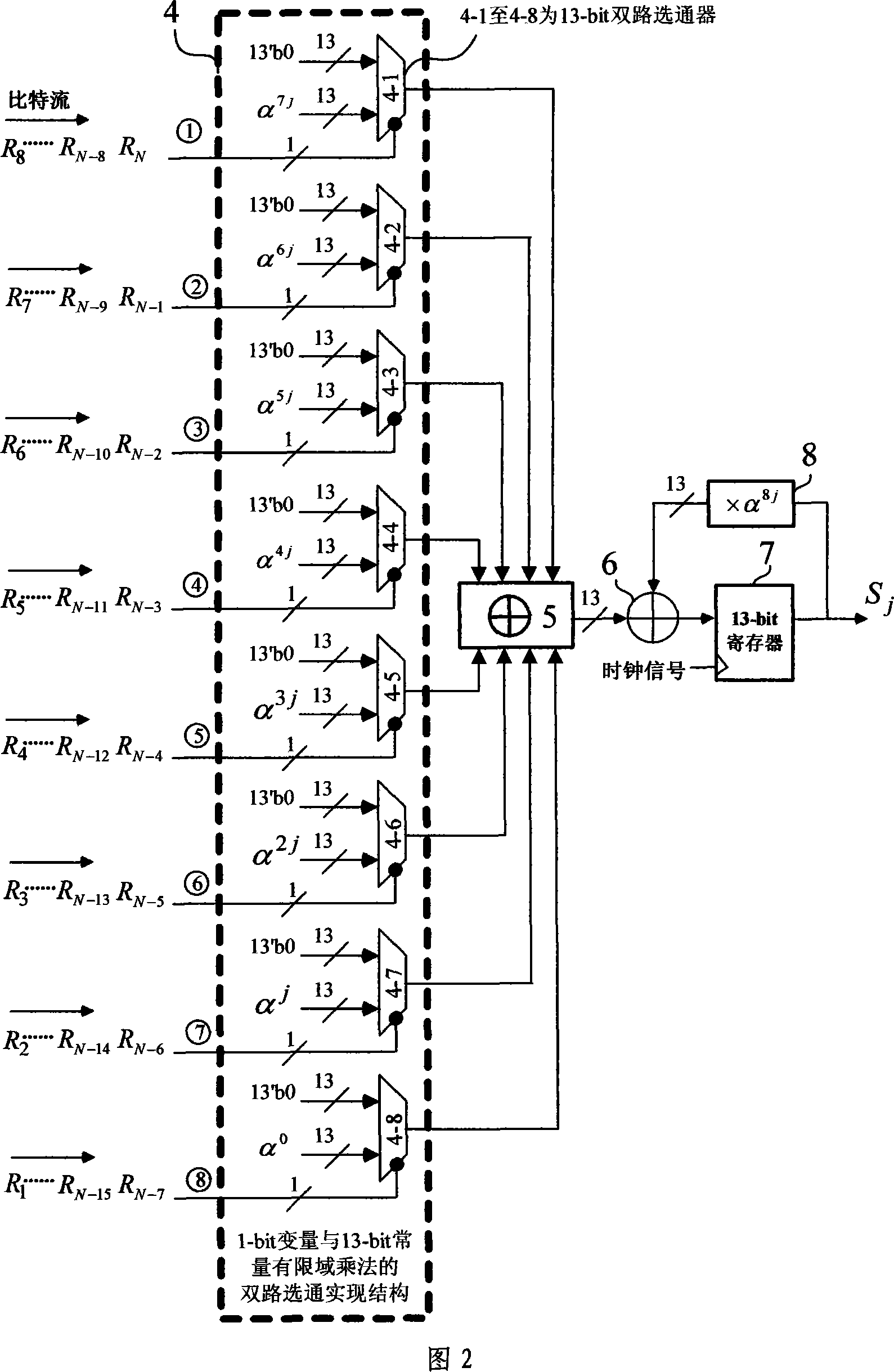

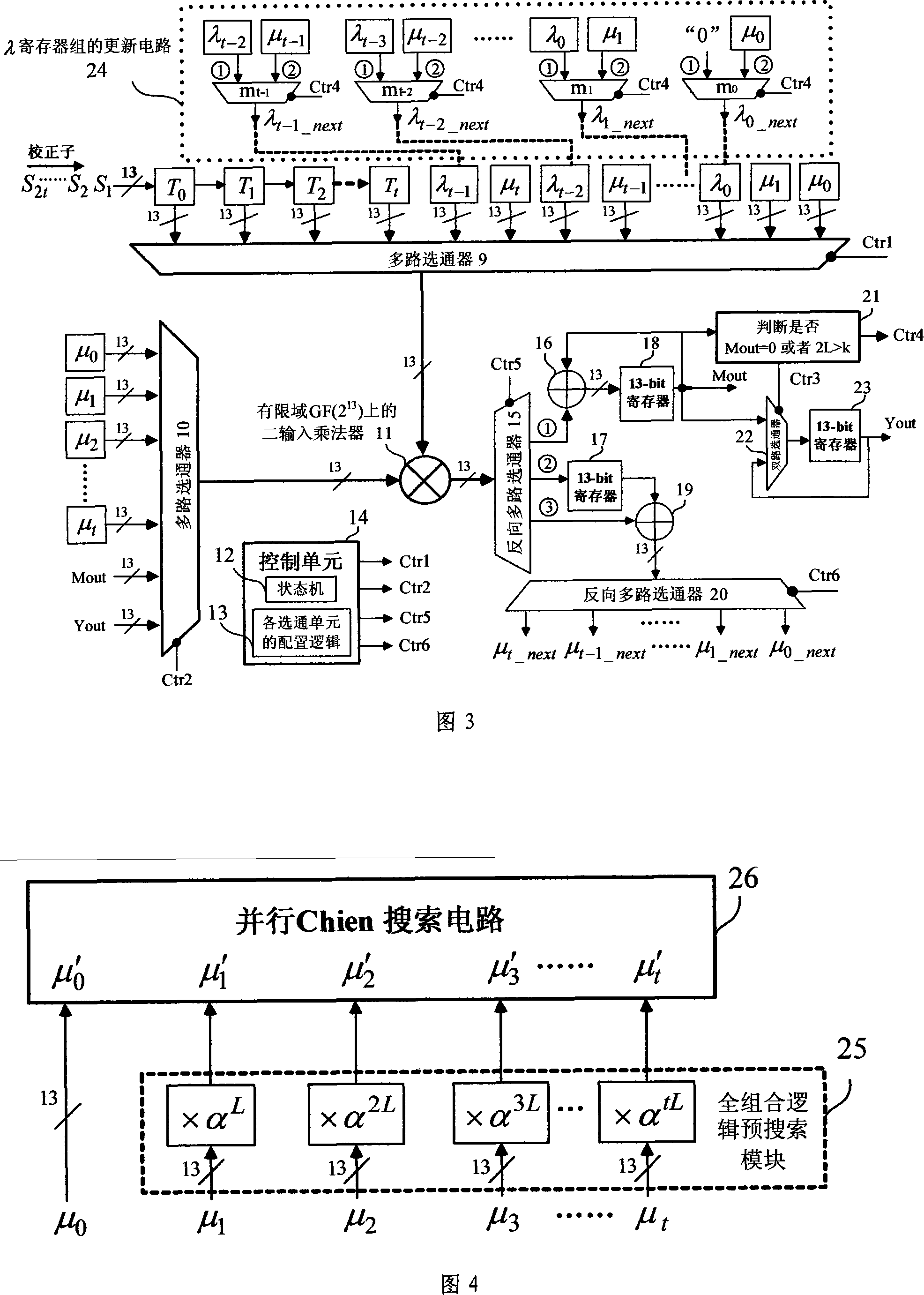

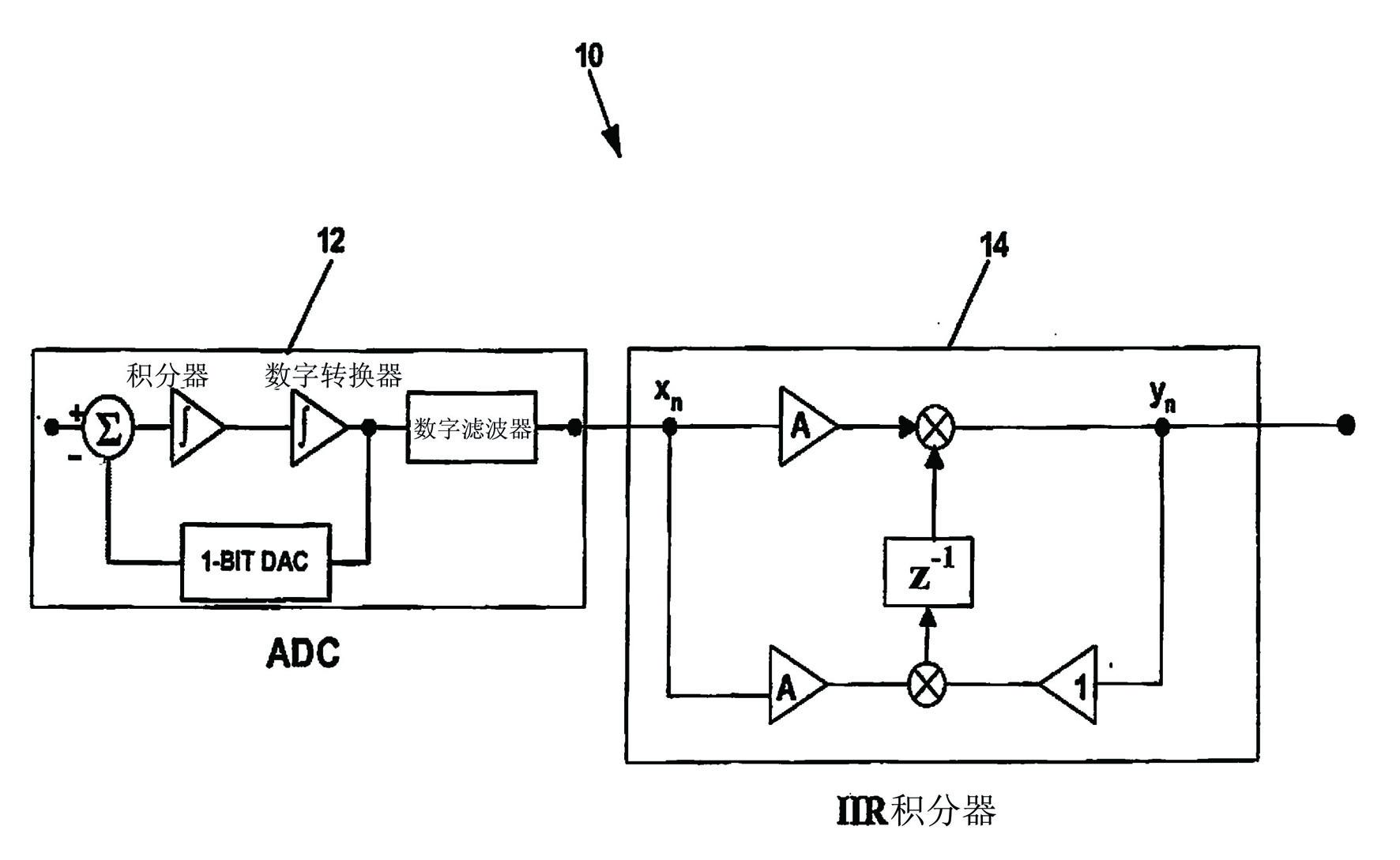

Area compact type BCH paralleling decoding circuit supporting pre searching

A compact BCH parallel decoding circuit which supports preview search works on a finite field GF(2<13>). The parallel decoding circuit comprises a syndrome arithmetic circuit(1), a realizing circuit(2)with multiple shoots in one round for IBM wrong position multinomial iterative computation in the finite field GF(2<13>), a wrong address search circuit(3) provided with a totally combined logic pre-search module and a multifunctional configurable data interface(27)of an encoder. Compared with prior art, the decoding circuit has the advantages that the hardware is of low degree of complexity, the circuit area is compact and the decoding circuit is low in cost; data throughput is high and wrong address research is quick; the interface is simple in design and is practical and multi-functional; correcting performance can be flexibly configured according to the length of the check element and is free from the change of the code length.

Owner:NATIONZ TECH INC

Integrated vibration measurement and analysis system

ActiveCN102374876AVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesVibration measurementRound complexity

A vibration data collection system performs an integration or differentiation process on incoming digitized vibration data in real time. The system uses a digital Infinite Impulse Response (IIR) filter running at the input data rate to provide the integration or differentiation function. With this approach, the system reduces hardware complexity and data storage requirements. Also, the system provides the ability to directly integrate or differentiate stored time waveforms without resorting to FFT processing methods.

Owner:CSI TECH

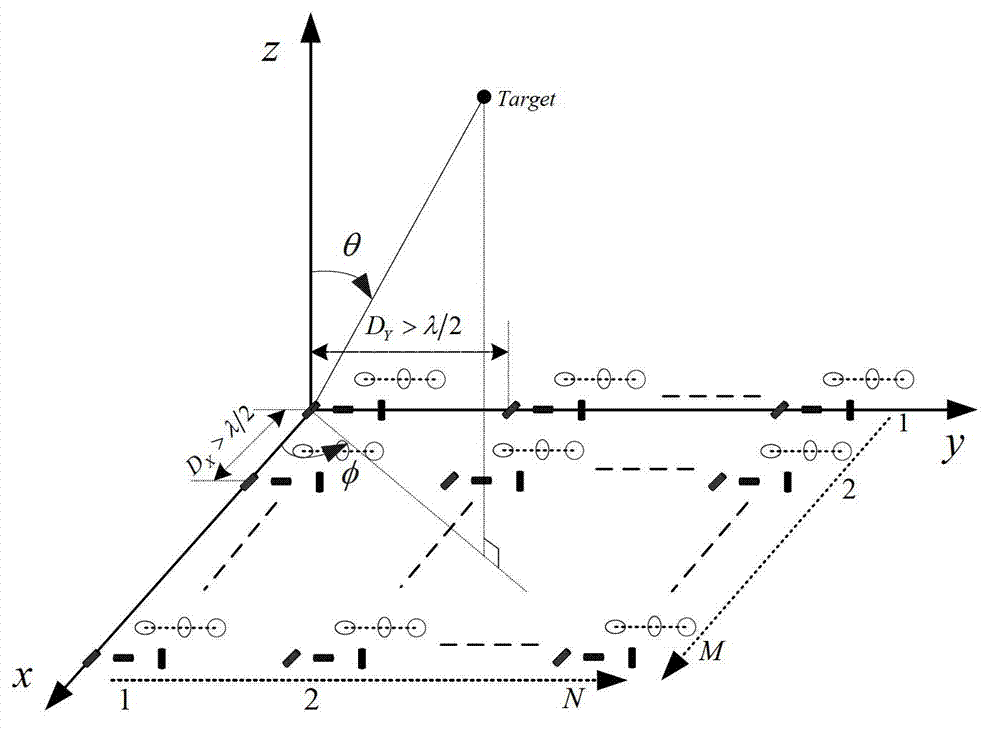

Bidimensional wave arrival direction estimation method based on non-concentric electromagnetic vector array radar

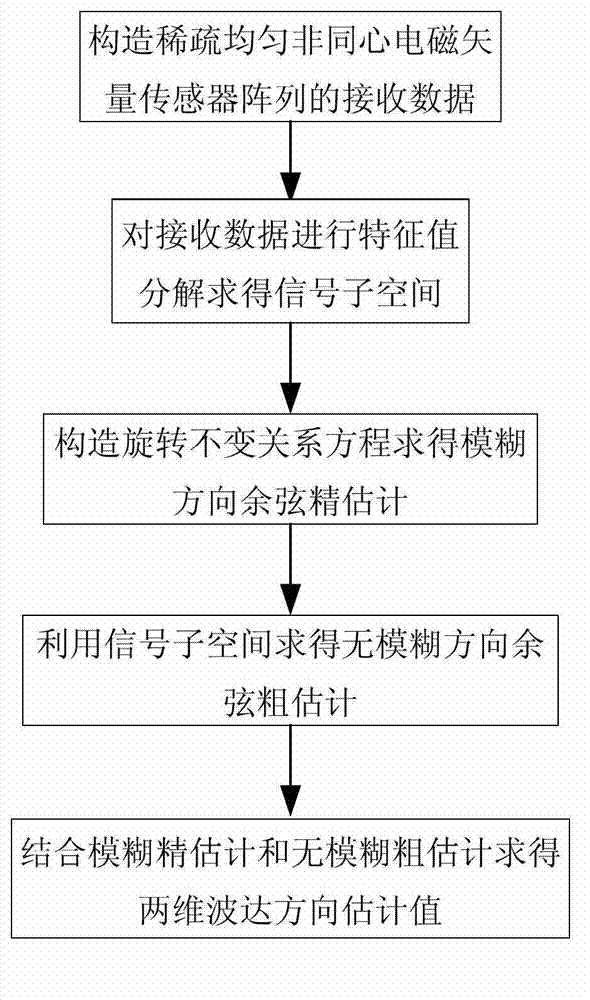

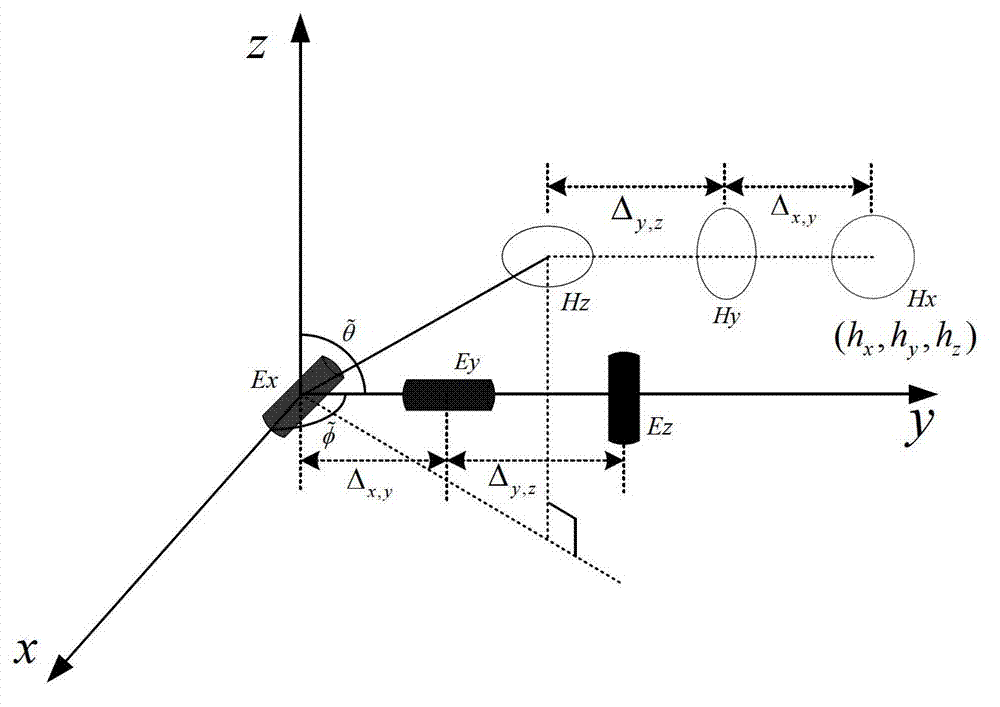

InactiveCN103091671AExtended physical apertureImprove estimation accuracyRadio wave reradiation/reflectionEstimation methodsCoupling

The invention discloses a bidimensional wave arrival direction estimation method based on a non-concentric electromagnetic vector array radar. The bidimensional wave arrival direction estimation method mainly solves the problems of serious cross coupling and low estimated accuracy of a polarization array radar in the process of target positioning and tracking. The method includes a first step of building receiving data of a sparse uniform non-concentric electromagnetic vector sensor array, a second step of carrying out eigenvalue decomposition to the received data to obtain a signal subspace, a third step of obtaining dim direction cosine precision estimation according to signal subspace tectonic rotation invariant relationship equation, and through utilization of the least square algorithm, a fourth step of obtaining non-dim-direction cosine rough estimation through utilization of the signal subspace, and a fifth step of combining the dim direction cosine precision estimation and the non-dim-direction cosine rough estimation, the bidimensional wave arrival direction estimation can be obtained. The bidimensional wave arrival direction estimation method effectively expands array physical apertures on the condition of not adding array elements and complexity of hardware, enables the bidimensional wave arrival direction estimation accuracy to be greatly improved, and can be applied to accurate positioning and tracking of the radar to targets.

Owner:XIDIAN UNIV

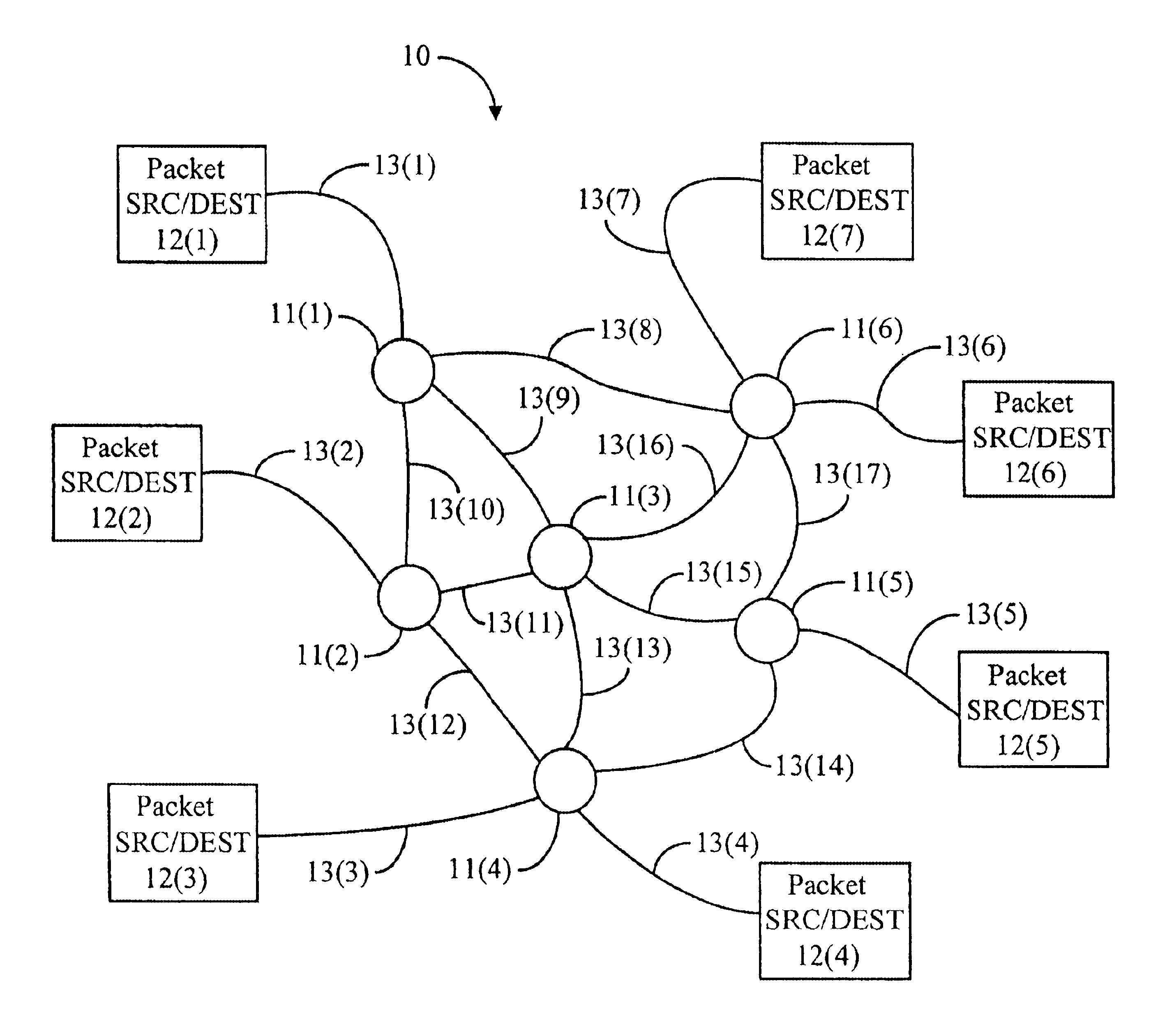

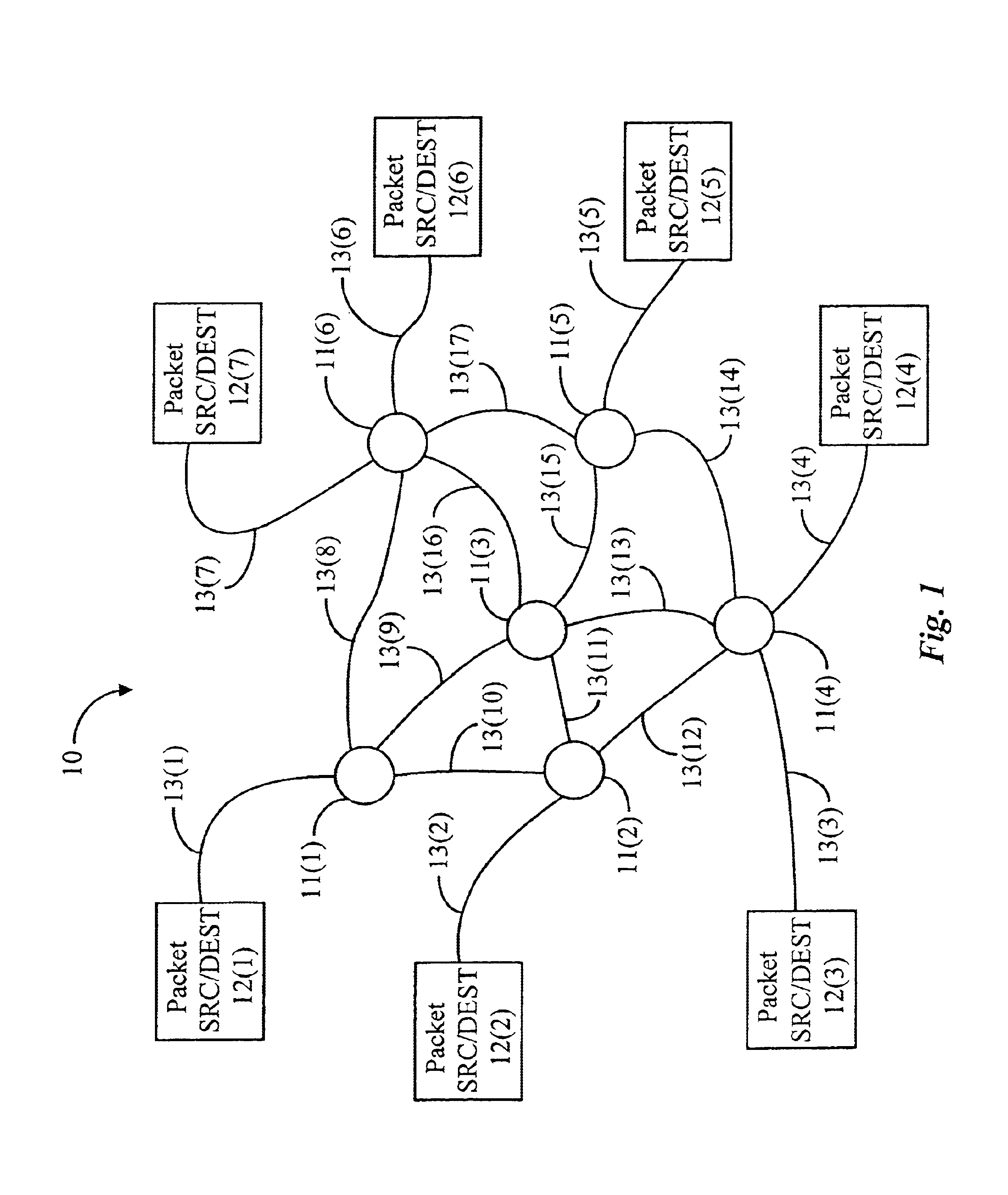

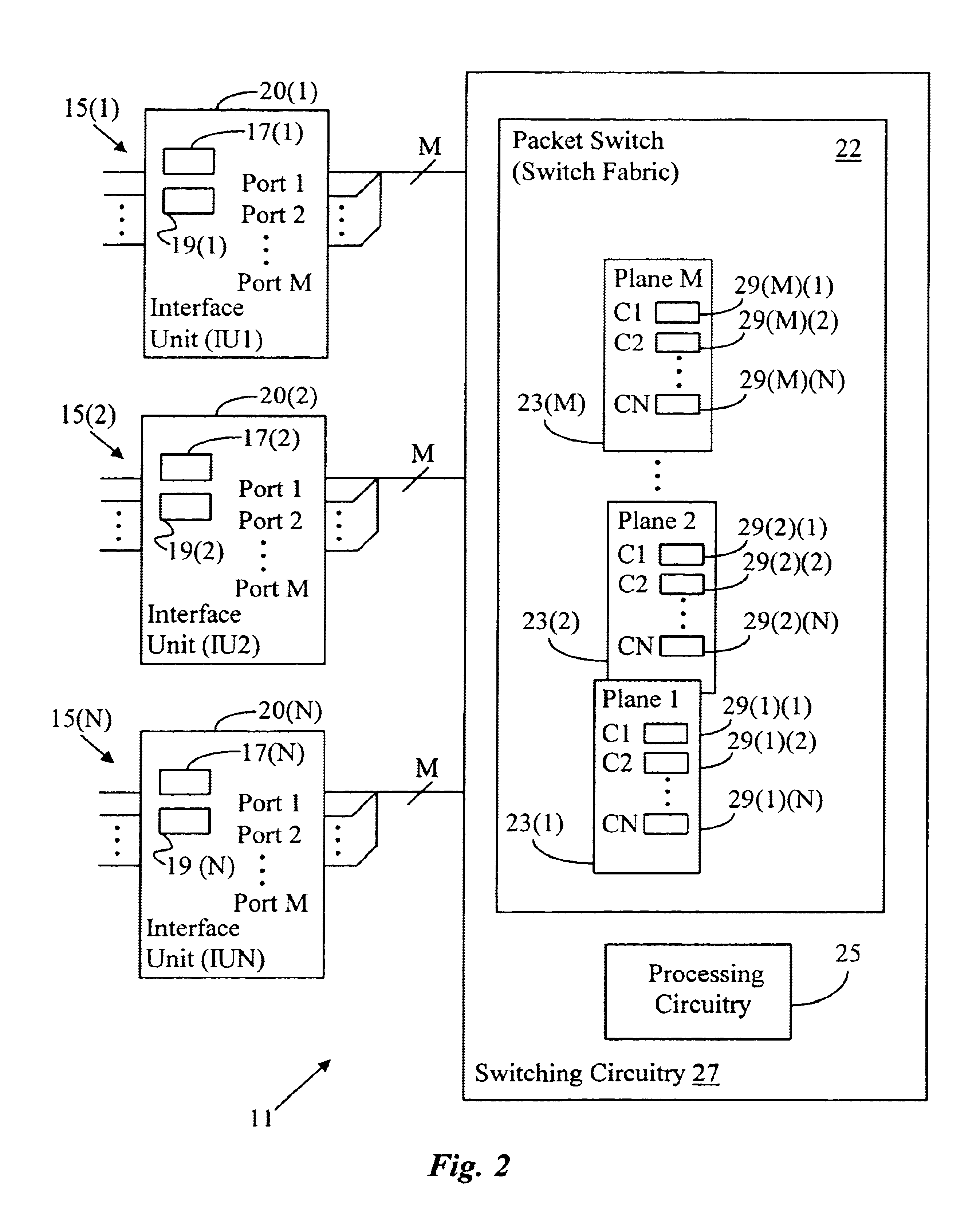

Apparatus and method for scaling a switching fabric in a network switching node

InactiveUS6891823B1Reduce in quantityReduce complexityMultiplex system selection arrangementsData switching by path configurationData portHardware complexity

A method and apparatus for reallocating switching circuitry in a switching fabric are disclosed. The switching fabric is used to permit data transfer among a plurality of interface units each having a plurality of data ports. The switching fabric is partitionable into a plurality of switch planes such that each switch plane can be assigned to transfer data associated with like data ports of the interface units. Each switch plane includes multiple switching channels each assignable to transfer data associated with one data port of one of the interface units, in a full implementation. The number of interface units is less than the number of switching channels in a switch plane, then the reallocation is performed such that multiple channels of at least one switch plane can be assigned to transfer data of multiple ports of at least one of the interface units. This results in switch plane channels that would otherwise be unused being utilized to transfer data. This reallocation of switch plane channels can result in the elimination of one or more switch planes from the switch fabric resulting in substantially reduced hardware complexity and cost.

Owner:PLURIS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com