Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

79 results about "Gate count" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In microprocessor design, gate count refers to the number of gates build with transistor and other electronic devices, that are needed to implement a design. Even with today's process technology providing what was formerly considered impossible numbers of gates on a single chip, gate counts remain one of the most important overall factors in the end price of a chip. Designs with fewer gates will typically cost less, and for this reason gate count remains a commonly used metric in the industry.

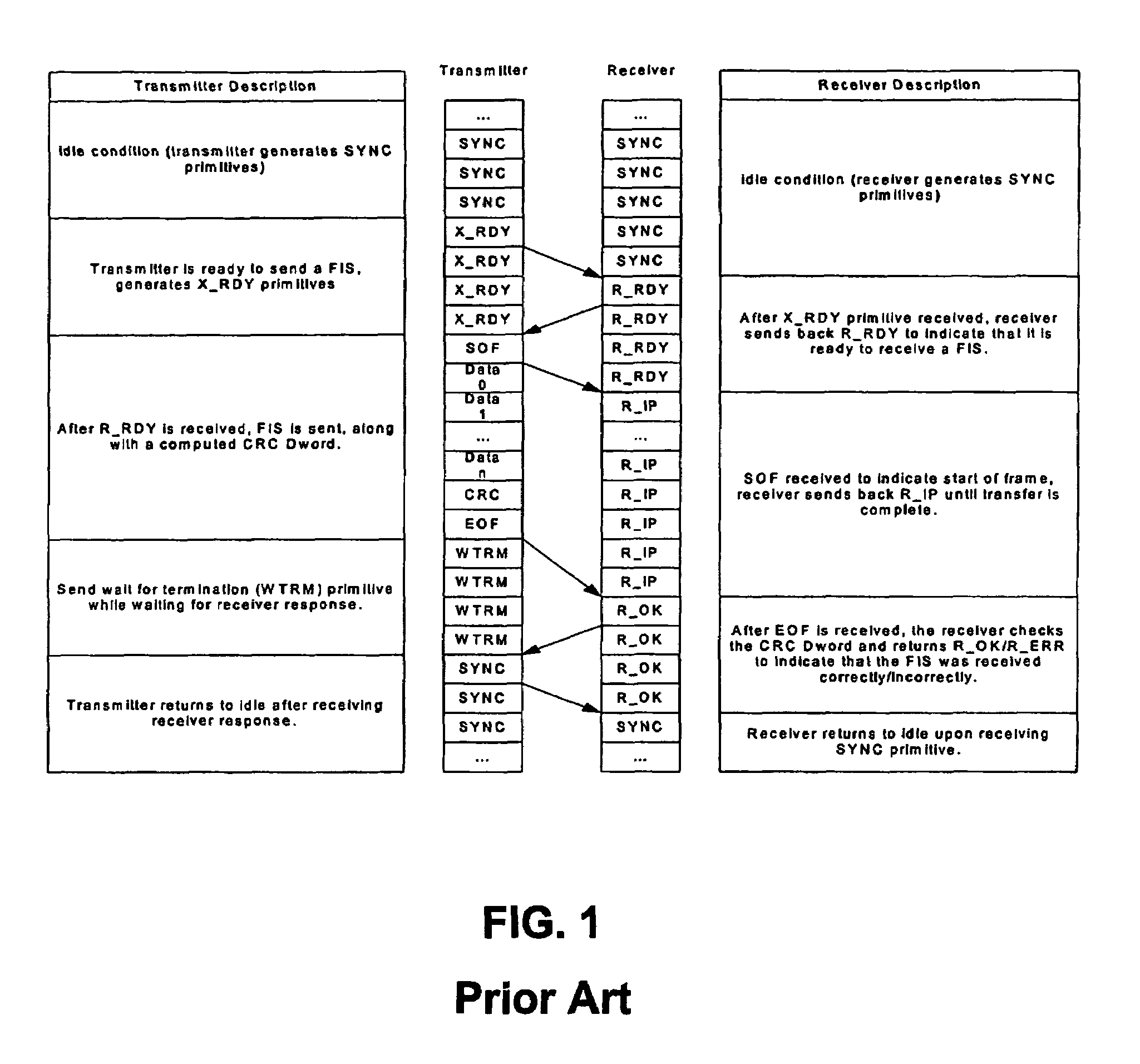

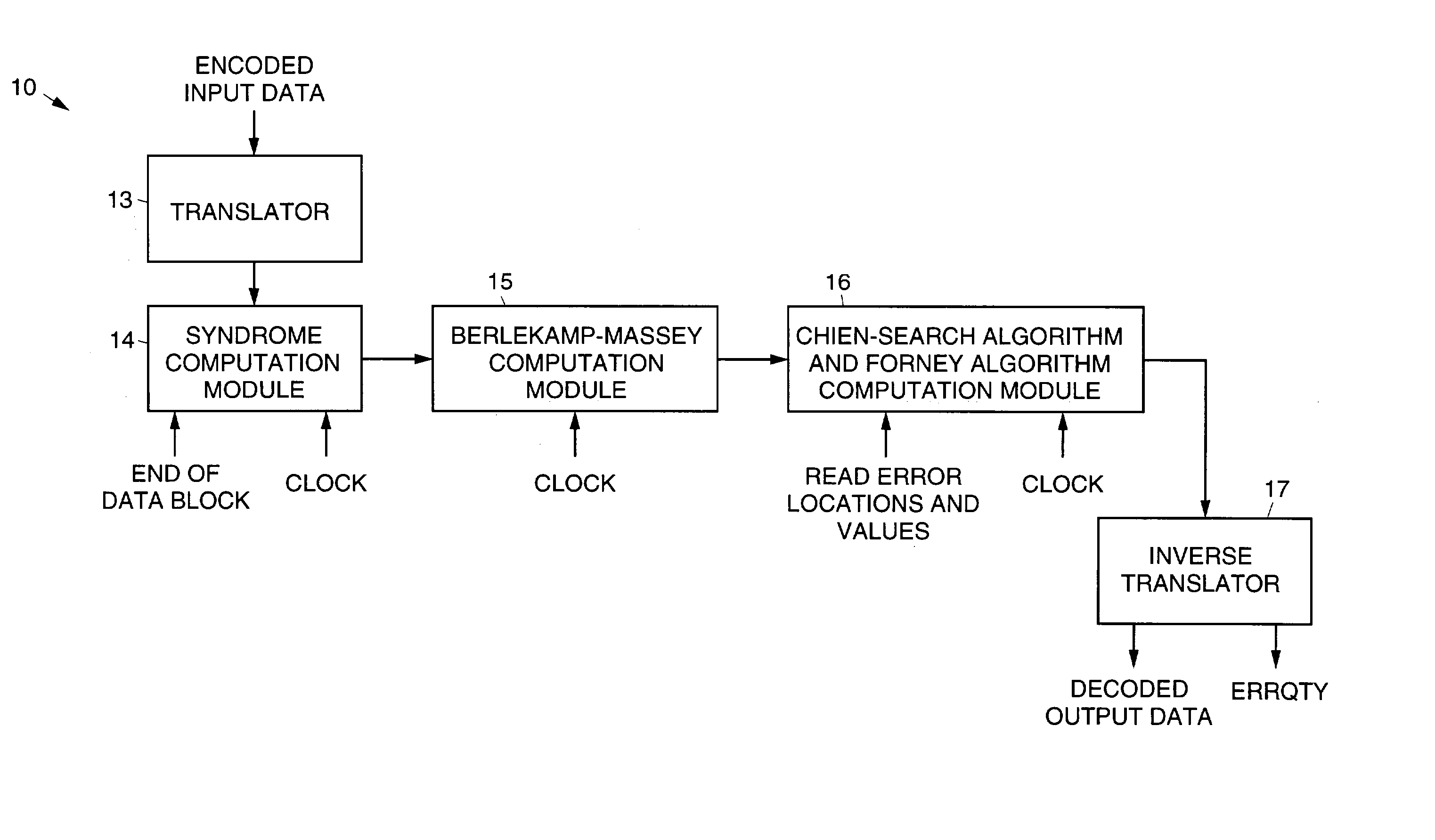

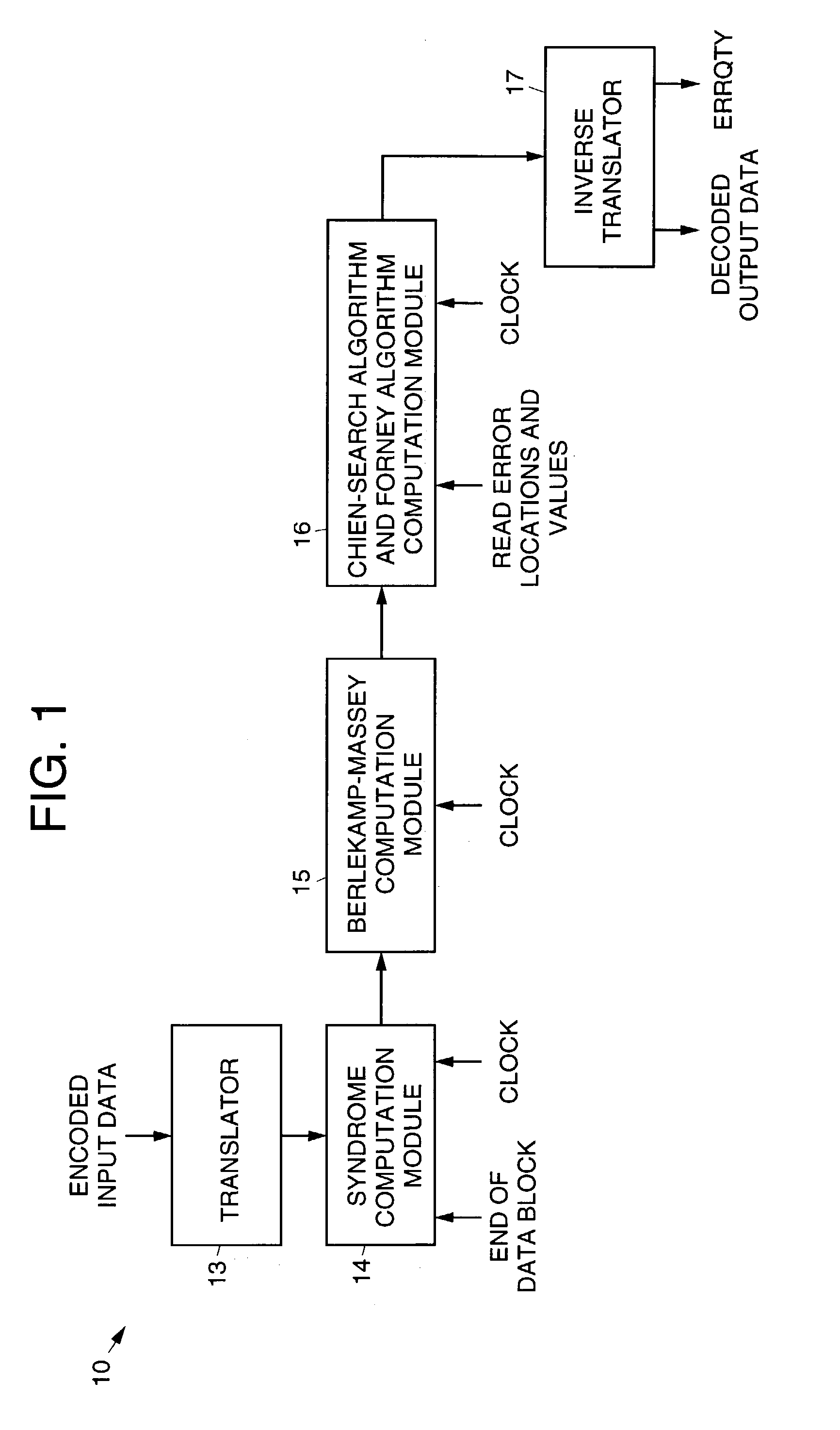

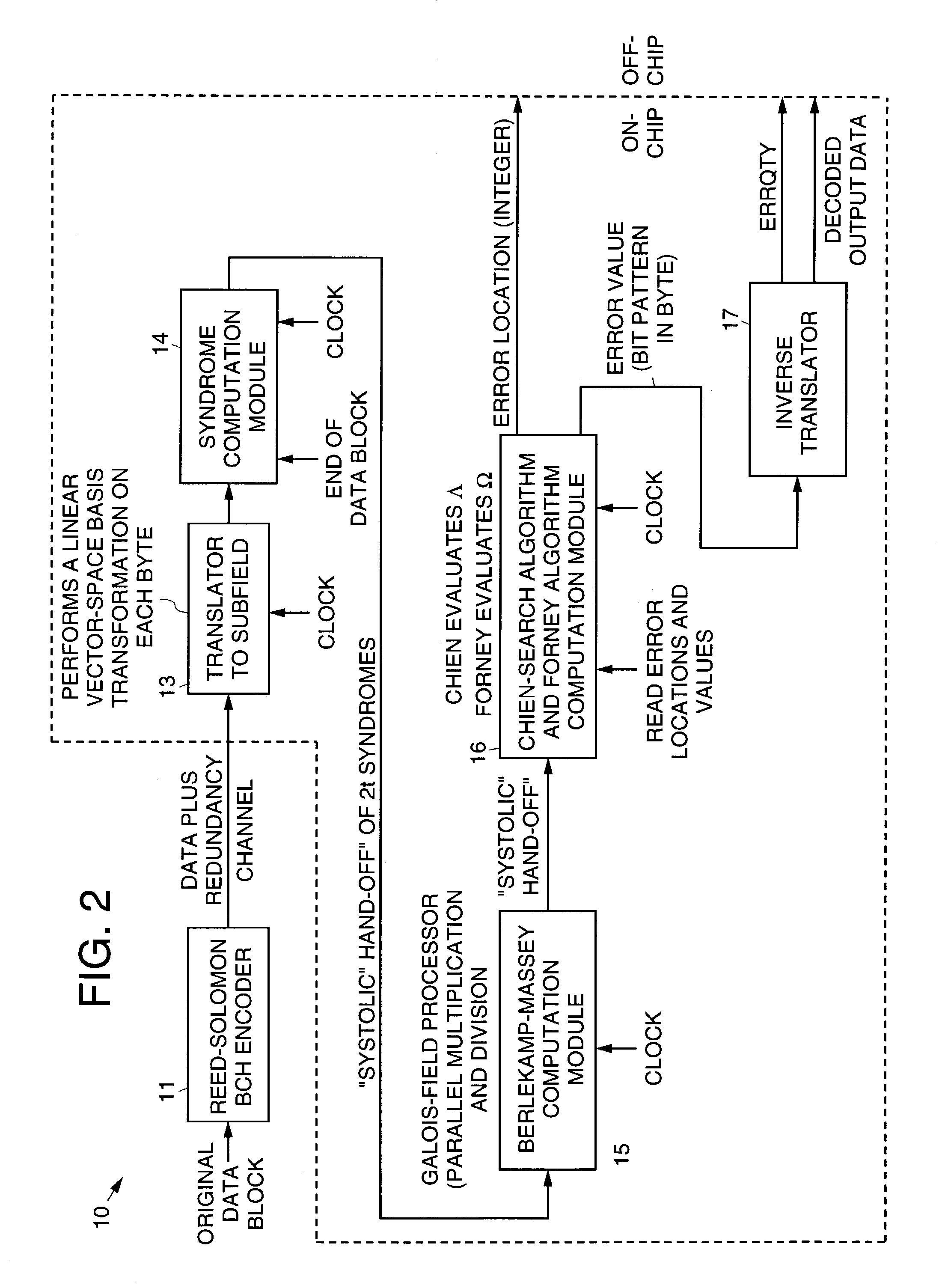

Reed-solomon decoder systems for high speed communication and data storage applications

InactiveUS20060059409A1Effective and reliable error correction functionalityReduce complexityCode conversionCoding detailsModem deviceHigh rate

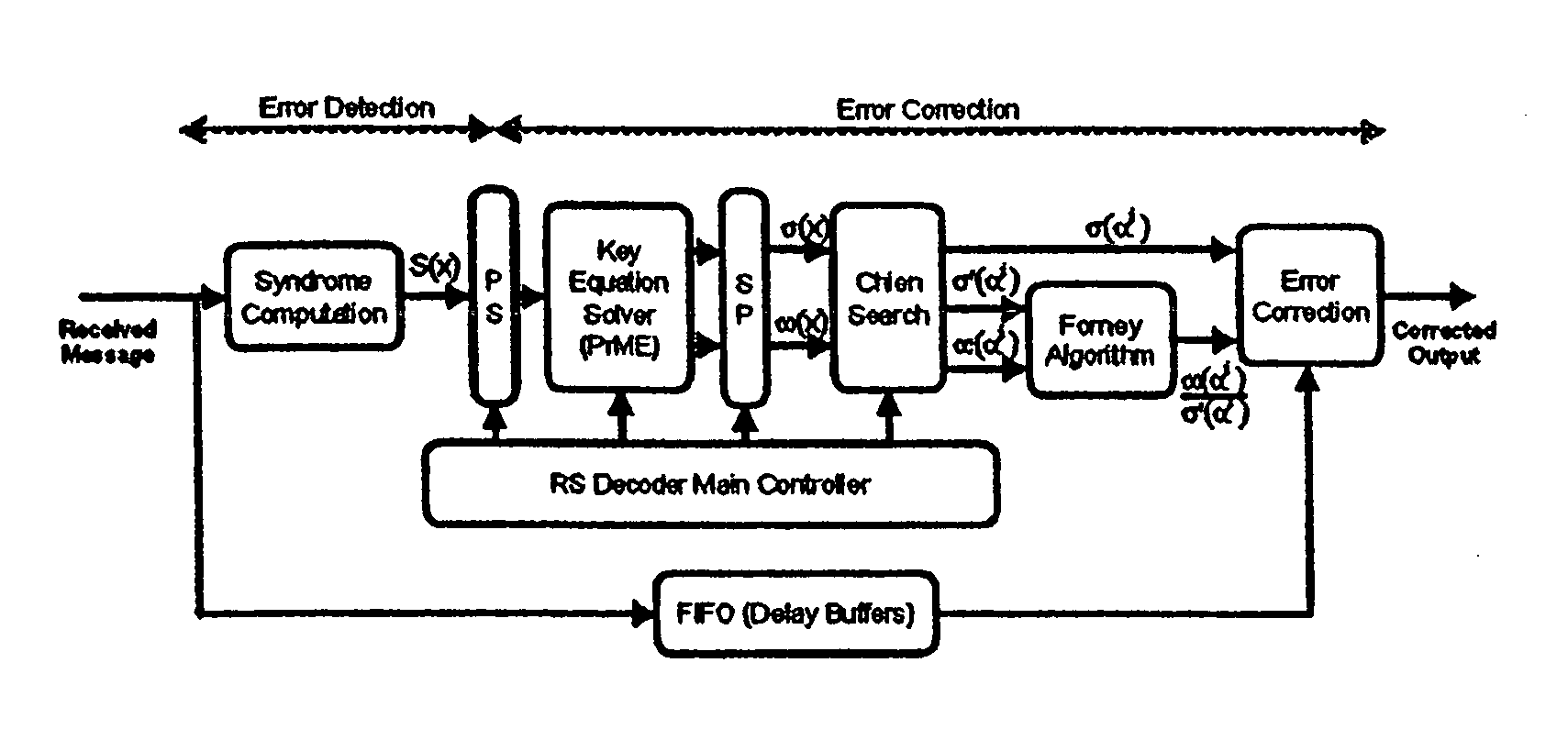

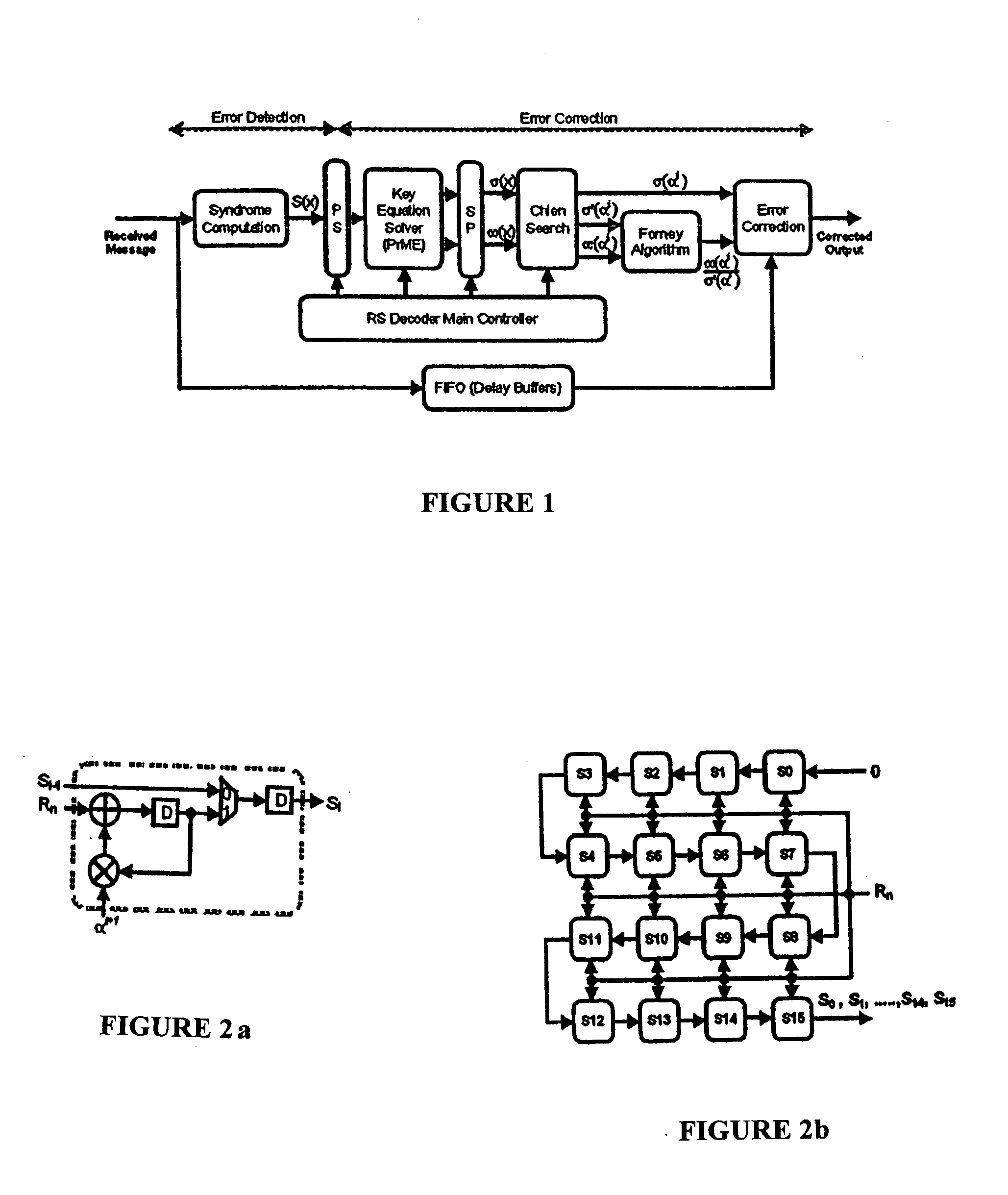

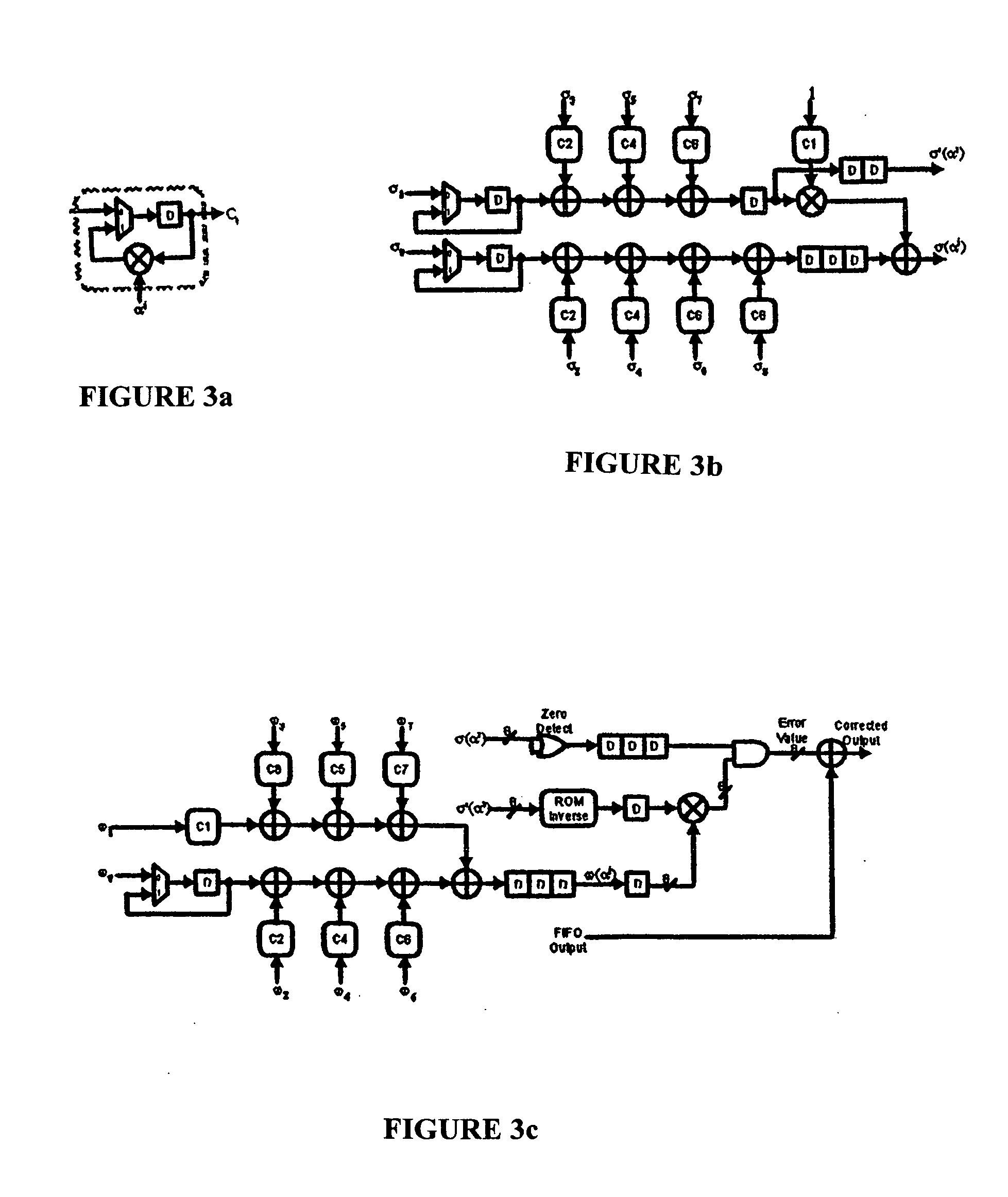

A high-speed, low-complexity Reed-Solomon (RS) decoder architecture using a novel pipelined recursive Modified Euclidean (PrME) algorithm block for very high-speed optical communications is provided. The RS decoder features a low-complexity Key Equation Solver using a PrME algorithm block. The recursive structure enables the low-complexity PrME algorithm block to be implemented. Pipelining and parallelizing allow the inputs to be received at very high fiber optic rates, and outputs to be delivered at correspondingly high rates with minimum delay. An 80-Gb / s RS decoder architecture using 0.13-μm CMOS technology in a supply voltage of 1.2 V is disclosed that features a core gate count of 393 K and operates at a clock rate of 625 MHz. The RS decoder has a wide range of applications, including fiber optic telecommunication applications, hard drive or disk controller applications, computational storage system applications, CD or DVD controller applications, fiber optic systems, router systems, wireless communication systems, cellular telephone systems, microwave link systems, satellite communication systems, digital television systems, networking systems, high-speed modems and the like.

Owner:UNIV OF CONNECTICUT

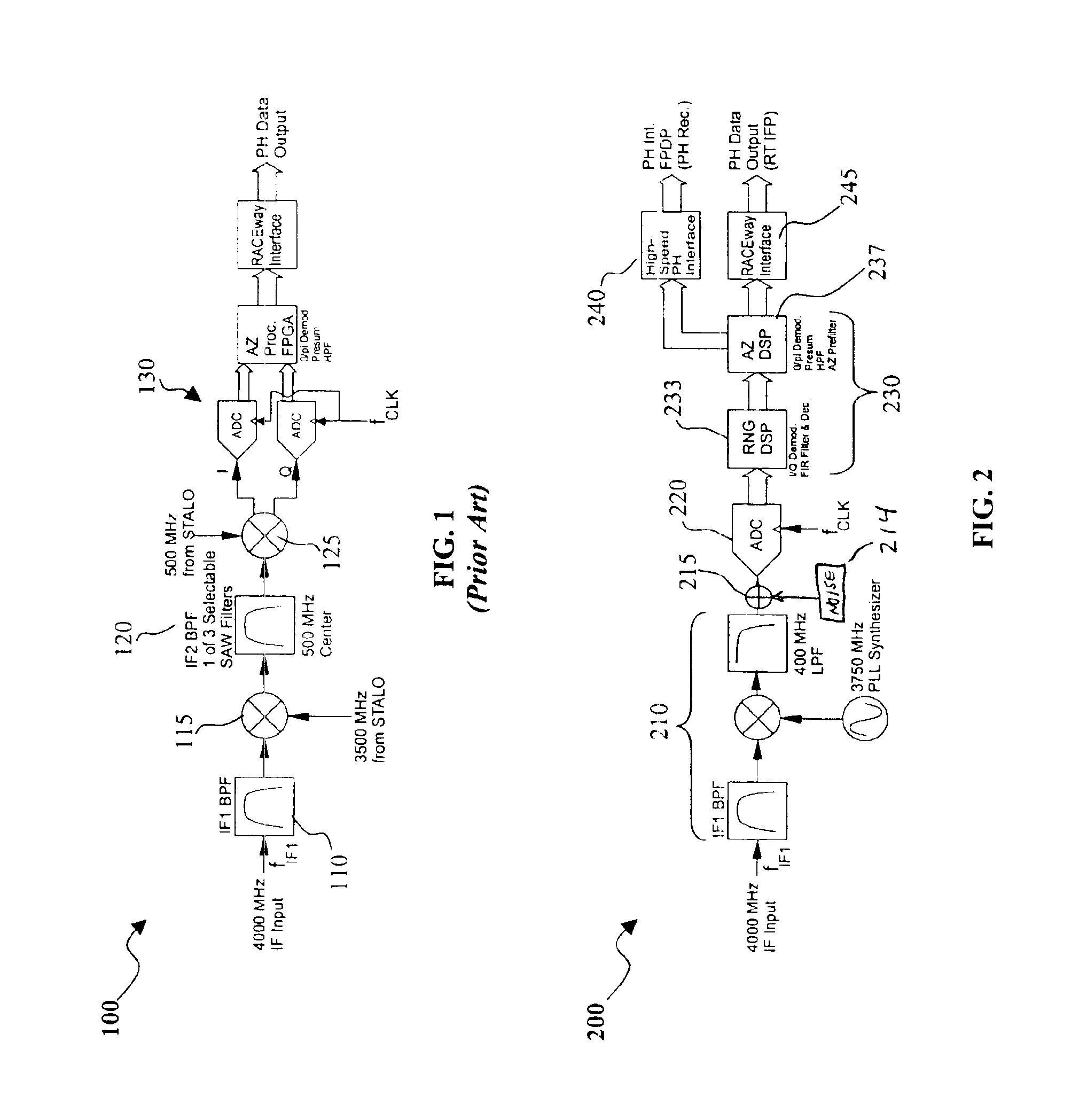

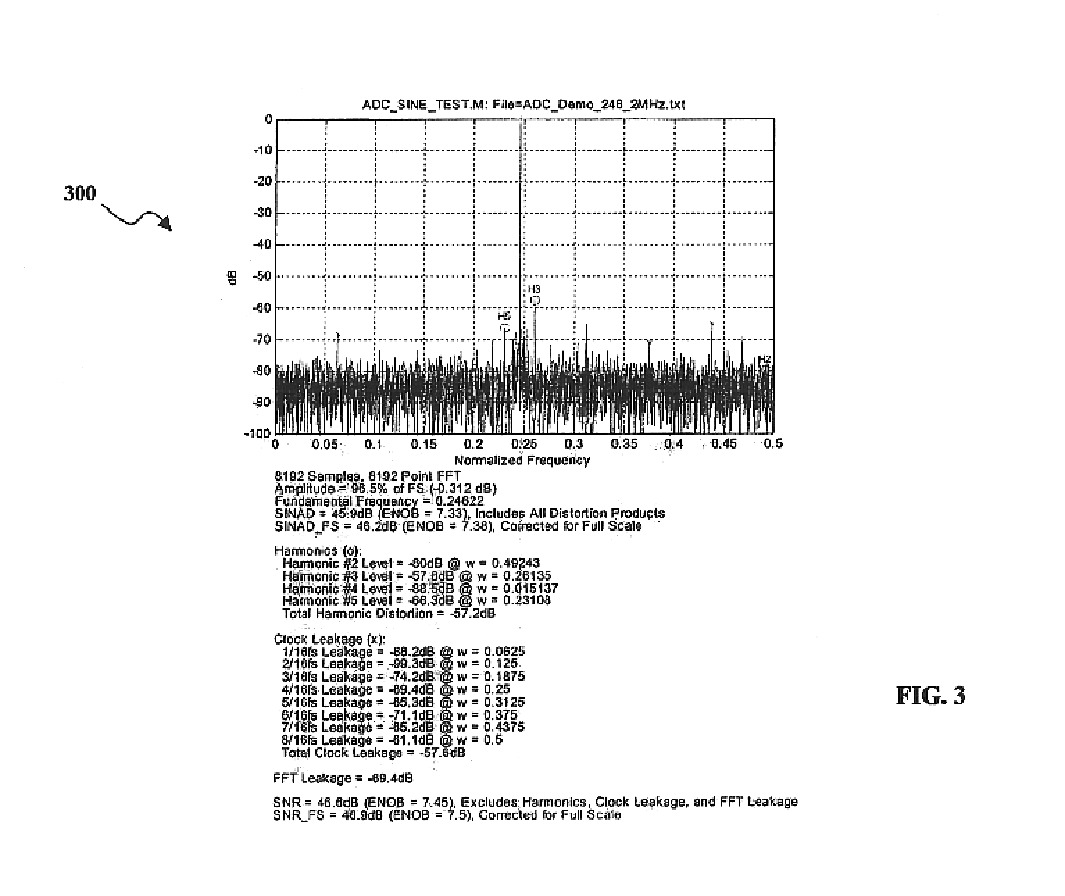

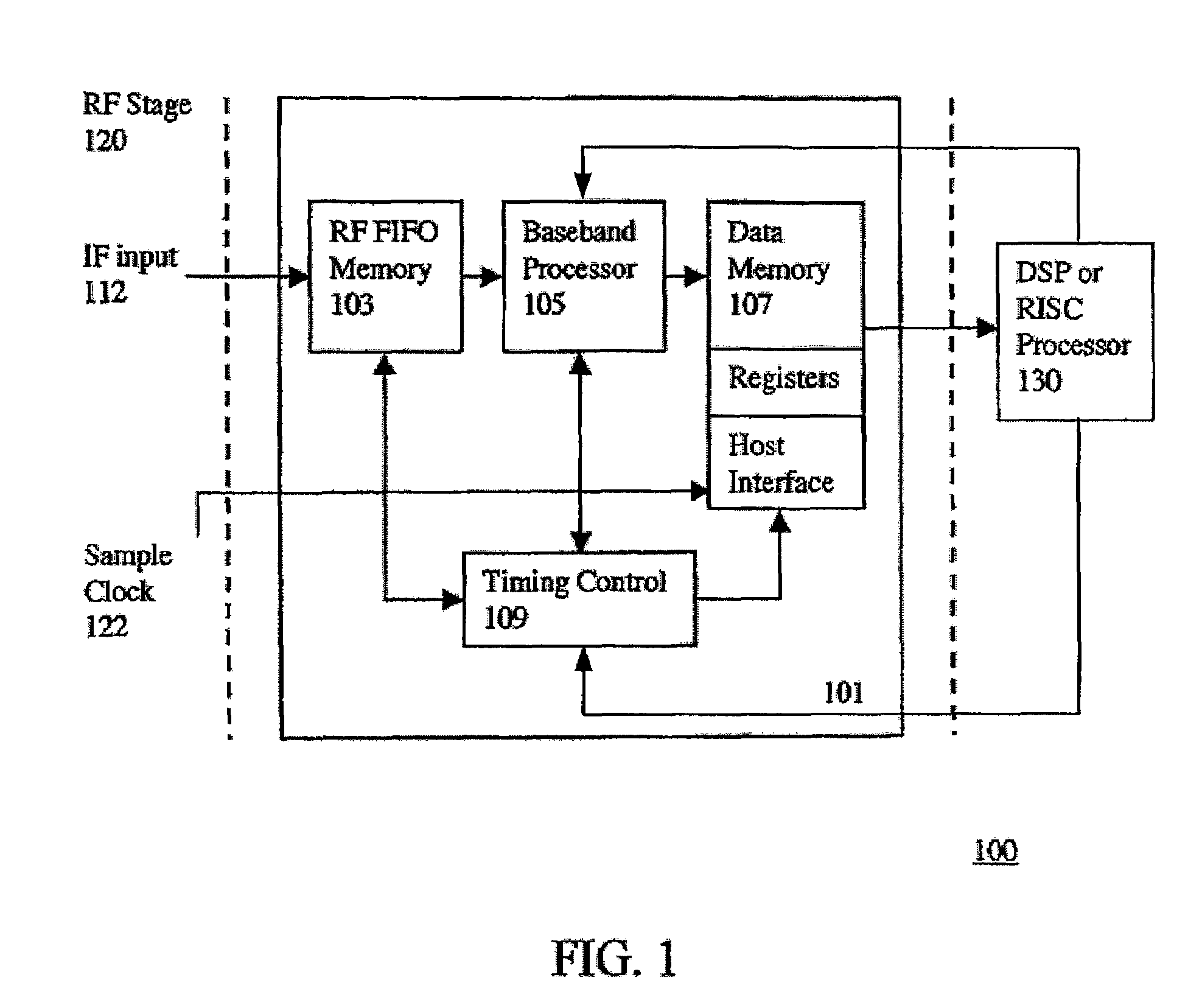

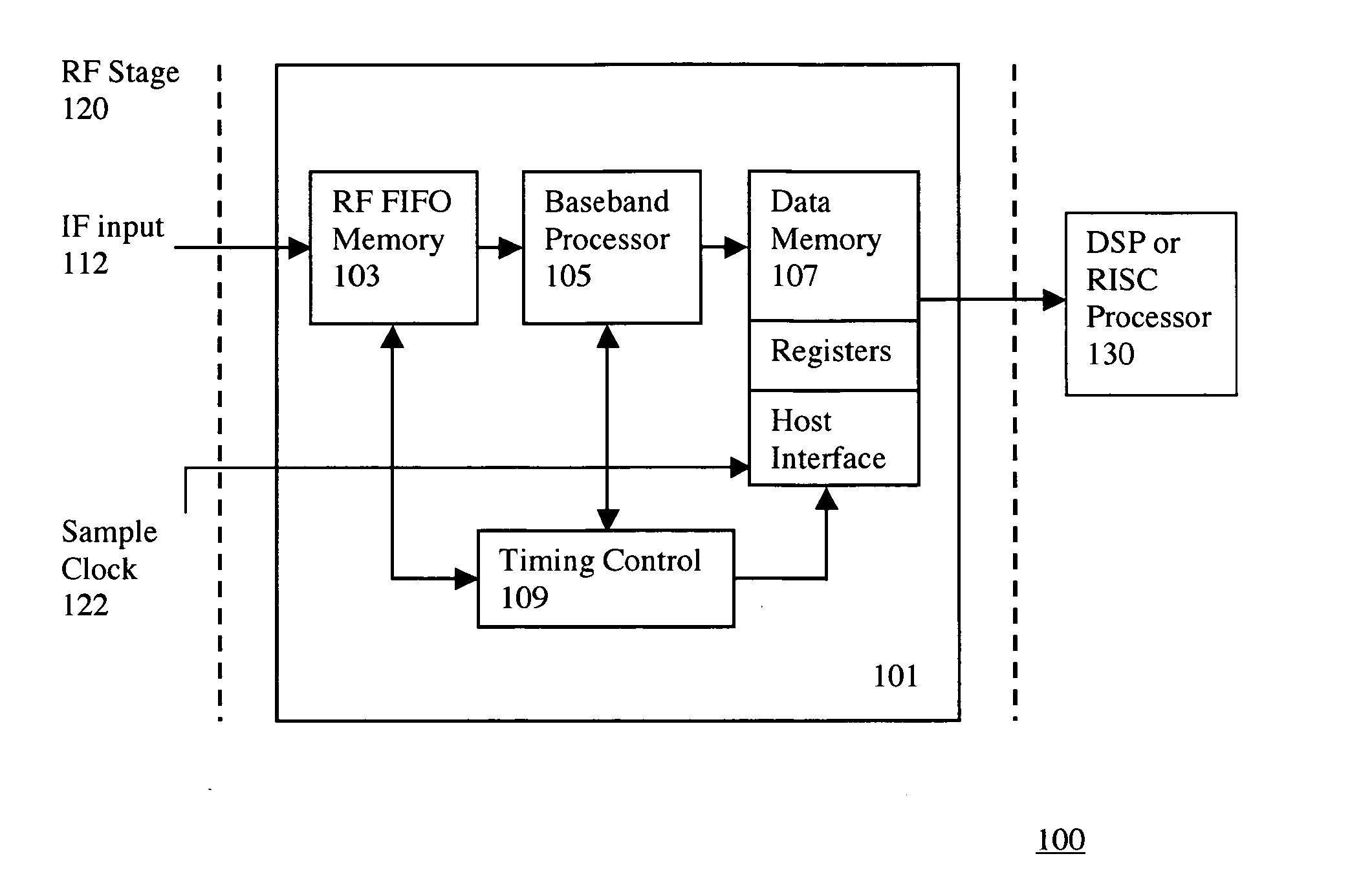

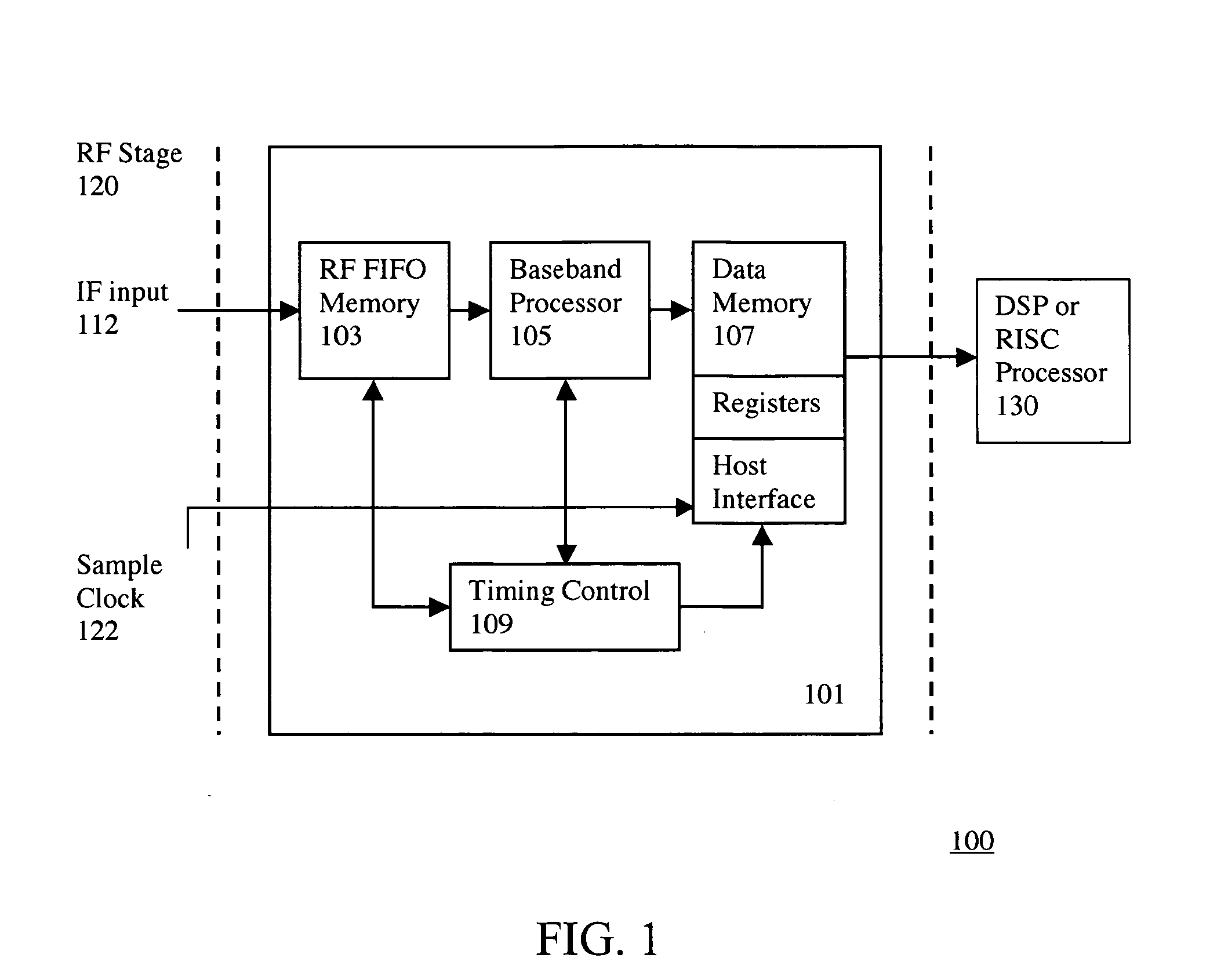

Digital intermediate frequency receiver module for use in airborne SAR applications

ActiveUS6864827B1Increase flexibilityIncrease spacingRadio wave reradiation/reflectionDigital signal processingRadar systems

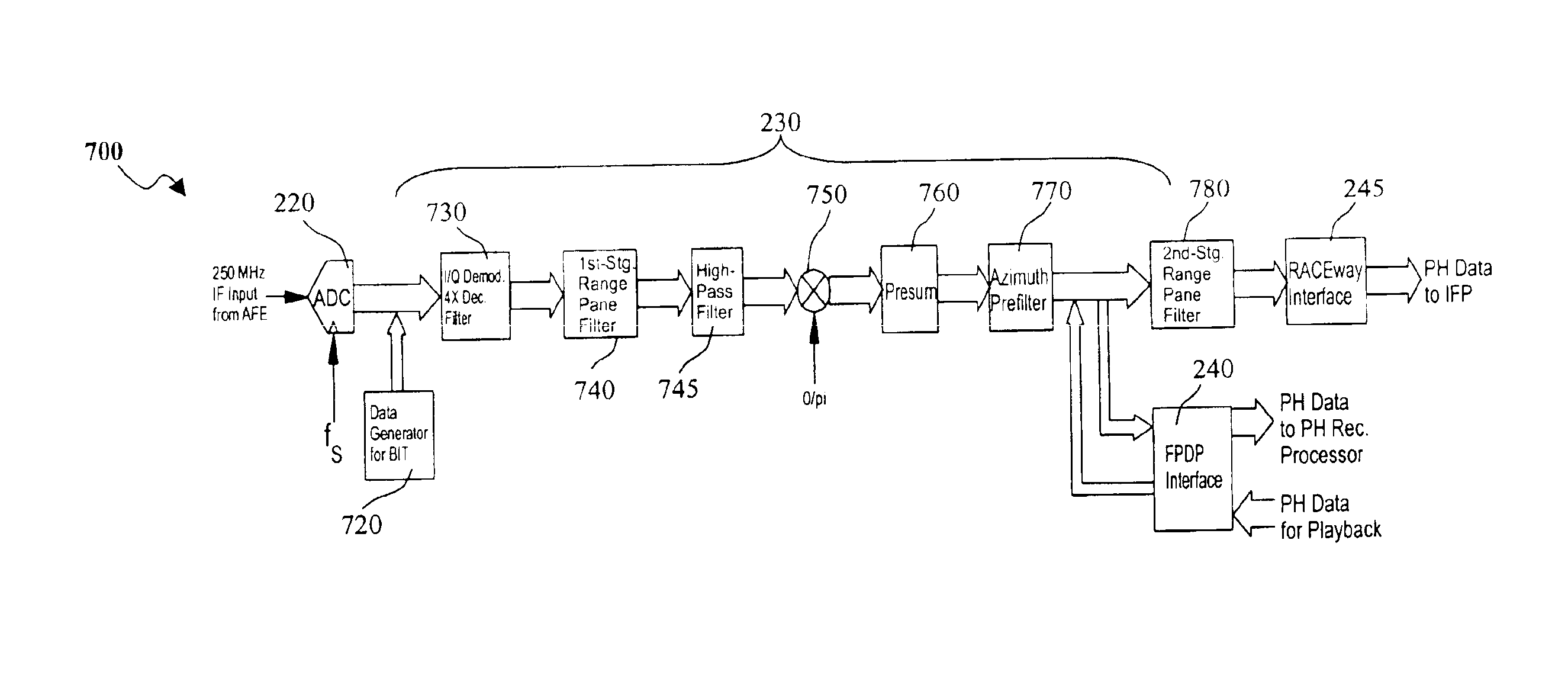

A digital IF receiver (DRX) module directly compatible with advanced radar systems such as synthetic aperture radar (SAR) systems. The DRX can combine a 1 G-Sample / sec 8-bit ADC with high-speed digital signal processor, such as high gate-count FPGA technology or ASICs to realize a wideband IF receiver. DSP operations implemented in the DRX can include quadrature demodulation and multi-rate, variable-bandwidth IF filtering. Pulse-to-pulse (Doppler domain) filtering can also be implemented in the form of a presummer (accumulator) and an azimuth prefilter. An out of band noise source can be employed to provide a dither signal to the ADC, and later be removed by digital signal processing. Both the range and Doppler domain filtering operations can be implemented using a unique pane architecture which allows on-the-fly selection of the filter decimation factor, and hence, the filter bandwidth. The DRX module can include a standard VME-64 interface for control, status, and programming. An interface can provide phase history data to the real-time image formation processors. A third front-panel data port (FPDP) interface can send wide bandwidth, raw phase histories to a real-time phase history recorder for ground processing.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

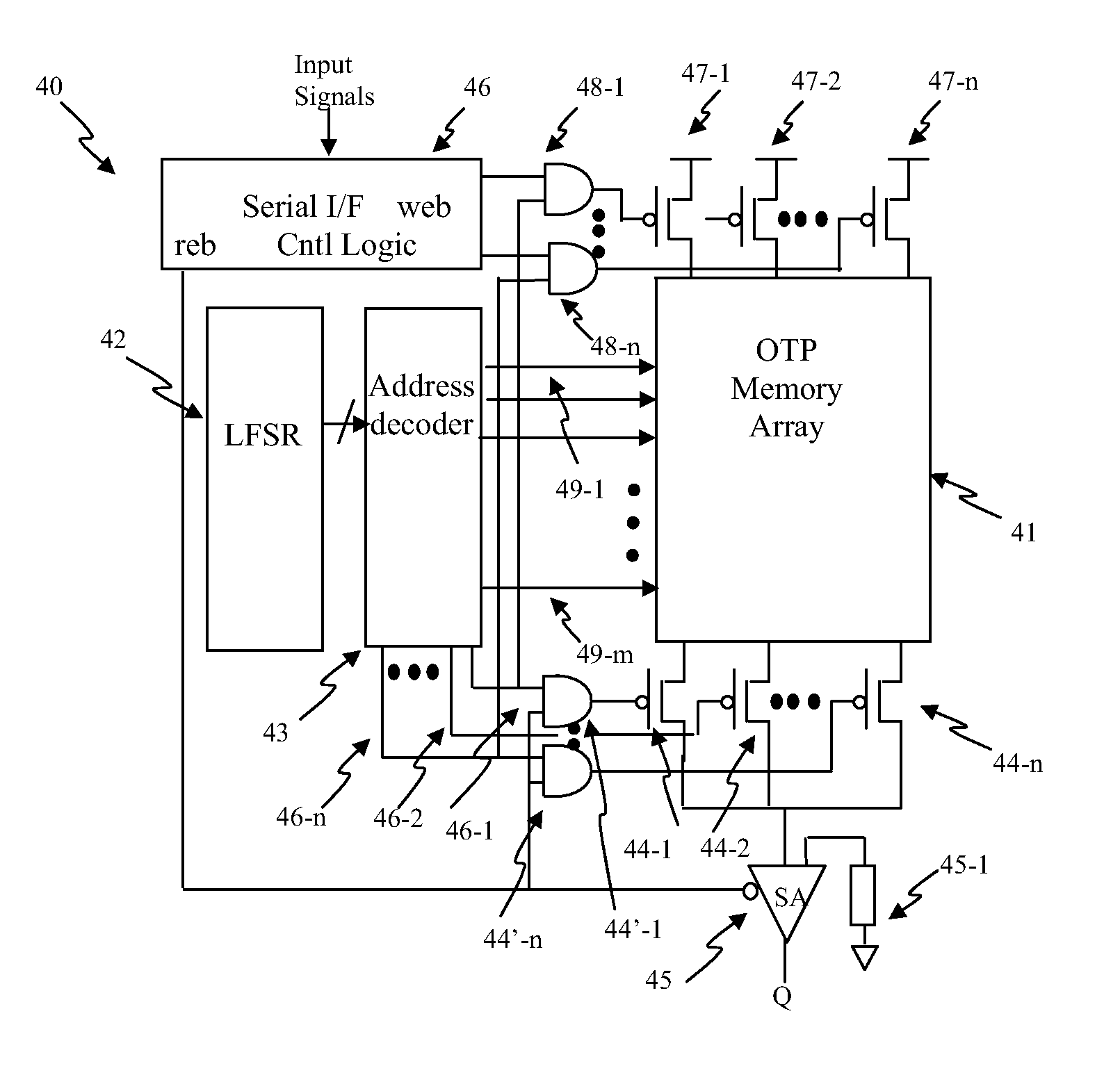

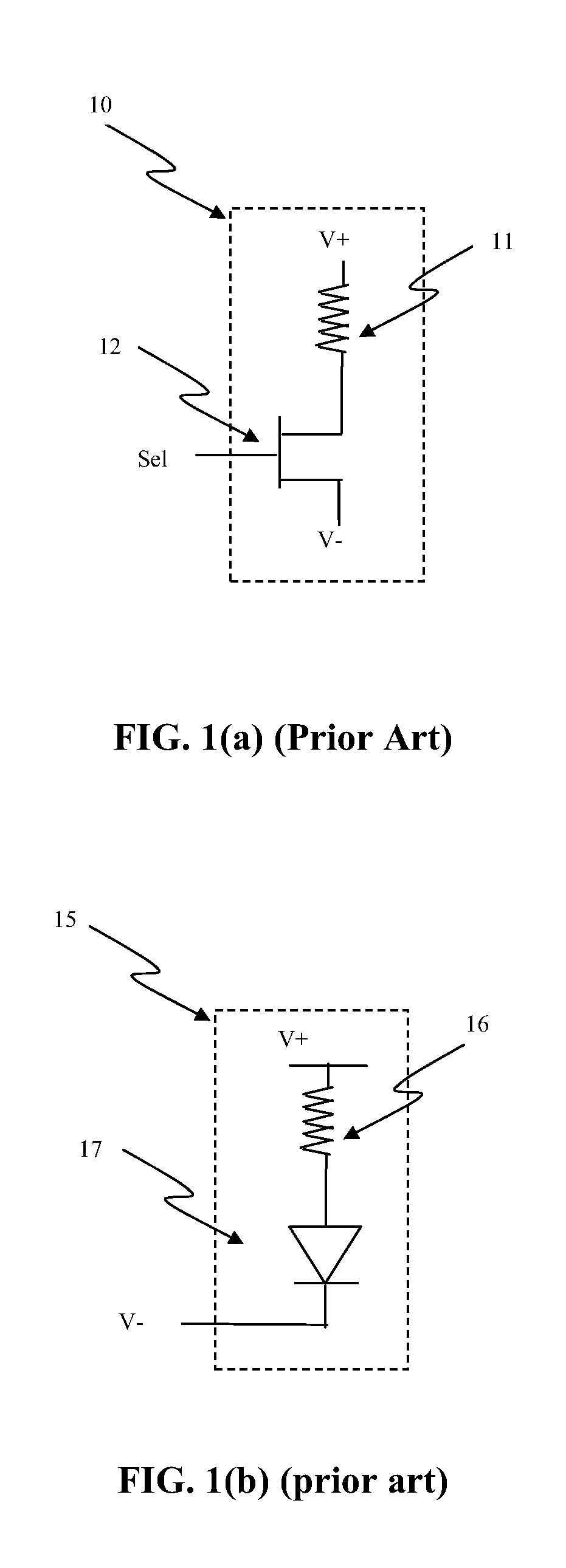

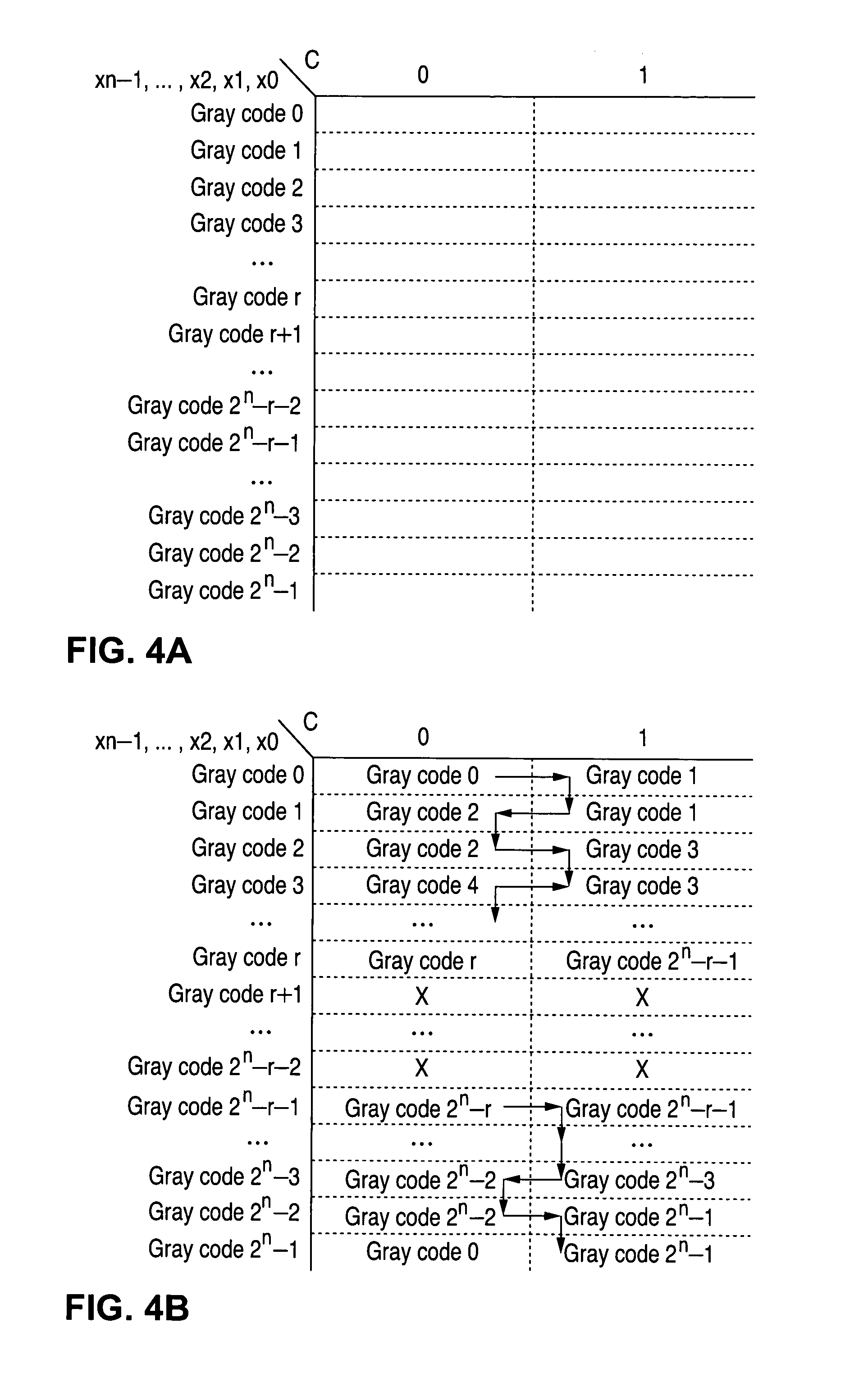

Circuit and System of a Low Density One-Time Programmable Memory

InactiveUS20130201745A1Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesAddress generatorHemt circuits

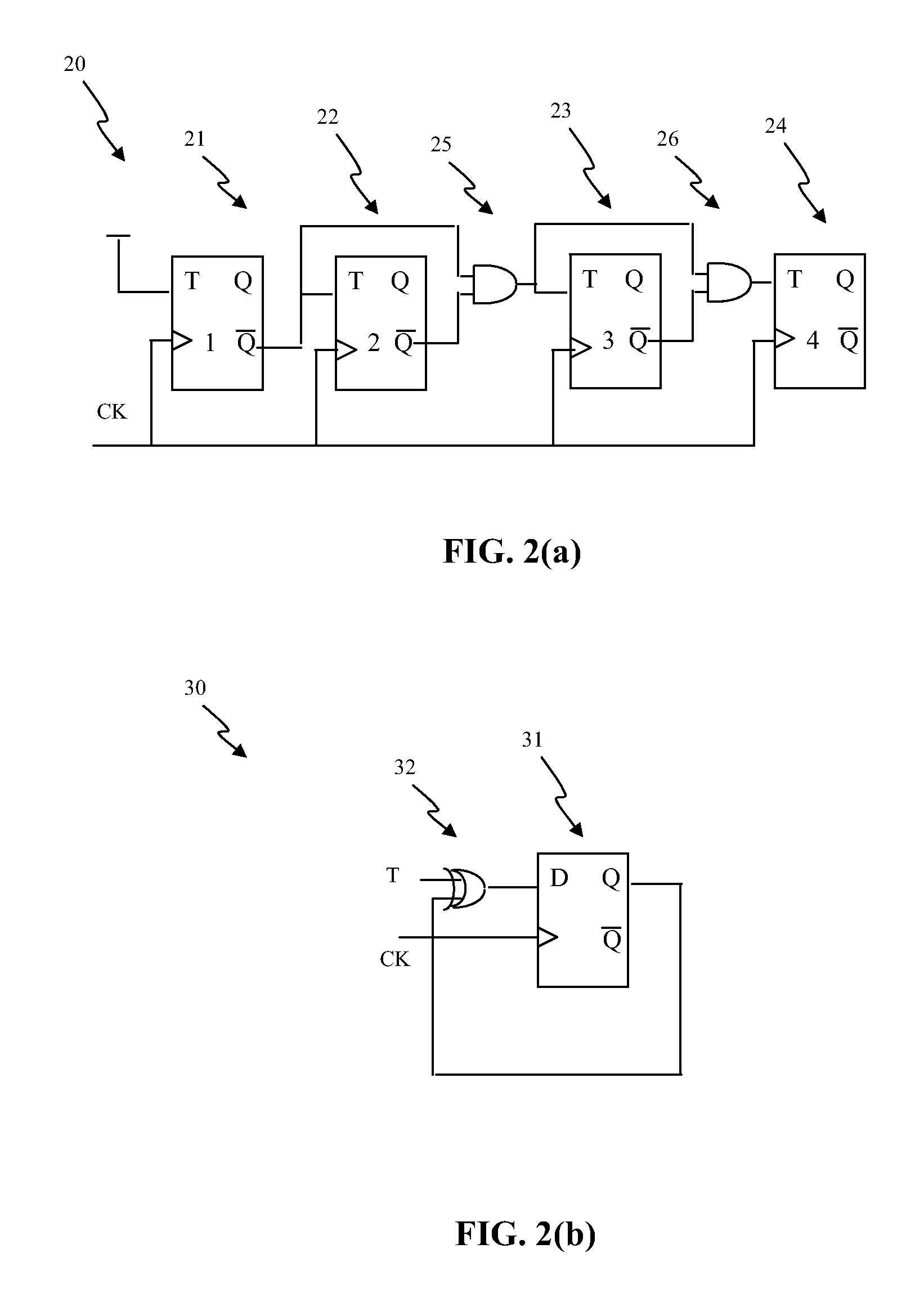

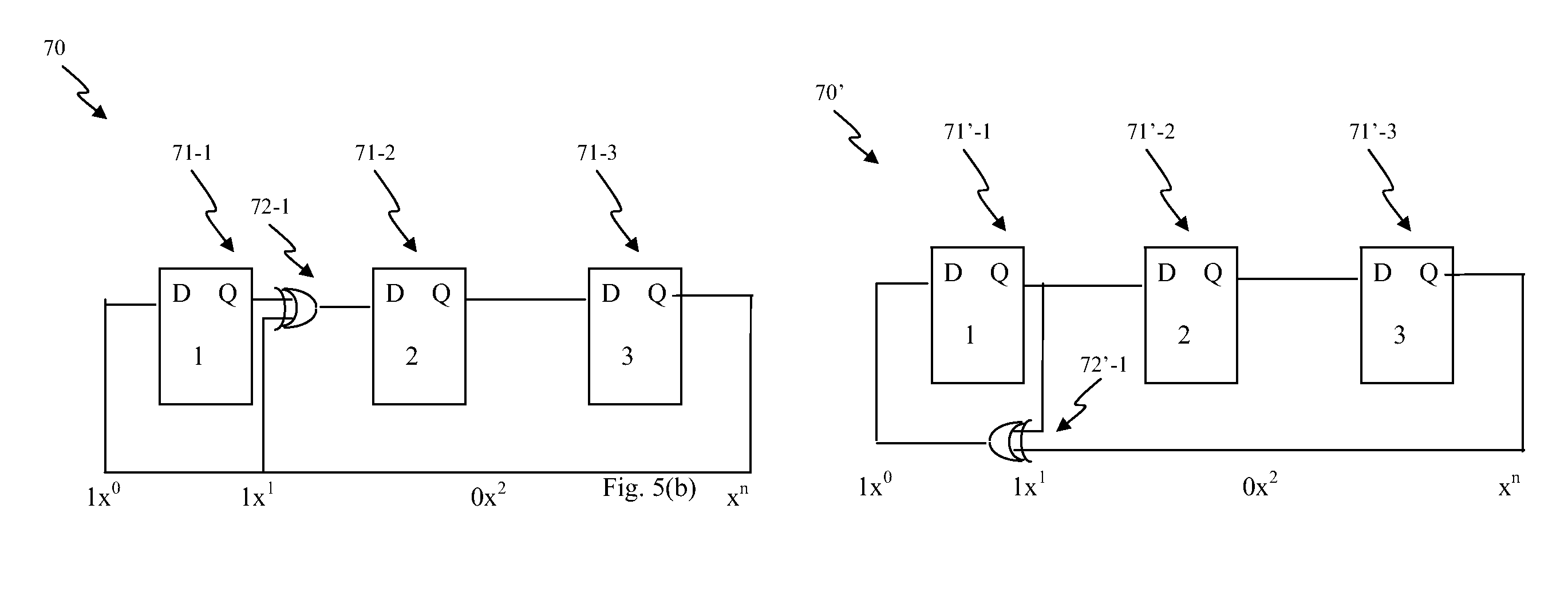

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

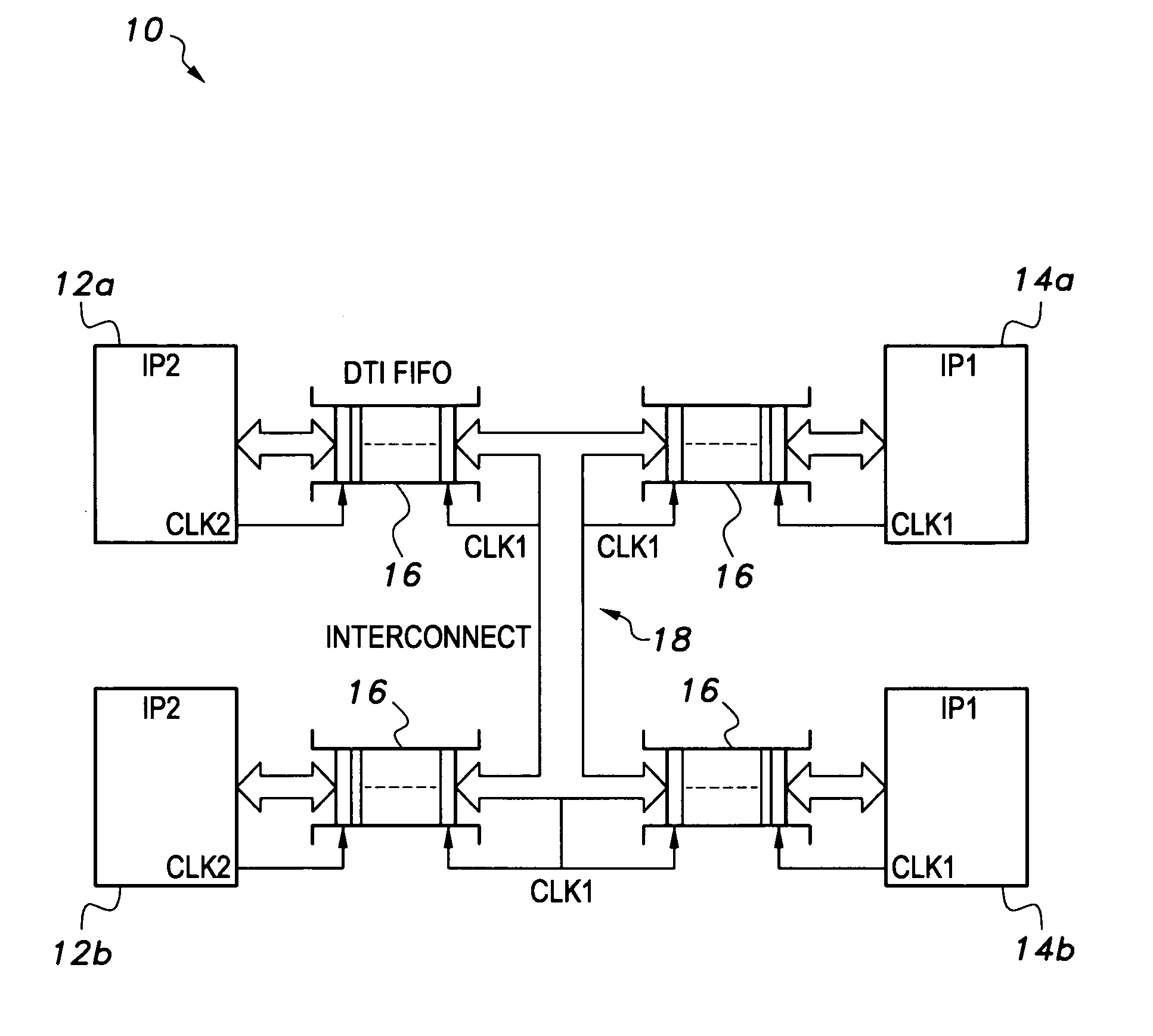

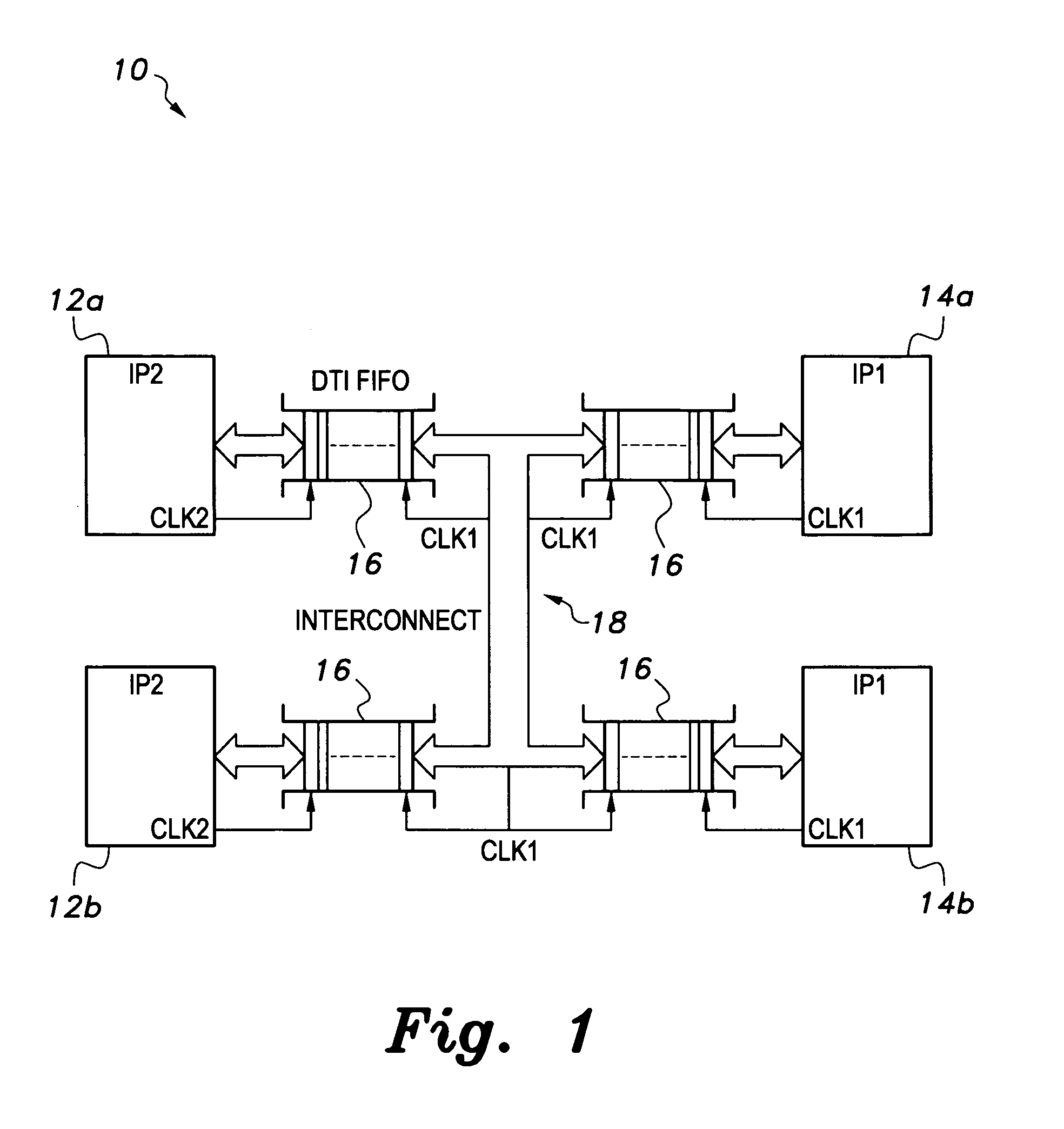

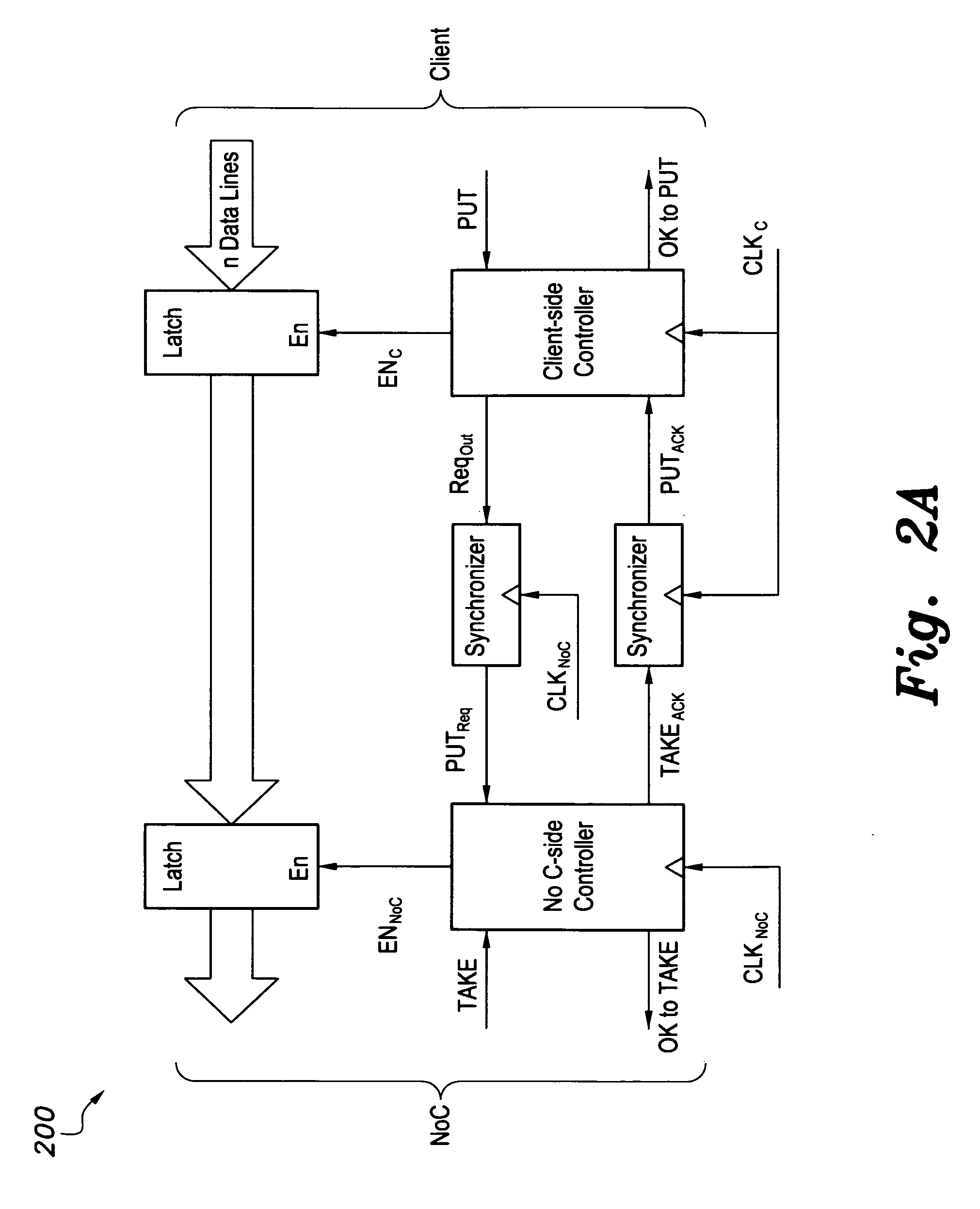

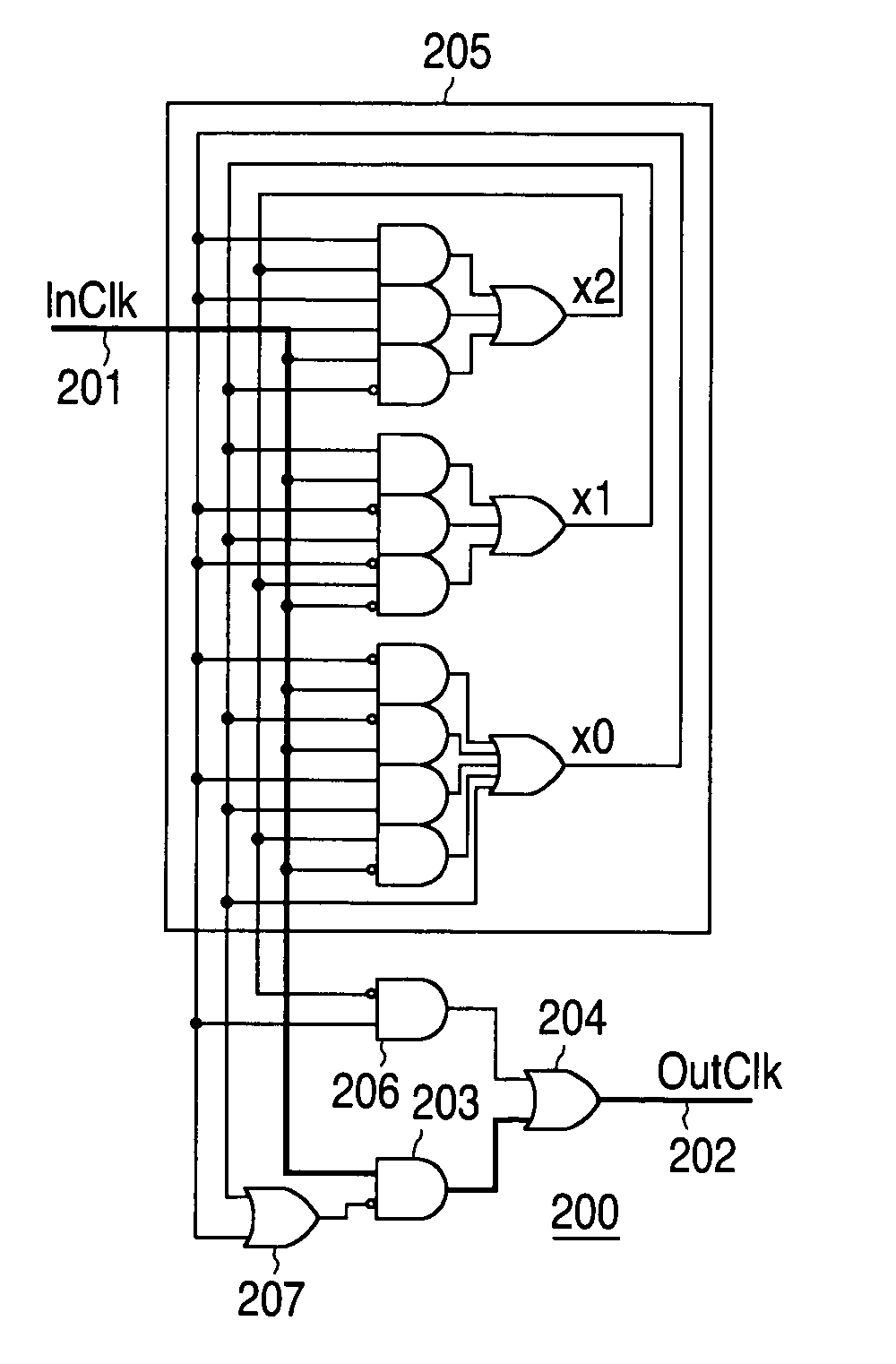

Inter-clock domain data transfer FIFO circuit

InactiveUS20110320854A1Reduce the number of gatesGenerating/distributing signalsData conversionClock rateData transmission

The inter-clock domain data transfer FIFO circuit provides a circuit that transfers data between two clock domains of unrelated frequencies. The gate count is kept relatively low, thereby allowing data transfer between the two clock domains at one data item per cycle of the lower of the two frequencies. Depending on the frequency difference between the data producer and consumer, the initial latency could be as low as a fraction of a cycle and no more than two cycles of the consumer's clock. The operation of the data transfer FIFO circuit has been verified using gate-level simulations for several ratios of clock frequencies.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

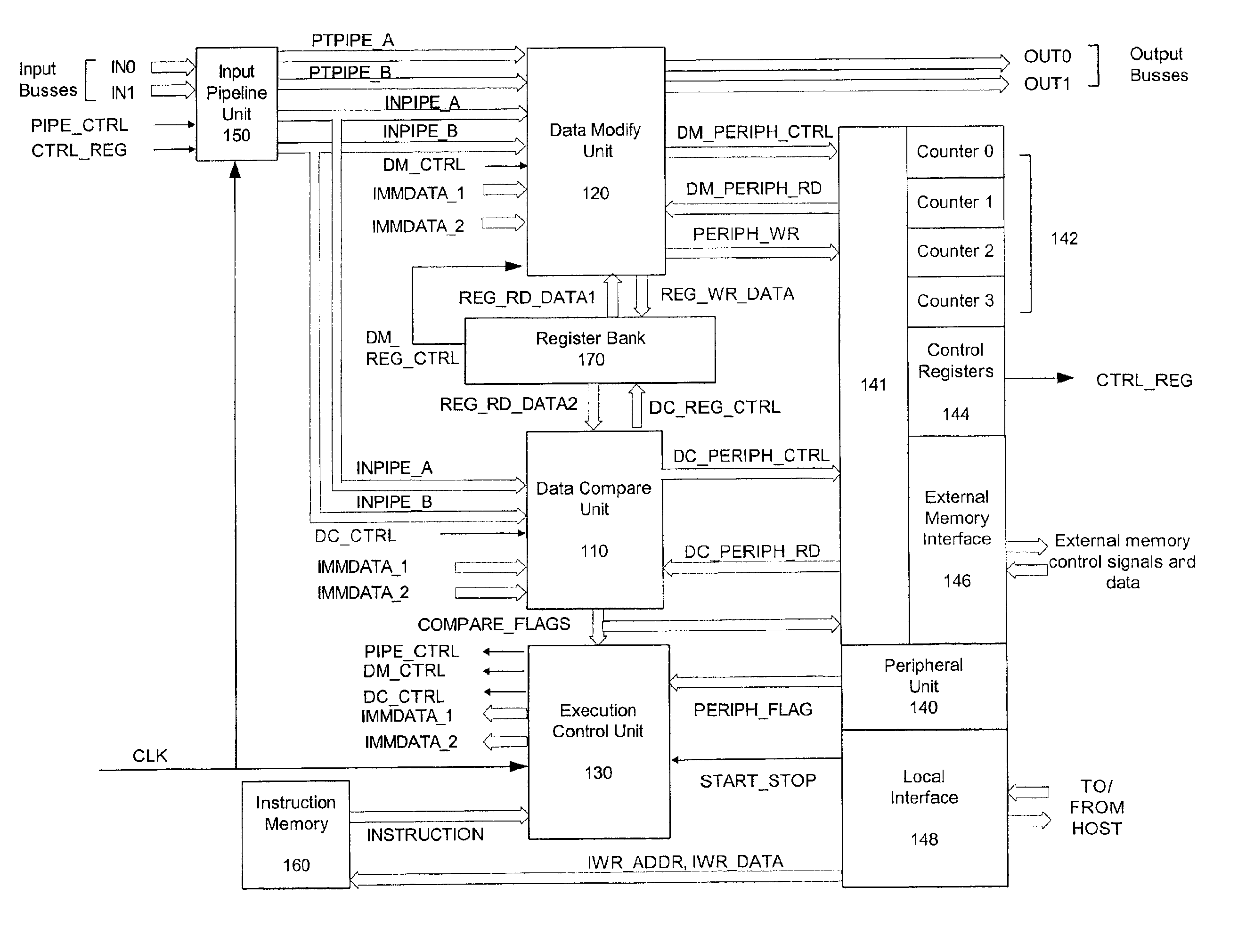

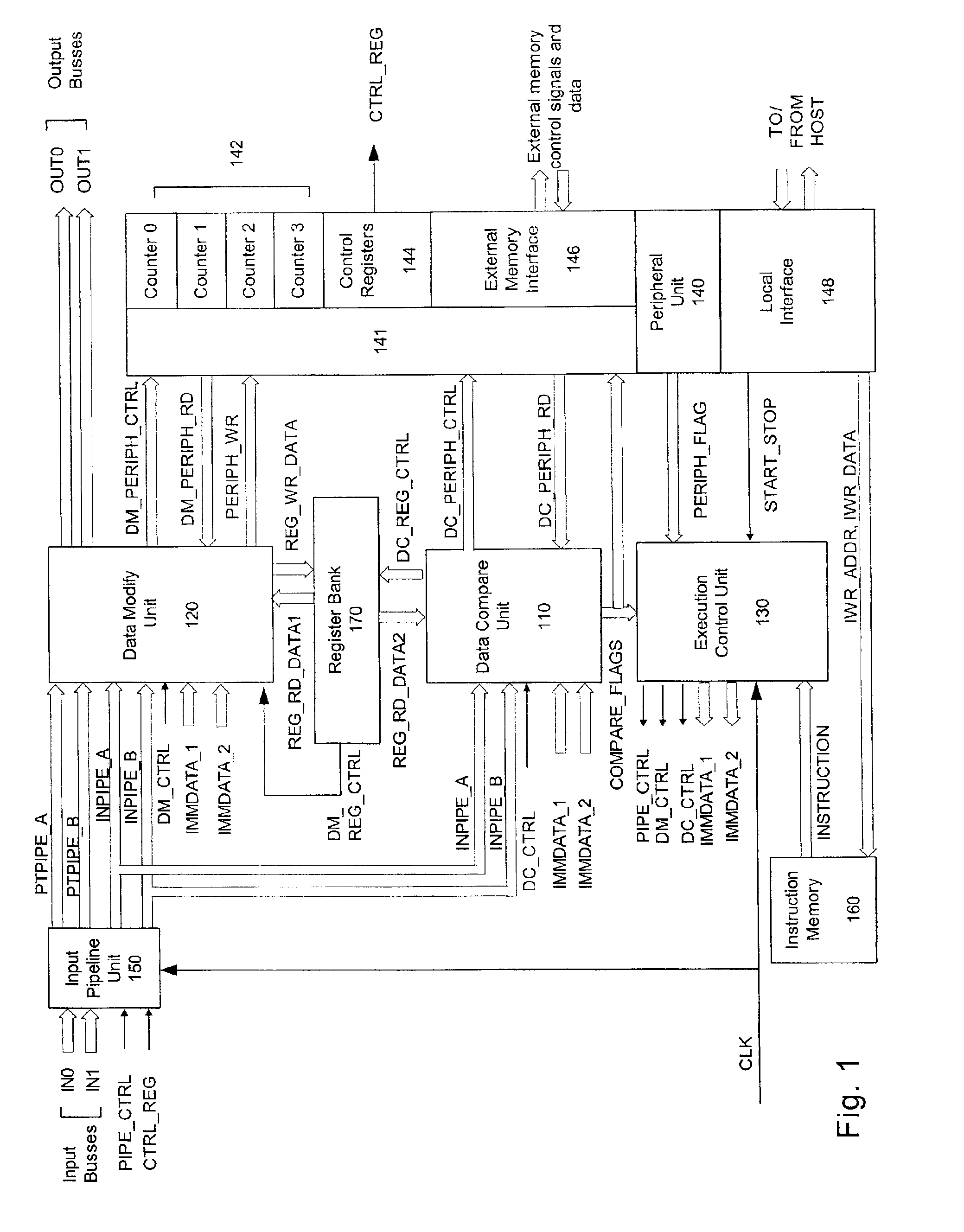

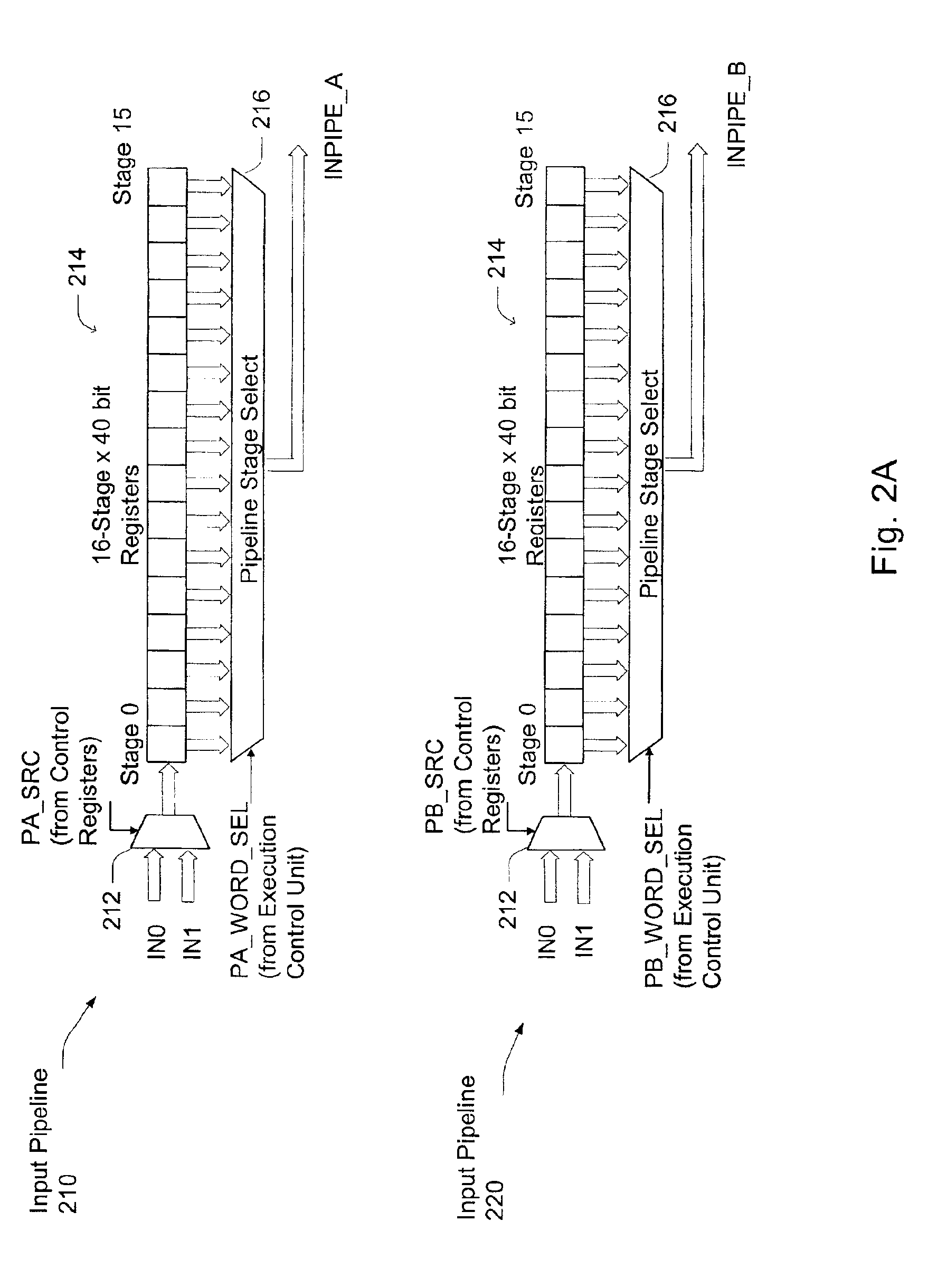

Synchronous network traffic processor

InactiveUS6880070B2Low costReduce developmentDigital computer detailsNext instruction address formationTraffic capacityWire speed

A synchronous network traffic processor that synchronously processes, analyzes and generates data for high-speed network protocols, on a wire-speed, word-by-word basis. The synchronous network processor is protocol independent and may be programmed to convert protocols on the fly. An embodiment of the synchronous network processor described has a low gate count and can be easily implemented using programmable logic. An appropriately programmed synchronous network traffic processor may replace modules traditionally implemented with hard-wired logic or ASIC.

Owner:VIAVI SOLUTIONS INC

Circuit and system of a low density one-time programmable memory

InactiveUS8861249B2Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesIp addressAddress generator

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

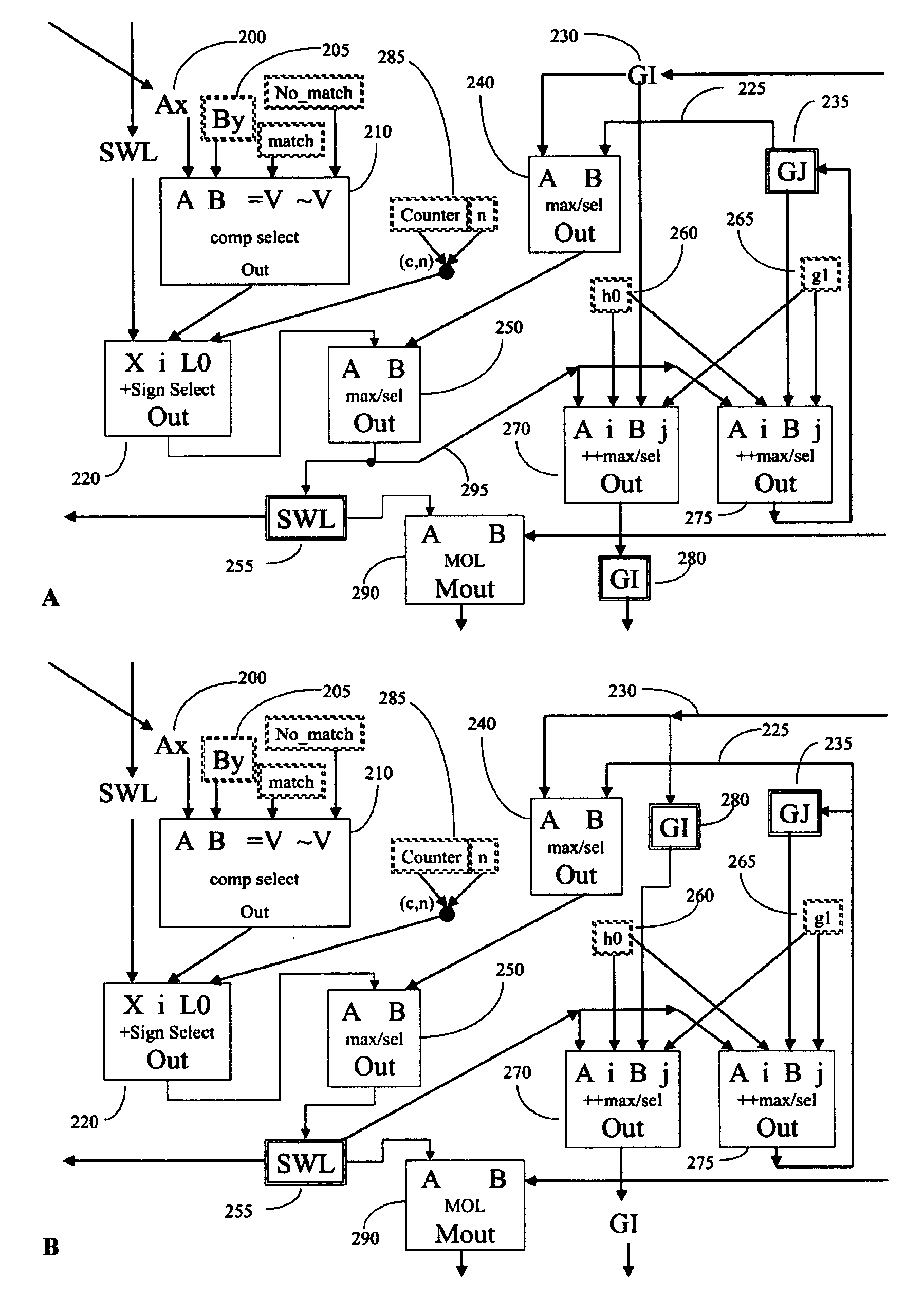

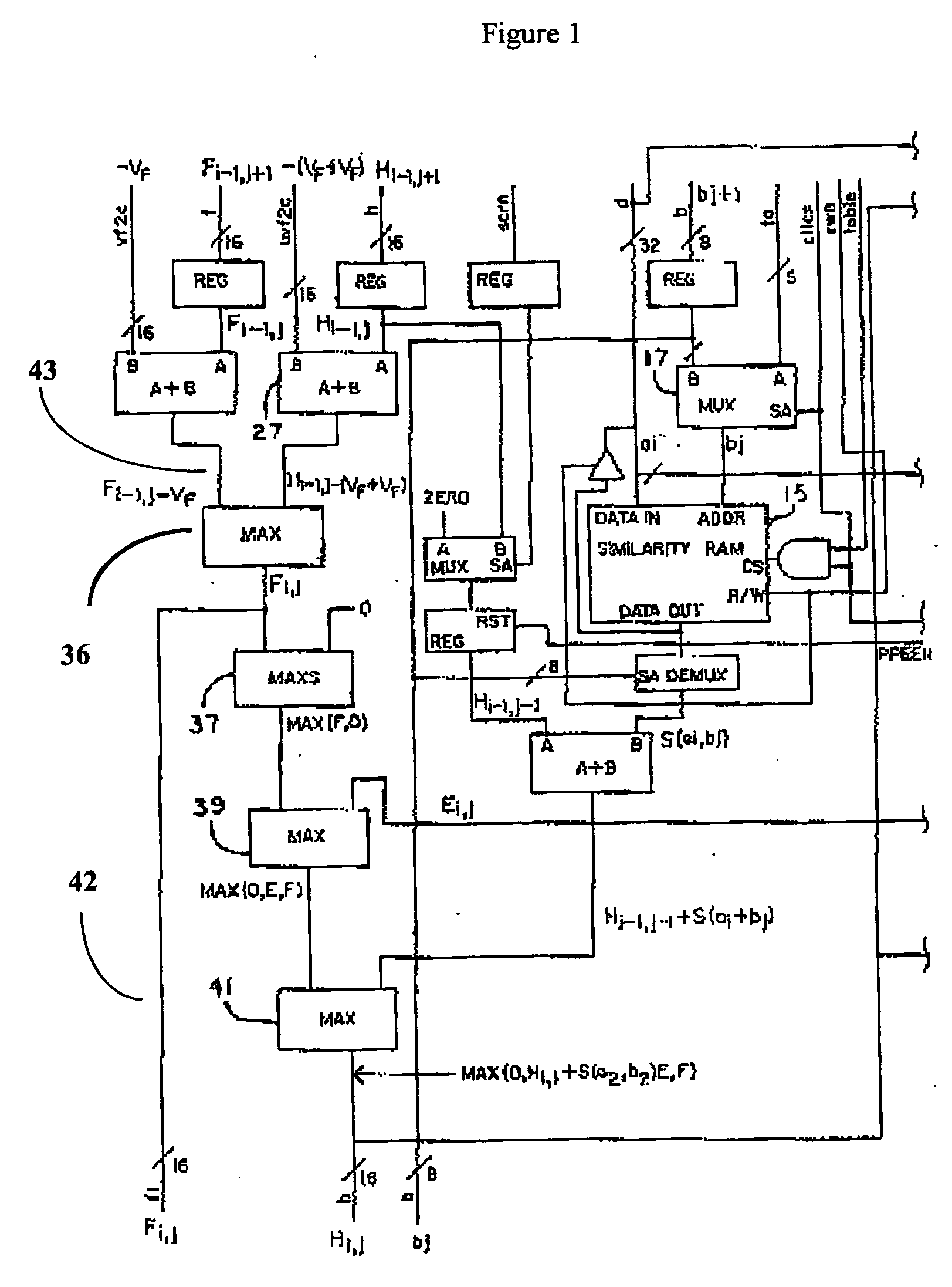

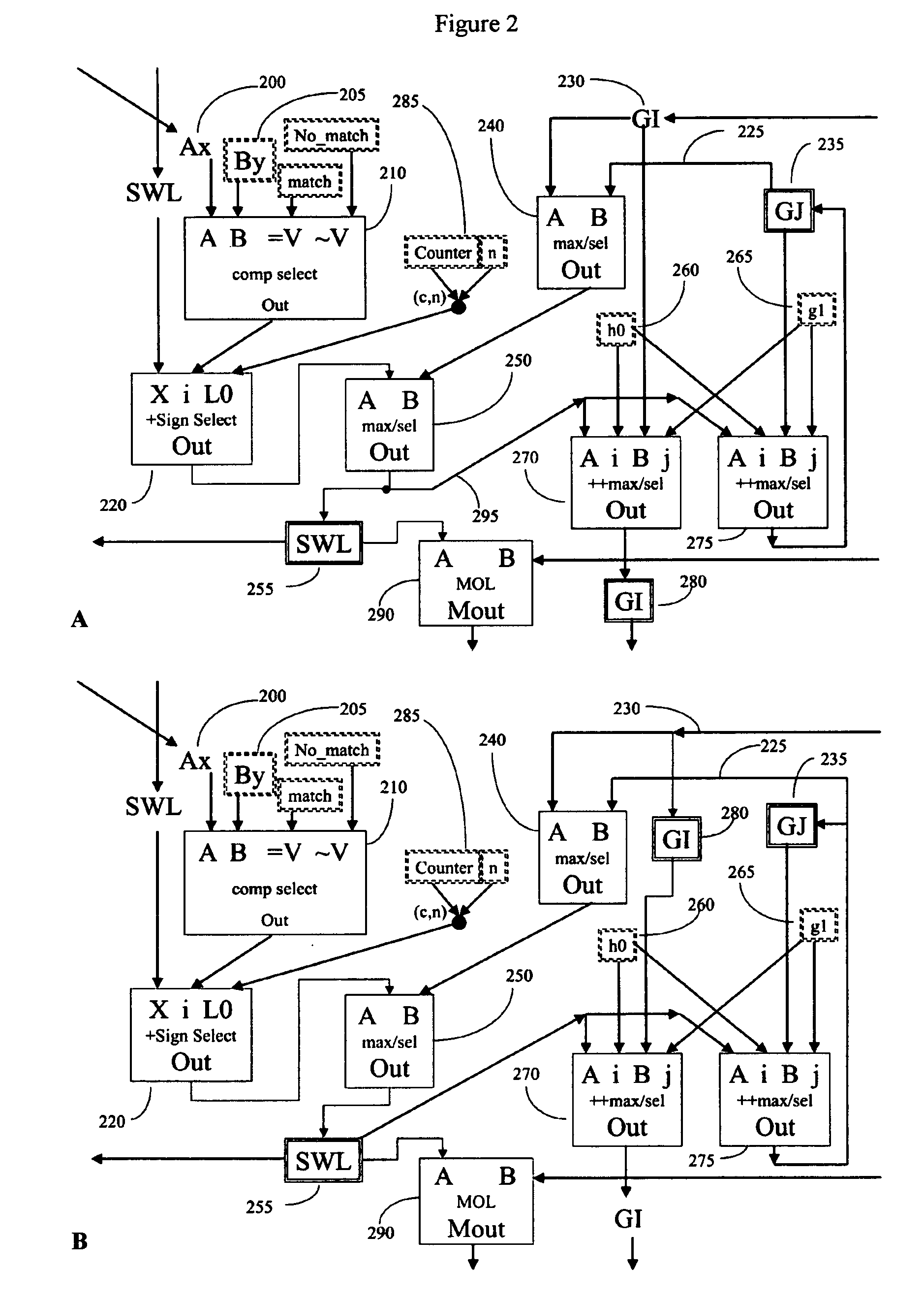

Processors for multi-dimensional sequence comparisons

InactiveUS20050228595A1Requirement to reduce computing speedEffect on its overall performanceDigital computer detailsBiological testingRecursive analysisHigh dimensional

Improved processors and processing methods are disclosed for high-speed computerized comparison analysis of multiple linear symbol or character sequences, such as biological nucleic acid sequences, protein sequences, or other long linear arrays of characters. These improved processors and processing methods, which are suitable for use with recursive analytical techniques such as the Smith-Waterman algorithm, and the like, are optimized for minimum gate count and maximum clock cycle computing efficiency. This is done by interleaving multiple linear sequence comparison operations per processor, which optimizes use of the processor's resources. In use, a plurality of such processors are embedded in high-density integrated circuit chips, and run synchronously to efficiently analyze long sequences. Such processor designs and methods exceed the performance of currently available designs, and facilitate lossless higher dimensional sequence comparison analysis between three or more linear sequences.

Owner:COOKE LAURENCE H +1

Inter-clock domain data transfer FIFO circuit

The inter-clock domain data transfer FIFO circuit provides a circuit that transfers data between two clock domains of unrelated frequencies. The gate count is kept relatively low, thereby allowing data transfer between the two clock domains at one data item per cycle of the lower of the two frequencies. Depending on the frequency difference between the data producer and consumer, the initial latency could be as low as a fraction of a cycle and no more than two cycles of the consumer's clock. The operation of the data transfer FIFO circuit has been verified using gate-level simulations for several ratios of clock frequencies.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

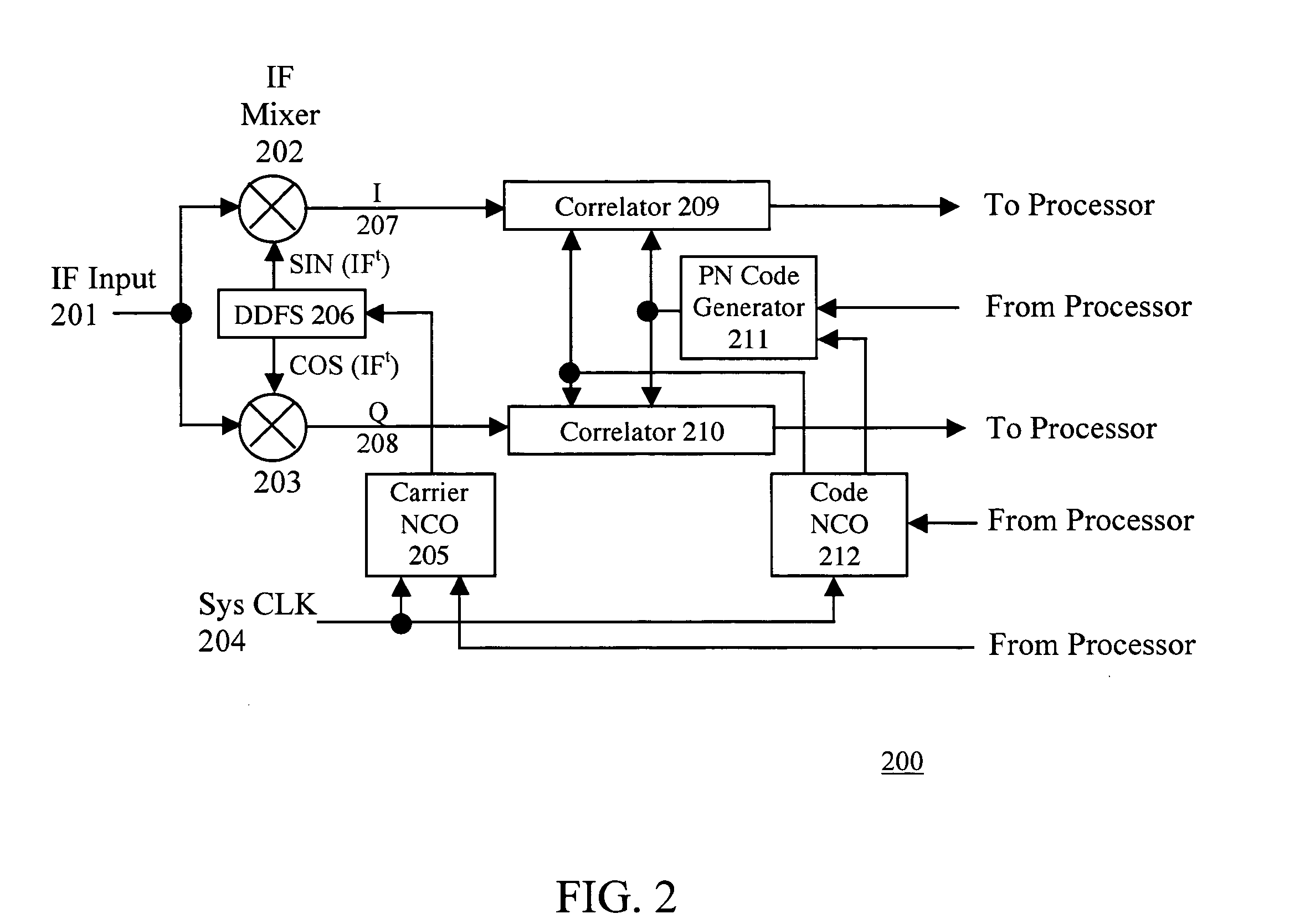

Efficient and flexible GPS receiver baseband architecture

ActiveUS7428259B2Minimize the numberEfficient powerColor television with pulse code modulationColor television with bandwidth reductionNCOSNumerically controlled oscillator

The present invention provides a new baseband integrated circuit (IC) architecture for direct sequence spread spectrum (DSSS) communication receivers. The baseband IC has a single set of baseband correlators serving all channels in succession. No complex parallel channel hardware is required. A single on-chip code Numerically Controlled Oscillator (NCO) drives a pseudorandom number (PN) sequence generator, generates all code sampling frequencies, and is capable of self-correct through feedback from an off-chip processor. A carrier NCO generates corrected local frequencies. These on-chip NCOs generate all the necessary clocks. This architecture advantageously reduces the total hardware necessary for the receiver and the baseband IC thus can be realized with a minimal number of gate count. The invention can accommodate any number of channels in a navigational system such as the Global Positioning System (GPS), GLONASS, WAAS, LAAS, etc. The number of channels can be increased by increasing the circuit clock speed.

Owner:CSR TECH HLDG

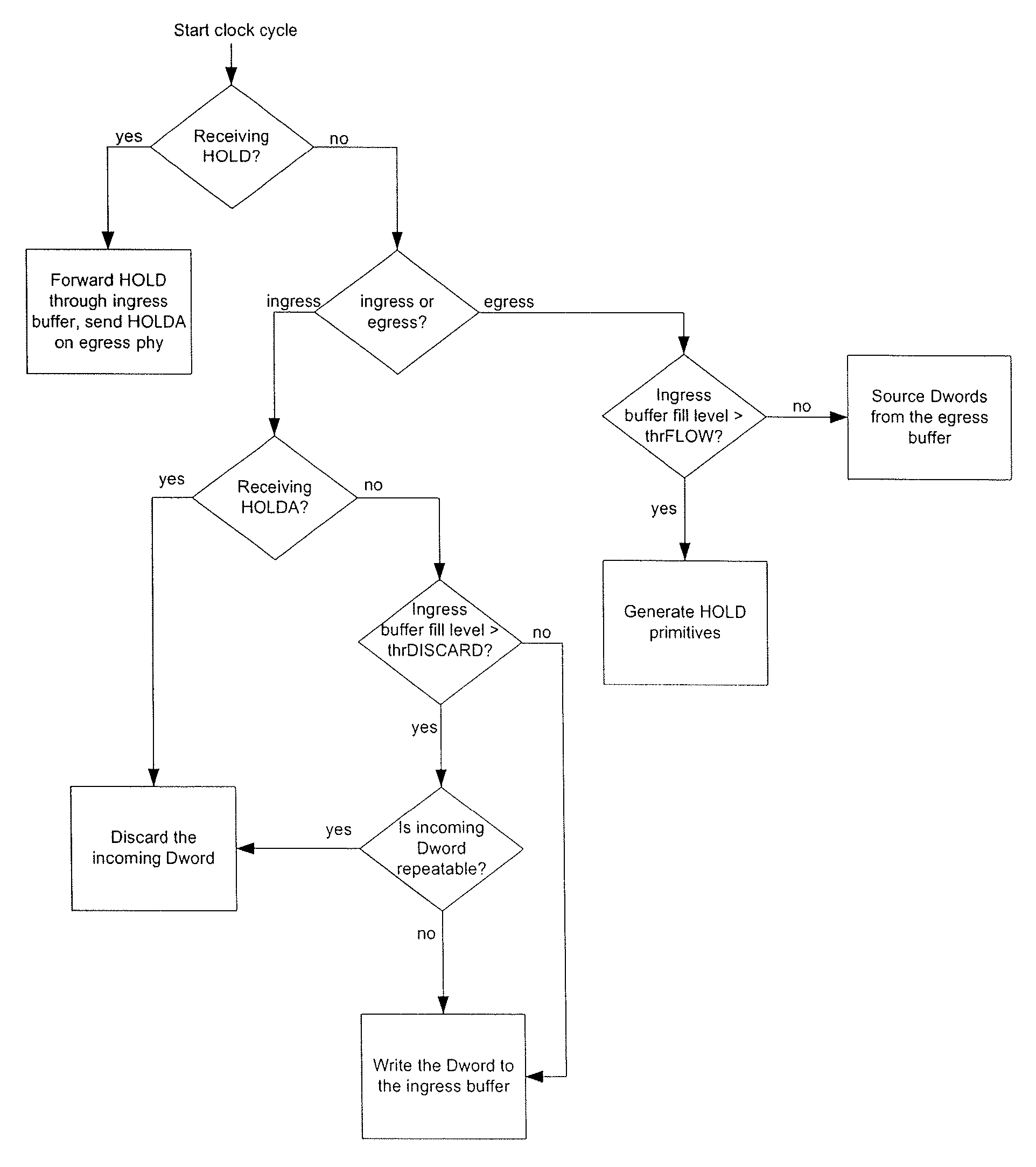

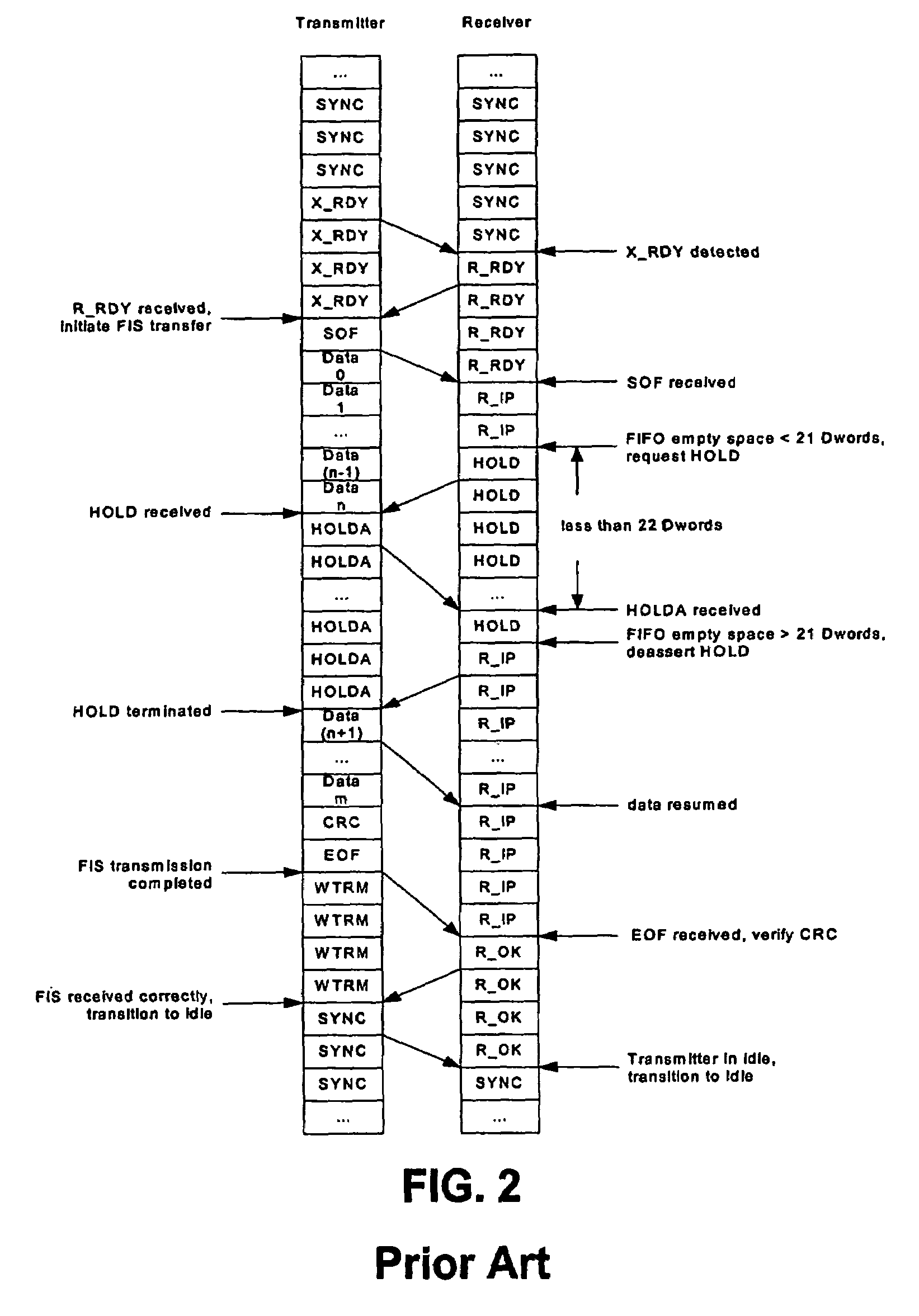

Serial tunneling protocol (STP) flow control in SAS expanders without SATA link state machine

ActiveUS7496700B1Improved STP flow control strategyMaintain integrityMultiple digital computer combinationsTransmissionTraffic capacityComputer science

A method and apparatus are disclosed for implementing STP flow control in SAS expander devices. SAS expanders are commonly used within a SAS network topology to allow multiple disk drives to connect to multiple host devices. Connections to a SATA HDD are supported using SATA Tunnelling Protocol (STP), which allows SATA traffic to be carried over a SAS network topology. Flow control in a STP connection is applied through a set of special SATA primitives, both for forward and backward flow control. A method is described herein in which STP flow control is supported without the use of a SATA link layer state machine. This allows STP flow control to be terminated on a hop-by-hop basis without knowing the data channel direction or maintaining a SATA link state machine, and while minimizing gate count.

Owner:MICROSEMI STORAGE SOLUTIONS

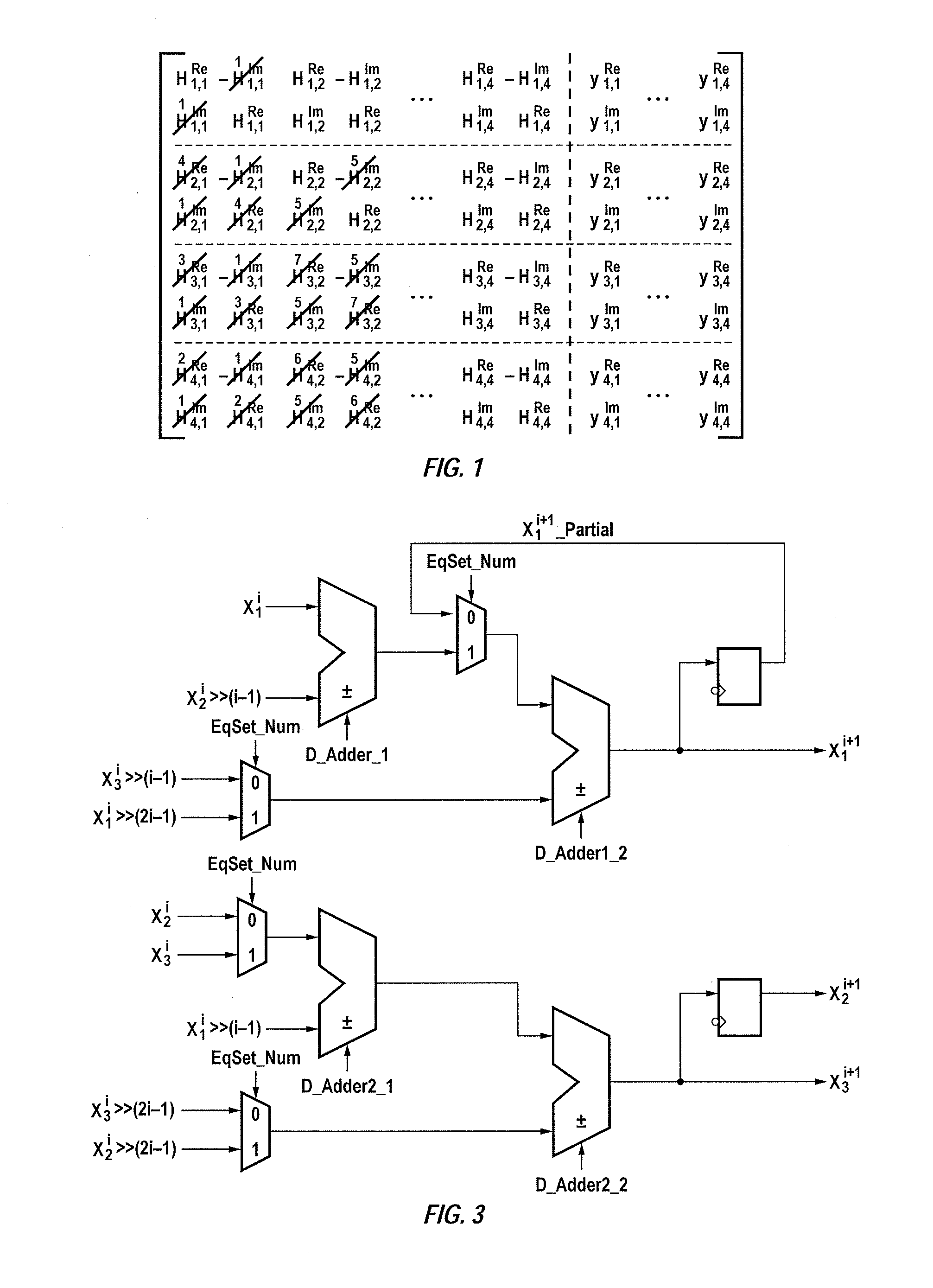

Signal processing block for a receiver in wireless communication

ActiveUS20110264721A1Digital computer detailsIndependent non-interacting antenna combinationsResource utilizationParallel computing

A QRD processor for computing input signals in a receiver for wireless communication relies upon a combination of multi-dimensional Givens Rotations, Householder Reflections and conventional two-dimensional (2D) Givens Rotations, for computing the QRD of matrices. The proposed technique integrates the benefits of multi-dimensional annihilation capability of Householder reflections plus the low-complexity nature of the conventional 2D Givens rotations. Such integration increases throughput and reduces the hardware complexity, by first decreasing the number of rotation operations required and then by enabling their parallel execution. A pipelined architecture is presented (290) that uses un-rolled pipelined CORDIC processors (245a to 245d) iteratively to improve throughput and resource utilization, while reducing the gate count.

Owner:MAXLINEAR INC

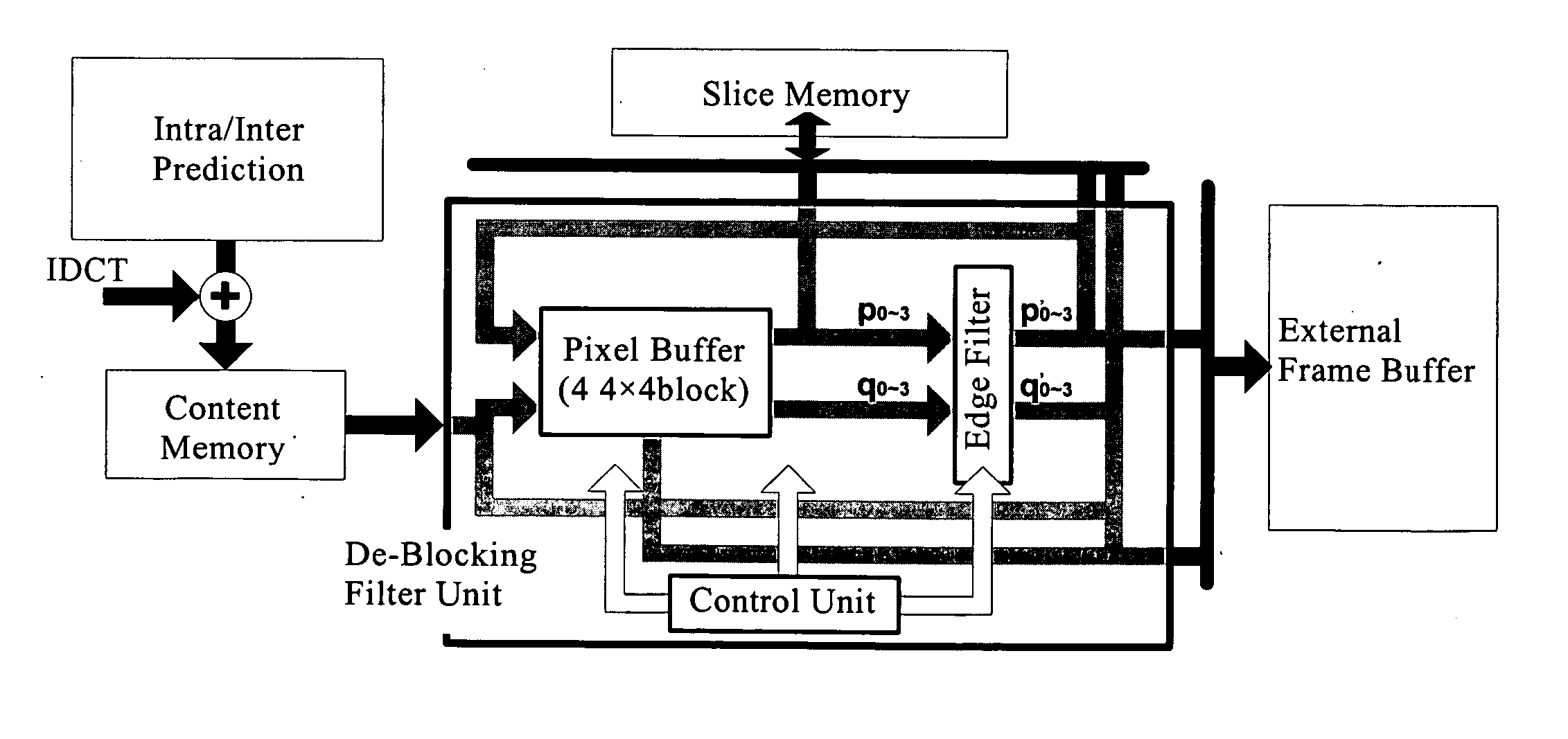

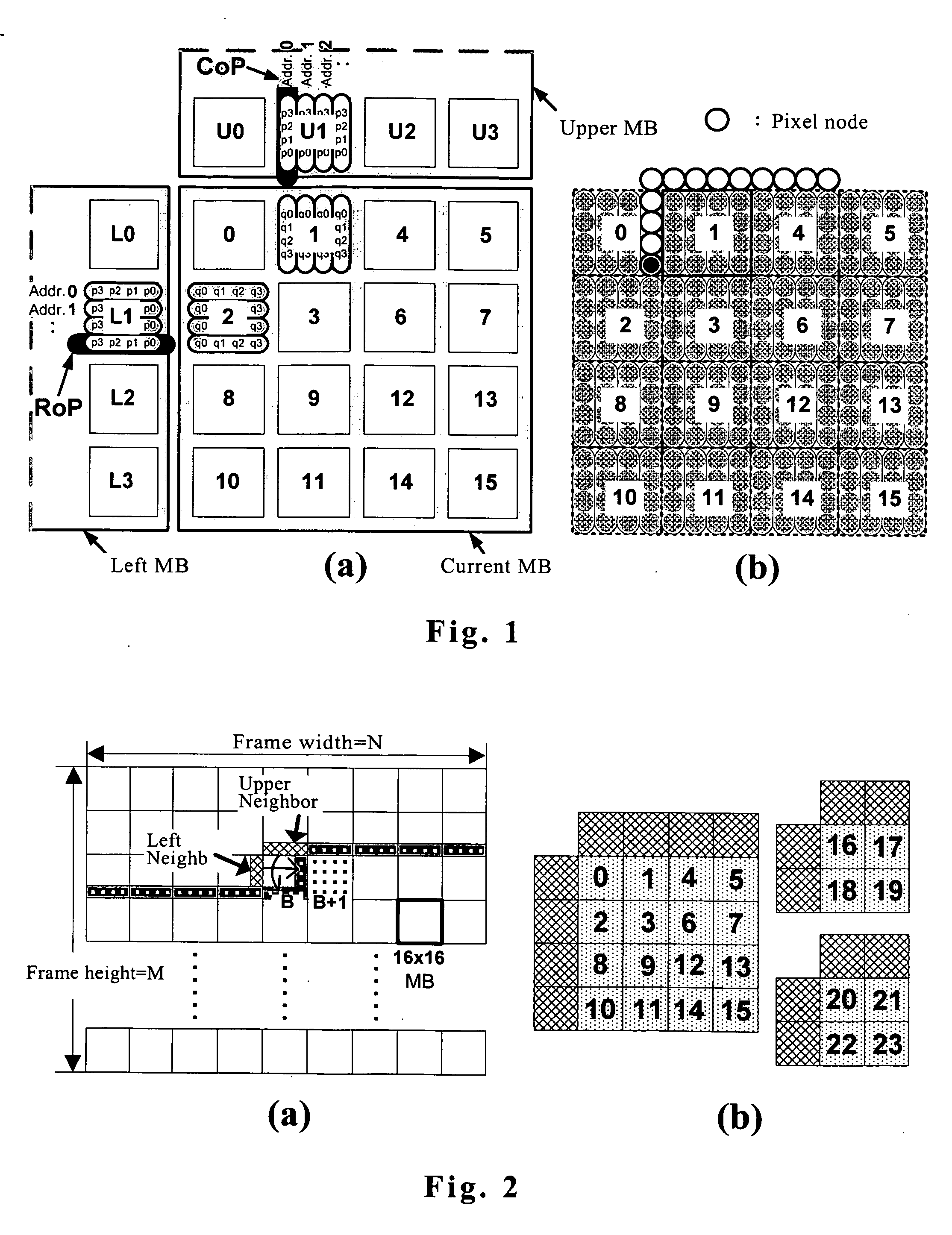

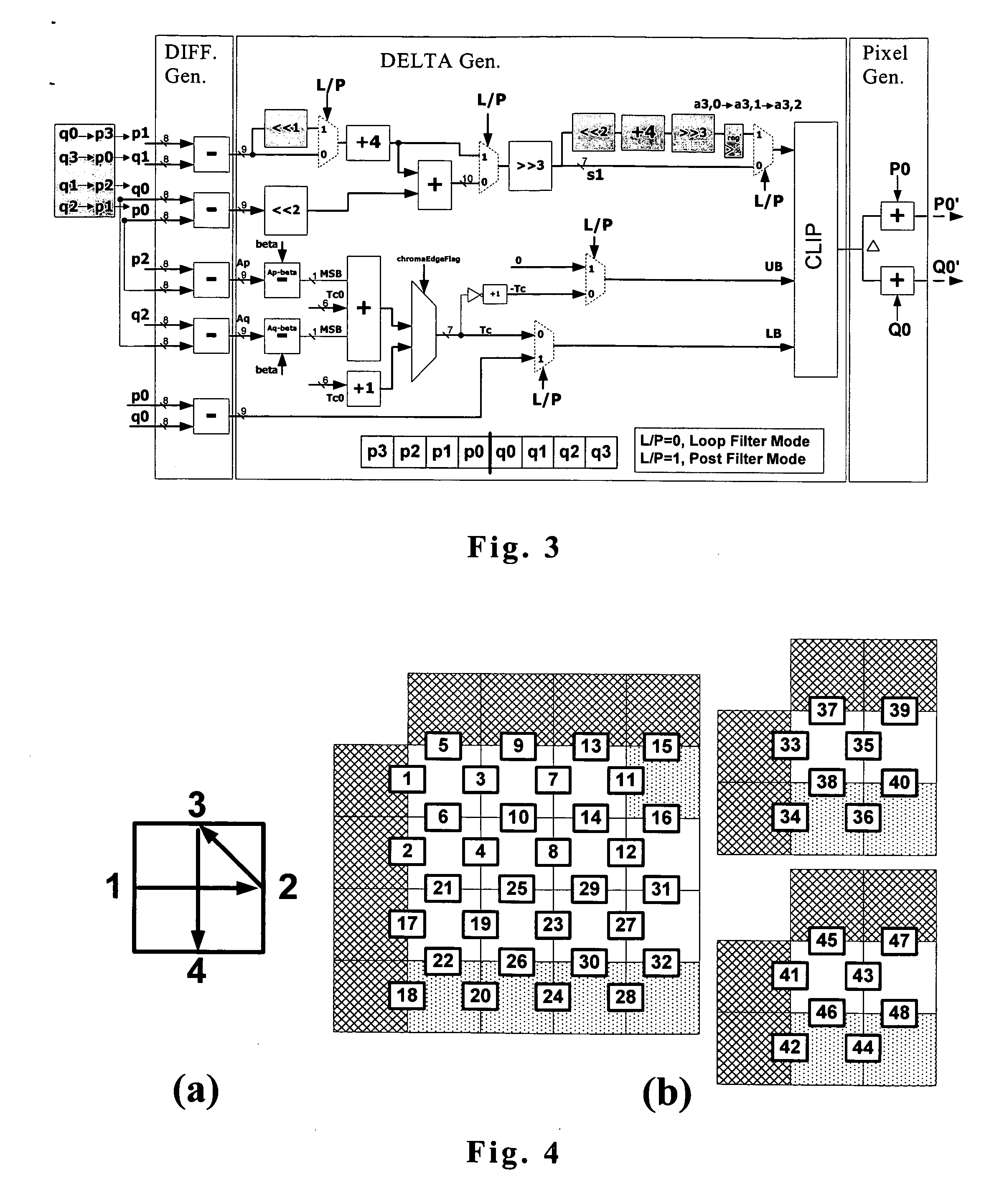

Dual-mode high throughput de-blocking filter

InactiveUS20060262990A1Easy to integrateReduce memory accessCharacter and pattern recognitionDigital video signal modificationLoop filterRound complexity

This invention provides the unique and high-throughput architecture for multiple video standards. Particularly, we propose a novel scheme to integrate the standard in-loop filter and the informative post-loop filter. Due to the non-standardization of post filter, it provides high freedom to develop a certain suitable algorithm for the integration with loop-filter. We modify the post filter algorithm to make a compromise between hardware integration complexity and performance loss. Further, we propose a hybrid scheduling to reduce the processing cycles and improve the system throughput. The main idea is that we use four pixel buffers to keep the intermediate pixel value and perform the horizontal and vertical filtering process in one hybrid scheduling flow. In our approach, we reduce processing cycles, and the synthesized gate counts are very small. Meanwhile, the synthesized results also indicate lower cost for hardware.

Owner:NAT CHIAO TUNG UNIV

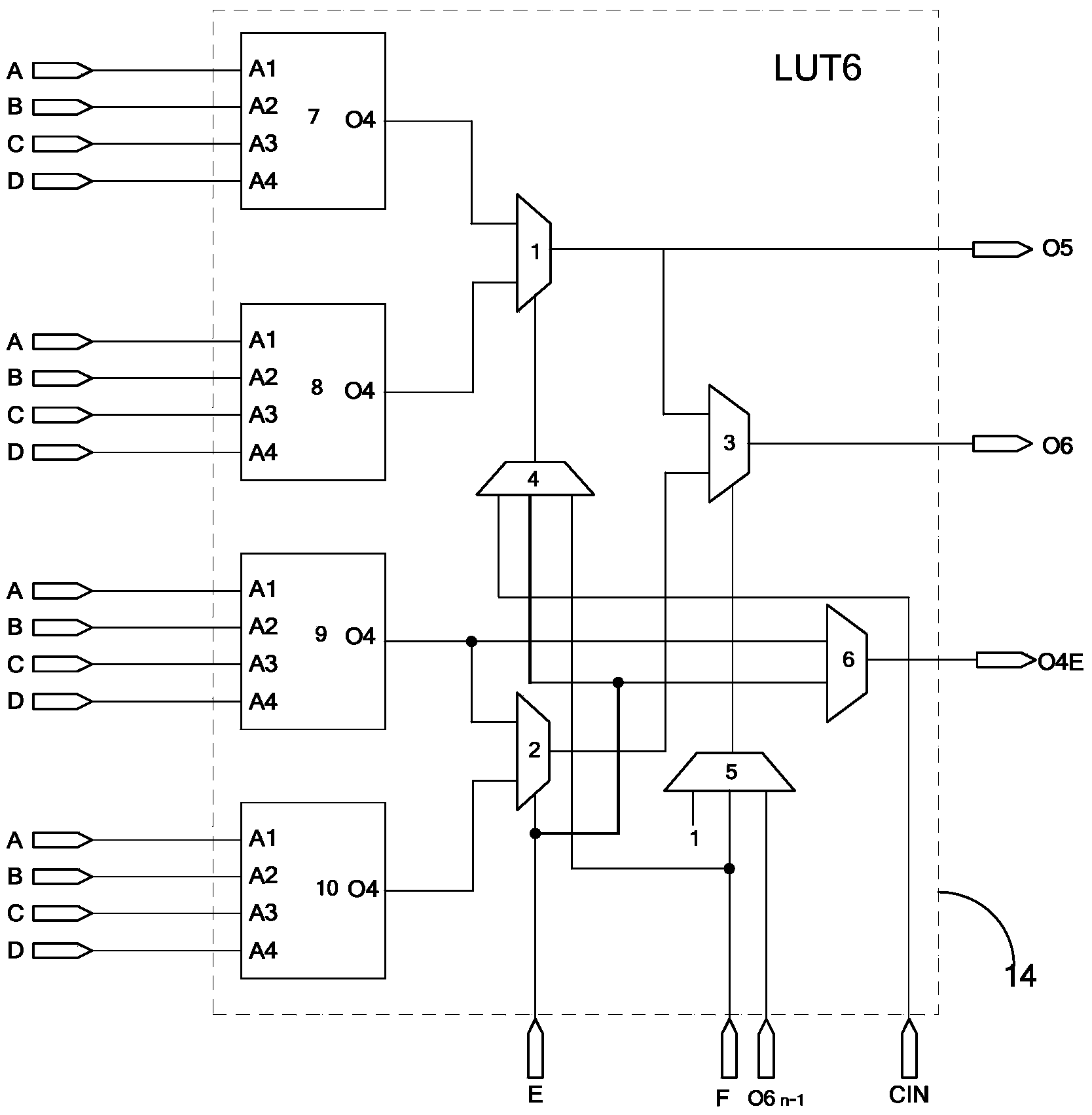

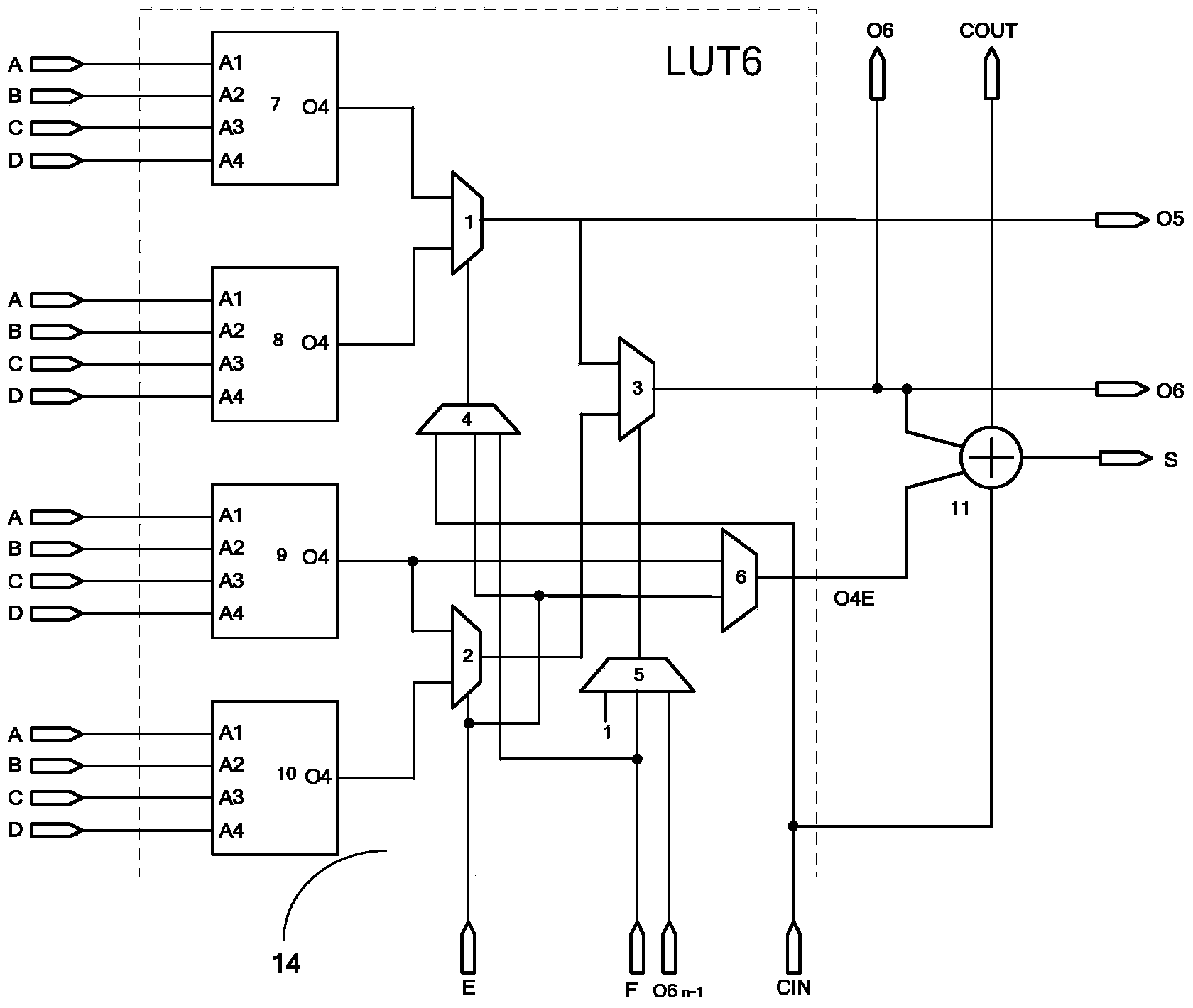

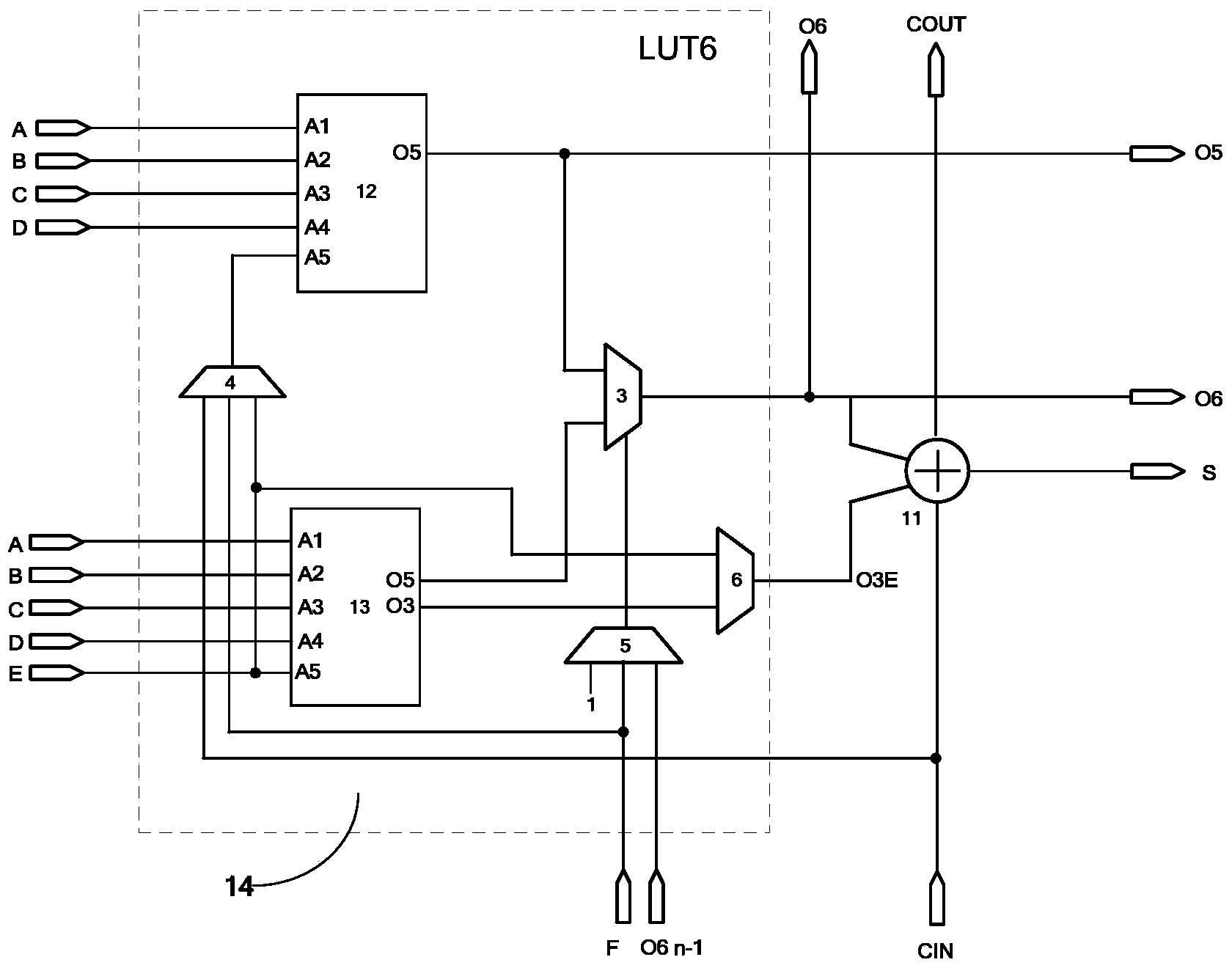

Multifunctional and configurable six-input lookup table structure

ActiveCN103762974AStrong configurabilityIncrease flexibilityLogic circuits using elementary logic circuit componentsOperandLookup table

The invention relates to a multifunctional and configurable six-input lookup table structure. The lookup table structure with different inputs and sharing with different signal numbers can be configured by flexibly selecting configuration signals, a function extension logic chain is designed, and a wide logic function can be achieved rapidly without external wiring. A special adder carry chain and an operand selection control end are designed, carry signals enter the lookup table through a four-input lookup table, and wide logic operation on a sum function of an adder and other operand can be achieved rapidly. Due to high flexibility and configuration capacity of the lookup table and the rapid carry of the carry chain, the wide logic function can be achieved through fewer logic resources, multiple functions are achieved, the utilization rate of wiring resources can be improved effectively, the occupied area of the resources is reduced, the working speed of a chip is improved, and more functions and applications can be achieved with limited gate counts.

Owner:WUXI ESIONTECH CO LTD

Modular Galois-field subfield-power integrated inverter-multiplier circuit for Galois-field division over GF(256)

ActiveUS7089276B2Lowering gateIncrease computing speedDigital computer detailsComputations using residue arithmeticSystems designModularity

A modular Galois-field subfield-power integrated inverter-multiplier circuit that may be used to perform Galois-field division over GF(245). The integrated inverter-multiplier circuit combines subfield-power and parallel multiplication and inversion operations performed therein. The circuit is modular, has a relatively low gate count, and is easily pipelined because it does not use random logic. The circuit implements mathematical calculations known as “Galois-field arithmetic” that are required for a variety of digital signaling and processing applications such as Reed-Solomon and Bose-Chaudhuri-Hochquenghem (BCH) error-correction coding systems. Galois-field division is particularly difficult, typically requiring either a great deal of time or highly complex circuits, or both. The circuit uses a unique combination of subfield and power inversion techniques to carry out multiplicative inversion. Furthermore, the circuit uniquely implements Galois-field division by carrying out the multiplicative inversion and the multiplication simultaneously and in parallel. This substantially increases computation speed. The modularity and pipelineability of the present invention also make system design easier and increases the speed and reduces the gate count of an integrated circuit embodying the inverter-multiplier circuit.

Owner:LOCKHEED MARTIN CORP

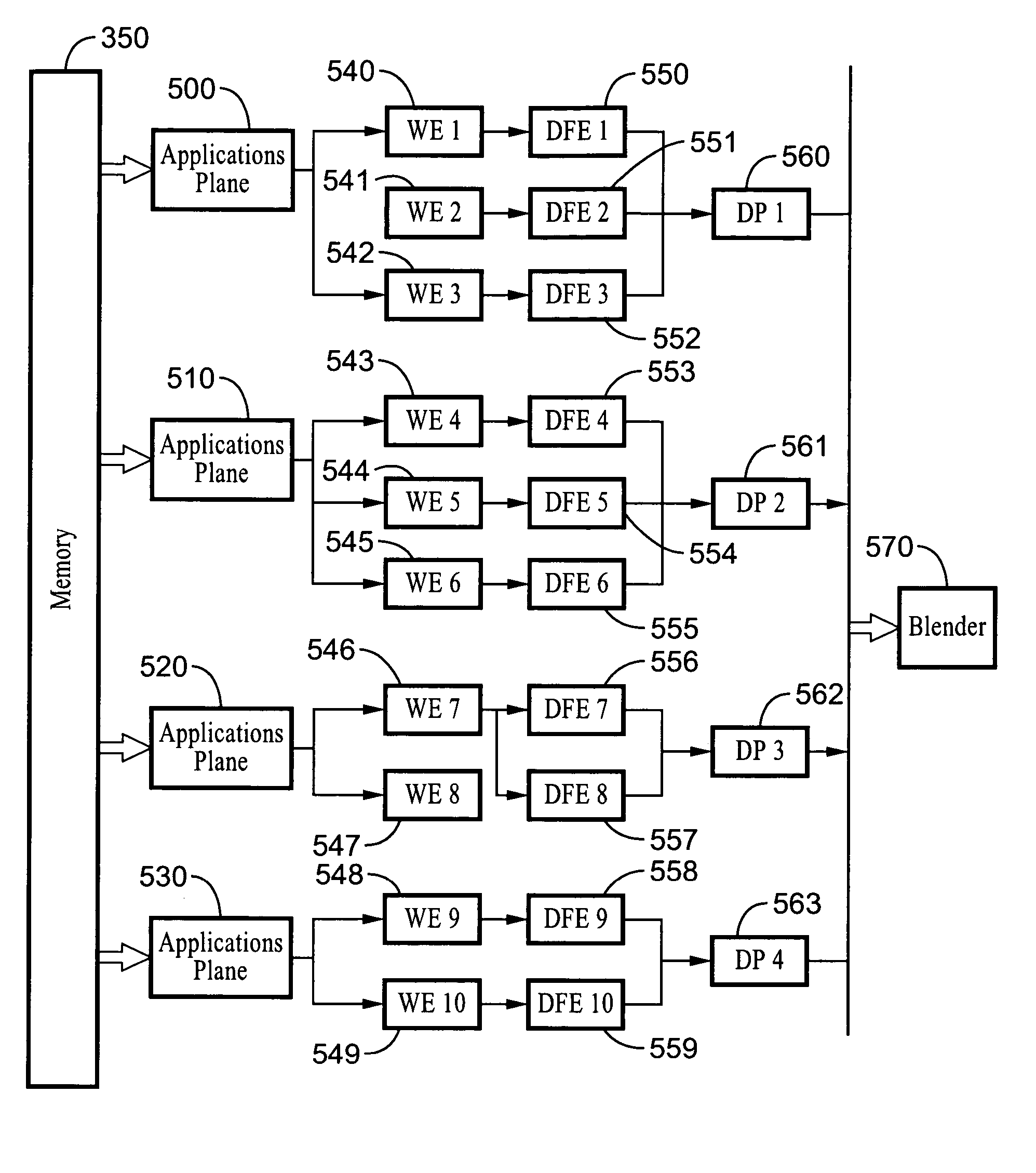

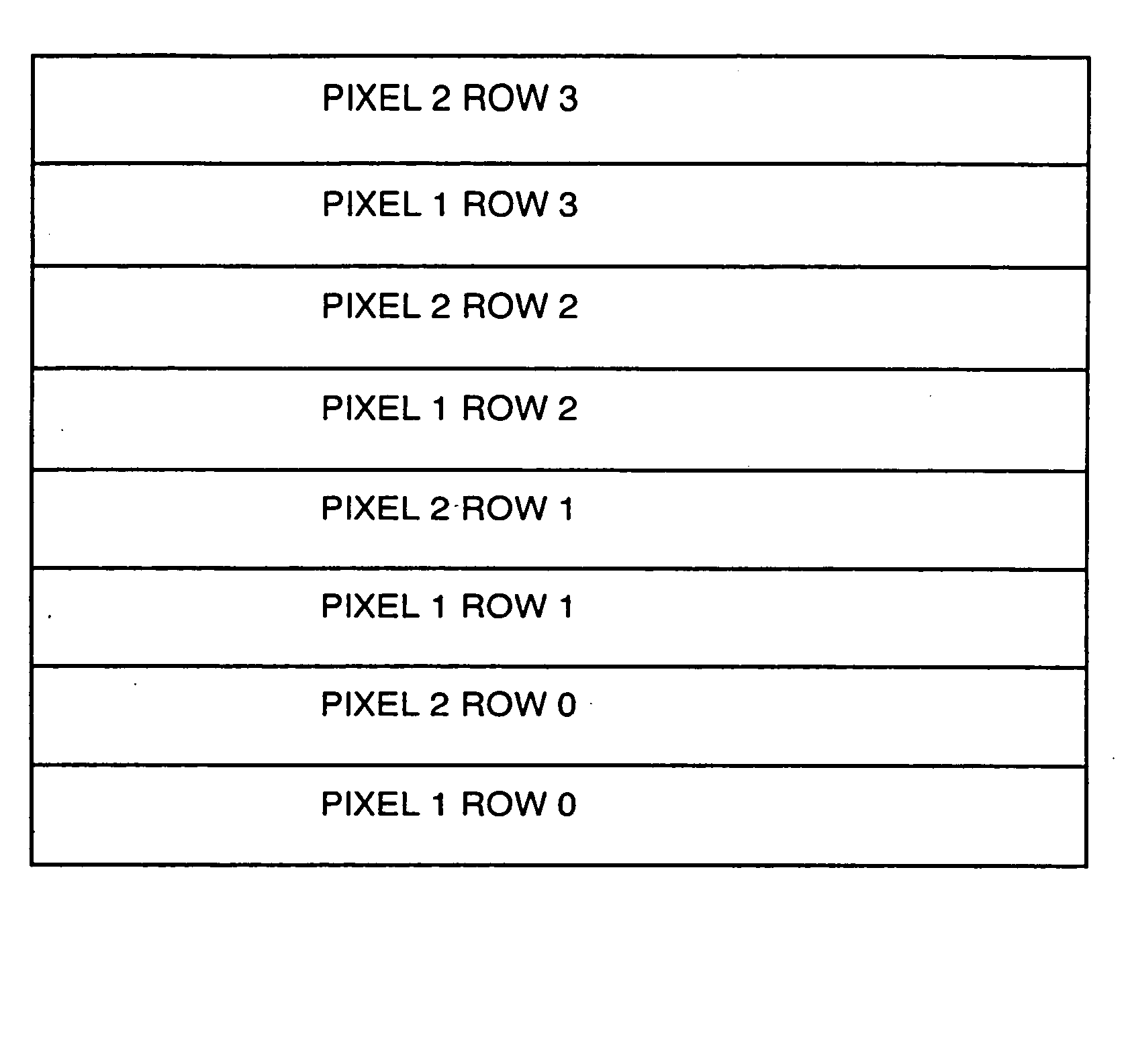

Time sliced architecture for graphics display system

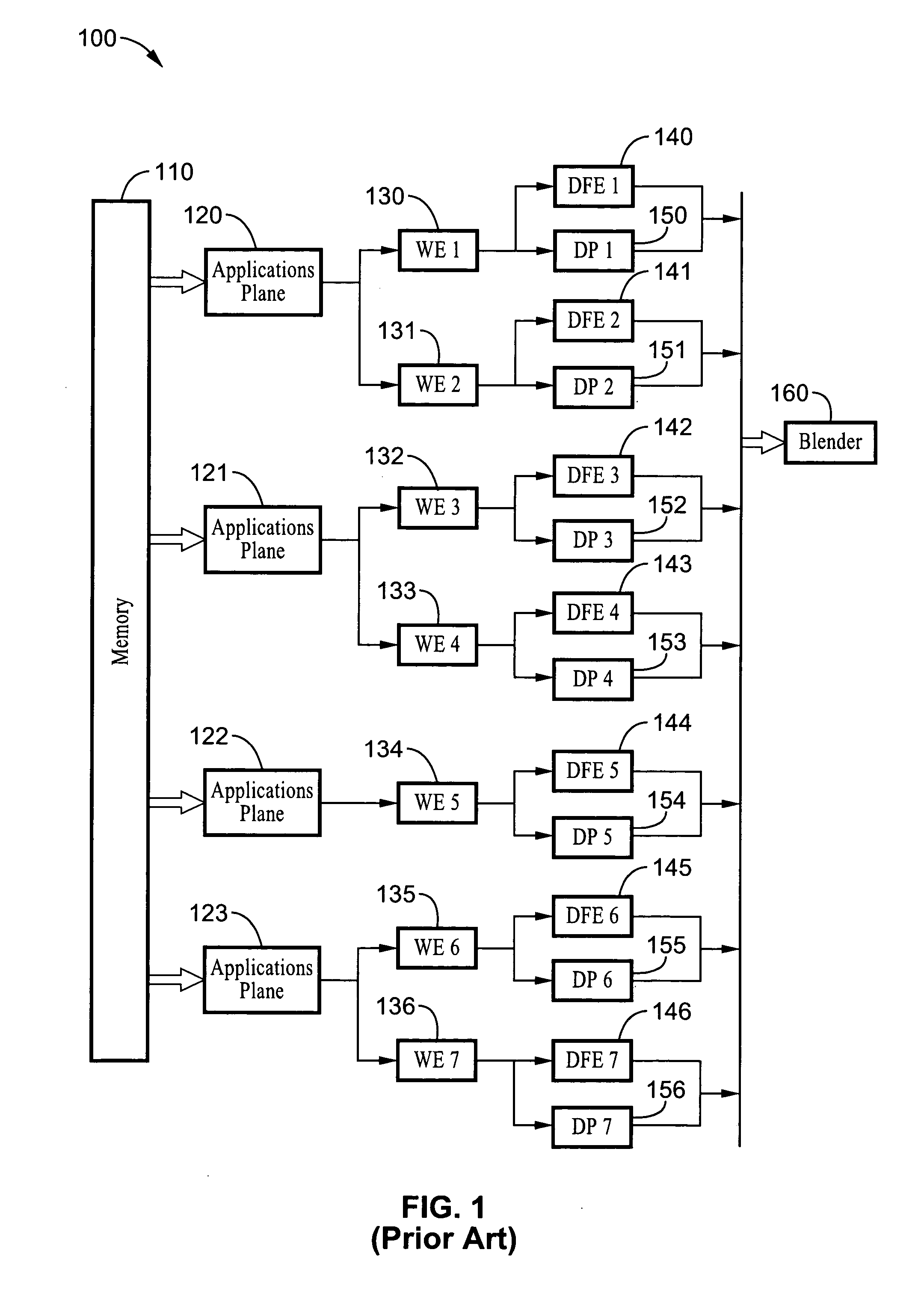

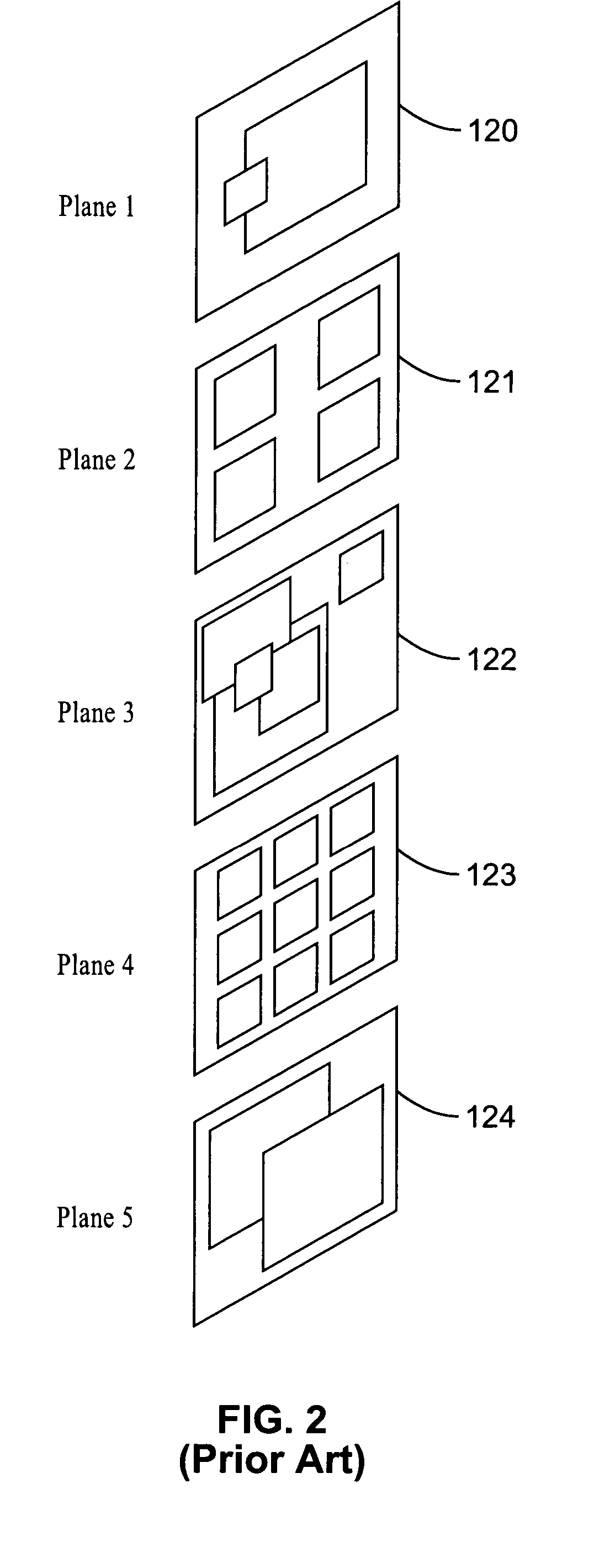

InactiveUS20050270297A1Reduce in quantityHighly area efficient designCathode-ray tube indicatorsMultiple digital computer combinationsGraphicsHigh-definition television

A system and method for rendering multiple windows across multiple display planes utilizing a sliced rendering data pathway architecture for achieving a highly area efficient design of the graphics display system. Windows across multiple display planes are rendered from direct memory access fetch engines retrieving pixel data from memory. Rendering data pathways are shared between direct memory access fetch engines directed to a single display plane. Furthermore, the rendering data pathways can be time sliced wherein data from multiple planes are time multiplexed through the rendering pathway. The invention allows creating a graphical engine with a lower gate count than conventional circuits. The resultant system is modular and scalable, while being customizable from lower power applications to HDTV sets.

Owner:SONY CORP +1

Efficient and flexible GPS receiver baseband architecture

ActiveUS20060251173A1Minimize the numberEfficient powerColor television with pulse code modulationColor television with bandwidth reductionNCOSCarrier signal

The present invention provides a new baseband integrated circuit (IC) architecture for direct sequence spread spectrum (DSSS) communication receivers. The baseband IC has a single set of baseband correlators serving all channels in succession. No complex parallel channel hardware is required. A single on-chip code Numerically Controlled Oscillator (NCO) drives a pseudorandom number (PN) sequence generator, generates all code sampling frequencies, and is capable of self-correct through feedback from an off-chip processor. A carrier NCO generates corrected local frequencies. These on-chip NCOs generate all the necessary clocks. This architecture advantageously reduces the total hardware necessary for the receiver and the baseband IC thus can be realized with a minimal number of gate count. The invention can accommodate any number of channels in a navigational system such as the Global Positioning System (GPS), GLONASS, WAAS, LAAS, etc. The number of channels can be increased by increasing the circuit clock speed.

Owner:CSR TECH HLDG

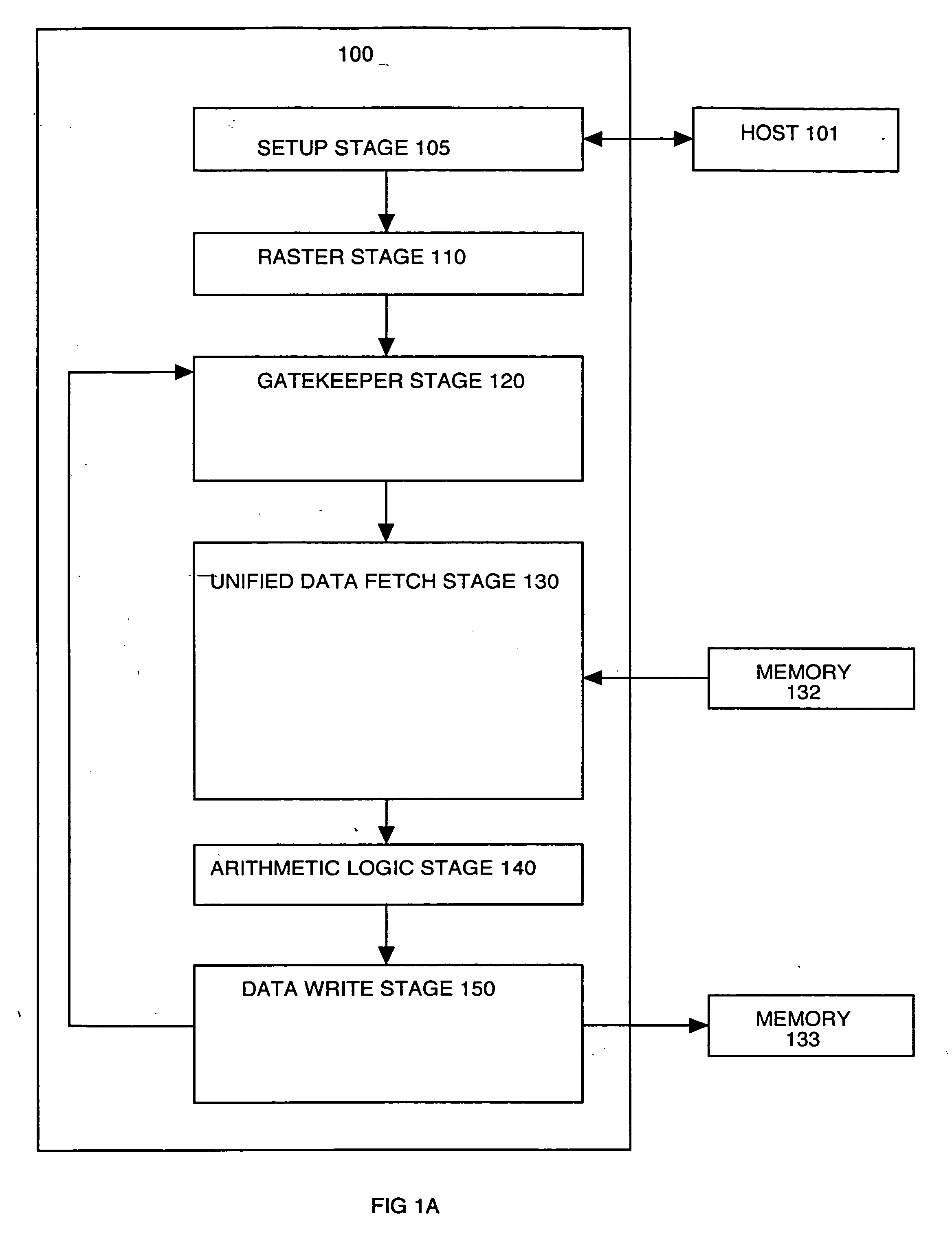

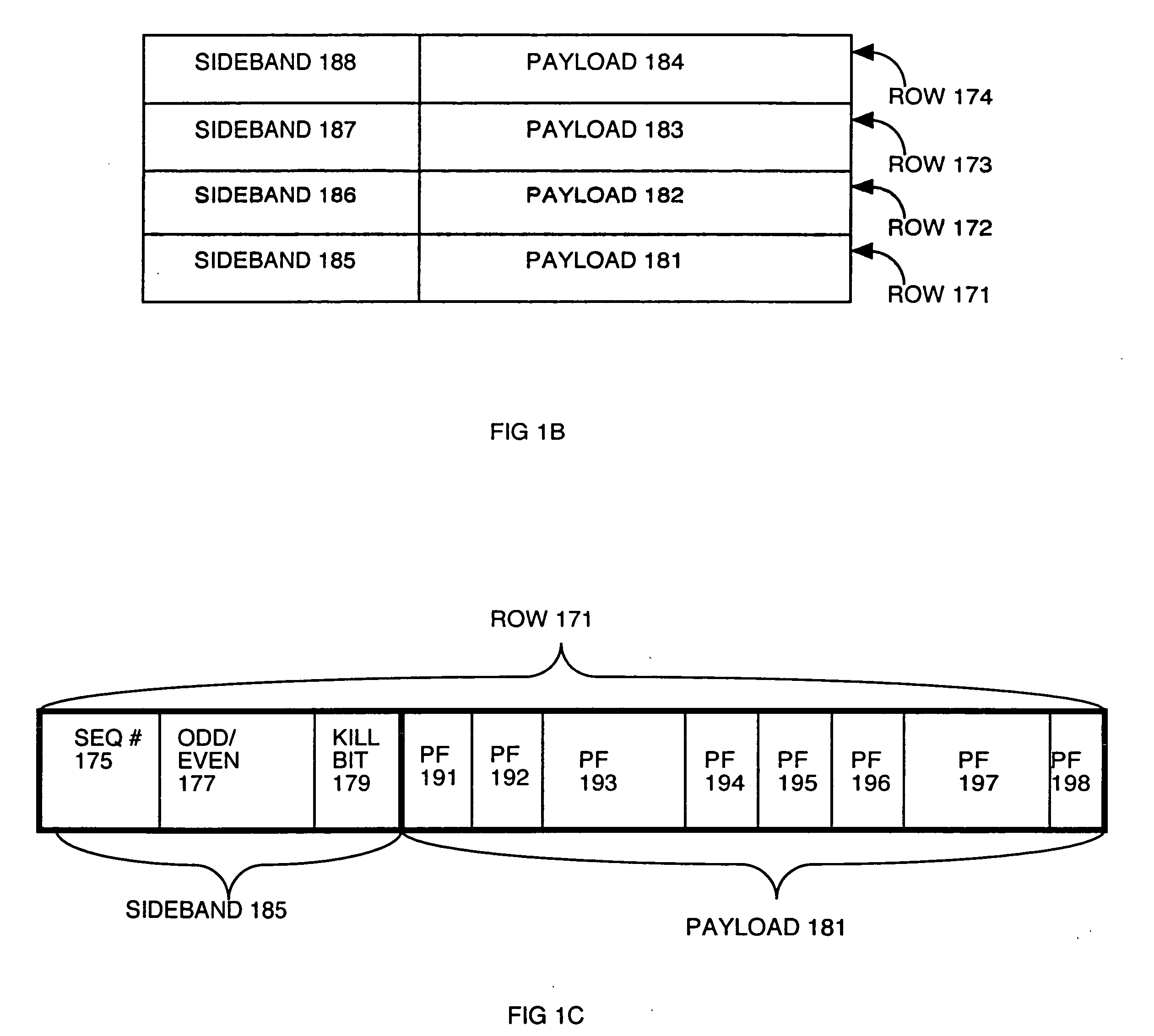

Kill bit graphics processing system and method

ActiveUS20050280655A1Efficient and convenient processingShorten the counting processCathode-ray tube indicators3D-image renderingGraphicsHandling system

A present invention pixel processing system and method permit complicated three dimensional images to be rendered with shallow graphics pipelines including reduced gate counts and also facilitates power conservation. Pixel packet information includes pixel surface attribute values are retrieved in a single unified data fetch stage. At a data fetch pipestage a determination may be made if the pixel packet information contributes to an image display presentation (e.g., a depth comparison of Z values is performed determine if the pixel is occluded). A pixel packet status indicator (e.g., a kill bit) is set in the sideband portion of a pixel packet and the pixel packet is forwarded for processing in accordance with the pixel packet status indicator. The status indicator is a kill bit is set to prevent logic components from clocking information for a payload portion of the pixel packet if the status indicator indicates the pixel packet payload does not contribute to the image display presentation while continuing to clock pixel packet sideband information.

Owner:NVIDIA CORP

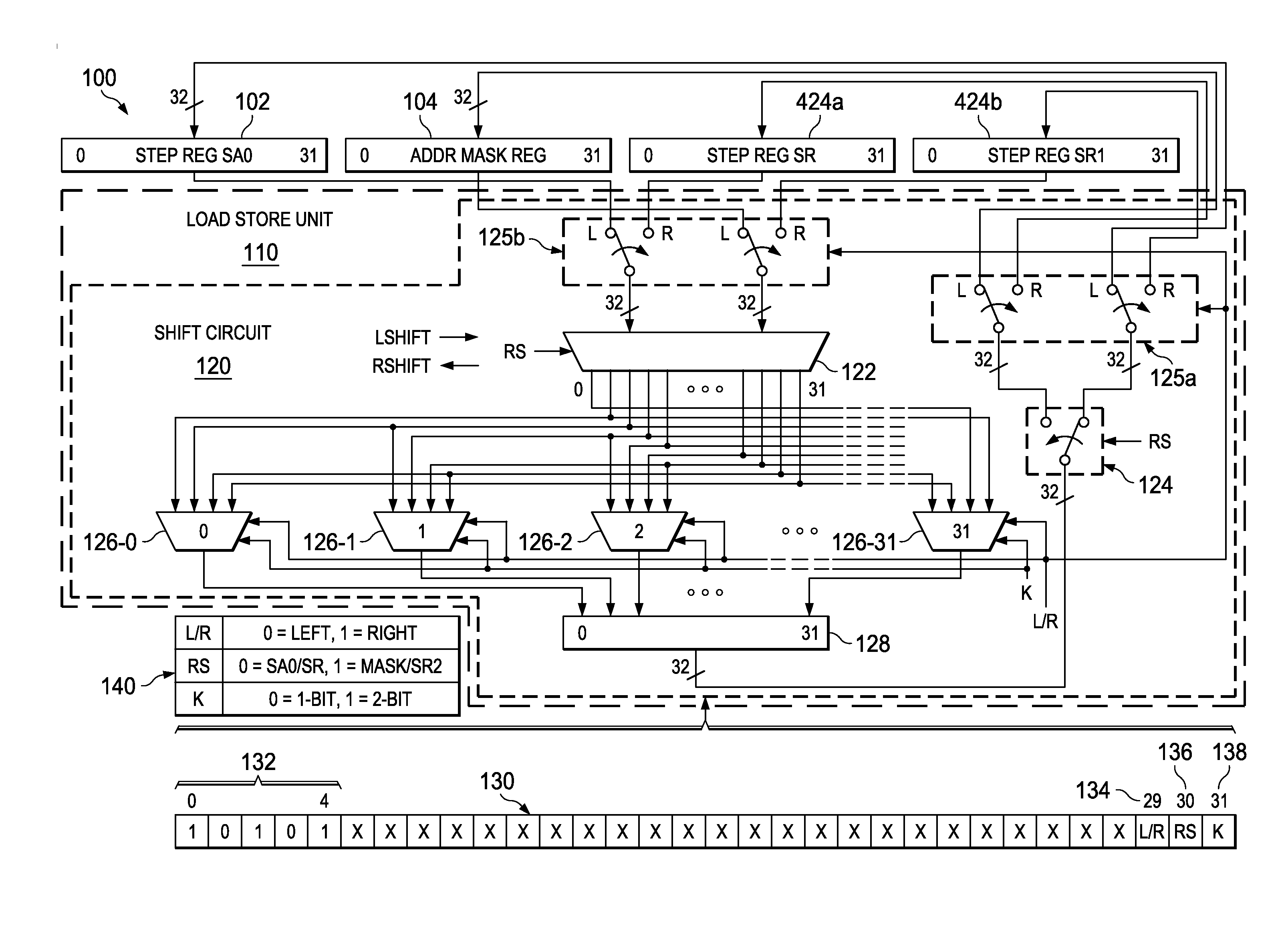

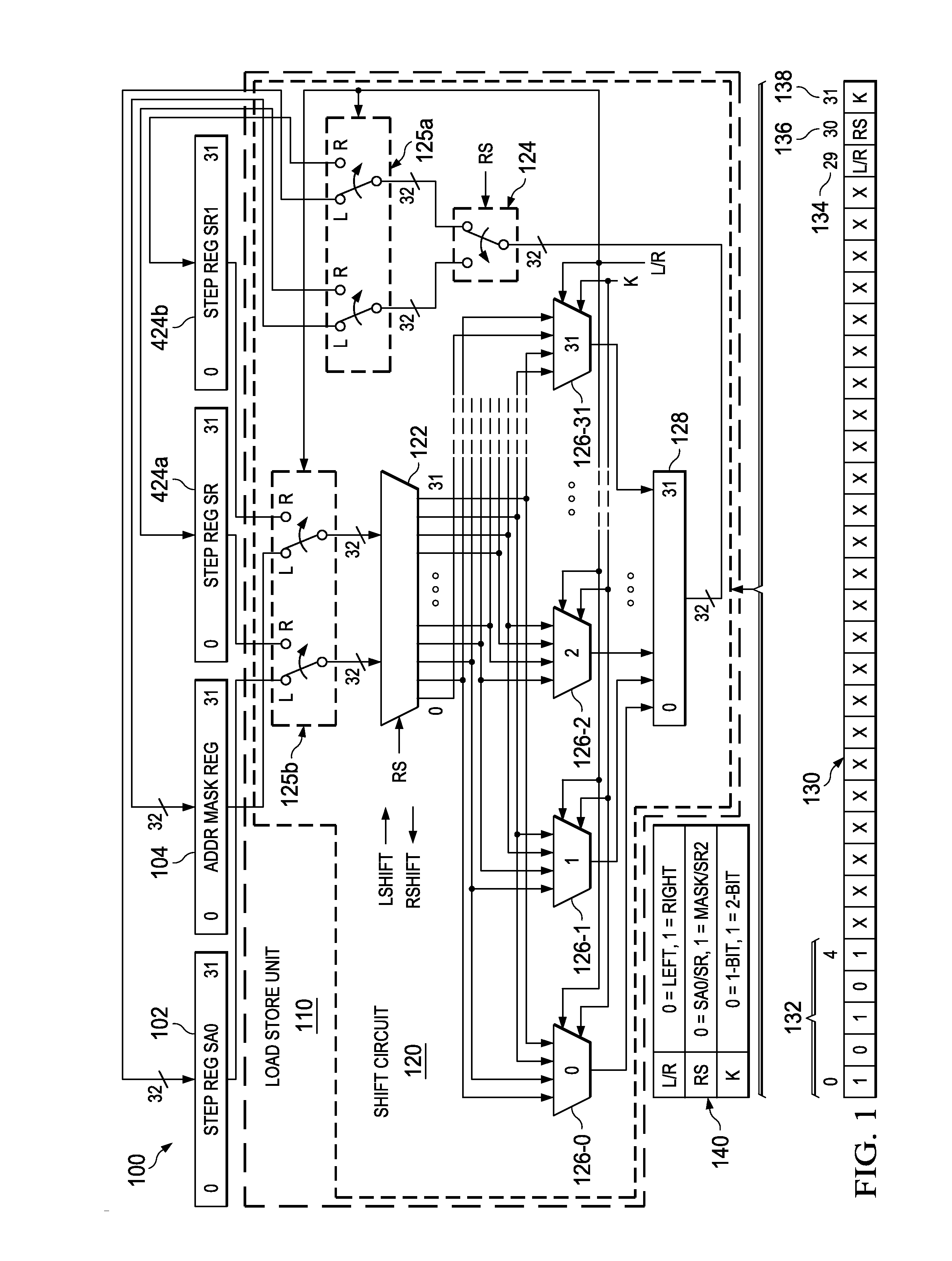

Load store circuit with dedicated single or dual bit shift circuit and opcodes for low power accelerator processor

PendingUS20170060586A1Without significant overheadEasy to operateRegister arrangementsEnergy efficient computingMicrocontrollerProcessor register

Described examples include integrated circuits such as microcontrollers with a low energy accelerator processor circuit or other application specific integrated processor circuit including a load store circuit operative to perform load and store operations associated with at least one register and a low gate count shift circuit to selectively shift the data of the register by only an integer number bits less than the register data width without using a barrel shifter for low power operation to support vector operations for FFT or filtering functions.

Owner:TEXAS INSTR INC

Authentication system executing an elliptic curve digital signature cryptographic process

ActiveUS7853012B2Improve parallelismImprove performanceDigital data processing detailsDigital computer detailsPower analysisDigital signature

An authentication system and a method for signing data are disclosed. The system uses a hardware software partitioned approach. In its implementation the system of the invention compares favourably with performance and other parameters with a complete hardware or full software implementation. Particularly, advantageously there is a reduced gate count. Also as disclosed in the invention the system makes it difficult for hackers to attack the system using simple power analysis.

Owner:TATA CONSULTANCY SERVICES LTD

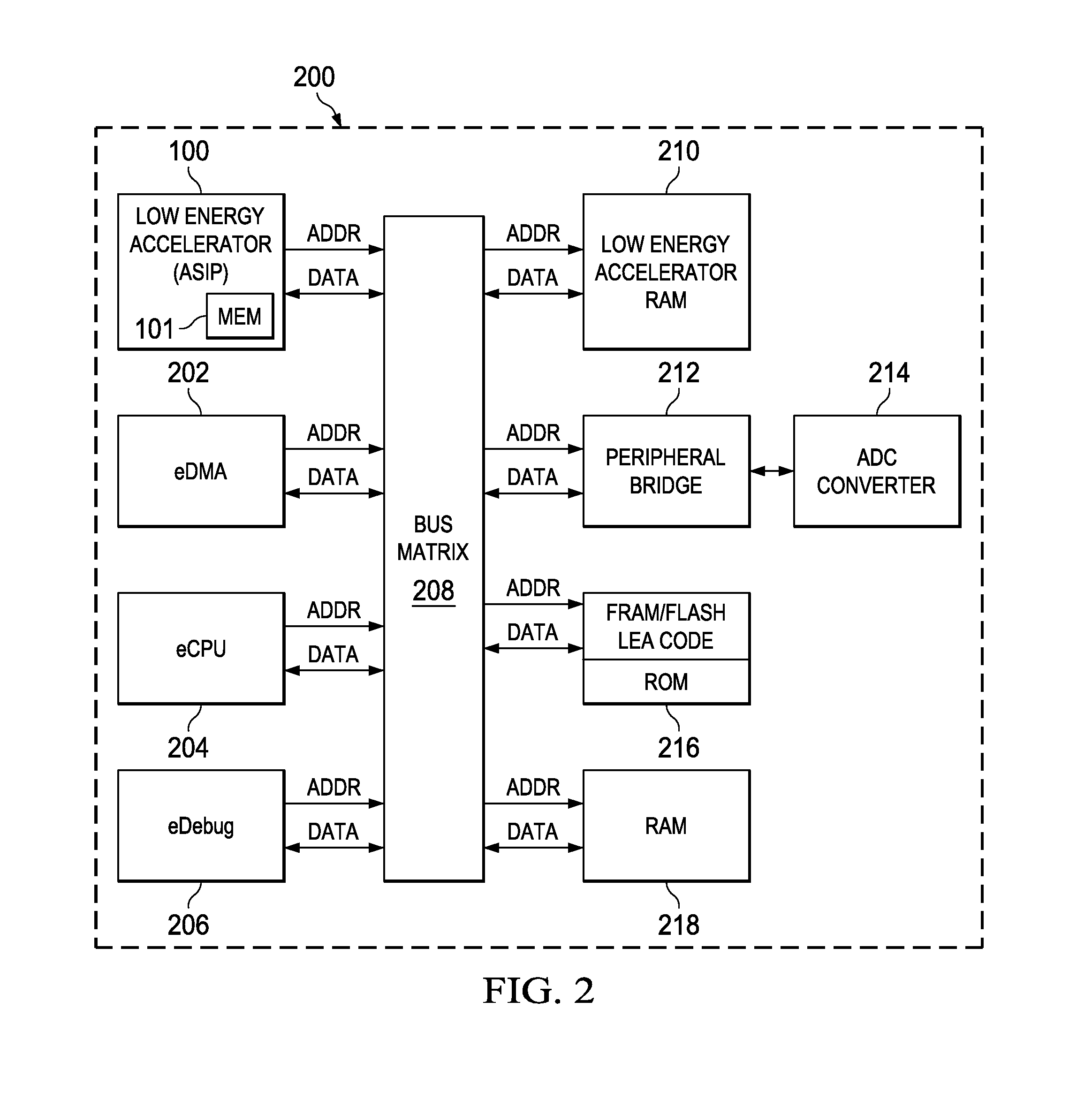

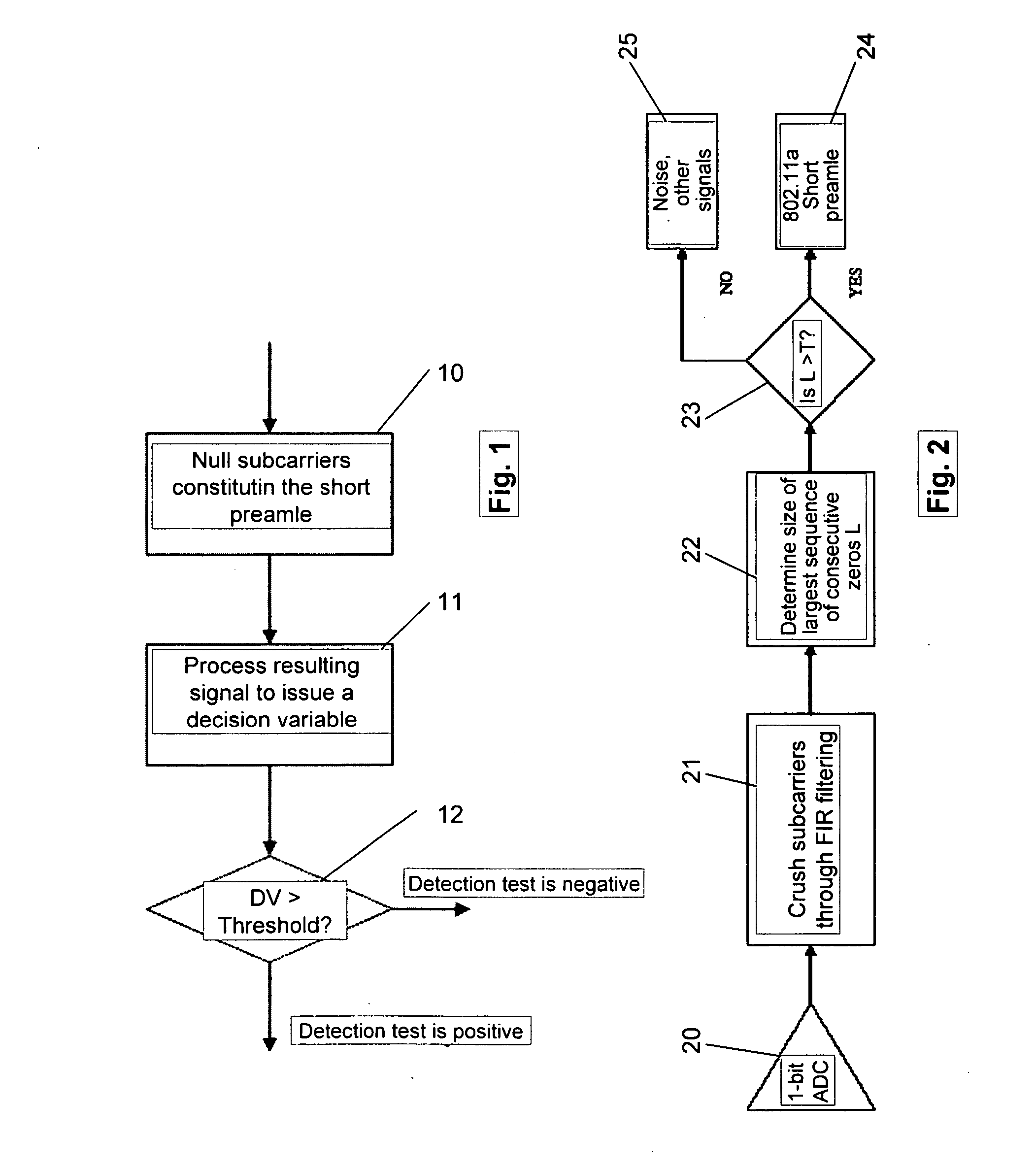

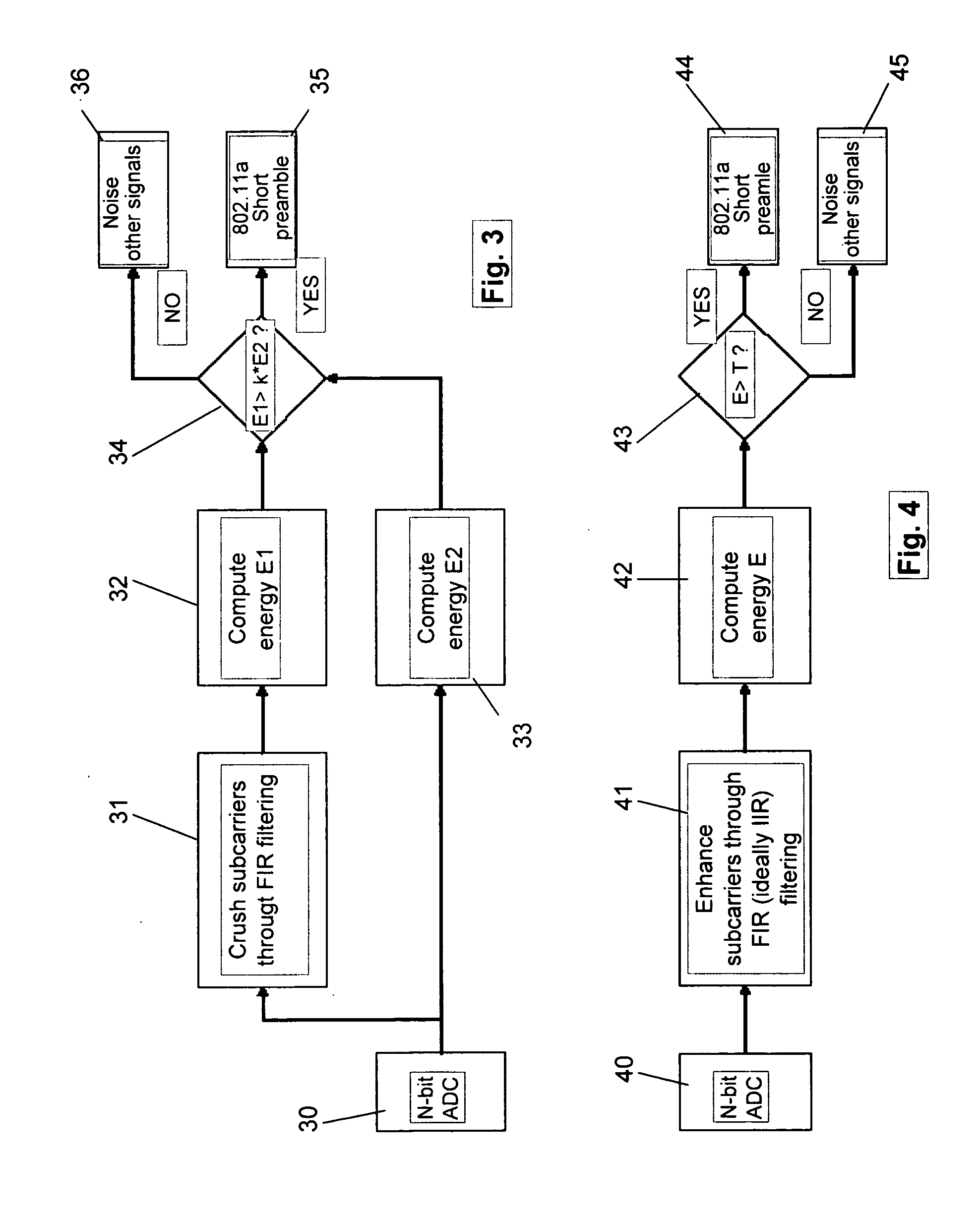

Apparatus and method for detecting preambles according to IEEE 802.11A wireless LAN standard

InactiveUS20060203926A1Reduce power consumptionReliable methodNetwork topologiesSecret communicationBandpass filteringWireless lan

A novel method and apparatus for short preamble detection within the framework of the 802.11a standard is described. The present invention can be easily implemented in both the radio part (preferred embodiment) and the baseband part (general case) of the receiver to provide short preamble detection. The inventive method and apparatus utilize either a notch comb filter to remove the rake of subcarriers composing the short preamble or a battery of bandpass filters to enhance them. A decision on the presence of the short preamble is made by comparing the magnitude associated to certain qualities of the input and output sequences to a preset threshold. The proposed innovation offers a significant advantage over conventional approaches in terms of gate count and power consumption.

Owner:NEWLOGIC TECH

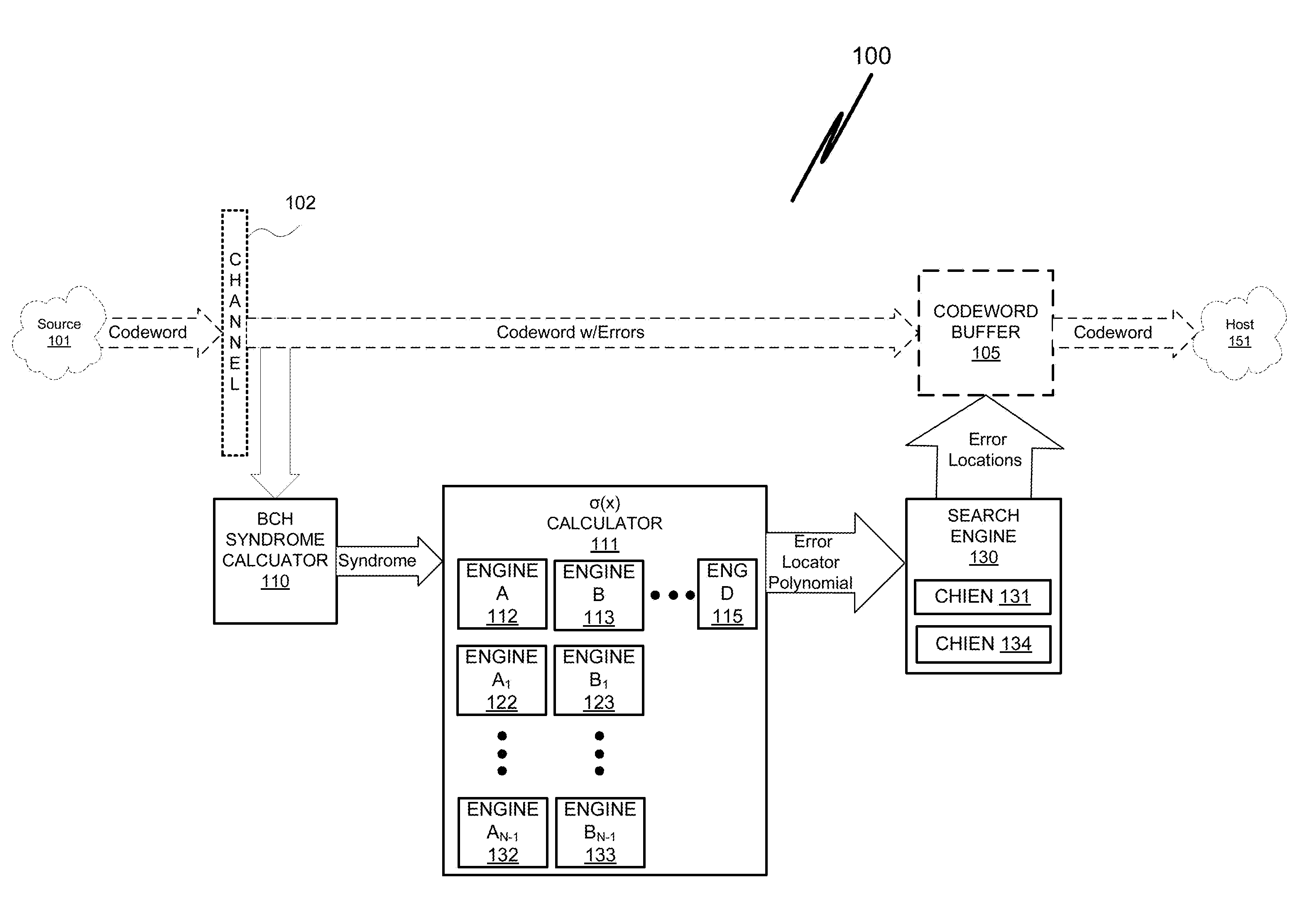

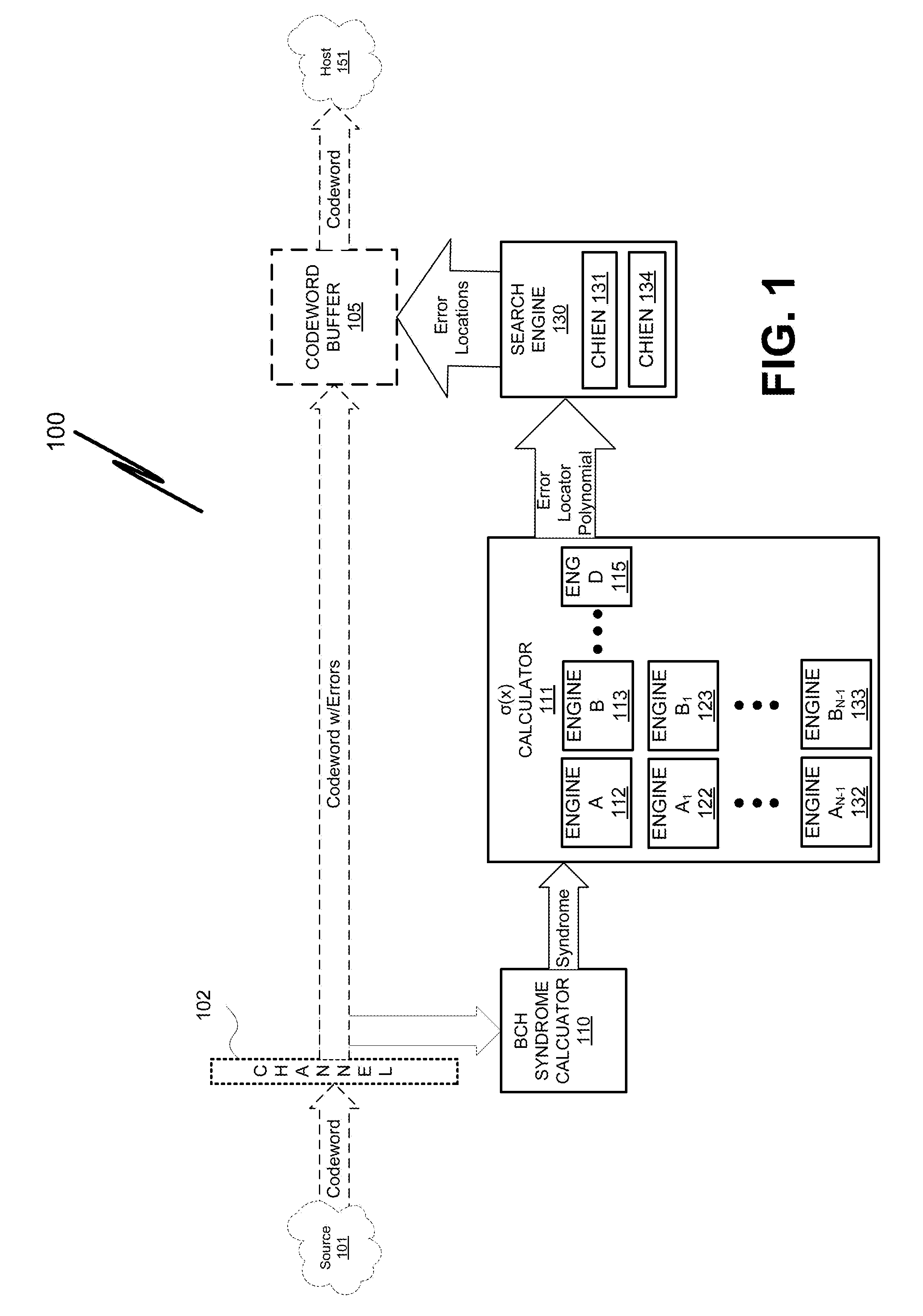

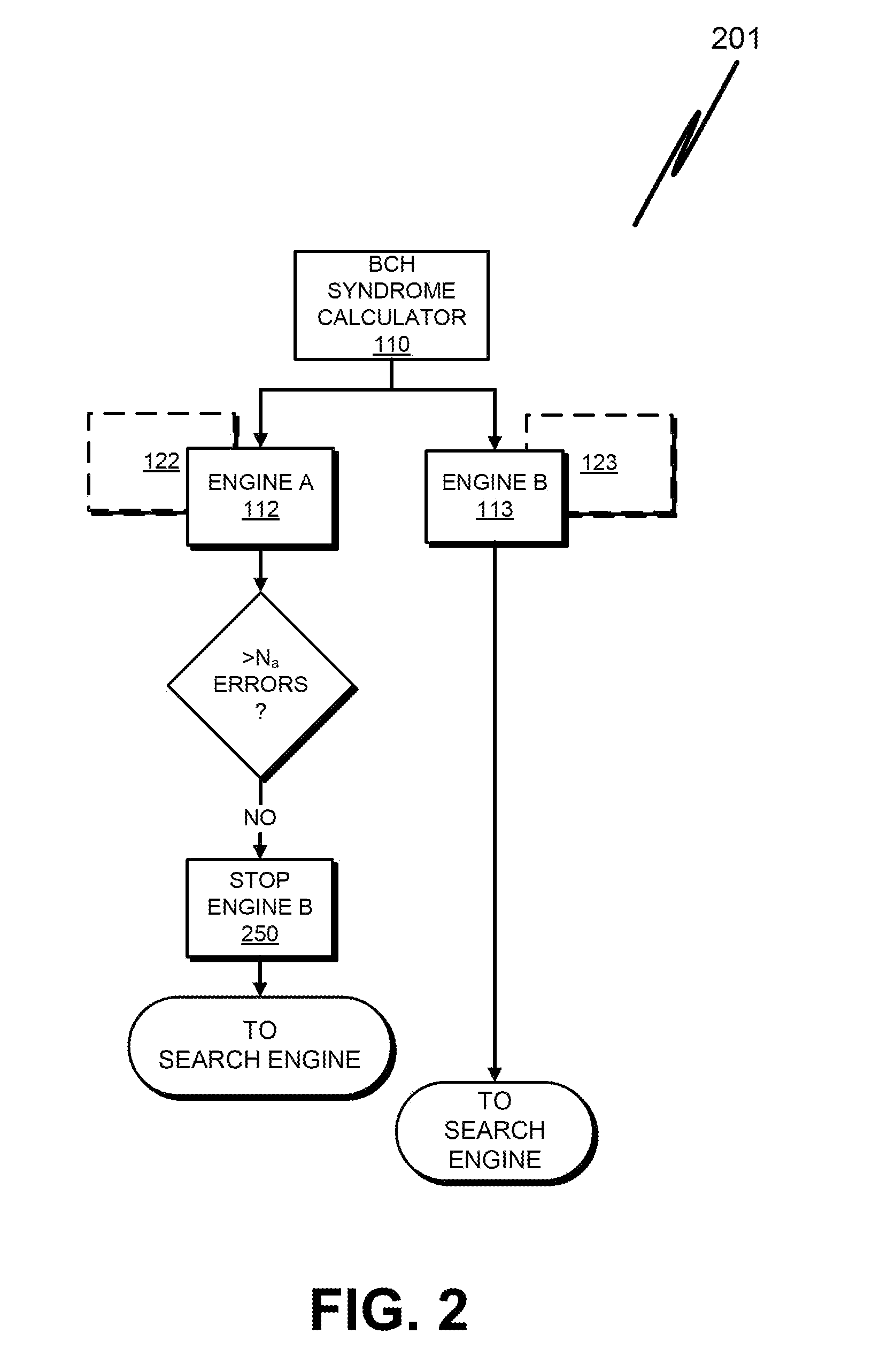

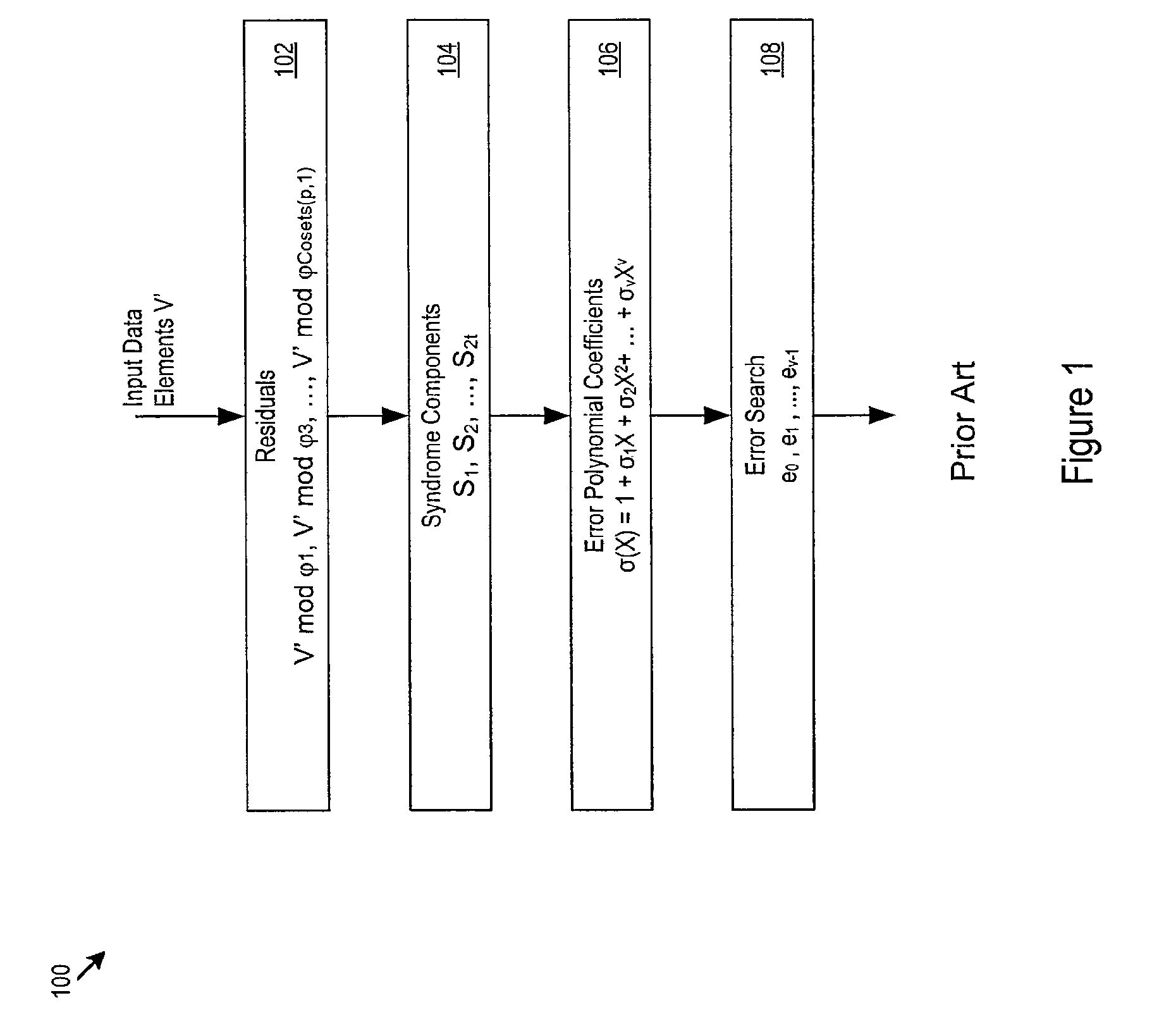

Bch decoding with multiple sigma polynomial calculation algorithms

Bose-Chaudhuri-Hocquenghem (BCH) decoder architectures which execute a plurality of different algorithms to calculate an error location polynomial. The multiple algorithms may be implemented in a storage controller for increased throughput per gate count. Codewords needing up to a threshold number of corrections may be processed via a first algorithm while those with a greater number of corrections may be processed via the second algorithm. In embodiments, the Peterson-Gorenstein-Zierler (PGZ) algorithm and the Berlekamp-Massey algorithm (BMA) are executed either serially or in parallel to increase throughput of the decoder.

Owner:SK HYNIX NAND PROD SOLUTIONS CORP

Efficient hardware implementation of tweakable block cipher

InactiveUS20080270505A1Efficient architectureDigital data processing detailsDigital computer detailsHardware implementationsComputer science

A combination of an infrequently-called tiny multiplication unit and a “differential” unit that quickly computes T (n+1) basing on known T n. The schedule (how often the multiplication unit is called) can be considered as a parameter of the algorithm. The proposed architecture of the “differential” unit is efficient both in terms of speed (delay) and area (gate count).

Owner:BROADCOM INT PTE LTD

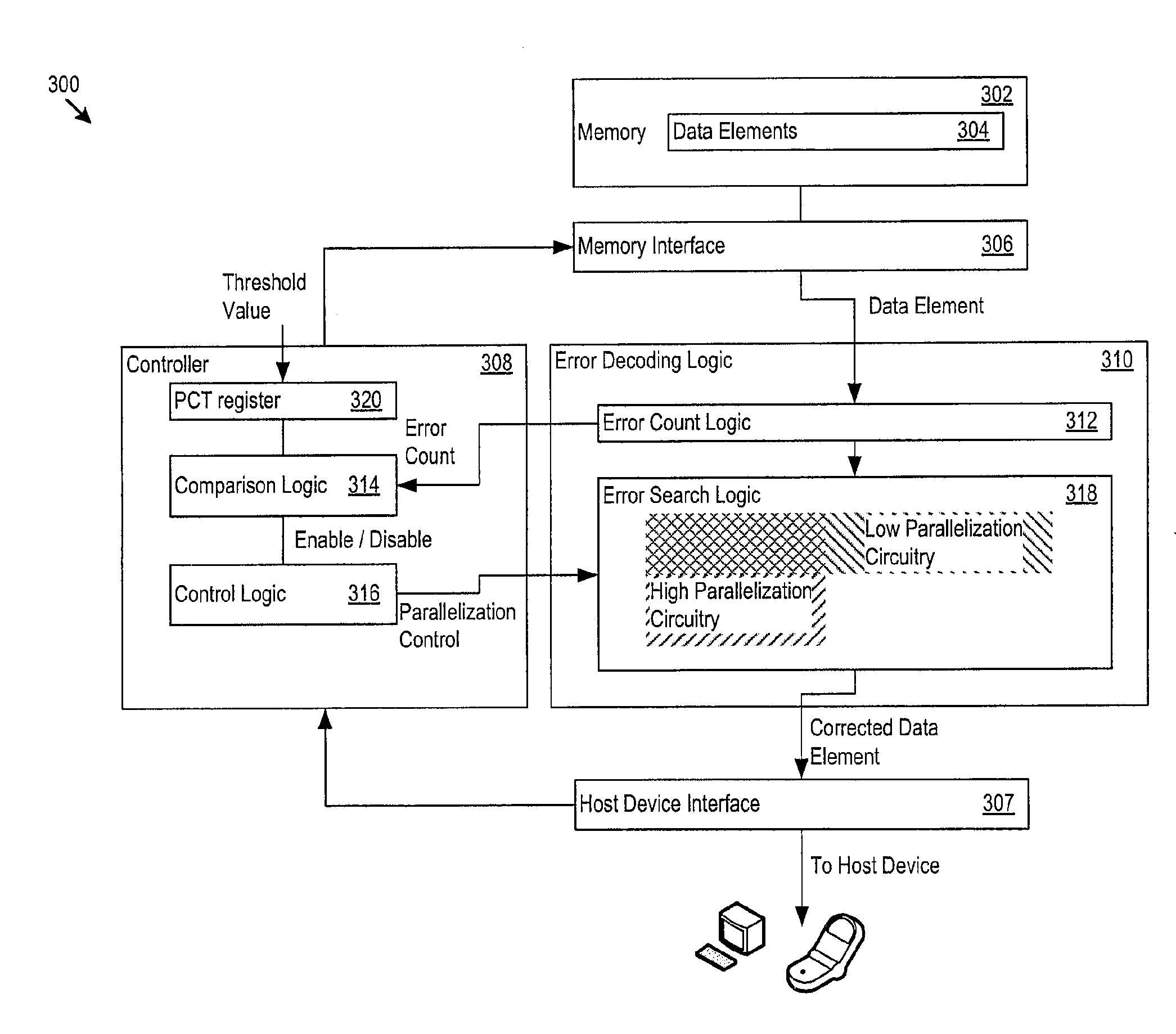

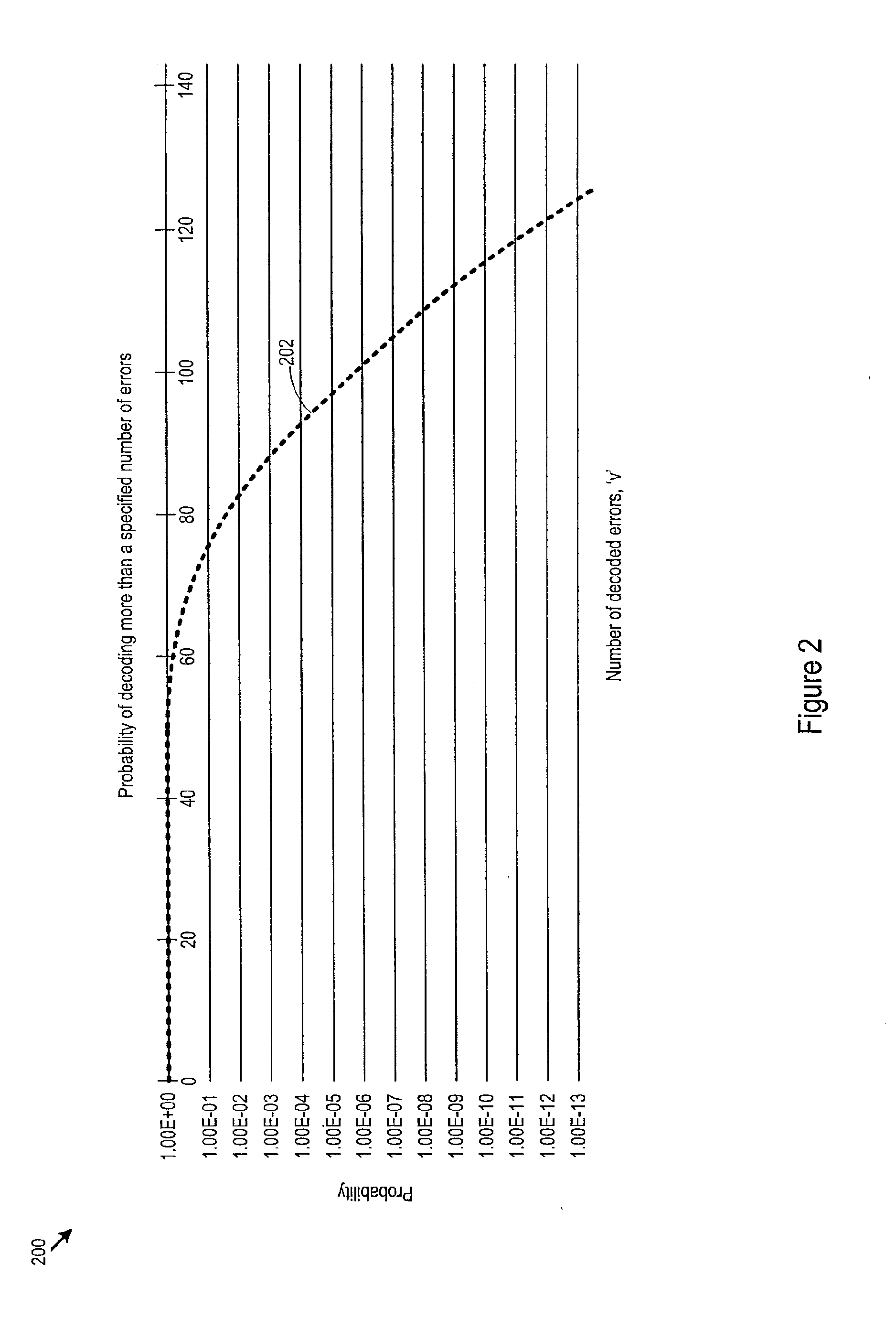

Parallelization of Error Analysis Circuitry for Reduced Power Consumption

ActiveUS20120246526A1Less configurationReduce power consumptionFault responseCode conversionPower efficientMostly True

A memory device (e.g., a flash memory device) includes power efficient codeword error analysis circuitry. The circuitry analyzes codewords stored in the memory of the memory device to locate and correct errors in the codewords before the codewords are communicated to a host device that requests the codewords from the memory device. The circuitry includes a highly parallel configuration with reduced complexity (e.g., reduced gate count) that a controller may cause to perform the error analysis under most circumstances. The circuitry also includes an analysis section of greater complexity with a less parallel configuration that the controller may cause to perform the error analysis less frequently. Because the more complex analysis section runs less frequently, the error analysis circuitry may provide significant power consumption savings in comparison to prior designs for error analysis circuitry.

Owner:WESTERN DIGITAL ISRAEL LTD

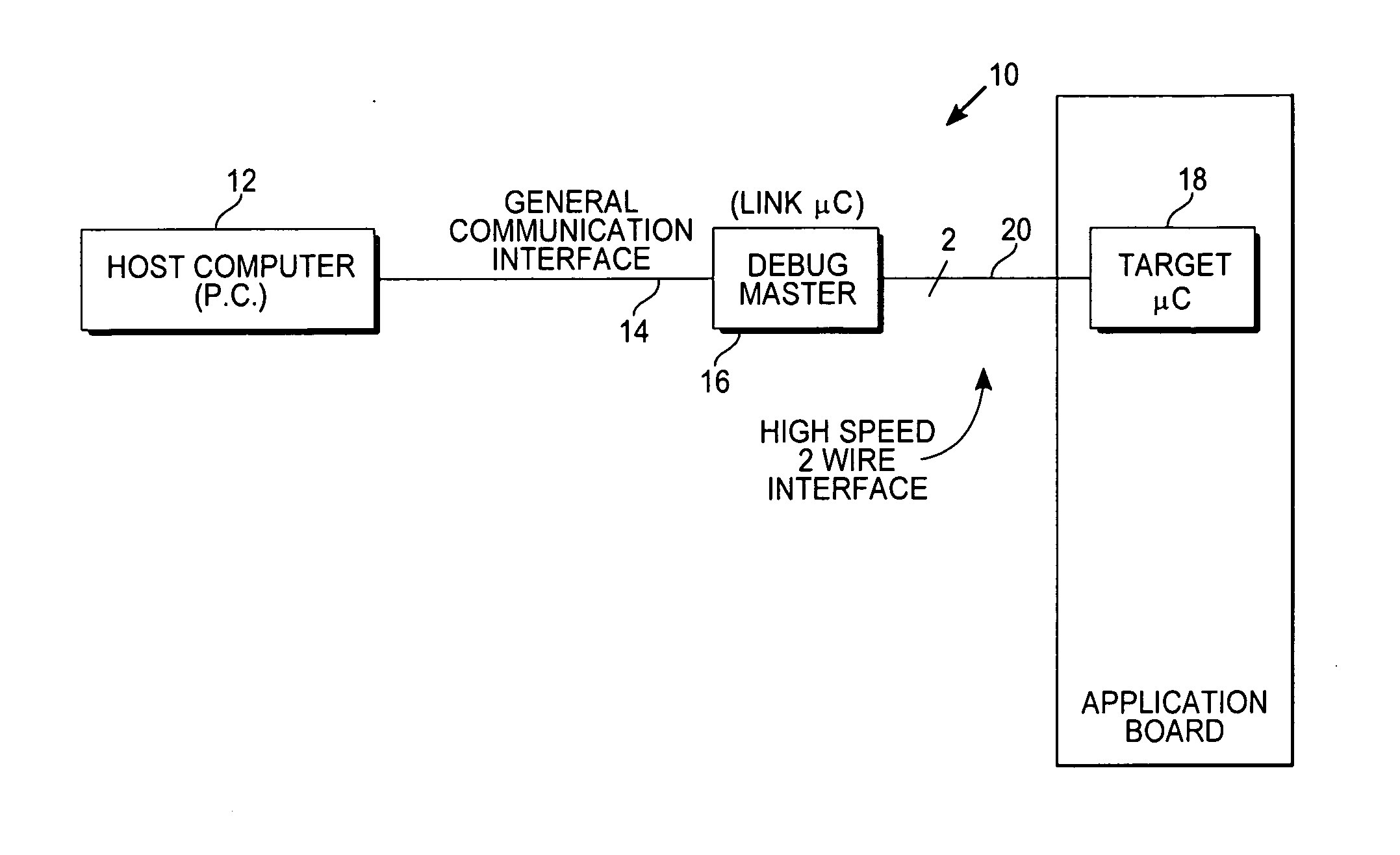

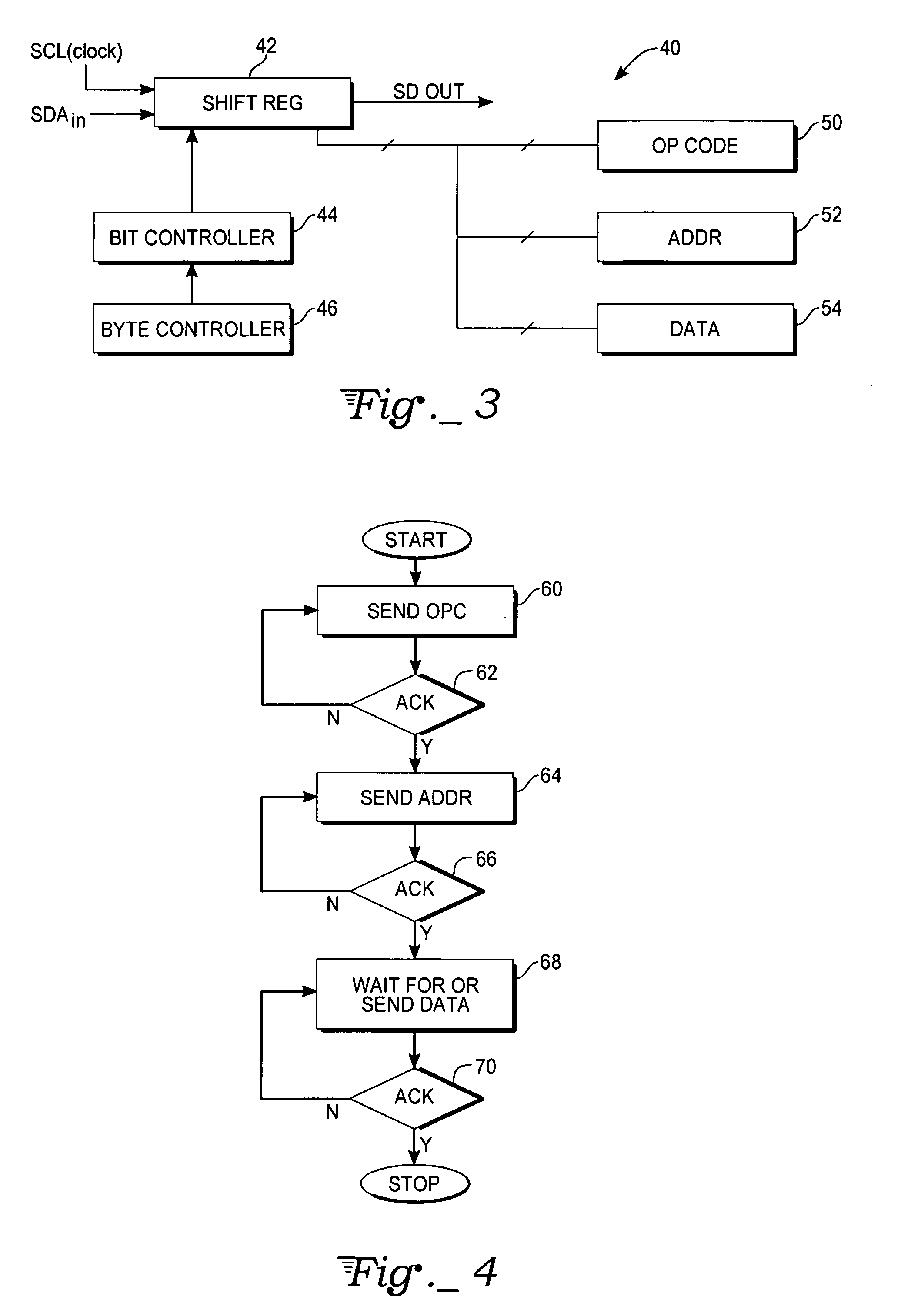

Dual CPU on-chip-debug low-gate-count architecture with real-time-data tracing

ActiveUS20070168731A1Reduce intrusionIncrease costError detection/correctionMicrocontrollerGeneral purpose

The same microcontroller chip is configured to be either a Target version or a Link version of a microcontroller. The Target version runs an application program. To debug the Target microcontroller, the Link version of the microcontroller functions as a master debug microcontroller to the slave Target microcontroller running the application program. The Link microcontroller runs an interface translator program between a Host computer that runs a debug program, and the Target microcontroller. The Link microcontroller communicates with the Target microcontroller using a fast, 2-wire interface. The Link microcontroller communicates with the Host computer through a general purpose interface.

Owner:ATMEL CORP

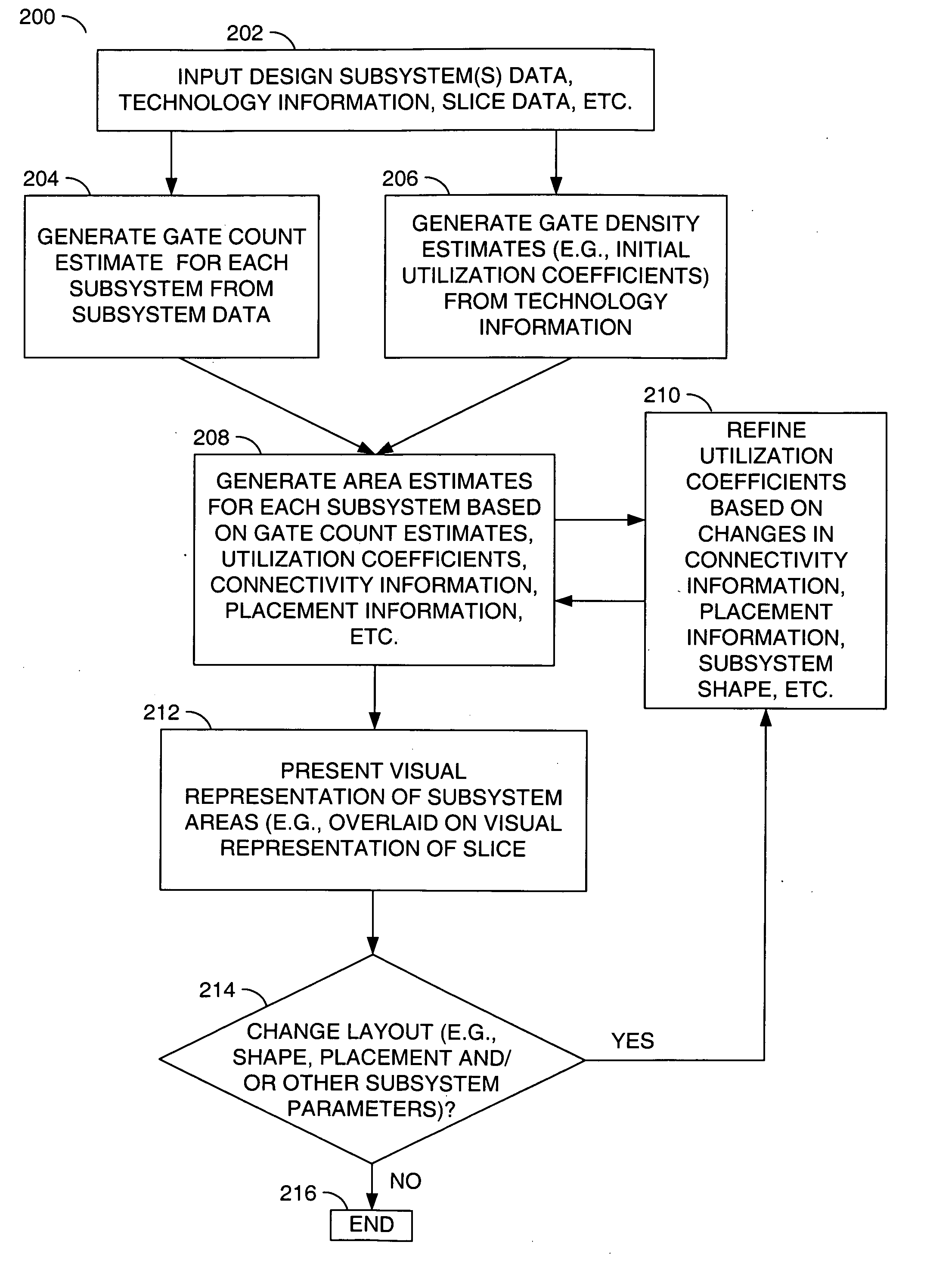

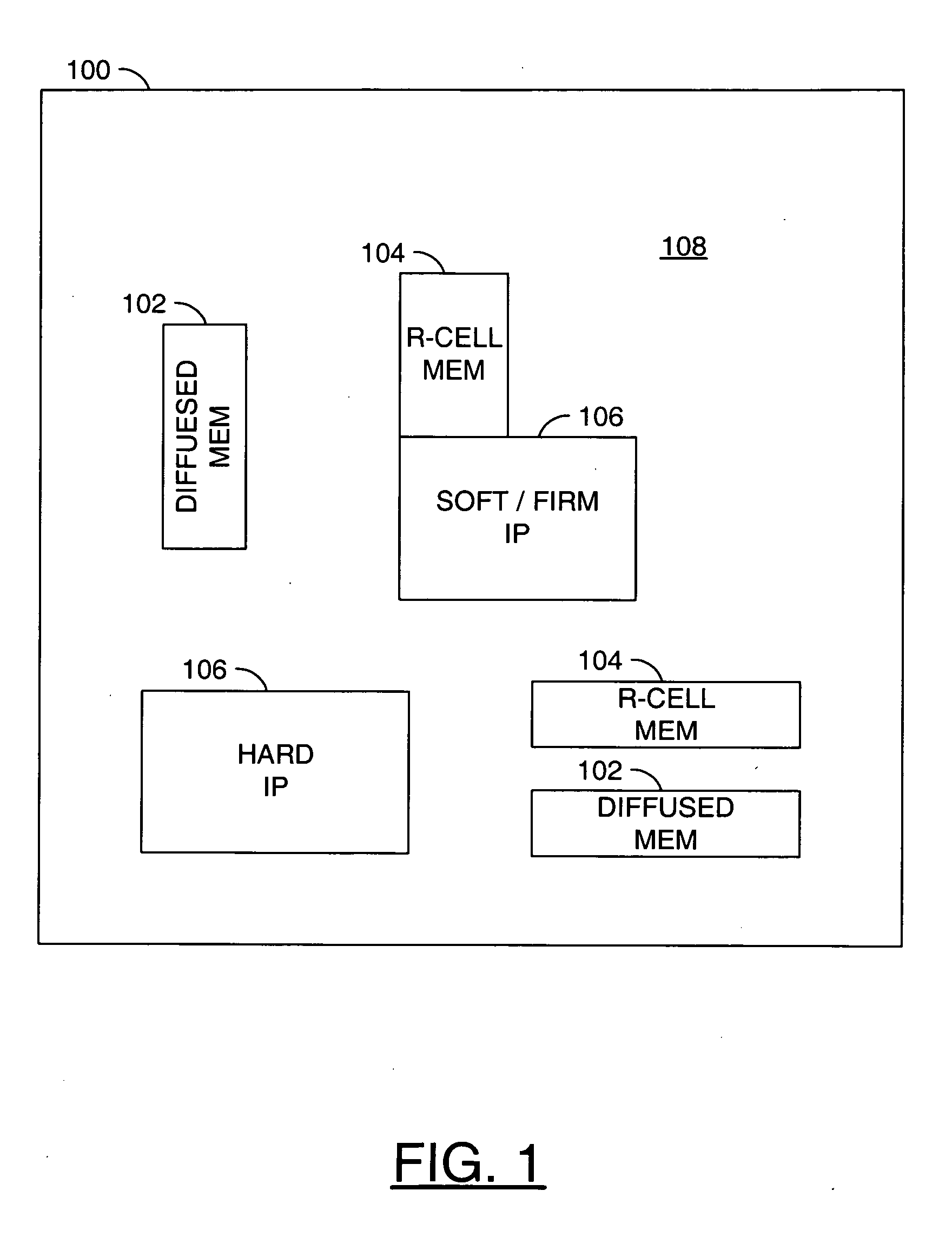

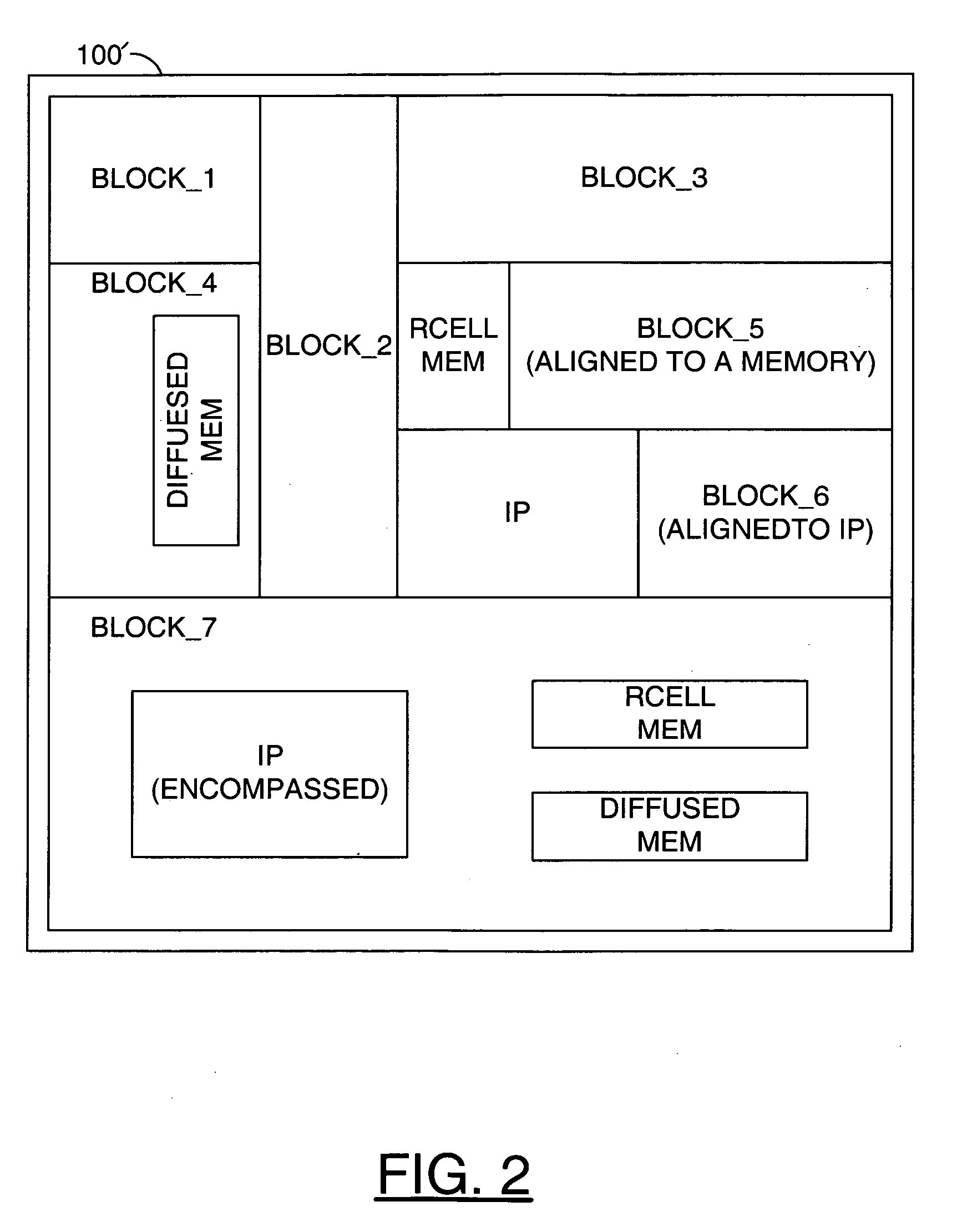

Floorplan visualization method

ActiveUS20060129963A1Facilitate R-cellFast and easy analysisComputer programmed simultaneously with data introductionComputer aided designComputer architectureDesign information

A method for floorplan visualization comprising the steps of (A) receiving design information for an integrated circuit design comprising one or more subsystems, (B) generating one or more gate count estimates for the one or more subsystems of the integrated circuit design, (C) generating one or more gate density estimates for gates of the one or more subsystems mapped to one or more programmable areas of a programmable platform device and (D) generating a visual representation of one or more area estimations for each of the one or more subsystems based on the one or more gate count estimates and the one or more gate density estimates.

Owner:BELL SEMICON LLC

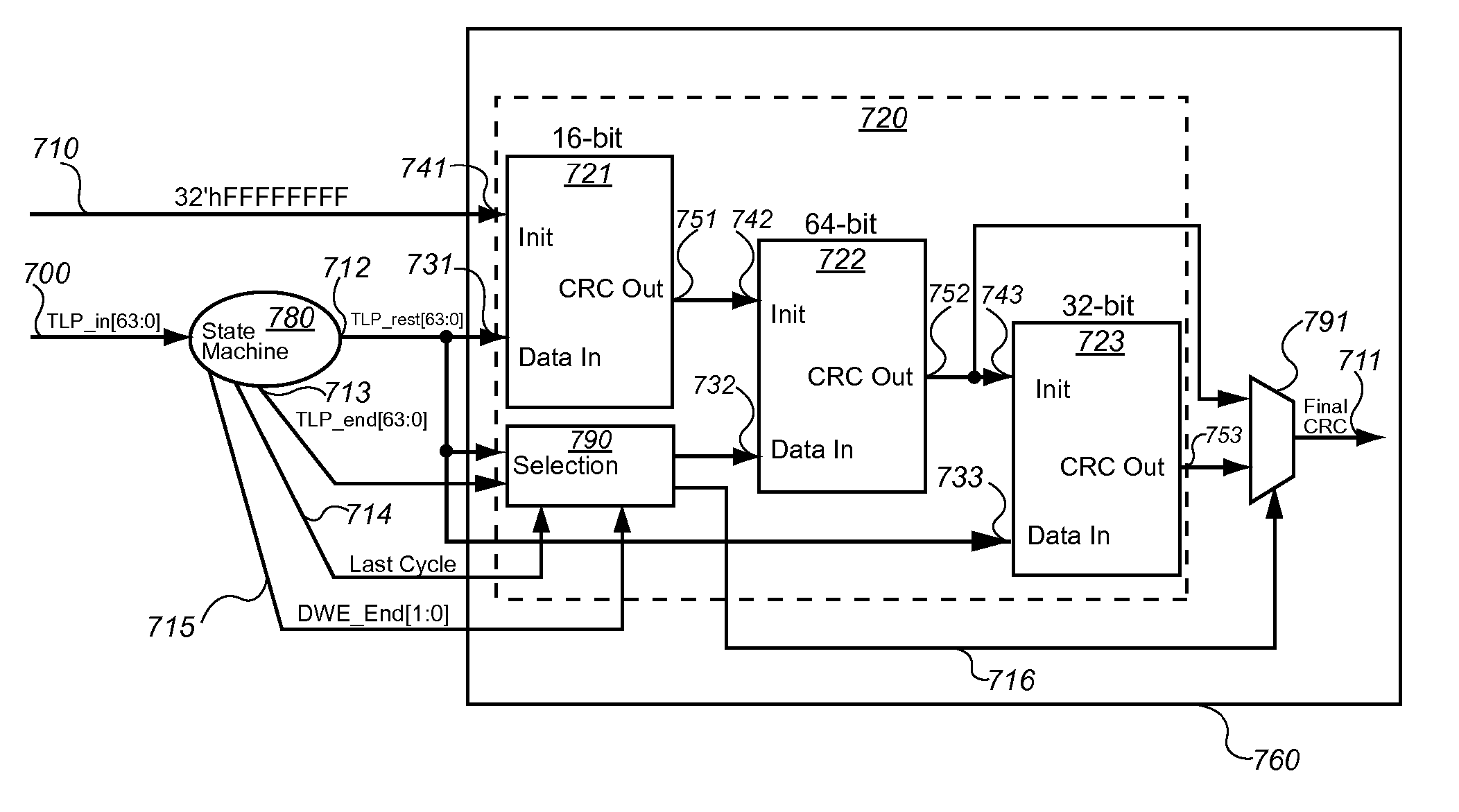

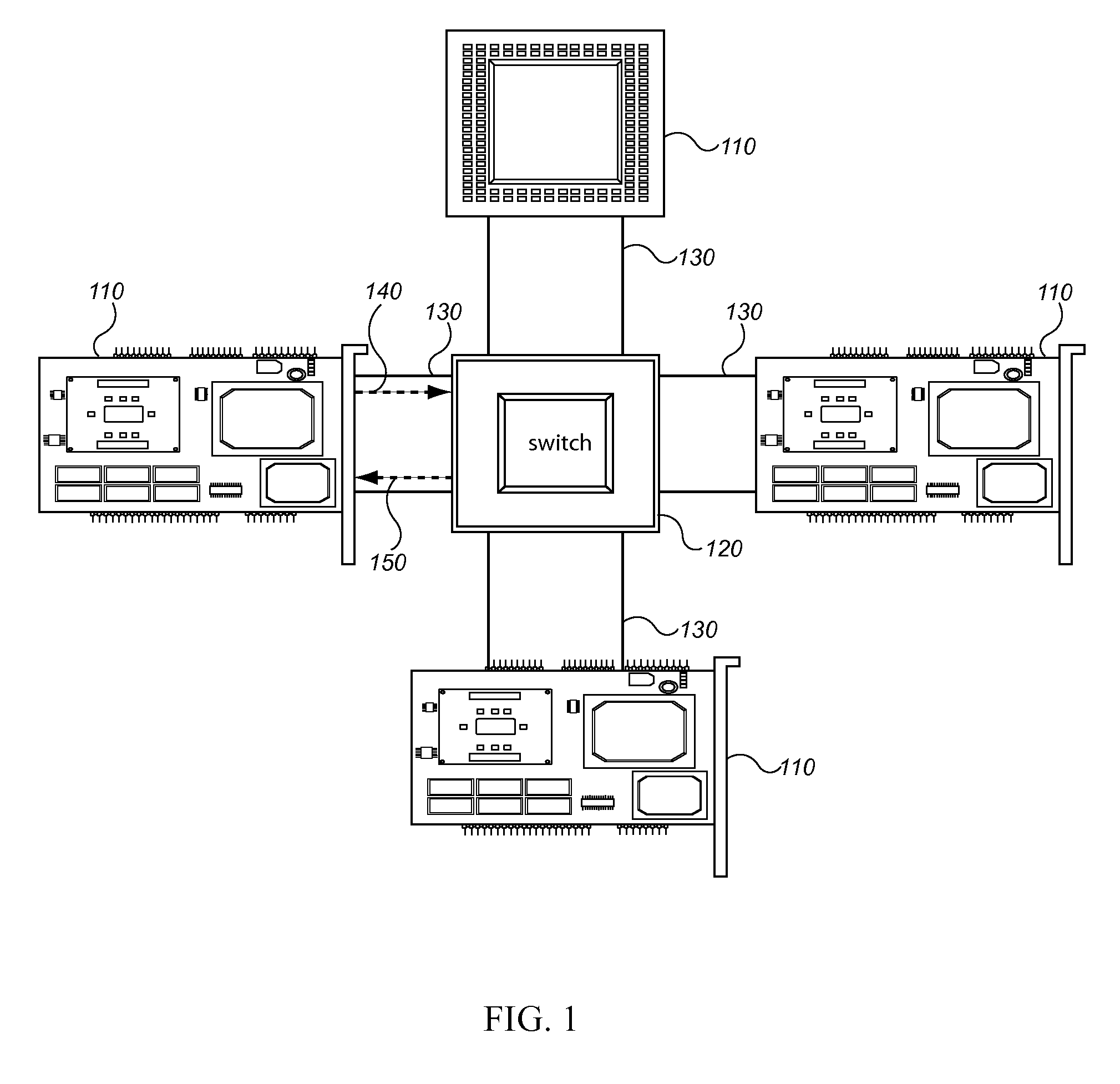

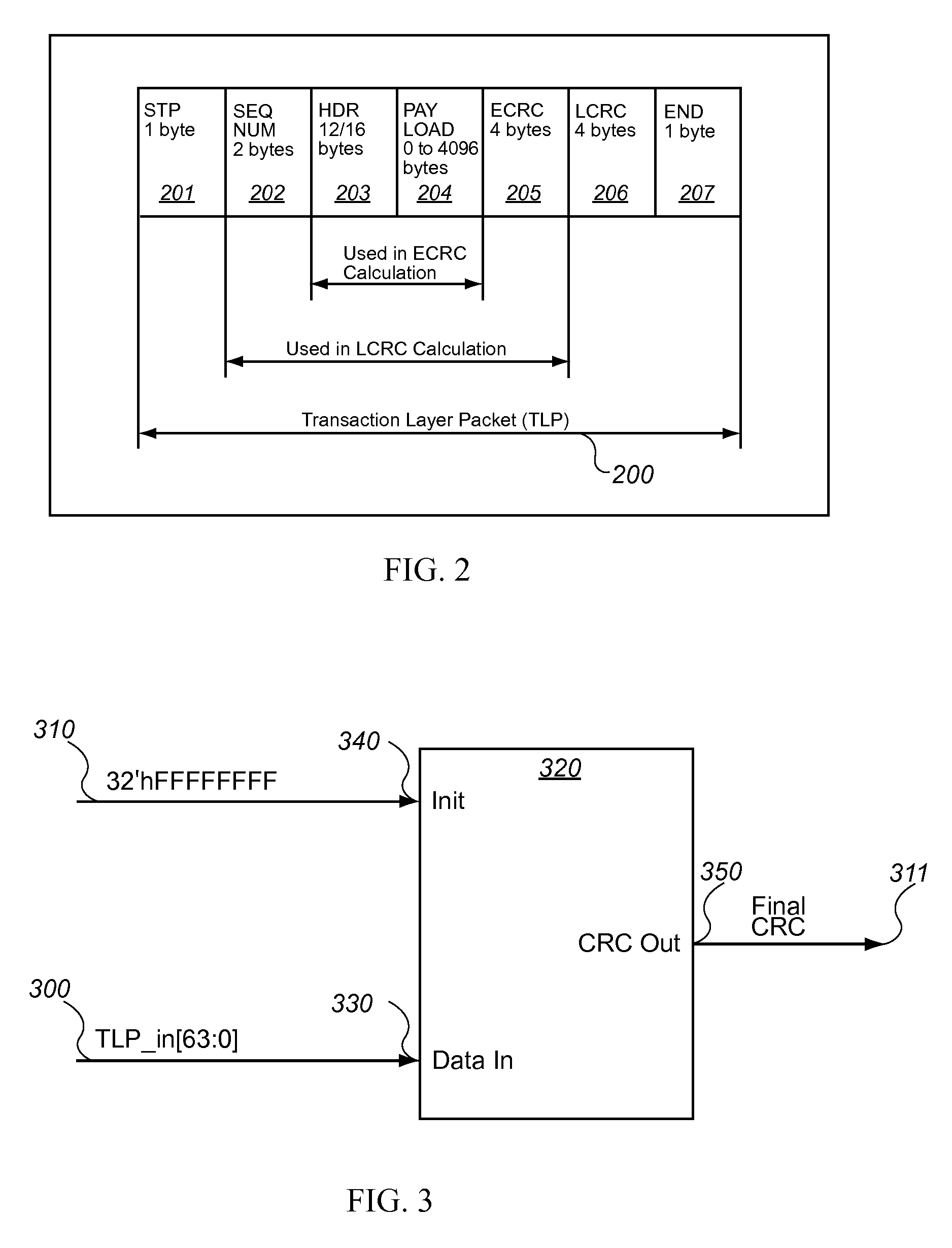

System and Method of Processing Received Line Traffic for PCI Express that Provides Line-Speed Processing, and Provides Substantial Gate-Count Savings

InactiveUS20070028152A1Less latencyError detection/correctionError detection onlyWire speedCarrier signal

A branch of CRC resources is configured to process back-to-back TLPs in a PCIe architecture. A state machine receives back-to-back TLPs and generates carrier signals, which it then routes to the branch of CRC resources. These signals are used to align the back-to-back TLPs such that a LCRC for each of the back-to-back TLPs is calculated by the branch of CRC resources at line speed. The system and method allow substantial gate-count savings to be realized, as the present invention minimizes the number of components necessary to achieve the desired results.

Owner:MISHRA KISHORE KUMAR +1

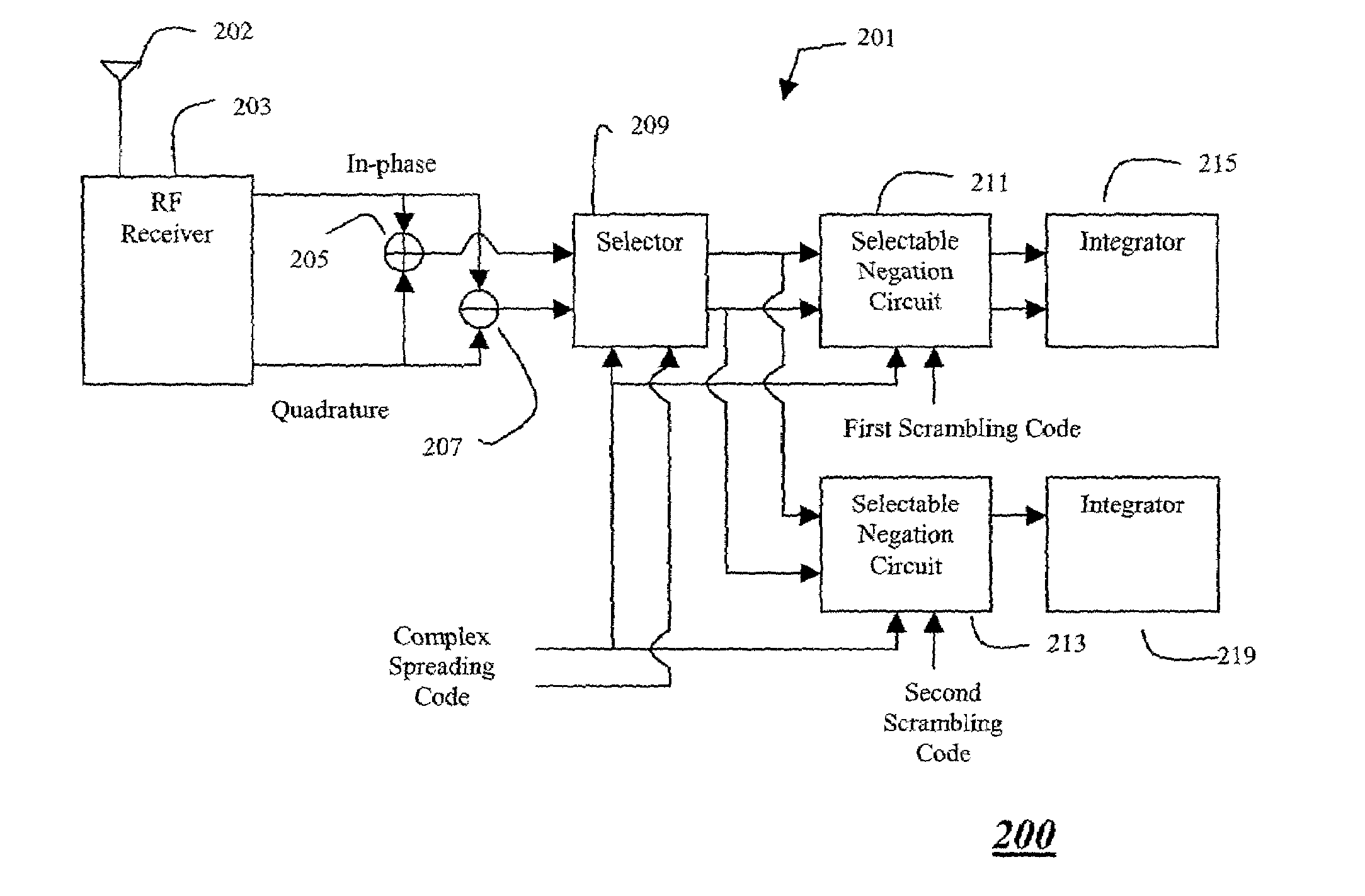

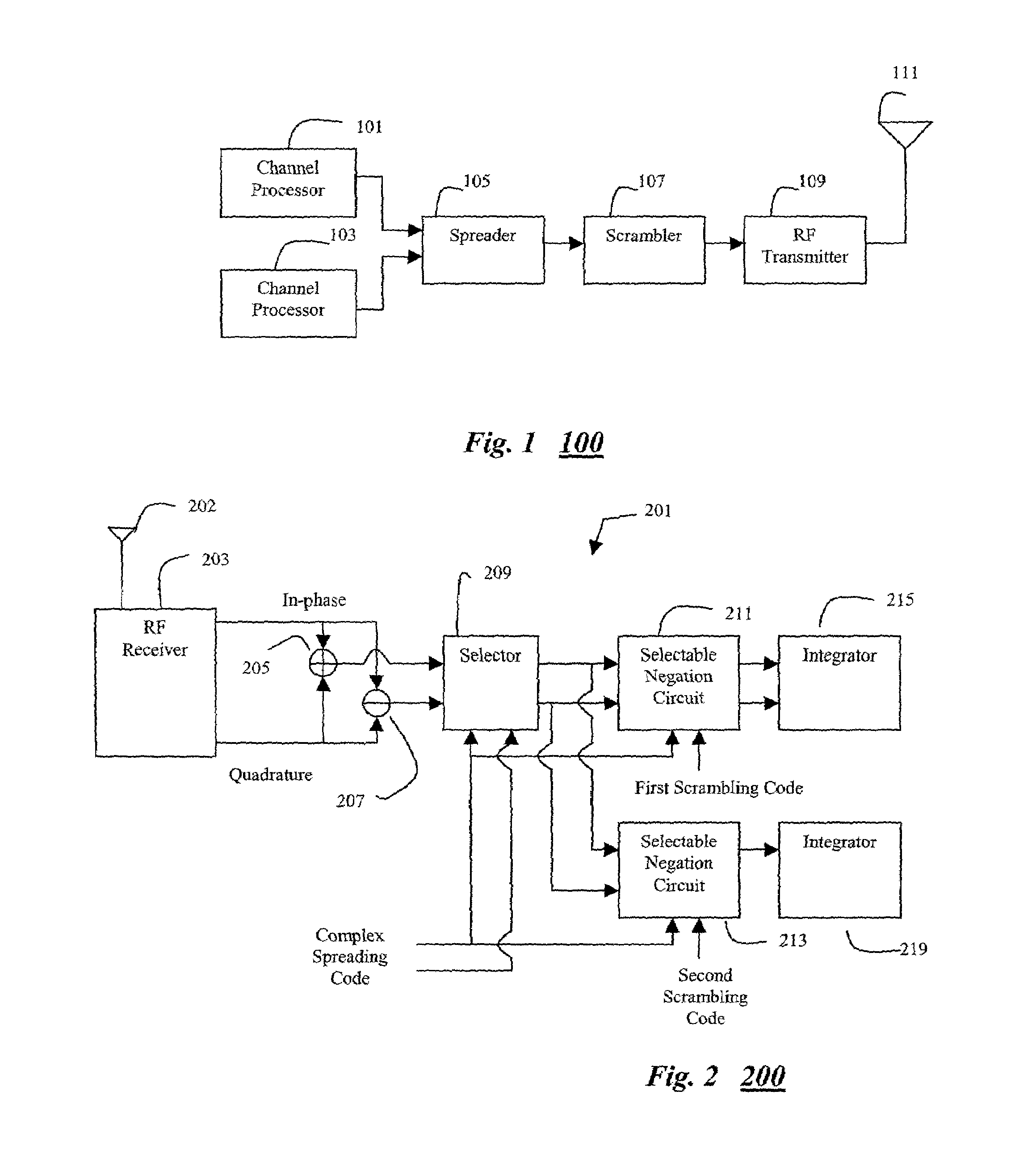

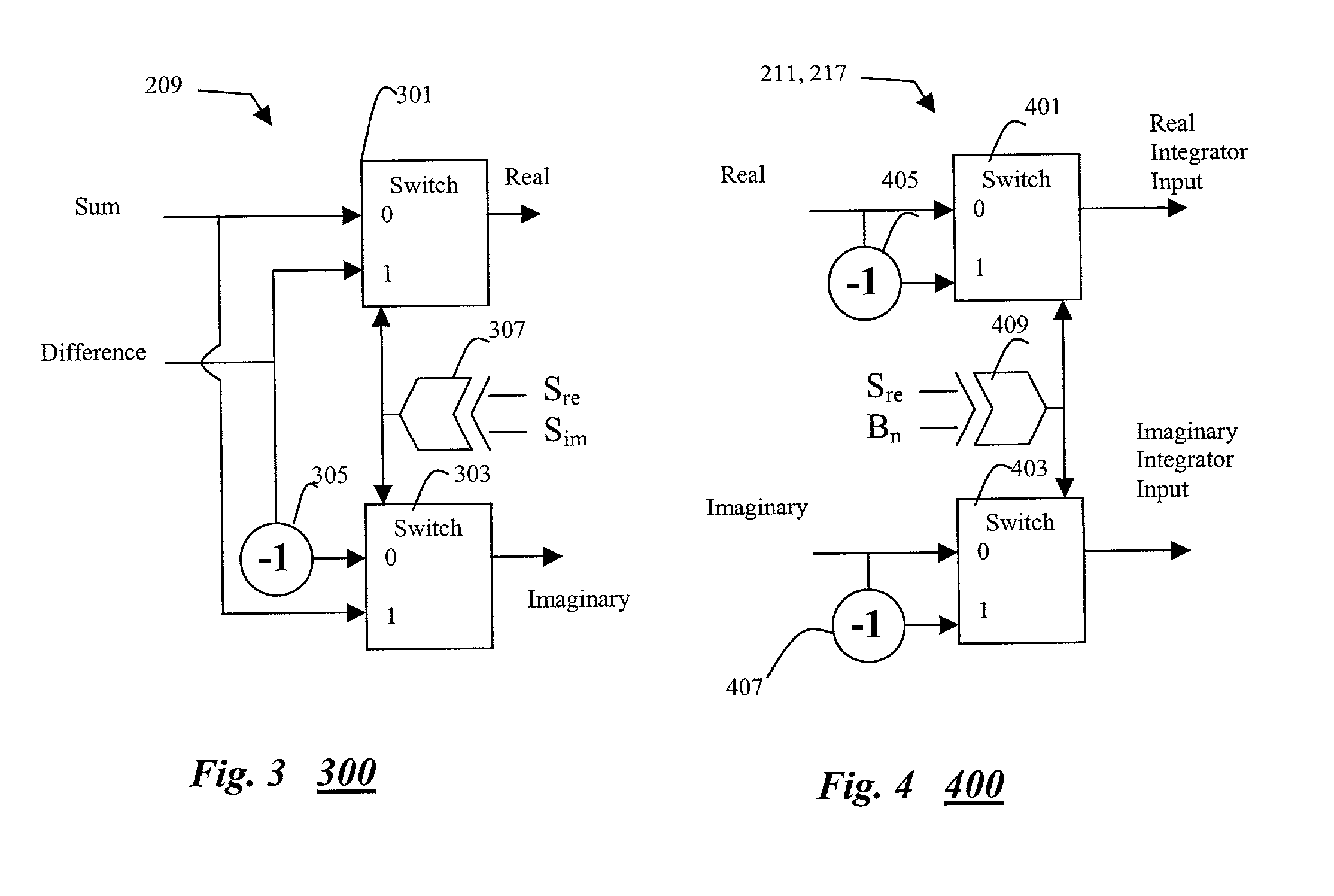

Multicode receiver

InactiveUS7016398B2Code division multiplexTransmissionCode division multiple accessFrequency-division multiple access

A code division multiple access (CDMA) receiver detects, de-scrambles, and de-spreads multiple channels that utilize different binary codes. The processing that is common to all channels can be performed once thus saving gate count and power consumption.

Owner:APPLE INC

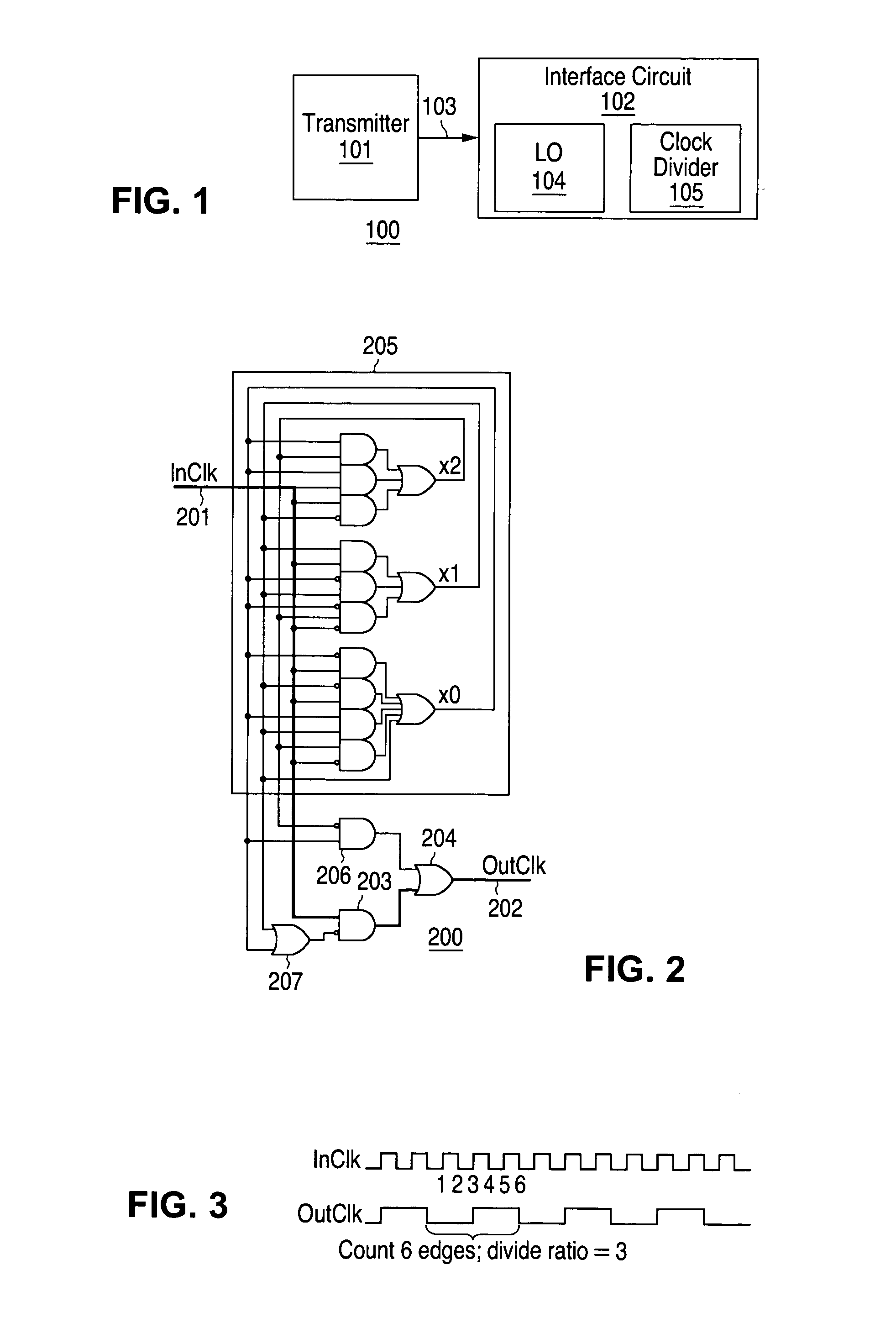

Minimum gate delay edge counter

ActiveUS7197104B1Counting chain pulse counters with non-natural counting orderCounting chain synchronous pulse countersSignal edgeEngineering

An edge counter counting both rising and falling edges of an input signal is implemented with combinational logic, without using flip-flops. The combinational logic is designed using intermediate signals and state transitions producing an output signal having a cycle corresponding to a predetermined odd or even number of input signal edges, with the logic optimized and protected against entry into “stuck” states. A low power, low gate count edge counter is thus implemented with an output signal duty cycle at least as balanced as the input counter duty cycle.

Owner:NAT SEMICON CORP

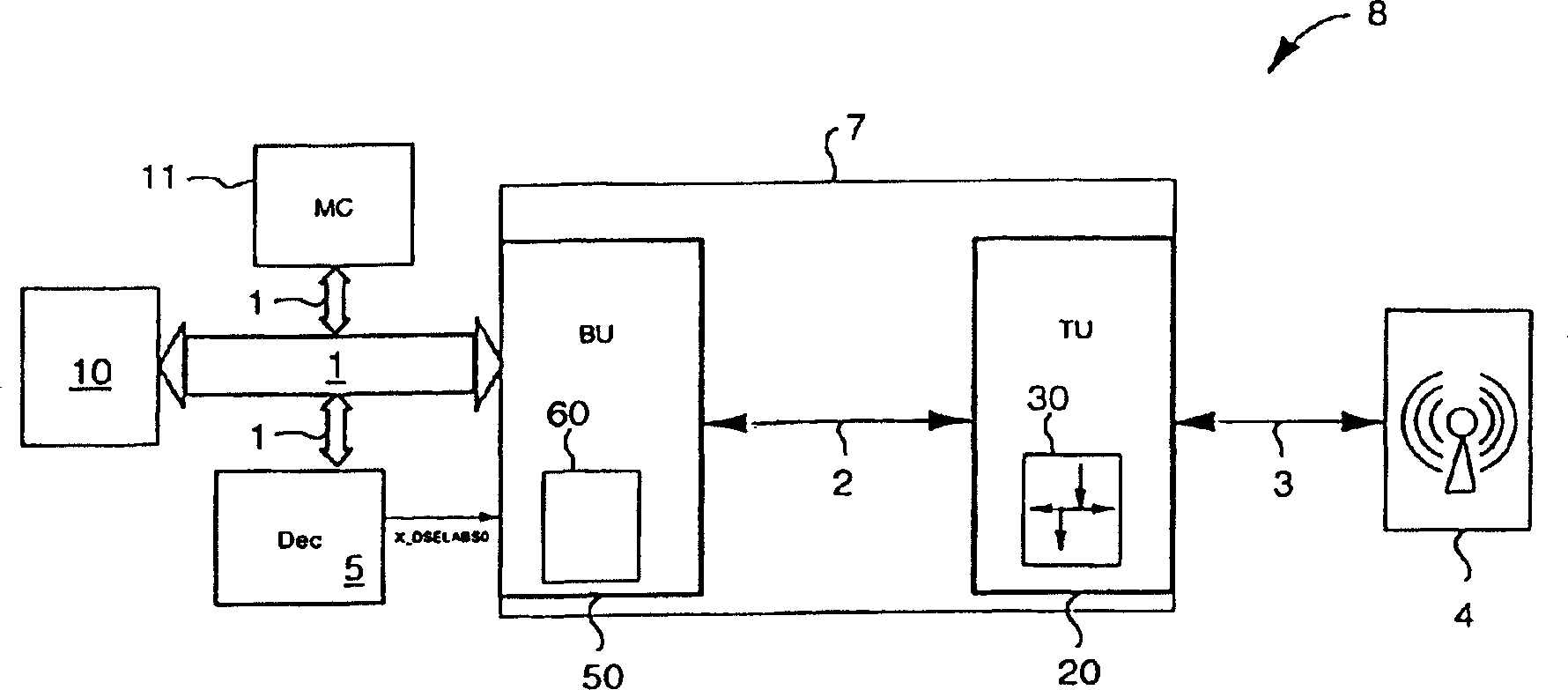

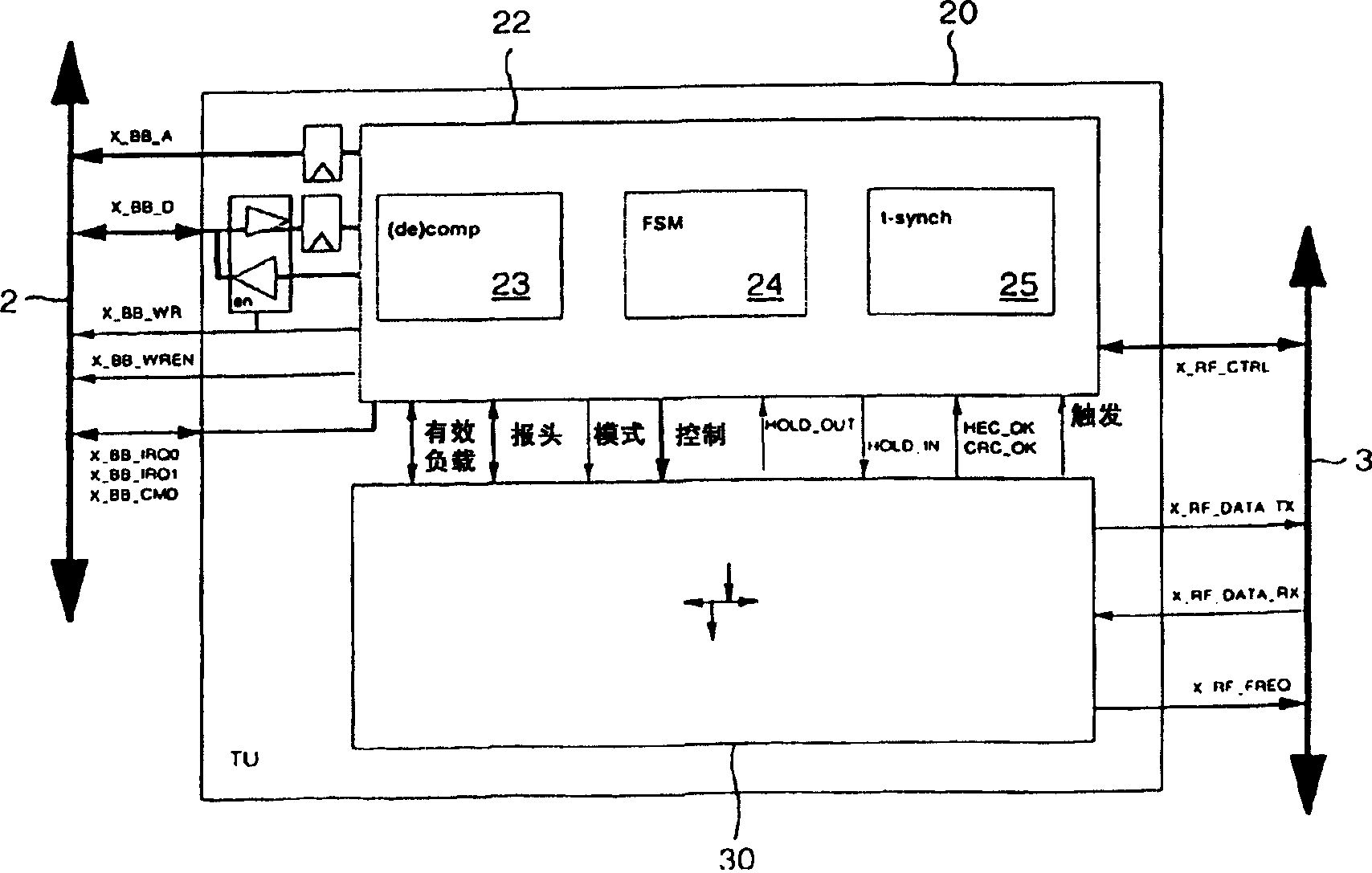

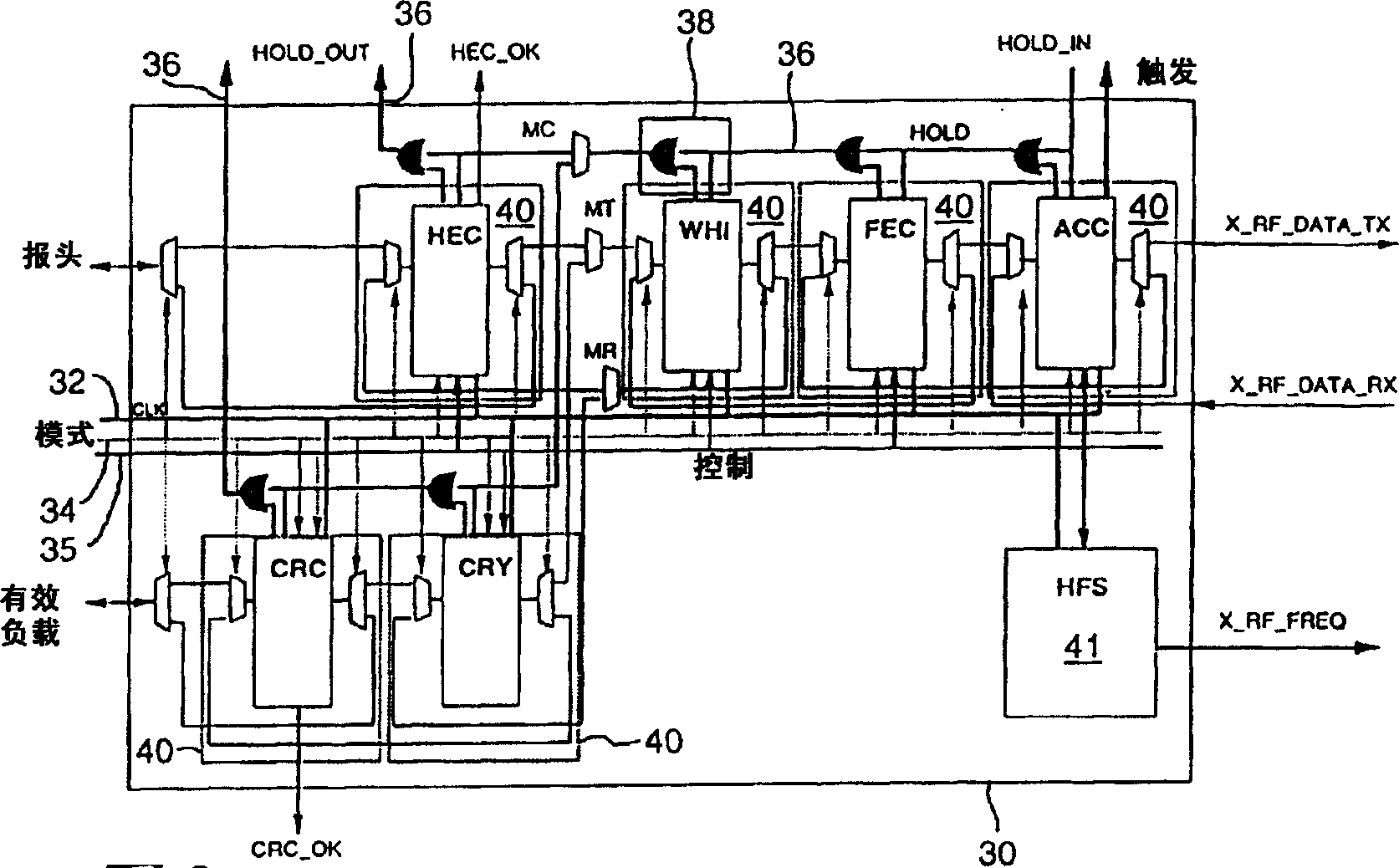

Digital baseband system

The invention provides a baseband system for a short-range radio communication system. The baseband system complies with the Bluetooth baseband specification and is well suited for efficient hardware implementation, providing low power, small size and low cost radio subsystem design. The baseband system includes a transceiver unit and a buffer unit so that the system has an efficient gate count and reduced power consumption. The transceiver unit design is based on pipelined signal processing with distributed datapath flow control. The transceiver unit processes outgoing and incoming packets and comprises several signal processing units connected in series so that each signal processing unit is clocked by a common clock signal. A mode line is connected to each signal processing unit for switching each signal processing unit between transmit mode and receive mode. Control lines connected to each signal processing unit convey flow control information to one or more preceding signal processing units in transmit mode, or to one or more subsequent signal processing units in receive mode. The buffer unit comprises a buffer system applying a flexible memory management concept that results in an efficient implementation of buffers or storage elements in terms of gate count and power consumption and provides the ability to dynamically allocate memory for variable length user packets flexibility. The buffer system holding the data of the first processing unit and the second processing unit comprises several storage elements such that each storage element has a first storage unit and a second storage unit. A switching subsystem is provided for switching the individual storage elements between the first and second modes. In the first mode, each first storage unit is addressable by a first processing unit and each second storage unit is addressable by a second processing unit. In the second mode, each second storage unit is addressable by the first processing unit, and each first storage unit is addressable by the second processing unit.

Owner:INT BUSINESS MASCH CORP

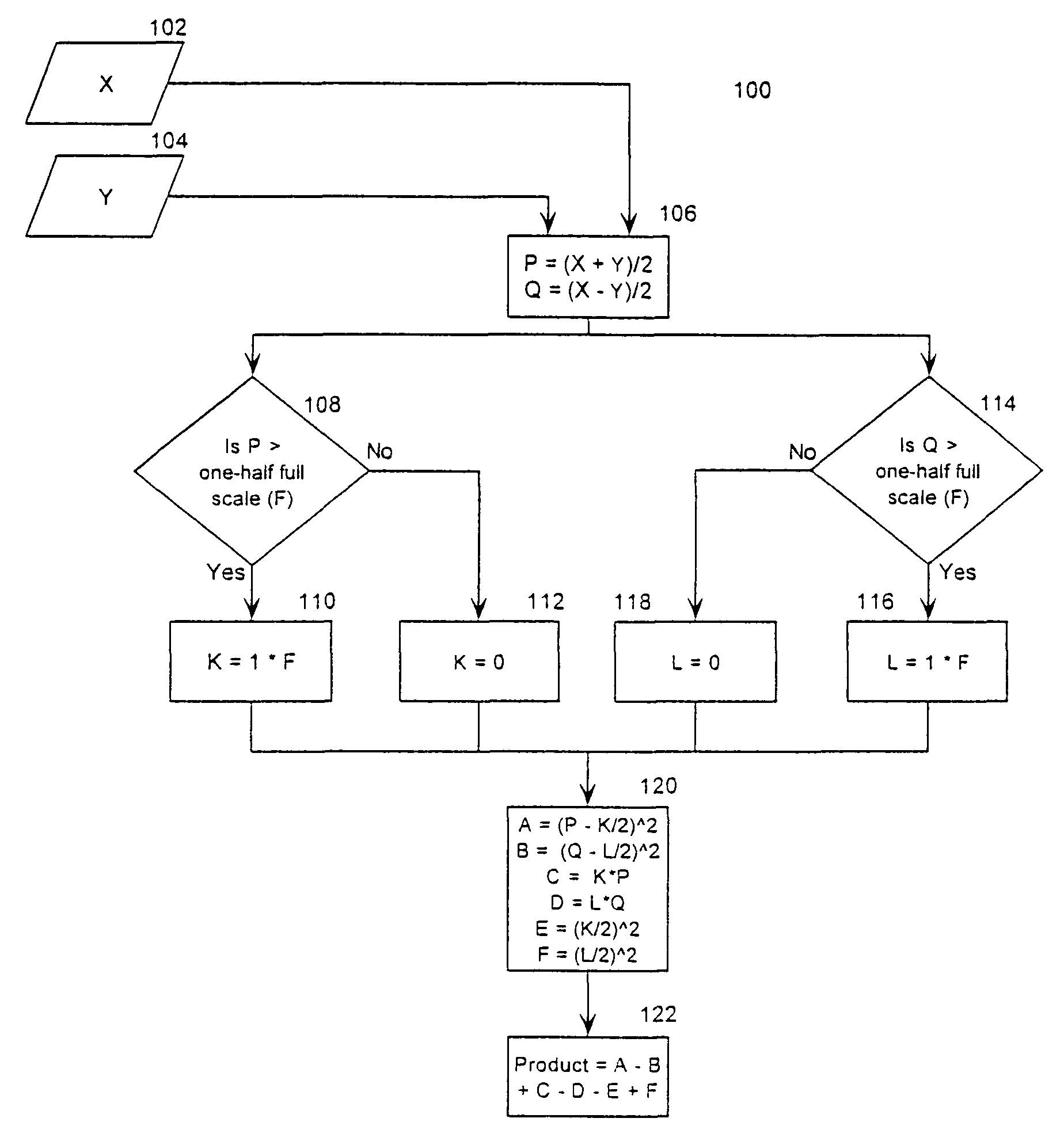

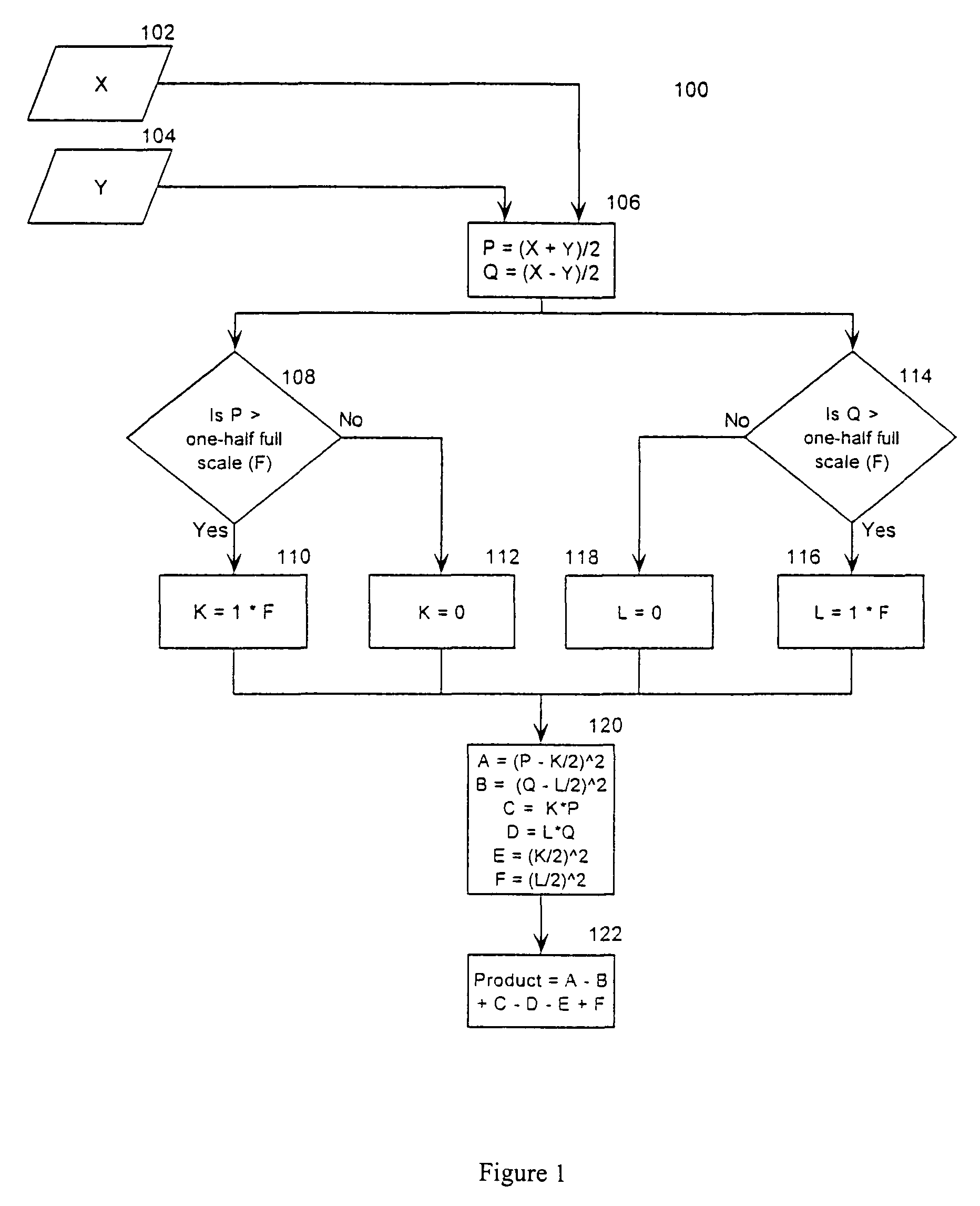

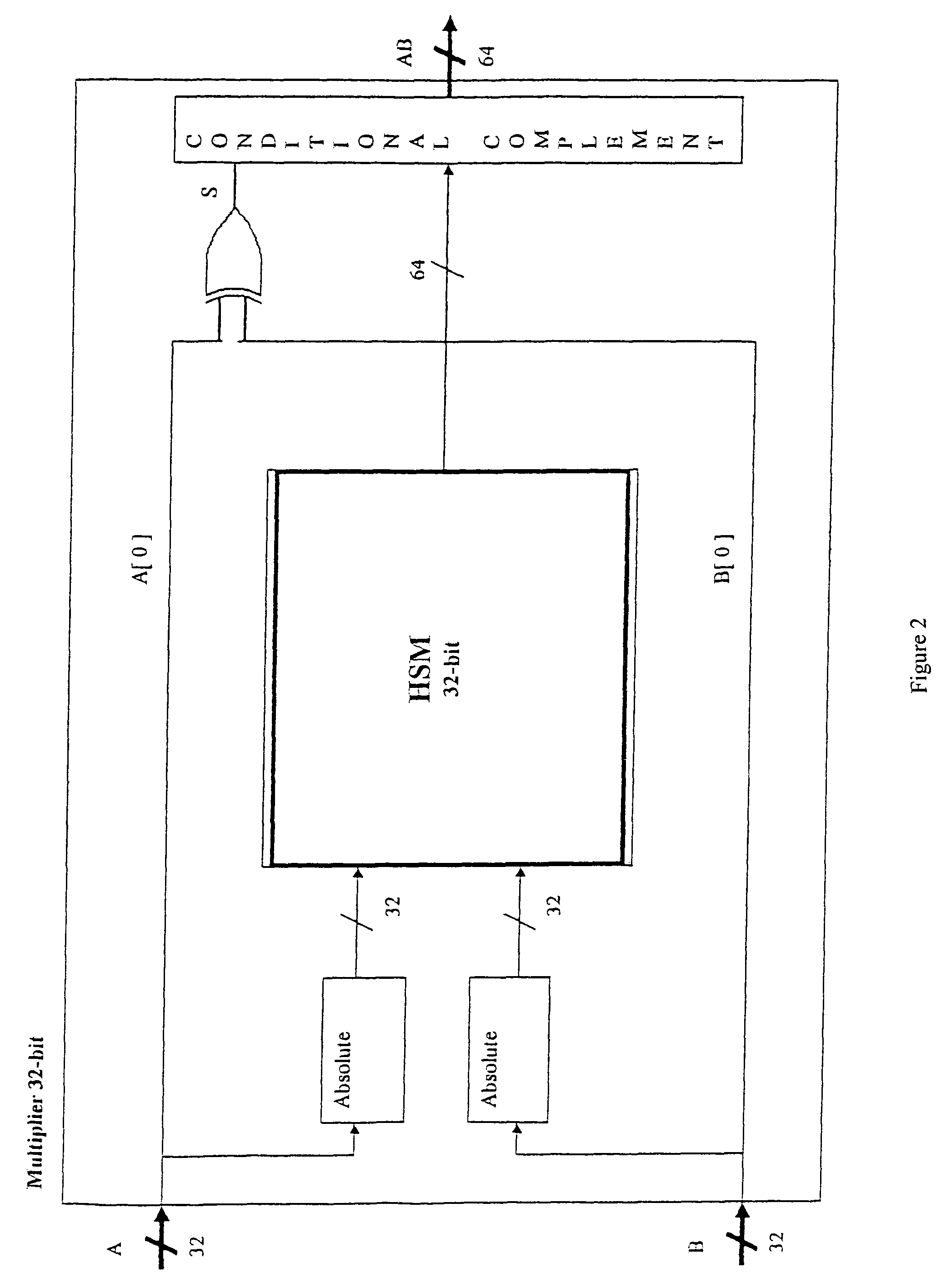

Dynamically reconfigurable power-aware, highly scaleable multiplier with reusable and locally optimized structures

InactiveUS7873823B2Reduce power consumptionReduce dissipationVolume/mass flow measurementComputation using non-contact making devicesComputer architectureTrade offs

A large bit width multiplier with multiple copies of a core small bit width multiplier and ROM cells. The present invention provides a power system that trades off processing speed against power dissipation. The present invention reduces power dissipation to about half of the best industry implementation at about half the speed. Its power dissipation is 10% of another industry standard implementation at 1.5 times the speed. The present invention has a gate count that is about twice the gate count for these implementations.

Owner:SHANKAR RAVI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com