Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

11623results about "Computer aided design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

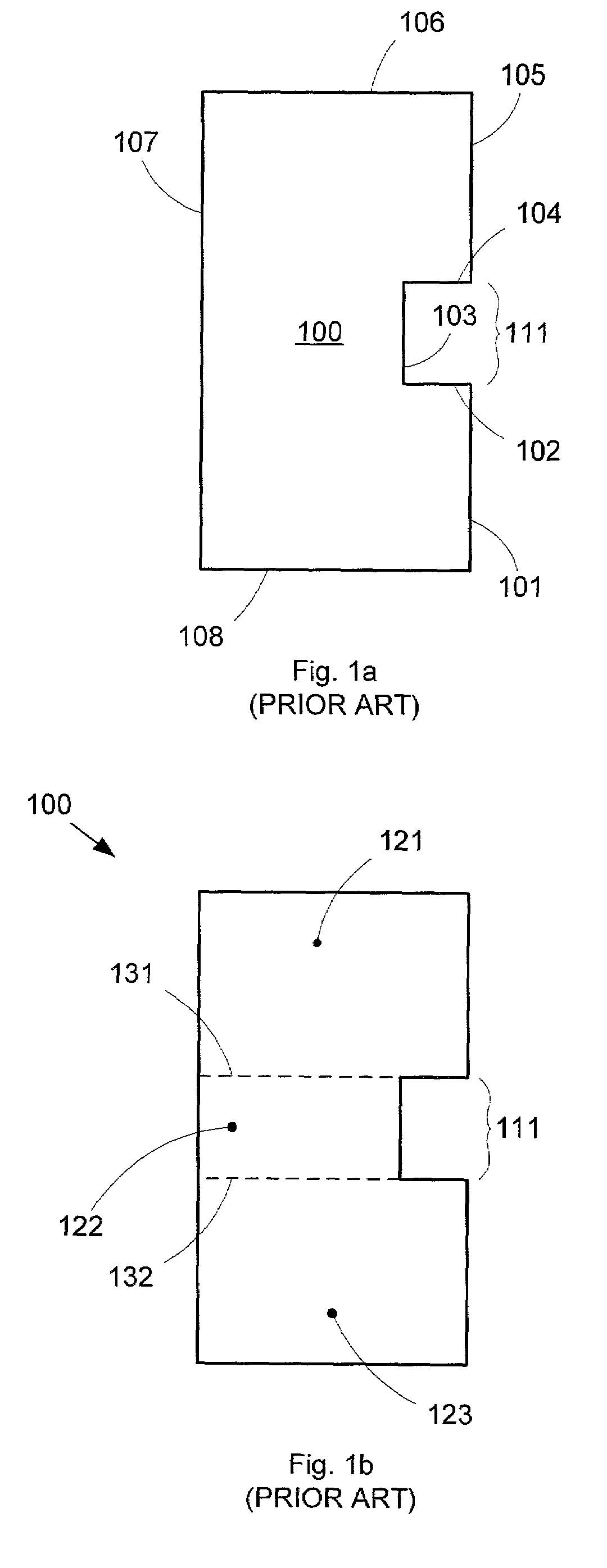

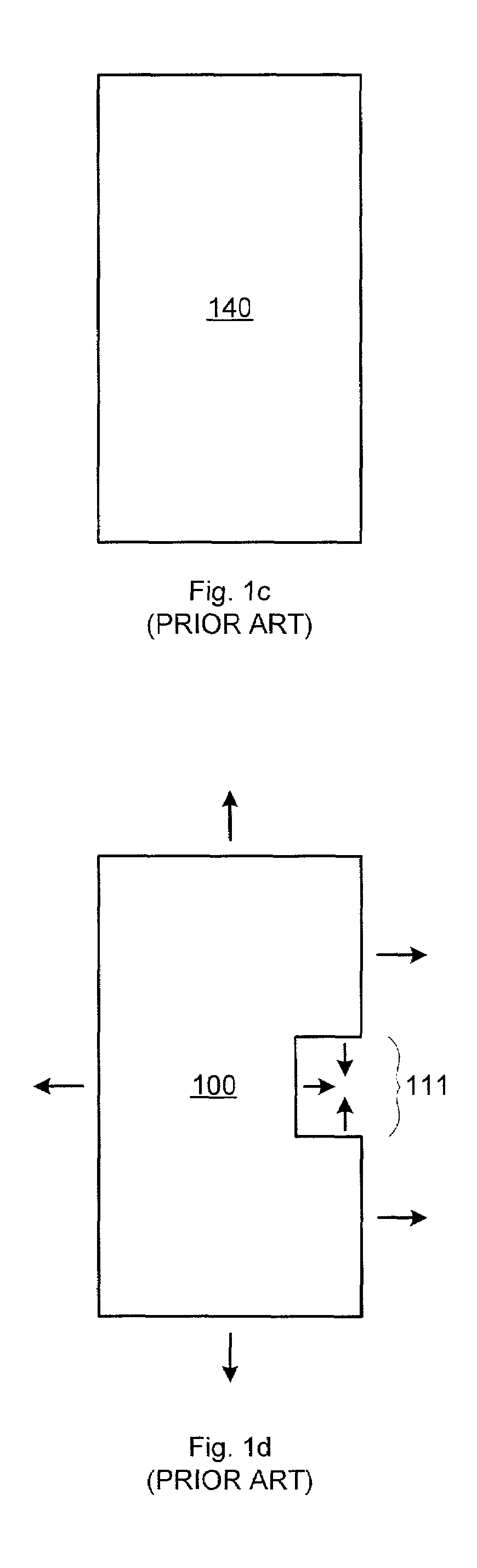

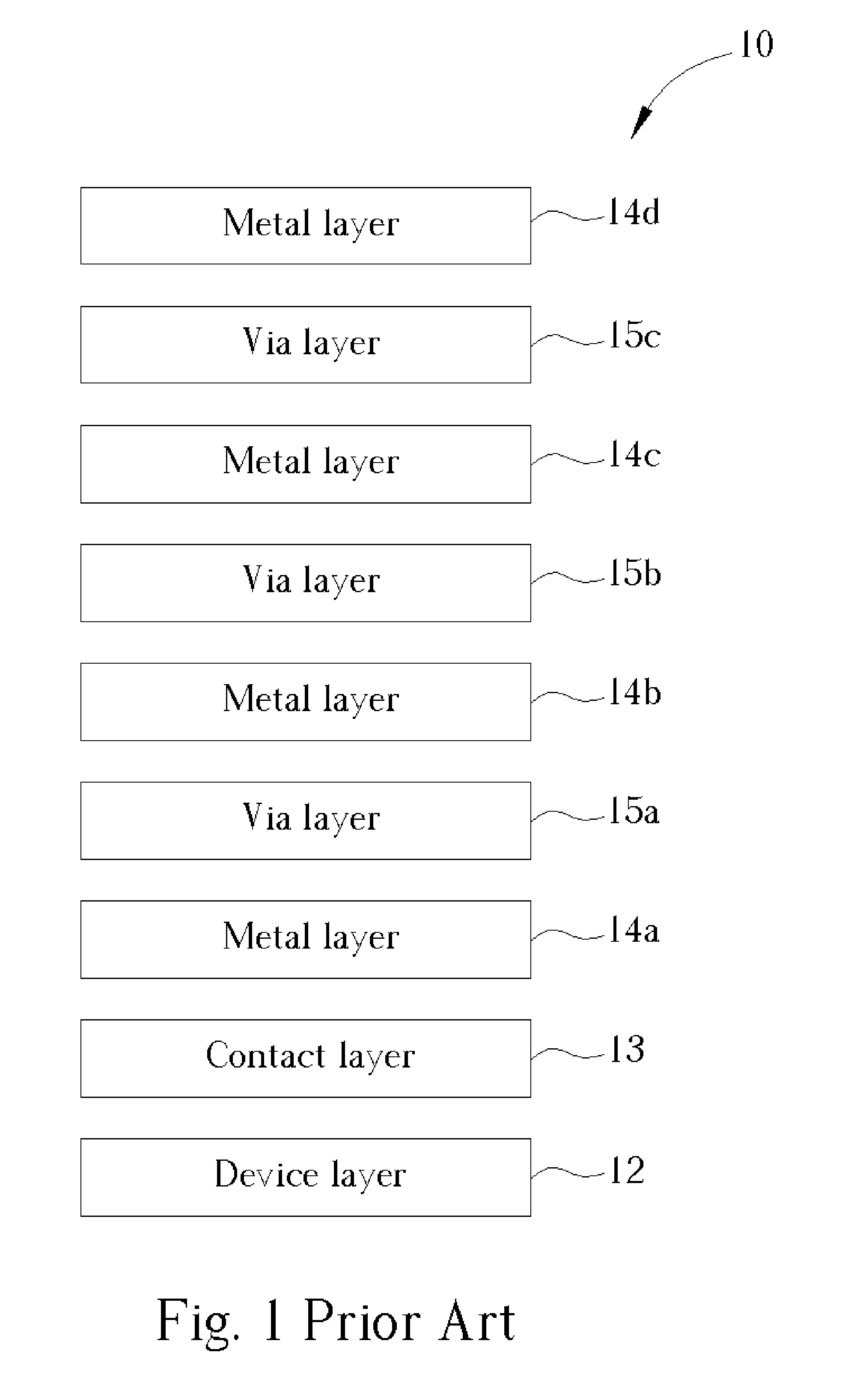

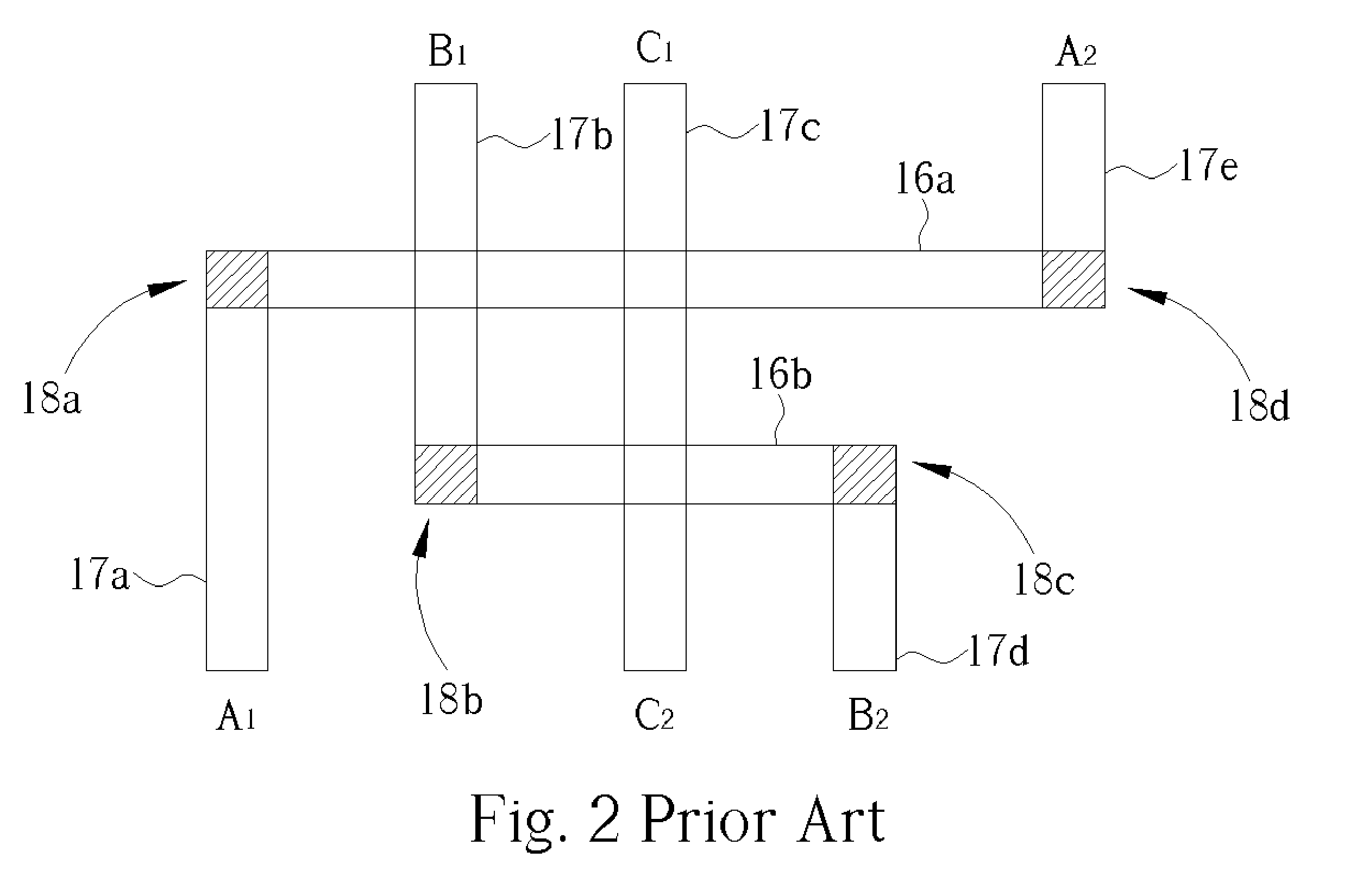

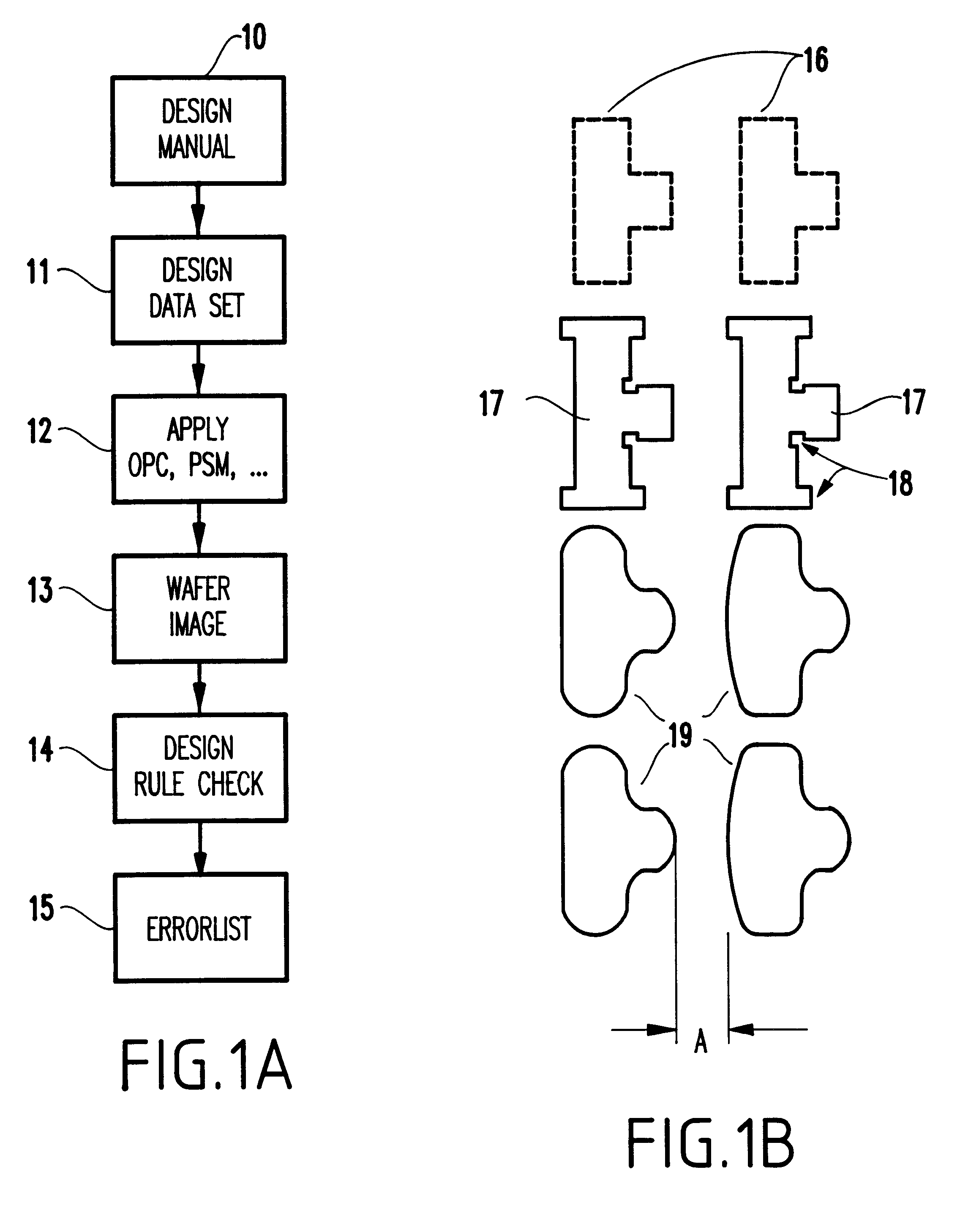

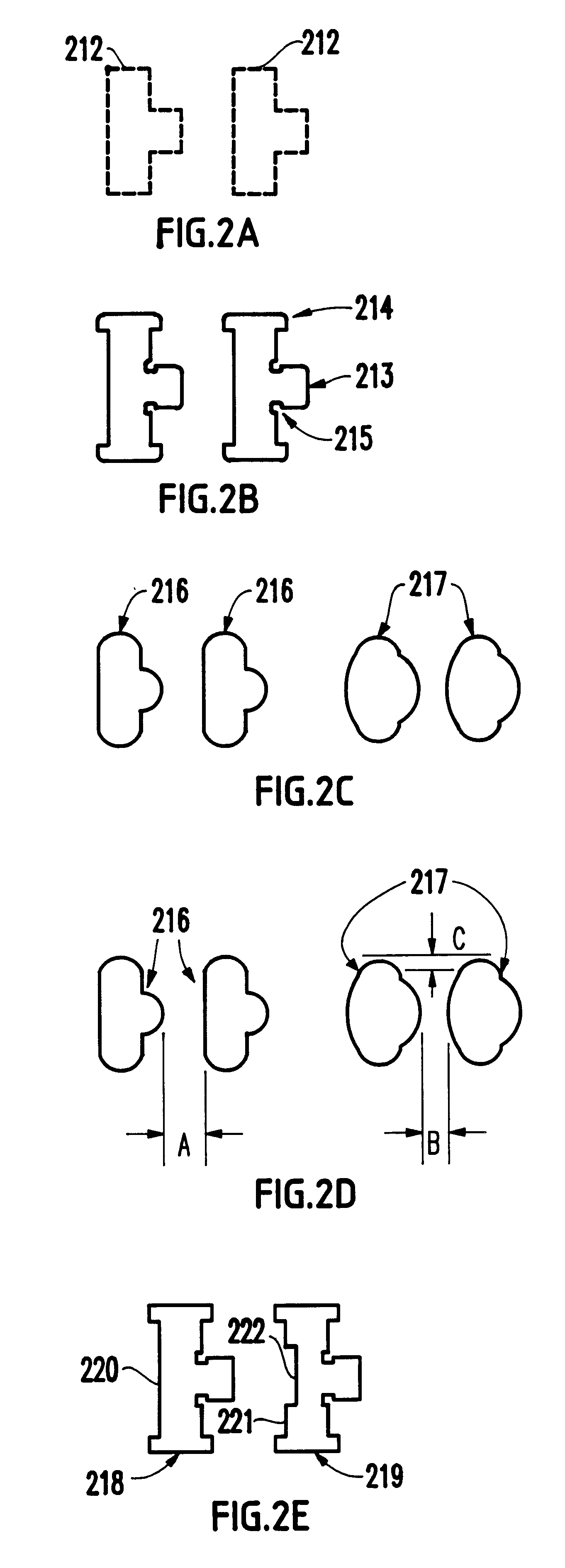

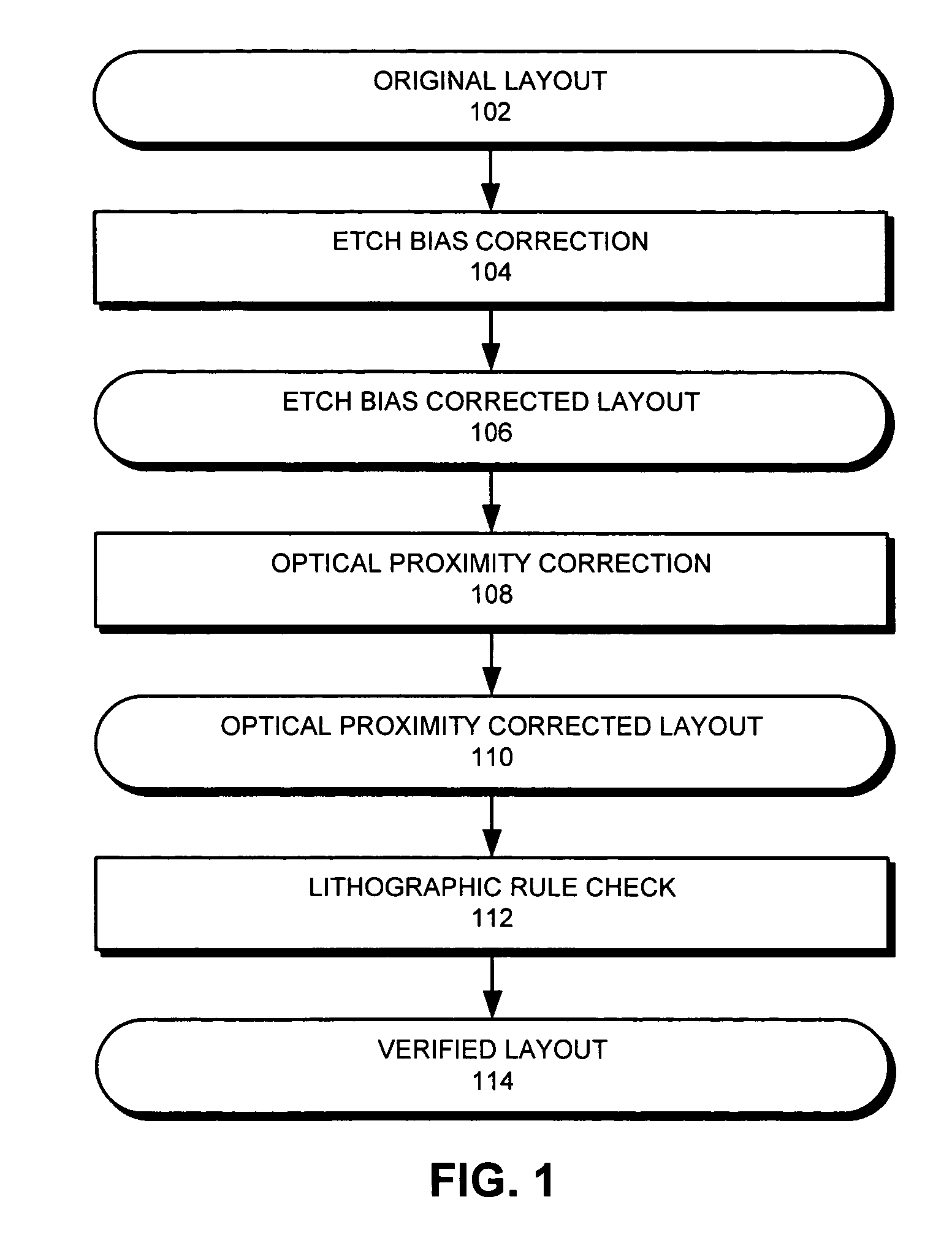

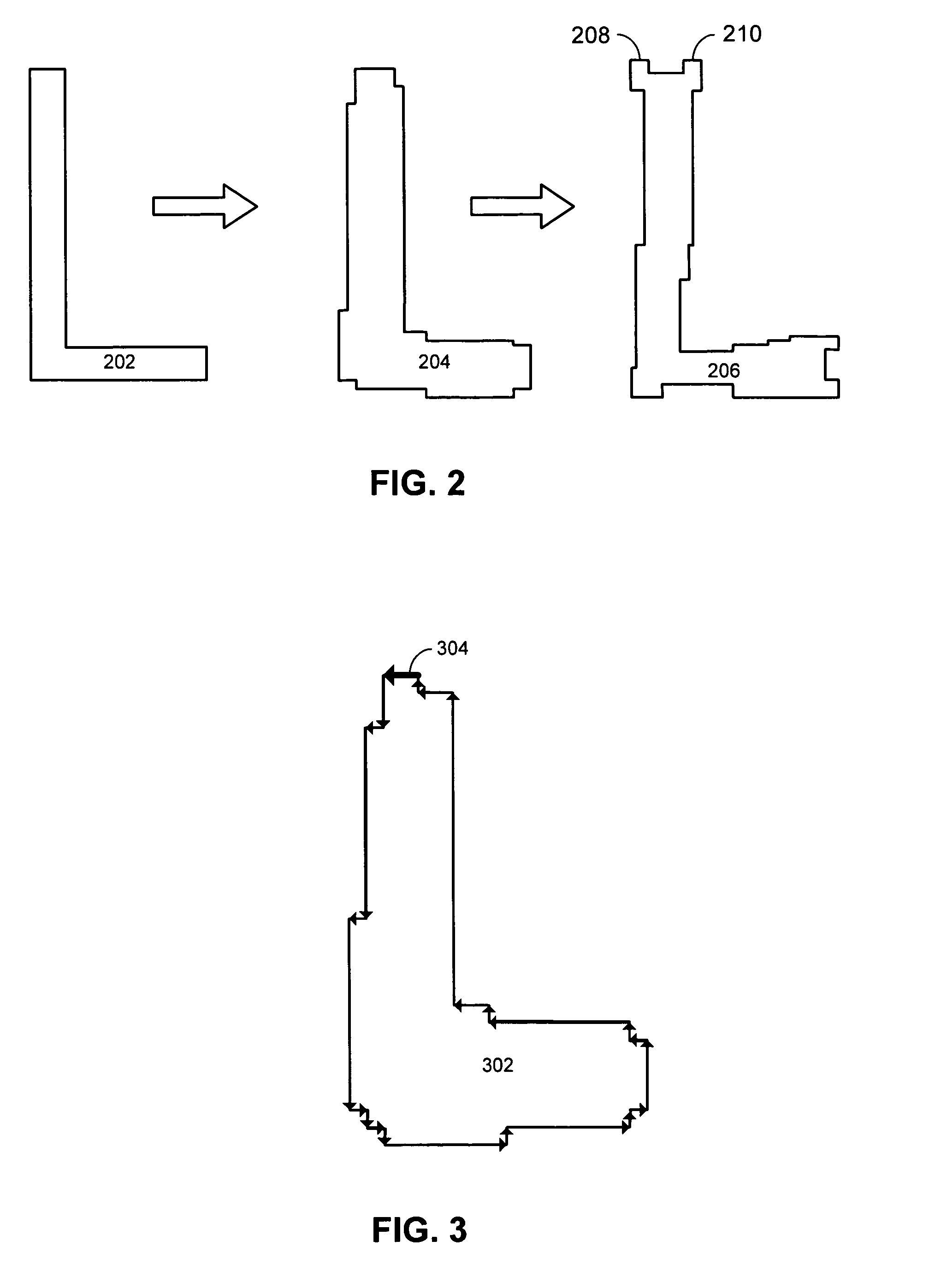

Design rule checking system and method

InactiveUS6470489B1Create efficientlyImprove system efficiencyOriginals for photomechanical treatmentComputer aided designDesign rule checkerLithography

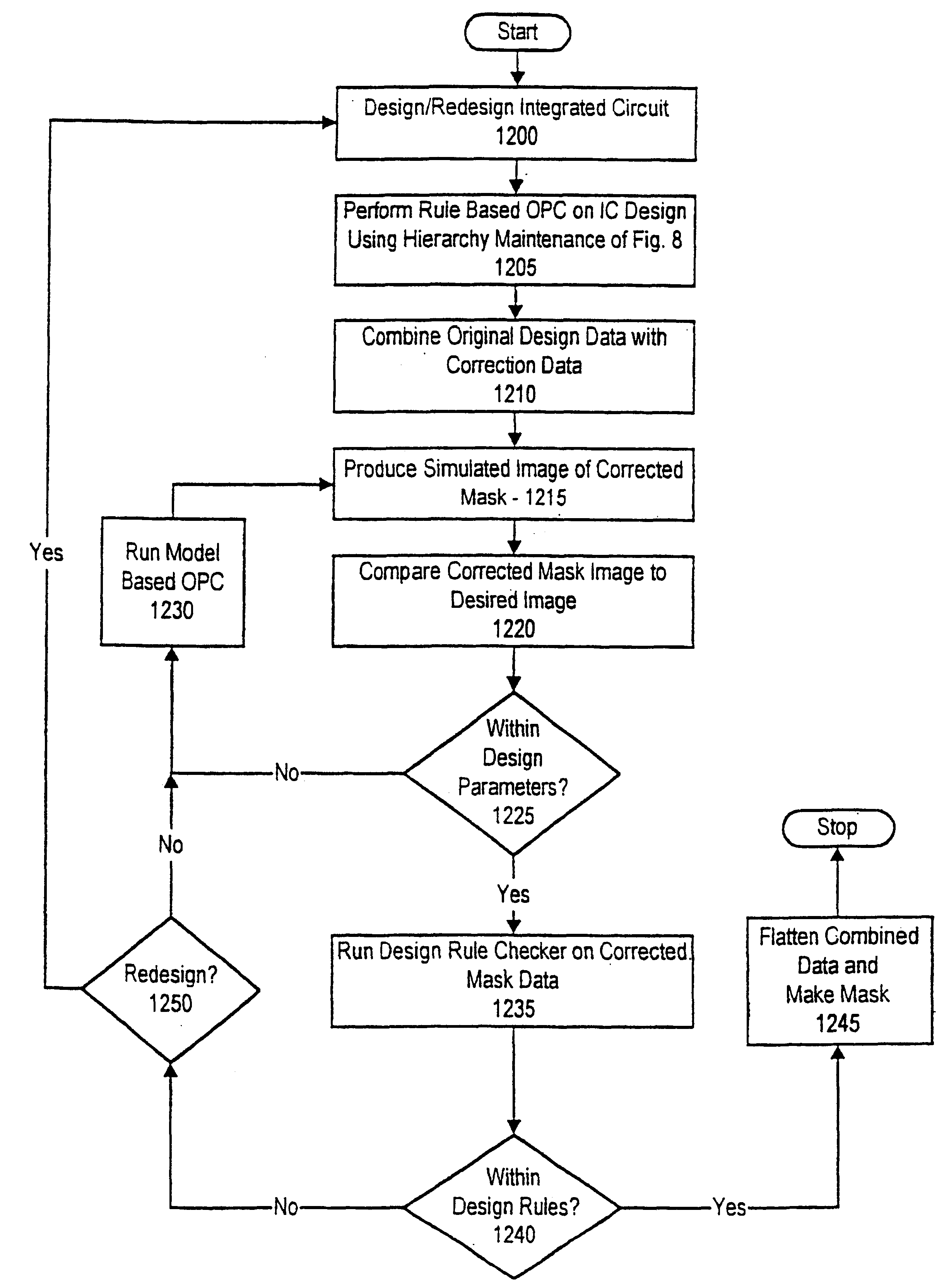

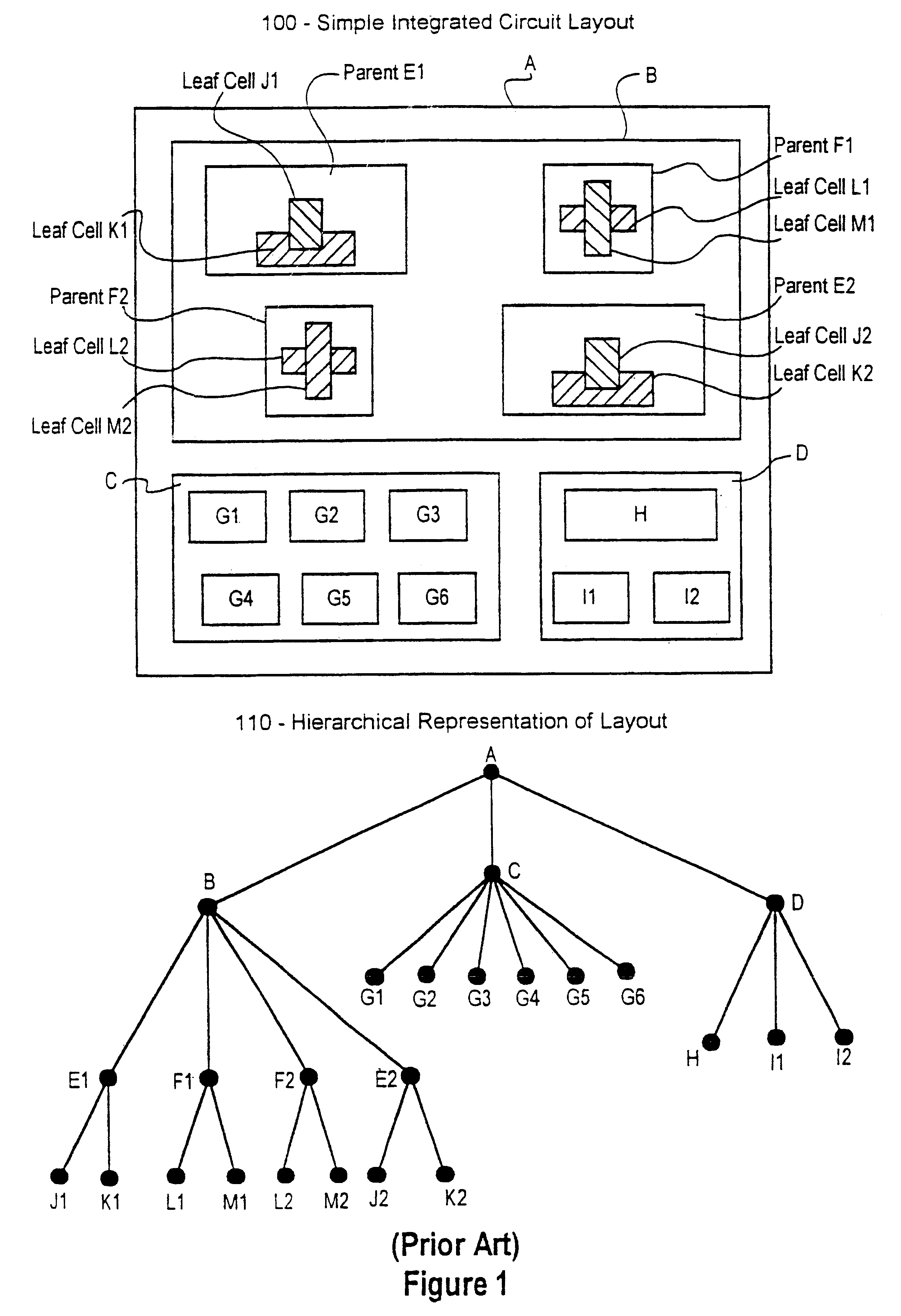

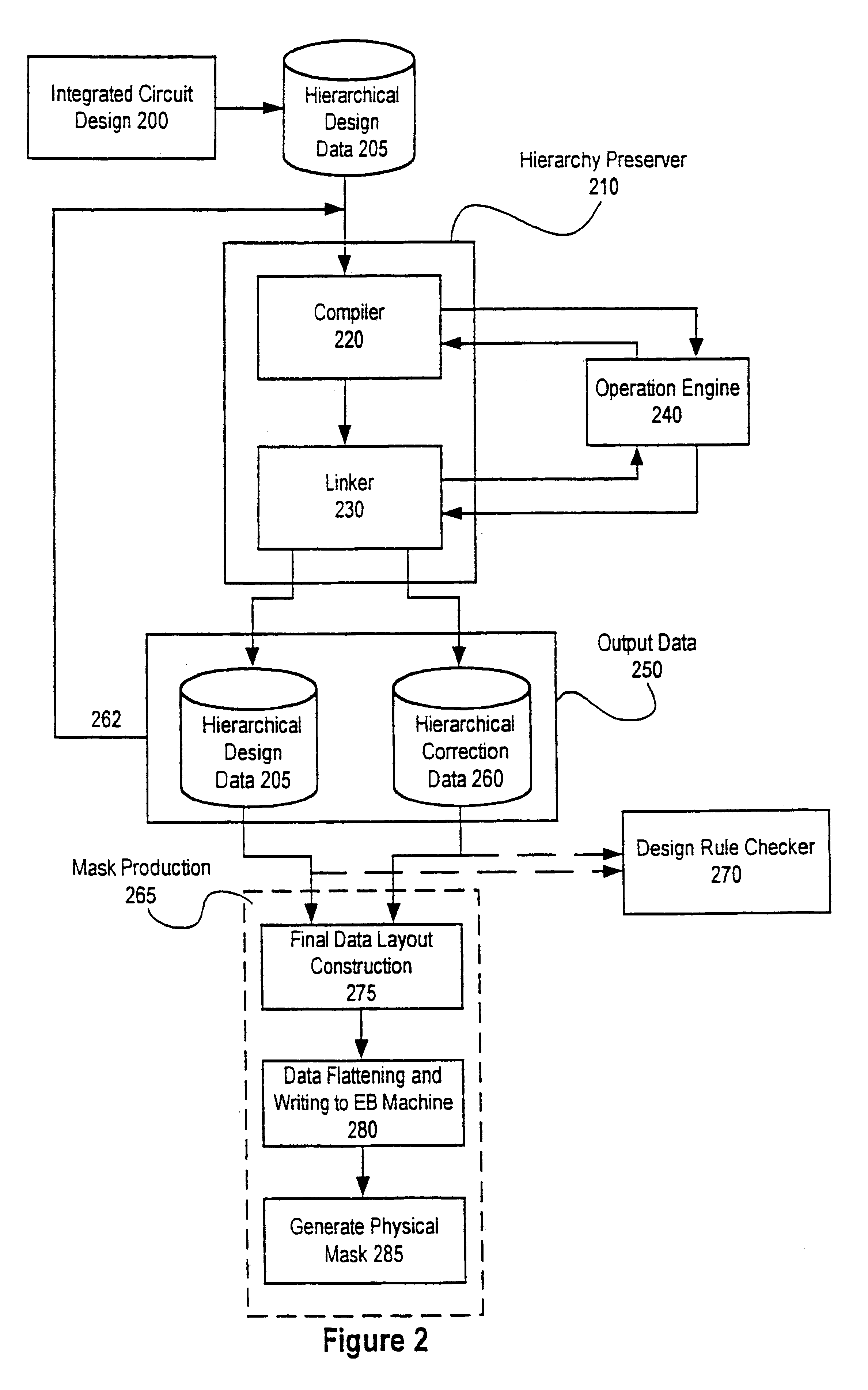

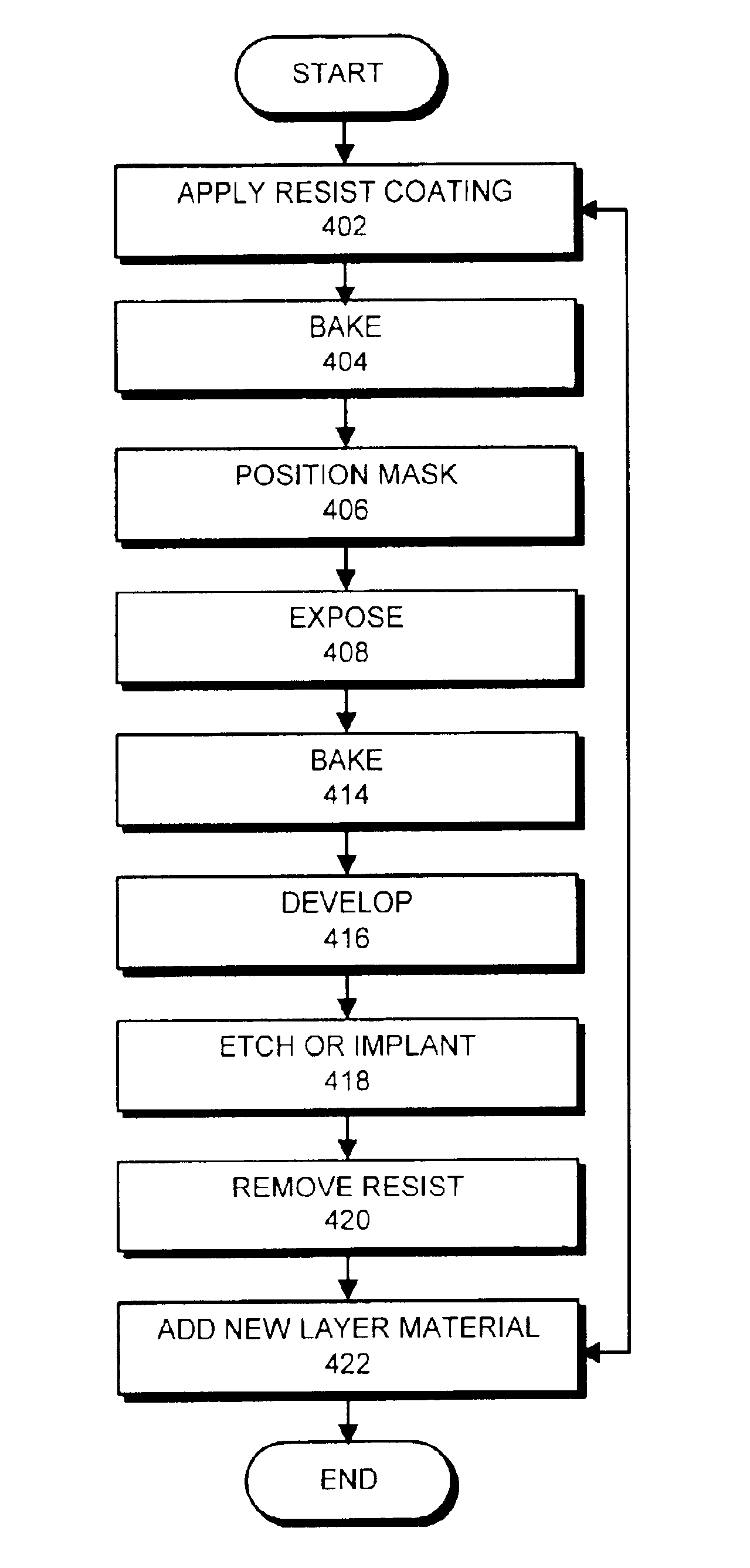

A method for performing design rule checking on OPC corrected or otherwise corrected designs is described. This method comprises accessing a corrected design and generating a simulated image. The simulated image corresponds to a simulation of an image which would be printed on a wafer if the wafer were exposed to an illumination source directed through the corrected design. The characteristics of the illumination source are determined by a set of lithography parameters. In creating the image, additional characteristics can be used to simulate portions of the fabrication process. However, what is important is that a resulting simulated image is created. The simulated image can then be used by the design rule checker. Importantly, the simulated image can be processed to reduce the number of vertices in the simulated image, relative to the number of vertices in the OPC corrected design layout. Also, the simulated image can be compared with an idea layout image, the results of which can then be used to reduce the amount of information that is needed to perform the design rule checking.

Owner:SYNOPSYS INC

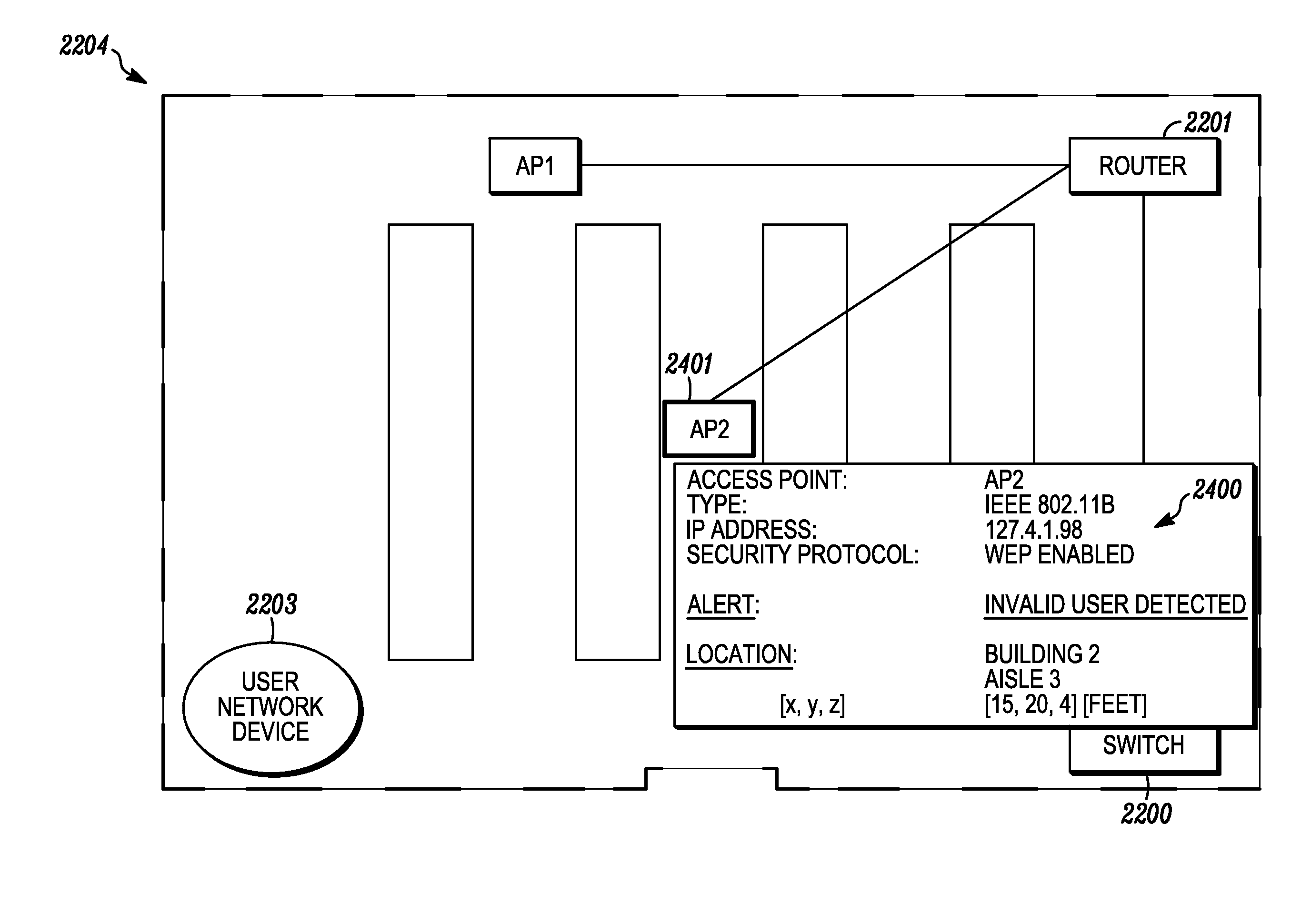

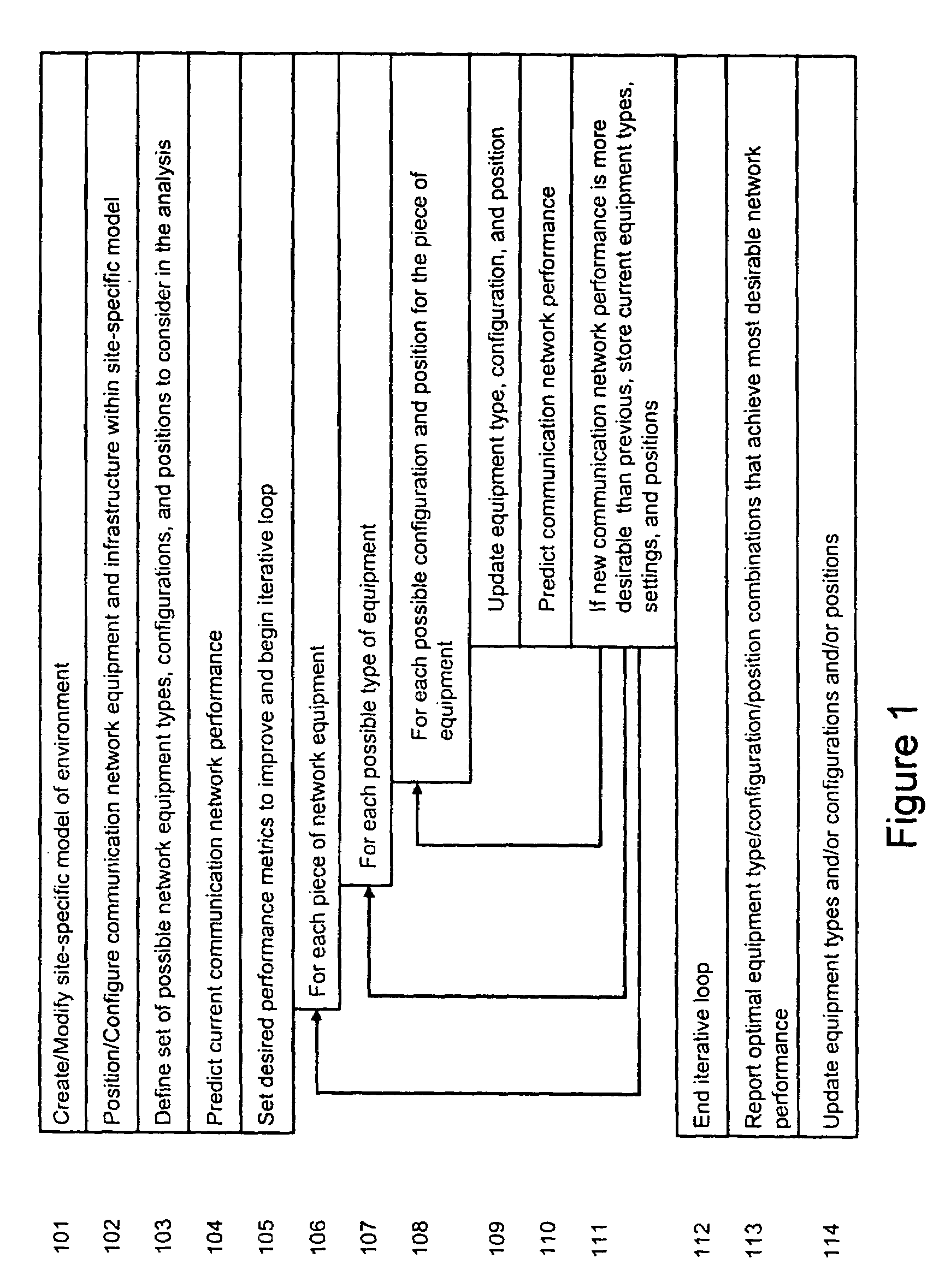

System and method for indicating the presence or physical location of persons or devices in a site specific representation of a physical environment

ActiveUS7295119B2Significant valueEasy to explainDigital data processing detailsBurglar alarm mechanical actuationCommunications systemDisplay device

A system and method for providing security to a wireless communication system having wireless communication components positioned at different locations within a physical environment are provided. The wireless communication components include an access point and a network device. A site-specific computerized representation of the physical environment displays the location of the wireless communication components including the access point and network device. The access point and network device identify the presence or a physical location of a possible intruder or intruder devices. An indicator is presented in the site-specific representation on the display when an erroneous authentication request or other undesired transmission is received by the network device or the access point.

Owner:EXTREME NETWORKS INC

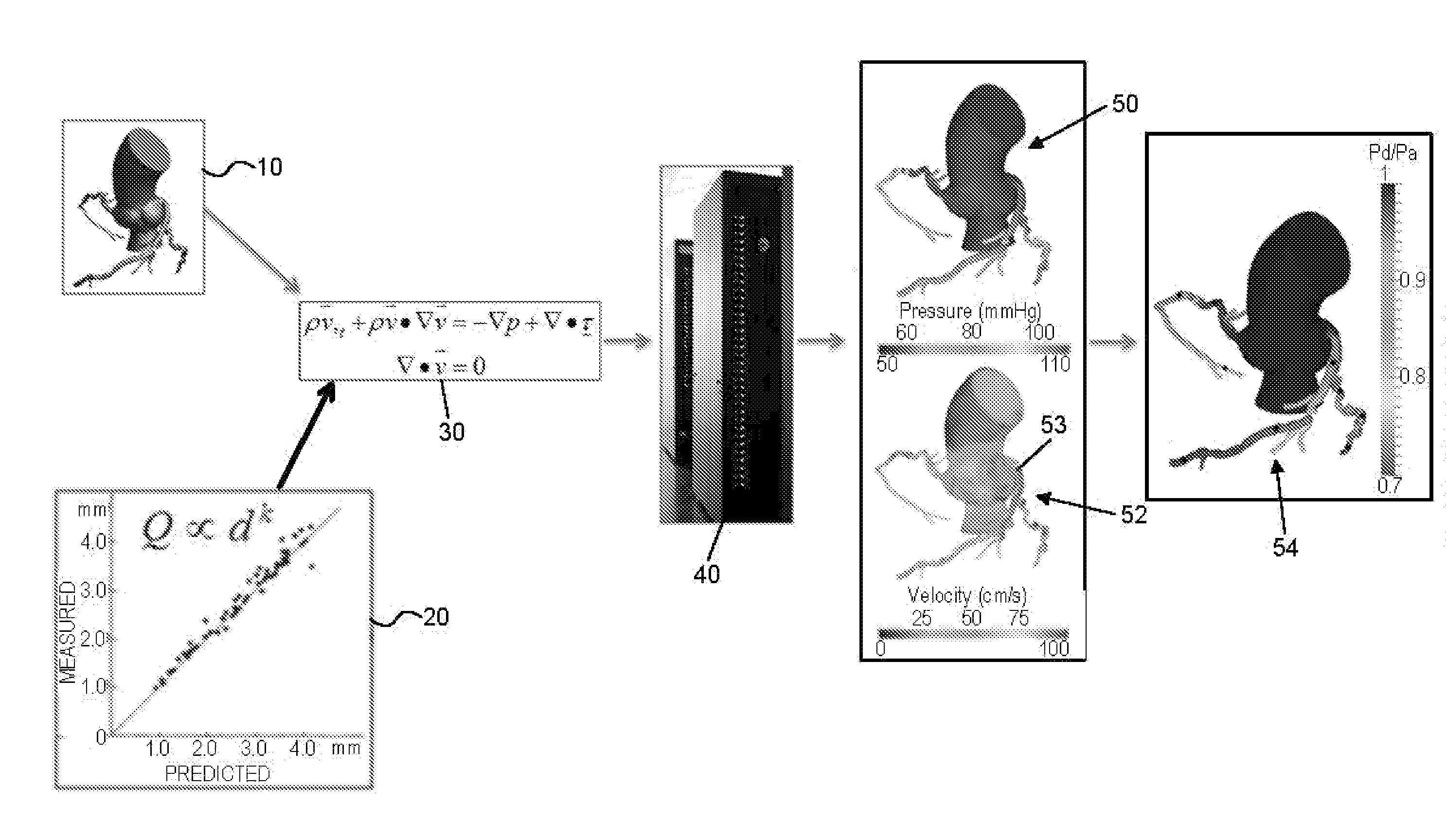

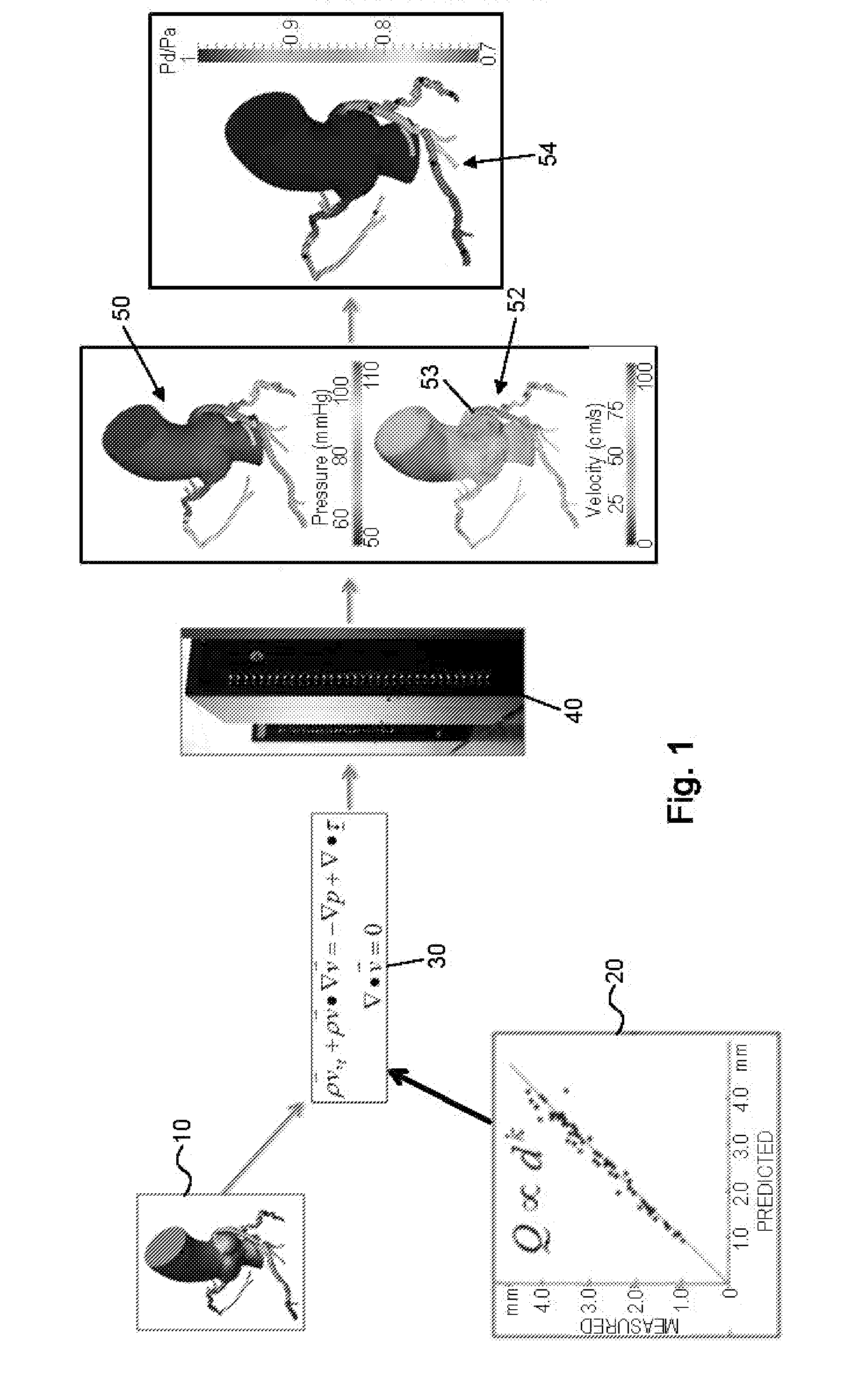

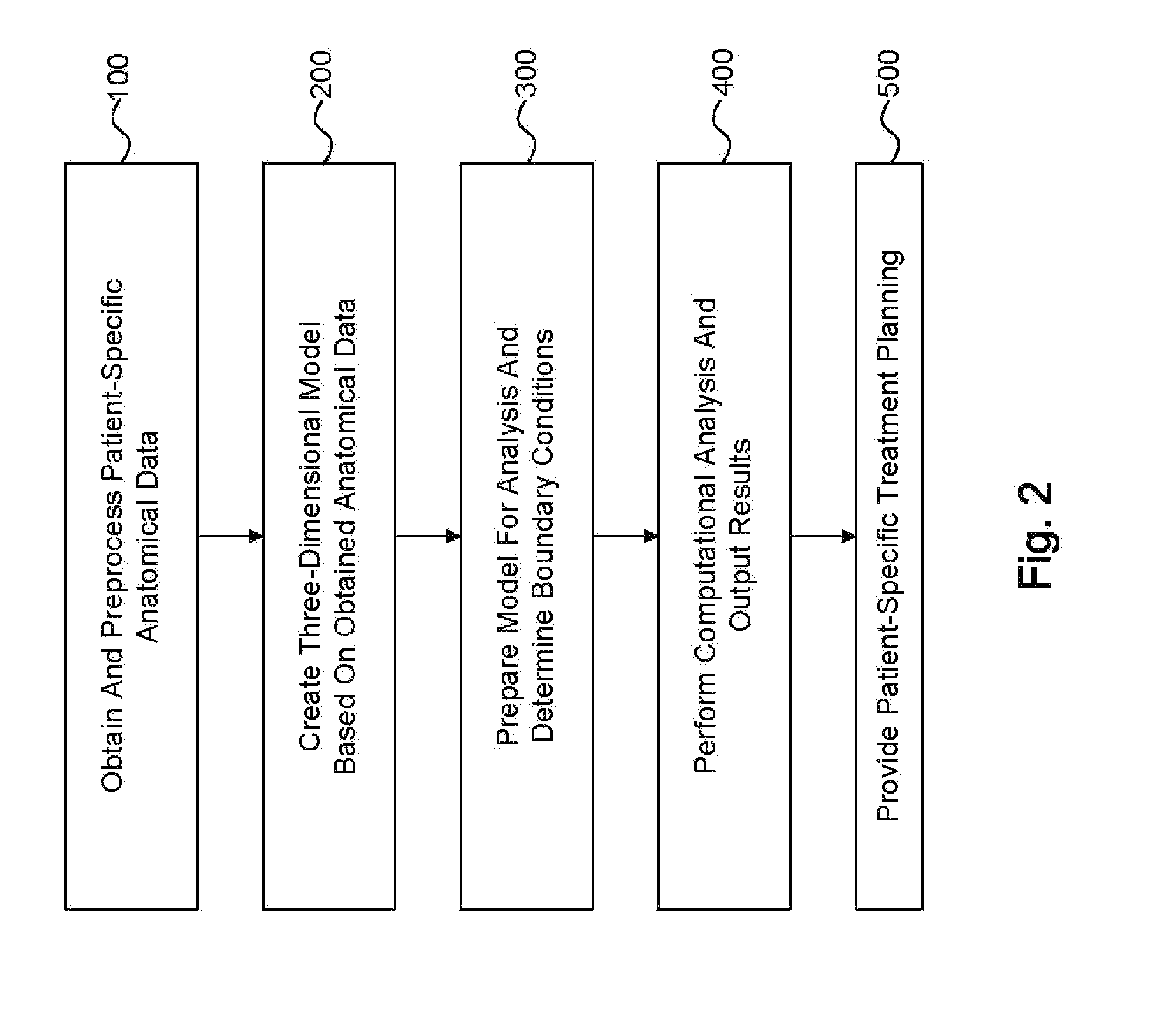

Method and system for patient-specific modeling of blood flow

Embodiments include a system for determining cardiovascular information for a patient. The system may include at least one computer system configured to receive patient-specific data regarding a geometry of the patient's heart, and create a three-dimensional model representing at least a portion of the patient's heart based on the patient-specific data. The at least one computer system may be further configured to create a physics-based model relating to a blood flow characteristic of the patient's heart and determine a fractional flow reserve within the patient's heart based on the three-dimensional model and the physics-based model.

Owner:HEARTFLOW

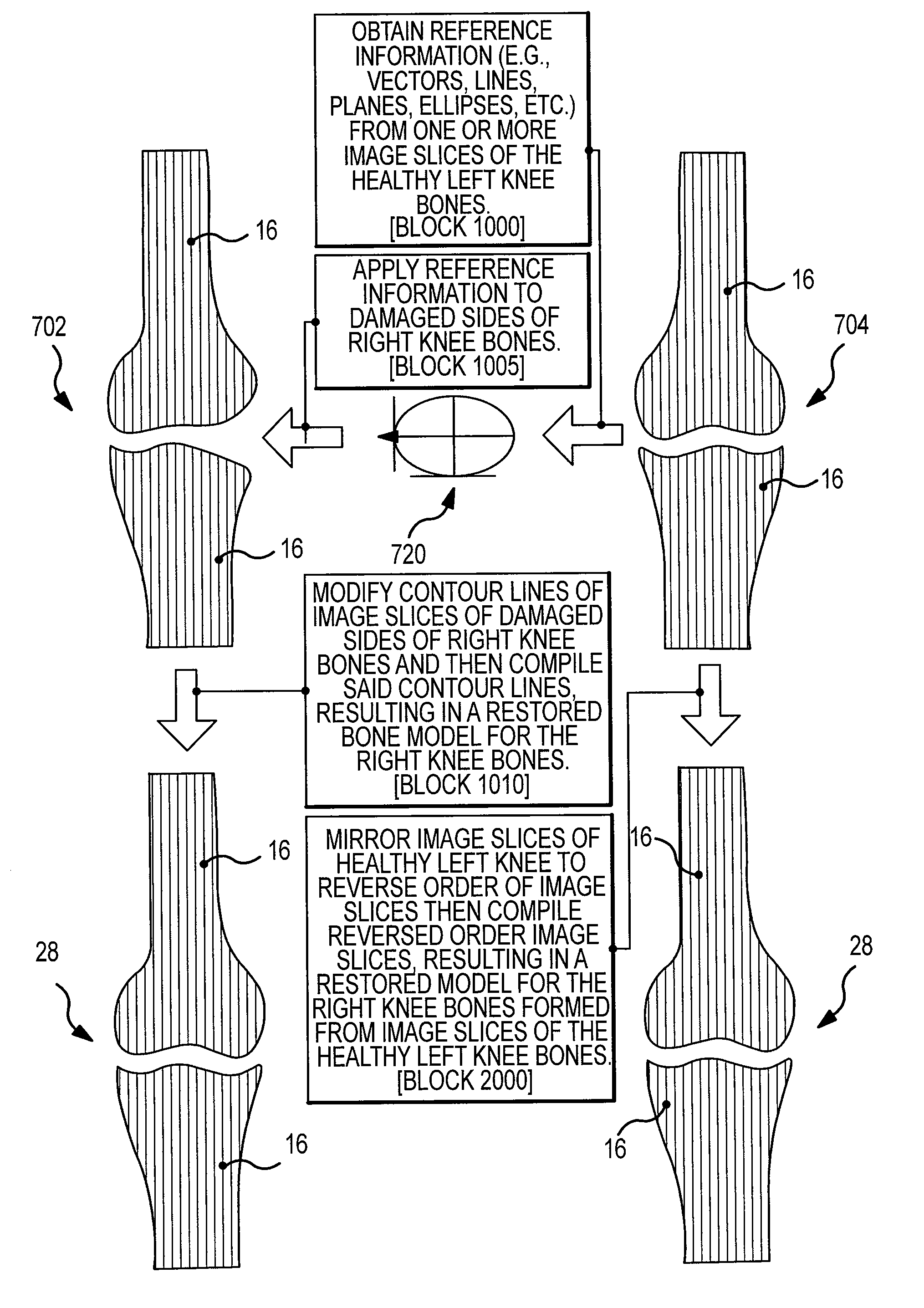

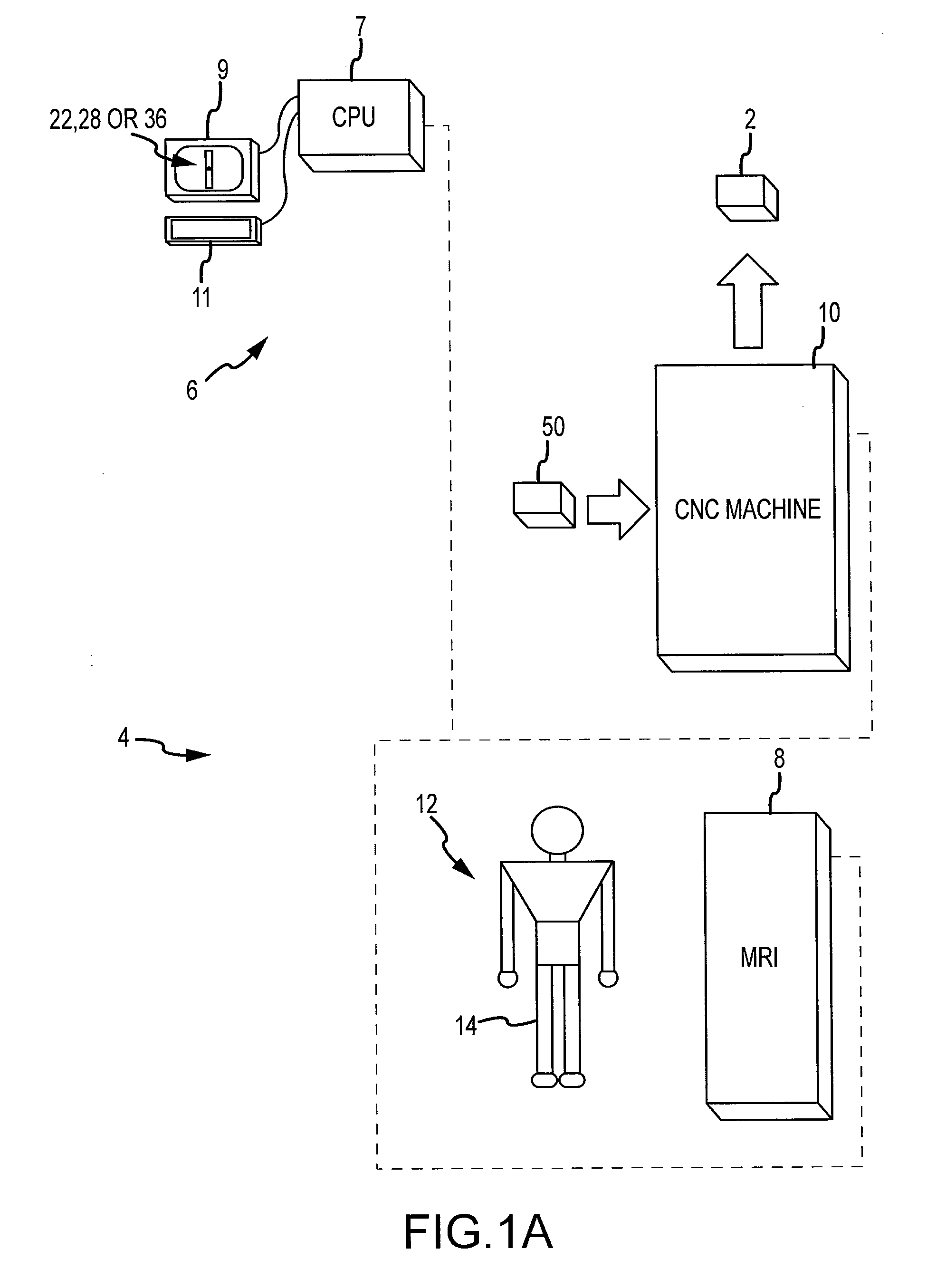

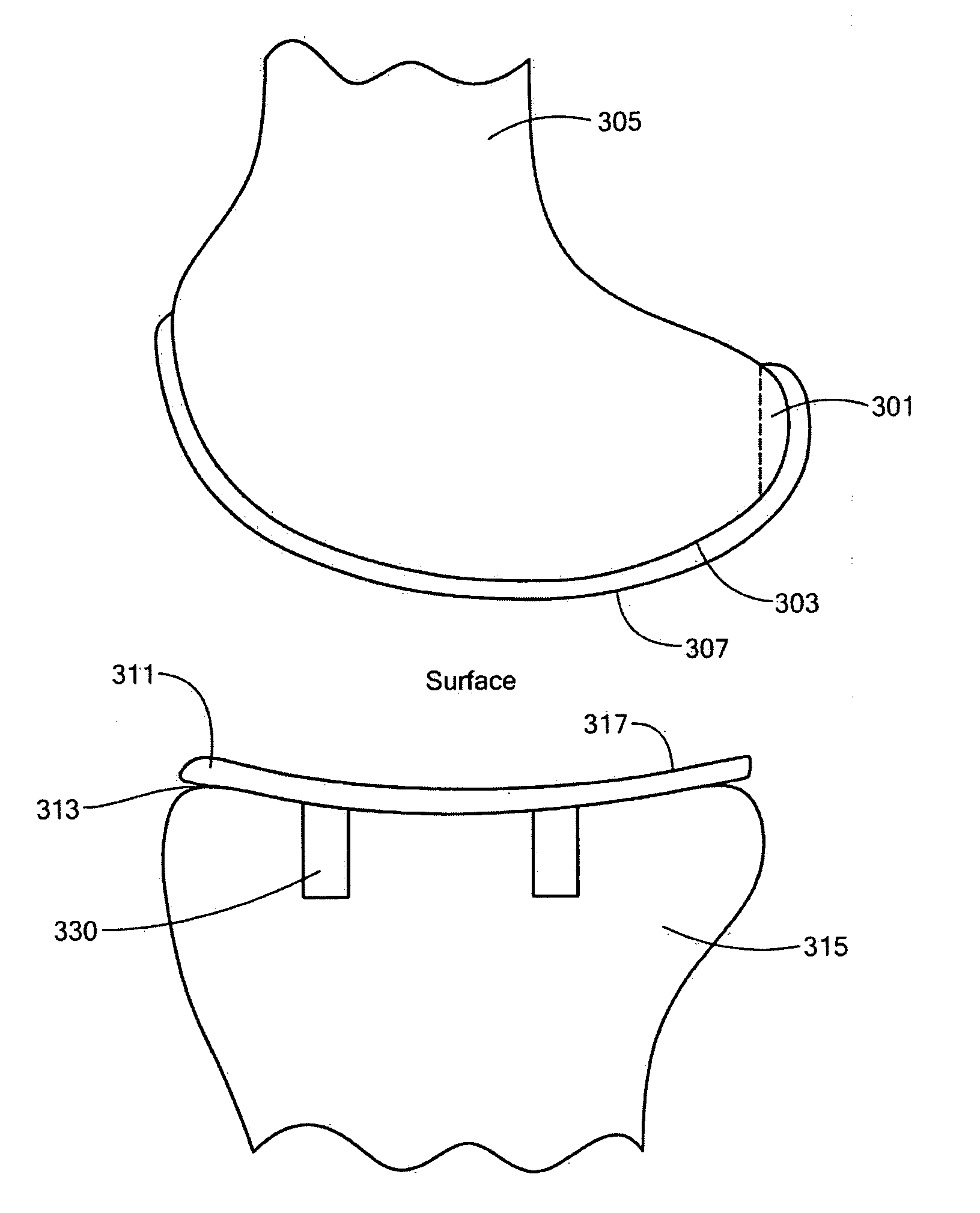

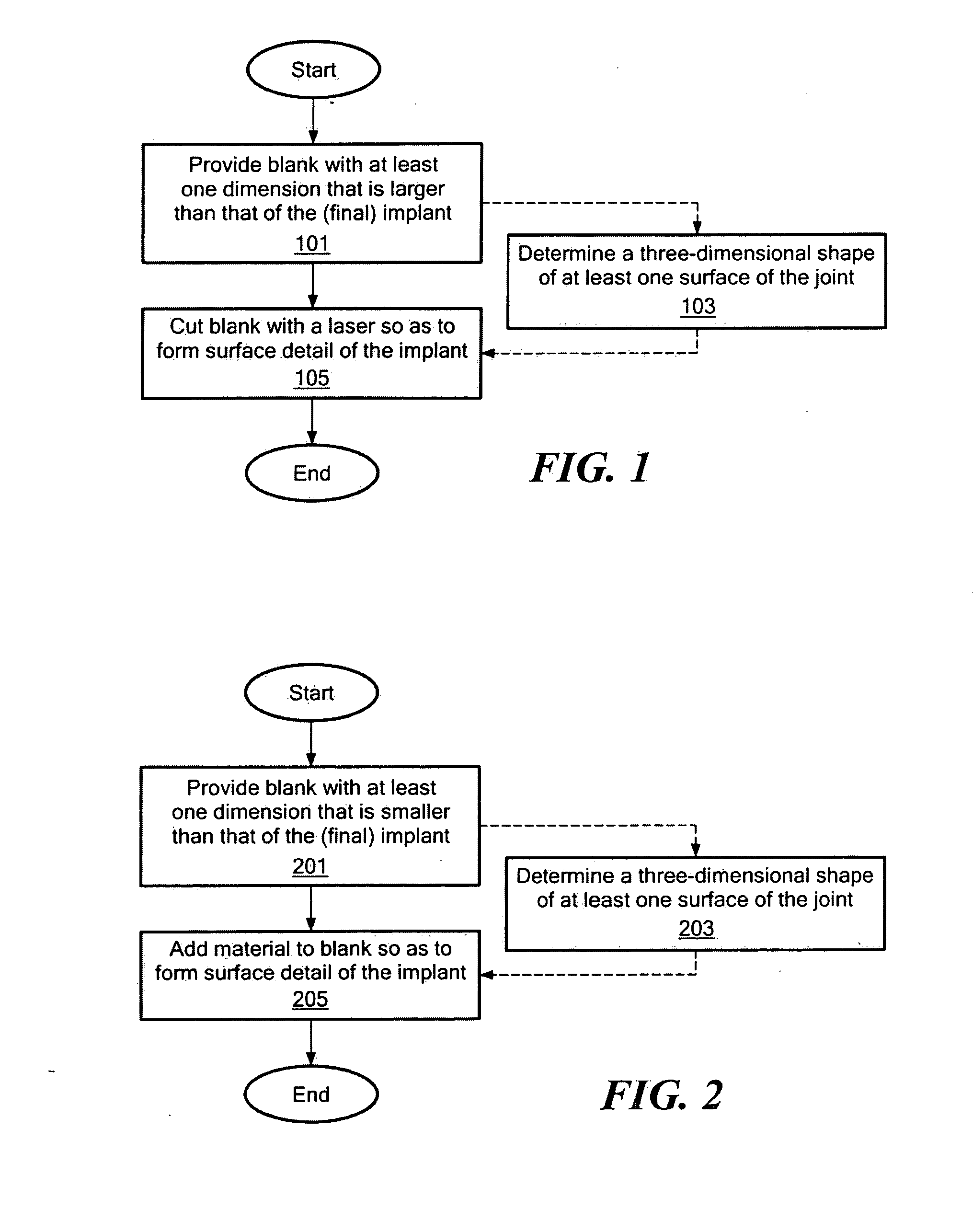

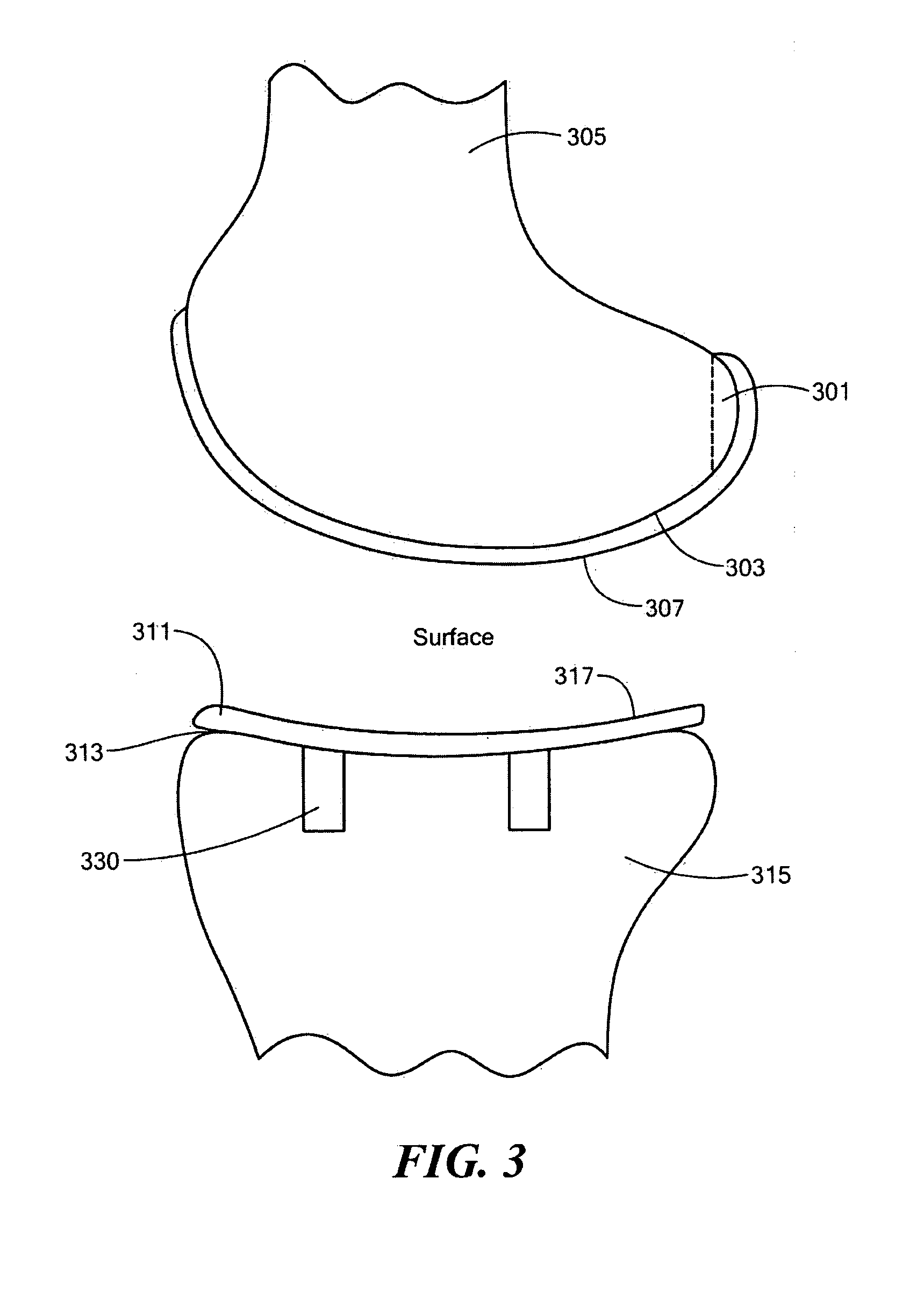

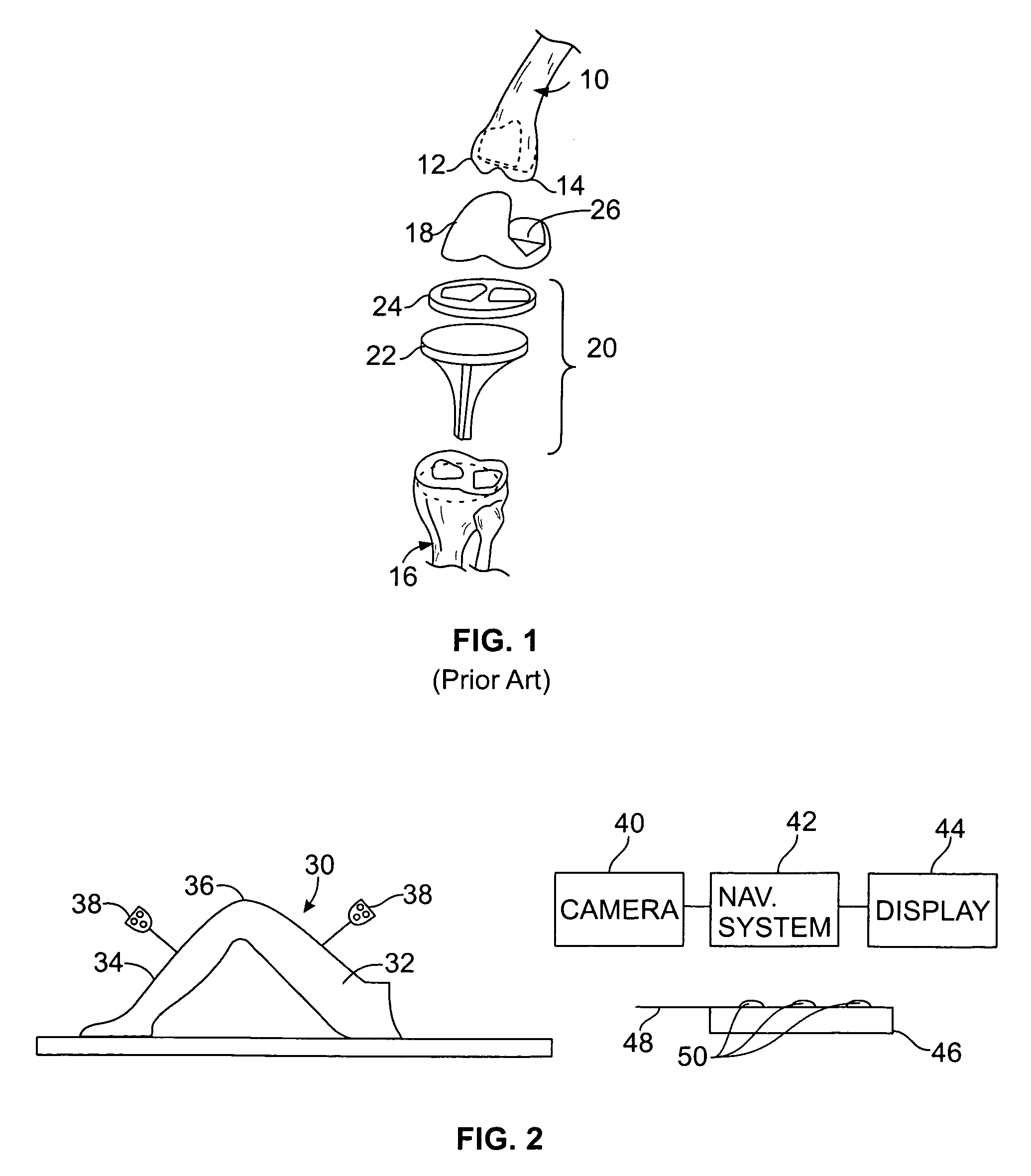

Generation of a computerized bone model representative of a pre-degenerated state and useable in the design and manufacture of arthroplasty devices

ActiveUS20090270868A1Reduce the possibilityIncrease success rateDiagnosticsAnalogue computers for chemical processesKnee JointProsthesis

Disclosed herein is a method of generating a computerized bone model representative of at least a portion of a patient bone in a pre-degenerated state. The method includes: generating at least one image of the patient bone in a degenerated state; identifying a reference portion associated with a generally non-degenerated portion of the patient bone; identifying a degenerated portion associated with a generally degenerated portion of the patient bone; and using information from at least one image associated with the reference portion to modify at least one aspect associated with at least one image associated the generally degenerated portion. The method may further include employing the computerized bone model representative of the at least a portion of the patient bone in the pre-degenerated state in defining manufacturing instructions for the manufacture of a customized arthroplasty jig. Also disclosed herein is a customized arthroplasty jig manufactured according to the above-described method. The customized arthroplasty jig is configured to facilitate a prosthetic implant restoring a patient joint to a natural alignment. The prosthetic implant may be for a total joint replacement or partial joint replacement. The patient joint may be a variety of joints, including, but not limited to, a knee joint.

Owner:HOWMEDICA OSTEONICS CORP

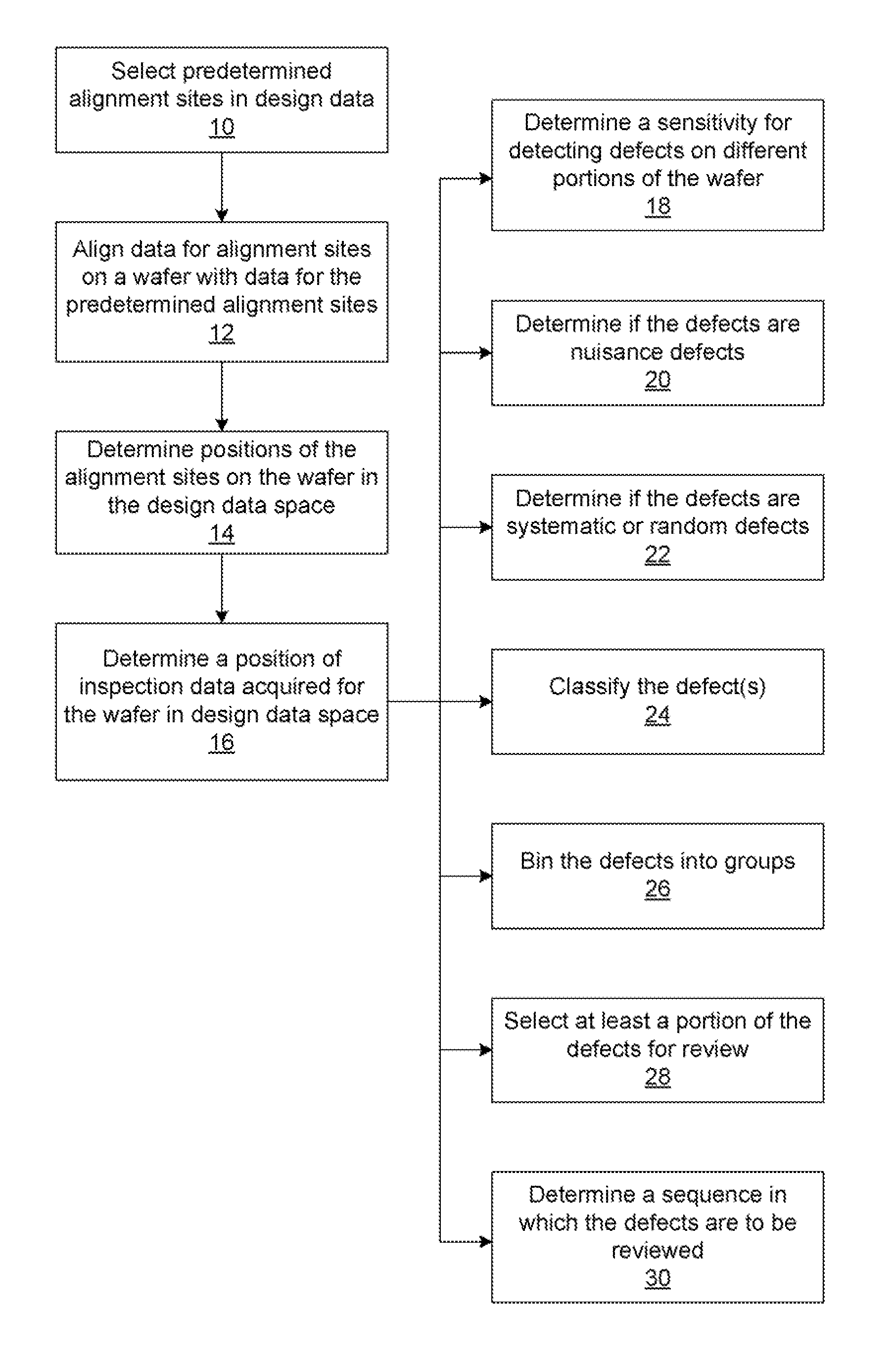

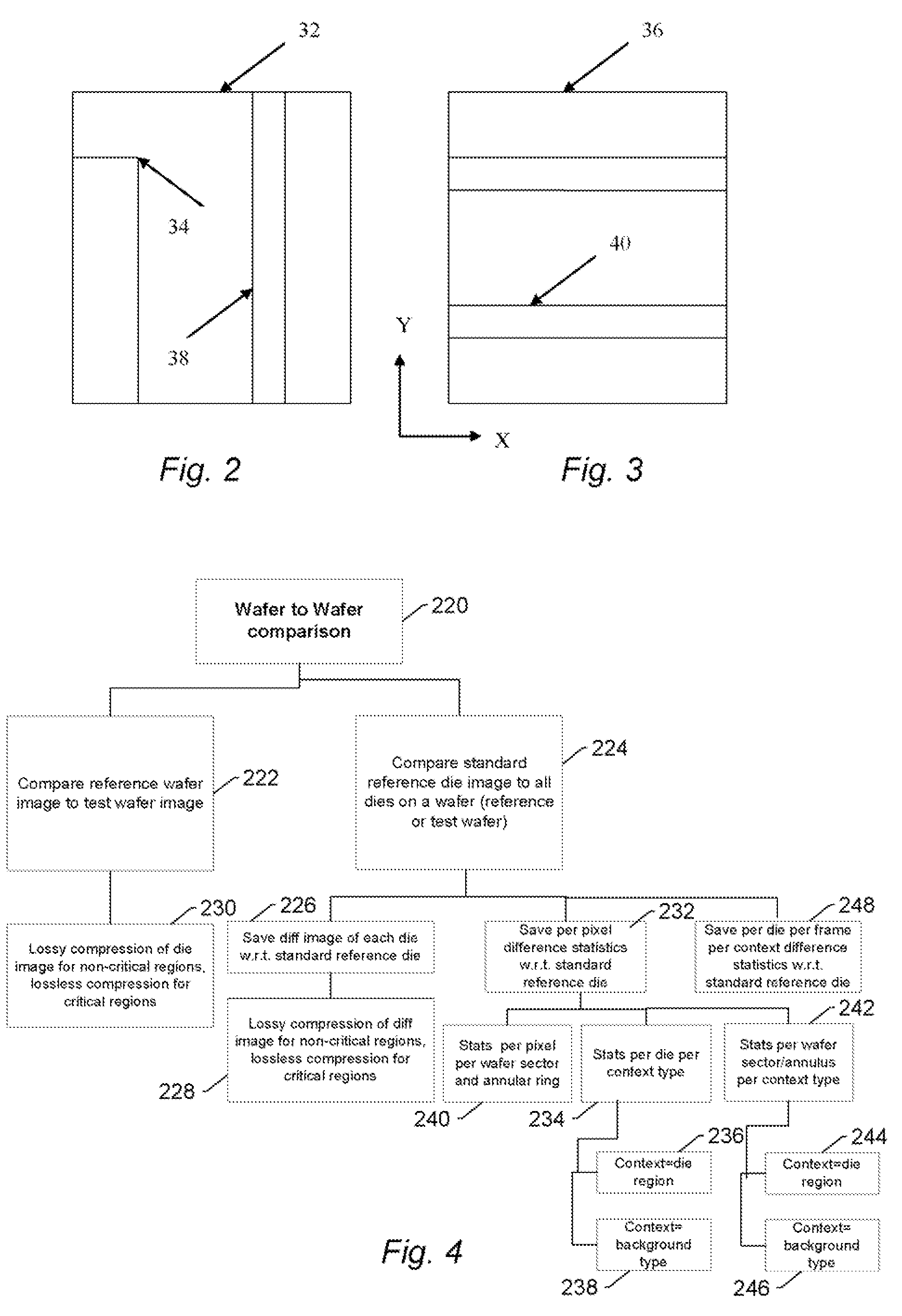

Methods and systems for utilizing design data in combination with inspection data

ActiveUS20070288219A1Increase catch rateReduce errorsImage enhancementImage analysisComputer scienceDesign data

Various methods and systems for utilizing design data in combination with inspection data are provided. One computer-implemented method for binning defects detected on a wafer includes comparing portions of design data proximate positions of the defects in design data space. The method also includes determining if the design data in the portions is at least similar based on results of the comparing step. In addition, the method includes binning the defects in groups such that the portions of the design data proximate the positions of the defects in each of the groups are at least similar. The method further includes storing results of the binning step in a storage medium.

Owner:KLA TENCOR CORP

Methods and systems for utilizing design data in combination with inspection data

ActiveUS7570796B2Reduce errorsImprove signal-to-noise ratioImage enhancementImage analysisComputer scienceDesign data

Owner:KLA TENCOR TECH CORP

Implant Device and Method for Manufacture

A knee implant includes a femoral component having first and second femoral component surfaces. The first femoral component surface is for securing to a surgically prepared compartment of a distal end of a femur. The second femoral component surface is configured to replicate the femoral condyle. The knee implant further includes a tibial component having first and second tibial component surfaces. The first tibial component surface is for contacting a proximal surface of the tibia that is substantially uncut subchondral bone. At least a portion of the first tibial component surface is a mirror image of the proximal tibial surface. The second tibial component surface articulates with the second femoral component surface.

Owner:CONFORMIS

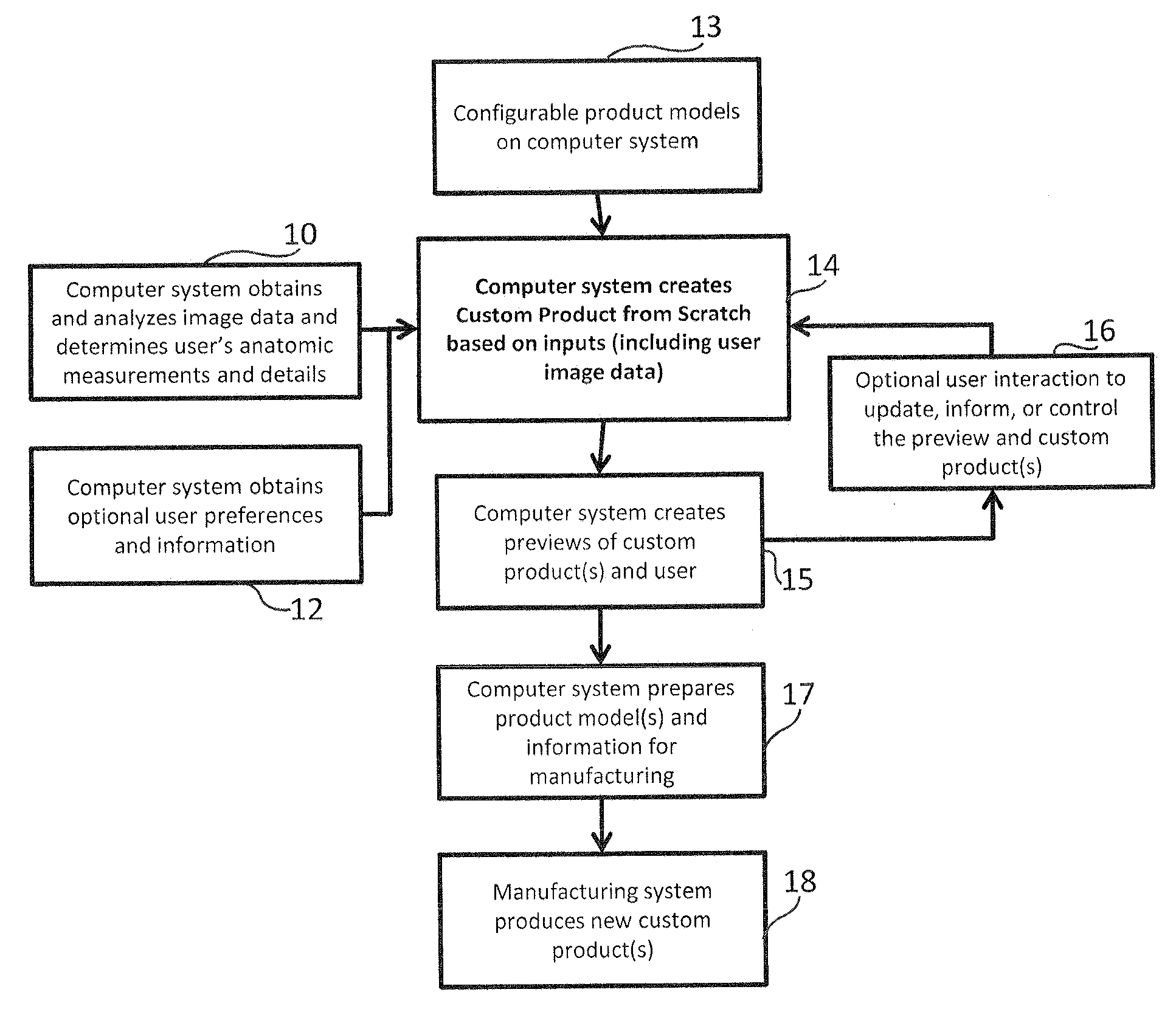

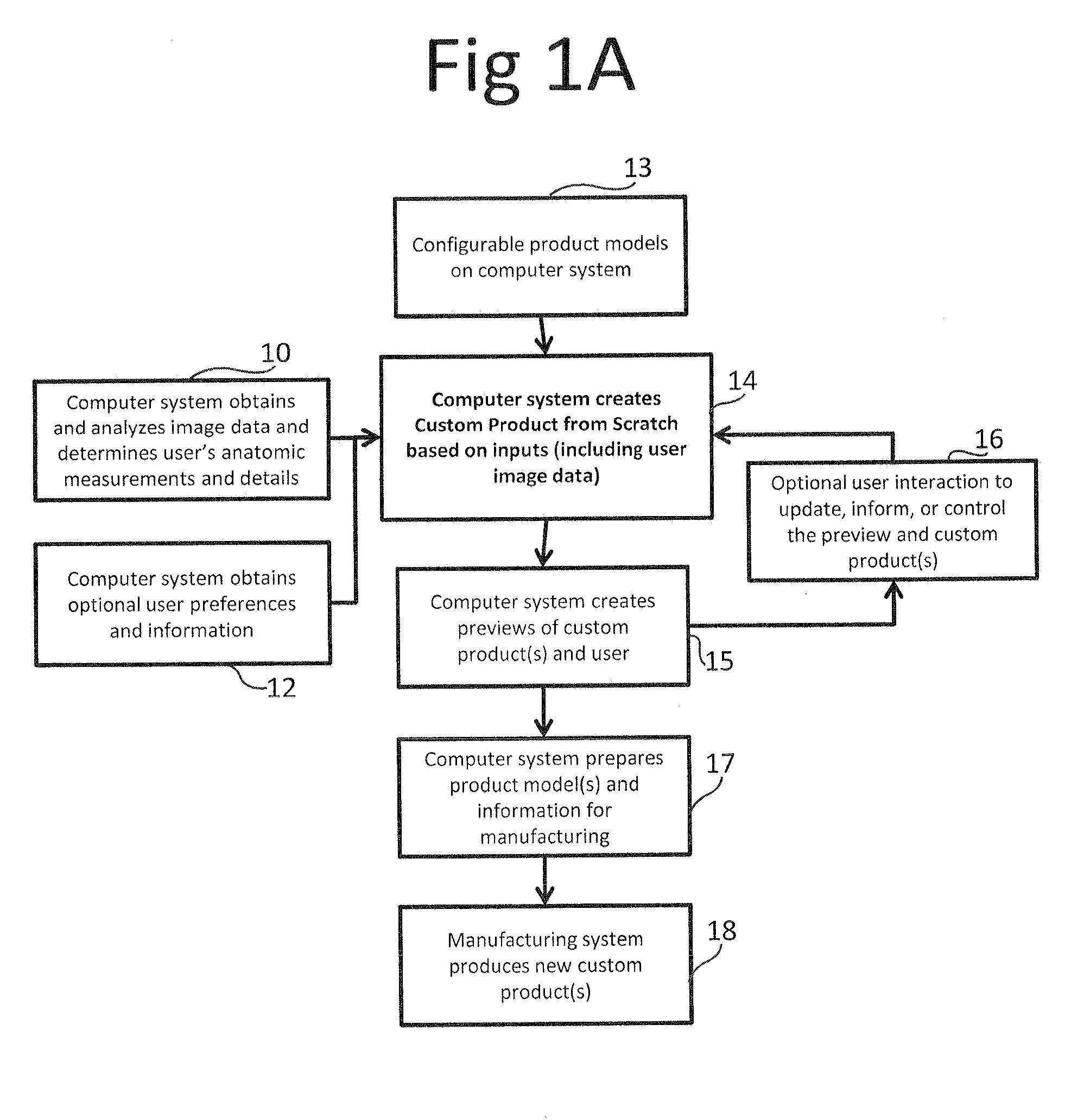

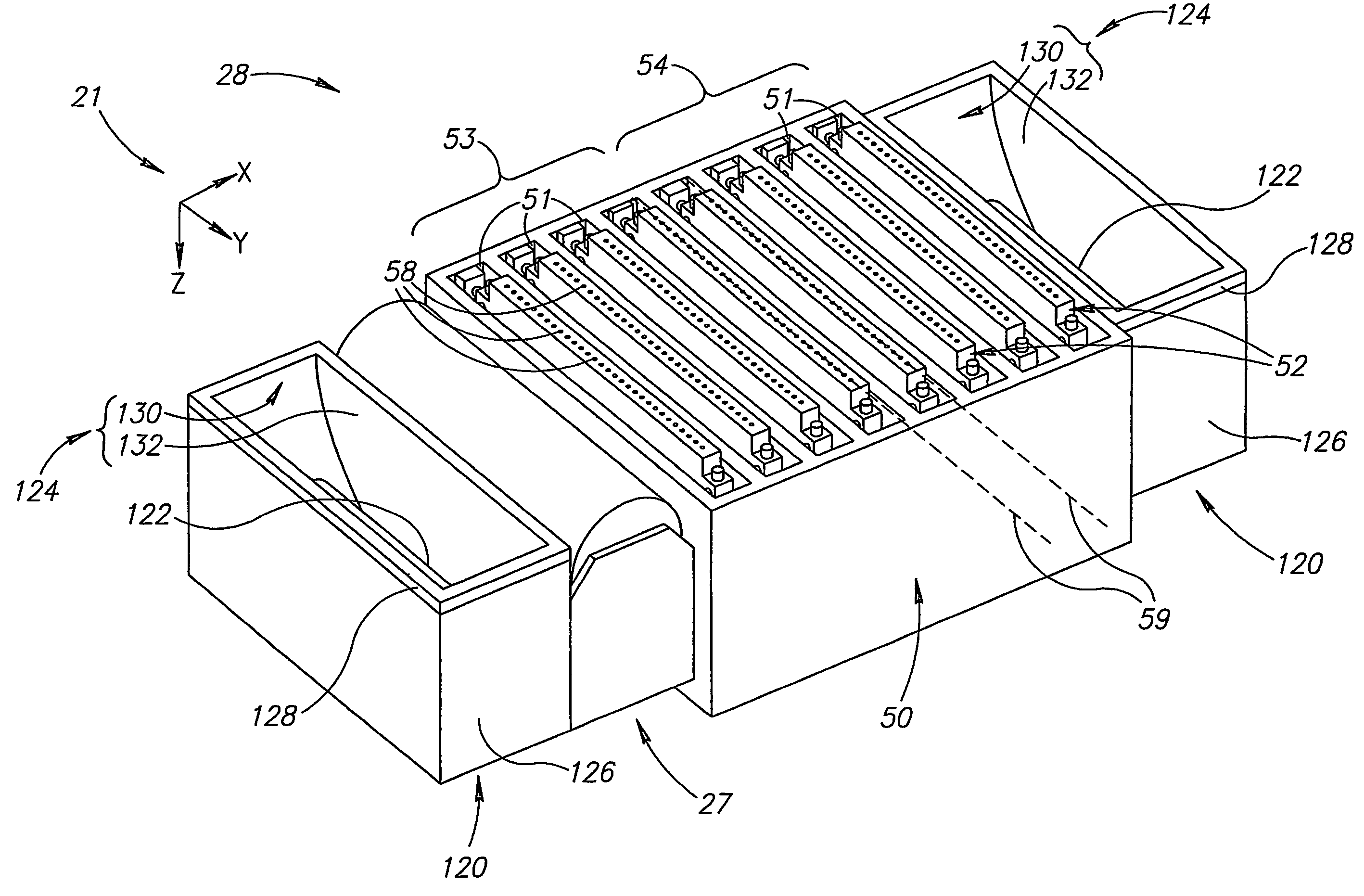

Method and system to create products

Systems and methods for creating fully custom products from scratch without exclusive use of off-the-shelf or pre-specified components. A system for creating custom products includes an image capture device for capturing image data and / or measurement data of a user. A computer is communicatively coupled with the image capture device and configured to construct an anatomic model of the user based on the captured image data and / or measurement data. The computer provides a configurable product model and enables preview and automatic or user-guided customization of the product model. A display is communicatively coupled with the computer and displays the custom product model superimposed on the anatomic model or image data of the user. The computer is further configured to provide the customized product model to a manufacturer for manufacturing eyewear for the user in accordance with the customized product model. The manufacturing system is configured to interpret the product model and prepare instructions and control equipment for the manufacturing of the customized product.

Owner:BIS

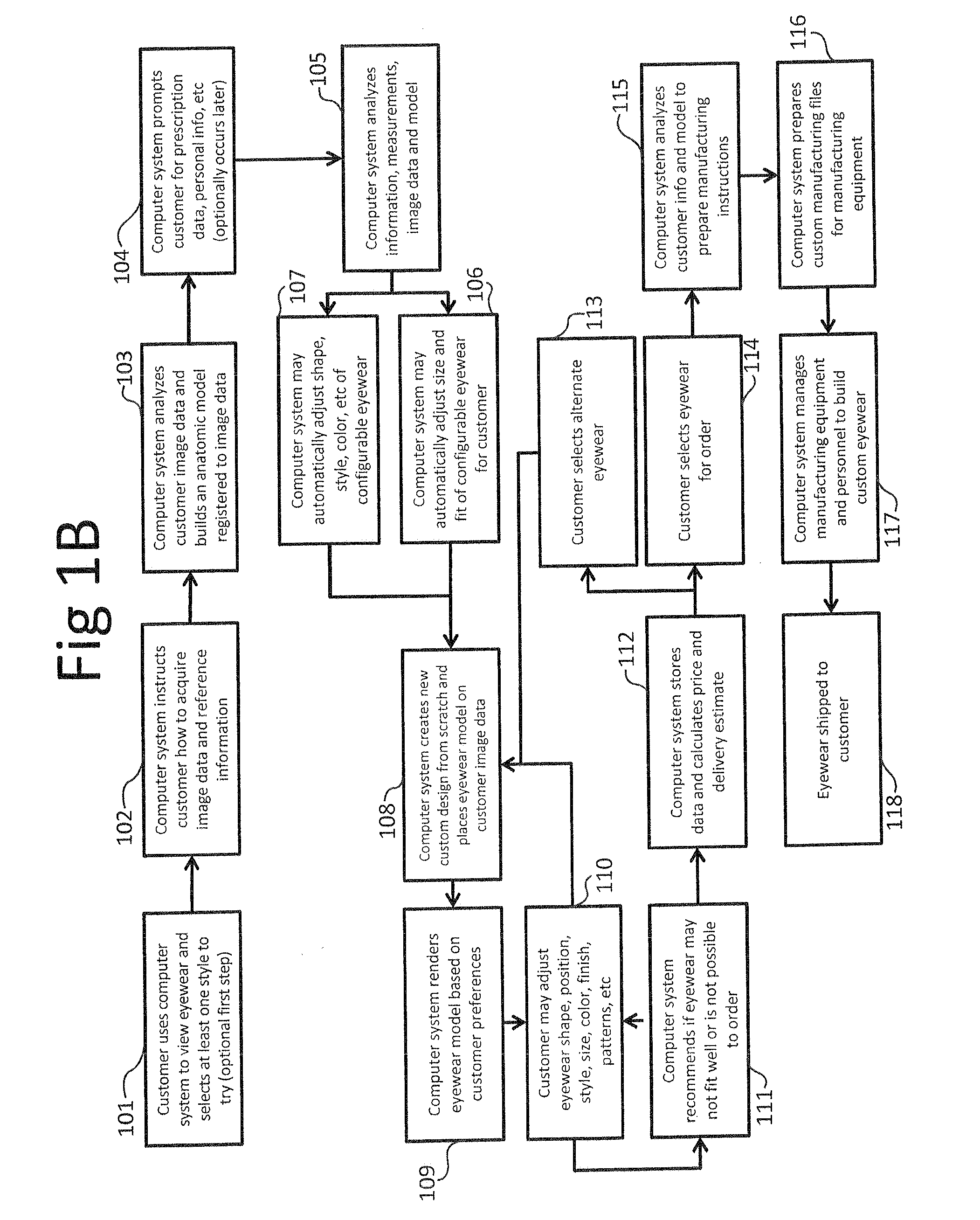

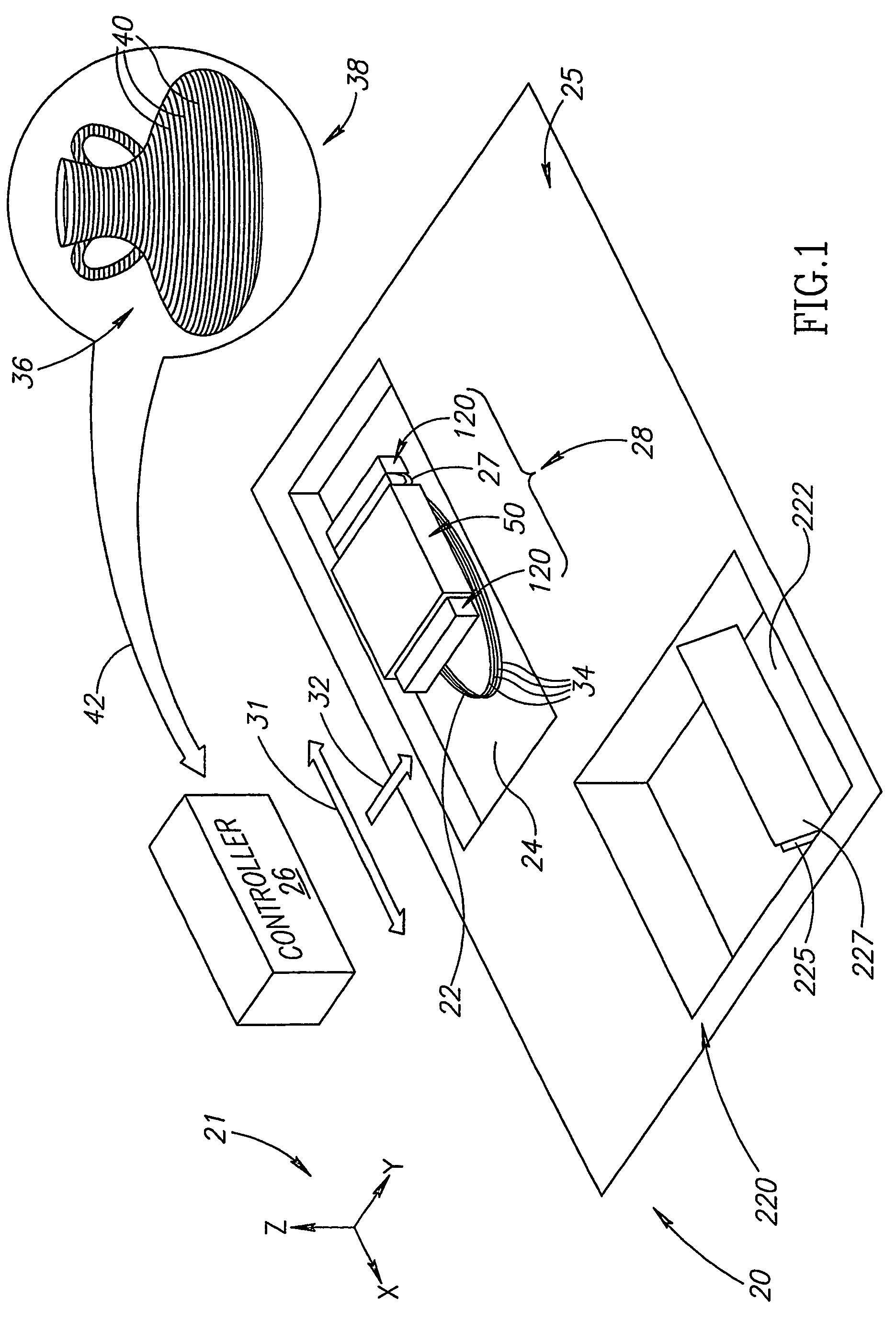

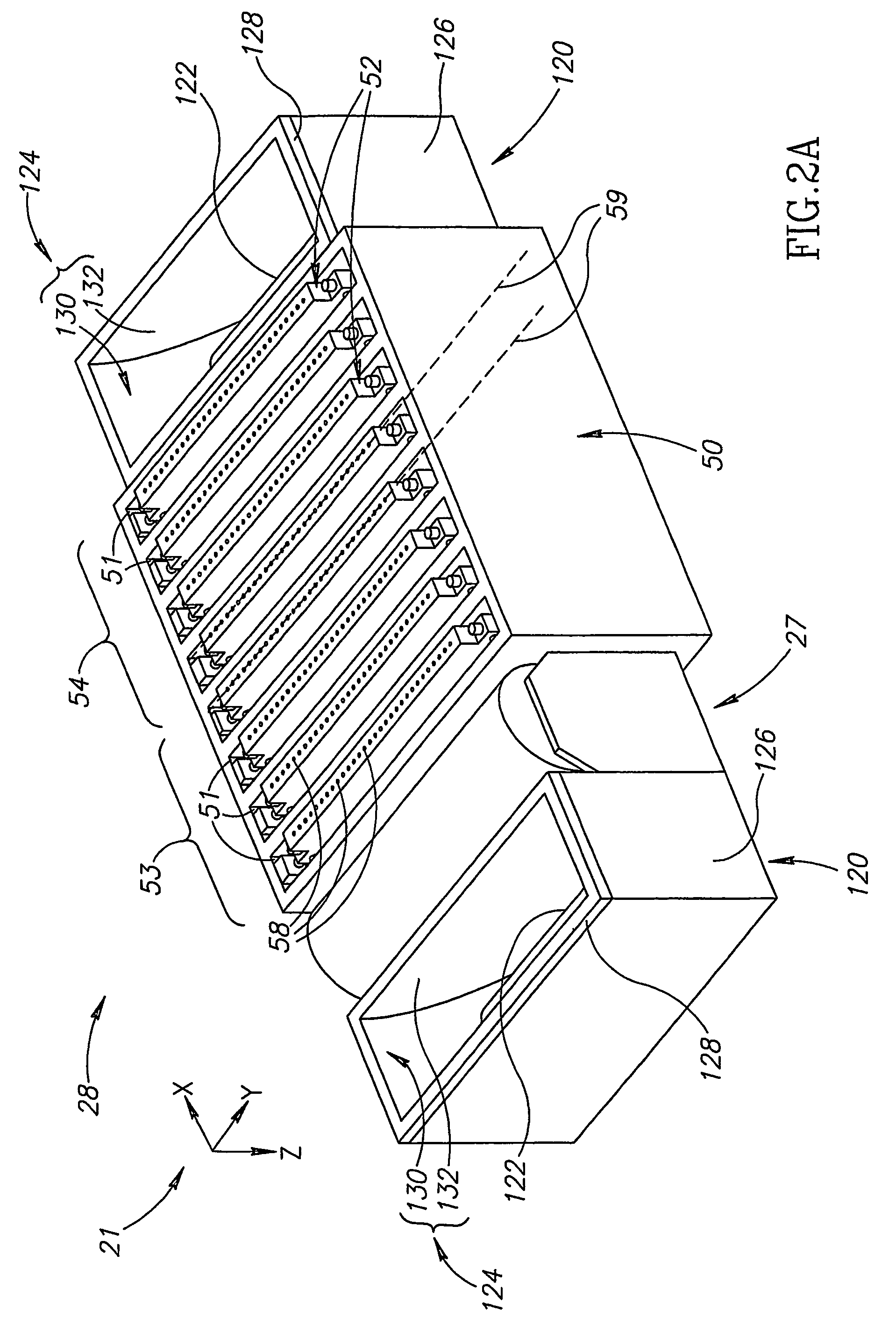

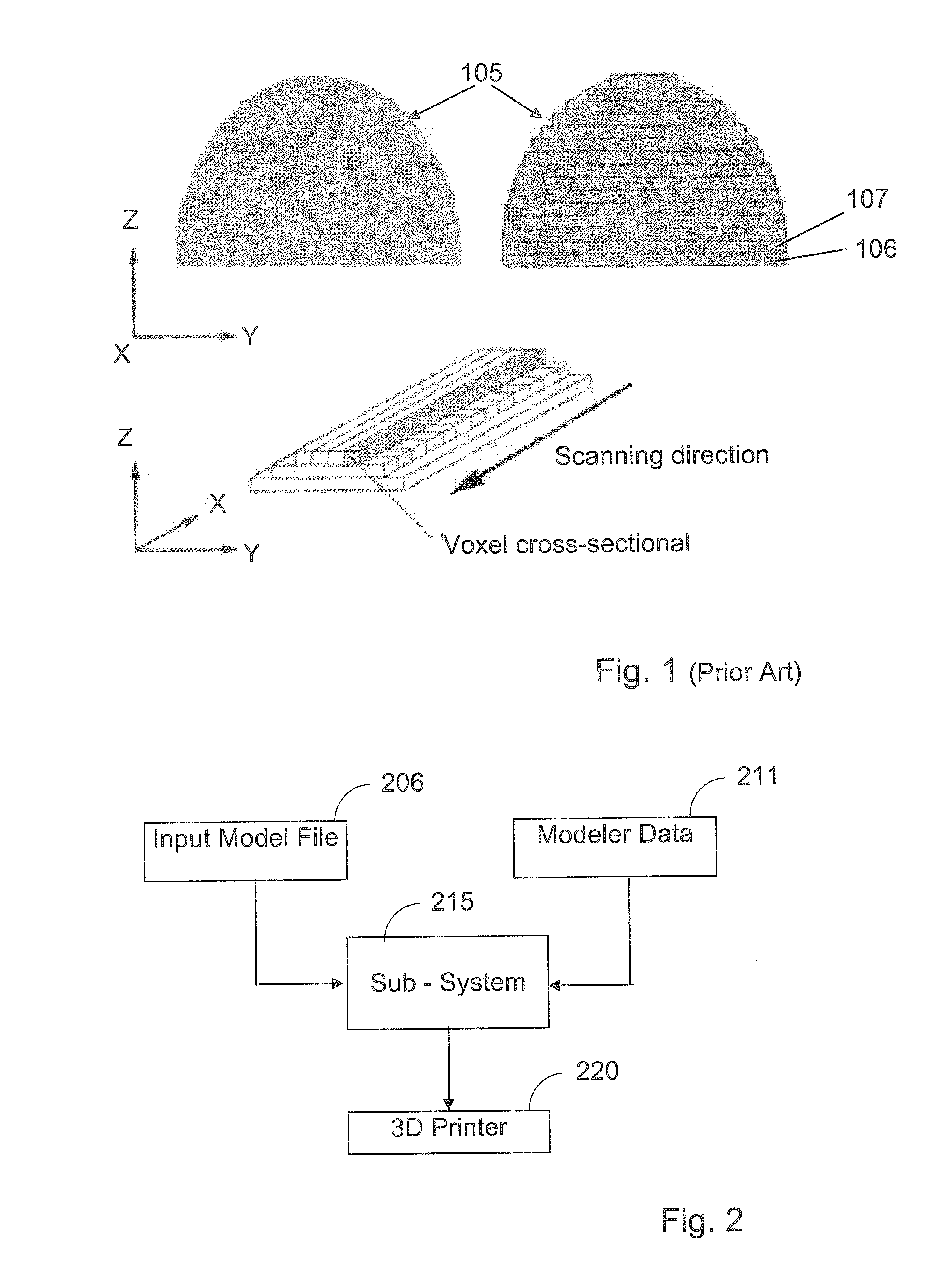

Rapid prototyping apparatus

ActiveUS7500846B2Improve operating characteristicsRapid productionConfectionerySweetmeatsThin layerEngineering

Apparatus for producing an object by sequentially forming thin layers of a construction material one on top of the other responsive to data defining the object, the apparatus comprising: a plurality of printing heads each having a surface formed with a plurality of output orifices and controllable to dispense the construction material through each orifice independently of the other orifices; a shuttle to which the printing heads are mounted; a support surface; and a controller adapted to control the shuttle to move back and forth over the support surface and as the shuttle moves to control the printing heads to dispense the construction material through each of their respective orifices responsive to the data to form a first layer on the support surface and thereafter, sequentially the other layers; wherein each printing head is dismountable from the shuttle and replaceable independently of the other printing heads.

Owner:OBJET GEOMETRIES

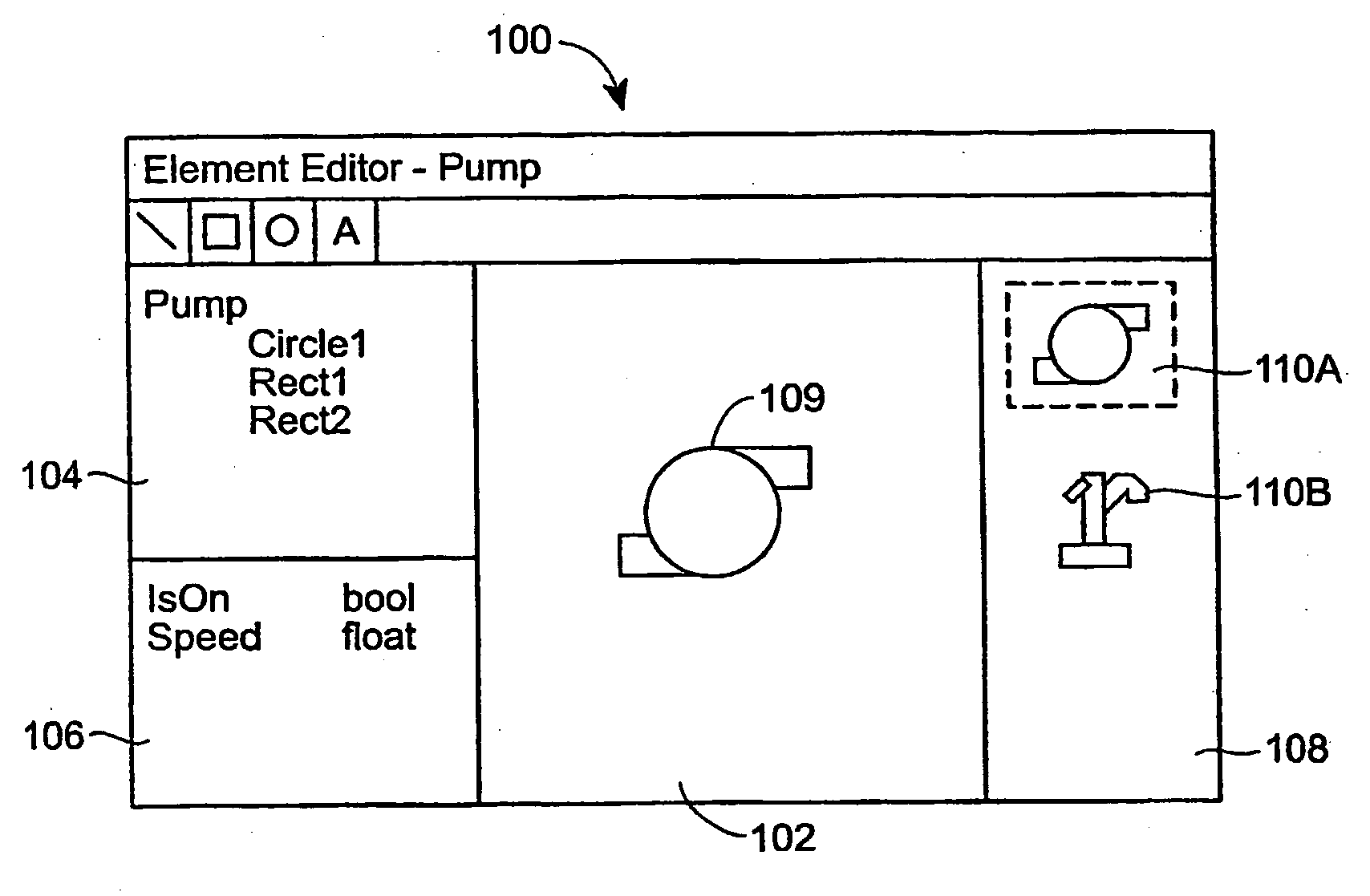

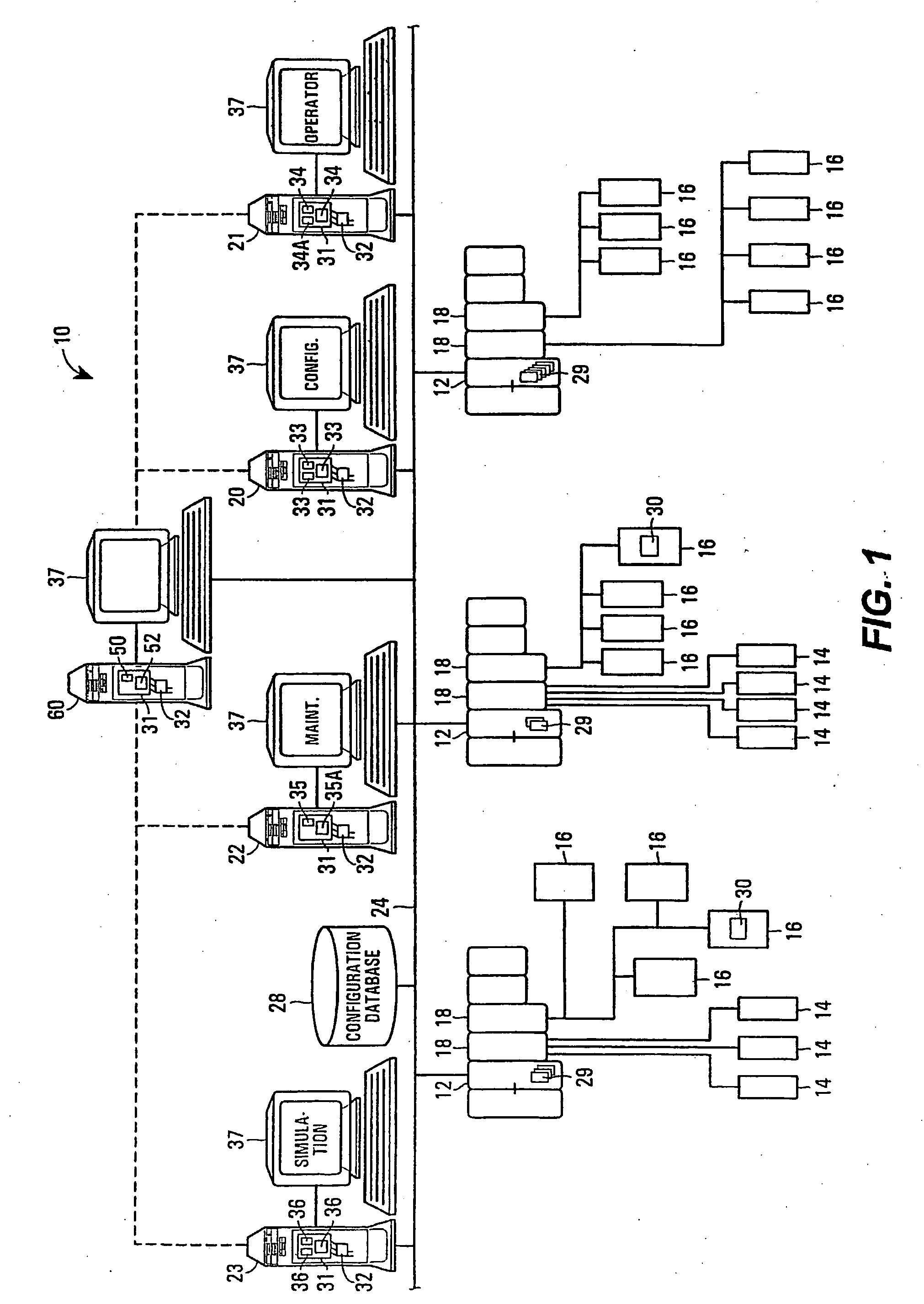

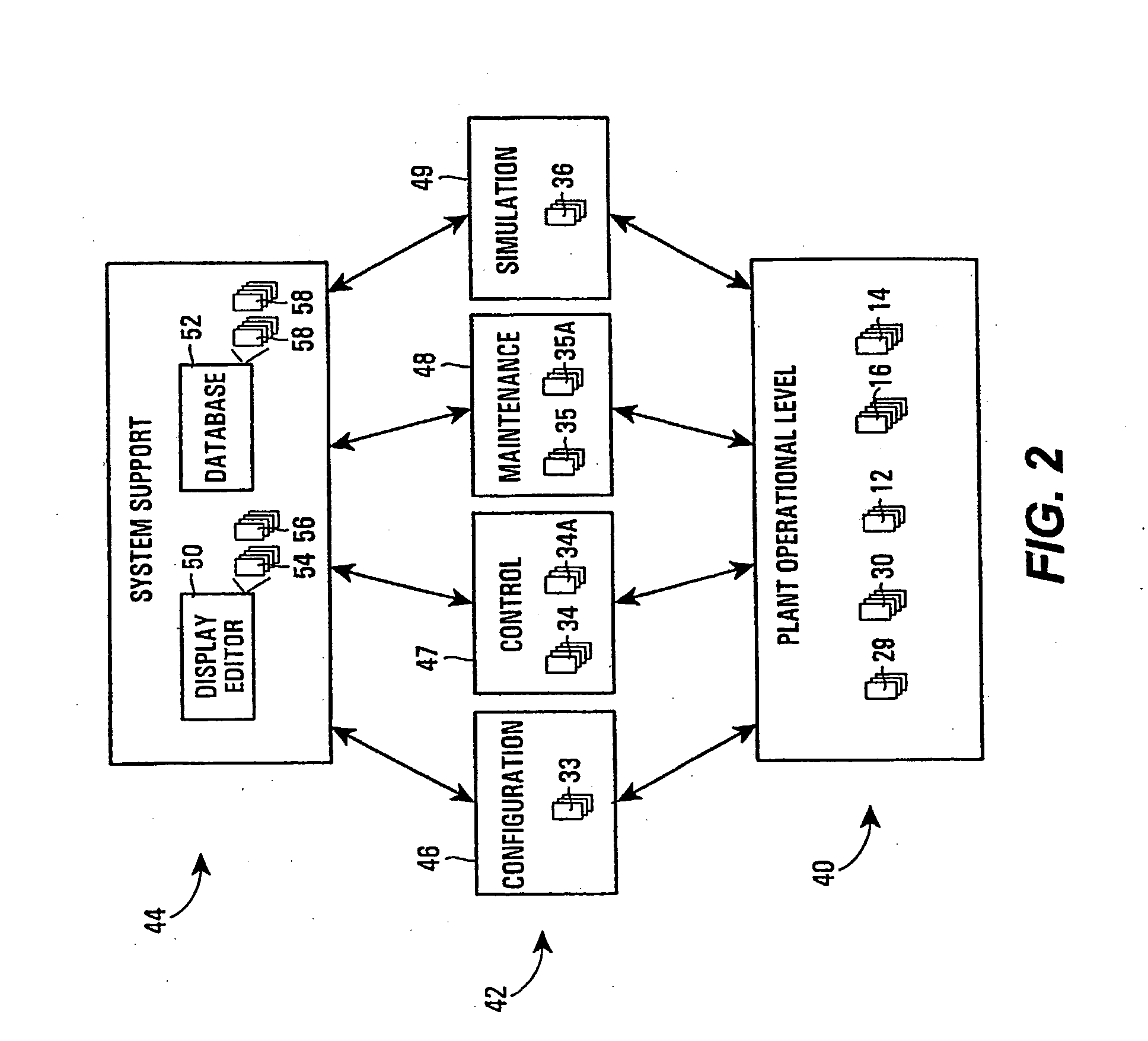

Graphic element with multiple visualizations in a process environment

ActiveUS20070132779A1Graphic element more versatileTechnology managementProgram controlGraphicsDisplay design

Smart graphic elements are provided for use as portions or components of one or more graphic displays, which may be executed in a process plant to display information to users about the process plant environment, such as the current state of devices within the process plant. Each of the graphic elements is an executable object that includes a property or a variable that may be bound to an associated process entity, like a field device, and that includes multiple visualizations, each of which may be used to graphically depict the associated process entity on a user interface when the graphic element is executed as part of the graphic display. Any of the graphic element visualizations may be used in any particular graphic display and the same graphic display may use different ones of the visualizations at different times. The different visualizations associated with a graphic element make the graphic element more versatile, at they allow the same graphic element to be used in different displays using different graphical styles or norms. These visualizations also enable the same graphic element to be used in displays designed for different types of display devices, such as display devices having large display screens, standard computer screens and very small display screens, such as PDA and telephone display screens.

Owner:FISHER-ROSEMOUNT SYST INC

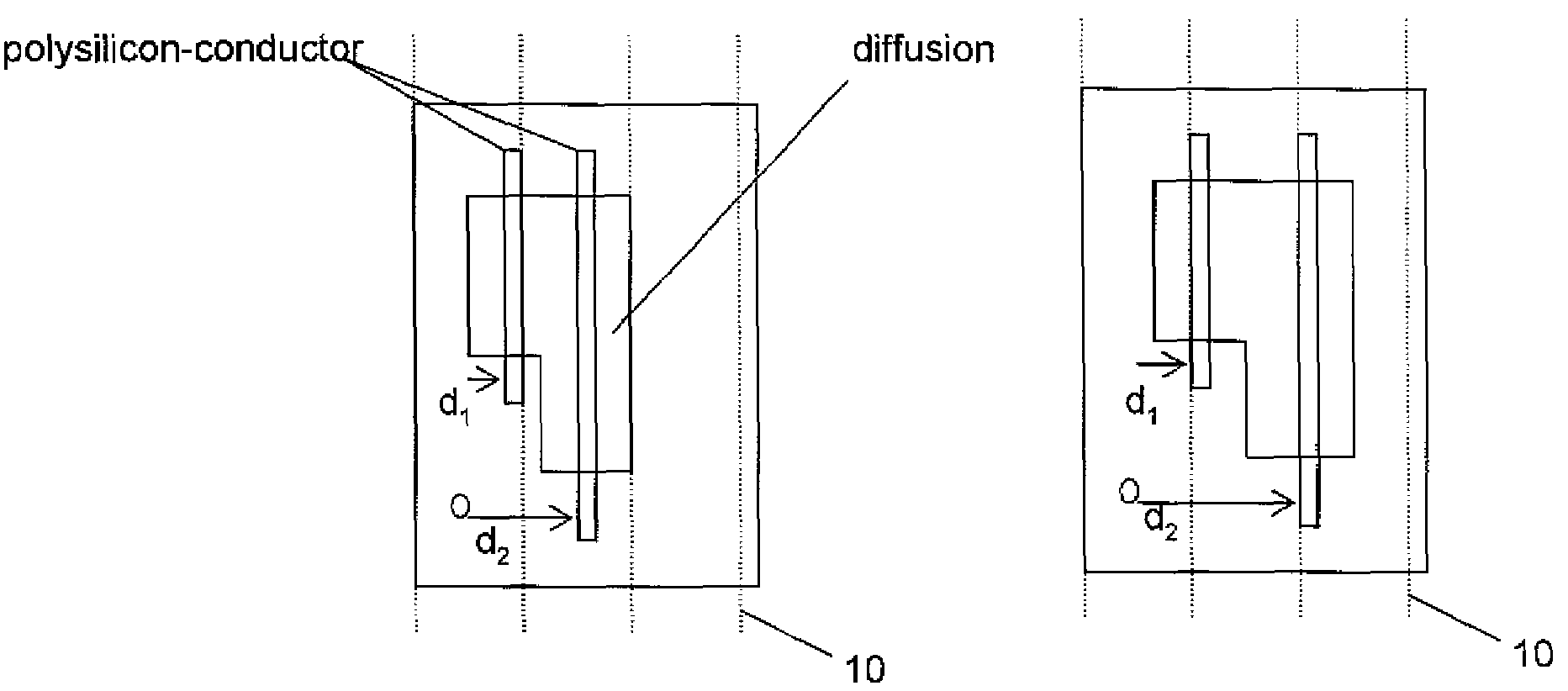

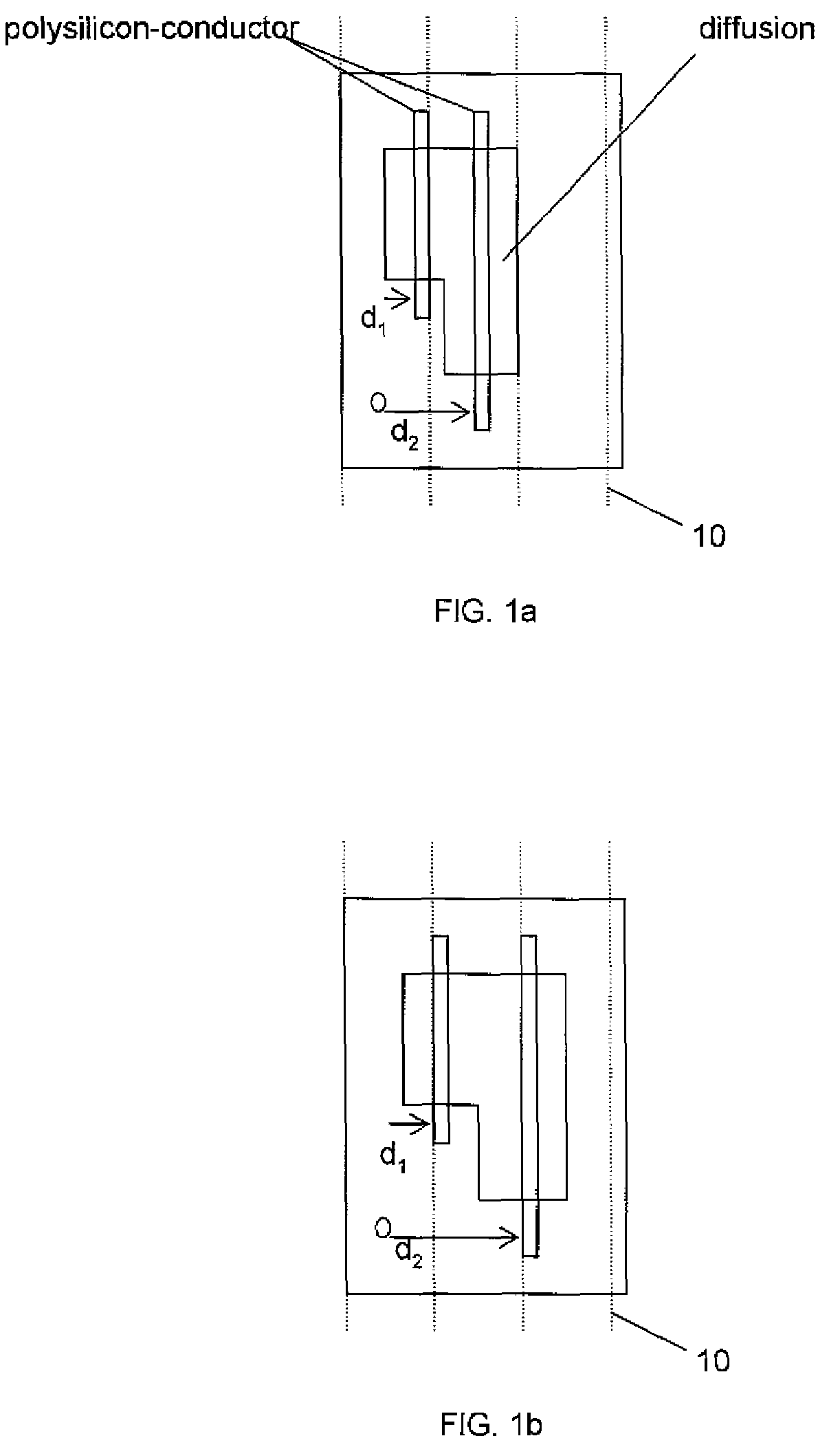

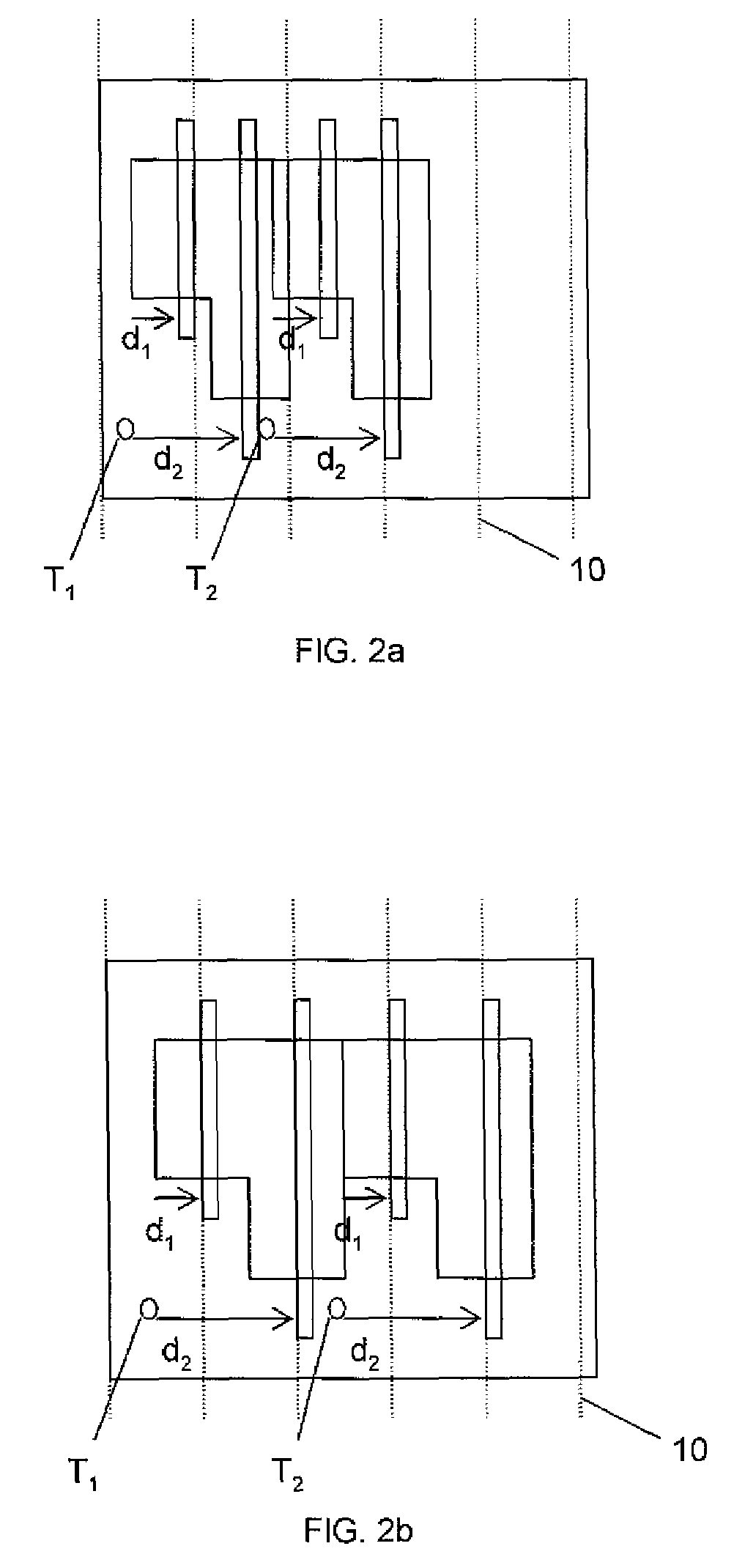

Minimum layout perturbation-based artwork legalization with grid constraints for hierarchical designs

InactiveUS7484197B2Computer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceHierarchical design

A method comprises extracting a hierarchical grid constraint set and modeling one or more critical objects of at least one cell as a variable set. The method further comprises solving a linear programming problem based on the hierarchical grid constraint set with the variable set to provide initial locations of the critical objects of the at least one cell and determining target on-grid locations of the one or more critical objects in the at least one cell using the results of the linear programming solution.

Owner:GLOBALFOUNDRIES INC

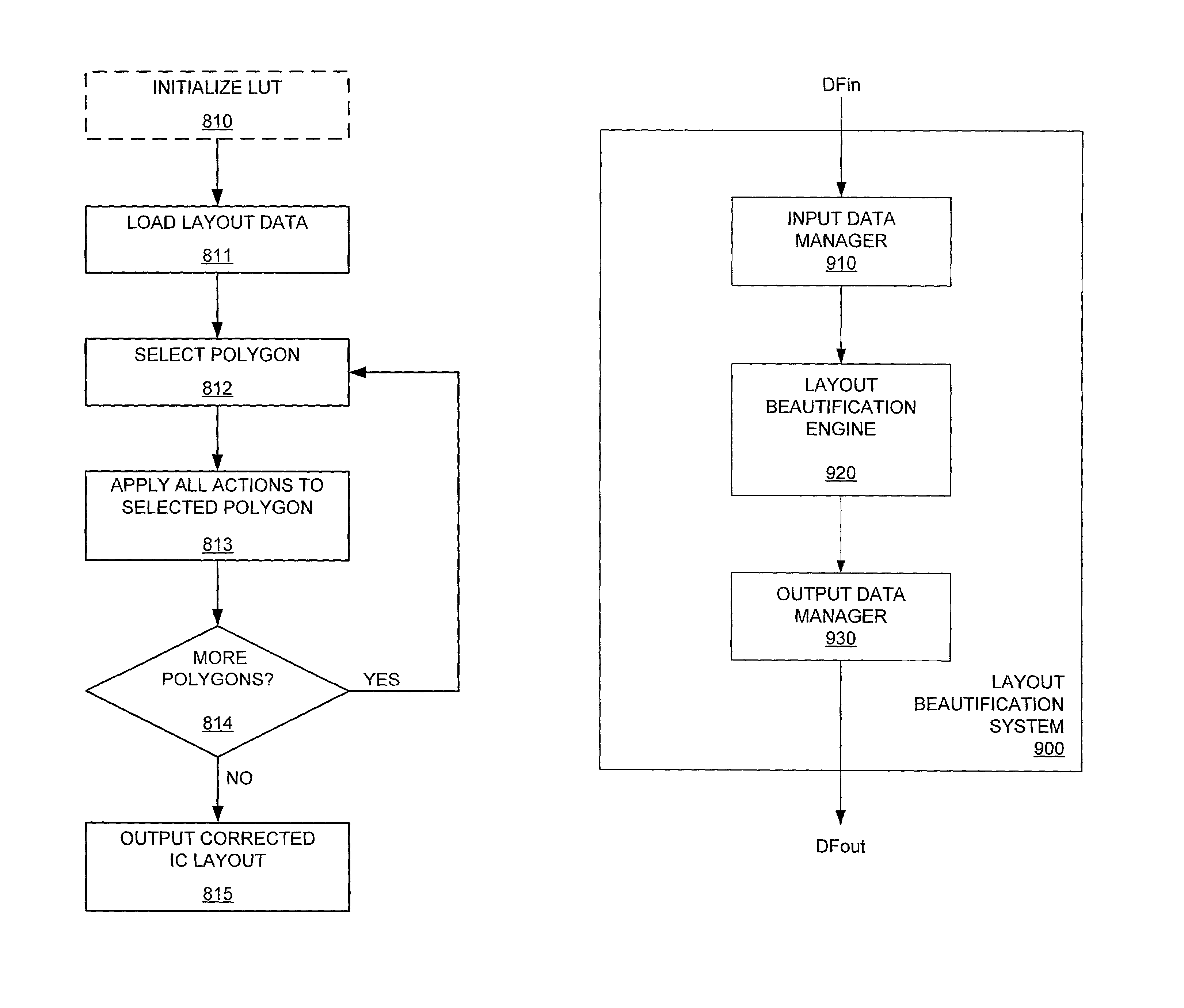

Shape-based geometry engine to perform smoothing and other layout beautification operations

ActiveUS7159197B2Efficient executionData be eliminatedOriginals for photomechanical treatmentComputer aided designData fileEngineering

A shape-based layout beautification operation can be performed on an IC layout to correct layout imperfections. A shape is described by edges (and vertices) related according to specified properties. Each shape can be configured to match specific layout imperfection types. Corrective actions can then be associated with the shapes, advantageously enabling efficient formulation and precise application of those corrective actions. Corrective actions can include absolute, adaptive, or replacement-type modifications to the detected layout imperfections. A concurrent processing methodology can be used to minimize processing overhead during layout beautification, and the actions can also be incorporated into a lookup table to further reduce runtime. A layout beautification system can also be connected to a network across which shapes, actions, and IC layout data files can be accessed and retrieved.

Owner:SYNOPSYS INC

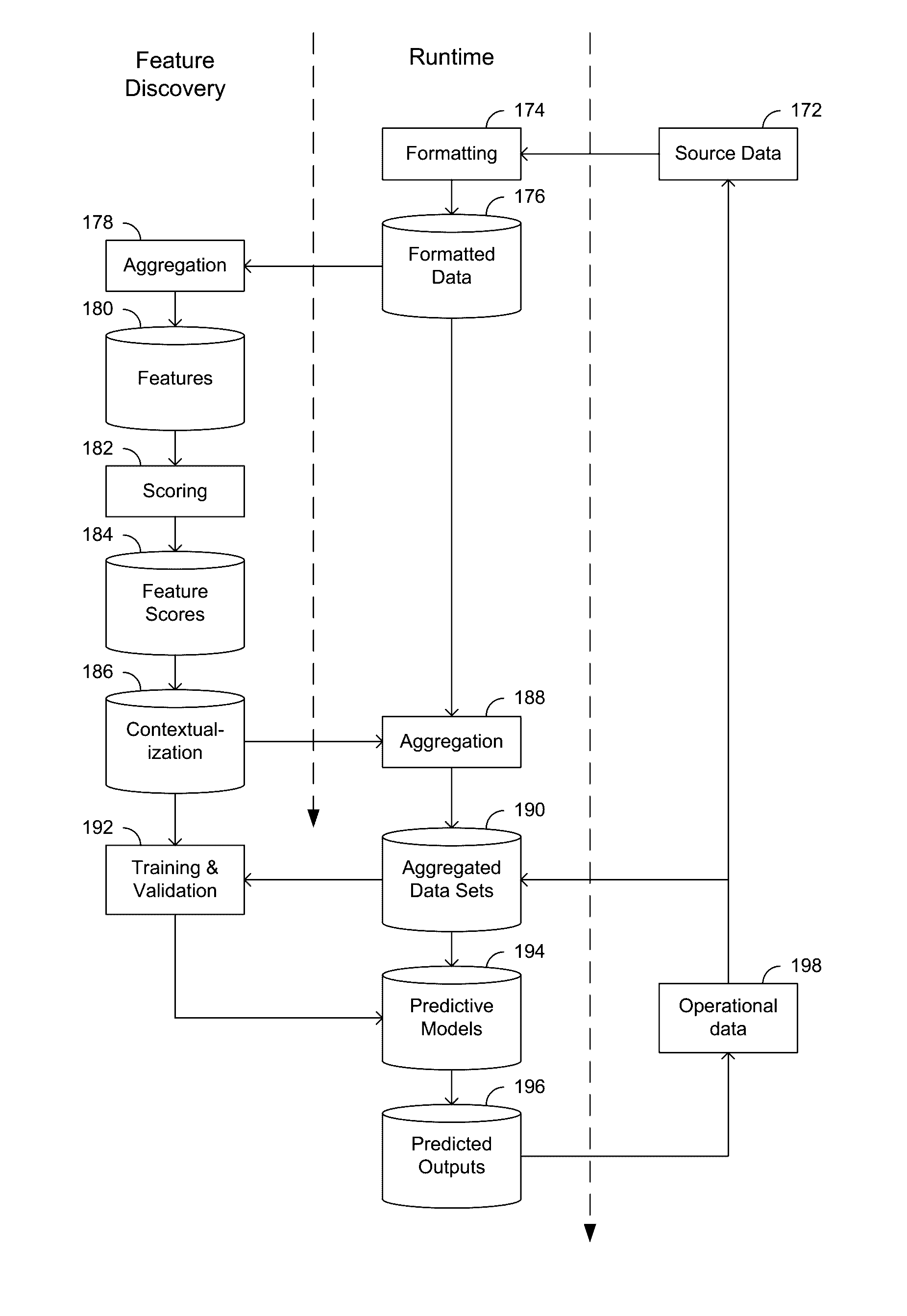

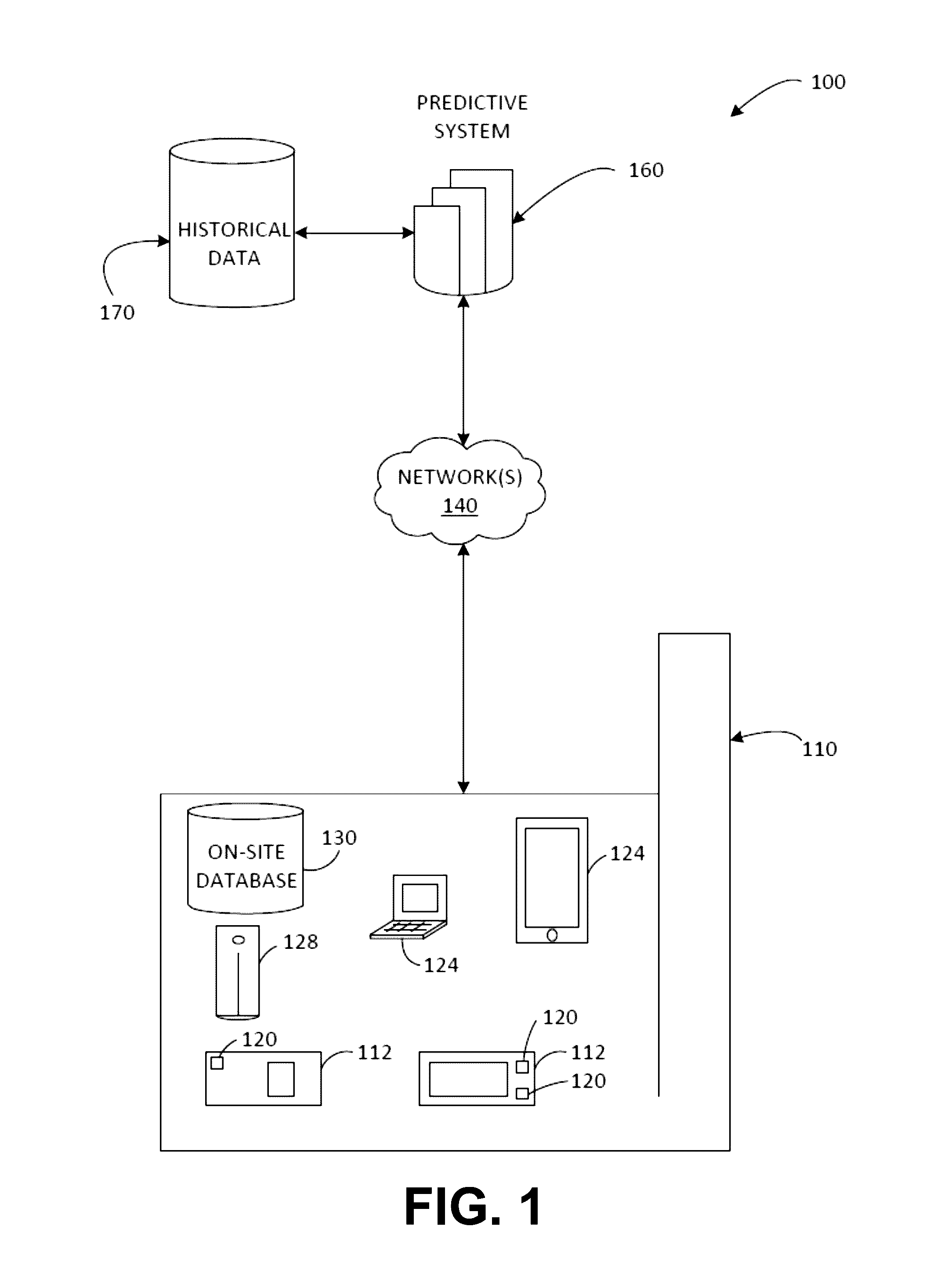

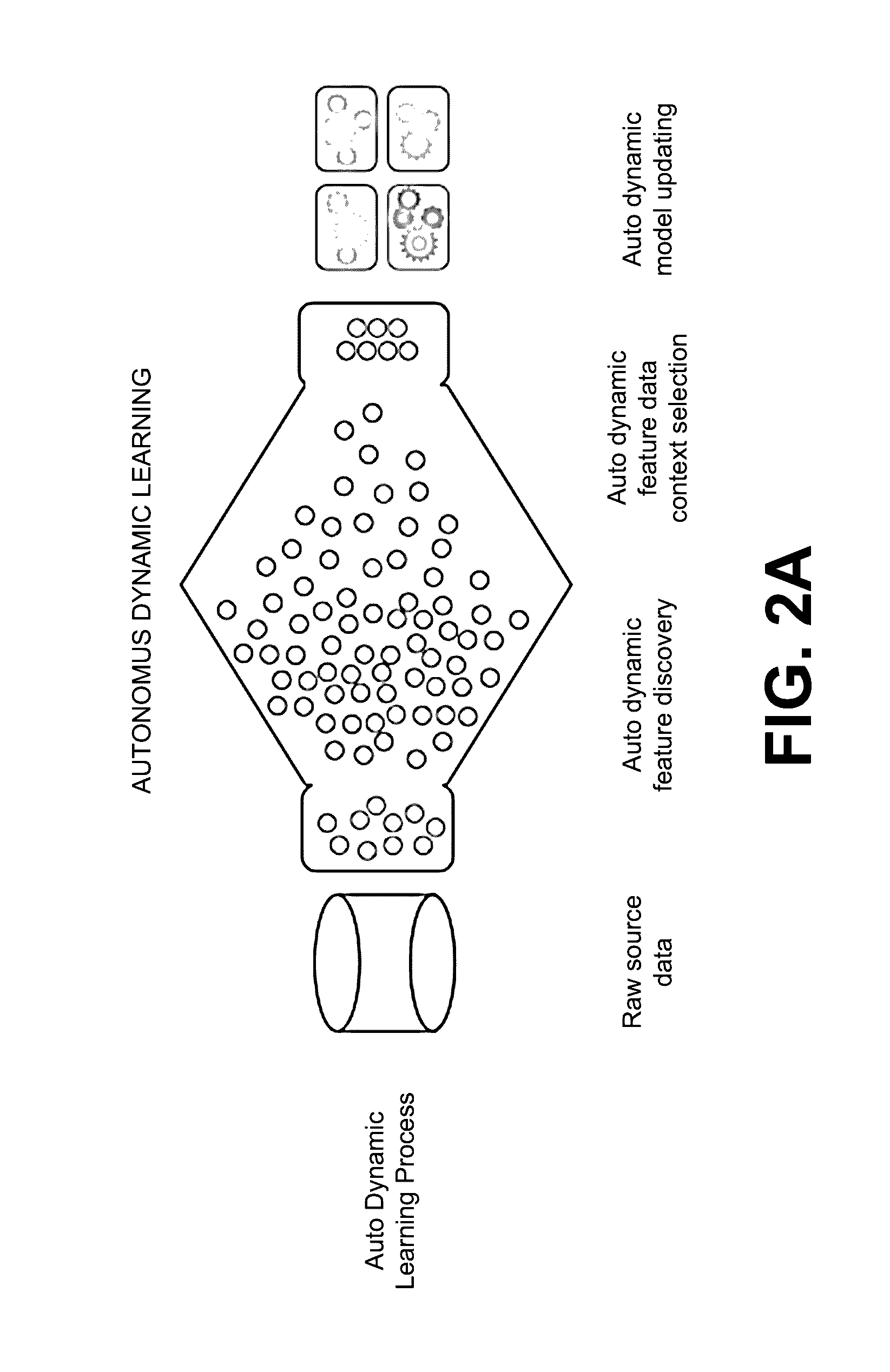

Dynamically updated predictive modeling of systems and processes

ActiveUS20160350671A1Testing/monitoring control systemsProbabilistic networksSufficient timeOperational system

Various examples are provided for dynamically updating or adapting predictive modeling for prediction of outcomes of interest for operating systems and processes. Embodiments of the disclosure may provide systems, apparatus, processes, and methods for generating and deploying dynamically updated predictive models. In some embodiments, the predictive model may be deployed for the purpose of predicting operational outcomes of interests in operating systems, hardware devices, machines and / or processes associated therewith prior to the operational outcomes of interest occurring. The predictions can, for example, provide sufficient time for maintenance or repairs to be scheduled and carried out to avoid the predicted operational outcome. Autonomous evaluation of features allows the predictive models to be dynamically updated in response to changes in the environment or monitored data.

Owner:RAYTHEON TECH CORP

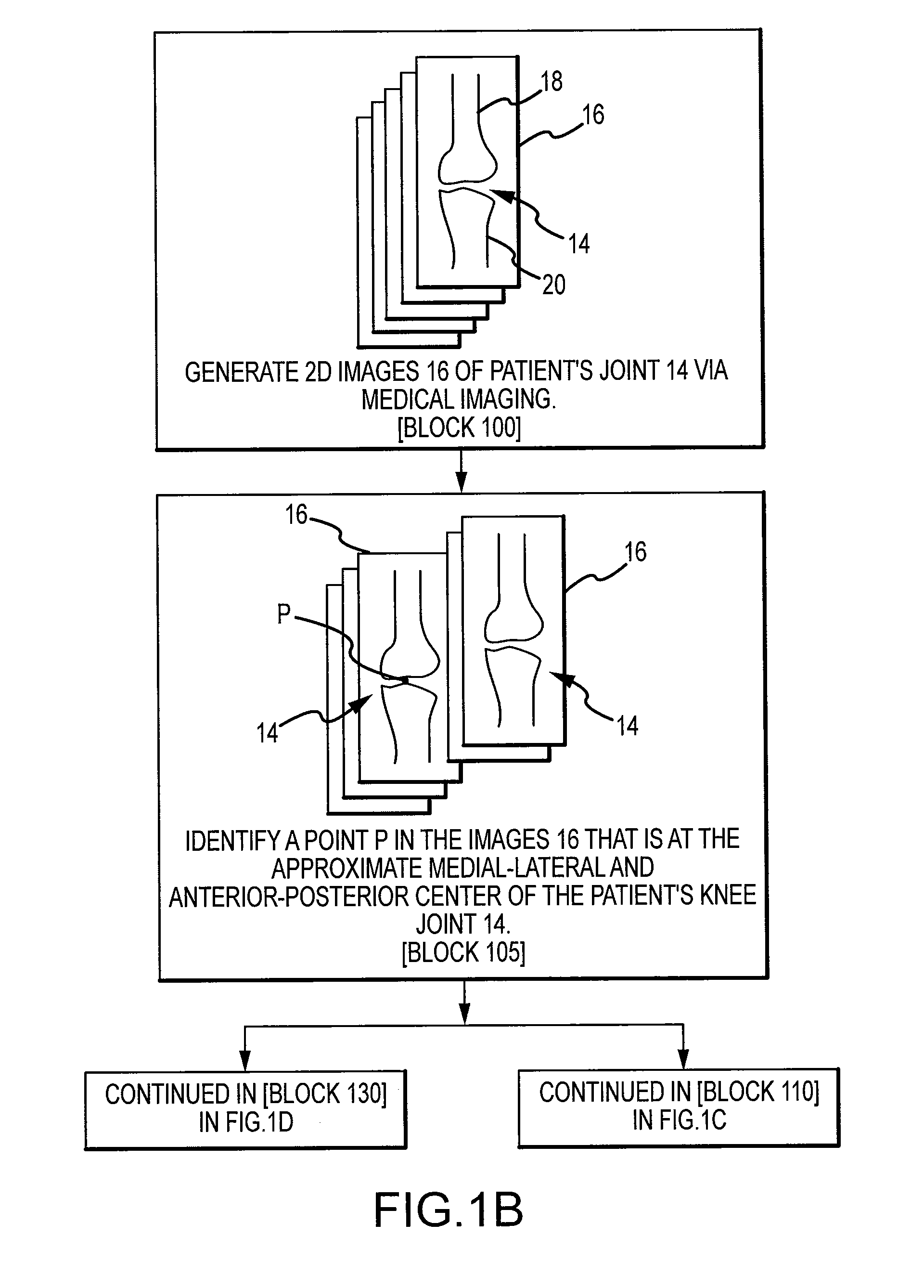

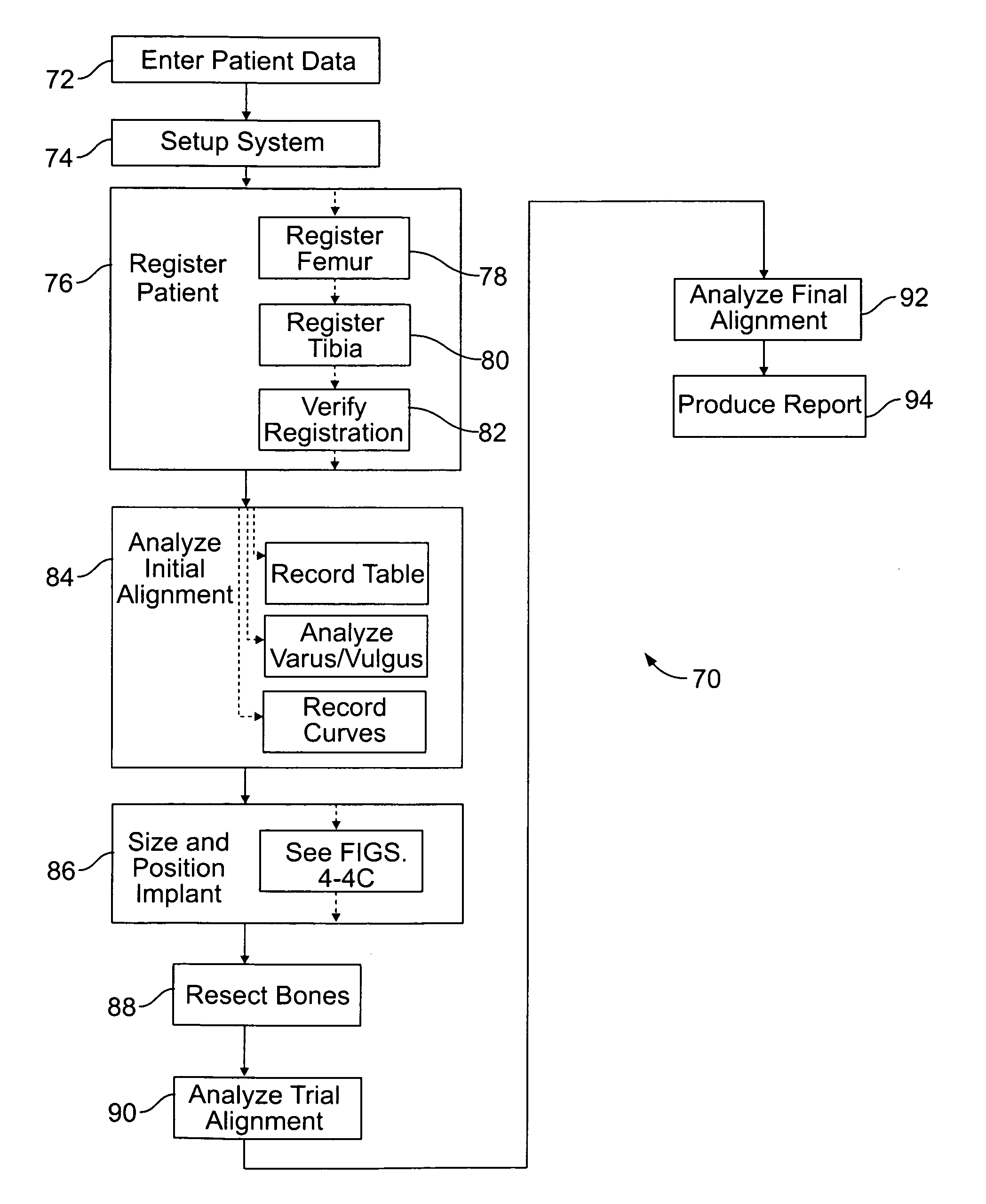

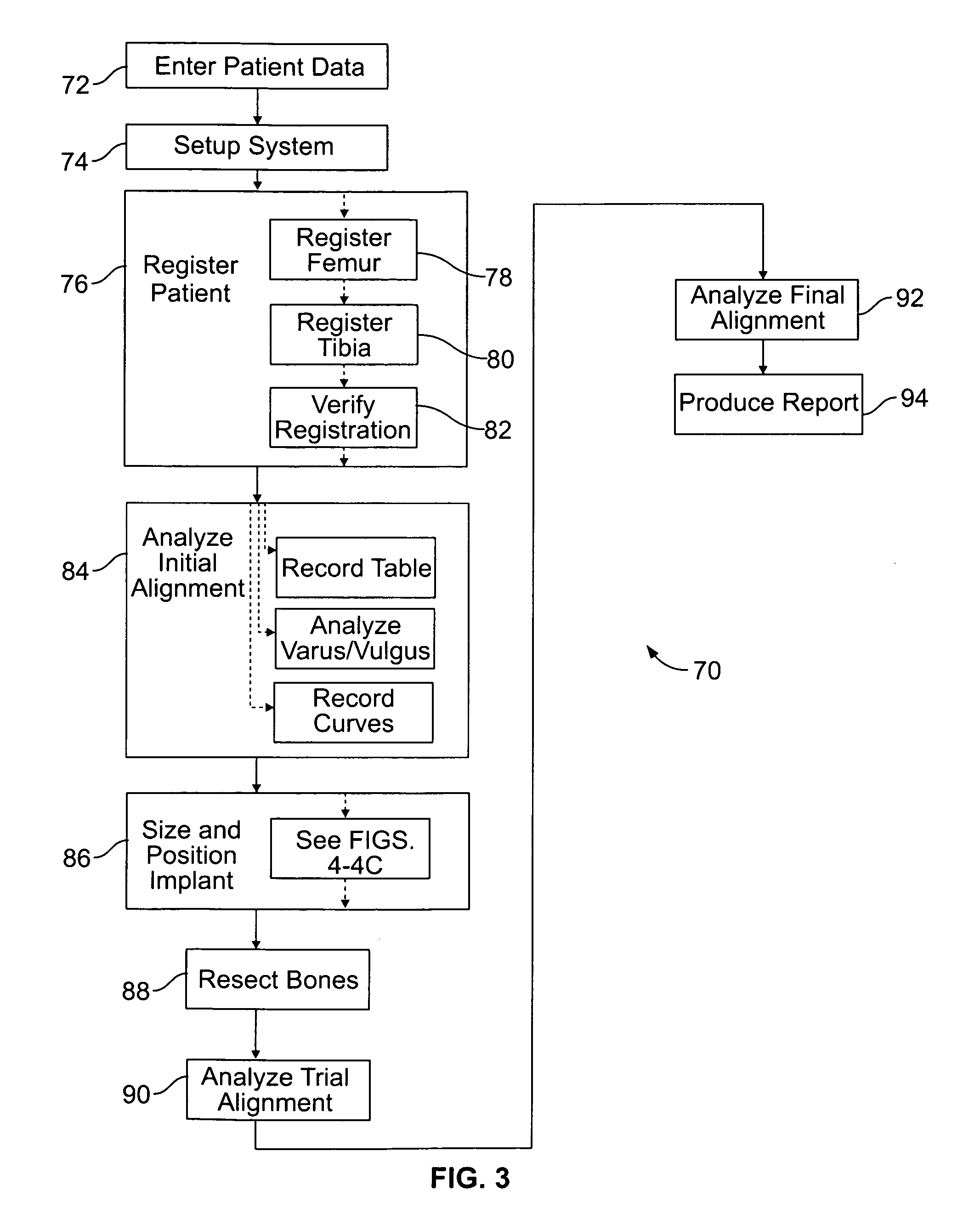

Method of and system for planning a surgery

ActiveUS20090043556A1Analogue computers for chemical processesDiagnostic recording/measuringSurgery procedureBiomedical engineering

A system for virtually planning a size and position of a prosthetic implant for a bone on a patient includes a database containing pre-defined form factor information for a plurality of different implants and a circuit for obtaining surface shape information of the bone. The system further includes a circuit for defining baseline location parameters for an implant location in relation to a virtual representation of the bone based on the surface shape information and a circuit for assessing a fit calculation of each implant in relation to the virtual representation of the bone based on the form factor in formation and a plurality of fit factors at each of a plurality of incremental positions in relation to the bone. Still further, the system includes a circuit for selecting a best fit implant size and position from all of the fit calculations.

Owner:STRYKER EURO OPERATIONS HLDG LLC

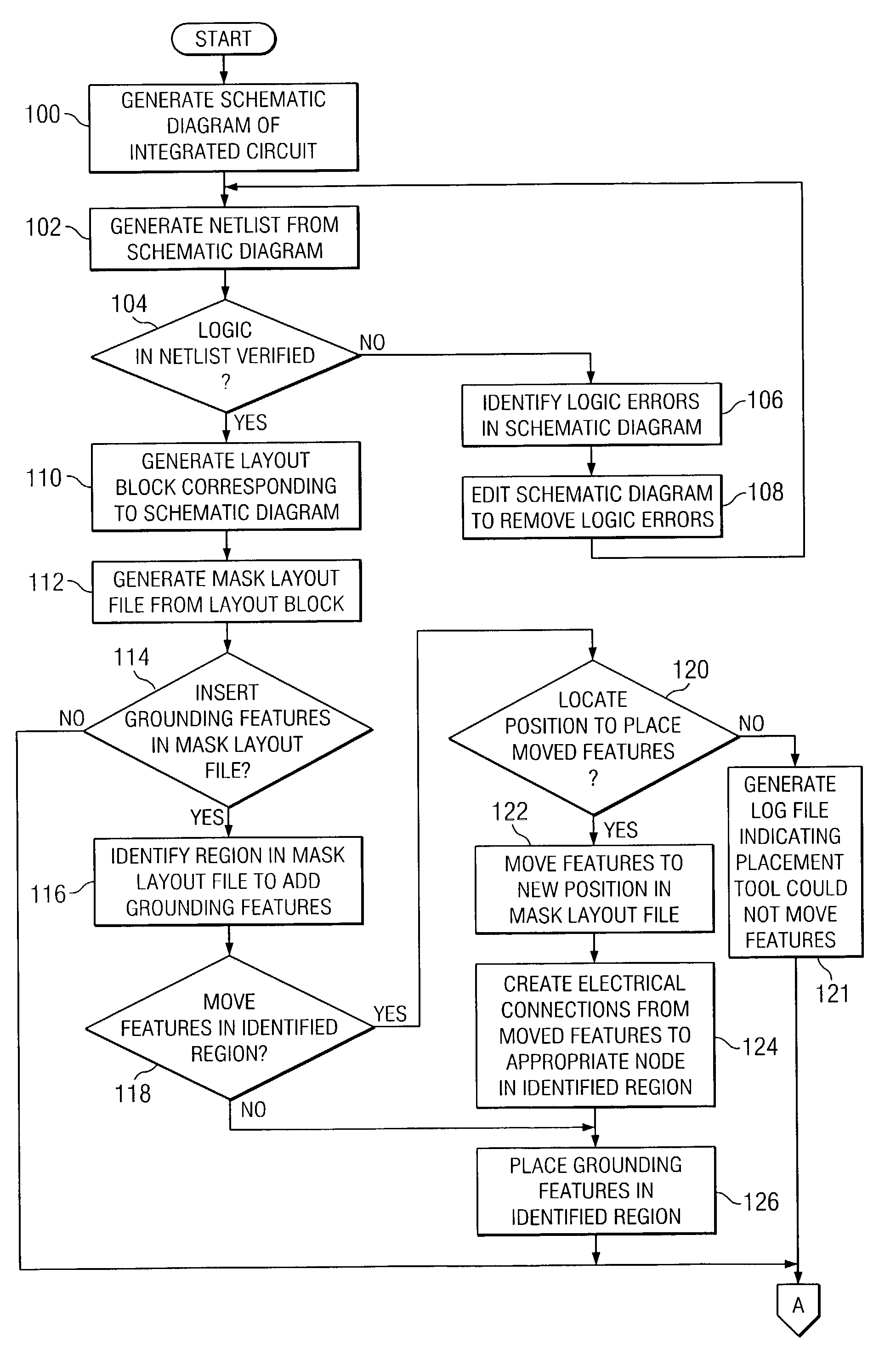

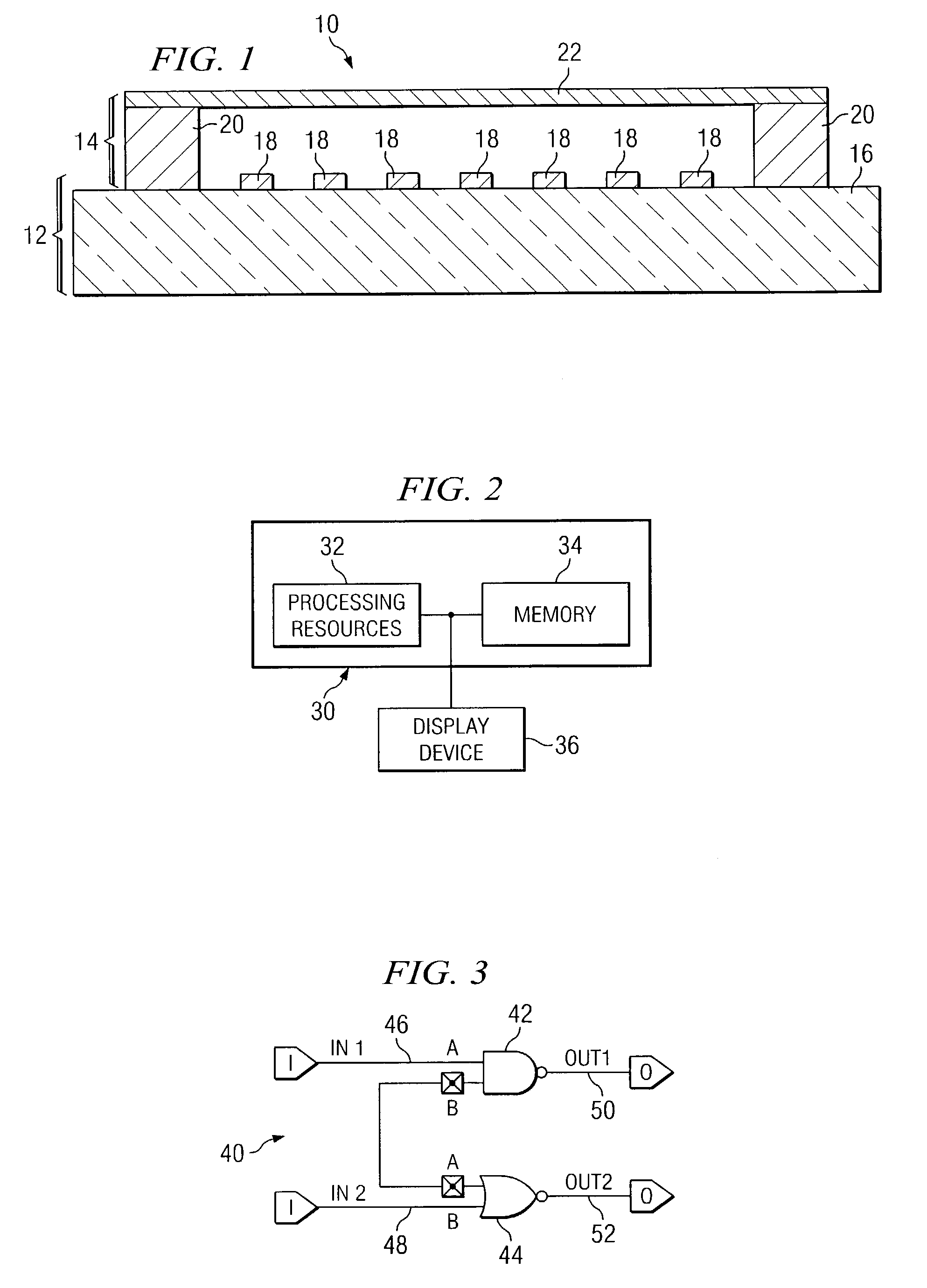

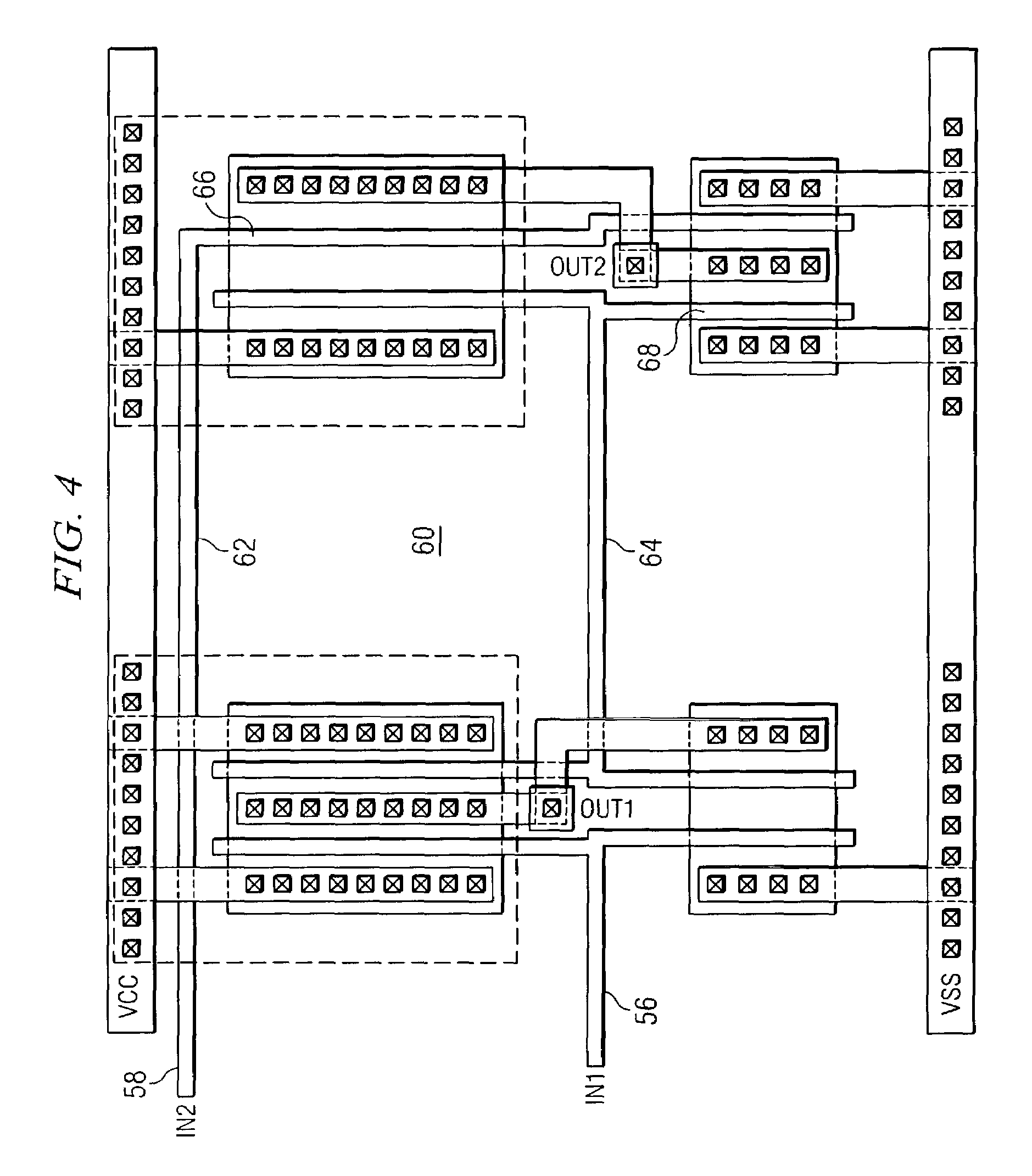

Photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufacture with same

InactiveUS6978437B1Increase antenna ratioRaise the ratioSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

A photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufactured with the photomask are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region including an antenna ratio less than a first design rule. A feature located in the identified region is moved based on a second design rule from a first position to a second position in the mask layout file to create a space in the identified region. A grounding feature is placed in the space and automatically connected to a gate feature in the mask layout file such that the antenna ratio is increased to greater than or approximately equal to the first design rule.

Owner:CELERICS TECH

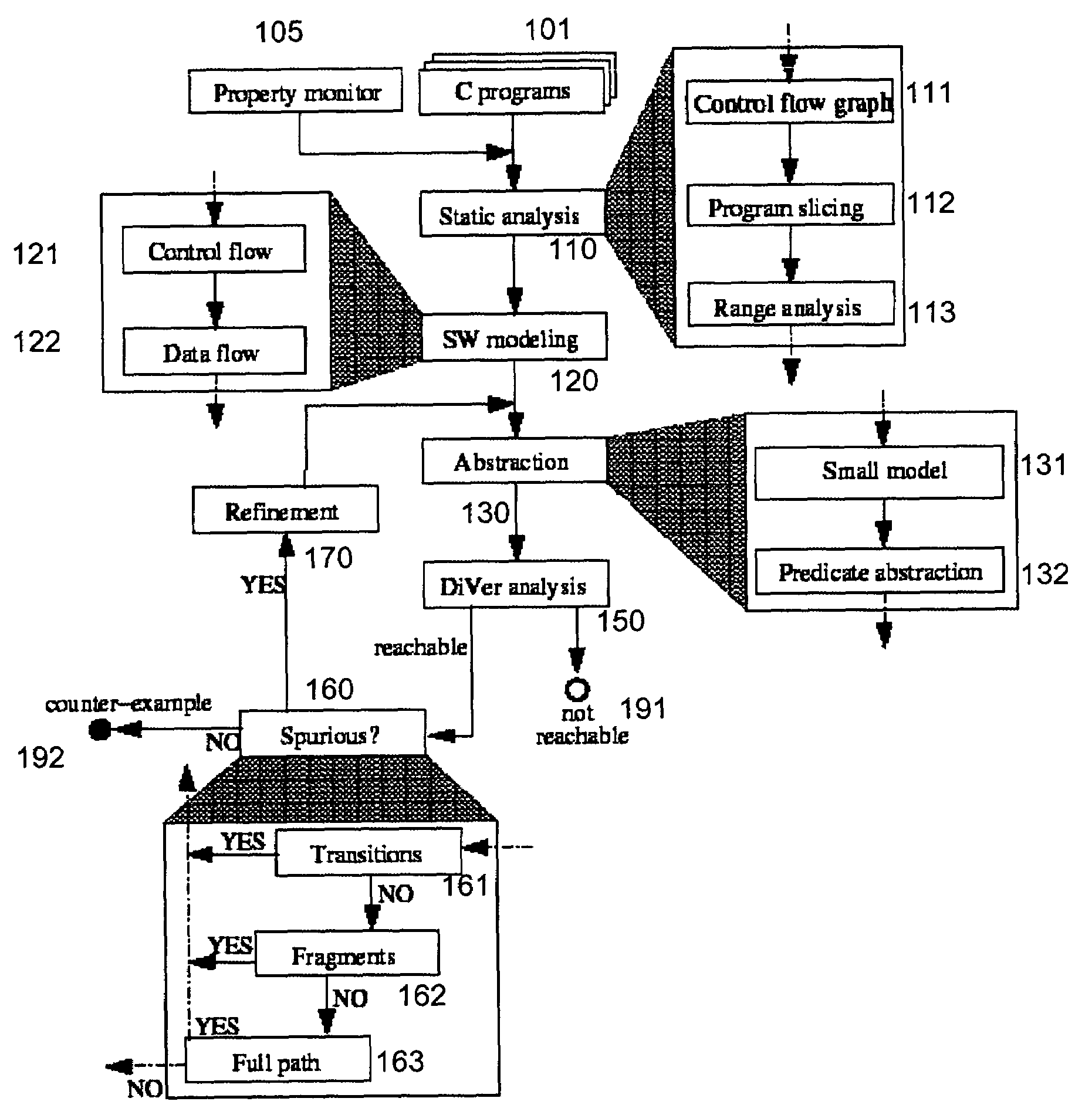

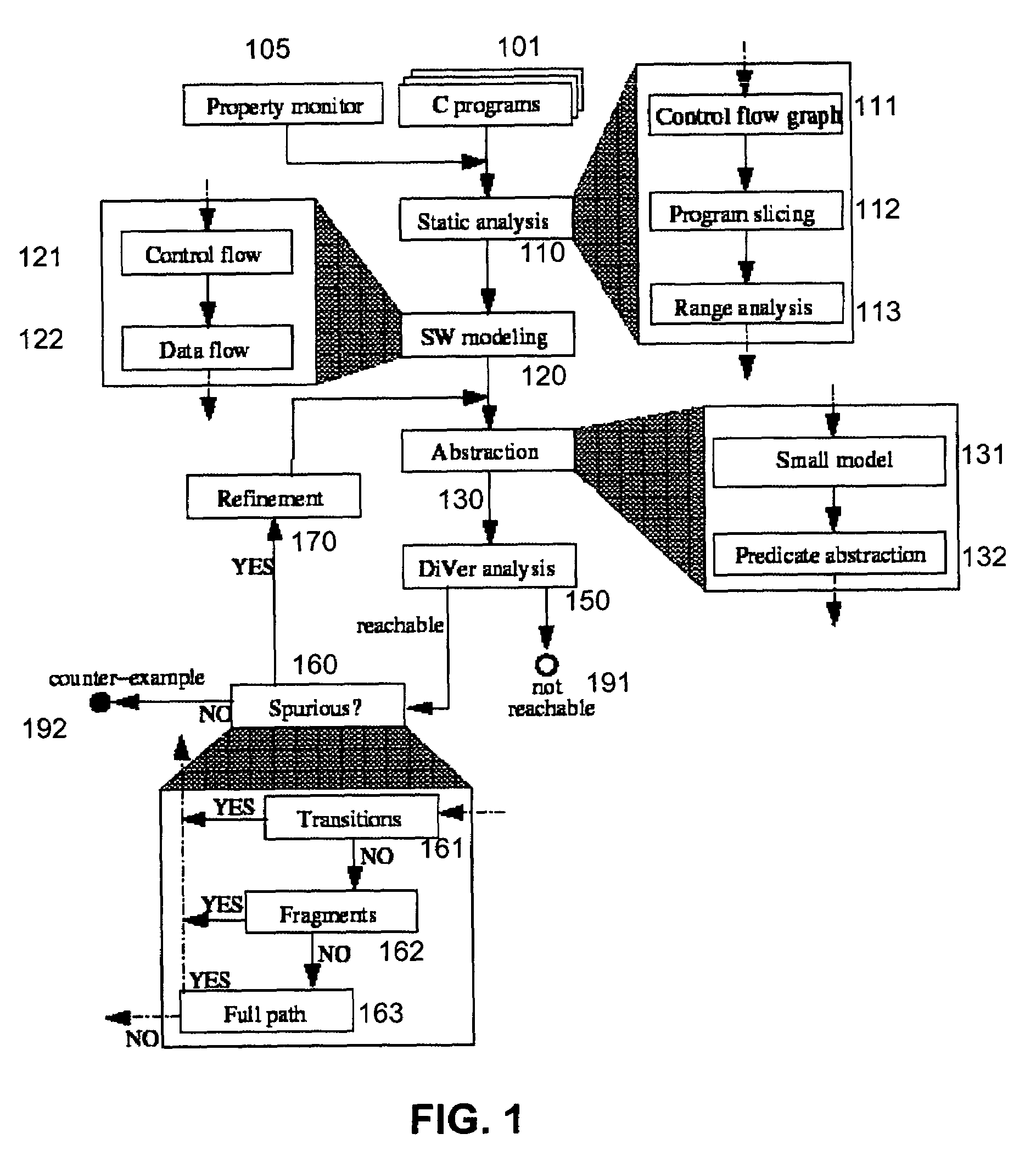

System and method for modeling, abstraction, and analysis of software

ActiveUS7346486B2Improve verification efficiencyImprove translationError detection/correctionComputation using non-denominational number representationBasic blockSoftware

A system and method is disclosed for formal verification of software programs that advantageously translates the software, which can have bounded recursion, into a Boolean representation comprised of basic blocks and which applies SAT-based model checking to the Boolean representation.

Owner:NEC CORP

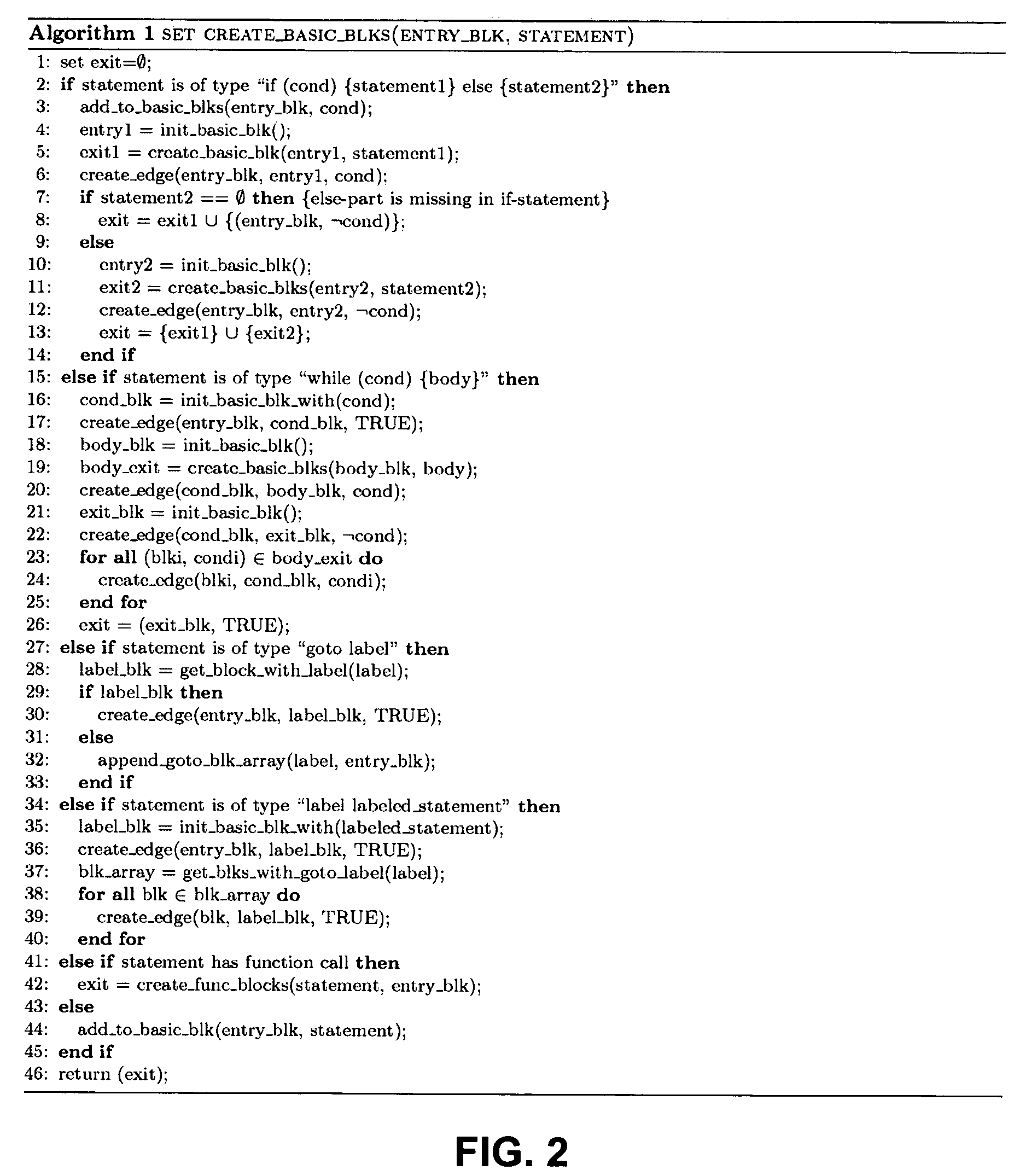

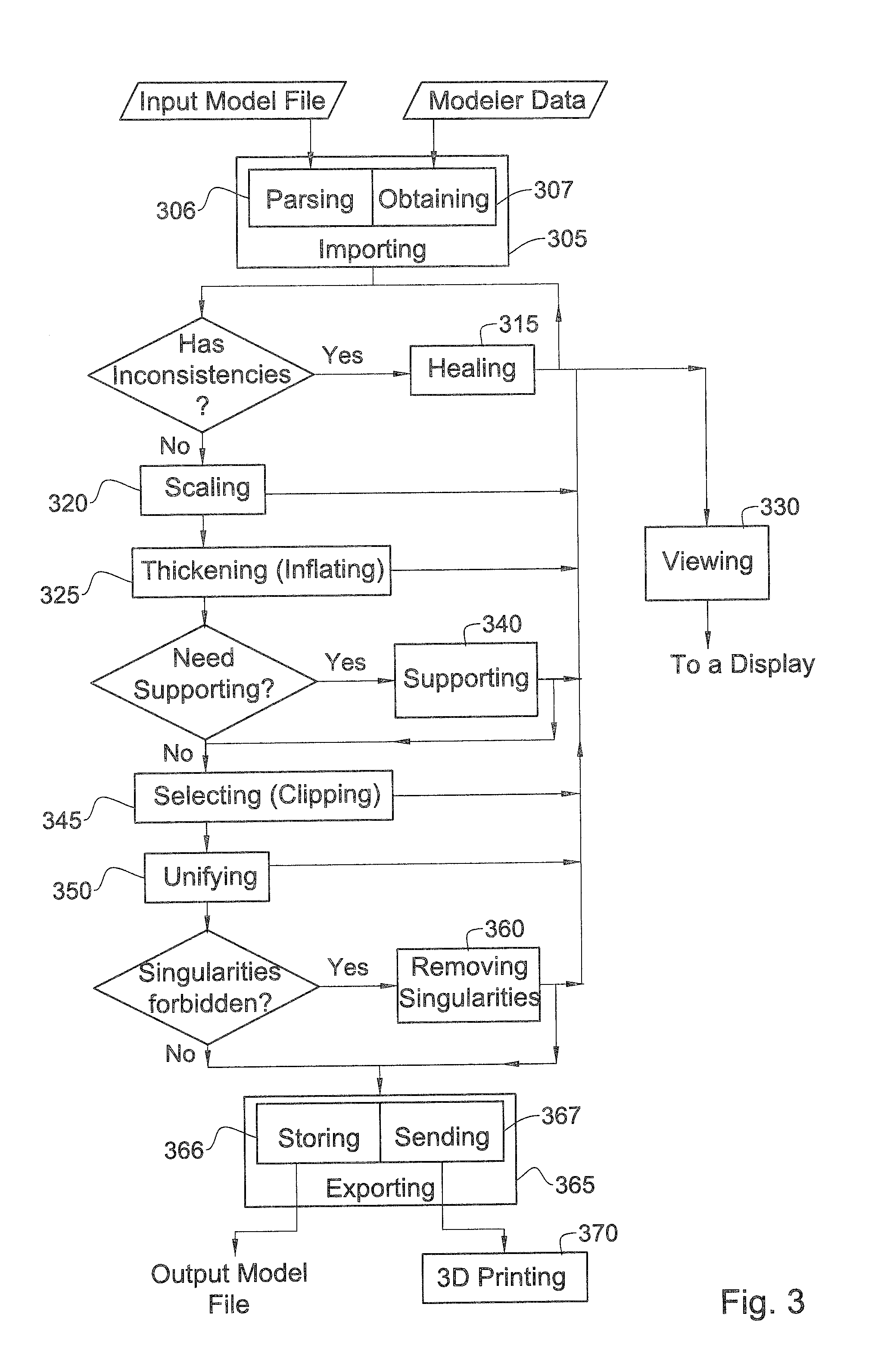

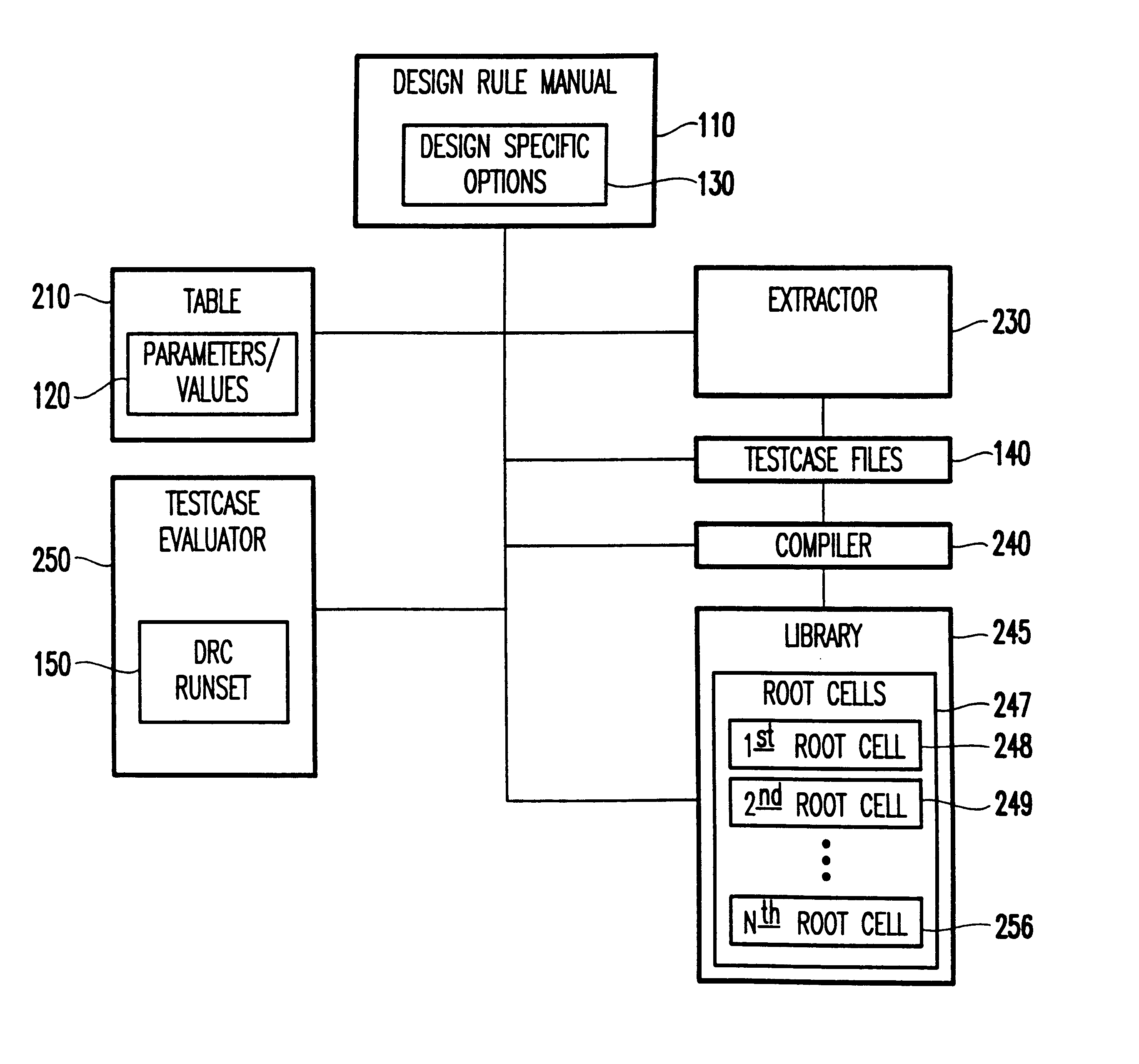

Methods and system for enabling printing three-dimensional object models

InactiveUS20110087350A1Additive manufacturing apparatusComputer aided designComputer scienceObject model

The present invention relates to a system and method of transforming an inconsistent 3D (three-dimensional) model of one or more 3D objects into a valid printable 3D model, said method comprising: (a) receiving an input model file and / or receiving modeler data, giving rise to an input 3D model having one or more parts; (b) analyzing said input 3D model and removing its one or more inconsistencies; (c) thickening the one or more parts of said 3D model, while preserving their functionality; and (d) unifying the union of interior volumes of said one or more parts, thereby removing self intersections and / or intersections between the two or more parts, giving rise to a valid printable 3D model.

Owner:3D M T P

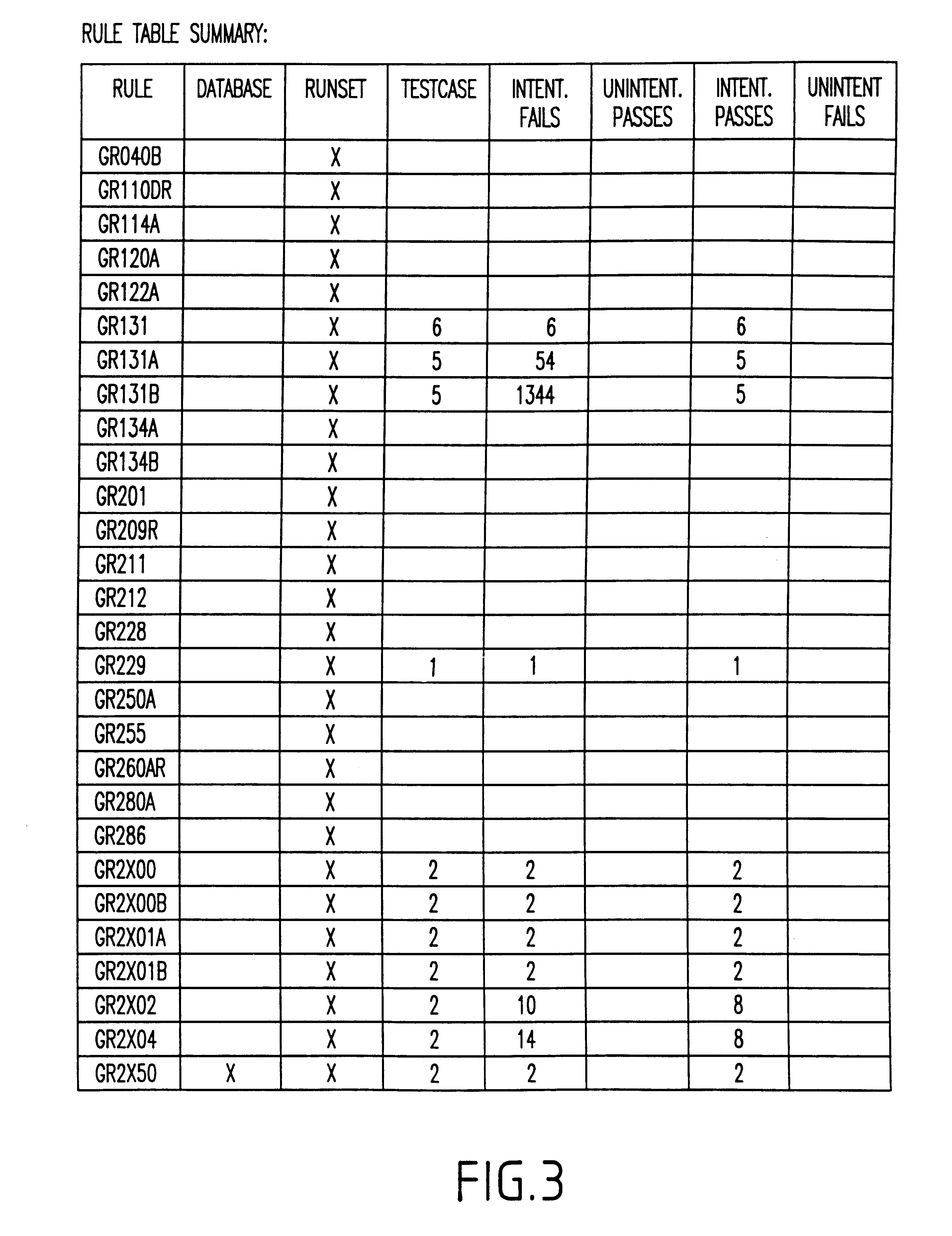

Method for comprehensively verifying design rule checking runsets

InactiveUS6732338B2Extraction of informationComputer aided designSoftware simulation/interpretation/emulationComputer architectureDesign rule checking

A system and method for automatically creating testcases for design rule checking comprises first creating a table with a design rule number, a description, and the values from a design rule manual. Next, any design specific options are derived that affect the flow of the design rule checking, including back end of the line stack options. Then, the design rule values and any design specific options (including back end of the line stack options) are extracted into testcases. Next, the testcases are organized such that there is one library with a plurality of root cells, further comprising one root cell for checking all rules pertaining to the front end of the line, and another root cell for checking design specific options including back end of the line stack options. Finally, the DRC runset is run against the testcases to determine if the DRC runset provides for design rule checking.

Owner:IBM CORP

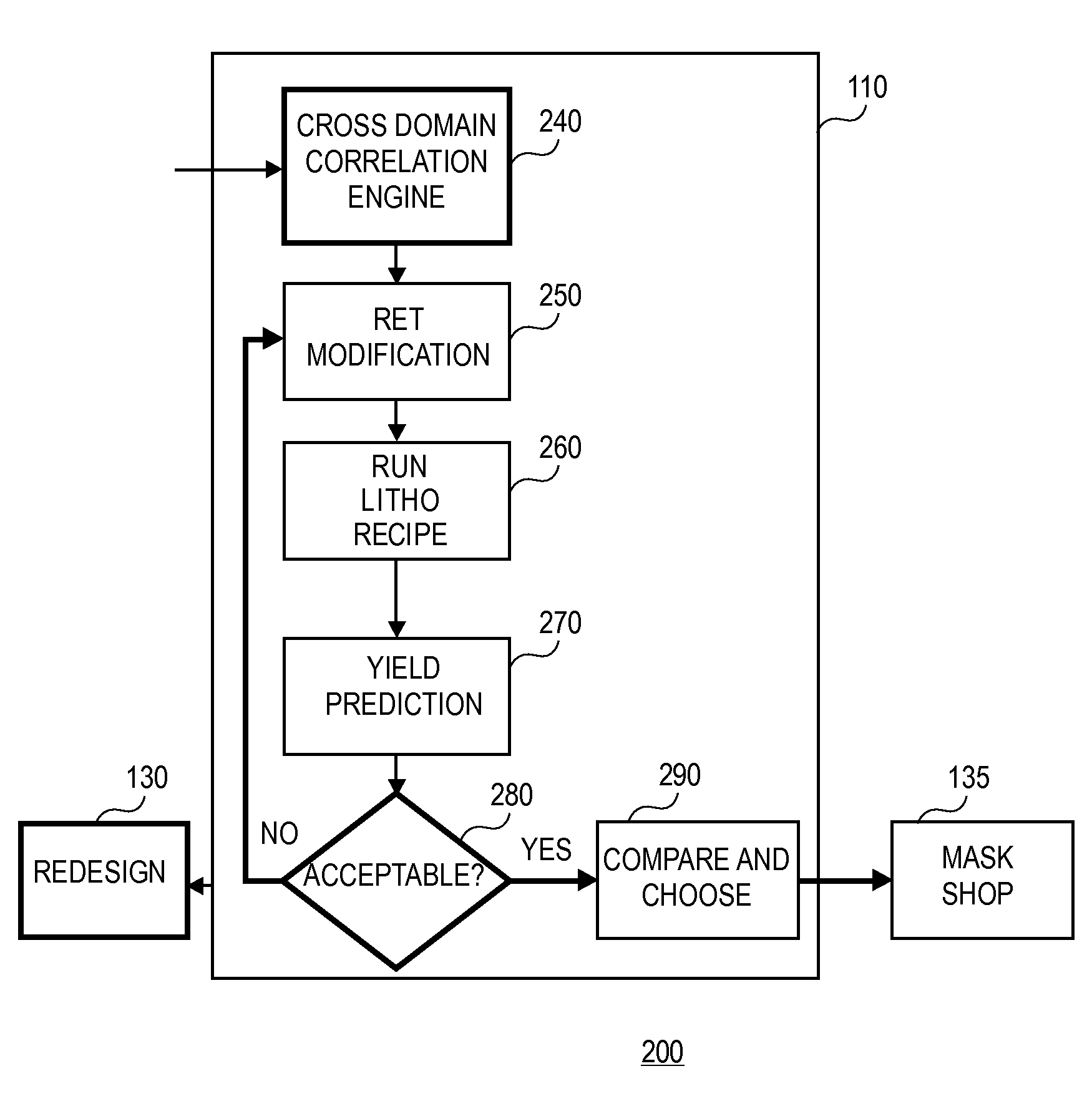

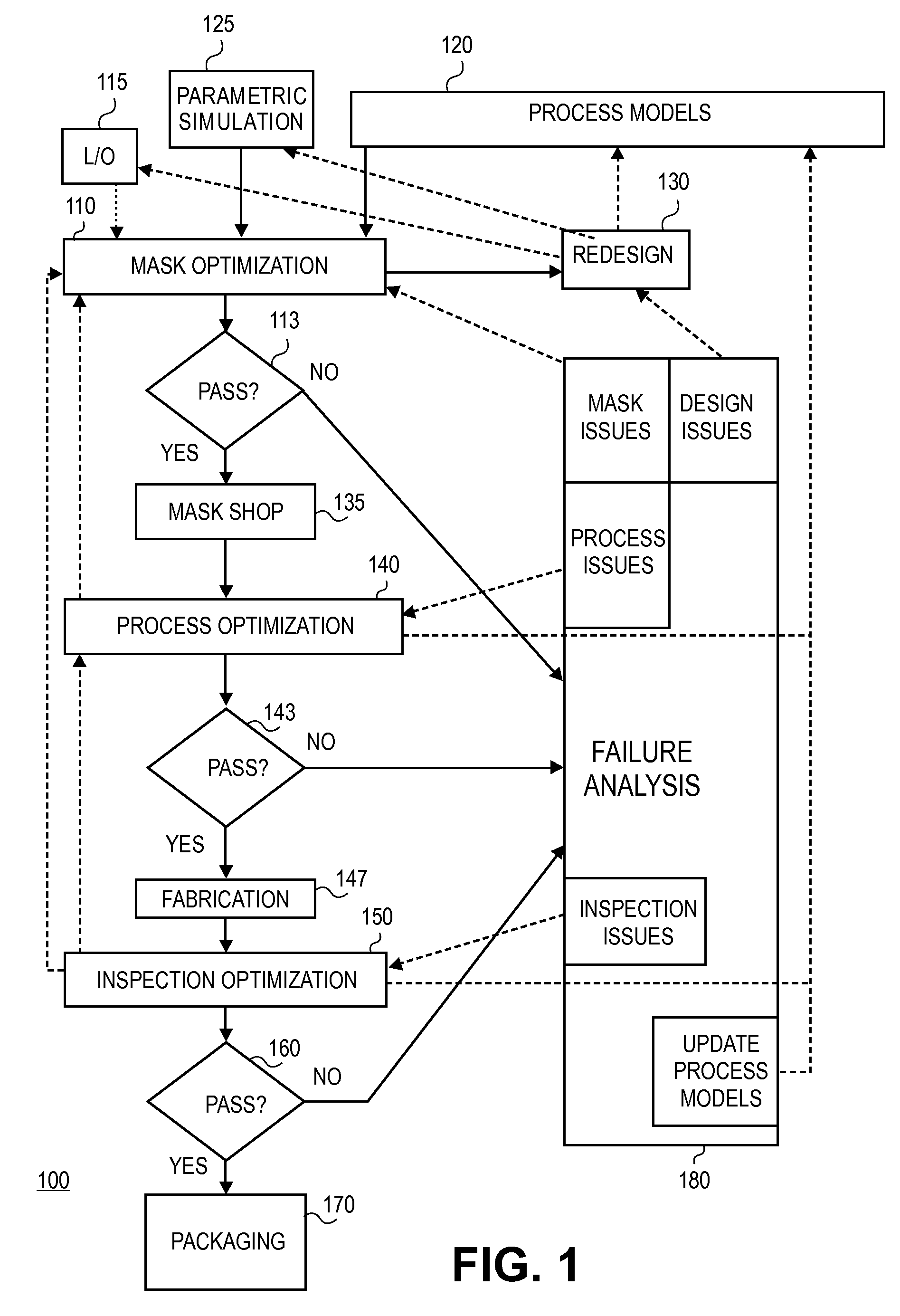

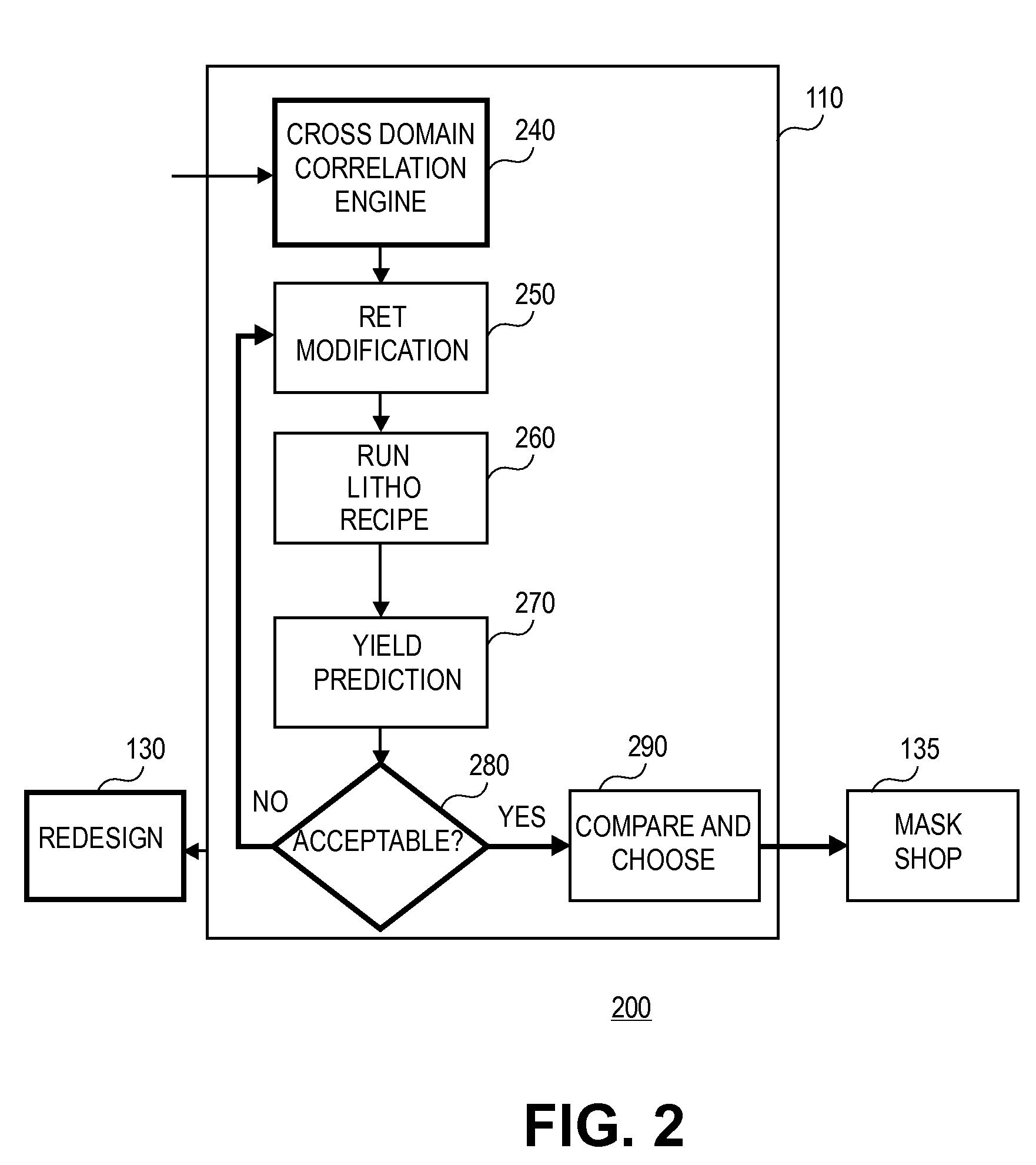

Method and system for mask optimization

ActiveUS20080148216A1Originals for photomechanical treatmentComputer aided designProcess engineering

Owner:CADENCE DESIGN SYST INC

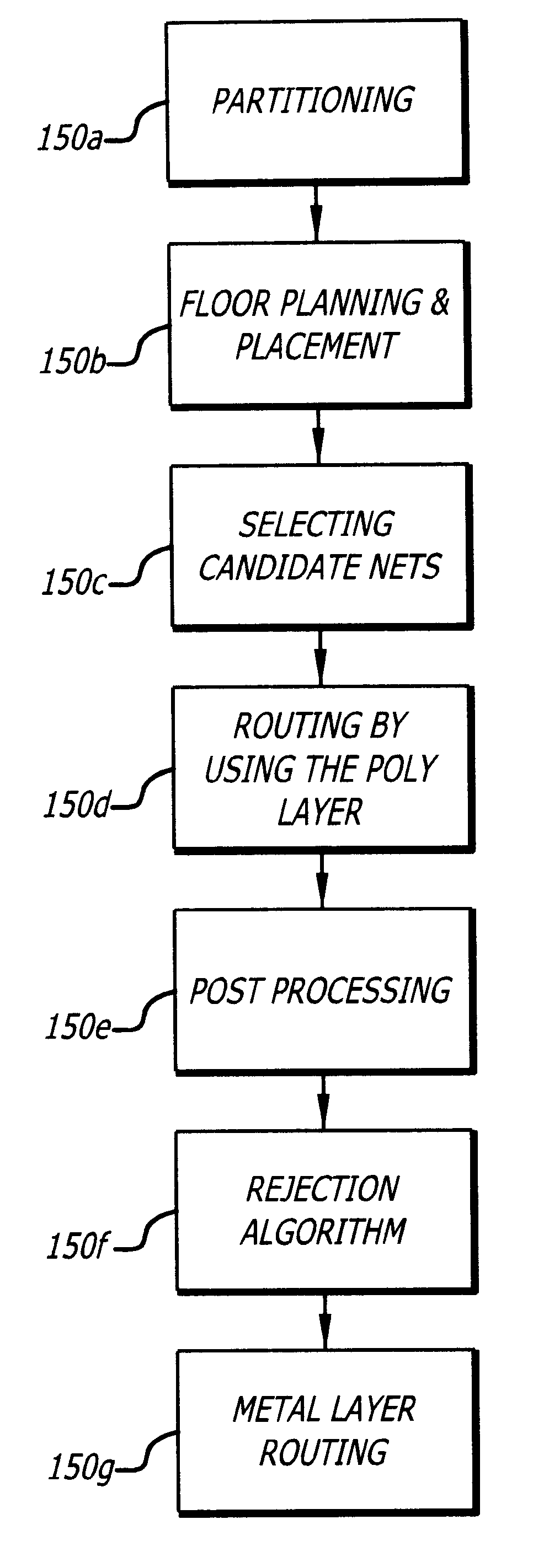

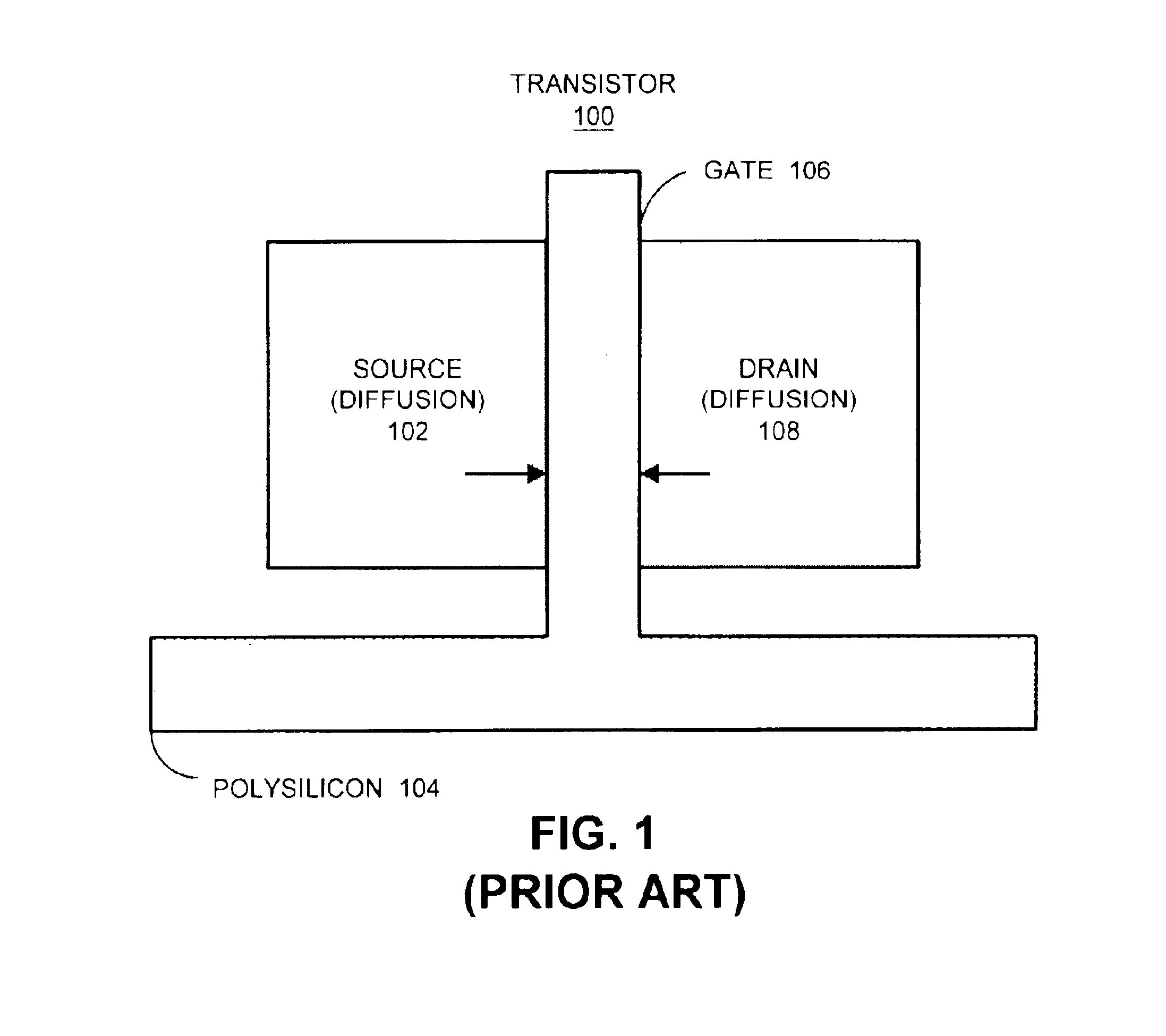

Poly routing for chip interconnects with minimal impact on chip performance

InactiveUS6240542B1Computer aided designSoftware simulation/interpretation/emulationFilter algorithmNetlist

Methods for using the polysilicon layer to route the cells in the ASIC are disclosed. The poly layer of an IC chip is used for routing chip interconnects with minimal impact on the chip performance by selecting nets in the IC chip based on a predetermined or a desired qualification. A maximum allowable length of the poly layer to be used for chip interconnects is determined based on the intended technology of the chip. A filtering algorithm filters the netlist to provide a set of candidate nets that are suitable for poly layer routing based on the predetermined or desired qualification. A routing tool routes the selected nets that have been selected by the filtering algorithm by using the poly layer. Some of the poly layer routings are further rejected by a post processing step.

Owner:BELL SEMICON LLC

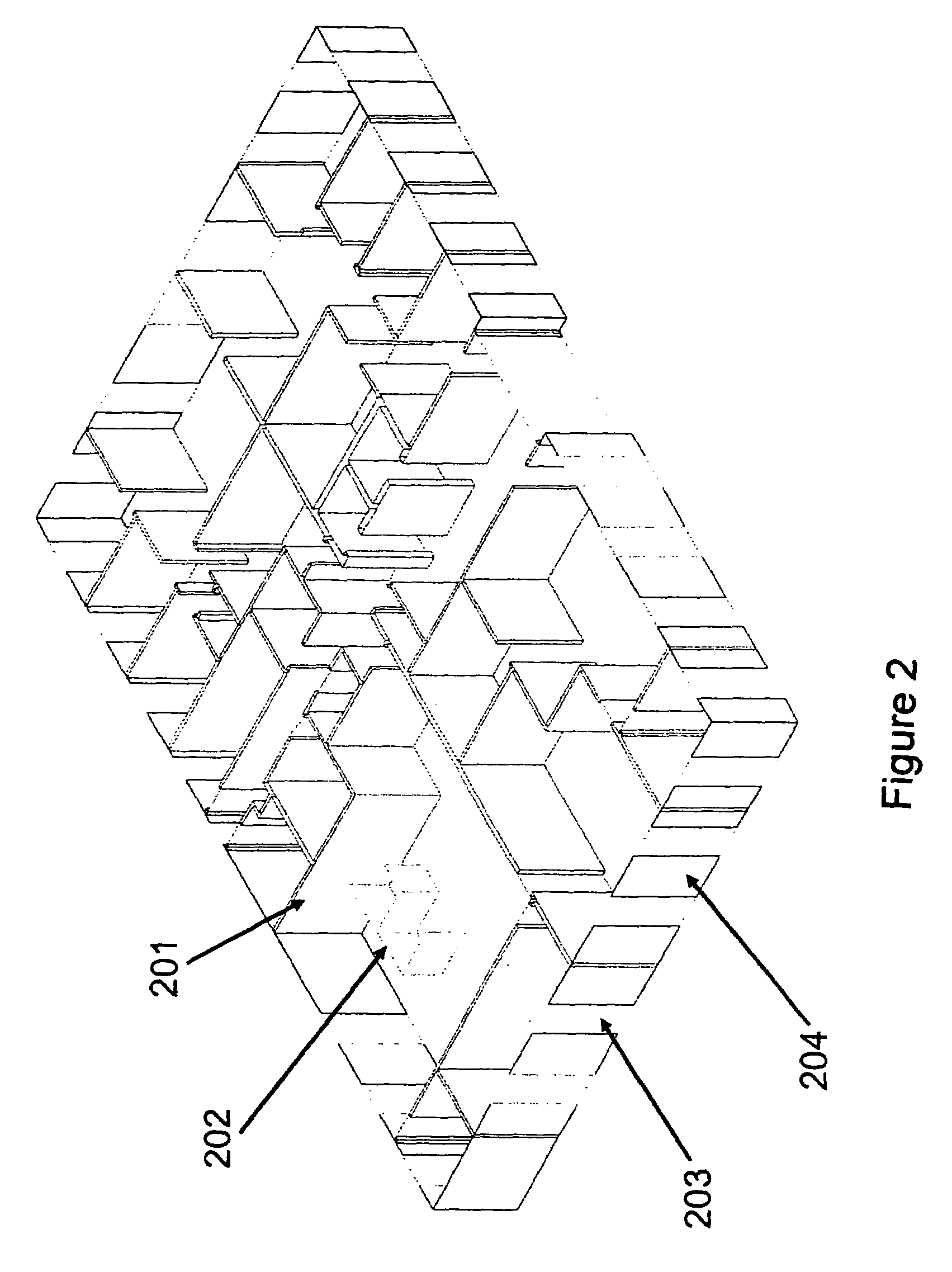

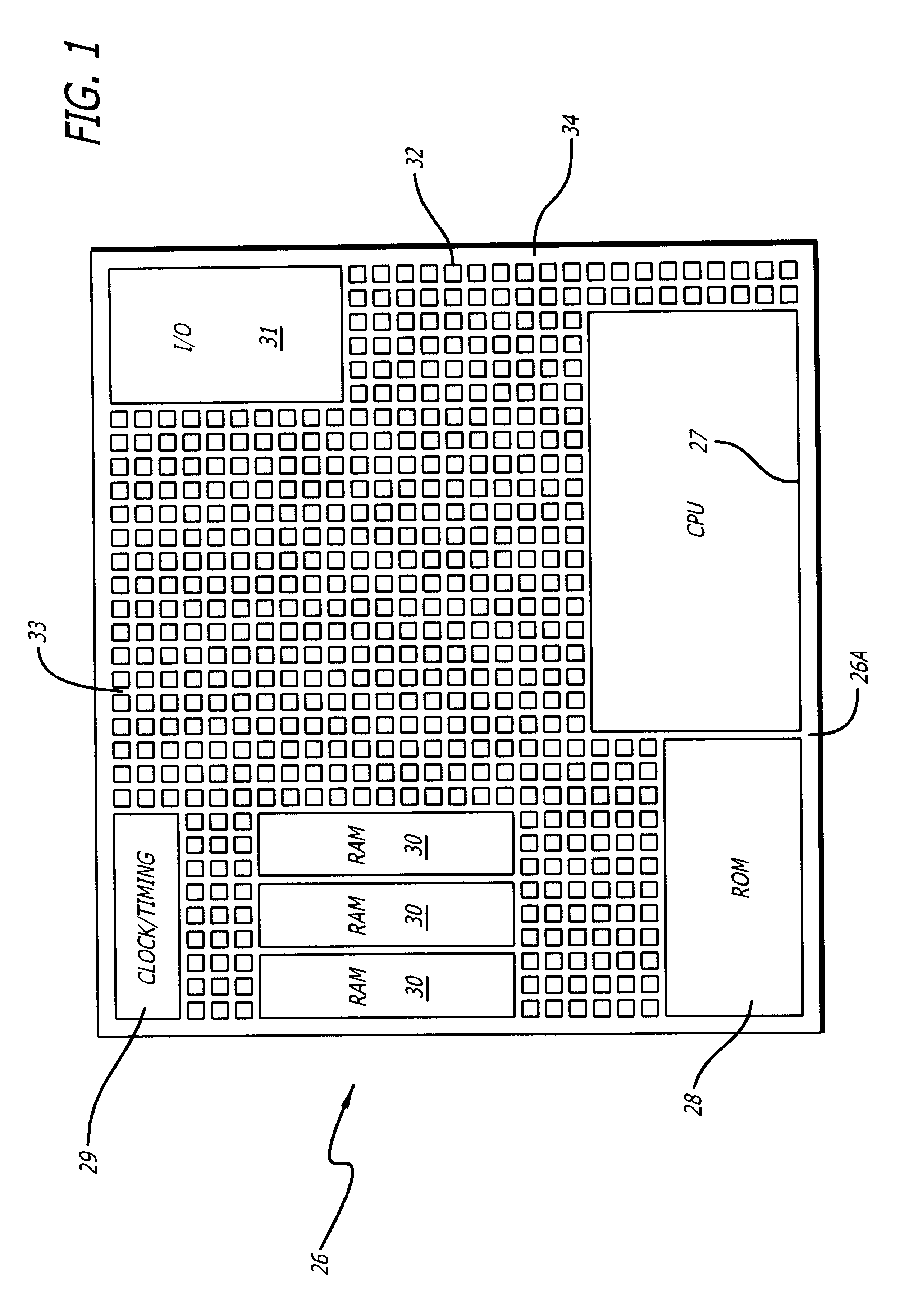

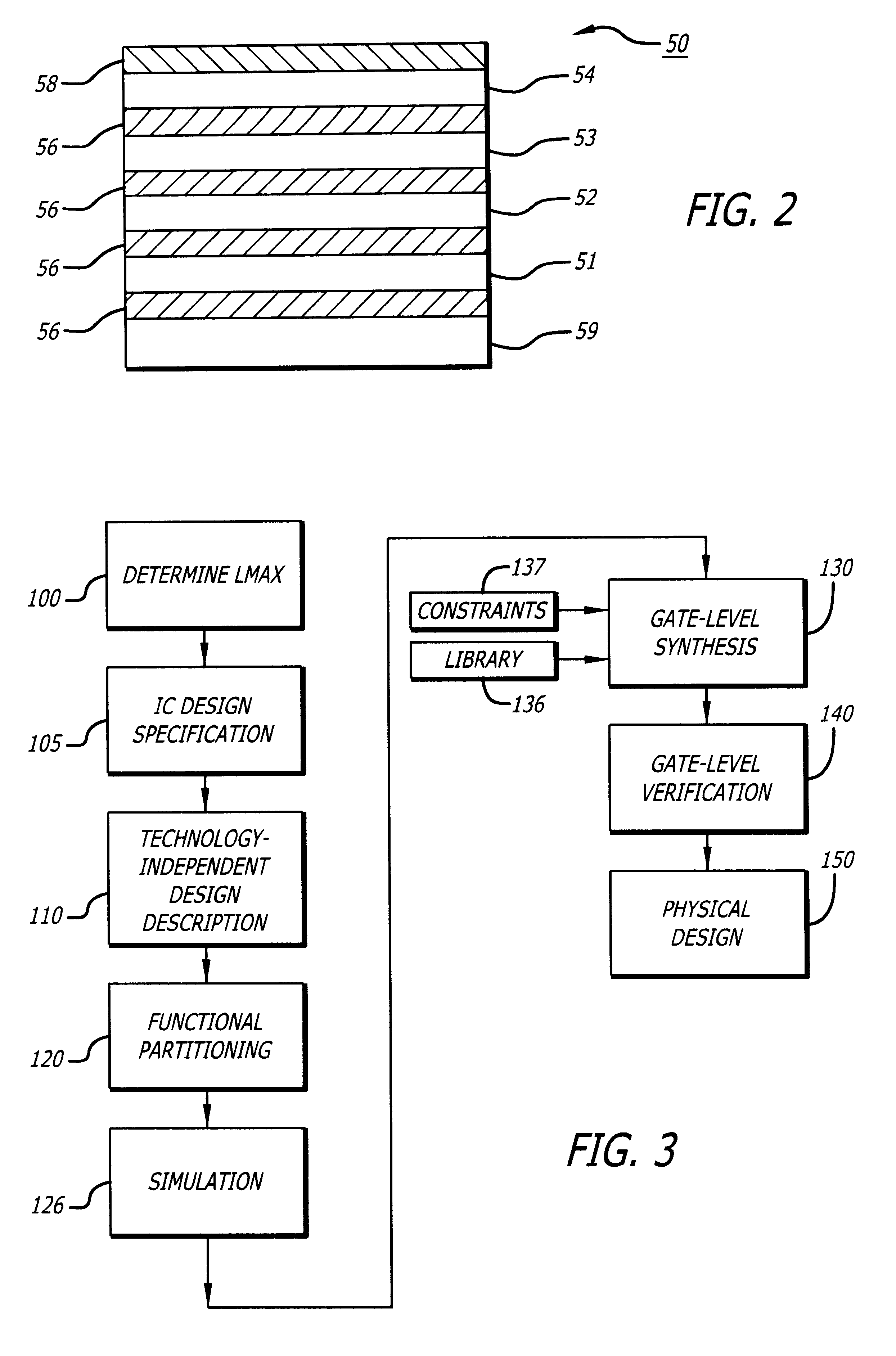

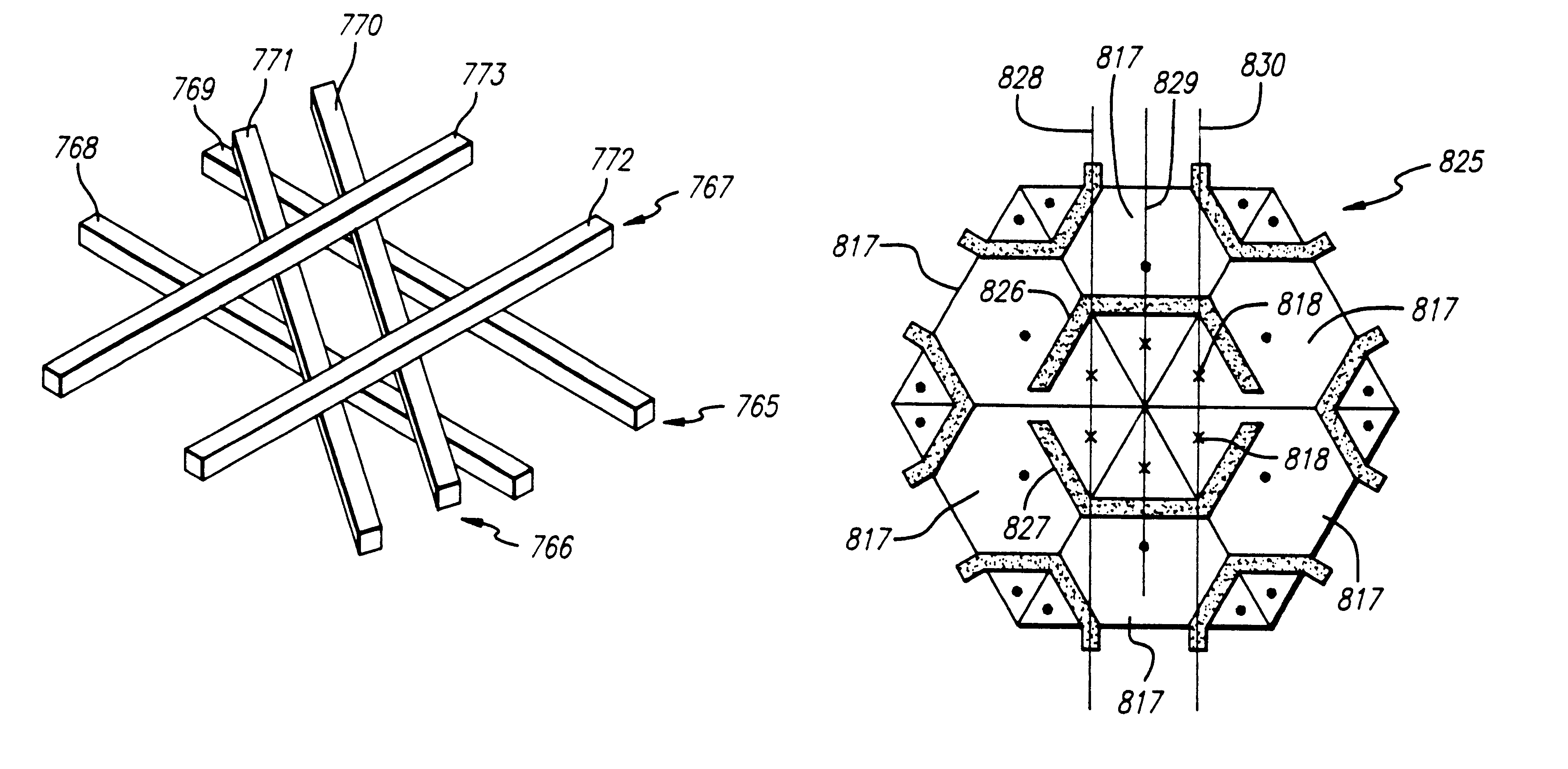

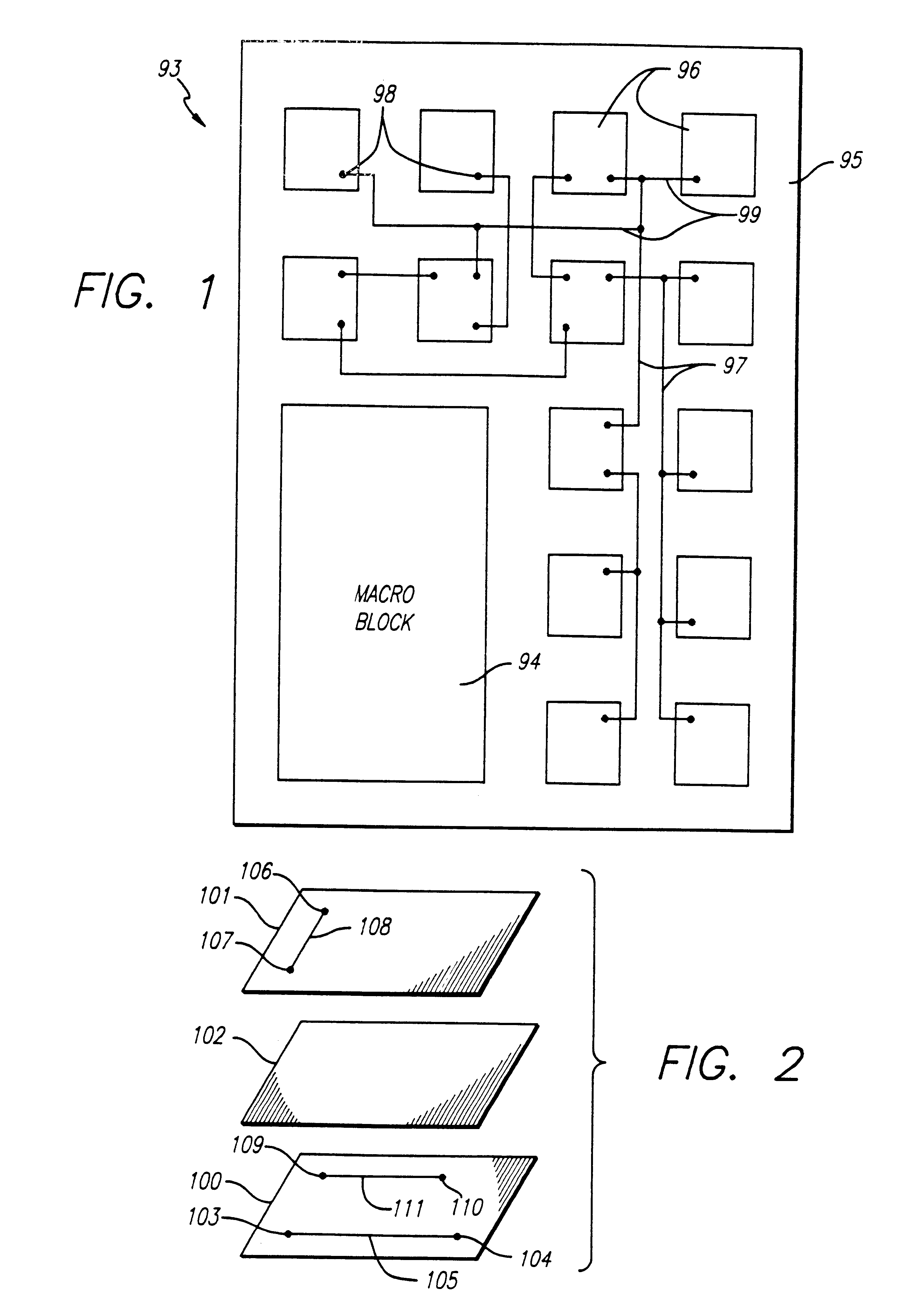

Hexagonal architecture

InactiveUS6407434B1Reduce total wirelength interconnect congestionReduce the numberTransistorSemiconductor/solid-state device detailsCapacitanceElectrical conductor

Several inventions are disclosed. A cell architecture using hexagonal shaped cells is disclosed. The architecture is not limited to hexagonal shaped cells. Cells may be defined by clusters of two or more hexagons, by triangles, by parallelograms, and by other polygons enabling a variety of cell shapes to be accommodated. Polydirectional non-orthogonal three layer metal routing is disclosed. The architecture may be combined with the tri-directional routing for a particularly advantageous design. In the tri-directional routing arraingement, electrical conductors for interconnecting terminals of microelectronic cells of an integrated circuit preferrably extend in three directions that are angularly displaced from each other by 60°. The conductors that extend in the three directions are preferrably formed in three different layers. A method of minimizing wire length in a semiconductor device is disclosed. A method of minimizing intermetal capacitance in a semiconductor device is disclosed. A novel device called a "tri-ister" is disclosed. Triangular devices are disclosed, including triangular NAND gates, triangular AND gates, and triangular OR gates. A triangular op amp and triode are disclosed. A triangular sense amplifier is disclosed. A DRAM memory array and an SRAM memory array, based upon triangular or parallelogram shaped cells, are disclosed, including a method of interconnecting such arrays. A programmable variable drive transistor is disclosed. CAD algorithms and methods are disclosed for designing and making semiconductor devices, which are particularly applicable to the disclosed architecture and tri-directional three metal layer routing.

Owner:BELL SEMICON LLC

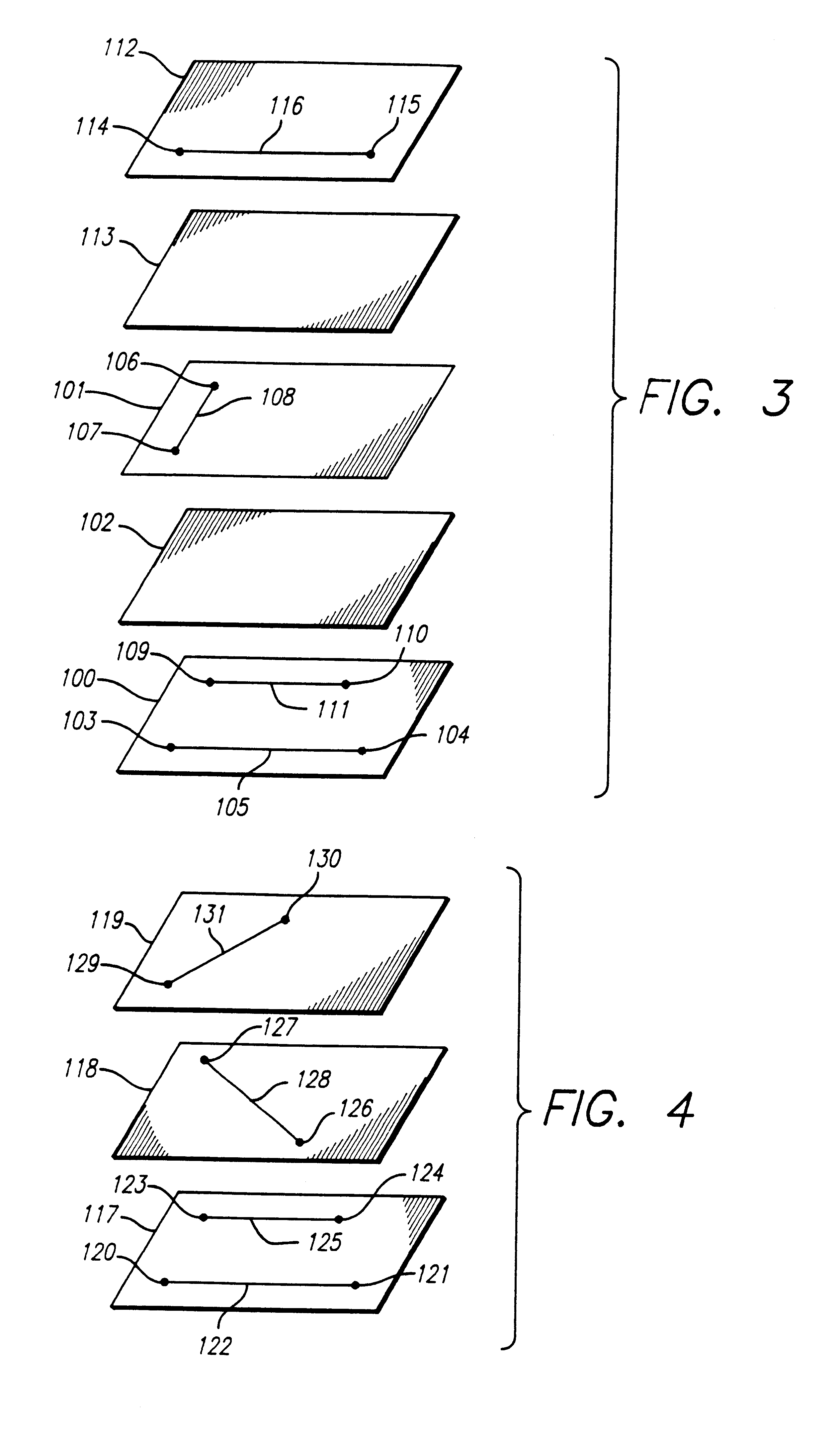

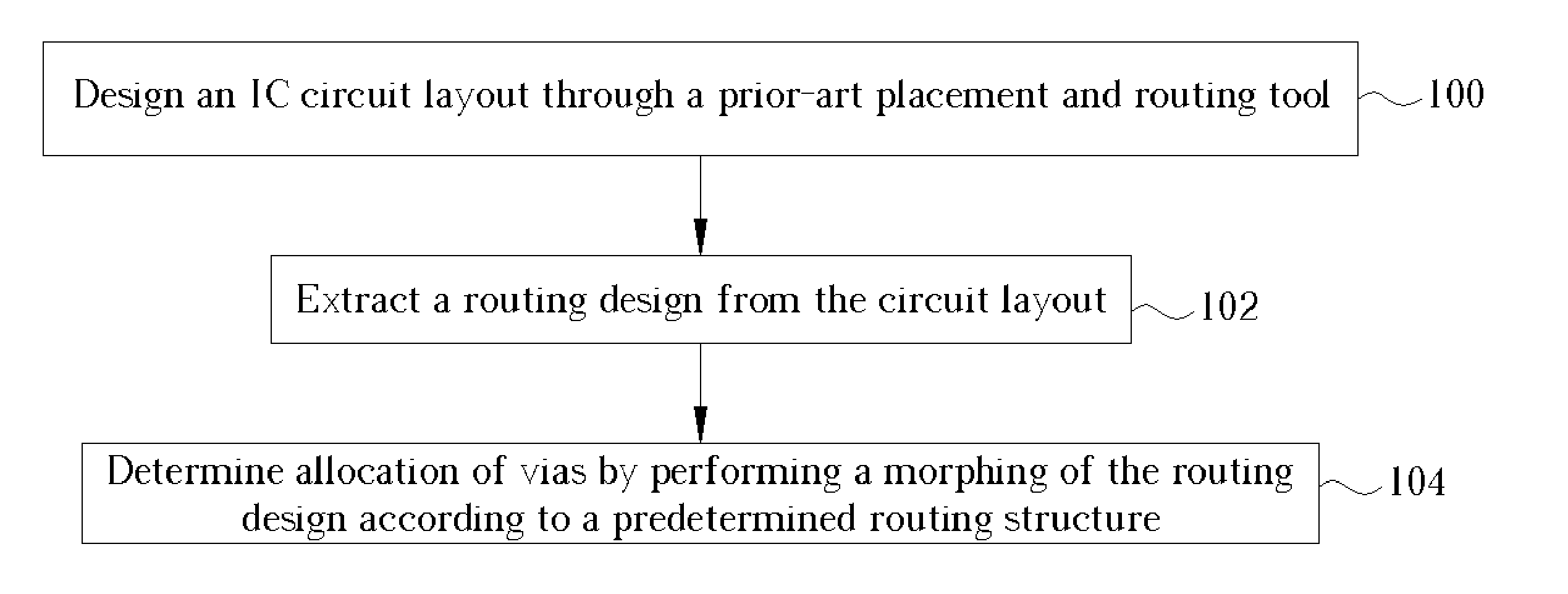

Method for programming a routing layout design through one via layer

ActiveUS20050055828A1Avoid feesPrinted circuit assemblingLine/current collector detailsComputer science

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

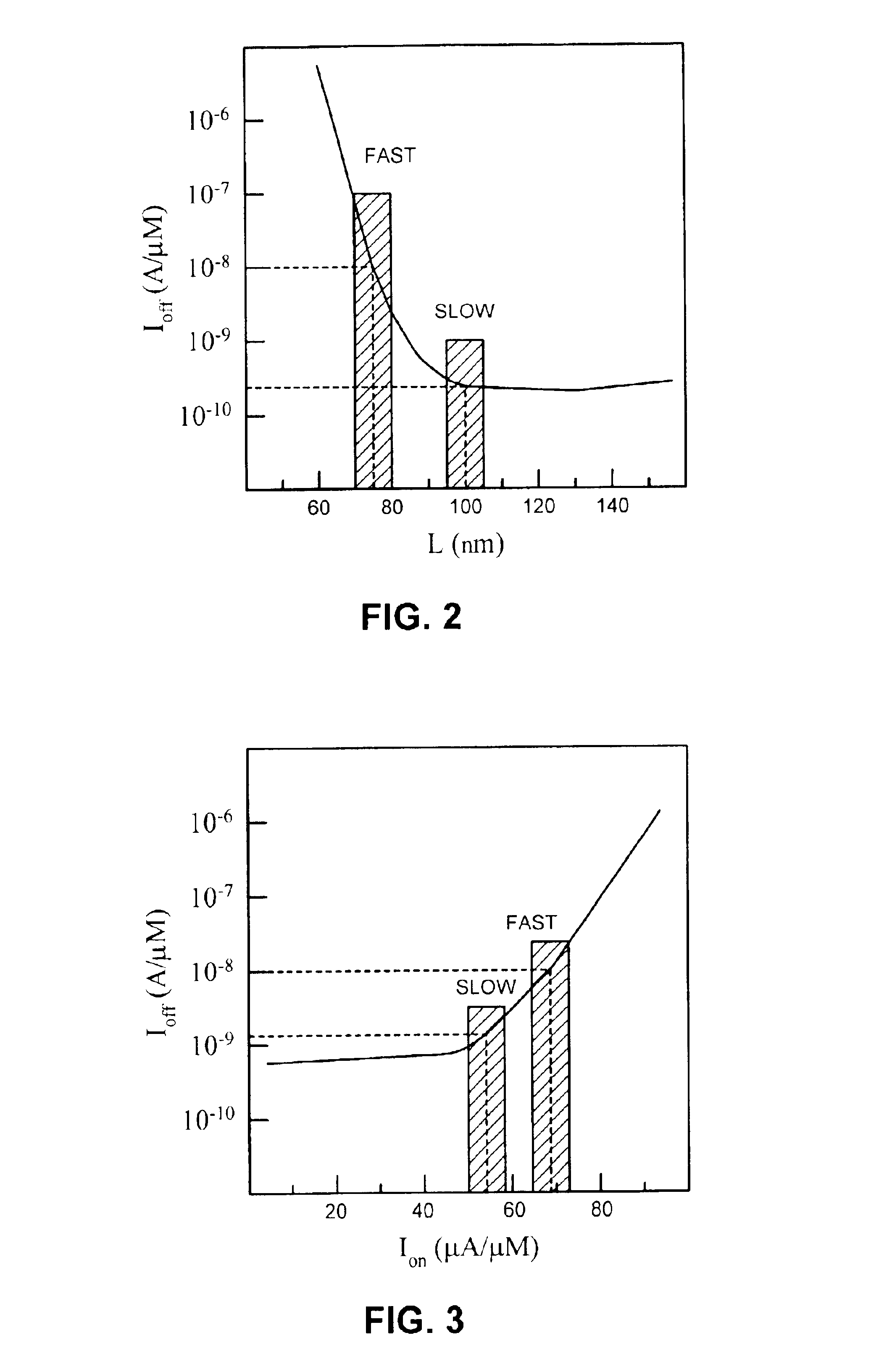

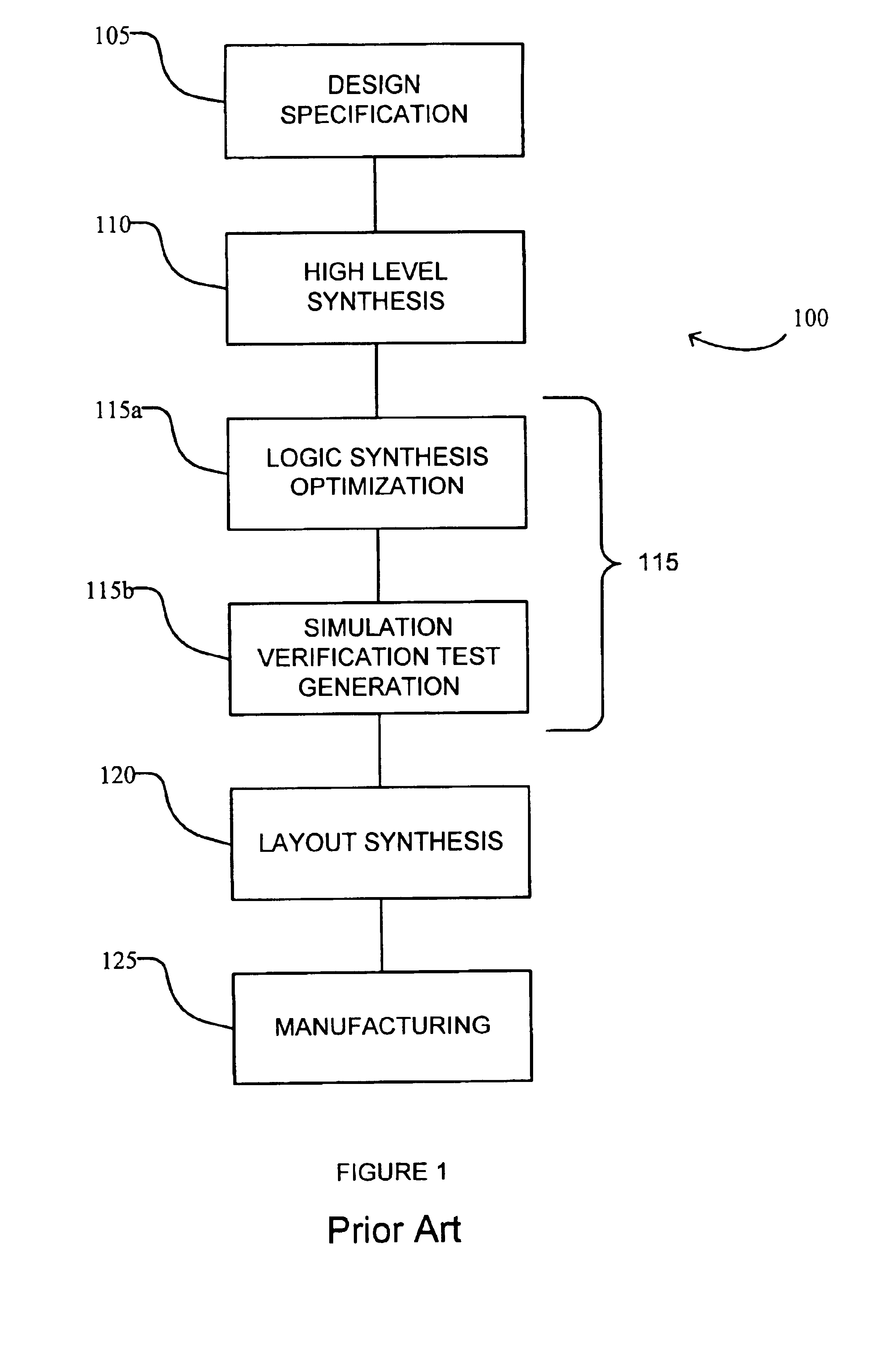

Selectively applying resolution enhancement techniques to improve performance and manufacturing cost of integrated circuits

InactiveUS6928635B2Reduce delaysReduction of gate lengthSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingResolution enhancement technologiesImage resolution

One embodiment of the present invention provides a system that applies resolution enhancement techniques (RETs) selectively to a layout of an integrated circuit. Upon receiving the layout of the integrated circuit, the system identifies a plurality of critical regions within the layout based on an analysis of one or more of, timing, dynamic power, and off-state leakage current. The system then performs a first set of aggressive RET operations on the plurality of critical regions. The system also performs a second set of less aggressive RET operations on other non-critical regions of the layout.

Owner:SYNOPSYS INC

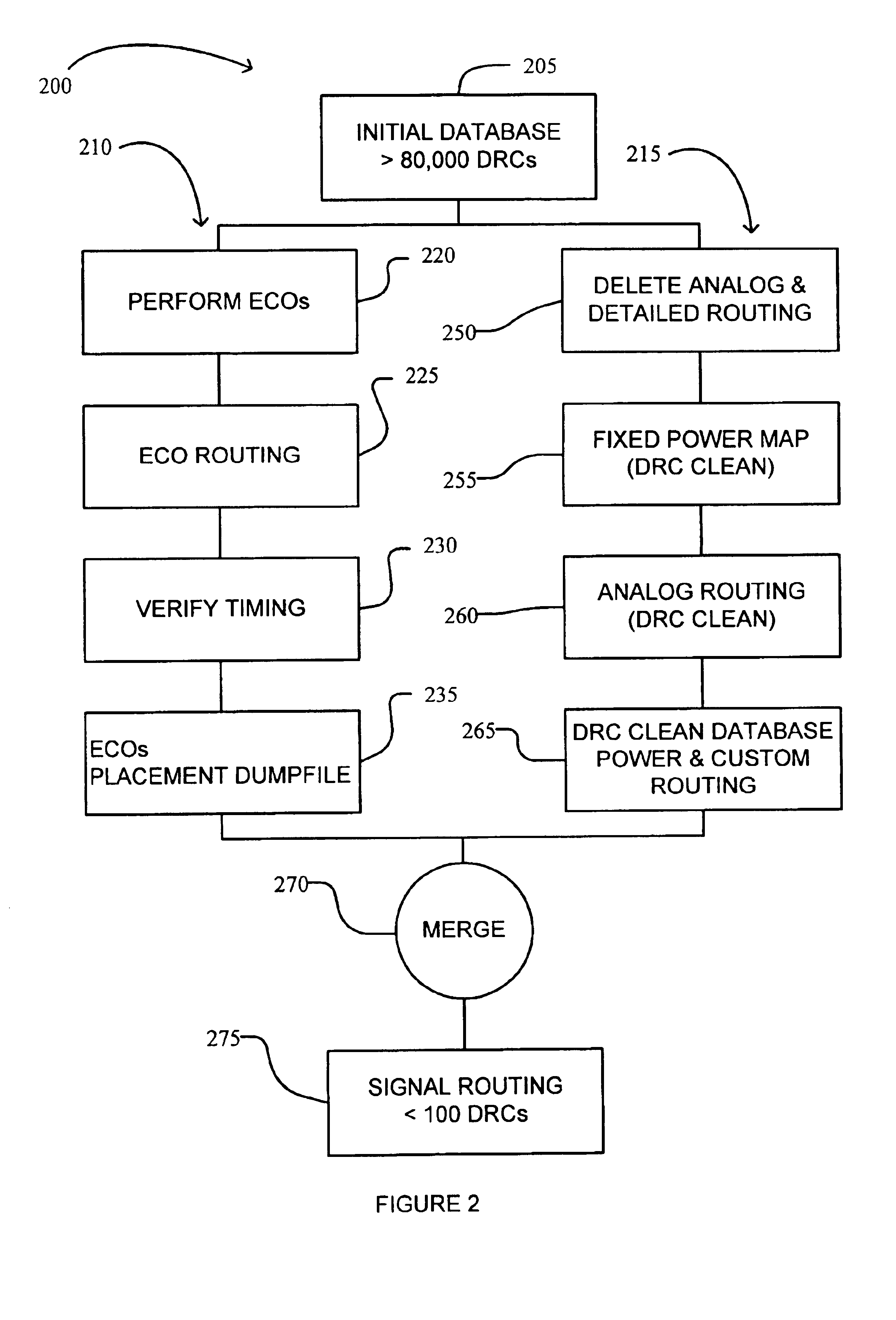

Split and merge design flow concept for fast turnaround time of circuit layout design

ActiveUS6898770B2Increase turnaround timeAccurate verificationComputer aided designSoftware simulation/interpretation/emulationSufficient timeTurnaround time

A method and system is disclosed to improve the turnaround time to provide adequate time to meet project schedules in the event that adjustments or modifications to the design are necessary. A method for improving a turnaround time for design verification of a process database representing a semiconductor design includes the steps of (a) deriving a timing database and a (DNE) database from the process database; (b) performing, using the timing database, one or more design changes and one or more timing verifications and corrections to generate a modified timing database; (c) initiating, using the process database, physical validation of the semiconductor design prior to completion of step (b) to generate a modified DNE database; (d) merging the modified timing database with the modified DNE database to form a modified process database; and (e) performing, using the modified process database, one or more design verification checks of the semiconductor design.

Owner:BELL SEMICON LLC

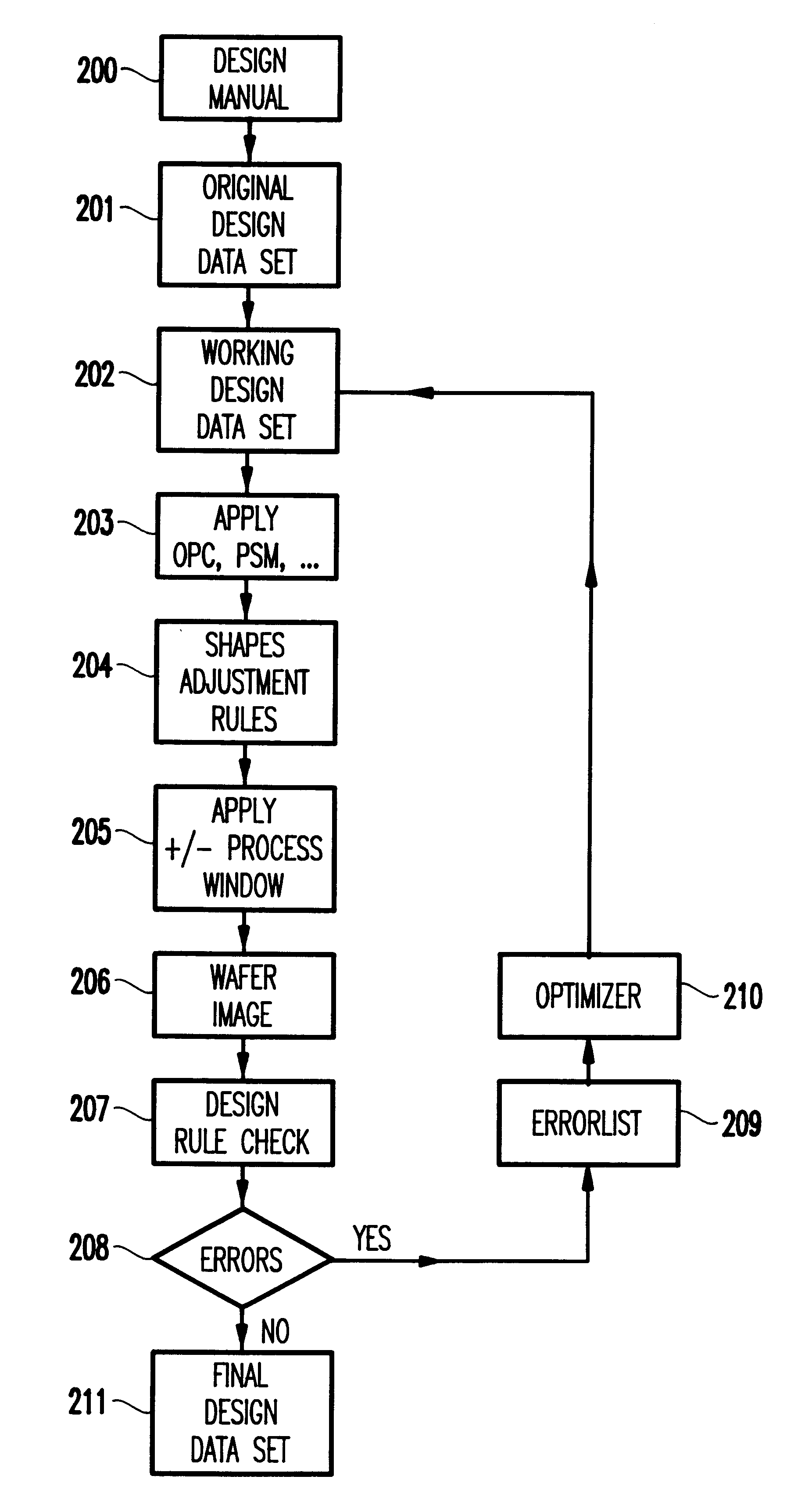

Auto correction of error checked simulated printed images

A method and computer system are provided for checking integrated circuit designs for design rule violations. The method may include generating a working design data set, creating a wafer image data set, comparing the wafer image data set to the design rules to produce an error list and automatically altering the working design data set when the comparing indicates a design rule violation. The method further automatically repeats the creating, the comparing and the automatically altering until no design rule violations occur or no solution to the errors exists.

Owner:IBM CORP

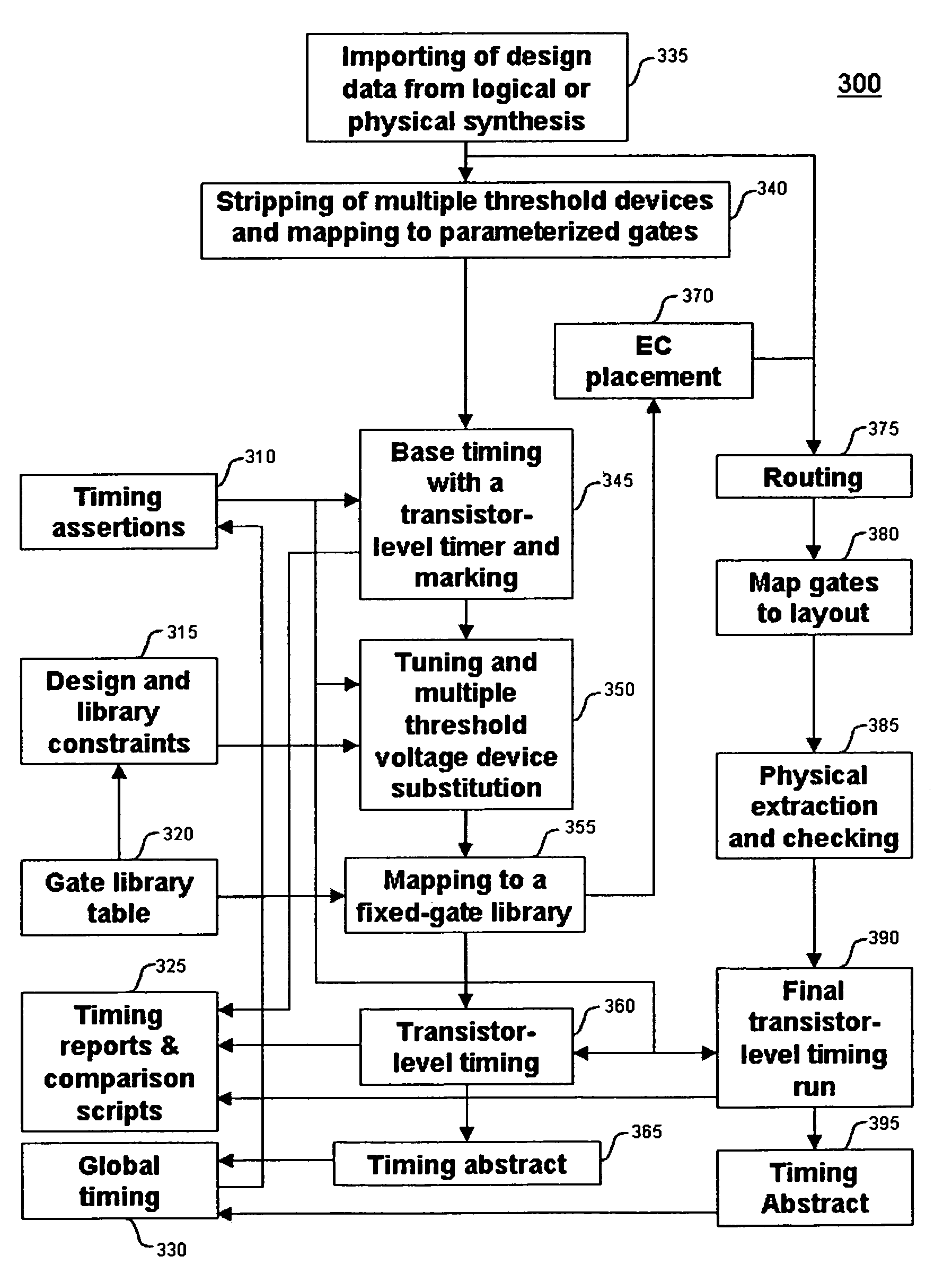

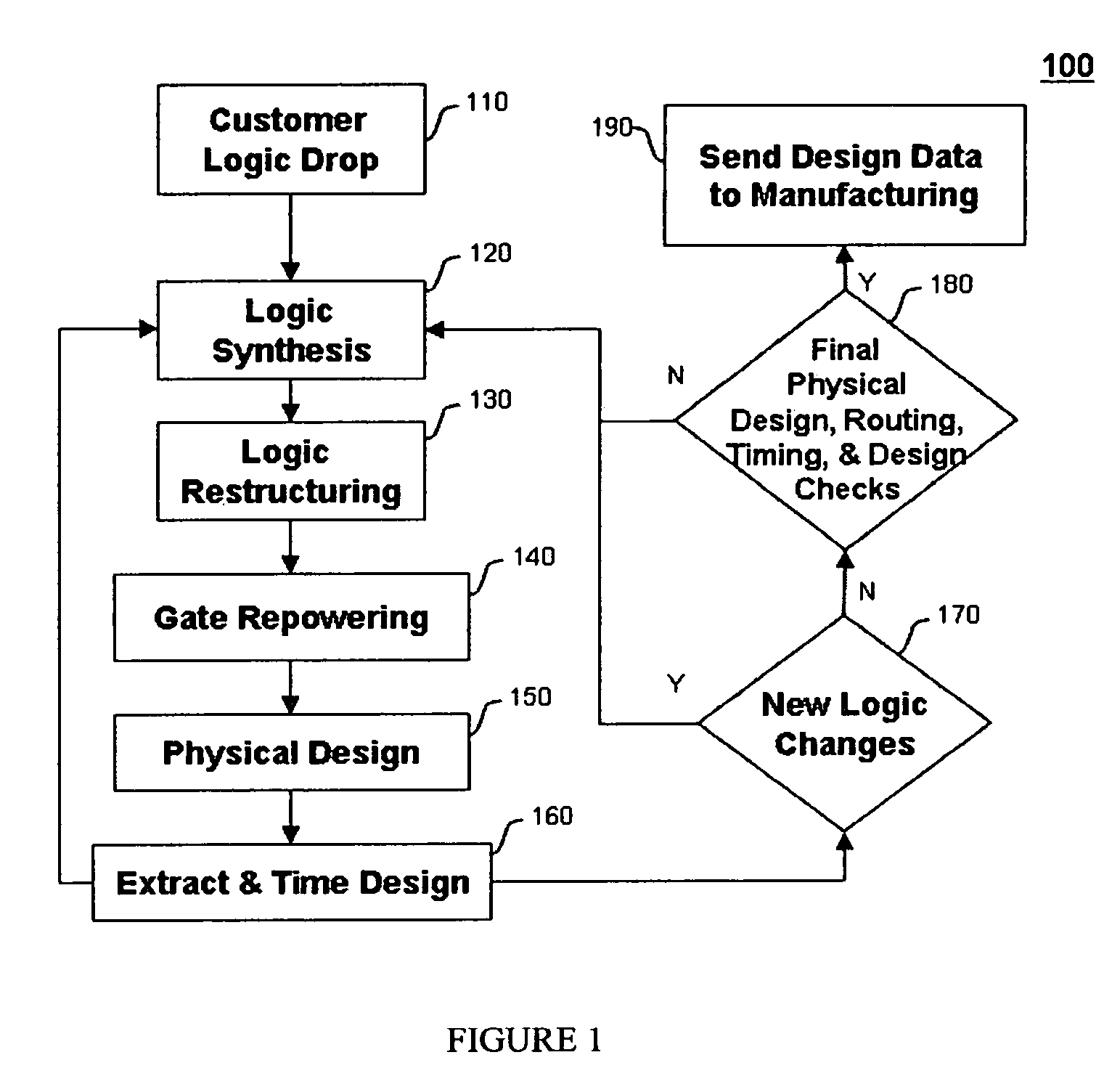

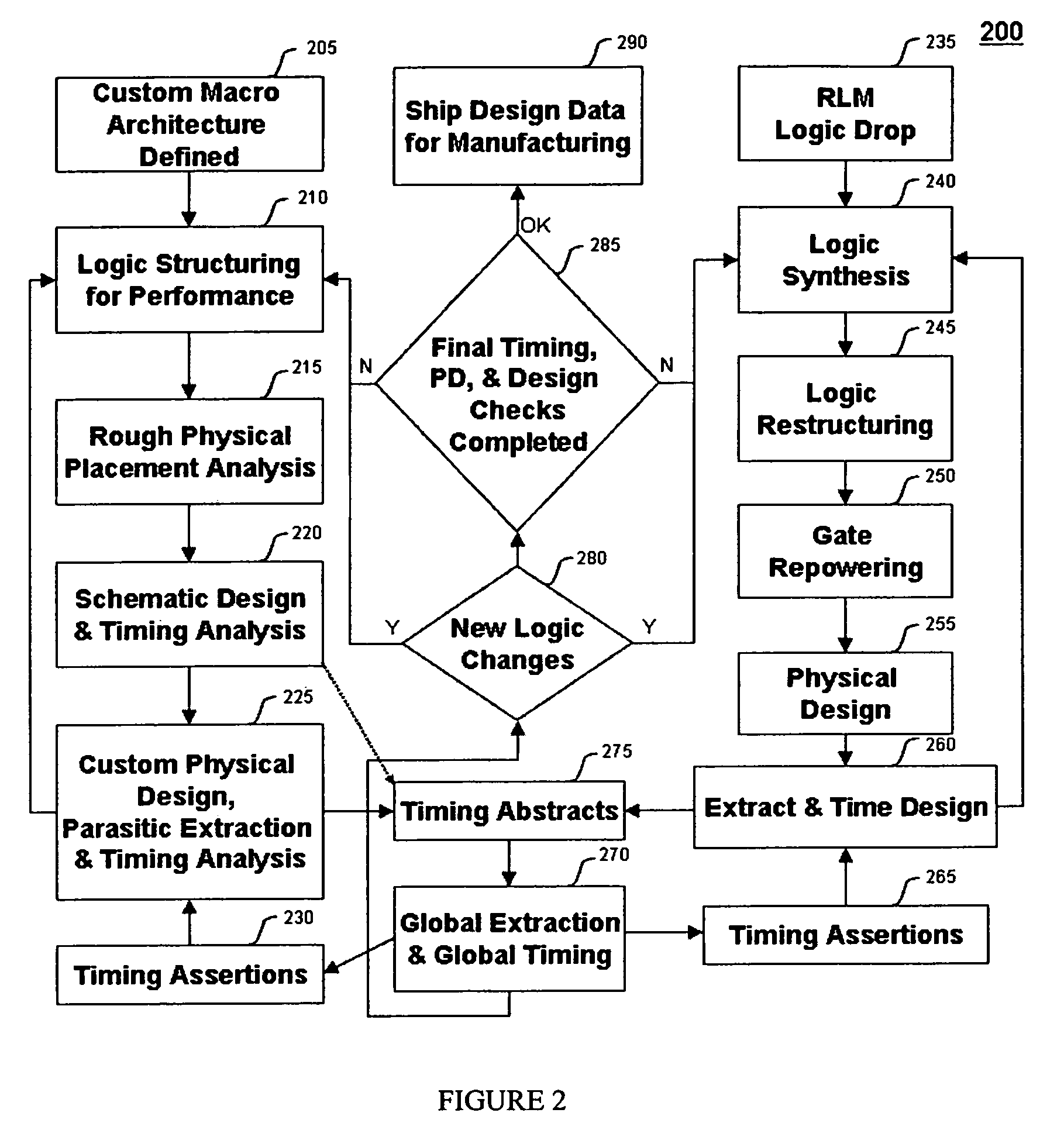

Method for tuning a digital design for synthesized random logic circuit macros in a continuous design space with optional insertion of multiple threshold voltage devices

InactiveUS7093208B2Efficient and effective methodologyError minimizationDigital storageComputer aided designContinuous designCritical section

A Digital Design Method which may be automated is for obtaining timing closure in the design of large, complex, high-performance digital integrated circuits. The methodincludes the use of a tuner on random logic macros that adjusts transistor sizes in a continuous domain. To accommodate this tuning, logic gates are mapped to parameterized cells for the tuning and then back to fixed gates after the tuning. Tuning is constrained in such a way as to minimize “binning errors” when the design is mapped back to fixed cells. Further, the critical sections of the circuit are marked in order to make the optimization more effective and to fit within the problem-size constraints of the tuner. A specially formulated objective function is employed during the tuning to promote faster global timing convergence, despite possibly incorrect initial timing budgets. The specially formulated objective function targets all paths that are failing timing, with appropriate weighting, rather than just targeting the most critical path. Finally, the addition of multiple threshold voltage gates allows for increased performance while limiting leakage power.

Owner:GLOBALFOUNDRIES INC

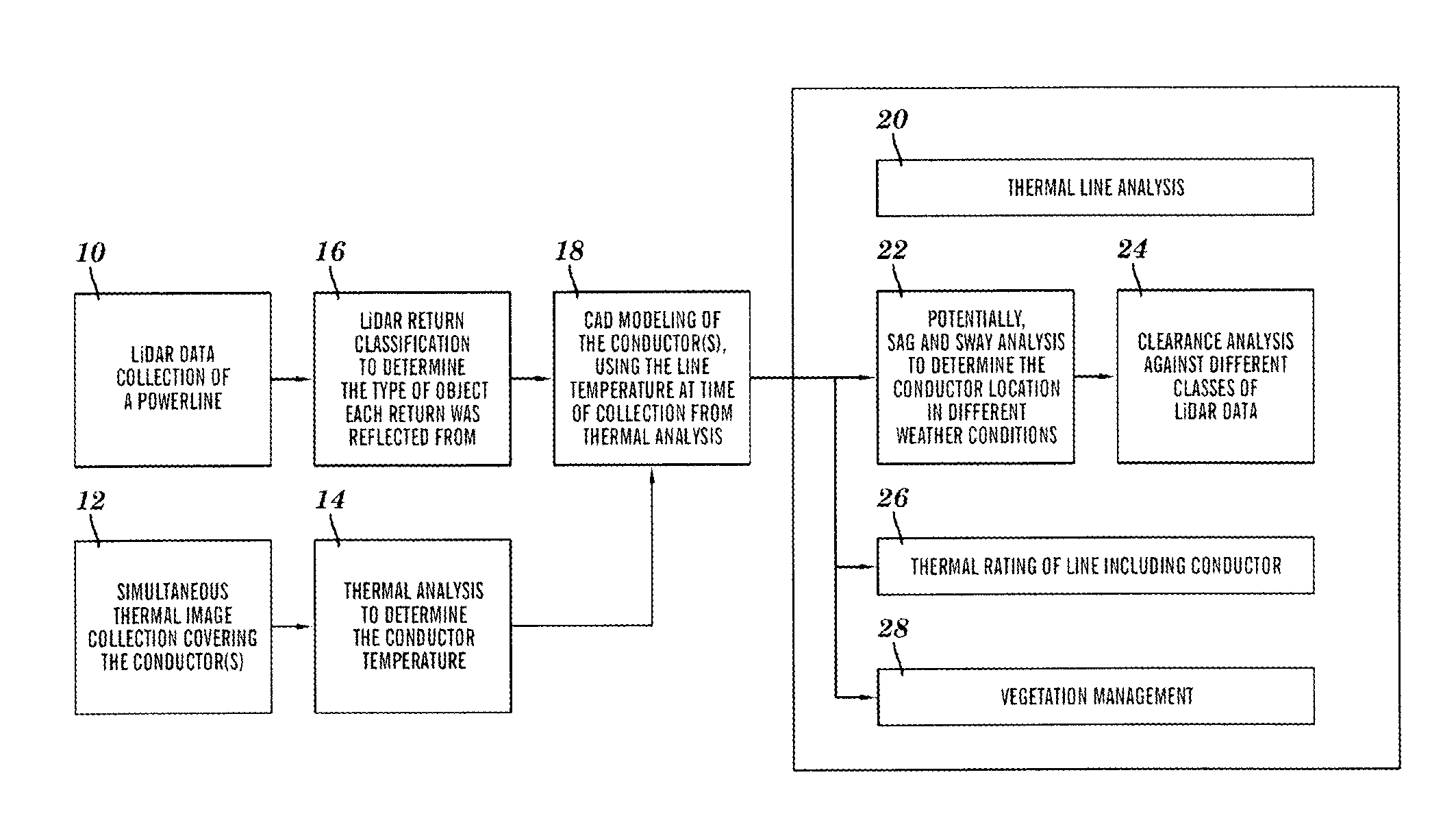

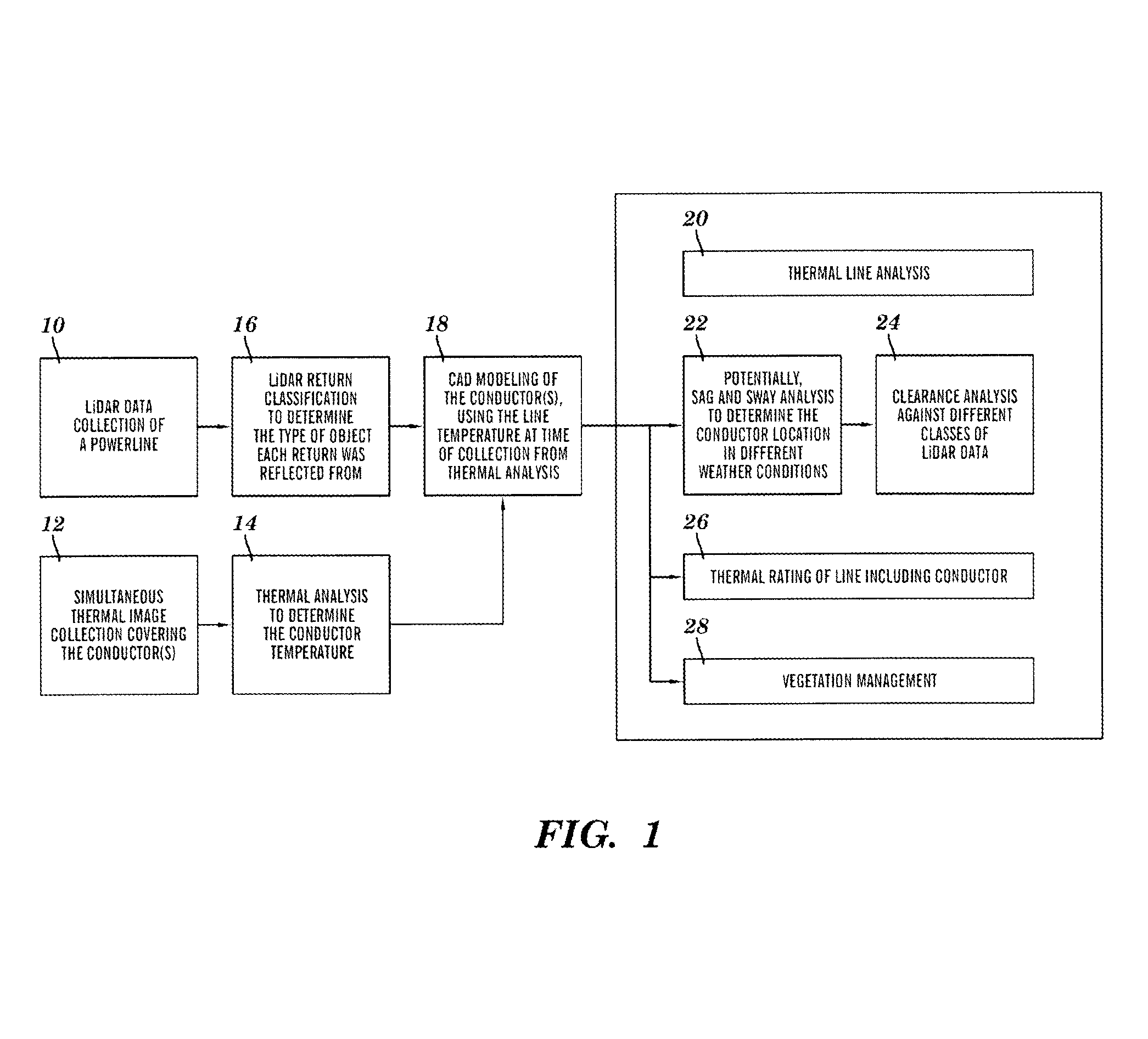

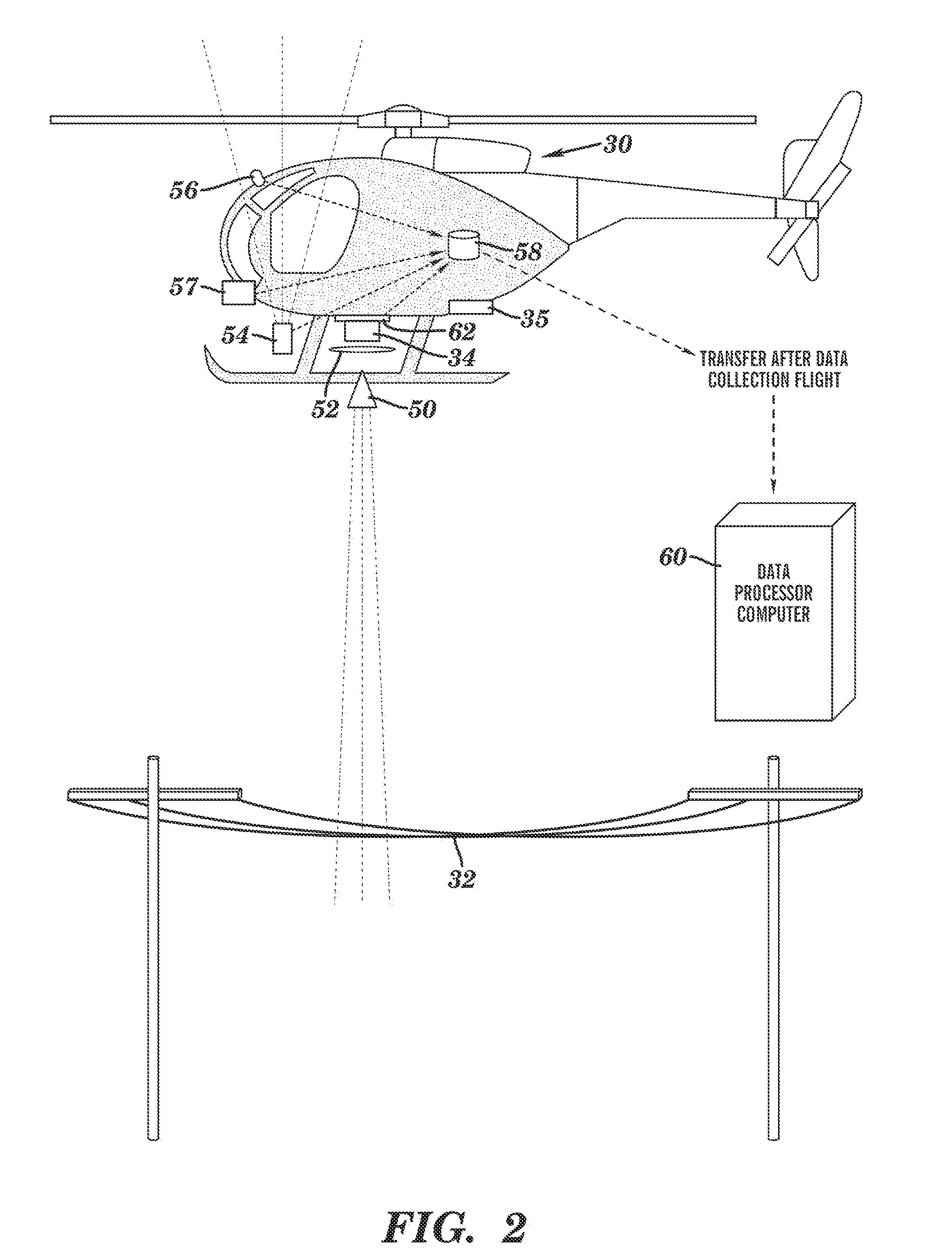

Thermal powerline rating and clearance analysis using thermal imaging technology

ActiveUS8374821B2Minimize impactThermometer detailsOverhead installationVegetationElectrical conductor

A method and apparatus are provided to acquire direct thermal measurements, for example, from a LiDAR collecting vehicle or air vessel, of an overhead electrical conductor substantially simultaneous with collection of 3-dimensional location data of the conductor, and utilize temperature information derived from the direct thermal measurements in line modeling, line rating, thermal line analysis, clearance analysis, and / or vegetation management.

Owner:HUDSON POWER TECH LLC

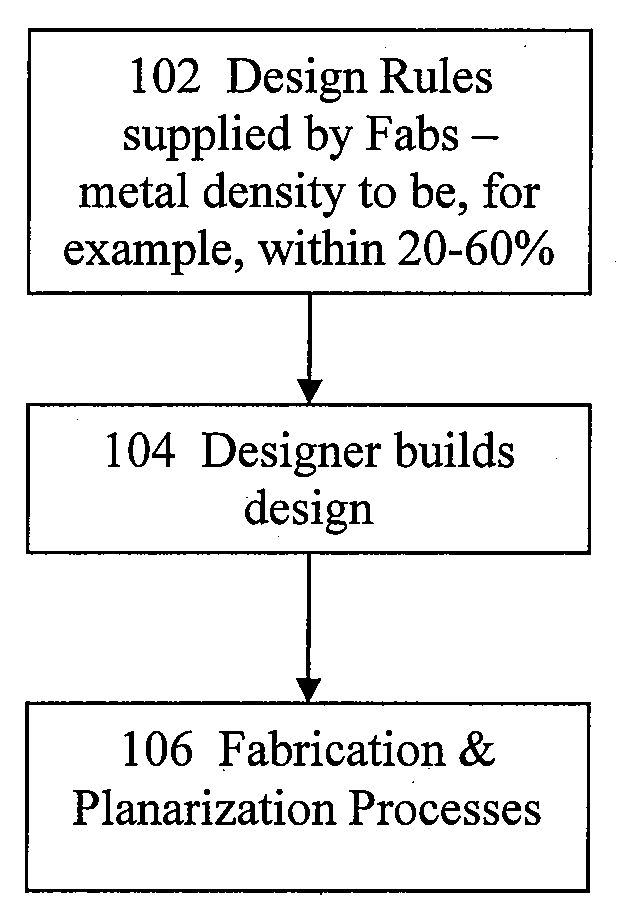

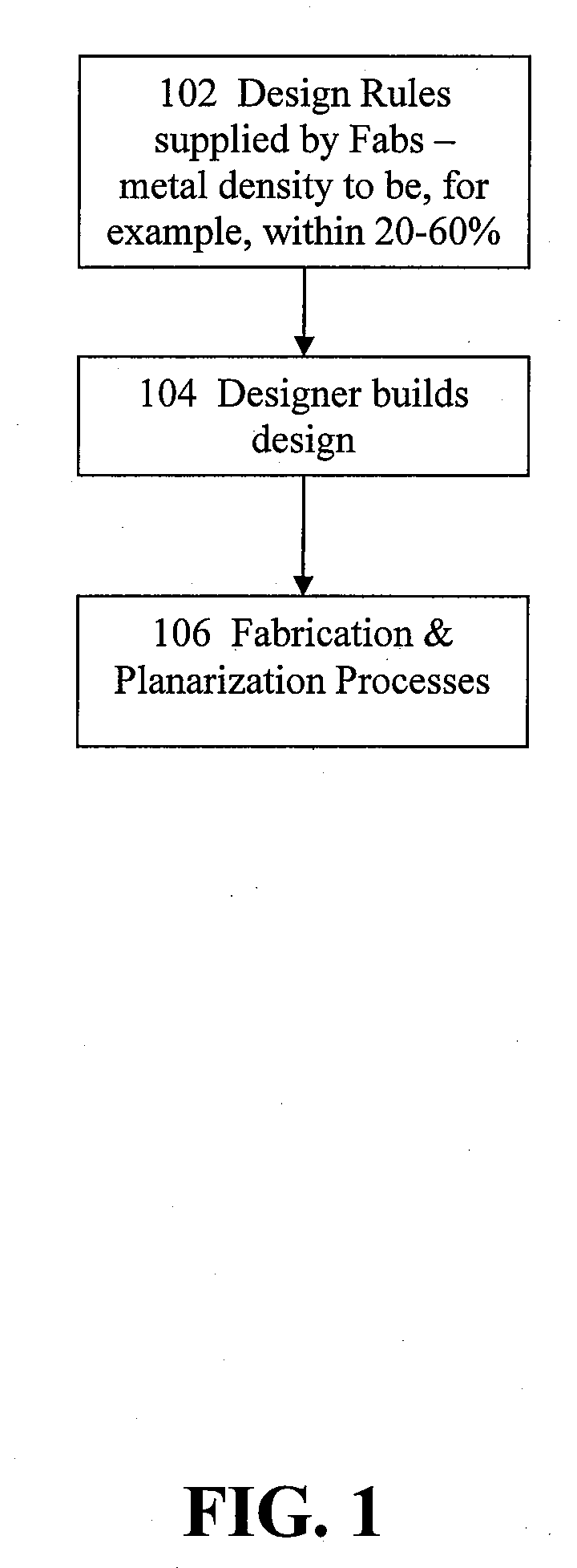

Supplant design rules in electronic designs

ActiveUS20080163141A1Interaction be complexComputer aided designSoftware simulation/interpretation/emulationFoundryComputer architecture

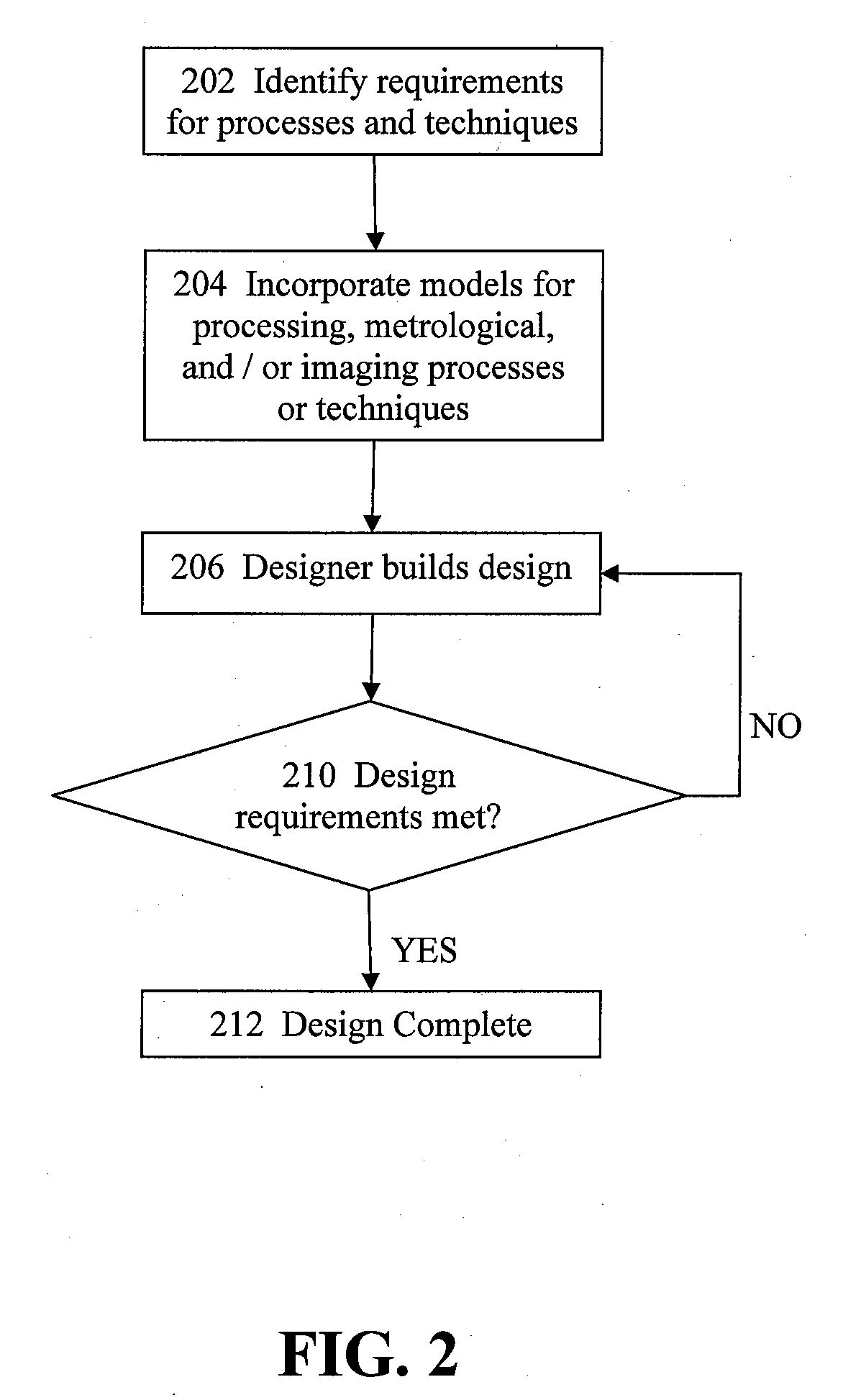

Disclosed is an improved method, system, and computer program product for electronic designs with supplant design rules. According to some embodiments of the invention, the foundry-imposed design rules are replaced by one or more supplant design requirements which define absolute or relative threshold(s) for a design feature characteristic. Some other embodiments of the invention, the foundry-imposed design rules are replaced by one or more supplant design requirements which define one or more ranges of absolute or relative values for a design feature characteristic. Some other embodiments of the invention further provide an EDA tool which takes into account a model for the electronic design, the processing, metrological, lithographic, or imaging processing processes or techniques, and the supplant design requirements to determine whether the features of an electronic design meet the design requirements.

Owner:CADENCE DESIGN SYST INC

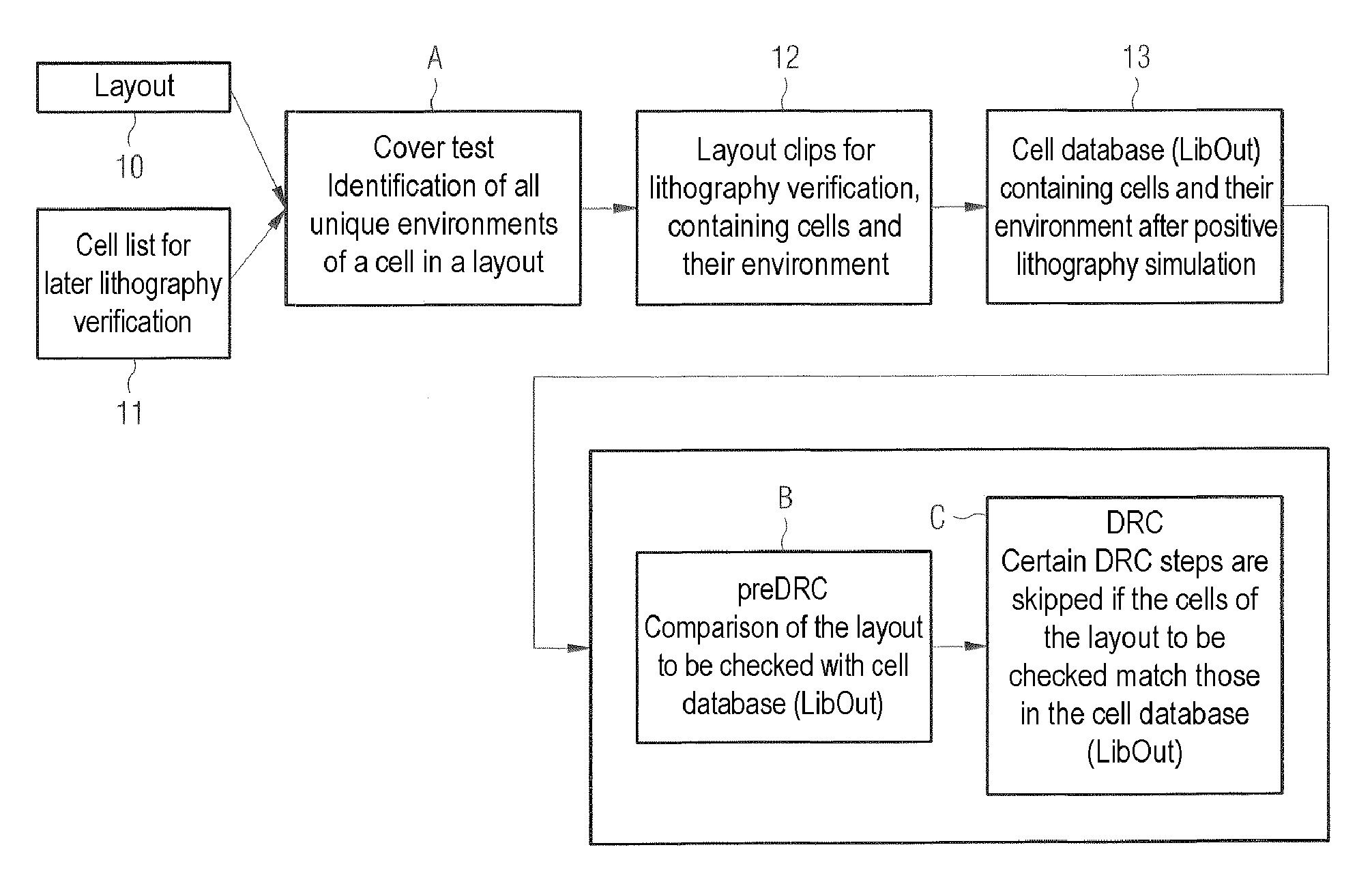

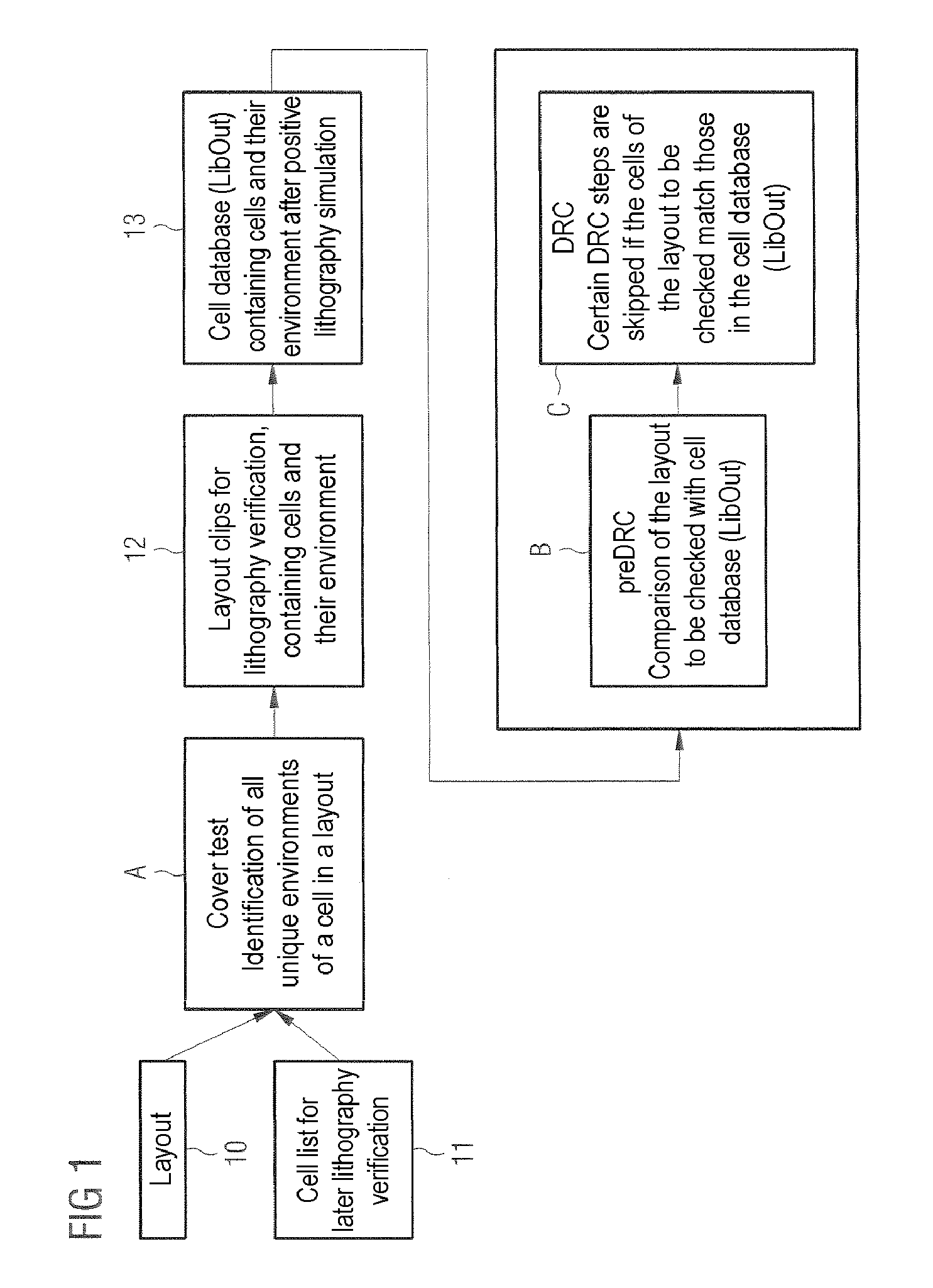

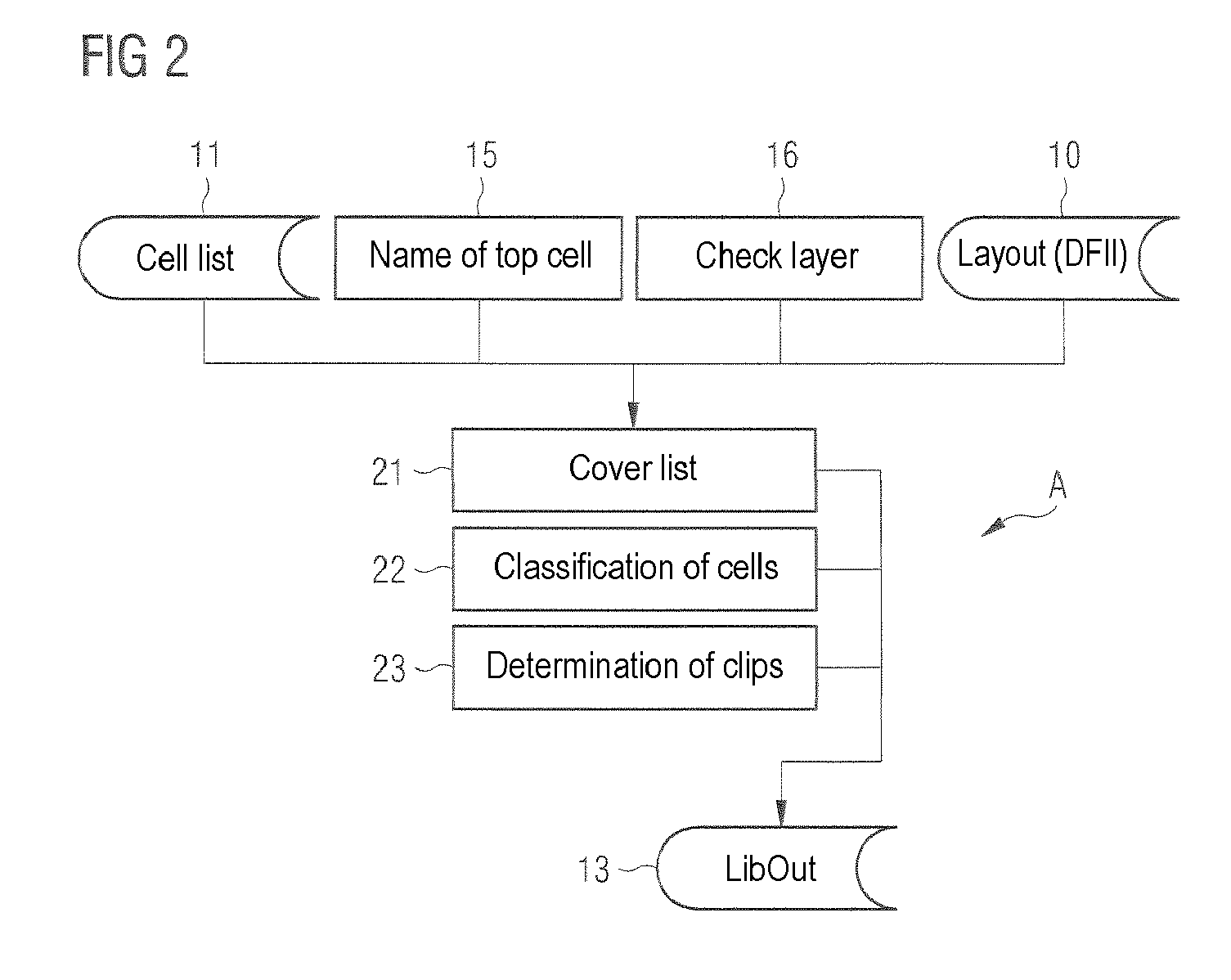

Method and device for classifying cells in a layout into a same environment and their use for checking the layout of an electronic circuit

InactiveUS7665051B2Originals for photomechanical treatmentComputer aided designComputer scienceSemiconductor components

A method and a device can be used for checking the layout of an electronic circuit of a semiconductor component. For example, the method includes an automatic classification of cells in at least one layout into a cell database, and an automatic layout checker comparing the cell database to a layout to be checked.

Owner:POLARIS INNOVATIONS LTD

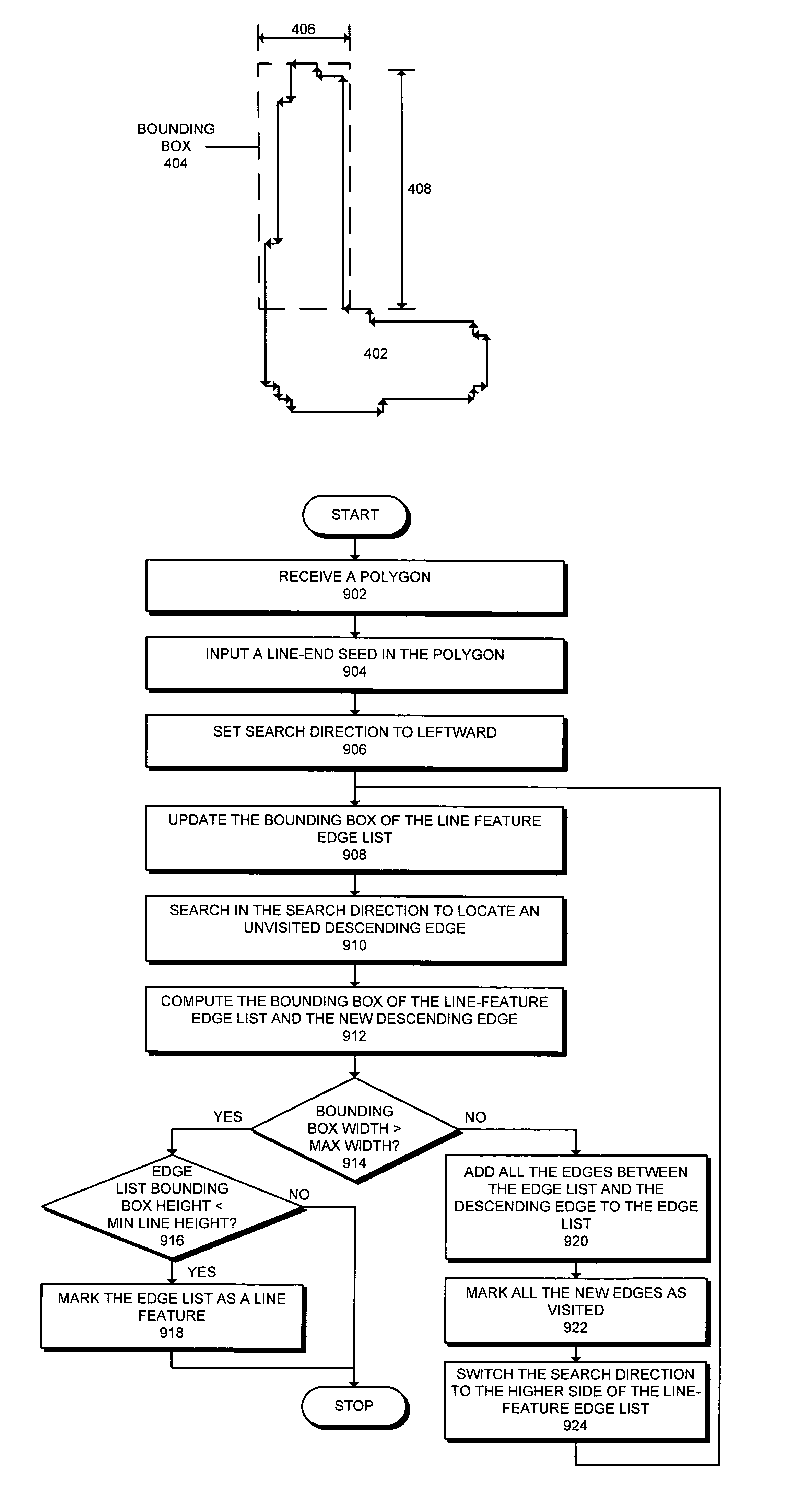

Method and apparatus for identifying line-end features for lithography verification

ActiveUS7194712B2Facilitates identifying line-end featureComputer aided designSpecial data processing applicationsLithographic artistEngineering

One embodiment of the invention provides a system that facilitates identifying line-end features in a layout for an integrated circuit. The system operates by first receiving the layout for the integrated circuit. Next, the system selects a polygon from the layout and marks a line-end seed on the polygon. The system then determines if the line-end seed is associated with a line feature, and if so, the system marks the line-end feature inside the line feature.

Owner:SYNOPSYS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com