Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1269 results about "Foundry" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A foundry is a factory that produces metal castings. Metals are cast into shapes by melting them into a liquid, pouring the metal into a mold, and removing the mold material after the metal has solidified as it cools. The most common metals processed are aluminium and cast iron. However, other metals, such as bronze, brass, steel, magnesium, and zinc, are also used to produce castings in foundries. In this process, parts of desired shapes and sizes can be formed.

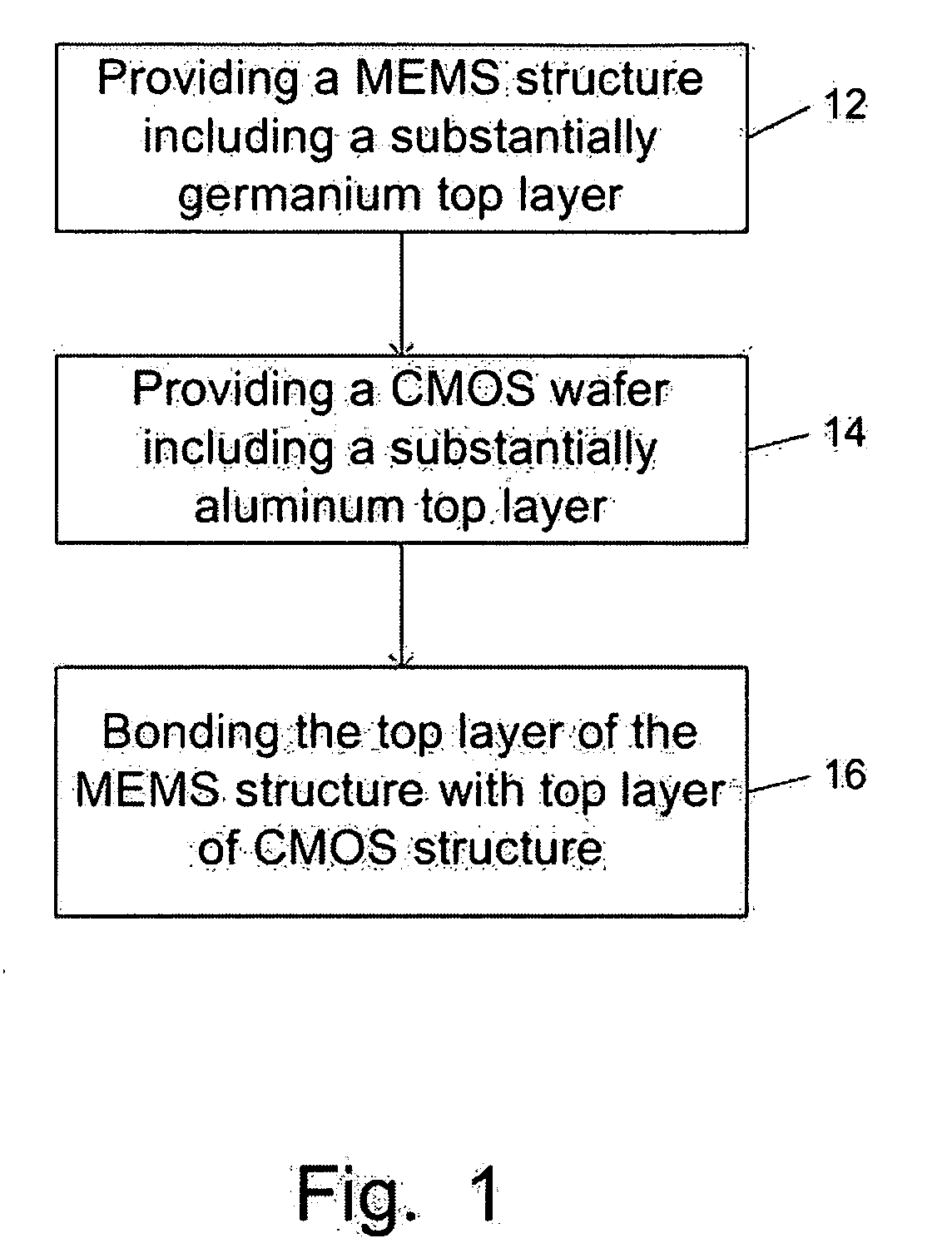

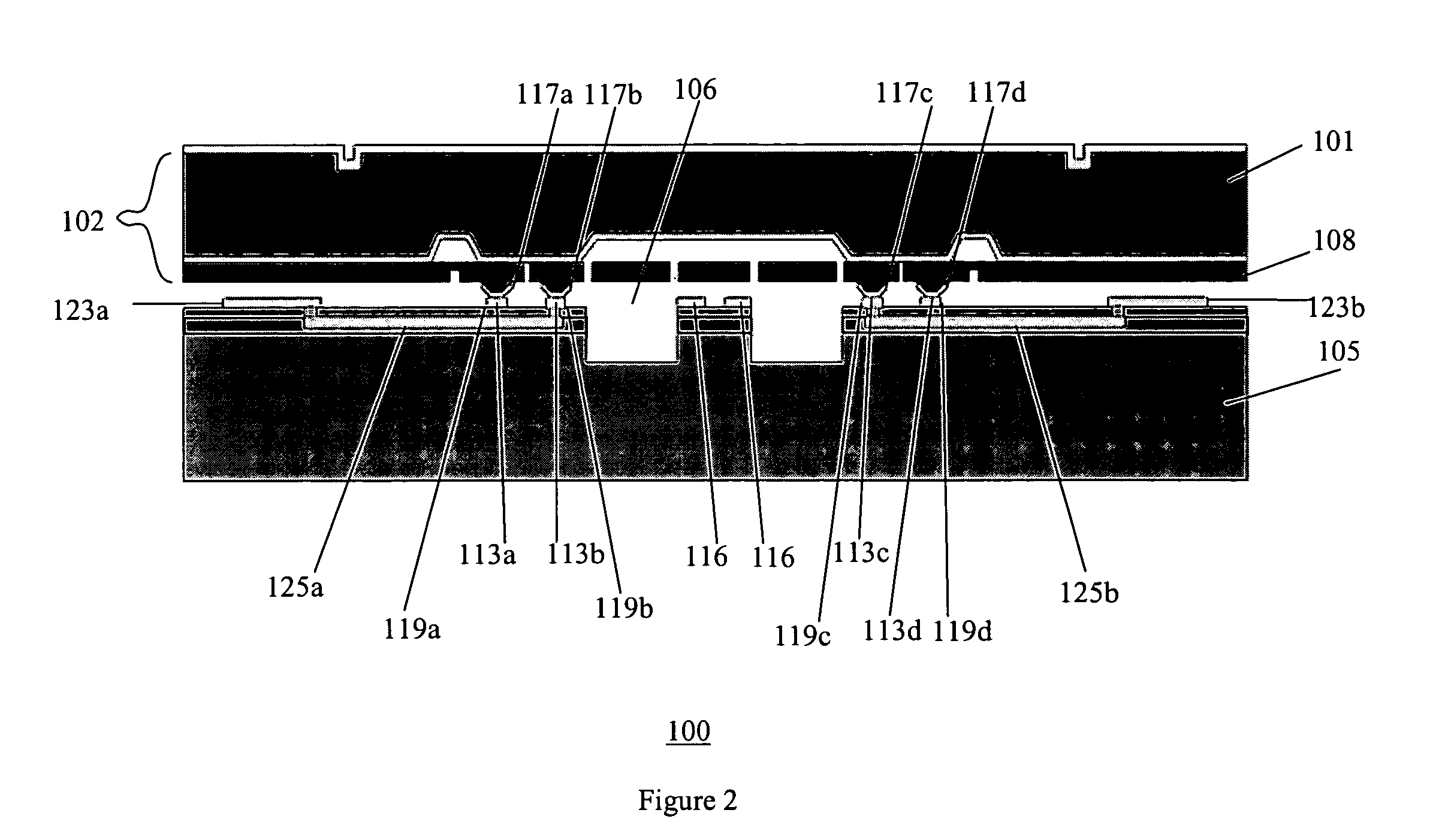

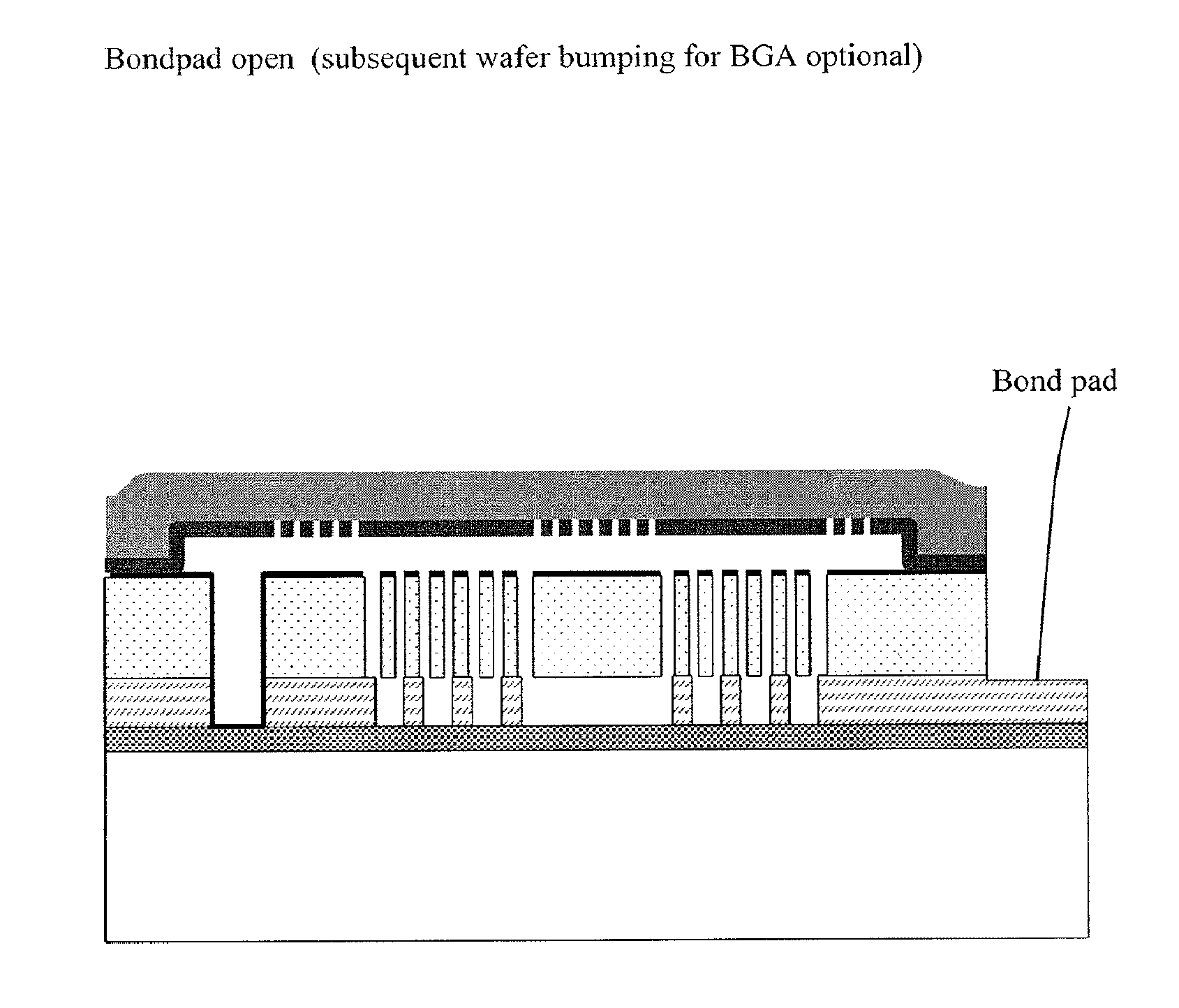

Method of fabrication of a AL/GE bonding in a wafer packaging environment and a product produced therefrom

ActiveUS7442570B2Robust and mechanical contactHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

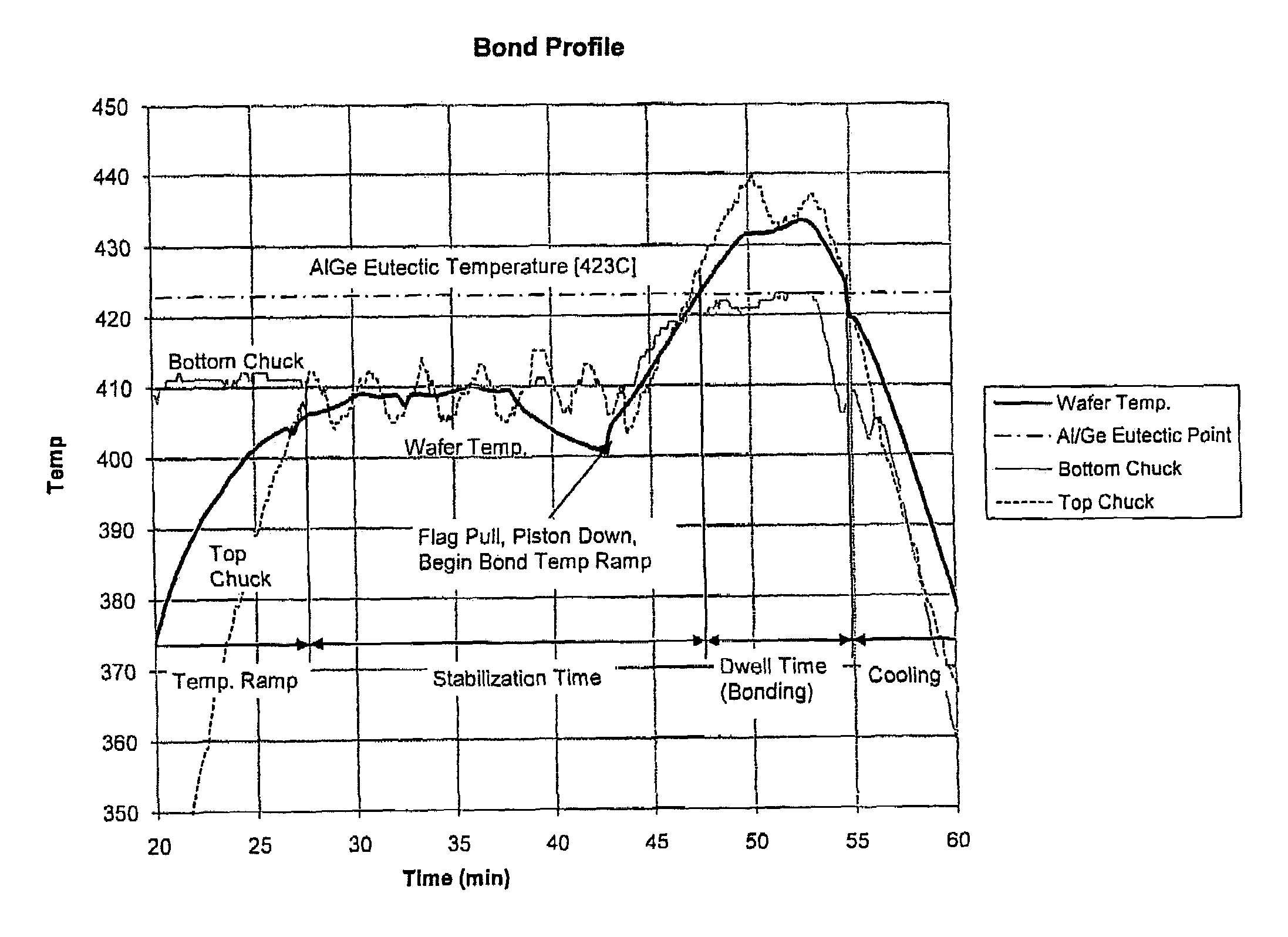

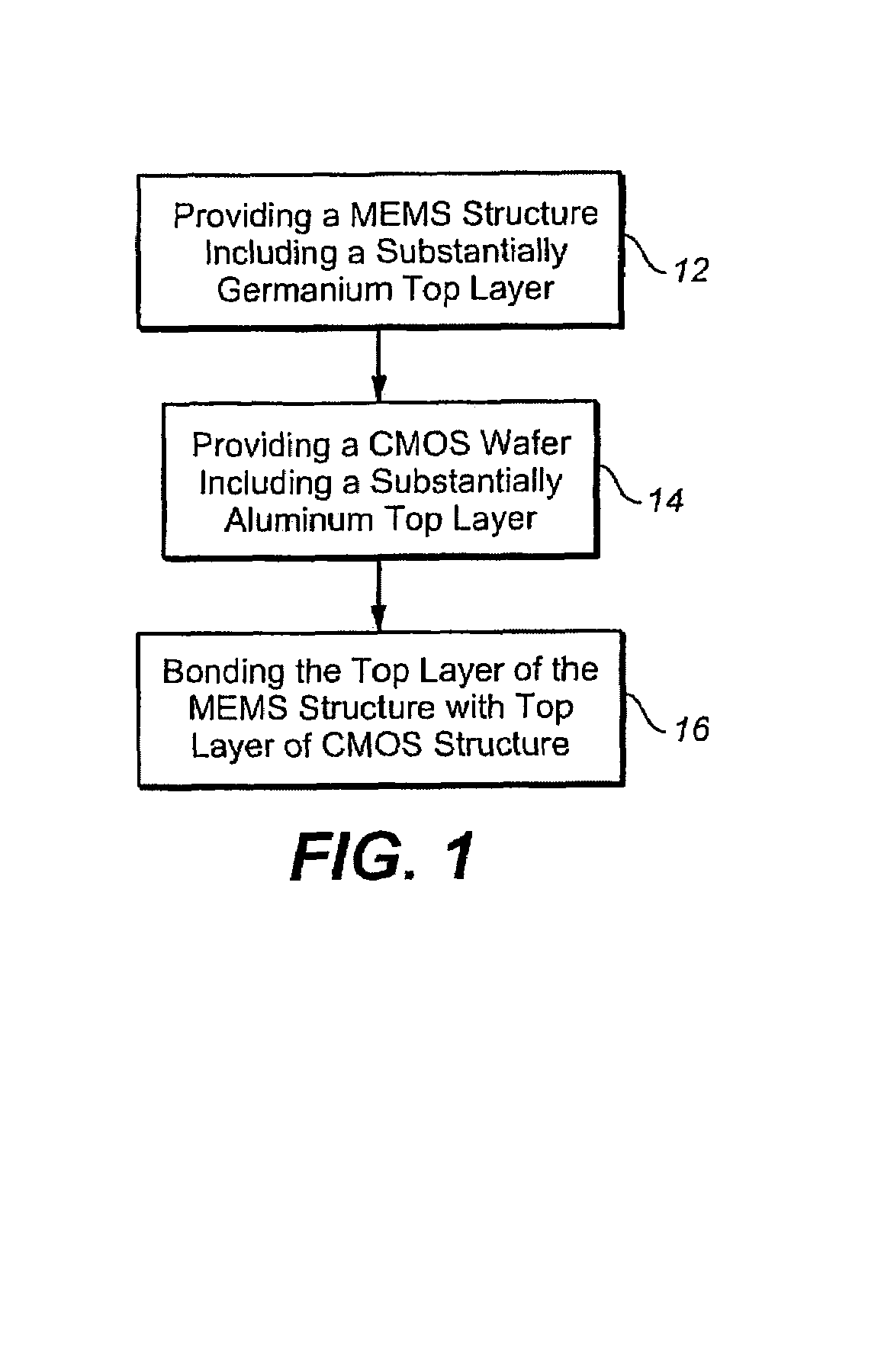

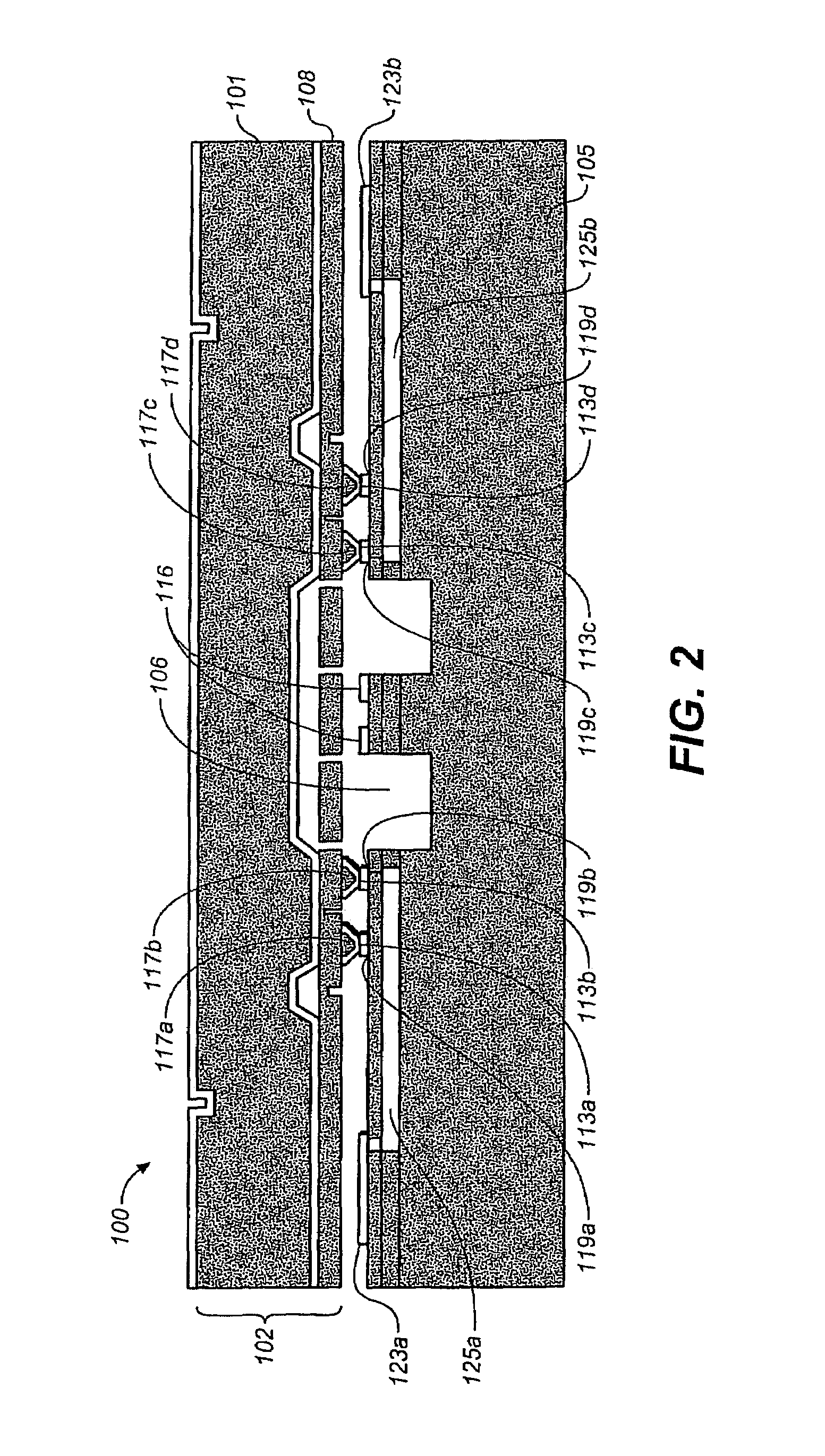

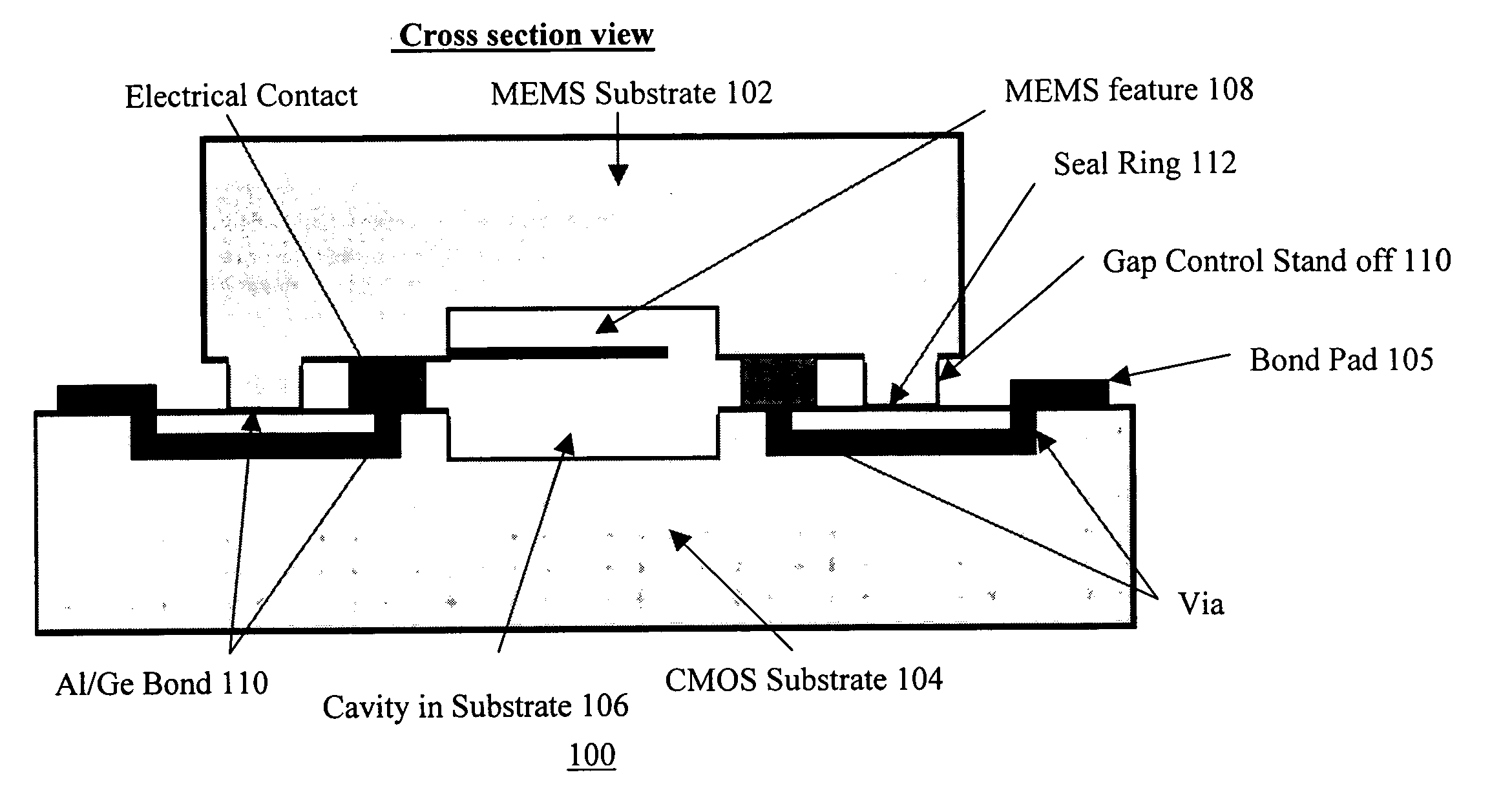

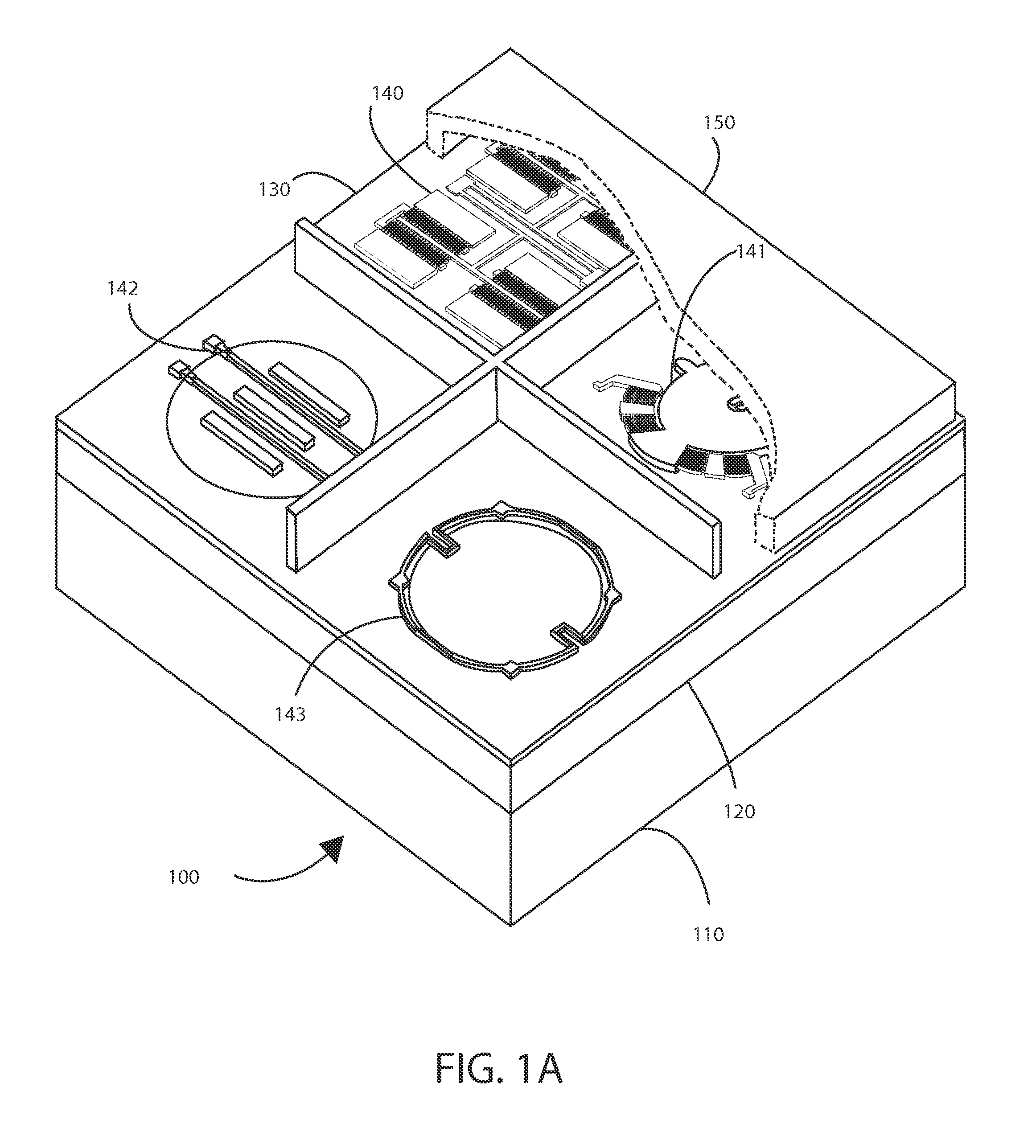

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

Method of fabrication of ai/ge bonding in a wafer packaging environment and a product produced therefrom

ActiveUS20060208326A1RobustHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

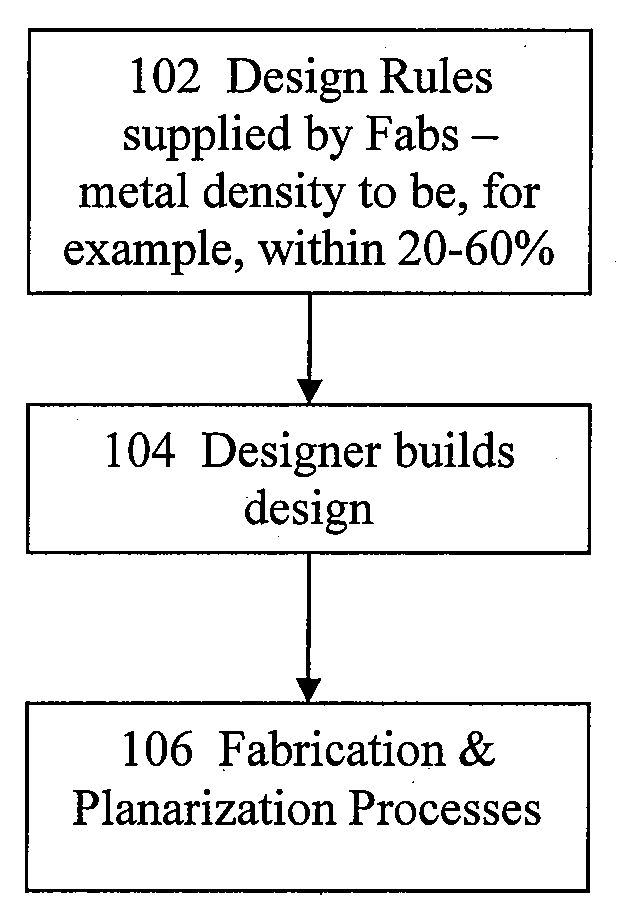

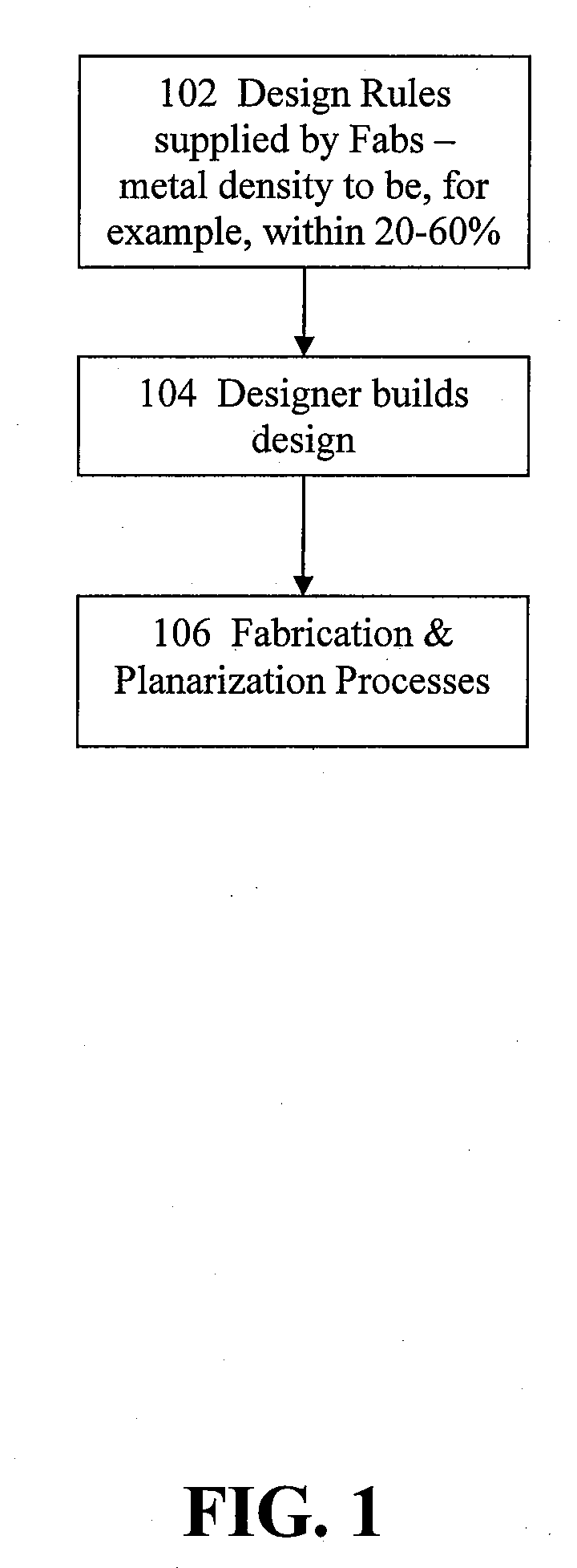

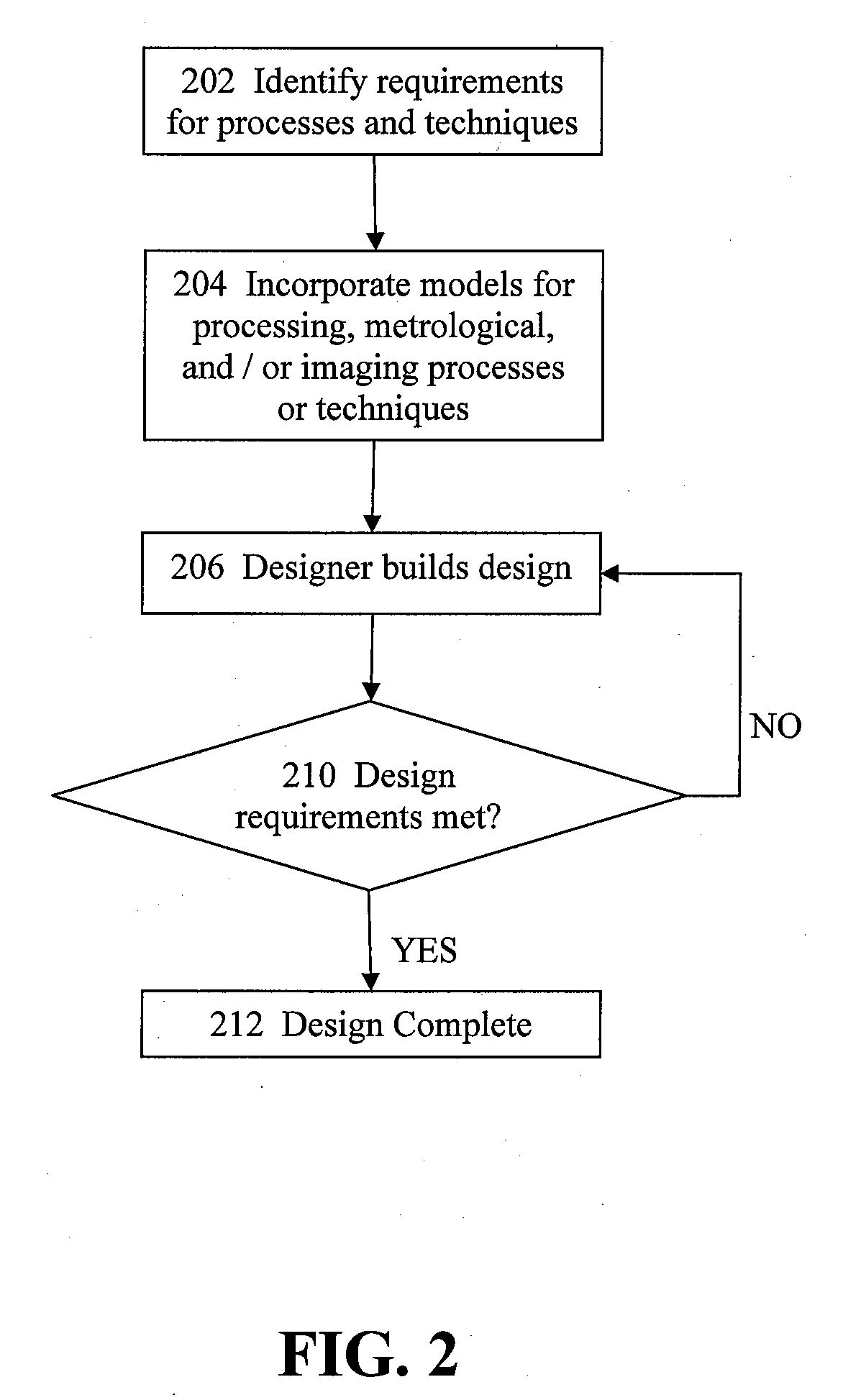

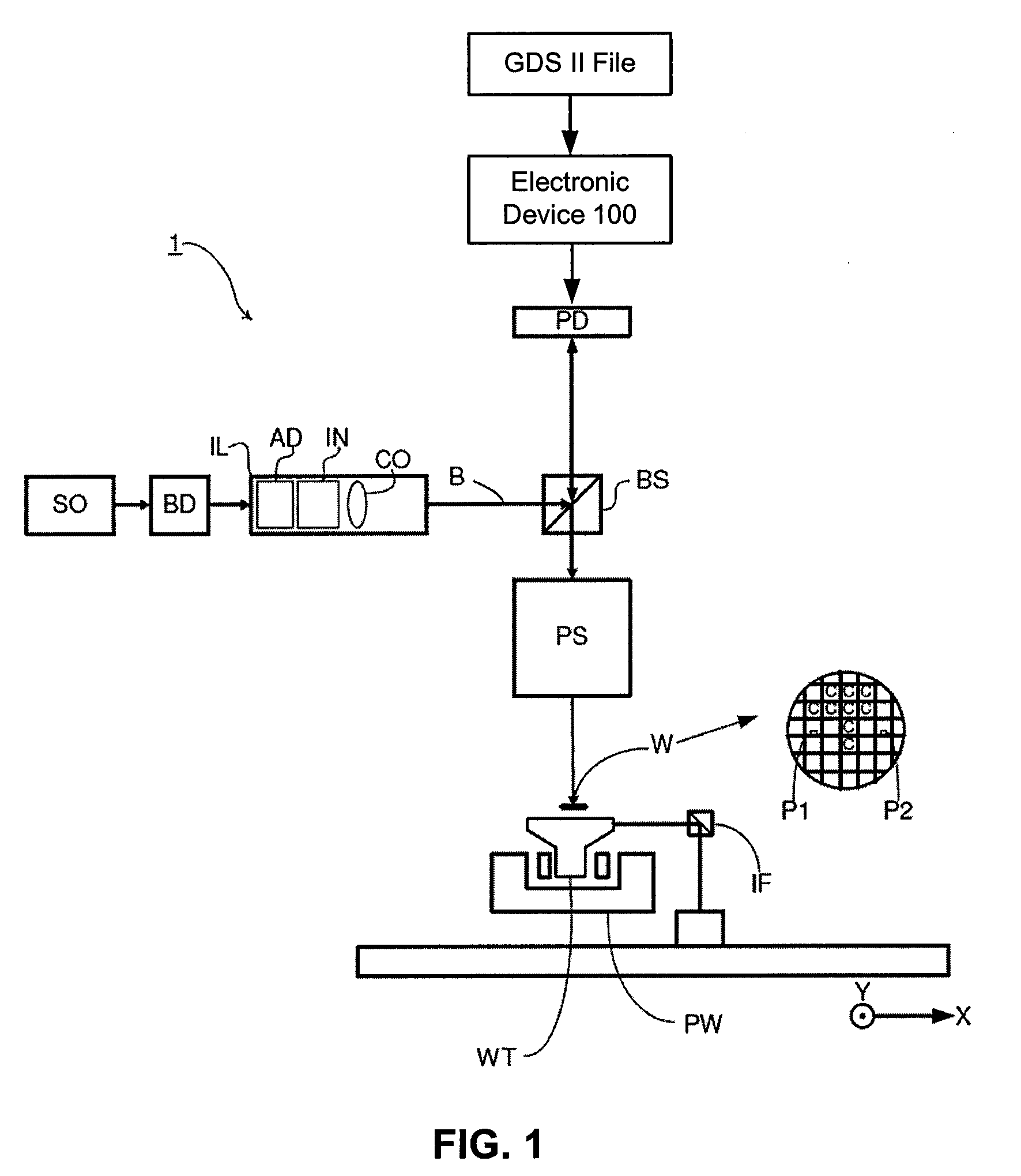

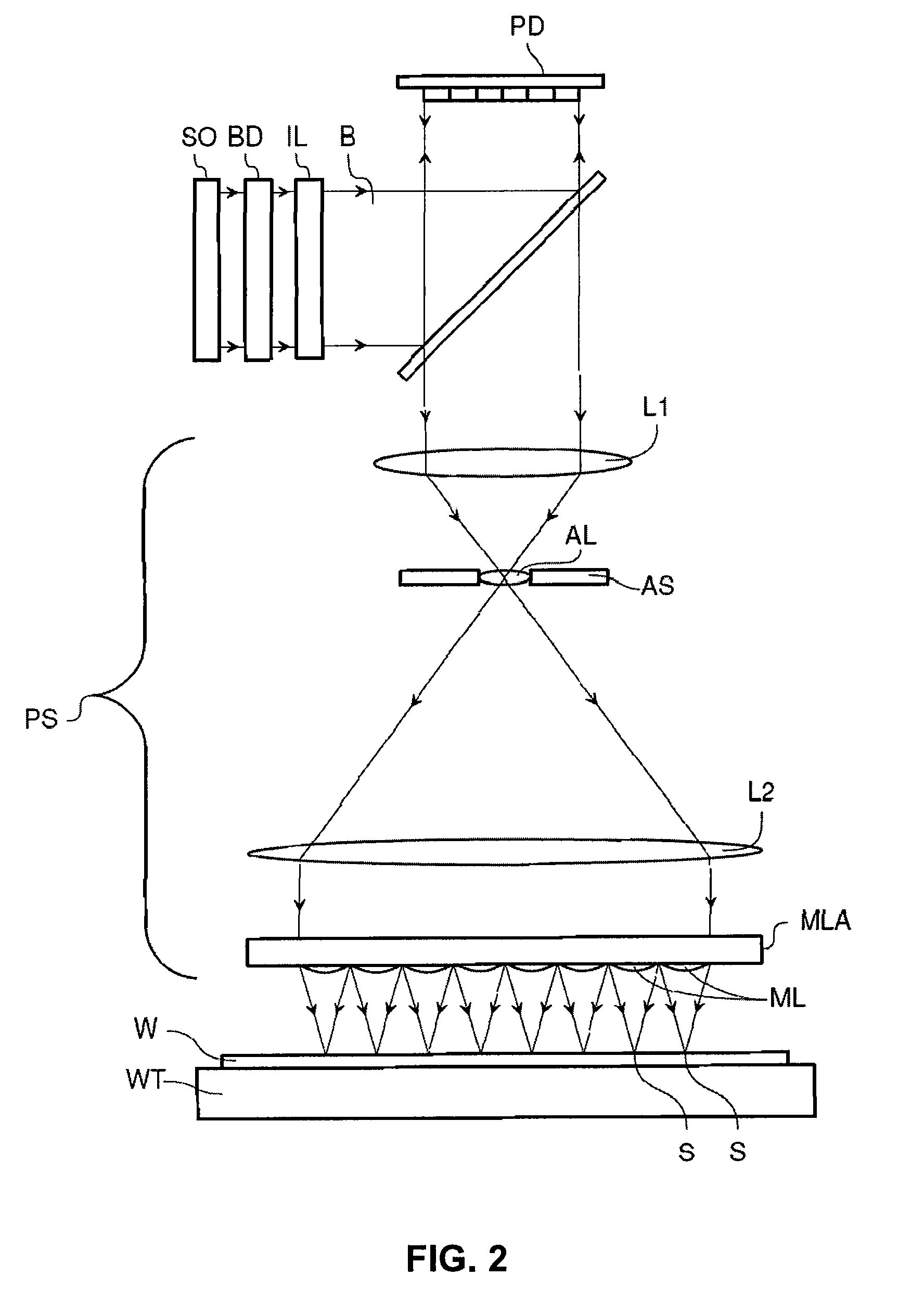

Supplant design rules in electronic designs

ActiveUS20080163141A1Interaction be complexComputer aided designSoftware simulation/interpretation/emulationFoundryComputer architecture

Disclosed is an improved method, system, and computer program product for electronic designs with supplant design rules. According to some embodiments of the invention, the foundry-imposed design rules are replaced by one or more supplant design requirements which define absolute or relative threshold(s) for a design feature characteristic. Some other embodiments of the invention, the foundry-imposed design rules are replaced by one or more supplant design requirements which define one or more ranges of absolute or relative values for a design feature characteristic. Some other embodiments of the invention further provide an EDA tool which takes into account a model for the electronic design, the processing, metrological, lithographic, or imaging processing processes or techniques, and the supplant design requirements to determine whether the features of an electronic design meet the design requirements.

Owner:CADENCE DESIGN SYST INC

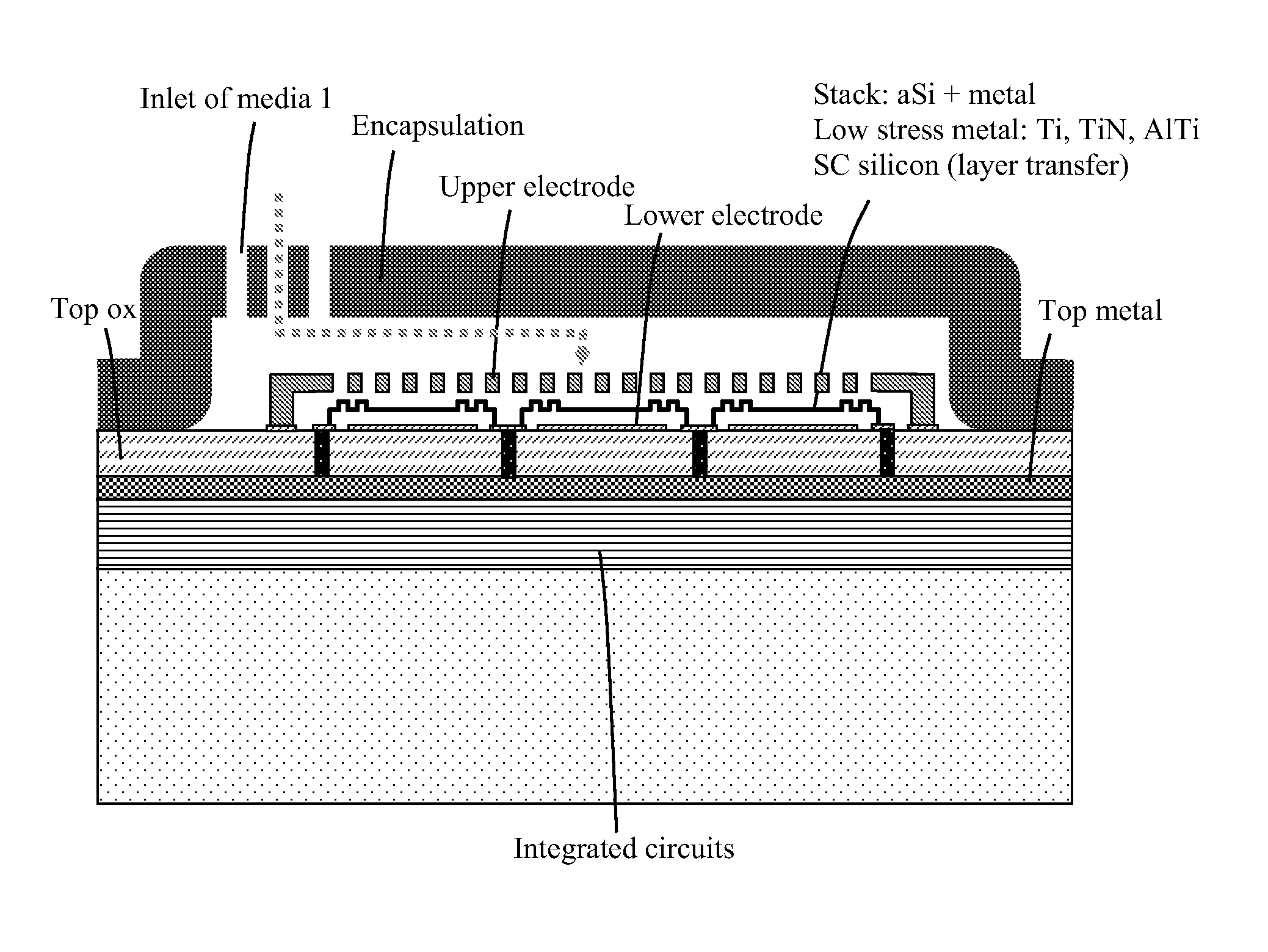

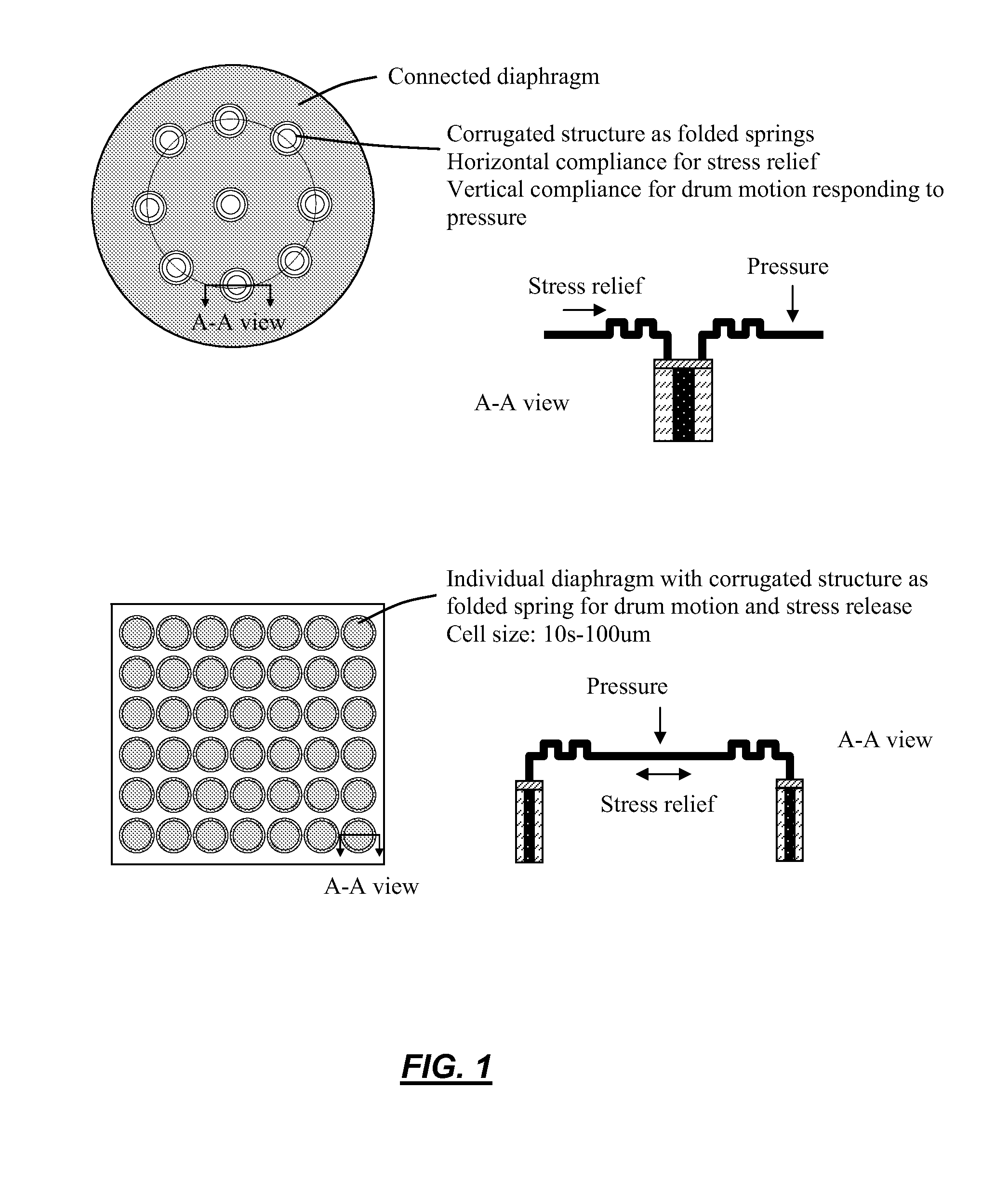

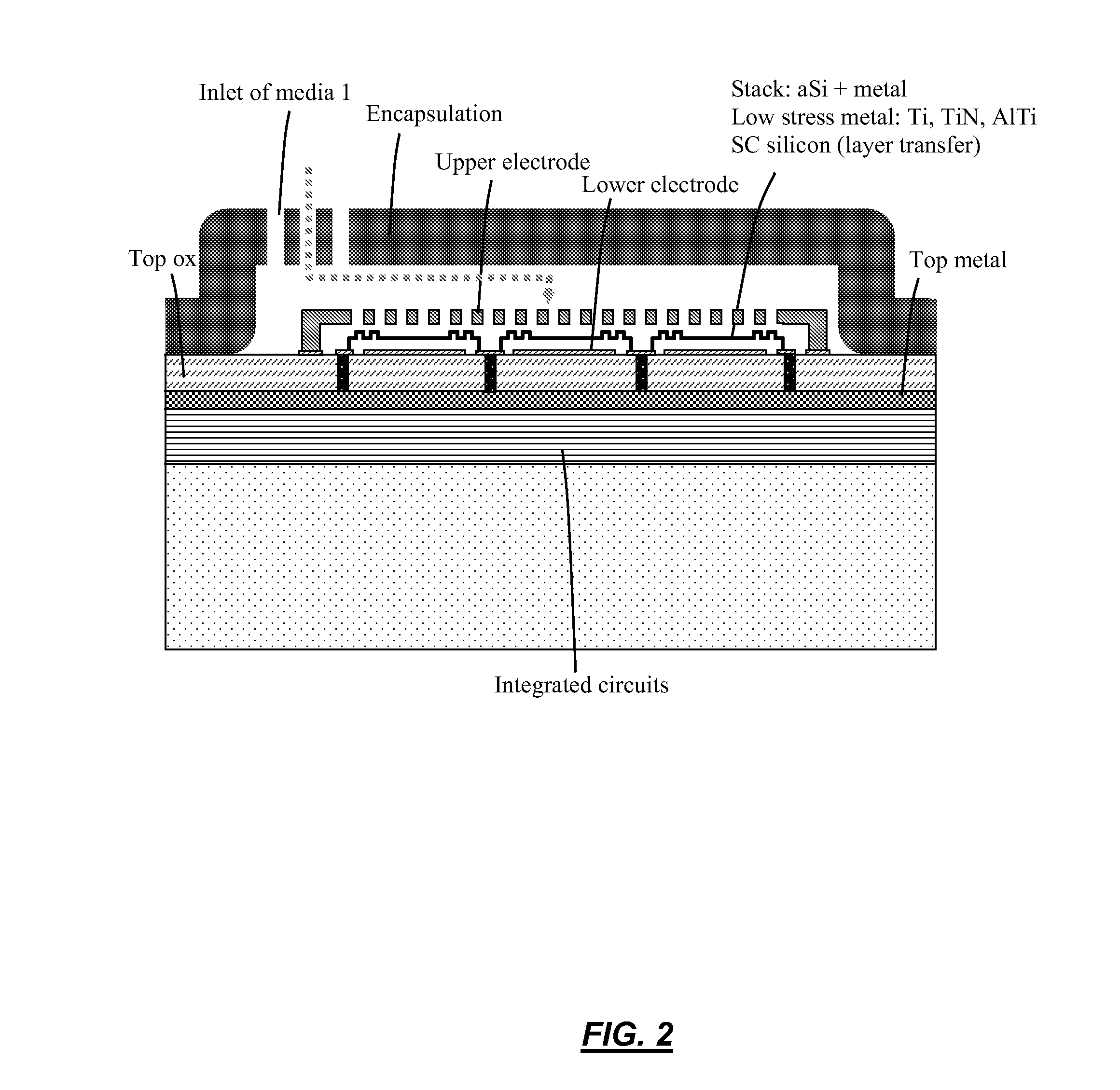

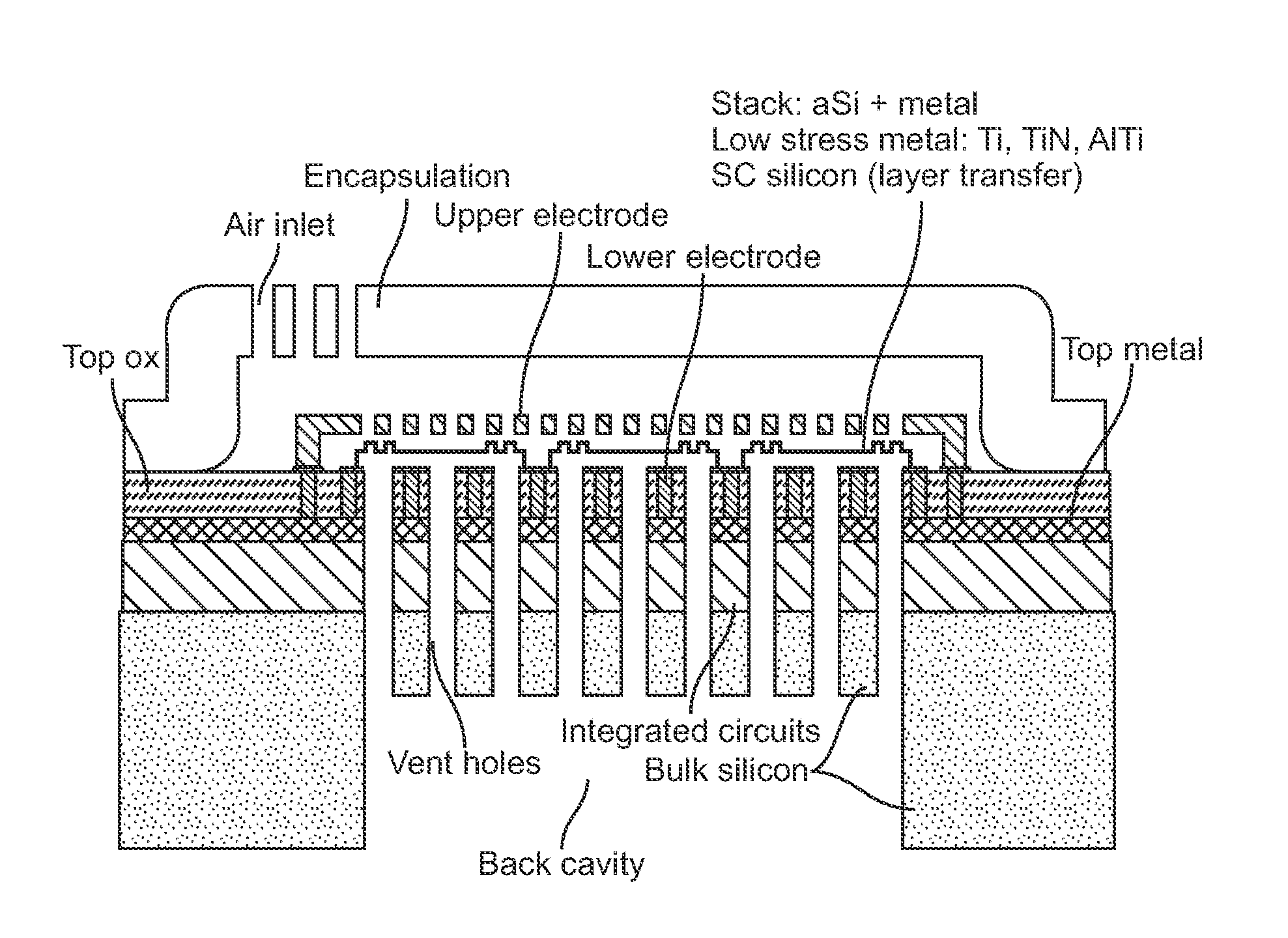

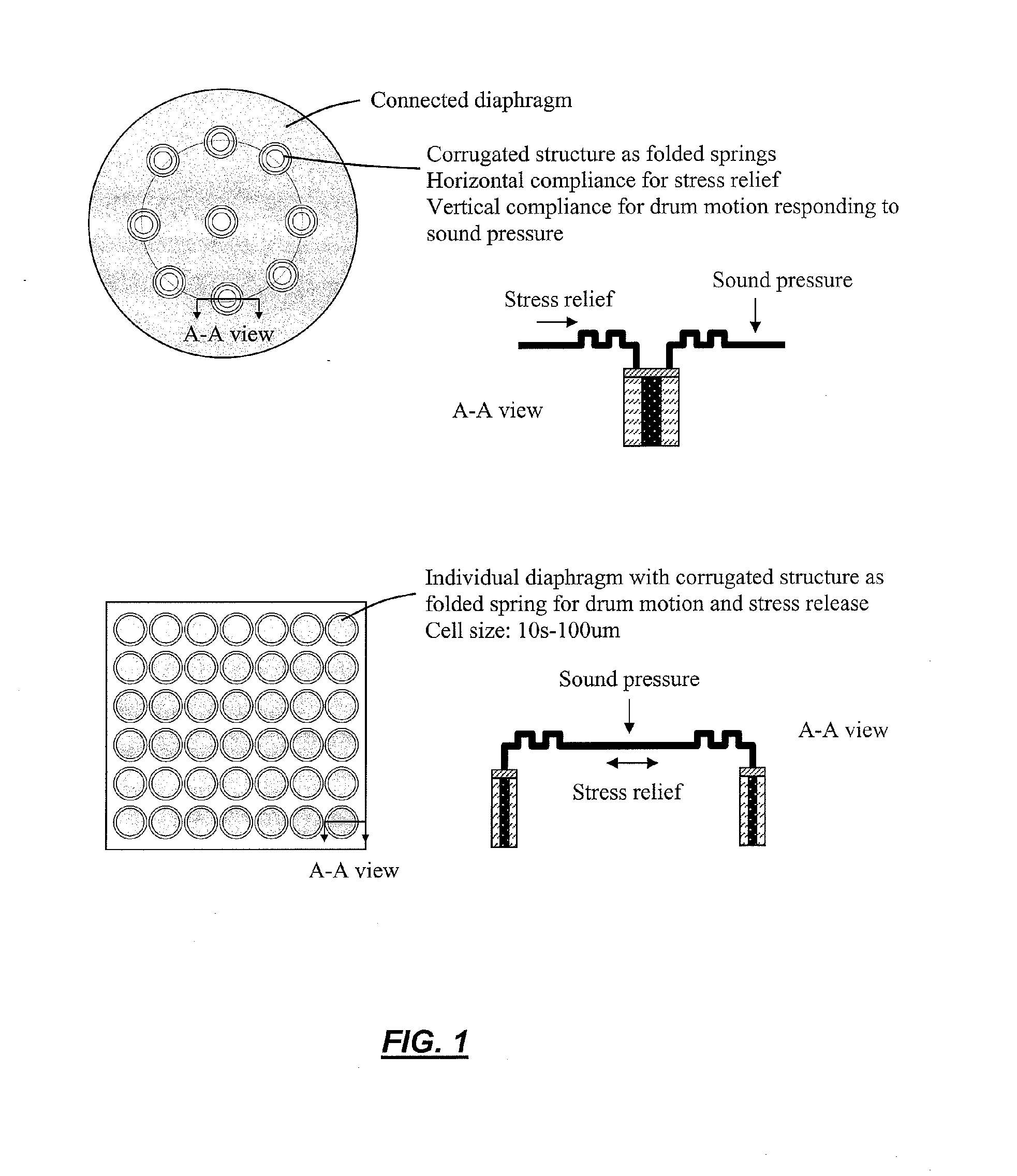

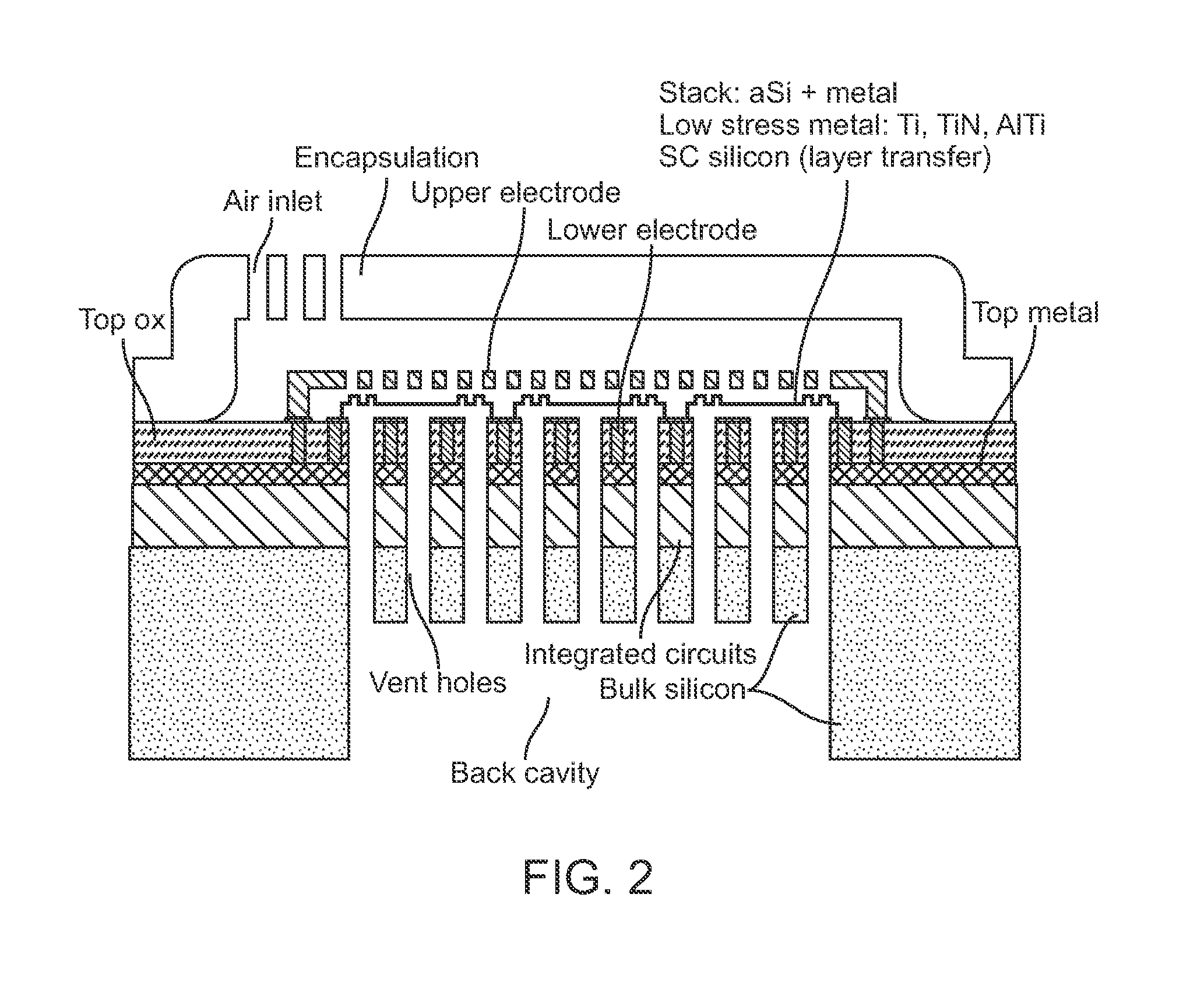

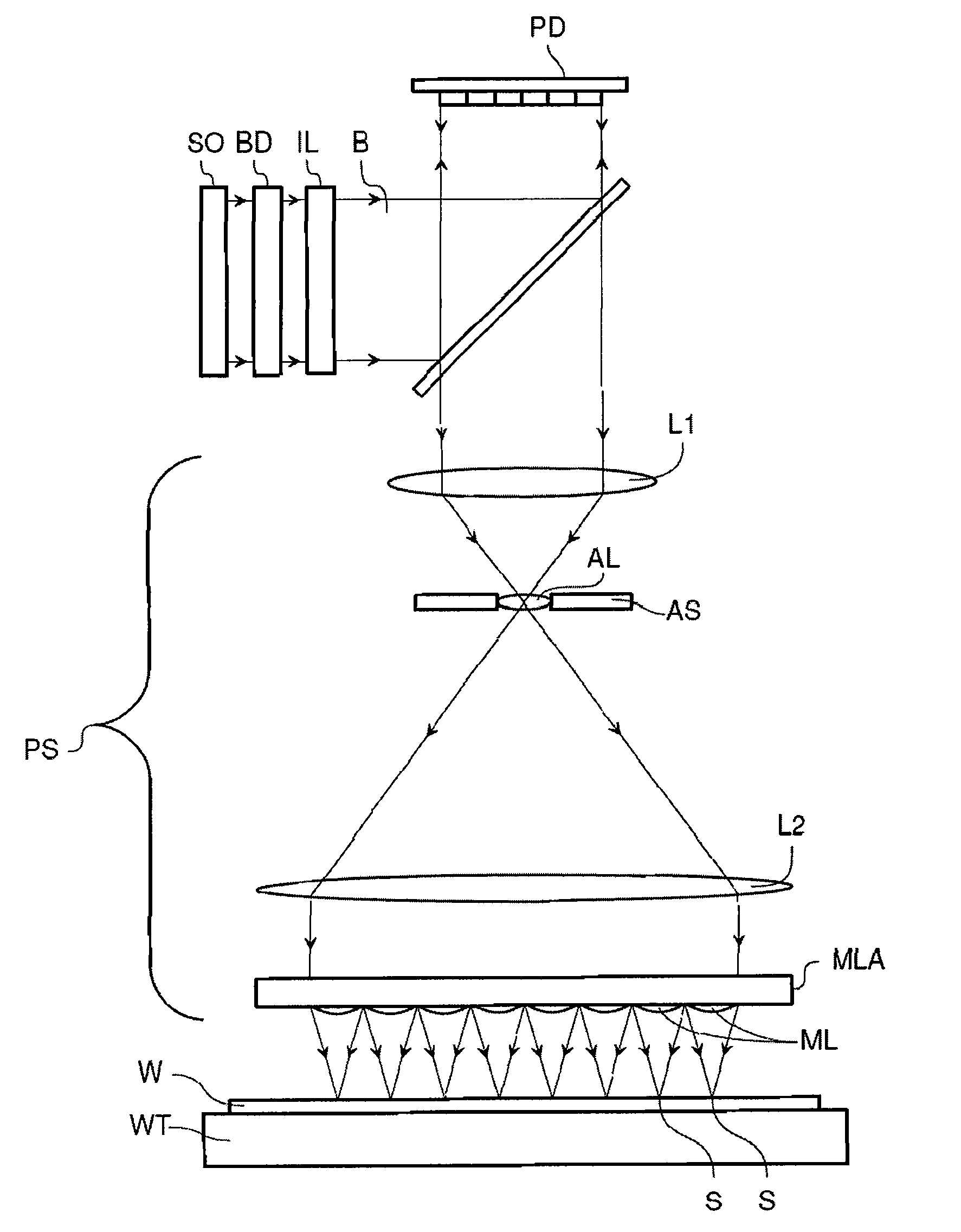

Method and structure of monolithically integrated pressure sensor using IC foundry-compatible processes

ActiveUS20100171153A1Improve performanceSmall sizeFluid pressure measurement by electric/magnetic elementsSemiconductor/solid-state device manufacturingCMOSFoundry

A monolithically integrated MEMS pressure sensor and CMOS substrate using IC-Foundry compatible processes. The CMOS substrate is completed first using standard IC processes. A diaphragm is then added on top of the CMOS. In one embodiment, the diaphragm is made of deposited thin films with stress relief corrugated structure. In another embodiment, the diaphragm is made of a single crystal silicon material that is layer transferred to the CMOS substrate. In an embodiment, the integrated pressure sensor is encapsulated by a thick insulating layer at the wafer level. The monolithically integrated pressure sensor that adopts IC foundry-compatible processes yields the highest performance, smallest form factor, and lowest cost.

Owner:MOVELLA INC

Method and structure of monolithetically integrated micromachined microphone using IC foundry-compatiable processes

A monolithically integrated MEMS and CMOS substrates provided by an IC-foundry compatible process. The CMOS substrate is completed first using standard IC processes. A diaphragm with stress relief corrugated structure is then fabricated on top of the CMOS. Air vent holes are then etched in the CMOS substrate. Finally, the microphone device is encapsulated by a thick insulating layer at the wafer level. The monolithically integrated microphone that adopts IC foundry-compatible processes yields the highest performance, smallest form factor, and lowest cost. Using this architecture and fabrication flow, it is feasible and cost-effective to make an array of Silicon microphones for noise cancellation, beam forming, better directionality and fidelity.

Owner:MOVELLA INC

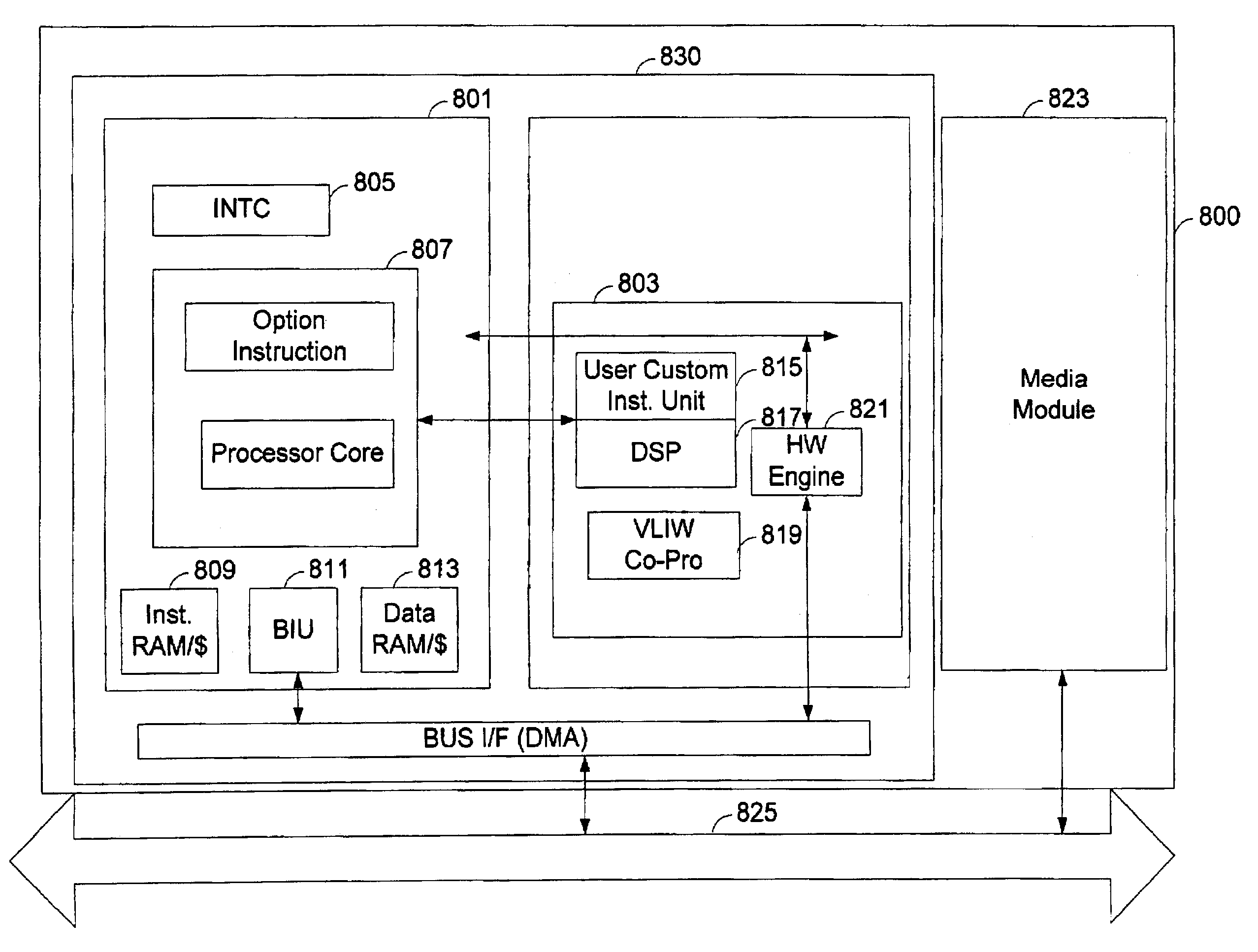

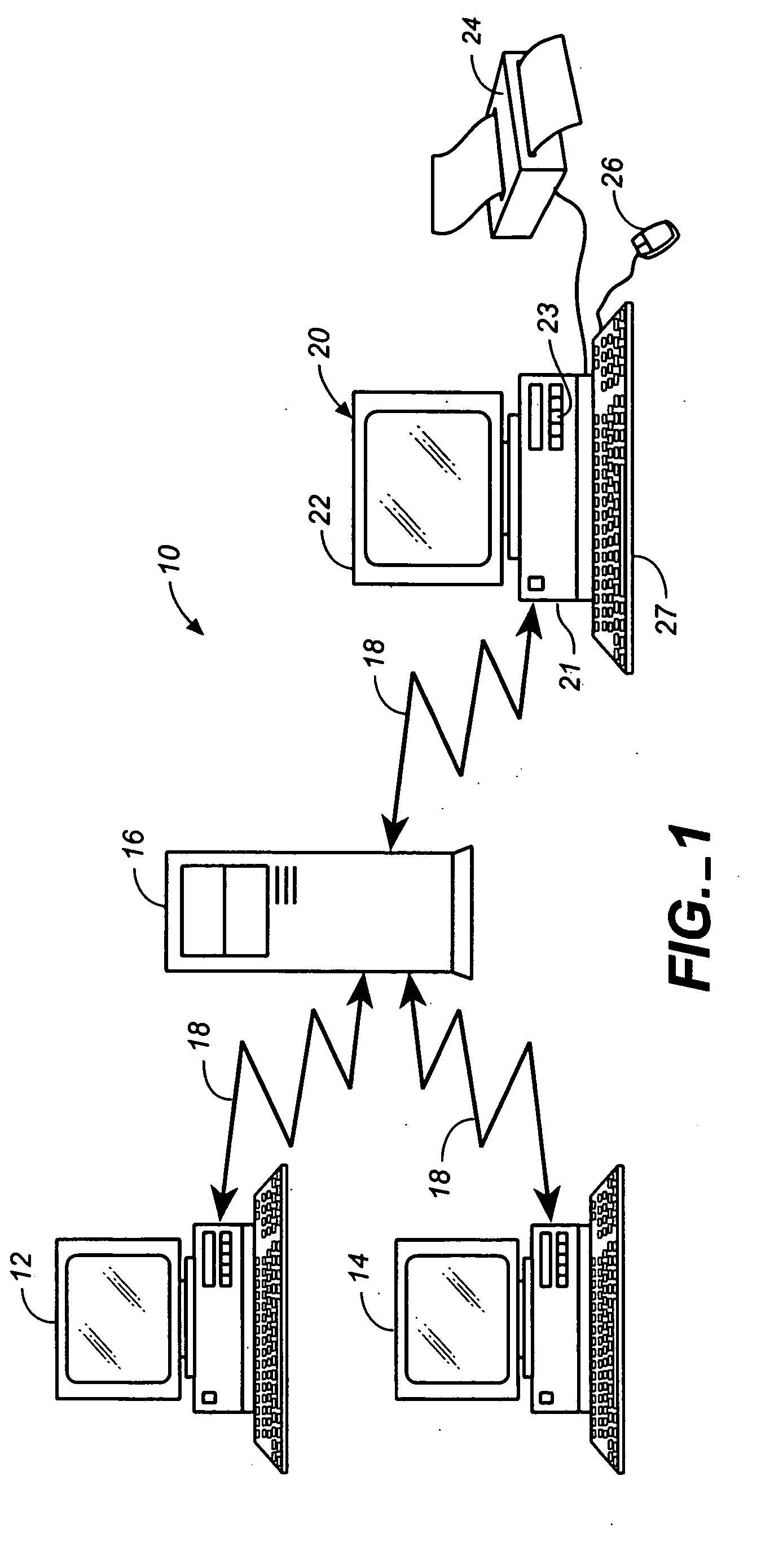

Software IP providing system and method, software IP obtaining method, and IP core designing and manufacturing method

InactiveUS7406716B2Easy to implementDigital data processing detailsUnauthorized memory use protectionFoundryWeb site

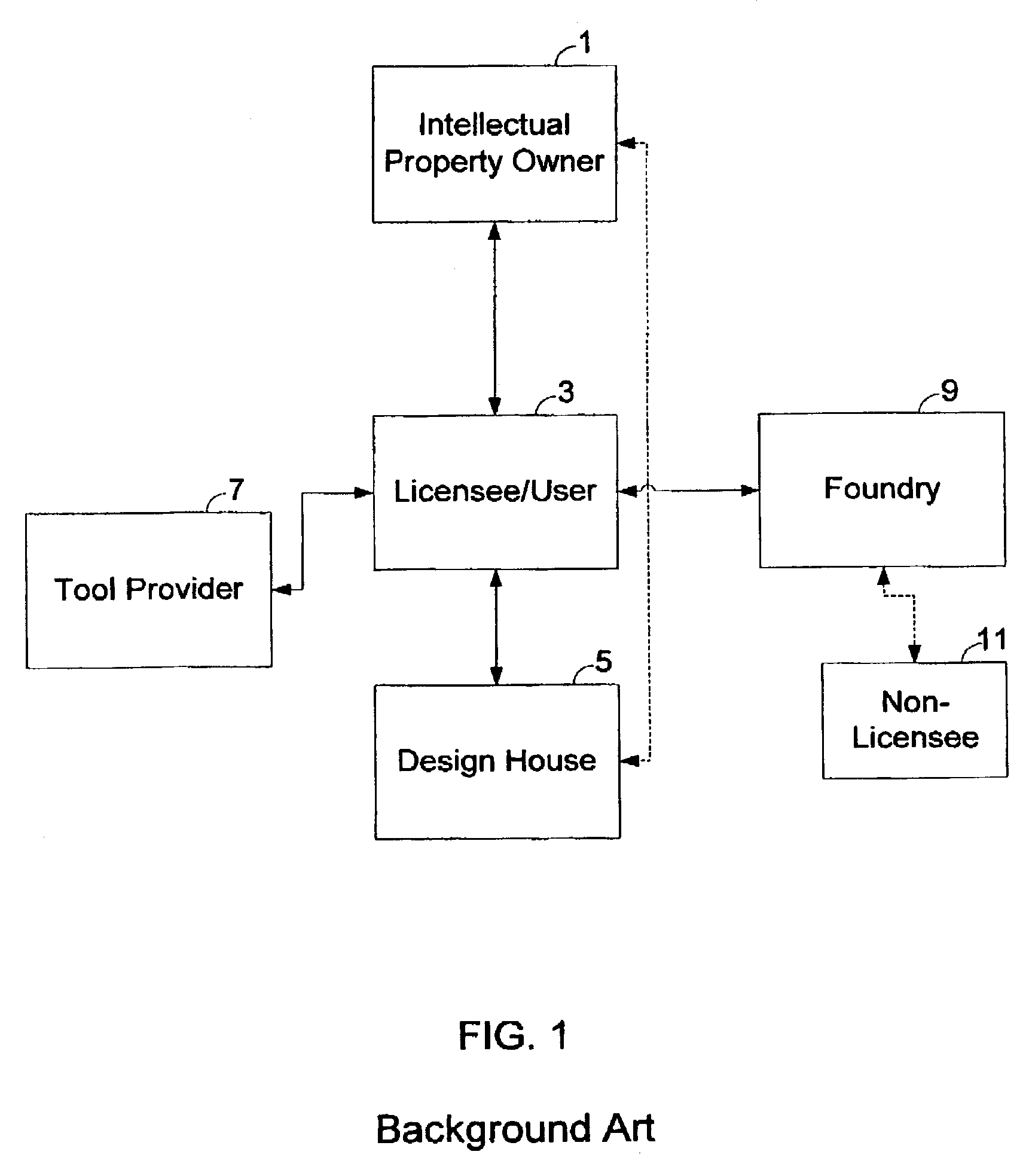

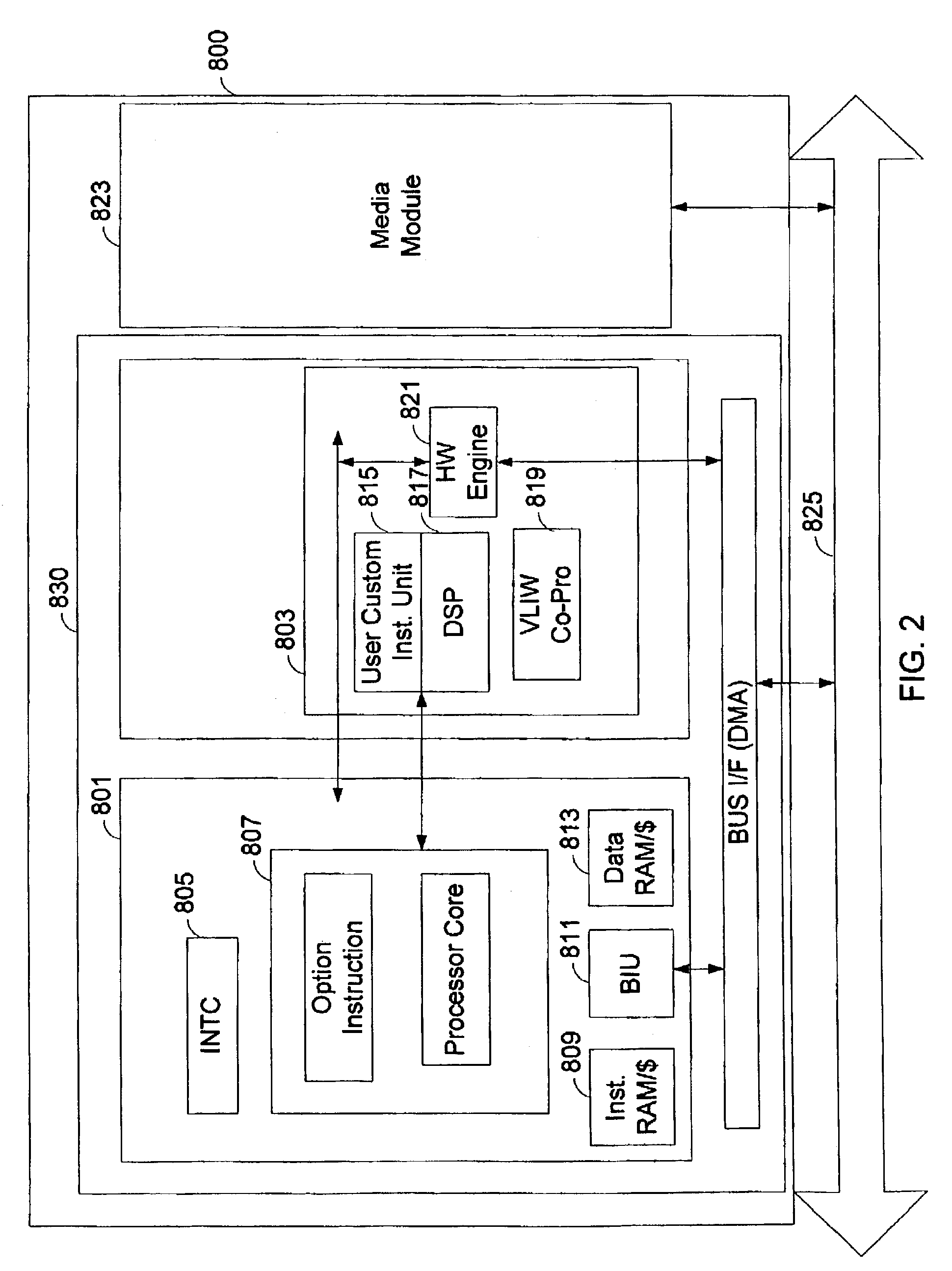

A system and method enables controlled distribution of processor IPinformation to users for evaluation, customization and / or production. One aspect of the system and method is a web site that helps coordinate the IP distribution of the processor IP information between a administrator and end-users, and affiliates of the end-users, namely design houses, tool providers and / or foundries. The processor IP information has a configuration specification including a definable portion of the user. By controlling the distribution of the processor IPinformation, while still allowing for convenient access, the system and method enable many users to customize the processor IPinformation for a variety of applications, with license condition being granted to the user to manufacture the customized units.

Owner:KK TOSHIBA

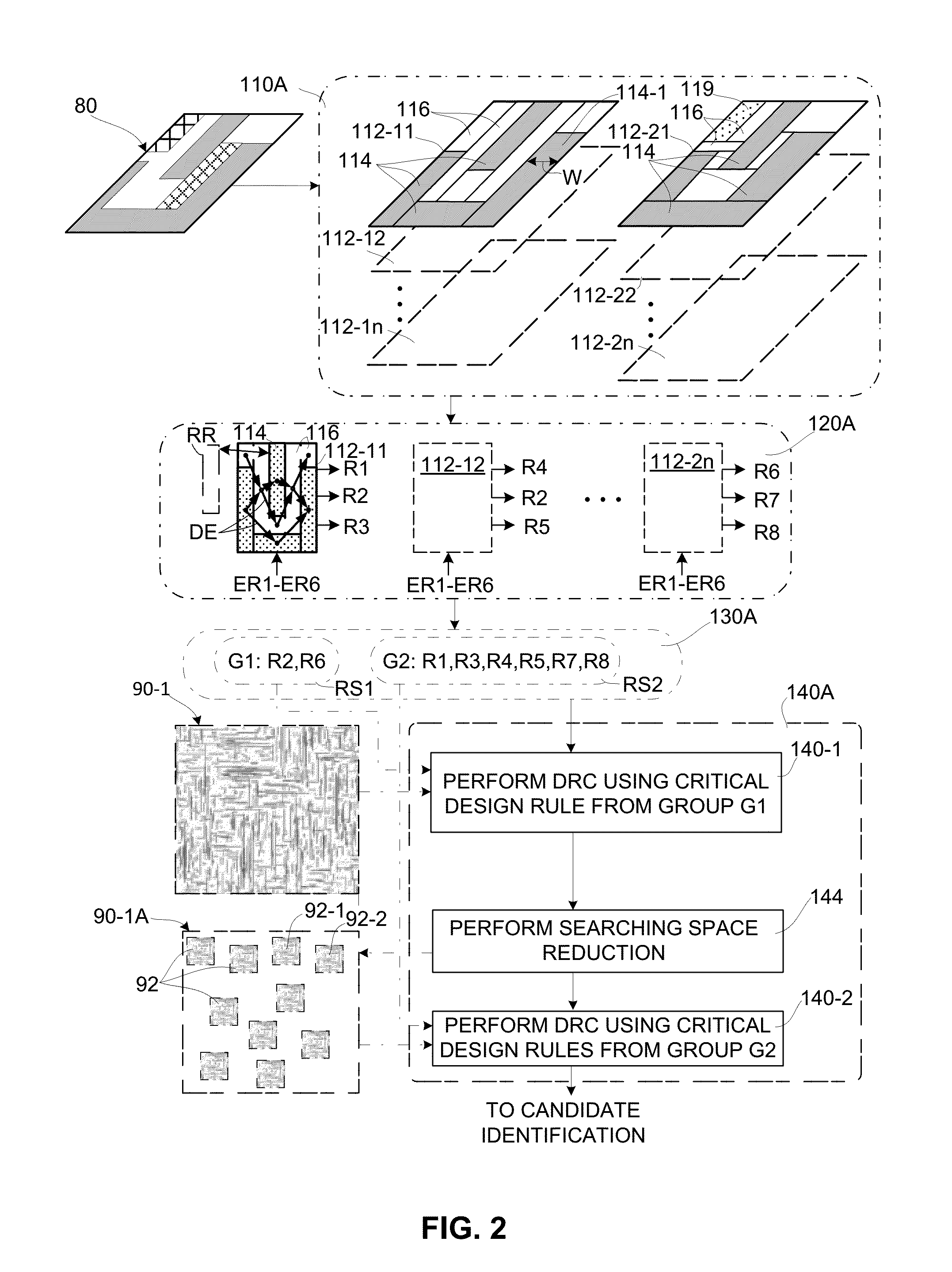

DRC-Based Hotspot Detection Considering Edge Tolerance And Incomplete Specification

ActiveUS20160125120A1Efficiently and accurately detectsFacilitates searching space reduction techniqueSemiconductor/solid-state device manufacturingComputer aided designLinear ScanFoundry

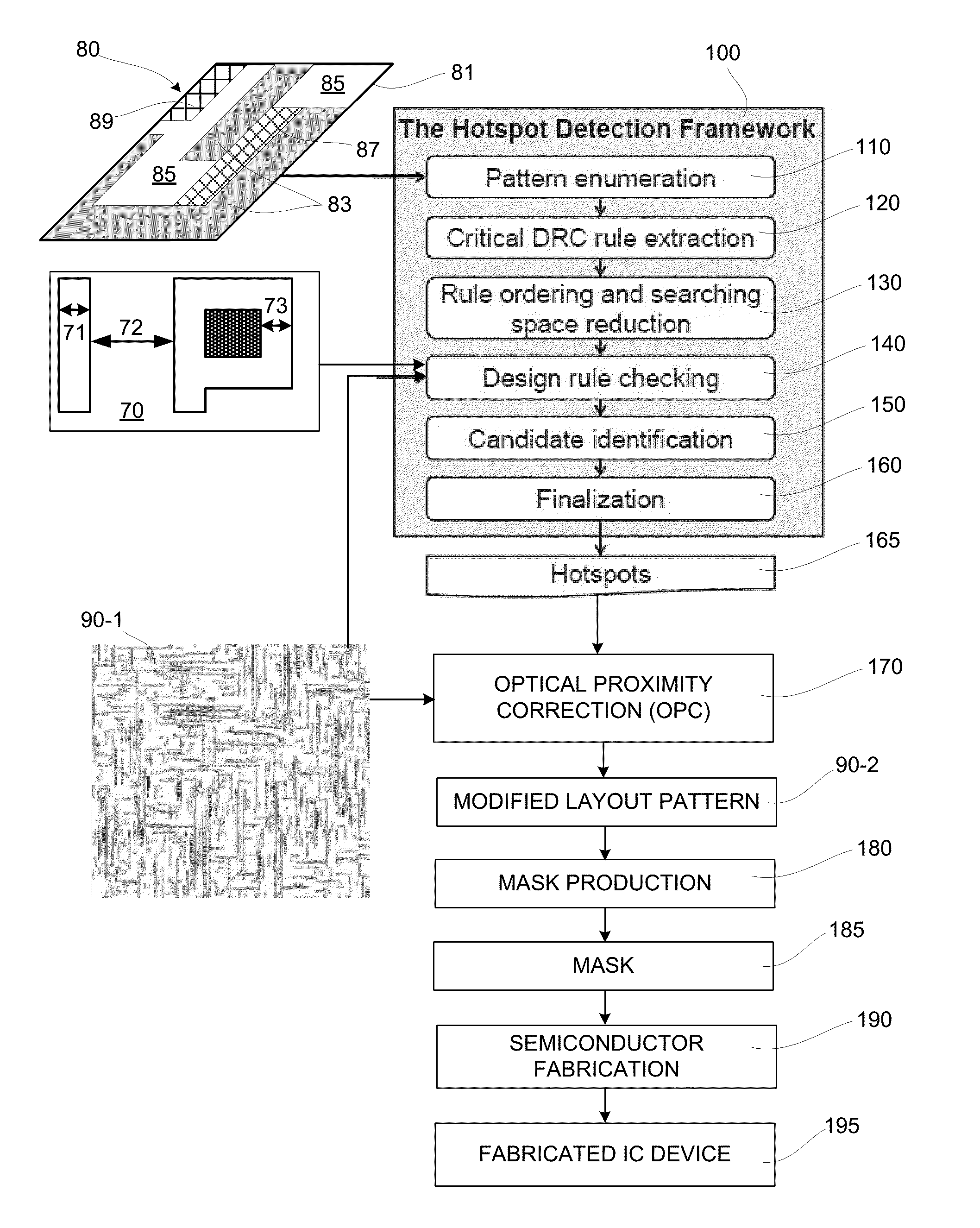

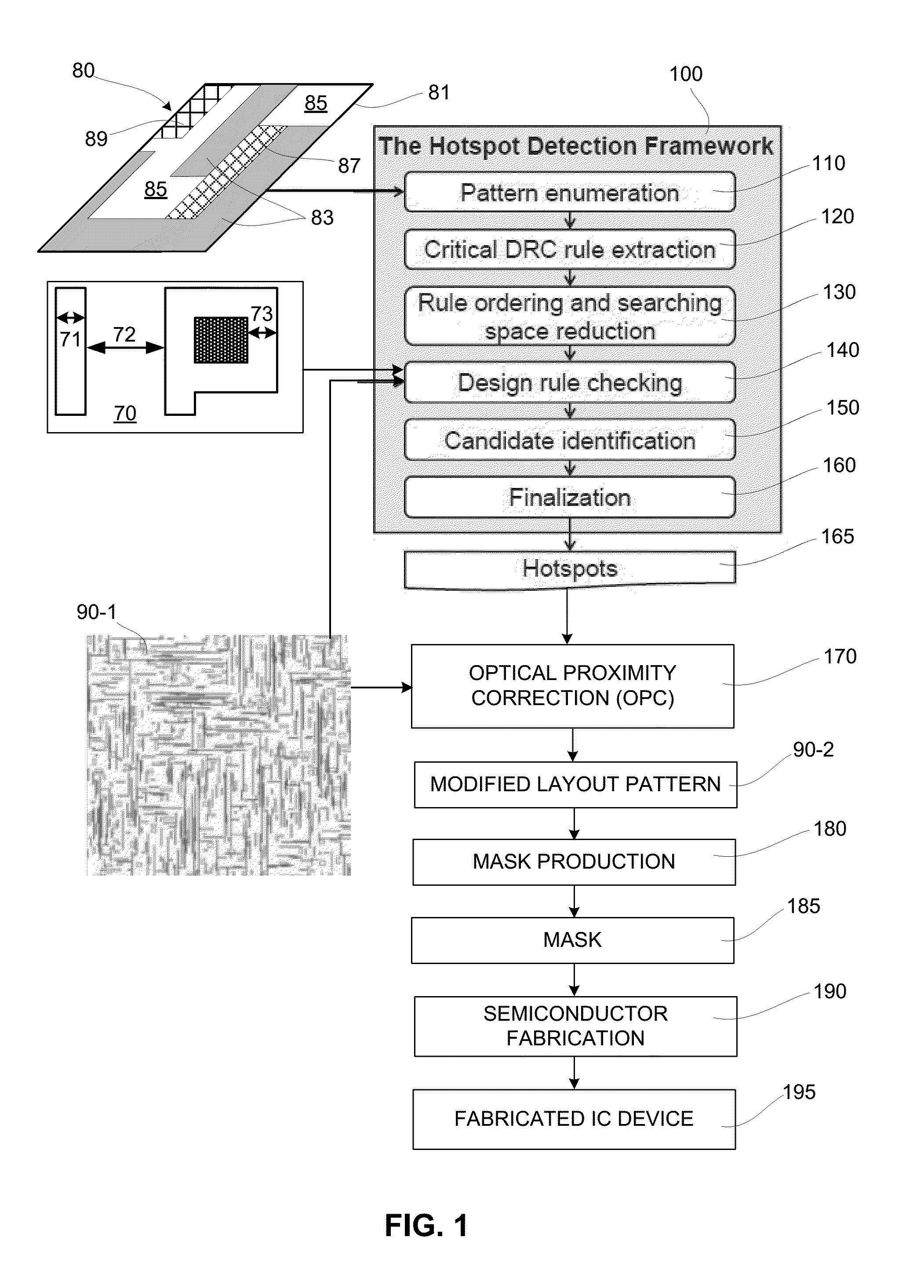

A range-pattern-matching-type DRC-based process hotspot detection is provided that considers edge tolerances and incomplete specification (“don't care”) regions in foundry-provided hotspot patterns. First, all possible topological patterns are enumerated for the foundry-provided hotspot pattern. Next, critical topological features are extracted from each pattern topology and converted to critical design rules using Modified Transitive Closure Graphs (MTCGs). Third, the extracted critical design rules are arranged in an order that facilitates searching space reduction techniques, and then the DRC process is sequentially repeated on a user's entire layout pattern for each critical design rule in a first group, then searching space reduction is performed to generate a reduced layout pattern, and then DRC process is performed for all remaining critical design rules using the reduced layout pattern. Candidate locations are then identified using the DRC results, and then the true hotspot locations are confirmed using longest common subsequence and linear scan techniques.

Owner:SYNOPSYS INC

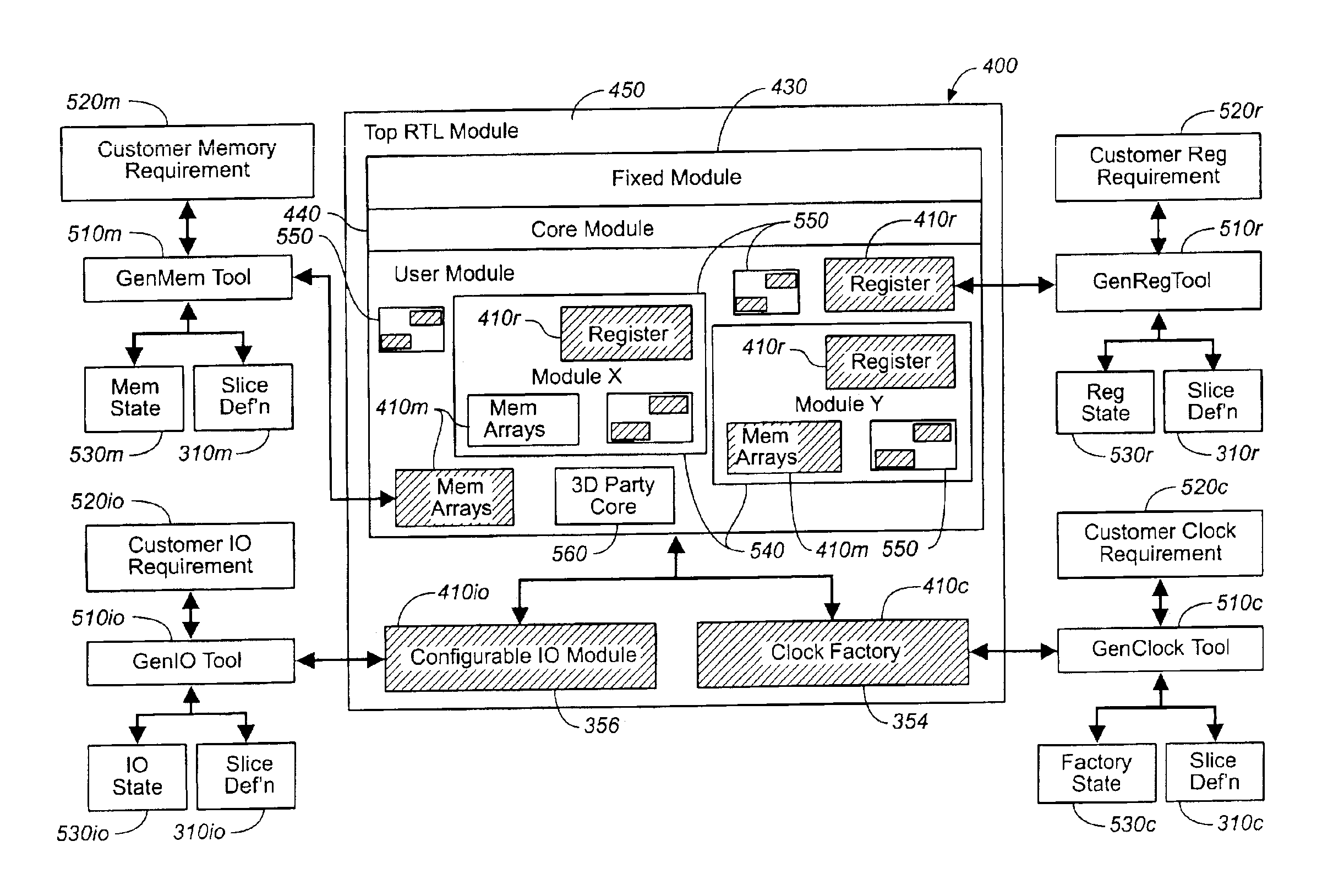

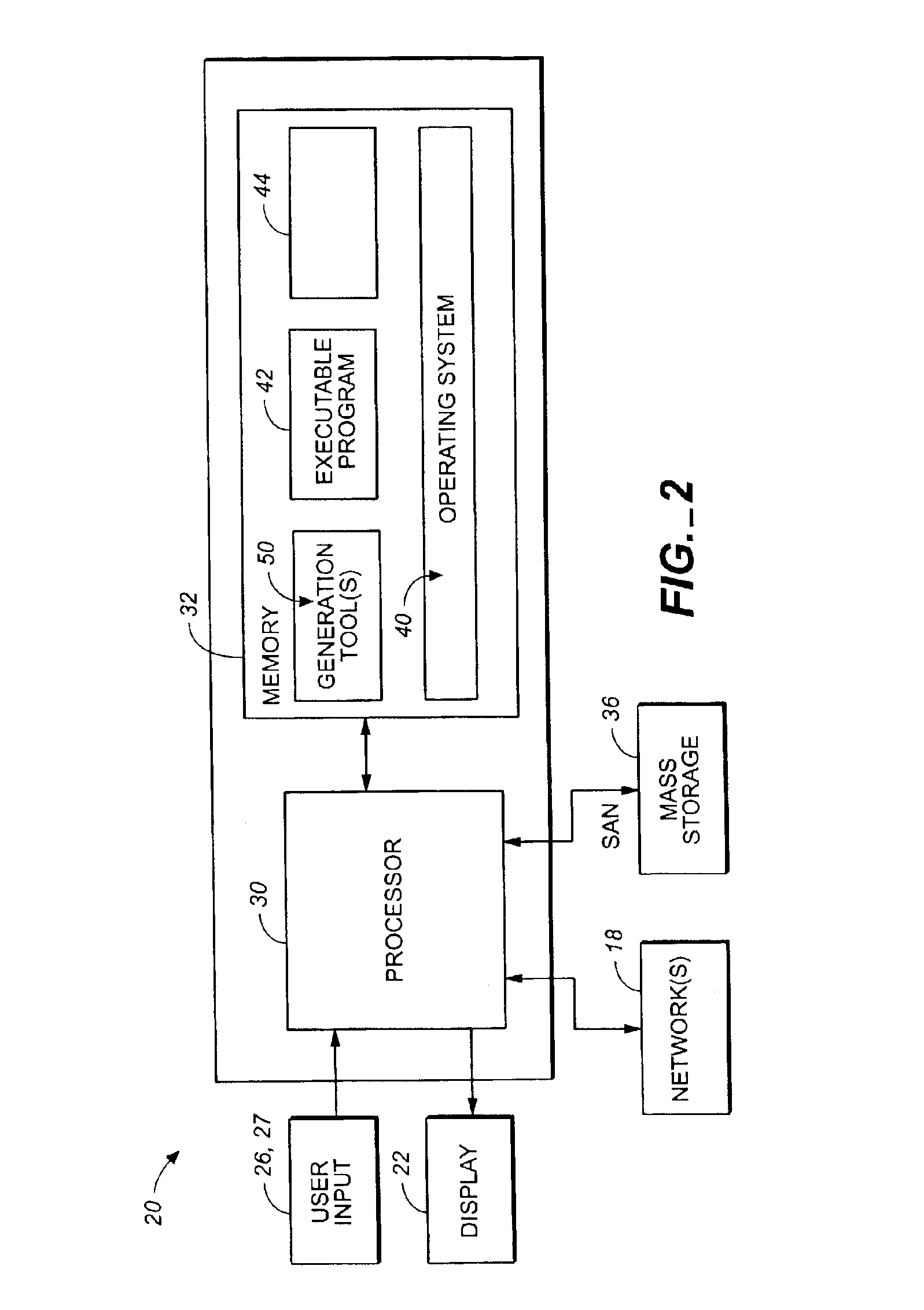

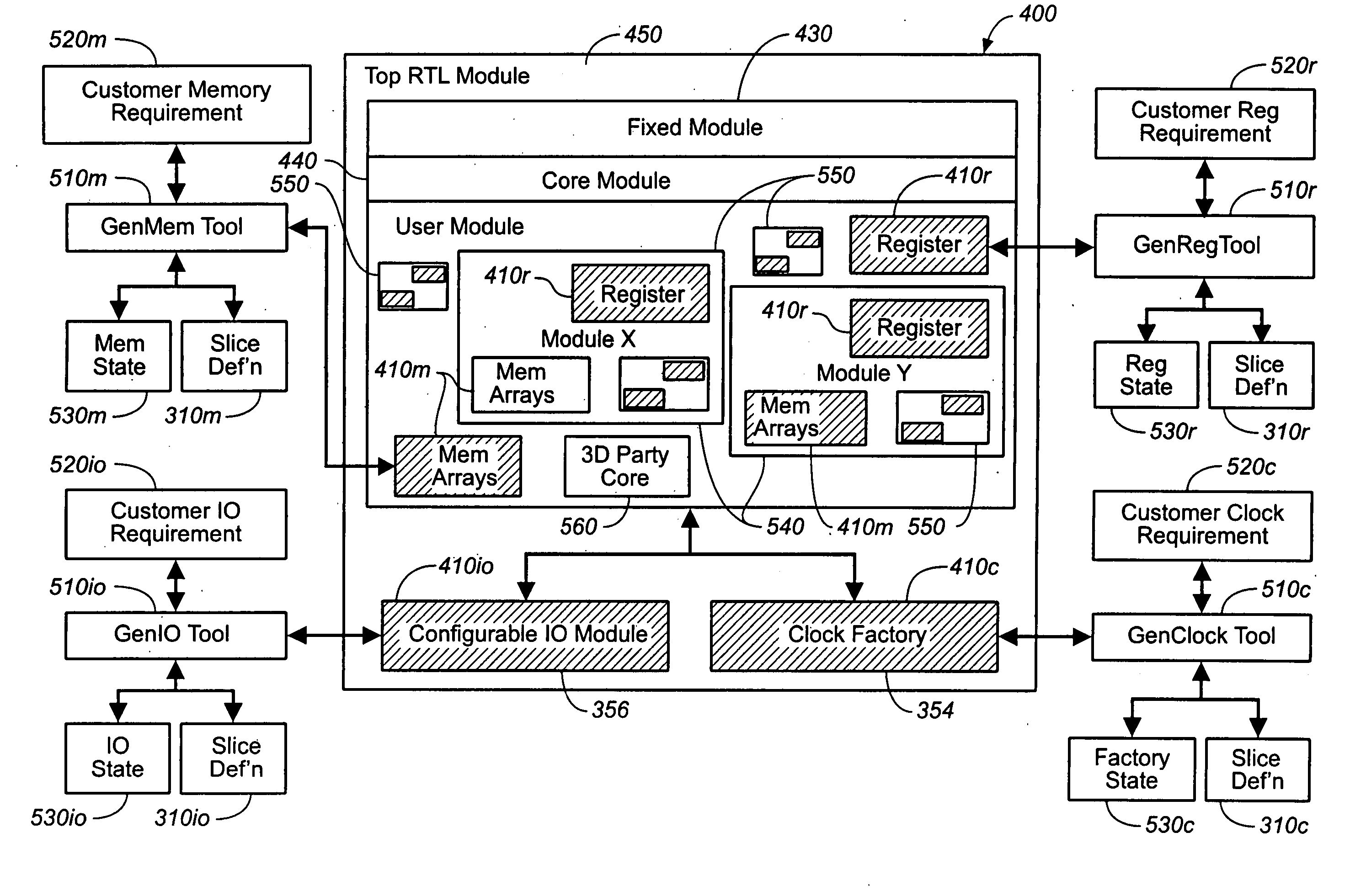

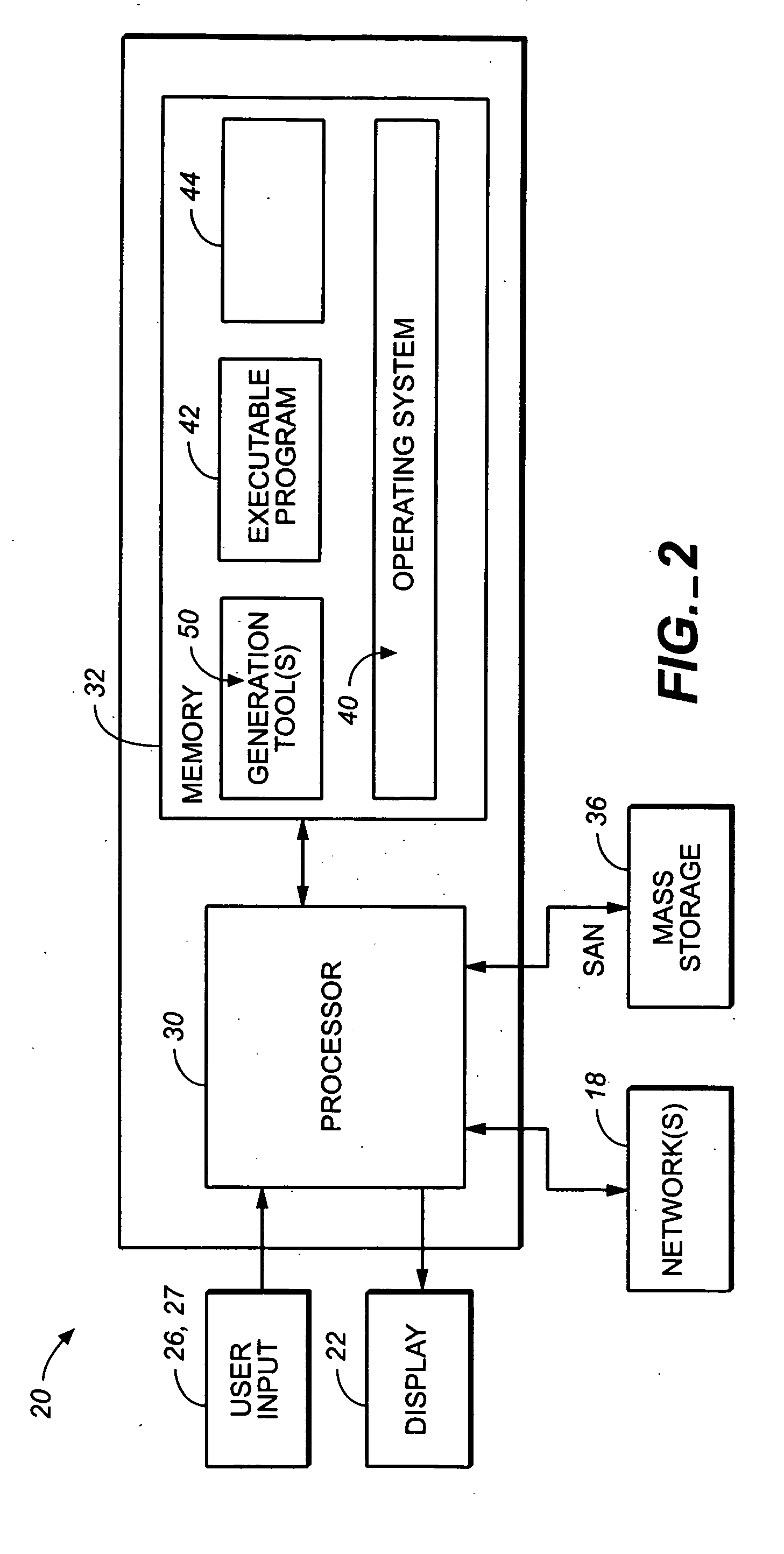

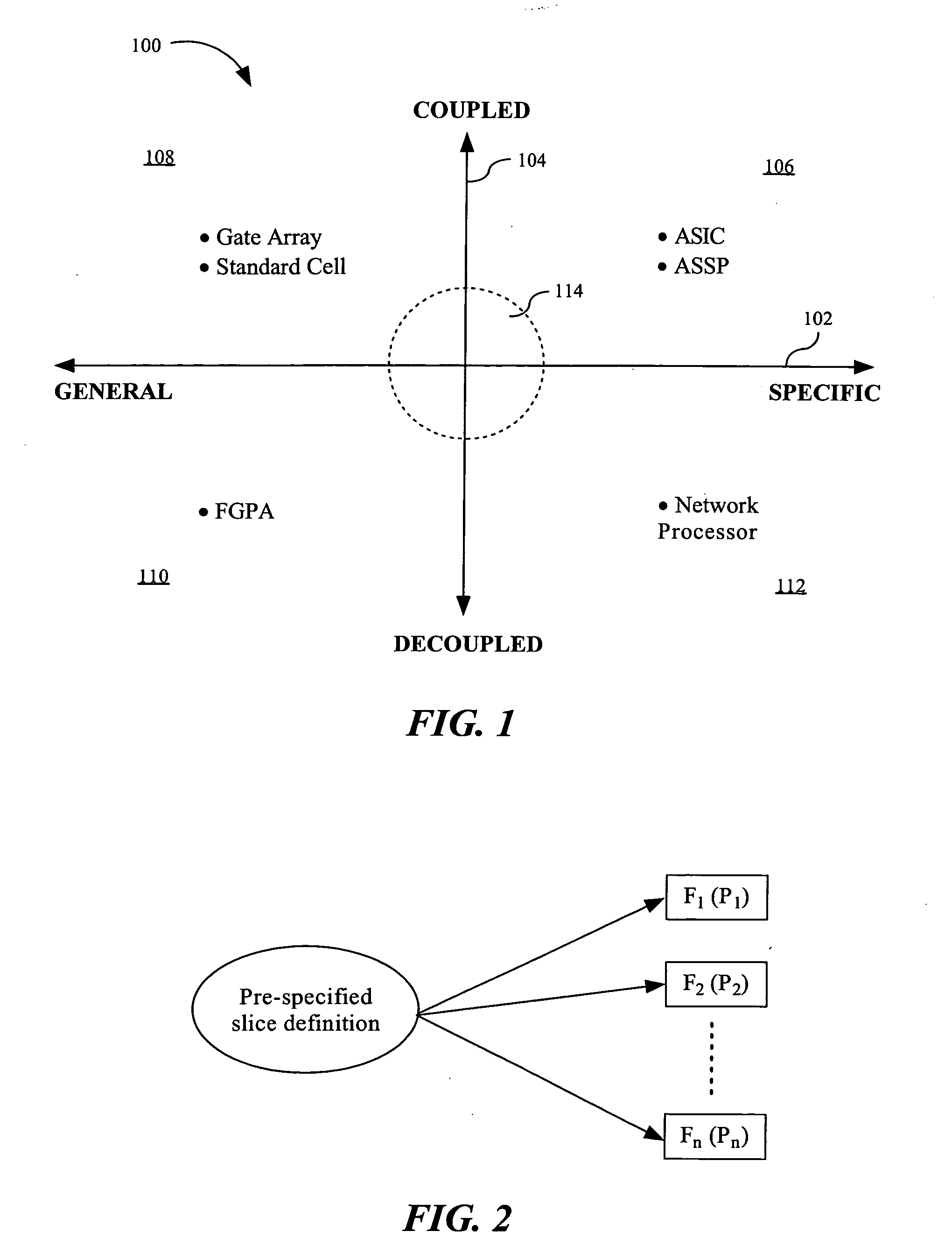

Simplified process to design integrated circuits

ActiveUS7055113B2Computer aided designSoftware simulation/interpretation/emulationCustomer requirementsFoundry

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

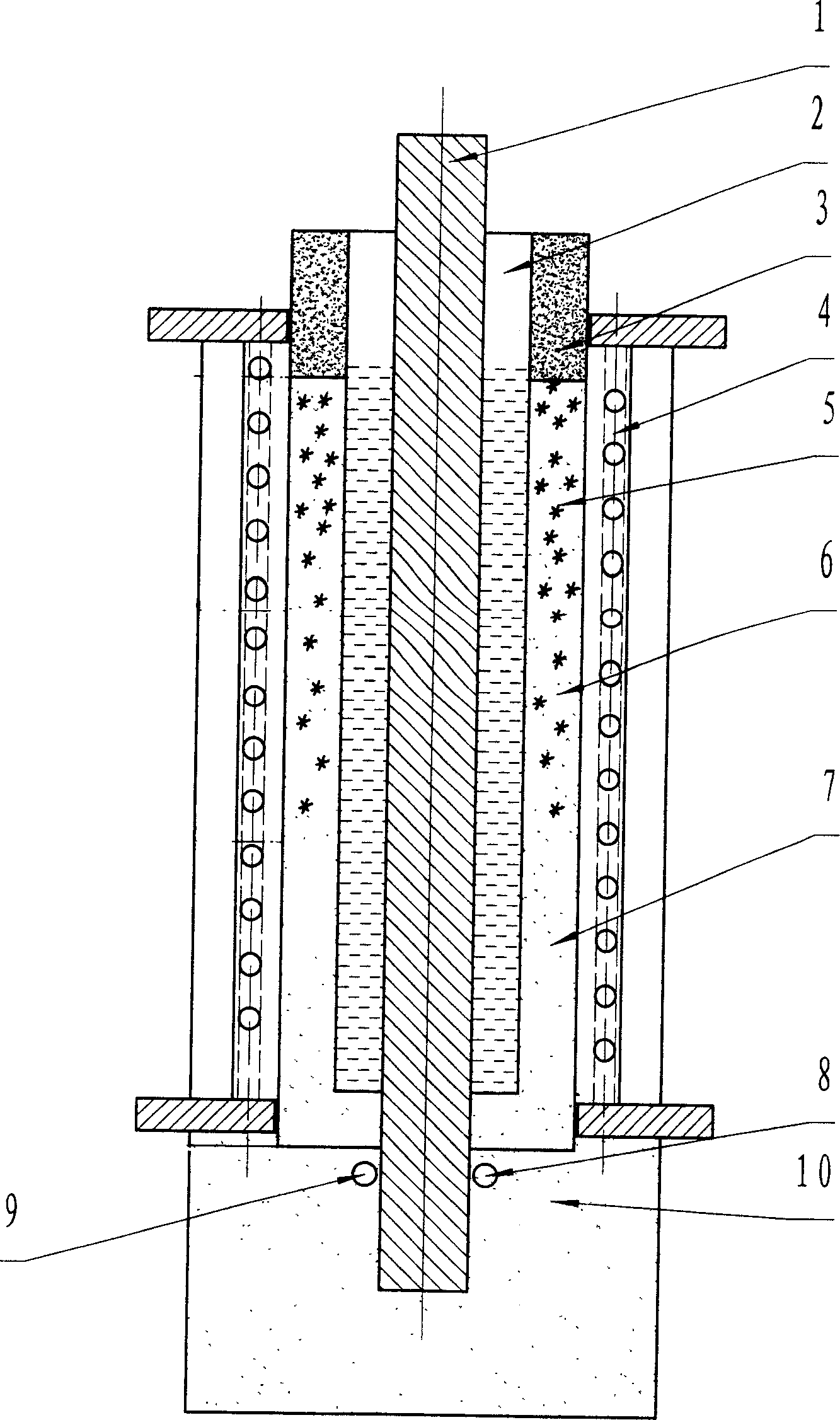

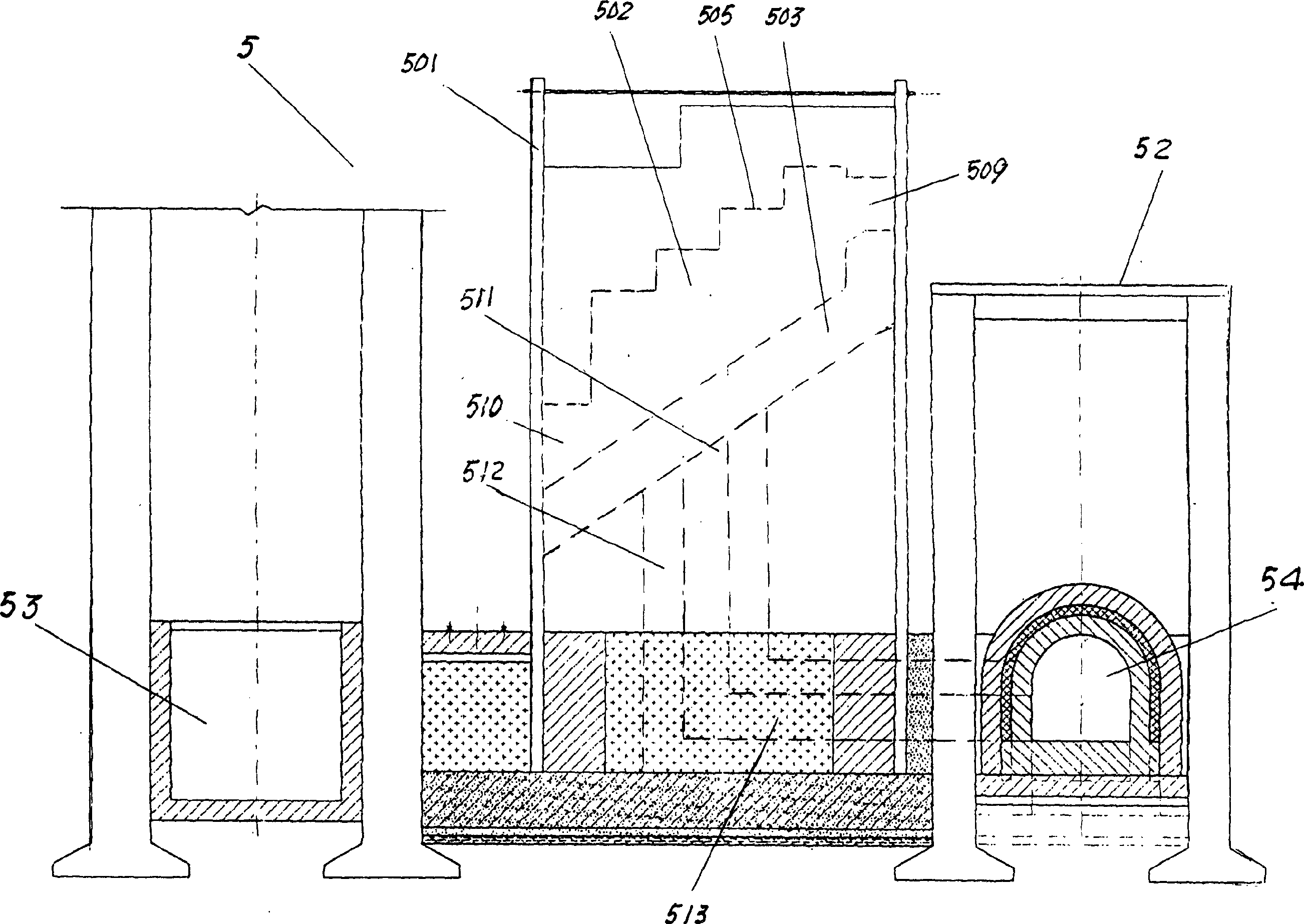

High-speed steel composite roller and casting method thereof

The invention belongs to the field of steel rolling manufacture, specifically is a high-speed steel composite roll for strip mill in steel rolling industry and casting method thereof. The outer layer of the composite roll is made of high-speed steel, the middle layer is made of ductile cast iron base iron or graphite semisteel, the core is made of ductile cast iron. The invention employs centrifugal compound foundry technique, the roll is moulded by three times of casting. Constant centrifugal rotating speed is kept in centrifuge, the metal material of the outer layer and the middle layer are mould cast, and then the metal of the roll core is statically cast to form the final product. Compared with former dual-layer or other three-layer composite high-speed steel rolling rolls, the three layers of metal of the high-speed steel composite roll of the invention are well combined and have high strength; the optimal selection of the material of the middle layer improves the strength of the bonding layer, the carbide affecting the binding performance in the middle layer is reduced, the spreading of alloy element in the outer layer high-speed steel to the core, which affects the core material performance, is also effectively avoided by the middle layer, cracking and dropping off of the working layer in hot processing and rolling process are prevented as well.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

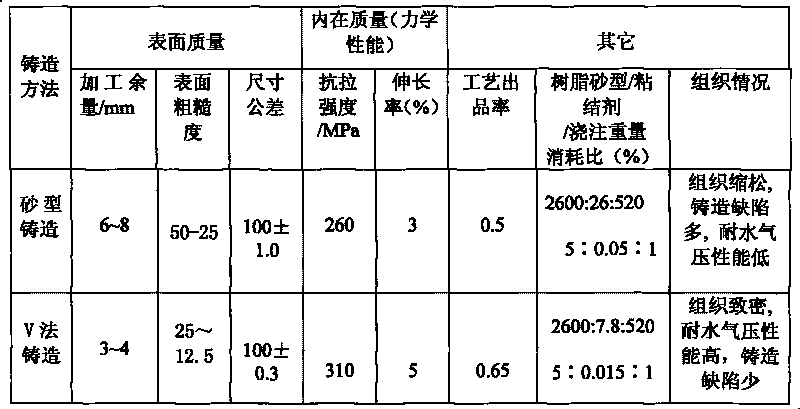

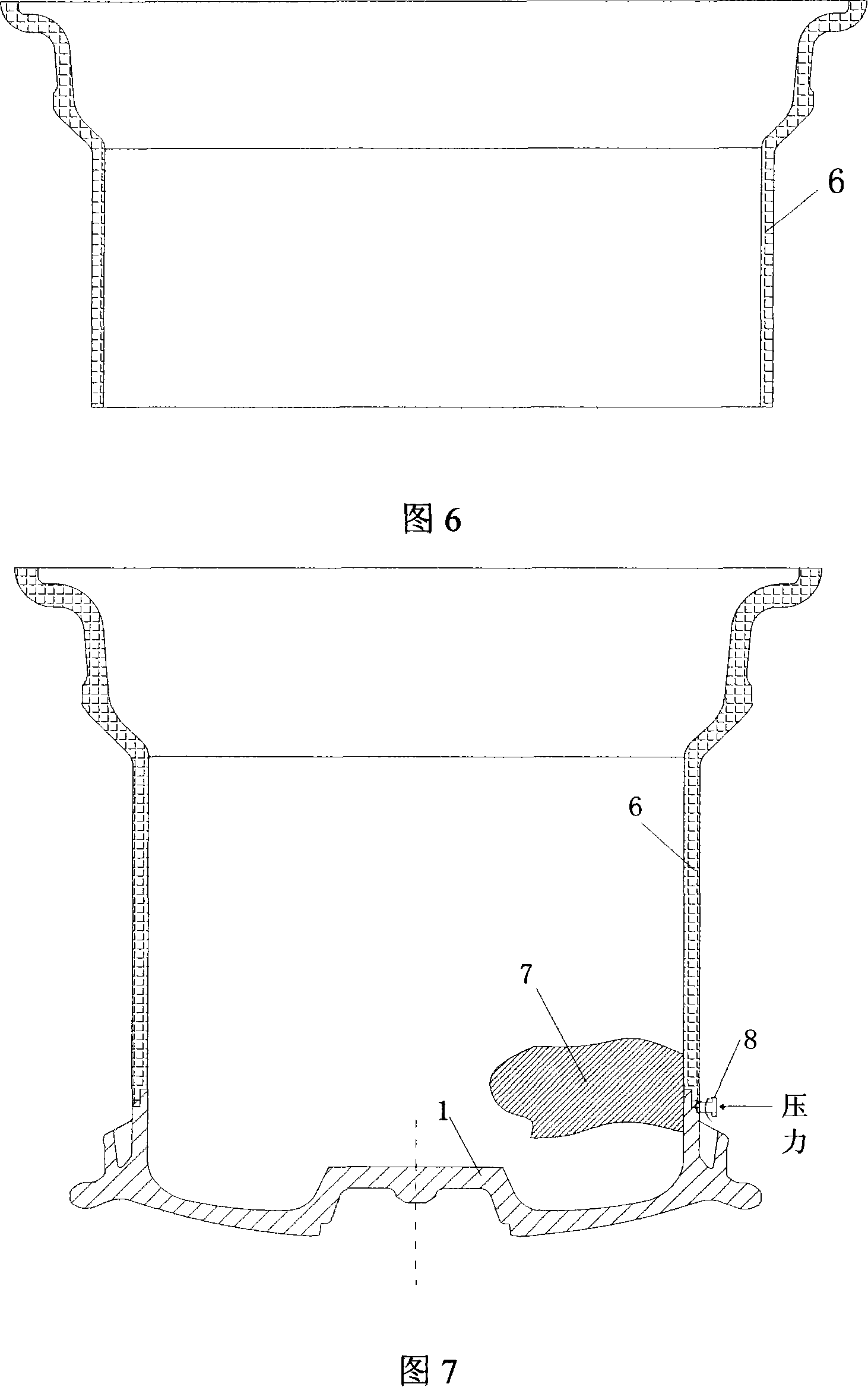

Method for producing voltage-bearing aluminum alloy tank body of ultra-high voltage switch by V-process

ActiveCN101693282AImprove mechanical propertiesImprove quality levelFoundry mouldsFoundry coresFoundryIntermediate frequency

The invention discloses a method for producing a voltage-bearing aluminum alloy tank body of an ultra-high voltage switch by a V-process, comprising the following steps: model making, thin film heating, thin film shaping (film absorbing), coating spraying, sandbox placing, ram-jolting by adding sand , back film covering, film loosening, core setting, box folding, pouring, removing box and shaking out. After the process is improved, an intermediate frequency furnace is utilized to melt and a crucible heat preserving furnace is utilized to modify and refine. When melting in the intermediate frequency furnace, microelements such as tombarthite and the like are replenished and a new non-stirring melting and refining technology is adopted so as to reduce oxide inclusion content in alloy liquid. Modification and refining treatment in the crucible heat preserving furnace ensures high purity degree and high component precision of aluminum liquid, and using pure aluminum alloy liquid can increase the ratio of acquiring qualified pressure-proof tank body foundry products.

Owner:NANYANG HUISEN PRECISION INSTR CASTING

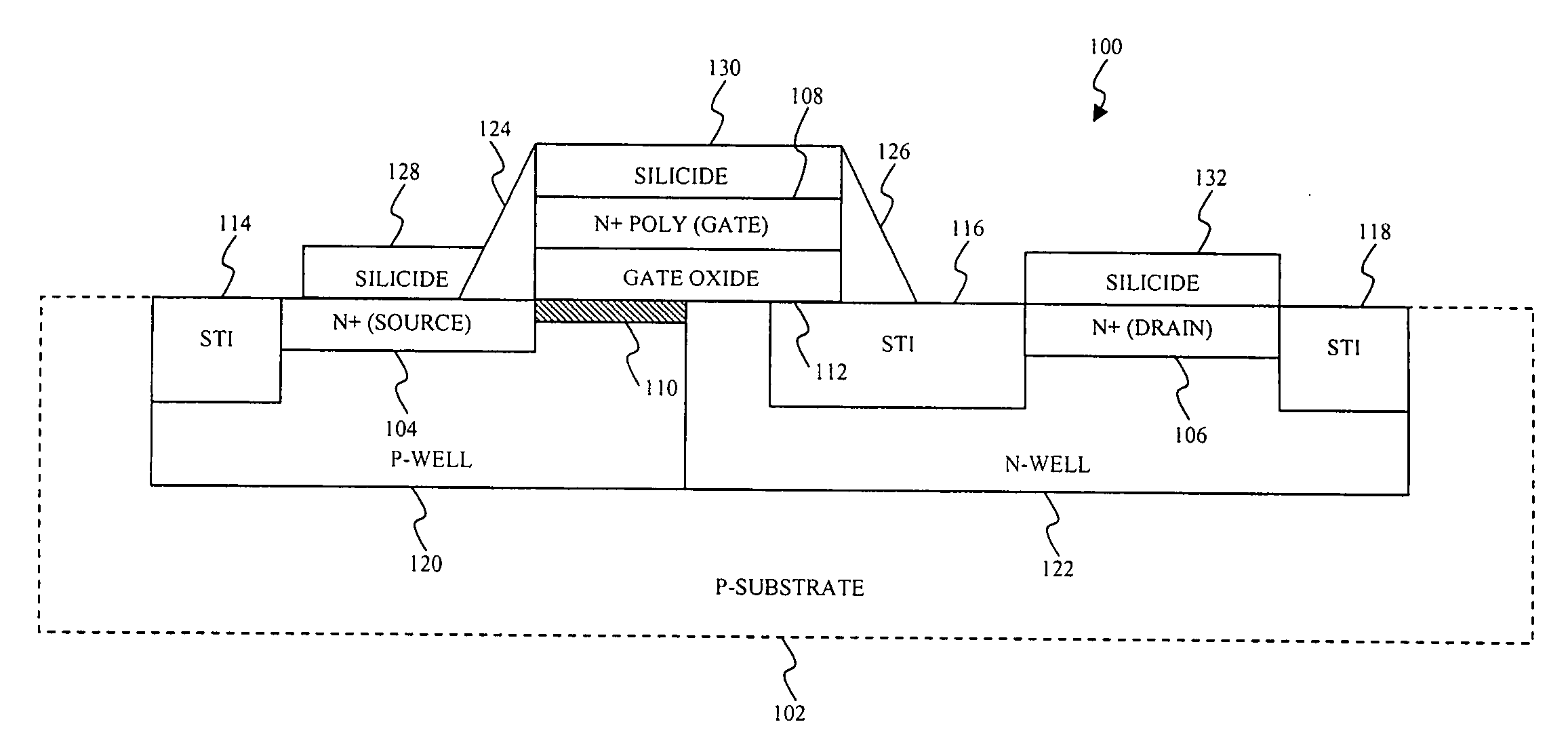

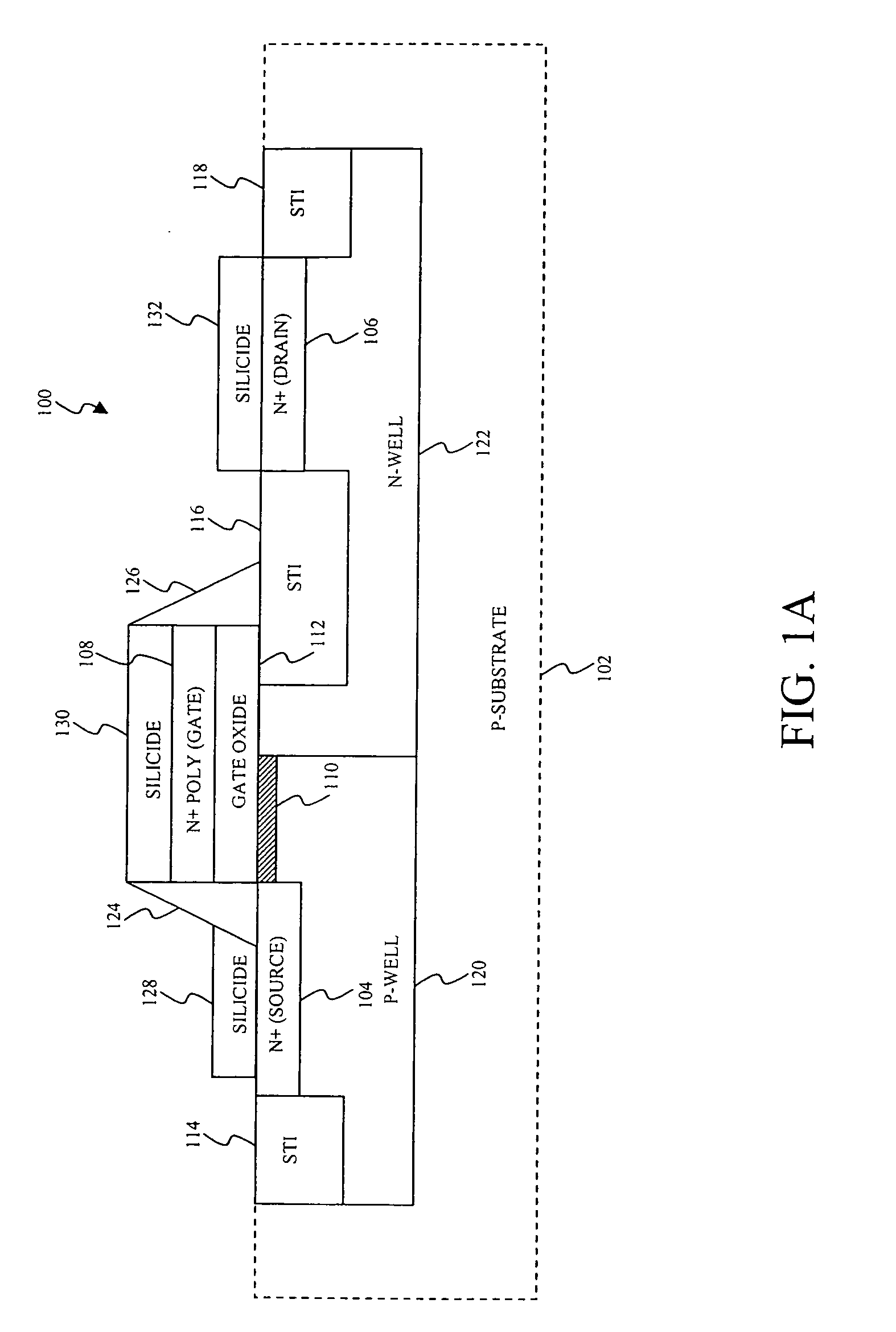

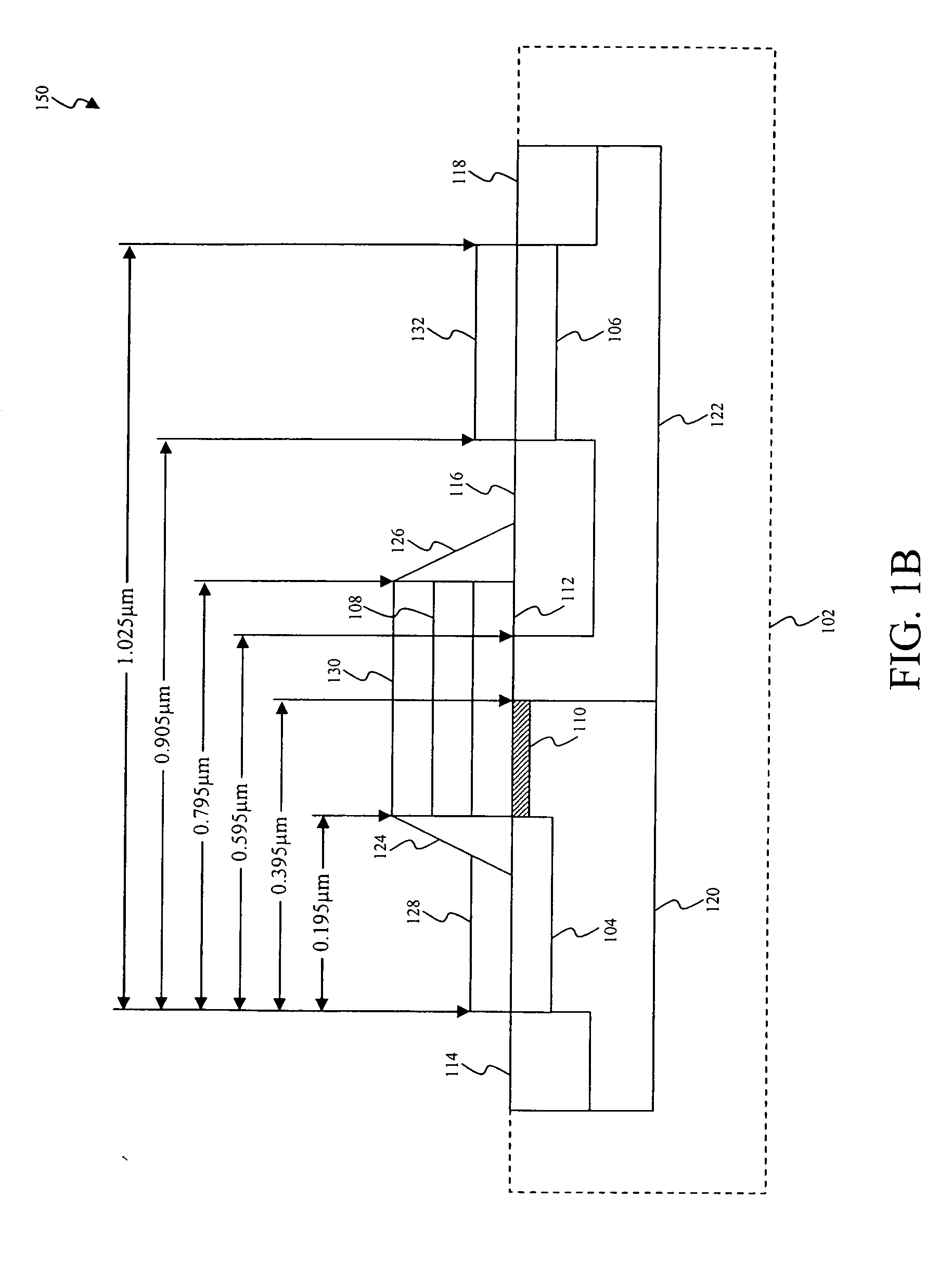

Shallow trench isolation (STI) based laterally diffused metal oxide semiconductor (LDMOS)

An apparatus is disclosed to increase a breakdown voltage of a semiconductor device. The semiconductor device includes a first heavily doped region to represent a source region. A second heavily doped region represents a drain region of the semiconductor device. A third heavily doped region represents a gate region of the semiconductor device. The semiconductor device further includes a shallow trench isolation (STI) region to increase the resistance from the drain region to the source region. The STI region includes a first side vertically aligned with a second side of the gate region. The STI region extends from the first side to a second side in contact with a second side of the drain region. The breakdown voltage of the n-type semiconductor device is directly proportional to a vertical length, or a depth, of the first side and / or the second side of the STI region. The horizontal length, or distance from the first side to the second side, of the STI region does not substantially contribute to the breakdown voltage of the semiconductor device. As a result, a conventional CMOS logic foundry technology may fabricate the STI region of the semiconductor device using a low operating voltage process minimum design rule.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

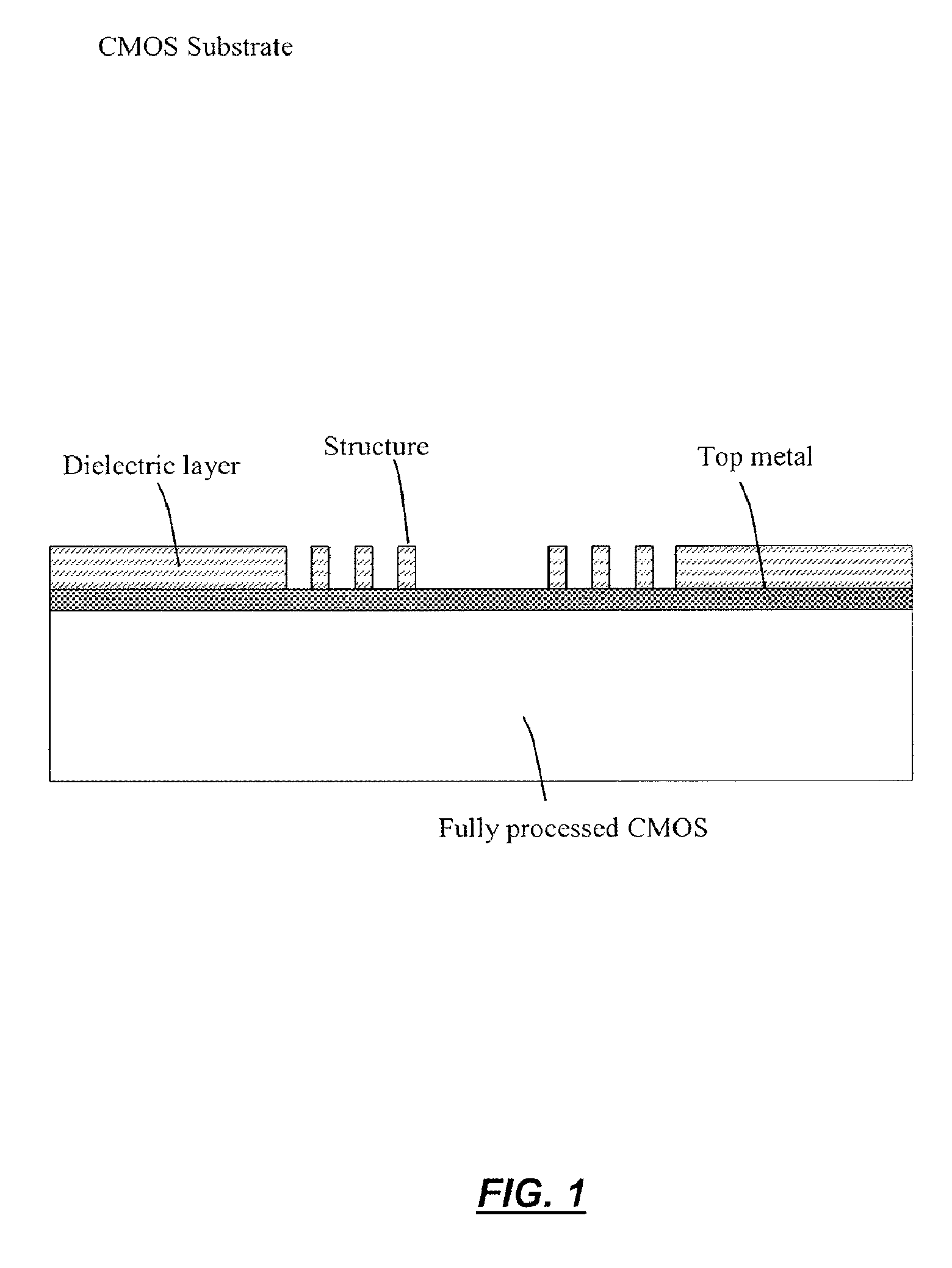

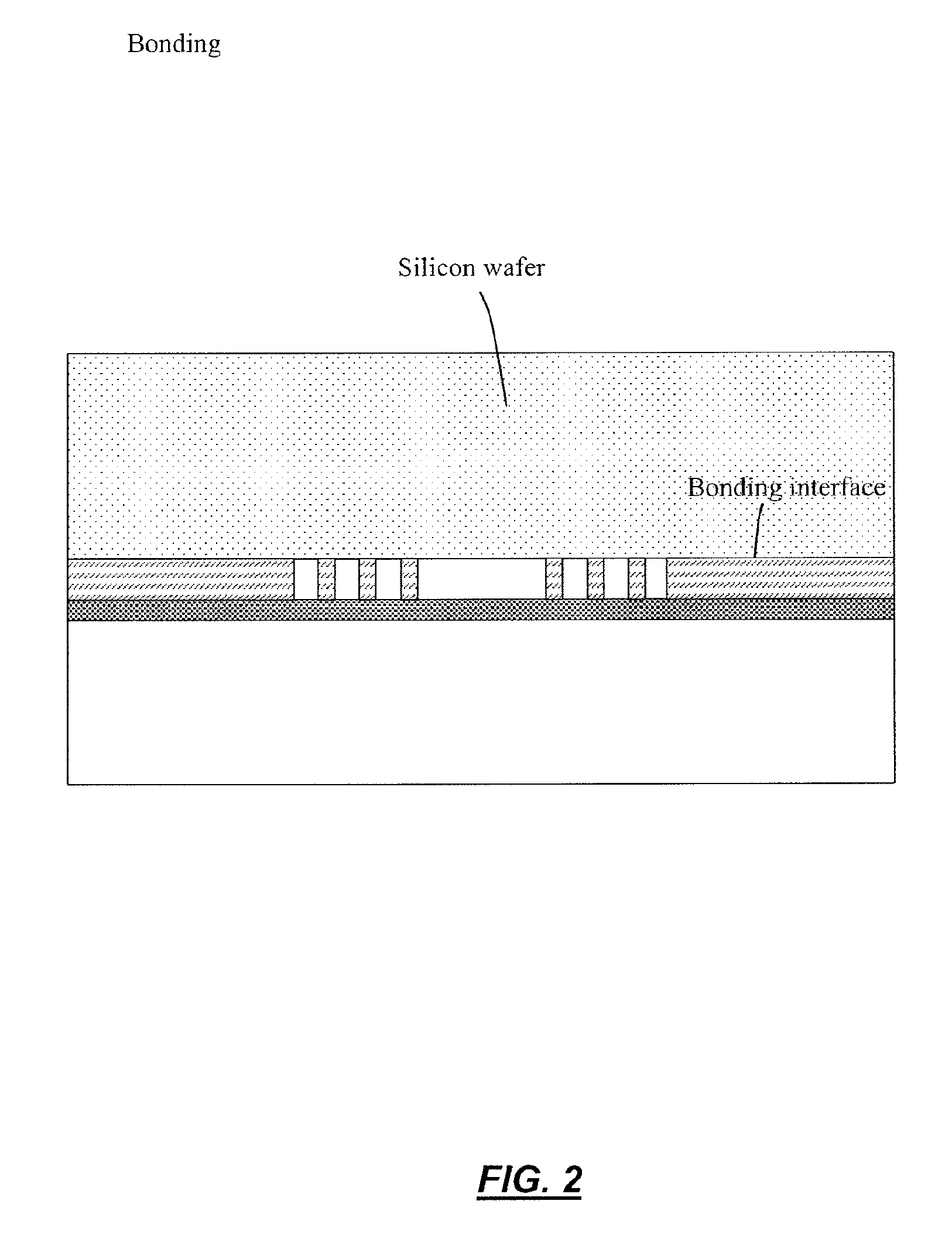

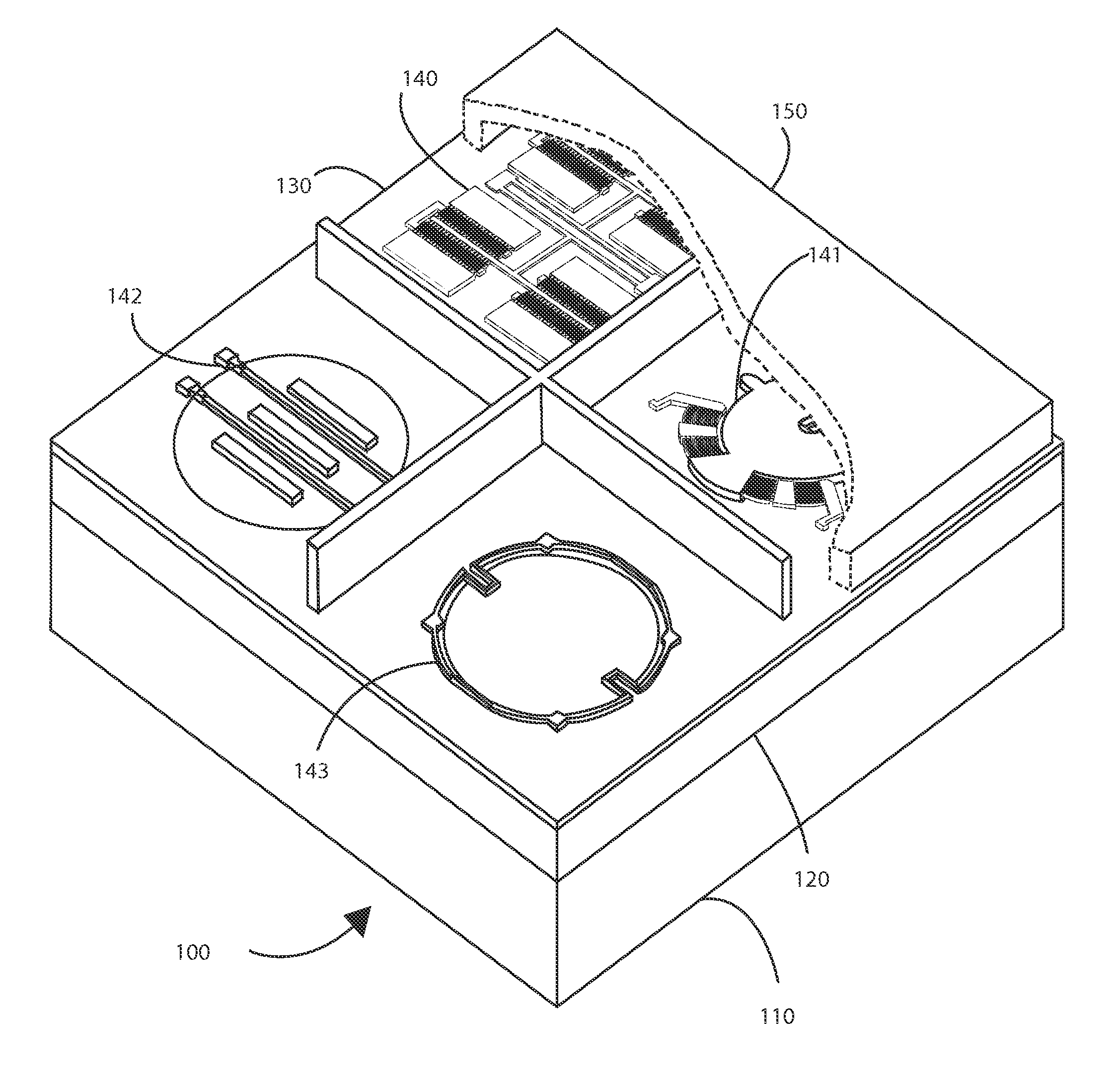

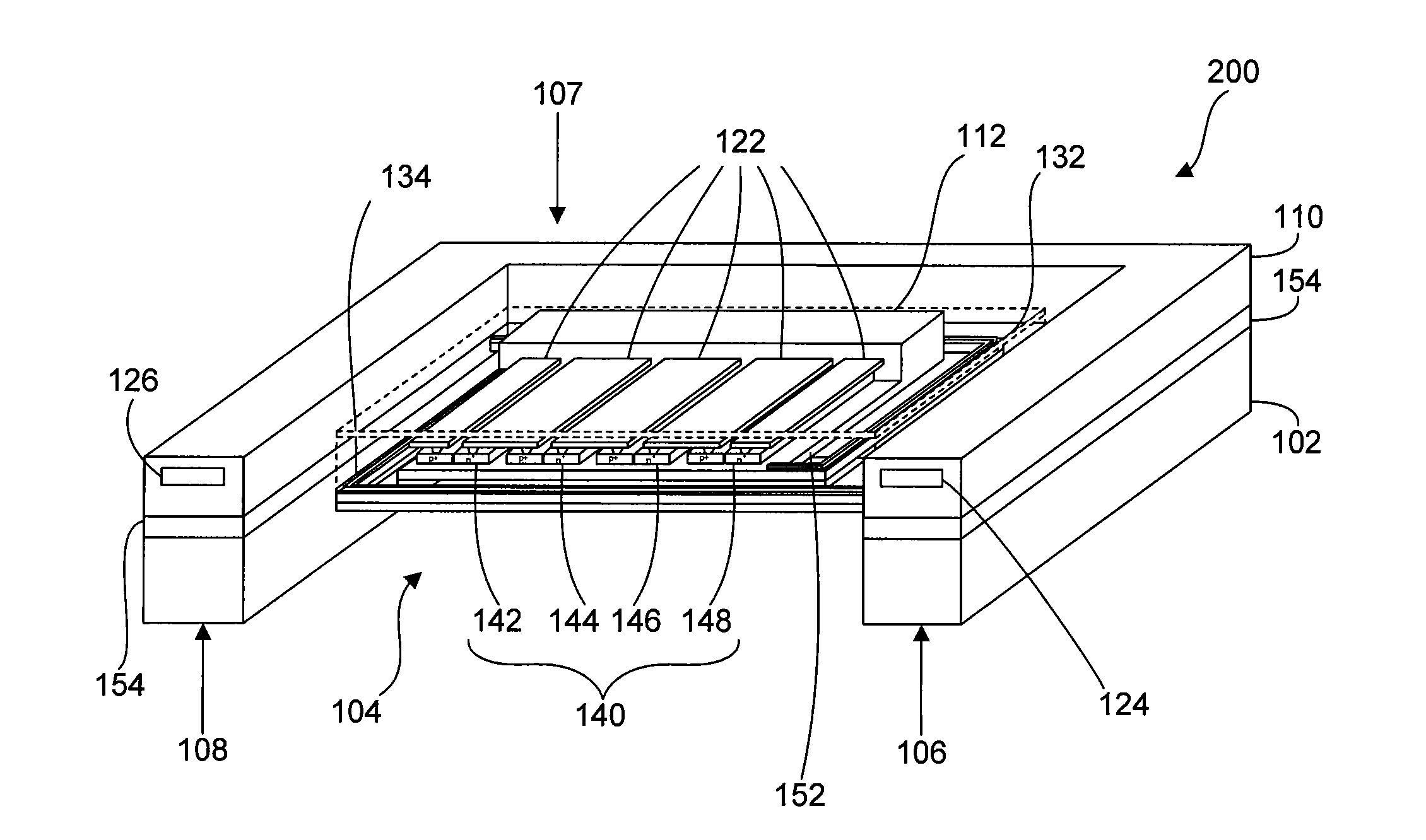

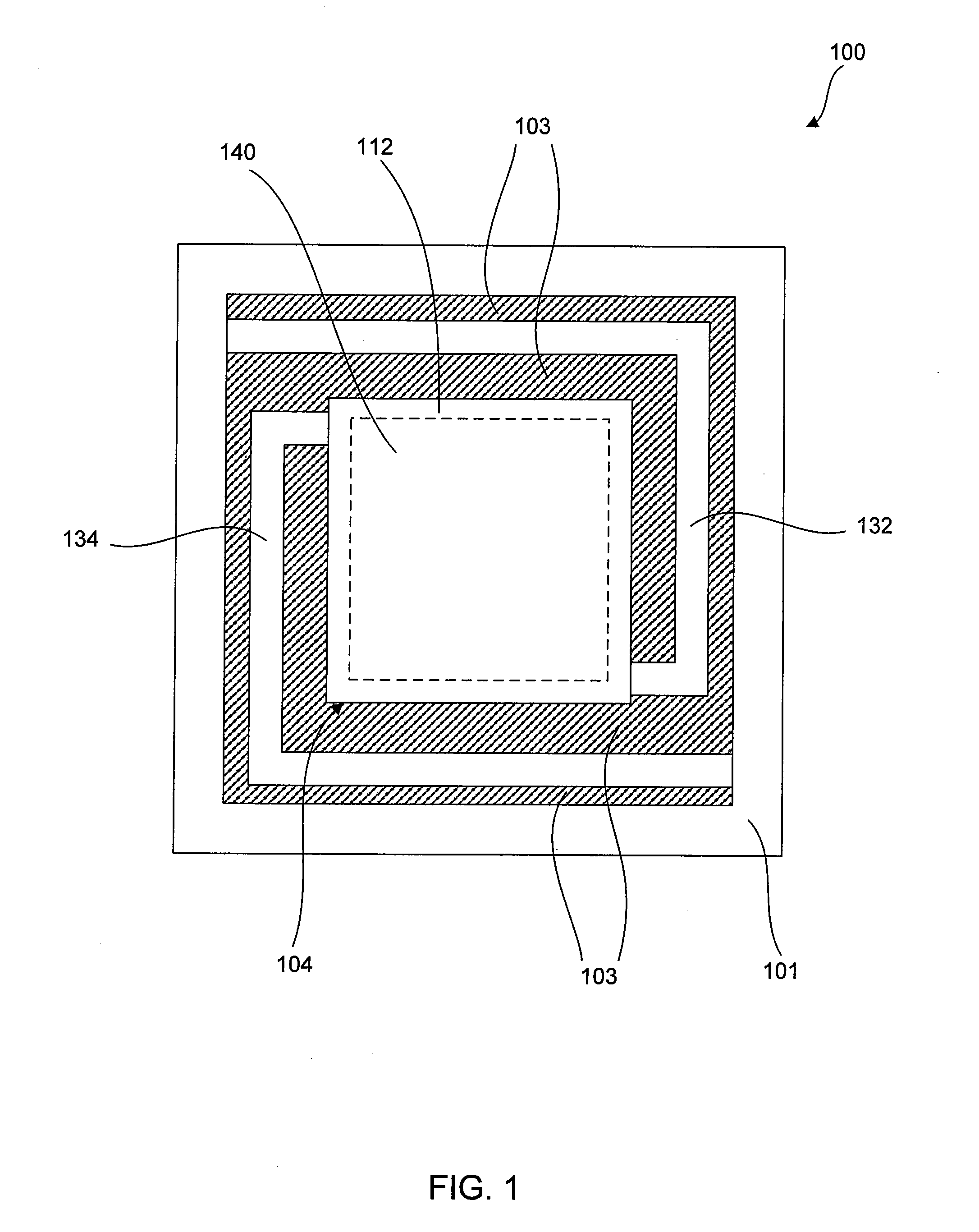

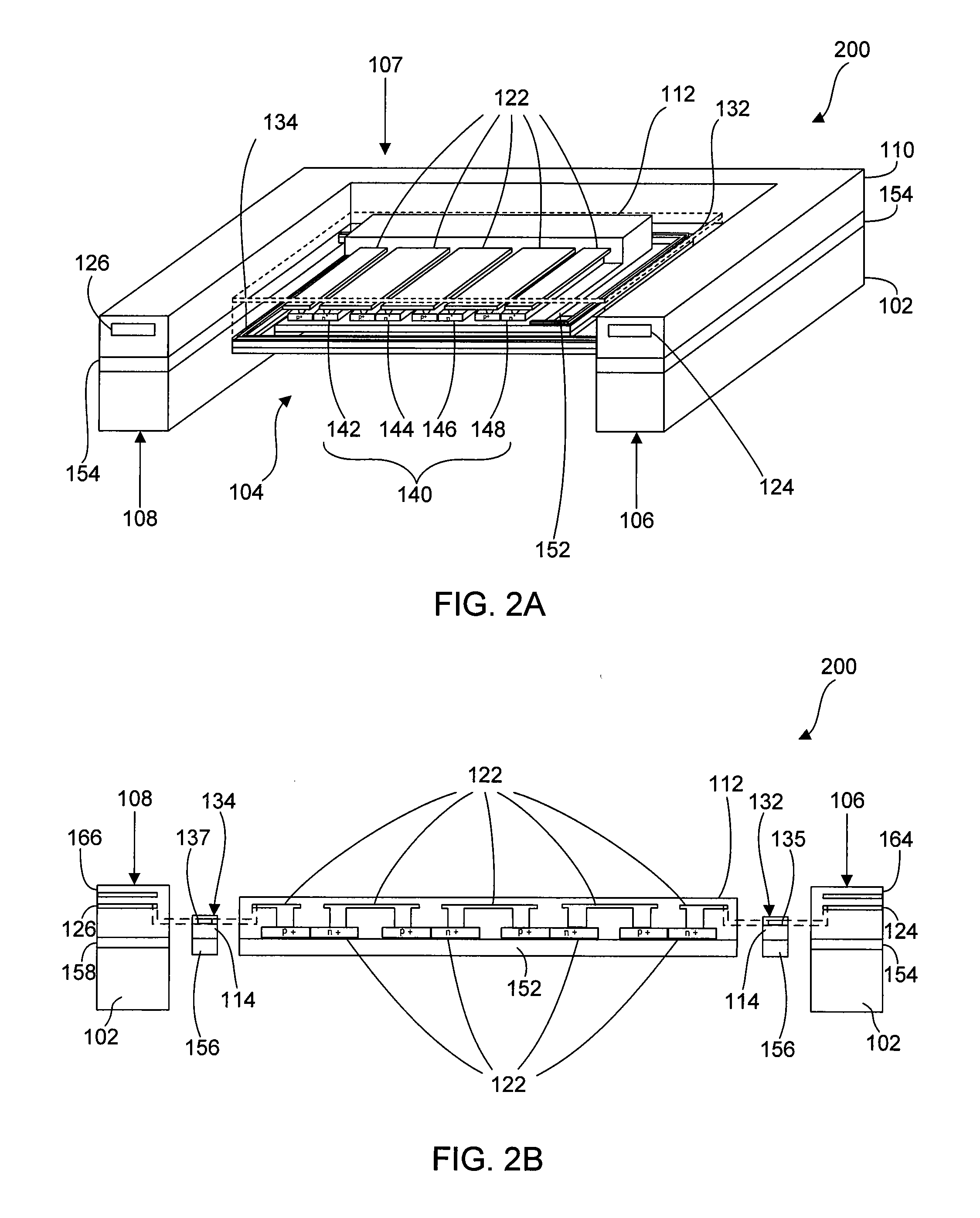

Method and structure of monolithetically integrated inertial sensor using IC foundry-compatible processes

ActiveUS8227285B1Reduce chip sizeReduce parasitismSemiconductor/solid-state device testing/measurementSolid-state devicesCMOSFoundry

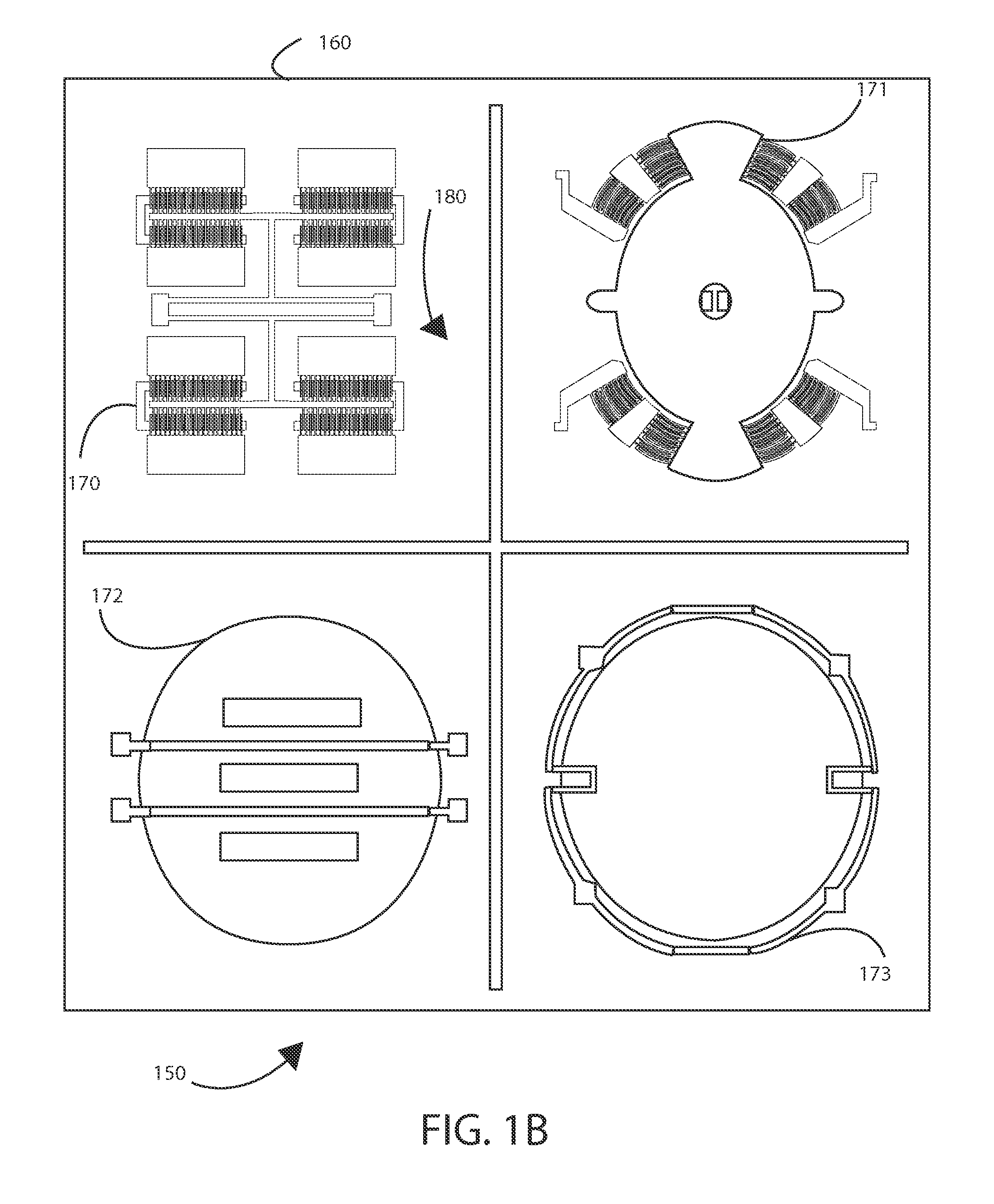

The present invention relates to integrating an inertial mechanical device on top of a CMOS substrate monolithically using IC-foundry compatible processes. The CMOS substrate is completed first using standard IC processes. A thick silicon layer is added on top of the CMOS. A subsequent patterning step defines a mechanical structure for inertial sensing. Finally, the mechanical device is encapsulated by a thick insulating layer at the wafer level. Comparing to the incumbent bulk or surface micromachined MEMS inertial sensors, the vertically monolithically integrated inertial sensors have smaller chip size, lower parasitics, higher sensitivity, lower power, and lower cost.

Owner:MOVELLA INC

Foundry compatible process for manufacturing a magneto meter using lorentz force for integrated systems

A method for fabricating an integrated electronic compass and circuit system. The fabrication method begins with providing a semiconductor substrate comprising a surface region. One or more CMOS integrated circuits are then formed on one or more portions of the semiconductor substrate. Once the CMOS circuits are formed, a thickness of dielectric material is formed overlying the one or more CMOS integrated circuits. A substrate is then joined overlying the thickness of the dielectric material. Once joined, the substrate is thinned to a predetermined thickness. Following the thinning process, an electric compass device is formed within one or more regions of the predetermined thickness of the substrate. Other mechanical devices or MEMS devices can also be formed within one or more regions of the thinned substrate.

Owner:MOVELLA INC

Suite of tools to design integrated circuits

InactiveUS20050240892A1Accelerate Design CycleI/O can be optimizedDetecting faulty computer hardwareComputer programmed simultaneously with data introductionFoundryCustomer requirements

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

Composite roller for high vanadium high speed steel and its production process

The invention offers the high V super-speed steel complex roller and its producing craft. The roller includes roller heart and roller shell, the roller heart uses low metal alloy steel or middle carbon steel to produce, the shell uses high V super-speed steel, whose main element is : C: 1.8--3.5A%, V: 7--12%, Cr: 4--5%, Mo: 2--4%, Ni: 0.5--1.5%, other is Fe. The producing craft is: melt and cast the heart and shell by responding heat way. The roller in the invention has good whet feature, high rate of feature and price, using safely. Fine roller, high strength of combination, no crush in use; it can reduce the stop times. It efficiently increase the roller tenacity and whet feature, solve the problems in the heart leaving foundry, and solve the problems of complicated craft and high cost.

Owner:HENAN UNIV OF SCI & TECH +1

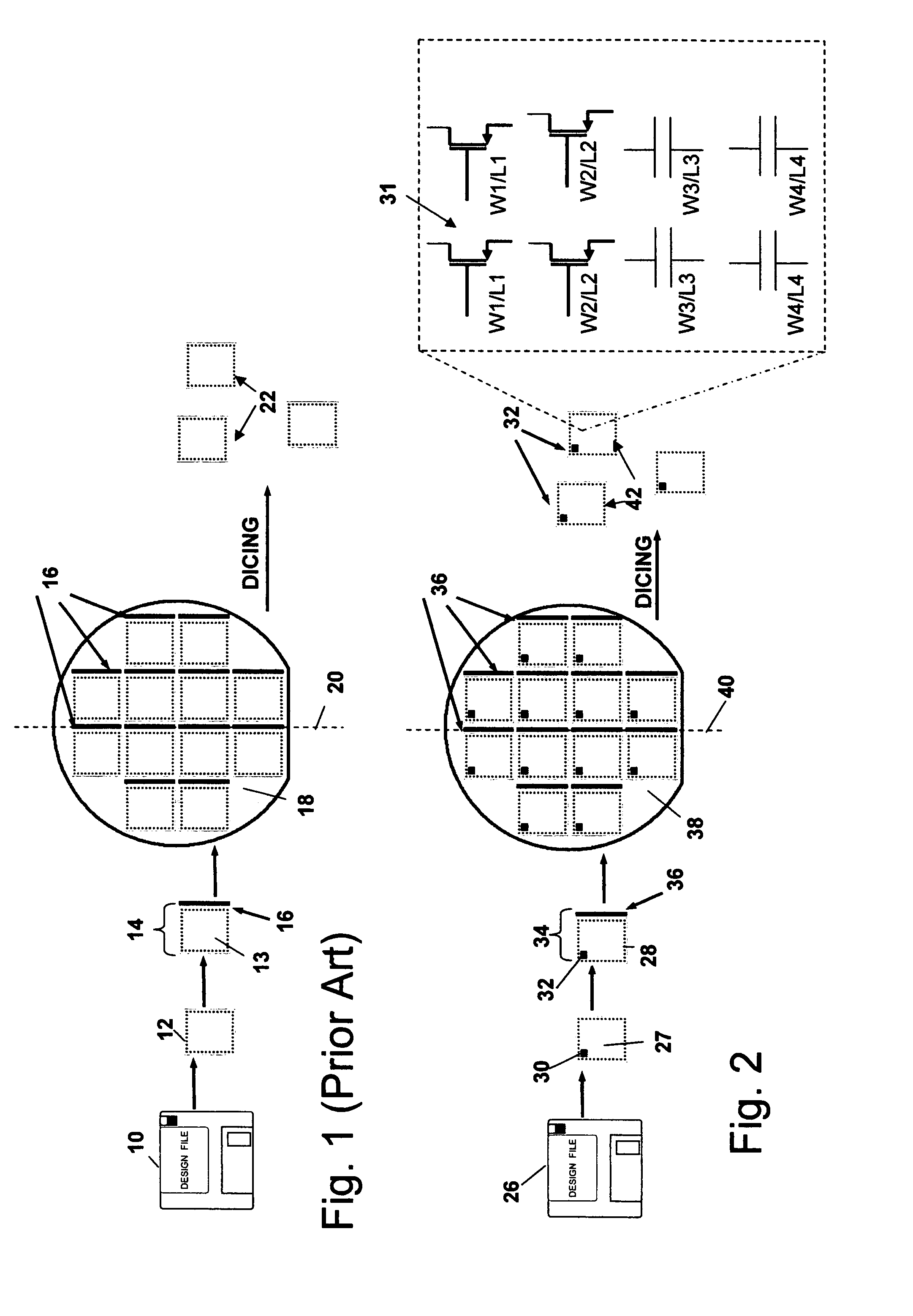

Die-level process monitor and method

InactiveUS7239163B1Minimized footprintReduce package sizeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsFoundryProcess engineering

A die-level process monitor (DLPM) provides a means for independently determining whether an IC malfunction is a result of the design or the manufacturing processing and further for gathering data on specific process parameters. The DLPM senses parameter variations that result from manufacturing process drift and outputs a measure of the process parameter. The DLPM will typically sense the mismatch of process parameters between two or more test devices as a measure of process variation between a like pair of production devices. The DLPM may be used as a diagnostic tool to determine why an IC failed to perform within specification or to gather statistics on measured process parameters for a given foundry or process.

Owner:RIDGETOP GROUP

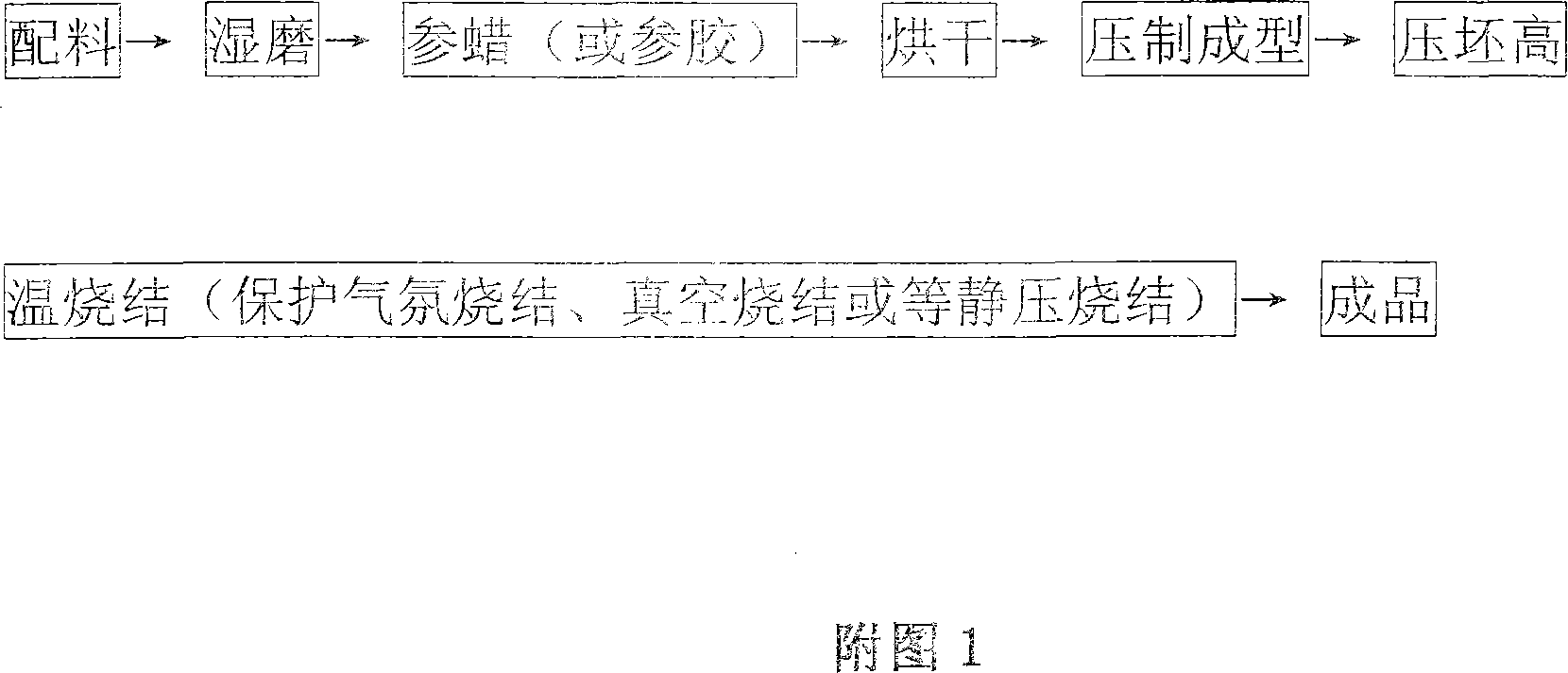

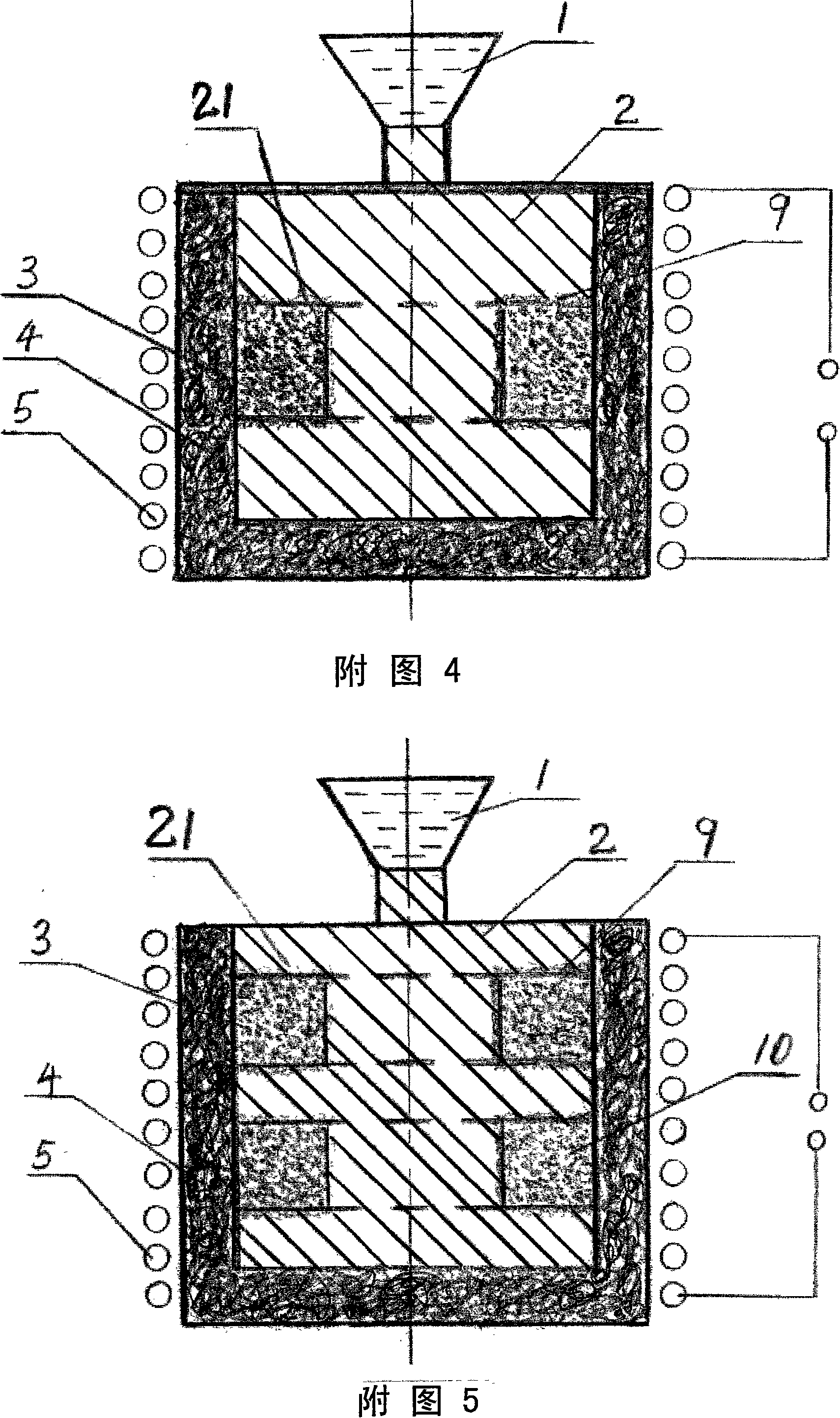

Hard alloy and double-metal composite technique and device

The utility model relates to a composite art and apparatus for hard alloy and bimetal, wherein the hard alloy is made of C with the content from 1.5 to 3.8 percent, Cr with the content from 15 to 27 percent, high chromium foundry iron with the content Fe used as binder, WC or TIC particles by the powder metallurgy technique, wherein the C and Cr are both accounted for 10-40 percent, the rest is the high chromium foundry iron, the WC or the TIC has the content from 90 to 60 percent. The hard alloy proceed composite casting with the C with the content from 1.5 to 3.8 percent, the Cr with the content from 15 to 25 percent, the rest high chromium foundry iron and spheroidal graphite cast iron in the mould provided with an electro-magnetism induction heater outside. The recombination of two materials is achieved by directly heating to the hard alloy and base metal liquid via the induction heater in the process of casting. The hard alloy produced by the invention has better wetting property and less bulking difference to the base metal, and is capable of achieving good recombination with the base metal. The invention has the advantages of simple recombination technique, easy achievement of technique, good property of the recombination products and low manufacturing costs.

Owner:丁家伟 +1

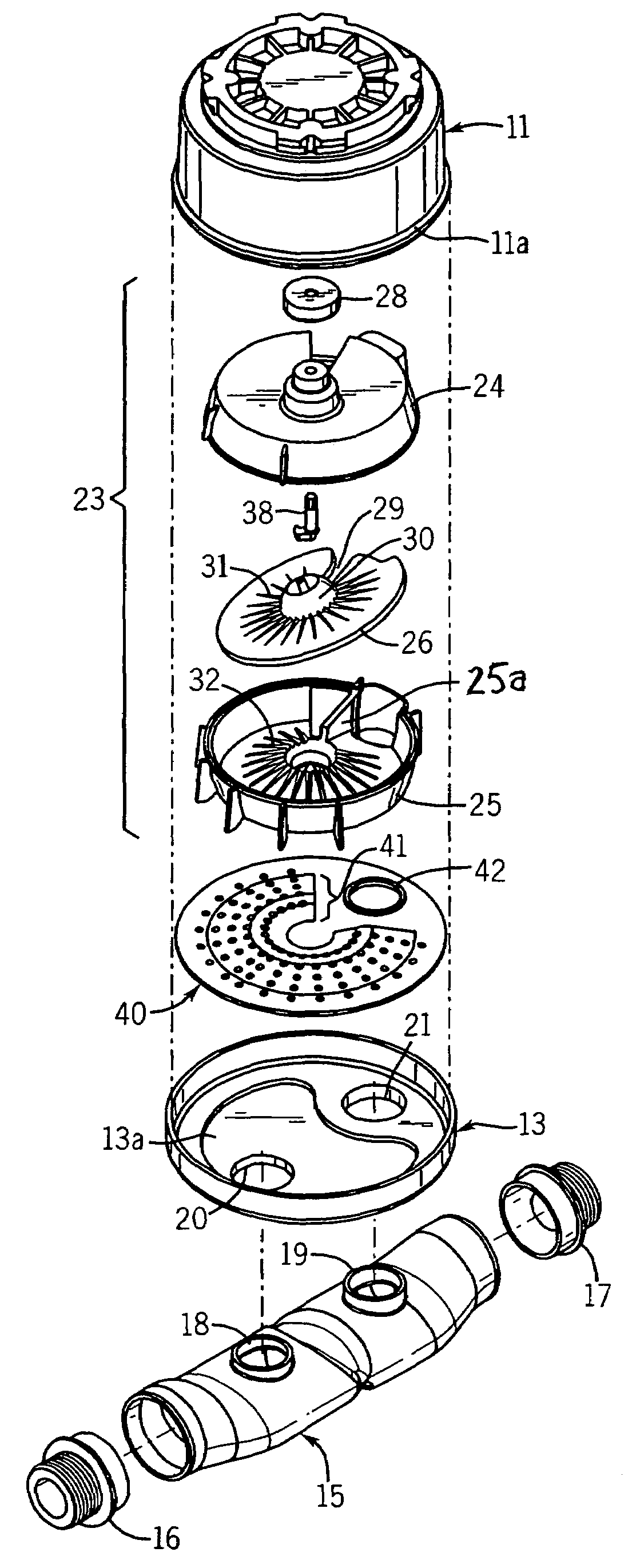

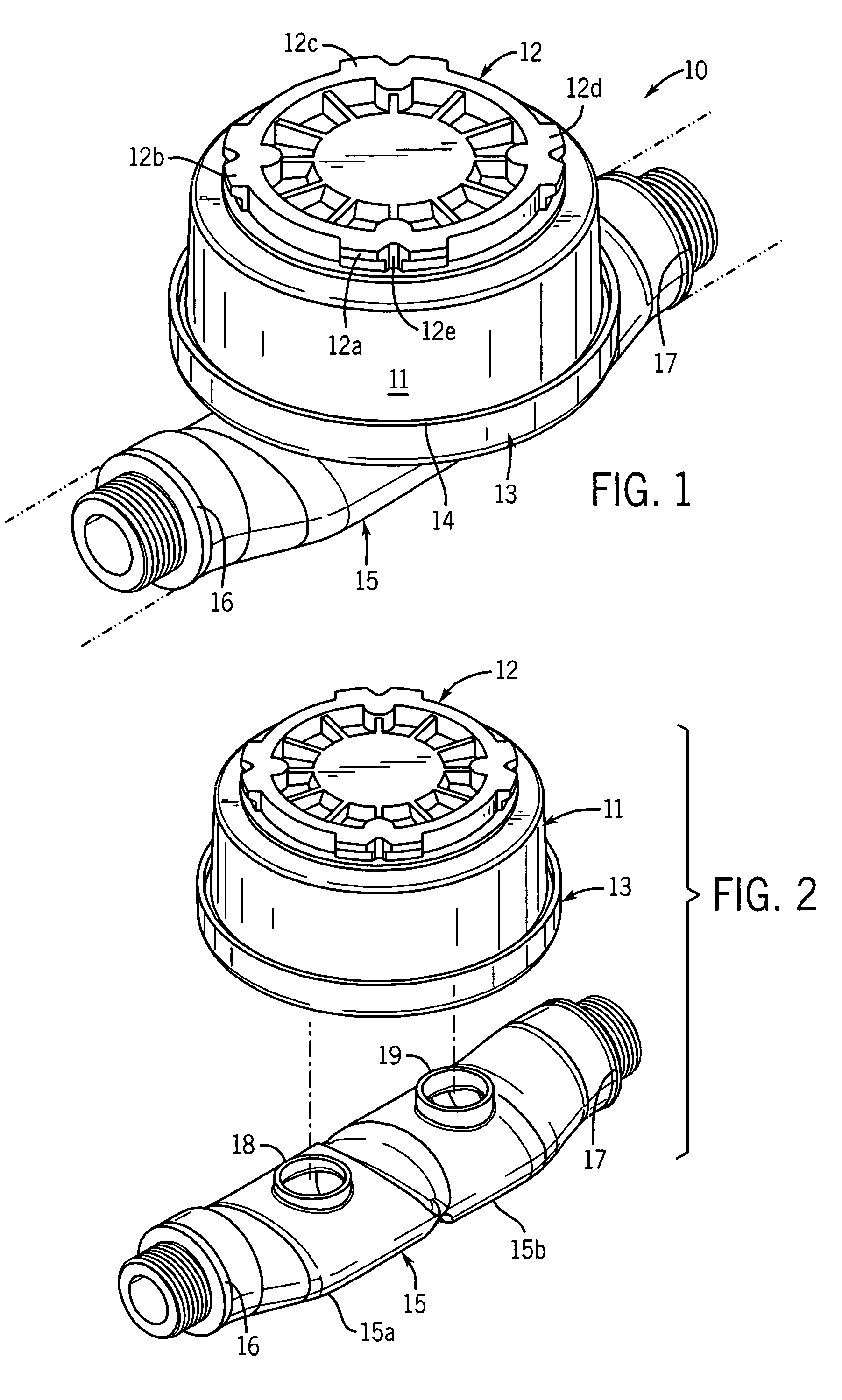

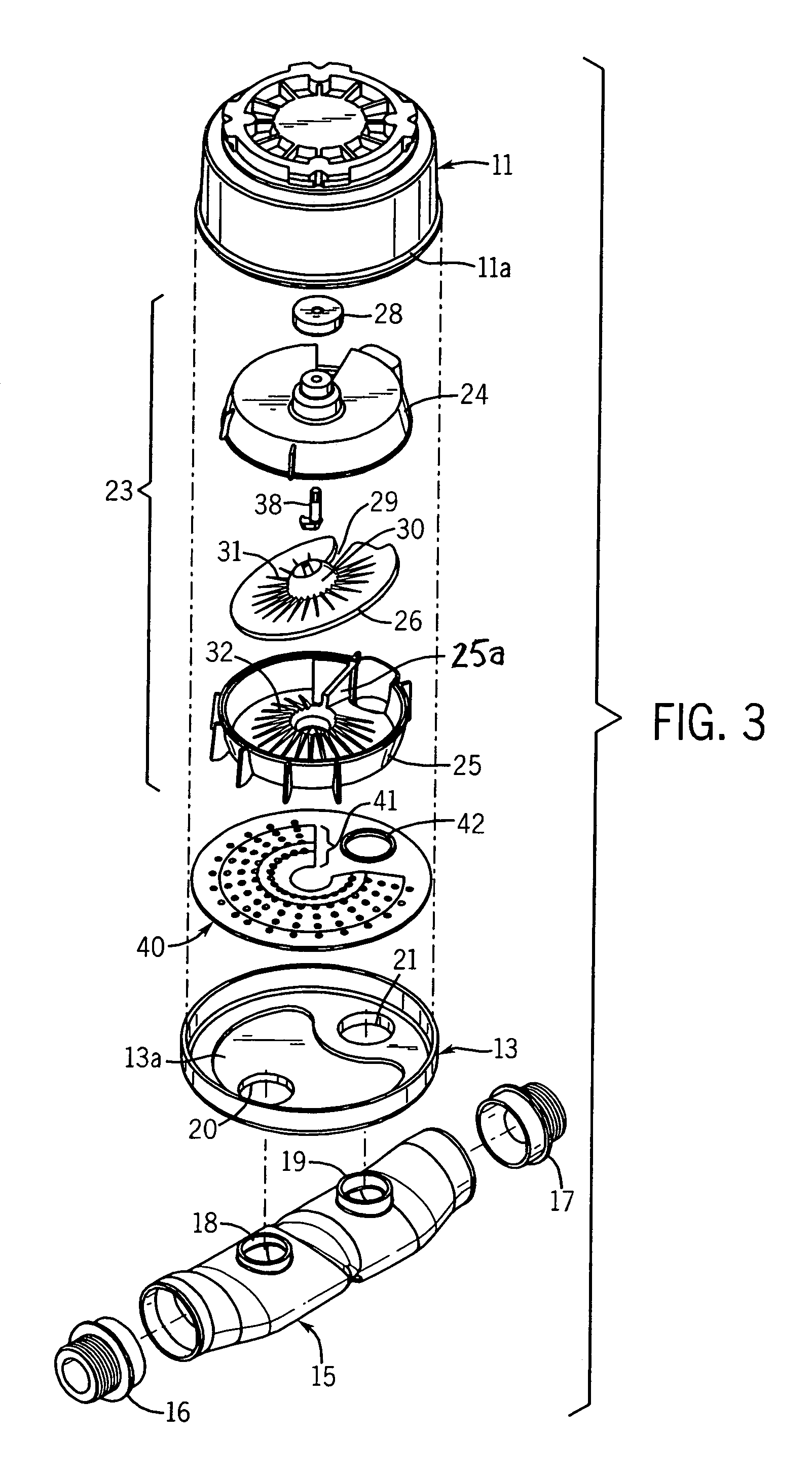

Meter housing assembly and method of assembly

ActiveUS7143645B2Reduce manufacturing costVolume/mass flow by mechanical effectsVolume meteringFoundryLine tubing

A water meter housing assembly (10) comprises a cylindrical, plastic housing body (11), a non-cast housing bottom (13) of hydroformable or stamped brass, a single-piece strainer and sealing member (40) that is disposed in the housing bottom (13) and portions of non-cast hydroformable or stamped brass tubing (15) with spud ends (16, 17) for connection in a water supply line. The brass consists essentially of lead-free material. The assembly (10) is designed to provide a lower cost alternative to foundry cast meter housings. The assembly (10) also provides advantages in a method of vertical assembly that saves manufacturing cost.

Owner:BAKER MARK +1

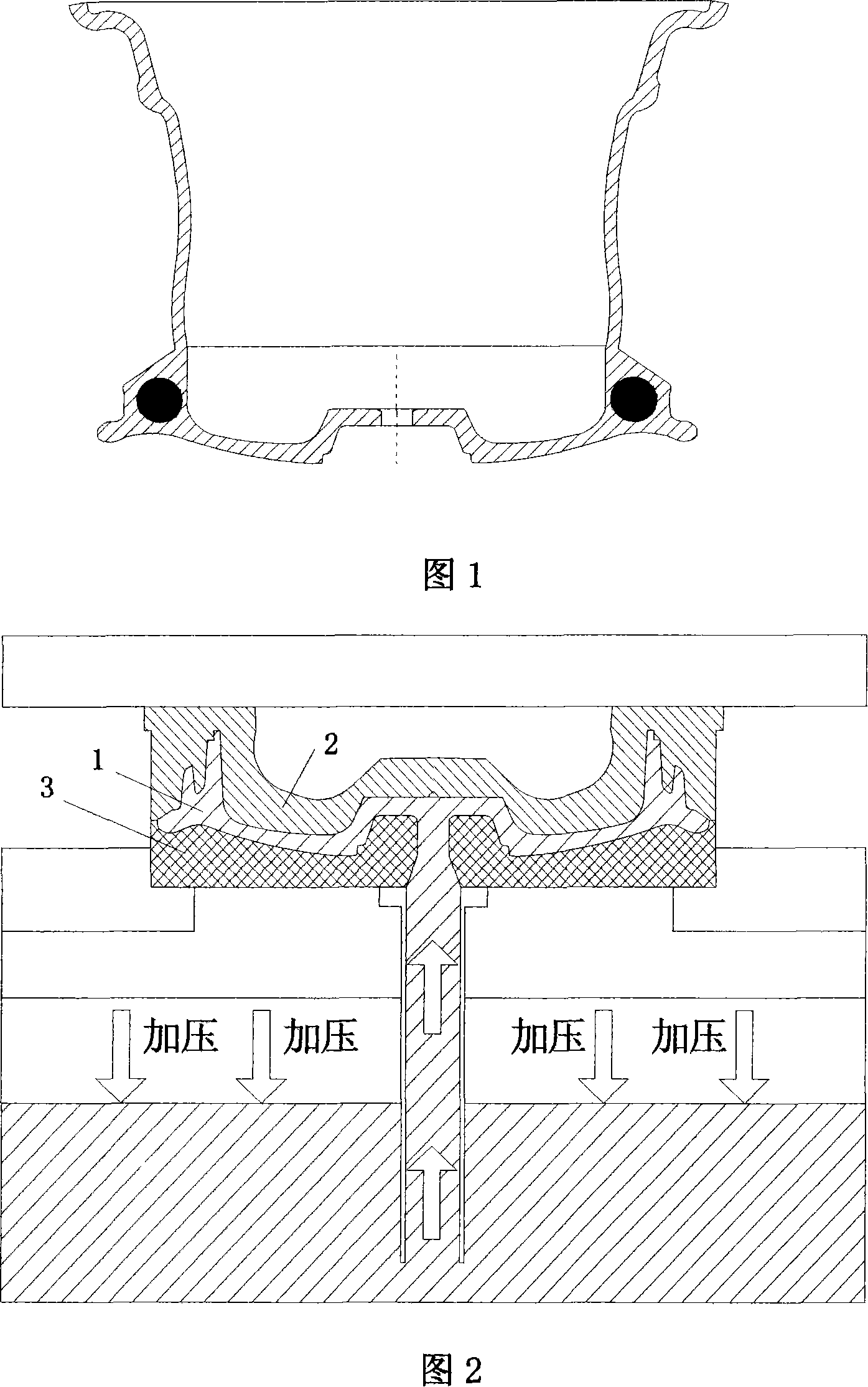

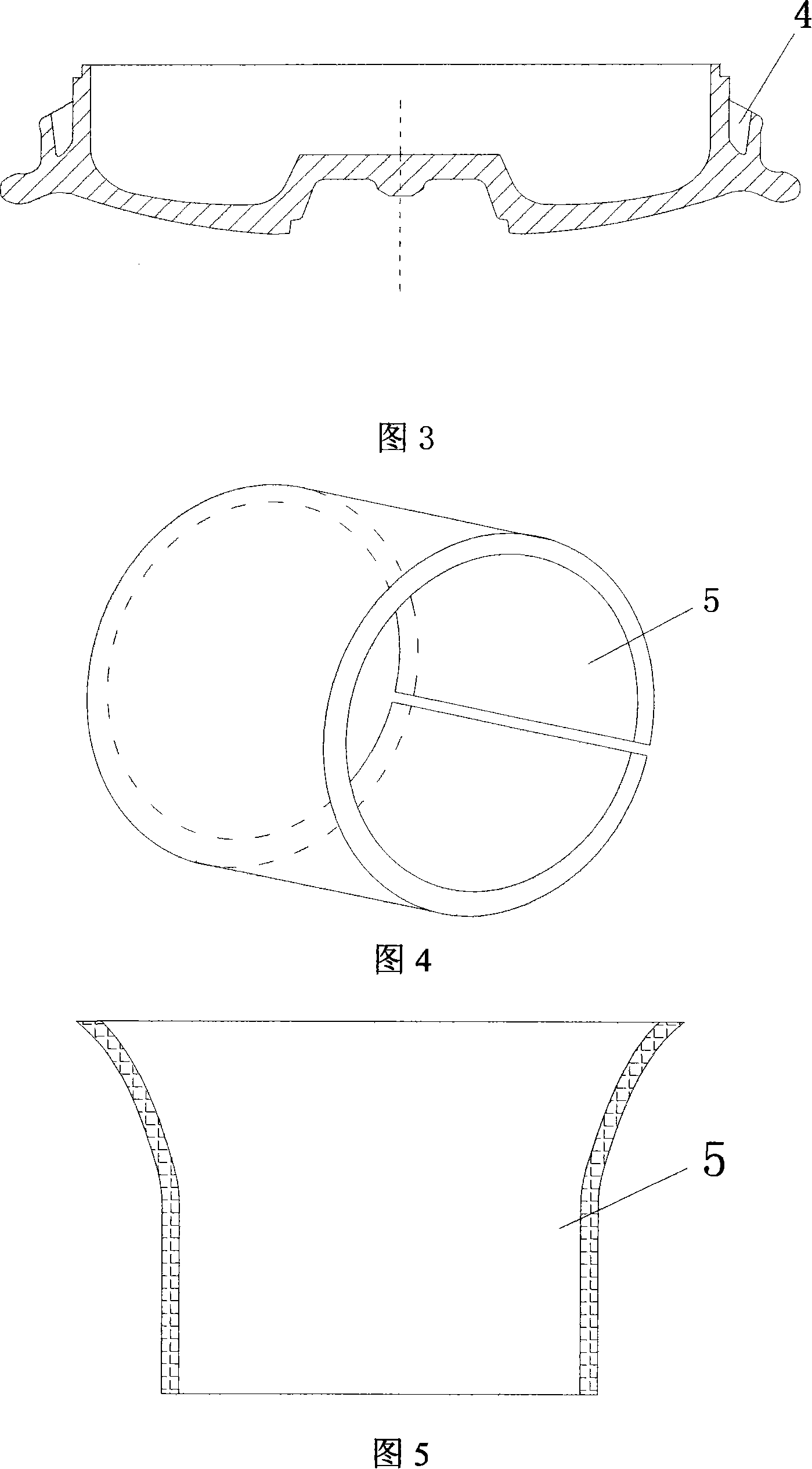

Hub manufacturing technology

The present invention discloses a production technique of a hub, which includes the following steps: (1) a rotary table is fabricated by the casting technique; (2) the cut plank stuff for a wheel felloe is rolled into a cylinder, the gap of which is welded and the burr of which is cleared out; (3) on a vertical press, the cylinder is pressed and flared; (4) on a spinning machine, the flared cylinder is formed into the wheel felloe by spinning; (5) on a positioning tooling workbench, the rotary table formed in the step (1) and the wheel felloe formed in the step (4) are welded by friction stir welding. The technique only applies the horizontally parted upper-lower mold type structure, thus leaving out the side form structure necessary for the traditional hubs, greatly simplifying the structure and the cost of foundry molds and avoiding the production of casting thermal centre in the process of casting. Because the wheel felloe and the rotary table are jointed by friction stir welding, which is a mature welding technique, the mechanical properties of the jointed part are ensured, and the problem of that the 90-degree impact experiment fails is resolved.

Owner:张新颖

High-strength casted air-colled bainite wear-resisting steel and preparing method

InactiveCN1775983AImprove mechanical propertiesImprove toughnessMolten metal pouring equipmentsFoundryWear resistant

The invention relates to a high strength foundry air cooling bainite wear resistant steel that the chemical constituents is 0.32-0.65 C, 0.8-3.0 Si, 1.2-3.0 Mn, 0.5-0.8 Cr, 0.3-0.8 Cu, 0.001-0.008 B, 0.18-0.35 Al, 0.05-0.15 Y, 0.05-0.20 Ti, 0-0.12 Mg, 0-0.12 Ca, 0-0.15 Zn, and 0.10<Mg+Ca+Zn<0.25, the else is Fe and trace impurities. The process includes the following steps: smelting waste steel, pig iron, ferrochrome iron and copper board, adding ferrosilicon and ferromanganese preliminary deoxidation into melting down and alloying; heating to 1600-1660 degree centigrade after adjusting the constituents adding aluminum deoxidatioin and alloying and blast furnace tapping; putting the compounding modification particle of Yt, boron, titanium, magnesium, calcium, and zinc on the bottom of pouring ladle, taking modification process to the molten steel; molding the molten steel after modification process into normal matrix for casting. The invention could prolong the useful life of antifriction component, improve working efficiency, and have good economic benefit.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

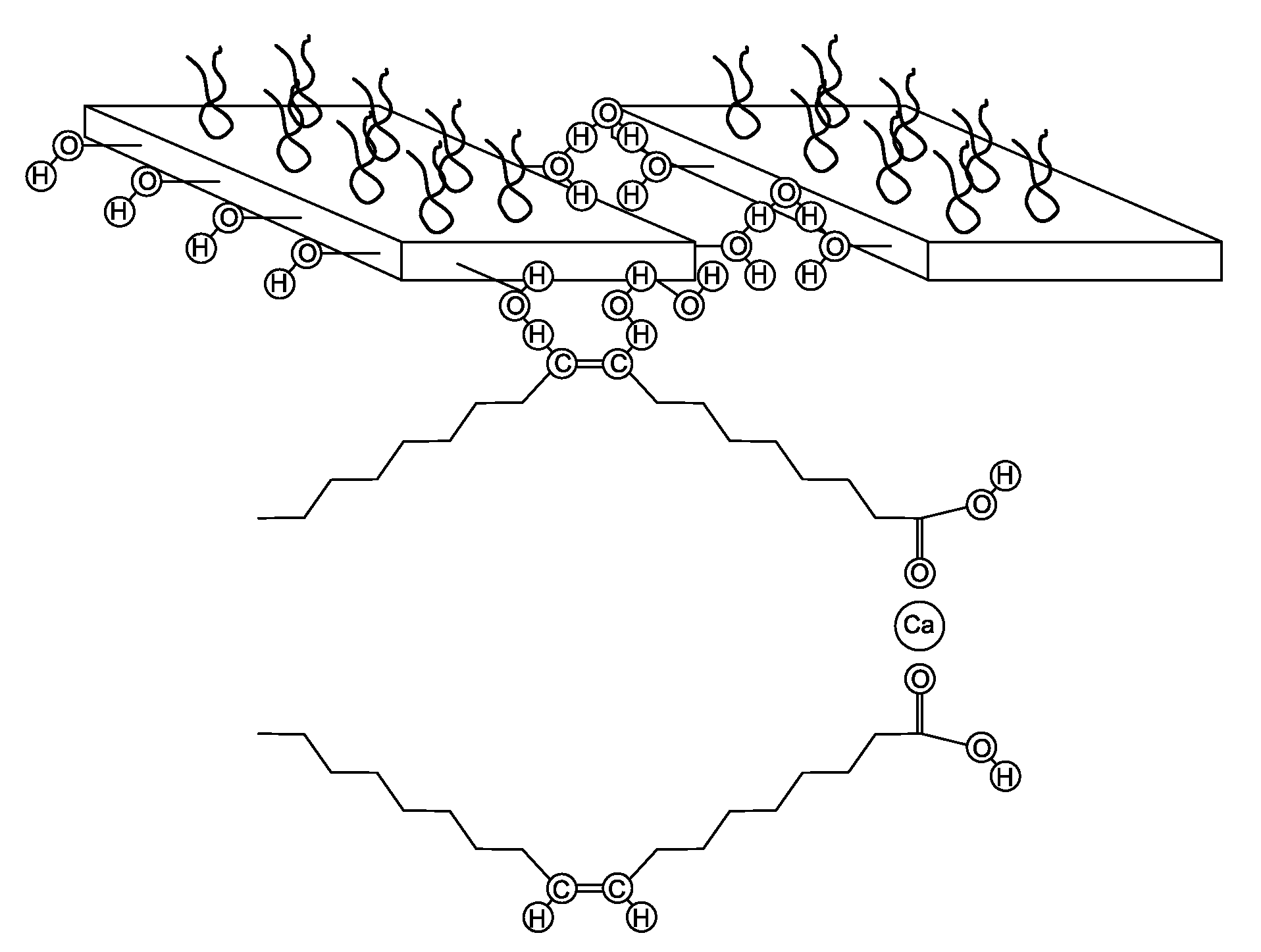

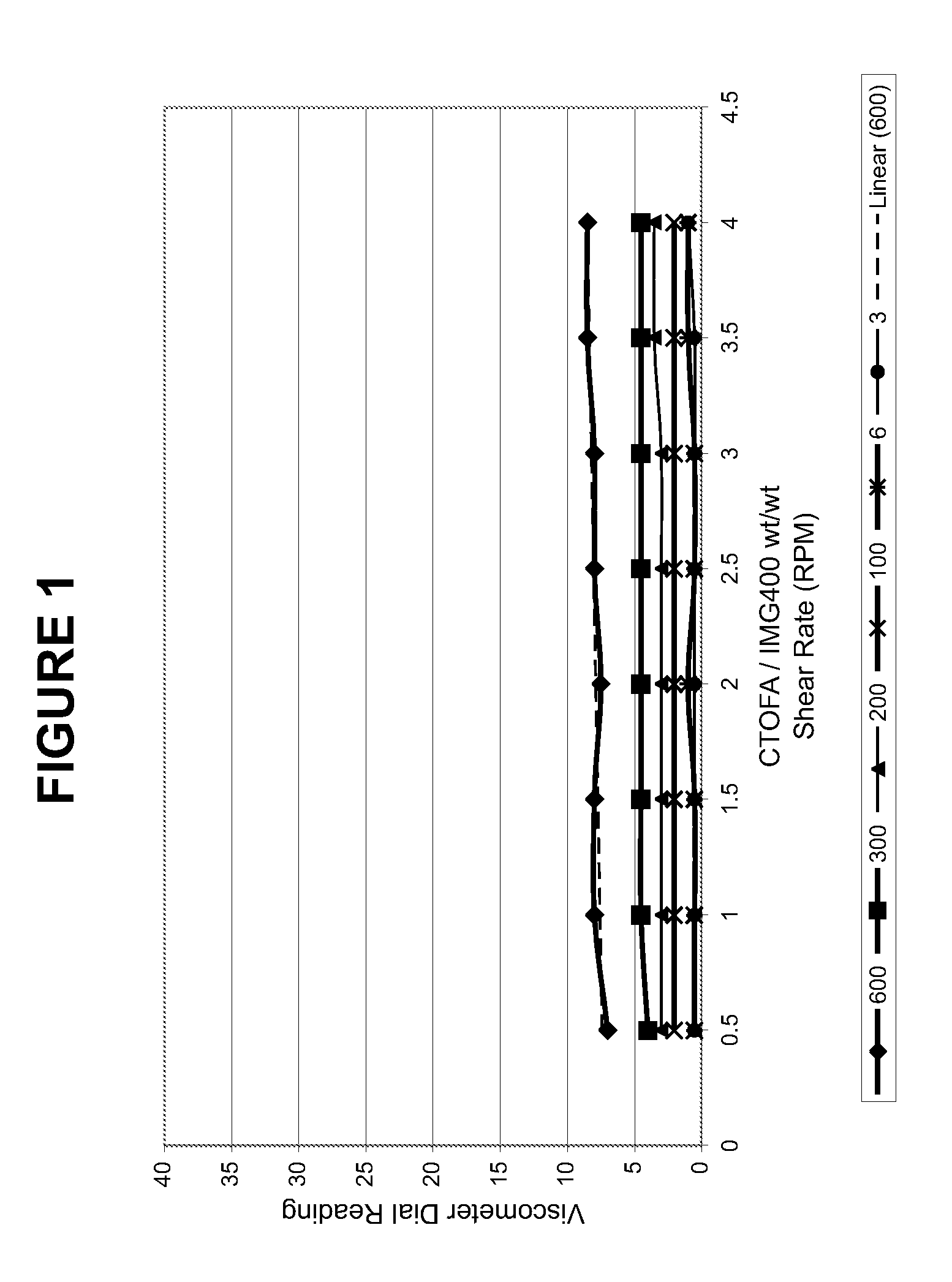

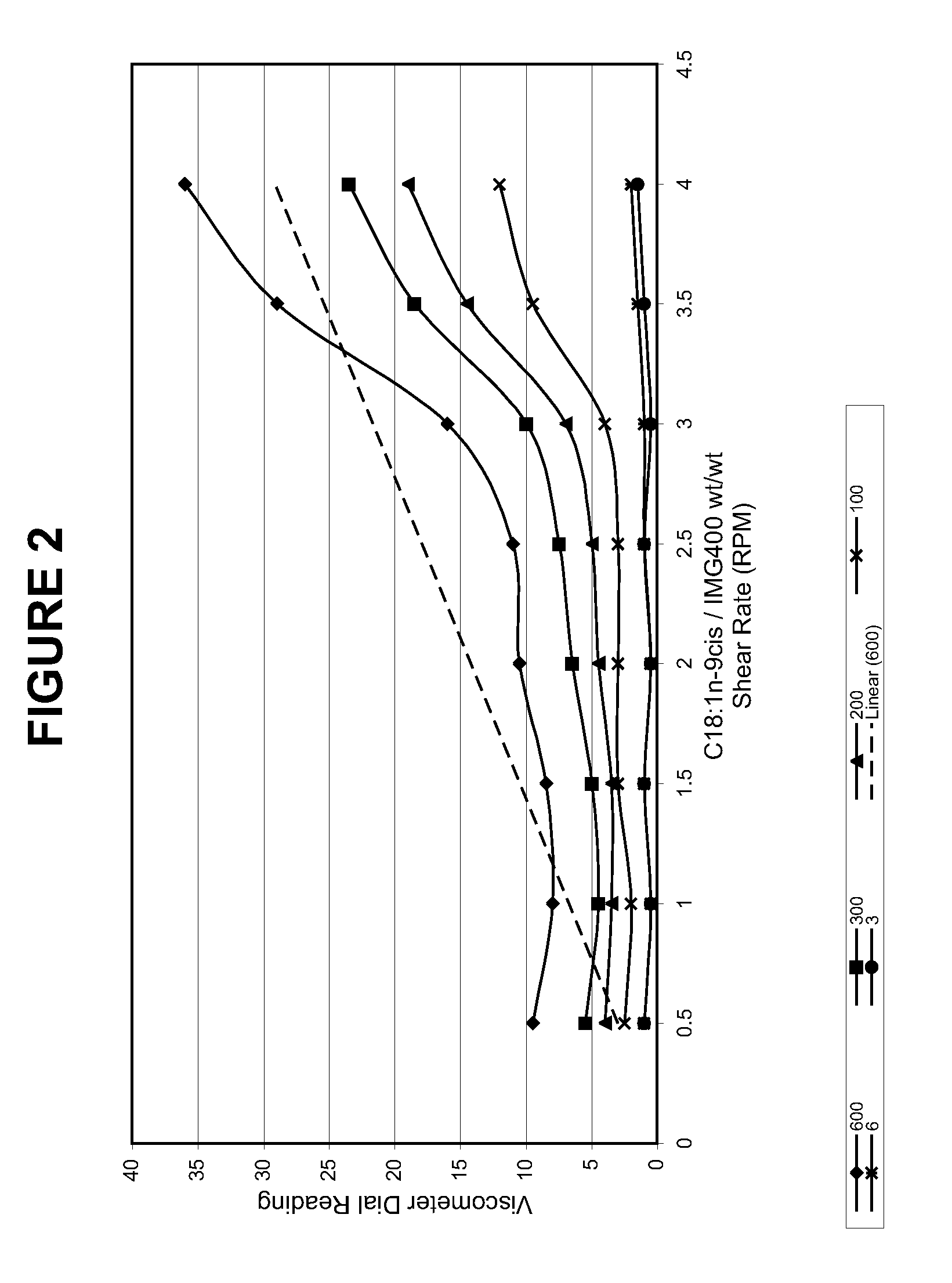

Methods Of Preparing Hydrocarbon, Water And Organophilic Clay Emulsions And Compositions Thereof

InactiveUS20090260885A1Low viscosityPerformance maximizationTransportation and packagingMixingPolyesterFoundry

This invention relates to compositions and methods for improving the performance of organophilic organic-clay complexes, which are dispersible in organic liquids to form a gel therein. Depending on the composition of the gel, such gels may be useful as lubricating greases, oil-based muds, oil base packer fluids, paint-varnish-lacquer removers, paints, foundry molding sand binders, adhesives and sealants, inks, polyester laminating resins, polyester gel coats, cosmetics, detergents, and the like.

Owner:ENGINEERED DRILLING SOLUTIONS

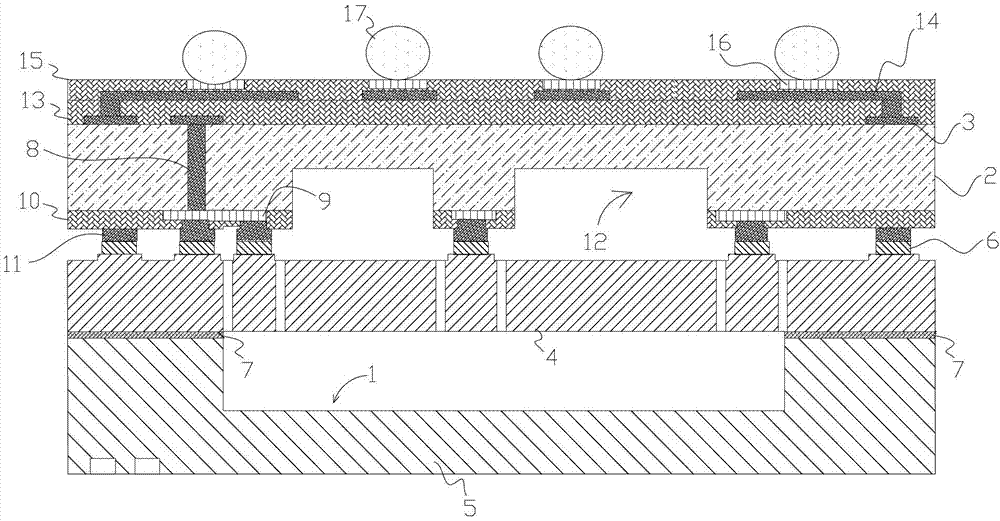

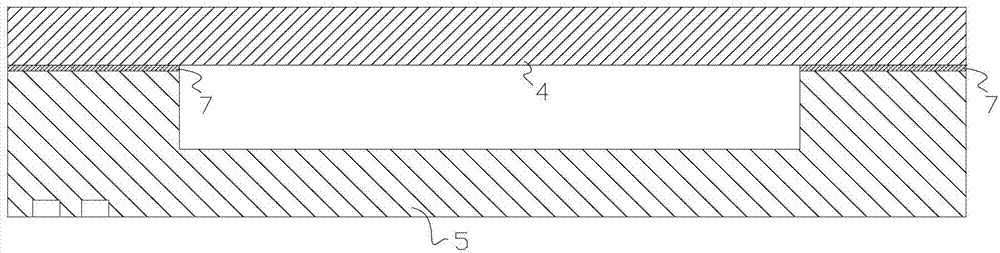

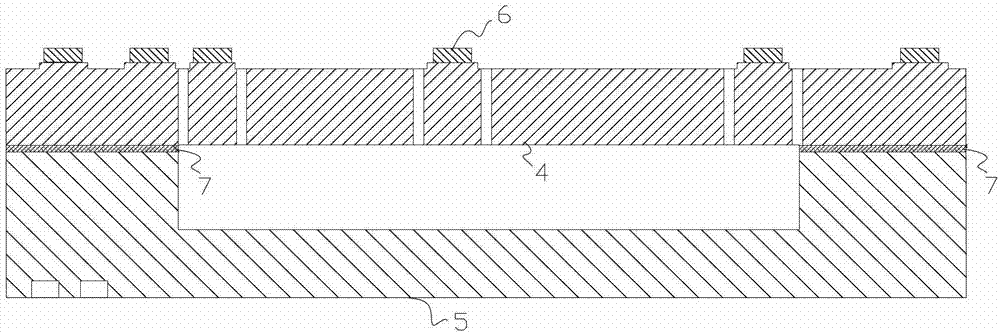

Inertial sensor production and wafer level package process based on MEMS (micro-electromechanical system)

InactiveCN103922267AEffective spaceImprove performanceDecorative surface effectsSolid-state devicesFoundryChip size

The invention discloses an inertial sensor production and wafer level package process based on an MEMS (micro-electromechanical system). The process includes the steps: 1) forming an E-SOI (engineering-silicon on insulator); 2) performing surface machining on an MEMS wafer; 3) producing an ASIC (application specific integrated circuit) wafer on a standard ASIC foundry; 4) performing metal eutectic bonding for the MEMS wafer and the ASIC wafer; 5) performing WLCSP (wafer level chip size packaging). The area of an ASIC chip is identical with that of an MEMS chip, the effective areas of the MEMS chip and the ASIC chip are sufficiently used, the most effective space is provided for the design of the MEMS chip and the ASIC chip, subsequent package procedures of the chips are omitted by the aid of the wafer level chip size packaging, Flip-Chip of a terminal circuit board is finished directly through a BGA (ball grid array), and the sizes of the chips and production cost are greatly reduced.

Owner:SENODIA TECH (SHANGHAI) CO LTD

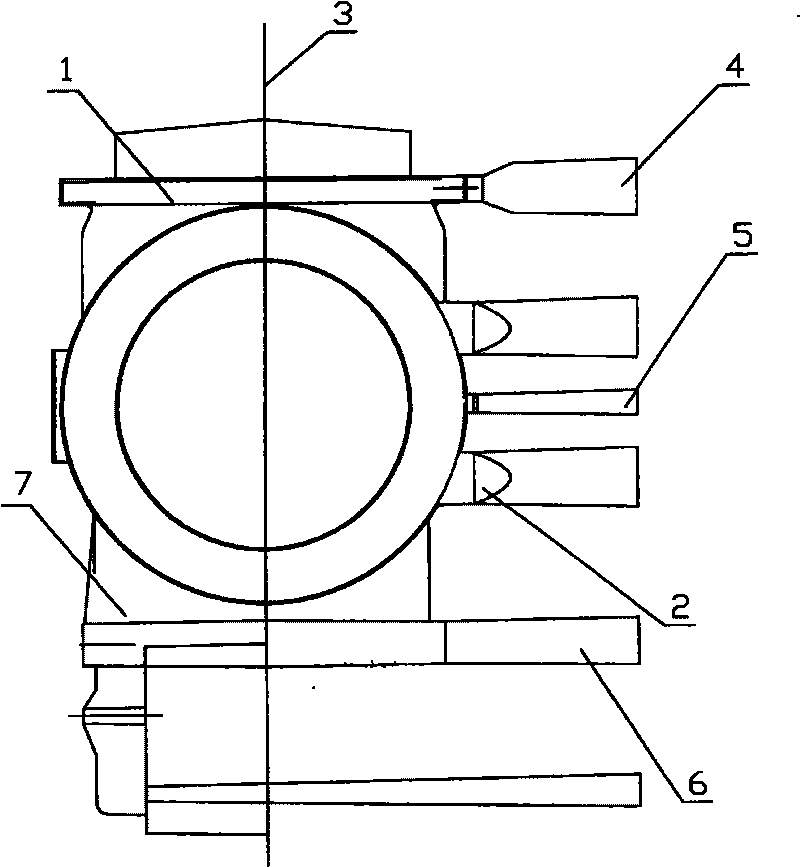

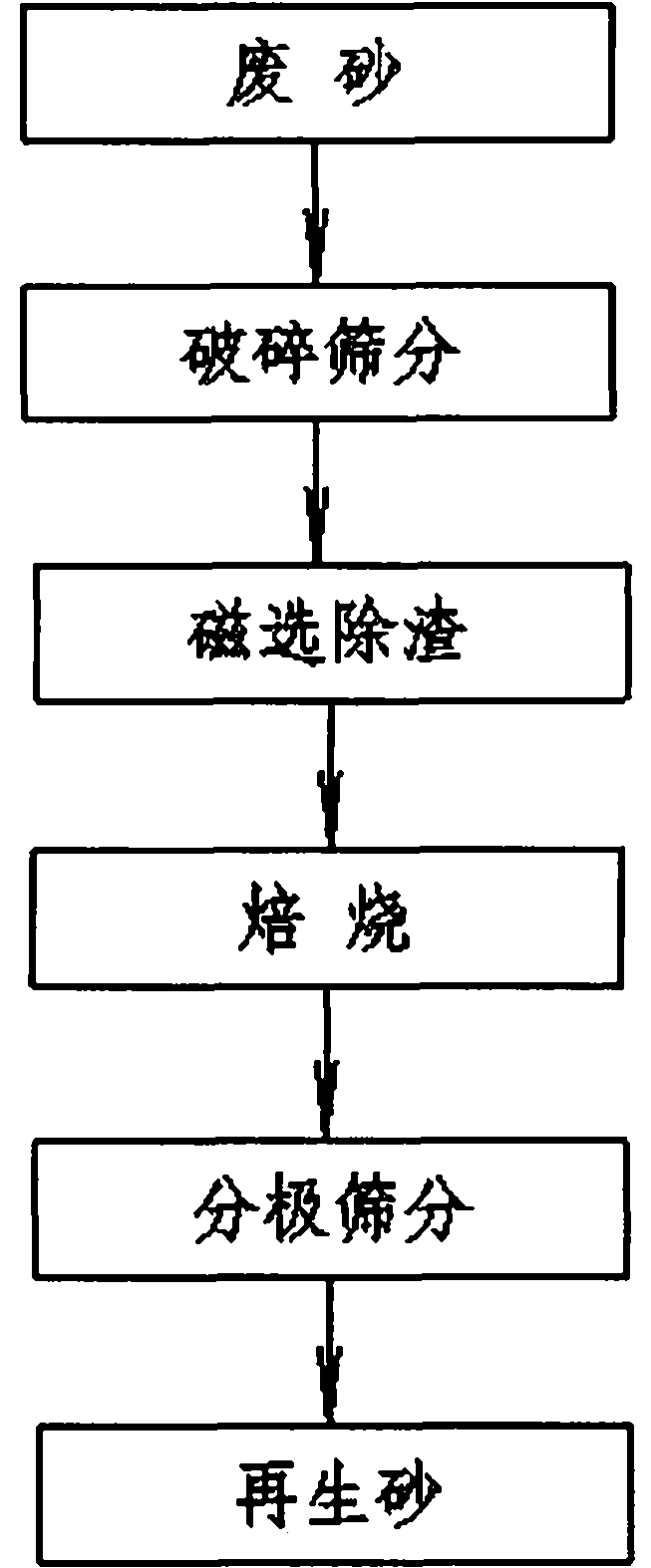

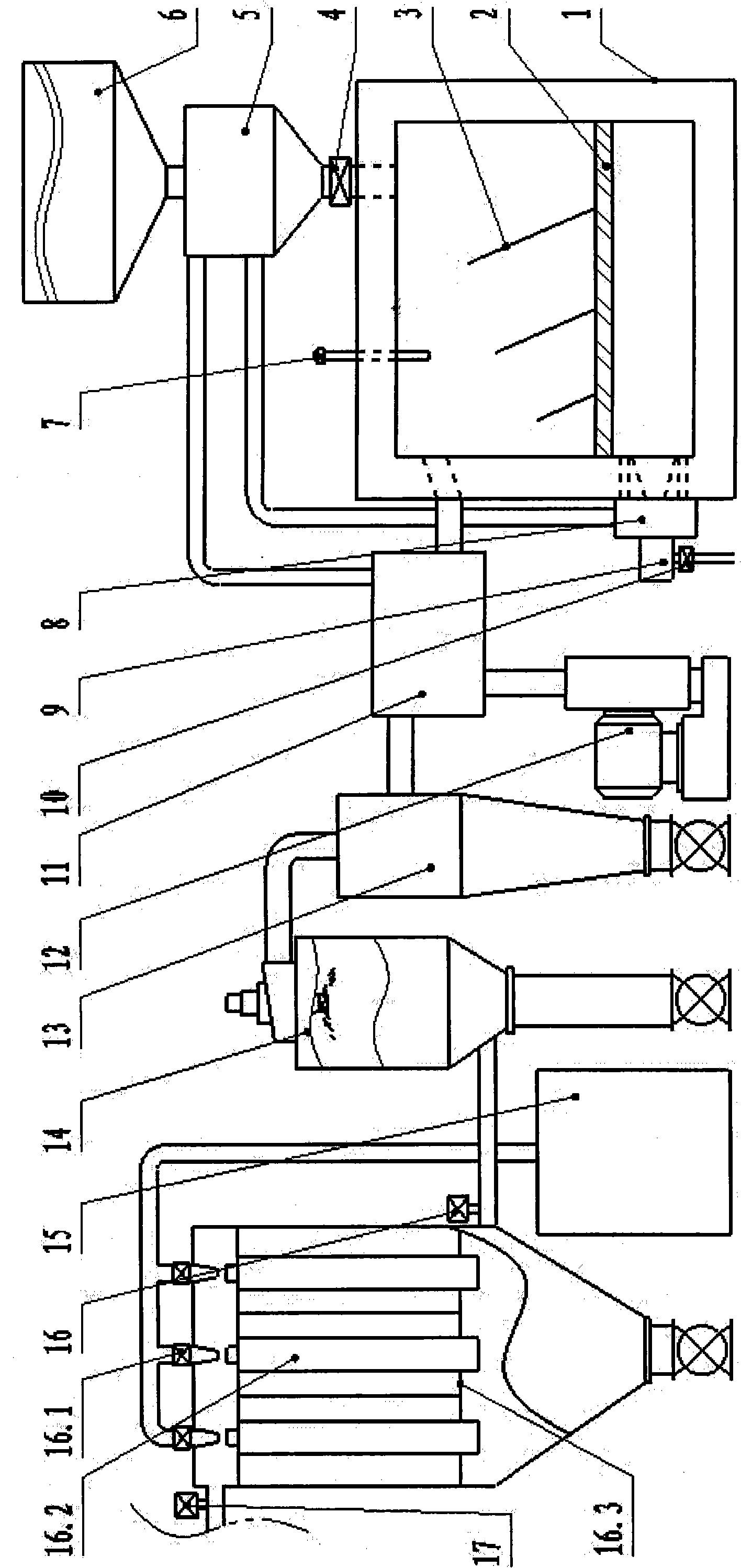

Waste foundry sand regenerating process method

InactiveCN102009122AReduce roasting energy consumptionMould handling/dressing devicesFoundryCombustor

The invention discloses a waste foundry sand regenerating process method, which comprises the processes of crashing and screening, magnetic separation, roasting and graded screening. The roasting process particular comprises the following steps of: preheating waste sand which does not enter a furnace and air for combustion by using the heat of hot sand which is discharged from the furnace; controlling the roasting temperature of a roasting furnace to be between 780 and 850 DEG C by controlling a roasting furnace burner and the flow of the waste sand entering the furnace; separating roasted waste sand from waste gas by using a cyclone dust collector, a spraying dust collector and a bag type dust collector; and exhausting the separated waste gas to the atmosphere after passing through an alkali liquor washing tank and an adsorption tank, wherein the bag type dust collector has a high-pressure air flow blowback control bag dust-removing structure; and the dust-removing process and the normal operation of a system are maintained by controlling the bag dust-removing cycle of the bag type dust collector. Compared with the conventional method, the waste foundry sand regenerating process method has the advantages of greatly reducing energy consumption and guaranteeing the cleaness of the exhausted waste gas.

Owner:LIUZHOU AOKAI ENG MACHINERY

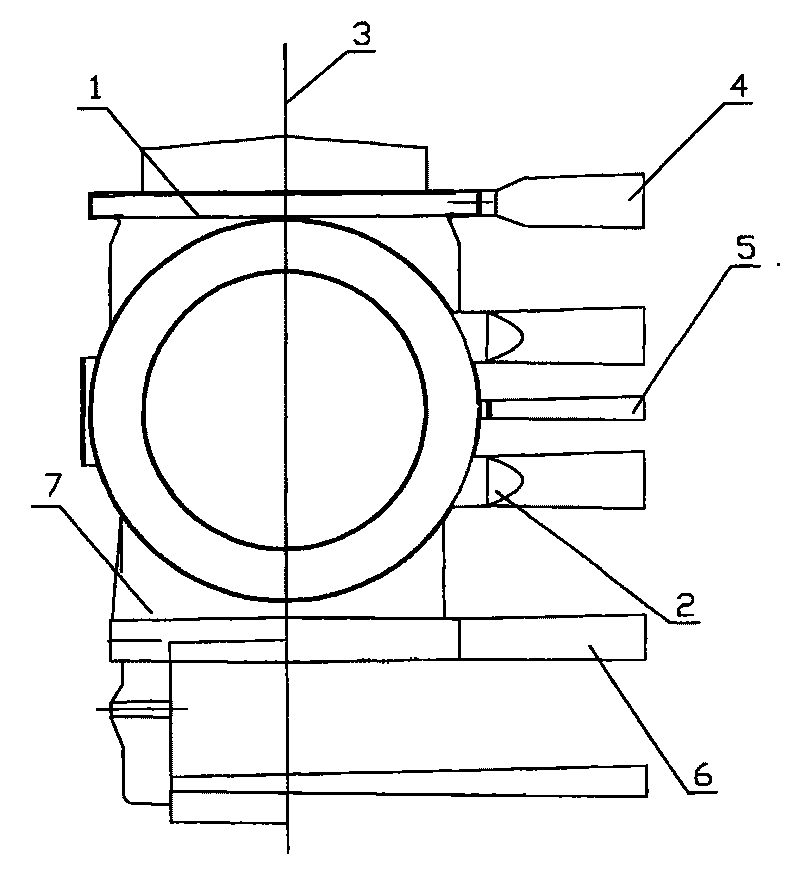

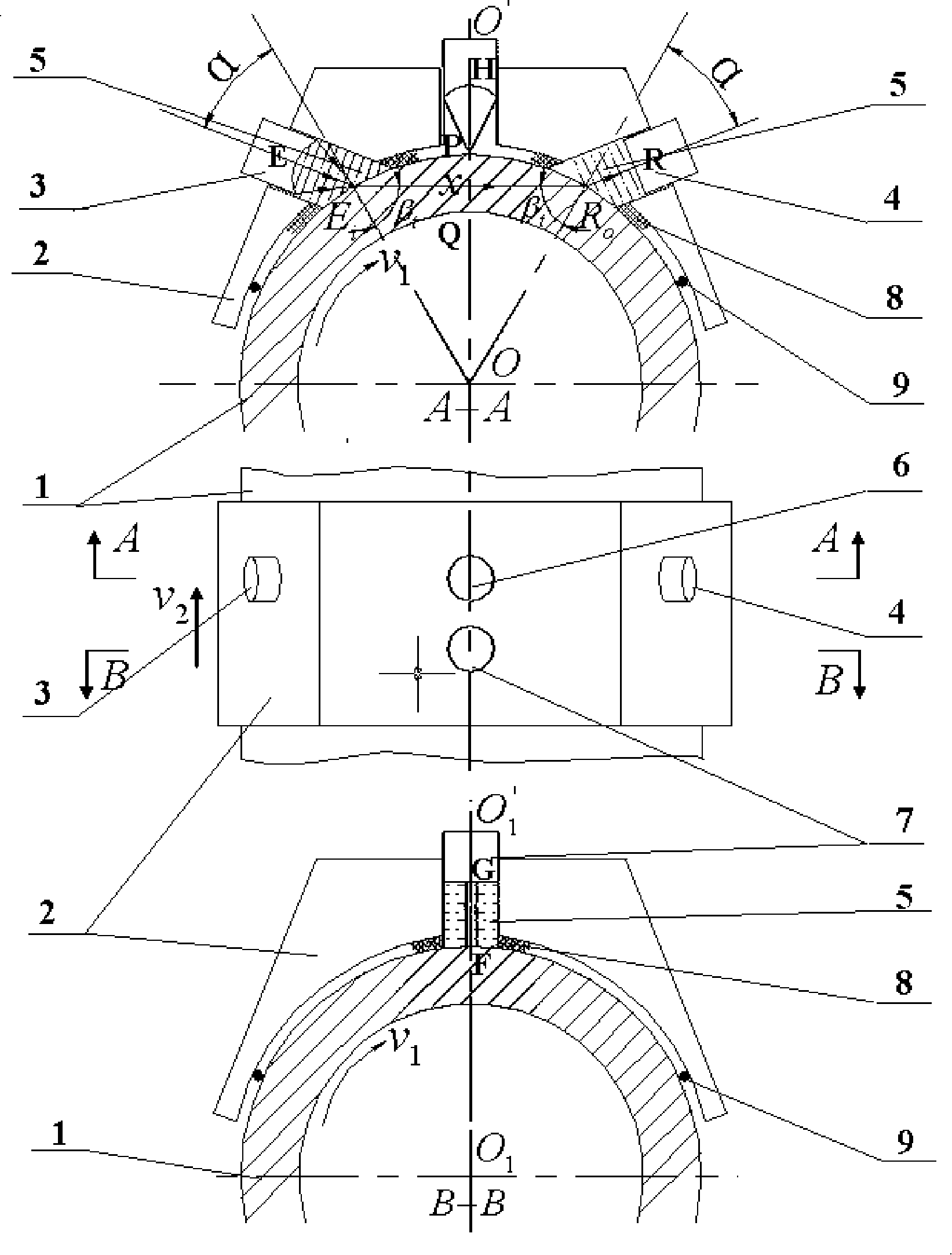

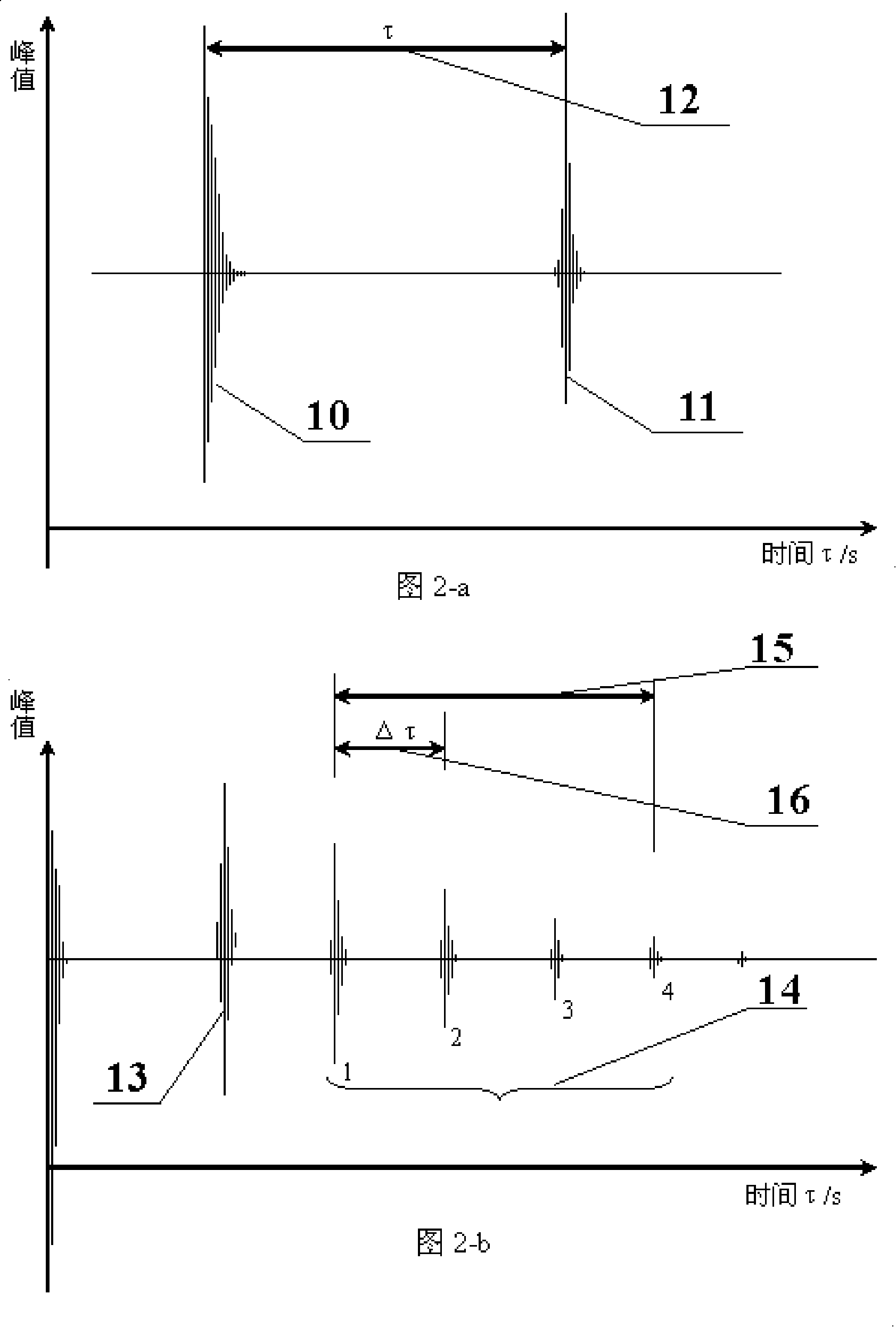

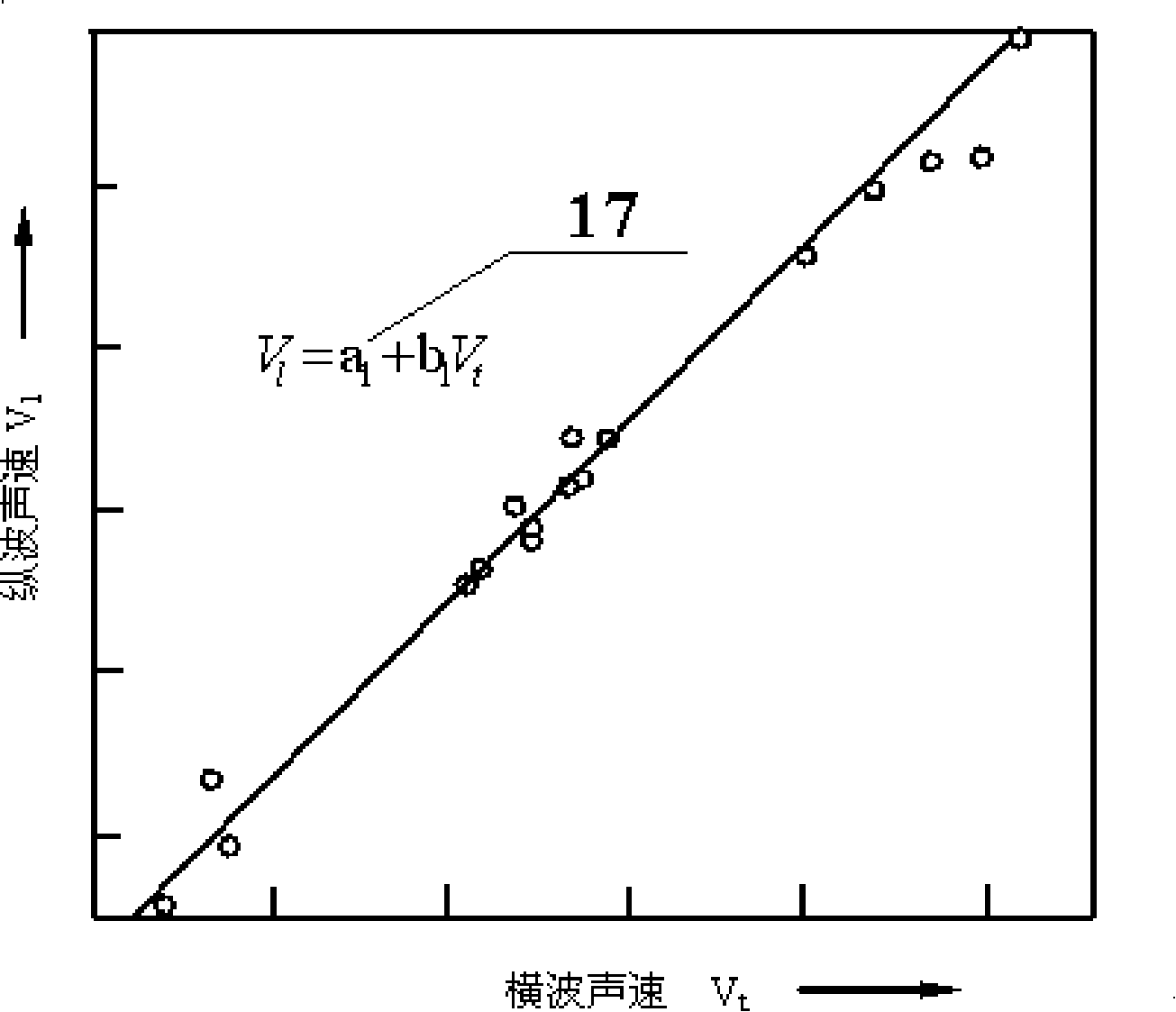

Eccentric ball iron pipe nodularity and wall thickness supersonic damage-free detection method

InactiveCN101187650AOvercoming Sound Velocity MeasurementsOvercoming detectionAnalysing solids using sonic/ultrasonic/infrasonic wavesUsing subsonic/sonic/ultrasonic vibration meansFoundrySonification

The invention belongs to the technical field of nondestructive detection of foundry industry, and relates to method for testing nodularity and wall thickness of centrifugal nodular cast iron tubes through ultrasonic and without deconstructions. The technological characteristics are that a certified orientation relationship between a probe and a tested tube can be guaranteed through a structural design of a sound path and a probe frame. The probe frame is motioned compositely and mutually with the tested tube, and coupling medium in a coupling medium chamber guarantees a dynamic coupling of the ultrasonic. A transmitting mode is adopted to test sound speed of ultrasonic shear waves inside a detecting tube wall, simultaneously an infrared temperature probe is used to test temperature of the detecting tube wall, after the sound speed of the ultrasonic shear waves is corrected by the temperature, the nodularity of the tube wall can be calculated out under normal temperature by the sound speed of the ultrasonic shear waves. The sound speed of the ultrasonic shear waves is transformed into longitudinal wave velocity, and a mode of ultrasonic pulse reflection is used to test the thickness of the tube wall. An effect and a benefit of the invention are that two projects can be tested in one test, influences of the thickness and the temperature to the test of the nodularity can be overcome, and a dynamic test can be used to test the whole surface of the testing tube, which increases testing efficiency and coverage rate.

Owner:DALIAN UNIV OF TECH

Uncooled infrared detector and methods for manufacturing the same

This disclosure discusses various methods for manufacturing uncooled infrared detectors by using foundry-defined silicon-on-insulator (SOI) complementary metal oxide semiconductor (CMOS) wafers, each of which may include a substrate layer, an insulation layer having a pixel region and a wall region surrounding the pixel region, a pixel structure formed on the pixel region of the insulation layer, a wall structure formed adjacent to the pixel structure and on the wall region of the insulation layer, a dielectric layer covering the pixel structure and the wall structure, a pixel mask formed within the dielectric layer and for protecting the pixel structure during a dry etching process, and a wall mask formed within the dielectric layer and for protecting the wall structure during the dry etching process, thereby releasing a space defined between the wall structure and the pixel structure after the dry etching process.

Owner:MIKROSENS ELEKTRONIK SAN & TIC A S

Securing Authenticity of Integrated Circuit Chip

ActiveUS20090100392A1Improve trustGreat customer interestPhotomechanical apparatusPhotographic printingFoundryNon destructive

A system and method are provided for securely manufacturing a device at a foundry. For example, an integrated circuit chip may be securely fabricated at an untrusted foundry by later verifying authenticity of the integrated circuit chip based on a valid usage of an original source code file associated with a semiconductor manufacturing process of the integrated circuit chip. The integrated circuit chip may be authenticated by matching a first set of unique daughter codes generated during fabrication with a second set of unique daughter codes generated independently by some entity other than the foundry. In this way, a trusted electronics integrator may compare the first and second unique daughter codes to nondestructively determine whether the integrated circuit chip is a trusted device or a tampered device.

Owner:ASML HLDG NV

Molding sand for aluminum casting and preparation technology thereof

ActiveCN101574725AImprove the finishImprove breathabilityFoundry mouldsFoundry coresFoundrySodium Bentonite

The invention belongs to the field of foundry industry, in particular relates to molding sand for aluminum casting and a preparation technology thereof. The molding sand for the aluminum casting comprises the following constituents: old sand, new sand, bentonite and water. The preparation technology of the molding sand for the aluminum casting comprises a sand-mixing method: weighting the old sand, the new sand and the bentonite according to a proportion, firstly mixing the same for 10 to 20 seconds, adding water to mix for 80 to 100 seconds and standing the mixed material for 20 seconds after the mixed material is well mixed. The invention has the advantages that the particle sizes of the sand are strictly controlled, the sand with the particle size of 200 / 100 meshes is selected, and the proportion of the sand failing to pass 200 meshes is larger than 50 percent so that both the surface smoothness of aloxite parts and the air permeability of the molding sand are favorable.

Owner:SHANDONG LIANCHENG PRECISION MFG CO LTD

Tooth form part foundry technique method

ActiveCN101249547AImprove working conditionsReduce the amount of sand usedFoundry mouldsFoundry coresFoundryMaterials science

The invention relates to a gear-like part casting technique, in particular to a technique for directly casting gear-like parts. The method can directly cast gear-like parts by using a gear-like cavity obtained by the iron-mold coated sand process. The technique has the advantages of no cutting or extremely less cutting, low cost and simple and feasible operation, and is applicable for most of enterprises.

Owner:山东时风(集团)有限责任公司

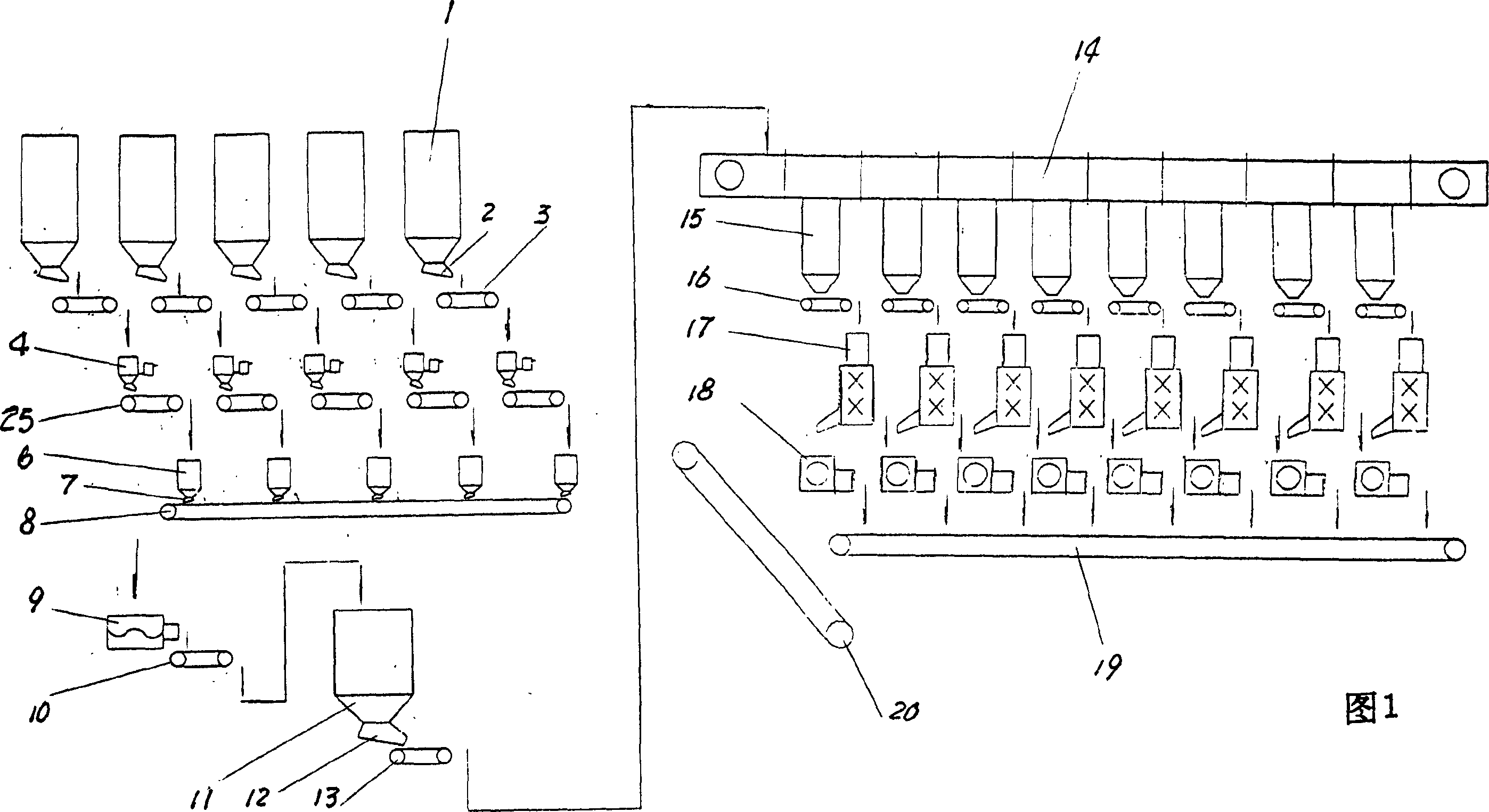

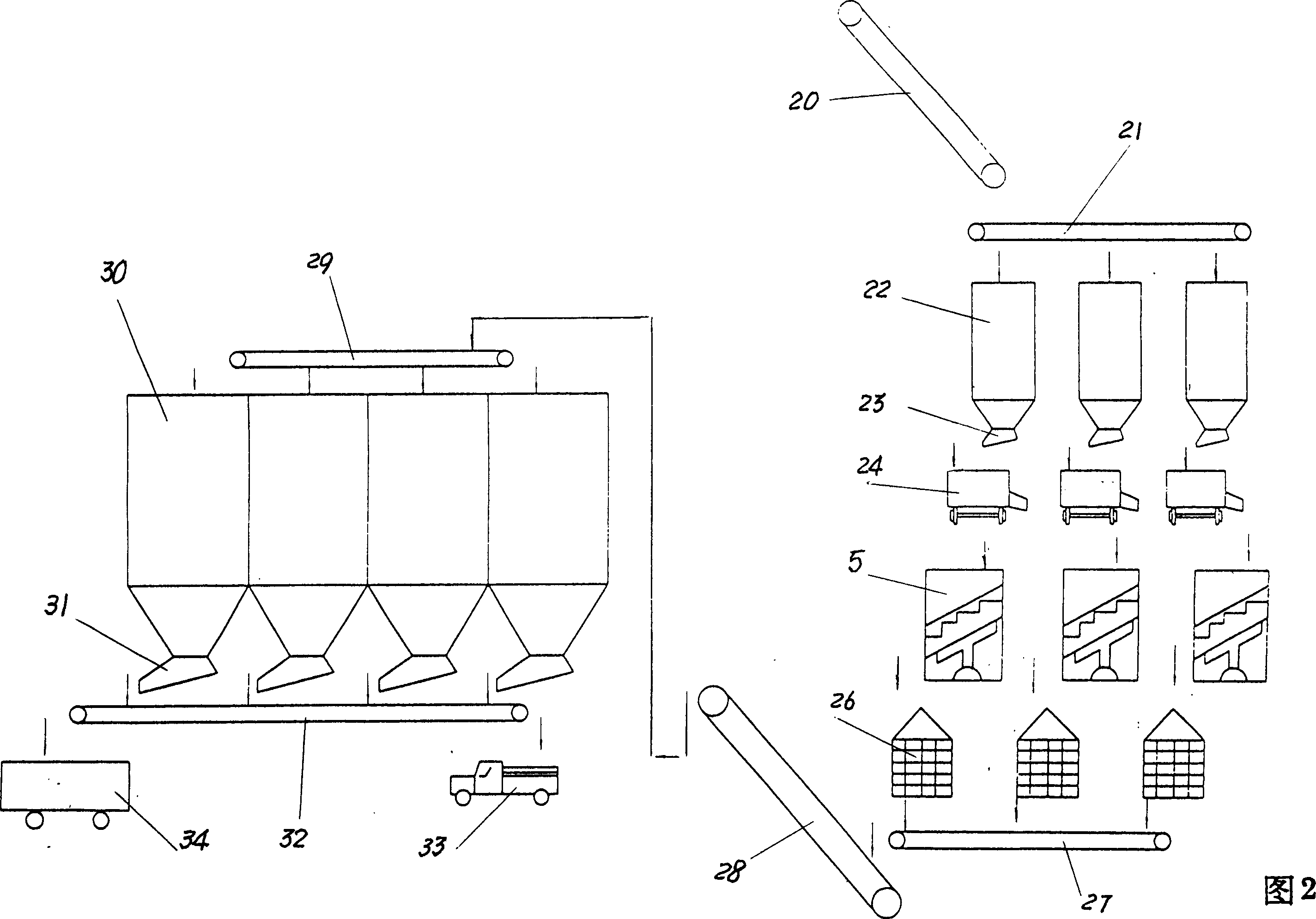

Casting type coke production method and apparatus system used thereof

The present invention relates to a production method of foundry shaped coke and its equipment system for producing said foundry shaped coke. Said method includes the procedures of preparing material,pulverizing, cold stirring, hot stirring, forming and carbonization and coking, and its equipment system includes material-preparing chamber, pulverizing machine, cold stirring machine, hot stirring machine, forming machine and carbonizing furnace, etc.

Owner:商丘市普天工贸有限公司煤化工研究所

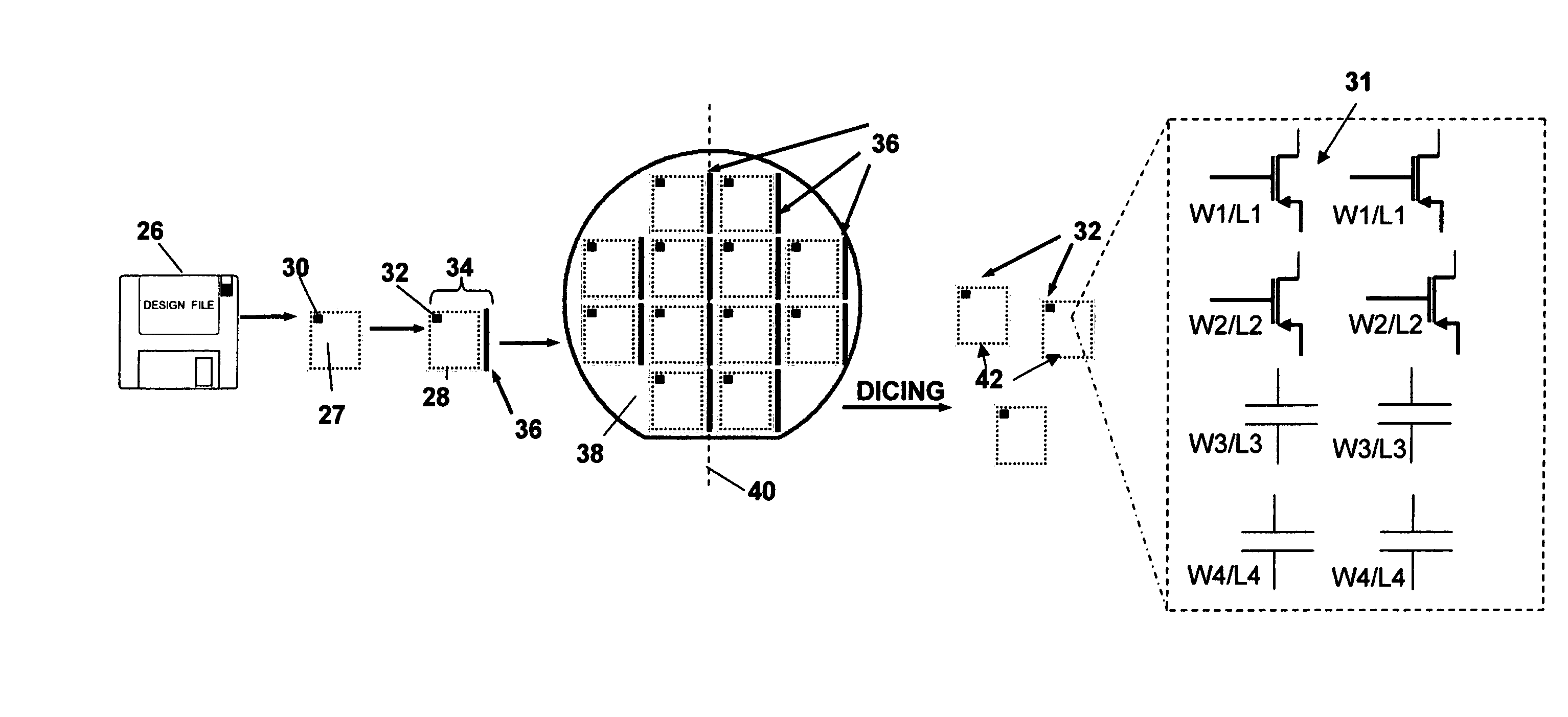

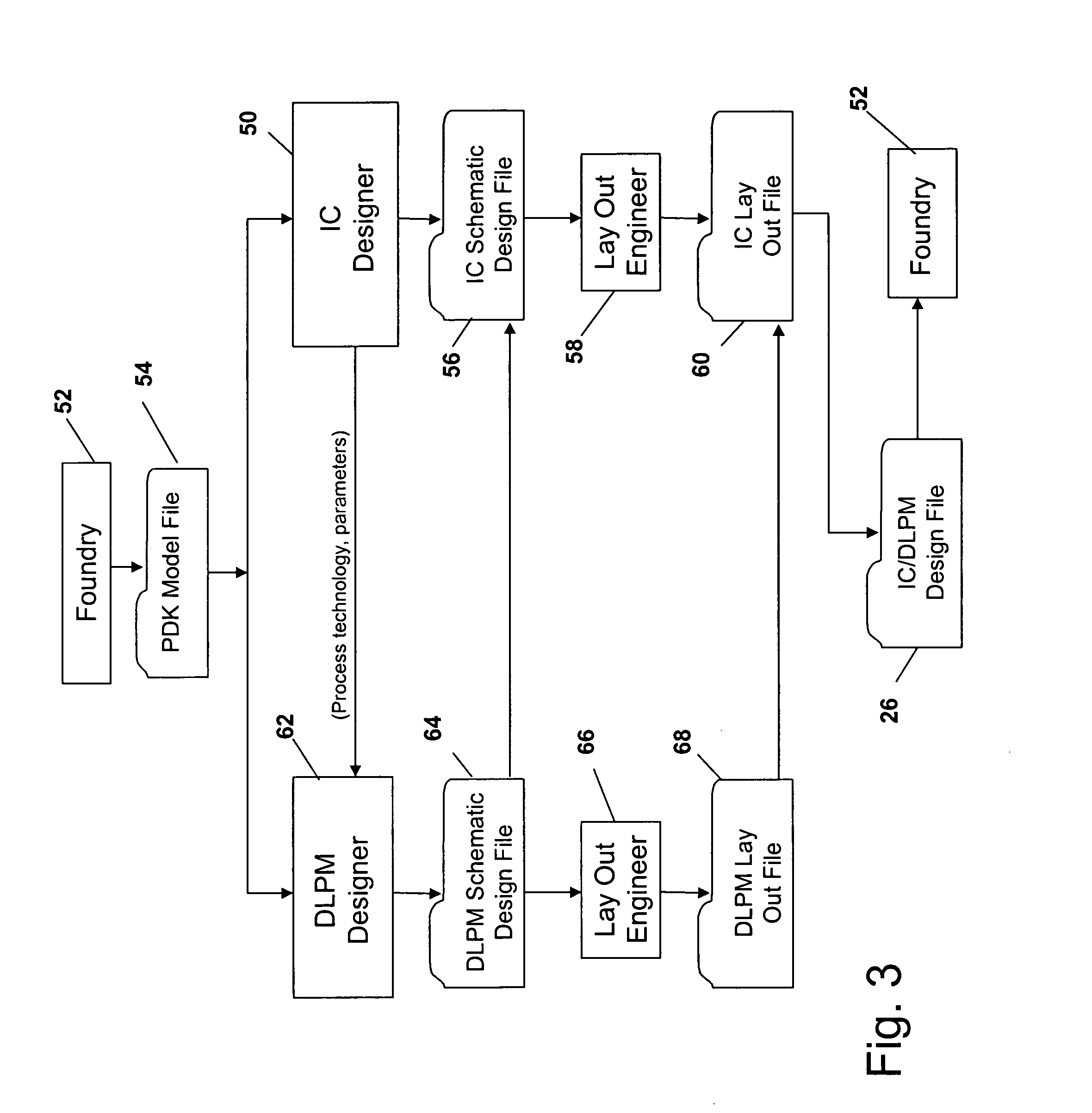

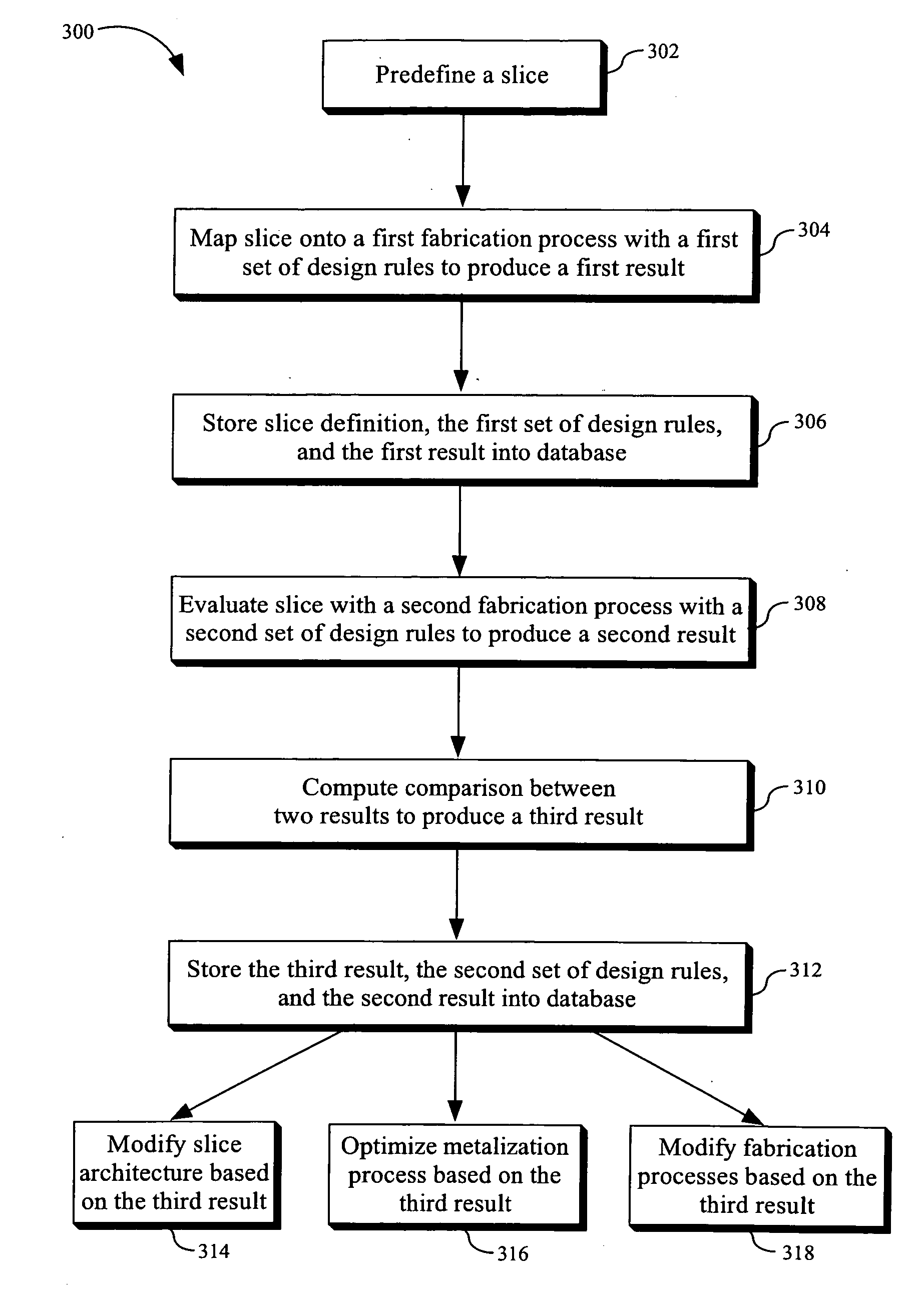

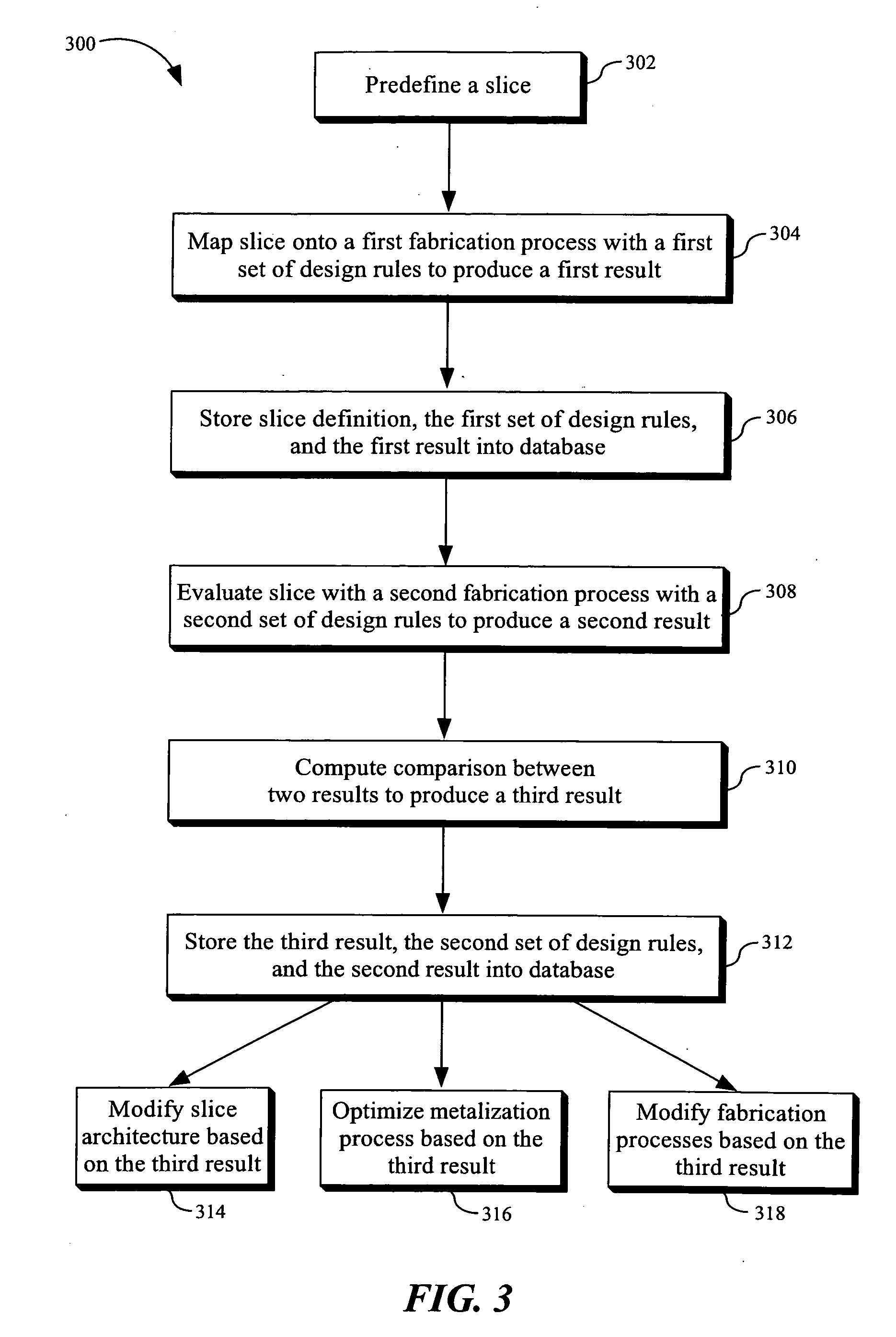

Method and apparatus for mapping platform-based design to multiple foundry processes

InactiveUS20050034087A1Computer aided designSoftware simulation/interpretation/emulationFoundryInterface layer

The present invention is directed to a method and apparatus for mapping platform-based design to multiple foundry processes. According to an exemplary aspect of the present invention, a method for mapping platform-based design to multiple foundry processes may include the following steps. First, availability of required features of a design in a target foundry process may be checked. The target foundry process must provide all the features that are used in the design. The design may include base wafer layers and metal stack layers. Then, a base wafer / metal stack interface layer for the design may be selected. Next, compatible blocks between different base wafer processes may be created. Then, a physical design library for the design may be created. Next, a logic design and timing library for the design may be created. This way, the design may be mapped to different foundry processes.

Owner:BELL SEMICON LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com