Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7356 results about "Germanium" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Germanium is a chemical element with the symbol Ge and atomic number 32. It is a lustrous, hard-brittle, grayish-white metalloid in the carbon group, chemically similar to its group neighbours silicon and tin. Pure germanium is a semiconductor with an appearance similar to elemental silicon. Like silicon, germanium naturally reacts and forms complexes with oxygen in nature.

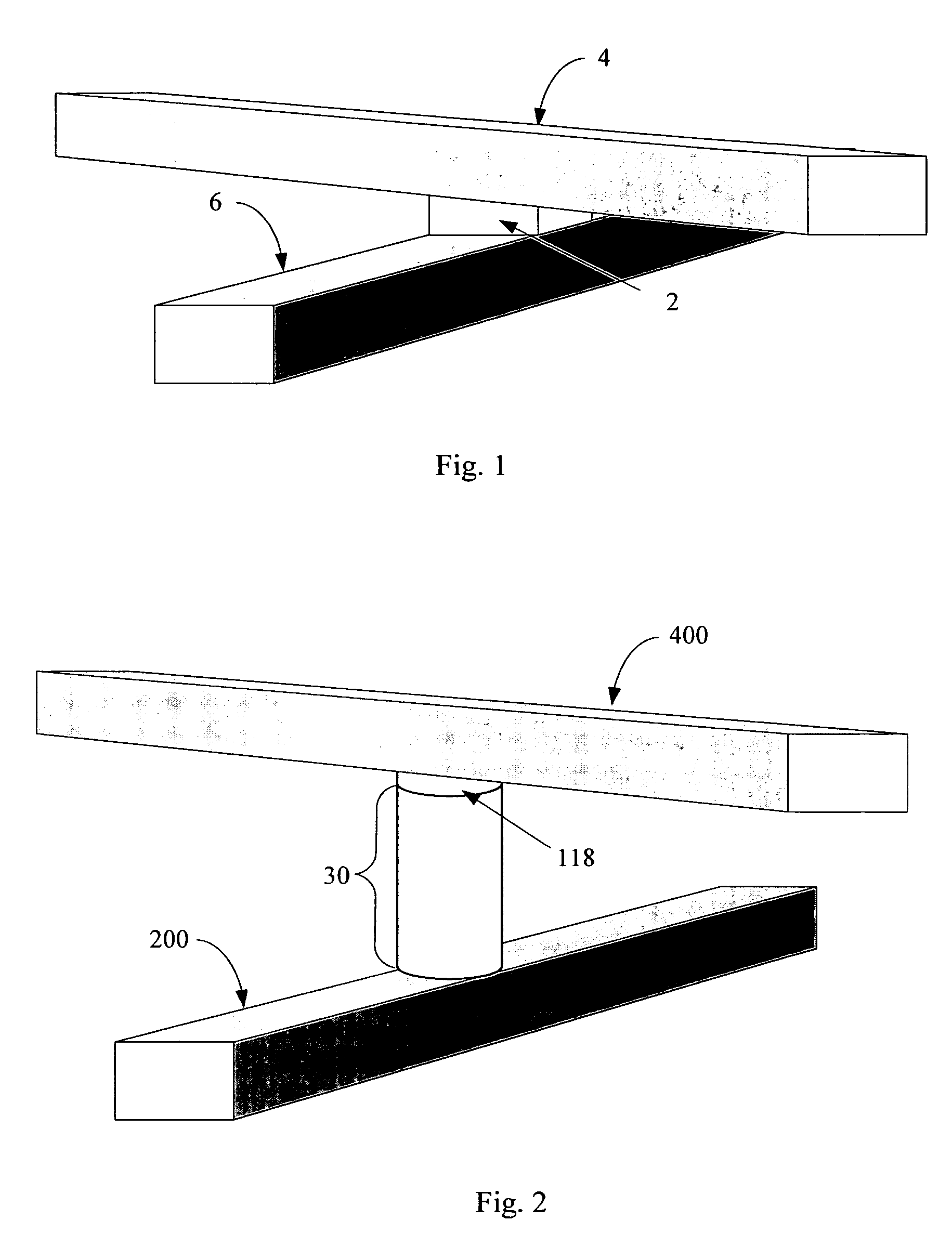

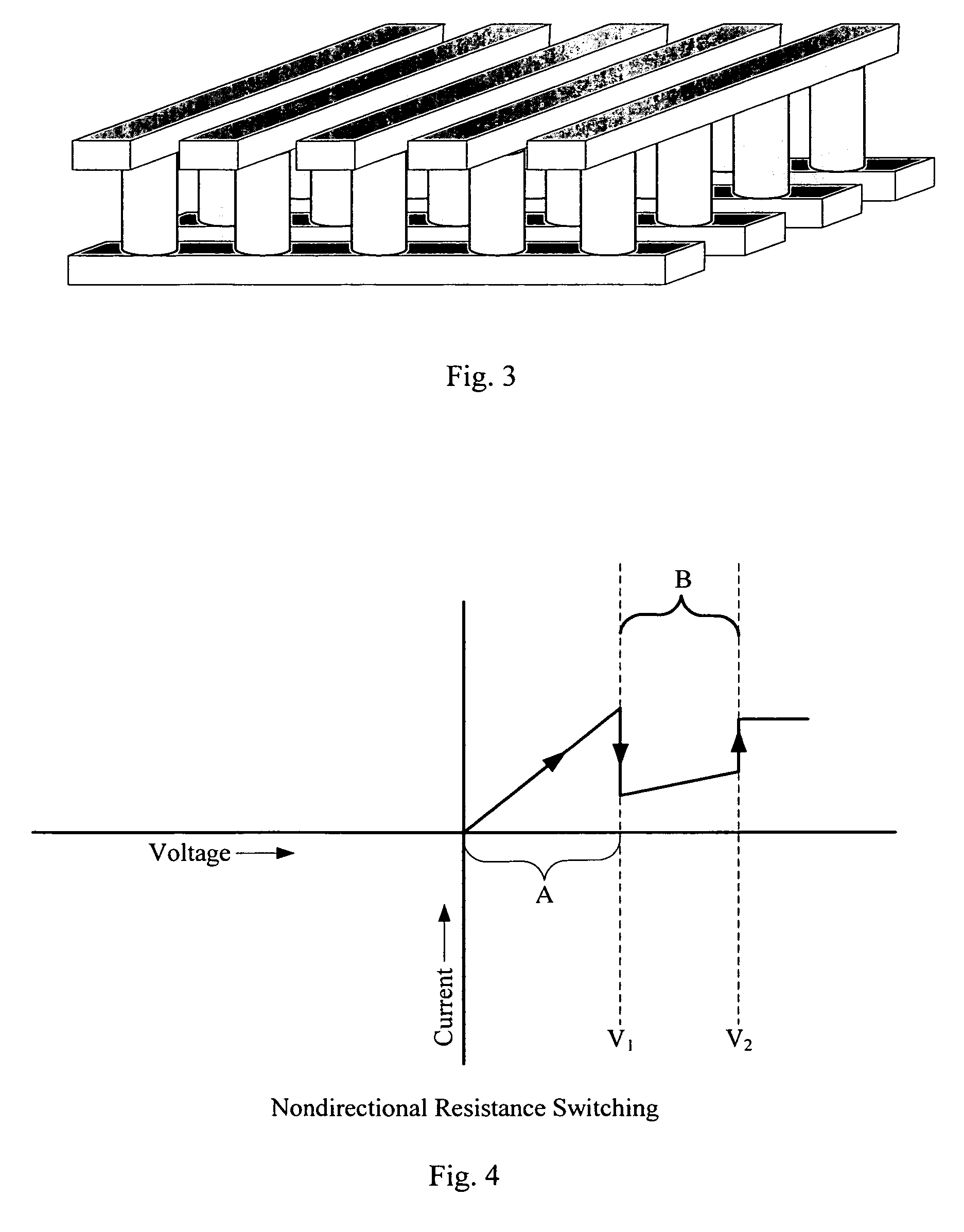

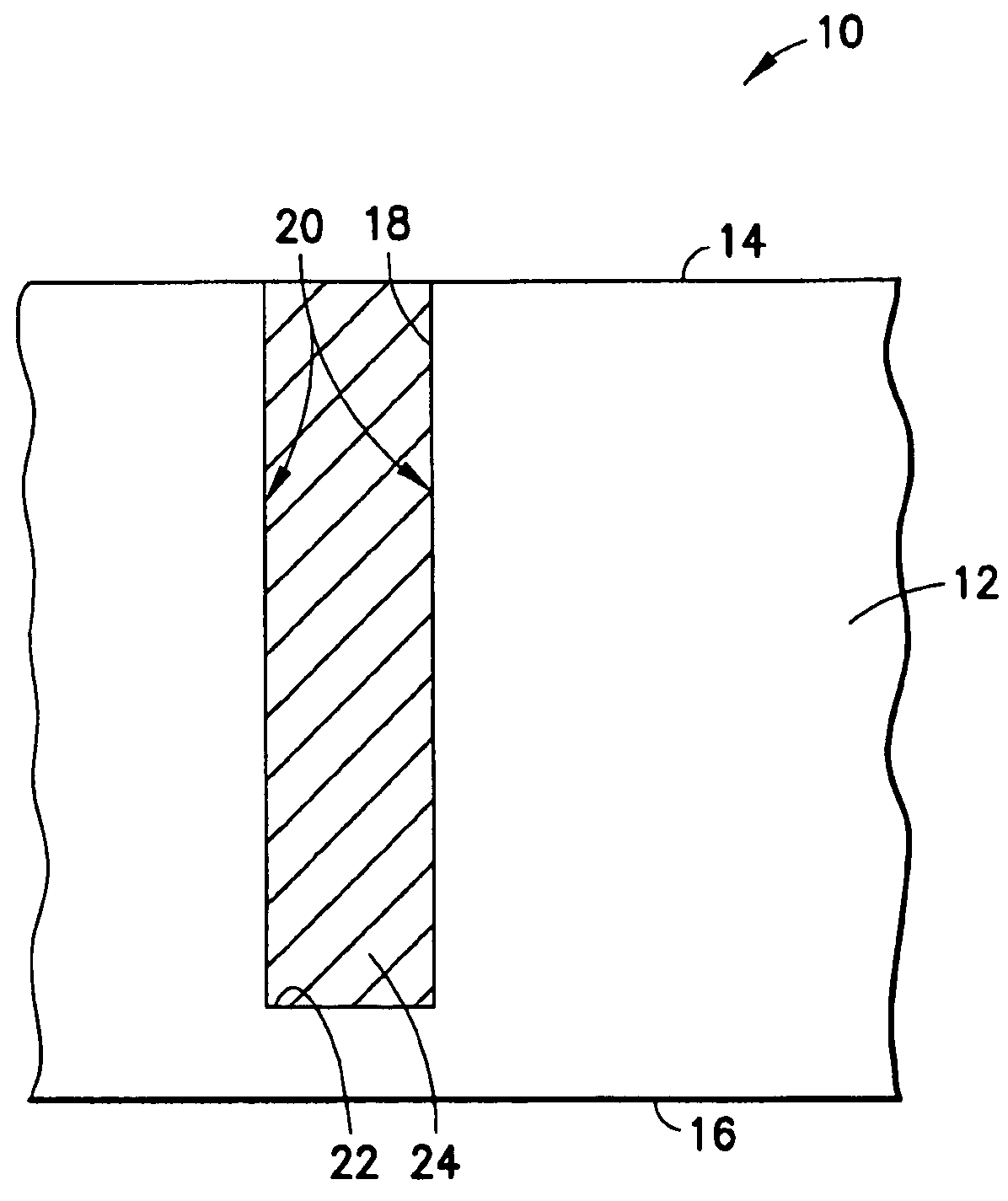

Rewriteable memory cell comprising a diode and a resistance-switching material

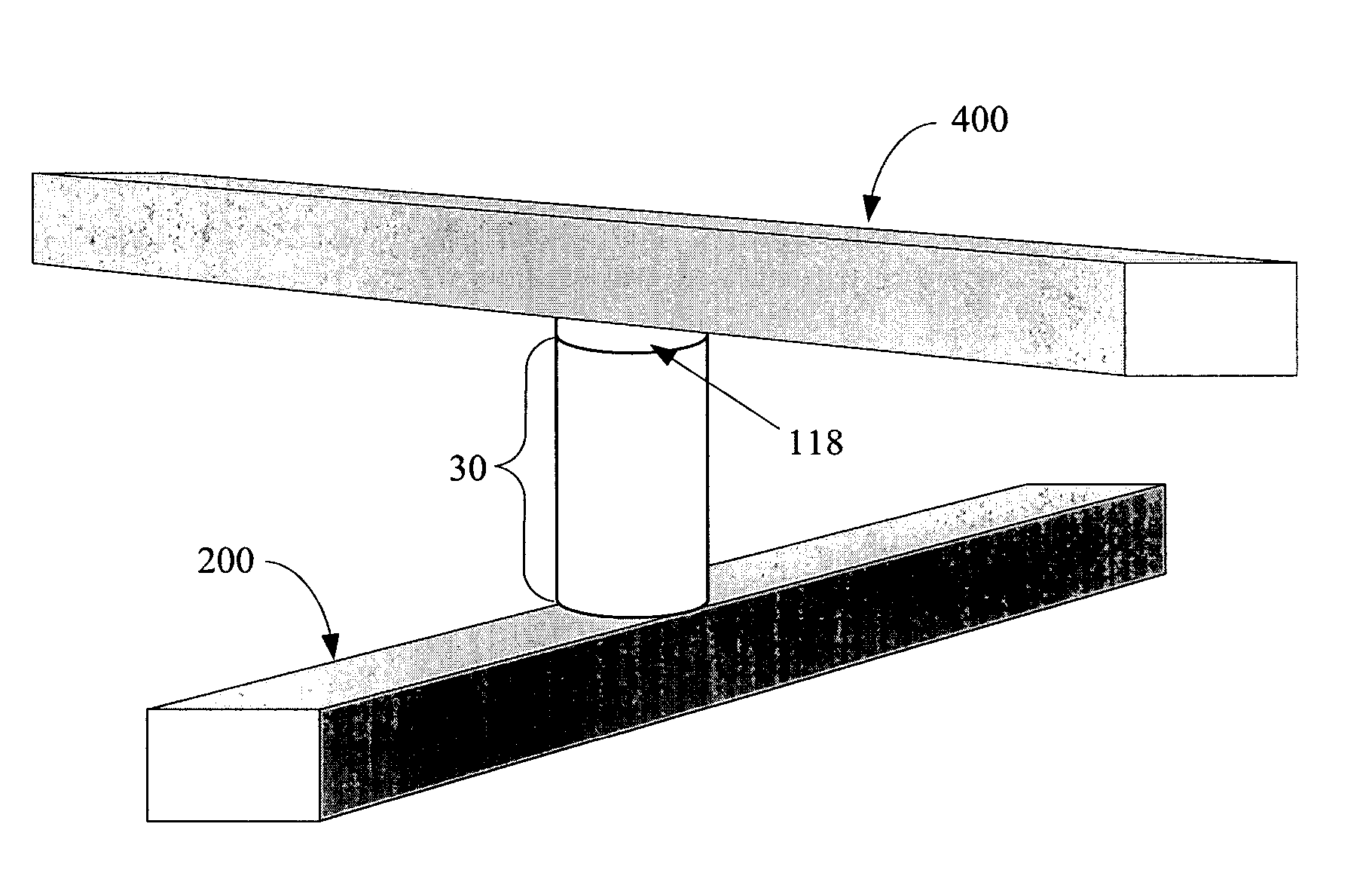

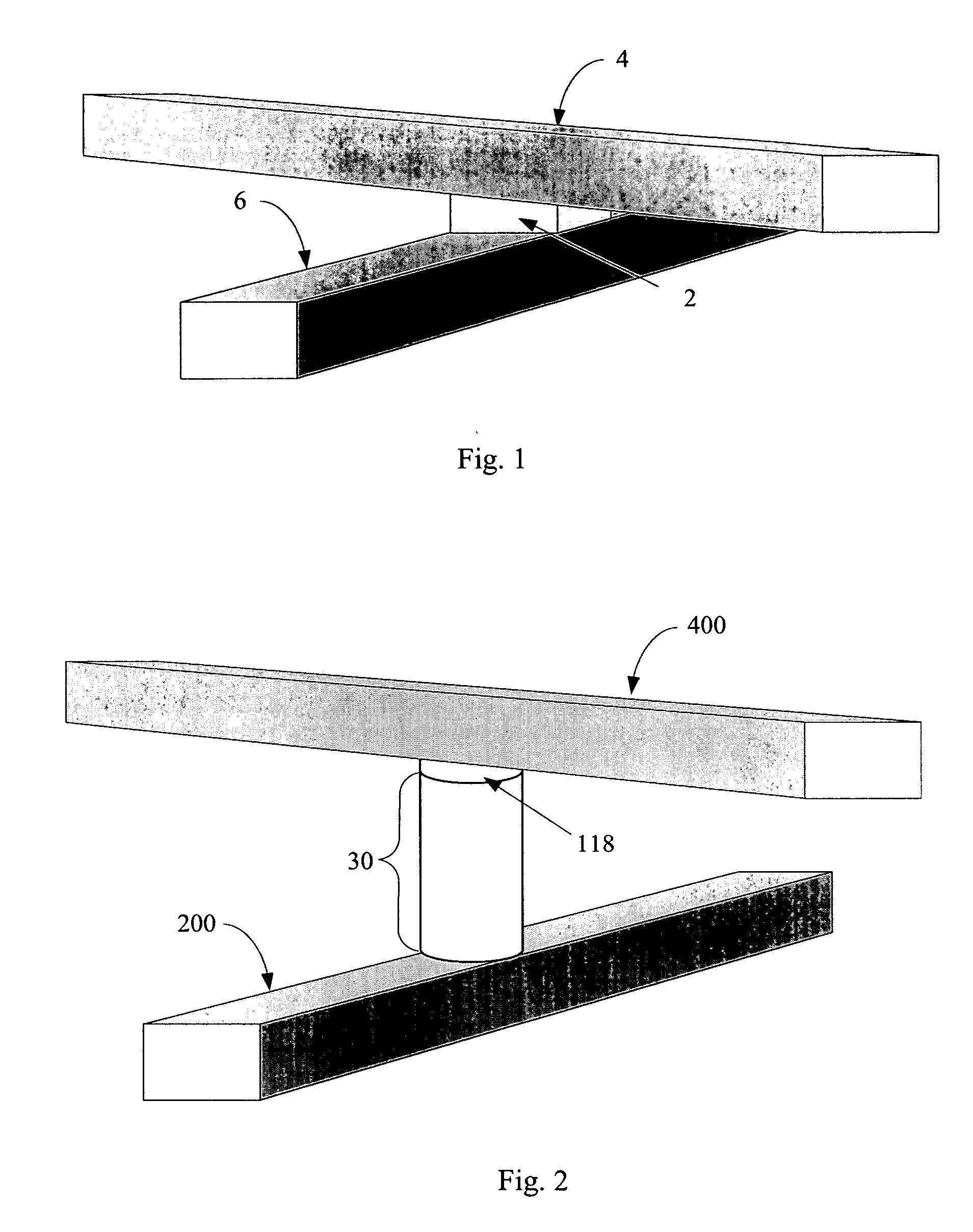

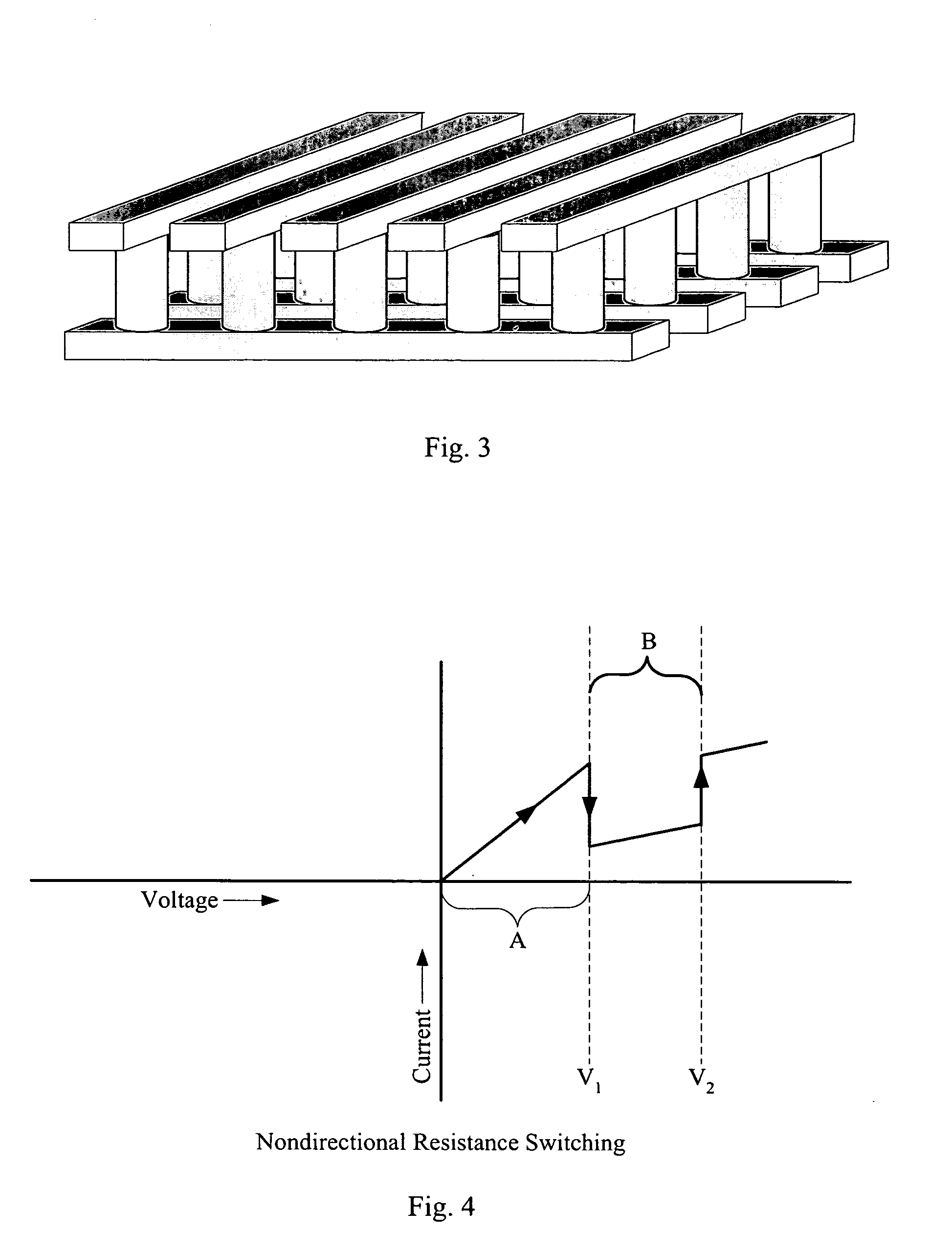

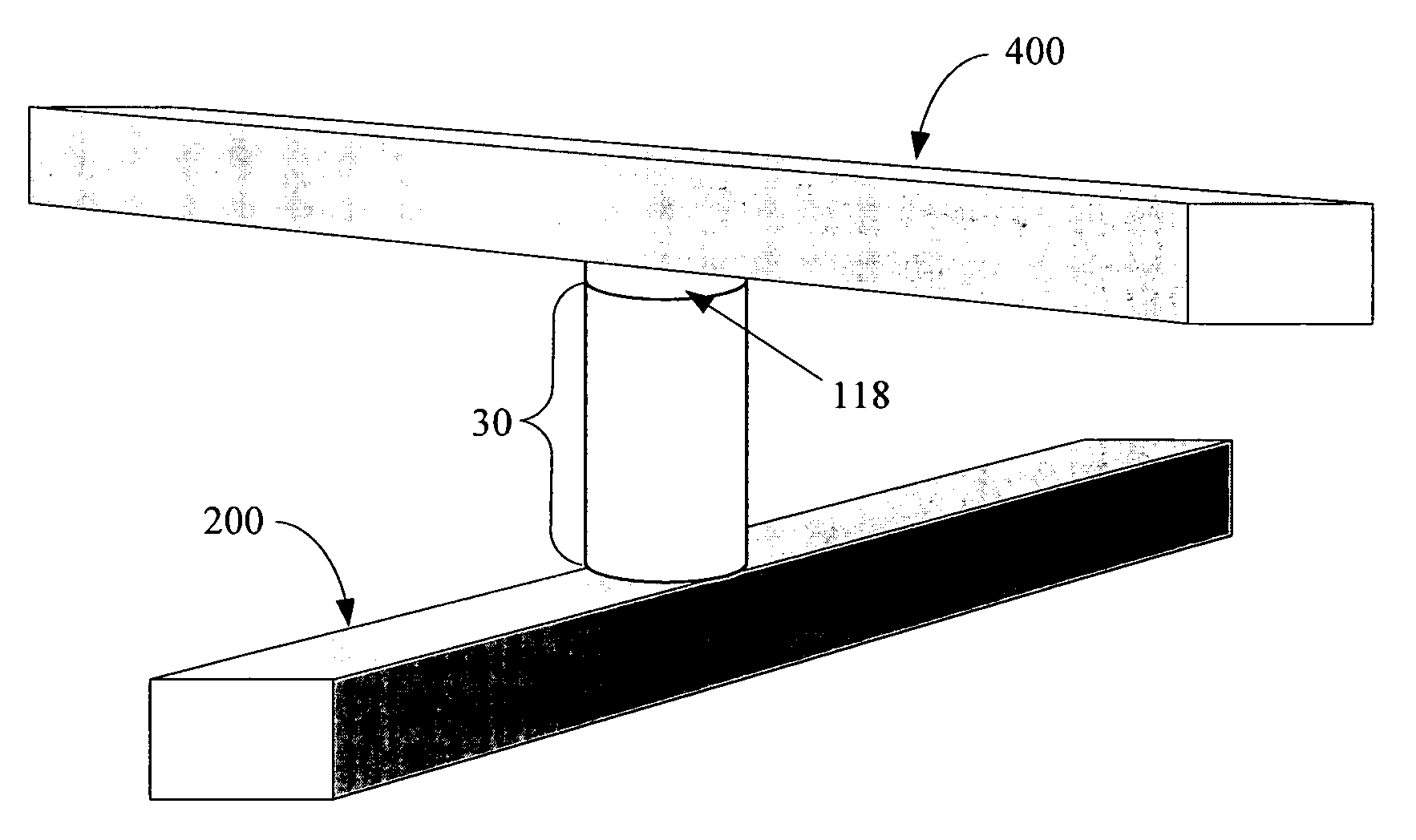

In a novel rewriteable nonvolatile memory cell formed above a substrate, a diode is paired with a reversible resistance-switching material, preferably a metal oxide or nitride such as, for example, NiO, Nb2O5, TiO2, HfO2, Al2O3, MgOx, CrO2, VO, BN, and AlN. In preferred embodiments, the diode is formed as a vertical pillar disposed between conductors. Multiple memory levels can be stacked to form a monolithic three dimensional memory array. In some embodiments, the diode comprises germanium or a germanium alloy, which can be deposited and crystallized at relatively low temperatures, allowing use of aluminum or copper in the conductors.

Owner:SANDISK TECH LLC

Nonvolatile memory cell comprising a diode and a resistance-switching material

In a novel nonvolatile memory cell formed above a substrate, a diode is paired with a reversible resistance-switching material, preferably a metal oxide or nitride such as, for example, NixOy, NbxOy, TixOy, HFxOy, AlxOy, MgxOy, CoxOy, CrxOy, VxOy, ZnxOy, ZrxOy, BxNy, and AlxNy. In preferred embodiments, the diode is formed as a vertical pillar disposed between conductors. Multiple memory levels can be stacked to form a monolithic three dimensional memory array. In some embodiments, the diode comprises germanium or a germanium alloy, which can be deposited and crystallized at relatively low temperatures, allowing use of aluminum or copper in the conductors. The memory cell of the present invention can be used as a rewriteable memory cell or a one-time-programmable memory cell, and can store two or more data states.

Owner:SANDISK TECH LLC

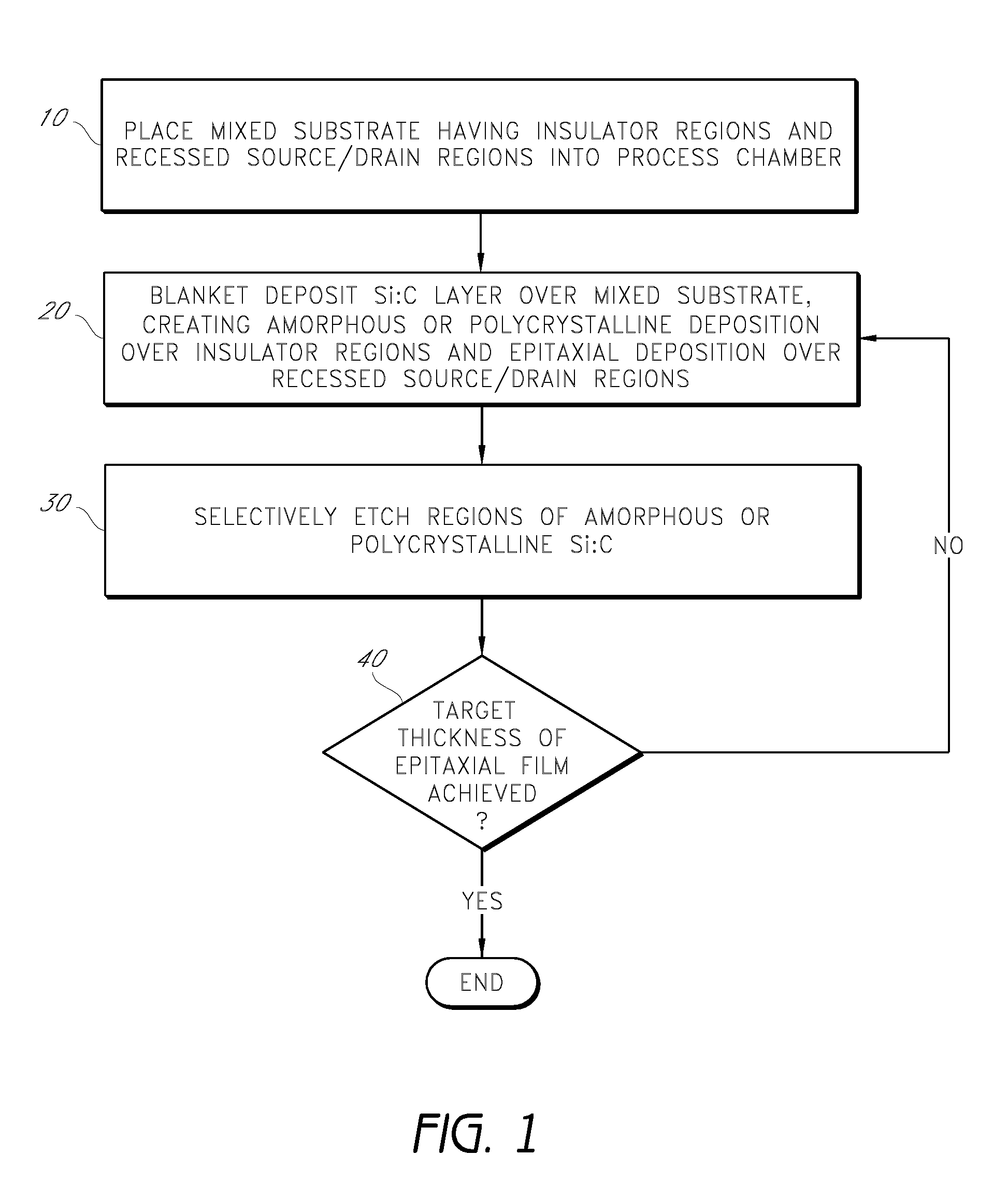

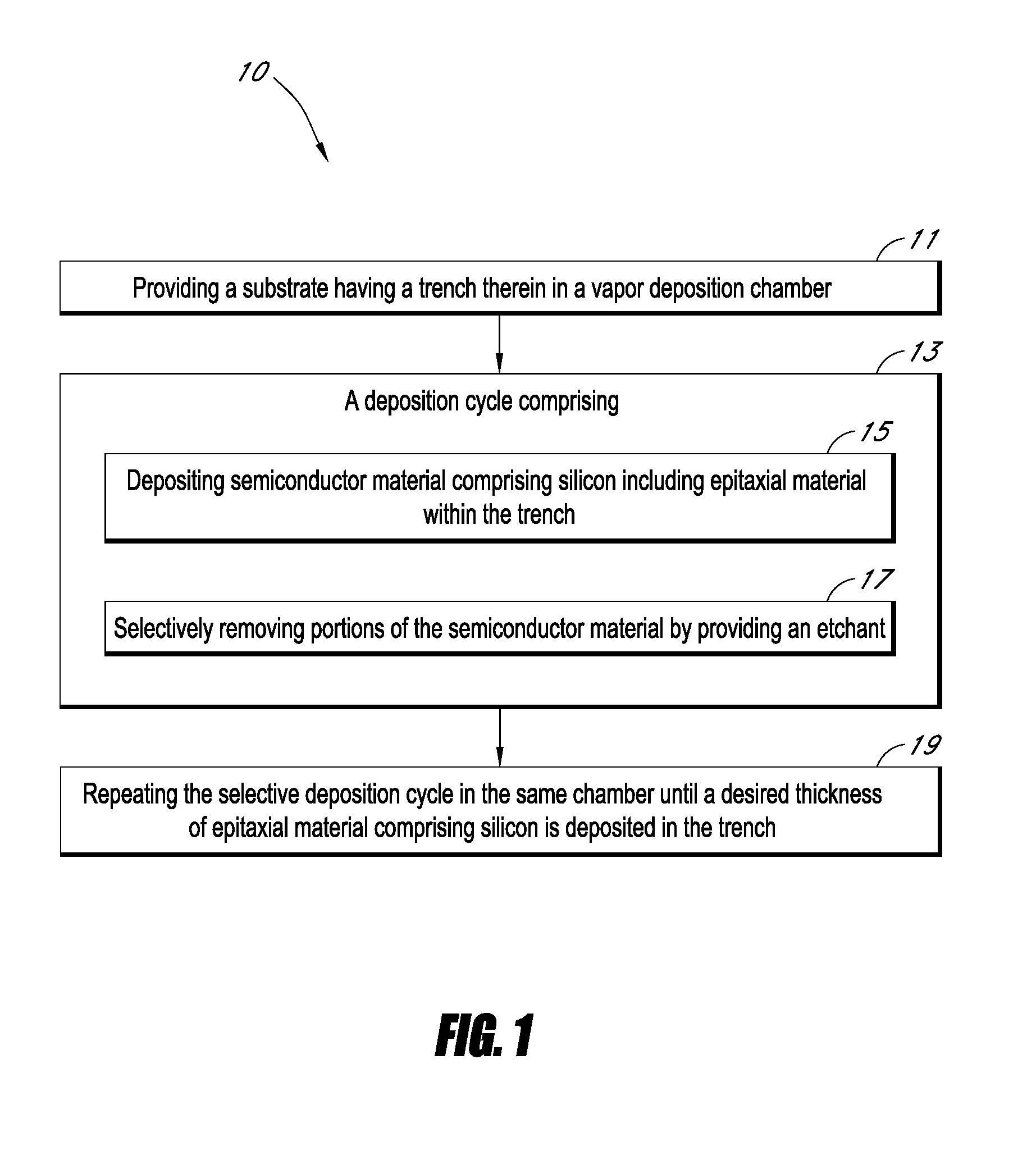

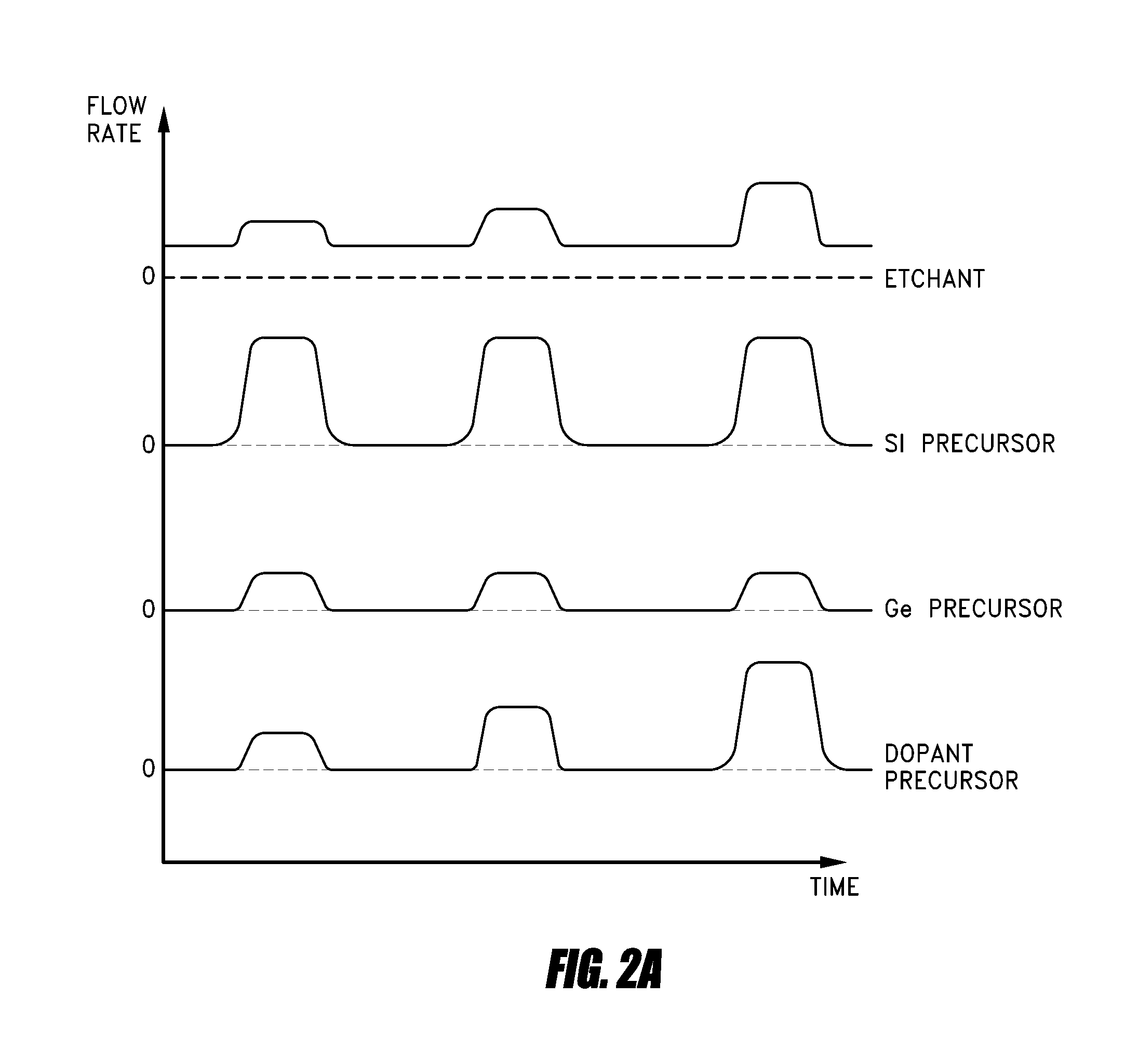

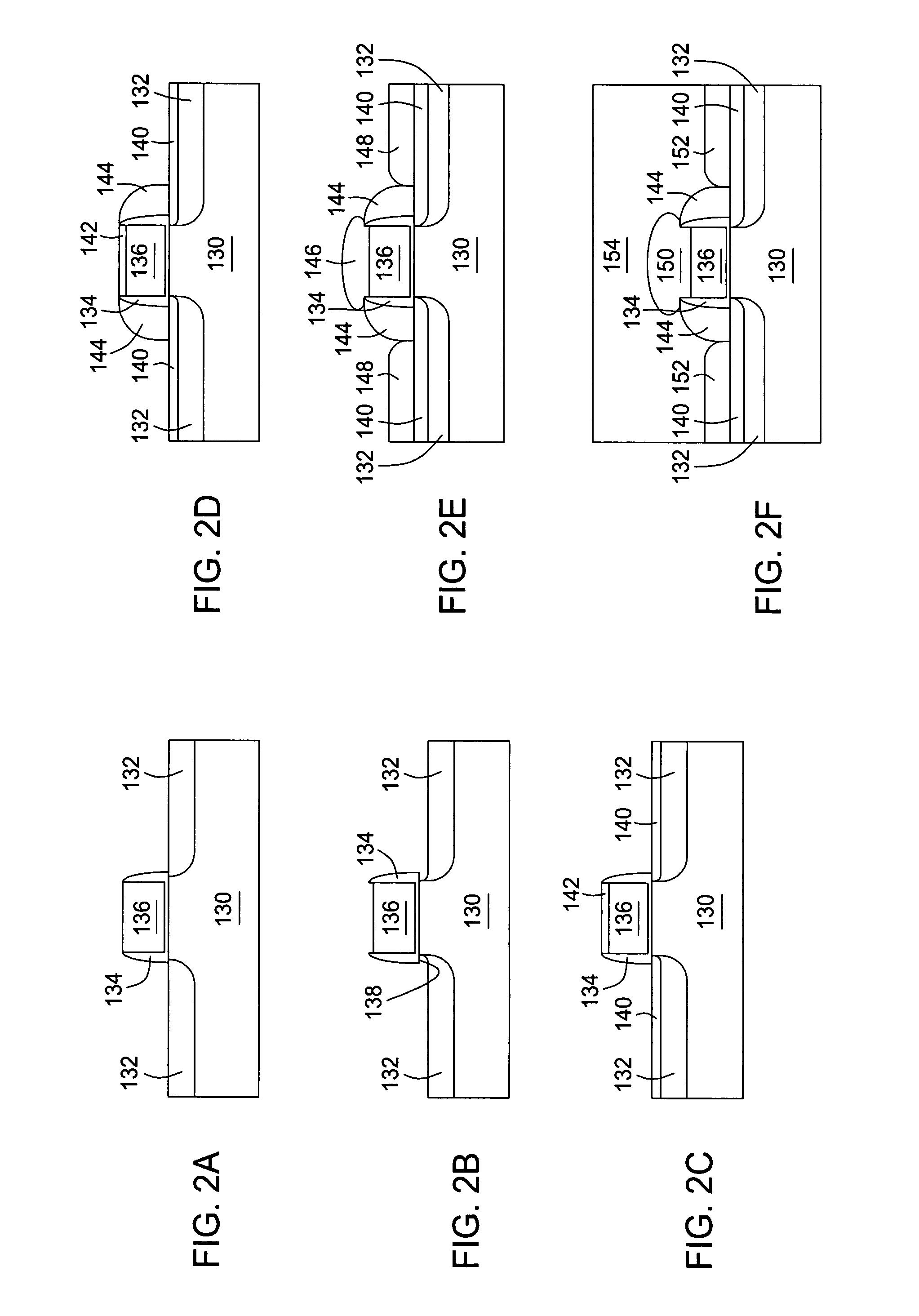

Selective epitaxial formation of semiconductor films

ActiveUS8278176B2Semiconductor/solid-state device manufacturingSemiconductor devicesCyclic processMetallurgy

Epitaxial layers are selectively formed in semiconductor windows by a cyclical process of repeated blanket deposition and selective etching. The blanket deposition phases leave non-epitaxial material over insulating regions, such as field oxide, and the selective etch phases preferentially remove non-epitaxial material while deposited epitaxial material builds up cycle-by-cycle. Quality of the epitaxial material improves relative to selective processes where no deposition occurs on insulators. Use of a germanium catalyst during the etch phases of the process aid etch rates and facilitate economical maintenance of isothermal and / or isobaric conditions throughout the cycles. Throughput and quality are improved by use of trisilane, formation of amorphous material over the insulating regions and minimizing the thickness ratio of amorphous:epitaxial material in each deposition phase.

Owner:ASM IP HLDG BV

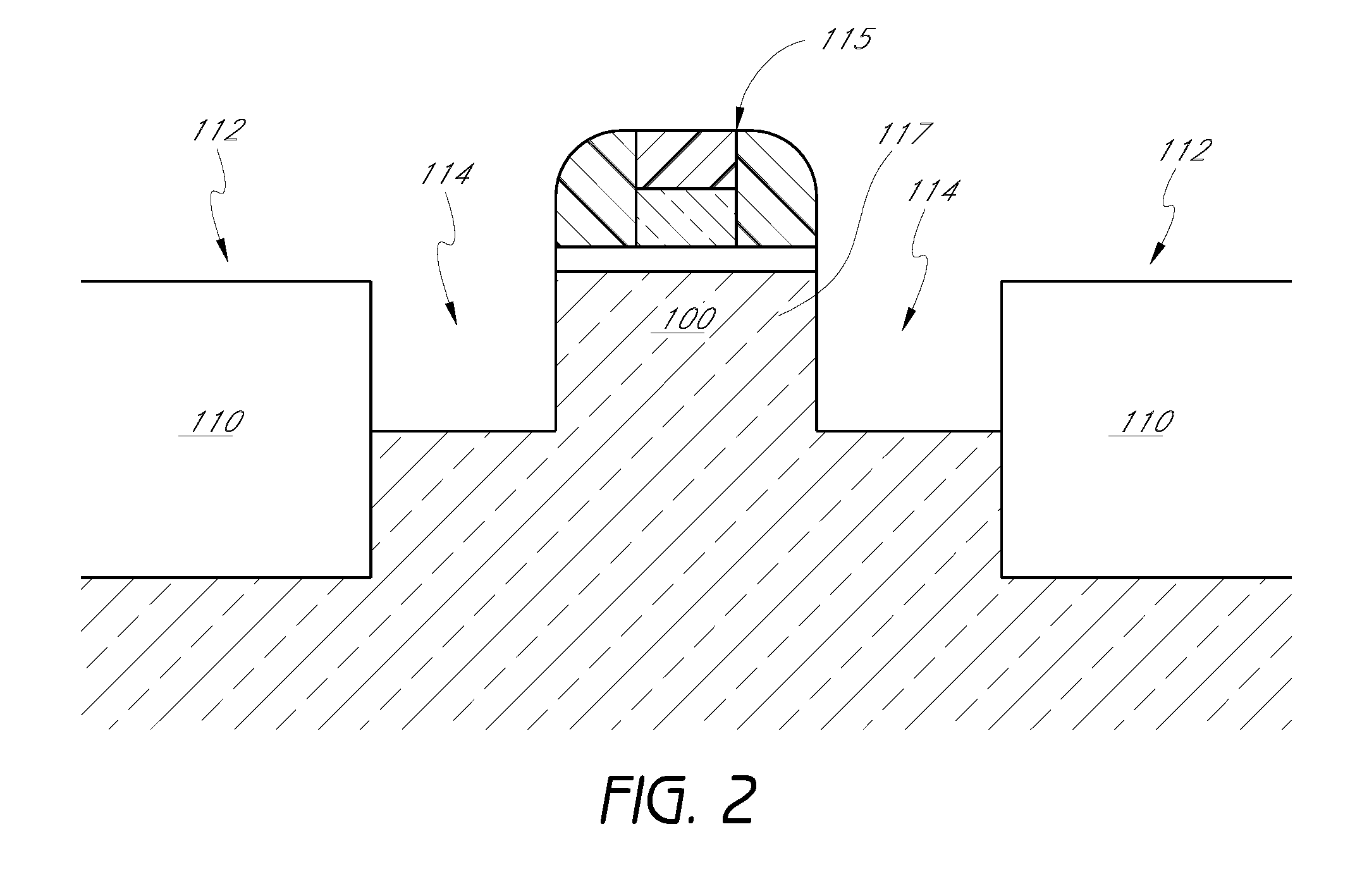

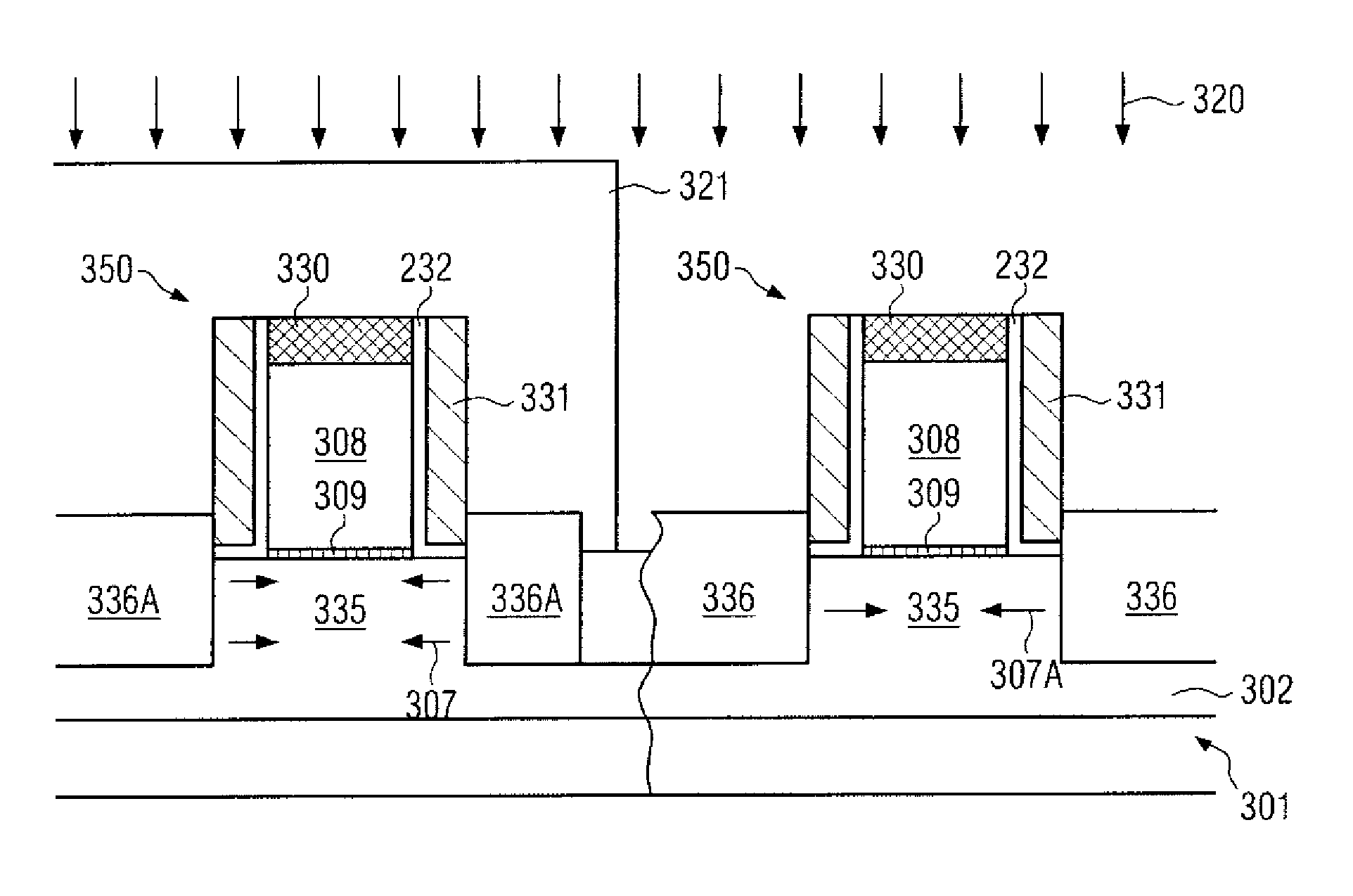

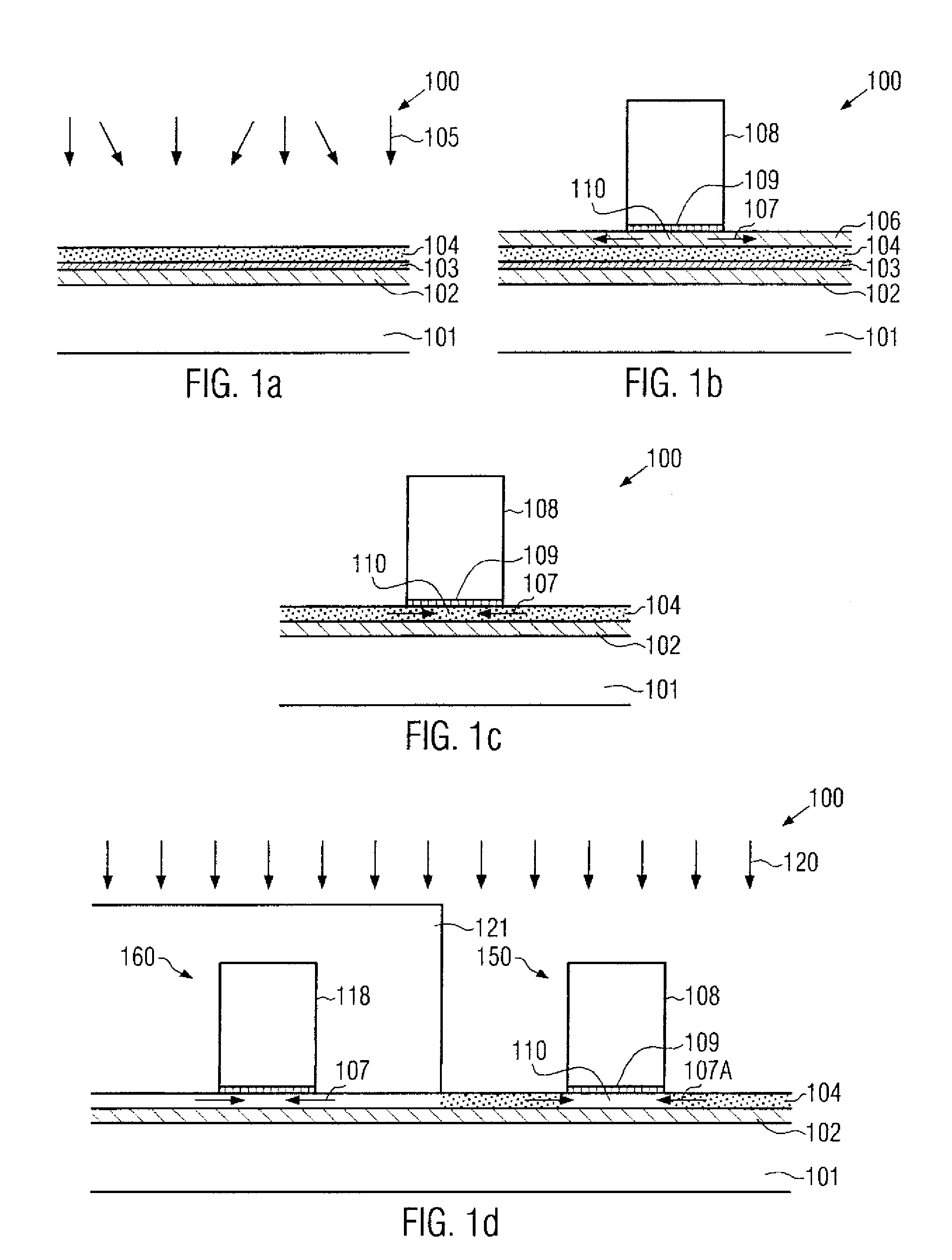

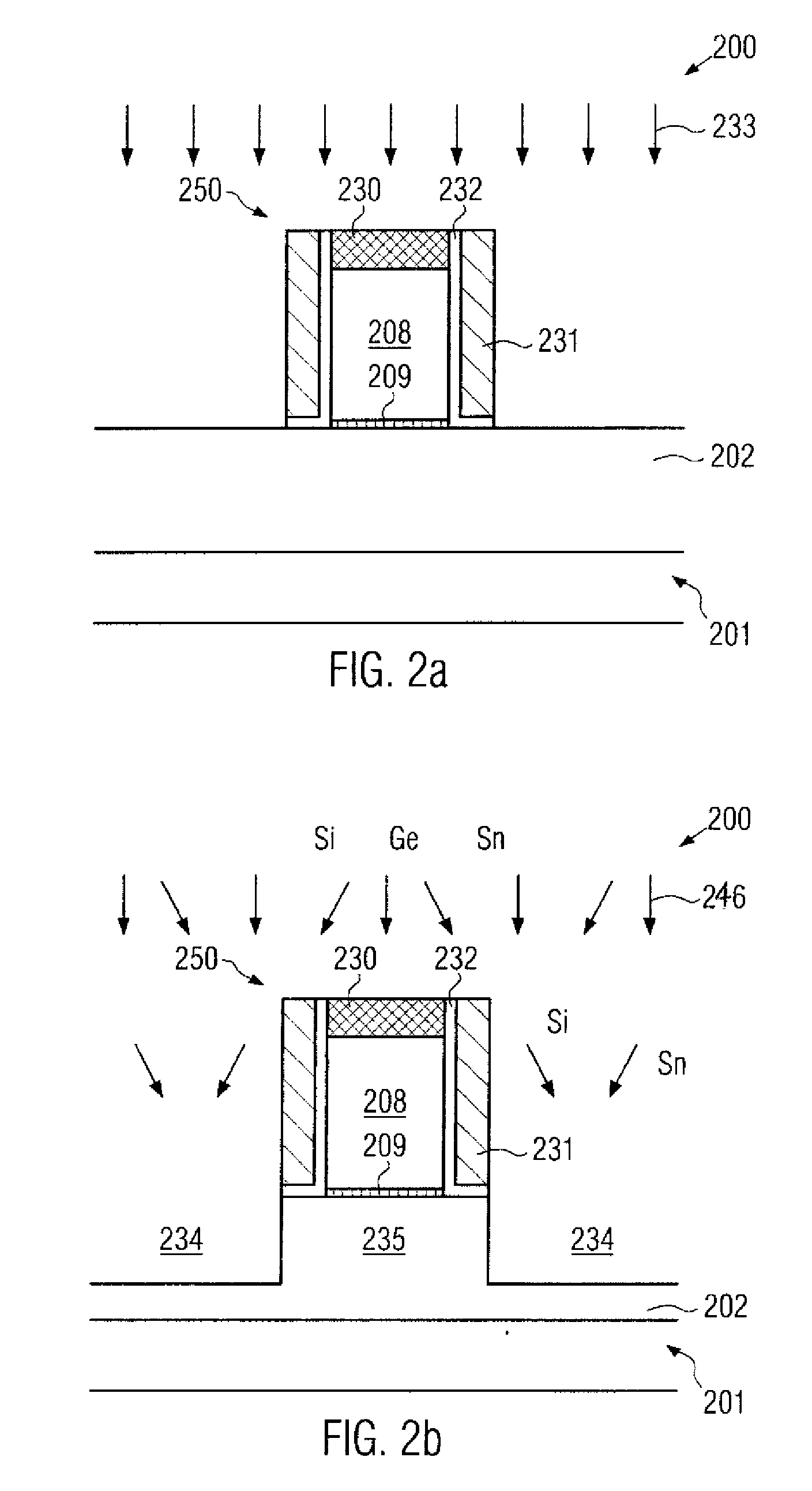

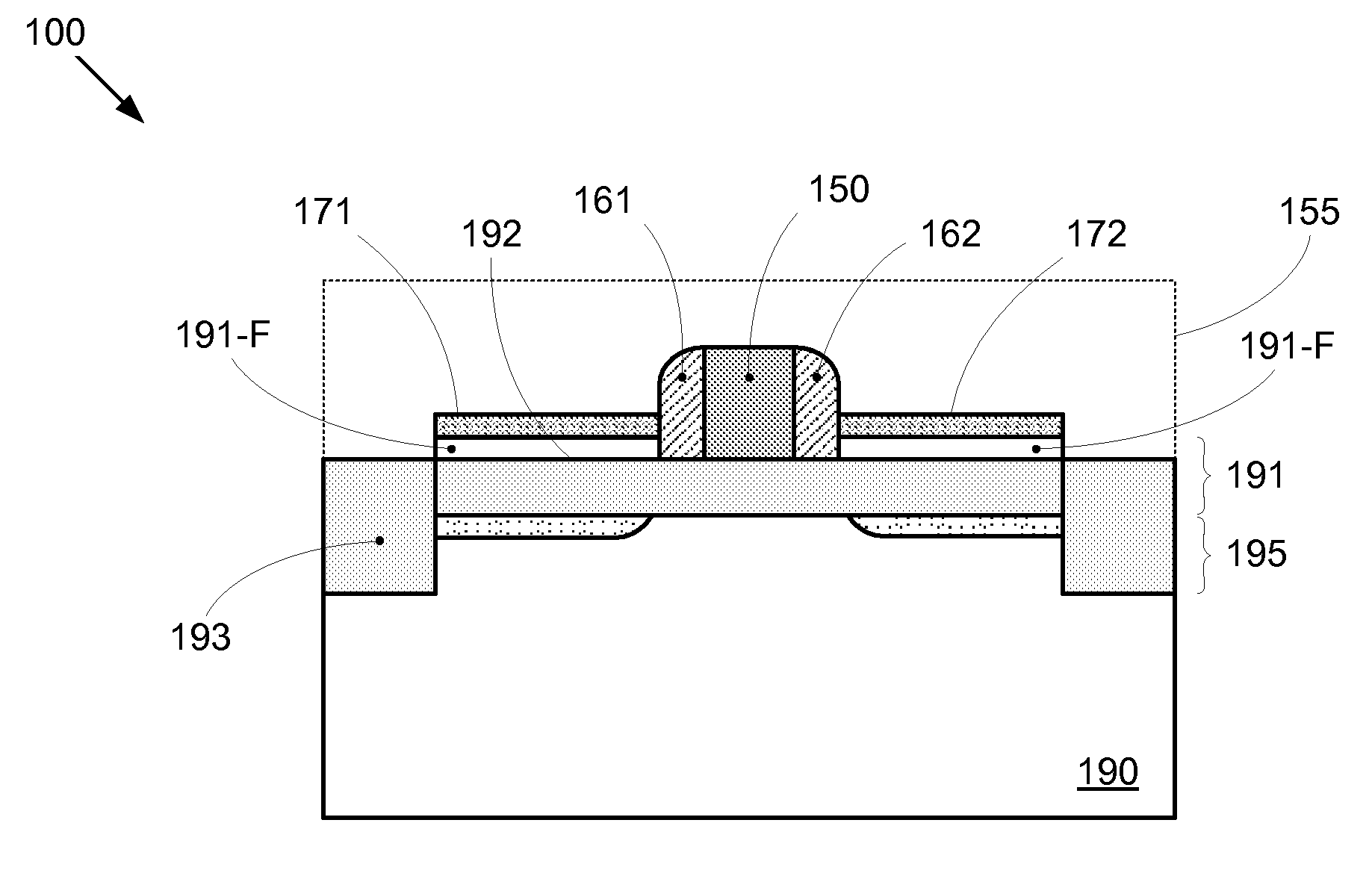

Technique for strain engineering in si-based transistors by using embedded semiconductor layers including atoms with high covalent radius

By incorporating an atomic species of increased covalent radius, which may at least partially substitute germanium, a highly efficient strain mechanism may be provided, in which the risk of stress relief due to germanium conglomeration and lattice defects may be reduced. The atomic species of increased radius, such as tin, may be readily incorporated by epitaxial growth techniques on the basis of tin hydride.

Owner:GLOBALFOUNDRIES INC

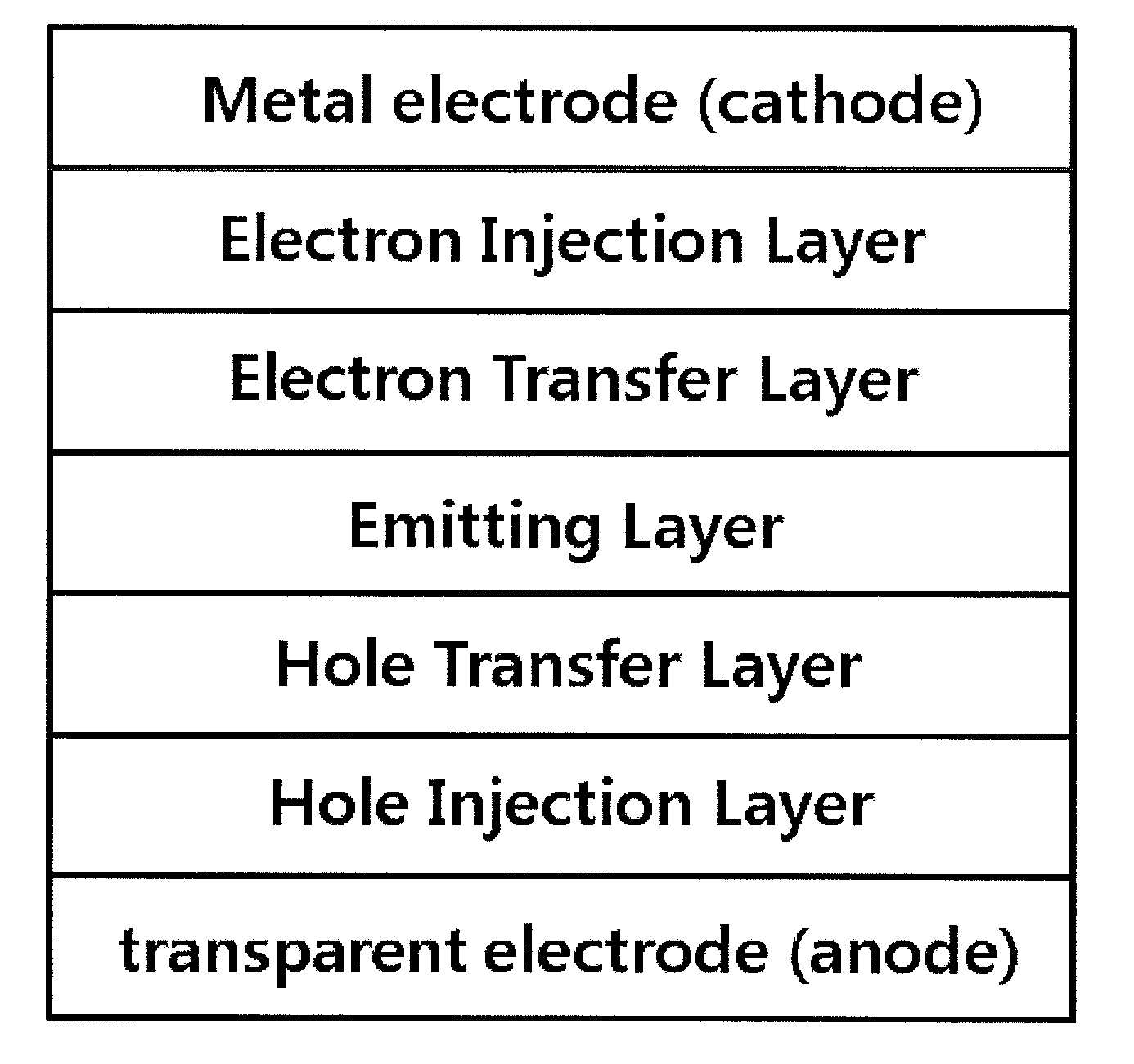

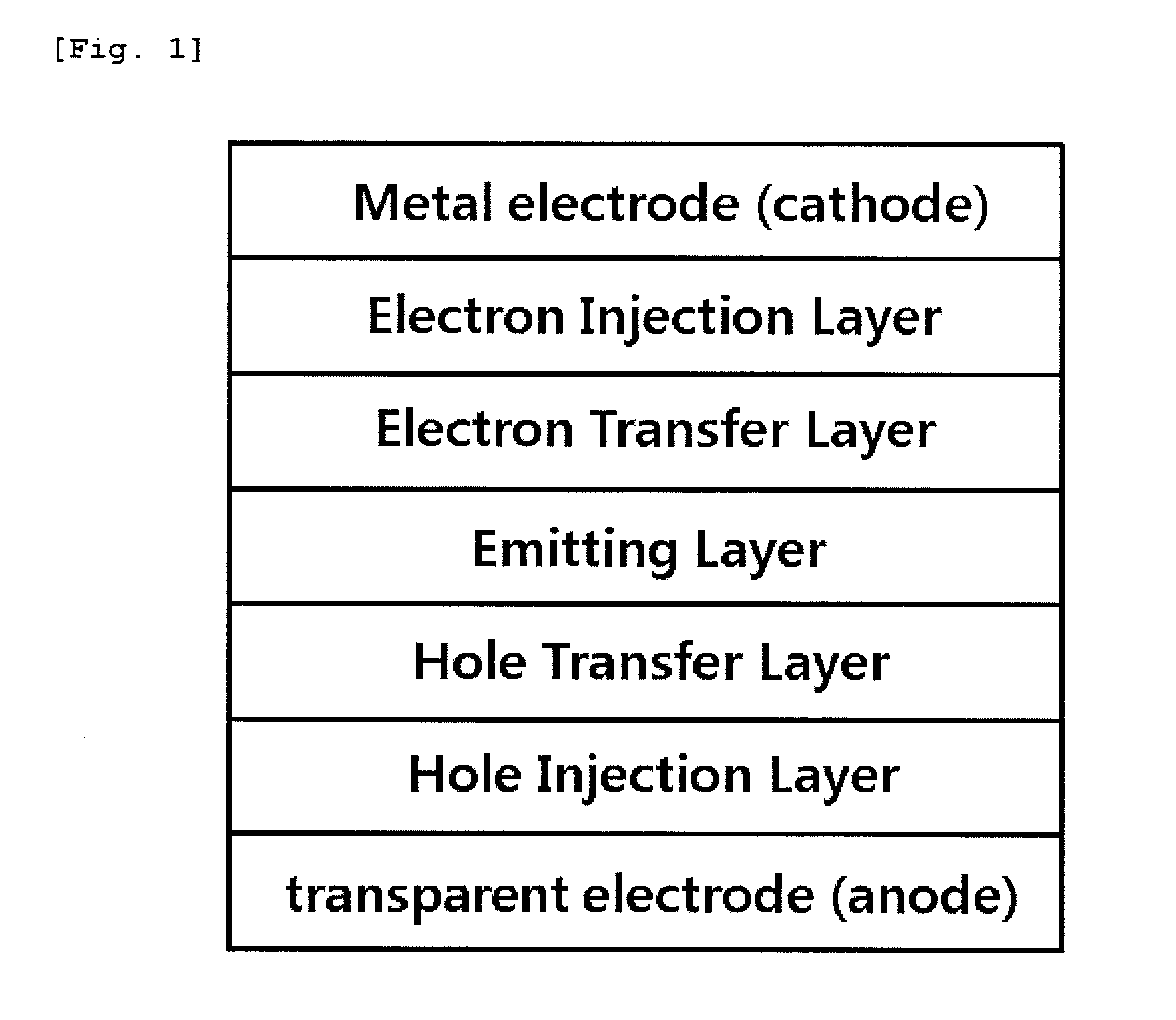

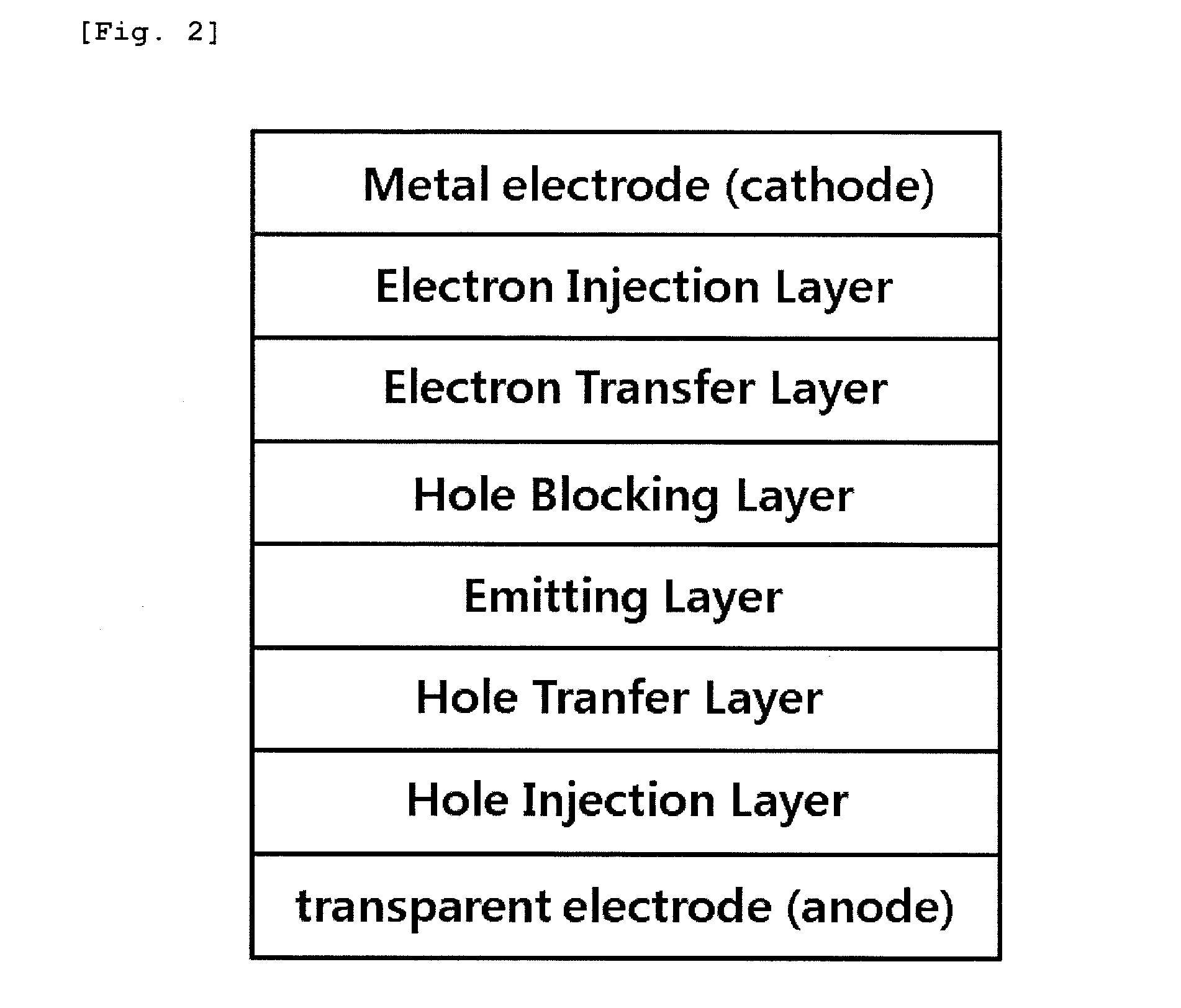

Novel organometallic compound, and organic light-emitting diode using same

ActiveUS20130334521A1Easy to useImprove emission efficiencyIndium organic compoundsElectroluminescent light sourcesLight-emitting diodeOLED

The present invention relates to a novel organometallic compound, and more particularly, to a luminescent organometallic compound in which intermolecular interaction is inhibited by means of introducing a germanium substituent, thereby improving light-emitting characteristics. The present invention also relates to an organic electronic device, specifically, to an organic light-emitting diode using the compound. According to the present invention, a germanium substituent is introduced to the parent organometallic iridium compound, thus inhibiting an intermolecular interaction in the solid state and enabling the compound of the present invention to be effectively used in solution processing. When the compound of the present invention is used as part of a light-emitting layer of an organic light-emitting diode, the light-emitting efficiency of the light-emitting diode may be significantly improved. Therefore, the compound of the present invention may be effectively used as a material for an organic light-emitting diode.

Owner:SAMSUNG ELECTRONICS CO LTD

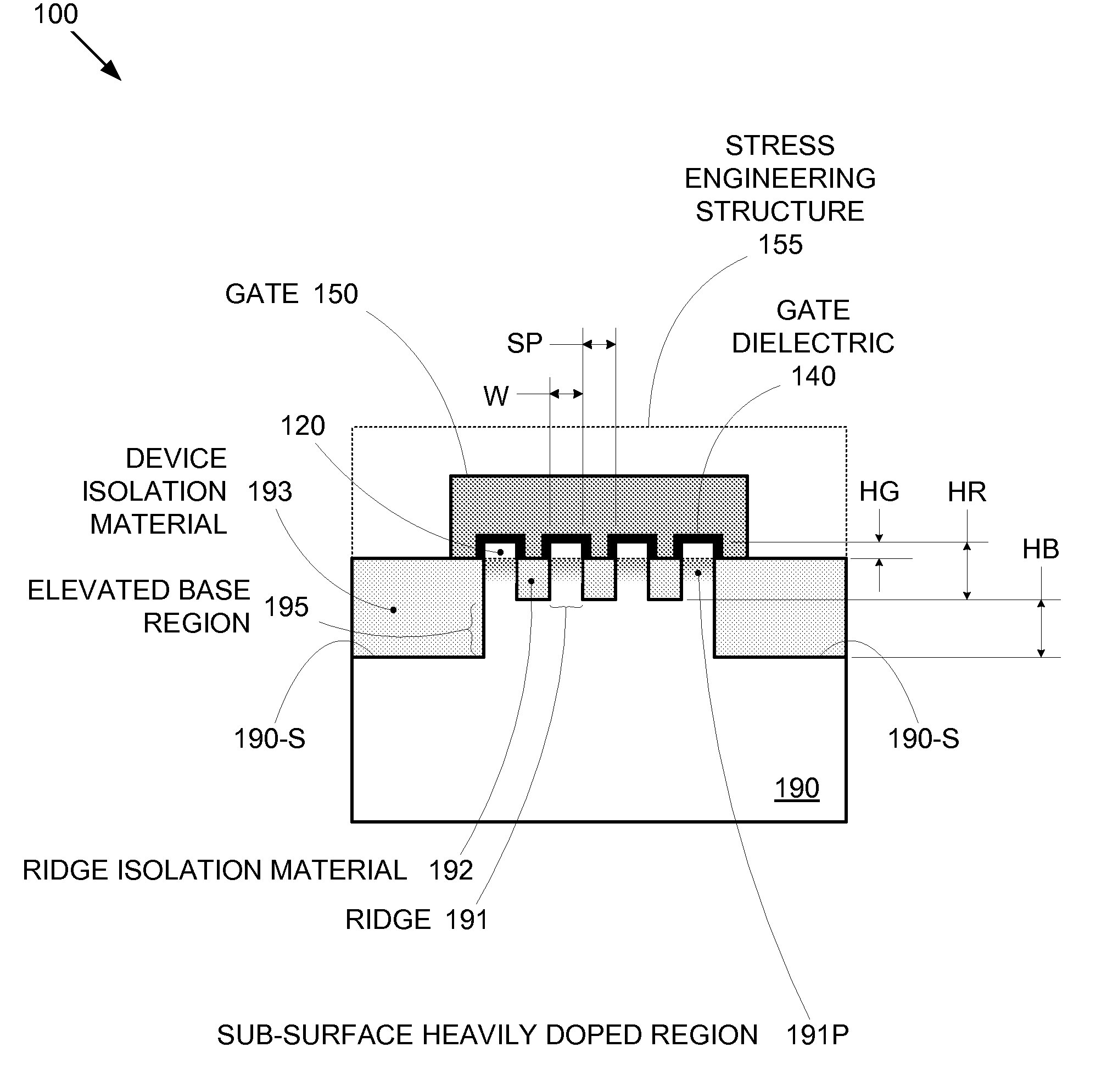

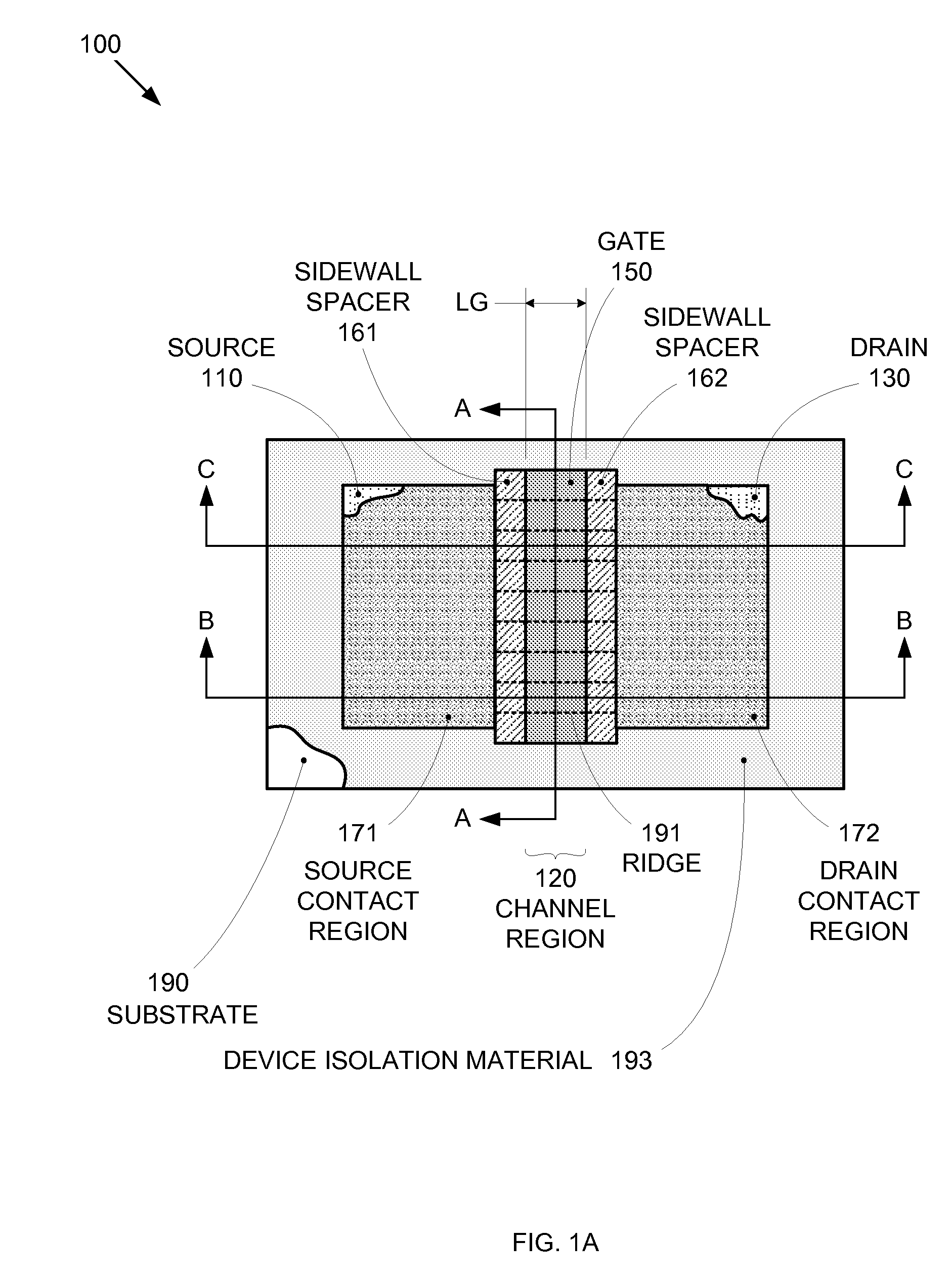

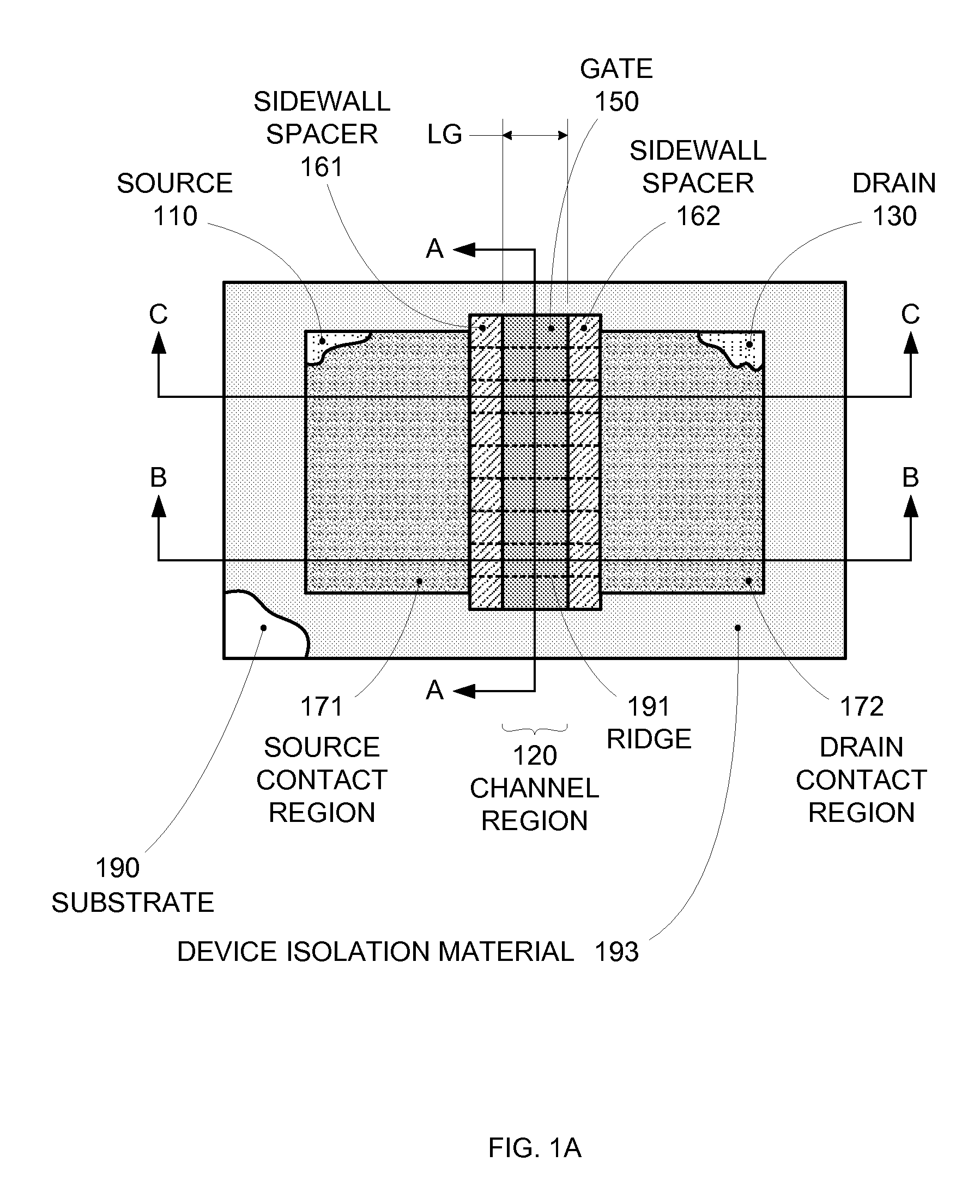

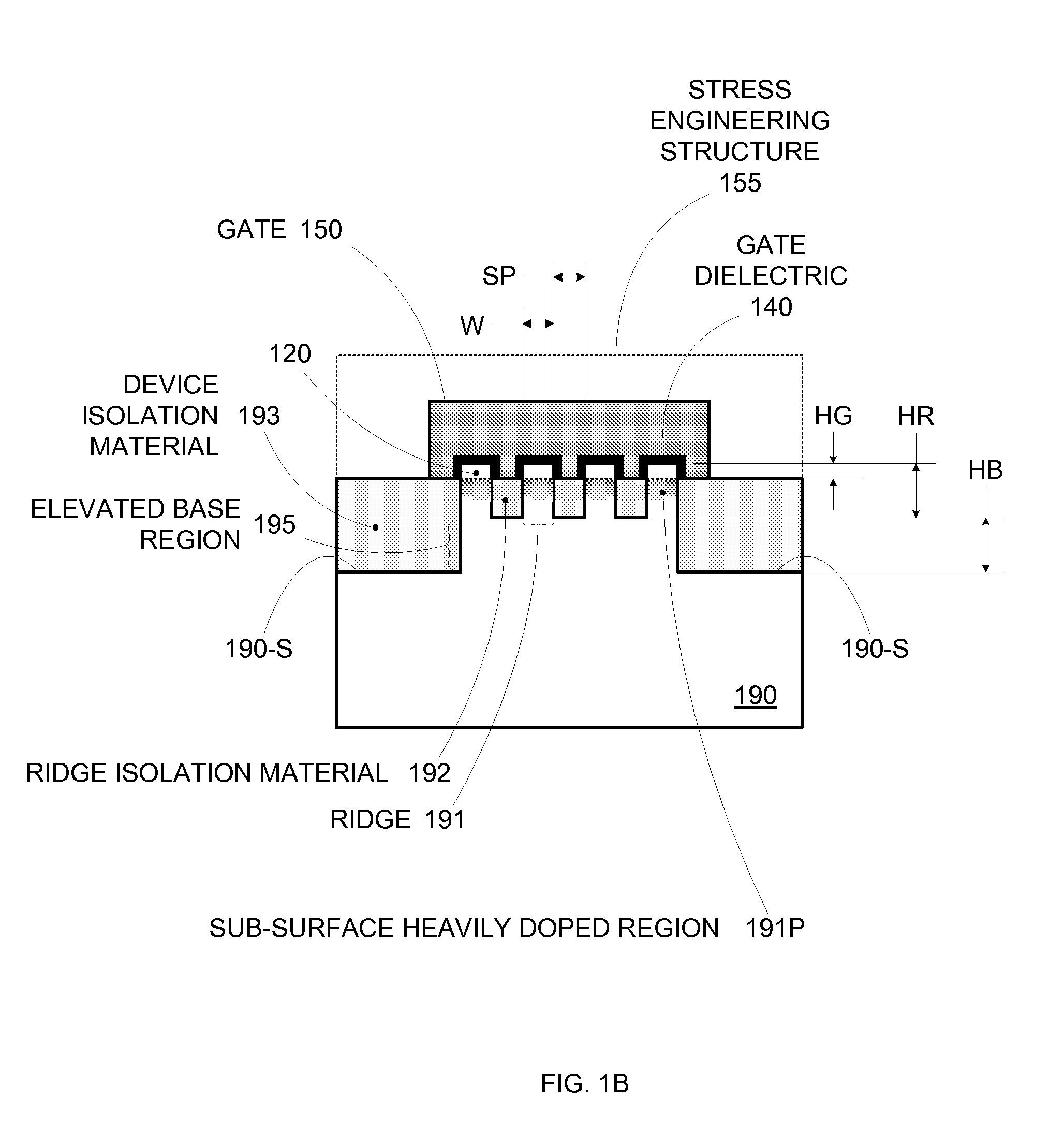

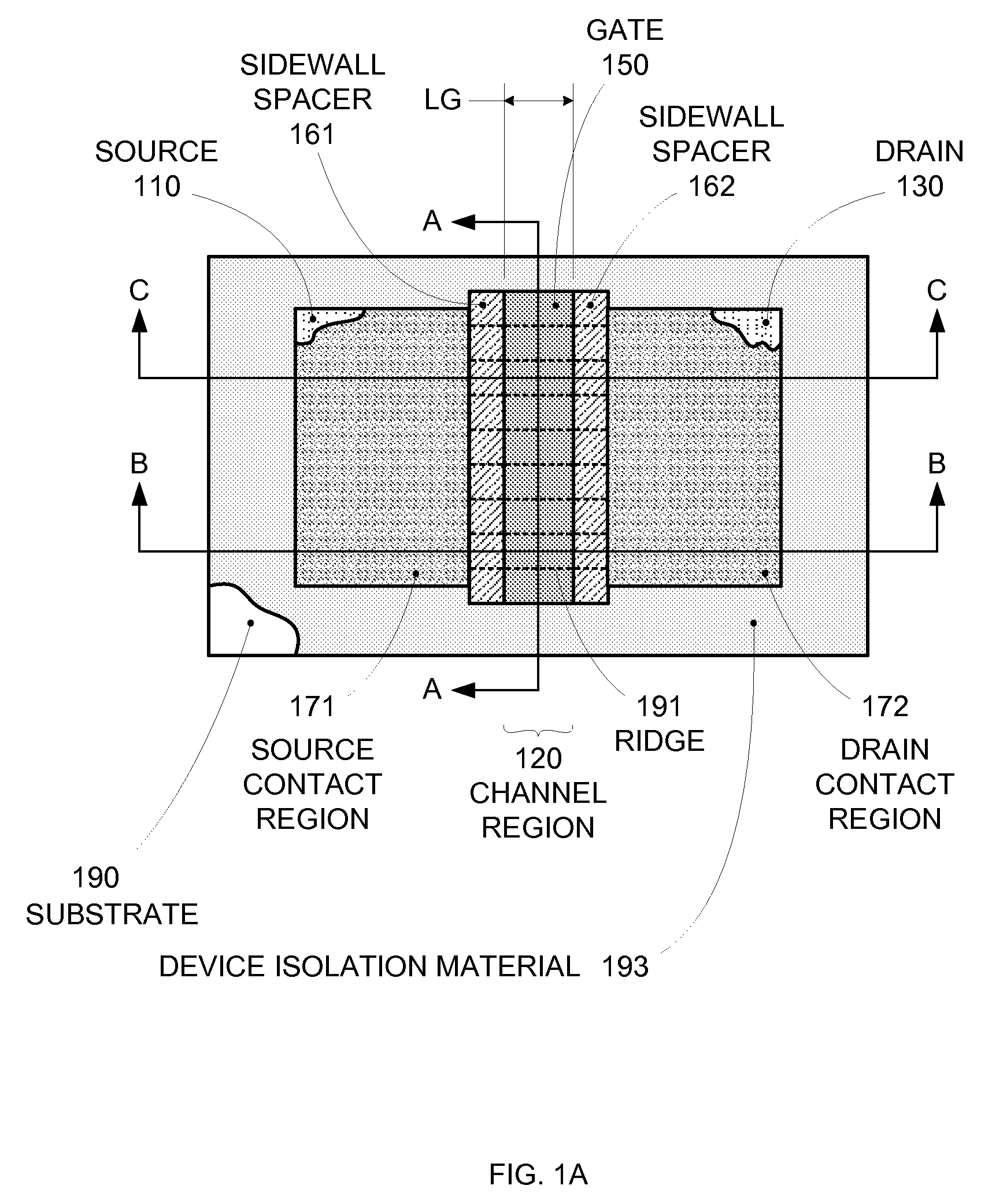

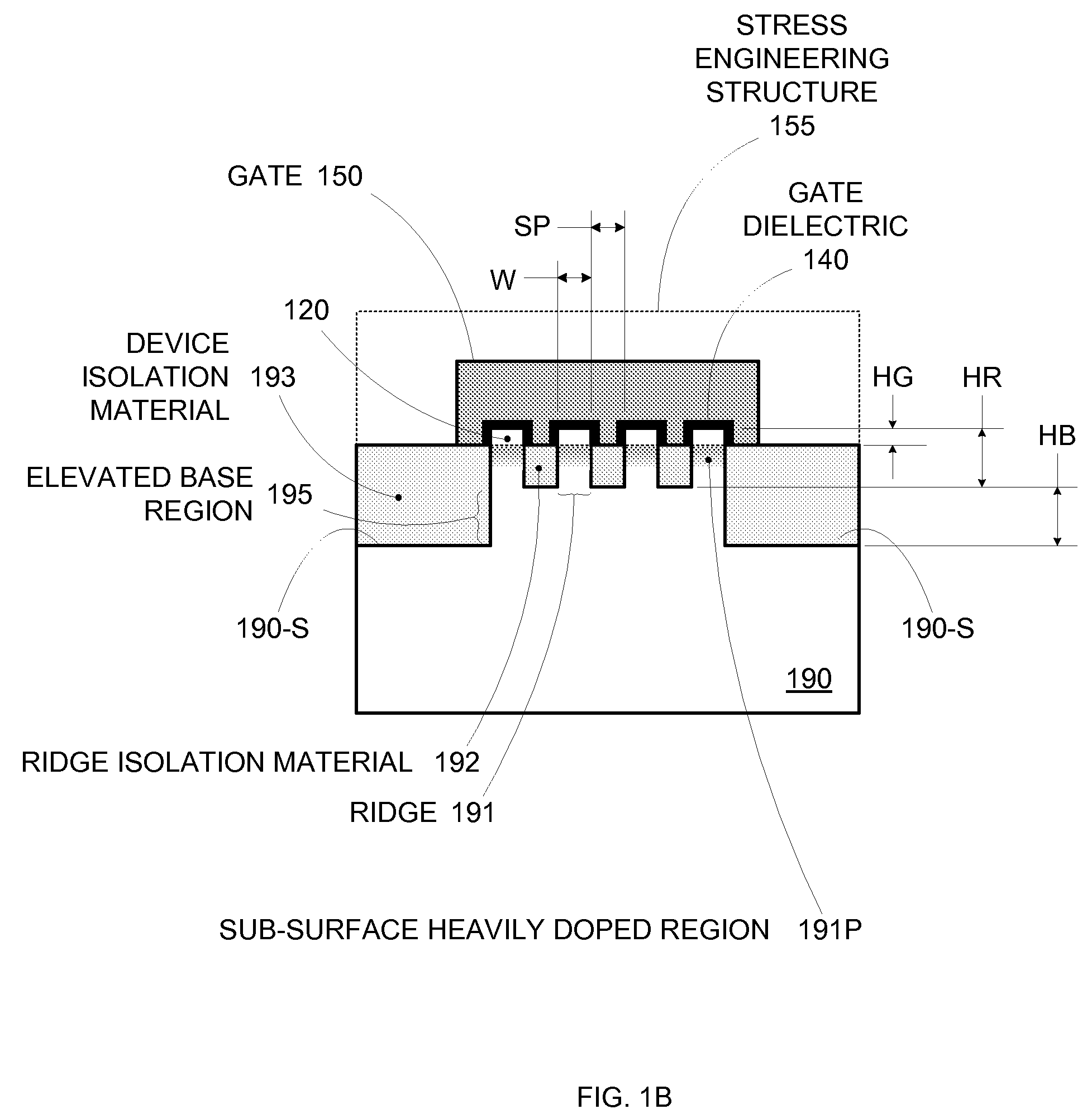

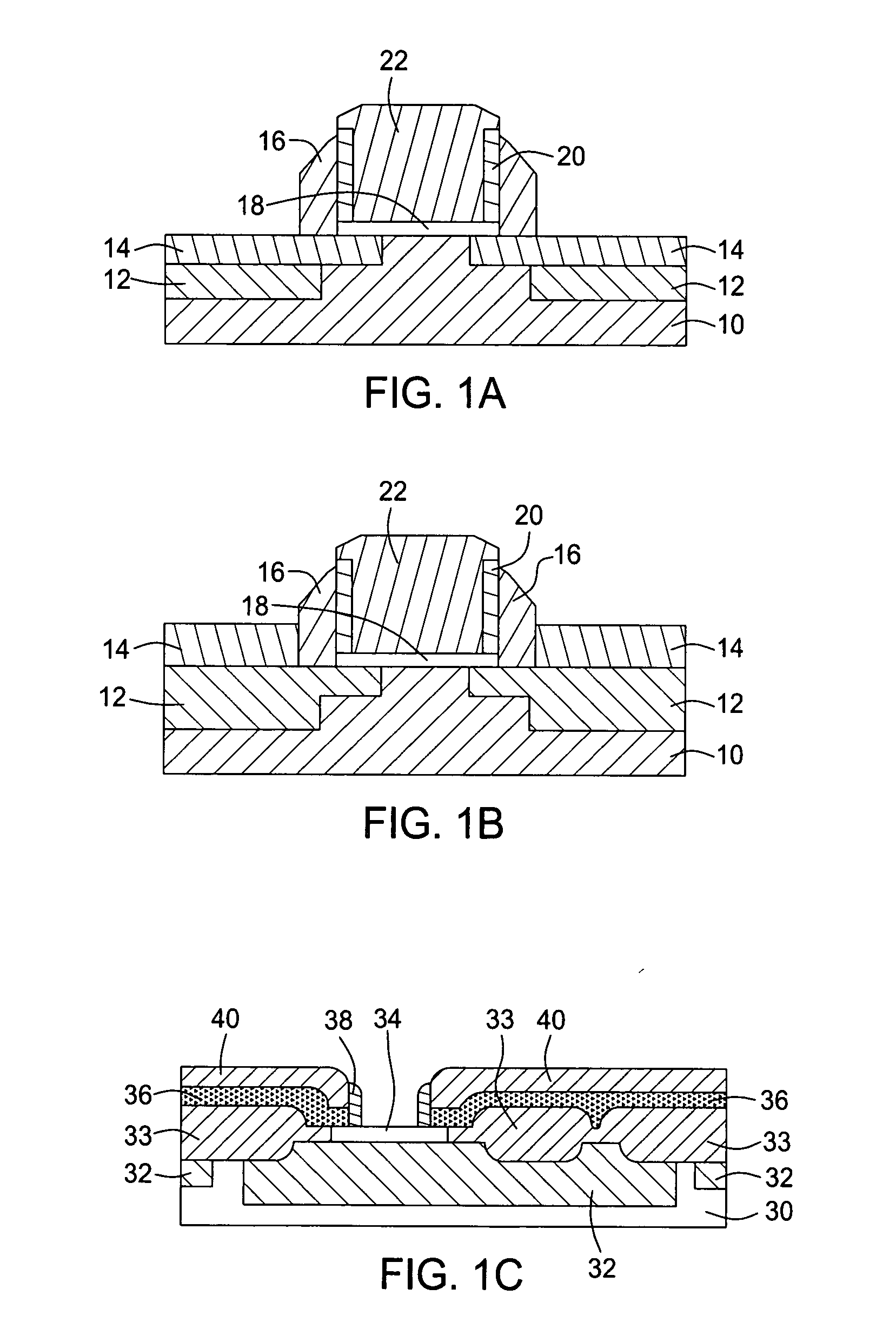

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

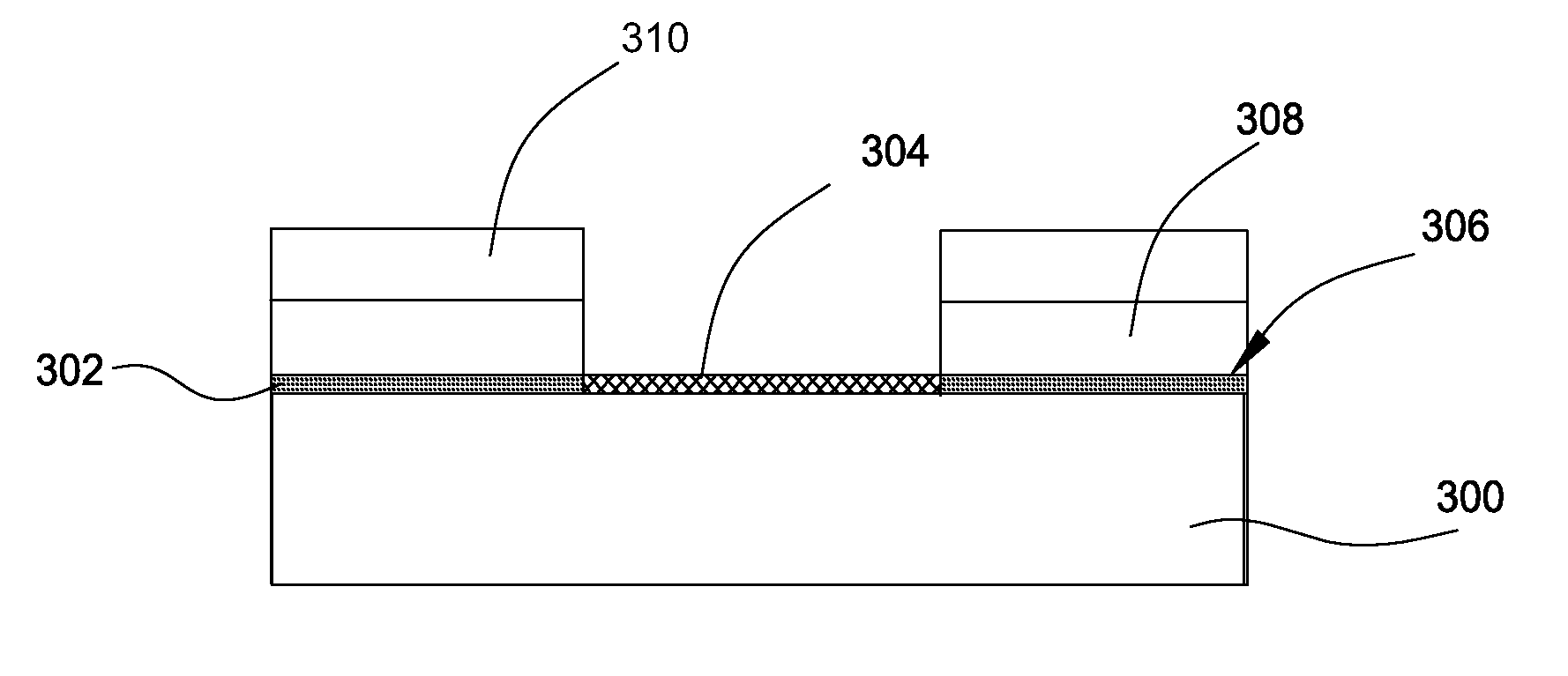

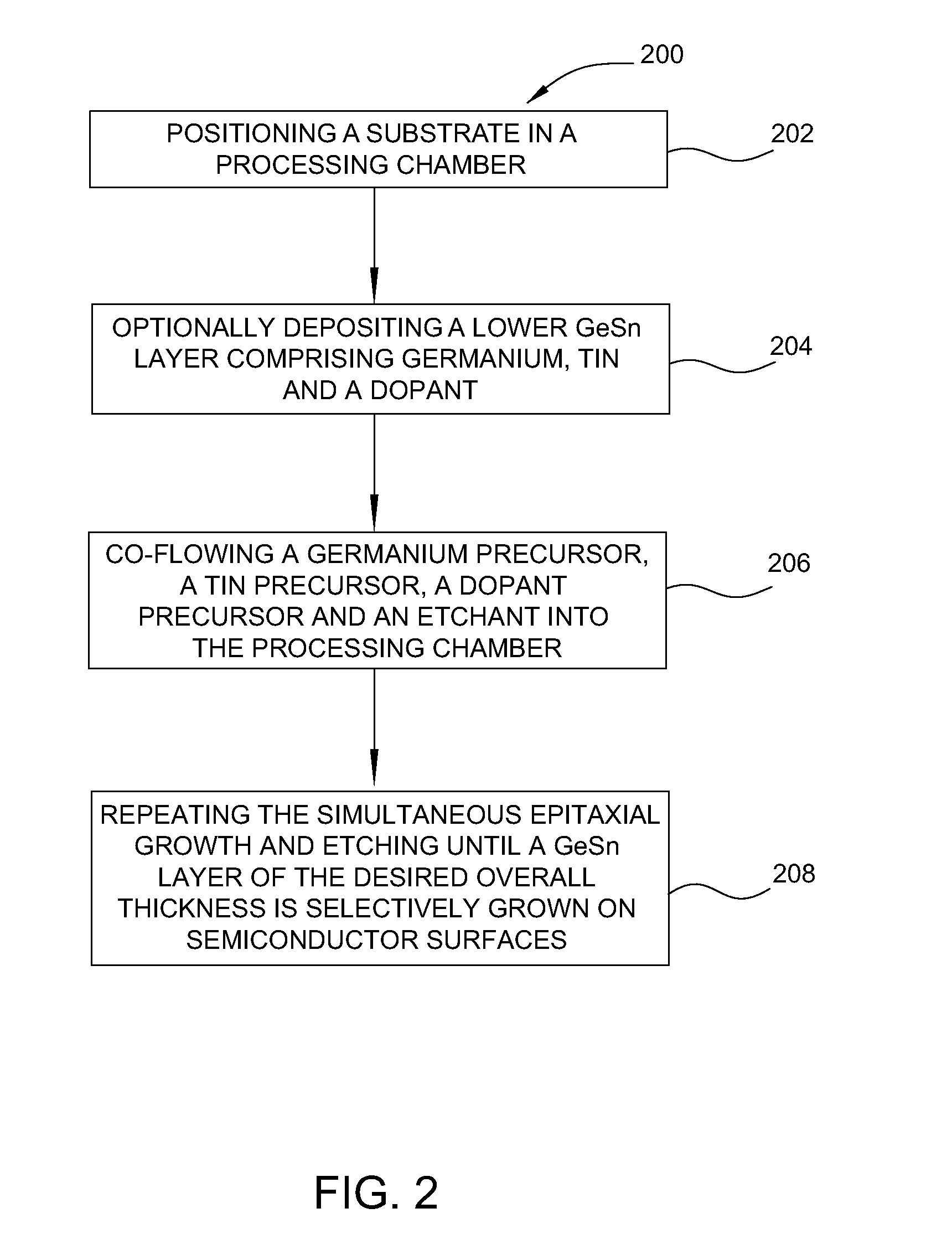

Method of epitaxial doped germanium tin alloy formation

ActiveUS20130256838A1Reduce lossesSemiconductor/solid-state device manufacturingSemiconductor devicesDopantAlloy

A method for forming germanium tin layers and the resulting embodiments are described. A germanium precursor and a tin precursor are provided to a chamber, and an epitaxial layer of germanium tin is formed on the substrate. The germanium tin layer is selectively deposited on the semiconductor regions of the substrate and can include thickness regions of varying tin and dopant concentrations. The germanium tin layer can be selectively deposited by either alternating or concurrent flow of a halide gas to etch the surface of the substrate.

Owner:APPLIED MATERIALS INC

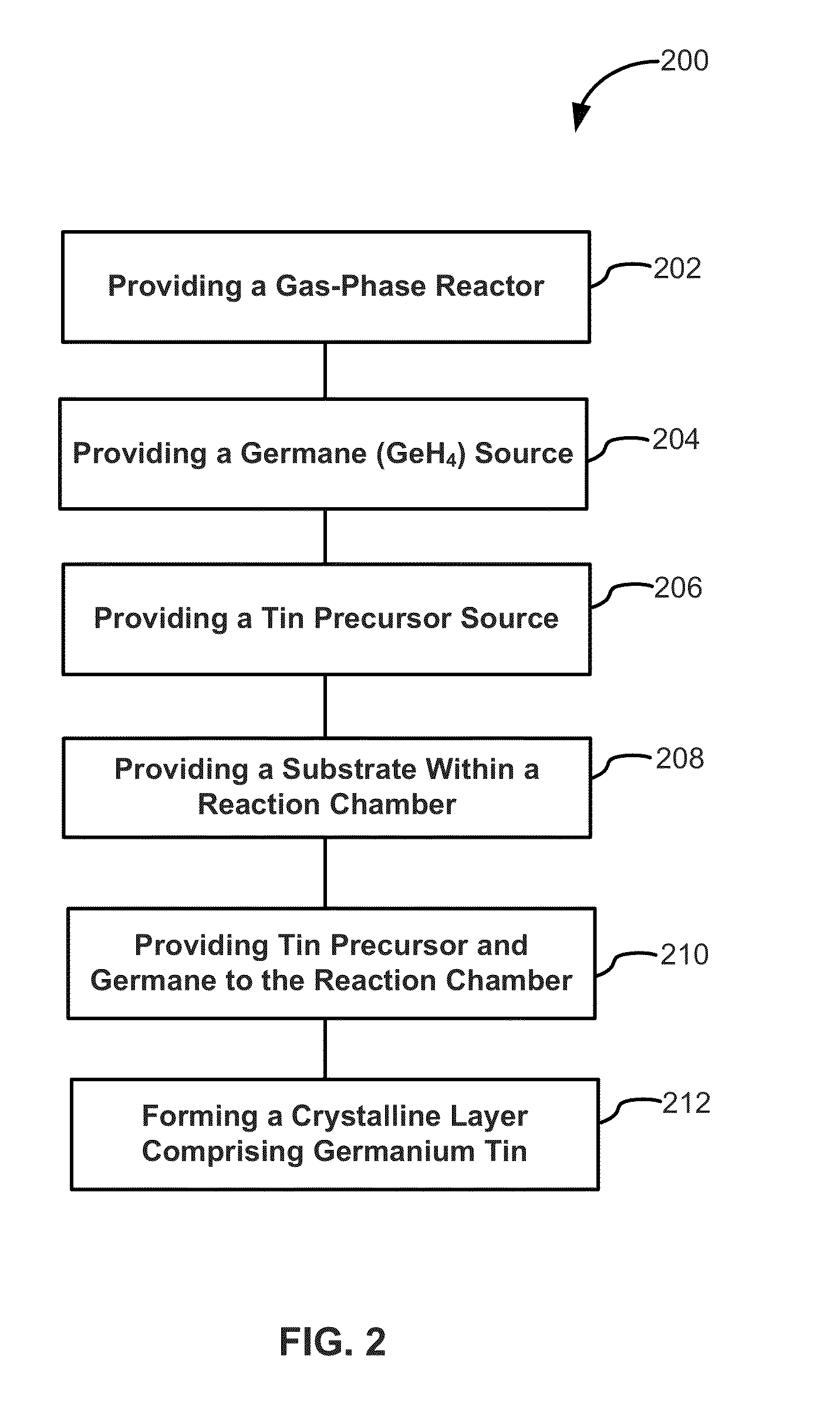

Methods of forming films including germanium tin and structures and devices including the films

ActiveUS9396934B2Polycrystalline material growthSemiconductor/solid-state device manufacturingGermananeChemical vapor deposition

Owner:ASM IP HLDG BV

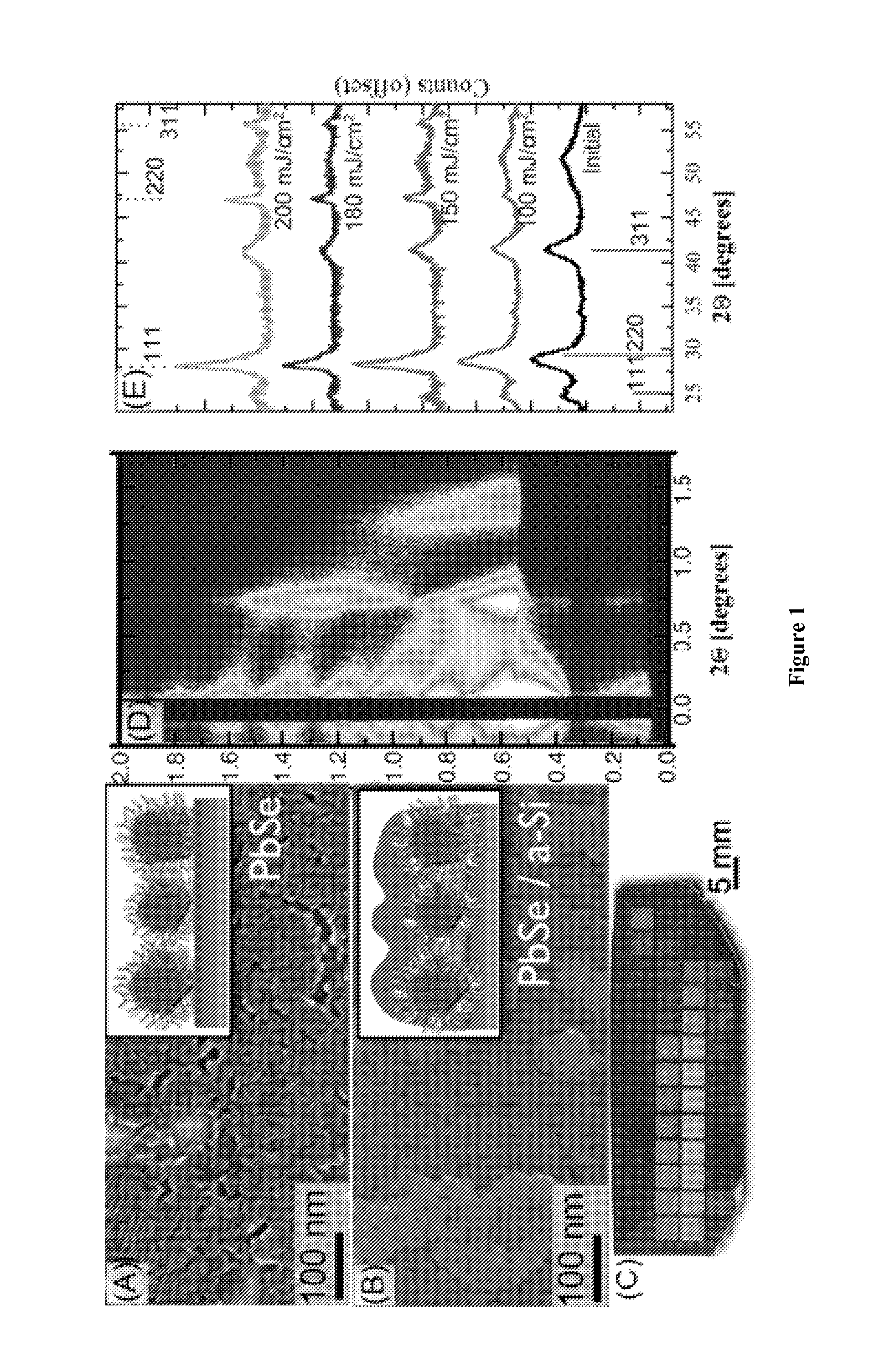

Inorganic Bulk Multijunction Materials and Processes for Preparing the Same

InactiveUS20110220874A1Material nanotechnologyFinal product manufactureAlloySemiconductor nanocrystals

A nanostructured composite material comprising semiconductor nanocrystals in a crystalline semiconductor matrix. Suitable nanocrystals include silicon, germanium, and silicon-germanium alloys, and lead salts such as PbS, PbSe, and PbTe. Suitable crystalline semiconductor matrix materials include Si and silicon-germanium alloys. A process for making the nanostructured composite materials. Devices comprising nanostructured composite materials.

Owner:CORNELL UNIVERSITY

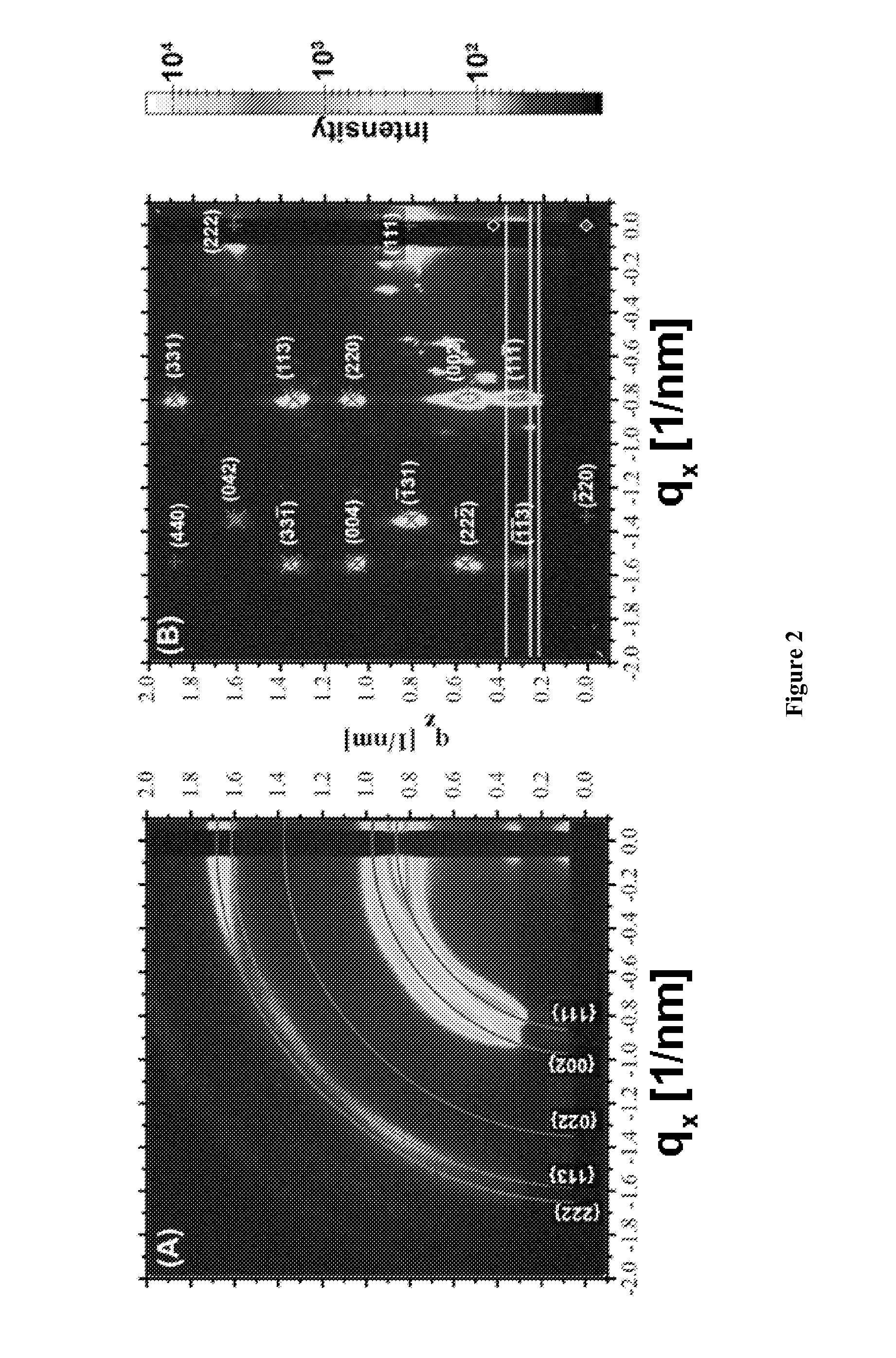

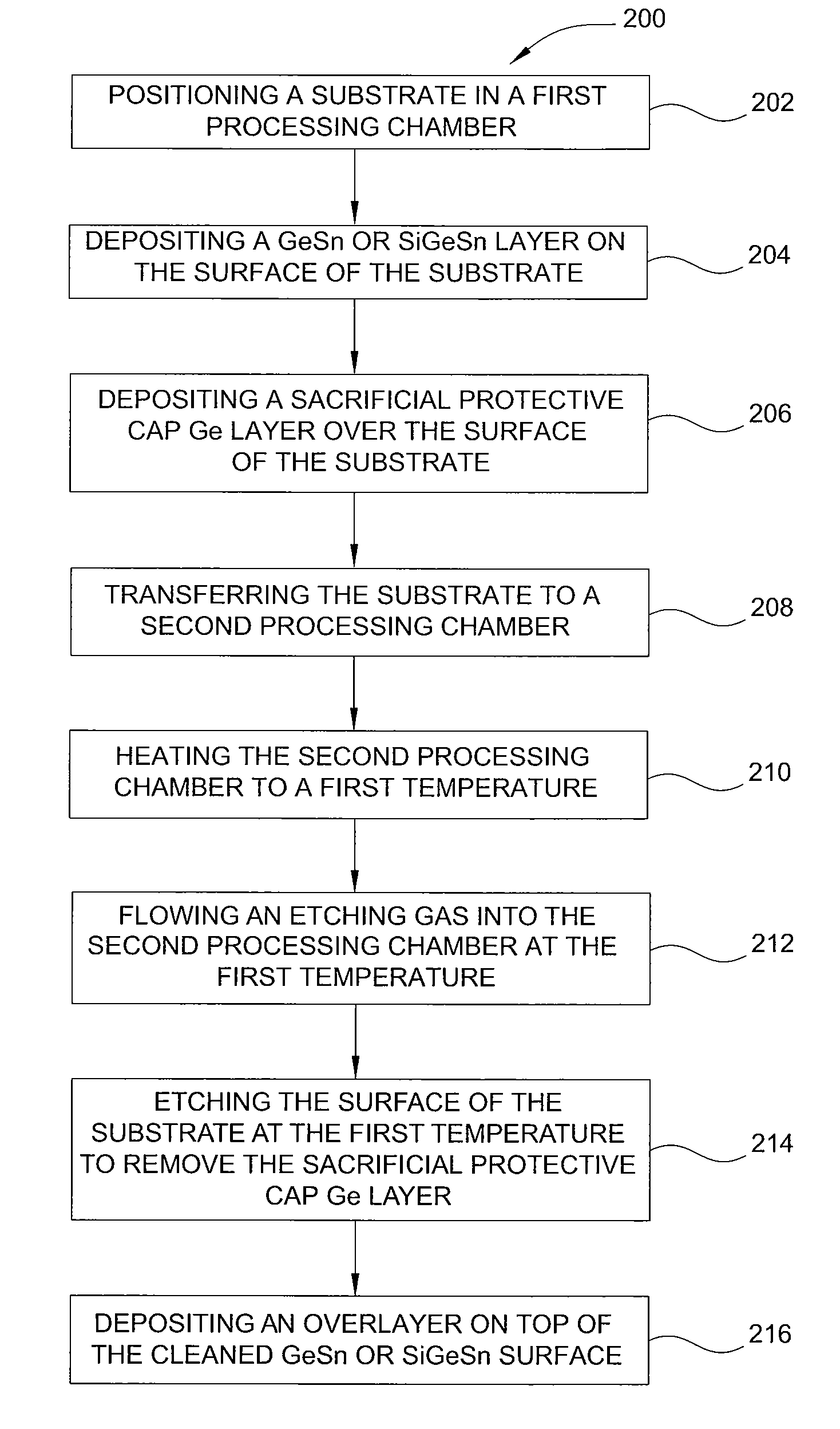

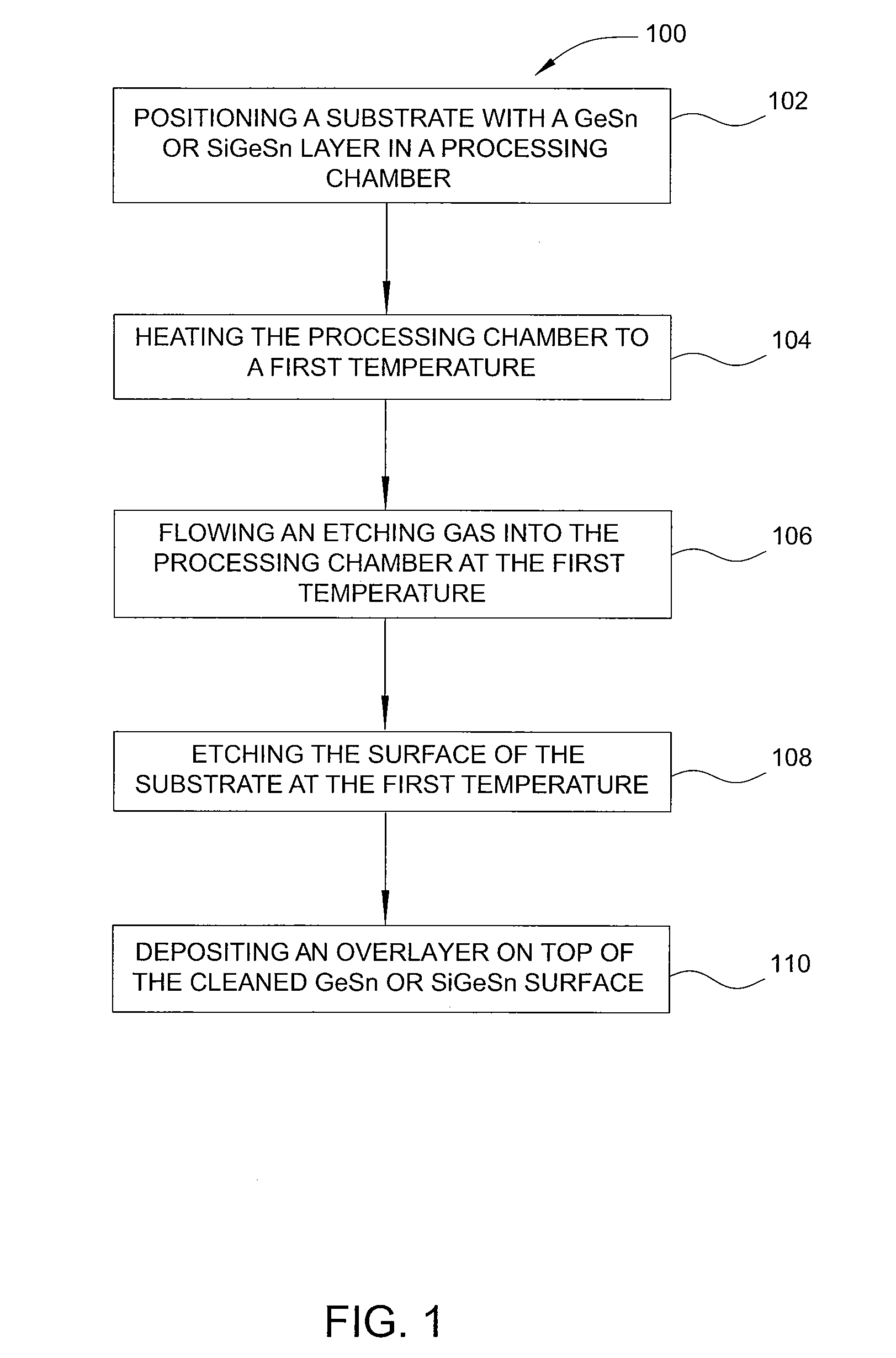

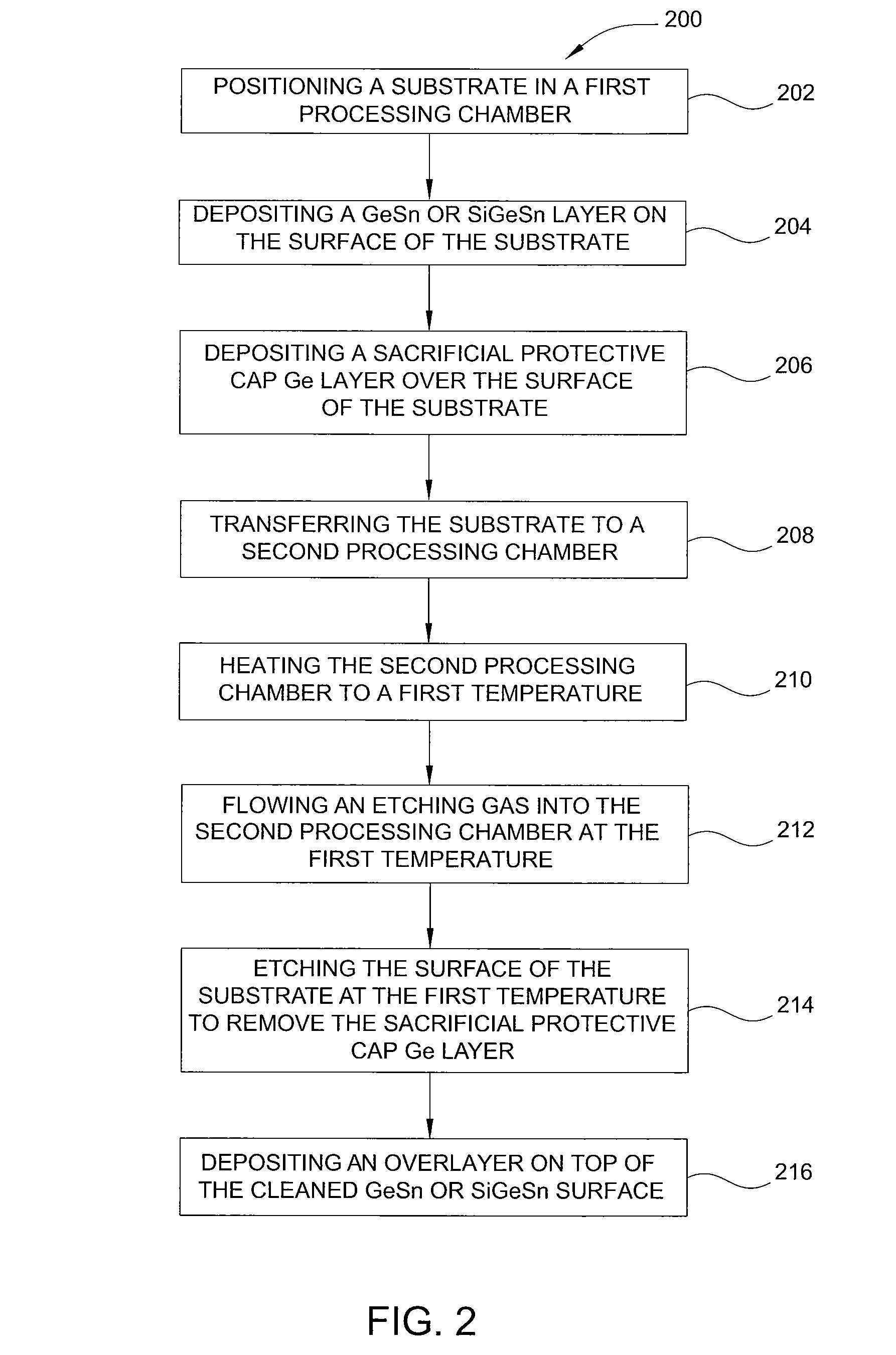

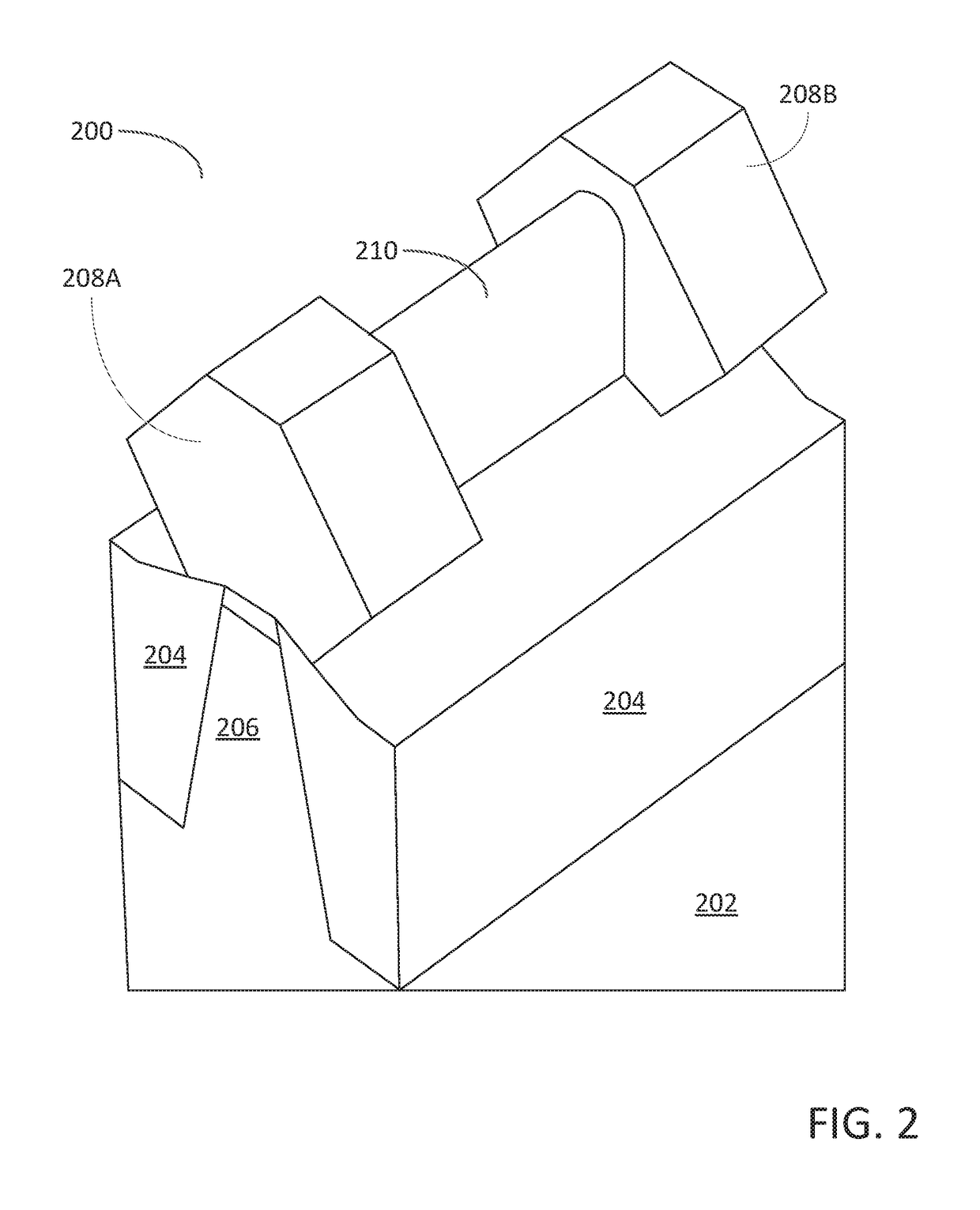

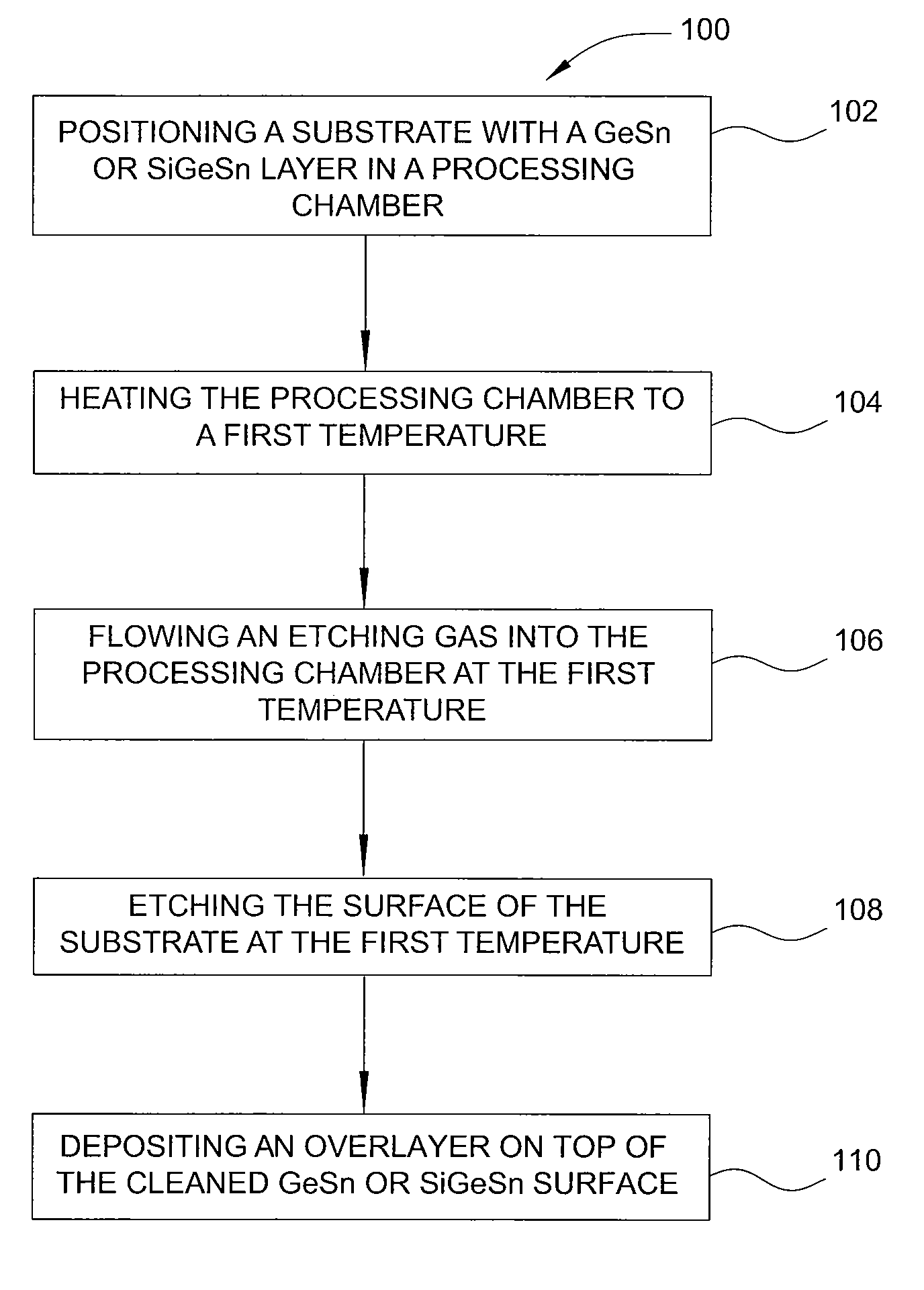

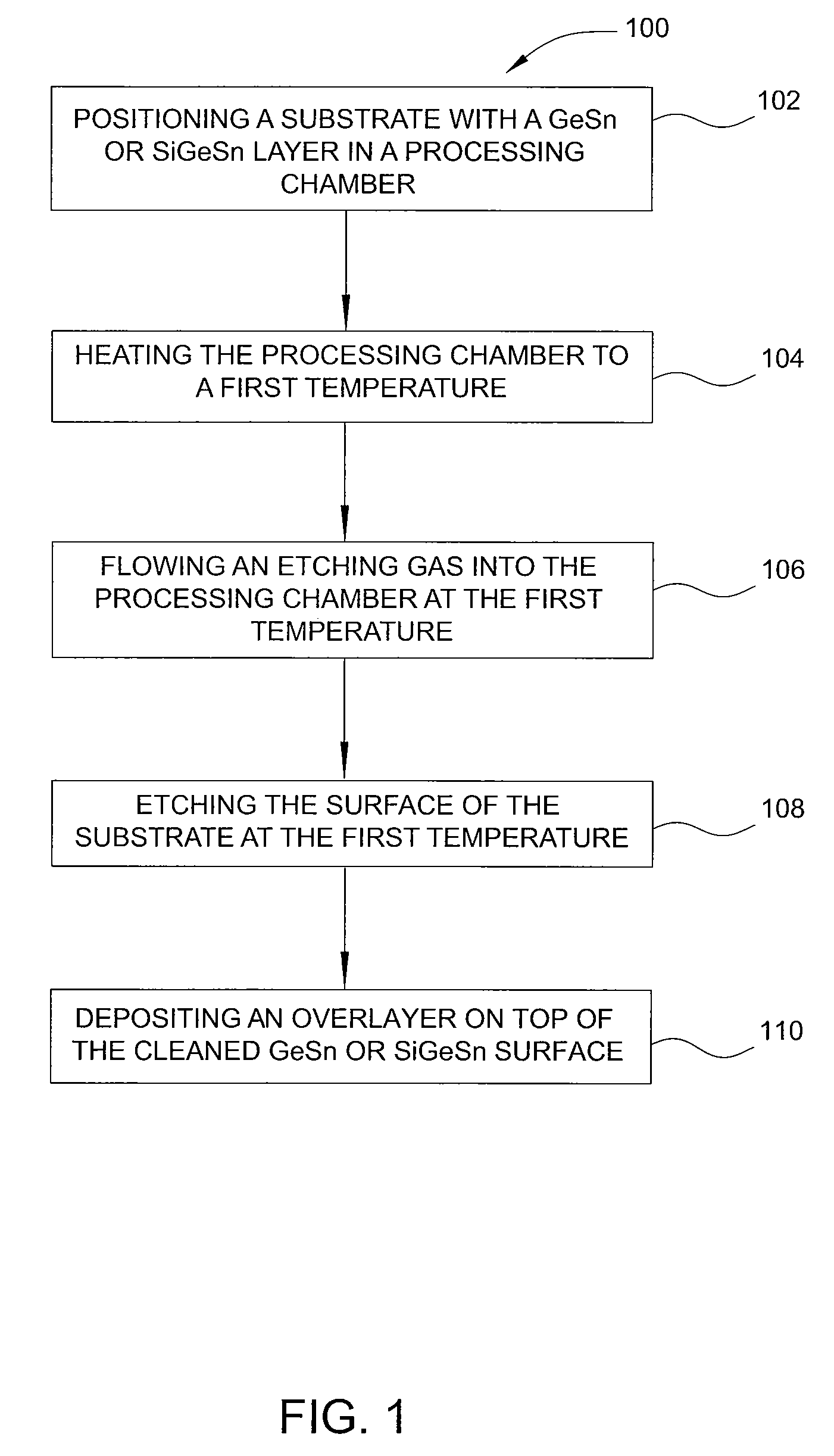

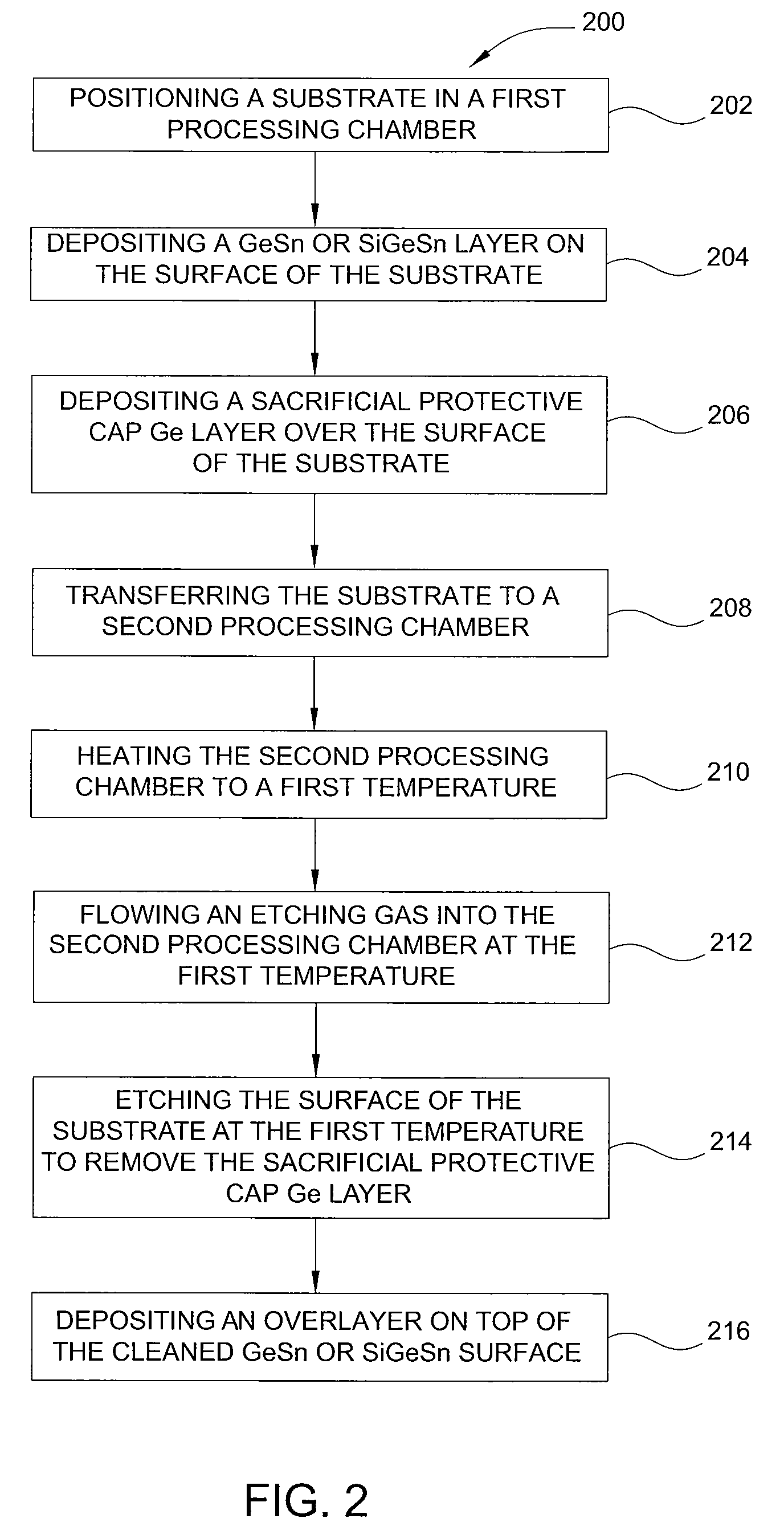

Method of epitaxial germanium tin alloy surface preparation

ActiveUS20130288480A1Increase temperatureStop the flowSemiconductor/solid-state device manufacturingPhotovoltaic energy generationEtchingRapid thermal annealing

Methods of preparing a clean surface of germanium tin or silicon germanium tin layers for subsequent deposition are provided. An overlayer of Ge, doped Ge, another GeSn or SiGeSn layer, a doped GeSn or SiGeSn layer, an insulator, or a metal can be deposited on a prepared GeSn or SiGeSn layer by positioning a substrate with an exposed germanium tin or silicon germanium tin layer in a processing chamber, heating the processing chamber and flowing a halide gas into the processing chamber to etch the surface of the substrate using either thermal or plasma assisted etching followed by depositing an overlayer on the substantially oxide free and contaminant free surface. Methods can also include the placement and etching of a sacrificial layer, a thermal clean using rapid thermal annealing, or a process in a plasma of nitrogen trifluoride and ammonia gas.

Owner:APPLIED MATERIALS INC

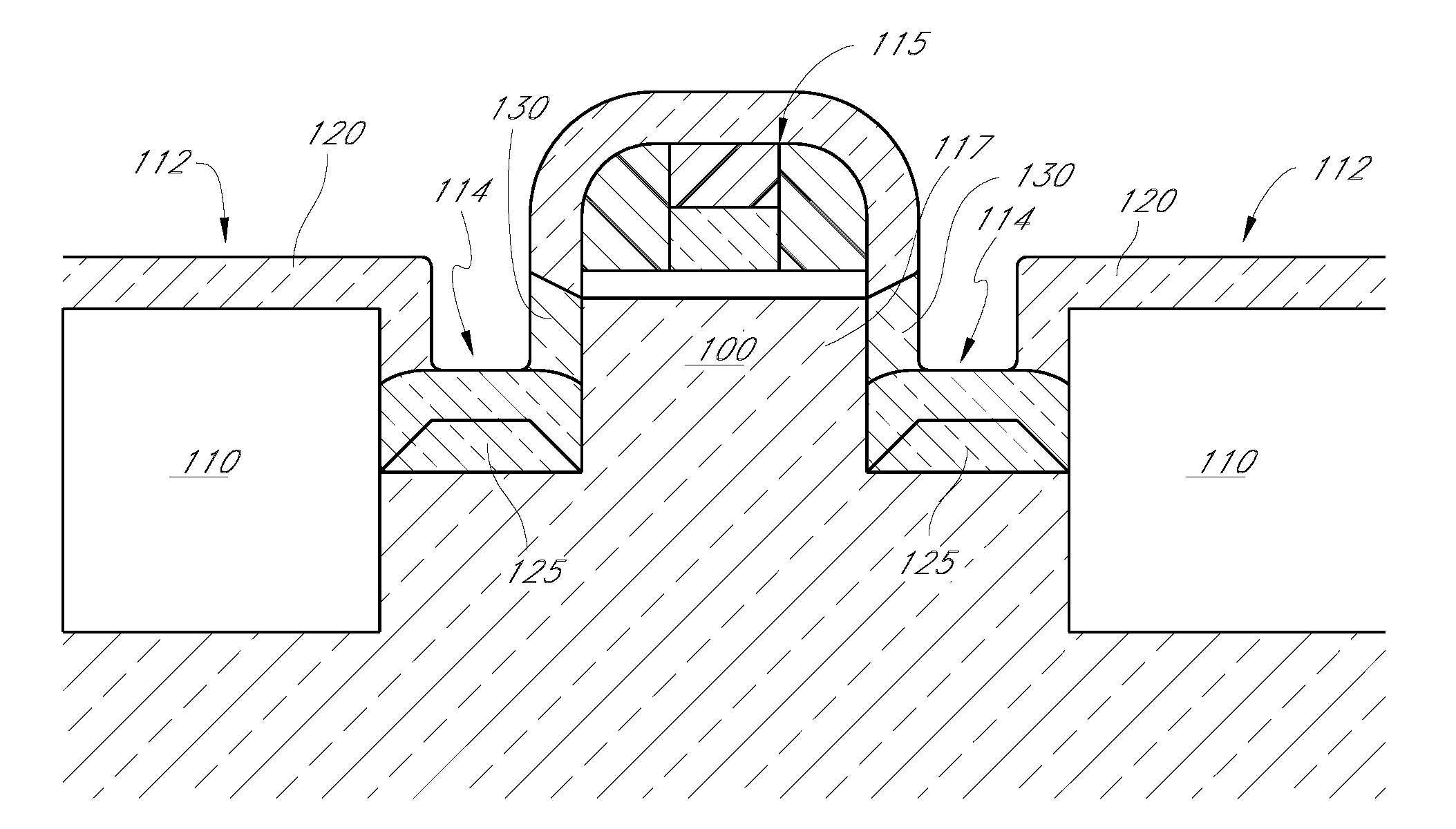

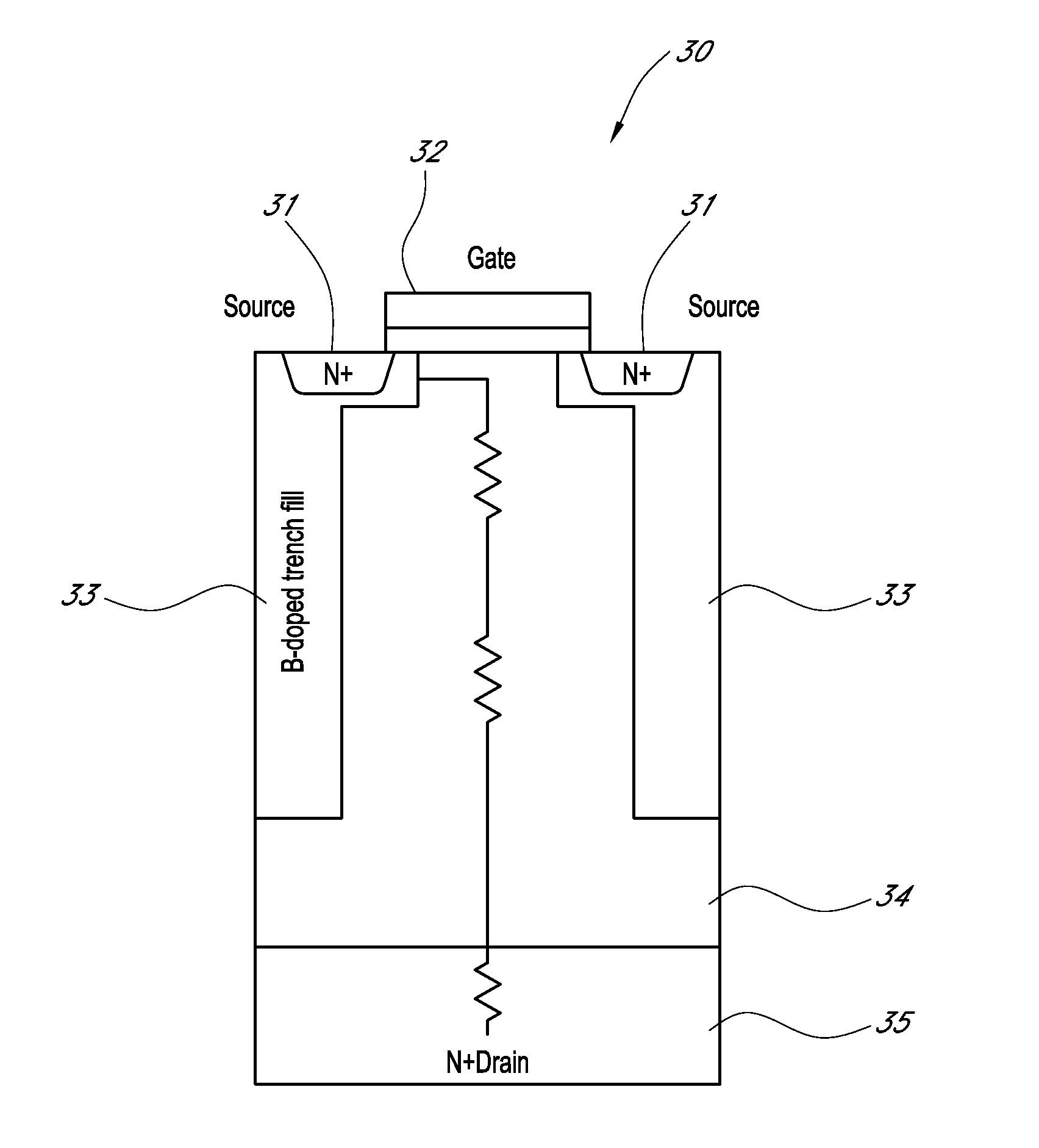

Processes and structures for dopant profile control in epitaxial trench fill

InactiveUS20130320429A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantEpitaxial material

Methods of depositing epitaxial material using a repeated deposition and etch process. The deposition and etch processes can be repeated until a desired thickness of silicon-containing material is achieved. During the deposition process, a doped silicon film can be deposited. The doped silicon film can be selectively deposited in a trench on a substrate. The trench can have a liner comprising silicon and carbon prior to depositing the doped silicon film. The doped silicon film may also contain germanium. Germanium can promote uniform dopant distribution within the doped silicon film.

Owner:ASM IP HLDG BV

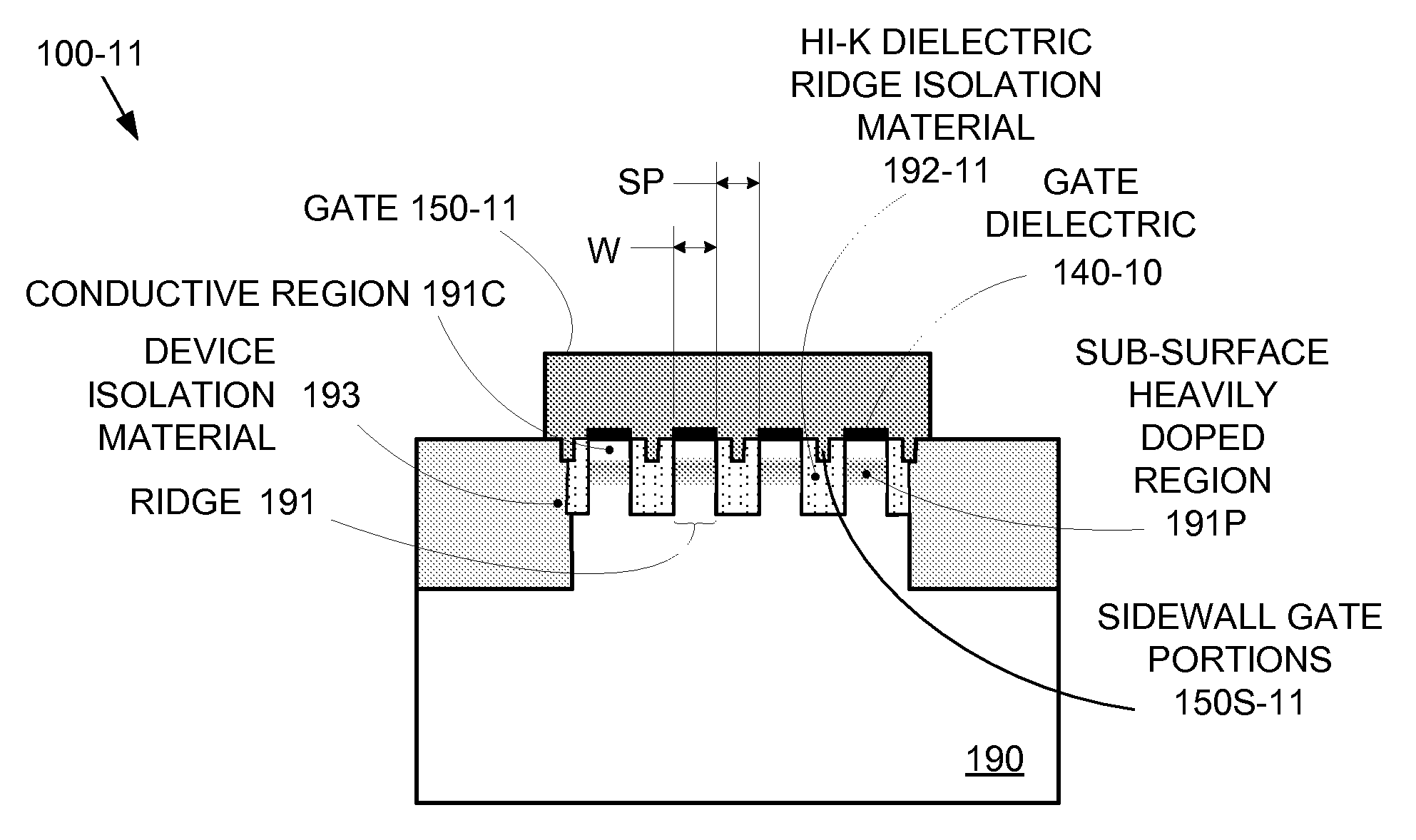

Enhanced Segmented Channel MOS Transistor with High-Permittivity Dielectric Isolation Material

ActiveUS20070122953A1Increase costImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

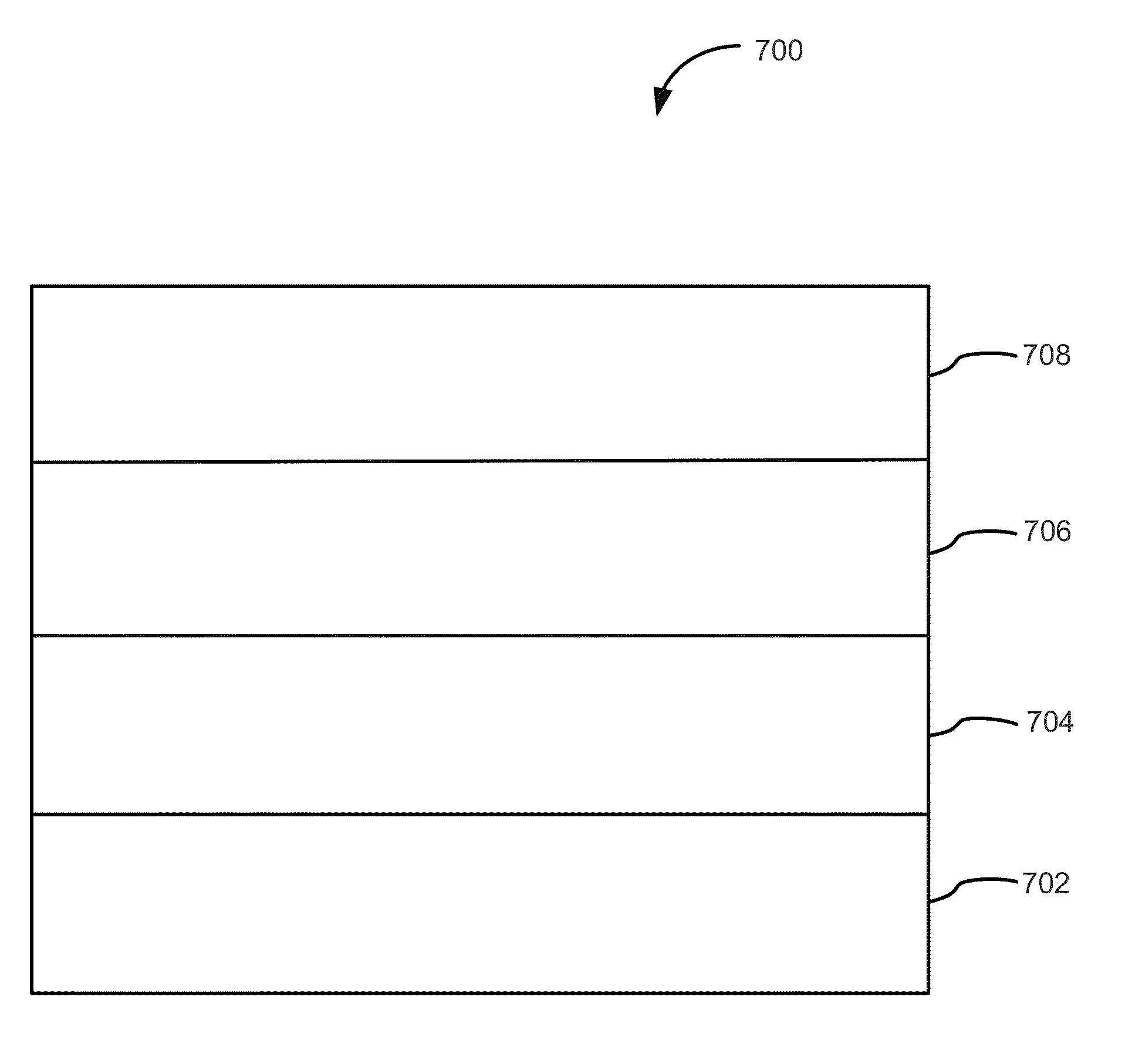

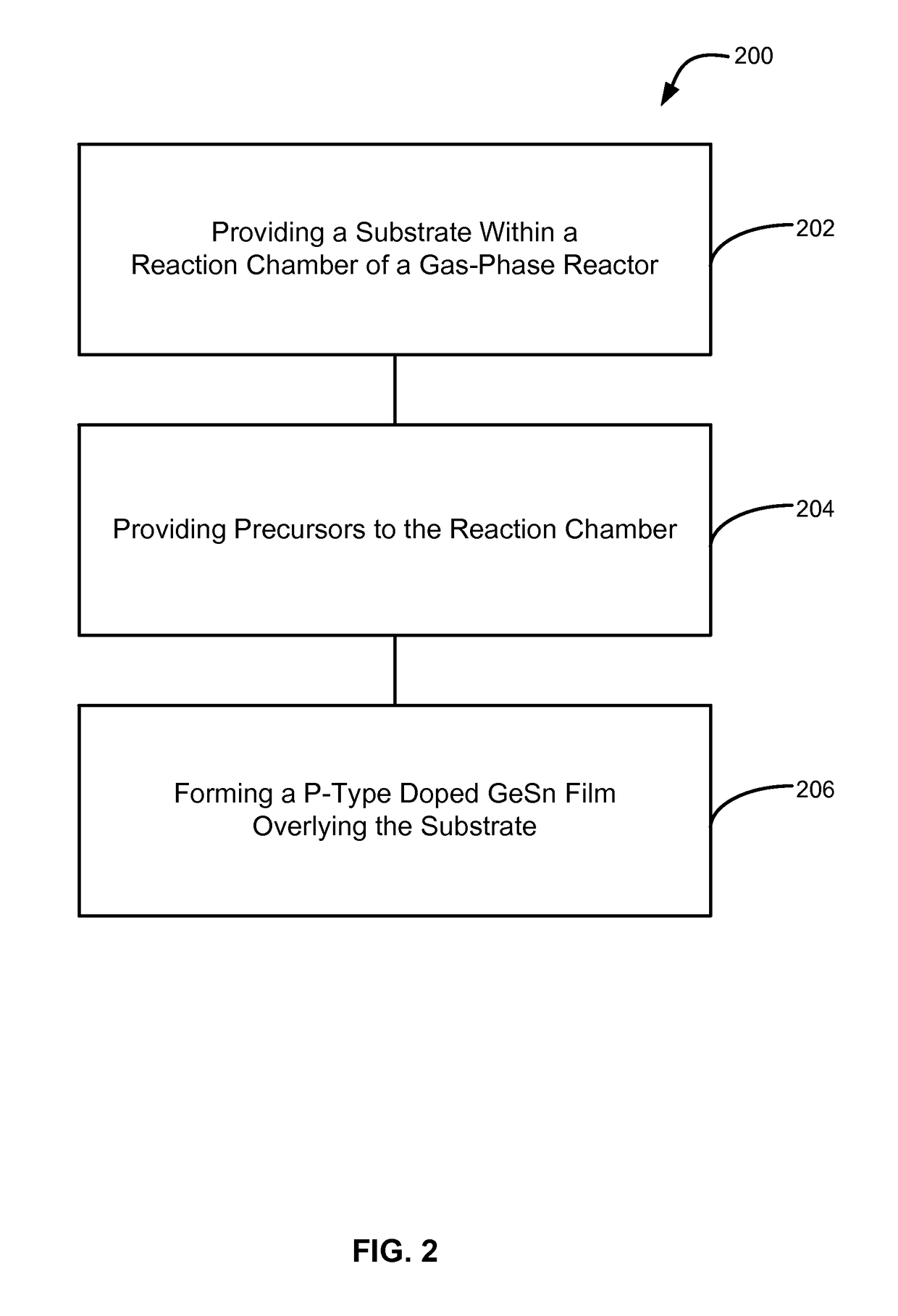

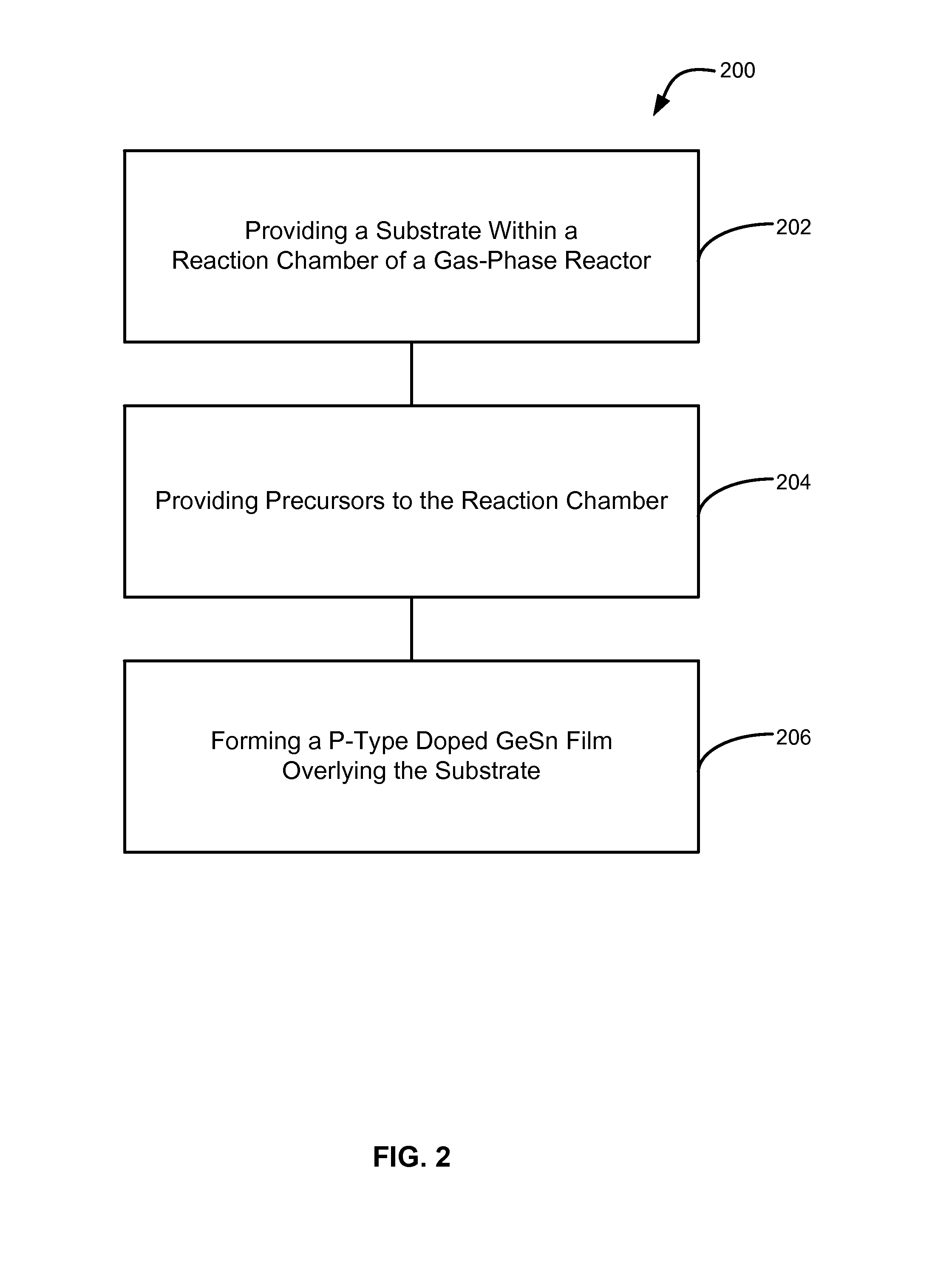

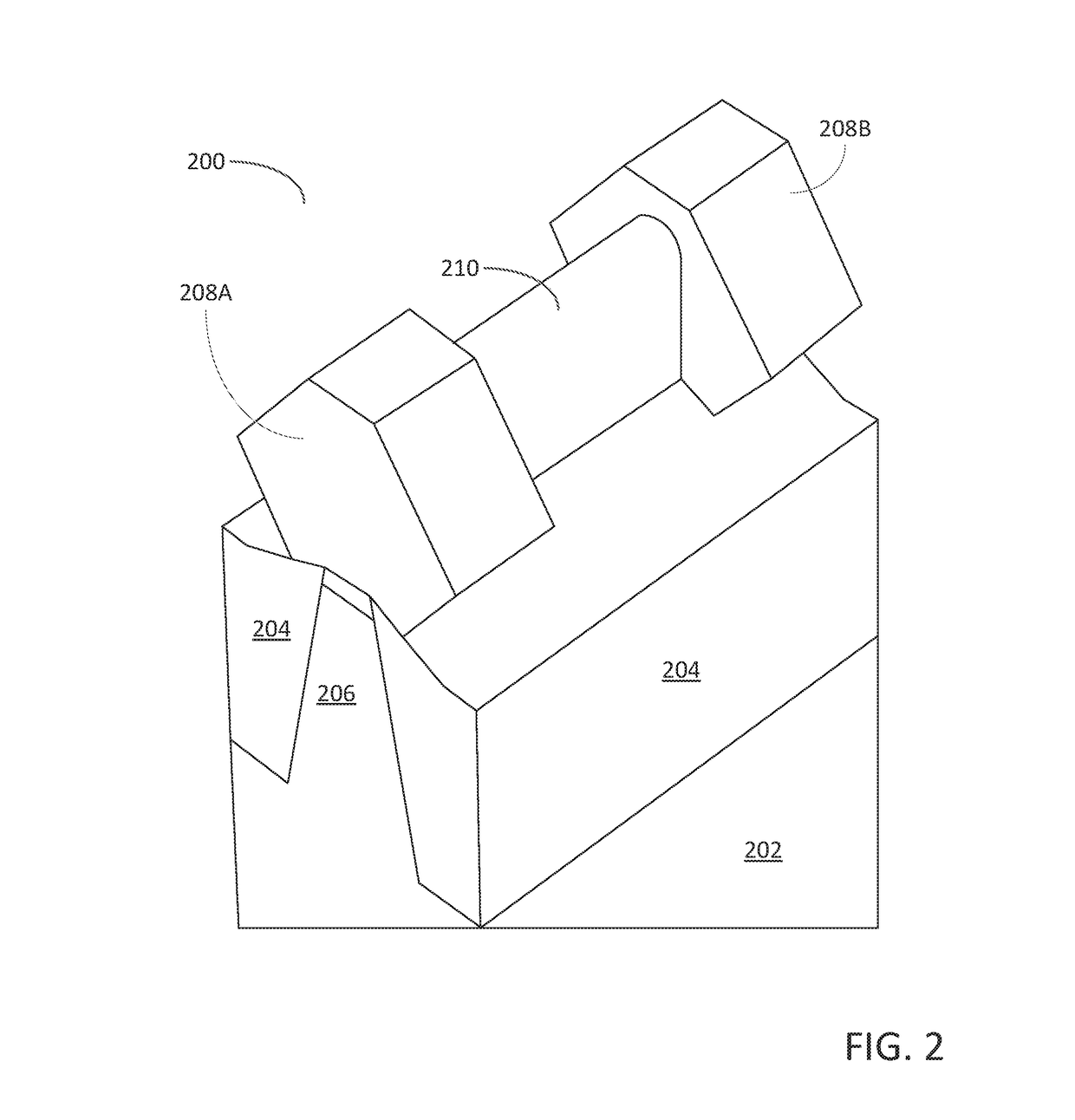

Methods of forming highly p-type doped germanium tin films and structures and devices including the films

ActiveUS9647114B2Polycrystalline material growthSemiconductor/solid-state device manufacturingDopantP type doping

Methods of forming p-type doped germanium-tin layers, systems for forming the p-type doped germanium-tin layers, and structures including the p-type doped germanium-tin layers are disclosed. The p-type doped germanium-tin layers include an n-type dopant, which allows relatively high levels of tin and / or p-type dopant to be included into the p-type doped germanium-tin layers.

Owner:ASM IP HLDG BV

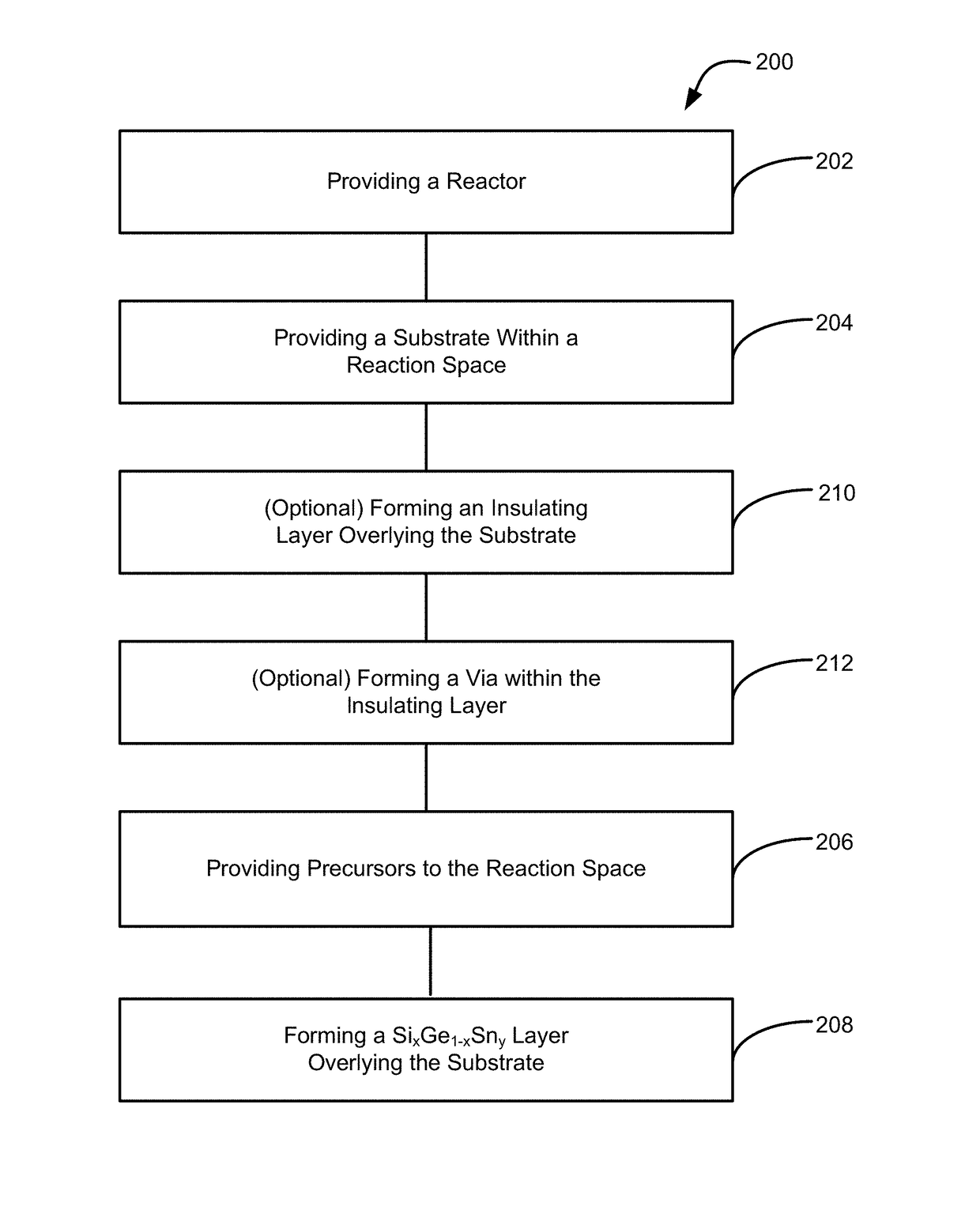

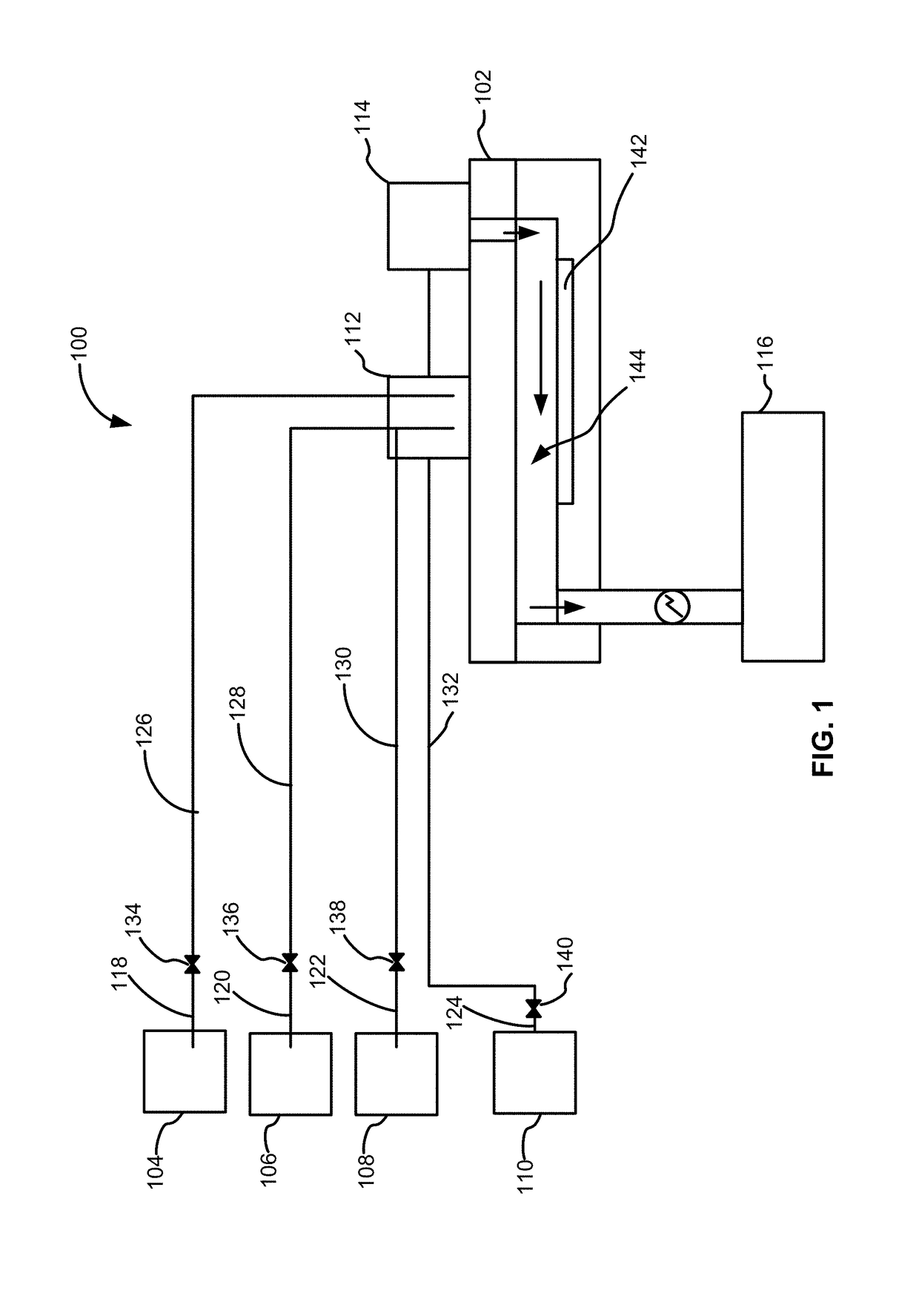

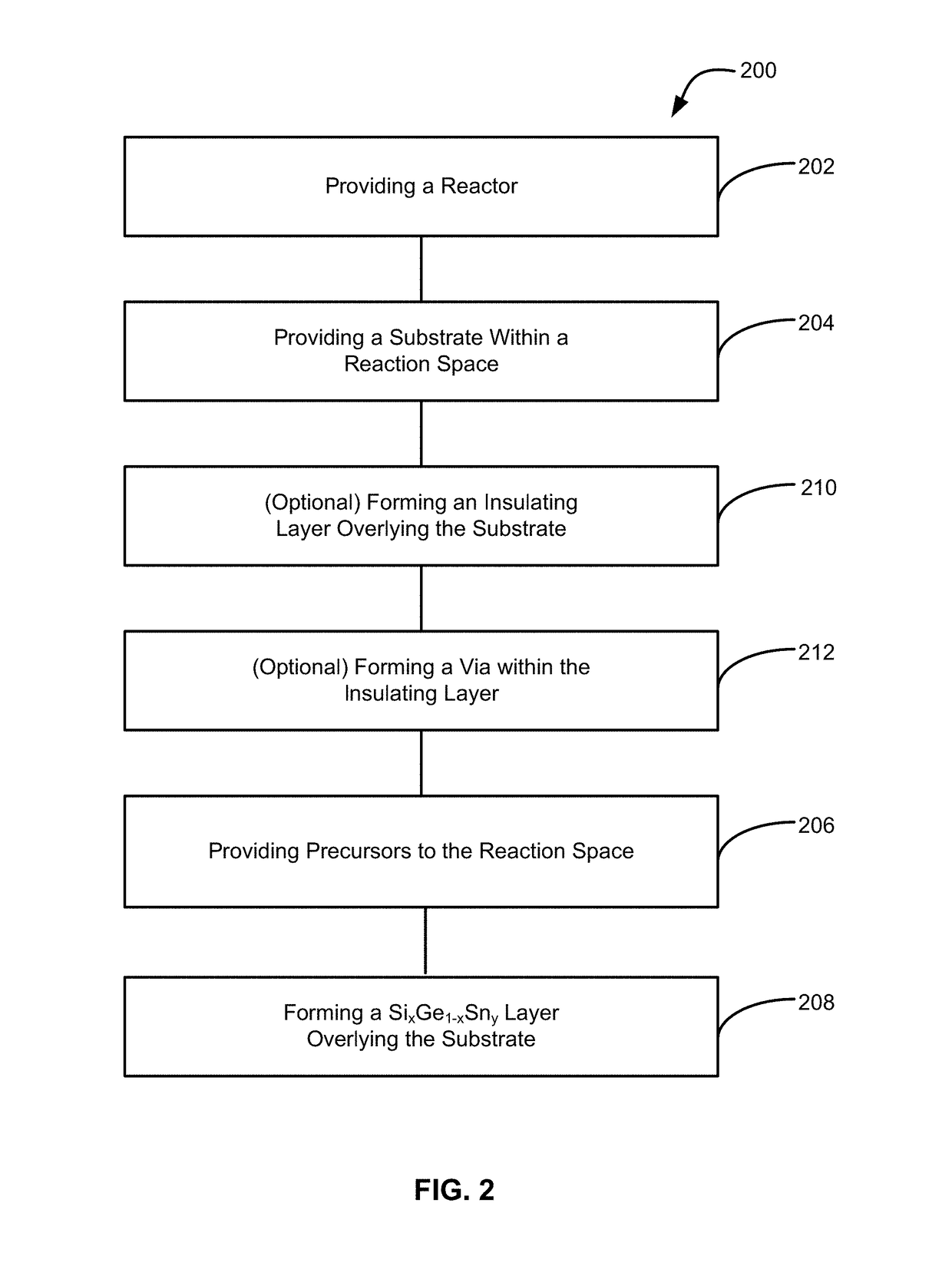

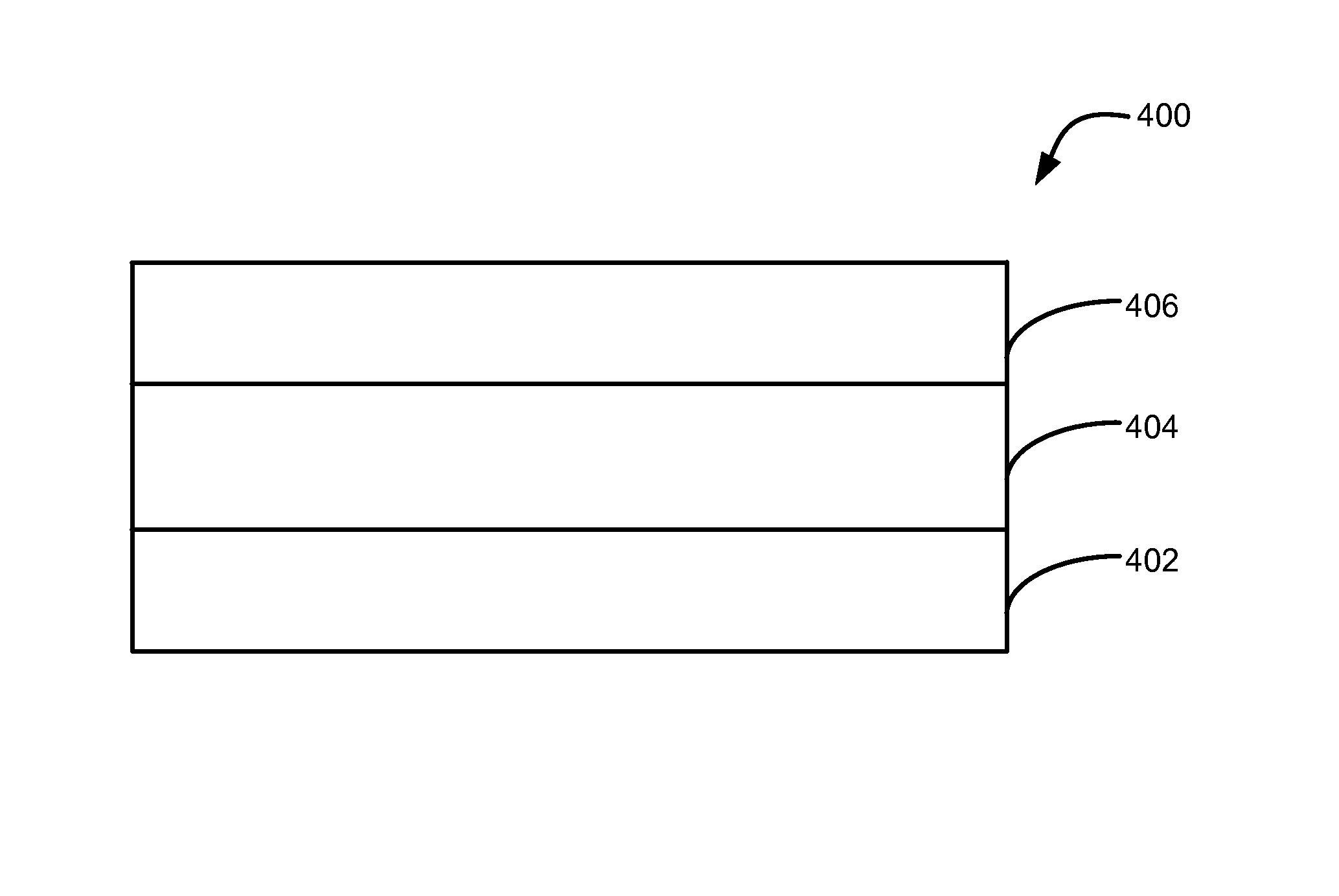

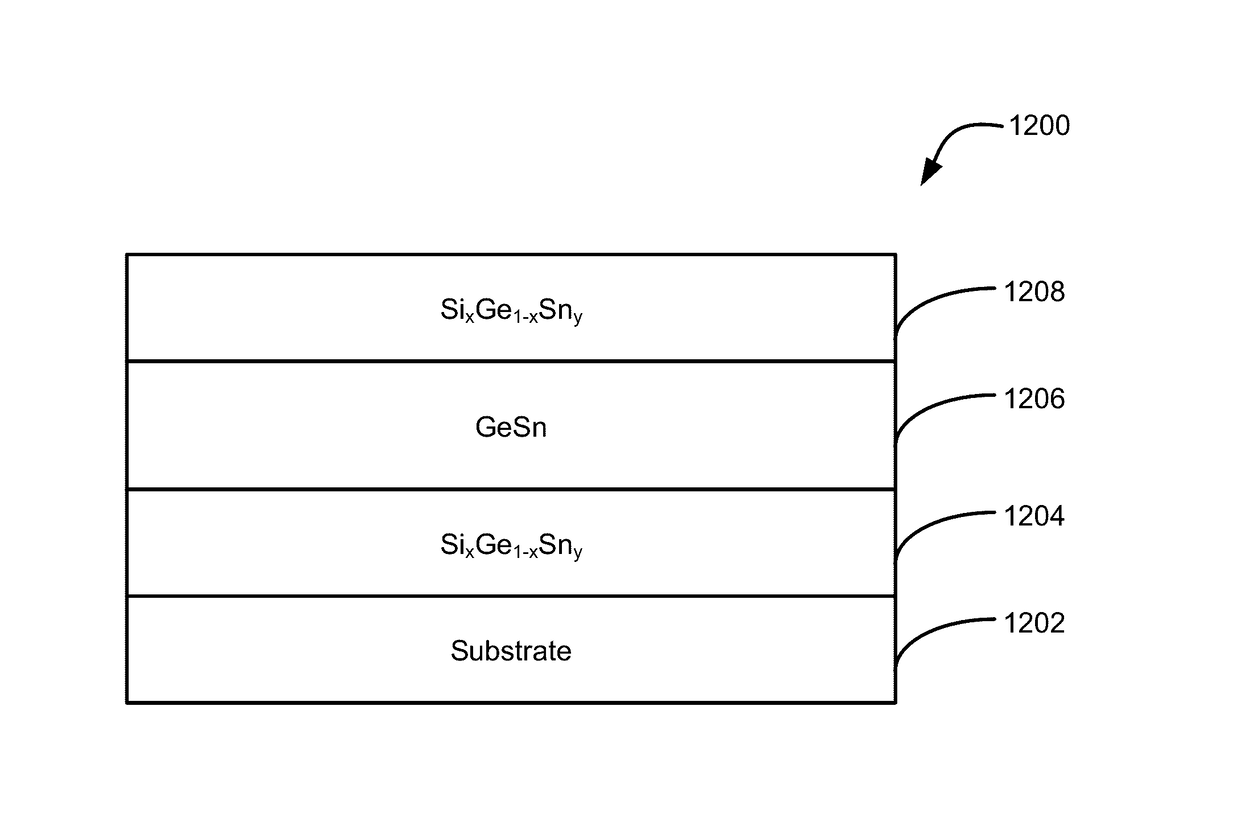

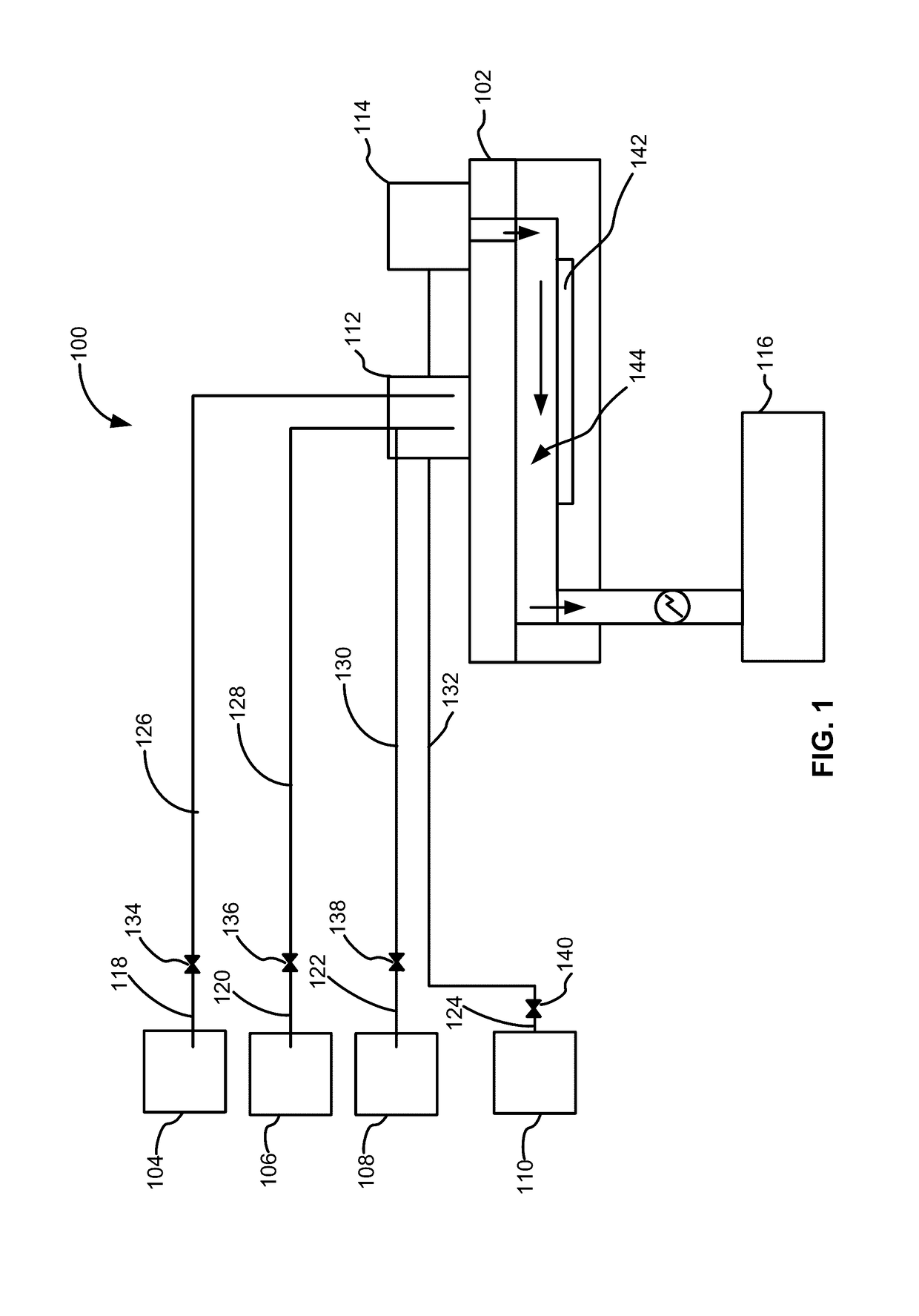

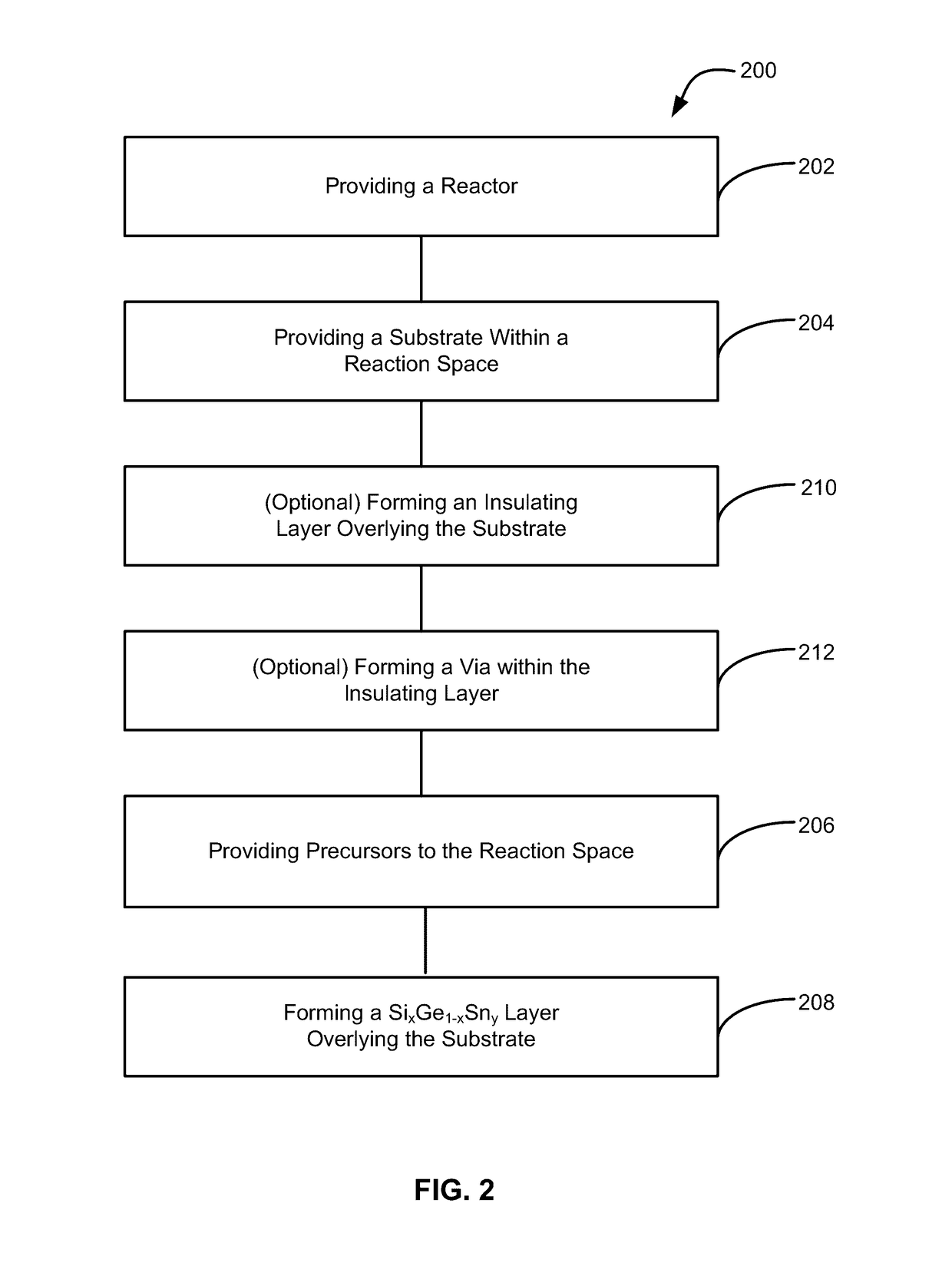

Methods of forming silicon germanium tin films and structures and devices including the films

ActiveUS9905420B2Semiconductor/solid-state device manufacturingSemiconductor devicesHigh volume manufacturingChemical vapor deposition

Methods of forming silicon germanium tin (SixGe1-xSny) films are disclosed. Exemplary methods include growing films including silicon, germanium and tin in an epitaxial chemical vapor deposition reactor. Exemplary methods are suitable for high volume manufacturing. Also disclosed are structures and devices including silicon germanium tin films.

Owner:ASM IP HLDG BV

Methods of forming highly p-type doped germanium tin films and structures and devices including the films

ActiveUS20170047446A1High tin contentSuitable for applicationPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantP type doping

Methods of forming p-type doped germanium-tin layers, systems for forming the p-type doped germanium-tin layers, and structures including the p-type doped germanium-tin layers are disclosed. The p-type doped germanium-tin layers include an n-type dopant, which allows relatively high levels of tin and / or p-type dopant to be included into the p-type doped germanium-tin layers.

Owner:ASM IP HLDG BV

Methods of selective deposition of heavily doped epitaxial SiGe

ActiveUS20050079691A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantSelective deposition

The invention generally teaches a method for depositing a silicon film or silicon germanium film on a substrate comprising placing the substrate within a process chamber and heating the substrate surface to a temperature in the range from about 600° C. to about 900° C. while maintaining a pressure in the range from about 0.1 Torr to about 200 Torr. A deposition gas is provided to the process chamber and includes SiH4, an optional germanium source gas, an etchant, a carrier gas and optionally at least one dopant gas. The silicon film or the silicon germanium film is selectively and epitaxially grown on the substrate. One embodiment teaches a method for depositing a silicon-containing film with an inert gas as the carrier gas. Methods may include the fabrication of electronic devices utilizing selective silicon germanium epitaxial films.

Owner:APPLIED MATERIALS INC

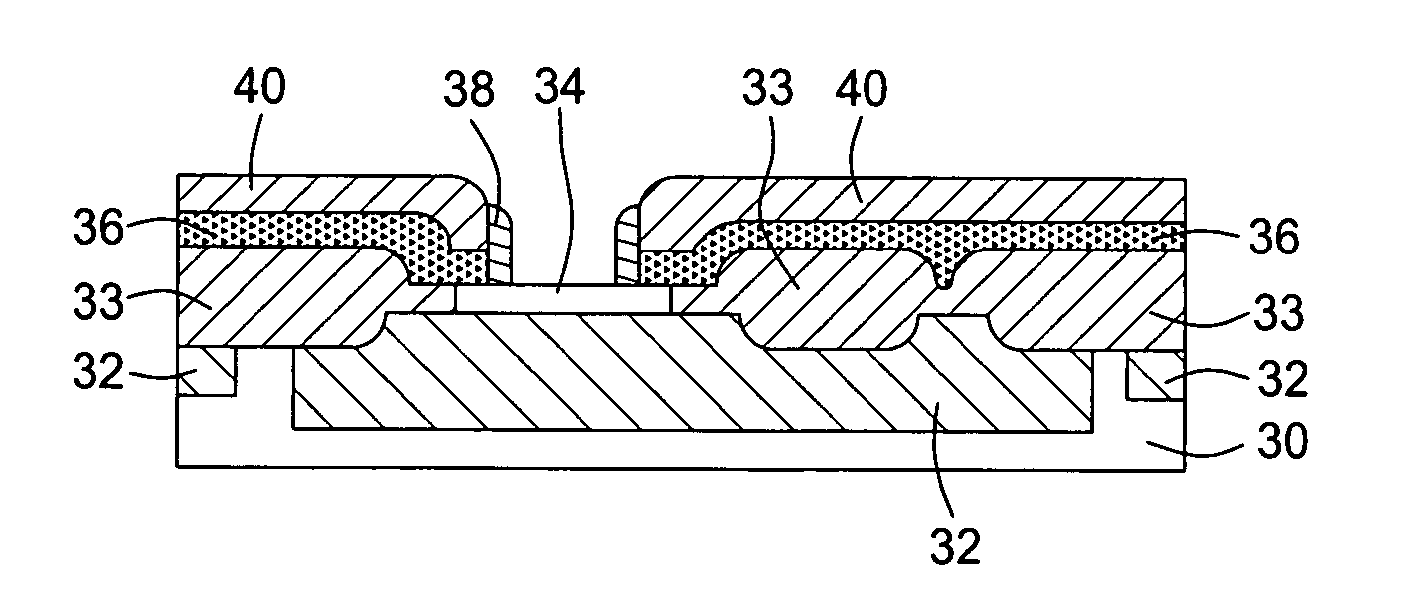

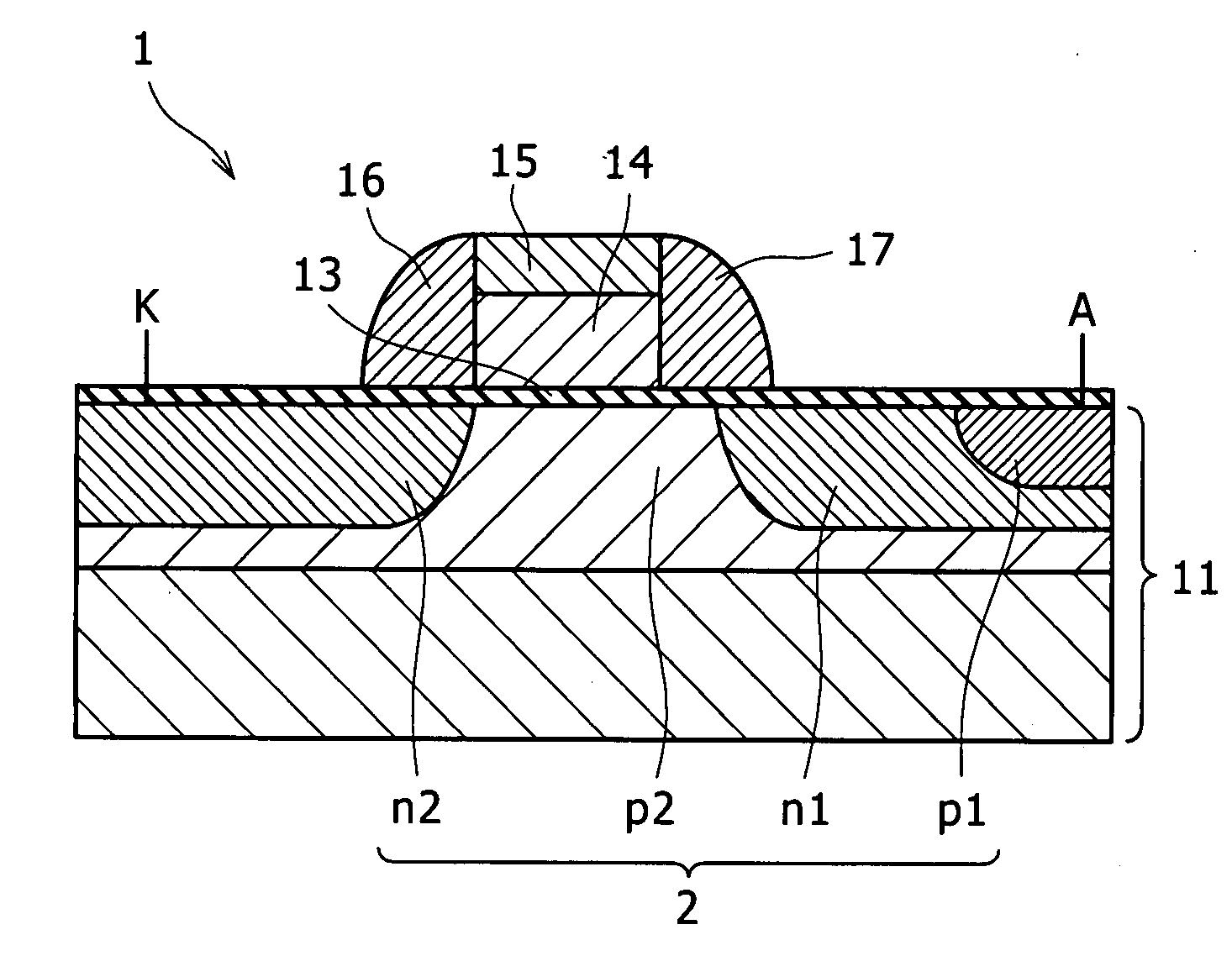

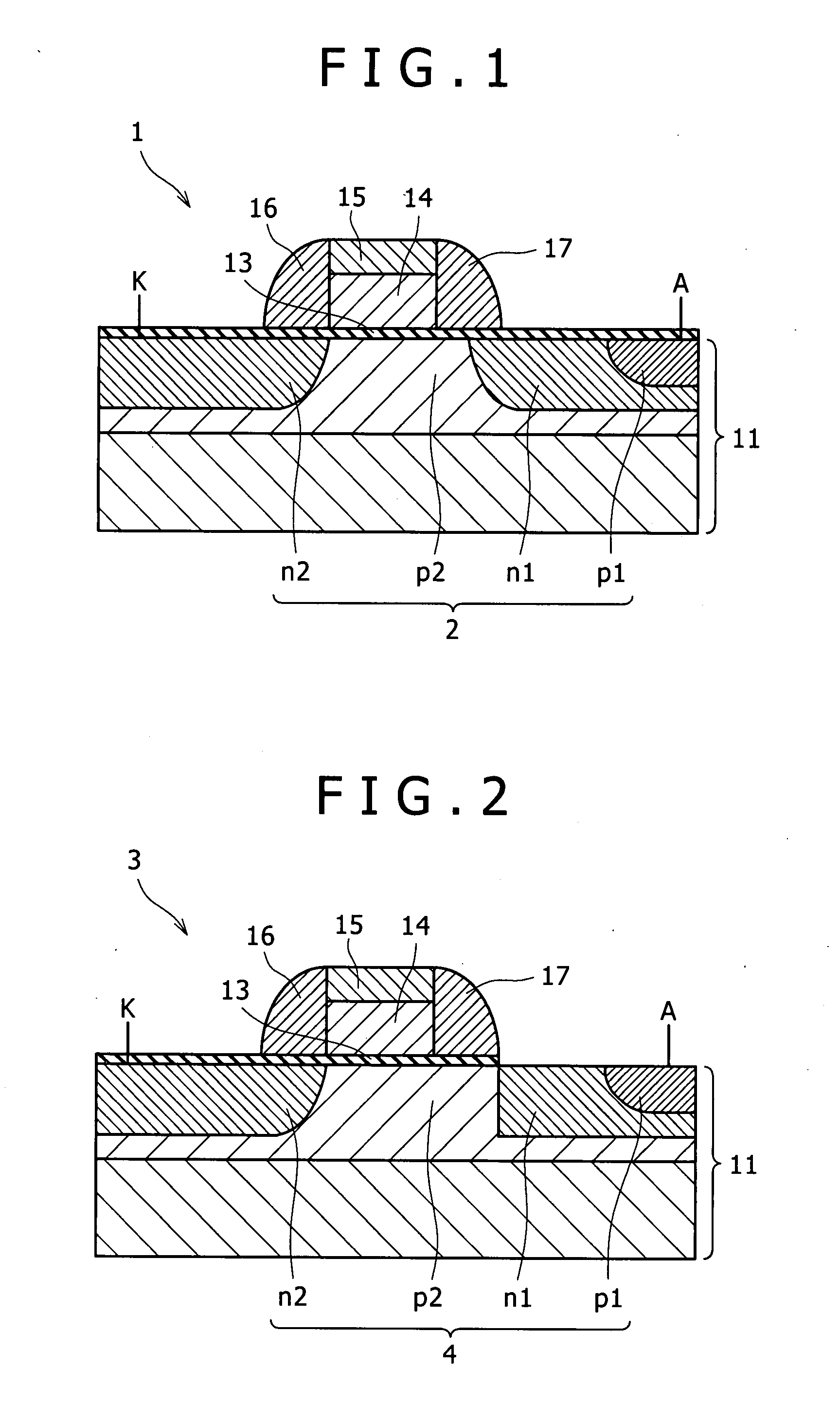

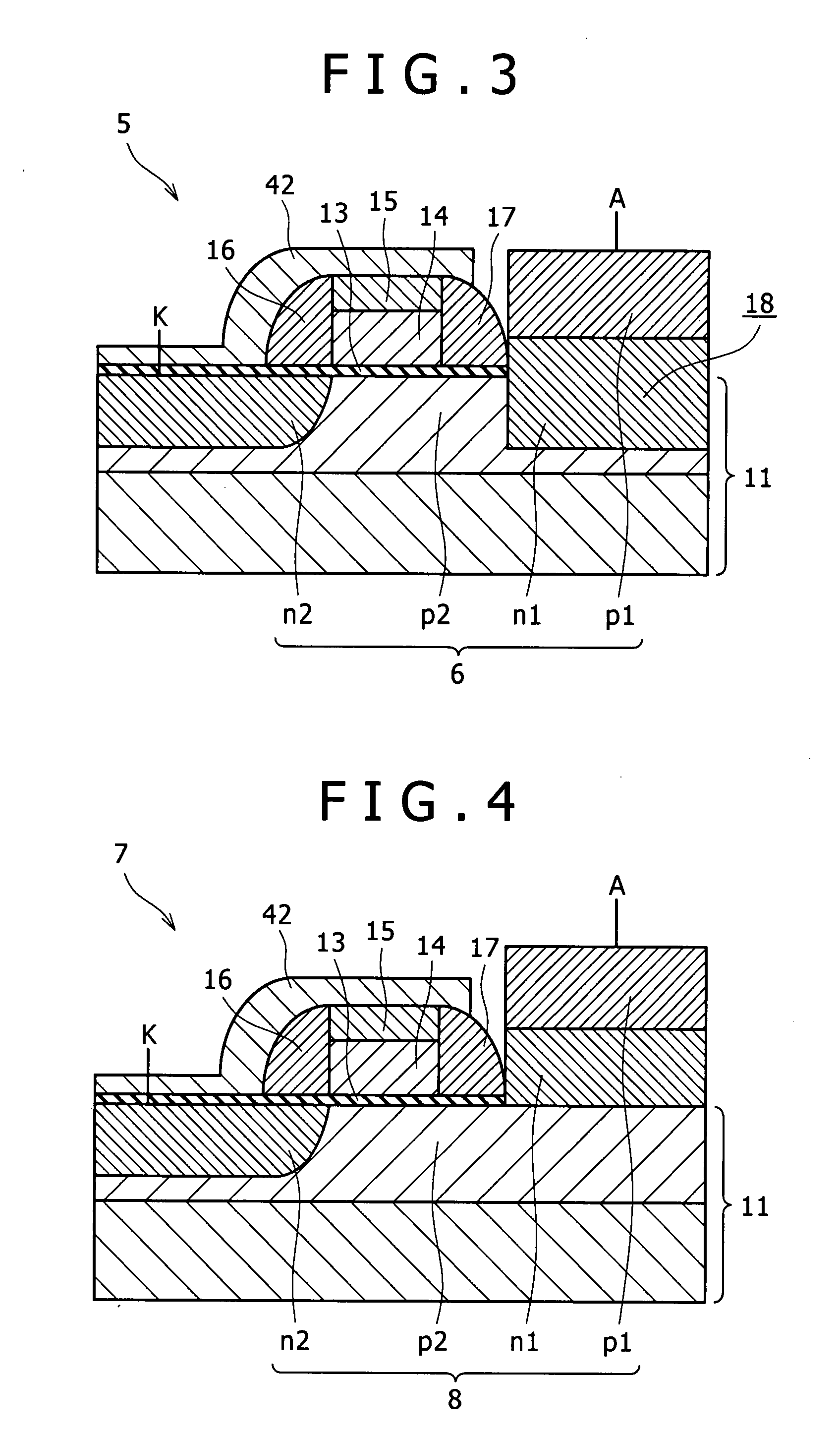

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20080042165A1Increase speedImprove mobilityThyristorSemiconductor/solid-state device manufacturingThyratronSemiconductor

A semiconductor device includes a thyristor configured to be formed through sequential joining of a first region of a first conductivity type, a second region of a second conductivity type opposite to the first conductivity type, a third region of the first conductivity type, and a fourth region of the second conductivity type, and have a gate formed over the third region. The first to fourth regions are formed in a silicon germanium region or germanium region.

Owner:SONY CORP

Pecvd microcrystalline silicon germanium (SIGE)

ActiveUS20150072509A1Enhanced vapor depositionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingCelsius DegreeMicrocrystalline silicon

Embodiments of the present invention generally relate to methods for forming a SiGe layer. In one embodiment, a seed SiGe layer is first formed using plasma enhanced chemical vapor deposition (PECVD), and a bulk SiGe layer is formed directly on the PECVD seed layer also using PECVD. The processing temperature for both seed and bulk SiGe layers is less than 450 degrees Celsius.

Owner:APPLIED MATERIALS INC

Methods of forming silicon germanium tin films and structures and devices including the films

ActiveUS20170154770A1Low throughput timeSemiconductor/solid-state device manufacturingSemiconductor devicesHigh volume manufacturingChemical vapor deposition

Methods of forming silicon germanium tin (SiGexGe1−xSny) films are disclosed. Exemplary methods include growing films including silicon, germanium and tin in an epitaxial chemical vapor deposition reactor. Exemplary methods are suitable for high volume manufacturing. Also disclosed are structures and devices including silicon germanium tin films.

Owner:ASM IP HLDG BV

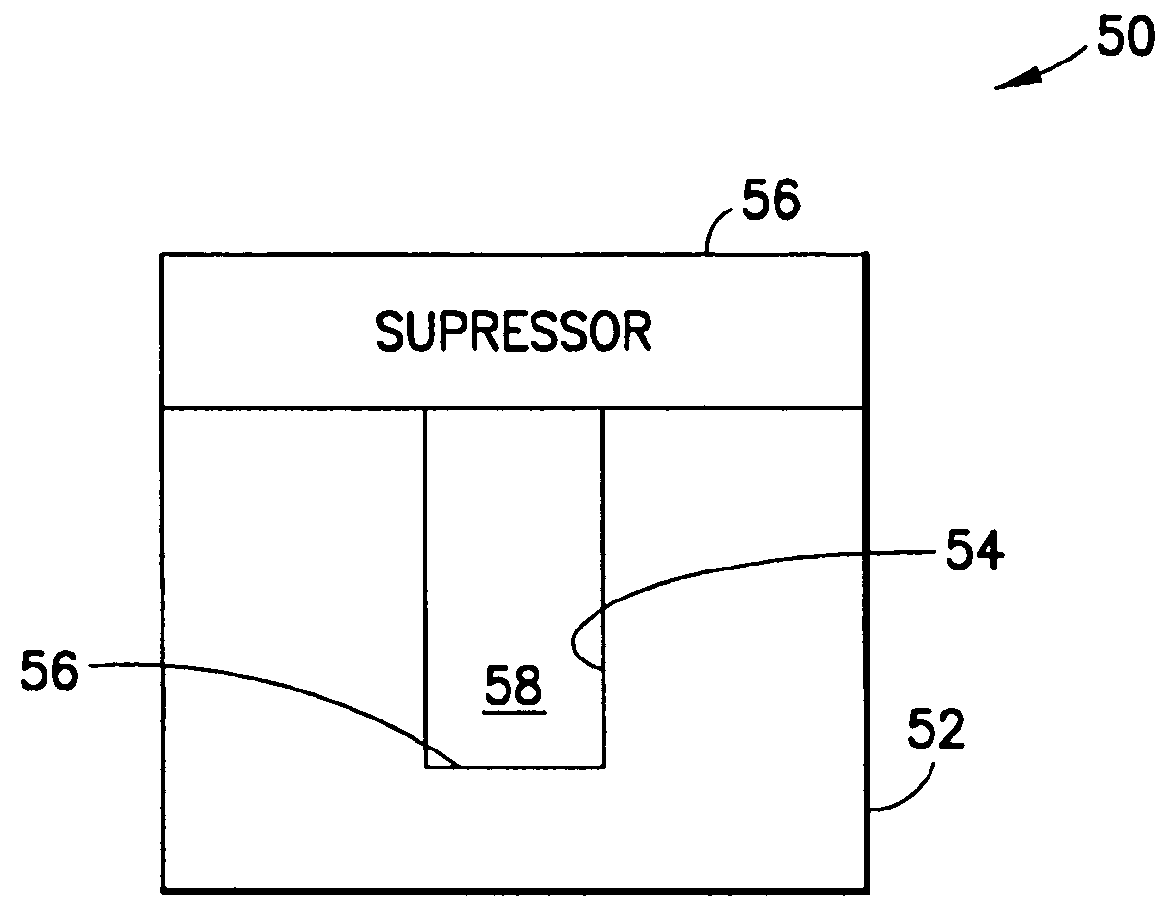

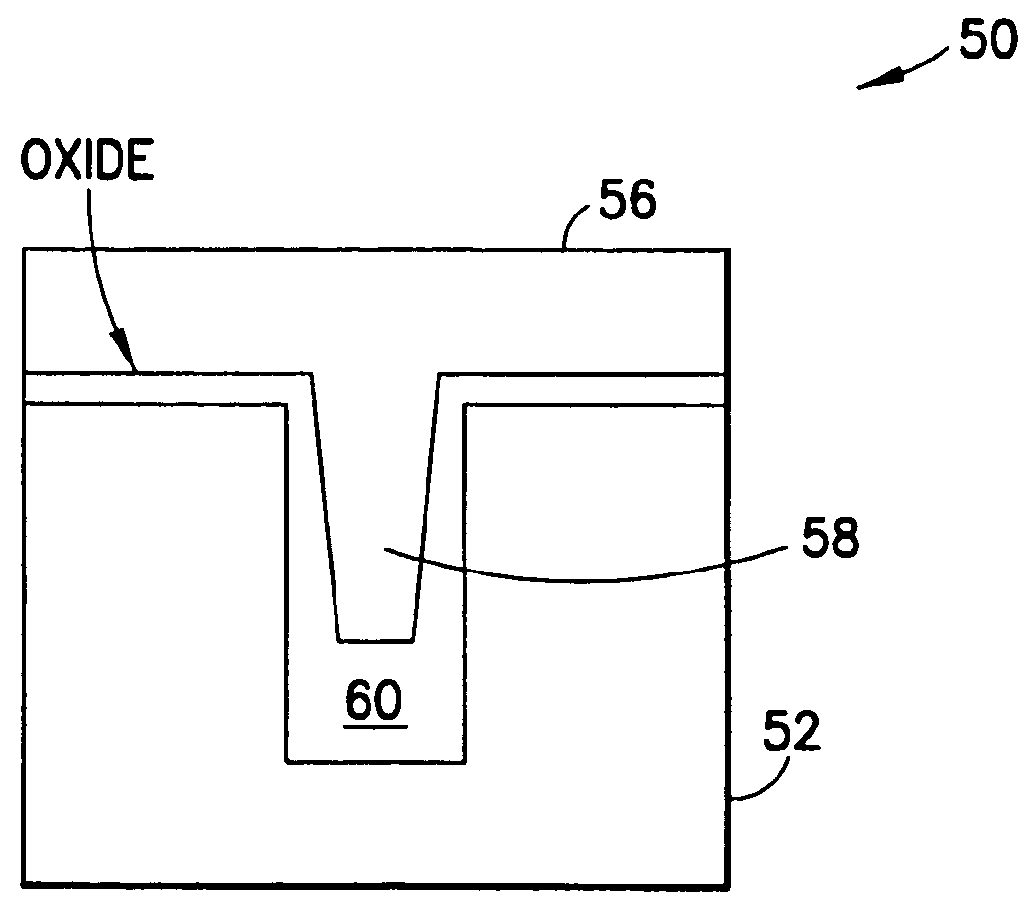

Precursors for silicon dioxide gap fill

ActiveUS9337054B2Adverse seam effectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingFilling materialsVolumetric Mass Density

A full fill trench structure is described, including a microelectronic device substrate having a high aspect ratio trench therein and filled with silicon dioxide of a substantially void-free character and substantially uniform density throughout its bulk mass. A method of manufacturing a semiconductor product also is described, involving use of specific silicon precursor compositions for forming substantially void-free and substantially uniform density silicon dioxide material in the trench. The precursor fill composition may include silicon and germanium, to produce a microelectronic device structure including a GeO2 / SiO2 trench fill material. A suppressor component may be employed in the precursor fill composition, to eliminate or minimize seam formation in the cured trench fill material.

Owner:ENTEGRIS INC

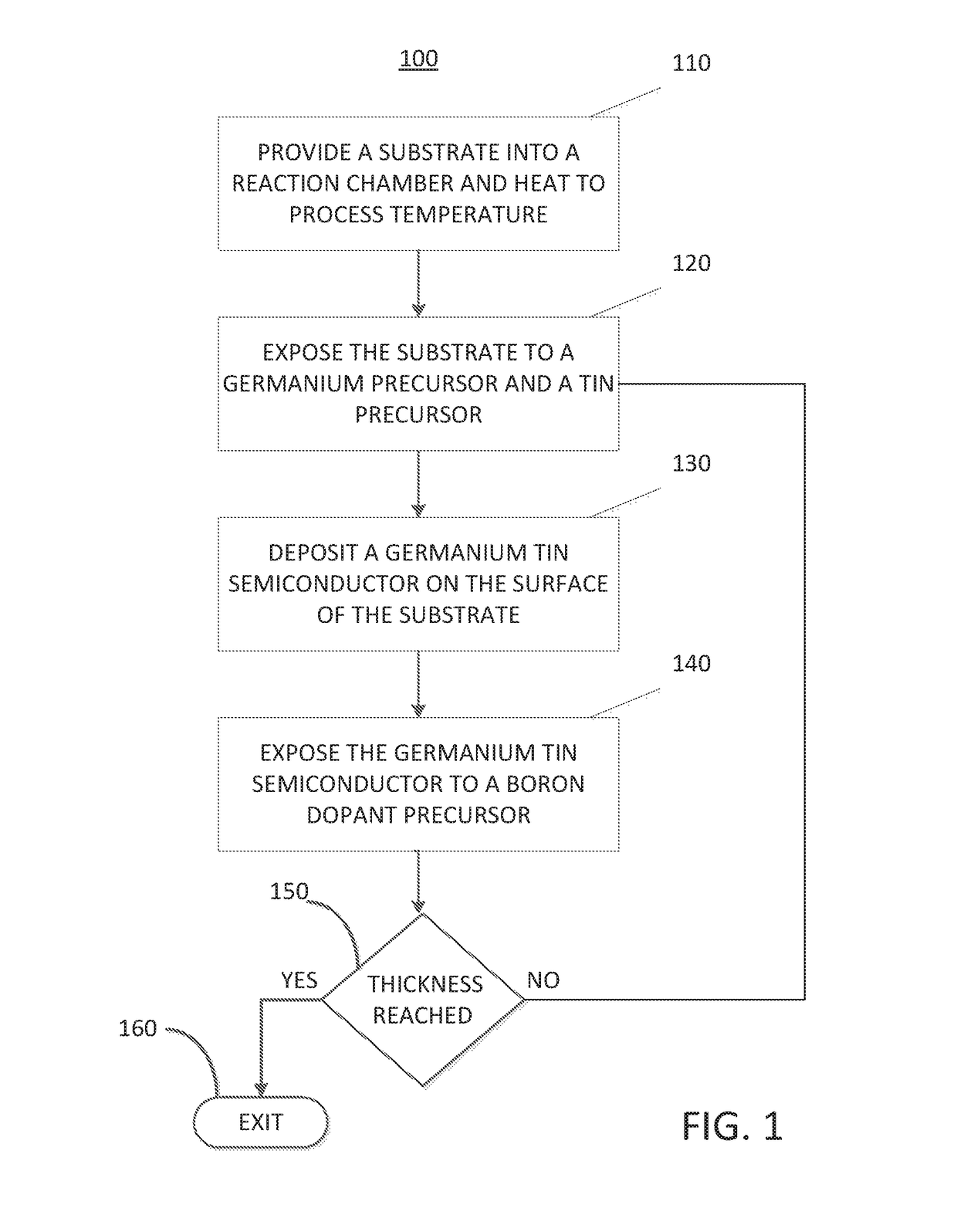

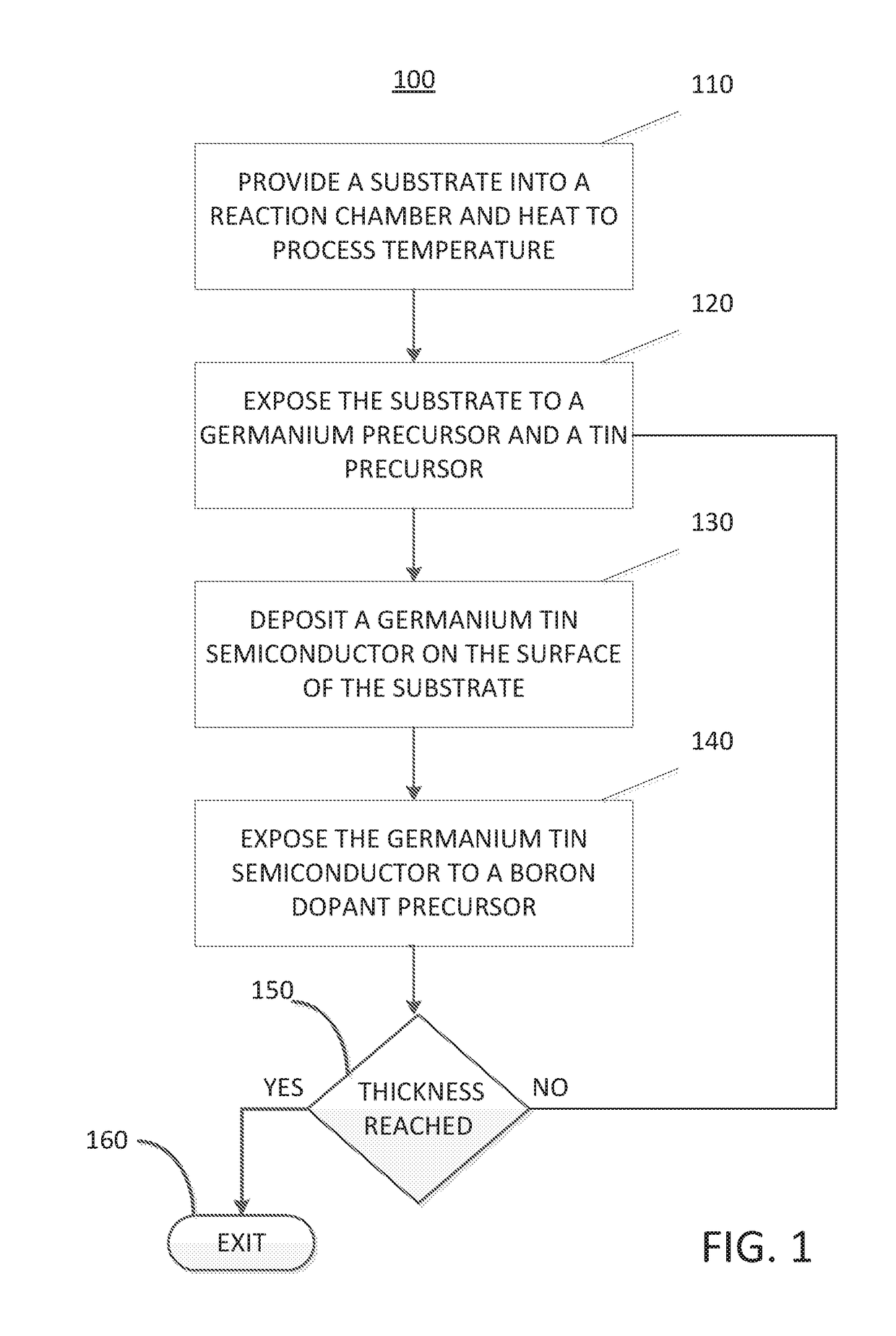

Methods for depositing a doped germanium tin semiconductor and related semiconductor device structures

ActiveUS10236177B1Polycrystalline material growthAfter-treatment detailsDopantDeposition temperature

A method for depositing a germanium tin (Ge1-xSnx) semiconductor is disclosed. The method may include; providing a substrate within a reaction chamber, heating the substrate to a deposition temperature and exposing the substrate to a germanium precursor and a tin precursor. The method may further include; depositing a germanium tin (Ge1-xSnx) semiconductor on the surface of the substrate, and exposing the germanium tin (Ge1-xSnx) semiconductor to a boron dopant precursor. Semiconductor device structures including a germanium tin (Ge1-xSnx) semiconductor formed by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

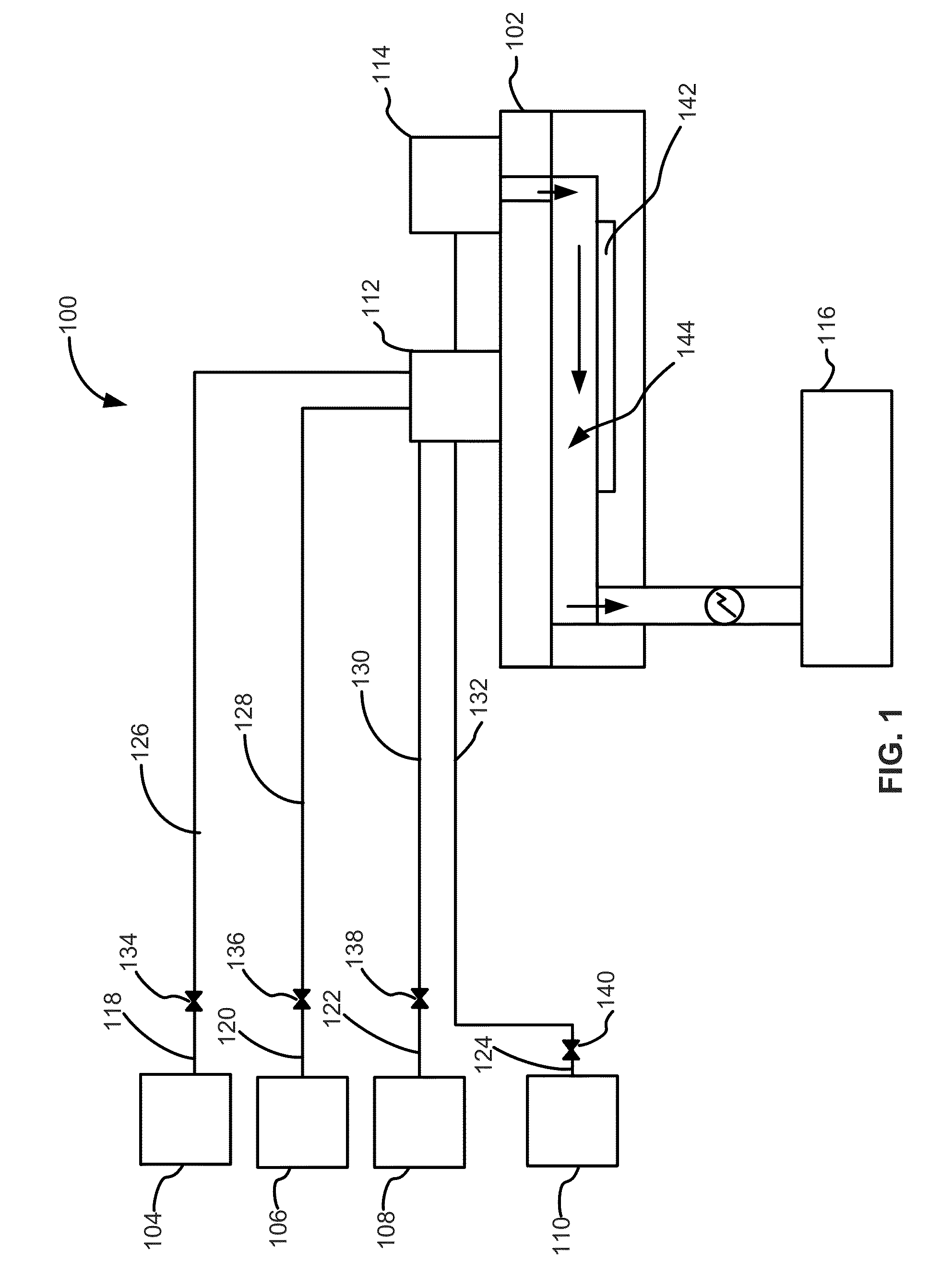

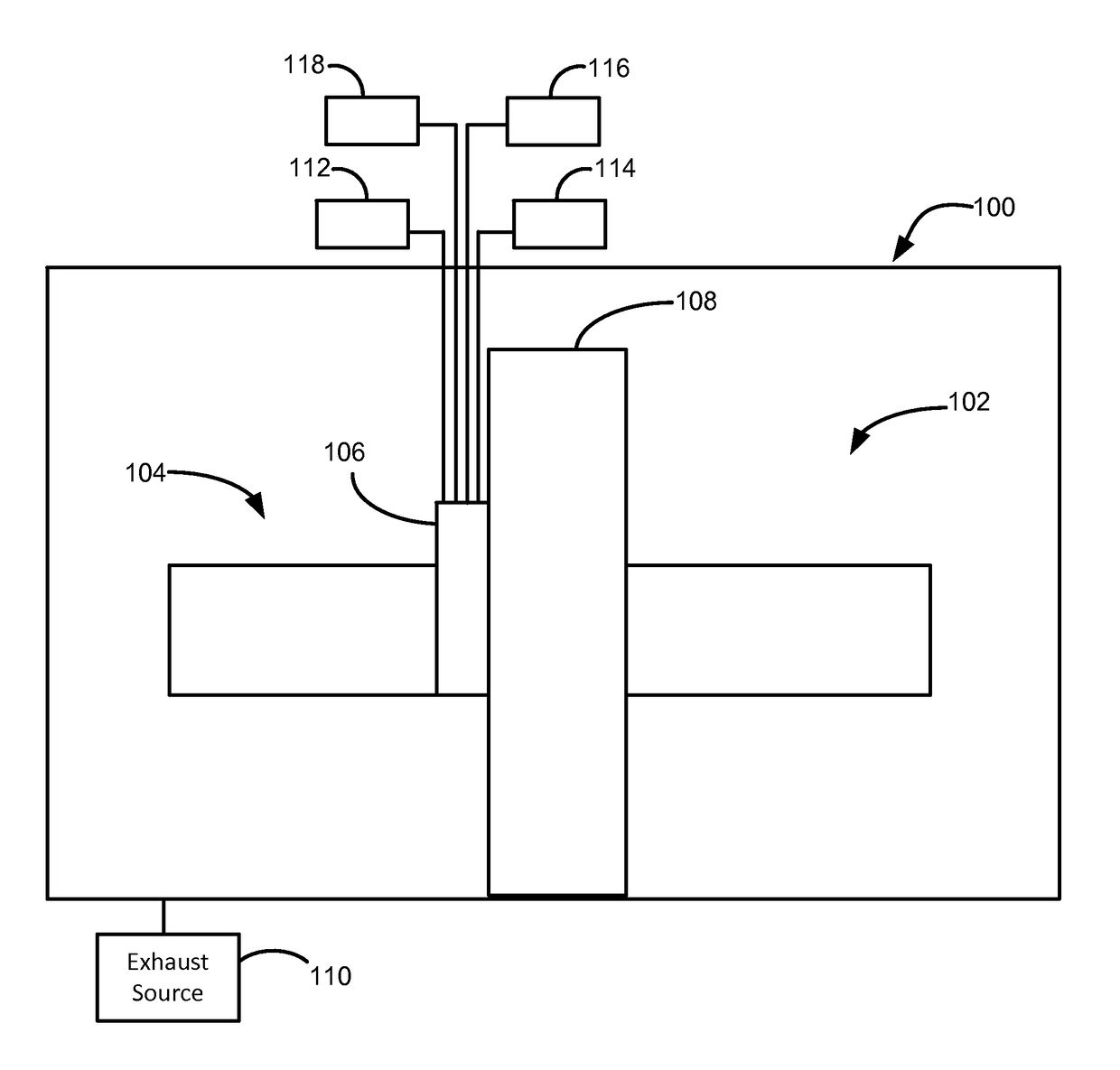

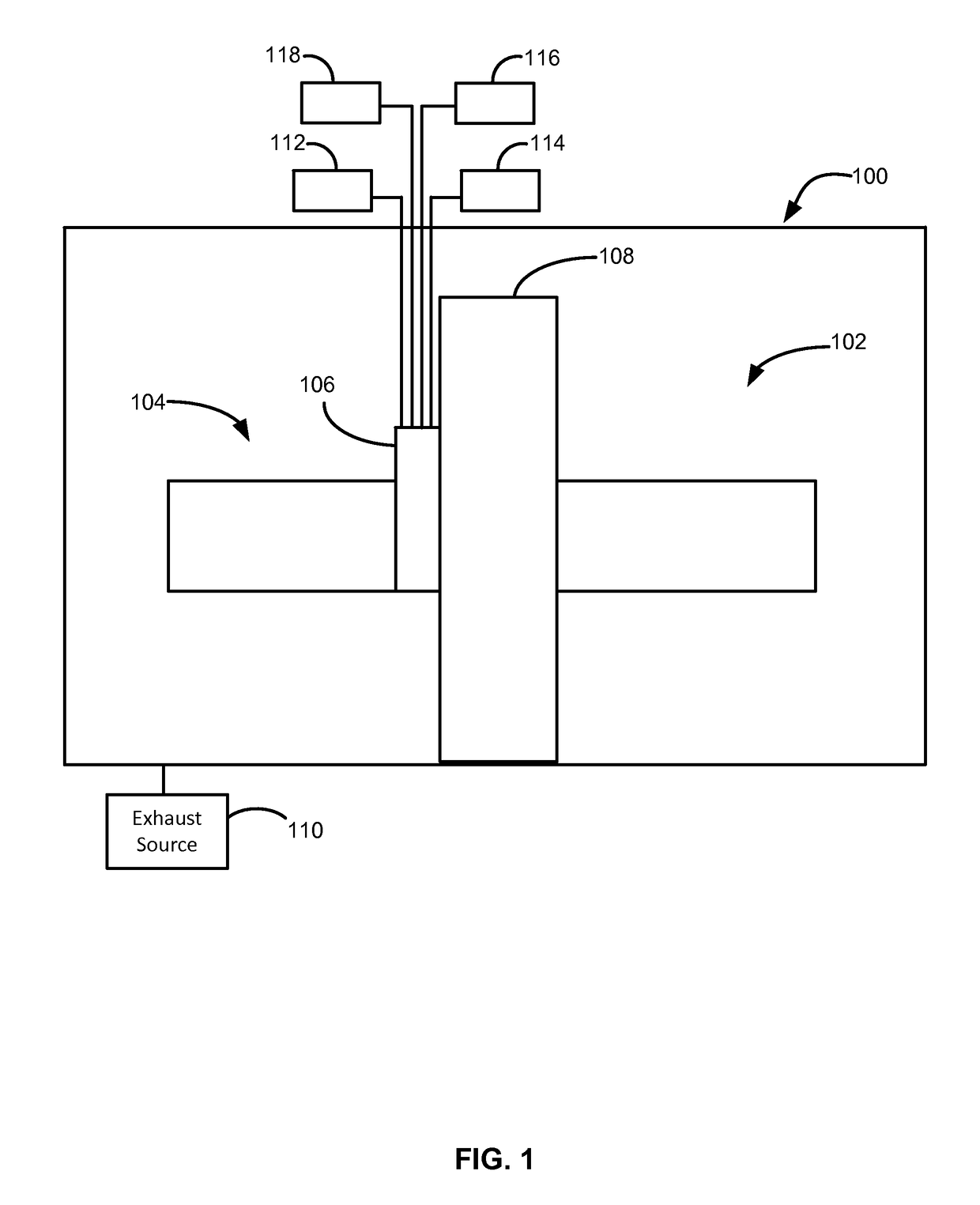

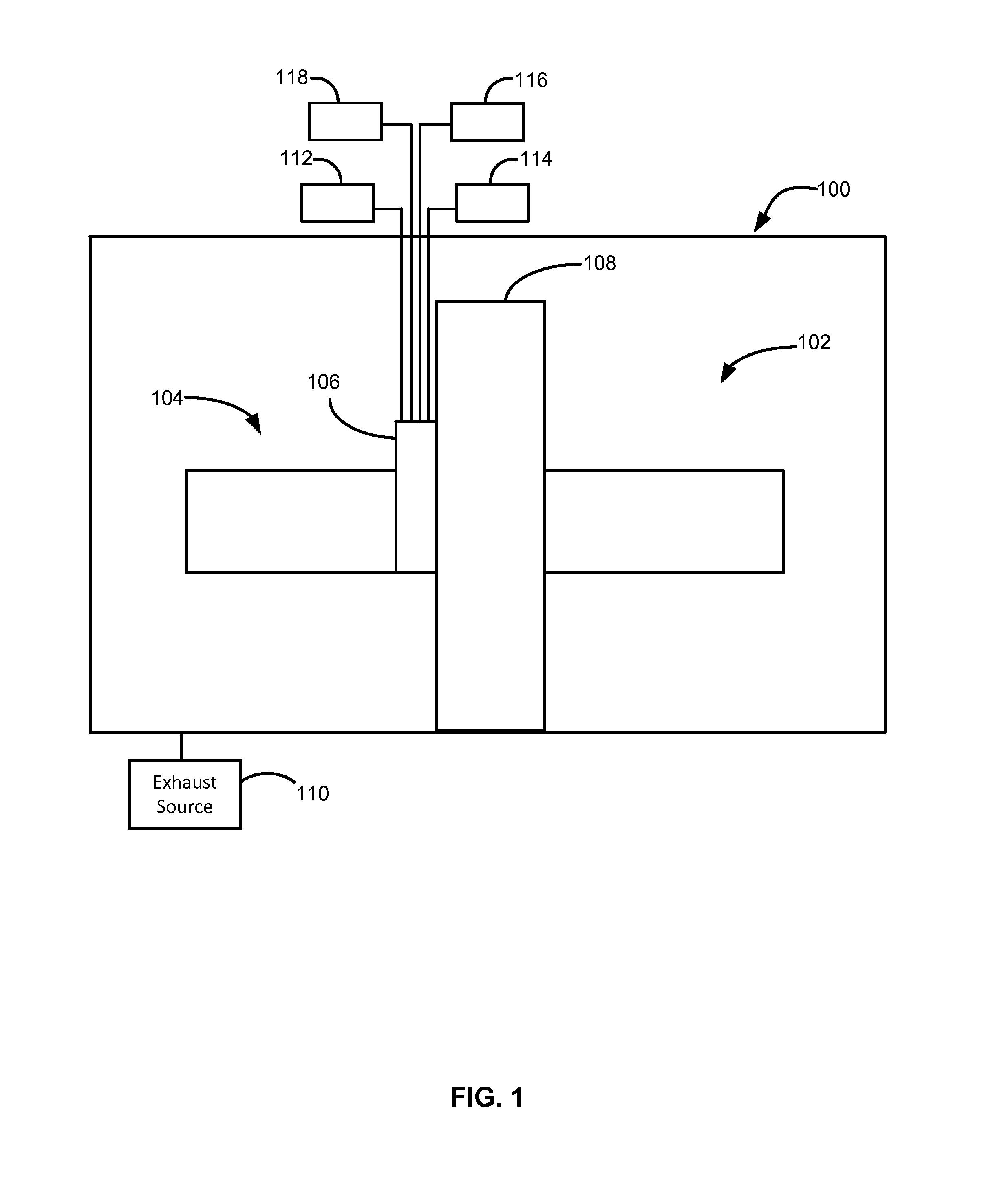

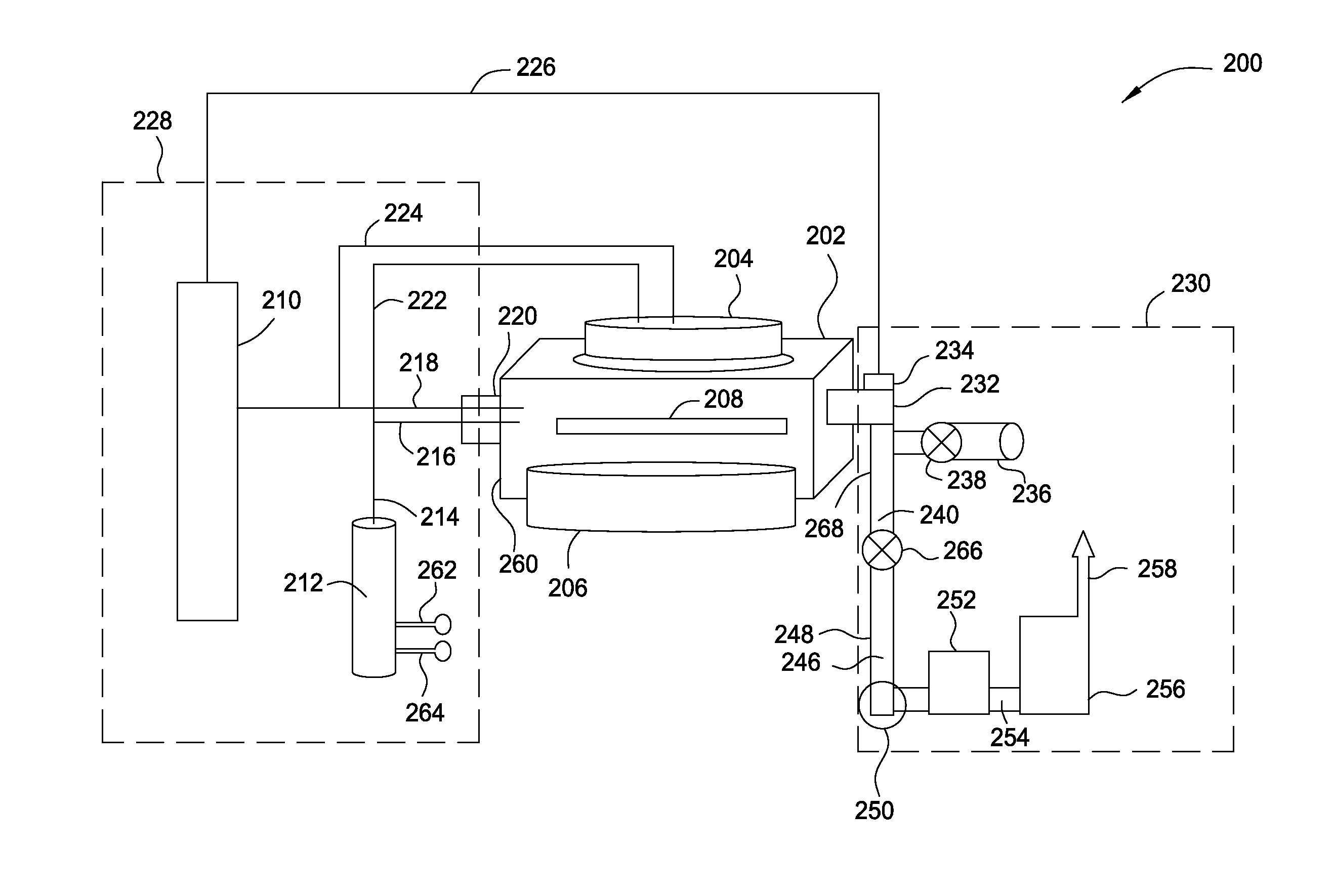

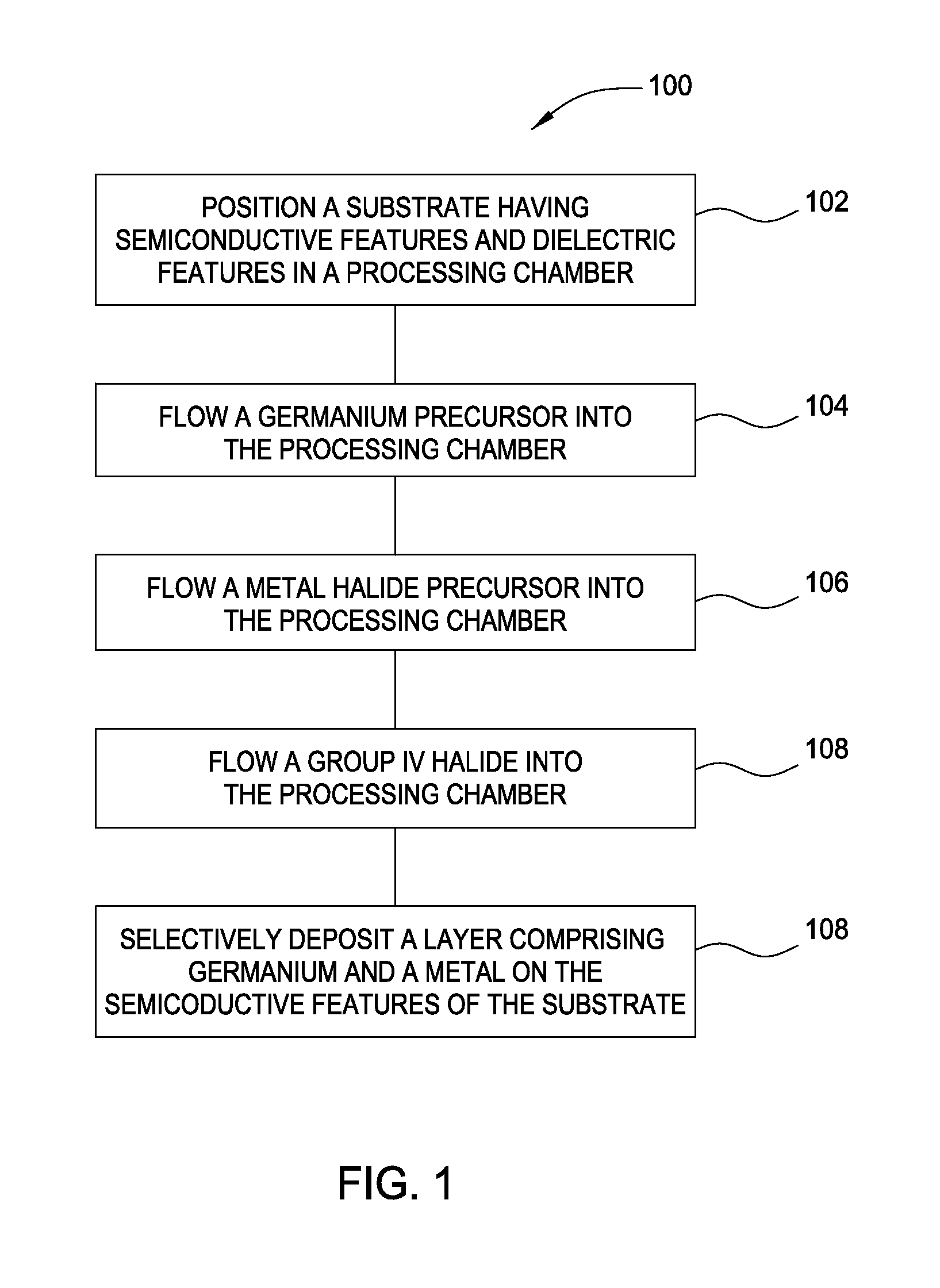

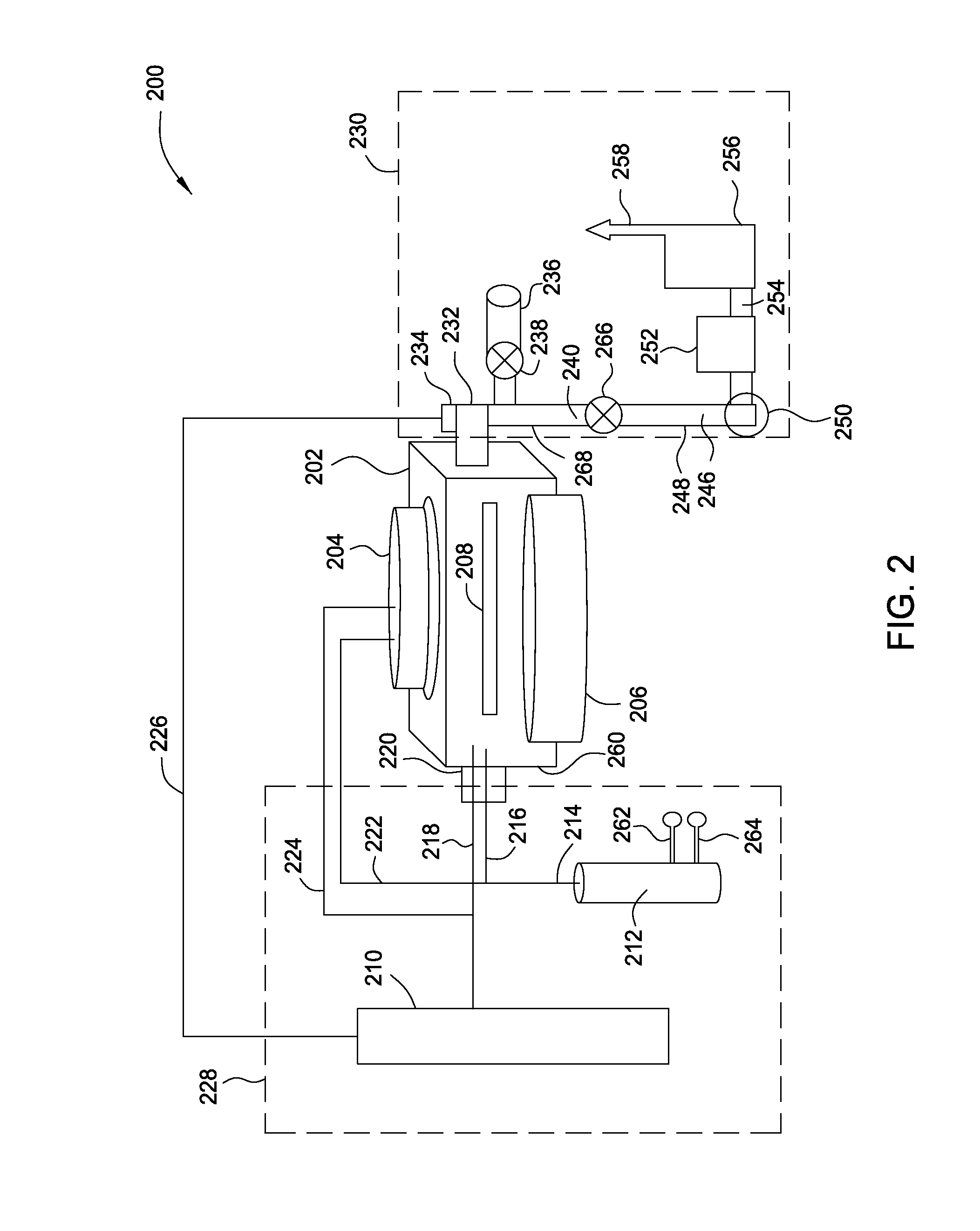

Method and apparatus for germanium tin alloy formation by thermal CVD

InactiveUS20130280891A1Polycrystalline material growthSemiconductor/solid-state device manufacturingSelective depositionLiquid metal

A method and apparatus for forming semiconductive semiconductor-metal alloy layers is described. A germanium precursor and a metal precursor are provided to a chamber, and an epitaxial layer of germanium-metal alloy, optionally including silicon, is formed on the substrate. The metal precursor is typically a metal halide, which may be provided by evaporating a liquid metal halide, subliming a solid metal halide, or by contacting a pure metal with a halogen gas. A group IV halide deposition control agent is used to provide selective deposition on semiconductive regions of the substrate relative to dielectric regions. The semiconductive semiconductor-metal alloy layers may be doped, for example with boron, phosphorus, and / or arsenic. The precursors may be provided through a showerhead or through a side entry point, and an exhaust system coupled to the chamber may be separately heated to manage condensation of exhaust components.

Owner:APPLIED MATERIALS INC

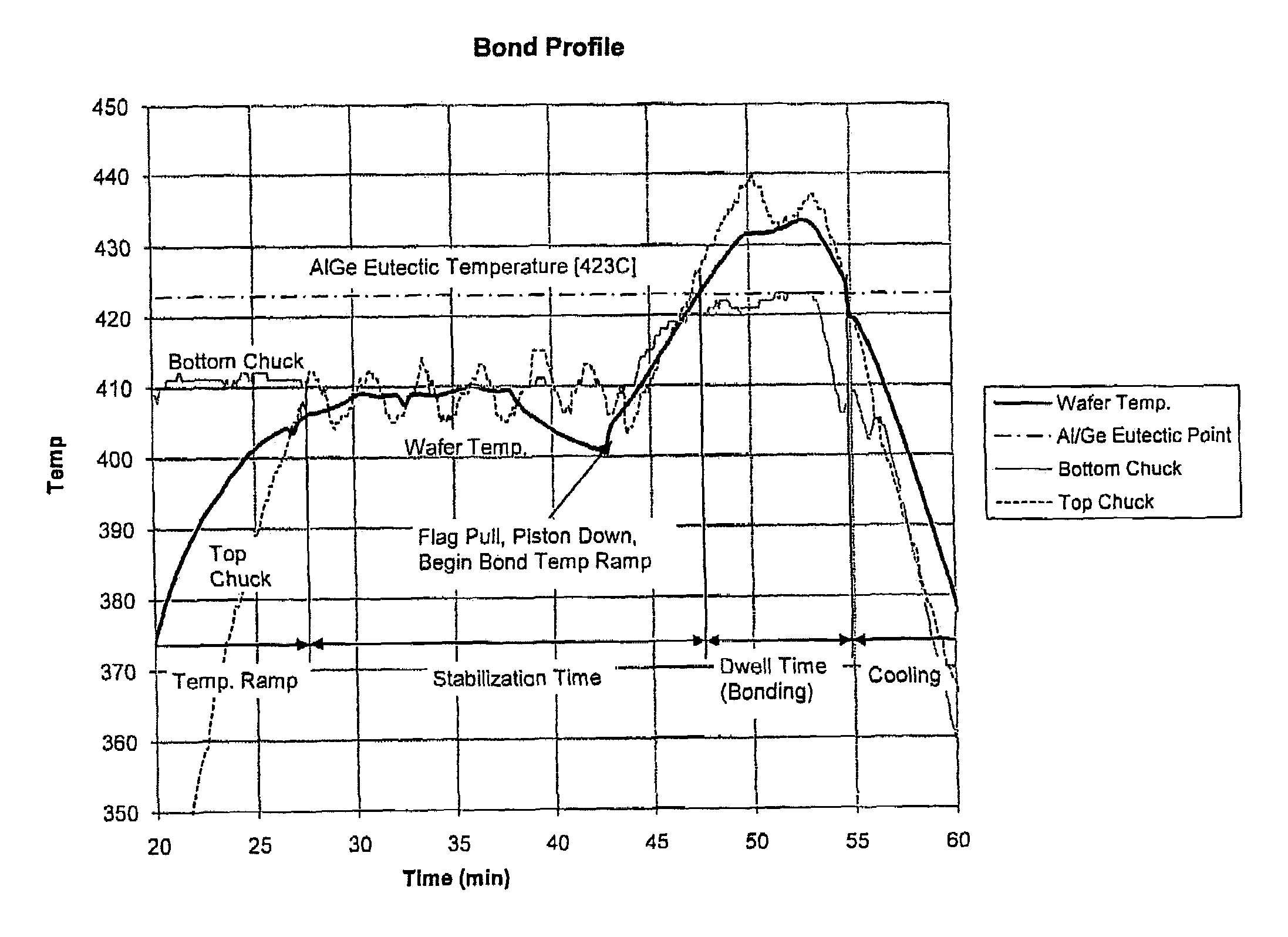

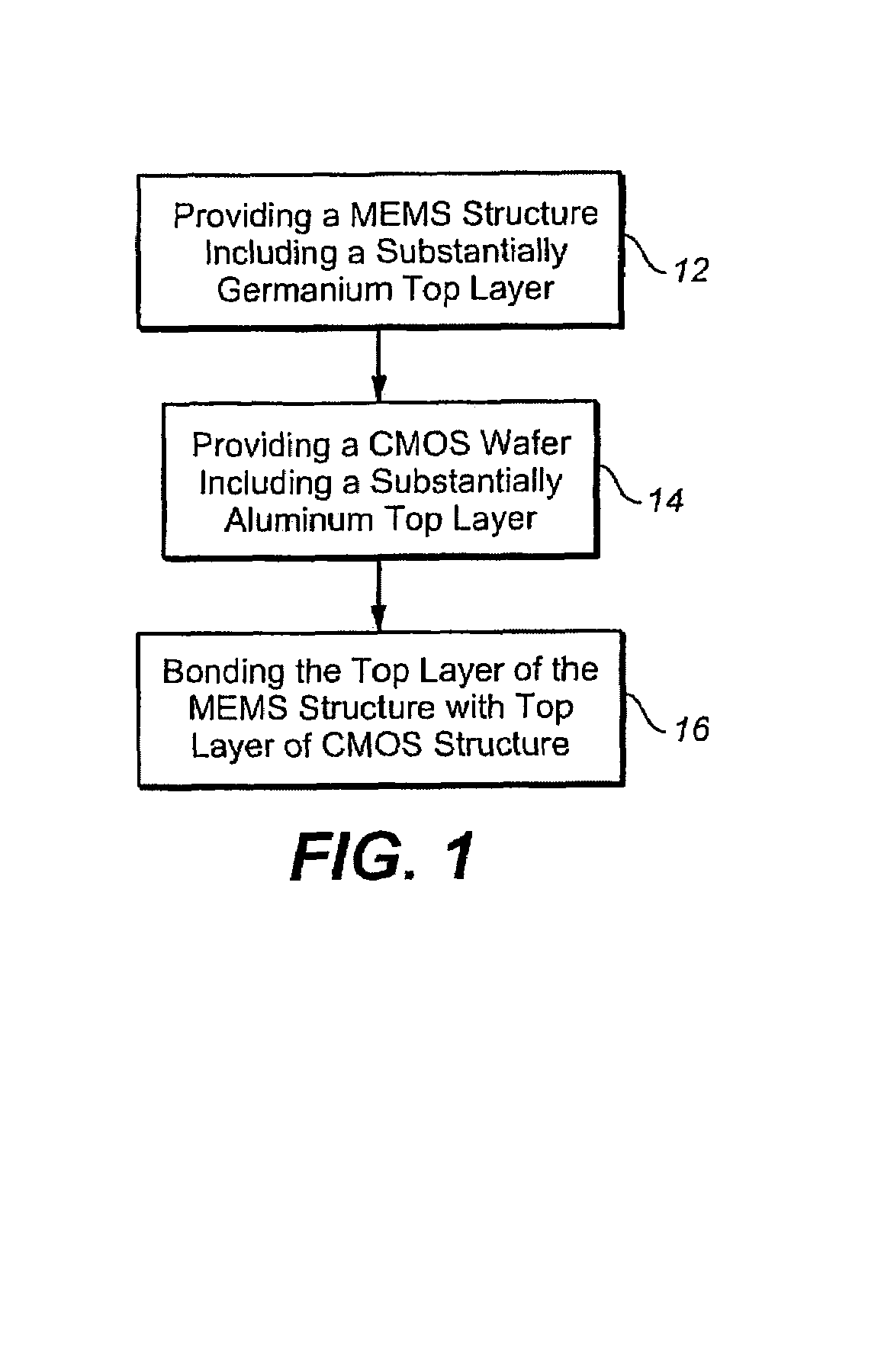

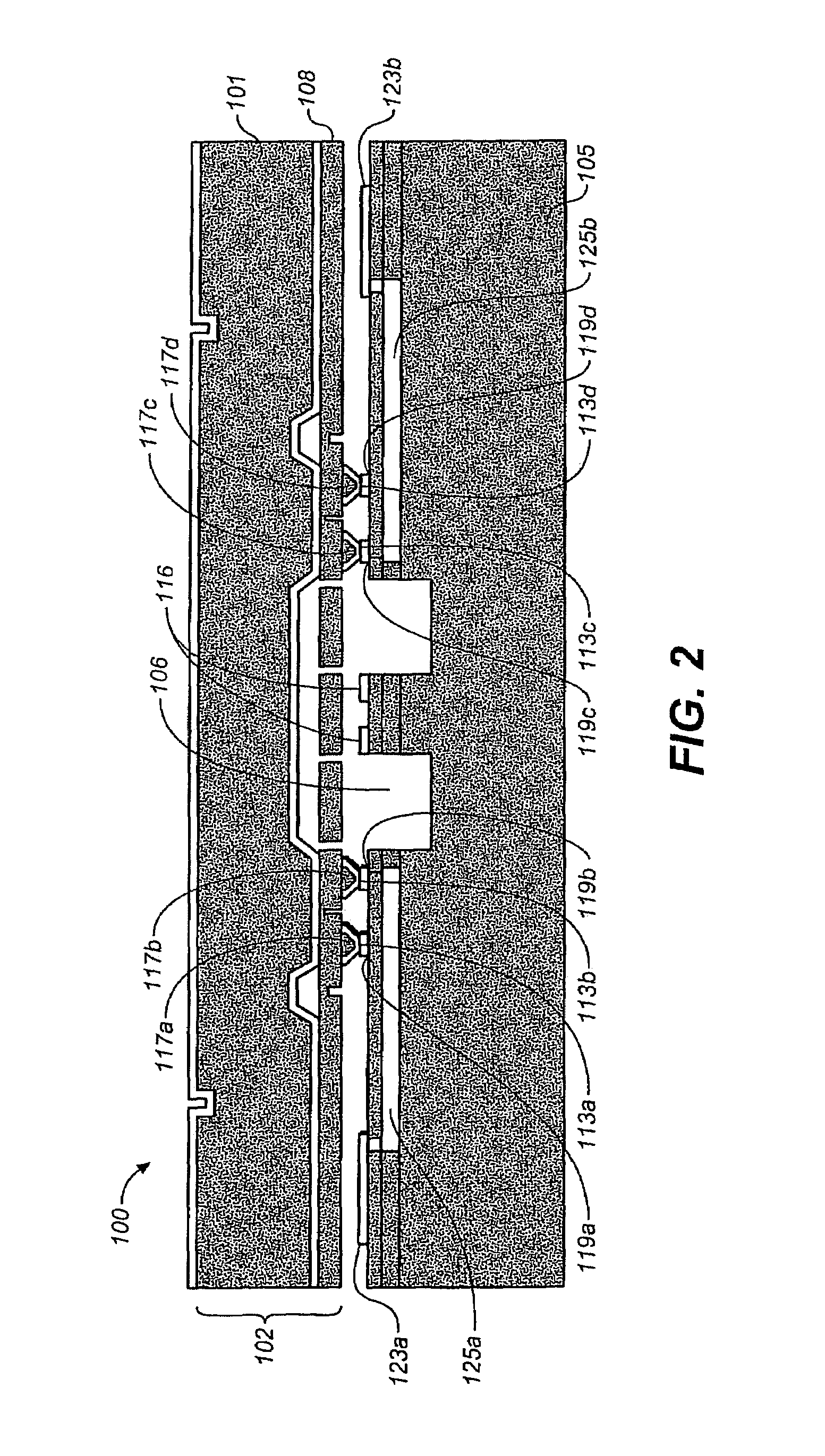

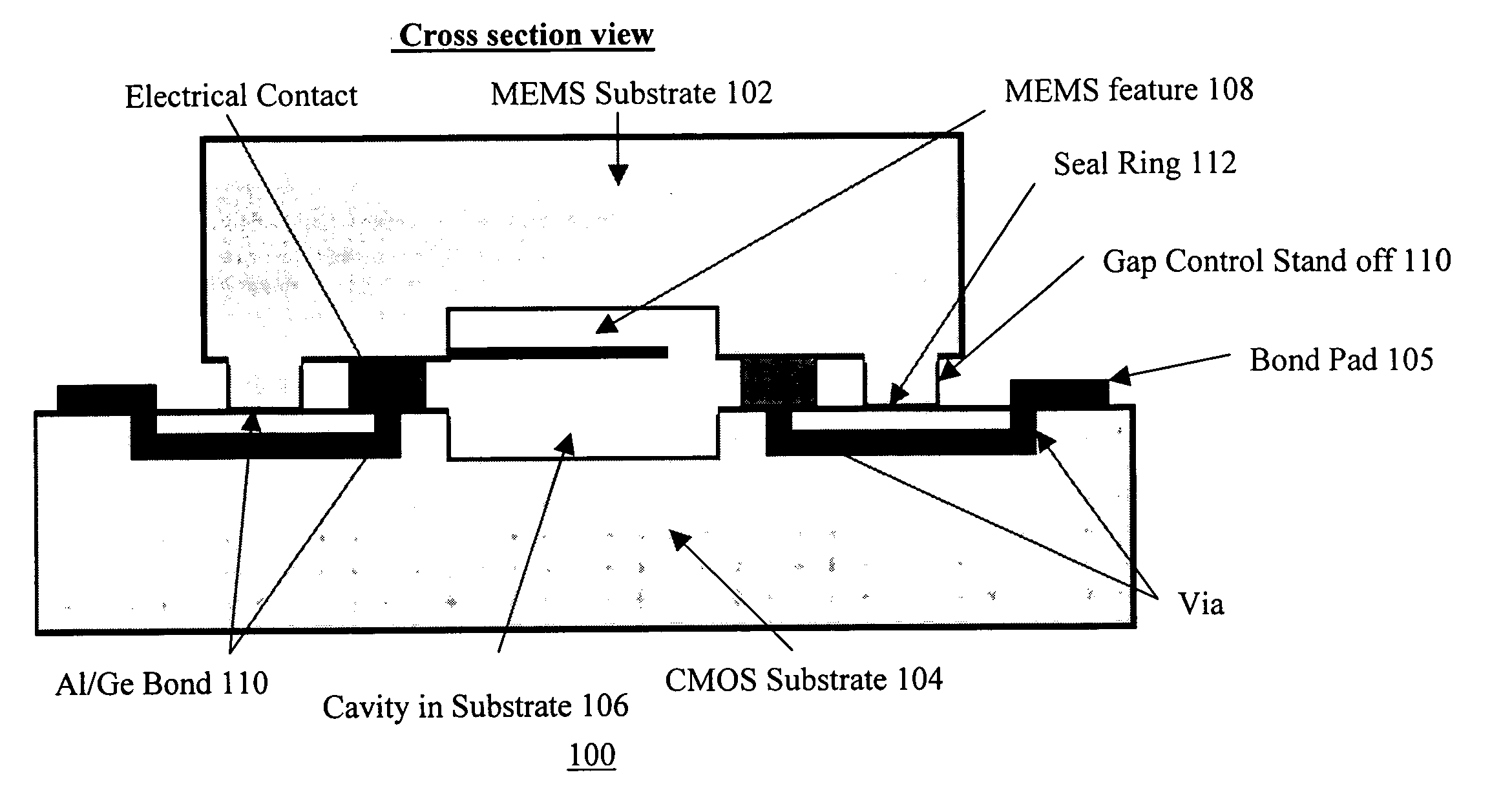

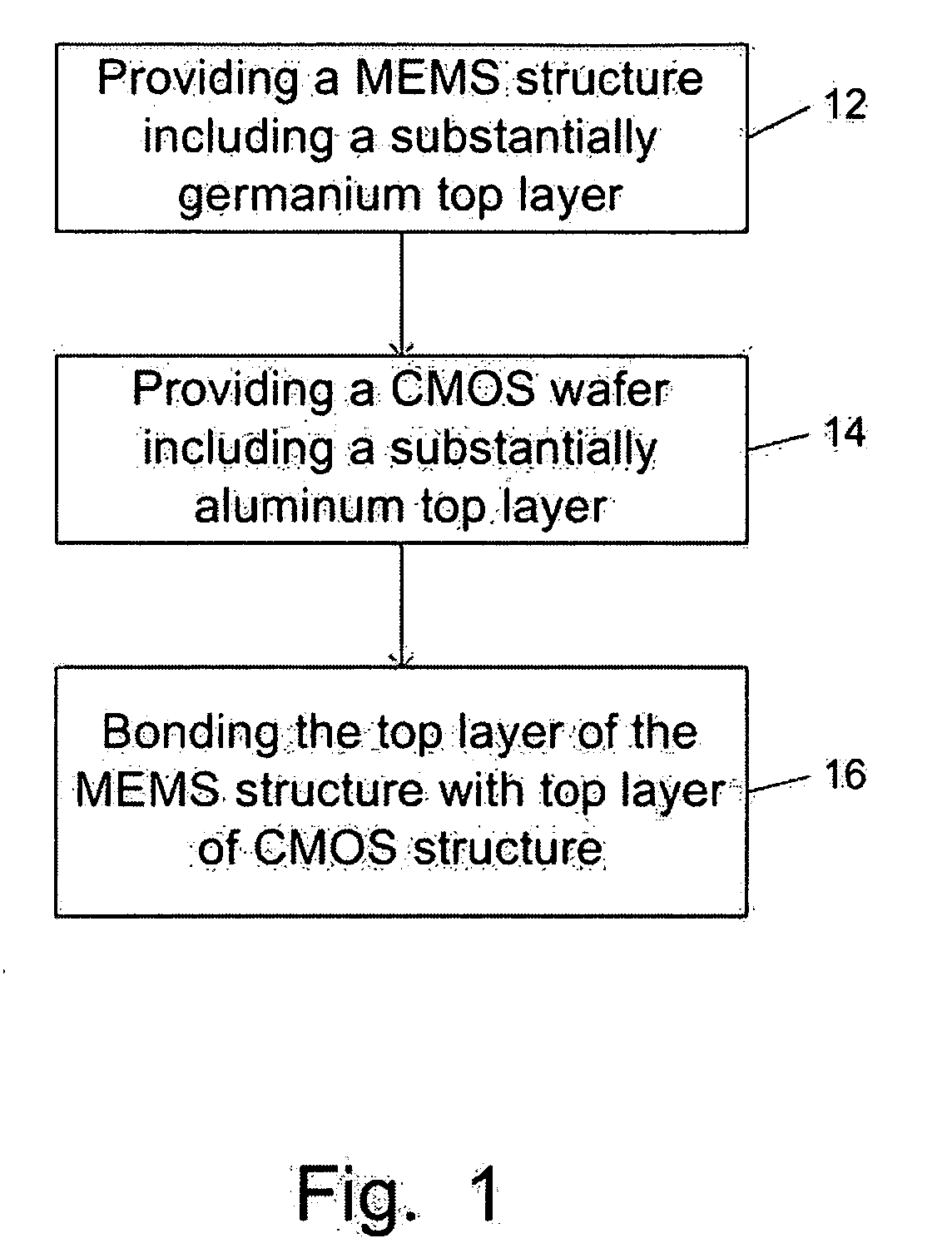

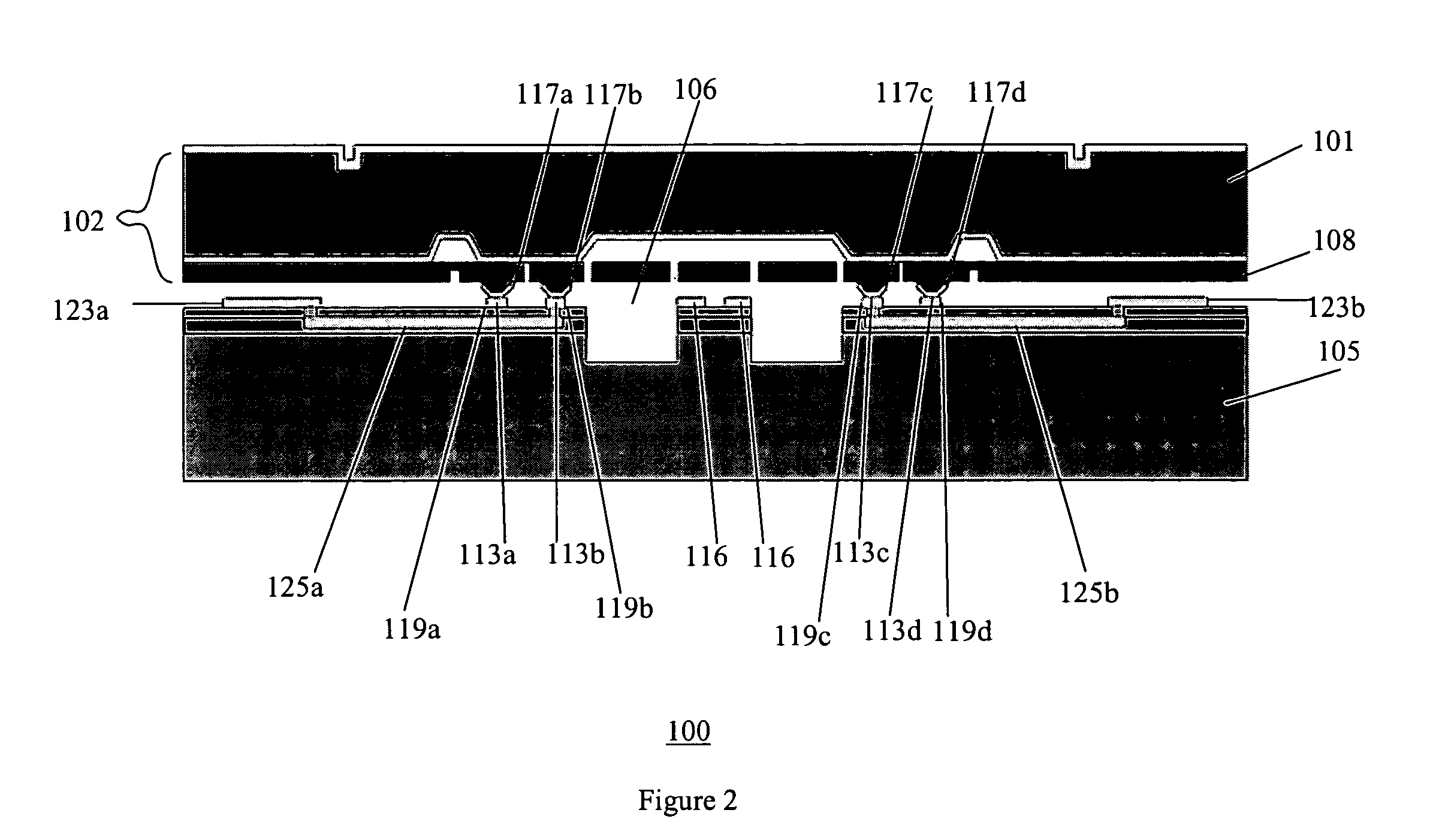

Method of fabrication of a AL/GE bonding in a wafer packaging environment and a product produced therefrom

ActiveUS7442570B2Robust and mechanical contactHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

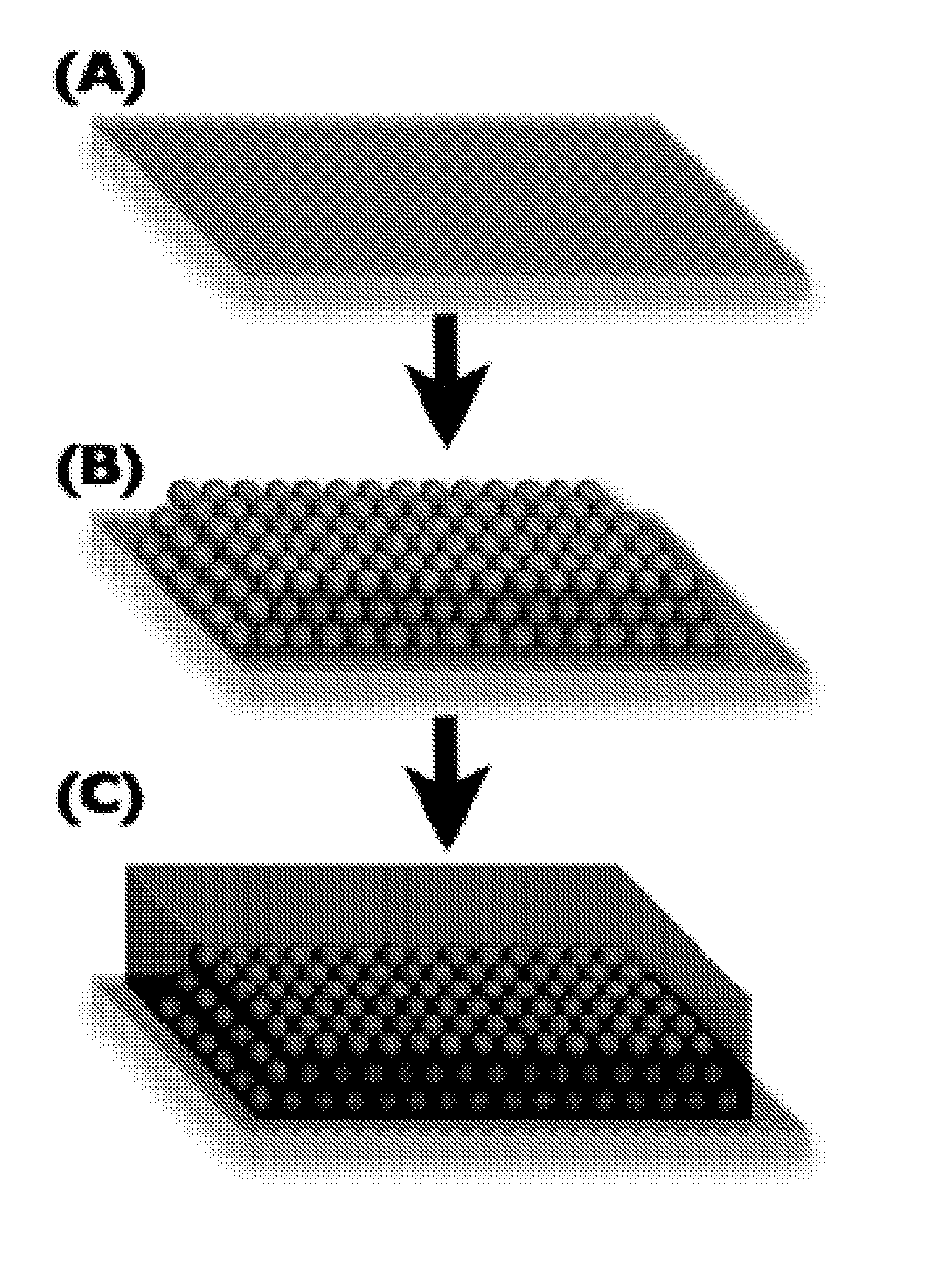

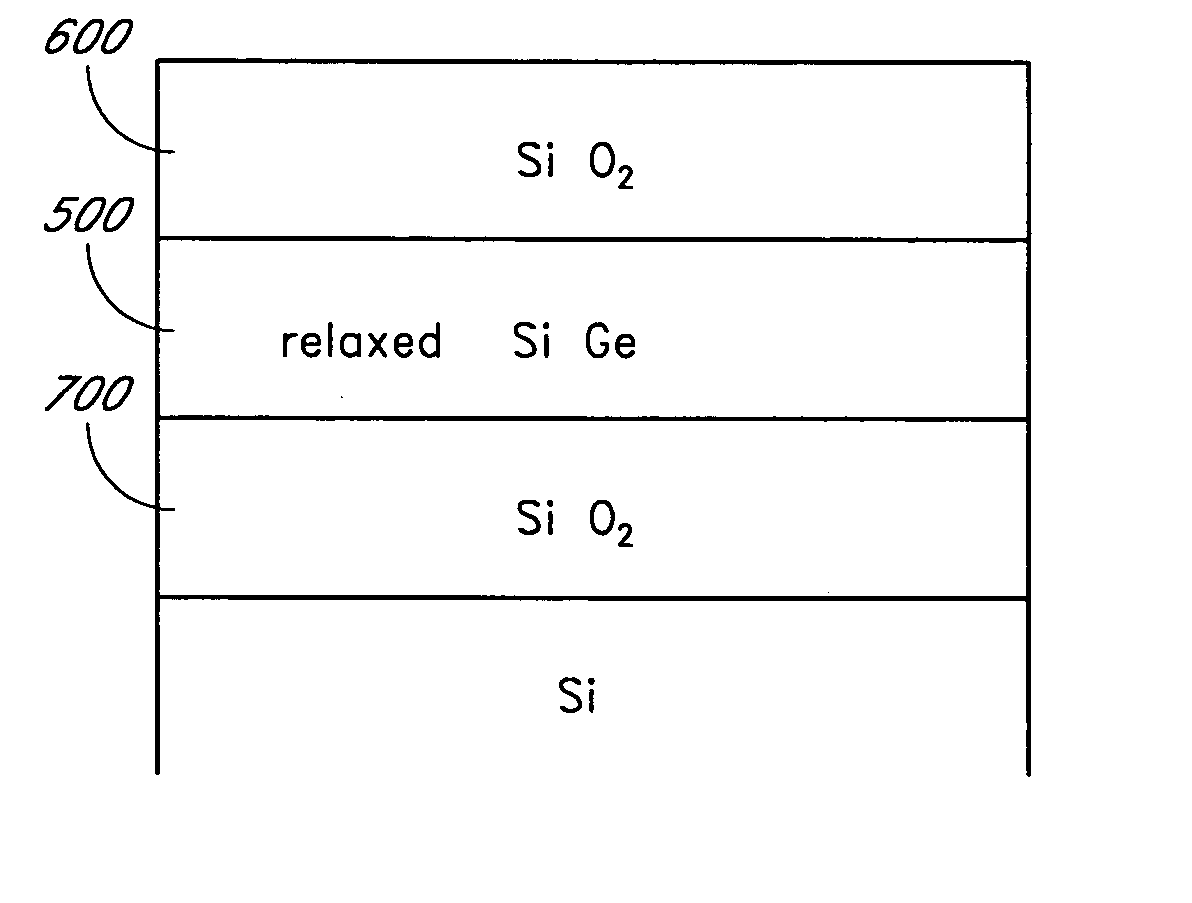

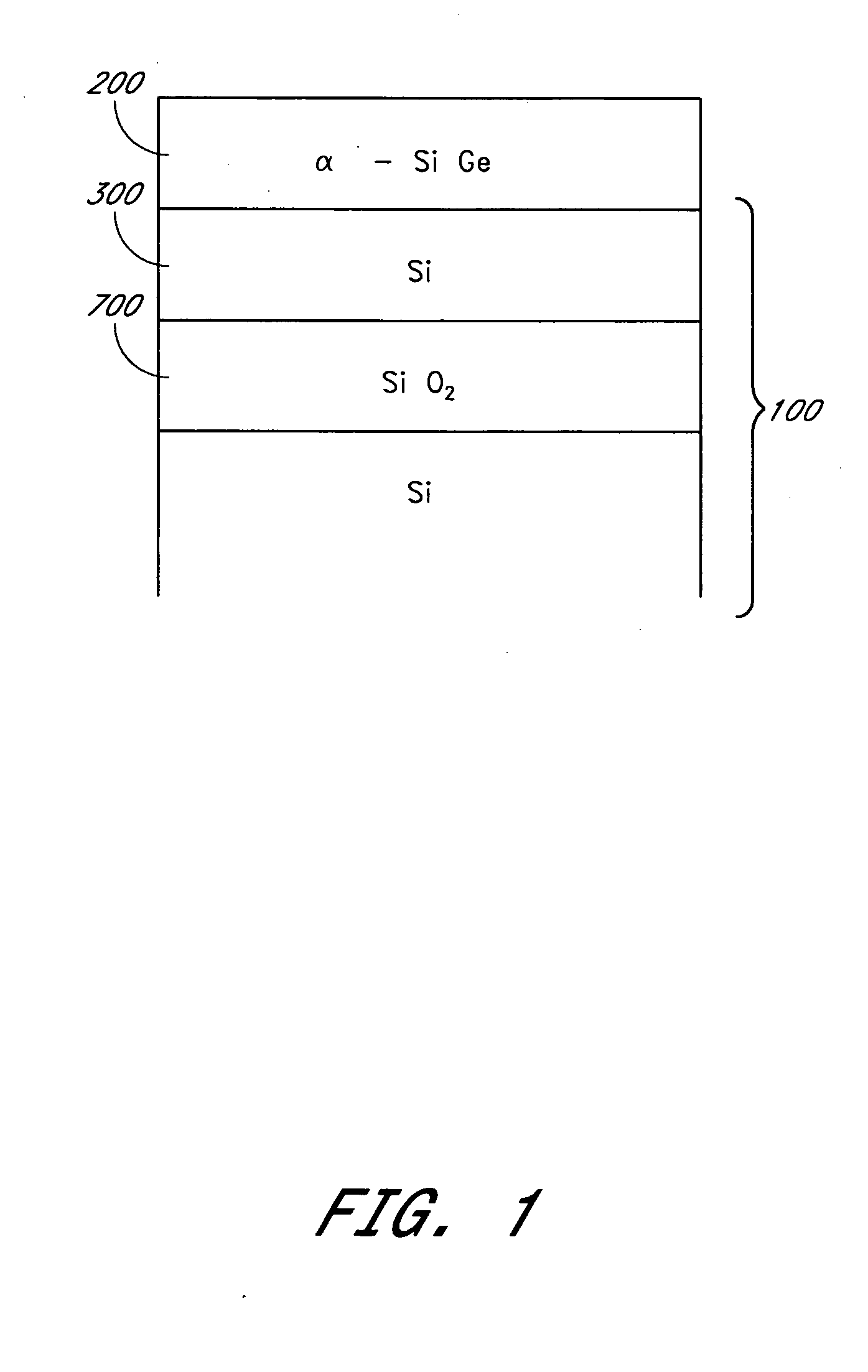

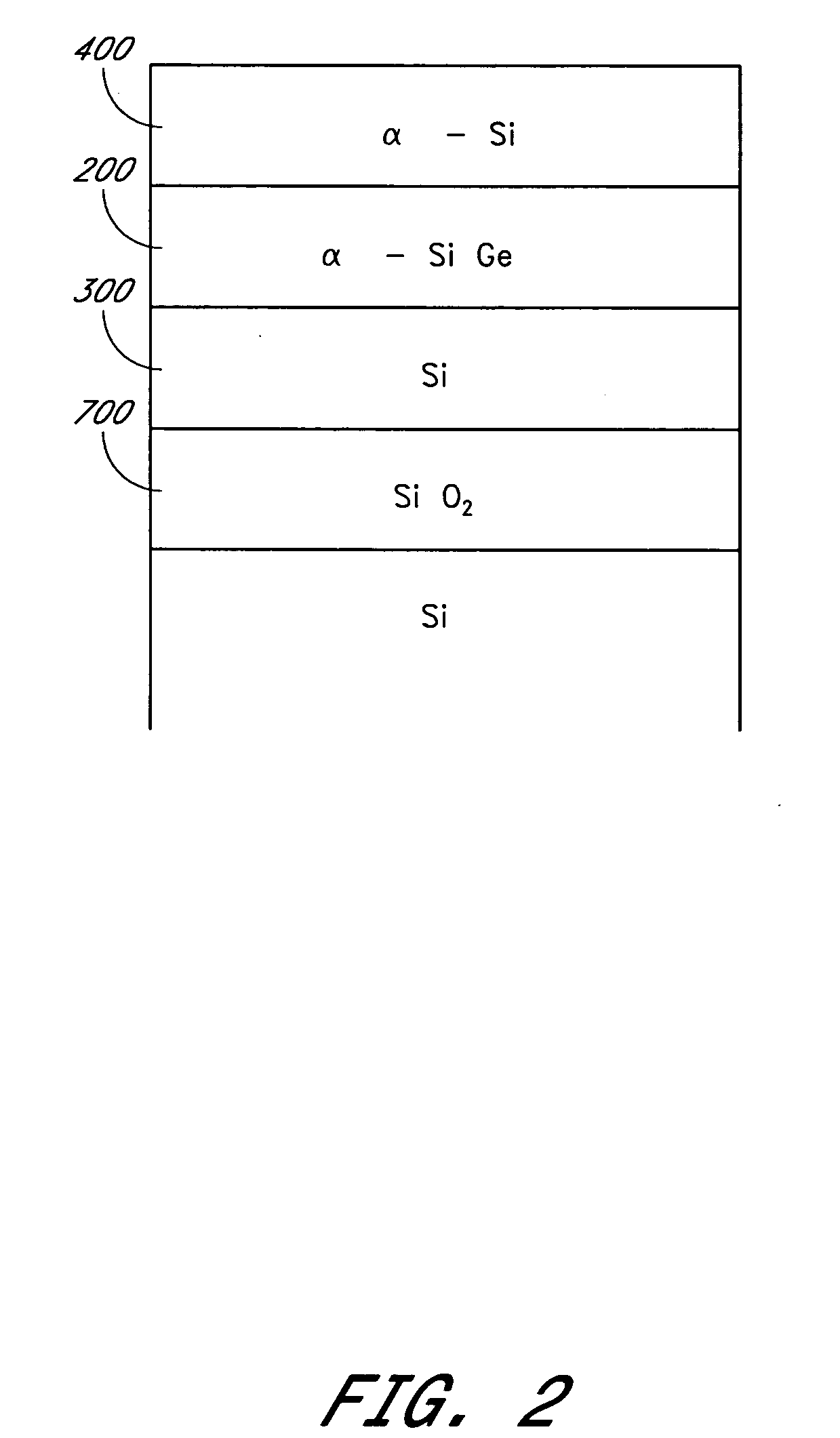

Deposition of silicon germanium on silicon-on-insulator structures and bulk substrates

Methods are provided for producing SiGe-on-insulator structures and for forming strain-relaxed SiGe layers on silicon while minimizing defects. Amorphous SiGe layers are deposited by CVD from trisilane and GeH4. The amorphous SiGe layers are recrystallized over silicon by melt or solid phase epitaxy (SPE) processes. The melt processes preferably also cause diffusion of germanium to dilute the overall germanium content and essentially consume the silicon overlying the insulator. The SPE process can be conducted with or without diffusion of germanium into the underlying silicon, and so is applicable to SOI as well as conventional semiconductor substrates.

Owner:ASM IP HLDG BV

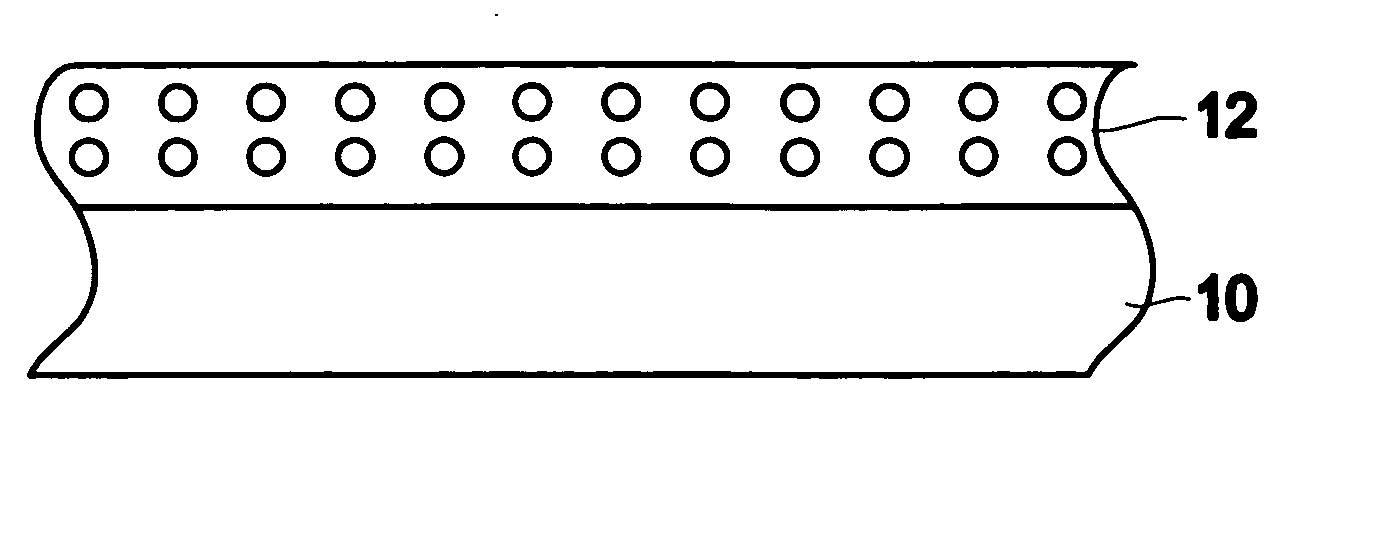

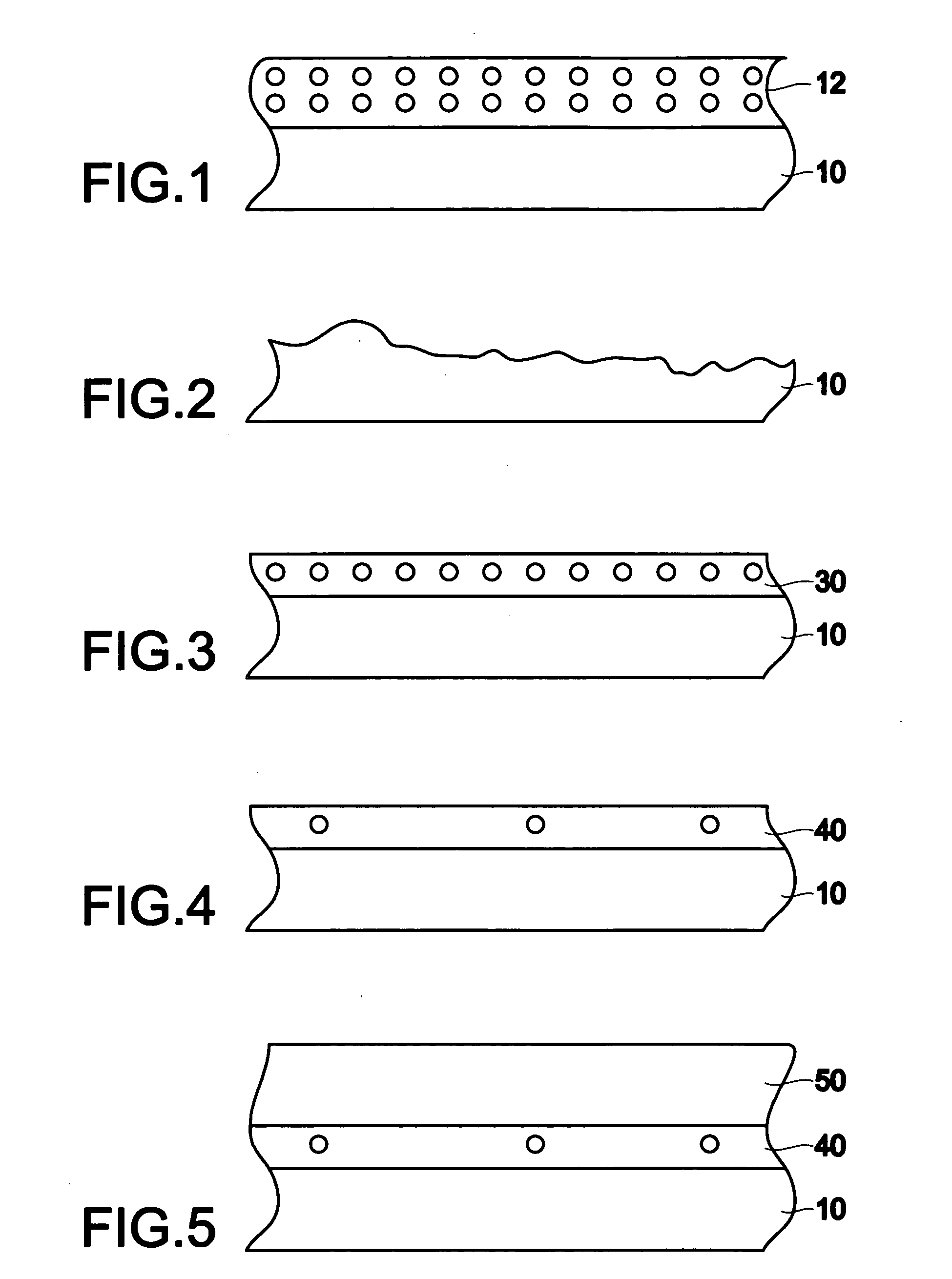

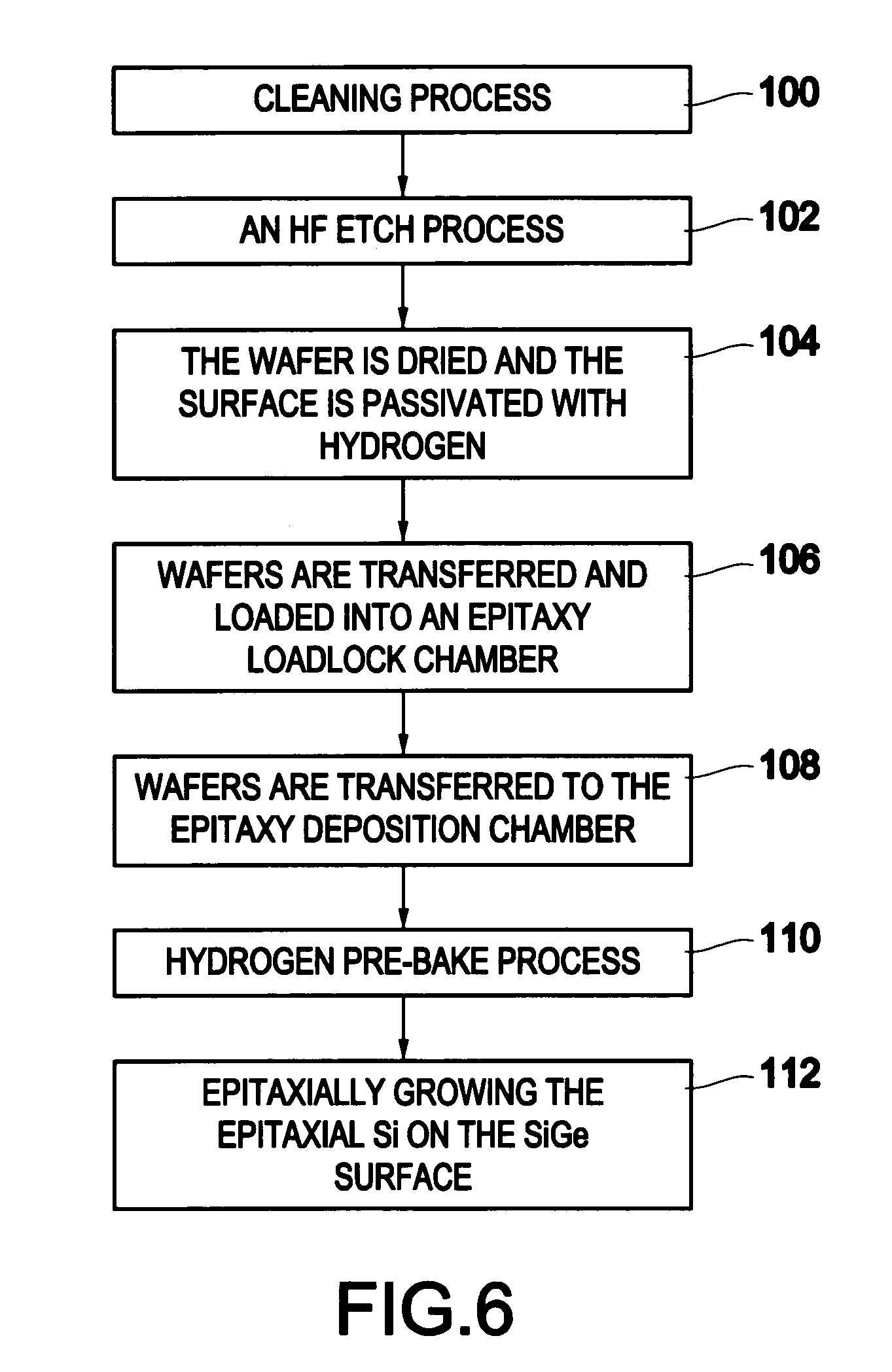

Method of preventing surface roughening during hydrogen pre-bake of SiGe substrates using chlorine containing gases

InactiveUS20050148162A1Prevent surfaceAvoid creatingPolycrystalline material growthSemiconductor/solid-state device manufacturingPartial oxidationSilicon on insulator

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves only a sub-monolayer of oxygen (typically 1×1013-1×1015 / cm2 of oxygen) at the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process in a chlorine containing environment which heats the silicon germanium, strained silicon, or thin silicon-on-insulator surface sufficiently to remove the remaining oxygen from the surface. By introducing a small amount of chlorine containing gases, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:IBM CORP

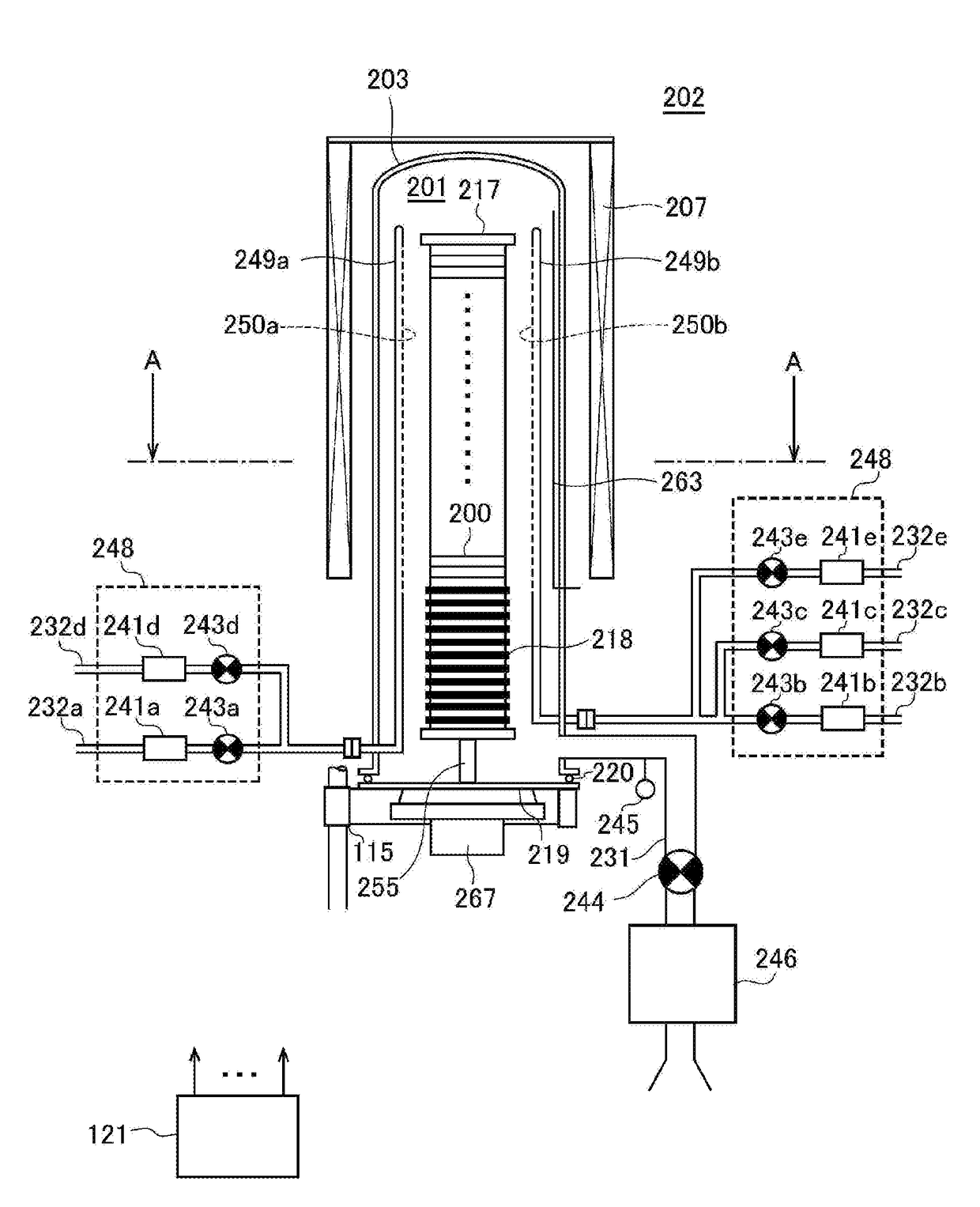

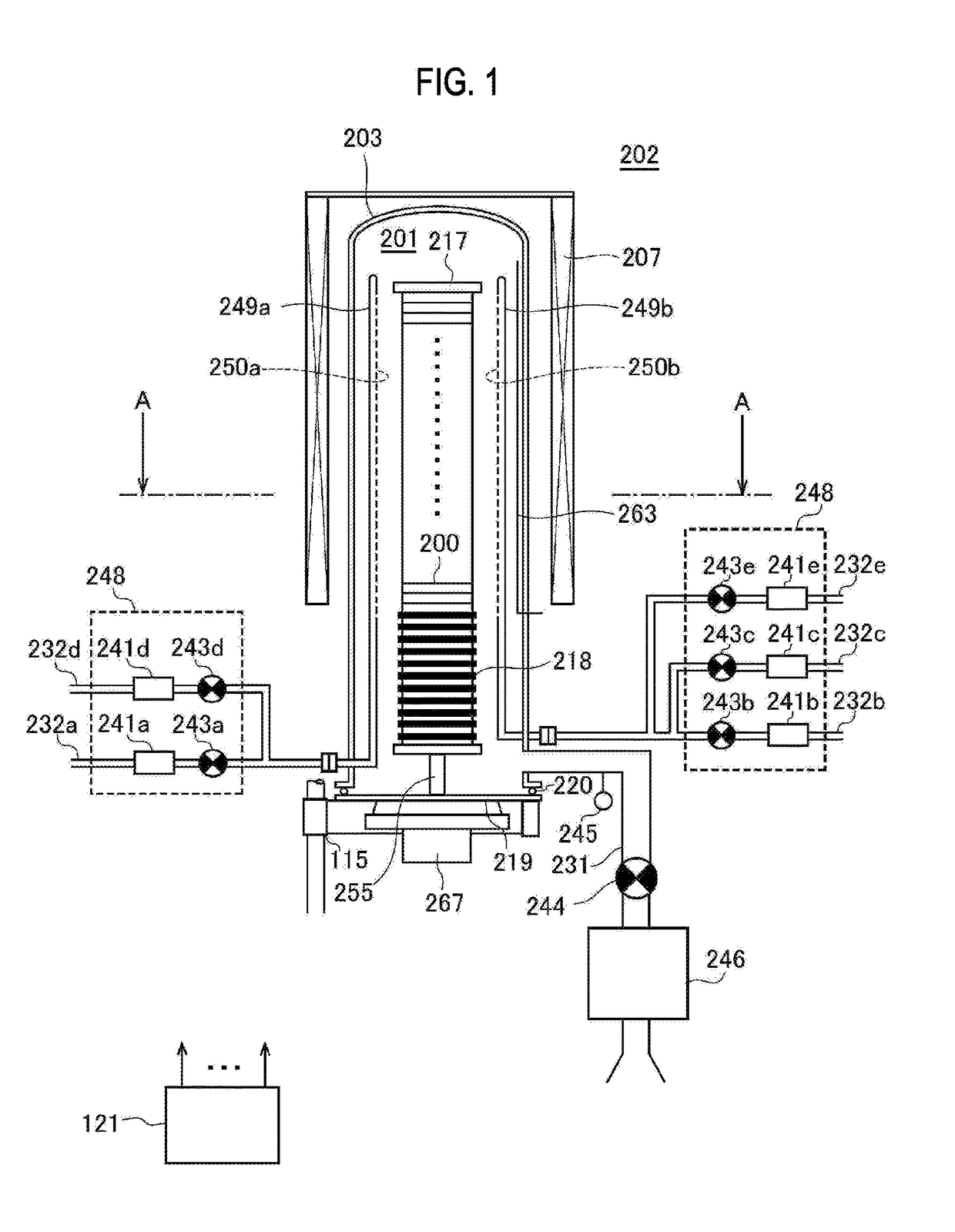

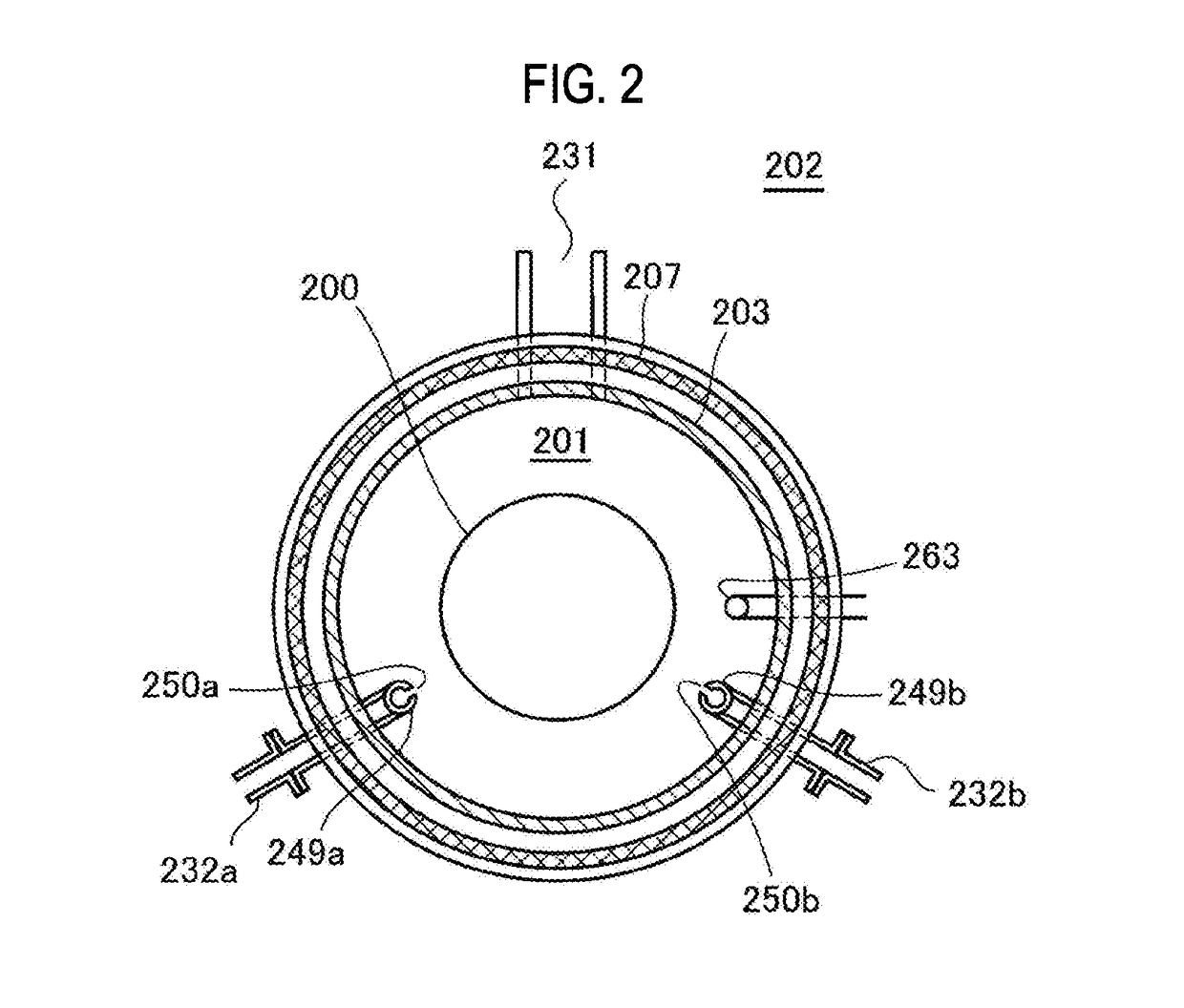

Method of manufacturing semiconductor device, substrate processing apparatus, and recording medium

ActiveUS20170365467A1Improve film qualitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingHalogenEngineering

There is provided a method of manufacturing a semiconductor device, which includes: forming a first seed layer containing silicon and germanium on a substrate by performing, a predetermined number of times, a cycle which includes supplying a first process gas containing silicon or germanium and containing a halogen element to the substrate, supplying a second process gas containing silicon and not containing a halogen element to the substrate, and supplying a third process gas containing germanium and not containing a halogen element to the substrate; and forming a germanium-containing film on the first seed layer by supplying a fourth process gas containing germanium and not containing a halogen element to the substrate.

Owner:KOKUSA ELECTRIC CO LTD

Methods for depositing a doped germanium tin semiconductor and related semiconductor device structures

ActiveUS20190067004A1Polycrystalline material growthAfter-treatment detailsDopantDeposition temperature

A method for depositing a germanium tin (Ge1-xSnx) semiconductor is disclosed. The method may include; providing a substrate within a reaction chamber, heating the substrate to a deposition temperature and exposing the substrate to a germanium precursor and a tin precursor. The method may further include; depositing a germanium tin (Ge1-xSnx) semiconductor on the surface of the substrate, and exposing the germanium tin (Ge1-xSnx) semiconductor to a boron dopant precursor. Semiconductor device structures including a germanium tin (Ge1-xSnx) semiconductor formed by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

Method of epitaxial germanium tin alloy surface preparation

Methods of preparing a clean surface of germanium tin or silicon germanium tin layers for subsequent deposition are provided. An overlayer of Ge, doped Ge, another GeSn or SiGeSn layer, a doped GeSn or SiGeSn layer, an insulator, or a metal can be deposited on a prepared GeSn or SiGeSn layer by positioning a substrate with an exposed germanium tin or silicon germanium tin layer in a processing chamber, heating the processing chamber and flowing a halide gas into the processing chamber to etch the surface of the substrate using either thermal or plasma assisted etching followed by depositing an overlayer on the substantially oxide free and contaminant free surface. Methods can also include the placement and etching of a sacrificial layer, a thermal clean using rapid thermal annealing, or a process in a plasma of nitrogen trifluoride and ammonia gas.

Owner:APPLIED MATERIALS INC

Method of fabrication of ai/ge bonding in a wafer packaging environment and a product produced therefrom

ActiveUS20060208326A1RobustHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com