Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Enhanced vapor deposition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Pecvd microcrystalline silicon germanium (SIGE)

ActiveUS20150072509A1Enhanced vapor depositionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingCelsius DegreeMicrocrystalline silicon

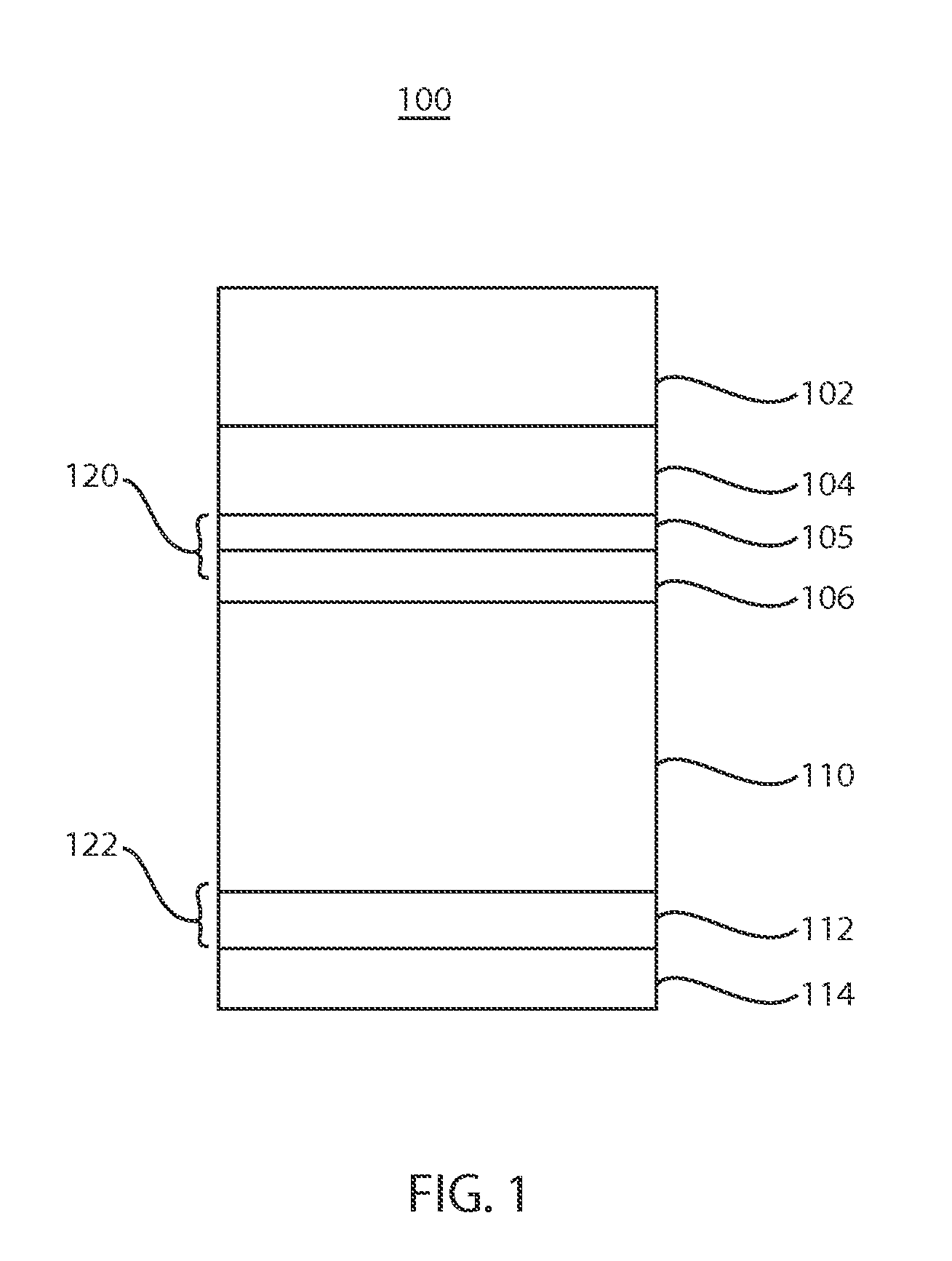

Embodiments of the present invention generally relate to methods for forming a SiGe layer. In one embodiment, a seed SiGe layer is first formed using plasma enhanced chemical vapor deposition (PECVD), and a bulk SiGe layer is formed directly on the PECVD seed layer also using PECVD. The processing temperature for both seed and bulk SiGe layers is less than 450 degrees Celsius.

Owner:APPLIED MATERIALS INC

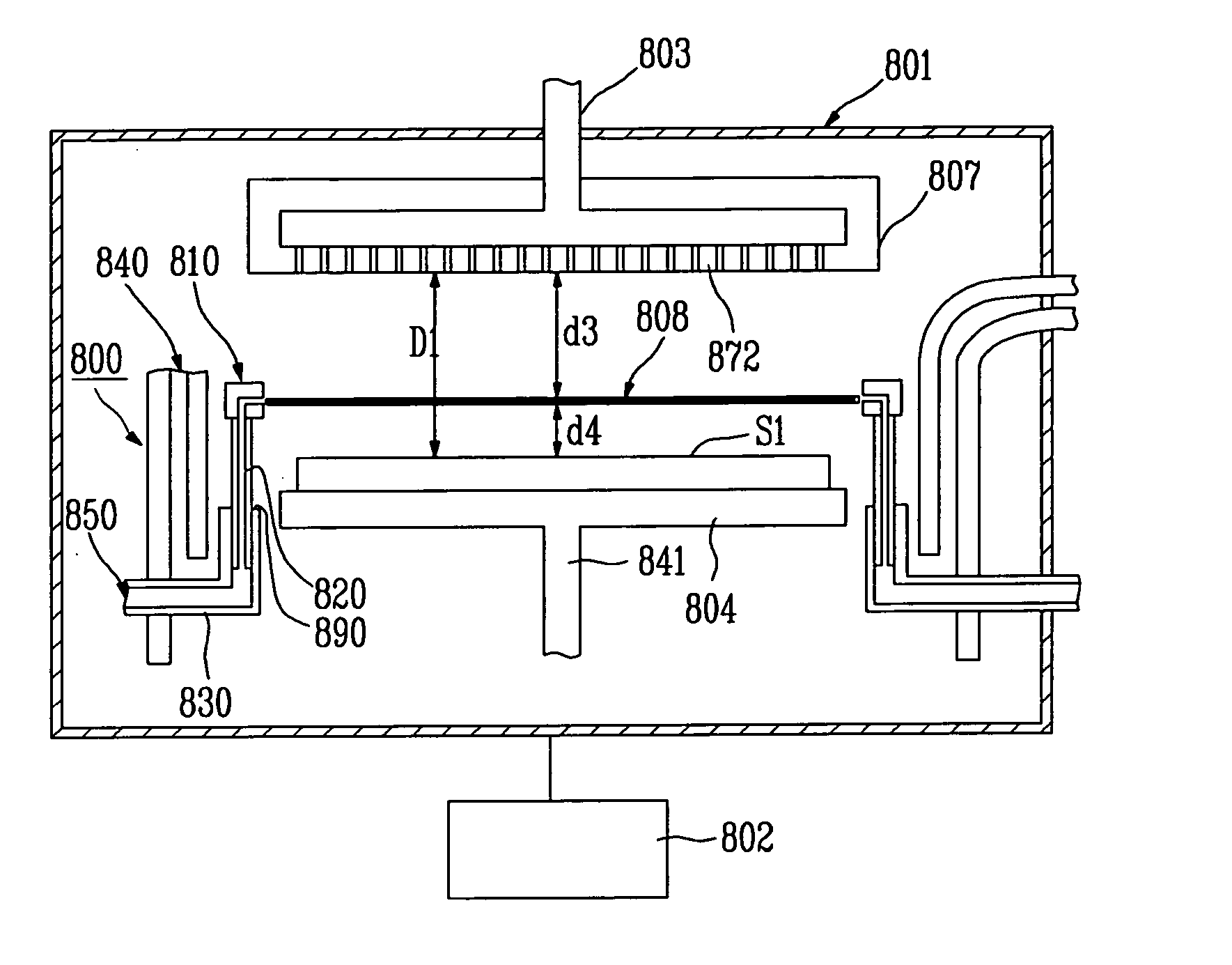

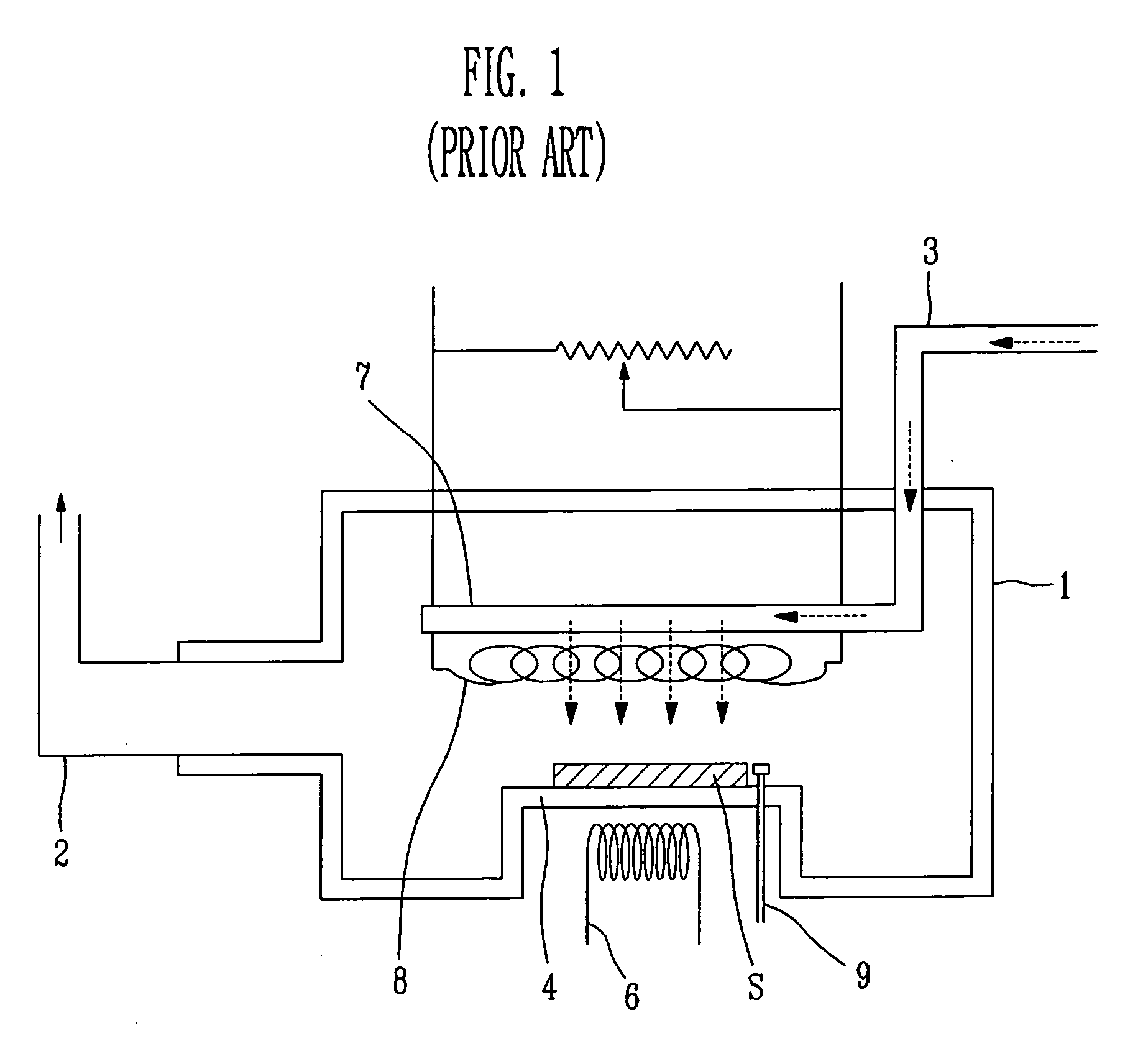

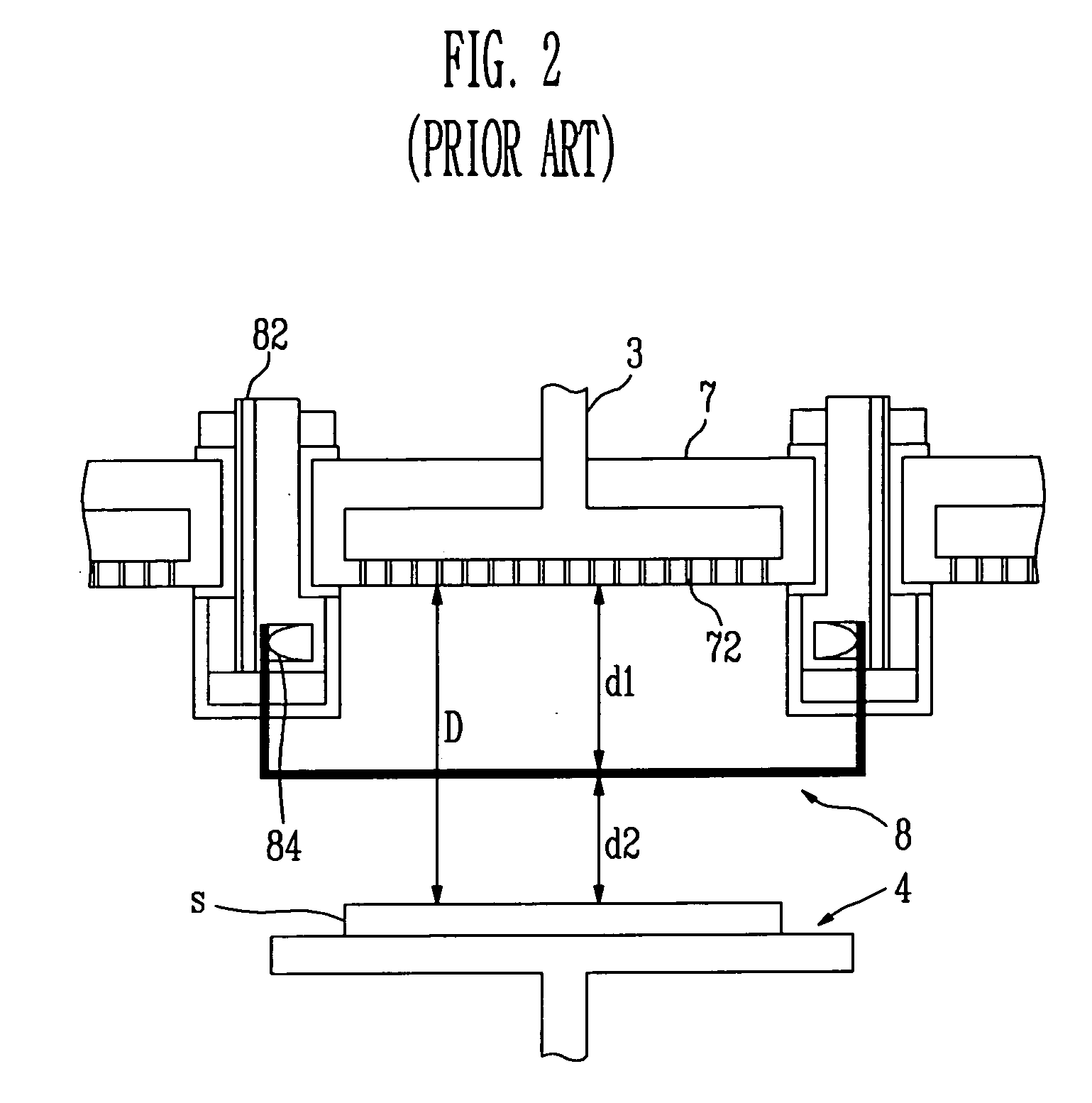

Catalyst enhanced chemical vapor deposition apparatus

InactiveUS20060254514A1Simple structureAvoid formingSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseChemical vapor deposition

A catalyst enhanced chemical vapor deposition (CECVD) apparatus is provided in which the showerhead and catalyst support are separated from each other. The CECVD apparatus has excellent spacing between the showerhead, catalyst wire and substrate and can be purged to prevent contaminants from forming on parts functioning at low temperatures. The CECVD apparatus comprises a reaction chamber, a showerhead for introducing reaction gas into the reaction chamber, a catalyst wire for decomposing the reaction gas, a catalyst support for supporting the catalyst wire, a substrate on which the decomposed gas is deposited, and a substrate support for supporting the substrate.

Owner:SAMSUNG DISPLAY CO LTD

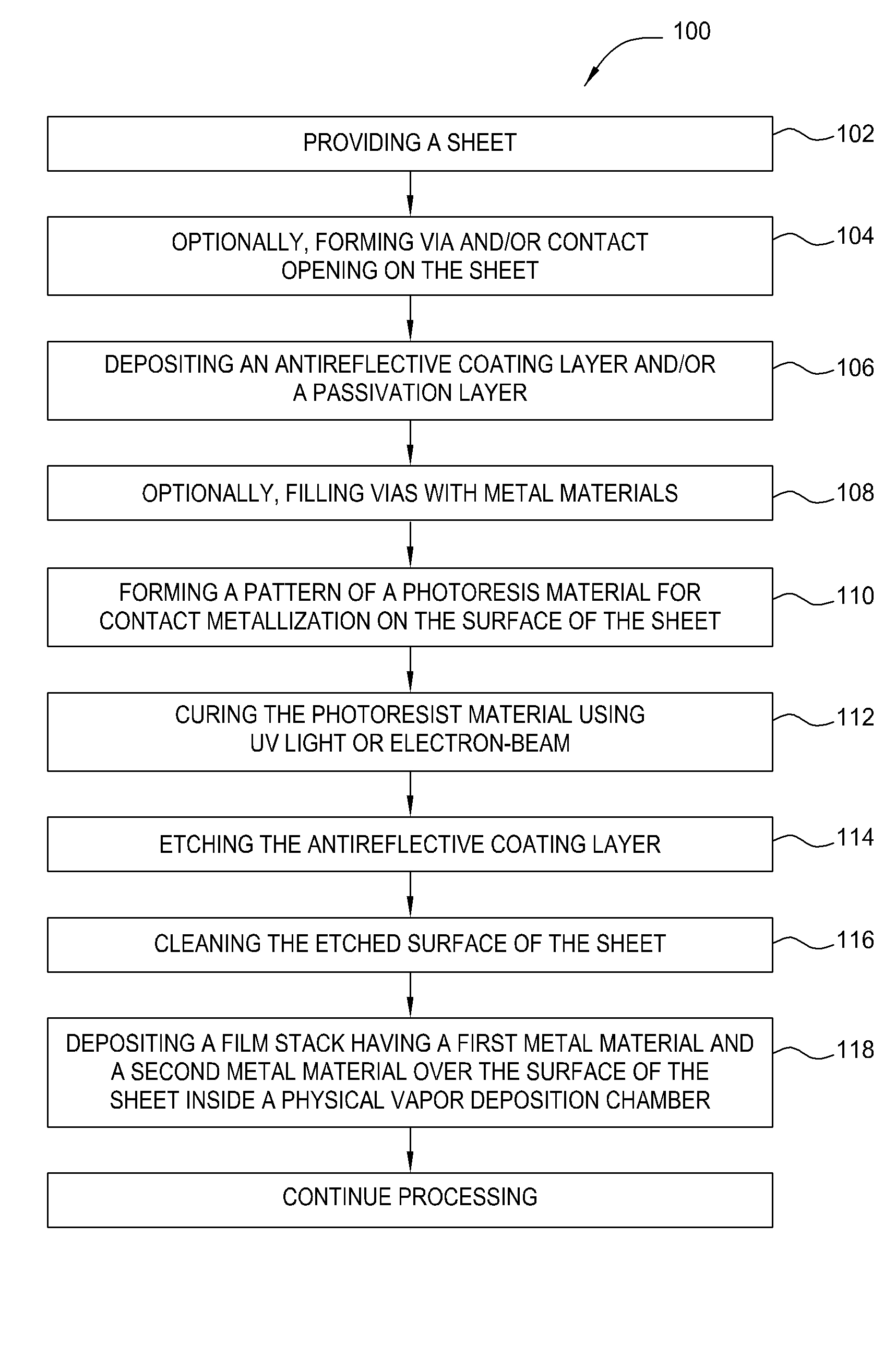

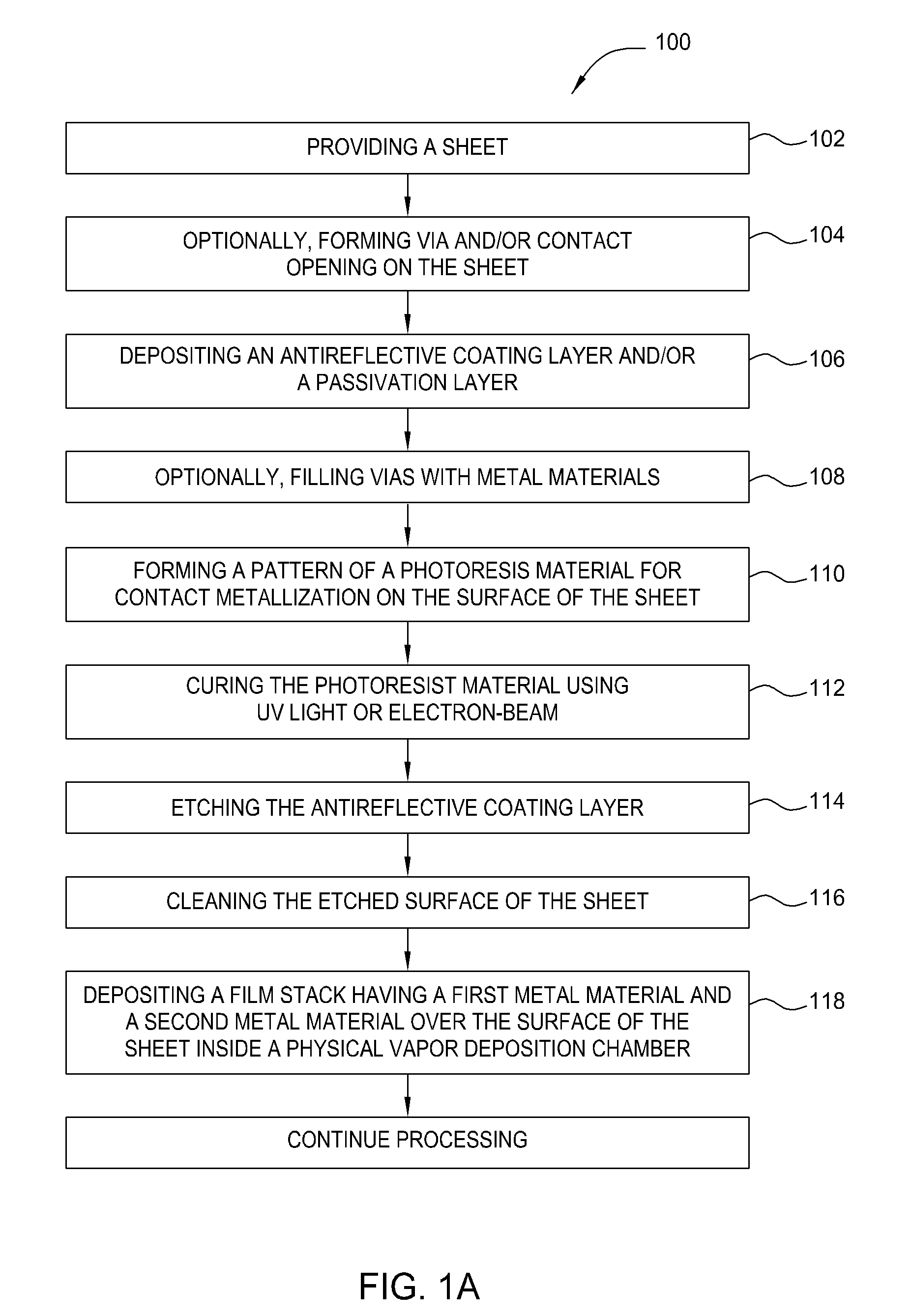

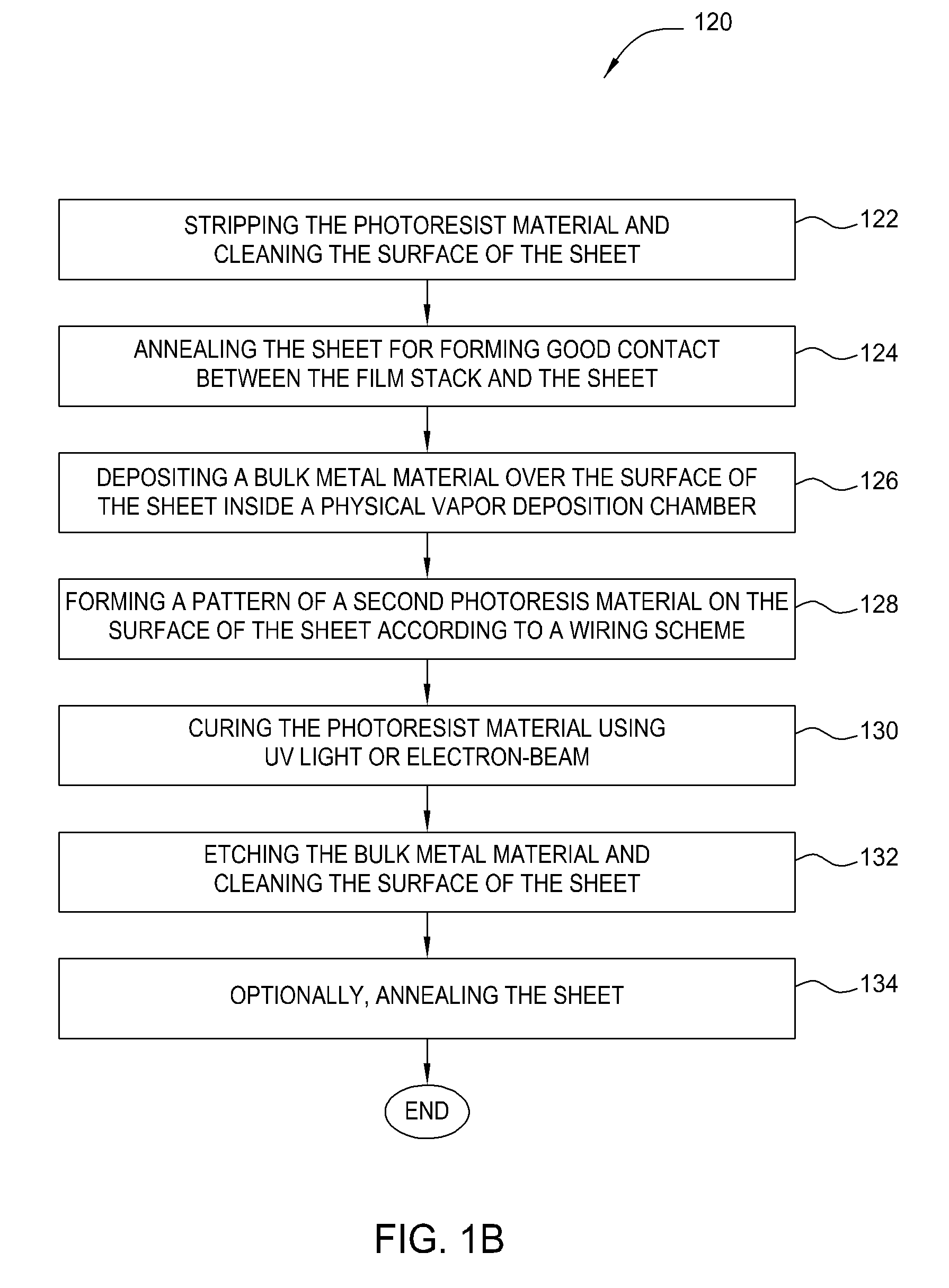

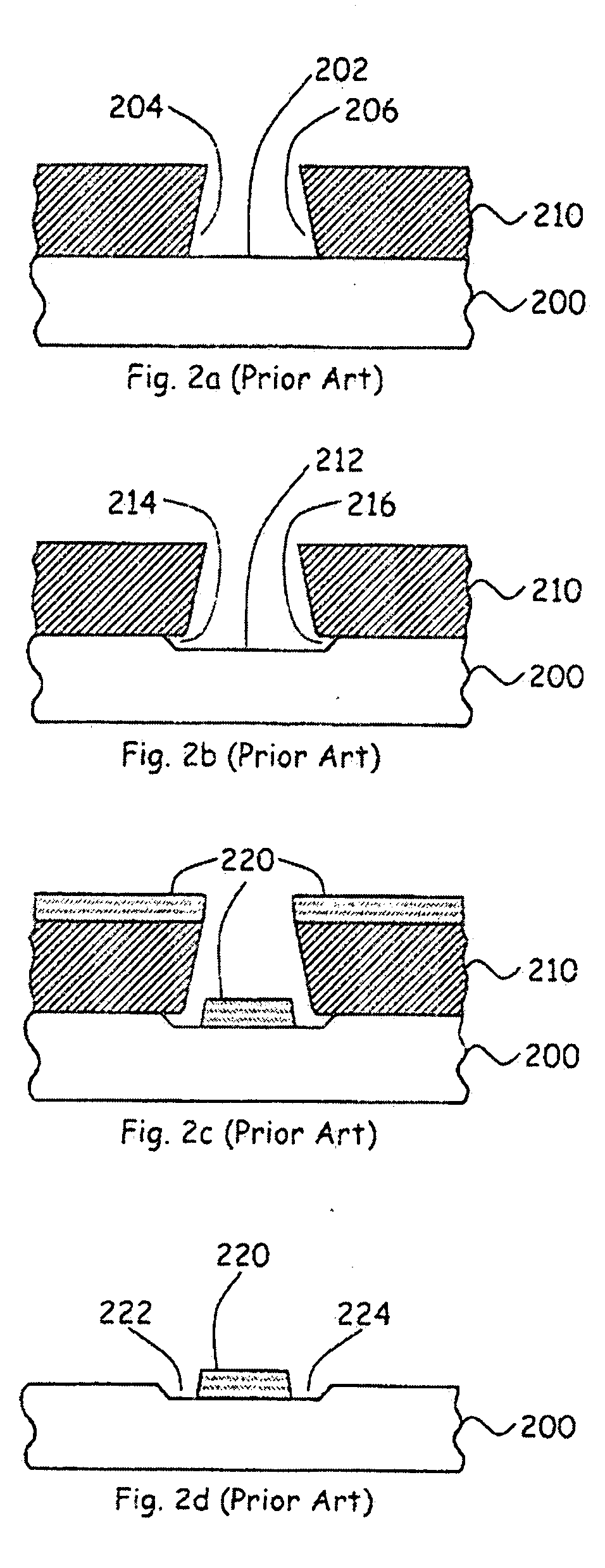

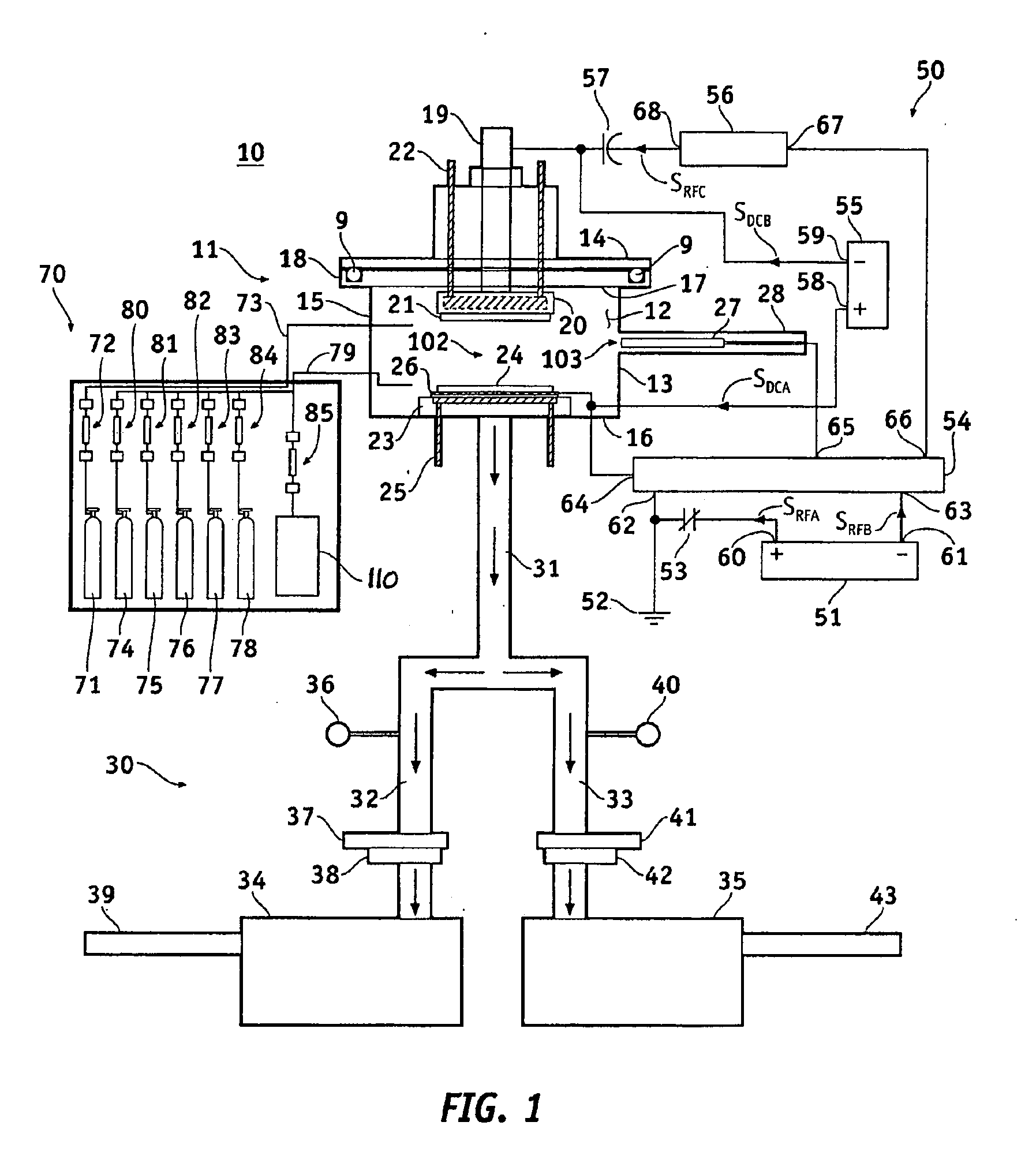

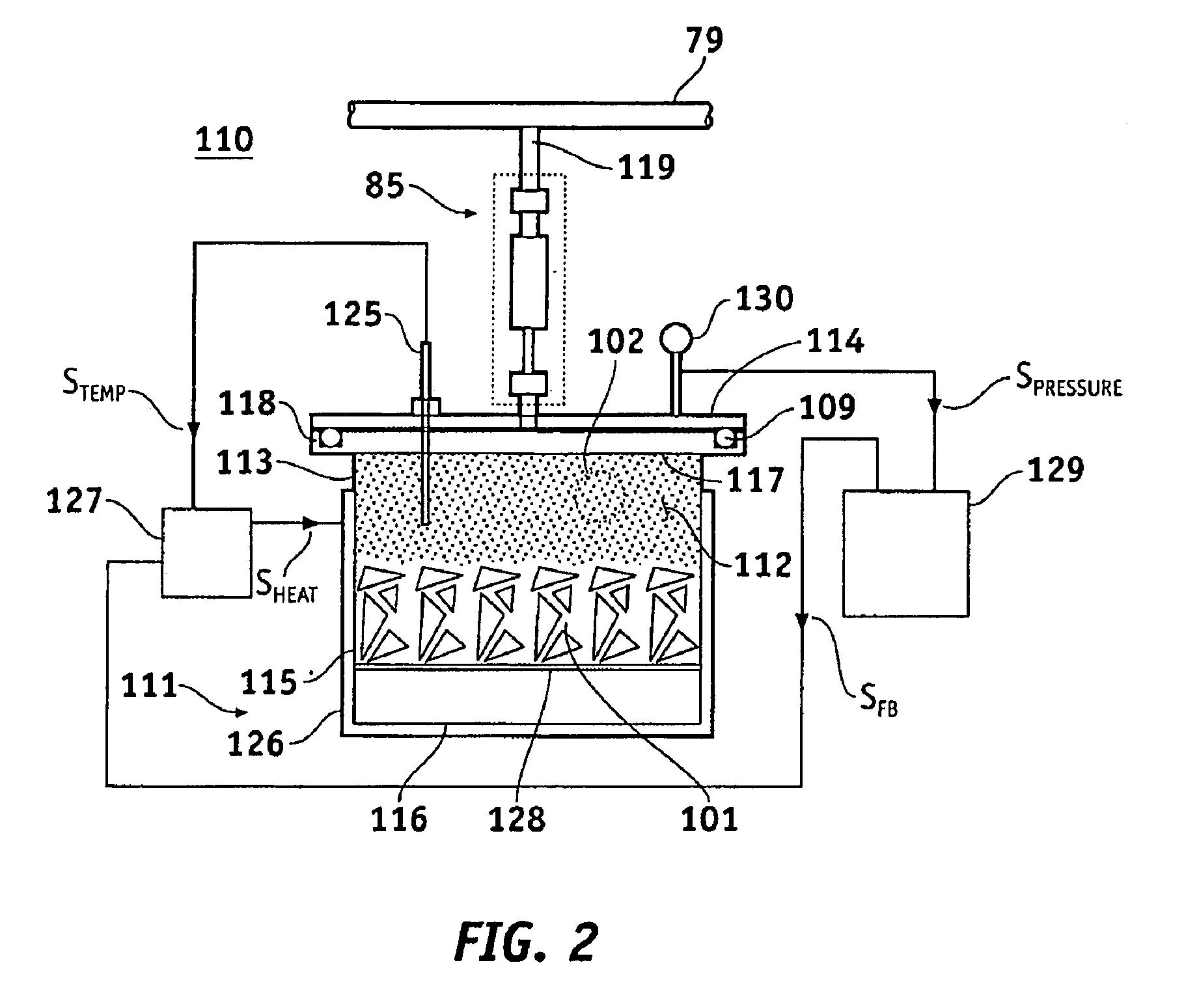

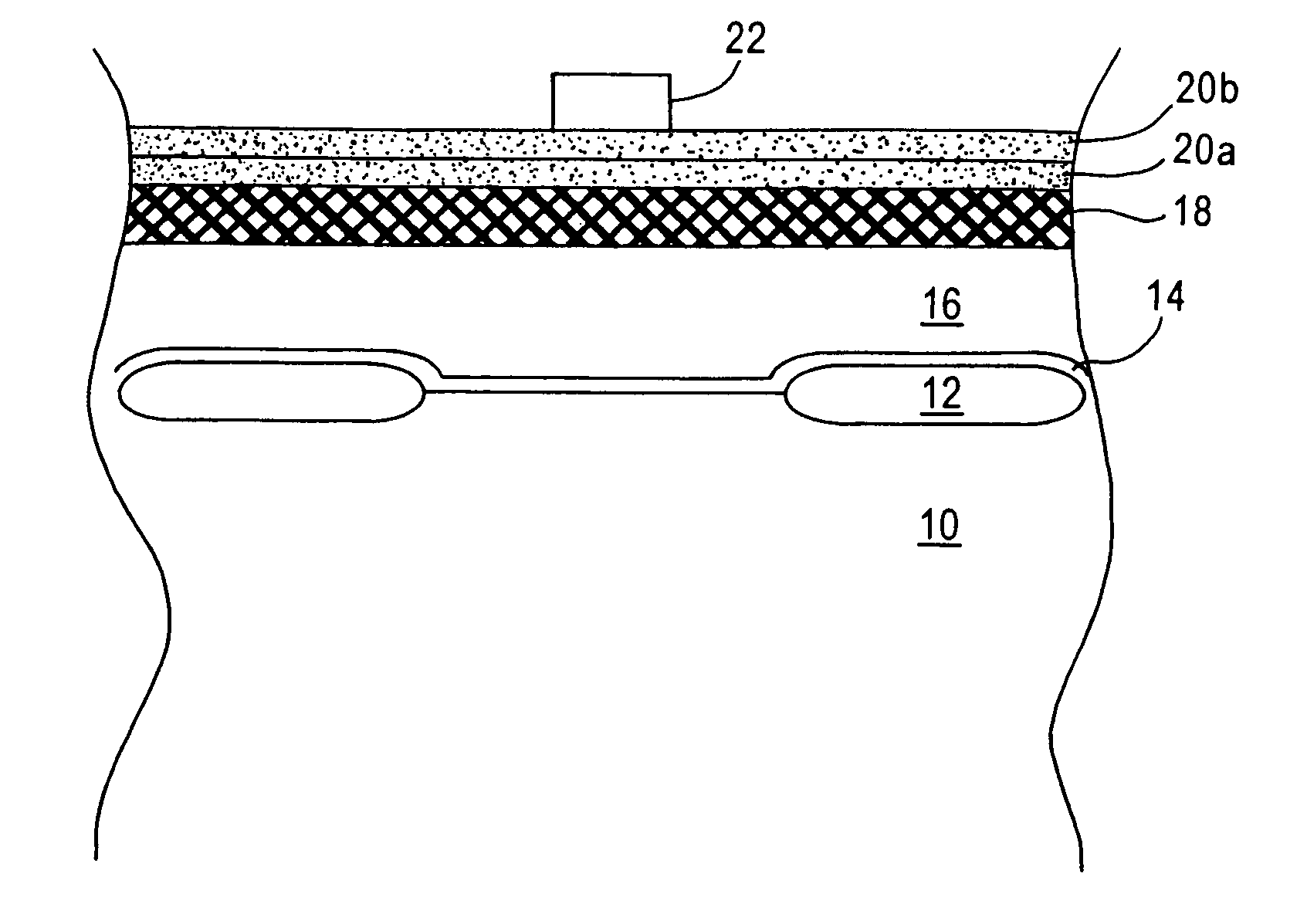

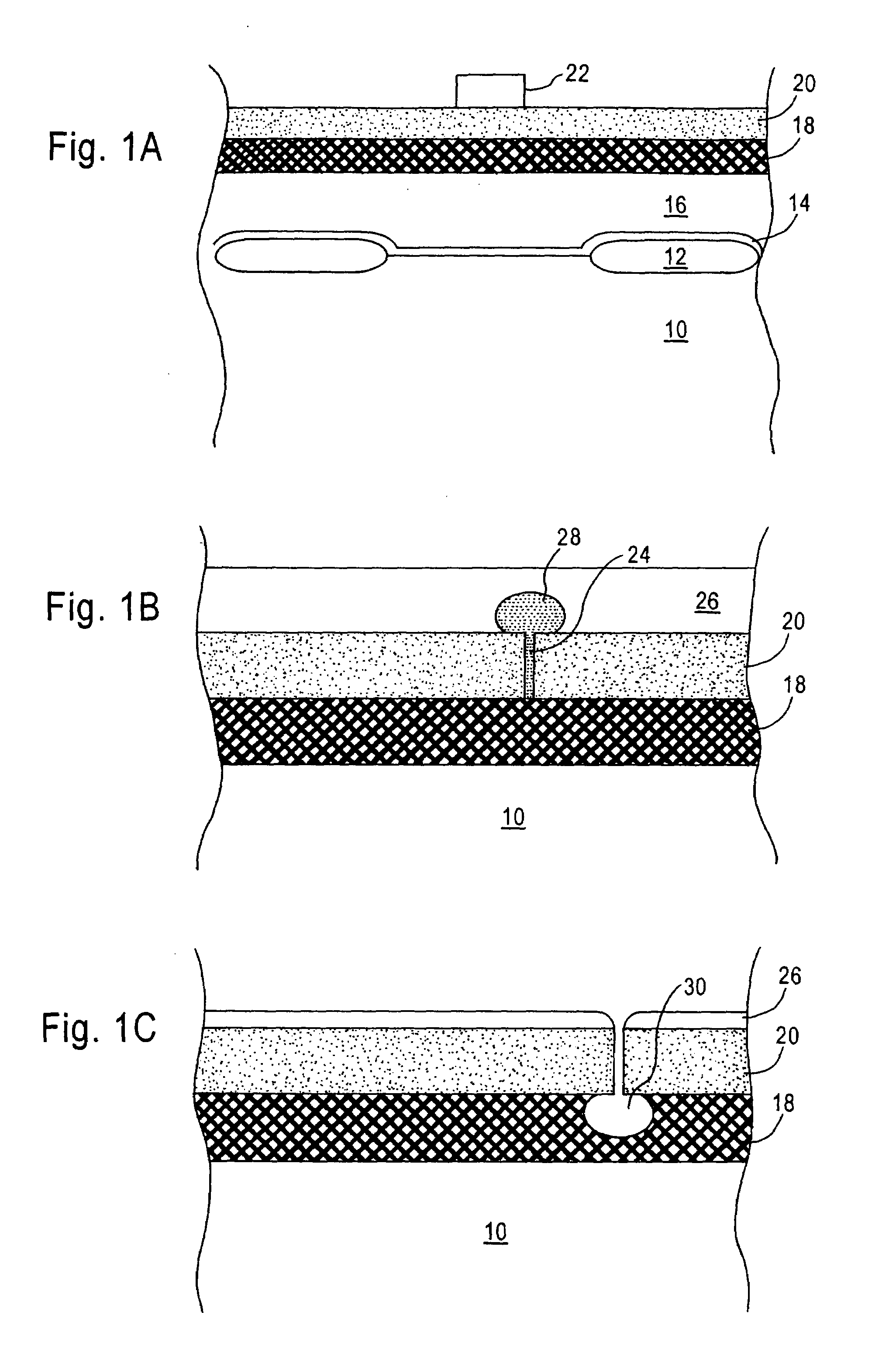

Photovoltaic contact and wiring formation

InactiveUS20070148336A1Reduce contact resistanceEnhanced vapor depositionVacuum evaporation coatingSputtering coatingEtchingGas phase

A method and apparatus for fabricating a solar cell and forming metal contact is disclosed. Solar cell contact and wiring is formed by depositing a thin film stack of a first metal material and a second metal material as an initiation layer or seed layer for depositing a bulk metal layer in conjunction with additional sheet processing, photolithography, etching, cleaning, and annealing processes. In one embodiment, the thin film stack for forming metal silicide with reduced contact resistance over the sheet is deposited by sputtering or physical vapor deposition. In another embodiment, the bulk metal layer for forming metal lines and wiring is deposited by sputtering or physical vapor deposition. In an alternative embodiment, electroplating or electroless deposition is used to deposit the bulk metal layer.

Owner:APPLIED MATERIALS INC

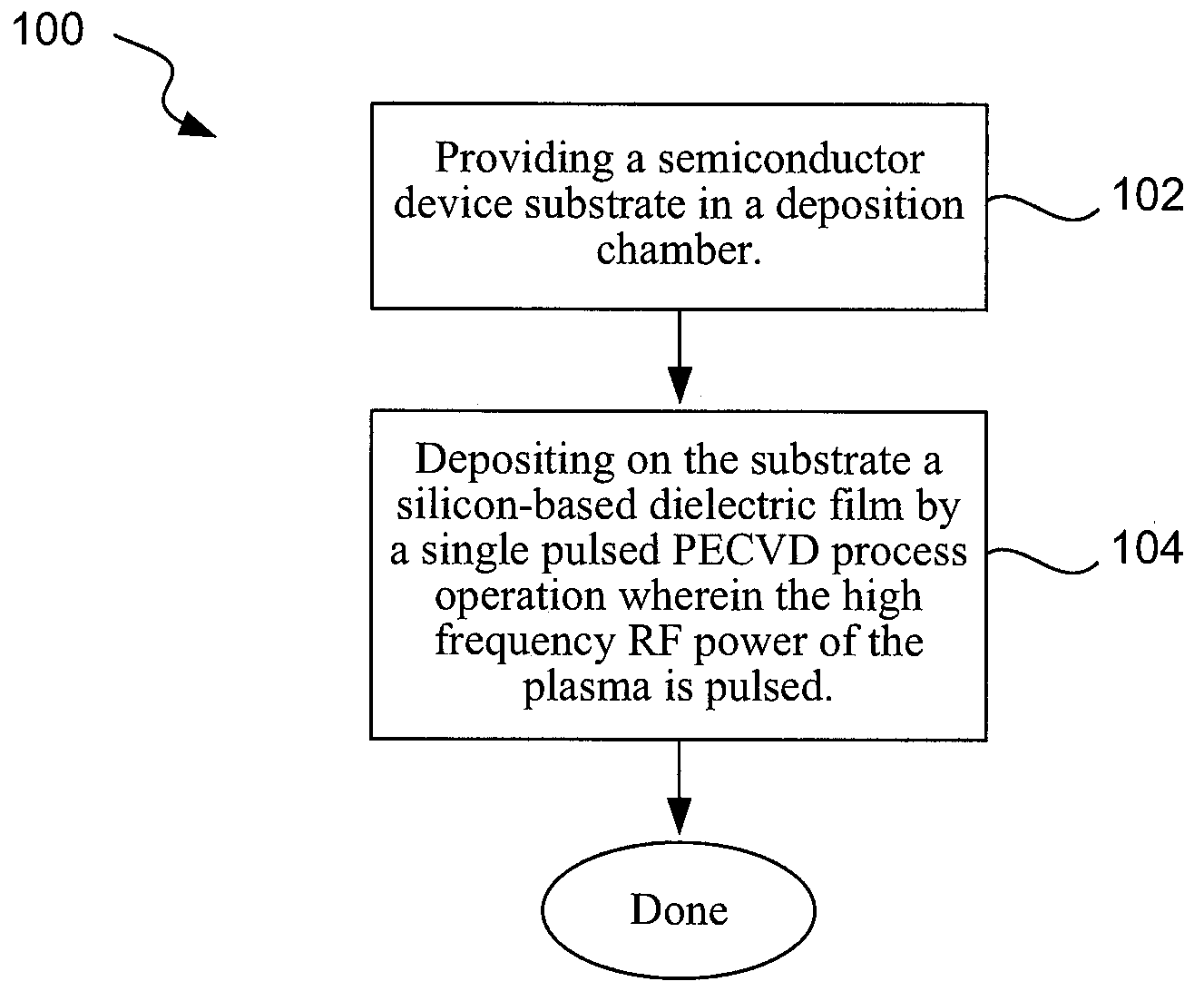

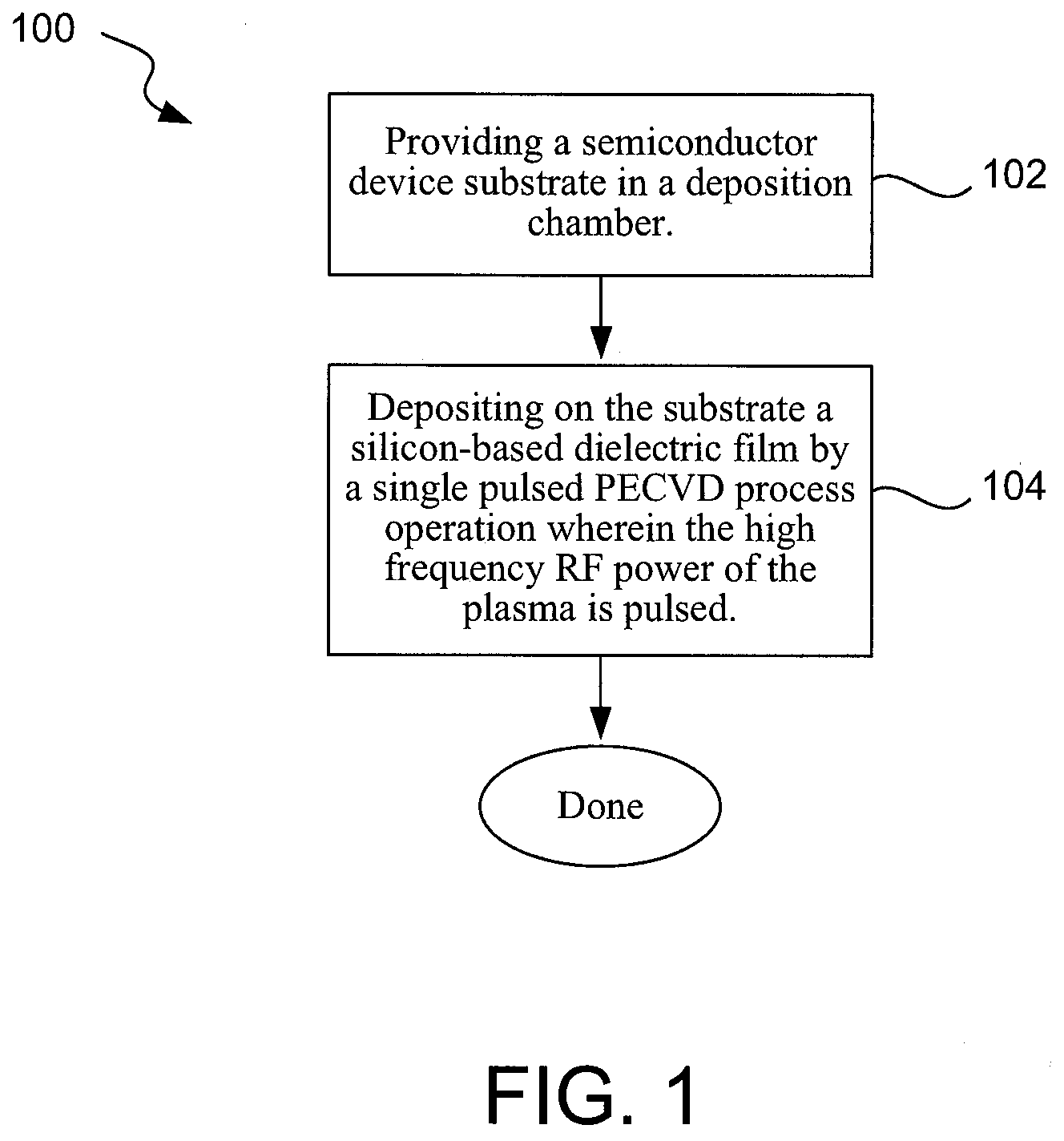

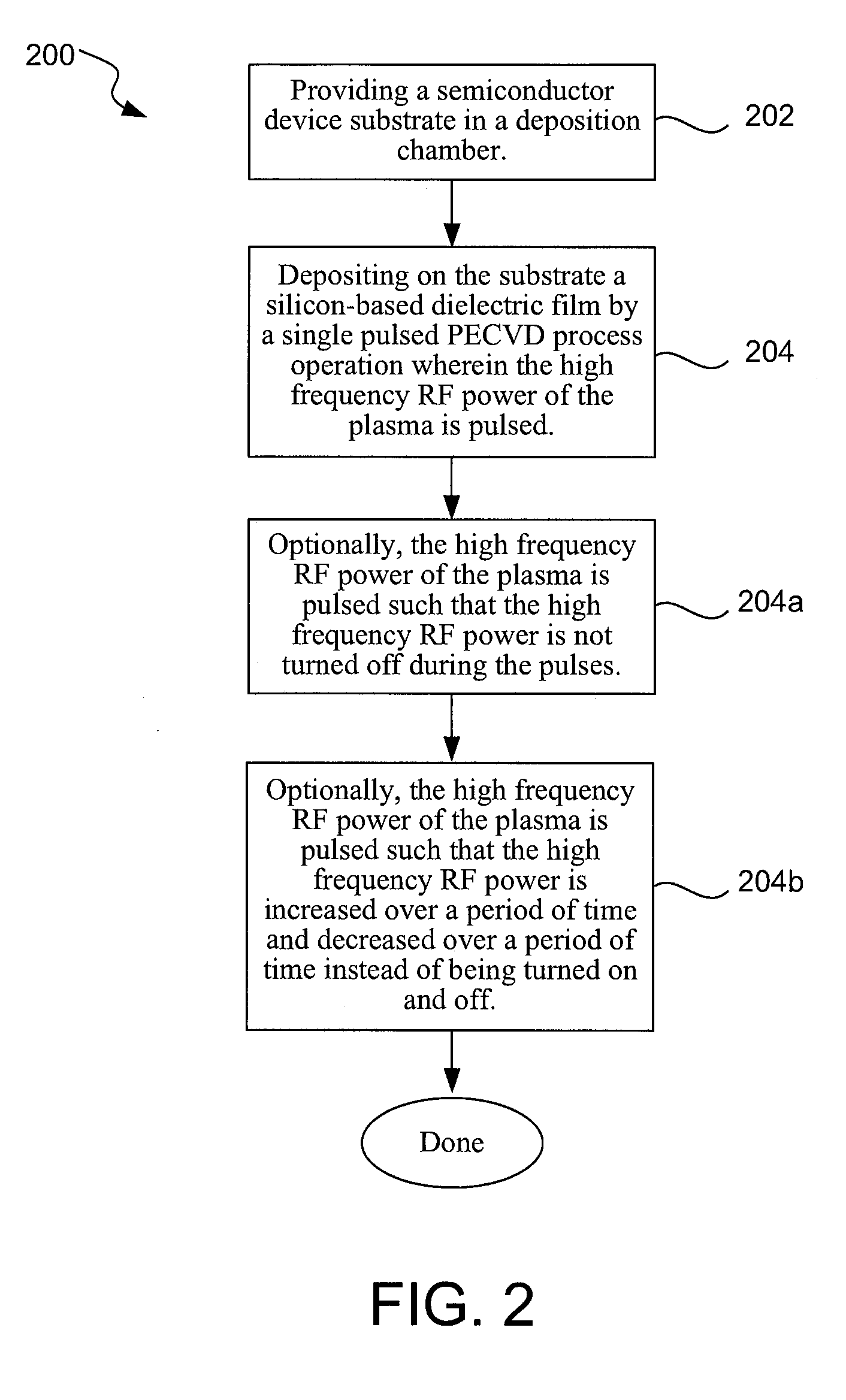

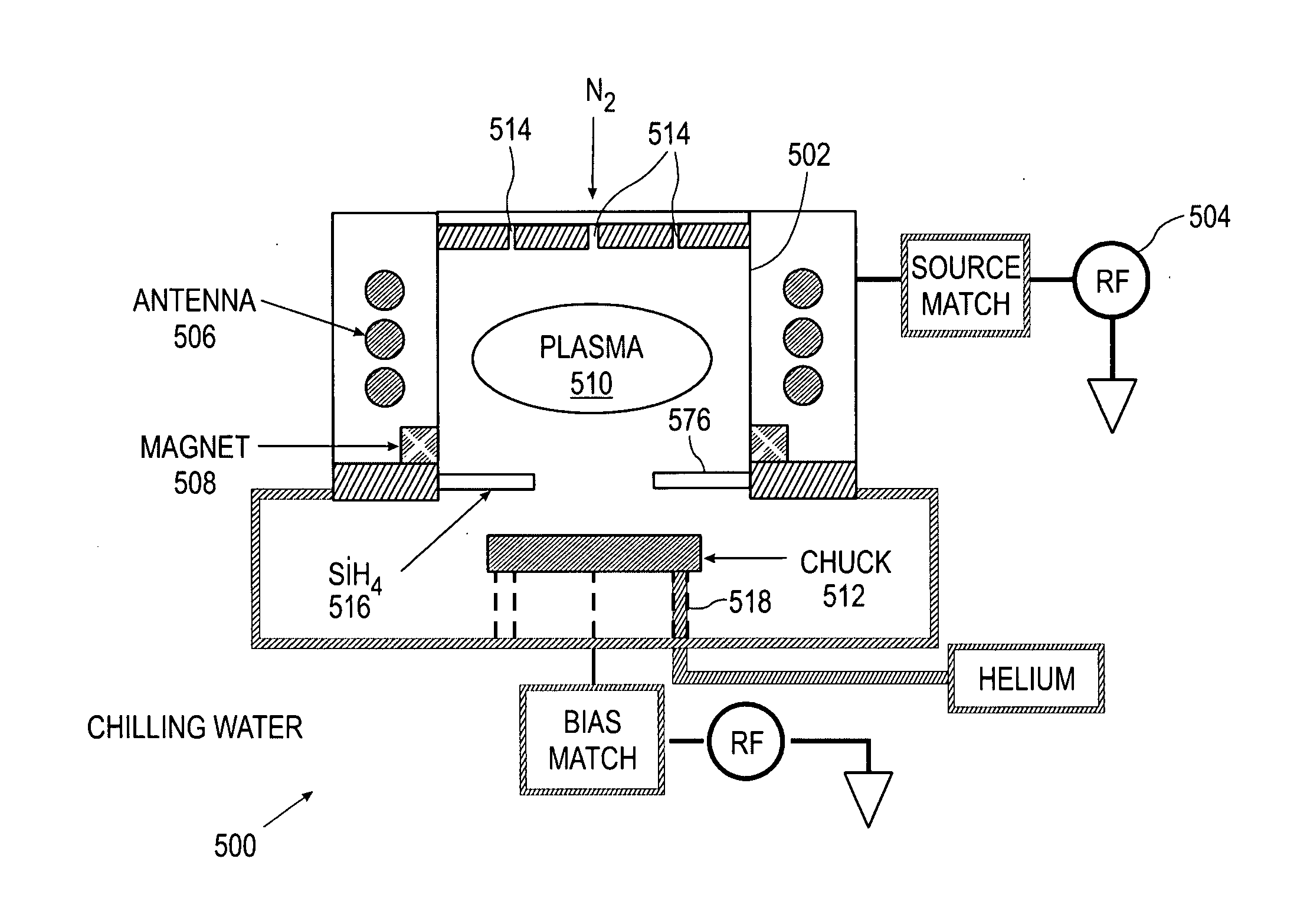

Method for improving process control and film conformality of pecvd film

ActiveUS20100099271A1More controllable depositionEnhanced vapor depositionLiquid surface applicatorsSemiconductor/solid-state device manufacturingDielectricEngineering

A method for forming a silicon-based dielectric film on a substrate with a single deposition process operation using pulsed plasma enhanced chemical vapor deposition (PECVD) wherein the high frequency radio frequency power of the plasma is pulsed, allows enhanced control, efficiency and product quality of the PECVD process. Pulsing the high frequency RF power of the plasma reduces the deposited film thickness per unit time the high frequency RF power of the plasma is on. This yields silicon-based dielectric films that are both thin and conformal.

Owner:NOVELLUS SYSTEMS

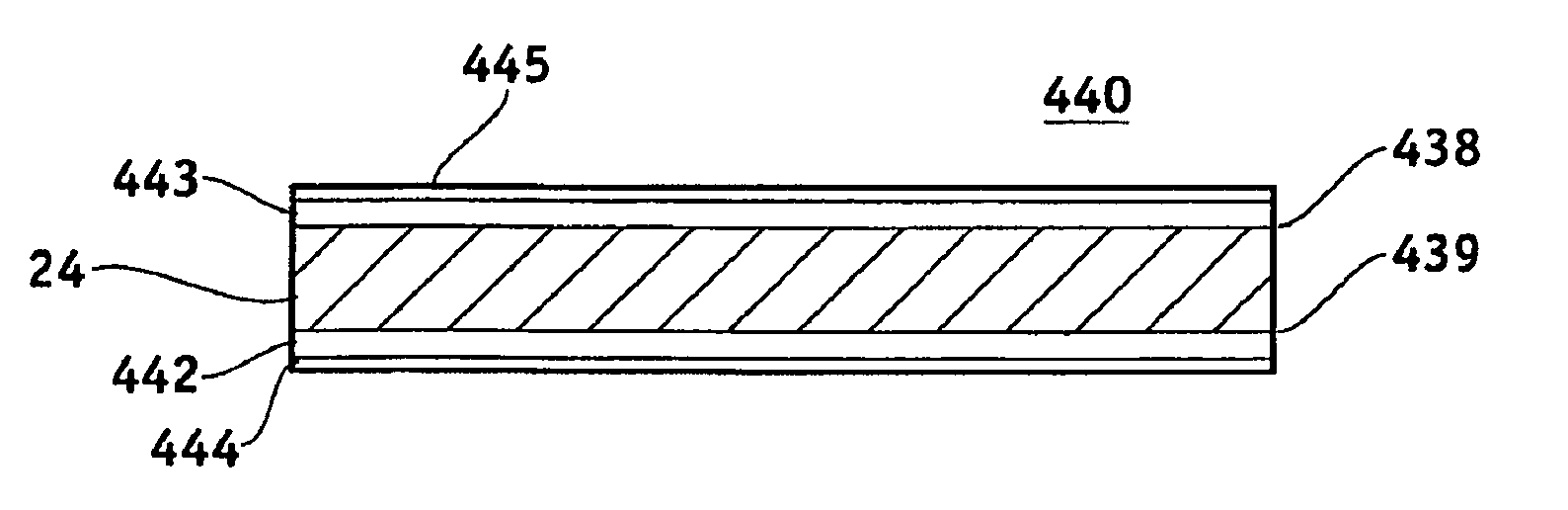

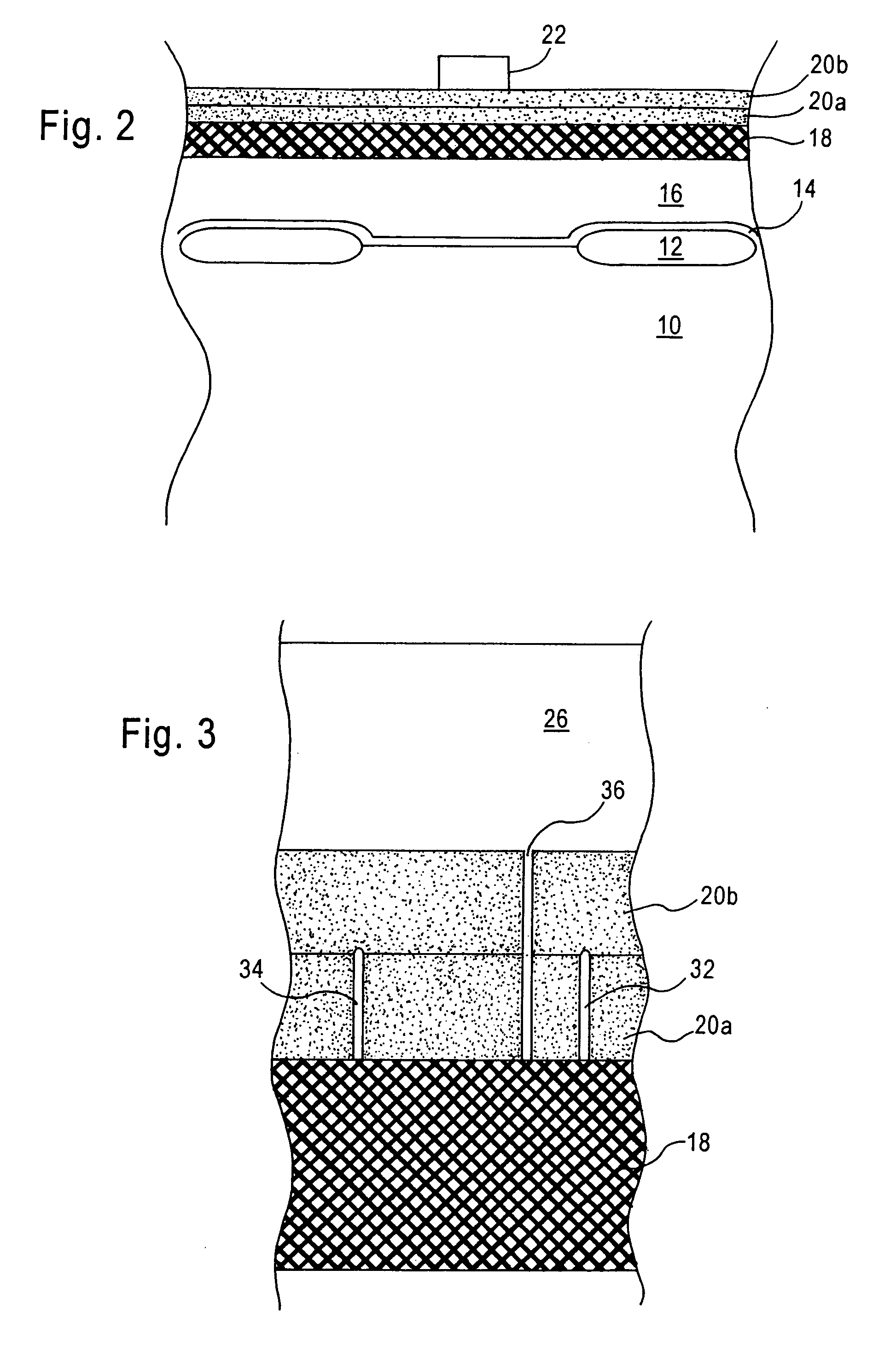

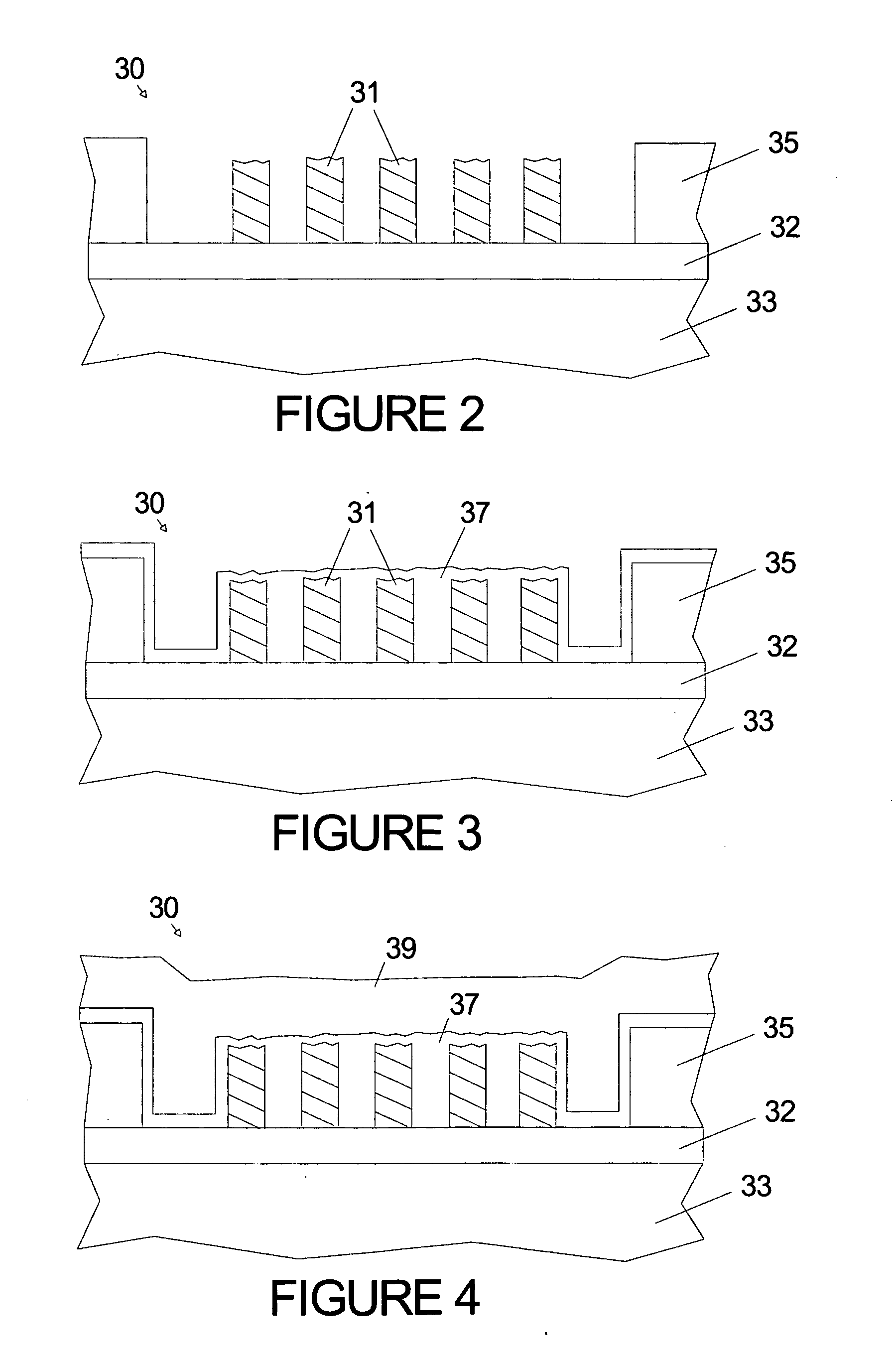

MEMS fabrication on a laminated substrate

ActiveUS20050062653A1Increasing energy of plasmaEnhanced vapor depositionSimultaneous aerial operationsAntenna supports/mountingsLow temperature depositionEngineering

Systems and methods are provided that facilitate the formation of micro-mechanical structures and related systems on a laminated substrate. More particularly, a micro-mechanical device and a three-dimensional multiple frequency antenna are provided for in which the micro-mechanical device and antenna, as well as additional components, can be fabricated together concurrently on the same laminated substrate. The fabrication process includes a low temperature deposition process allowing for deposition of an insulator material at a temperature below the maximum operating temperature of the laminated substrate, as well as a planarization process allowing for the molding and planarizing of a polymer layer to be used as a form for a micro-mechanical device.

Owner:RGT UNIV OF CALIFORNIA

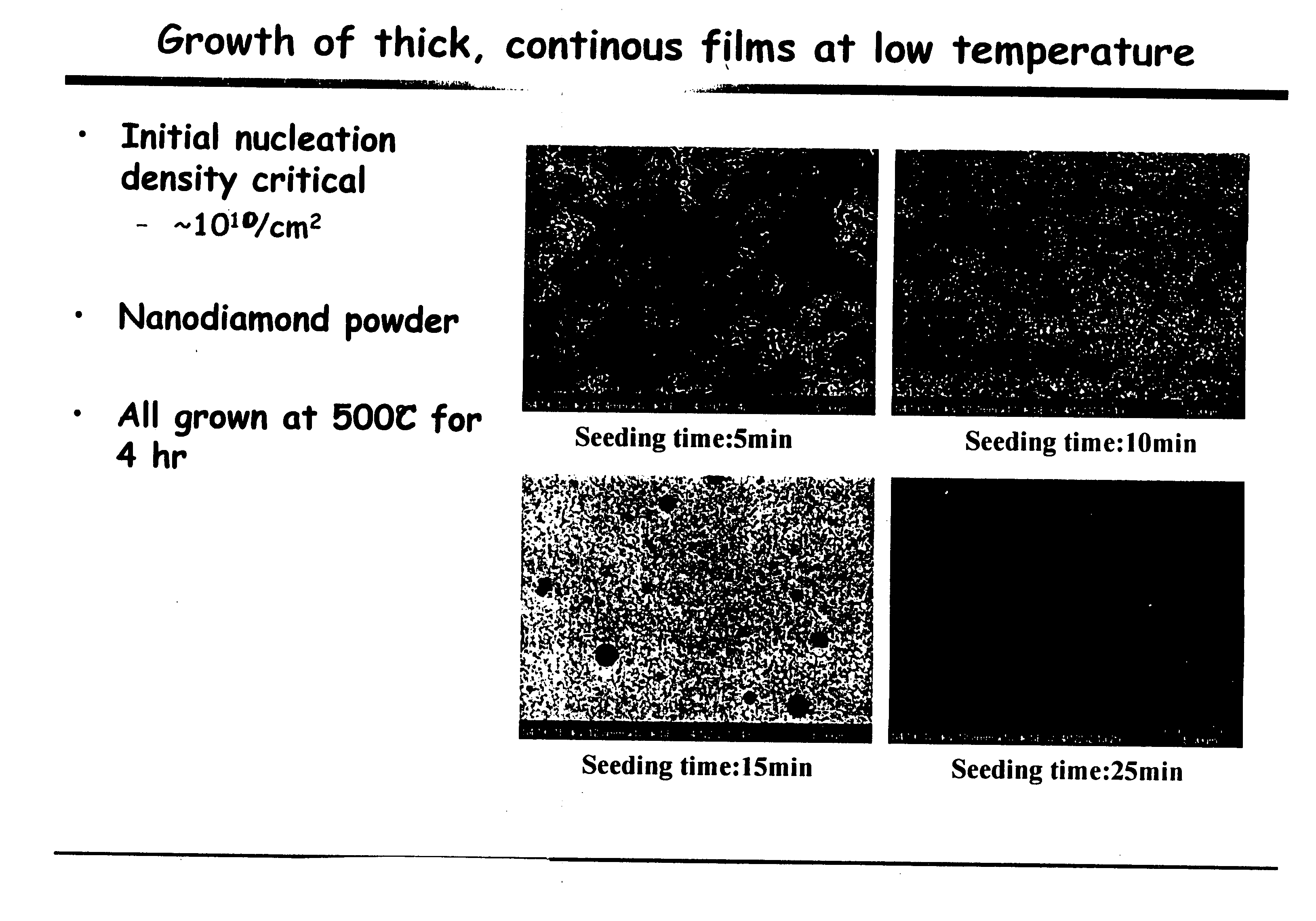

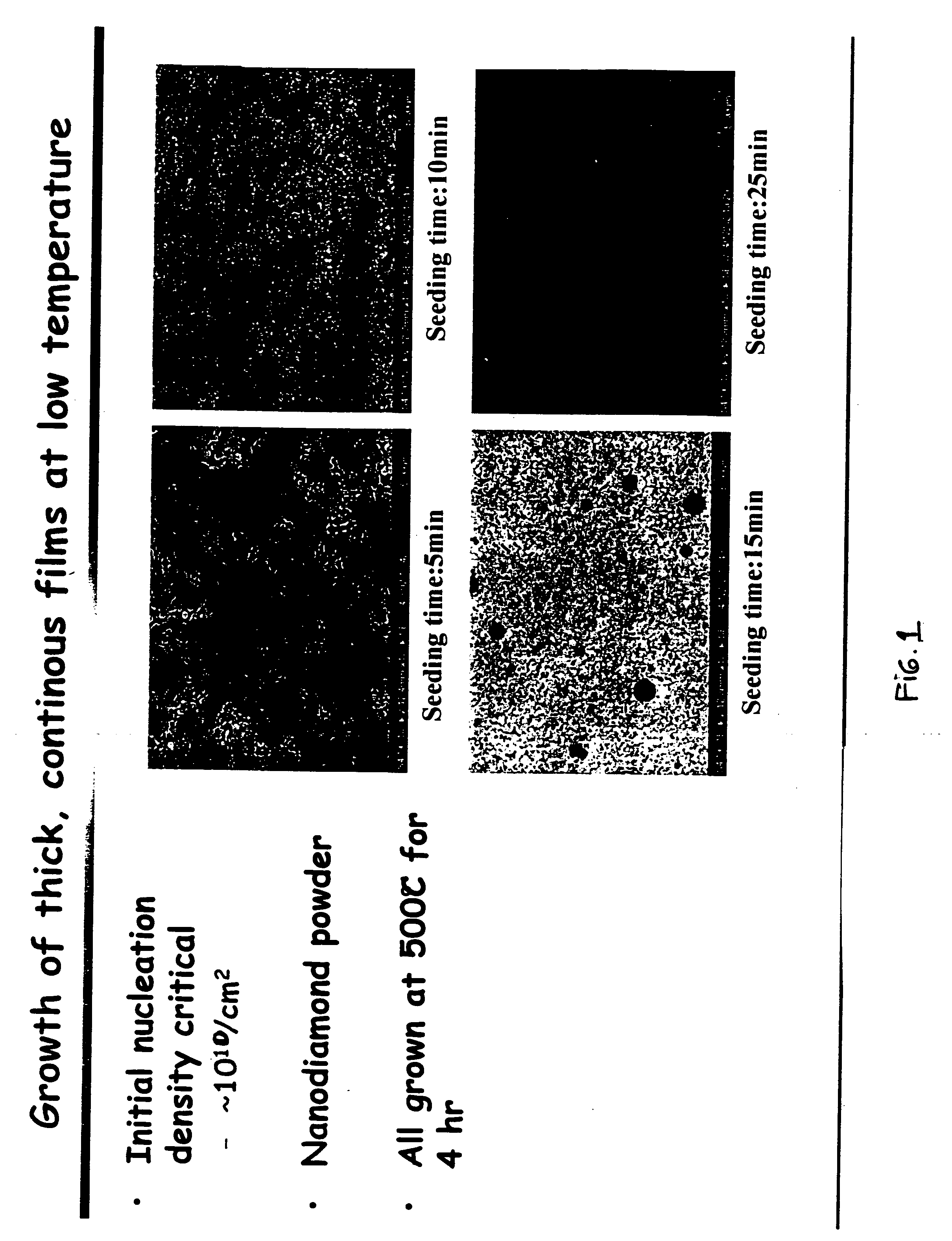

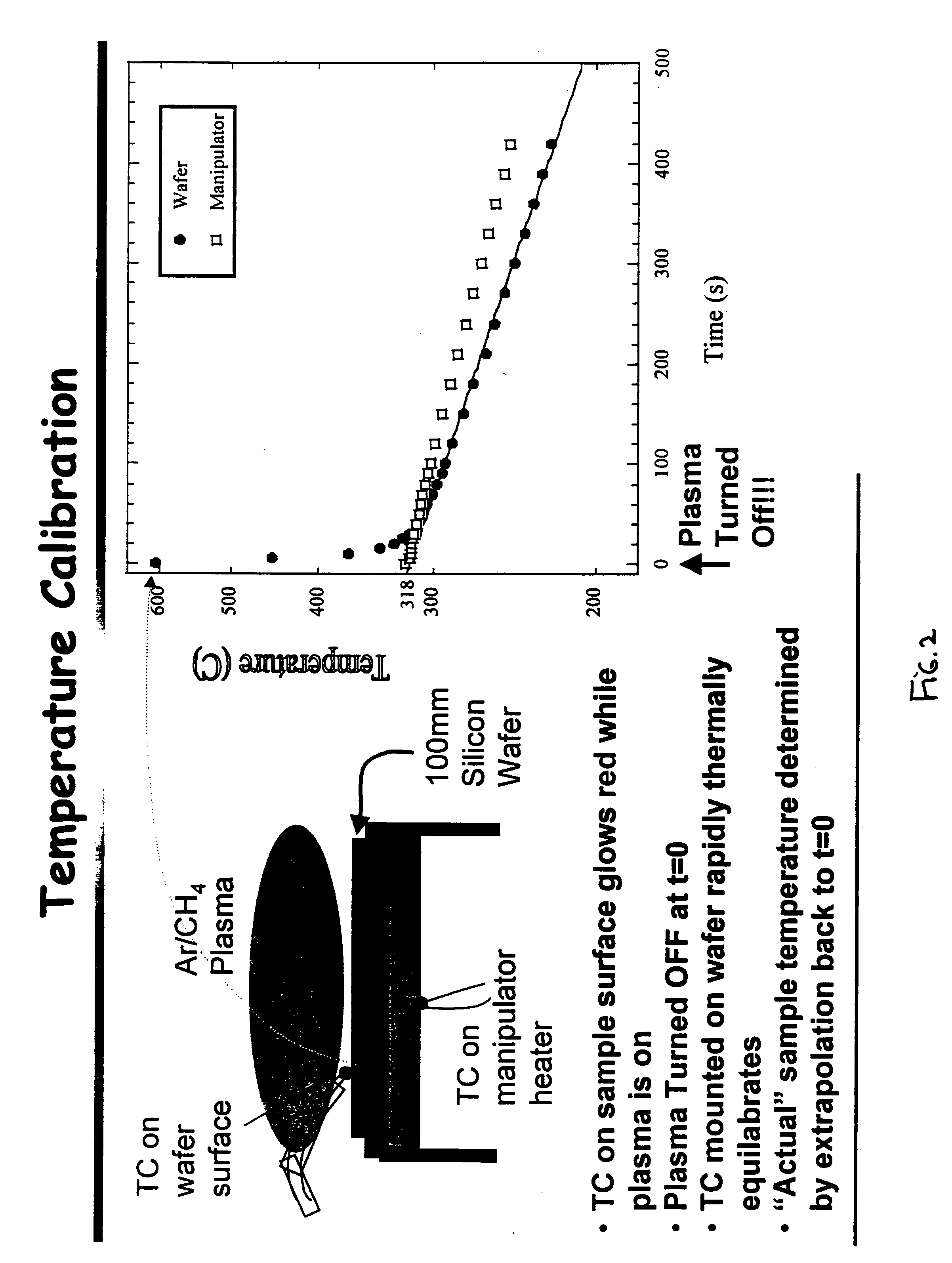

Method to grow pure nanocrystalline diamond films at low temperatures and high deposition rates

ActiveUS20050031785A1Increase deposition rateEnhanced vapor depositionLayered productsSemiconductor/solid-state device manufacturingMetallurgyVolumetric Mass Density

A method of depositing nanocrystalline diamond film on a substrate at a rate of not less than about 0.2 microns / hour at a substrate temperature less than about 500° C. The method includes seeding the substrate surface with nanocrystalline diamond powder to an areal density of not less than about 1010sites / cm2, and contacting the seeded substrate surface with a gas of about 99% by volume of an inert gas other than helium and about 1% by volume of methane or hydrogen and one or more of acetylene, fullerene and anthracene in the presence of a microwave induced plasma while maintaining the substrate temperature less than about 500° C. to deposit nanocrystalline diamond on the seeded substrate surface at a rate not less than about 0.2 microns / hour. Coatings of nanocrystalline diamond with average particle diameters of less than about 20 nanometers can be deposited with thermal budgets of 500° C.-4 hours or less onto a variety of substrates such as MEMS devices.

Owner:UCHICAGO ARGONNE LLC

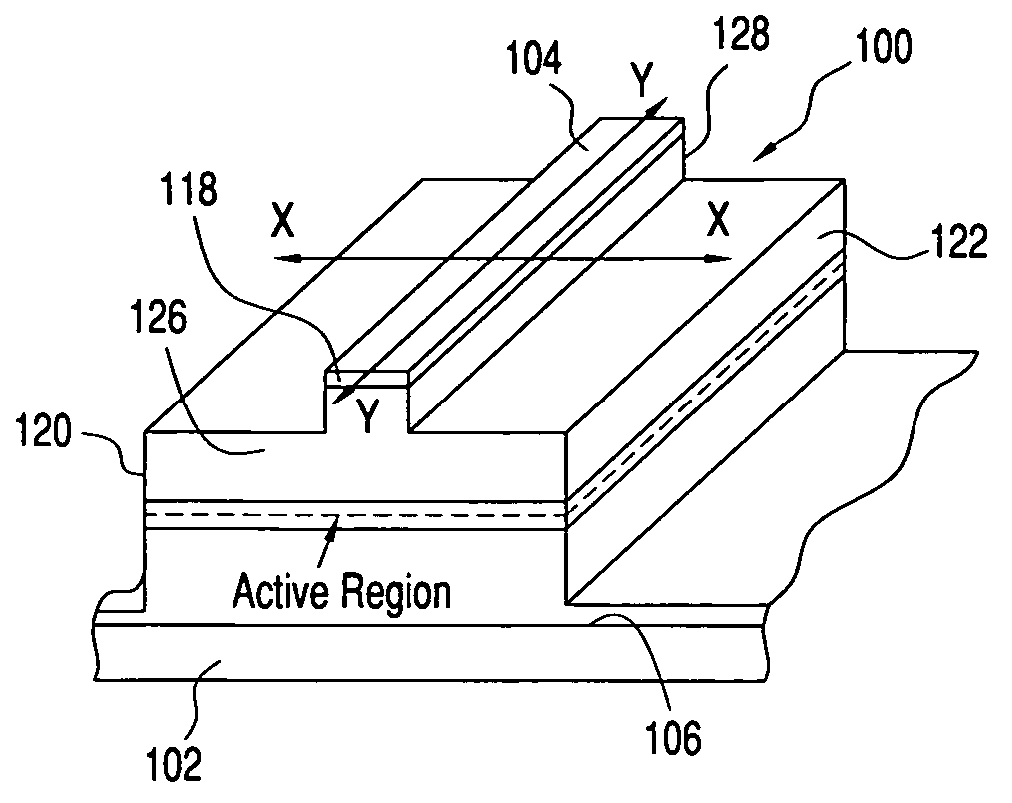

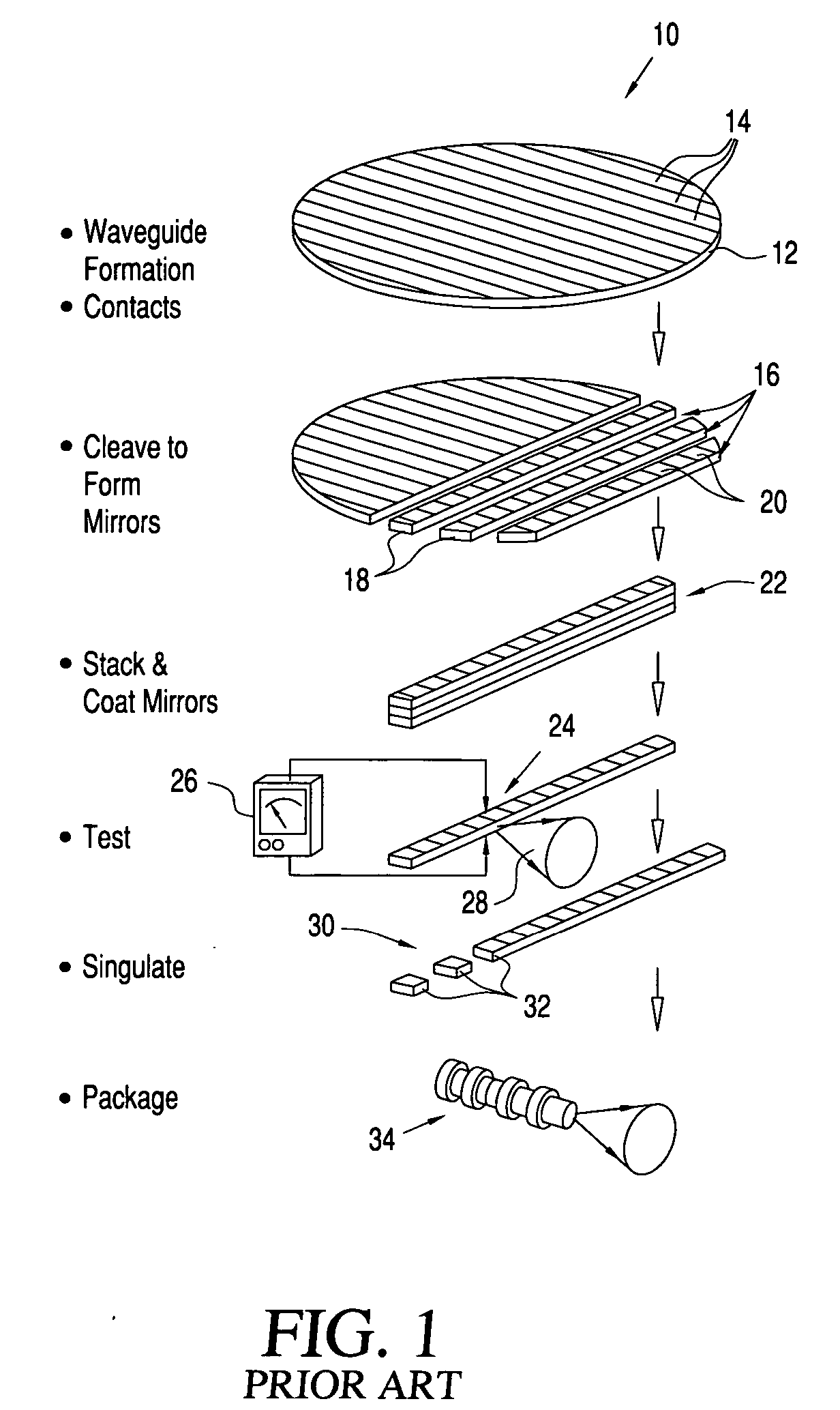

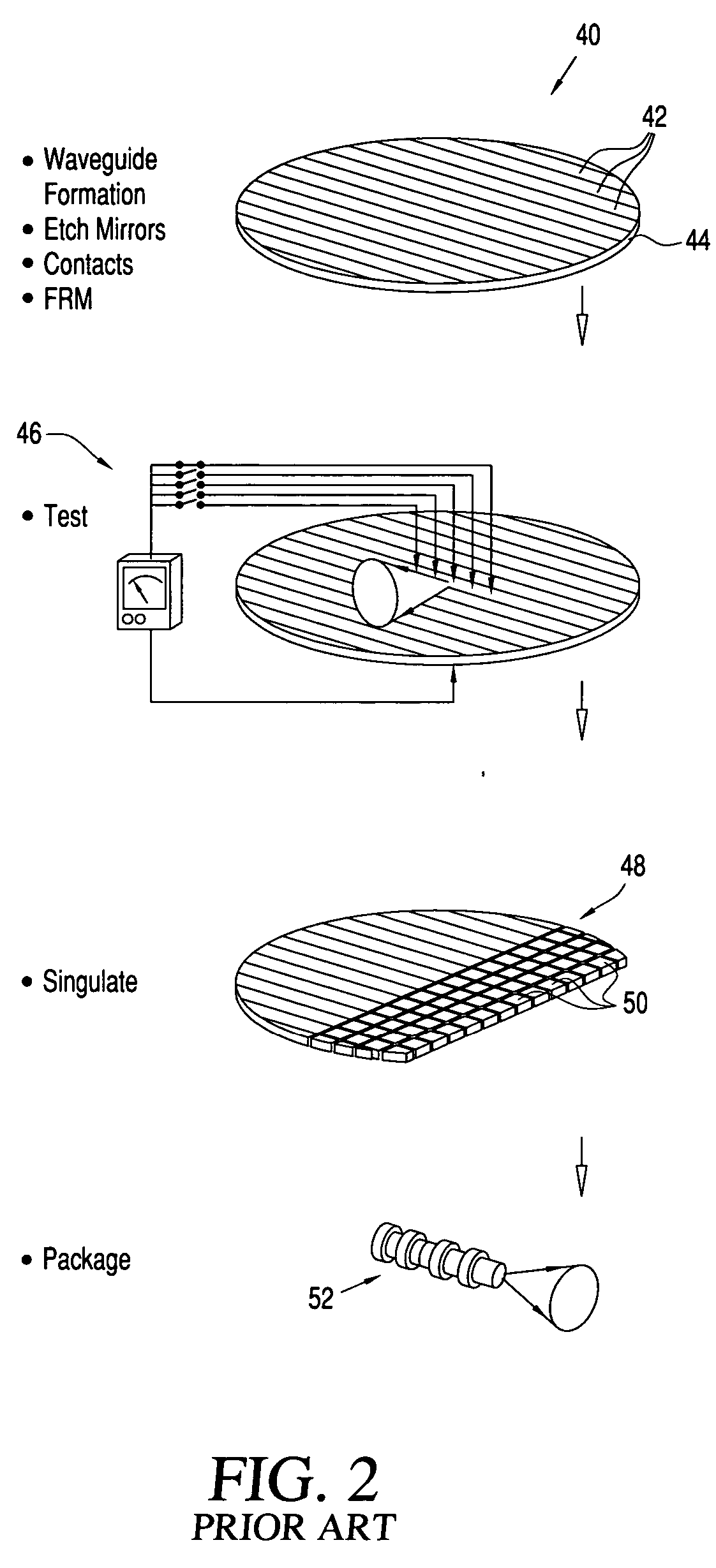

High reliability etched-facet photonic devices

ActiveUS20060187985A1Improve reliabilityGuaranteed uptimeOptical wave guidanceLaser optical resonator constructionPhotonicsFaceting

Semiconductor photonic device surfaces are covered with a dielectric or a metal protective layer. The protective layer covers the entire device, including regions near facets at active regions, to prevent bare or unprotected semiconductor regions, thereby to form a very high reliability etched facet photonic device.

Owner:MACOM TECH SOLUTIONS HLDG INC

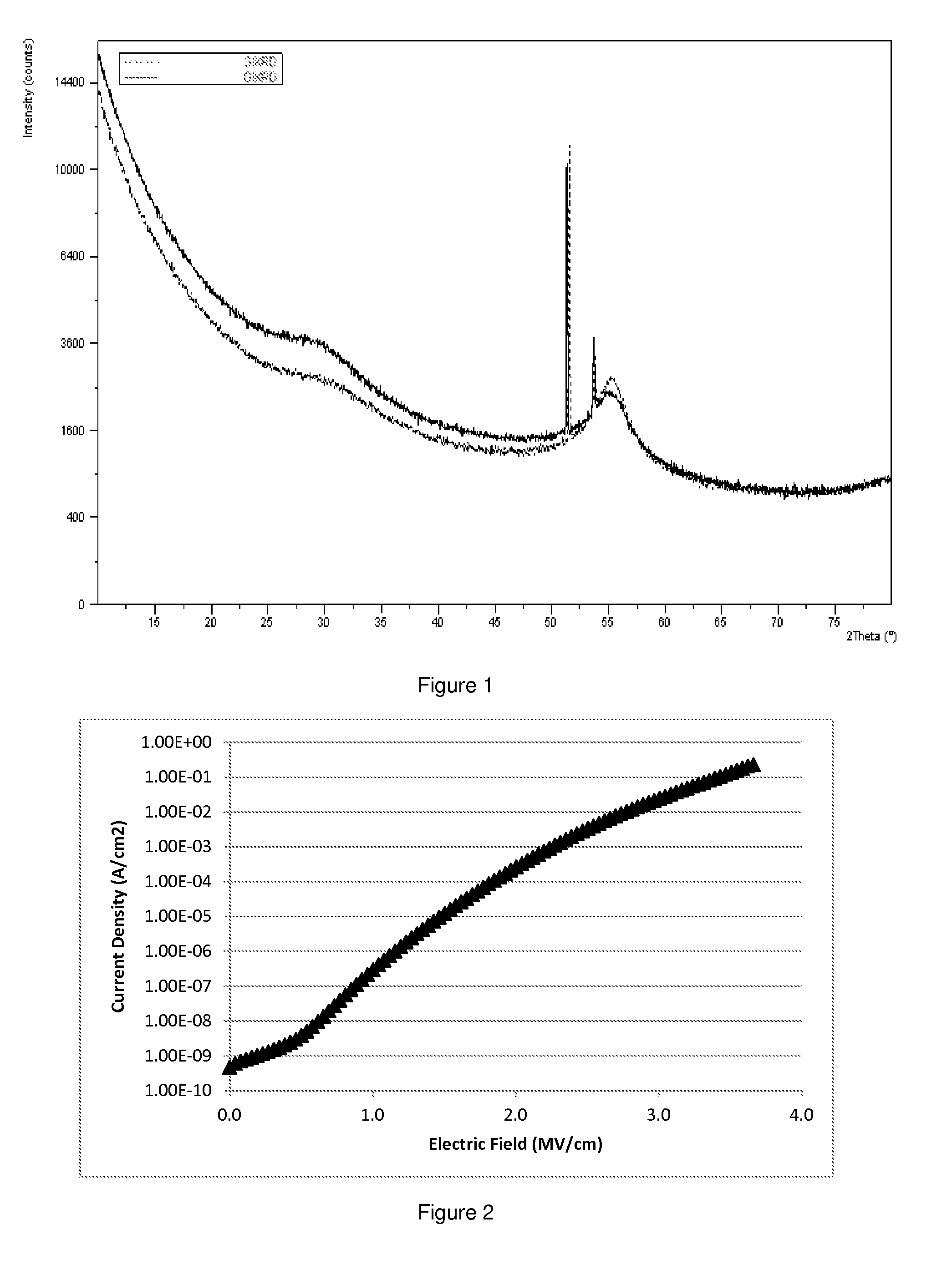

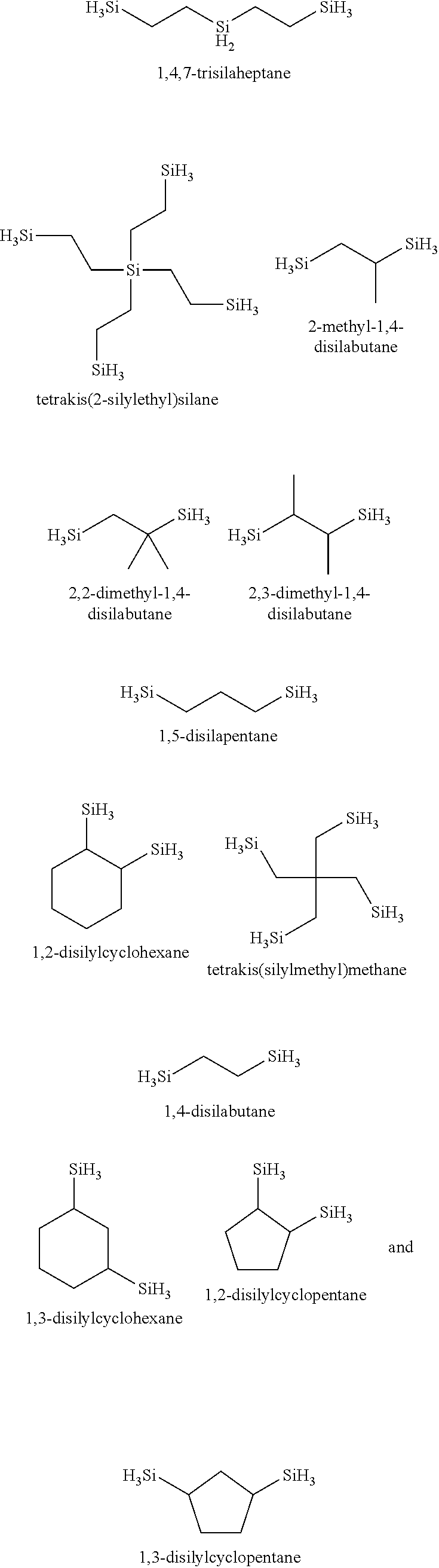

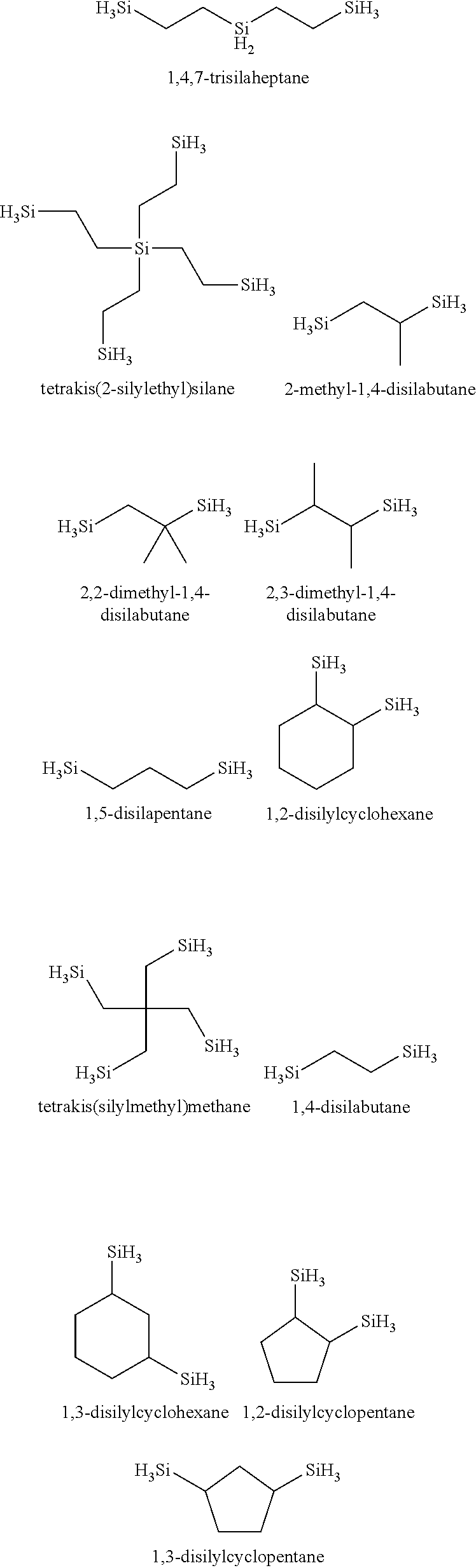

Non-oxygen containing silicon-based films and methods of forming the same

ActiveUS20140030448A1Enhanced vapor depositionChemical vapor deposition coatingPlasma techniqueOxygenChemistry

Disclosed herein are non-oxygen containing silicon-based films, and methods for forming the same. The non-oxygen silicon-based films contain >50 atomic % of silicon. In one aspect, the silicon-based films have a composition SixCyNz wherein x is about 51 to 100, y is 0 to 49, and z is 0 to 50 atomic weight (wt.) percent (%) as measured by XPS. In one embodiment, the non-oxygen silicon-based films were deposited using at least one organosilicon precursor having at least two SiH3 groups with at least one C2-3 linkage between silicon atoms such as 1,4-disilabutane.

Owner:VERSUM MATERIALS US LLC

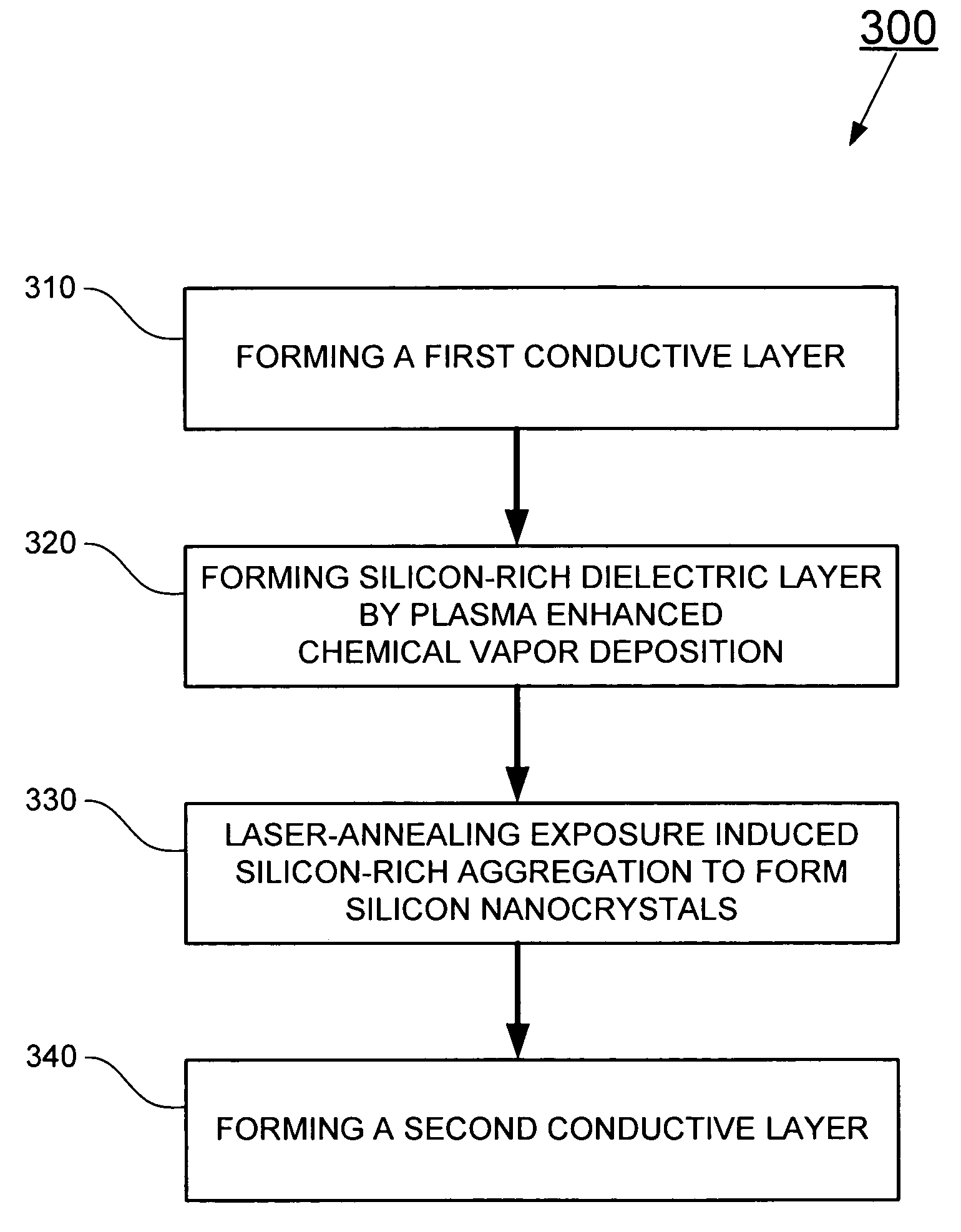

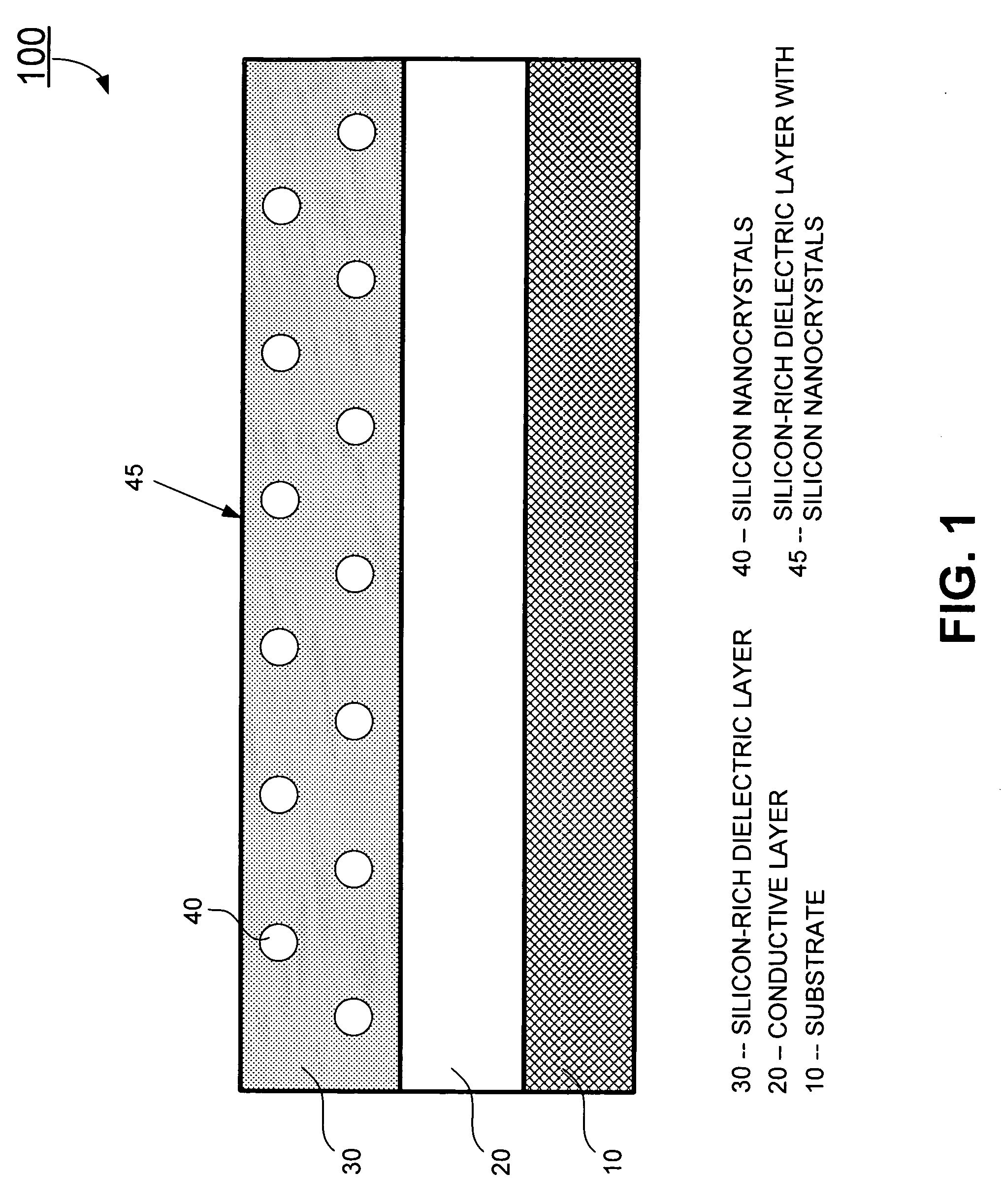

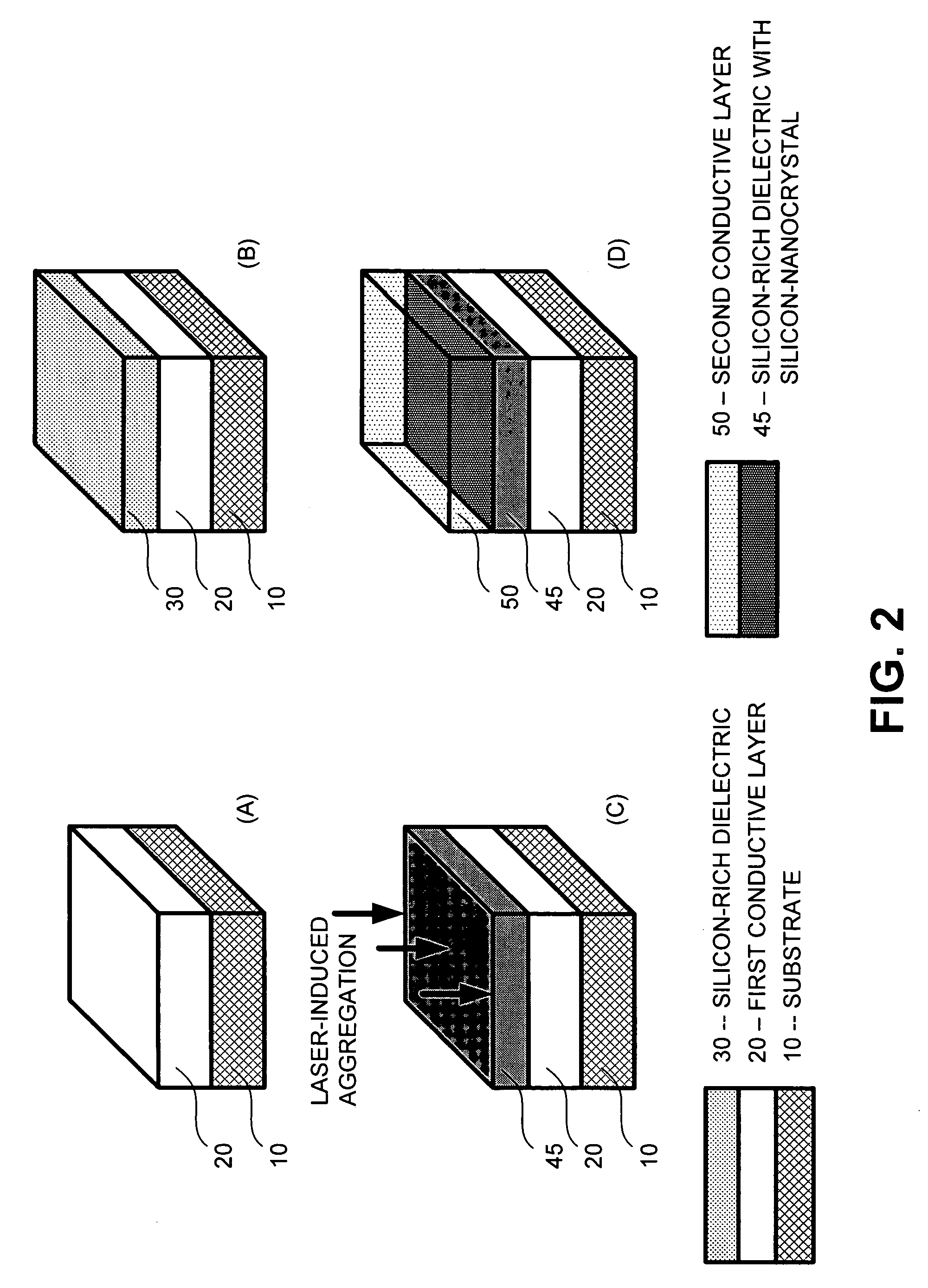

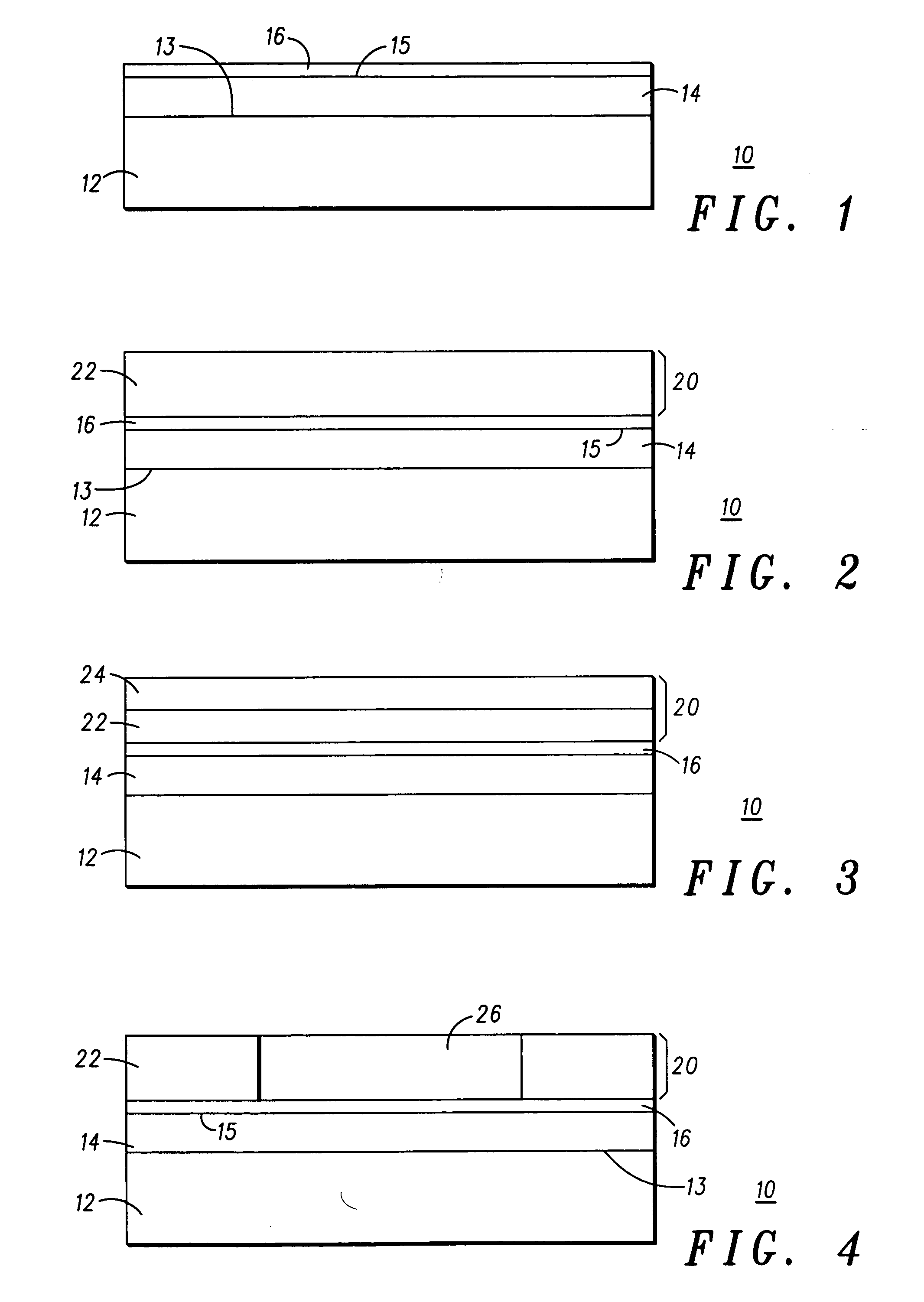

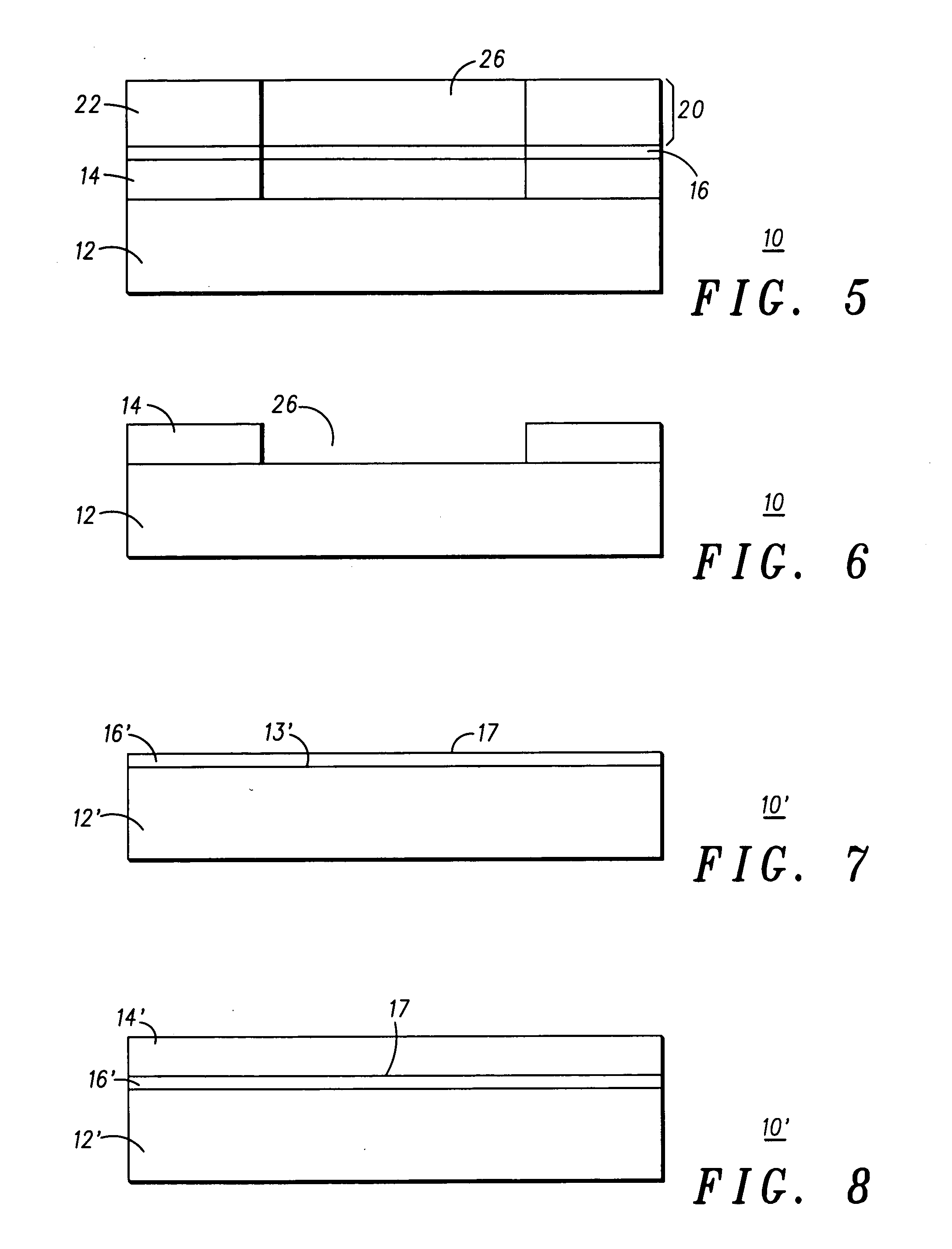

Methods of forming silicon nanocrystals by laser annealing

ActiveUS20080178794A1Enhanced vapor depositionPolycrystalline material growthNanotechSilicon nanocrystalsPhotodetector

The present invention relates to a method for forming a layered structure with silicon nanocrystals. In one embodiment, the method comprises the steps of: (i) forming a first conductive layer on a substrate, (ii) forming a silicon-rich dielectric layer on the first conductive layer, and (iii) laser-annealing at least the silicon-rich dielectric layer to induce silicon-rich aggregation to form a plurality of silicon nanocrystals in the silicon-rich dielectric layer. The silicon-rich dielectric layer is one of a silicon-rich oxide film having a refractive index in the range of about 1.4 to 2.3, or a silicon-rich nitride film having a refractive index in the range of about 1.7 to 2.3. The layered structure with silicon nanocrystals in a silicon-rich dielectric layer is usable in a solar cell, a photodetector, a touch panel, a non-volatile memory device as storage node, and a liquid crystal display.

Owner:AU OPTRONICS CORP

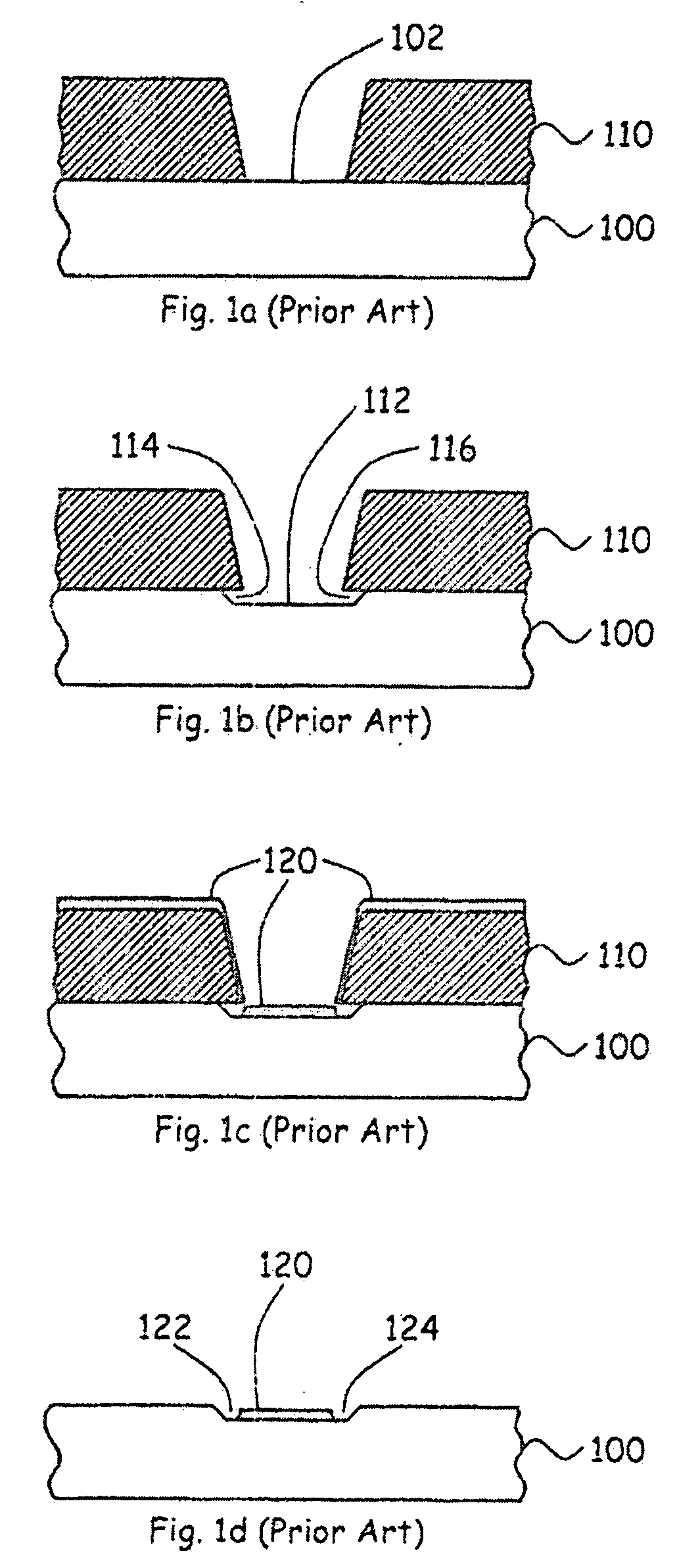

Methods of Minimizing Etch Undercut and Providing Clean Metal Liftoff

ActiveUS20090111061A1Inhibition effectAdequate step coverageSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusResistOxygen

A method of minimizing etch undercut and providing clean metal liftoff in subsequent metal deposition is provided. In one embodiment a bilayer resist mask is employed and used for etching of underlying substrate material and subsequent metal liftoff. In one embodiment, the top layer resist such as positive photoresist which is sensitive to selected range of energy, such as near UV or violet light, is first patterned by standard photolithography techniques and resist development in a first developer to expose portion of a bottom resist layer which is sensitive to a different selected range of energy, such as deep UV light. The exposed portion of the bottom layer resist is then removed by anisotropic etching such as oxygen reactive ion etching using the top layer resist as the etch mask to expose portion of the underlying substrate. This minimizes the undercut in the bottom resist around the top photoresist opening. The resultant patterned bilayer resist stack is then used as the etch mask for the subsequent etching of the exposed portion of the underlying substrate material. Because there is no undercut in the bottom resist layer, the etch undercut in the substrate material is also minimized relative to the edges of the top photoresist opening.

Owner:TRIQUINT SEMICONDUCTOR

Formation of photoconductive and photovoltaic films

InactiveUS20090120501A1Enhanced vapor depositionIncrease depositionElectric discharge tubesVacuum evaporation coatingP–n junctionSilicon

The present application discloses a method and system of depositing a lead selenide film onto another material. The lead selenide film may used in a photoconductive application or a photovoltaic application. Furthermore, the applications may be responsive to infrared radiation at ambient temperature. In one embodiment, a method includes sputtering the lead selenide film, performing a sensitization process, and applying a passivation film. In one exemplary embodiment, a p-n junction is formed by directly adhering a lead selenide film to a silicon substrate.

Owner:ADVANCED INTEGRATION

Multi-chamber deposition of silicon oxynitride film for patterning

InactiveUS7033960B1Improve reliabilityAccurately dimensioned device featureSemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyTotal thickness

Pinholes in a silicon oxynitride film are reduced by PECVD deposition of a plurality of silicon oxynitride sub-layers in a PECVD apparatus containing multiple chambers. Embodiments include forming a layer of amorphous carbon over a conductive layer, such as doped polycrystalline silicon, on a substrate, transferring the substrate to a multi-chamber PECVD tool and depositing 2 to 7, e.g., 5, sub-layers of dense silicon oxynitride at a total thickness of 300 to 700 Å.

Owner:GLOBALFOUNDRIES INC

Device including an amorphous carbon layer for improved adhesion of organic layers and method of fabrication

ActiveUS20050079650A1Enhanced vapor depositionSemiconductor/solid-state device detailsNanoinformaticsGas phaseDevice material

A novel device, such as a semiconductor device, a microfluidic device, a surface acoustic wave device an imprint template, or the like, including an amorphous carbon layer for improved adhesion of organic layers and method of fabrication. The device includes a substrate having a surface, an amorphous carbon layer, formed overlying the surface of the substrate, and a low surface energy material layer overlying the surface of the substrate. The device is formed by providing a substrate having a surface, depositing a low surface energy material layer and an amorphous carbon layer overlying the surface of the substrate adjacent the low surface energy material layer using plasma enhanced chemical vapor deposition (PECVD) or sputtering.

Owner:NXP USA INC

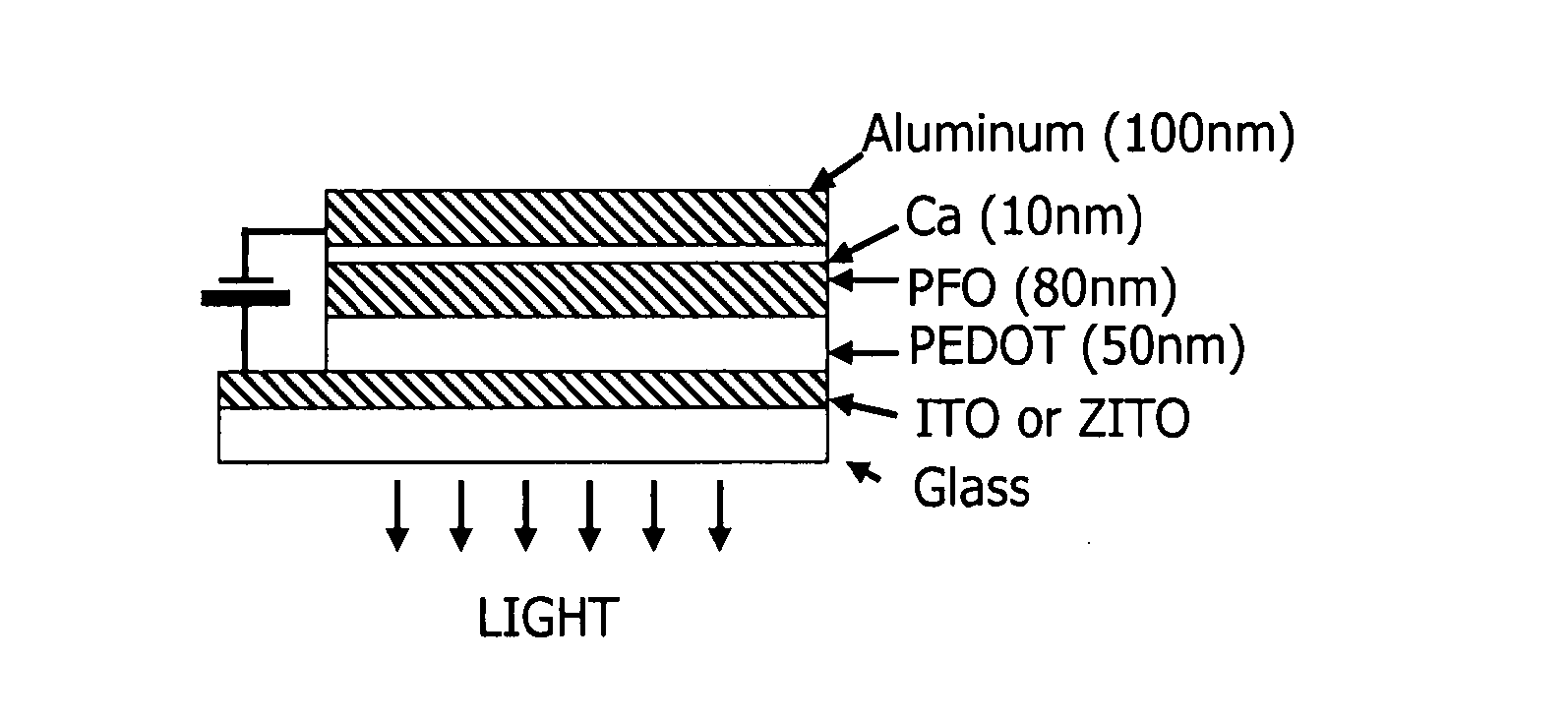

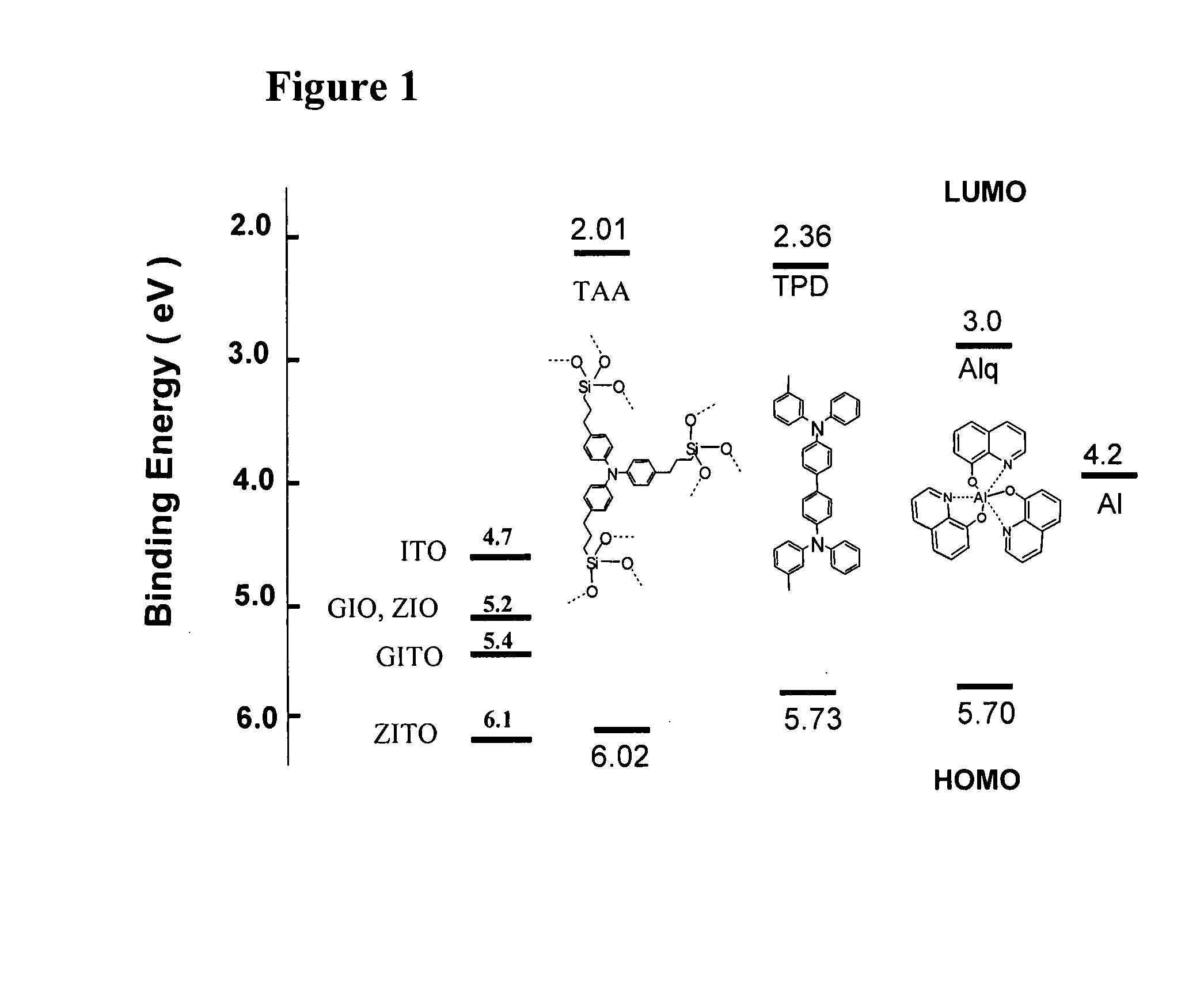

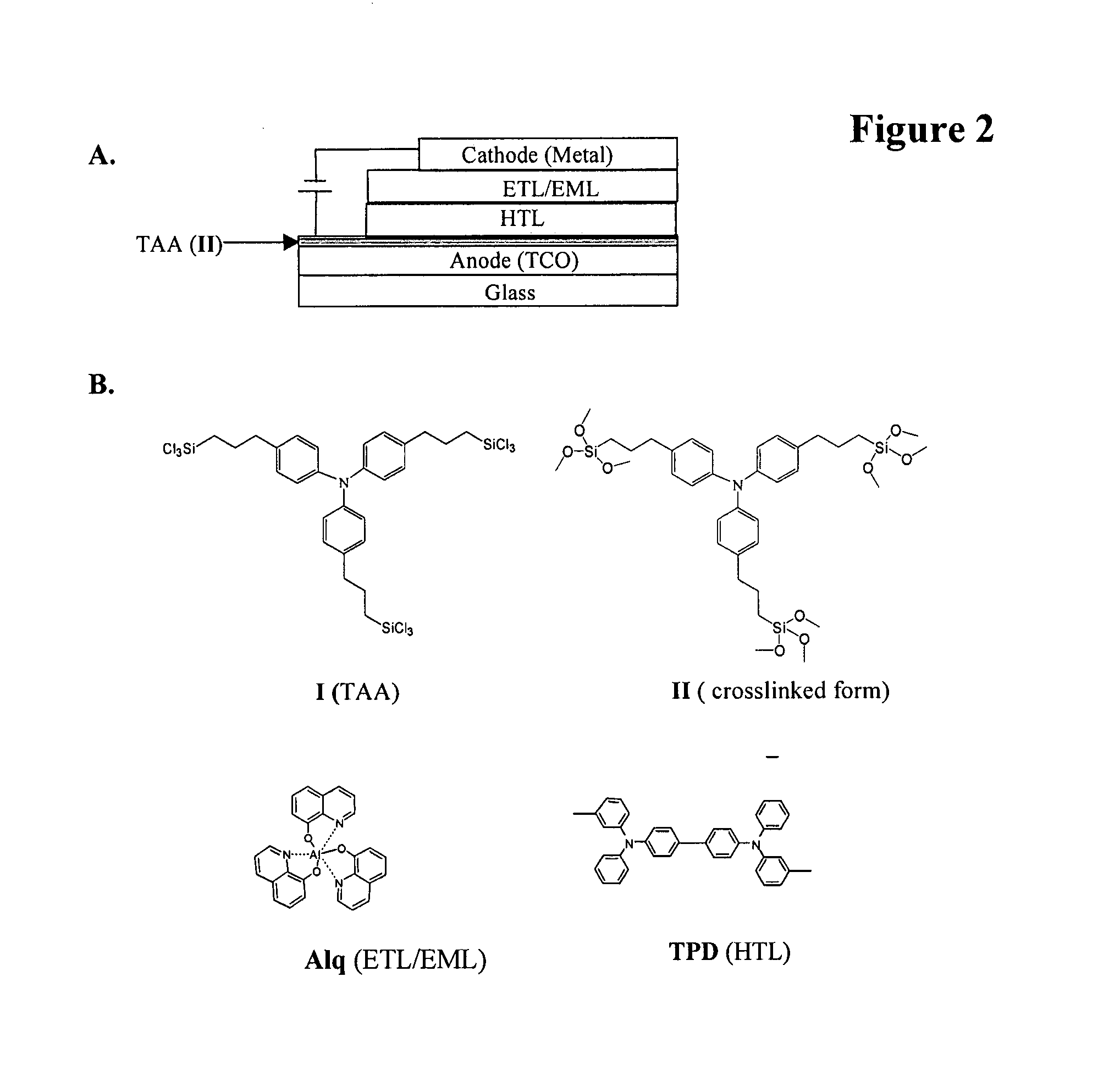

Transparent conducting oxide thin films and related devices

ActiveUS20080024055A1Satisfactory surface smoothnessEnhanced vapor depositionLiquid crystal compositionsConductive materialIndiumOrganic electroluminescence

Transparent conducting oxide thin films having a reduced indium content and / or an increased tin content are provided. In addition, processes for producing the same, precursors for producing the same, and transparent electroconductive substrate for display panels and organic electroluminescence devices, both including the transparent conducting oxide thin films, are provided.

Owner:NORTHWESTERN UNIV

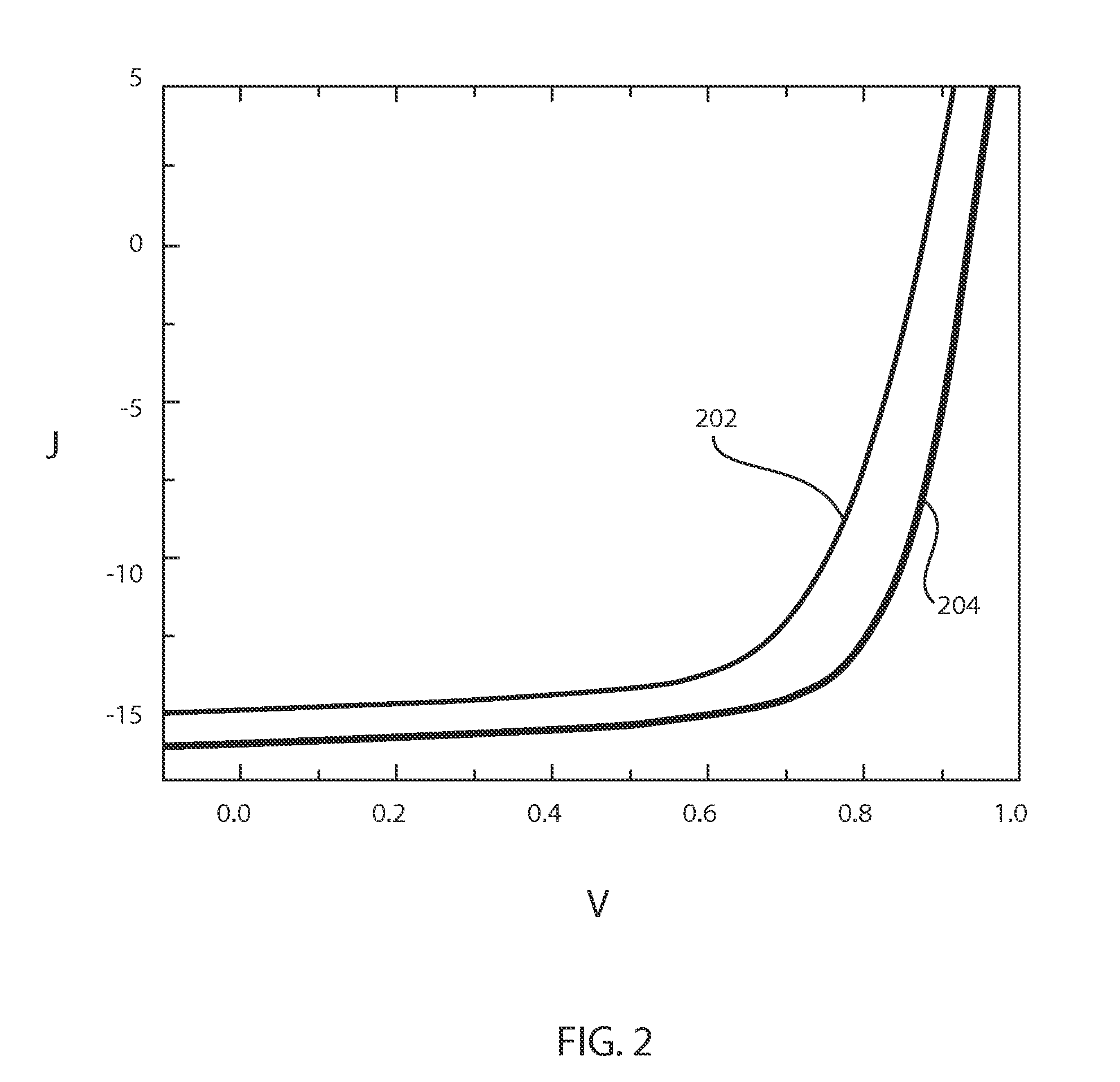

High efficiency solar cells fabricated by inexpensive pecvd

ActiveUS20140004651A1Improve performanceIncrease deposition rateFinal product manufactureSemiconductor/solid-state device manufacturingElectrical batterySolar cell

A method for forming a photovoltaic device includes depositing one or more layers of a photovoltaic stack on a substrate by employing a high deposition rate plasma enhanced chemical vapor deposition (HDR PECVD) process. Contacts are formed on the photovoltaic stack to provide a photovoltaic cell. Annealing is performed on the photovoltaic cell at a temperature and duration configured to improve overall performance.

Owner:GLOBALFOUNDRIES US INC

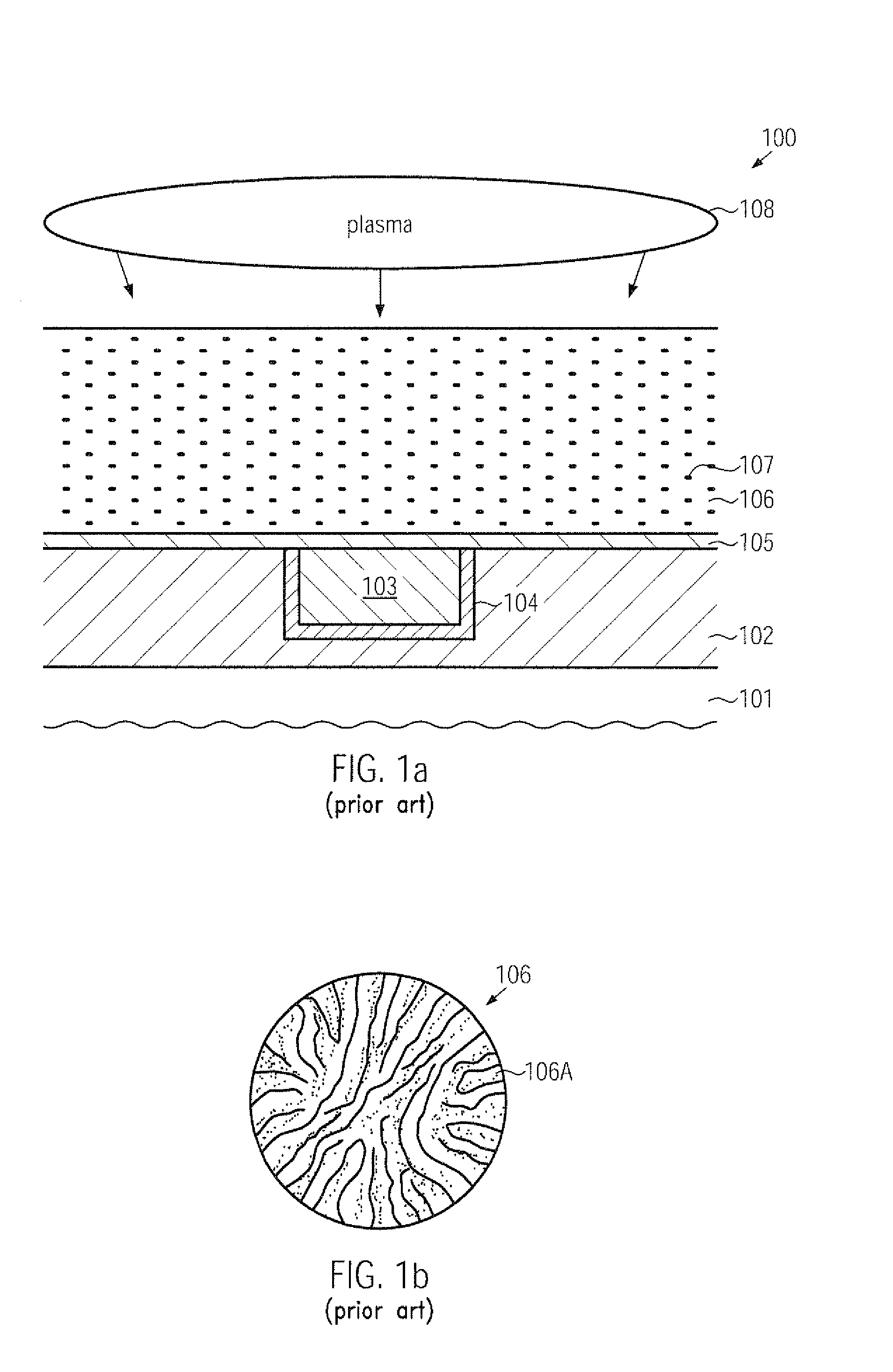

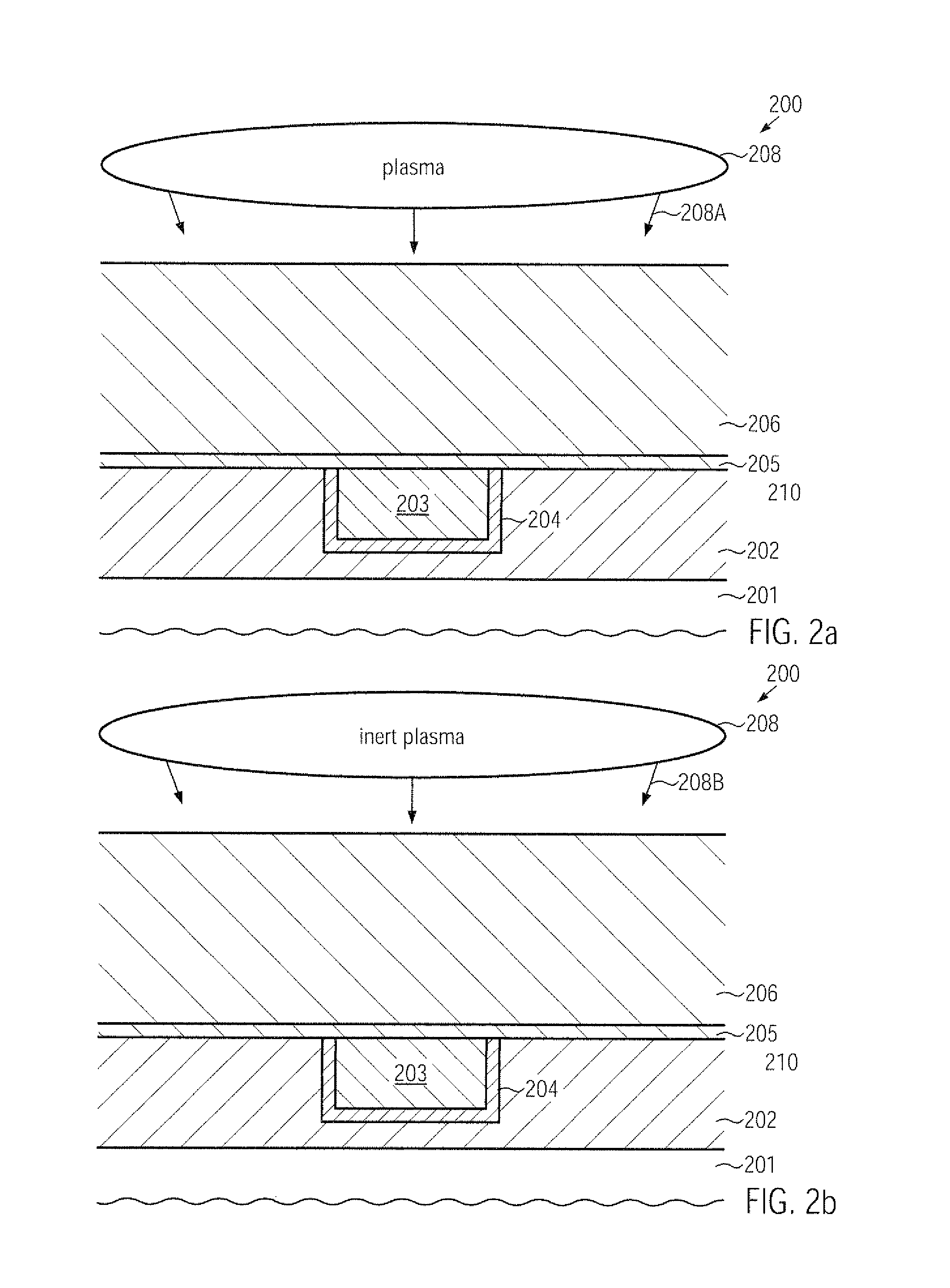

Particle reduction in pecvd processes for depositing low-k material by using a plasma assisted post-deposition step

InactiveUS20100055899A1Reduce defective rateReduce the impactSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricDeposition process

When forming dielectric materials of reduced dielectric constant in sophisticated metallization systems, the creation of defect particles on the dielectric material may be reduced during a plasma enhanced deposition process by inserting an inert plasma step after the actual deposition step.

Owner:ADVANCED MICRO DEVICES INC

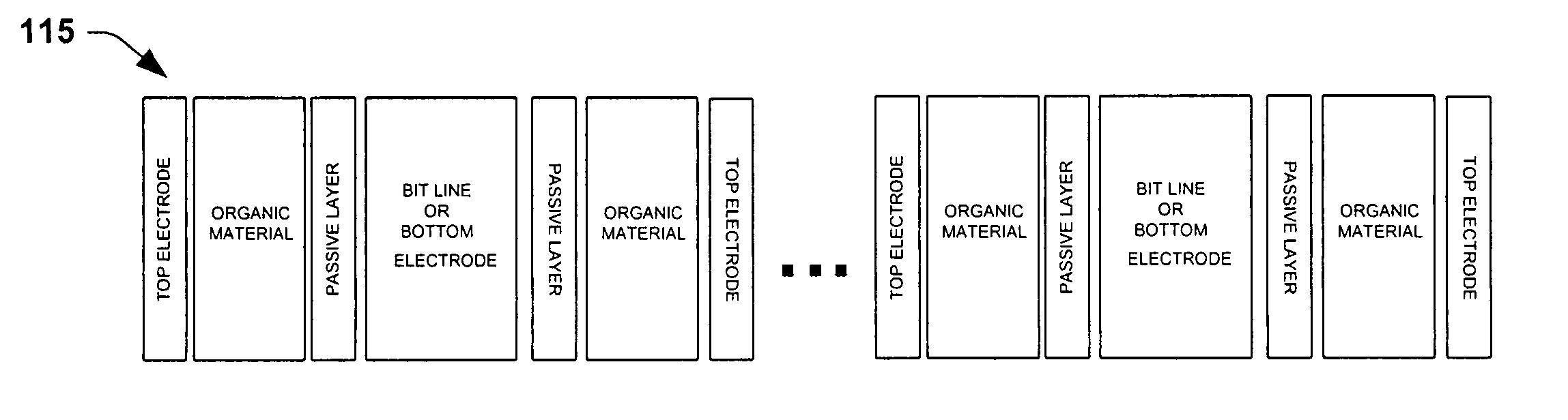

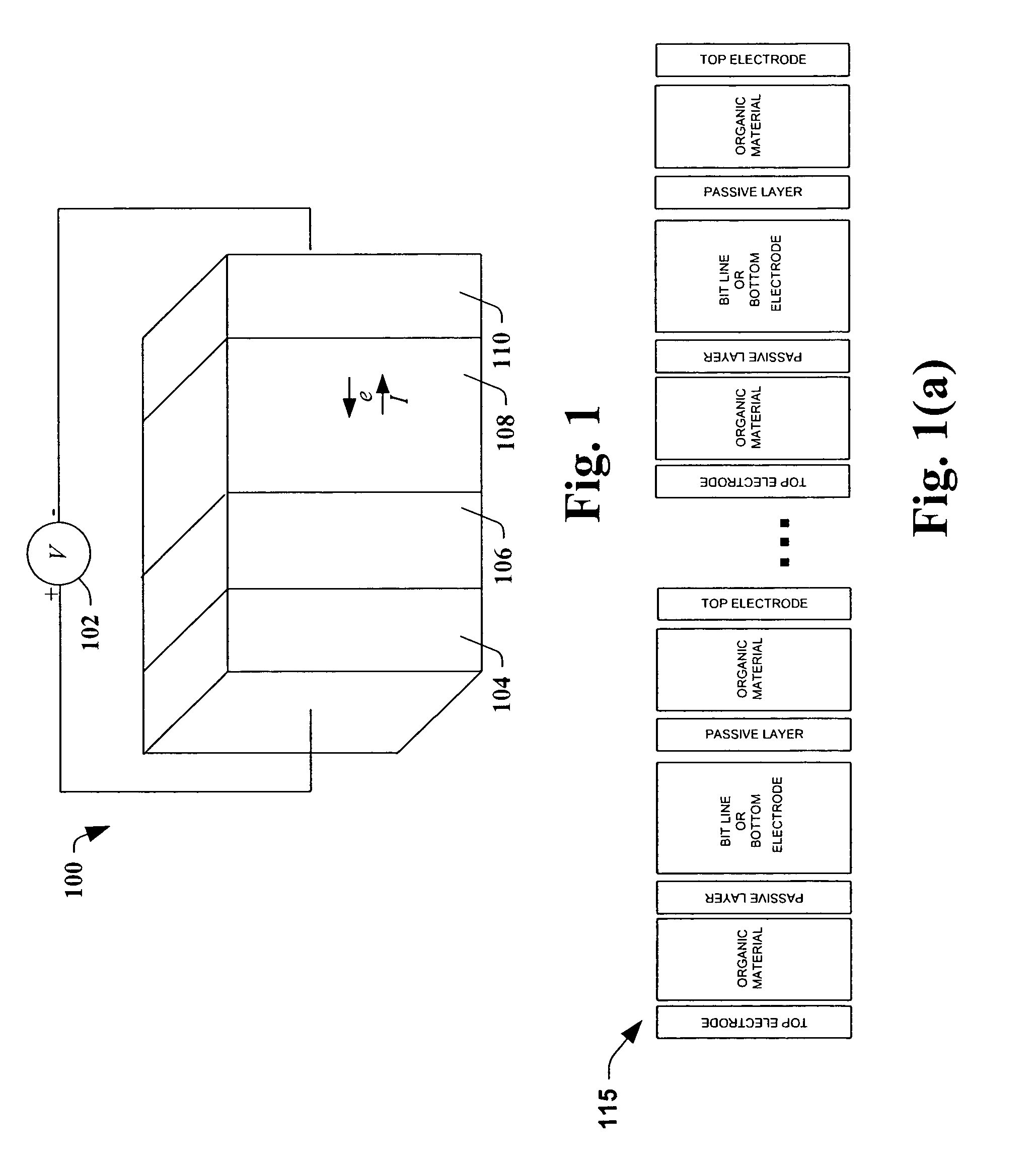

Sidewall formation for high density polymer memory element array

ActiveUS20050092983A1Facilitate depositionEnhanced vapor depositionTransistorSemiconductor/solid-state device detailsBit lineHigh density

Systems and methodologies are disclosed for increasing the number of memory cells associated with a lithographic feature. The systems comprise memory elements that are formed on the sidewalls of the lithographic feature by employing various depositing and etching processes. The side wall memory cells can have a bit line of the wafer as the first electrode and operate with a second formed electrode to activate a portion of an organic matter that is formed there between.

Owner:CYPRESS SEMICON CORP

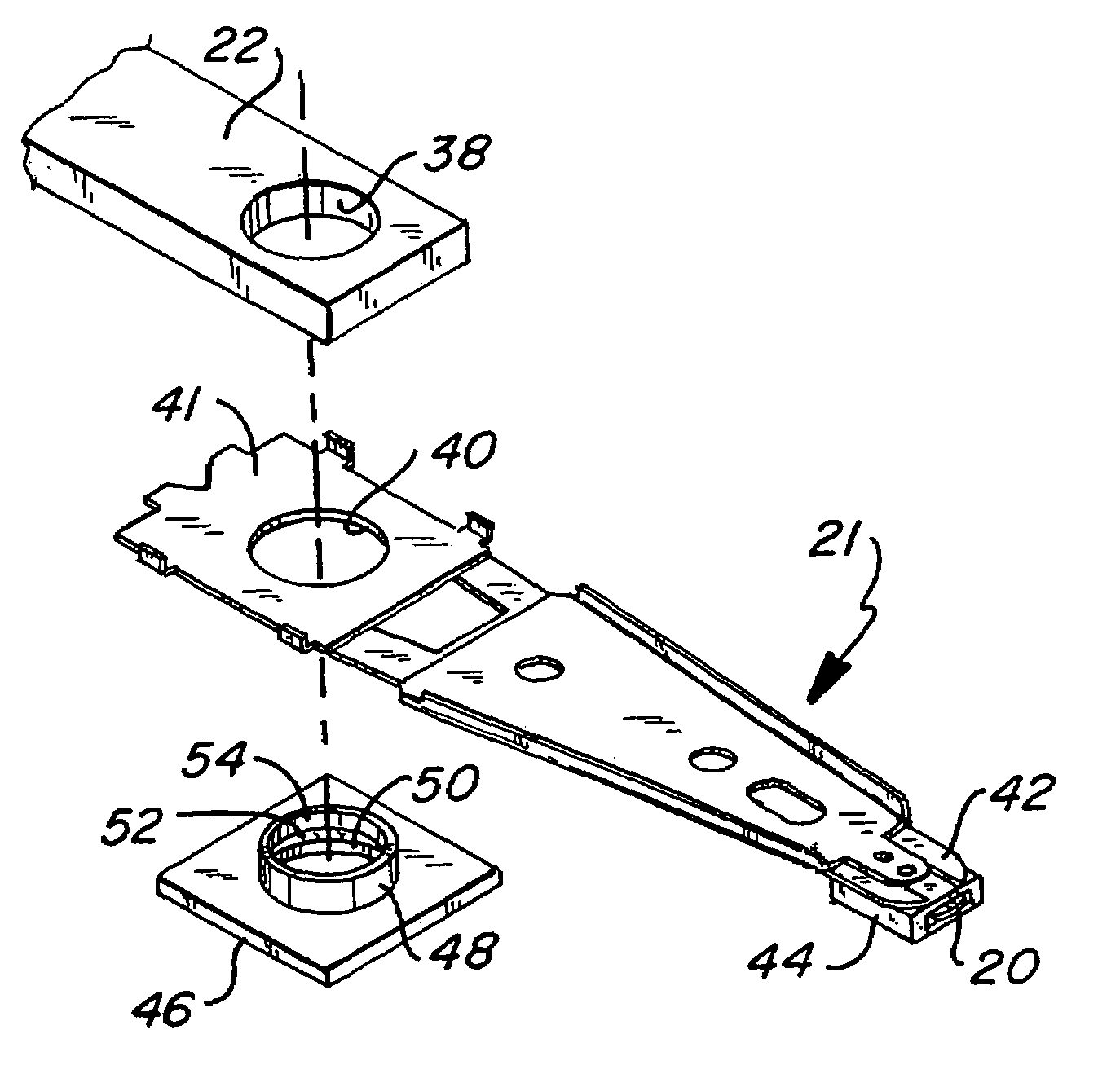

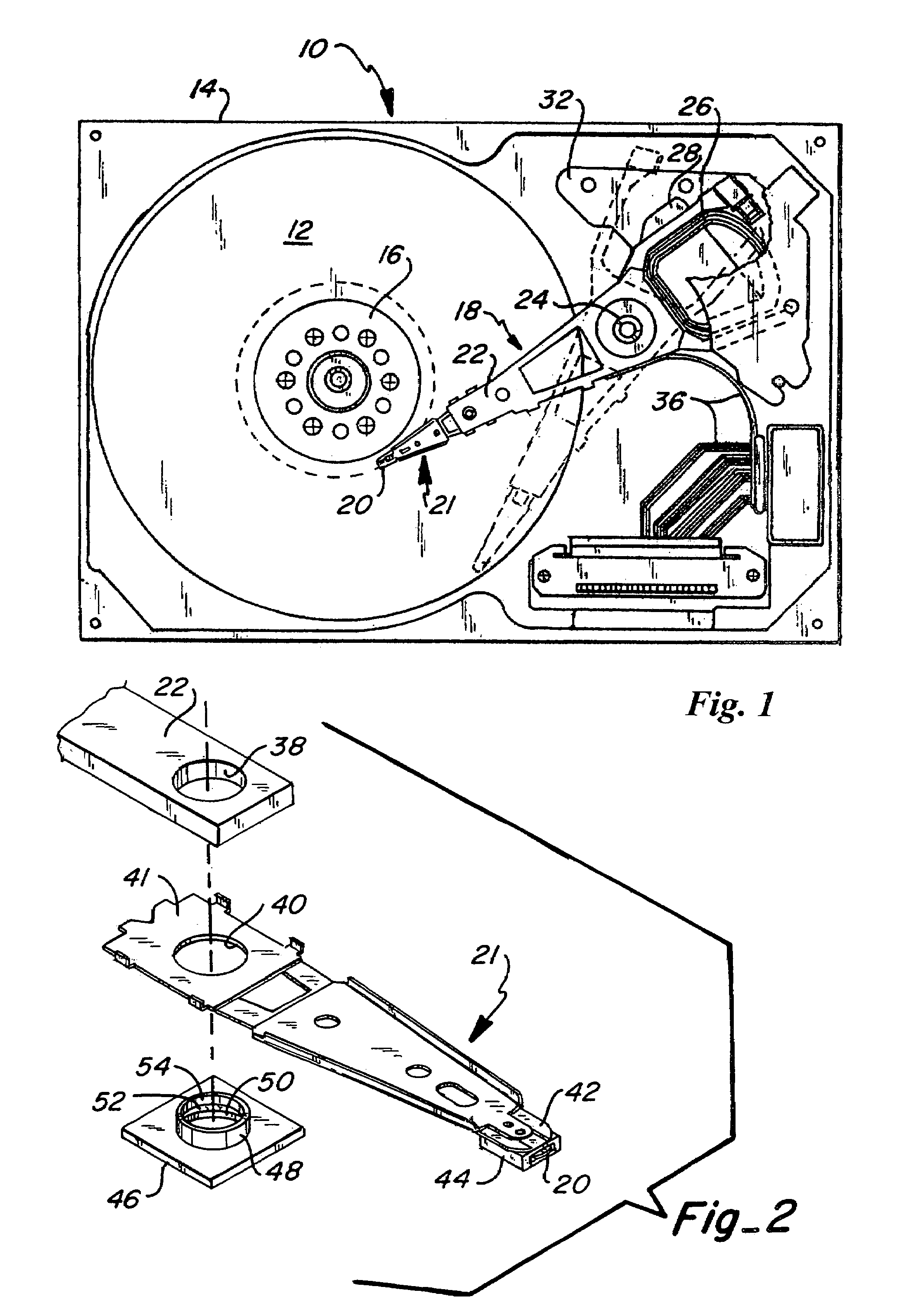

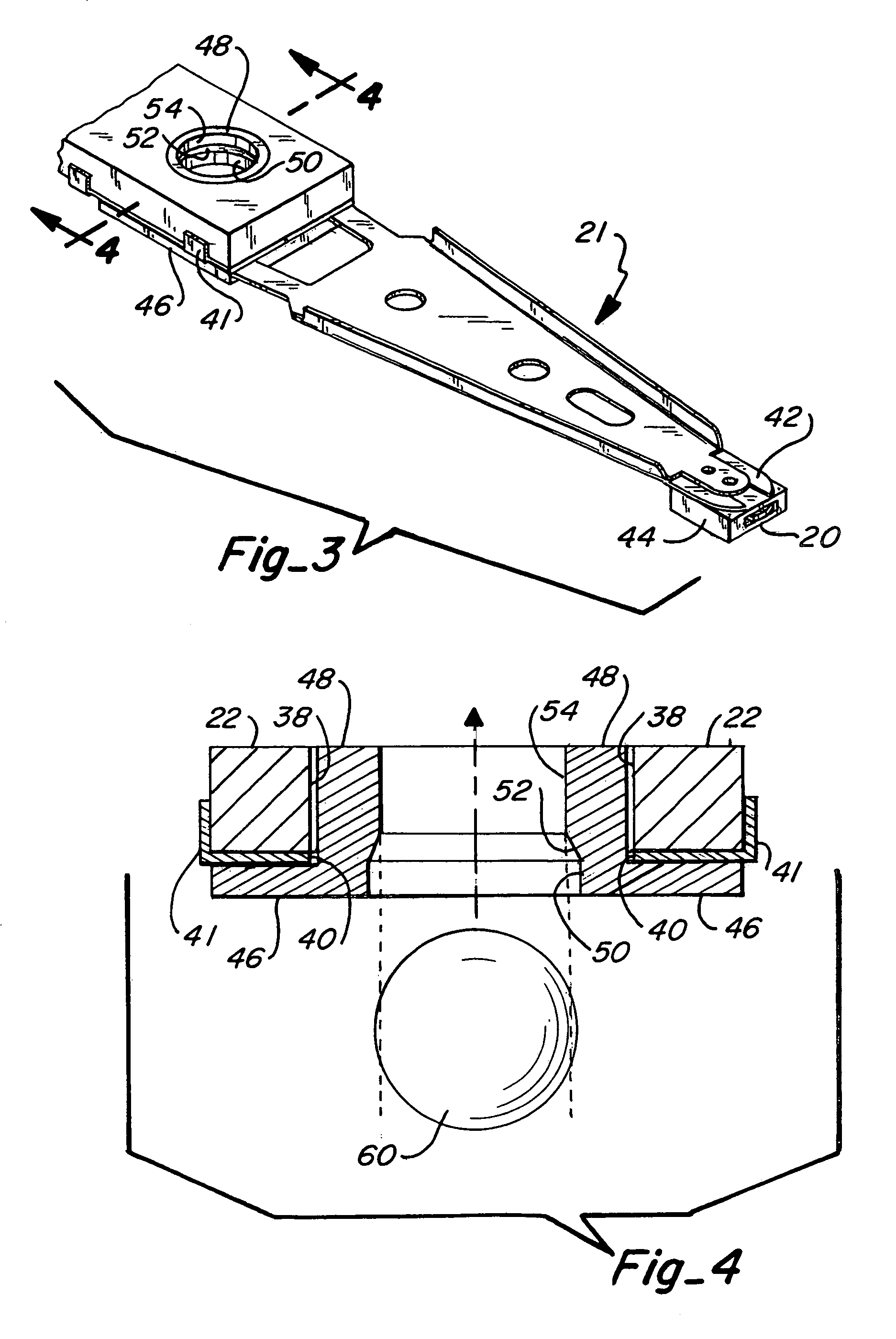

Method of assembling an actuator assembly of a disk drive and of reducing torque out retention values in subsequent de-swaging

InactiveUS7024754B1Reduced retention torqueGood deformation propertiesElectrical transducersManual lubricationGramSwaging

A method is provided for assembling an actuator assembly of a disk drive. The method includes providing an actuator arm, providing a suspension arm, fixing a swage plate to the suspension arm, the swage plate including a swage boss extending therefrom, depositing a film lubricant upon at least an outer surface of the swage boss, and attaching the suspension arm to the actuator arm by swaging. A method is also provided for reducing torque out retention values between the actuator arm and the suspension arm when the actuator arm and suspension arm must be separated in a subsequent de-swaging process. This method includes providing an outer surface of the swage boss, and applying a lubricant film coating to the outer surface of the swage boss. A preferred thin film lubricant may be applied by emersion and draining, localized spraying, or various deposition processes. Application of the lubricant has also shown to improve gram load uniformity and to reduce adverse distortion to the actuator assembly which otherwise occurs during swaging.

Owner:MAXTOR

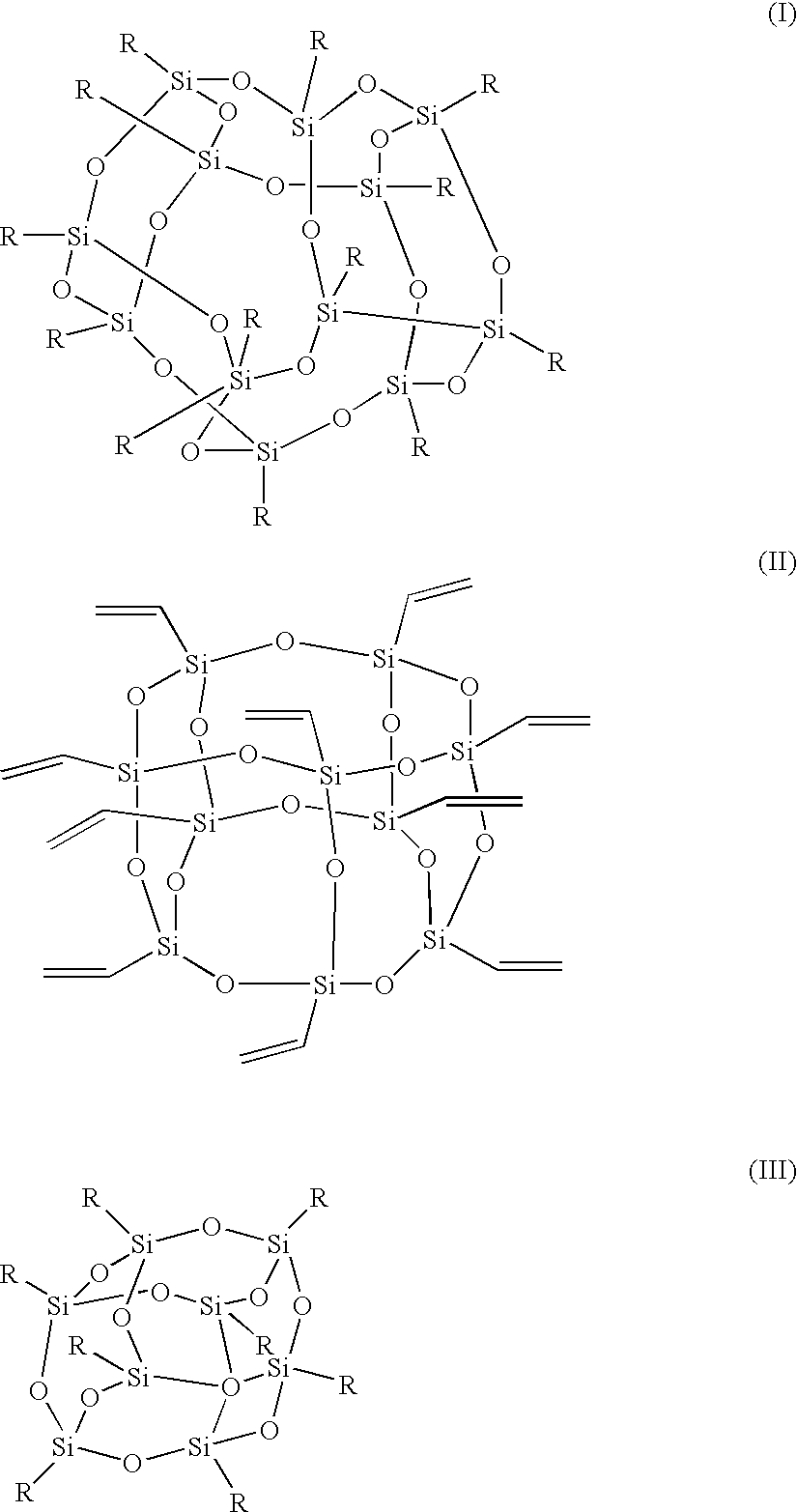

Methods for forming low-k dielectric films

InactiveUS6936537B2Enhanced vapor depositionGolf teesPhotometrySilsesquioxaneChemical vapor deposition

The use of a polyhedral oligomeric silsesquioxane compound and linking agent to form an ultra low-k dielectric film on semiconductor or integrated circuit surfaces is disclosed. The reaction between the polyhedral oligomeric silsesquioxane compound and linking agent is done in a chemical vapor deposition chamber.

Owner:BOC GRP INC

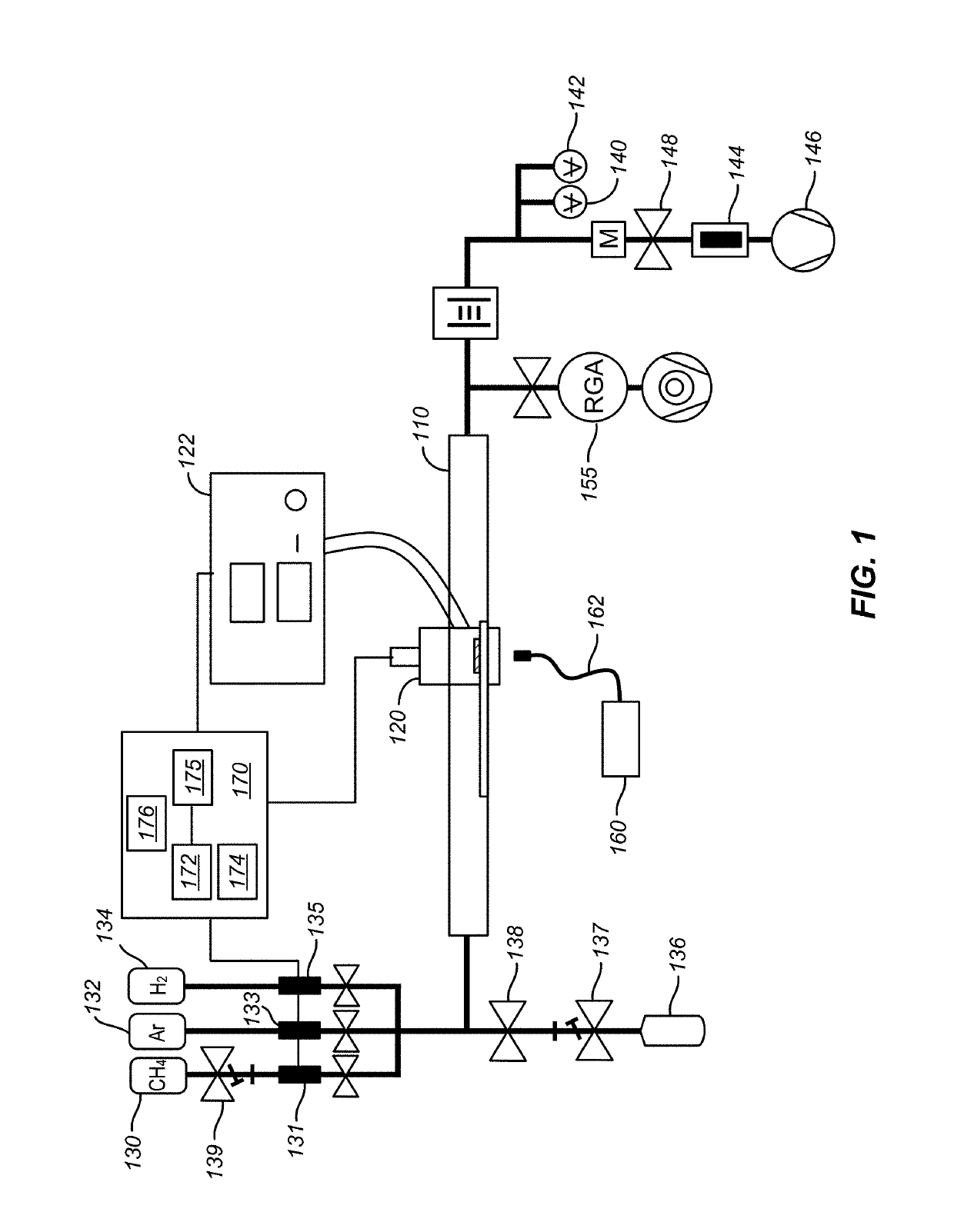

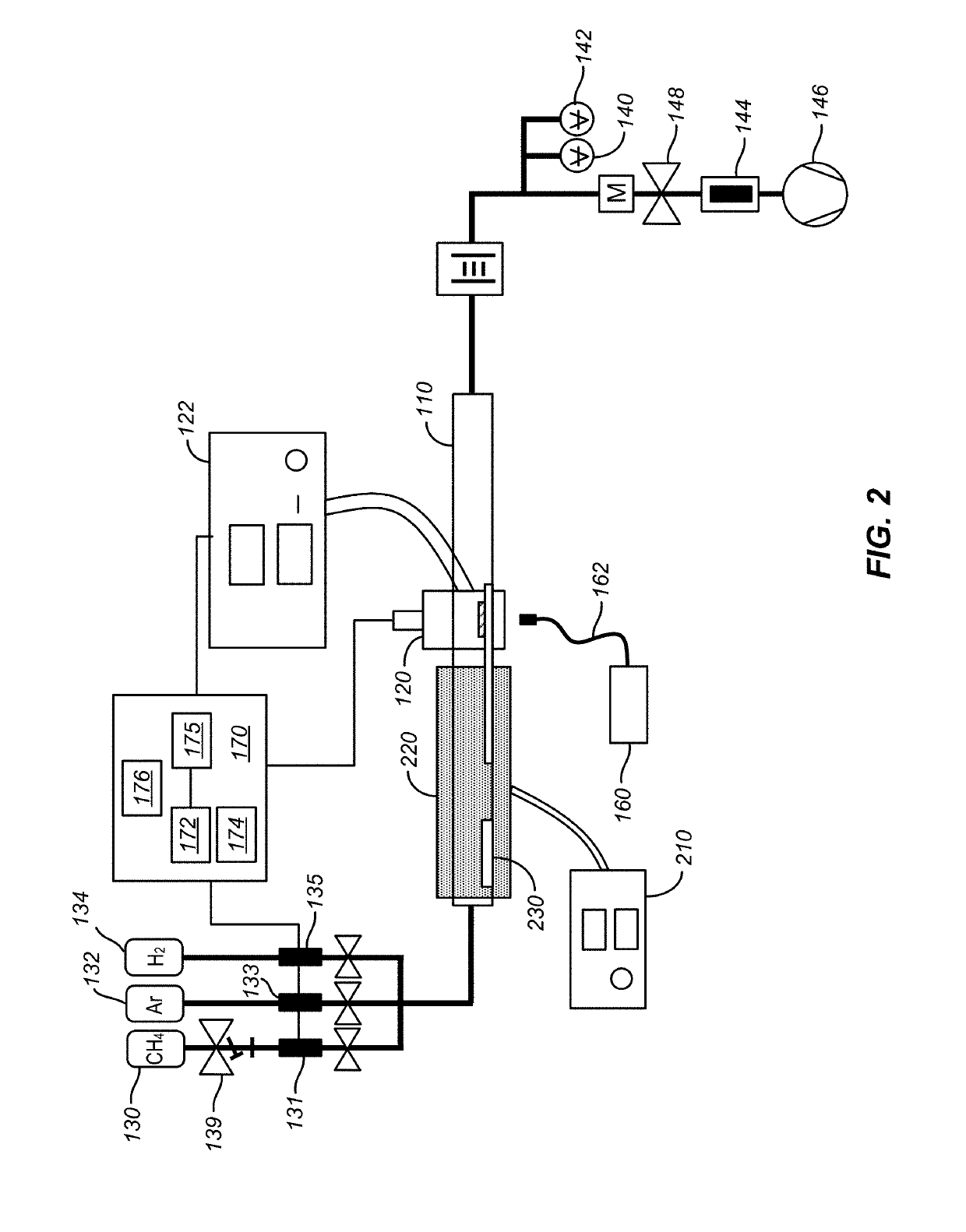

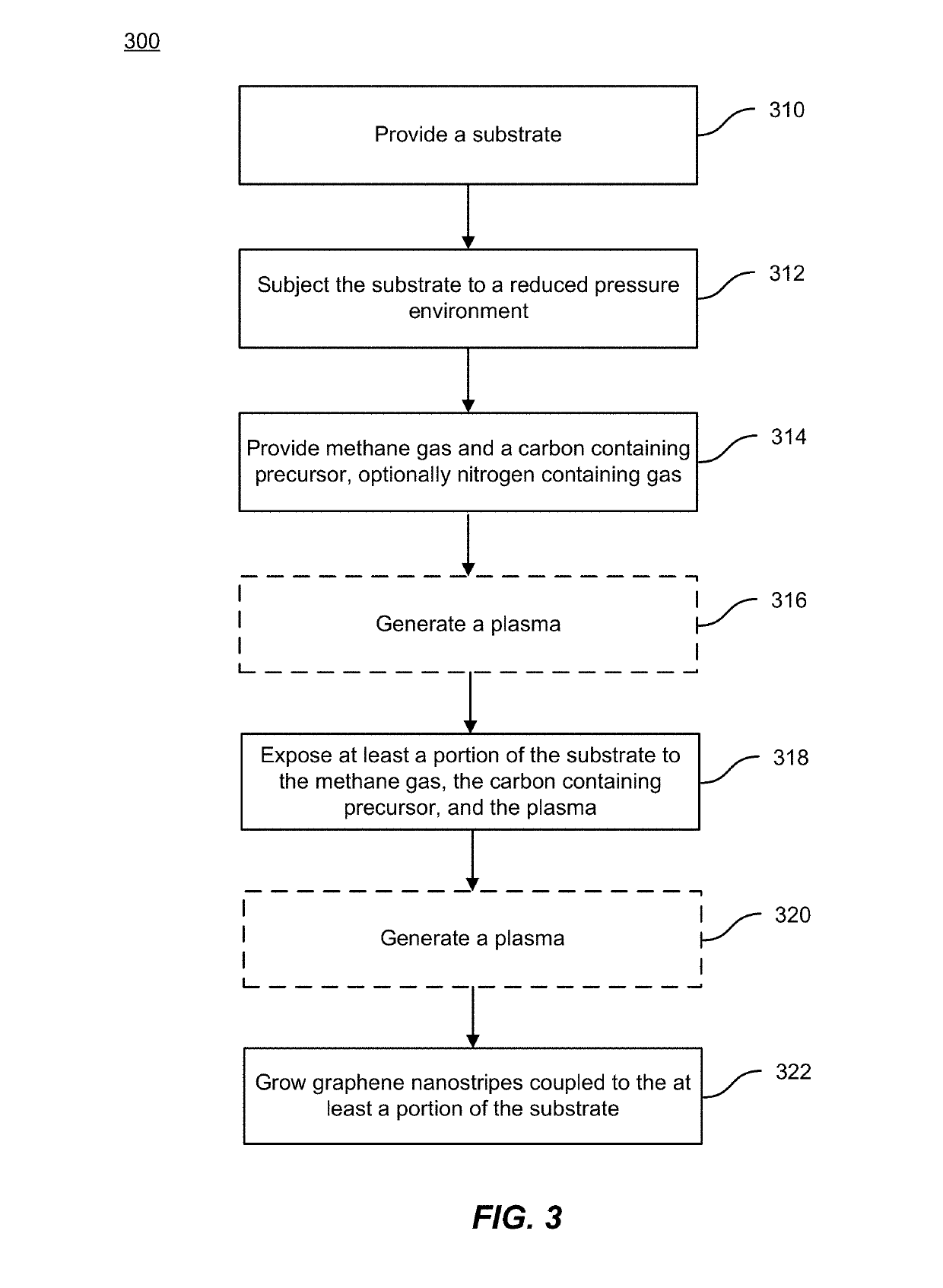

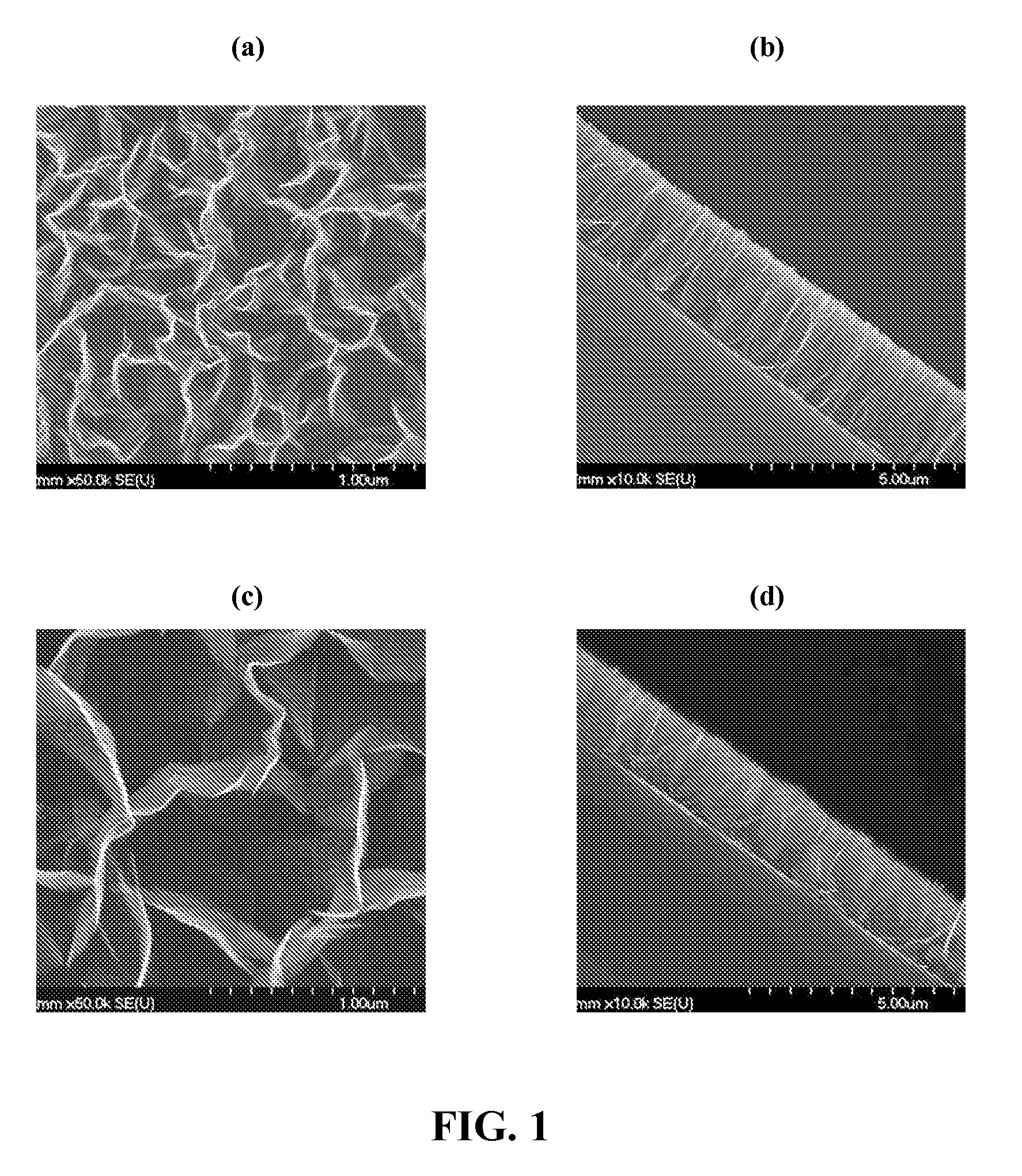

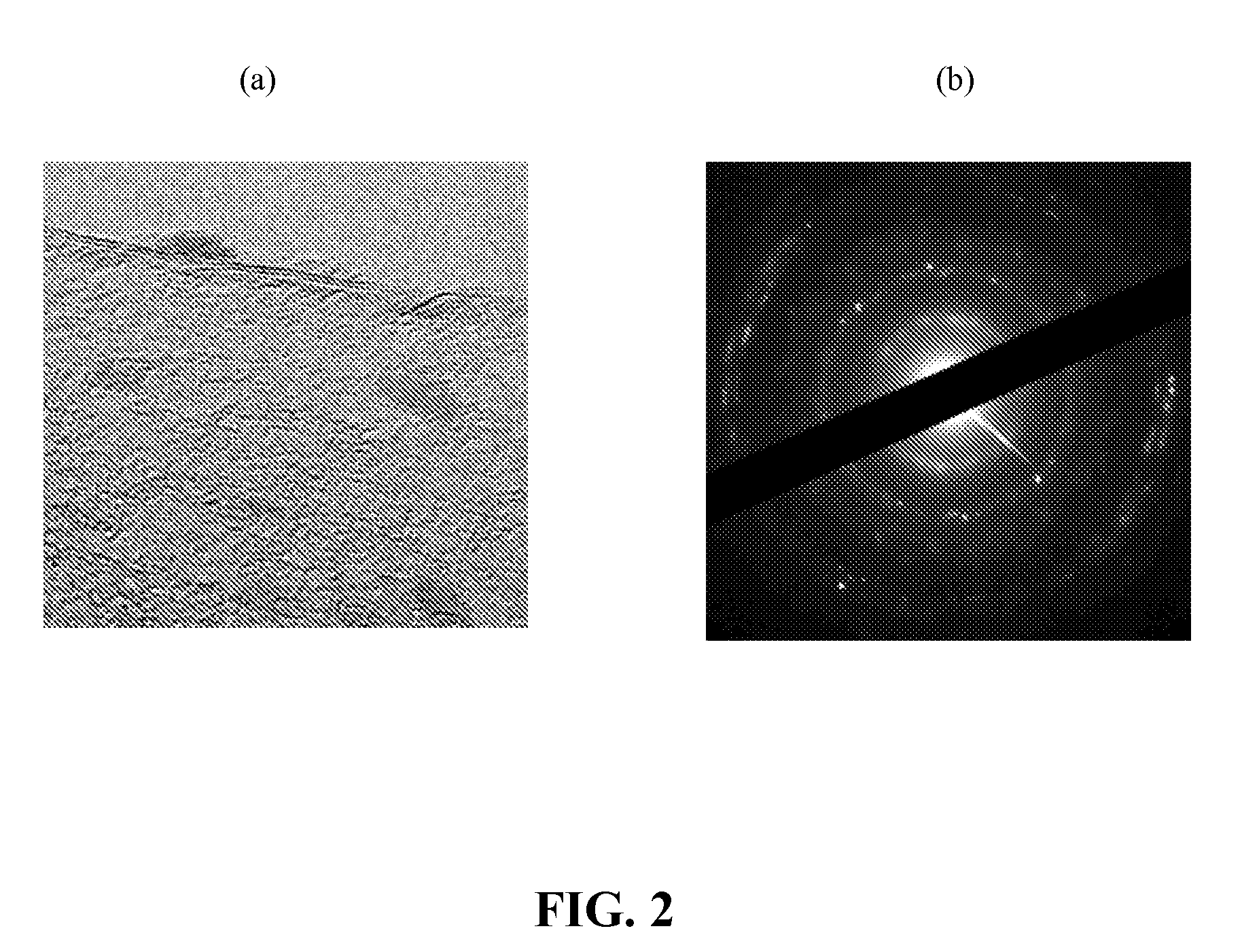

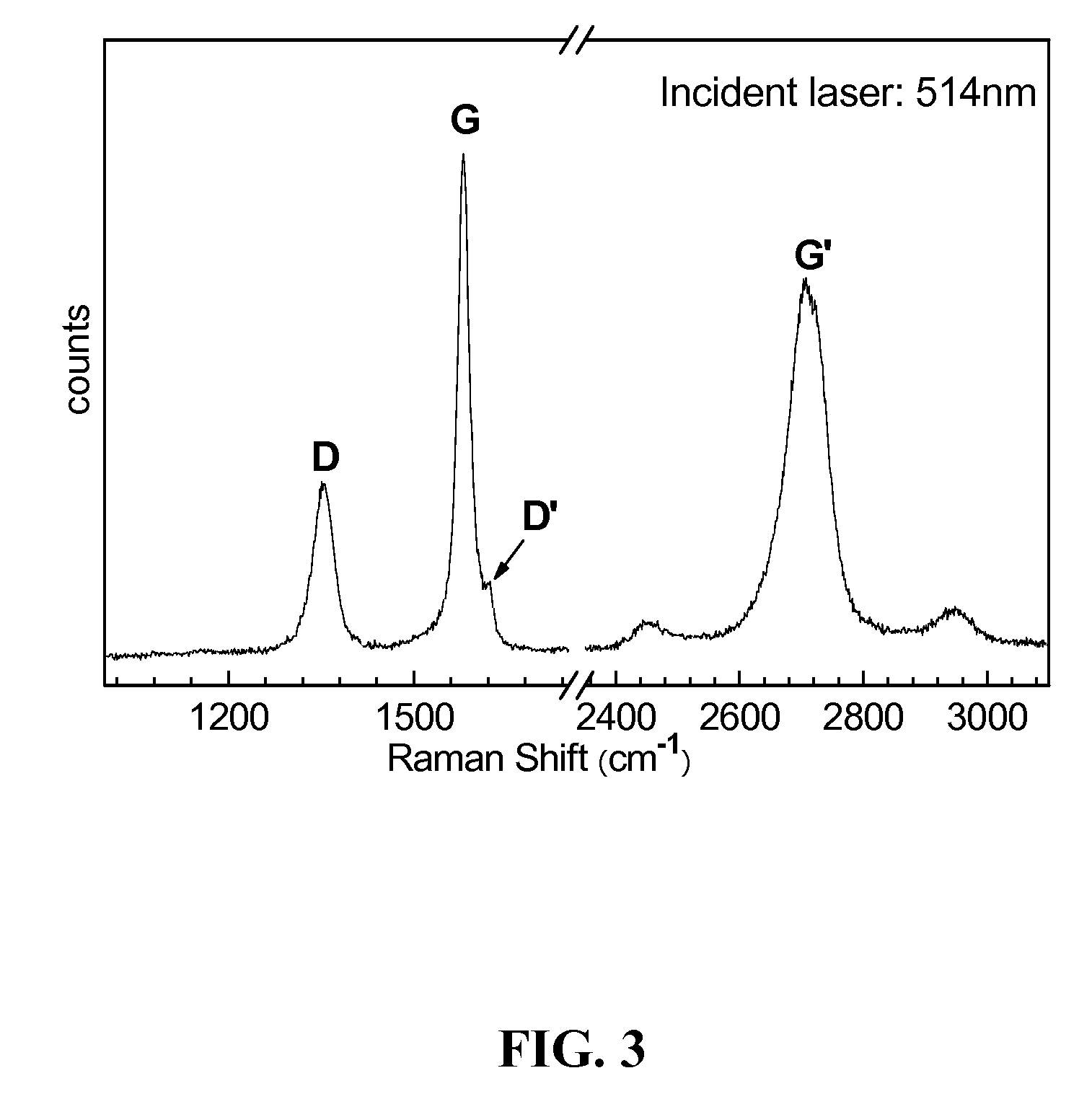

Method and system for growth of graphene nanostripes by plasma enhanced chemical vapor deposition

ActiveUS20190093227A1High yieldEnhanced vapor depositionChlorine/hydrogen-chlorideMaterial nanotechnologyGraphene nanoribbonsGas phase

A method of forming graphene nanostripes includes providing a substrate comprising at least one of copper foil or nickel foam and subjecting the substrate to a reduced pressure environment in a processing chamber. The method also includes providing methane gas and 1,2-dichlorobenzene (1,2-DCB) gas, flowing the methane gas and the 1,2-DCB into the processing chamber, and establishing a partial pressure ratio of 1,2-DCB gas to methane gas in the processing chamber. The partial pressure ratio is between 0 and 3. The method further includes generating a plasma, thereafter, exposing the at least a portion of the substrate to the methane gas, the 1,2-DCB gas, and the plasma, and growing the graphene nanostripes coupled to the at least a portion of the substrate.

Owner:CALIFORNIA INST OF TECH

Carbon Nanoflake Compositions and Methods of Production

InactiveUS20090011241A1Enhanced vapor depositionMore vertical orientationMaterial nanotechnologySynthetic resin layered productsHigh concentrationProduct gas

Novel compositions and morphologies of carbon nanoflakes are described, as well as methods for making carbon nanoflakes using a radio frequency plasma enhanced chemical vapor deposition (RF-PECVD) process. Acetylene is used as a CVD source gas. By utilizing high concentrations of acetylene in the CVD source gas at relatively low temperatures, carbon nanoflake growth rate and robustness are improved, and the resulting carbon nanoflakes have enhanced height uniformity.

Owner:COLLEGE OF WILLIAM & MARY

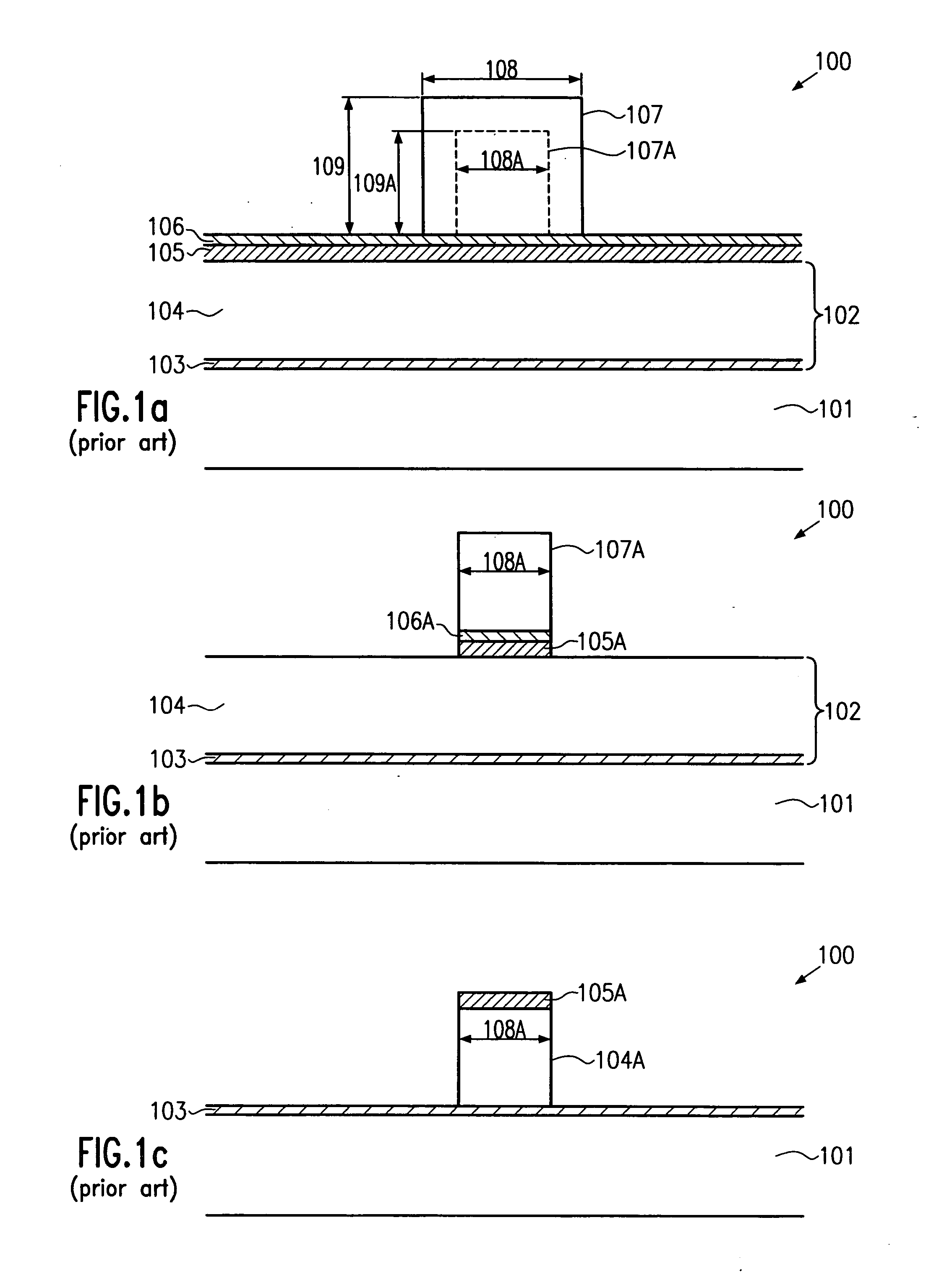

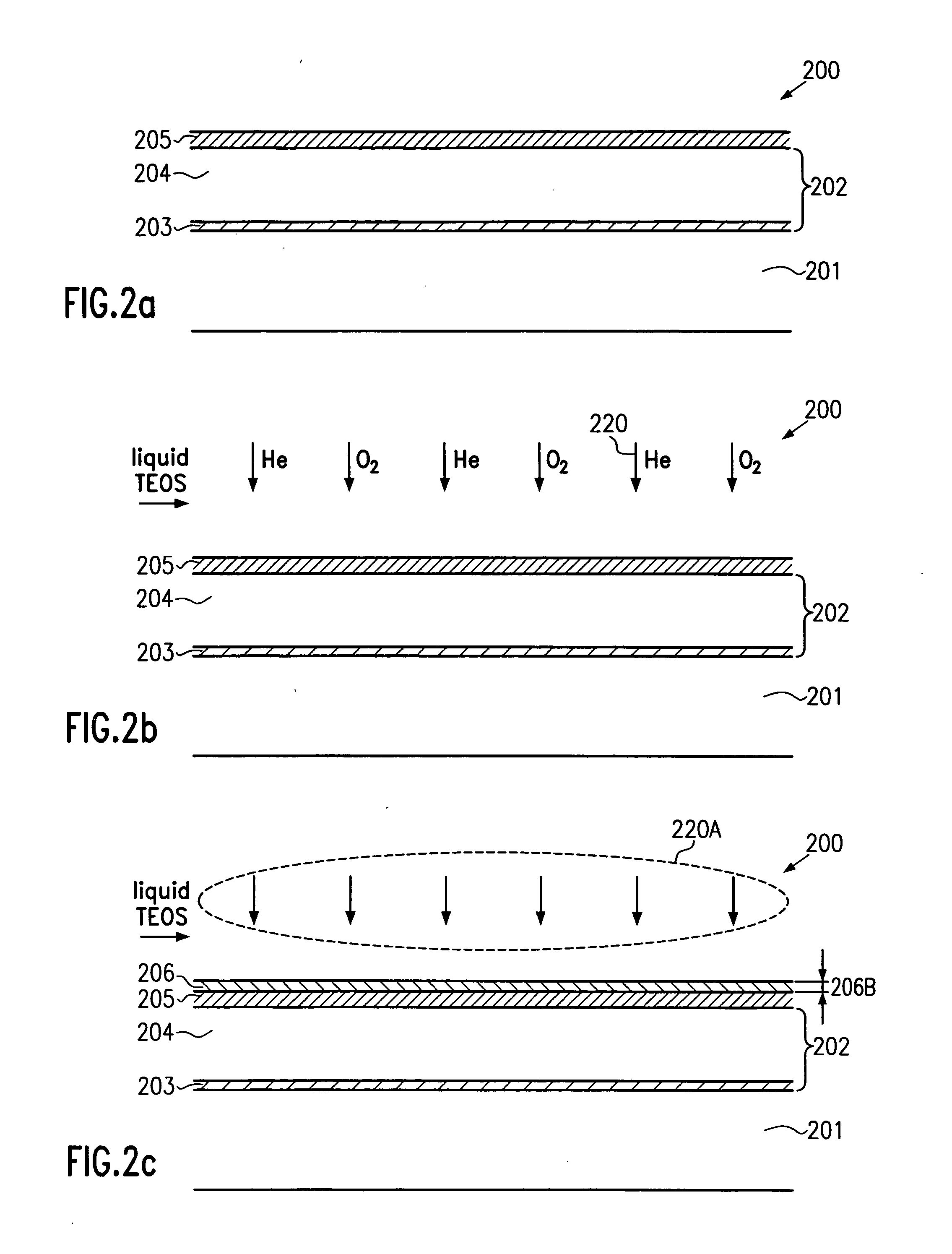

Method of forming a teos cap layer at low temperature and reduced deposition rate

InactiveUS20050048222A1Reduce defectsReliable controlSemiconductor/solid-state device manufacturingChemical vapor deposition coatingLow temperature plasmaLayer thickness

The present invention discloses a method for forming a silicon dioxide cap layer for a carbon hard mask layer for patterning of polysilicon line features having critical dimensions of 50 nm and less. To this end, a low temperature plasma enhanced CVD process is used in which the deposition rate is maintained low to provide improved controllability of the layer thickness and, thus, of the optical characteristics of the silicon dioxide layer.

Owner:GLOBALFOUNDRIES INC

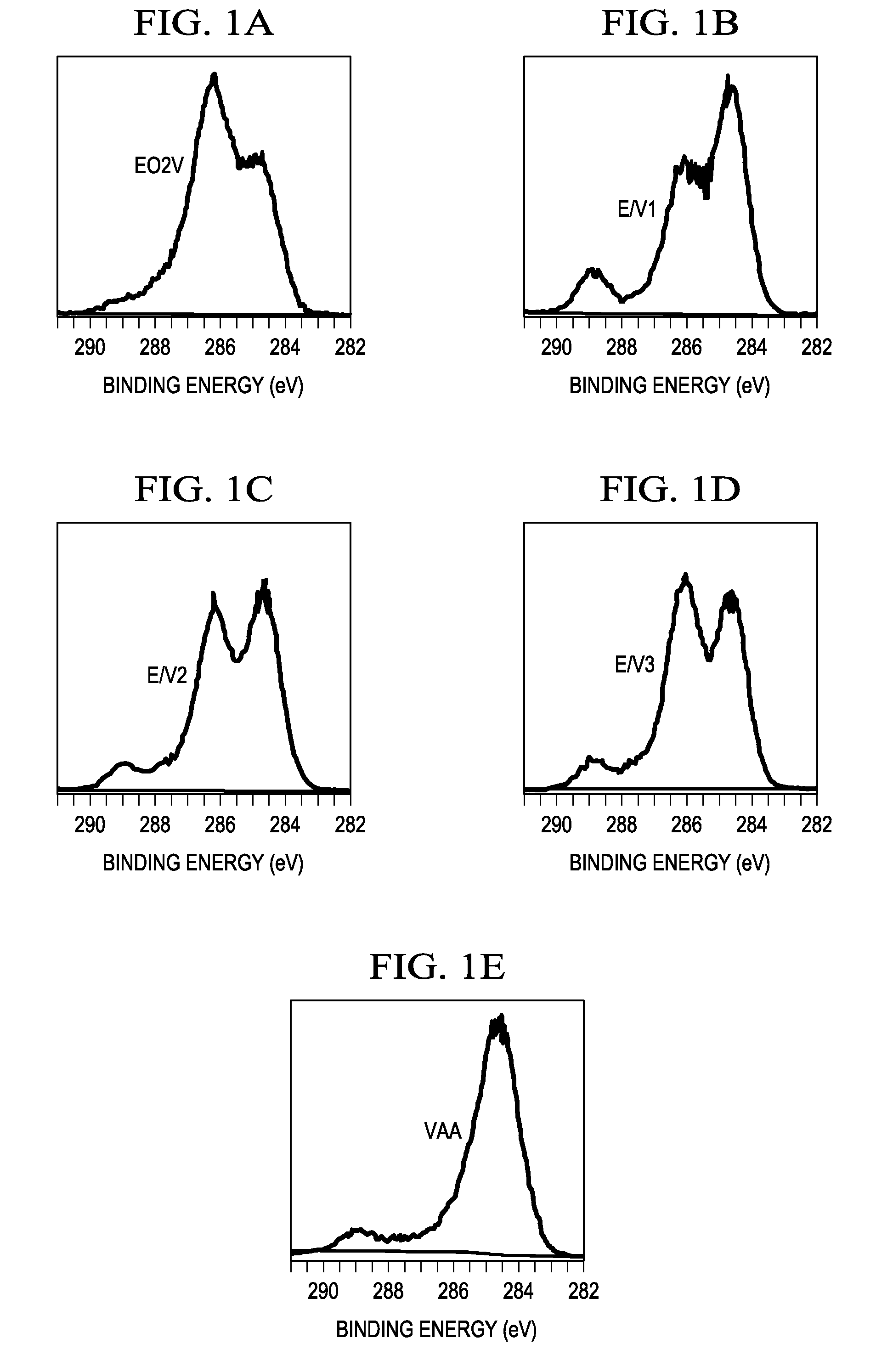

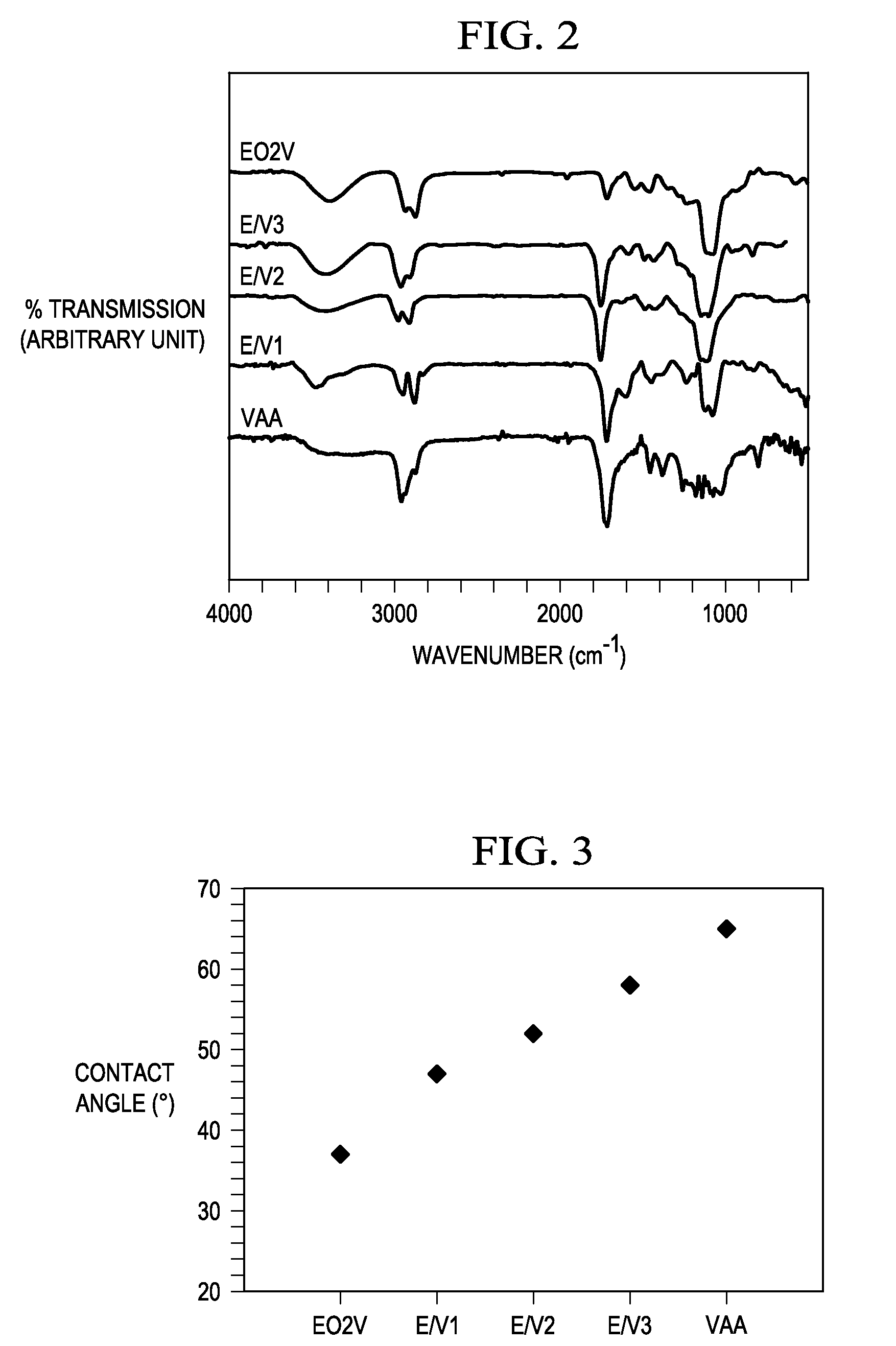

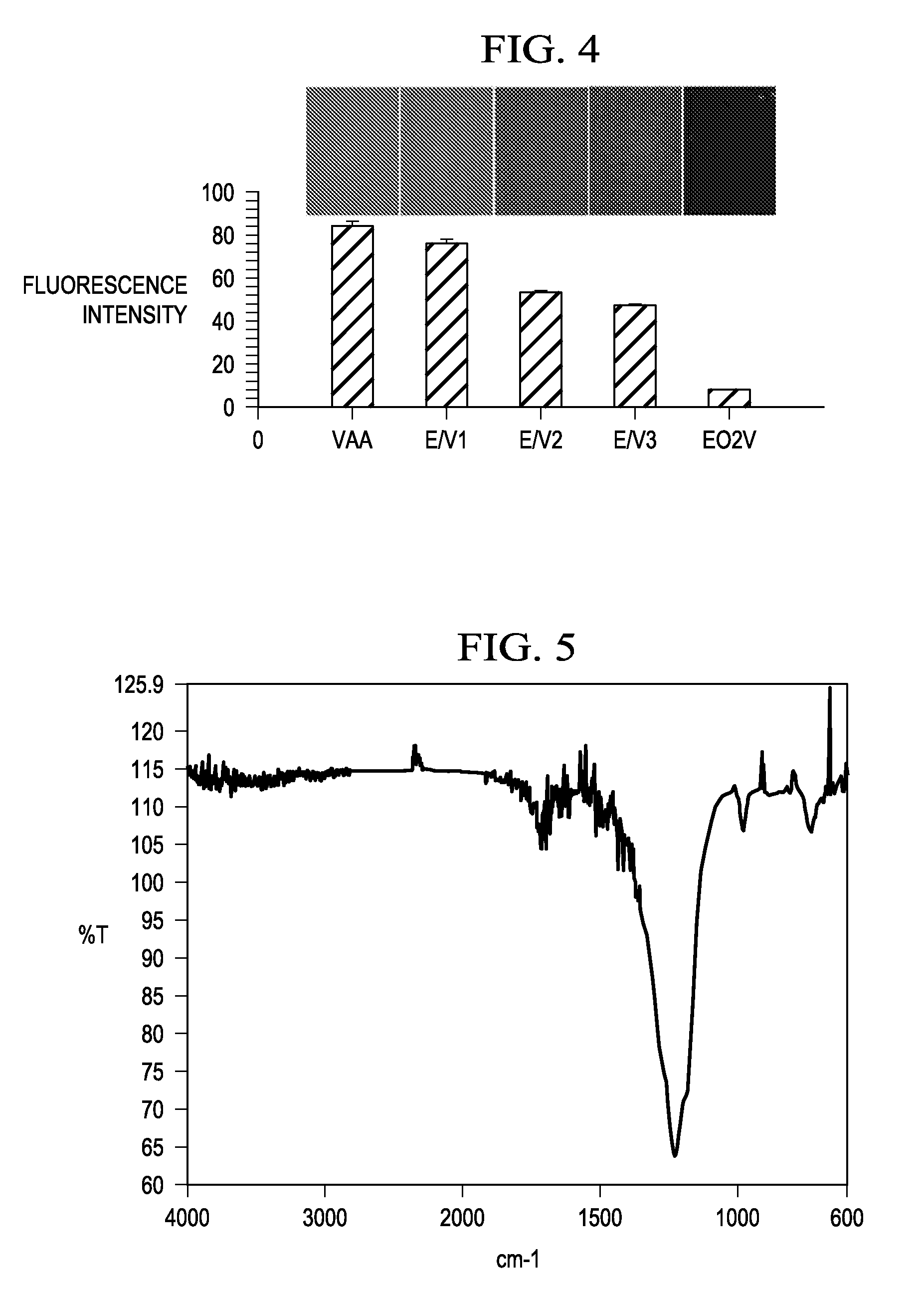

Non-Fouling Receptor Labeled Multi-Functional Surfaces

InactiveUS20100305291A1Reduce adsorptionDegrading moisture resistancePlasma techniquePolymer scienceMonomer

The present invention provides compositions and methods of forming a multifunctional polymer film by plasma discharge by providing one or more monomers to a plasma discharge reactor, wherein the one or more monomers comprising one or more functional groups; polymerizing the one or more monomers into a multifunctional polymer; and forming a polymer film from the multifunctional polymer on a surface.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST +1

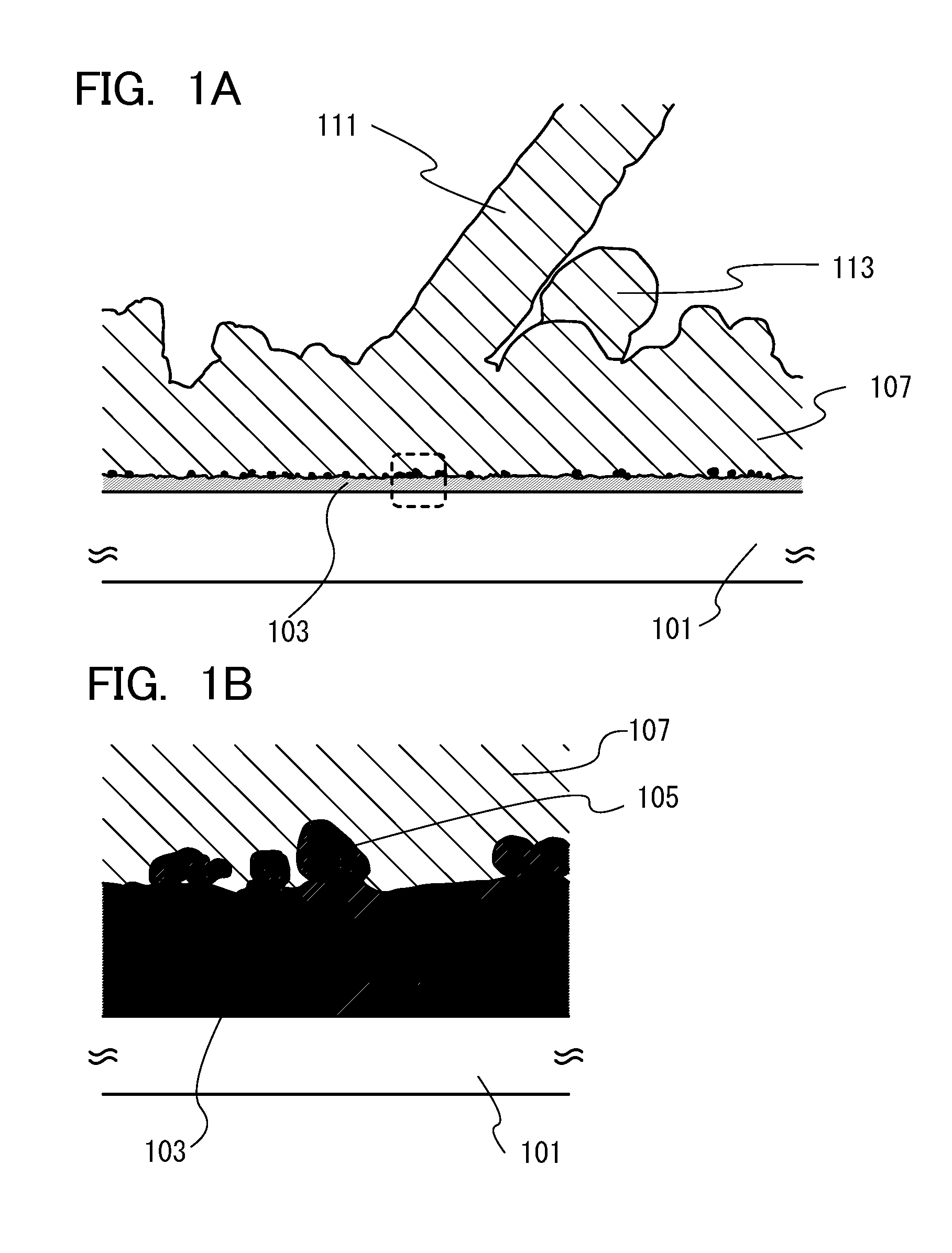

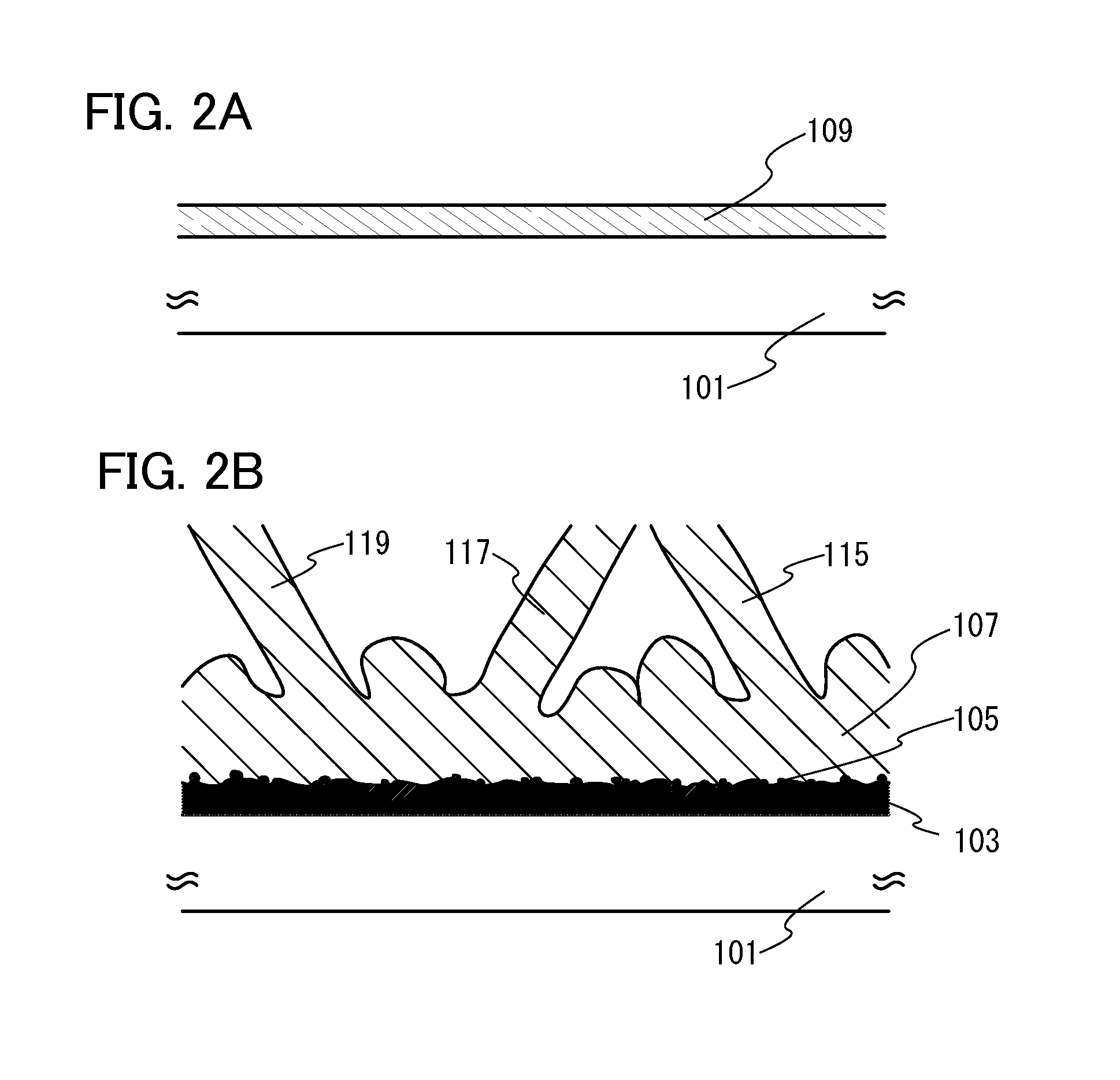

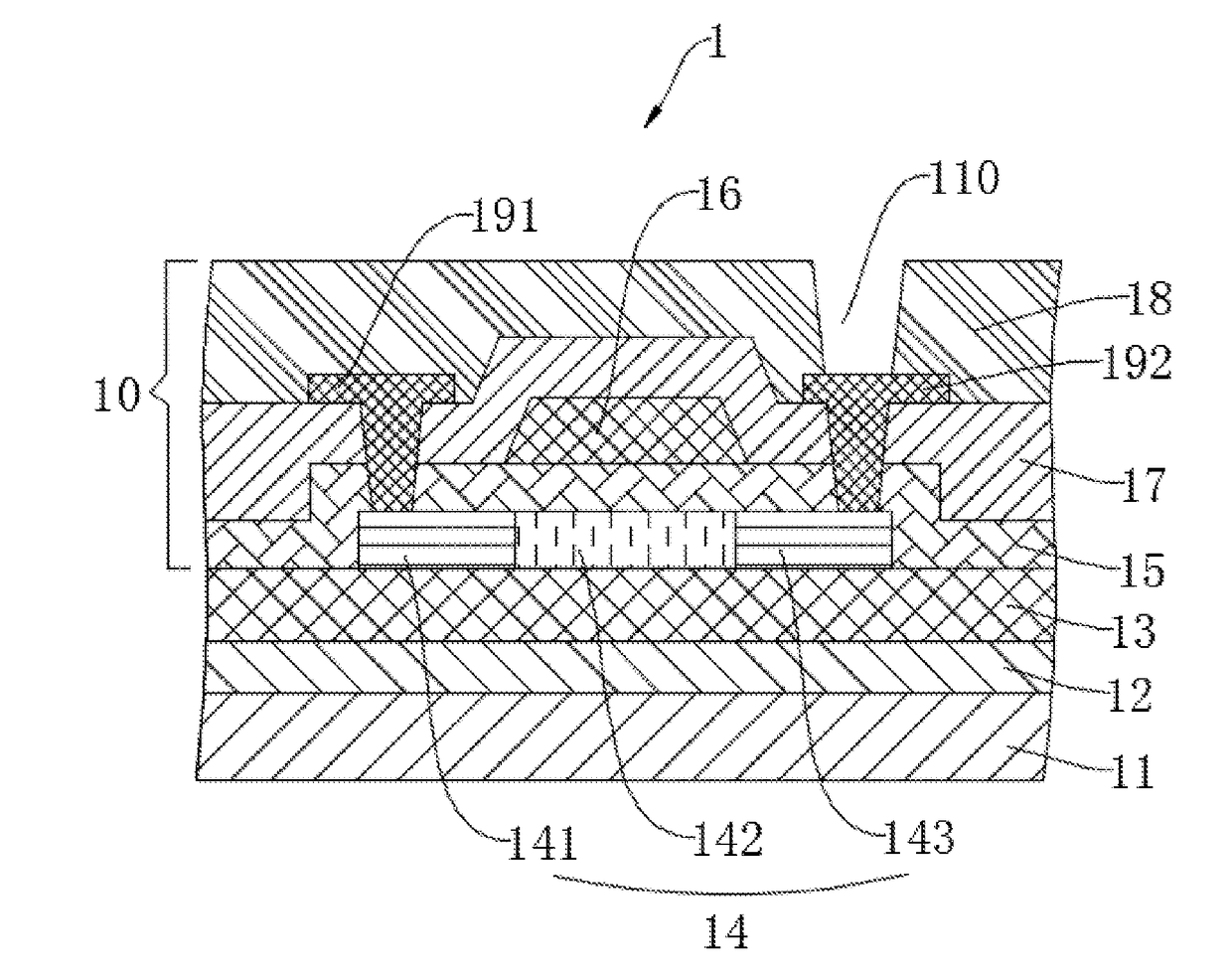

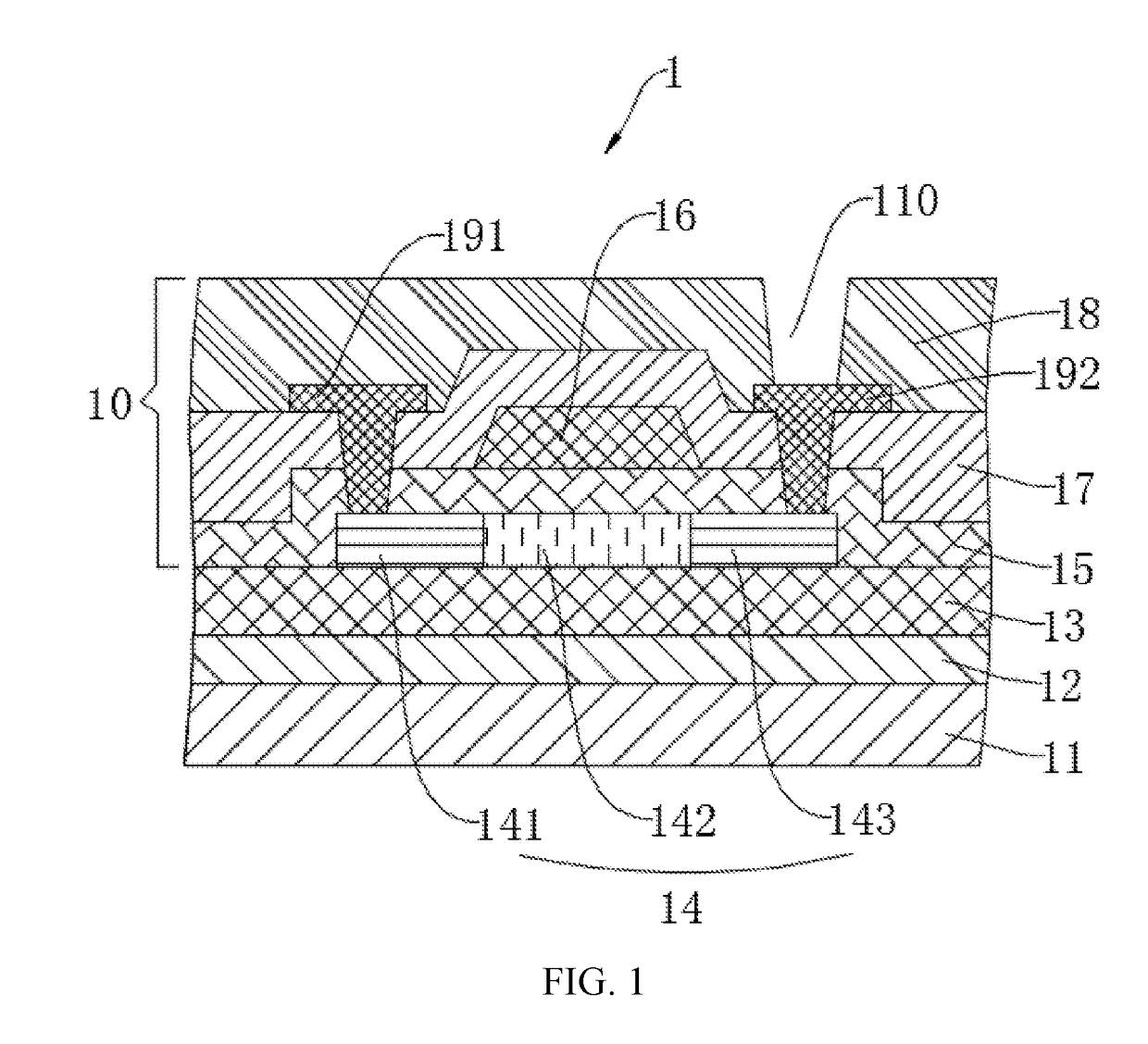

Semiconductor film, method for manufacturing the same, and power storage device

ActiveUS20120135302A1High charge and discharge capacityEnhanced vapor depositionHybrid capacitor electrodesSemiconductor/solid-state device detailsHigh densityCharge discharge

Provided are a semiconductor film including silicon microstructures formed at high density, and a manufacturing method thereof. Further, provided are a semiconductor film including silicon microstructures whose density is controlled, and a manufacturing method thereof Furthermore, a power storage device with improved charge-discharge capacity is provided. A manufacturing method in which a semiconductor film with a silicon layer including silicon structures is formed over a substrate with a metal surface is used. The thickness of a silicide layer formed by reaction between the metal and the silicon is controlled, so that the grain sizes of silicide grains formed at an interface between the silicide layer and the silicon layer are controlled and the shapes of the silicon structures are controlled. Such a semiconductor film can be applied to an electrode of a power storage device.

Owner:SEMICON ENERGY LAB CO LTD

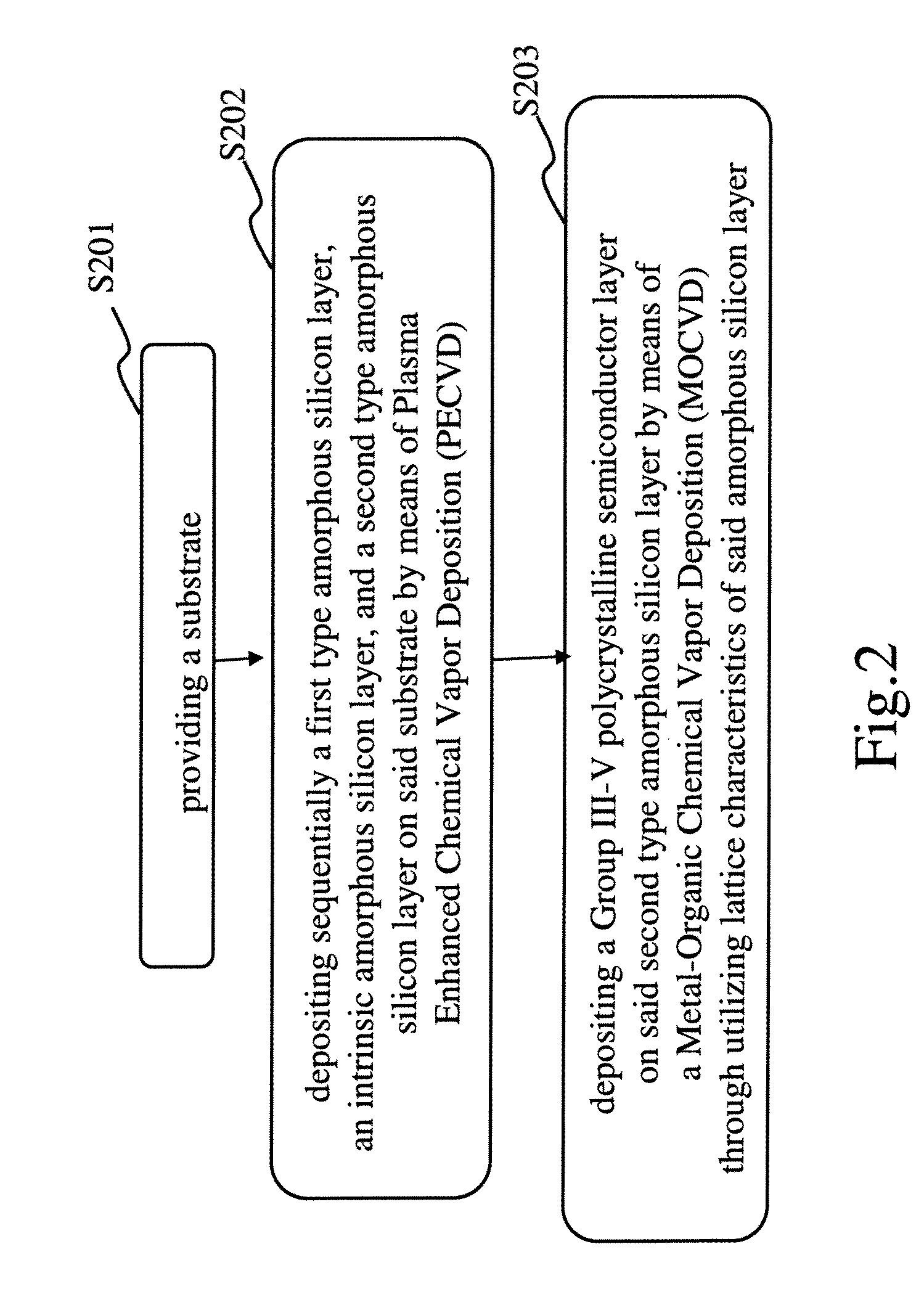

Group iii-v solar cell and method of manufacturing the same

InactiveUS20110308607A1Improve photoelectric conversion efficiencyEnhanced Vapor DepositionFinal product manufactureSemiconductor/solid-state device manufacturingAmorphous siliconPhotoelectric conversion

A Group III-V solar cell and a manufacturing method thereof, wherein, three amorphous silicon layers are formed on a substrate, which includes a first type amorphous silicon layer, an intrinsic amorphous silicon layer, and a second type amorphous silicon layer. The lattice characteristics of amorphous silicon layer are utilized, and a Group III-V polycrystalline semiconductor layer is formed on said amorphous silicon layer, such that amorphous silicon and Group III-V material are able to perform photoelectric conversion simultaneously in raising photoelectric conversion efficiency of said Group III-V solar cell effectively by means of a direct energy gap of said Group III-V material.

Owner:CHING NEW ENERGY MACHINERY & EQUIP

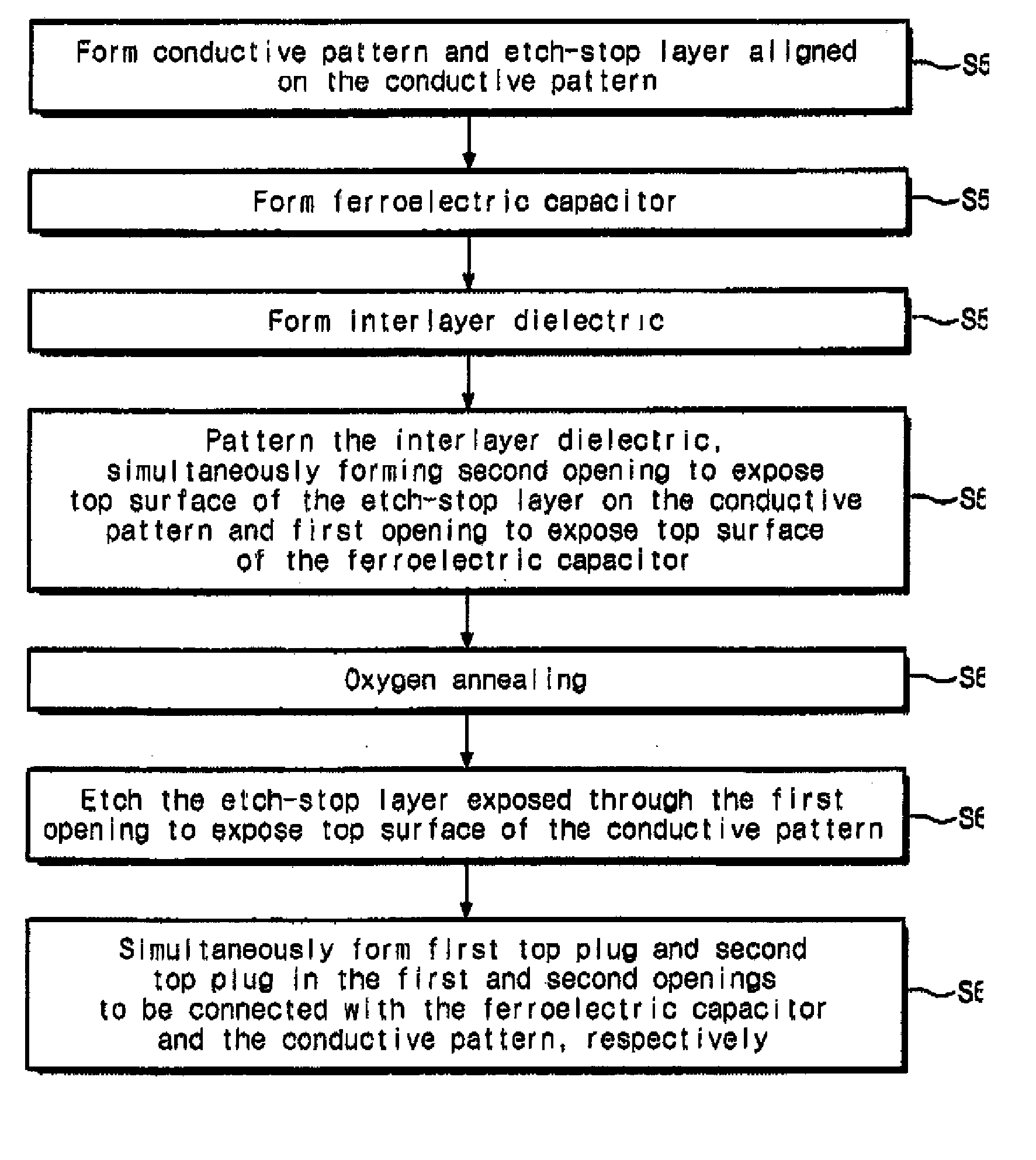

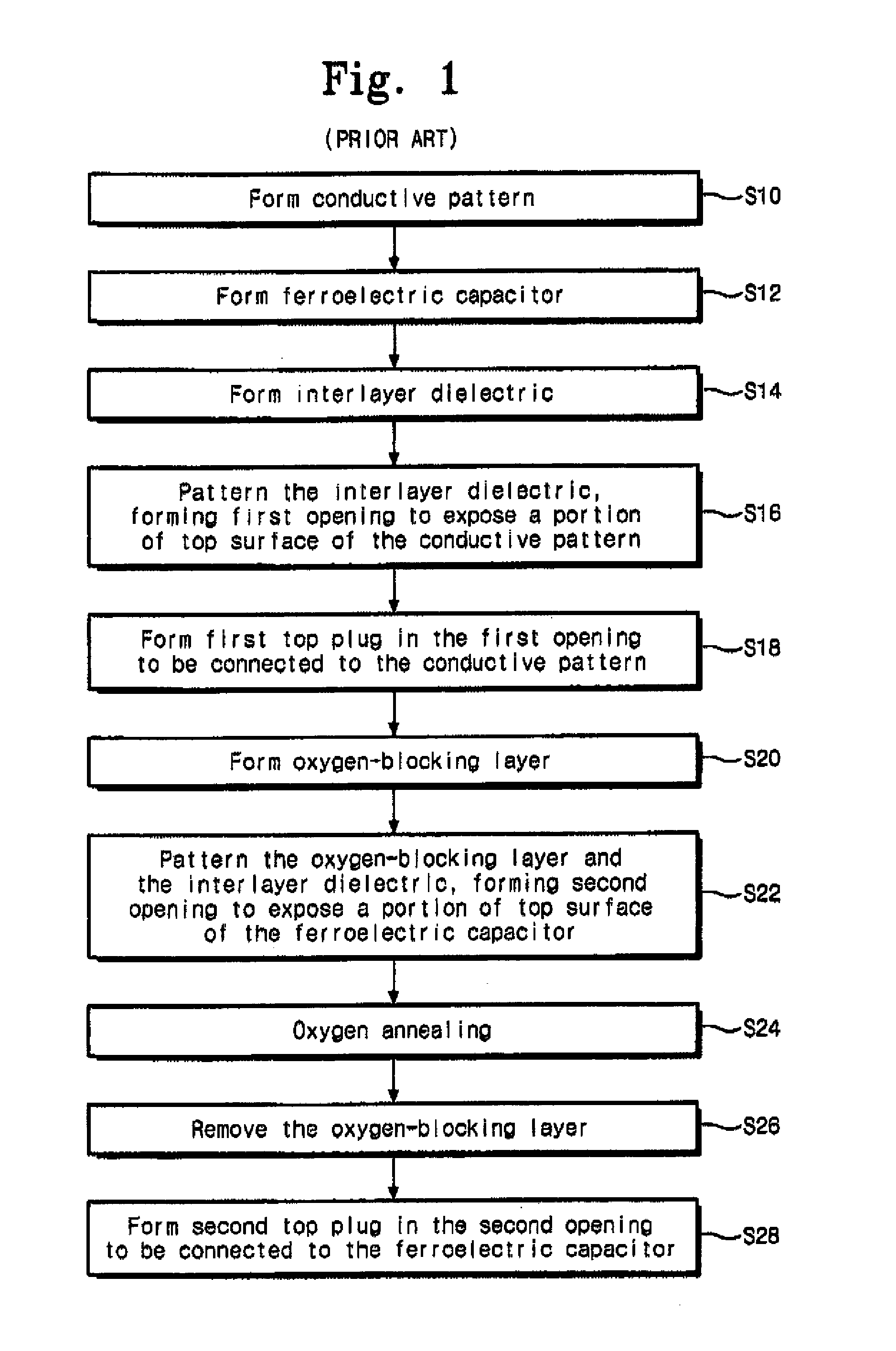

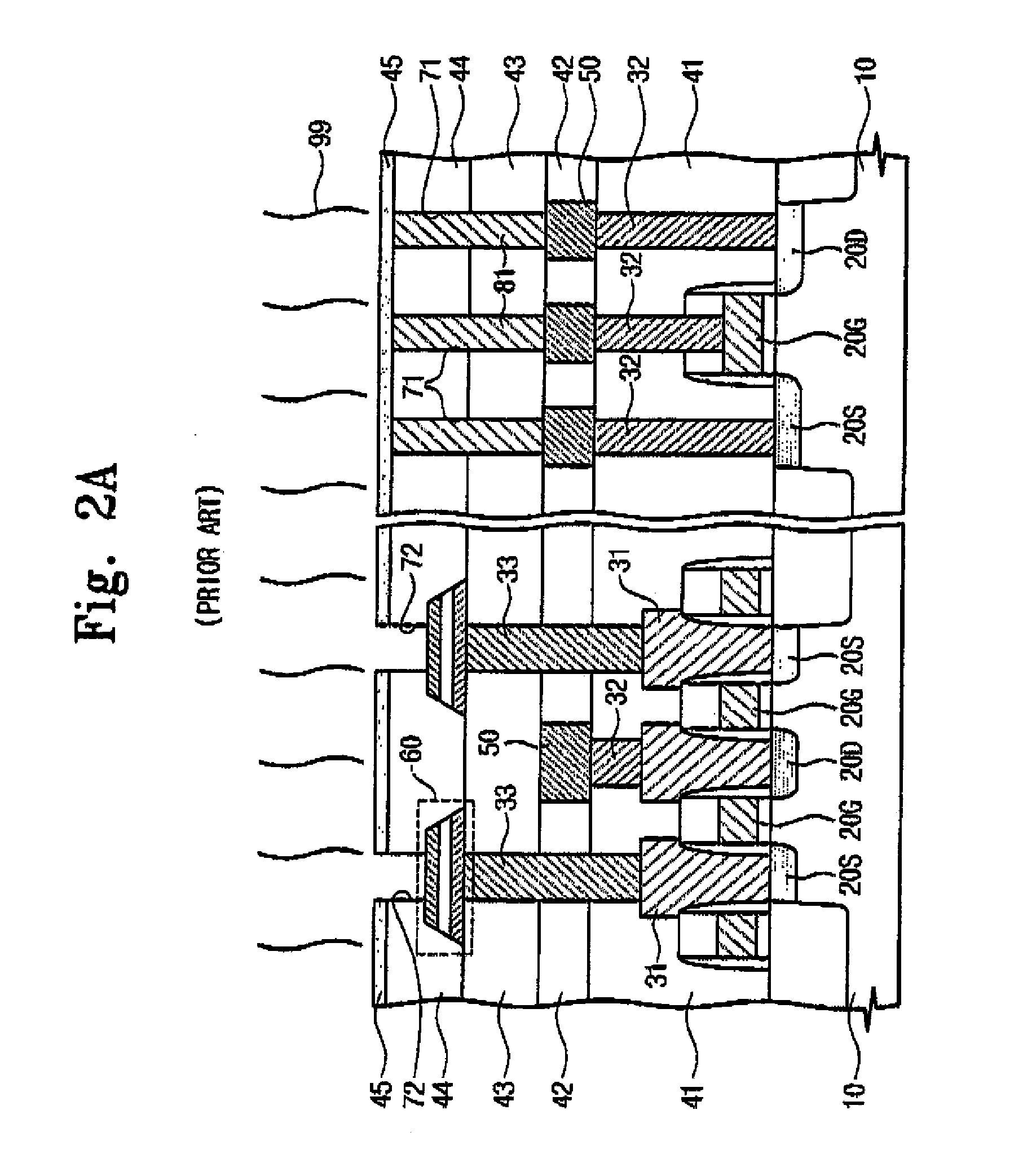

Ferroelectric random access memory and methods of fabricating the same

InactiveUS20080087926A1Enhanced vapor depositionPrevent penetrationTransistorSolid-state devicesDielectricRandom access memory

A method of forming a ferroelectric random access memory includes sequentially forming a conductive pattern, an etch-stop layer, a ferroelectric capacitor and an interlayer dielectric on a semiconductor substrate, which includes a first region and a second region. The ferroelectric capacitor is formed on the first region and the conductive pattern is formed on the second region. The interlayer dielectric is patterned to simultaneously form a first opening to expose a top surface of the ferroelectric capacitor and a second opening to expose a top surface of the etch-stop layer. The patterned interlayer dielectric is annealed in an ambient atmosphere, including oxygen atoms. The etch-stop layer exposed through the second opening is etched to expose a top surface of the conductive pattern. First and second top plugs are formed to connect to the ferroelectric capacitor and the conductive pattern through the first and second openings, respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

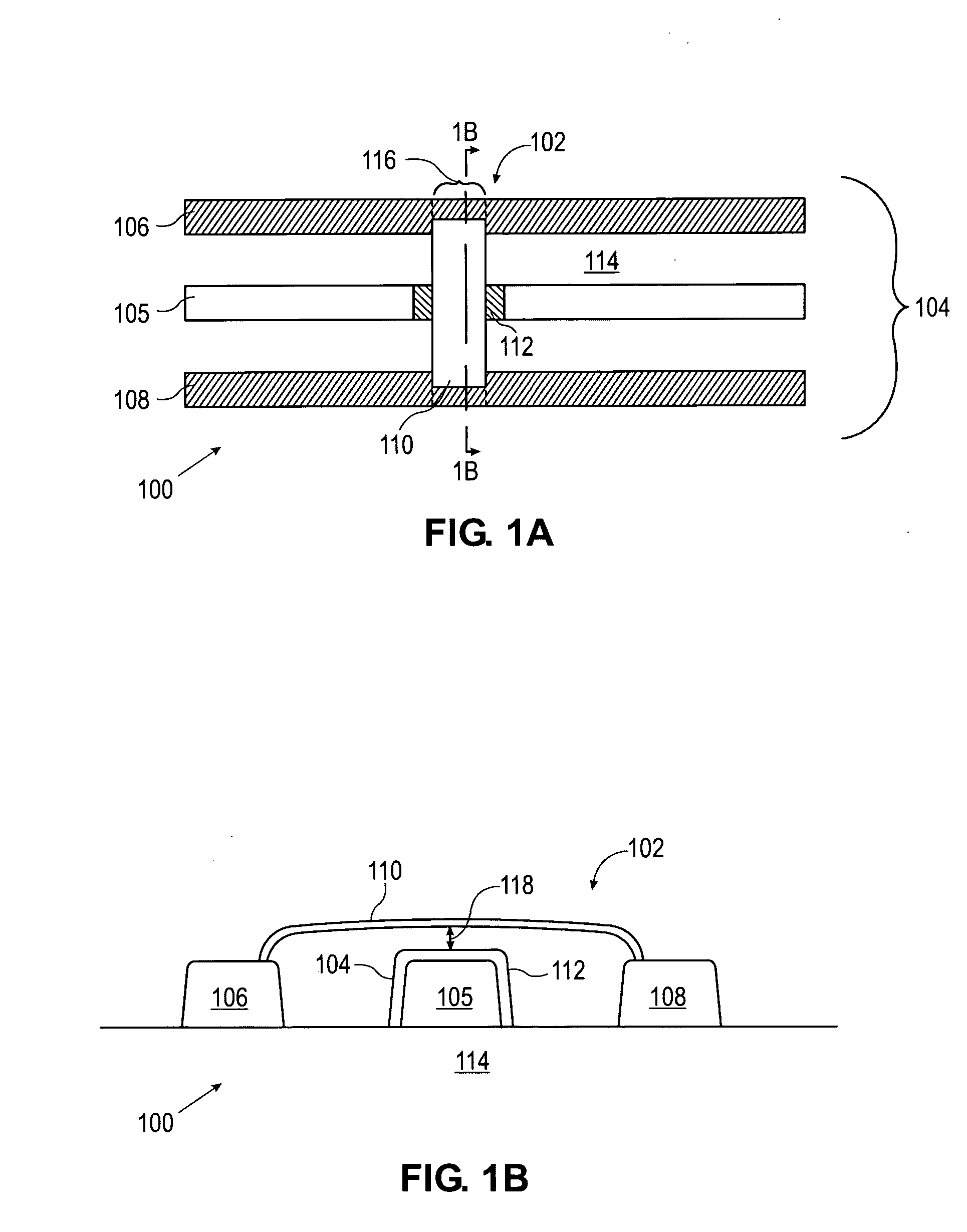

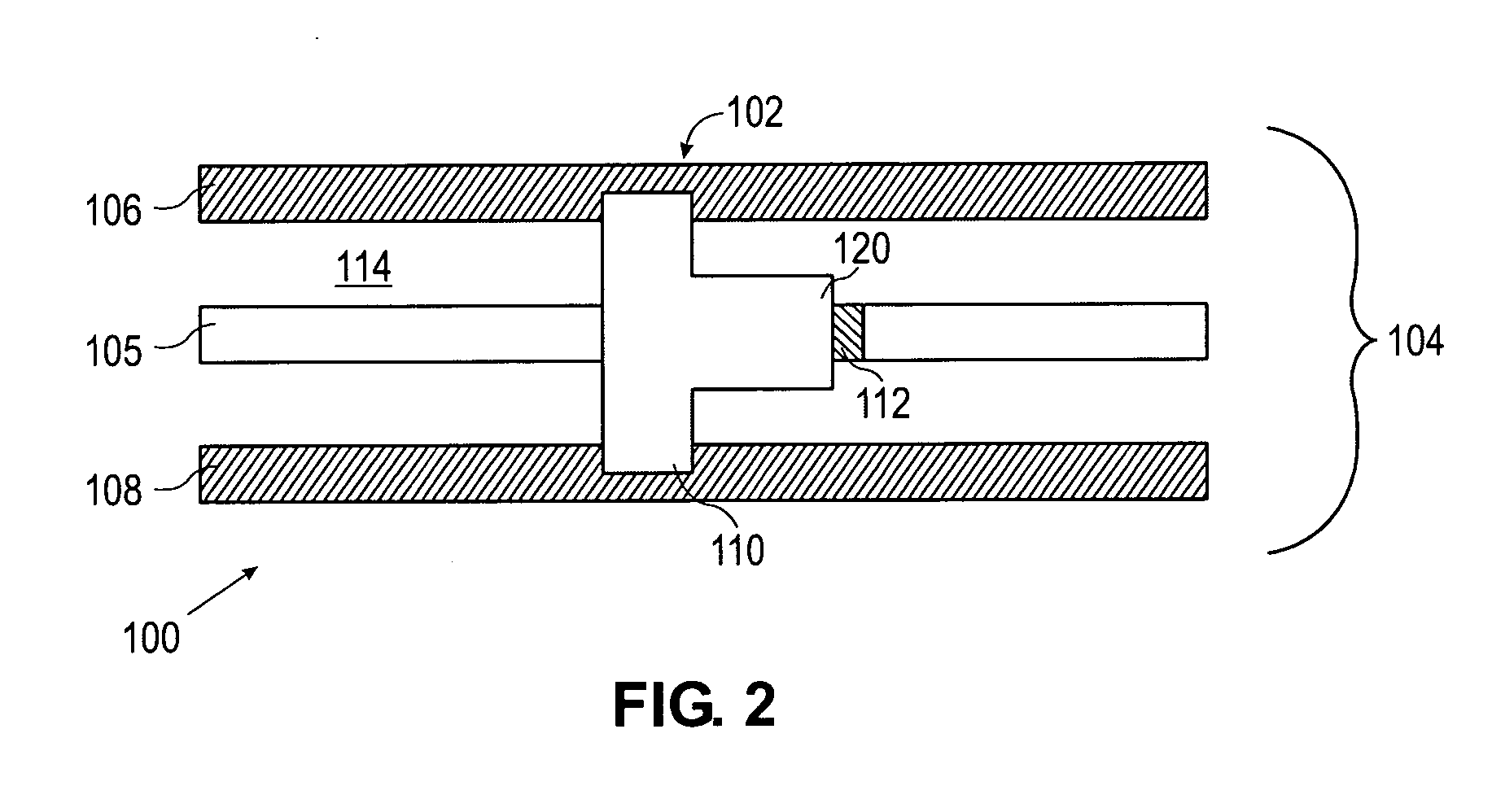

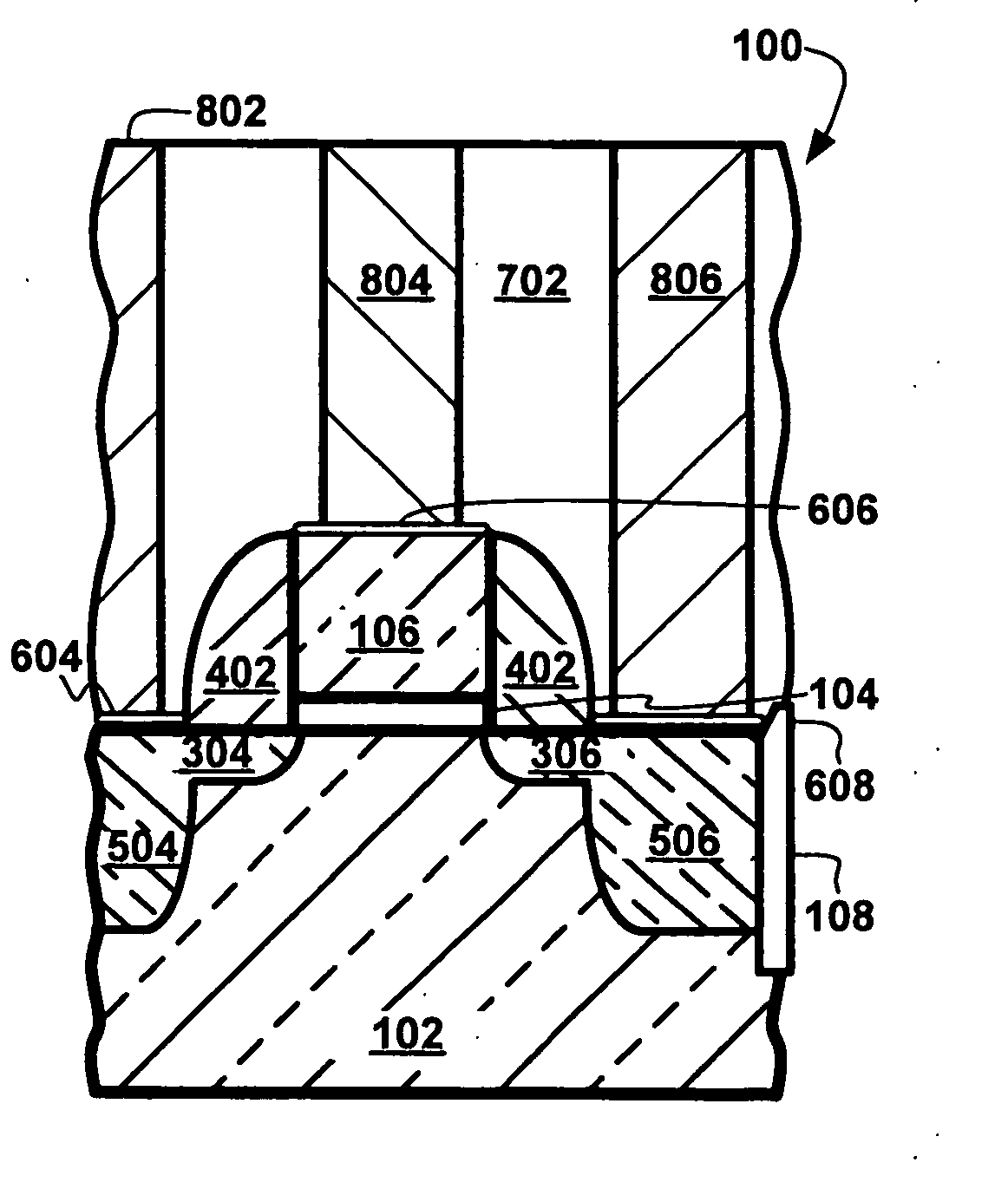

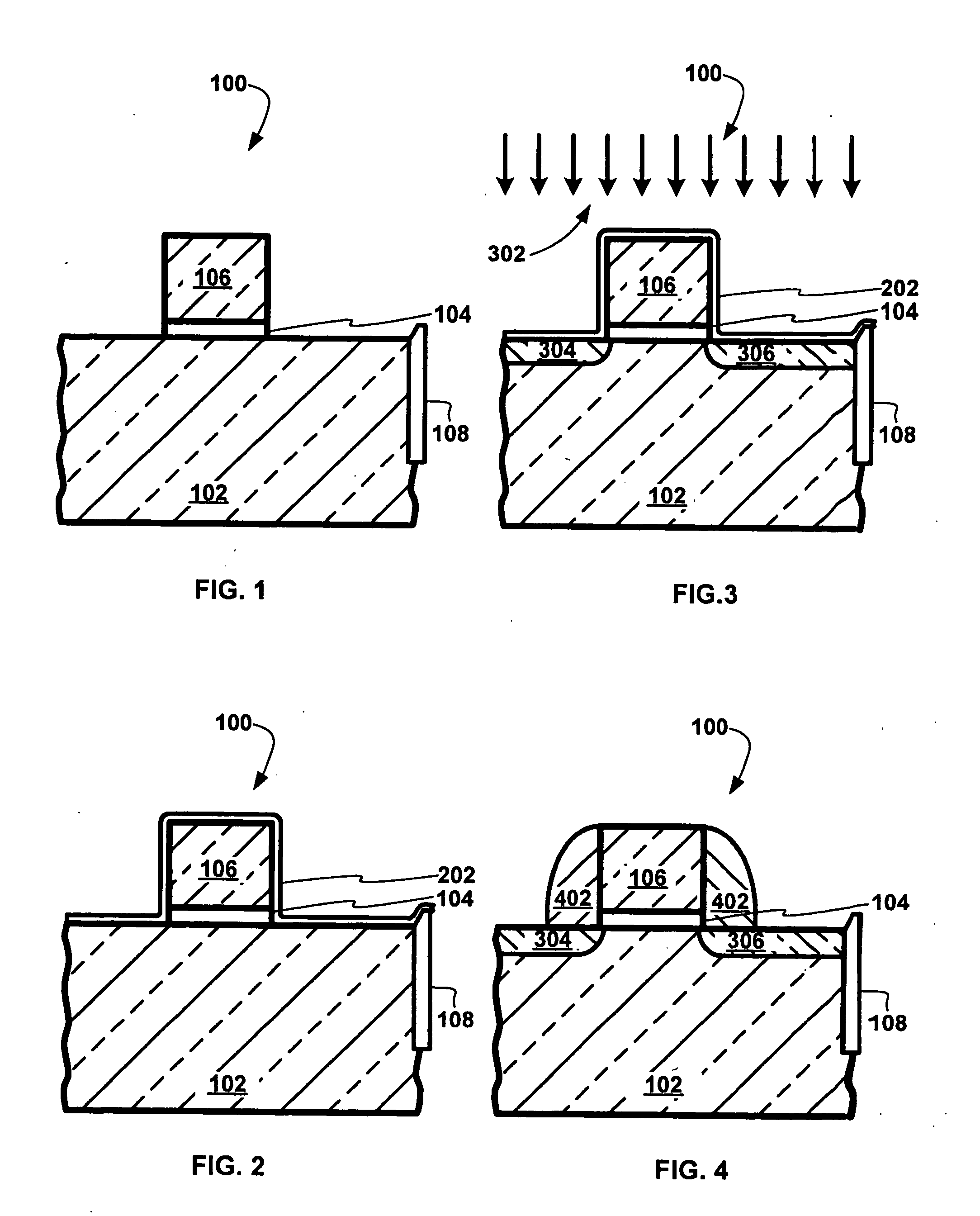

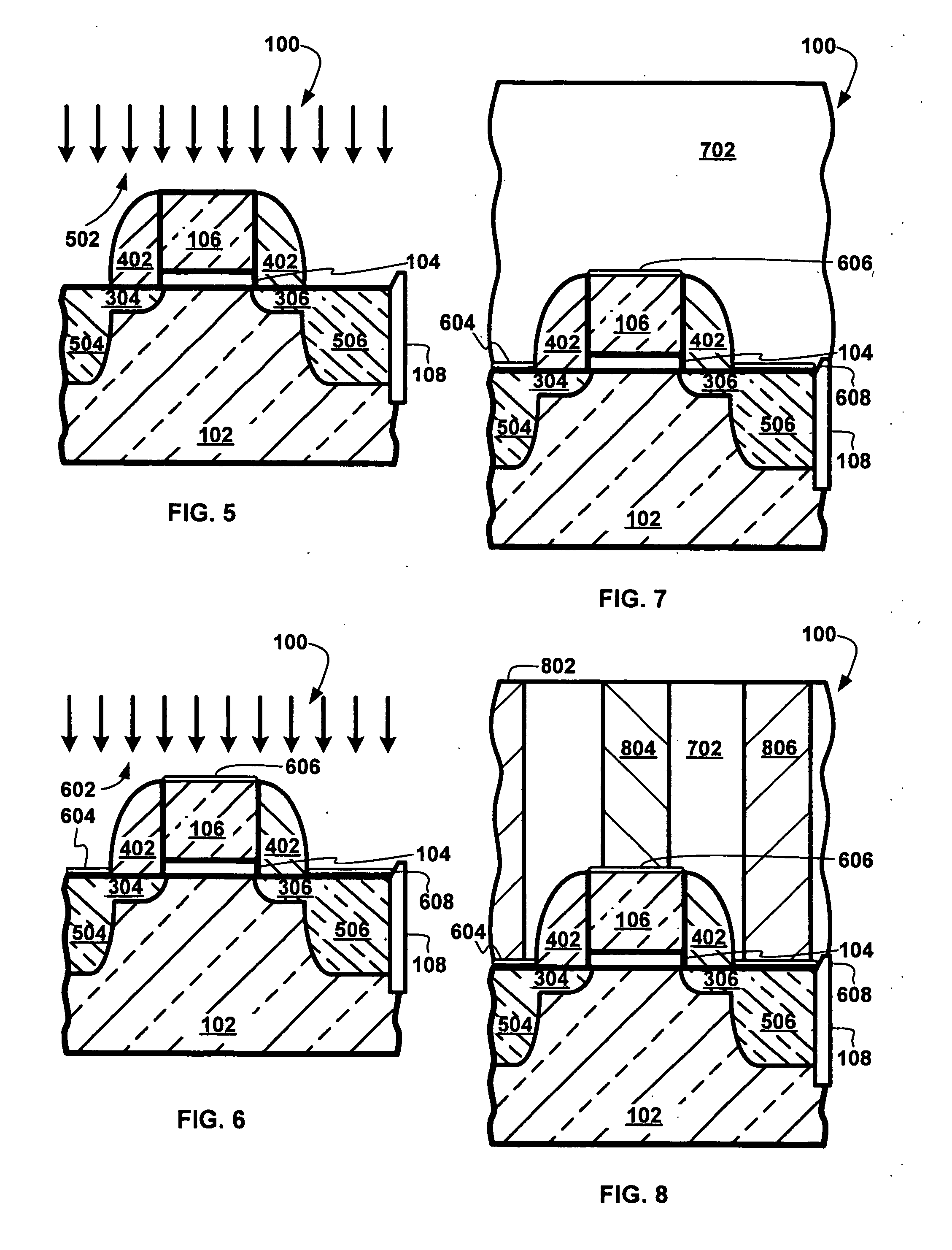

Low stress sidewall spacer in integrated circuit technology

ActiveUS20050153496A1Lower resistanceImprove performanceTransistorSemiconductor/solid-state device manufacturingSalicideDielectric

A method of forming an integrated circuit with a semiconductor substrate is provided. A gate dielectric is formed on the semiconductor substrate, and a gate is formed on the gate dielectric. Source / drain junctions are formed in the semiconductor substrate. A sidewall spacer is formed around the gate using a low power plasma enhanced chemical vapor deposition process A silicide is formed on the source / drain junctions and on the gate, and an interlayer dielectric is deposited above the semiconductor substrate. Contacts are then formed in the interlayer dielectric to the silicide.

Owner:INNOVATIVE FOUNDRY TECH LLC

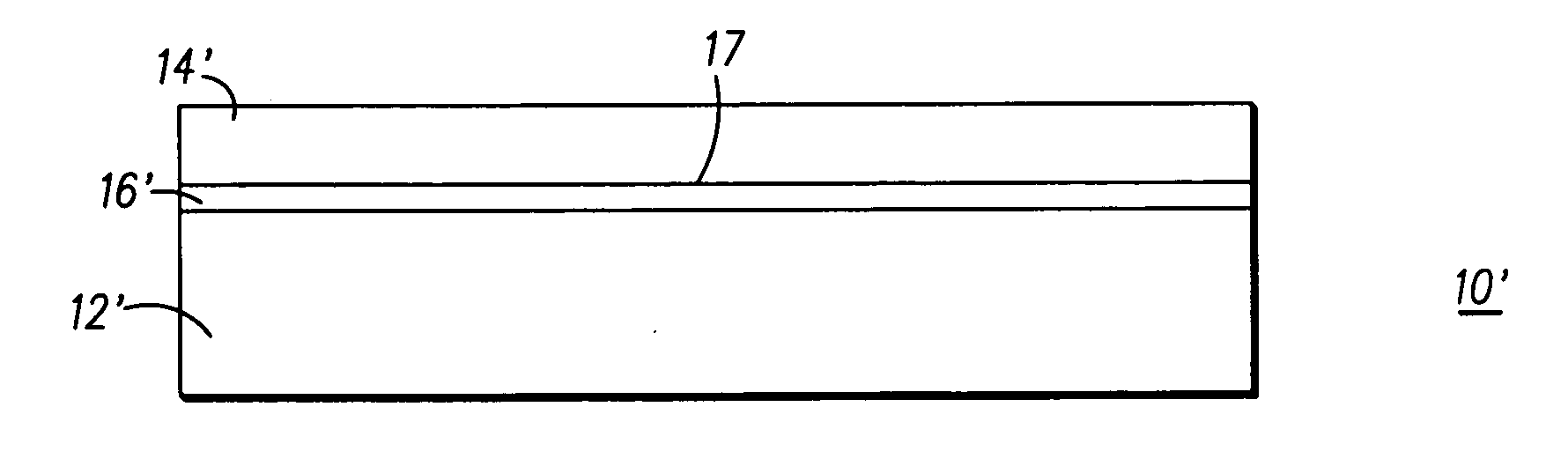

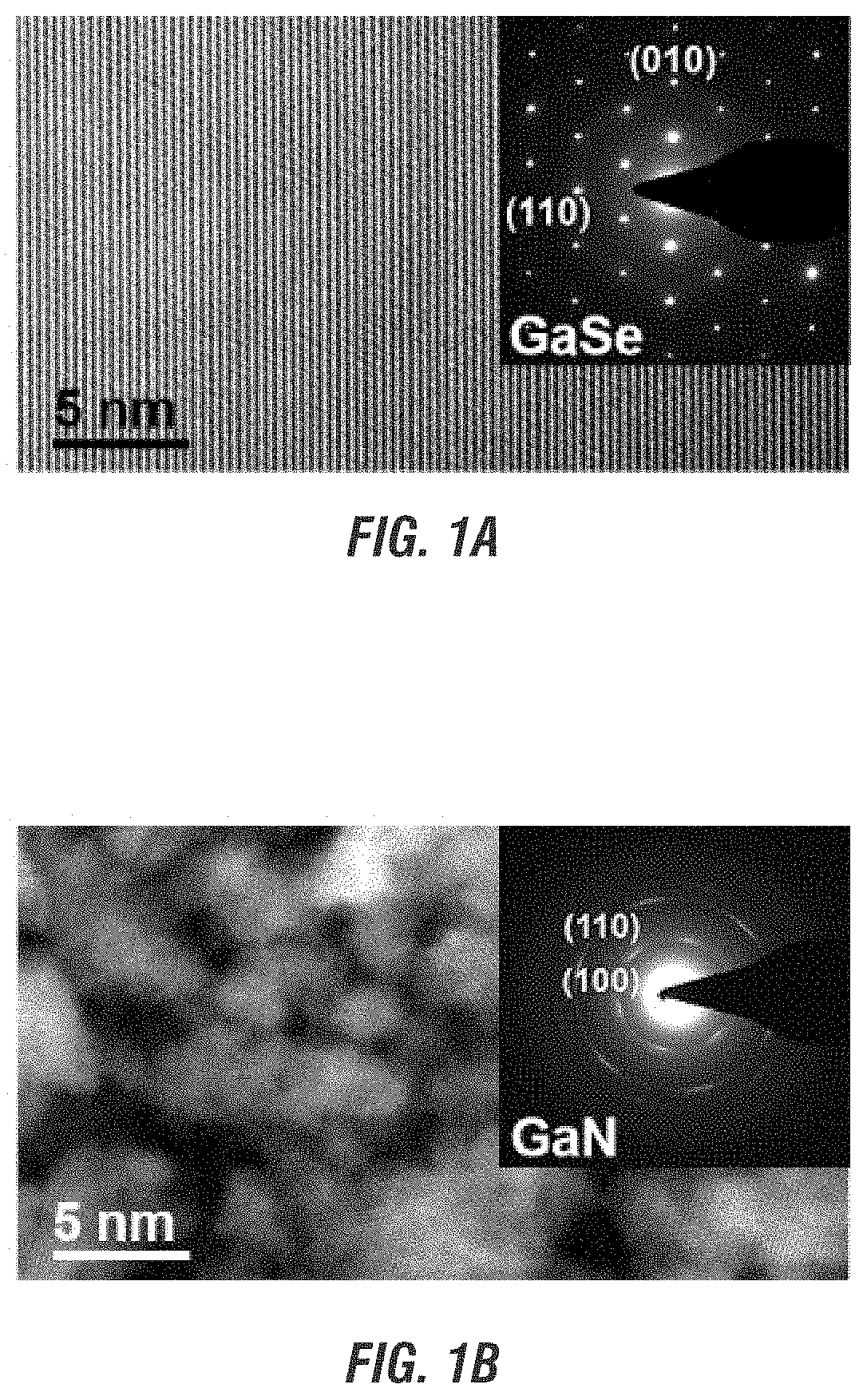

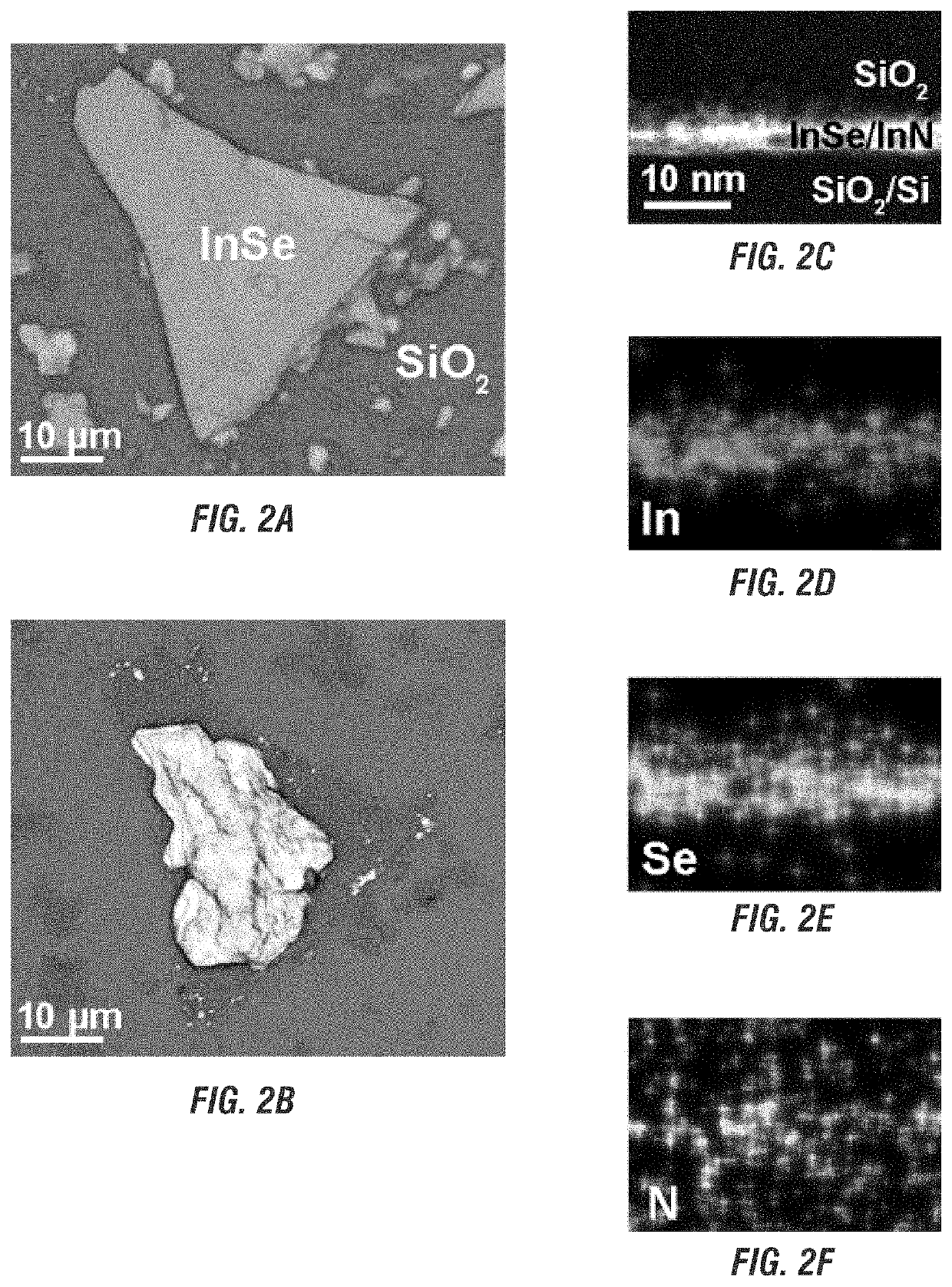

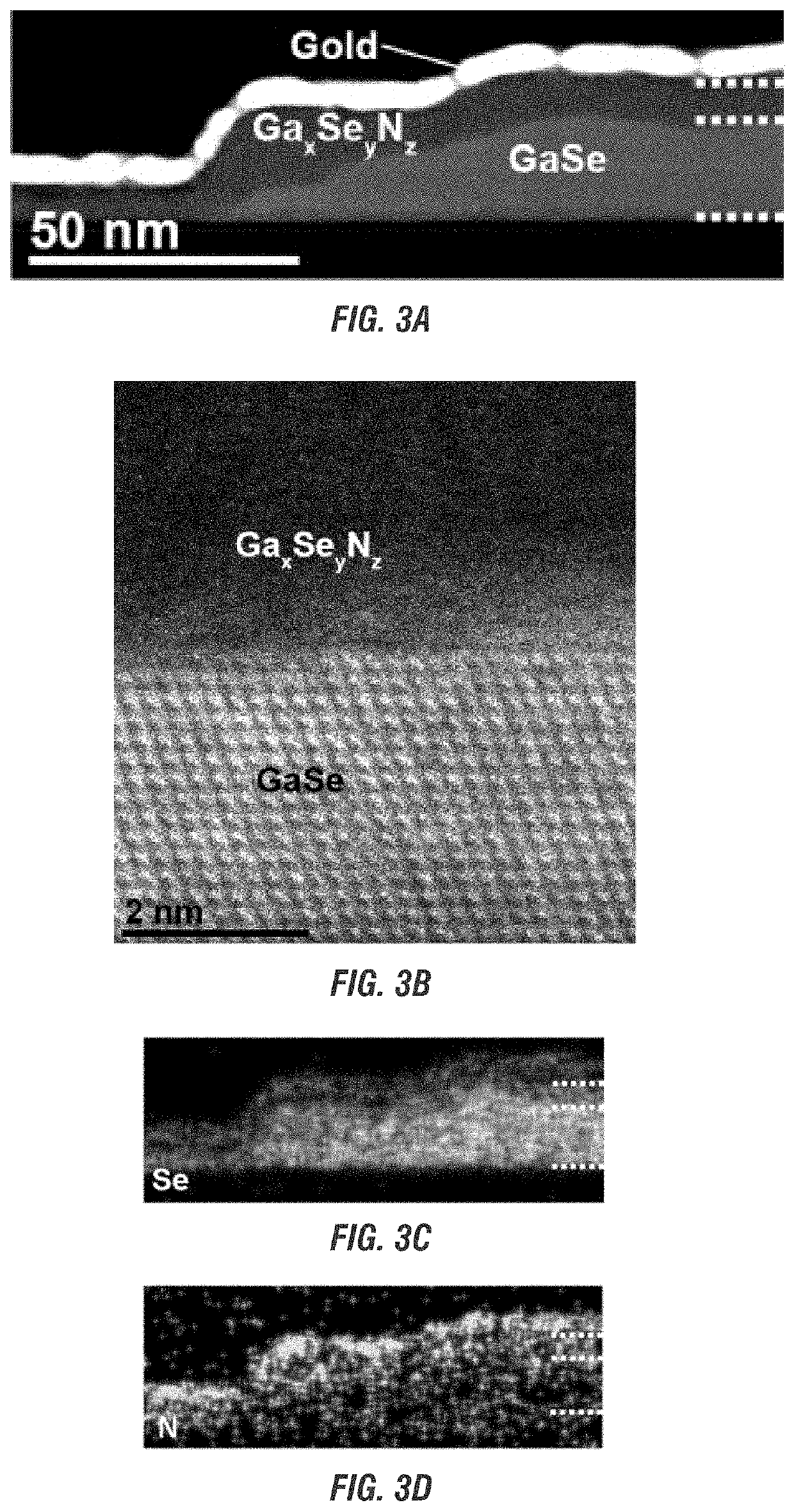

Method of growing crystalline layers on amorphous substrates using two-dimensional and atomic layer seeds

ActiveUS20210217617A1Enhanced vapor depositionPolycrystalline material growthFrom solid stateThin membraneMaterials science

This disclosure relates to methods of growing crystalline layers on amorphous substrates by way of an ultra-thin seed layer, methods for preparing the seed layer, and compositions comprising both. In an aspect of the invention, the crystalline layers can be thin films. In a preferred embodiment, these thin films can be free-standing.

Owner:PENN STATE RES FOUND

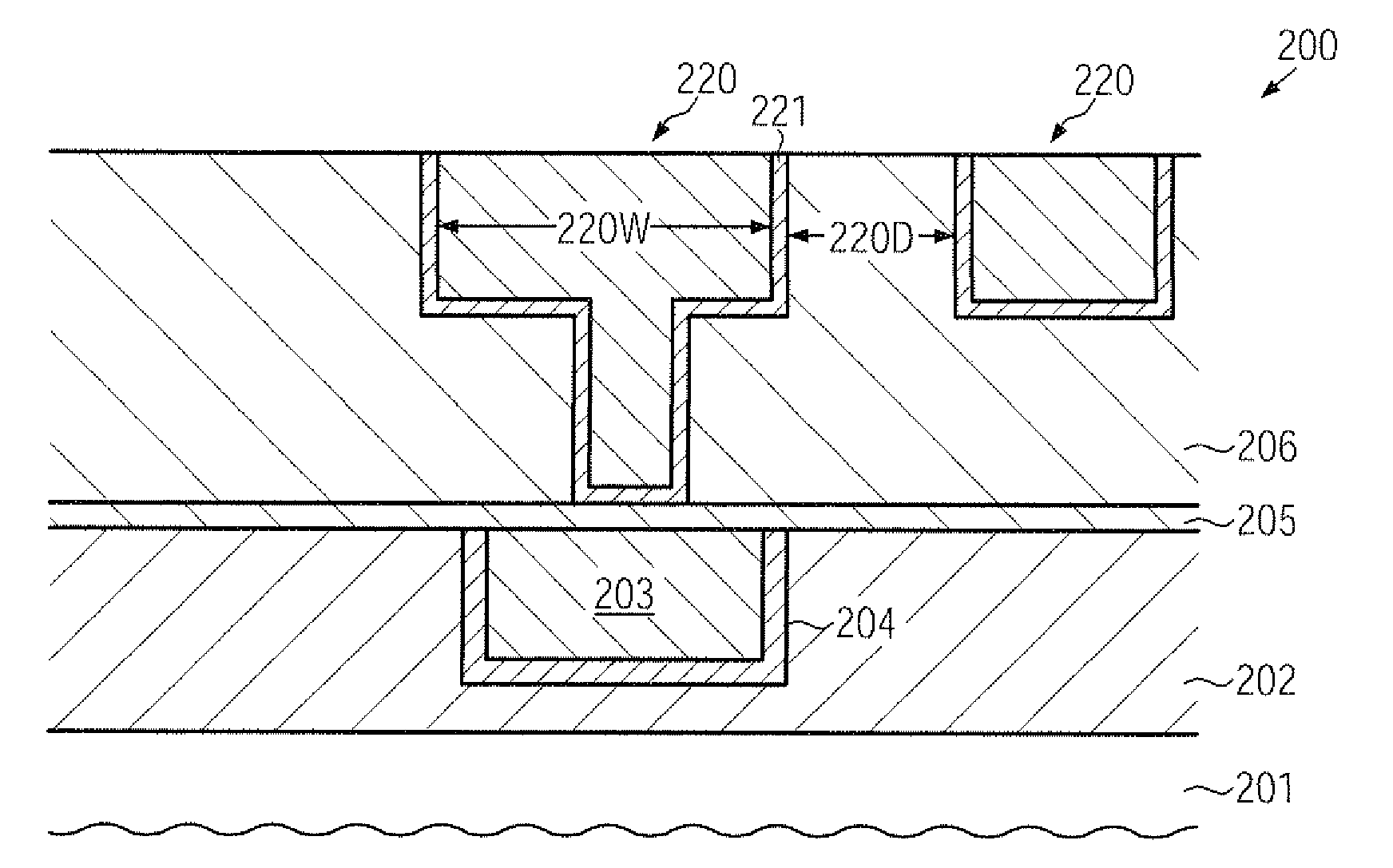

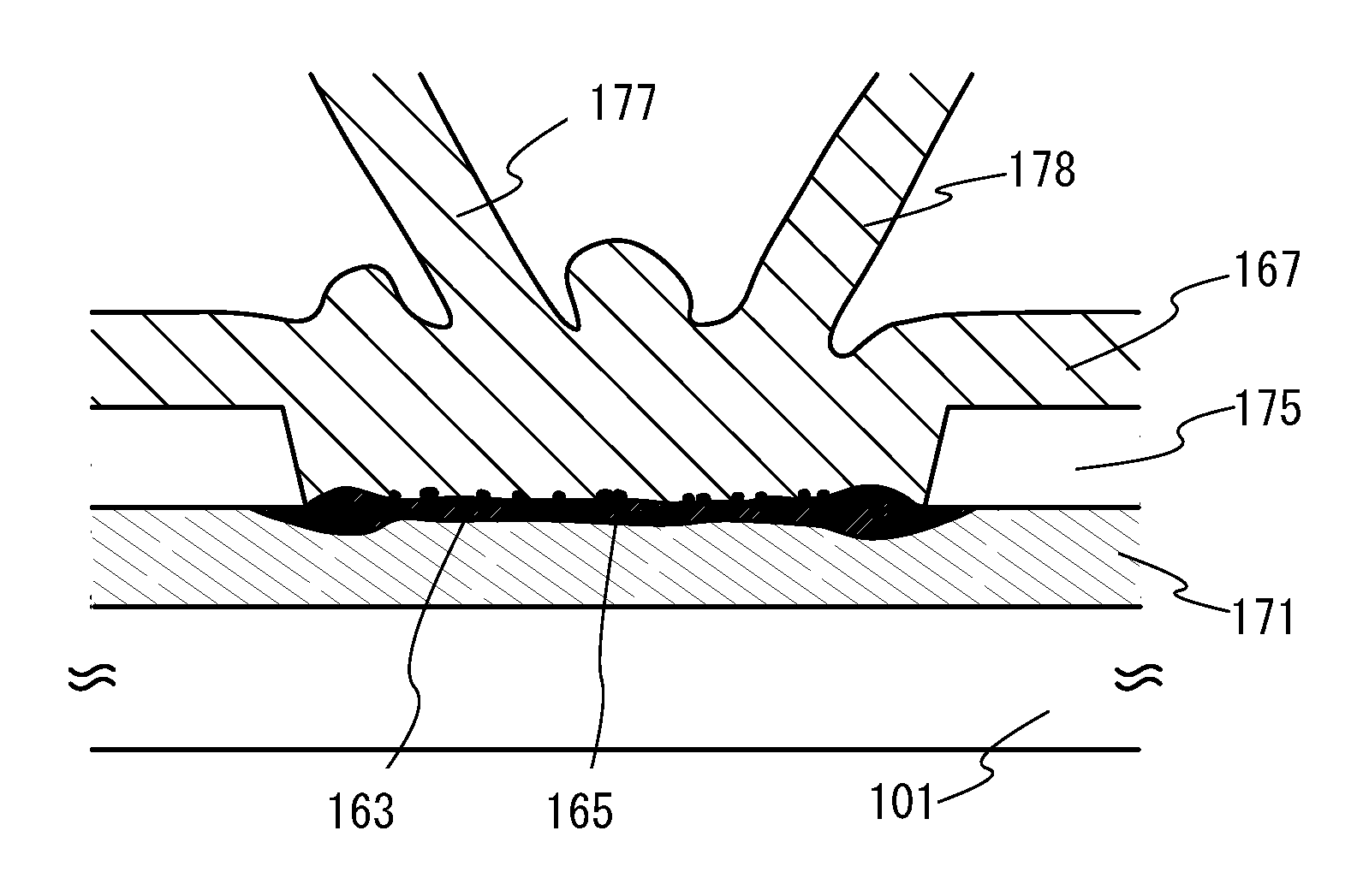

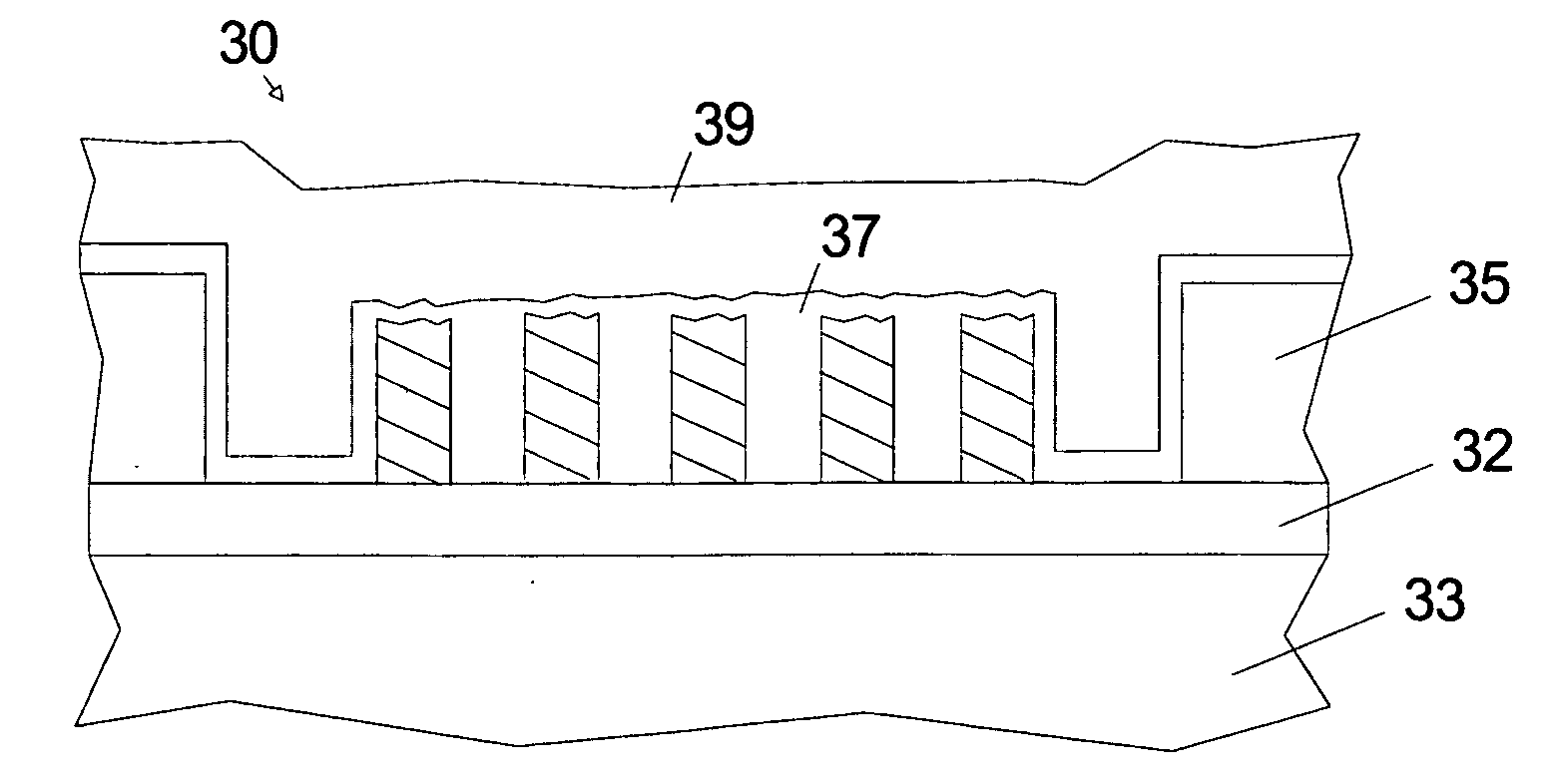

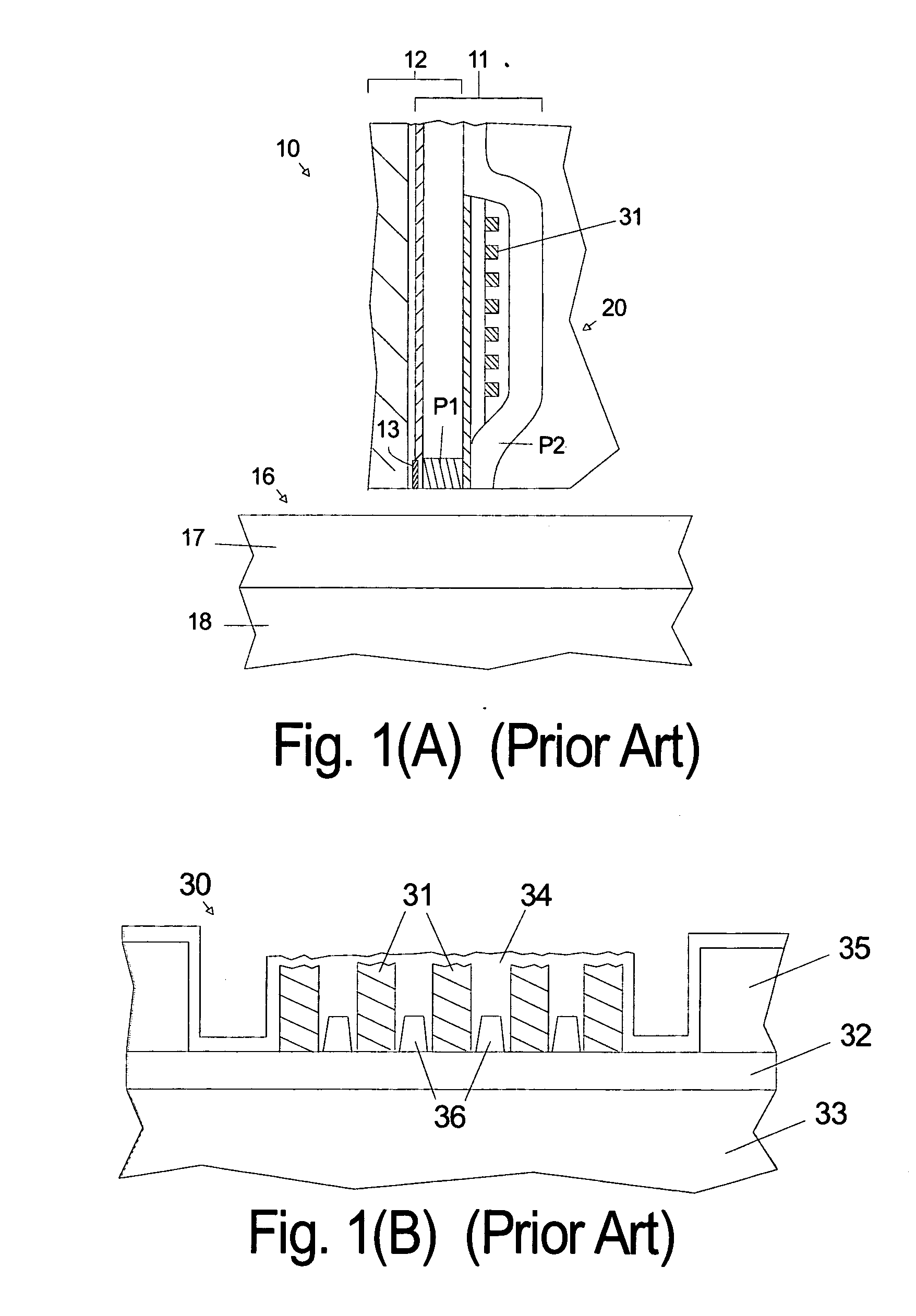

Method for using CVD process to encapsulate coil in a magnetic write head

InactiveUS20060215313A1Improvement in thermal protrusion characteristicEnhanced Vapor DepositionConstruction of head windingsElectrical transducersGas phaseThermal expansion

Applicant discloses a method for fabricating a magnetic write head with a coil with a high aspect ratio using a Chemical Vapor Deposition process such as Atomic Layer Deposition (ALD), High Speed ALD, Plasma Enhanced ALD (PEALD), Plasma Enhanced Chemical Vapor Deposition (PECVD) or Low Pressure Chemical Vapor Deposition (LPCVD) to form encapsulating films over the coils without voids. Materials which can be used for encapsulation include Al2O3, SiO2, AlN, Ta2O5, HfO2, ZrO2, and YtO3. The use of an ultra-conformal deposition process allows the pitch of the coils to be smaller than it is possible in the prior art. The method according to the invention also allows materials with a smaller coefficient of thermal expansion than hardbake photoresist to be used with resulting improvements in thermal protrusion characteristics.

Owner:WESTERN DIGITAL TECH INC

Array substrate, display device and manufacturing method for array substrate

ActiveUS20180175078A1Reduce heat transferEnhanced Vapor DepositionFinal product manufactureSolid-state devicesMetallic materialsDisplay device

An array substrate is disclosed. The array substrate includes: a substrate adopting an organic material; an isolation layer adopting a metal material, and the isolation layer is formed on the substrate; and a buffering layer formed at a side of the isolation layer away from the substrate. In the array substrate of the present invention, in a high-temperature PECVD process, a pollution problem caused by the plasma directly bombarding the substrate made of an organic material can be avoid. A display device applying the array substrate and a manufacturing method for an array substrate are also disclosed.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com