Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7368results about How to "Reduce contact resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

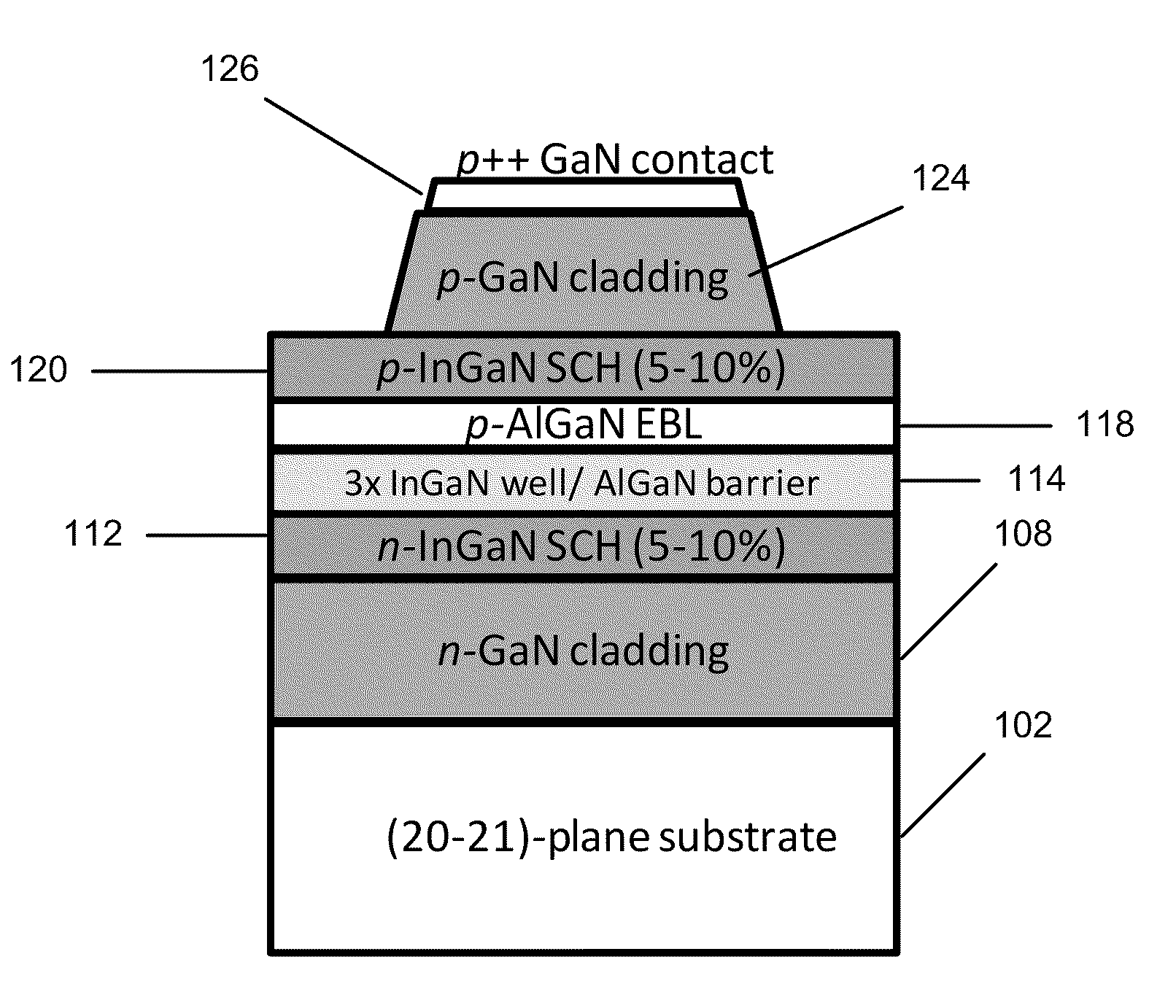

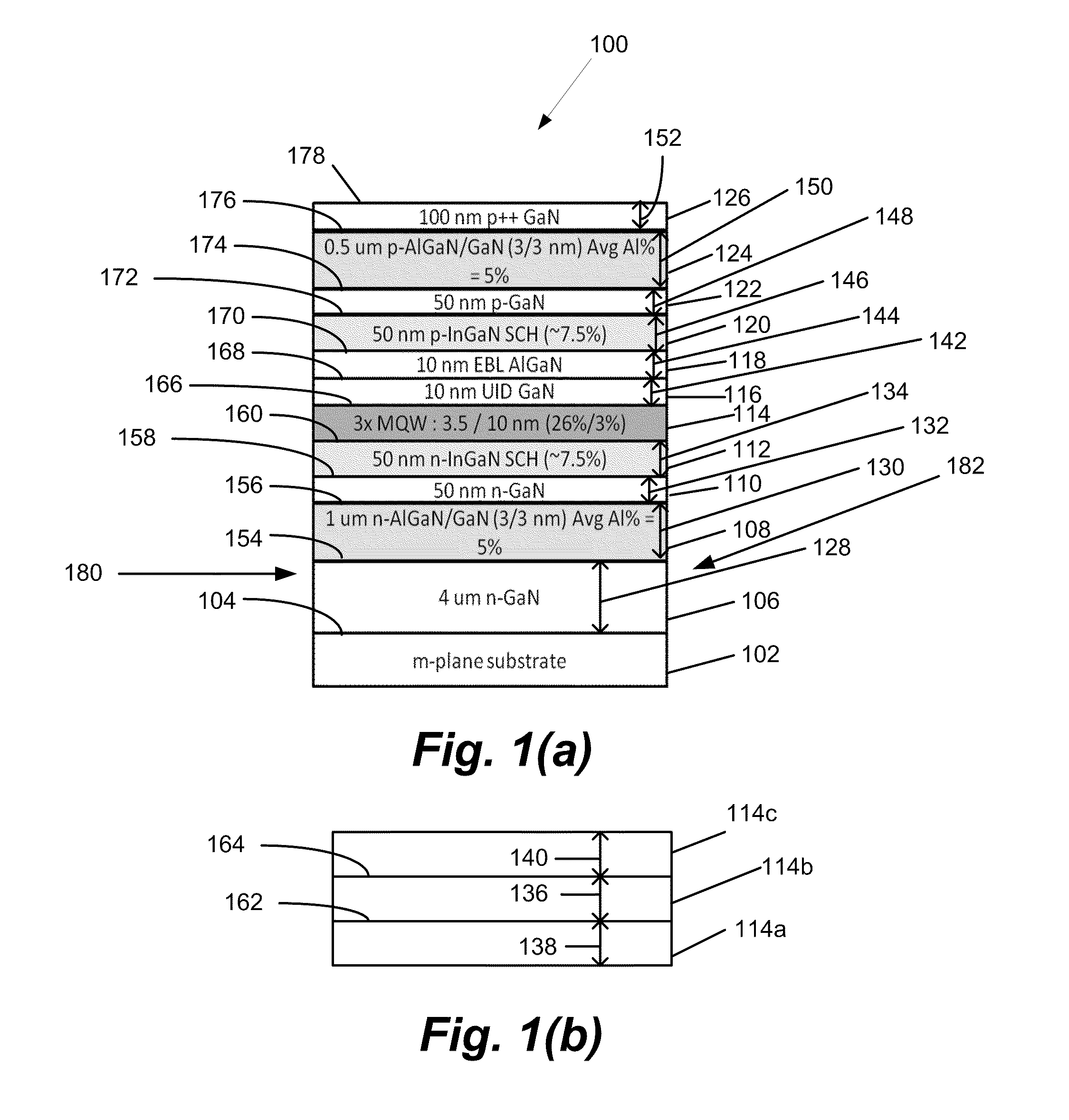

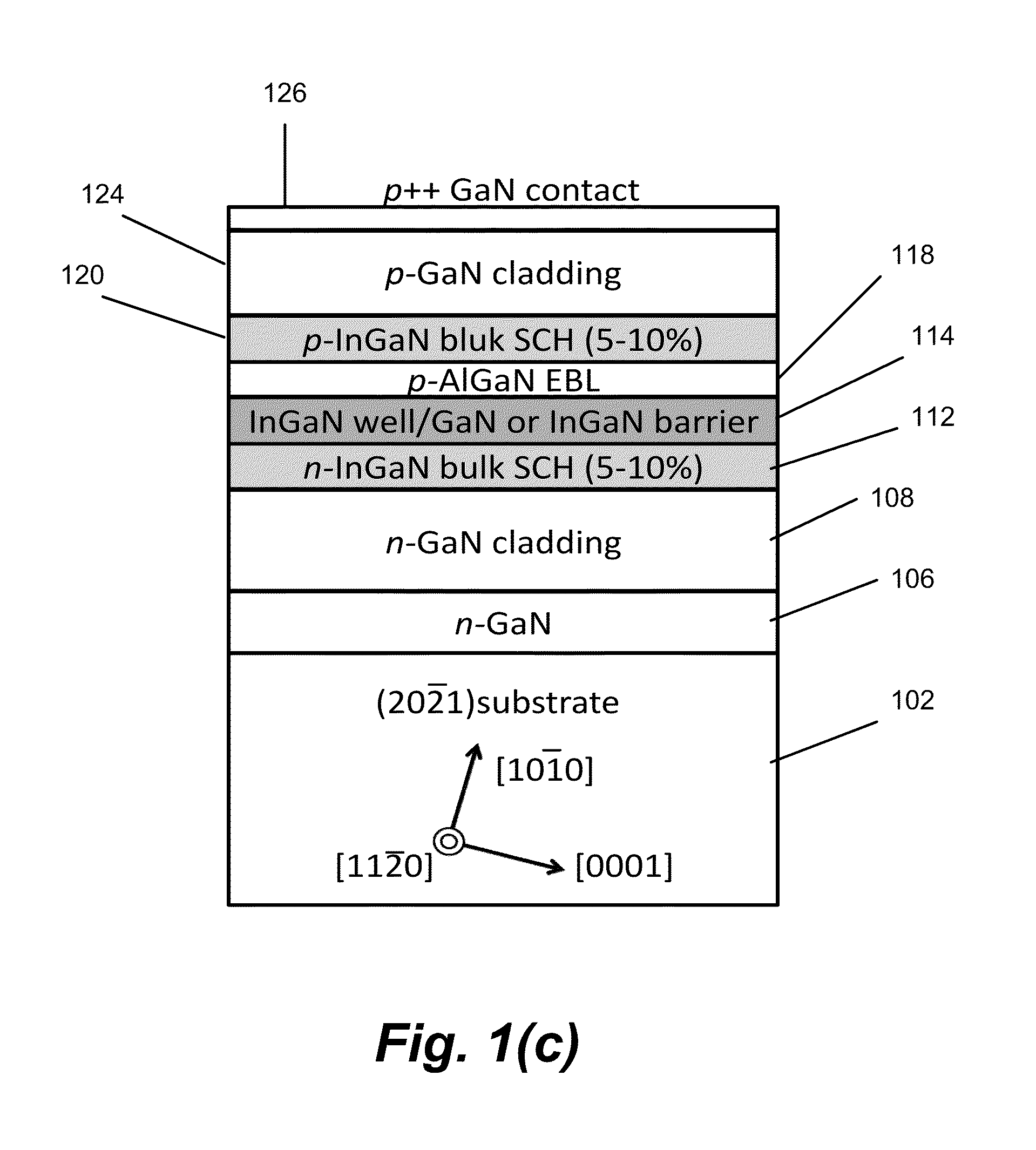

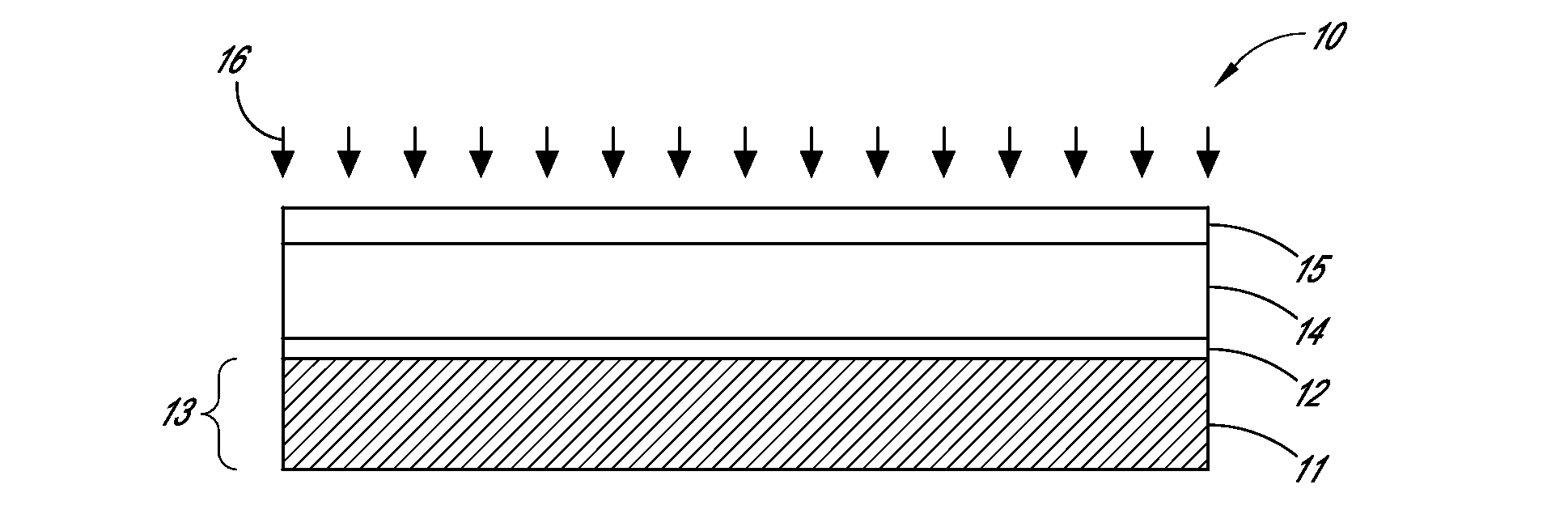

LONG WAVELENGTH NONPOLAR AND SEMIPOLAR (Al,Ga,In)N BASED LASER DIODES

InactiveUS20100309943A1Simple structureImprove electricityOptical wave guidanceLaser detailsContact layerStimulated emission

A laser diode, grown on a miscut nonpolar or semipolar substrate, with lower threshold current density and longer stimulated emission wavelength, compared to conventional laser diode structures, wherein the laser diode's (1) n-type layers are grown in a nitrogen carrier gas, (2) quantum well layers and barrier layers are grown at a slower growth rate as compared to other device layers (enabling growth of the p-type layers at higher temperature), (3) high Al content electron blocking layer enables growth of layers above the active region at a higher temperature, and (4) asymmetric AlGaN SPSLS allowed growth of high Al containing p-AlGaN layers. Various other techniques were used to improve the conductivity of the p-type layers and minimize the contact resistance of the contact layer.

Owner:RGT UNIV OF CALIFORNIA

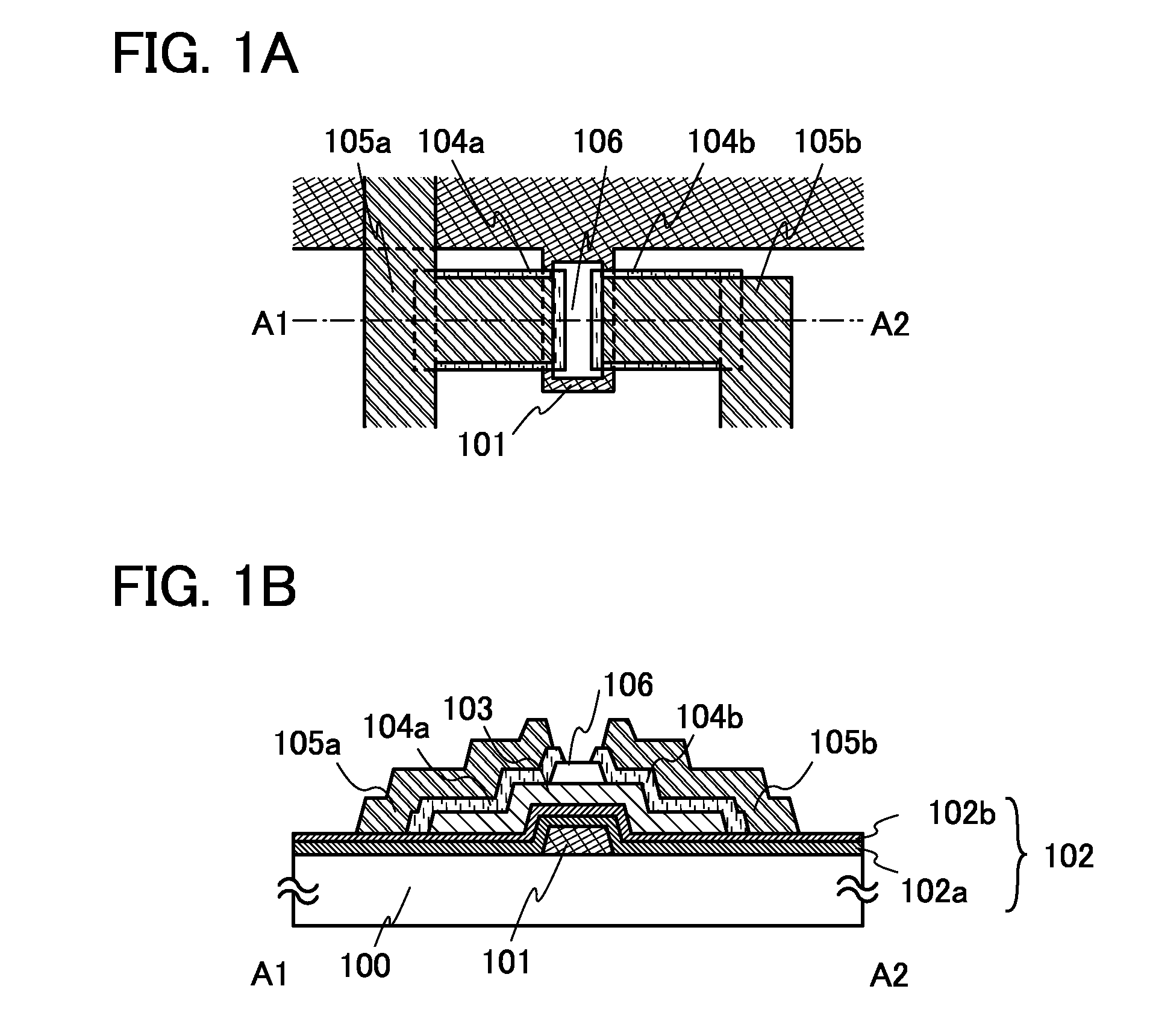

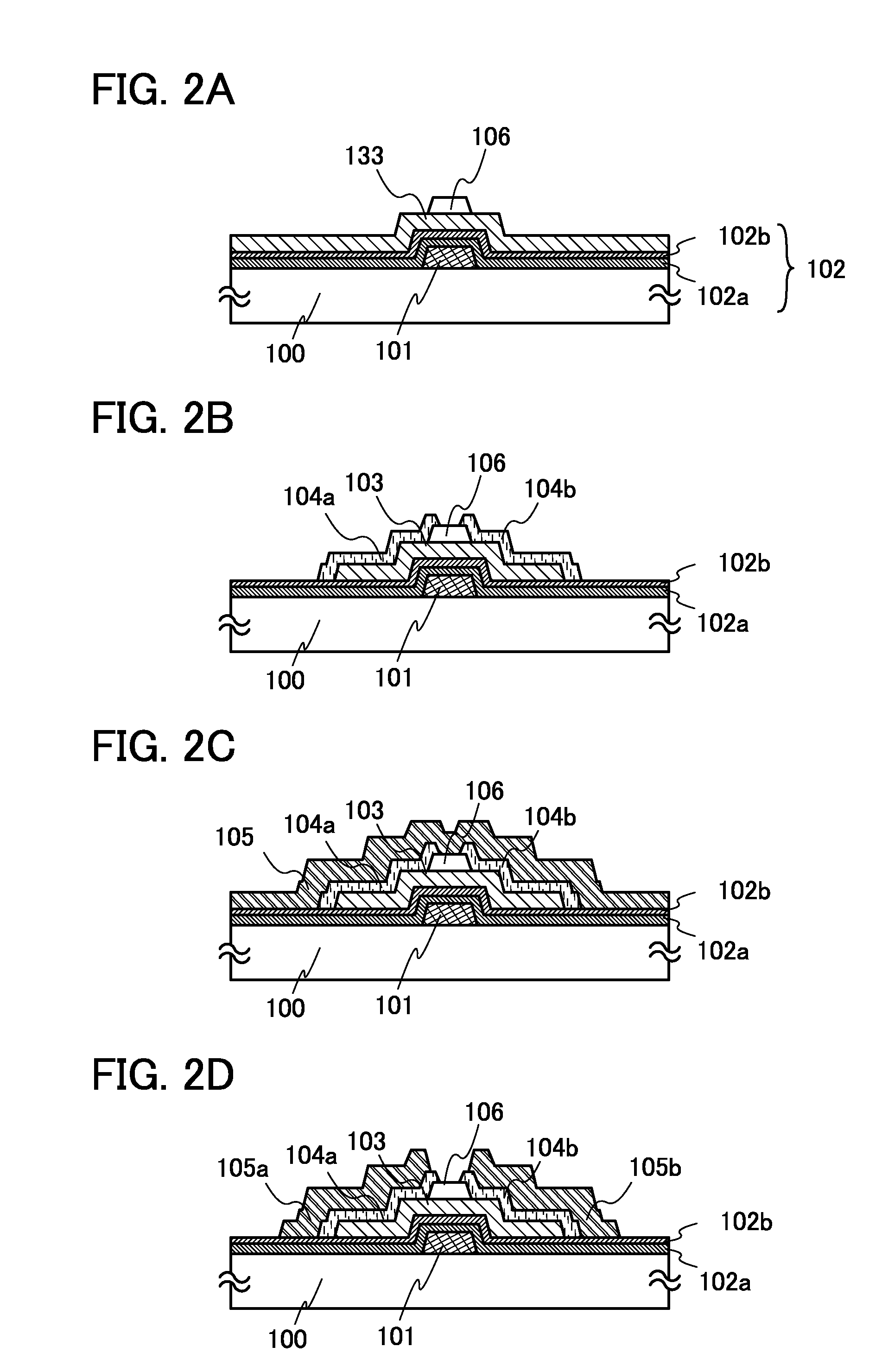

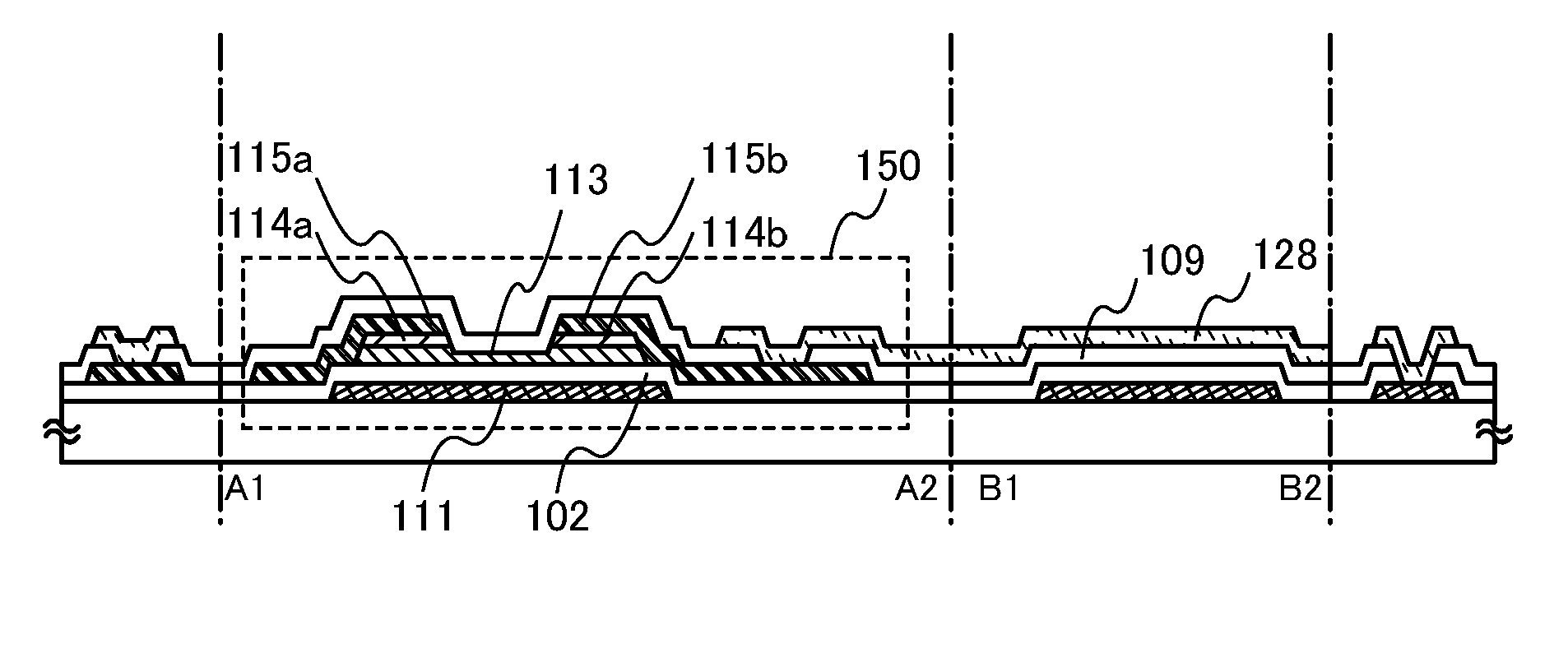

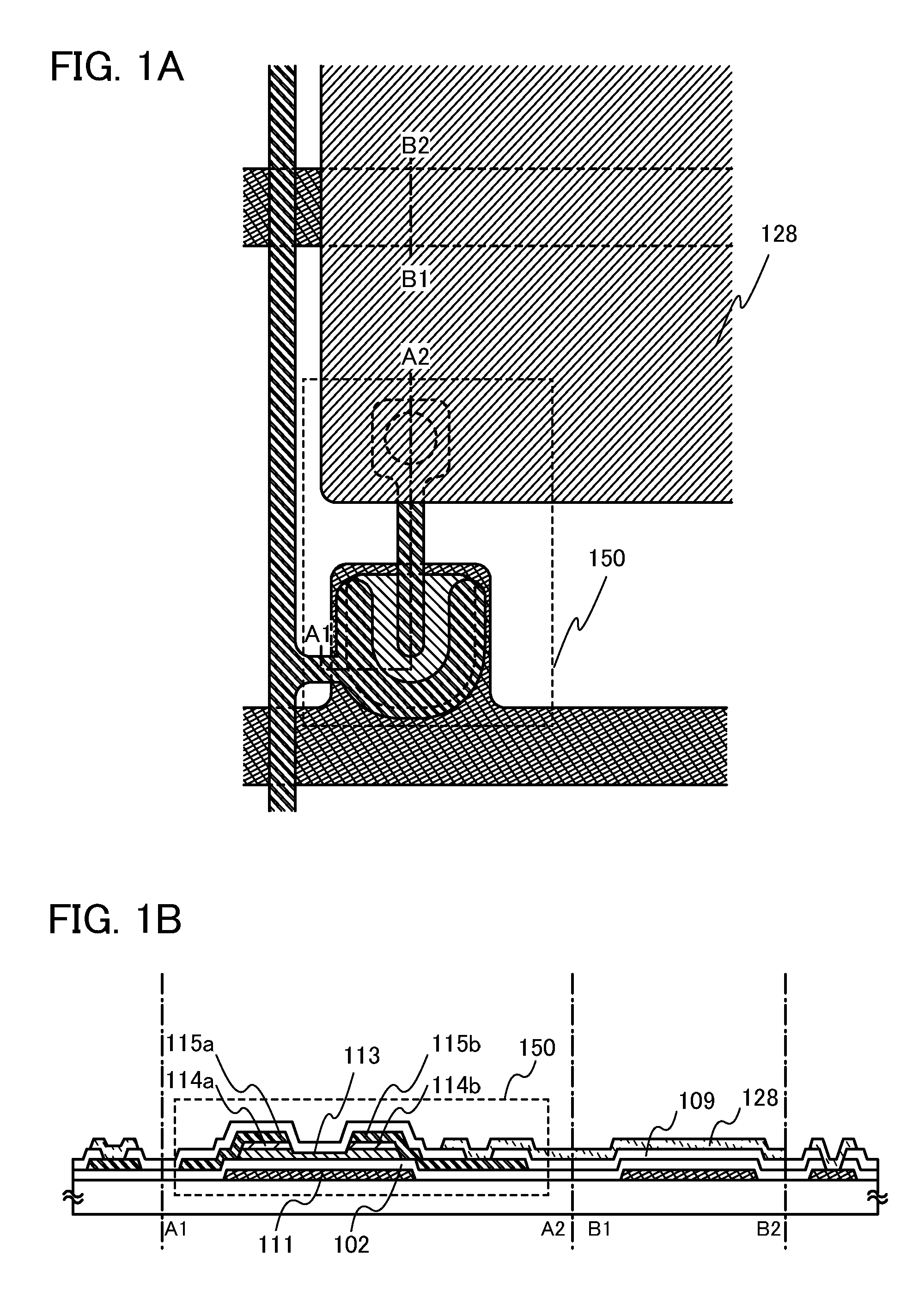

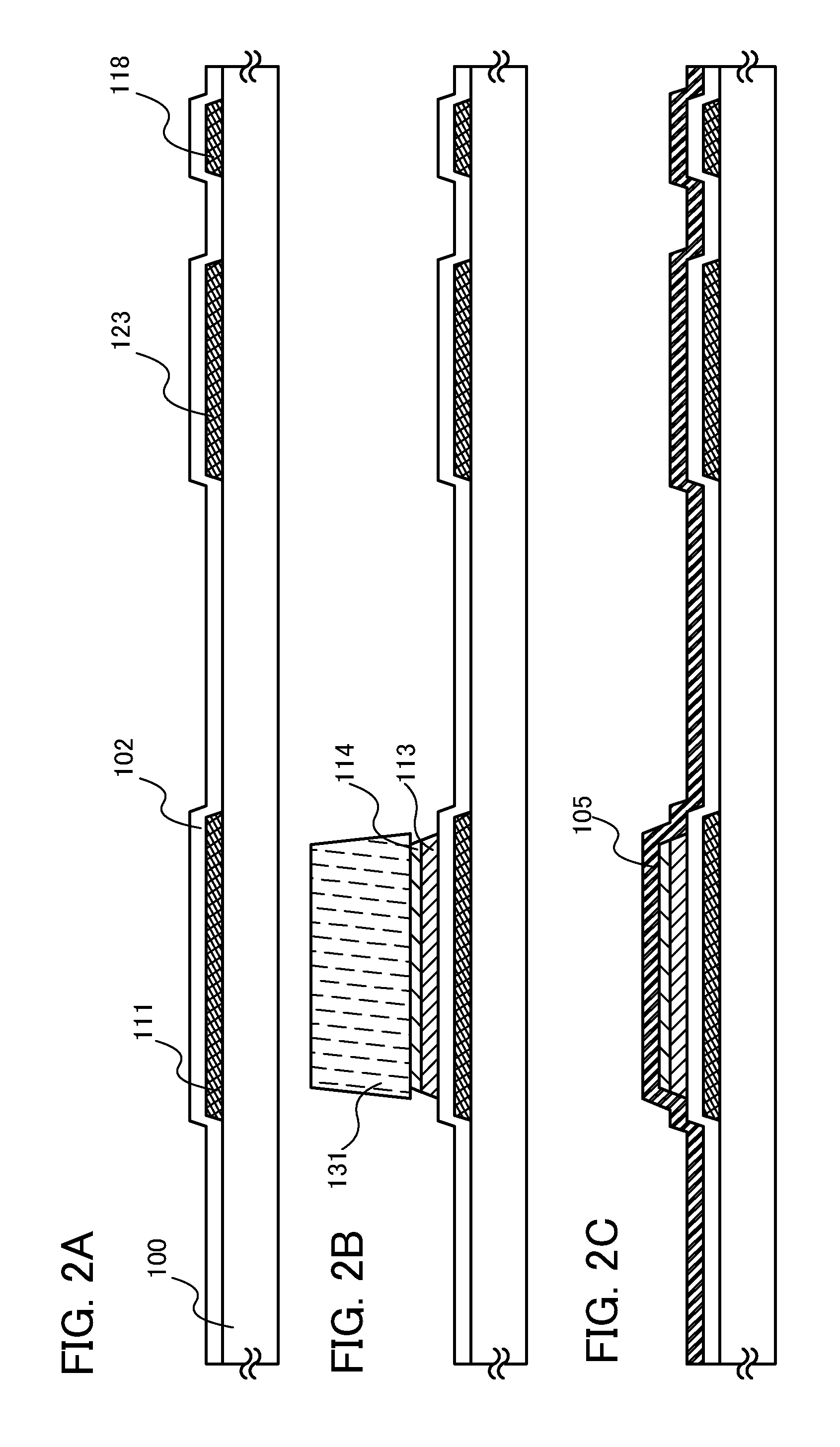

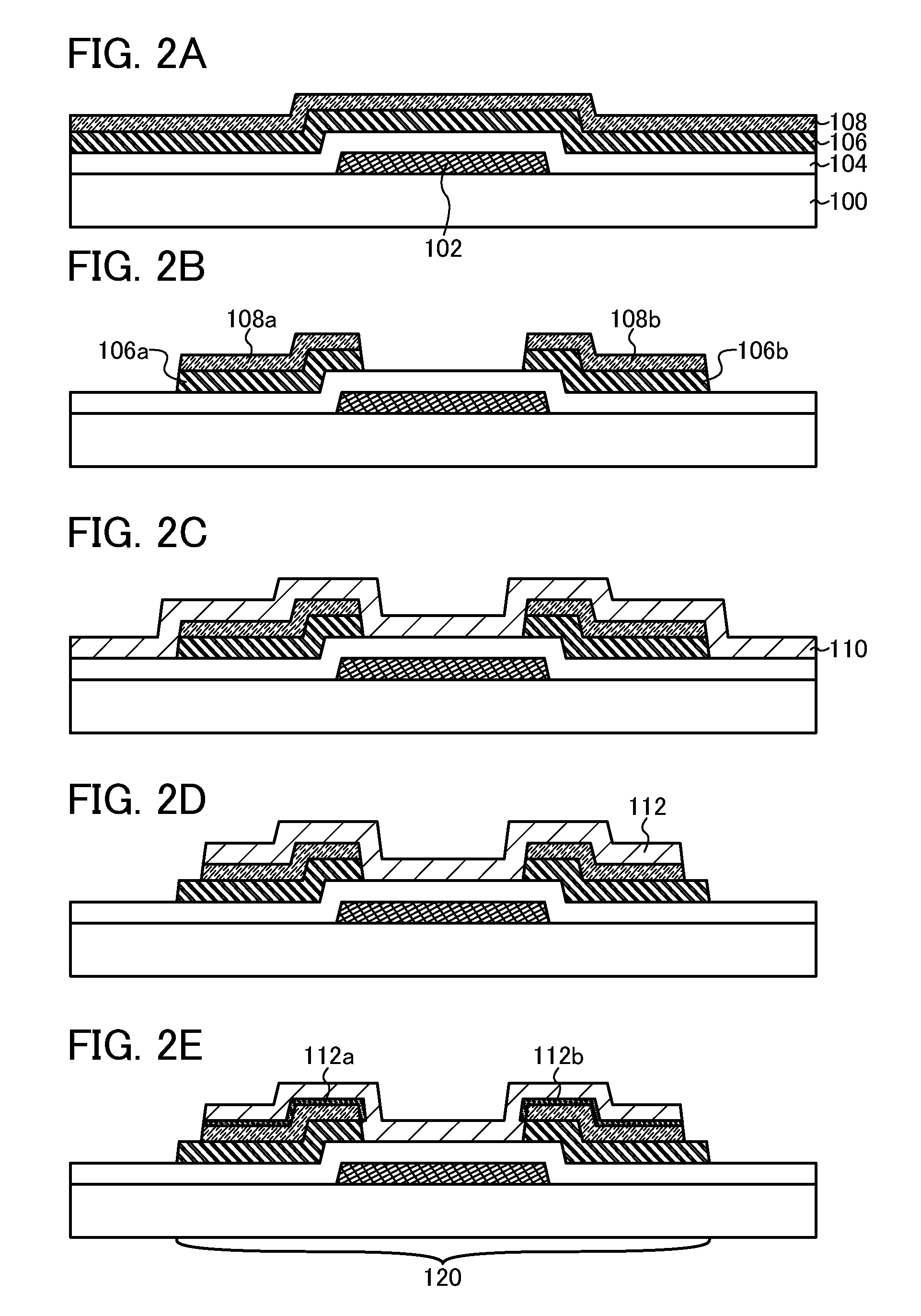

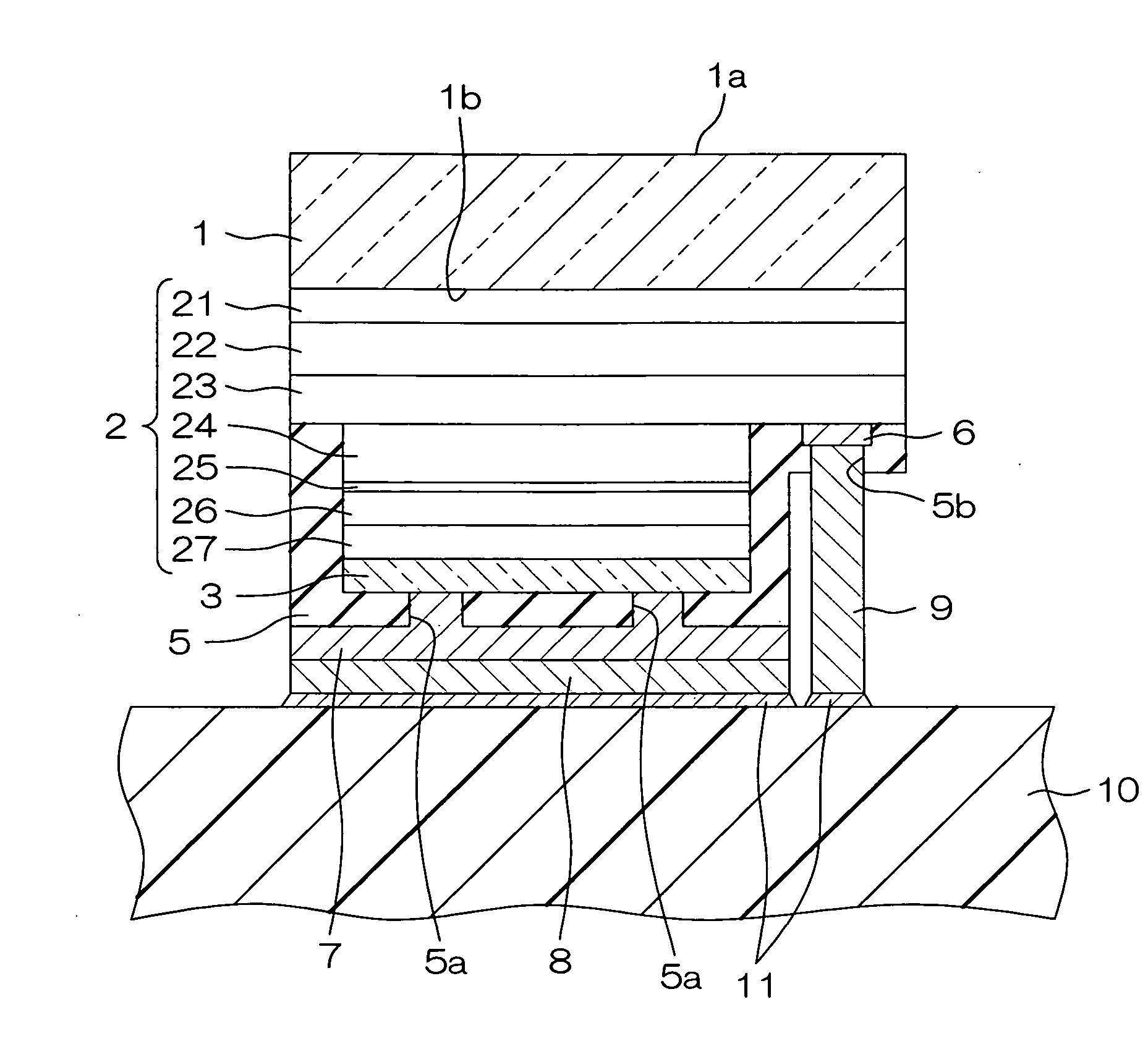

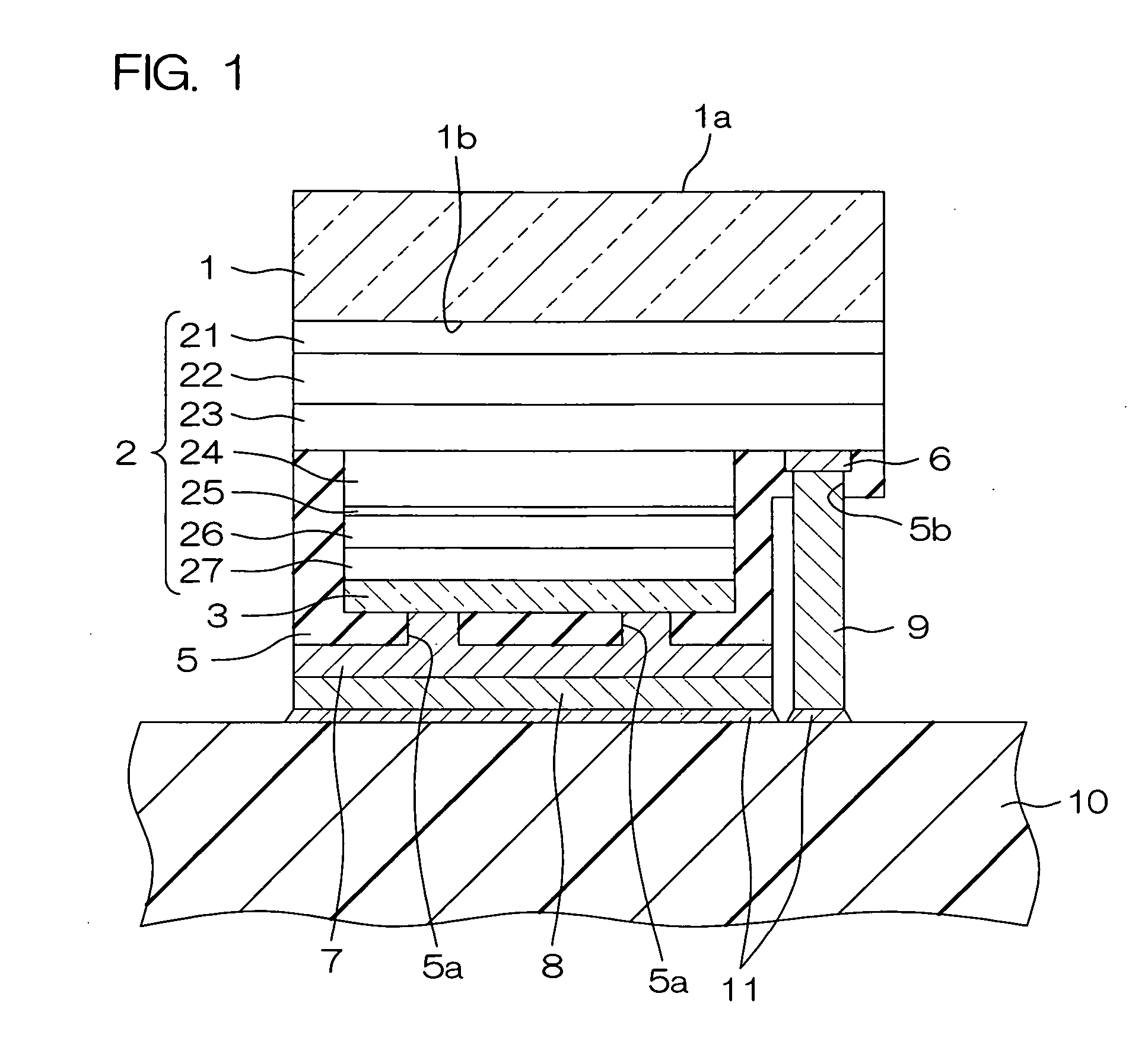

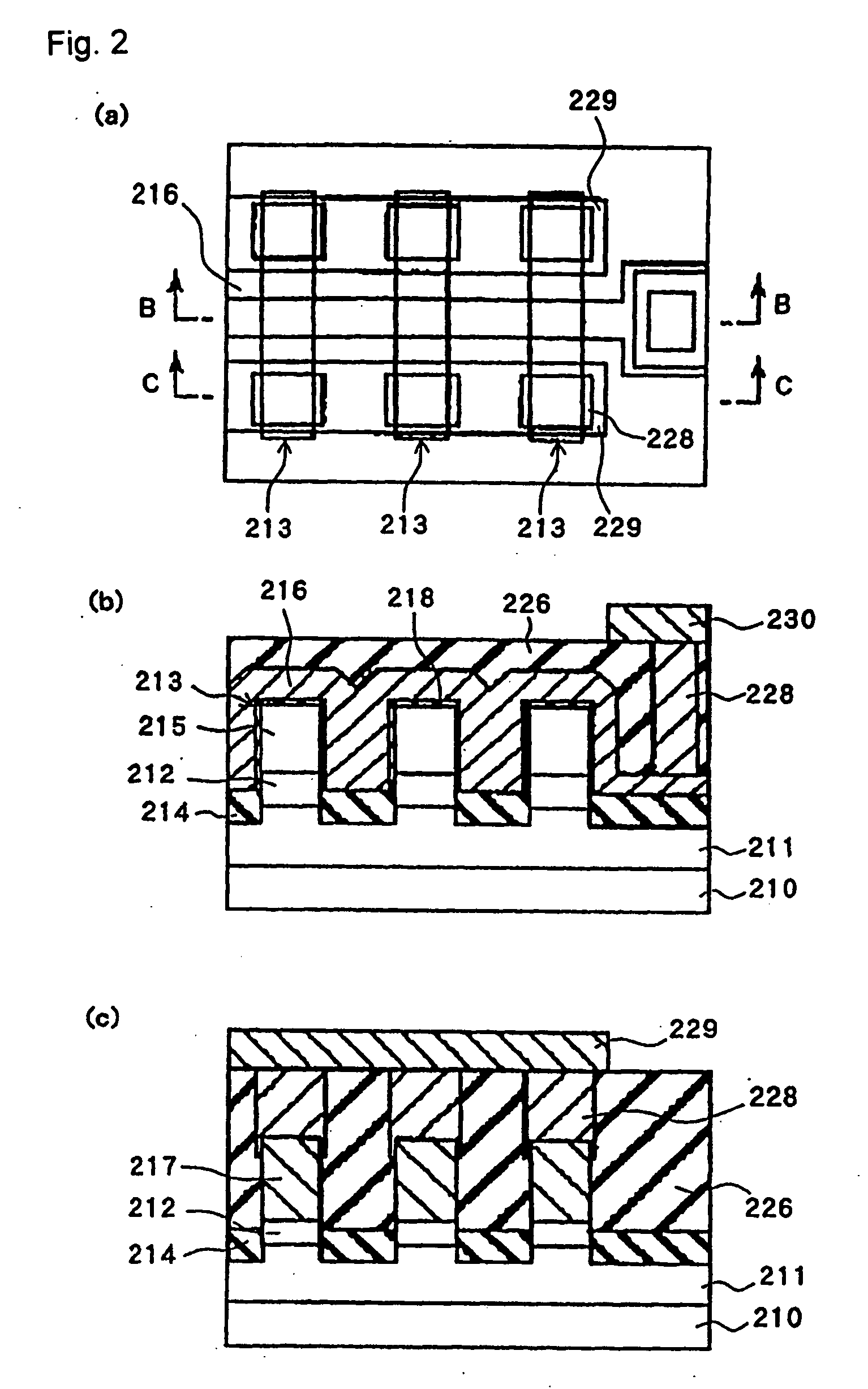

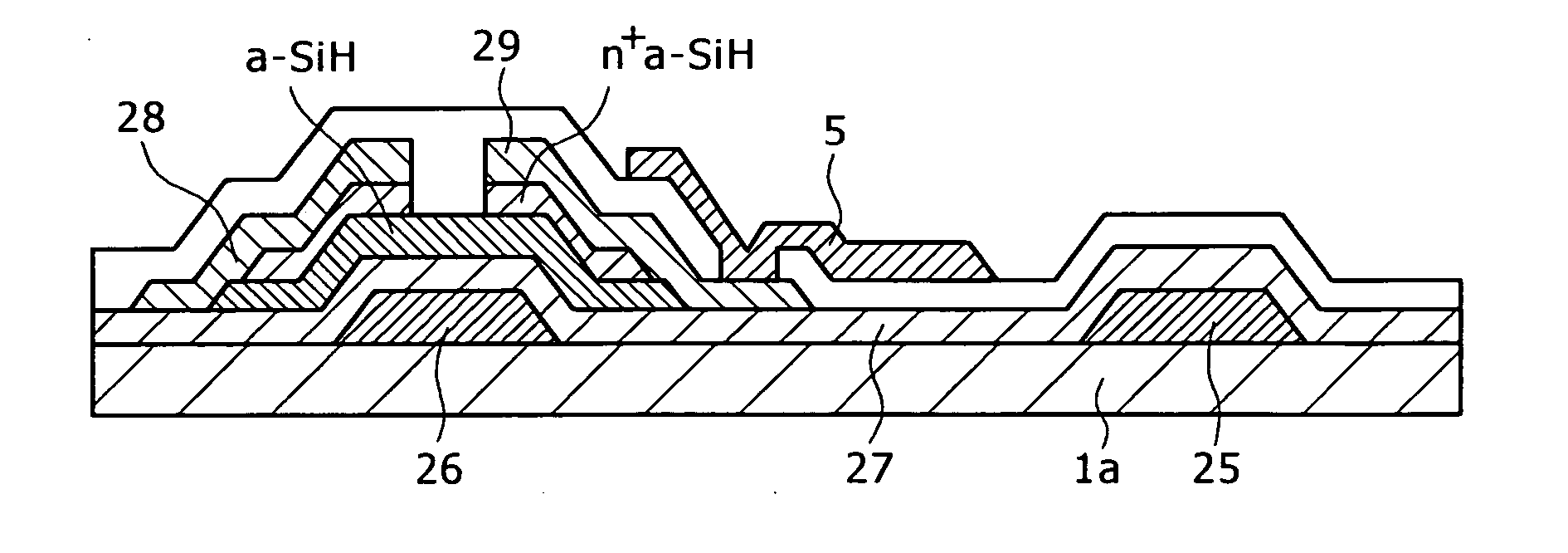

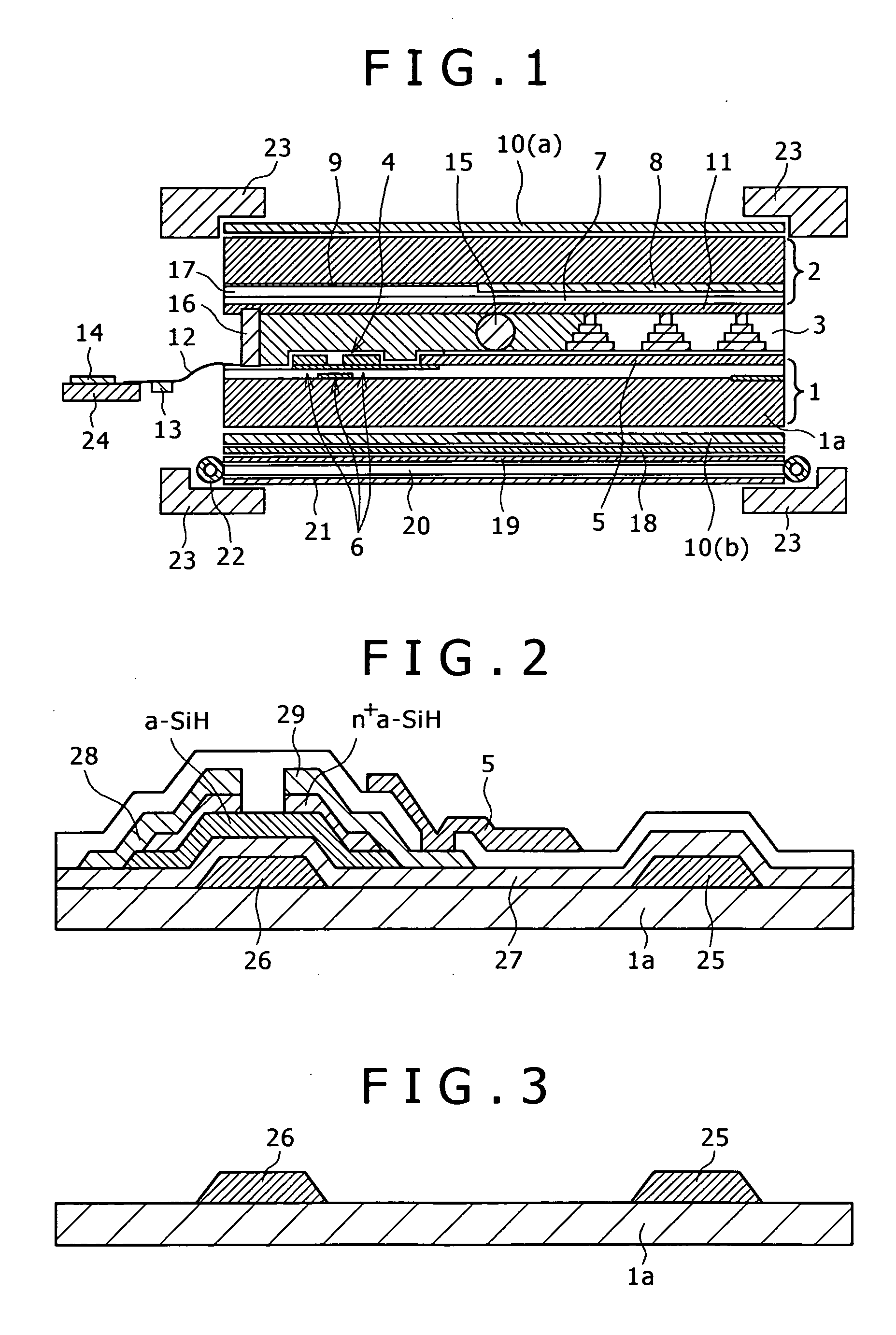

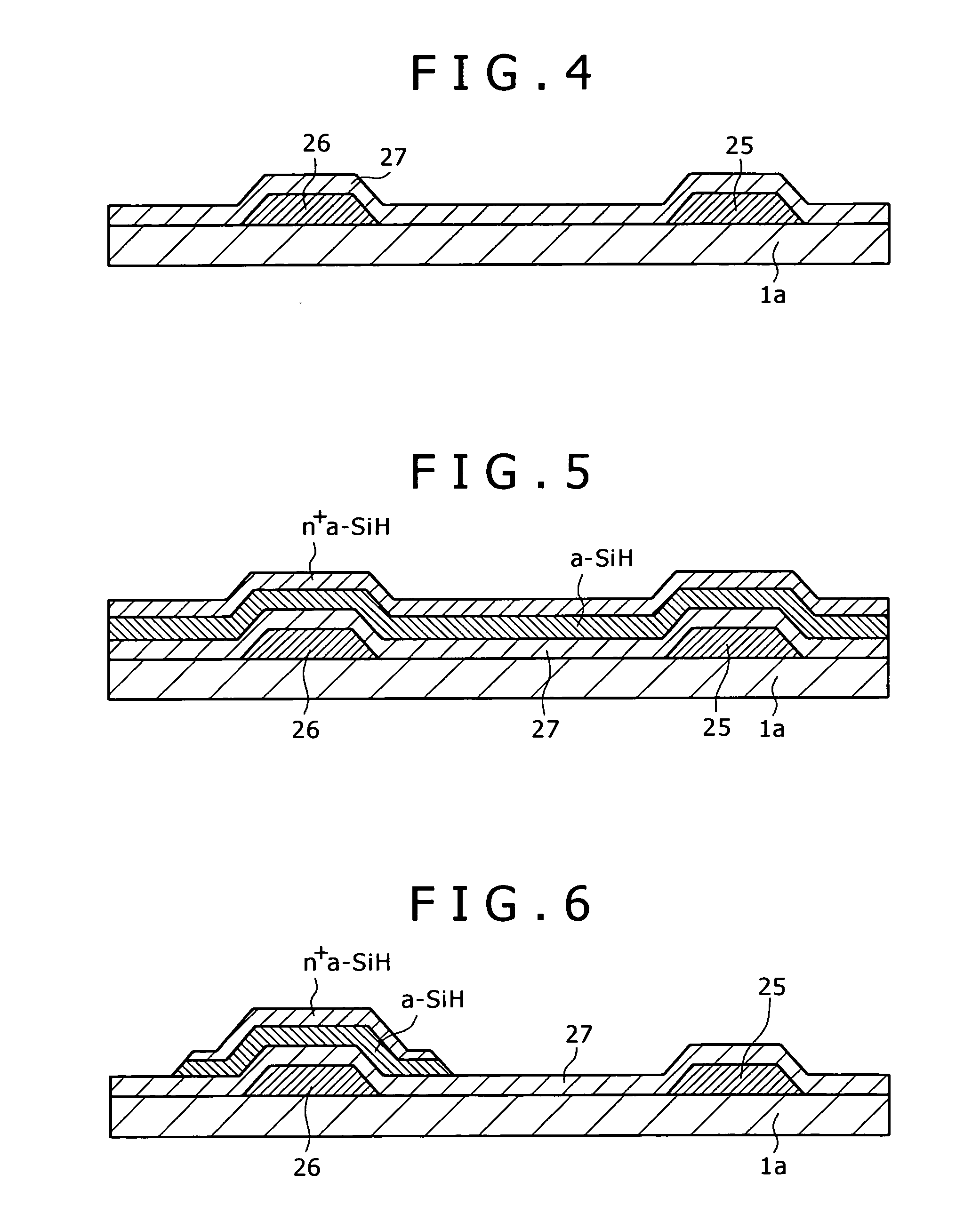

Semiconductor device and manufacturing method thereof

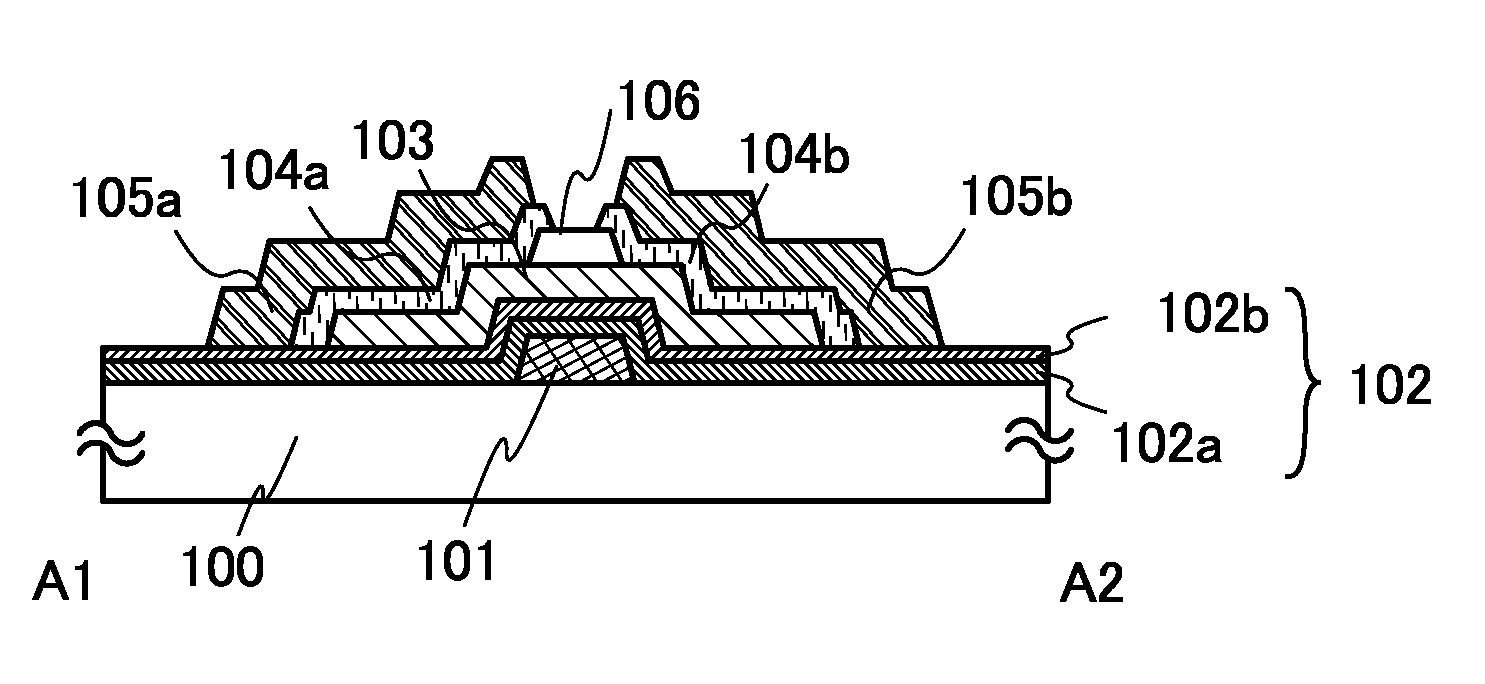

ActiveUS20100025677A1Small amount of photocurrentReduce parasitic capacitanceTransistorElectroluminescent light sourcesProduction rateCharge carrier

To provide a semiconductor device including a thin film transistor having excellent electric characteristics and high reliability and a manufacturing method of the semiconductor device with high mass productivity. The summary is that an inverted-staggered (bottom-gate) thin film transistor is included in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer, a channel protective layer is provided in a region that overlaps a channel formation region of the semiconductor layer, and a buffer layer is provided between the semiconductor layer and source and drain electrodes. An ohmic contact is formed by intentionally providing the buffer layer having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

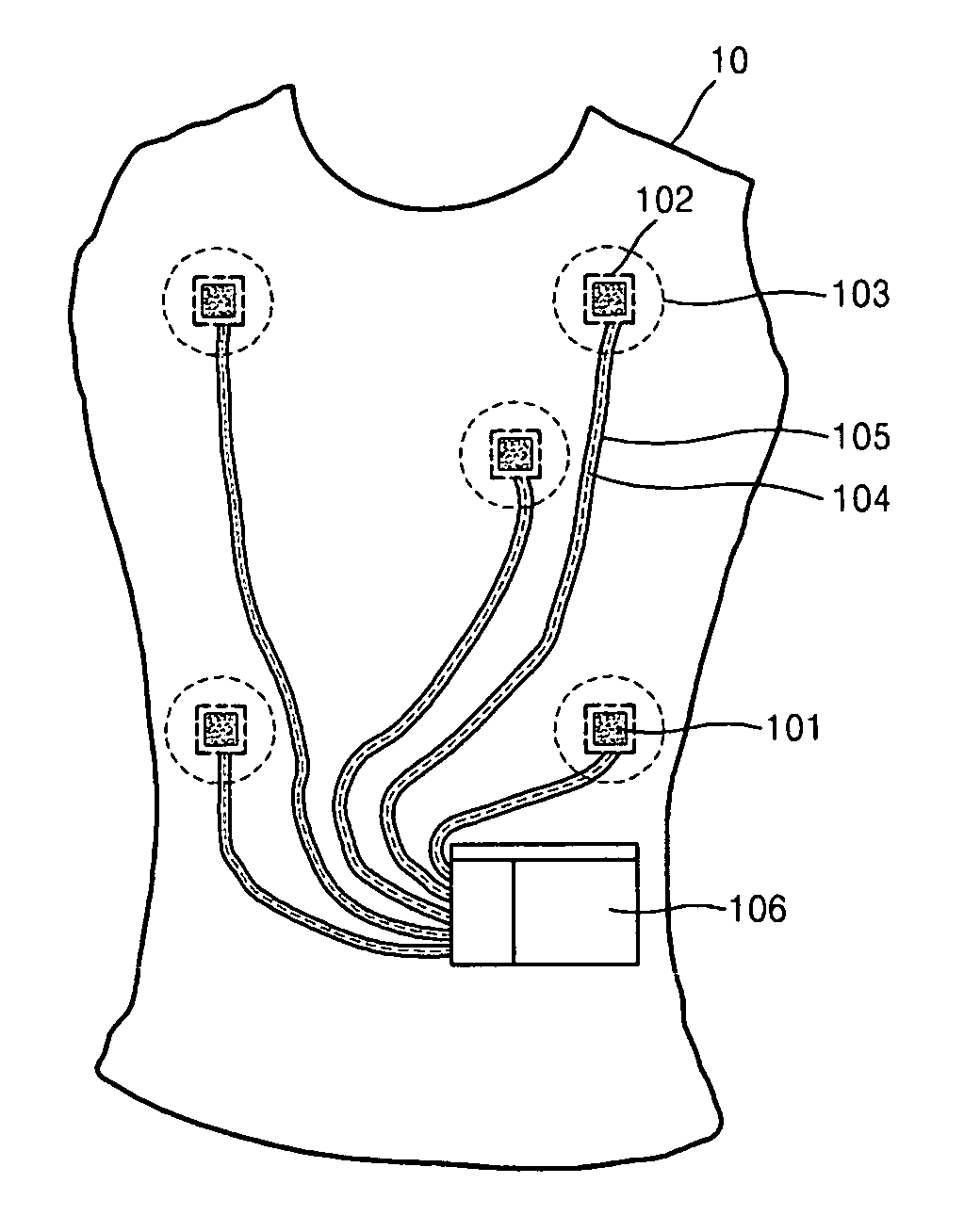

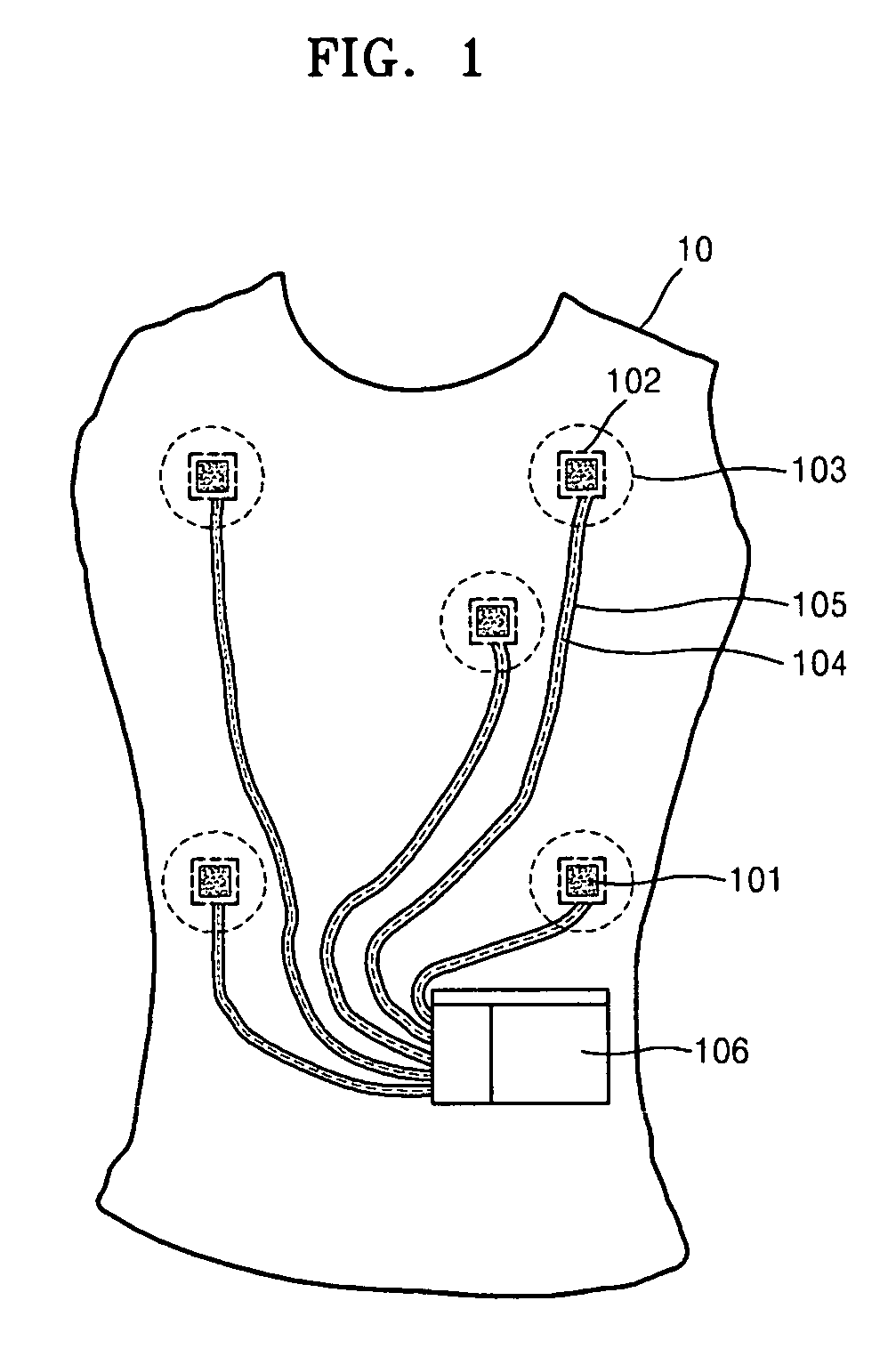

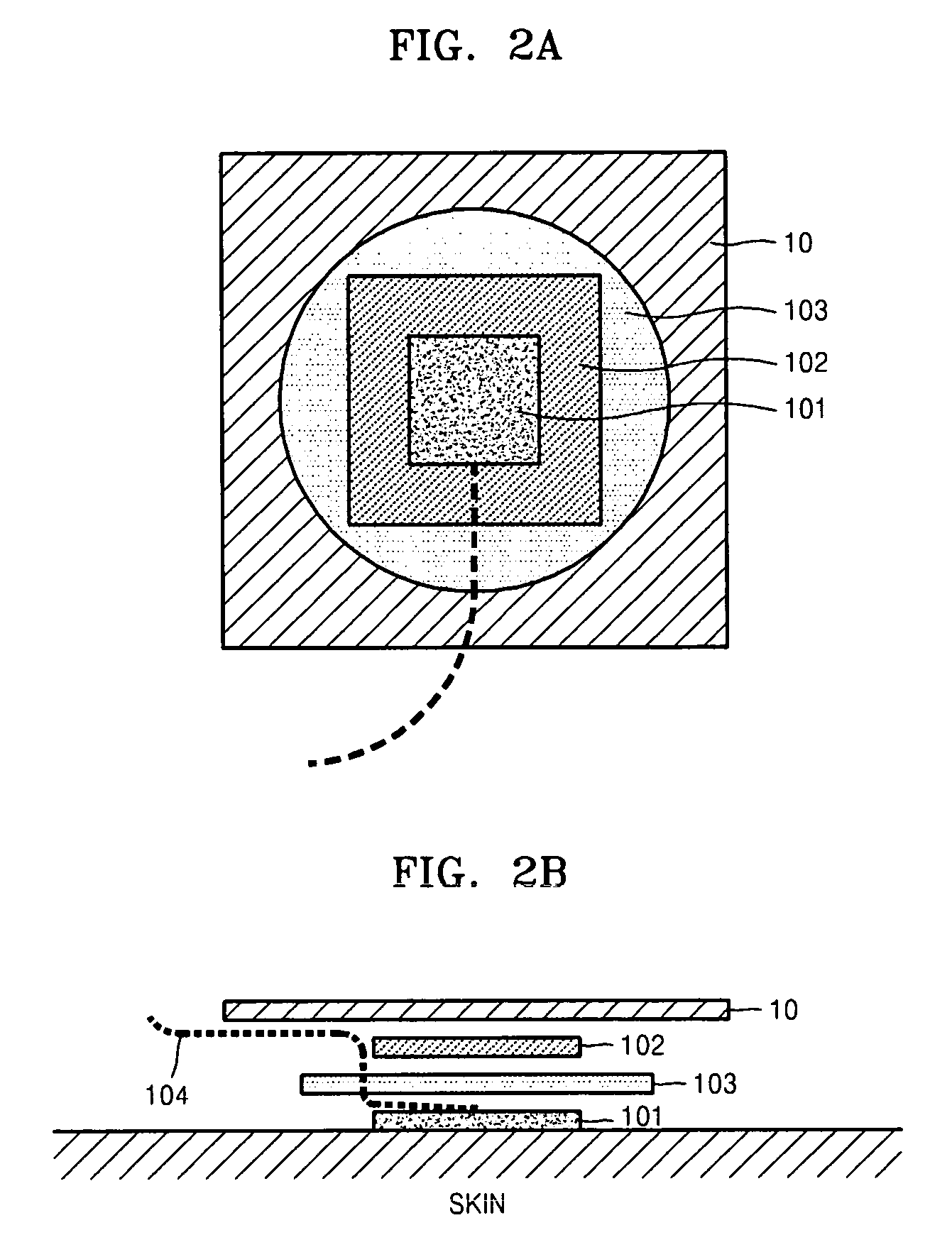

Garment for measuring physiological signal

InactiveUS20070038057A1Reduce contact resistanceReduce noiseElectrocardiographyNon-adhesive dressingsEngineeringBody condition

Provided is a smart garment for measuring a physiological signal which can improve comfort and convenience of wear and correctly measure a physiological signal. The smart garment for measuring physiological signals includes an electrode which is made of an electro-conductive fabric and detects a physiological signal, a physiological signal transmission line through which the detected physiological signal is transmitted, a physiological signal measuring unit which is connected to the transmission line, receives the physiological signal, and measures information regarding body conditions related to the physiological signal, and a pocket where the physiological signal measuring unit in inserted.

Owner:THE IND & ACADEMIC COOPERATION & CHUNGNAM NAT UNIV +1

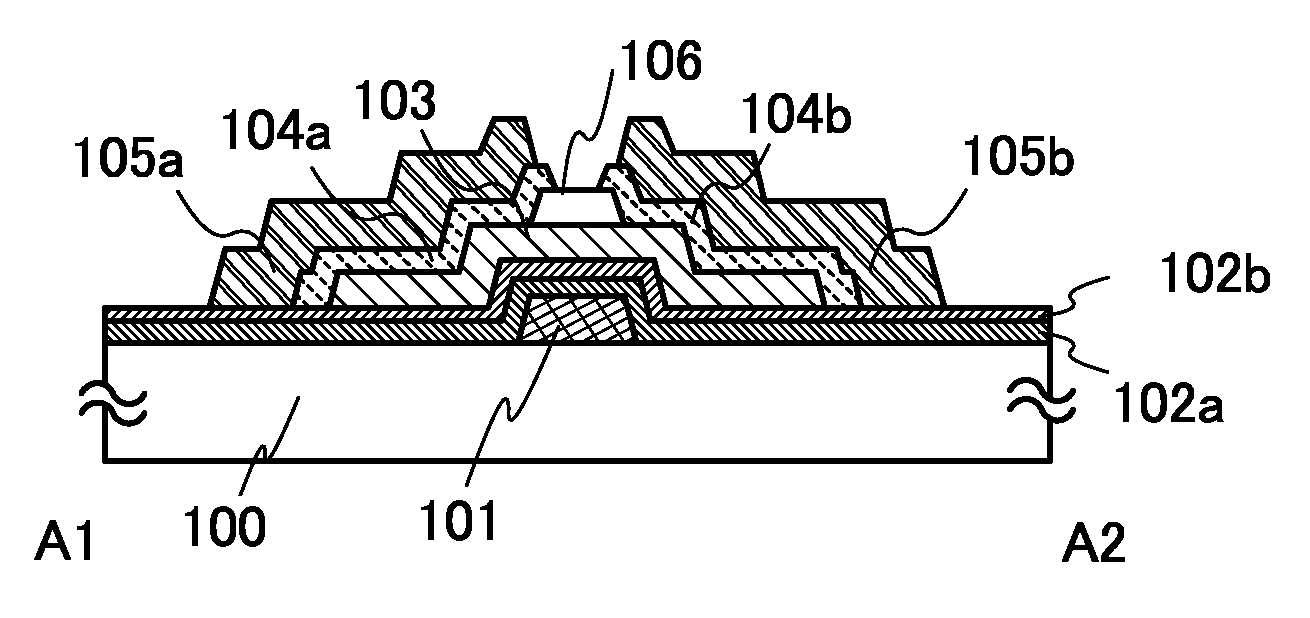

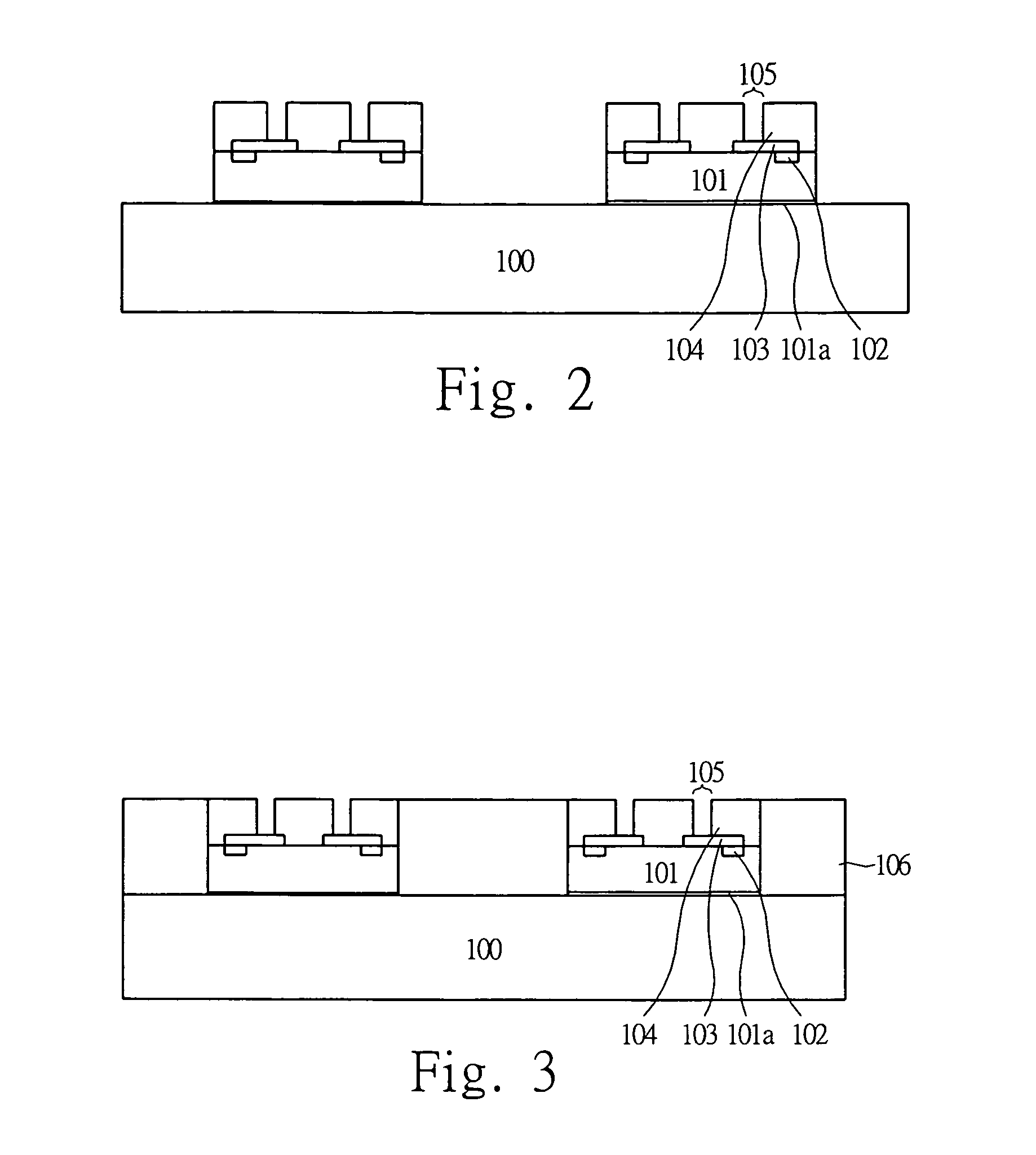

Vertical light emitting diode and method of manufacturing the same

ActiveUS20090221110A1Fine surfaceImprove thermal stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesActive layerLight-emitting diode

Provided is a vertical LED including an n-electrode; an n-type GaN layer formed under the n-electrode, the n-type GaN layer having a surface coming in contact with the n-electrode, the surface having a Ga+N layer containing a larger amount of Ga than that of N; an active layer formed under the n-type GaN layer; a p-type GaN layer formed under the active layer; a p-electrode formed under the p-type GaN layer; and a structure support layer formed under the p-electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

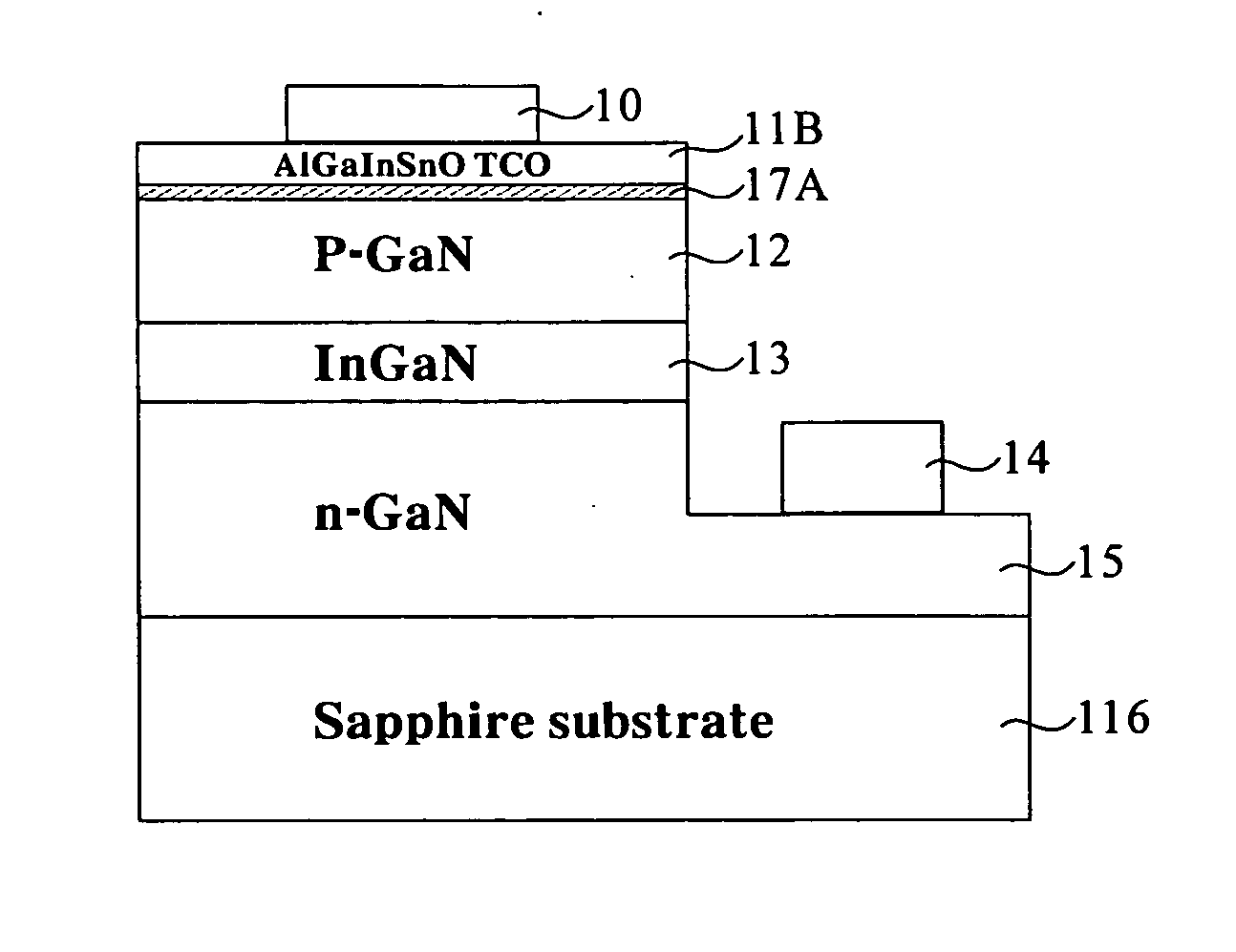

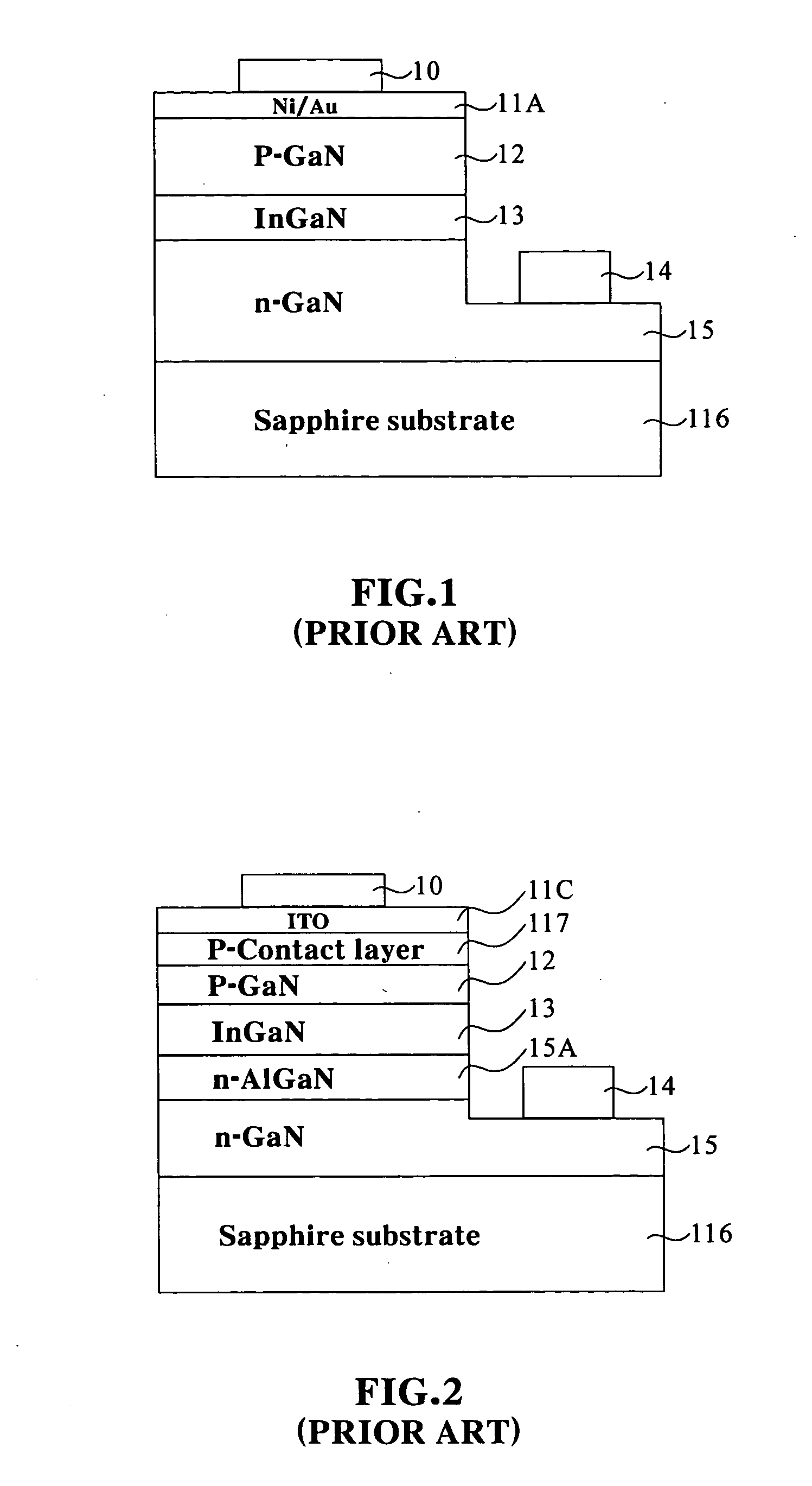

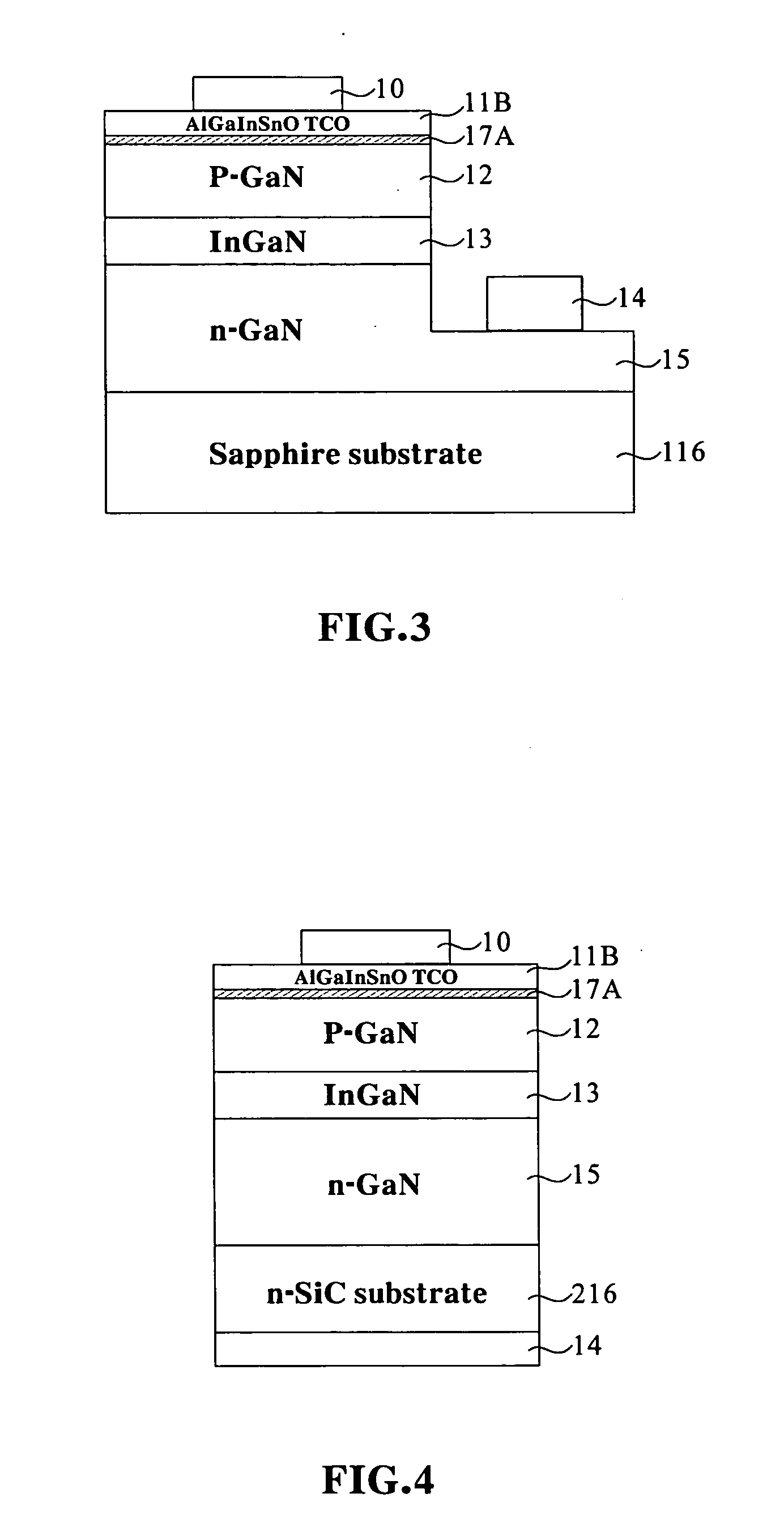

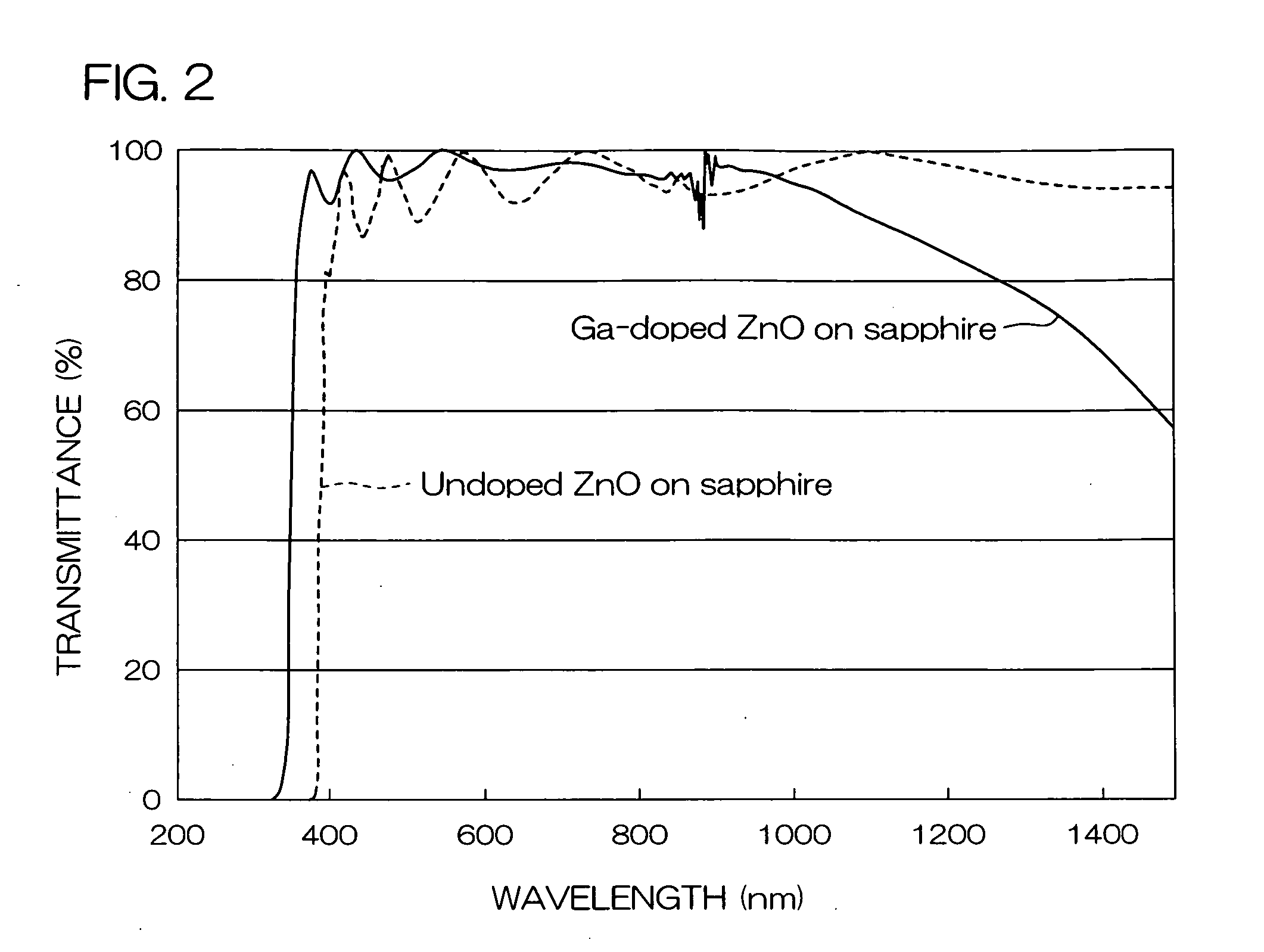

High brightness gallium nitride-based light emitting diode with transparent conducting oxide spreading layer

InactiveUS20050230701A1Reduce contact resistanceReduce the impactFibre treatmentSolid-state devicesOptical propertyGallium

A new transparent conducting oxide (TCO), which can be expressed as AlxGa3−x−yIn5+ySn2−zO16−2z; 0≦x<1, 0<y<3, 0≦z<2, has been used to improve the brightness and current spreading in GaN base LED process. The optical properties of this system are superior to regular Ni / Au transparent conducting layer in blue-green region, and the new Al2O3—Ga2O3—In2O3—SnO2 system is able to increase the brightness at 1.5˜2.5 time to compare to regular process. Furthermore, the new transparent conducting oxide thin film has the highest conductivity, which is better than the Ni / Au transparent conducting thin film.

Owner:ARIMA OPTOELECTRONICS

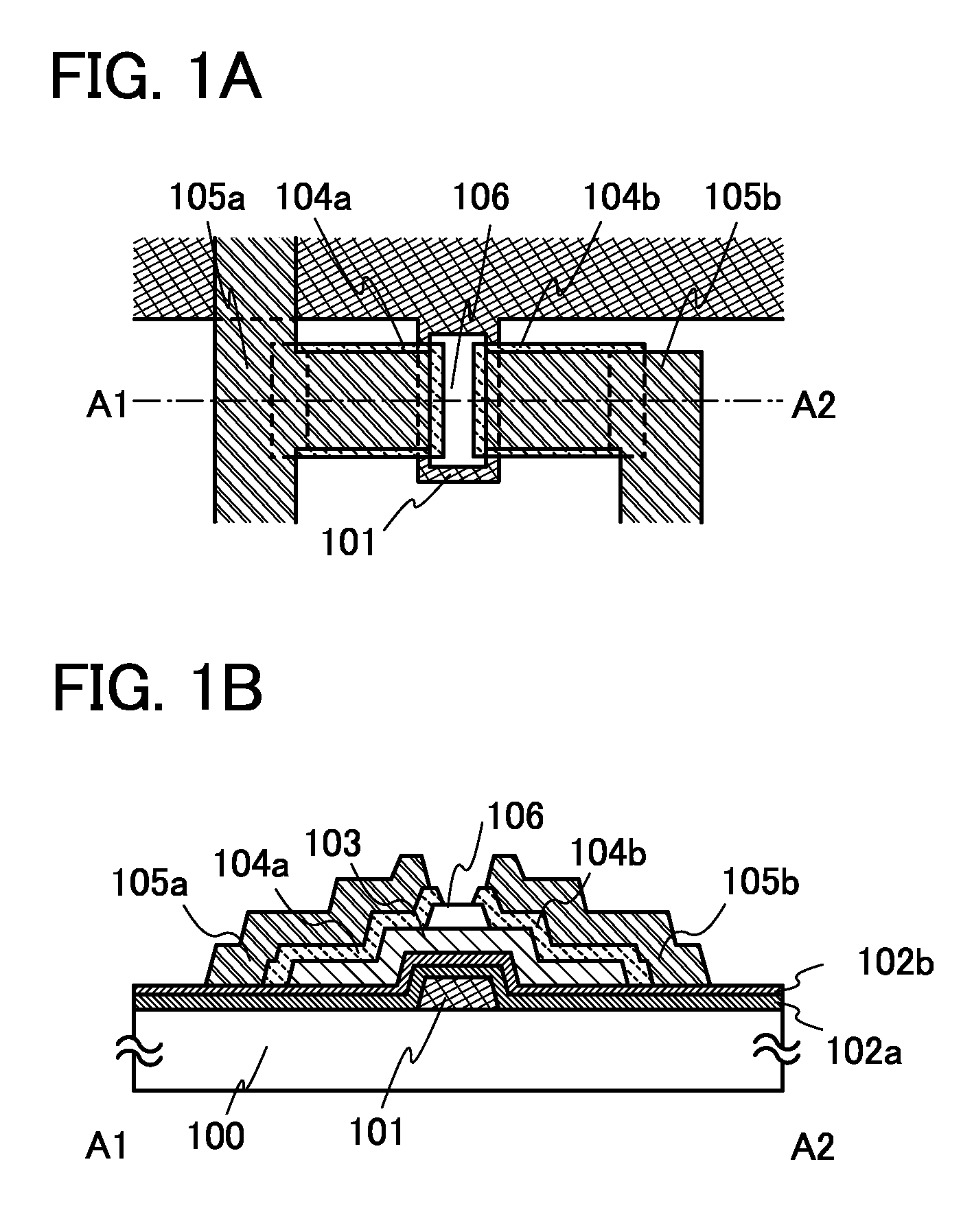

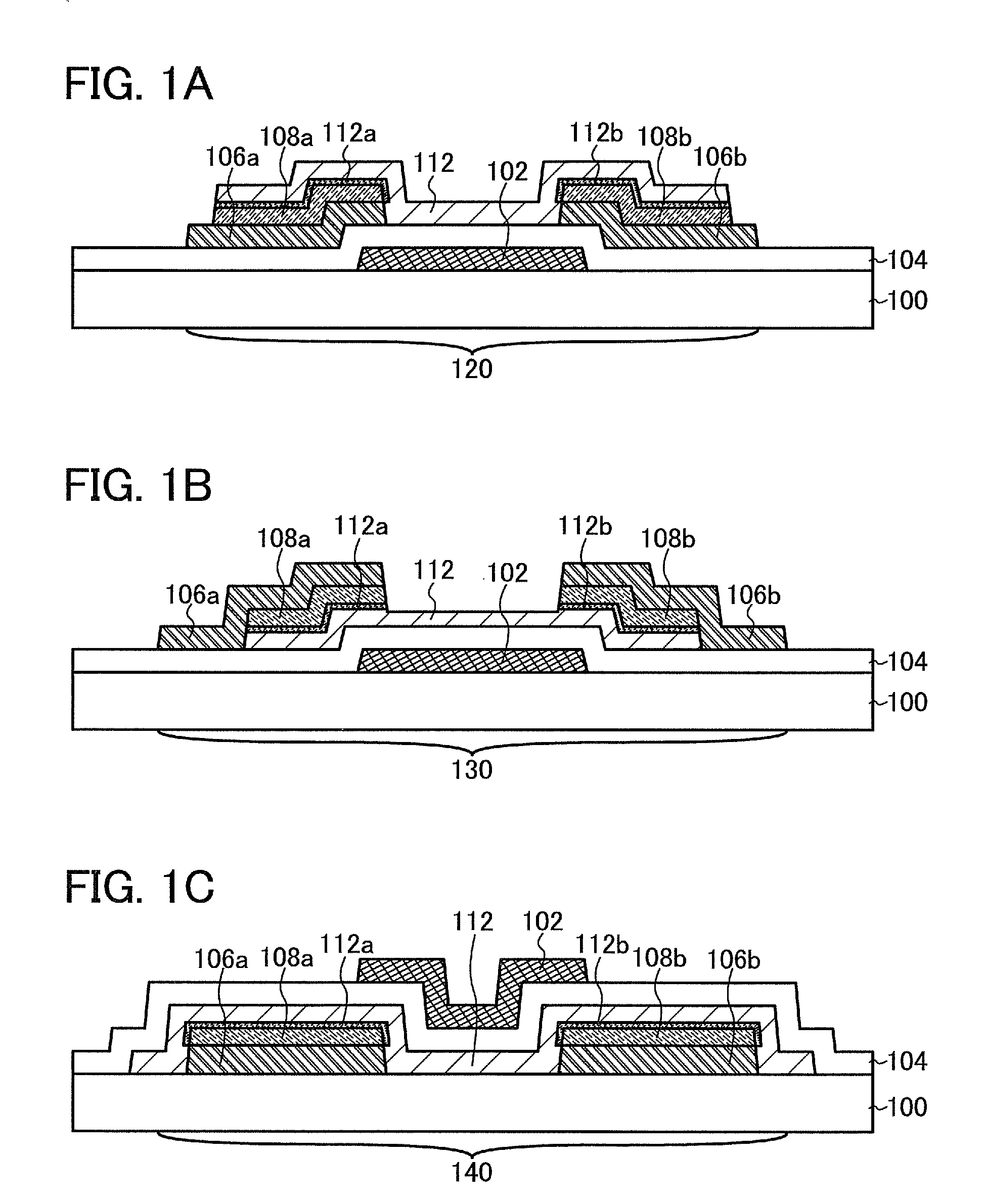

Semiconductor device and manufacturing method thereof

ActiveUS20100025676A1Small amount of photocurrentReduce parasitic capacitanceTransistorSolid-state devicesCharge carrierOhmic contact

To offer a semiconductor device including a thin film transistor having excellent characteristics and high reliability and a method for manufacturing the semiconductor device without variation. The summary is to include an inverted-staggered (bottom-gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used for a semiconductor layer and a buffer layer is provided between the semiconductor layer and source and drain electrode layers. An ohmic contact is formed by intentionally providing a buffer layer containing In, Ga, and Zn and having a higher carrier concentration than the semiconductor layer between the semiconductor layer and the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

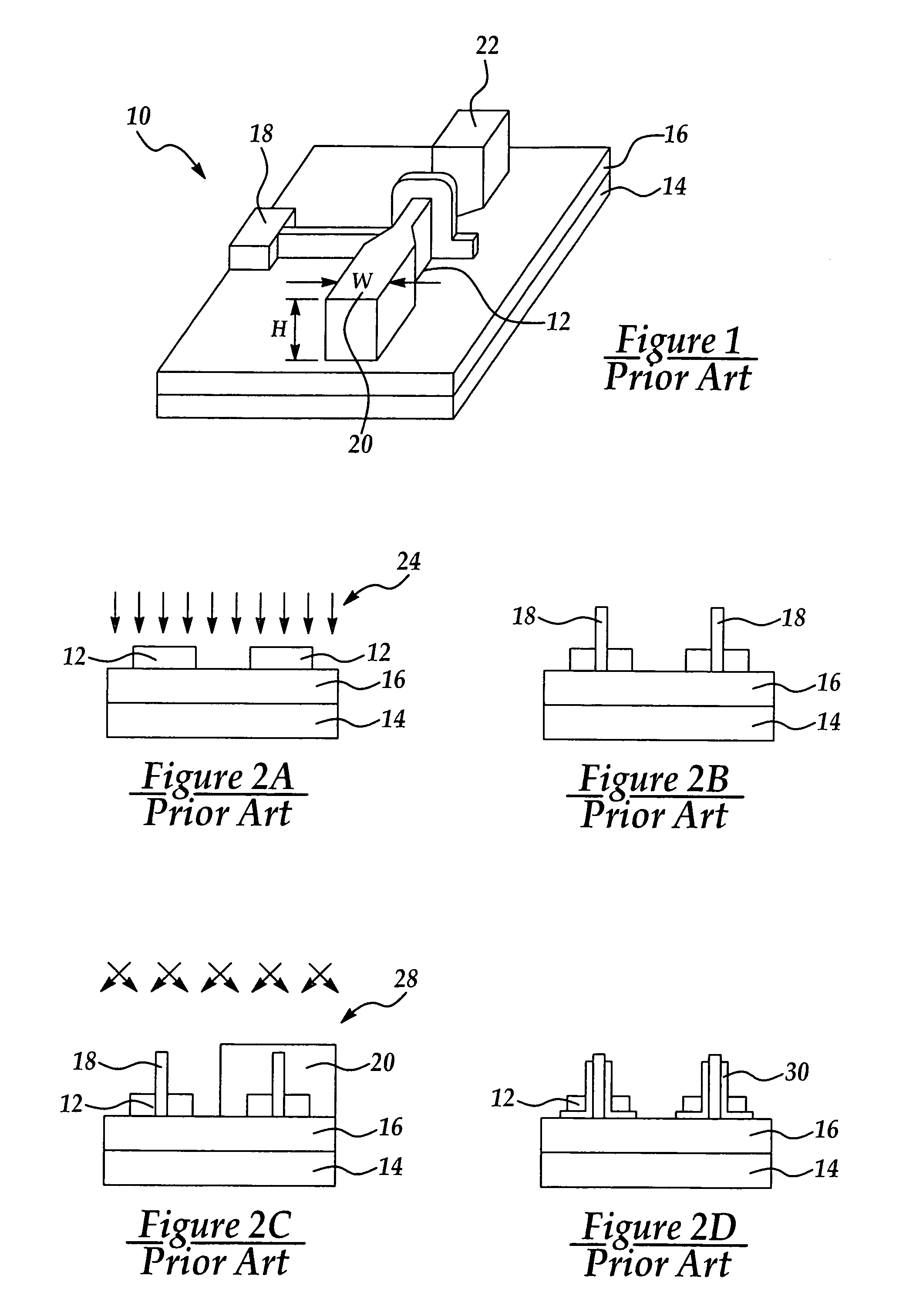

Method of fabricating a MOS transistor with a raised source/drain extension

InactiveUS6121100AReduce parasitic resistanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor materials

A method of forming a MOS transistor. According to the method of the present invention, a pair of source / drain contact regions are formed on opposite sides of a gate electrode. After forming the pair of source / drain contact regions, semiconductor material is deposited onto opposite sides of the gate electrode. Dopants are then diffused from the semiconductor material into the substrate beneath the gate electrode to form a pair of source / drain extensions.

Owner:INTEL CORP

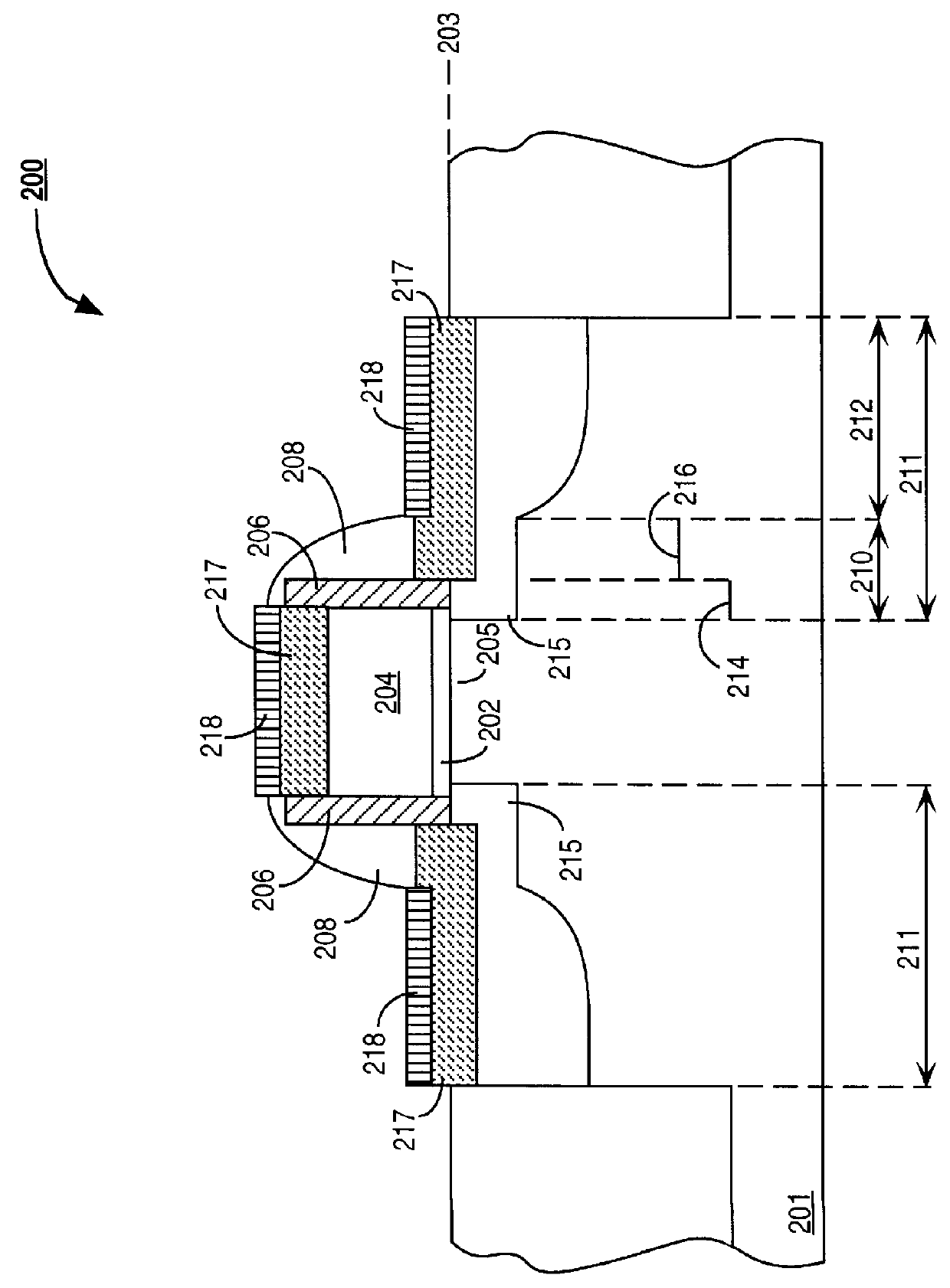

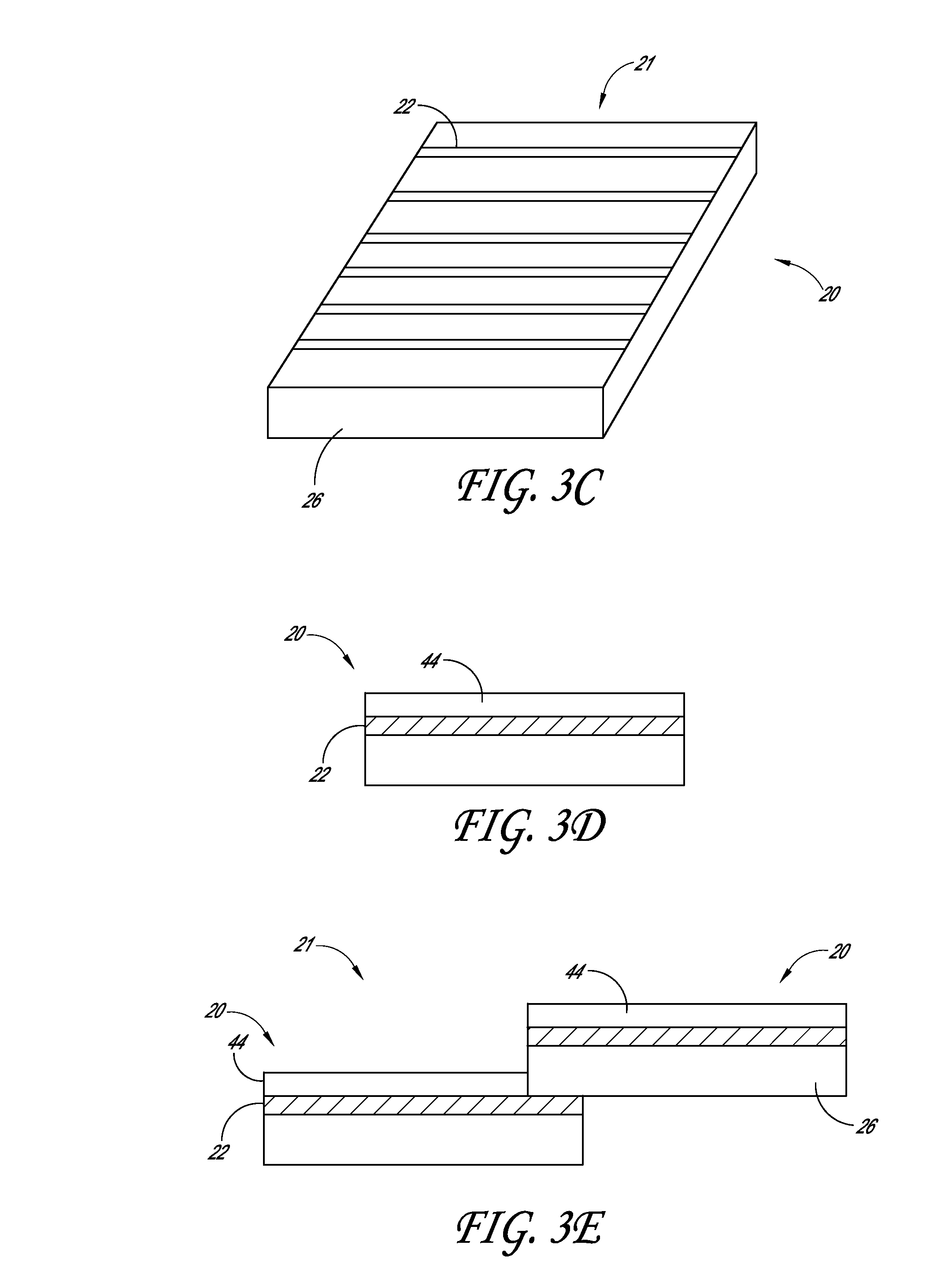

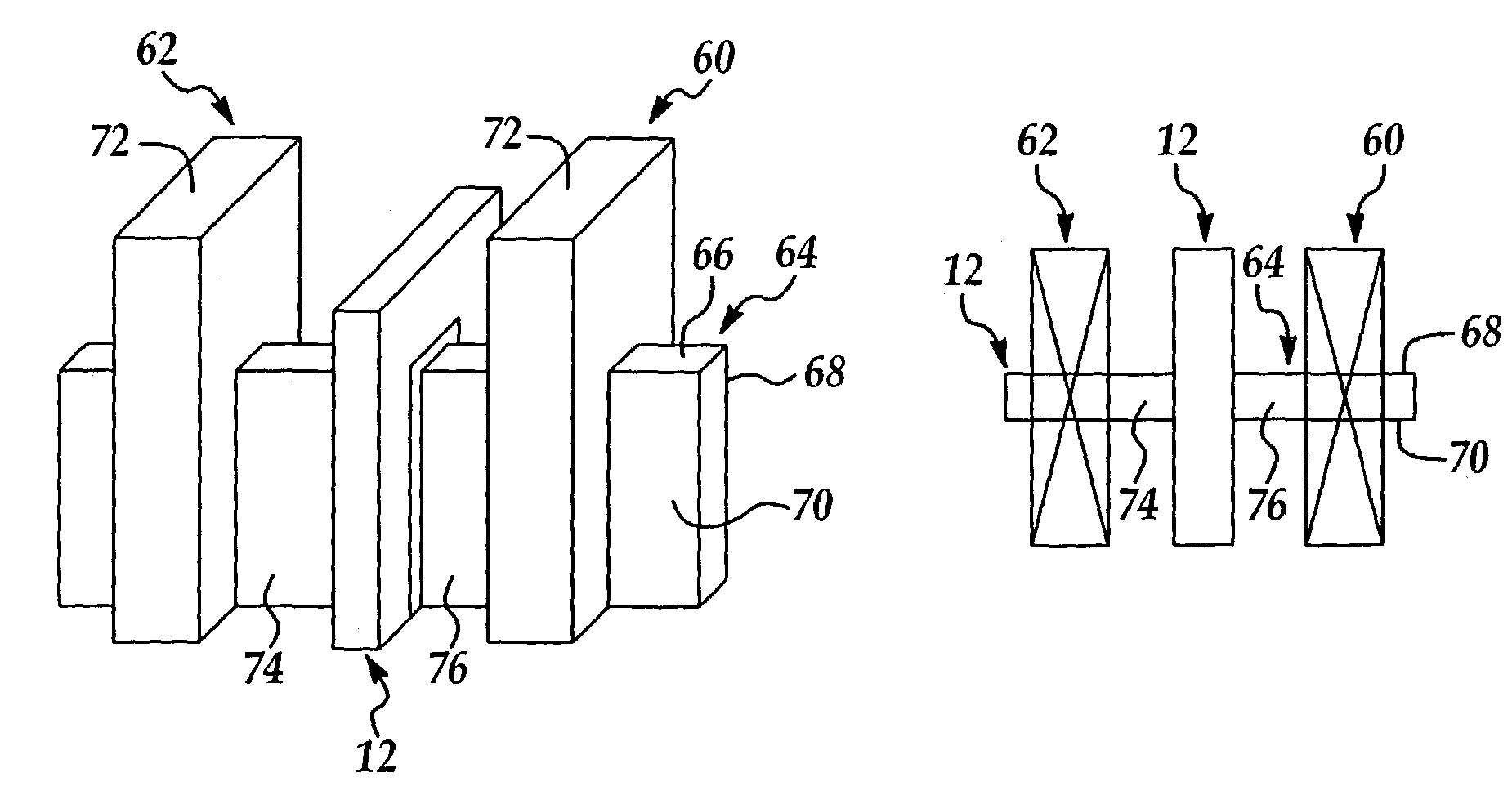

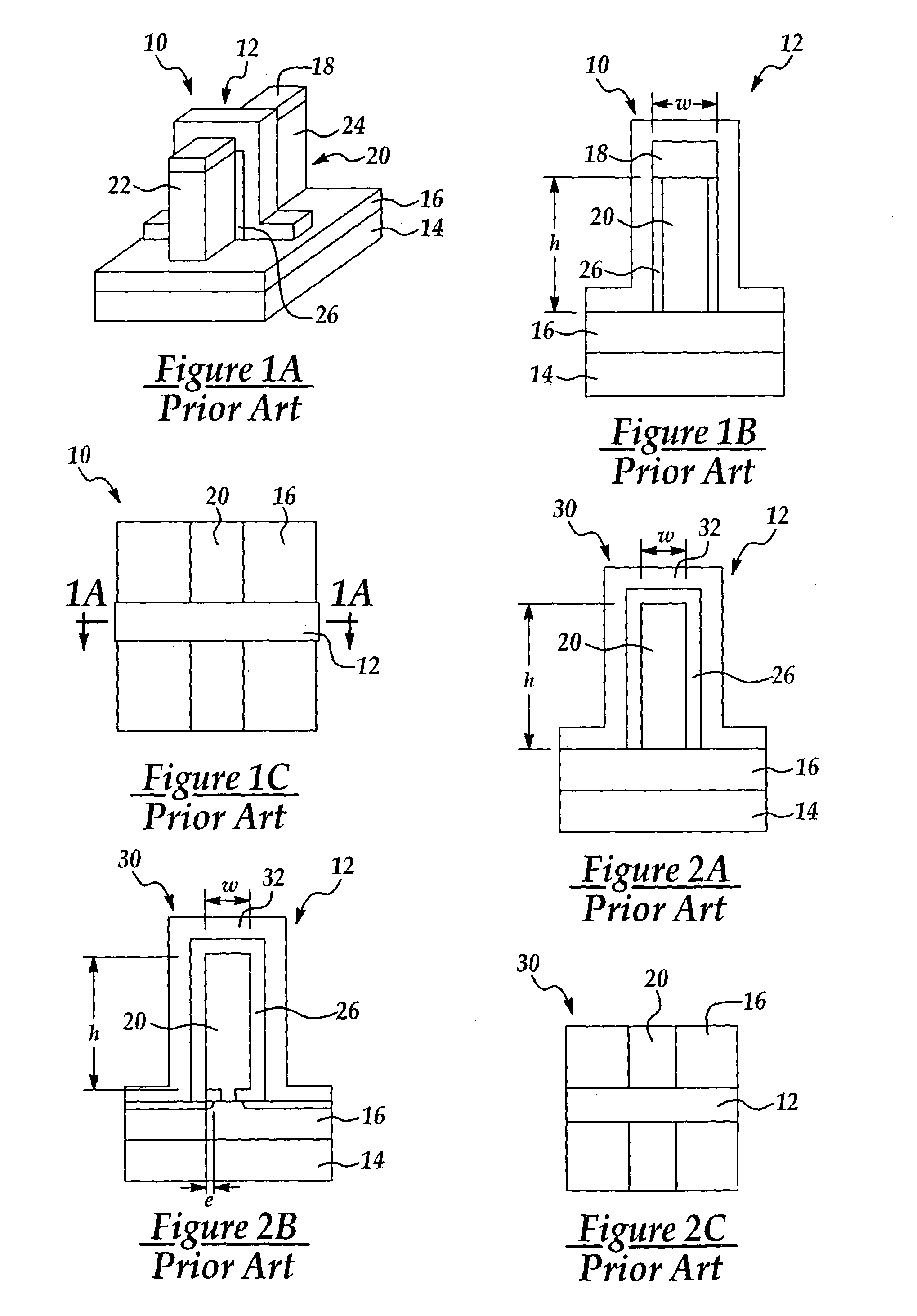

FinFET transistor device on SOI and method of fabrication

ActiveUS7300837B2Thin body”Reduce contact resistanceTransistorSolid-state devicesSilicate glassEngineering

A FinFET transistor on SOI device and method of fabrication is provided. At least two FinFET fins each having an upper poly-silicate glass portion and a lower silicon portion are formed using spacer patterning technology. Each fin is formed on a sacrificial SiN mask layer having a sacrificial support structure. The SiN mask is removed and then a breakthrough etch is applied to remove an underlying pad oxide layer. A PSG layer defining a width of each of the fins on a sidewall of each of the support structures is deposited on each of the support structures. At least two fins each having a narrow fin pitch of about 0.25 μm. are formed. The fins provide a seed layer for at least two selective epitaxially raised source and drain regions, wherein each raised source-drain associated with each fin are interconnected thus forming a source pad and a drain pad.

Owner:TAIWAN SEMICON MFG CO LTD

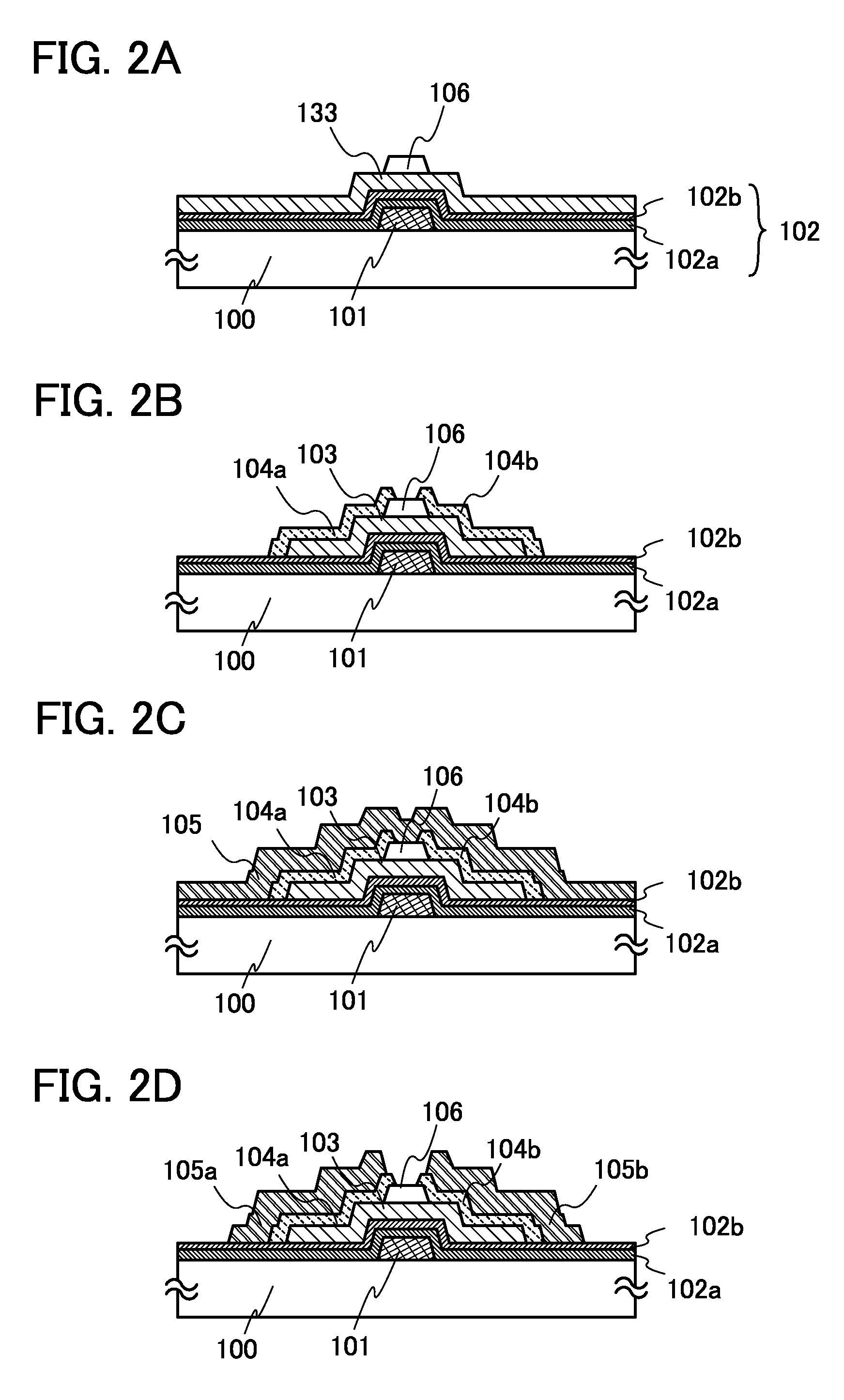

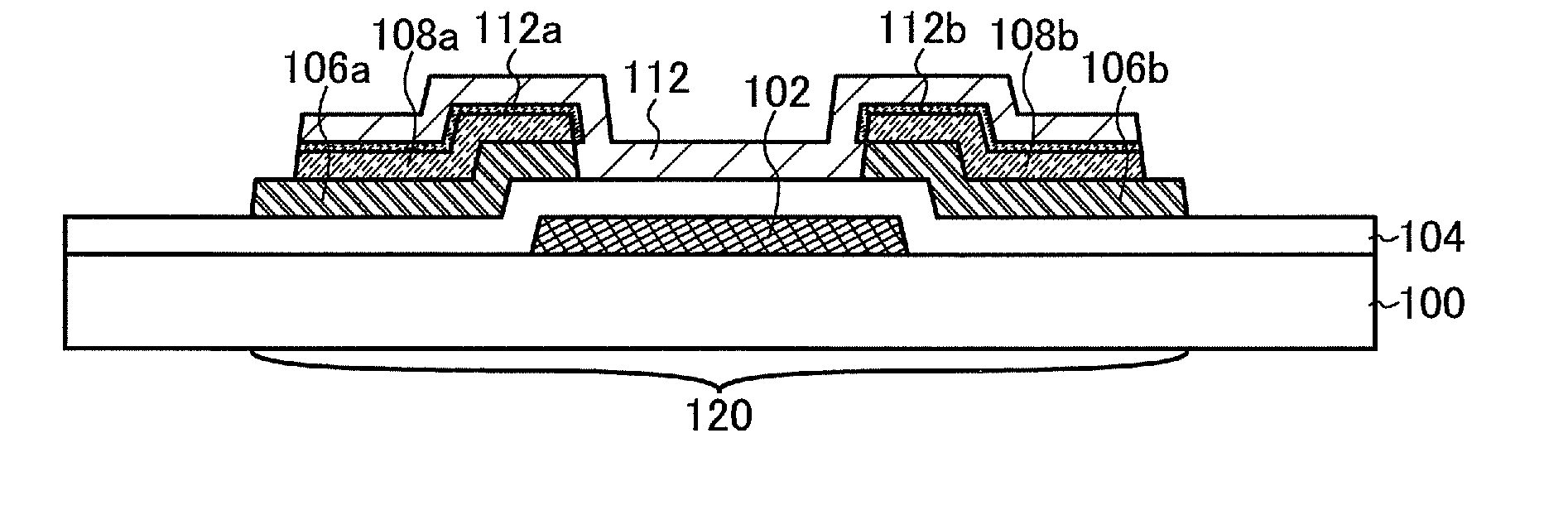

Semiconductor device and method for manufacturing the same

ActiveUS20100117073A1Small parasitic capacitanceHigh on-off ratioTransistorElectroluminescent light sourcesIndiumNitrogen

In a thin film transistor which uses an oxide semiconductor, buffer layers containing indium, gallium, zinc, oxygen, and nitrogen are provided between the oxide semiconductor layer and the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

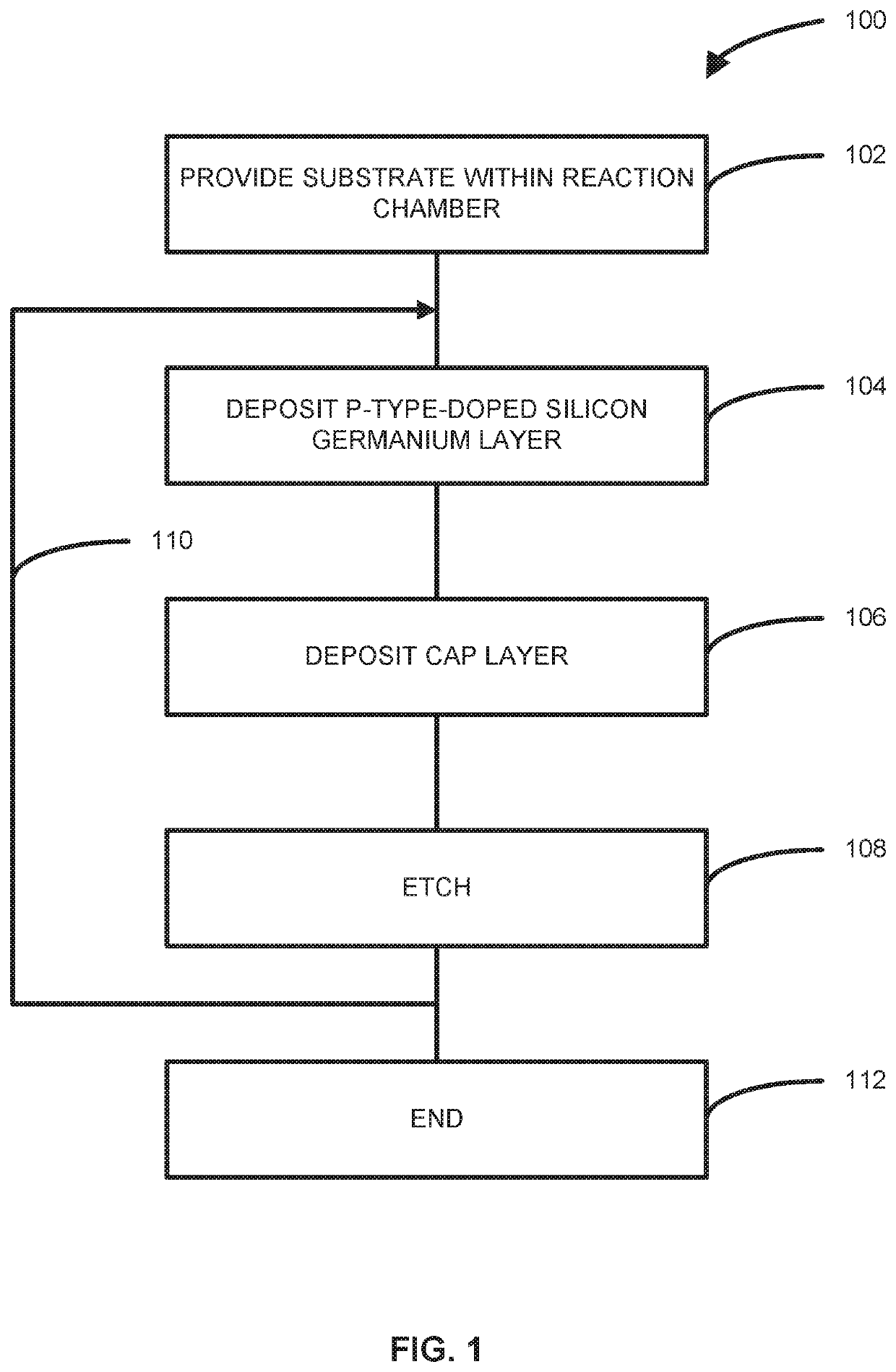

Methods for selective deposition using a sacrificial capping layer

ActiveUS20210066079A1Reduce contact resistanceIncrease contact resistanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSelective depositionMaterials science

Methods and systems for selectively depositing a p-type doped silicon germanium layer and structures and devices including a p-type doped silicon germanium layer are disclosed. An exemplary method includes providing a substrate, comprising a surface comprising a first area comprising a first material and a second area comprising a second material, within a reaction chamber; depositing a p-type doped silicon germanium layer overlying the surface, the p-type doped silicon germanium layer comprising gallium; and depositing a cap layer overlying the p-type doped silicon germanium layer. The method can further include an etch step to remove the cap layer and the p-type doped silicon germanium layer overlying the second material.

Owner:ASM IP HLDG BV

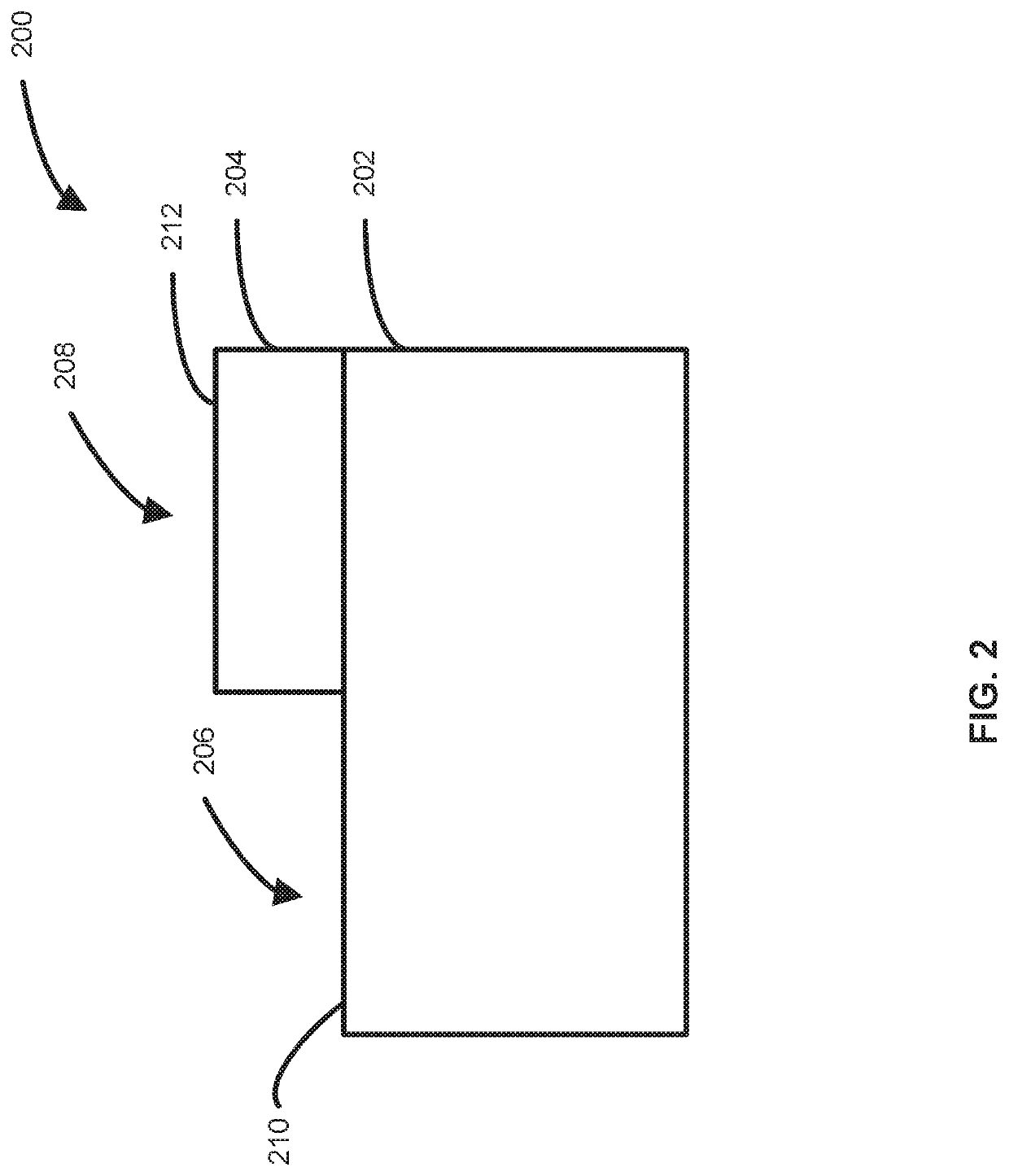

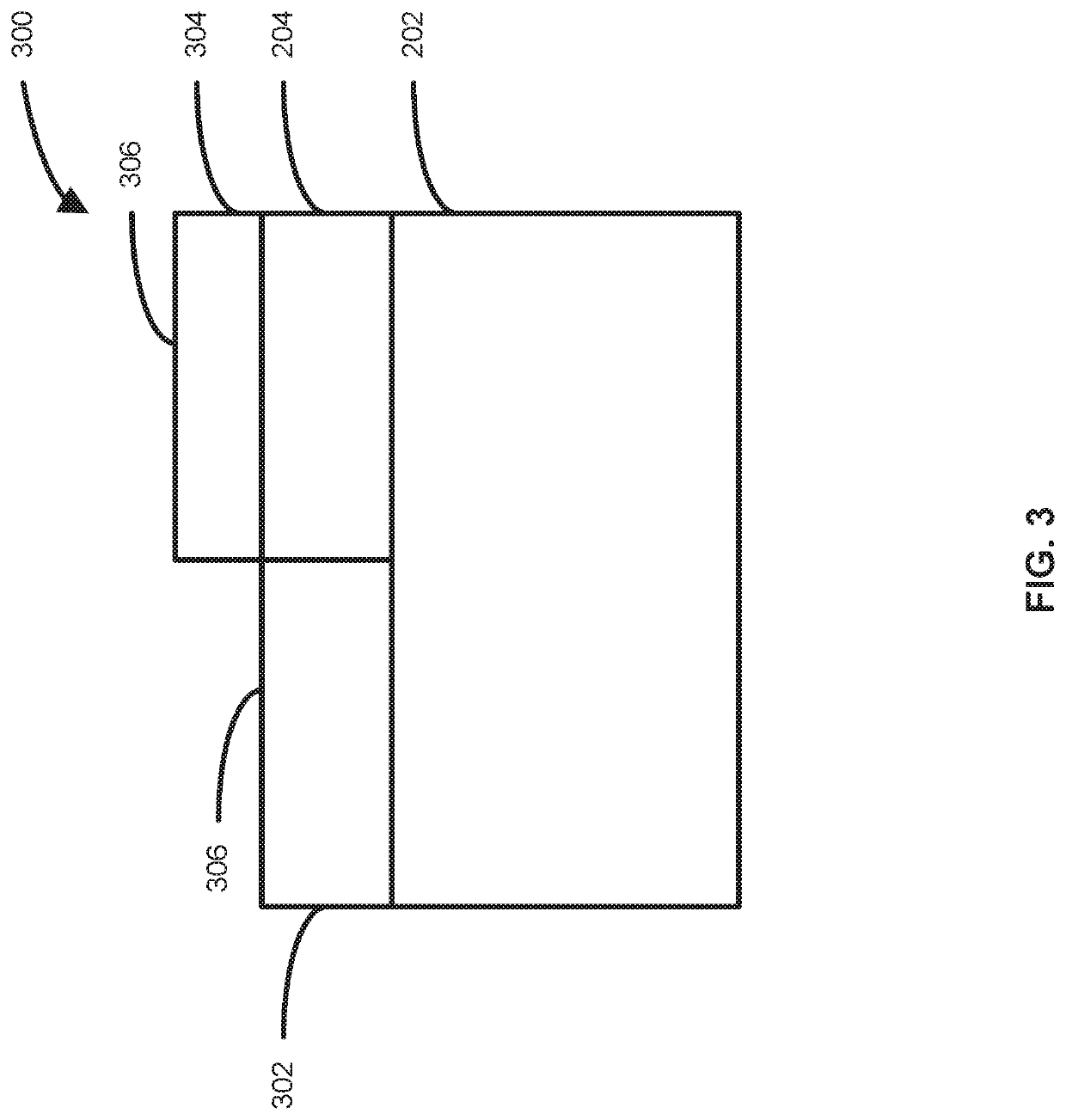

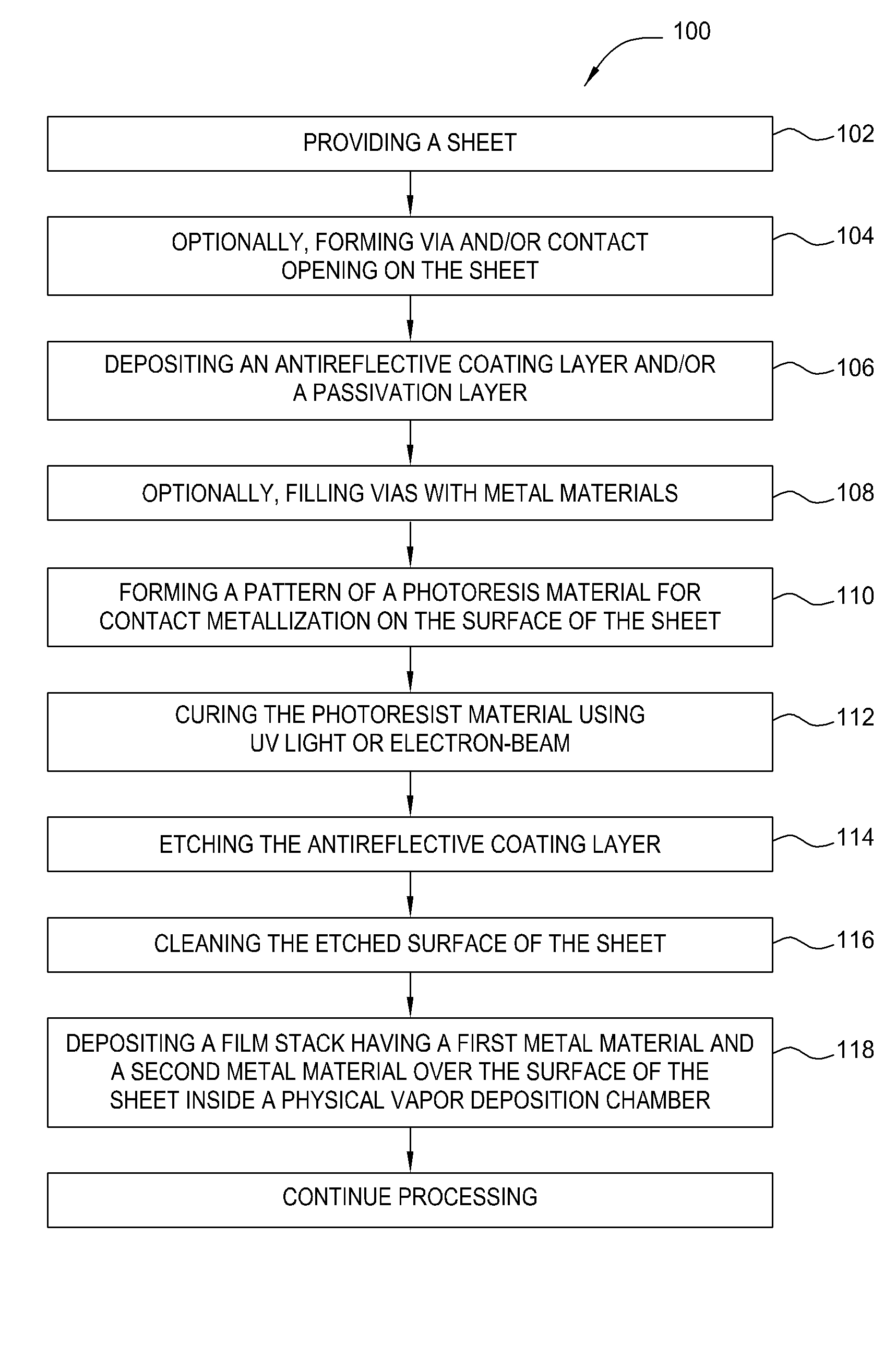

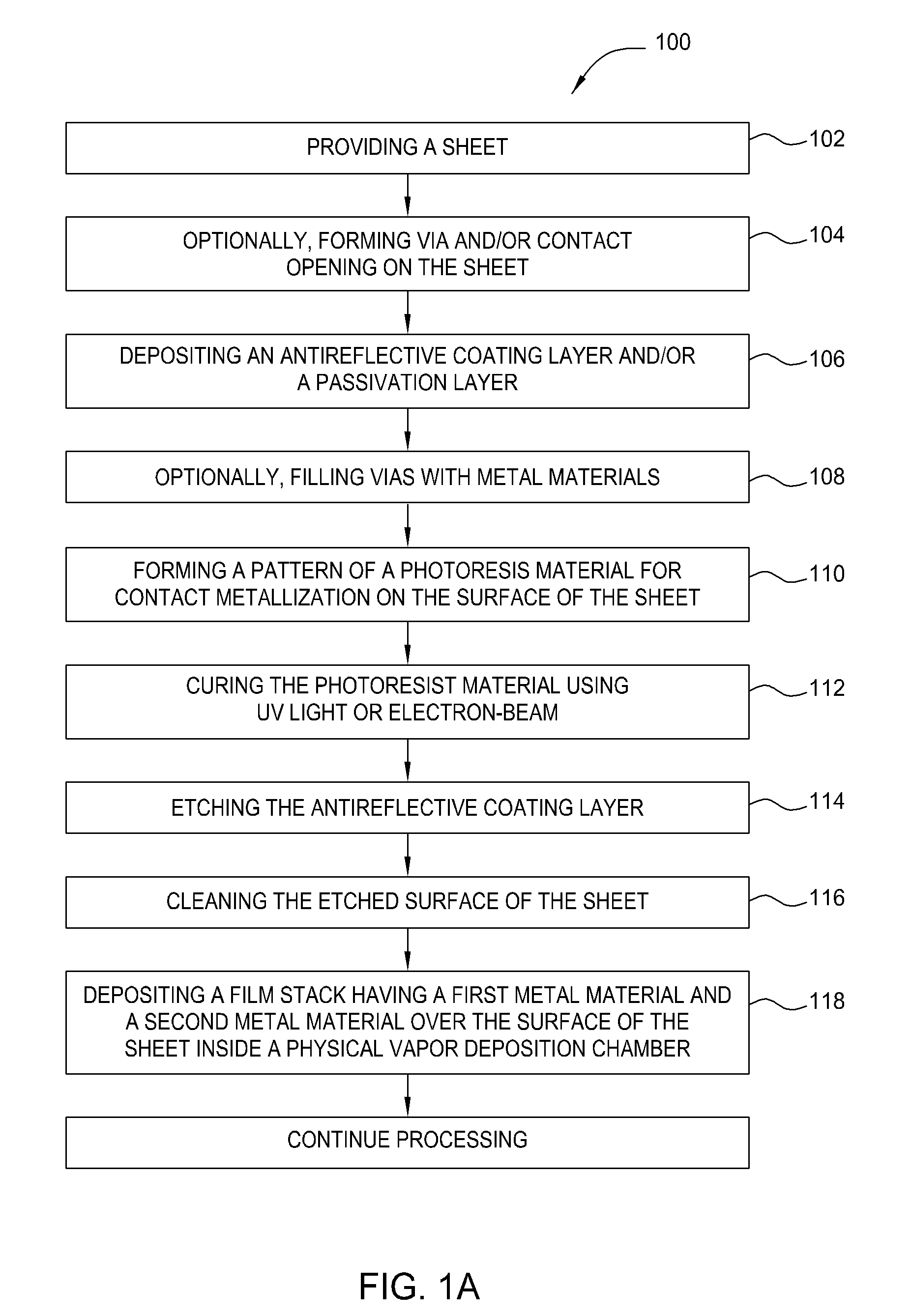

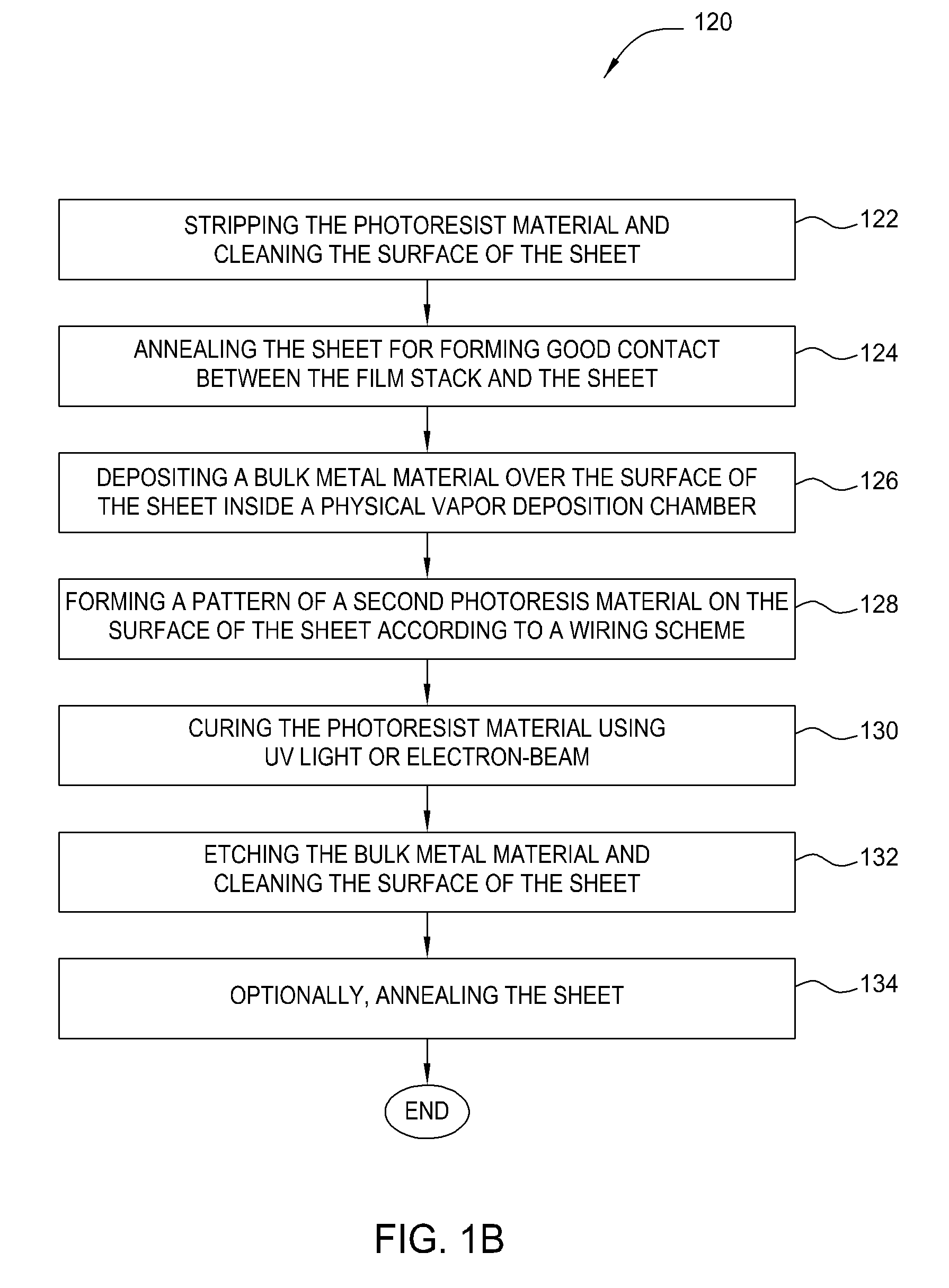

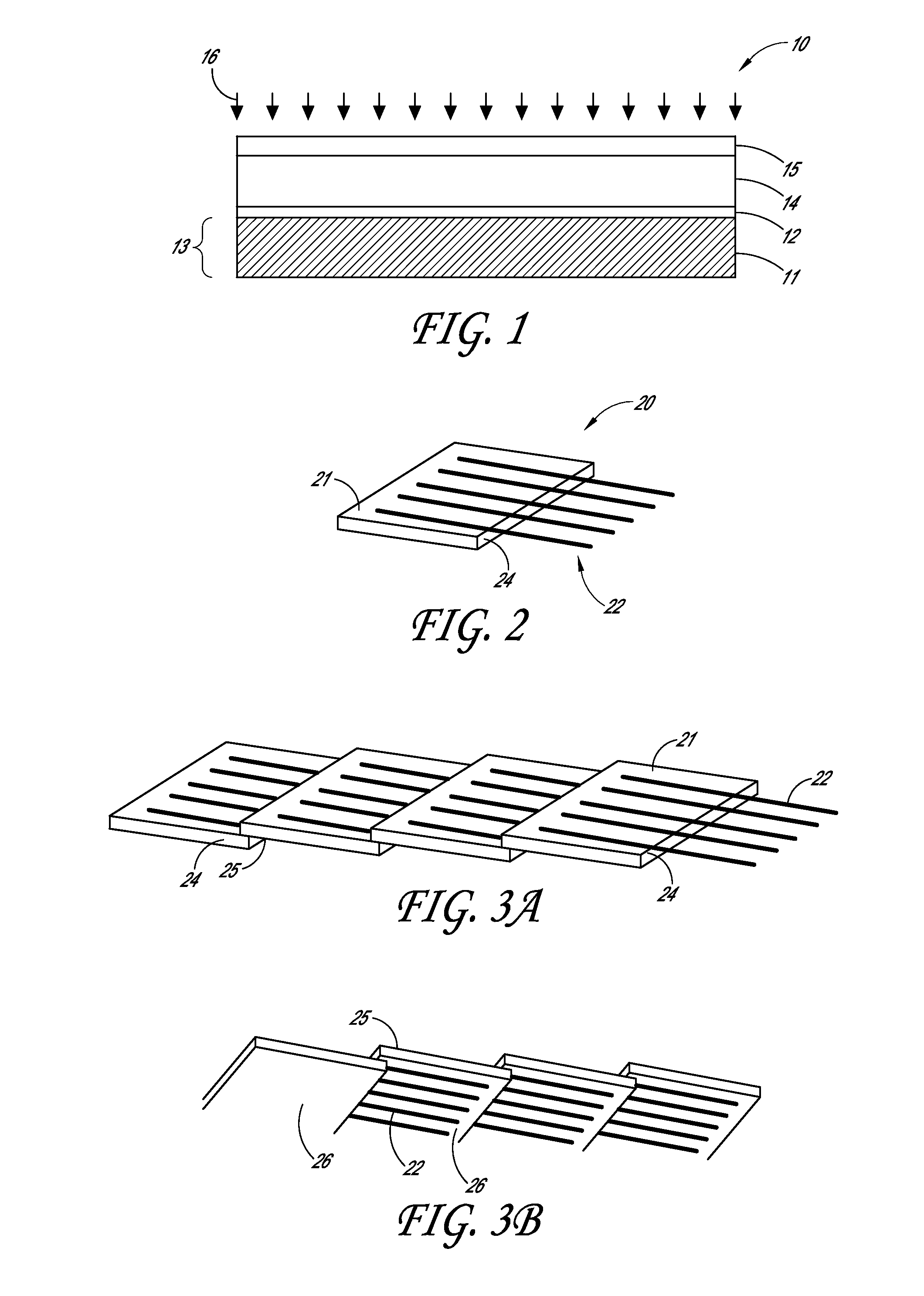

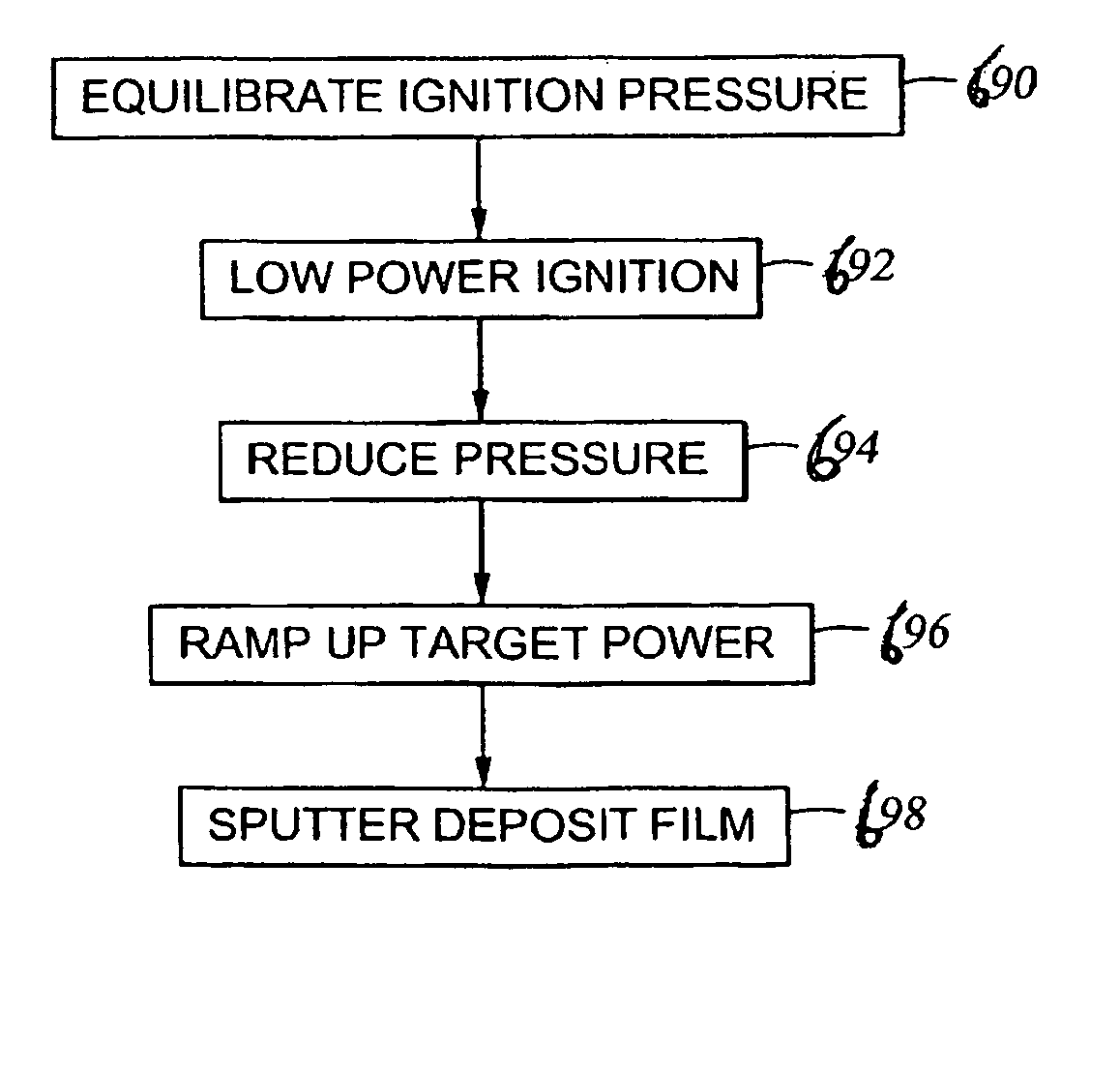

Photovoltaic contact and wiring formation

InactiveUS20070148336A1Reduce contact resistanceEnhanced vapor depositionVacuum evaporation coatingSputtering coatingEtchingGas phase

A method and apparatus for fabricating a solar cell and forming metal contact is disclosed. Solar cell contact and wiring is formed by depositing a thin film stack of a first metal material and a second metal material as an initiation layer or seed layer for depositing a bulk metal layer in conjunction with additional sheet processing, photolithography, etching, cleaning, and annealing processes. In one embodiment, the thin film stack for forming metal silicide with reduced contact resistance over the sheet is deposited by sputtering or physical vapor deposition. In another embodiment, the bulk metal layer for forming metal lines and wiring is deposited by sputtering or physical vapor deposition. In an alternative embodiment, electroplating or electroless deposition is used to deposit the bulk metal layer.

Owner:APPLIED MATERIALS INC

Transistor and method for manufacturing the transistor

ActiveUS20100193782A1Reduce variationContact resistanceTransistorSolid-state devicesCrystal structureSemiconductor

It is an object to reduce characteristic variation among transistors and reduce contact resistance between an oxide semiconductor layer and a source electrode layer and a drain electrode layer, in a transistor where the oxide semiconductor layer is used as a channel layer. In a transistor where an oxide semiconductor is used as a channel layer, at least an amorphous structure is included in a region of an oxide semiconductor layer between a source electrode layer and a drain electrode layer, where a channel is to be formed, and a crystal structure is included in a region of the oxide semiconductor layer which is electrically connected to an external portion such as the source electrode layer and the drain electrode layer.

Owner:SEMICON ENERGY LAB CO LTD

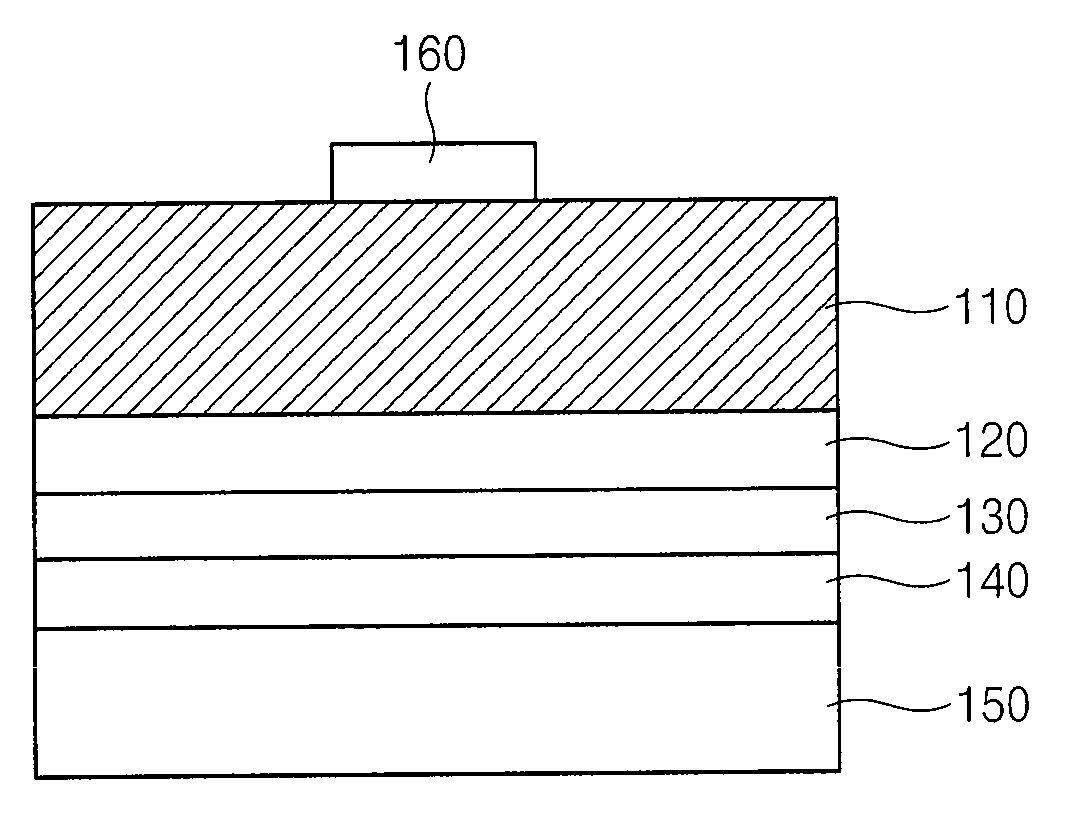

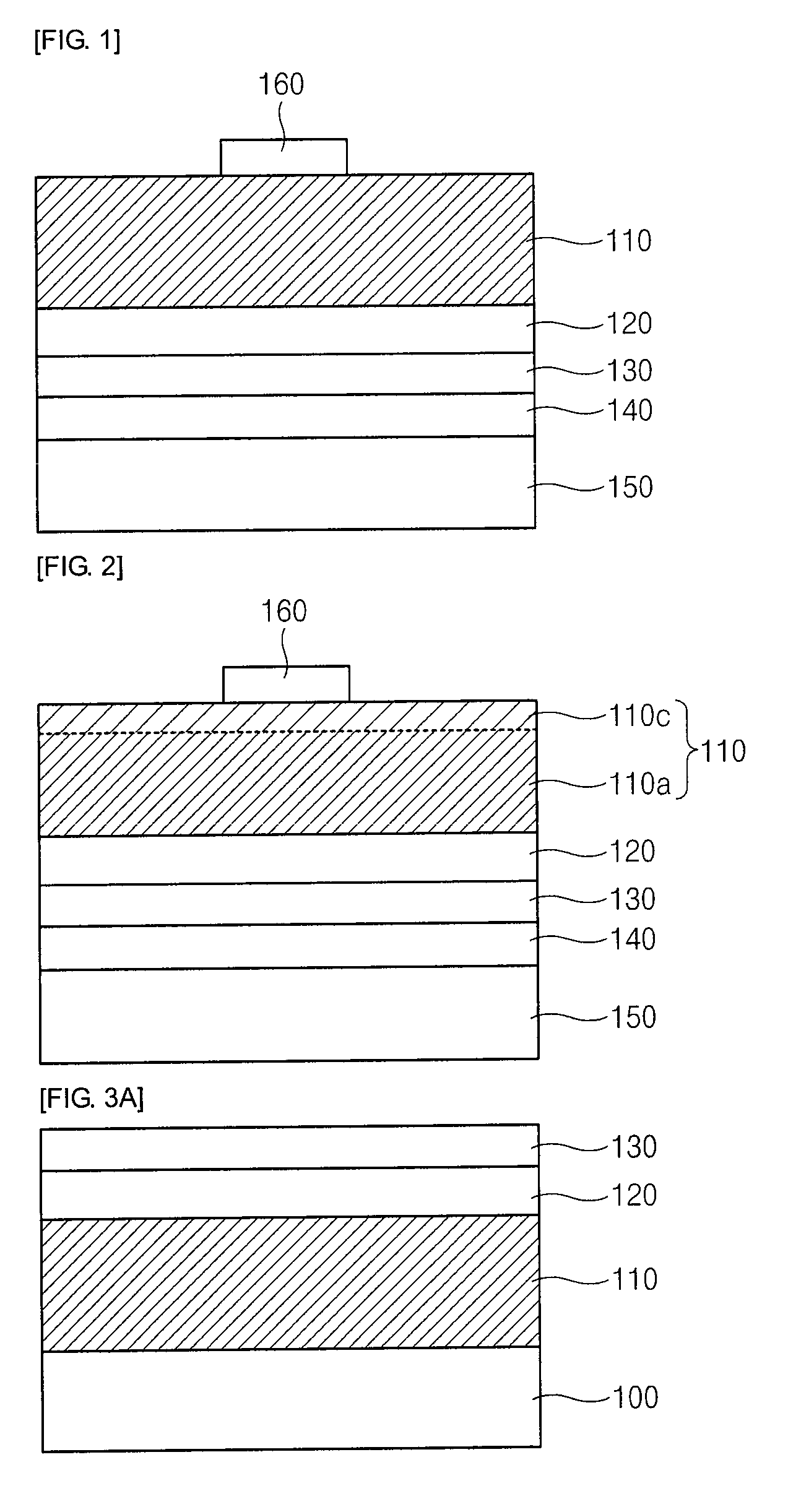

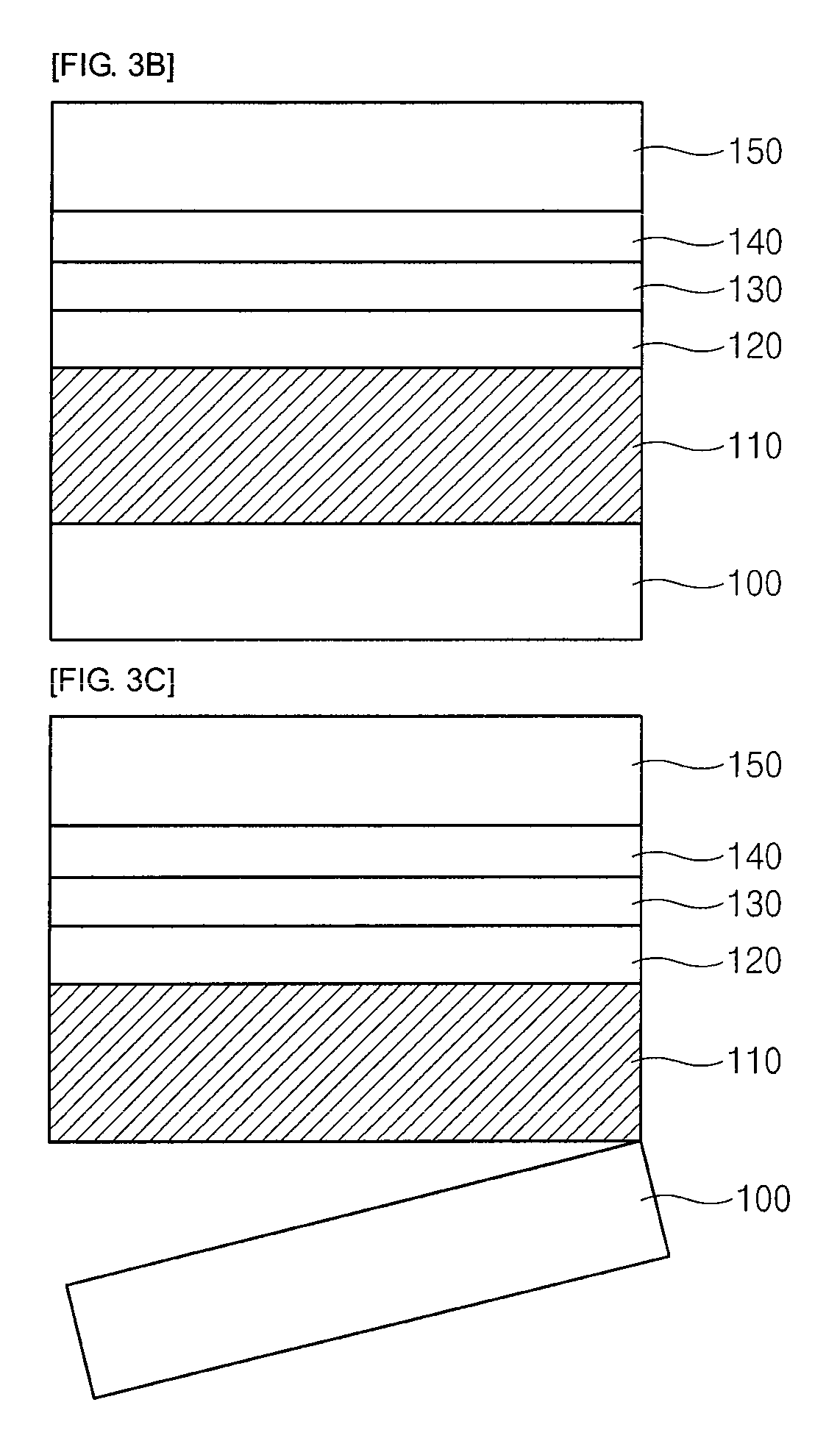

Semiconductor light emitting device

ActiveUS20060273335A1Good ohmic contactReduce contact resistanceSolid-state devicesSemiconductor devicesOhmic contactLength wave

A semiconductor light emitting device includes a semiconductor light emitting portion having a first contact layer of a first conductivity, a second contact layer of a second conductivity and an active layer sandwiched between the first and second contact layers. The device further includes a transparent electrode which substantially entirely covers a surface of the second contact layer in ohmic contact with the surface of the second contact layer and is transparent to a wavelength of light emitted from the semiconductor light emitting portion, and a metal reflection film which is opposed to substantially the entire surface of the transparent electrode and electrically connected to the transparent electrode, and reflects the light emitted from the semiconductor light emitting portion and passing through the transparent electrode toward the semiconductor light emitting portion.

Owner:ROHM CO LTD

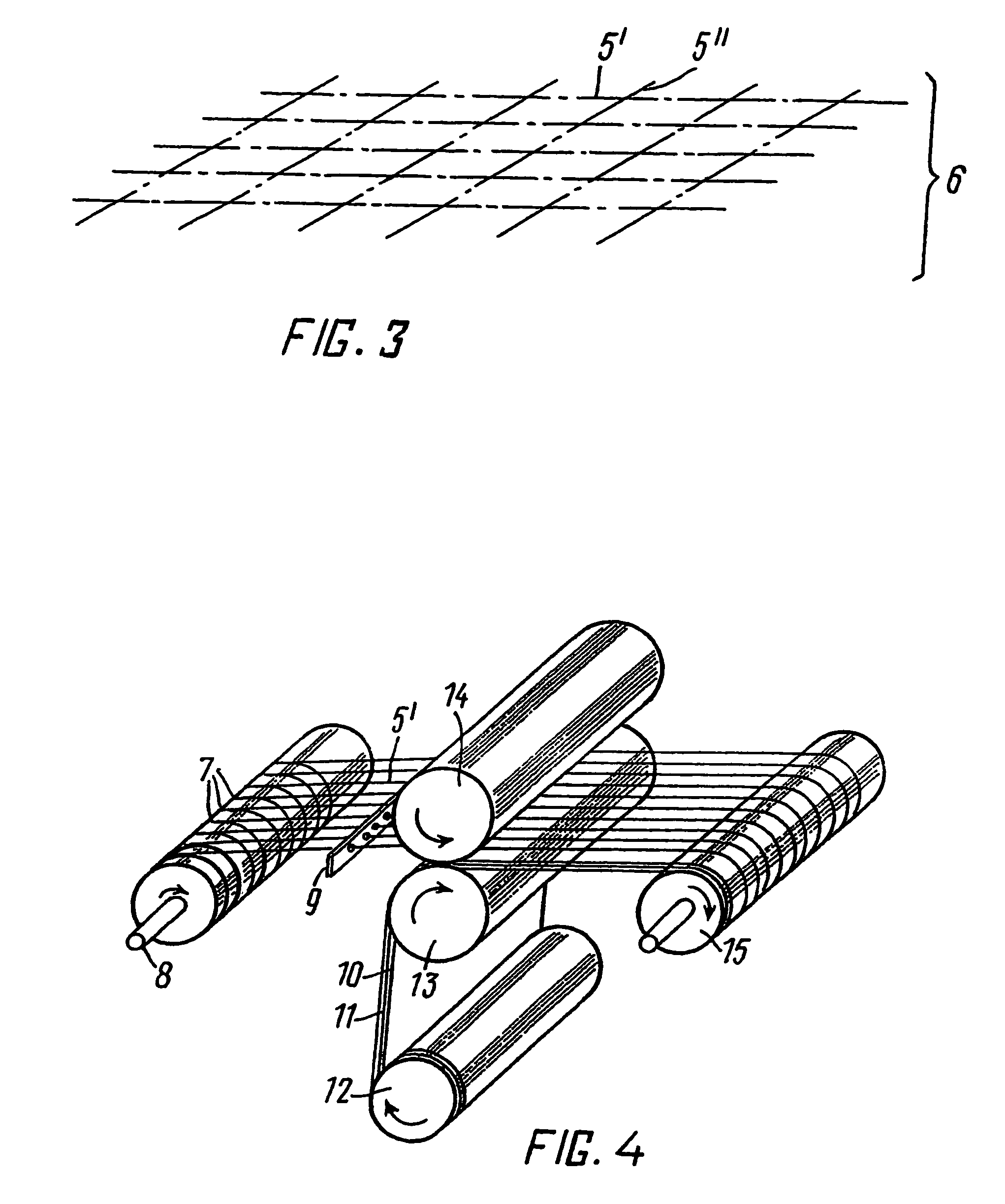

Solar cells with grid wire interconnections

InactiveUS20120325282A1Robust handlingReduce contact resistancePV power plantsSemiconductor/solid-state device manufacturingElectrical and Electronics engineeringElectrode

A plurality of solar cells is connected together in a shingled fashion. Each of the solar cells includes grid wires that are attached to an electrode of the solar cell so as to receive charge carriers produced when photons are absorbed by the solar cell. The grid wires are then interconnected with adjacent solar cells when the solar cells are shingled together. The grid wires may be applied to the solar cells via a laminate and the electrical interconnection of the grid wires may be achieved by the use of a conductive epoxy.

Owner:SOLOPOWER

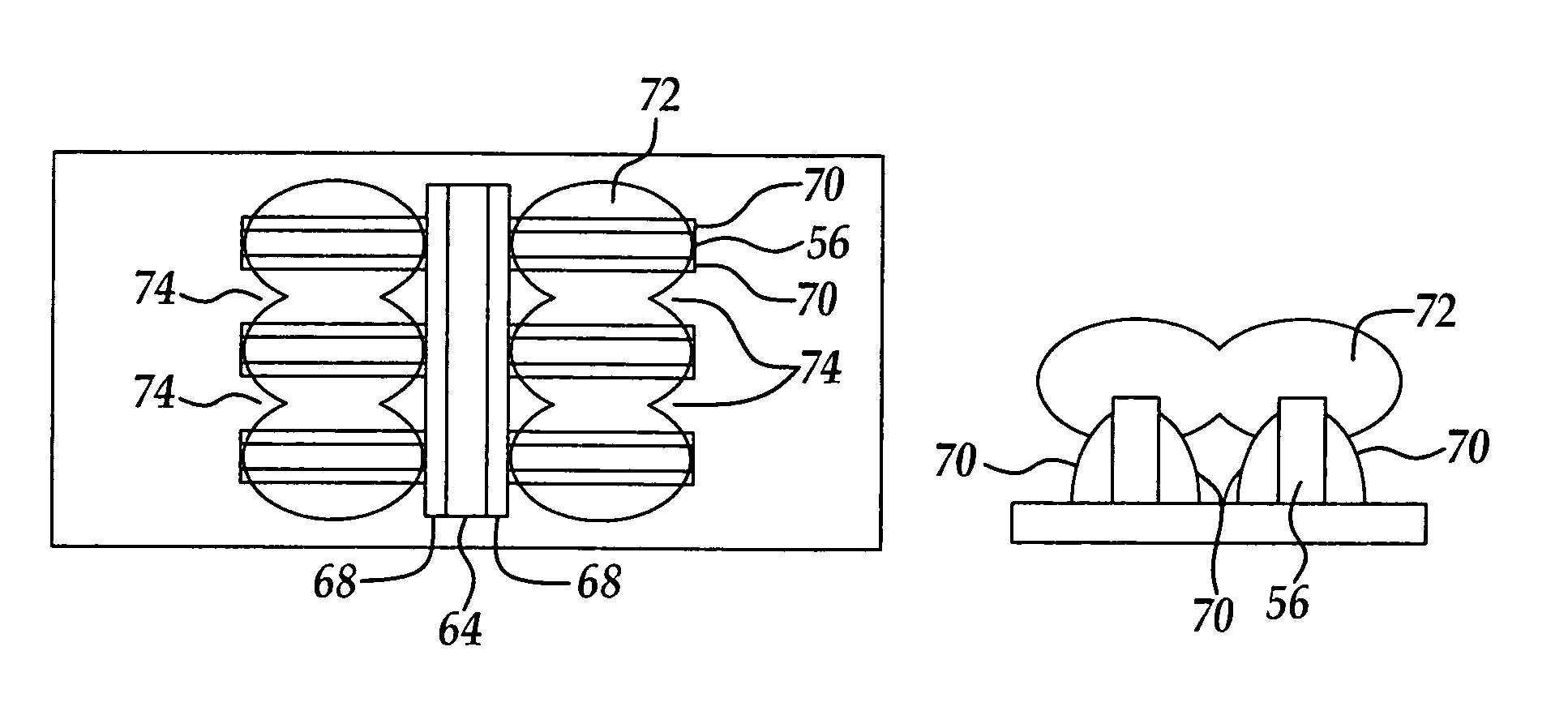

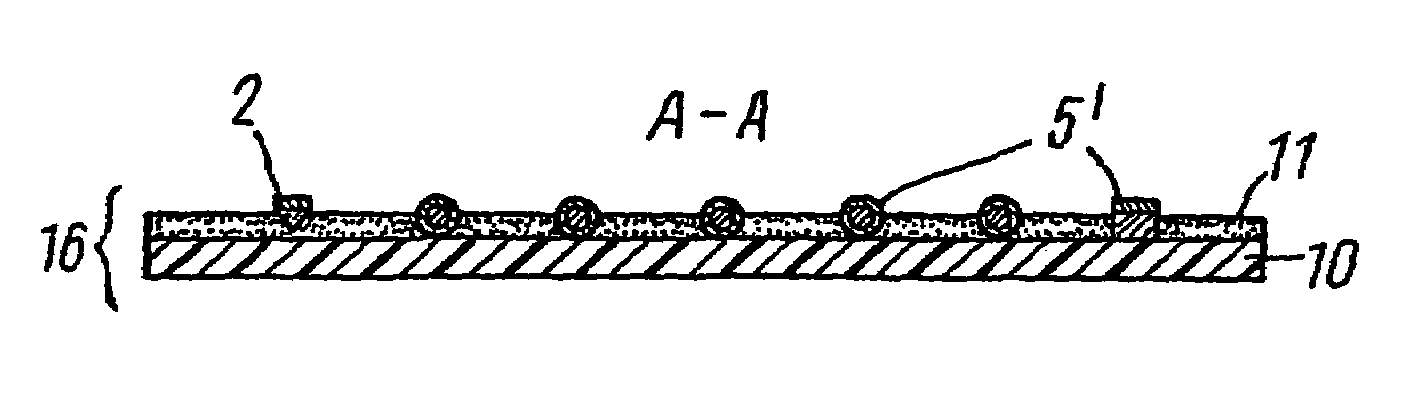

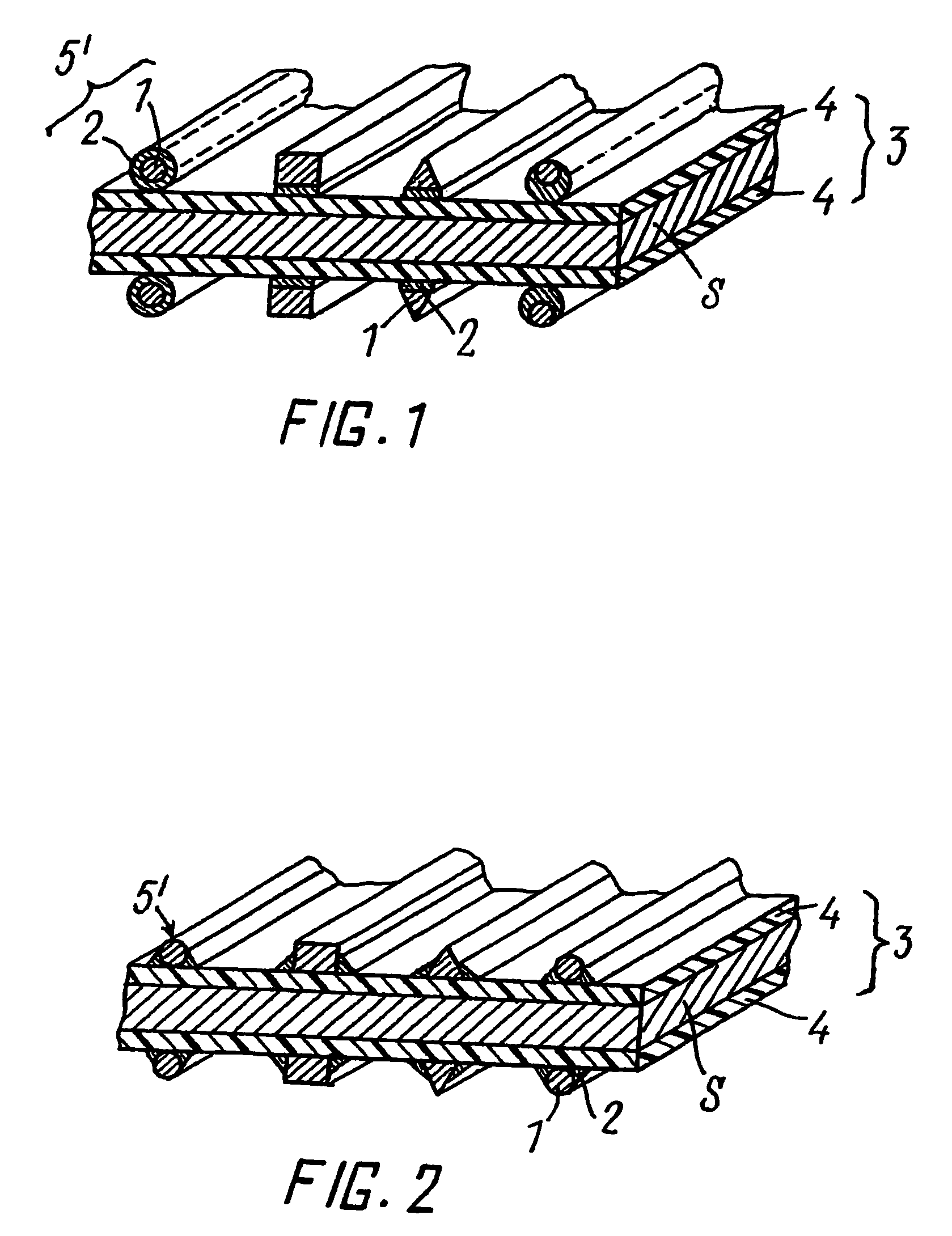

Electrode for photovoltaic cells, photovoltaic cell and photovoltaic module

ActiveUS7432438B2Low production costReduce contact resistancePV power plantsSolid-state devicesAlloyLow melting point

An electrode for contacting an electrically conductive surface of a photovoltaic element includes an electrically insulating optically transparent film, an adhesive layer provided on a planar surface of the film, and a plurality of substantially parallel, electrically conductive wires embedded into the adhesive layer. The plurality of wires lies over the planar surface of the film. A part of the surfaces of the wires protrude from the adhesive layer. At least the part of the surfaces protruding from the adhesive layer are covered by a coating consisting of an alloy having a low melting point to solder the wires to the electrically conductive surface and to a first terminal bar. The adhesive layer has a thickness less that a thickness of the wires embedded therein.

Owner:MEYER BURGER AG

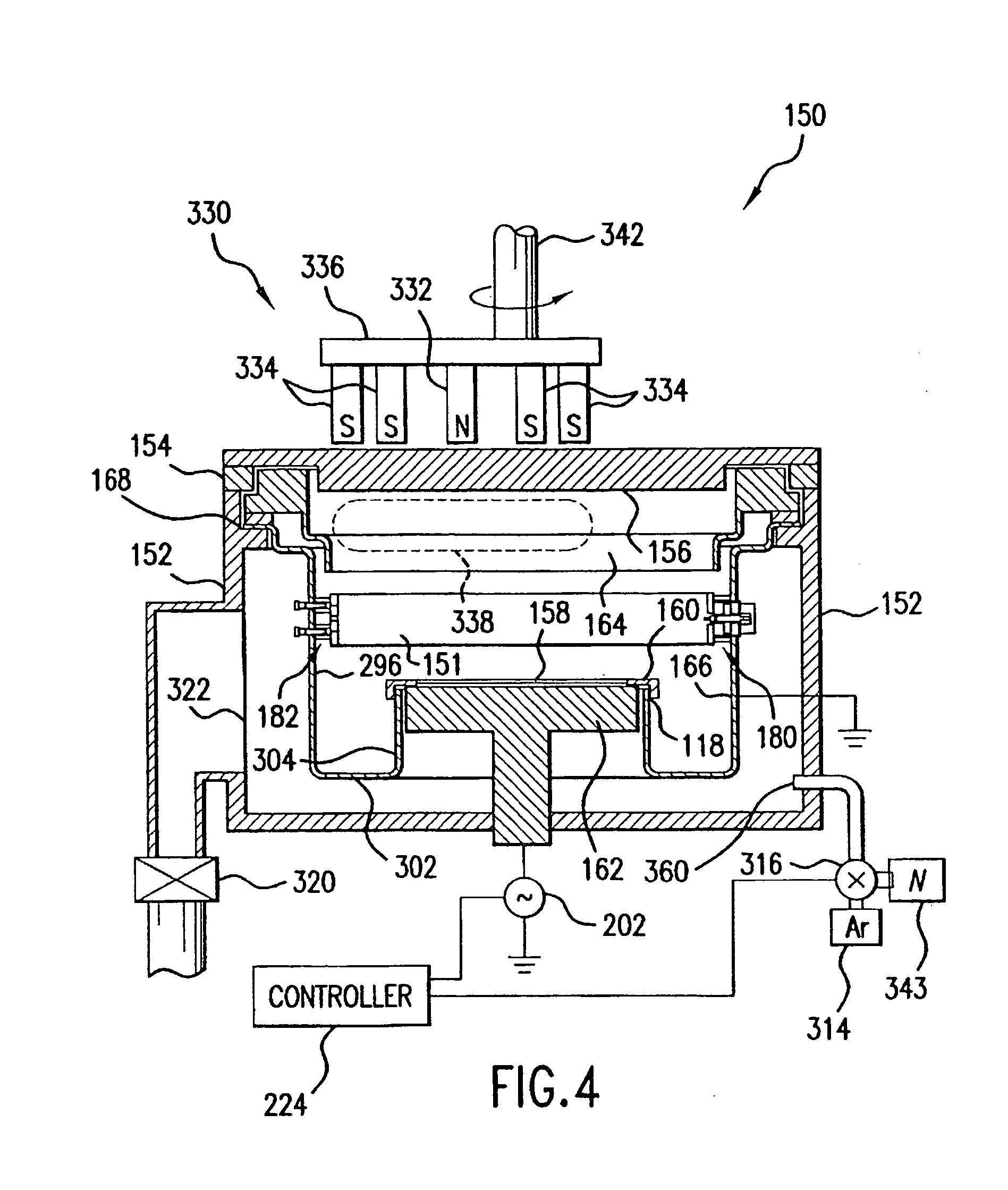

Self-ionized and inductively-coupled plasma for sputtering and resputtering

InactiveUS20050006222A1Raise the ratioReduce layer thicknessCellsElectric discharge tubesSputteringInductively coupled plasma

A magnetron sputter reactor (410) and its method of use, in which SIP sputtering and ICP sputtering are promoted is disclosed. In another chamber (412) an array of auxiliary magnets positioned along sidewalls (414) of a magnetron sputter reactor on a side towards the wafer from the target is disclosed. The magnetron (436) preferably is a small one having a stronger outer pole (442) of a first polarity surrounding a weaker inner pole (440) of a second polarity all on a yoke (444) and rotates about the axis (438) of the chamber using rotation means (446, 448, 450). The auxiliary magnets (462) preferably have the first polarity to draw the unbalanced magnetic field (460) towards the wafer (424), which is on a pedestal (422) supplied with power (454). Argon (426) is supplied through a valve (428). The target (416) is supplied with power (434).

Owner:APPLIED MATERIALS INC

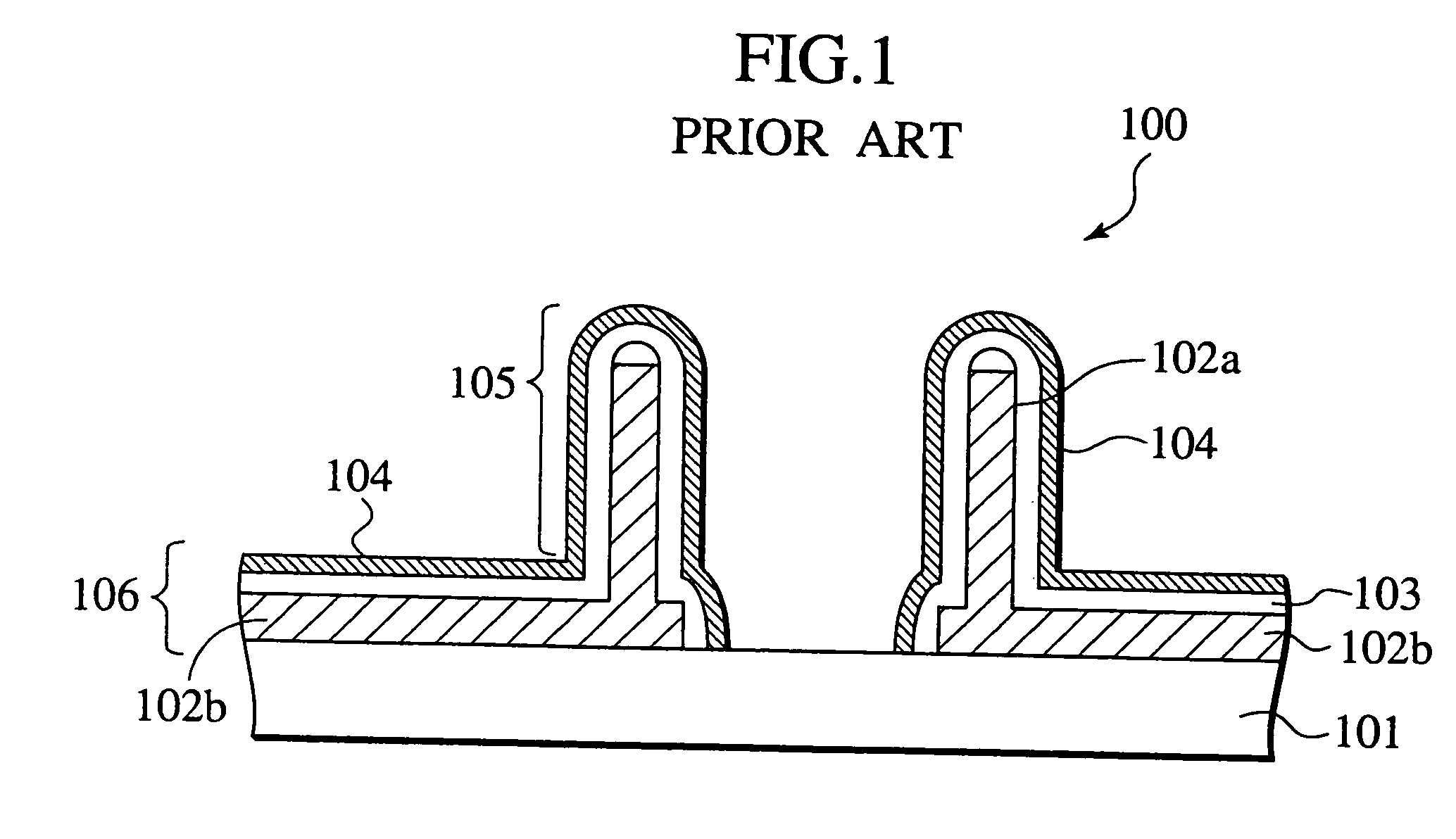

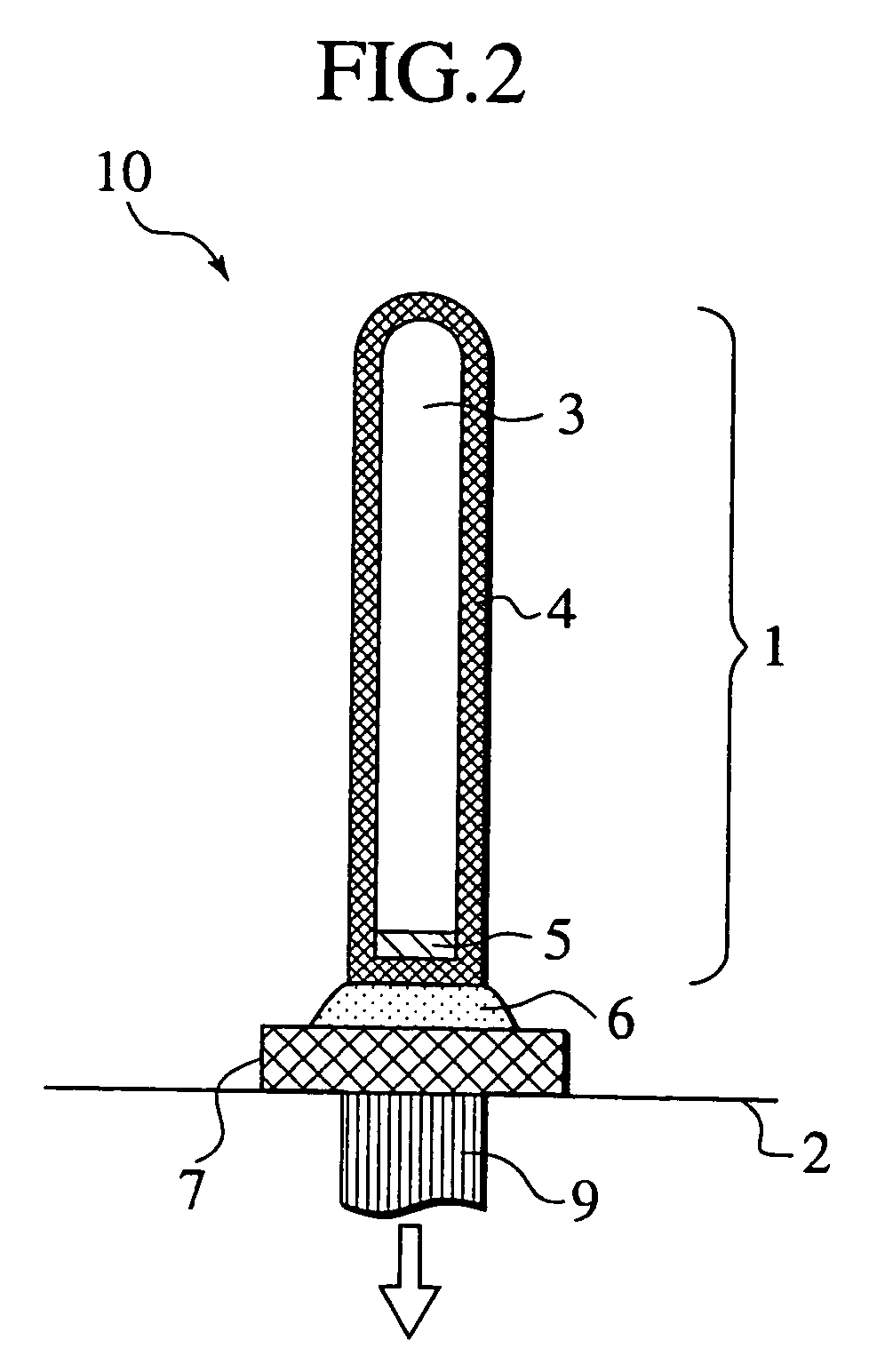

Method for fabricating a probe pin for testing electrical characteristics of an apparatus

InactiveUS7032307B2Reduce contact resistancePitch of probe pins to be reducedLine/current collector detailsSemiconductor/solid-state device testing/measurementProbe cardHigh density

A probe pin for testing electric characteristics of a semiconductor device comprises a silicon pin core (3, 23, 33), and a conductive film (4, 24, 34) covering the entire surface, including the bottom face, of the pin core. The bottom face of the probe pin is connected directly to an electrode (7, 37) positioned in or on a print wiring board. A number of probe pins can be connected to the associated electrodes at a high density, thereby forming a fine-pitch probe card having a superior high-frequency signal characteristic.

Owner:KK TOSHIBA

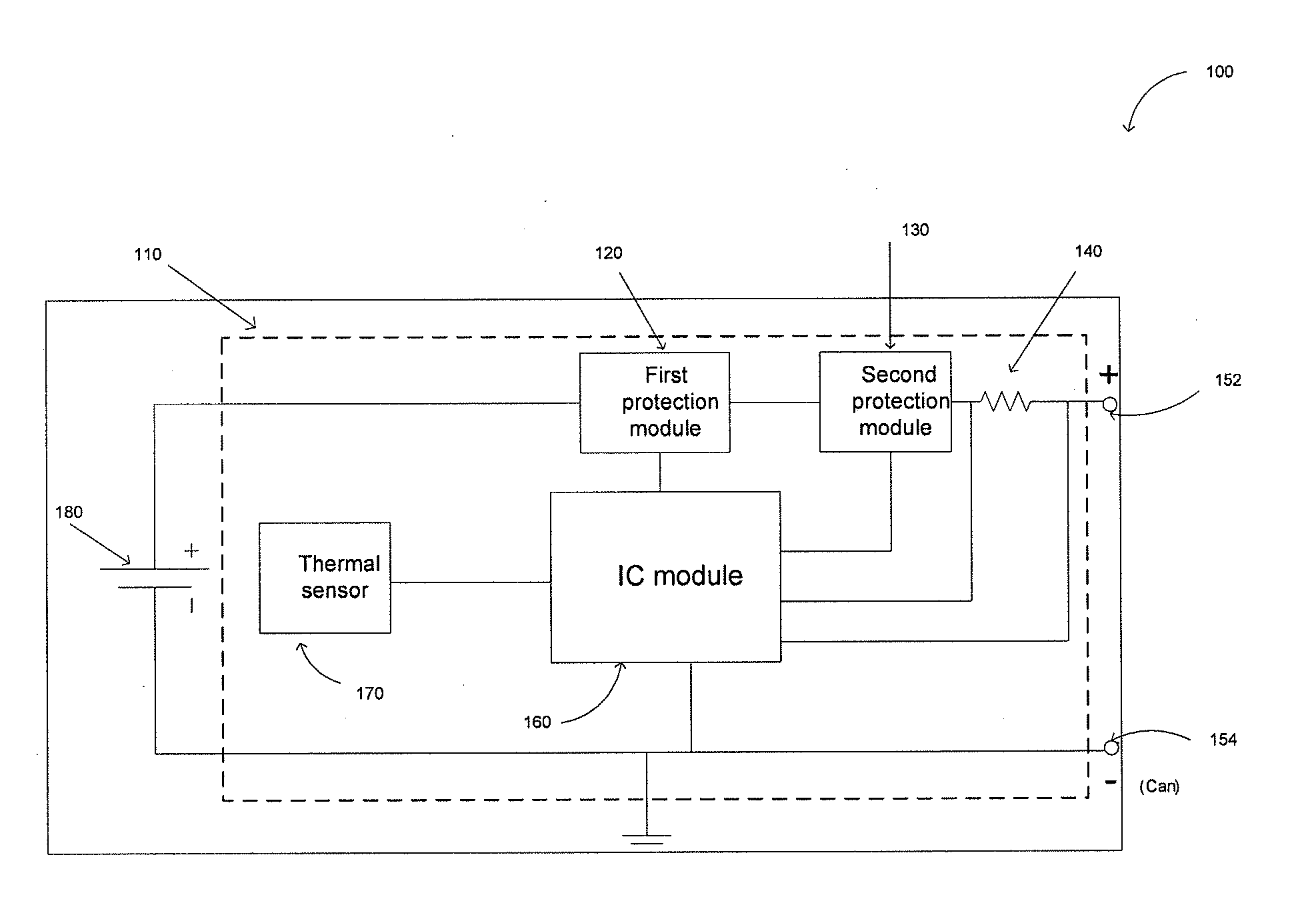

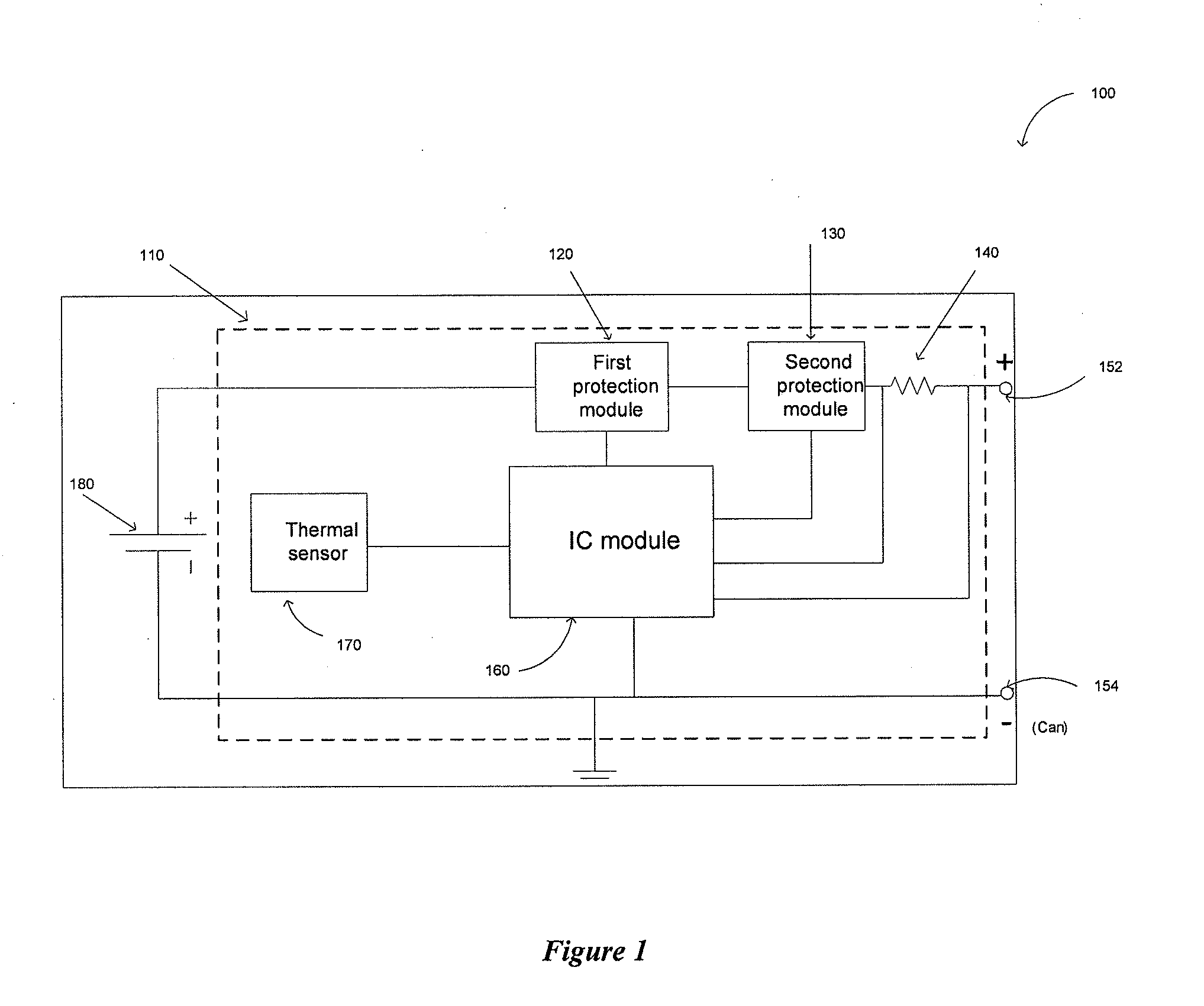

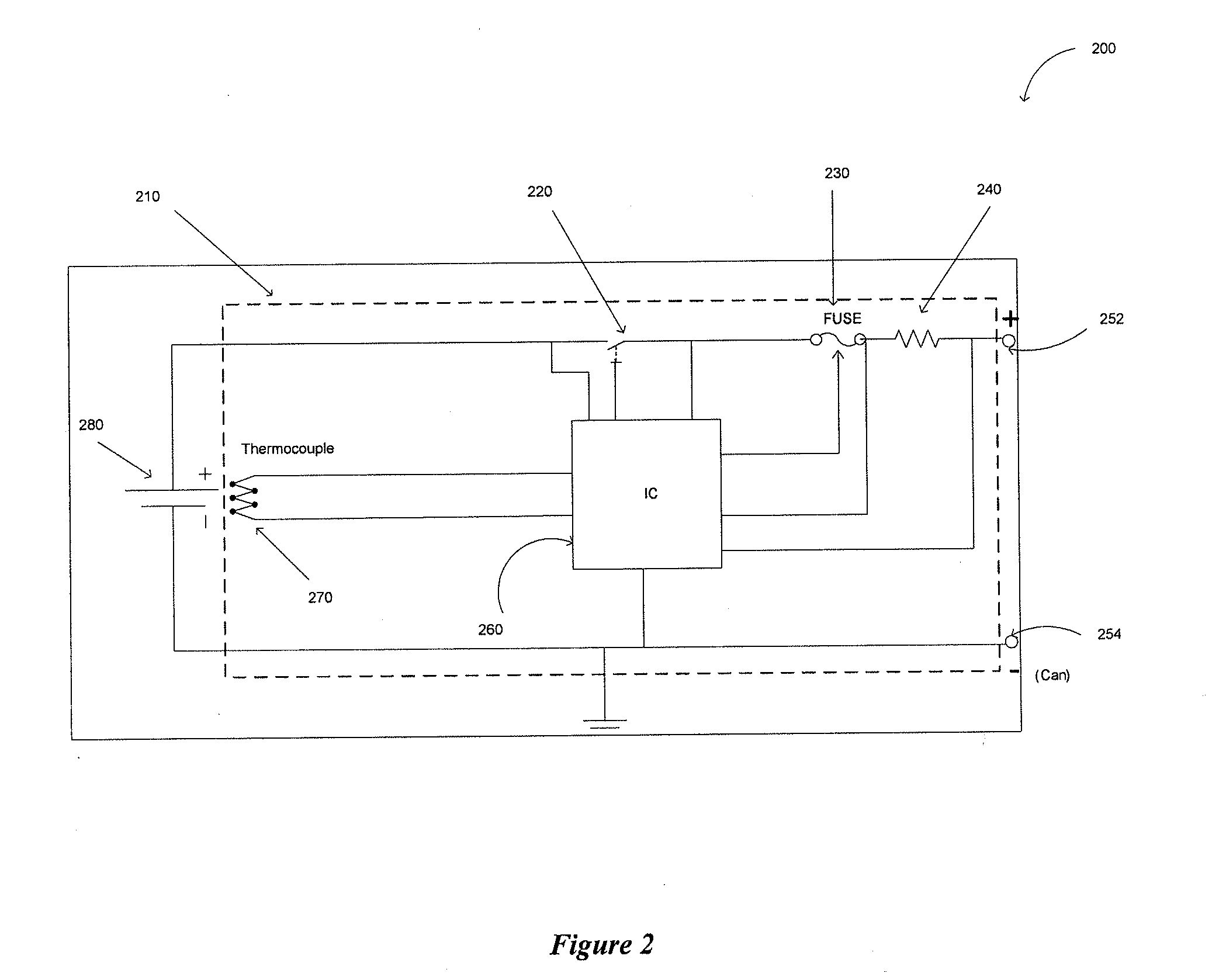

Electronic current interrupt device for battery

InactiveUS20100119881A1Low resistance contactReduce contact resistanceEmergency protective circuit arrangementsElectrical testingLithiumThermocouple

The present invention provides a protection circuit disposed in a lithium-ion cell for protection of the lithium-ion cell. The protection circuit includes a first protection module, a second protection module, an integrated circuit module, a thermal sensor or thermocouple, a switch, a fuse and / or a resistor.

Owner:LEYDEN ENERGY

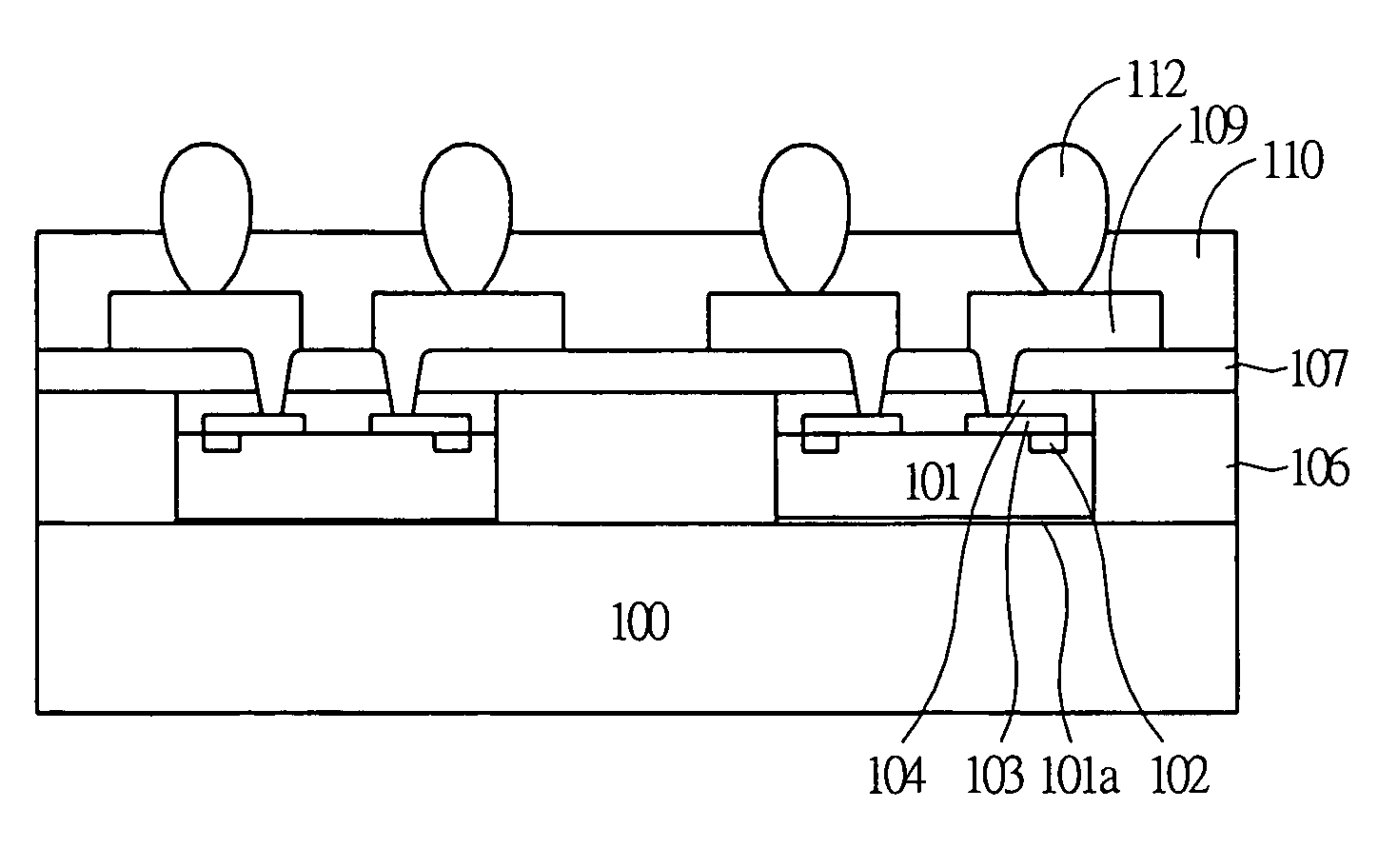

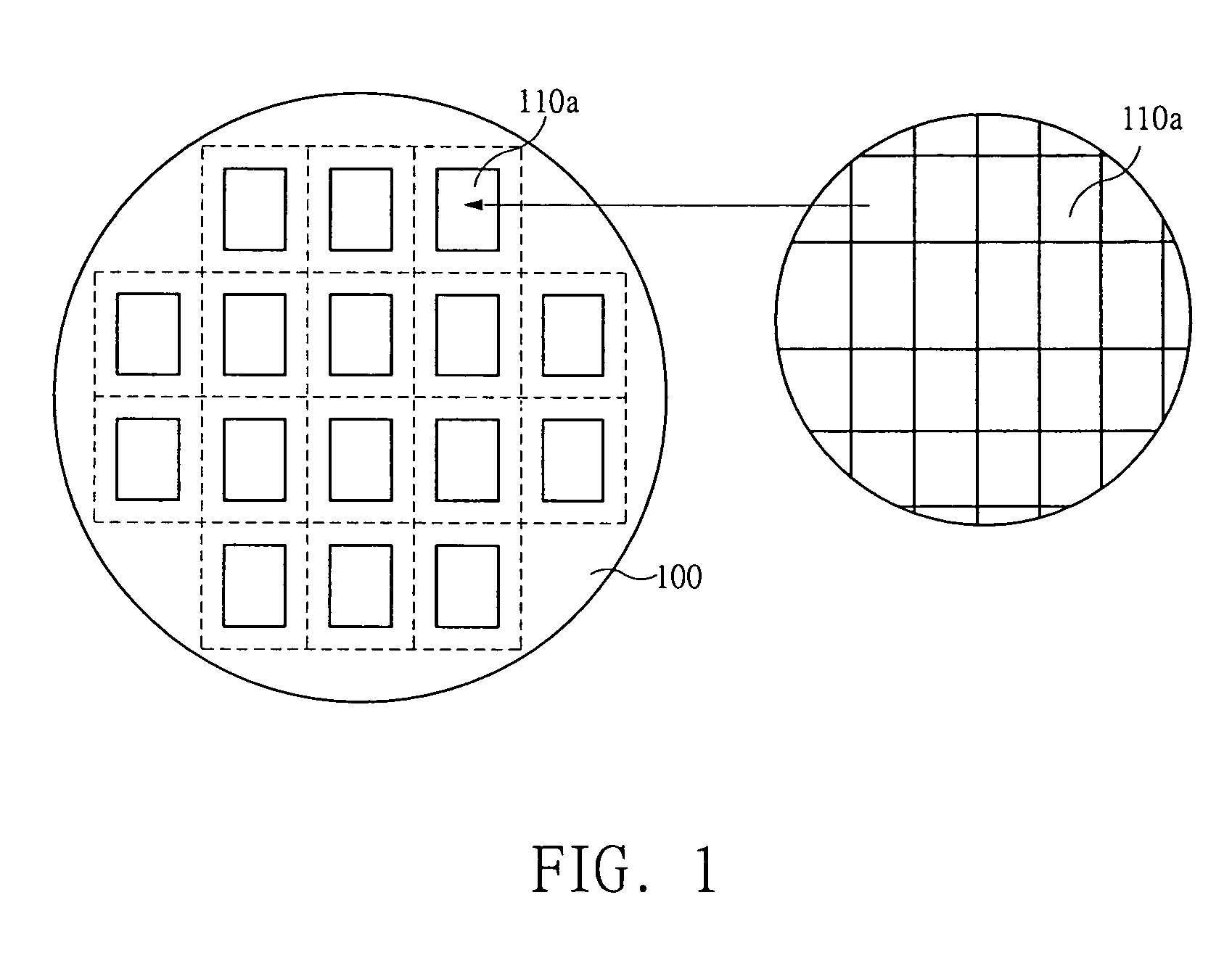

Chip-size package structure and method of the same

ActiveUS7238602B2Reduce contact resistanceLow costSemiconductor/solid-state device detailsSolid-state devicesChip sizeSolder ball

Owner:ADL ENERGY CORP

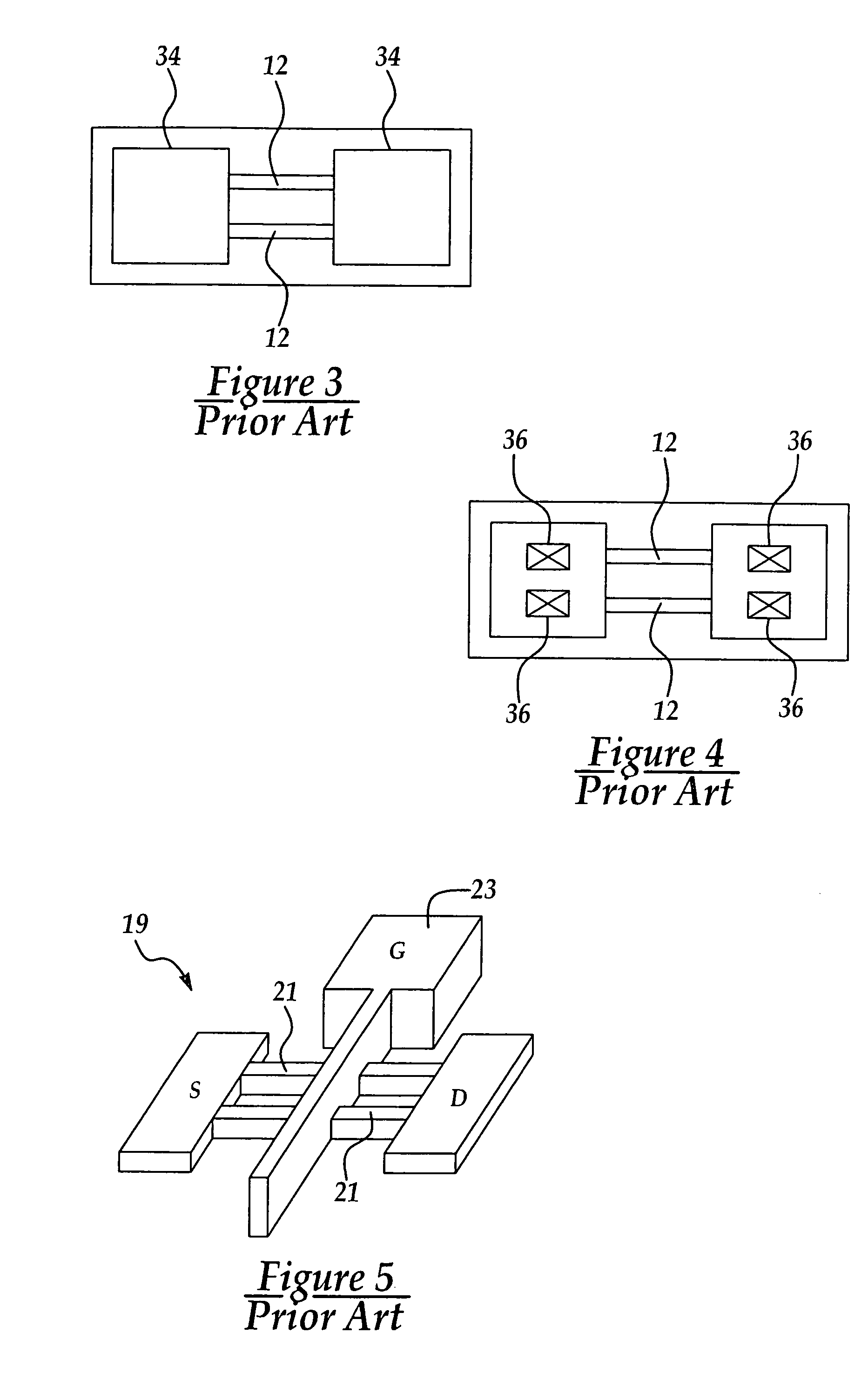

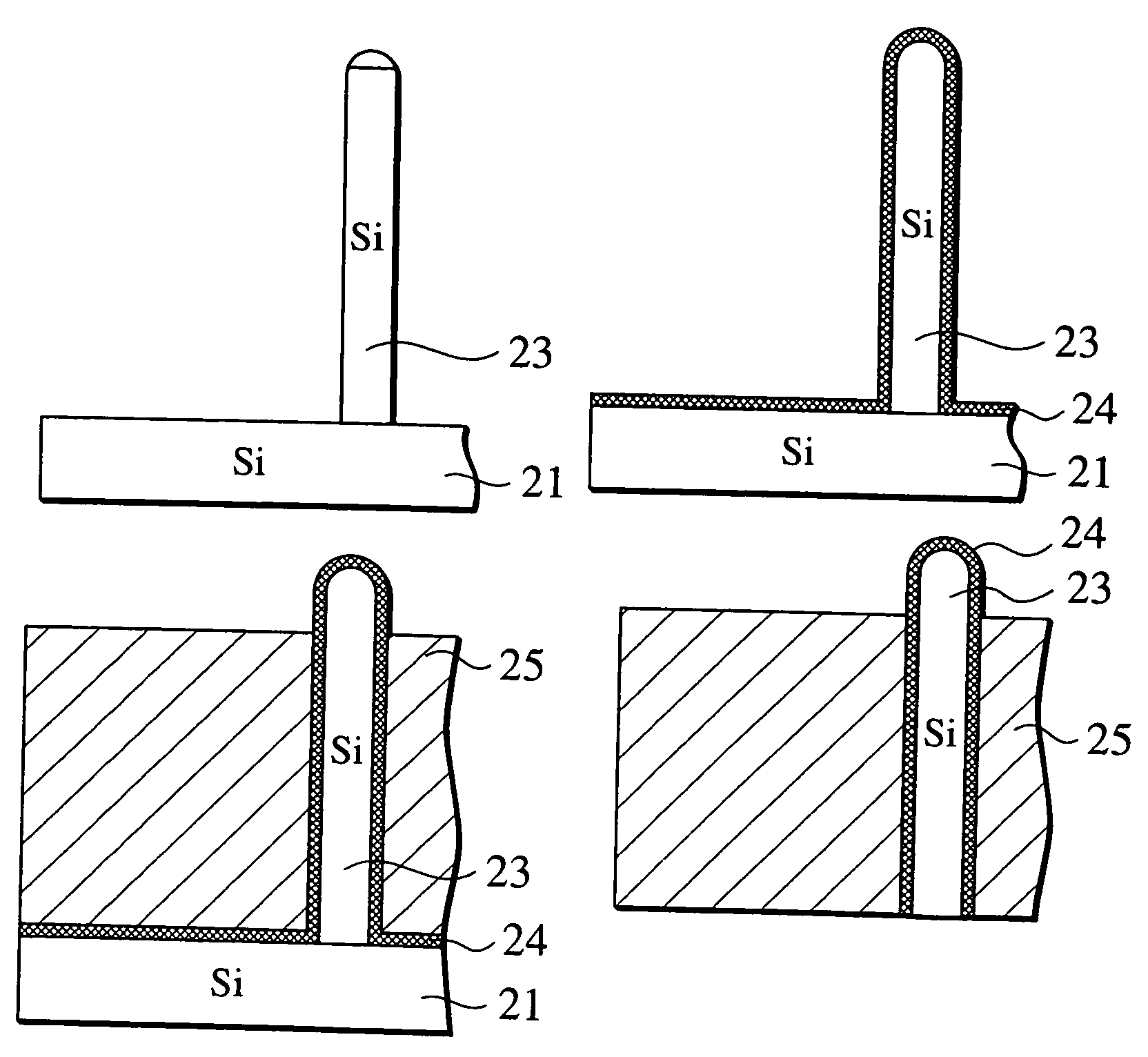

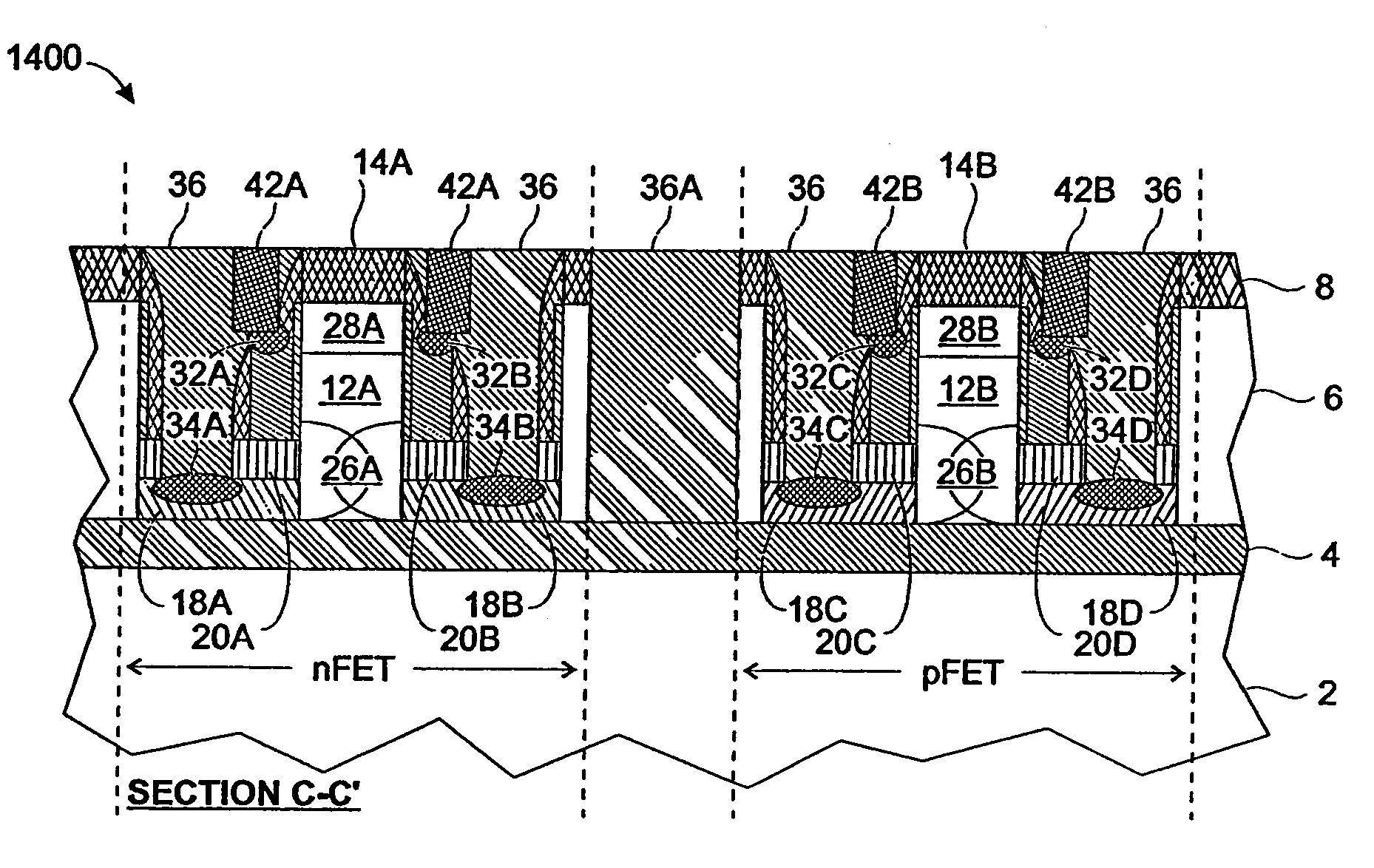

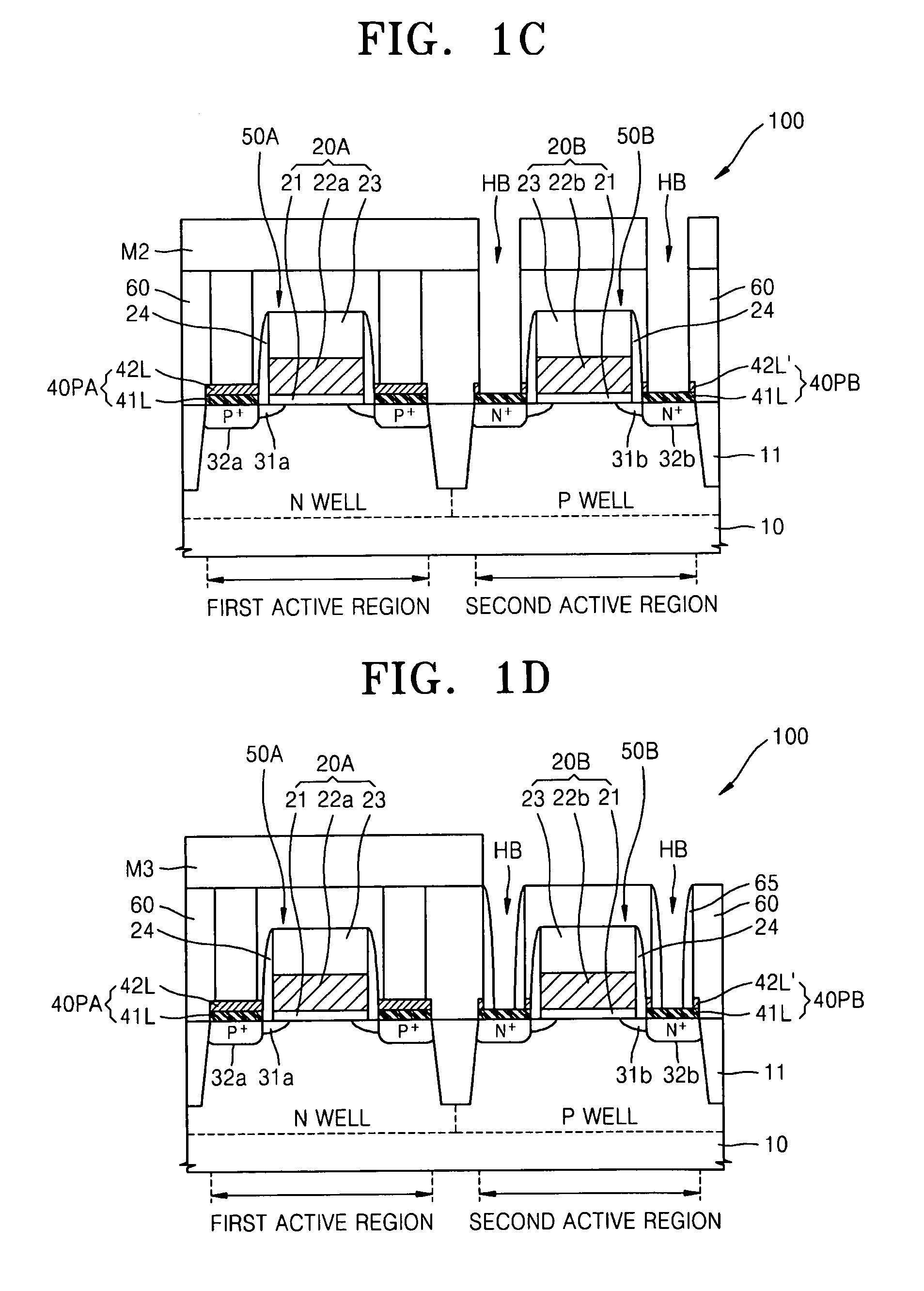

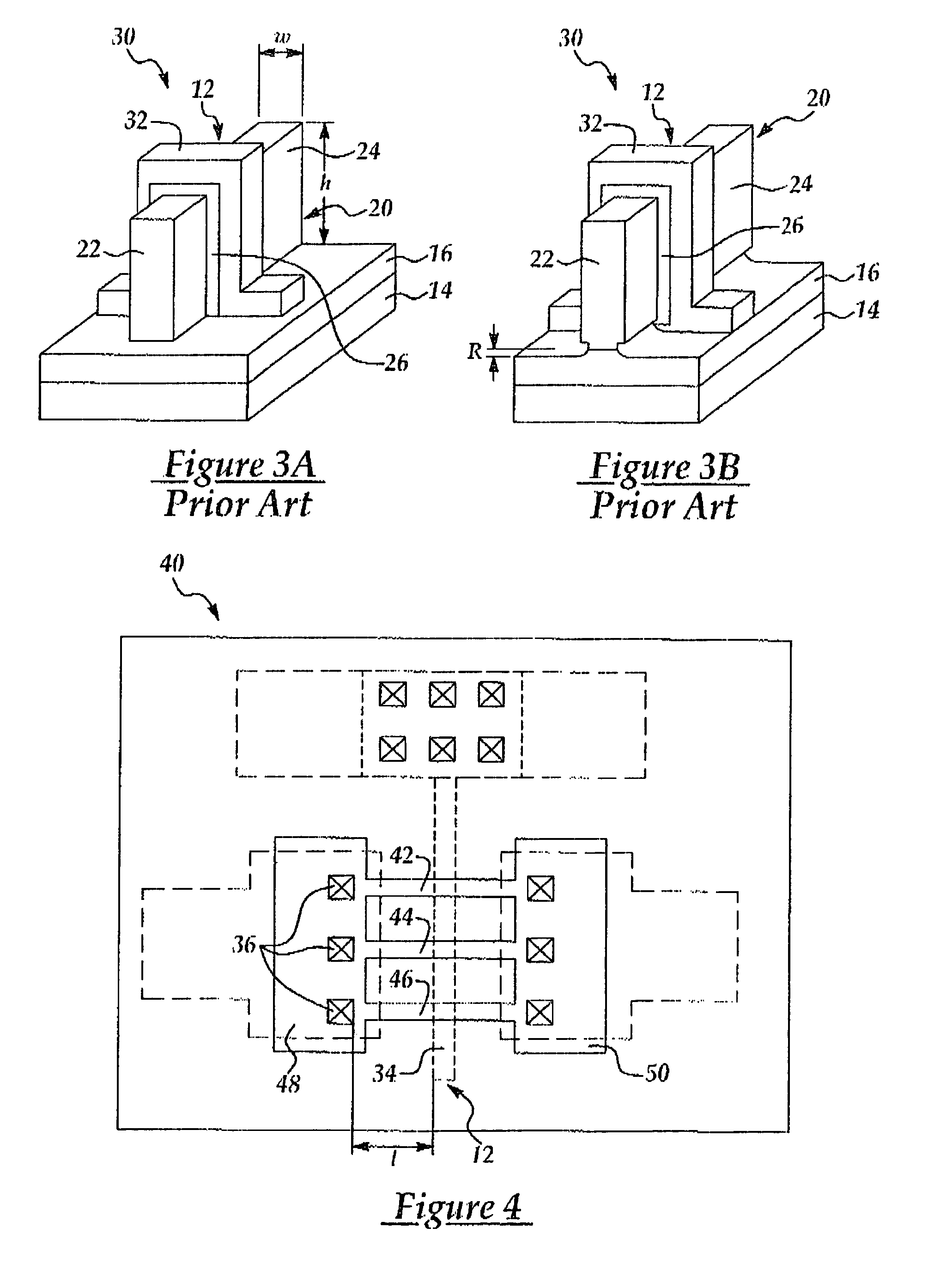

Vertical fin-fet mos devices

ActiveUS20090200604A1Reduce contact resistanceImprove current carrying capacityTransistorSolid-state devicesElectrical resistance and conductanceHigh density

A new class of high-density, vertical Fin-FET devices that exhibit low contact resistance is described. These vertical Fin-FET devices have vertical silicon “fins” (12A) that act as the transistor body. Doped source and drain regions (26A, 28A) are formed at the bottoms and tops, respectively, of the fins (12A). Gates (24A, 24B) are formed along sidewalls of the fins. Current flows vertically through the fins (12A) between the source and drain regions (26A, 28A) when an appropriate bias is applied to the gates (24A, 24B). An integrated process for forming pFET, nFET, multi-fin, single-fin, multi-gate and double-gate vertical Fin-FETs simultaneously is described.

Owner:GLOBALFOUNDRIES US INC

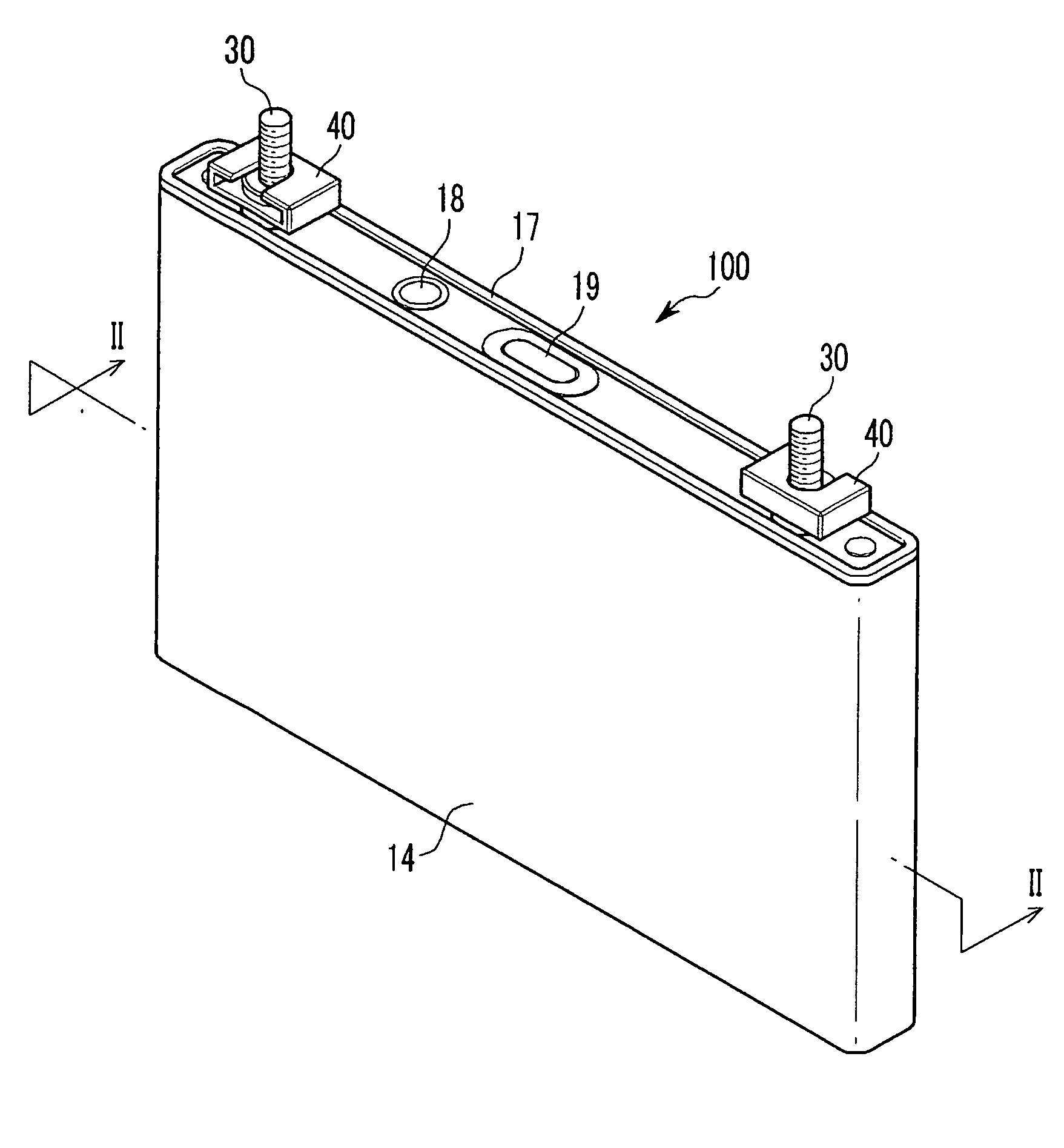

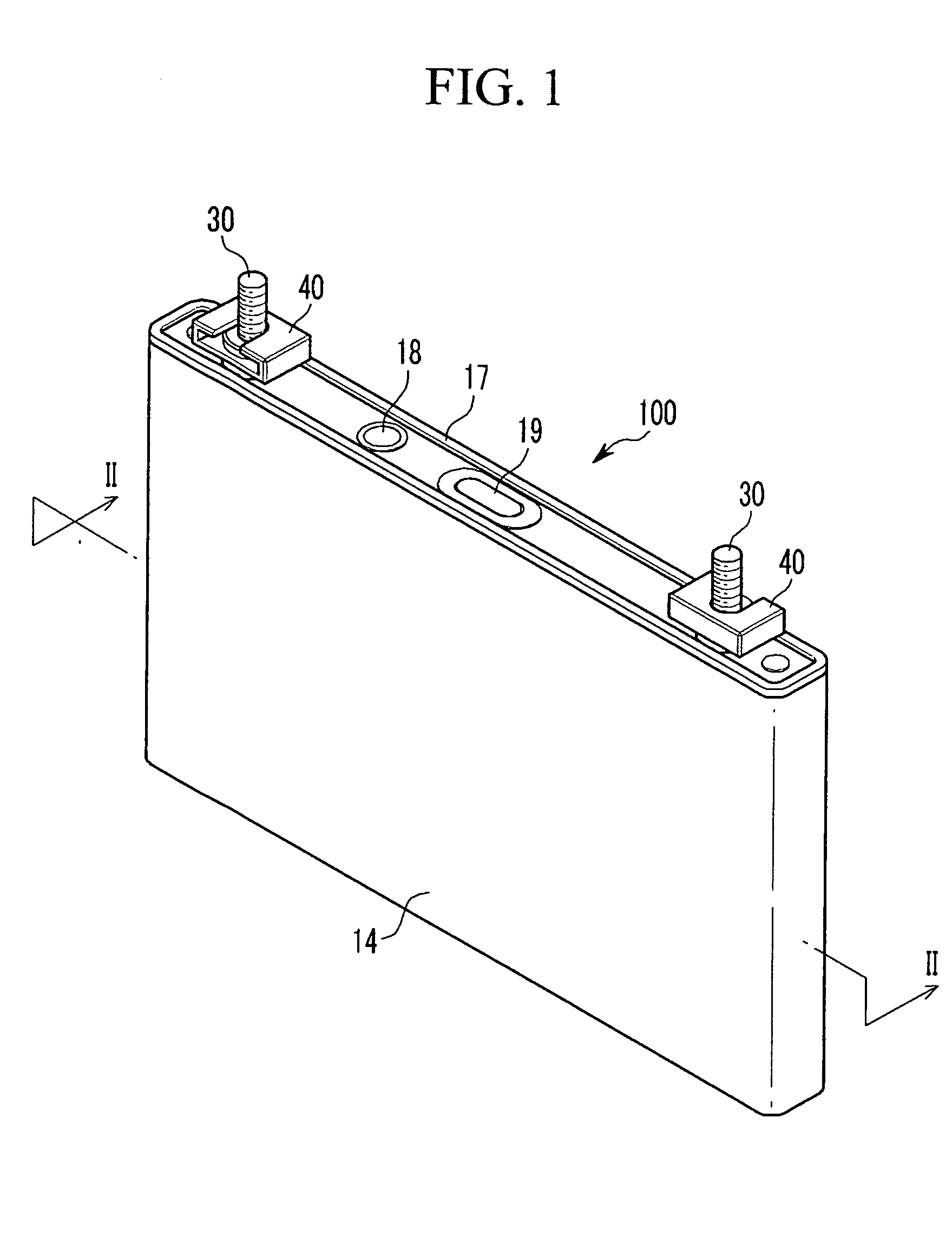

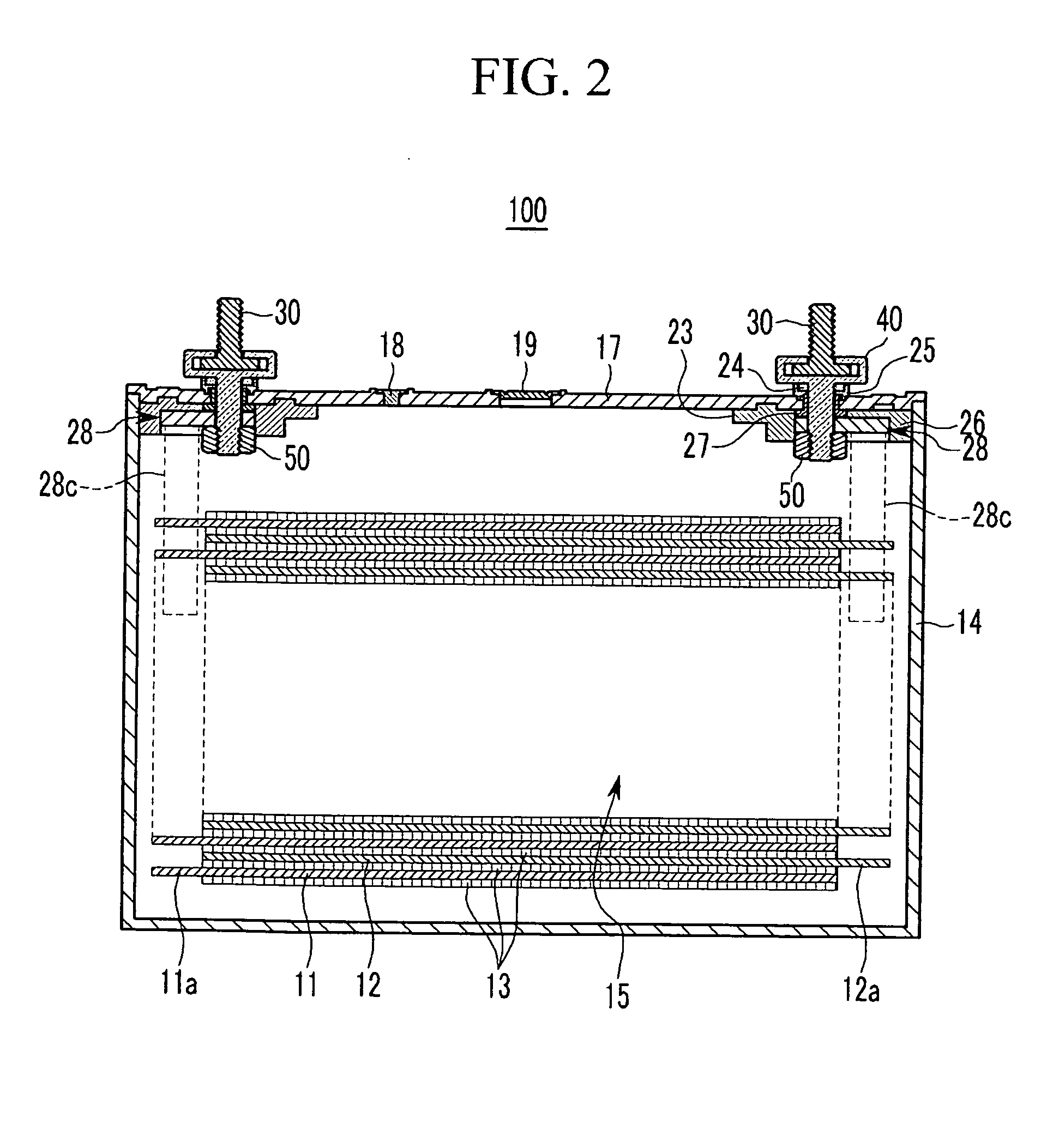

Rechargeable battery and battery module using the same

ActiveUS20100143786A1Reduce materialEasily releasing heatPrimary cell to battery groupingSmall-sized cells cases/jacketsElectricityRechargeable cell

A rechargeable battery includes an electrode group for producing electricity, a case for housing the electrode group, a cap plate combined with the case, an electrode terminal electrically coupled to the electrode group, and a fixing member disposed inside the case and combined to the support shaft portion. The electrode terminal includes a head portion disposed outside the case, and a support shaft portion protruding from the head portion and penetrating the cap plate. Contact resistance of the rechargeable battery can be reduced with this configuration. A battery module includes a plurality of rechargeable batteries and bus bars electrically connecting at least two of the rechargeable batteries, wherein each rechargeable battery includes a case with an internal space, a cap plate combined with the case, an electrode terminal including a head portion caught on the cap plate and a support shaft portion protruding from the head portion and penetrating the cap plate, and a fixing member disposed inside the case and combined to the support shaft portion.

Owner:SAMSUNG SDI CO LTD

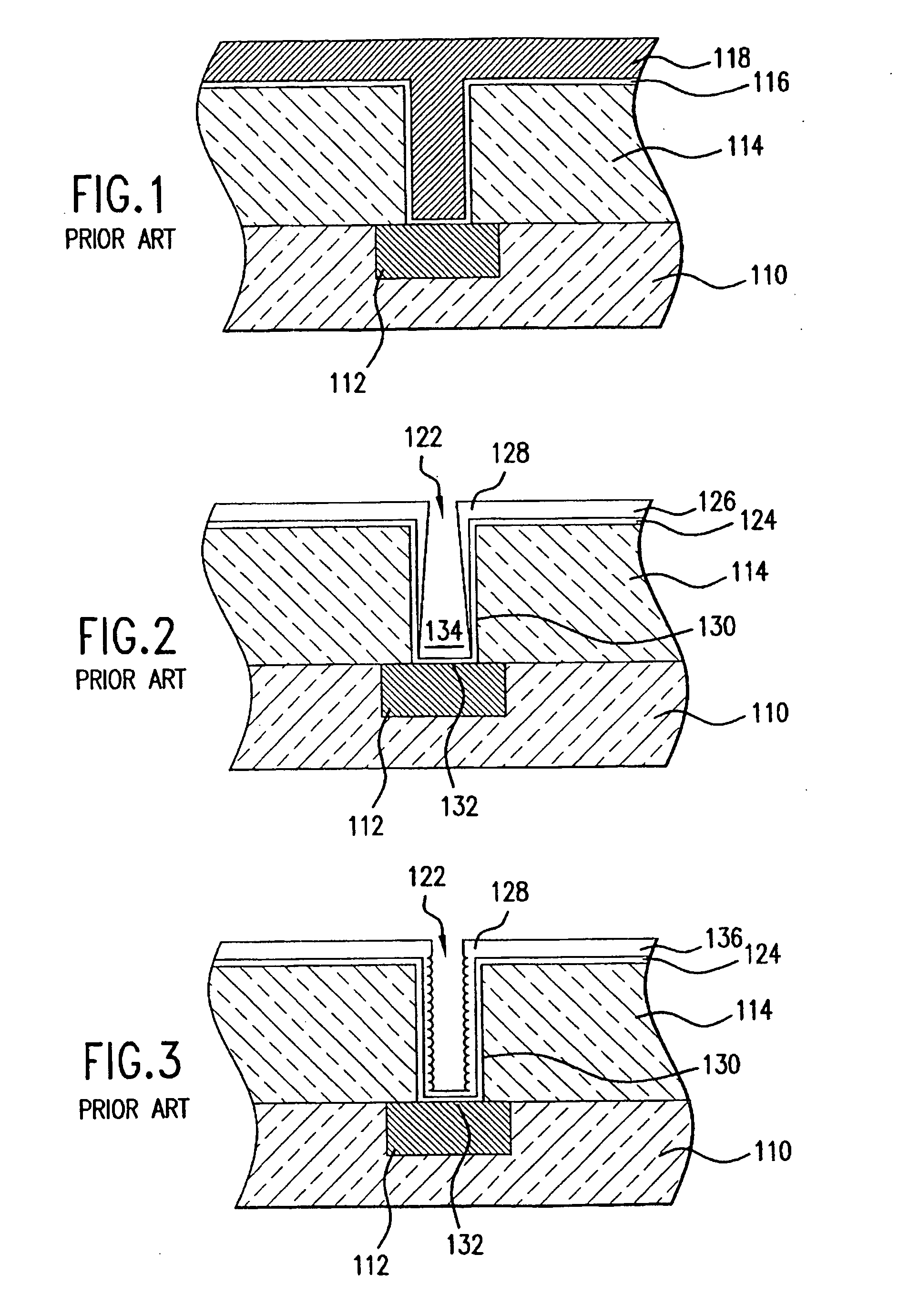

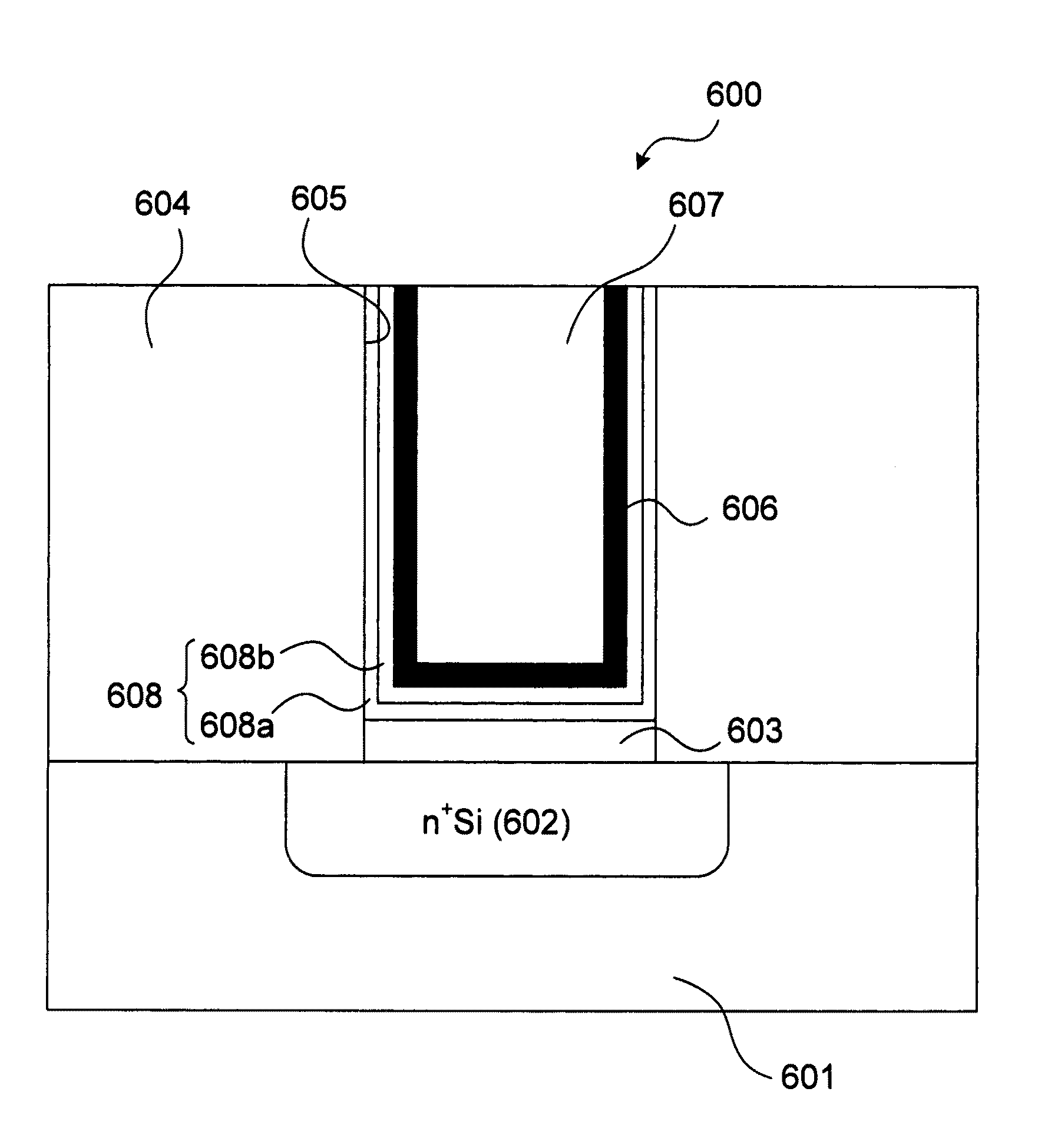

Contact plug structure, semiconductor device, and method for forming contact plug

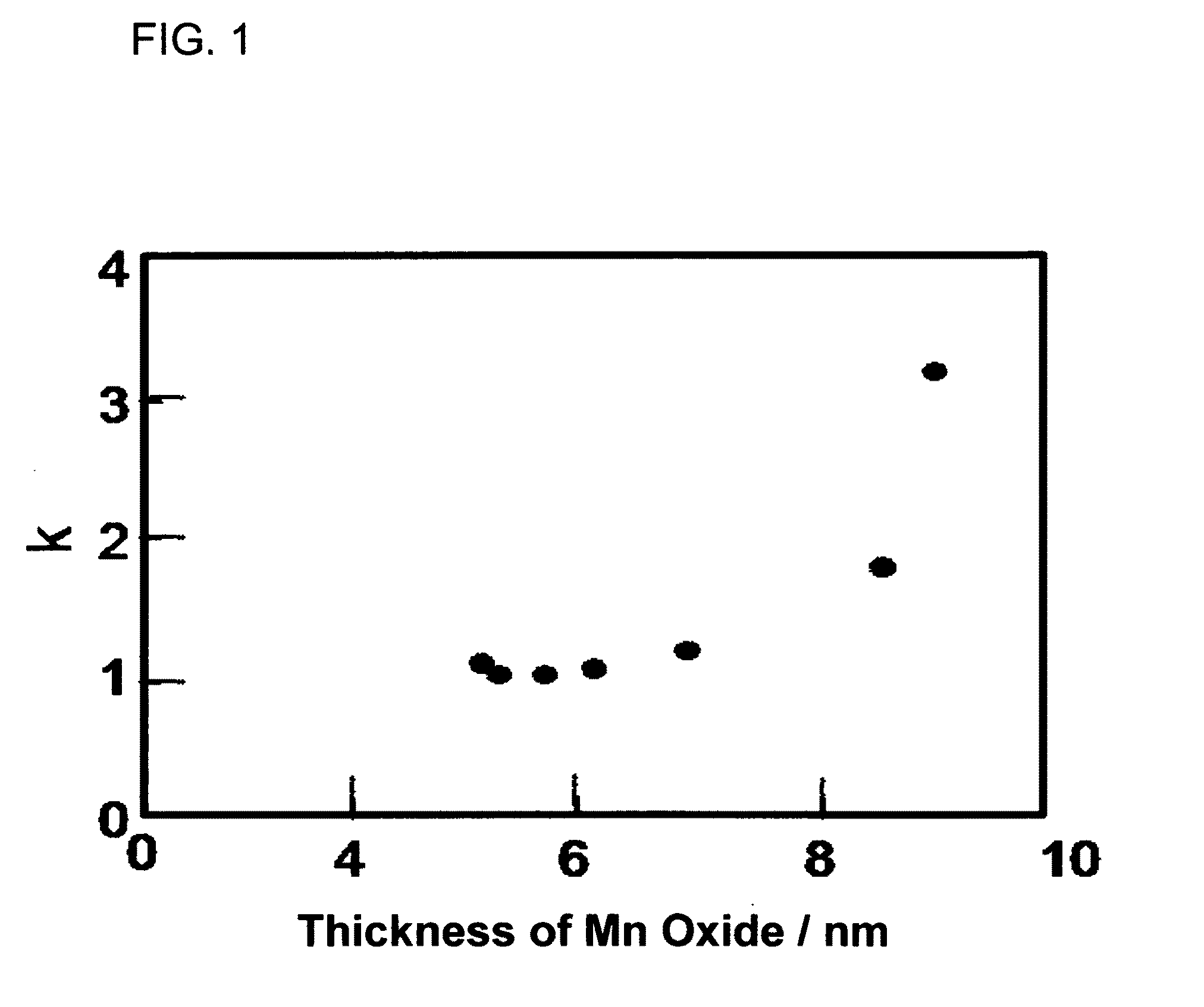

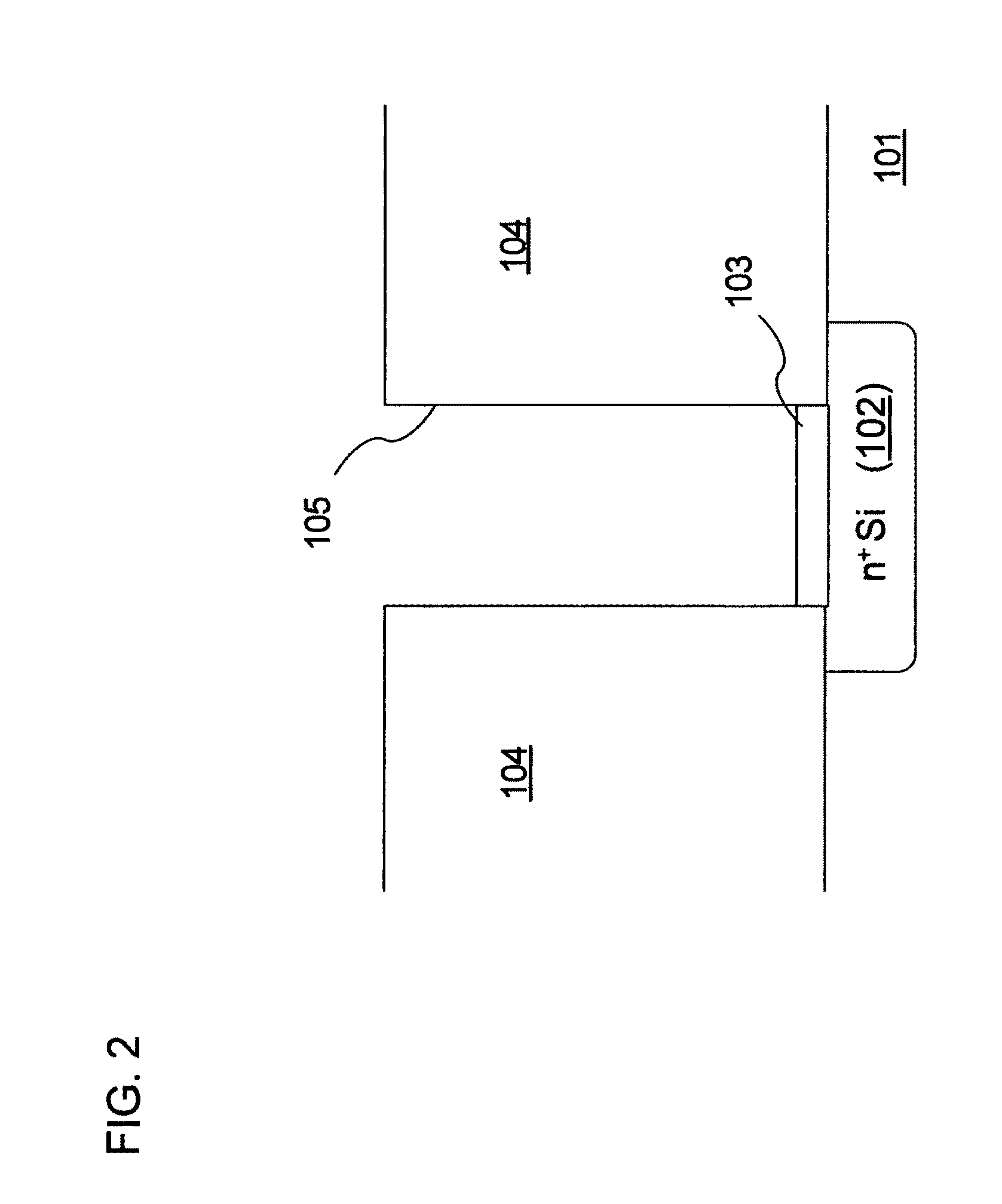

InactiveUS20110057317A1Suppress DiffuseReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesMetal silicideManganese oxide

A contact plug structure formed on a contact hole of an insulating layer of a semiconductor device includes a metal silicide layer formed on a bottom part of the contact hole of the insulating layer, a manganese oxide layer formed on the metal silicide layer in the contact hole, and a buried copper formed on the manganese oxide layer which substantially fills the contact hole.

Owner:ADVANCED INTERCONNECT MATERIAL

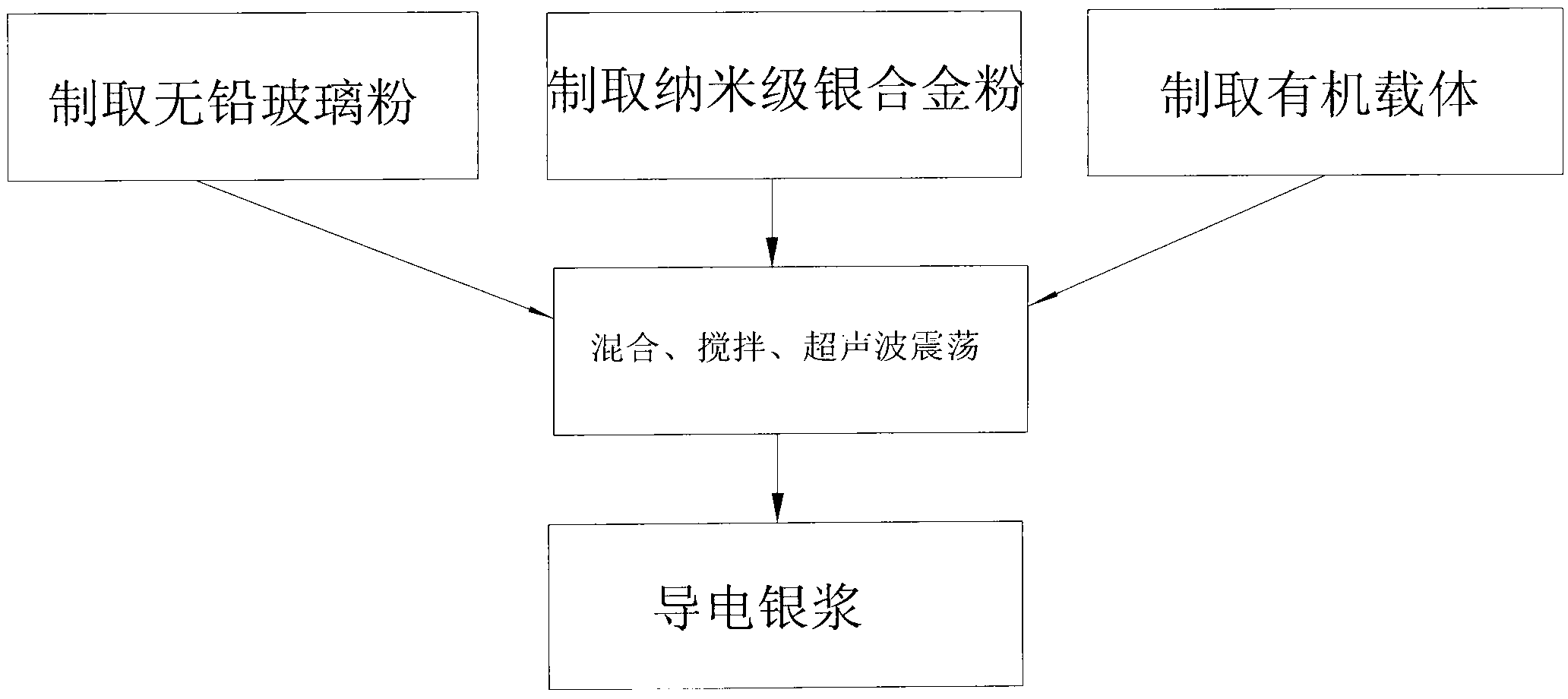

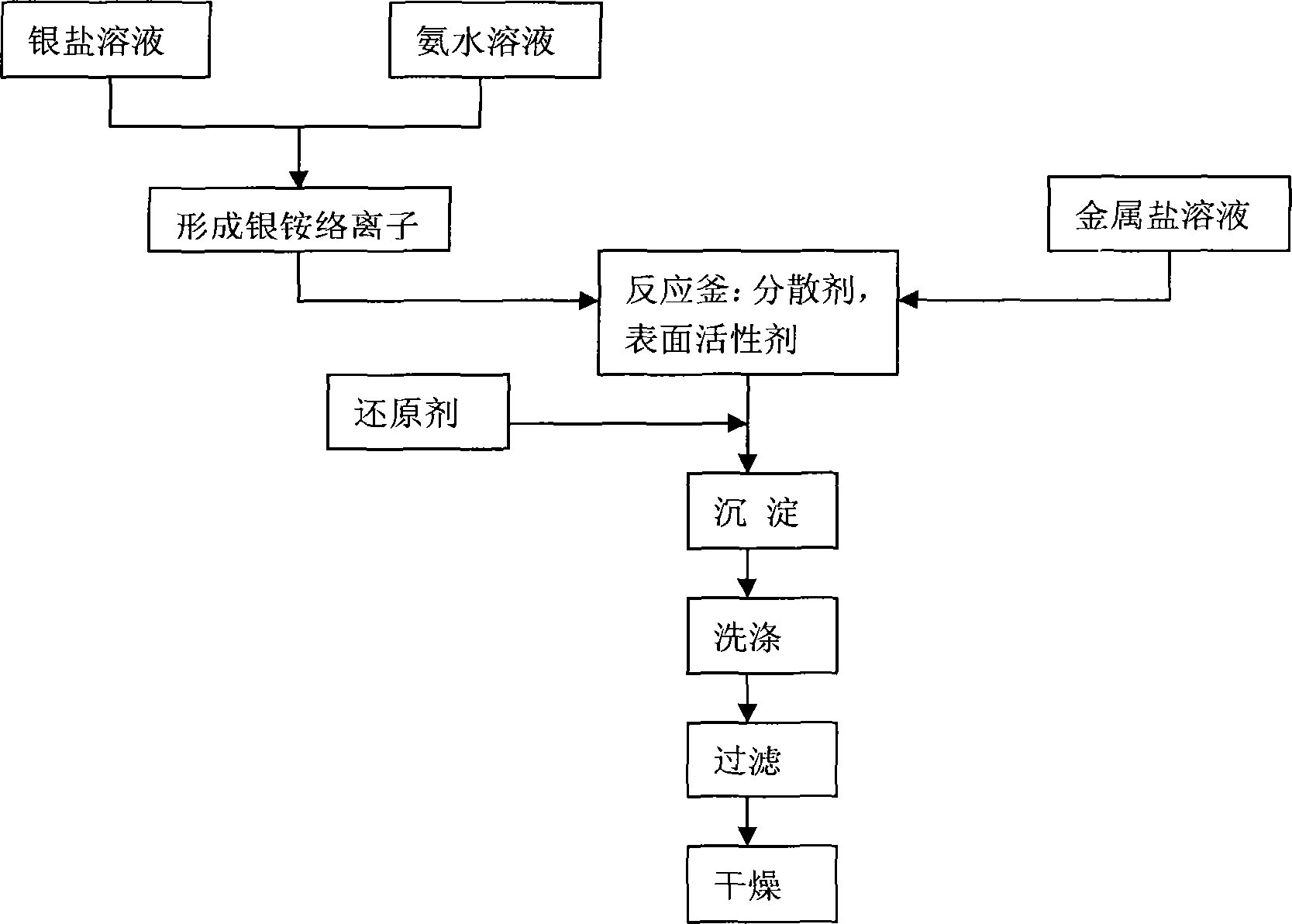

Electric conductive silver paste and manufacturing method thereof

ActiveCN103258584AEnhanced interconnectionIncrease contact areaNon-conductive material with dispersed conductive materialCable/conductor manufactureSilver pasteMetal alloy

The invention discloses electric conductive silver paste and a manufacturing method of the electric conductive silver paste. The electric conductive silver paste comprises, by mass percentage, 35 - 65 % of micron-sized silver powder, 1-10 % of nanometer-sized silver powder of or 1-20 % of nanometer-sized silver and other metal alloy powder, and 1-10 % of an organic carrier; for ceramics, solar cell silver paste comprises 2-15 % of unleaded glass powder, each component is manufactured in parts, weighed, mixed and stirred or mixed and rapidly scattered, and ultrasonic-vibrated or fine adjusted of viscosity of solvent, and therefore the electric conductive silver paste is obtained. Due to the fact that the nanometer-sized silver powder or the nanometer-sized silver alloy powder is mixed with the micron-sized silver powder, intensity of conductivity and a circuit is improved, adhesive force of crushing resistance and a base plate is improved, at the same time unleaded slurry good in thixotropy, low in contacting resistance and low in piece-needed slurry amount replaces lead slurry materials, the electric conductive silver paste is used for manufacturing crystalline silicon solar cells, improves photoelectric conversion efficiency, accords with environmental-protection ideas, and can be produced in large scales continuously.

Owner:SHENZHEN CHENGGONG CHEM

Coatable conductive polyethylenedioxythiophene with carbon nanotubes

InactiveUS20060062983A1High transparencyImprove conductivityMaterial nanotechnologyNanoinformaticsCarbon nanotube

Owner:EASTMAN KODAK CO

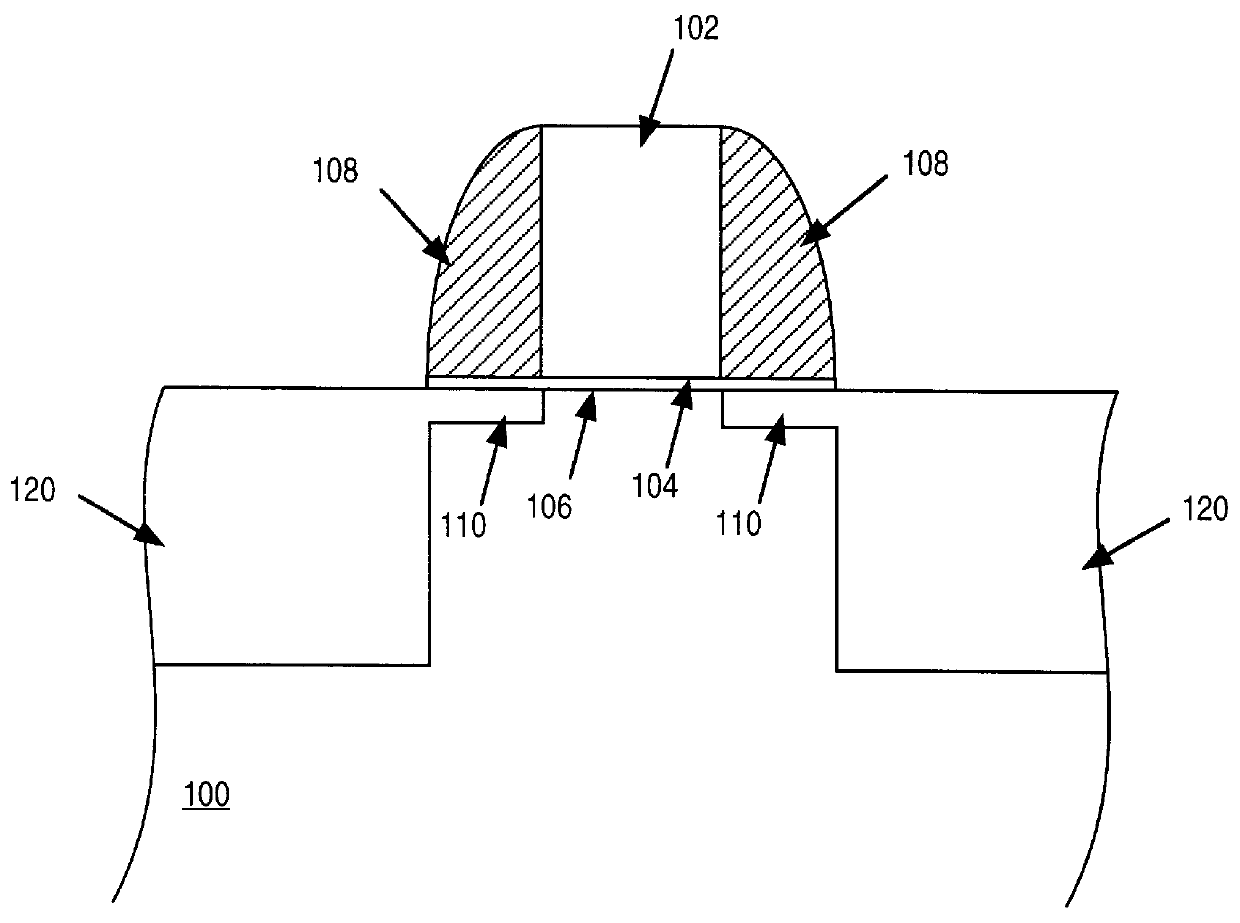

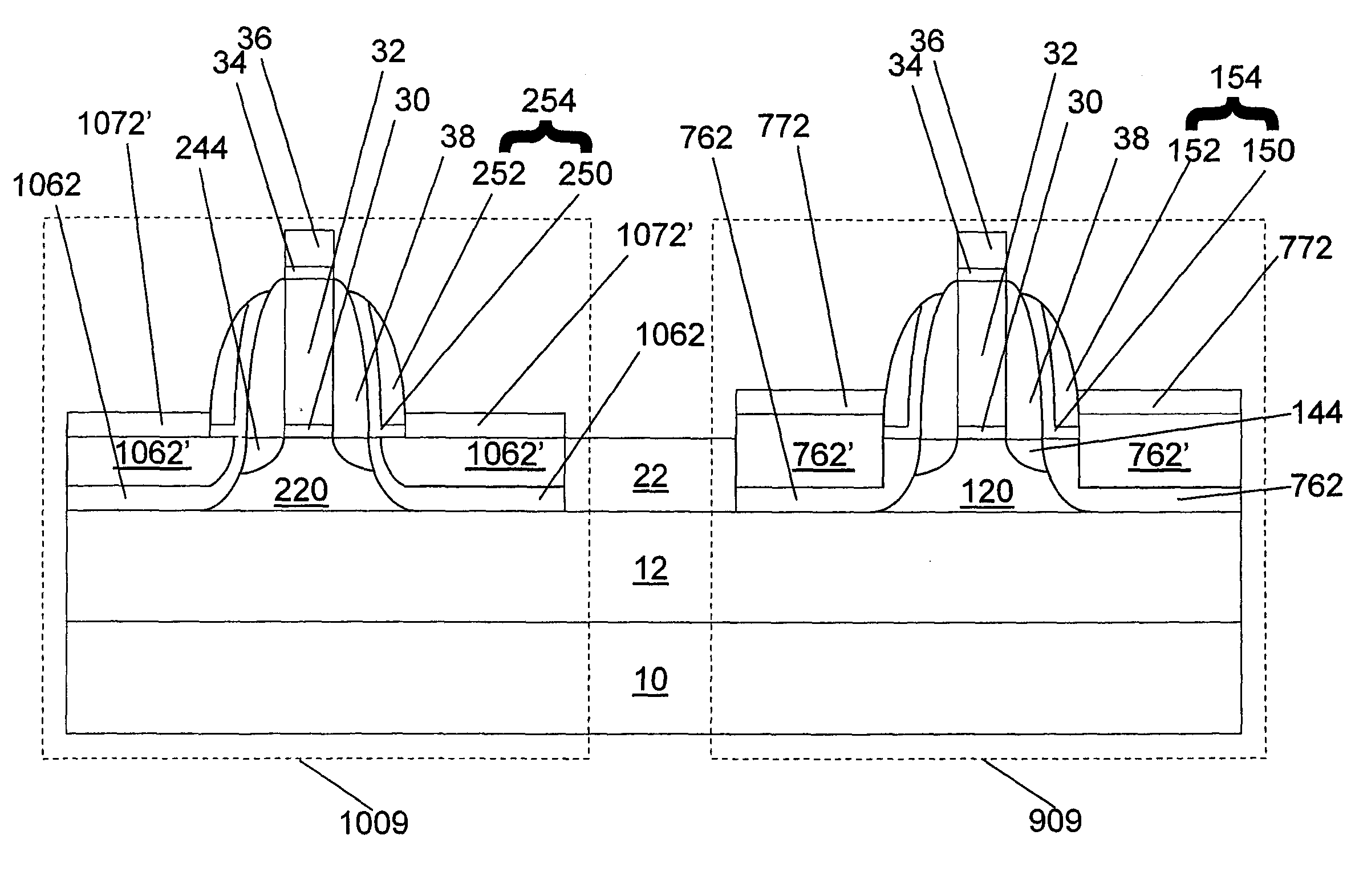

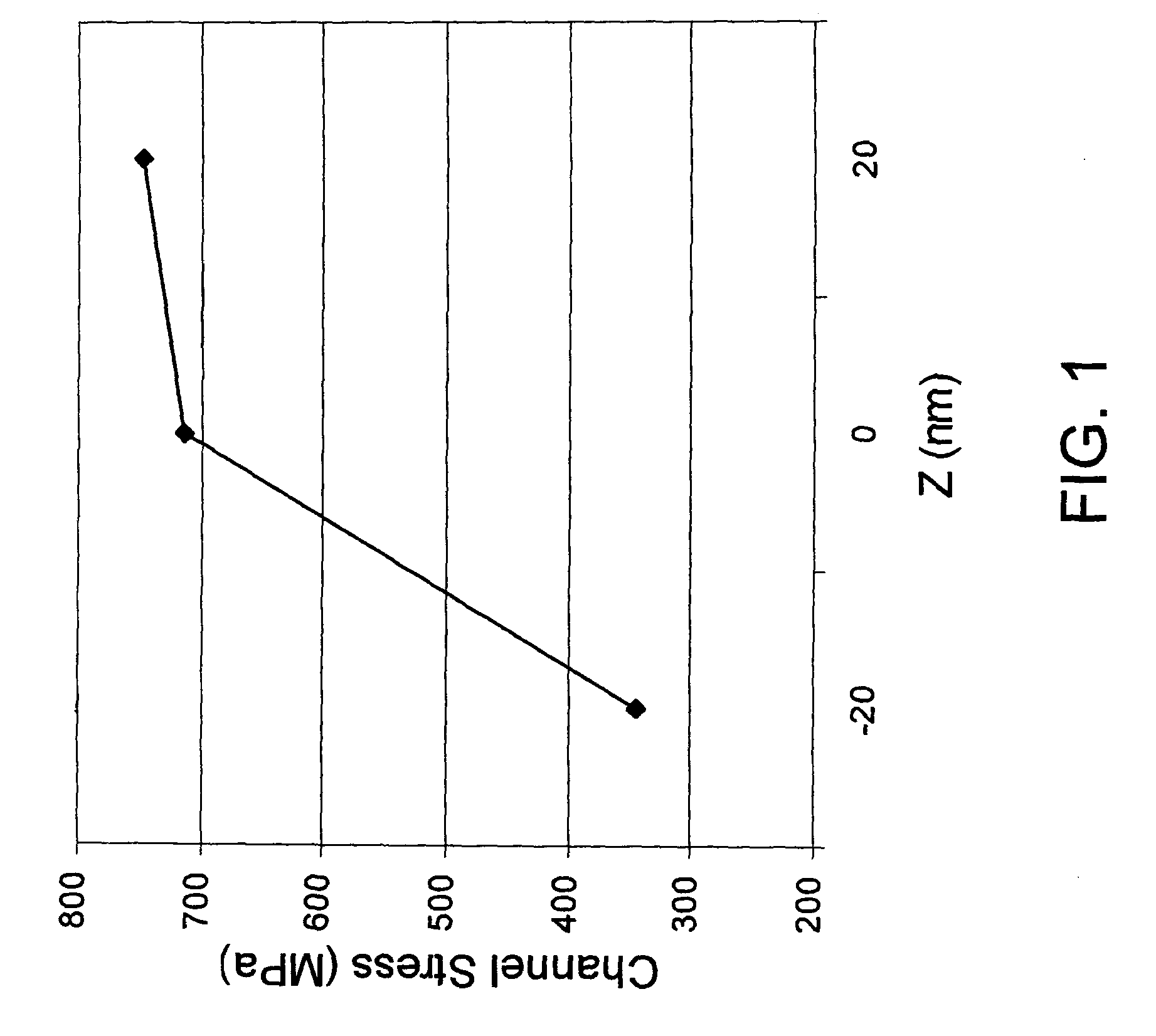

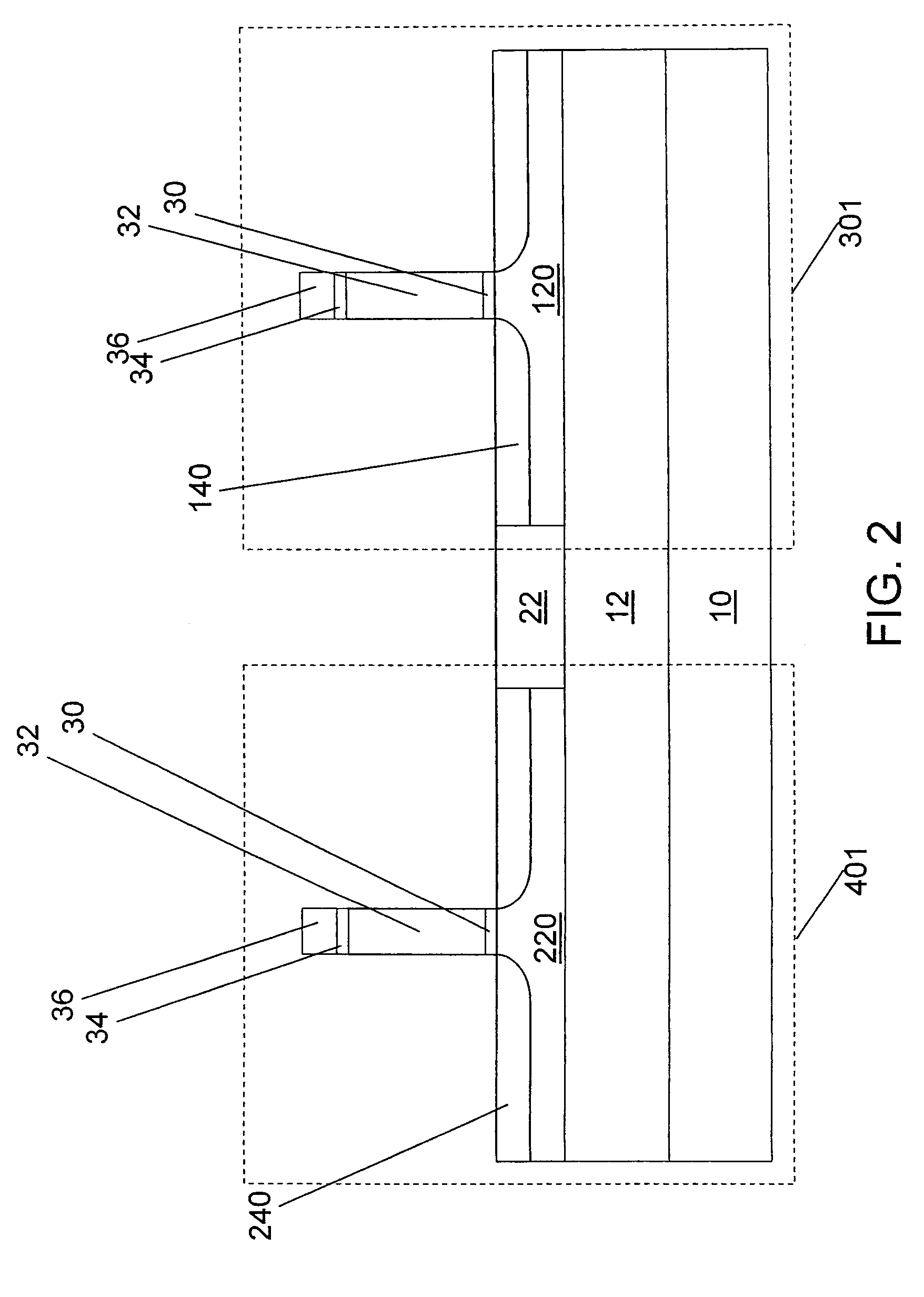

Structure and method for mobility enhanced MOSFETs with unalloyed silicide

ActiveUS8217423B2Stable and low contact resistanceReduce contact resistanceTransistorSolid-state devicesMOSFETSalicide

While embedded silicon germanium alloy and silicon carbon alloy provide many useful applications, especially for enhancing the mobility of MOSFETs through stress engineering, formation of alloyed silicide on these surfaces degrades device performance. The present invention provides structures and methods for providing unalloyed silicide on such silicon alloy surfaces placed on semiconductor substrates. This enables the formation of low resistance contacts for both mobility enhanced PFETs with embedded SiGe and mobility enhanced NFETs with embedded Si:C on the same semiconductor substrate. Furthermore, this invention provides methods for thick epitaxial silicon alloy, especially thick epitaxial Si:C alloy, above the level of the gate dielectric to increase the stress on the channel on the transistor devices.

Owner:AURIGA INNOVATIONS INC

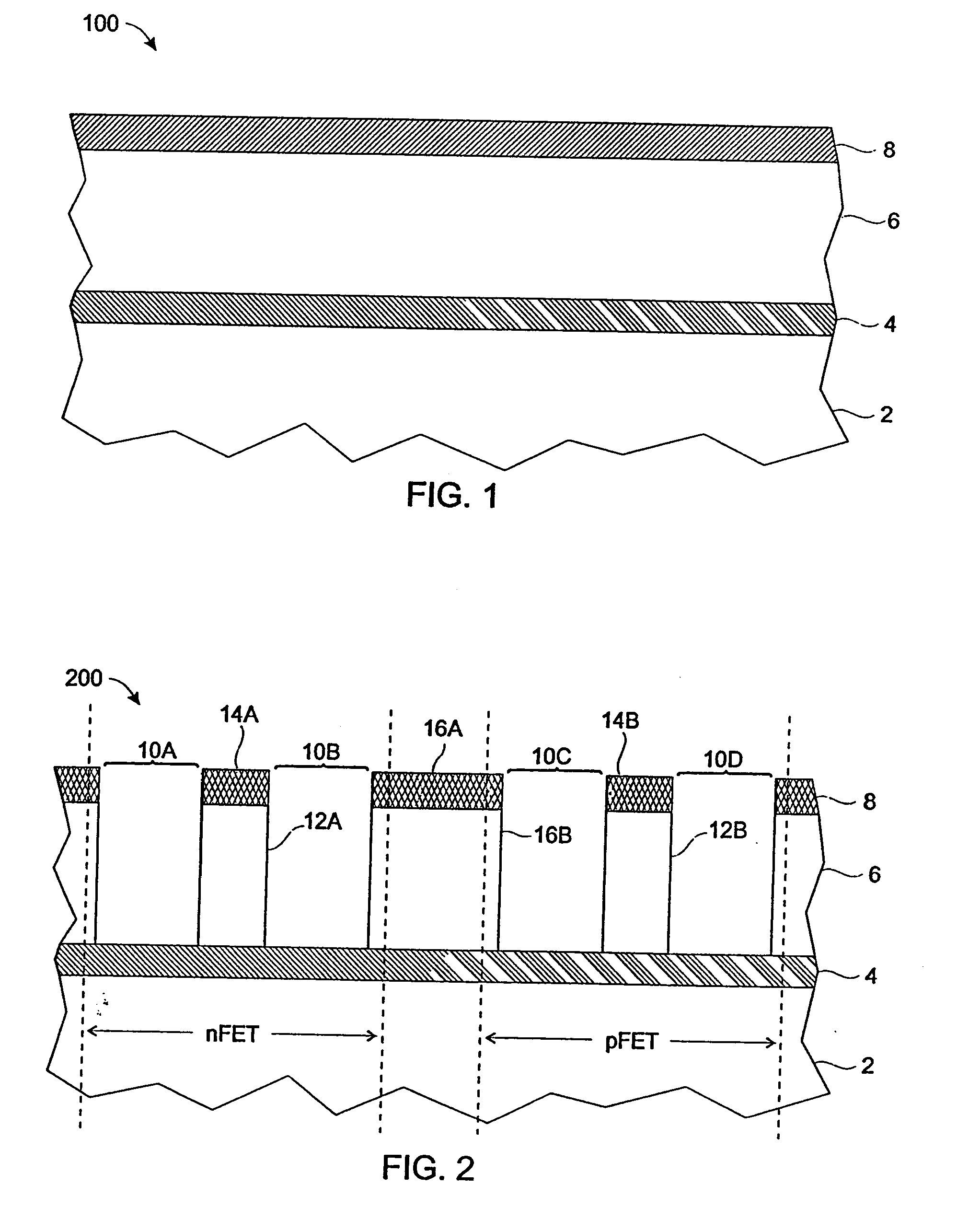

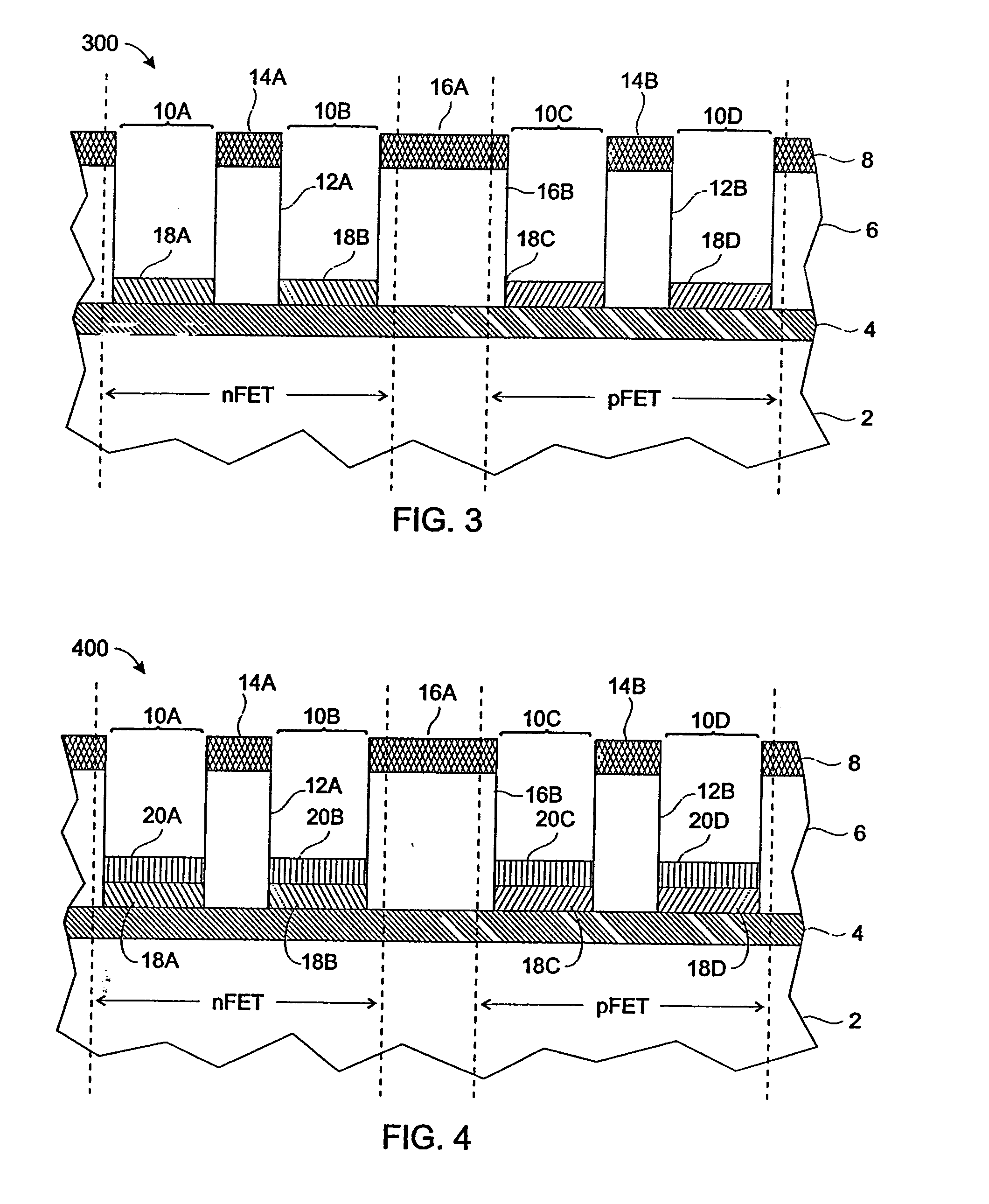

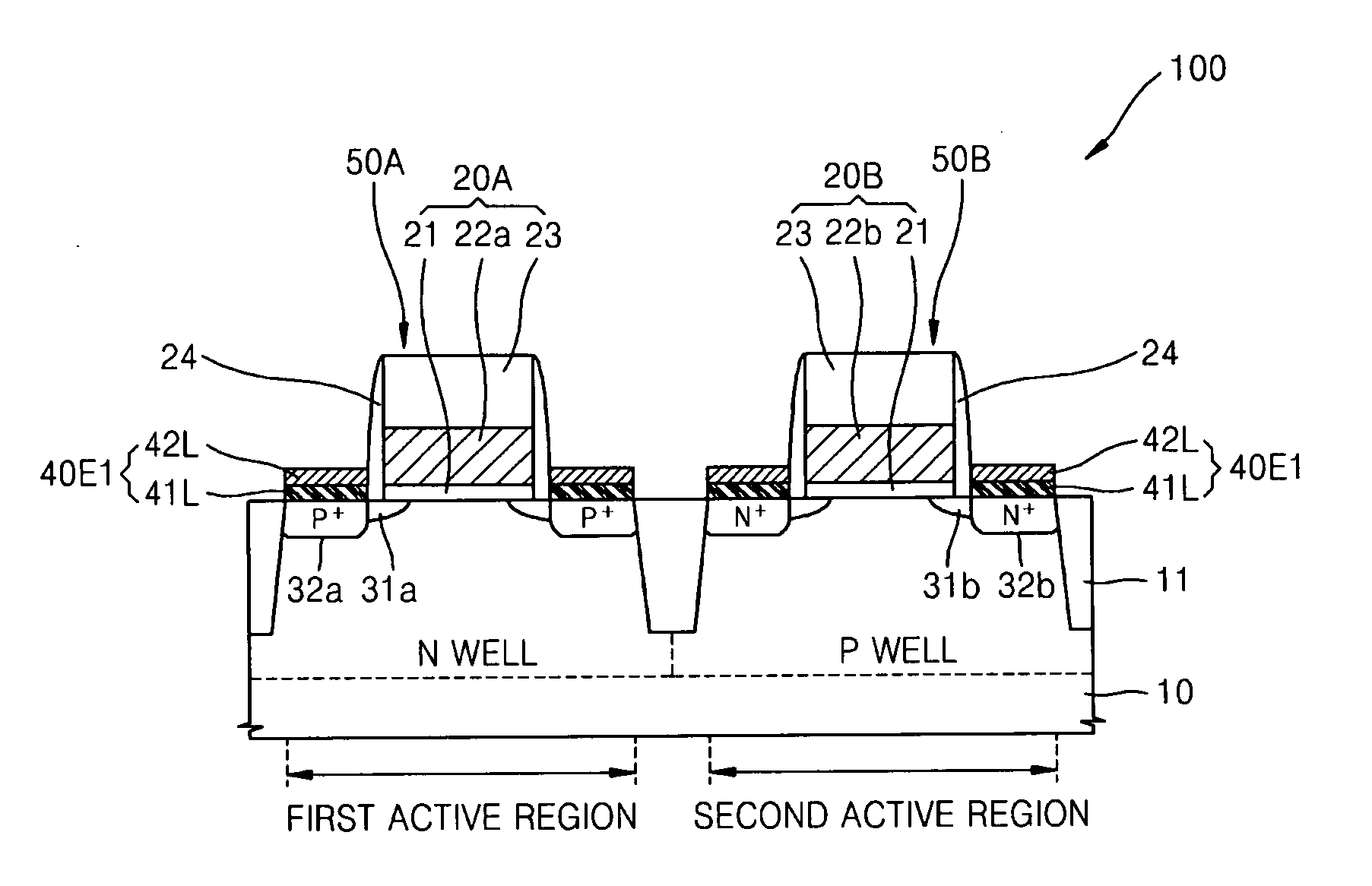

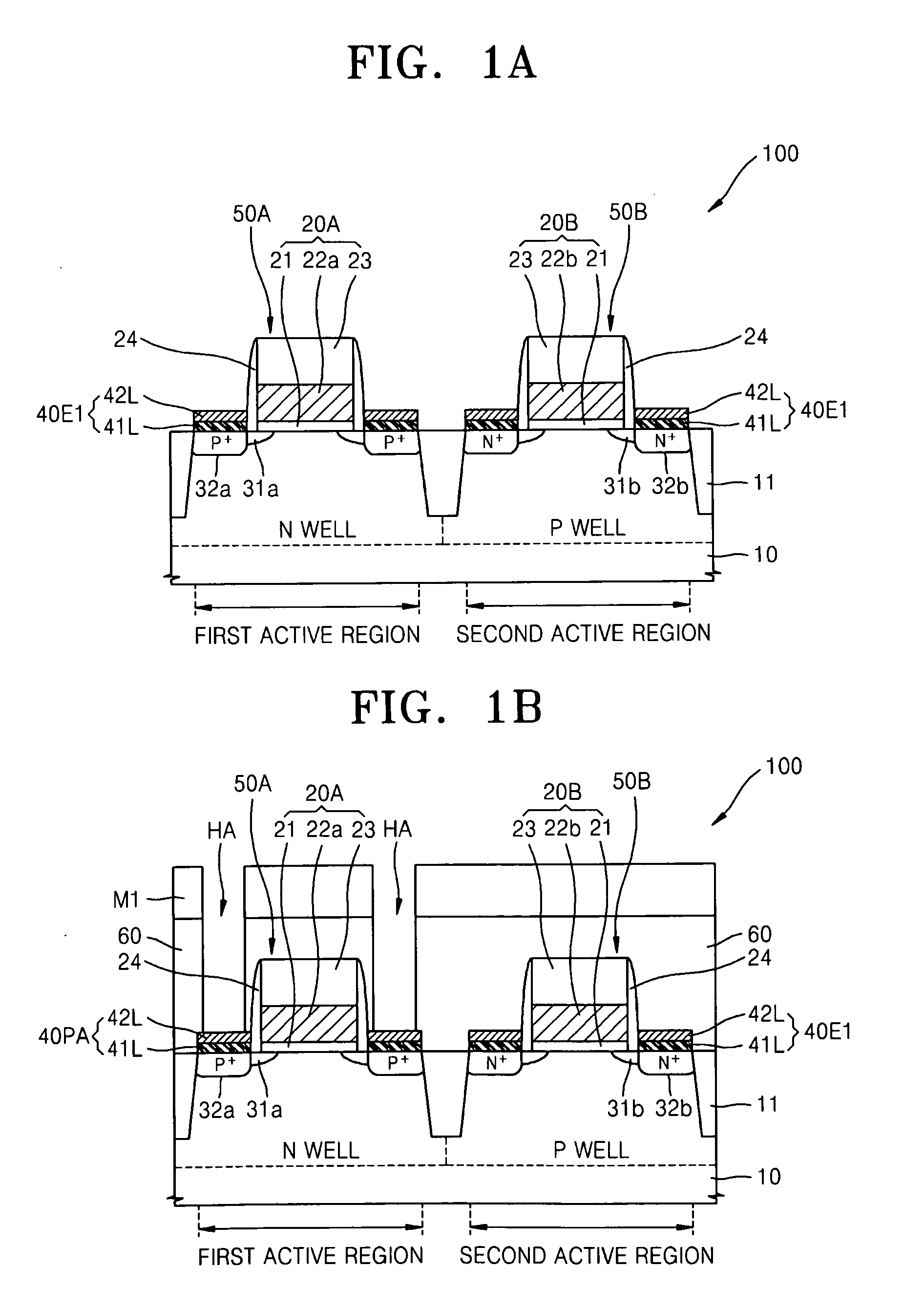

Semiconductor devices and methods of manufacturing the same

ActiveUS20100123198A1Reduce contact resistanceTransistorSemiconductor/solid-state device detailsContact padDevice material

Provided are semiconductor devices having low resistance contacts and methods of manufacturing the same. One or more of the semiconductor devices include a substrate having first and second active regions; a P-channel field-effect transistor associated with the first active region and including at least one of the source and drain regions; a N-channel field-effect transistor associated with the second active region and including at least one of the source and drain regions; a first contact pad layer comprising silicon (Si) and SiGe epitaxial layers on the at least one of the source and drain regions of the P-channel field-effect transistor, the SiGe epitaxial layer being sequentially stacked on the Si epitaxial layer; a second contact pad layer comprising silicon (Si) and SiGe epitaxial layers on the at least one of the source and drain regions of the N-channel field-effect transistor, the SiGe epitaxial layer being sequentially stacked on the Si epitaxial layer; an interlayer insulating film formed on the P-channel and the N-channel field-effect transistors and including first and second contact holes, wherein the first contact hole includes a first lower region that exposes the SiGe epitaxial layer of the first contact pad layer and the second contact hole includes a second lower region that penetrates through the SiGe epitaxial layer of the second contact pad layer to expose the Si epitaxial layer of the second contact pad layer; first and second metal silicide films formed respectively in the first and second lower regions of the contact holes; and contact plugs formed on the first and second metal silicide films and filled in the first and second contact holes.

Owner:SAMSUNG ELECTRONICS CO LTD

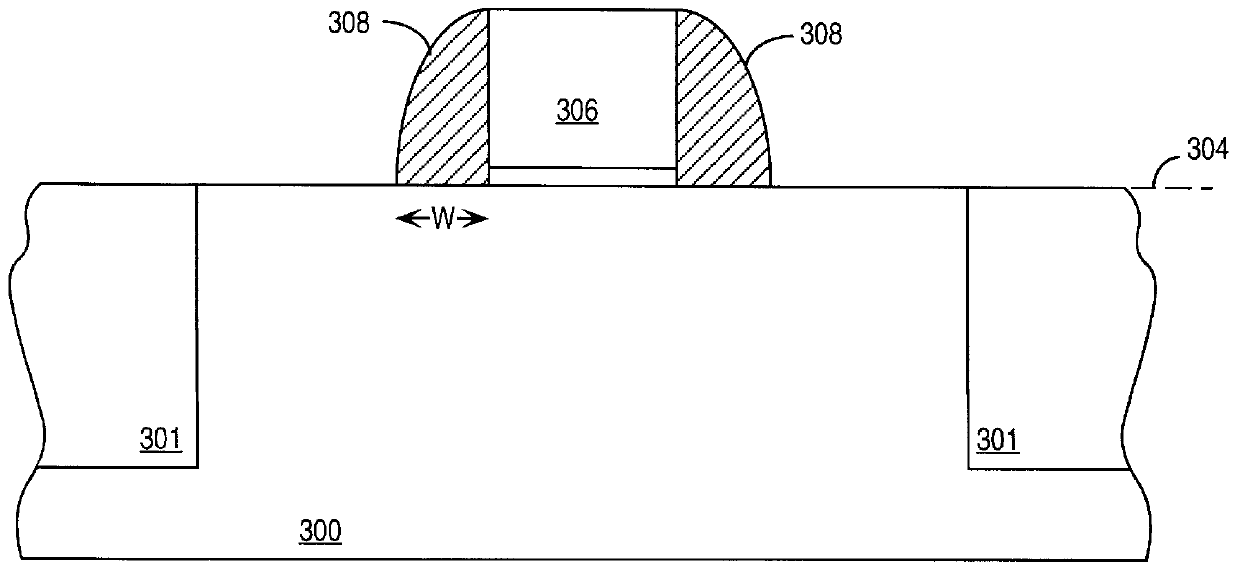

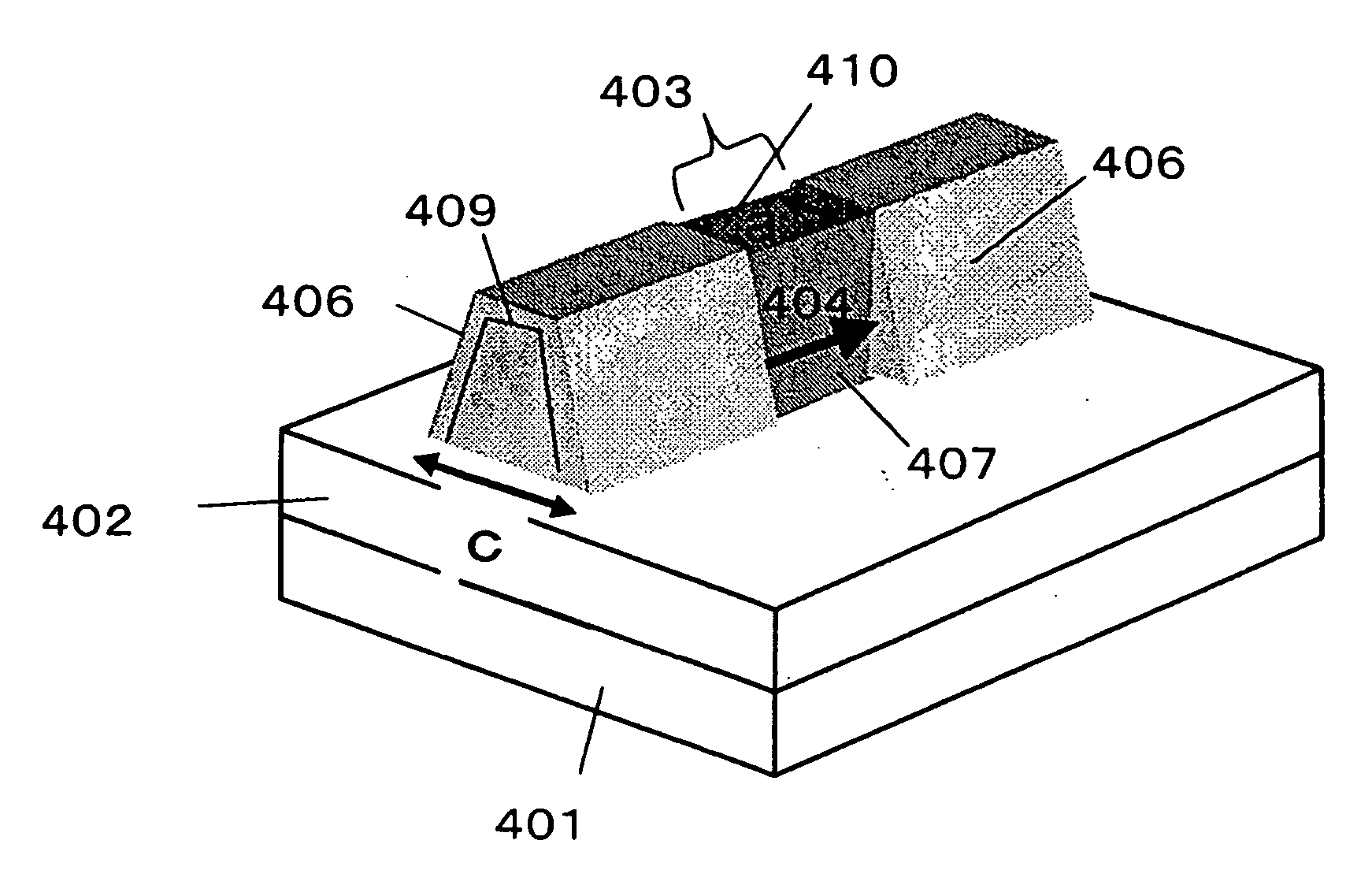

Semiconductor device and manufacturing process therefor

InactiveUS20070075372A1Easy alignmentReduce contact resistanceTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

There is provided a semiconductor device wherein at least the largest width of a source / drain region is larger than the width of a semiconductor region and the source / drain region has a slope having a width continuously increasing from the uppermost side to the substrate side, and a silicide film is formed in the surface of the slope.

Owner:NEC CORP

Display device

InactiveUS20060275618A1Low electrical connection resistivityImprove display qualitySolid-state devicesNatural mineral layered productsLiquid-crystal displayDisplay device

A display device in which interconnection—electrode comprising a Cu alloy film having a lower electrical resistivity than Al alloy and a transparent conductive film are directly connected not by way of a refractory metal thin film, wherein the Cu alloy film contains Zn and / or Mg in a total amount from 0.1 to 3.0 at %, or Ni and / or Mn in a total amount from 0.1 to 5 at %, thereby enabling the direct connection at low resistivity between the Cu alloy film and the transparent electrode without using a barrier metal, and giving high display quality in a case of application, for example, to a liquid crystal display.

Owner:KOBE STEEL LTD

Contacts to semiconductor fin devices

InactiveUS7105894B2Reduce contact resistanceIncrease contact areaTransistorSemiconductor/solid-state device detailsConductive materialsEngineering

A method for forming a contact to a semiconductor fin which can be carried out by first providing a semiconductor fin that has a top surface, two sidewall surfaces and at least one end surface; forming an etch stop layer overlying the fin; forming a passivation layer overlying the etch stop layer; forming a contact hole in the passivation layer exposing the etch stop layer; removing the etch stop layer in the contact hole; and filling the contact hole with an electrically conductive material.

Owner:TAIWAN SEMICON MFG CO LTD

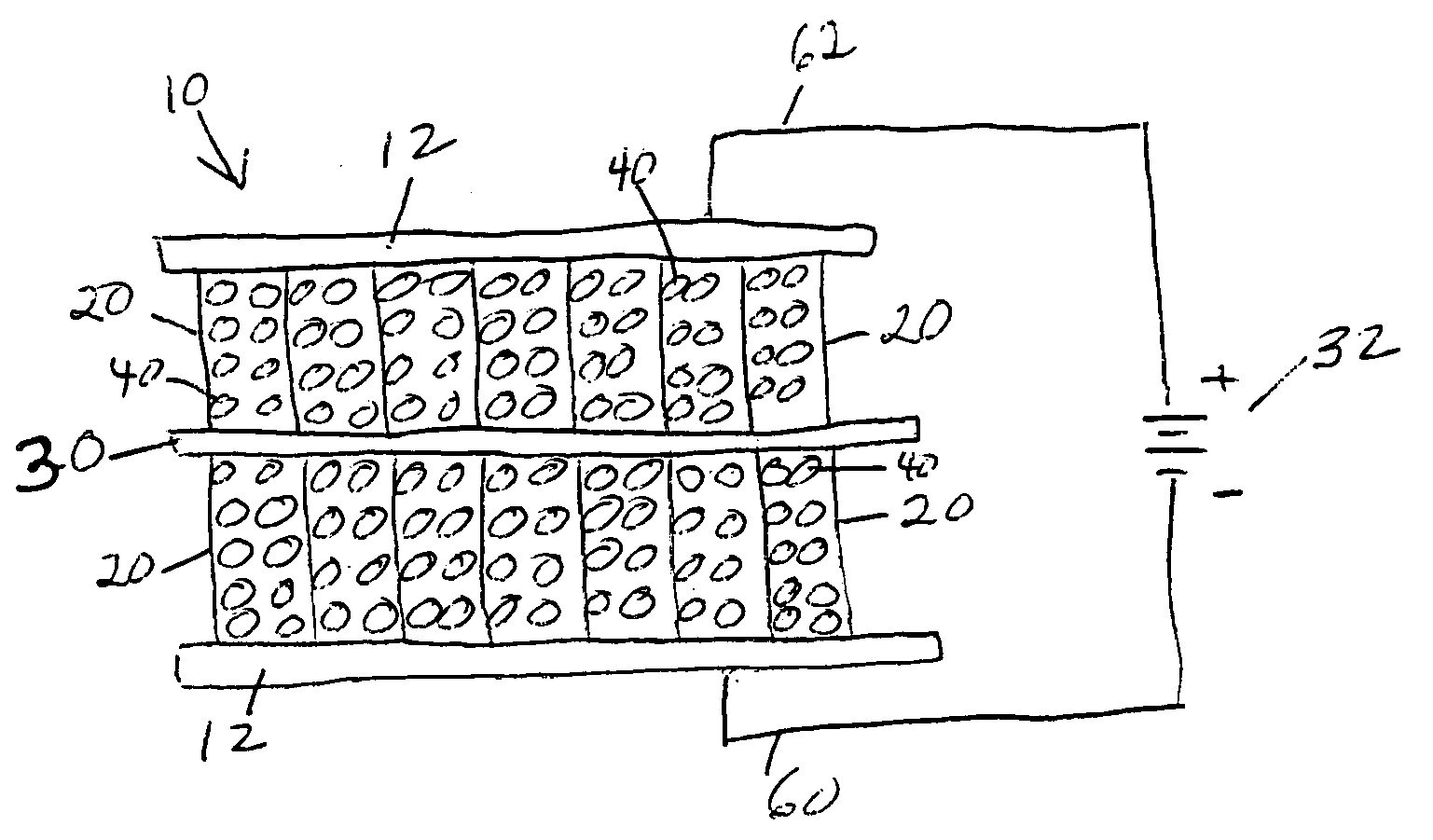

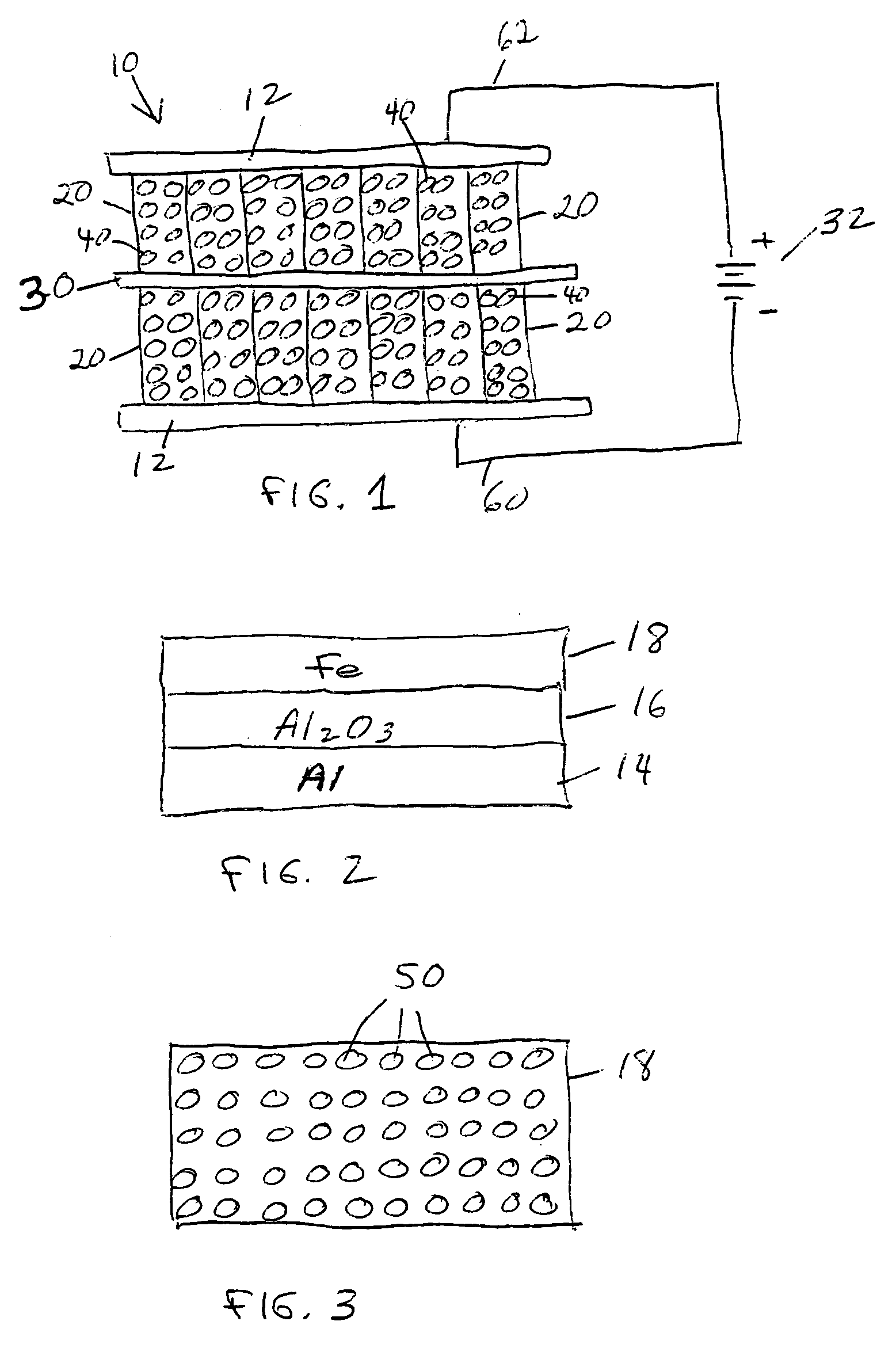

Engineered structure for charge storage and method of making

InactiveUS20070258192A1High capacitanceHigh immunityMaterial nanotechnologyHybrid capacitor separatorsIonEngineering

Engineered structure for charge storage. An electrolyte is disposed between two electrically conducting plates, each plate serving as a base for an aligned array of electrically conducting nanostructures extending from the surface of each plate into the electrolyte. The nanostructures have diameter and spacing comparable to the dimension of an ion of the electrolyte. An electrically insulating separator is disposed between the two plates. A CVD process (or other processes yielding similar results) is used to make the aligned array of electrically conducting nanostructures.

Owner:MASSACHUSETTS INST OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com