Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

329results about How to "High capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Solvent-free process based graphene electrode for energy storage devices

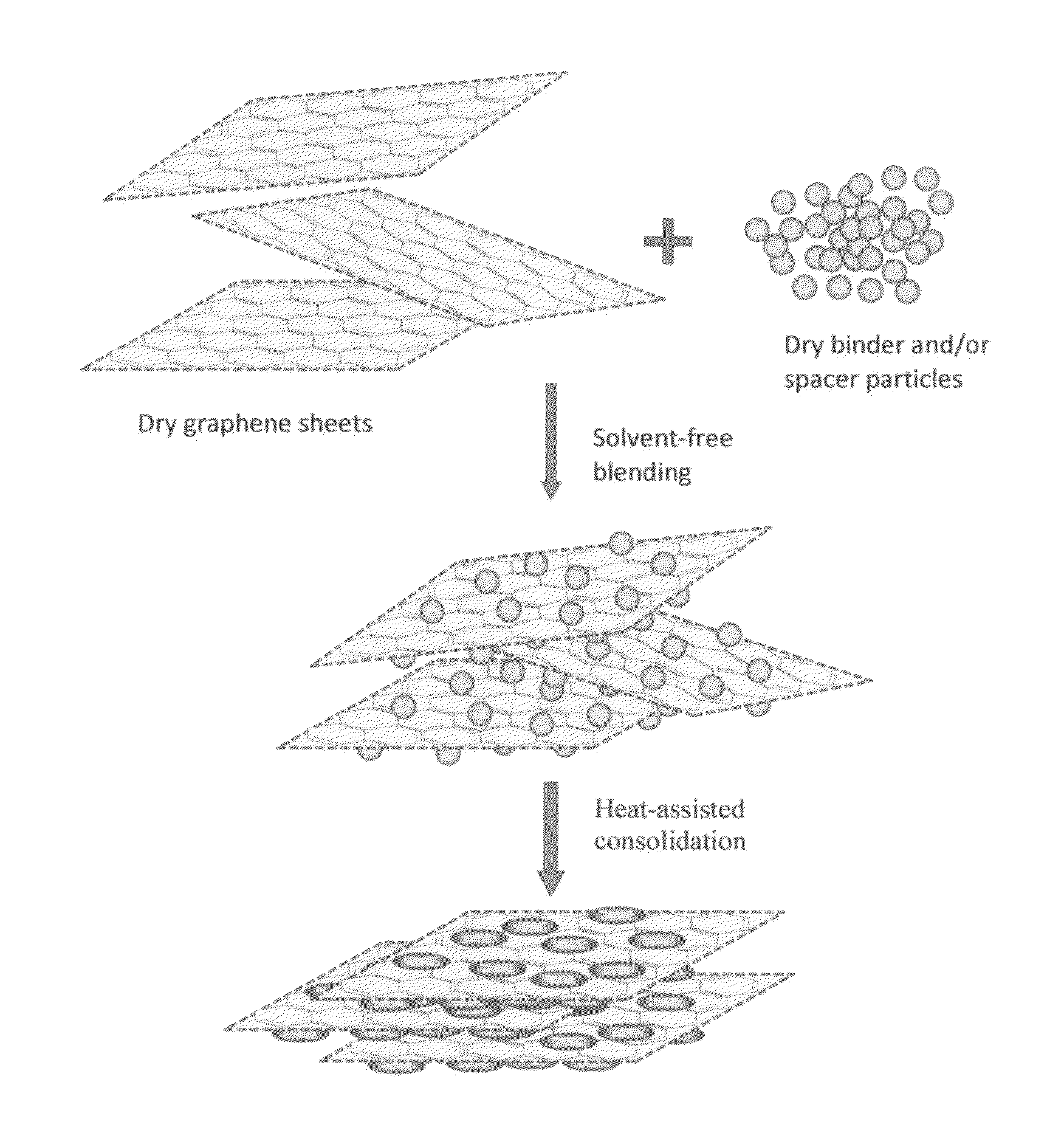

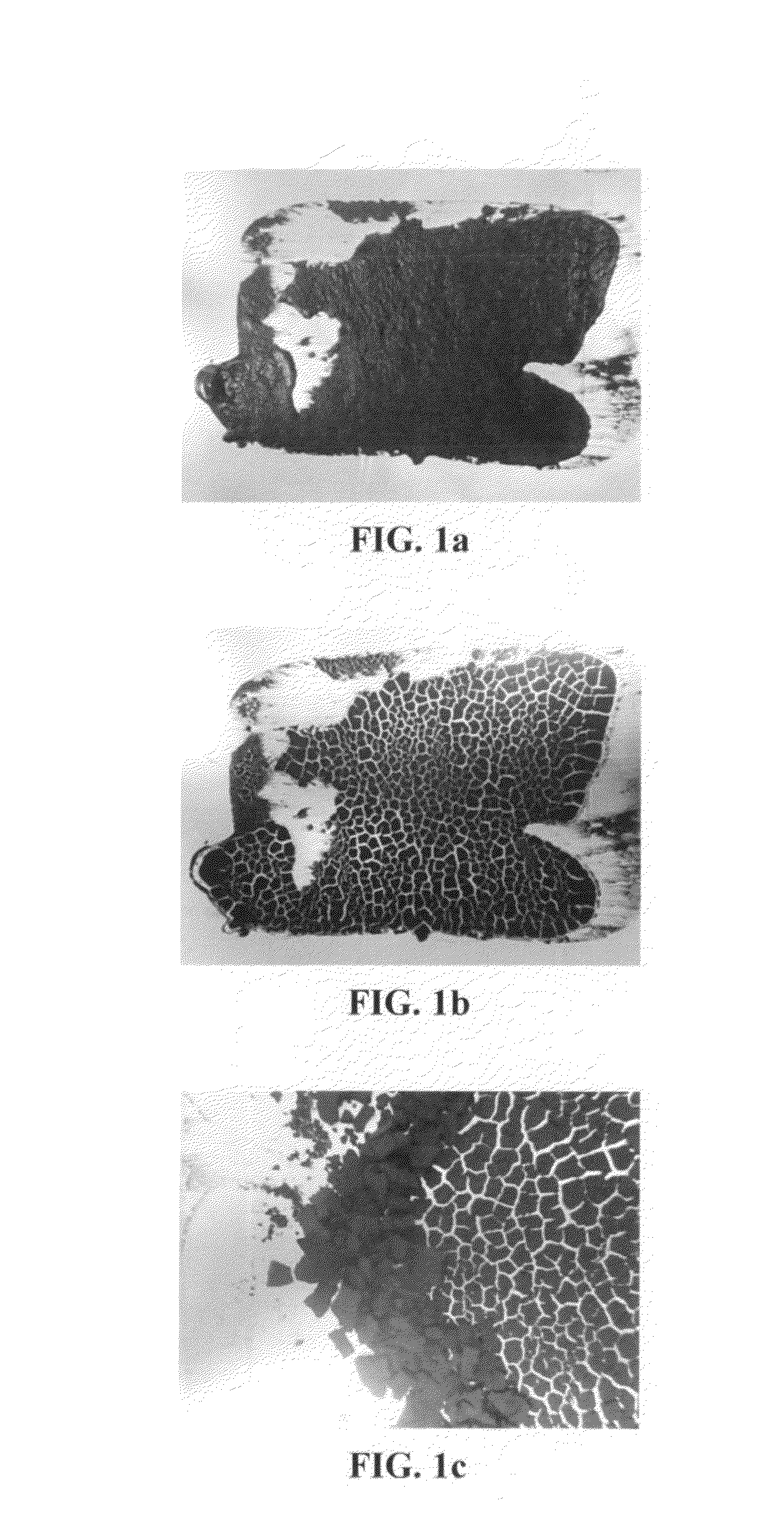

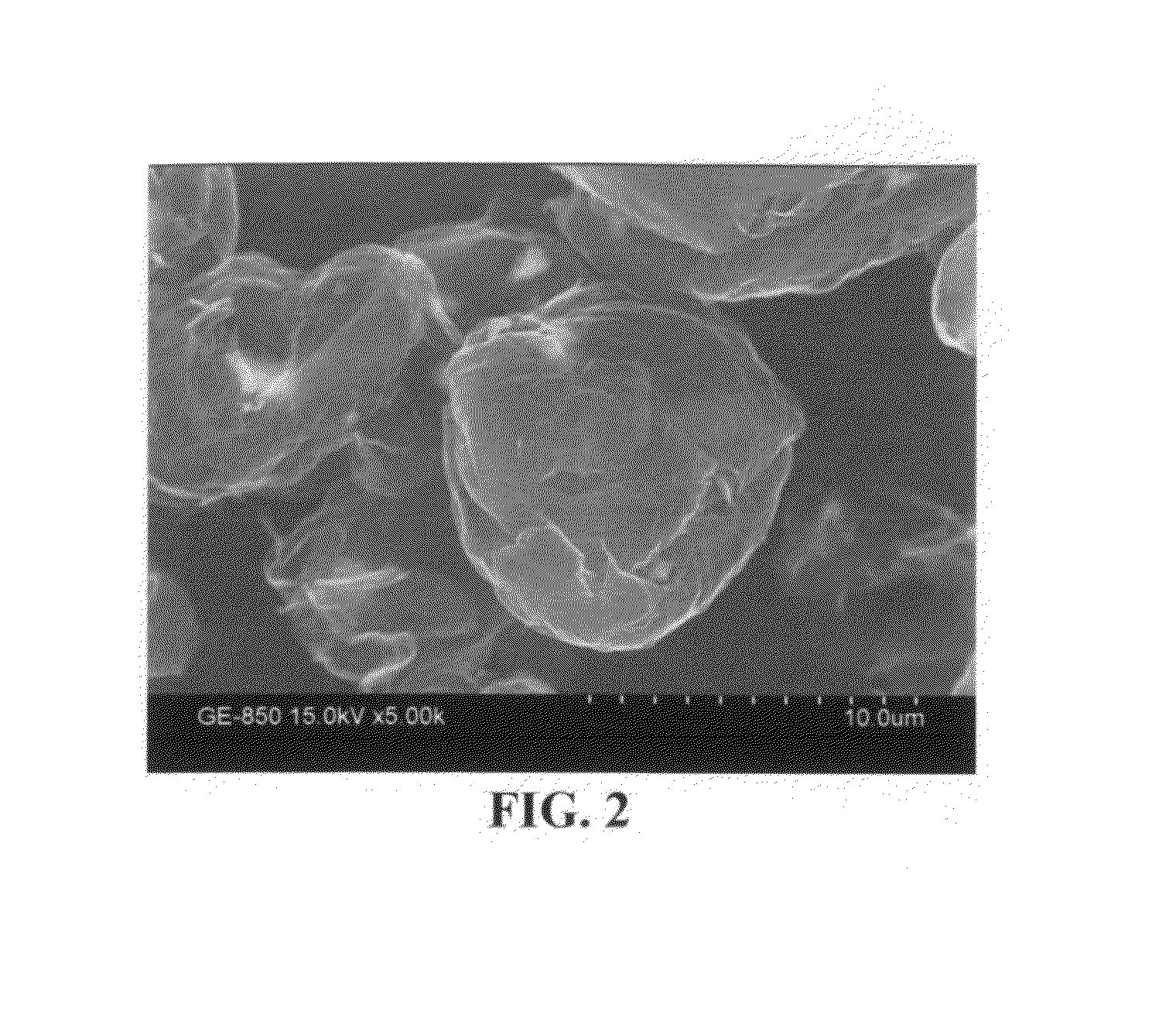

PendingUS20140030590A1Inexpensive and durable and highly reliableHigh capacitanceMaterial nanotechnologyHybrid capacitor electrodesGraphene flakeSolvent free

Disclosed is an electrode for an electrochemical energy storage device, the electrode comprising a self-supporting layer of a mixture of graphene sheets and spacer particles and / or binder particles, wherein the electrode is prepared without using water, solvent, or liquid chemical. The graphene electrode prepared by the solvent-free process exhibits many desirable features and advantages as compared to the corresponding electrode prepared by a known wet process. These advantages include a higher electrode specific surface area, higher energy storage capacity, improved or higher packing density or tap density, lower amount of binder required, lower internal electrode resistance, more consistent and uniform dispersion of graphene sheets and binder, reduction or elimination of undesirable effect of electrolyte oxidation or decomposition due to the presence of water, solvent, or chemical, etc.

Owner:GLOBAL GRAPHENE GRP INC

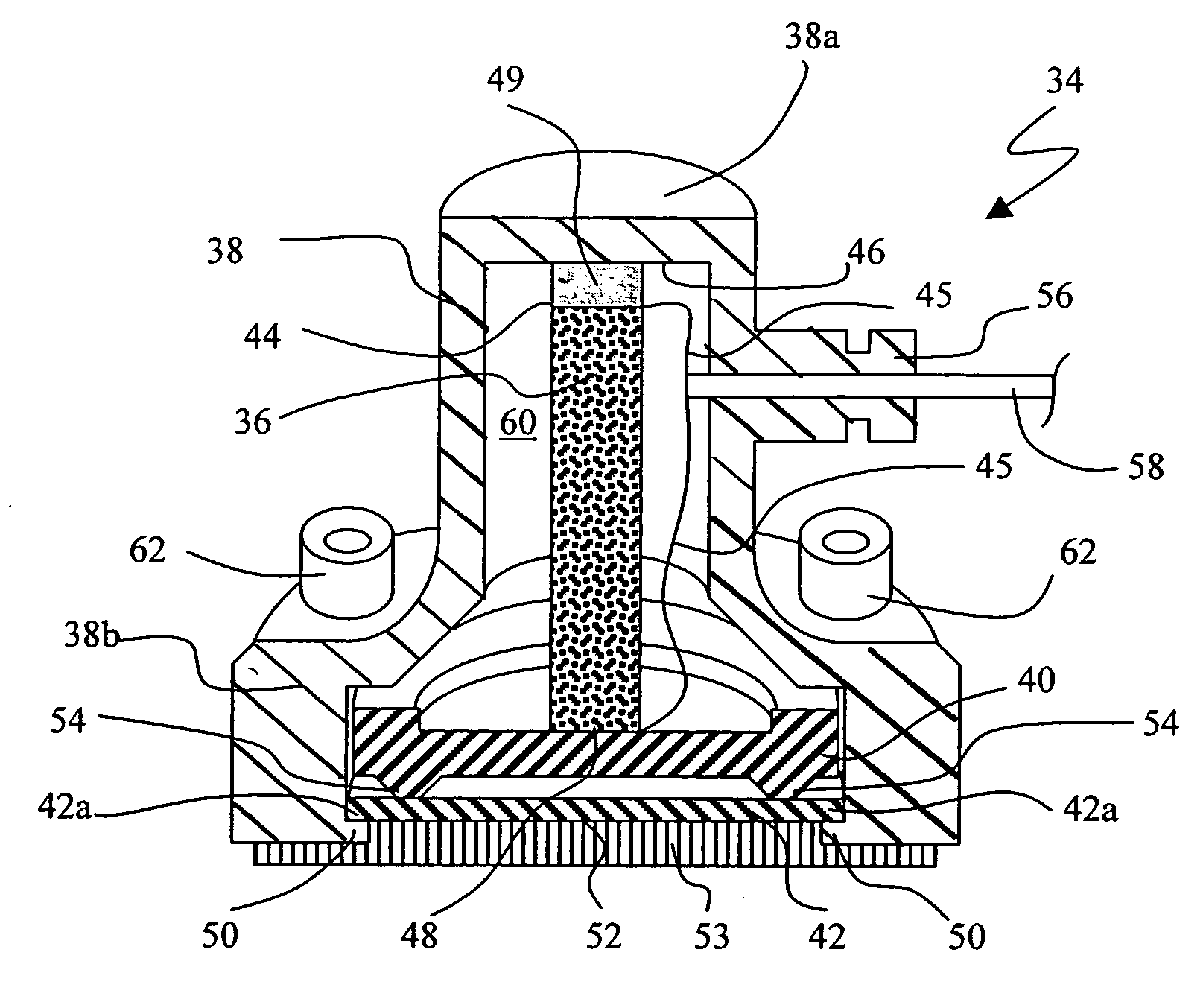

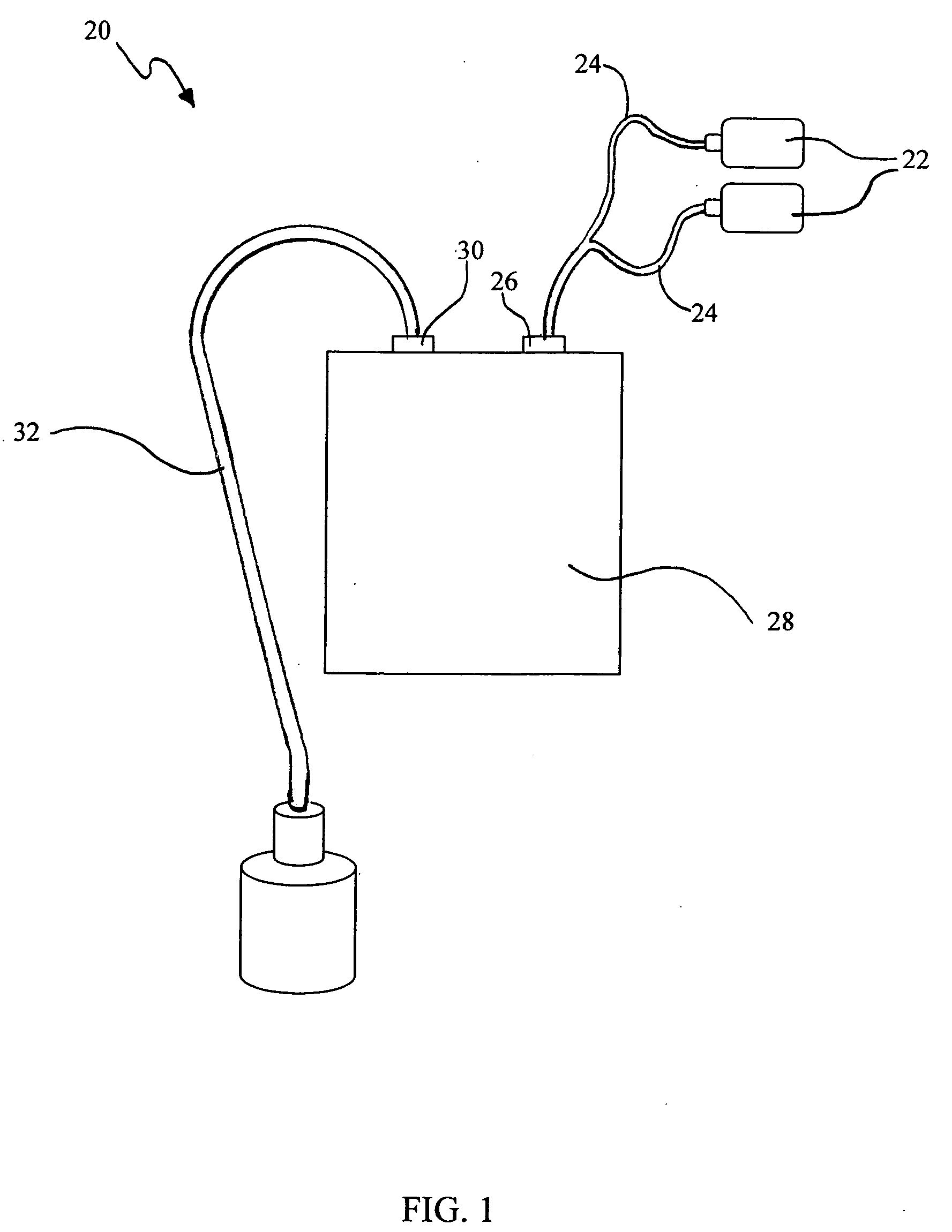

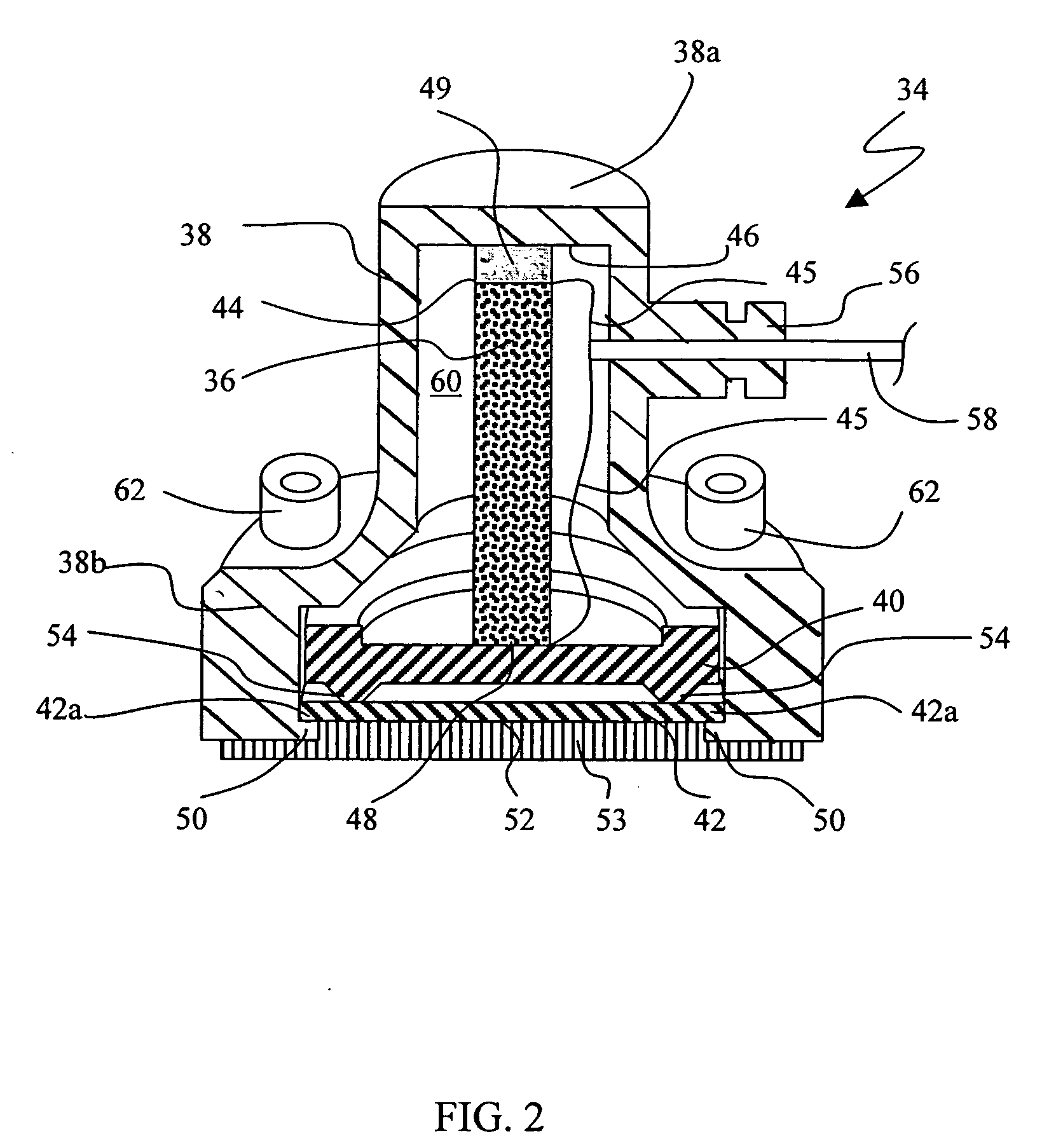

High sensitivity noise immune stethoscope

ActiveUS20070165872A1Efficient couplingHigh elastic modulusTransducer detailsStethoscopeEngineeringActive systems

A physiological sensing stethoscope suitable for use in high-noise environments is disclosed. The stethoscope is designed to be substantially matched to the mechanical impedance of monitored physiological activity and substantially mismatched to the mechanical impedance of air-coupled acoustic activity. One embodiment of the stethoscope utilizes a passive acoustic system. Another embodiment utilizes an active Doppler system. The passive and active systems can be combined in one stethoscope enabling switching from a passive mode to an active mode suitable for use in very high-noise environments. The stethoscope is suitable for use in environments having an ambient background noise of 100 dBA and higher. The passive includes a head having a housing, a flexural disc mounted with the housing, and an electromechanical stack positioned between the housing and the flexural disc in contact with the skin of a patient. The active system detects Doppler shifts using a high-frequency transmitter and receiver.

Owner:ACTIVE SIGNAL TECH

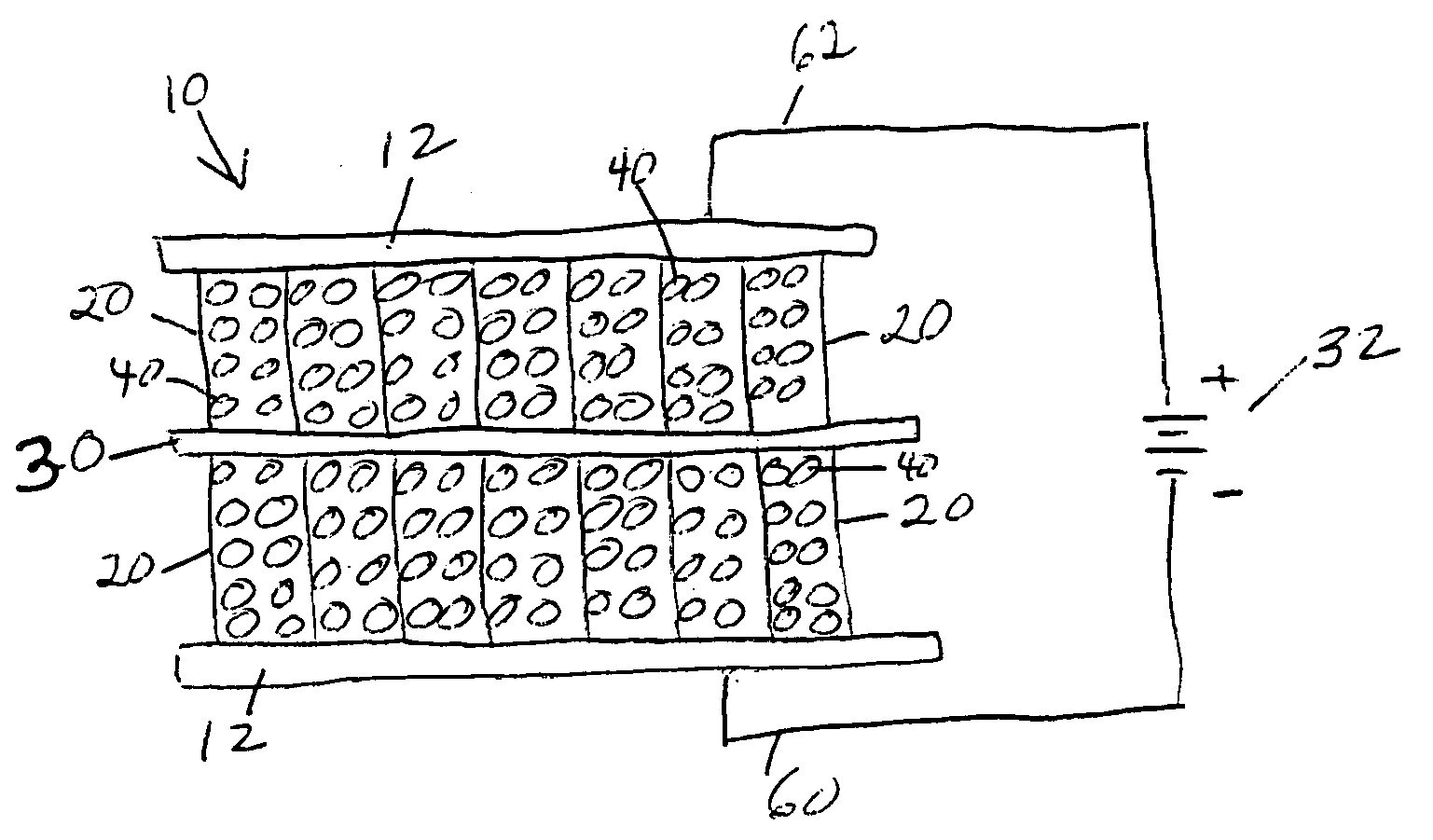

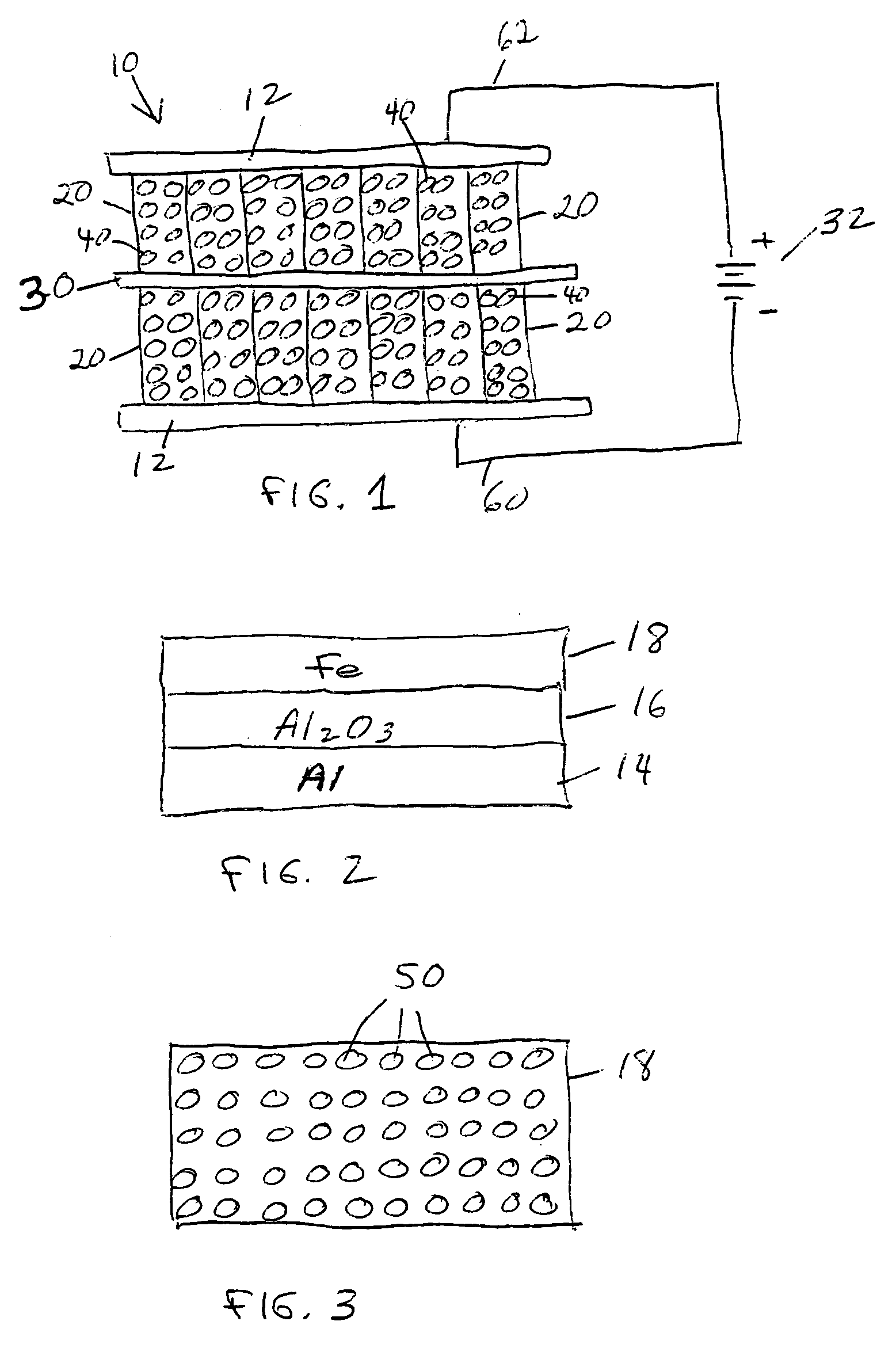

Engineered structure for charge storage and method of making

InactiveUS20070258192A1High capacitanceHigh immunityMaterial nanotechnologyHybrid capacitor separatorsIonEngineering

Engineered structure for charge storage. An electrolyte is disposed between two electrically conducting plates, each plate serving as a base for an aligned array of electrically conducting nanostructures extending from the surface of each plate into the electrolyte. The nanostructures have diameter and spacing comparable to the dimension of an ion of the electrolyte. An electrically insulating separator is disposed between the two plates. A CVD process (or other processes yielding similar results) is used to make the aligned array of electrically conducting nanostructures.

Owner:MASSACHUSETTS INST OF TECH

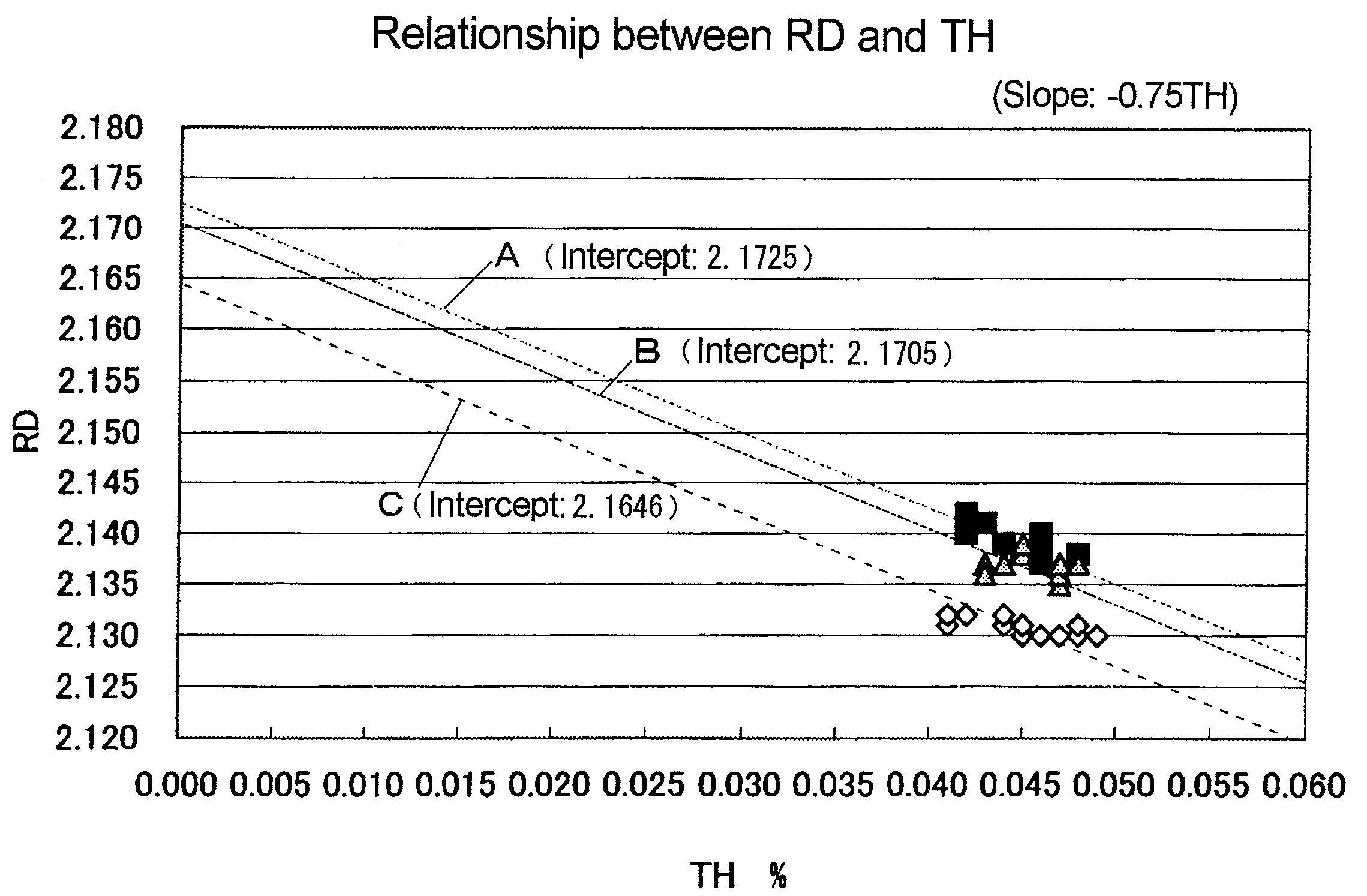

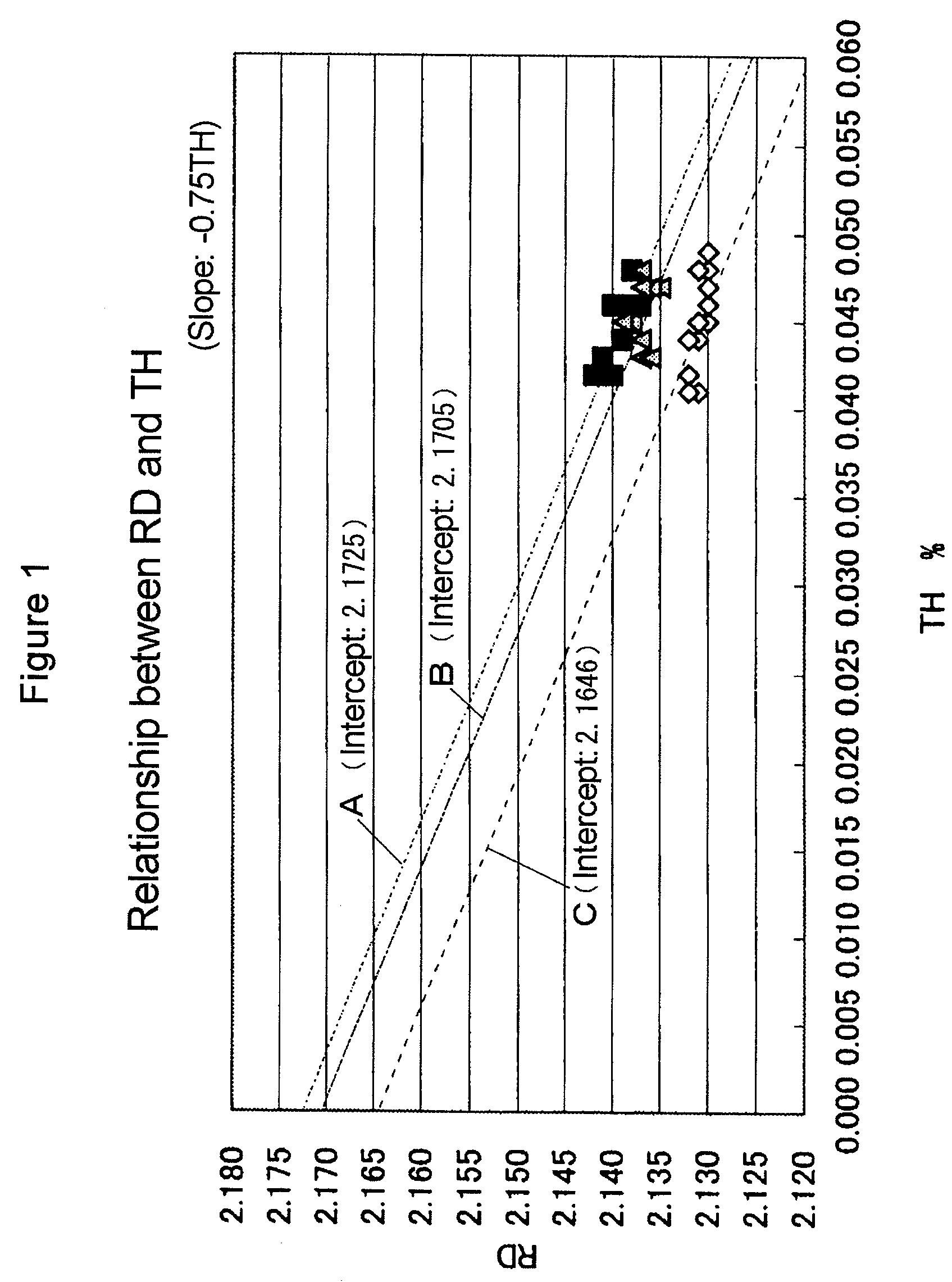

Raw material carbon composition for carbon material for electrode in electric double layer capacitor

ActiveUS7582902B2Improve the level ofGood reproducibilityTransistorCarbon compoundsMetallurgyHydrogen content

Owner:NIPPON OIL CORP

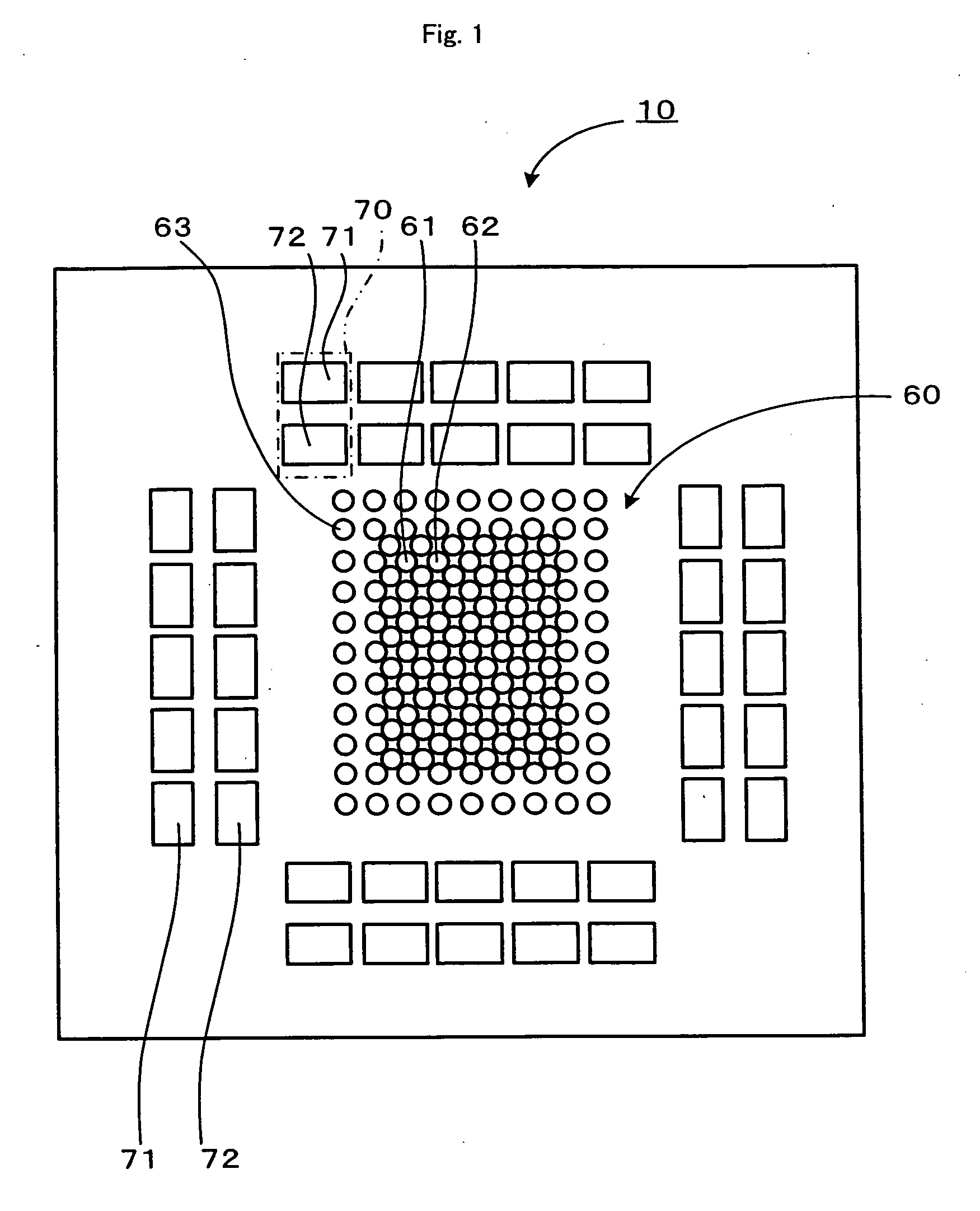

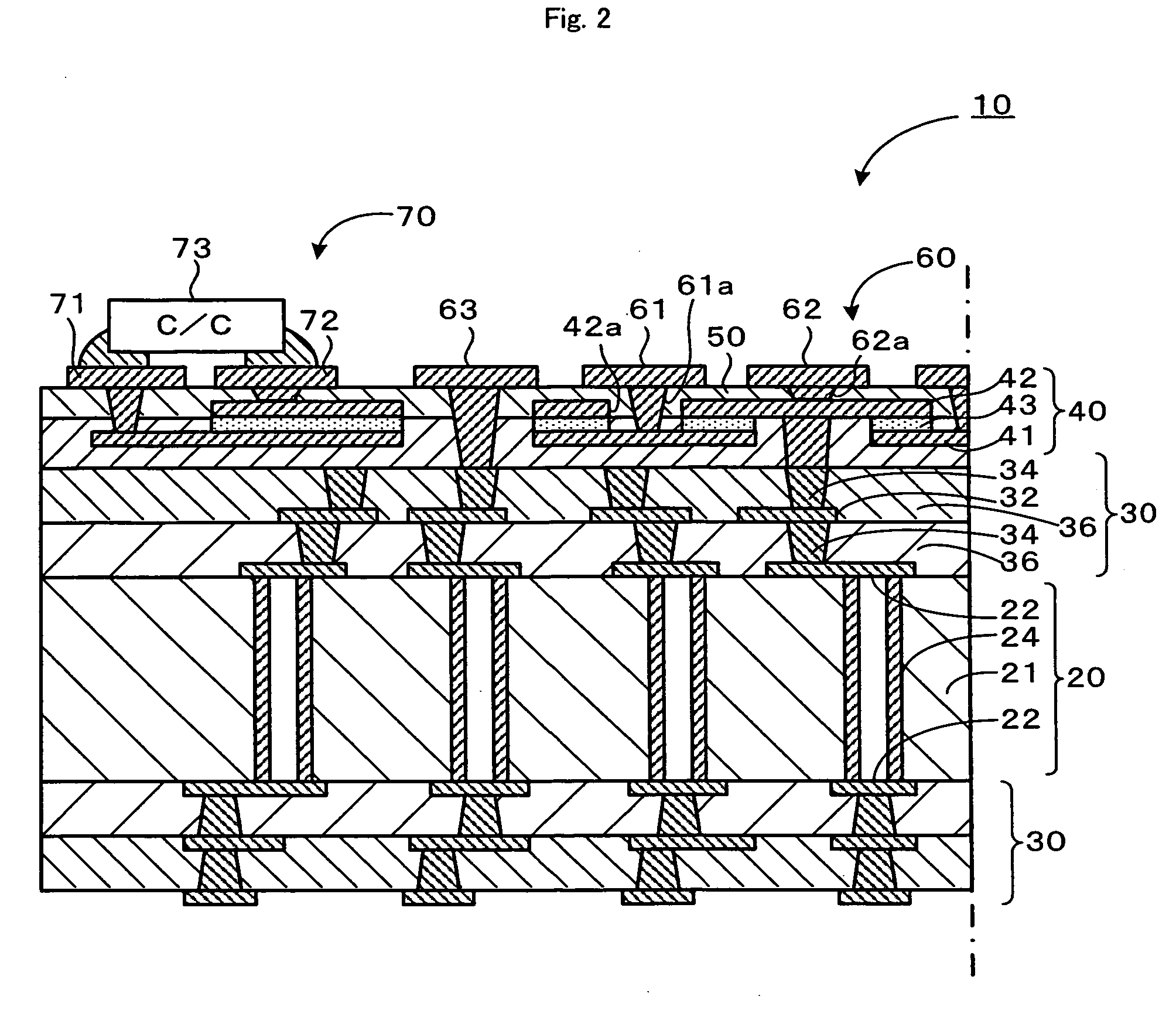

Multilayer printed wiring board

ActiveUS20060137905A1High capacitanceAdequate decoupling effectCross-talk/noise/interference reductionPrinted circuits stress/warp reductionCapacitanceEngineering

A multilayer printed wiring board 10 includes: a mounting portion 60 on the top surface of which is mounted a semiconductor element that is electrically connected to a wiring pattern 32, etc.; and a capacitor portion 40 having a high dielectric constant layer 43, formed of ceramic and first and second layer electrodes 41 and 42 that sandwich the high dielectric constant layer 43. One of either of the first and second layer electrodes 41 and 42 is connected to a power supply line of the semiconductor element and the other of either of the first and second layer electrodes 41 and 42 is connected to a ground line. In this multilayer printed wiring board 10, high dielectric constant layer 43 included in the layered capacitor portion 40, which is connected between the power supply line and the ground line, is formed of ceramic. With this structure, the static capacitance of the layered capacitor portion 40 can be high, and an adequate decoupling effect is exhibited even under circumstances in which instantaneous potential drops occur readily.

Owner:IBIDEN CO LTD

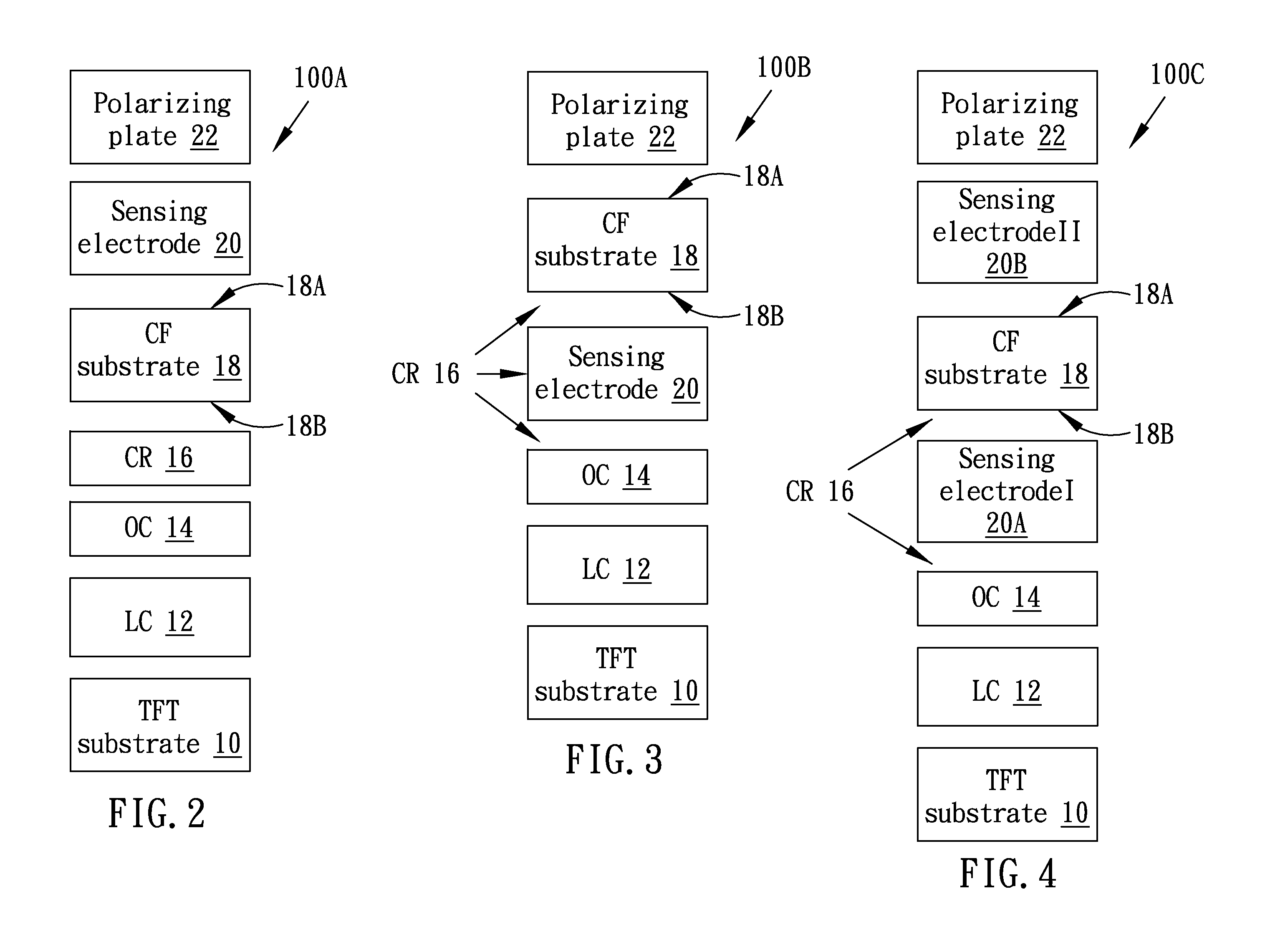

Touch sensitive ips liquid crystal display

ActiveUS20100321327A1Improve accuracyImprove Sensing PerformanceNon-linear opticsInput/output processes for data processingLiquid-crystal displayActive matrix

A touch sensitive in-plane switching (IPS) liquid crystal display (LCD) includes a liquid crystal layer, an active-matrix transistor layer with an electrode pair, a color filter substrate, and a sensing electrode layer. The sensing electrode layer may be disposed above or below the color filter substrate, and the sensing electrode layer may include two parts that are disposed above and below the color filter layer respectively.

Owner:TRENDON TOUCH TECHNOLOGY CORPORATION

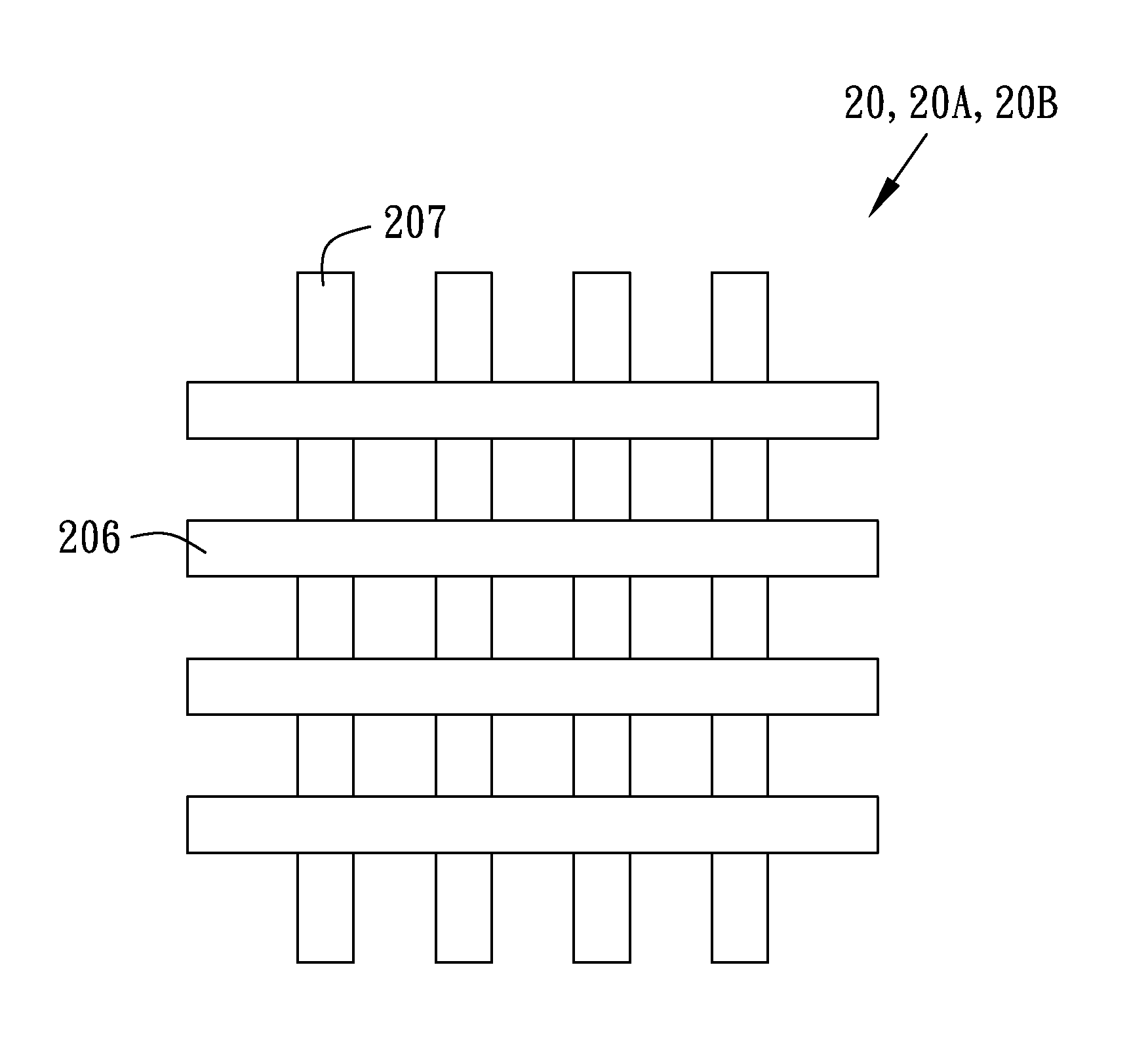

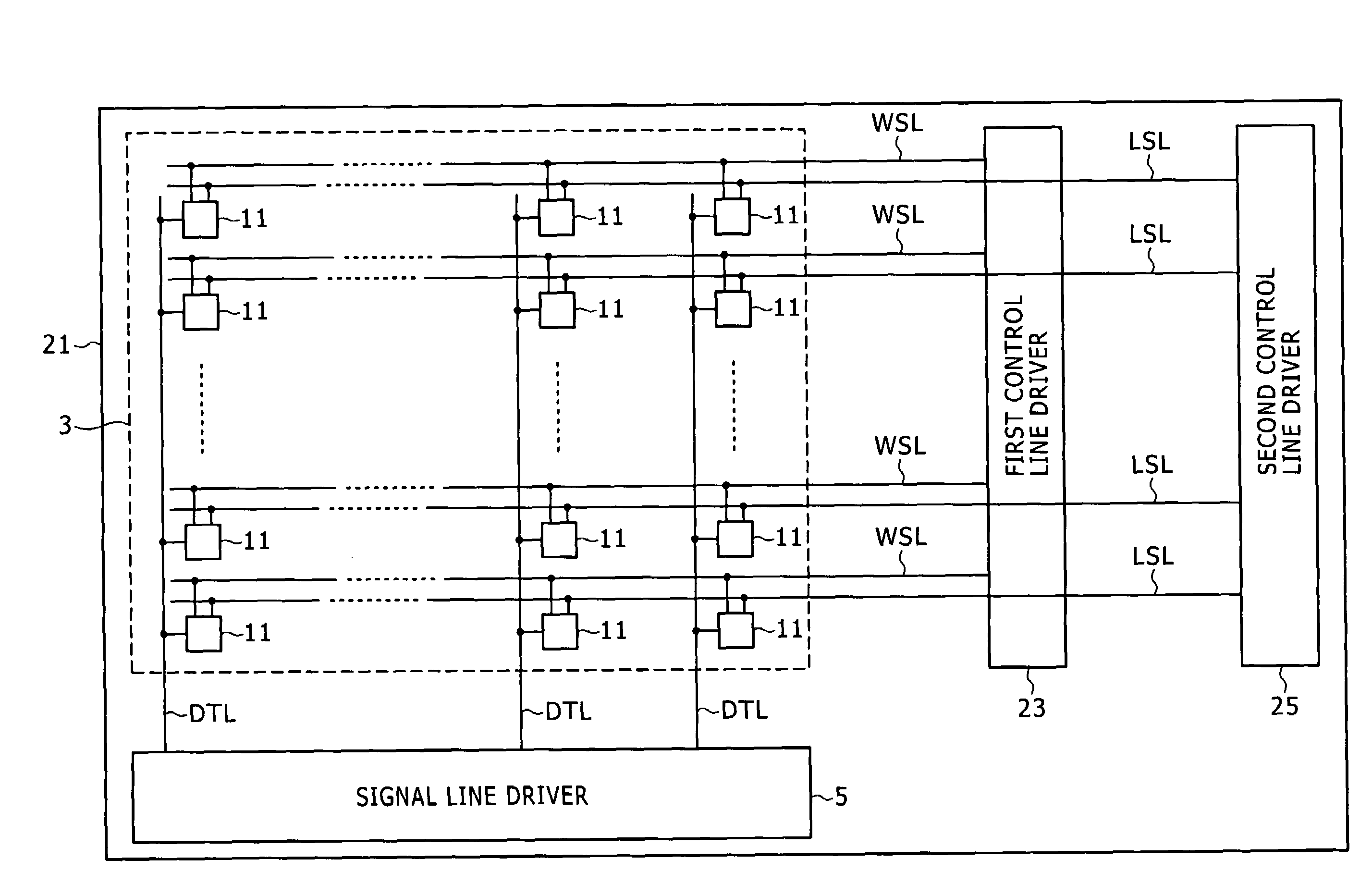

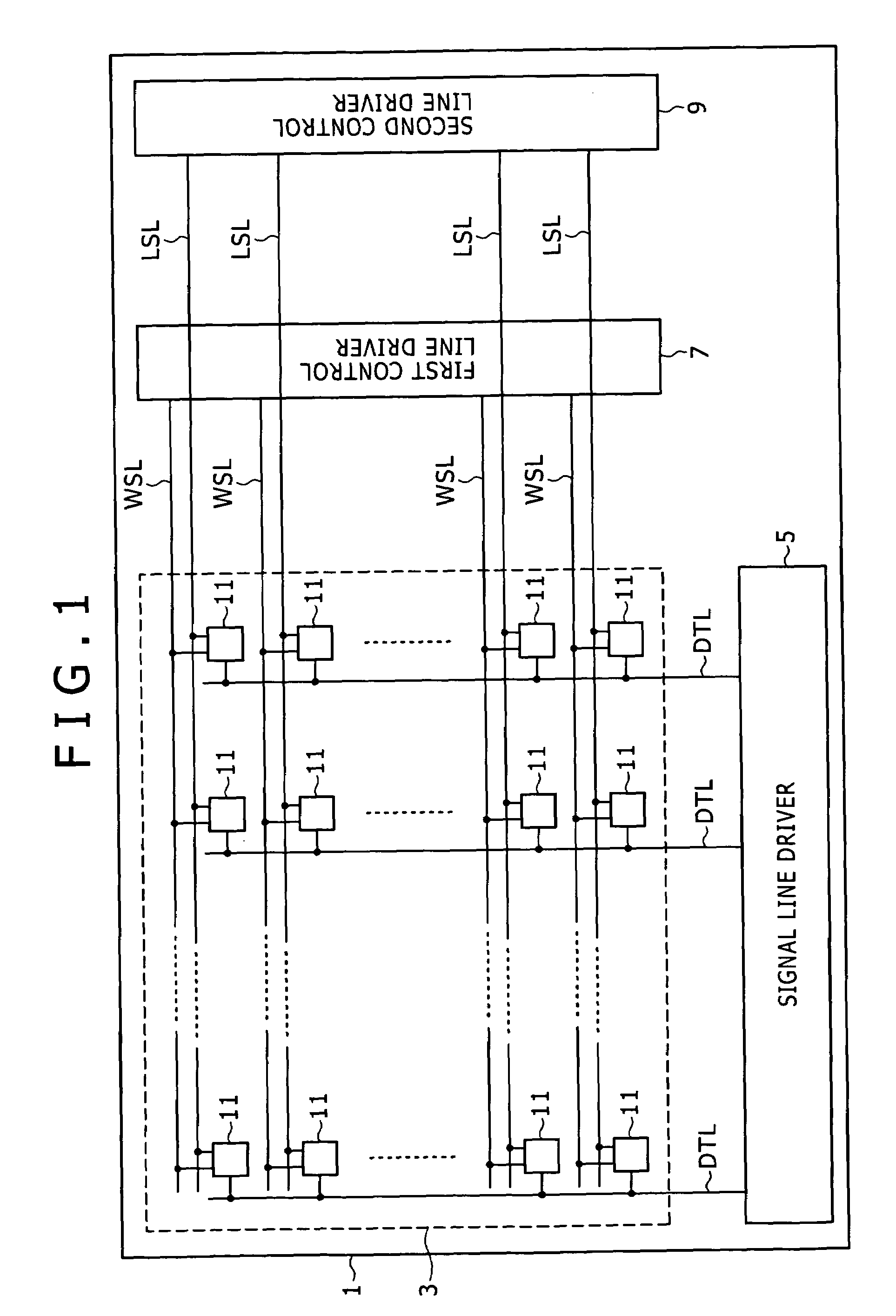

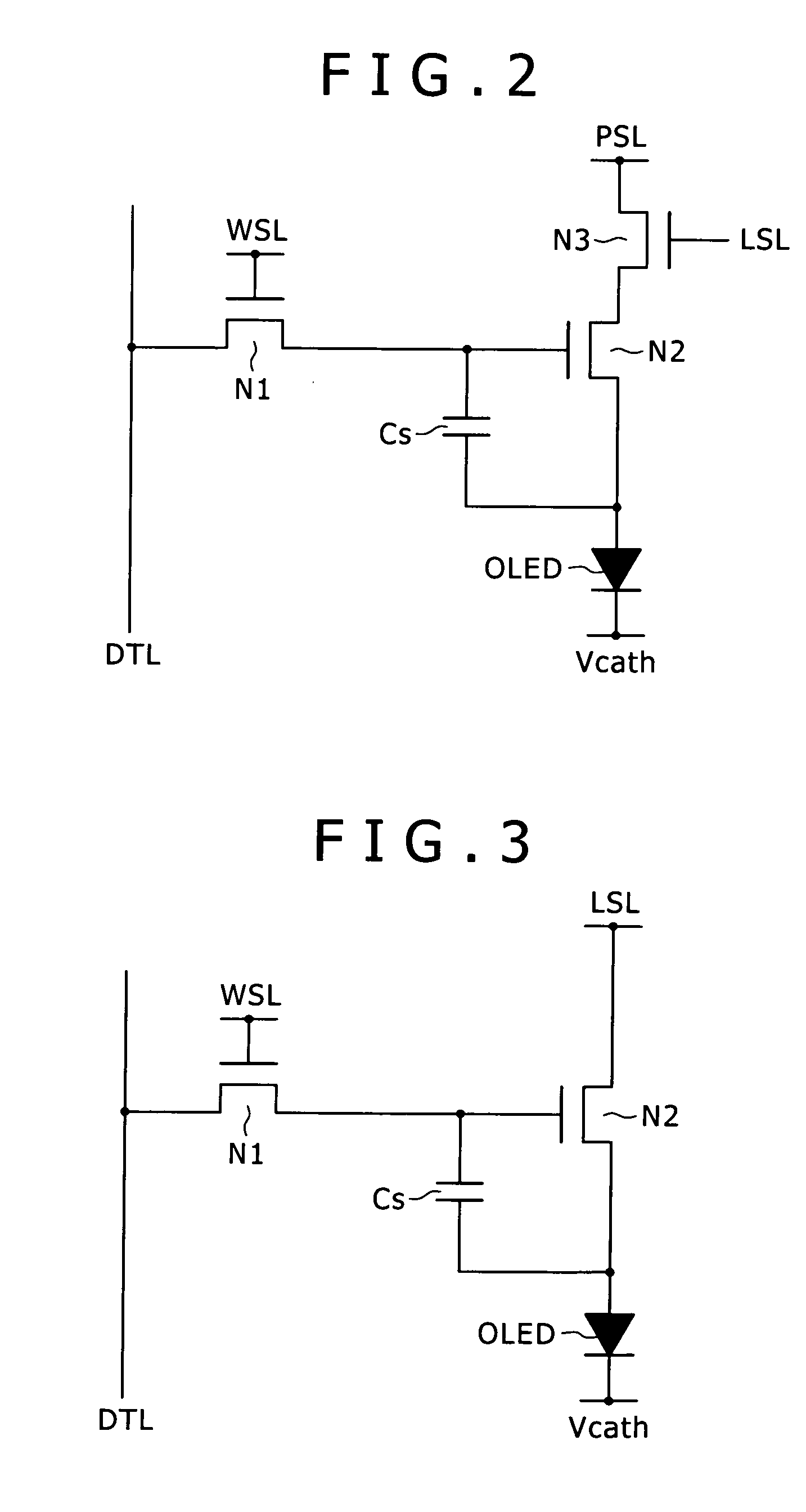

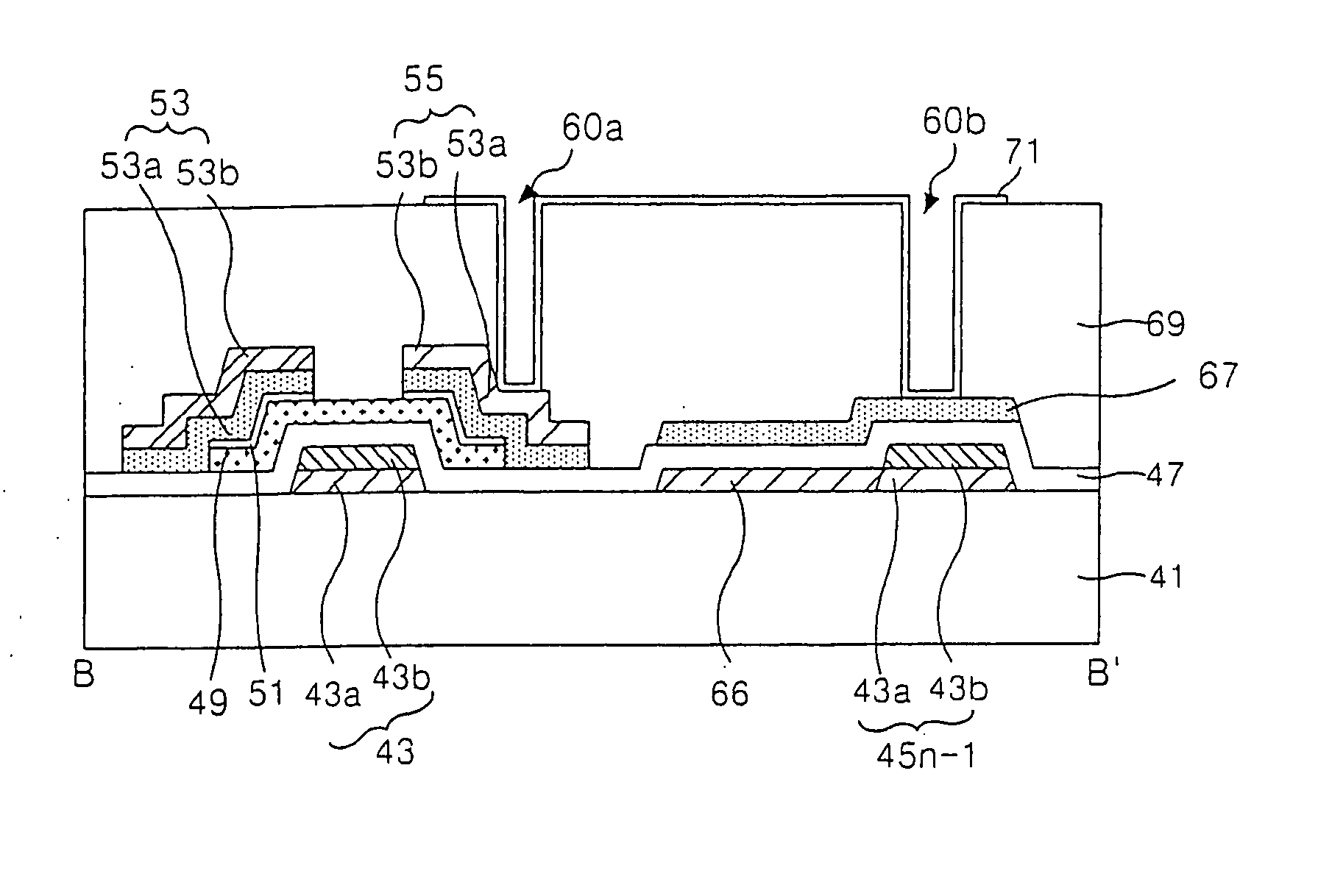

Shift register circuit, display panel, and electronic apparatus

InactiveUS20090251443A1Increase in sizeHigh capacitanceCathode-ray tube indicatorsDigital storageShift registerHemt circuits

Disclosed herein is a shift register circuit that is formed on an insulating substrate with thin film transistors having channels of the same conductivity type and includes shift stages, each of the shift stages including: a first thin film transistor; a second thin film transistor; a 3(1)-th thin film transistor; a 3(2)-th thin film transistor; a 4(1)-th thin film transistor; a 4(2)-th thin film transistor; a fifth thin film transistor; and a sixth thin film transistor.

Owner:SONY CORP

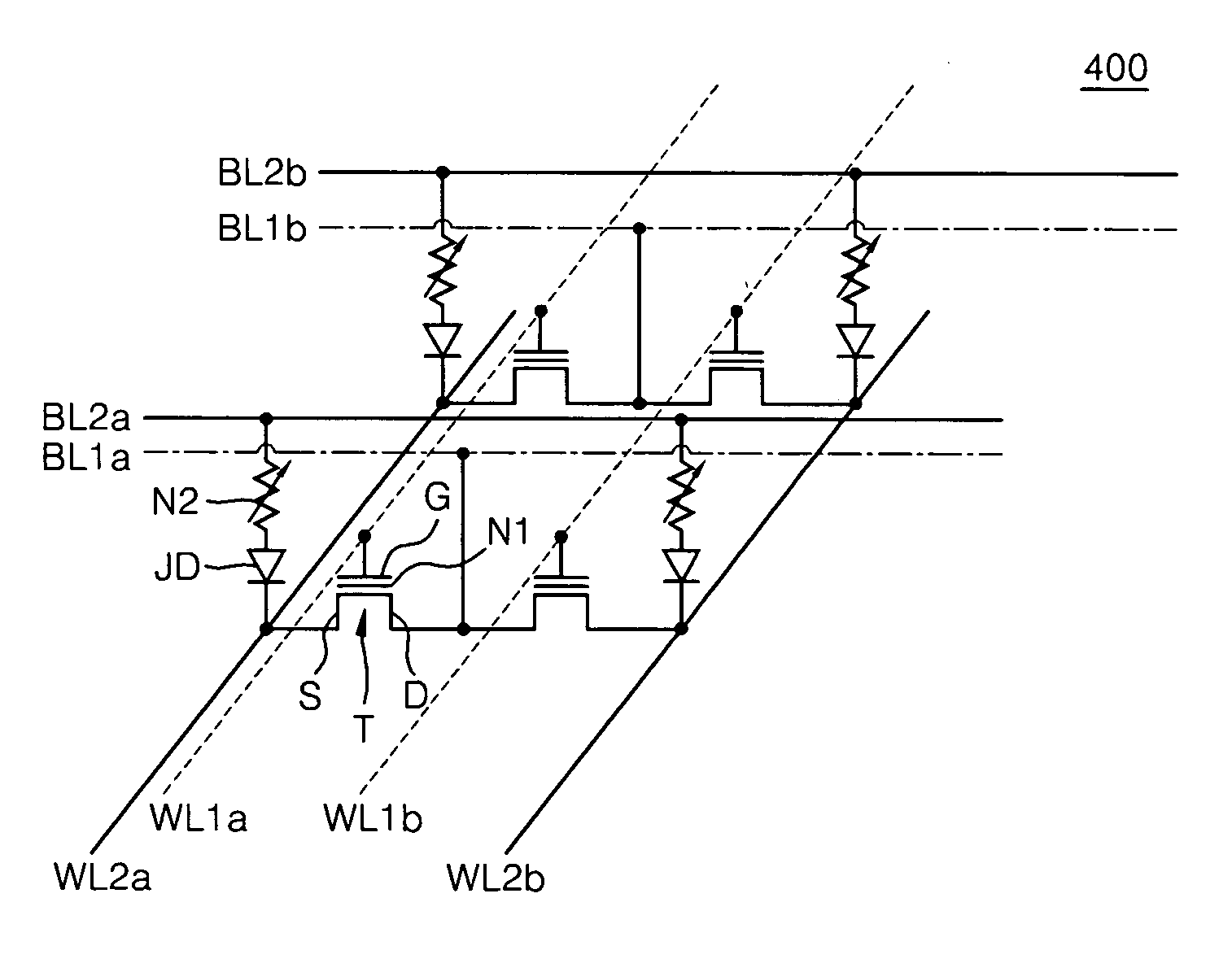

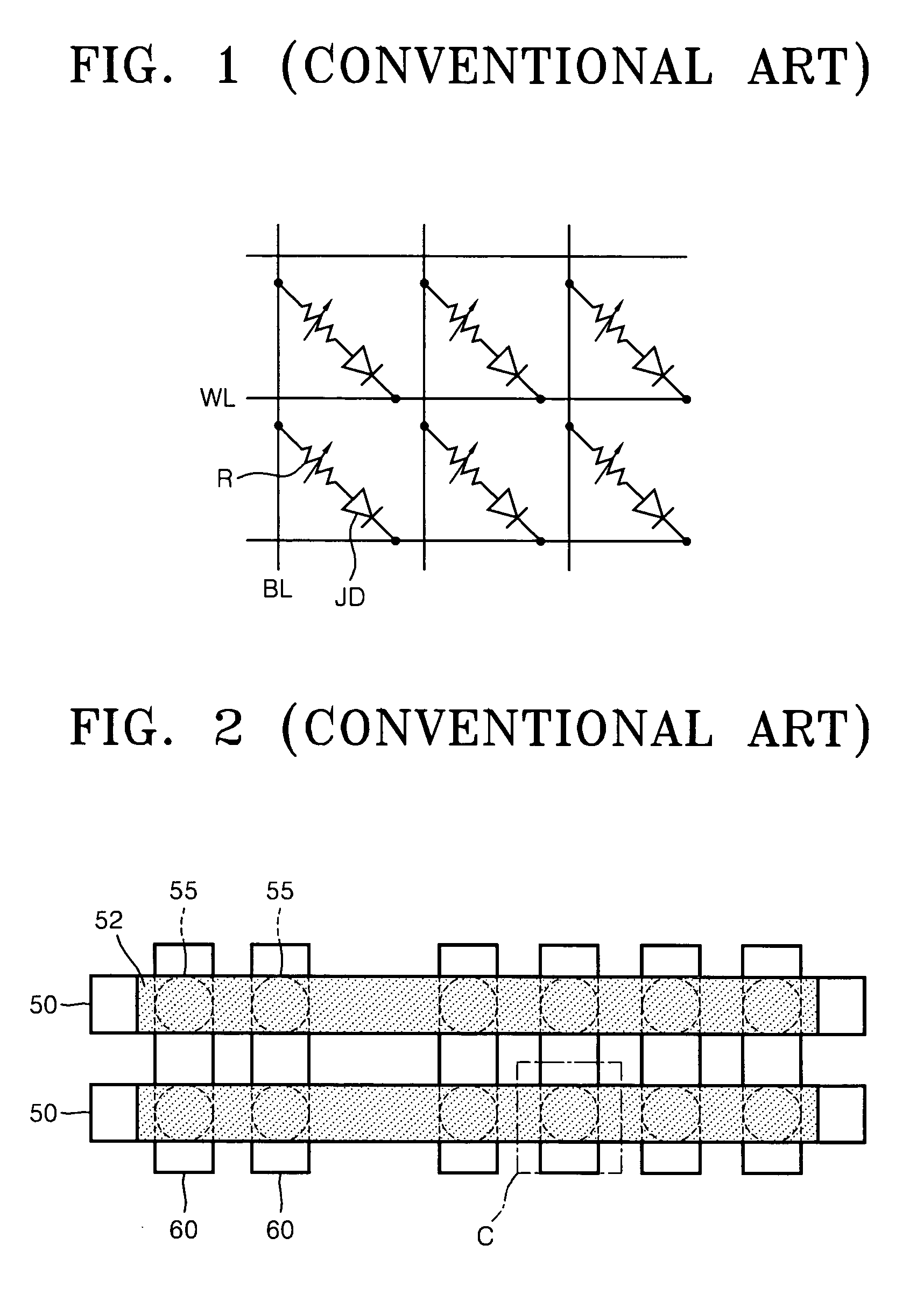

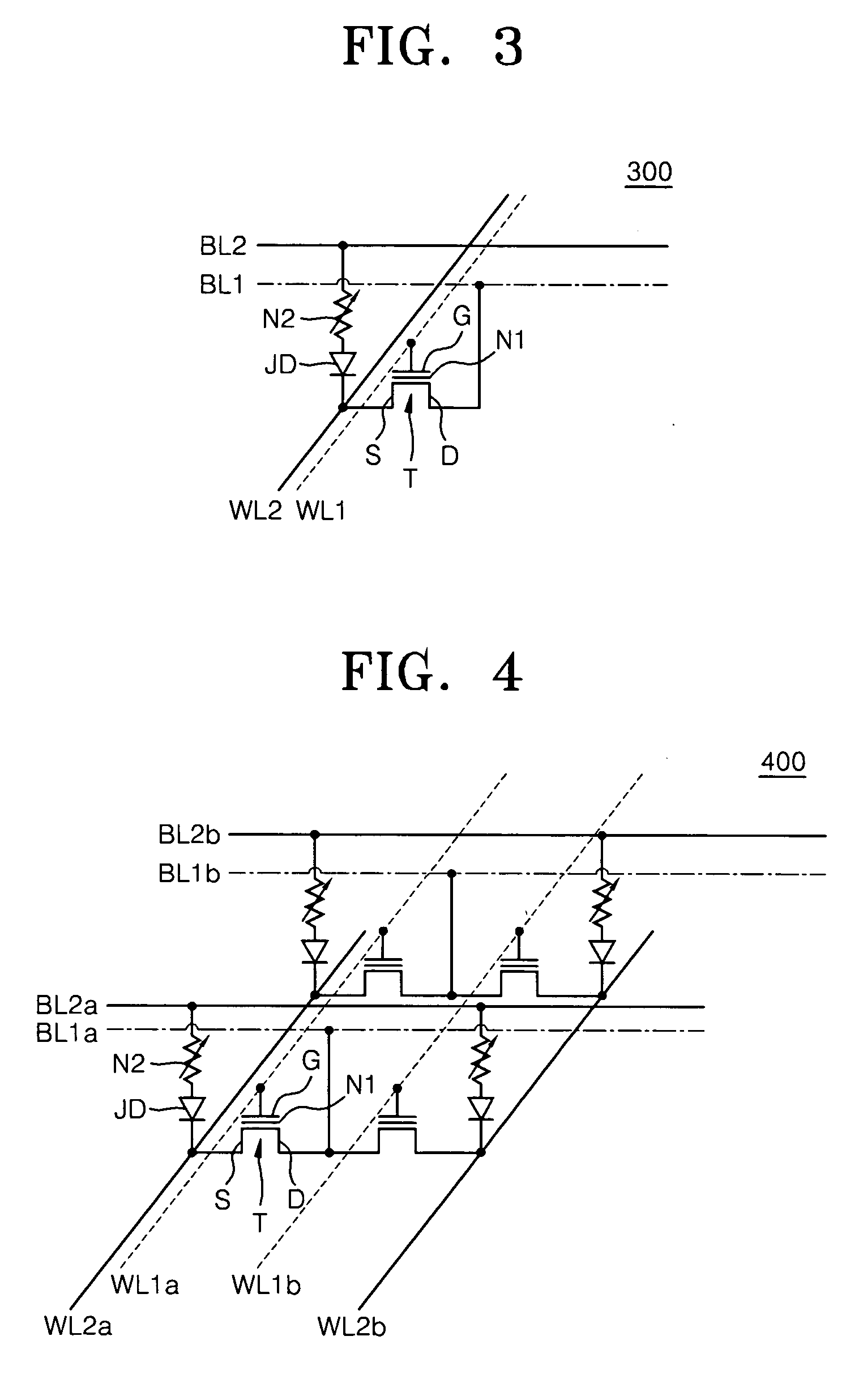

Non-volatile memory devices and method thereof

ActiveUS20070103963A1High capacitanceSolid-state devicesRead-only memoriesSemiconductorVolatile memory

Non-volatile memory devices and a method thereof are provided. A non-volatile memory device according to an example embodiment of the present invention may include a first transistor including a source, a drain, and a control gate, a first storage node coupled to the first transistor, the first storage node configured to store information in a first manner, a first diode having a first end connected to the source of the transistor, the first diode configured to rectify a flow of current from the source of the transistor and a second storage node connected to a second end of the first diode, the second storage node configured to store information in a second manner. Another non-volatile memory device according to another example embodiment of the present invention may include a semiconductor substrate having a first conductivity type including an active region defined by a device isolating layer, a source region and a drain region formed by doping an impurity having a second conductivity type in the active region, a control gate electrode insulated from the active region, the control gate electrode extending across the active region disposed between the source region and the drain region, a first storage node layer interposed between the active region and the control gate electrode configured to store information in a first manner, a second storage node layer disposed on the source region configured to store information in a second manner and a diode interposed between the source region and the second storage node layer to rectify a flow of current to the source region. The example method may be directed to obtaining a higher storage capacity per cell area in either of the above-described example non-volatile memory devices.

Owner:SAMSUNG ELECTRONICS CO LTD

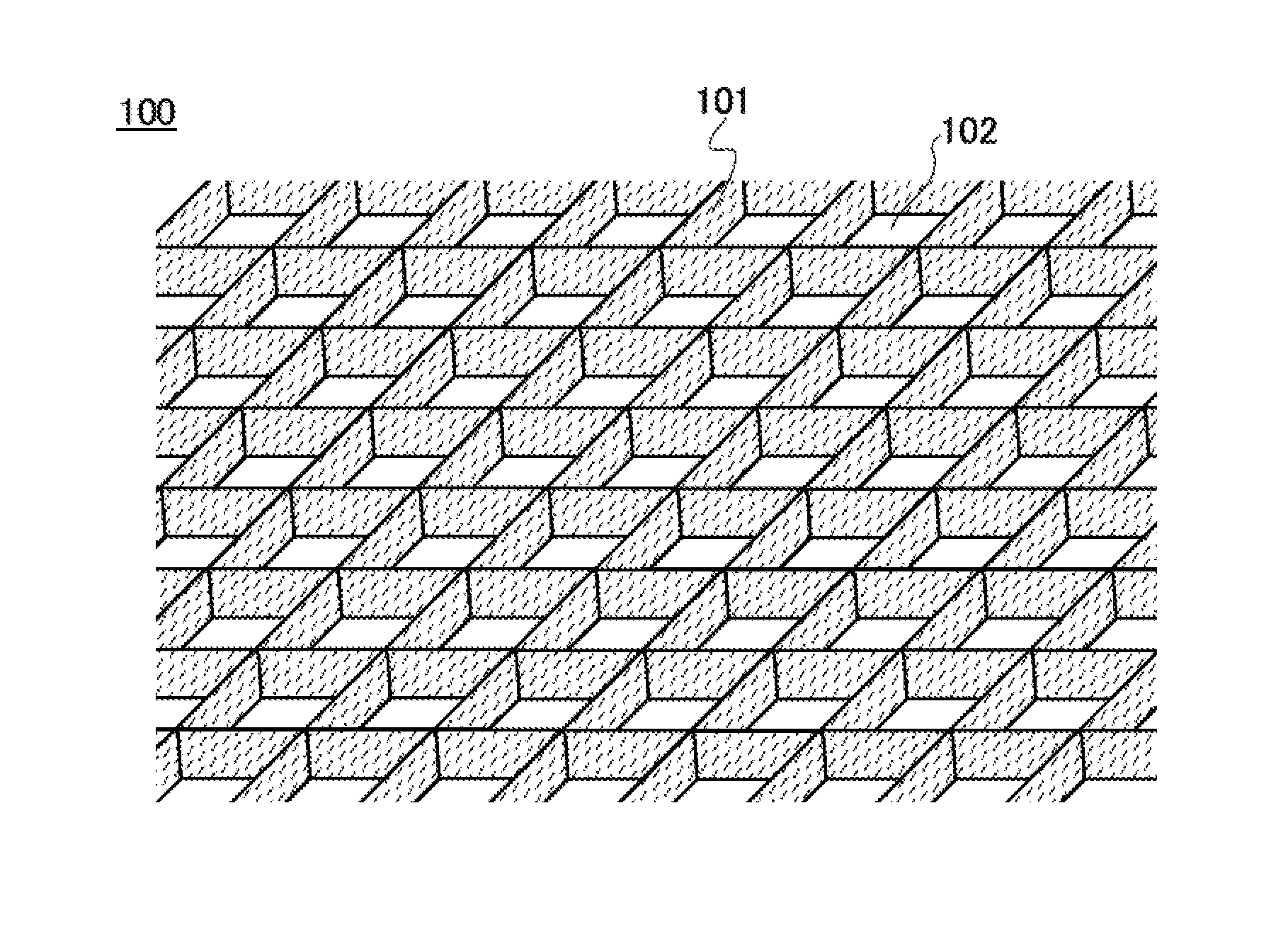

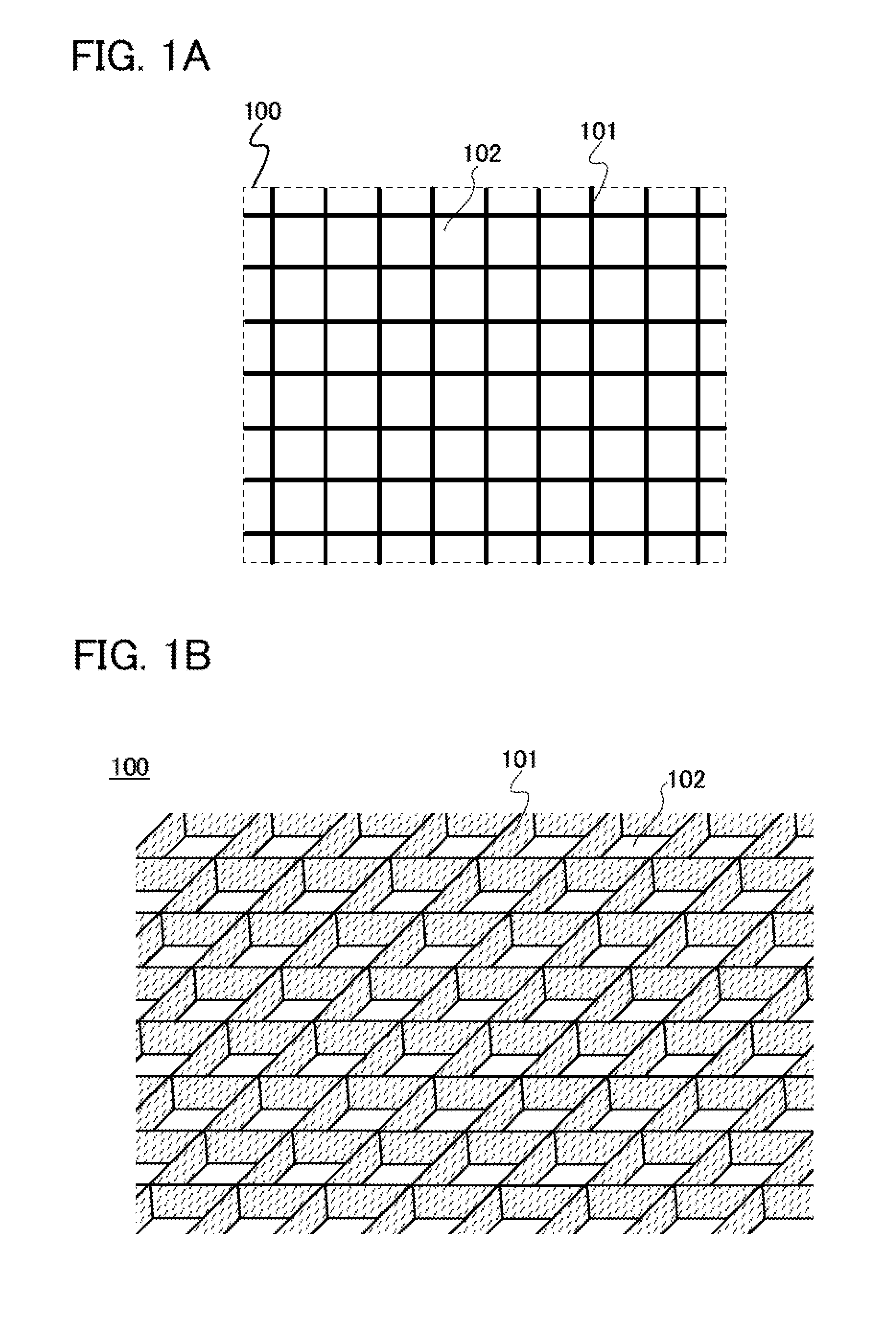

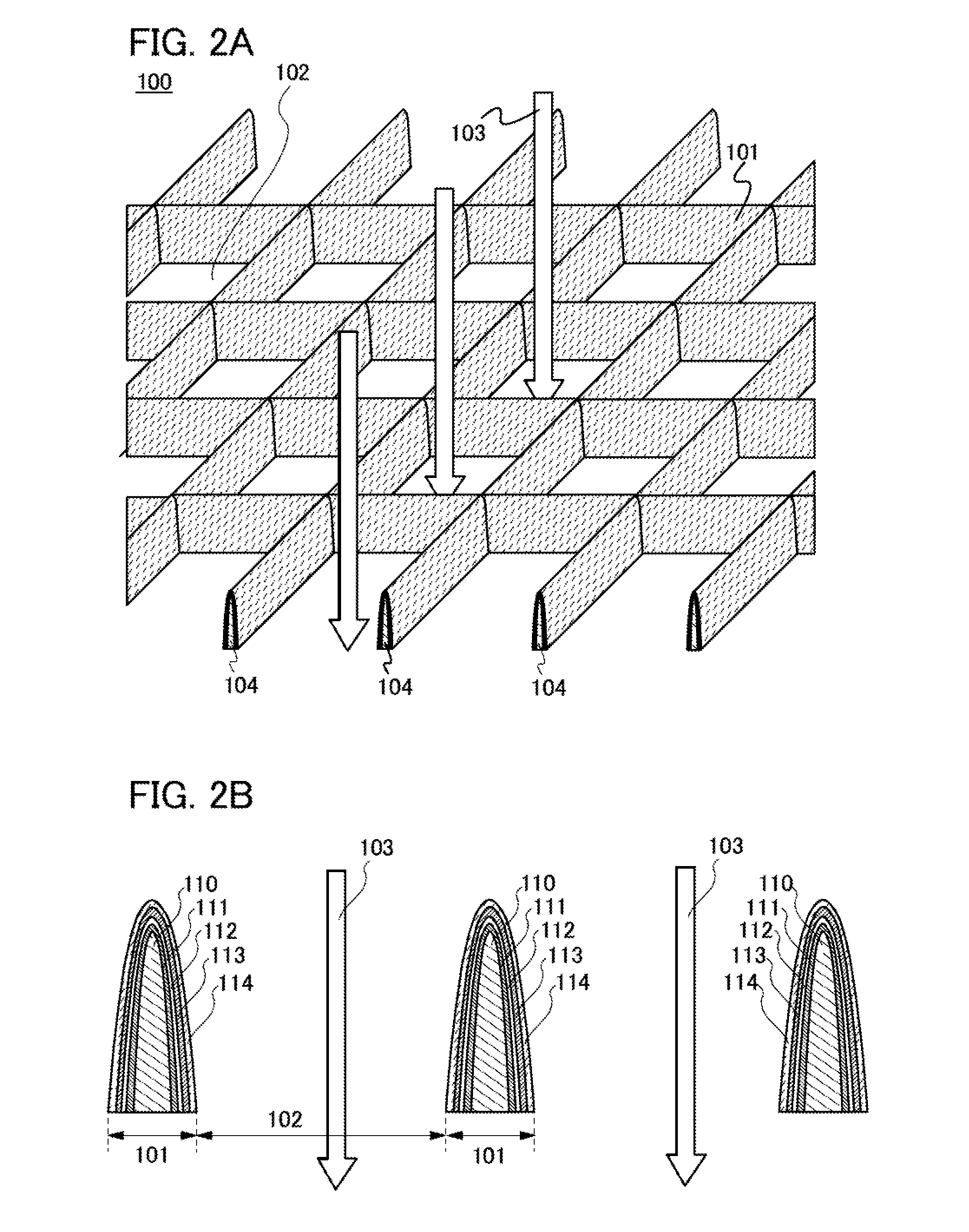

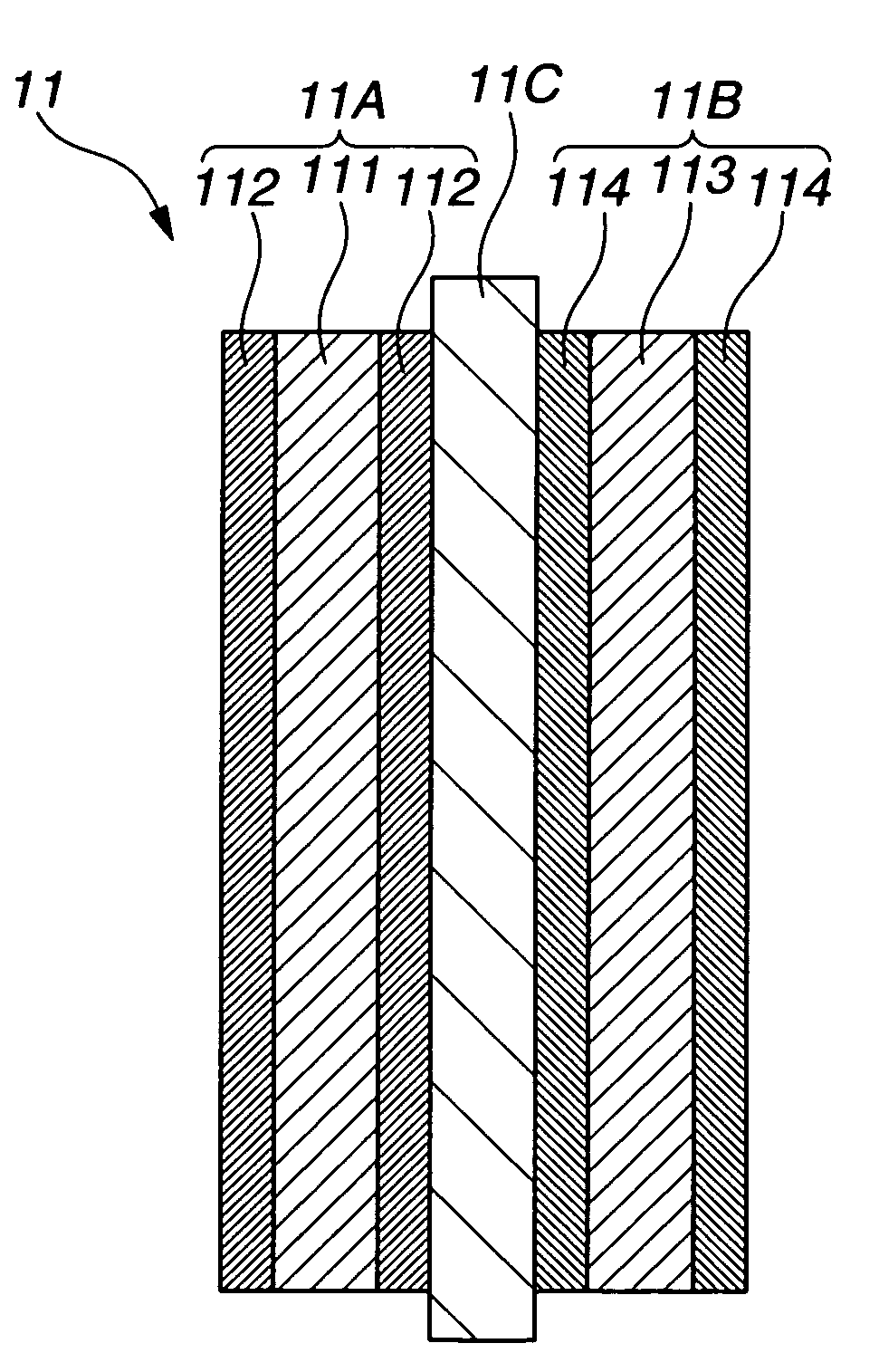

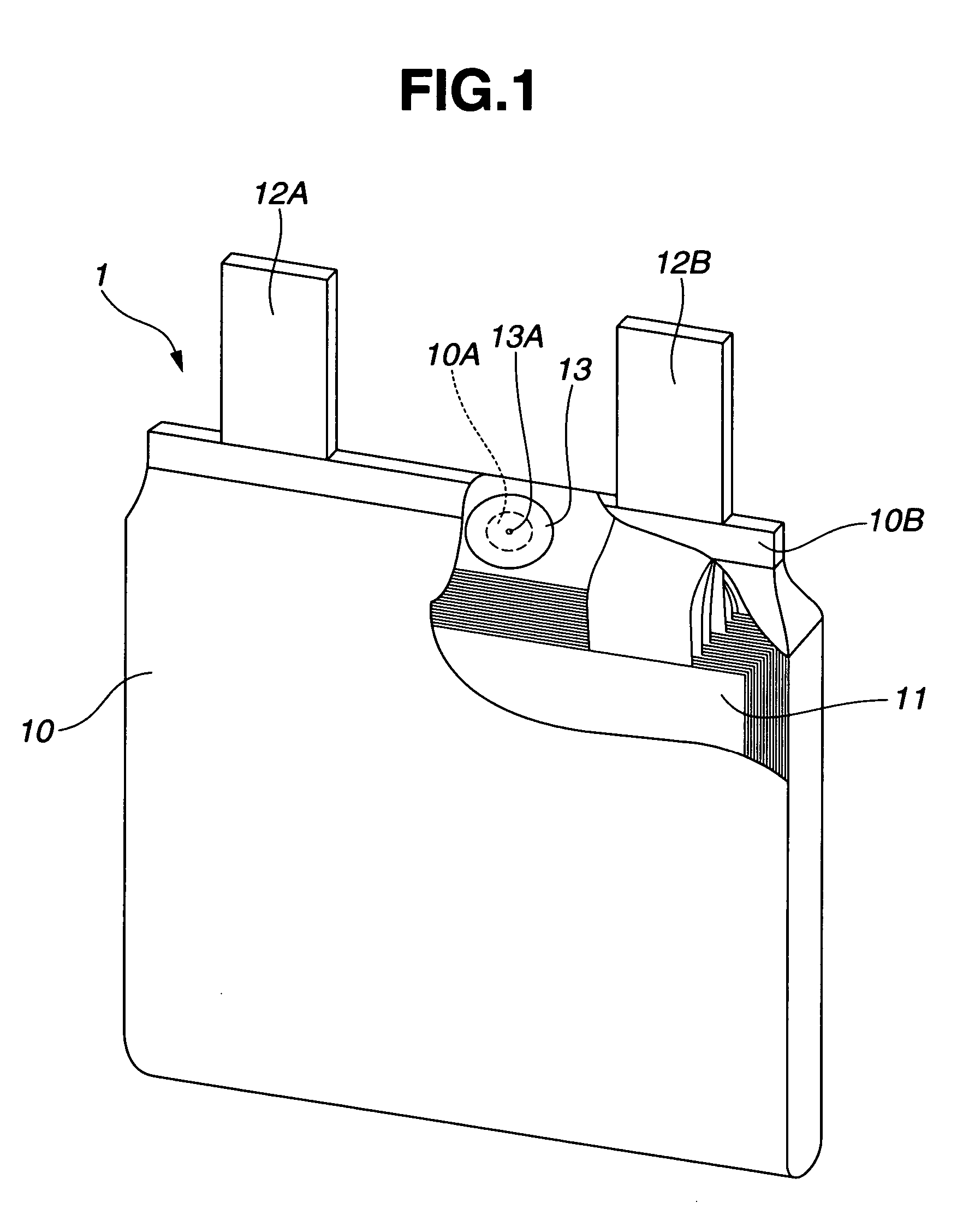

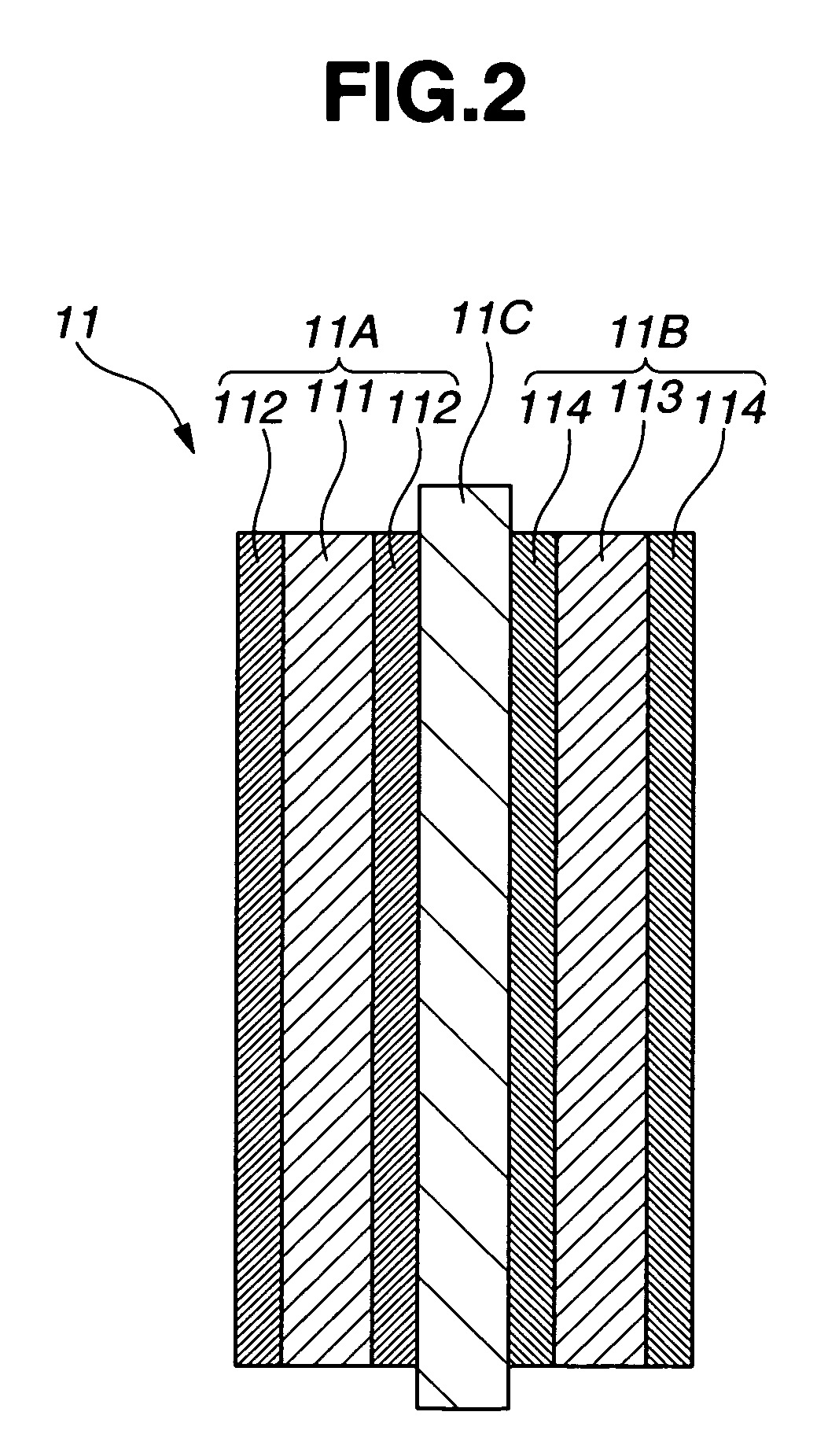

Power storage device and electric device

ActiveUS20130252089A1High strengthImprove securityHybrid capacitor electrodesElectrolytic capacitorsCapacitanceEngineering

Provided is a power storage device having a high discharge capacitance and a light-transmitting property. The power storage device includes a first current collector having a net-like planar shape; a first active material layer over the first current collector; a solid electrolyte layer over the first active material layer; a second active material layer over the solid electrolyte layer; and a second current collector over the second active material layer.

Owner:SEMICON ENERGY LAB CO LTD

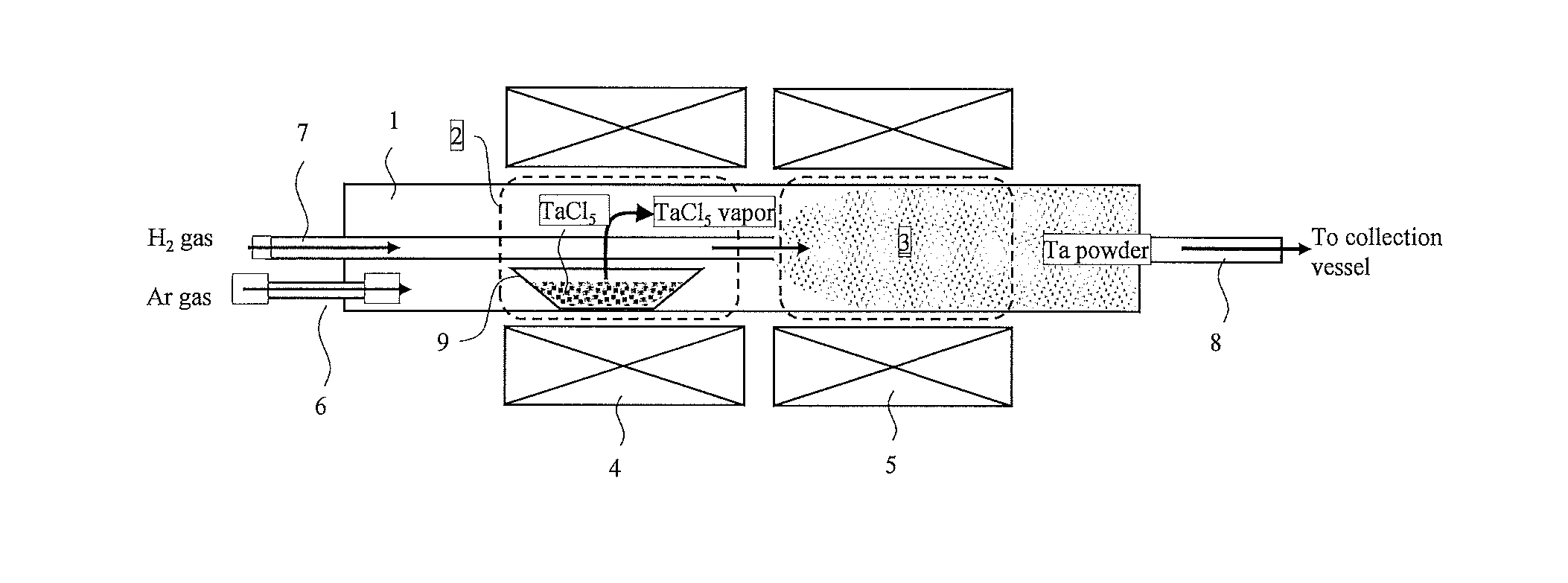

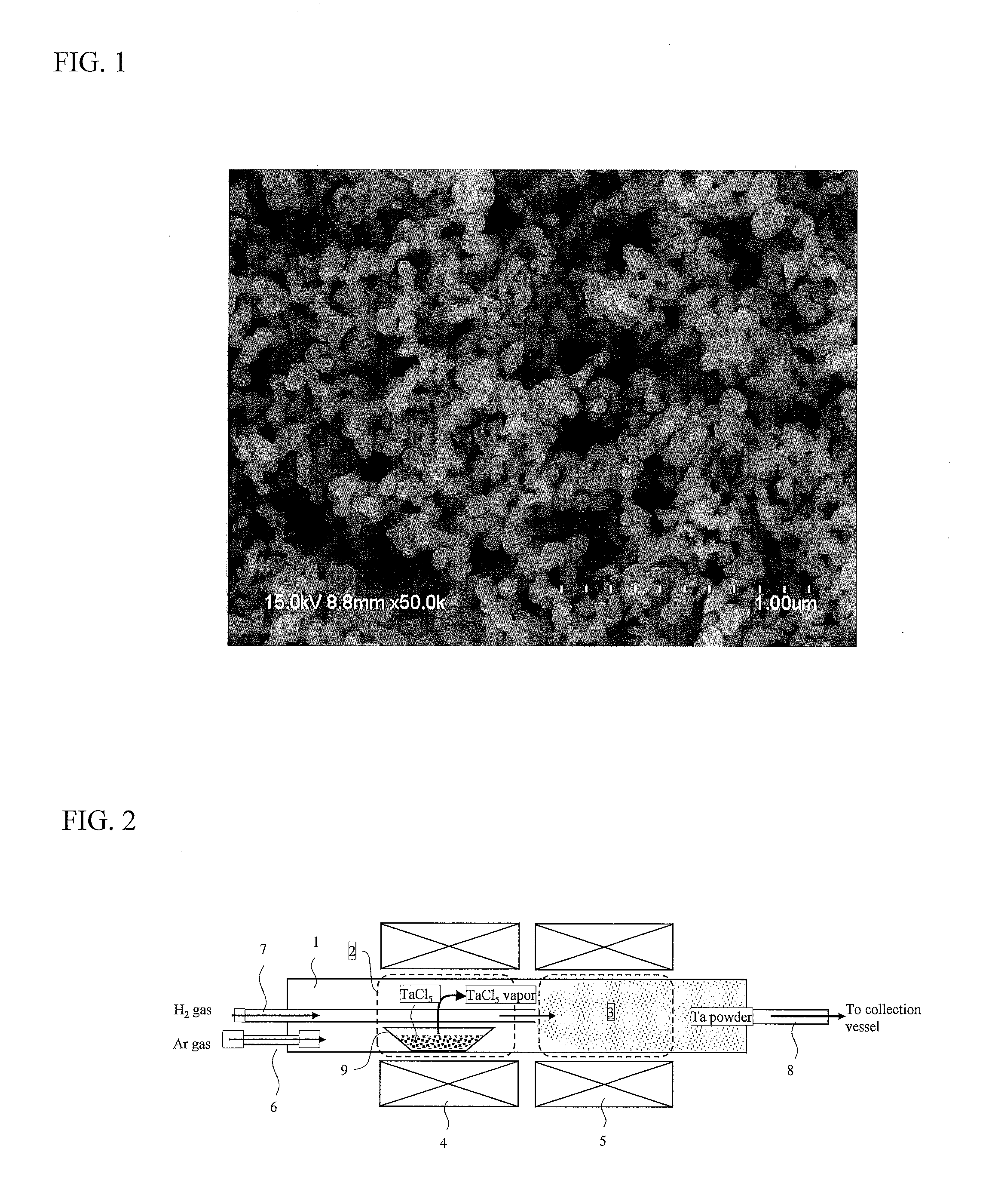

Ta powder, production method therefor, and ta granulated powder

InactiveUS20160104580A1Improved characteristicHigh electrostatic capacitySolid electrolytic capacitorsTransportation and packagingTACLSingle phase

Method of producing Ta powder for tantalum solid electrolytic capacitor capable of stably providing CV value of more than 220 k and to provide the Ta powder and its Ta granulated powder. In method of producing Ta powder by vaporizing TaCl5 through heating and reducing with H2 gas, the reduction is performed under conditions that feeding rate of TaCl5 vapor passing through section area of reaction field of 1 cm2 for 1 minute is 0.05˜5.0 g / cm2·min and residence time of TaCl5 vapor in the reduction reaction field is 0.1˜5 seconds and reduction temperature of TaCl5 is 1100˜1600° C., whereby Ta powder including a single phase of β-Ta of tetragonal system or mixed phase of β-Ta and α-Ta of cubic system and having average particle size of 30˜150 nm is obtained. Further, Ta granulated powder is obtained by granulating the Ta powder.

Owner:ISHIHARA CHEM

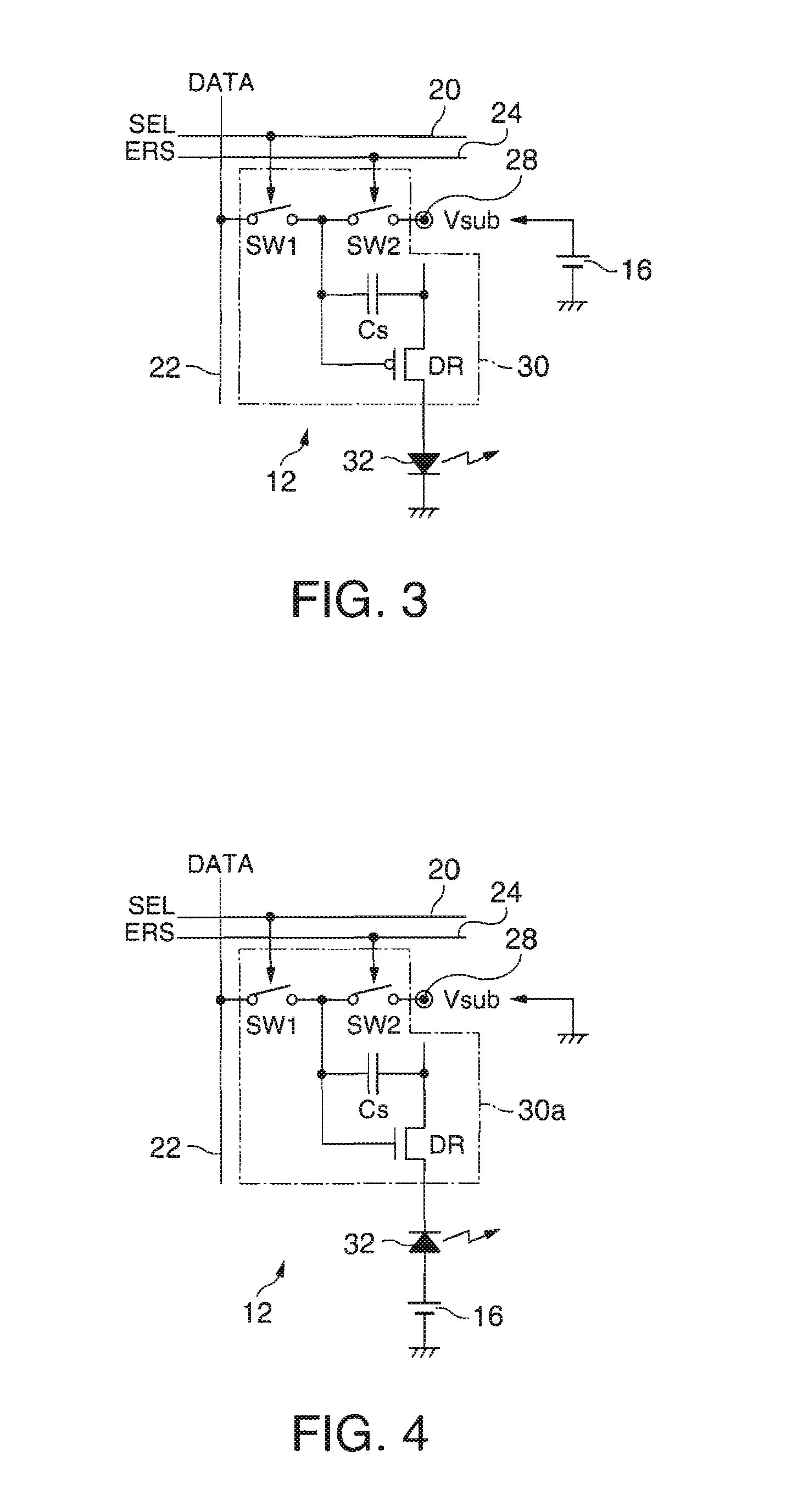

Electroluminescence device, manufacturing method thereof, and electronic apparatus

InactiveUS7435633B2Increase capacitanceReduce parasitic capacitanceElectroluminescent light sourcesSolid-state devicesEngineeringOrganic electroluminescence

An organic electroluminescence device including: a substrate having conductivity on at least one side; a first insulation film, formed on one side of the substrate, while having an aperture which partially exposes the same side of the substrate; a semiconductor film, formed on the first insulation film, while covering a part of the first insulation film; a second insulation film formed on the first insulation film, while covering the semiconductor film and contacting the same side of the substrate via the aperture; a capacitor electrode, formed on the aperture, while sandwiching the second insulation film so as to face the substrate; a gate electrode formed on the semiconductor film, so as to sandwich the second insulation film; and an organic electroluminescence element, formed on the second insulation film, electrically connected to the semiconductor film.

Owner:SEIKO EPSON CORP

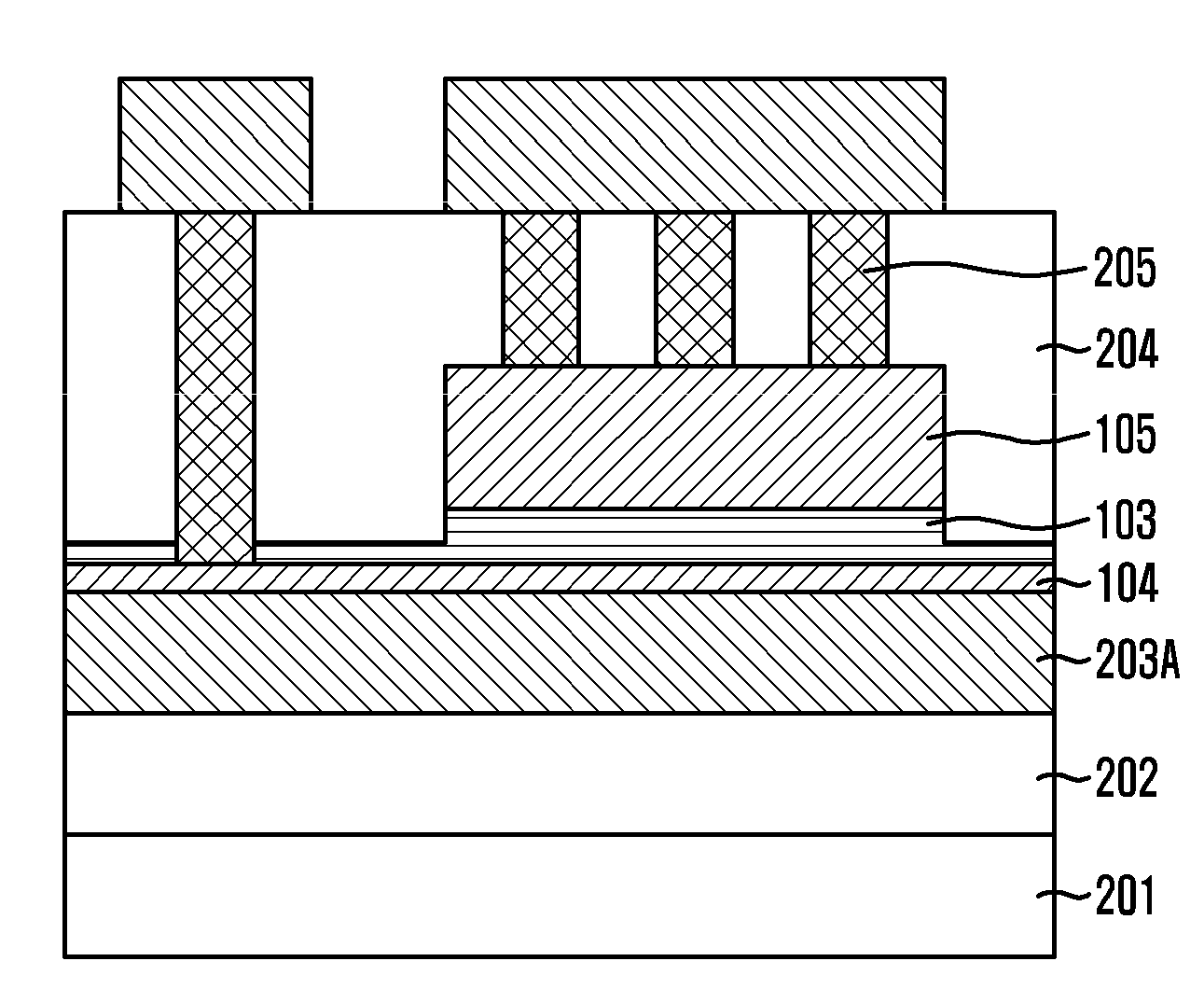

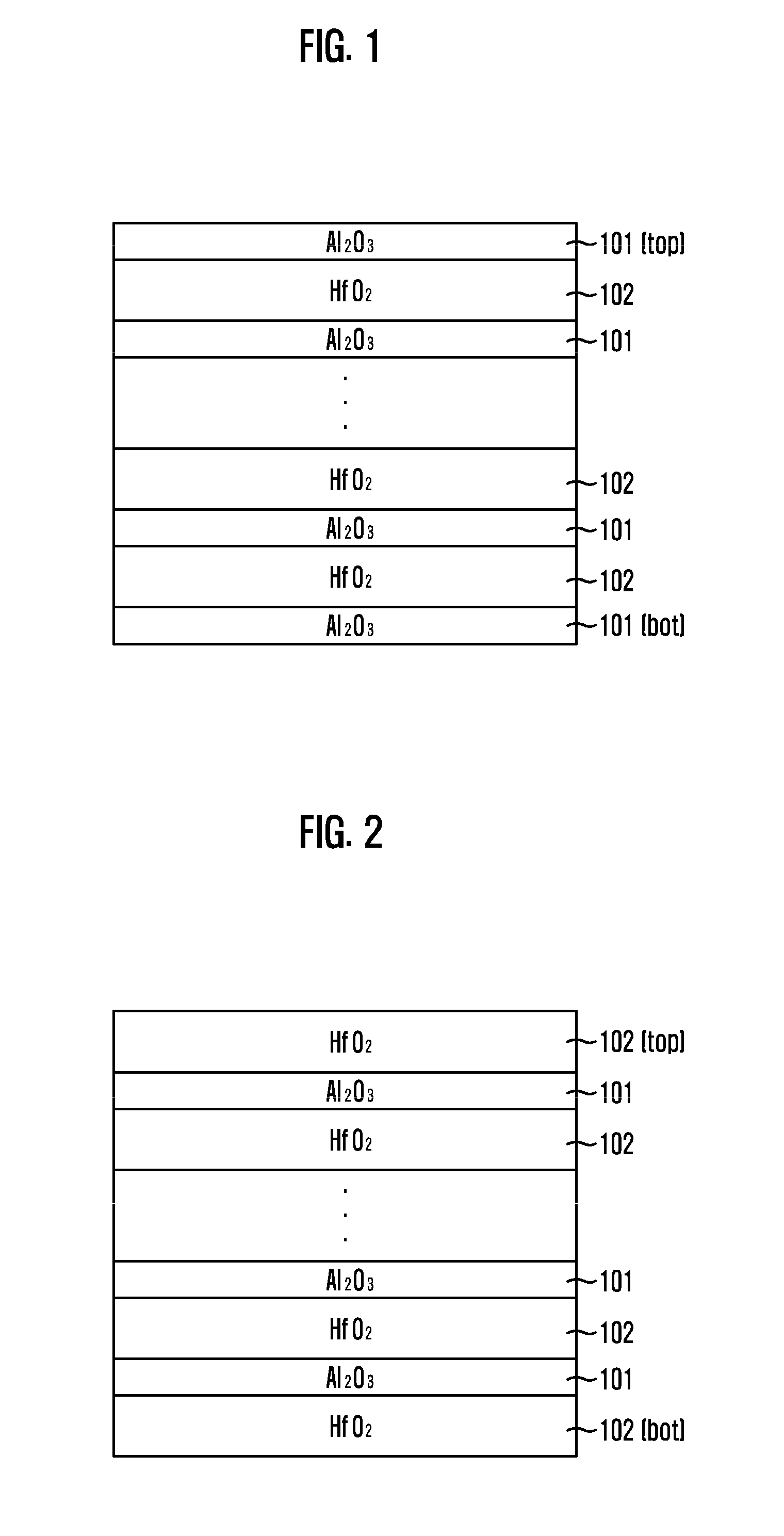

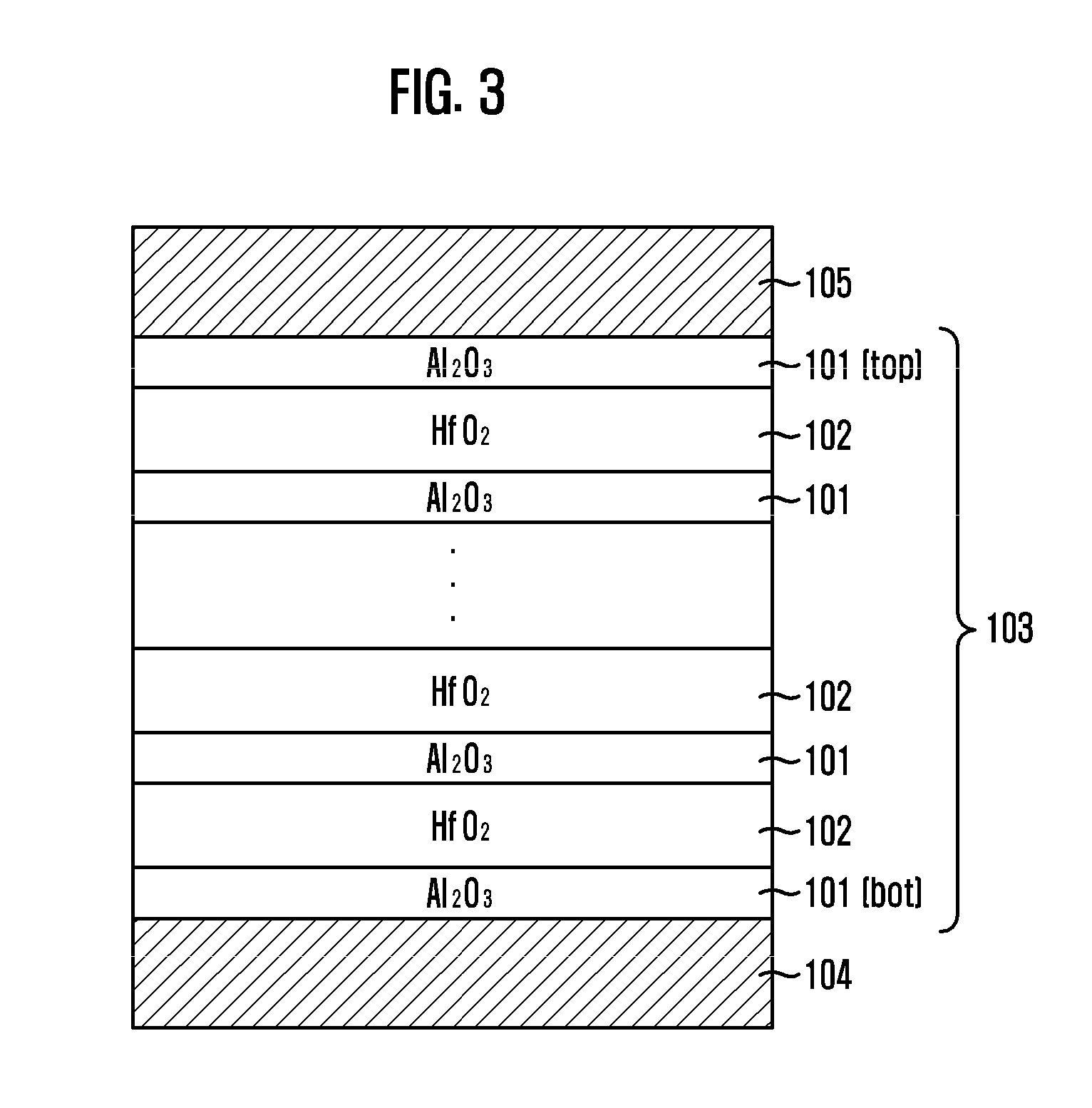

Insulator, capacitor with the same and fabrication method thereof, and method for fabricating semionductor device

ActiveUS20100091428A1High capacitanceGood leakage current characteristicSemiconductor/solid-state device detailsSolid-state devicesEngineeringMetal-insulator-metal

Disclosed is a multilayer insulator, a metal-insulator-metal (MIM) capacitor with the same, and a fabricating method thereof. The capacitor includes: a first electrode; an insulator disposed on the first electrode, the insulator including: a laminate structure in which an aluminum oxide (Al2O3) layer and a hafnium oxide (HfO2) layer are laminated alternately in an iterative manner and a bottom layer and a top layer are formed of the same material; and a second electrode disposed on the insulator.

Owner:KEY FOUNDRY CO LTD

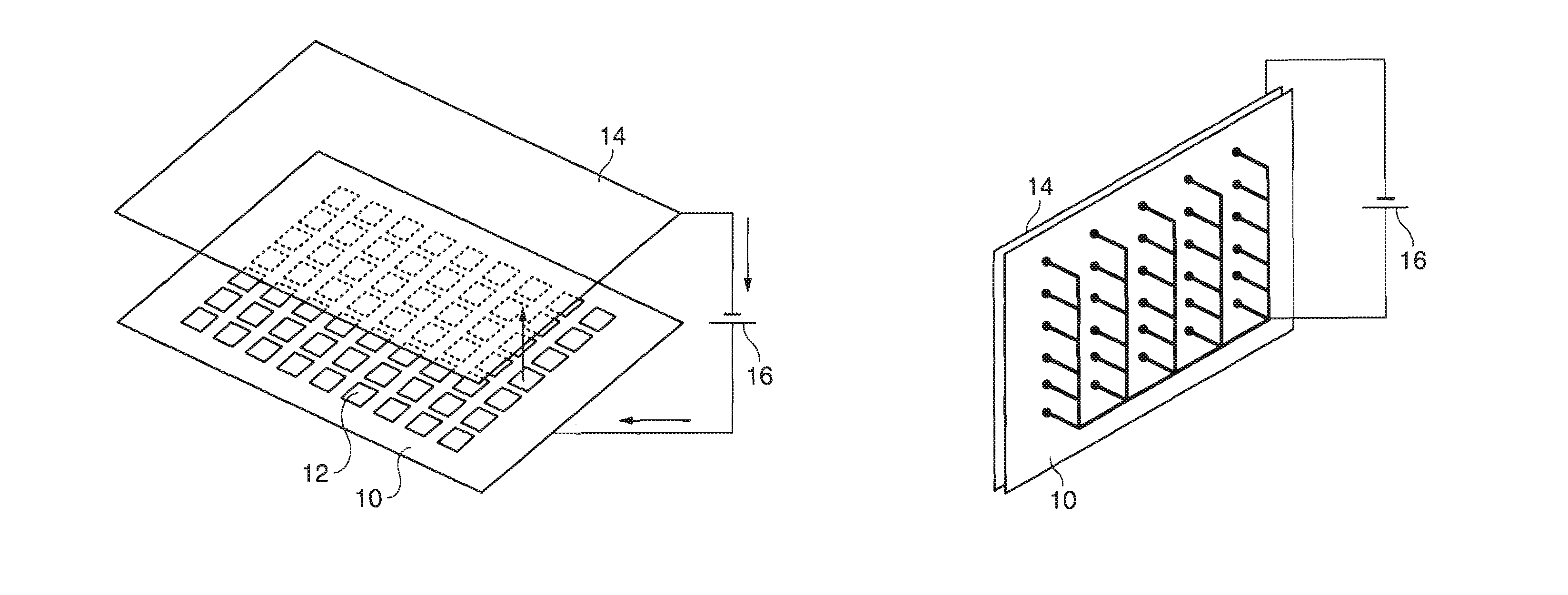

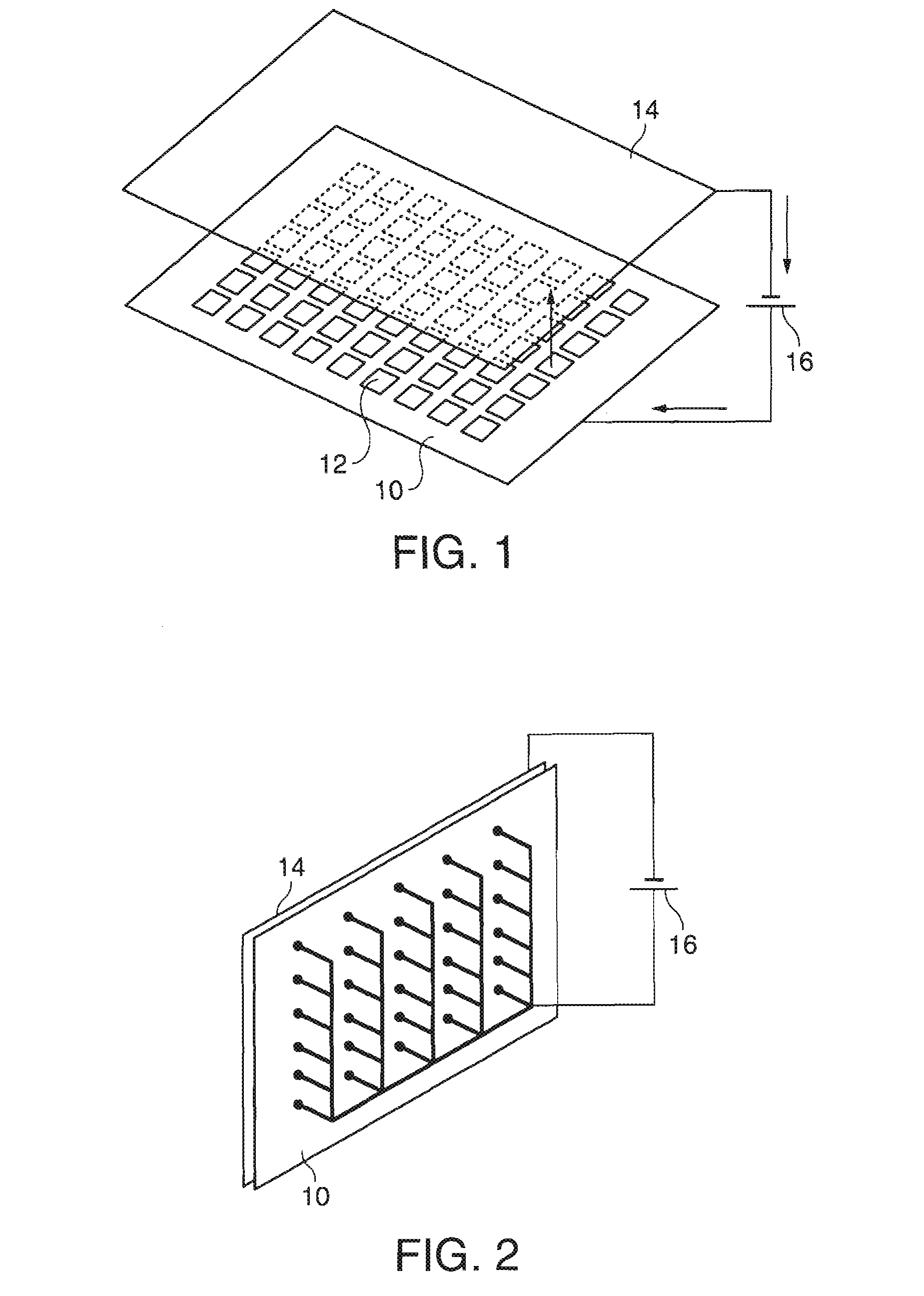

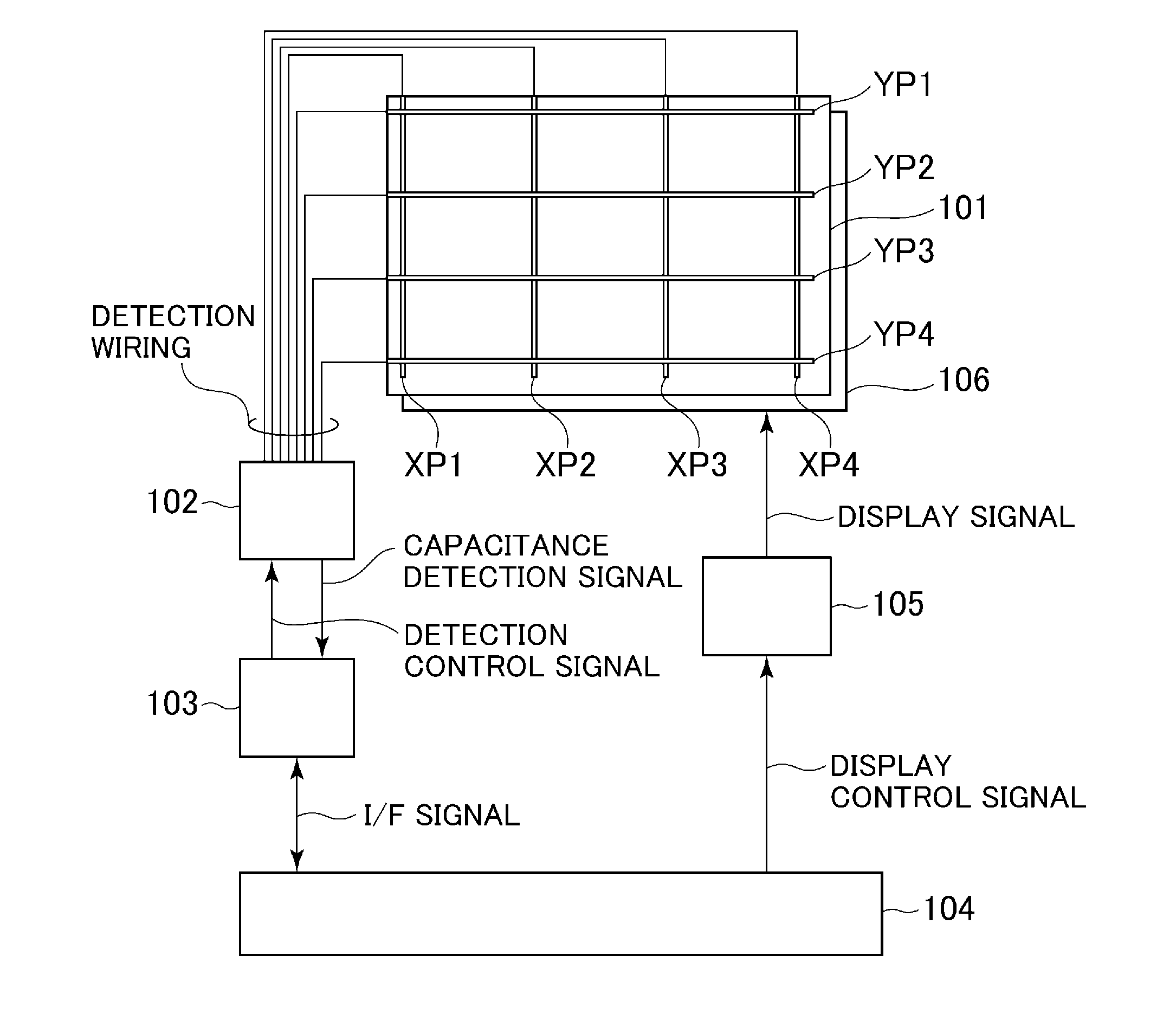

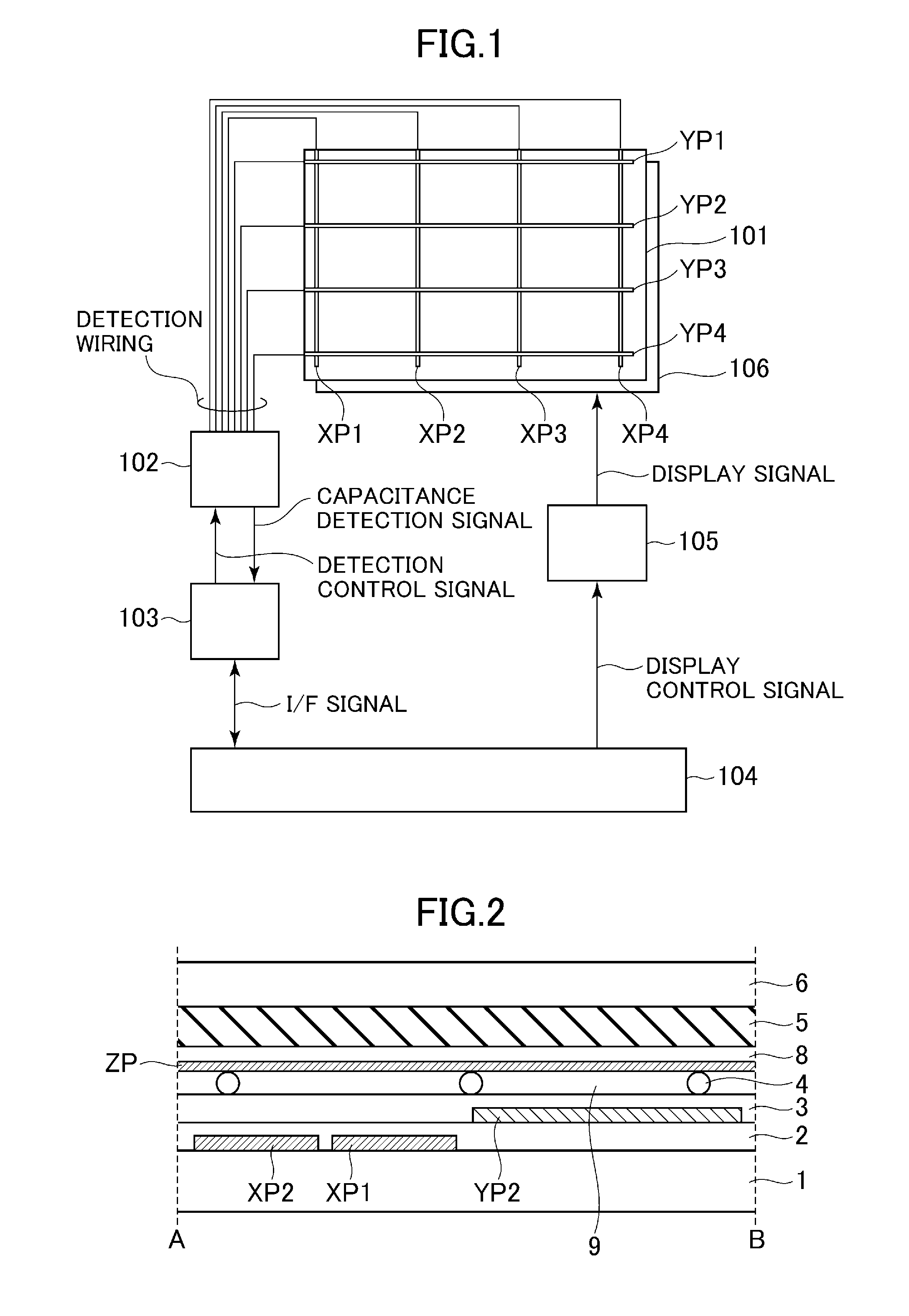

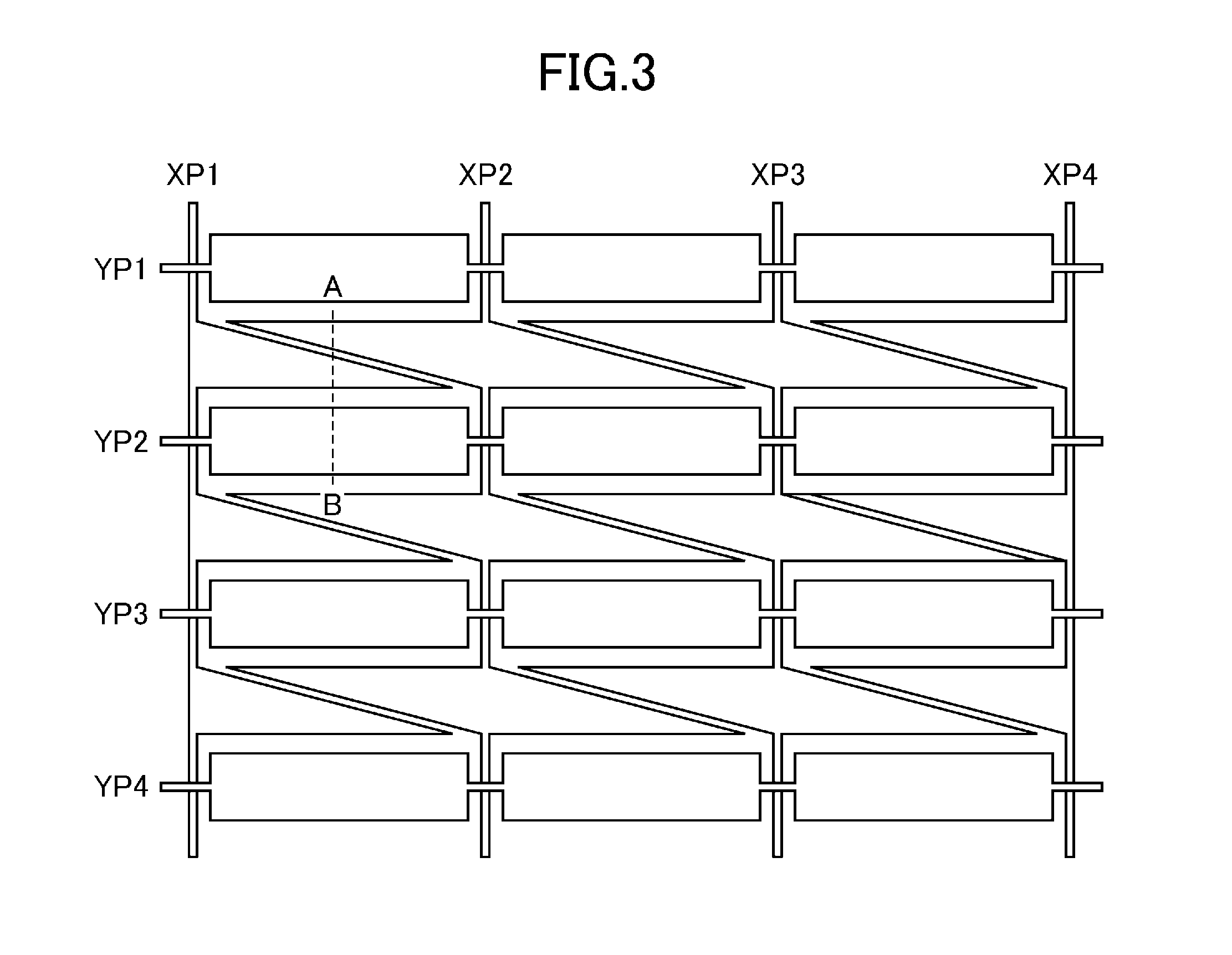

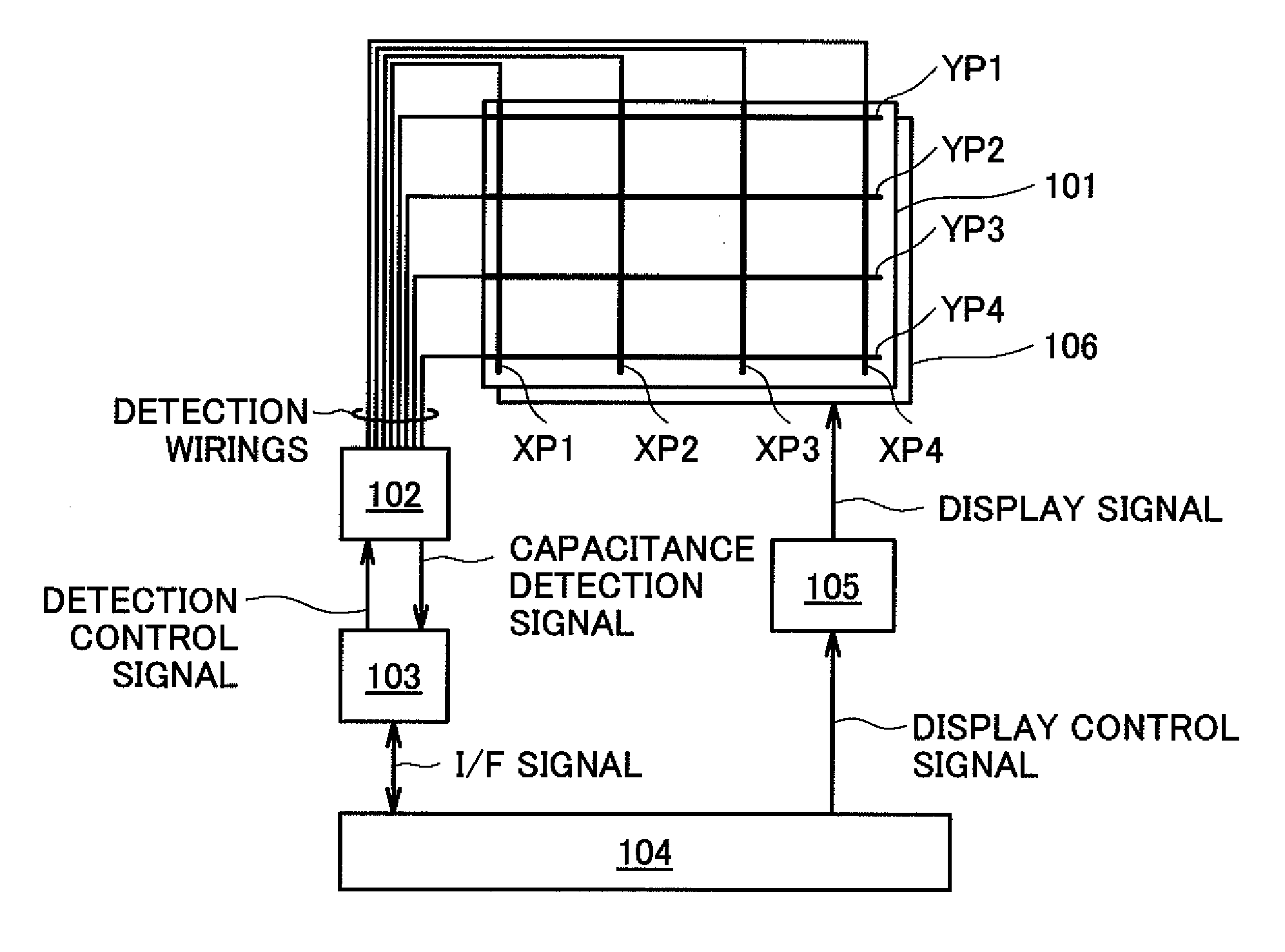

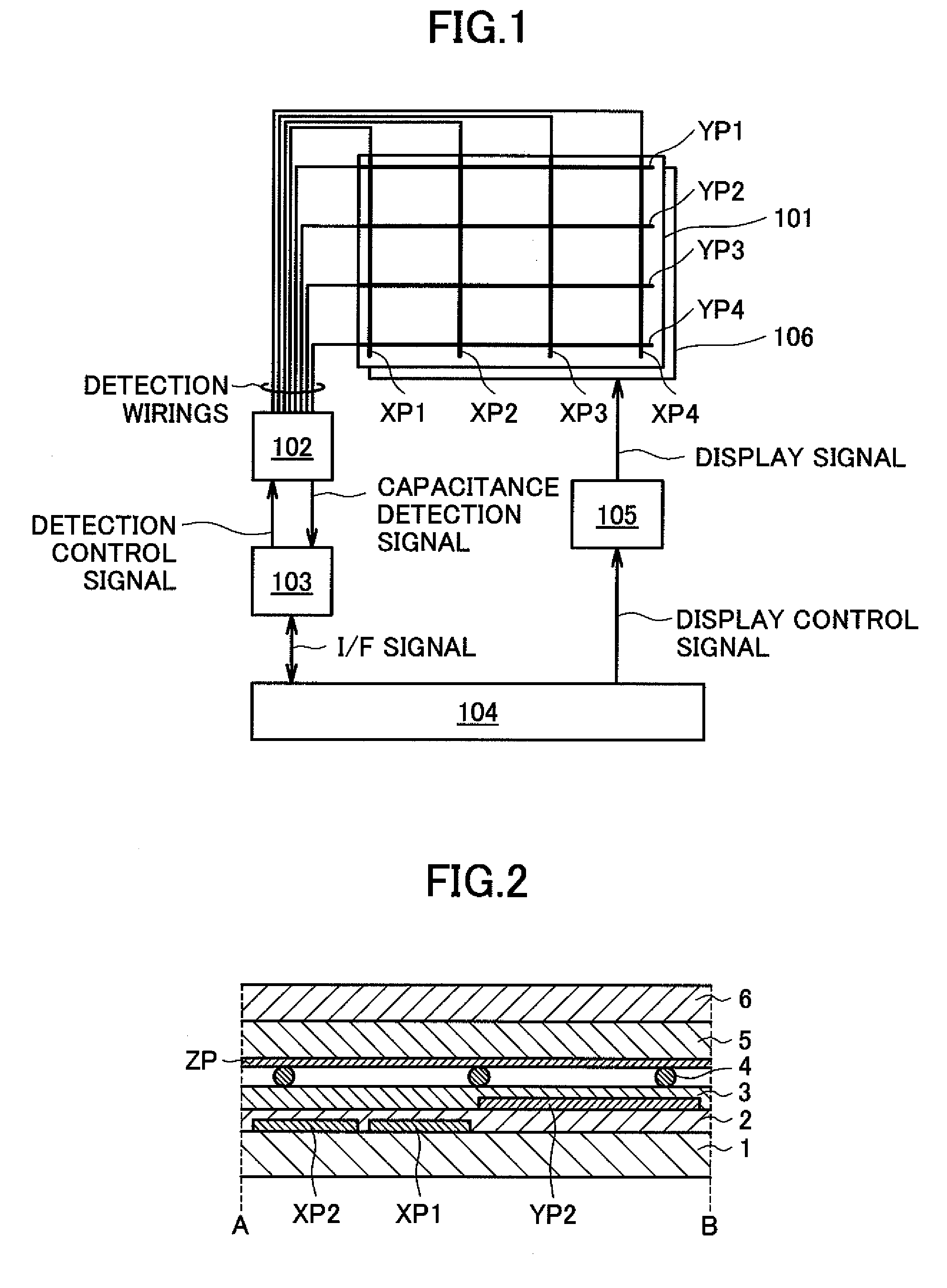

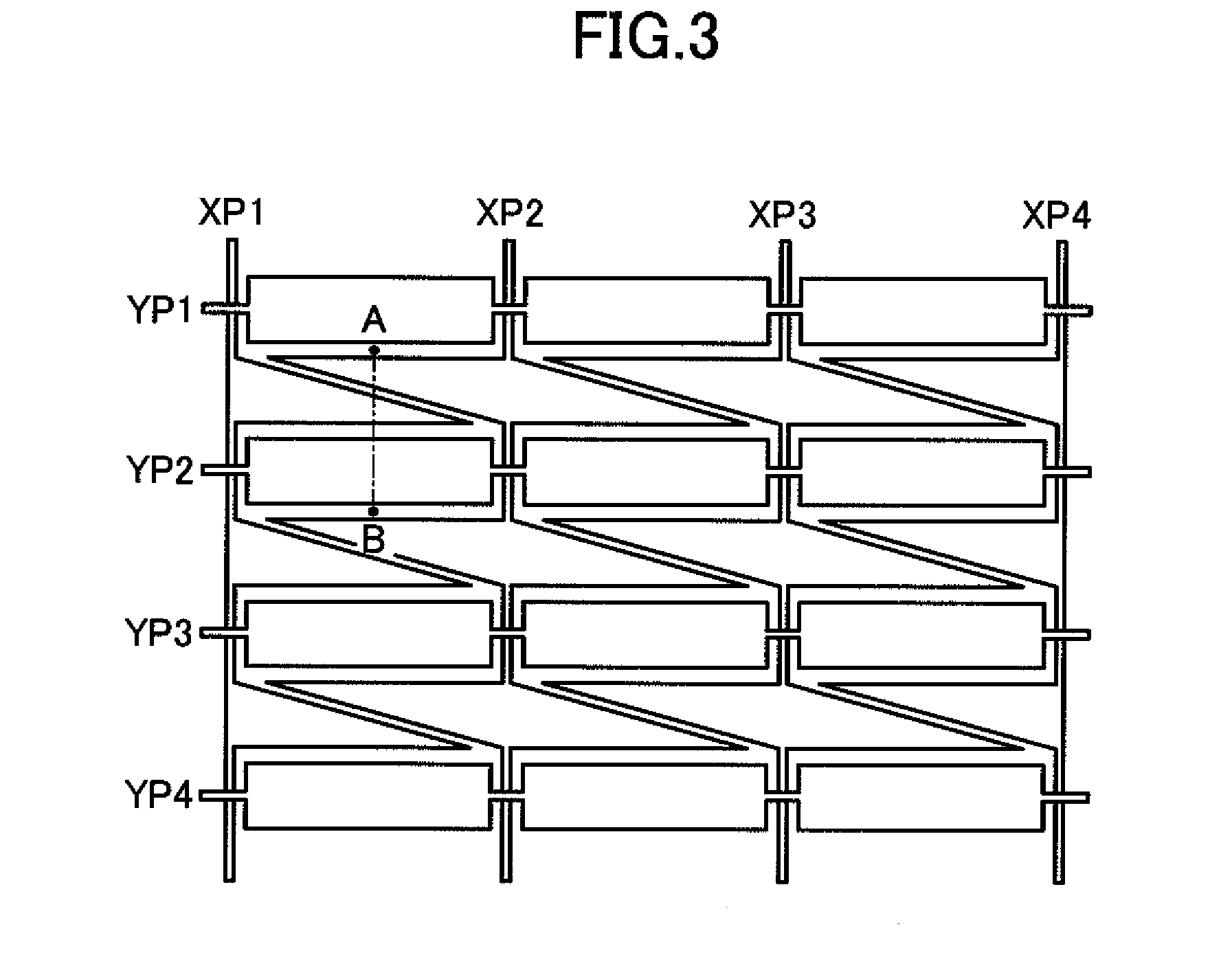

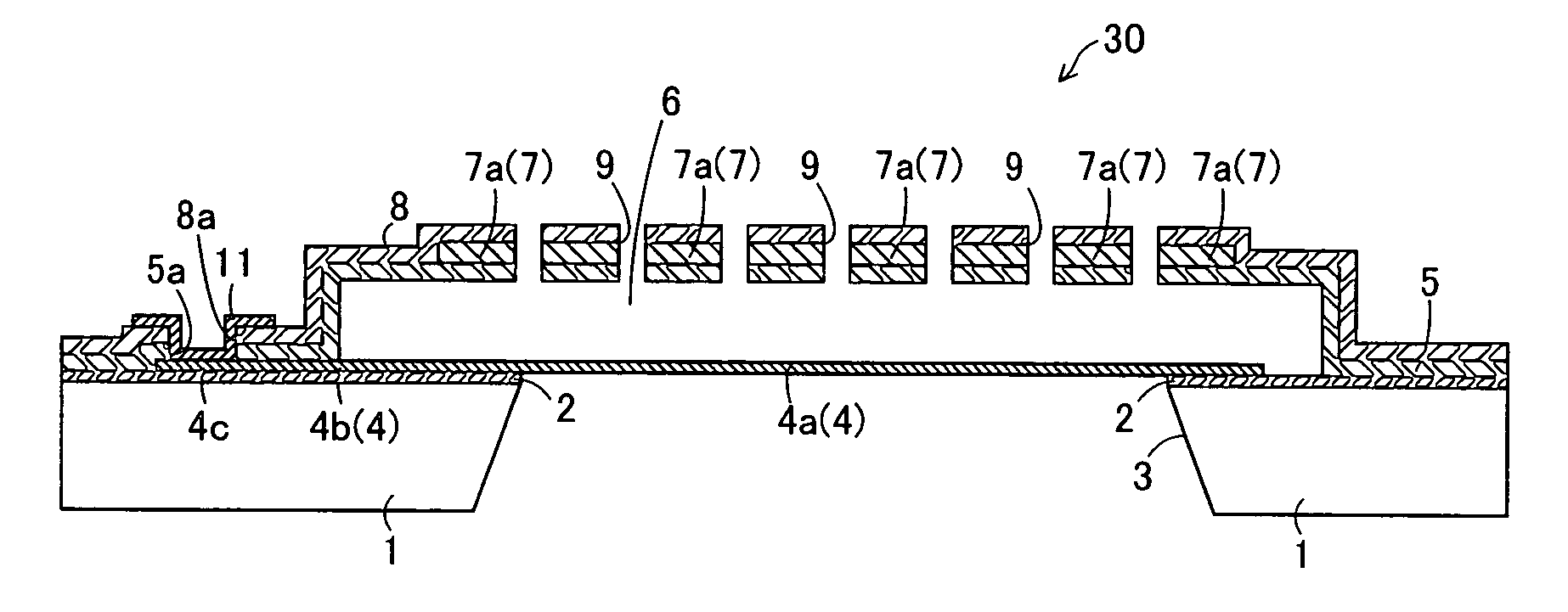

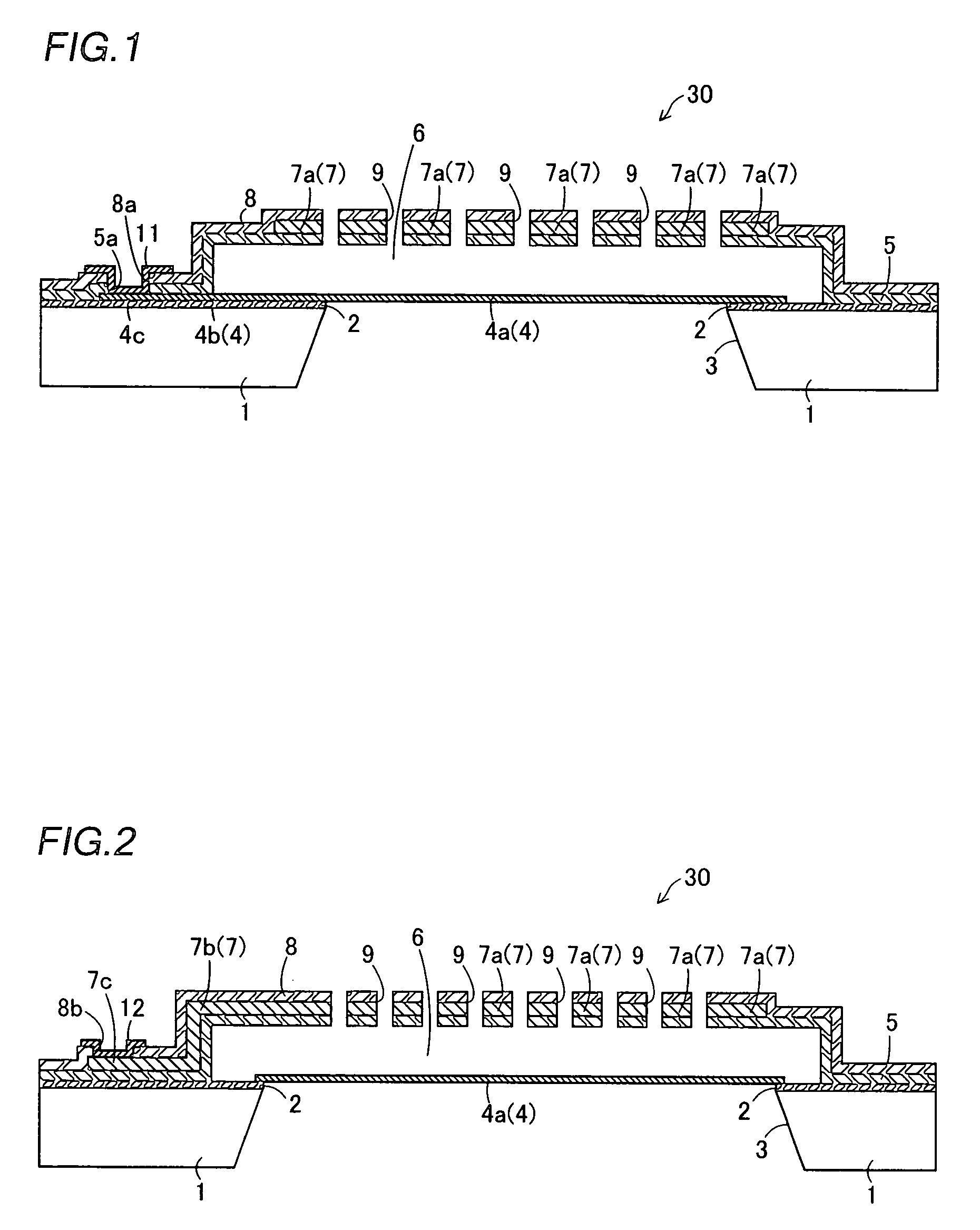

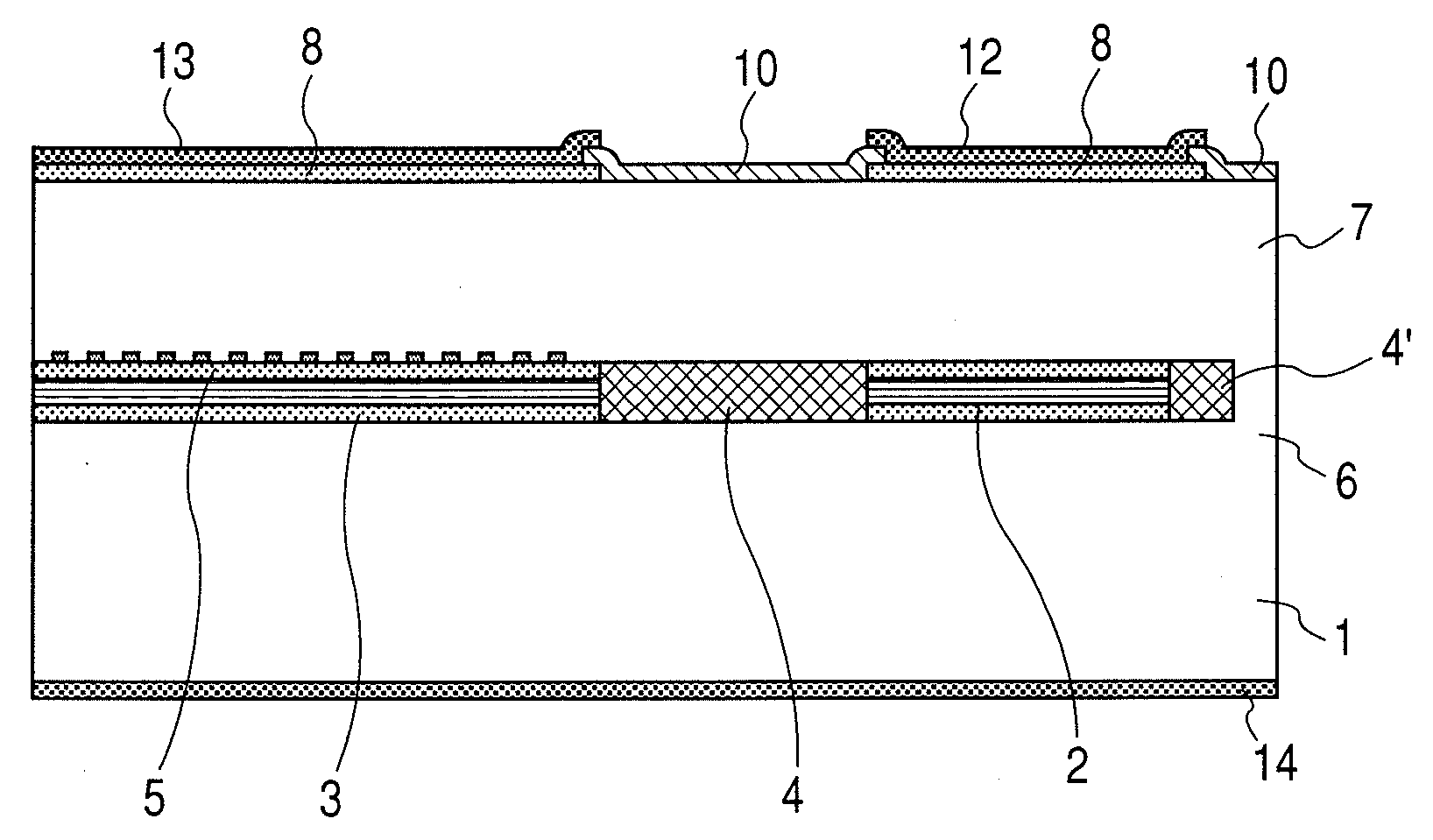

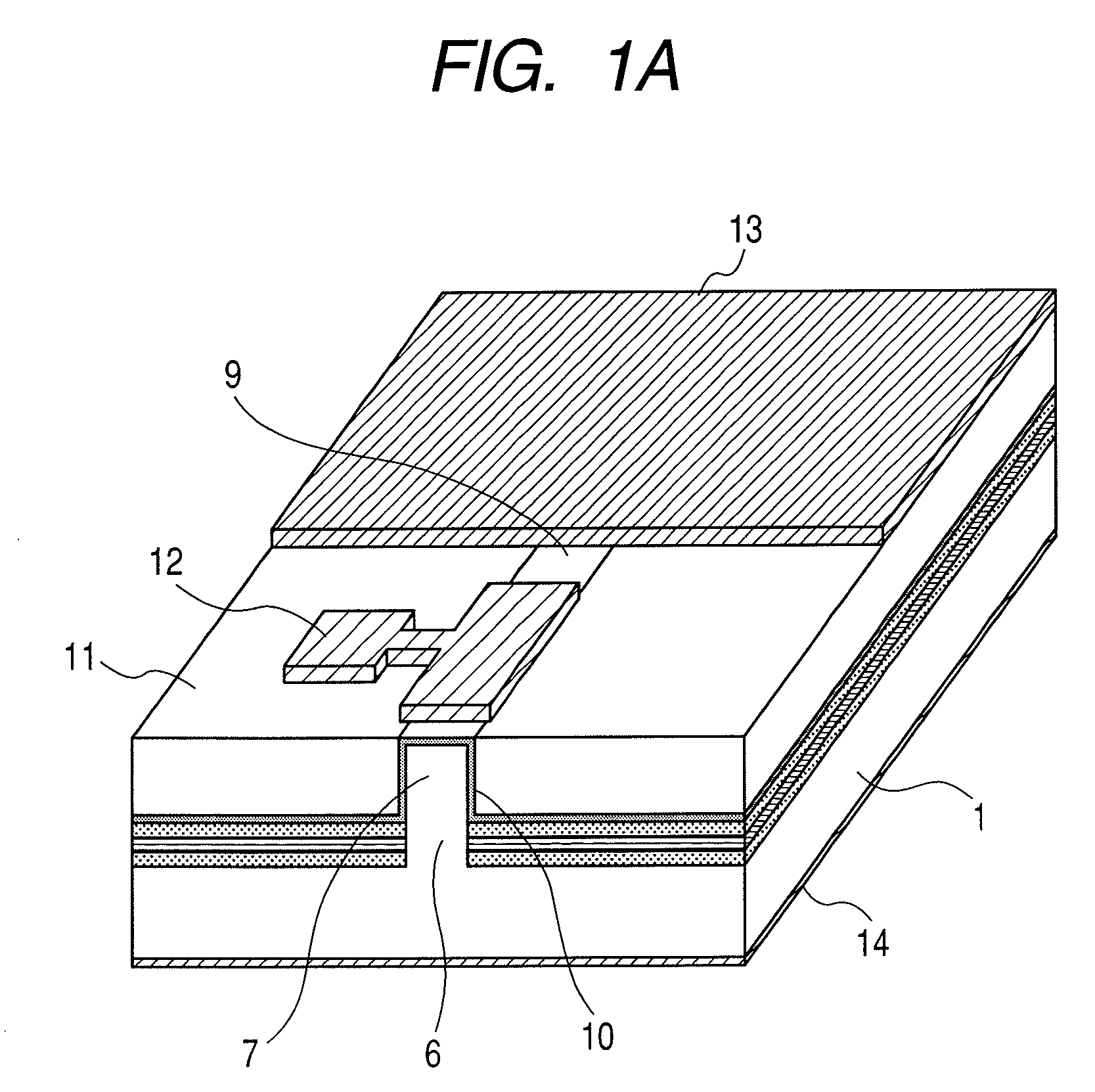

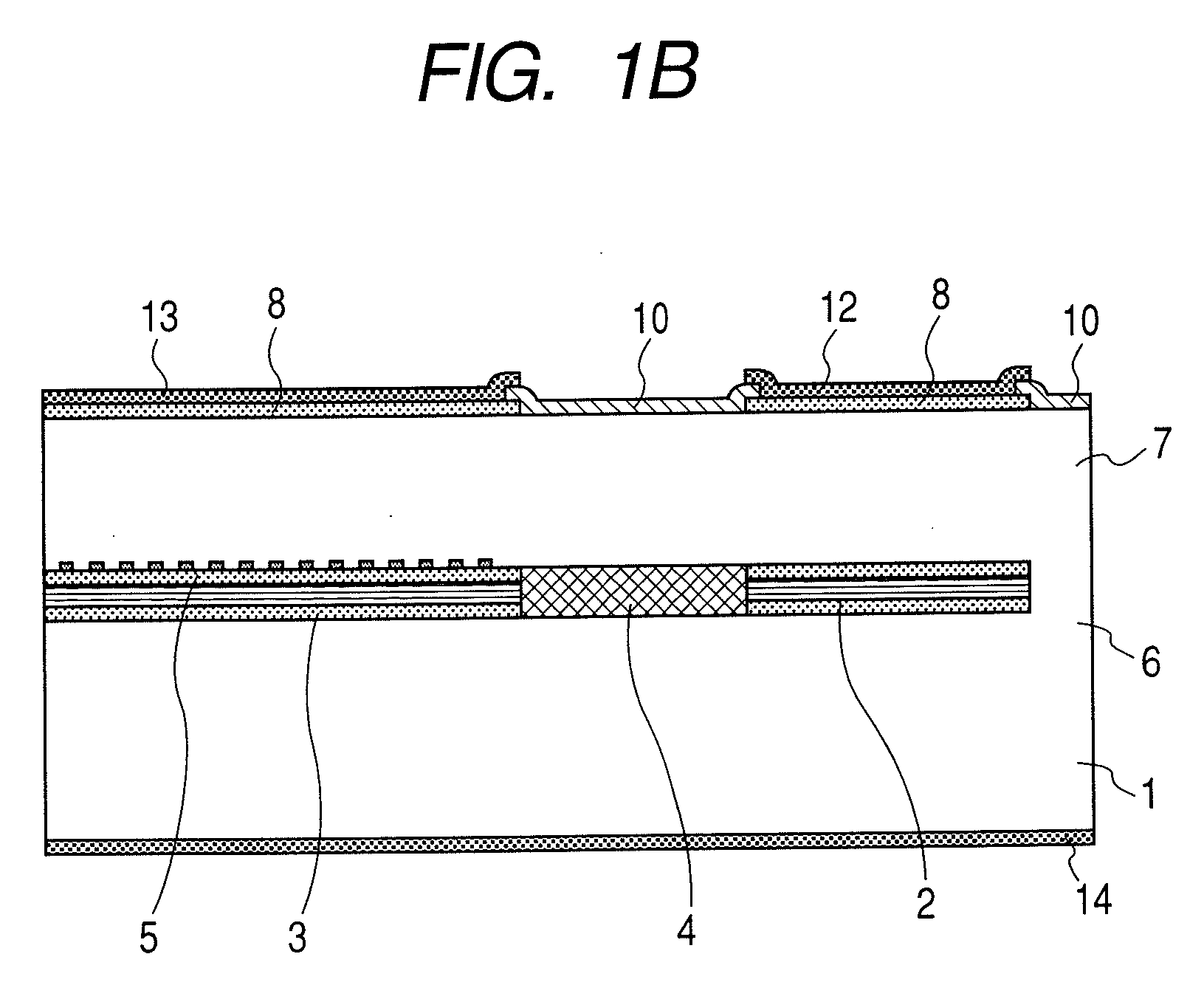

Touch panel and display device using the same

InactiveUS20110181548A1High capacitanceAvoid crackingInput/output processes for data processingCapacitanceCapacitive coupling

Provided is a capacitive coupling type touch panel, including: a plurality of coordinate detection electrodes (XP1, XP2, YP) for detecting X-Y position coordinates; a first substrate including the plurality of coordinate detection electrodes; and a second substrate (6) disposed to be opposed to the first substrate, in which: the capacitive coupling type touch panel further includes, between the first substrate (1) and the second substrate (6): a conductive layer (ZP) having conductivity; a nonconductive layer (8) supporting the conductive layer; a plurality of nonconductive spacers (4) that are formed at intervals in a plane direction of the first substrate and the second substrate; and an elastic layer (5) that is lower in rigidity than the first substrate, the second substrate, and the plurality of nonconductive spacers.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

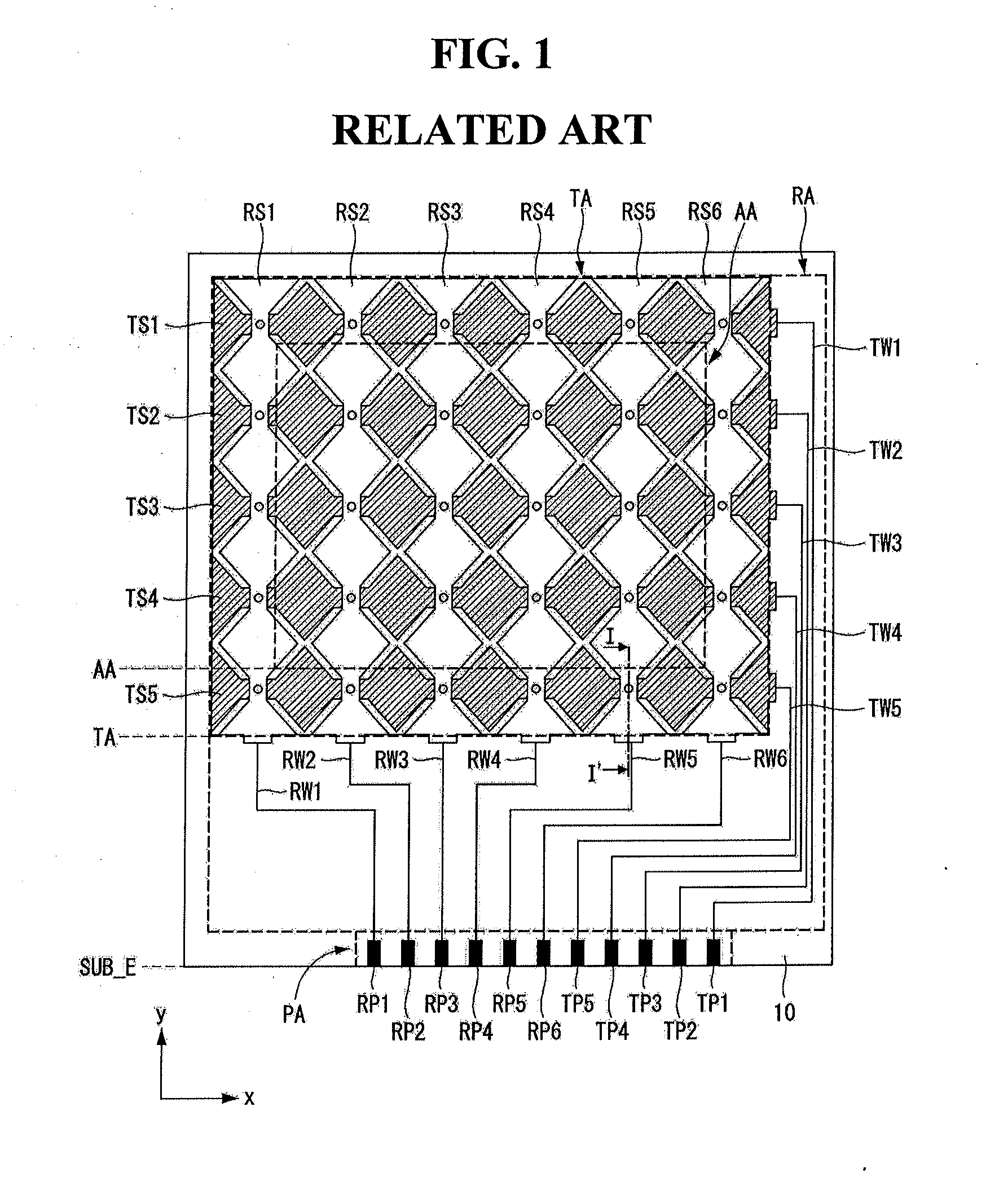

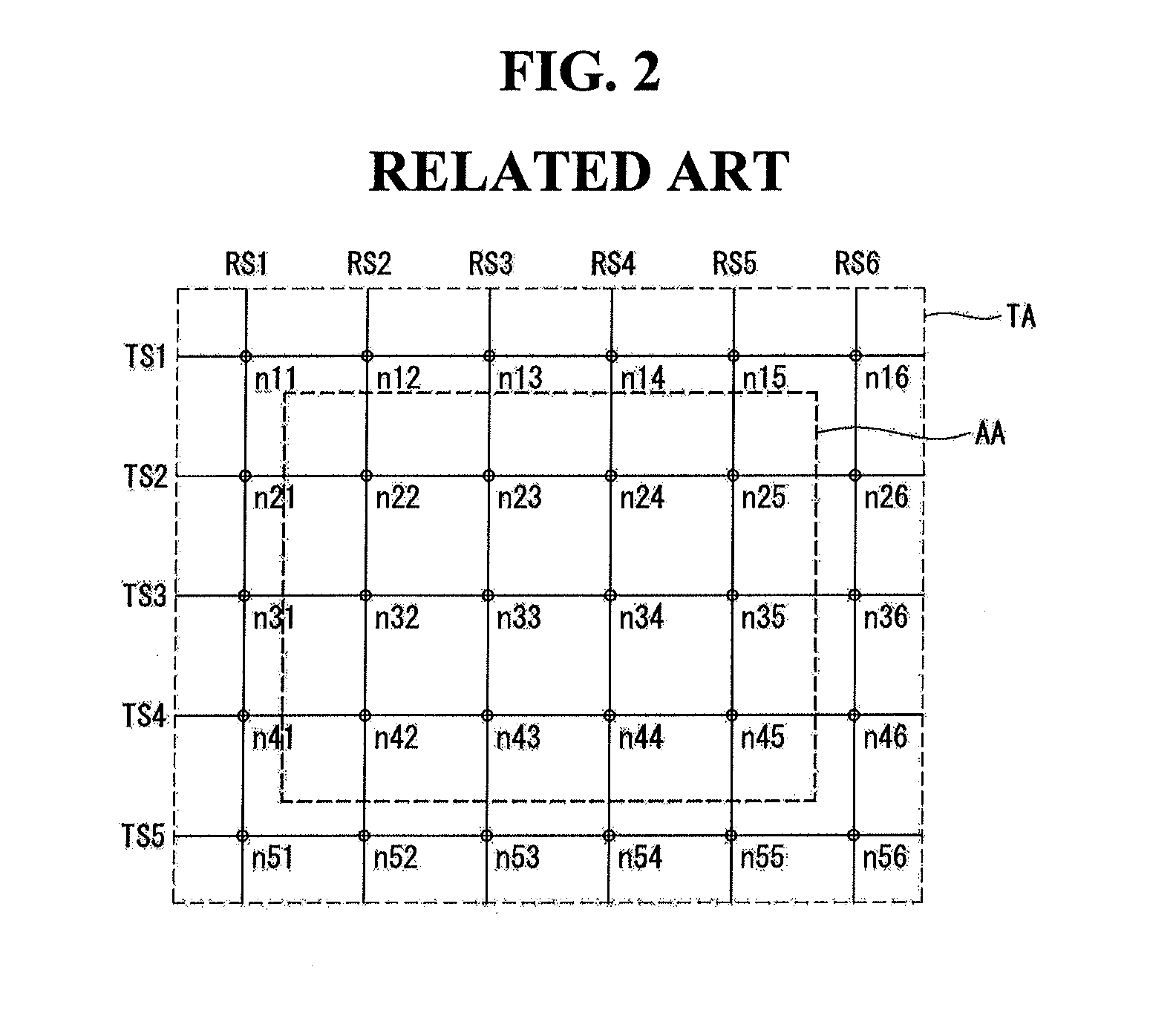

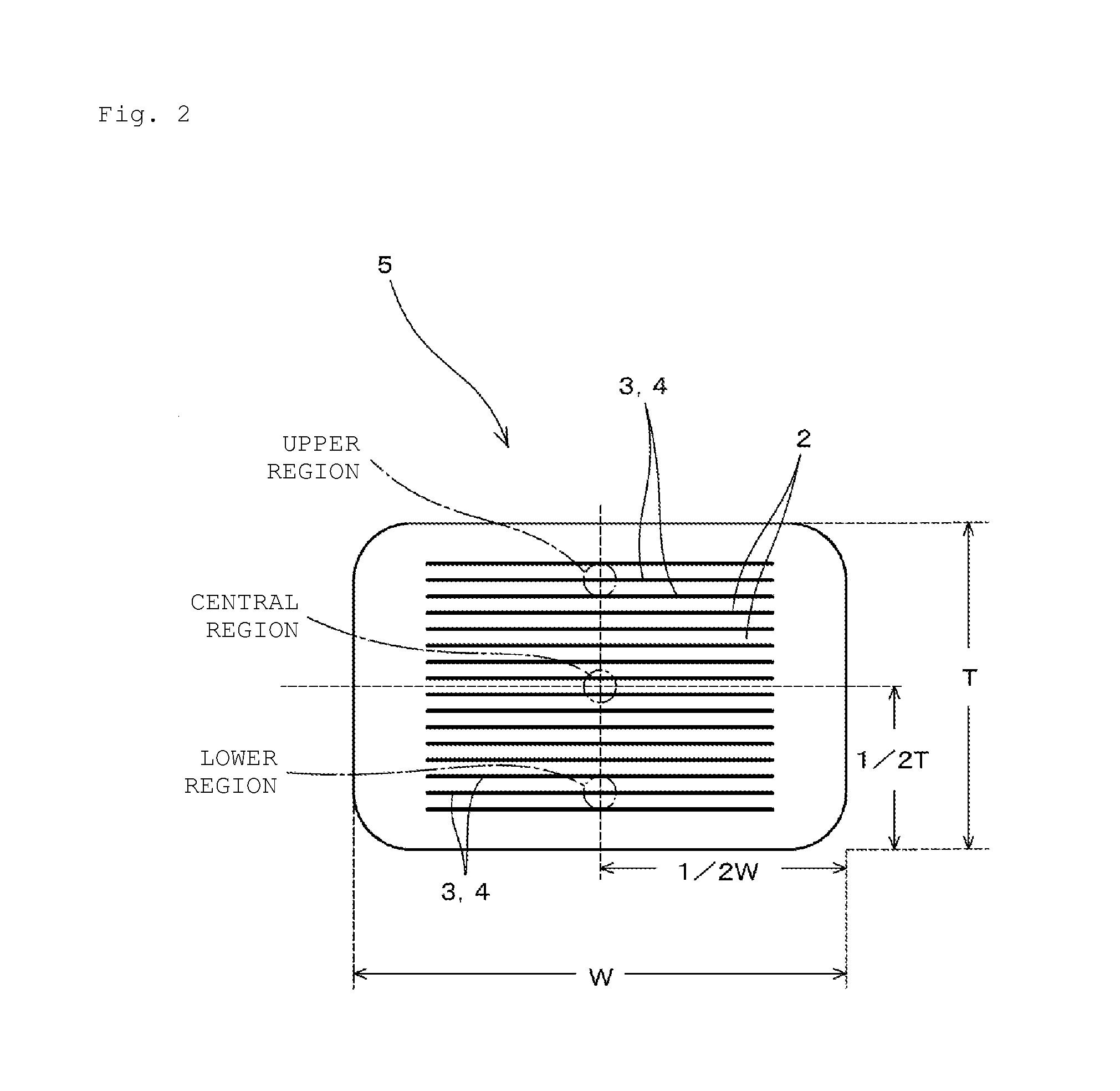

Electrostatic capacitive touch-sensitive panel for display device

ActiveUS20150060256A1Improve touch accuracyMinimize the differenceElectronic switchingInput/output processes for data processingDisplay deviceElectrode

An electrostatic capacitive touch-sensitive panel has an active area; a touch electrode forming area; a routing wire forming area disposed; a plurality of first touch electrode lines disposed in the active area, with both ends extending to a plurality of electrode pattern extension regions; a plurality of second touch electrode lines disposed in the active area to cross the first direction so as to cross the first touch electrode lines without contact; a plurality of first routing wires connected to the plurality of first touch electrode lines, respectively; and a plurality of second routing wires connected to the plurality of second touch electrode lines, respectively. Each of the second touch electrode lines includes a plurality of second touch electrode patterns and a plurality of second connecting portions connecting neighboring second touch electrode patterns. The second touch electrode pattern has an asymmetrical portion.

Owner:LG DISPLAY CO LTD

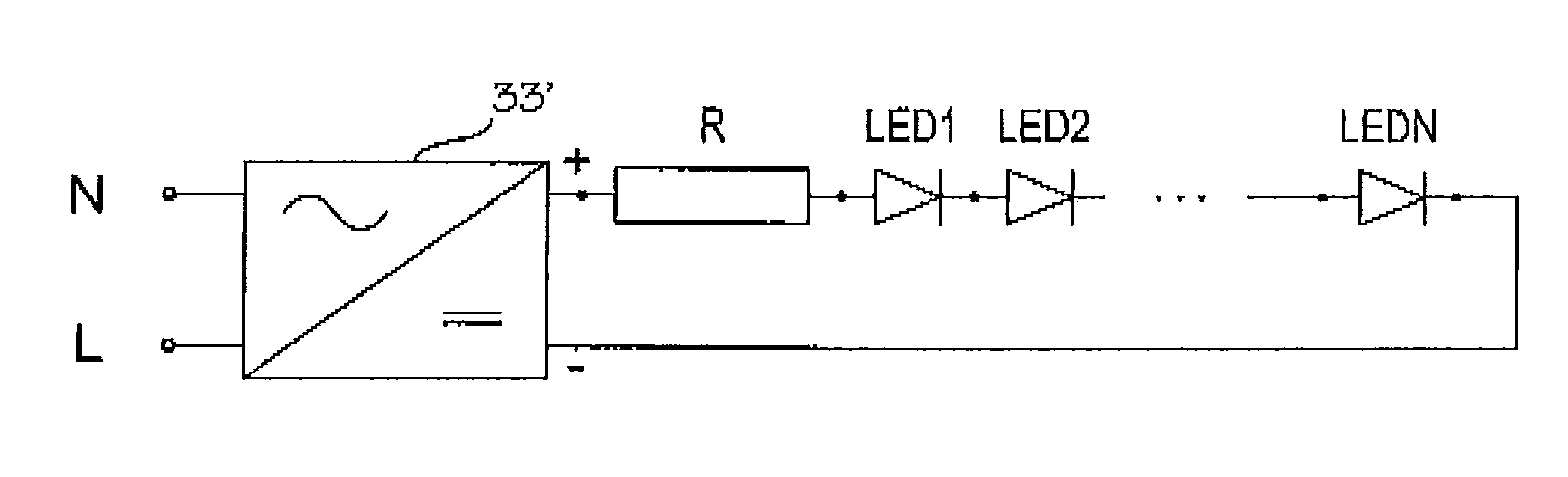

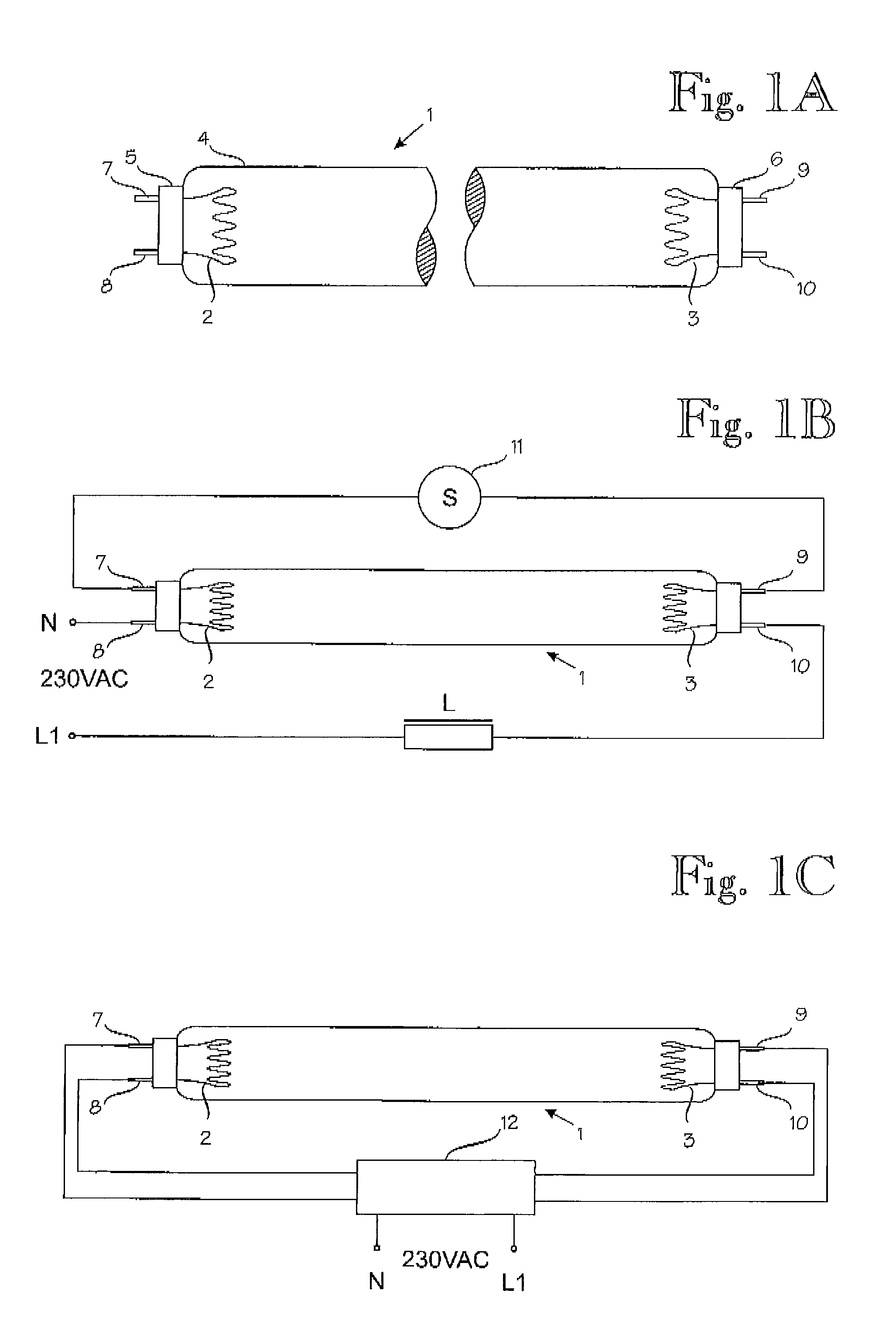

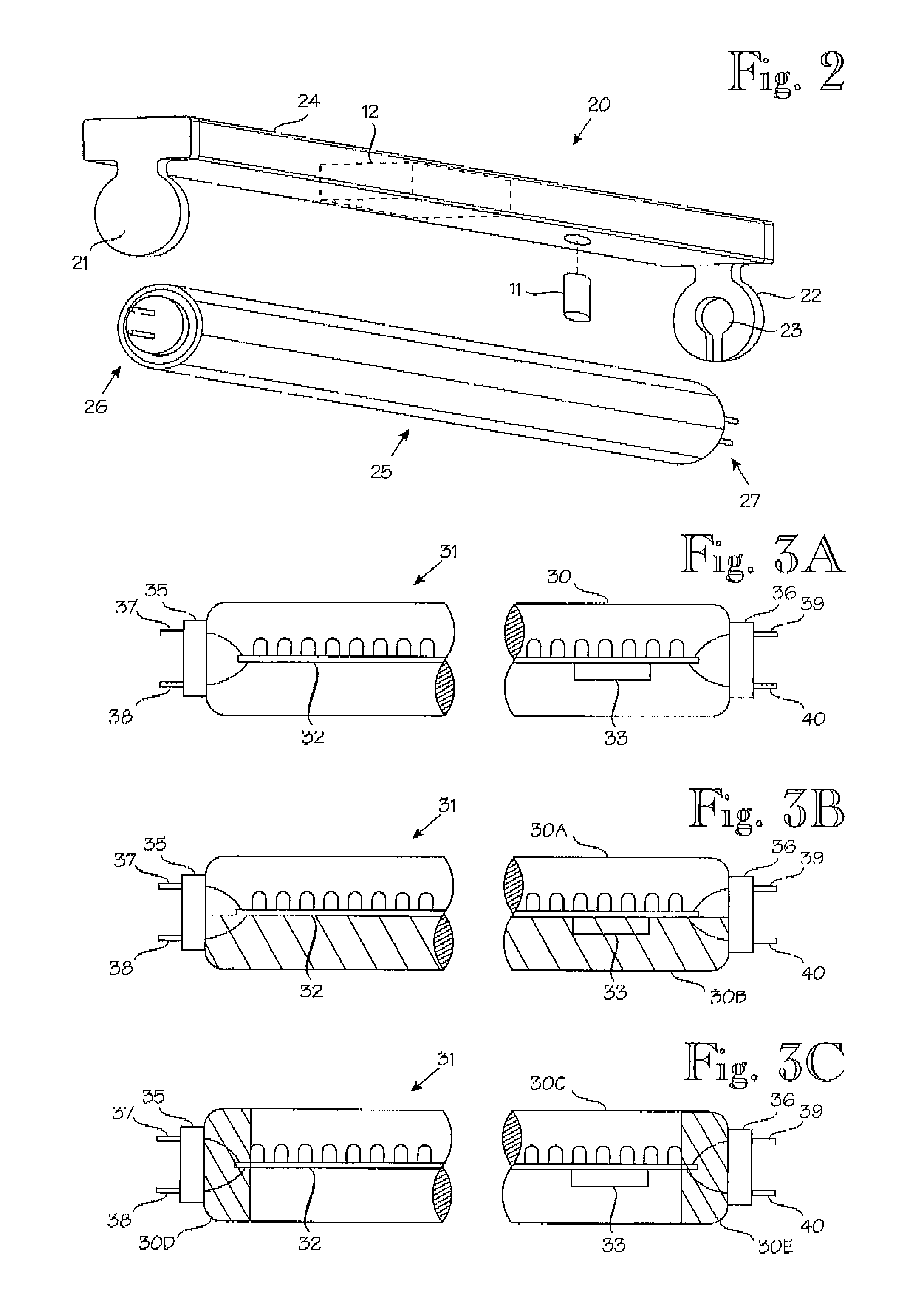

LED tube and lighting fixture arrangement

ActiveUS20110260622A1Preventing situationDistributed capacitance can be relatively highPoint-like light sourceElongate light sourcesPower flowEffect light

A LED tube includes a substantially fluorescent-tube-shaped and fluorescent-tube-sized translucent or fluorescent tube having one or more LED components and a current control unit installed therein. Both ends of the LED tube are provided with a pair of contact pins for connecting the LED tube mechanically and electrically to the tube holders of the fluorescent tube lighting fixture. The tube has a safety unit arranged to prevent a voltage from transferring through the tube from its one end to the other until a voltage supplied from the corresponding tube holder of the lighting fixture to the pair of contact pins has been detected at each end of the tube separately. Electric power or switching control of electric power is cross-connected between the ends of the LED tube.

Owner:TEKNOWARE

Organic Electrolyte Capacitor Using a Mesopore Carbon Material as a Negative Electrode

ActiveUS20080165471A1Increase energy densityImprove pressure resistanceHybrid capacitor electrolytesHybrid capacitor electrodesCapacitanceLithium

An organic electrolyte capacitor having a high energy density and a high power and having a high capacitance even at −20° C. is provided.According to the organic electrolyte capacitor of the present invention, an organic electrolyte capacitor having a high discharge capacity even at a low temperature state as low as −20° C. while having a high voltage and a high energy density can be attained in an organic electrolyte capacitor having a positive electrode, a negative electrode, and an electrolyte capable of transporting lithium ions, in which the positive electrode can reversibly support lithium ions and anions, and the negative electrode can reversibly support the lithium ions by using a mesopored carbon material having a pore volume of 0.10 ml / g or more for pore diameter of 3 nm or larger.

Owner:SUBARU CORP

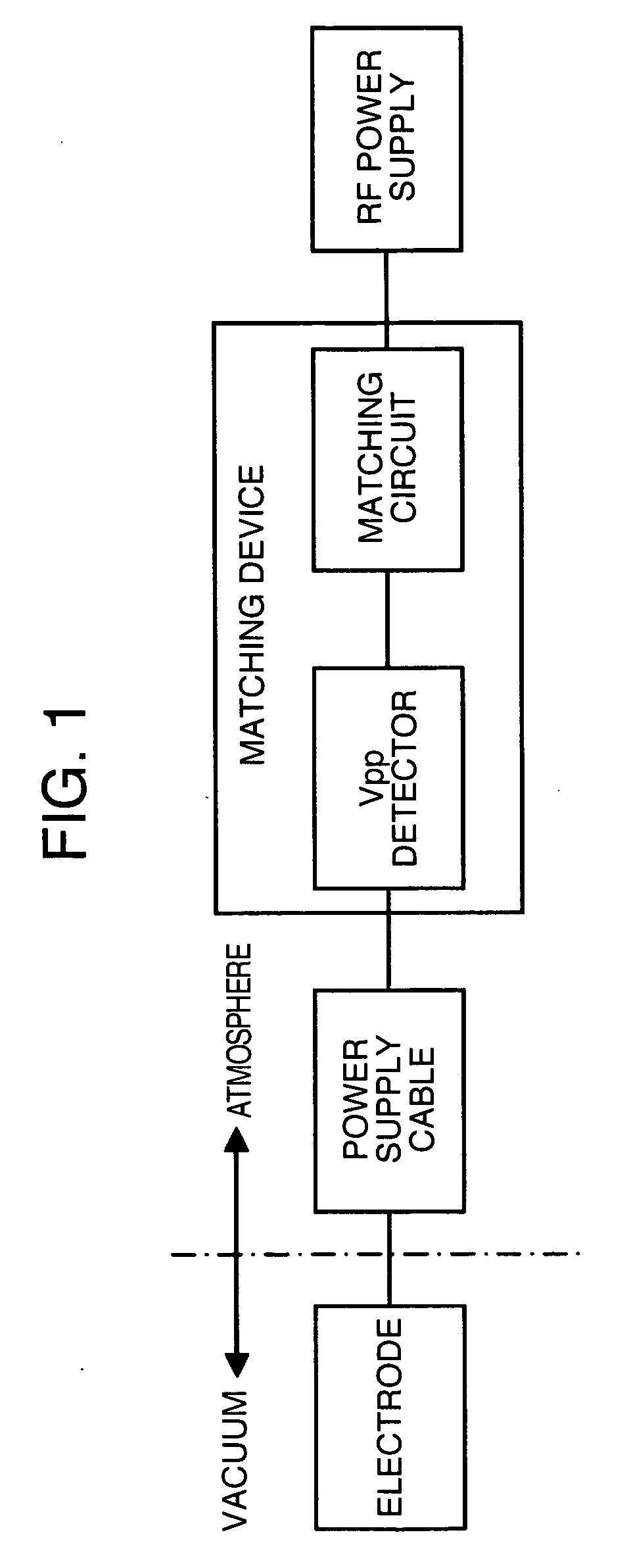

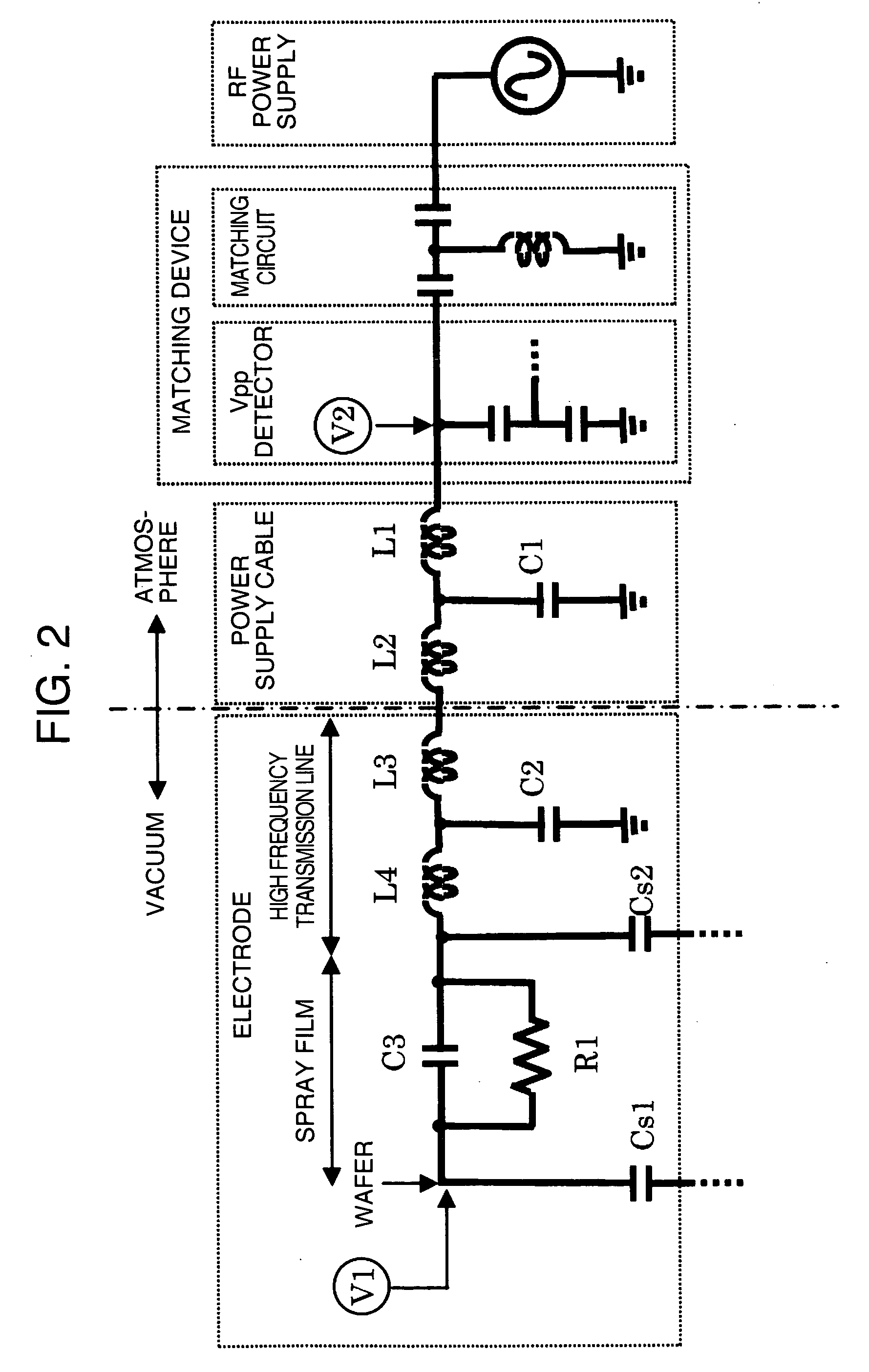

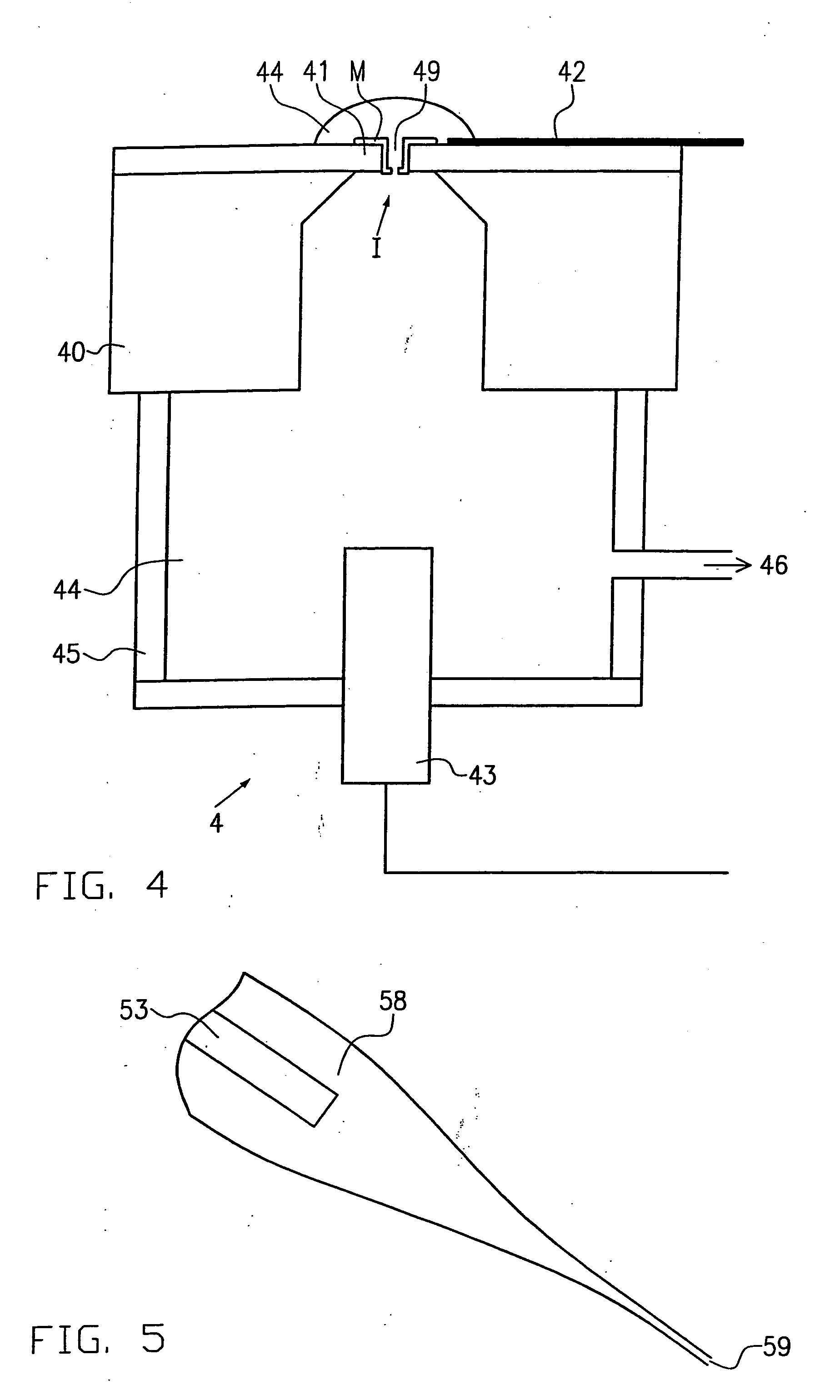

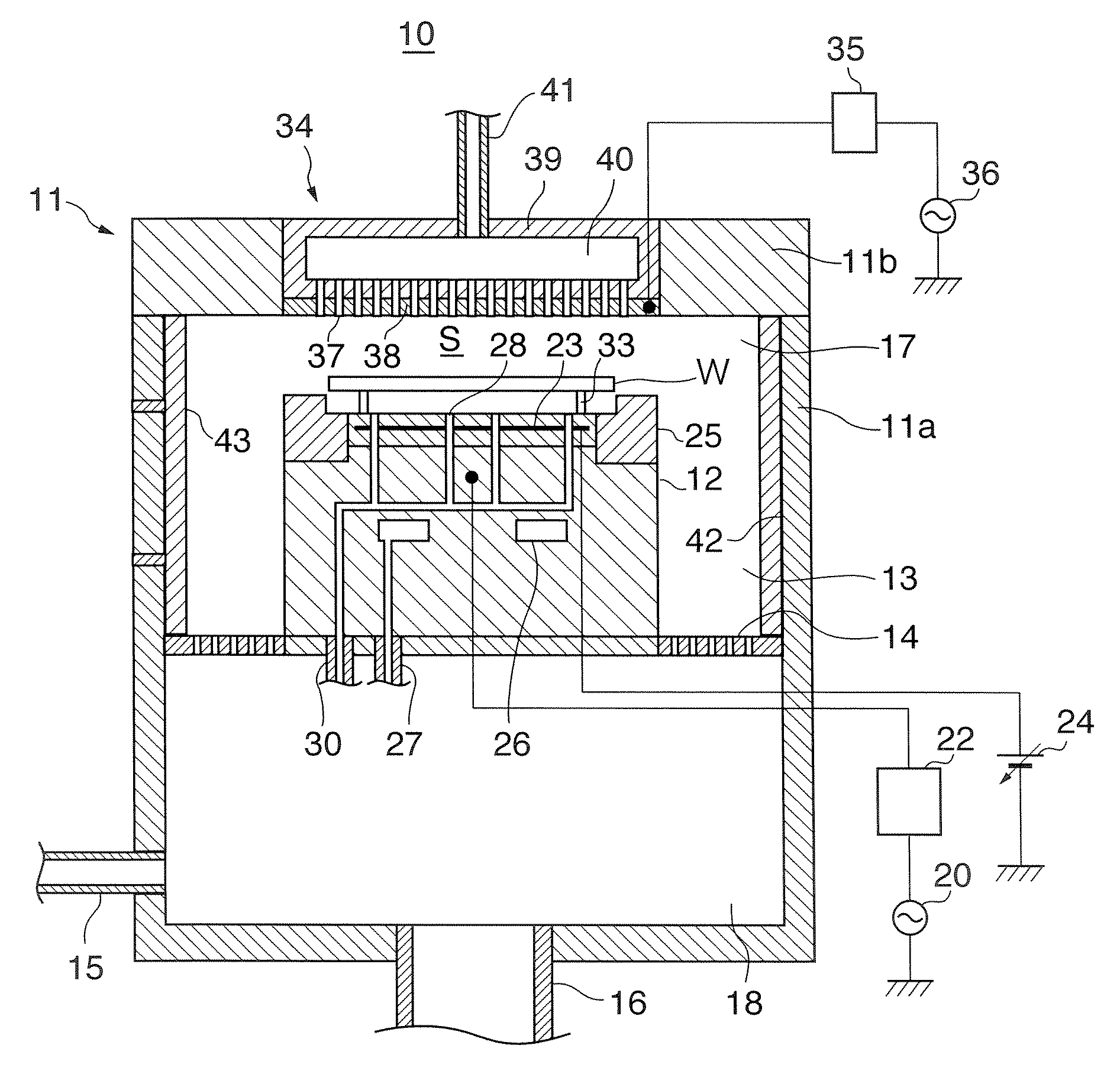

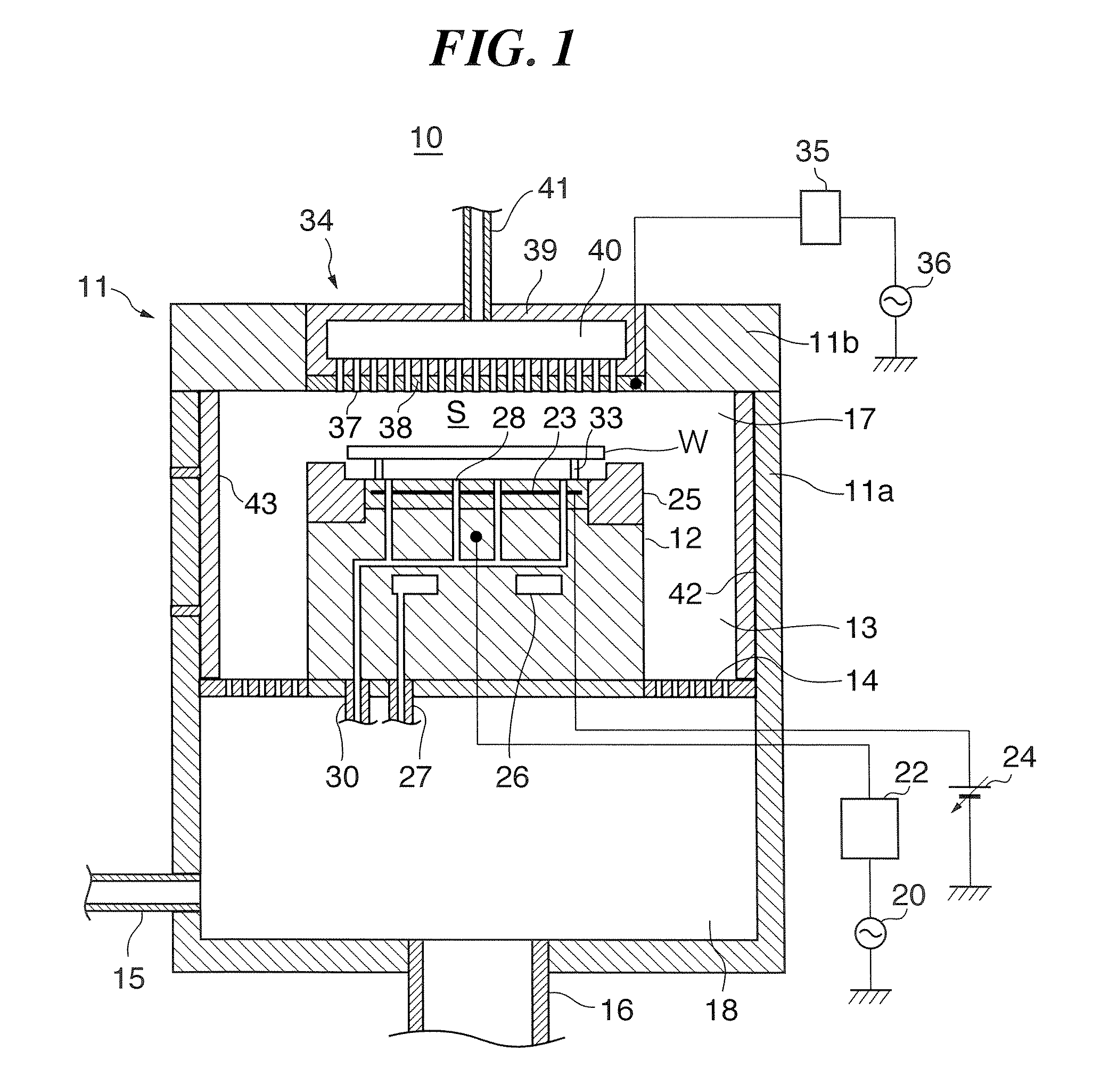

Plasma processing apparatus with resonance countermeasure function

InactiveUS20070181254A1Reduce manufacturing costHigh capacitanceElectric discharge tubesSemiconductor/solid-state device manufacturingInternal pressureHigh frequency power

A plasma processing apparatus has a processing chamber connected to an exhaust system so that the inside pressure can be reduced, a gas feeding unit for supplying gas to the processing chamber, a wafer, and a substrate electrode on which the wafer can be placed. The plasma processing apparatus also has an antenna electrode provided in opposition to the substrate electrode to generate plasma, a plasma generating high-frequency power supply connected to the antenna electrode, and a wafer biasing power supply connected to the substrate electrode. In addition, a coaxial line and a coaxial waveguide are optimized by using a coaxial model, and a voltage measuring circuit is mounted right under the coaxial line.

Owner:HITACHI HIGH-TECH CORP

Input device and display device having the same

InactiveUS20100271328A1DistanceElectrostatic capacitanceTransmission systemsInput/output processes for data processingCapacitanceCapacitive coupling

An electrostatic capacitive coupling-type touch panel is provided which interacts not only with a finger-based input but also with a touch using non-conductive input means. The touch panel includes coordinate detection electrodes for detecting XY position coordinates and transparent Z electrodes. The Z electrodes are arranged over the coordinate detection electrodes at certain intervals with spacers disposed therebetween. An elastic layer that is deformed along the shape of the spacers by compressive force resulting from touch pressing presses the Z electrodes.

Owner:JAPAN DISPLAY INC +1

Array substrate of liquid crystal display and fabricating method thereof

InactiveUS20070188671A1High capacitanceReduce the ratioNon-linear opticsLiquid-crystal displayDisplay device

An array substrate of a liquid crystal device has a plurality of gate lines, data lines, pixel areas, and thin film transistors, wherein the gate lines are formed from a material of a first and second metal layer, and wherein the first metal layer of the gate line is extended on the pixel area. Also, a display device has first and second gate lines and a data line on a substrate, a thin film transistor, a pixel electrode, a first storage electrodes extending from the second gate line and wherein at least one of the first and second gate lines and the data line includes first and second line layers respectively formed of an oxidized metal later and a metal layer.

Owner:LG DISPLAY CO LTD

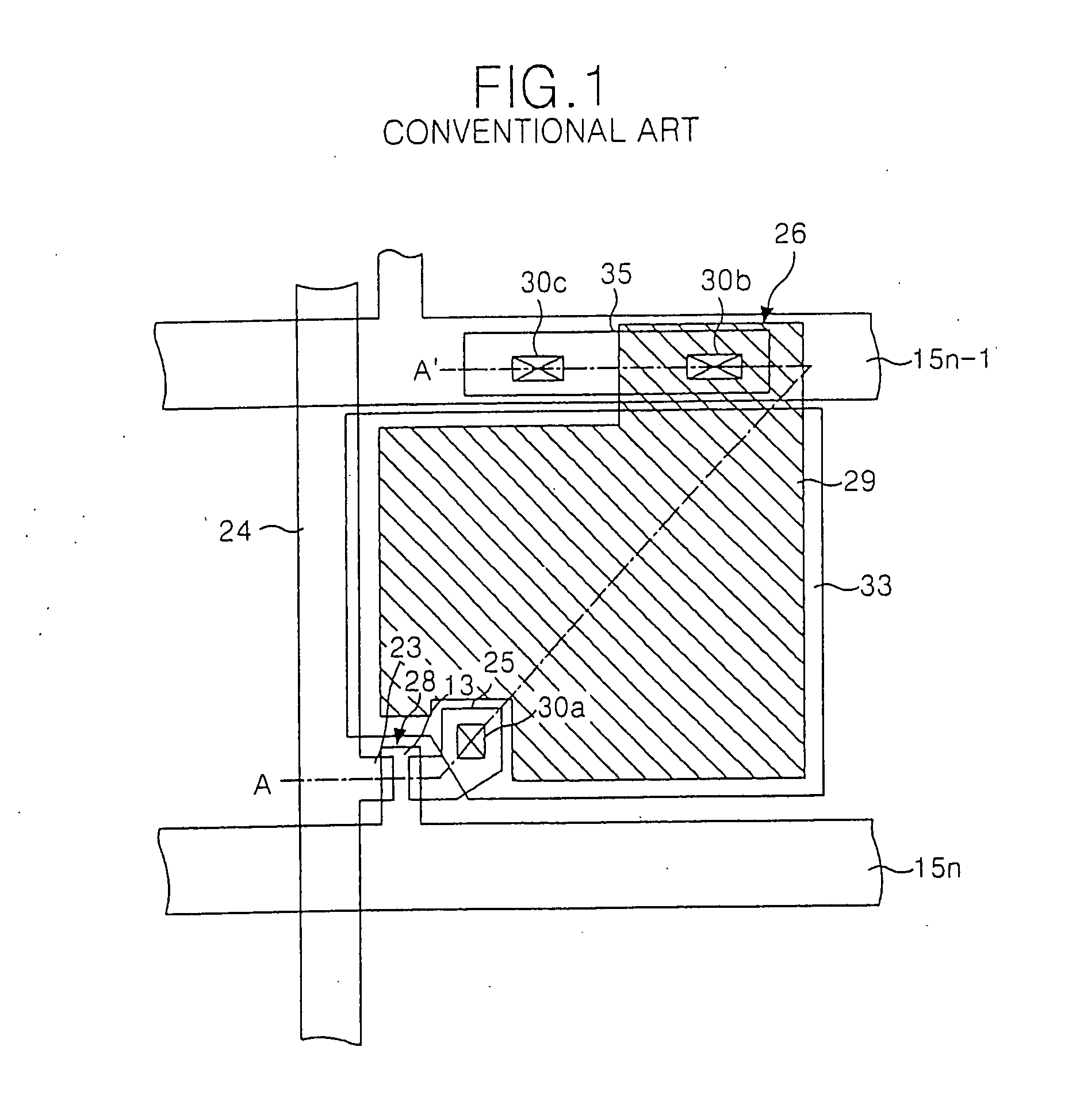

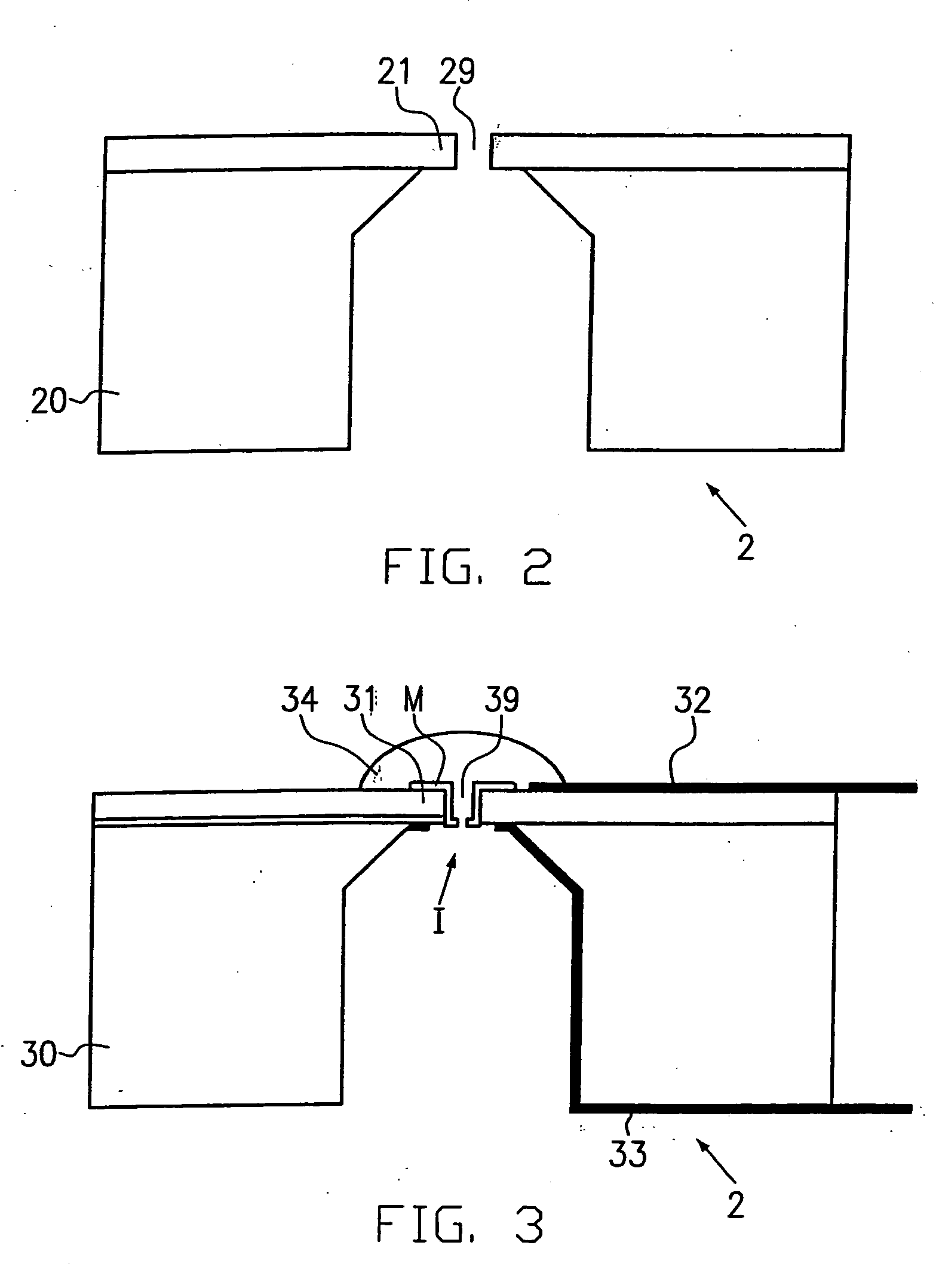

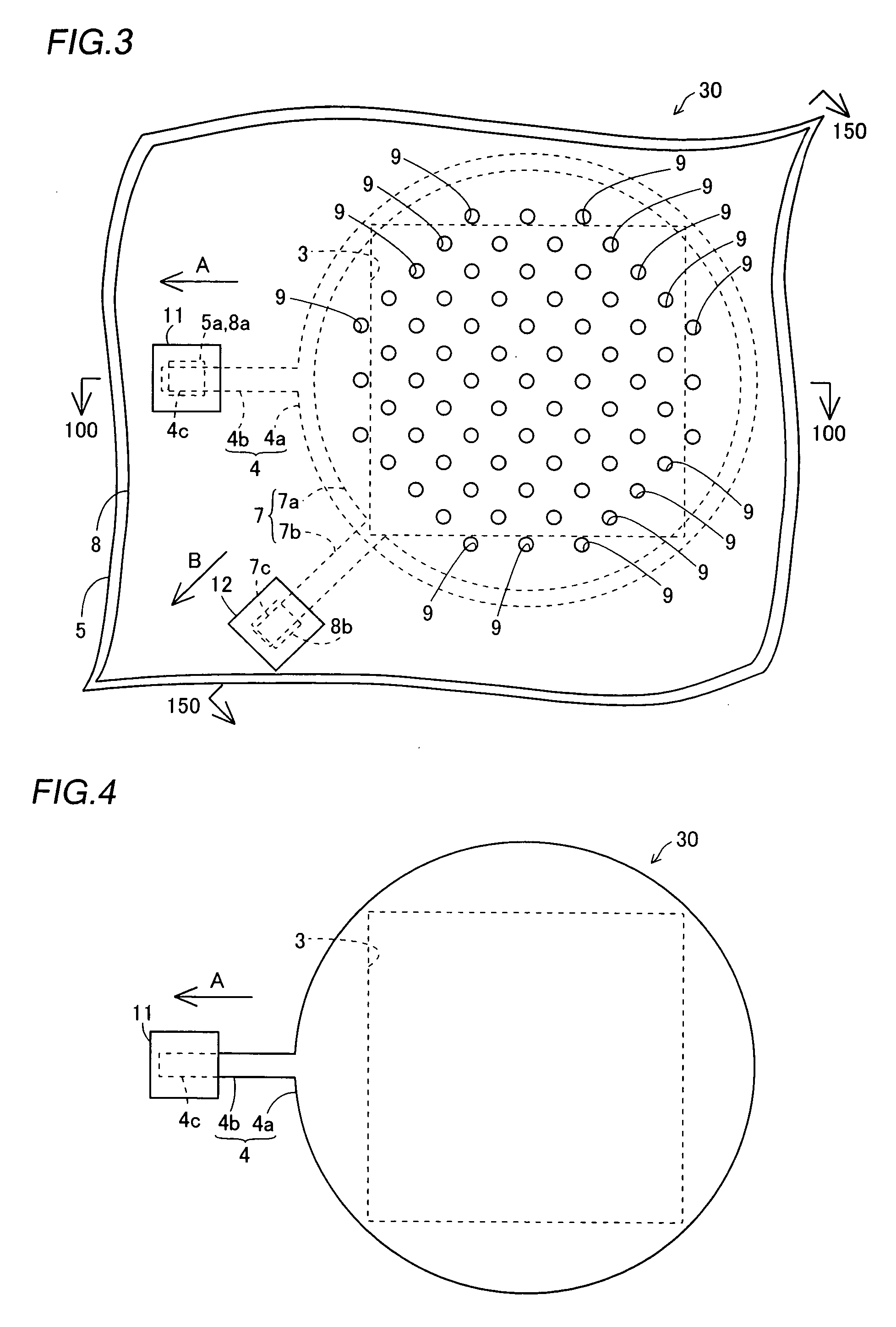

Device and method for analyzing ion channels in membranes

InactiveUS20050009171A1High capacitanceImprove signal-to-noise ratioBioreactor/fermenter combinationsBiological substance pretreatmentsLipid formationCell membrane

The present invention relates to devices and methods for analyzing ion channels in membranes. The invention is characterized by a biochip comprising a substrate in which openings are provided in the form of an M×N matrix for receiving therein a cell membrane including at least one ion channel (I) or an artificial lipid membrane (Me), wherein M≧1 and N≧1.

Owner:FERTIG NIELS +2

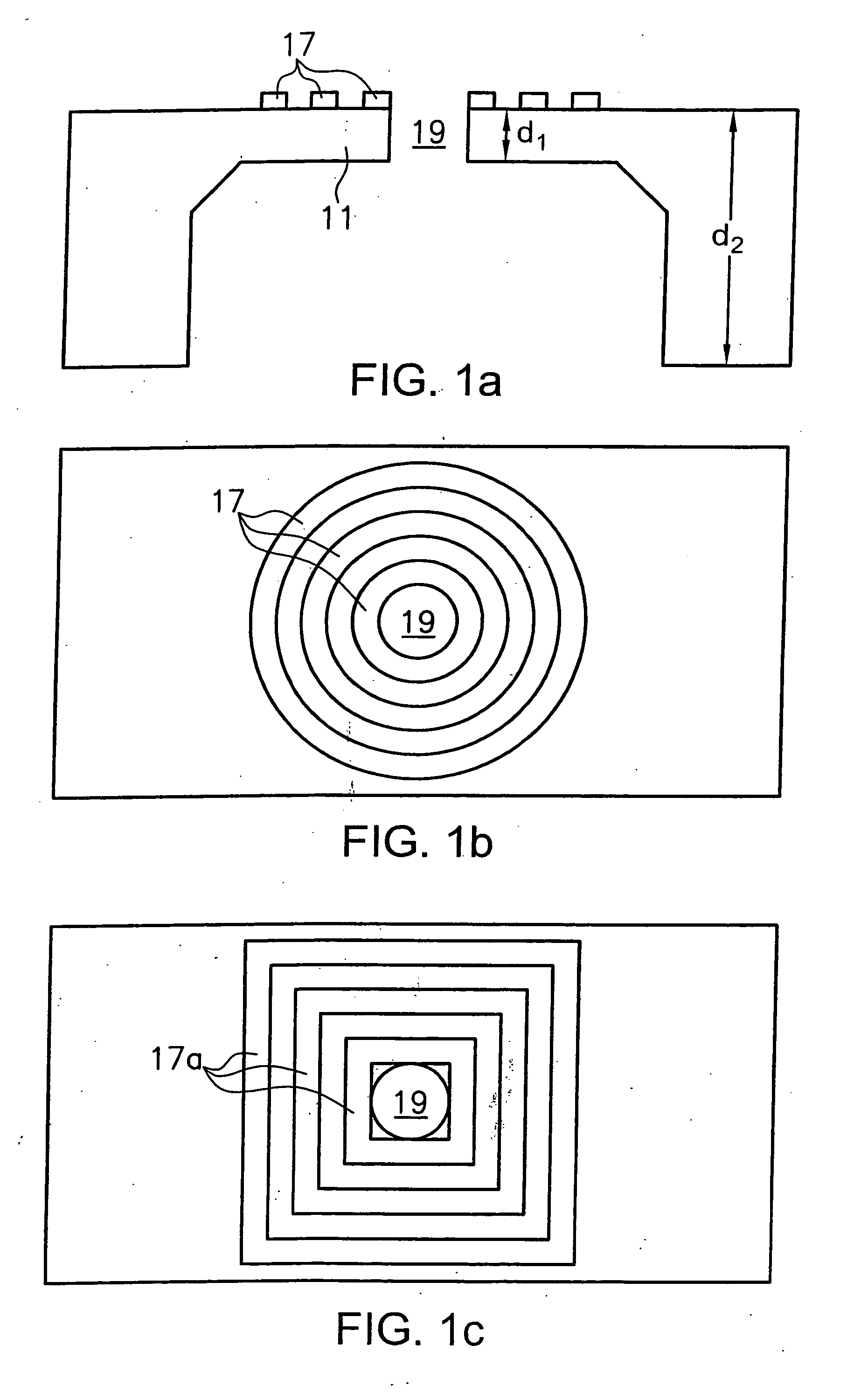

Sensor

InactiveUS20070045757A1Change capacitanceIncreasing the thicknessResistance/reactance/impedenceSemiconductor electrostatic transducersEngineeringElectric signal

A sensor capable of increasing an electric signal output therefrom by inhibiting an electrode plate from vibration is obtained. This sensor comprises a diaphragm provided in a vibrative manner, an electrode plate, opposed to the diaphragm at a prescribed distance, having a hole and a support made of a material having an elastic modulus higher than the elastic modulus of a material constituting the electrode plate for supporting the electrode plate. The support is so formed as to cover at least two of the upper surface and the lower surface of the electrode plate and the side surface of the hole.

Owner:SANYO ELECTRIC CO LTD

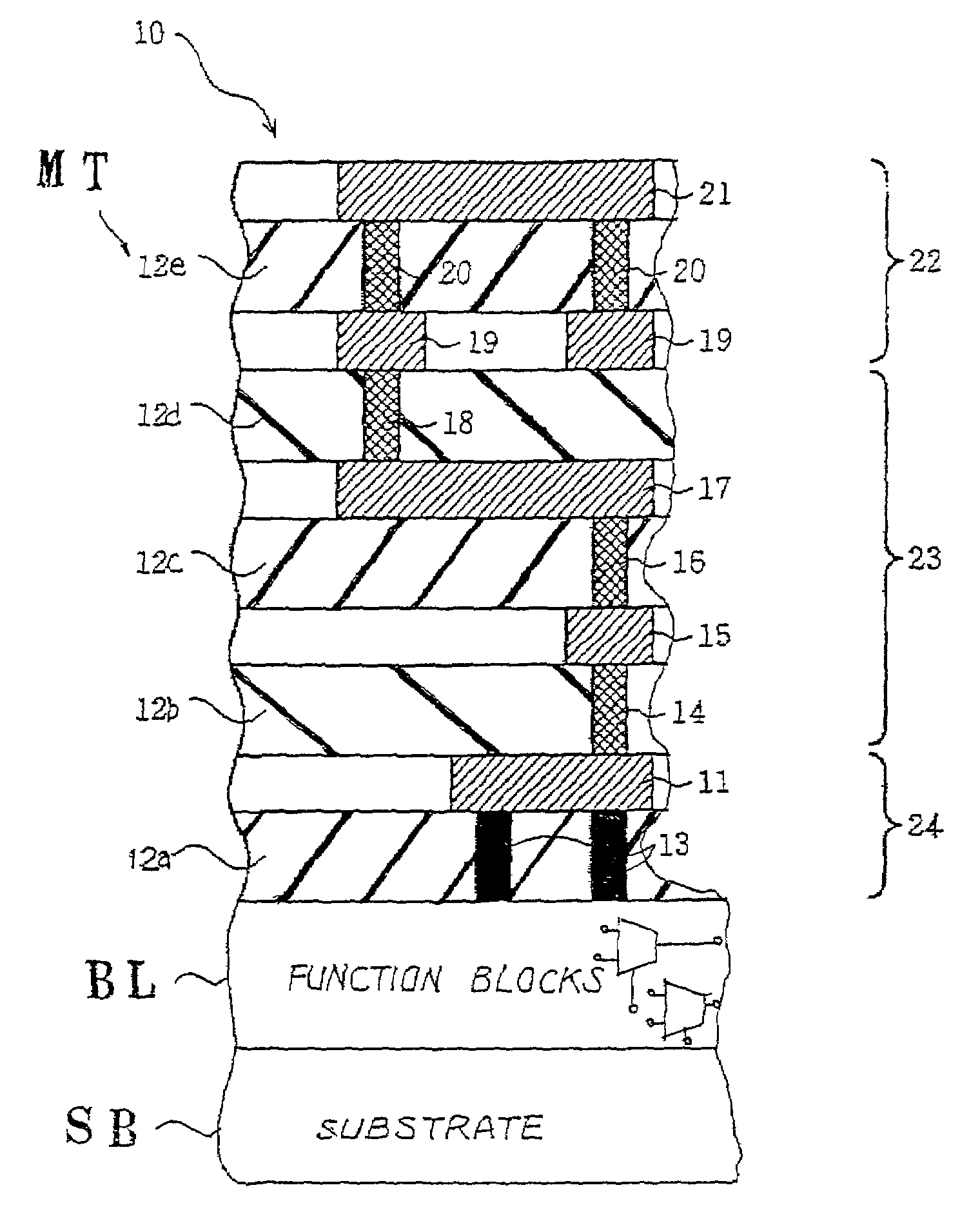

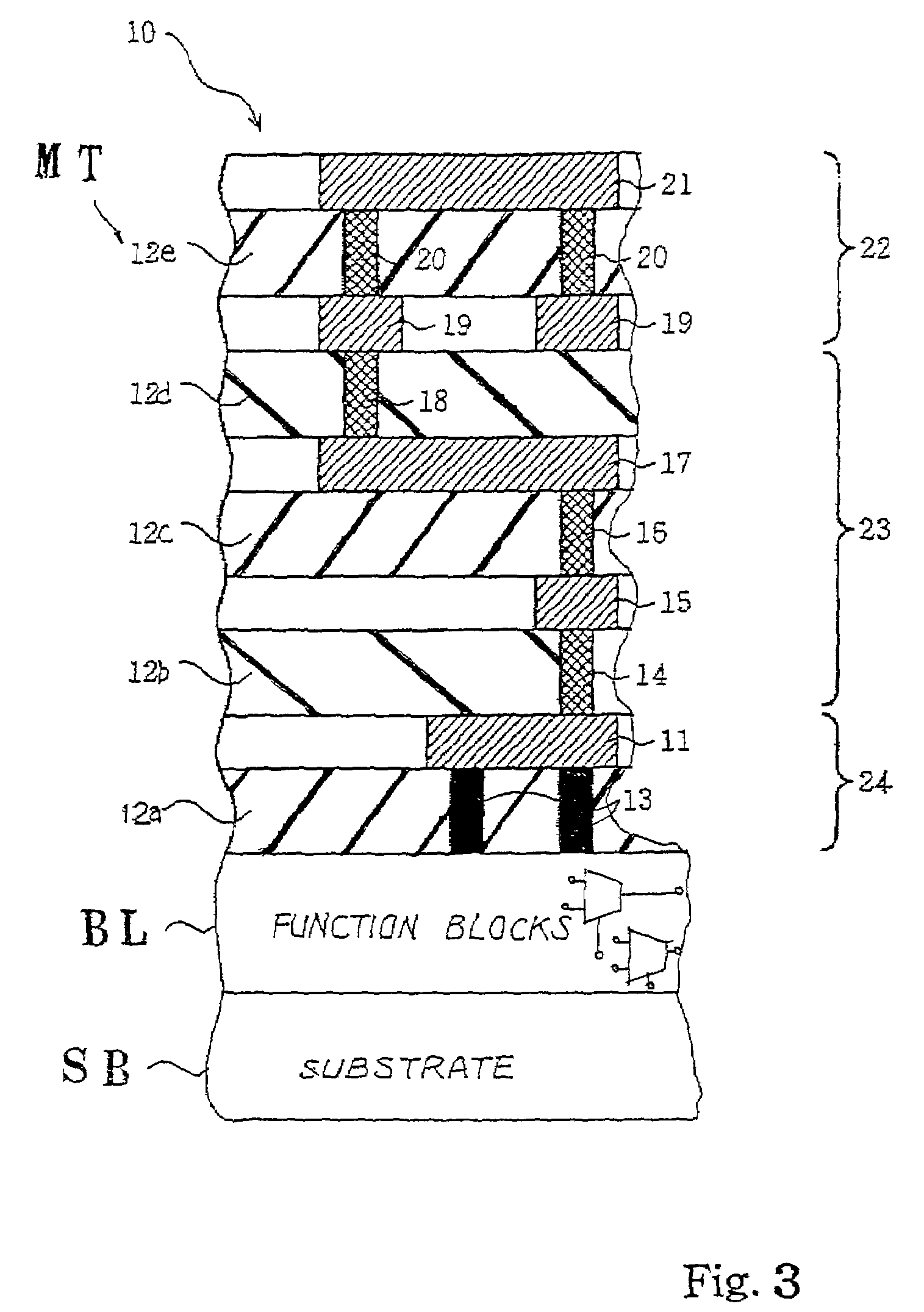

Semi-custom-made semiconductor integrated circuit device, method for customization and method for redesign

InactiveUS7047514B2High capacitanceHigh degreeSolid-state devicesSemiconductor/solid-state device manufacturingLogic cellParasitic capacitance

An ASIC includes a function layer formed with plural universal logic cells, a common layer formed with conductive strips connected to the universal logic cells and common to other ASICs and a customized layer having at least two metallization layers assigned to conductive strips extending in certain directions parallel to one another and other conductive strips extending in perpendicular directions to the certain directions, respectively, and an inter-layered insulating layer formed with conductive plugs selectively connected between the conductive strips and the other conductive strips, wherein the conductive strips have respective values of length such that the conductive plugs are located on both ends thereof, whereby the conductive strips, other conductive strips and the conductive plugs form plural signal paths reduced in total contact resistance and parasitic capacitance.

Owner:RENESAS ELECTRONICS CORP

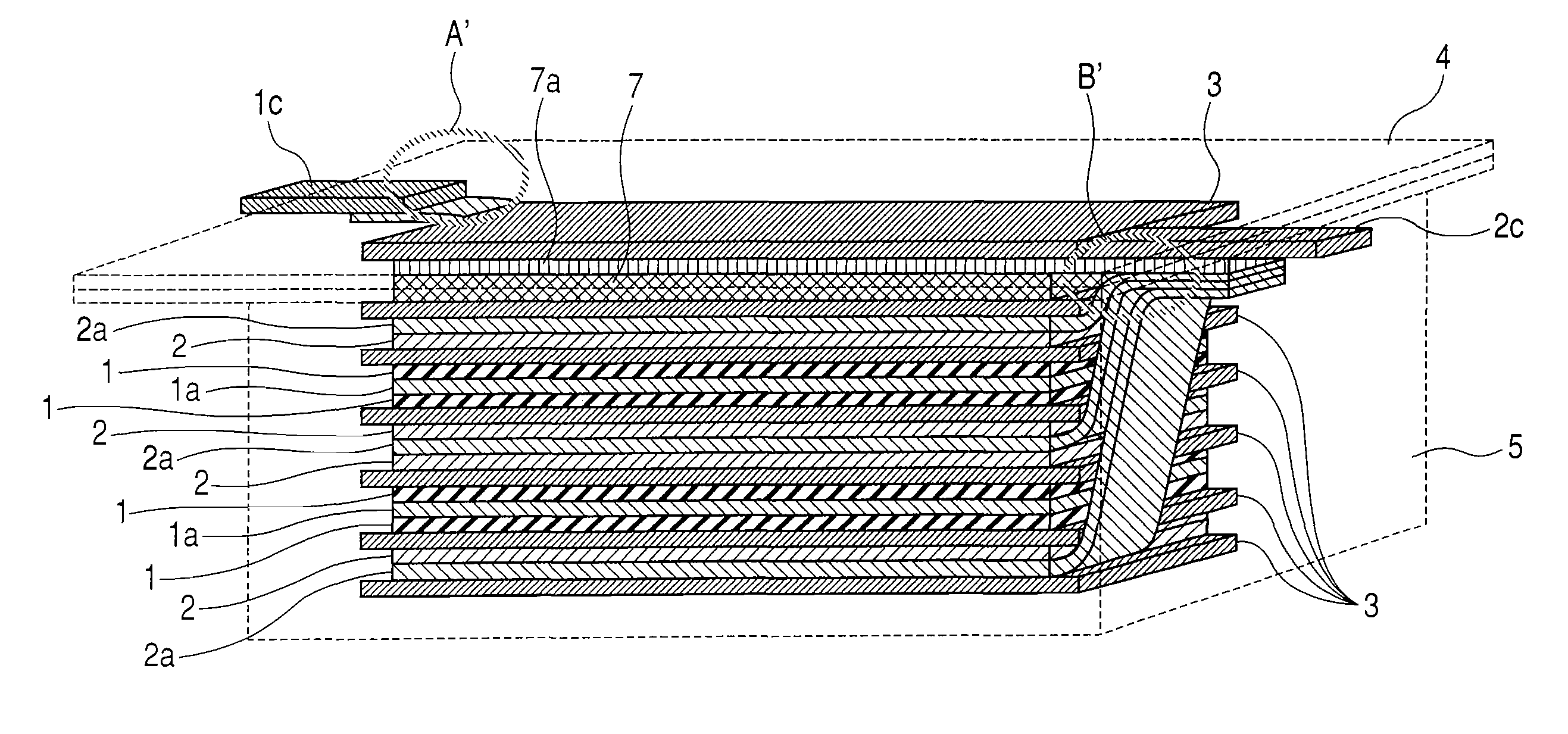

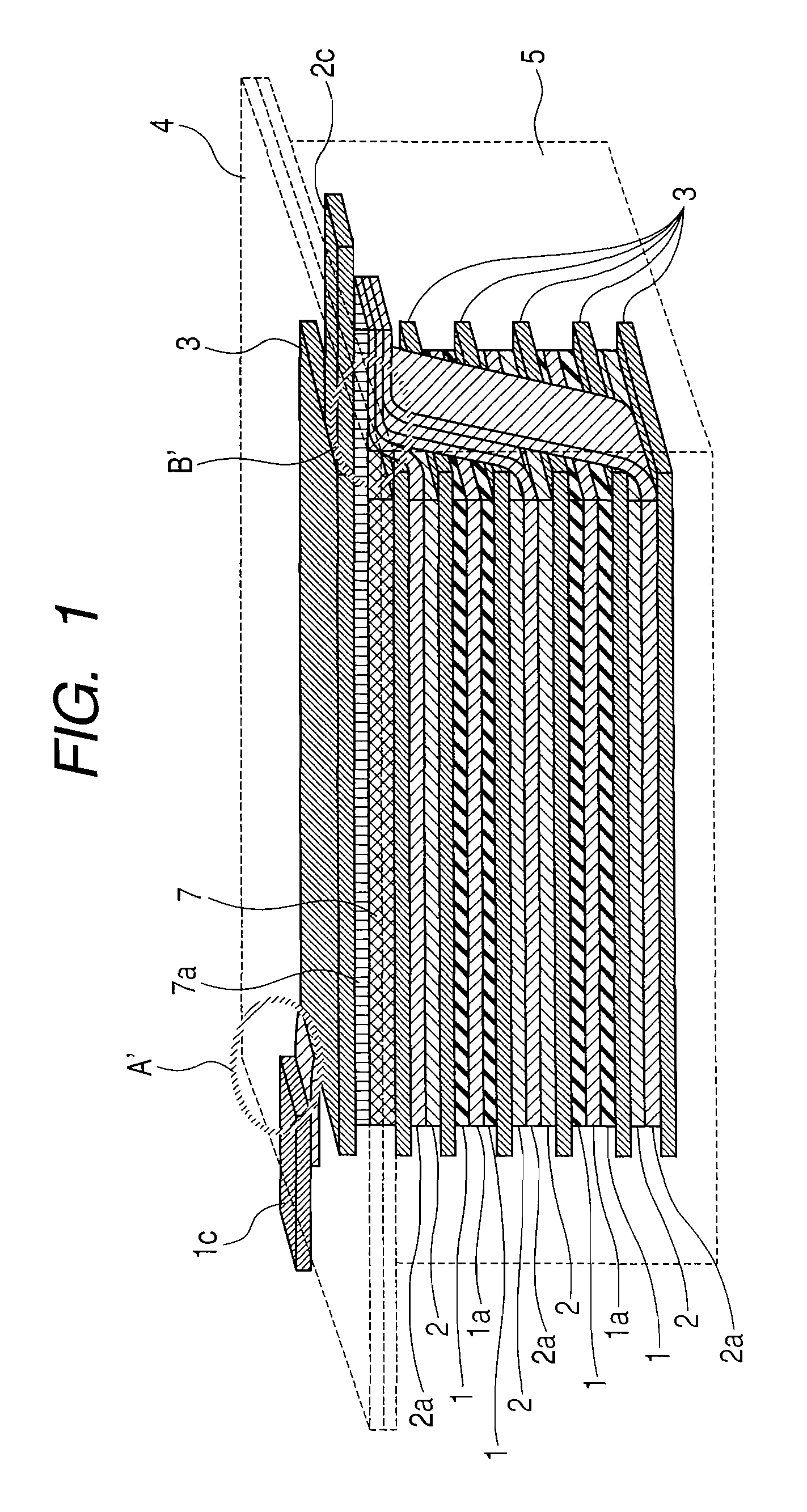

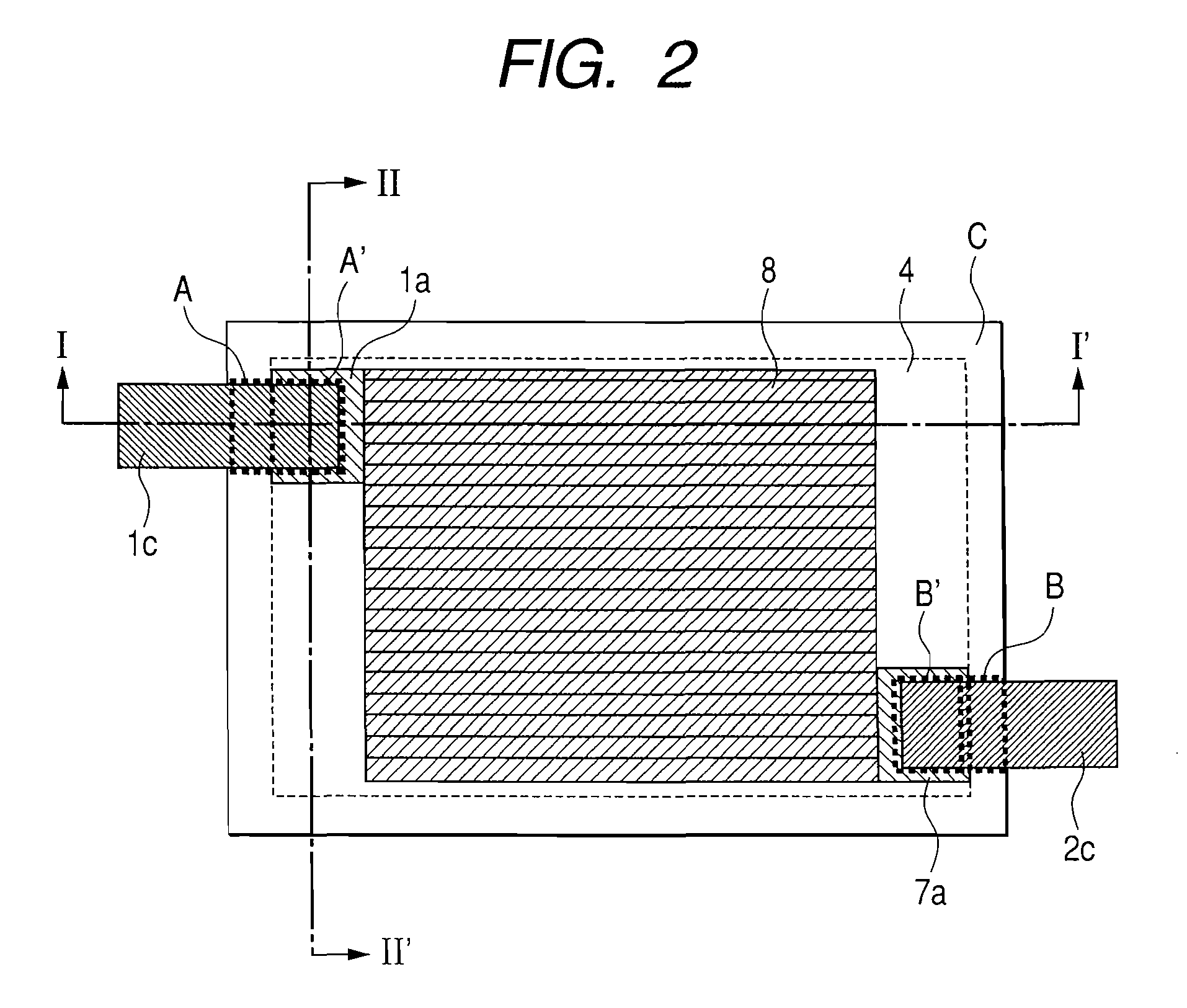

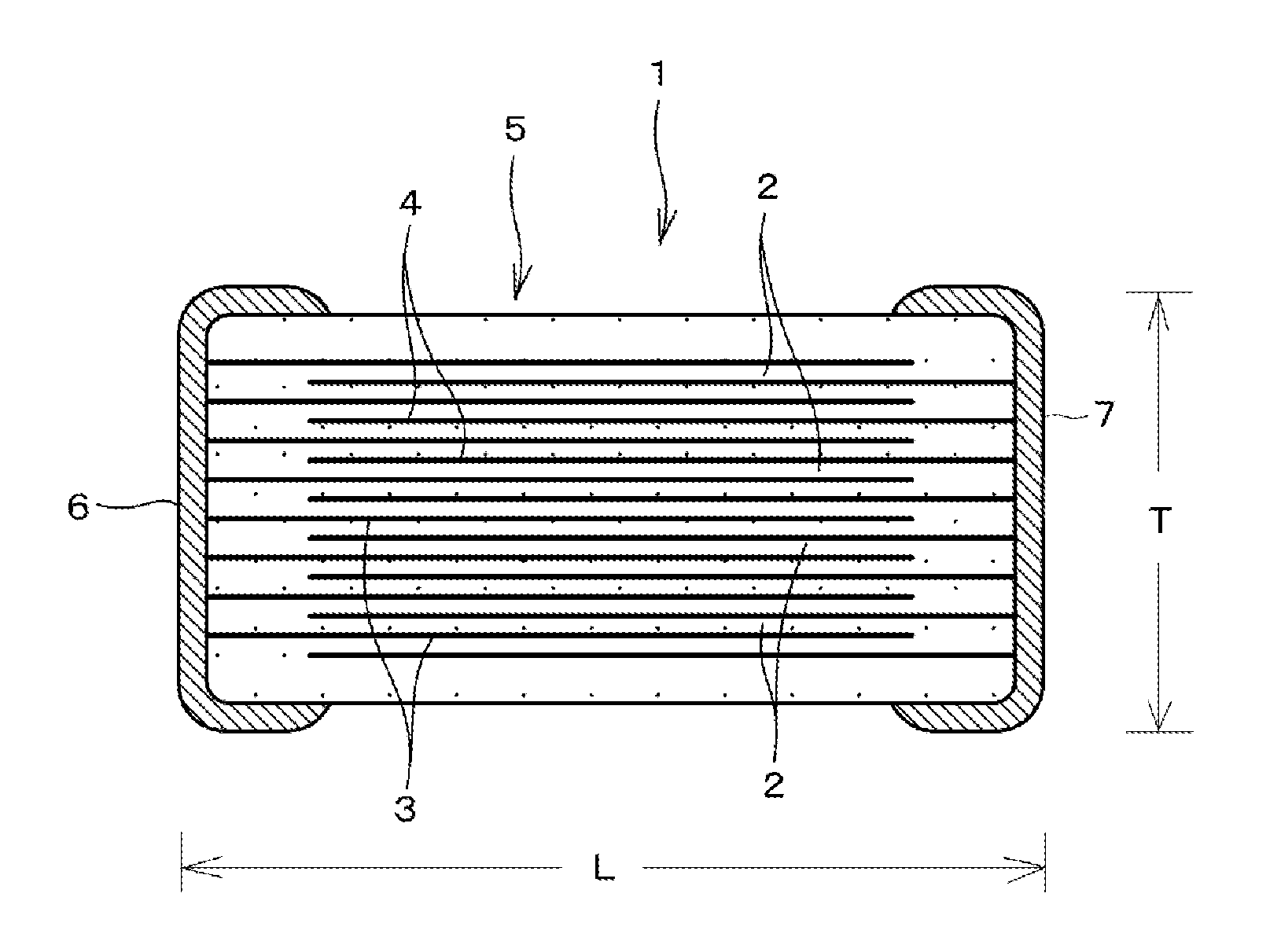

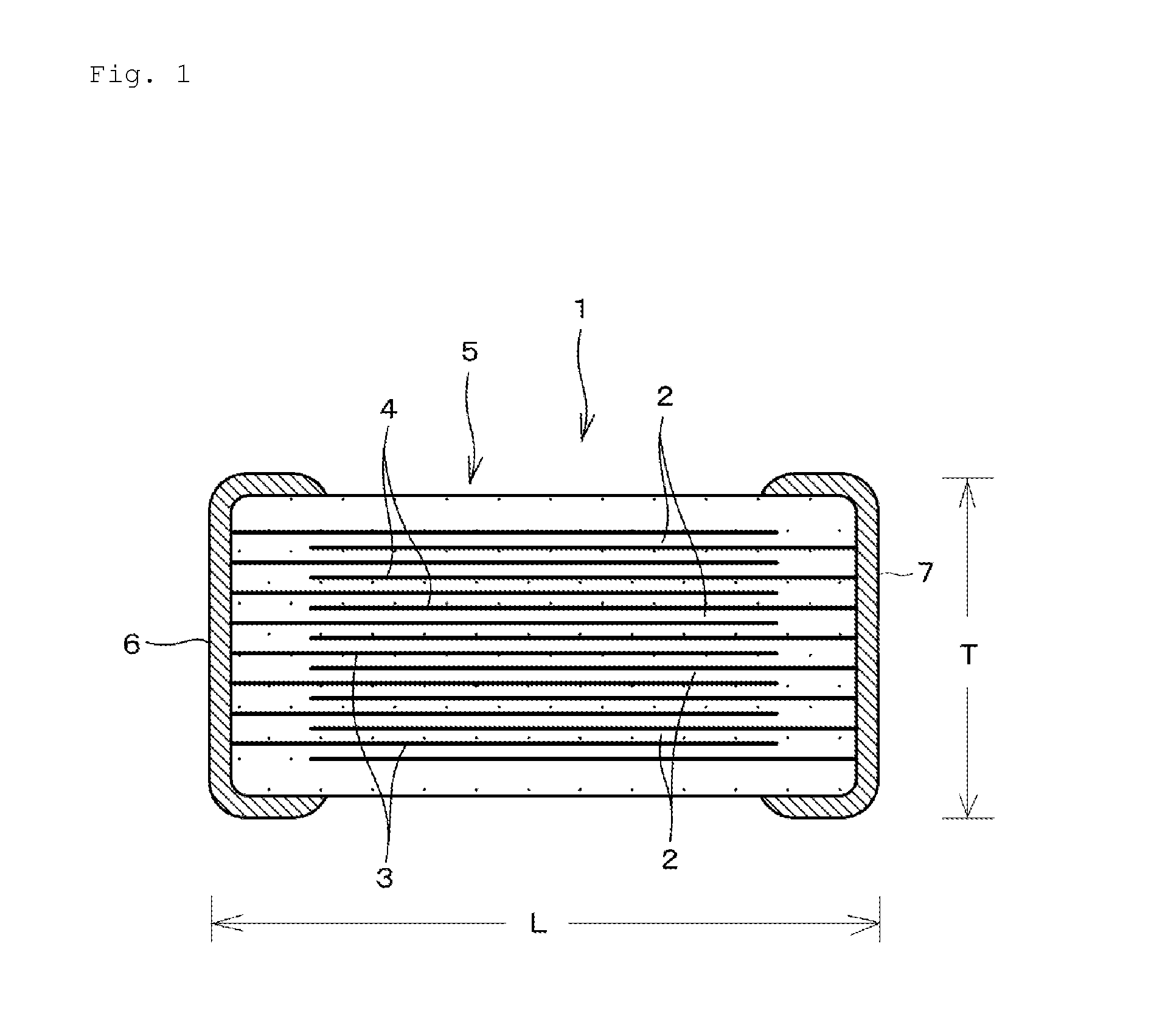

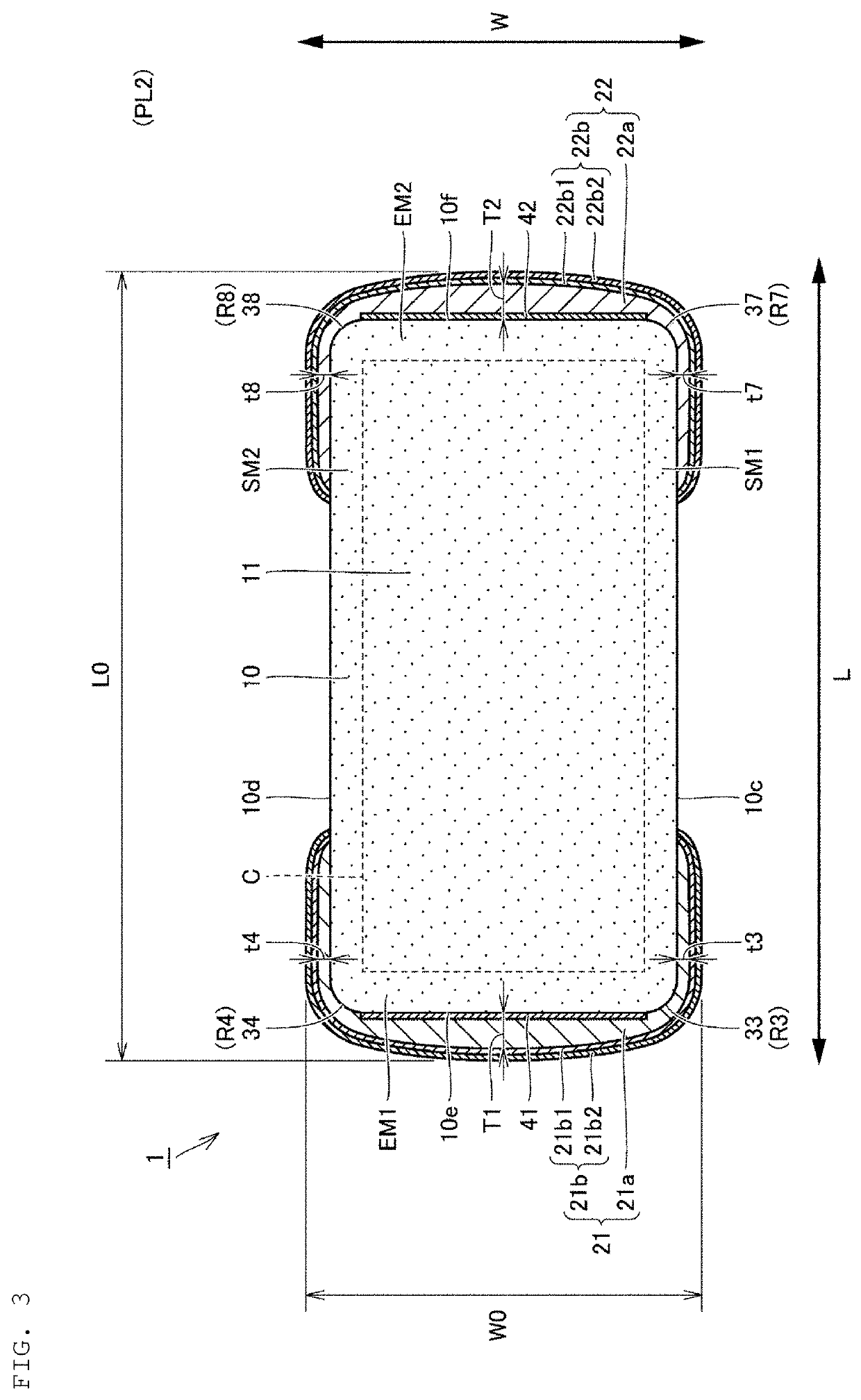

Laminated ceramic capacitor and method for manufacturing laminated ceramic capacitor

ActiveUS20150155098A1Improve reliabilityExcellent in high-temperature load lifeFixed capacitor electrodesFixed capacitor dielectricMetallurgyCeramic capacitor

A laminated ceramic capacitor that includes a ceramic laminated body having a stacked plurality of ceramic dielectric layers and a plurality of internal electrodes opposed to each other with the ceramic dielectric layers interposed therebetween, and external electrodes on the outer surface of the ceramic laminated body and electrically connected to the internal electrodes. The internal electrodes contain Ni and Sn, a proportion of the Sn / (Ni+Sn) ratio is 0.001 or more in molar ratio is 75% or more in a region of the internal electrode at a depth of 20 nm from a surface opposed to the ceramic dielectric layer, and the proportion of the Sn / (Ni+Sn) ratio is 0.001 or more in molar ratio is less than 40% in a central region in a thickness direction of the internal electrode.

Owner:MURATA MFG CO LTD

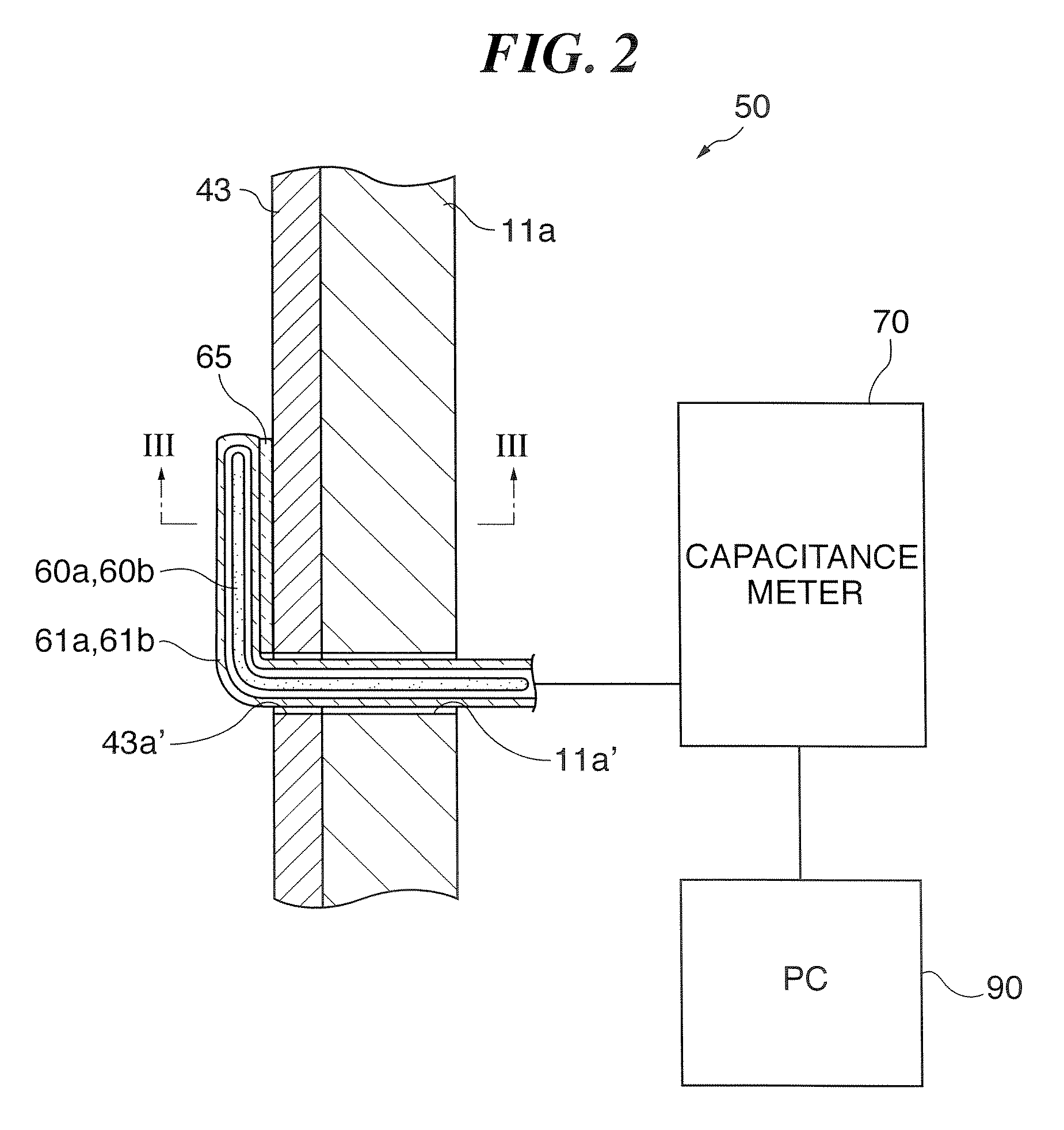

Substrate processing apparatus, deposit monitoring apparatus, and deposit monitoring method

InactiveUS20070215044A1High capacitanceHigh permittivityLiquid surface applicatorsSemiconductor/solid-state device testing/measurementCapacitanceEngineering

A substrate processing apparatus enable fouling due to deposit to be monitored in real time. To monitor deposit attached to an inner wall surface of a processing chamber in which processing is carried out on a substrate, a deposit monitoring apparatus of the substrate processing apparatus includes a sensor for measuring a capacitance between two conductors spaced apart from each other and both connected to the sensor. The capacitance between the conductors increases with increase in an mount of deposit and reflects the state of fouling due to deposit.

Owner:TOKYO ELECTRON LTD

Electric double layer capacitor

InactiveUS7283349B2Decrease riseIncreased durabilityClosuresHybrid capacitor electrodesCapacitanceActivated carbon

Owner:NISSHINBO IND INC

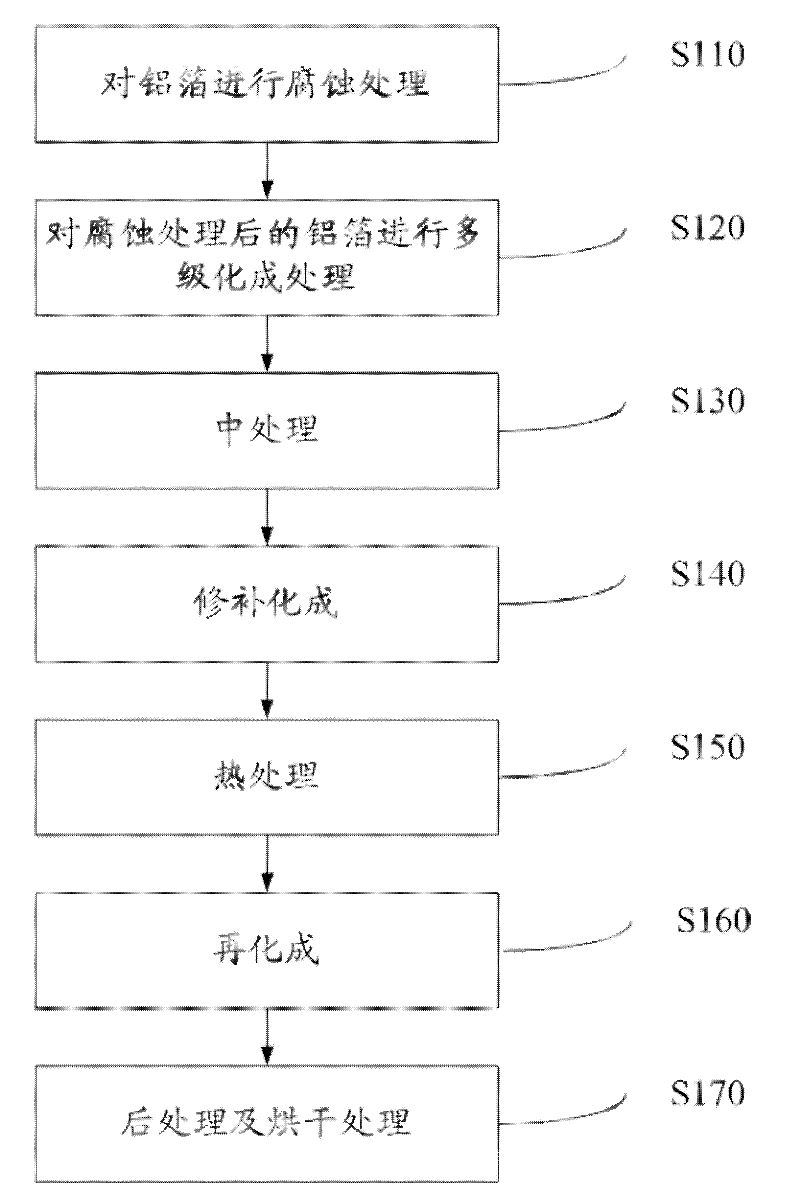

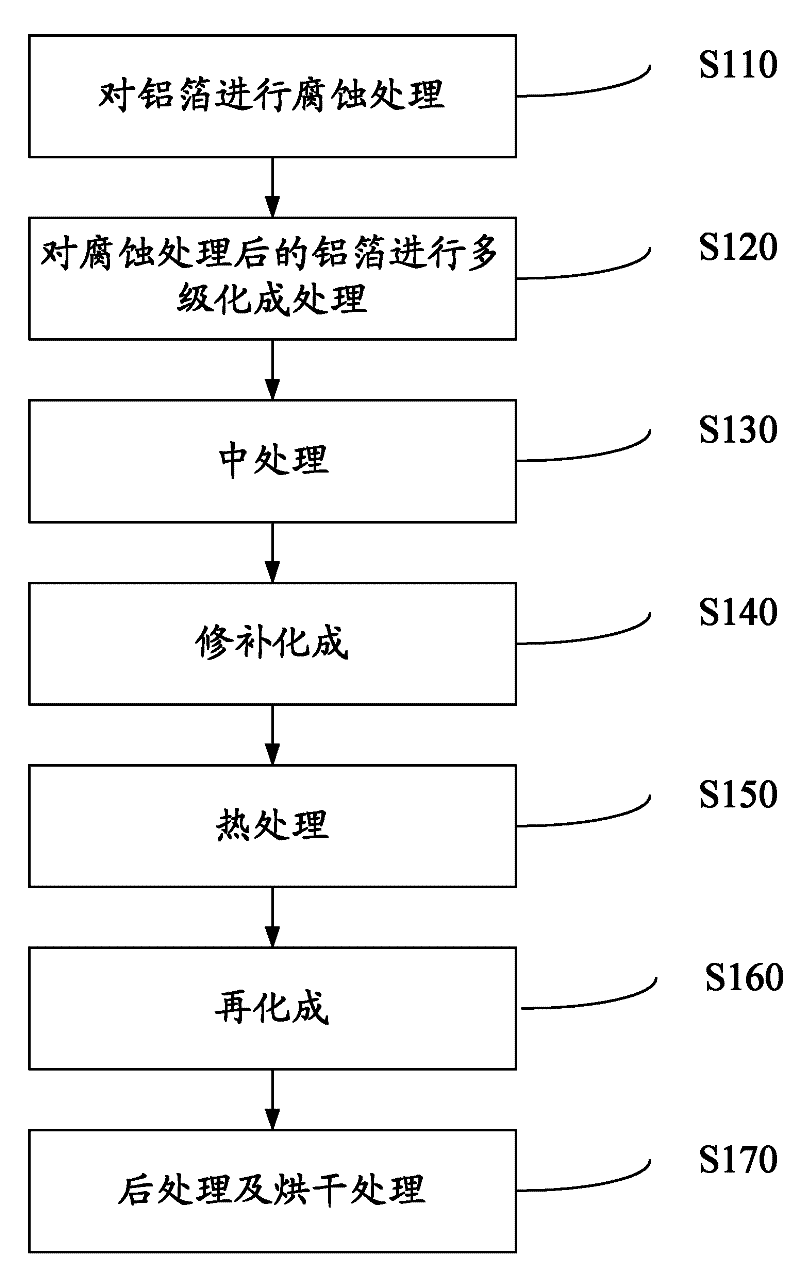

Electrolyte for melting aluminum foil of anode of capacitor and aluminum foil melting method

ActiveCN102212861AHigh capacitanceImprove pressure resistanceSurface reaction electrolytic coatingAluminum foilCapacitor

The invention relates to an electrolyte for melting an aluminum foil and an aluminum foil melting method. The capacitor anode aluminum foil melting method comprises the steps of corrosion, multi-stage melting, intermediate treatment, heat treatment, re-melting and post treatment of the aluminum foil. The electrolyte used for melting in the first stage of the multi-stage melting comprises 0.2 to 1.0 percent of oxalate, 3.5 to 7 percent of ammonium adipate and the balance of water according to weight percentage. The aluminum foil of the capacitor anode, which is prepared by the method, has higher electrostatic capacity and withstand voltage.

Owner:富德(清远)电子铝箔有限公司

Cold cathode tube lamp, lighting device, and display device

InactiveUS20060197424A1Reduce weightLow costElectrode assembly support/mounting/spacing/insulationControl electrodesCapacitanceCold cathode

A cold cathode tube lamp is fed with power from a first conductive member and a second conductive member provided outside in a mounted state, and includes a glass tube, first and second internal electrodes provided inside the glass tube, a first external electrode provided outside the glass tube and connected to the first internal electrode, a second external electrode provided outside the glass tube and connected to the second internal electrode, a first insulating layer coated on the first external electrode, and a second insulating layer coated on the second external electrode. In a mounted state, the first conductive member and the first external electrode are capacitively coupled together, and the second conductive member and the second external electrode are capacitively coupled together. With such a structure, parallel lighting can be achieved by parallel driving.

Owner:SHARP KK

Semiconductor Optical Device and Manufacturing Method Thereof

ActiveUS20080219315A1Less chirpingMaintain good propertiesLaser detailsLaser optical resonator constructionParasitic capacitanceRefractive index

A low reflective window structure in an existent electro-absorption optical modulator involves a trading off problem between the increase in the parasitic capacitance and the pile-up. This is because the capacitance density of the pn junction in the window structure is higher compared with the pin junction as the optical absorption region, and the application of electric field to the optical absorption region becomes insufficient in a case of receding the electrode structure from the junction between the optical absorption region and the window structure making it difficult to discharge photo-carriers generated in the optical absorption region. An undope waveguide structure comprising a structure having such compositional wavelength and a film thickness that the compositional wavelength for each of multi-layers constituting the waveguide structure is sufficiently shorter than that of the signal light and the average refractive index is about identical with that in the optical absorption region may be disposed. In a case of forming the electrode structure so as to overlap the junction boundary between the optical absorption region and the undope waveguide, and do not extend on the joined boundary between the undope waveguide and the window structure, increase in the parasitic capacitance due to the pn junction of the window structure and pile up can be suppressed simultaneously.

Owner:LUMENTUM JAPAN INC

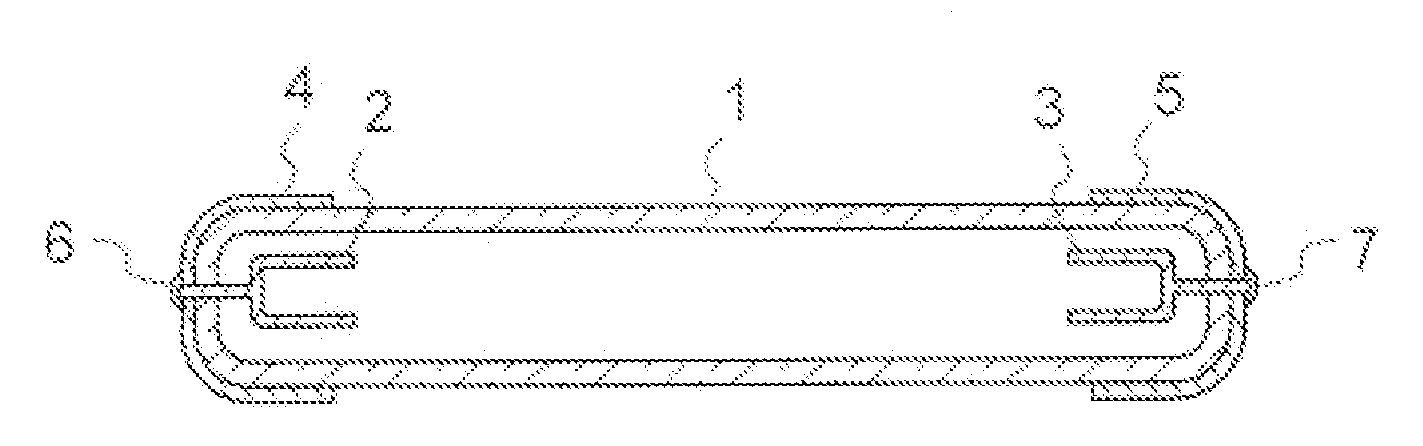

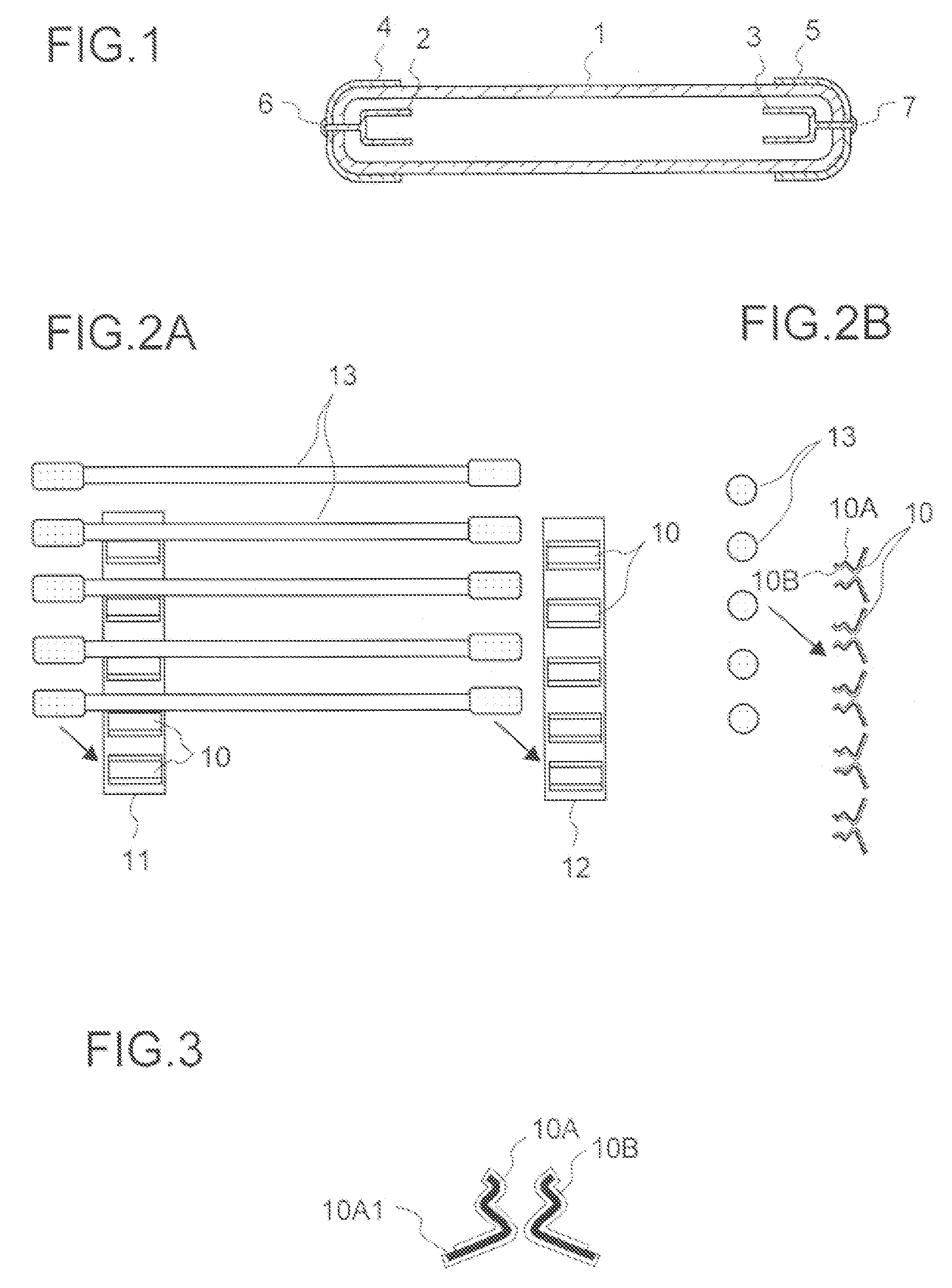

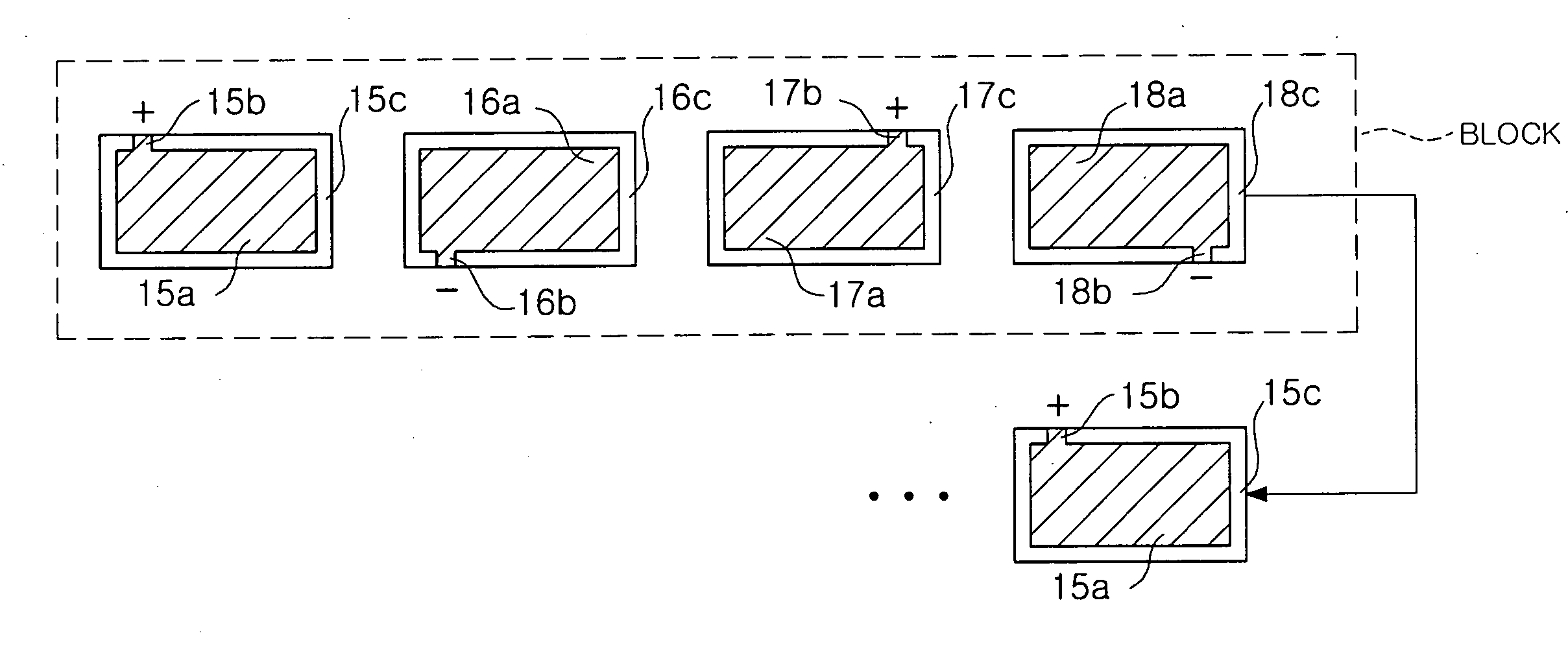

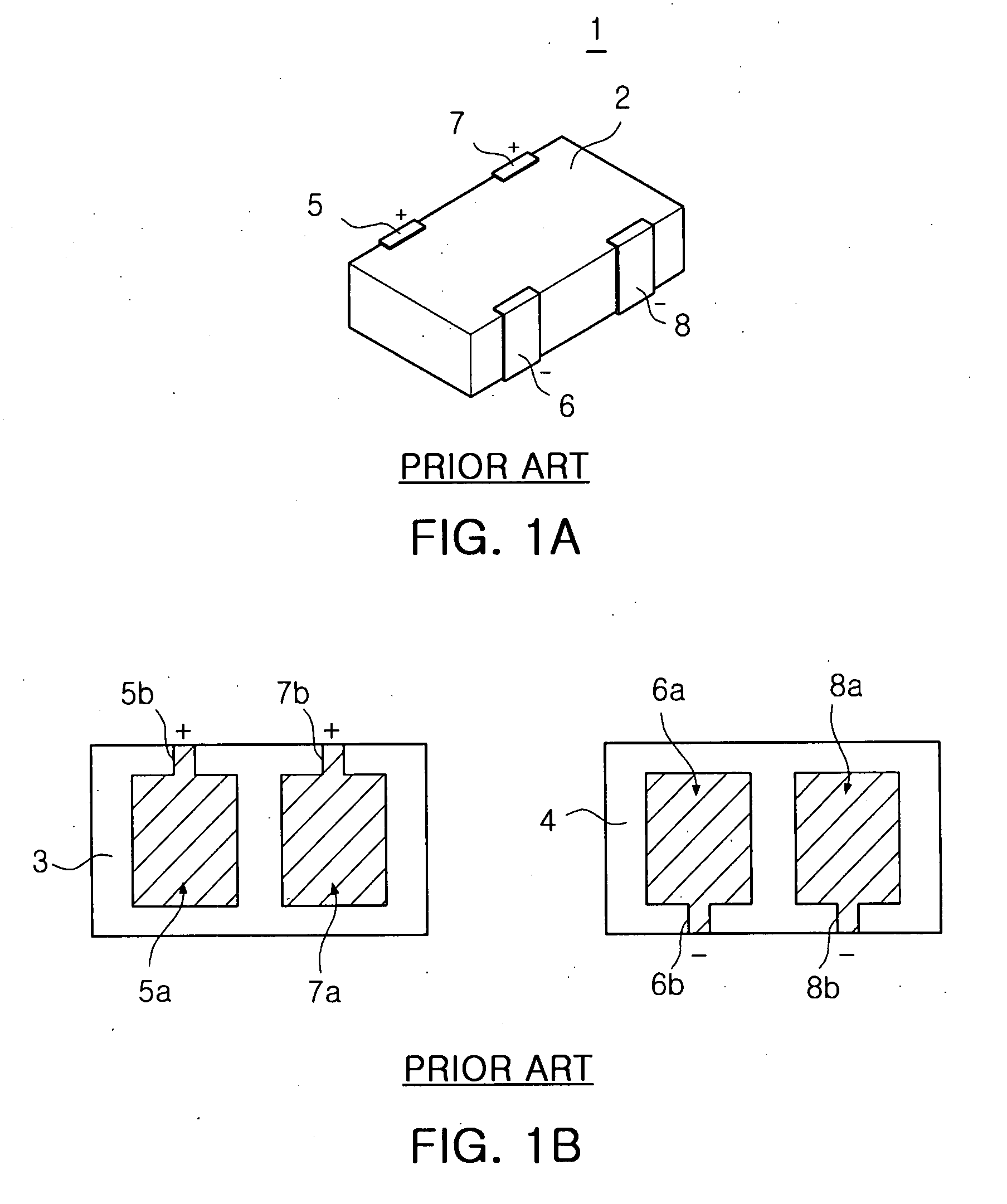

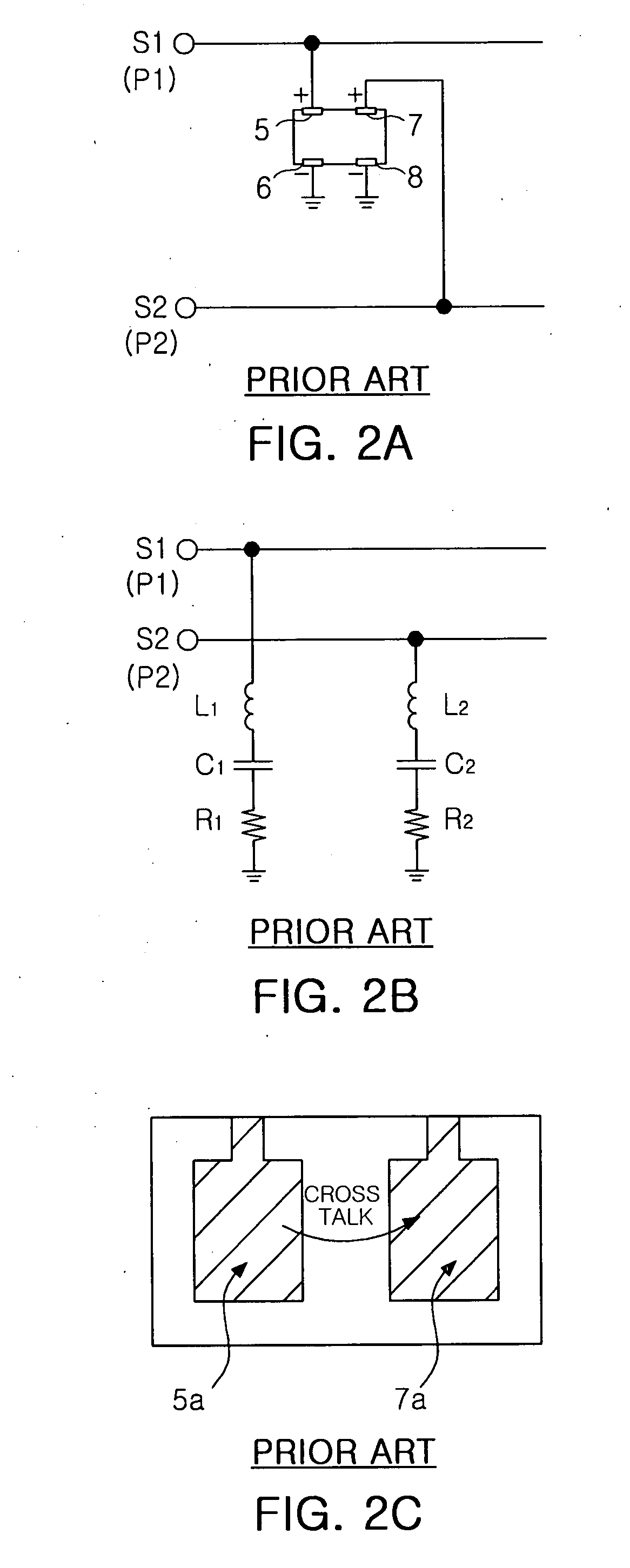

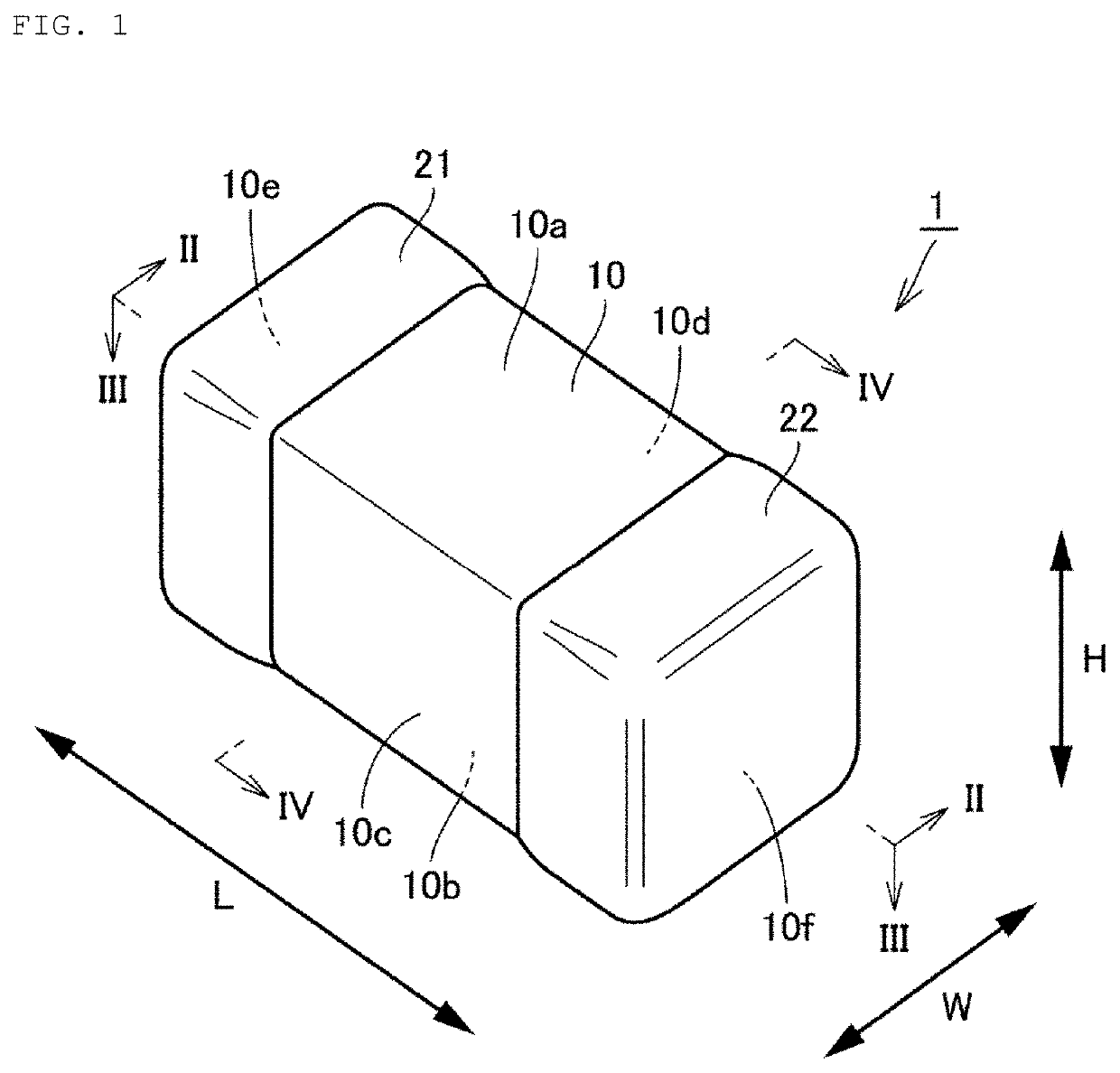

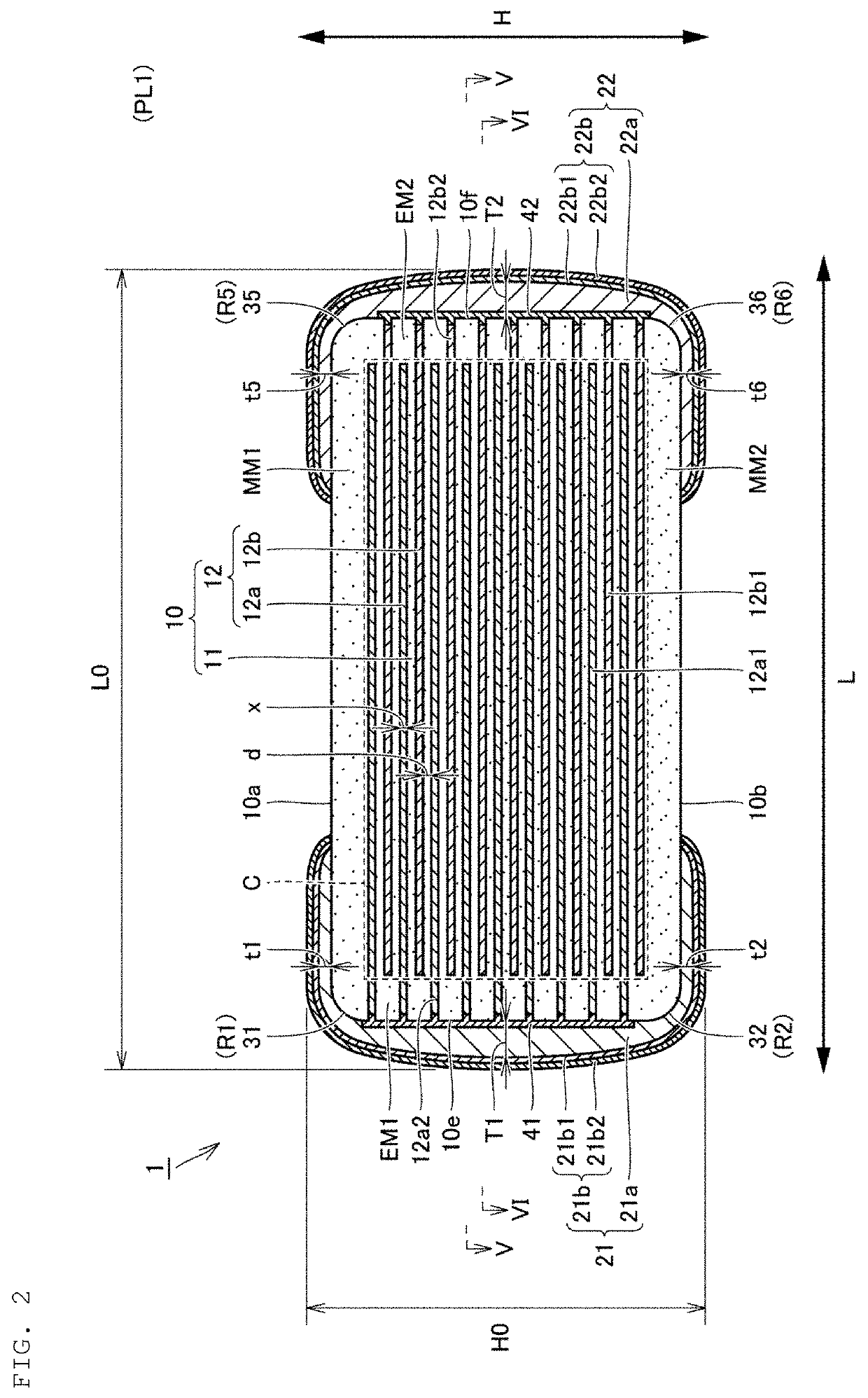

Multilayer capacitor array

ActiveUS20080158773A1High capacitancePrevent delamination and crosstalk phenomenonMultiple fixed capacitorsFixed capacitor electrodesCapacitanceSingle electrode

A multilayer capacitor array having a plurality of multilayer capacitor devices formed in a single multilayer structure, the multilayer capacitor array including: a capacitor body formed by depositing a plurality of dielectric layers and having first and second side surfaces opposite to each other; a plurality of first polarity internal electrodes and second polarity internal electrodes, disposed oppositely to each other in the capacitor body, interposing the dielectric layer there between, and formed of a single electrode plate comprising a single lead, respectively; and a plurality of first polarity external electrodes and second polarity external electrodes, formed on the first side surface and second side surface, respectively, and connected to a correspondent polarity internal electrode via the lead, the first polarity external electrode formed on the first side surface and the second polarity external electrode formed on the second side surface, wherein the numbers of the first polarity external electrodes and the second polarity external electrodes are two or more, respectively, and are identical to each other, and a total number of the multilayer capacitor devices in the multilayer capacitor array is identical to the number of the first polarity external electrodes.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Multilayer ceramic capacitor

ActiveUS20190355518A1High capacitanceEnsure moisture resistanceFixed capacitor electrodesStacked capacitorsCeramic capacitorAlloy

A multilayer ceramic capacitor includes a laminate including dielectric layers and internal electrode layers, and first and second external electrodes respectively including first and second base electrode layers. The internal electrode layers, and the first and second base electrode layers are connected through first and second alloy layers that cover first and second end surfaces of the laminate. A predetermined portion of ridges between each of the first and second end surfaces, and each of first and second principal surfaces and first and second side surfaces, among ridges of the laminate, has a curvature radius of about 5.4 μm or more and about 10 μm or less, and the first and second external electrodes extend from the first and second end surfaces to cover the ridges.

Owner:MURATA MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com