Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3425 results about "Ceramic capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

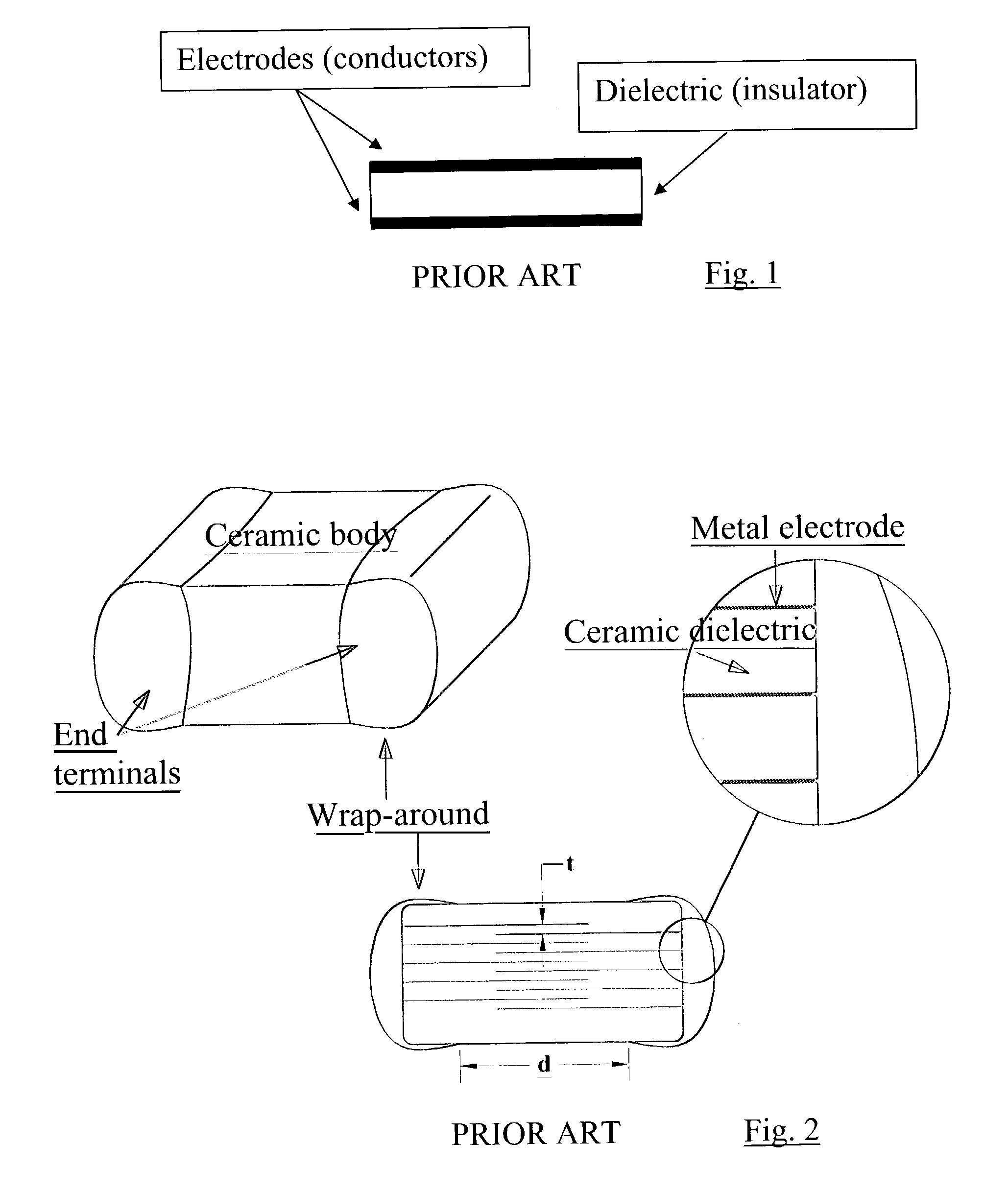

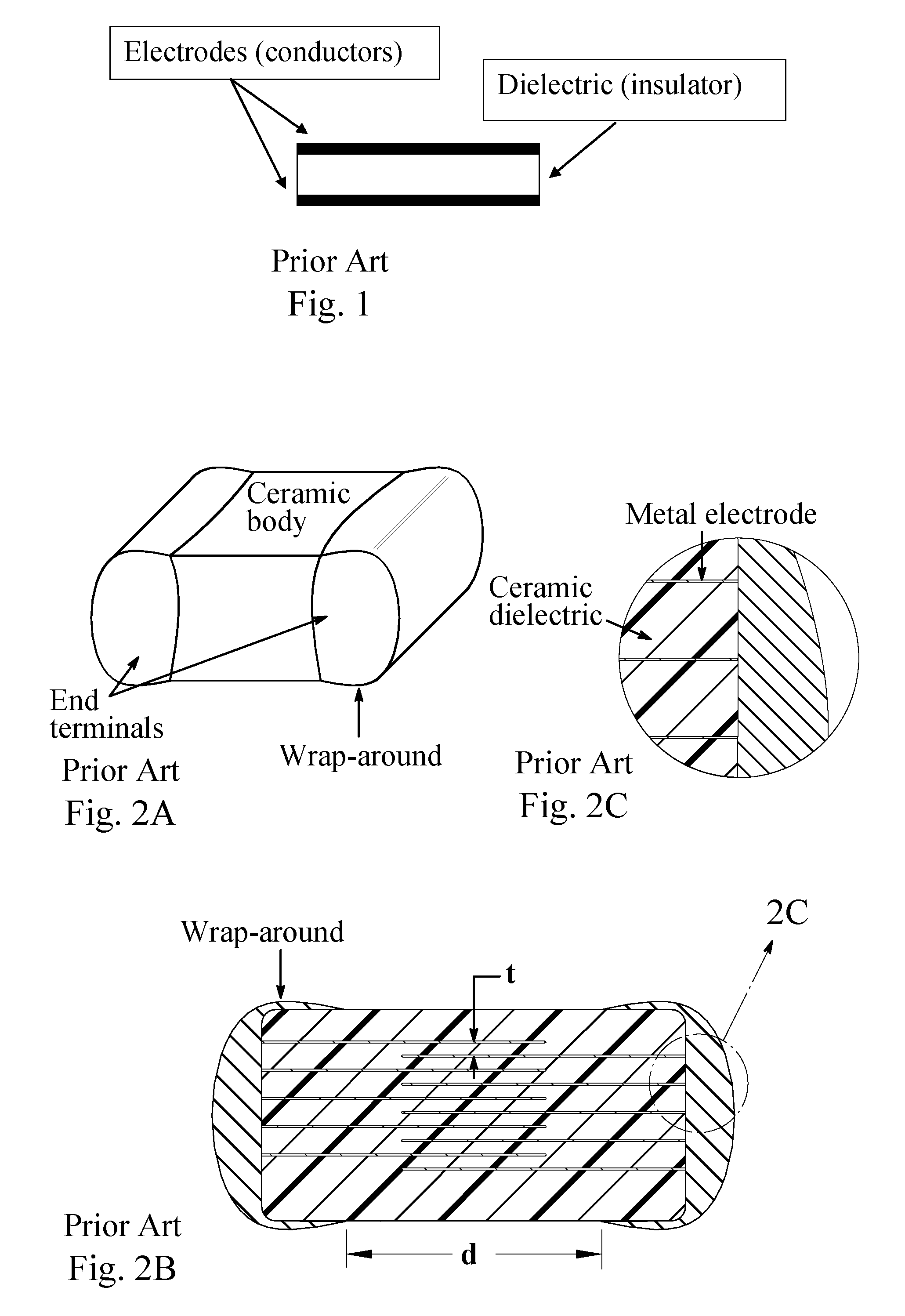

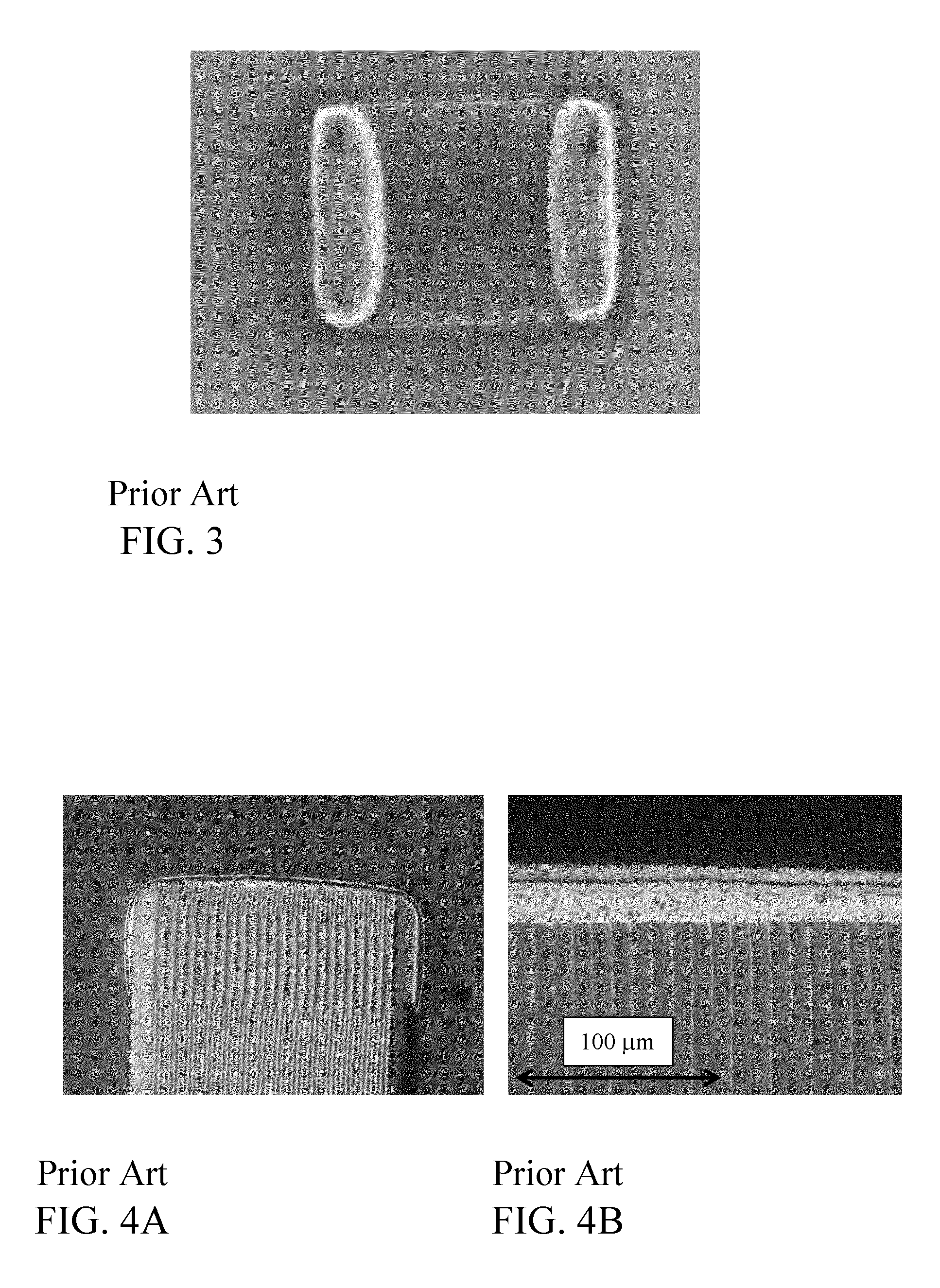

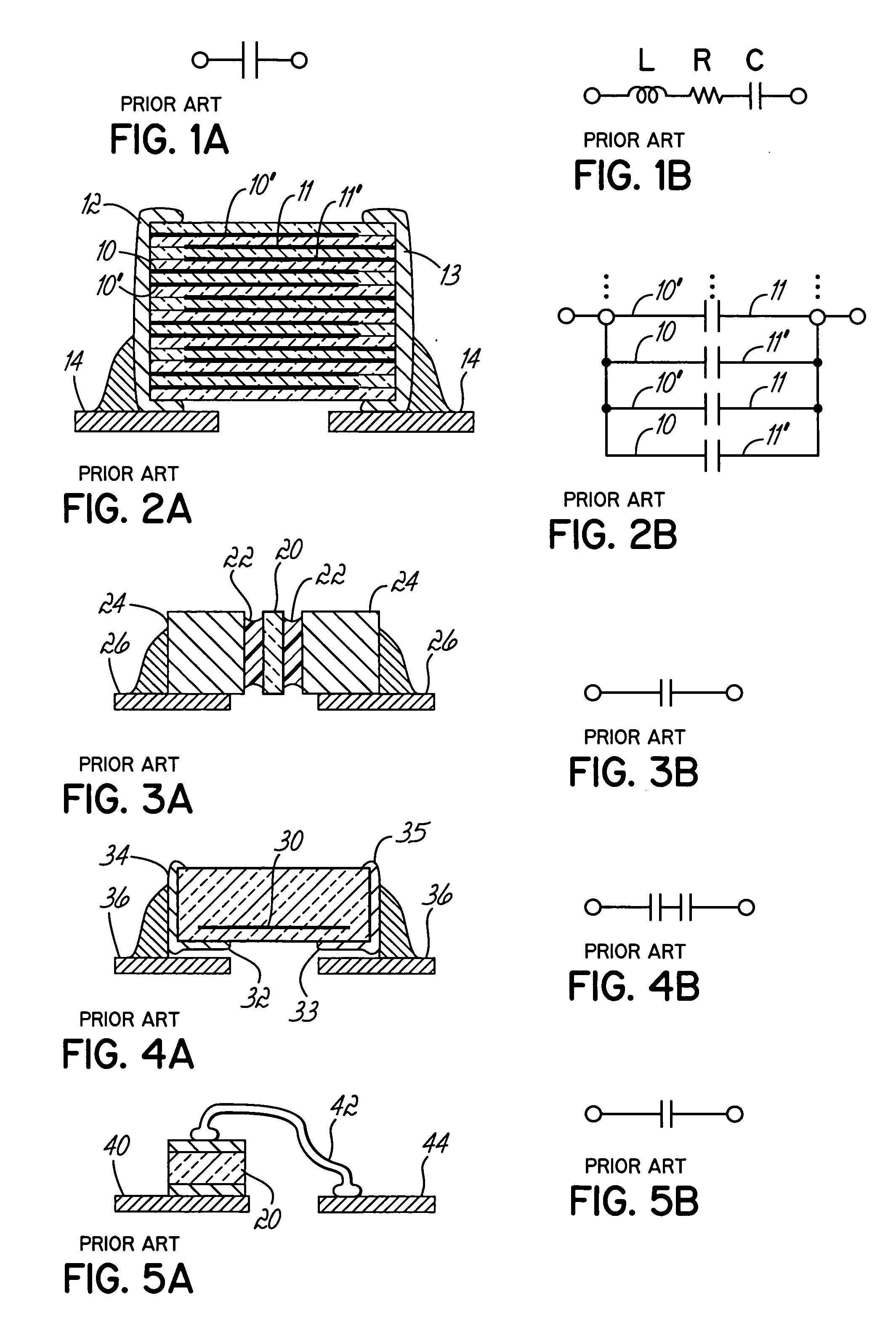

A ceramic capacitor is a fixed-value capacitor where the ceramic material acts as the dielectric. It is constructed of two or more alternating layers of ceramic and a metal layer acting as the electrodes. The composition of the ceramic material defines the electrical behavior and therefore applications.

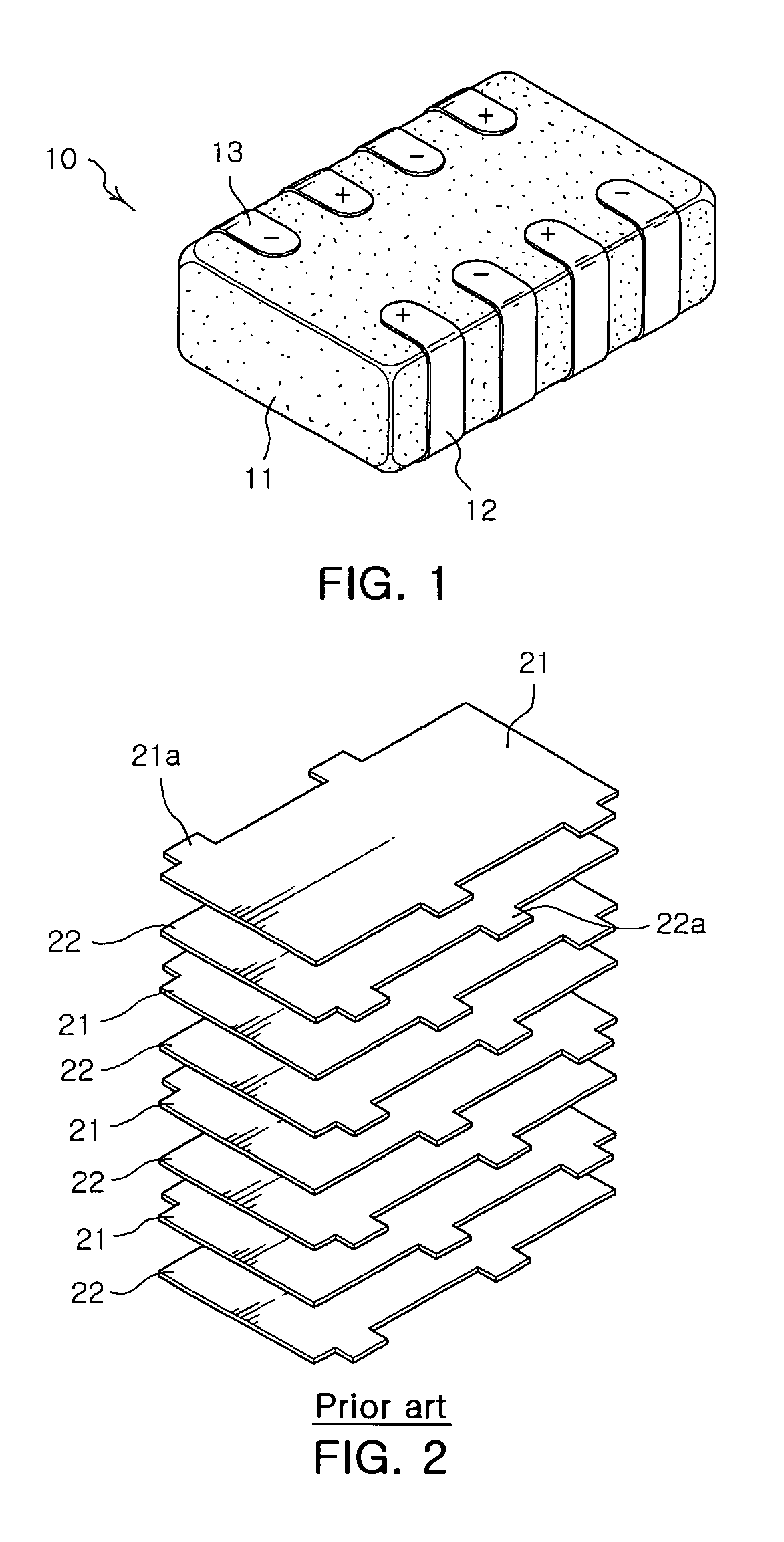

Multilayer ceramic capacitor with terminal formed by electroless plating

InactiveUS7345868B2High strengthFixed capacitor electrodesFixed capacitor dielectricElectrolysisCeramic capacitor

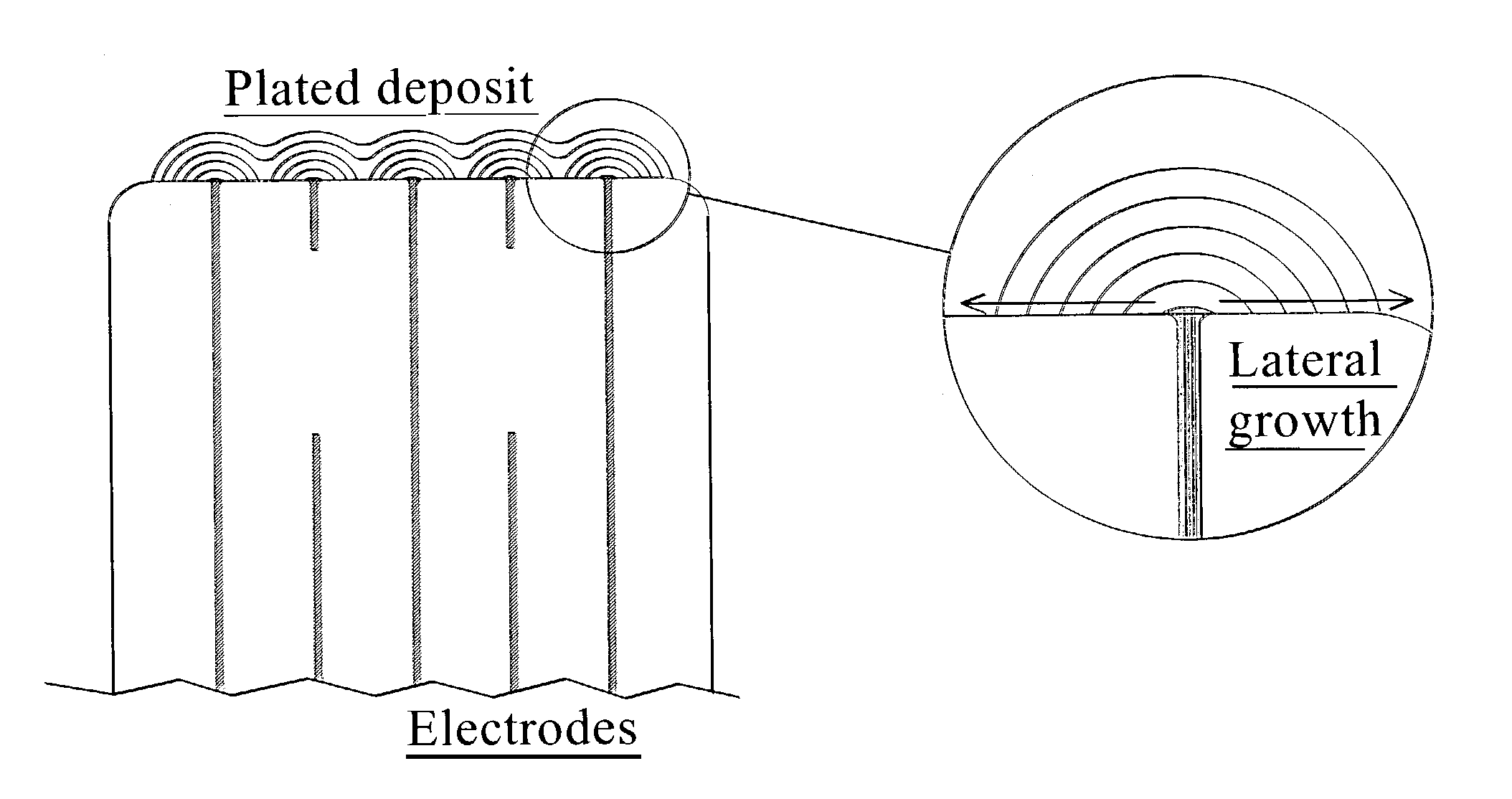

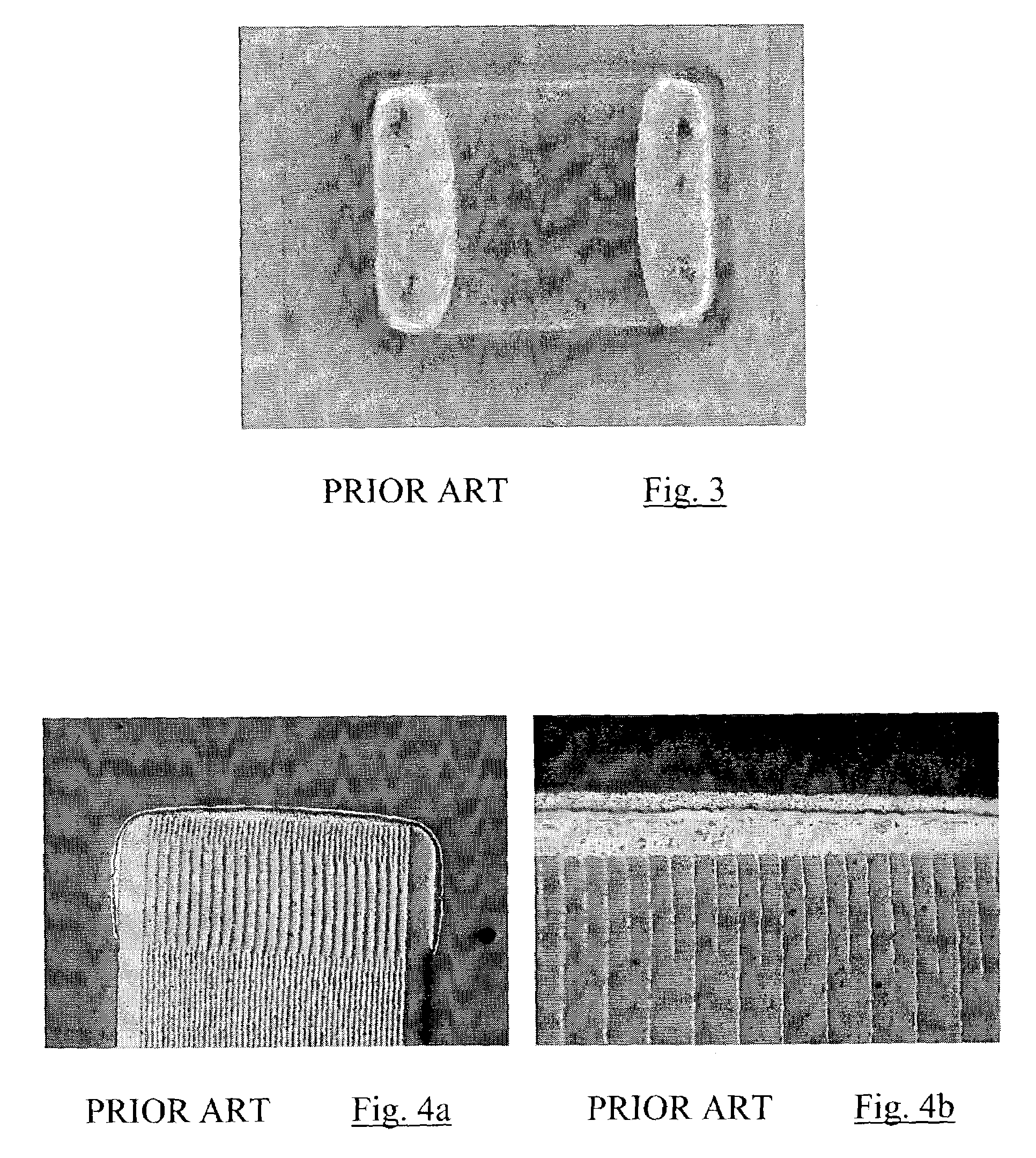

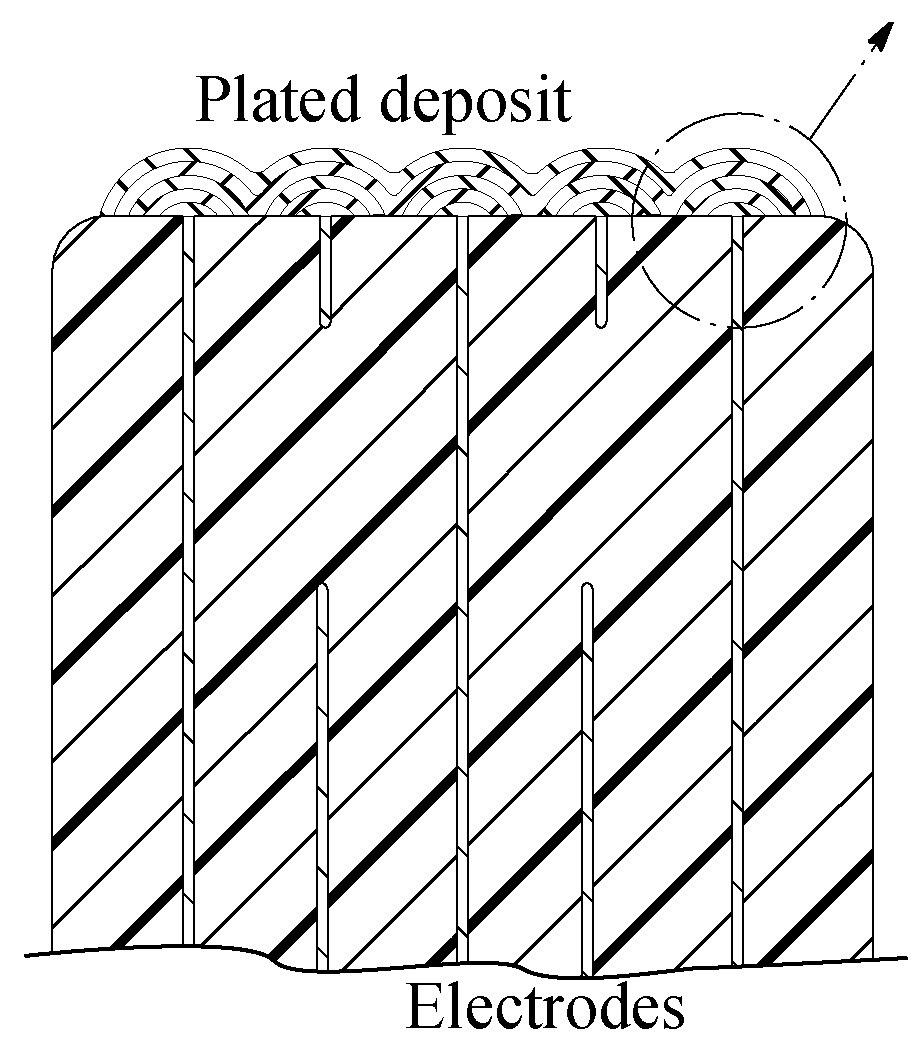

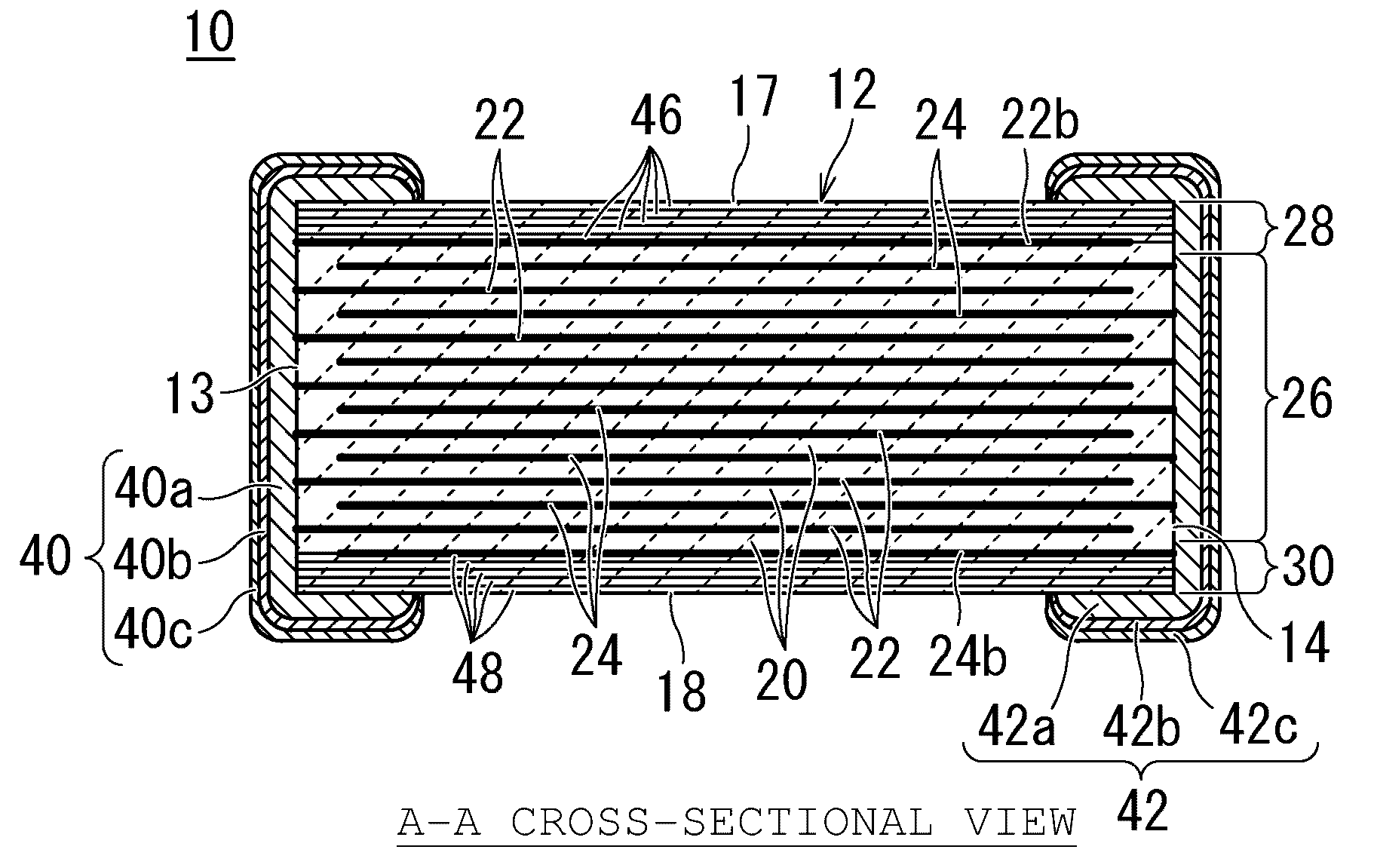

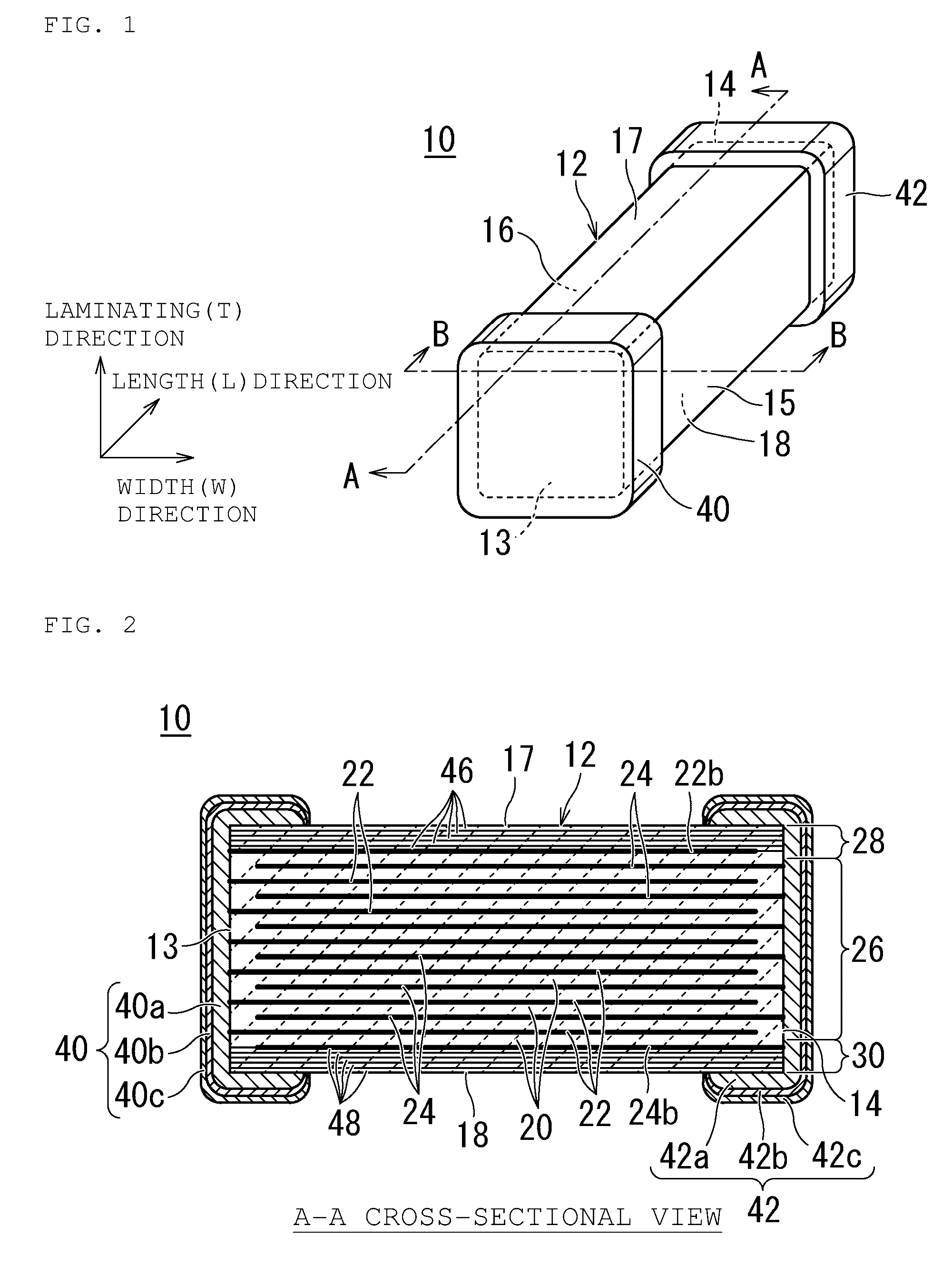

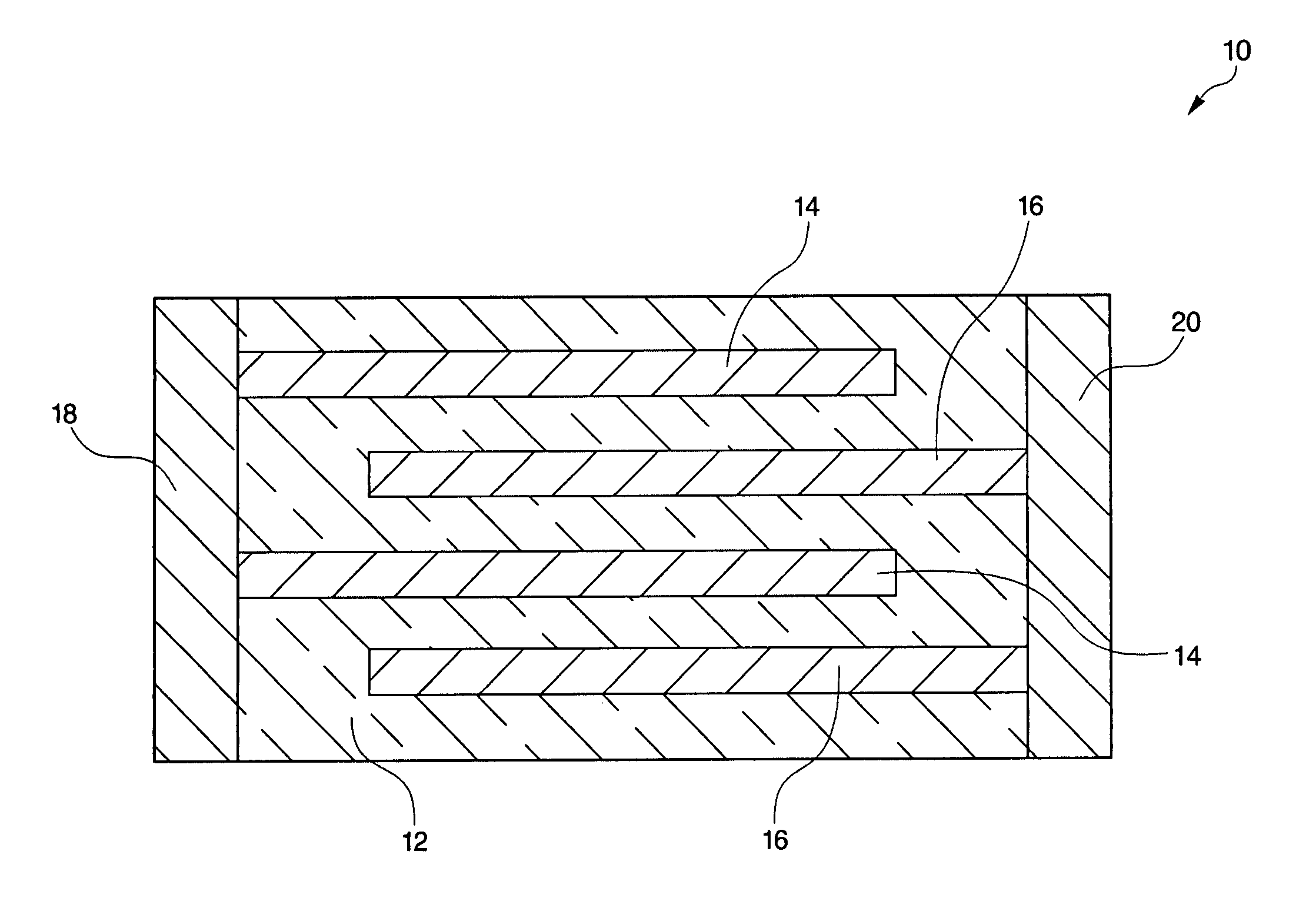

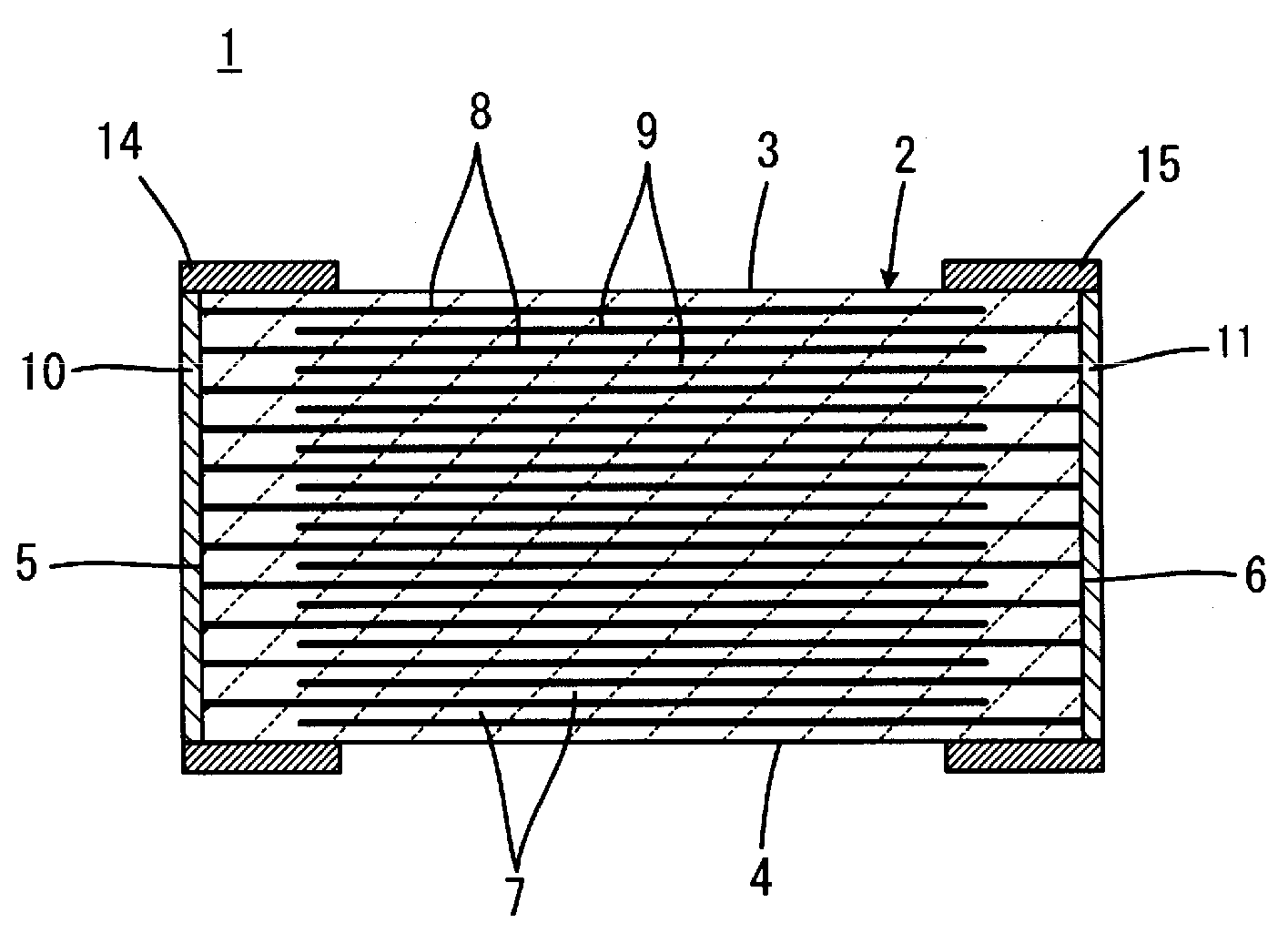

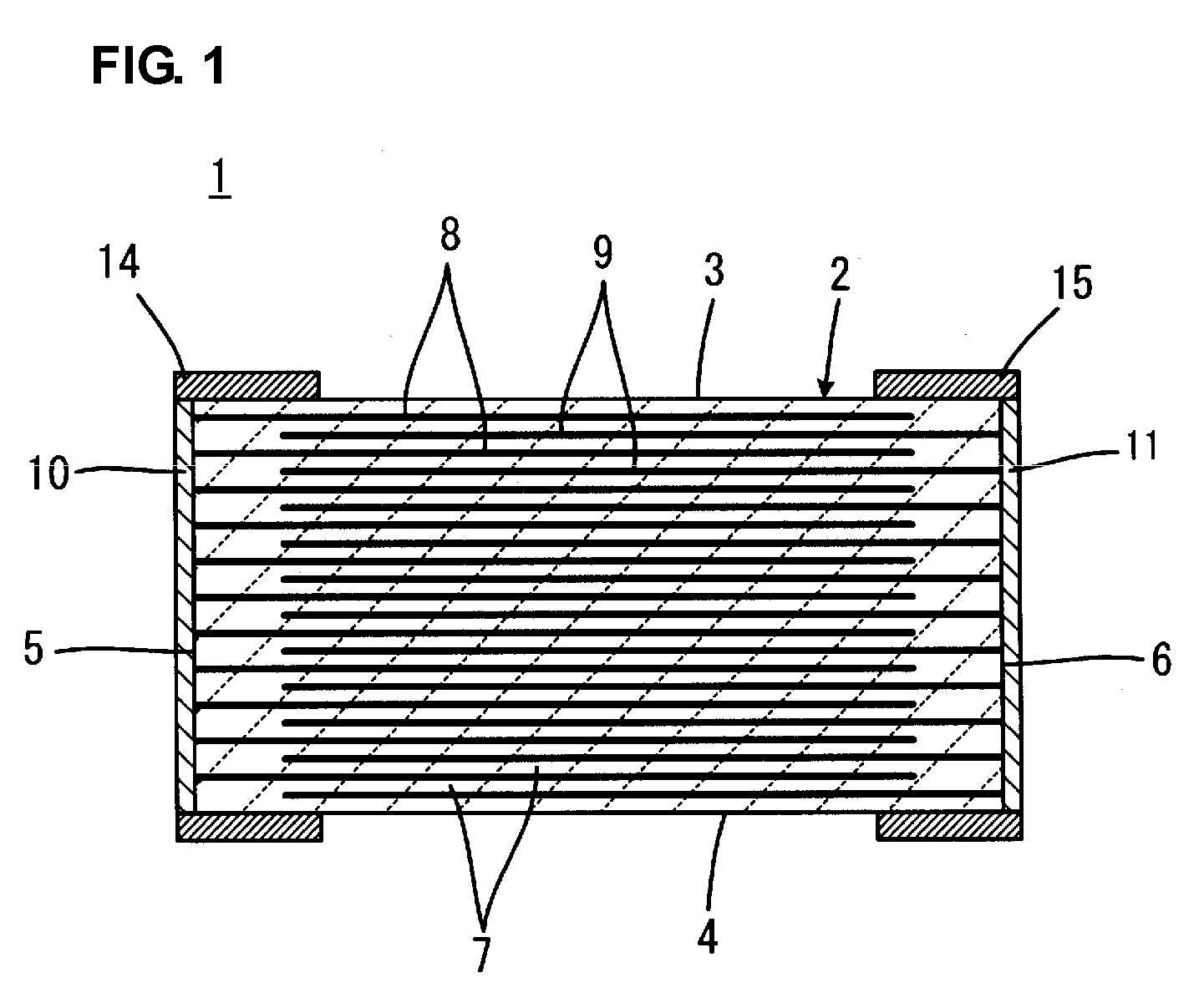

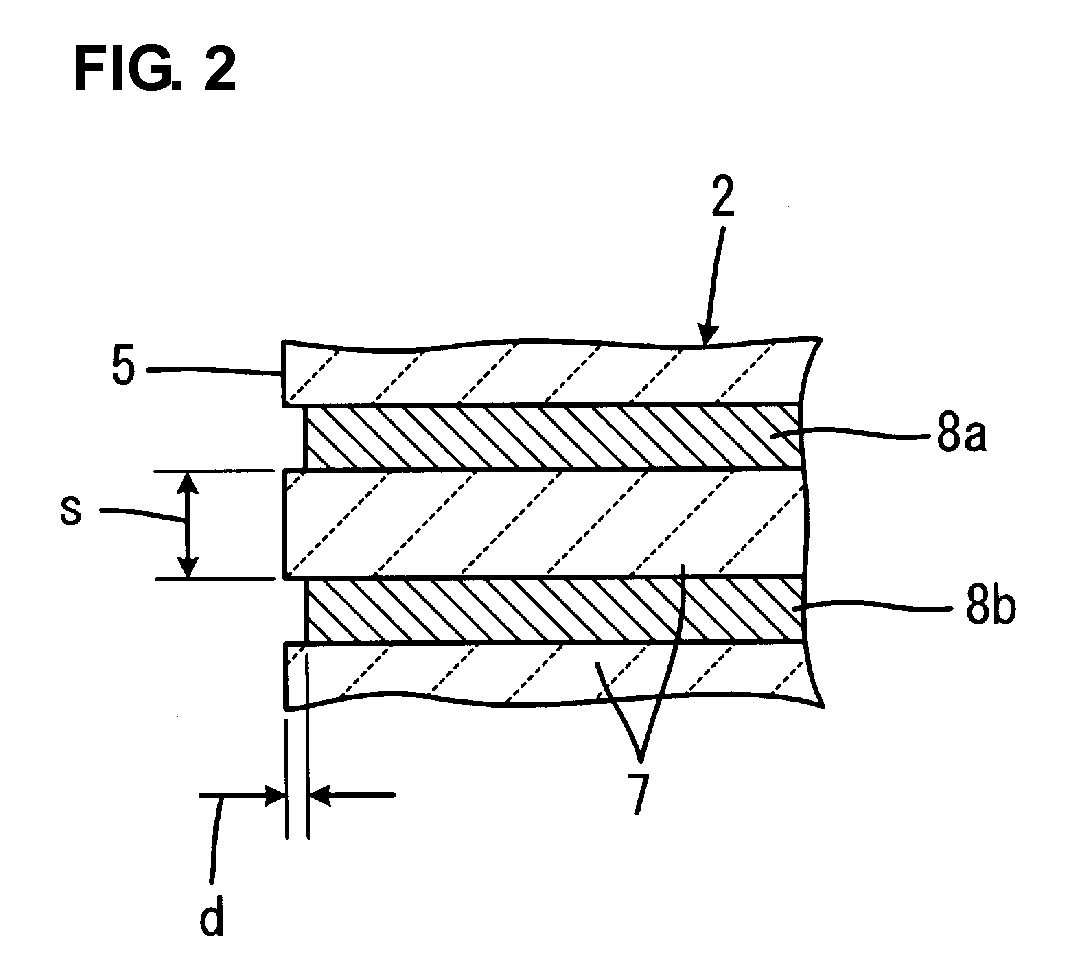

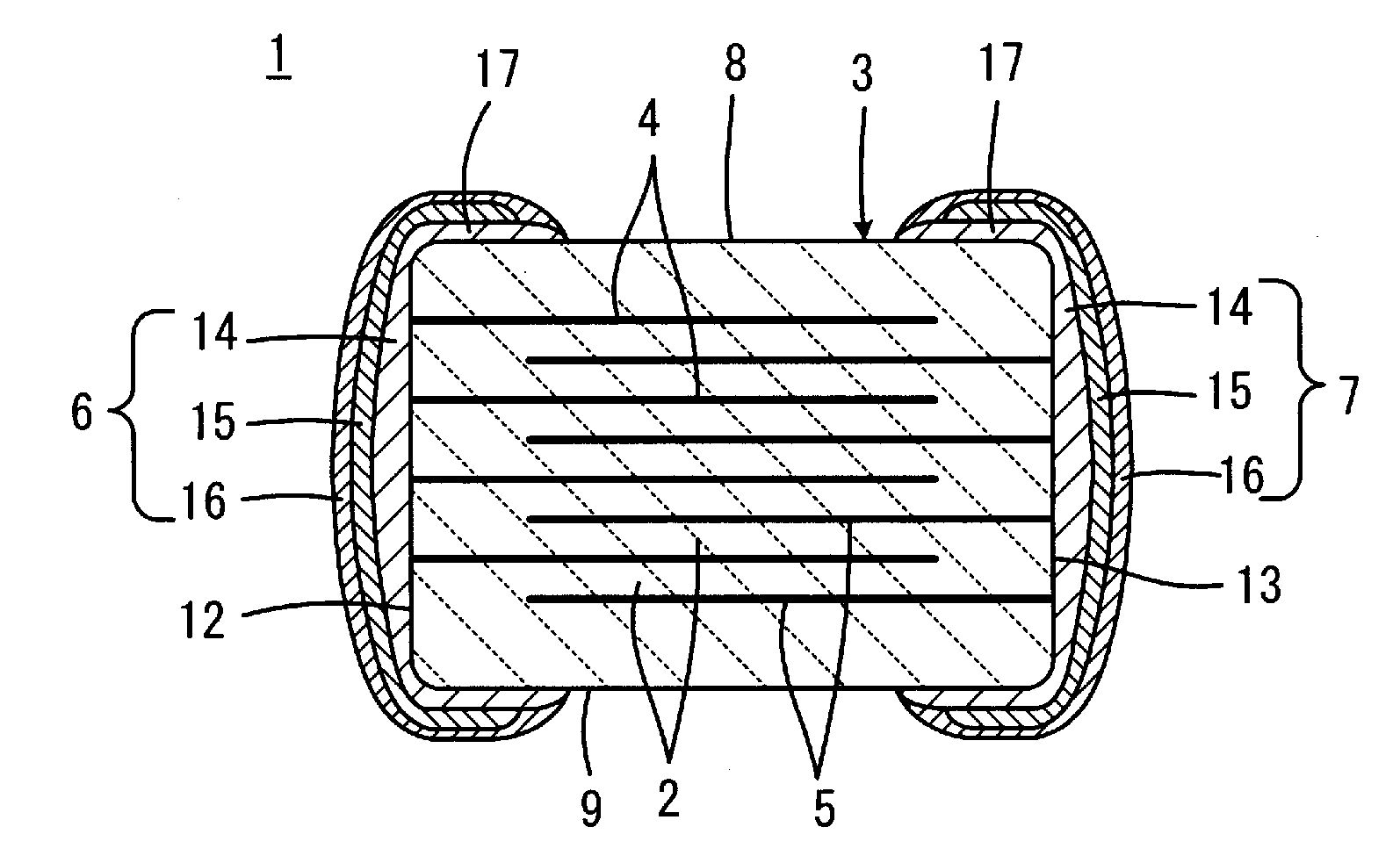

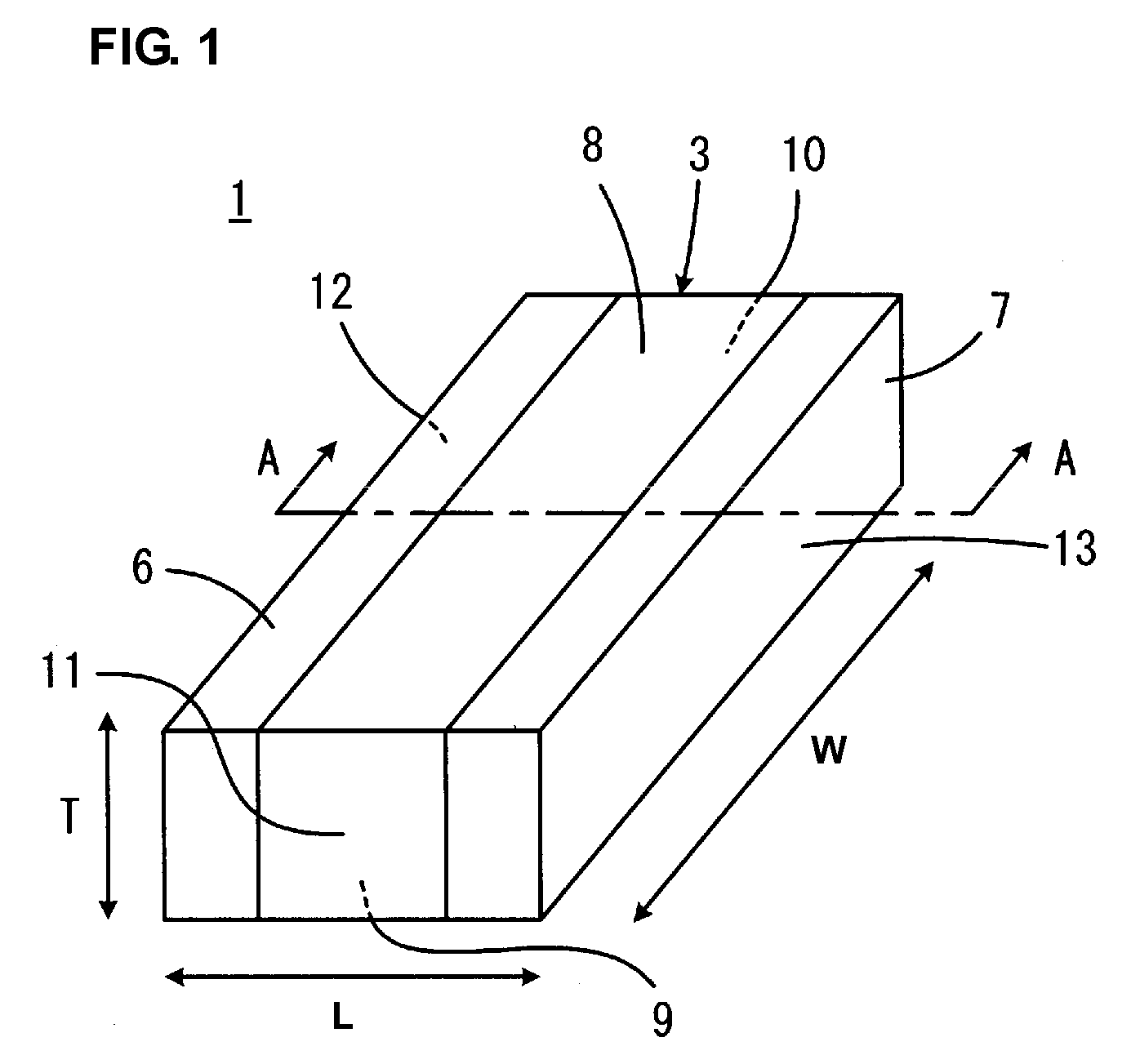

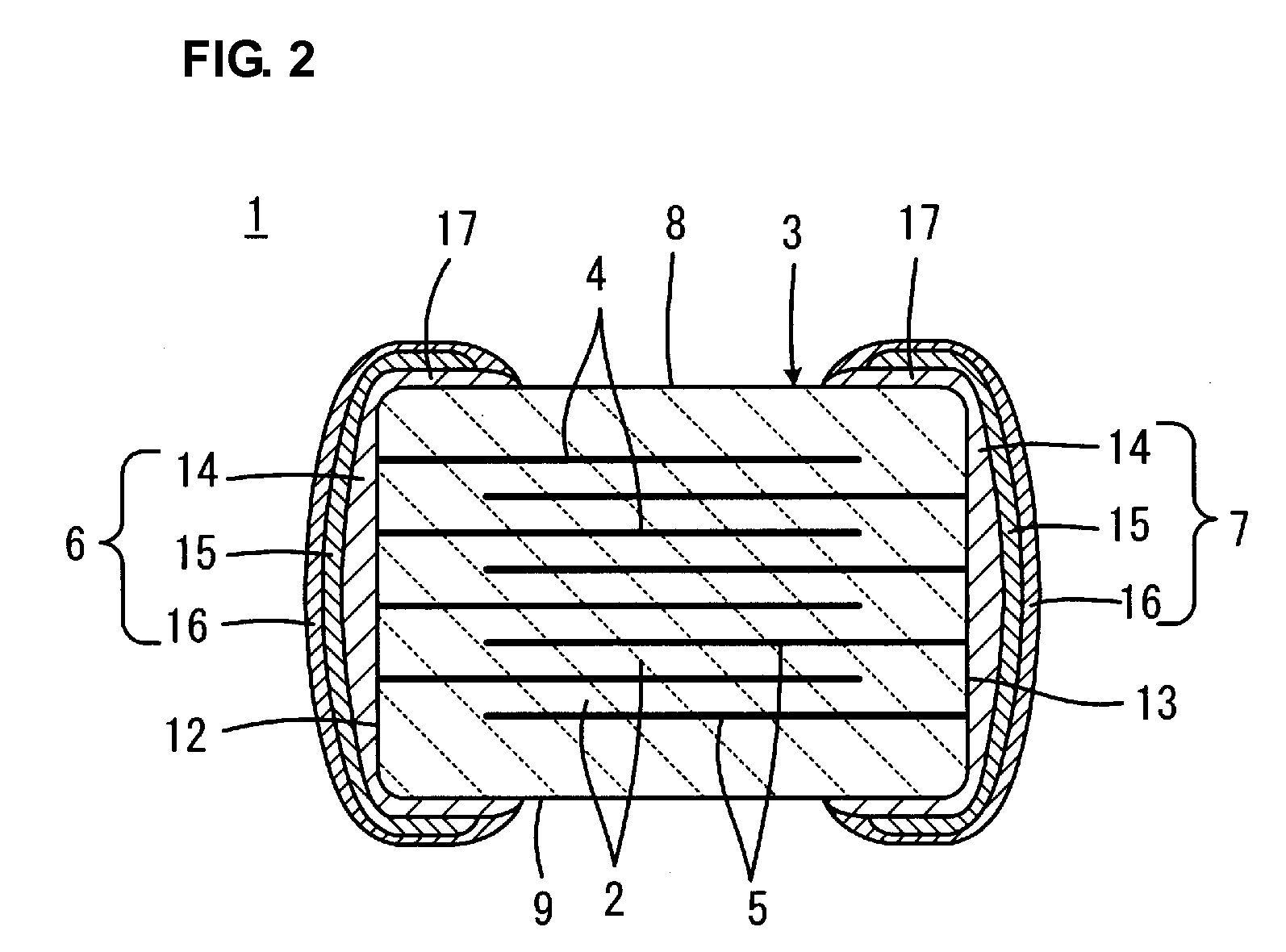

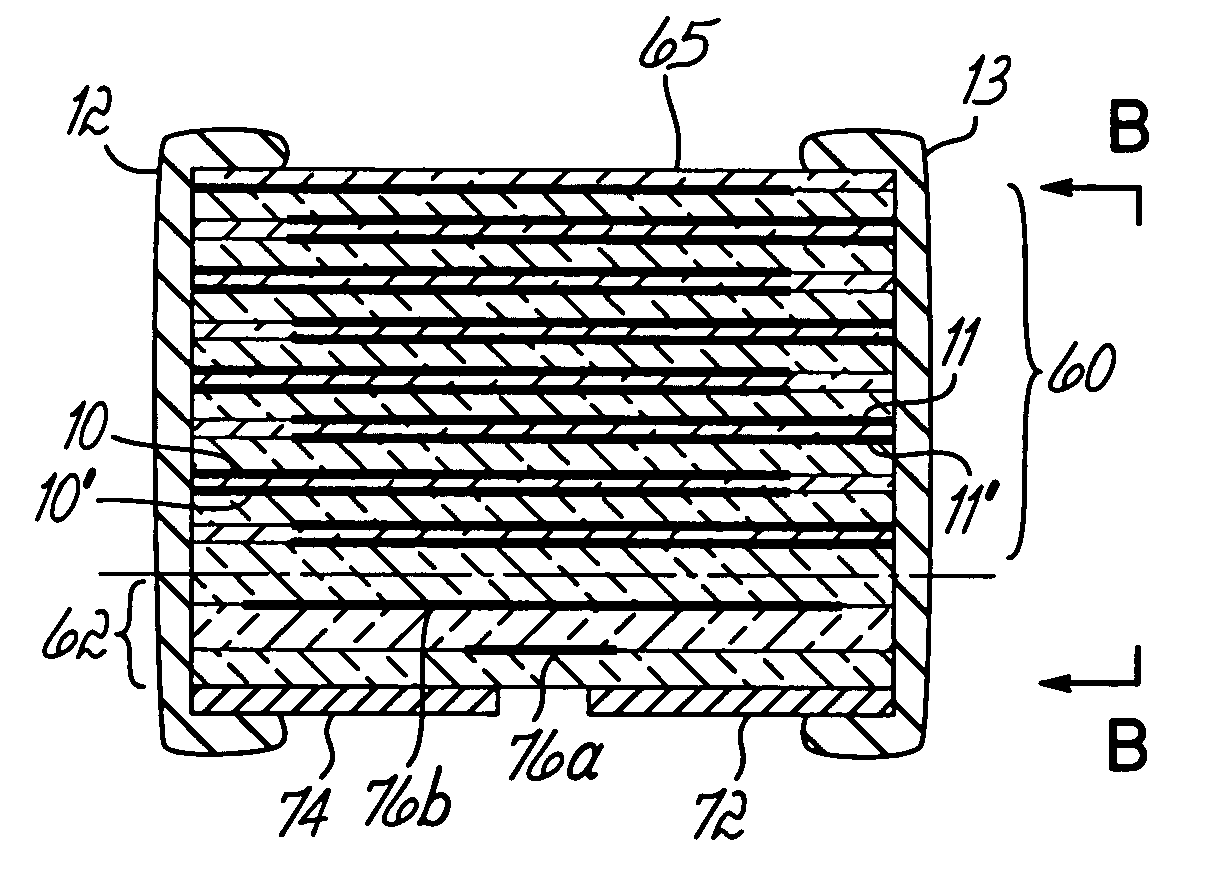

A terminal to, most commonly, a ceramic capacitor, most commonly a multilayer ceramic capacitor (MLCC), is formed by electroless plating, also known as electroless deposition or simply as electrodeposition. In the MLCC having a multiple parallel interior plates brought to, and exposed at, at least one, first, surface, an electrically-conductive first-metal layer, preferably Cu, is electrolessly deposited upon this first surface directly in contact with, mechanically connected to, and electrically connected to, the edges of these interior plates. Lateral growth of the electrolessly-deposited first-metal is sufficient to span from exposed plate to exposed plate, electrically connecting the plates. One or more top layers, preferably one of Ni and one of Sn and Pb, are deposited, preferably by plating and more preferably by electrolytic plating, on top of the electrolessly-deposited Cu.

Owner:PRESIDIO COMPONENTS

Multilayer ceramic capacitor with terminal formed by electroless plating

InactiveUS20080158774A1High strengthFixed capacitor electrodesFixed capacitor dielectricCeramic capacitorElectroless deposition

A terminal to, most commonly, a ceramic capacitor, most commonly a multilayer ceramic capacitor (MLCC), is formed by electroless plating, also known as electroless deposition or simply as electrodeposition. In the MLCC having a multiple parallel interior plates brought to, and exposed at, at least one, first, surface, an electrically-conductive first-metal layer, preferably Cu, is electrolessly deposited upon this first surface directly in contact with, mechanically connected to, and electrically connected to, the edges of these interior plates. Lateral growth of the electrolessly-deposited first-metal is sufficient to span from exposed plate to exposed plate, electrically connecting the plates. One or more top layers, preferably one of Ni and one of Sn and Pb, are deposited, preferably by plating and more preferably by electrolytic plating, on top of the electrolessly-deposited Cu.

Owner:PRESIDIO COMPONENTS

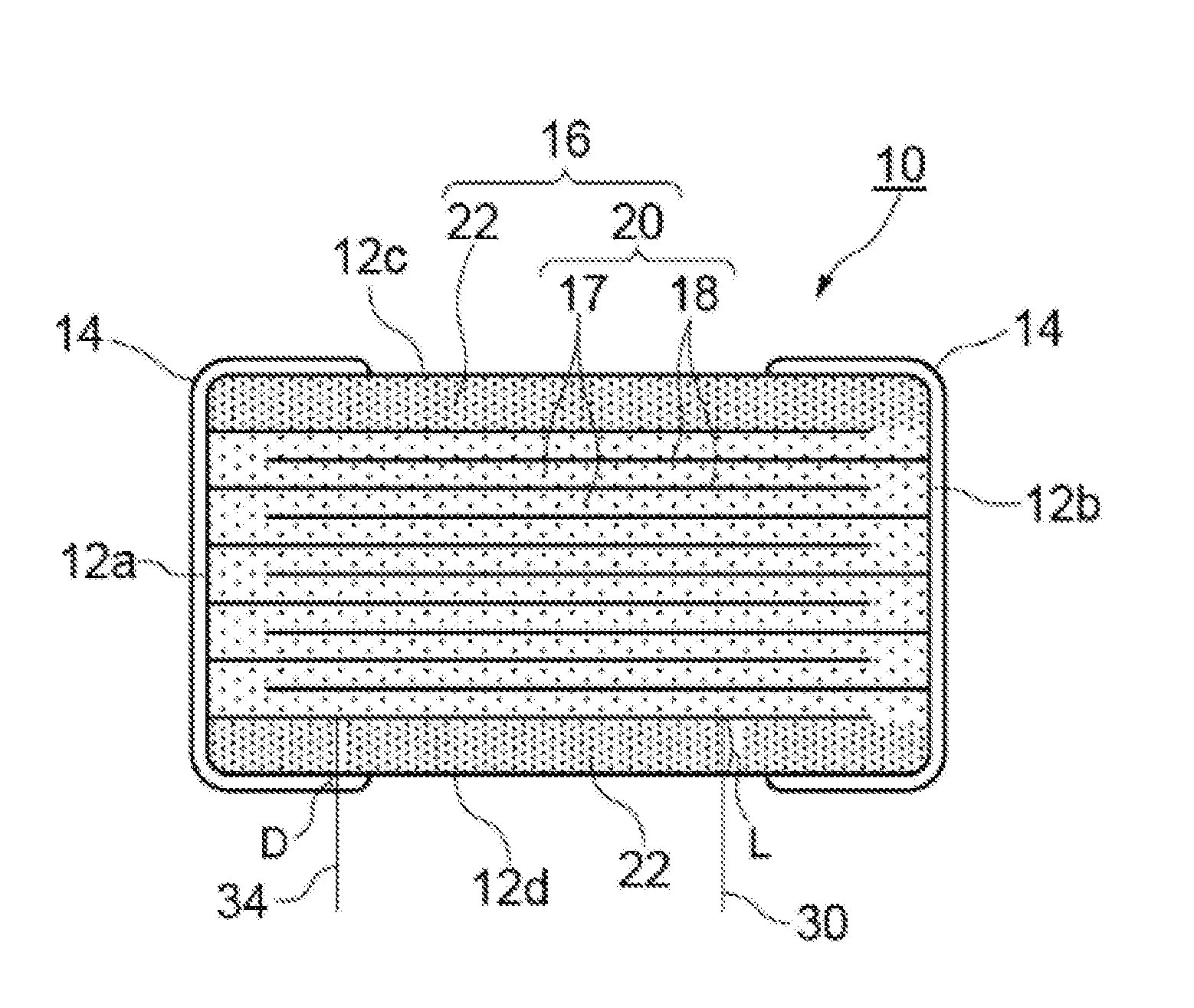

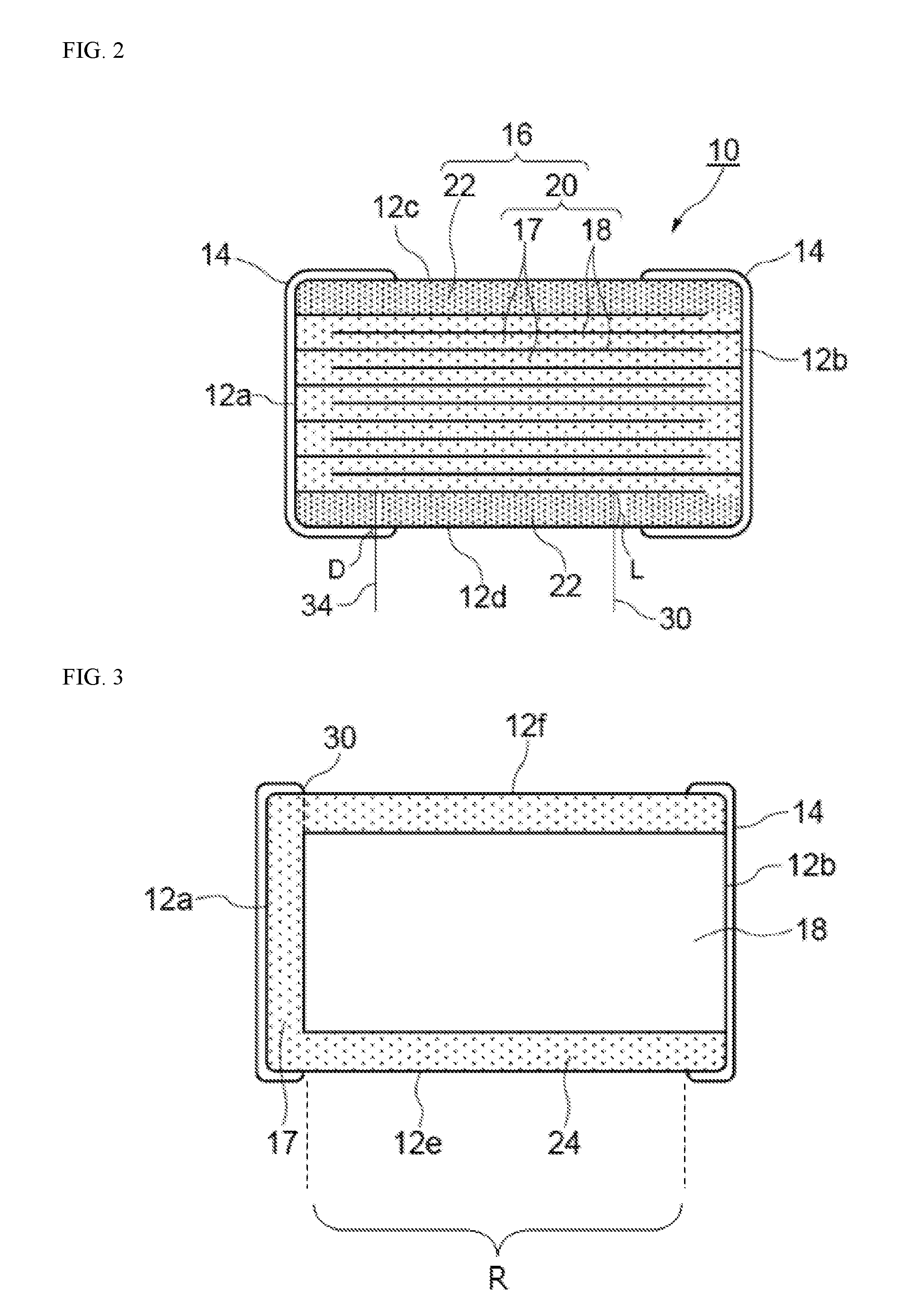

Multilayer ceramic capacitor

ActiveUS20170018363A1Solve the lack of reliabilityImprove side strengthFixed capacitor electrodesFixed capacitor dielectricCeramic capacitorMaterials science

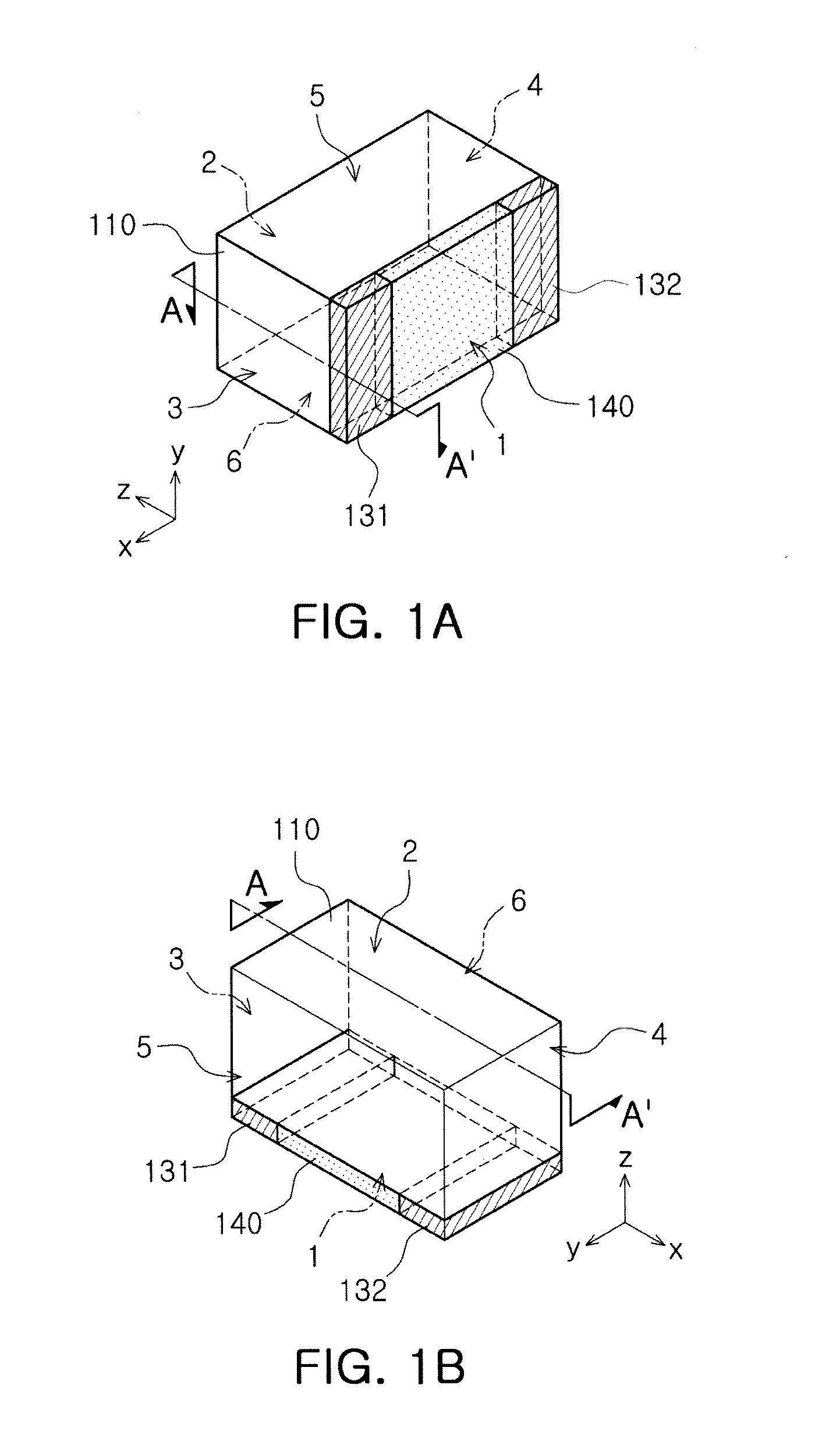

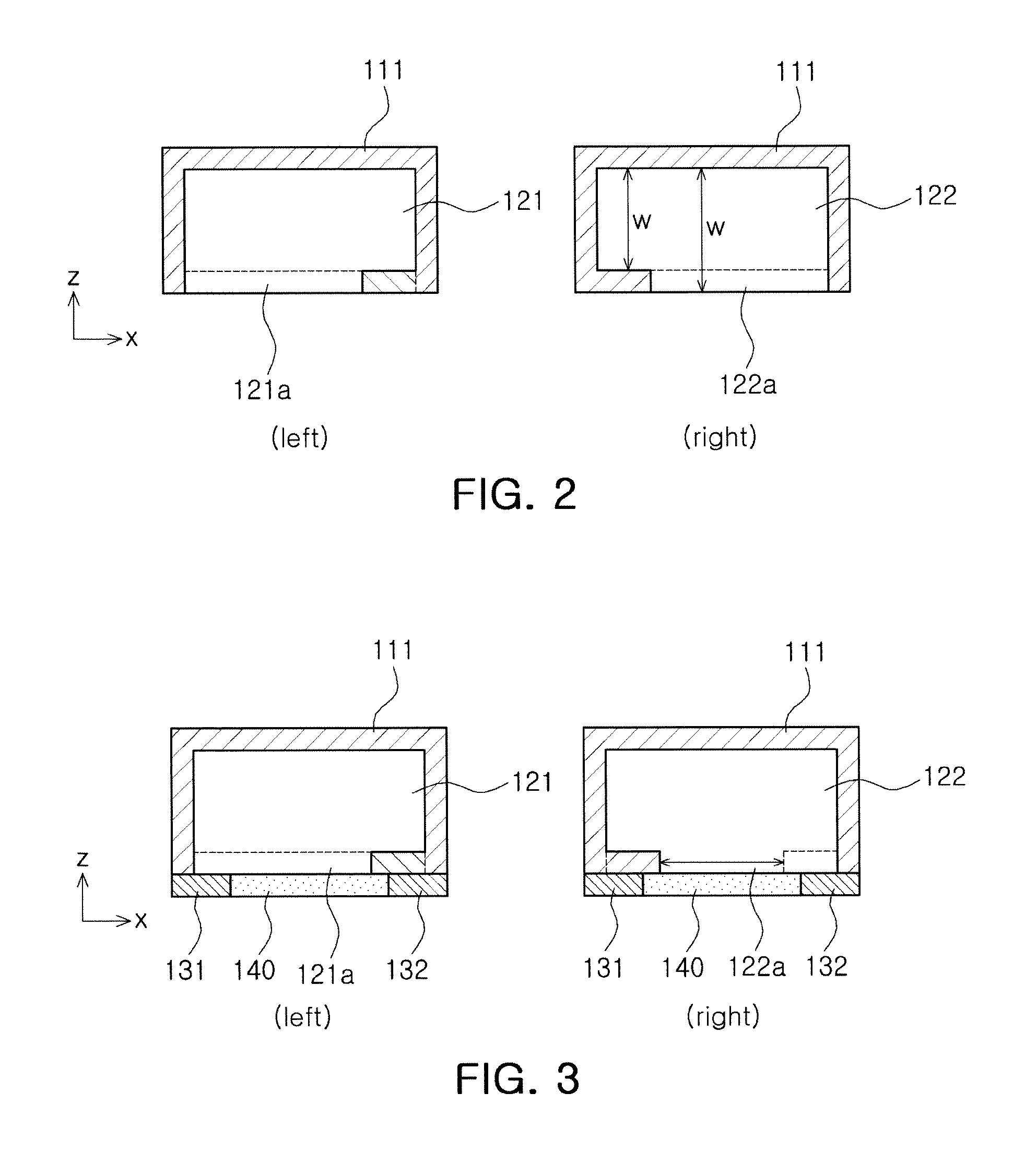

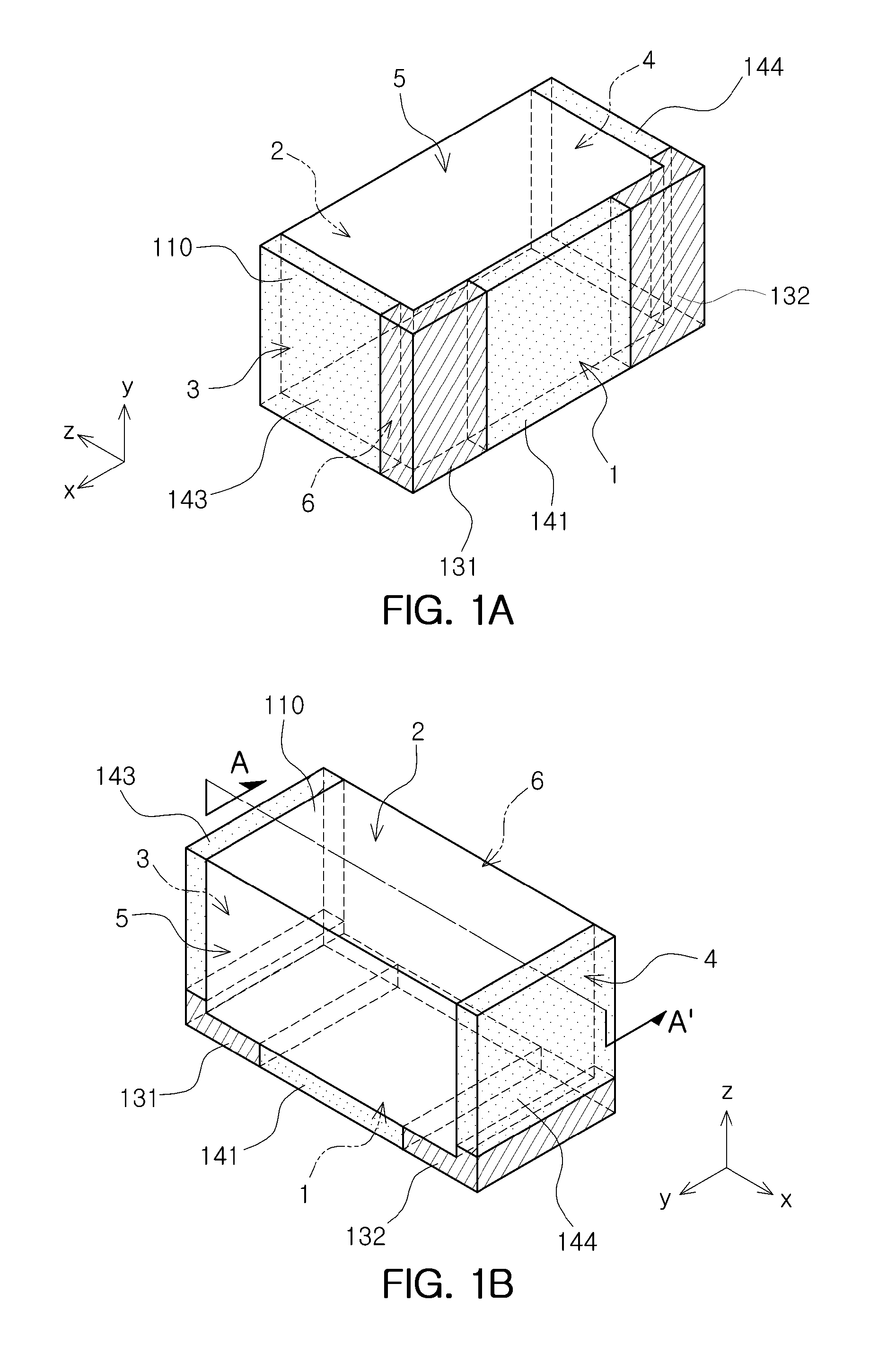

A multilayer ceramic capacitor includes a laminated body and first and second external electrodes respectively on both end surfaces of the laminated body. When regions where first internal electrodes or second internal electrodes are not present are regarded as side margin portions in a cross section of the laminated body as viewed from the laminating direction, the side margin portions include multiple side margin layers, and the content of Si in the side margin layer closest to the internal electrode is lower than that in the side margin layer other than the side margin layer closest to the internal electrode.

Owner:MURATA MFG CO LTD

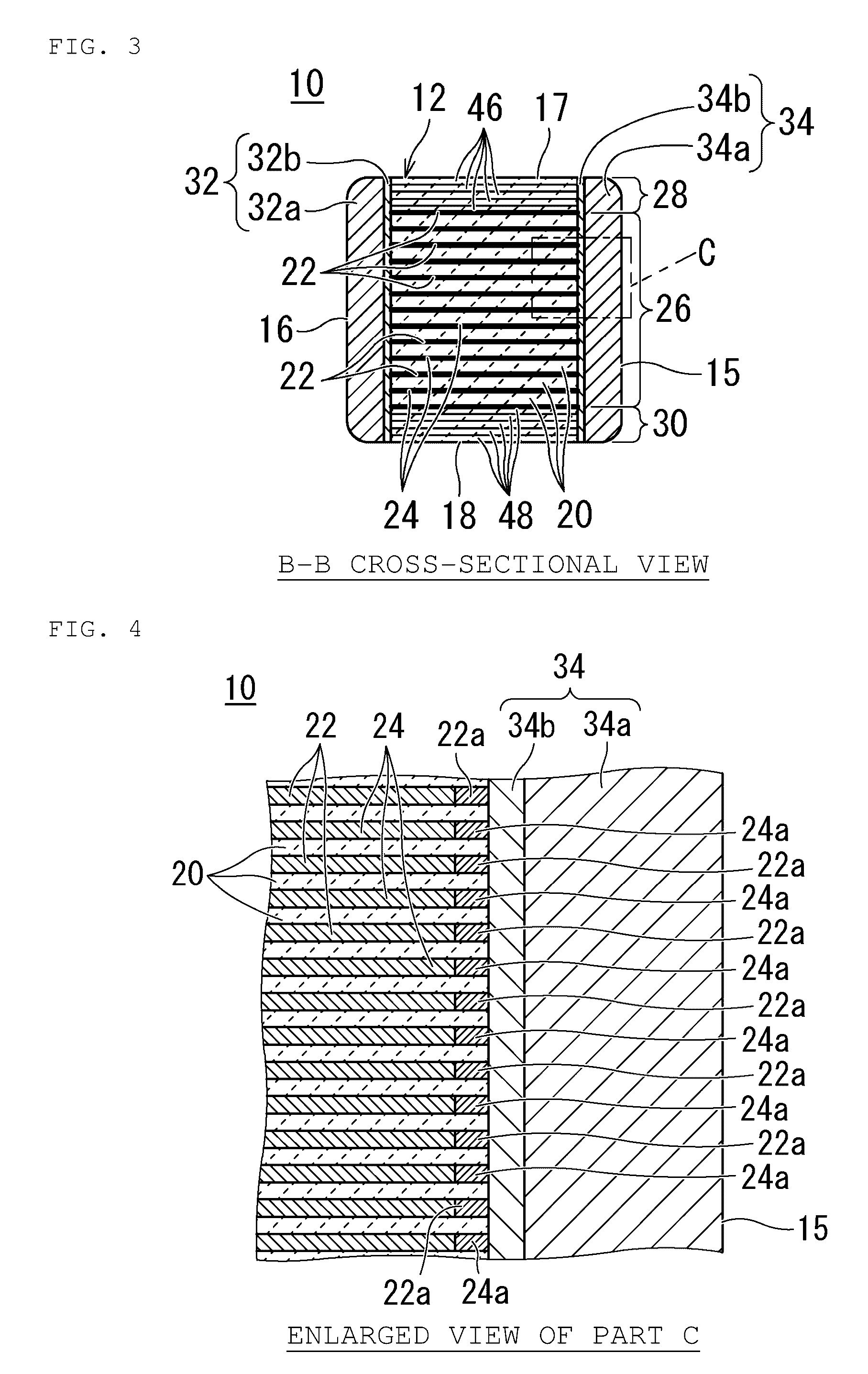

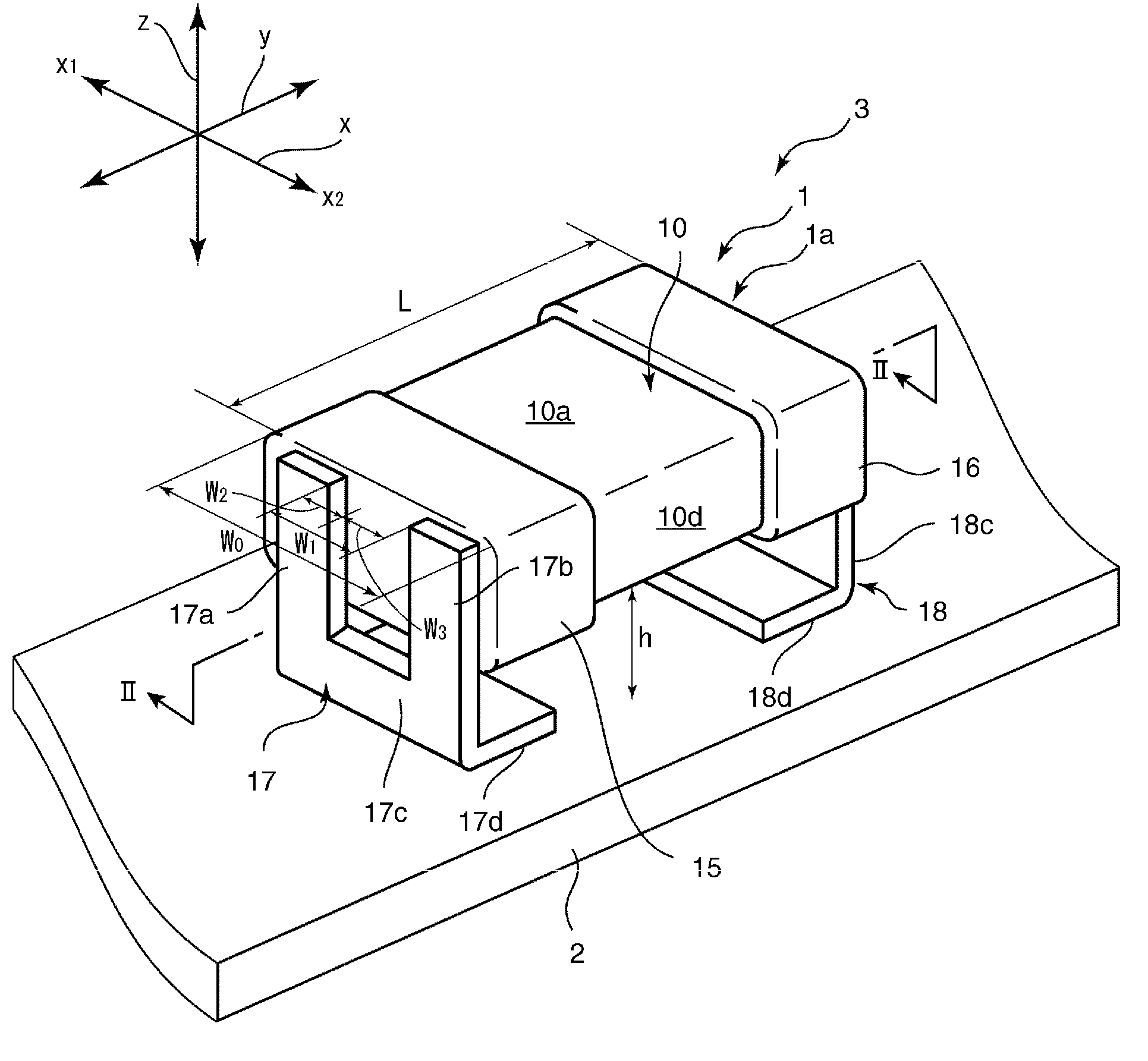

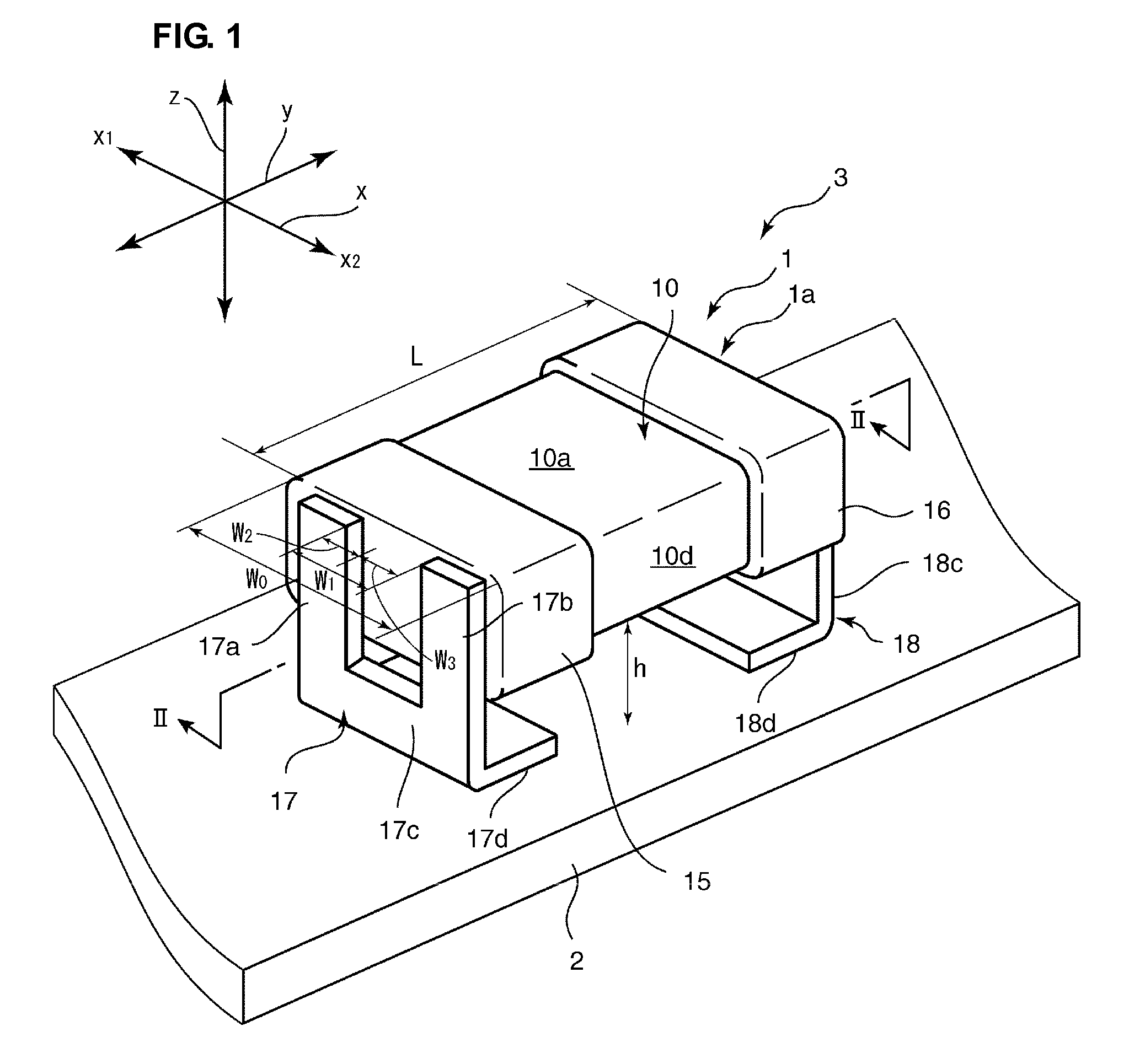

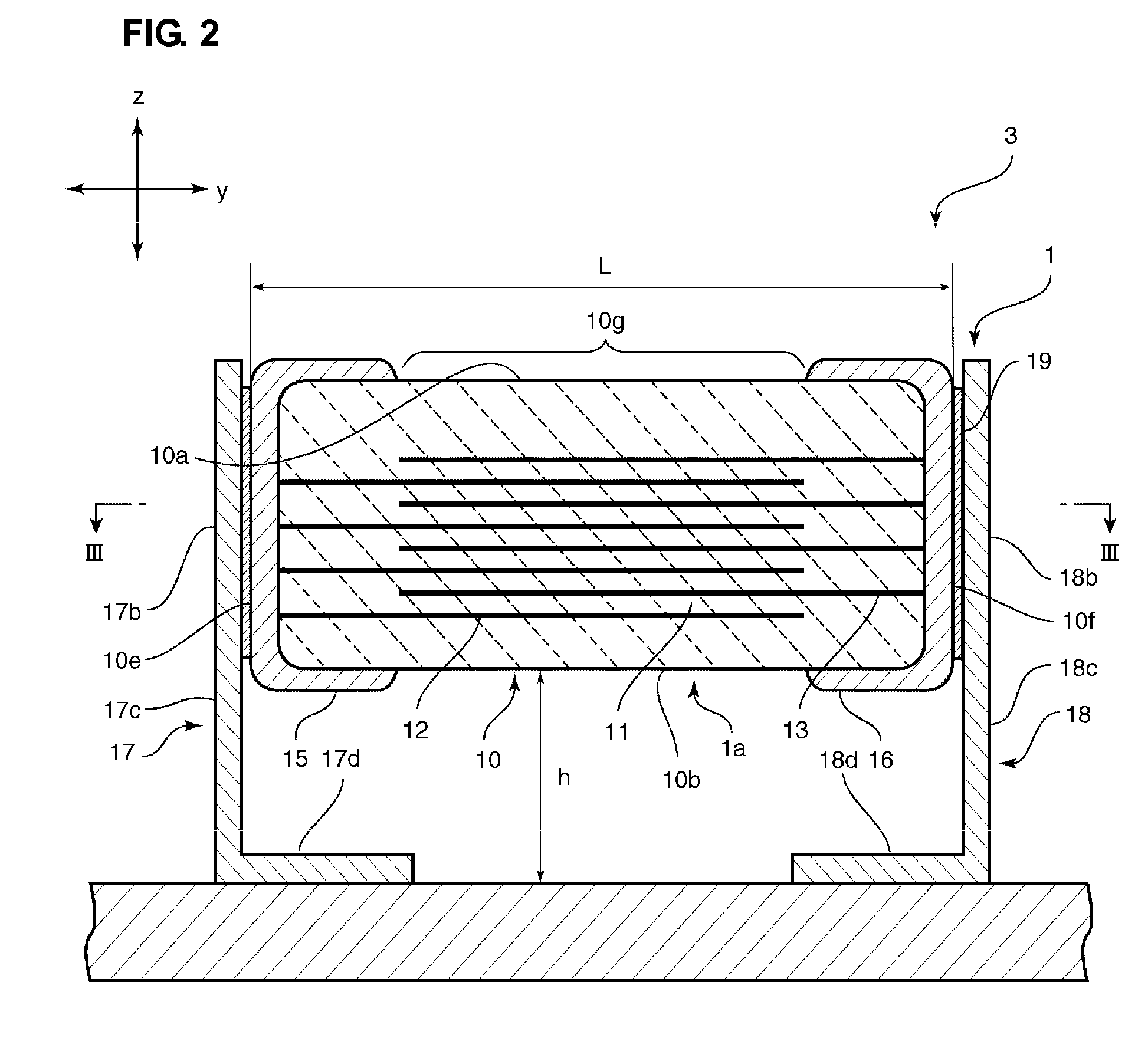

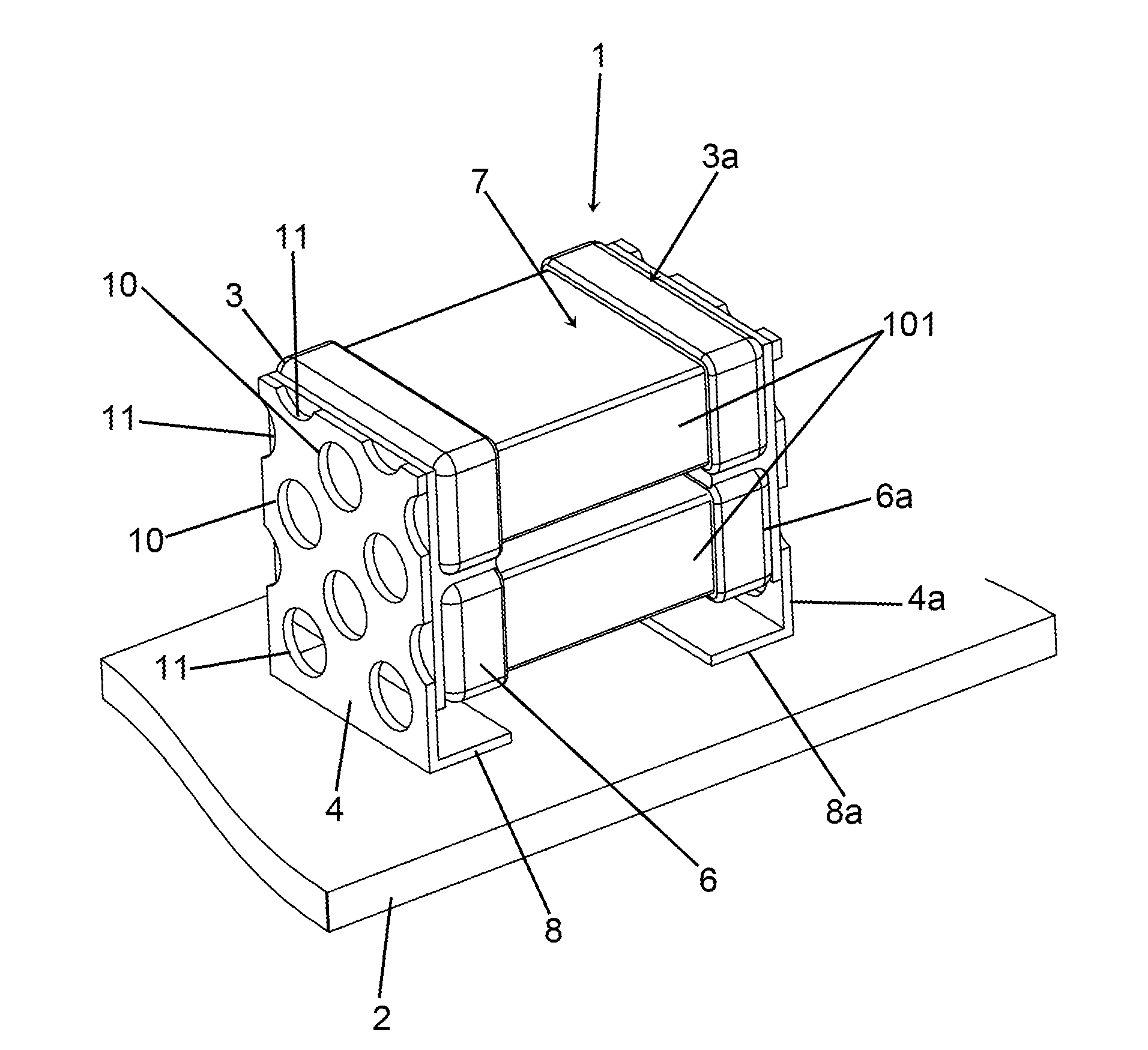

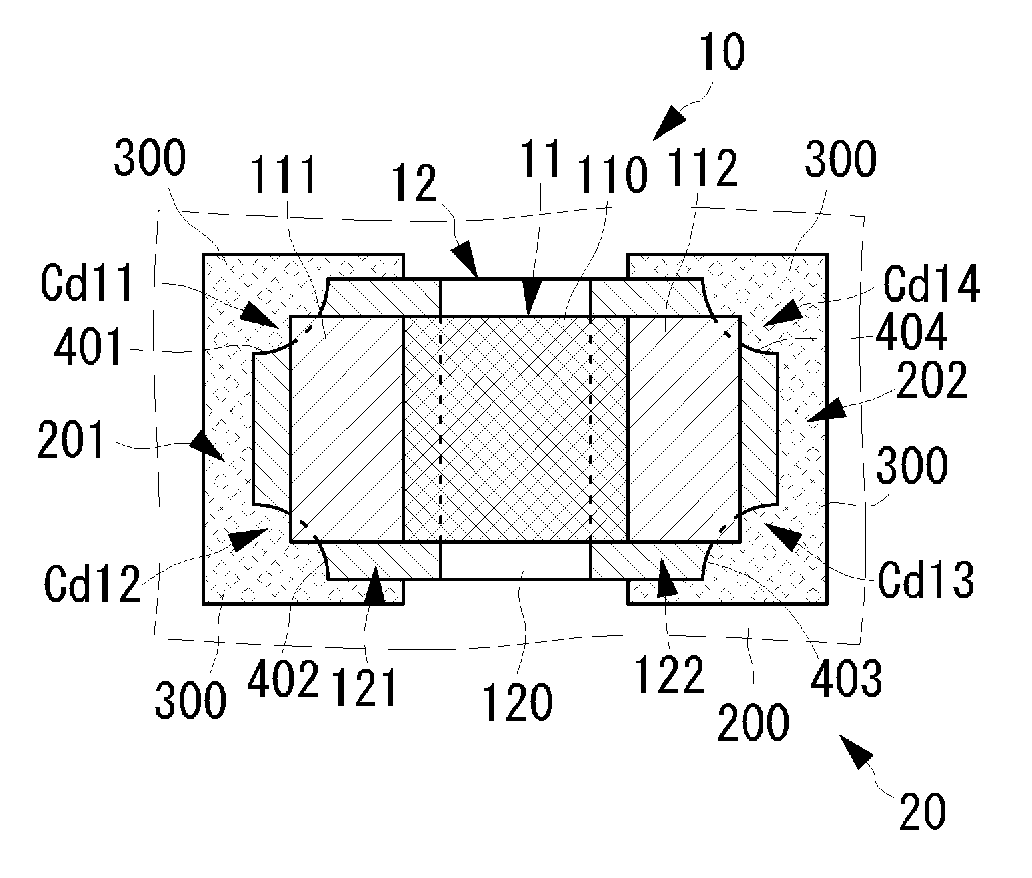

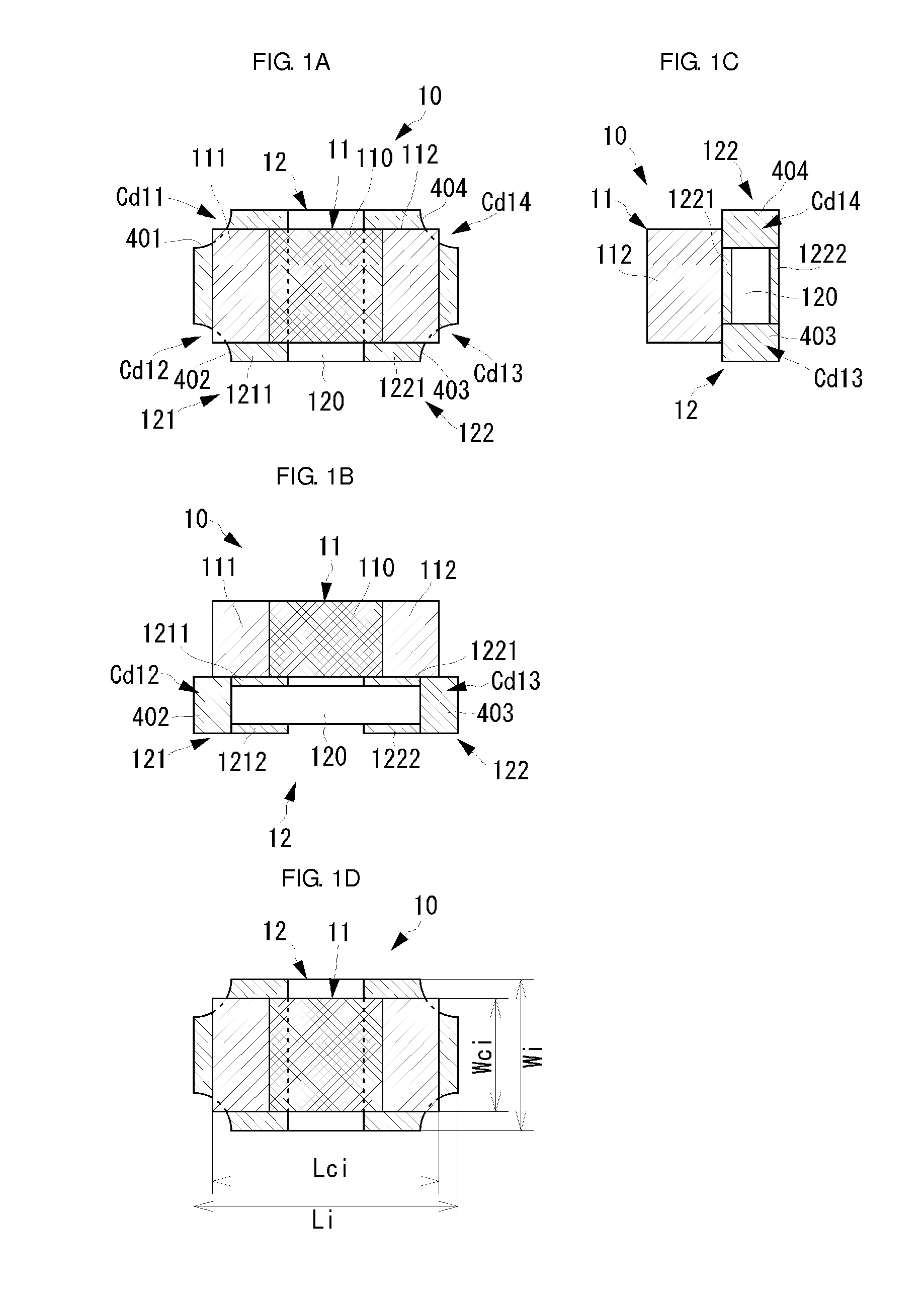

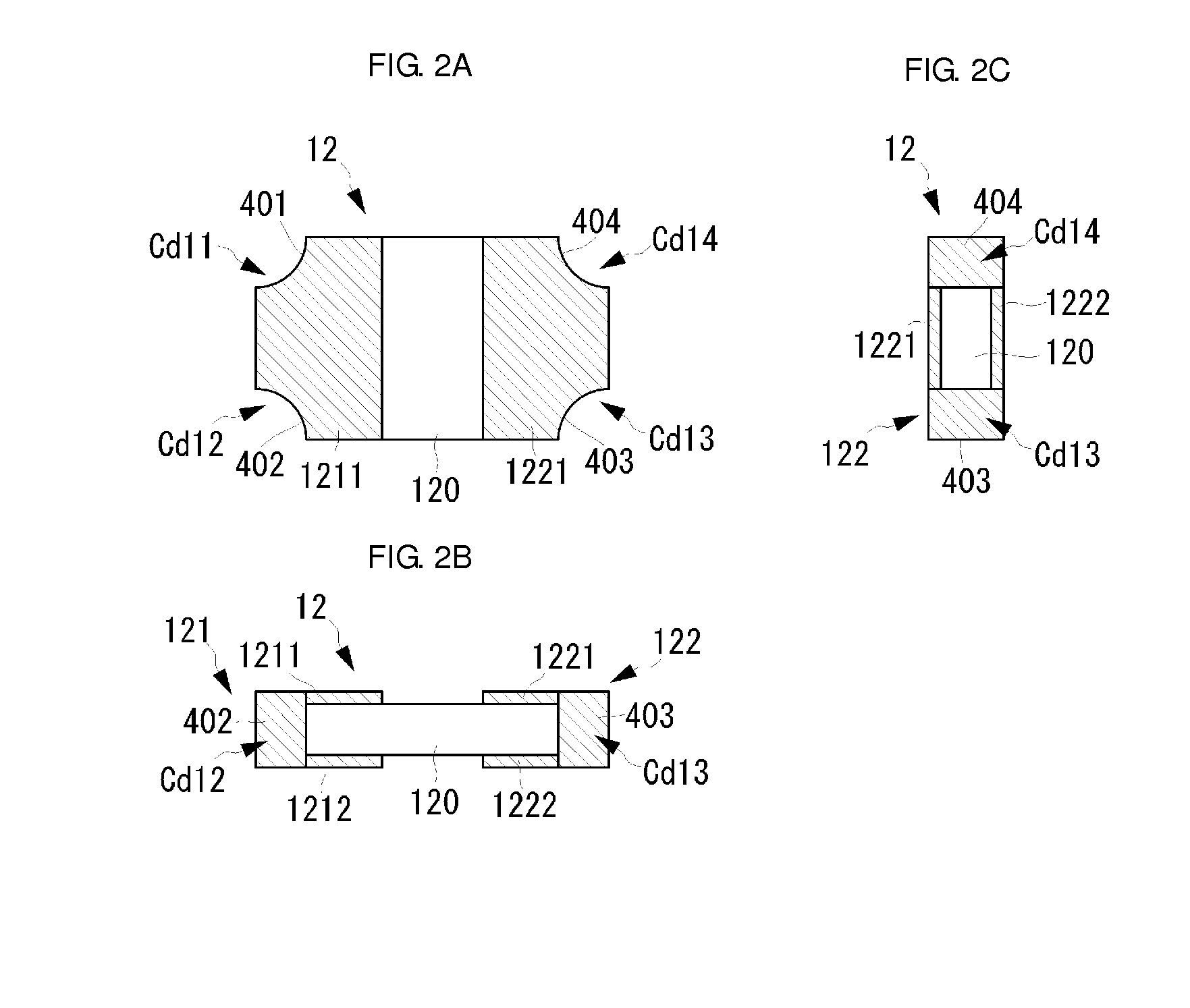

Ceramic capacitor and electronic component including the same

ActiveUS20100123995A1Avoid noiseFinal product manufactureFixed capacitor dielectricCeramic capacitorElectronic component

In a ceramic capacitor, first and second electrode terminals each include a bonded-to-substrate portion, a first bonded-to-electrode portion bonded to a first edge of one of first and second external electrodes, a second bonded-to-electrode portion bonded to a second edge of the one of first and second external electrodes and disposed at a distance from the first bonded-to-electrode portion in the first directions, and a connecting portion connecting the first and second bonded-to-electrode portions and the bonded-to-substrate portion. W1 / W0 is about 0.3 or more, and h / L is about 0.1 or more.

Owner:MURATA MFG CO LTD

Pressure sensor apparatus and method

InactiveUS7082835B2Fluid pressure measurement using elastically-deformable gaugesFluid pressure measurement by electric/magnetic elementsHermetic sealCeramic capacitor

A pressure sensor apparatus is disclosed herein, which generally includes a sensor element, a flexible sensor diaphragm in intimate contact with the sensor element at all pressure levels and temperatures, and a package base and a package cover for hermetically sealing the sensor element and the flexible sensor diaphragm within a hermetically sealed sensor package to provide pressure sensor data thereof. The sensor element can be implemented as a quartz sense element to produce a SAW pressures sensor. The pressure sensor apparatus can be alternatively based on other sensing technologies, such as silicon piezoresistive, ceramic capacitive and others.

Owner:HONEYWELL INT INC

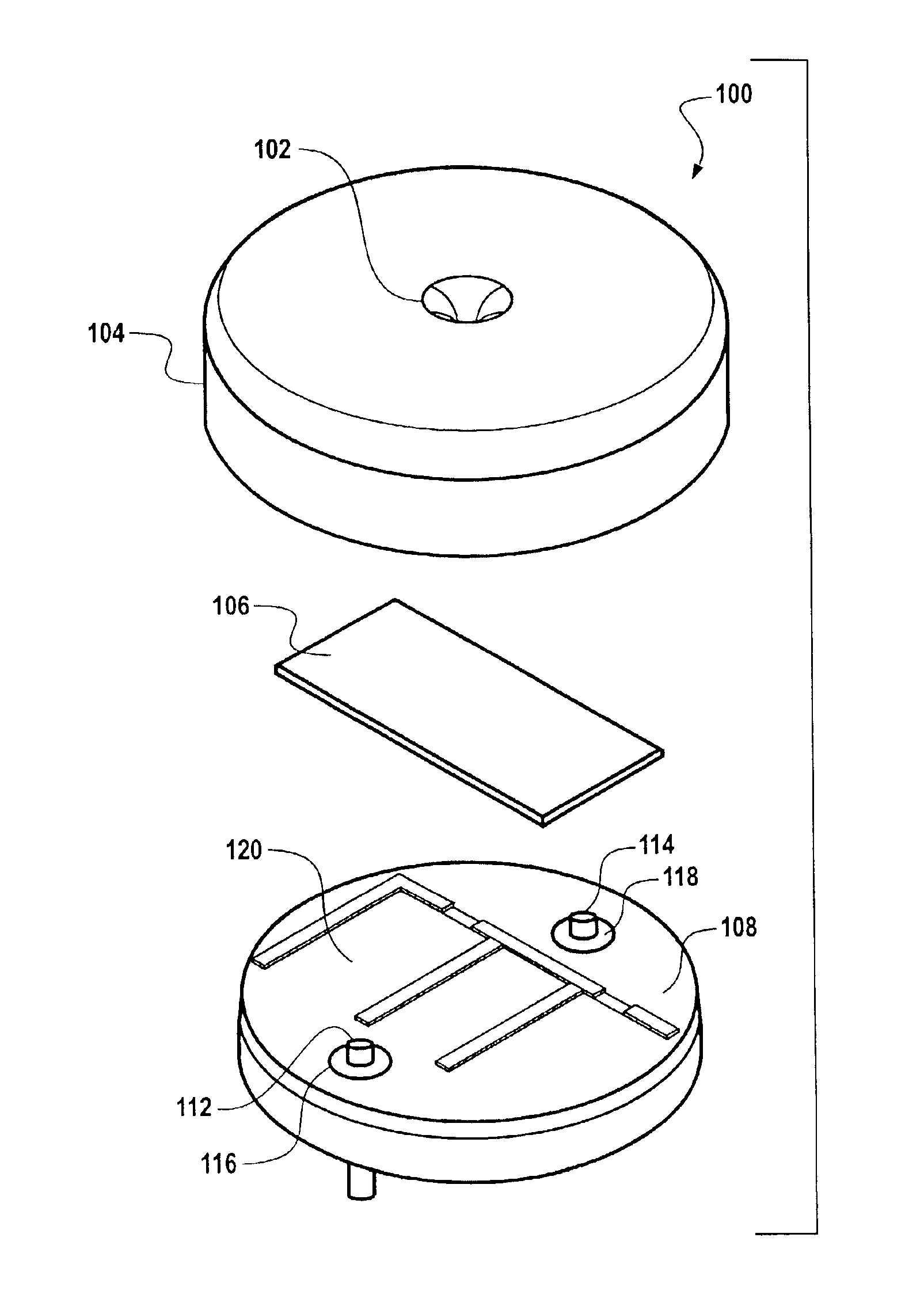

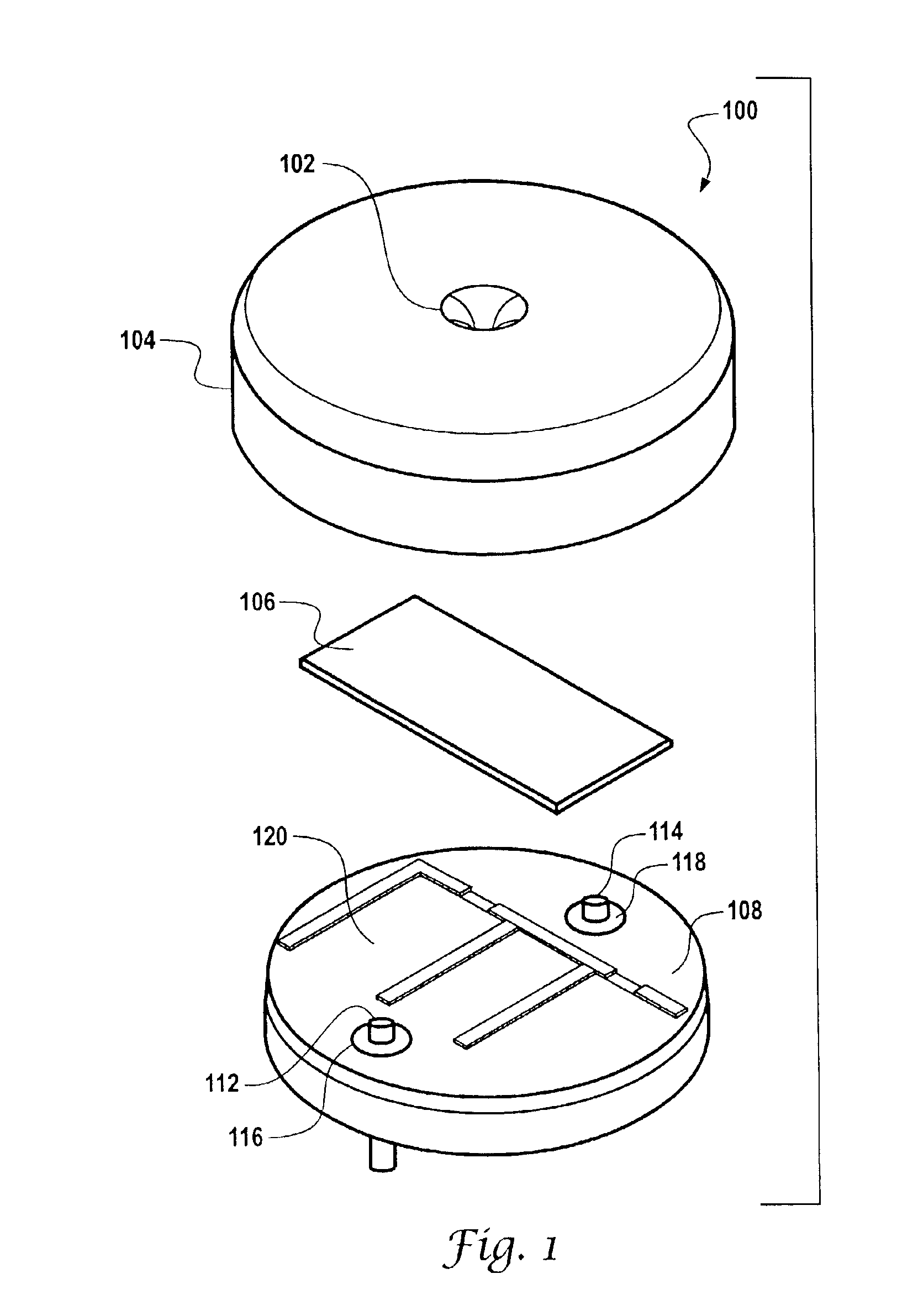

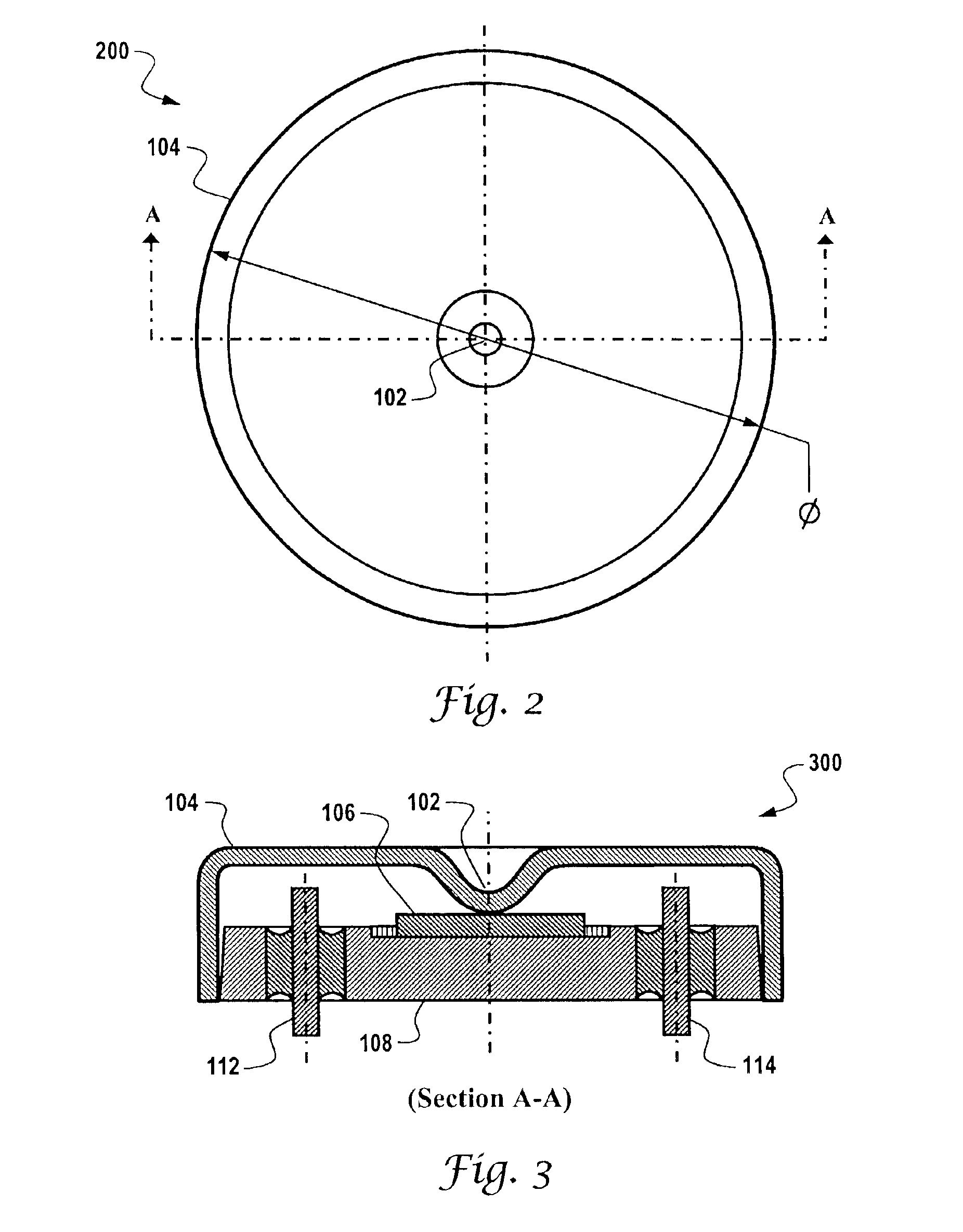

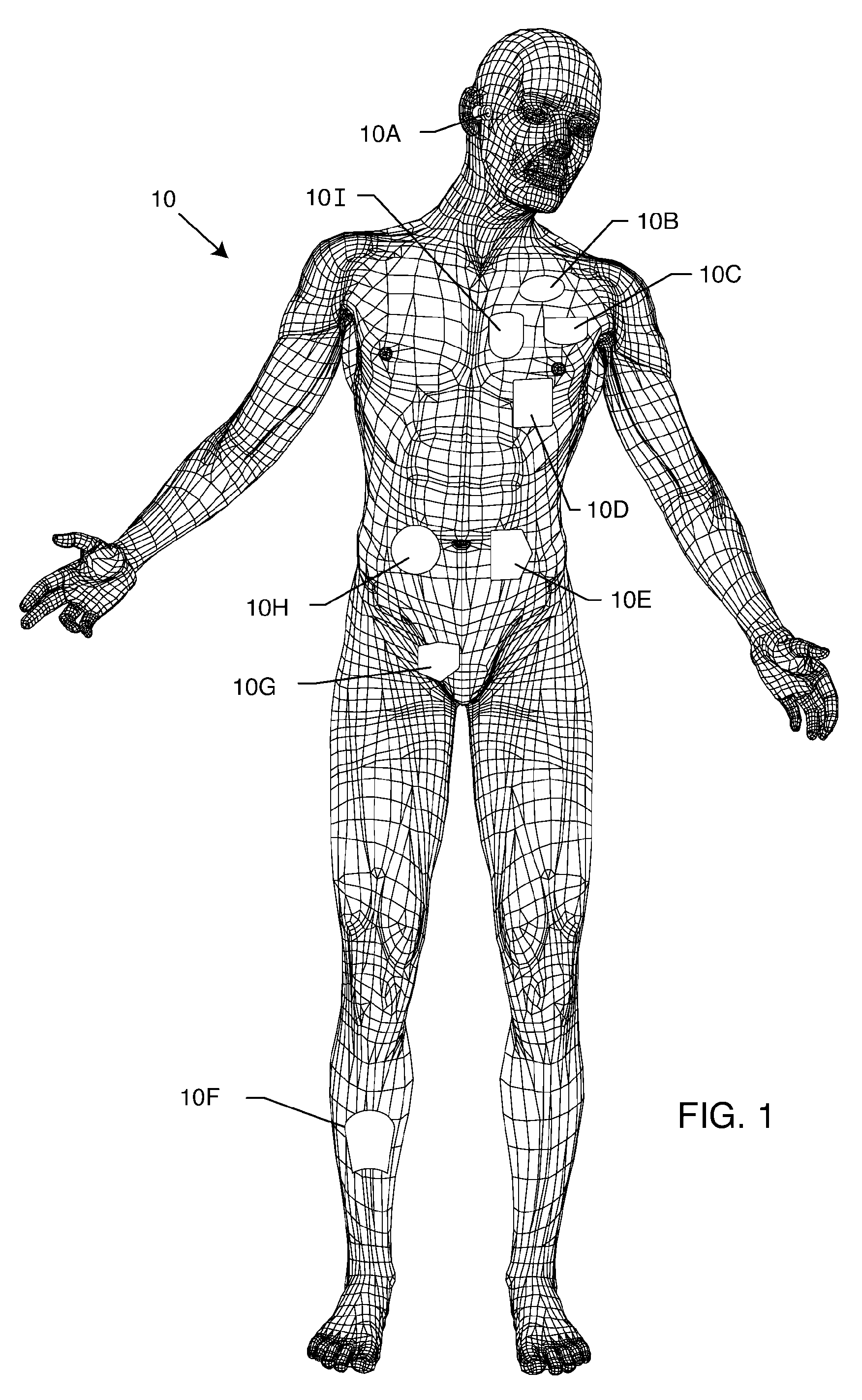

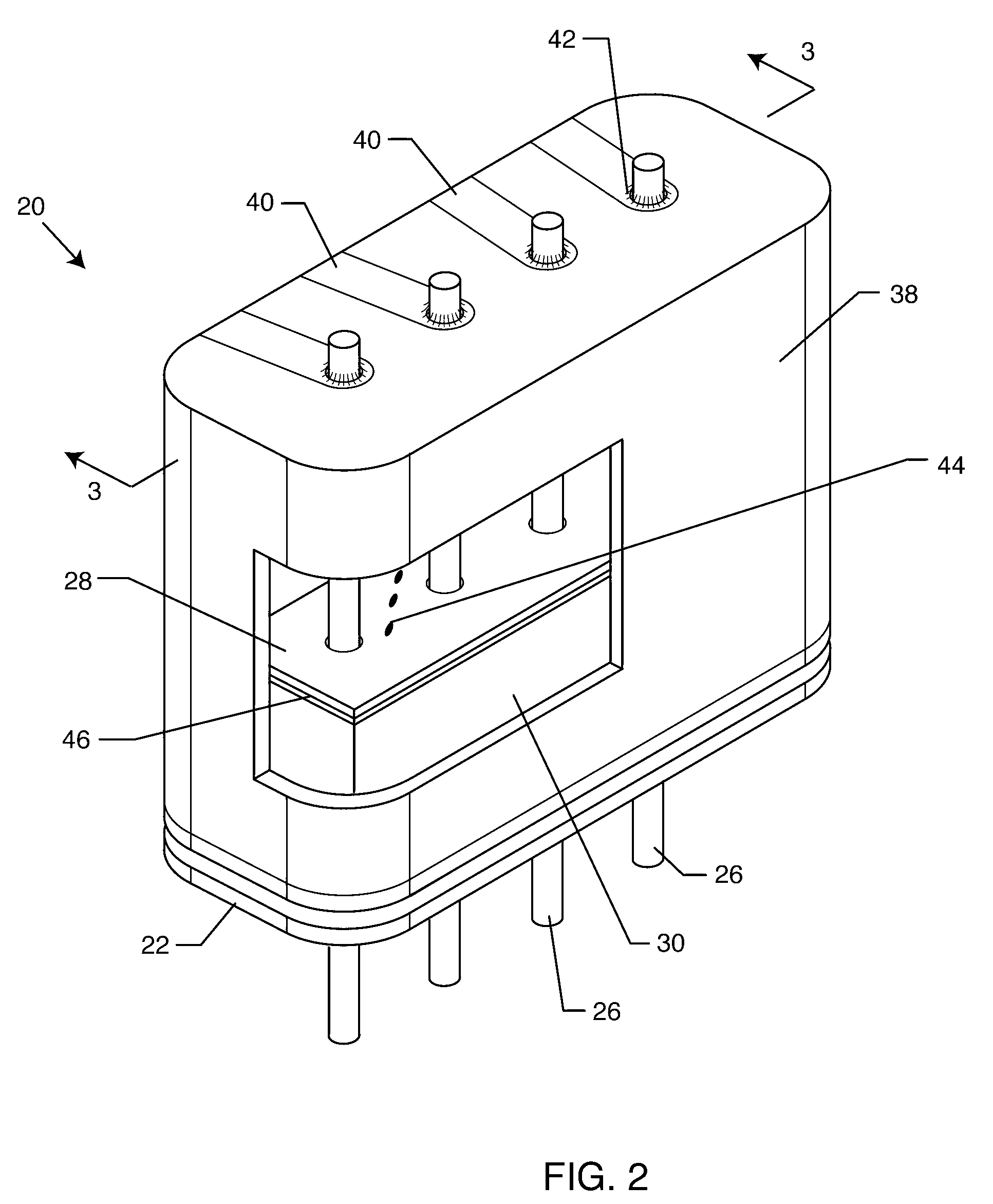

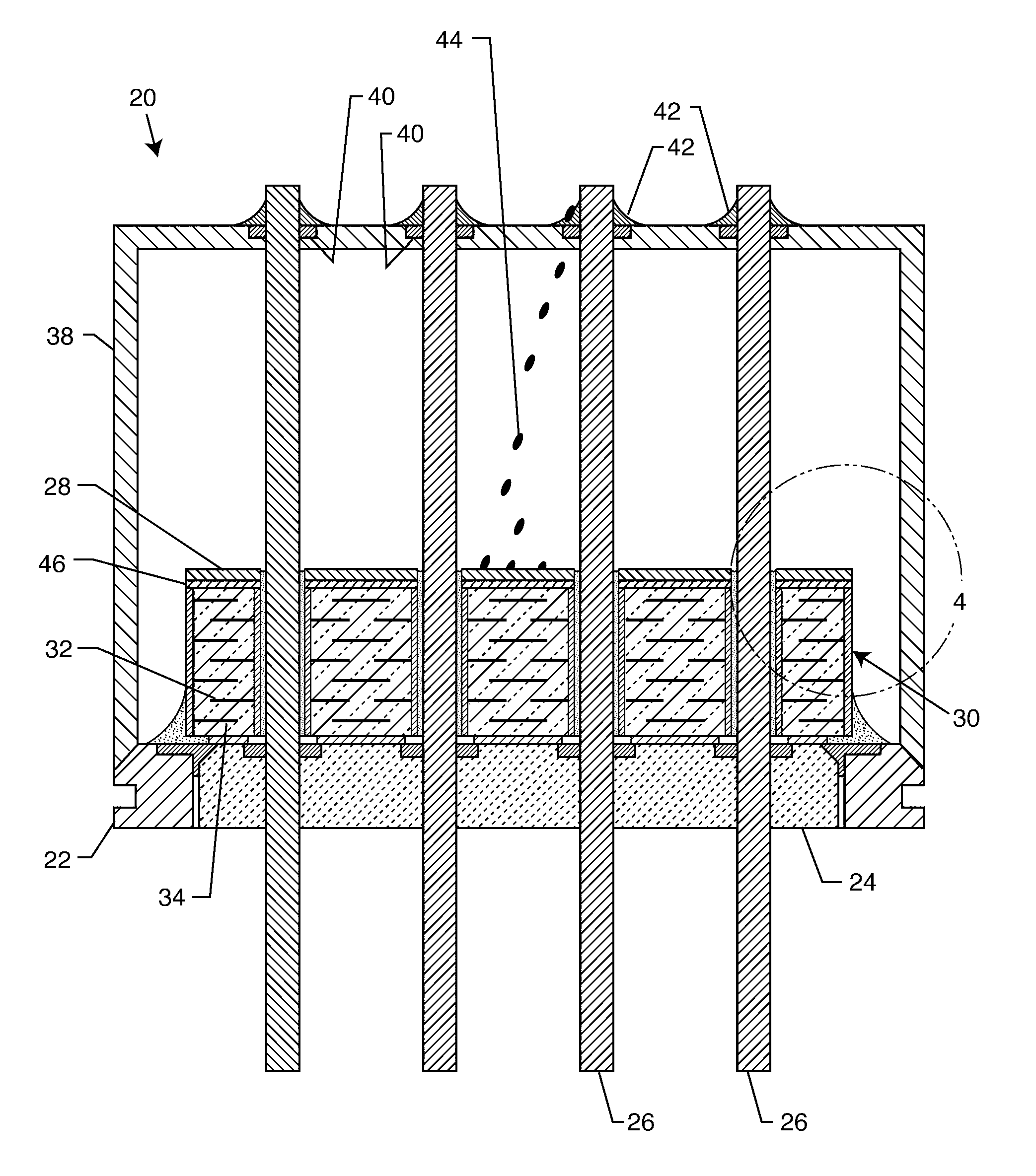

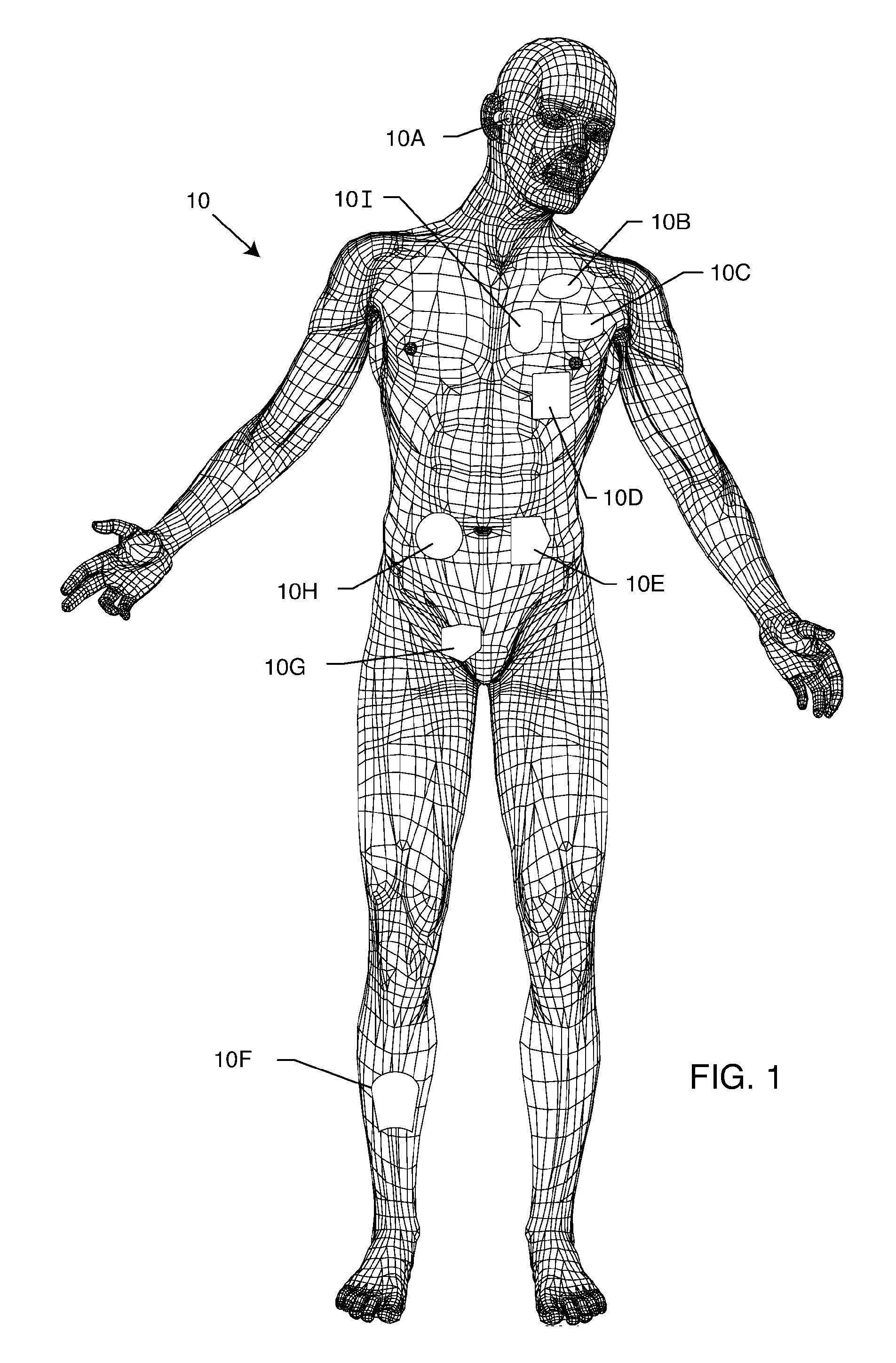

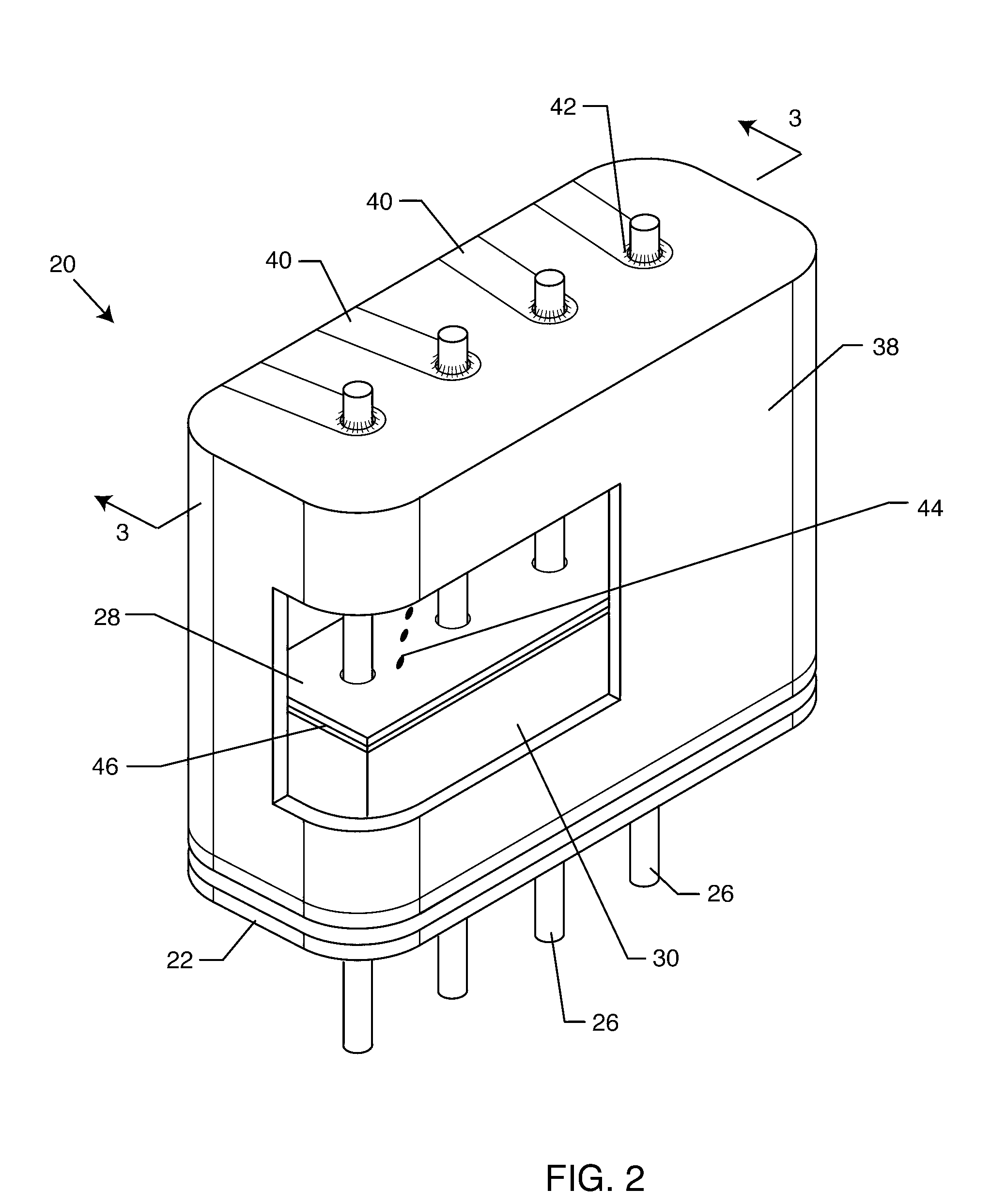

Device to protect an active implantable medical device feedthrough capacitor from stray laser weld strikes, and related manufacturing process

An insulative shield is co-bonded to the top of a ceramic capacitor in a feedthrough terminal assembly on an active implantable medical device. The insulative shield is a thin substrate that provides protection against damage and degradation of the feedthrough capacitor and / or its conformal coating from heat, splatter or debris resulting from the electromechanical connection of components during construction of the assembly. Laser welding, thermal or ultrasonic bonding, soldering, brazing or related lead attachment techniques can create such heat, splatter or debris. In a preferred embodiment, the insulative shield is co-bonded using the capacitor's own conformal coating.

Owner:WILSON GREATBATCH LTD

Device to protect an active implantable medical device feedthrough capacitor from stray laser weld strikes, and related manufacturing process

InactiveUS20060028784A1Protect the surfaceAnti-noise capacitorsElectrotherapyManufacturing technologyCeramic capacitor

An insulative shield is co-bonded to the top of a ceramic capacitor in a feedthrough terminal assembly on an active implantable medical device. The insulative shield is a thin substrate that provides protection against damage and degradation of the feedthrough capacitor and / or its conformal coating from heat, splatter or debris resulting from the electromechanical connection of components during construction of the assembly. Laser welding, thermal or ultrasonic bonding, soldering, brazing or related lead attachment techniques can create such heat, splatter or debris. In a preferred embodiment, the insulative shield is co-bonded using the capacitor's own conformal coating.

Owner:WILSON GREATBATCH LTD

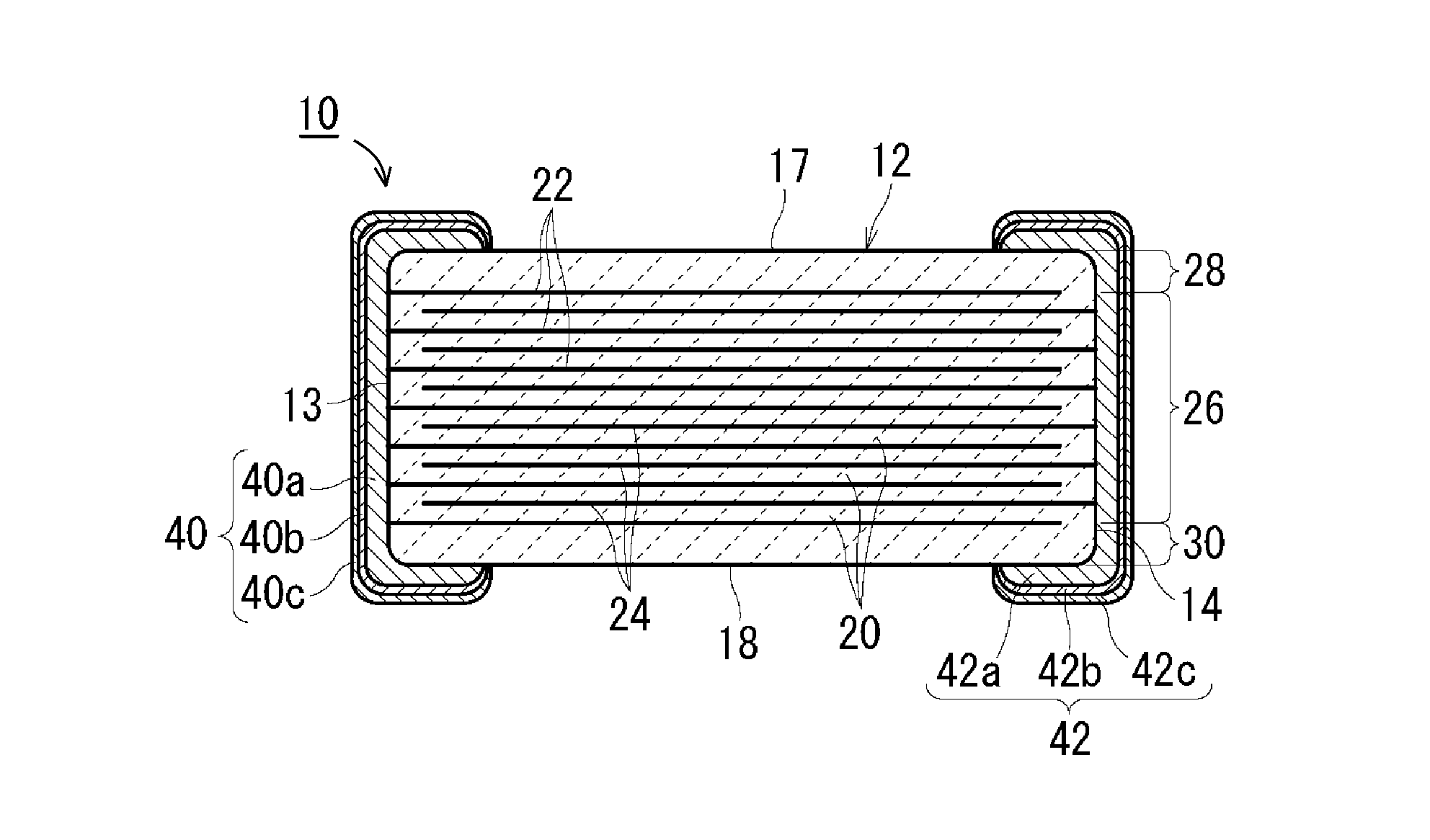

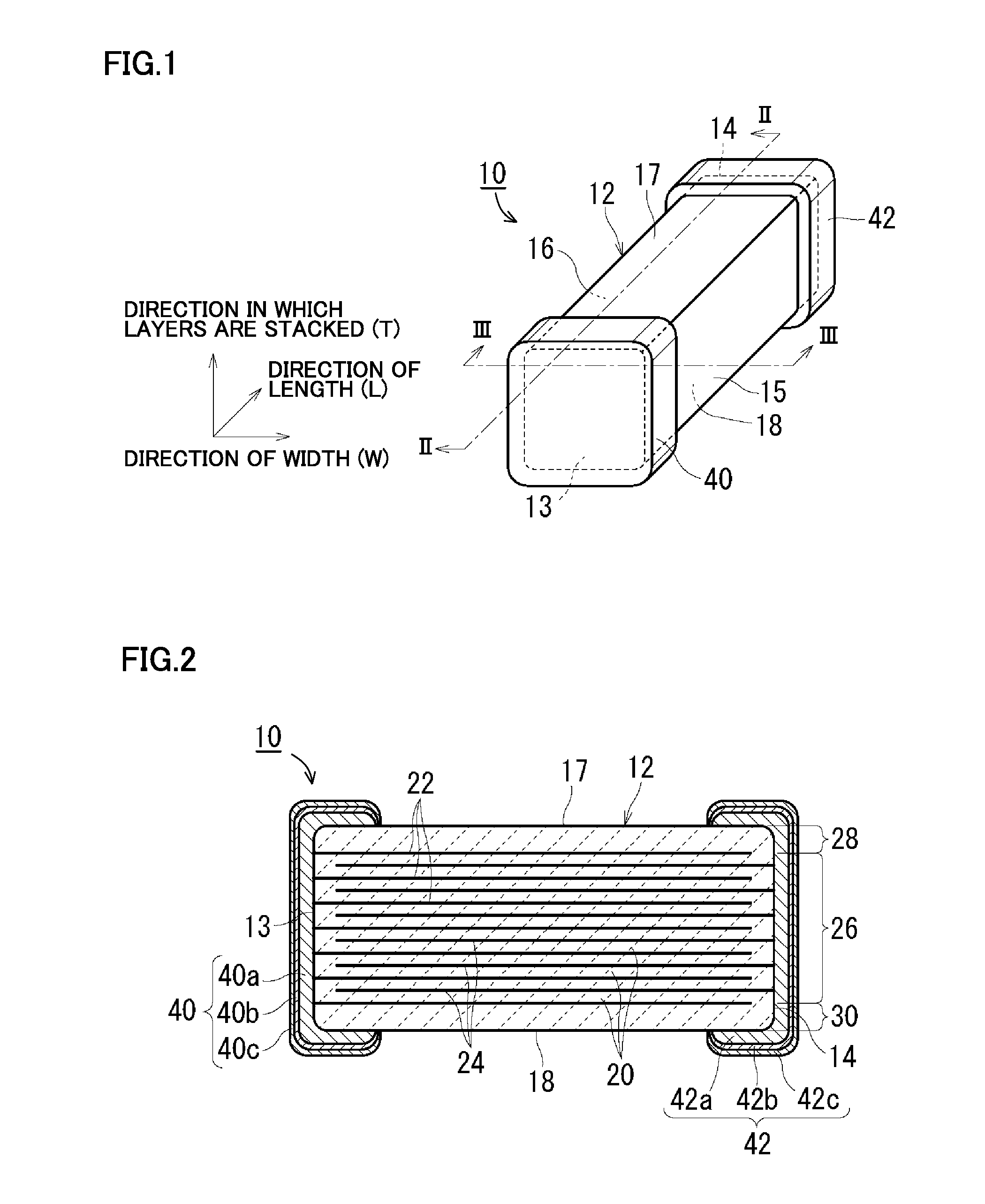

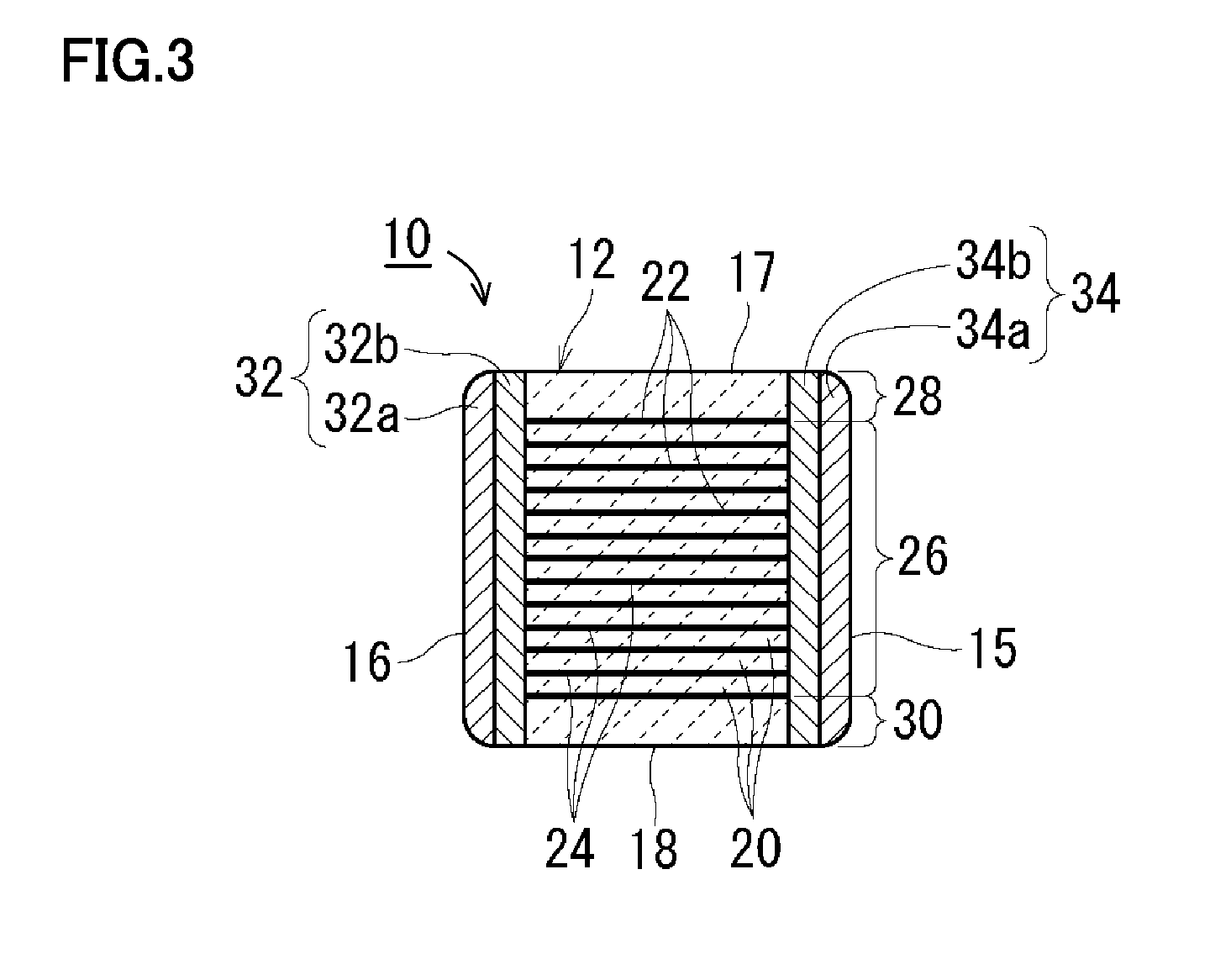

Multilayer ceramic capacitor

ActiveUS20150340155A1Reduce moistureImprove moisture resistanceFixed capacitor electrodesFixed capacitor dielectricMetallurgyCeramic capacitor

A multilayer ceramic capacitor includes a ceramic body and external electrodes provided on opposite end surfaces of the ceramic body. The ceramic body includes an inner layer portion including a plurality of ceramic layers defining inner layers and a plurality of first and second internal electrodes each disposed at an interface of adjacent ones of the ceramic layers defining the inner layers, outer layer portions sandwiching the inner layer portion in a direction in which the layers are stacked, and side margin portions sandwiching the inner layer portion and the outer layer portions in a widthwise direction. The side margin portion includes pores that decrease in number along a direction from inside to outside of the ceramic body.

Owner:MURATA MFG CO LTD

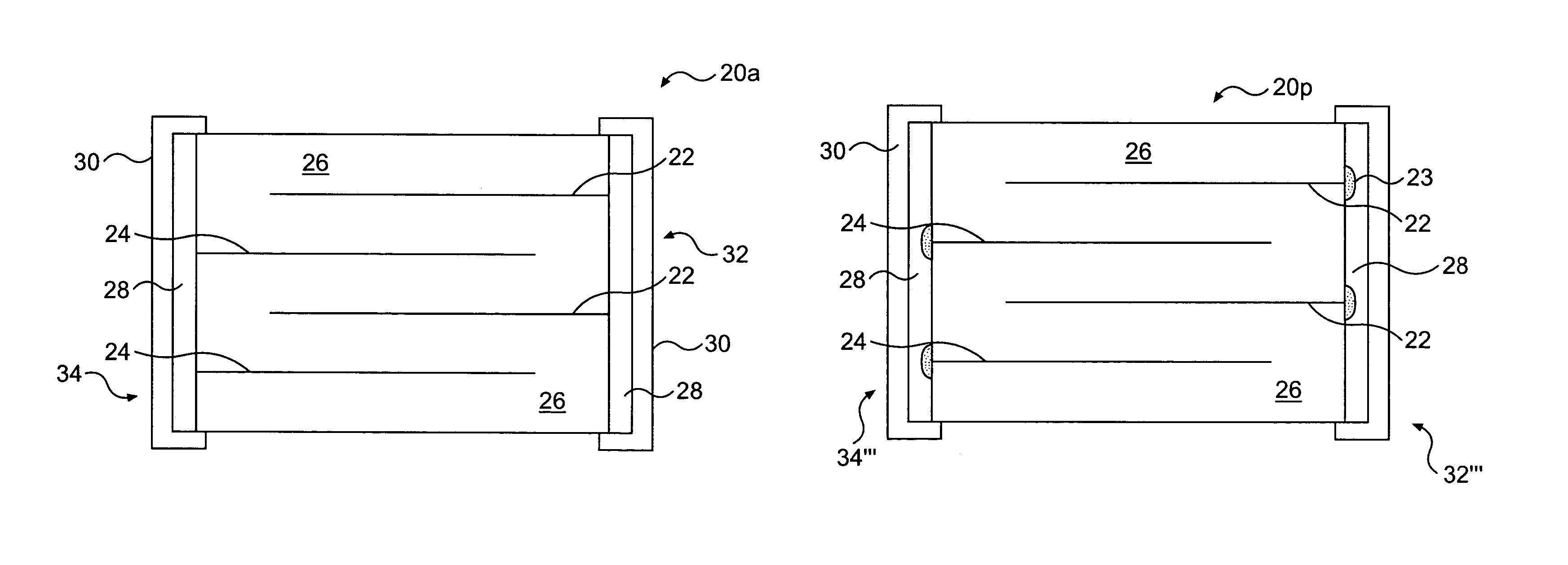

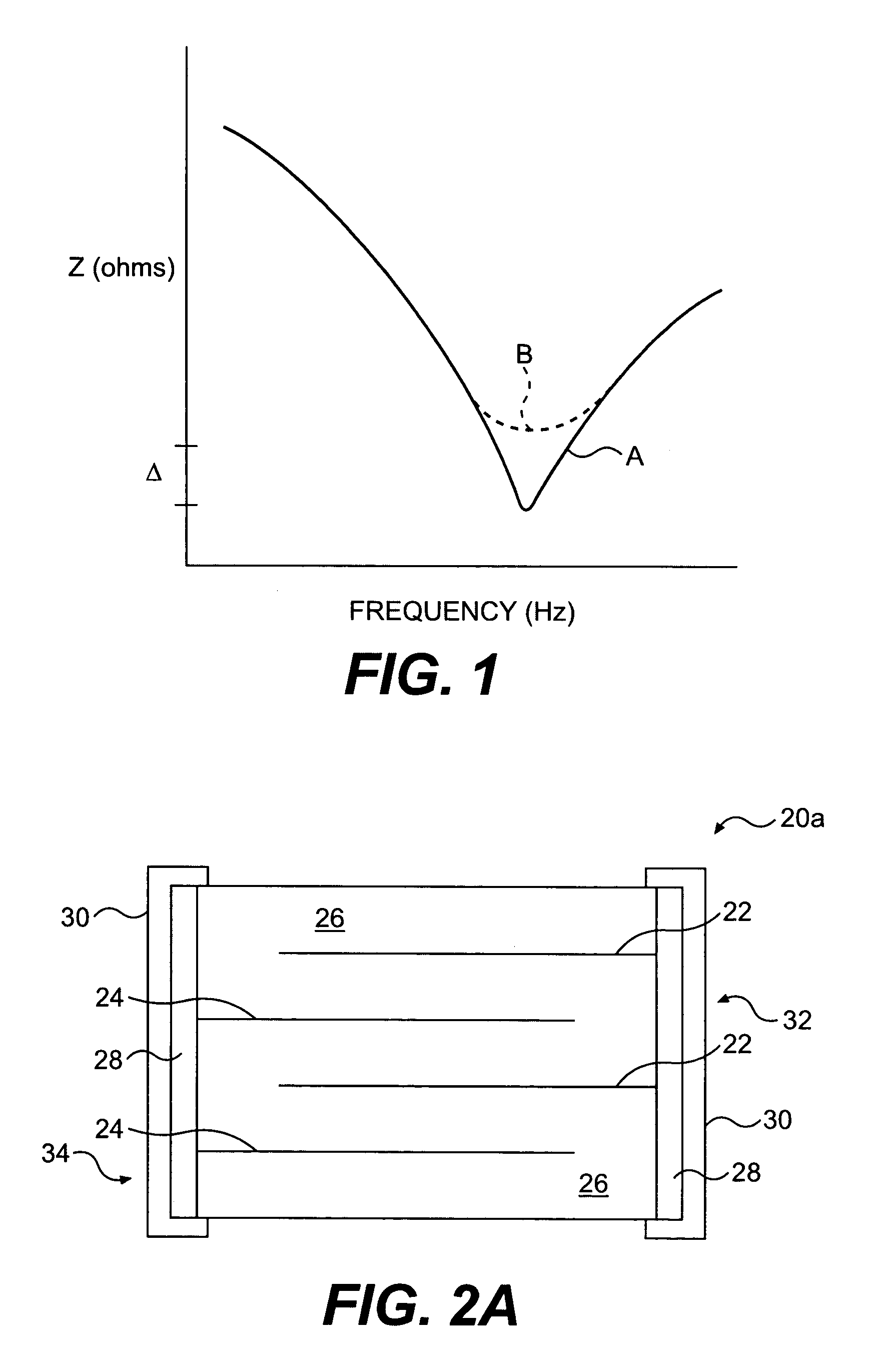

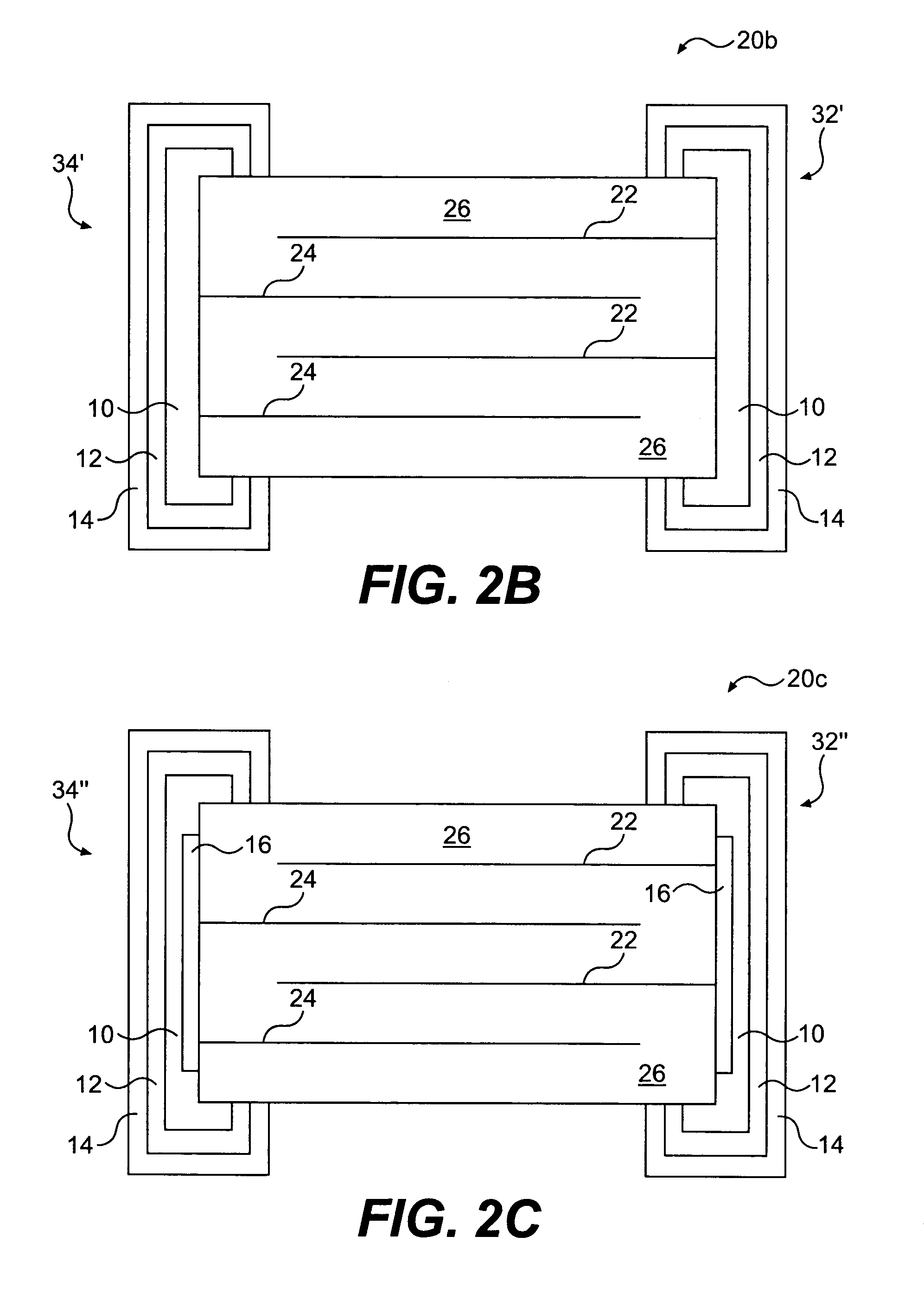

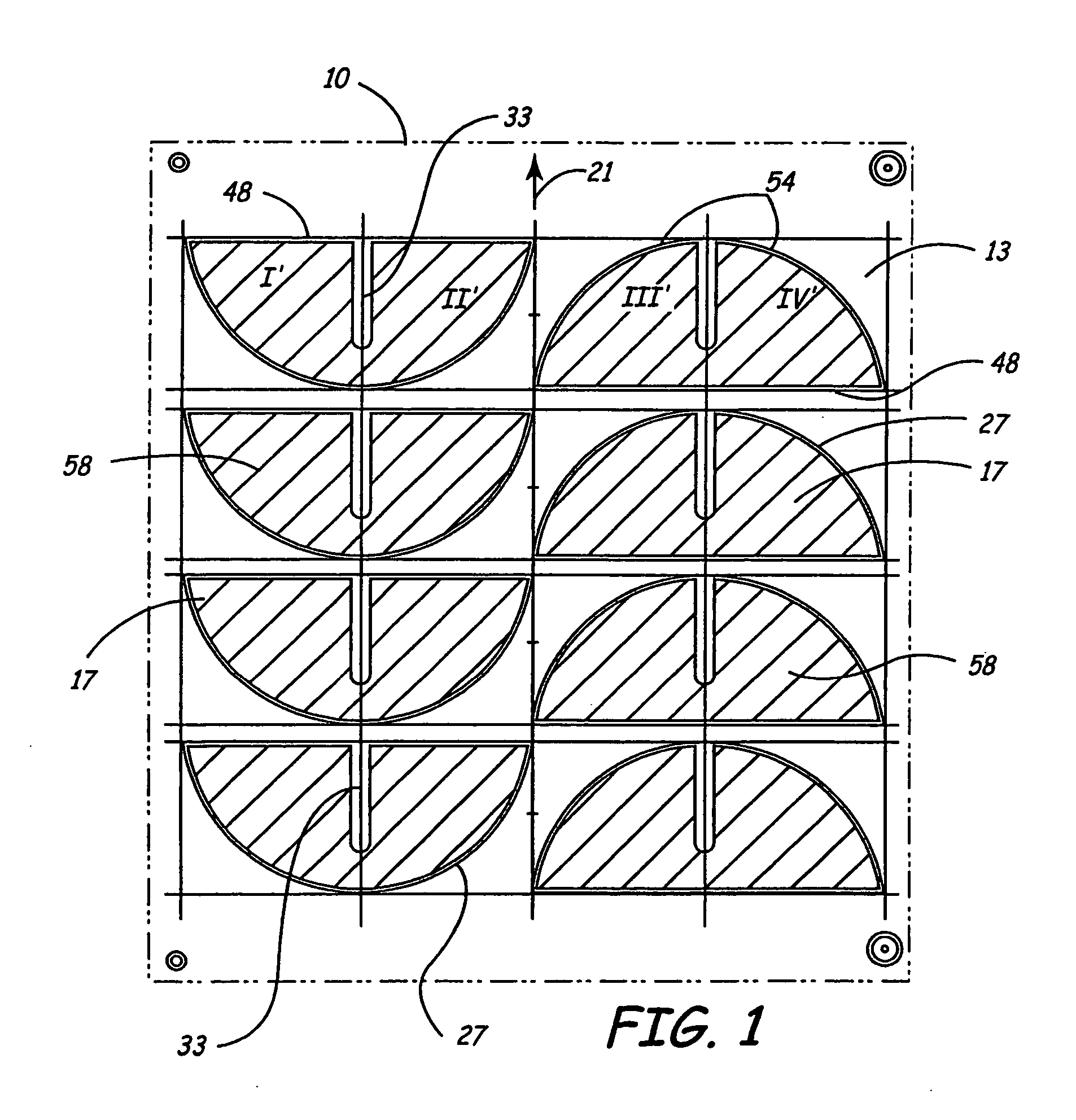

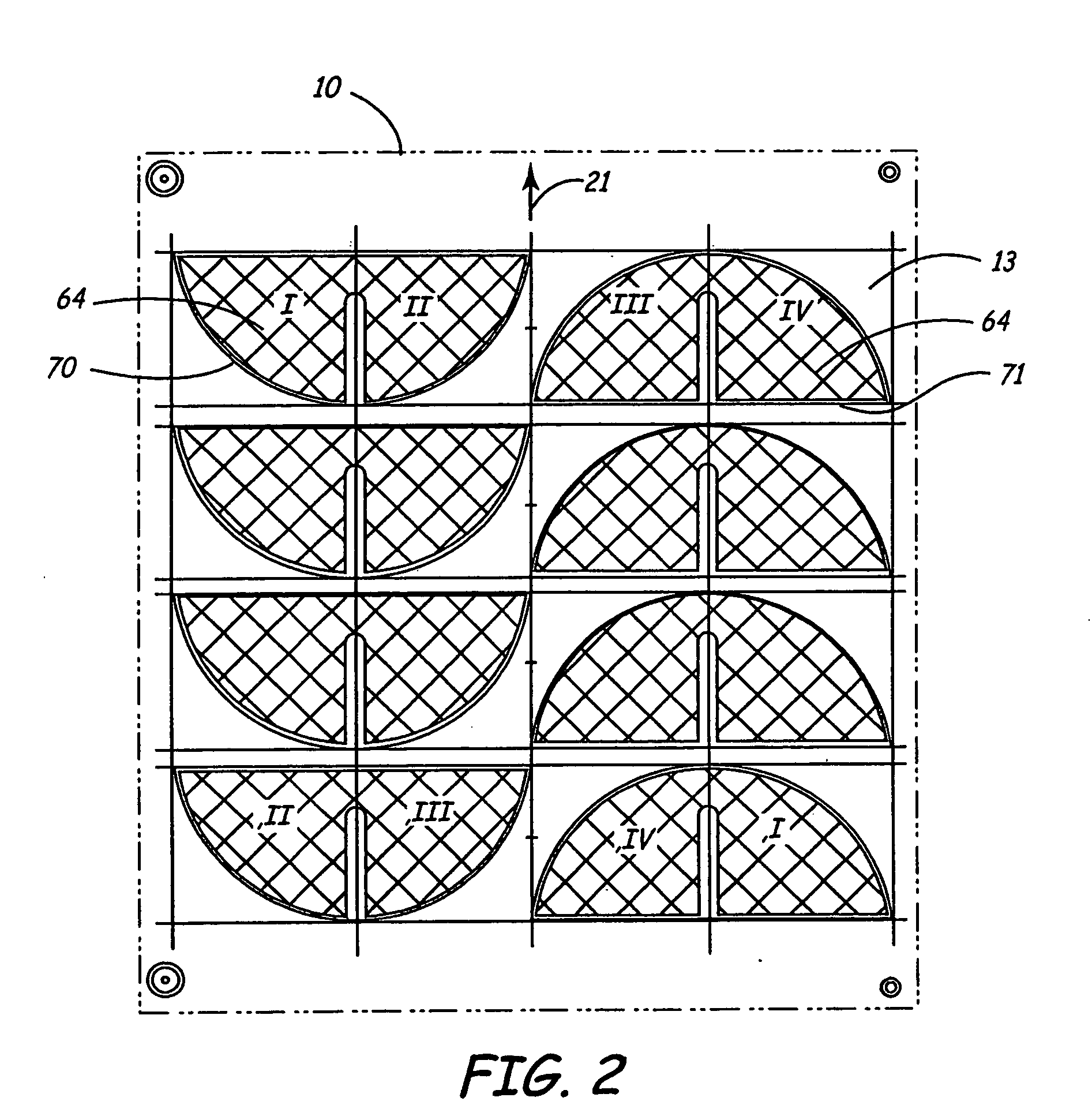

Controlled ESR low inductance multilayer ceramic capacitor

InactiveUS7054136B2Increase the lengthIncrease the equivalent series resistanceFixed capacitor dielectricStacked capacitorsDielectricElectrical resistance and conductance

A multilayer ceramic capacitor assembly capable of exhibiting low high-frequency inductance and a controlled equivalent series resistance (ESR) while maintaining a useful capacitance value includes respective pluralities of first and second electrode elements interleaved to form a stack. Controlled ESR is achieved either through inclusion of specific types of materials or through alteration of the shape of various component parts. A resistive material may be used in typical end terminations, via terminations, electrode elements or connective tab structures. Additionally, the dielectric may be made lossy so as to enhance resistivity without overly affecting device capacitance. Still further, an additional layer of resistive material may be added to an outer device surface to connect filled-via terminations to end terminations or radial resistive prints may be used to only partially fill the vias. Finally, various electrode element configurations, such as flat plate, serpentine, mesh, L-, O- or U-shaped patterns, may be employed.

Owner:KYOCERA AVX COMPONENTS CORP

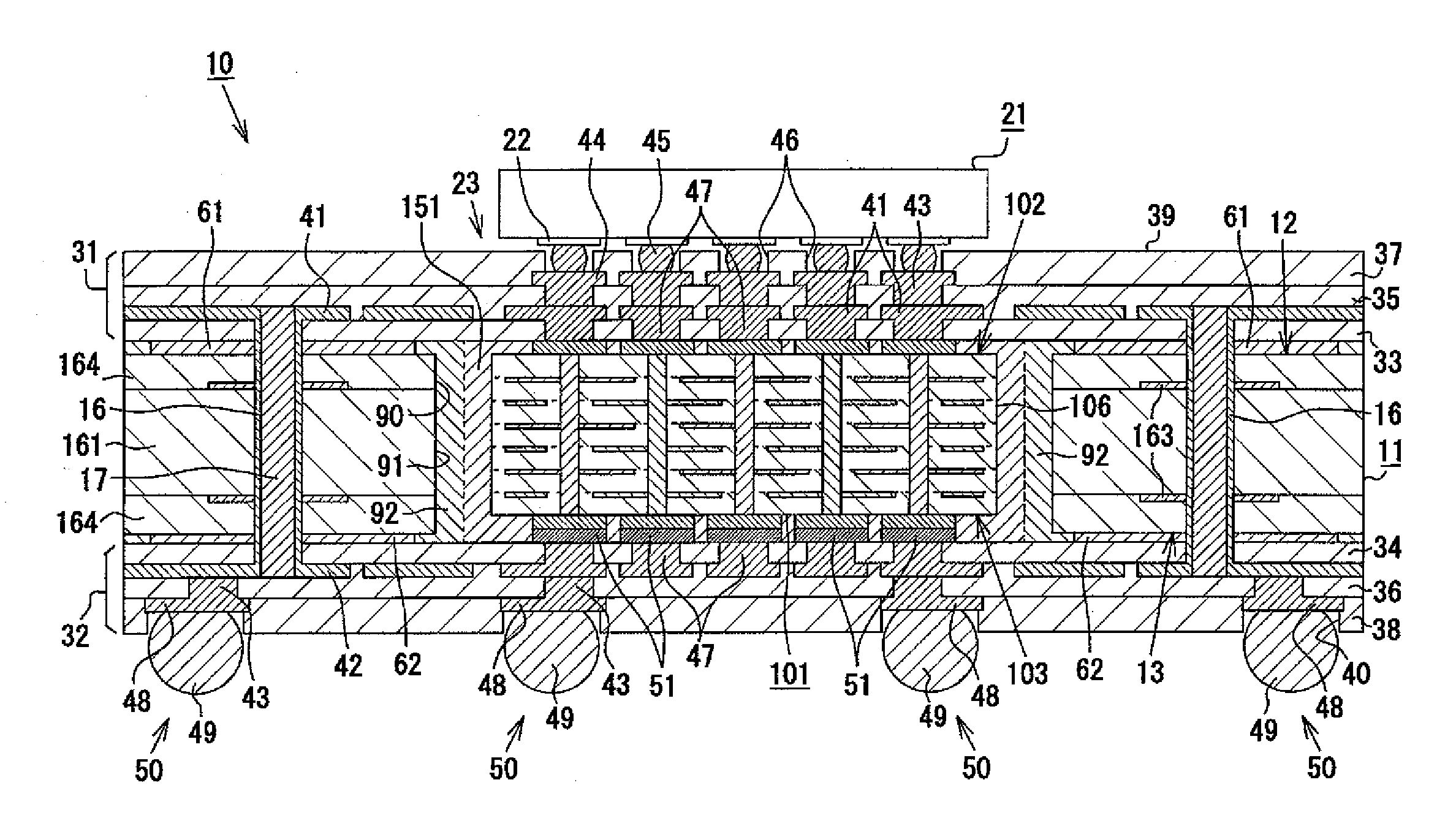

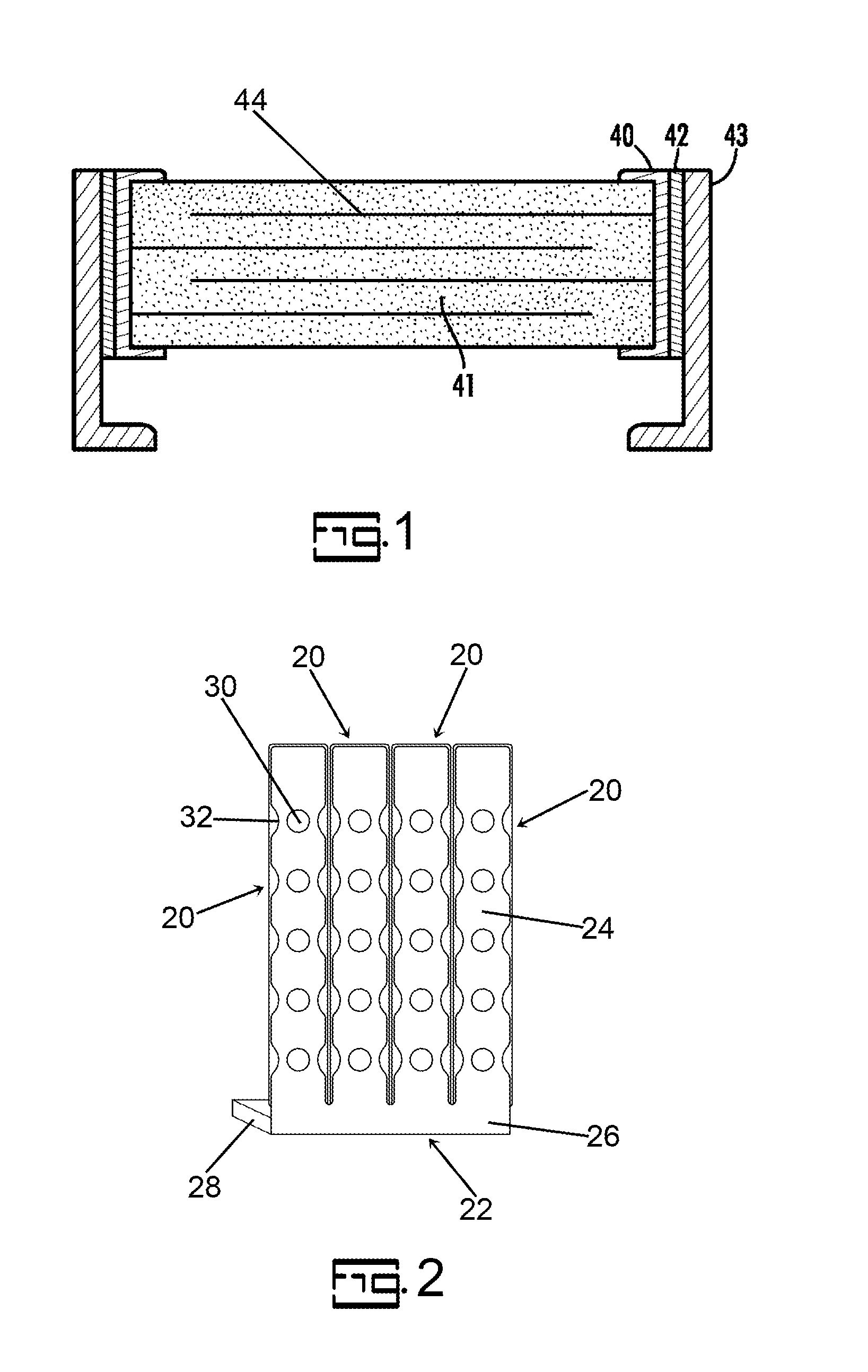

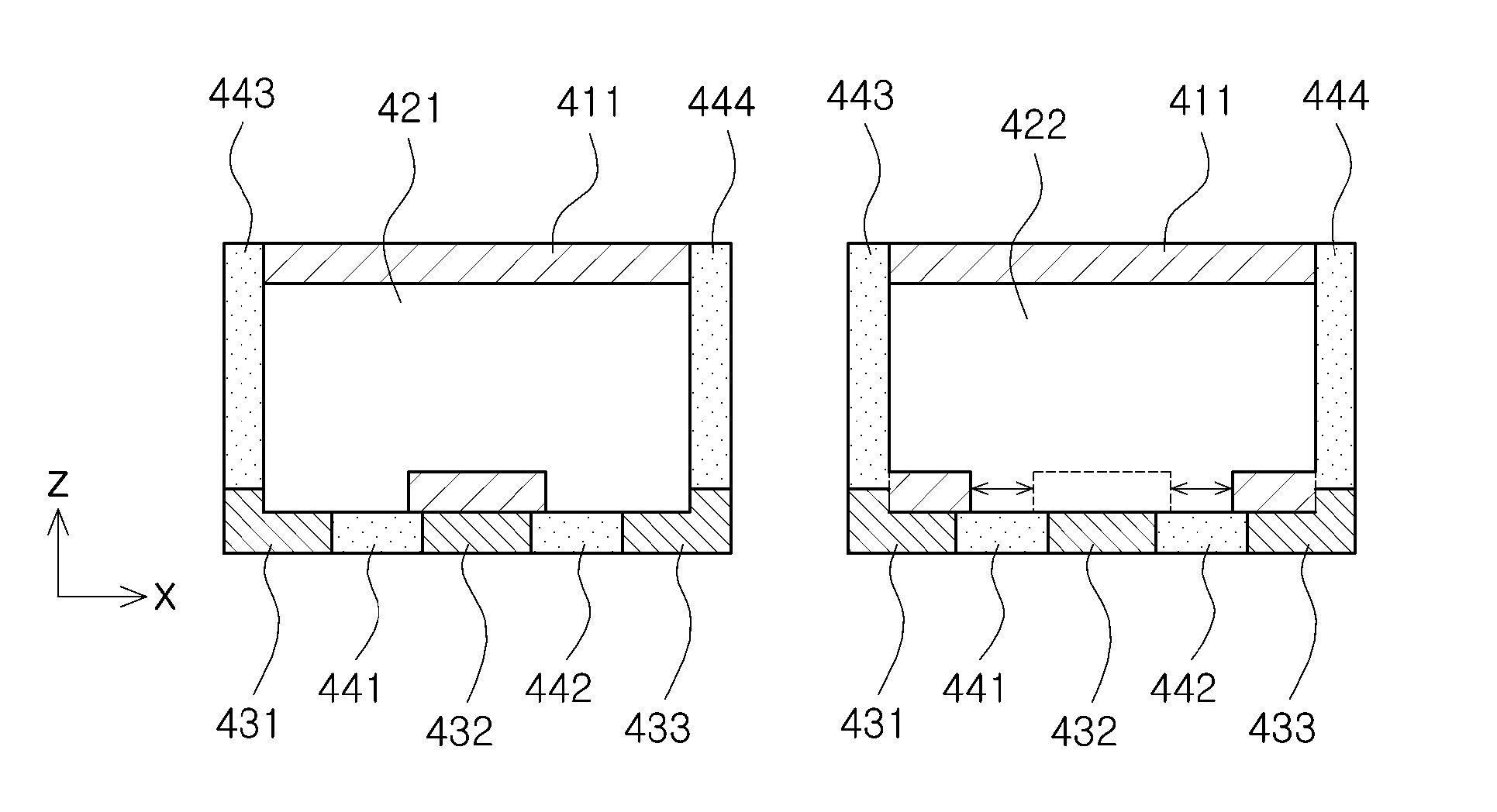

Wiring board with built-in component and method for manufacturing the same

InactiveUS20080277150A1Avoid defectsImprove reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorCeramic capacitor

A method for manufacturing a wiring board with built-in component. The method provides a secure connection between a component and interlayer insulating layers so that the wiring board with built-in component has excellent reliability. The wiring board is manufactured through a core board preparation step, a component preparation step, an accommodation step and a height alignment step. In the core board preparation step, a core board having an accommodation hole therein is prepared. In the component preparation step, a ceramic capacitor having therein a plurality of protruding conductors which protrudes from a capacitor rear surface is prepared. In the accommodation step, the ceramic capacitor is accommodated in the accommodation hole with the core rear surface facing the same side as the capacitor rear surface. In the height alignment step, a surface of a top portion of the protruding conductor and a surface of a conductor layer formed on the core rear surface are aligned to the same height.

Owner:NGK SPARK PLUG CO LTD

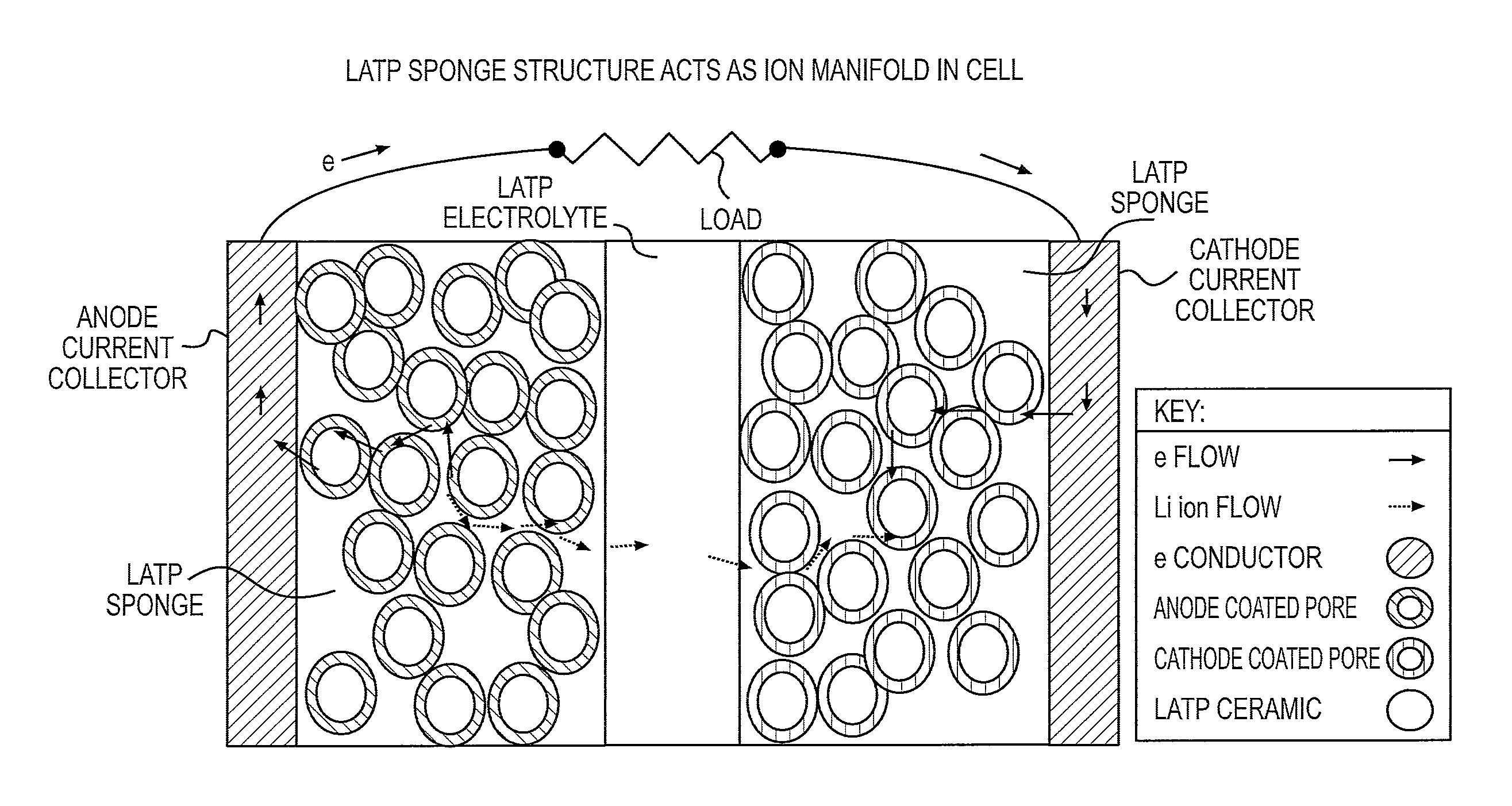

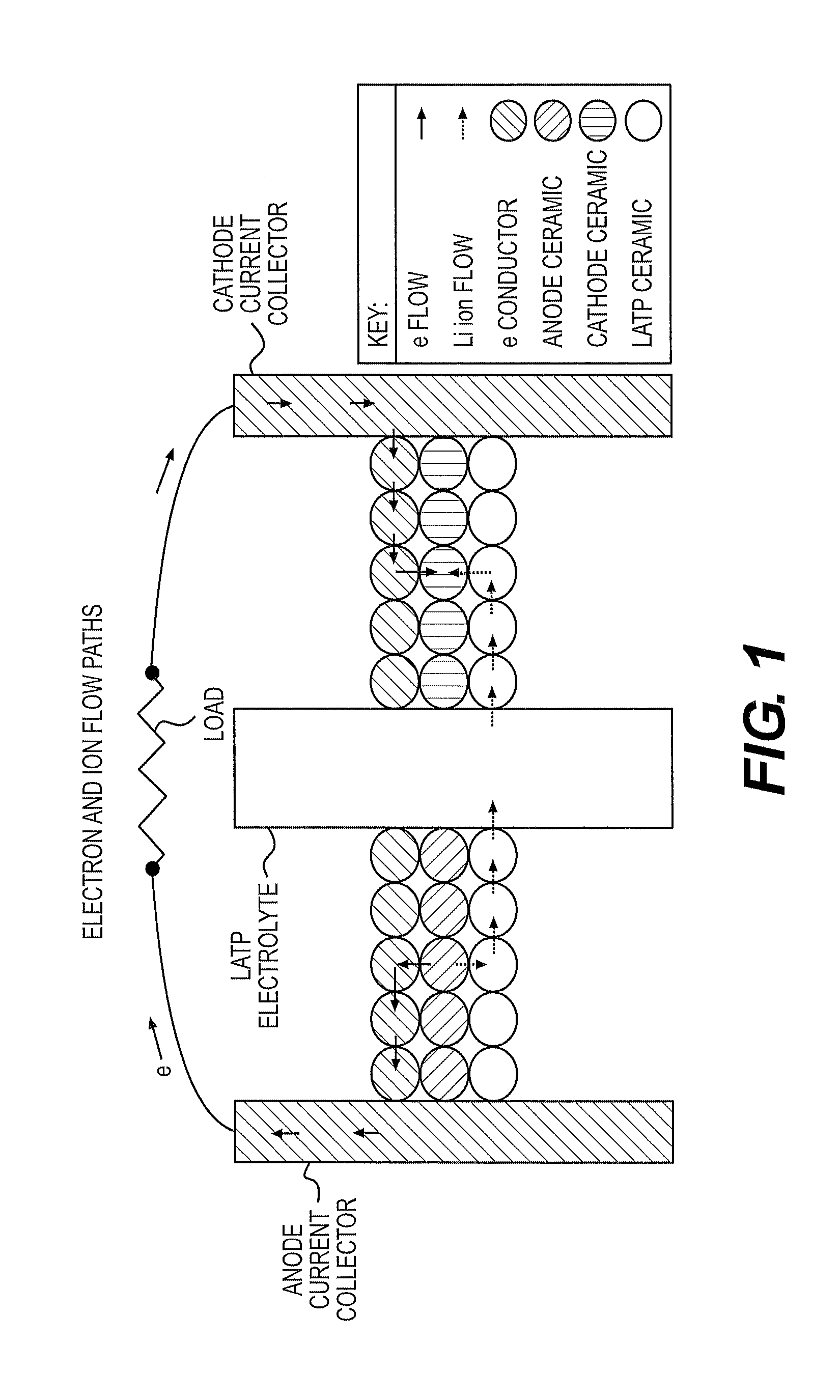

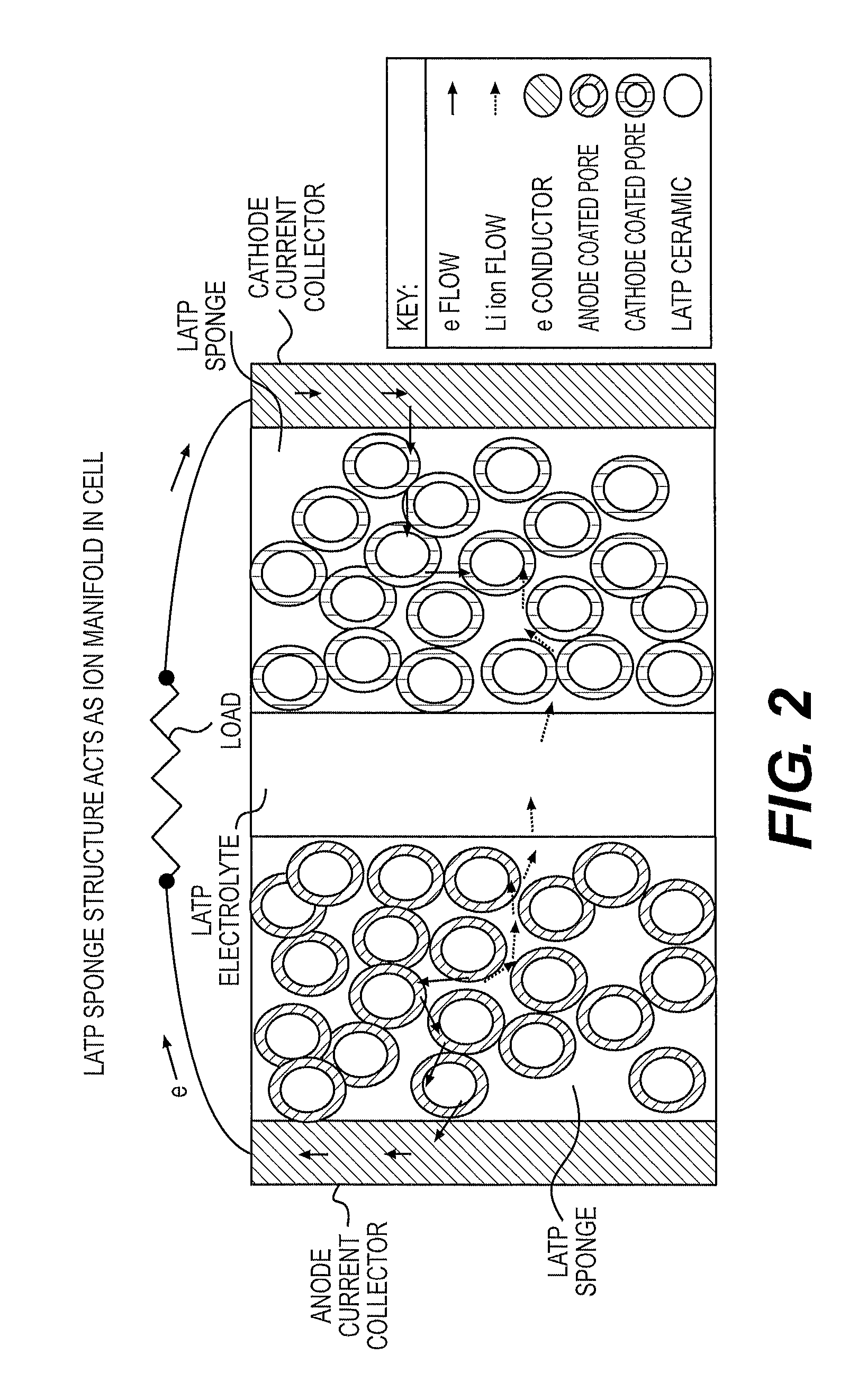

Multi layer ceramic battery

ActiveUS8304115B1High energyIncrease powerNon-aqueous electrolyte accumulatorsCell electrodesSolid state electrolyteMetallurgy

A practical solid-state battery composed primarily of ceramic or glass materials and containing no liquid, gel or polymeric electrolytes. The invention utilizes solid-state electrolyte materials with solid-state anode and cathode materials along with construction concepts utilized in the multi layered ceramic capacitor (MLCC) industry to result in a compact primary or secondary battery.

Owner:POLYMER INNOVATIONS

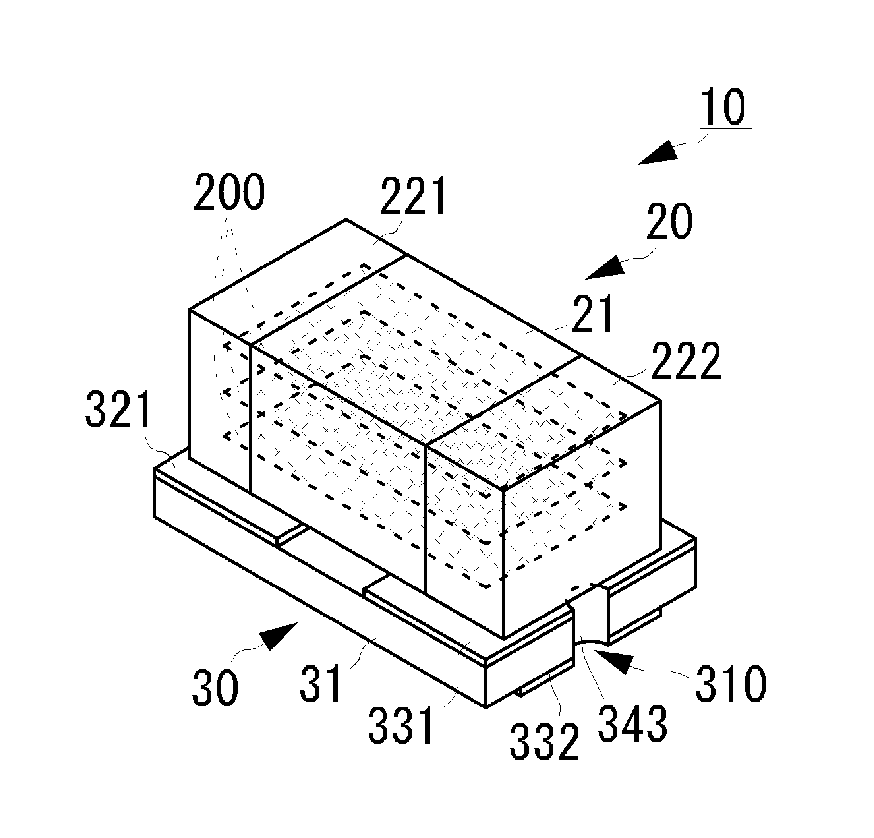

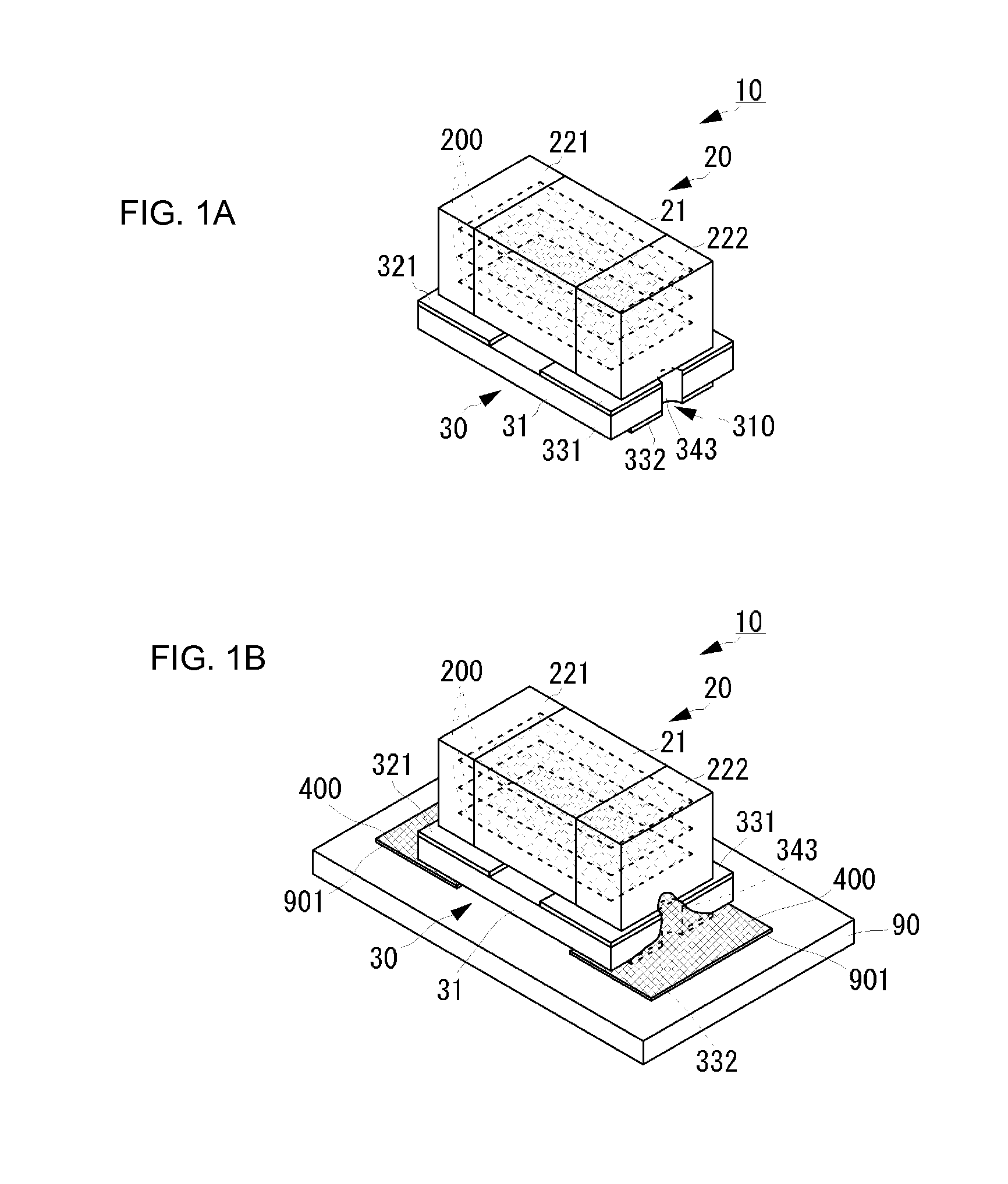

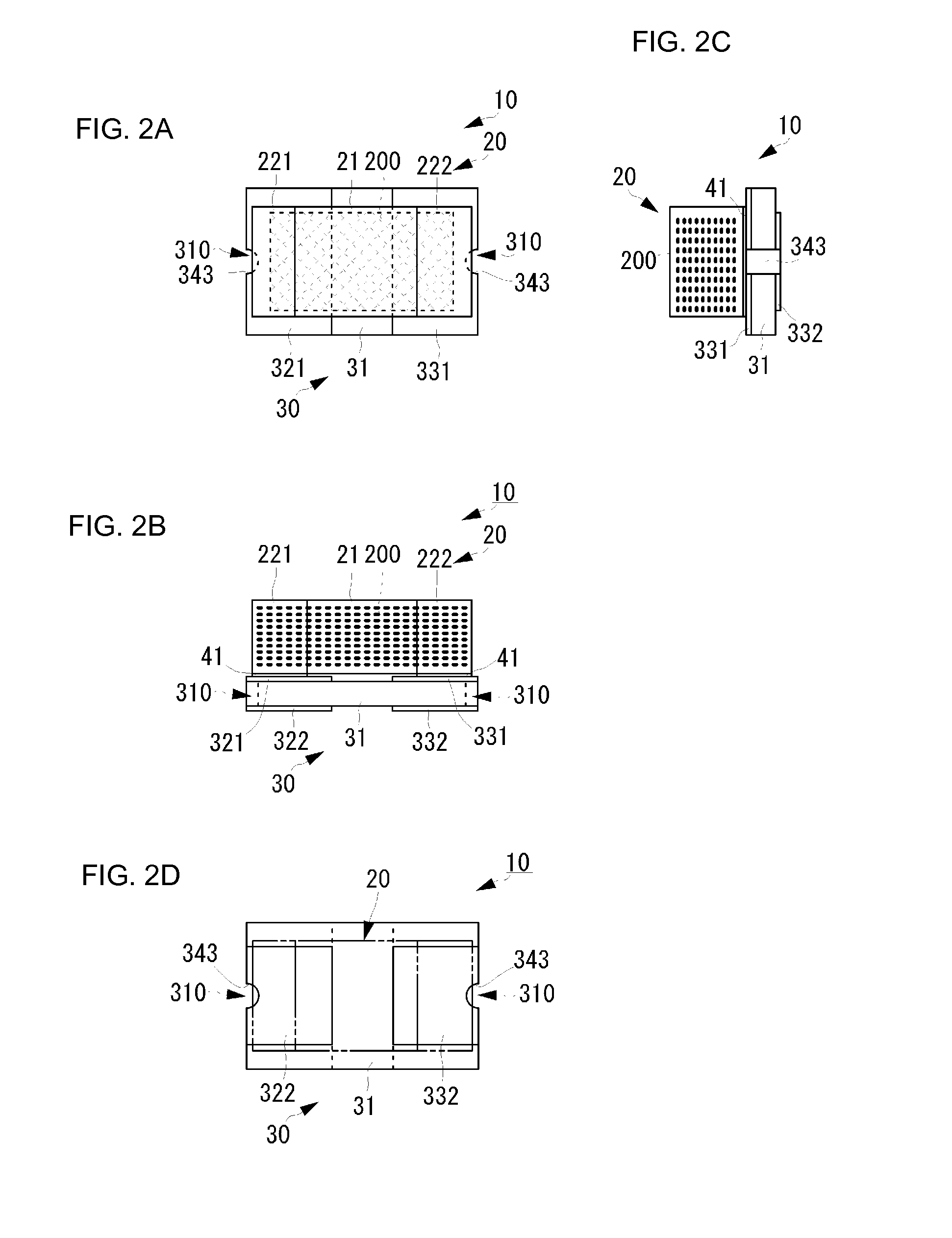

Electronic component

ActiveUS20140016242A1Reduce adhesionSimple structureFixed capacitor electrodesFinal product manufactureCeramic capacitorInterposer

A multilayer ceramic capacitor includes flat-shaped inner electrodes that are laminated. An interposer includes an insulating substrate that is larger than contours of the multilayer ceramic capacitor. A first mounting electrode that mounts the multilayer ceramic capacitor is located on a first principal surface of the insulating substrate, and a first external connection electrode for connection to an external circuit board located on a second principal surface. The multilayer ceramic capacitor is mounted onto the interposer in such a way that the principal surfaces of the inner electrodes are parallel or substantially parallel to the principal surface of the interposer, that is, the first and second principal surfaces of the insulating substrate.

Owner:MURATA MFG CO LTD

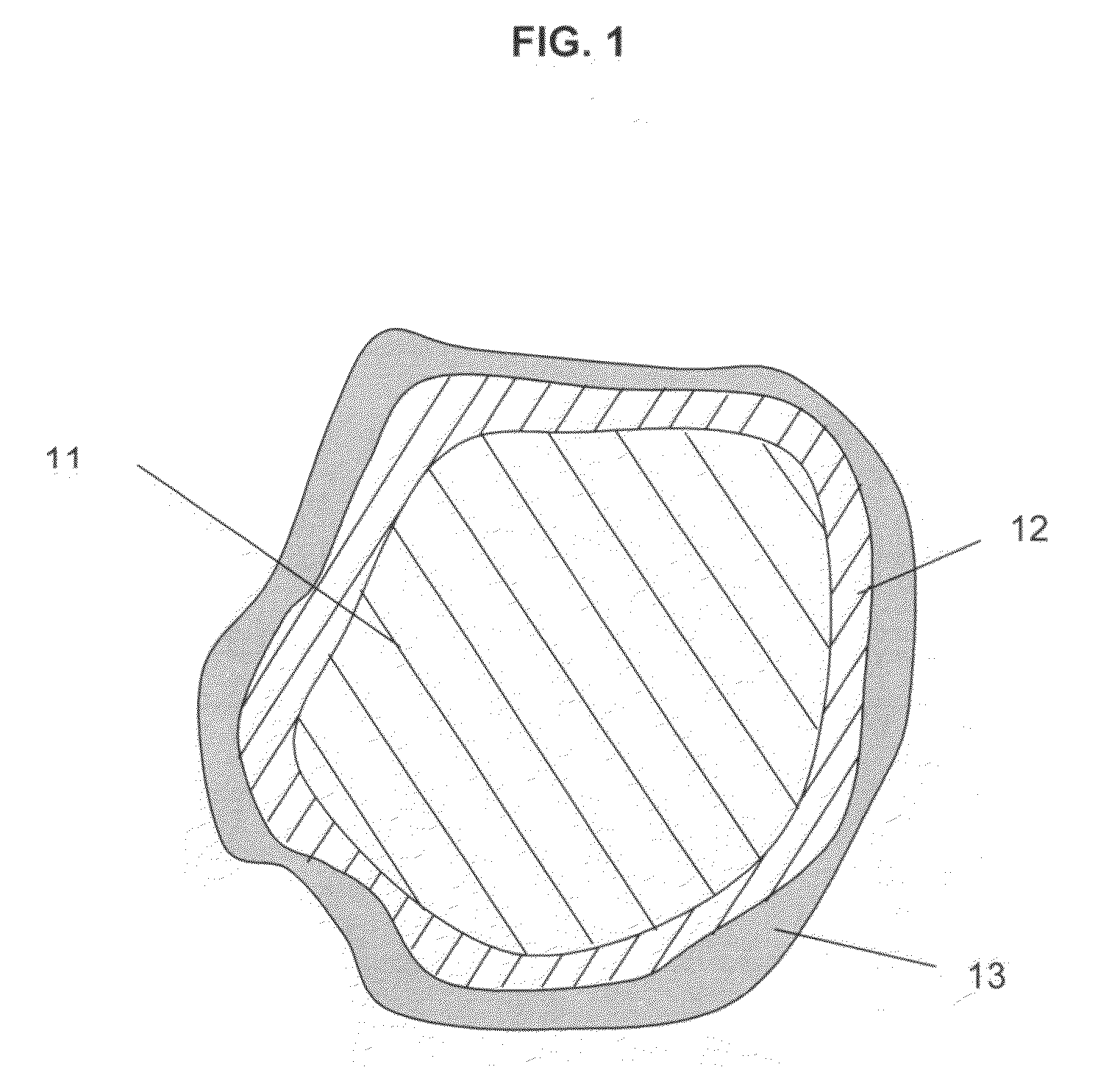

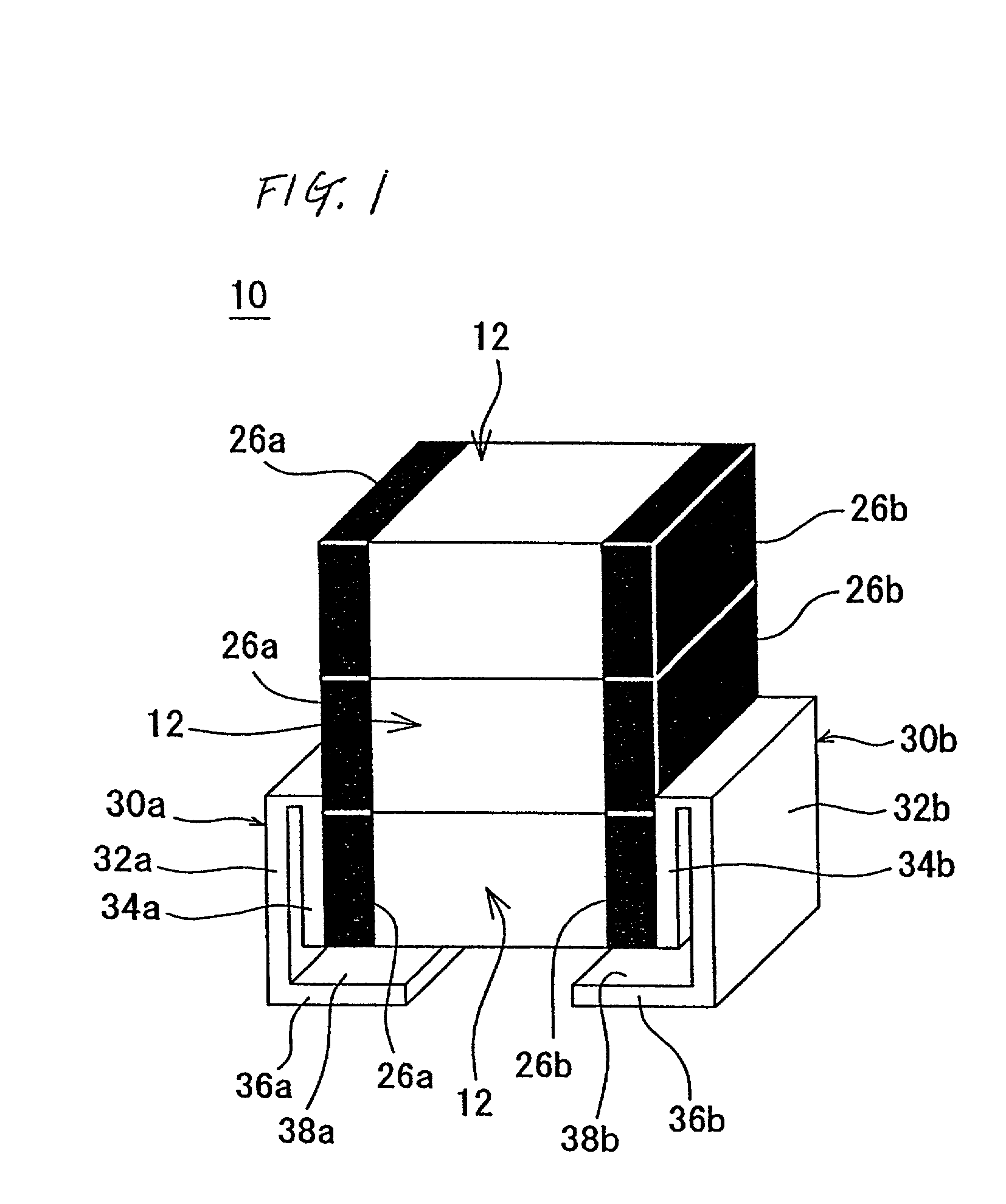

High temperature ceramic dielectric composition and capacitors made from the composition

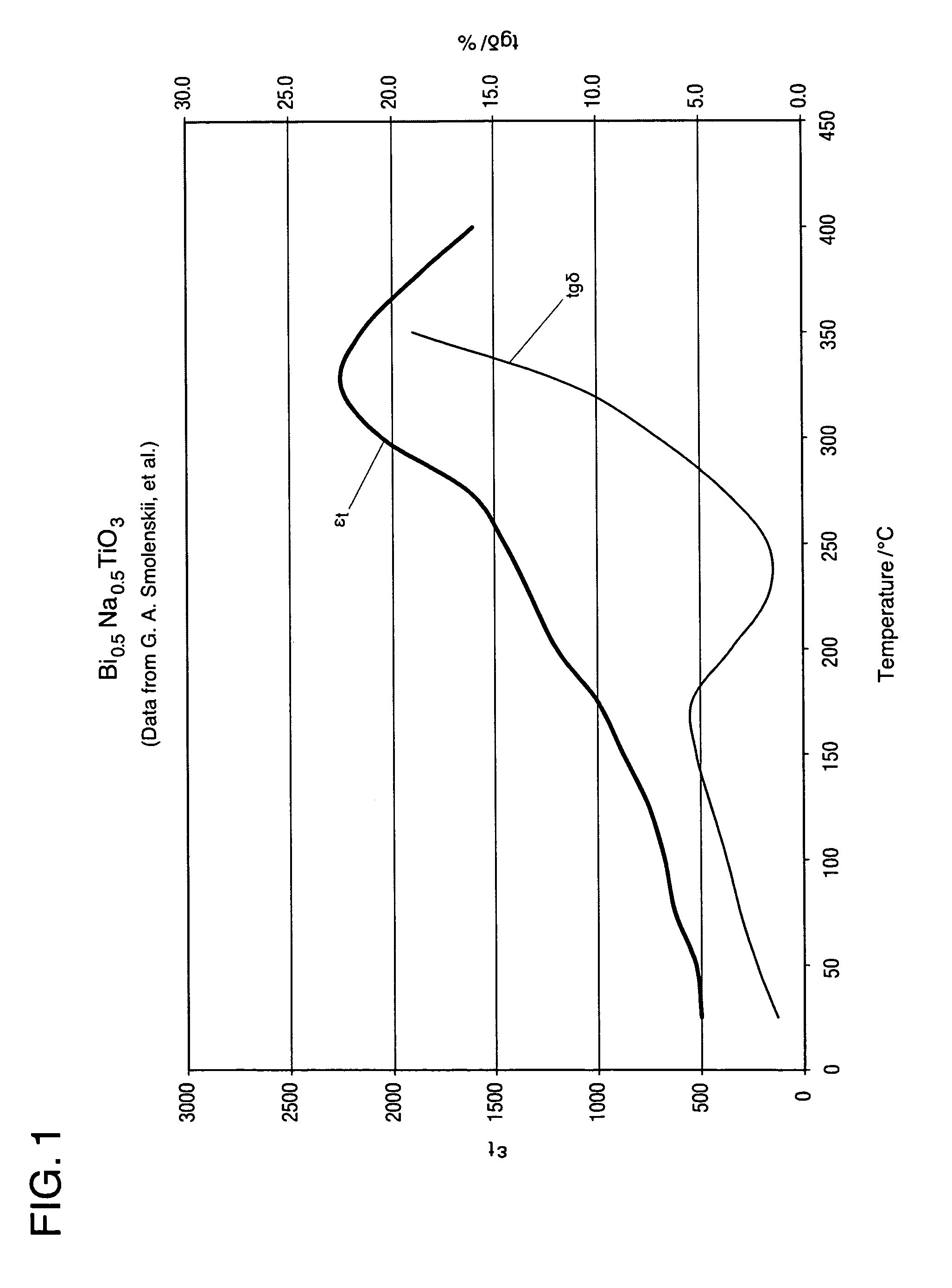

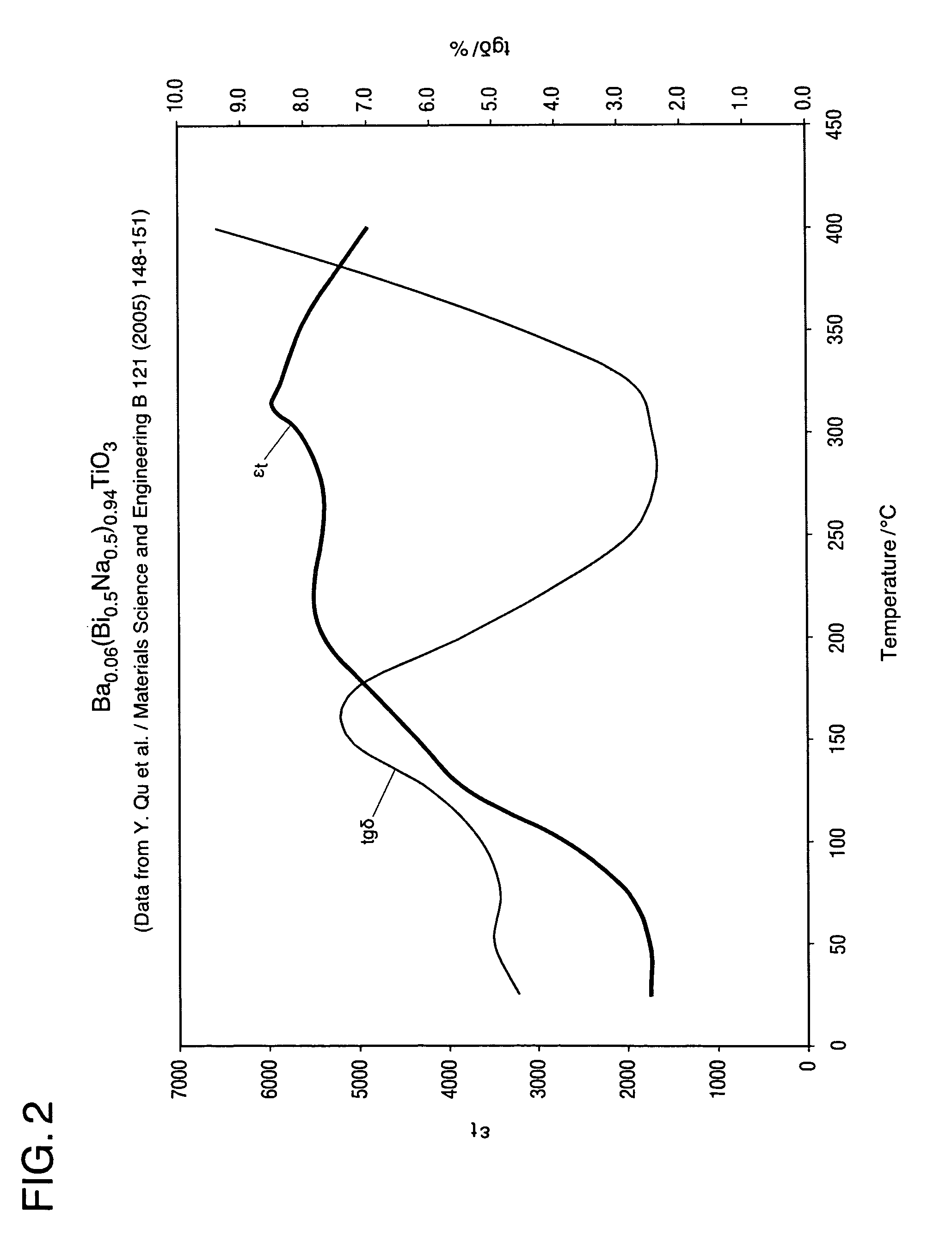

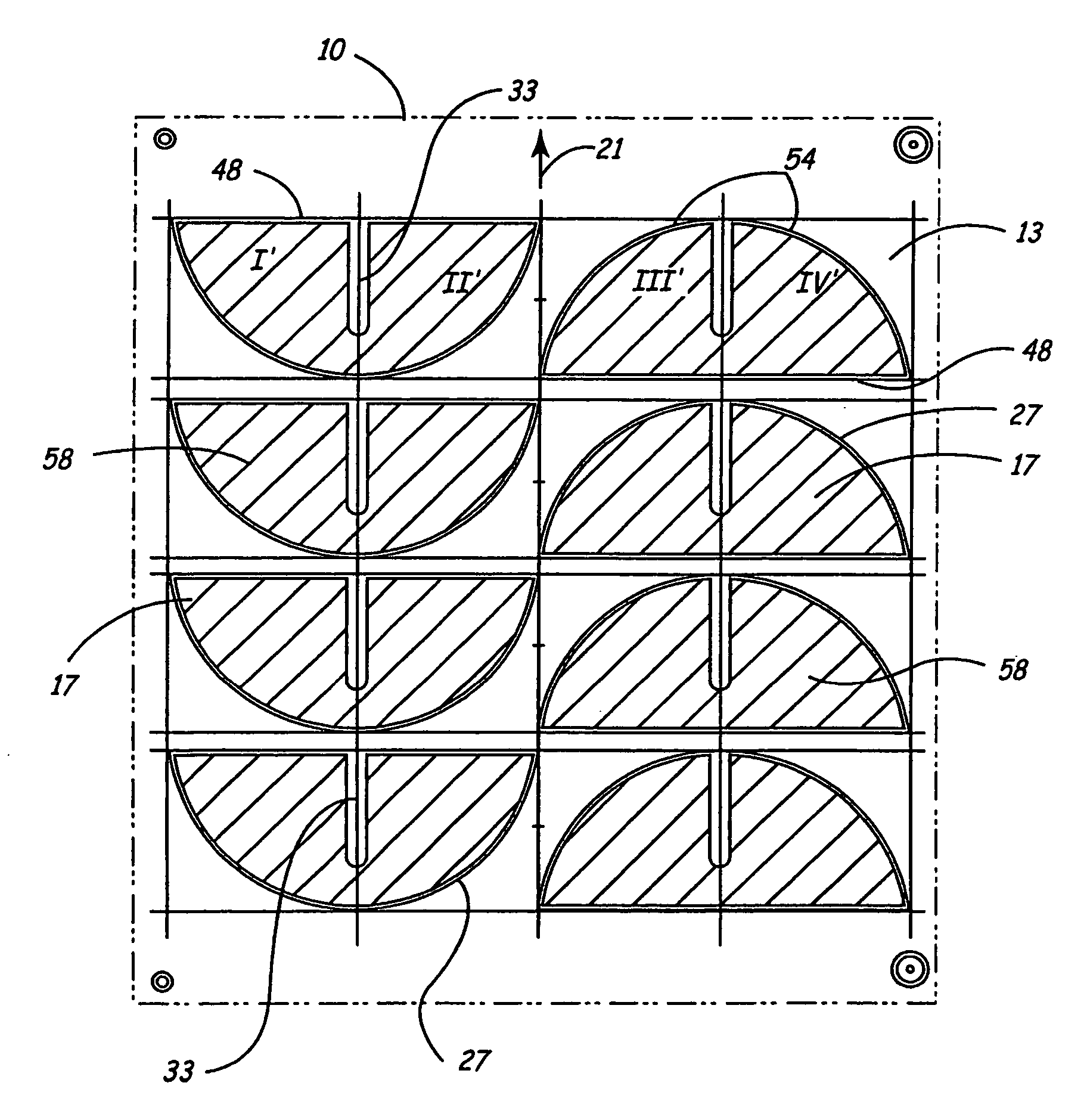

ActiveUS8076257B1Highly desirable propertyExcellent dielectric constant/voltage characteristicFixed capacitor dielectricStacked capacitorsCapacitanceDielectric

A bismuth sodium titanate (Bi0.5Na0.5TiO3) base material is modified by the partial substitution of aliovalent A-site cations such as barium (as BaO) or strontium (as SrO), as well as certain b-site donor / acceptor dopants and sintering aids to form a multi-phase system, much like known “core / shell” X7R dielectrics based solely on BaTiO3. The resulting ceramic dielectric composition is particularly suitable for producing a multilayer ceramic capacitor (10) that maintains high dielectric constant (and thus the capability of maintaining high capacitance) over a broad temperature range of from about 150° C. to about 300° C. Such capacitors (10) are appropriate for high temperature power electronics applications in fields such as down-hole oil and gas well drilling.

Owner:FERRO CORP

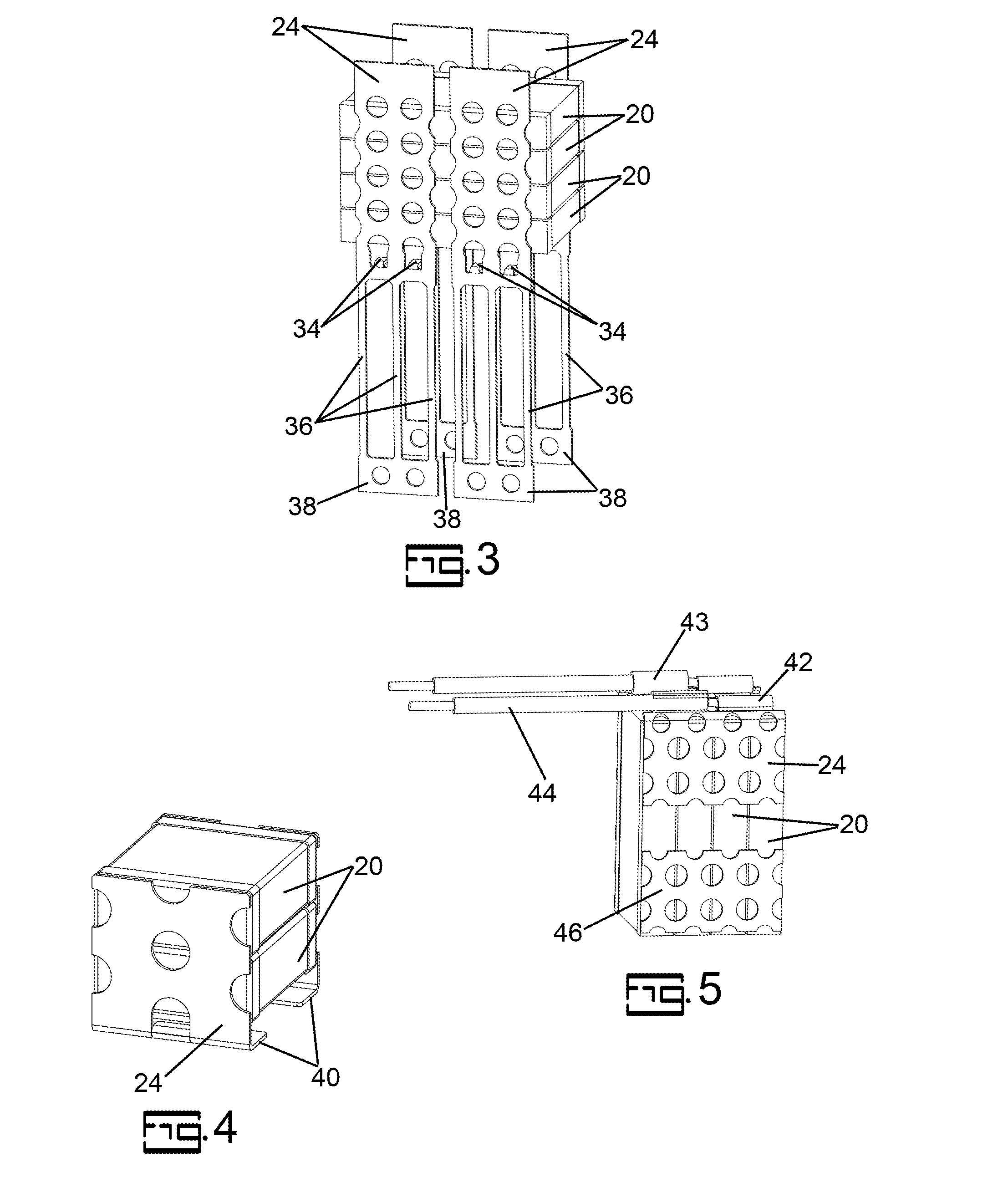

Complex-shaped ceramic capacitors for implantable cardioverter defibrillators and method of manufacture

InactiveUS20060126265A1Efficient use ofLower the volumeHeart defibrillatorsStacked capacitorsHigh energyCeramic capacitor

An improved manufacturing and packaging process for optimizing the size of various implanted medical devices is disclosed. Specifically, complex shapes involving ceramic capacitors with various other shapes are manufactured to optimize fit and shapes within the device housing. The manufacturing process includes various techniques and electrode material selections, including manufacturing processes that enable high energy discharge capacitors to be made in compliant shapes to fit in small ICD footprints.

Owner:MEDTRONIC INC

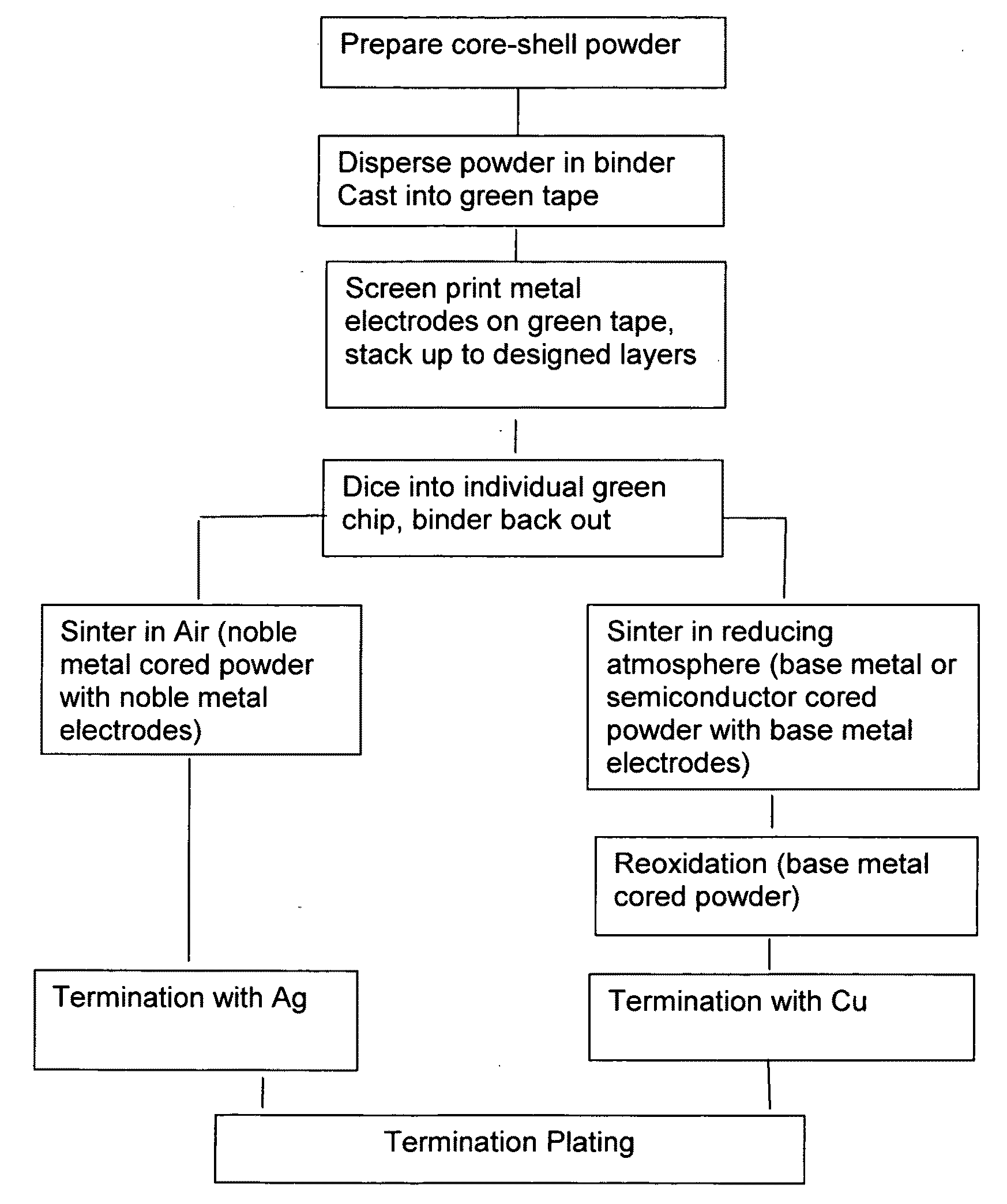

Core-shell structured dielectric particles for use in multilayer ceramic capacitors

InactiveUS20100110608A1Simplifies MLCC manufacturing processImprove propertiesFixed capacitor dielectricStacked capacitorsCapacitanceThin shells

This invention provides a method to make core-shell structured dielectric particles which consist of a conductive core and at least one layer of insulating dielectric shell for the application of multilayer ceramic capacitors (MLCC). The use of said core-shell instead of conventionally solid dielectric particles as the capacitor's active layers simplifies the MLCC manufacturing processes and effectively improves the MLCC properties. In particular, the use of core-shell particles with a thin shell of high permittivity dielectric material improves the capacitance volumetric efficiency, and the use of core-shell particles with a thick shell of dielectric will improve capacitor device's energy storage capacity as the results of improved electrical and mechanical strength.

Owner:WEI FRANK +1

Wiring board construction including embedded ceramic capacitors(s)

ActiveUS20070045815A1Small sizeMultiple fixed capacitorsCross-talk/noise/interference reductionCeramic capacitorEngineering

A wiring board includes a substrate core, ceramic capacitors and a built-up layer. The substrate core has a housing opening portion therein which opens at a core main surface. The ceramic capacitors are accommodated in the housing opening portion and oriented such that the core main surface and a capacitor main surface of each capacitor face the same way. The built-up layer includes semiconductor integrated circuit element mounting areas at various locations on a surface thereof. In the substrate core, each ceramic capacitor is respectively disposed in an area corresponding to each semiconductor integrated circuit element mounting area.

Owner:NGK SPARK PLUG CO LTD

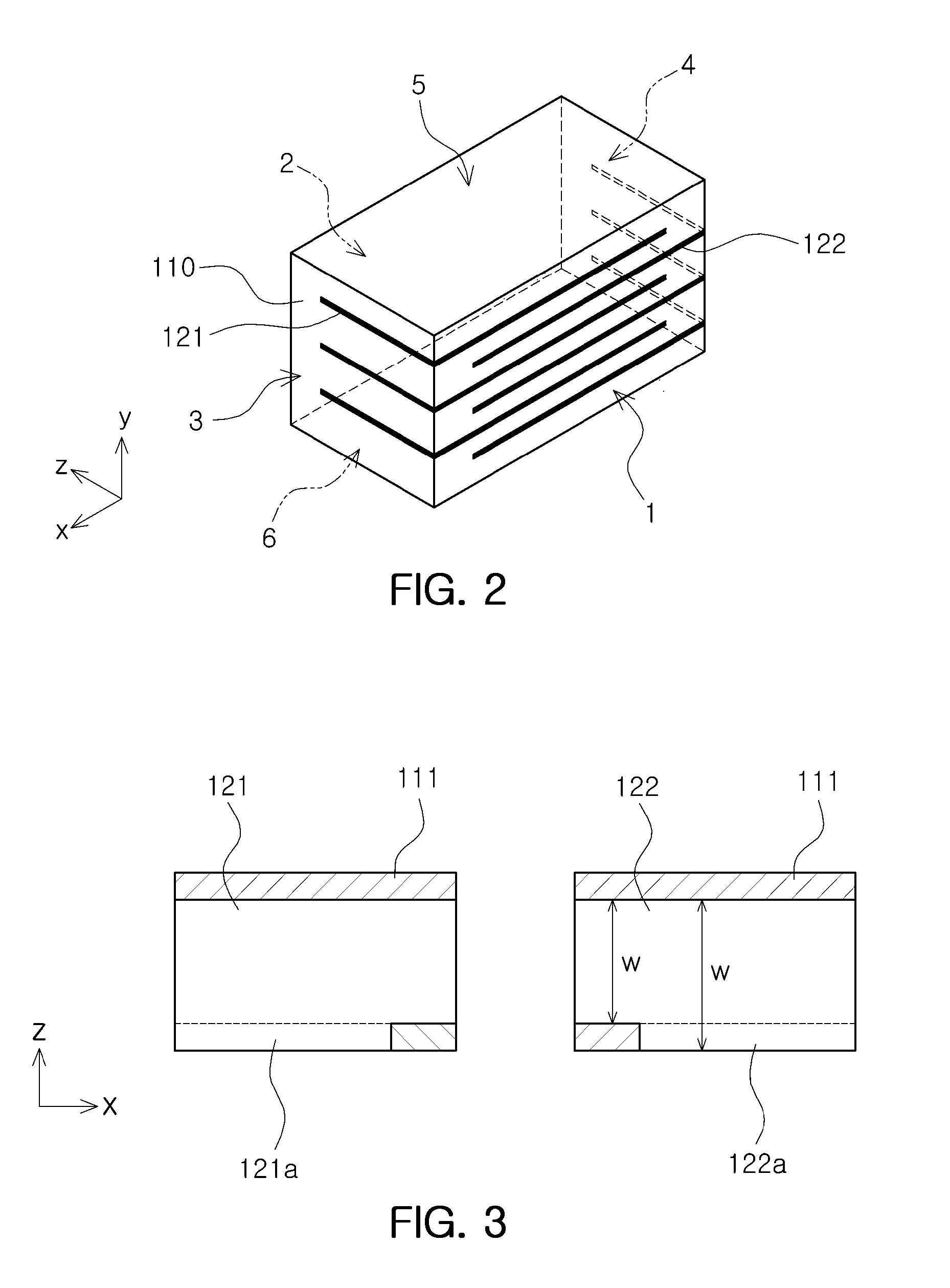

Multilayer ceramic capacitor

ActiveUS20130050893A1Increase capacitanceHigh strengthFixed capacitor dielectricStacked capacitorsInsulation layerMetallurgy

There is provided a multilayer ceramic capacitor including: a ceramic body; first and second internal electrodes including respective lead-out portions having an overlapping area, the overlapping area being exposed to one surface of the ceramic body; first and second external electrodes extended from the one surface of the ceramic body to side surfaces thereof in a y-direction, in which the first and second internal electrodes are laminated, and connected to the respective lead-out portions; and an insulation layer formed on the one surface of the ceramic body.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

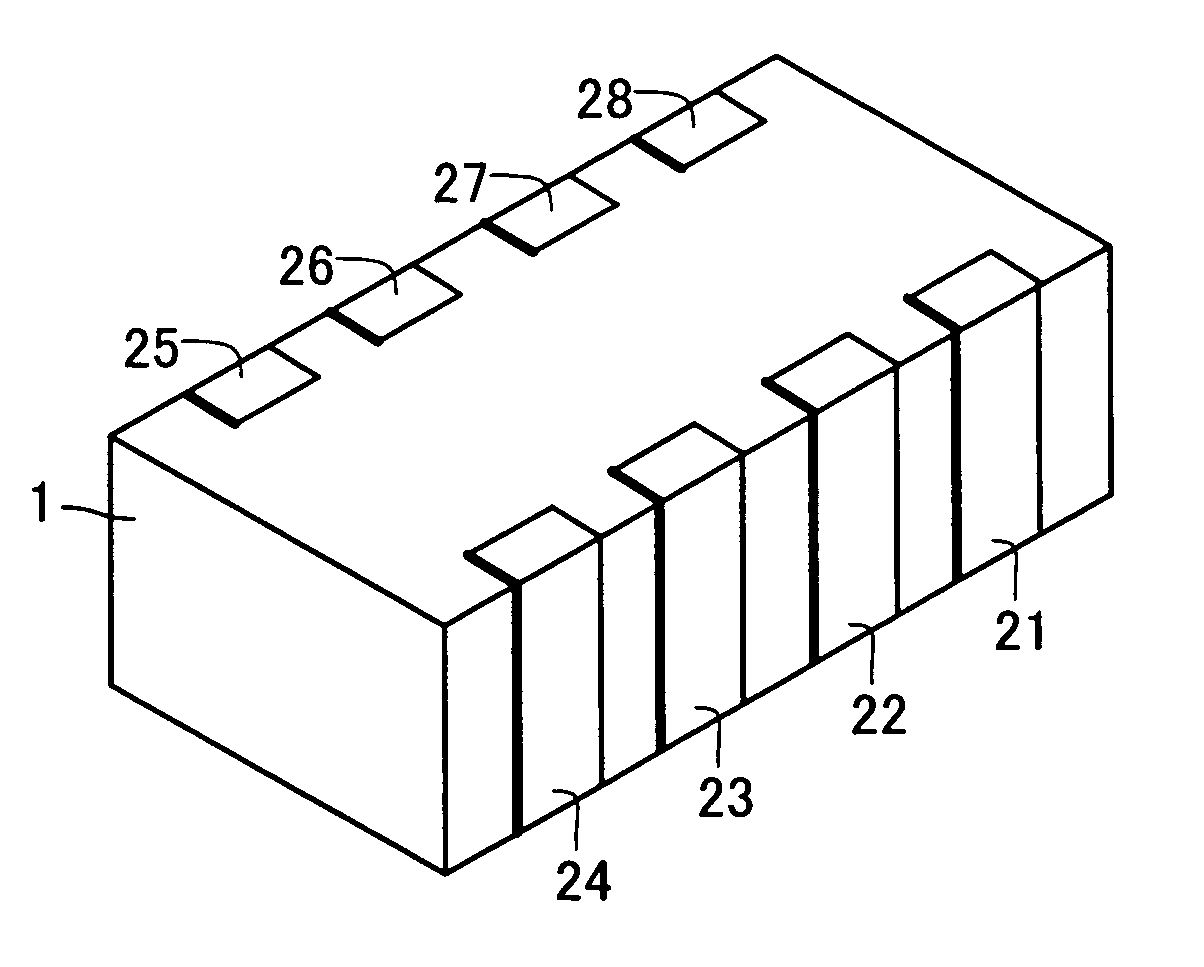

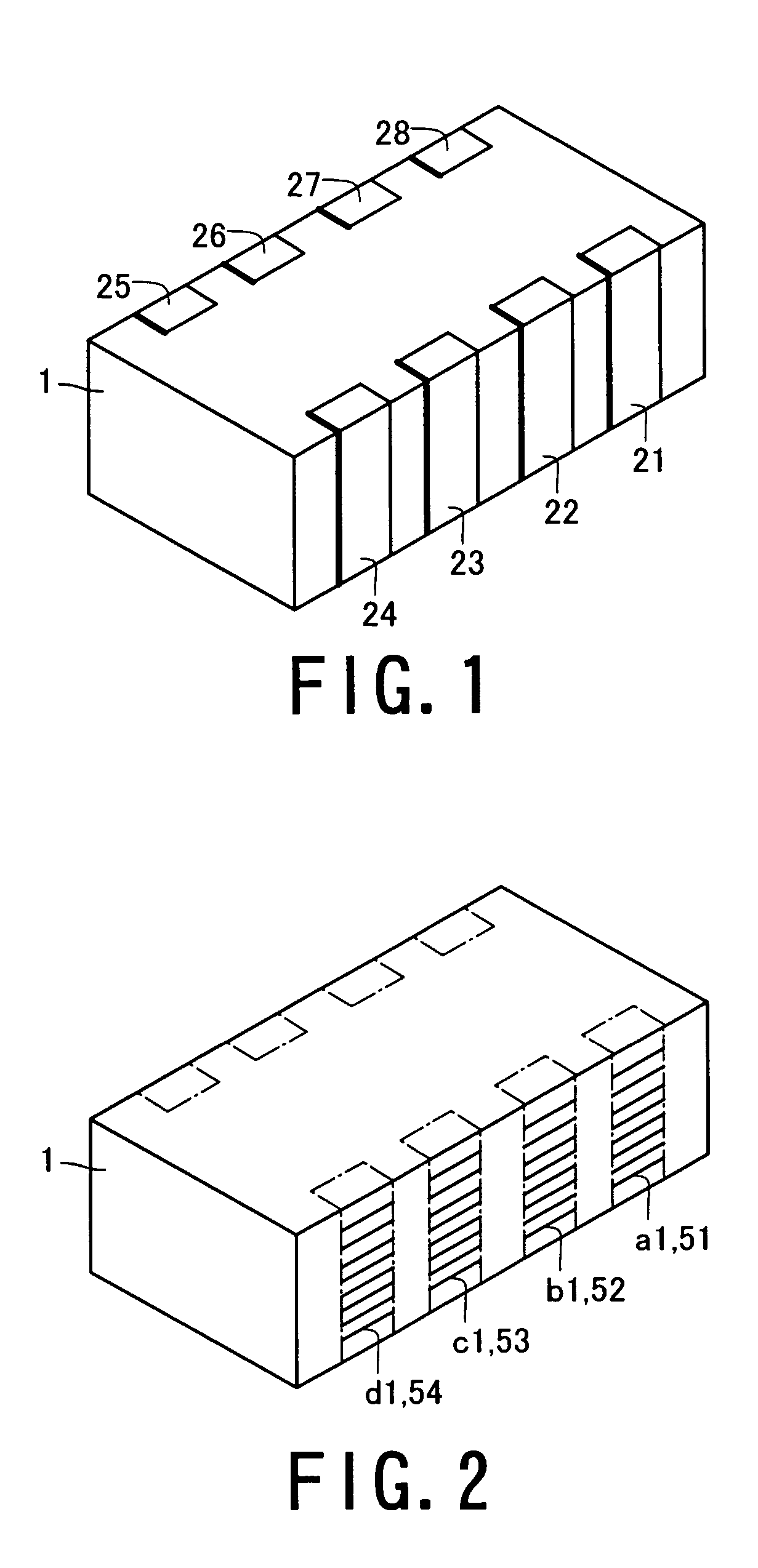

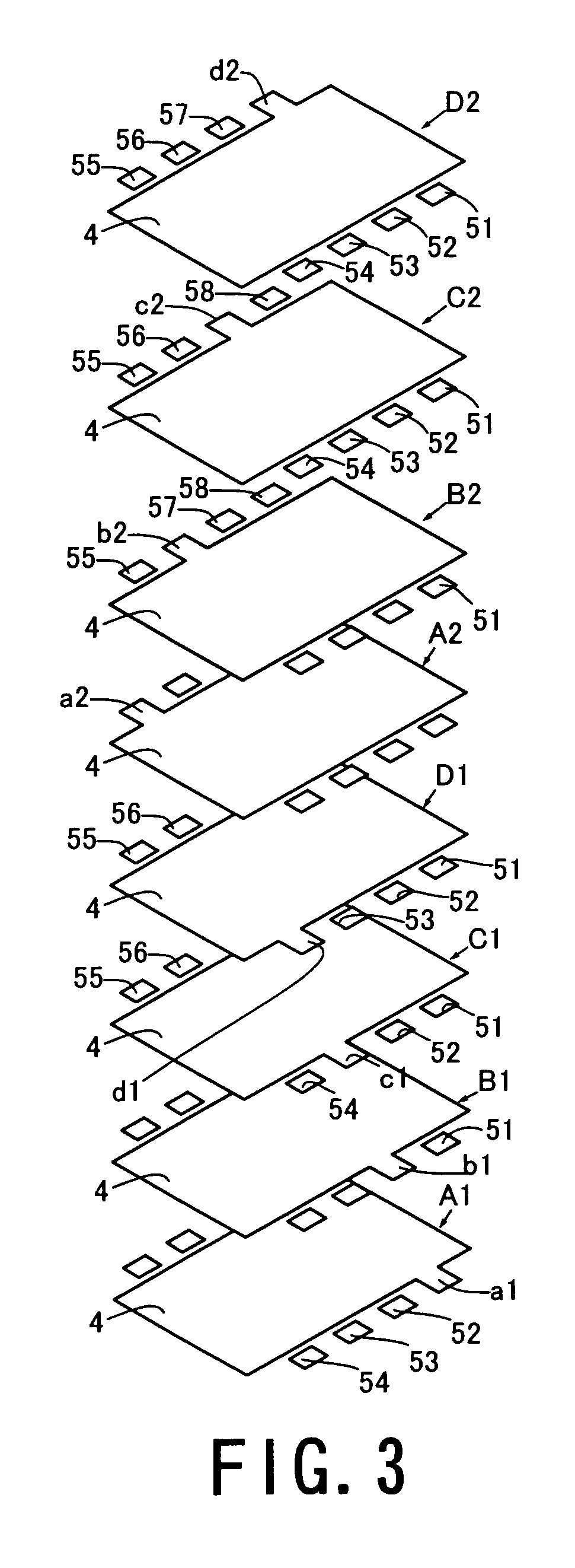

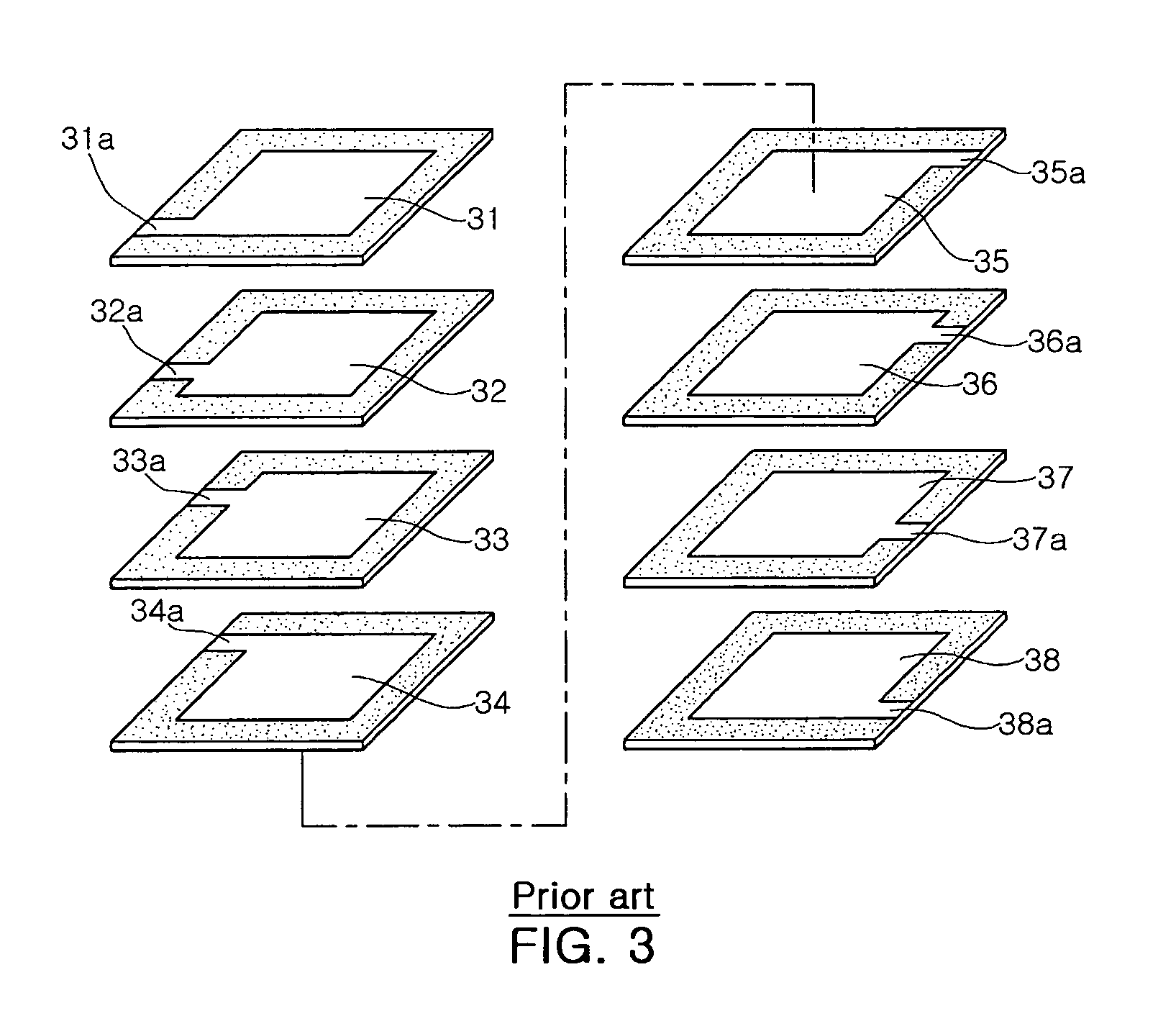

Laminated ceramic capacitor

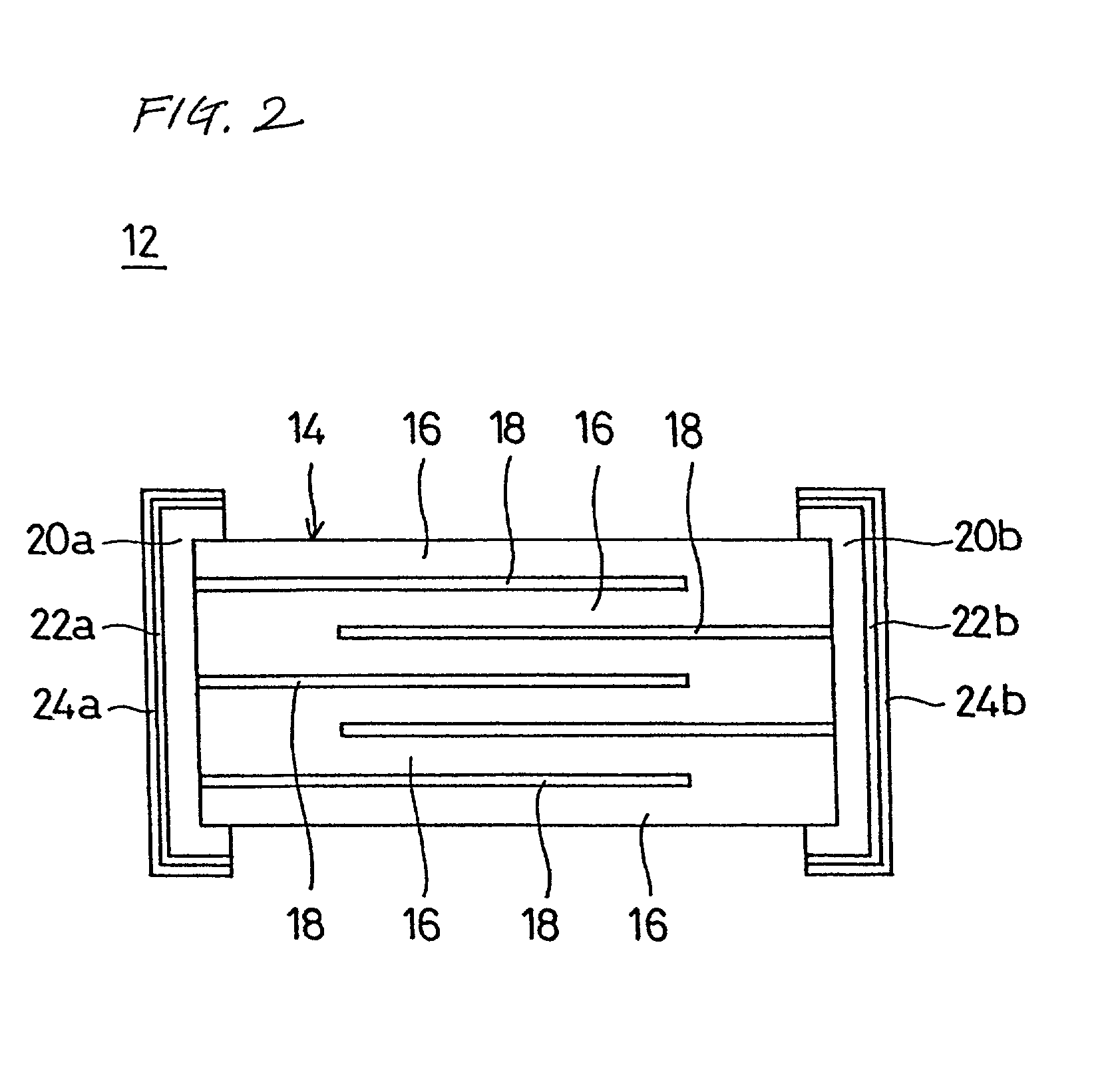

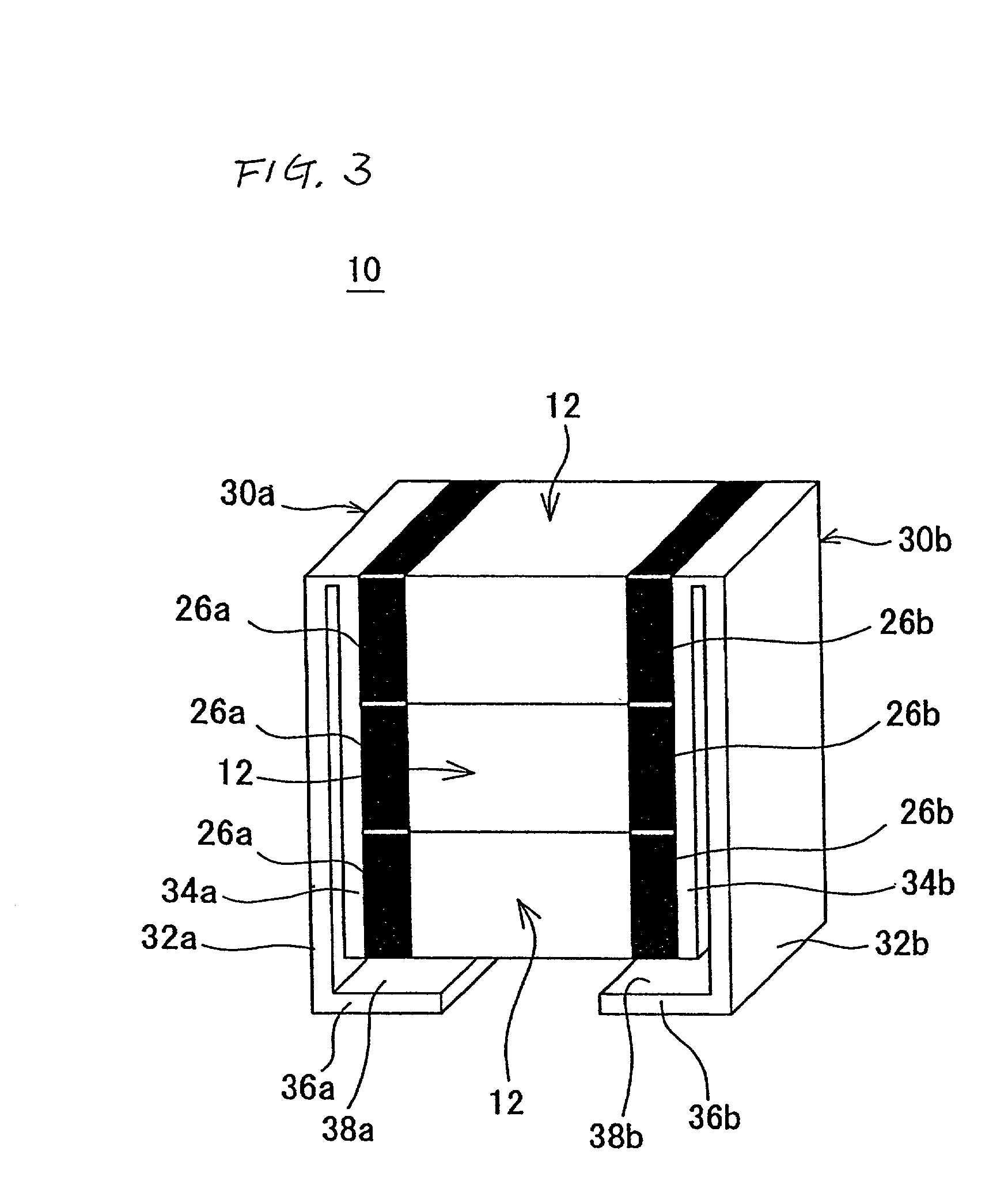

ActiveUS7050288B2Reduce connectionsReducing occurrence of delaminationMultiple fixed capacitorsFixed capacitor electrodesCeramic capacitorEngineering

Internal electrodes A1 to D1 and A2 to D2 are laid in layers at spaces in the direction of thickness of a ceramic body 1. Lead electrodes a1 to d1 and a2 to d2 are led out to a side face to form lead portions. Dummy electrodes 51 to 58 have one-side ends led out to a side face to form lead portions in layers provided with the internal electrodes A1 to D1 and A2 to D2. The lead portion of a lead electrode a1 to d1 or a2 to d2 of each layer is superposed over the lead portion of a dummy electrode 51 to 58 belonging to another layer in the direction of thickness.

Owner:TDK CORPARATION

Multilayer ceramic capacitor

InactiveUS20160293331A1Reduce the effective areaReduce capacitanceFixed capacitor dielectricStacked capacitorsCapacitanceCeramic capacitor

A multilayer ceramic capacitor includes an element body of roughly rectangular solid shape which is constituted by dielectric layers alternately stacked with internal electrode layers having different polarities, with a pair of cover layers formed on it to cover the top and bottom faces in the direction of lamination of the foregoing, and which has a pair of principal faces, a pair of end faces, and a pair of side faces, wherein external electrodes are formed on the pair of end faces and at least one of the pair of principal faces of the element body, and Tt representing the thickness of the external electrode and Tc representing the thickness of the cover layer satisfy the relationship of Tt≦Tc. The multilayer ceramic capacitor has large capacitance and also exhibits excellent thermal shock resistance while sufficiently suppressing generation of cracks.

Owner:TAIYO YUDEN KK

Monolithic capacitor

InactiveUS20010007522A1Improve thermal shock resistancePrinted circuit assemblingMultiple fixed capacitorsCeramic capacitorMaterials science

A monolithic capacitor includes a plurality of monolithic ceramic capacitor elements provided with external electrodes at both ends thereof, solder layers arranged on the entire surfaces of the external electrodes of the monolithic ceramic capacitor elements, and metal terminals electrically connected to the external electrodes of the monolithic ceramic capacitor elements. The monolithic ceramic capacitor elements are joined to each other by the solder layers and are stacked on each other. The external electrodes of the monolithic ceramic capacitor elements are electrically connected to each other by the solder layers.

Owner:MURATA MFG CO LTD

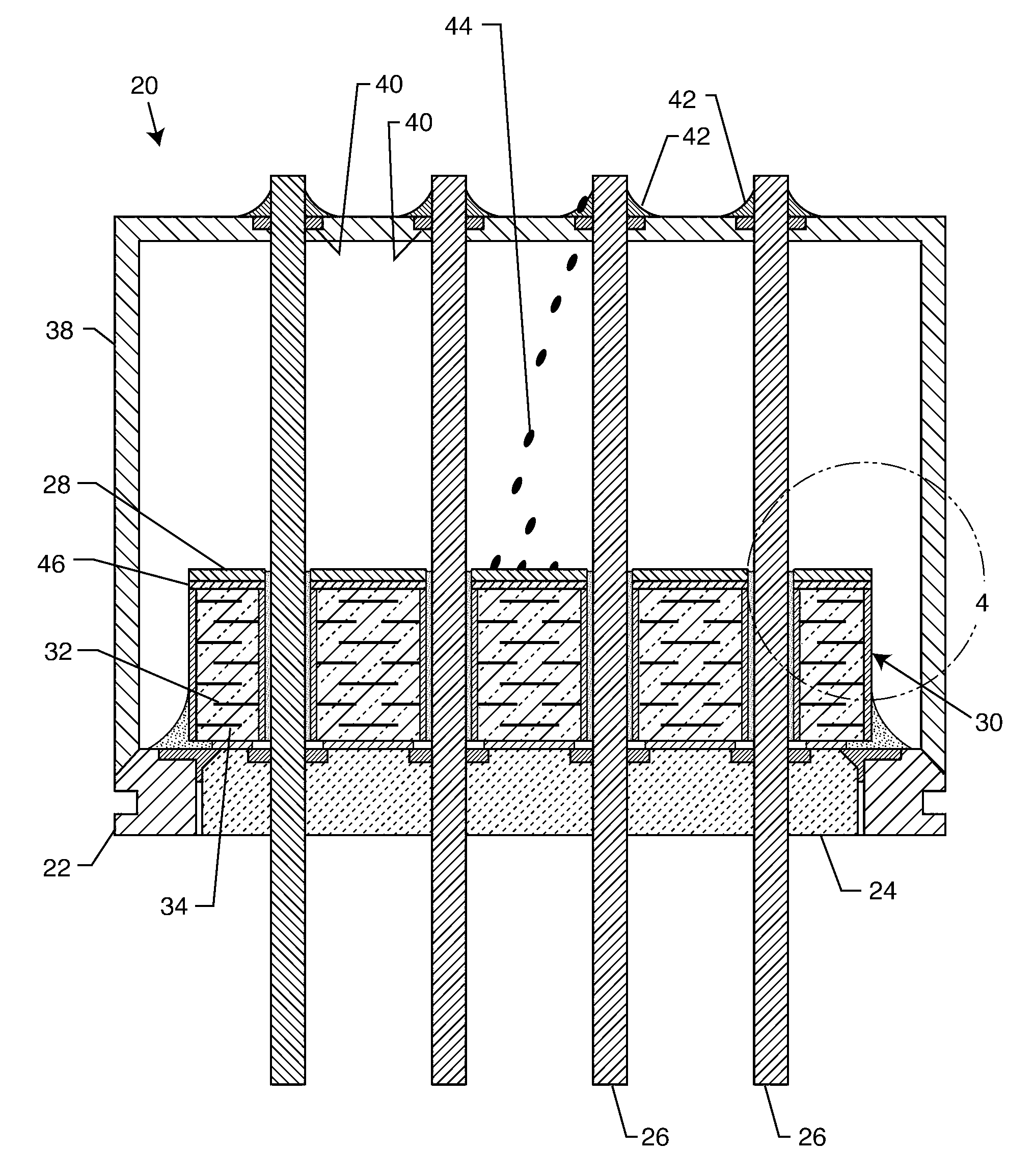

Electro-pyrotechnic initiator

InactiveUS6324979B1Small sizeLow costBlasting cartridgesElectric fuzesElectrical resistance and conductancePyrotechnic initiator

An device for use in an electro-pyrotechnic initiator comprises a header, a foil resistive strip, a substrate, and a current source. The substrate is mounted on the header. The foil resistive strip is mounted on the substrate. The energy source is connected to the resistive strip. When current flows through the resistive strip, the resistive strip generates enough heat to spark autoignition of a pyrotechnic material. The pyrotechnic material is in direct contact with the resistive strip. For an energy input of up to 115 microjoules, the resistive strip can cause autoignition in less than 25 microseconds. In a second embodiment, an electro-pyrotechnic initiator for use in a "smart" airbag system comprises a header, a foil resistive strip, a substrate, a current source connected to the resistive strip, and a control circuit. The control circuit is designed such that it will cause current to flow through the resistive strip when the circuit receives an appropriate signal. A ceramic capacitor can be used as an energy source for the resistive strip.

Owner:VISHAY INTERTECHNOLOGY INC

Multilayer electronic component and method for manufacturing multilayer electronic component

ActiveUS20080239617A1Large effective volumeImprove welding reliabilityStacked capacitorsFixed capacitor terminalsConductive pasteCeramic capacitor

A method for manufacturing a laminated ceramic capacitor includes a step of preparing a laminate which has a first principal surface, a second principal surface, a first end surface, a second end surface, a first side surface, and a second side surface and which includes insulating layers and internal electrodes having end portions exposed at the first or second end surface; a step of forming external electrodes on the first and second end surfaces such that plating deposits are formed on the exposed end portions of the internal electrodes so as to be connected to each other; and a step of forming thick end electrodes electrically connected to the external electrodes such that a conductive paste is applied onto edge portions of the first and second principal surfaces and first and second side surfaces of the laminate and then baked.

Owner:MURATA MFG CO LTD

Laminated ceramic capacitor

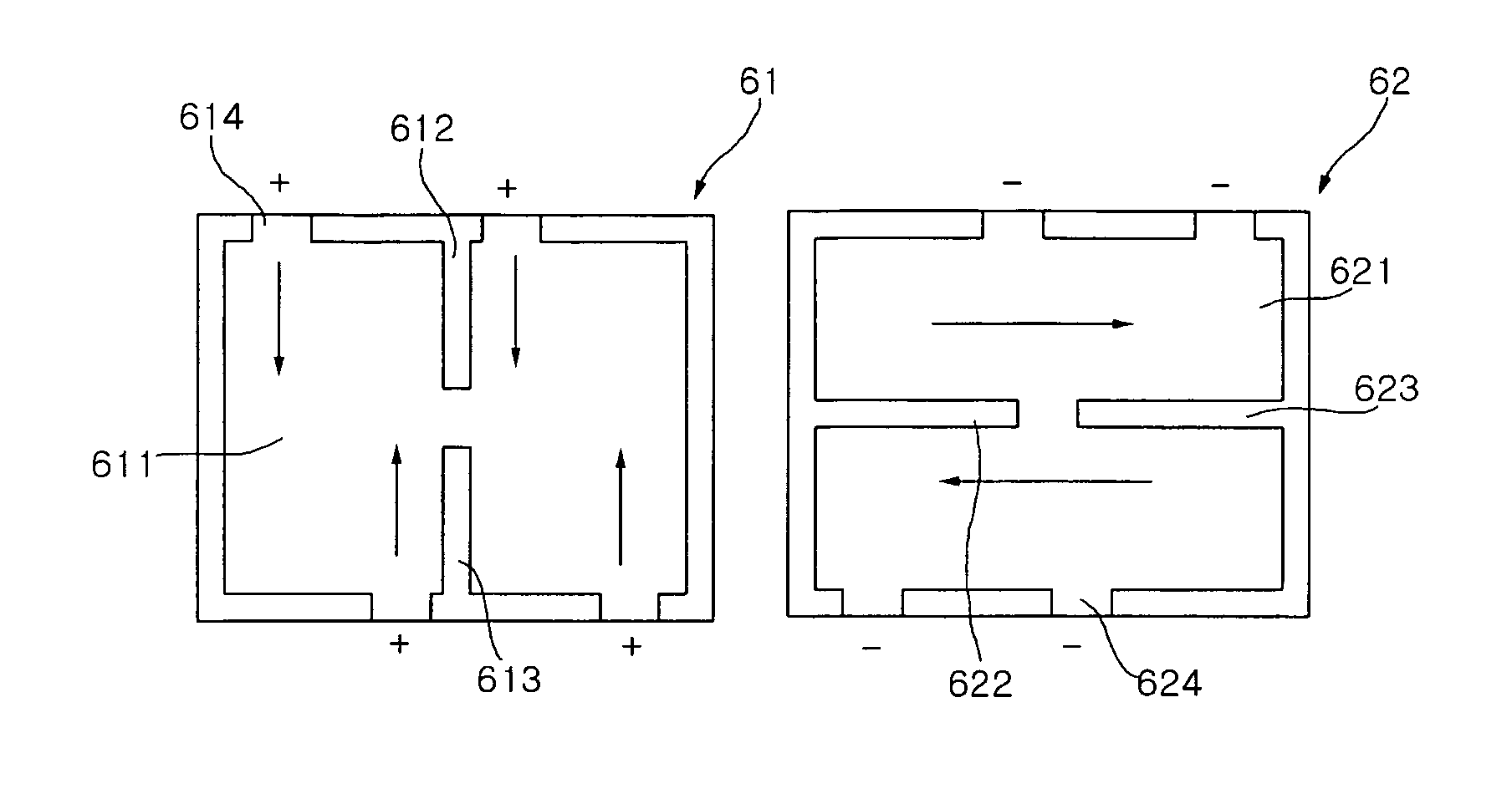

InactiveUS7046500B2Reduce capacitanceFixed capacitor electrodesFixed capacitor dielectricMetallurgyCeramic capacitor

A laminated ceramic capacitor includes a ceramic block formed by laminating a plurality of ceramic sheets, a plurality of external electrodes formed on outer surfaces of the ceramic block facing each other, and set as a positive terminal and a negative terminal, respectively, one or more first and second internal electrodes alternately arranged within the ceramic block such that electric currents flow in opposite directions in the internal electrodes, and a plurality of withdrawing patterns for connecting the first and second internal electrodes to the external electrodes, respectively.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Ceramic Capacitors with Improved Lead Designs

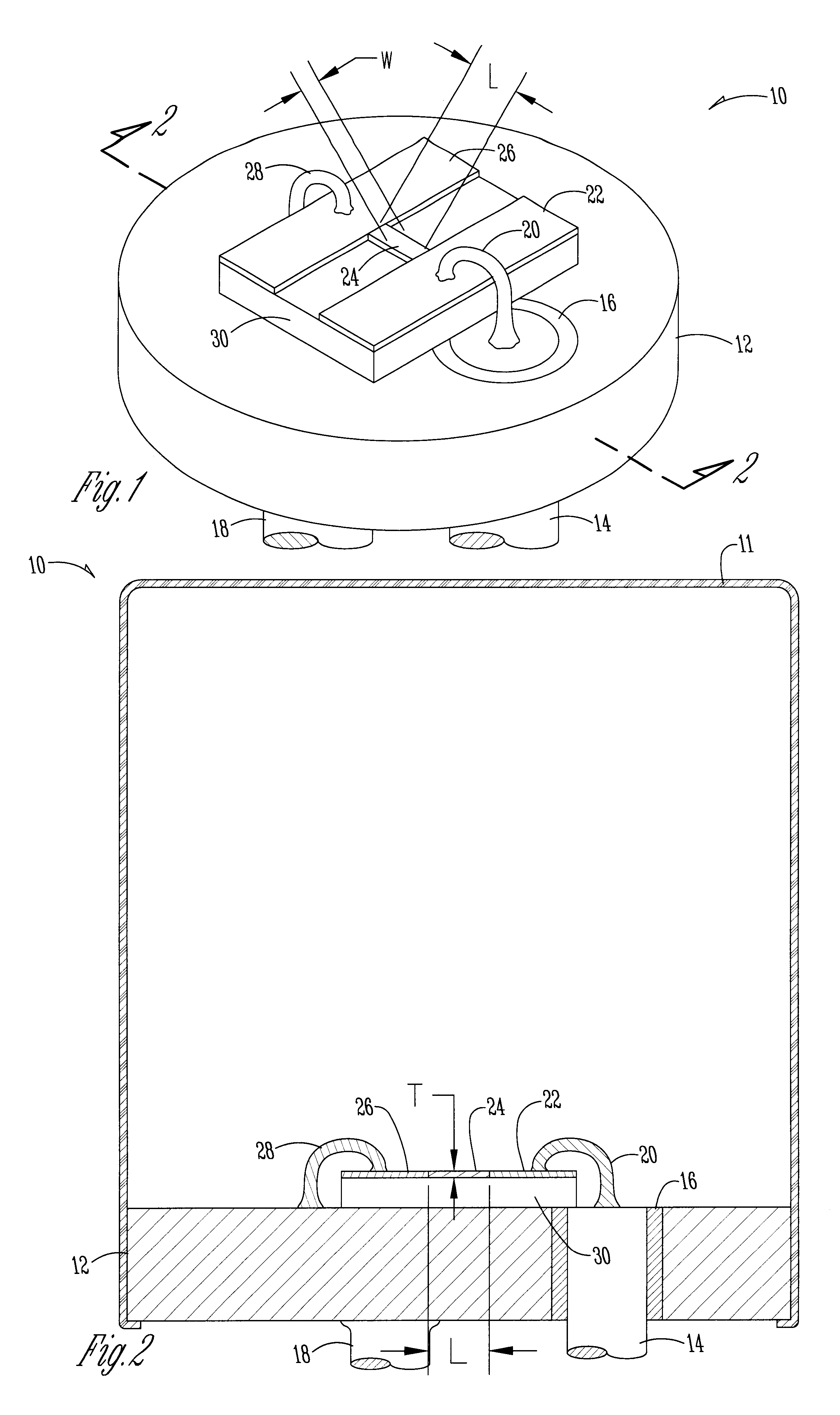

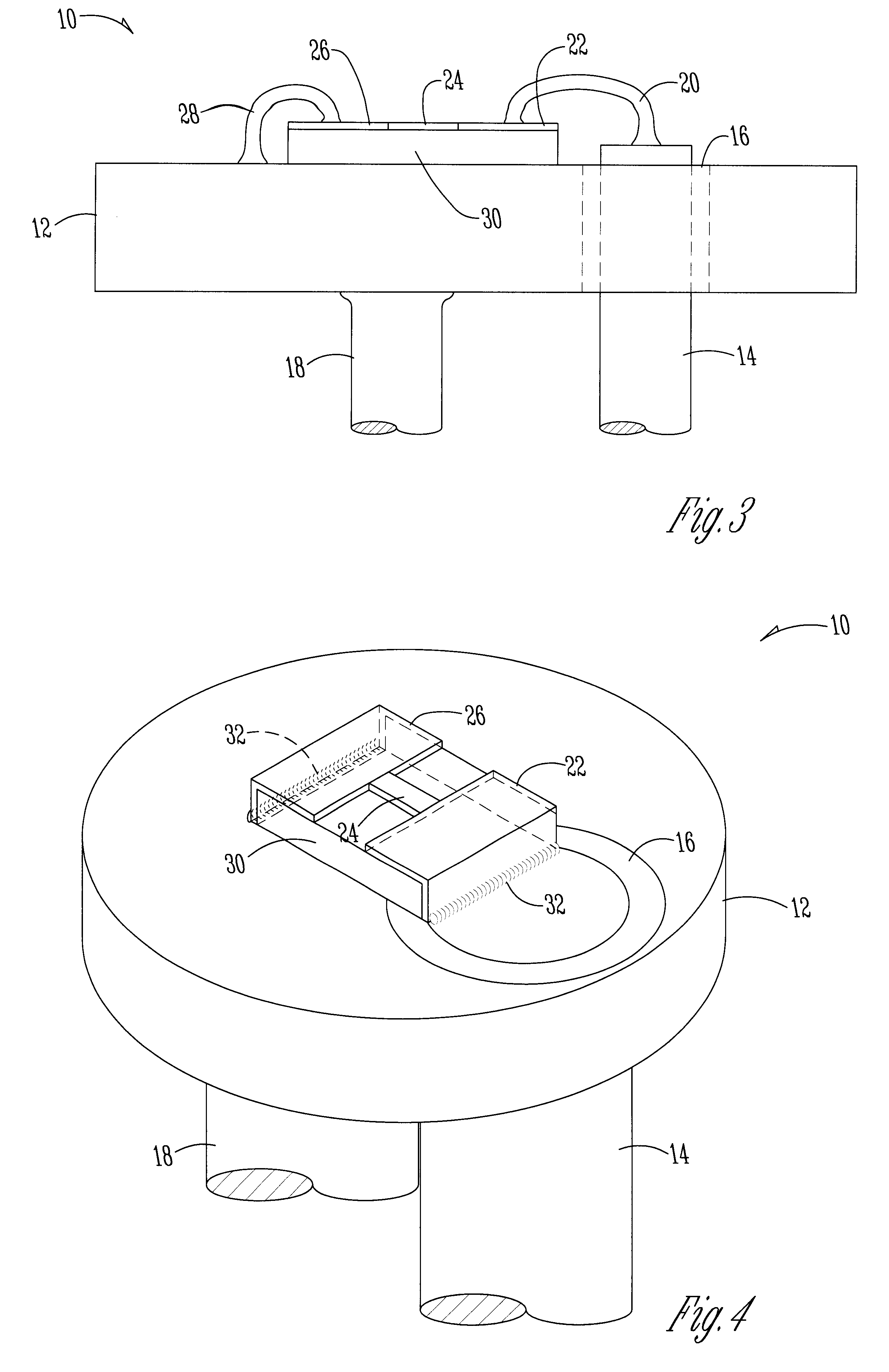

InactiveUS20150114697A1High mechanical strengthRelieve pressureFixed capacitor dielectricSemiconductor/solid-state device detailsCapacitanceDielectric

An electronic component is provided with improved thermal stability. The electronic component comprises at least one capacitive element wherein the capacitive element comprises internal electrodes of alternating polarity separated by a dielectric. External terminations with a first external termination of the external terminations are in electrical contact with internal electrodes of a first polarity and a second external termination of the external terminations are in electrical contact with internal electrodes of a second polarity. A first external lead frame is in electrical contact with the first external termination with a conductive bond there between wherein the first external lead frame comprises at least one feature selected from the group consisting of a perforation, a protrusion and an edge indentation.

Owner:KEMET ELECTRONICS CORP

Electronic component

ActiveUS20130284507A1Easy to installOccurrence can be reduced and preventedFinal product manufacturePrinted electric component incorporationCeramic capacitorInterposer

In an electronic component, upper surface electrodes are located on one main surface of an insulating substrate of an interposer on which a multilayer ceramic capacitor is mounted. The insulating substrate has substantially the same shape as that of the multilayer ceramic capacitor, viewed from a direction perpendicular or substantially perpendicular to the main surface, and has the multilayer ceramic capacitor mounted thereon so that the length direction of the multilayer ceramic capacitor substantially coincides with the length direction of the insulating substrate. The insulating substrate includes cutouts that include connection electrodes, respectively, and that are located at the four corners viewed from the direction perpendicular or substantially perpendicular to the main surface. The upper surface electrodes on the one main surface are connected via the connection electrodes to lower surface electrodes, respectively, that are located on the other main surface and are connected to a circuit board.

Owner:MURATA MFG CO LTD

Monolithic ceramic capacitor

ActiveUS20090002920A1Improve installabilityLow reliabilityFixed capacitor electrodesFixed capacitor dielectricCeramic capacitorOptoelectronics

In an LW-reverse-type monolithic ceramic capacitor including external terminal electrodes each including a resistance component, internal electrodes include nickel or a nickel alloy, and the external terminal electrodes each include a first layer, a second layer provided on the first layer, and a third layer provided on the second layer. The first layer has a wrap-around portion extending from an end surface to principal surfaces and side surfaces of a capacitor main body, and contains a glass component and a compound oxide that reacts with Ni or the Ni alloy. The second layer covers the first layer such that the edge of the wrap-around portion of the first layer remains exposed, and contains a metal. The third layer covers the edge of the wrap-around portion of the first layer and the second layer, and is formed by plating.

Owner:MURATA MFG CO LTD

Multilayer ceramic capacitor

ActiveUS20130050897A1Increase capacitanceLow equivalent series inductanceFixed capacitor electrodesFixed capacitor dielectricInsulation layerMetallurgy

There is provided a multilayer ceramic capacitor including: a ceramic body; first and second internal electrodes provided within the ceramic body and including respective lead-out portions exposed to a first surface of the ceramic body and a third or fourth surface thereof connected to the first surface and having an overlapping area, the overlapping area being exposed to the first surface of the ceramic body; first and second external electrodes extended from the first surface of the ceramic body to the third or fourth surface thereof connected to the first surface and connected to the respective lead-out portions; and an insulation layer formed on the first surface of the ceramic body and the third and fourth surfaces thereof connected to the first surface.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

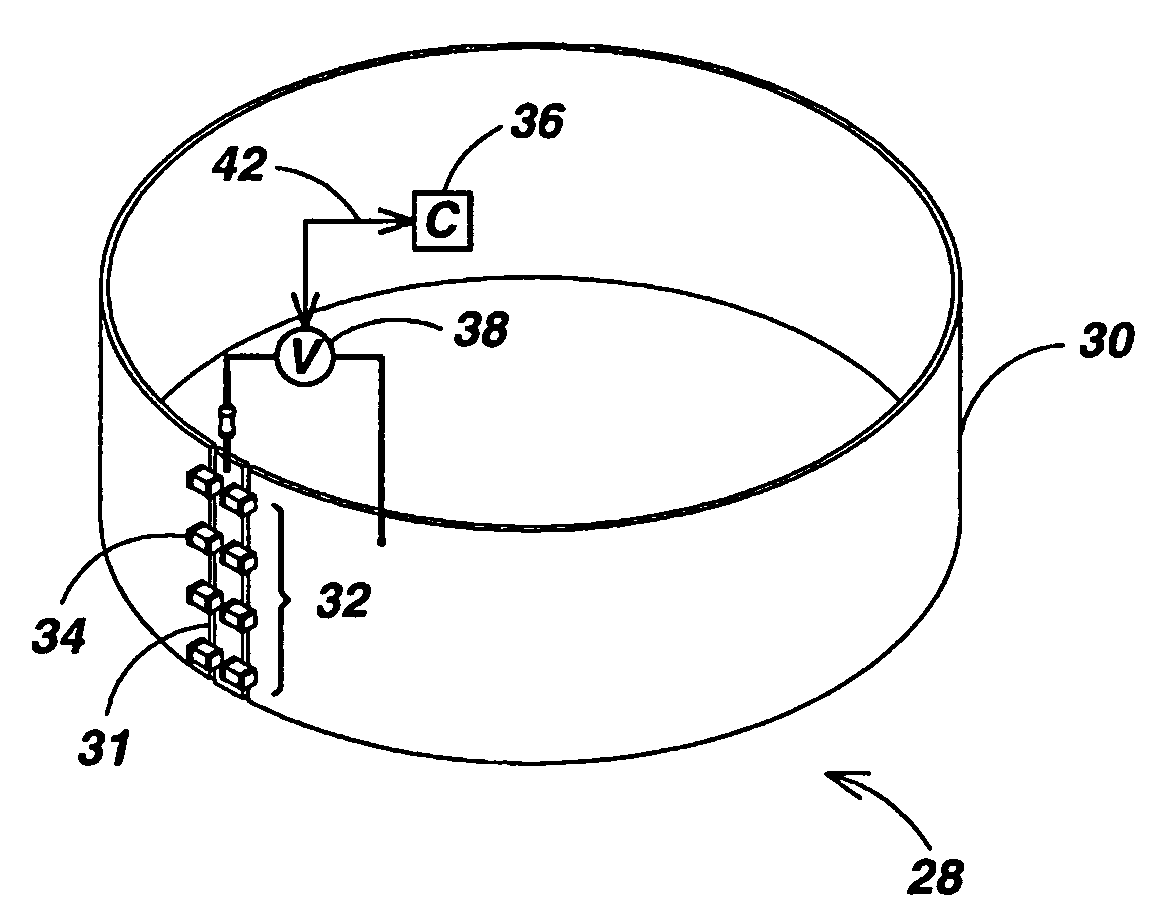

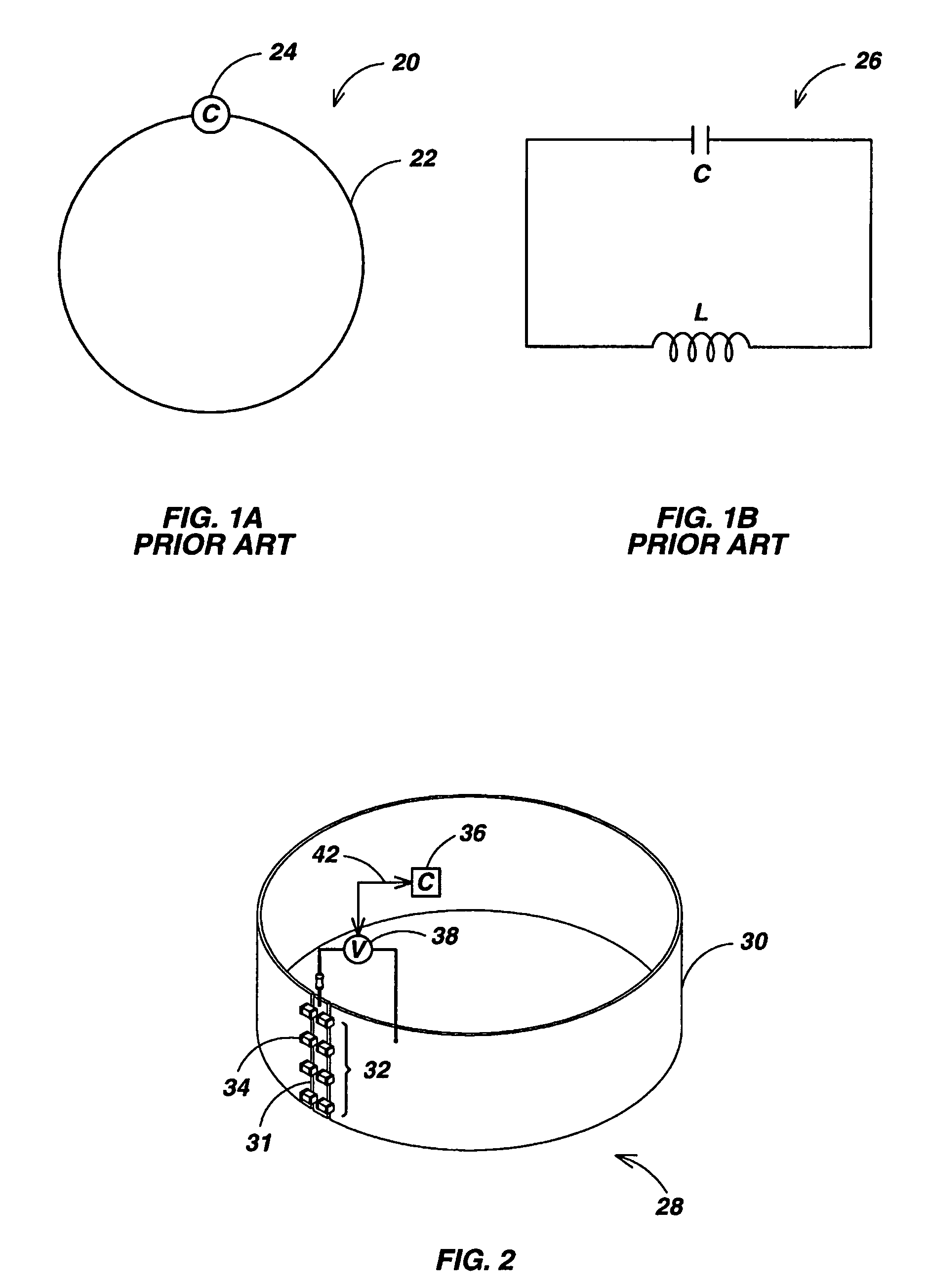

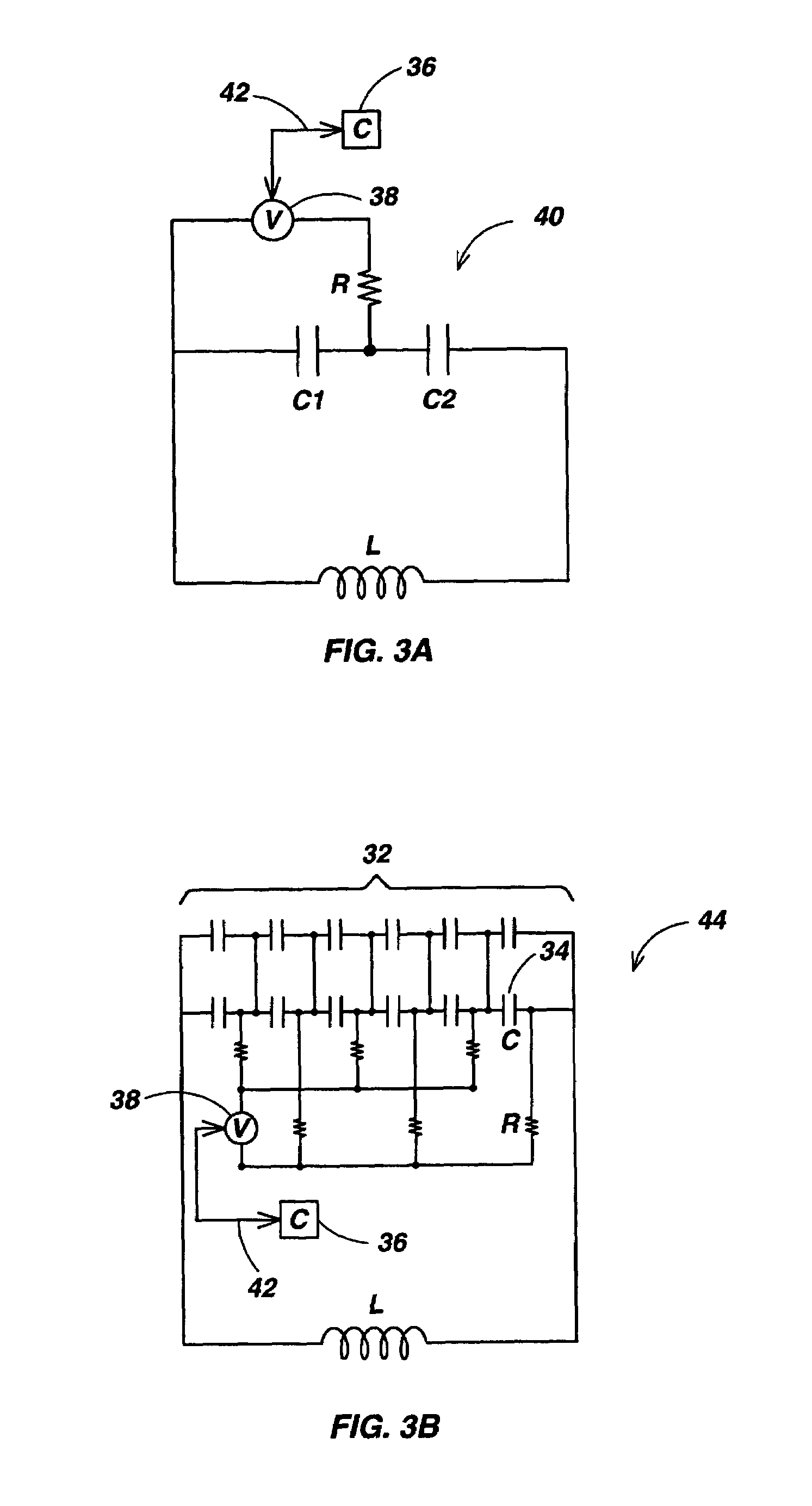

Compact self-tuned electrical resonator for buried object locator applications

ActiveUS7276910B2Improved efficiency and induced output powerLower equivalent series resistanceDetection of traffic movementResonatorsCapacitanceElectrical conductor

A self-tuning resonator for use in a transmitter apparatus for inducing alternating currents in a buried conductor. The resonator is dynamically tuned at frequencies below 500 kHz by exploiting the inherent voltage-variability of net capacitance in multilayer ceramic capacitors. The transmitter apparatus provides improved efficiency and induced output power suitable for use in a man-portable locator system, providing a very high magnetic field output from a physically small battery-powered resonator at frequencies under 500 kHz. The resonator exhibits a very low equivalent series resistance (ESR) and is adaptively returned to a predetermined resonant frequency responsive to any changes in resonance arising from phenomena such as component heating, thereby supporting very high tank circuit currents from battery-powered source to produce very high magnetic flux output.

Owner:SEEK TECH

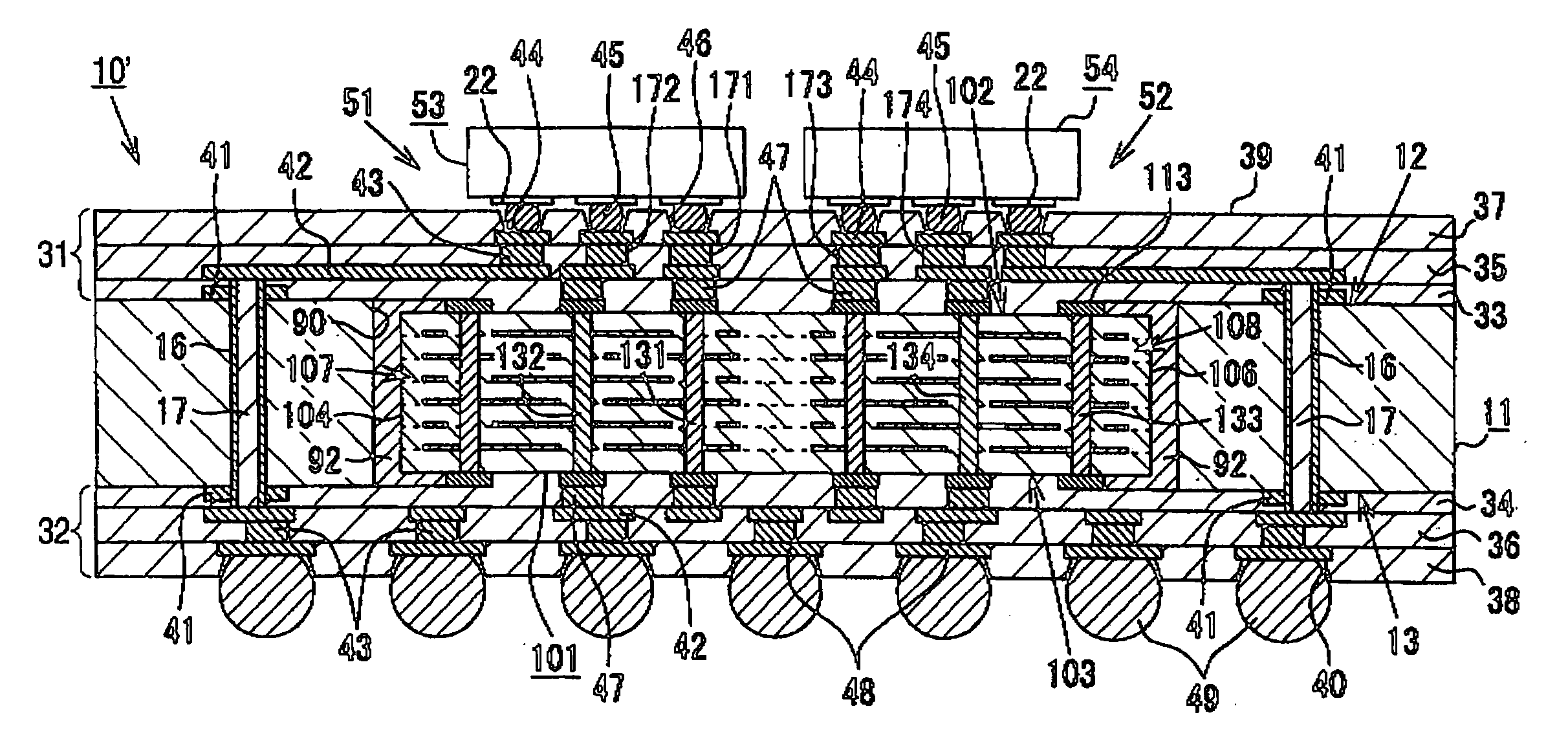

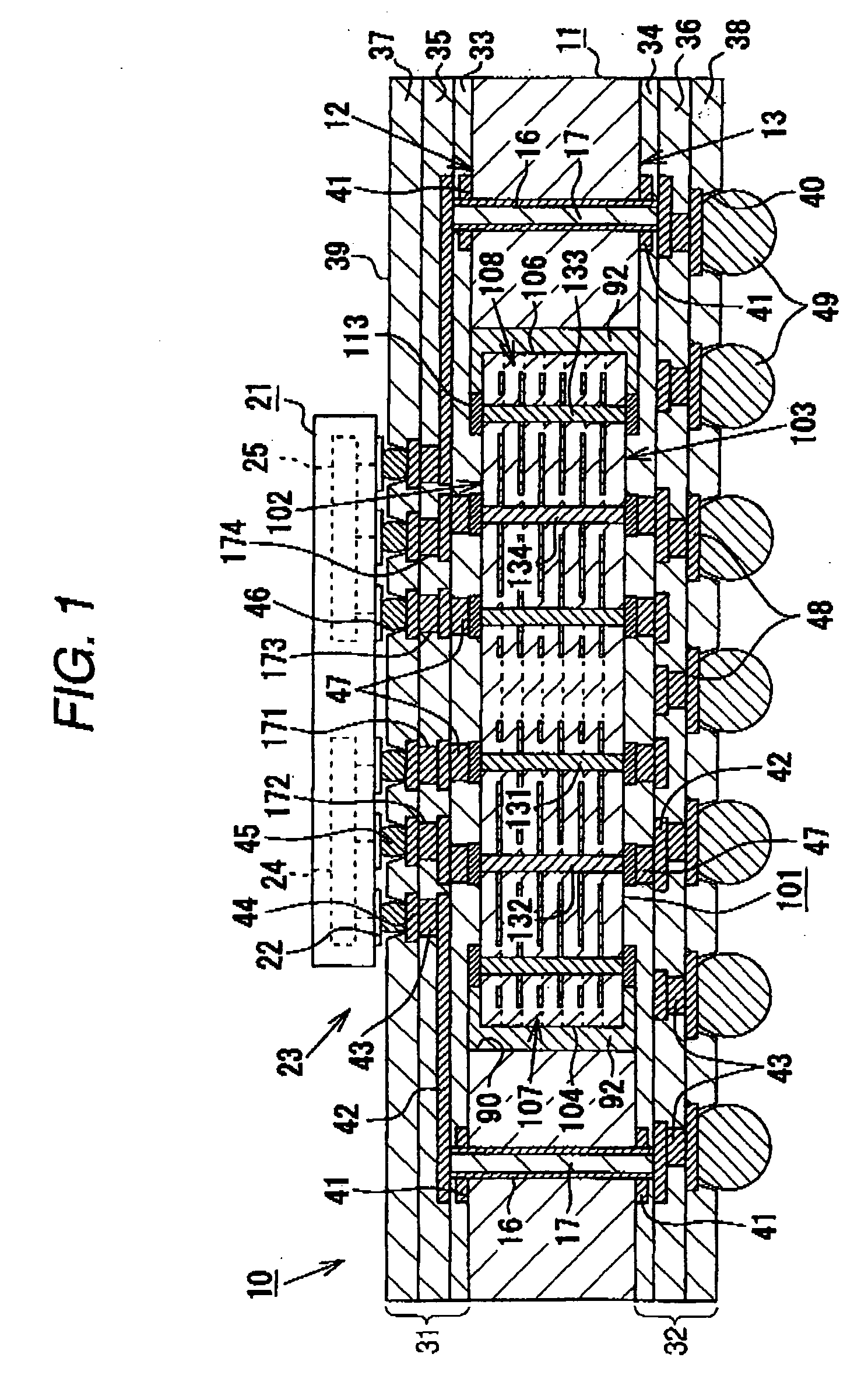

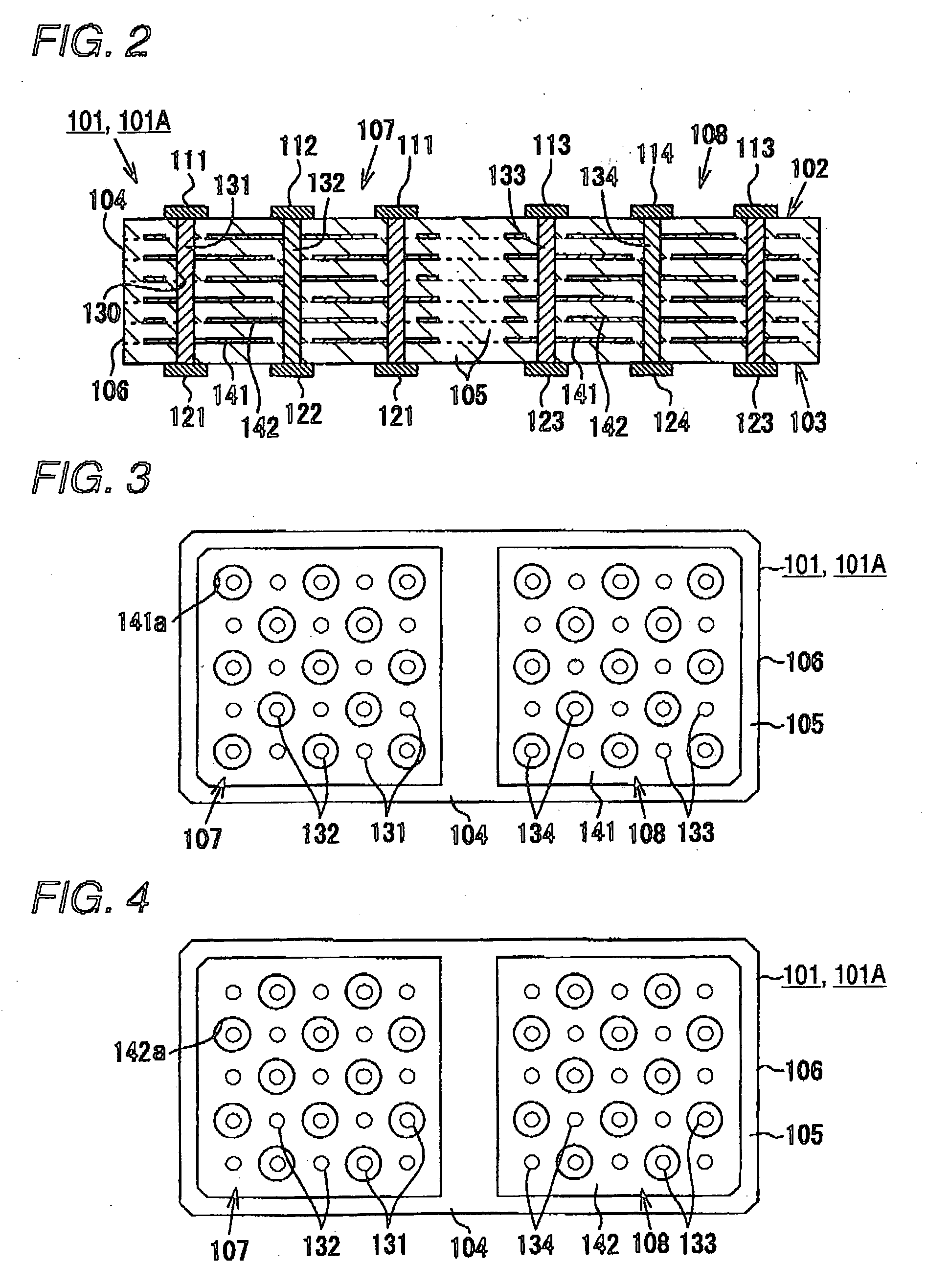

Ceramic capacitor

ActiveUS20070064375A1Effective noise reductionImprove performanceSemiconductor/solid-state device detailsCross-talk/noise/interference reductionCapacitanceElectrical conductor

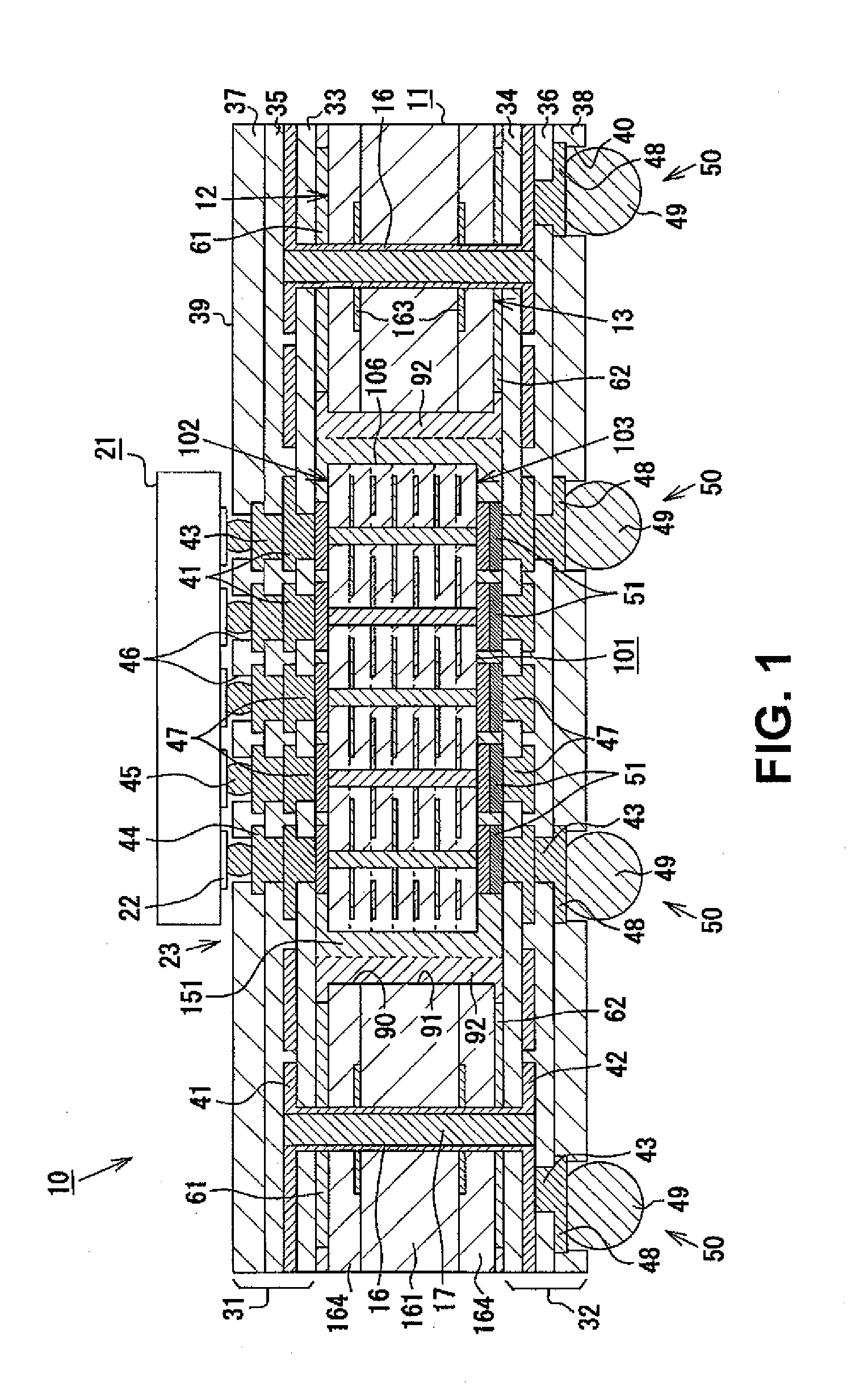

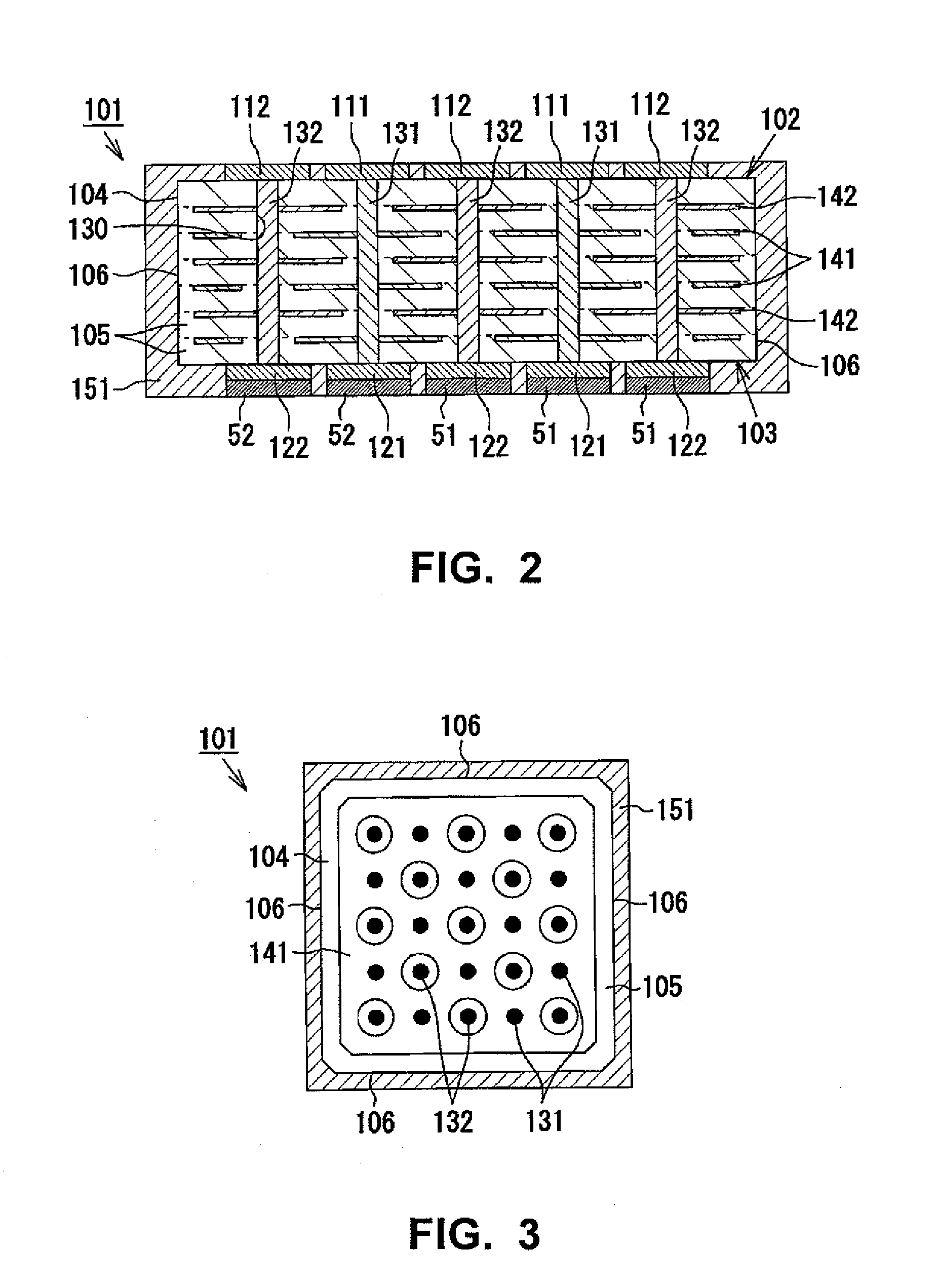

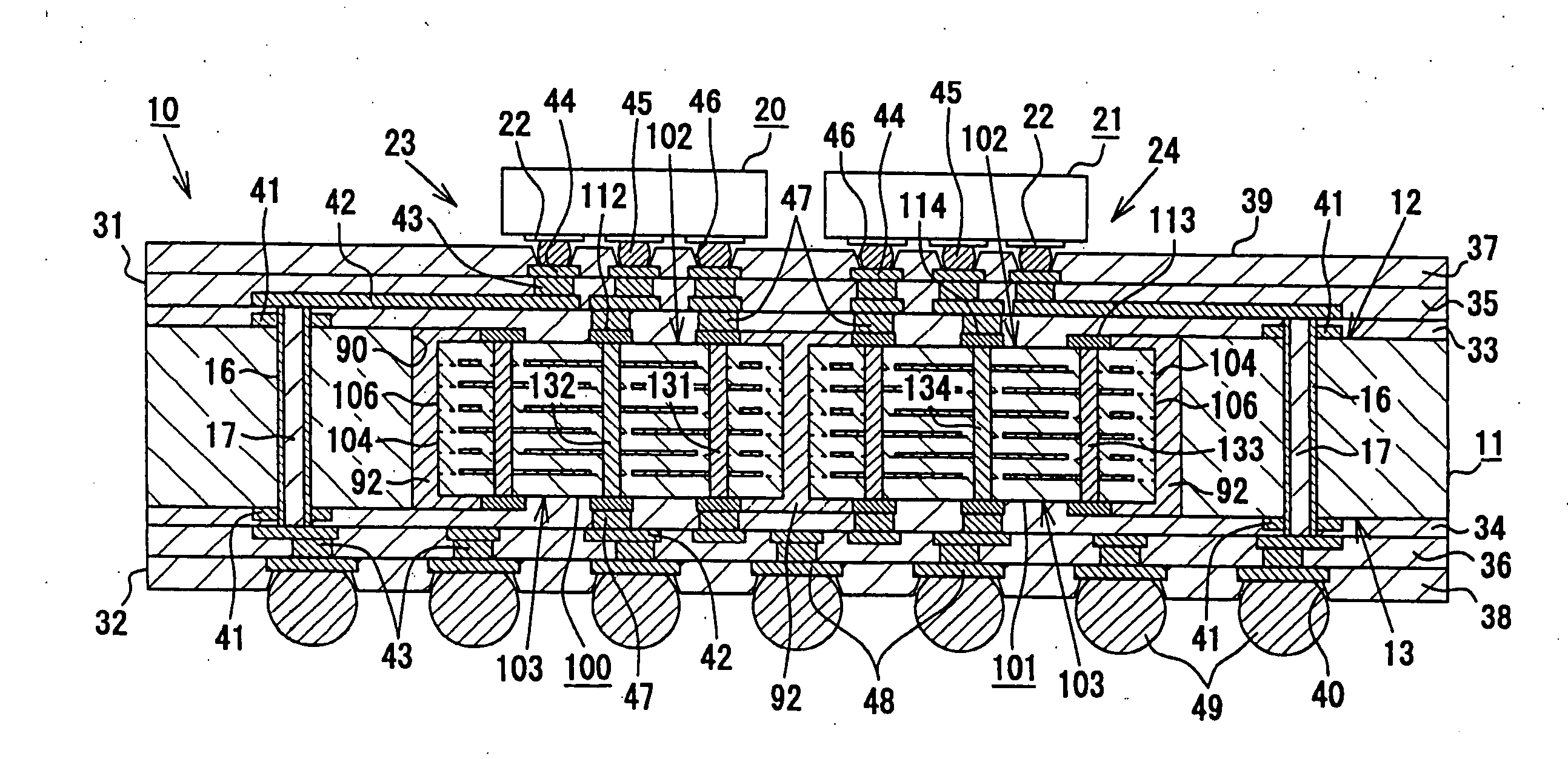

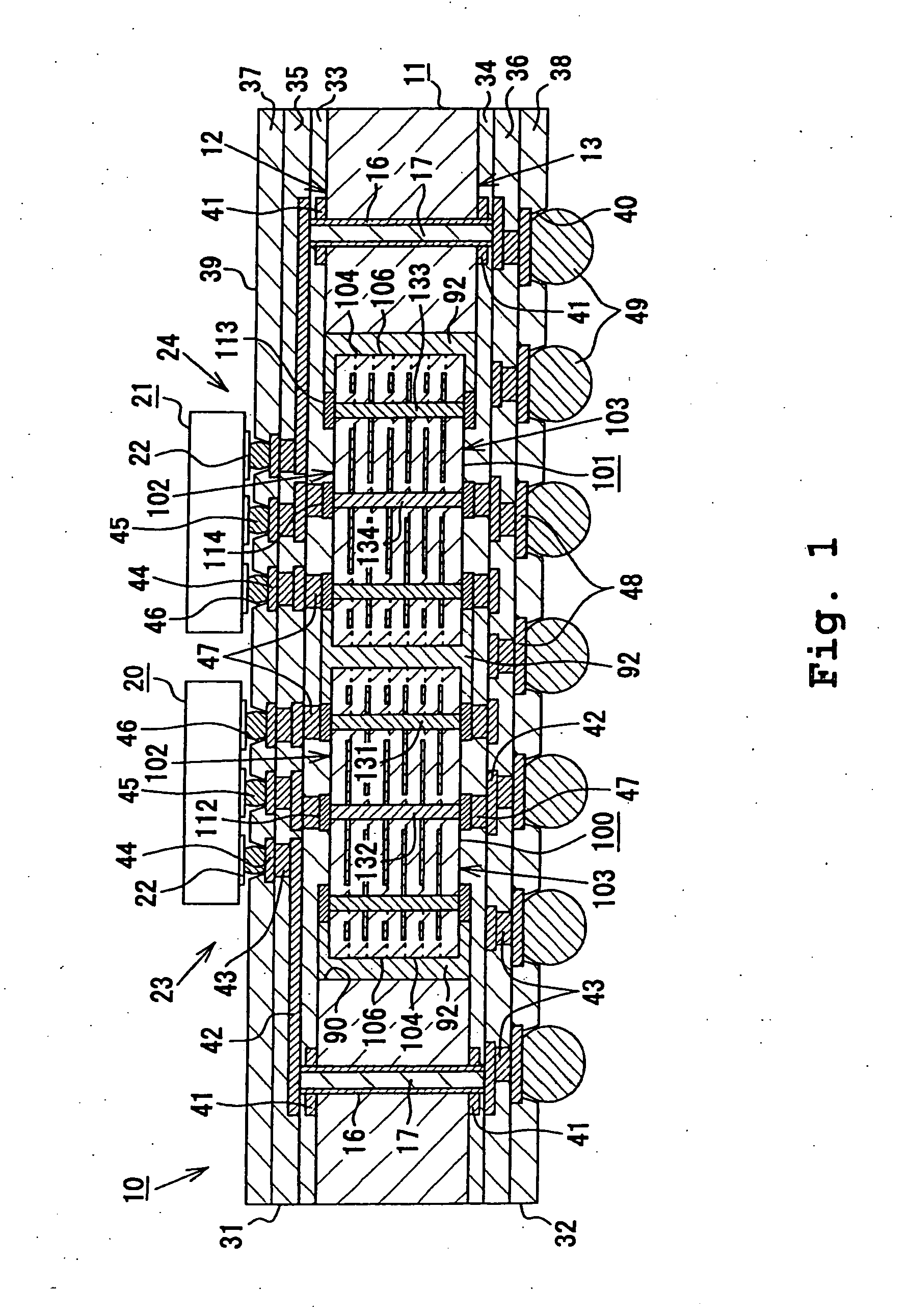

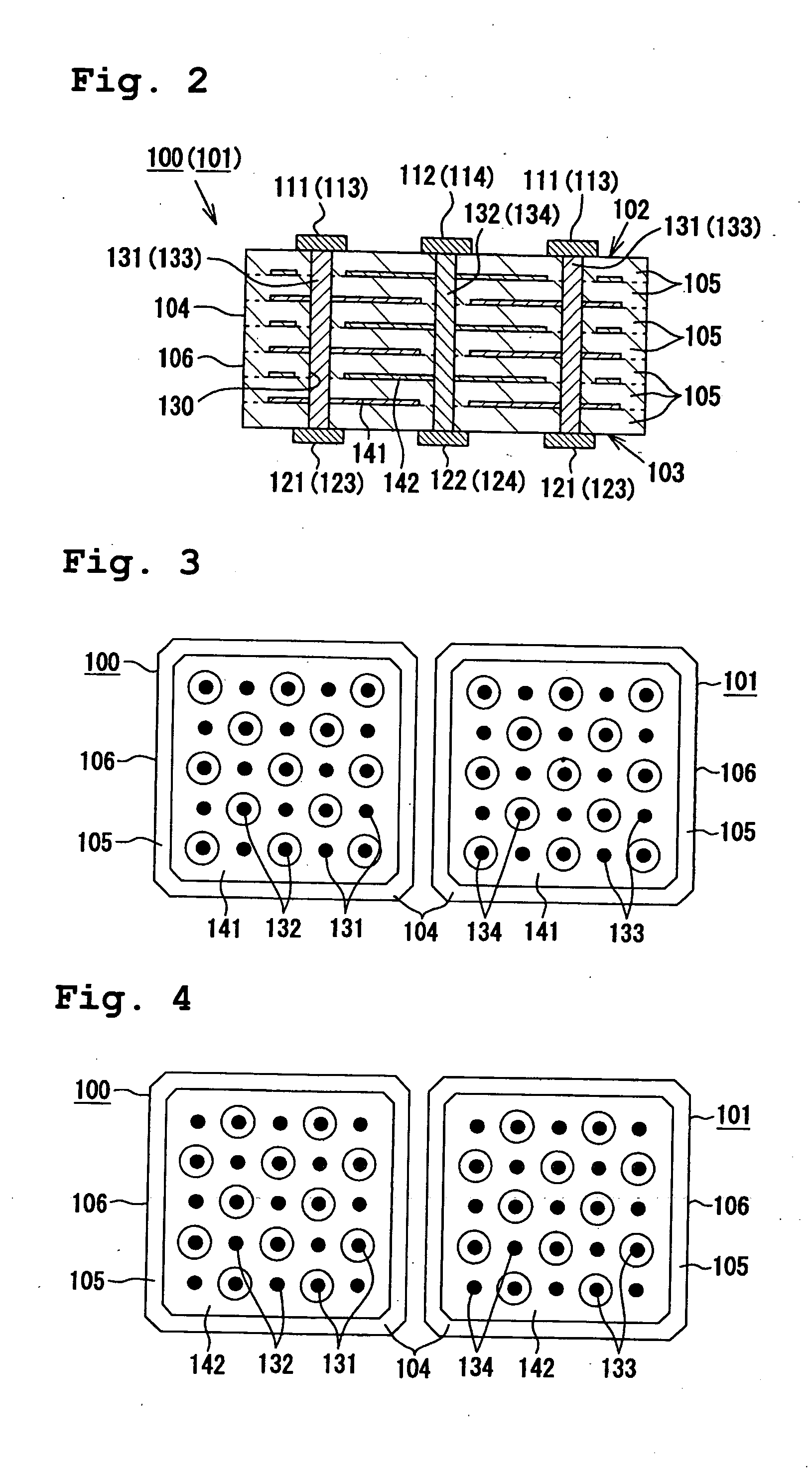

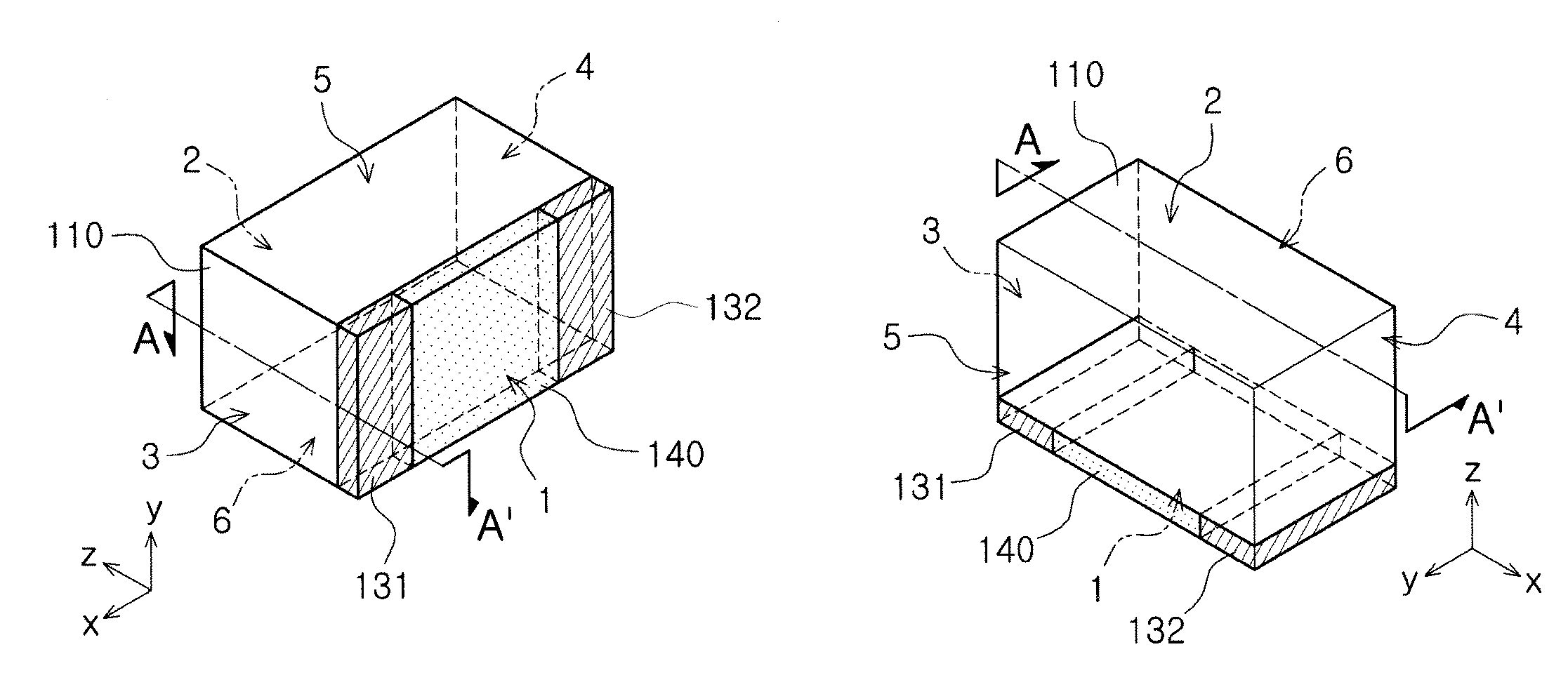

A circuit board (10, 10″, 10″′) comprising: a board core (11) having a main core surface (12) and a rear core surface (13); a ceramic capacitor (101, 101′, 101″, 101″′, 101″″, 101″″′, 101″″″) having a main capacitor surface (102) and a rear capacitor surface (103), having a structure in which a first inner electrode layer (141) and a second inner electrode layer (142) are alternately stacked with a ceramic dielectric layer (105) interposed therebetween, and having a plurality of capacitor function units (107, 108) being electrically independent from each other, the ceramic capacitor (101, 101′, 101″, 101″′, 101″″, 101″″′, 101″″″) being buried in the board core (11) in a state where the main core surface (12) and the main capacitor surface (102) are directed in a same direction; and a buildup layer (31) having a structure in which an interlayer insulating layer (33, 35) and a conductor layer (42) are alternately stacked on the main core surface (12) and the main capacitor surface (102) and having a semiconductor integrated circuit device mounting region (23, 51, 52) for mounting a semiconductor integrated circuit device (21, 53, 54) having a plurality of processor cores (24, 25) on a surface (39) of the buildup layer (31), wherein the plurality of capacitor function units (107, 108) are capable of being electrically connected to the plurality of processor cores (24, 25), respectively.

Owner:NGK SPARK PLUG CO LTD

Integrated broadband ceramic capacitor array

InactiveUS6970341B1Effective wideband performanceImprove performanceMultiple fixed capacitorsFixed capacitor electrodesCeramic capacitorEngineering

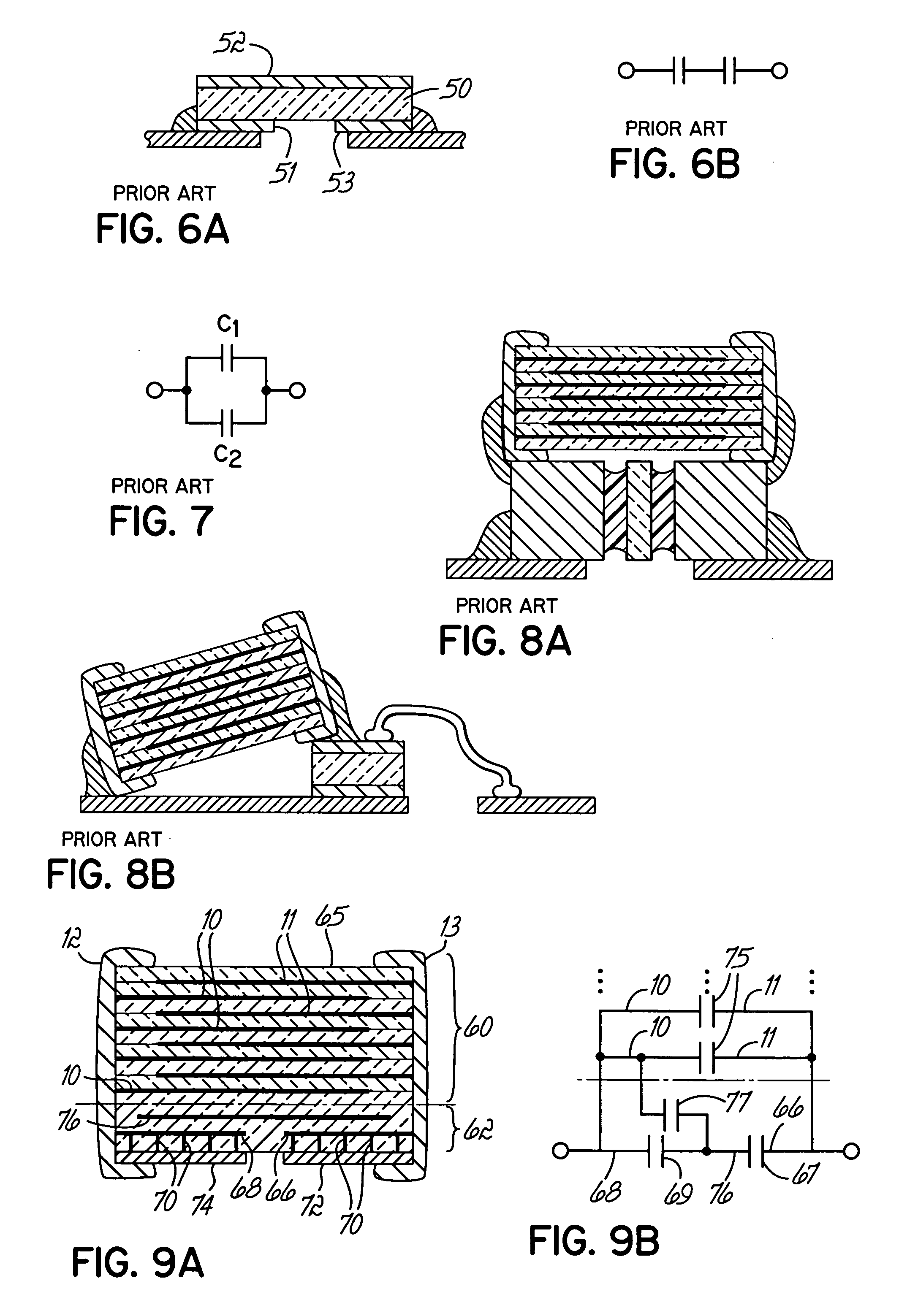

A monolithic capacitor structure includes opposed and overlapping plates within a dielectric body, which are arranged to form a lower frequency, higher value capacitor. Other conductive structure is located either inside the dielectric body or on an external surface thereof and is effective to form a higher frequency, lower value capacitor in parallel with the lower frequency, higher value capacitor. The resulting array of combined series and parallel capacitors integral with the dielectric body provides effective wideband performance in an integrated, cost-effective structure.

Owner:DEVOE DANIEL +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com