Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3622results about How to "Reduce capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

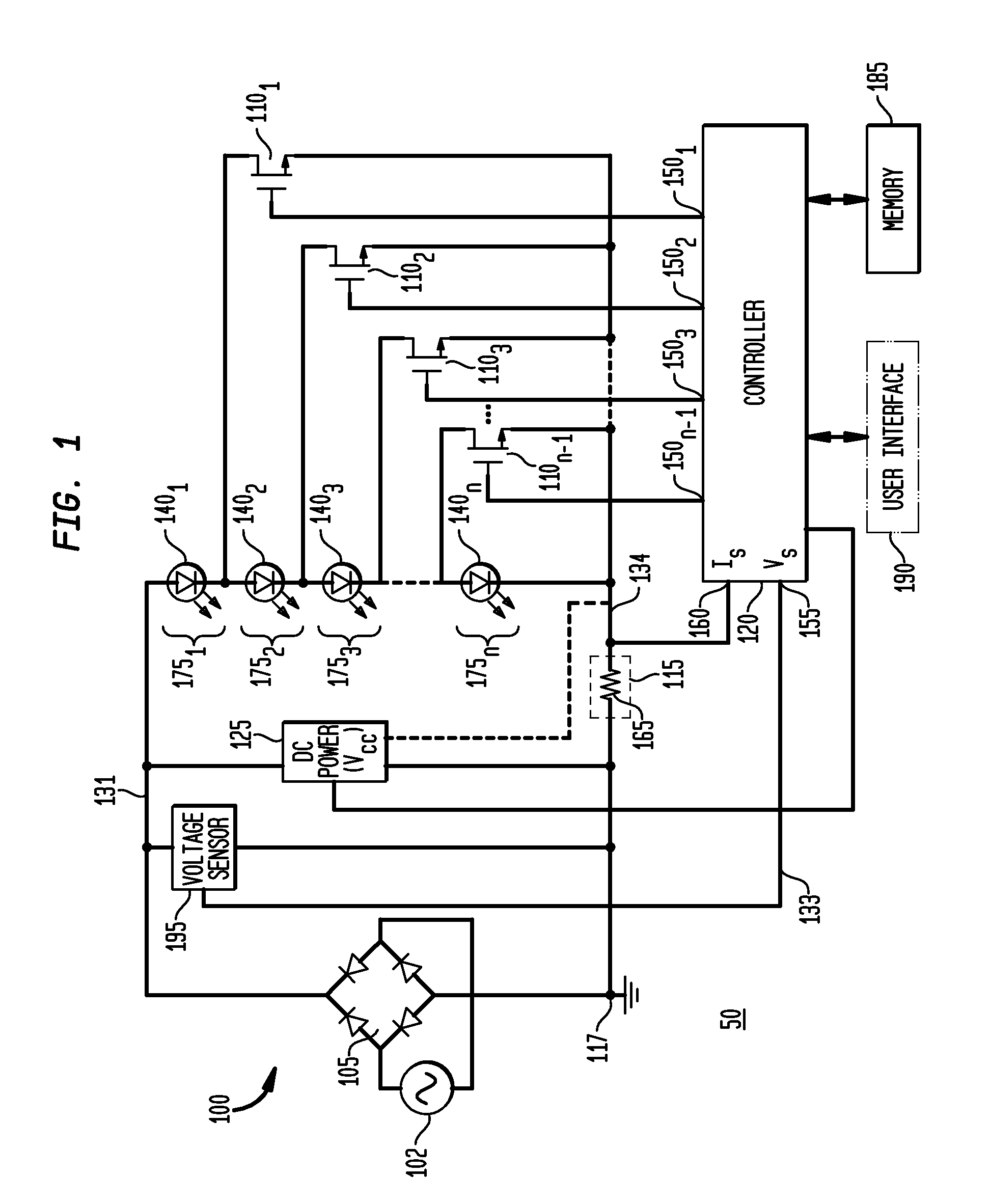

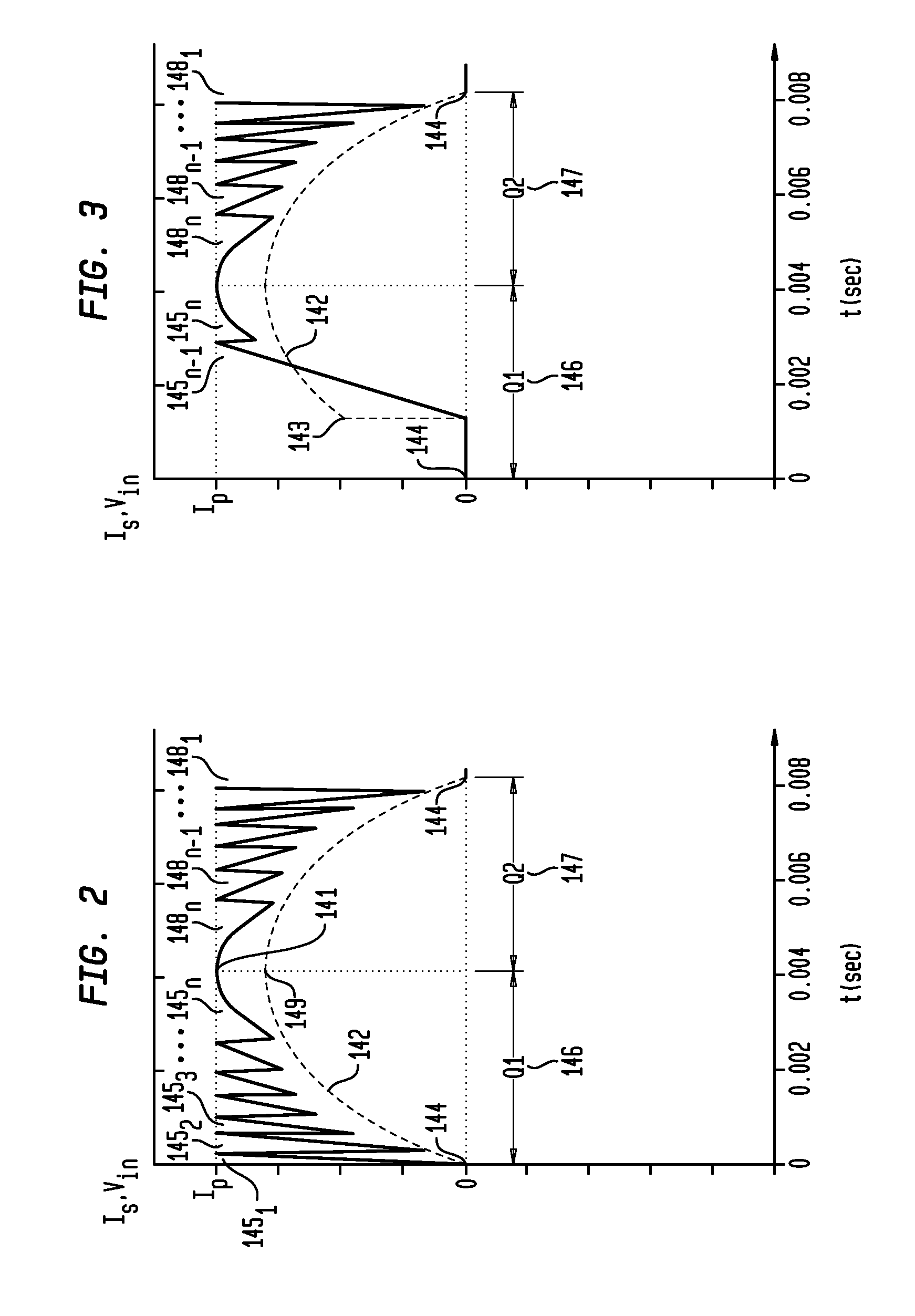

Apparatus, Method and System for Providing AC Line Power to Lighting Devices

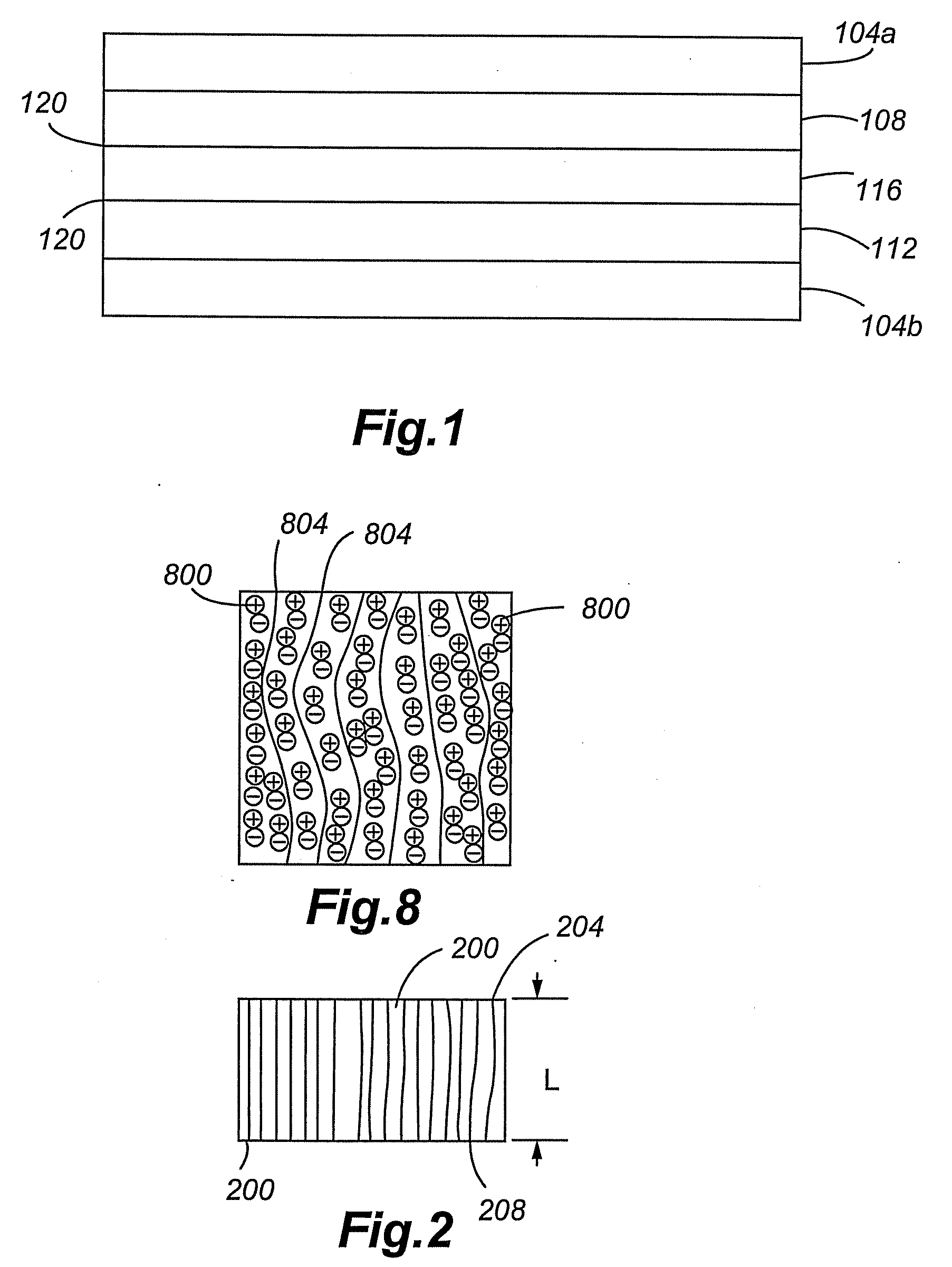

ActiveUS20120081009A1Reduction in size and costImprove Utilization and EfficiencyElectrical apparatusElectroluminescent light sourcesLight equipmentVoltage regulation

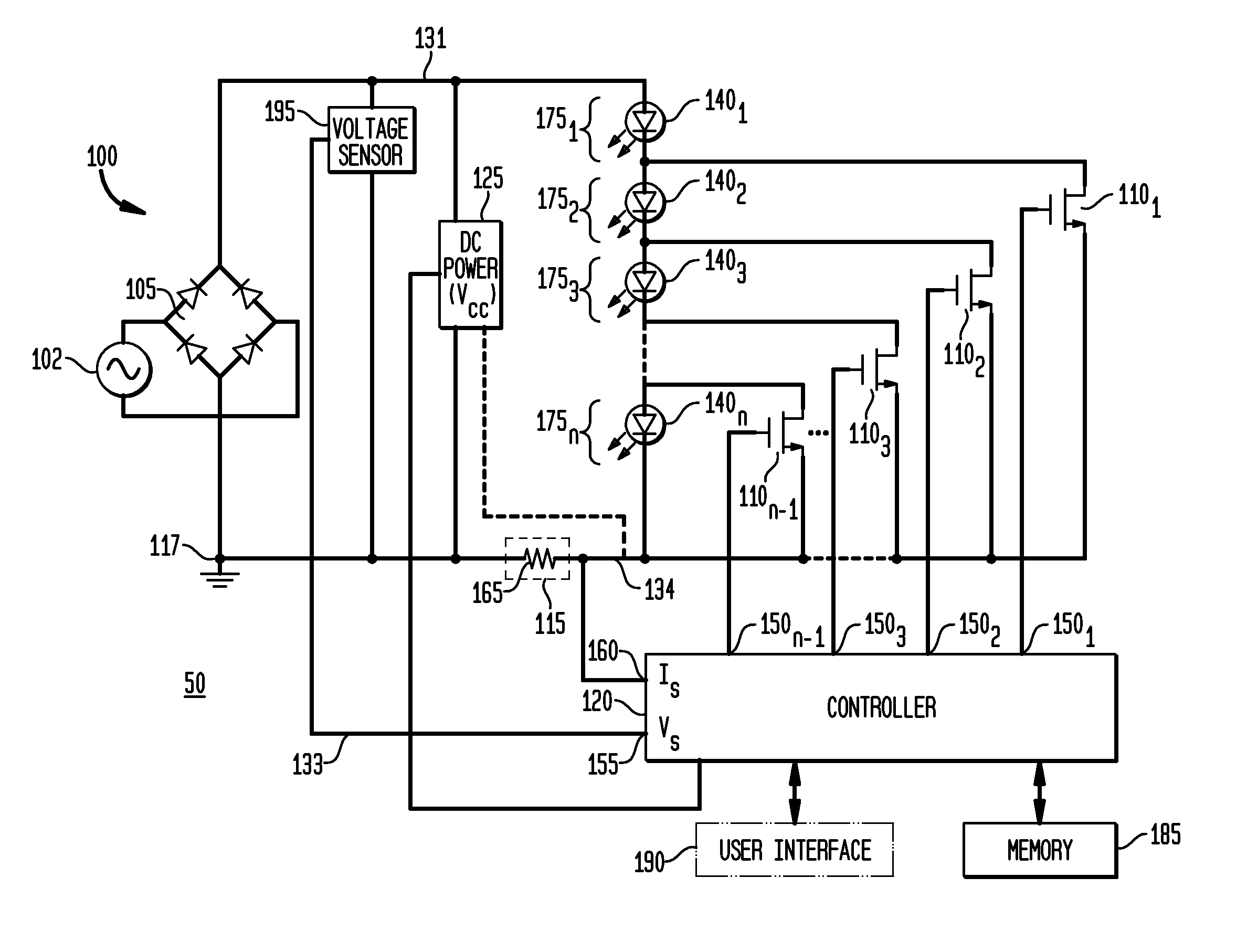

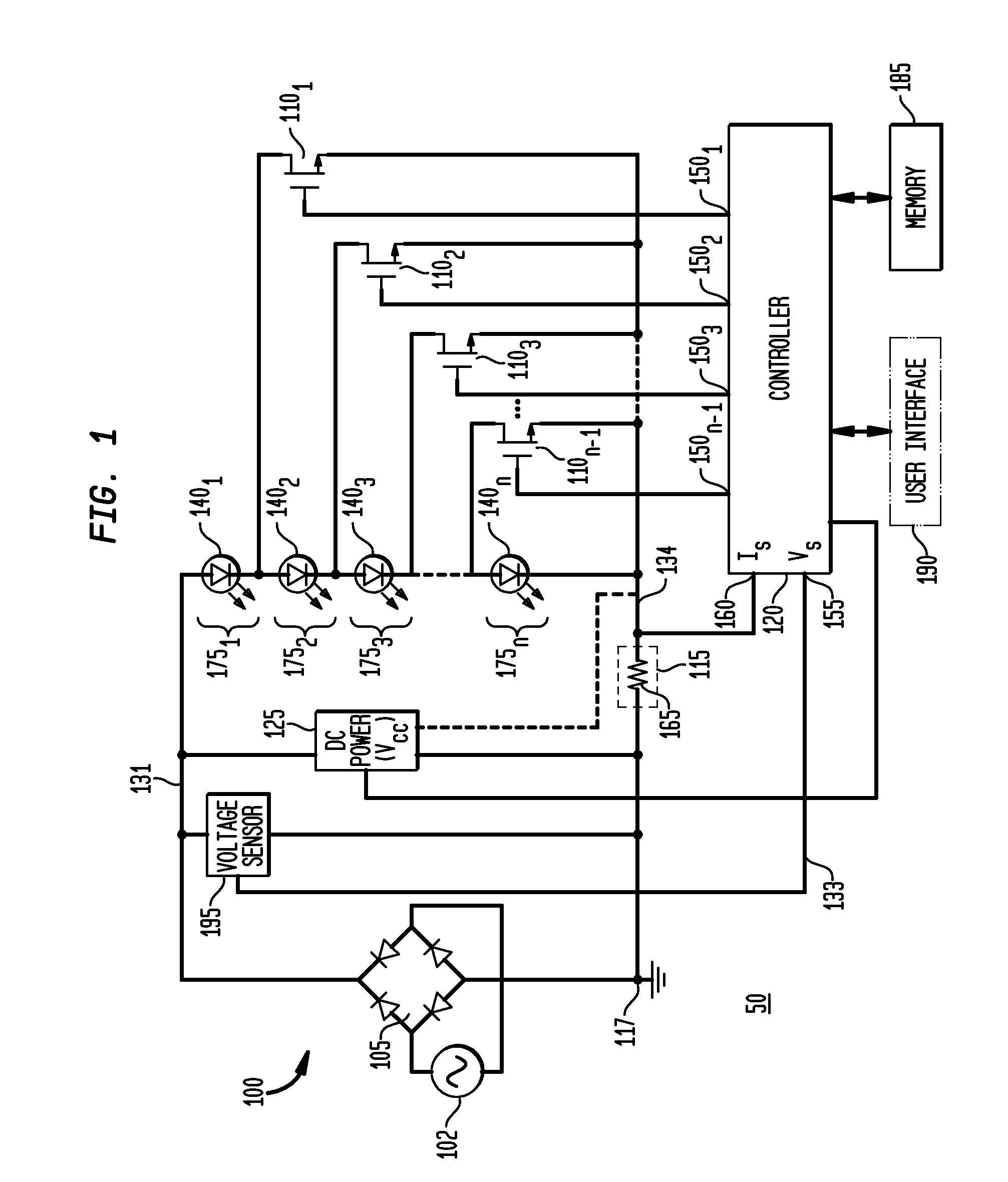

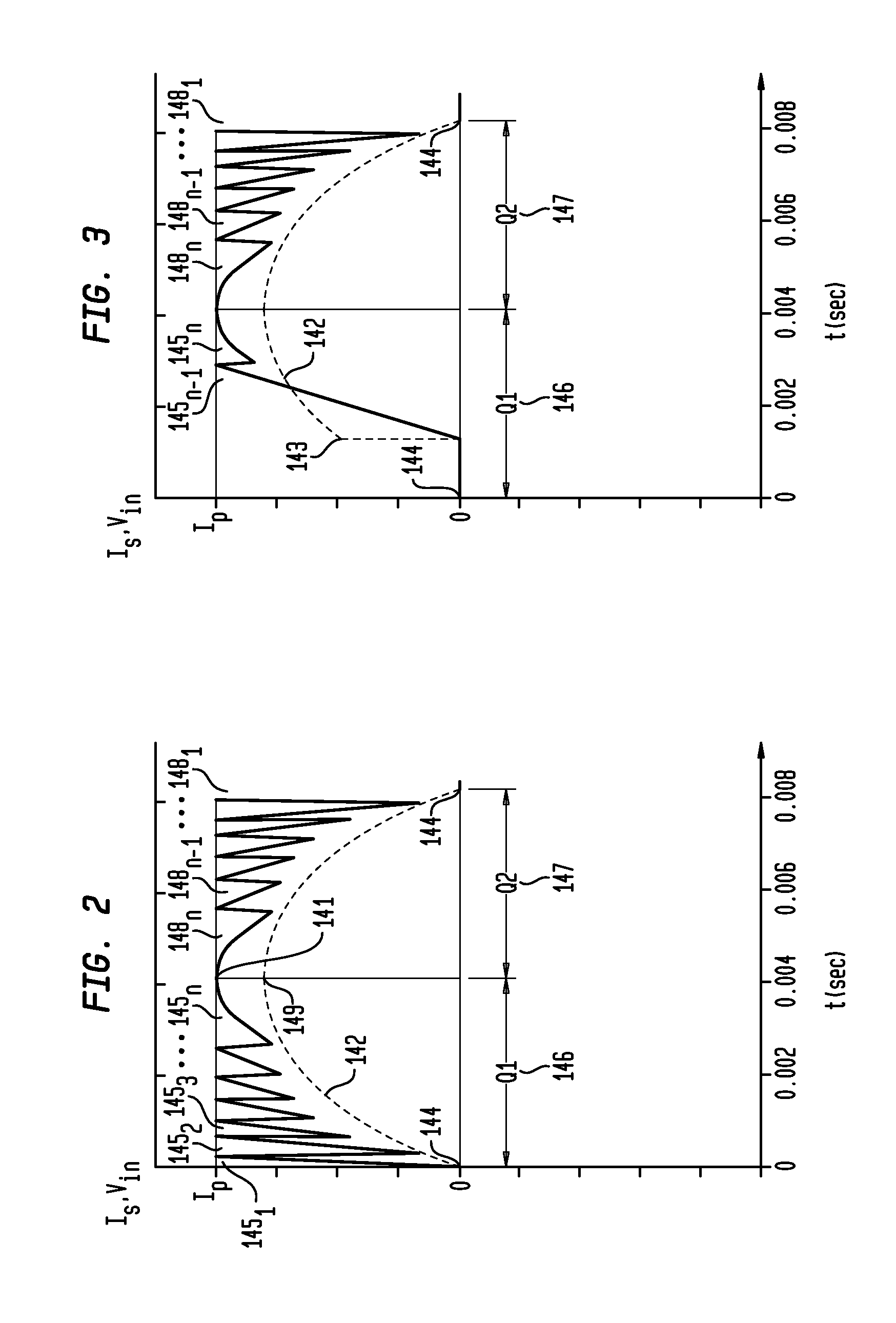

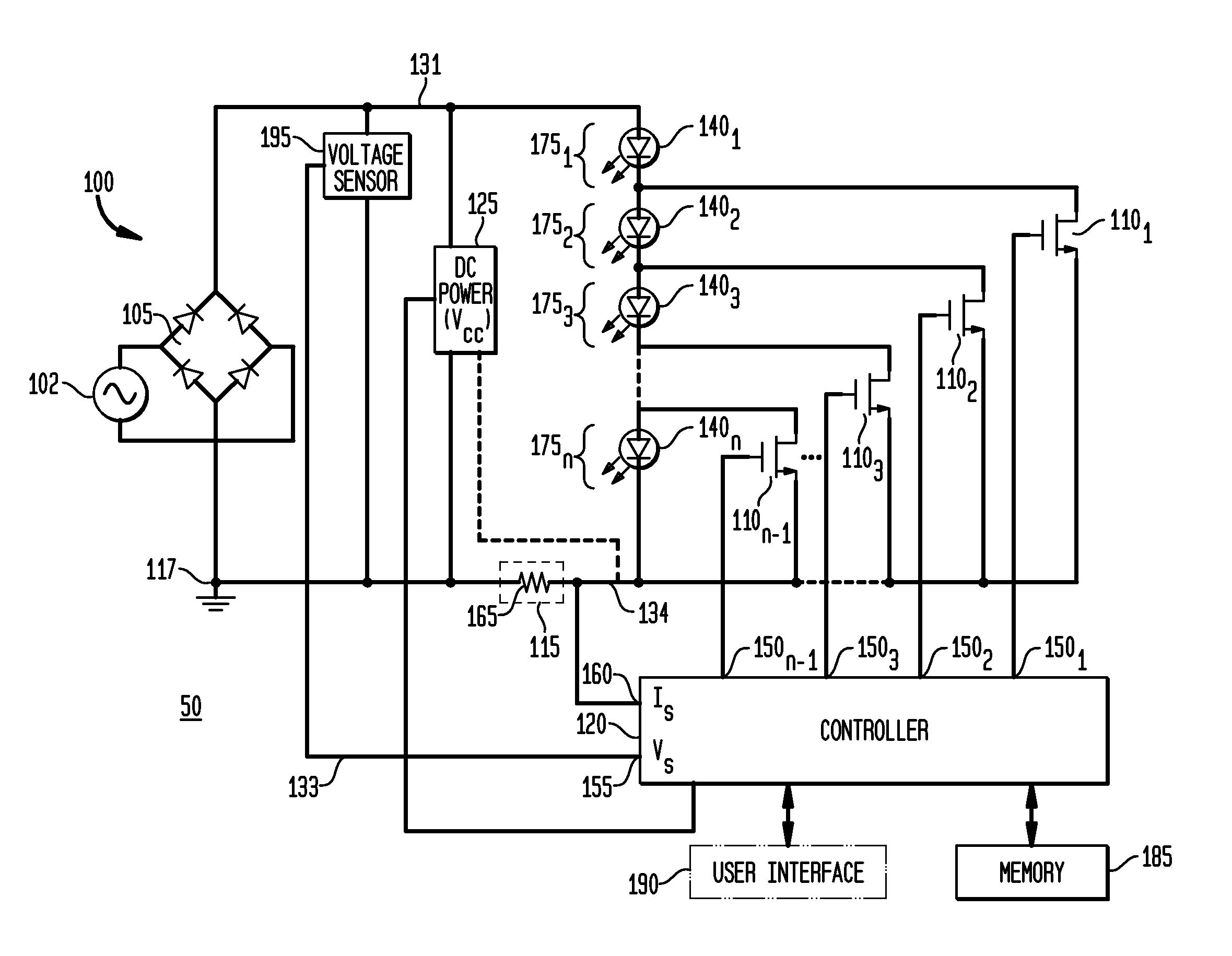

An apparatus, method and system are disclosed for providing AC line power to lighting devices such as light emitting diodes (“LEDs”). An exemplary apparatus comprises: a plurality of LEDs coupled in series to form a plurality of segments of LEDs; first and second current regulators; a current sensor; and a controller to monitor a current level through a series LED current path, and to provide for first or second segments of LEDs to be in or out of the series LED current path at different current levels. A voltage regulator is also utilized to provide a voltage during a zero-crossing interval of the AC voltage. In an exemplary embodiment, first and second segments of LEDs are both in the series LED current path regulated at a lower current level compared to when only the first segment of LEDs is in the series LED current path.

Owner:CHEMTRON RES

Apparatus, Method and System for Providing AC Line Power to Lighting Devices

ActiveUS20100308739A1Reduction in size and costImprove Utilization and EfficiencyElectrical apparatusElectroluminescent light sourcesLight equipmentControl signal

An apparatus, method and system are disclosed for providing AC line power to lighting devices such as light emitting diodes (“LEDs”). An exemplary apparatus comprises: a plurality of LEDs coupled in series to form a first plurality of segments of LEDs; a plurality of switches coupled to the plurality of segments of LEDs to switch a selected segment into or out of a series LED current path in response to a control signal; a memory; and a controller which, in response to a first parameter and during a first part of an AC voltage interval, determines and stores in the memory a value of a second parameter and generates a first control signal to switch a corresponding segment of LEDs into the series LED current path; and during a second part of the AC voltage interval, when a current value of the second parameter is substantially equal to the stored value, generates a second control signal to switch a corresponding segment of LEDs out of the first series LED current path.

Owner:CHEMTRON RES

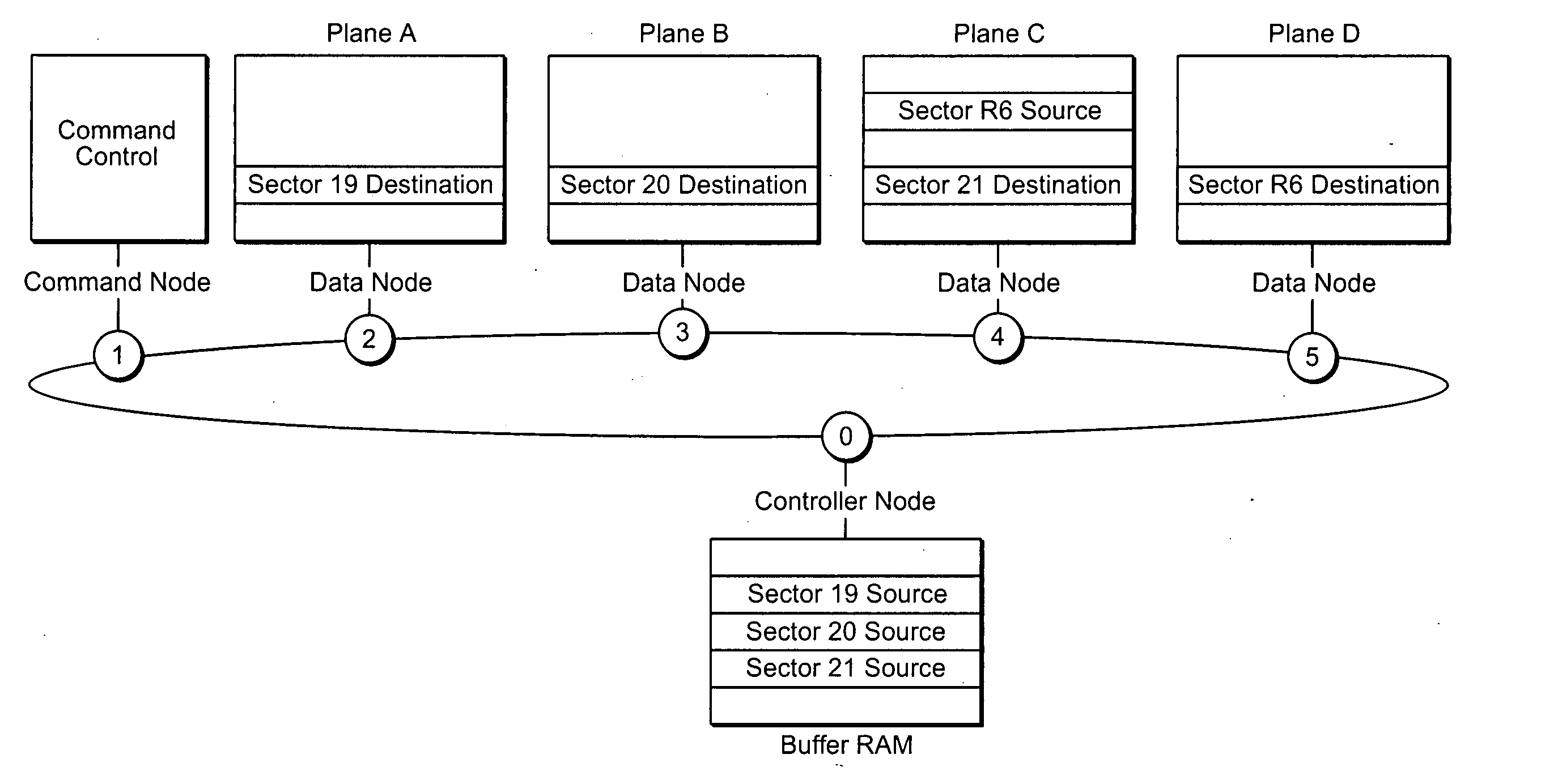

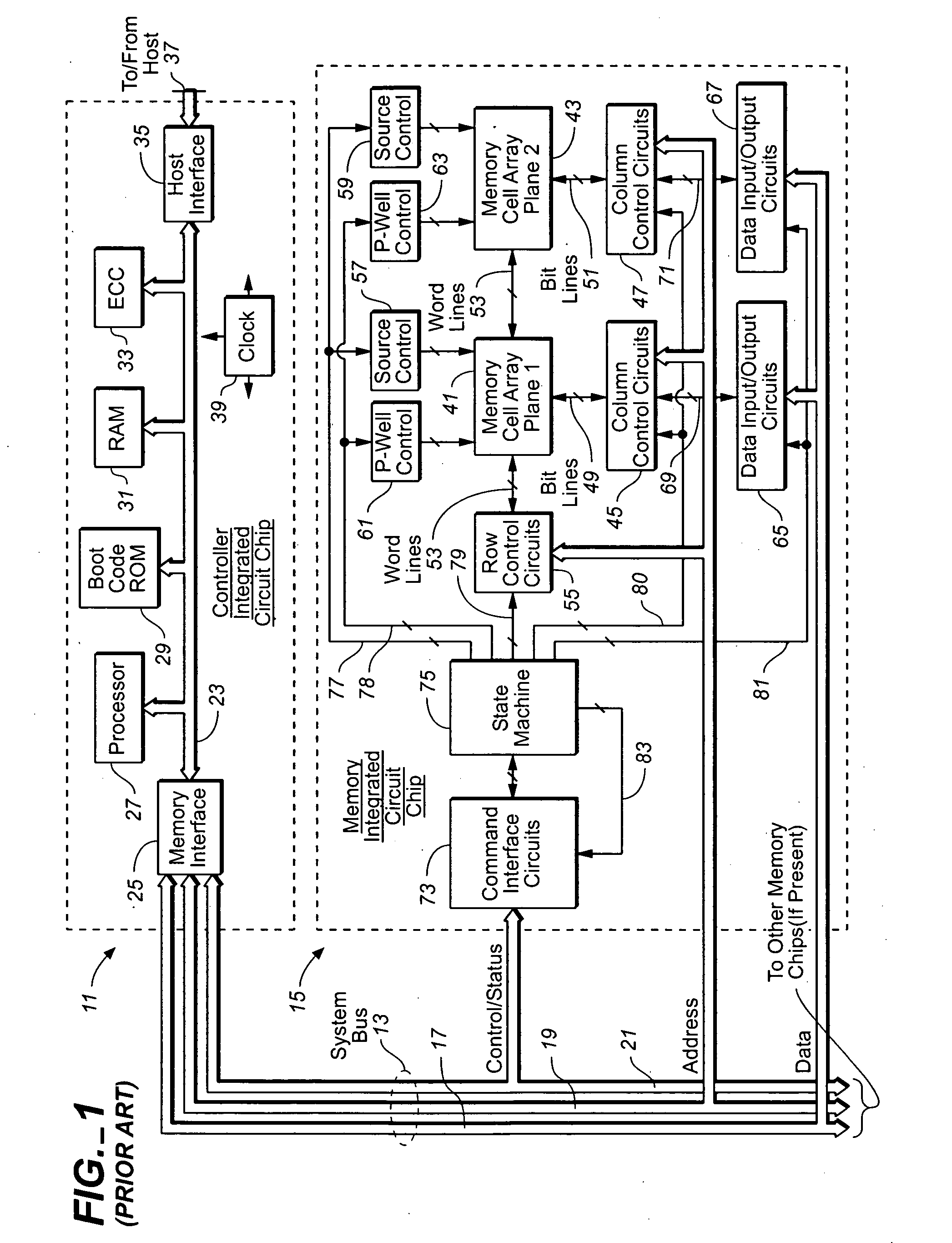

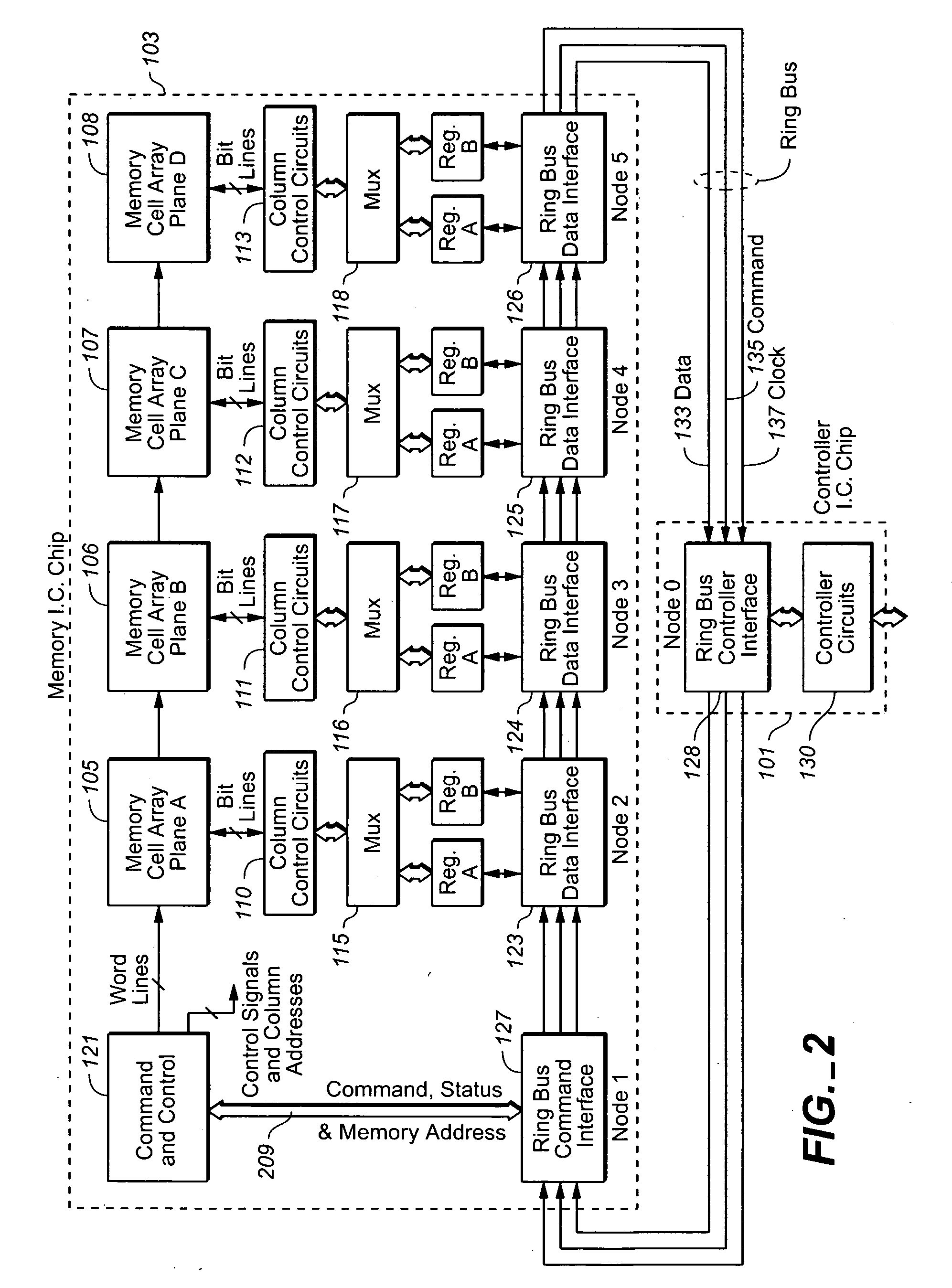

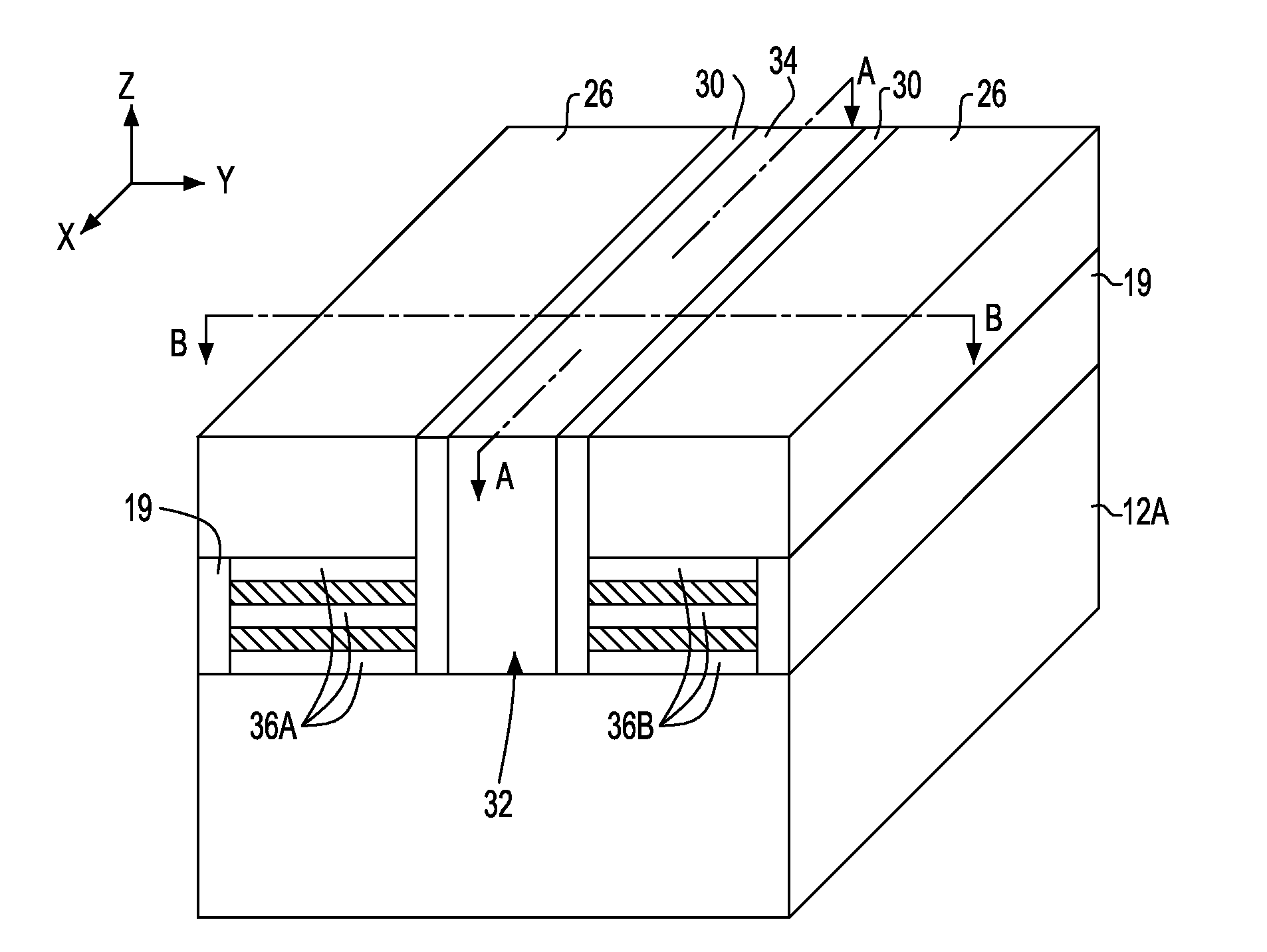

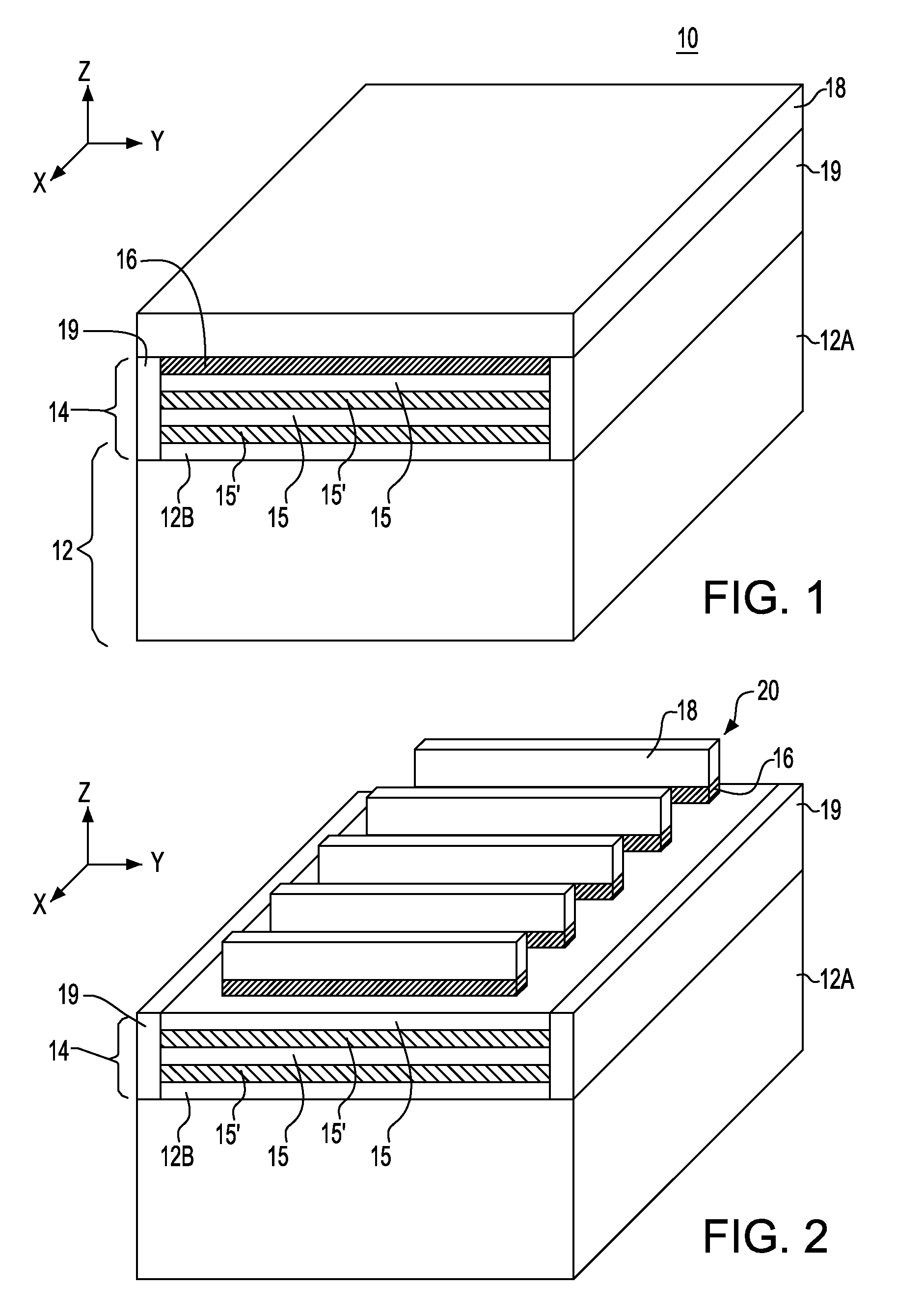

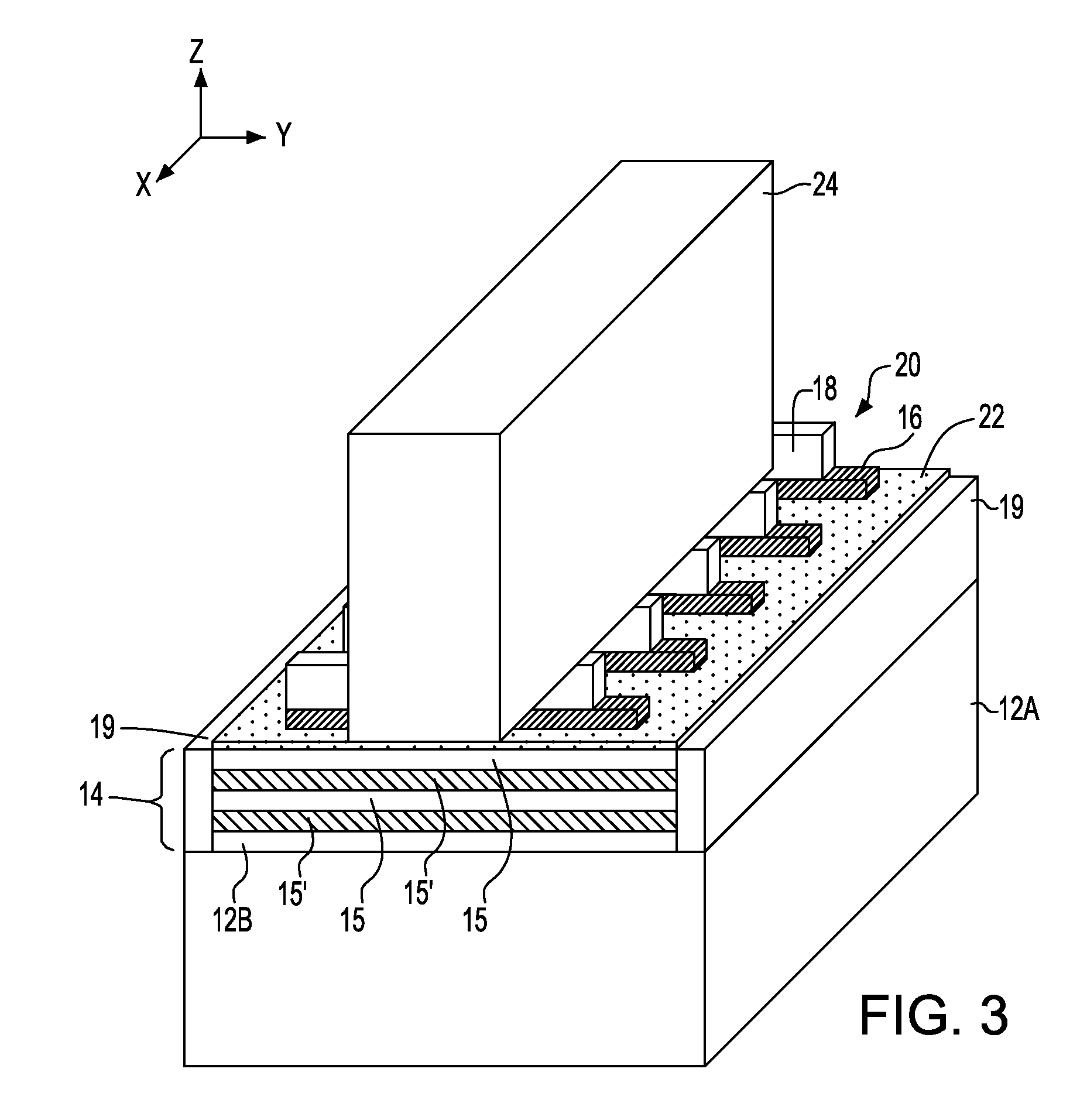

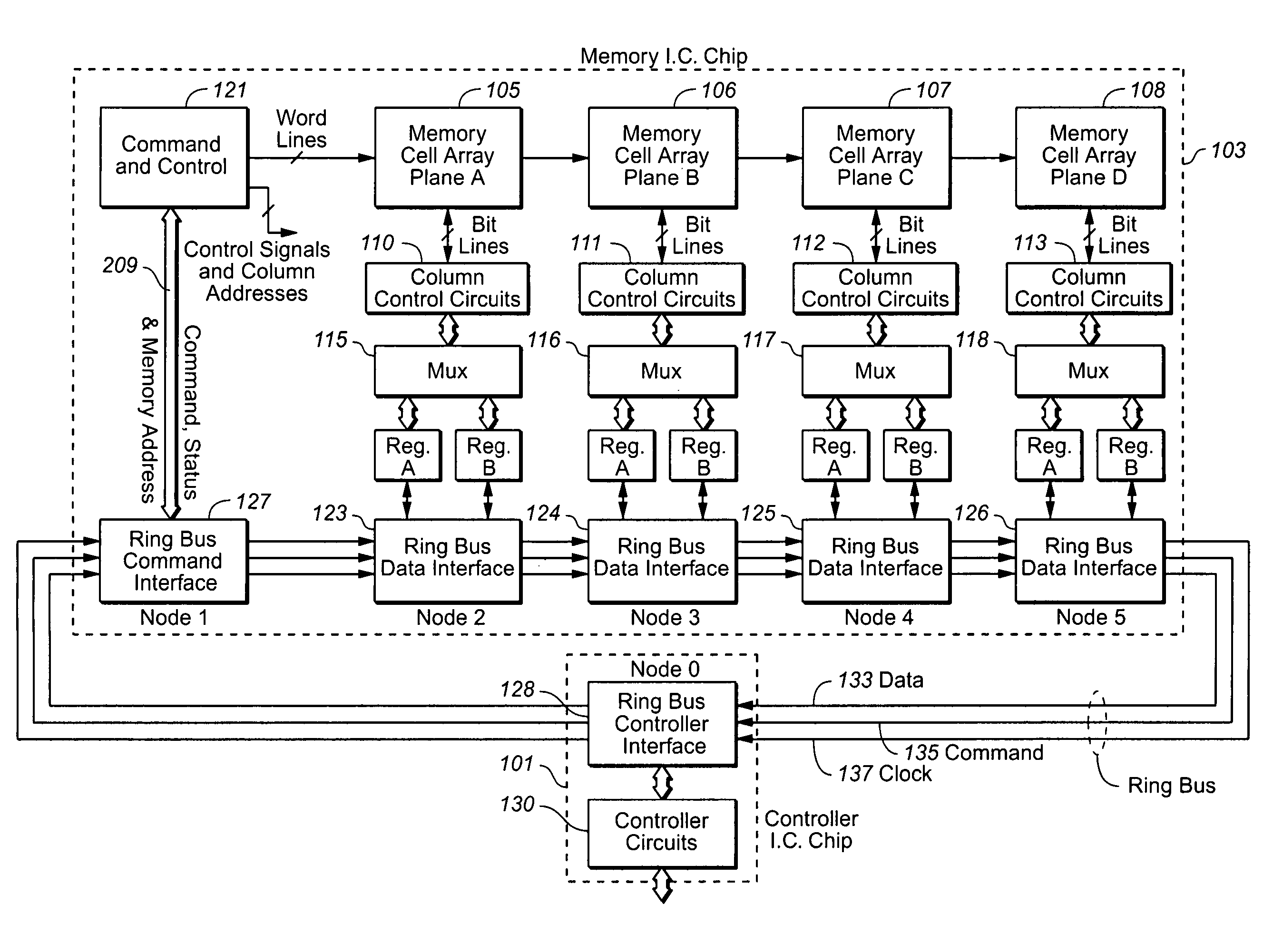

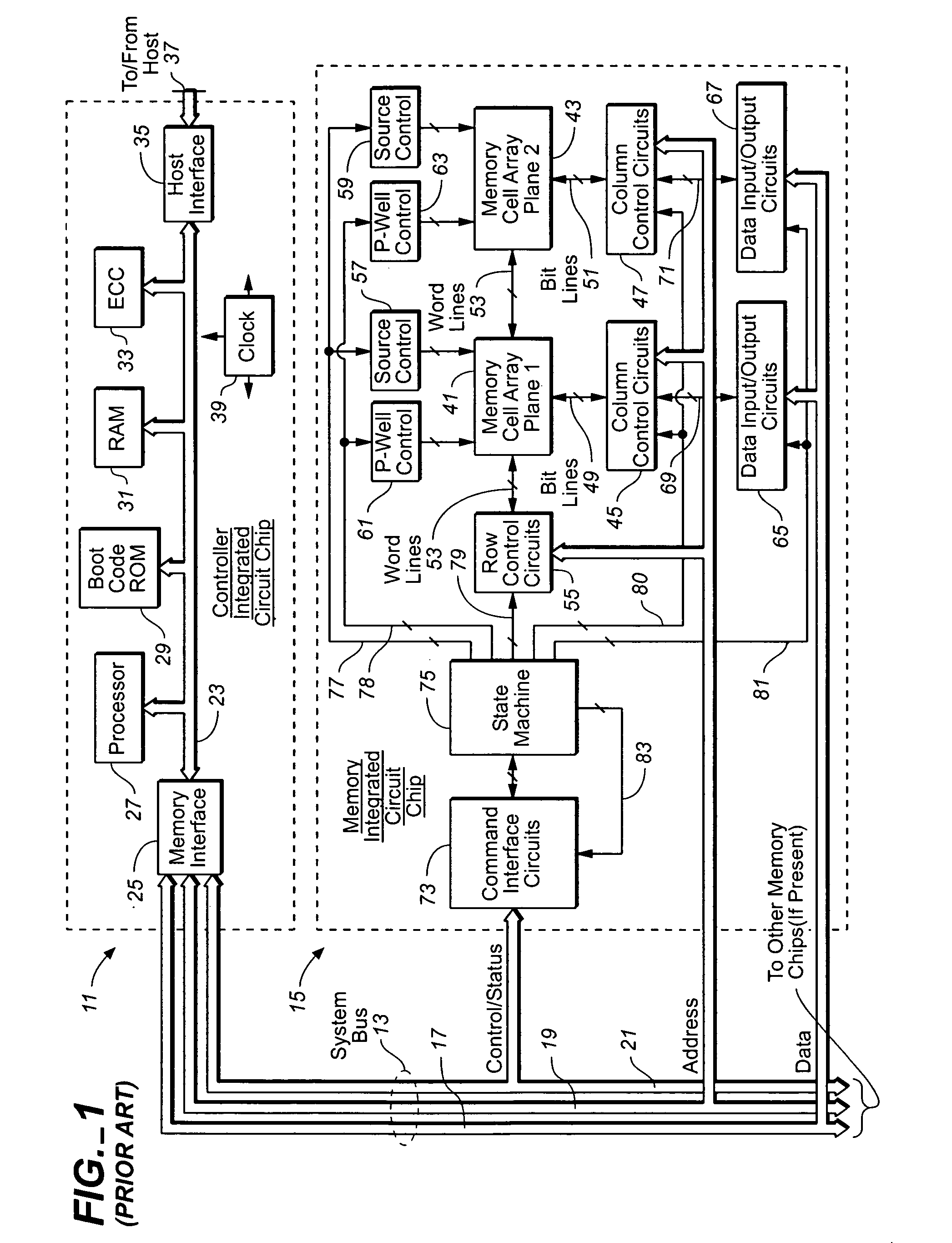

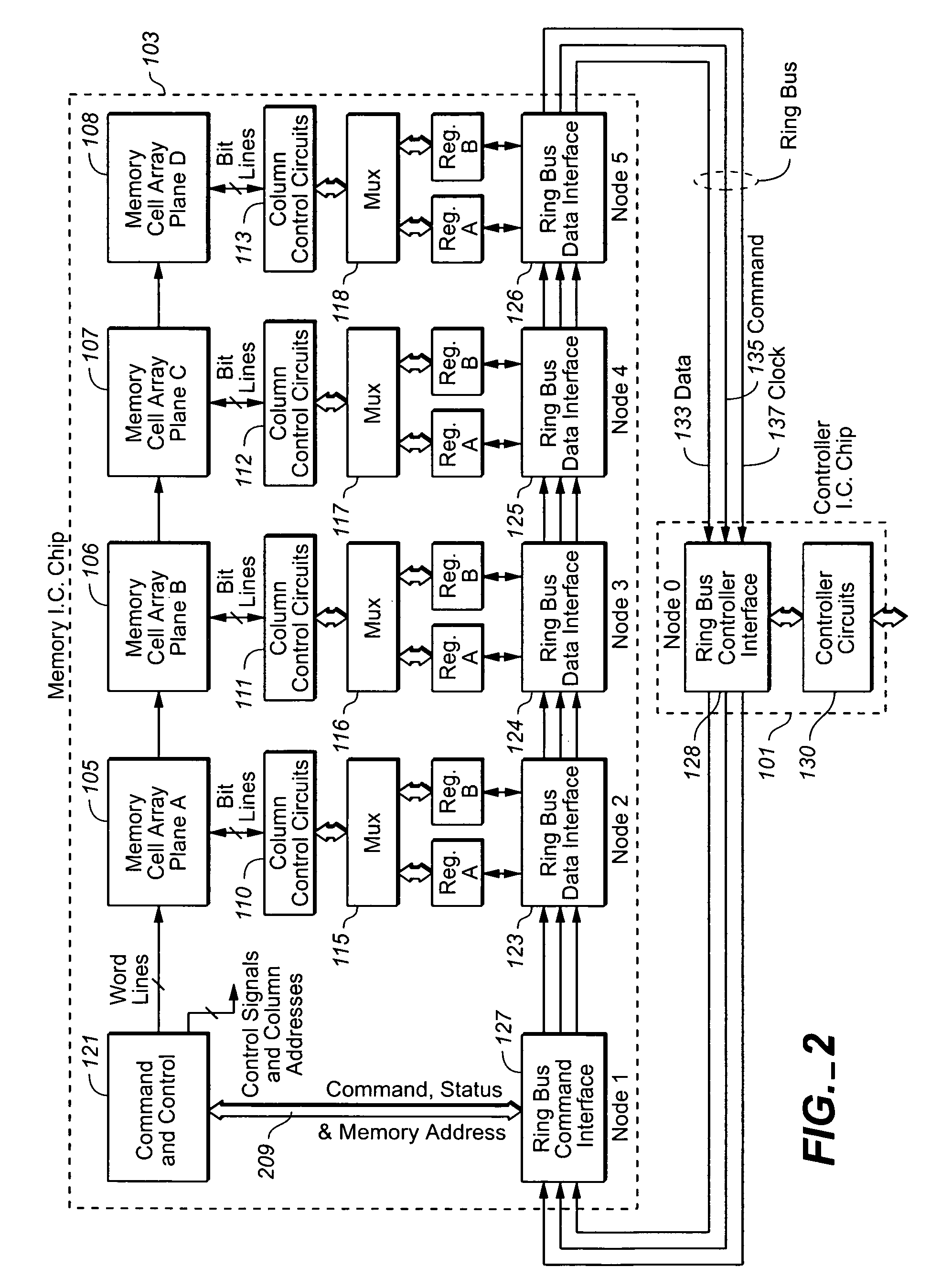

Ring bus structure and its use in flash memory systems

ActiveUS20060031593A1Easy to checkIncrease flexibilityMultiple digital computer combinationsElectric digital data processingSystem controllerNon-volatile memory

A system and integrated circuit chips used in the system utilize a bus in the form of a ring to interconnect nodes of individual components for transfer of data and commands therebetween. An example system described is a memory having one or more re-programmable non-volatile memory cell arrays connected to each other and to a system controller by a ring bus.

Owner:SANDISK TECH LLC

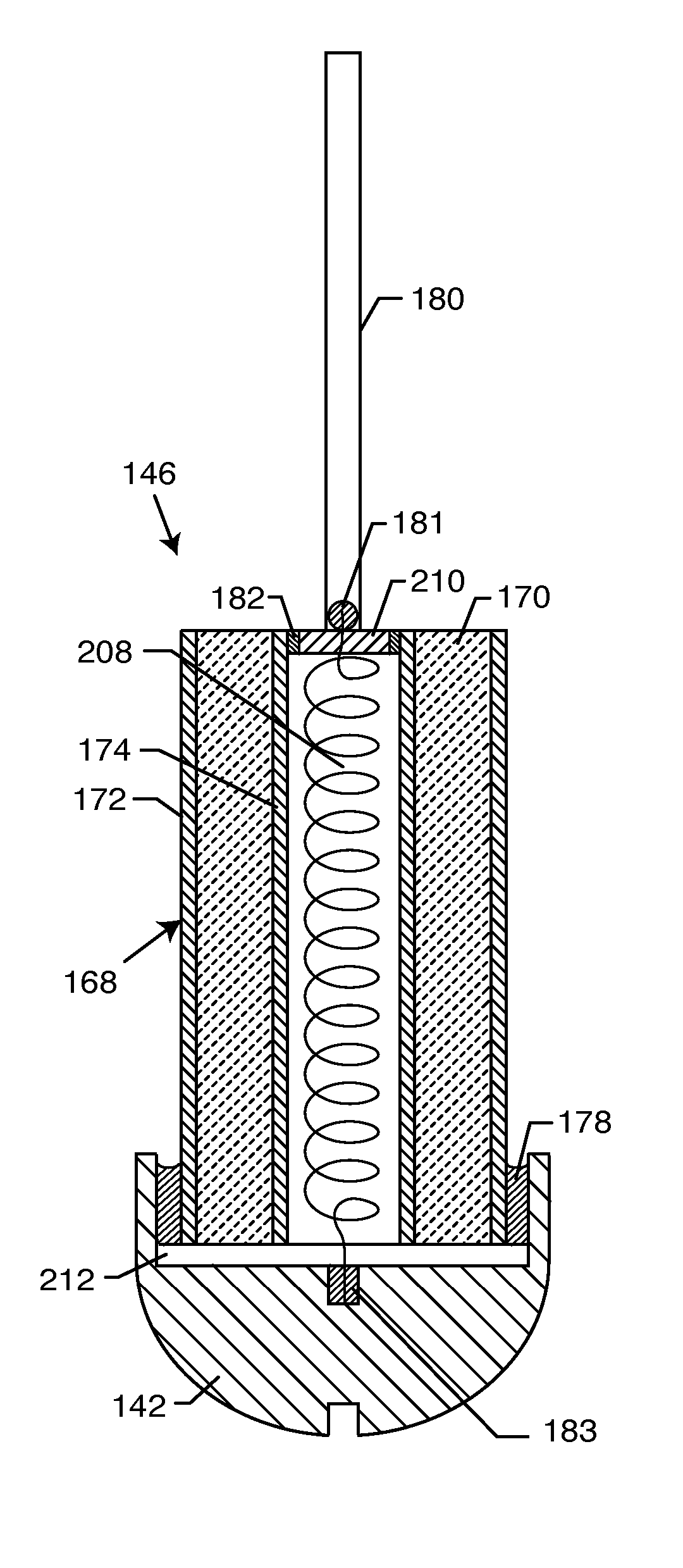

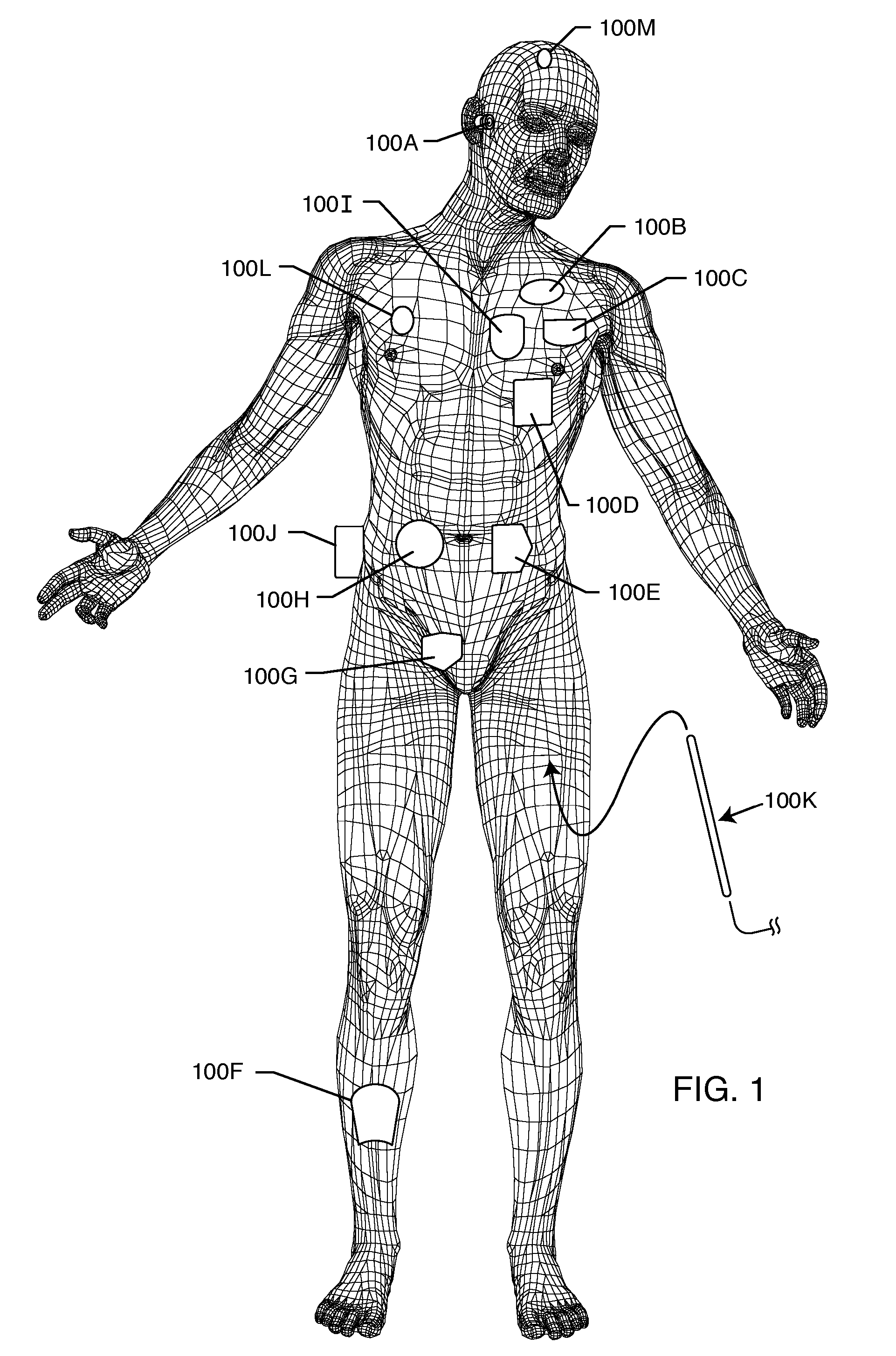

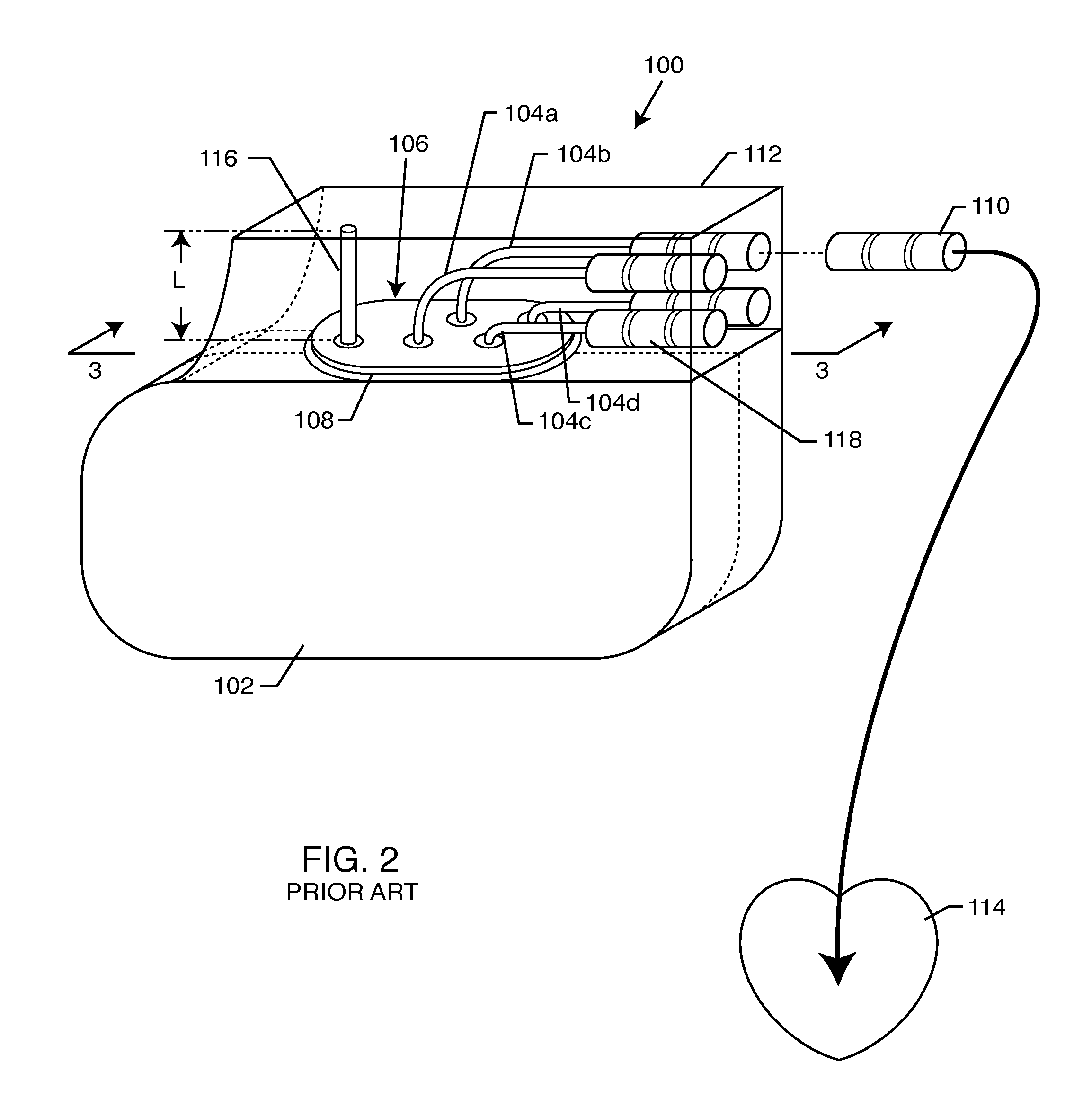

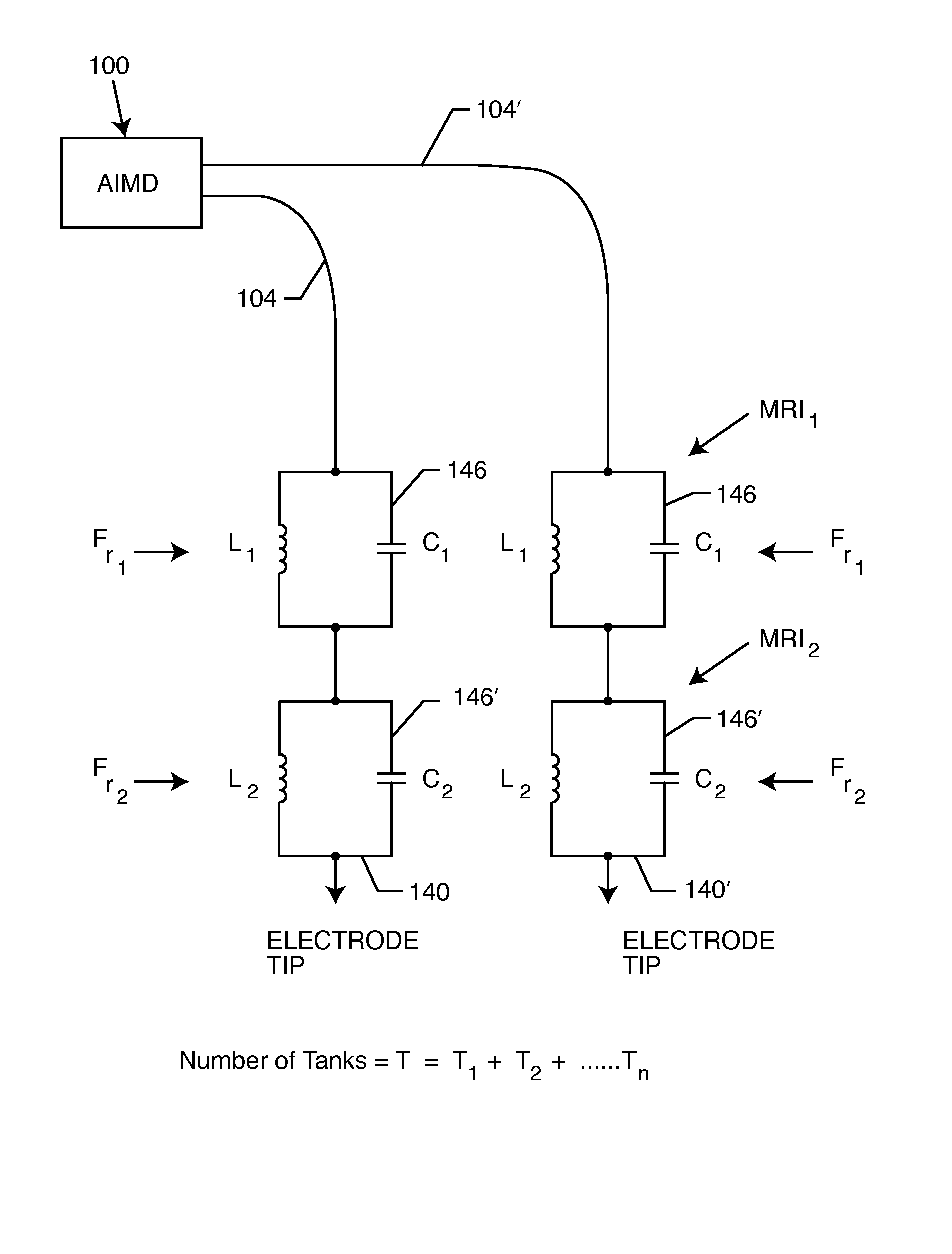

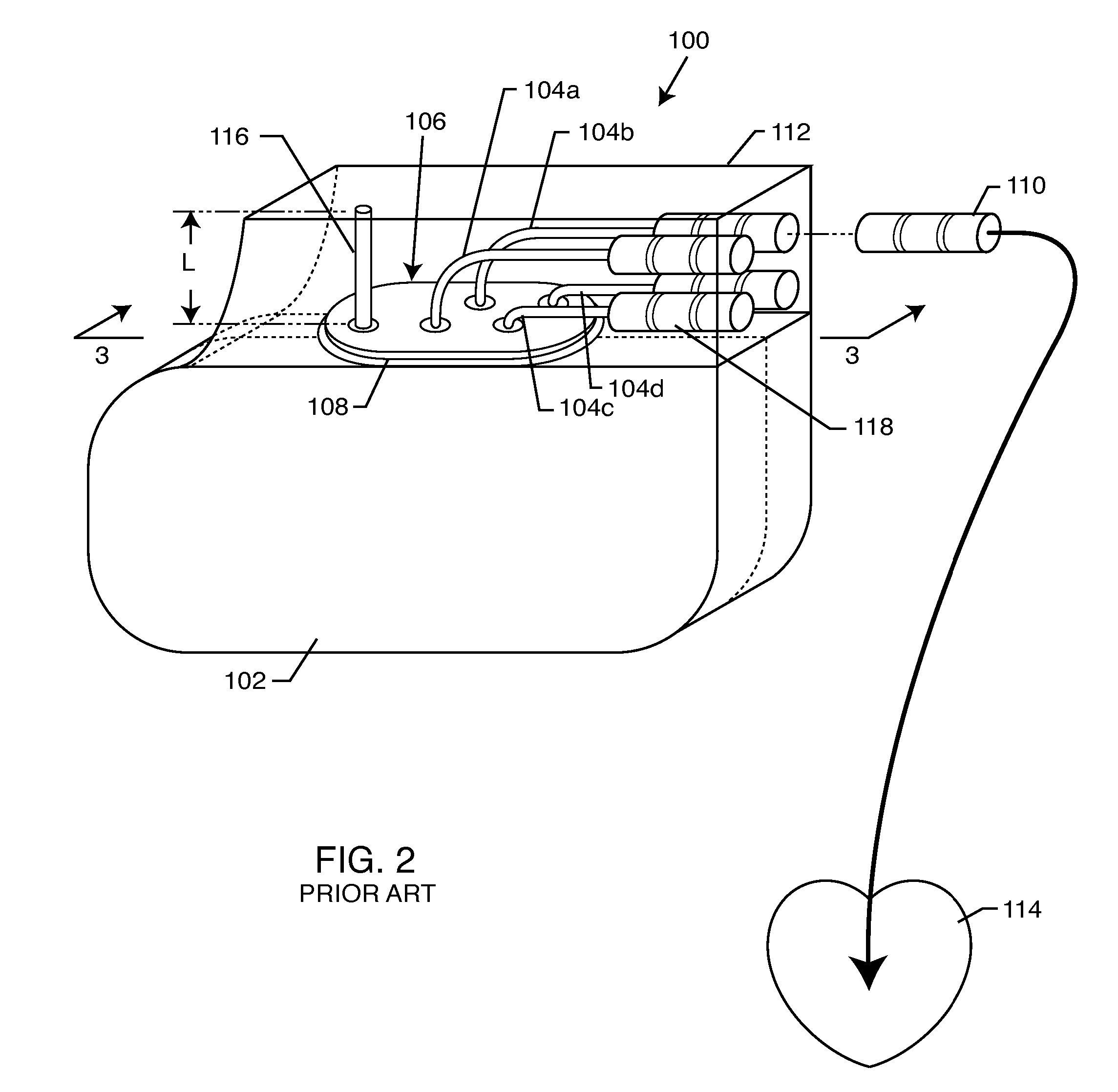

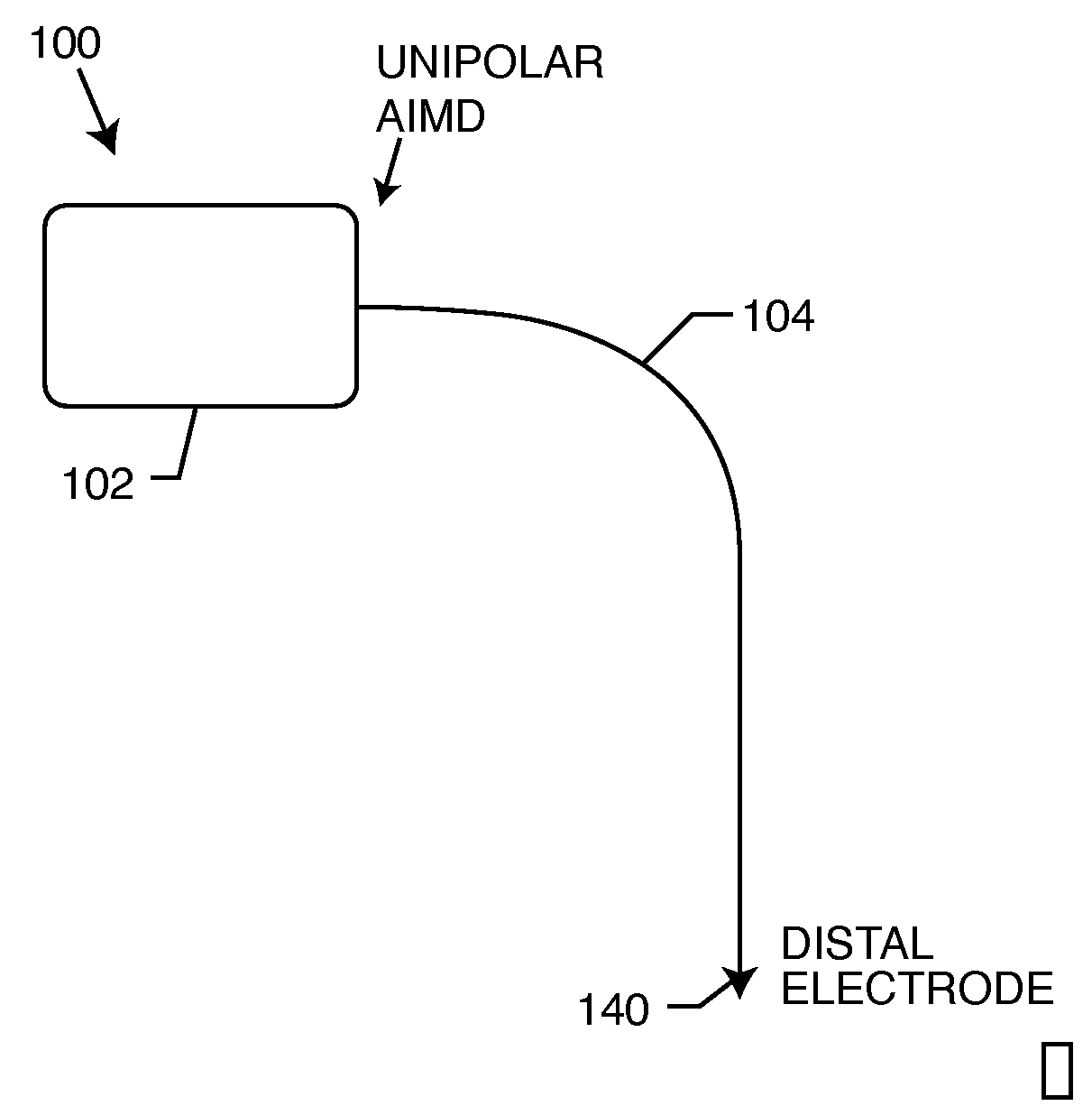

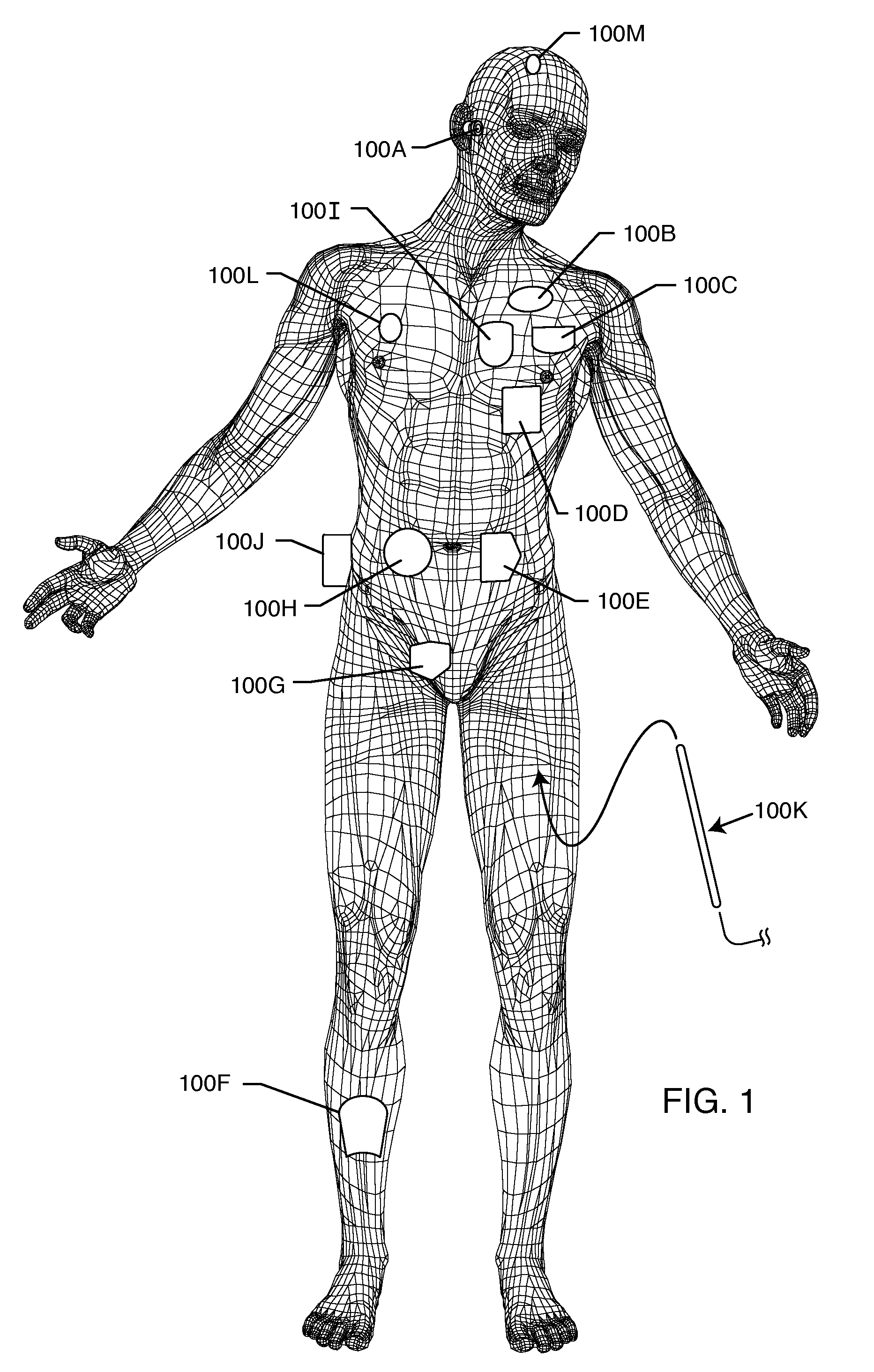

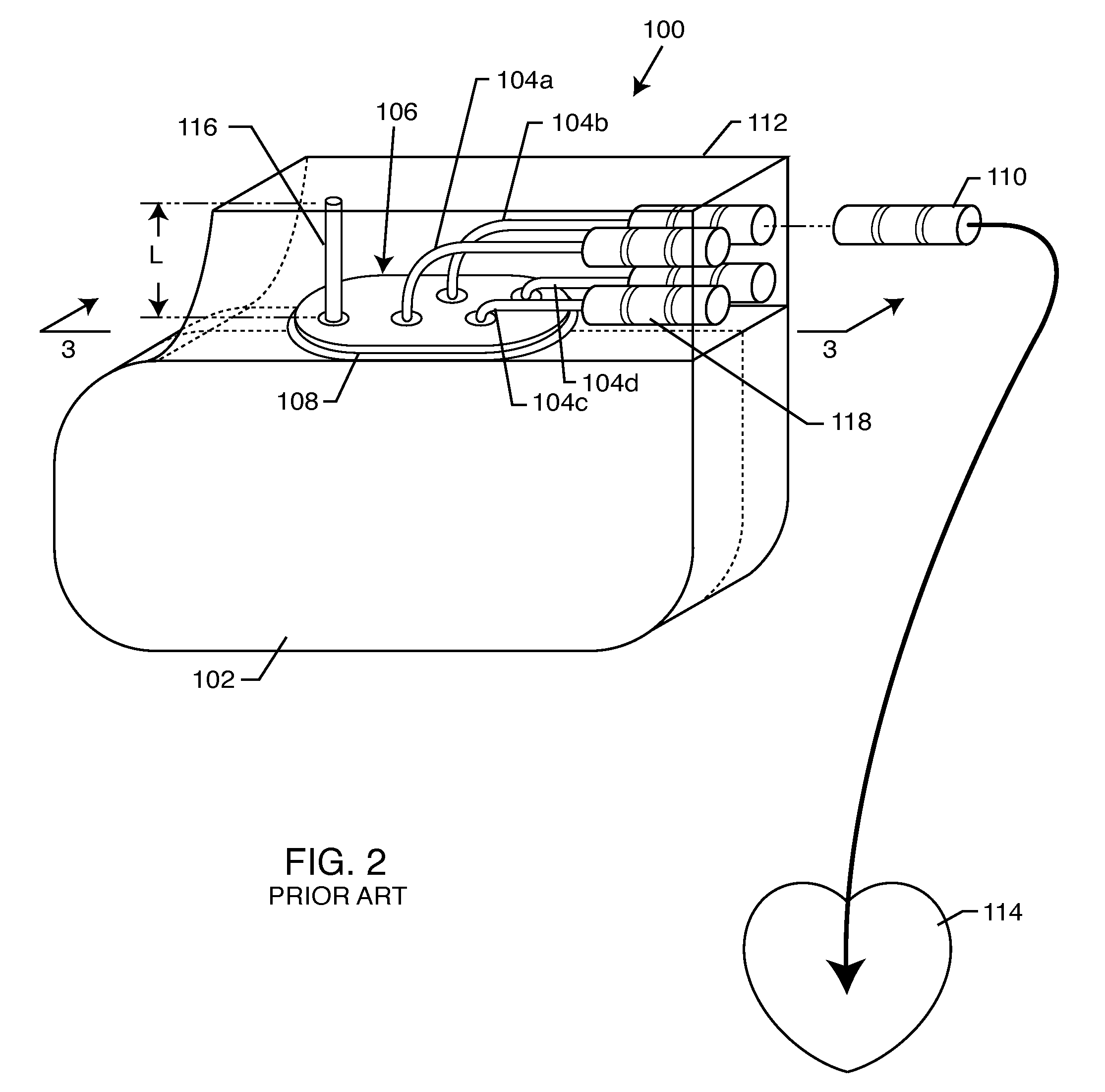

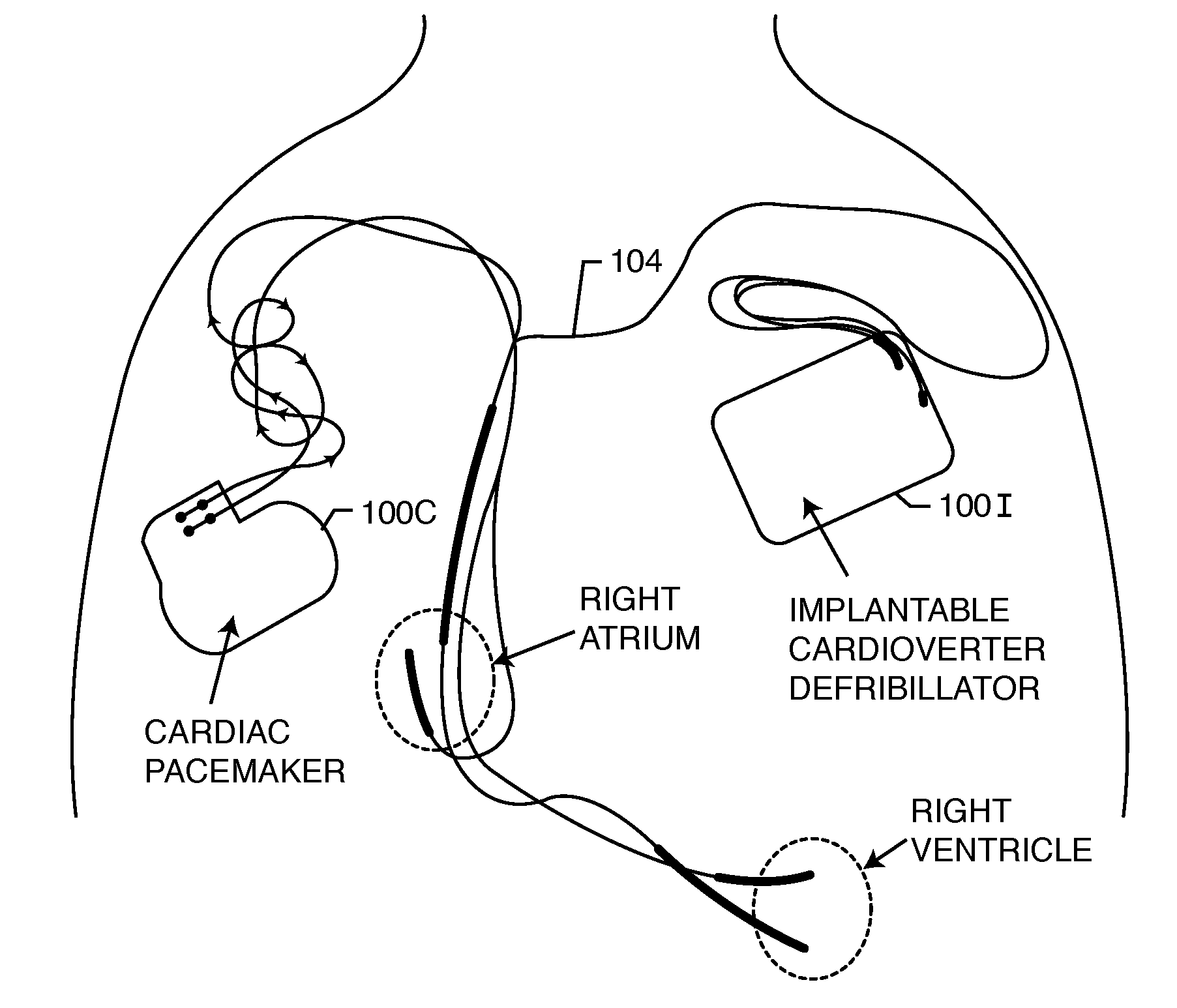

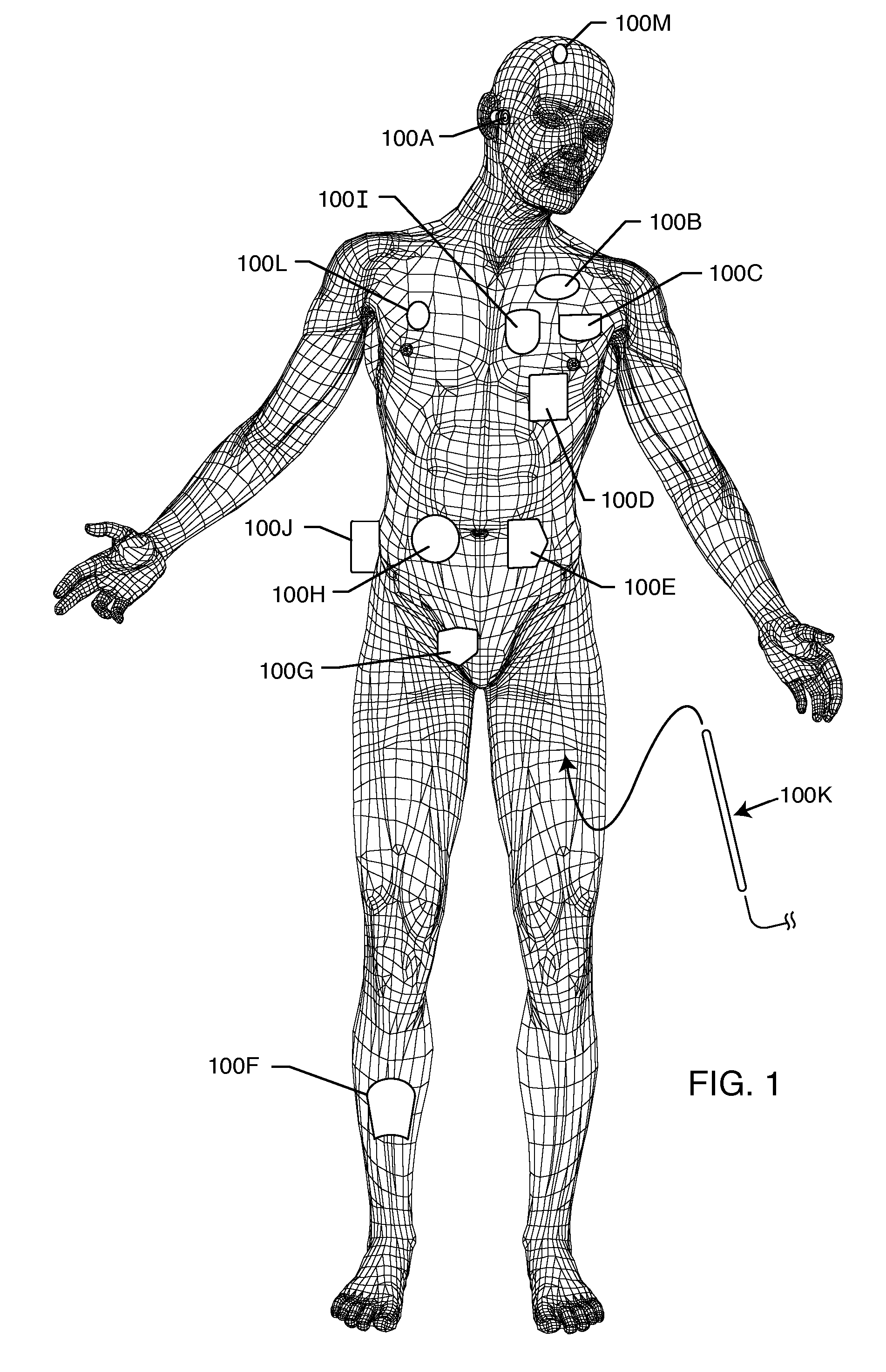

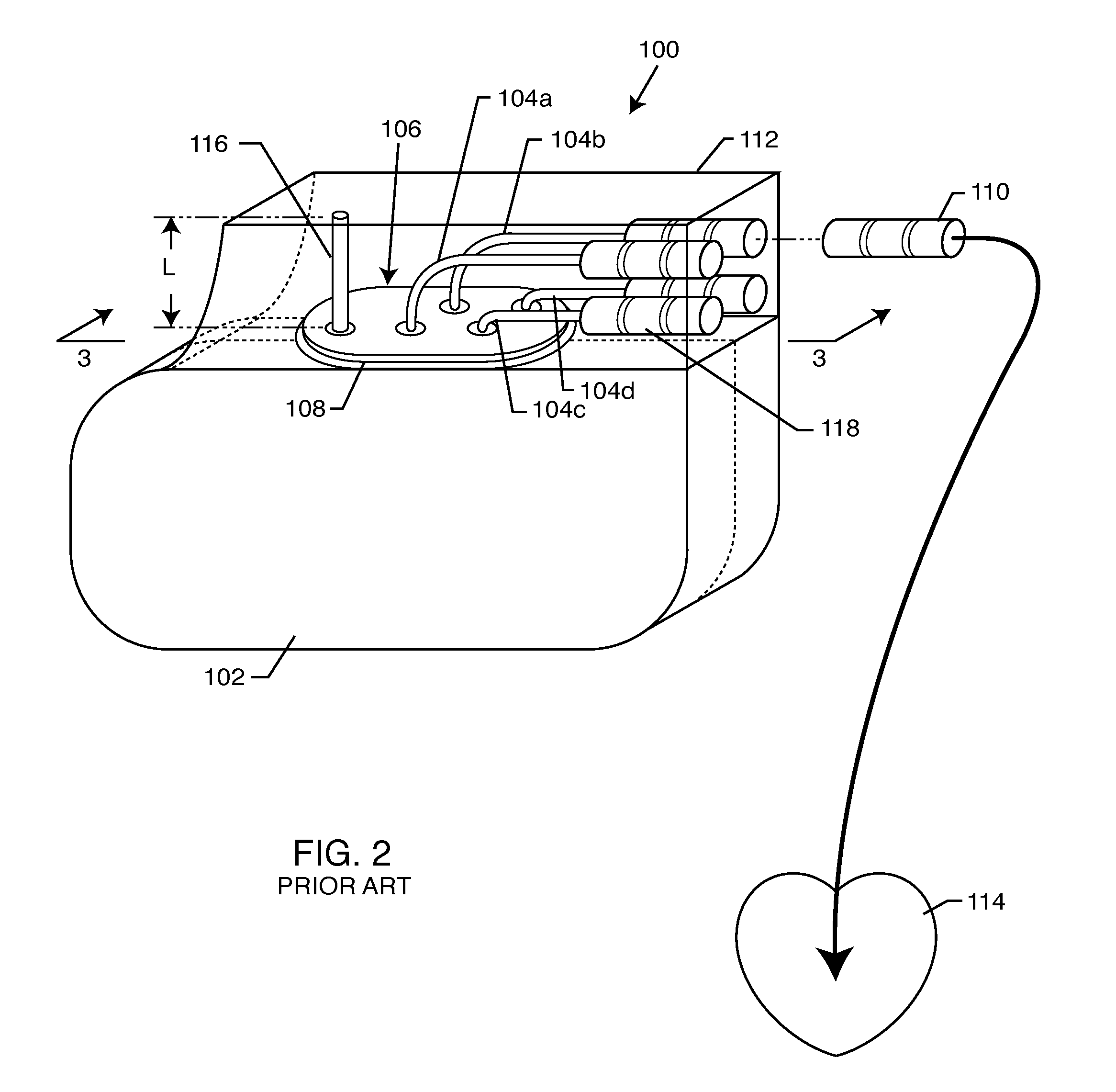

Tank filters placed in series with the lead wires or circuits of active medical devices to enhance MRI compatibility

ActiveUS20070112398A1Rapid imageryReduce sensitivityMultiple-port networksAnti-noise capacitorsMri compatibilityInductor

A TANK filter is provided for a lead wire of an active medical device (AMD). The TANK filter includes a capacitor in parallel with an inductor. The parallel capacitor and inductor are placed in series with the lead wire of the AMD, wherein values of capacitance and inductance are selected such that the TANK filter is resonant at a selected frequency. The Q of the inductor may be relatively maximized and the Q of the capacitor may be relatively minimized to reduce the overall Q of the TANK filter to attenuate current flow through the lead wire along a range of selected frequencies. In a preferred form, the TANK filter is integrated into a TIP and / or RING electrode for an active implantable medical device.

Owner:WILSON GREATBATCH LTD

Non-ferromagnetic tank filters in lead wires of active implantable medical devices to enhance MRI compatibility

InactiveUS20080049376A1High impedanceMuch smaller and volumetrically efficientMultiple-port networksAnti-noise capacitorsCapacitanceEngineering

A TANK filter is provided for a lead wire of an active medical device (AMD). The TANK filter includes a capacitor in parallel with an inductor. The parallel capacitor and inductor are placed in series with the lead wire of the AMD, wherein values of capacitance and inductance are selected such that the TANK filter is resonant at a selected frequency. In a preferred form, the TANK filter reduces or even eliminates the use of ferro-magnetic materials, and instead uses non-ferromagnetic materials so as to reduce or eliminate MRI image artifacts or the force or torque otherwise associated during an MRI image scan.

Owner:WILSON GREATBATCH LTD

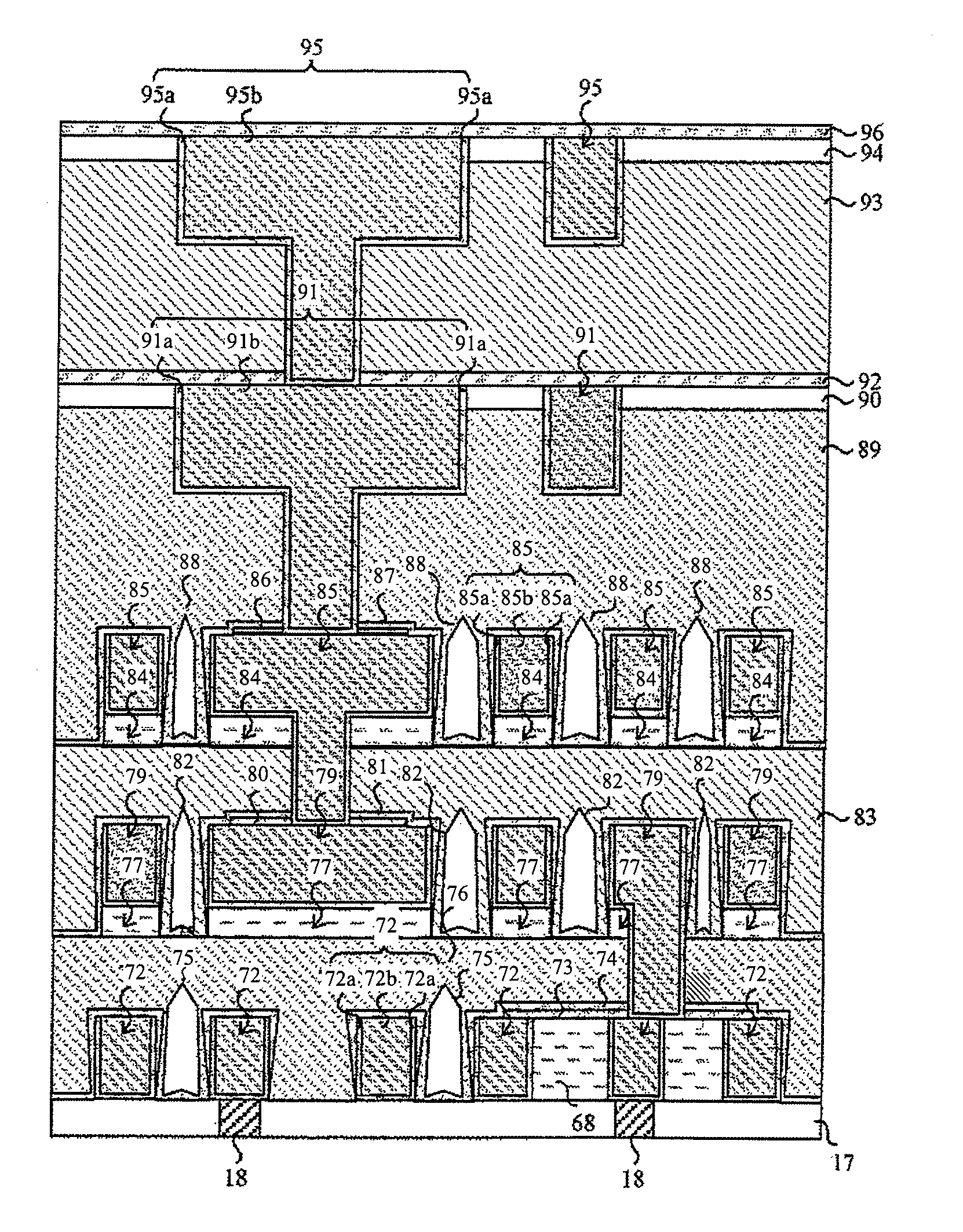

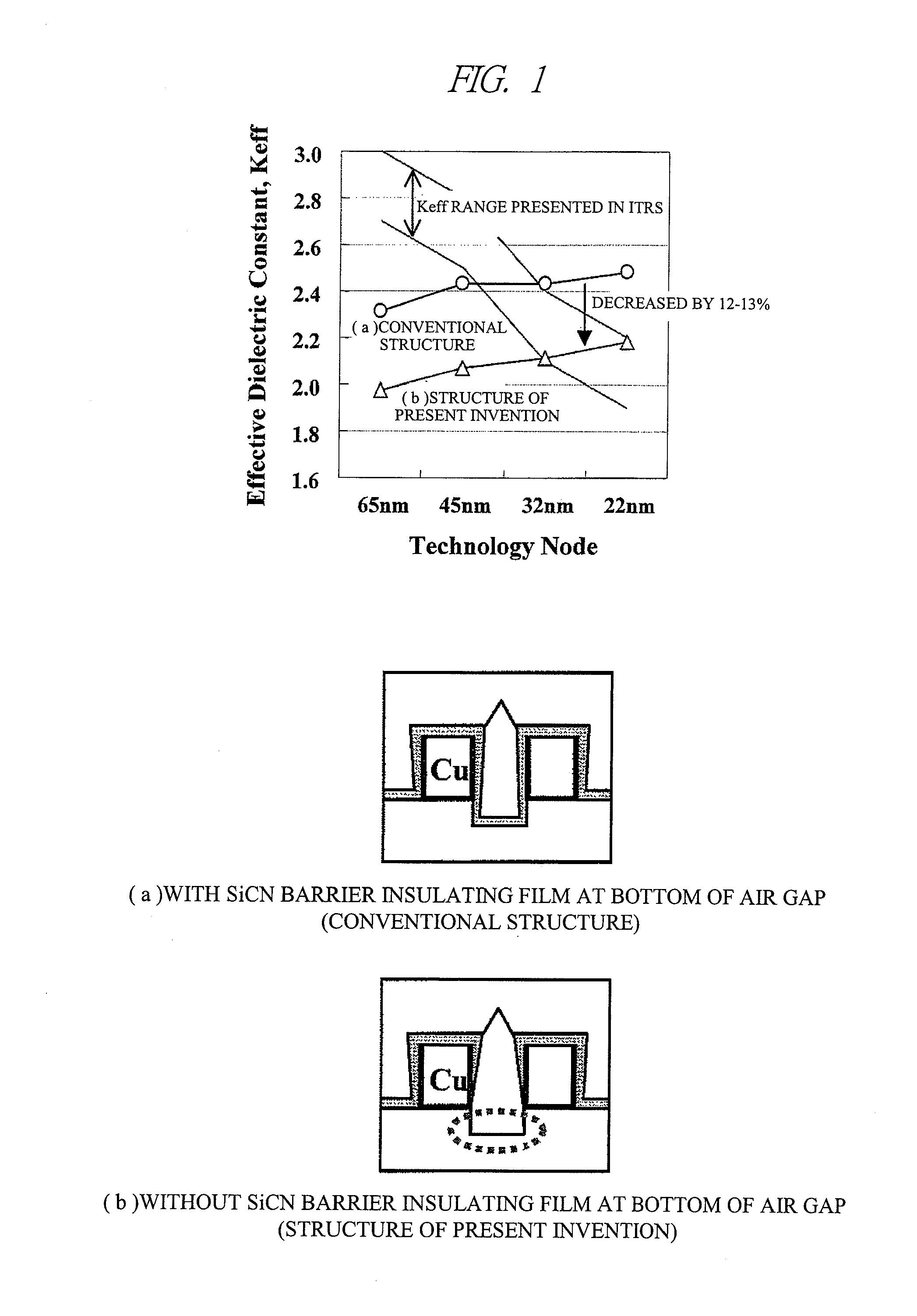

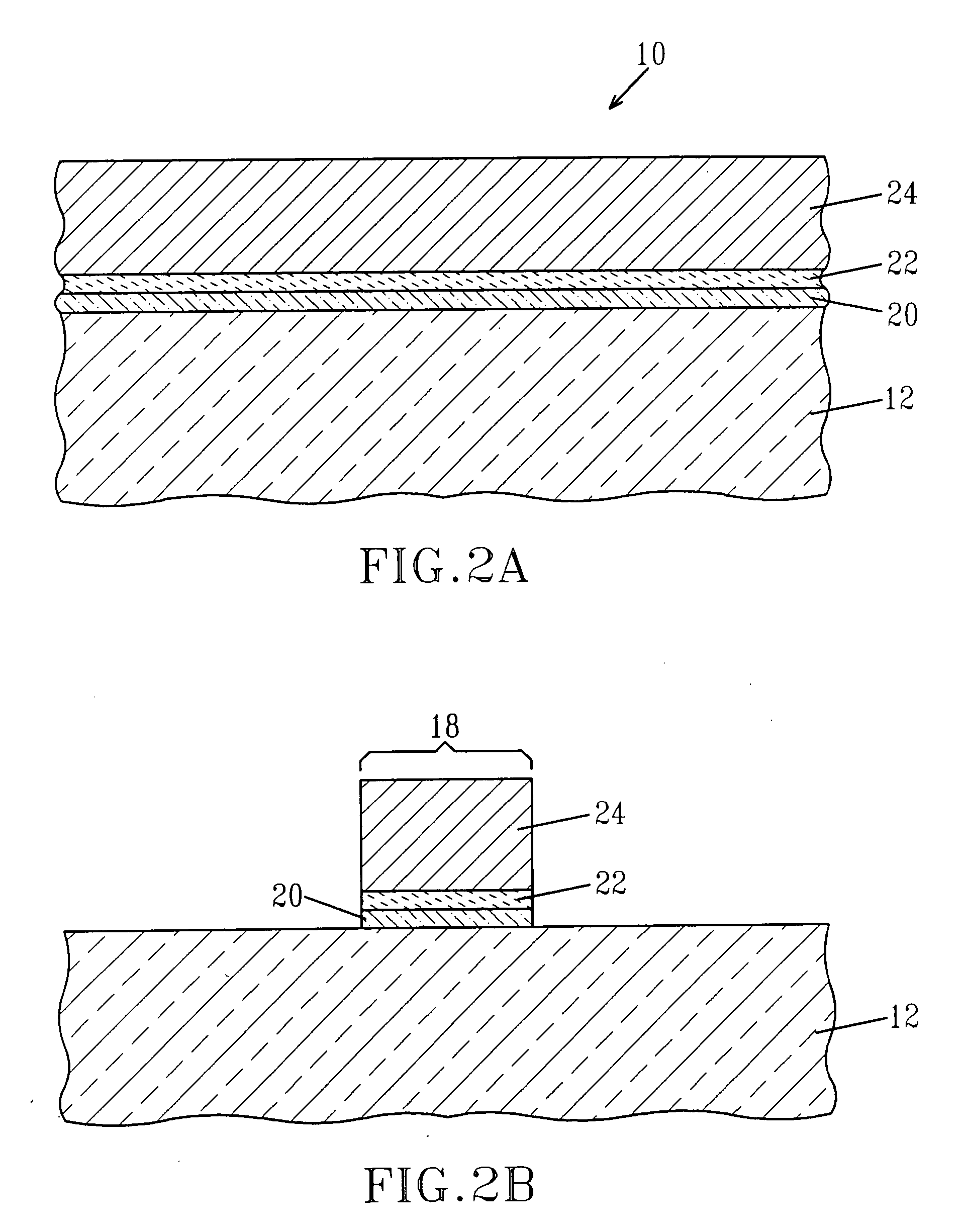

Semiconductor device and manufacturing method thereof

ActiveUS20100130001A1Reduce capacitanceEffective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesCapacitanceCopper

Wirings mainly containing copper are formed on an insulating film on a substrate. Then, after forming insulating films for reservoir pattern and a barrier insulating film, an insulating film for suppressing or preventing diffusion of copper is formed on upper and side surfaces of the wirings, the insulating film on the substrate, and the barrier insulating film. Here, thickness of the insulating film for suppressing or preventing diffusion of copper at the bottom of a narrow inter-wiring space is made smaller than that on the wirings, thereby efficiently reducing wiring capacitance of narrow-line pitches. Then, first and second low dielectric constant insulating films are formed. Here, a deposition rate of the first insulating film at an upper portion of the side surfaces of facing wirings is made higher than that at a lower portion thereof, thereby forming air gaps. Finally, the second insulating film is planarized by interlayer CMP.

Owner:KOKUSA ELECTRIC CO LTD

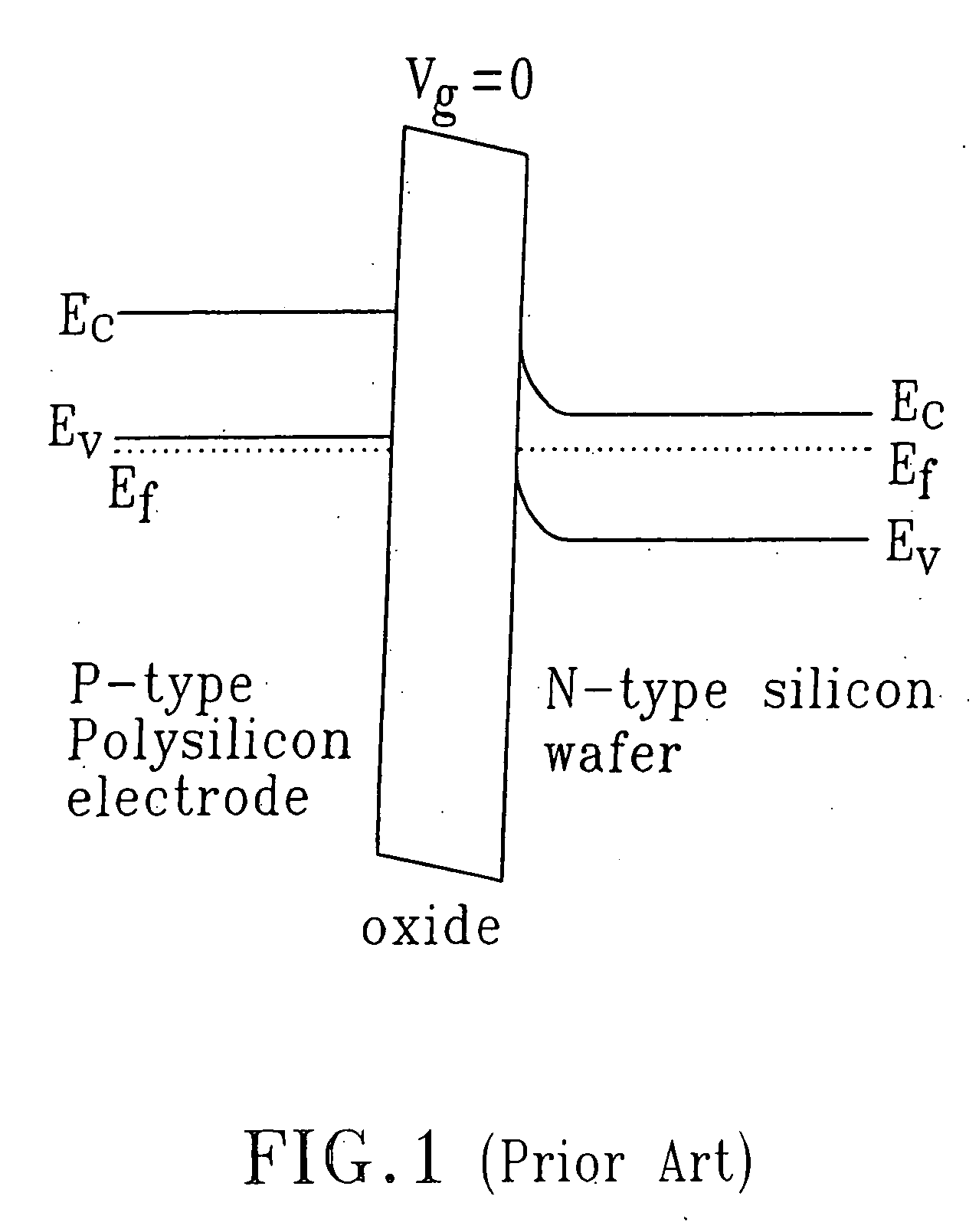

Nitrogen-containing field effect transistor gate stack containing a threshold voltage control layer formed via deposition of a metal oxide

InactiveUS20060102968A1Raise the threshold voltageImprove voltage stabilityTransistorSemiconductor/solid-state device detailsGate dielectricControl layer

A semiconductor structure is provided that includes a Vt stabilization layer between a gate dielectric and a gate electrode. The Vt stabilization layer is capable of stabilizing the structure's threshold voltage and flatband voltage to a targeted value and comprises a nitrided metal oxide, or a nitrogen-free metal oxide, with the proviso that when the Vt stabilization layer comprises a nitrogen-free metal oxide, at least one of the semiconductor substrate or the gate dielectric includes nitrogen. The present invention also provides a method of fabricating such a structure.

Owner:GLOBALFOUNDRIES INC

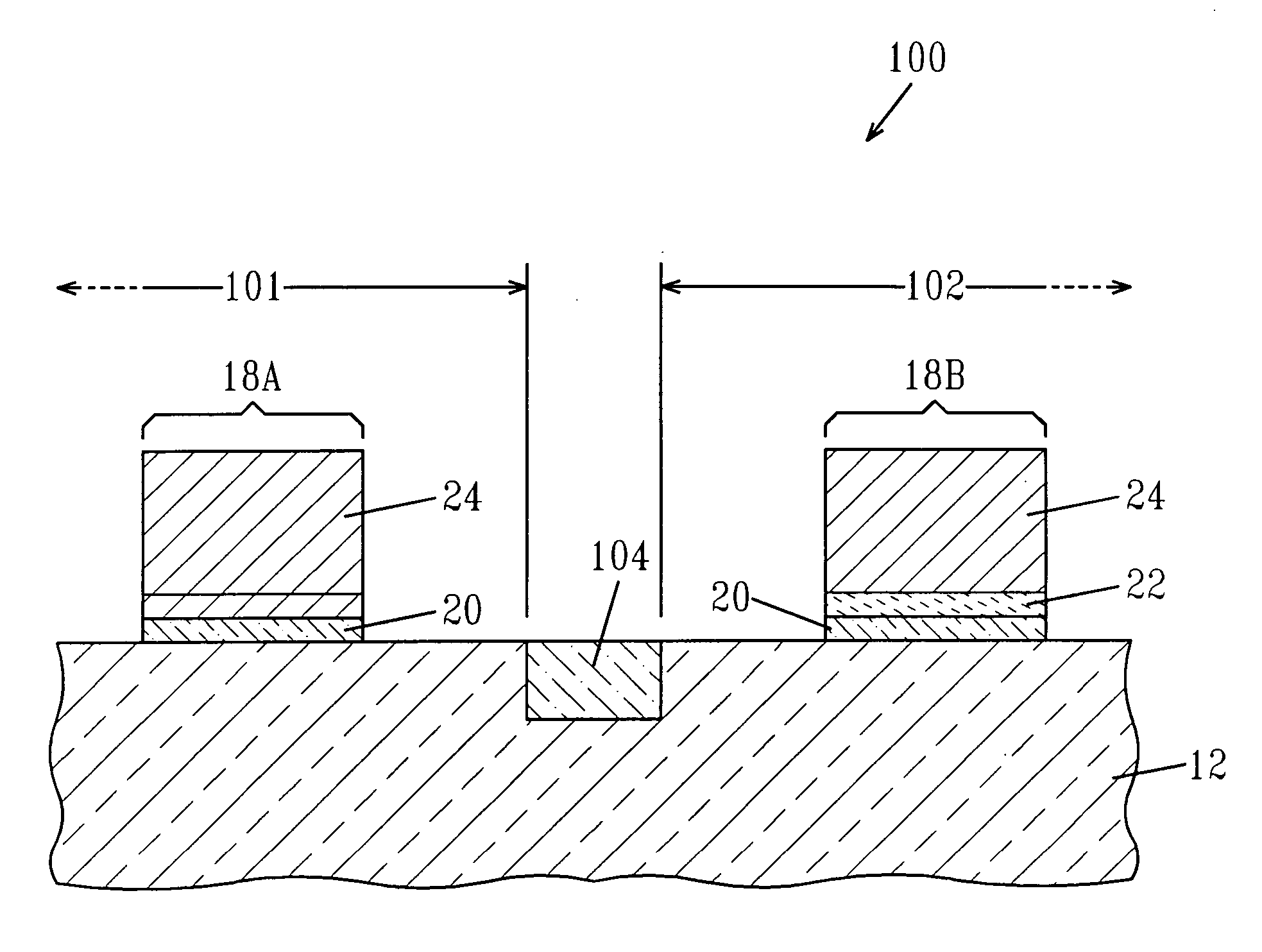

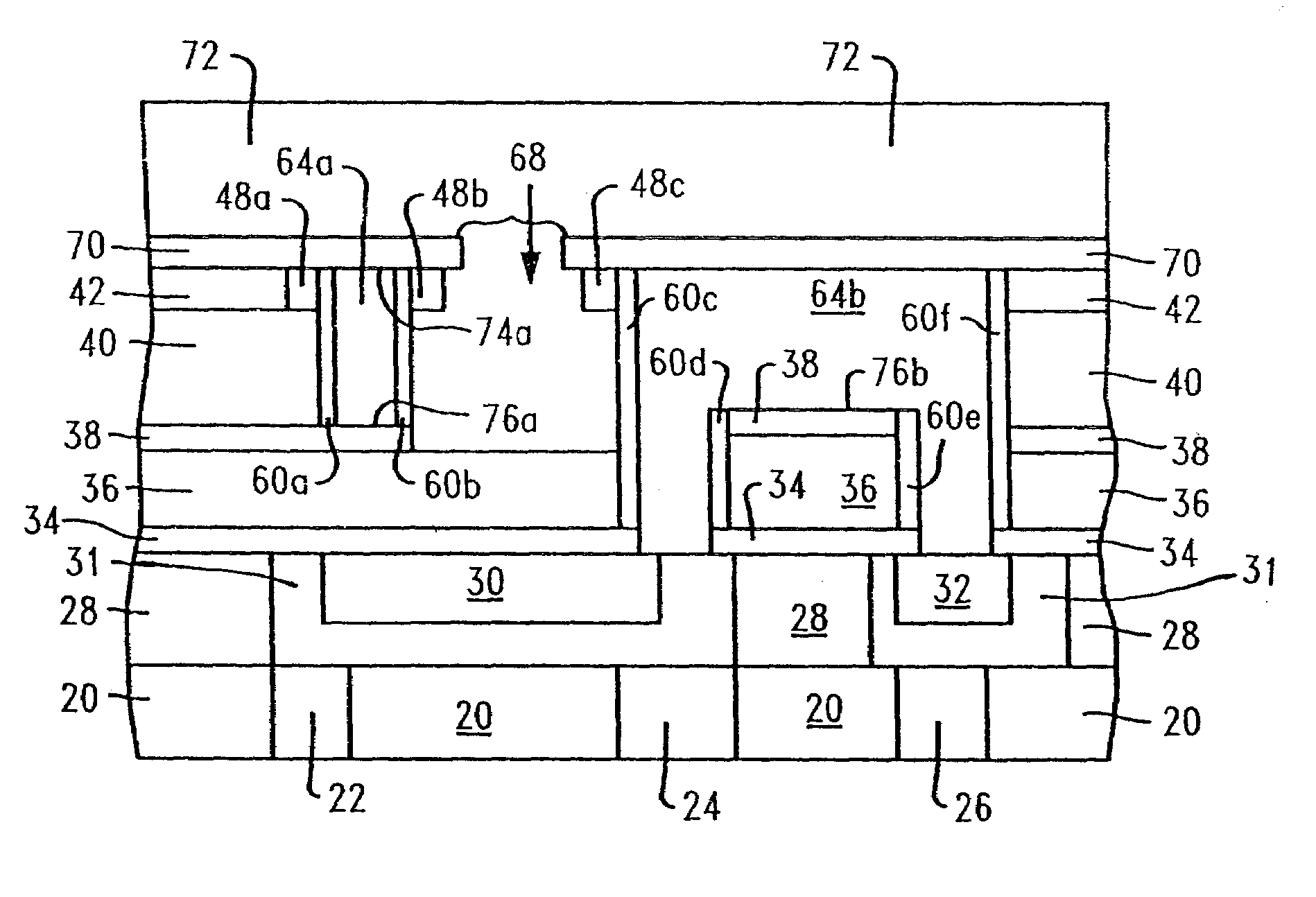

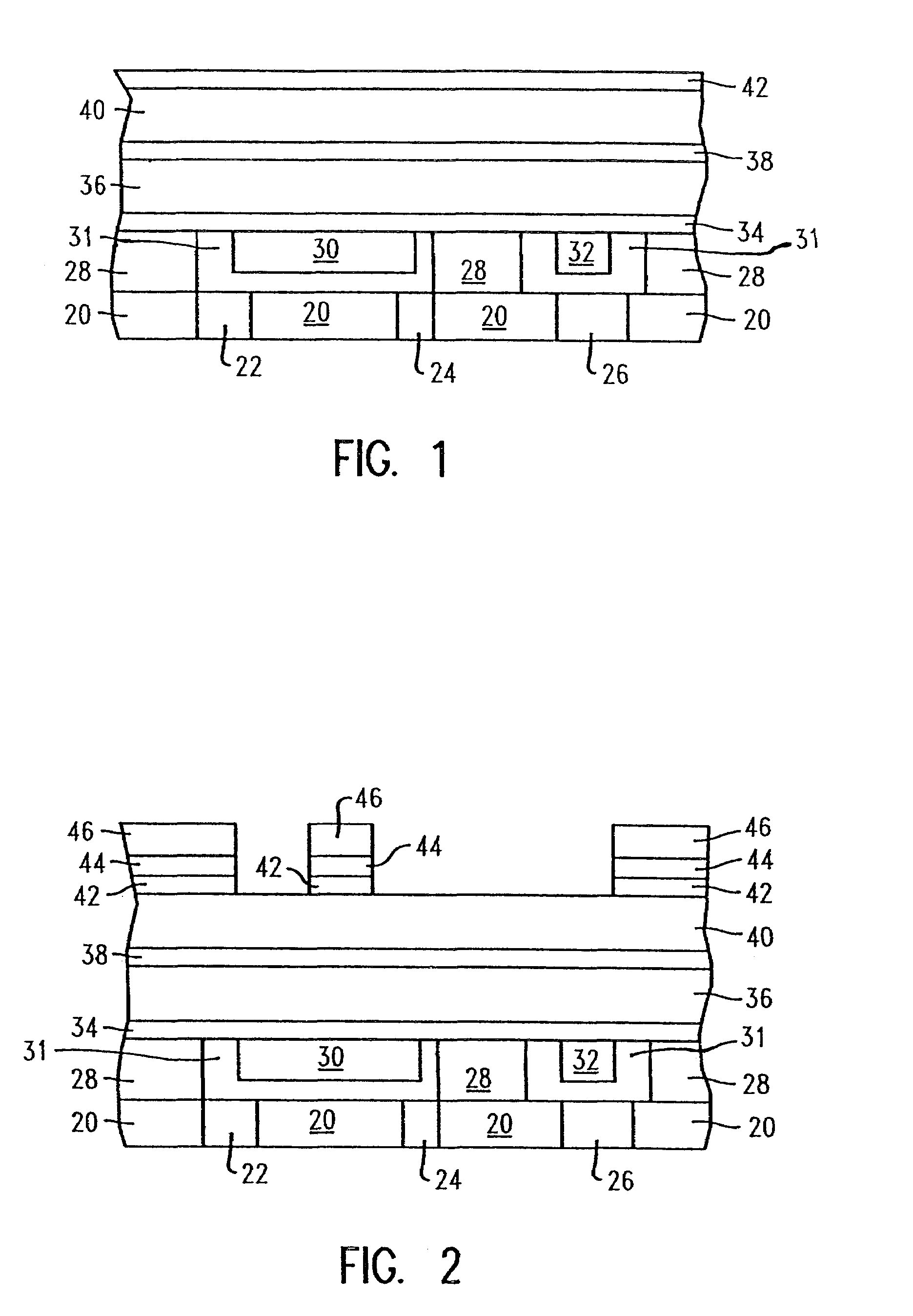

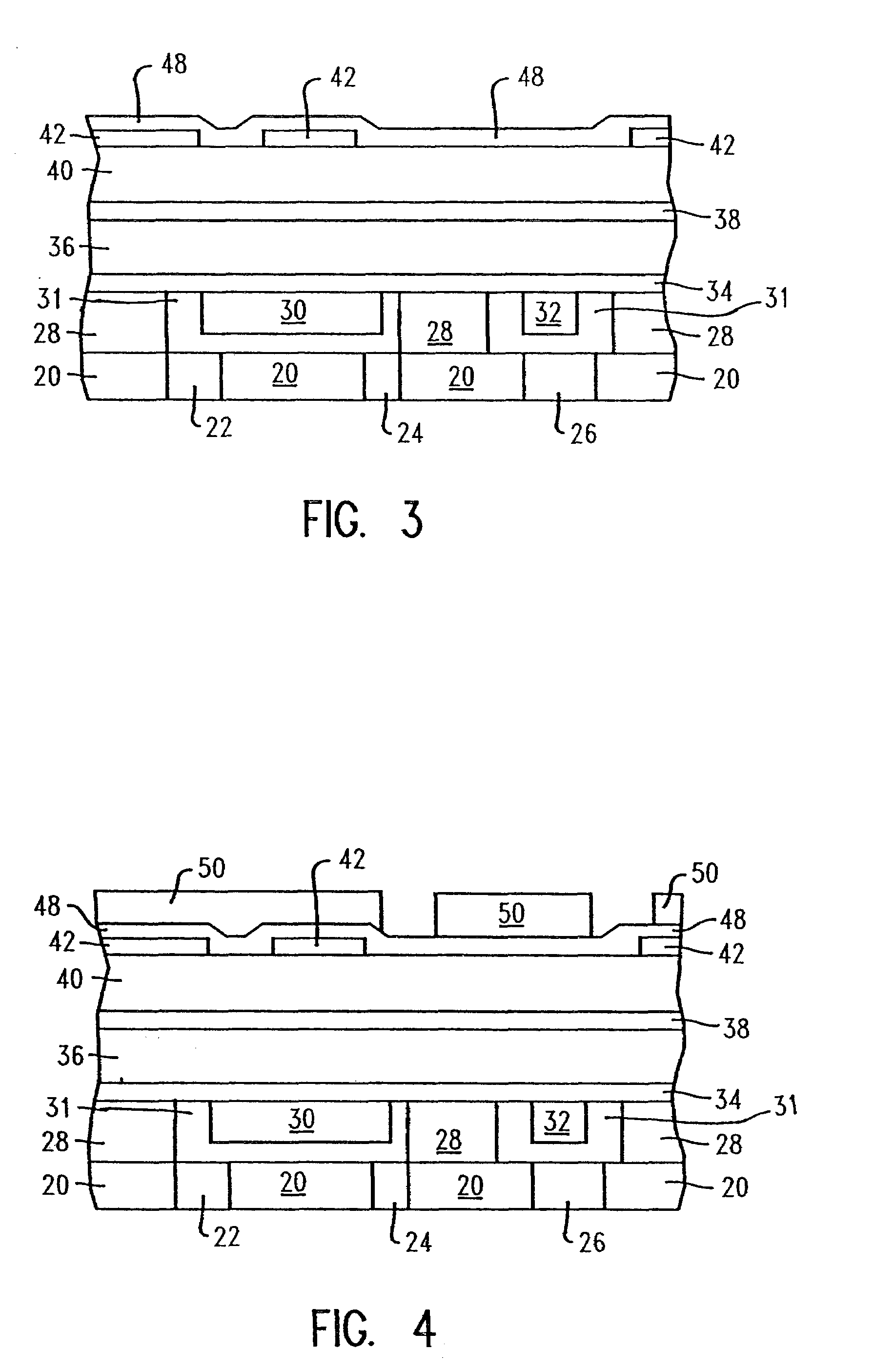

Adjustable self-aligned air gap dielectric for low capacitance wiring

ActiveUS7071532B2Reduce capacitanceReduce line widthSemiconductor/solid-state device detailsSolid-state devicesDielectricCapacitance

Owner:GLOBALFOUNDRIES U S INC

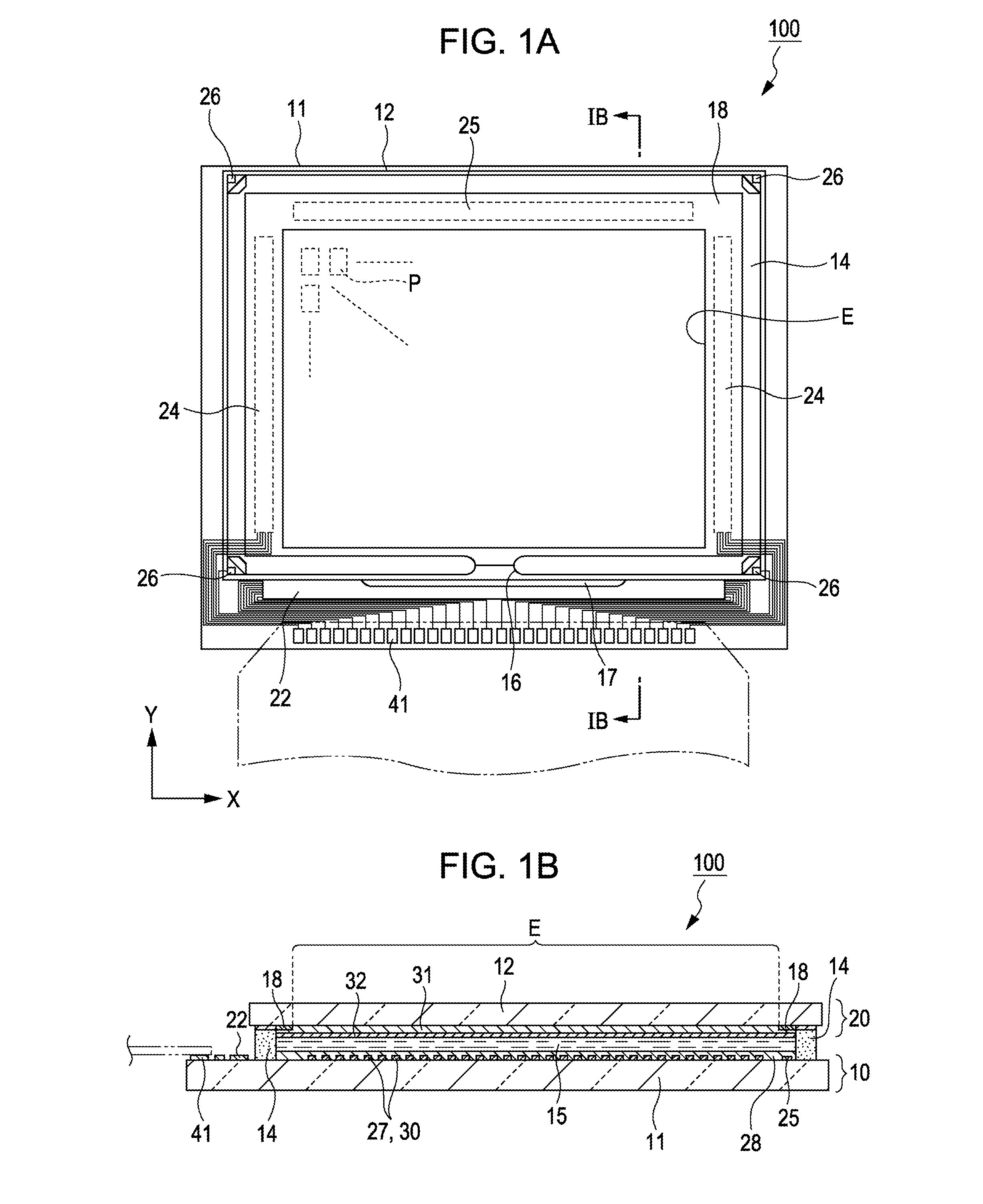

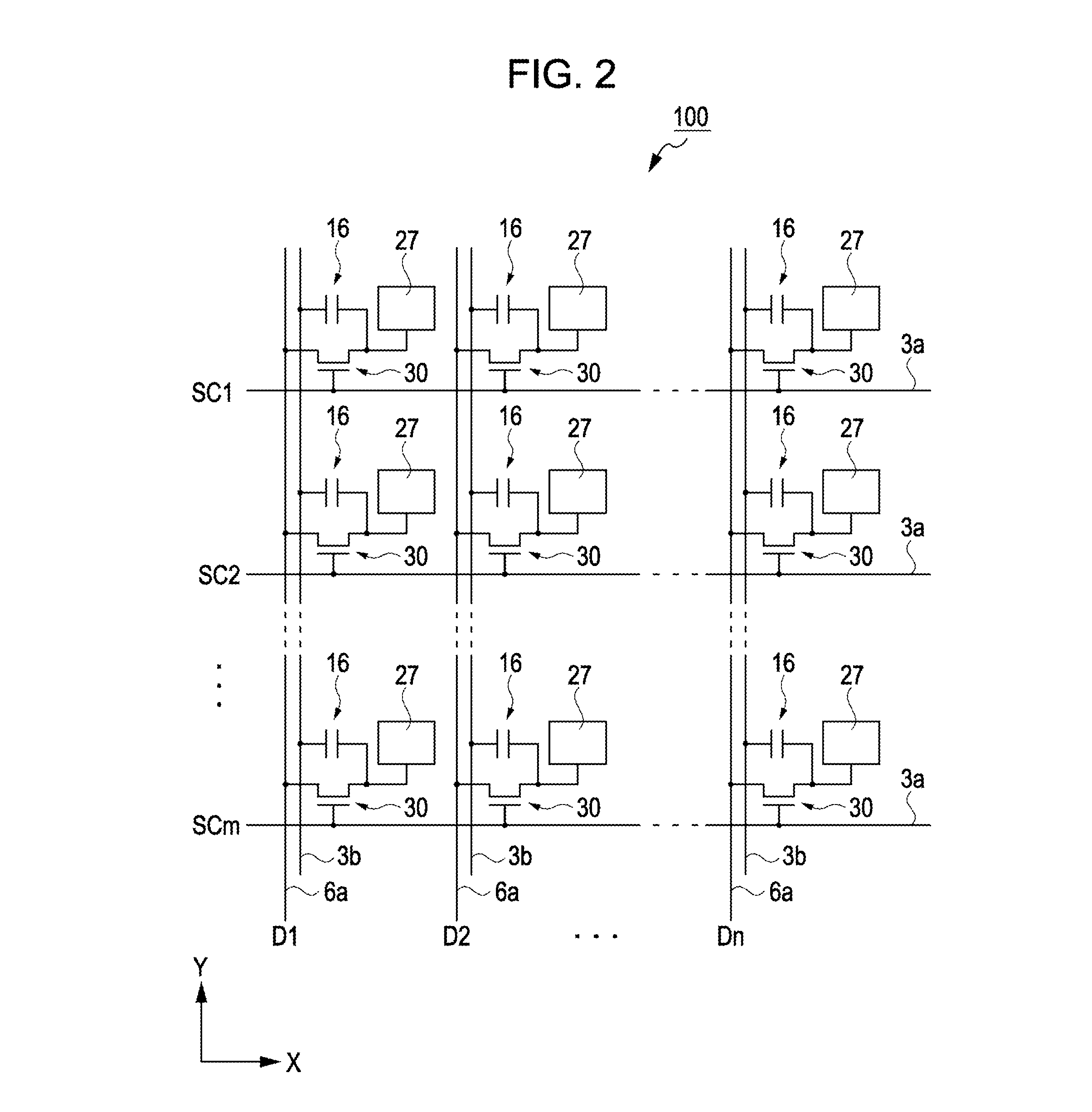

Electro-optical device and electronic apparatus

Disclosed is a pixel electrode which is electrically connected to a scanning line electrically connected to a gate electrode, a data line electrically connected to a data line side source and drain region, and a pixel electrode side source and drain region; and a capacitance element which has a first capacitance electrode which is electrically connected to a capacitance line, a second capacitance electrode which is provided to oppose the first capacitance electrode, and a dielectric layer which is interposed between the first capacitance electrode and the second capacitance electrode, where the first capacitance electrode is arranged to be covered with the dielectric layer and the second capacitance electrode between a layer where the transistor, the scanning line, and the data line are provided and a layer where the pixel electrode is provided.

Owner:138 EAST LCD ADVANCEMENTS LTD

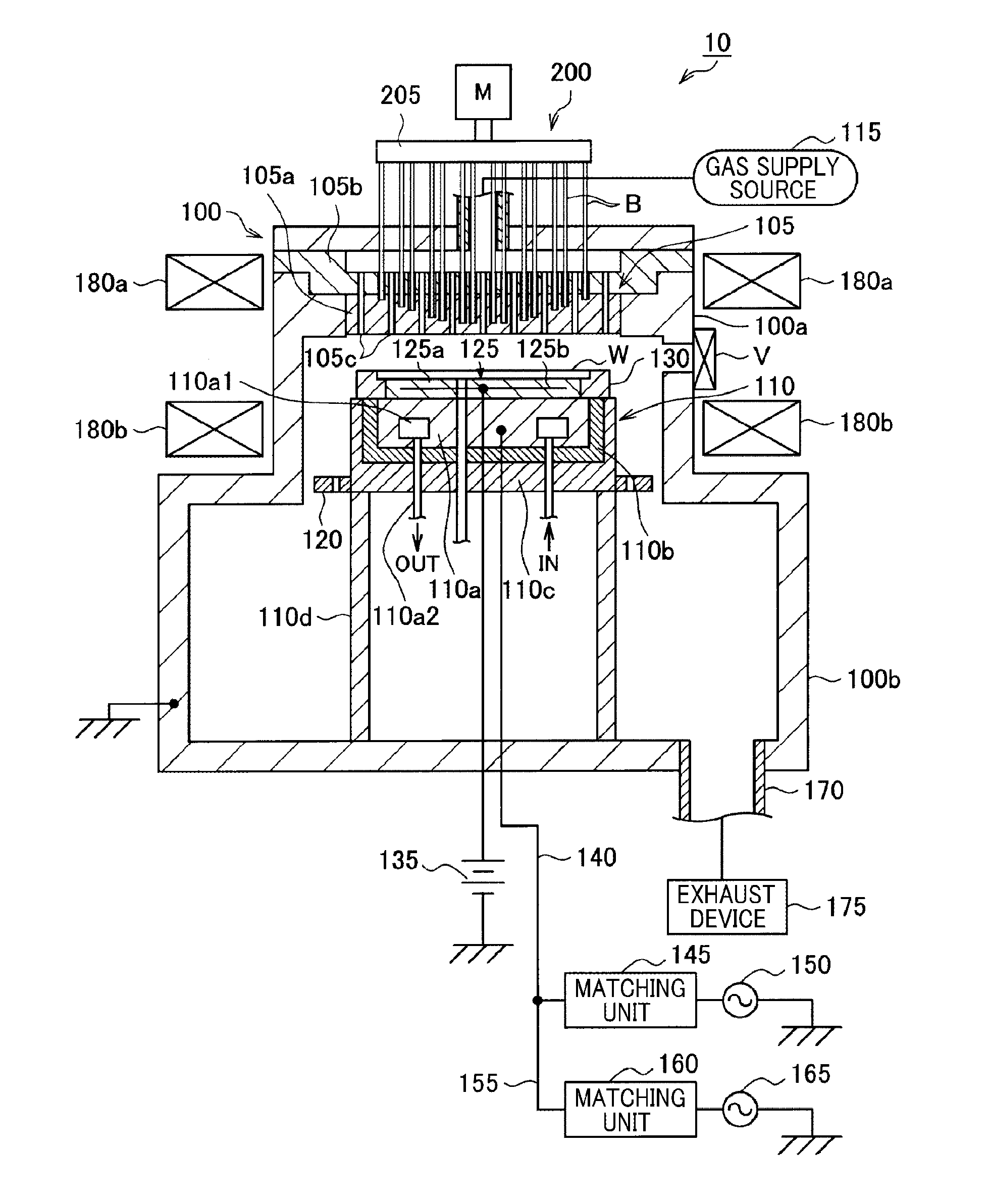

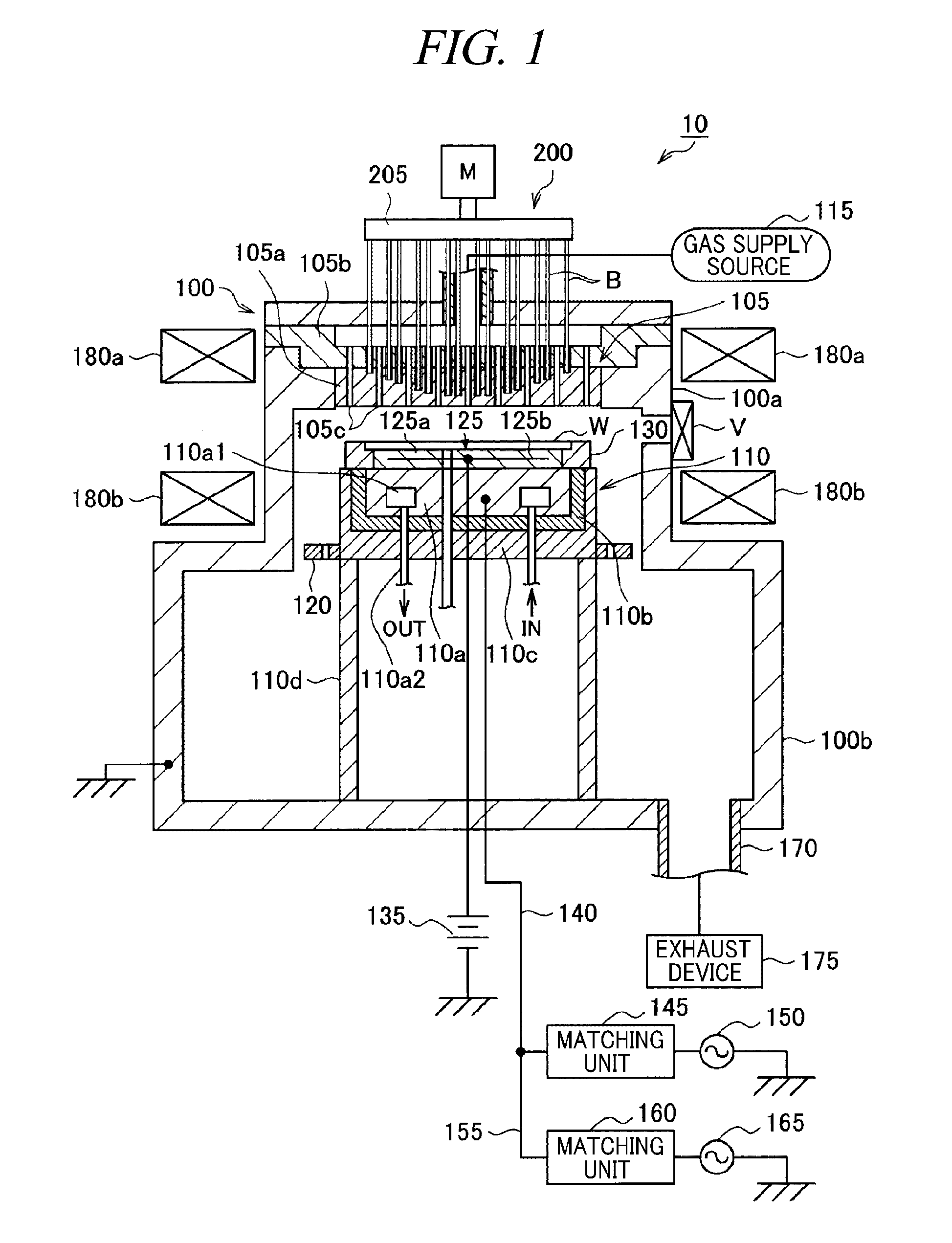

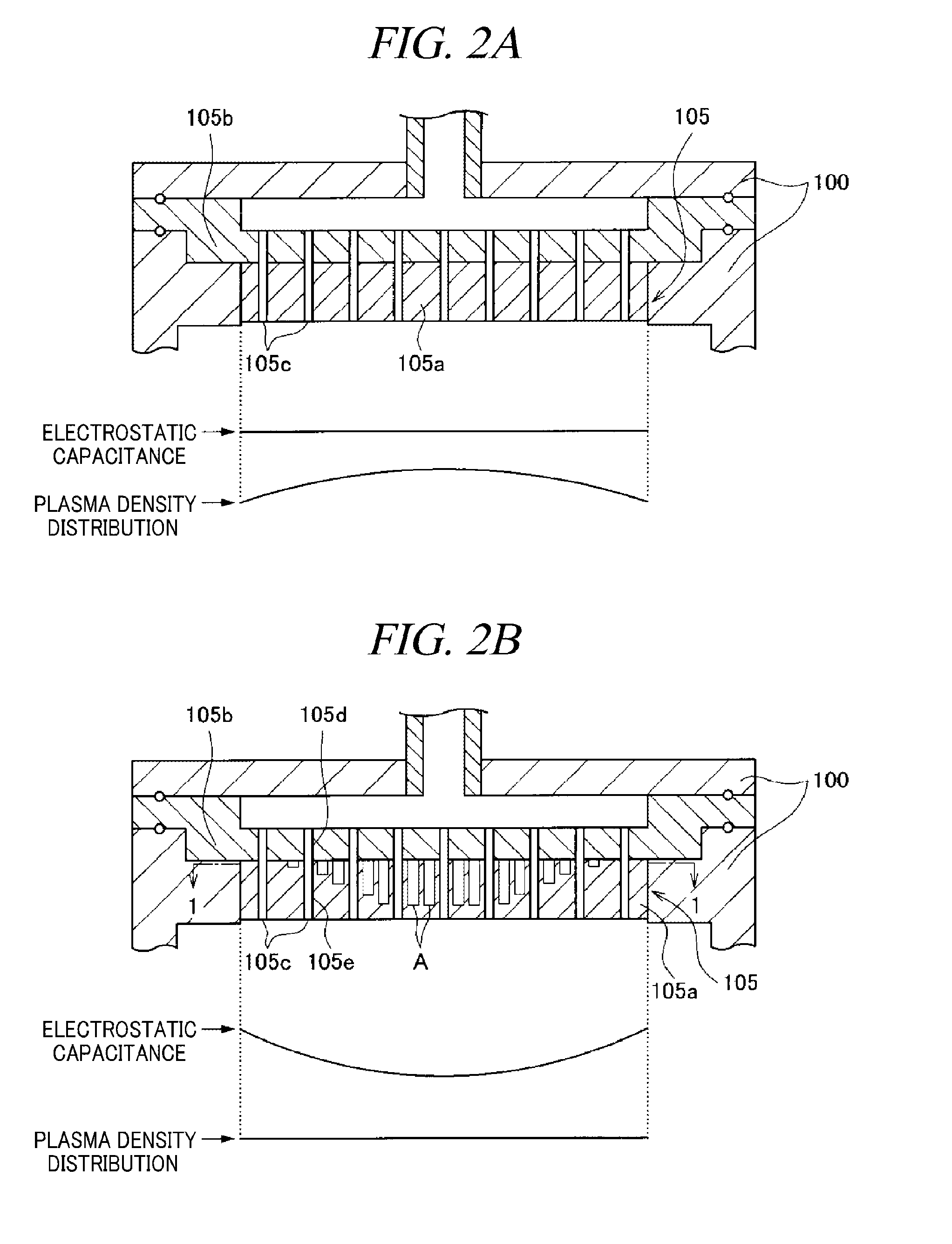

Plasma processing apparatus

ActiveUS20110226421A1Reduce capacitanceUniform intensity distributionElectric discharge tubesSemiconductor/solid-state device manufacturingHigh frequency powerProduct gas

An intensity distribution of an electric field of a high frequency power used for generating plasma is controlled by using an electrode made of a homogeneous material and a moving body. There is provided a plasma processing apparatus for introducing a processing gas into an evacuable processing chamber 100 and generating plasma by a high frequency power and performing a plasma process on a wafer W by the plasma. The plasma processing apparatus includes a dielectric base 105a having a multiple number of fine holes A; a varying member 200 as the moving body provided with a multiple number of rod-shaped members B capable of being inserted into and separated from the fine holes A; and a driving mechanism 215 configured to drive the varying member 200 to allow the rod-shaped members B to be inserted into and separated from the fine holes A.

Owner:TOKYO ELECTRON LTD

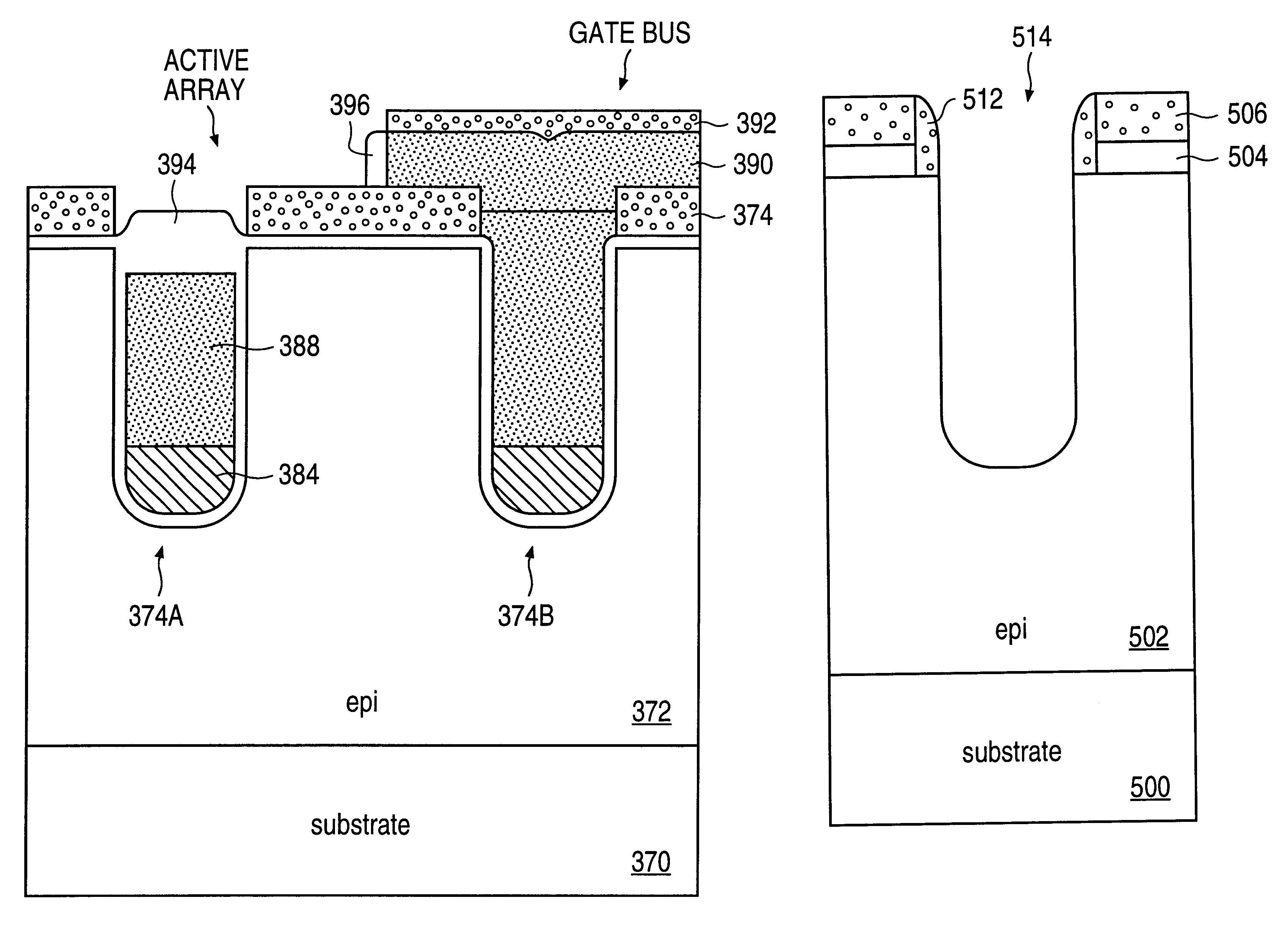

Process of manufacturing Trench gate semiconductor device having gate oxide layer with multiple thicknesses

InactiveUS6291298B1Reduced strengthReduce capacitanceSemiconductor/solid-state device manufacturingDiodePhysicsPhotoresist

The a trench semiconductor device such as a power MOSFET the high electric field at the corner of the trench is diminished by increasing the thickness of the gate oxide layer at the bottom of the trench. Several processes for manufacturing such devices are described. In one group of processes a directional deposition of silicon oxide is performed after the trench has been etched, yielding a thick oxide layer at the bottom of the trench. Any oxide which deposits on the walls of the trench is removed before a thin gate oxide layer is grown on the walls. The trench is then filled with polysilicon in or more stages. In a variation of the process a small amount of photoresist is deposited on the oxide at the bottom of the trench before the walls of the trench are etched. Alternatively, polysilicon can be deposited in the trench and etched back until only a portion remains at the bottom of the trench. The polysilicon is then oxidized and the trench is refilled with polysilicon. The processes can be combined, with a directional deposition of oxide being followed by a filling and oxidation of polysilicon. A process of forming a "keyhole" shaped gate electrode includes depositing polysilicon at the bottom of the trench, oxidizing the top surface of the polysilicon, etching the oxidized polysilicon, and filling the trench with polysilicon.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

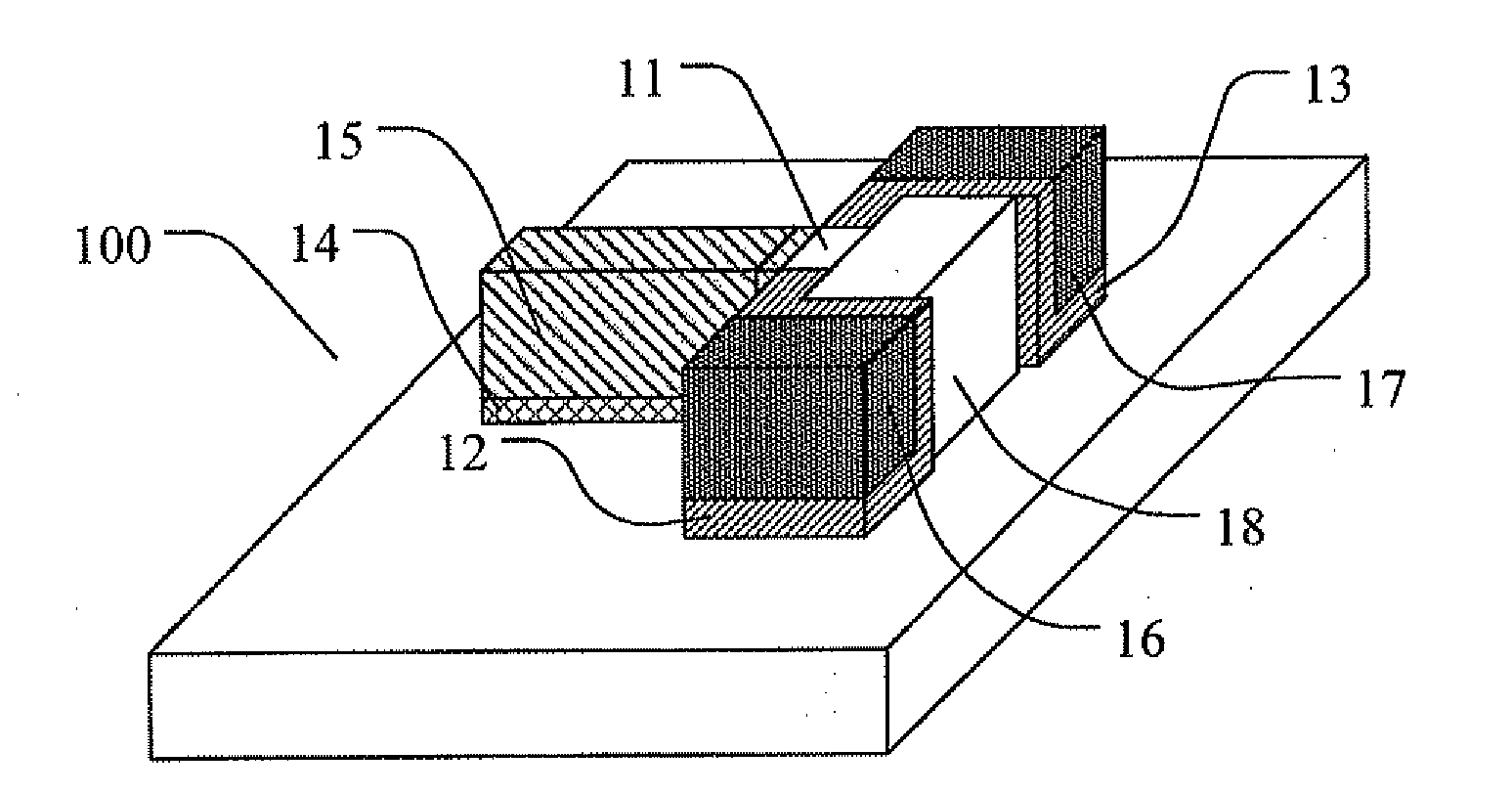

Nanowire mesh device and method of fabricating same

ActiveUS20100207208A1Improved contact schemeImprove scalabilityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireGate dielectric

A semiconductor structure is provided that includes a plurality of vertically stacked and vertically spaced apart semiconductor nanowires (e.g., a semiconductor nanowire mesh) located on a surface of a substrate. One end segment of each vertically stacked and vertically spaced apart semiconductor nanowires is connected to a source region and another end segment of each vertically stacked and vertically spaced apart semiconductor nanowires is connected to a drain region. A gate region including a gate dielectric and a gate conductor abuts the plurality of vertically stacked and vertically spaced apart semiconductor nanowires, and the source regions and the drain regions are self-aligned with the gate region.

Owner:GLOBALFOUNDRIES US INC

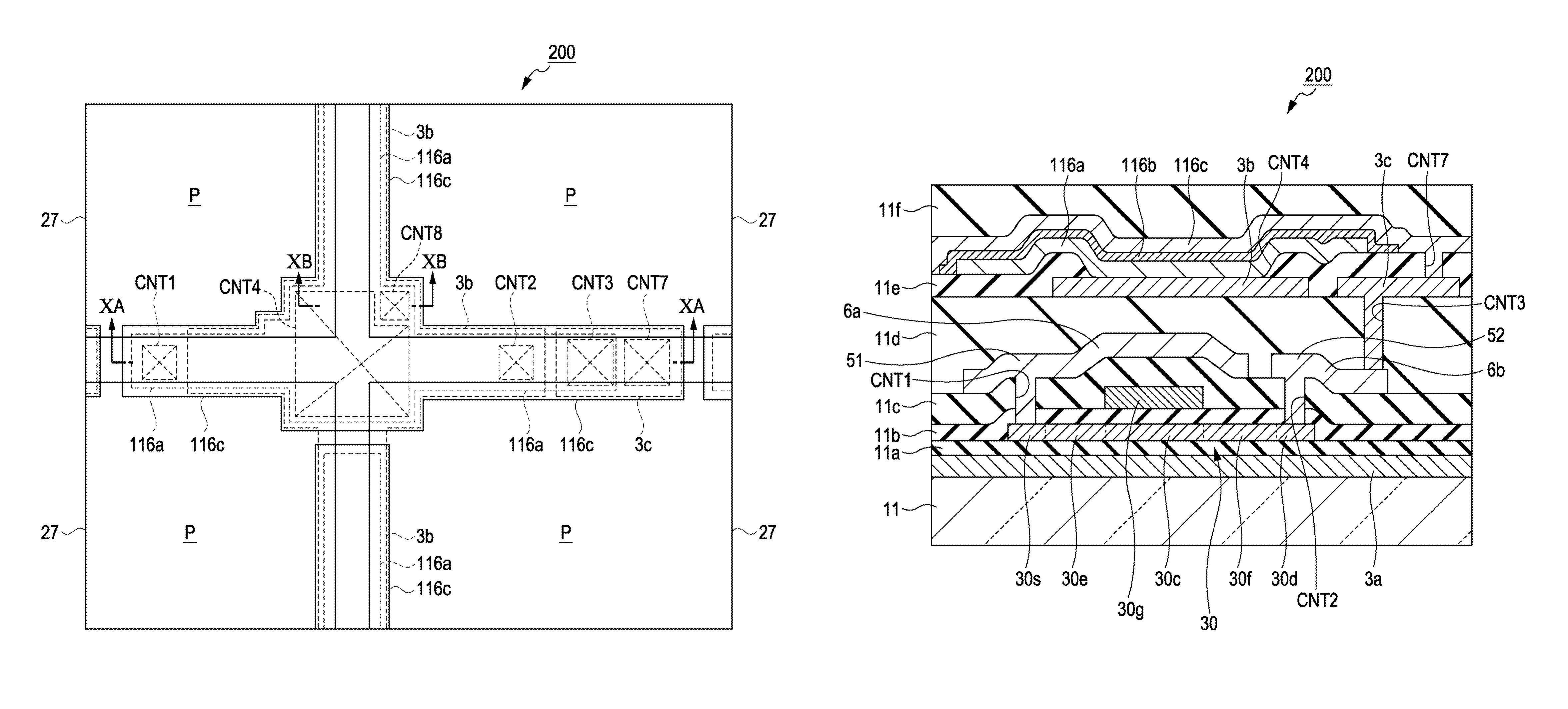

Ring bus structure and its use in flash memory systems

ActiveUS8375146B2Reduce capacitanceIncrease working frequencyMultiple digital computer combinationsElectric digital data processingSystem controllerBus

A system and integrated circuit chips used in the system utilize a bus in the form of a ring to interconnect nodes of individual components for transfer of data and commands therebetween. An example system described is a memory having one or more re-programmable non-volatile memory cell arrays connected to each other and to a system controller by a ring bus.

Owner:SANDISK TECH LLC

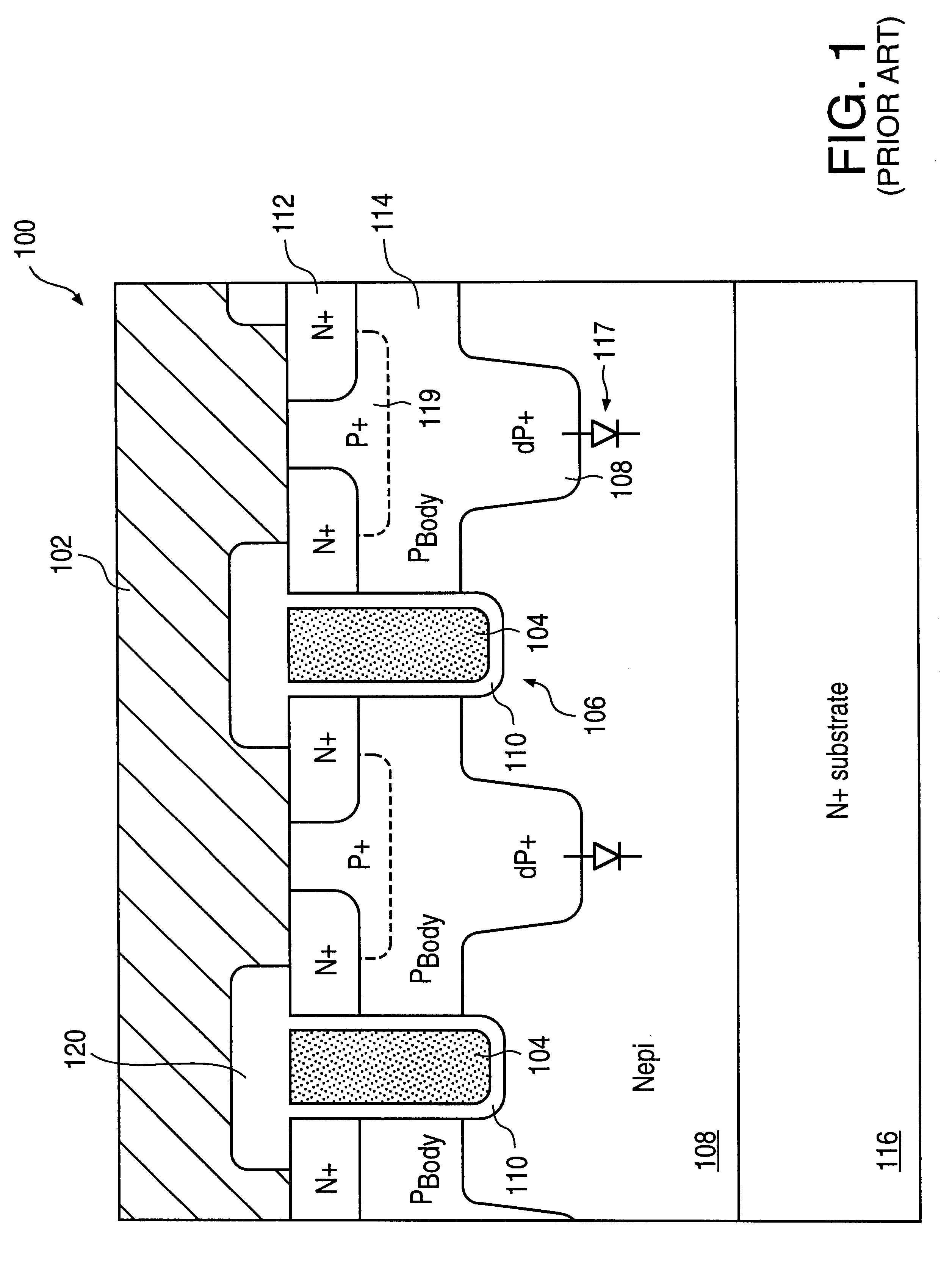

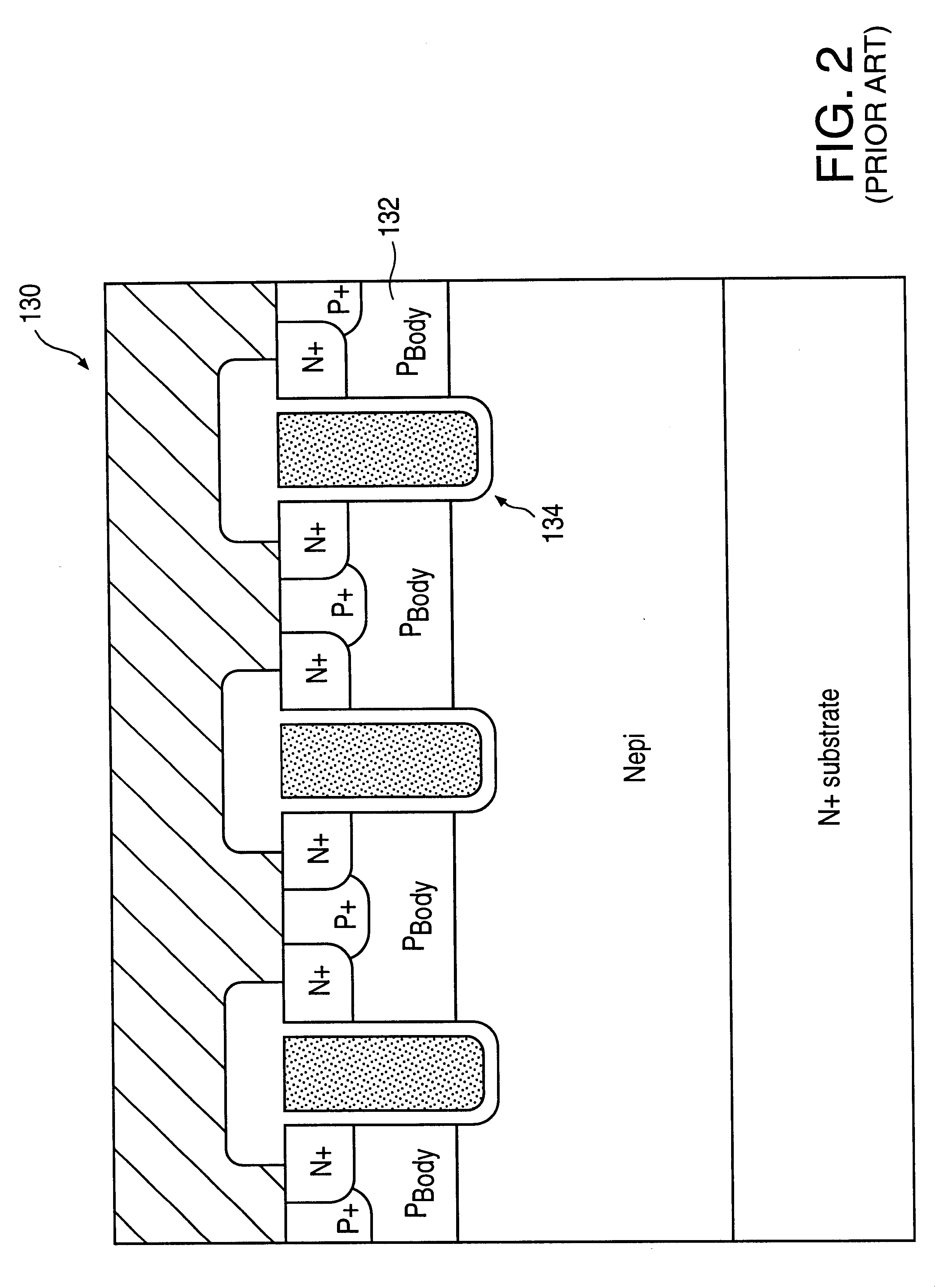

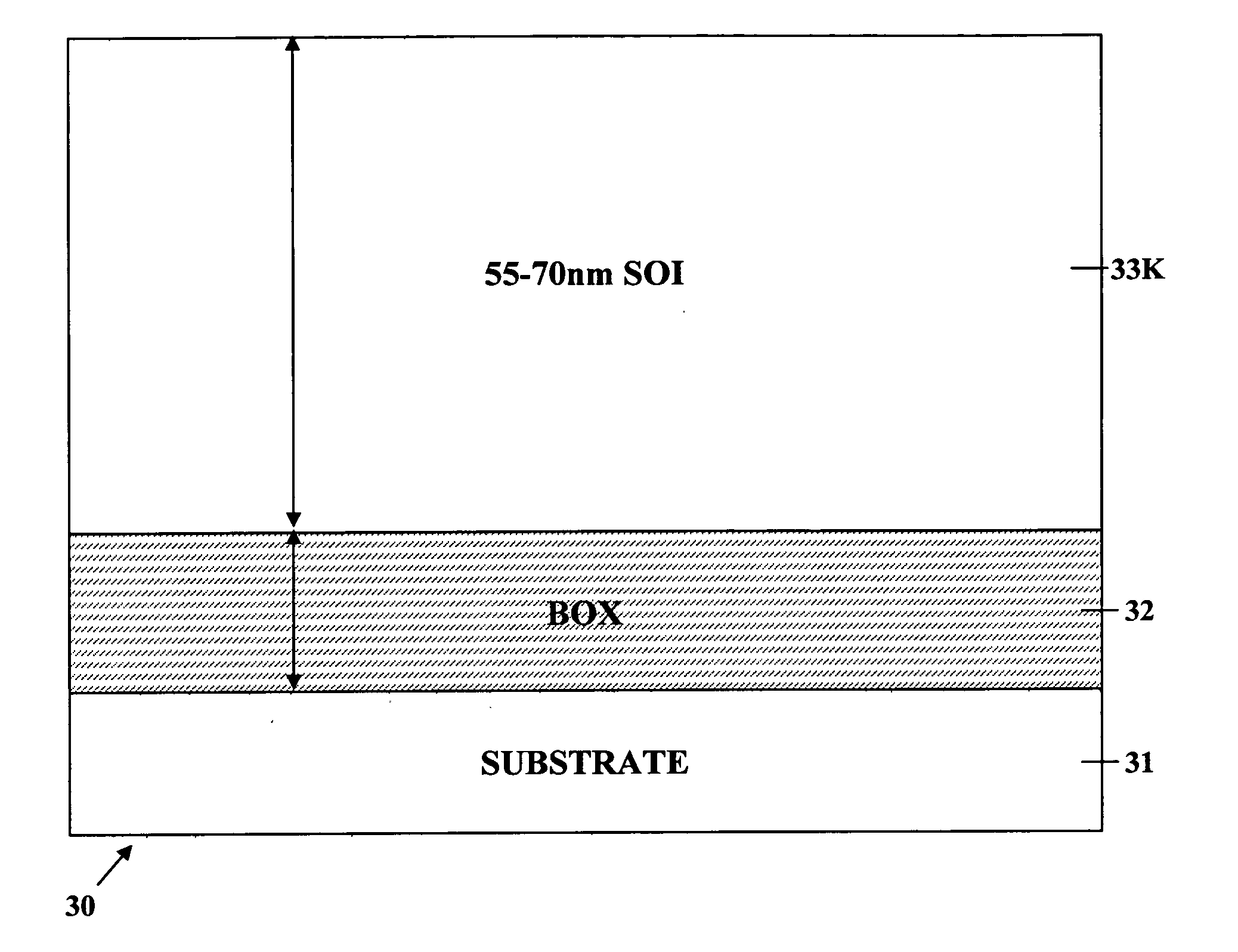

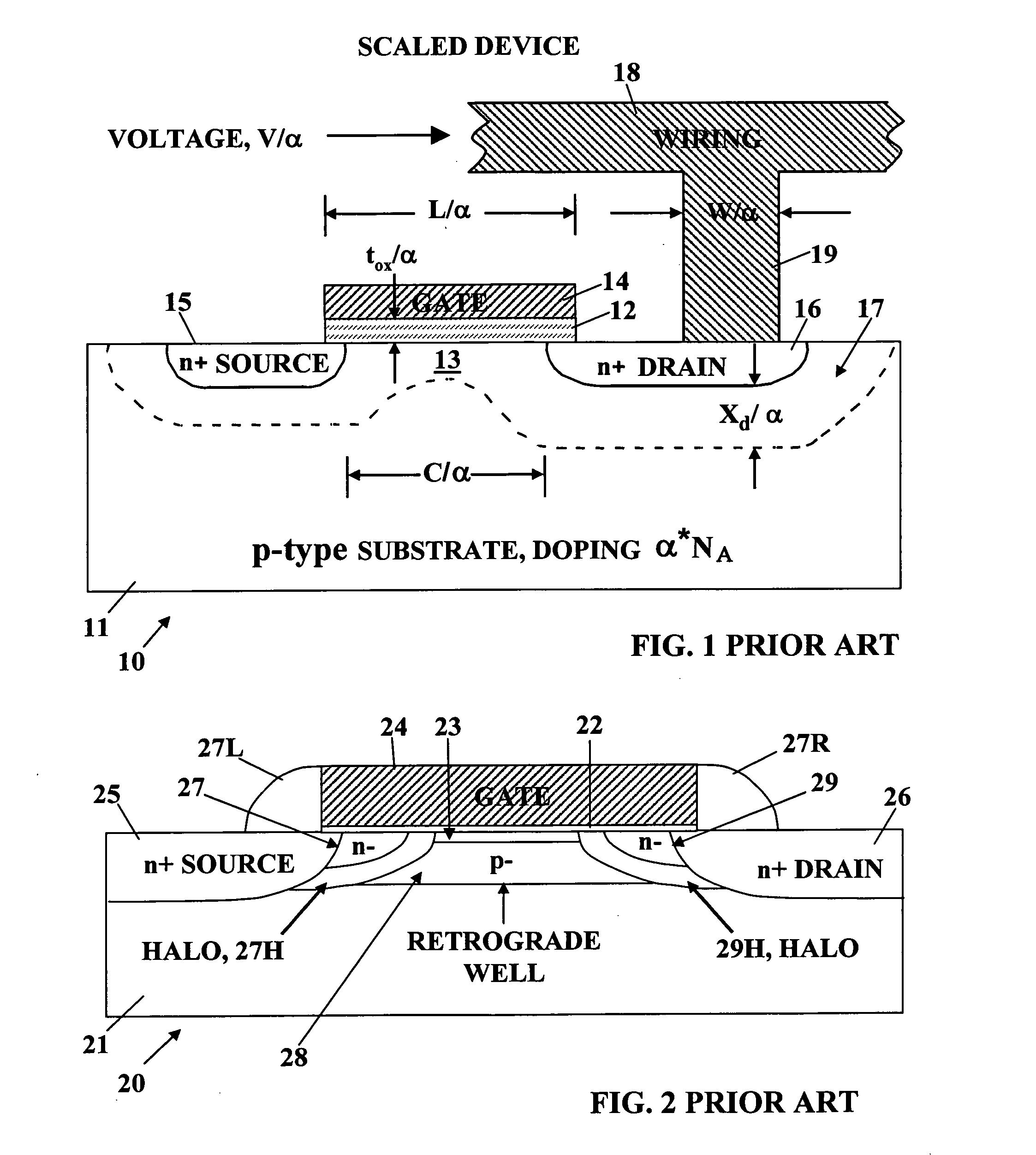

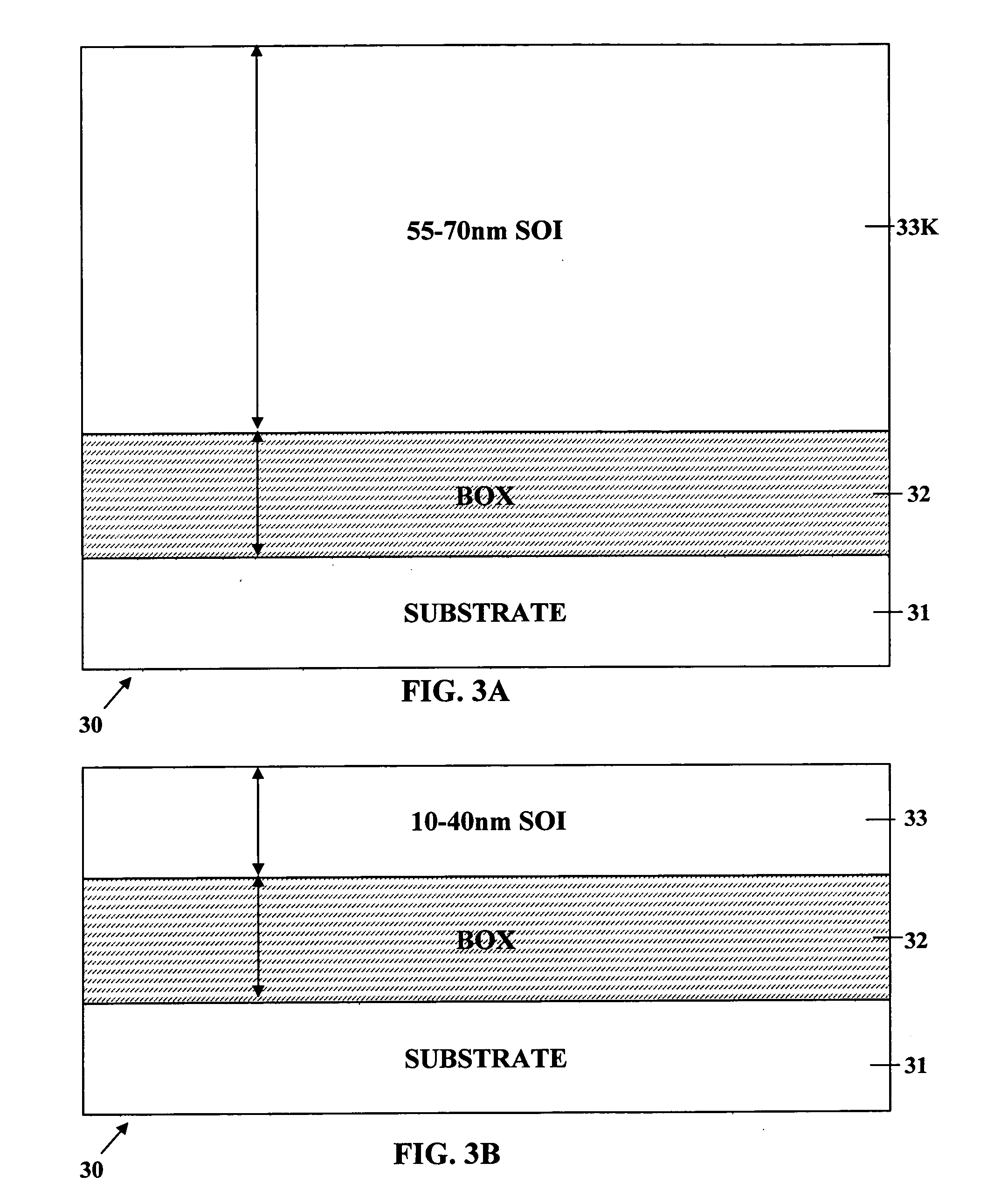

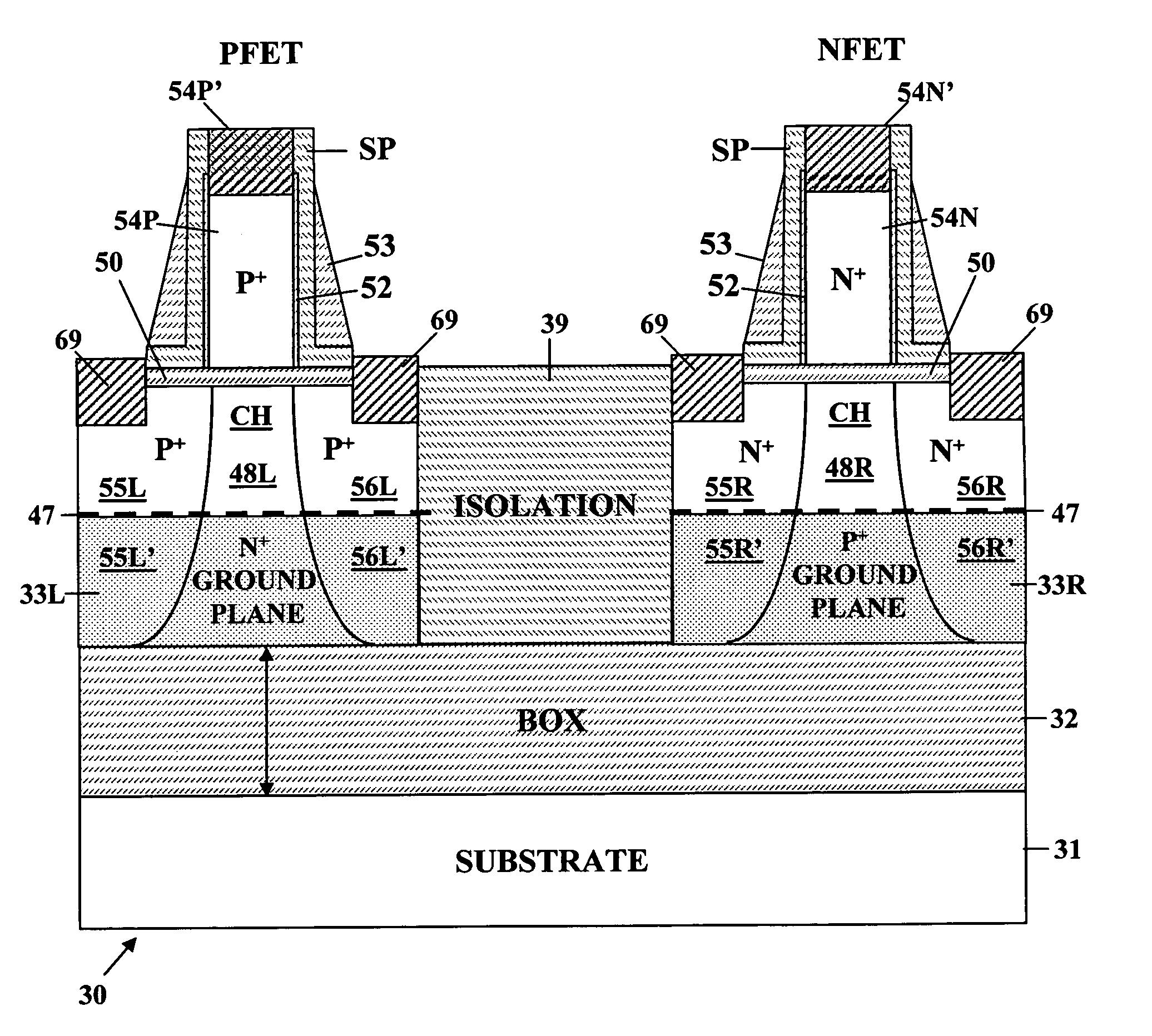

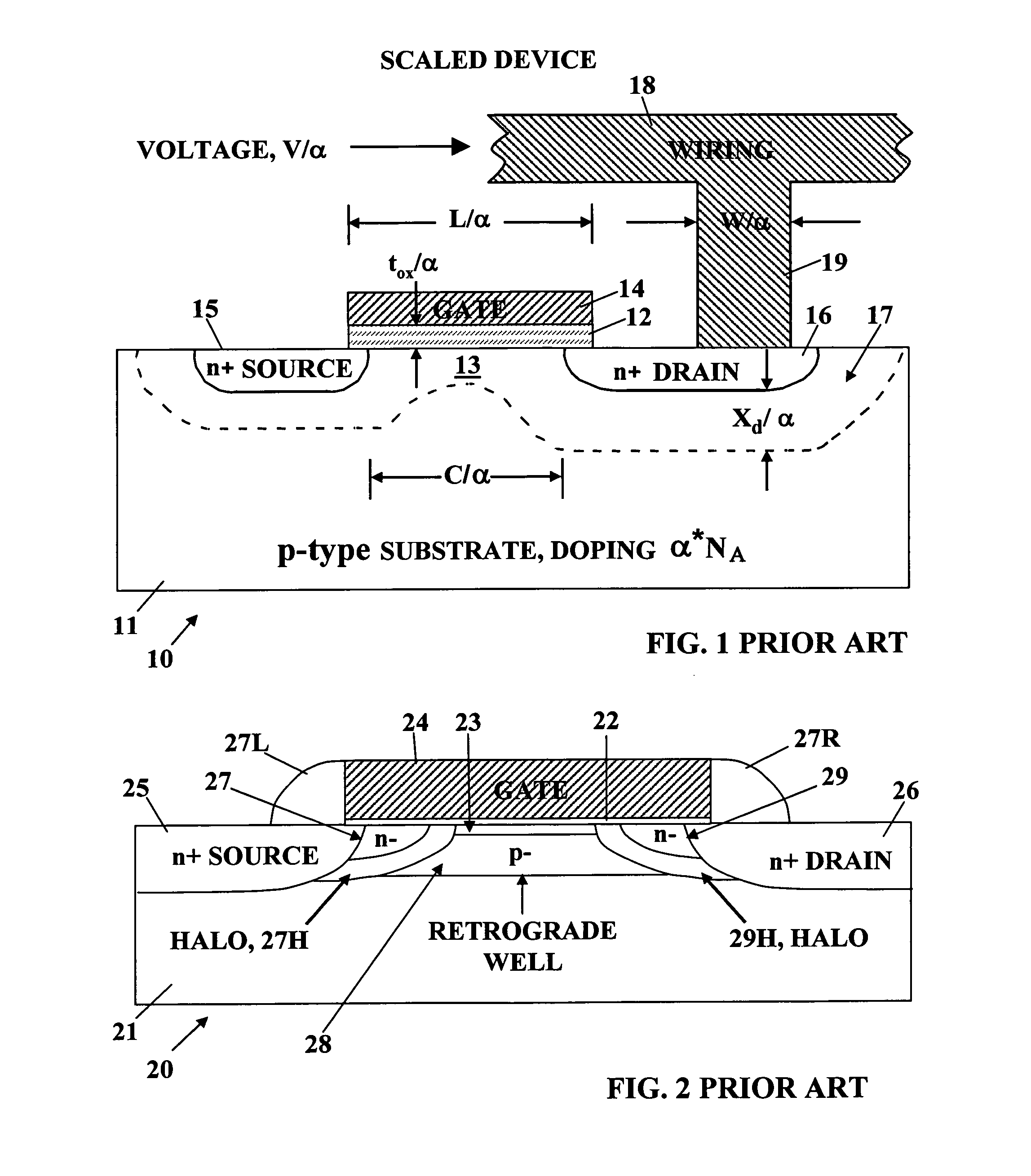

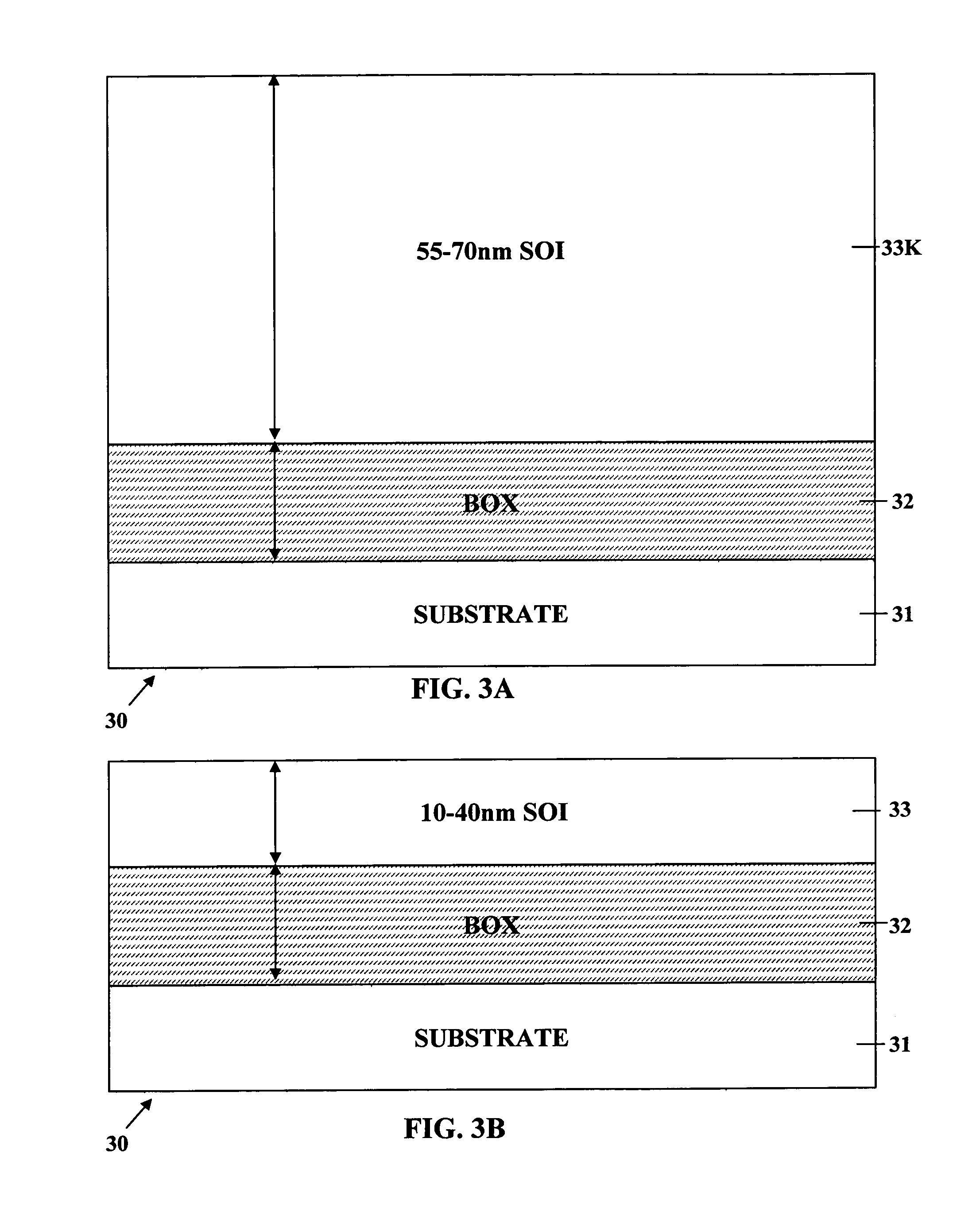

Ultra-thin body super-steep retrograde well (SSRW) FET devices

ActiveUS20060022270A1Minimize space-charge related fluctuationReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

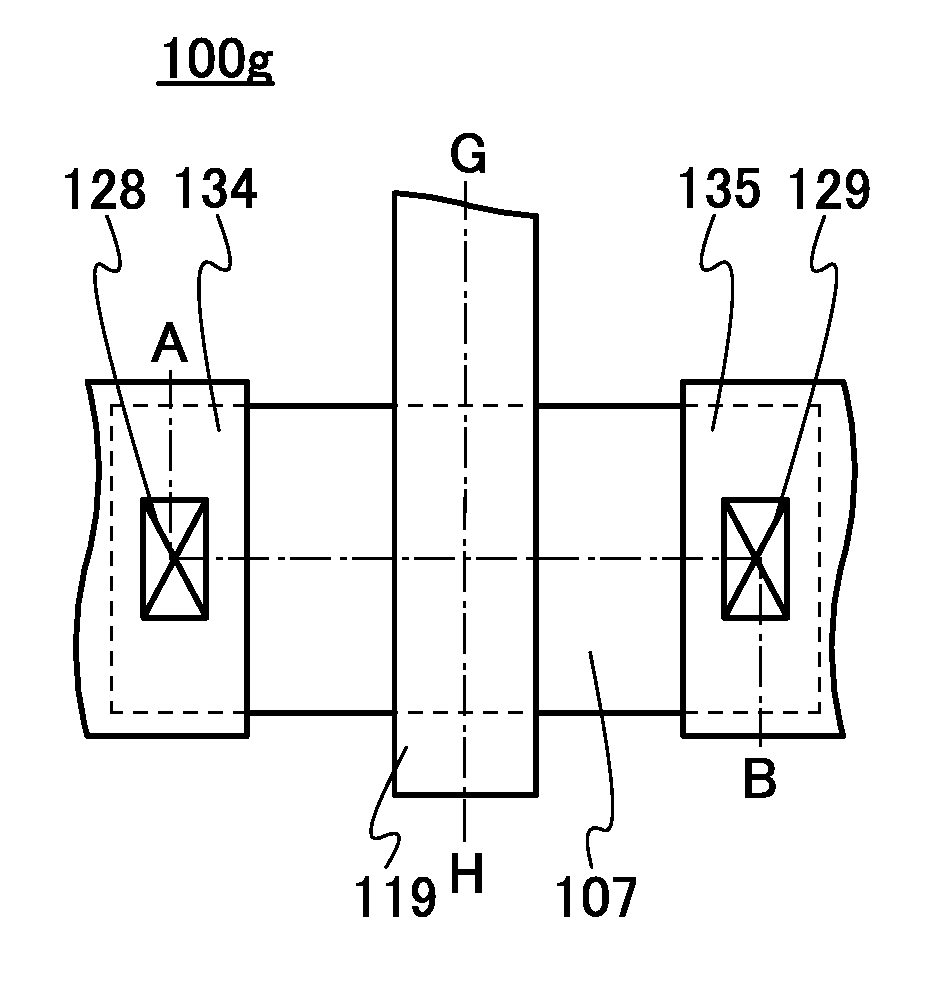

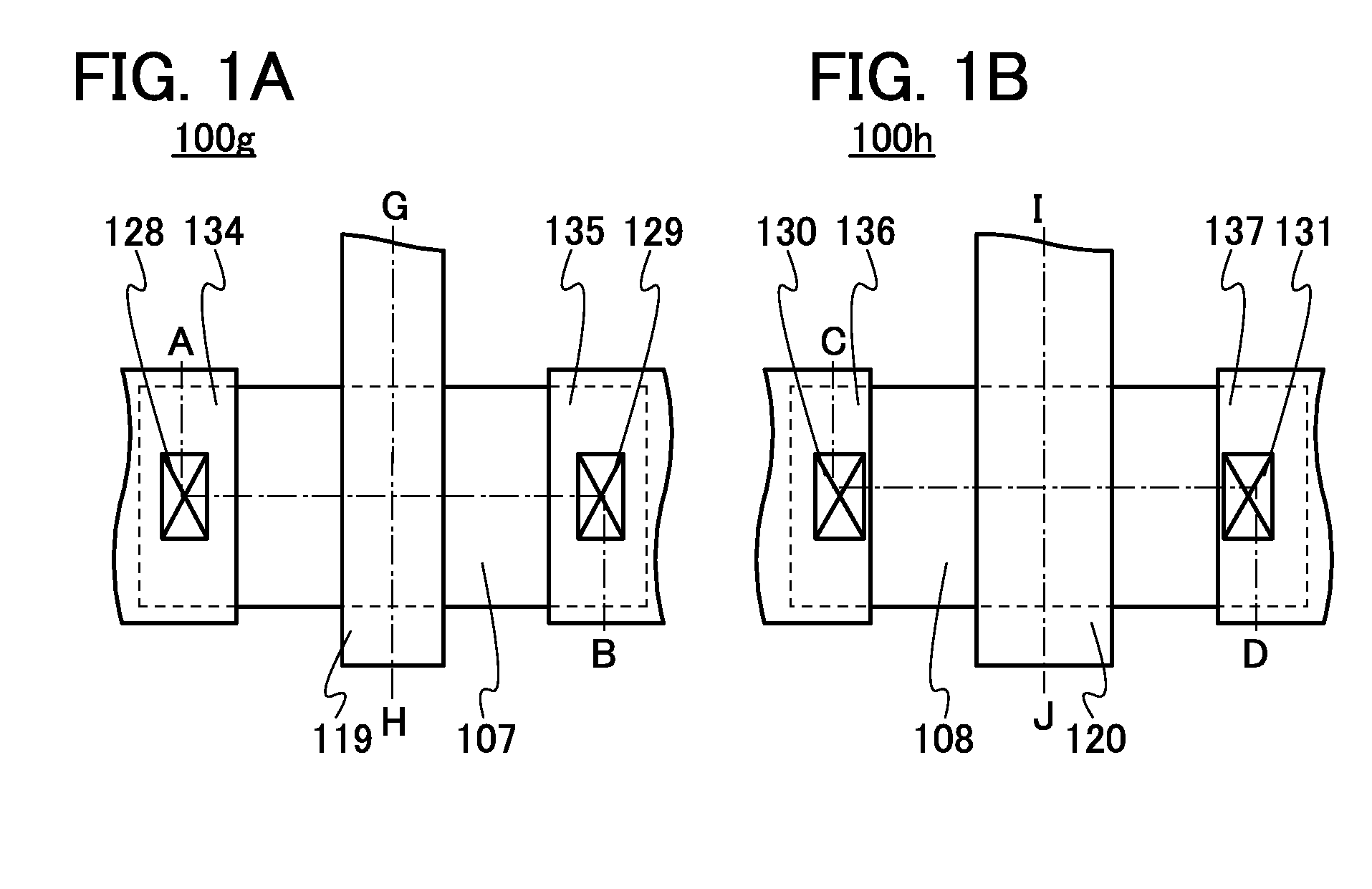

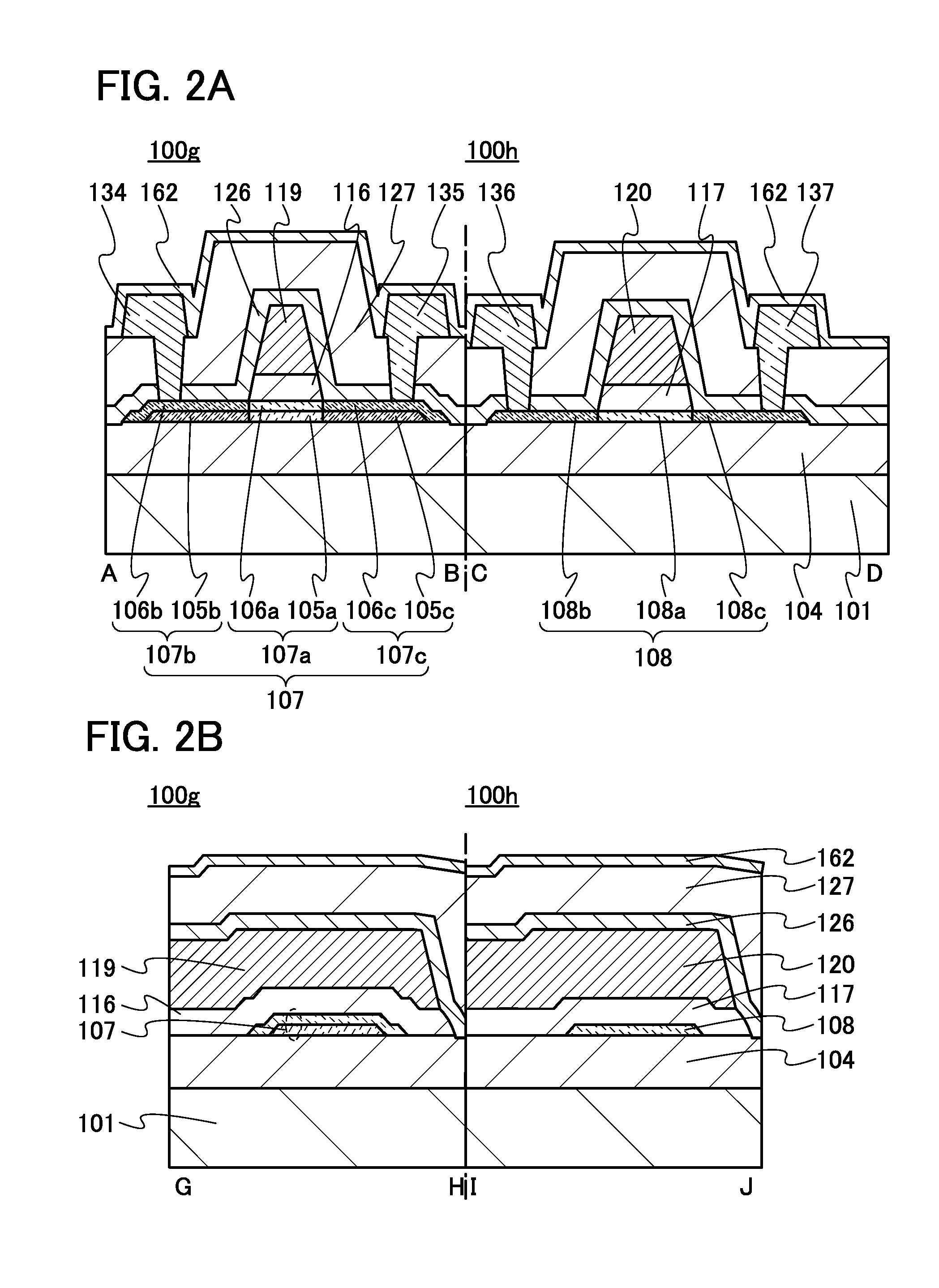

Semiconductor device

ActiveUS20150228803A1Stable semiconductor characteristicSimple manufacturing processTransistorSolid-state devicesDriver circuitHydrogen

The semiconductor device includes a first transistor provided in a driver circuit portion and a second transistor provided in a pixel portion; the first transistor and the second transistor have different structures. In an oxide semiconductor film of each of the transistors, an impurity element is contained in regions which do not overlap with a gate electrode. The regions of the oxide semiconductor film which contain the impurity element function as low-resistance regions. Furthermore, the regions of the oxide semiconductor film which contain the impurity element are in contact with a film containing hydrogen. Furthermore, the first transistor provided in the driver circuit portion may include the oxide semiconductor film in which a first film and a second film are stacked, and the second transistor provided in the pixel portion may include the oxide semiconductor film which differs from the first film in the atomic ratio of metal elements.

Owner:SEMICON ENERGY LAB CO LTD

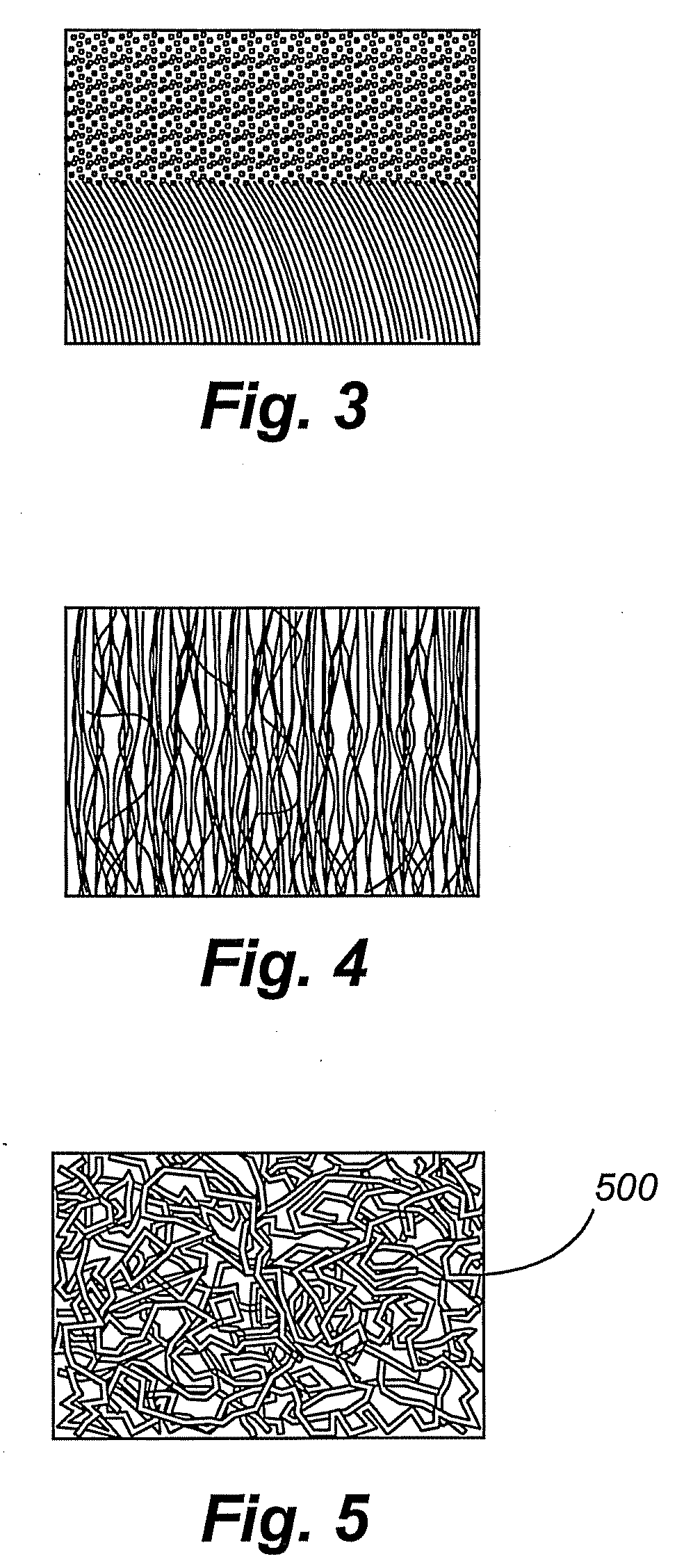

Negative pixel compensation

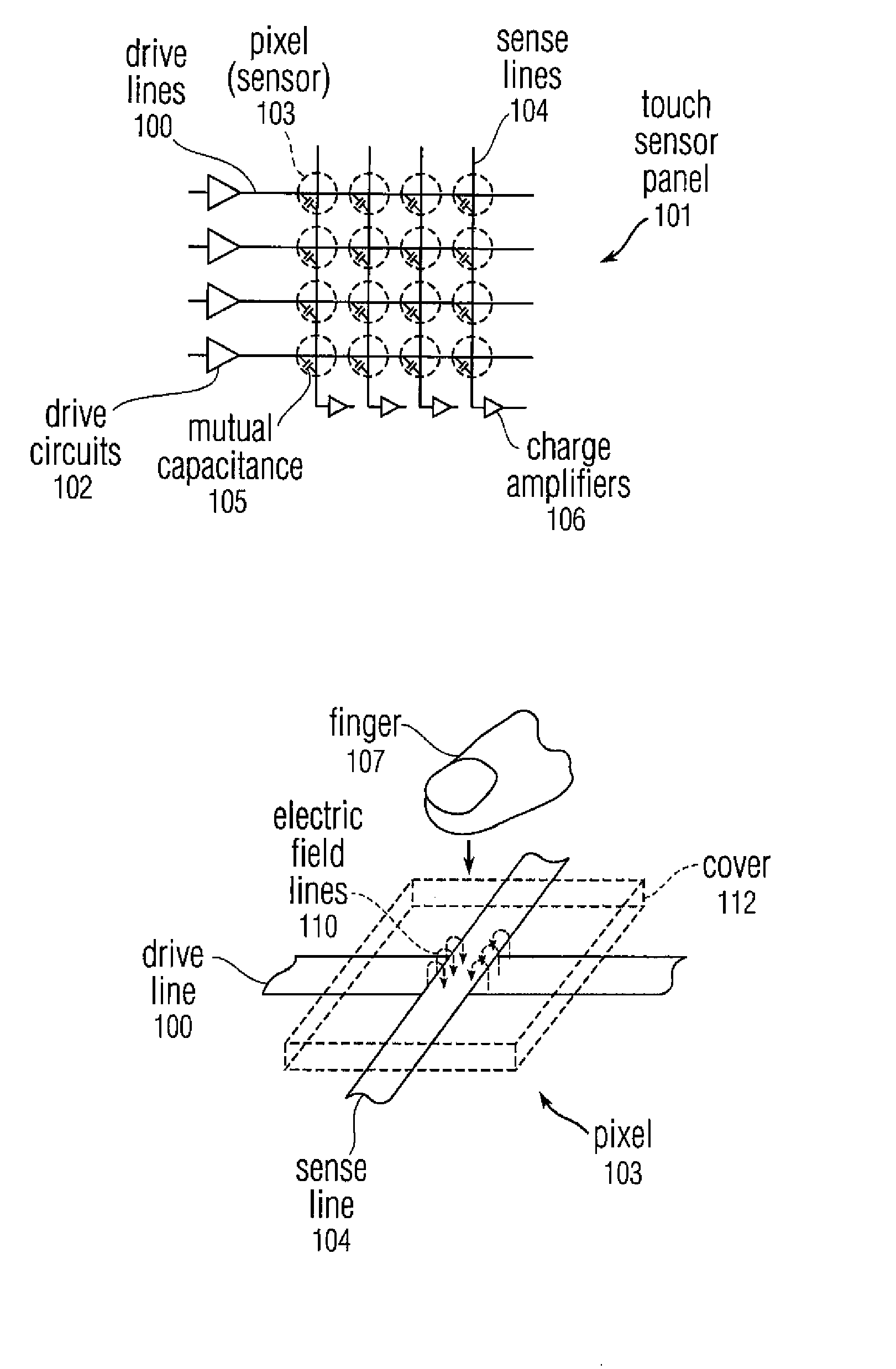

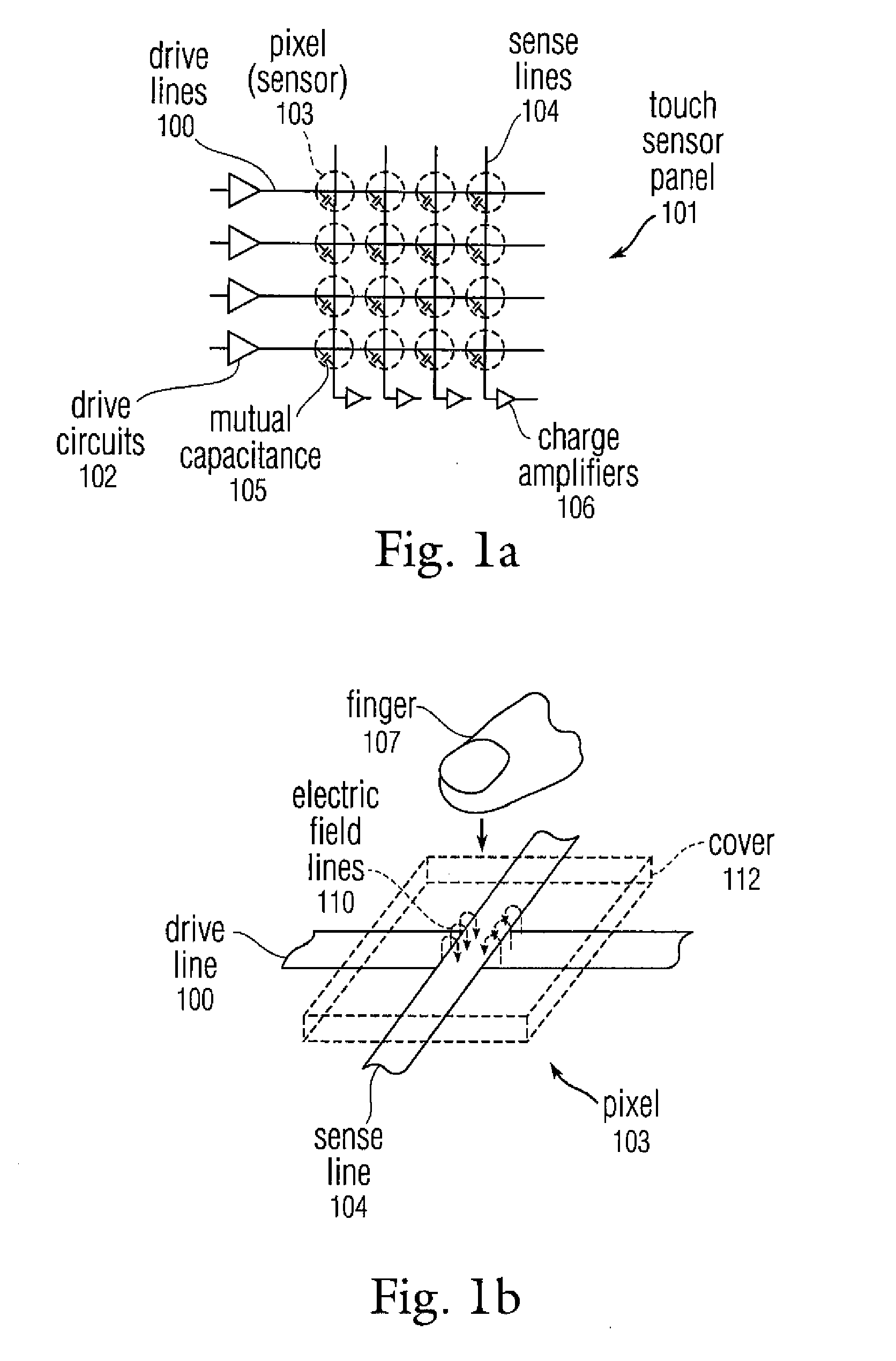

ActiveUS20090160787A1Minimize negative pixelsReduce capacitanceInput/output processes for data processingPattern recognition

Compensation of pixels that generate erroneous readings (so-called “negative pixels”), produced when multiple touch events are generated by the same poorly grounded object on a touch sensor panel is disclosed. To minimize negative pixels, a thicker cover material and / or a lower dielectric constant can be used. Alternatively, narrower drive and sense lines can be employed. To compensate for negative pixels, a predicted negative pixel value can be computed as an indicator of pixels that are likely to be distorted. The negative pixel value for any particular pixel can be computing by summing up the touch output values for pixels in the drive line of that pixel, summing up the touch output values for pixels in the sense line of that pixel, and then multiplying these two sums. The predicted negative pixel value is added to the measured touch output value for the pixel to compensate for artificially negative readings.

Owner:APPLE INC

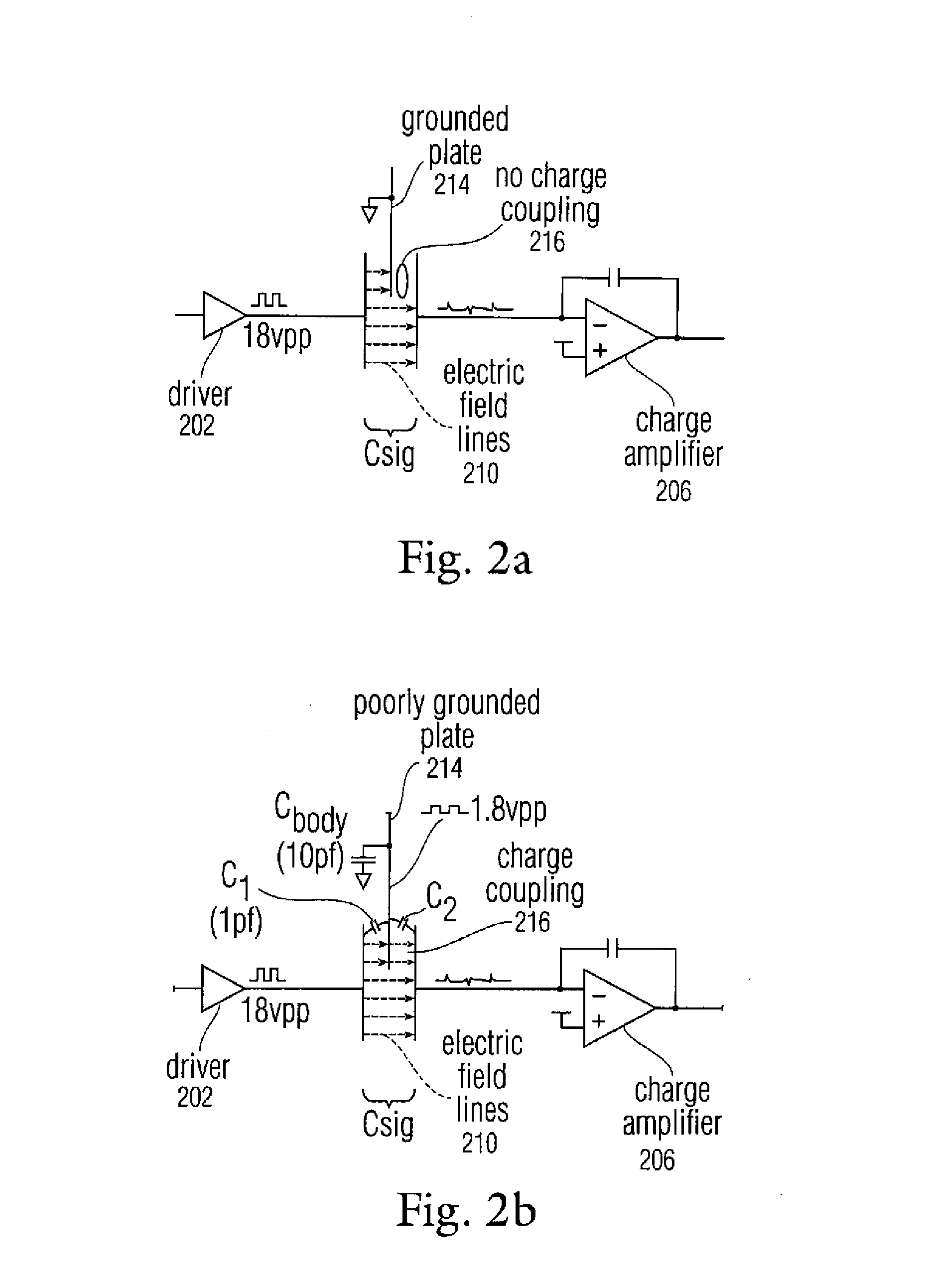

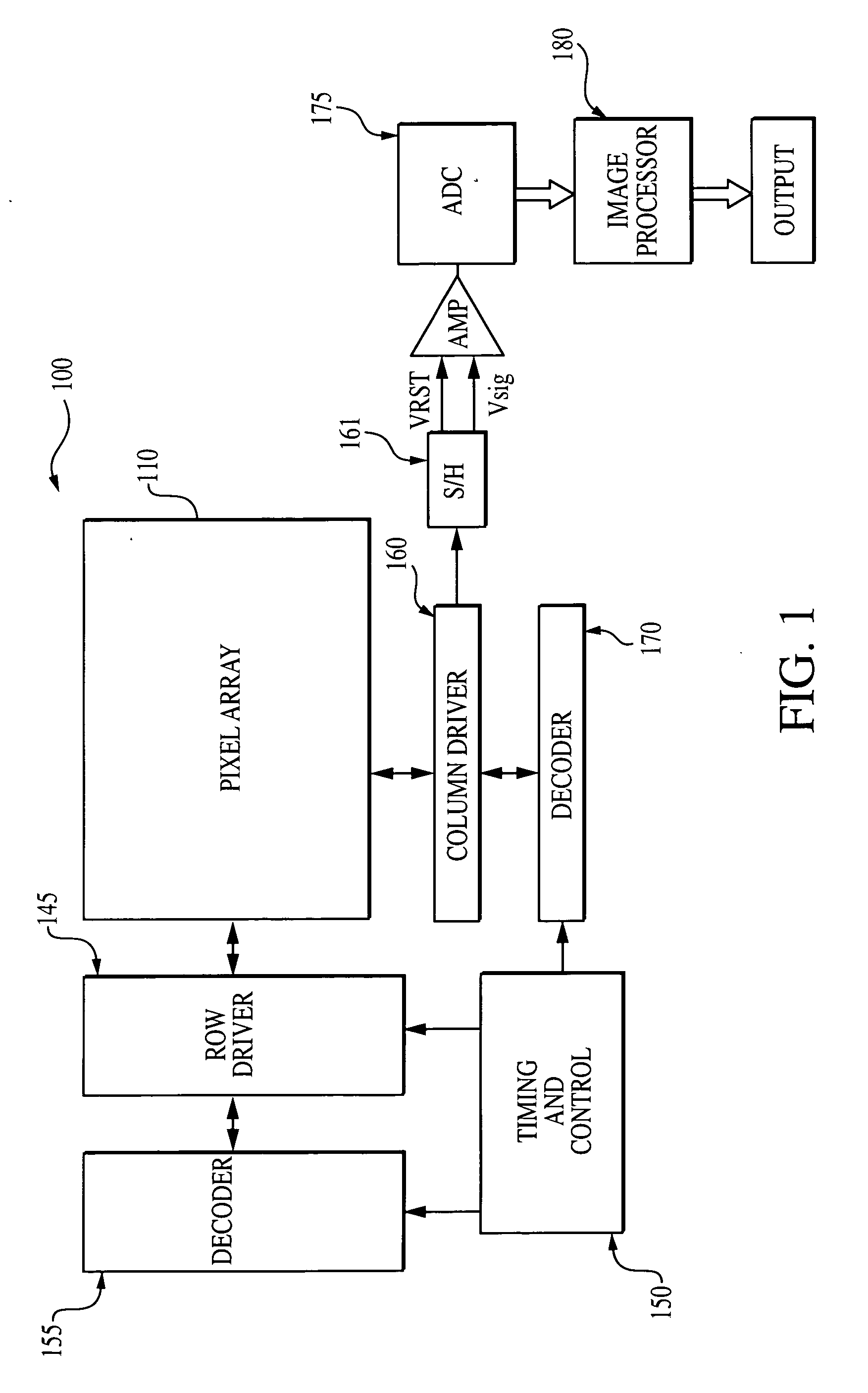

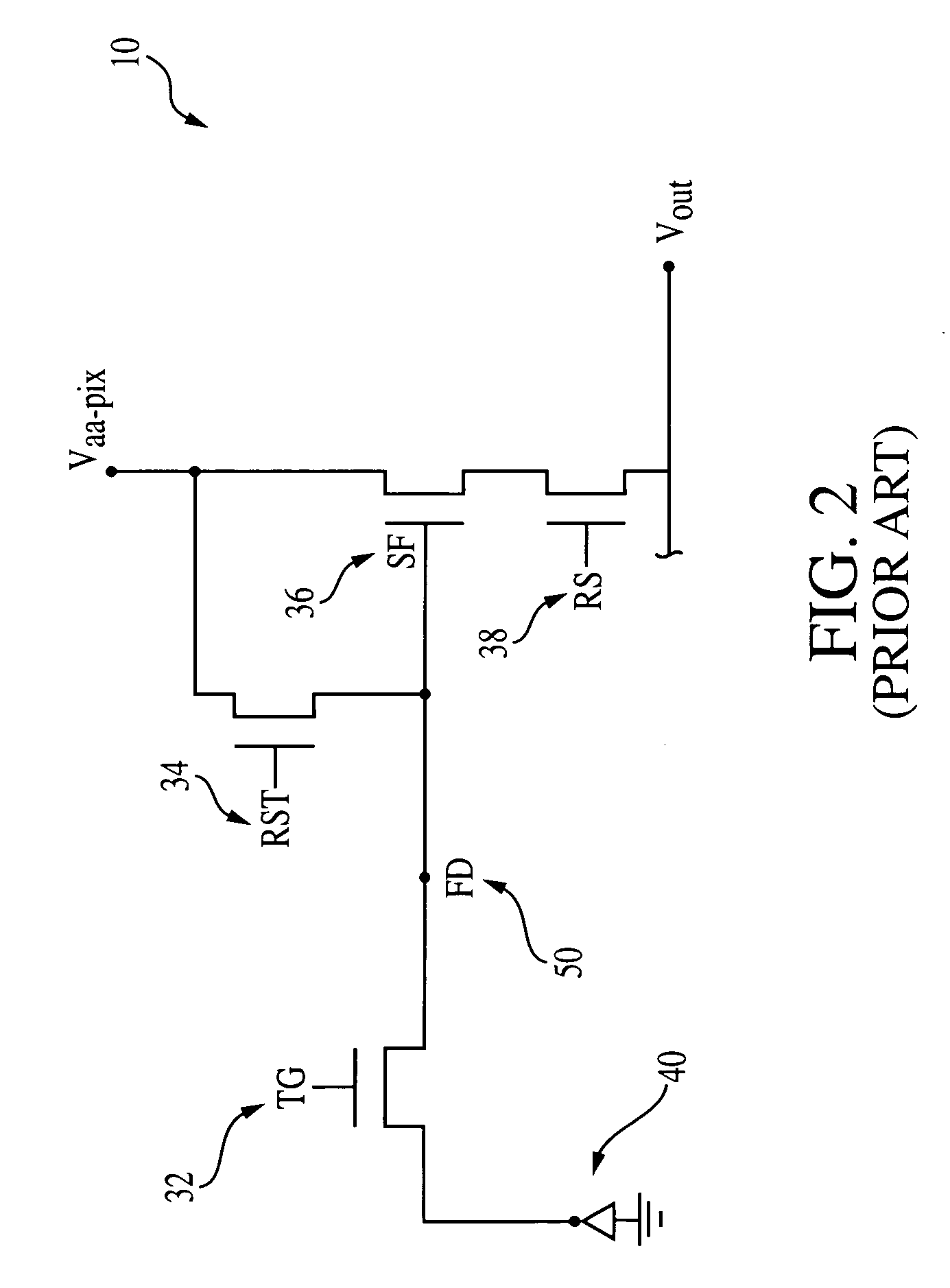

High dynamic range pixel amplifier

ActiveUS20050224843A1Increase capacitanceReduce capacitanceTelevision system detailsTelevision system scanning detailsCapacitanceEngineering

A pixel cell with increased dynamic range is formed by providing a floating diffusion region having a variable capacitance, controlled by at least one gate having source and drain regions commonly connected to the floating diffusion region. The gate has an intrinsic capacitance which, when the gate is activated, is added to the capacitance of the floating diffusion region, providing a low conversion gain readout. When the gate is off, the floating diffusion region capacitance is minimized, providing a high conversion gain readout. The gate may also be selectively switched to mid-level. At mid-level, a mid-level conversion gain, which is between the high and low conversion gains, readout is provided, but the gate still provides some capacitance to prevent the floating diffusion region from saturating.

Owner:APTINA IMAGING CORP

Tank filters adaptable for placement with a guide wire, in series with the lead wires or circuits of active medical devices to enhance MRI compatibility

InactiveUS20080161886A1Reduce sensitivityReduce heatMultiple-port networksAnti-noise capacitorsEngineeringInductor

A tank filter is provided for a lead wire of an active medical device (AMD). The tank filter includes a capacitor in parallel with an inductor. The parallel capacitor and inductor are placed in series with the lead wire of the AMD, wherein values of capacitance and inductance are selected such that the tank filter is resonant at a selected frequency. A passageway through the tank filter permits selective slidable passage of a guide wire therethrough for locating the lead wire in an implantable position. The Q of the inductor may be relatively maximized and the Q of the capacitor may be relatively minimized to reduce the overall Q of the tank filter to attenuate current flow through the lead wire along a range of selected frequencies. In a preferred form, the tank filter is integrated into a TIP and / or RING electrode for an active implantable medical device.

Owner:WILSON GREATBATCH LTD

Tank filters utilizing very low k materials, in series with lead wires or circuits of active medical devices to enhance MRI compatibility

ActiveUS20080071313A1Low dielectric constantHigh strengthMultiple-port networksAnti-noise capacitorsCapacitanceEngineering

A TANK filter is provided for a lead wire of an active medical device (AMD). In a preferred form, the TANK filter is integrated into a TIP and / or RING electrode for an active implantable medical device. The TANK filter includes a capacitor in parallel with an inductor. The parallel capacitor and inductor are placed in series with the lead wire of the AMD, wherein values of capacitance and inductance are selected such that the TANK filter is resonant at a selected frequency to attenuate current flow through the lead wire along a range of selected frequencies. In a particularly preferred form, the TANK filter is manufactured using very low k materials of sufficient strength to handle forces applied thereto during installation and use.

Owner:WILSON GREATBATCH LTD

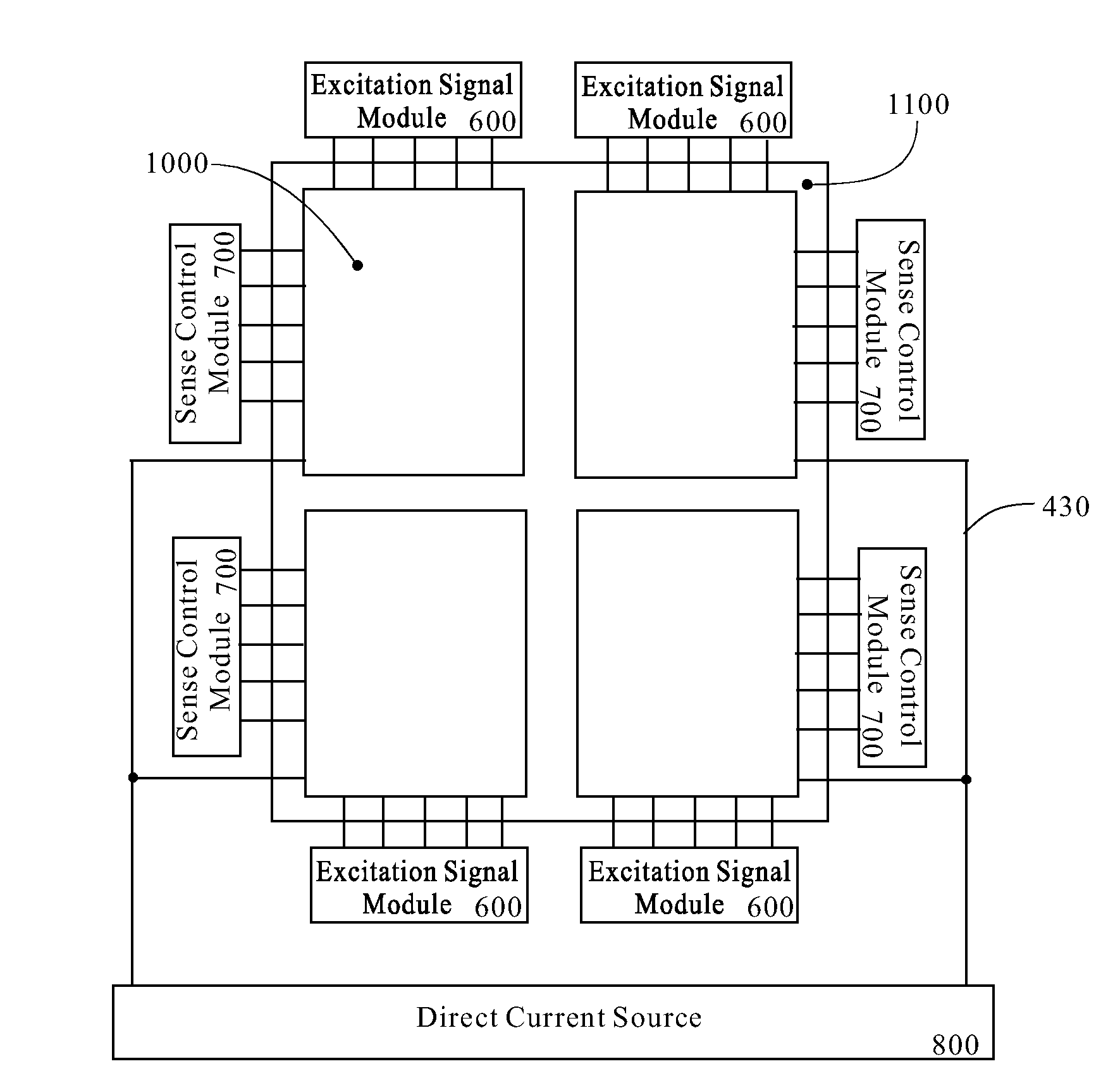

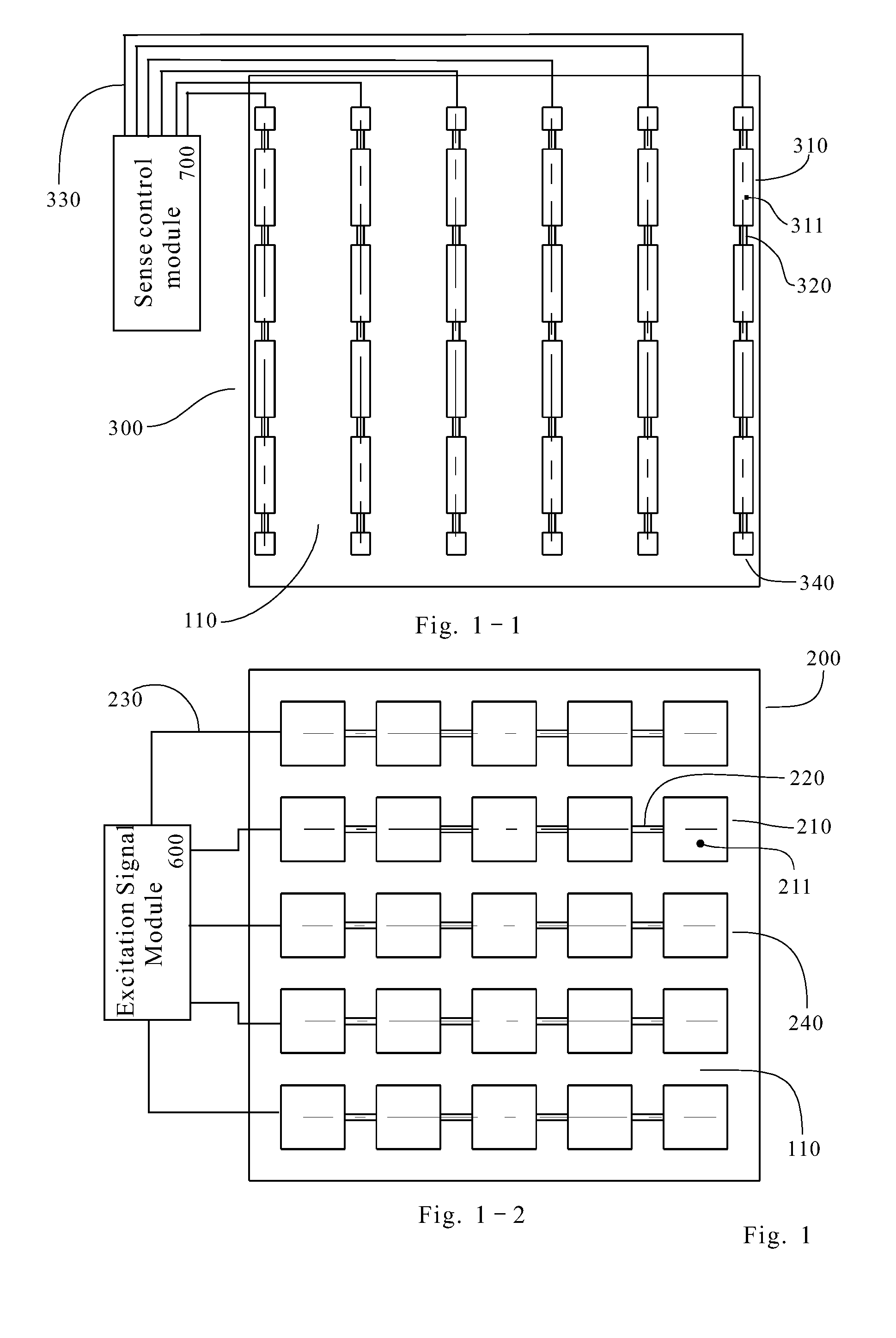

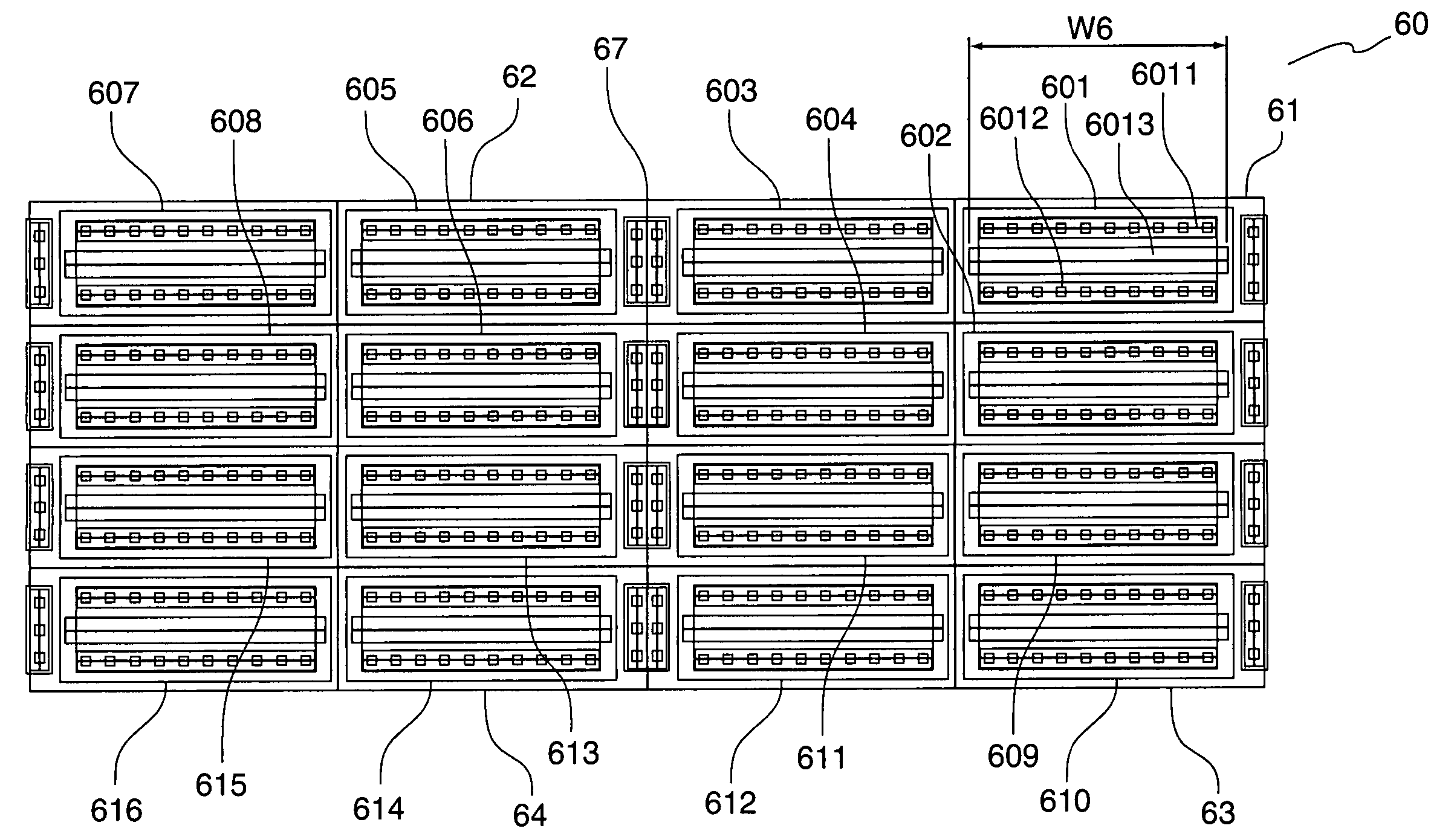

Mutual capacitance touch screen and combined mutual capacitance touch screen

InactiveUS20100110038A1Increase capacitanceReduce capacitanceInput/output processes for data processingEngineeringComputational physics

A mutual capacitance touch screen and a combined mutual capacitance touch screen formed by the combination of mutual capacitance touch screens. A driving layer and a sensor layer are included, wherein the driving layer comprises driving electrodes distributed at intervals in the same plane; the sensor layer comprises sense electrodes distributed at intervals in the same plane; and the places where the sense electrodes are distributed in the sensor layer are just over against the intervals between the driving electrodes in the driving layer so that the driving electrodes and the sense electrodes together fill the touch area of the touch screen. The driving electrodes are not over against the sense electrodes in terms of space positions to increase the proportion of capacitance CT to mutual capacitance C, wherein the capacitance CT is formed between the driving electrodes and the top of the sense electrodes; consequently, the effective capacitivity of the mutual capacitance touch screen is effectively increased.

Owner:FOCALTECH SYST LTD

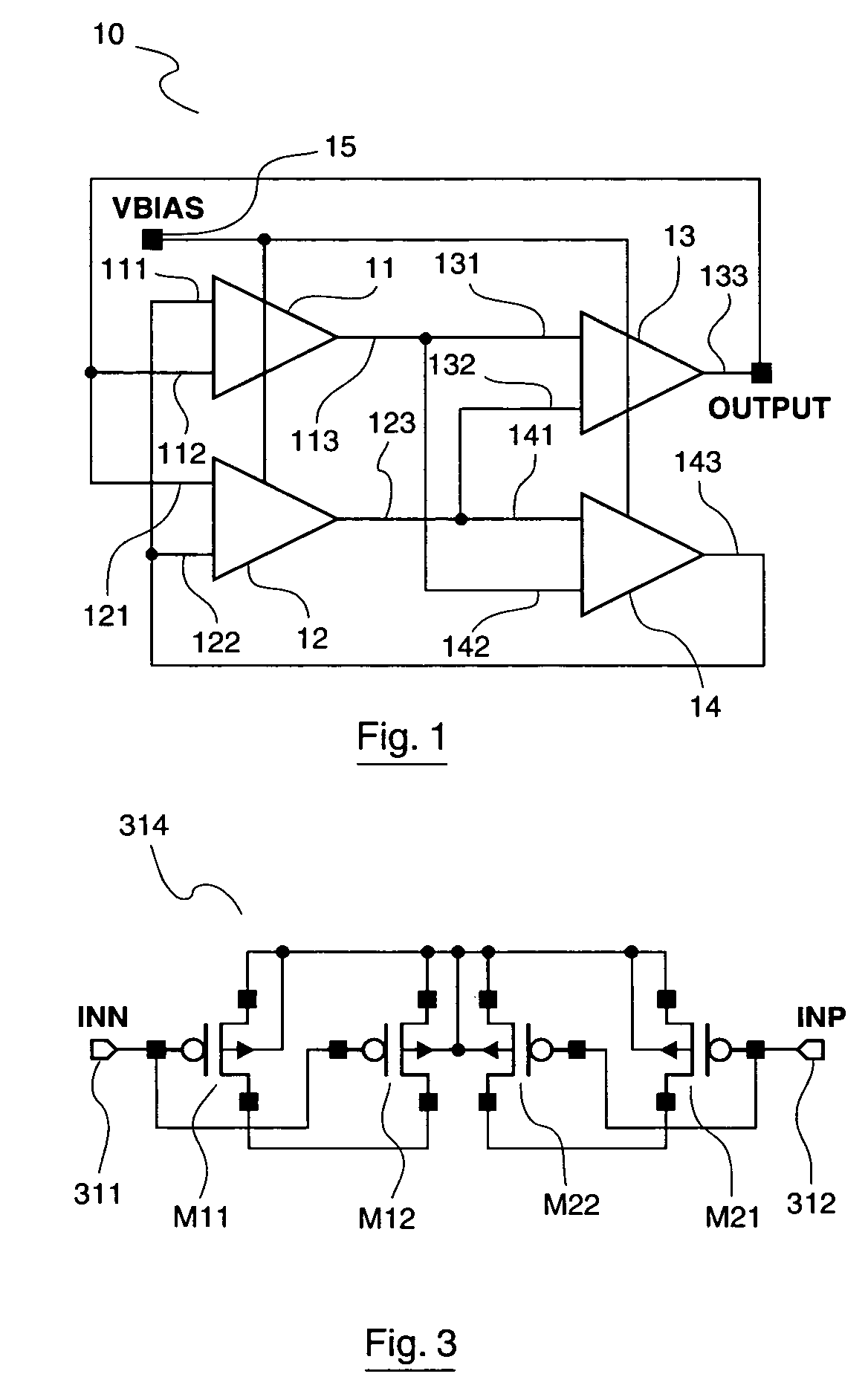

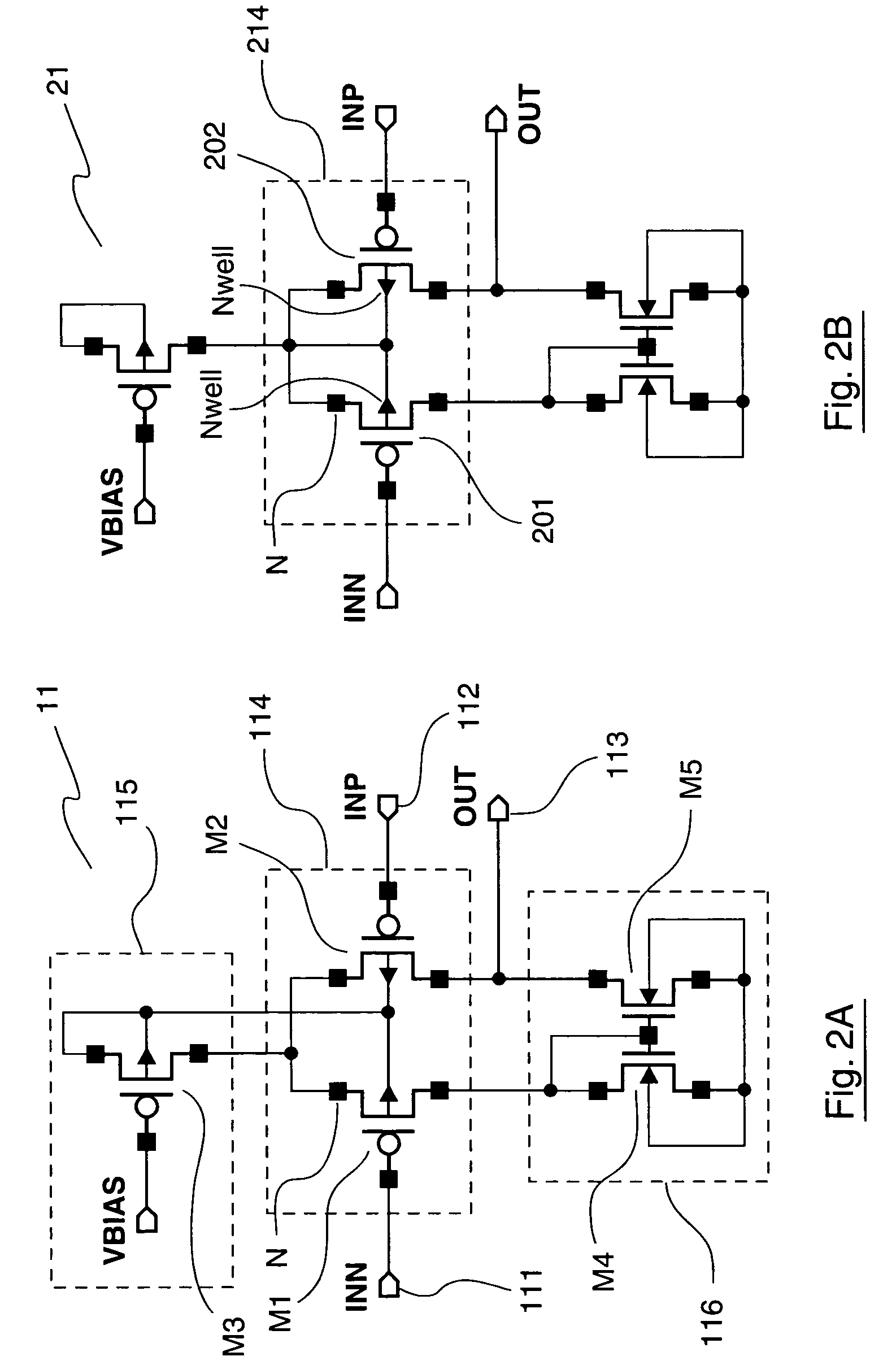

Electronic circuit including at least one first and one second differential pair with the transistors sharing one and the same well

ActiveUS20060158270A1Reduce capacitanceReduce surfaceSolid-state devicesAmplifier with semiconductor-devices/discharge-tubesEngineeringTransistor

The disclosure relates to an electronic circuit including at least one first and one second differential pair each including a plurality of transistors. All the transistors of said first and second differential pair are included in a single well.

Owner:ATMEL CORP

Ultra-thin body super-steep retrograde well (SSRW) FET devices

ActiveUS7002214B1Reduce capacitanceReduce junctionSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

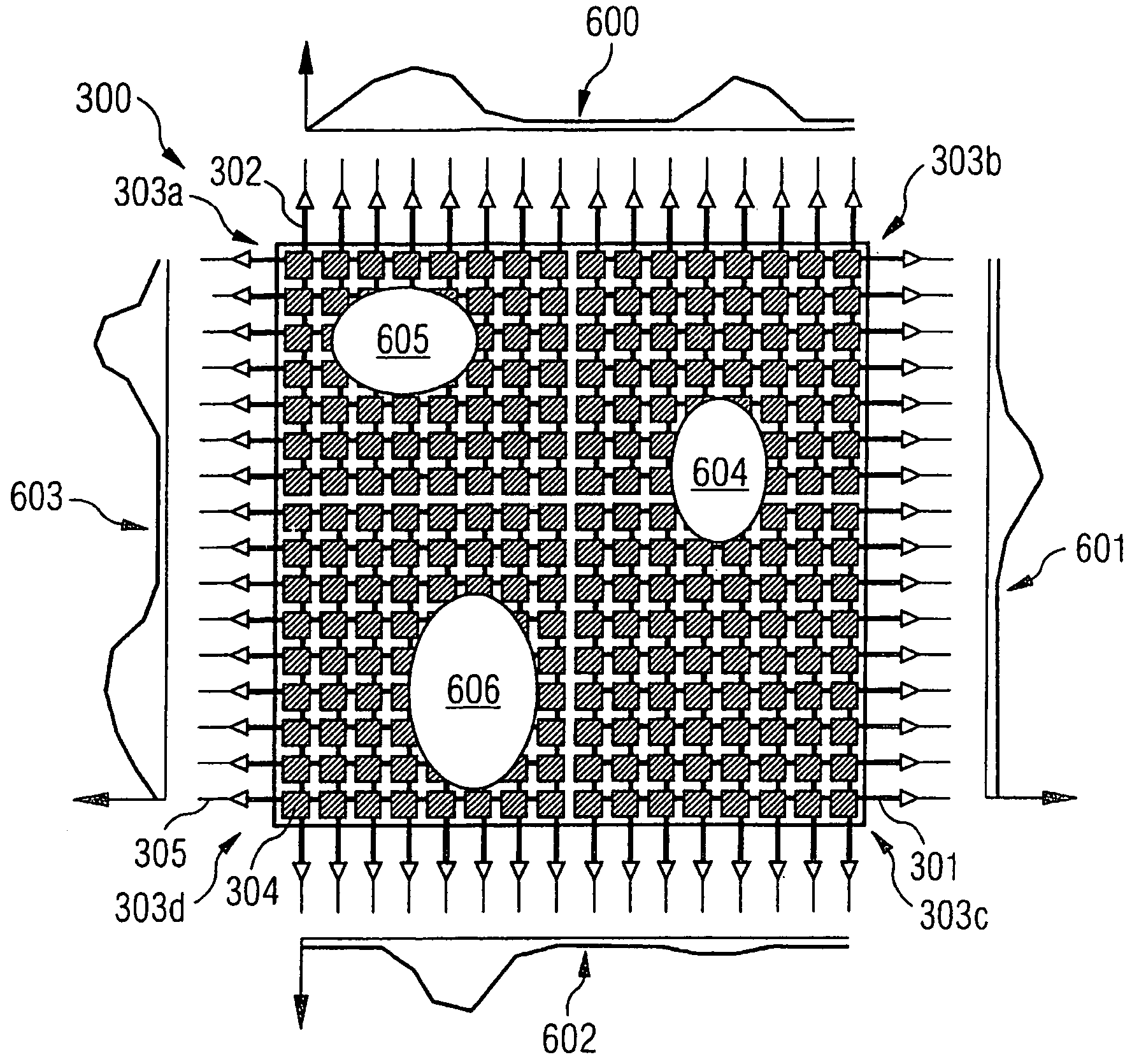

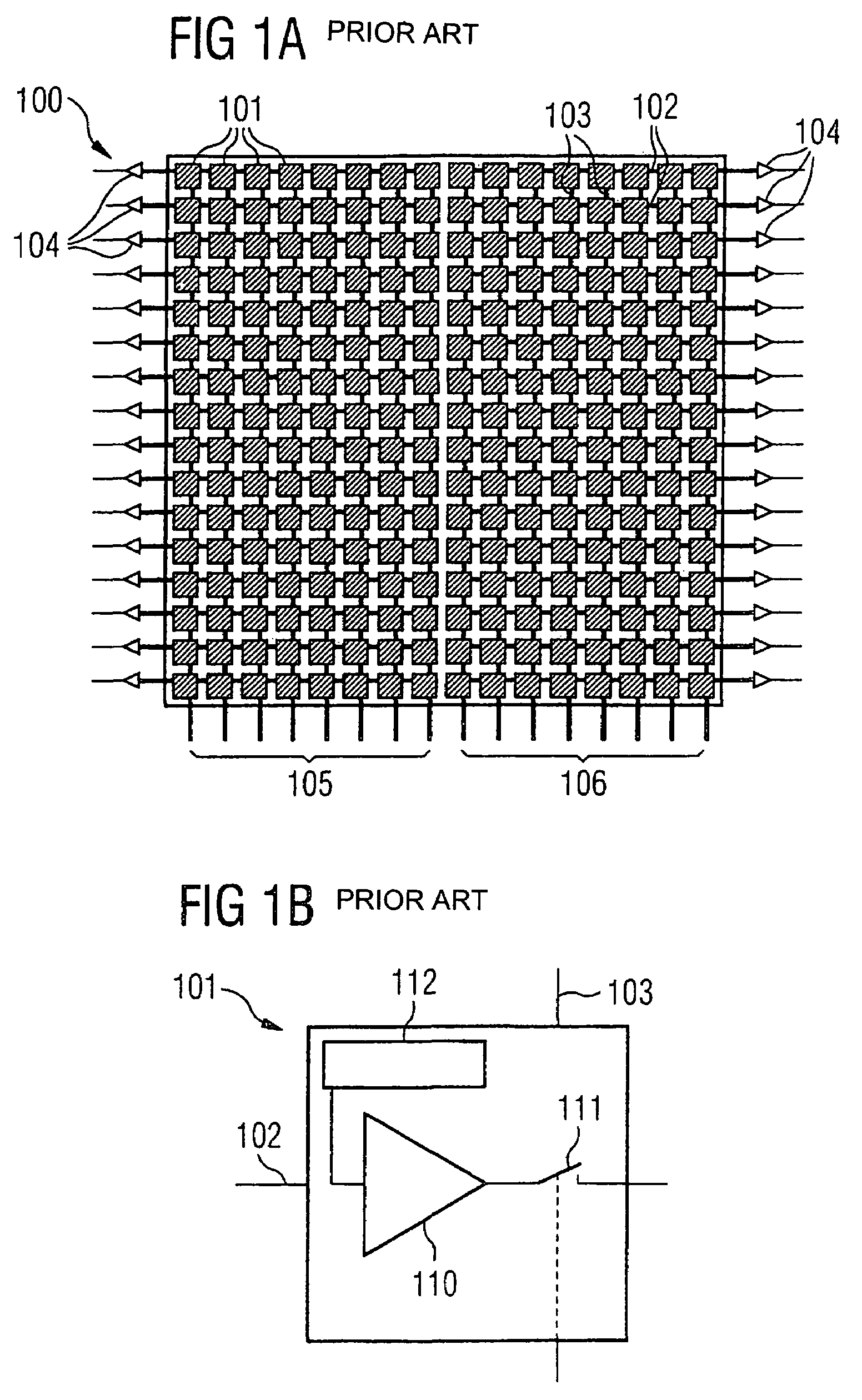

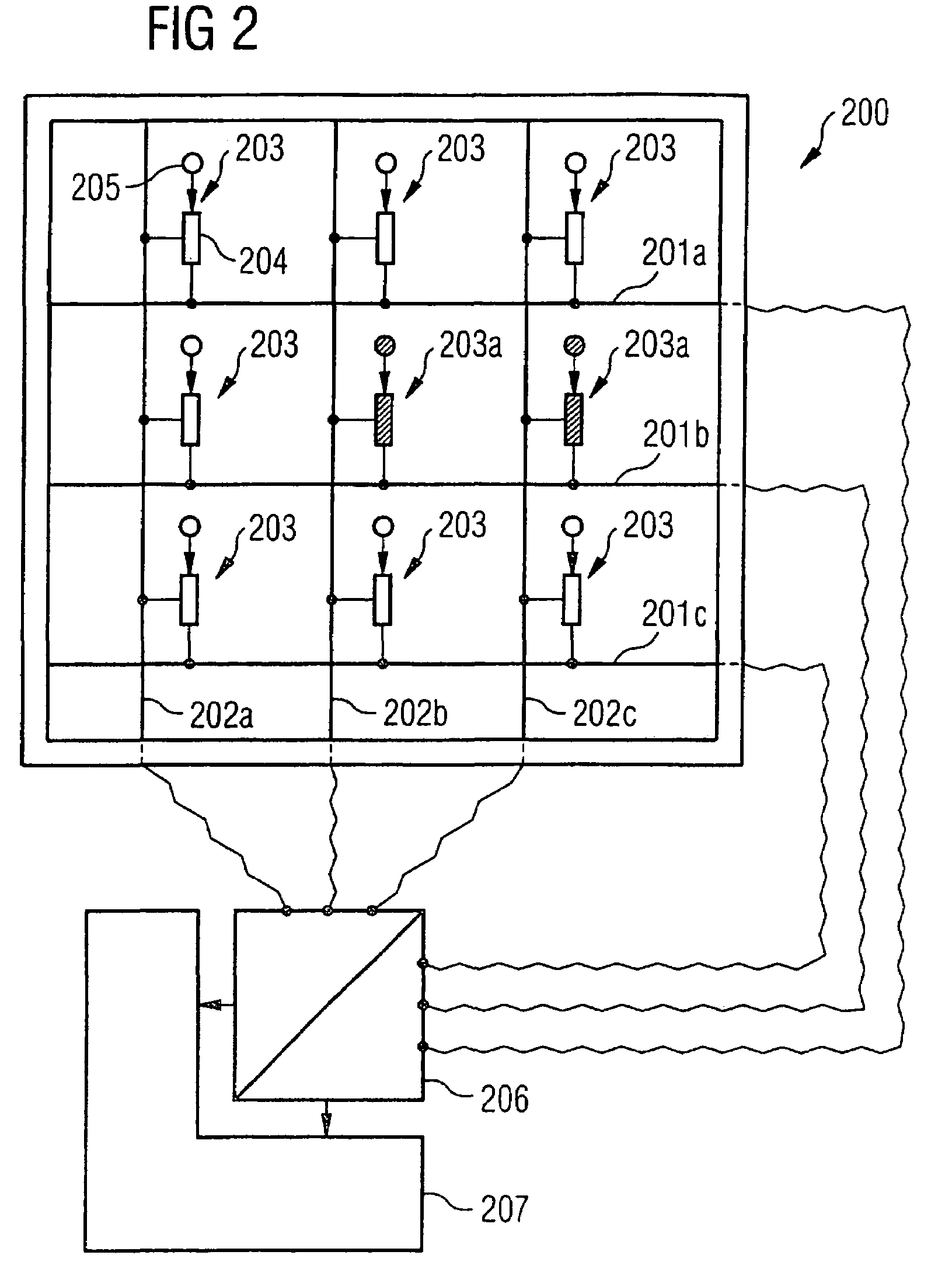

Sensor arrangement

ActiveUS7470352B2Reduced dimensionImprove read rateImmobilised enzymesBioreactor/fermenter combinationsSensor arrayElectricity

Sensor arrangement having row and column lines arranged in first and second directions, respectively, sensor arrays arranged in crossover regions of the row and column lines, a detector, and a decoding device. The sensor arrays have a coupling device for electrically coupling respective row and column lines, and a sensor element to influence electric current flow through the coupling device. The detector is electrically coupled to a respective end section of at least a portion of the row and column lines, and detects a respective accumulative current flow from the individual electrical current flows provided by the sensor arrays of the respective lines. The decoding device is coupled to the row and column lines, and evaluates at least a portion of the accumulative electric current flows fed to the decoding device via the row and column lines to determine at which of the sensor elements a sensor signal is present.

Owner:INFINEON TECH AG

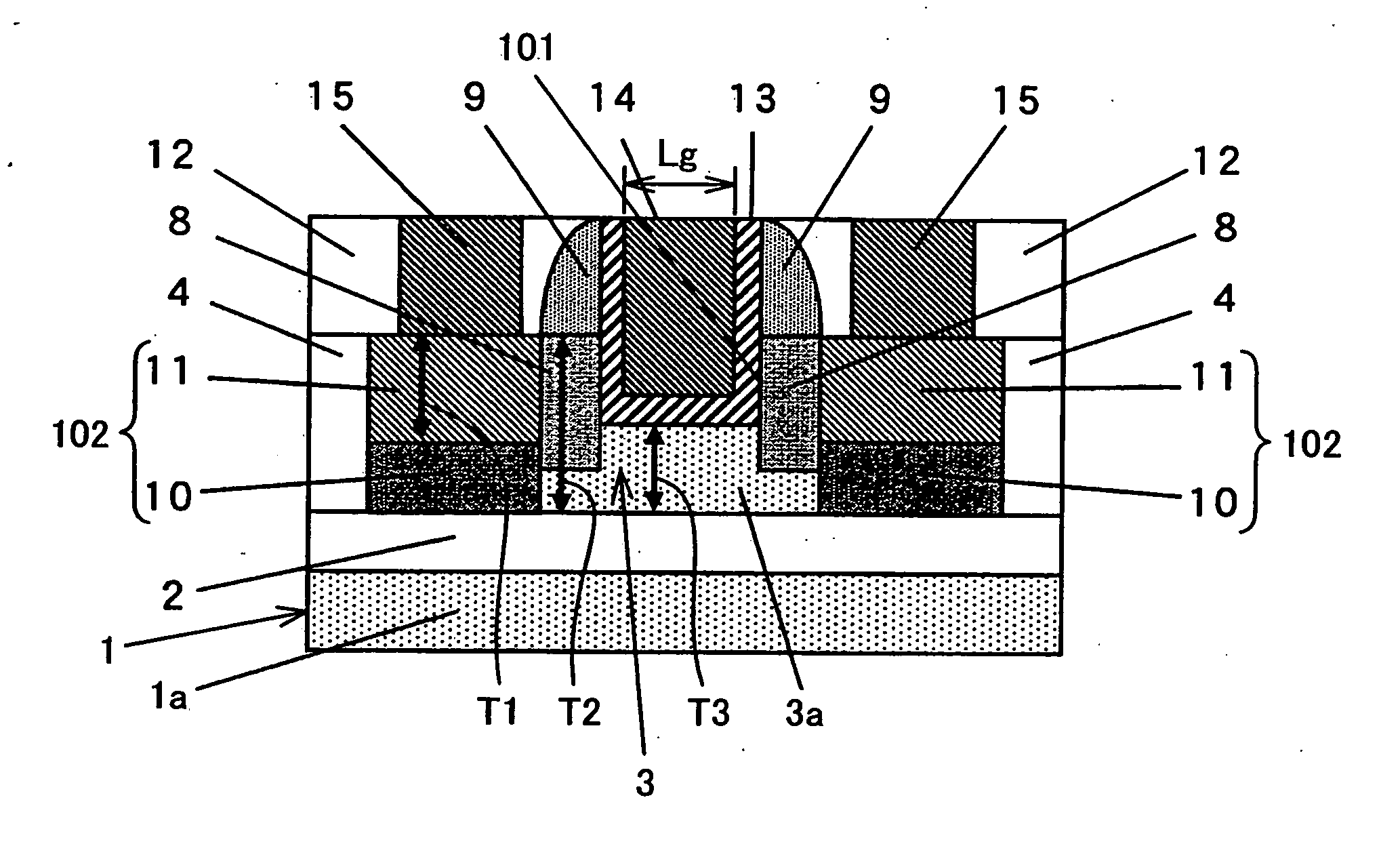

Semiconductor device and method of fabricating the same

InactiveUS20070108514A1Reduce capacitanceTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device according to the present invention, which comprises a MISFET, has a semiconductor layer (3) having a recessed portion (101) formed in the surface thereof, the recessed portion (101) having an opening the outer circumference of which is closed, a gate insulating film (13) formed so as to cover at least the inner face of the recessed portion (3), a gate electrode (14) filling the recessed portion (101) such that the gate insulating film (13) is interposed between the gate electrode (14) and the inner face of the recessed portion (101), and a pair of source / drains (102), located on both sides of the gate electrode (14) when viewed in plan and formed to a predetermined depth from the surface of the semiconductor layer (3).

Owner:PANASONIC CORP

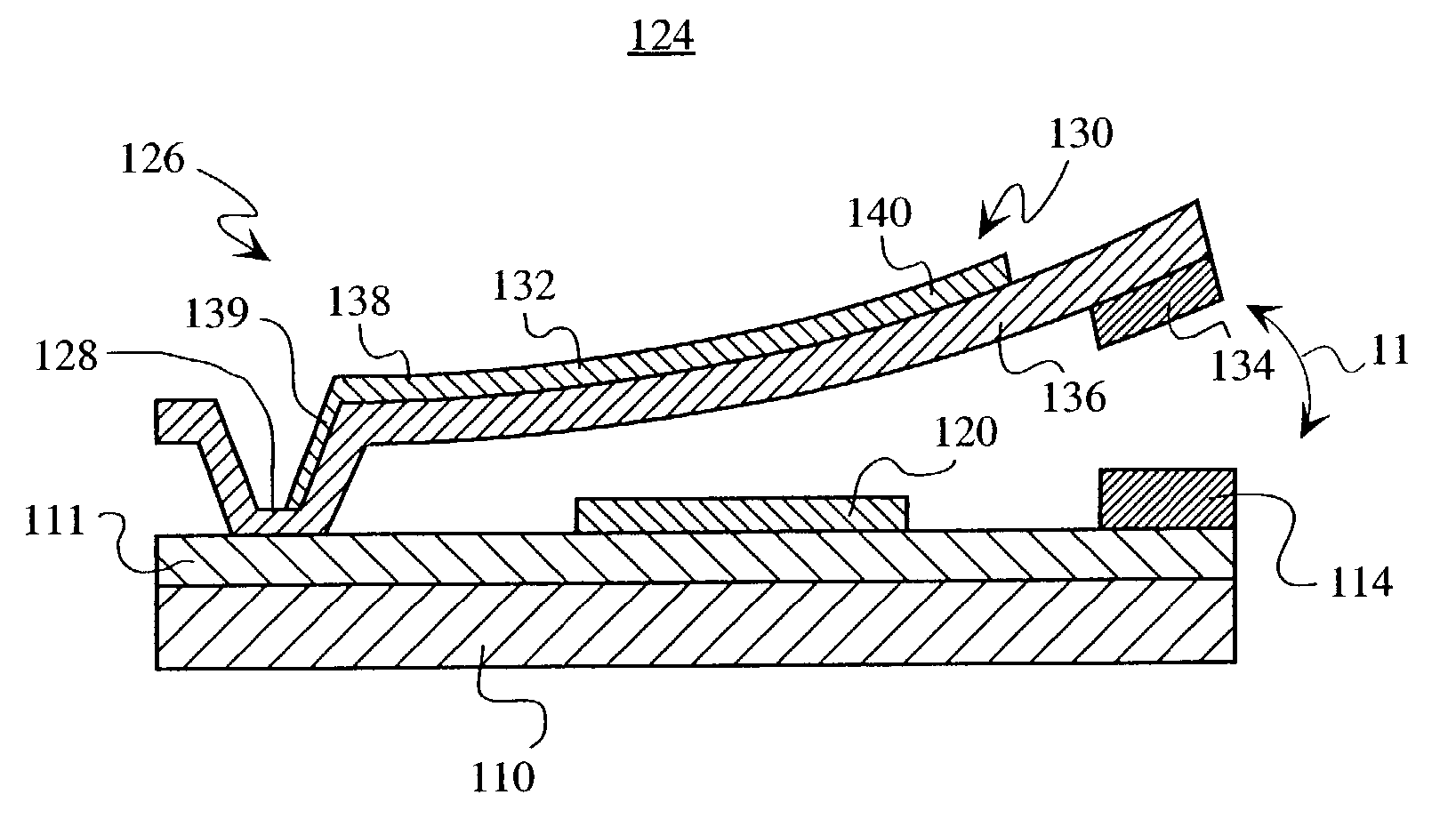

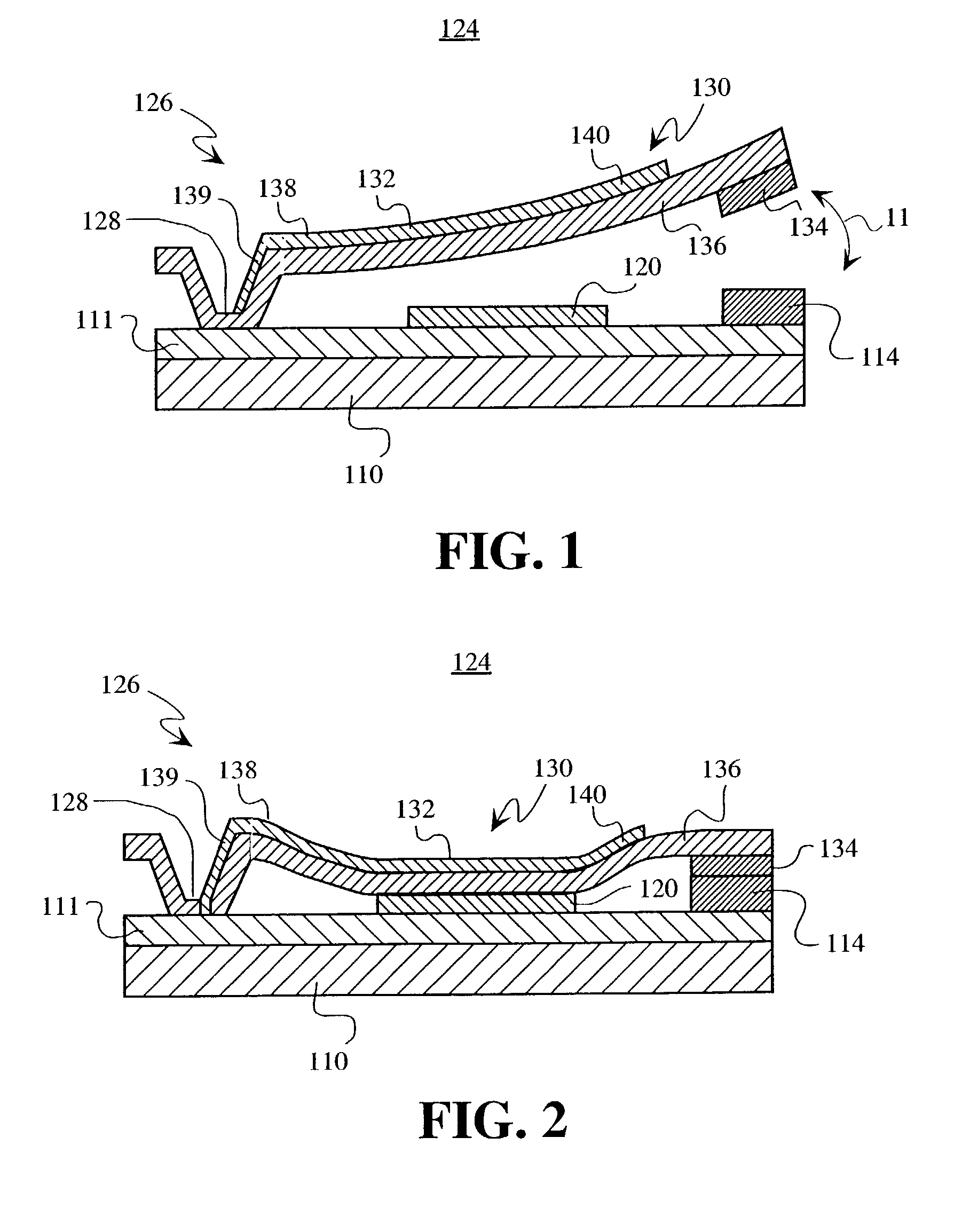

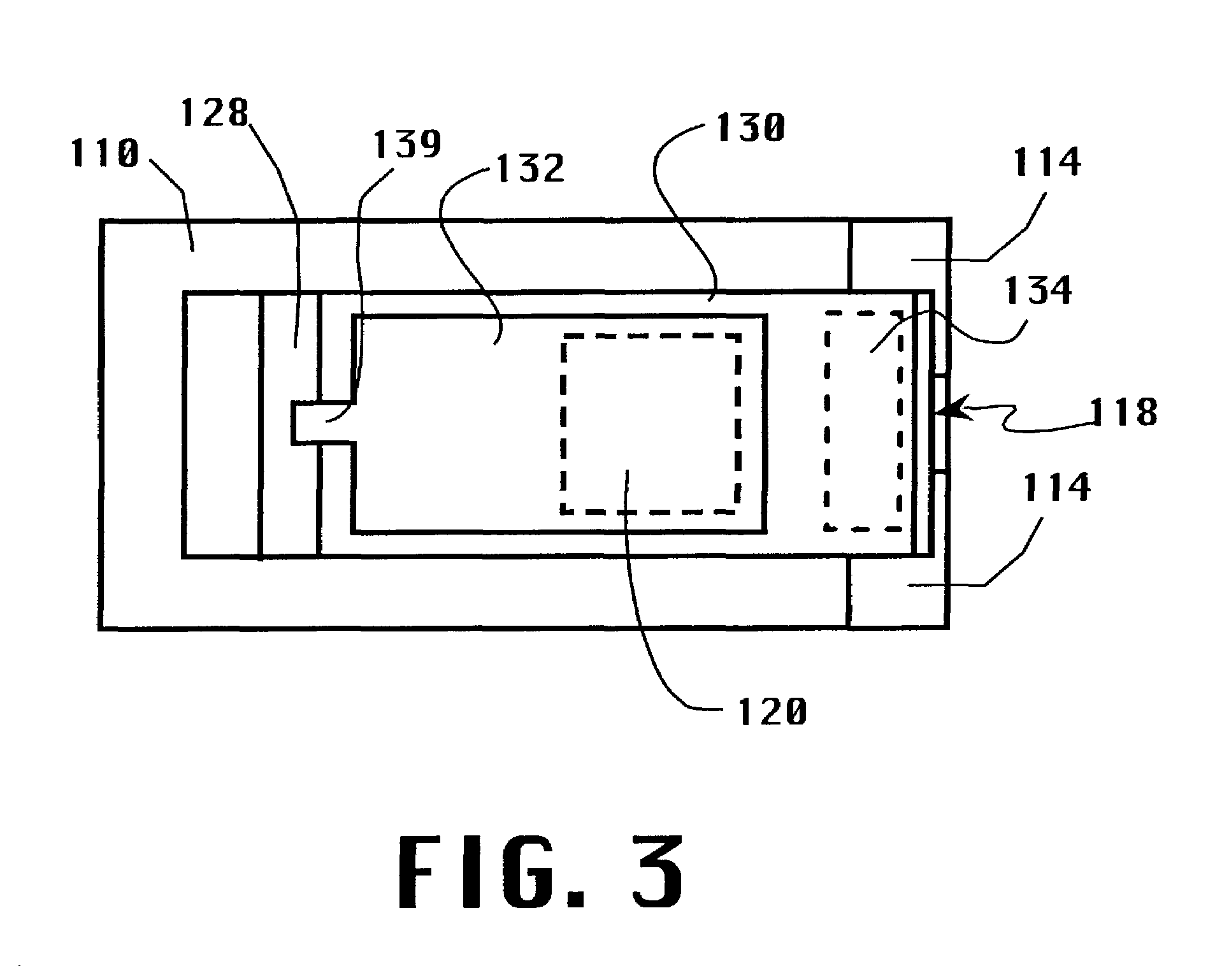

Stress bimorph MEMS switches and methods of making same

InactiveUS7053737B2Reduce capacitanceMinimize OFF-state capacitanceElectrostatic/electro-adhesion relaysCapacitor with electrode distance variationEngineeringCantilever

A micro-electromechanical system (MEMS) switch formed on a substrate, the switch comprising a transmission line formed on the substrate, a substrate electrostatic plate formed on the substrate, and an actuating portion. The actuating portion comprises a cantilever anchor formed on the substrate and a cantilevered actuator arm extending from the cantilever anchor. Attraction of the actuator arm toward the substrate brings an electrical contact into engagement with the portions of the transmission line separated by a gap, thus bridging the transmission line gap and closing the circuit. In order to maximize electrical isolation between the transmission line and the electrical contact in an OFF-state while maintaining a low actuation voltage, the actuator arm is bent such that the minimum separation distance between the transmission line and the electrical contact is equal to or greater than the maximum separation distance between the substrate electrostatic plate and arm electrostatic plate.

Owner:HRL LAB +1

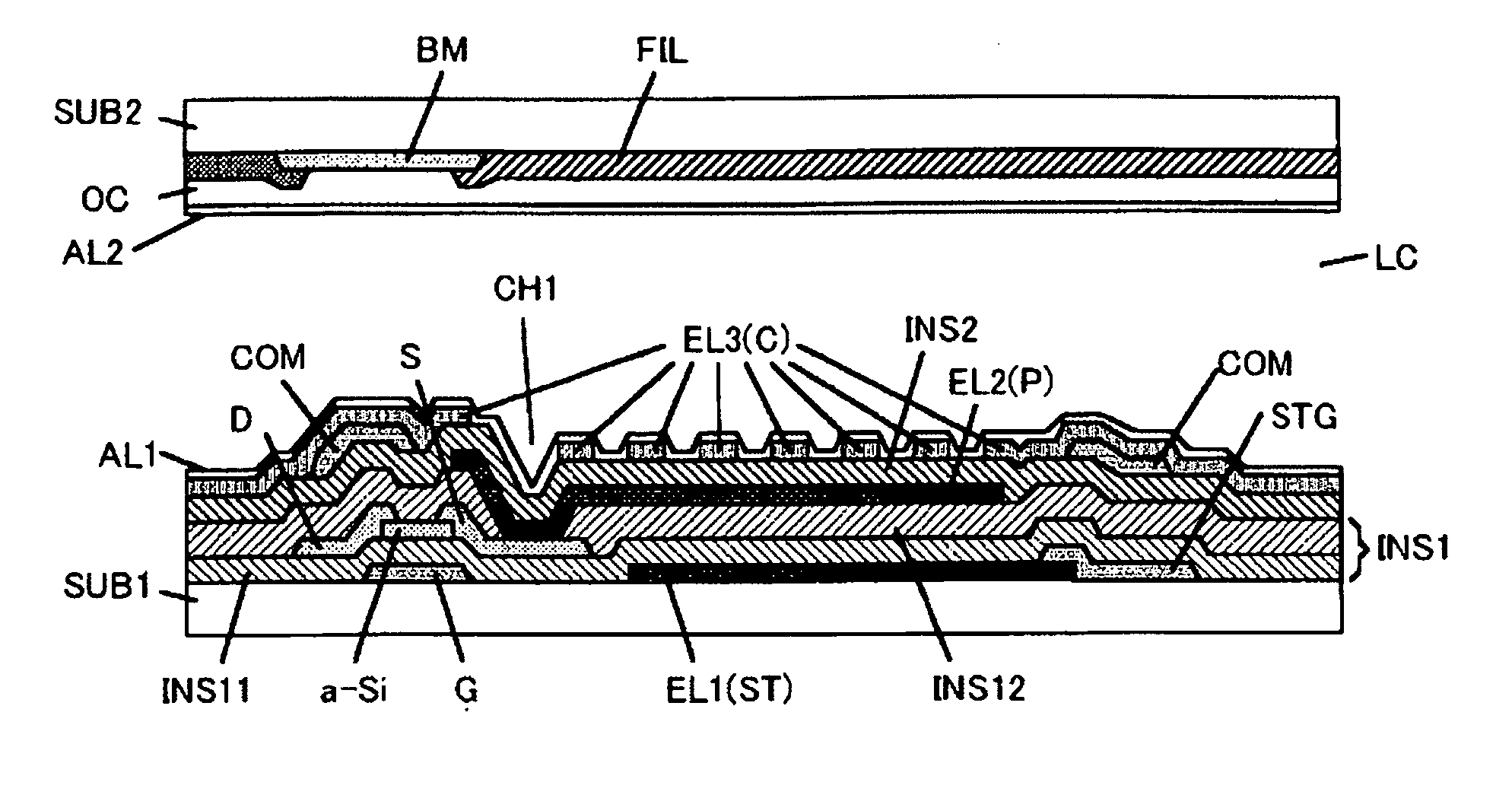

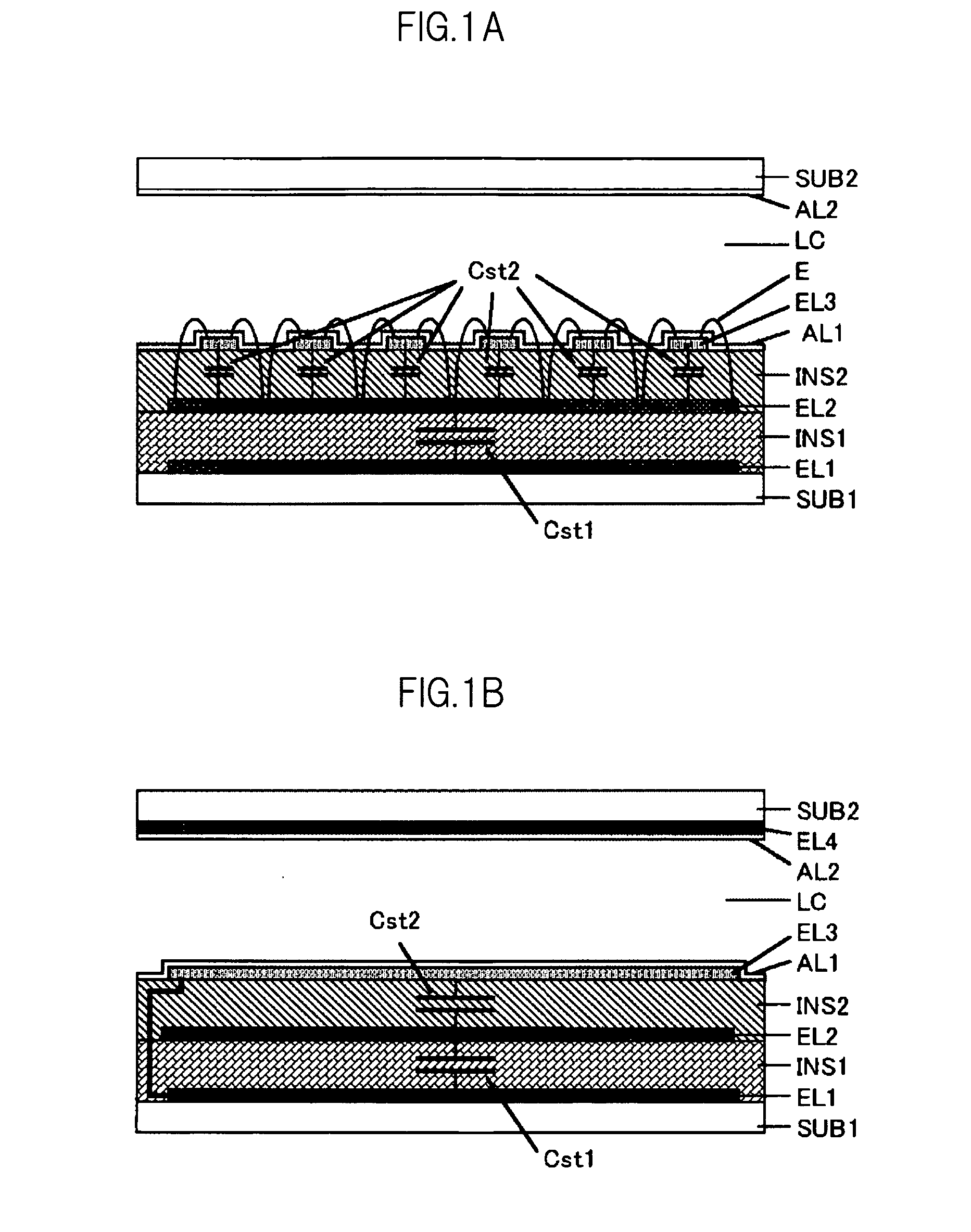

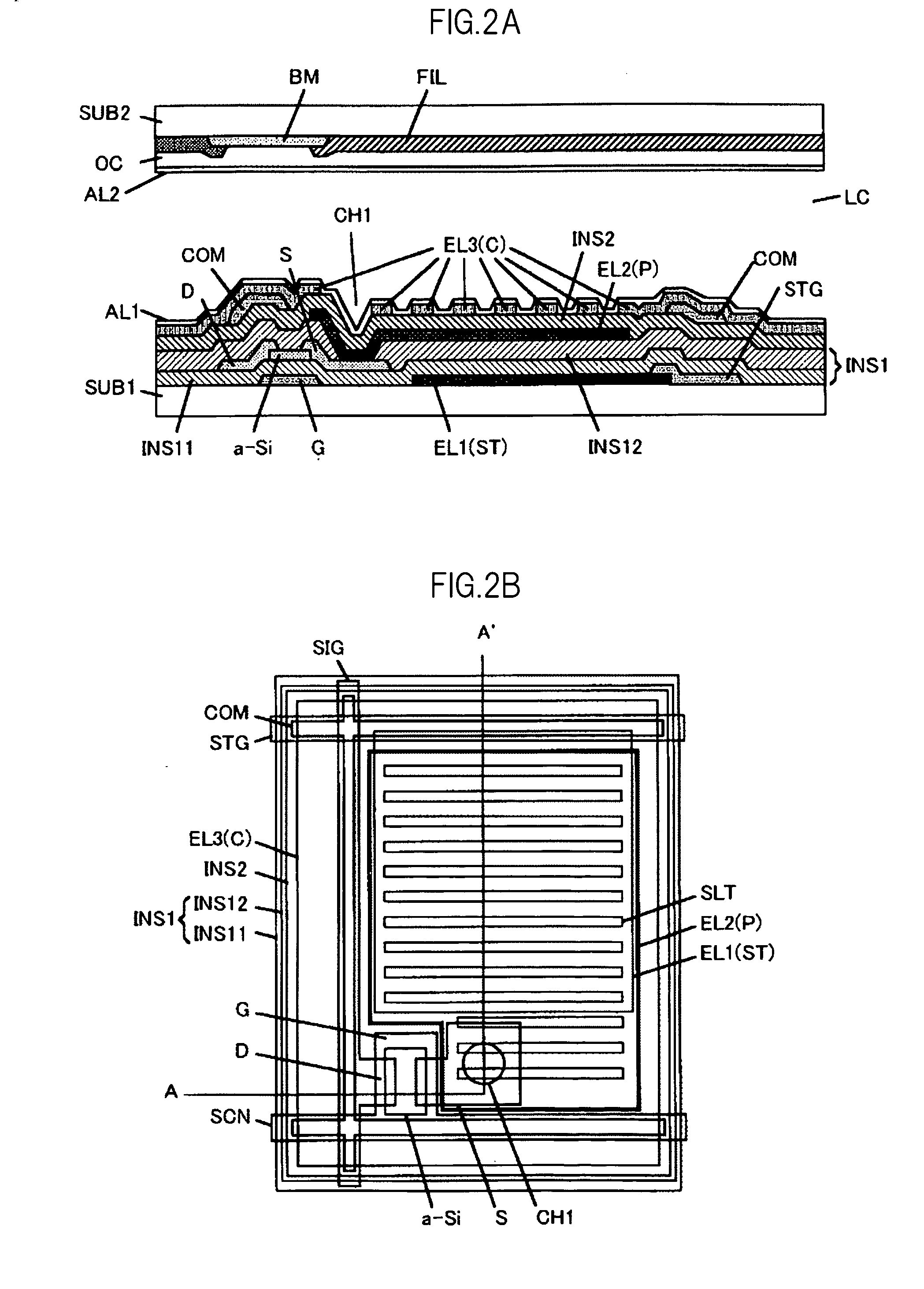

Liquid crystal display device

ActiveUS20090059110A1Reduce areaReduce capacitanceSolid-state devicesNon-linear opticsLiquid-crystal displayEngineering

To form a sufficiently large storage capacitor, a liquid crystal display device includes a liquid crystal display panel having a first substrate, a second substrate, and a liquid crystal held between the first substrate and the second substrate, the liquid crystal display panel having multiple pixels arranged in matrix. The first substrate has, in a transmissive display area provided in each of the pixels, a laminated structure containing a first transparent electrode, a first insulating film, a second transparent electrode, a second insulating film, and a third transparent electrode which are laminated in this order. The first transparent electrode and the second transparent electrode are electrically insulated from each other and together form a first storage capacitor through the first insulating film, and the second transparent electrode and the third transparent electrode are electrically insulated from each other and together form a second storage capacitor through the second insulating film.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

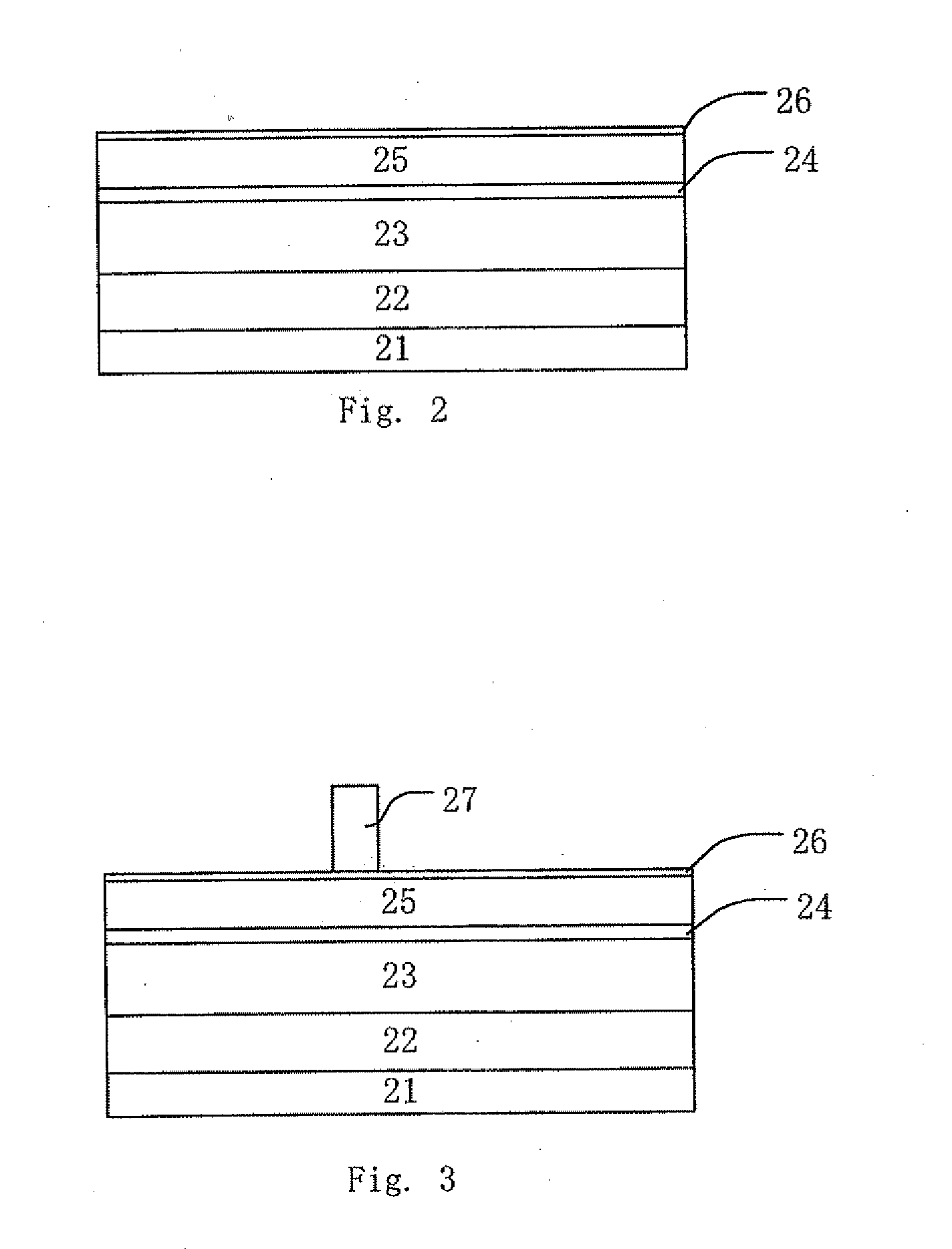

Semiconductor device and method for manufacturing the same

ActiveUS20110193164A1Reduce parasitic capacitanceLarge thicknessSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceGate dielectric

The present application discloses a semiconductor device formed on a SOI substrate which comprises a buried insulating layer and a semiconductor layer on the buried insulating layer and a method for manufacturing the same, wherein a fin of semiconductive material having two opposing sides perpendicular to a main surface of the SOI substrate is provided in the semiconductor layer, said semiconductor device comprising: a source region and a drain region provided at two ends of the fin respectively; a channel region provided at a central portion of the fin; and a stack of gate dielectric and gate conductor provided at one side of the fin, where the gate conductor is isolated from the channel region by the gate dielectric, wherein the gate conductor extends away from the one side of the fin in a direction parallel to the main surface of the SOI substrate. The semiconductor device has an improved short channel effect and a reduced parasitic capacitance and resistance, which contributes to an improved electrical property and facilitates scaling down of the transistor.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

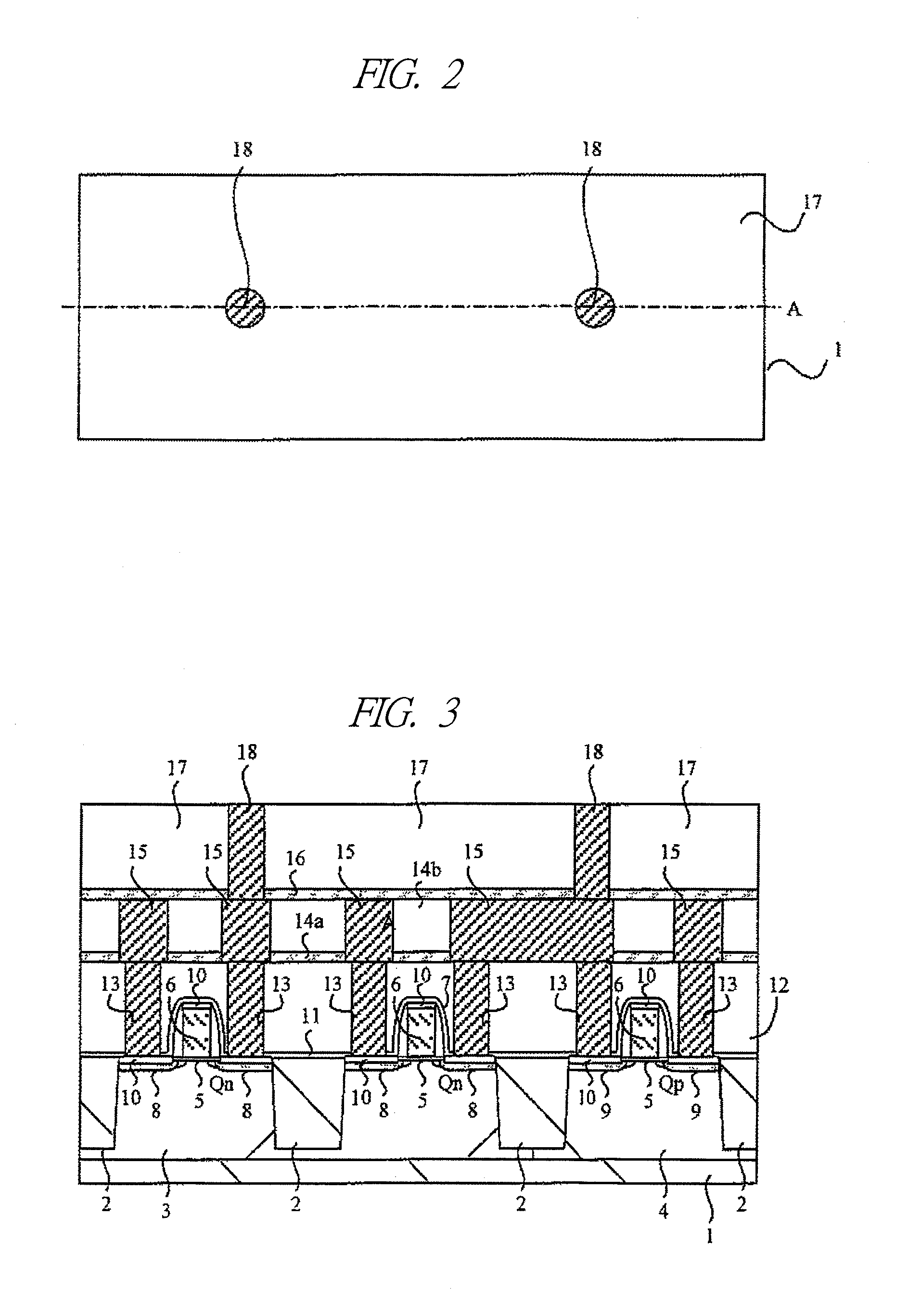

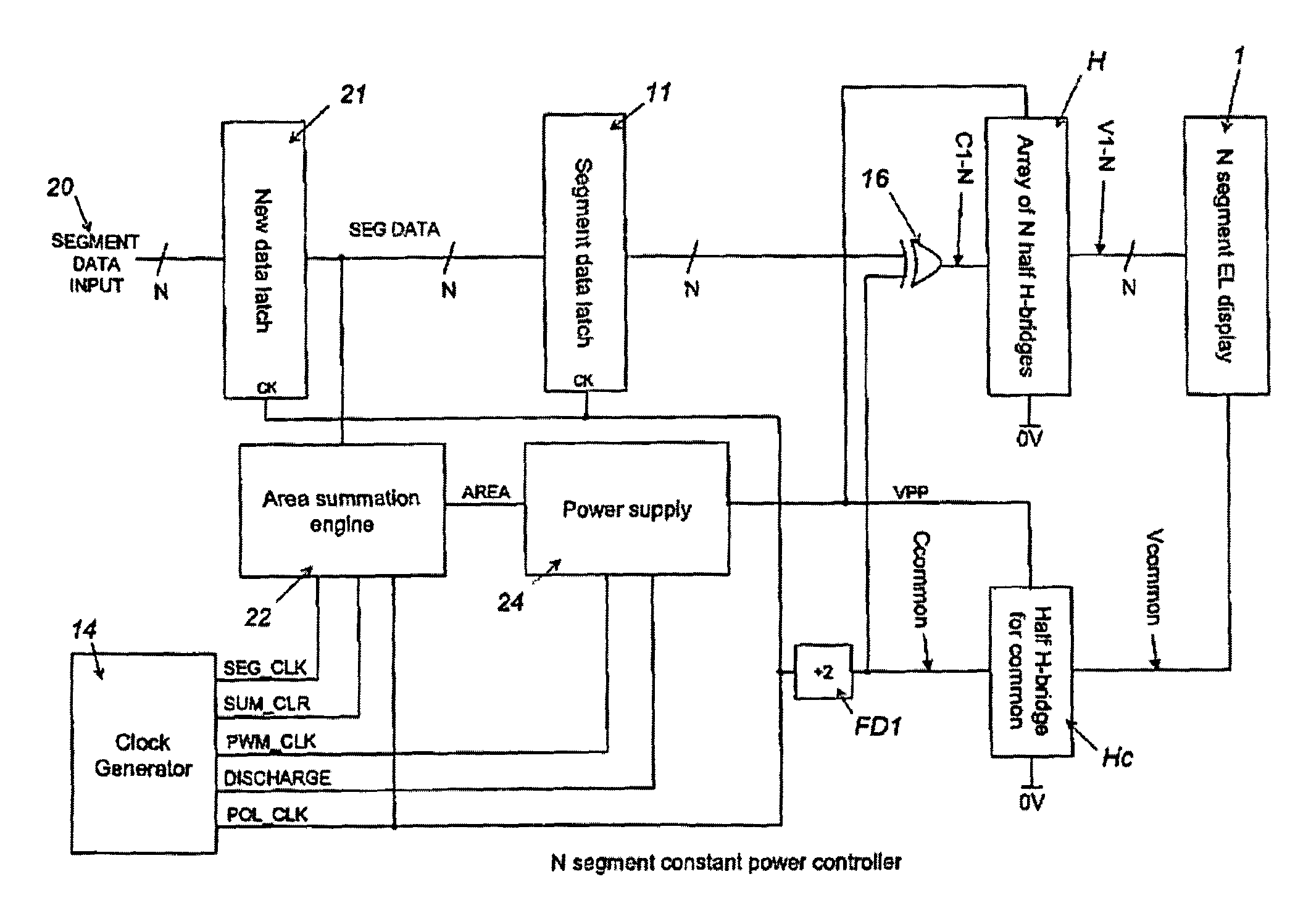

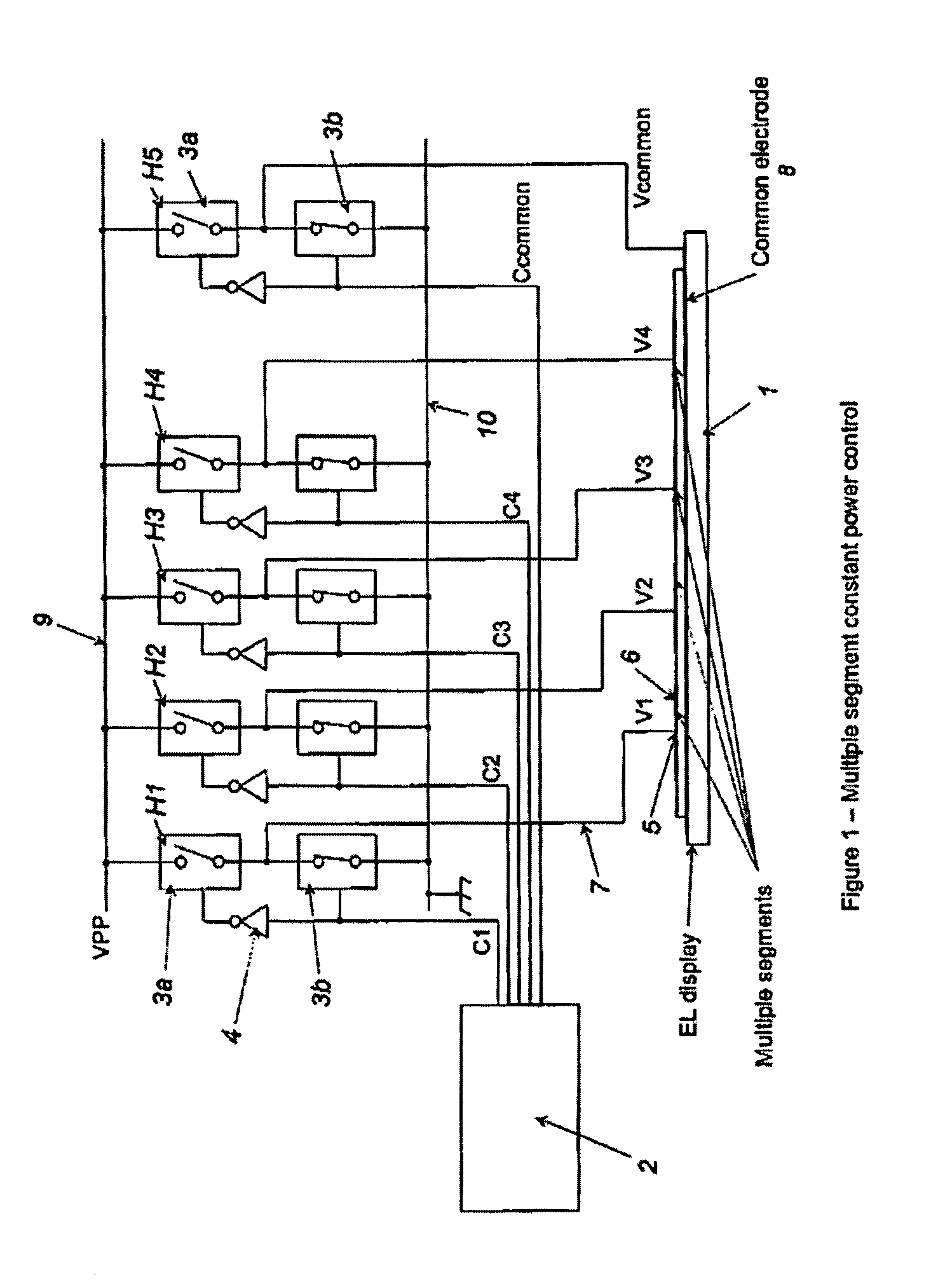

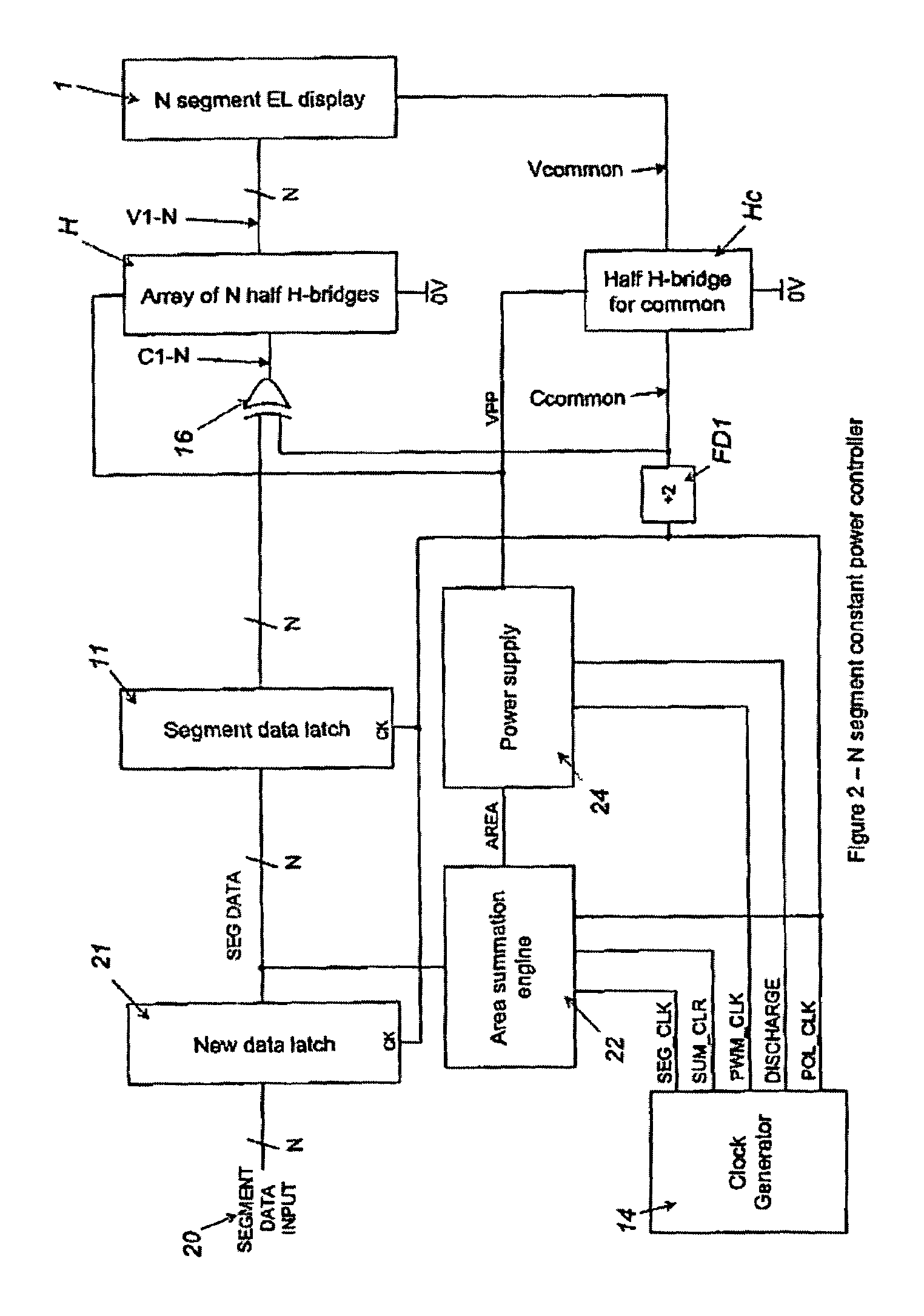

Control of electroluminescent displays

InactiveUS7119493B2Remove loadSmall voltage dropElectrical apparatusElectroluminescent light sourcesElectricityControl signal

A controller for use with a multi-segment electroluminescent display 1. Control signals C1–CN control a plurality of half H-bridges H and Hc, the terminals of the half H-bridges being connected respectively to ground and to a high voltage DC supply 9. One of said half H-bridges provides a common output Vcommon and the remaining H-bridges provide drive voltages V1–VN for the segments of the display. The H bridges are driven by an oscillator 14 so that an AC voltage is selectively applied to the segments of the display. A power supply 24 provides a predetermined amount of power per unit area of the display. This is controlled by an area summation engine 22 having a segment data input, a segment counter and a memory containing area data corresponding to the segment(s) of the display. Based on the input from the segment data input, the area(s) of the segment(s) that are to be lit are obtained from the memory and summed to provide the total area to be lit. This is fed to the power supply 24, which then feeds the correct amount of power to display 1 via the half H-bridges.

Owner:PELIKON

High performance ultracapacitors with carbon nanomaterials and ionic liquids

InactiveUS20080192407A1Excellent electrolyte accessibilityImprove performanceHybrid capacitor electrolytesElectrolytic capacitorsSupercapacitorCarbon nanomaterials

The present invention is directed to the use of carbon nanotubes and / or electrolyte structures comprising ionic liquids in various electrochemical devices, such as ultracapacitors.

Owner:ADA TECH

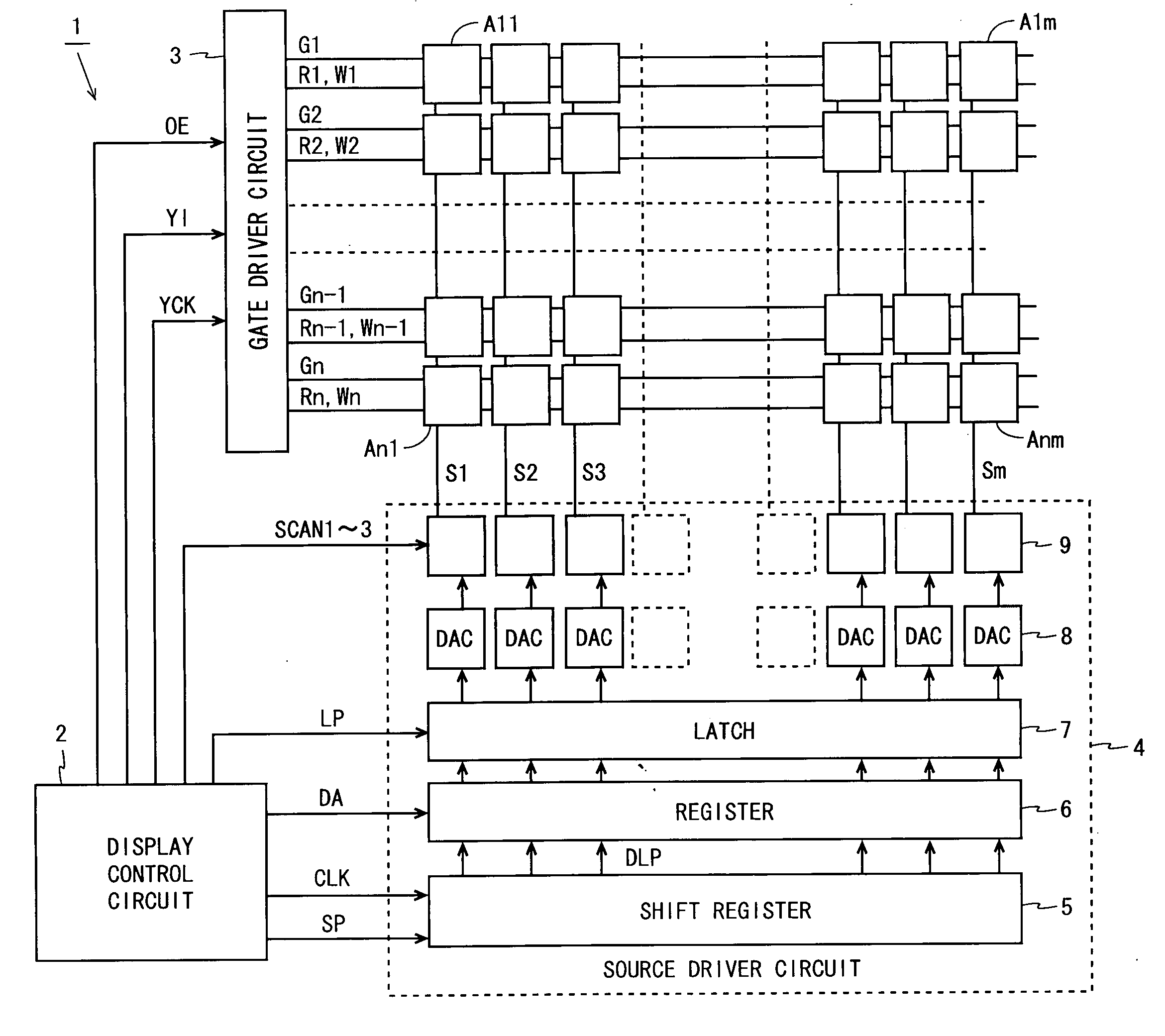

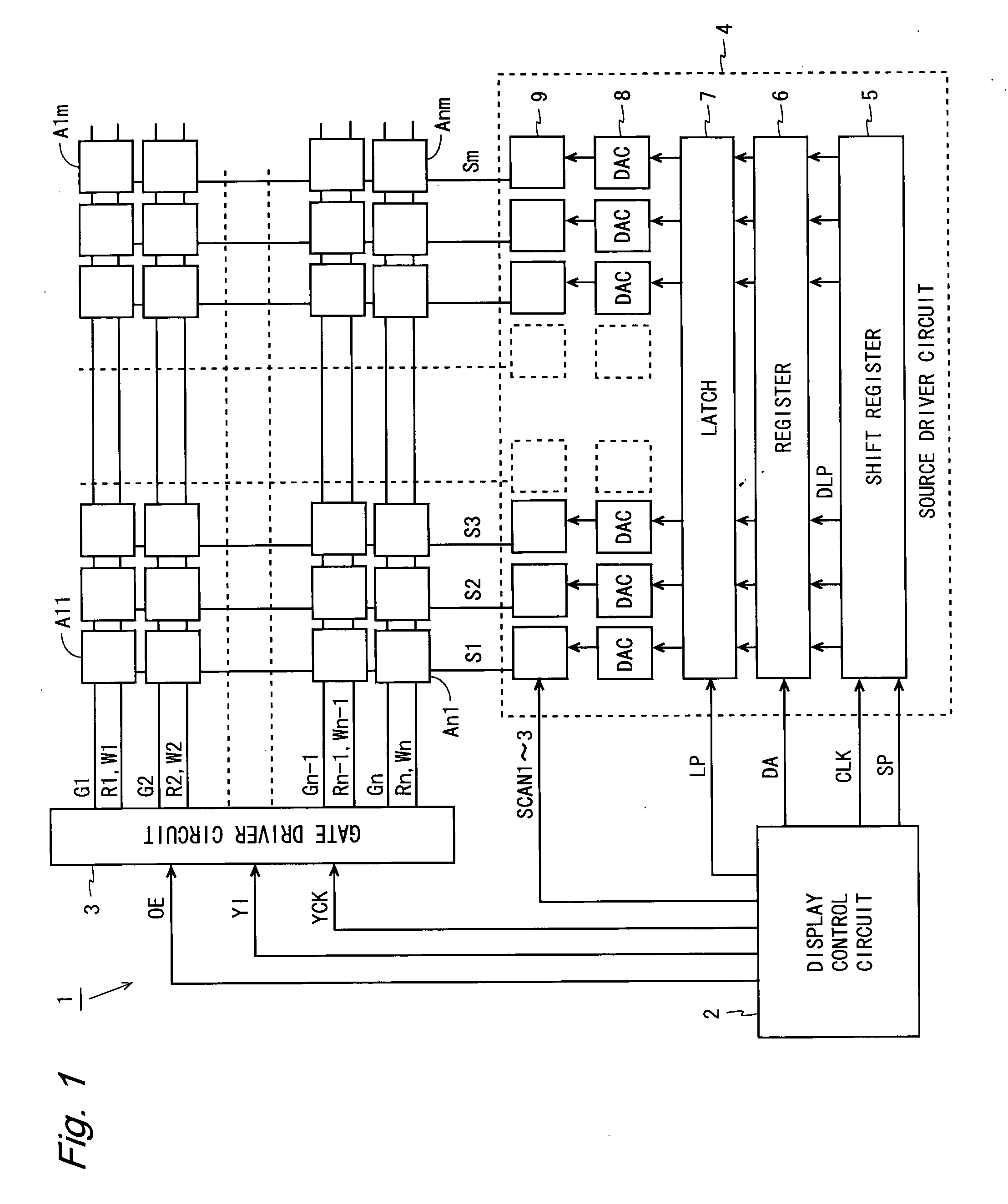

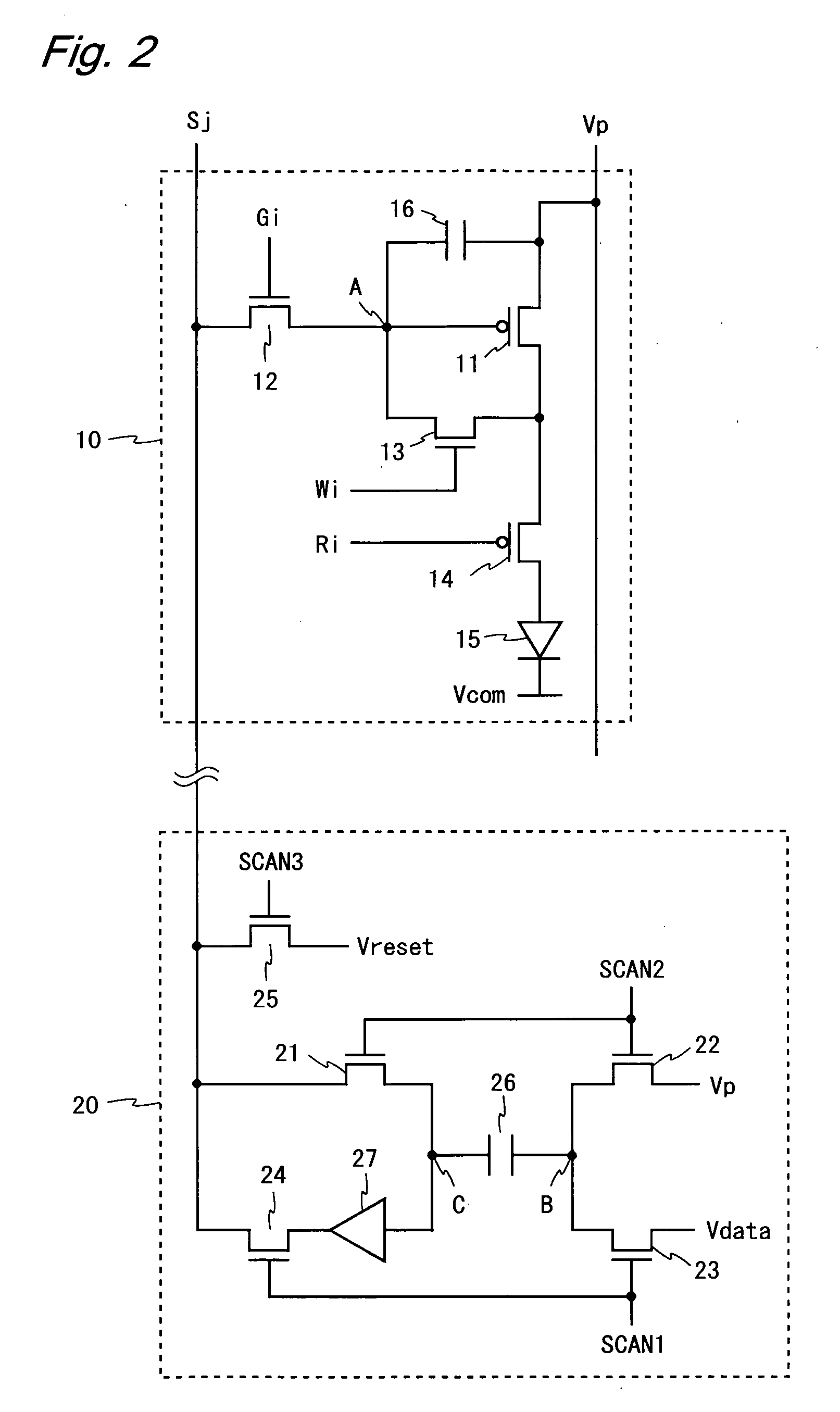

Display device and its driving method

ActiveUS20100045646A1Reduce scaleReduce areaCathode-ray tube indicatorsInput/output processes for data processingDriver circuitDisplay device

In a pixel circuit 10, TFTs 12 and 13 are turned on while a TFT 14 is turned off, and a voltage (VDD+Vx) which depends on a threshold voltage Vth of a driving TFT 11 is read onto a data line Sj. Moreover, switches 21 and 22 in a source driver circuit are turned on, and a voltage Vx is held at a capacitor 26. Next, the TFT 13 is turned off, states of switches 21 to 24 are switched, and a voltage (Vdata+Vx) is applied to the data line Sj. Further, the TFT 12 is turned off while the TFT 14 is turned on. An amount of an electric current flowing through an organic EL element 15 after the turn-on of the TFT 14 is determined from the voltage (Vdata+Vx) of a gate terminal of the driving TFT 11. Thus, it is possible to efficiently utilize an amplitude of a data voltage and compensate variations in threshold voltage of the driving TFT 11 with high accuracy, without increasing a scale of the pixel circuit 10.

Owner:SHARP KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com