Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2470results about How to "Reduced dimension" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

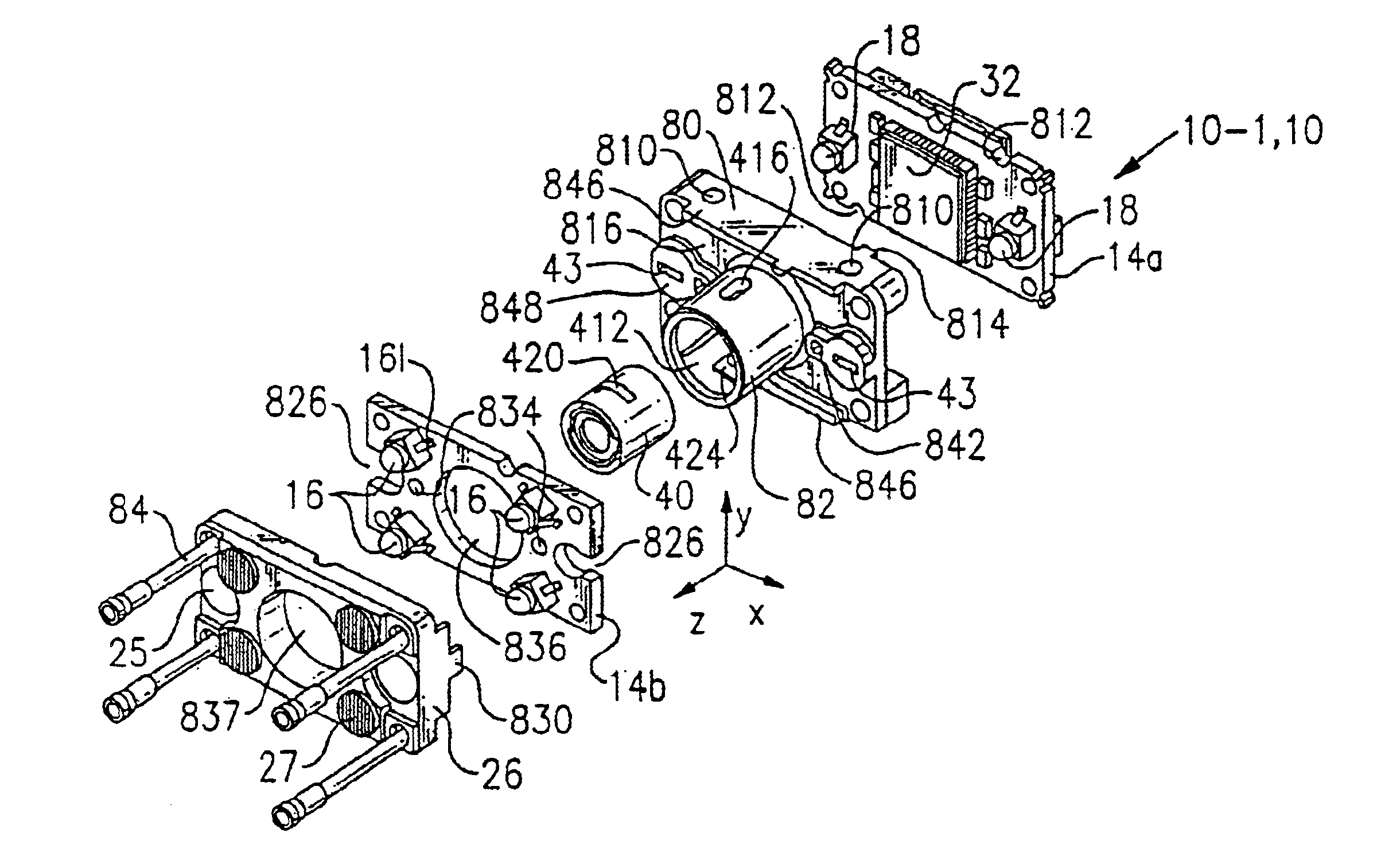

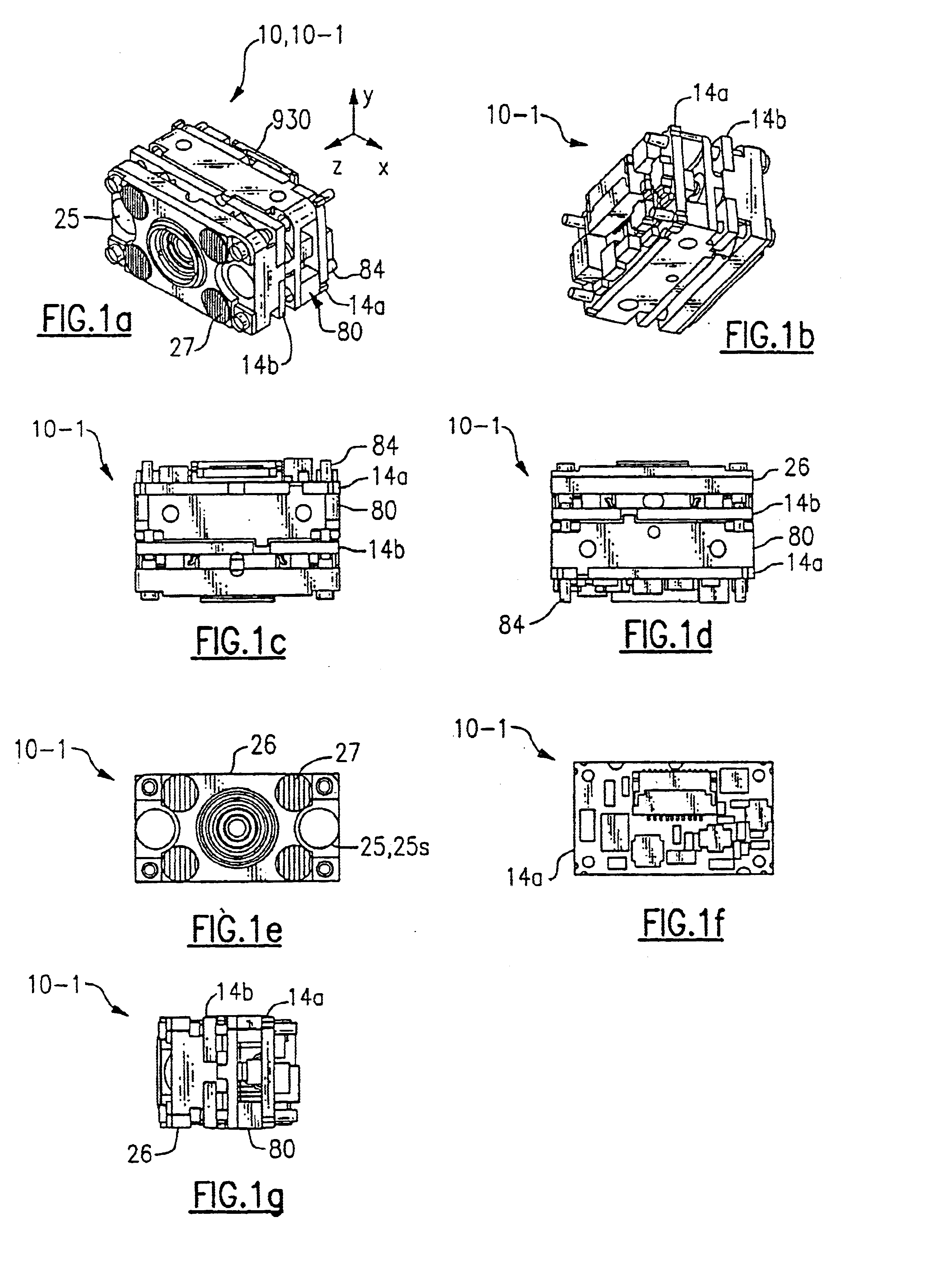

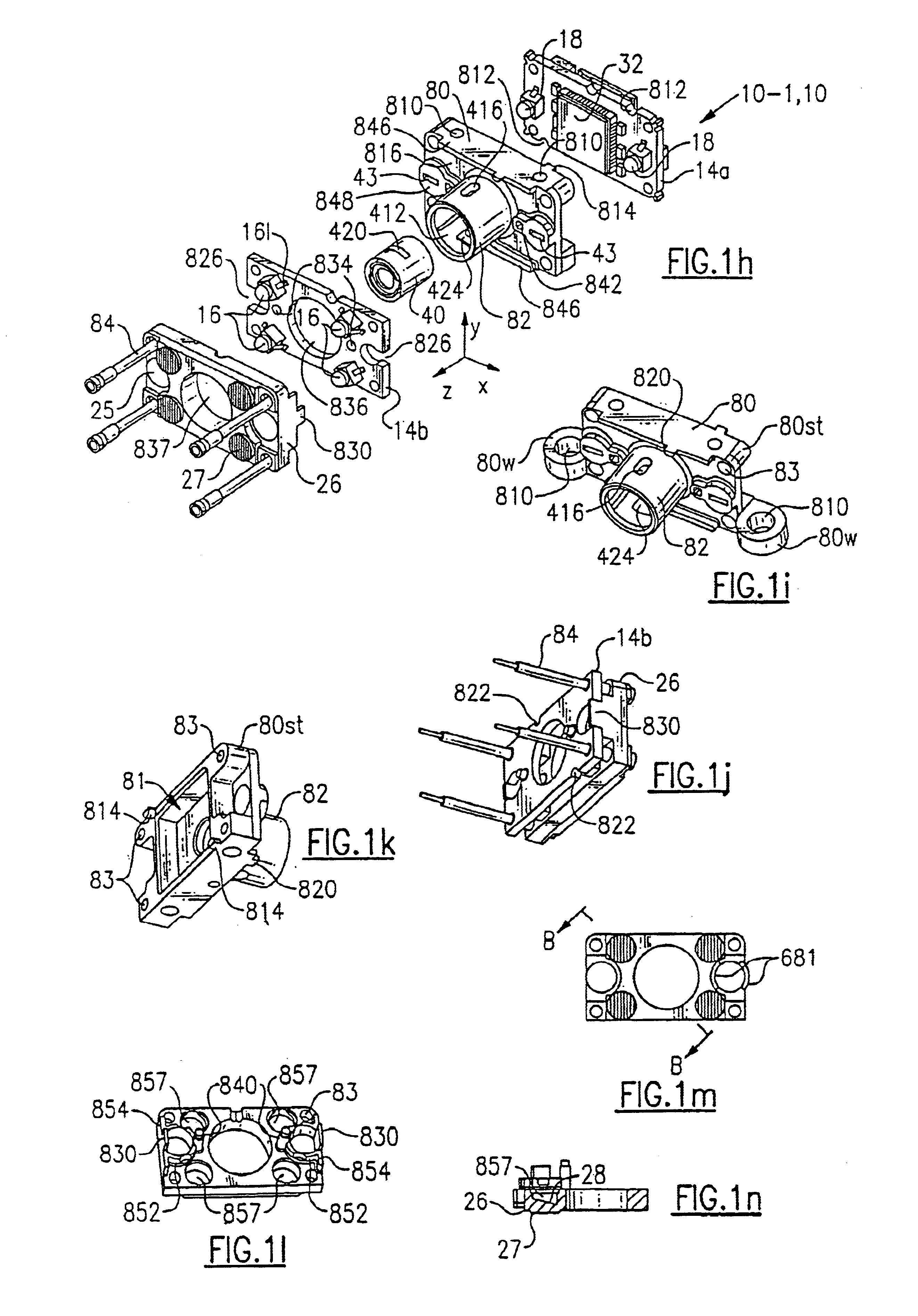

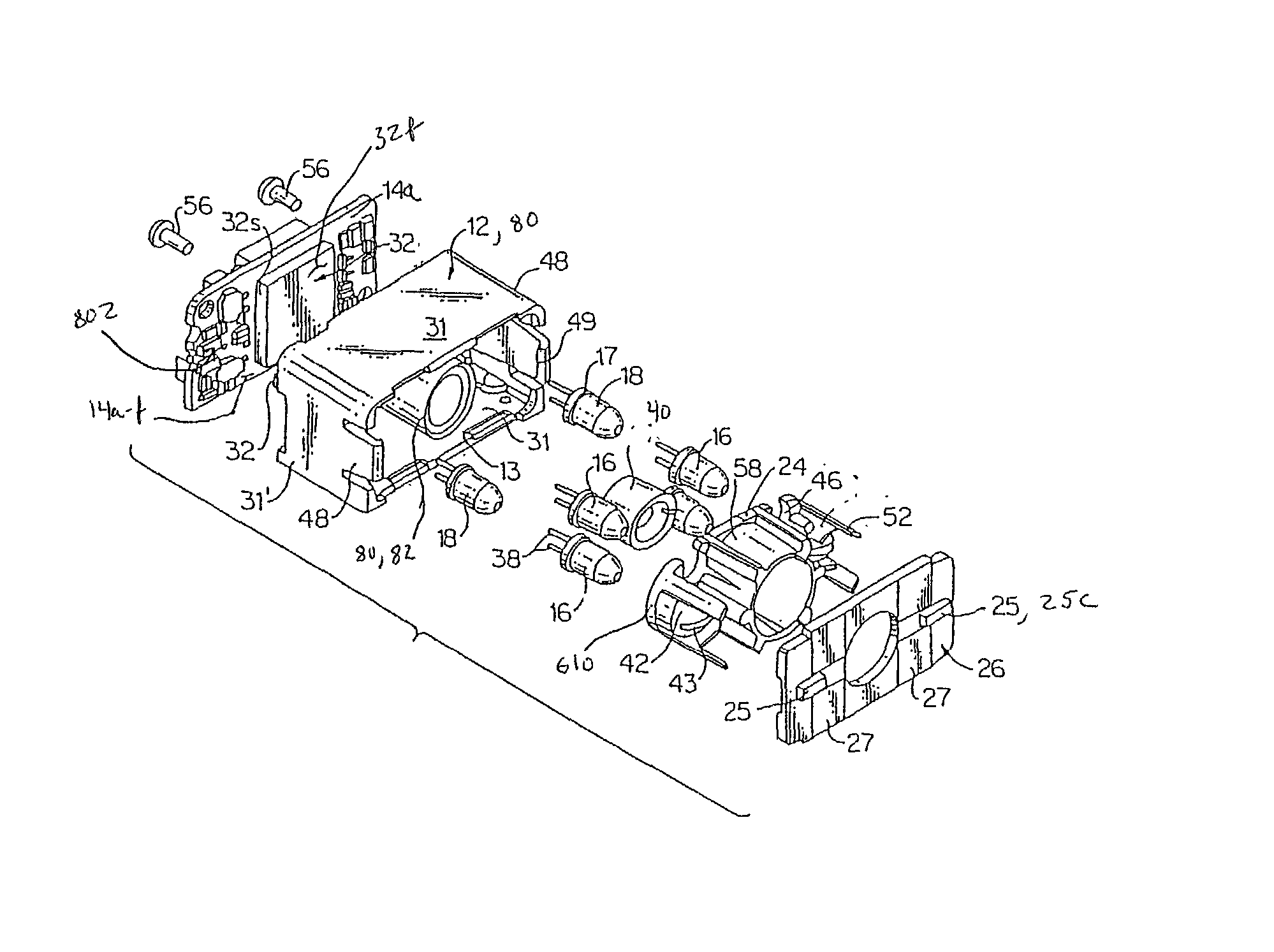

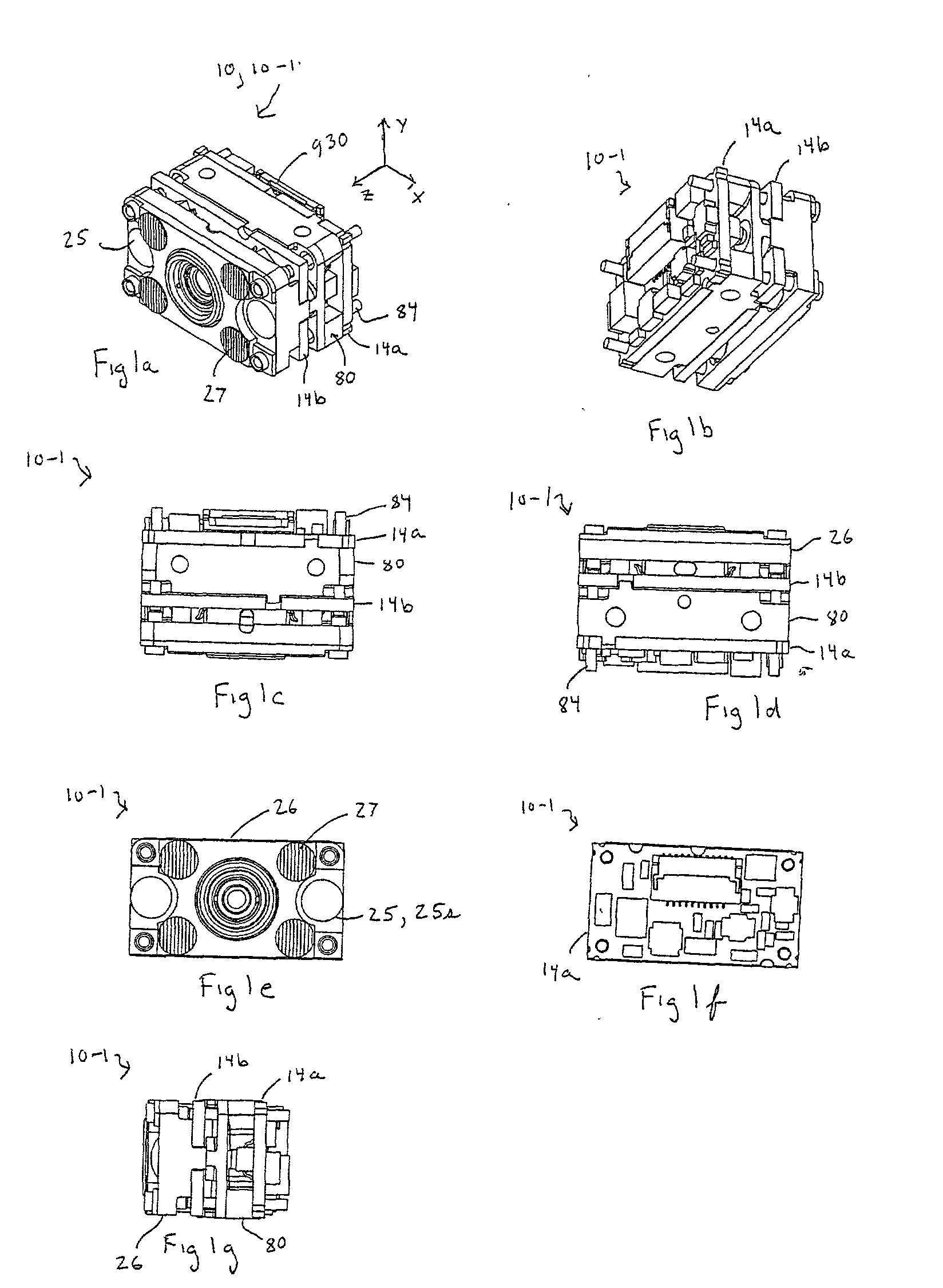

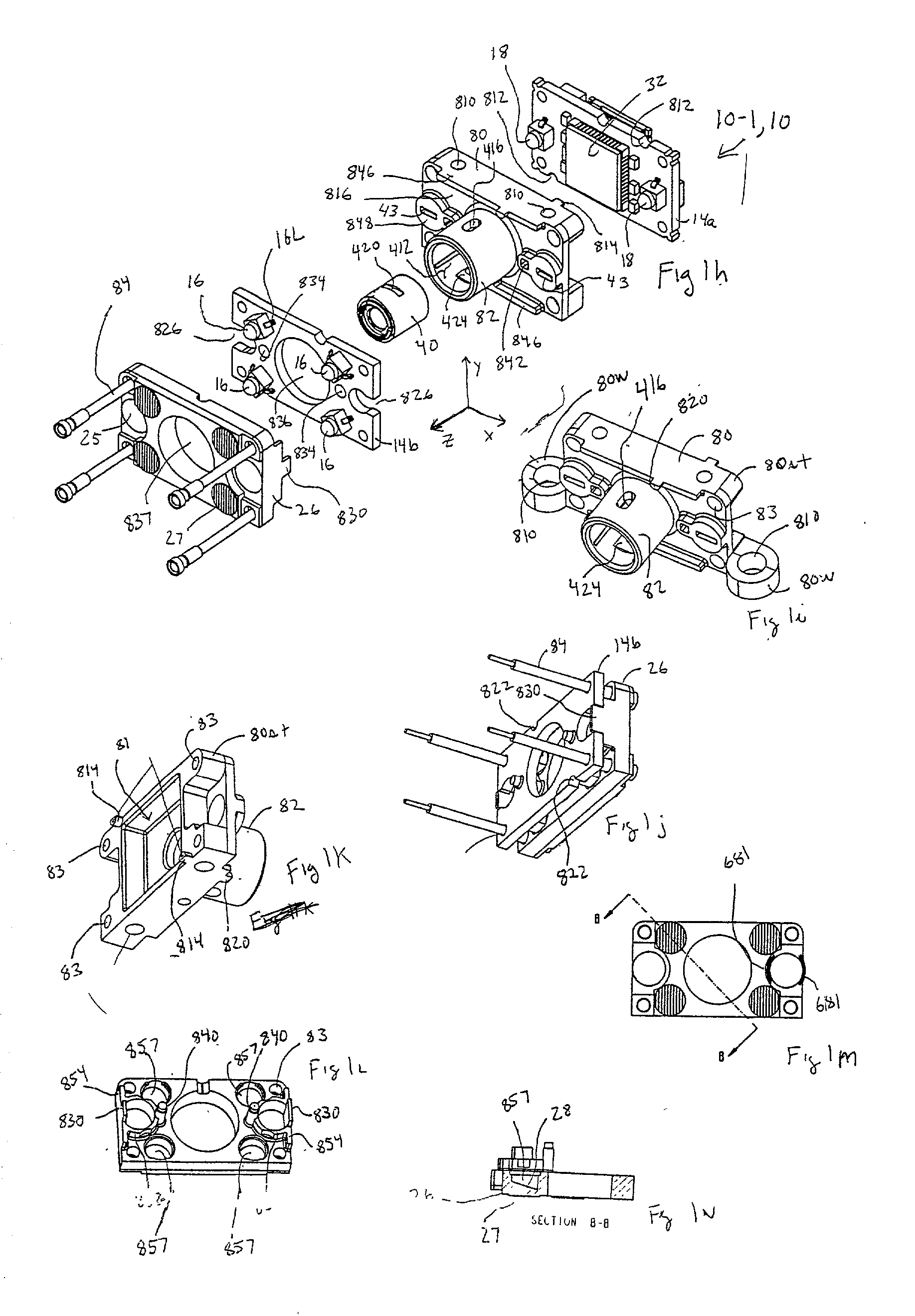

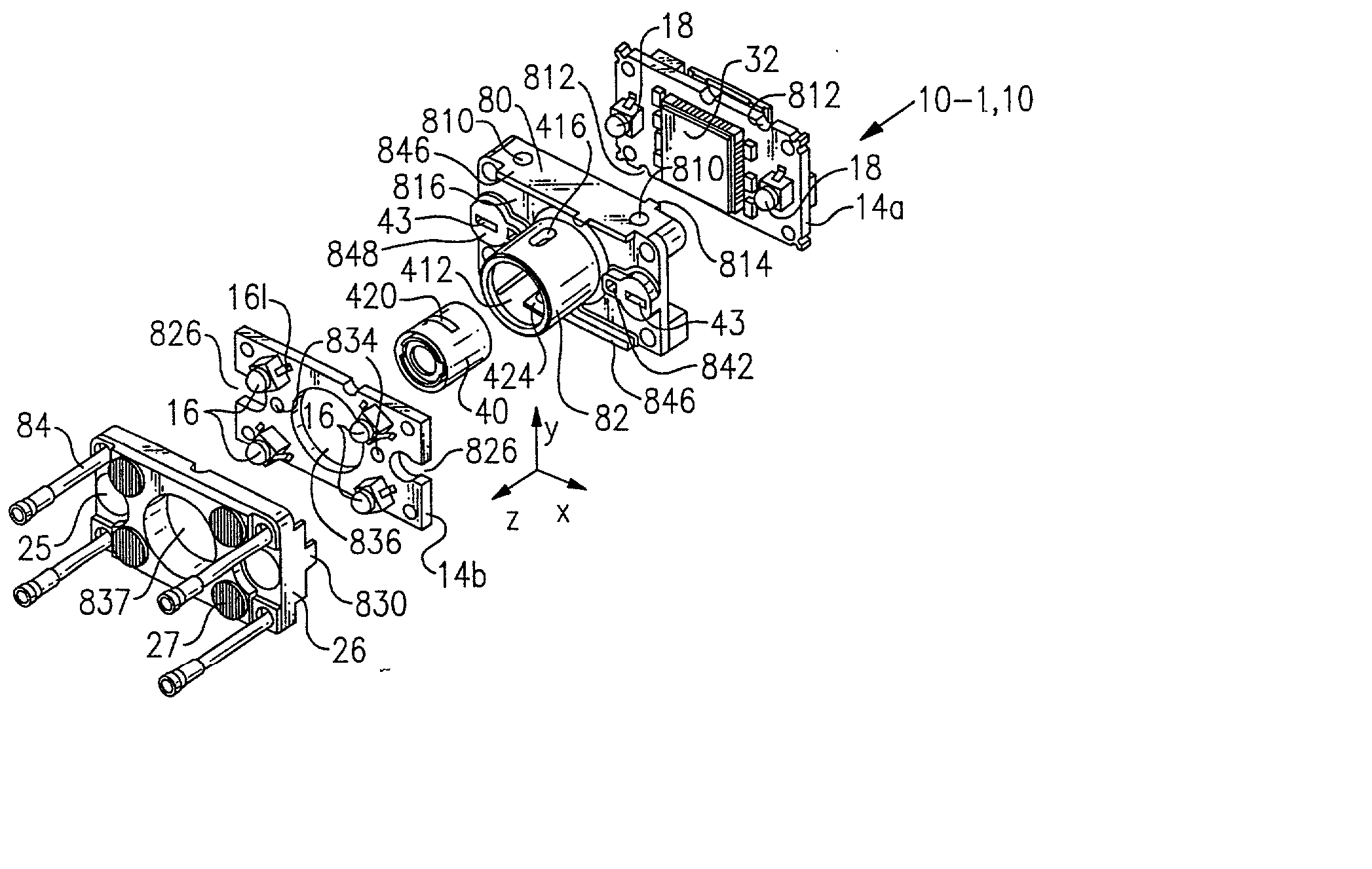

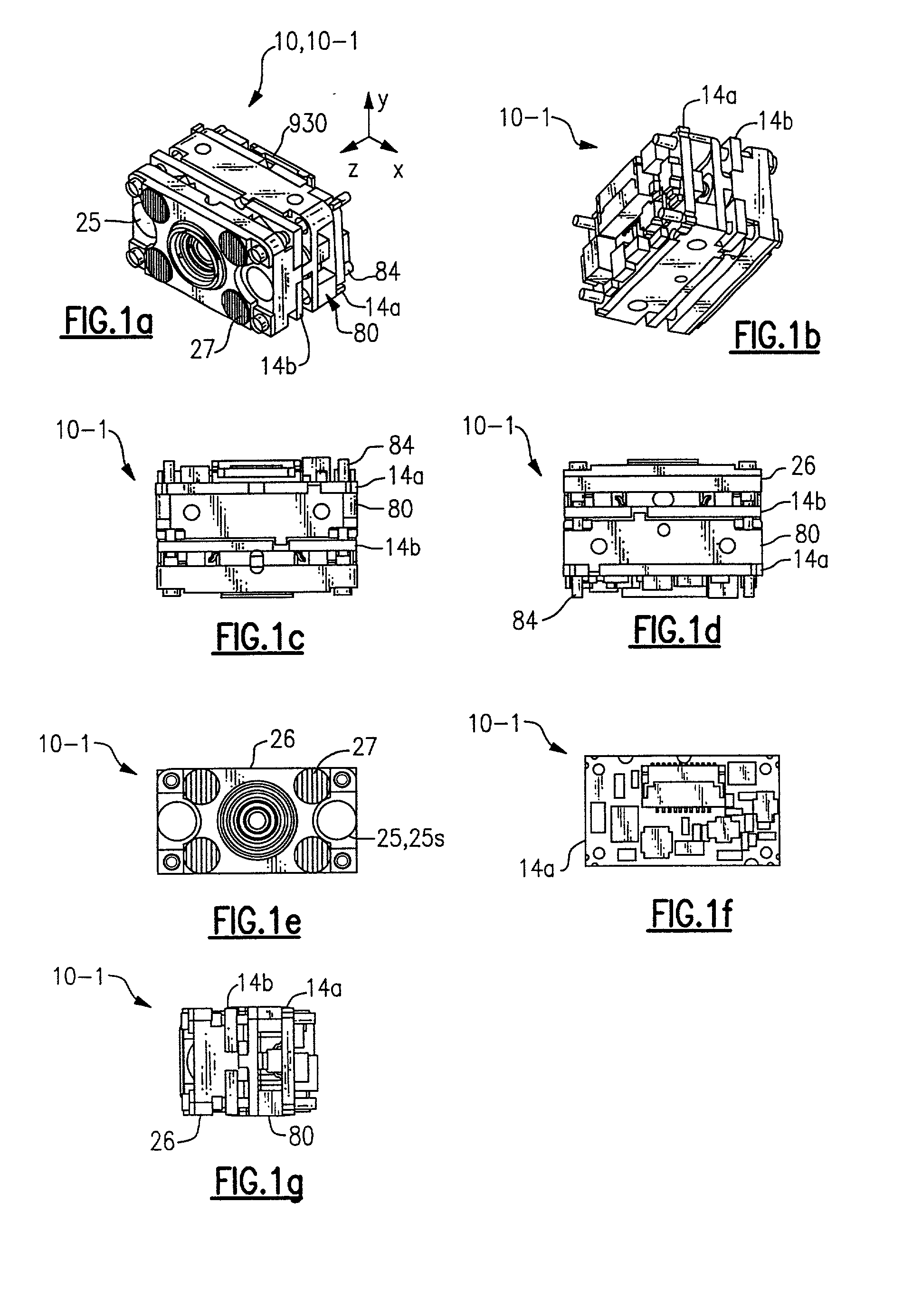

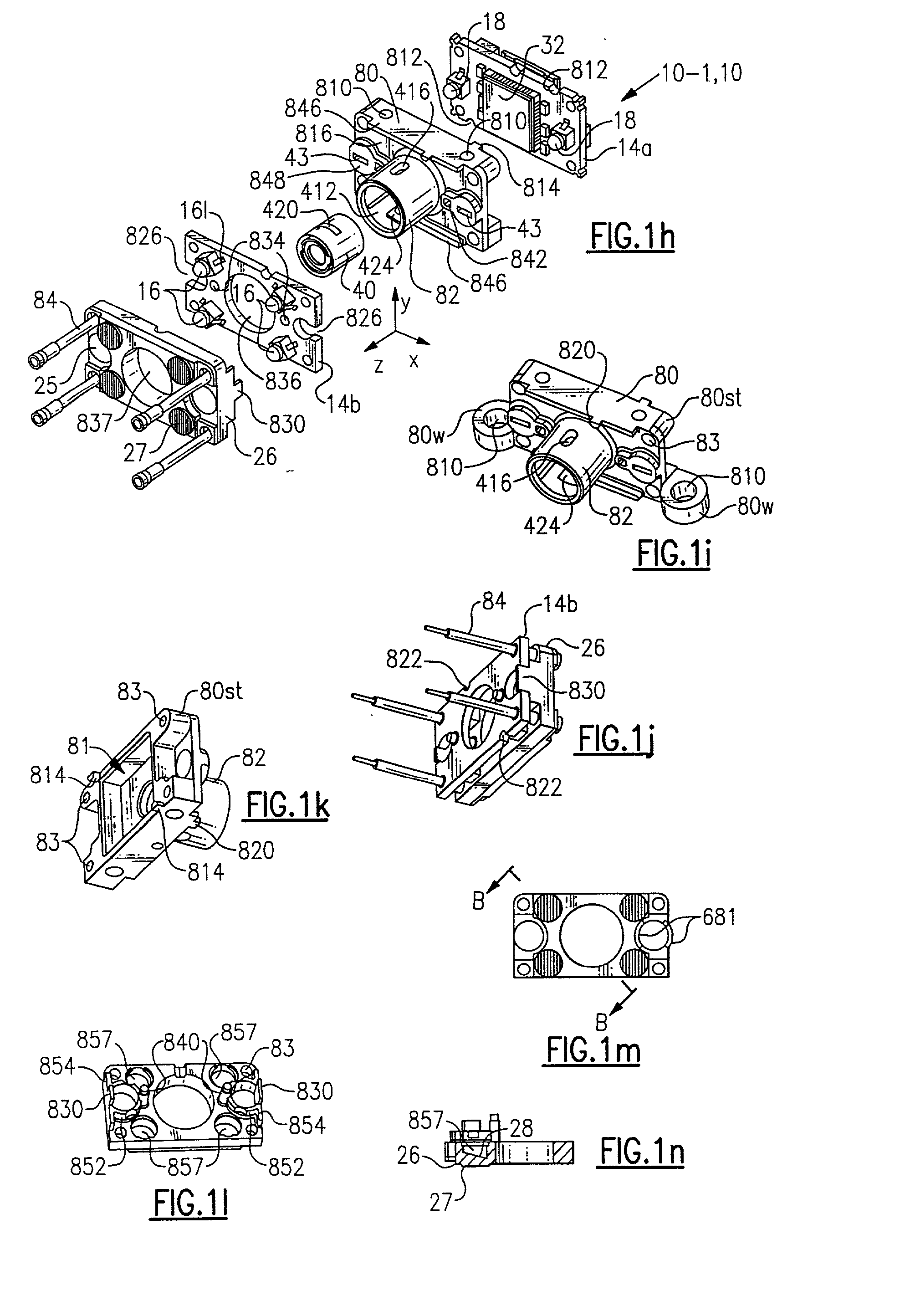

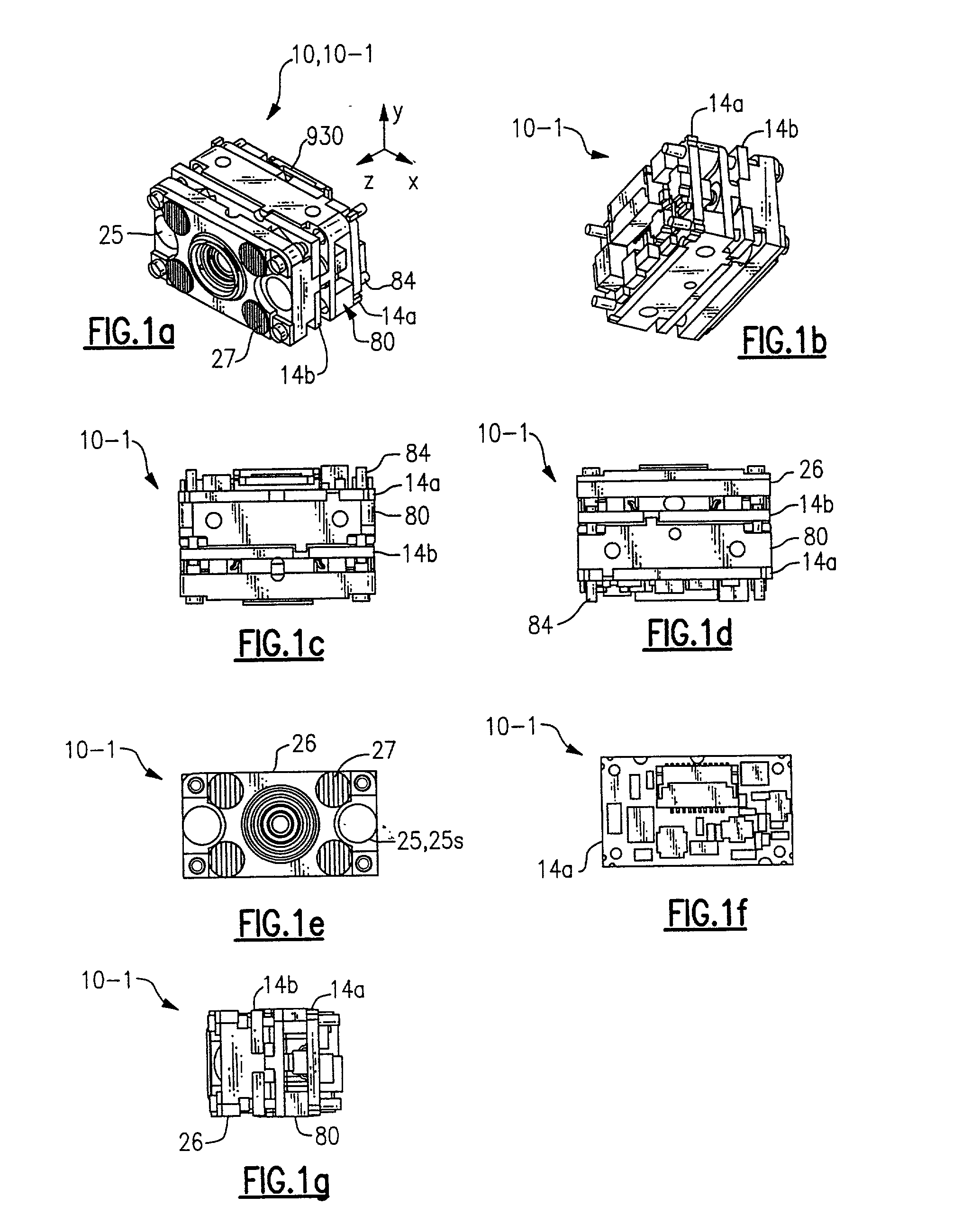

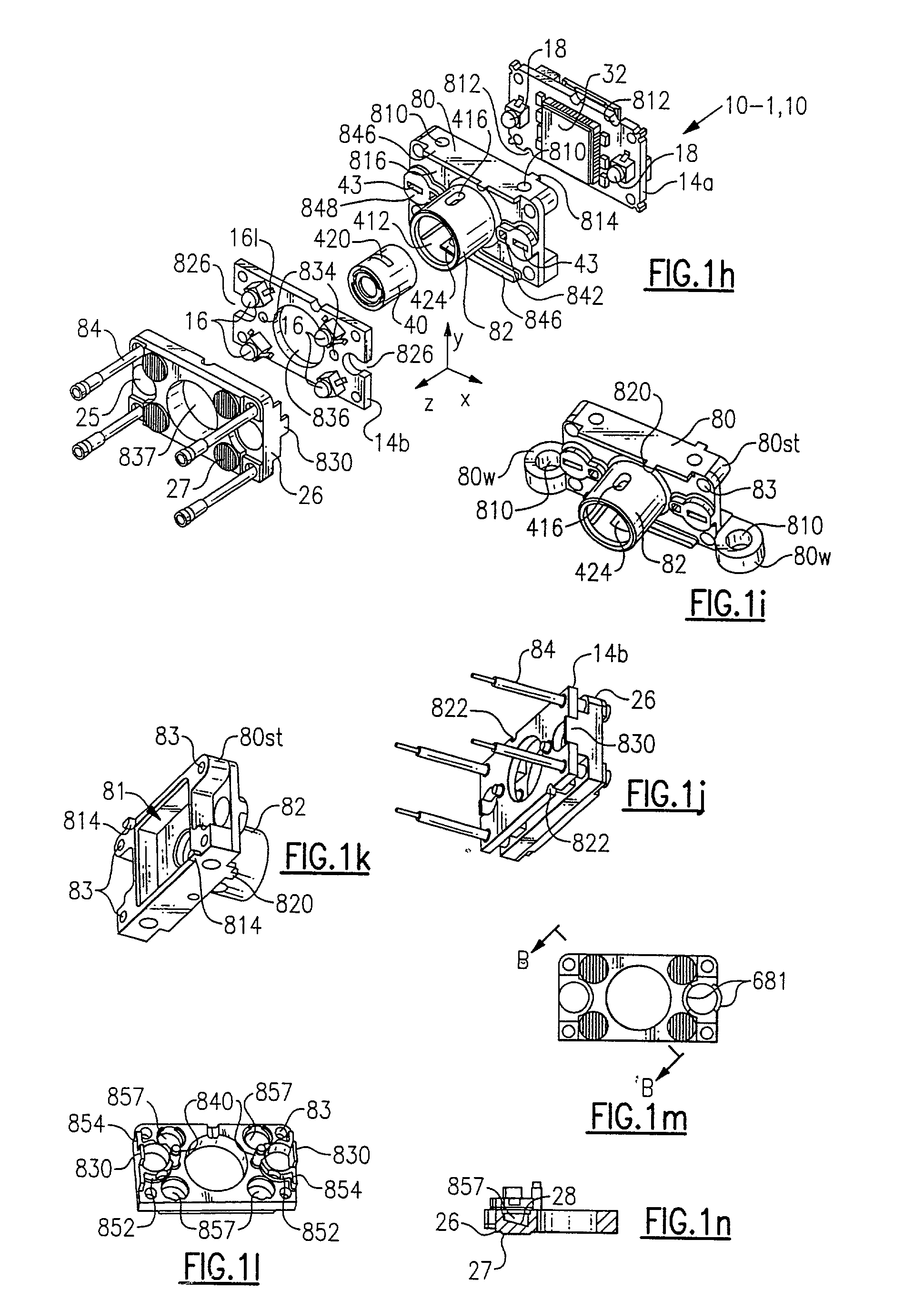

Optical reader comprising multiple color illumination

InactiveUS6832725B2Reduced dimensionOptimize architectureConveying record carriersCharacter and pattern recognitionComputer moduleLength wave

An imaging module in one embodiment includes at least one multiple color emitting light source comprising a plurality of different colored LED dies each independently driveable so that the overall color emitted by the light source can be controlled and varied. The multiple color emitting light source can be controlled so that the color emitted by the light source is optimized for imaging or reading in a present application environment of the module. Further, the module can be configured so that control of the multiple color emitting light source automatically varies depending on a sensed condition, such a color present in a field of view of the module, the distance of the module to a target, and / or a predetermined criteria being met so that feedback is provided to a user. The module in a further aspect can include illumination light sources and aiming light sources which project light in different wavelength emission bands.

Owner:HAND HELD PRODS

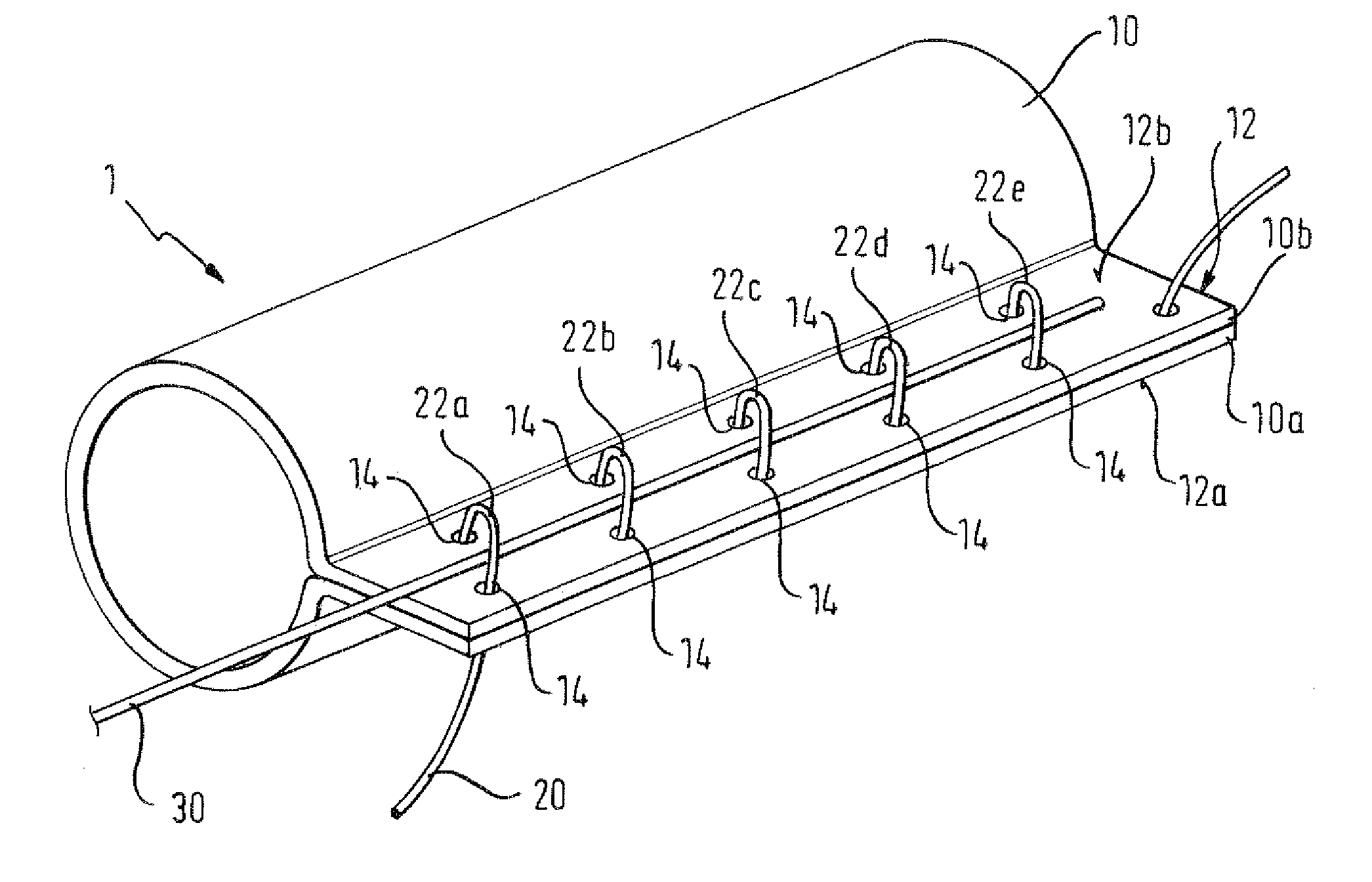

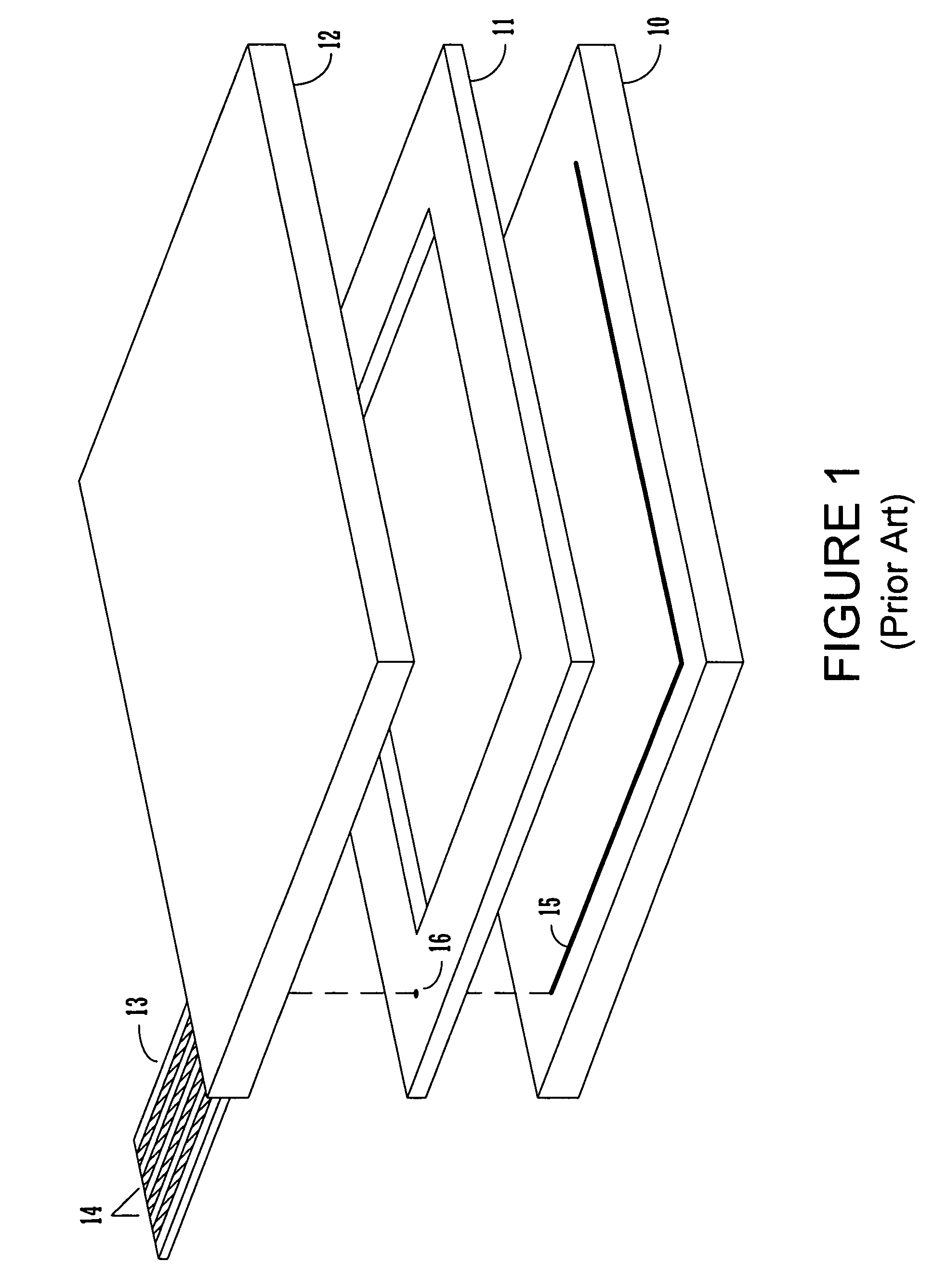

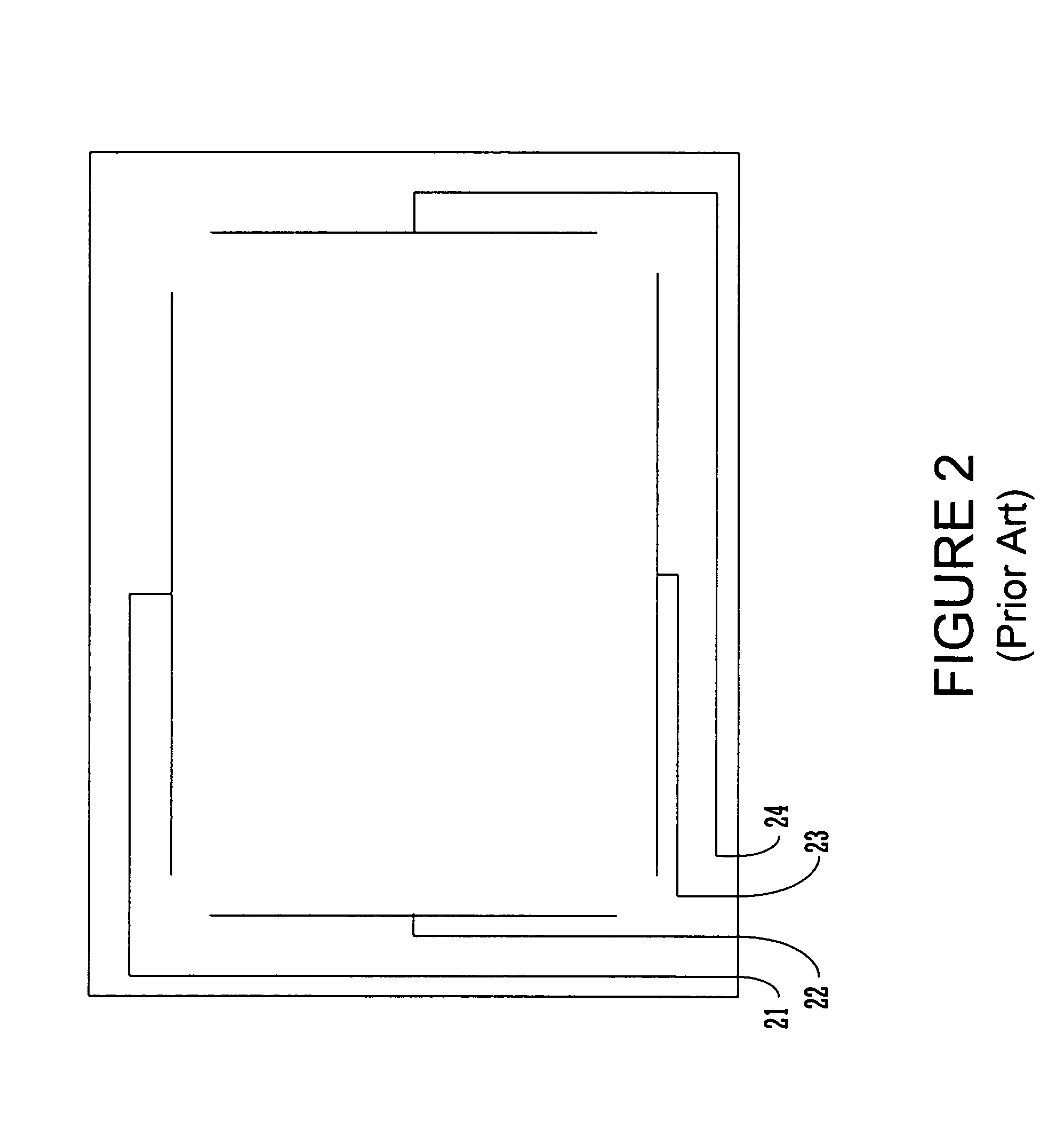

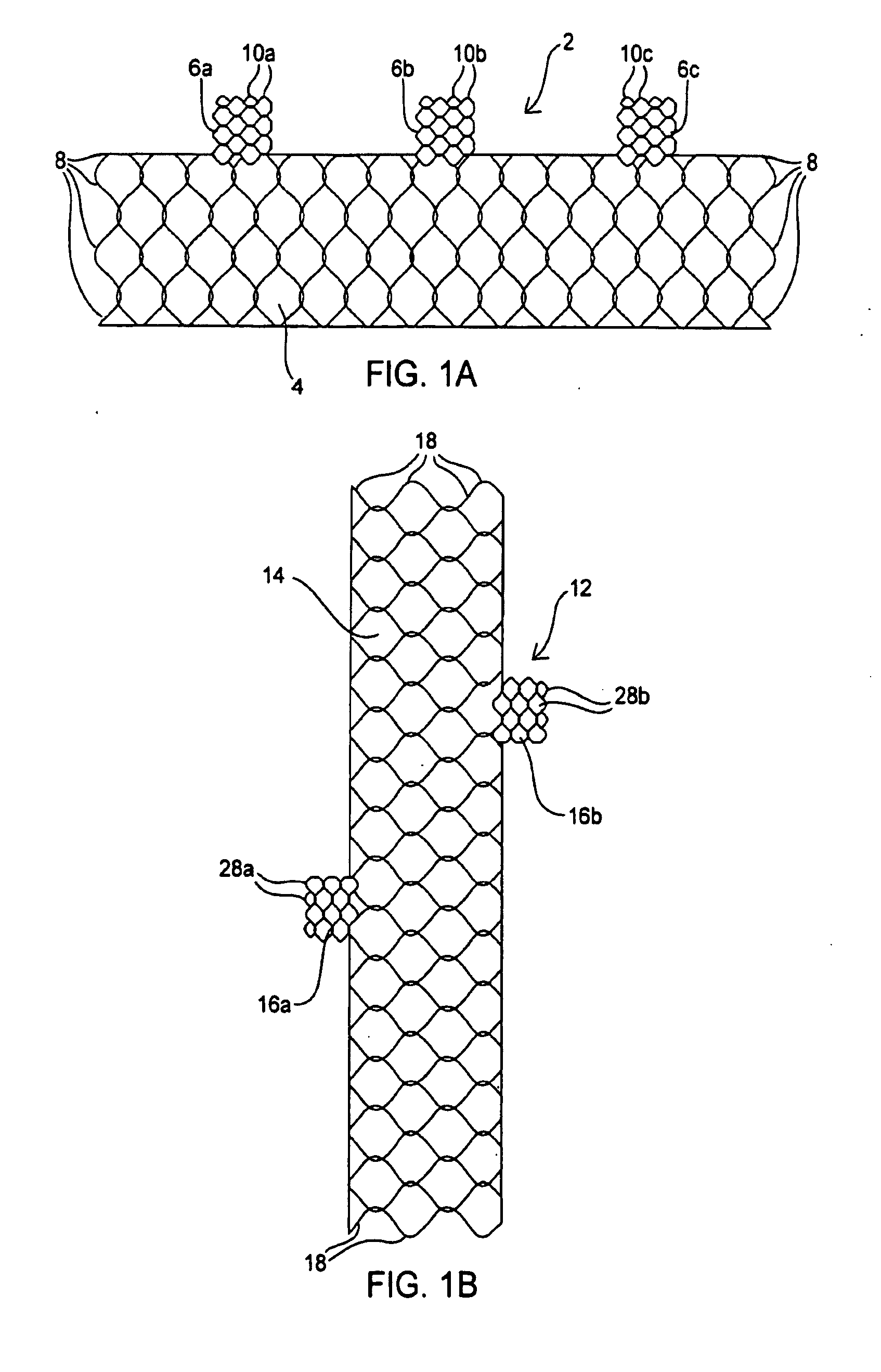

Catheter sheath for implant delivery

ActiveUS9060894B2Increase deflectionLarge radiusStentsBlood vesselsBiomedical engineeringCatheter sheath

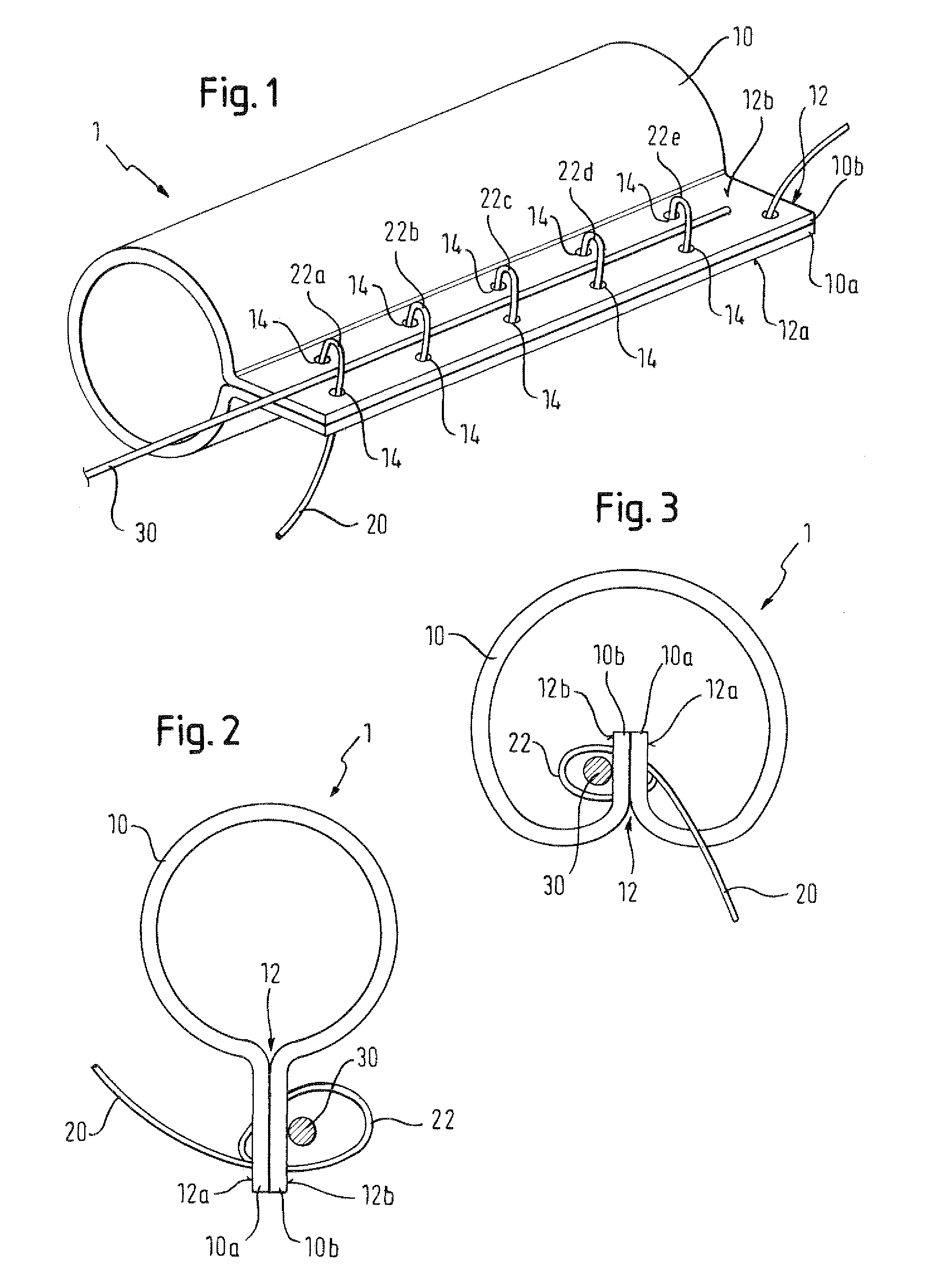

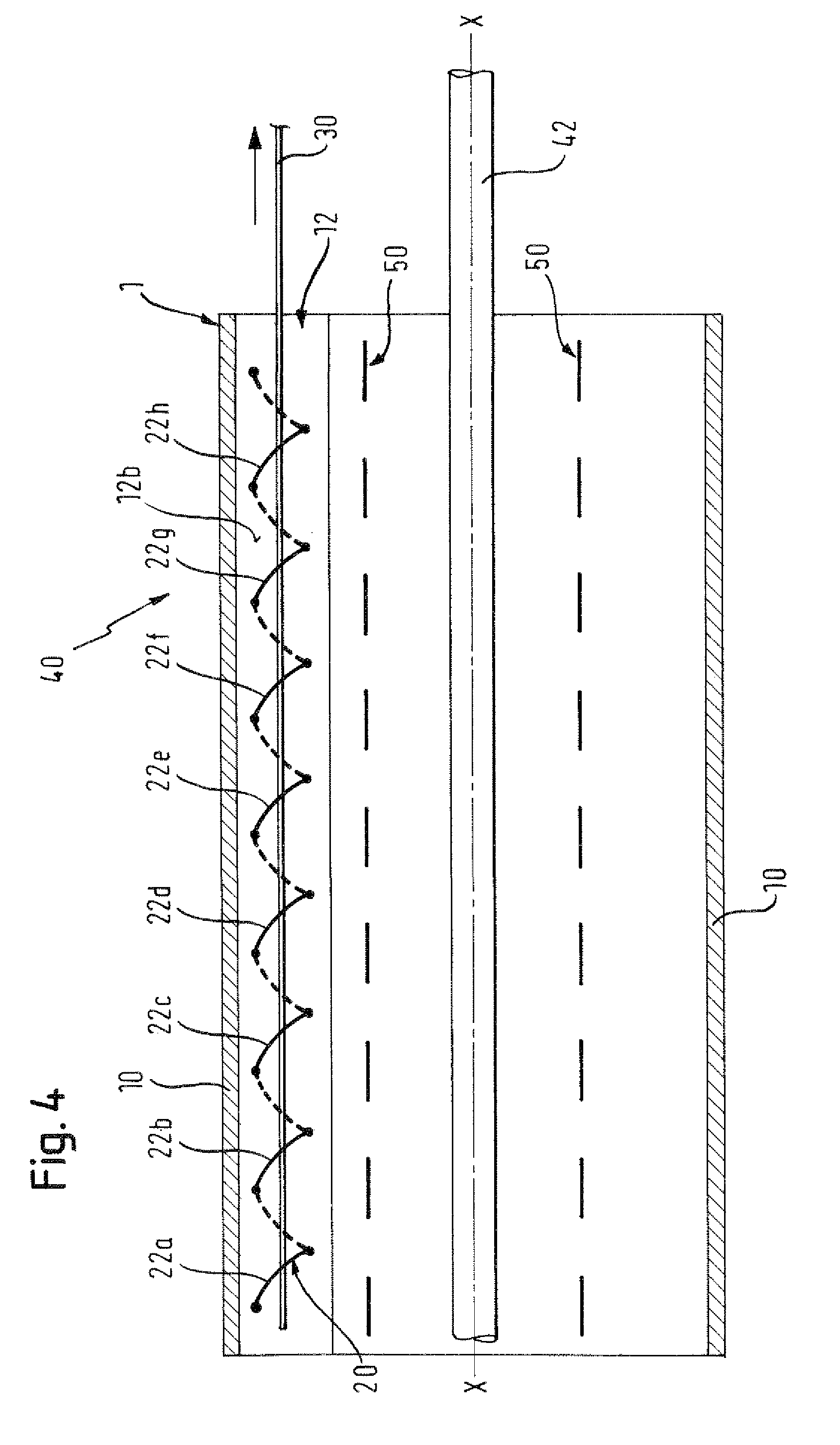

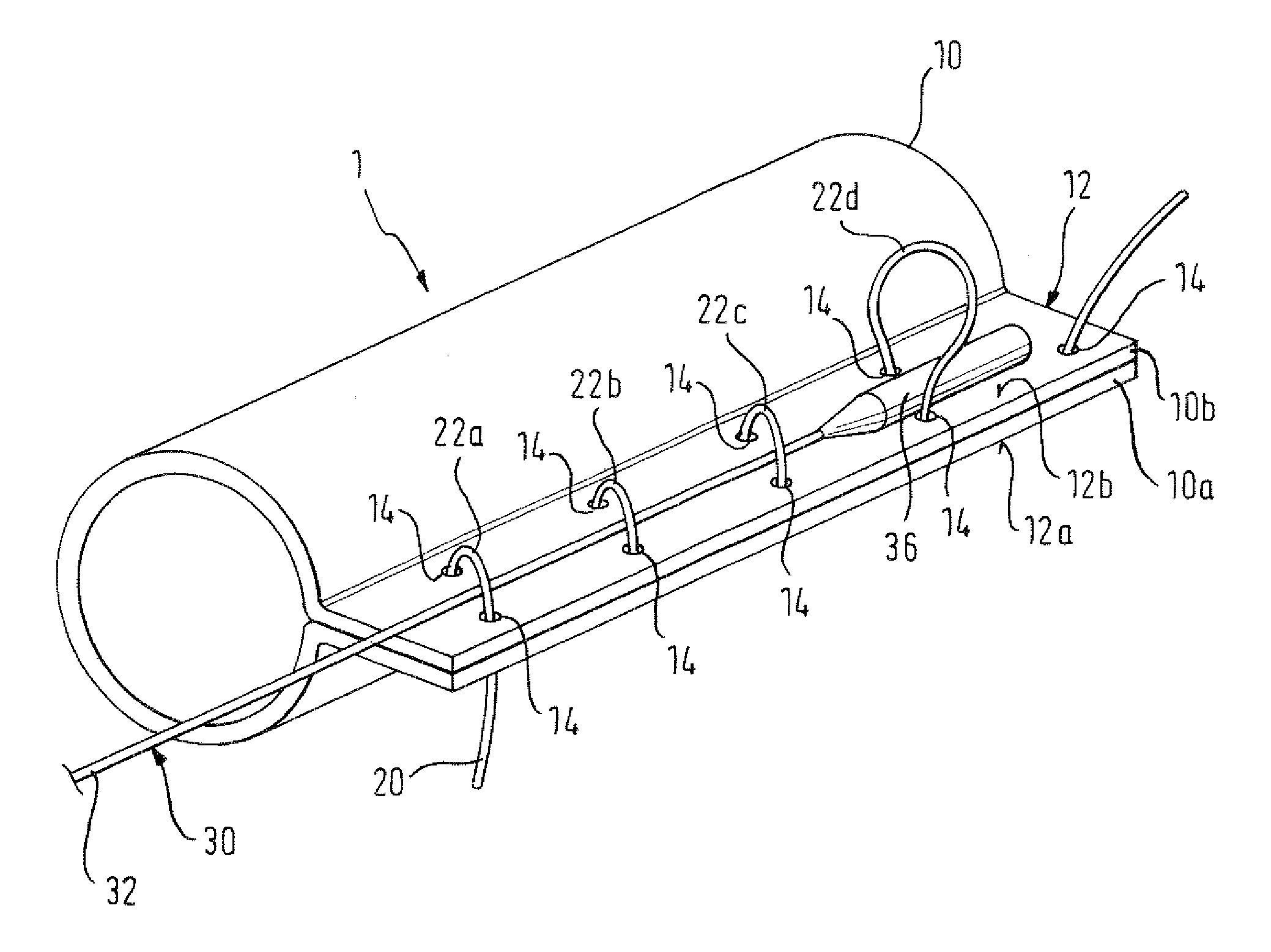

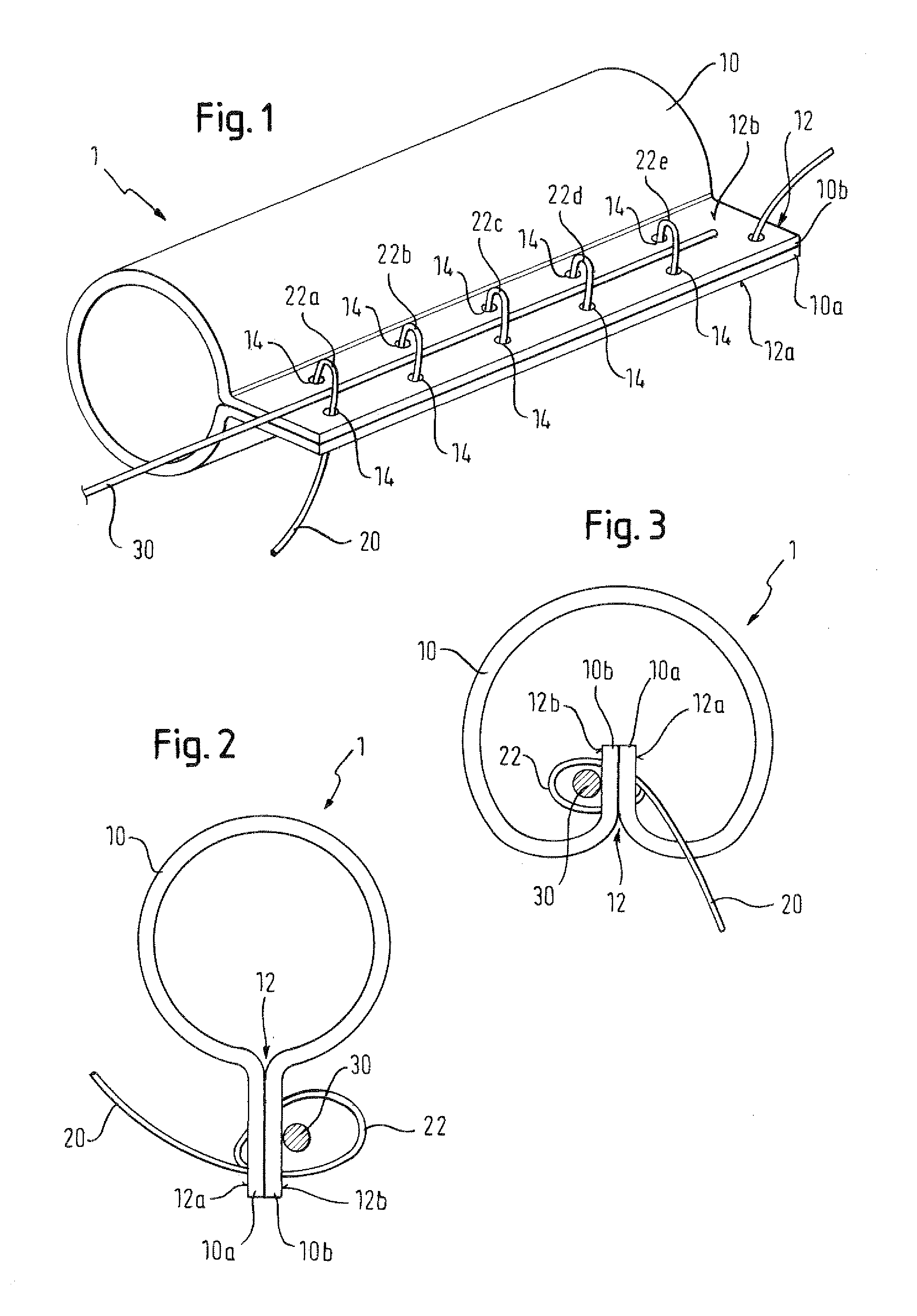

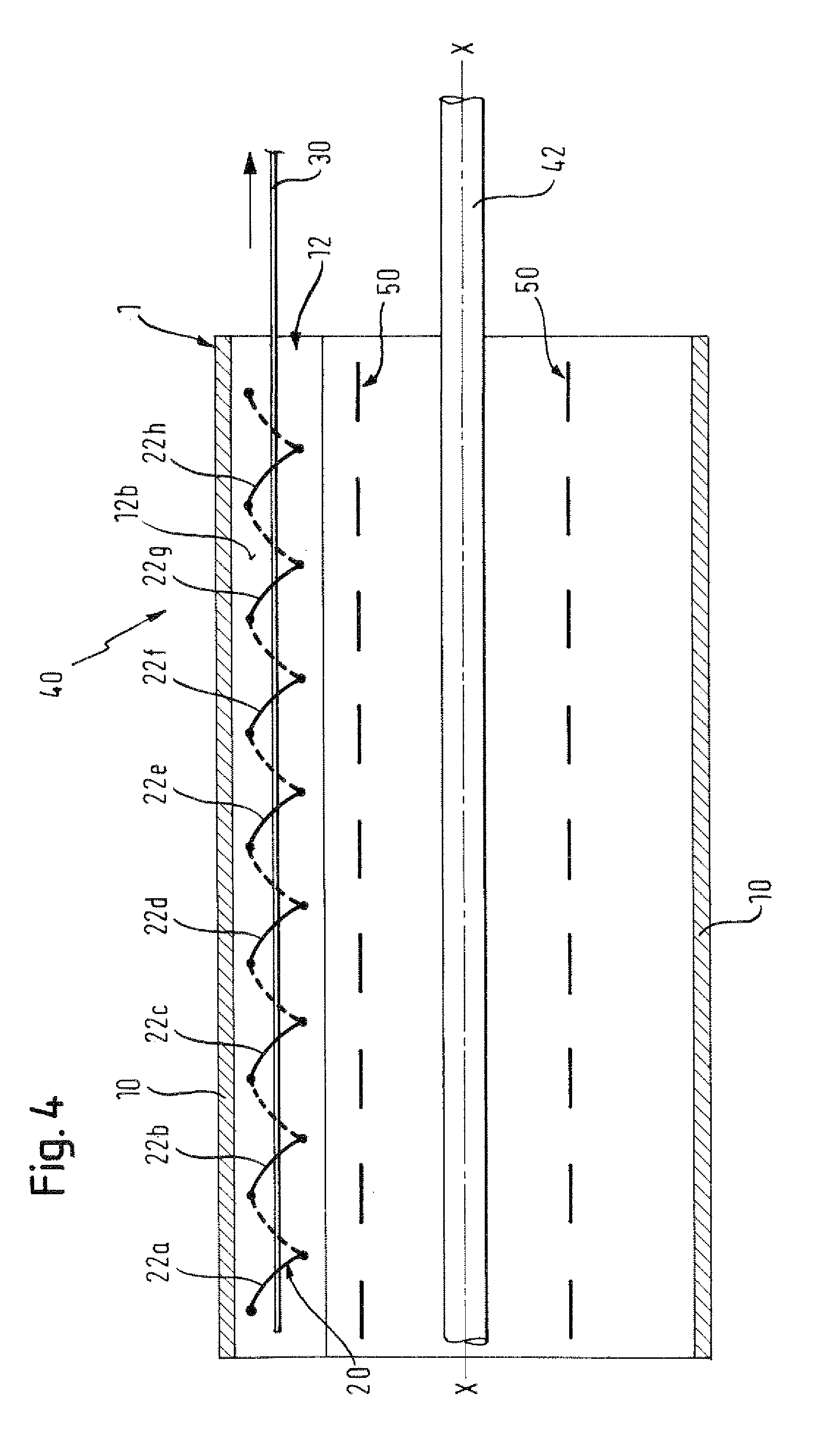

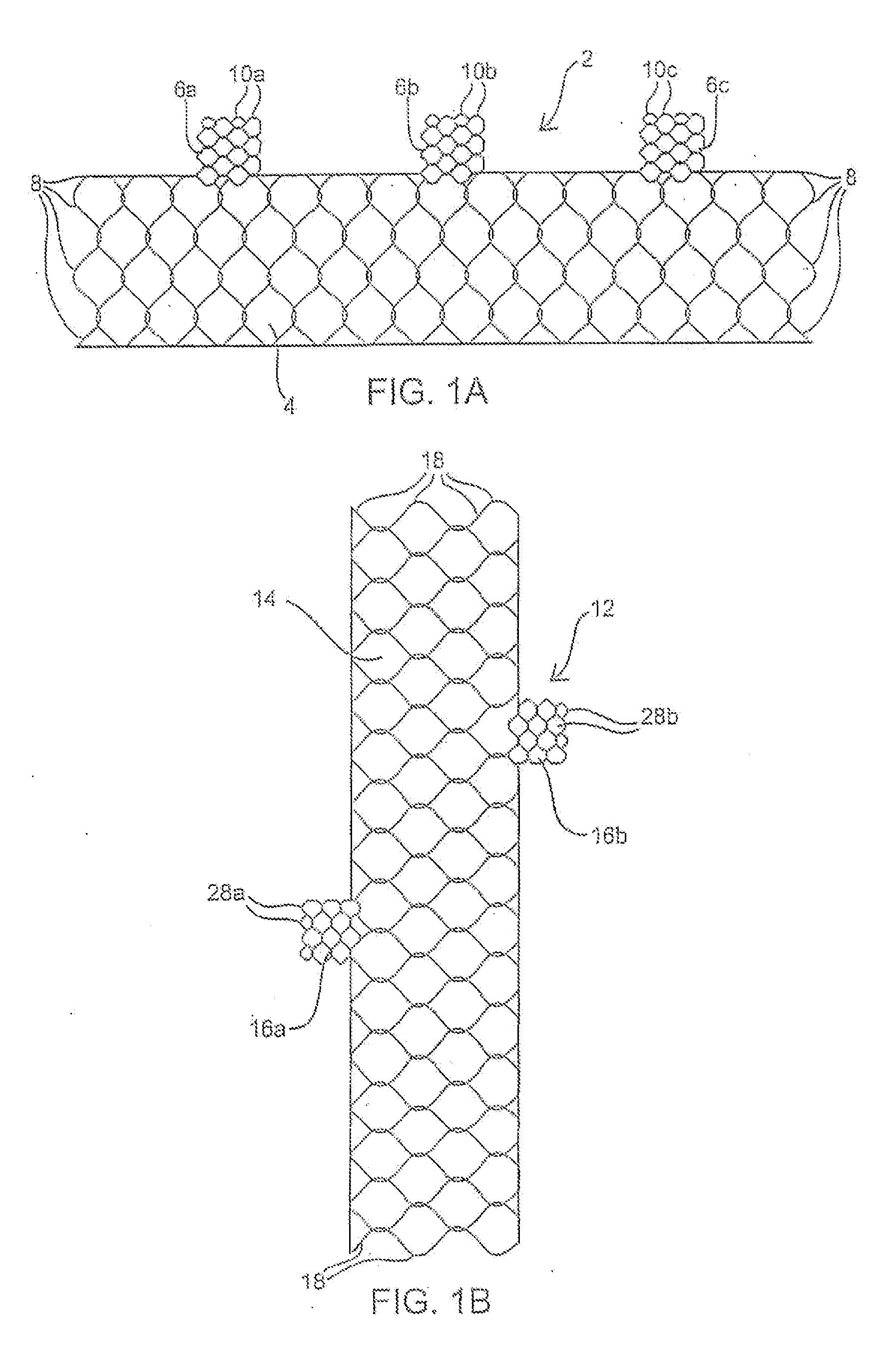

There is disclosed herein a tube of material (1) having a seam (12) extending between a proximal end and a distal end, two edges (10a, 10b) of the material meeting and at least partially overlapping along the seam (12) and being sewn together at the seam by stitches (21, 22, 24) of relatively flexible thread (20), the thread of one or more of the stitches (22, 24) passing from a first side (12a) of the overlapped edges (10a, 10b) of material, through both layers of overlapped material, crossing a relatively rigid member (30) which is disposed on a second, opposite side (12b) of the overlapped edges of material, and passing back to the first side (12a). There is further disclosed an implant delivery catheter (40) incorporating the tube of material (1), and associated methods for its manufacture.

Owner:CR BARD INC

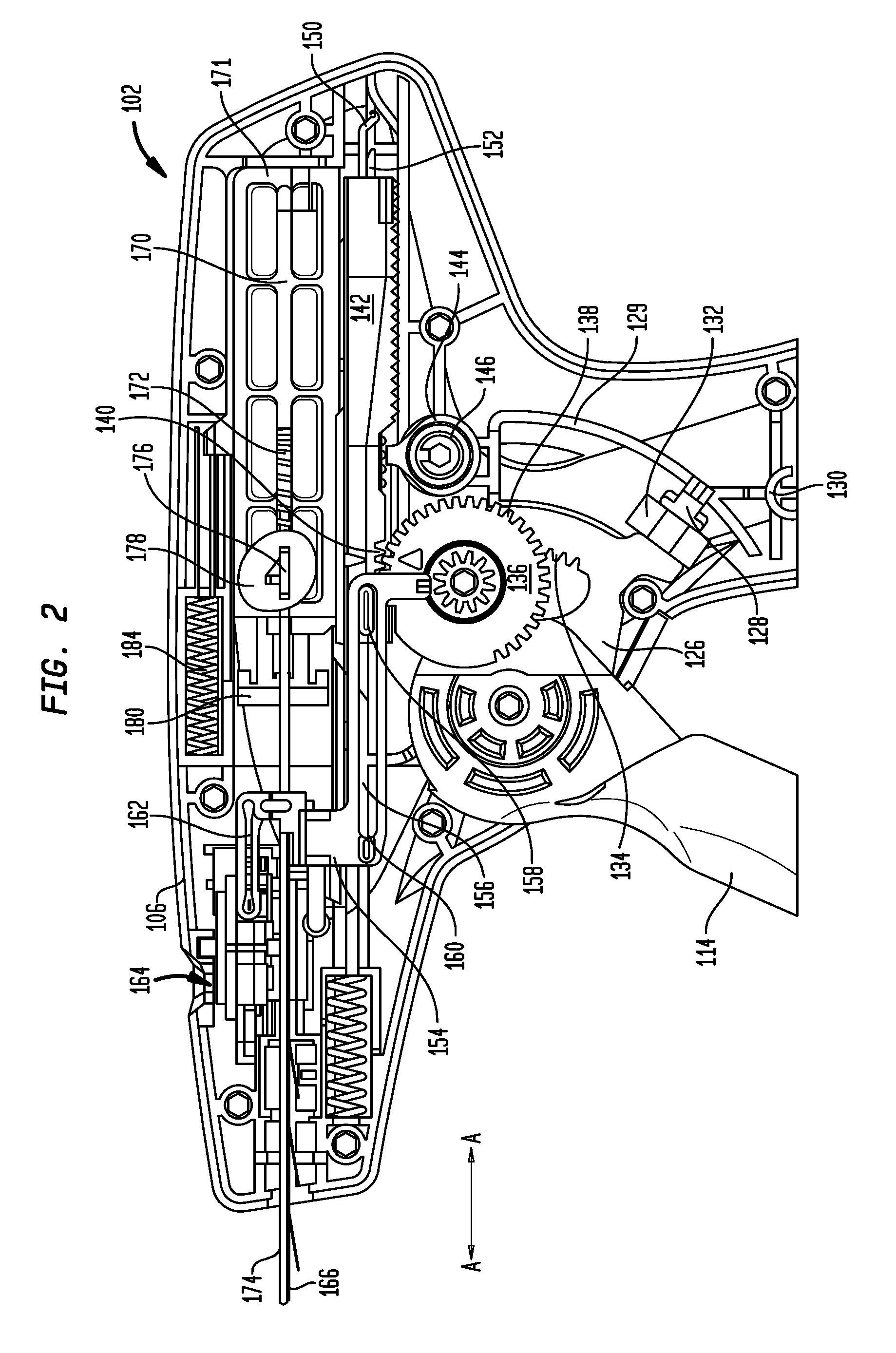

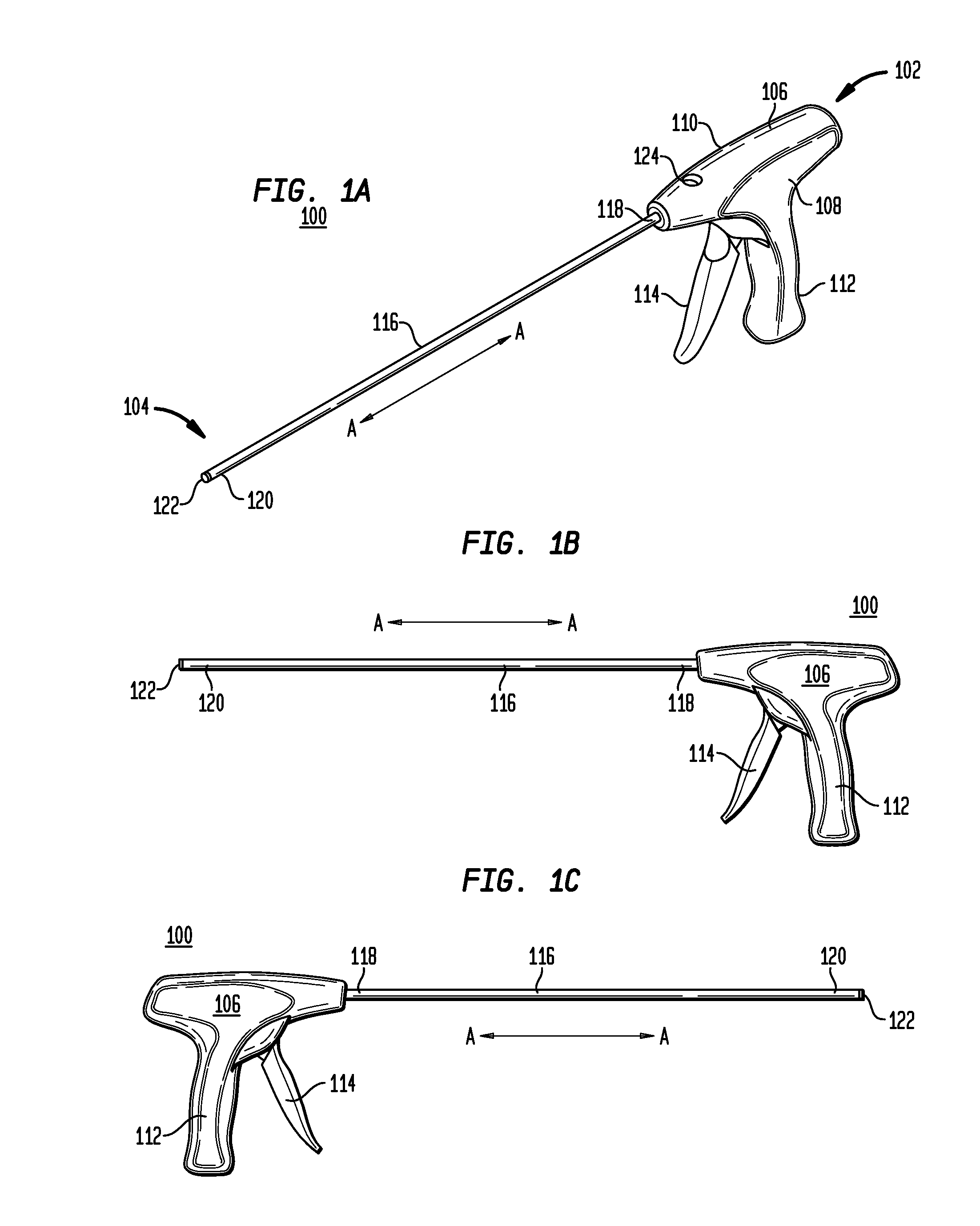

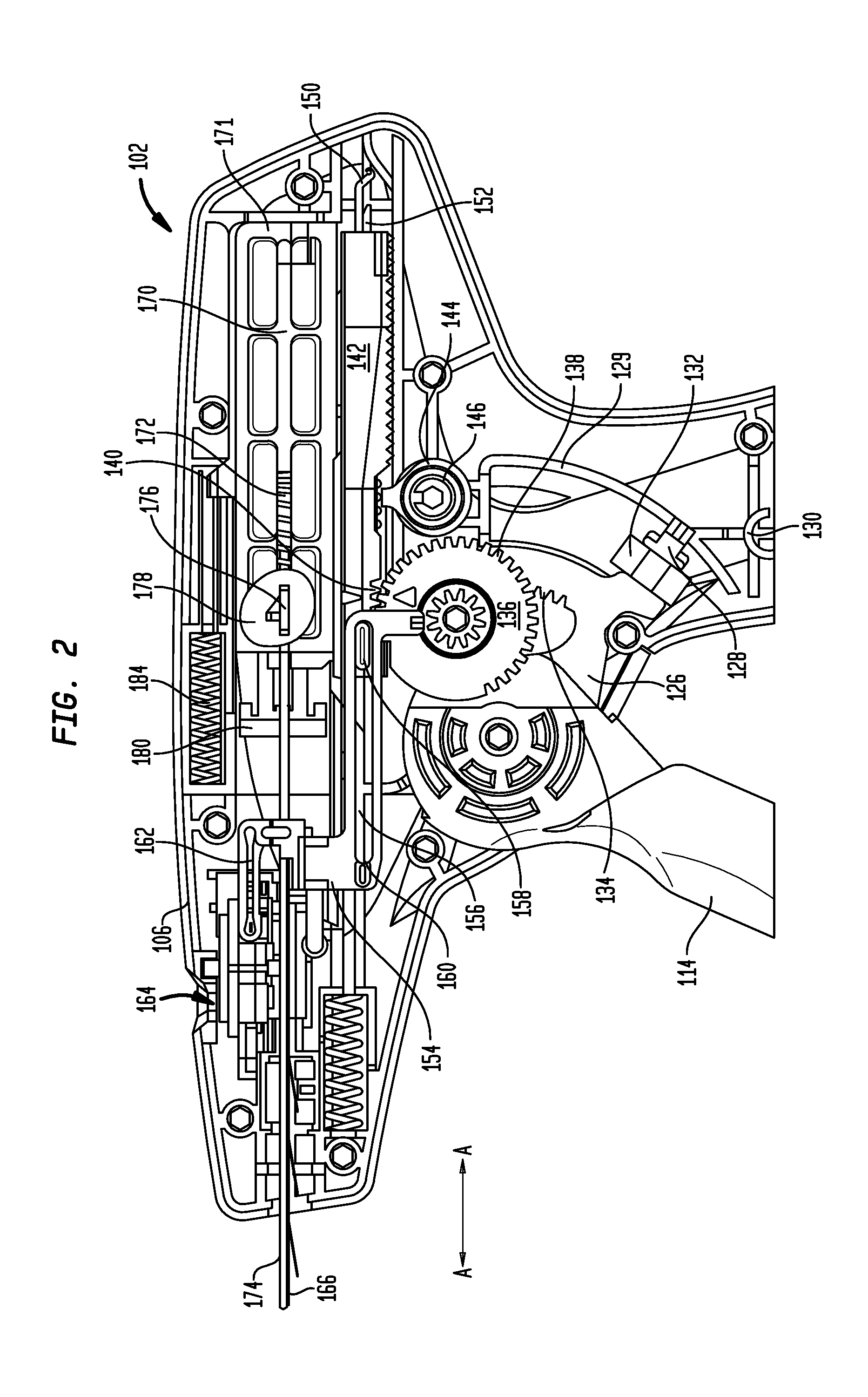

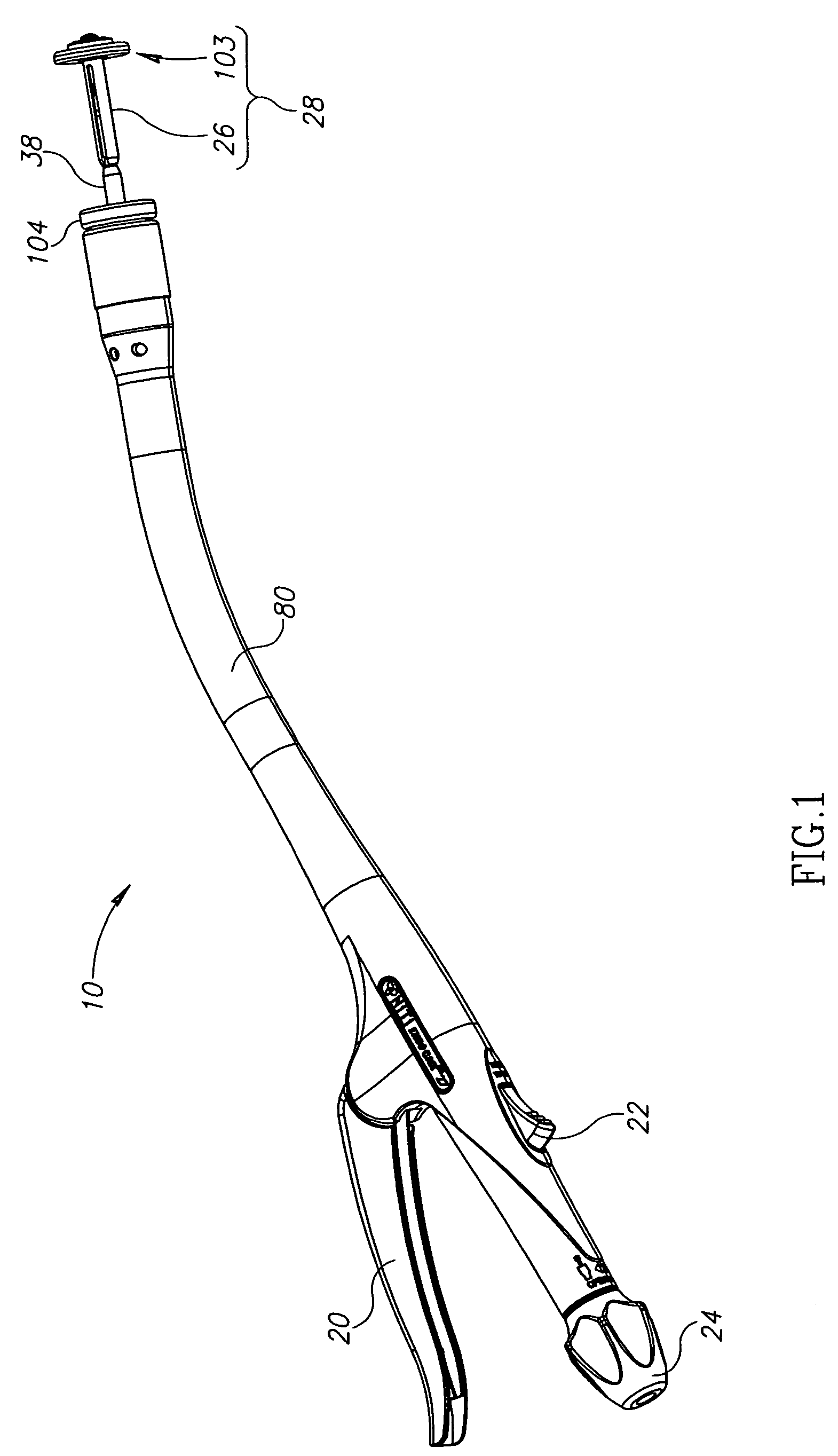

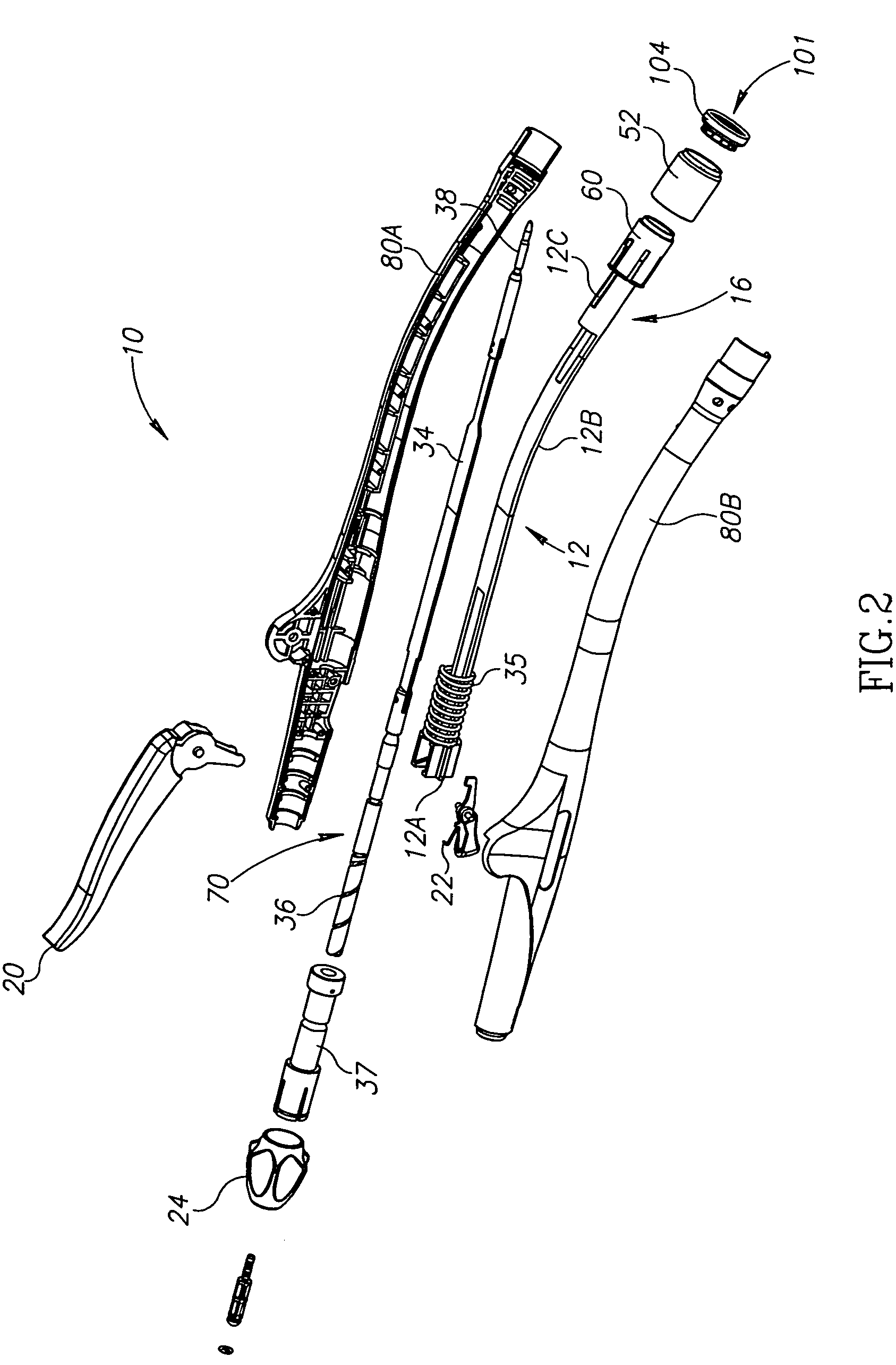

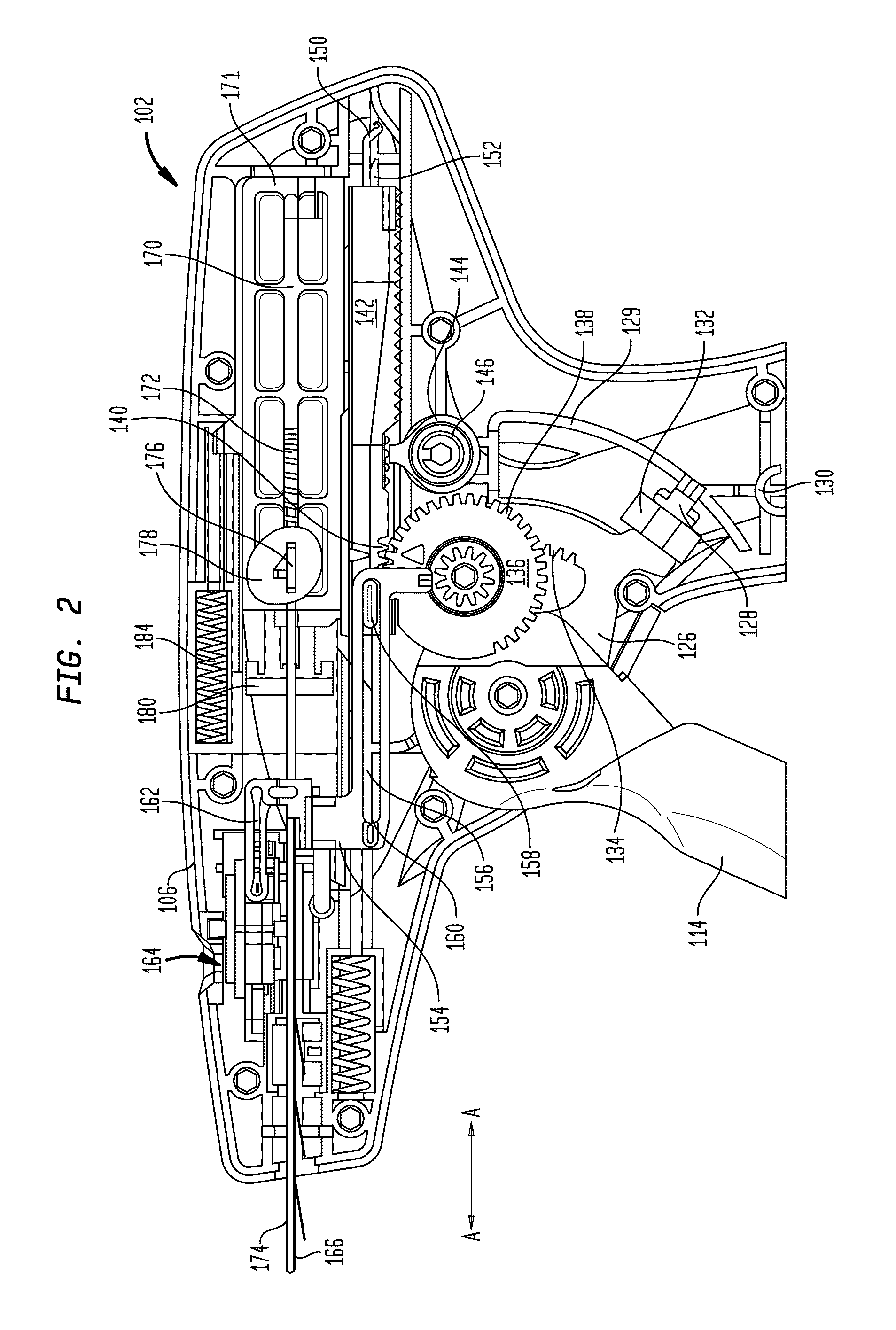

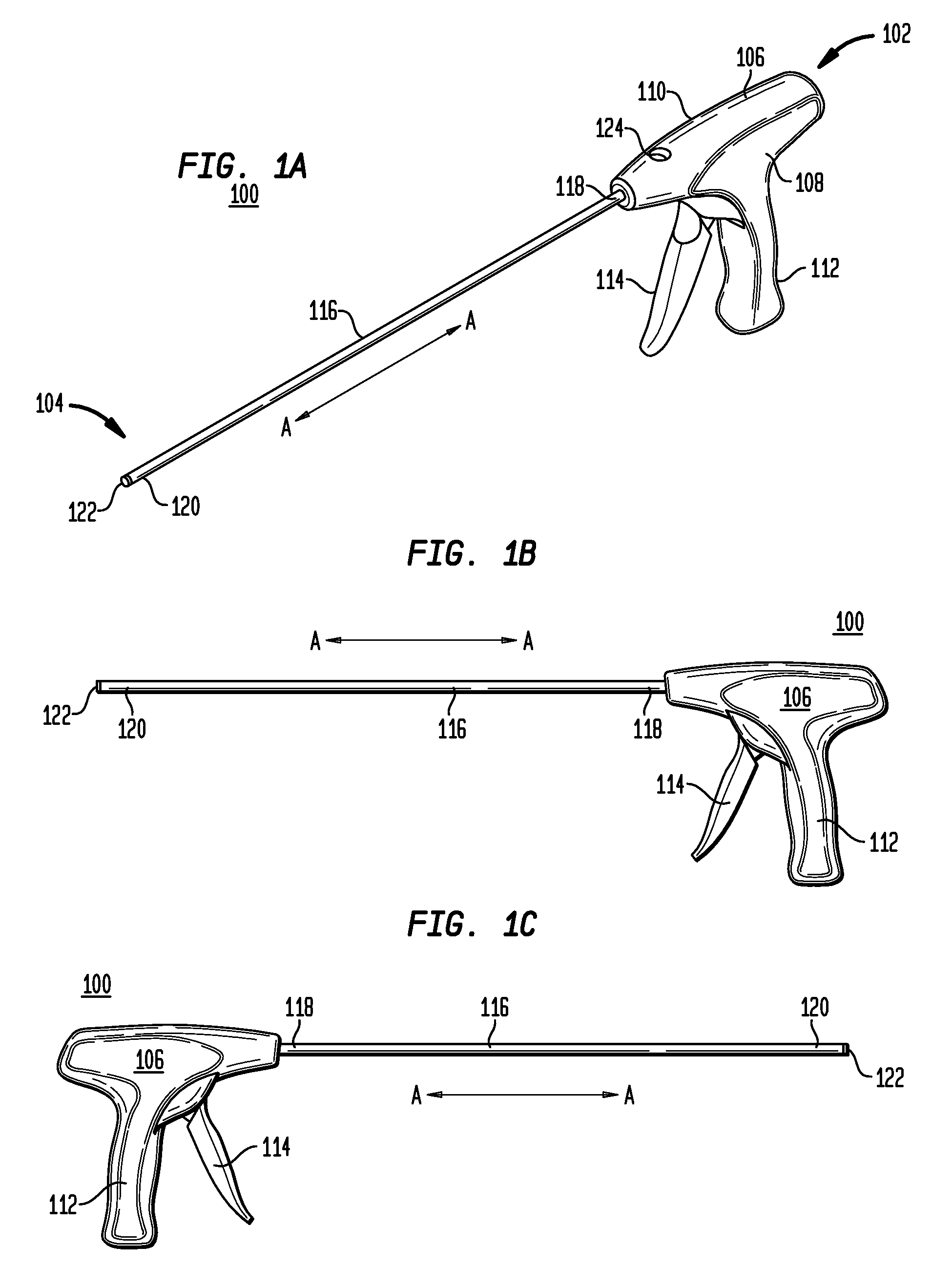

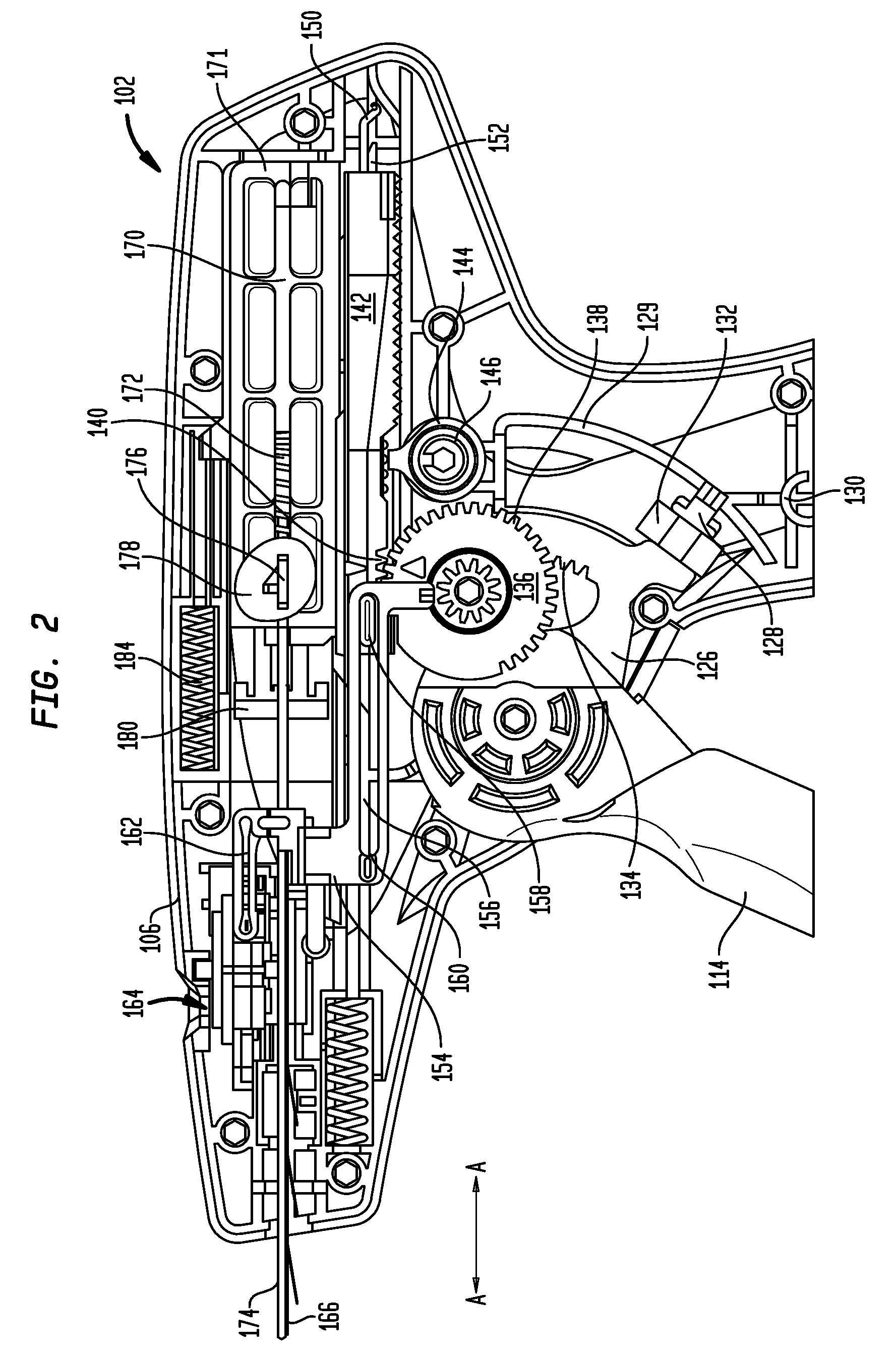

Surgical fasteners, applicator instruments, and methods for deploying surgical fasteners

ActiveUS8728099B2Accurate insertionGuarantees proper engagementSuture equipmentsStapling toolsEngineeringSurgical Fasteners

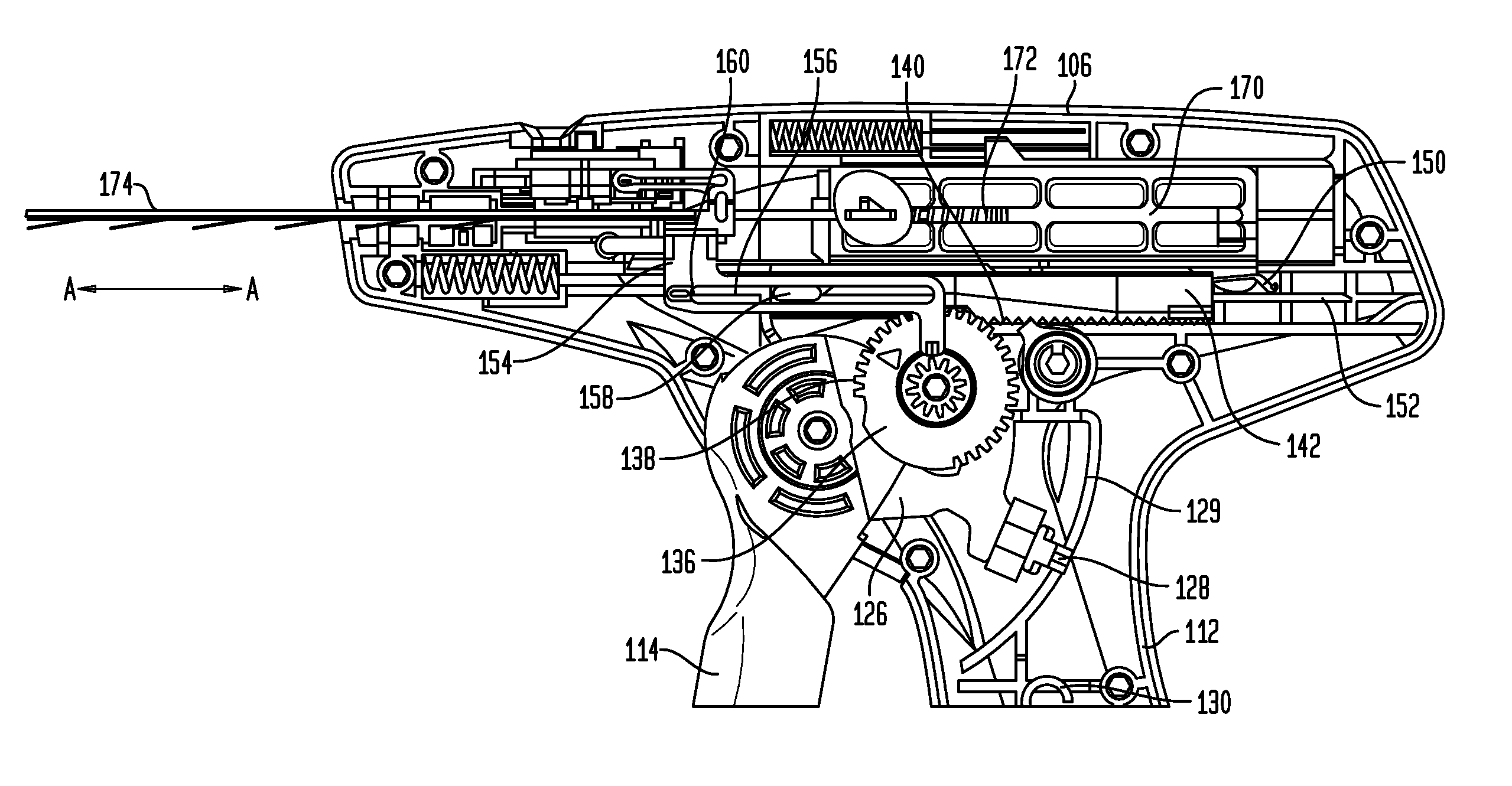

A firing system for an applicator instrument adapted to dispense surgical fasteners includes a housing, an elongated shaft extending from the housing, a firing rod disposed within the elongated shaft, a firing rod release engageable with the firing rod for preventing distal movement of the firing rod during at least one stage of a firing cycle, a trigger mounted to the housing, and a firing spring having a first end connected with the firing rod and a second end adapted for being sequentially coupled and decoupled from the trigger during the firing cycle. The firing cycle includes an initial stage in which the trigger is open and decoupled from the energy storing element, and the firing spring is at least partially compressed, and a piloting stage during which the firing rod release is disengaged from the firing rod for enabling distal movement of the firing rod.

Owner:ETHICON INC

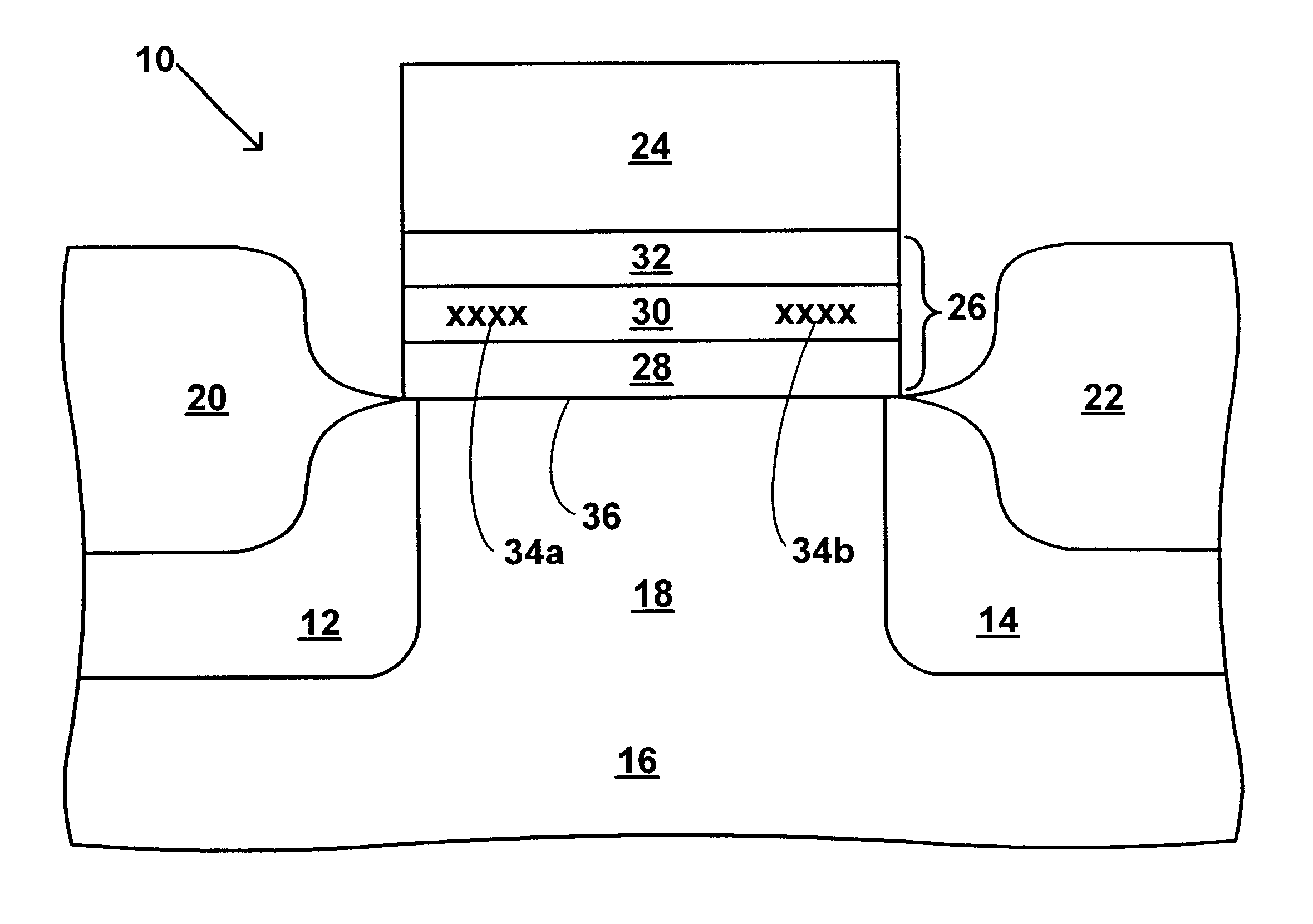

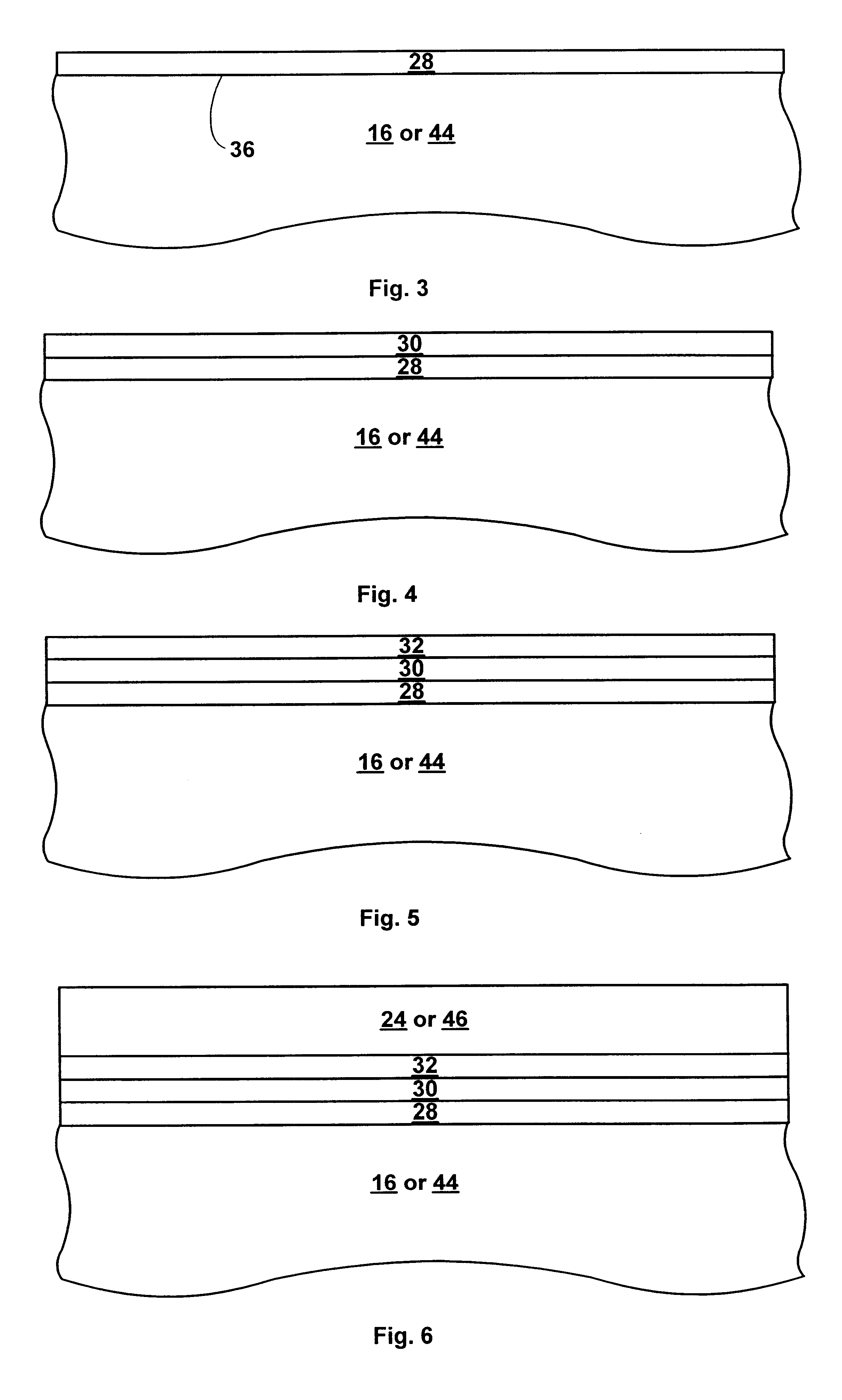

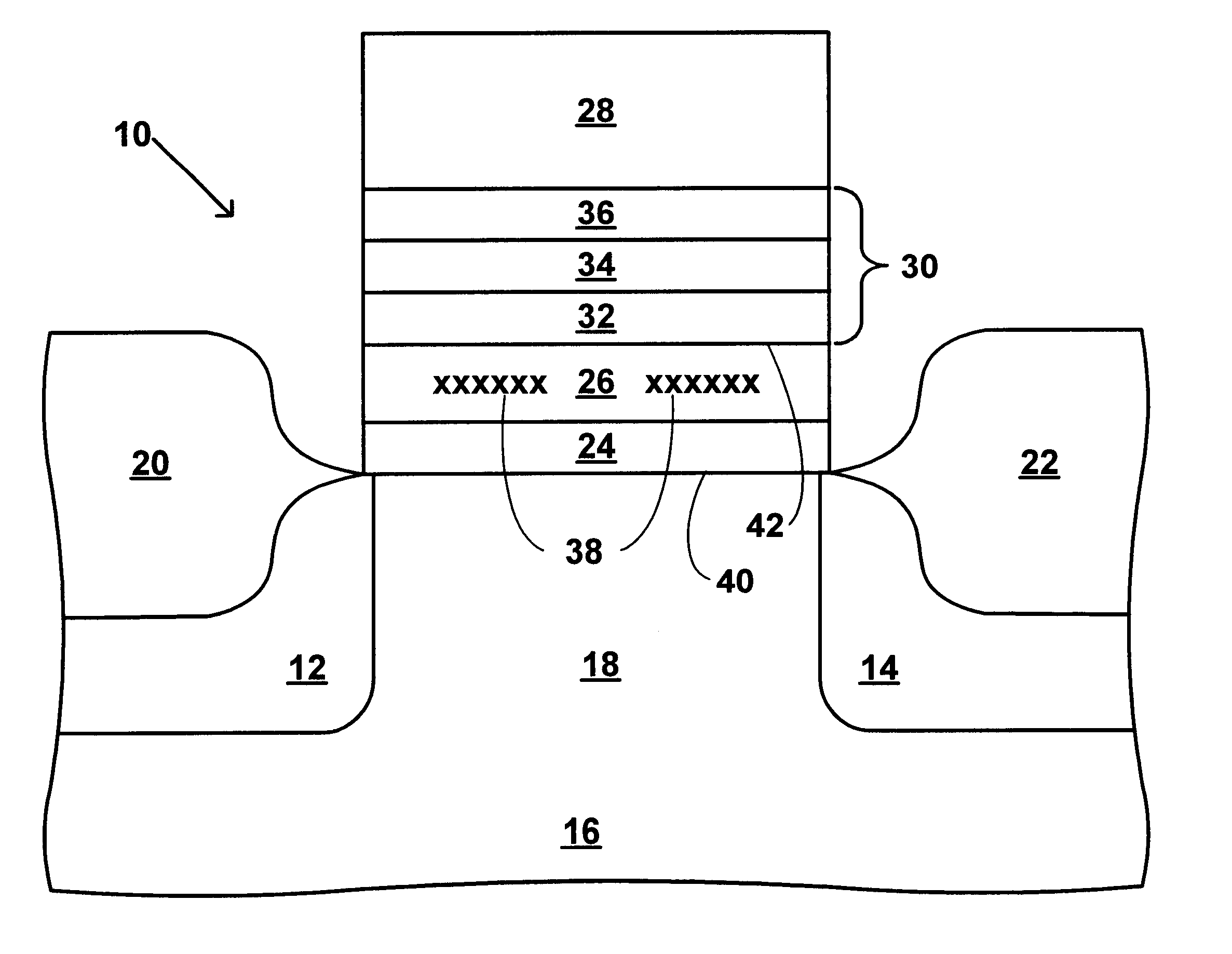

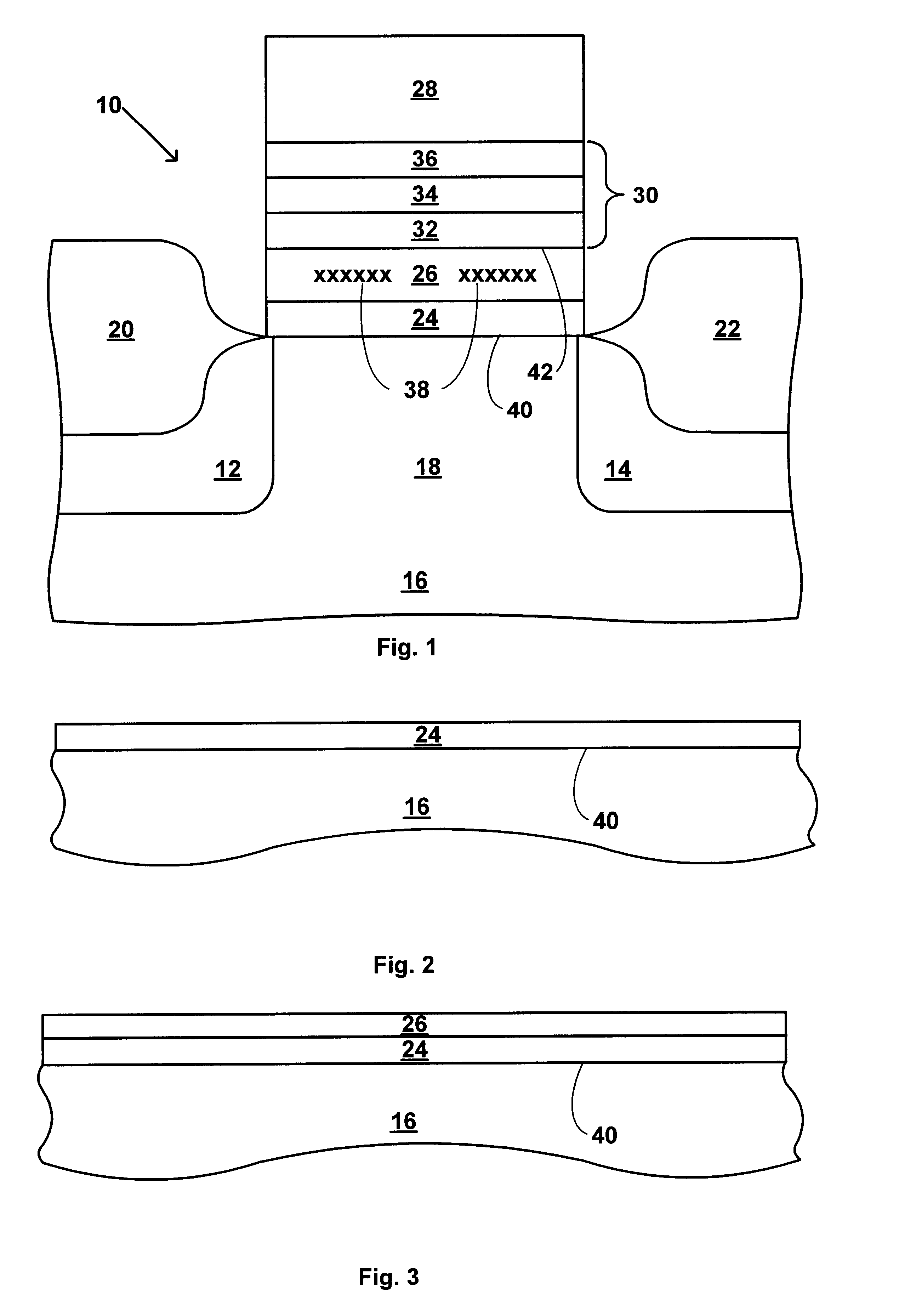

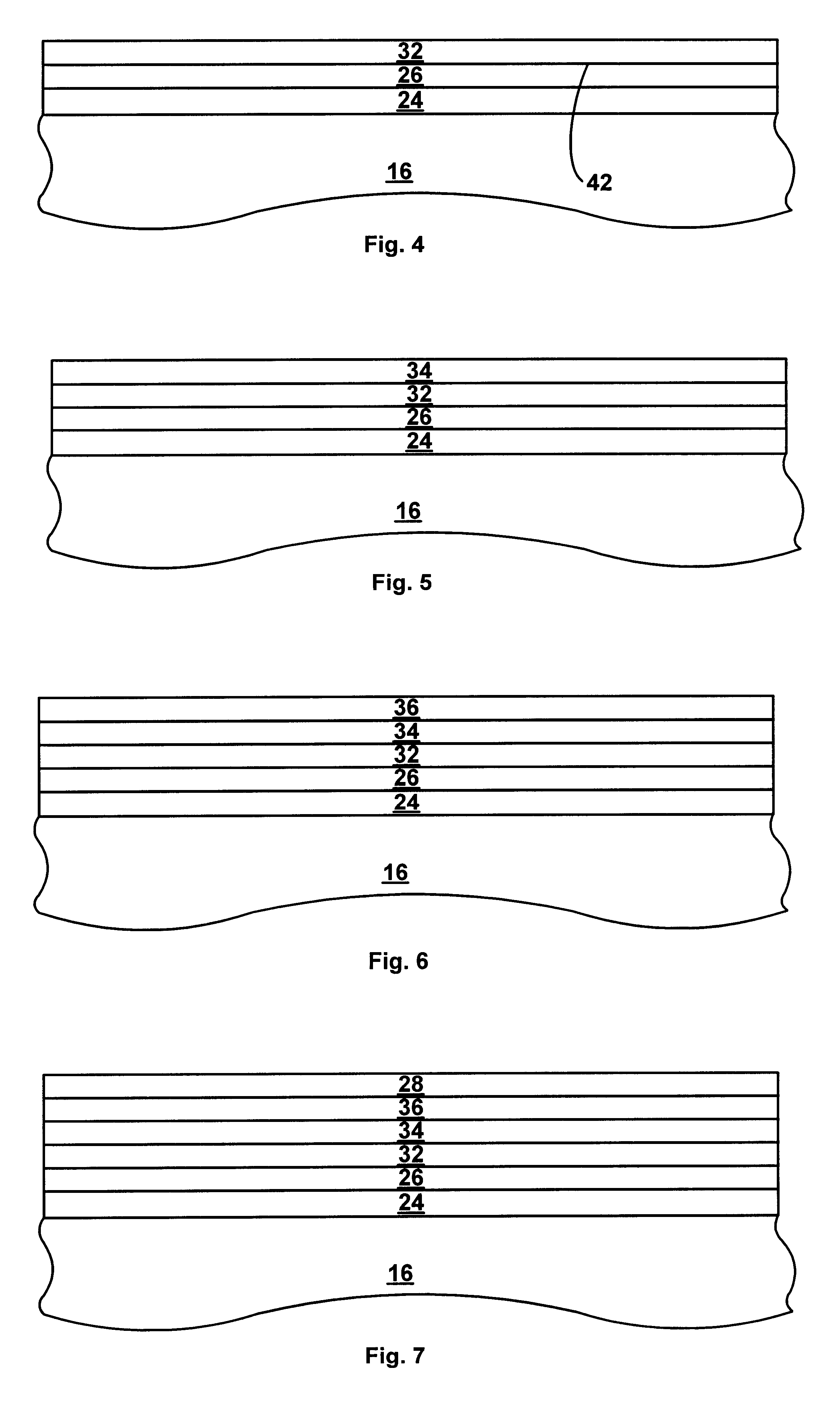

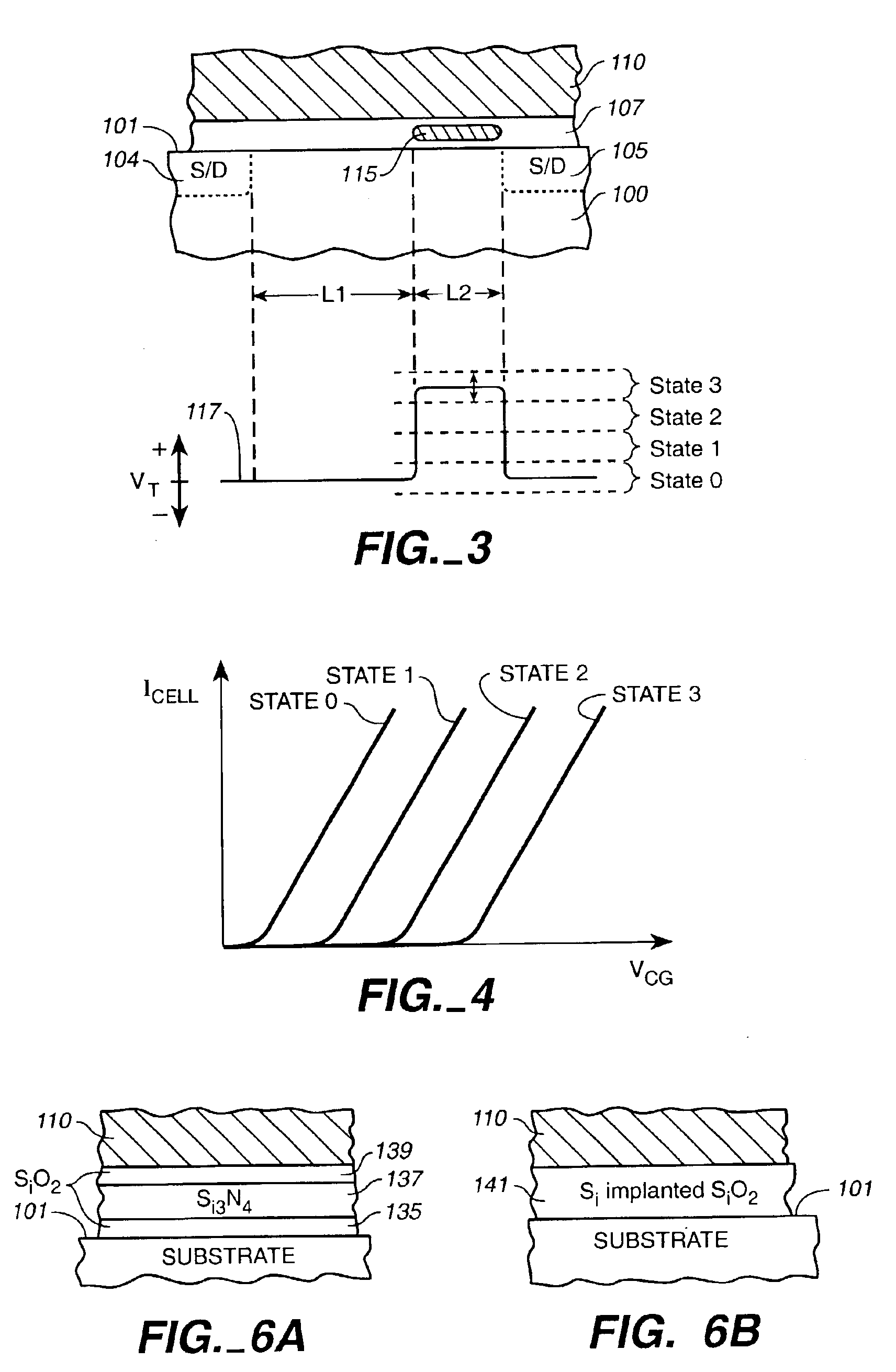

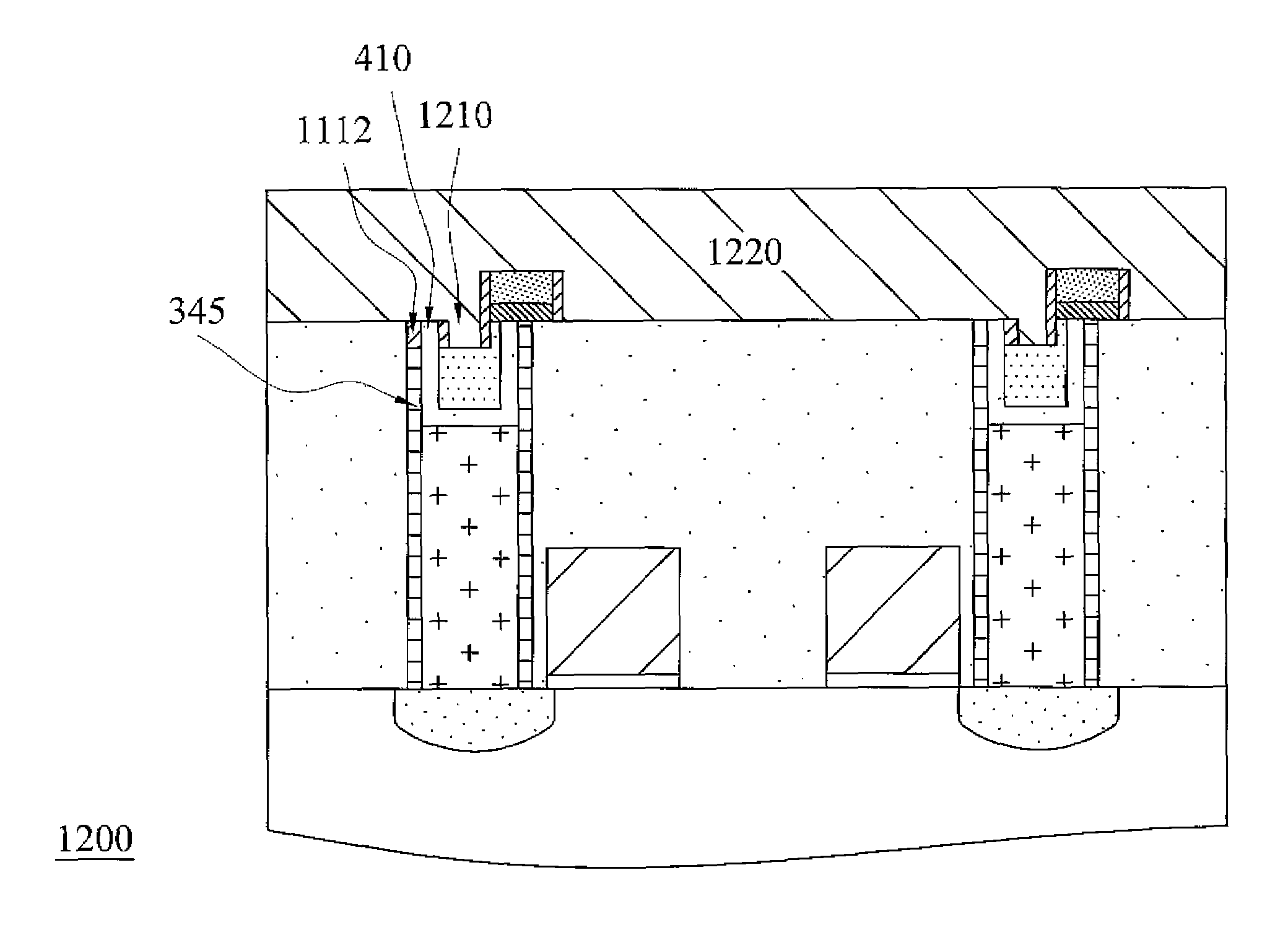

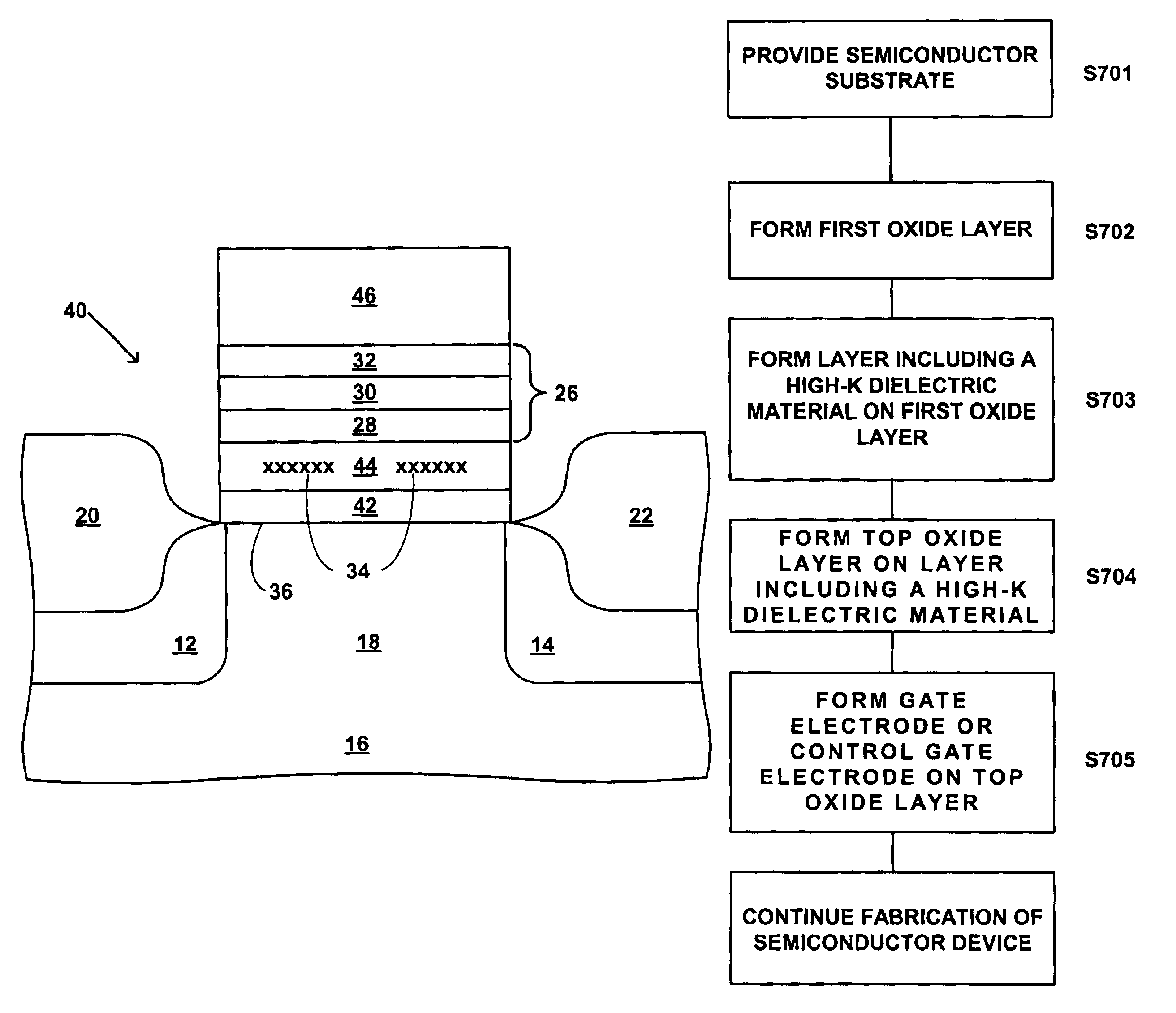

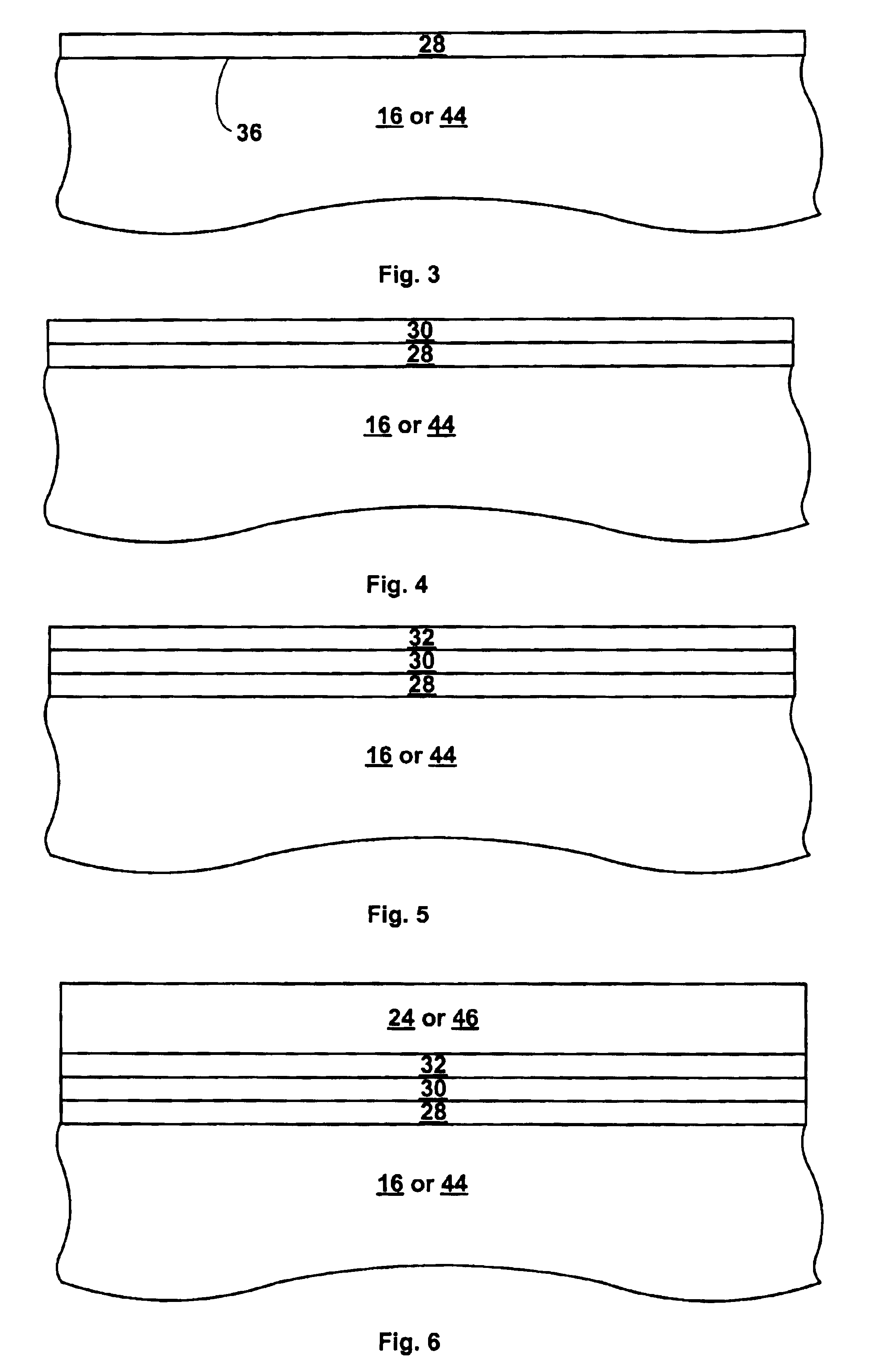

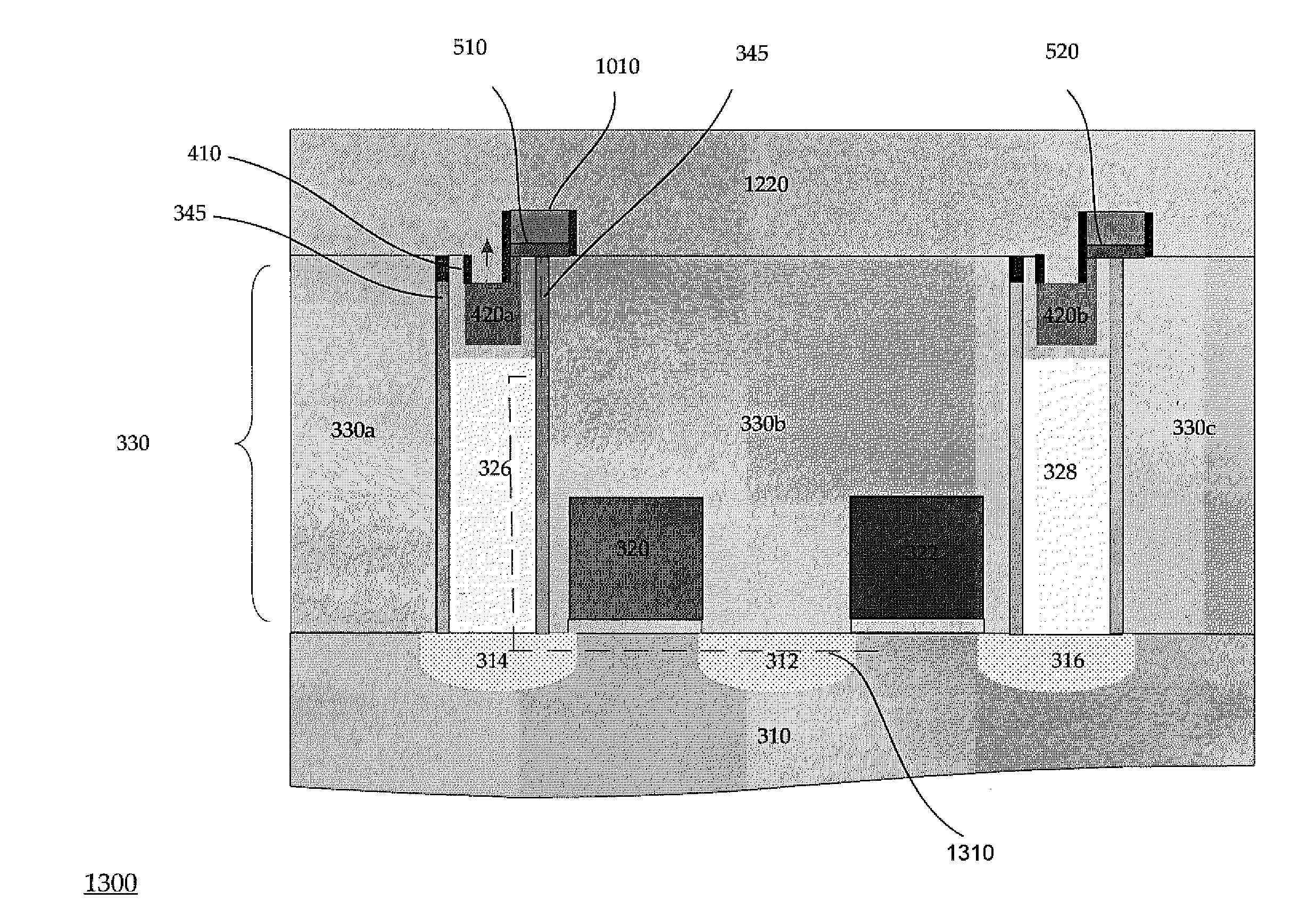

Use of high-k dielectric materials in modified ONO structure for semiconductor devices

InactiveUS6674138B1Reduced dimensionSacrificing charge trapping abilityTransistorSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

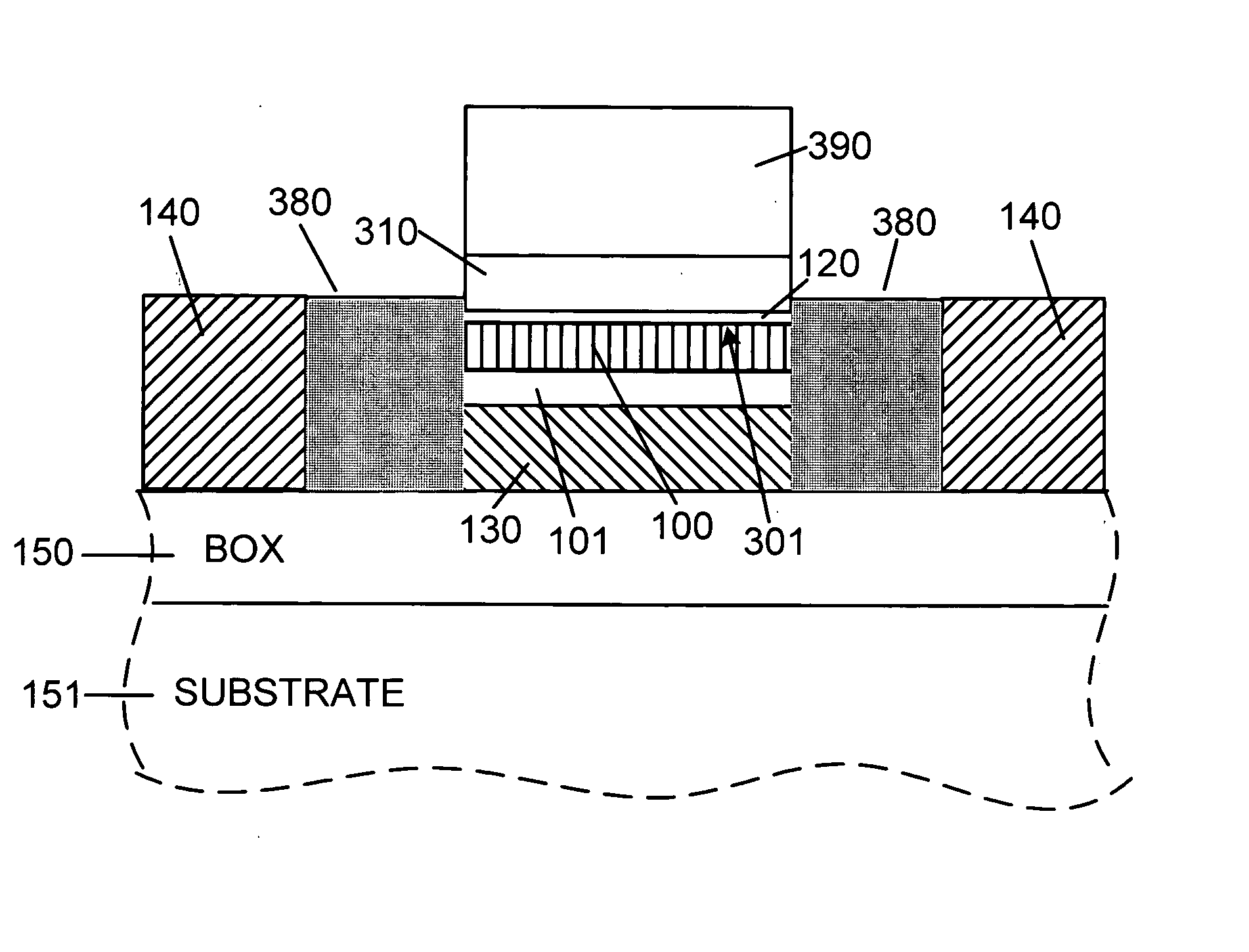

A process for fabrication of a semiconductor device including a modified ONO structure, including forming the modified ONO structure by providing a semiconductor substrate; forming a first oxide layer on the semiconductor substrate; depositing a layer comprising a high-K dielectric material on the first oxide layer; and forming a top oxide layer on the layer comprising a high-K dielectric material. The semiconductor device may be, e.g., a MIRRORBIT(TM) two-bit EEPROM device or a floating gate flash device including a modified ONO structure.

Owner:MONTEREY RES LLC

Catheter sheath for implant delivery

ActiveUS20120022630A1Increase deflectionLarge radiusStentsLeather sewingBiomedical engineeringCatheter sheath

There is disclosed herein a tube of material (1) having a seam (12) extending between a proximal end and a distal end, two edges (10a, 10b) of the material meeting and at least partially overlapping along the seam (12) and being sewn together at the seam by stitches (21, 22, 24) of relatively flexible thread (20), the thread of one or more of the stitches (22, 24) passing from a first side (12a) of the overlapped edges (10a, 10b) of material, through both layers of overlapped material, crossing a relatively rigid member (30) which is disposed on a second, opposite side (12b) of the overlapped edges of material, and passing back to the first side (12a). There is further disclosed an implant delivery catheter (40) incorporating the tube of material (1), and associated methods for its manufacture.

Owner:CR BARD INC

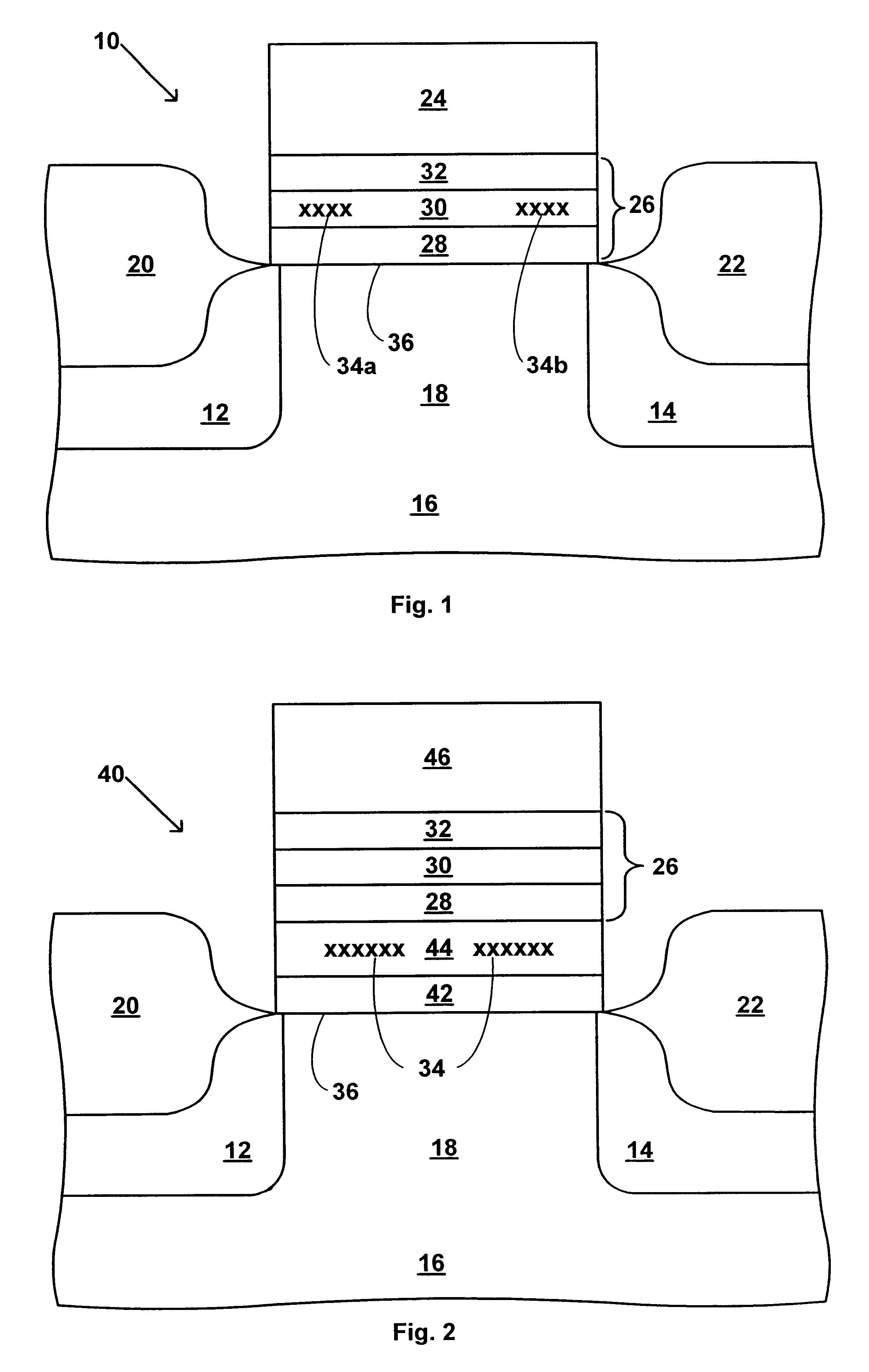

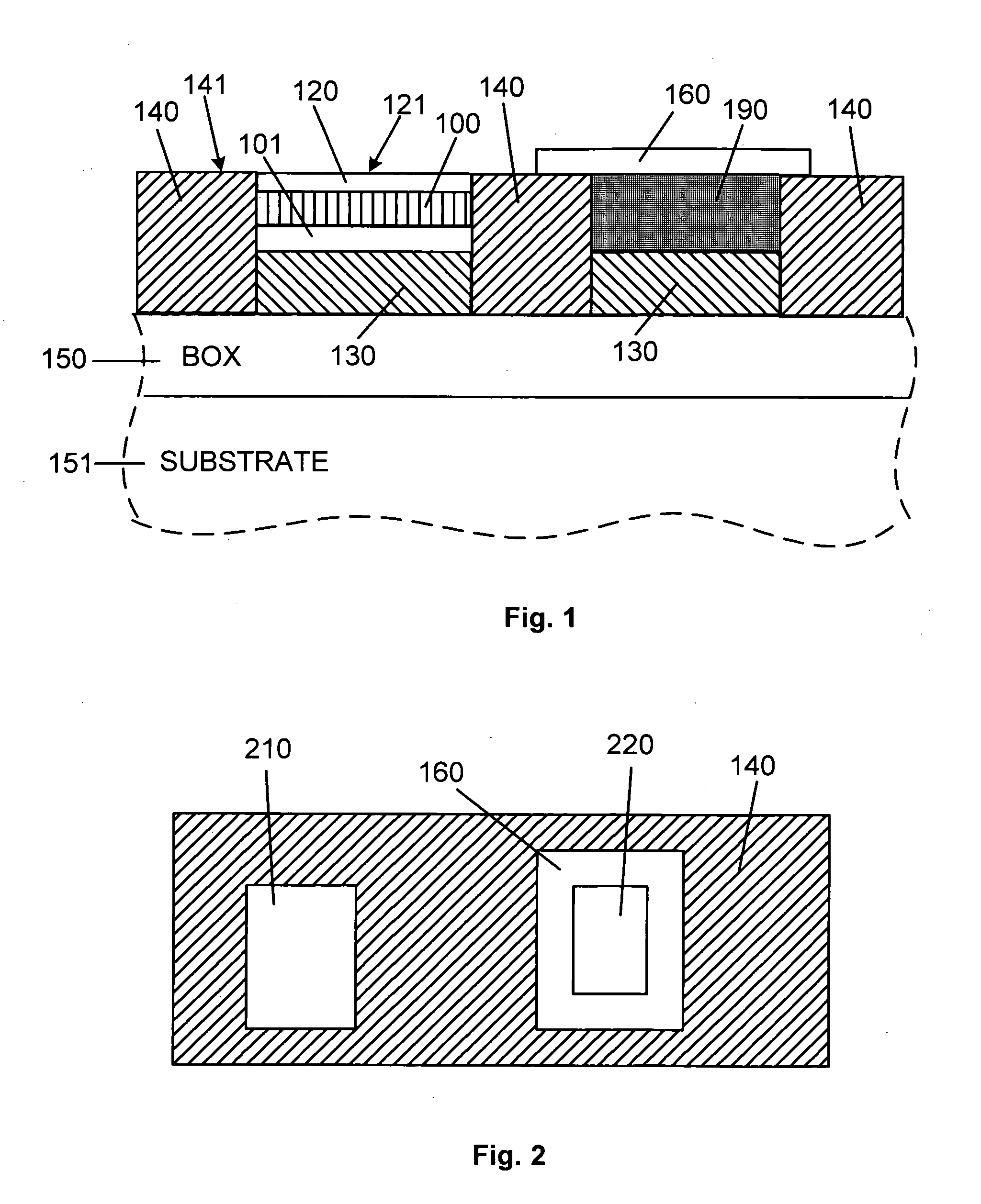

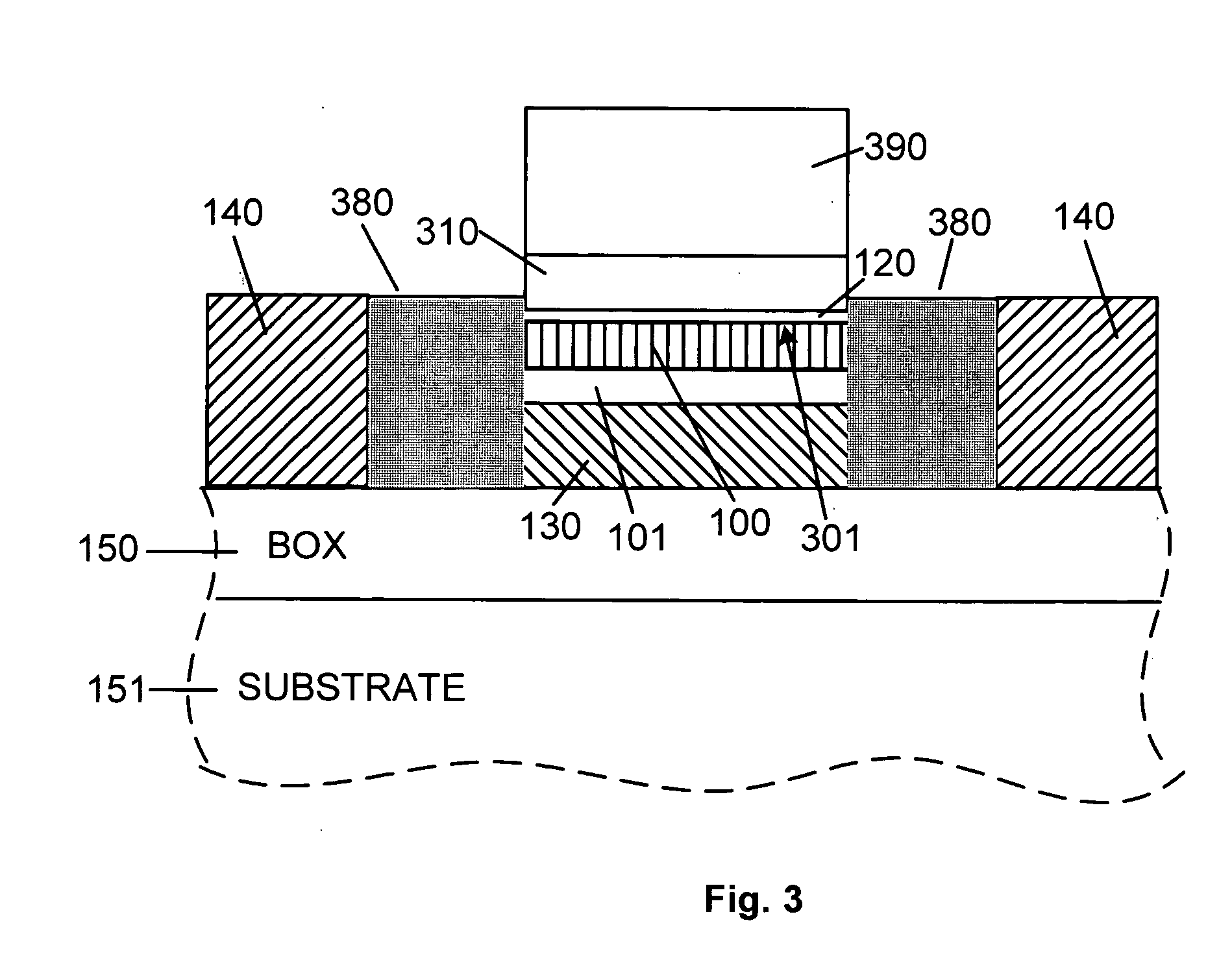

Integration of strained Ge into advanced CMOS technology

InactiveUS20050285097A1Improve mobilityImprove scalabilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSEngineering

A structure and method of fabrication for PFET devices in a compressively strained Ge layer is disclosed. The fabrication method of such devices is compatible with standard CMOS technology and it is fully scalable. The processing includes selective epitaxial depositions of an over 50% Ge content buffer layer, a pure Ge layer, and a SiGe top layer. Fabricated buried channel PMOS devices hosted in the compressively strained Ge layer show superior device characteristics relative to similar Si devices.

Owner:GLOBALFOUNDRIES INC

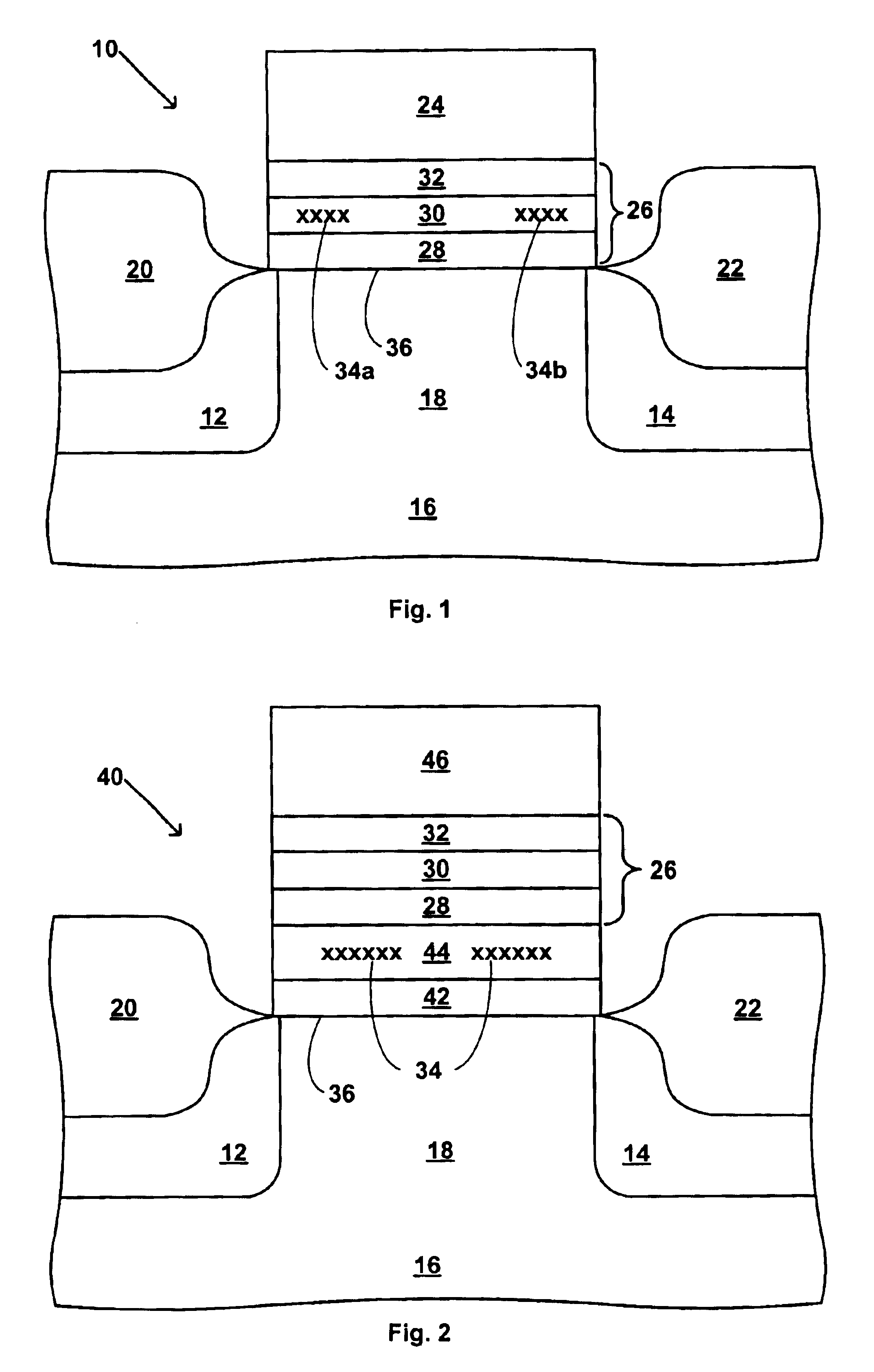

Use of high-K dielectric material for ONO and tunnel oxide to improve floating gate flash memory coupling

InactiveUS6617639B1Enhanced couplingReduce equivalent oxide thicknessTransistorSemiconductor/solid-state device manufacturingCouplingDielectric layer

A floating gate flash memory device including a substrate comprising a source region, a drain region, and a channel region positioned therebetween; a floating gate electrode positioned above the channel region and separated from the channel region by a tunnel dielectric material layer; and a control gate electrode positioned above the floating gate electrode and separated from the floating gate electrode by an interpoly dielectric layer, the interpoly dielectric layer comprising a modified ONO structure having a bottom dielectric material layer adjacent to the floating gate electrode, a top dielectric material layer adjacent to the control gate electrode, and a center layer comprising a nitride and positioned between the bottom dielectric material layer and the top dielectric material layer, in which the tunnel dielectric material layer, and at least one of the bottom dielectric material layer and the top dielectric material layer, comprise a high-K dielectric material.

Owner:MONTEREY RES LLC

Optical reader comprising multiple color illumination

InactiveUS20030062413A1Reduced dimensionOptimize architectureConveying record carriersCharacter and pattern recognitionLength waveComputer science

An imaging module in one embodiment includes at least one multiple color emitting light source comprising a plurality of different colored LED dies each independently driveable so that the overall color emitted by the light source can be controlled and varied. The multiple color emitting light source can be controlled so that the color emitted by the light source is optimized for imaging or reading in a present application environment of the module. Further, the module can be configured so that control of the multiple color emitting light source automatically varies depending on a sensed condition, such a color present in a field of view of the module, the distance of the module to a target, and / or a predetermined criteria being met so that feedback is provided to a user. The module in a further aspect can include illumination light sources and aiming light sources which project light in different wavelength emission bands.

Owner:HAND HELD PRODS

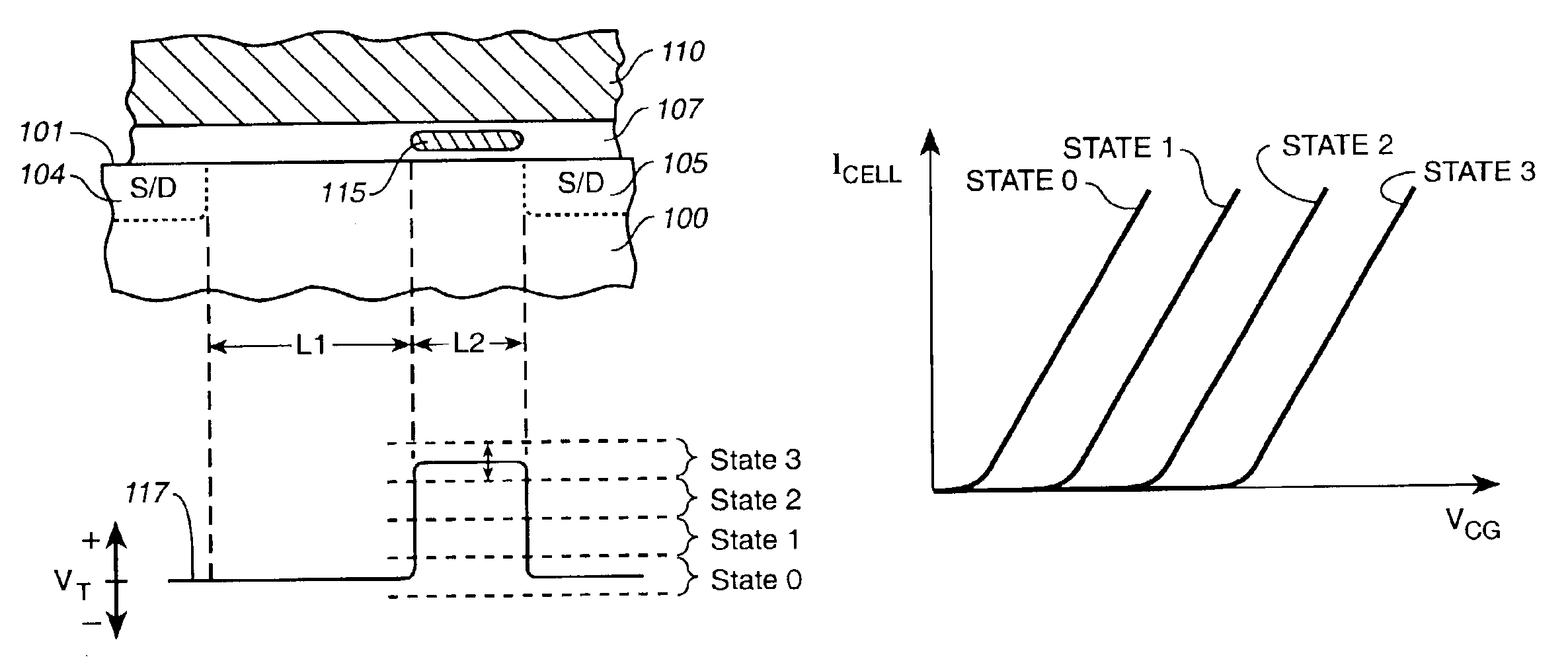

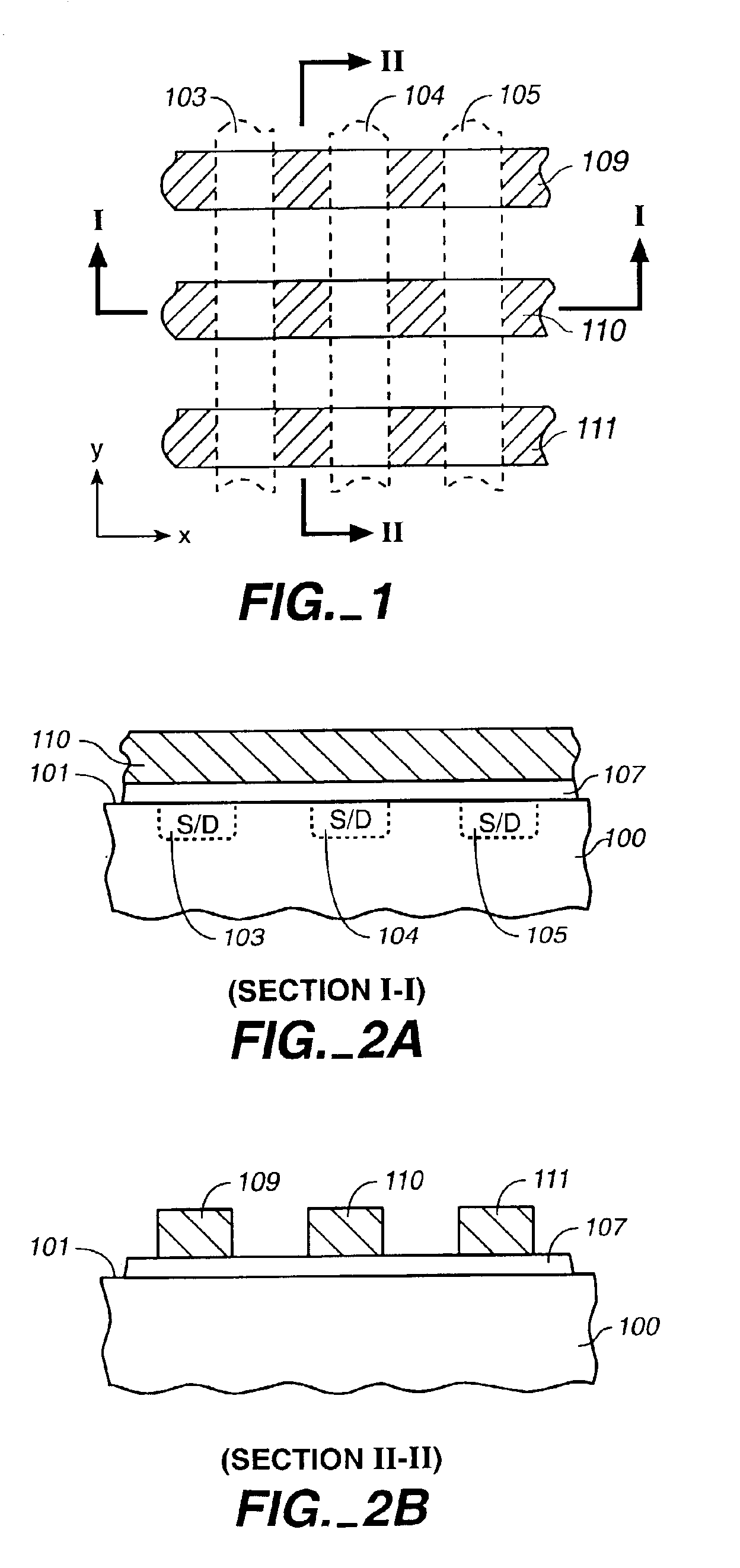

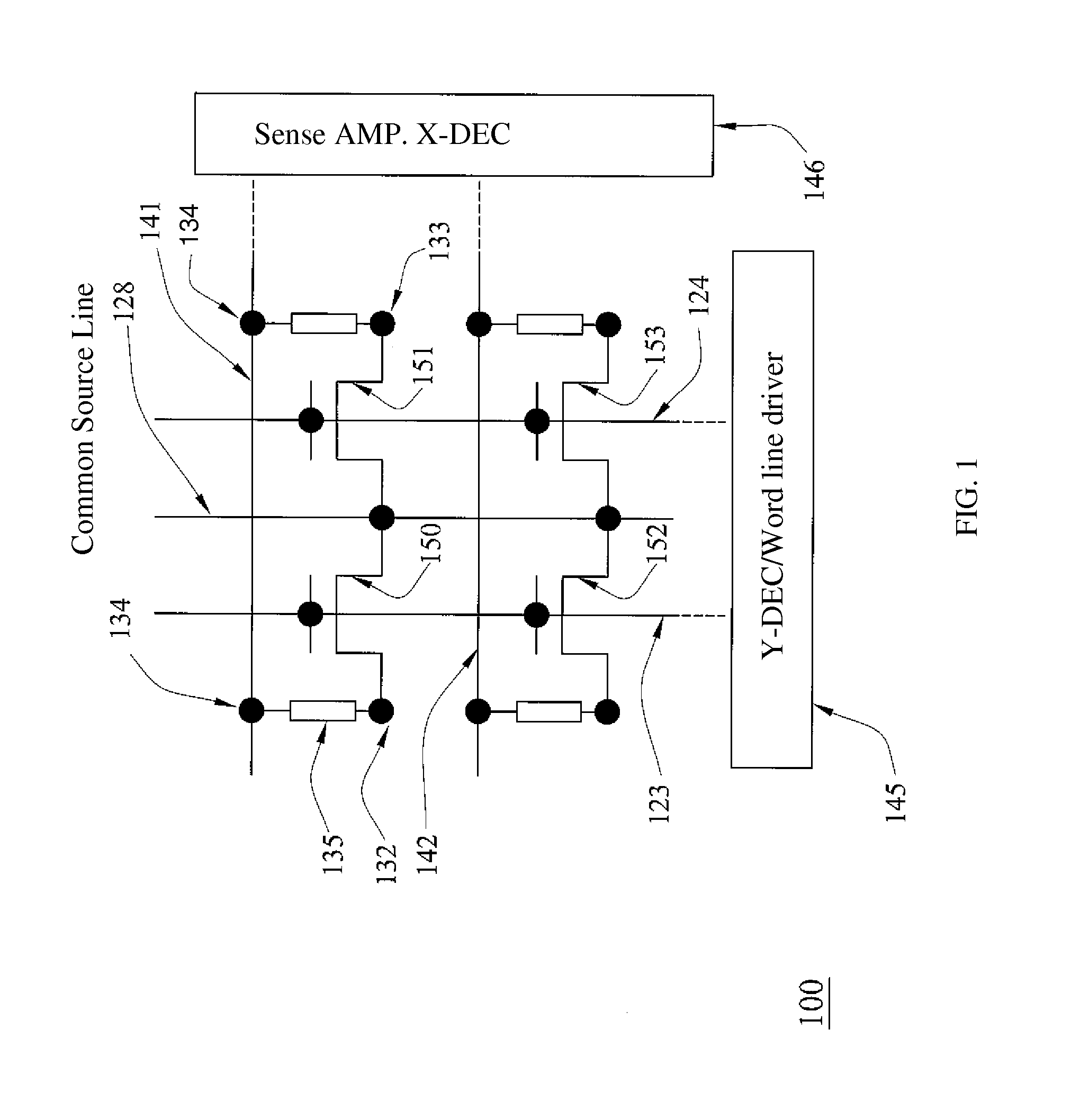

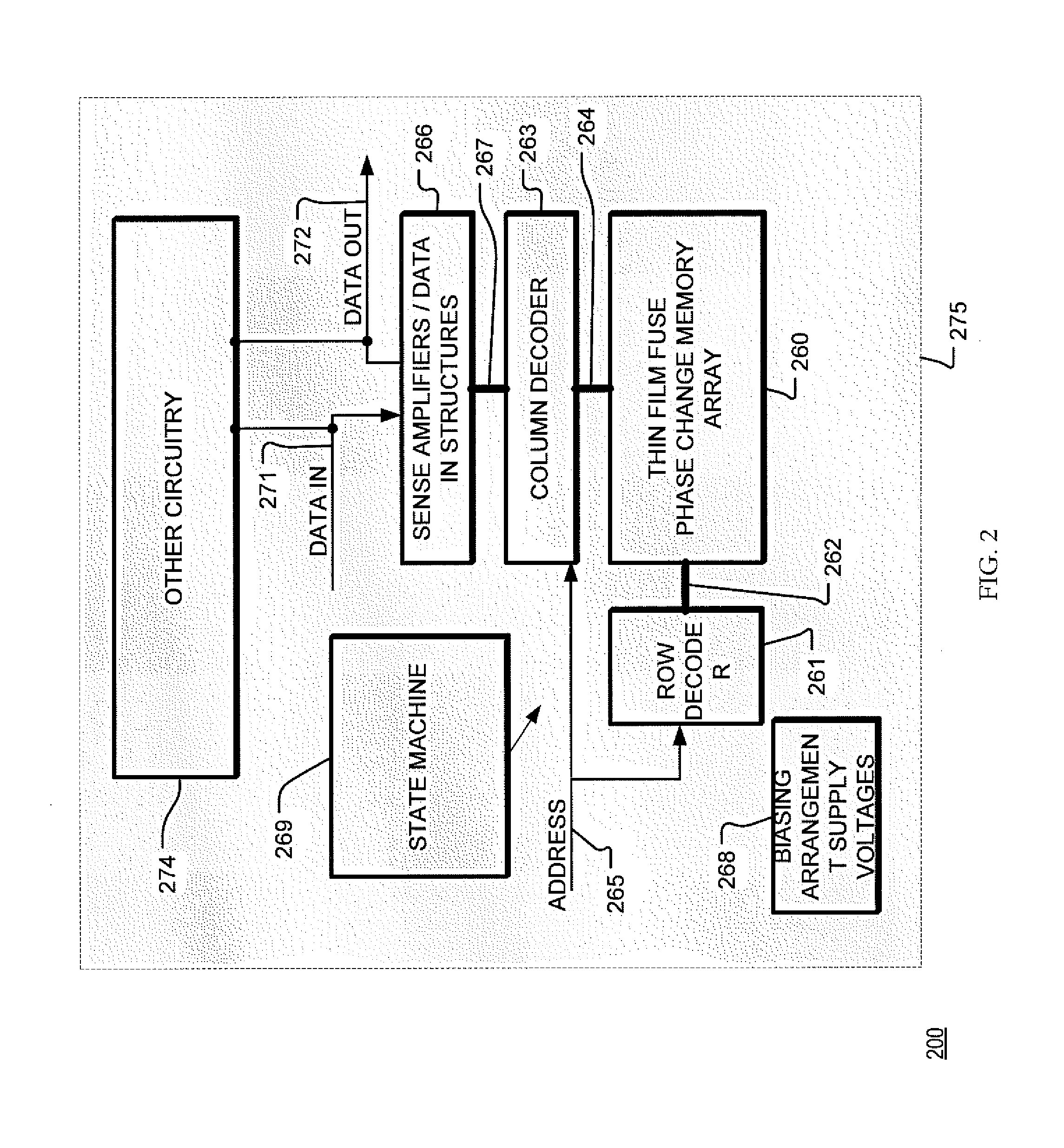

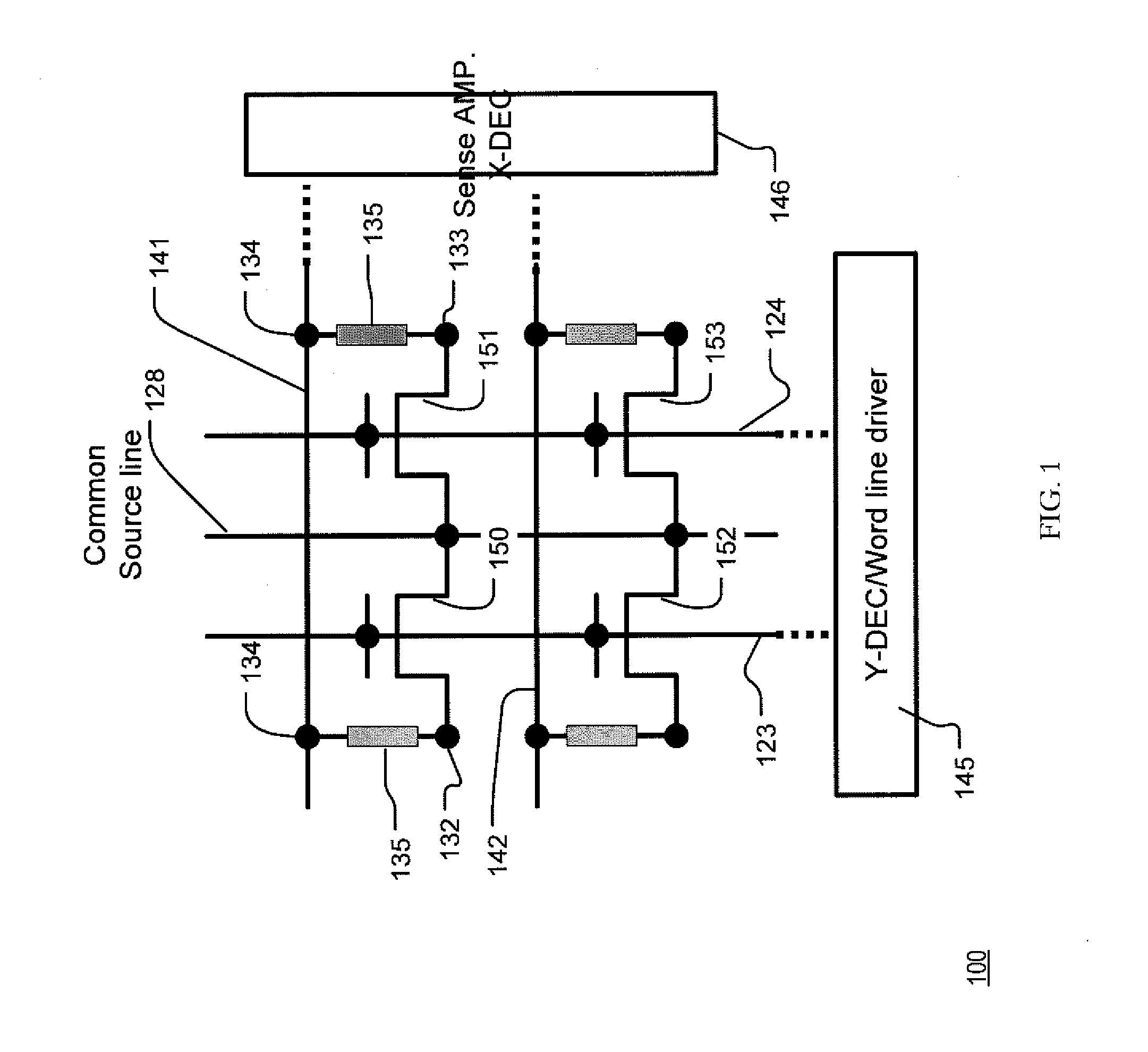

Multi-state non-volatile integrated circuit memory systems that employ dielectric storage elements

InactiveUS6925007B2Increase the number ofExtend effective lifeTransistorNanoinformaticsEngineeringDielectric layer

Non-volatile memory cells store a level of charge corresponding to the data being stored in a dielectric material storage element that is sandwiched between a control gate and the semiconductor substrate surface over channel regions of the memory cells. More than two memory states are provided by one of more than two levels of charge being stored in a common region of the dielectric material. More than one such common region may be included in each cell. In one form, two such regions are provided adjacent source and drain diffusions in a cell that also includes a select transistor positioned between them. In another form, NAND arrays of strings of memory cells store charge in regions of a dielectric layer sandwiched between word lines and the semiconductor substrate.

Owner:SANDISK TECH LLC

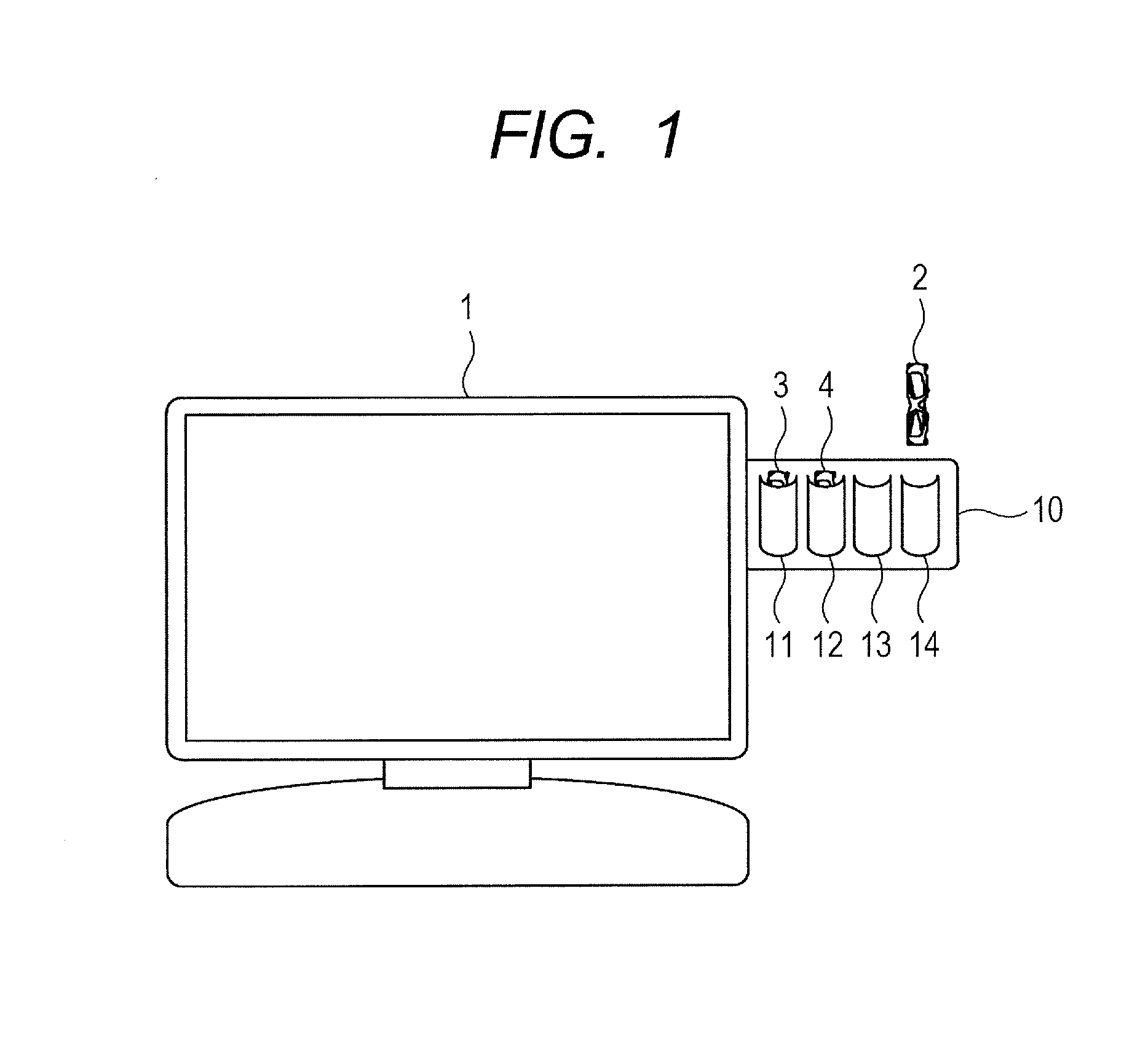

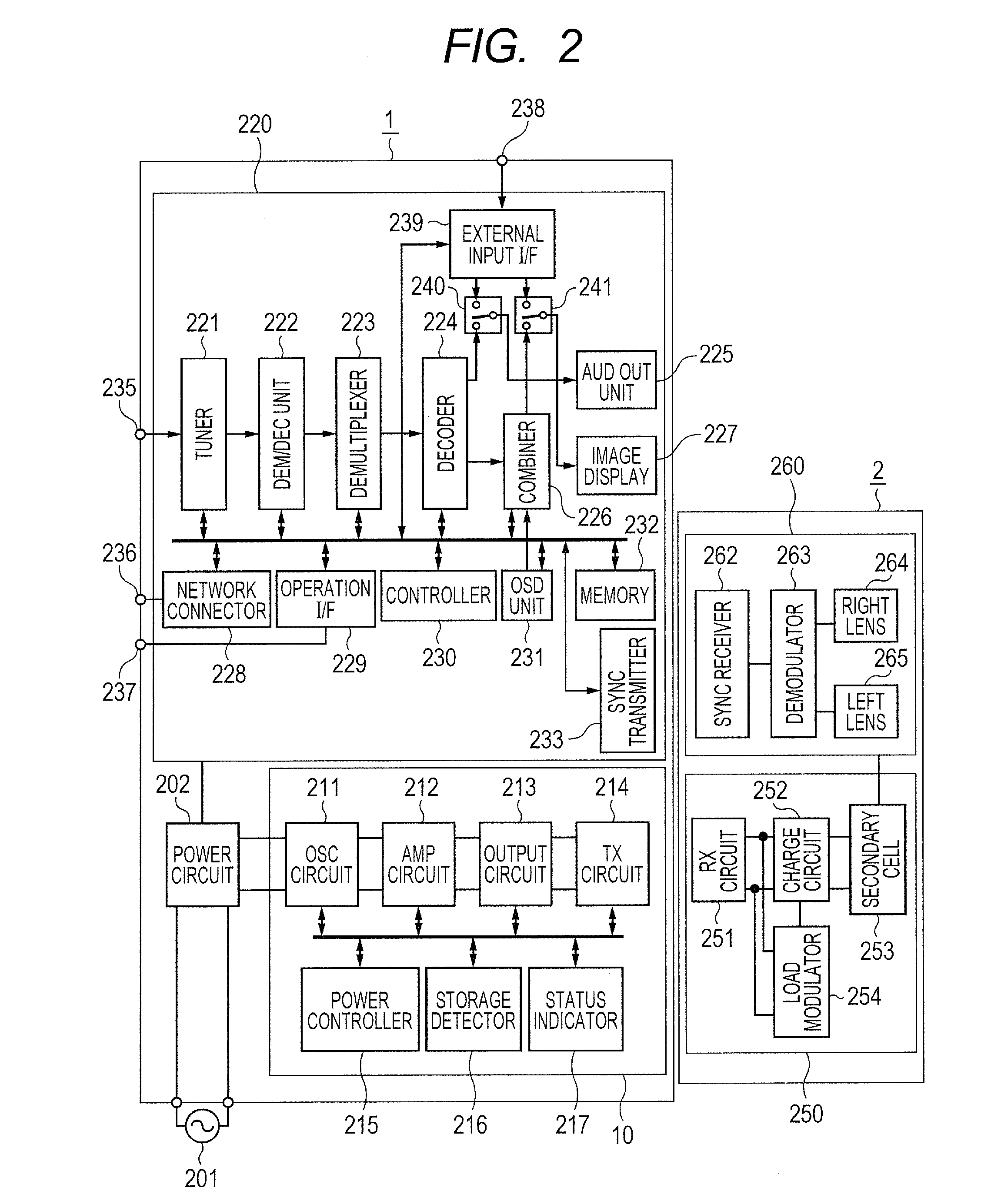

Contact-less Power Transmitter and Contact-less Power Transmission System

InactiveUS20130107023A1Power transmission be stopSimple device structureNear-field transmissionTransformersElectric power transmissionVariator

In a non-contact electric power transmission system that electrically charges a device in a non-contact fashion, a transmitter includes excitation and resonance elements, and transmits power from a specified storage pocket under a control signal from a transmission controller. The transmission controller, upon insertion of an object being detected, uses information from an output detector to determine the object to be a destination device to which power is to be transmitted, and controls the corresponding transmitter circuit to transmit the power. The information from the output detector can include a transmission rate, or a differential between a load modulation period of a receiver and that of the transmitter. The transmission controller acquires charge information on the receiver inserted in one of the storage pockets to control the power transmission. This simplifies the device to be charged for non-contact device charging, and reduces the device in dimensions and weight.

Owner:HITACHI CHEM CO LTD

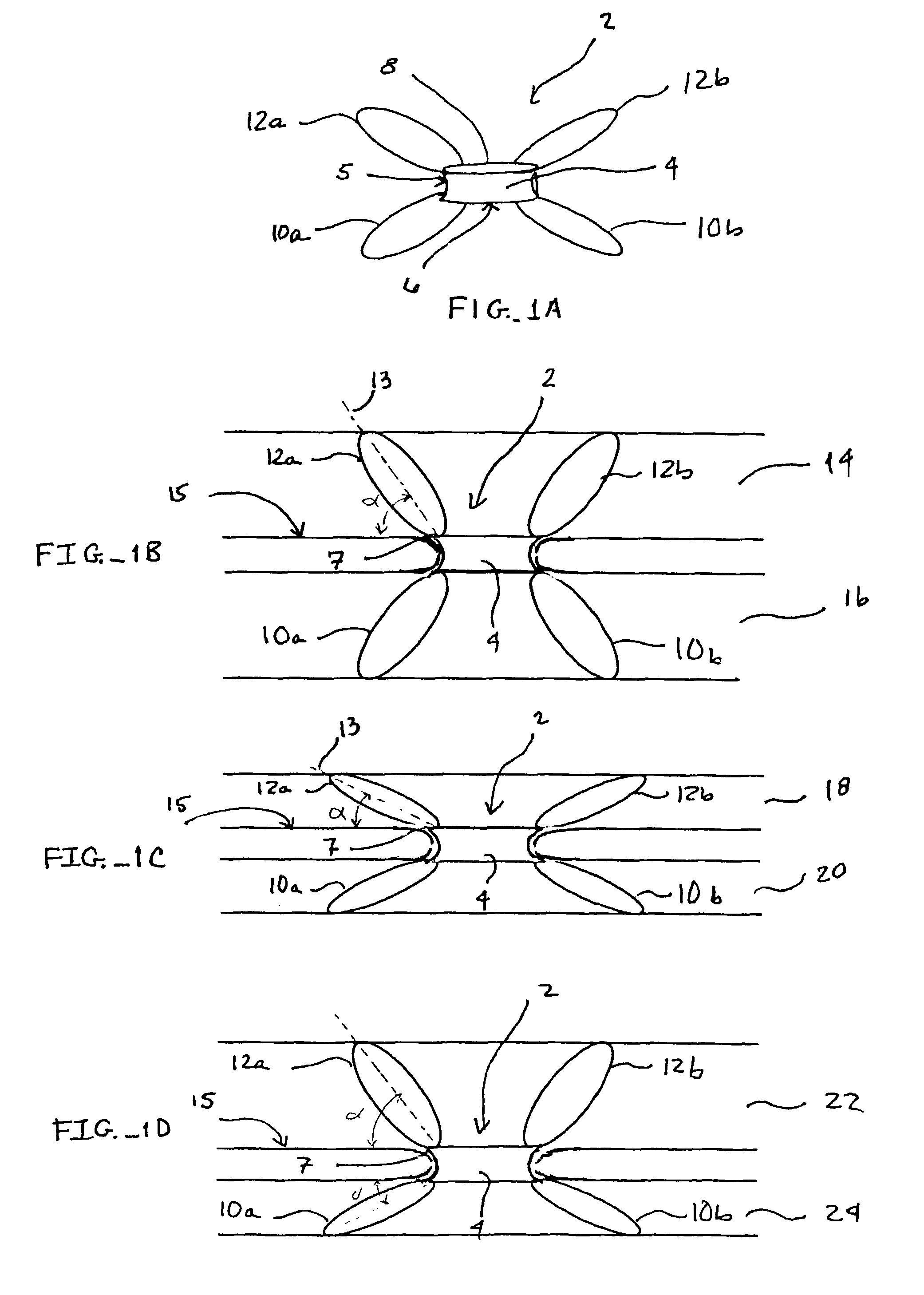

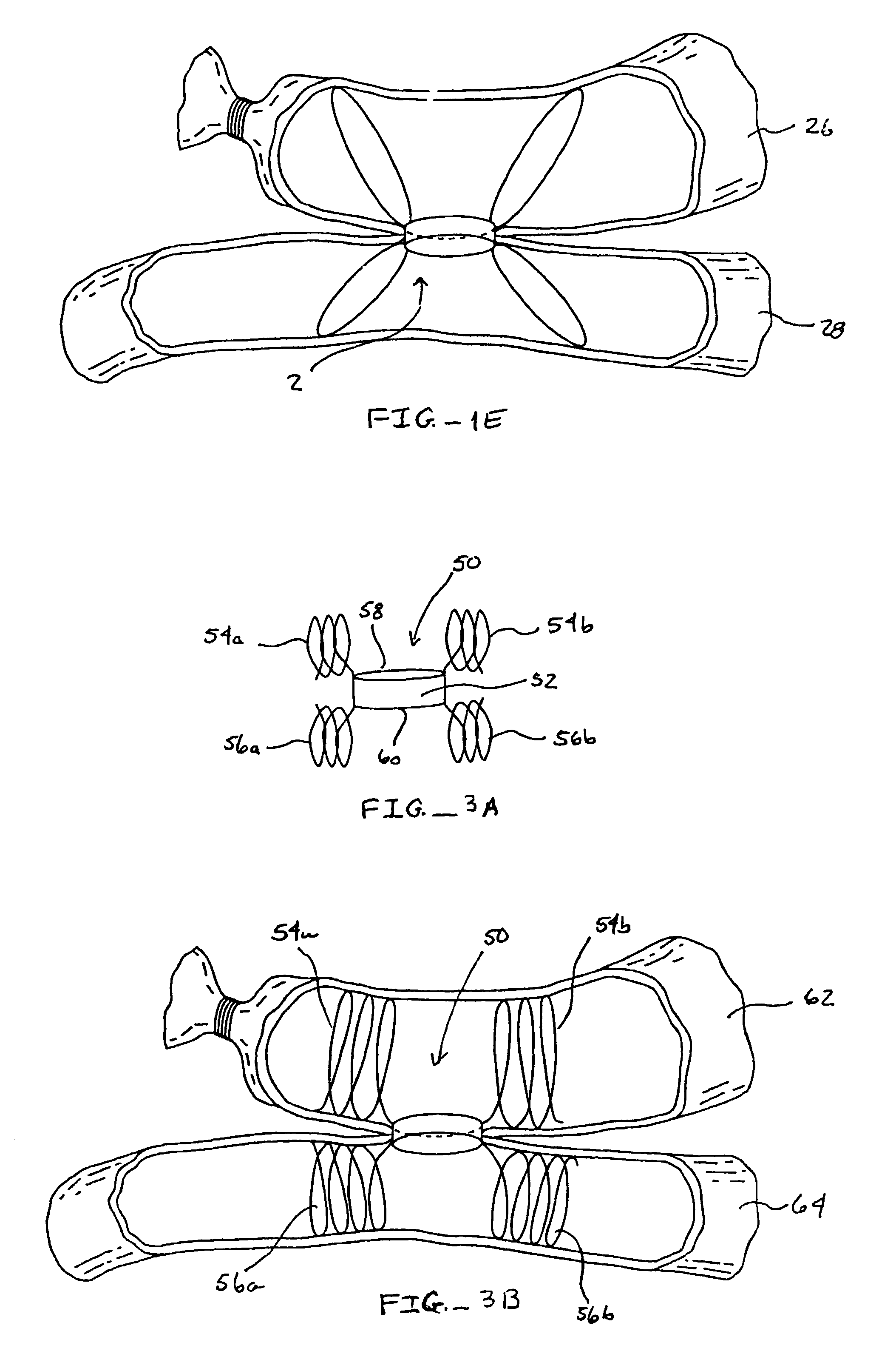

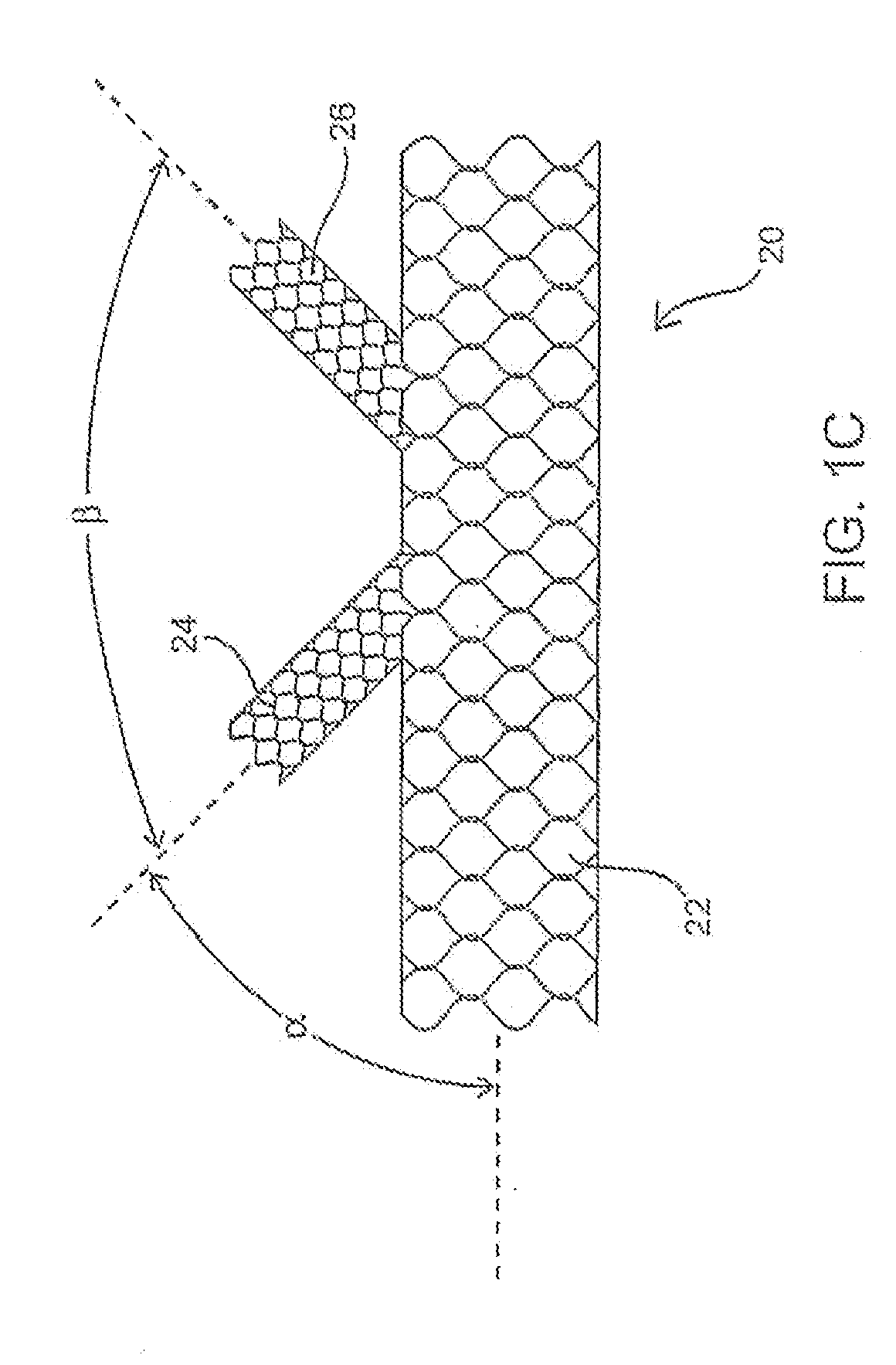

Surgical fasteners, applicator instruments, and methods for deploying surgical fasteners

ActiveUS20100292715A1Easy to collapseImprove abilitiesSuture equipmentsDiagnosticsProsthesisSurgical Fasteners

A surgical fastener for securing a prosthetic device to tissue includes a first leg having a distal end, a proximal end, and a first insertion tip at the distal end of the first leg, and a second leg including a distal end, a proximal end, and a second insertion tip at the distal end of the second leg. A bridge connects the proximal ends of the first and second legs for forming a closed end of the surgical fastener. The first insertion tip has a first insertion tool seating surface, and the second insertion tip has a second insertion tool seating surface. The first insertion tool seating surface is closer to the distal end of the first leg than the proximal end of the first leg, and the second insertion tool seating surface is closer to the distal end of the second leg than the proximal end of the second leg. The first and second legs extend along respective longitudinal axes, and the first and second insertion tips are skewed outwardly relative to the respective longitudinal axes.

Owner:ETHICON LLC

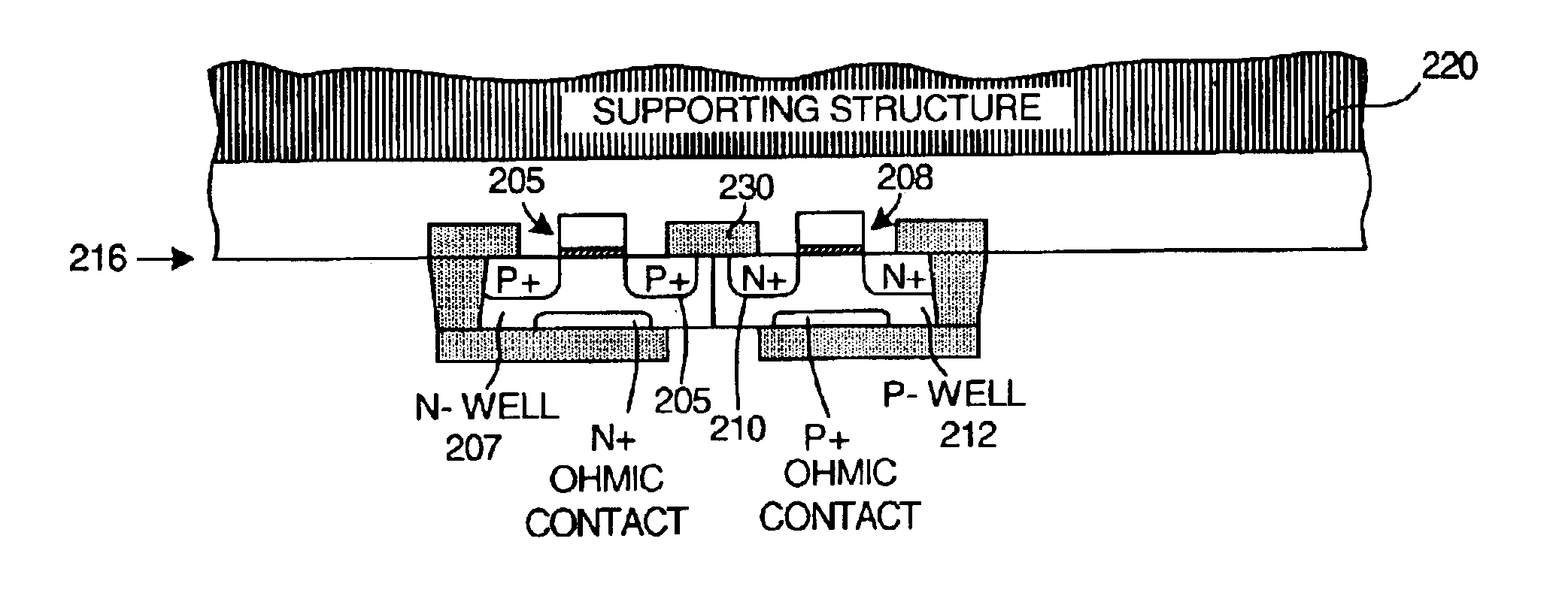

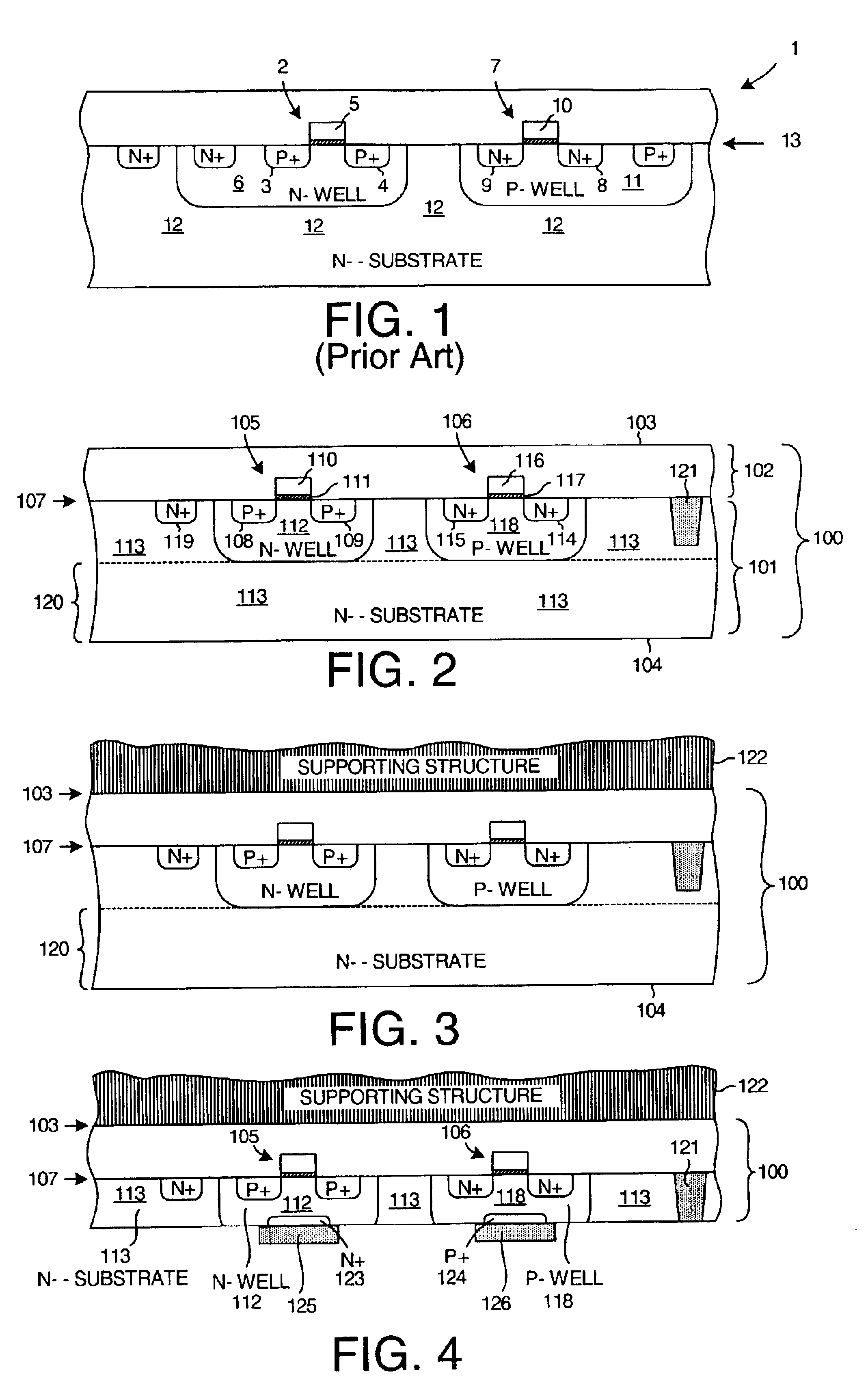

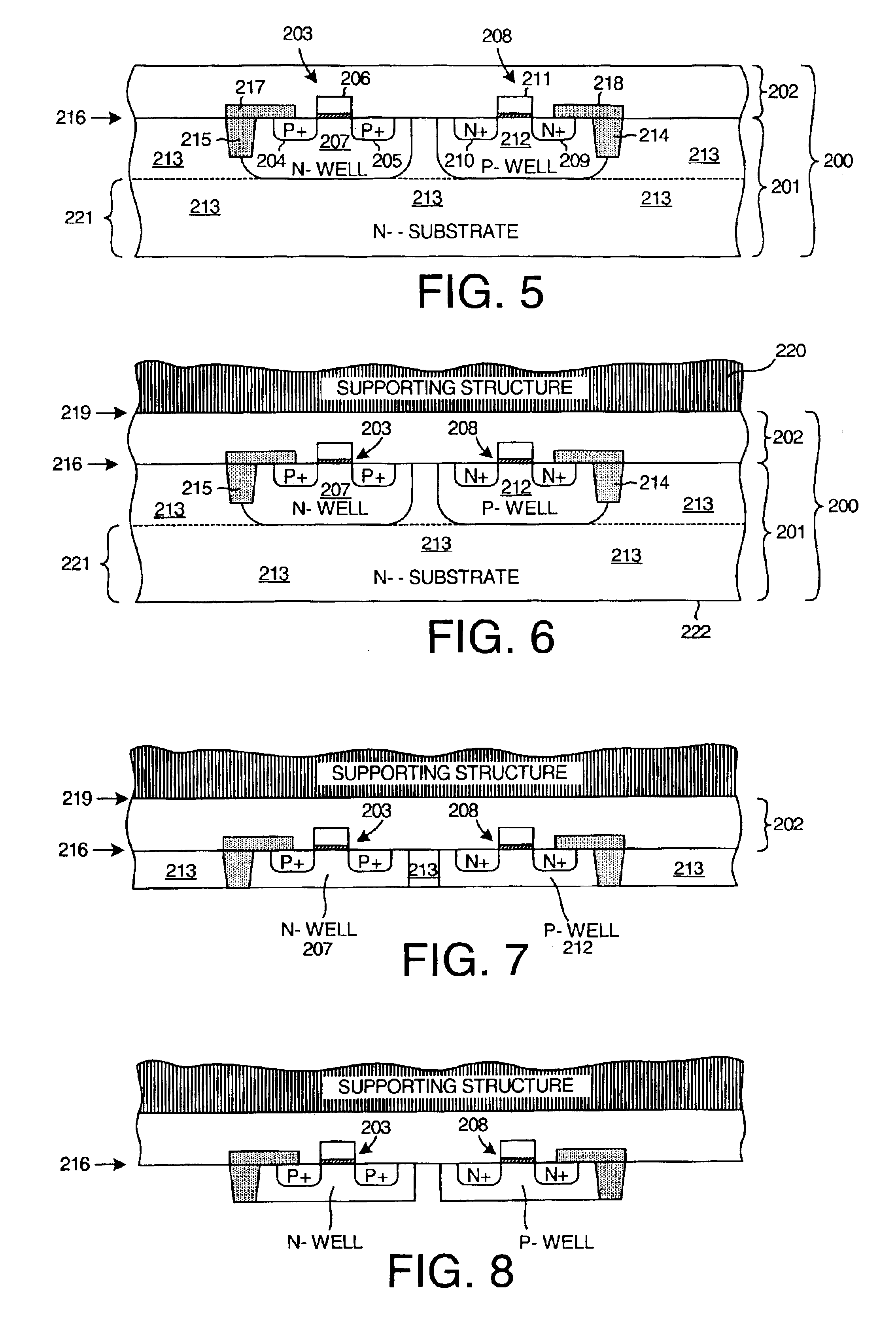

Semiconductor wafer with well contacts on back side

InactiveUS6864156B1Little source-to-wellImprove leakageTransistorSolid-state devicesCapacitanceEngineering

A supporting structure is wafer-bonded to the upper face side of a partially or fully processed device wafer. The device wafer includes a transistor having a well region that extends into the substrate material of the device wafer. The source and drain regions of the transistor extend into the well region. After attachment of the supporting structure, the device wafer is thinned from the back side until the bottom of the well region is reached. To reduce source and drain junction capacitances, etching can continue until the source and drain regions are reached. In one embodiment, all of the well-to-substrate junction is removed in a subsequent etching step, thereby reducing or eliminating the well-to-substrate junction capacitance of the resulting transistor. Resistance between the well electrode and the transistor channel is reduced because the well contact is disposed on the back side of the device wafer directly under the gate of the transistor.

Owner:XILINX INC

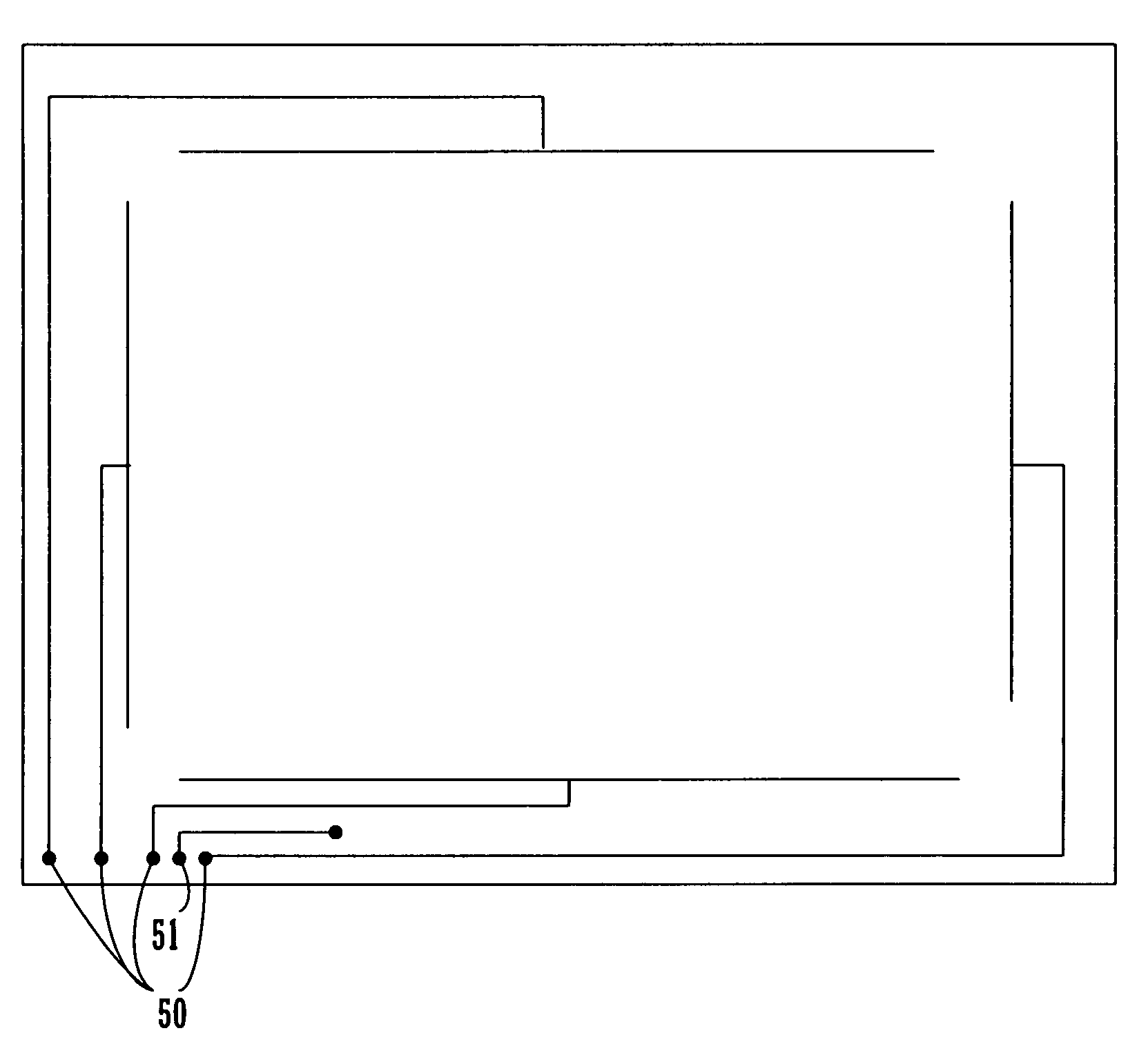

Compact integrated touch panel display for a handheld device

InactiveUS6965375B1Minimizing length of busReduction in size of handheldTransmission systemsCathode-ray tube indicatorsFlexible circuitsElectrical connection

A handheld device with a compact integrated touch panel is disclosed. A handheld device incorporating a touch panel display requiring electrical connections is reduced in size by incorporating electrical pathways within the support structure of the touch panel display, obviating the need for a flex circuit extension from the touch panel display for connection to the handheld device. A further reduction in size is obtained by providing an inherent visually homogeneous perimeter for the touch panel display by matching the colors of the conductive and dielectric materials, thereby eliminating the need for a bezel.

Owner:QUALCOMM INC

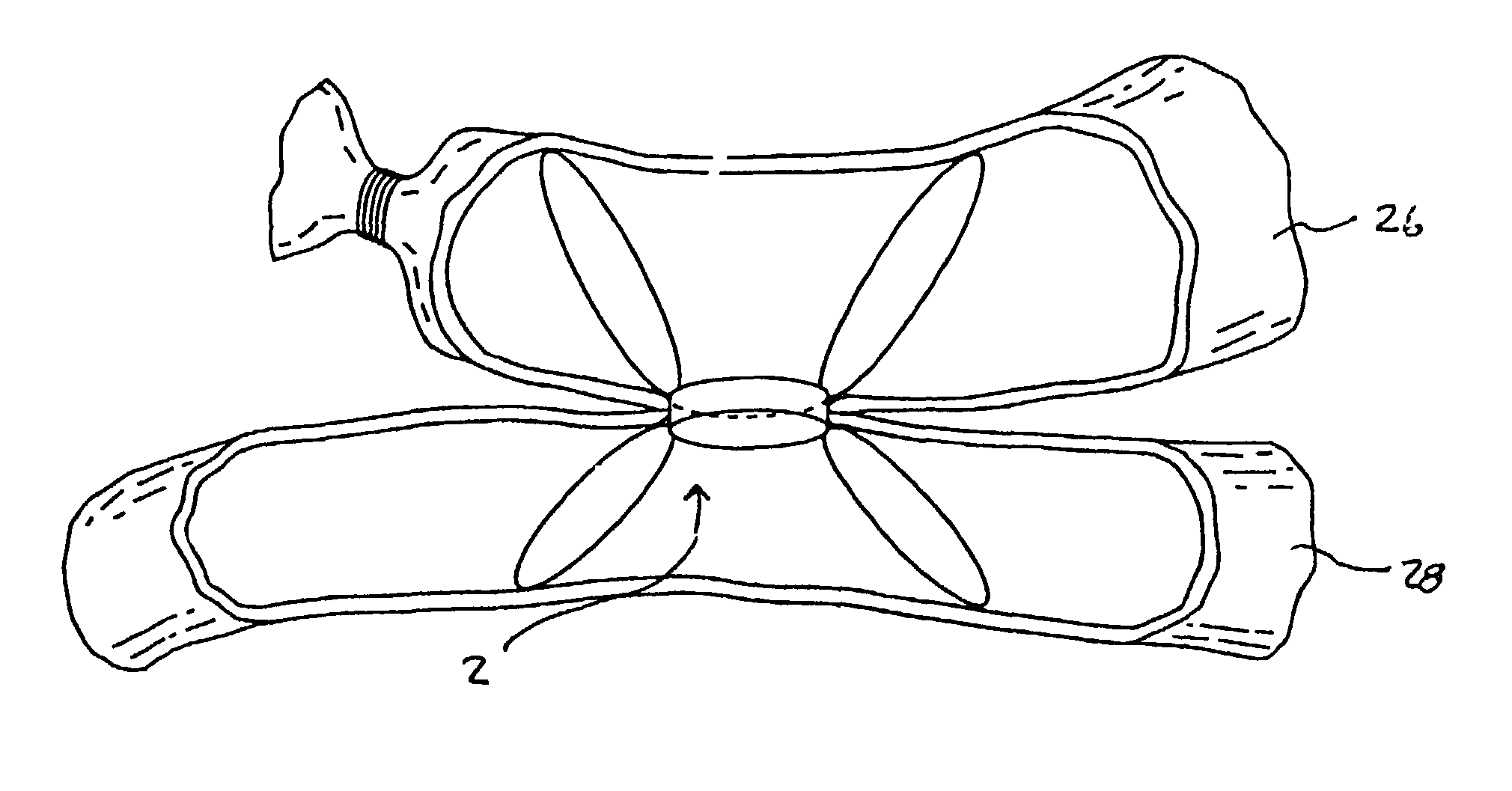

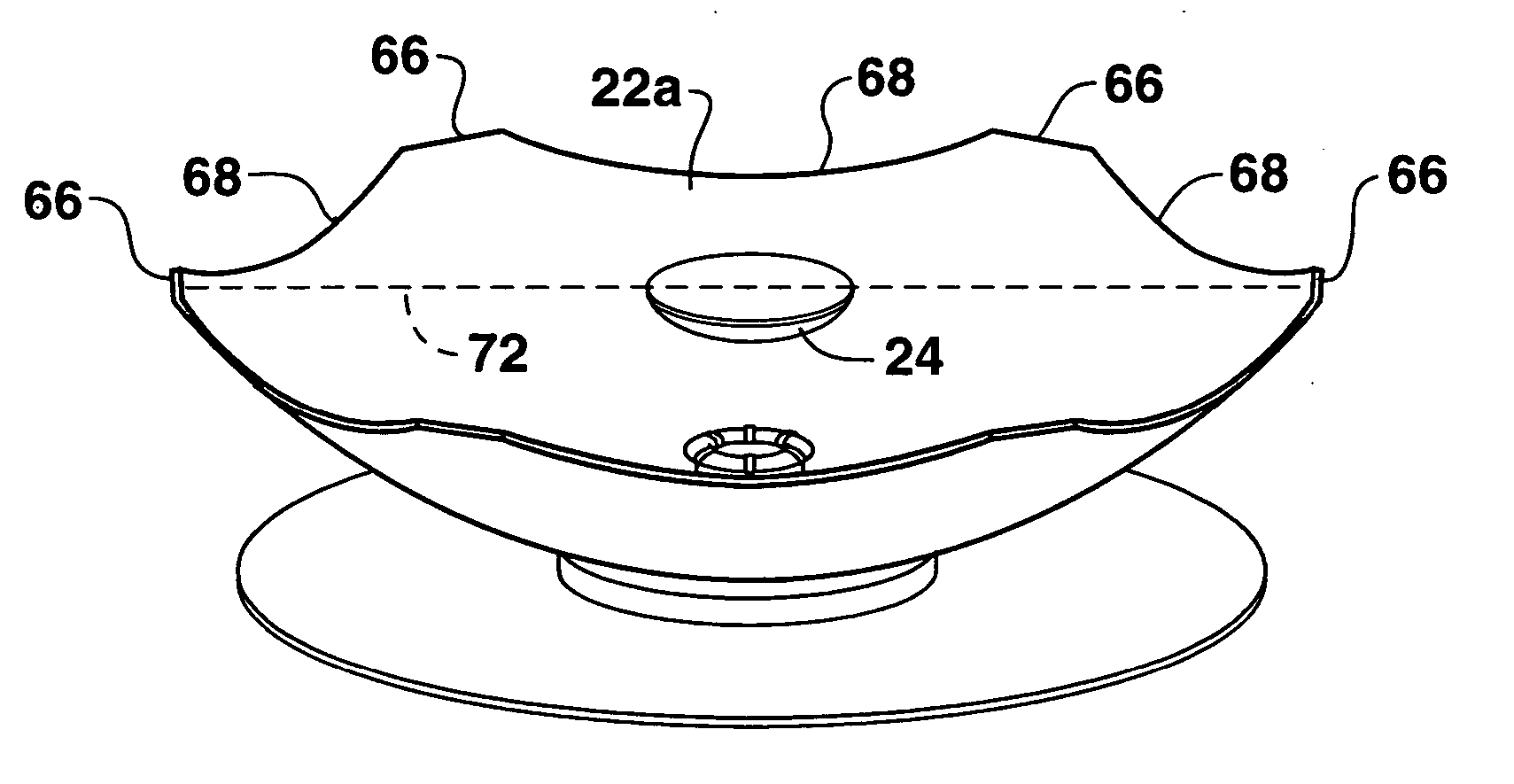

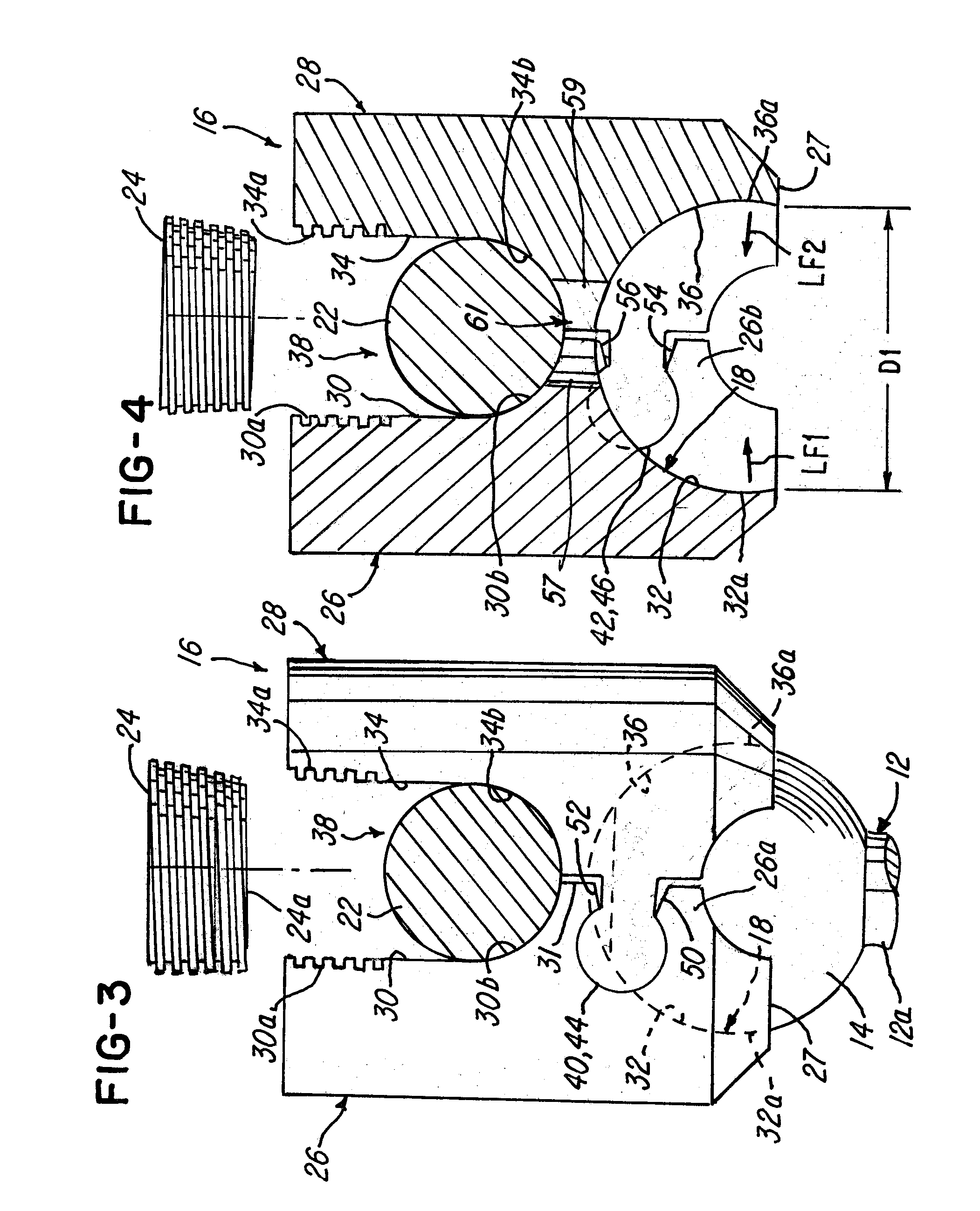

Compression anastomosis ring assembly and applicator for use therewith

InactiveUS7527185B2Reduced dimensionIncrease rangeSuture equipmentsStapling toolsOrgan wallShape-memory alloy

A compression anastomosis ring (CAR) assembly for use in joining severed organ wall portions of a hollow organ. The assembly comprises a first portion which includes an anvil assembly and a second portion which comprises a bottom ring, at least one ring element, and at least one spring element formed of a shape-memory alloy. The at least one spring element provides a restorative force and is in compressive force contact with the bottom ring and the tissue to be joined is positioned between the anvil ring and the bottom ring. A plurality of needles on one of the ring elements is operative, upon application of a closure force, to pierce the tissue and the anvil ring, holding the anvil ring to the second portion of the CAR assembly. An applicator for applying the CAR assembly and a method for using the assembly and applicator are taught.

Owner:NITI SURGICAL SOLUTIONS

Bridge resistance random access memory device with a singular contact structure

ActiveUS7608848B2Reduced dimensionSolid-state devicesBulk negative resistance effect devicesBit lineEdge surface

A resistance random access memory in a bridge structure is disclosed that comprises a contact structure where first and second electrodes are located within the contact structure. The first electrode has a circumferential extending shape, such as an annular shape, surrounding an inner wall of the contact structure. The second electrode is located within an interior of the circumferential extending shape and separated from the first electrode by an insulating material. A resistance memory bridge is in contact with an edge surface of the first and second electrodes. The first electrode in the contact structure is connected to a transistor and the second electrode in the contact structure is connected to a bit line. A bit line is connected to the second electrode by a self-aligning process.

Owner:MACRONIX INT CO LTD

Devices and methods for interconnecting vessels

ActiveUS7892247B2Quickly and efficiently performingMinimize tensionSurgical furnitureDiagnosticsEngineeringBlood vessel

Owner:BIOCONNECT SYST

Optical reader aiming assembly comprising aperture

InactiveUS20030019934A1Reduced dimensionOptimize architectureConveying record carriersCharacter and pattern recognitionOptical readerLight source

An imaging module in one embodiment includes an aiming system having a light source, an aperture and an optical element positioned optically forward of the aperture wherein the aiming system projects a crisp and sharp aiming pattern onto a target over a wide range of distances. In one embodiment, an aiming system is configured so that a lens operates as an aperture to project a crisp sharp aiming pattern over a wide range of distances including distances at which the aiming pattern is less than optimally focused. In another embodiment an aiming system is configured so that light emanating from a thin aperture is imaged in such manner that a crisp, sharp aiming pattern is defined over a wide range of distances. The aiming pattern in one embodiment includes sharply defined lateral edges which are useful in sighting target indicia.

Owner:HAND HELD PRODS

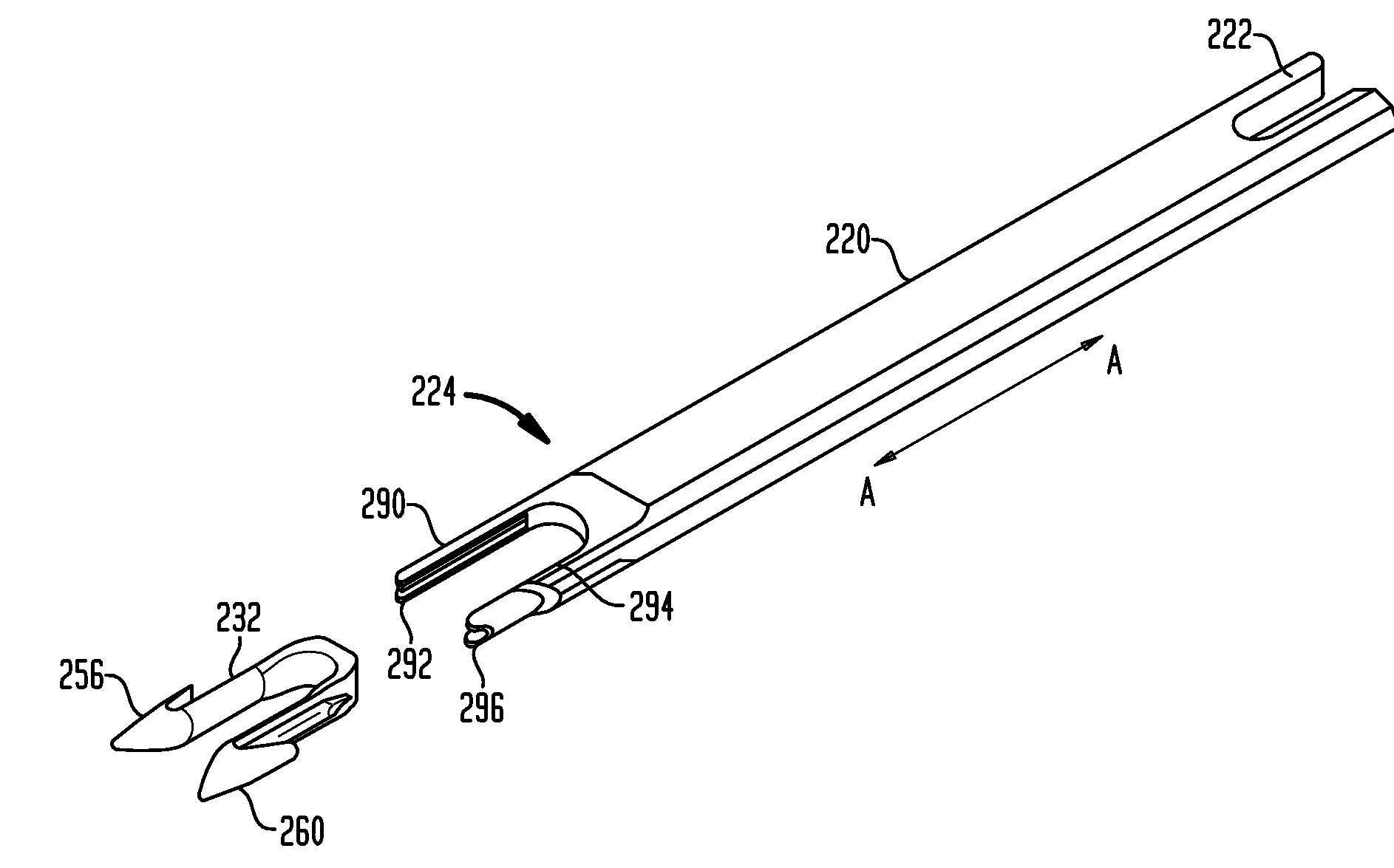

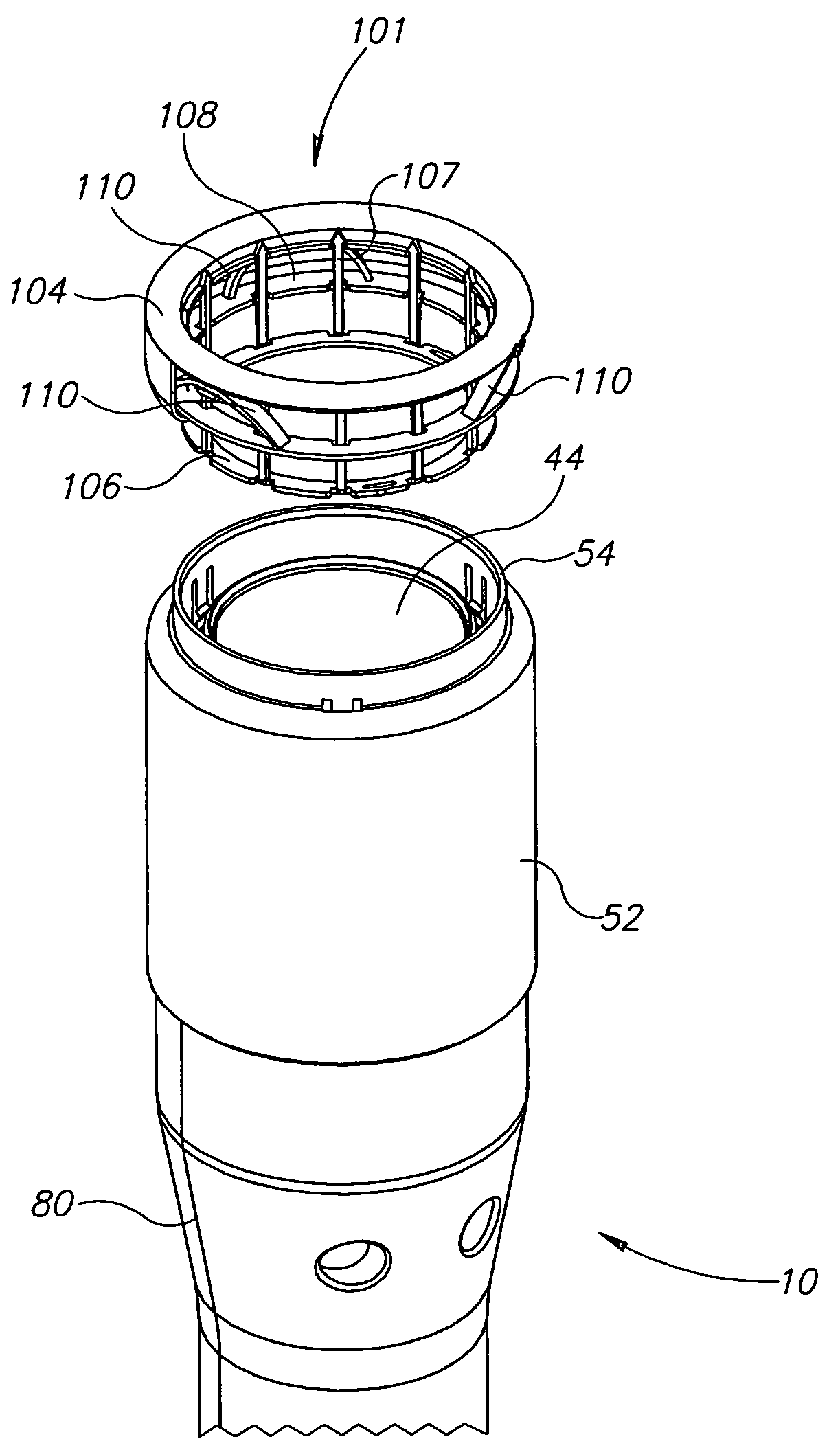

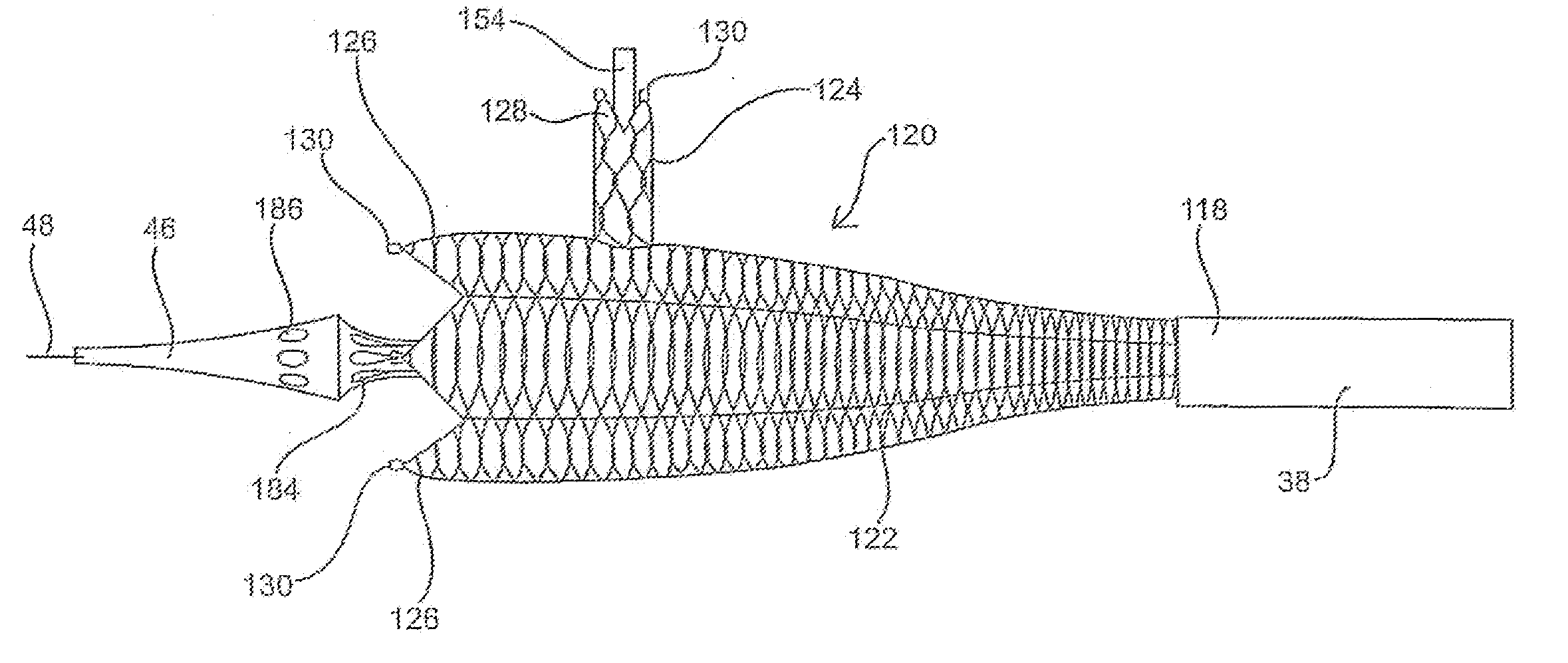

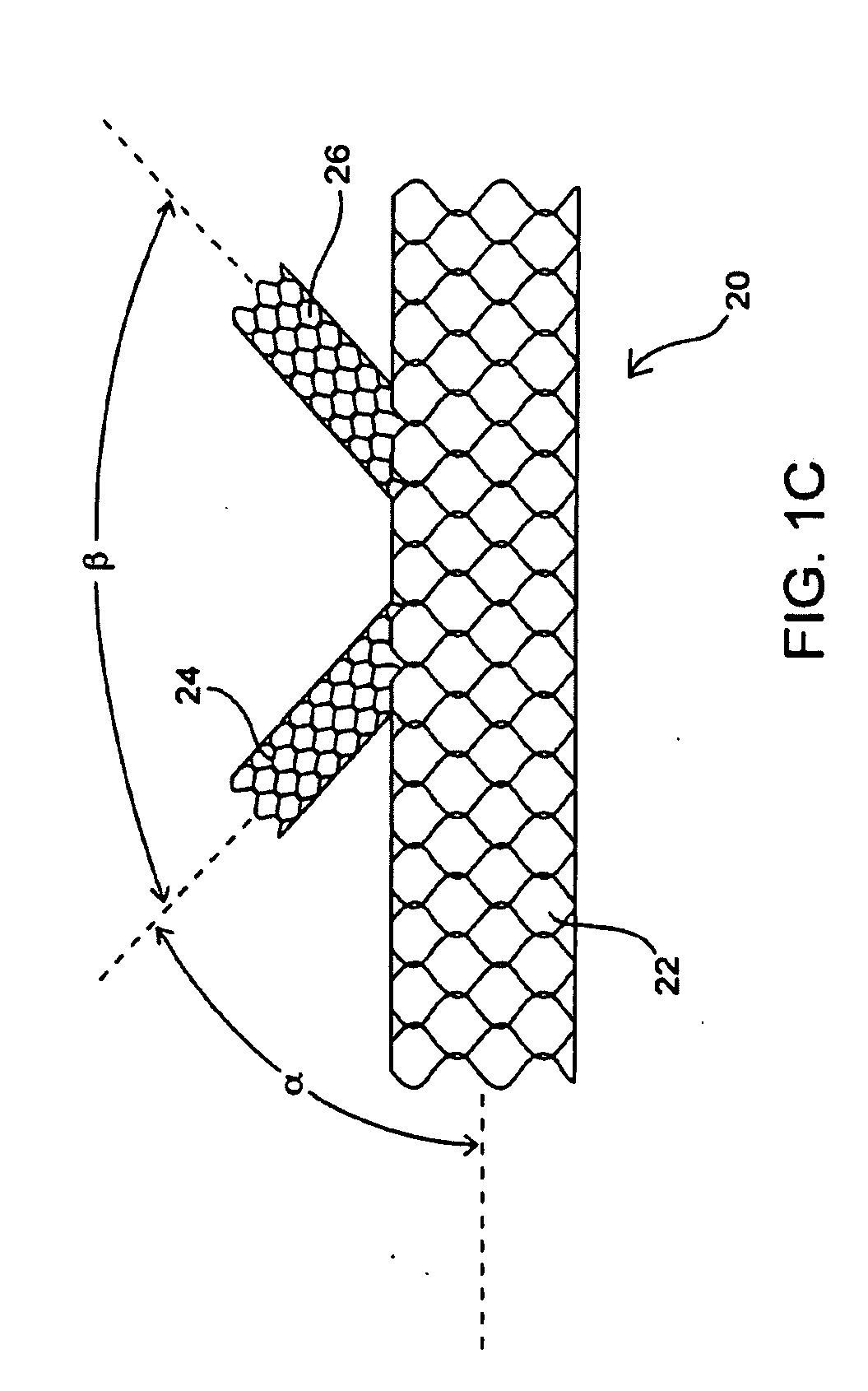

Apparatus and method for deploying an implantable device within the body

ActiveUS20070167955A1Satisfactory resultReduced dimensionStentsEar treatmentBiomedical engineeringCatheter

The present invention provides systems and methods for deploying implantable devices within the body. The delivery and deployment systems include at least one catheter or an assembly of catheters for selectively positioning the lumens of the implant to within target vessels. Various deployment and attachment mechanisms are provided for selectively deploying the implants.

Owner:TAHERI LADUCA

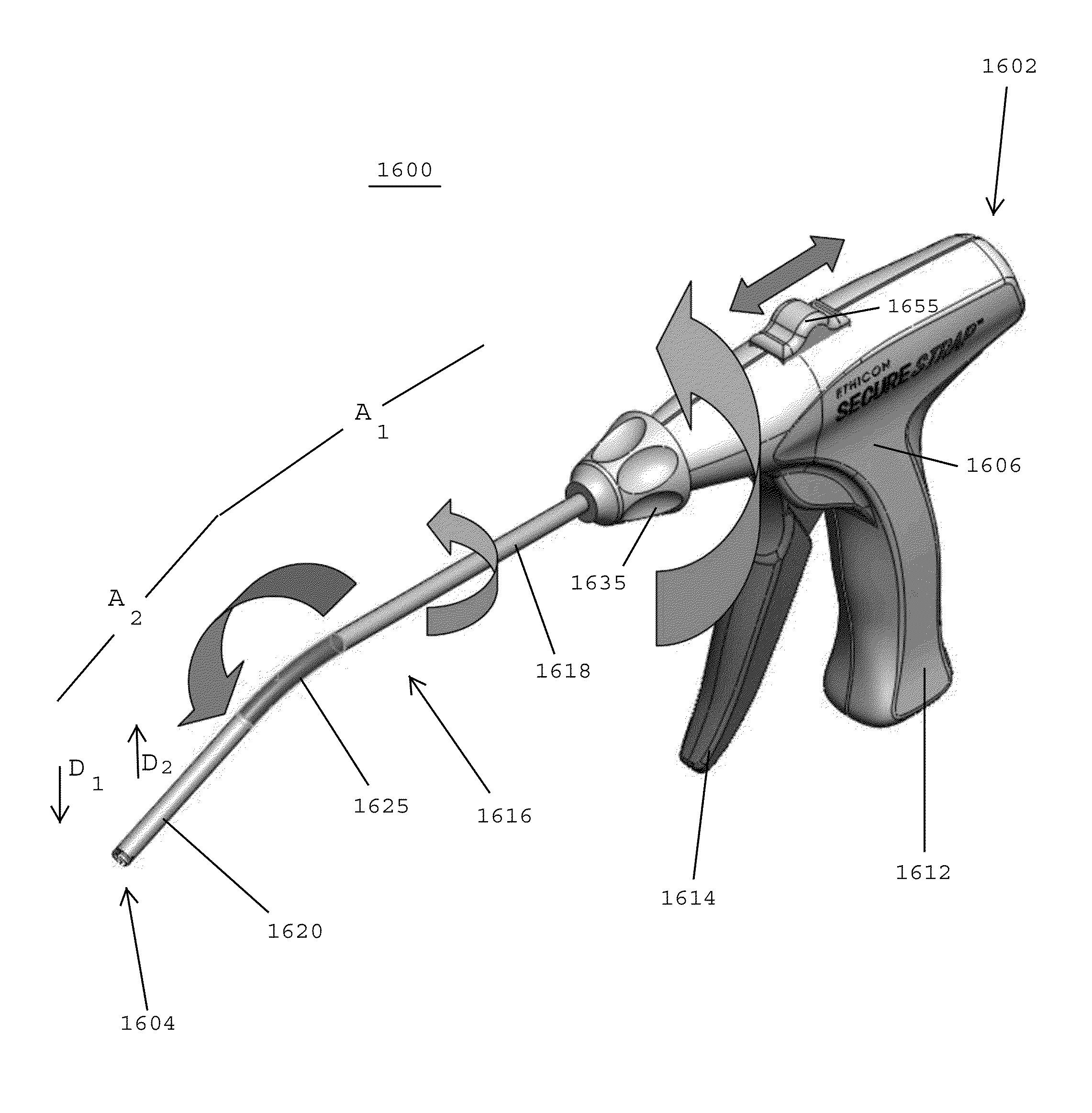

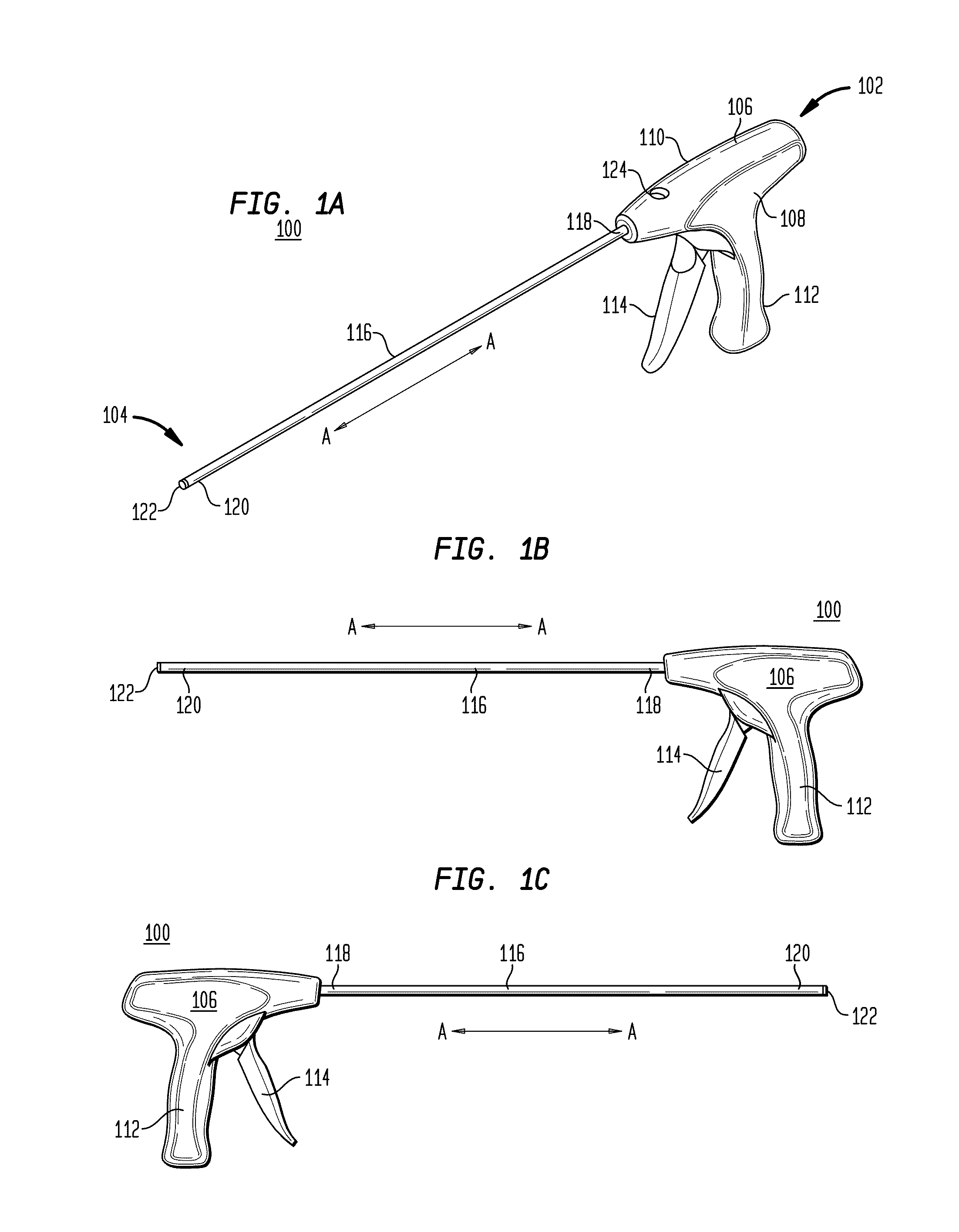

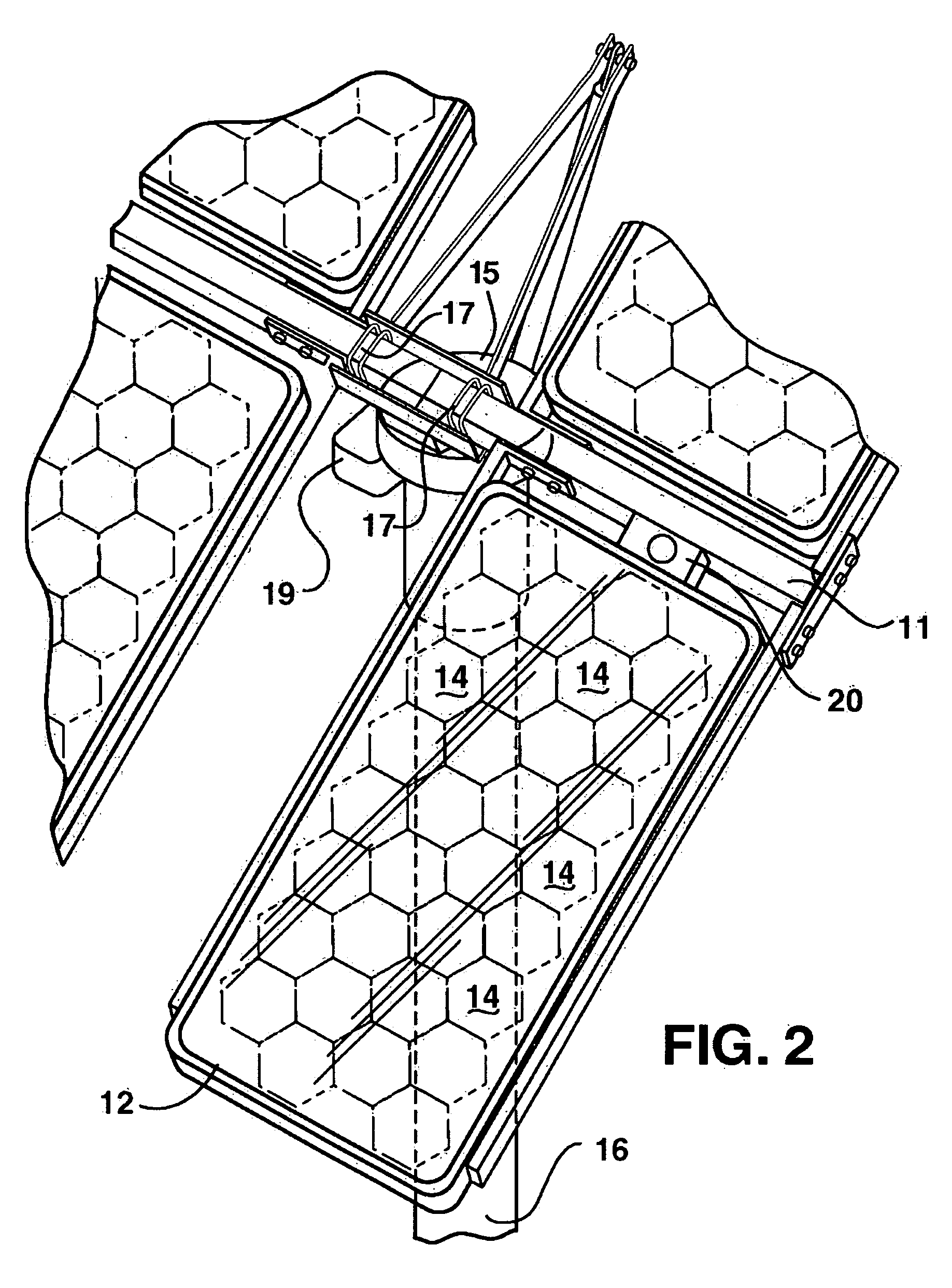

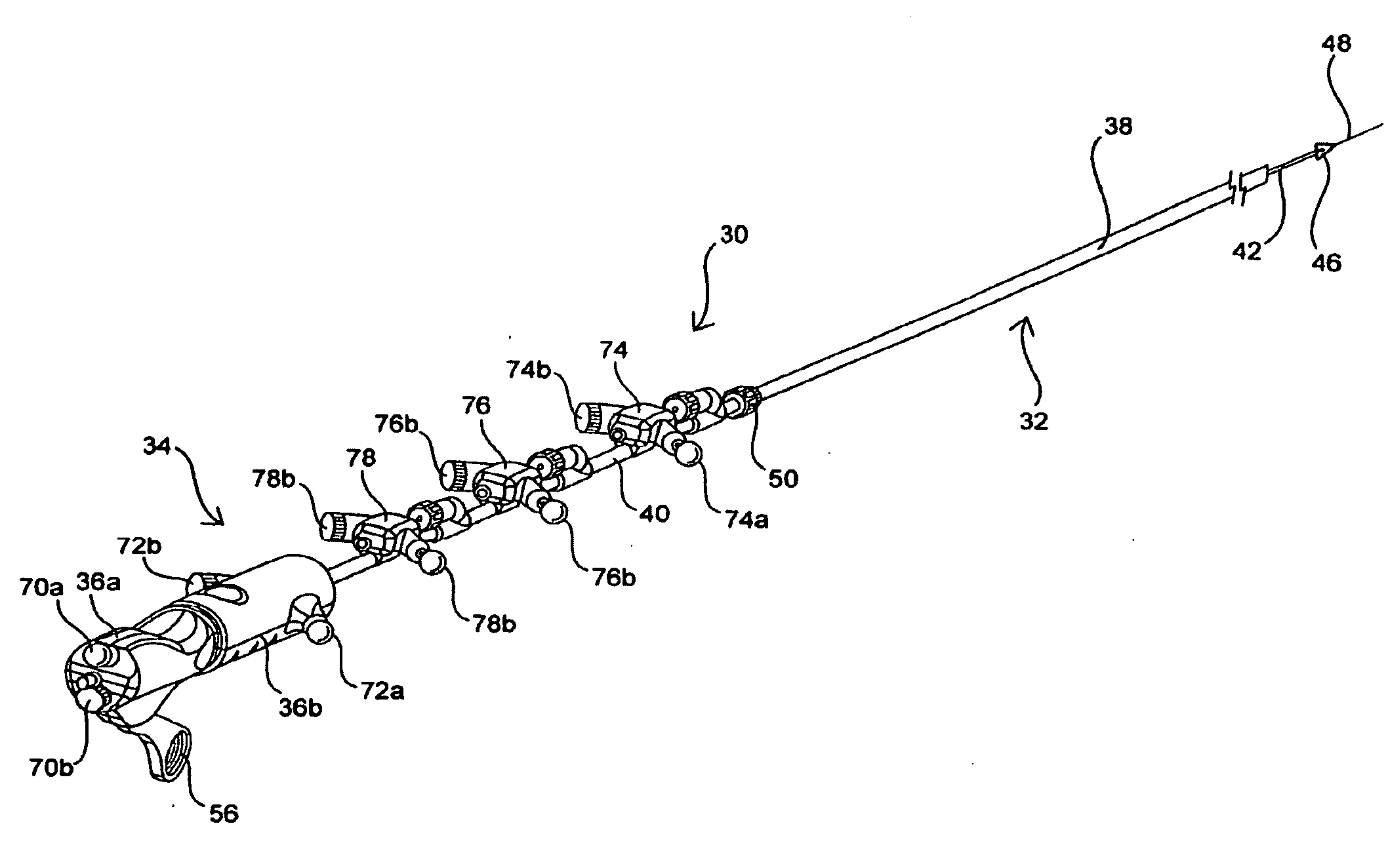

Applicator instruments having curved and articulating shafts for deploying surgical fasteners and methods therefor

ActiveUS20110079627A1Easy to collapseImprove abilitiesSuture equipmentsStapling toolsBiomedical engineeringSurgical Fasteners

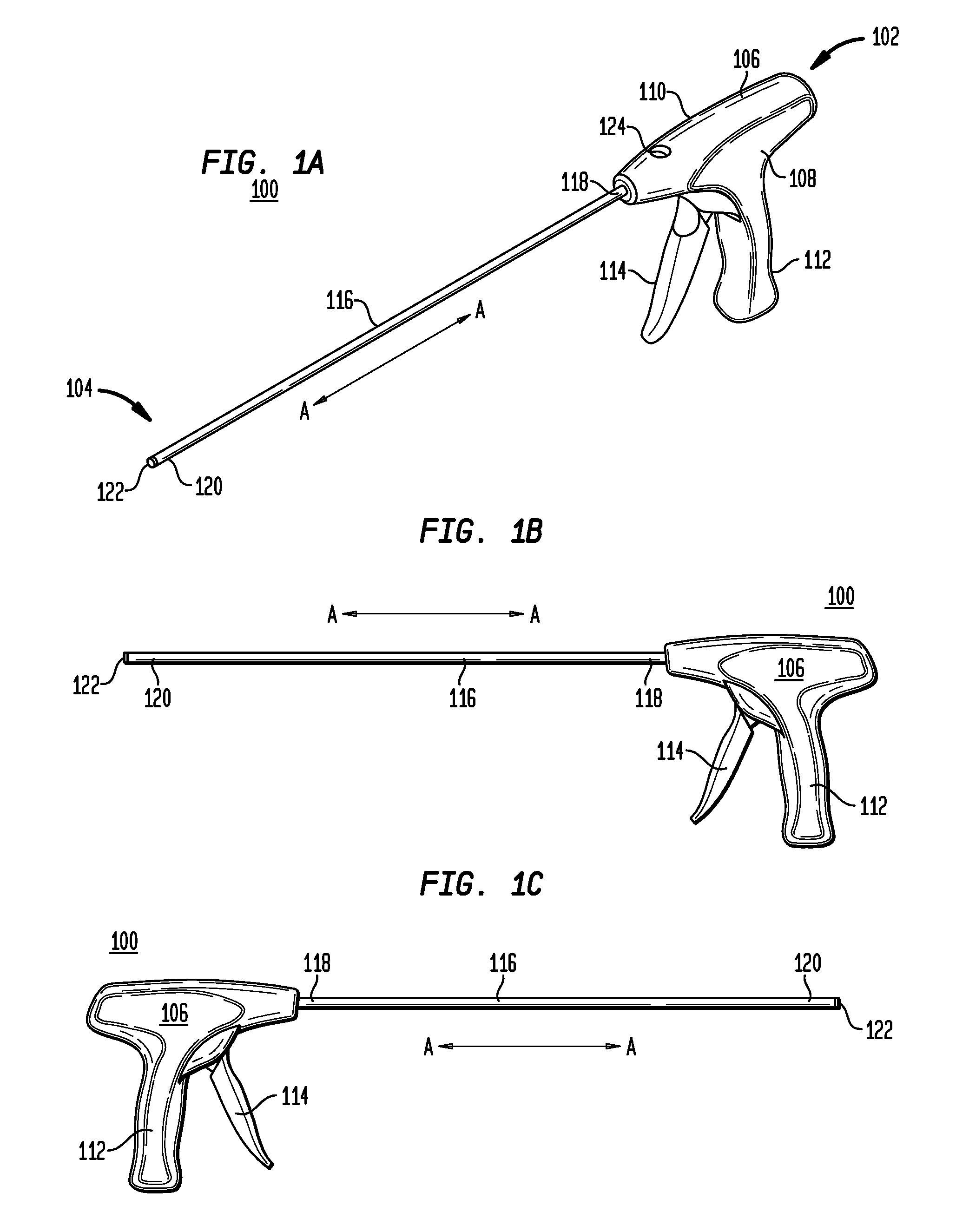

An applicator instrument for dispensing surgical fasteners includes a housing and a curved shaft. Surgical fasteners are disposed within the curved shaft for being dispensed from the distal end of the curved shaft. An advancer is disposed inside the curved shaft for shifting the surgical fasteners one position closer to the distal end of the curved shaft each time the advancer moves distally. A firing element is disposed inside the curved shaft and is movable between the proximal and distal ends of the curved shaft for dispensing the surgical fasteners from the distal end of the curved shaft. A staging assembly is adapted to receive a leading one of the surgical fasteners from the advancer as the advancer moves distally to shift the leading surgical fastener into substantial alignment with the firing element when the advancer moves proximally.

Owner:ETHICON LLC

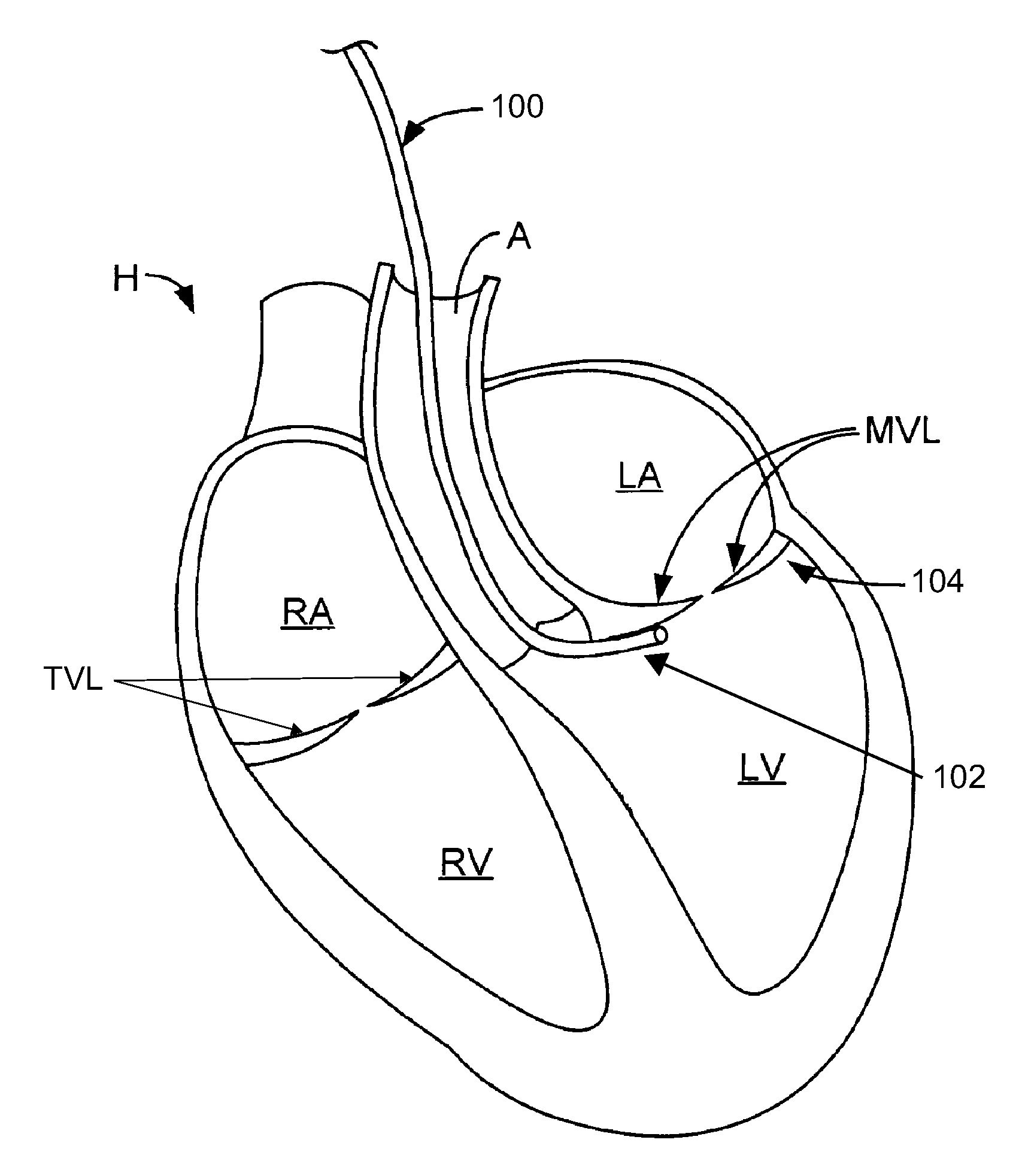

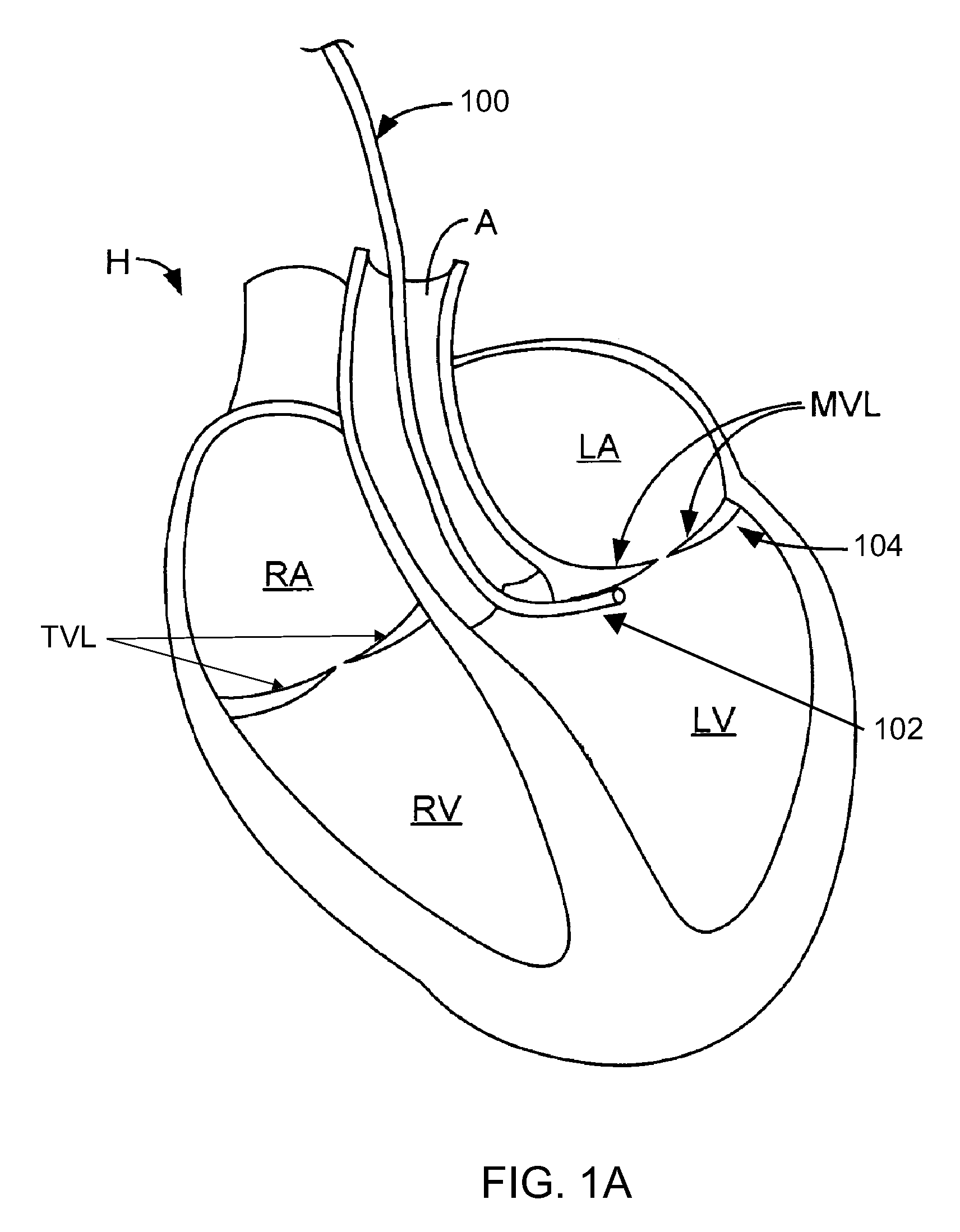

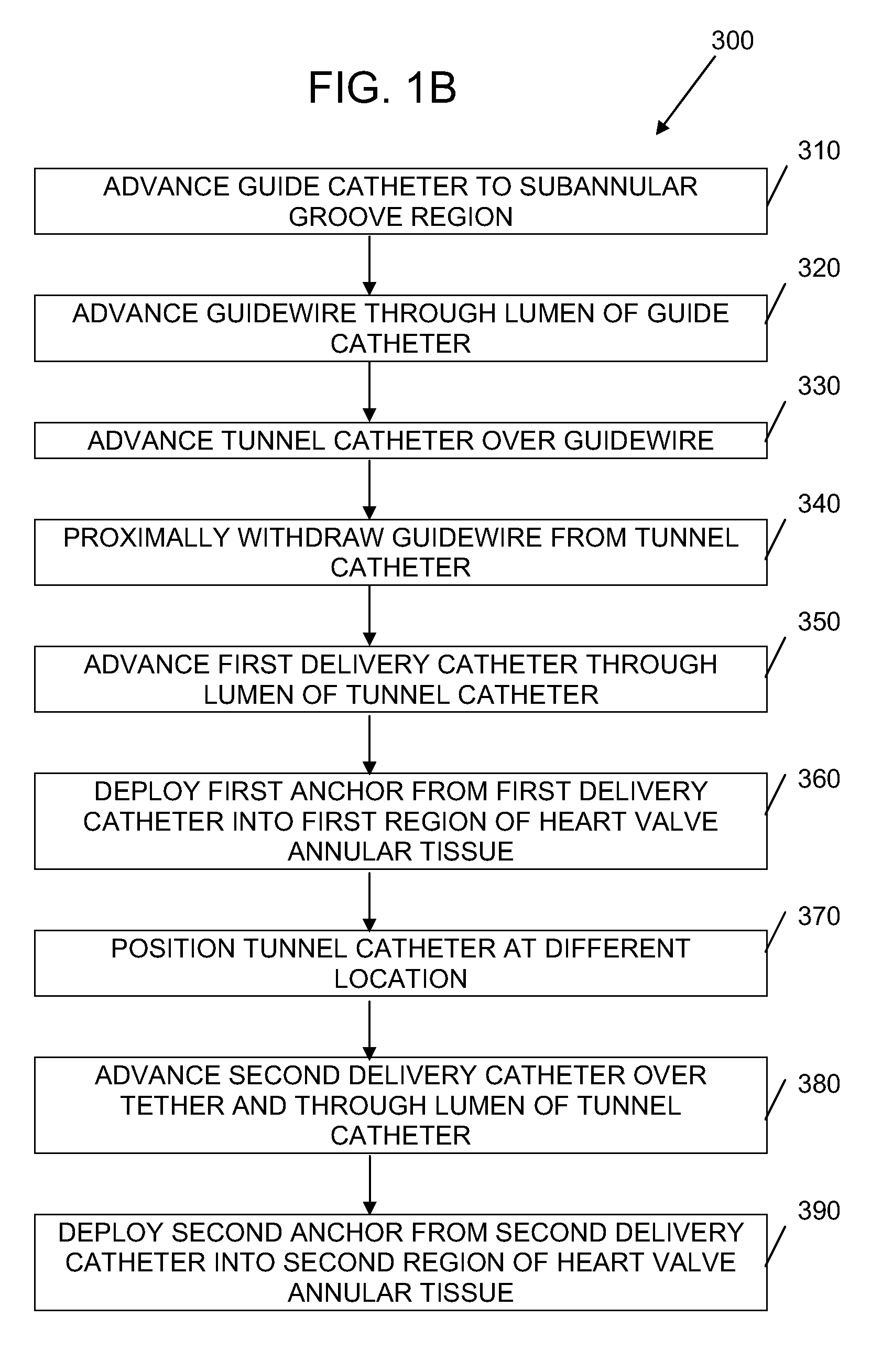

Systems and methods for cardiac remodeling

ActiveUS20090234318A1Improve hemodynamic functionReduced dimensionSuture equipmentsBone implantHemodynamicsCombined use

Described herein are devices and methods for improving the hemodynamic function of a patient. In particular, a first device adapted to reshape an atrio-ventricular valve is used in combination with a second device configured to further alter the blood flow through the valve. The first device is typically an implant positioned in the subvalvular space of a ventricle. The second device may be an annuloplasty implant, a non-annulus valve apparatus implant, a ventriculoplasty implant, or a cardiac rhythm management device.

Owner:ANCORA HEART INC

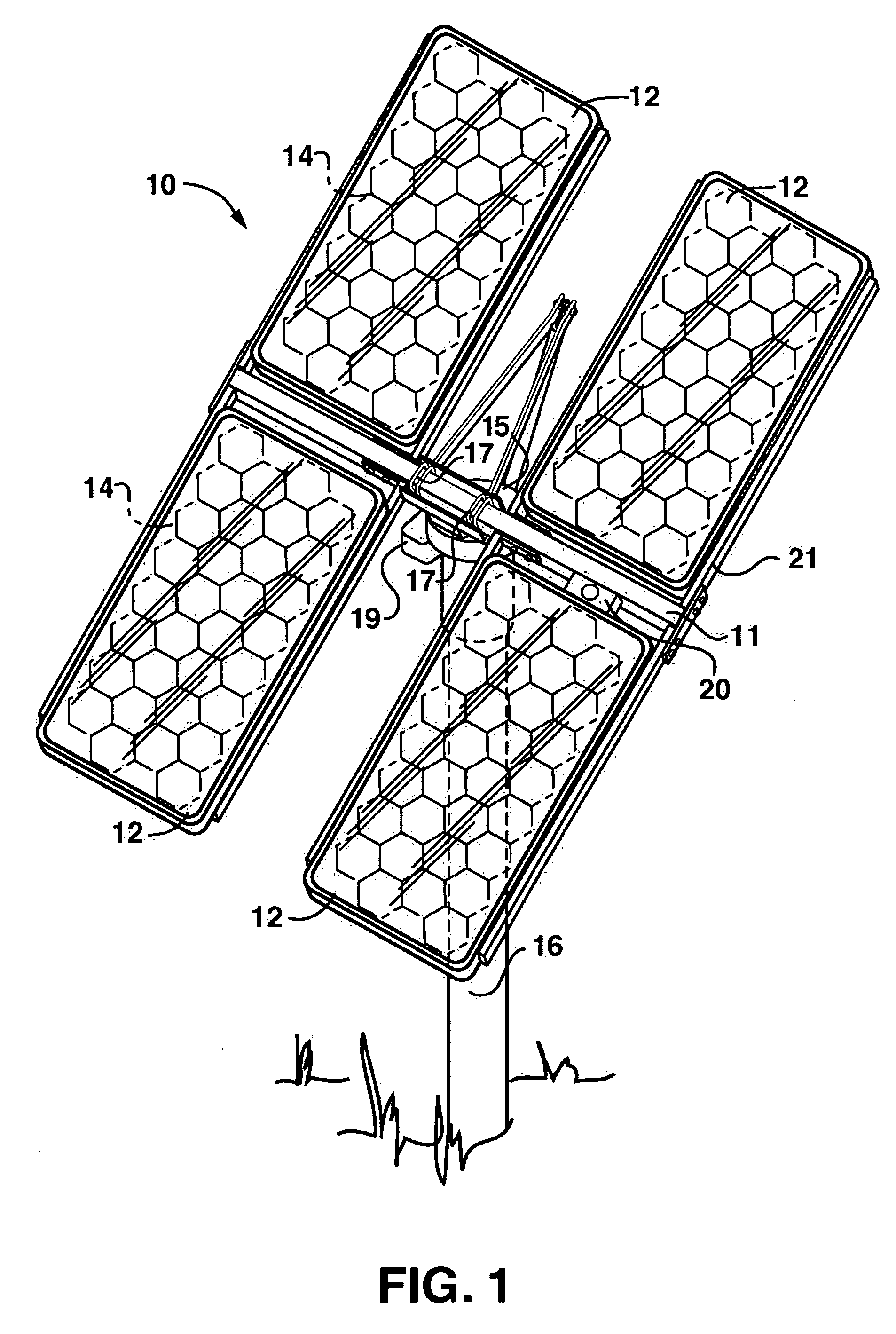

Concentrator solar photovoltaic array with compact tailored imaging power units

InactiveUS20060266408A1Low costEasy to assembleSolar heating energyMirrorsMechanical componentsEngineering

Solar panels and assembled arrays thereof include a collection of relatively compact, high-capacity power units. Optical components of each power unit include a front window or surface glazing, a primary mirror, secondary mirror and receiver assembly. Primary and secondary mirrors are defined by respective perimeters, at least a portion of which may be substantially coplanar and in contact with the front window. Some primary mirrors are configured with a perimeter of alternating full and truncated sections, and are curved to a base portion forming a pilot hole therein. Receiver assembly mechanical components include an alignment tube for mating with the primary mirror's pilot hole and for housing a photovoltaic solar cell. A base plate provided adjacent to the alignment tube serves to radiate heat emitted by the solar cell, and in some embodiments an additional heat sink provides further passive cooling. A tapered optical rod also provided within the receiver assembly directs received sunlight to the solar cell where electrical current is generated.

Owner:H2GO

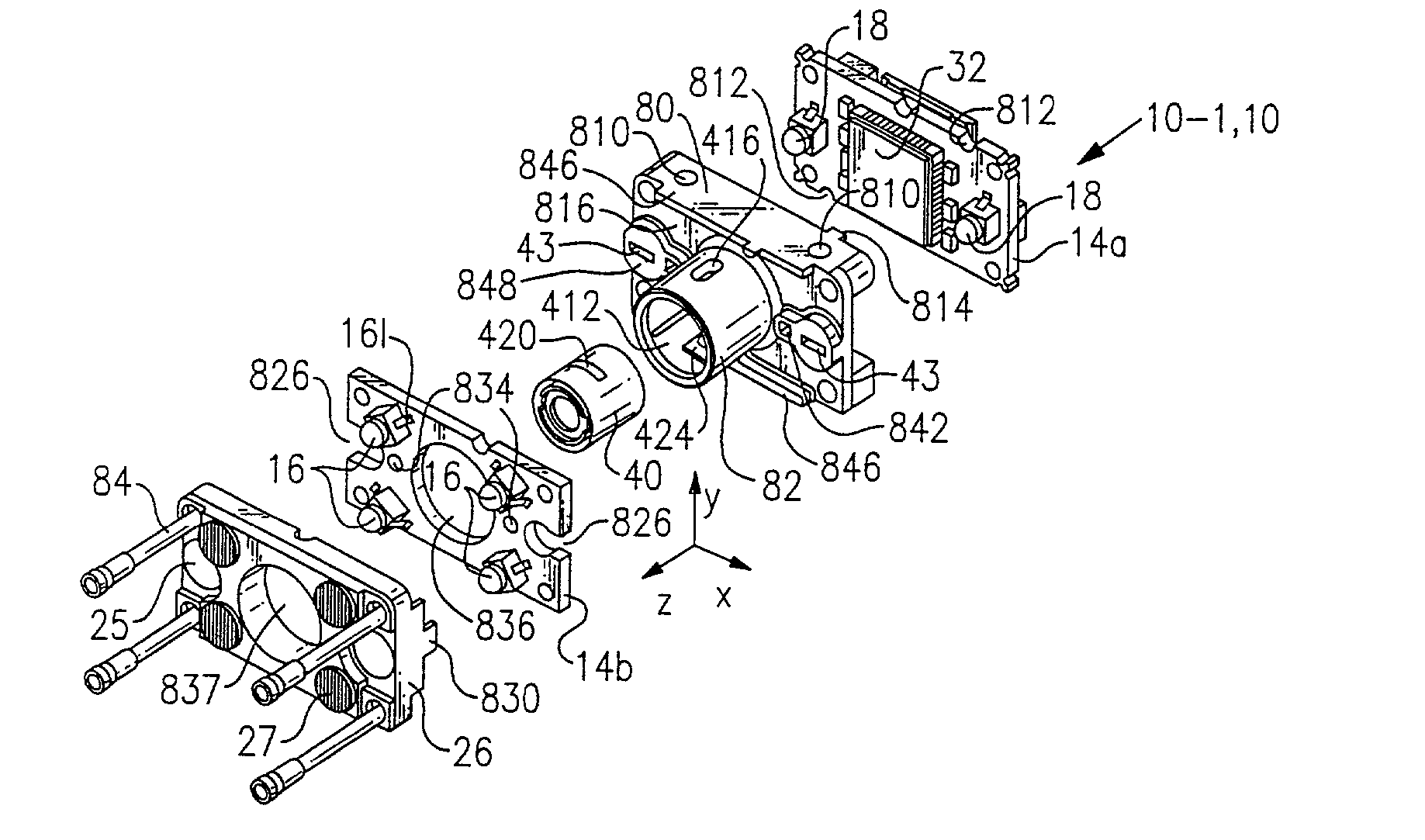

Optical reader for imaging module

InactiveUS20030029917A1Reduced dimensionOptimize architectureConveying record carriersPrinted circuits structural associationsElectricityComputer module

An imaging module in one embodiment includes a printed circuit board, an image sensor electrically connected to the printed circuit board, a support assembly for supporting at least one optical element, and an illumination system for generating an illumination pattern onto a target. The illumination system may include illumination light sources and diffusers for diffusing light from the illumination light sources. The module may further include an aiming system having an aiming light source, an aperture for stopping light from the aiming light source, and an optical element for projecting an aiming pattern into target area. Either or both of the illumination and aiming systems may include light redirecting elements such as mirrors or prisms.

Owner:HAND HELD PRODS

Use of high-K dielectric material in modified ONO structure for semiconductor devices

InactiveUS6803272B1Reduced dimensionSacrificing charge trapping abilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

Owner:MONTEREY RES LLC

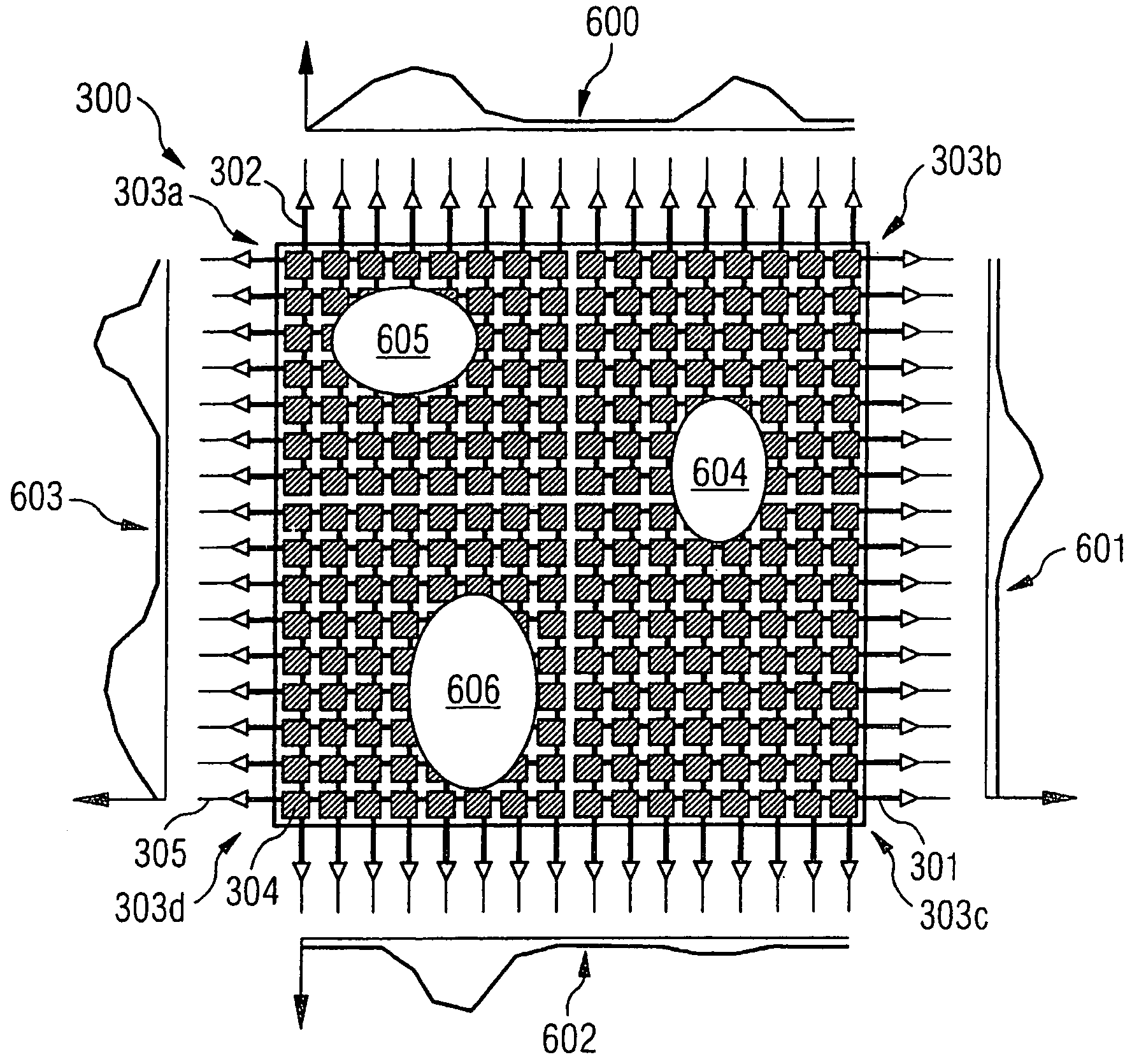

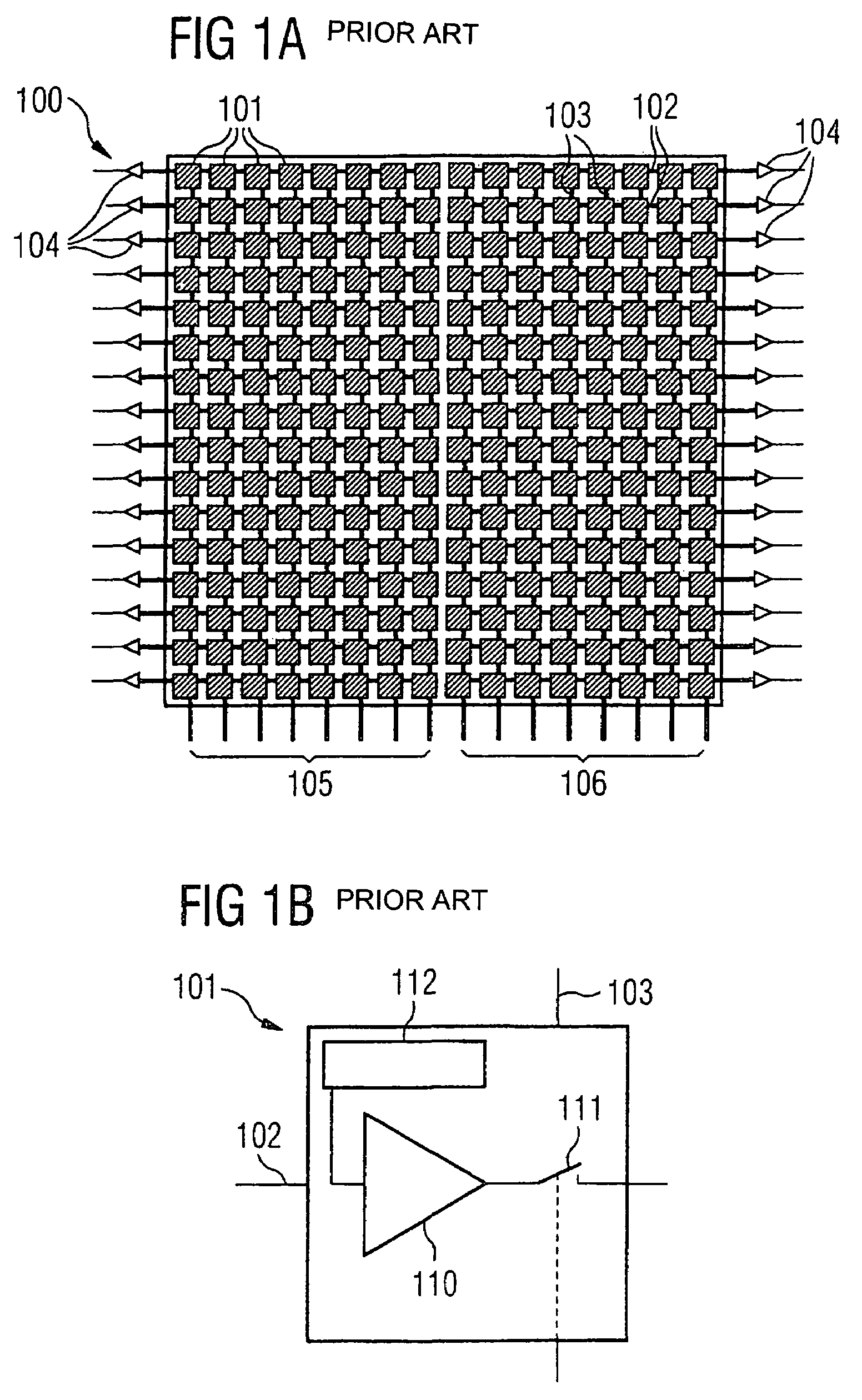

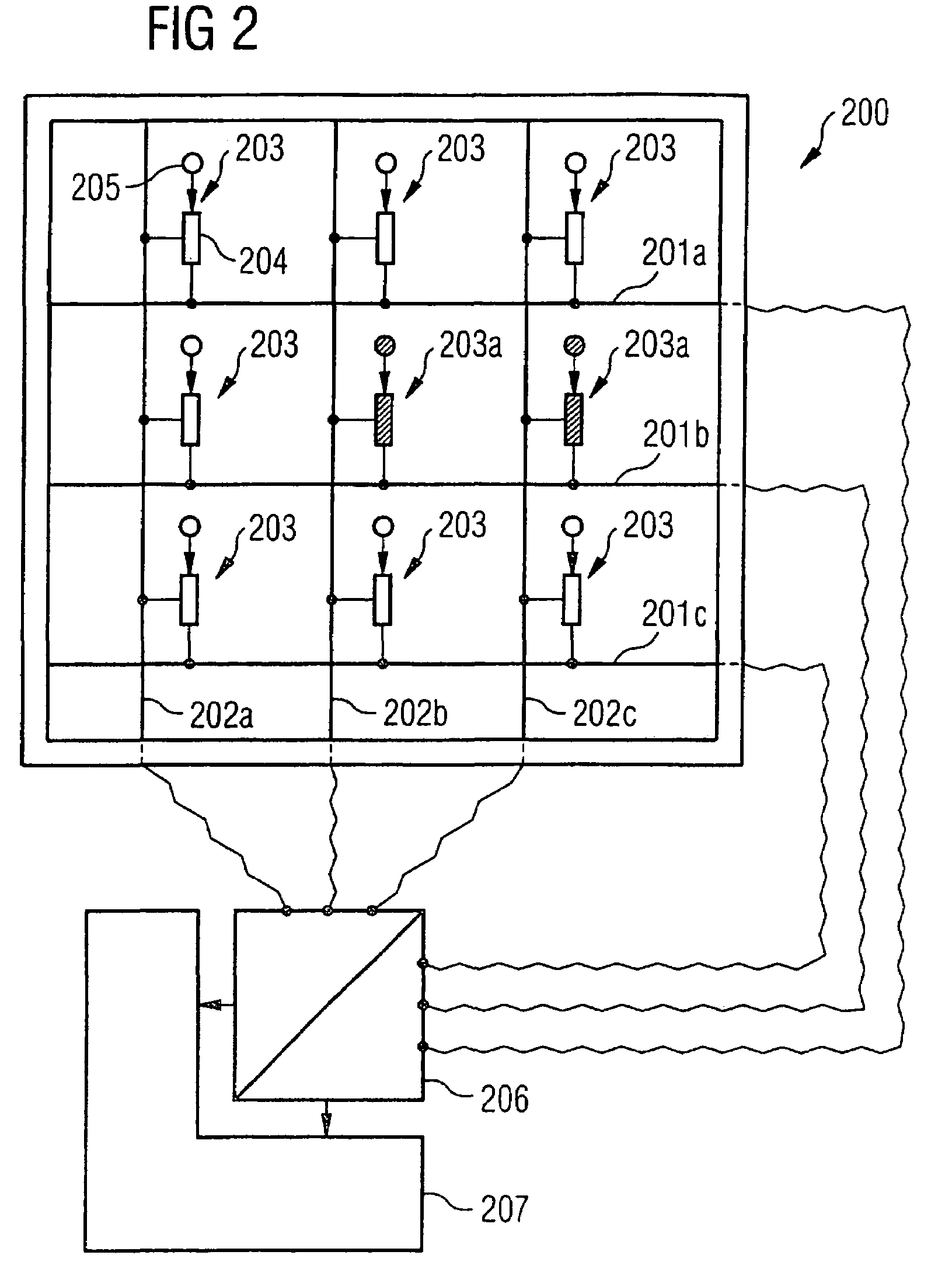

Sensor arrangement

ActiveUS7470352B2Reduced dimensionImprove read rateImmobilised enzymesBioreactor/fermenter combinationsSensor arrayElectricity

Sensor arrangement having row and column lines arranged in first and second directions, respectively, sensor arrays arranged in crossover regions of the row and column lines, a detector, and a decoding device. The sensor arrays have a coupling device for electrically coupling respective row and column lines, and a sensor element to influence electric current flow through the coupling device. The detector is electrically coupled to a respective end section of at least a portion of the row and column lines, and detects a respective accumulative current flow from the individual electrical current flows provided by the sensor arrays of the respective lines. The decoding device is coupled to the row and column lines, and evaluates at least a portion of the accumulative electric current flows fed to the decoding device via the row and column lines to determine at which of the sensor elements a sensor signal is present.

Owner:INFINEON TECH AG

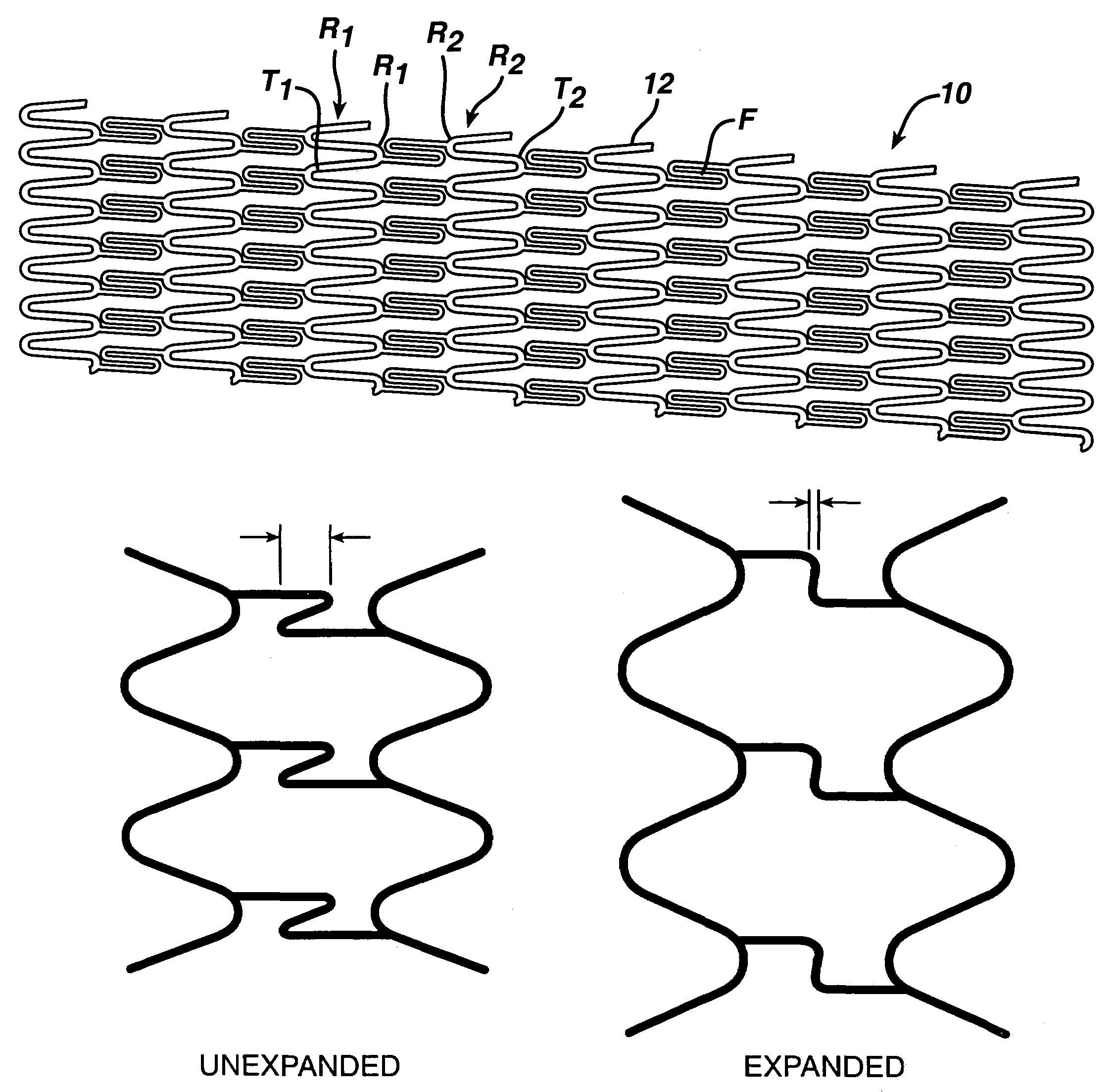

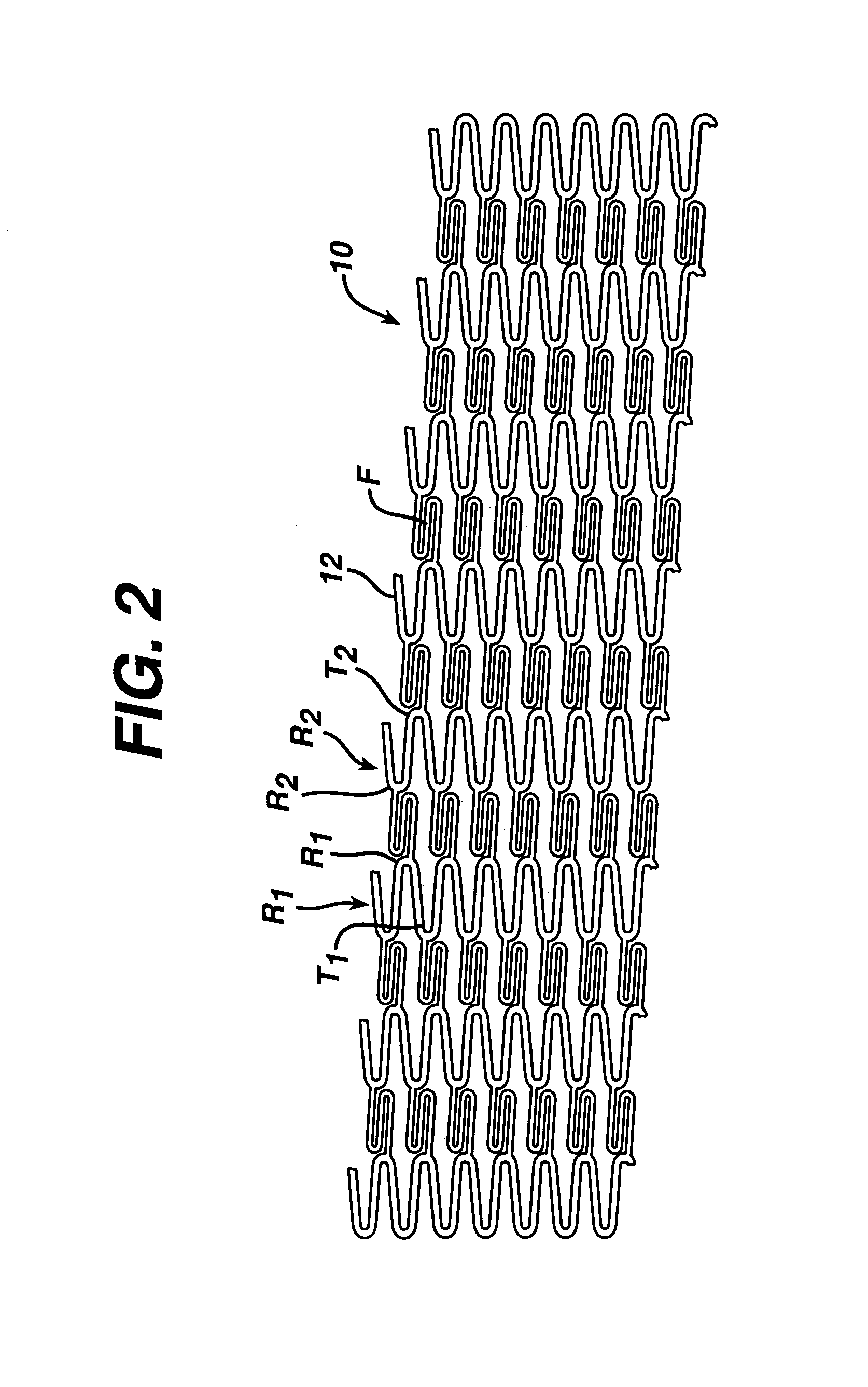

Stent with enhanced crossability

InactiveUS7029493B2Reduce dimensionDimension of opening can be reducedStentsSurgerySmooth surfaceStent design

A stent design is disclosed which has a flexible connector which has flexible arcs and flexible struts aligned similarly to the radial arcs and radial struts, such that the alignment of the flexible connector within the stent decreases the likelihood of the stent's catching on a non-smooth surface.

Owner:CARDINAL HEALTH SWITZERLAND 515 GMBH

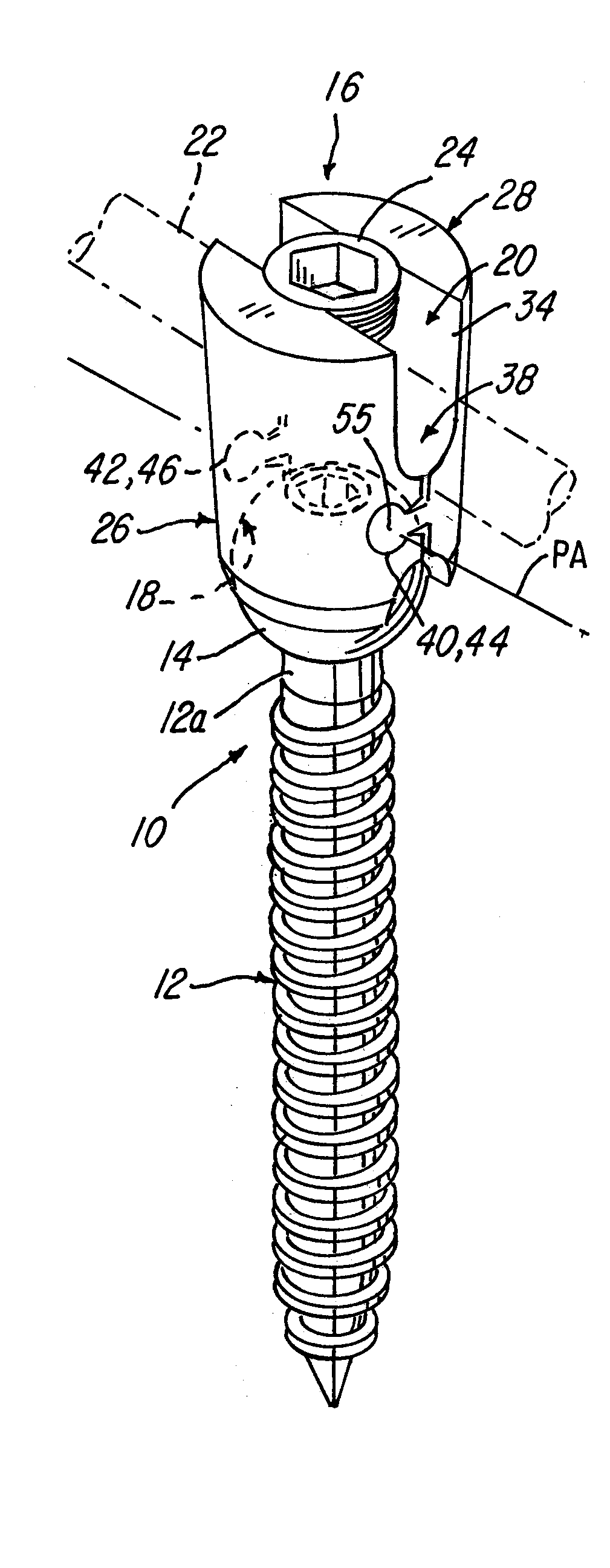

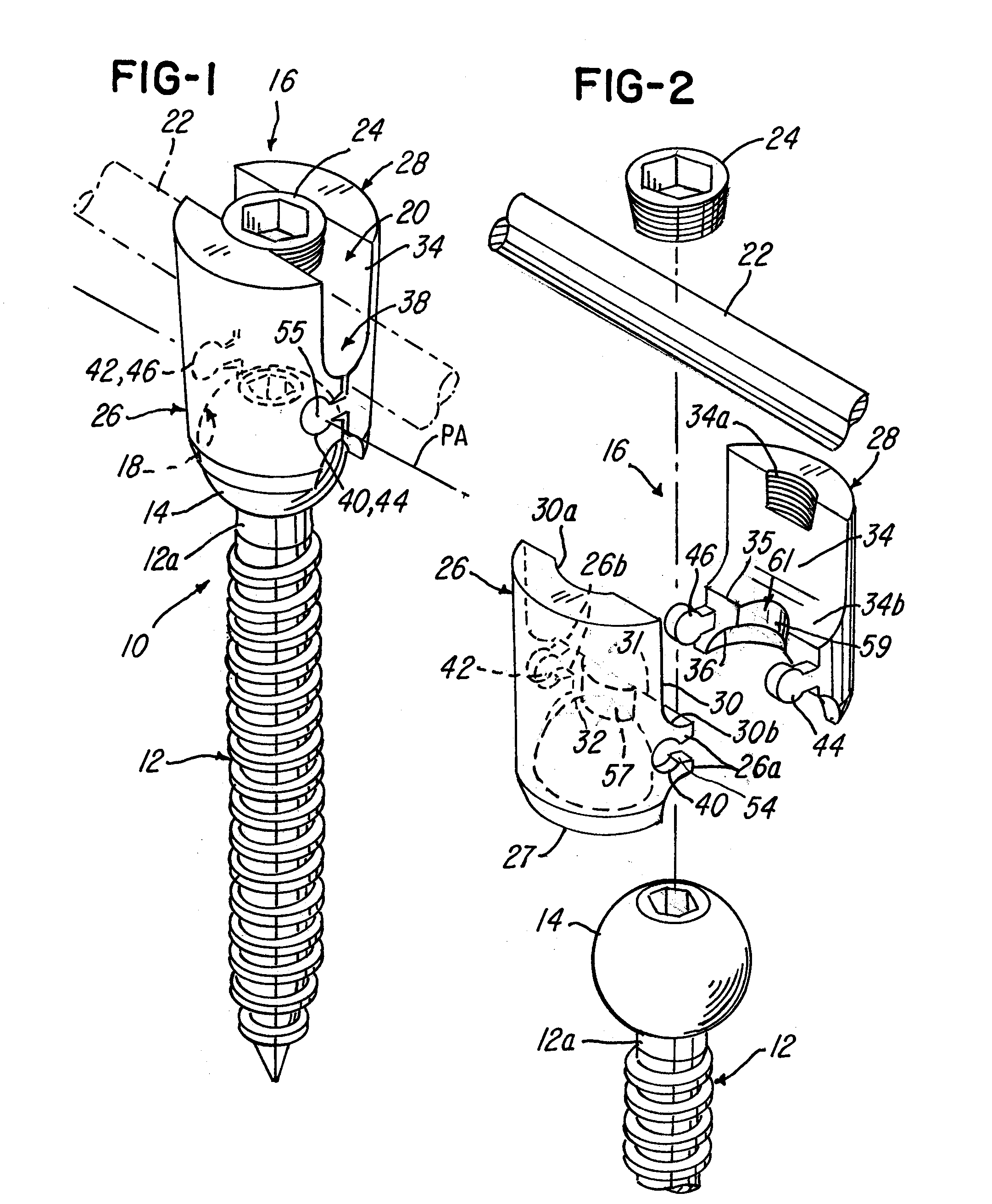

Polyaxial screw system and method having a hinged receiver

InactiveUS20080312655A1Firmly connectedReduced dimensionSuture equipmentsInternal osteosythesisScrew systemIliac screw

A polyaxial screw system and method are provided. The system comprises a receiver having a pivot area defined by a pivot joint or a material between a pair of receiver walls or members that permit the receiver walls or members to move or pivot relative to each other so that a dimension of a socket area can be changed. The socket area is defined by socket walls that when at least one of the receiver members pivots relative to another receiver member or wall, a distance between the socket walls gets smaller so that the socket walls can engage and lock against a head of a polyaxial screw.

Owner:X SPINE SYST

Apparatus and method for deploying an implantable device within the body

The present invention provides systems and methods for deploying implantable devices within the body. The delivery and deployment systems include at least one catheter or an assembly of catheters for selectively positioning the lumens of the implant to within target vessels. Various deployment and attachment mechanisms are provided for selectively deploying the implants.

Owner:TAHERI LADUCA

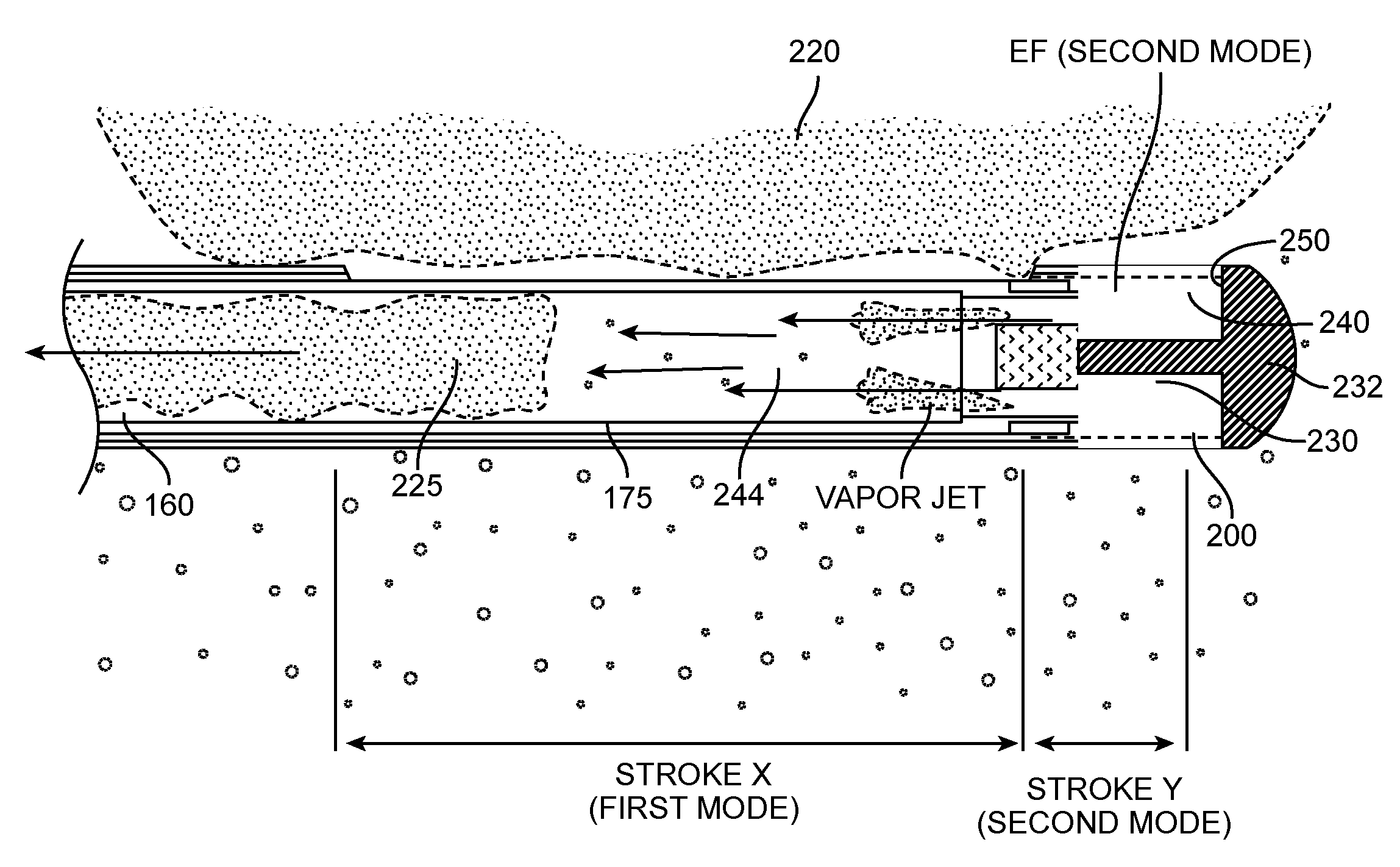

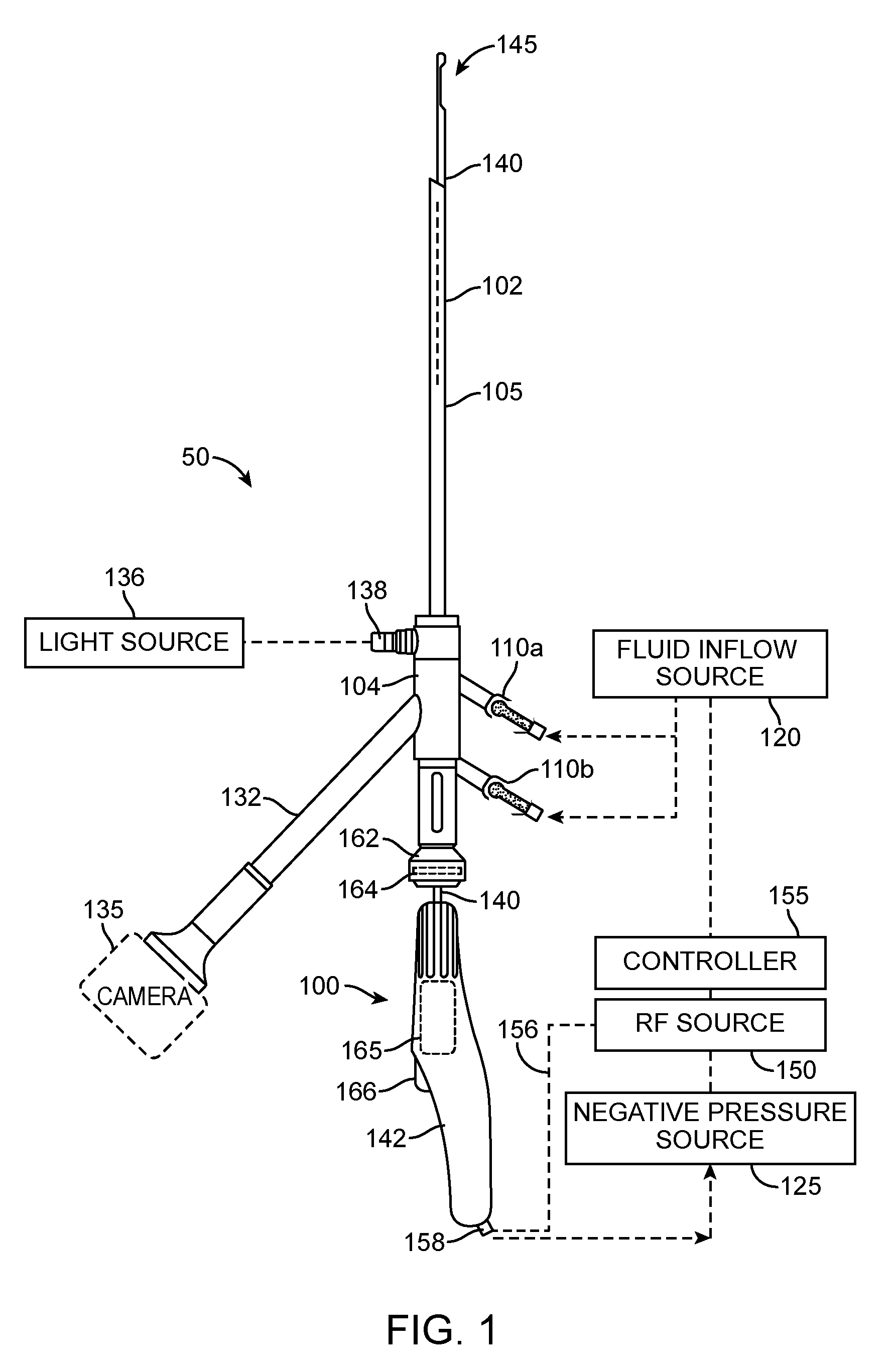

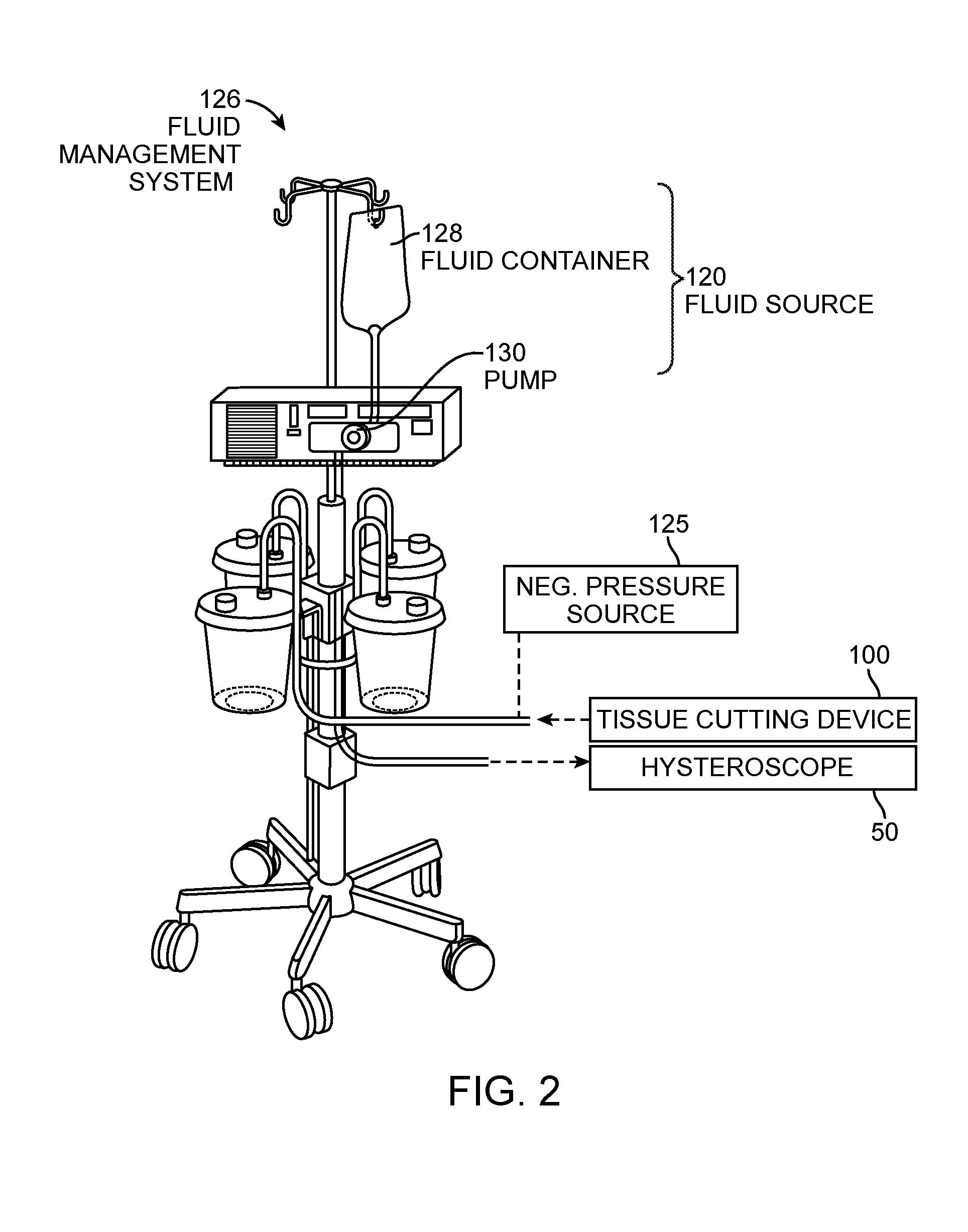

Tissue extraction devices and methods

ActiveUS20120330292A1Reduced dimensionVaporization fastEndoscopesExcision instrumentsPower flowVaporization

Tissue may be cut and extracted from an interior location in a patient's body using a probe or tool which both effects cutting and causes vaporization of a liquid or other fluid to propel the cut tissue through an extraction lumen of the cutting device. The cutting may be achieved using an electrosurgical electrode assembly, including a first electrode on a cutting member and a second electrode within a cutting probe or tool. Thus, over a first cutting portion, radio frequency current may help cut the tissue and over a second or over transition region, the RF current may initiate vaporization of the fluid or other liquid to propel the tissue from the cutting device.

Owner:MINERVA SURGICAL

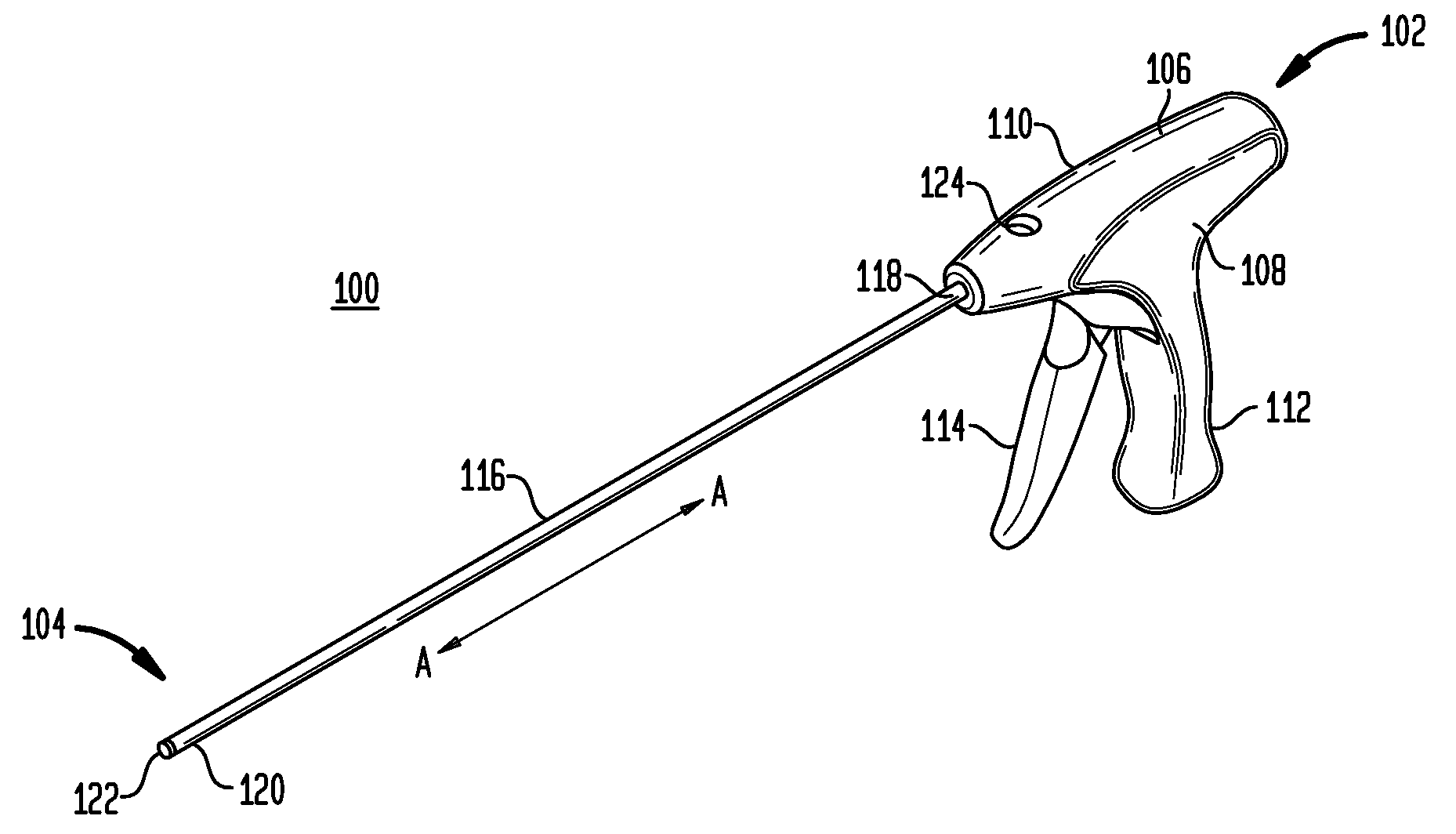

Surgical fasteners, applicator instruments, and methods for deploying surgical fasteners

ActiveUS20100292710A1Easy to collapseImprove abilitiesSuture equipmentsDiagnosticsEngineeringSurgical department

An applicator instrument for dispensing surgical fasteners includes a housing, an elongated shaft extending from the housing, the elongated shaft having a proximal end coupled with the housing and a distal end remote therefrom, and a firing system for dispensing surgical fasteners from the distal end of the elongated shaft. The firing system includes a firing rod disposed in the elongated shaft, the firing system having a firing cycle with a first stage for advancing the firing rod toward the distal end of the elongated shaft at a first rate of speed and a second stage for advancing the firing rod toward the distal end of the elongated shaft at a second rate of speed that is greater than the first rate of speed.

Owner:ETHICON INC

Bridge Resistance Random Access Memory Device and Method With A Singular Contact Structure

ActiveUS20070262388A1Reduced dimensionSemiconductor/solid-state device detailsSolid-state devicesBit lineEdge surface

A resistance random access memory in a bridge structure is disclosed that comprises a contact structure where first and second electrodes are located within the contact structure. The first electrode has a circumferential extending shape, such as an annular shape, surrounding an inner wall of the contact structure. The second electrode is located within an interior of the circumferential extending shape and separated from the first electrode by an insulating material. A resistance memory bridge is in contact with an edge surface of the first and second electrodes. The first electrode in the contact structure is connected to a transistor and the second electrode in the contact structure is connected to a bit line. A bit line is connected to the second electrode by a self-aligning process.

Owner:MACRONIX INT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com