Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2638results about "Bulk negative resistance effect devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory cell incorporating a chalcogenide element and method of making same

Owner:ROUND ROCK RES LLC

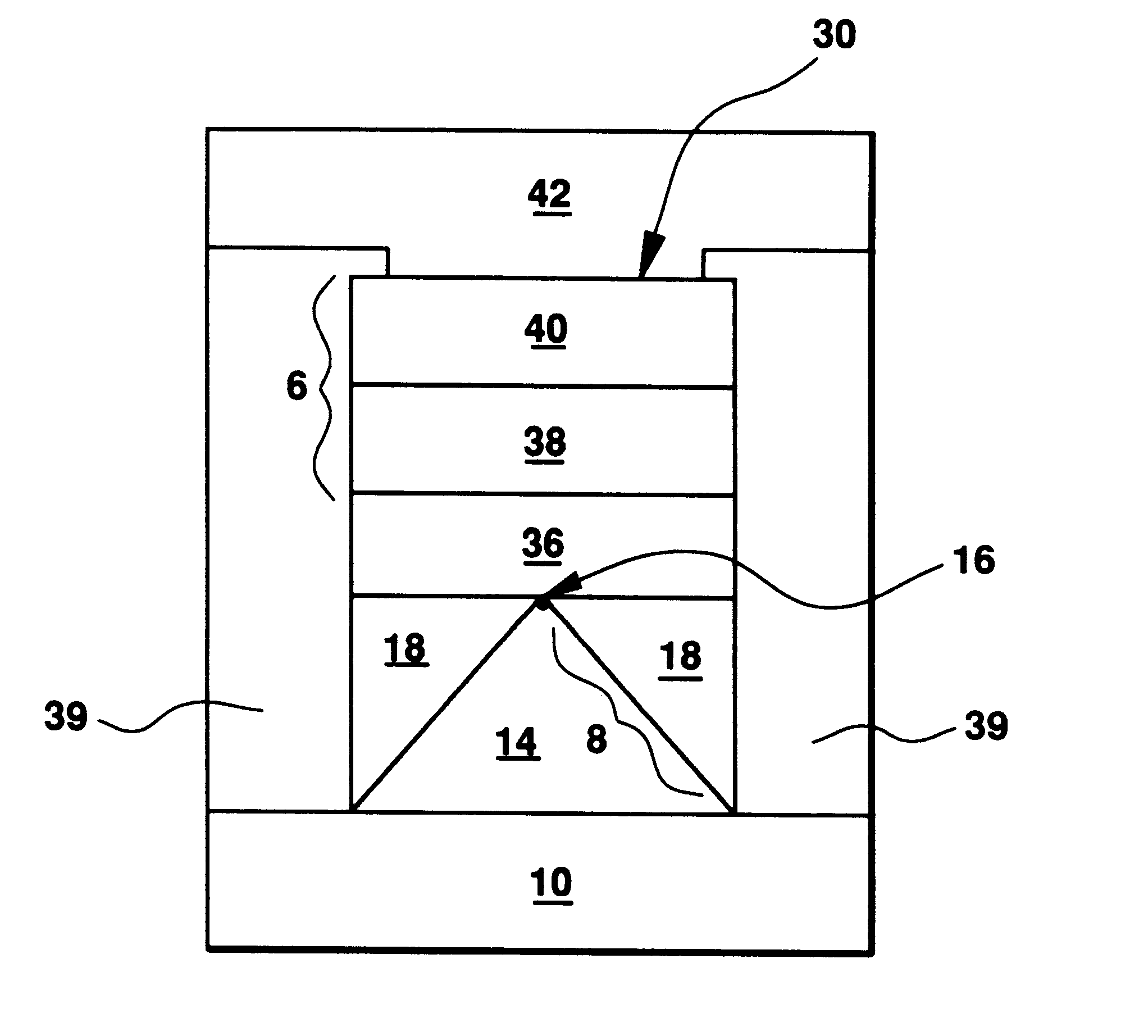

Multibit single cell memory element having tapered contact

InactiveUSRE37259E1Large electric resistance valueSolid-state devicesRead-only memoriesPeak valueEngineering

An electrically operated, directly overwritable, multibit, single-cell chalcogenide memory element with multibit storage capabilities and having at least one contact for supplying electrical input signals to set the memory element to a selected resistance value, the second contact tapering to a peak adjacent to the memory element. In this manner the tapered contact helps define the size and position of a conduction path through the memory element.

Owner:OVONYX MEMORY TECH LLC

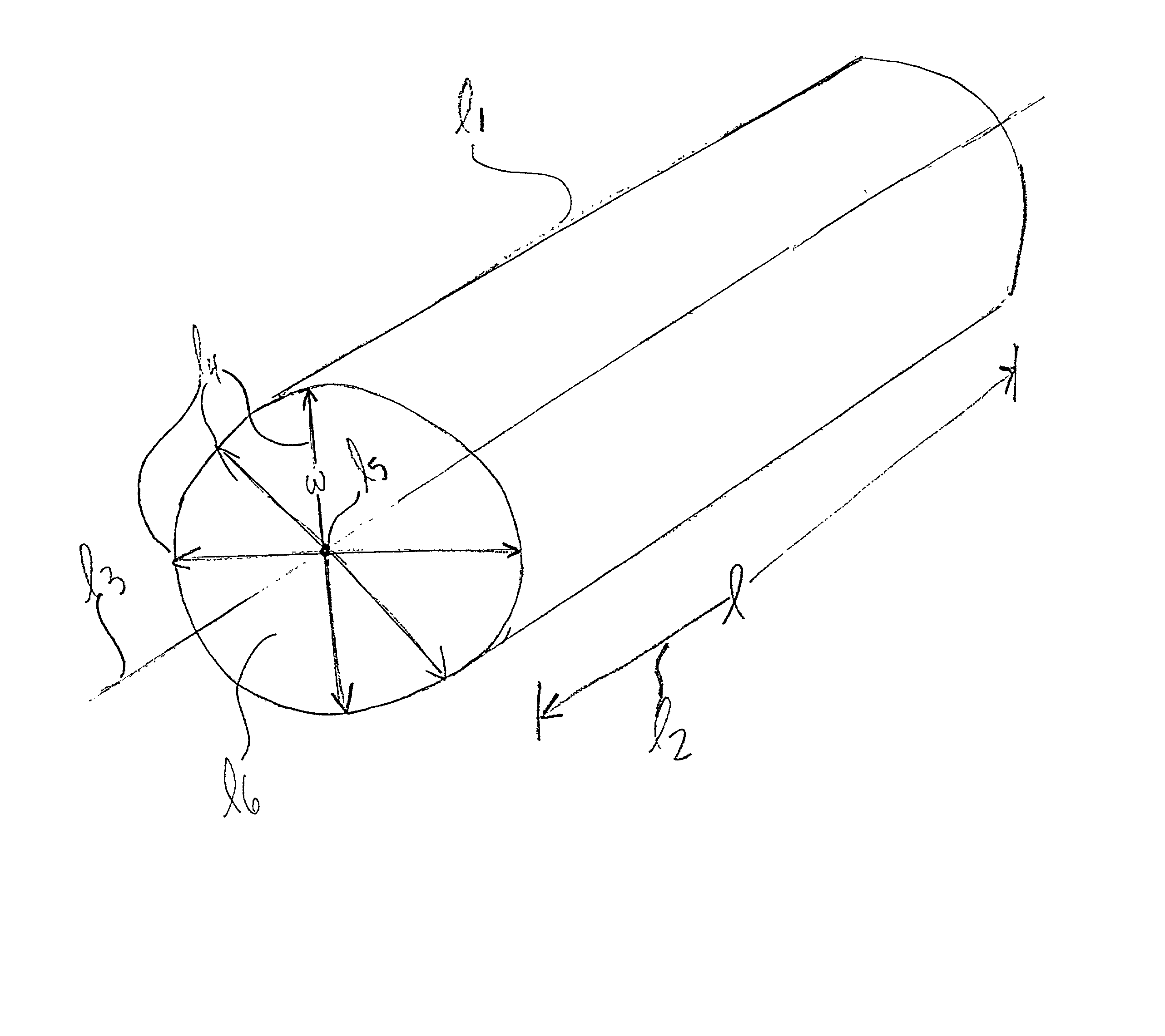

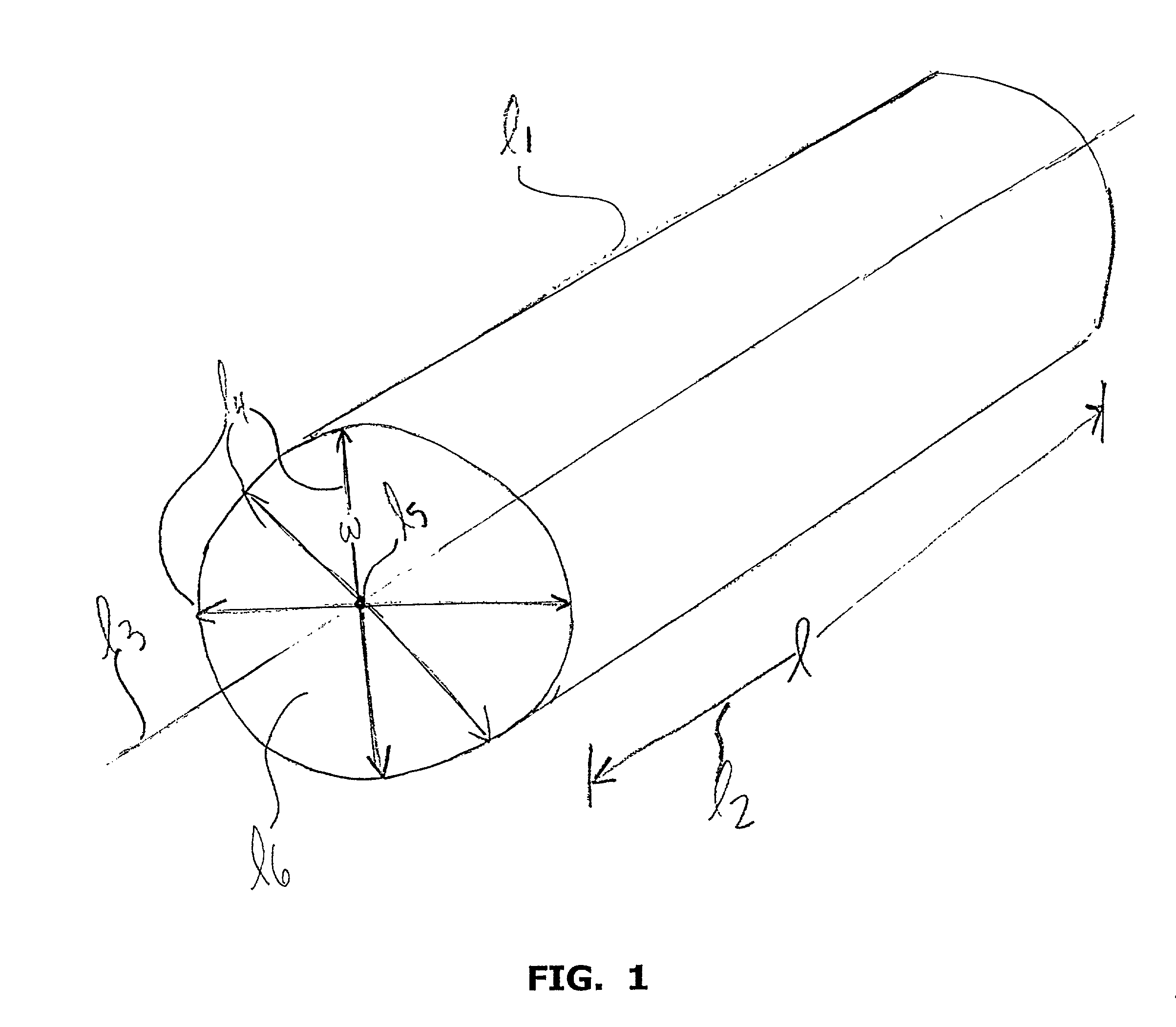

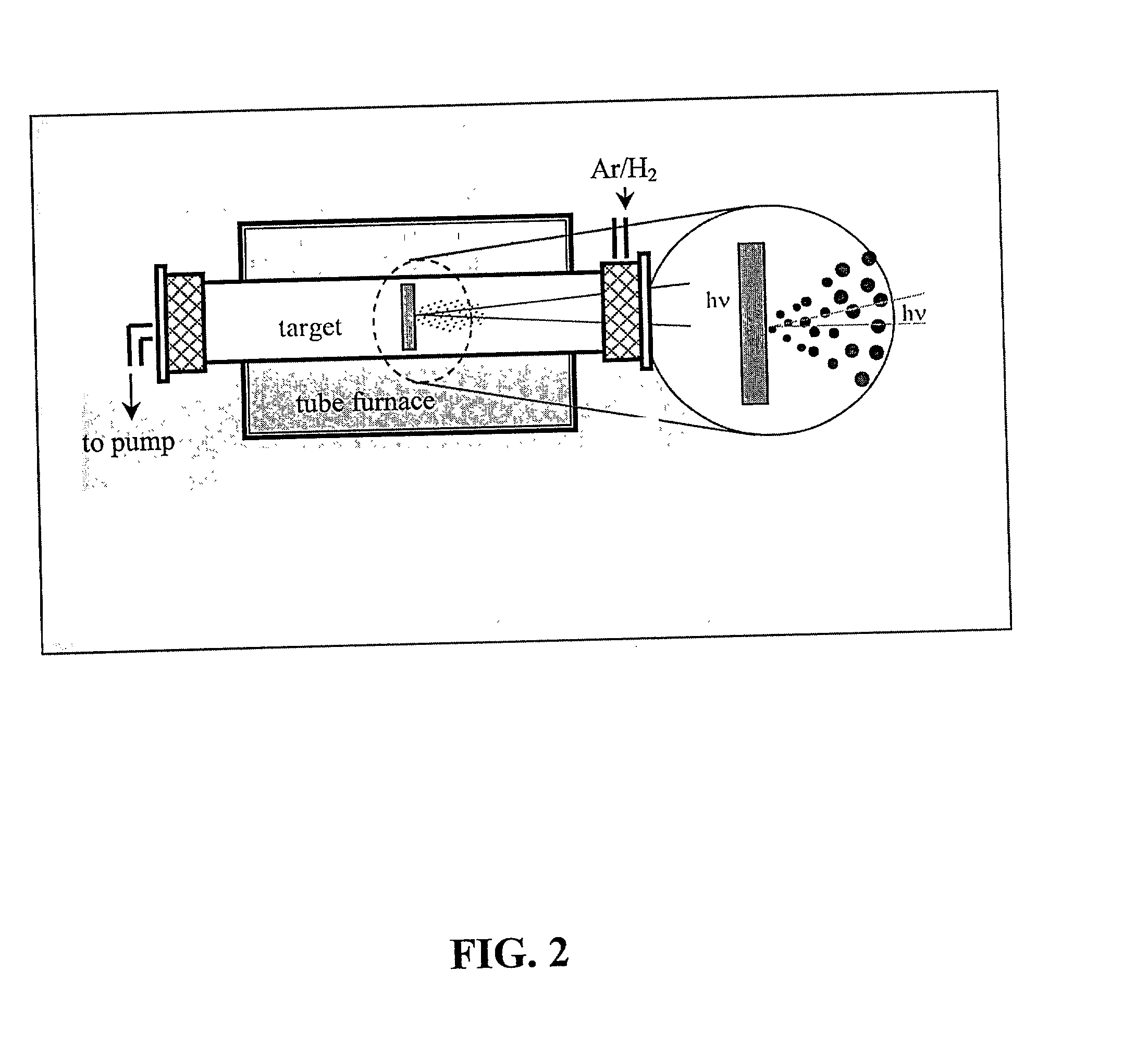

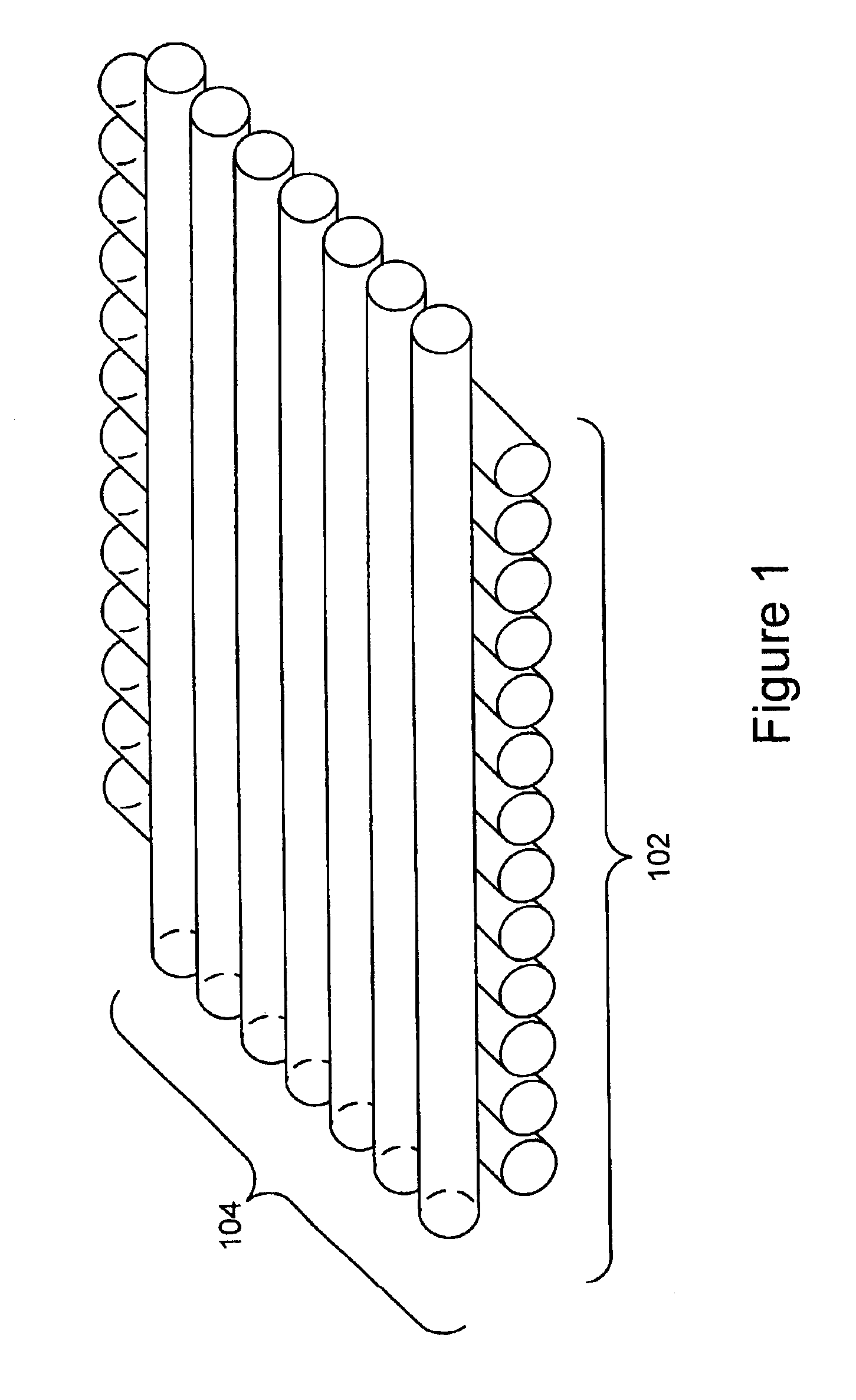

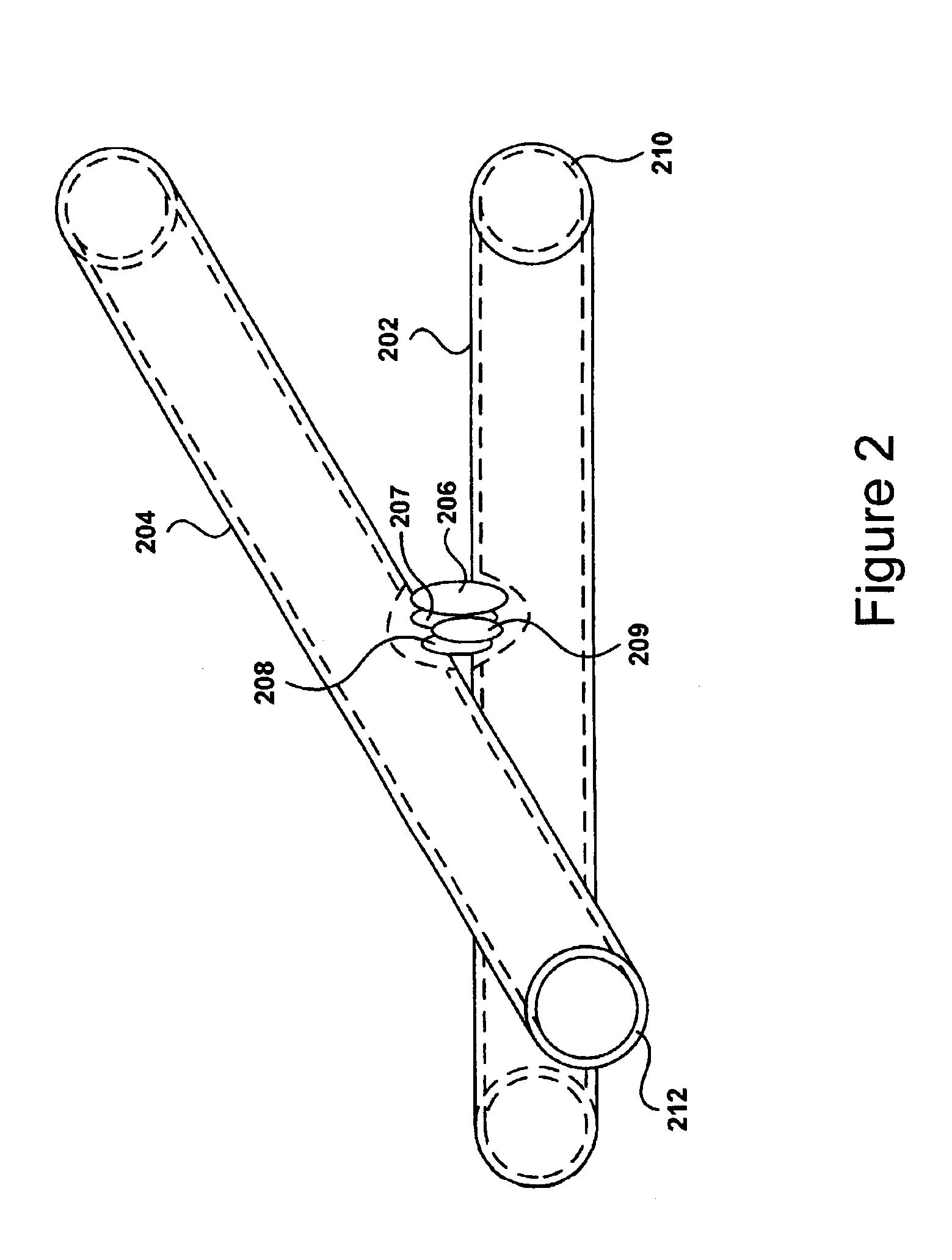

Doped elongated semiconductors, growing such semiconductors, devices including such semiconductors and fabricating such devices

A bulk-doped semiconductor that is at least one of the following: a single crystal, an elongated and bulk-doped semiconductor that, at any point along its longitudinal axis, has a largest cross-sectional dimension less than 500 nanometers, and a free-standing and bulk-doped semiconductor with at least one portion having a smallest width of less than 500 nanometers. Such a semiconductor may comprise an interior core comprising a first semiconductor; and an exterior shell comprising a different material than the first semiconductor. Such a semiconductor may be elongated and my have, at any point along a longitudinal section of such a semiconductor, a ratio of the length of the section to a longest width is greater than 4:1, or greater than 10:1, or greater than 100:1, or even greater than 1000:1. At least one portion of such a semiconductor may a smallest width of less than 200 nanometers, or less than 150 nanometers, or less than 100 nanometers, or less than 80 nanometers, or less than 70 nanometers, or less than 60 nanometers, or less than 40 nanometers, or less than 20 nanometers, or less than 10 nanometers, or even less than 5 nanometers. Such a semiconductor may be a single crystal and may be free-standing. Such a semiconductor may be either lightly n-doped, heavily n-doped, lightly p-doped or heavily p-doped. Such a semiconductor may be doped during growth. Such a semiconductor may be part of a device, which may include any of a variety of devices and combinations thereof, and, and a variety of assembling techniques may be used to fabricate devices from such a semiconductor. Two or more of such a semiconductors, including an array of such semiconductors, may be combined to form devices, for example, to form a crossed p-n junction of a device. Such devices at certain sizes may exhibit quantum confinement and other quantum phenomena, and the wavelength of light emitted from one or more of such semiconductors may be controlled by selecting a width of such semiconductors. Such semiconductors and device made therefrom may be used for a variety of applications.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

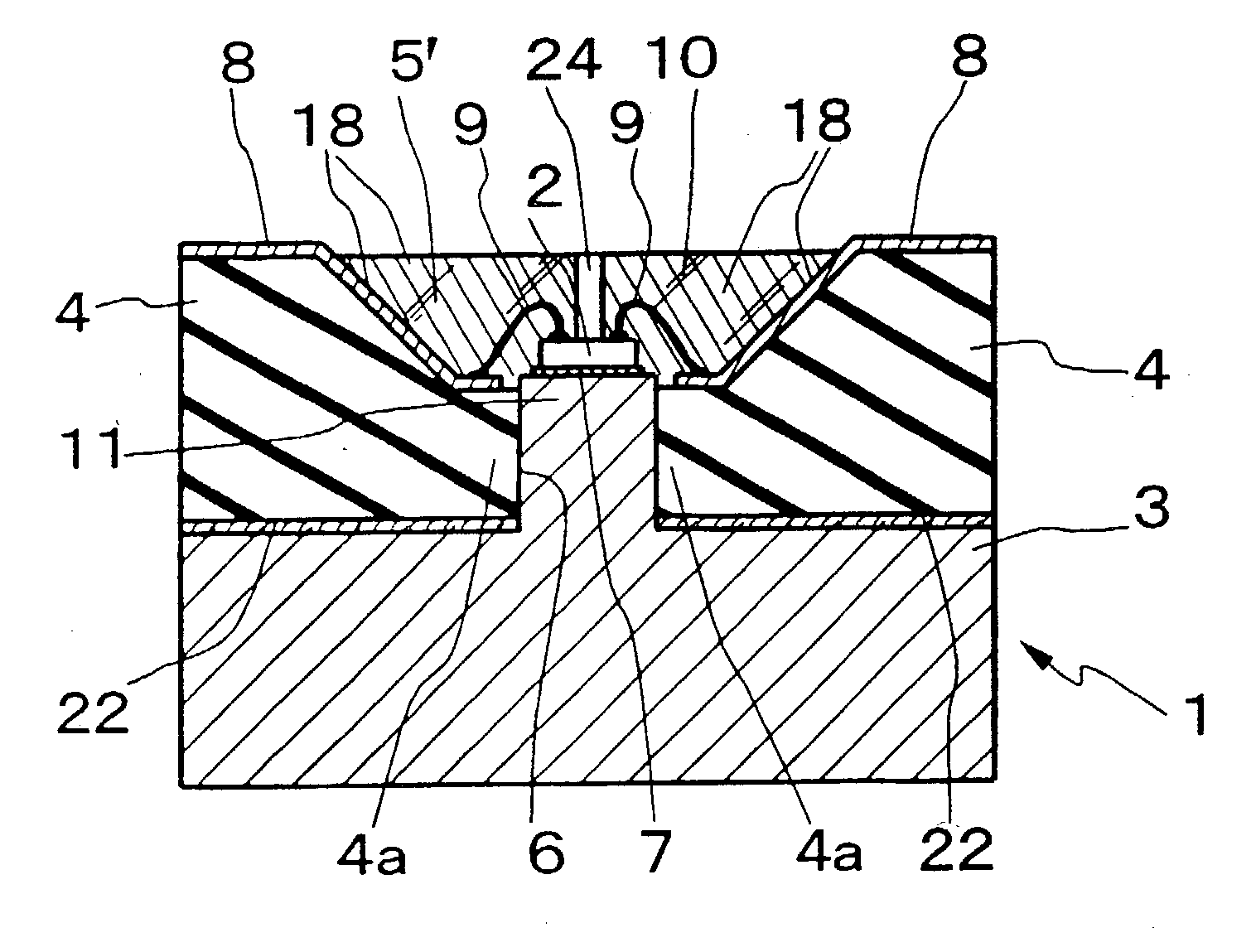

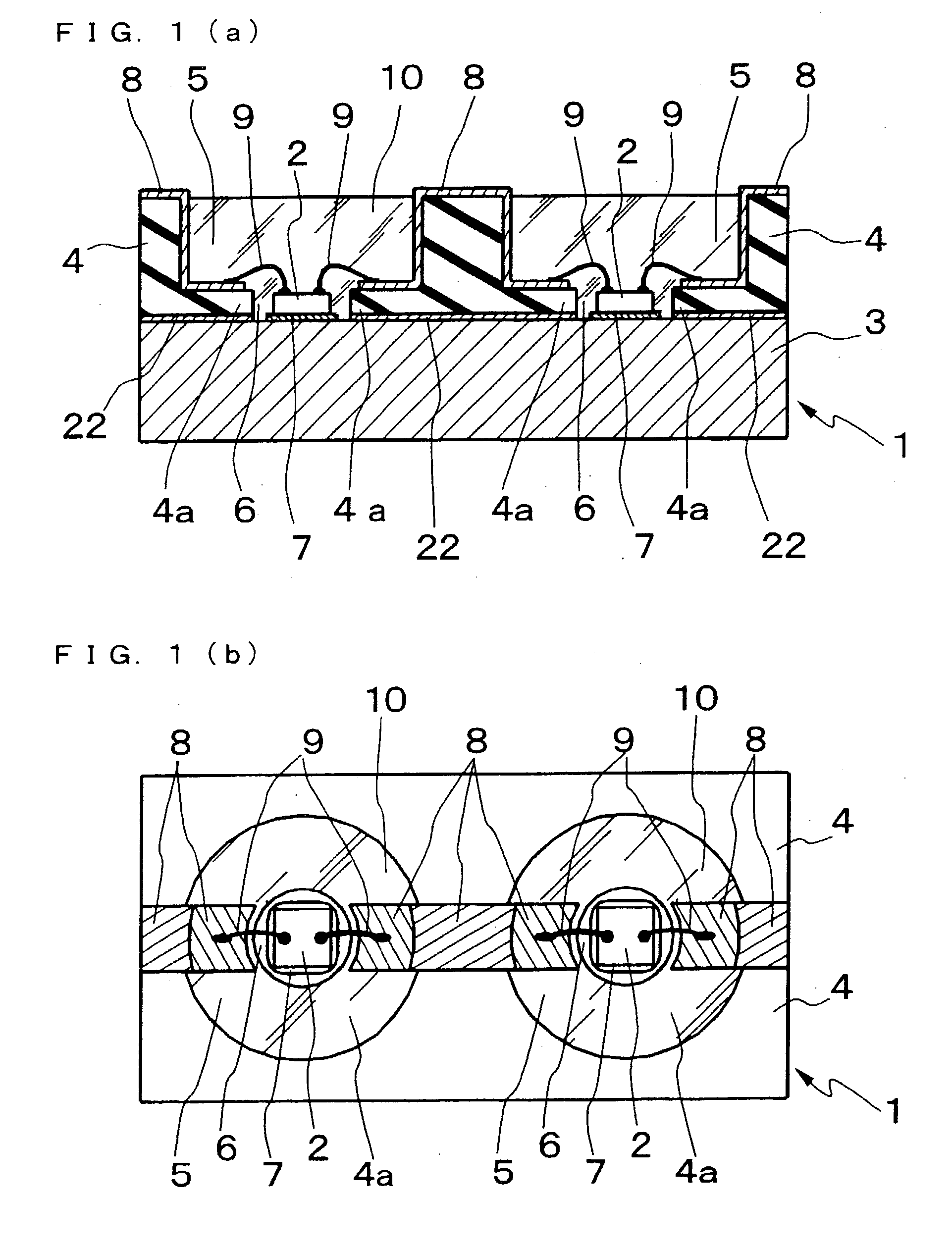

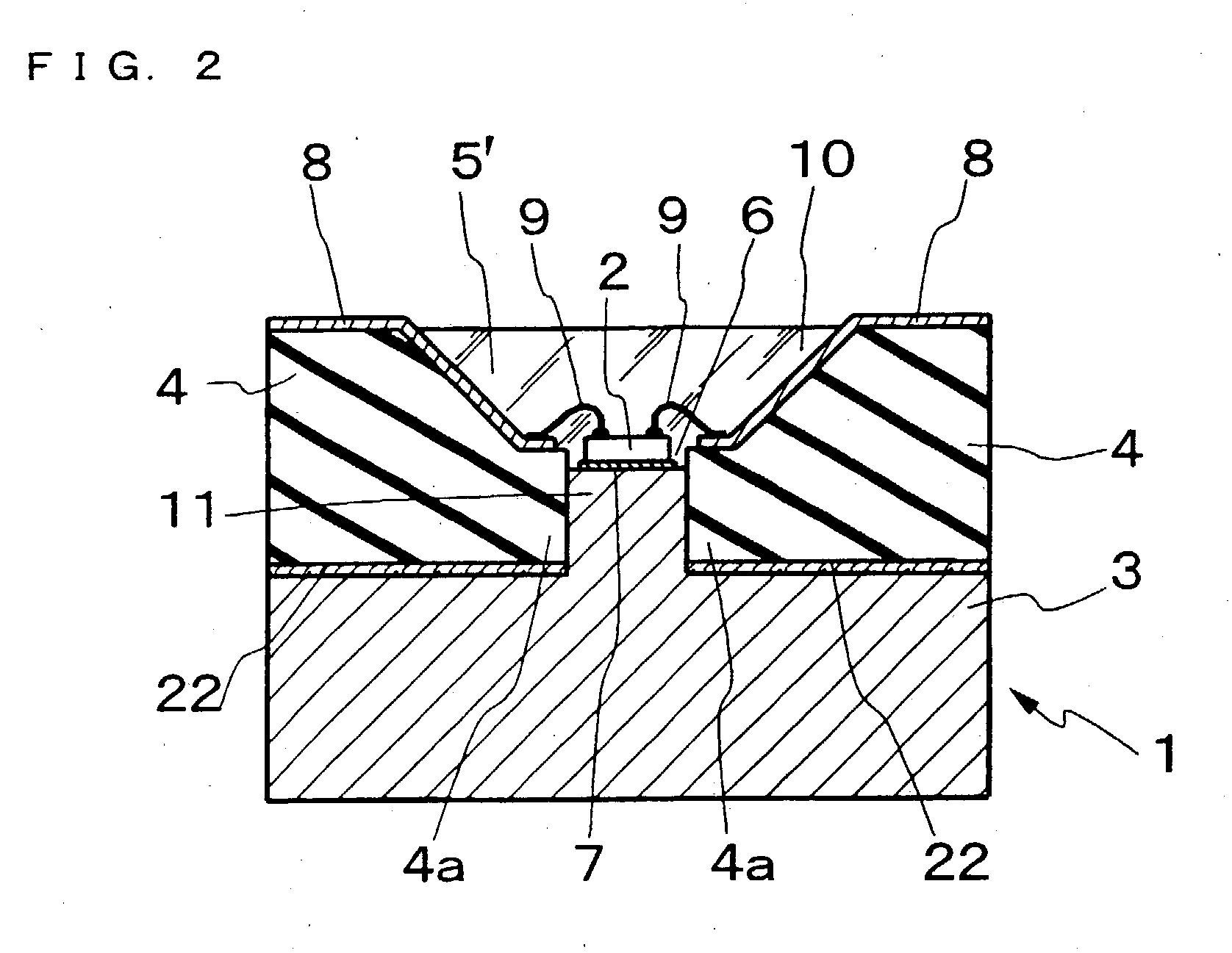

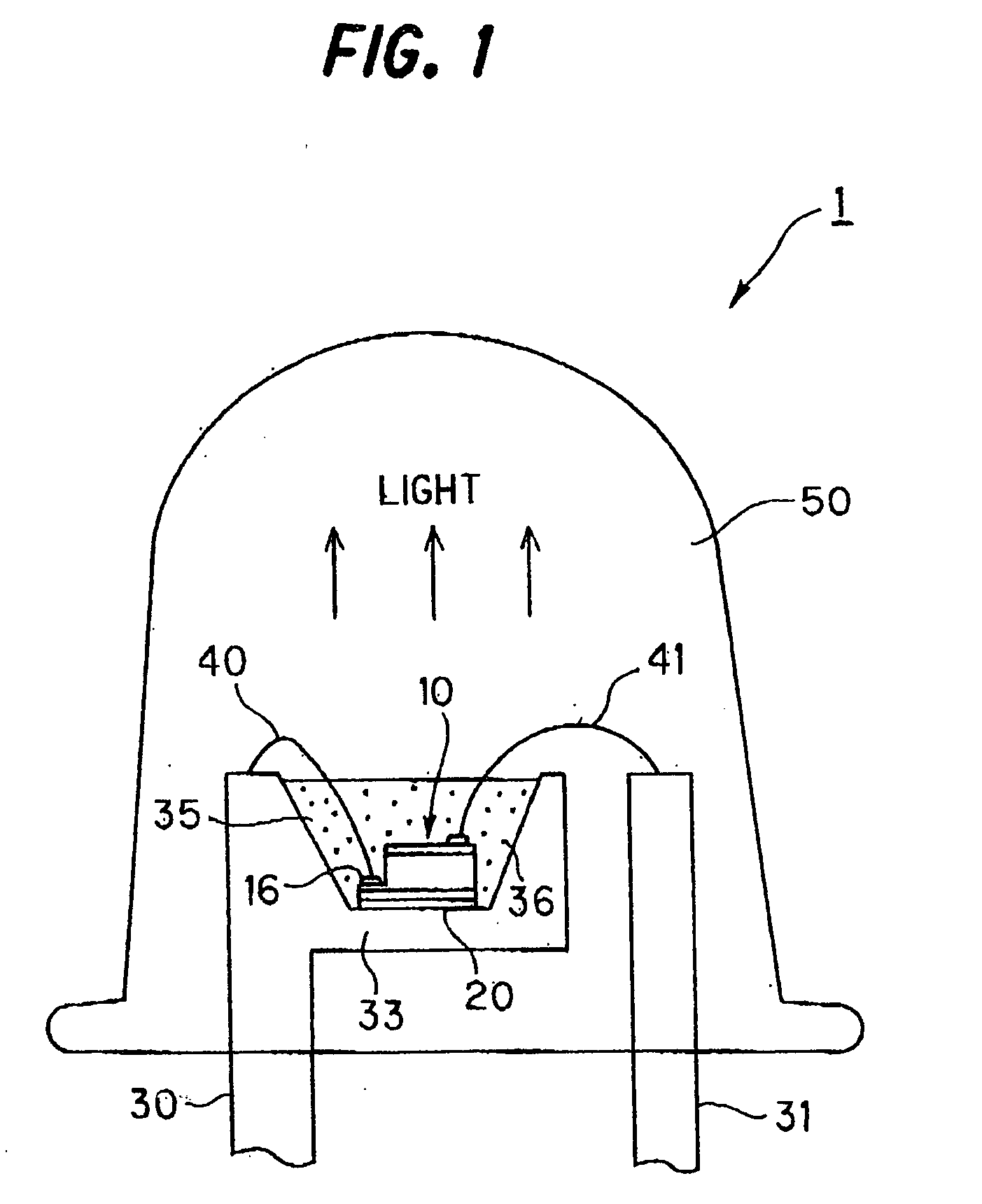

Light source device using led, and method of producing same

InactiveUS20030189830A1Easy to controlImprove powerLighting heating/cooling arrangementsSolid-state devicesLight emissionOperating life

A light source apparatus which is improved in the efficiency of light emission thus to increase the operating life and the mechanical strength and a method of producing the same are provided. The light source apparatus 1 comprises a radiator plate 3 having thermally conductive properties, an insulating member 4 coupled to at least one side of the radiator plate 3 and having a through hole 6 provided in the side thereof facing the radiator plate 3, an LED chip 2 installed and thermally coupled to an exposed portion of the radiator plate 3 facing the through hole 6, an extension 4a inwardly projecting at the hole 6 from the radiator plate 3 end of the insulating member 4, a wiring pattern 8 provided on the insulating member 4 and electrically isolated by the insulating member 4 from the radiator plate 3, bonding wires 9 electrically connecting between portions of the wiring pattern 8 extended to the extension 4a and the electrodes of the LED chip 2, and a light-transmissive sealing material 10 filled in the through hole 6 for entirely encapsulating the LED chip 2 and the bonding wires 9.

Owner:SIGNIFY HLDG BV

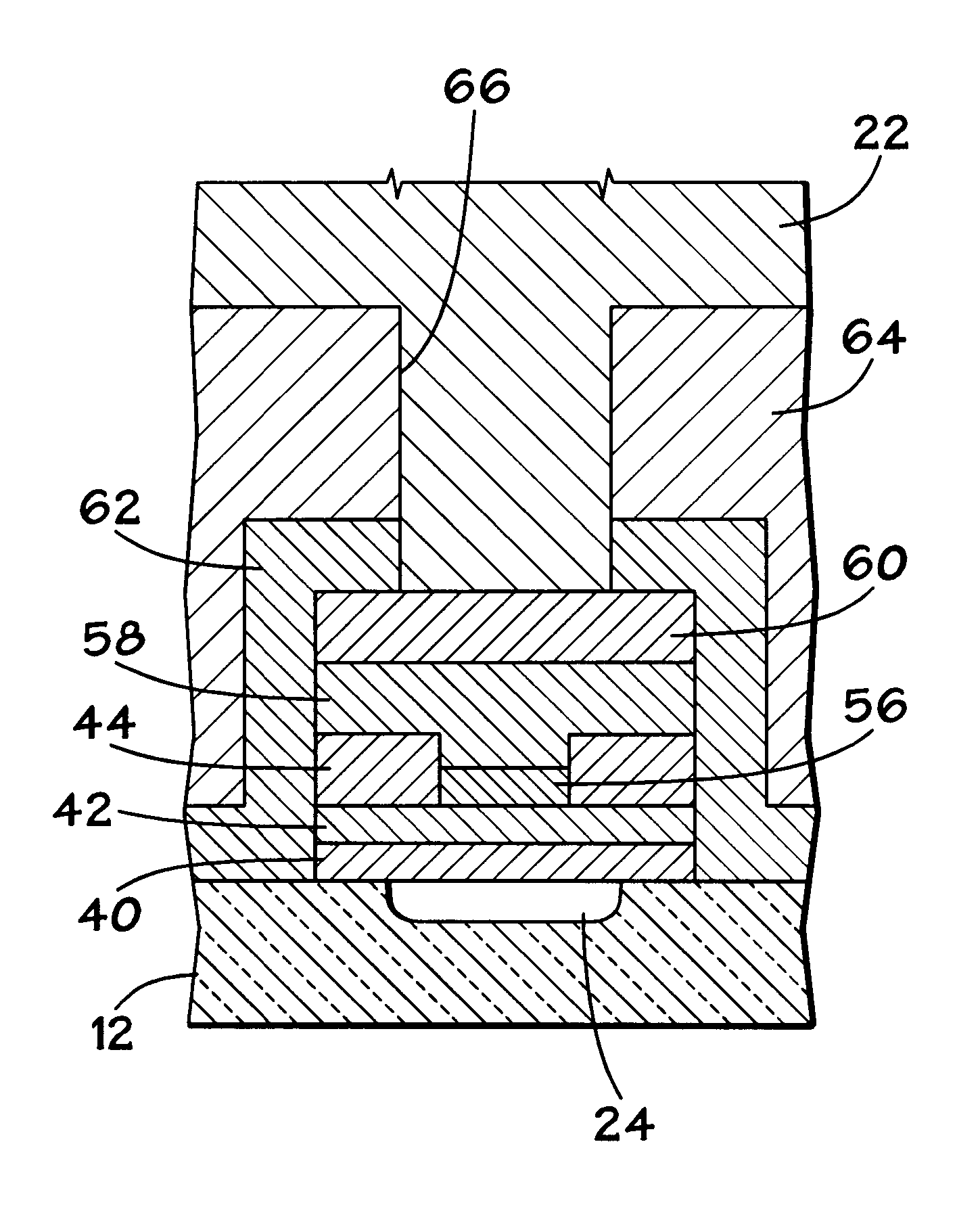

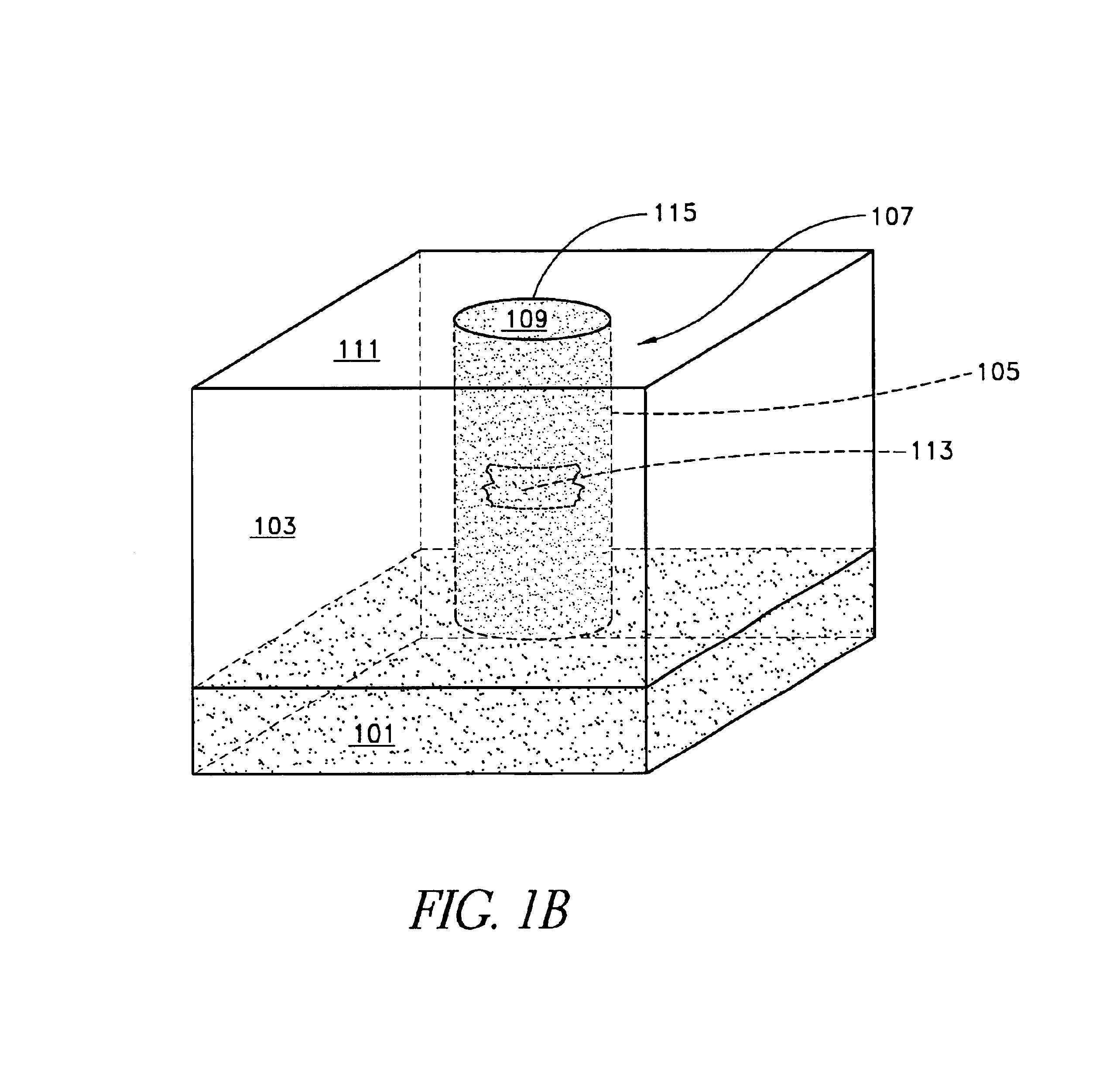

Small electrode for a chalcogenide switching device and method for fabricating same

InactiveUS6189582B1Solid-state devicesSemiconductor/solid-state device manufacturingDielectric layerElectrode material

A memory cell and a method of fabricating the memory cell having a small active area. By forming a spacer in a window that is sized at the photolithographic limit, a pore may be formed in dielectric layer which is smaller than the photolithographic limit. Electrode material is deposited into the pore, and a layer of structure changing material, such as chalcogenide, is deposited onto the lower electrode, thus creating a memory element having an extremely small and reproducible active area.

Owner:ROUND ROCK RES LLC

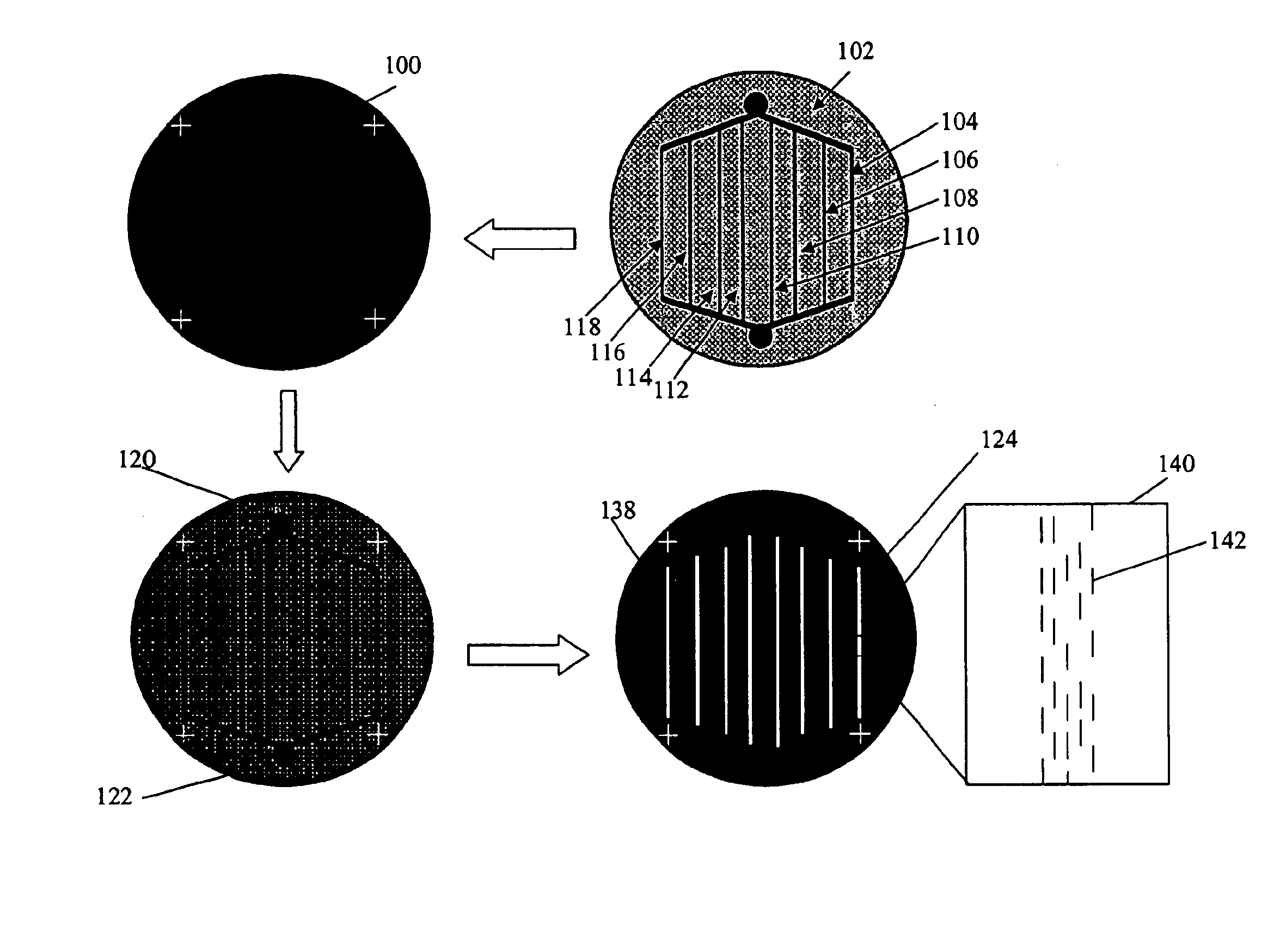

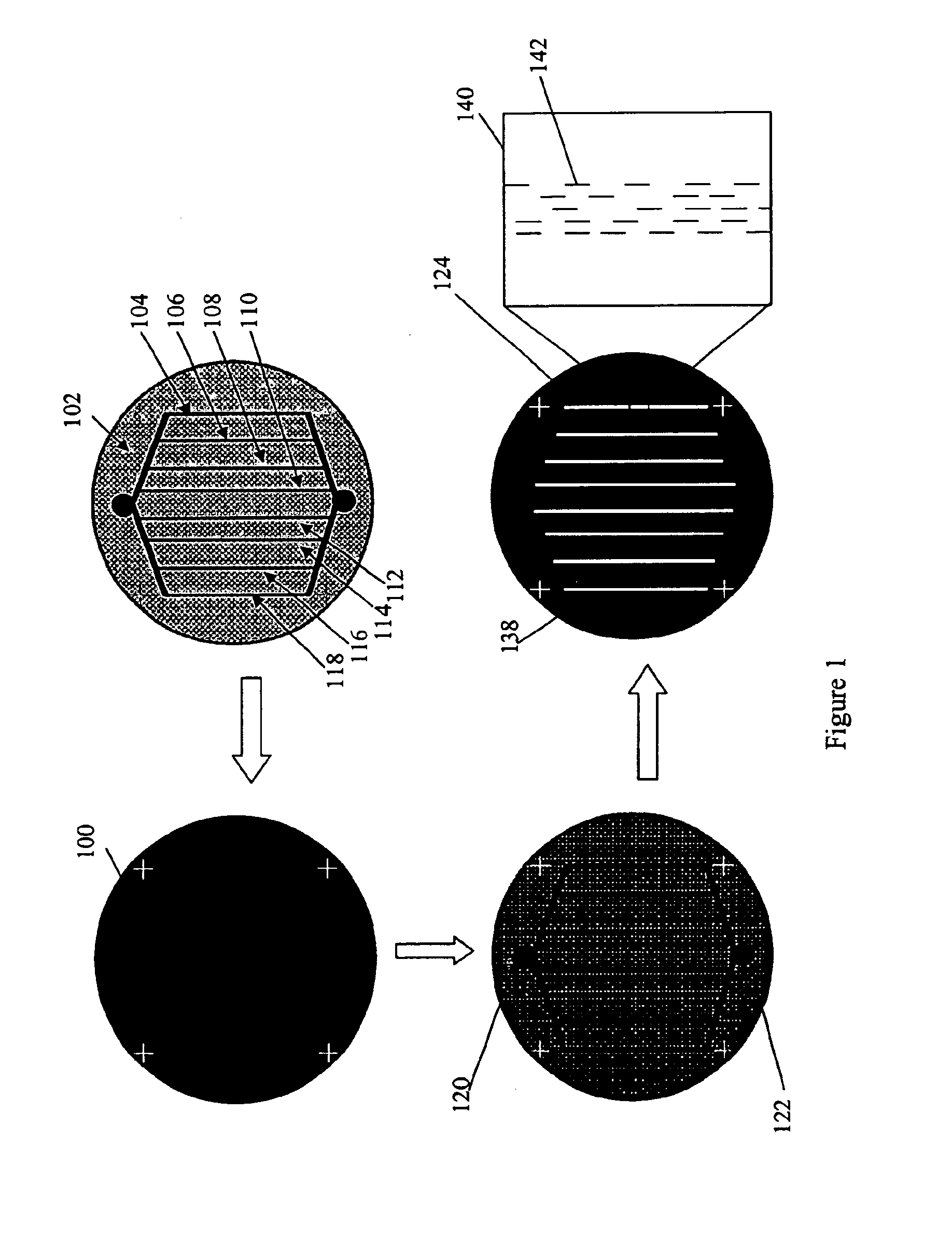

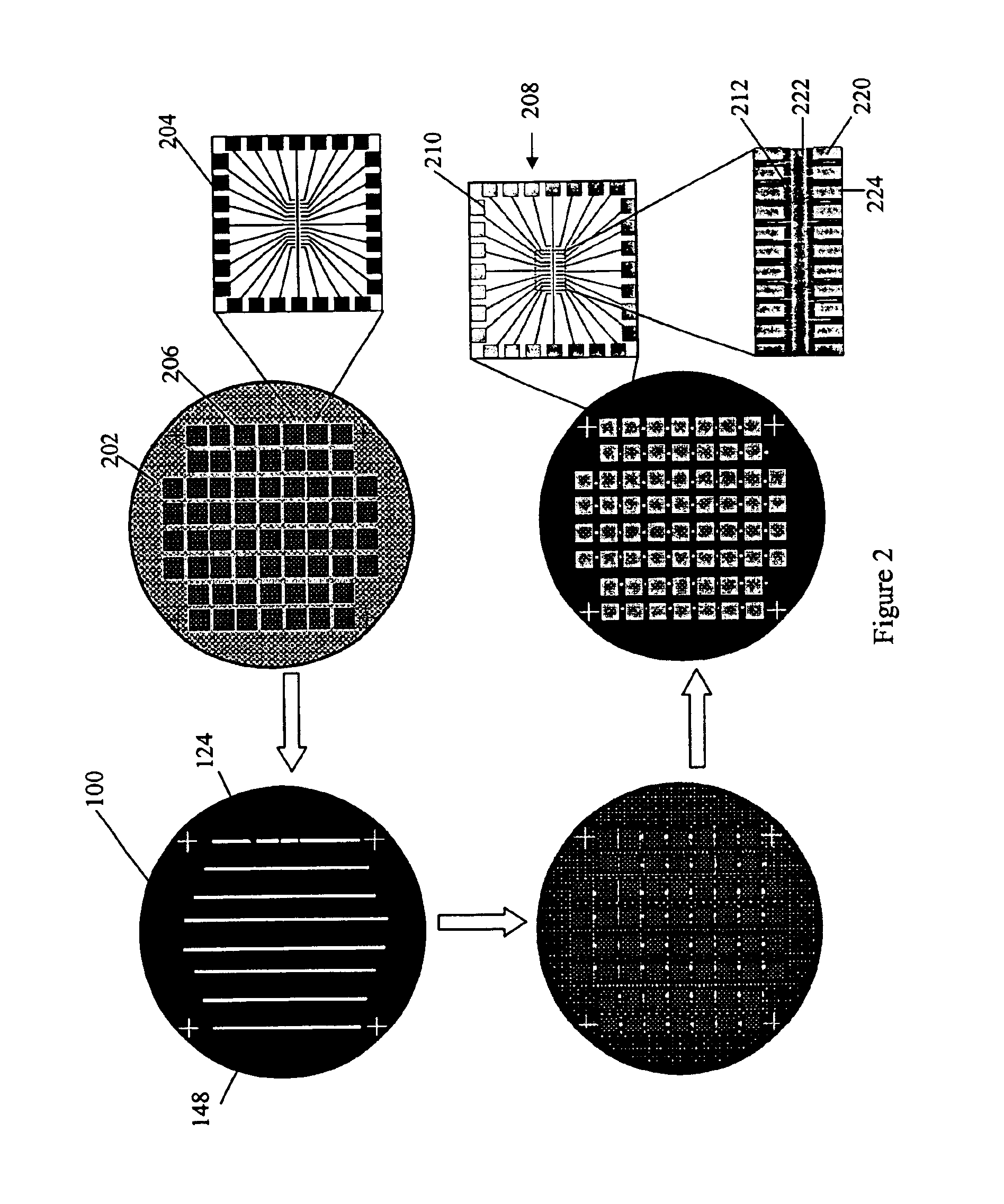

Methods of positioning and/or orienting nanostructures

Methods of positioning and orienting nanostructures, and particularly nanowires, on surfaces for subsequent use or integration. The methods utilize mask based processes alone or in combination with flow based alignment of the nanostructures to provide oriented and positioned nanostructures on surfaces. Also provided are populations of positioned and / or oriented nanostructures, devices that include populations of positioned and / or oriented nanostructures, systems for positioning and / or orienting nanostructures, and related devices, systems and methods.

Owner:ONED MATERIAL INC

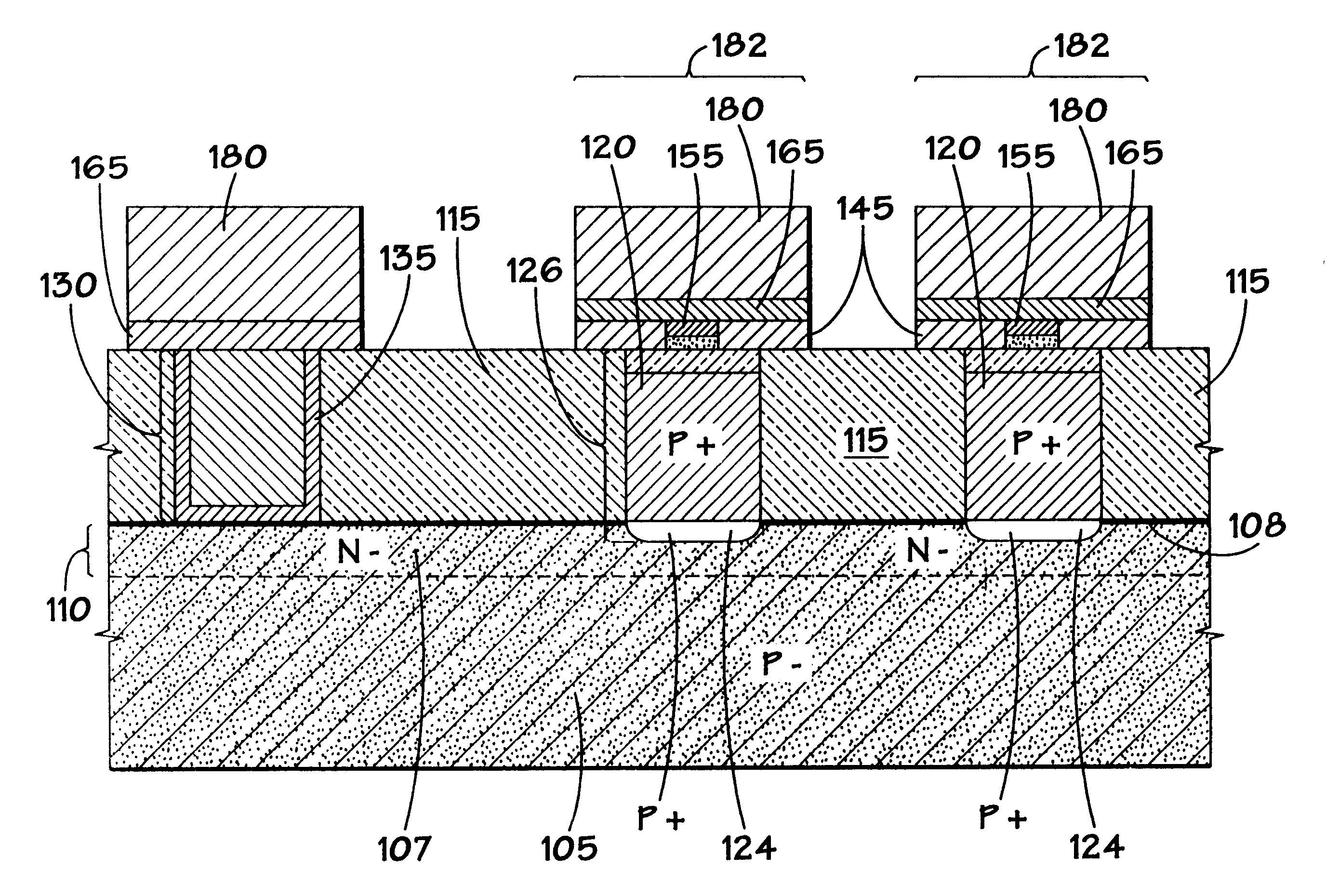

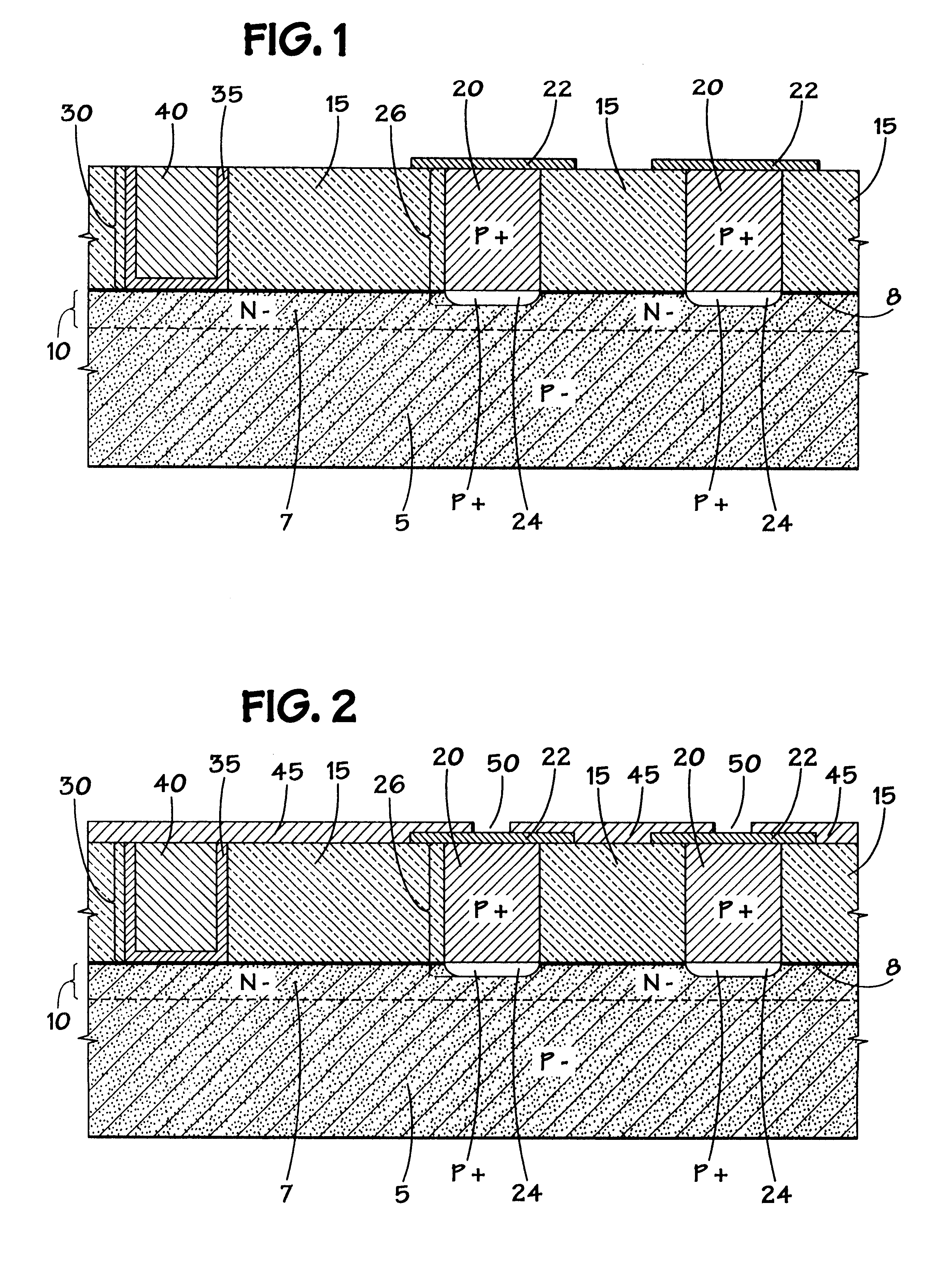

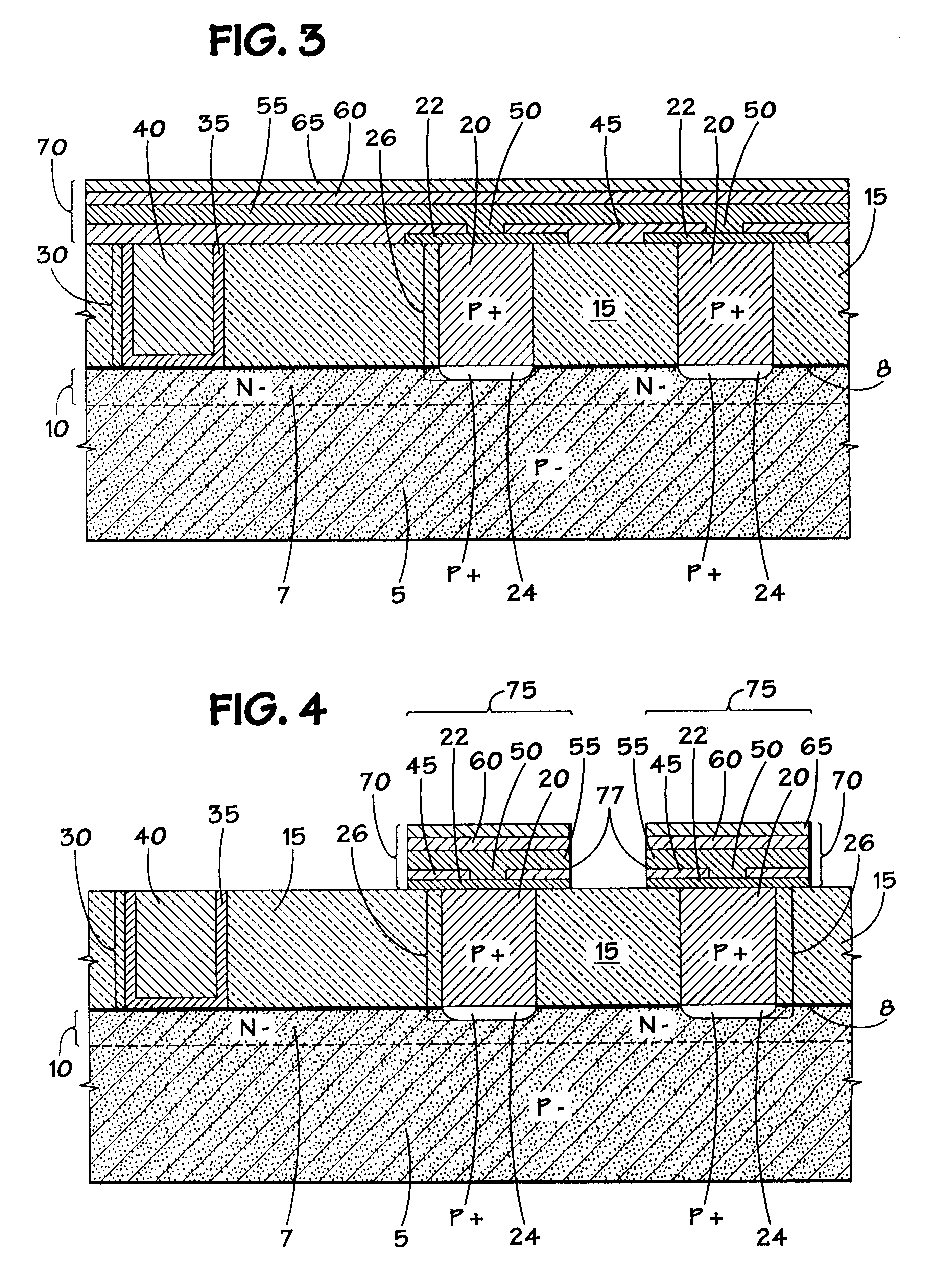

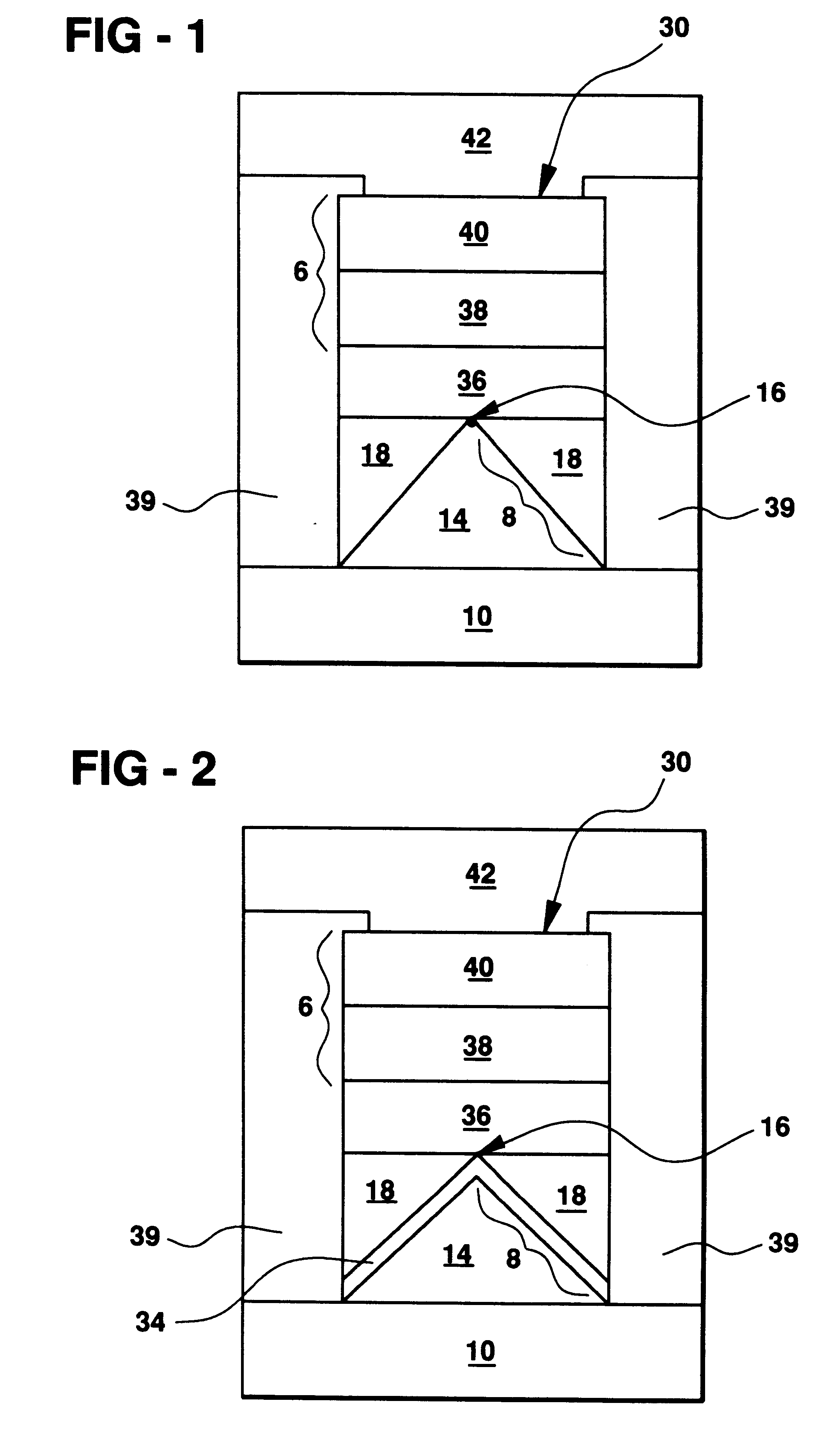

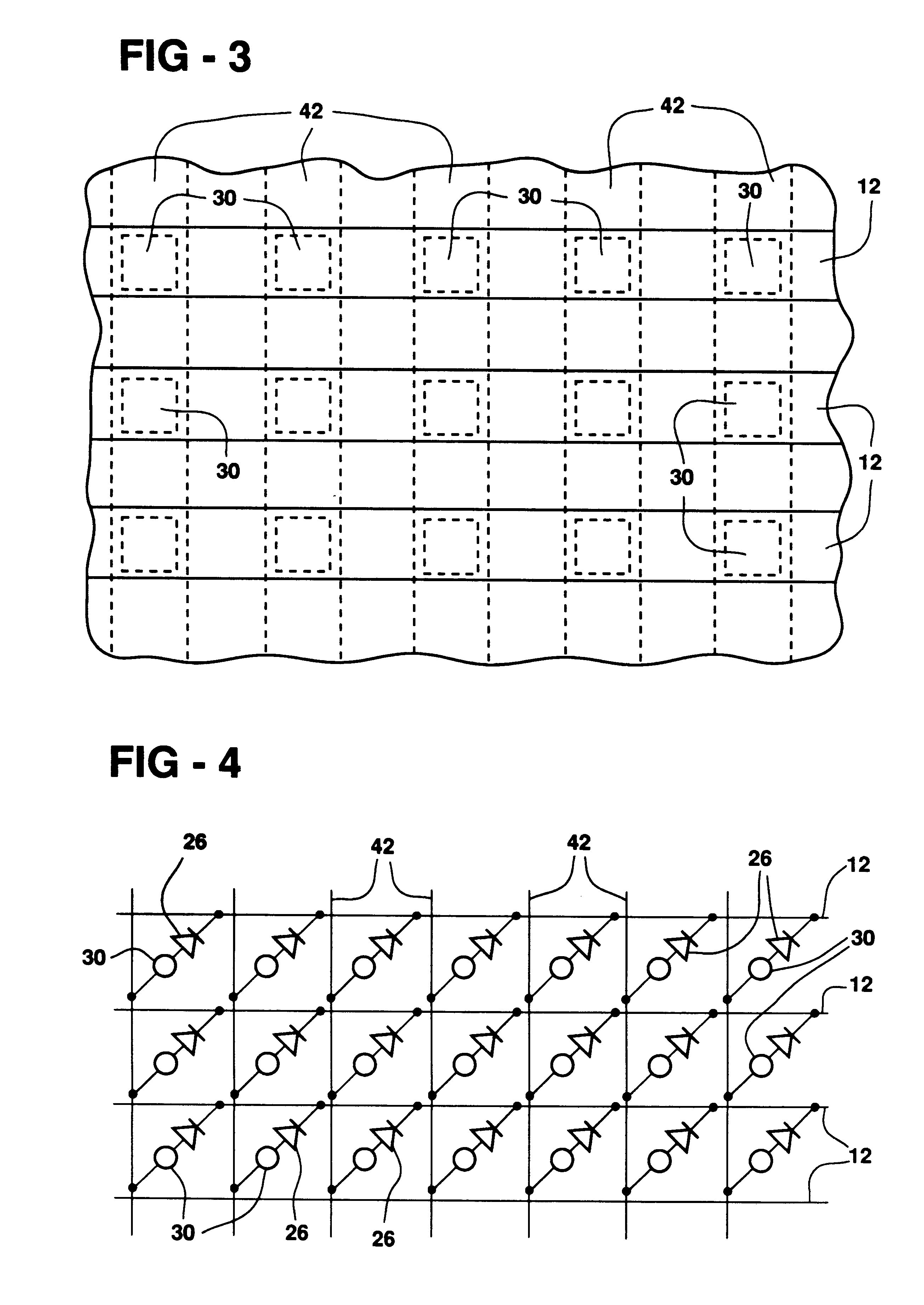

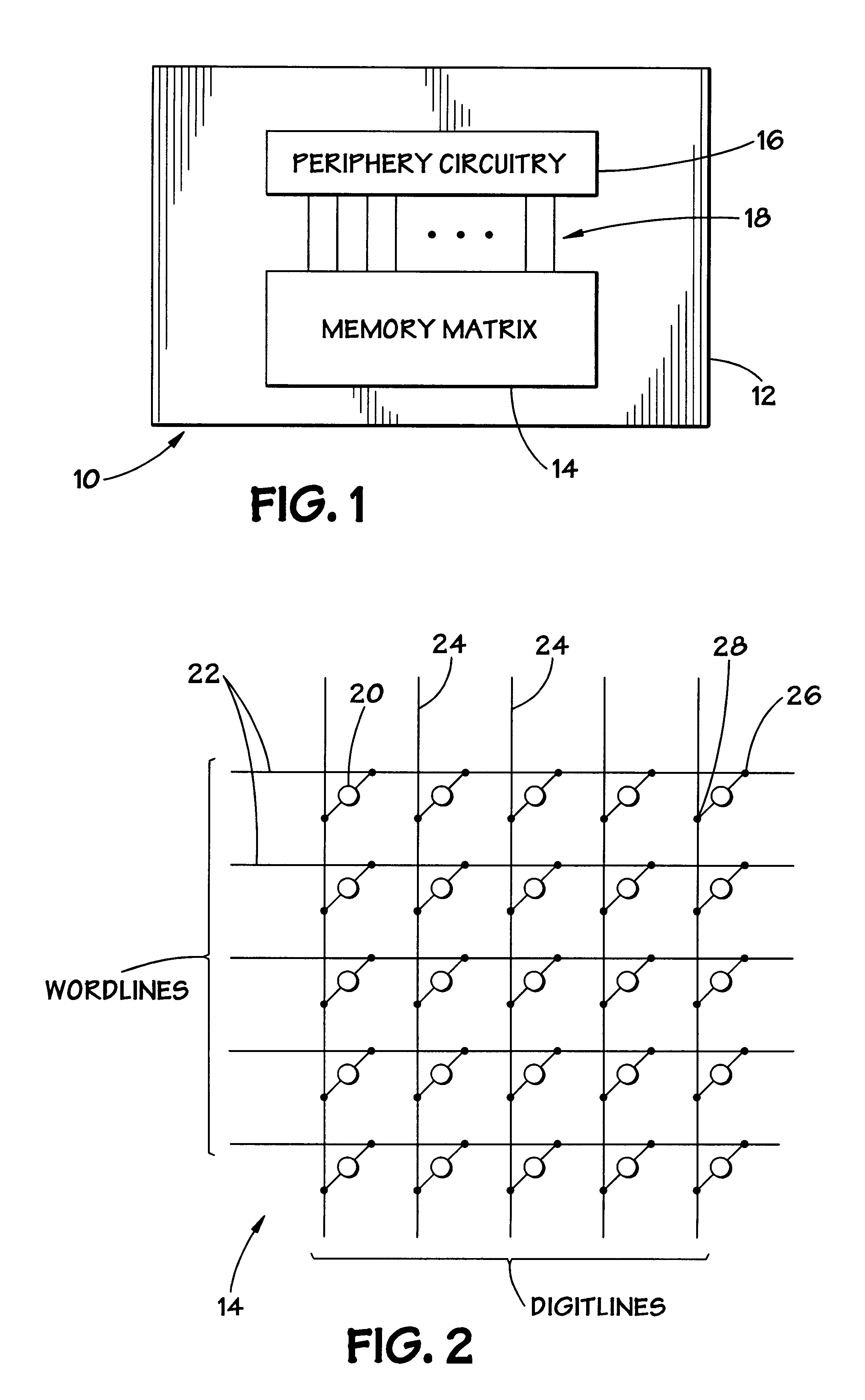

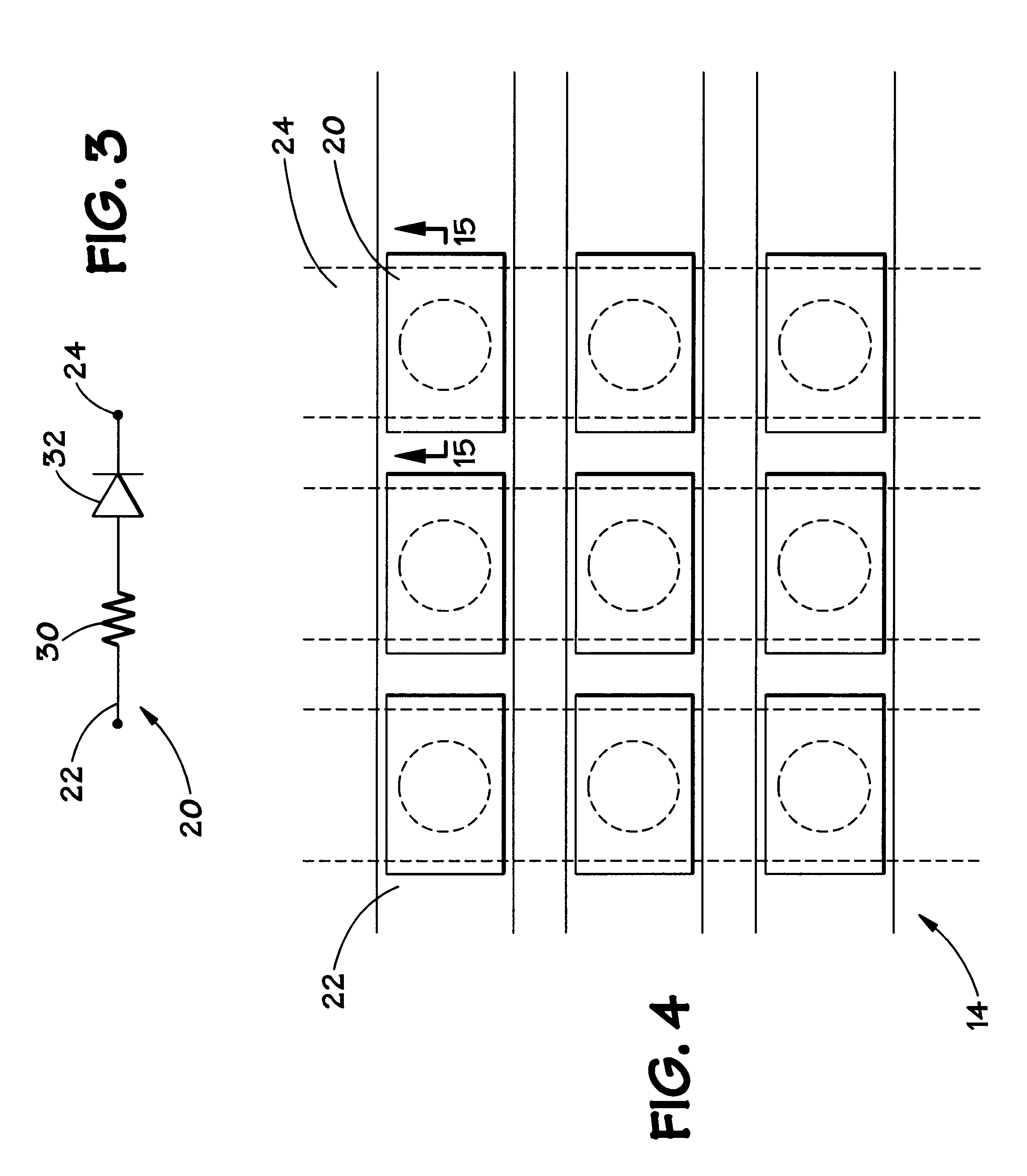

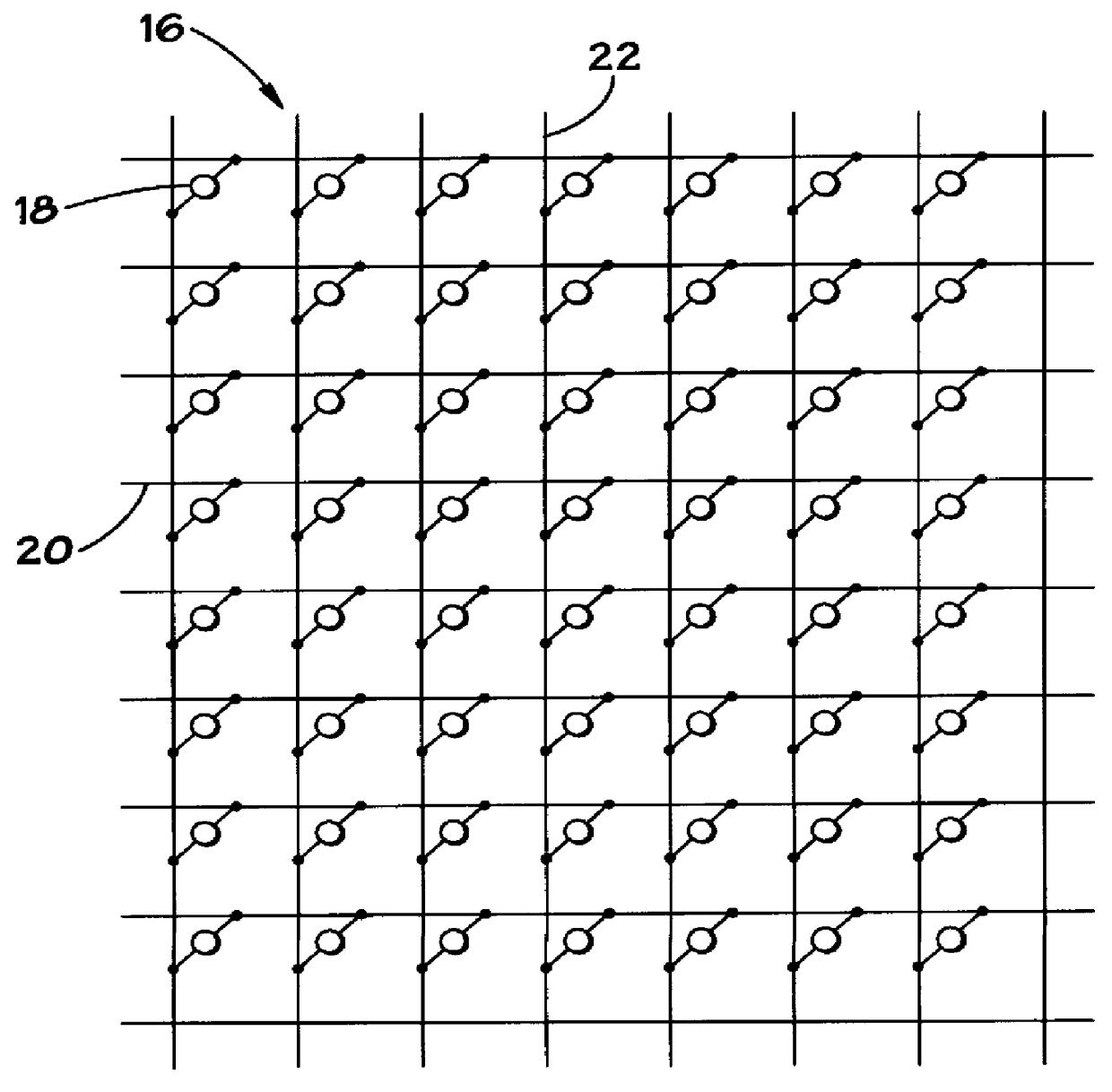

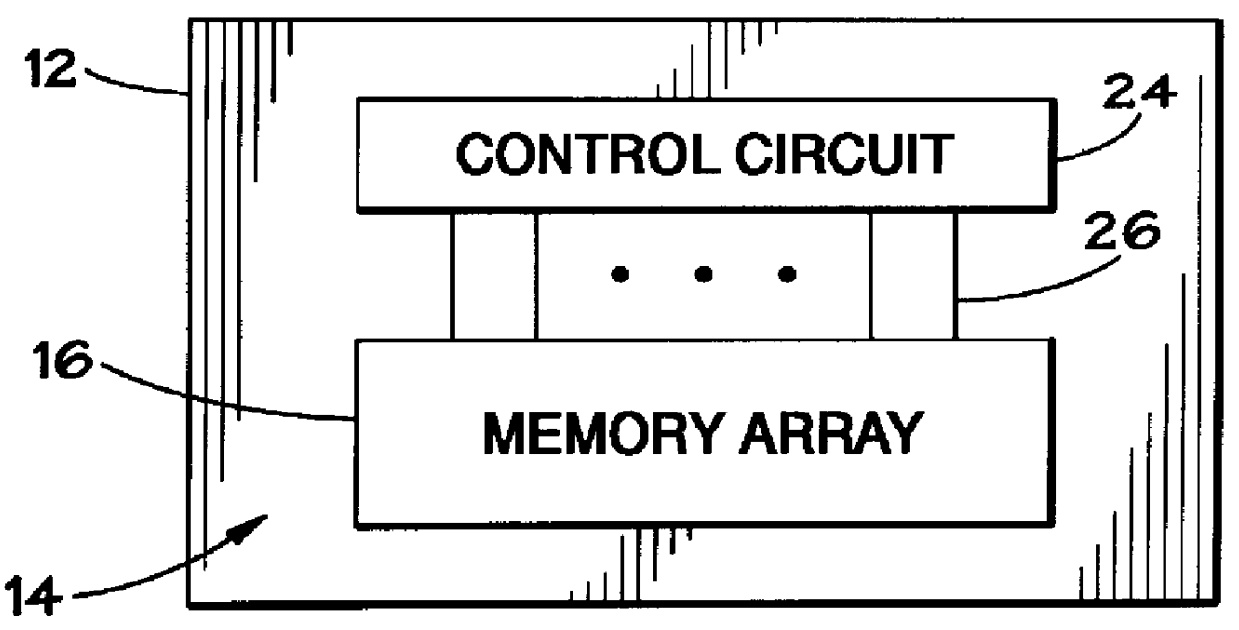

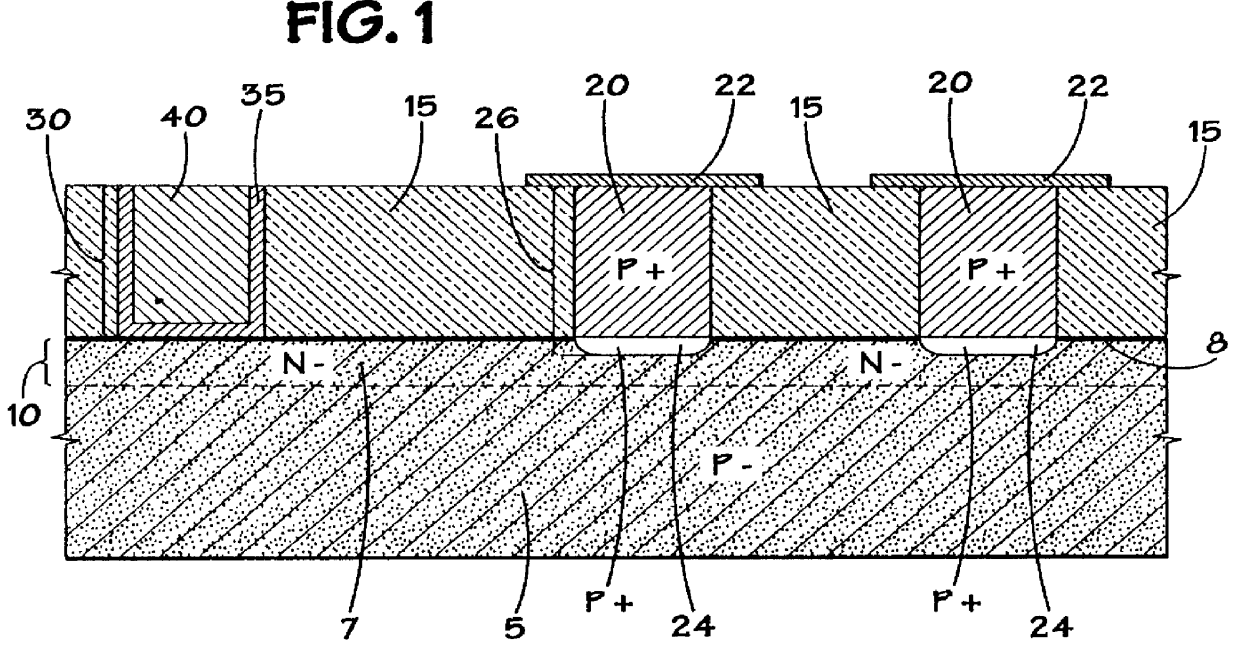

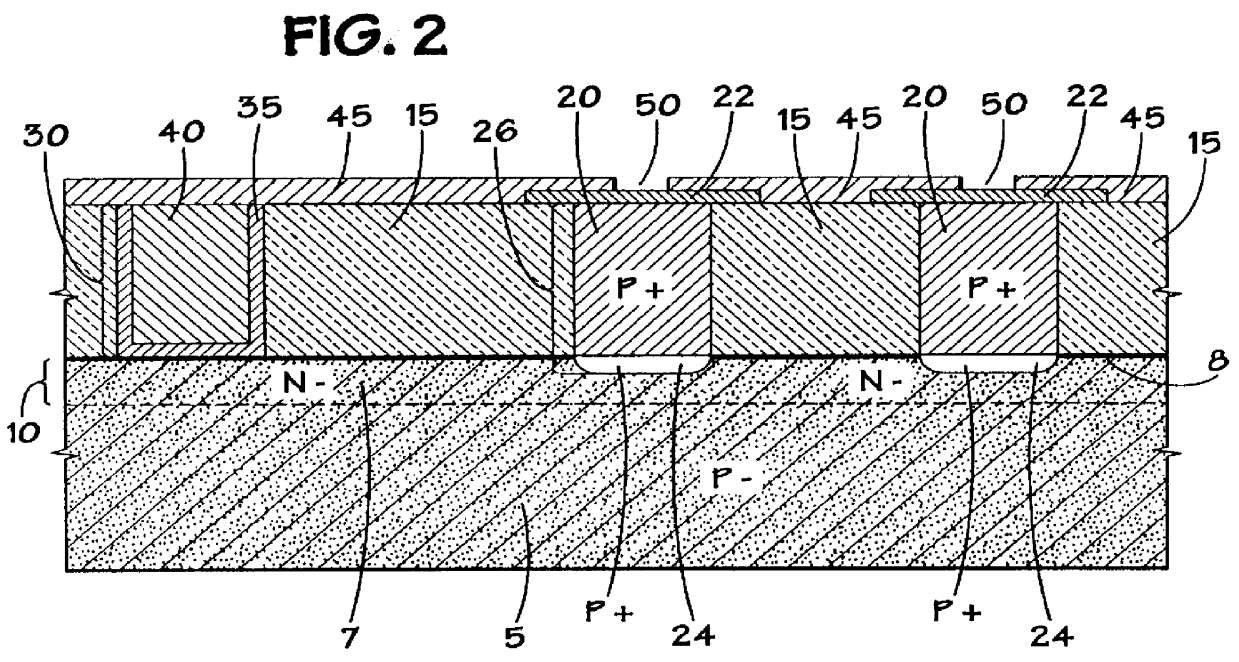

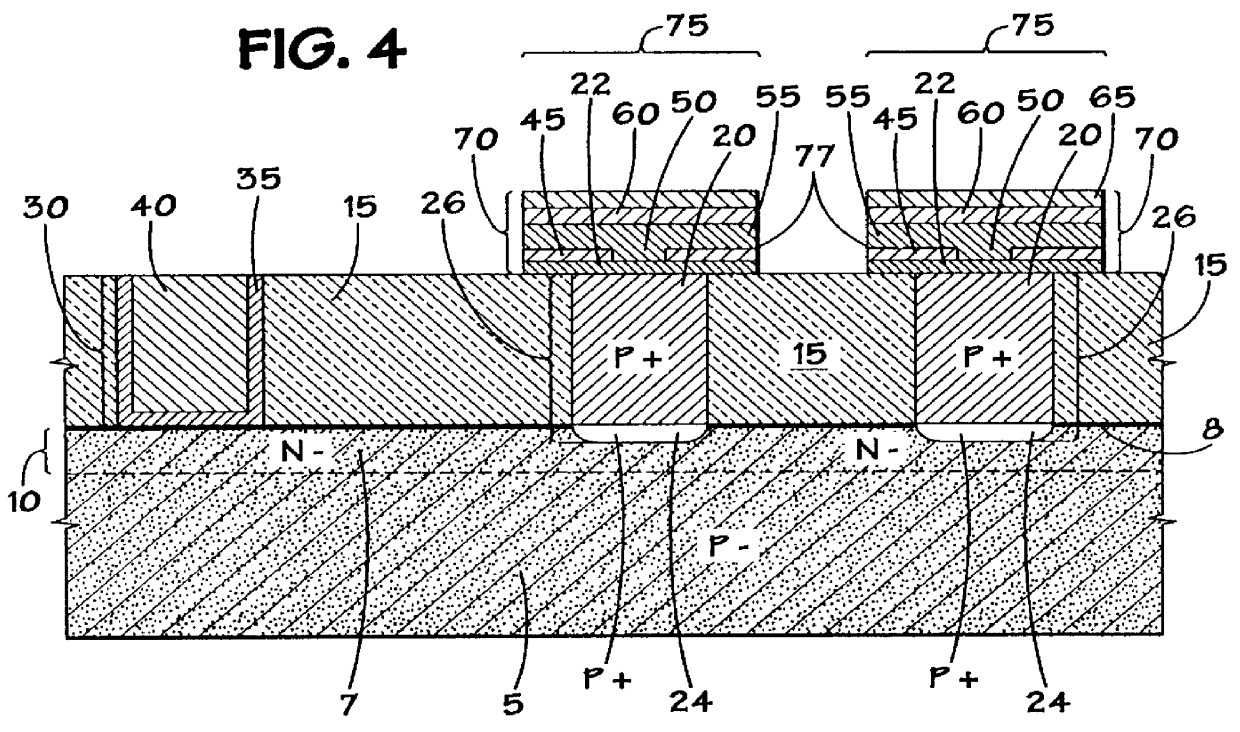

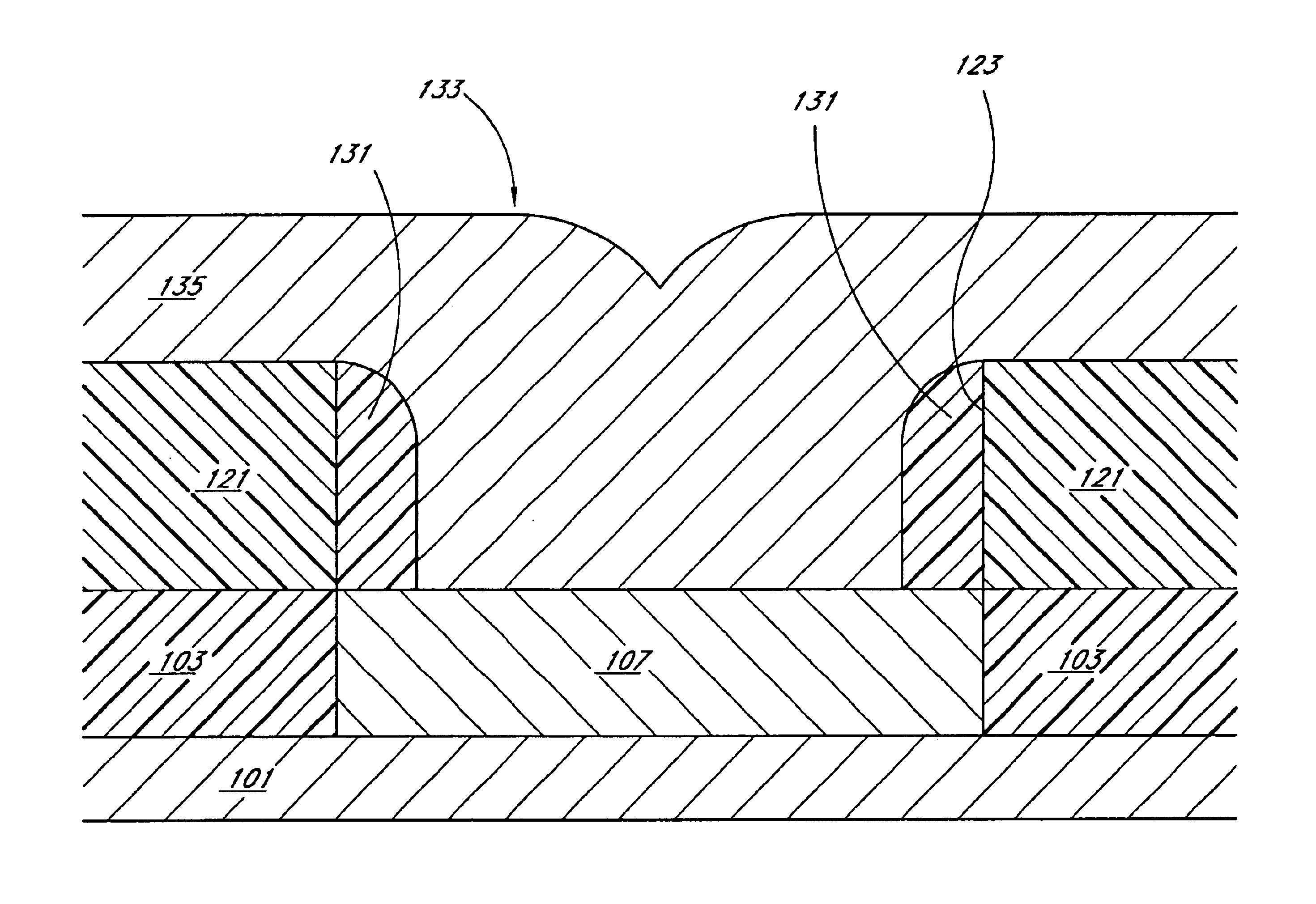

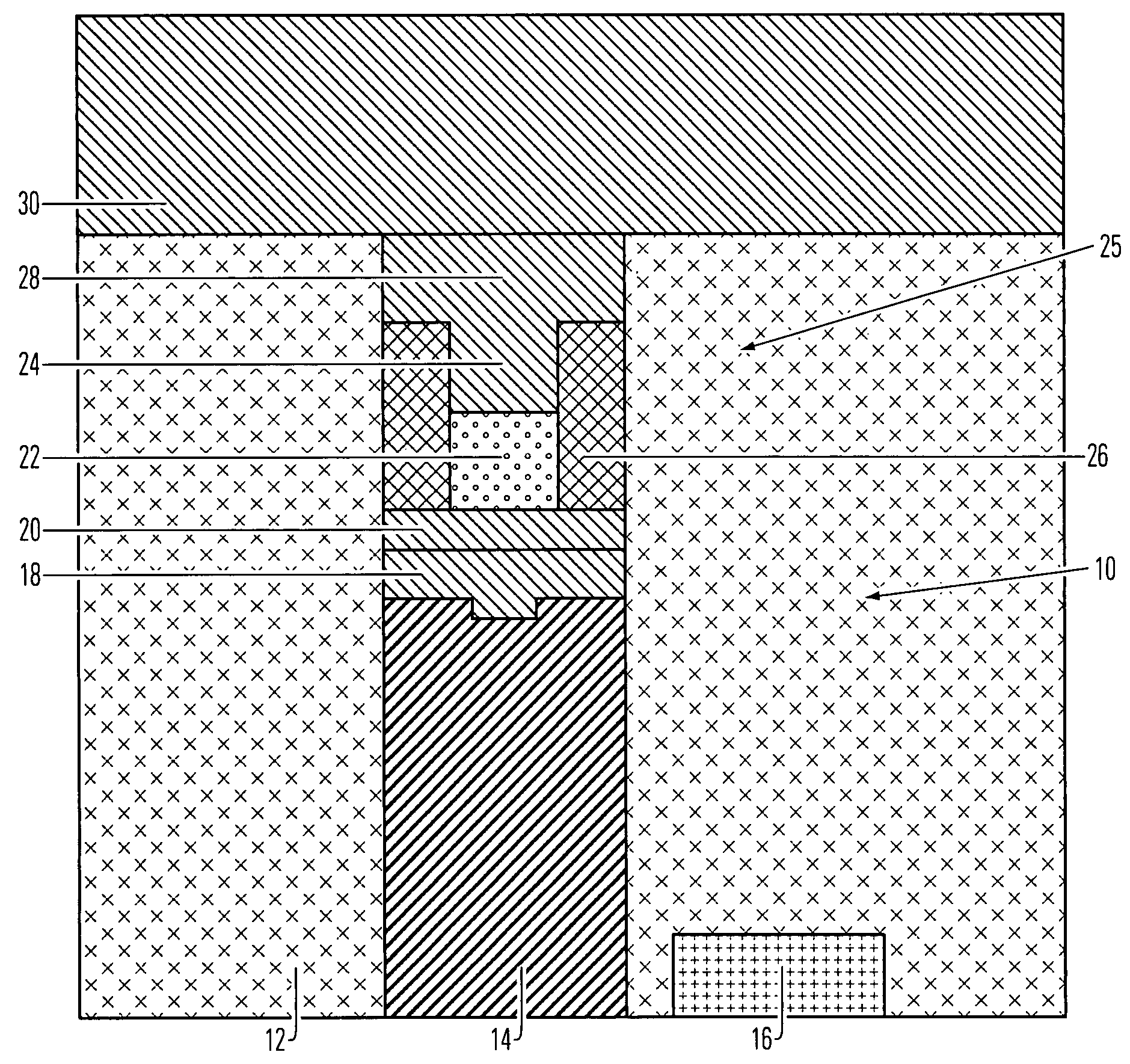

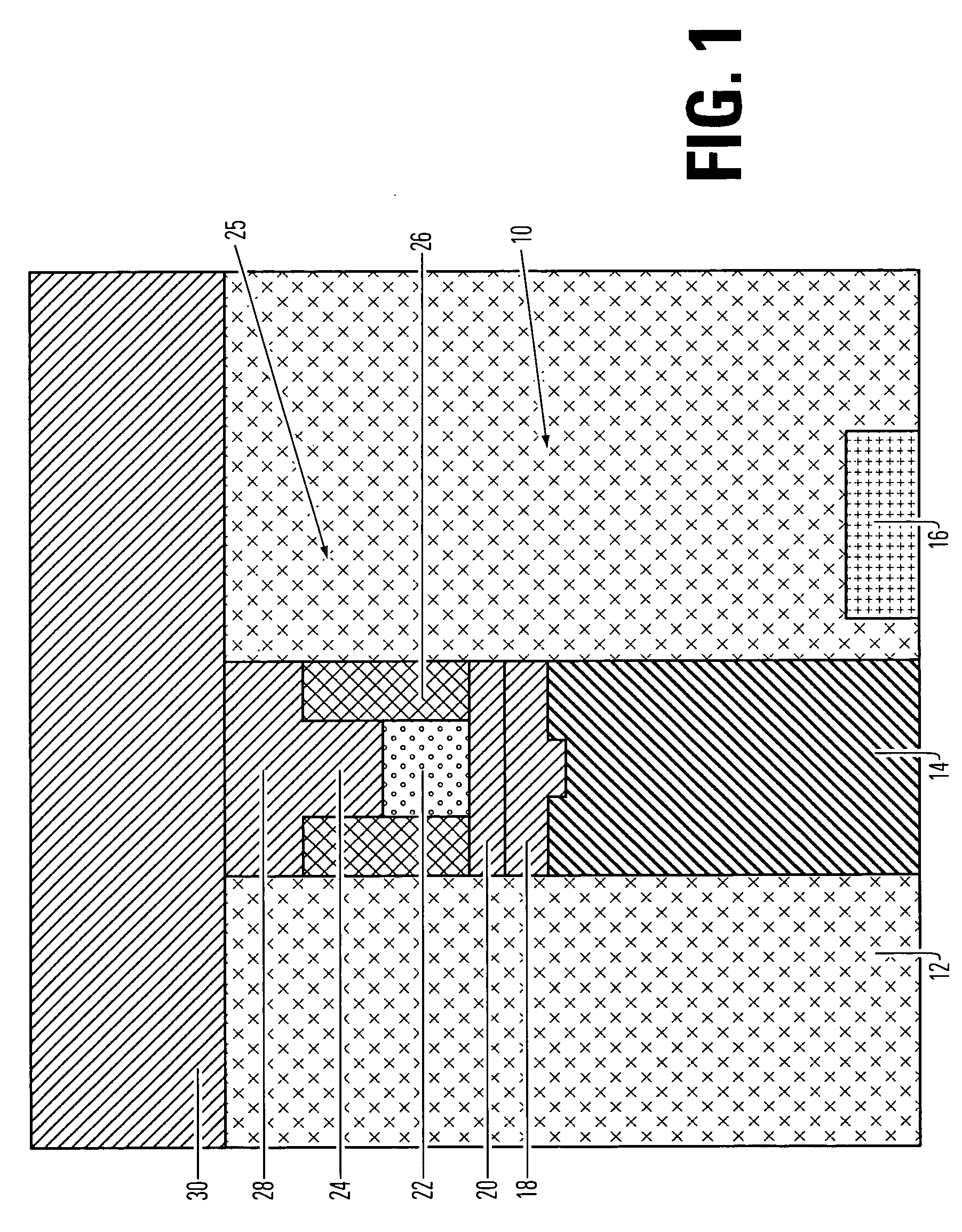

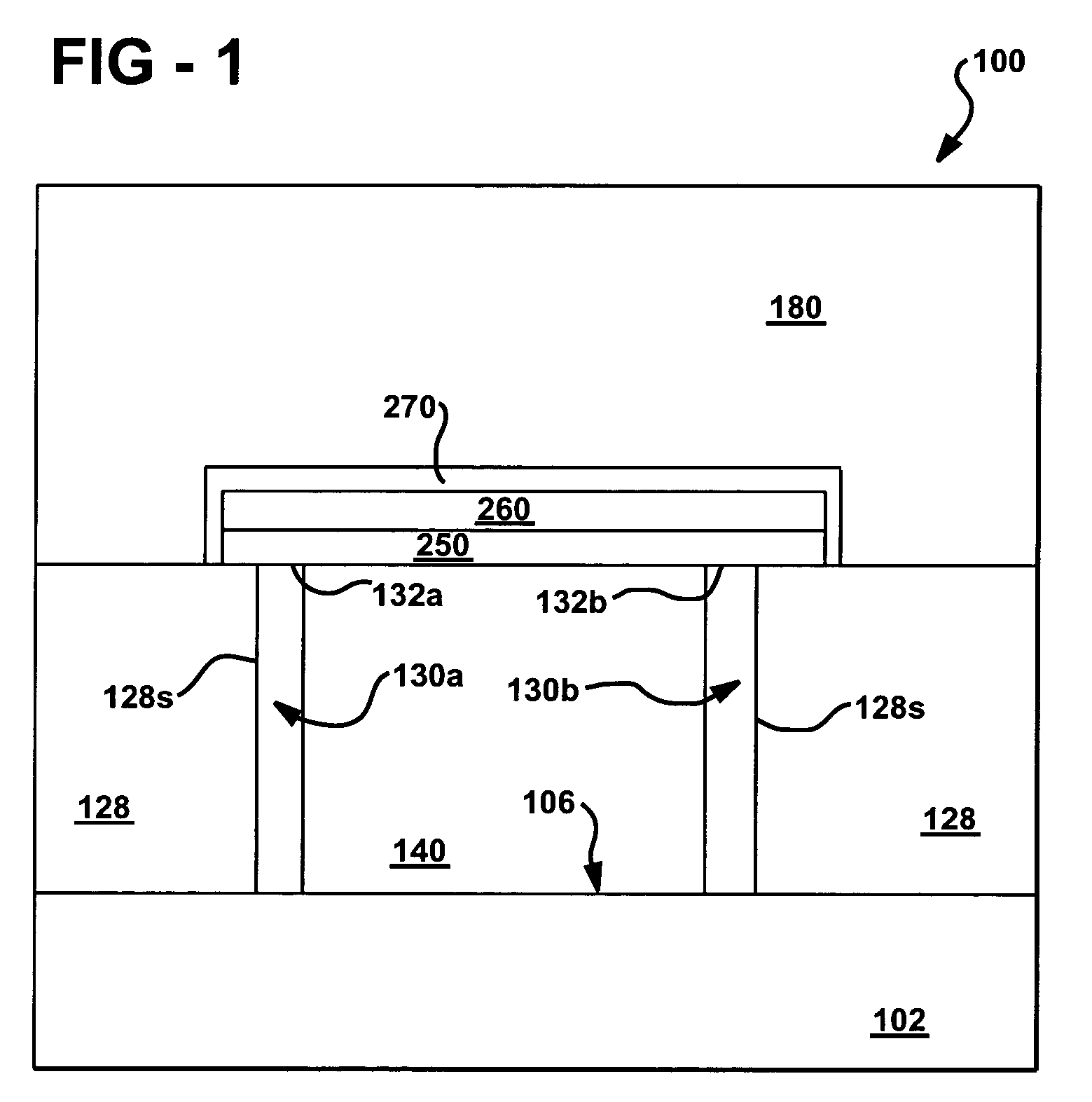

Integrated circuit memory cell having a small active area and method of forming same

InactiveUS6114713ASemiconductor/solid-state device detailsSolid-state devicesBit lineElectrical conductor

A method for manufacturing a memory device having a plurality of memory cells. Each memory cell has a non-volatile resistive memory element with a small active area. A plurality of memory cells are formed at selected locations of at least a portion of a semiconductor wafer. To form the memory cells, a lower electrode layer and a memory material layer are deposited over at least a portion of the wafer. Patterns are formed over desired contact locations of the memory material layer and etching is used to remove portions of the memory material layer. The etching step undercuts the patterns and forms memory elements having a protruding contact portion with an apex contact area. The pattern is removed, and an upper electrode is formed and electrically coupled to the contact area. Corresponding access devices and word / bit line conductor grids are provided and coupled to the memory cells.

Owner:ROUND ROCK RES LLC

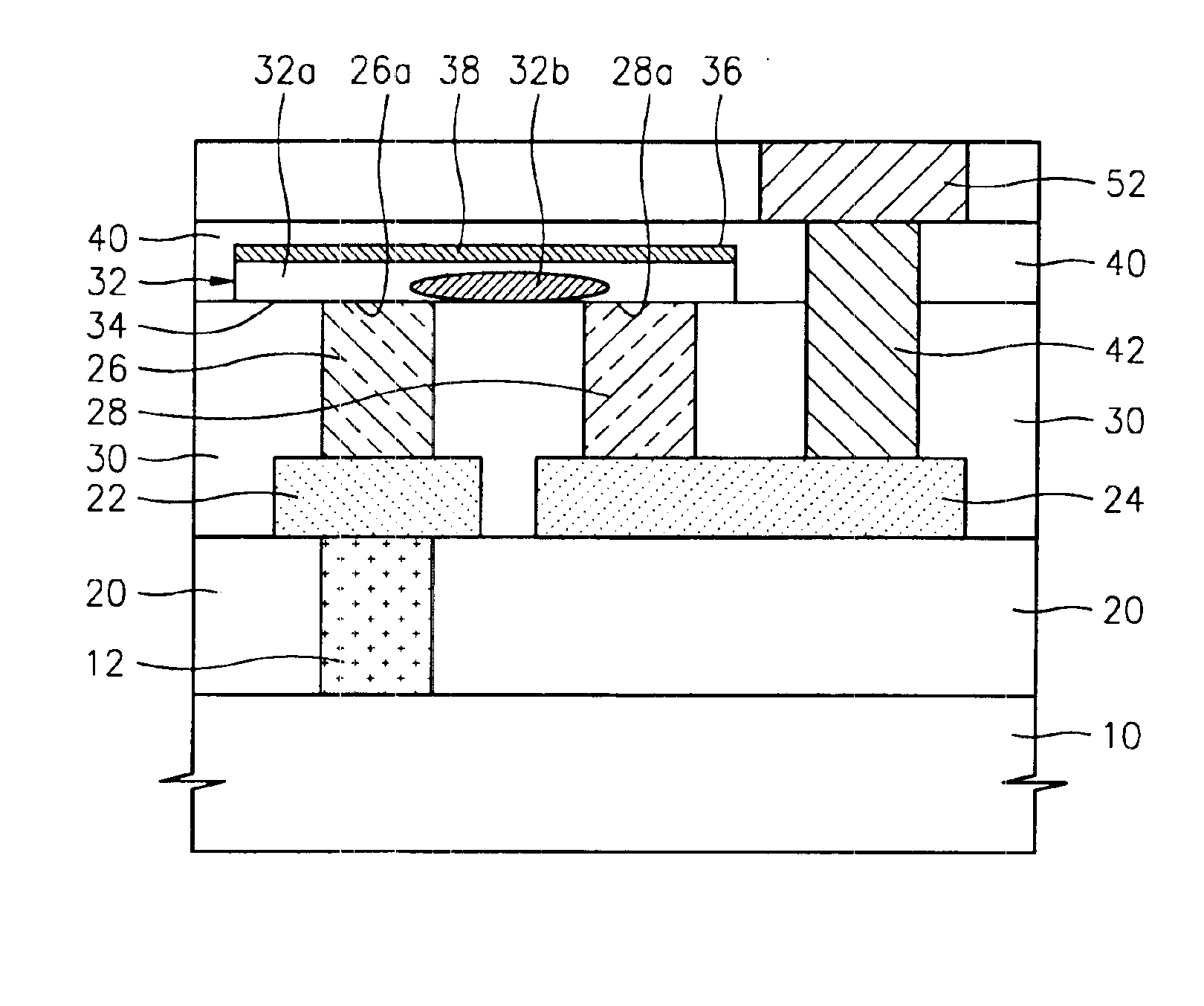

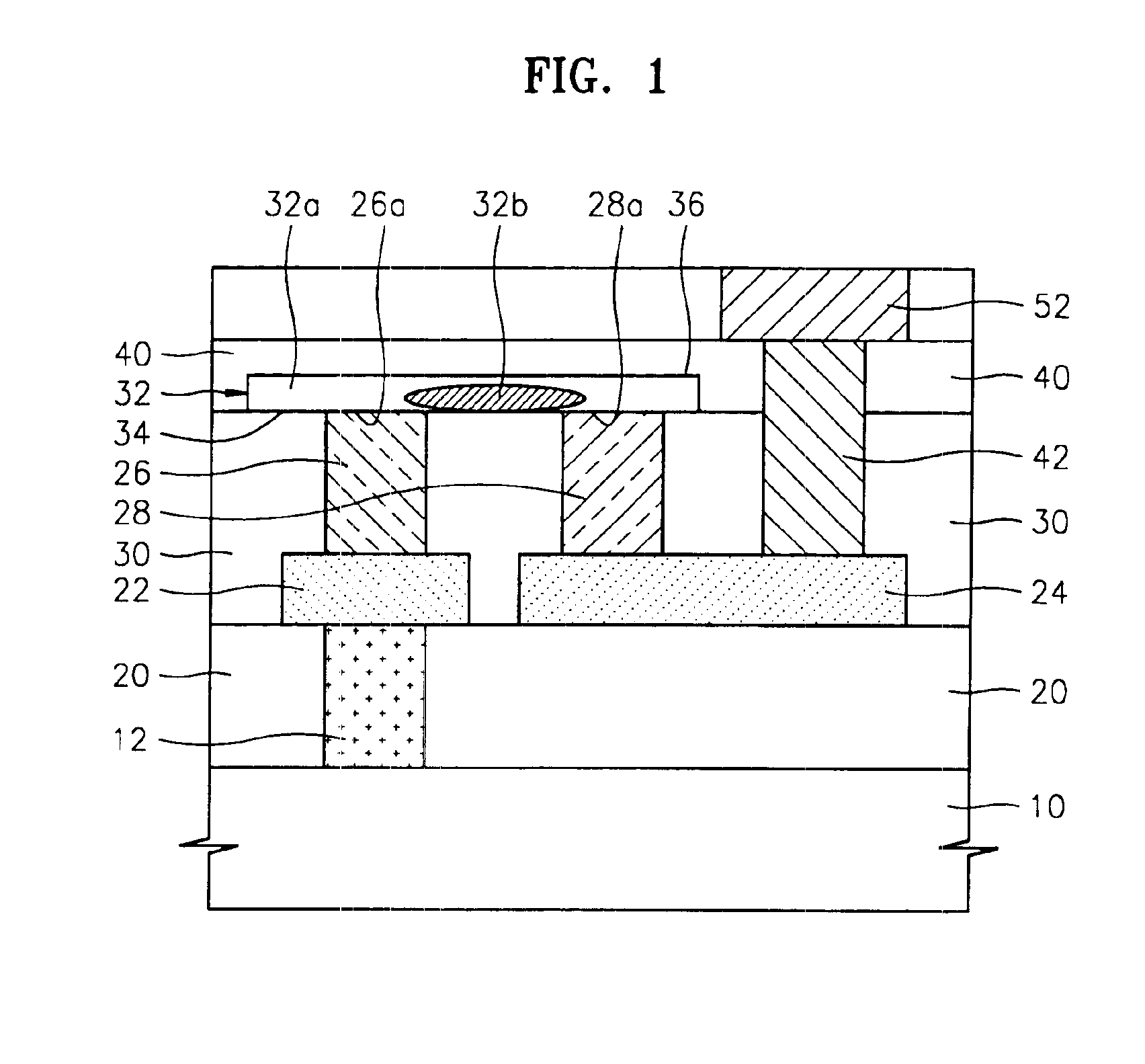

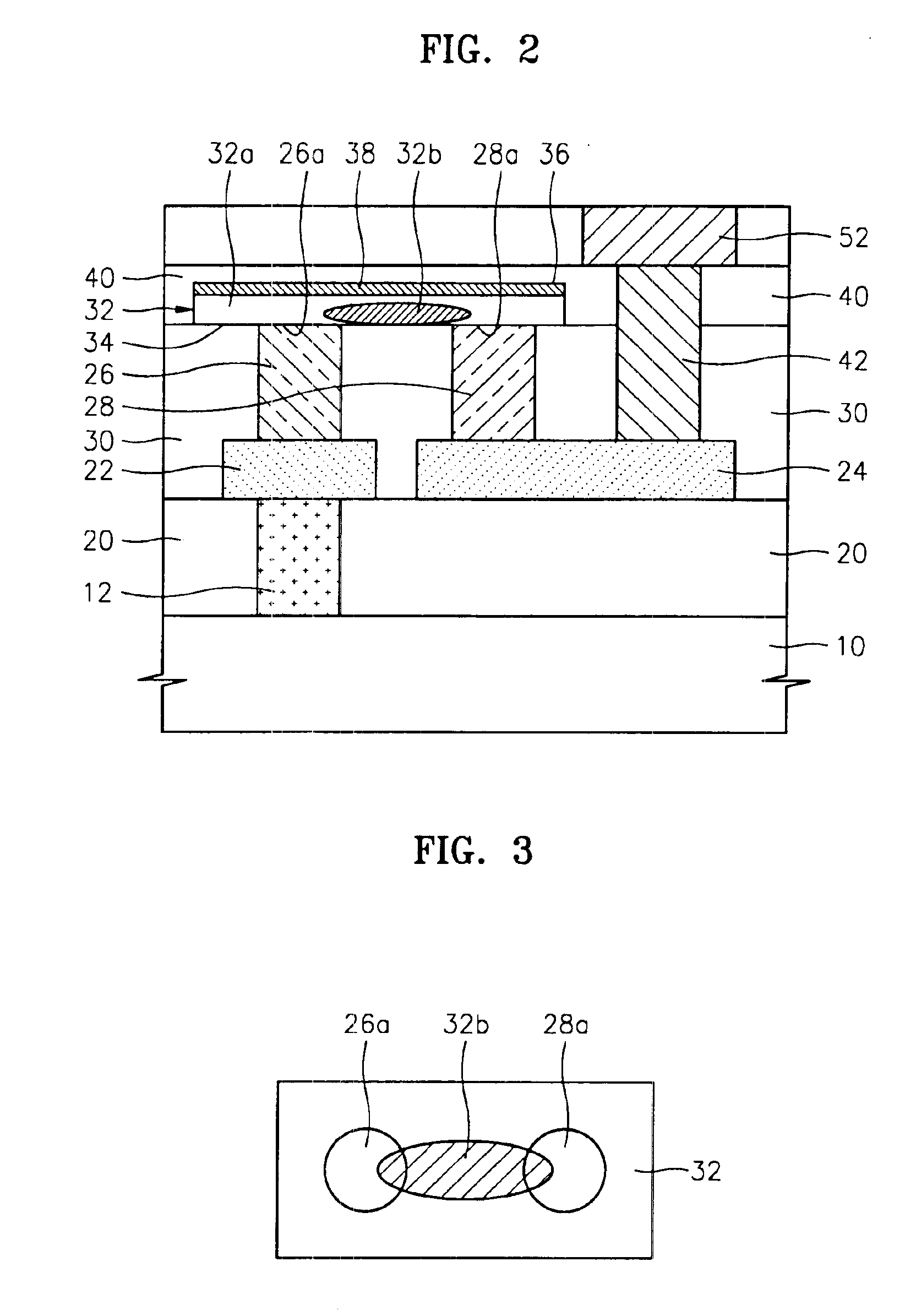

Phase-change memory devices with a self-heater structure

ActiveUS6894305B2Semiconductor/solid-state device detailsSolid-state devicesPhase-change memorySemiconductor

Phase change memory devices include a phase-change memory layer on a semiconductor substrate. The phase-change memory layer has a major axis that is substantially parallel to a major axis of the semiconductor substrate and has a first surface and a second surface opposite the first surface that are substantially parallel to the major axis of the phase-change memory layer. A first electrode is provided on the semiconductor substrate that is electrically connected to the first surface of the phase-change memory layer in a first contact region of the phase-change memory layer. A second electrode is provided on the semiconductor substrate that is electrically connected to the phase-change memory layer in a second contact region of the phase-change memory layer. The second contact region is space apart from the first contact region.

Owner:SAMSUNG ELECTRONICS CO LTD

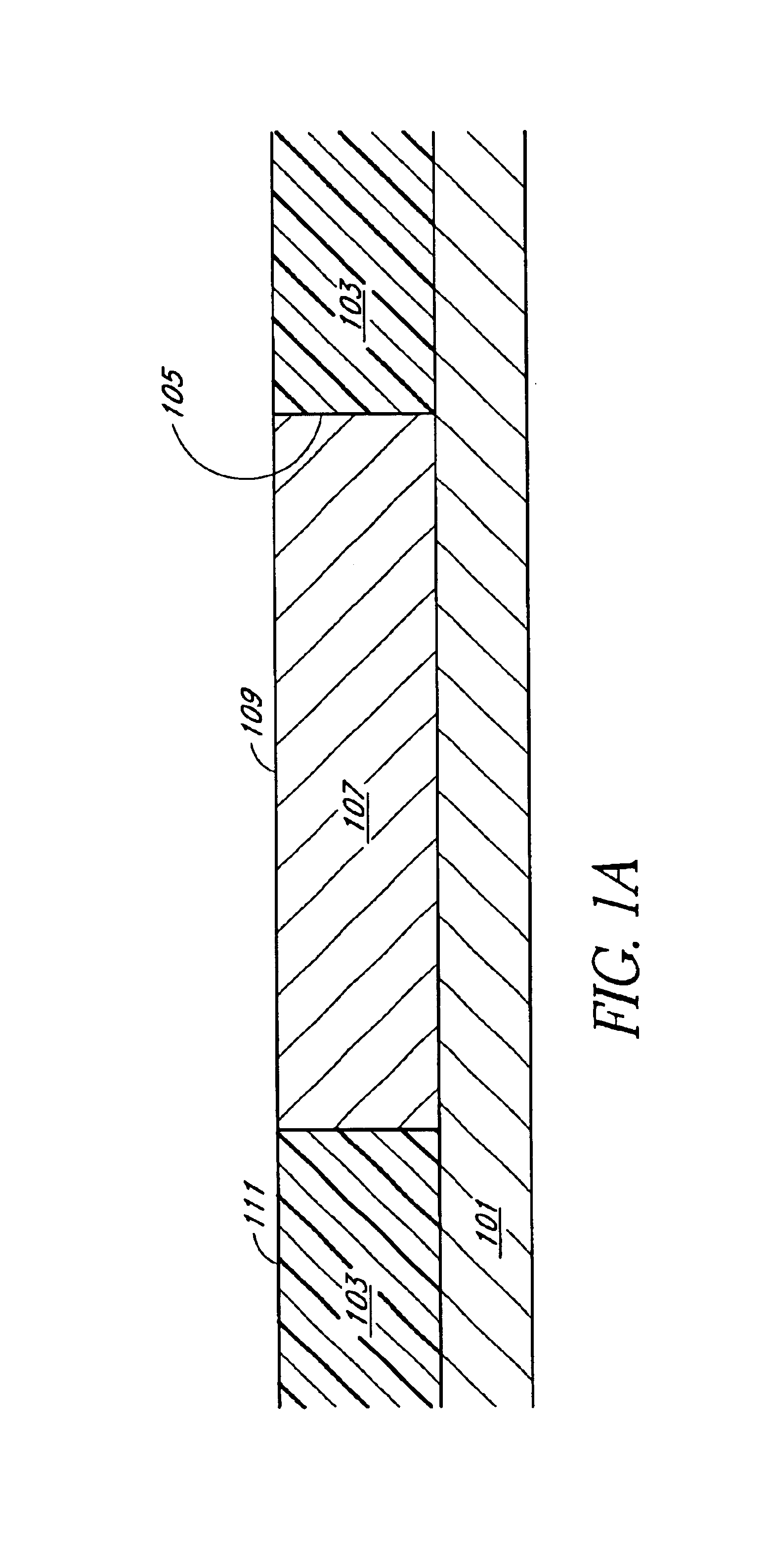

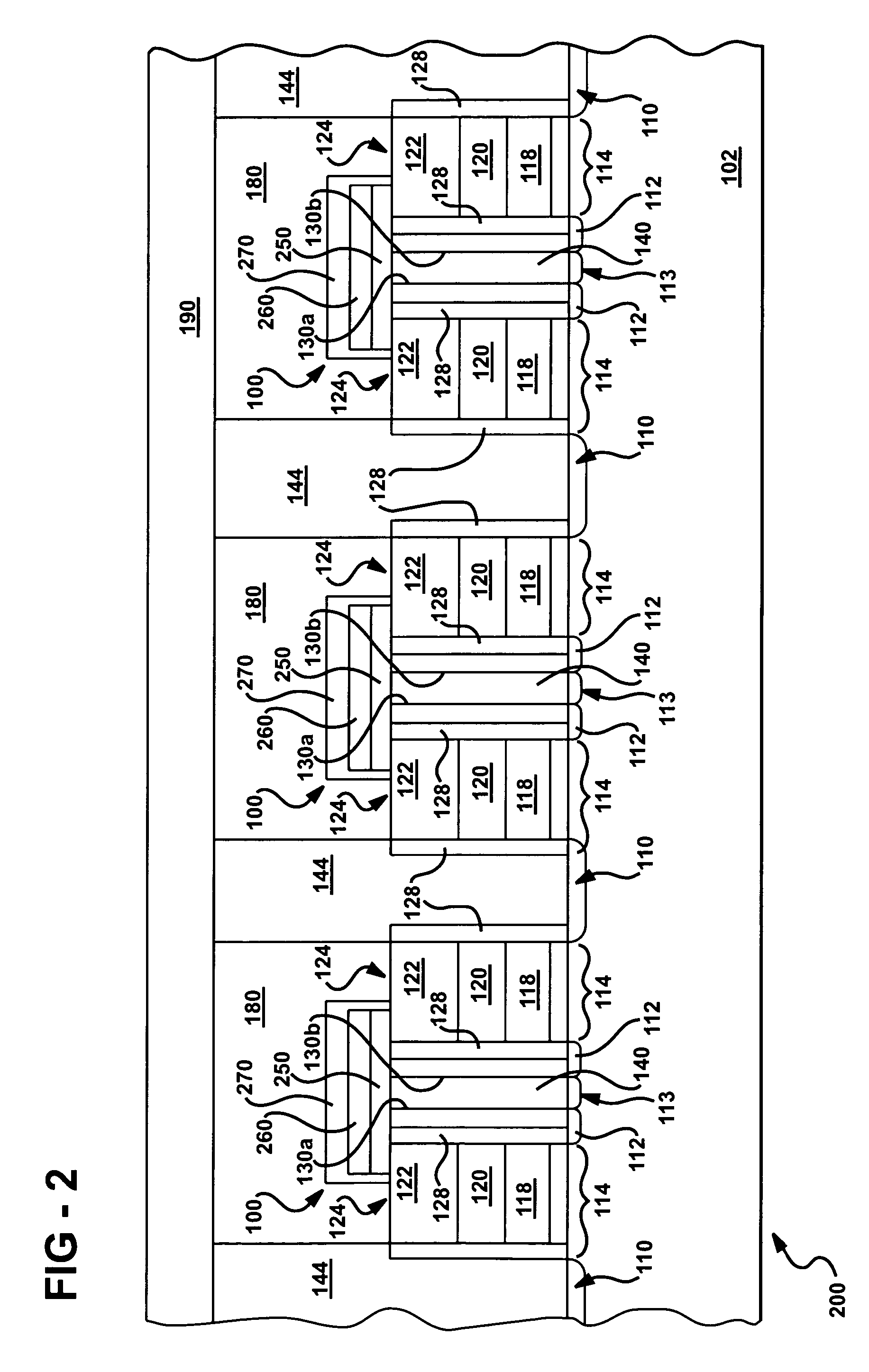

Memory cell incorporating a chalcogenide element

A memory cell incorporating a chalcogenide element and a method of making same is disclosed. In the method, a doped silicon substrate is provided with two or more polysilicon plugs to form an array of diode memory cells. A layer of silicon nitride is disposed over the plugs. Using a poly-spacer process, small pores are formed in the silicon nitride to expose a portion of the polysilicon plugs. A chalcogenide material is disposed in the pores by depositing a layer of chalcogenide material on the silicon nitride layer and planarizing the chalcogenide layer to the silicon nitride layer using CMP. A layer of TiN is next deposited over the plugs, followed by a metallization layer. The TiN and metallization layers are then masked and etched to define memory cell areas.

Owner:ROUND ROCK RES LLC

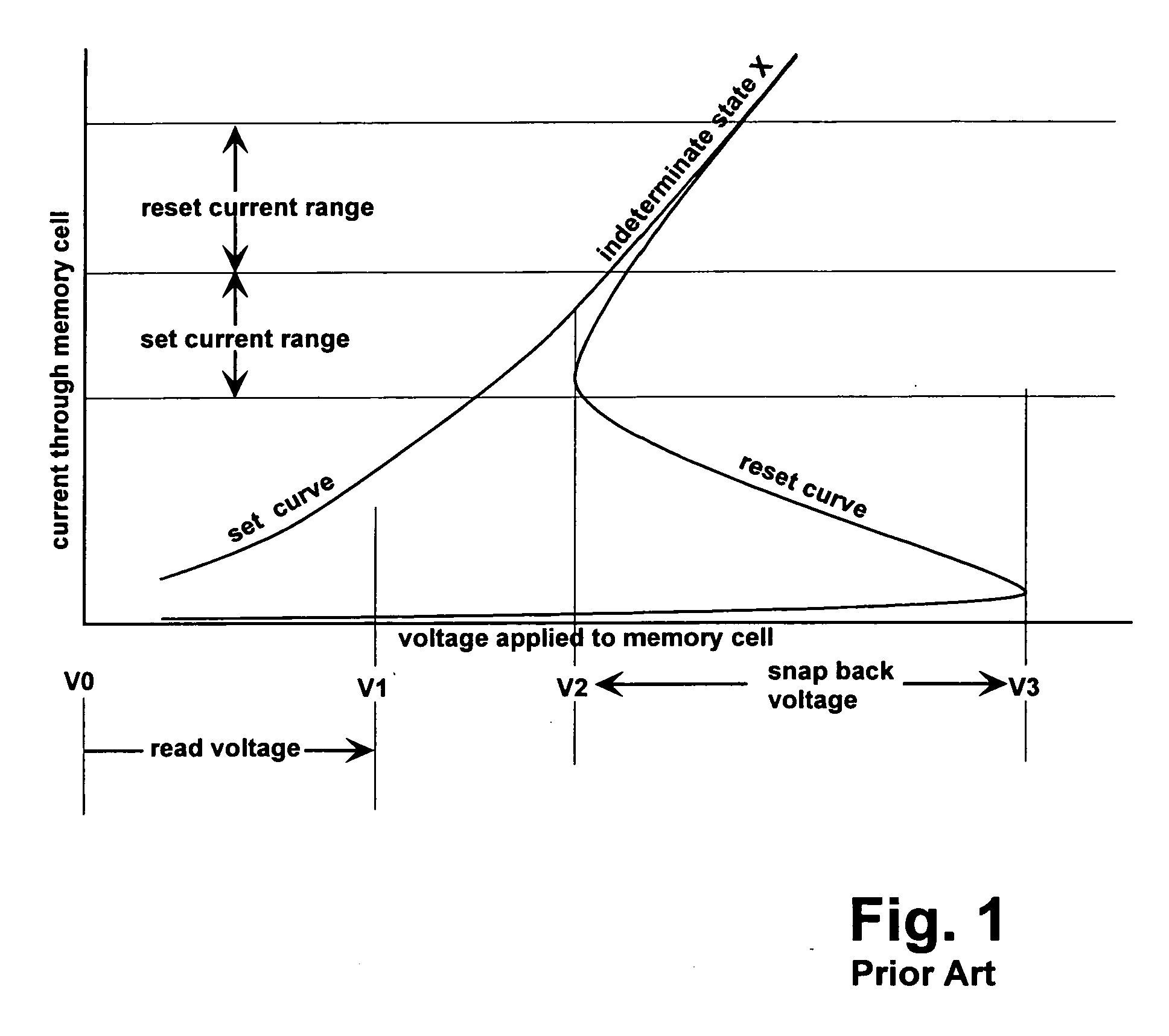

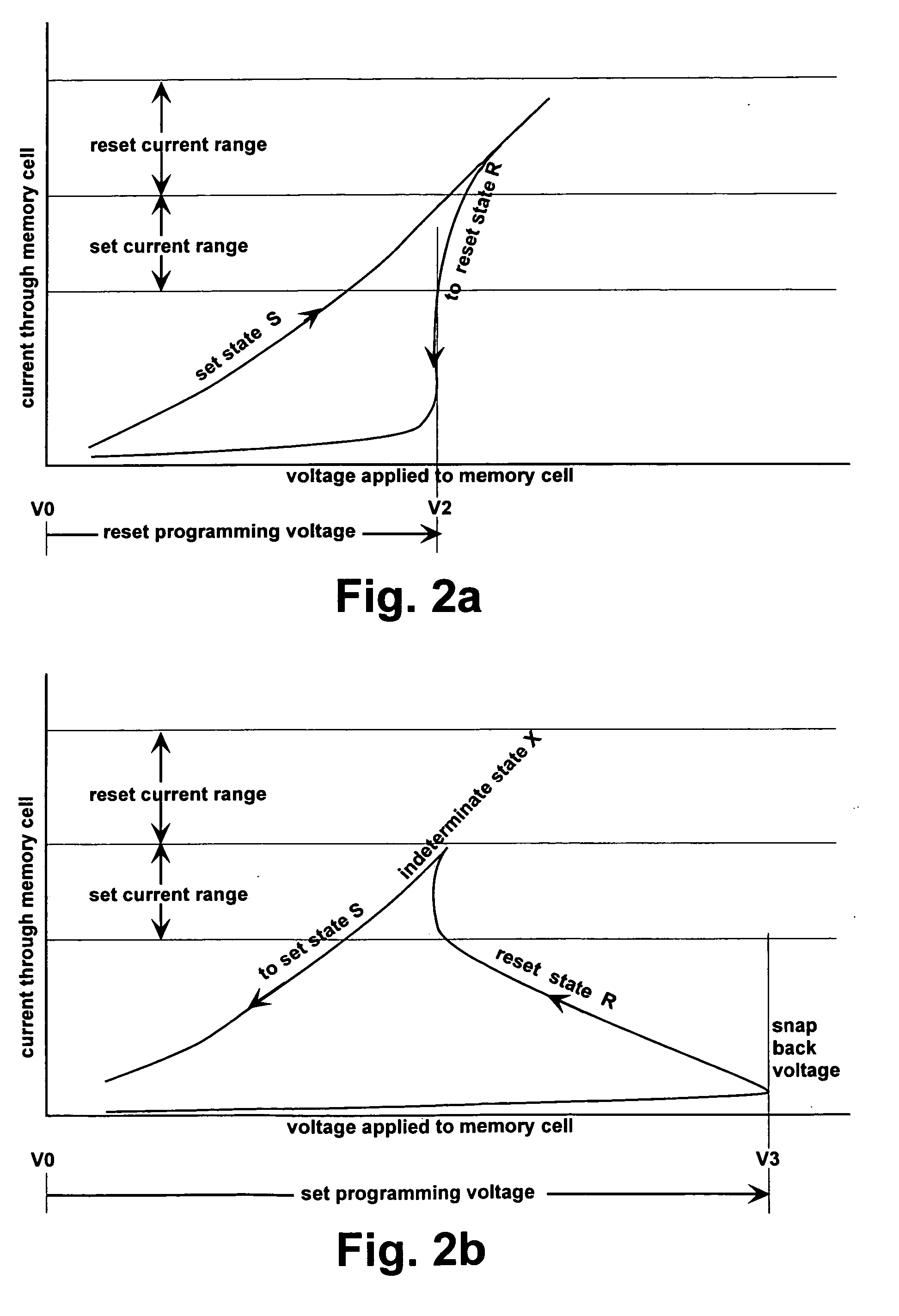

Nonvolatile memory device using a varistor as a current limiter element

ActiveUS20130214232A1Reduce voltageTotal current dropSolid-state devicesSemiconductor/solid-state device manufacturingSoftware engineeringMusic player

Embodiments of the invention include a method of forming a nonvolatile memory device that contains a resistive switching memory element that has improved device switching performance and lifetime, due to the addition of a current limiting component disposed therein. The electrical properties of the current limiting component are configured to lower the current flow through the variable resistance layer during the logic state programming steps by adding a fixed series resistance in the resistive switching memory element of the nonvolatile memory device. In some embodiments, the current limiting component comprises a varistor that is a current limiting material disposed within a resistive switching memory element in a nonvolatile resistive switching memory device. Typically, resistive switching memory elements may be formed as part of a high-capacity nonvolatile memory integrated circuit, which can be used in various electronic devices, such as digital cameras, mobile telephones, handheld computers, and music players.

Owner:KK TOSHIBA +1

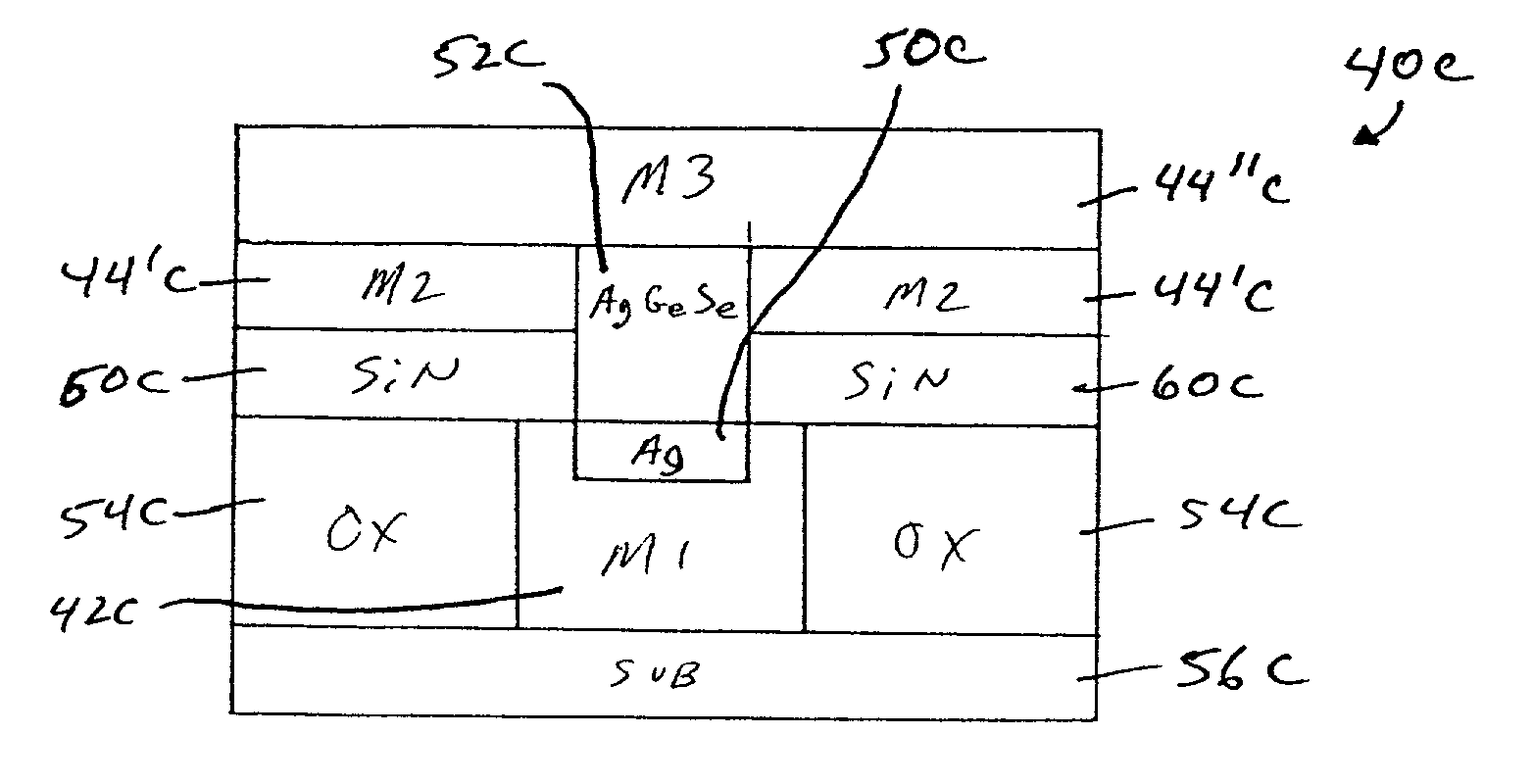

Programmable conductor memory cell structure

In programmable conductor memory cells, metal ions precipitate out of a glass electrolyte element in response to an applied electric field in one direction only, causing a conductive pathway to grow from cathode to anode. The amount of conductive pathway growth, and therefore the programming, depends, in part, on the availability of metal ions. It is important that the metal ions come only from the solid solution of the memory cell body. If additional metal ions are supplied from other sources, such as the sidewall edge at the anode interface, the amount of metal ions may not be directly related to the strength of the electric field, and the programming will not respond consistently from cell to cell. The embodiments described herein provide new and novel structures that block interface diffusion paths for metal ions, leaving diffusion from the bulk glass electrolyte as the only supply of metal ions for conductive pathway formation.

Owner:OVONYX MEMORY TECH LLC

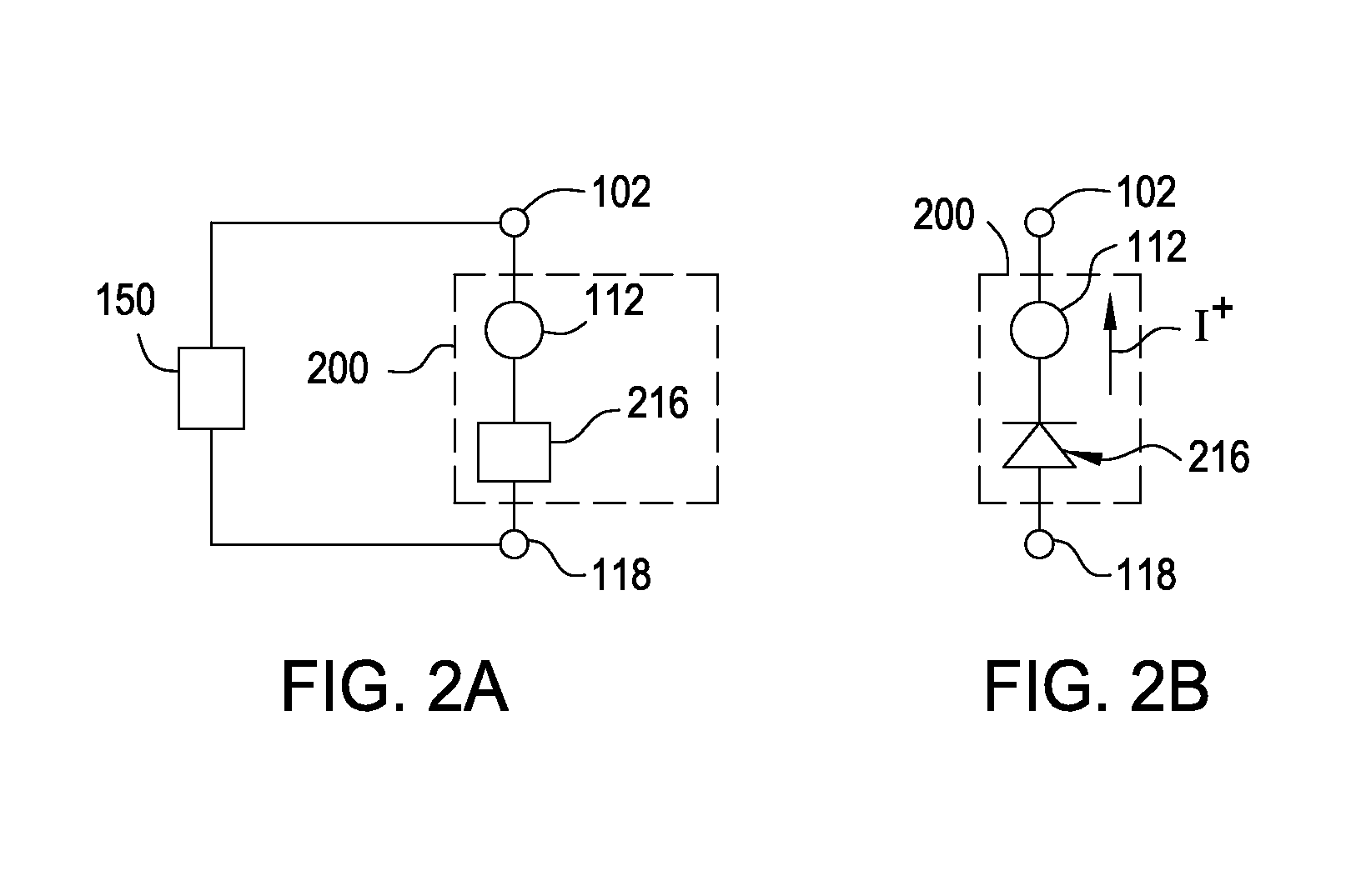

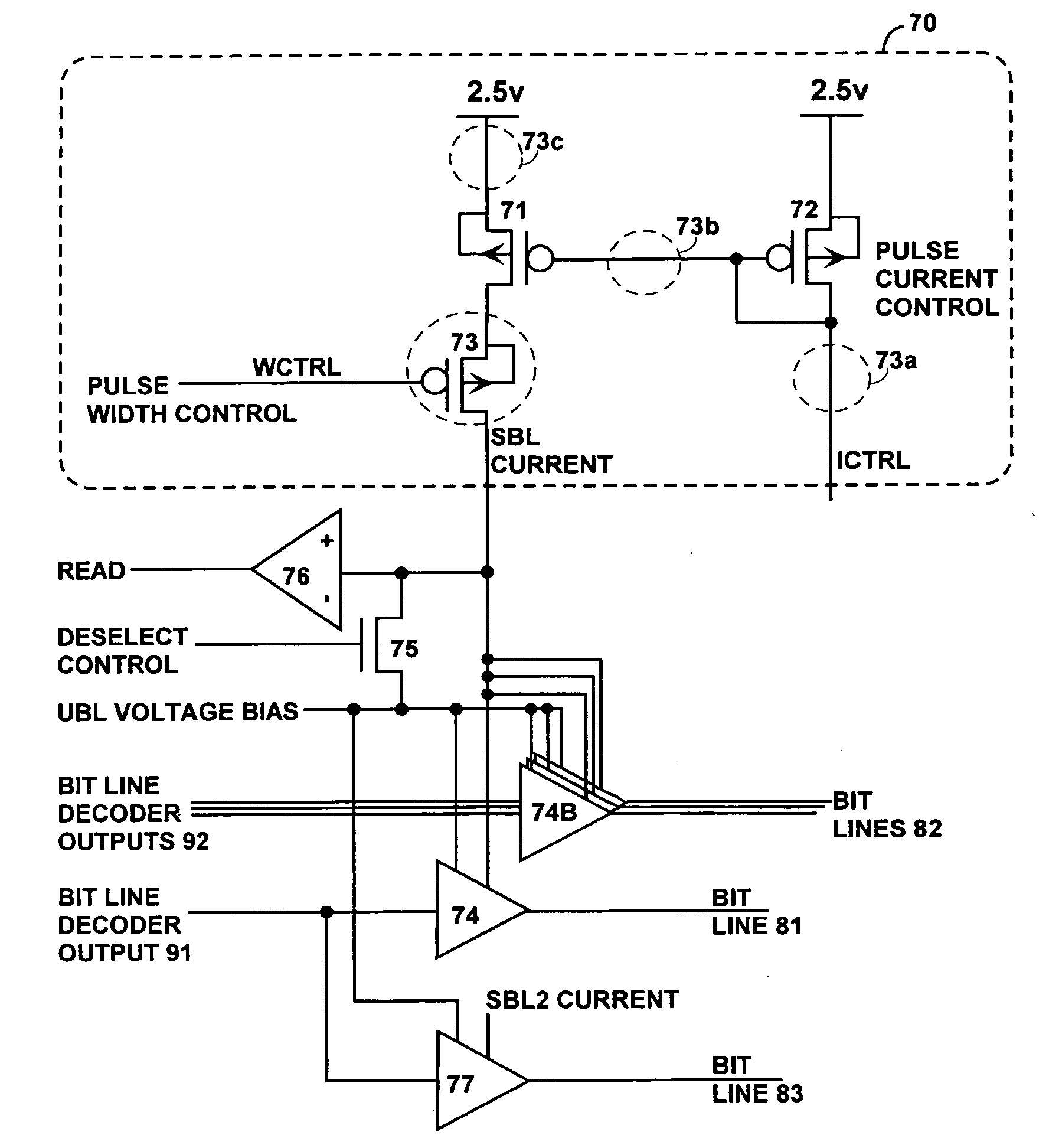

Structure and method for biasing phase change memory array for reliable writing

ActiveUS20060157679A1Minimize leakage currentReduce the possibilitySolid-state devicesDigital storageBit linePhase-change memory

A memory array having memory cells comprising a diode and a phase change material is reliably programmed by maintaining all unselected memory cells in a reverse biased state. Thus leakage is low and assurance is high that no unselected memory cells are disturbed. In order to avoid disturbing unselected memory cells during sequential writing, previously selected word and bit lines are brought to their unselected voltages before new bit lines and word lines are selected. A modified current mirror structure controls state switching of the phase change material.

Owner:SANDISK TECH LLC

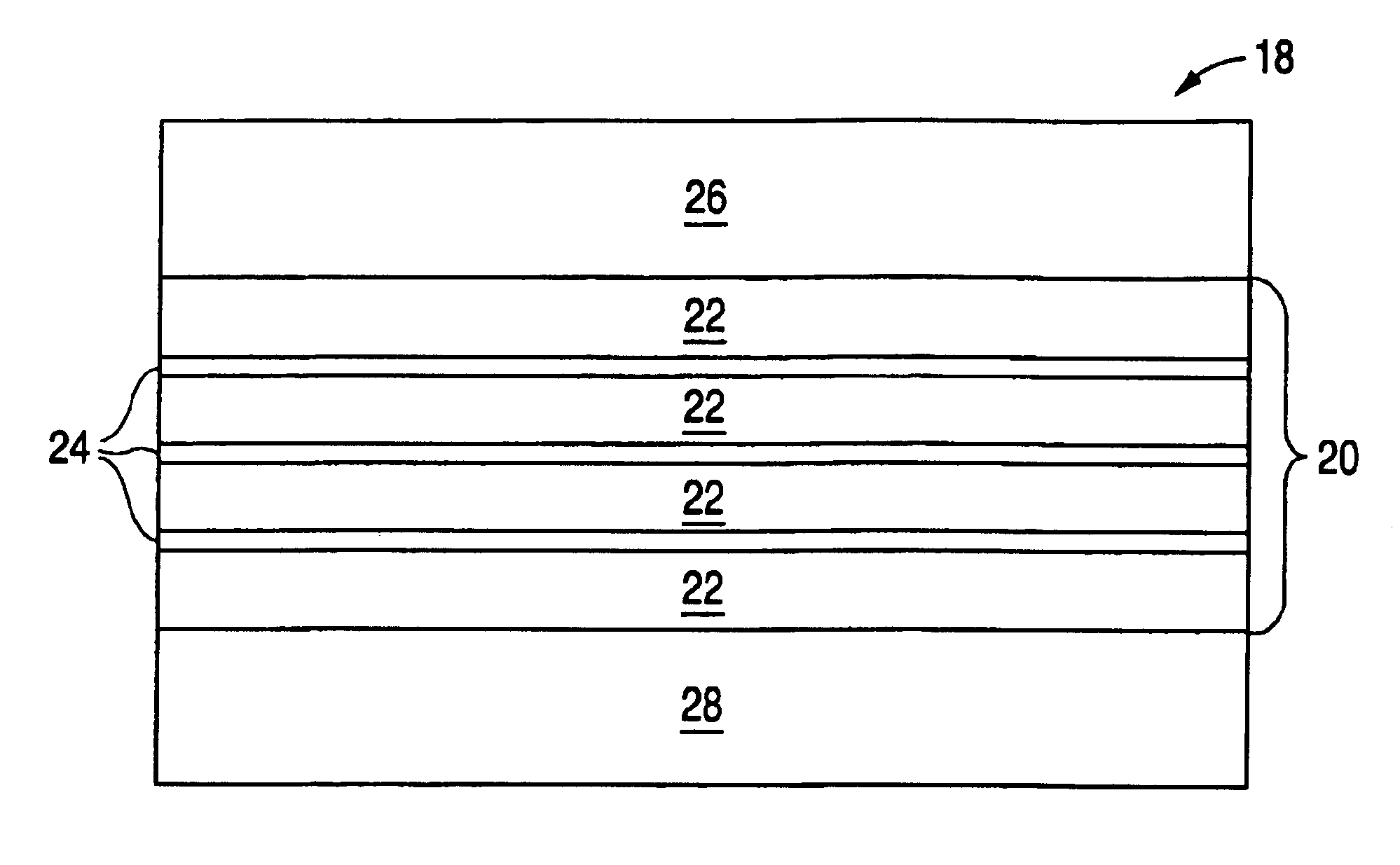

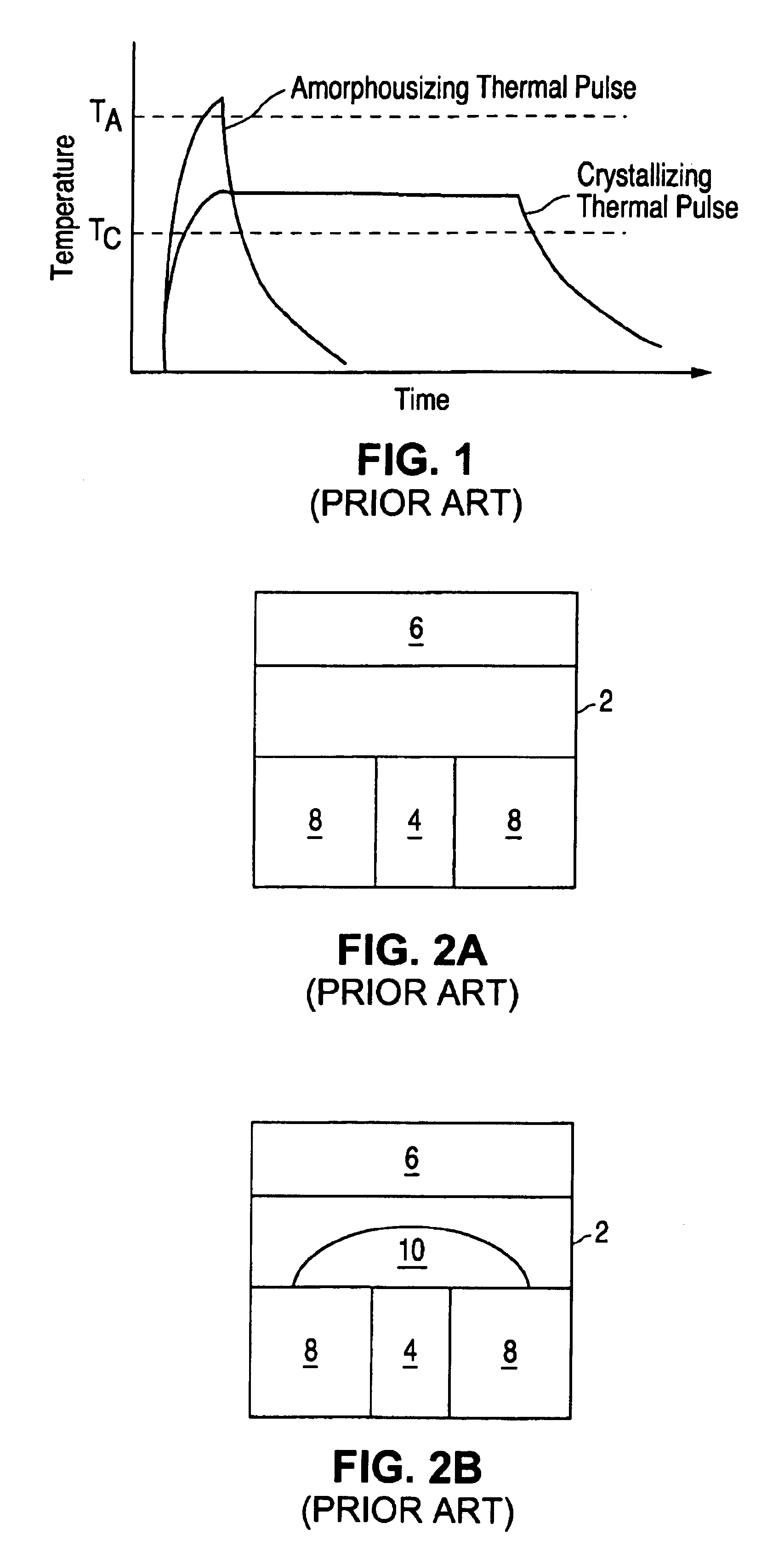

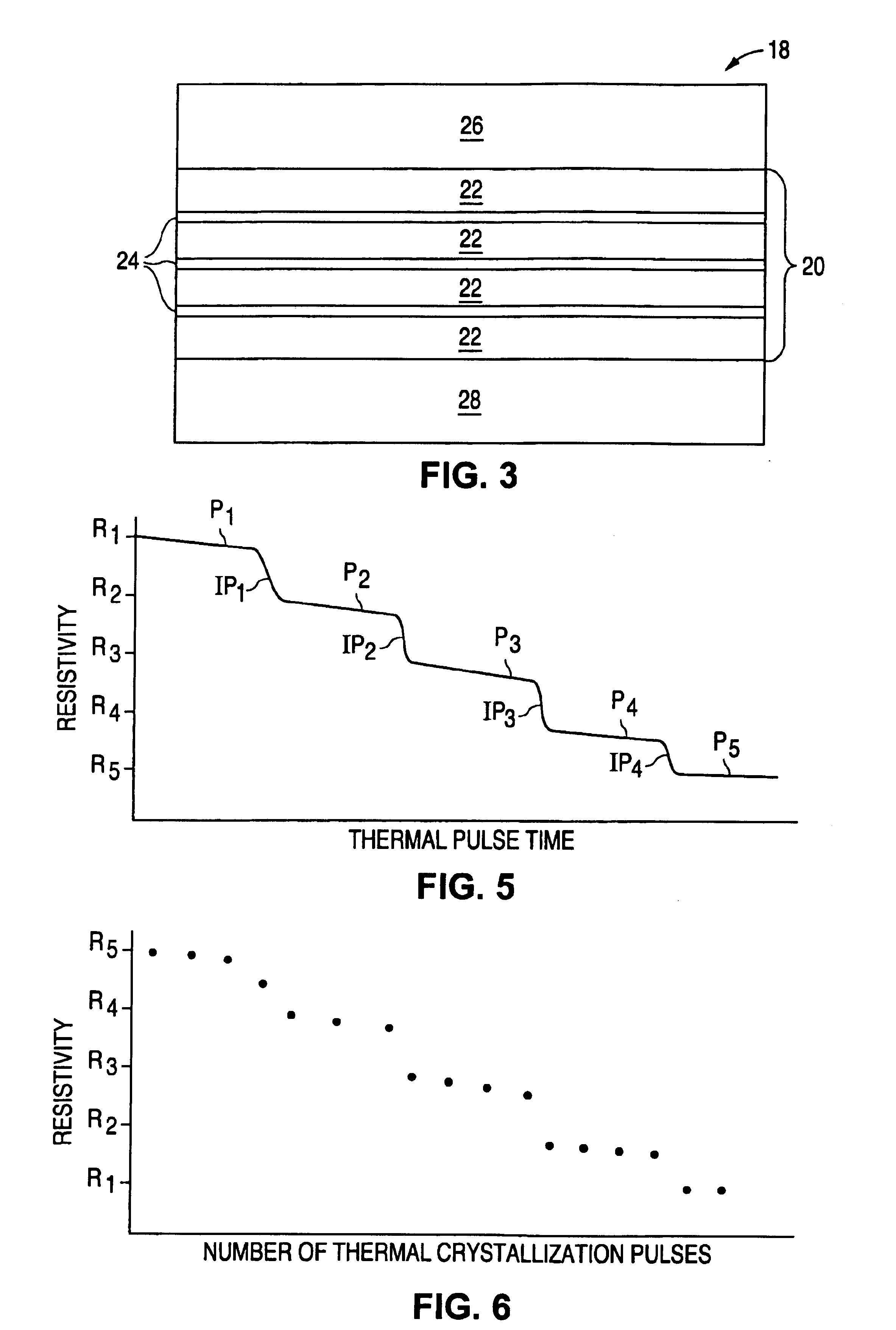

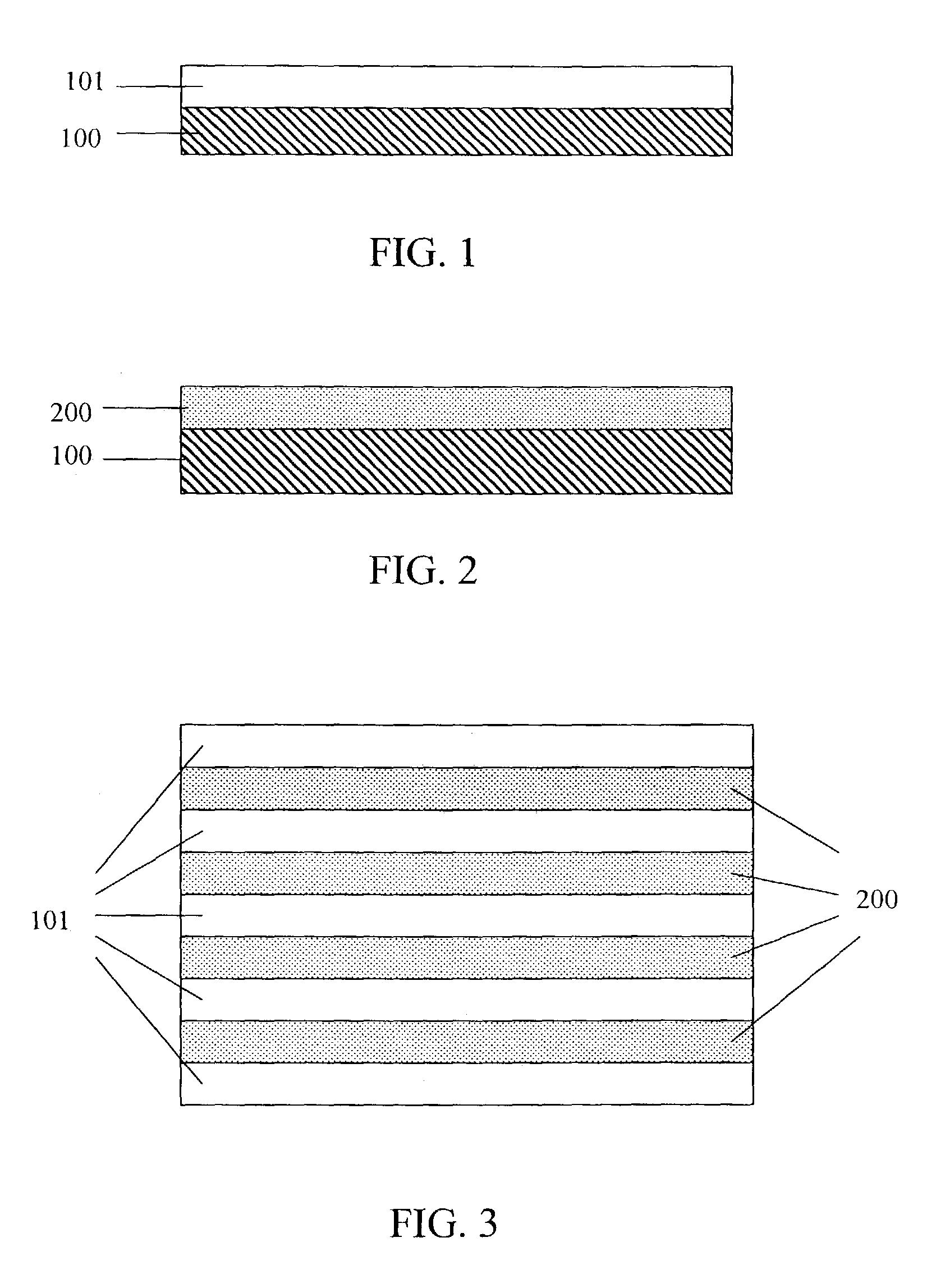

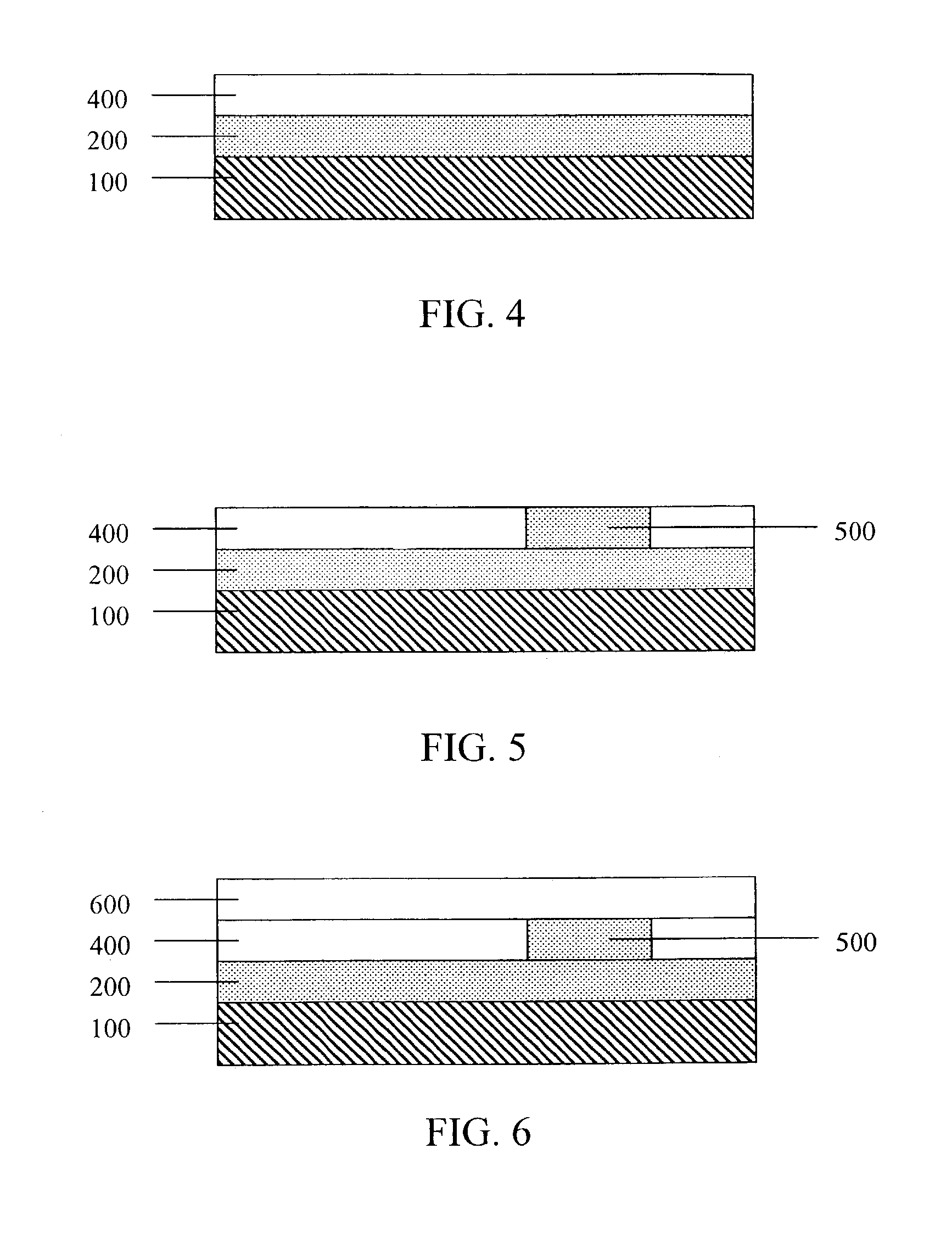

Memory device with discrete layers of phase change memory material

InactiveUS6927410B2Reliably and more repeatedly programmableSemiconductor/solid-state device detailsSolid-state devicesPhase-change memoryInterface layer

A phase changing memory device, and method of making the same, that includes programmable memory material disposed between a pair of electrodes. The programmable memory material includes discrete layers of phase change material, separated by conductive interface layers, that exhibits relatively stable resistivity values over discrete ranges of crystallizing and amorphousizing thermal pulses applied thereto, for multi-bit storage. The memory material and one of the electrodes can be disposed along spacer material surfaces to form an electrical current path that narrows in width as the current path approaches the other electrode, such that electrical current passing through the current path generates heat for heating the memory material disposed between the electrodes.

Owner:SILICON STORAGE TECHNOLOGY

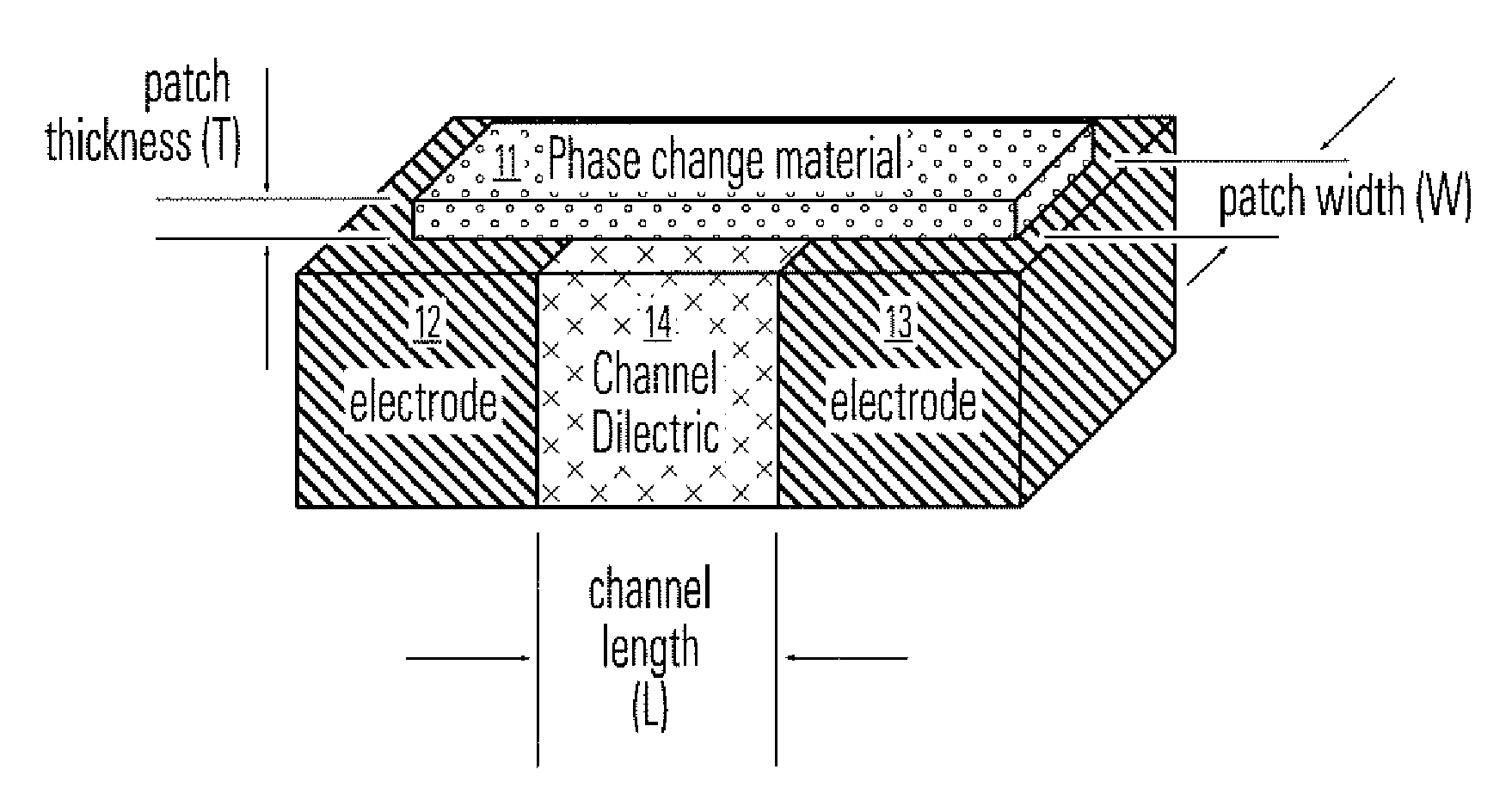

Structure for confining the switching current in phase memory (PCM) cells

InactiveUS20060226409A1Heat dissipation is limitedHigh densityBulk negative resistance effect devicesSemiconductor devicesPhase-change memorySwitched current

Disclosed are a phase change memory cell and a method of forming the memory cell. The memory cell comprises a main body of phase change material connected directly to a bottom contact and via a narrow channel of phase change material to a top contact. The channel is tapered from the top contact towards the main body. A minimum width of the channel has a less than minimum lithographic dimension and is narrower than a width of the main body. Therefore, the channel provides a confined region for the switching current path and restricts phase changing to within the channel. In addition an embodiment of the memory cell isolates the main body of phase change material by providing a space between the phase change material and the cell walls. The space allows the phase change material to expand and contract and also limits heat dissipation.

Owner:IBM CORP

Semiconductor Memory and Method of Manufacturing the Same

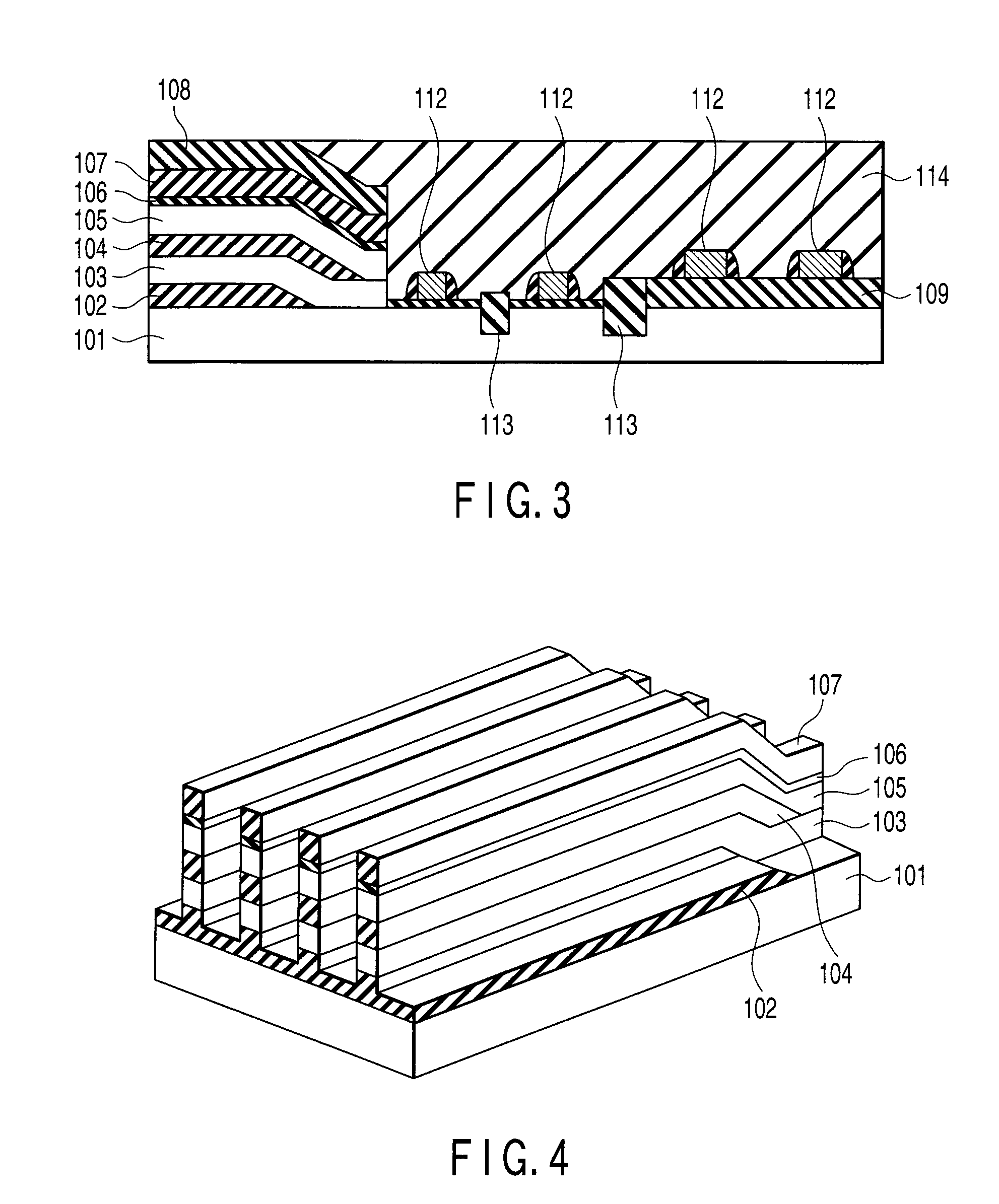

ActiveUS20080073635A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A semiconductor memory includes a plurality of stripe-like active areas formed by stacking, in a direction perpendicular to a substrate, a plurality of layers extending parallel to the substrate, a first gate electrode formed on first side surfaces of the active areas, the first side surfaces being perpendicular to the substrate, a second gate electrode formed on second side surfaces of the active areas, the second side surfaces being perpendicular to the substrate. The layers are patterned in self-alignment with each other, intersections of the active areas and the first gate electrode form a plurality of memory cells, and the plurality of memory cells in an intersecting plane share the first gate electrode.

Owner:KIOXIA CORP

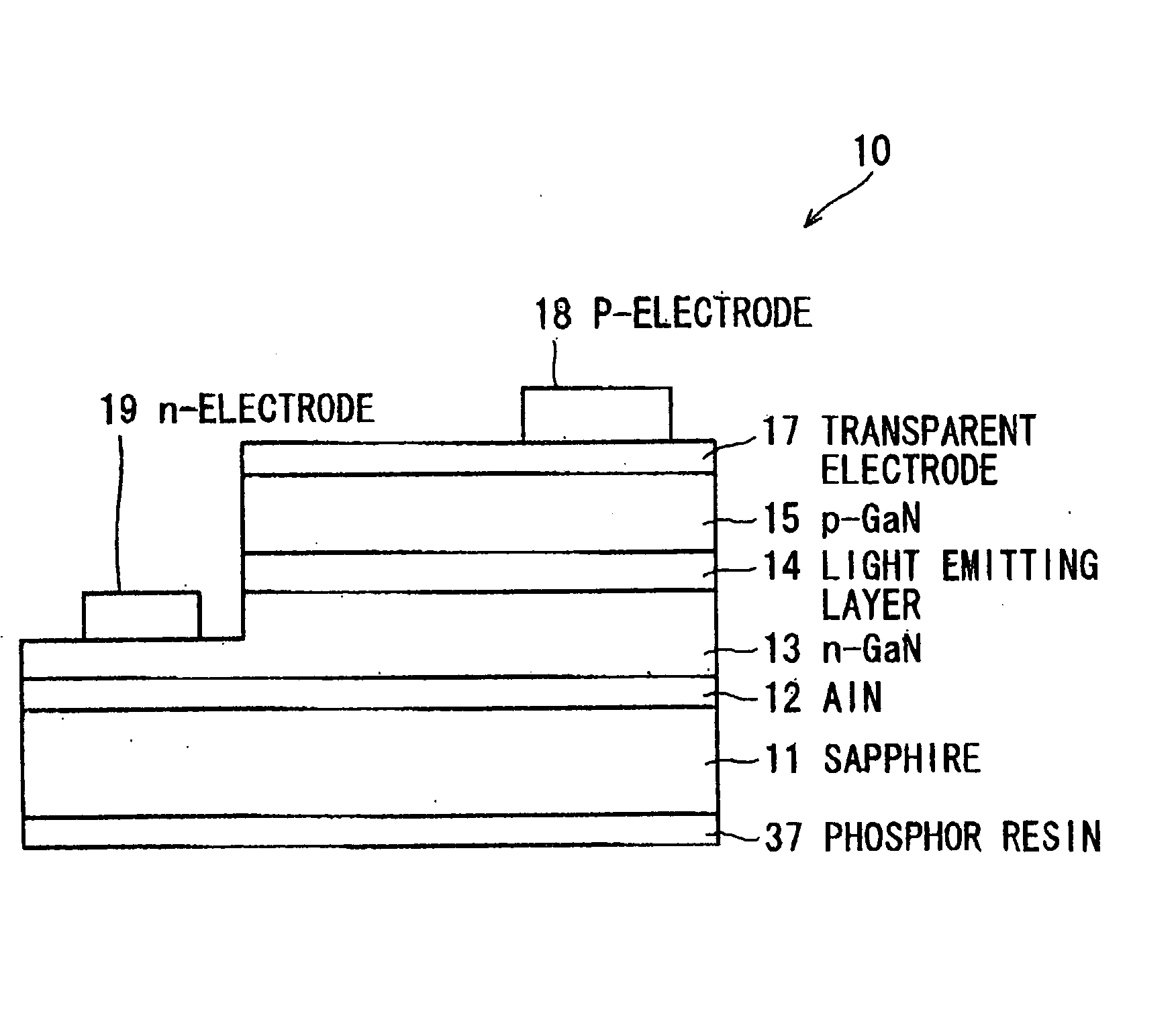

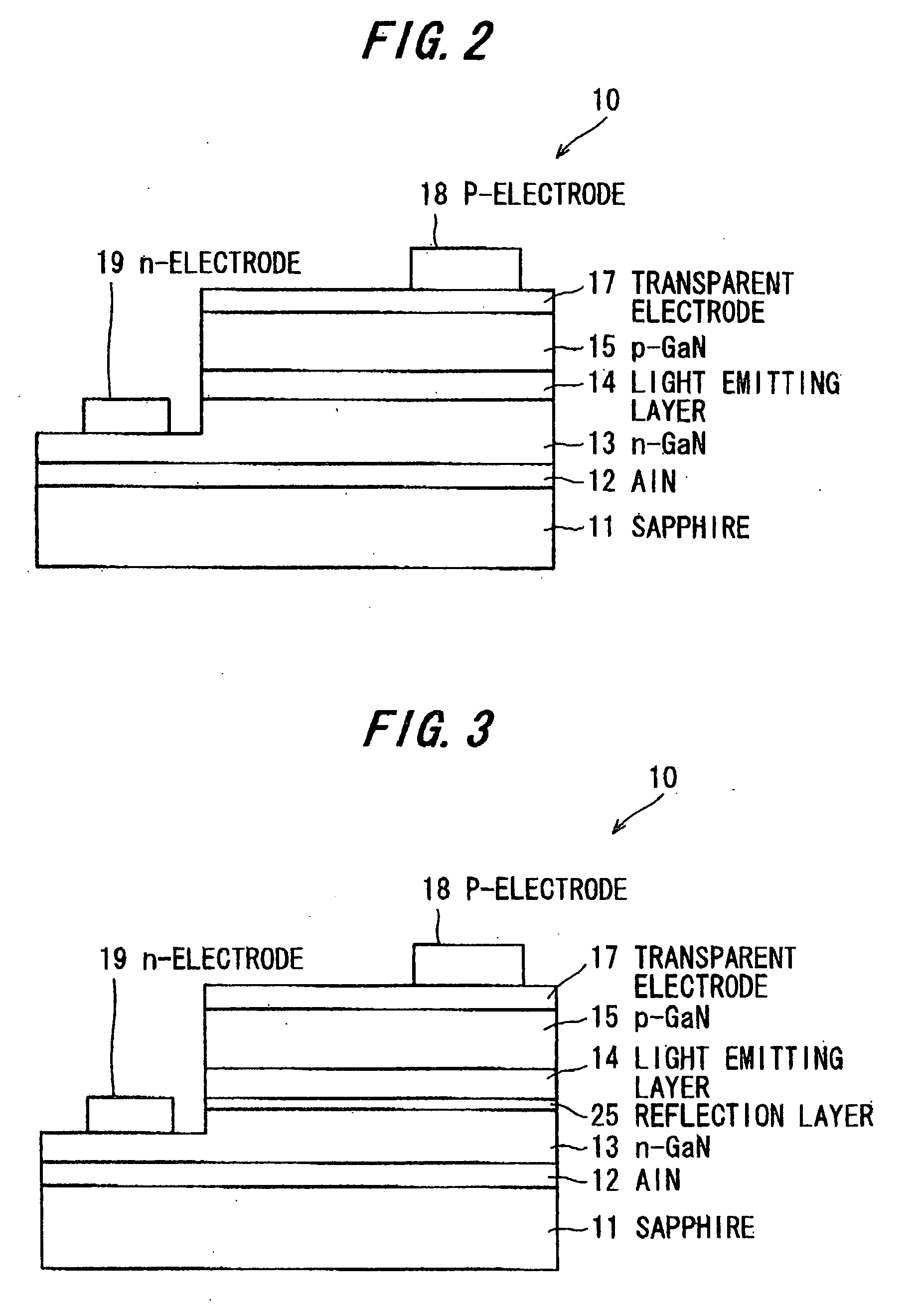

Light emitting apparatus and light emitting method

InactiveUS20050001225A1Improve propertiesIncrease brightnessSolid-state devicesBulk negative resistance effect devicesRare-earth elementSilicon nitride

A light emitting apparatus has a light emitting element with an emission wavelength in the range of 360 to 550 nm and a rare-earth element doped oxide nitride phosphor or cerium ion doped lanthanum silicon nitride phosphor. Part of light radiated from the light emitting element is wavelength-converted by the phosphor. The light emitting apparatus radiates white light generated by a mixture of the wavelength-converted light and the other part of light radiated from the light emitting element.

Owner:TOYODA GOSEI CO LTD +1

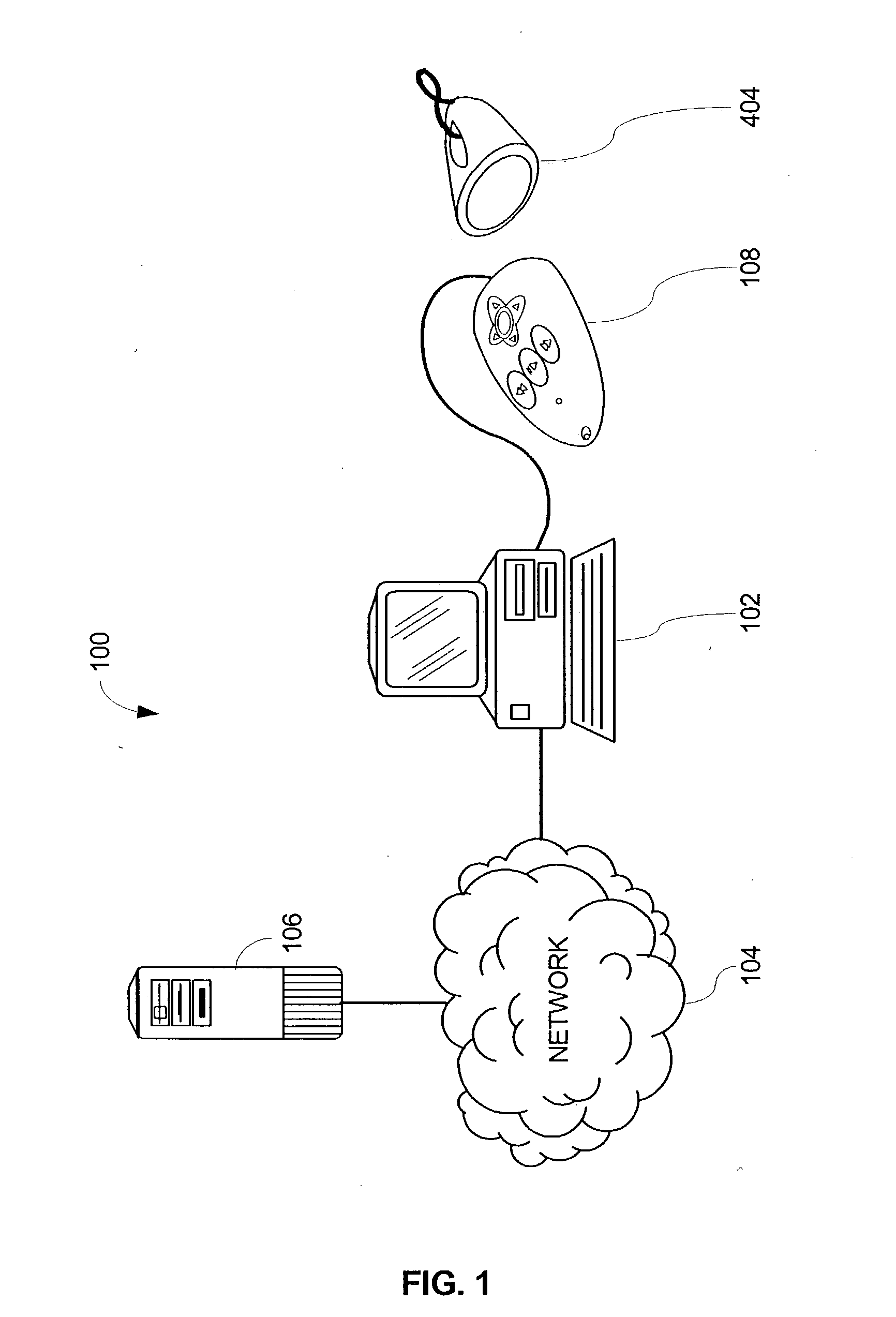

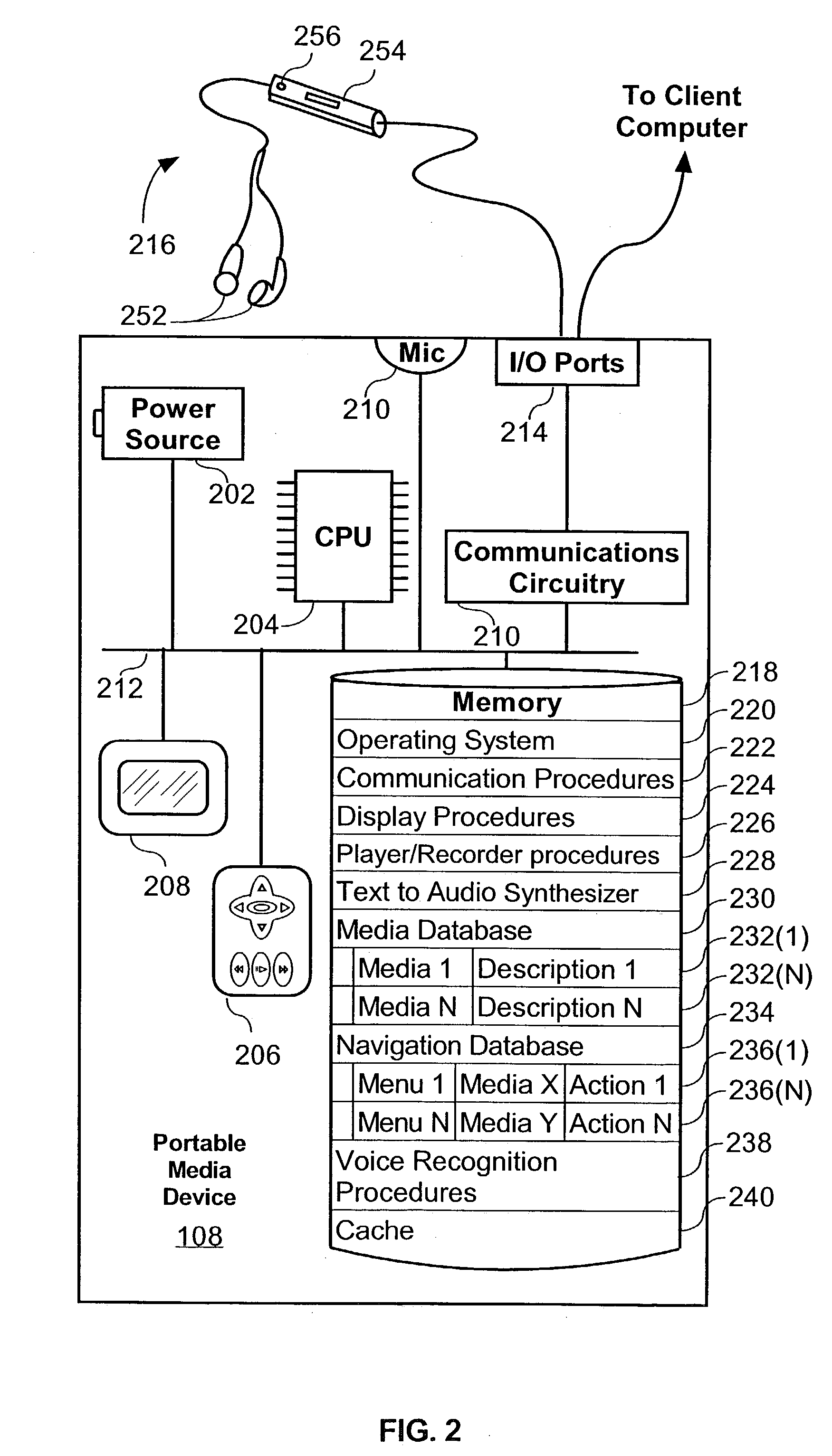

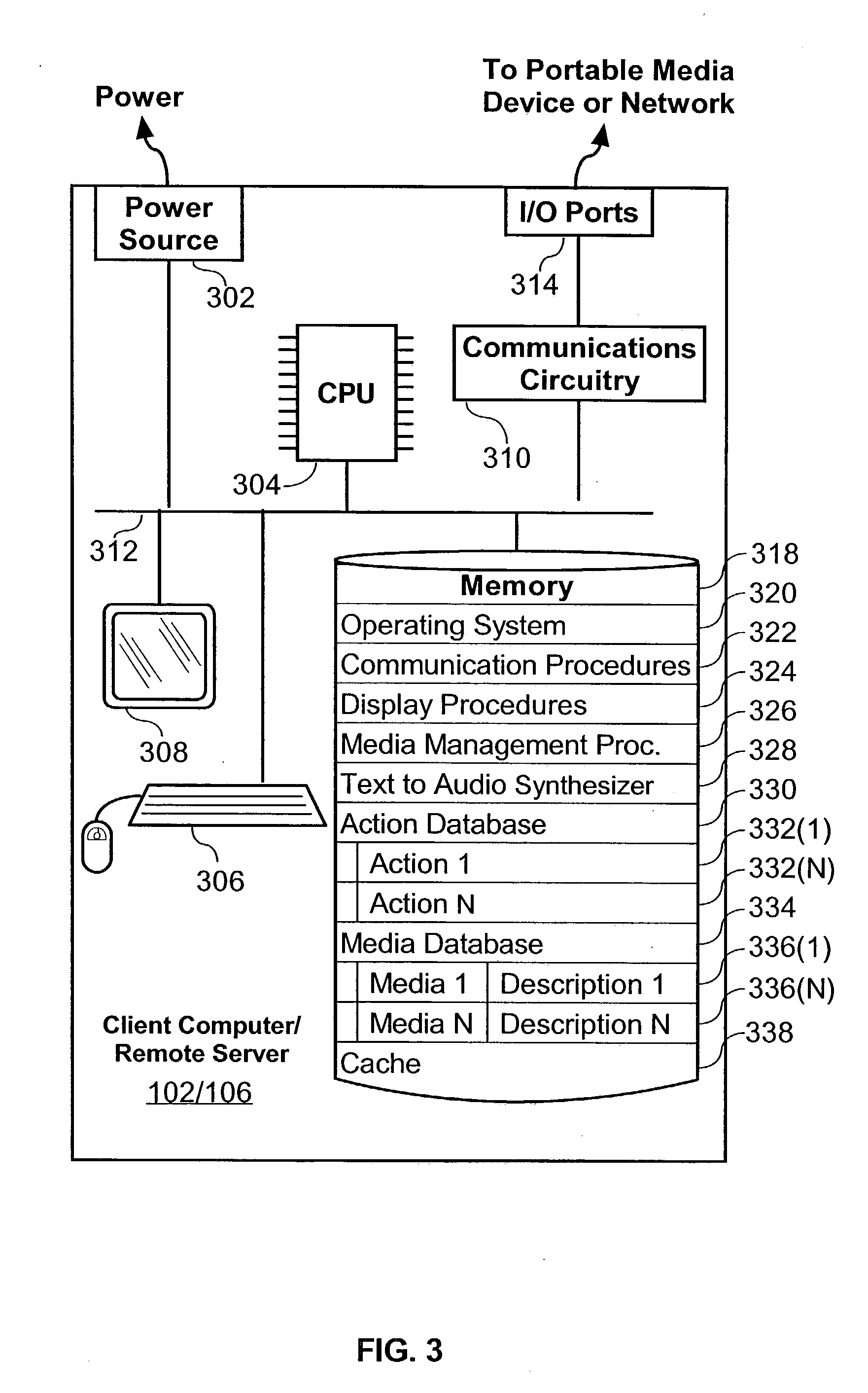

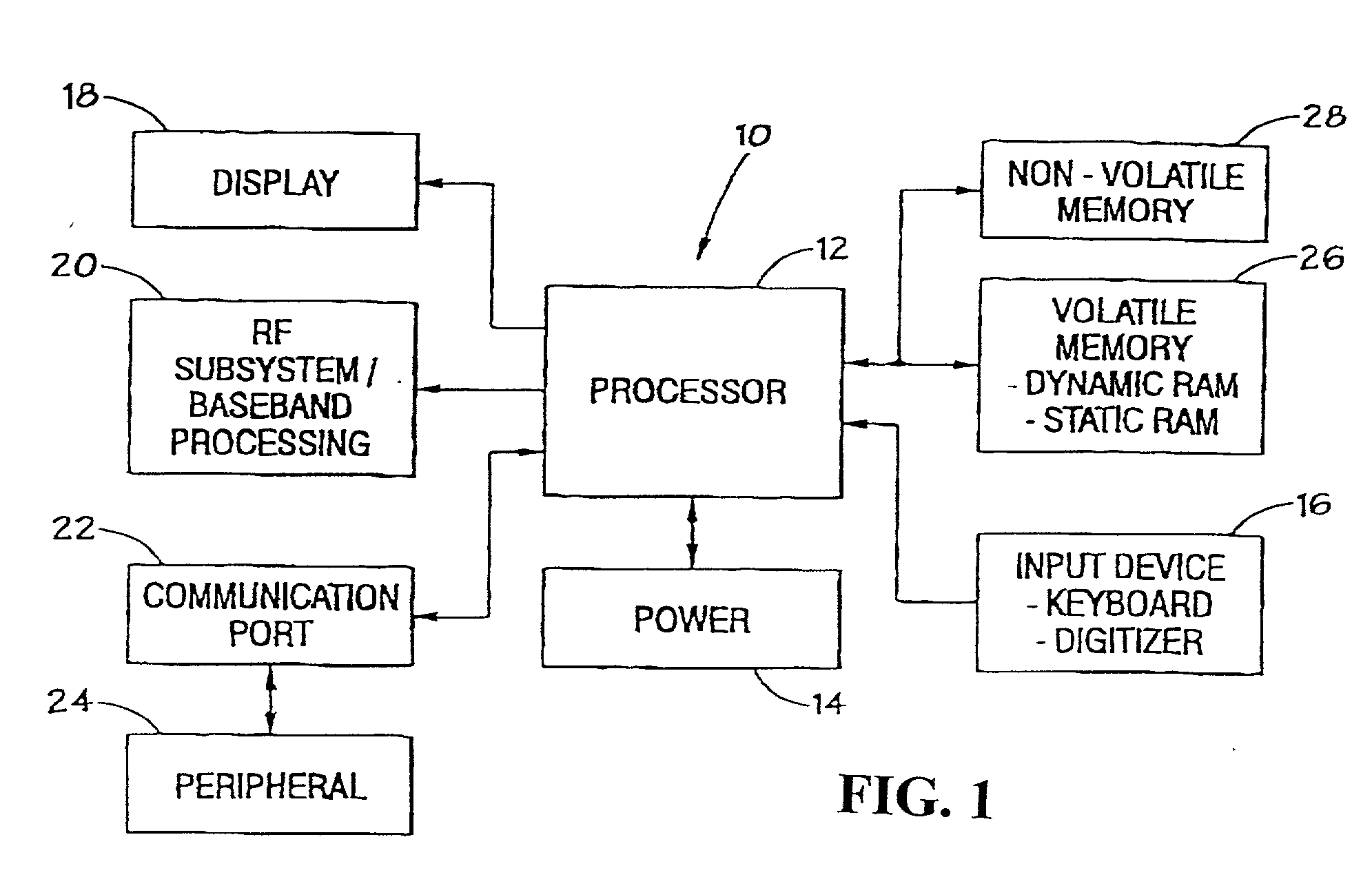

Portable media device with audio prompt menu

InactiveUS20050045373A1Improve the display effectLow costSemiconductor/solid-state device detailsElectronic editing digitised analogue information signalsOperational systemRemote computer

Once an audio prompt has been stored on the portable media device, the audio prompt menu is played. Subsequently, an input from a user of the portable media device is then received in response to the audio prompt menu. A command is subsequently transmitted to a remote computer. The command requests the remote computer to perform an action based on the user's input. The portable media device includes a portable media device housing containing a processor, a power source, a user interface device, communications circuitry, at least one input / output (i / o) port, and a memory. The memory includes an operating system, a media database, communication procedures for communicating with a remote computer, and instructions for performing the above described method.

Owner:NEUROS AUDIO

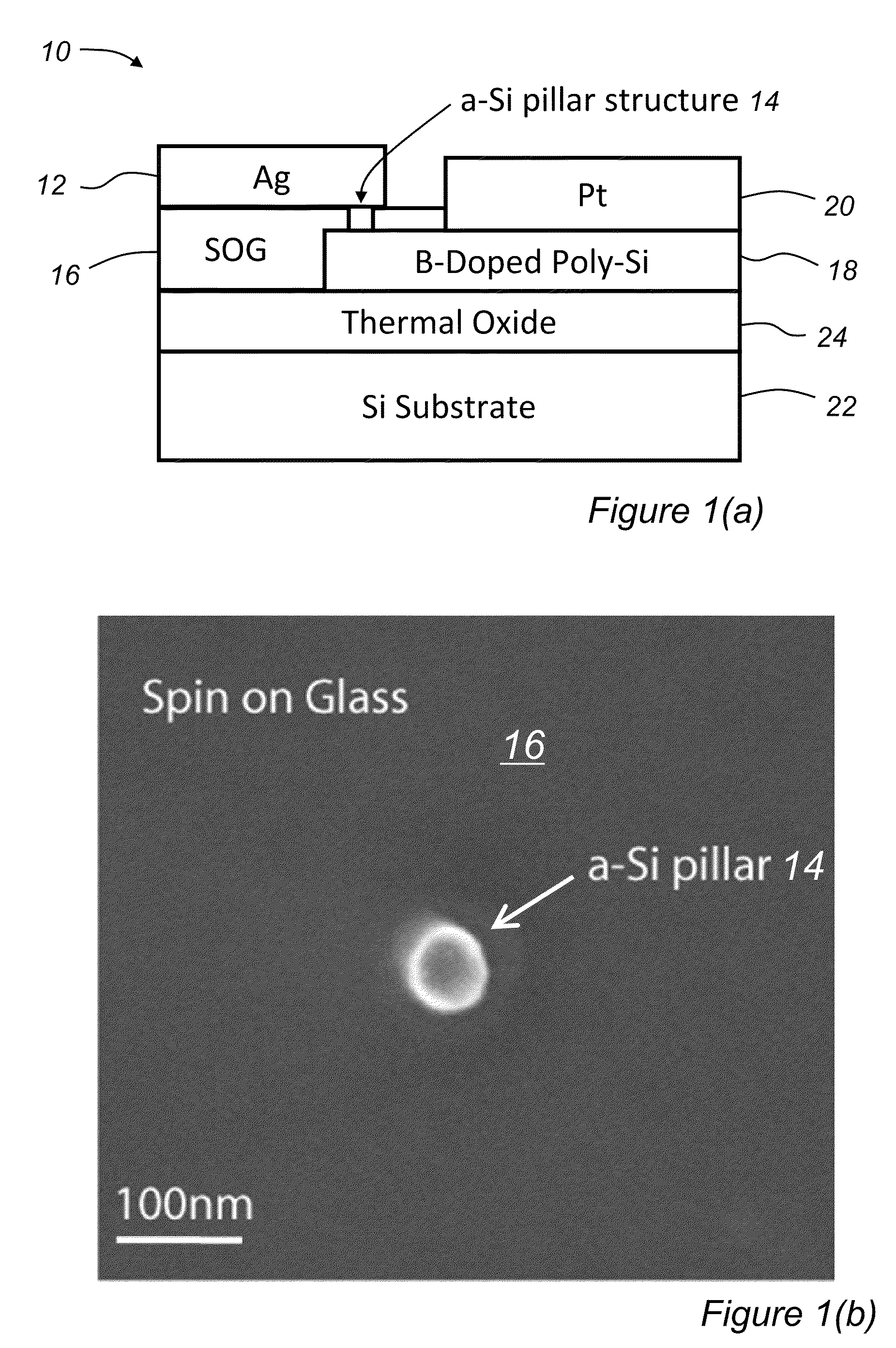

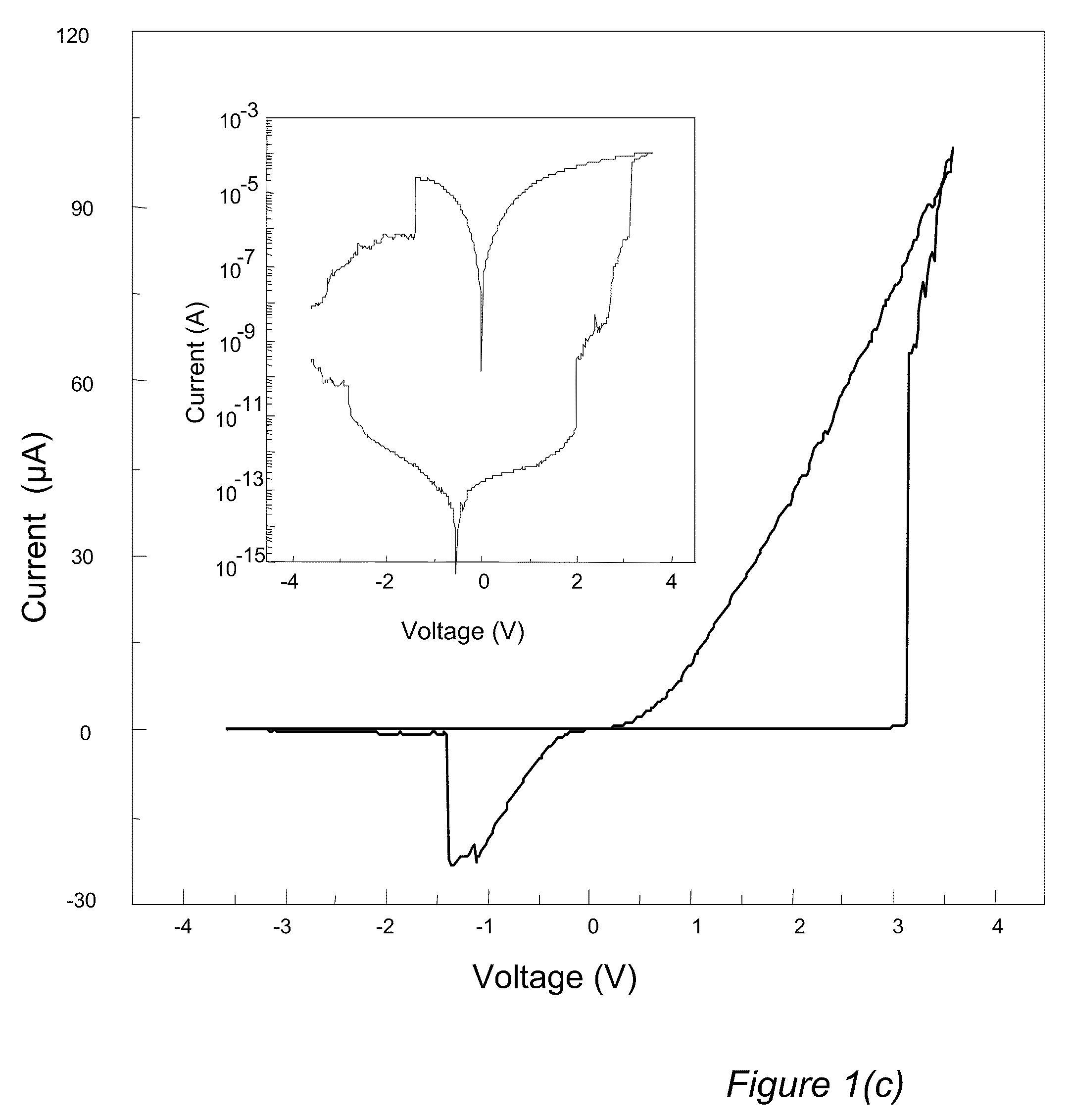

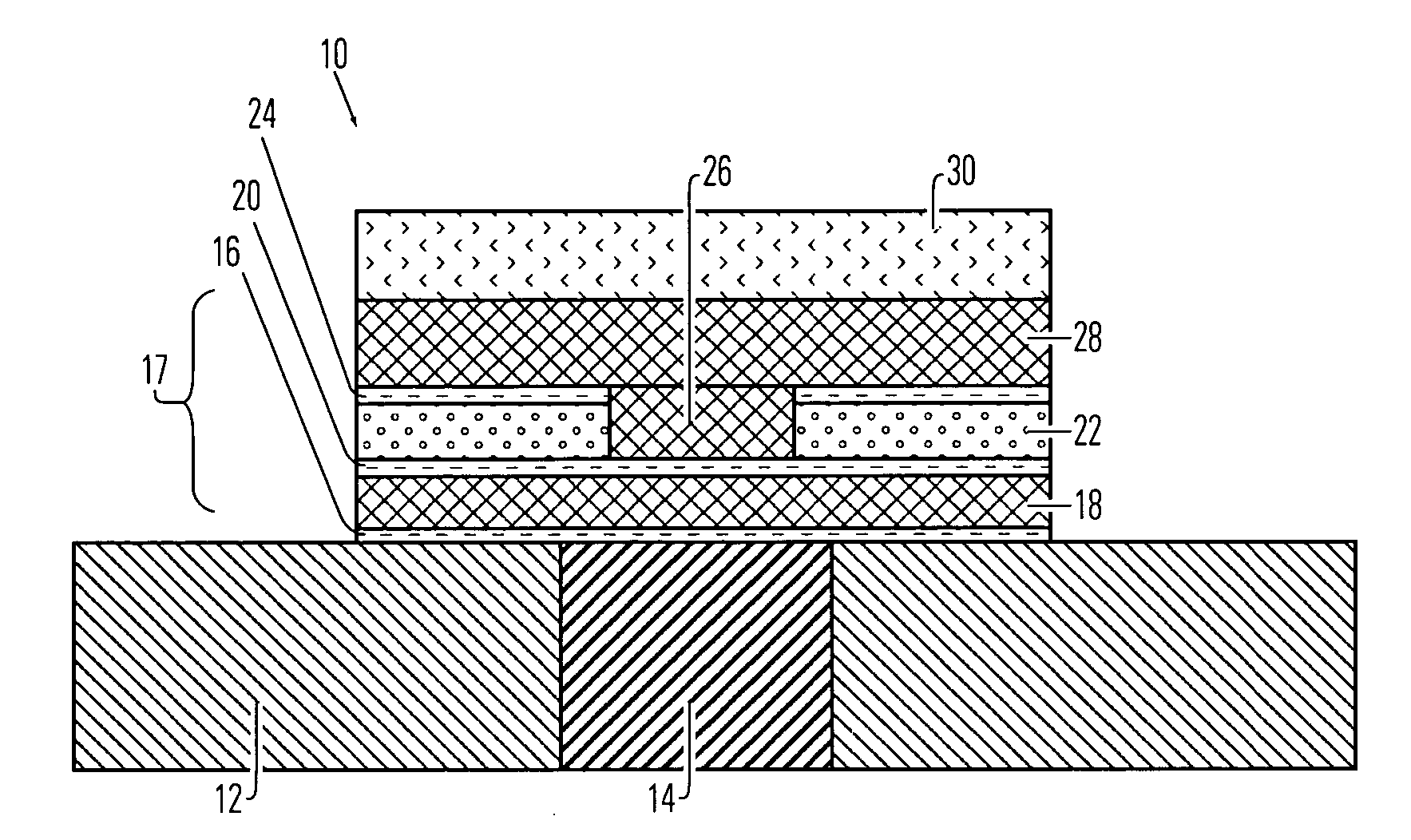

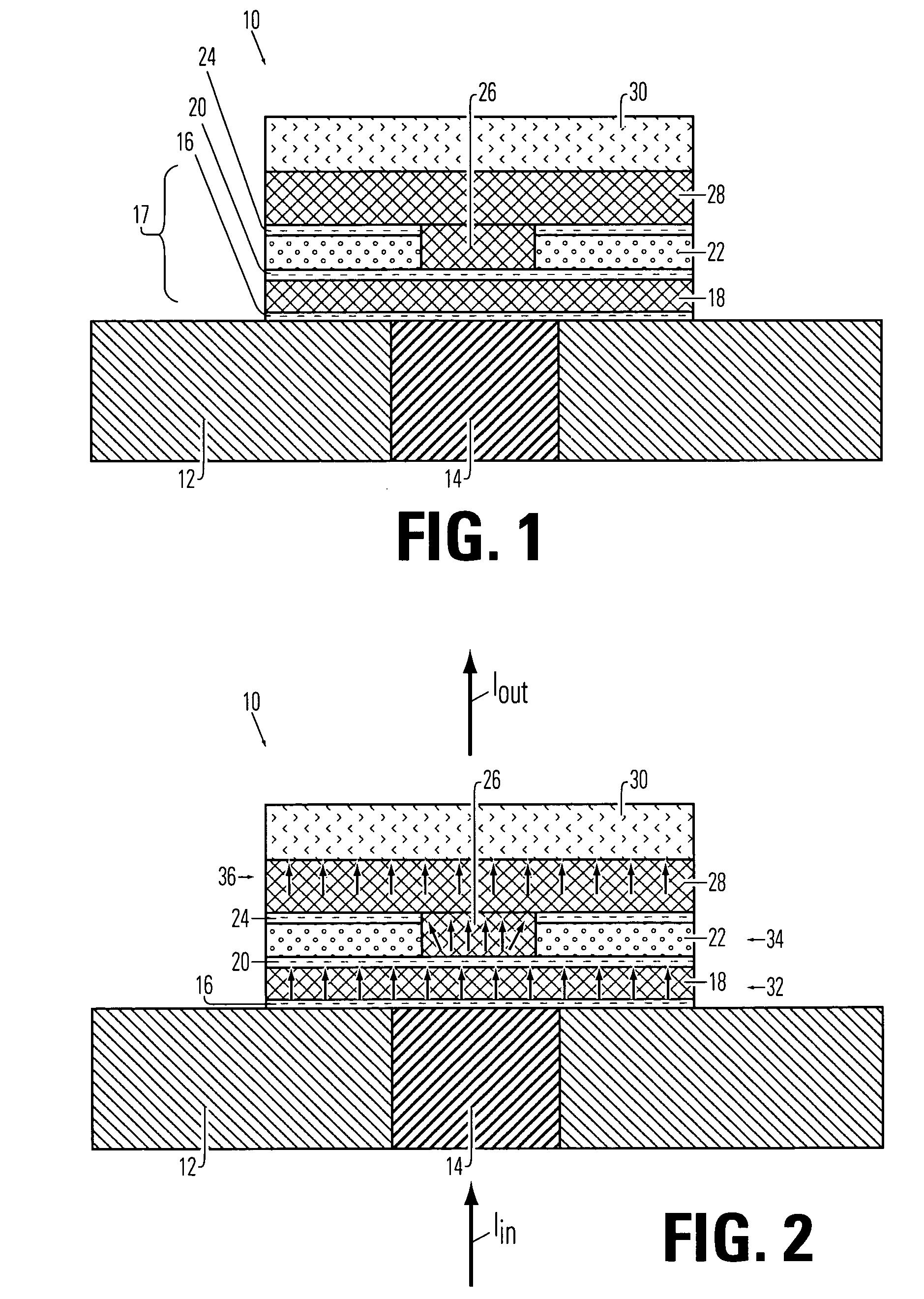

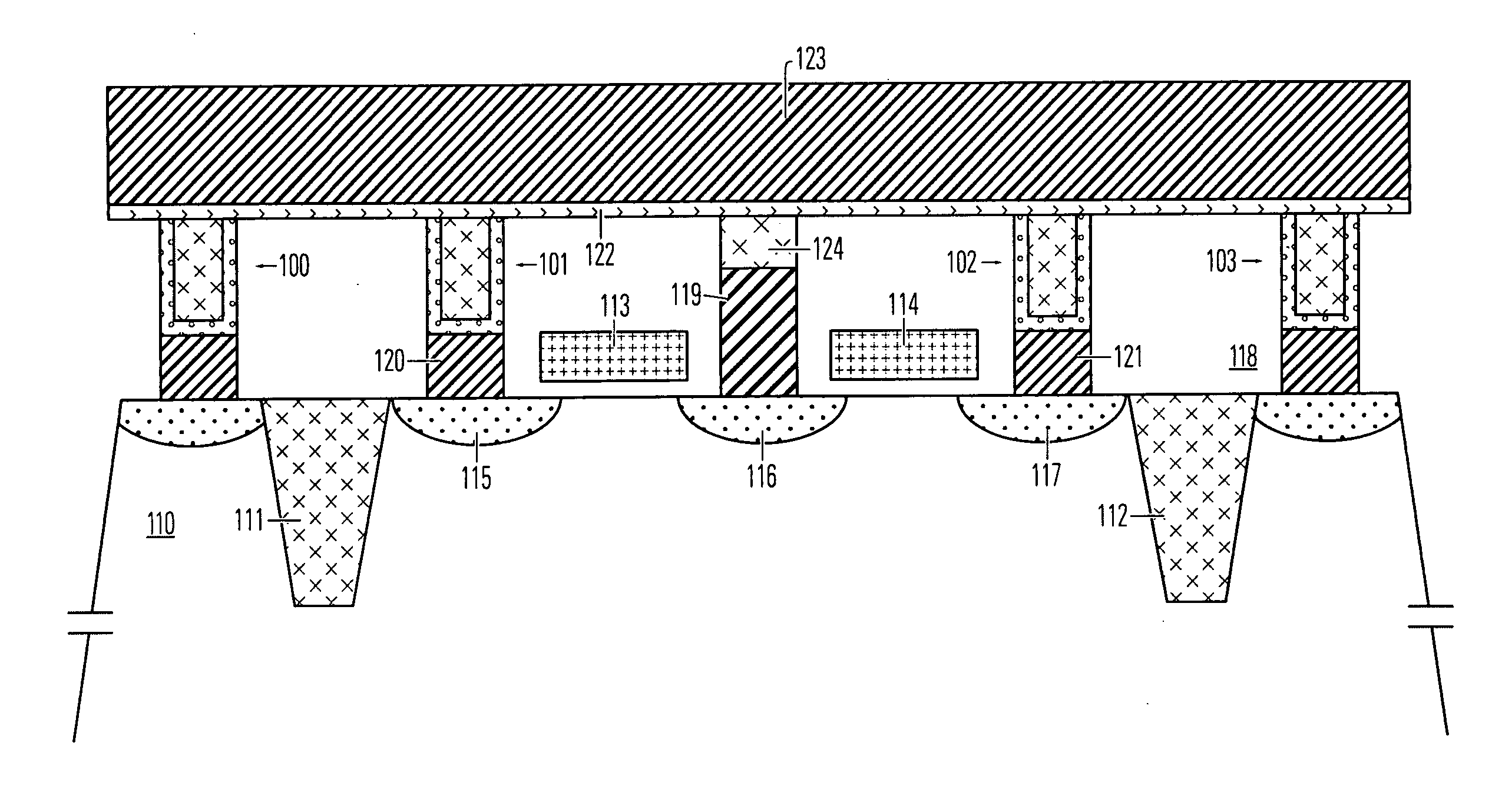

Silicon-based nanoscale resistive device with adjustable resistance

A non-volatile solid state resistive device that includes a first electrode, a p-type poly-silicon second electrode, and a non-crystalline silicon nanostructure electrically connected between the electrodes. The nanostructure has a resistance that is adjustable in response to a voltage being applied to the nanostructure via the electrodes. The nanostructure can be formed as a nanopillar embedded in an insulating layer located between the electrodes. The first electrode can be a silver or other electrically conductive metal electrode. A third (metal) electrode can be connected to the p-type poly-silicon second electrode at a location adjacent the nanostructure to permit connection of the two metal electrodes to other circuitry. The resistive device can be used as a unit memory cell of a digital non-volatile memory device to store one or more bits of digital data by varying its resistance between two or more values.

Owner:RGT UNIV OF MICHIGAN

I-shaped phase change memory cell

A memory device includes two electrodes, vertically separated and having mutually opposed contact surfaces, between which lies a phase change cell. The phase change cell includes an upper phase change member, having a contact surface in electrical contact with the first electrode; a lower phase change member, having a contact surface in electrical contact with the second electrode; and a kernel member disposed between and in electrical contact with the upper and lower phase change members. The phase change cell is formed of material having at least two solid phases, and the lateral extent of the upper and lower phase change members is substantially greater than that of the kernel member. An intermediate insulating layer is disposed between the upper and lower phase change members adjacent to the kernel member.

Owner:MACRONIX INT CO LTD

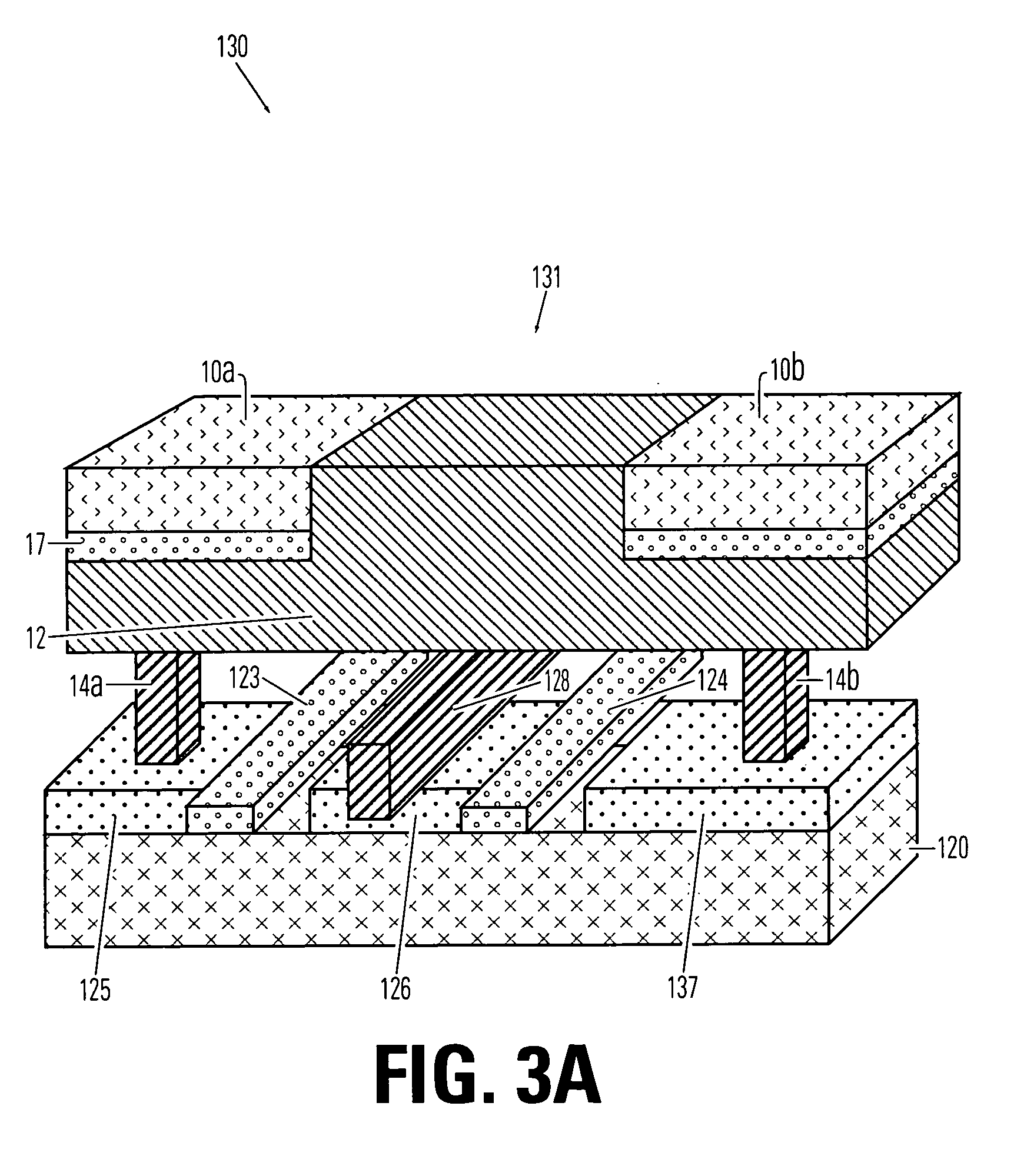

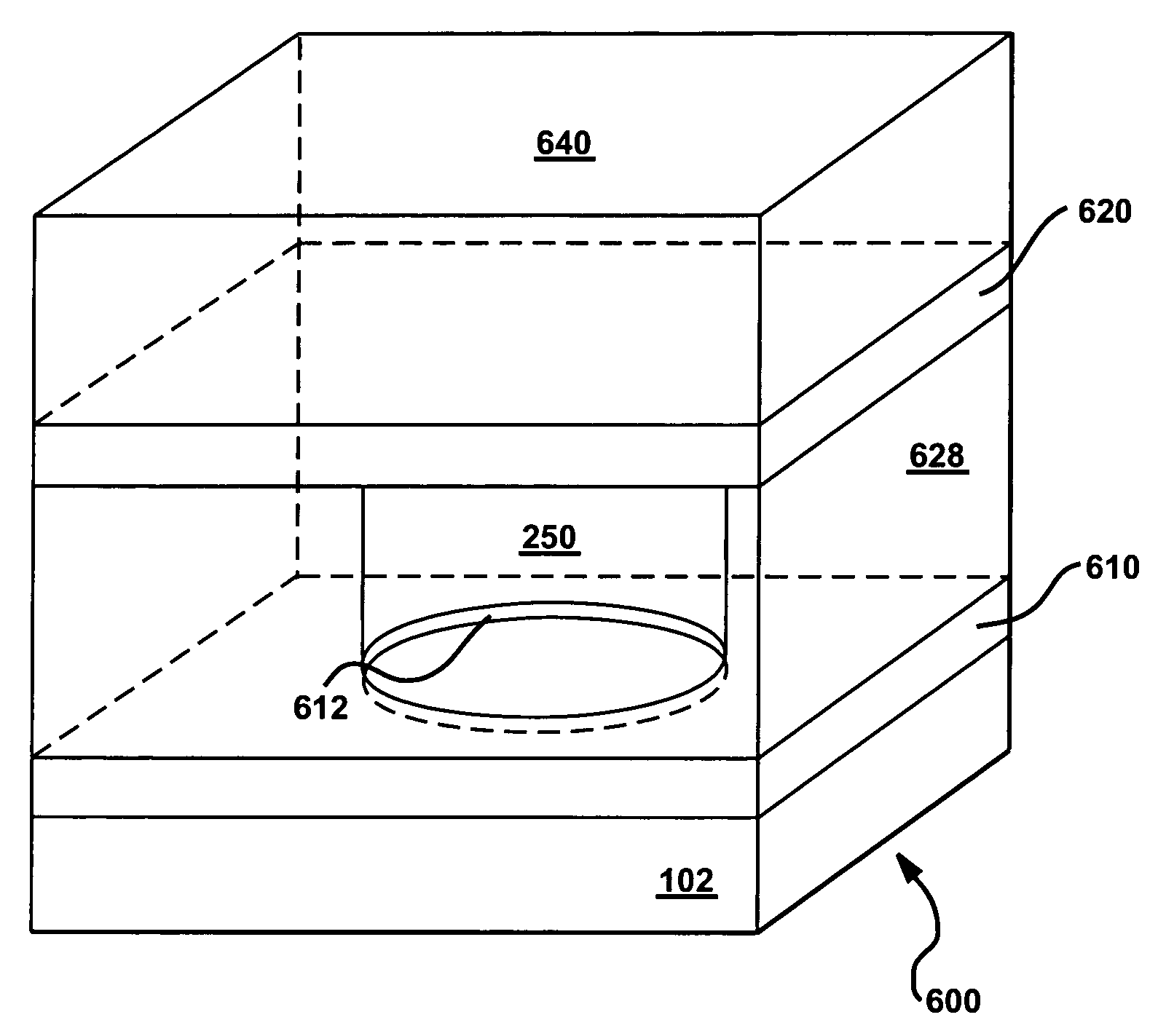

Thermally contained/insulated phase change memory device and method (combined)

ActiveUS20070108430A1Improve heat transfer characteristicsImprove insulation performanceSolid-state devicesBulk negative resistance effect devicesPhase-change memoryDielectric layer

A memory device with improved heat transfer characteristics. The device first includes a dielectric material layer; first and second electrodes, vertically separated and having mutually opposed contact surfaces. A phase change memory element is encased within the dielectric material layer, including a phase-change layer positioned between and in electrical contact with the electrodes, wherein the lateral extent of the phase change layer is less than the lateral extent of the electrodes. An isolation material is positioned between the phase change layer and the dielectric layer, wherein the thermal conductivity of the isolation material is lower than the thermal conductivity of the dielectric material.

Owner:MACRONIX INT CO LTD

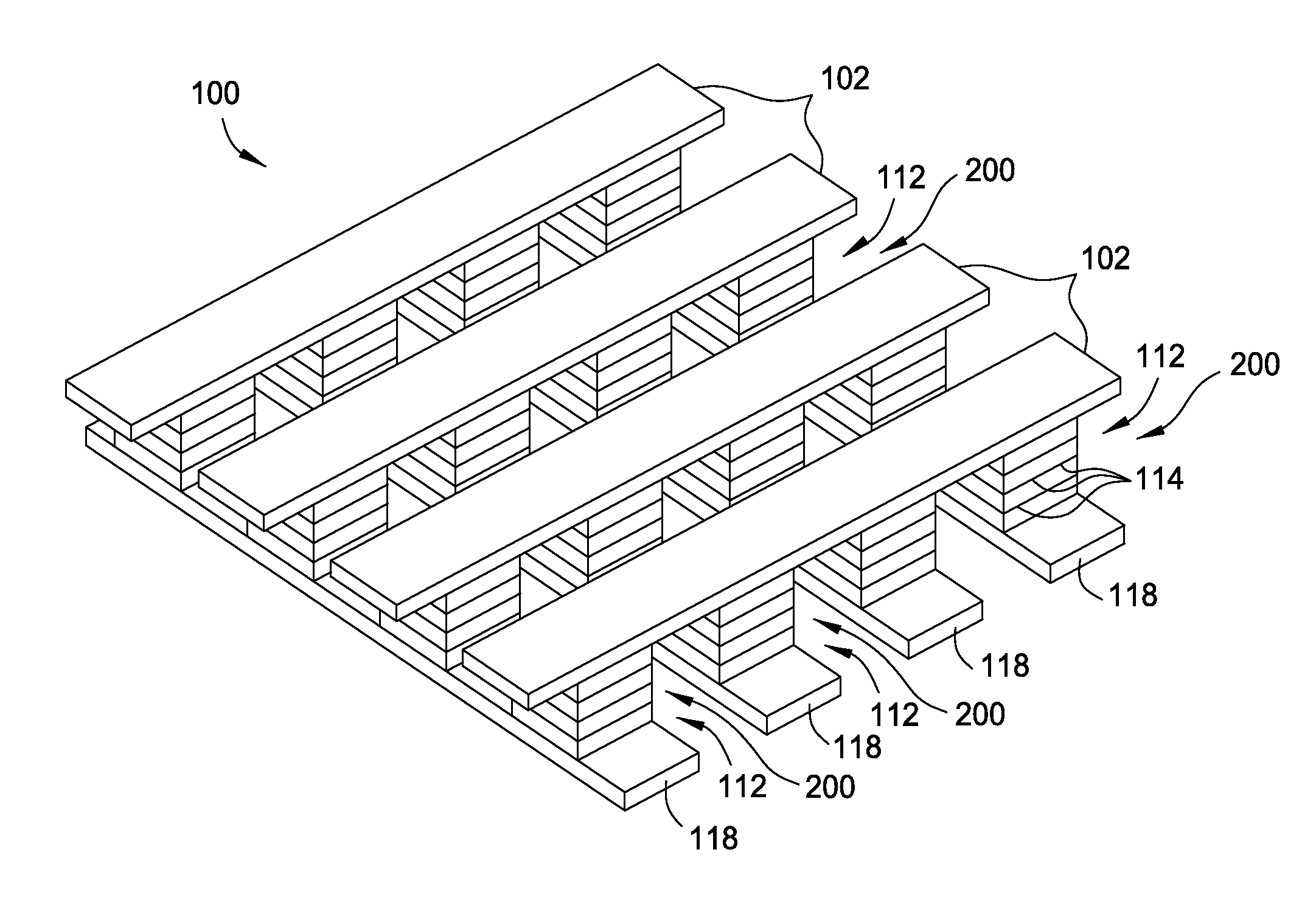

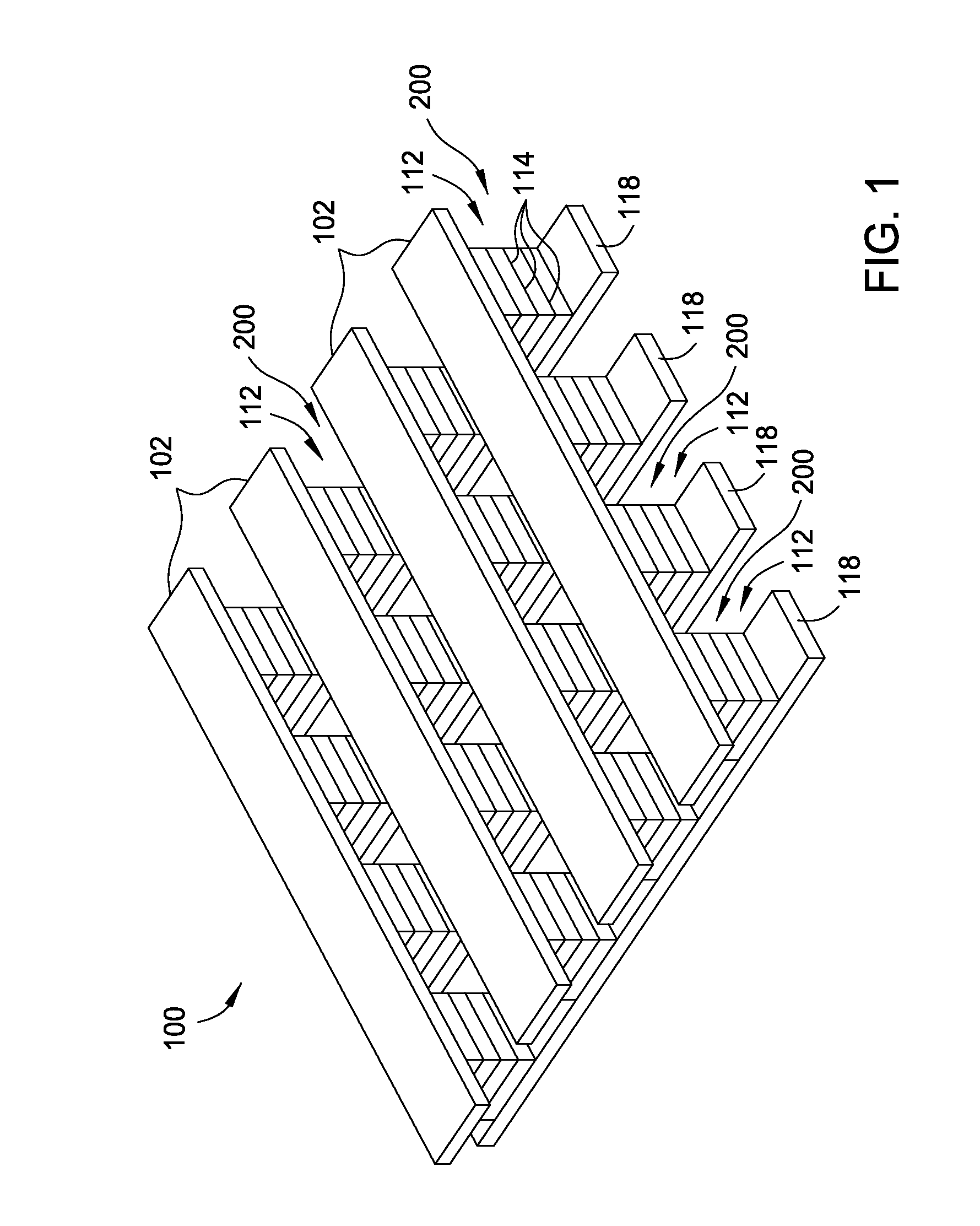

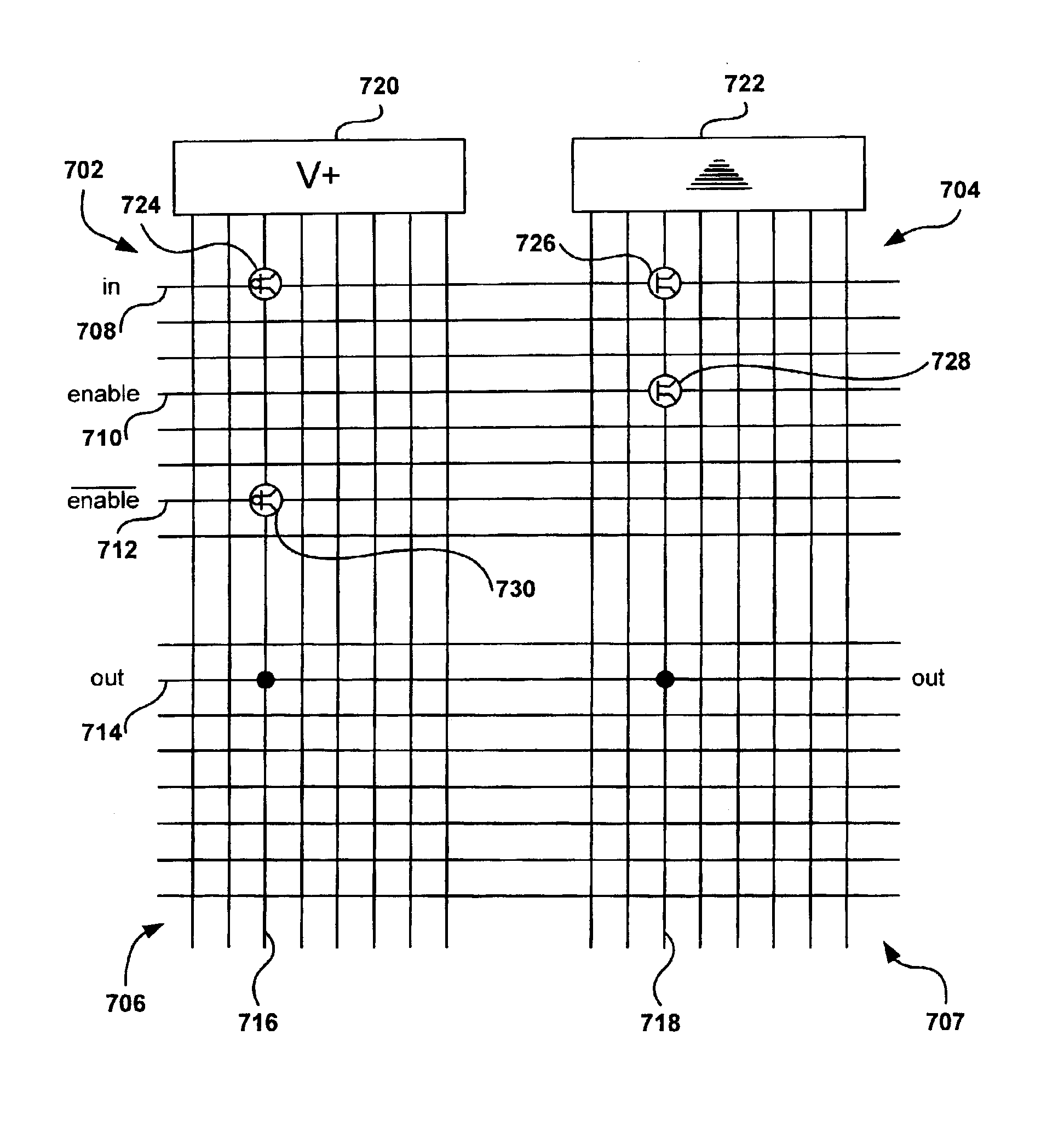

Molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits, and more complex circuits composed, in part, from molecular-junction-nanowire-crossbar-based inverter, latch, and flip-flop circuits

InactiveUS6919740B2High densityLittle powerLogic circuits characterised by logic functionNanoinformaticsCrossbar switchNanowire

Methods for implementing familiar electronic circuits at nanoscale sizes using molecular-junction-nanowire crossbars, and nanoscale electronic circuits produced by the methods. In one embodiment of the present invention, a 3-state inverter is implemented. In a second embodiment of the present invention, two 3-state inverter circuits are combined to produce a transparent latch. The 3-state inverter circuit and transparent-latch circuit can then be used as a basis for constructing additional circuitry, including master / slave flip-flops, a transparent latch with asynchronous preset, a transparent latch with asynchronous clear, and a master / slave flip-flop with asynchronous preset. 3-state inverters can thus be used to compose latches and flip-flops, and latches and flip-flops can be used, along with additional Boolean circuitry, to compose a wide variety of useful, state-maintaining circuits, all implementable within molecular-junction-nanowire crossbars by selectively configuring junctions within the molecular-junction-nanowire crossbars.

Owner:HEWLETT PACKARD DEV CO LP

Electrically programmable memory element with improved contacts

Owner:OVONYX MEMORY TECH LLC

PCRAM memory cell and method of making same

InactiveUS20020168852A1Semiconductor/solid-state device manufacturingBulk negative resistance effect devicesConductive materialsCopper

An inverted PCRAM cell is formed by plating the bottom electrode, made of copper for example, with a conductive material, such as silver. Chalcogenide material is disposed over the plated electrode and subjected to a conversion process so that ions from the plated material diffuse into the chalcogenide material.

Owner:OVONYX MEMORY TECH LLC

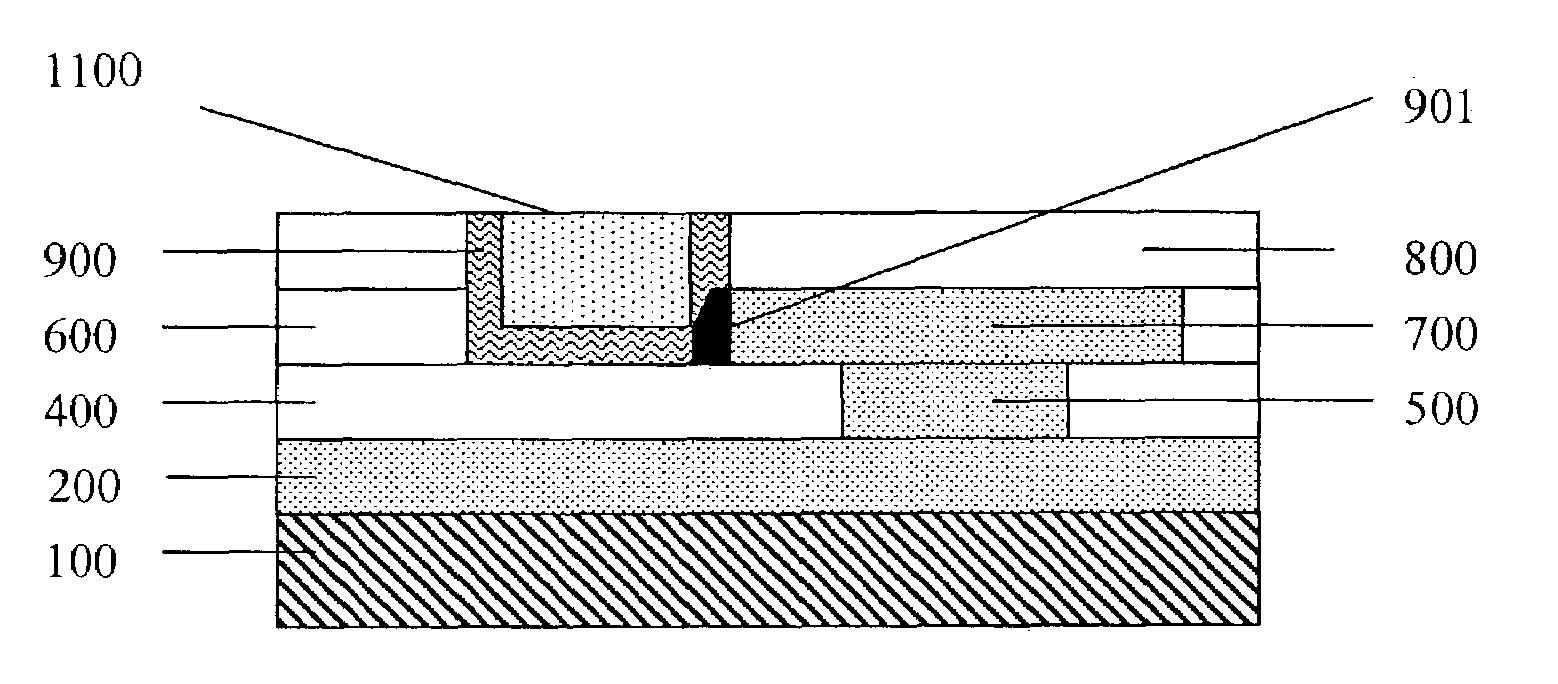

Bottom electrodes for use with metal oxide resistivity switching layers

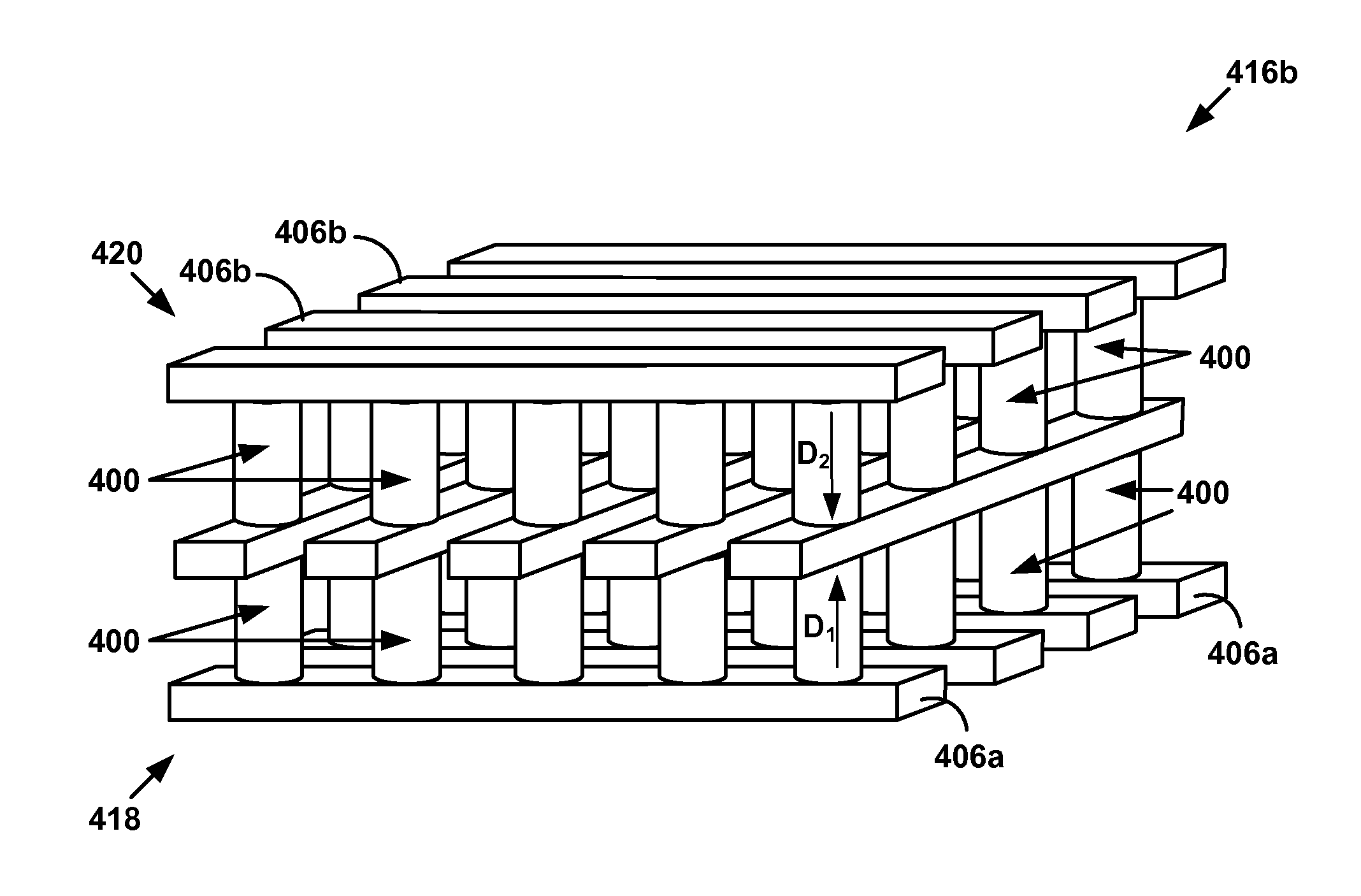

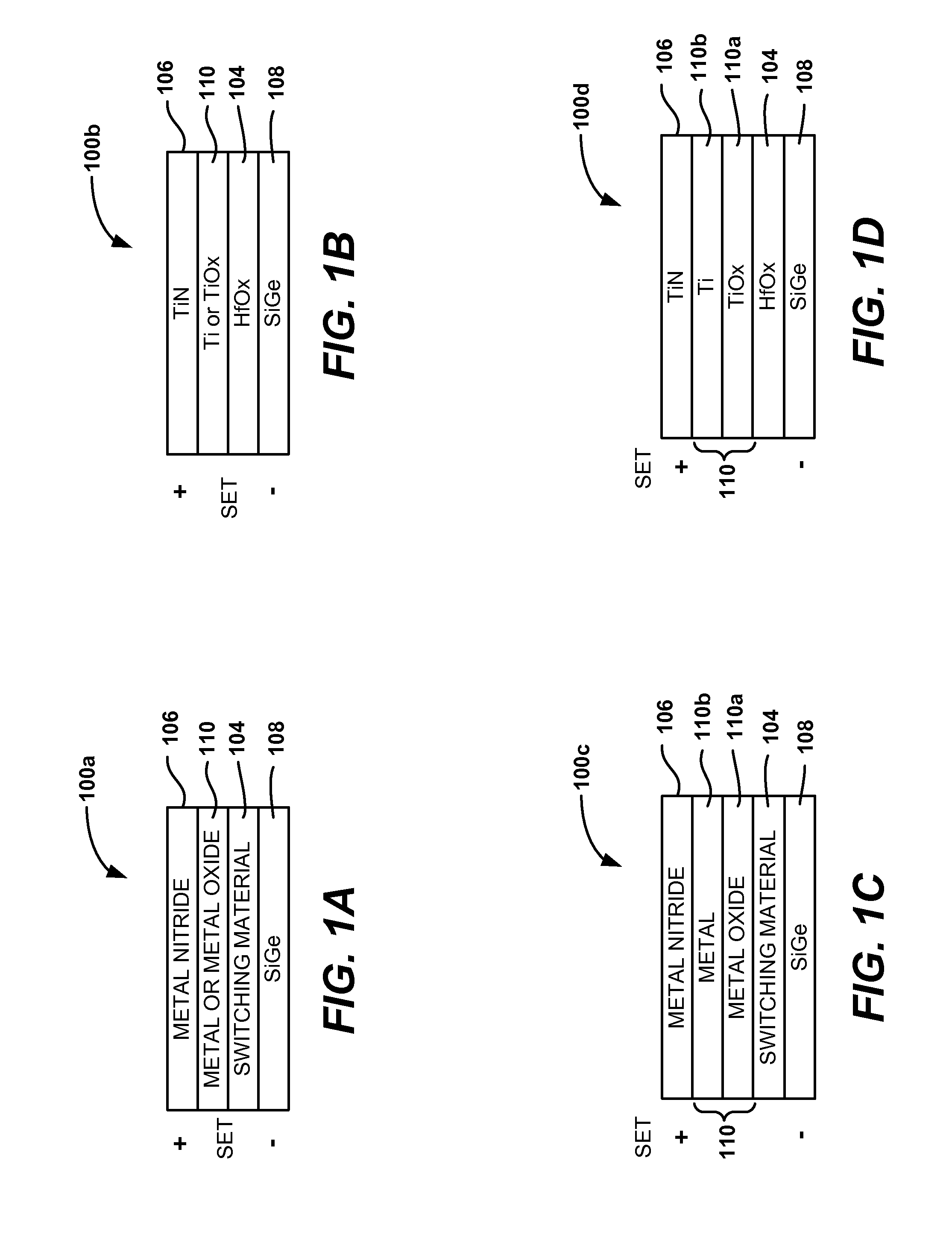

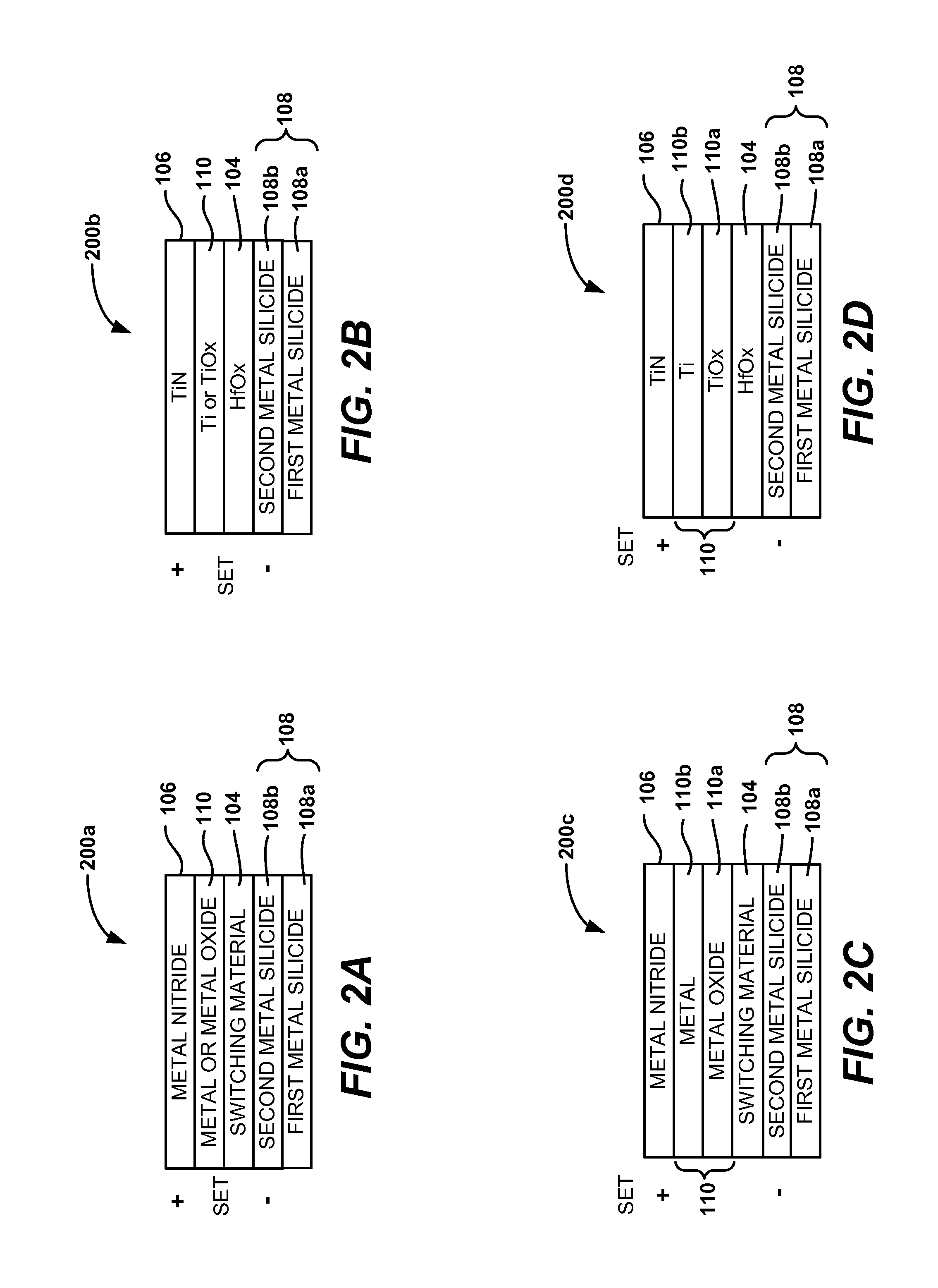

ActiveUS20110227028A1Solid-state devicesSemiconductor/solid-state device manufacturingMetal silicideOptoelectronics

In a first aspect, an MIM stack is provided that includes (1) a first conductive layer comprising a first metal-silicide layer and a second metal-silicide layer; (2) a resistivity-switching layer comprising a metal oxide layer formed above the first conductive layer; and (3) a second conductive layer formed above the resistivity-switching layer. A memory cell may be formed from the MIM stack. Numerous other aspects are provided.

Owner:SANDISK TECH LLC

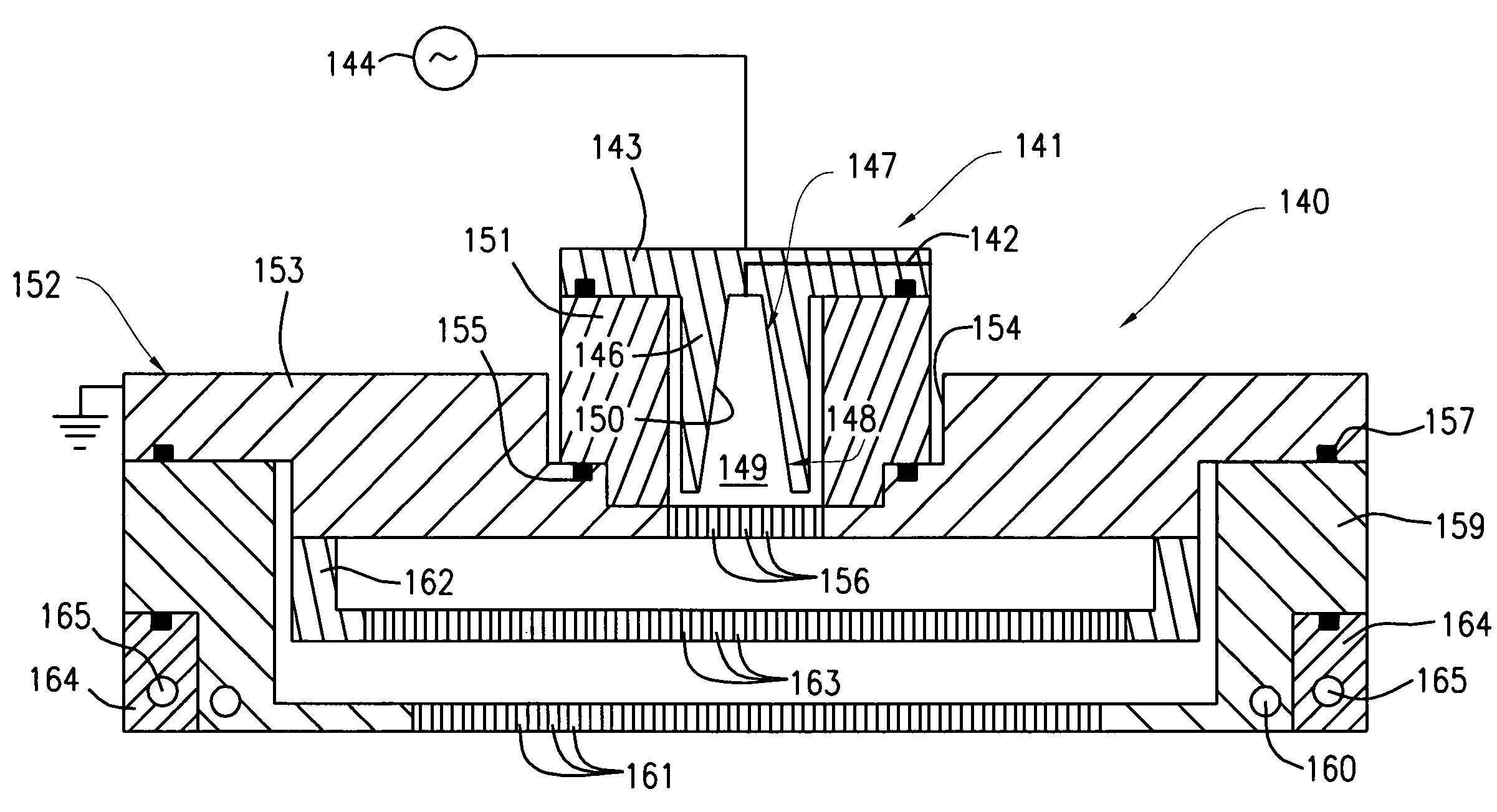

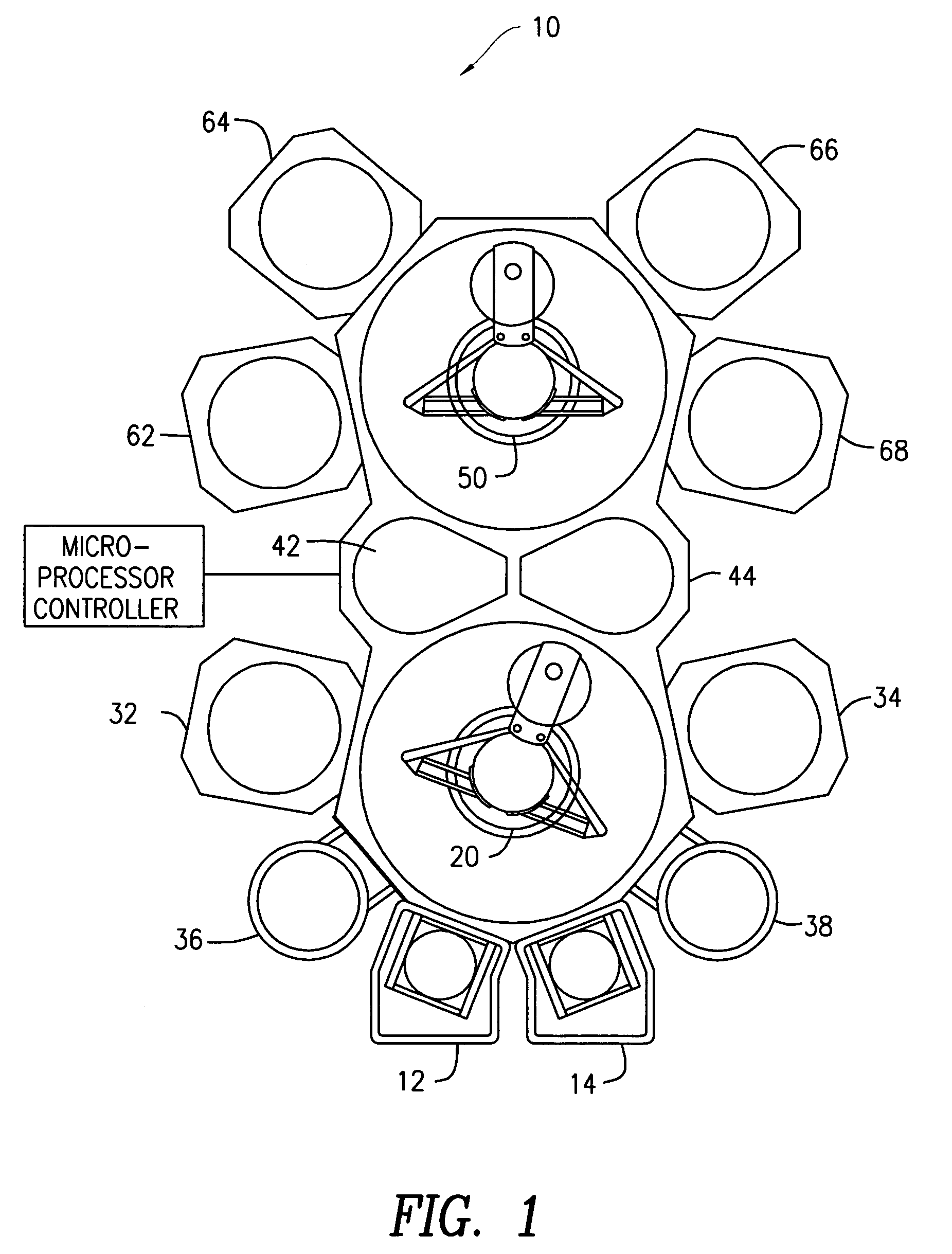

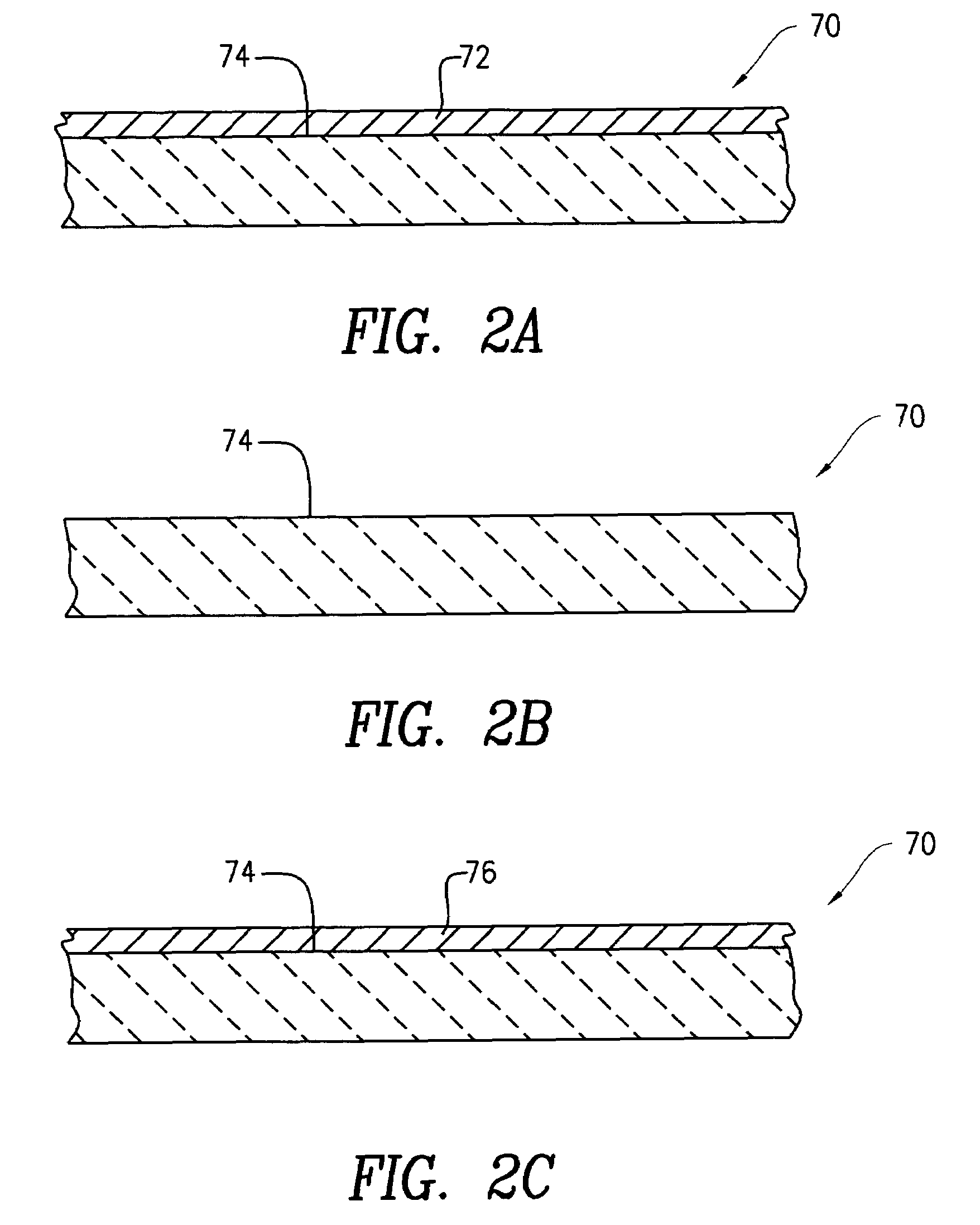

Epitaxial deposition process and apparatus

InactiveUS7494545B2Polycrystalline material growthSemiconductor/solid-state device manufacturingReactive gasDeposition process

An epitaxial deposition process including a dry etch process, followed by an epitaxial deposition process is disclosed. The dry etch process involves placing a substrate to be cleaned into a processing chamber to remove surface oxides. A gas mixture is introduced into a plasma cavity, and the gas mixture is energized to form a plasma of reactive gas in the plasma cavity. The reactive gas enters into the processing chamber and reacts with the substrate, forming a thin film. The substrate is heated to vaporize the thin film and expose an epitaxy surface. The epitaxy surface is substantially free of oxides. Epitaxial deposition is then used to form an epitaxial layer on the epitaxy surface.

Owner:APPLIED MATERIALS INC

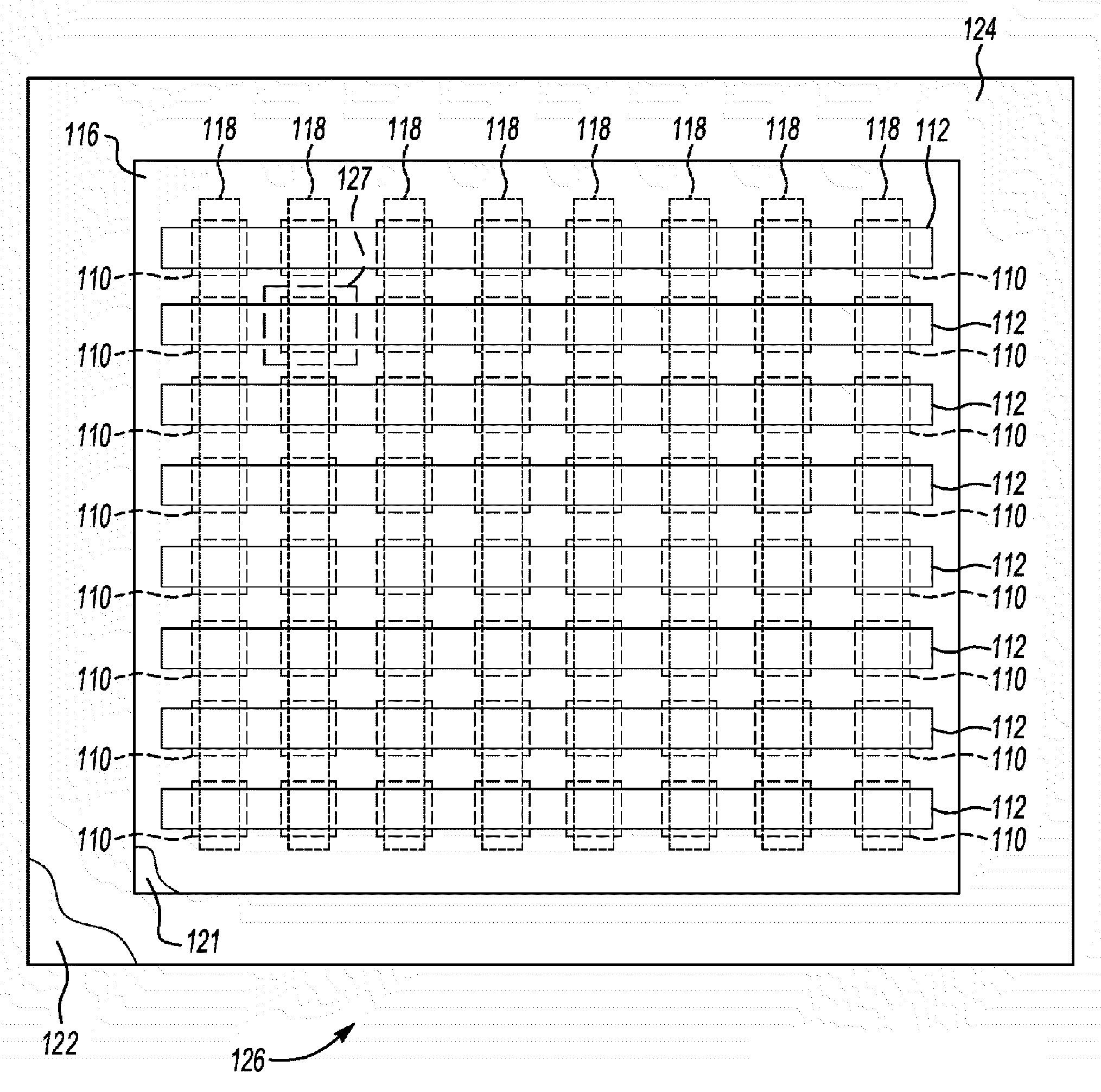

High density chalcogenide memory cells

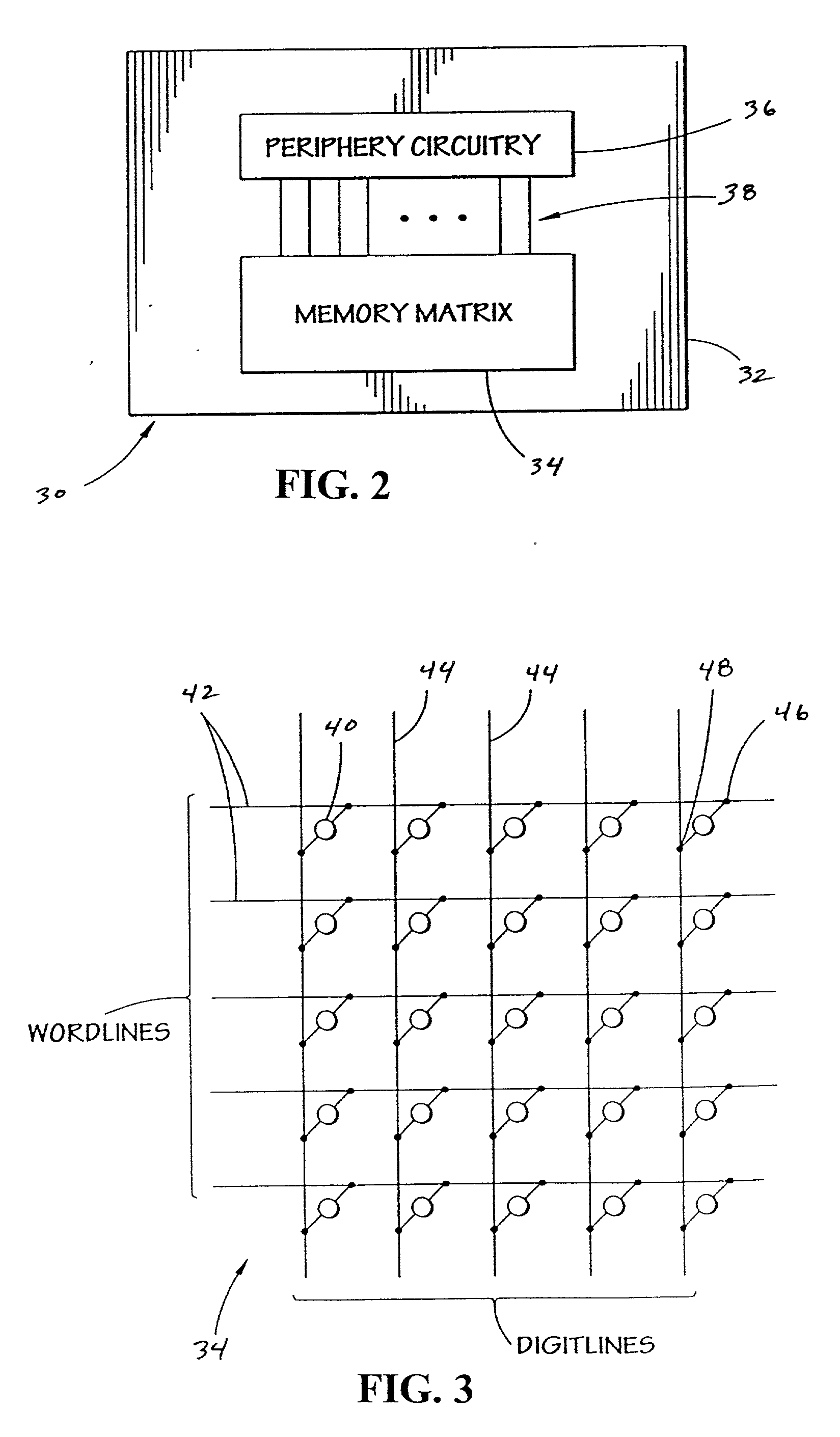

InactiveUS7067865B2Tight and repeatable controlImprove electrical isolationTransistorSolid-state devicesHigh densityAlloy

A non-volatile memory cell is constructed from a chalcogenide alloy structure and an associated electrode side wall. The electrode is manufactured with a predetermined thickness and juxtaposed against a side wall of the chalcogenide alloy structure, wherein at least one of the side walls is substantially perpendicular to a planar surface of the substrate. The thickness of the electrode is used to control the size of the active region created within the chalcogenide alloy structure. Additional memory cells can be created along rows and columns to form a memory matrix. The individual memory cells are accessed through address lines and address circuitry created during the formation of the memory cells. A computer can thus read and write data to particular non-volatile memory cells within the memory matrix.

Owner:MACRONIX INT CO LTD

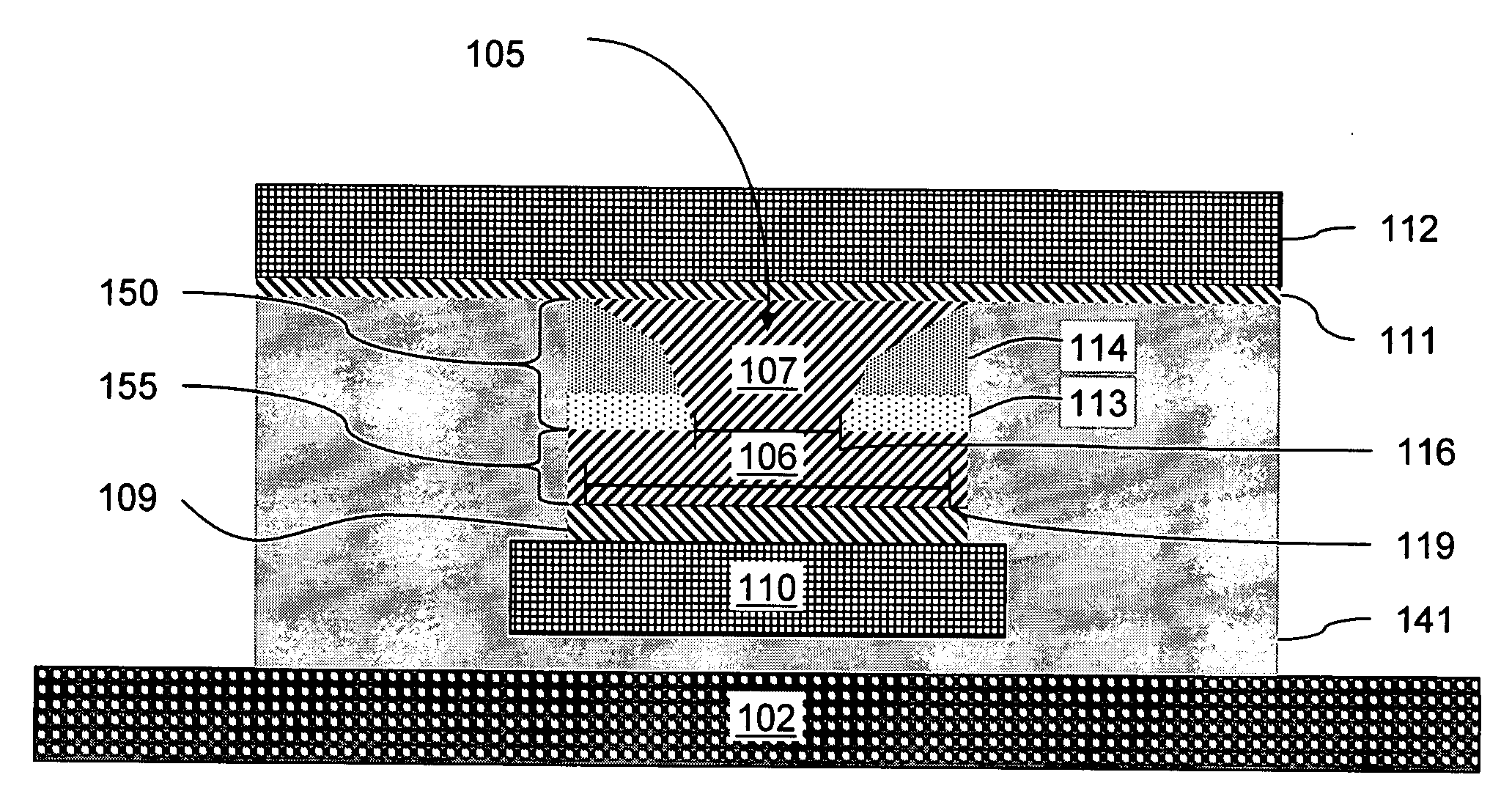

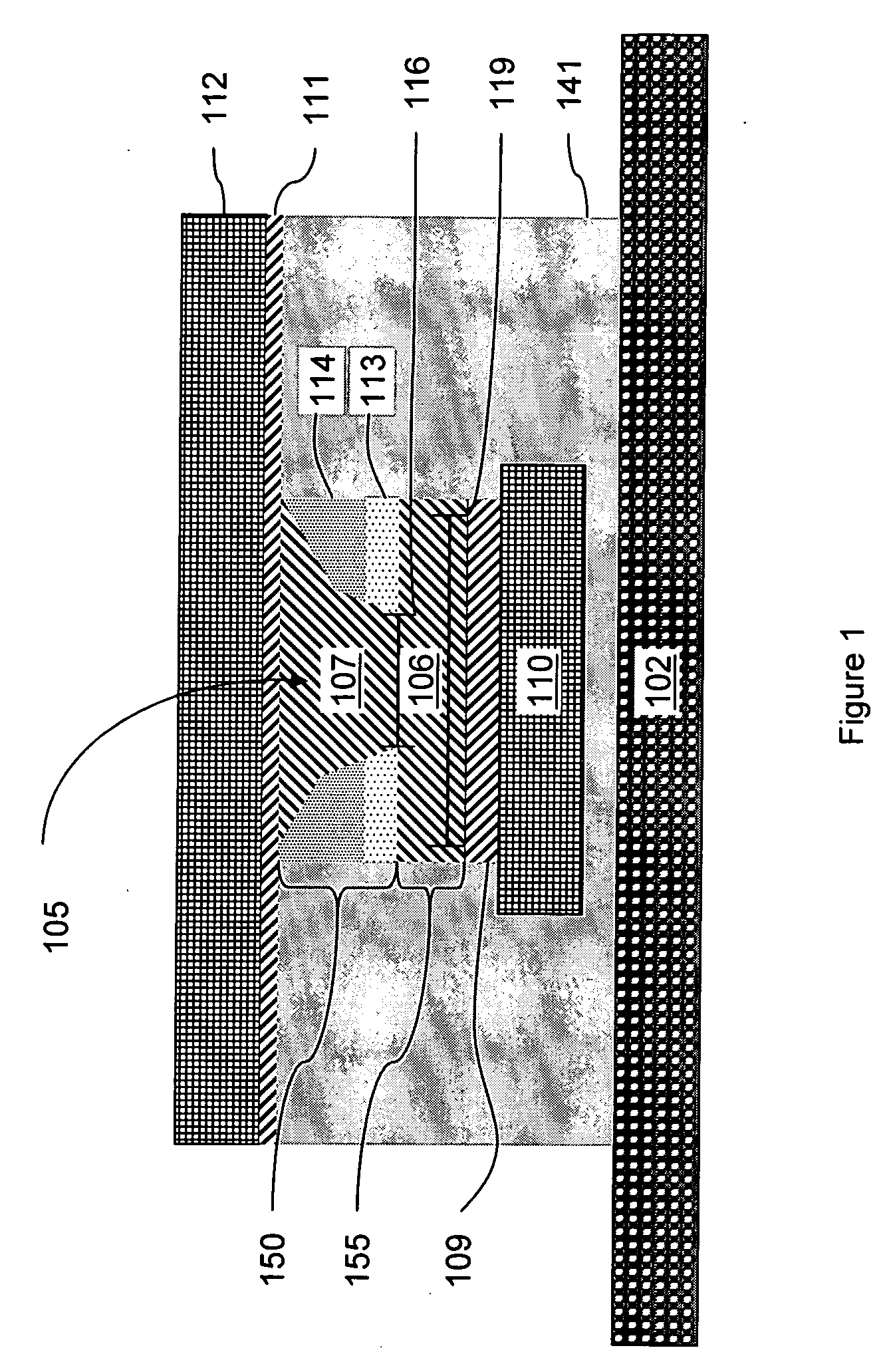

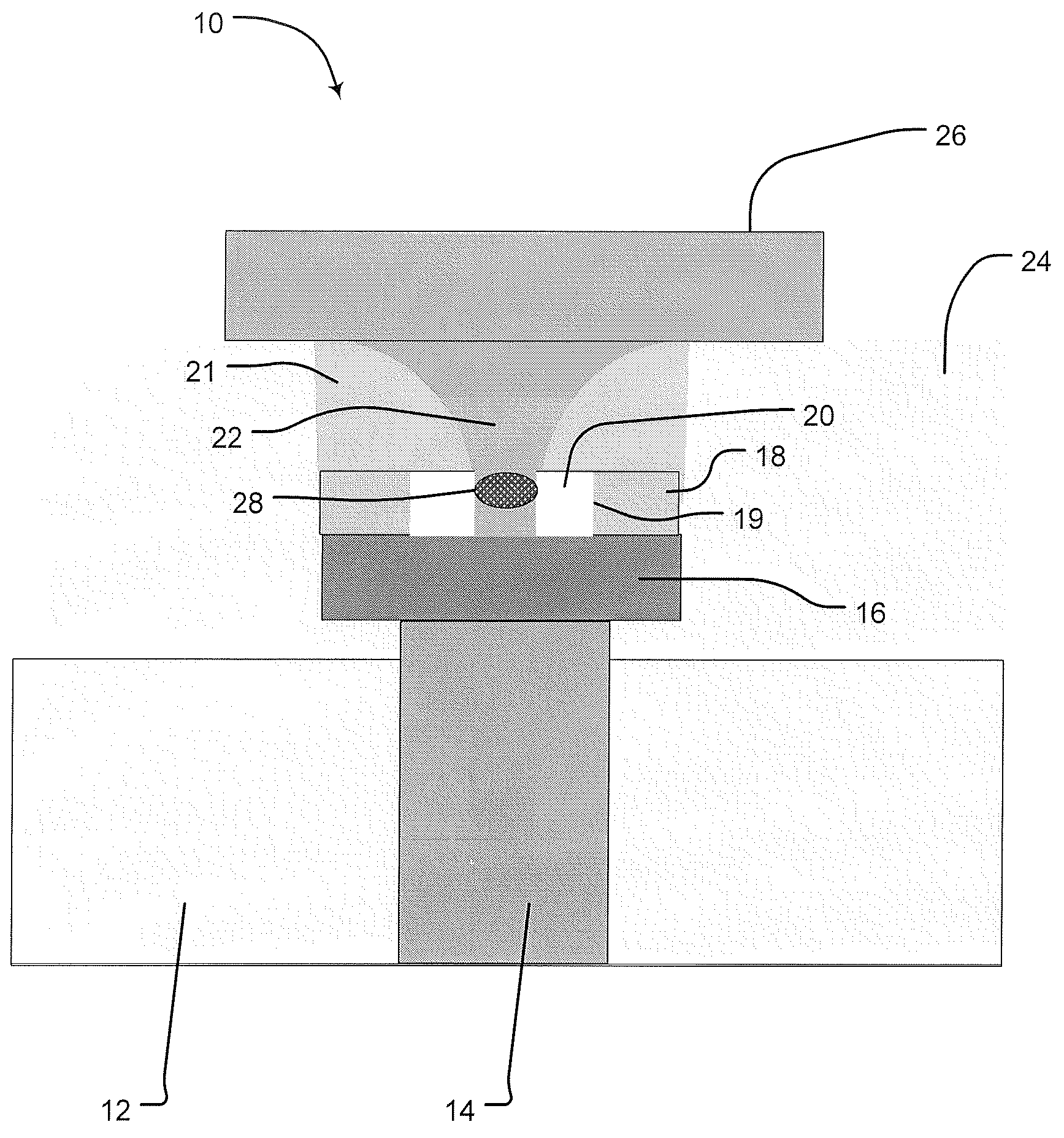

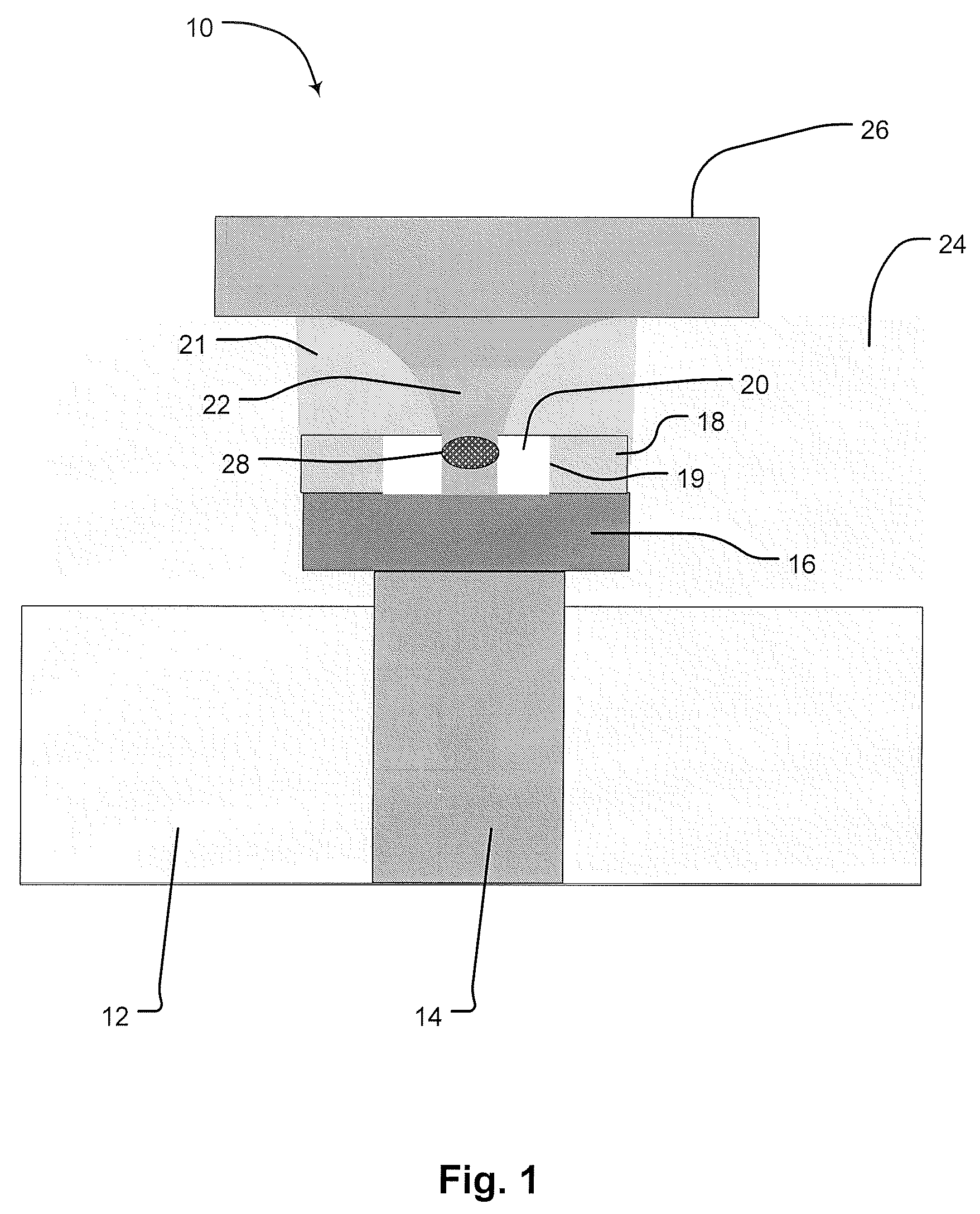

Method for Forming Self-Aligned Thermal Isolation Cell for a Variable Resistance Memory Array

A non-volatile method with a self-aligned RRAM element. The method includes a lower electrode element, generally planar in form, having an inner contact surface. At the top of the device is a upper electrode element, spaced from the lower electrode element. A containment structure extends between the upper electrode element and the lower electrode element, and this element includes a sidewall spacer element having an inner surface defining a generally funnel-shaped central cavity, terminating at a terminal edge to define a central aperture; and a spandrel element positioned between the sidewall spacer element and the lower electrode, having an inner surface defining a thermal isolation cell, the spandrel inner walls being spaced radially outward from the sidewall spacer terminal edge, such that the sidewall spacer terminal edge projects radially inward from the spandrel element inner surface. ARRAM element extends between the lower electrode element and the upper electrode, occupying at least a portion of the sidewall spacer element central cavity and projecting from the sidewall spacer terminal edge toward and making contact with the lower electrode. In this manner, the spandrel element inner surface is spaced from the RRAM element to define a thermal isolation cell adjacent the RRAM element.

Owner:MACRONIX INT CO LTD

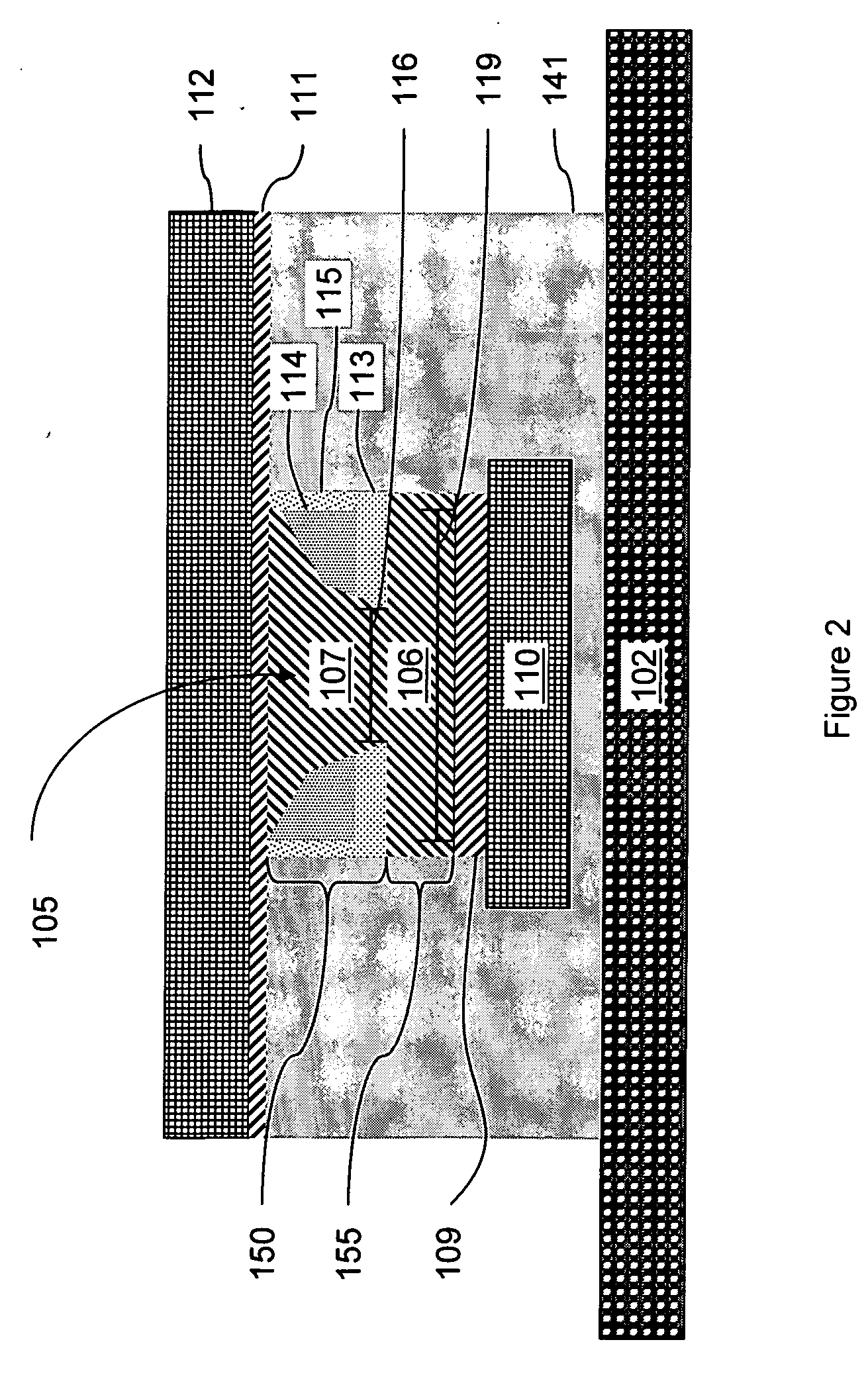

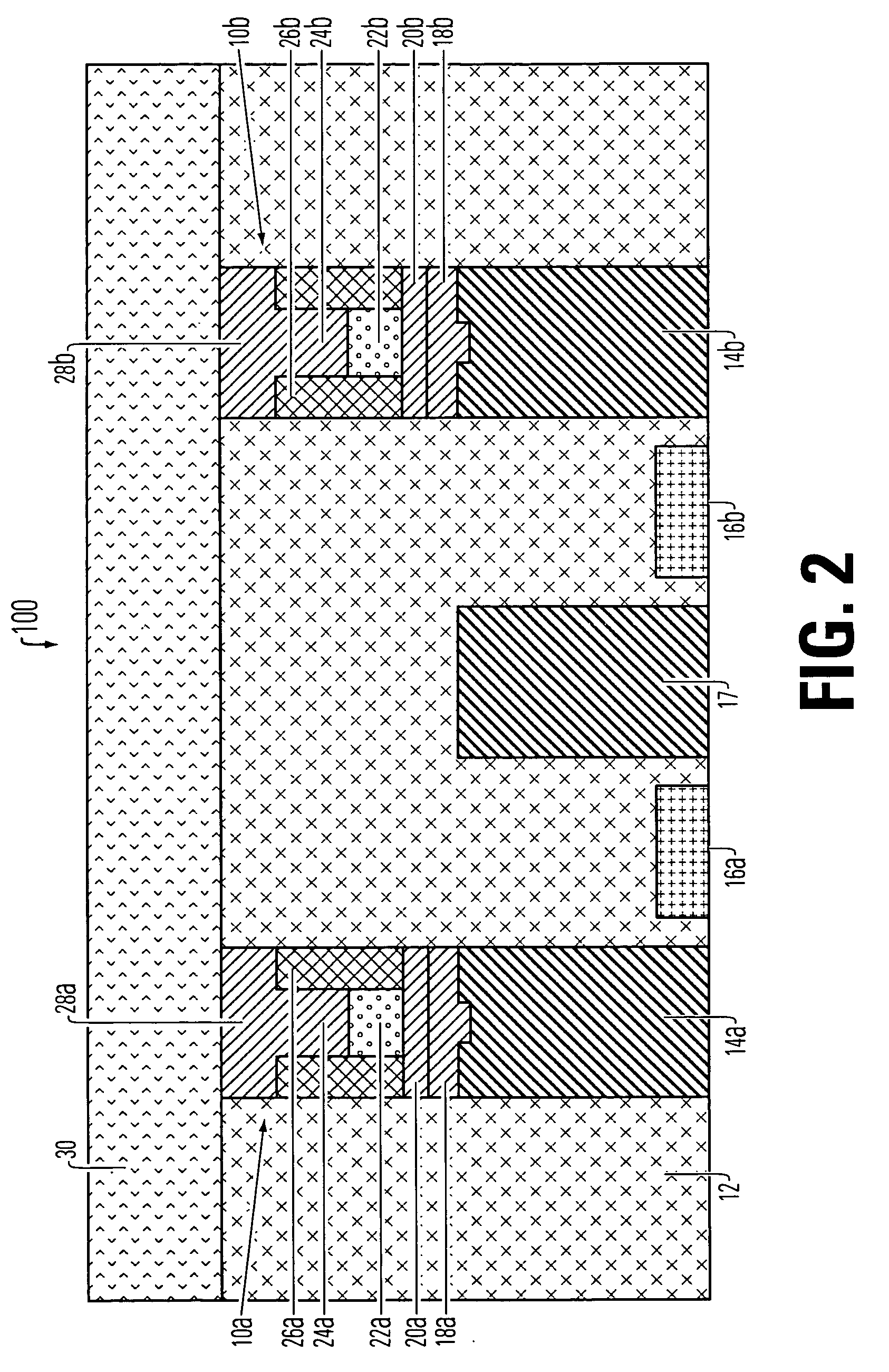

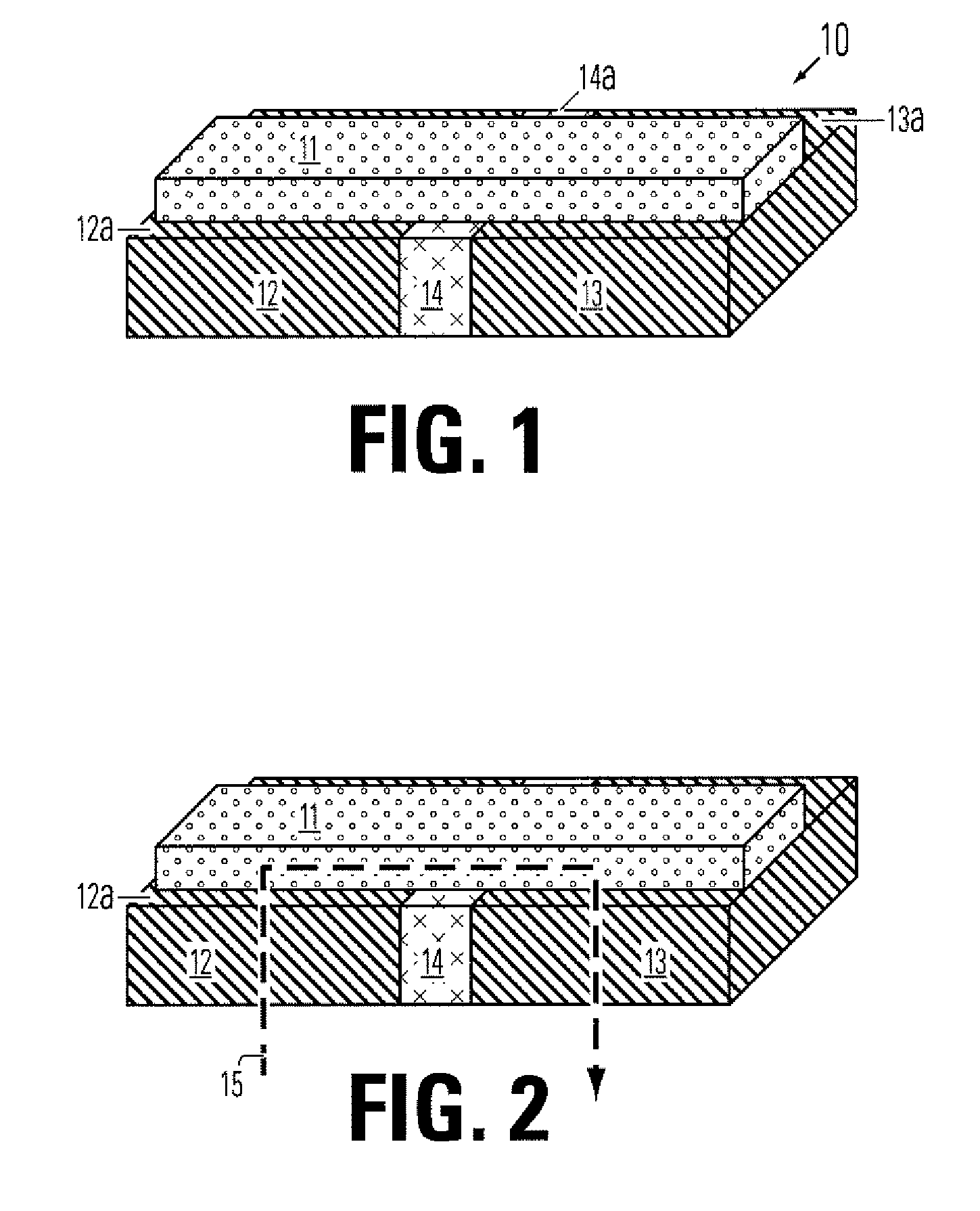

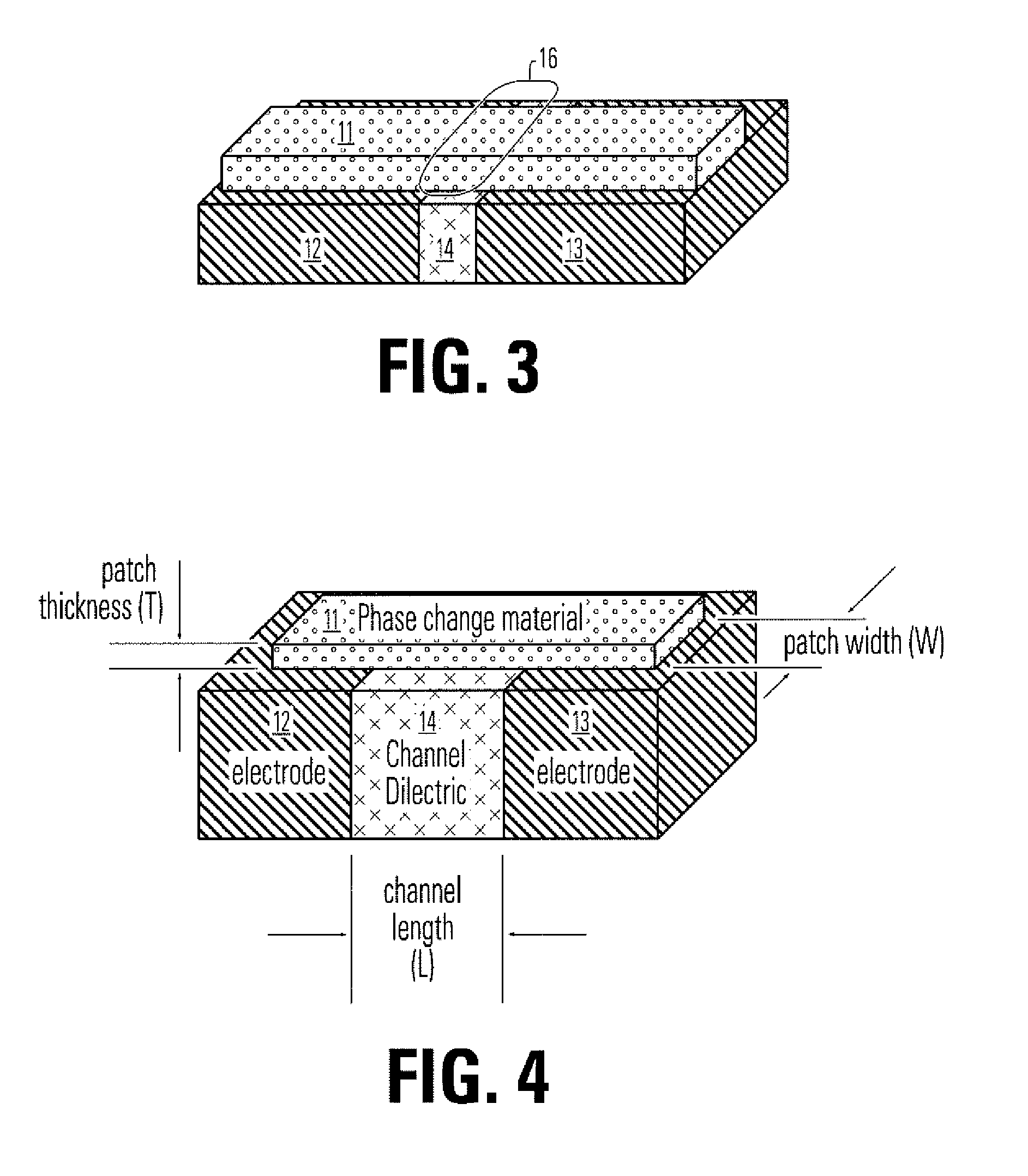

Self-aligned, embedded phase change ram and manufacturing method

ActiveUS20060284158A1Simple structureReduce power consumptionSolid-state devicesDigital storageElectrical conductorEngineering

An integrated circuit with an embedded memory comprises a substrate and a plurality of conductor layers arranged for interconnecting components of the integrated circuit. An intermediate layer in the plurality of conductor layers includes a first electrode having a top surface, a second electrode having a top surface, an insulating member between the first electrode and the second electrode. A bridge overlies the intermediate layer between the first and second electrodes across the insulating member, wherein the bridge comprises a programmable resistive memory material, such as a phase change material. A conductor in at least one layer in the plurality of conductor layers over said intermediate layer is connected to said bridge.

Owner:MACRONIX INT CO LTD

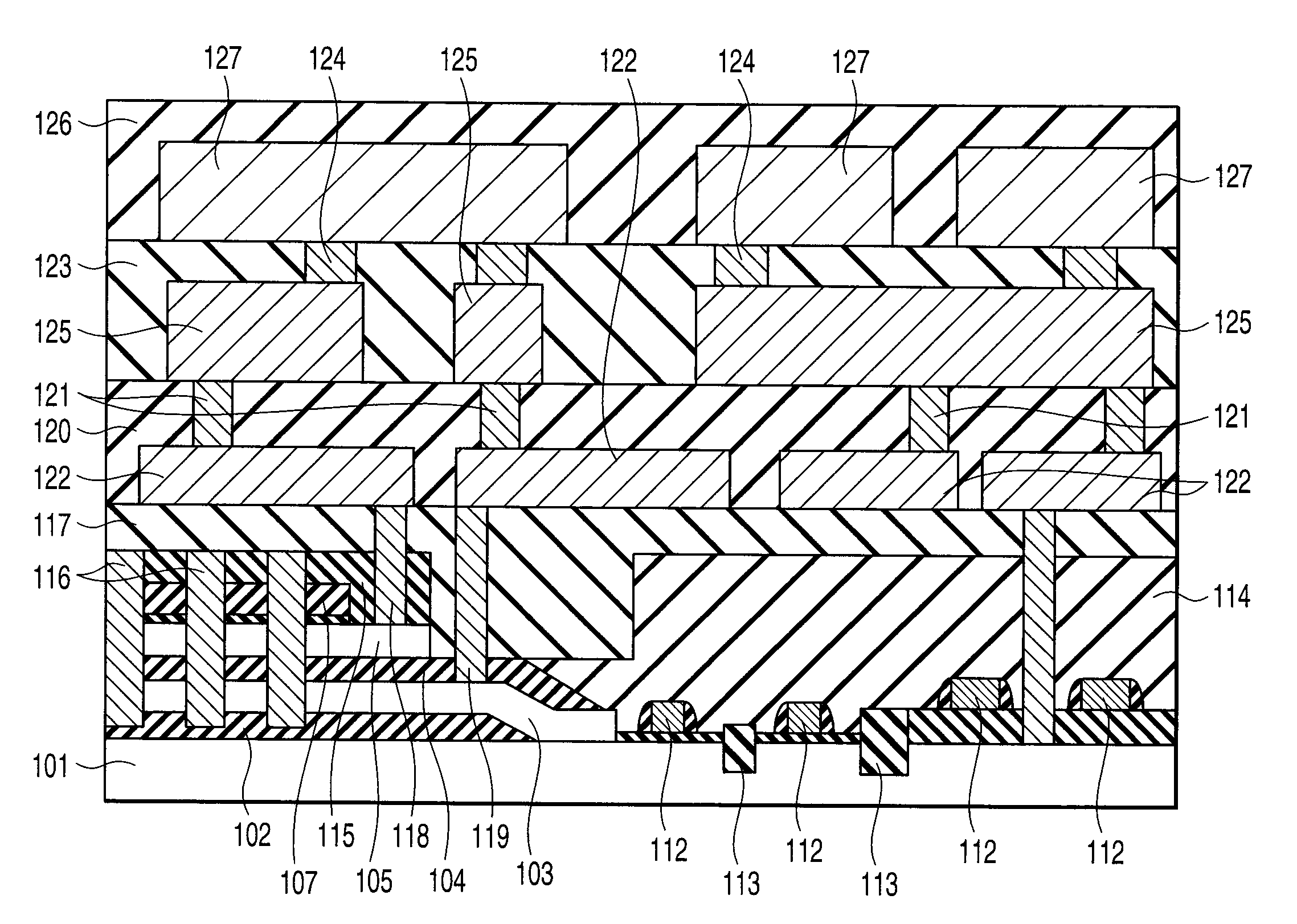

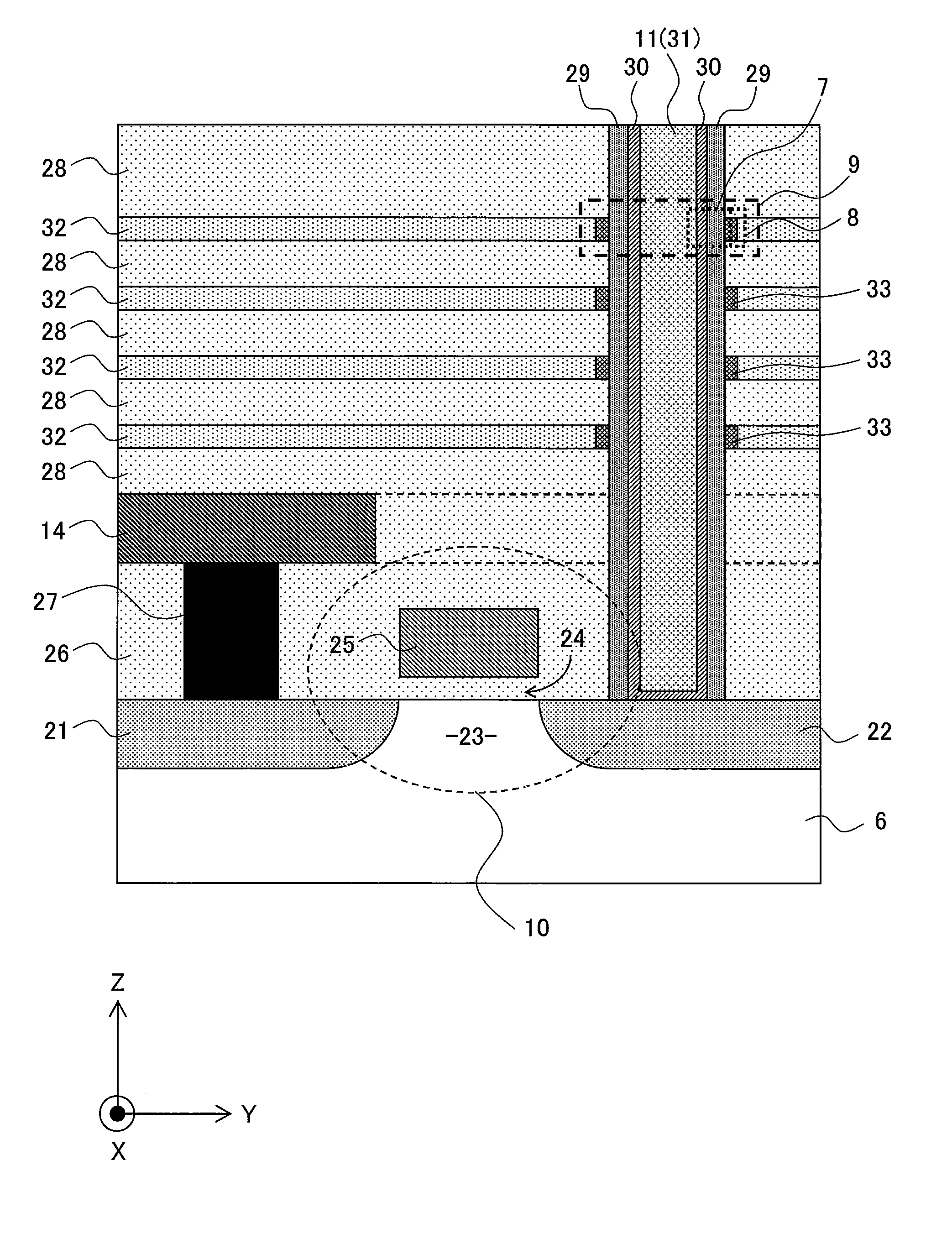

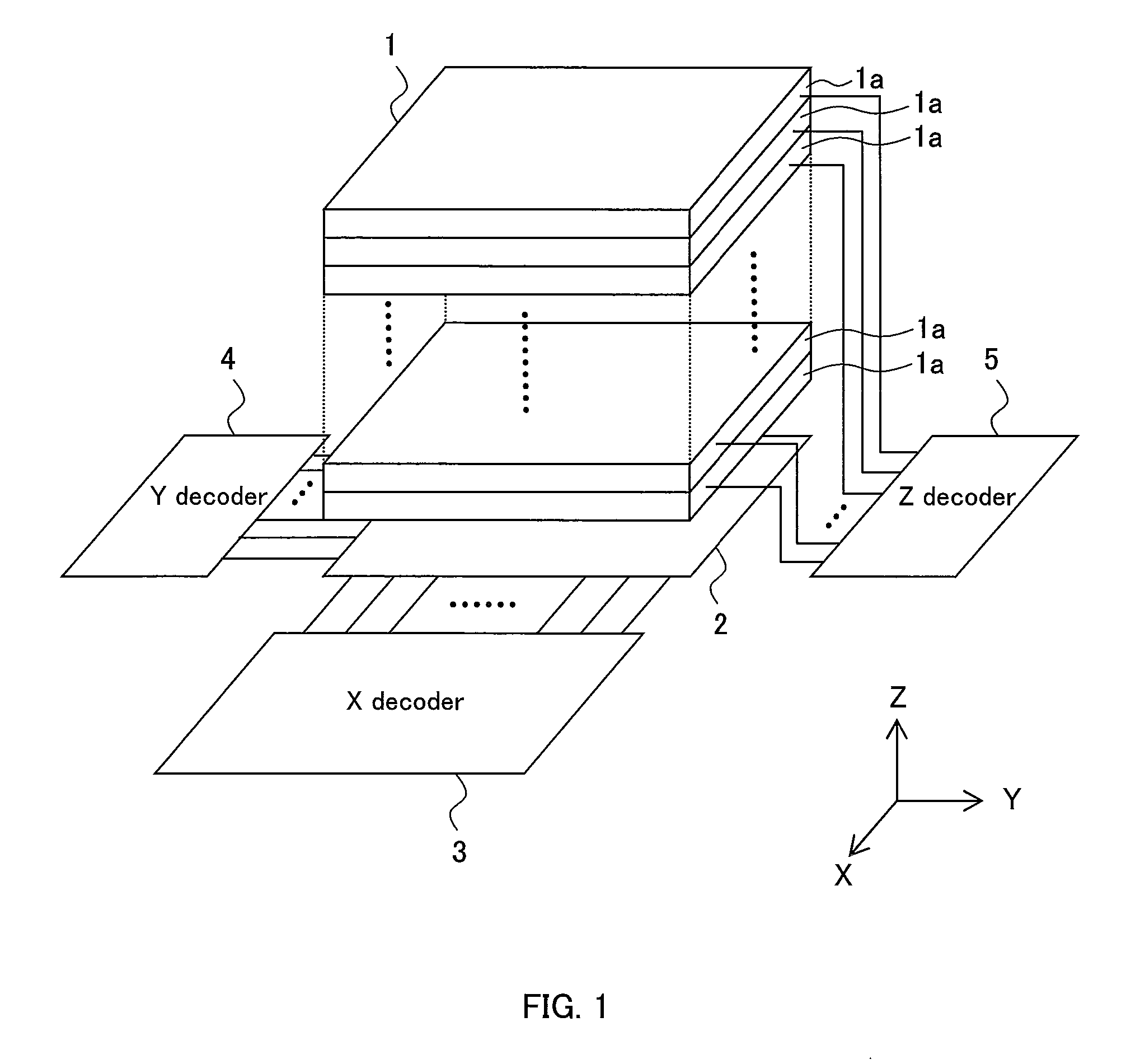

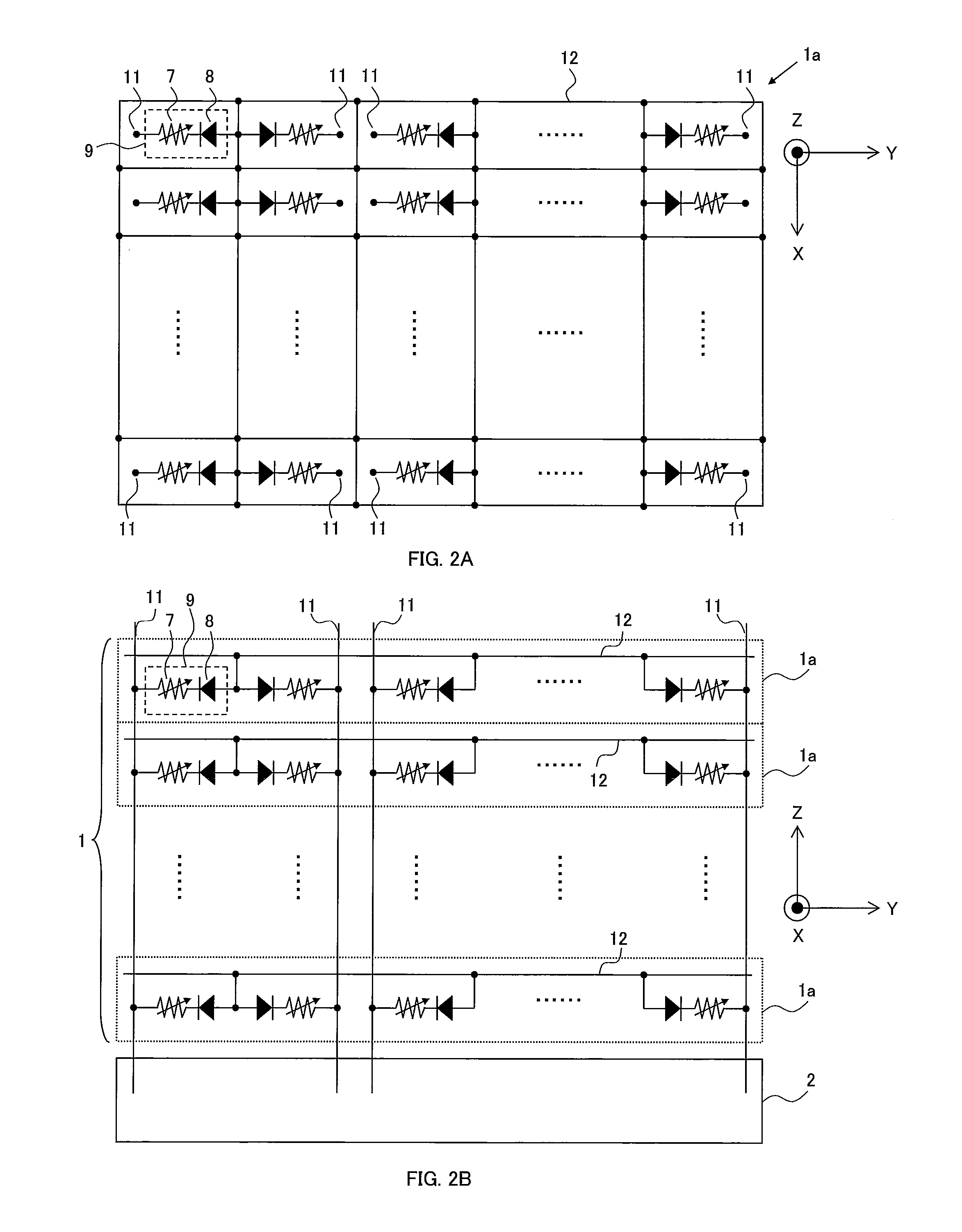

Nonvolatile semiconductor memory device and manufacturing method for same

InactiveUS20100219392A1Large capacityLow costSolid-state devicesSemiconductor/solid-state device manufacturingStorage cellTransistor

A three-dimensional memory cell array of memory cells with two terminals having a variable resistive element is formed such that: one ends of memory cells adjacent in Z direction are connected to one of middle selection lines extending in Z direction aligned in X and Y directions; the other ends of the memory cells located at the same point in Z direction are connected to one of third selection lines aligned in Z direction; a two-dimensional array where selection transistors are aligned in X and Y directions is adjacent to the memory cell array in Z direction; gates of selection transistors adjacent in X direction, drains of selection transistors adjacent in Y direction and sources of selection transistors are connected to same first selection line, second selection line, and different middle selection lines, respectively; and first, second and third selection lines are connected to X, Y and Z decoders, respectively.

Owner:SHARP KK

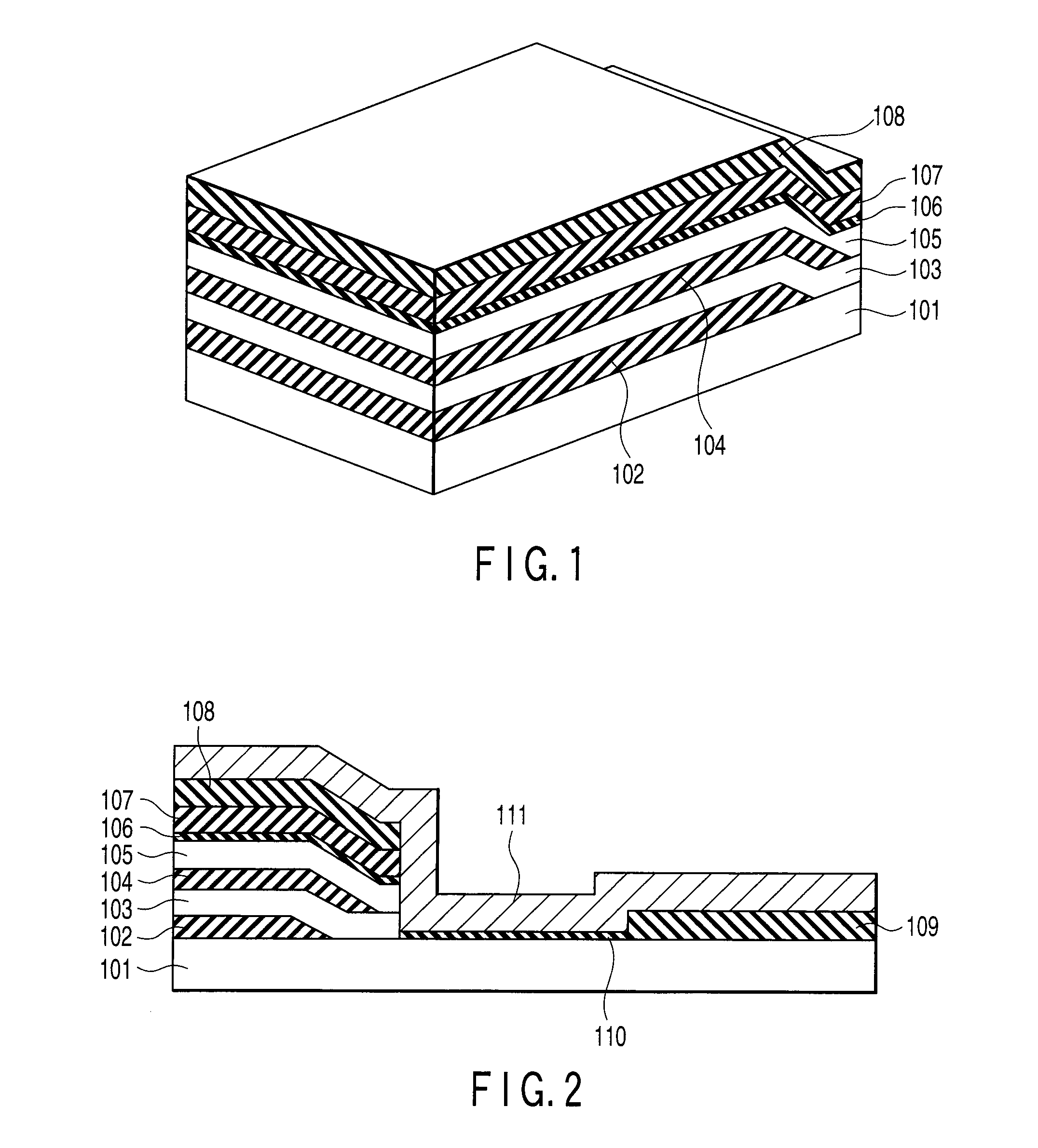

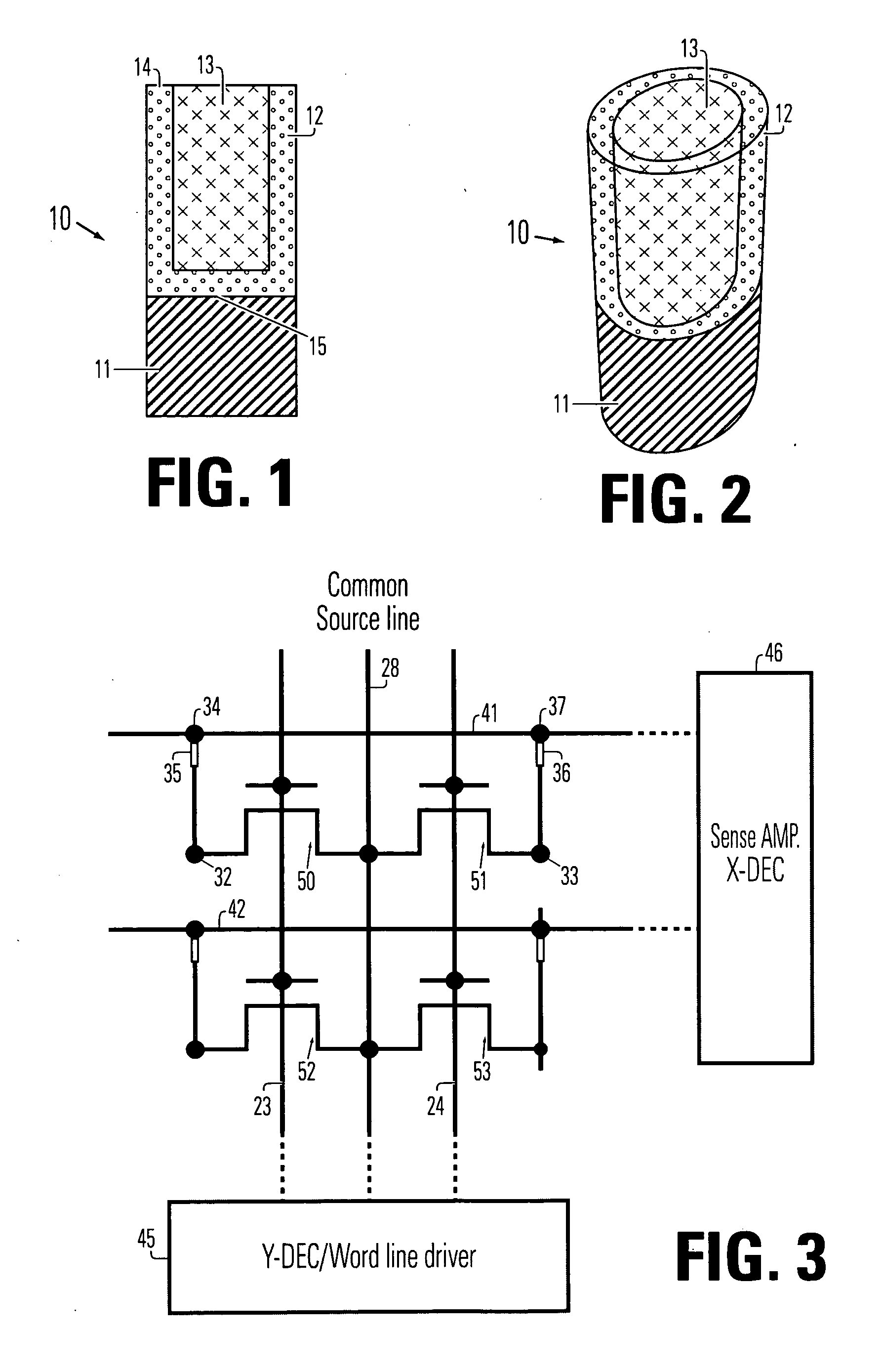

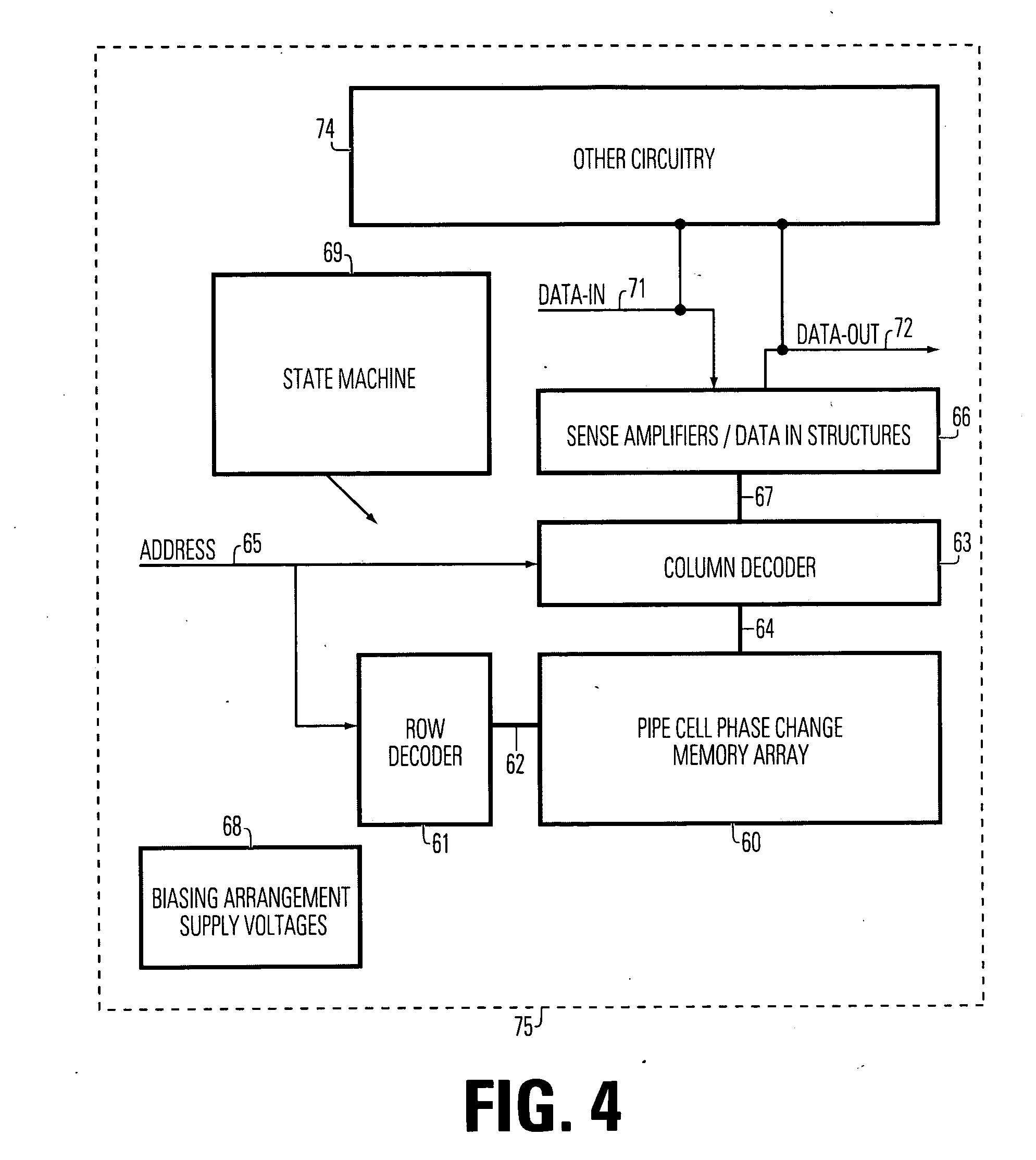

Pipe shaped phase change memory

ActiveUS20070108429A1High resistivityLow thermal conductivitySolid-state devicesBulk negative resistance effect devicesPhase-change memoryEngineering

A memory cell device includes a bottom electrode, pipe shaped member comprising phase change material and a top electrode in contact with the pipe-shaped member. An electrically and thermally insulating material is inside the pipe-shaped member. An integrated circuit including an array of pipe-shaped phase change memory cells is described.

Owner:MACRONIX INT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com