Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

320 results about "Doped oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

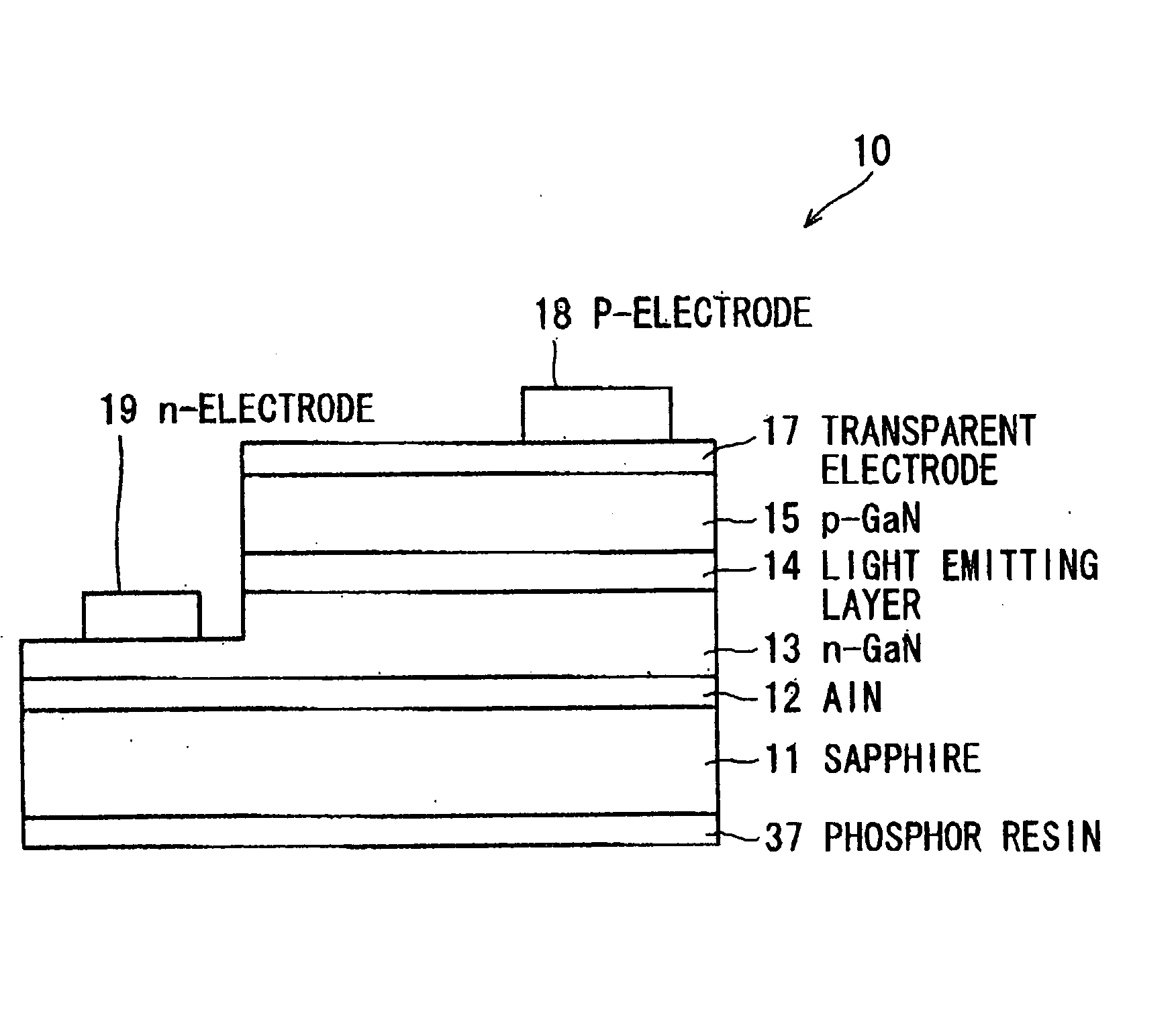

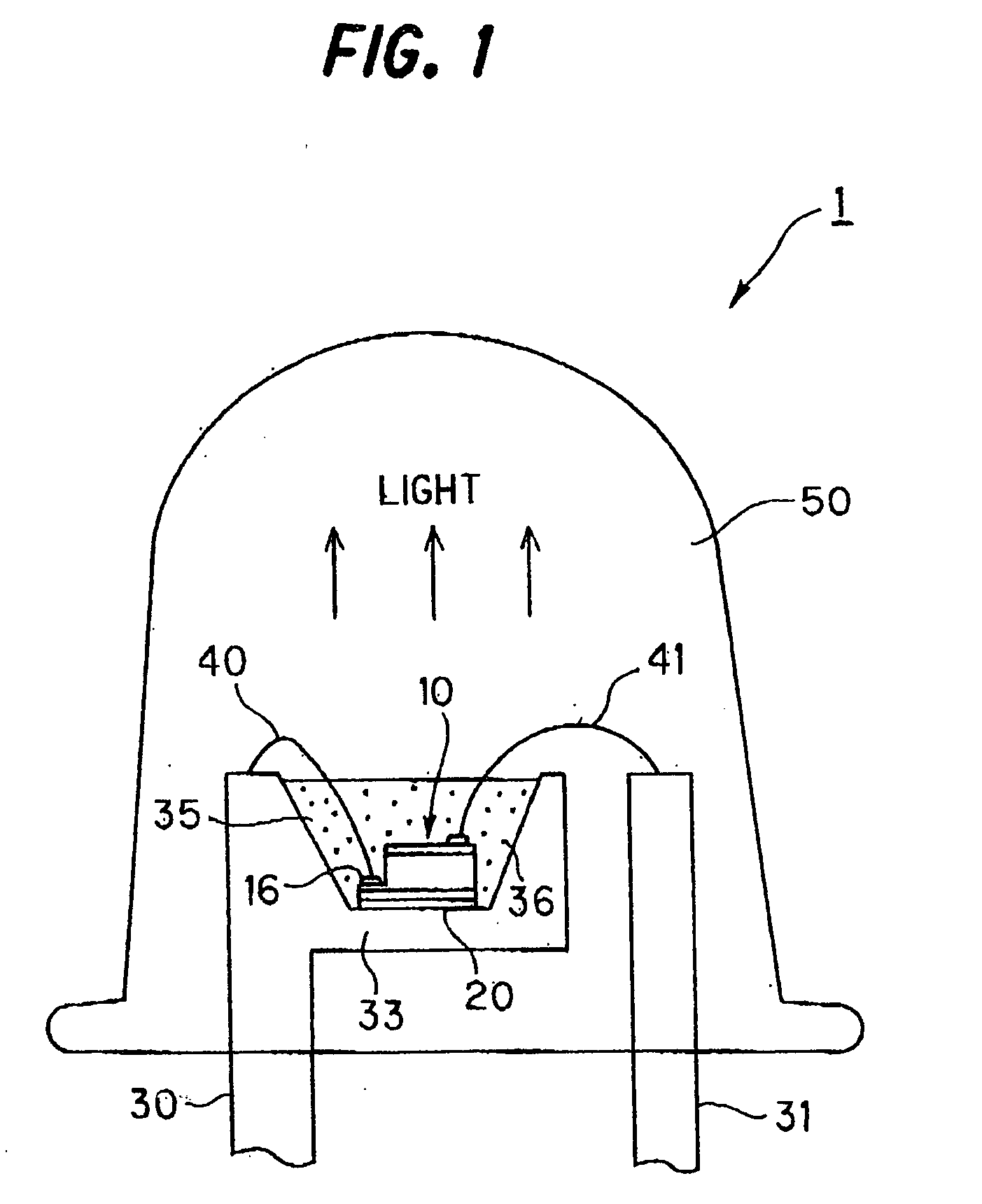

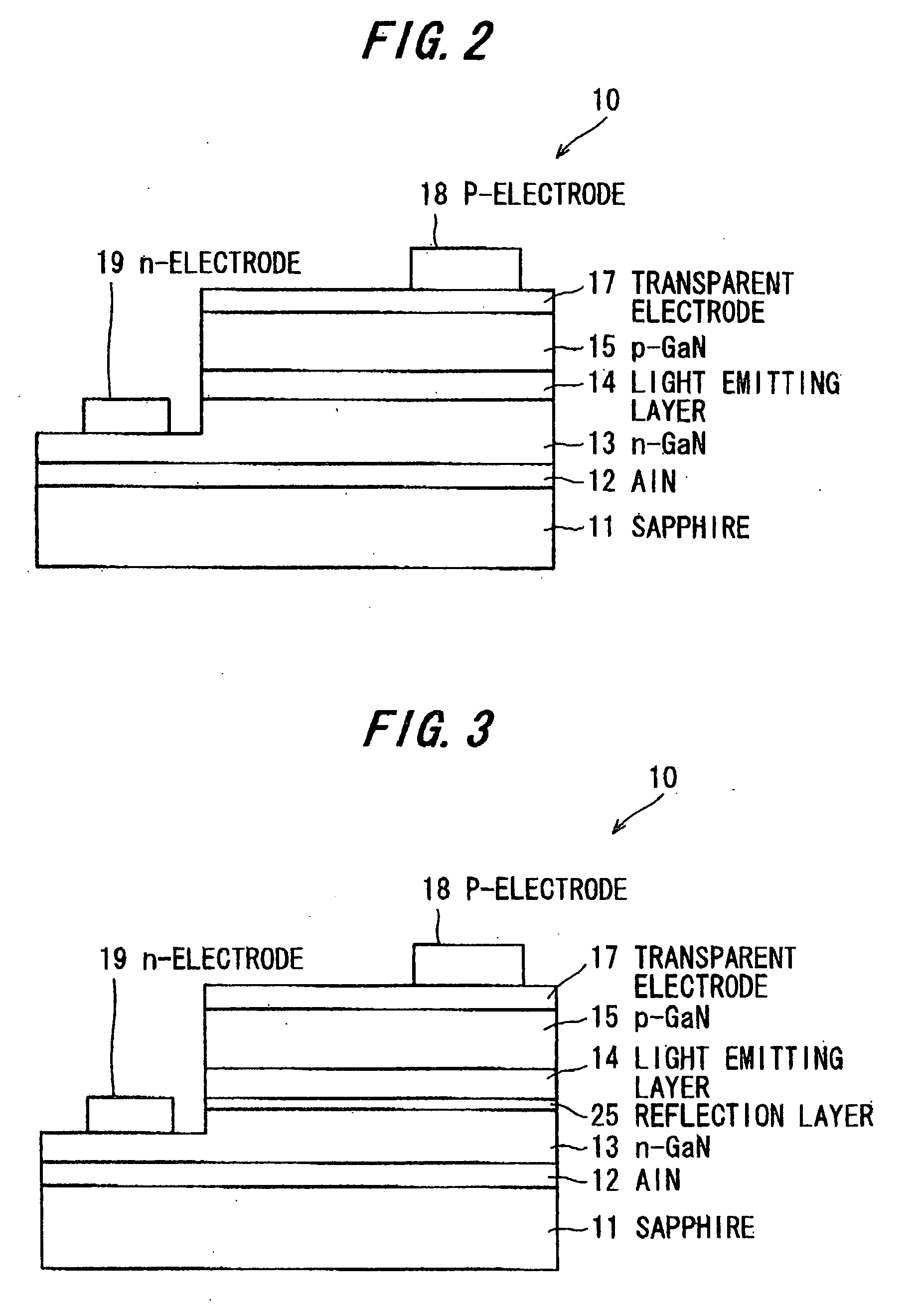

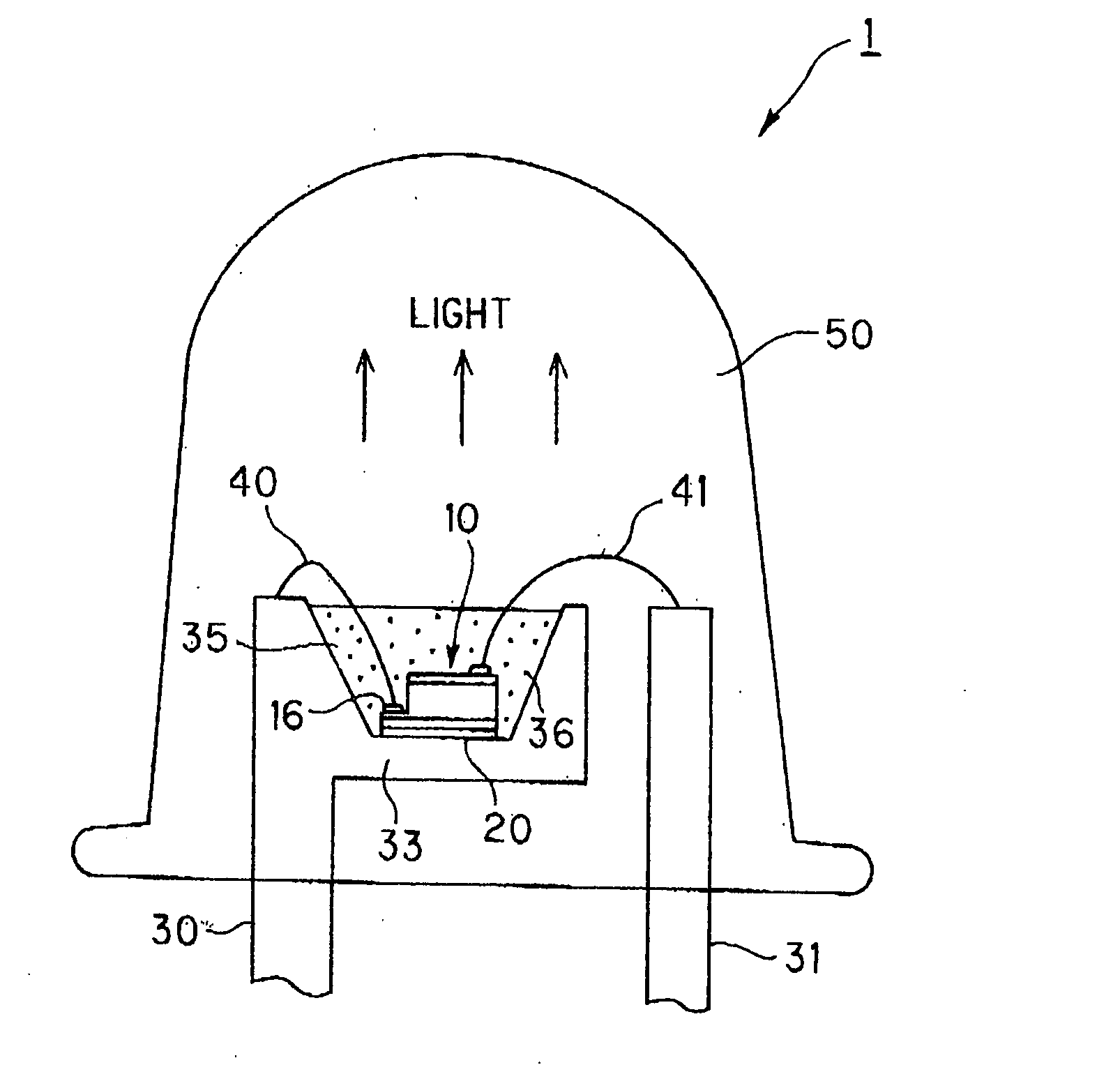

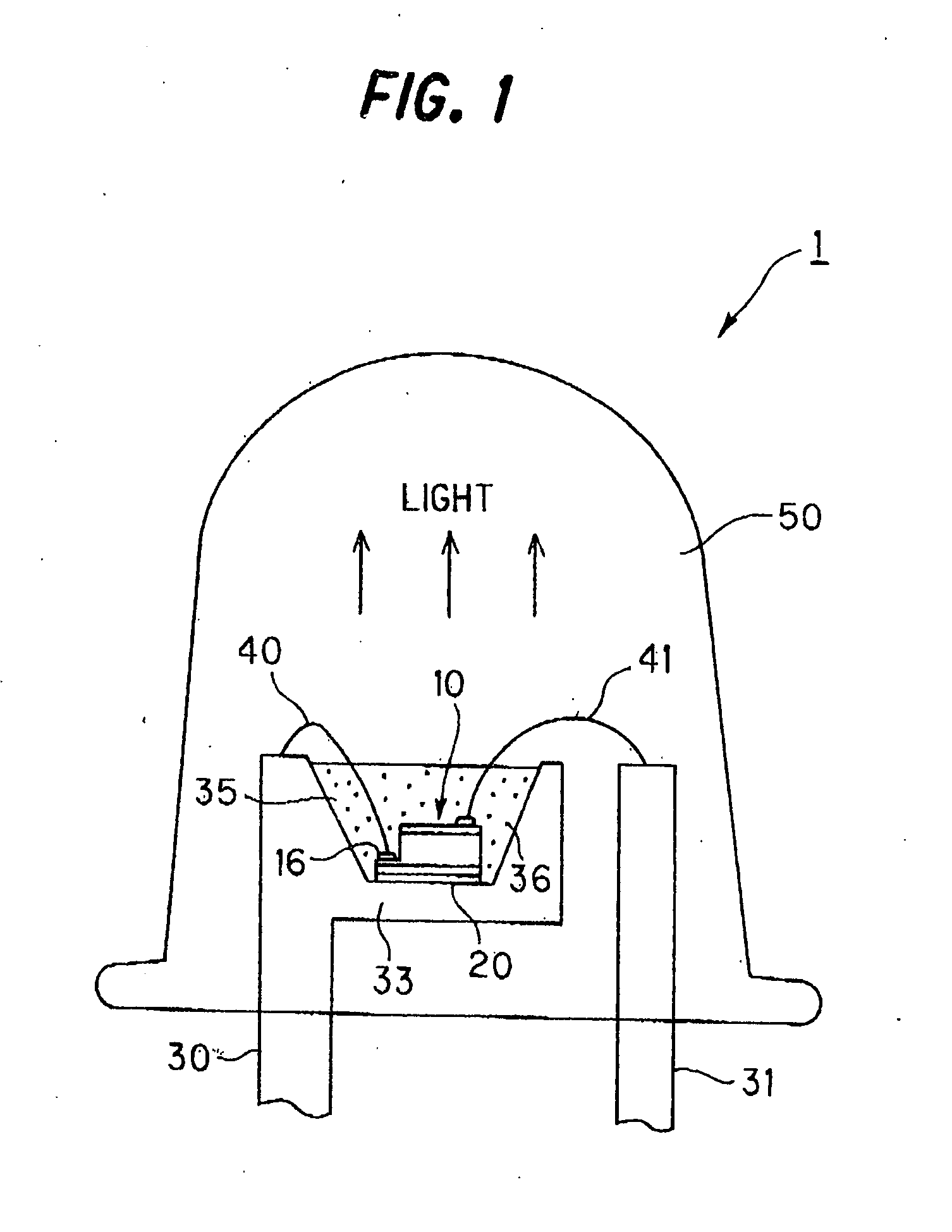

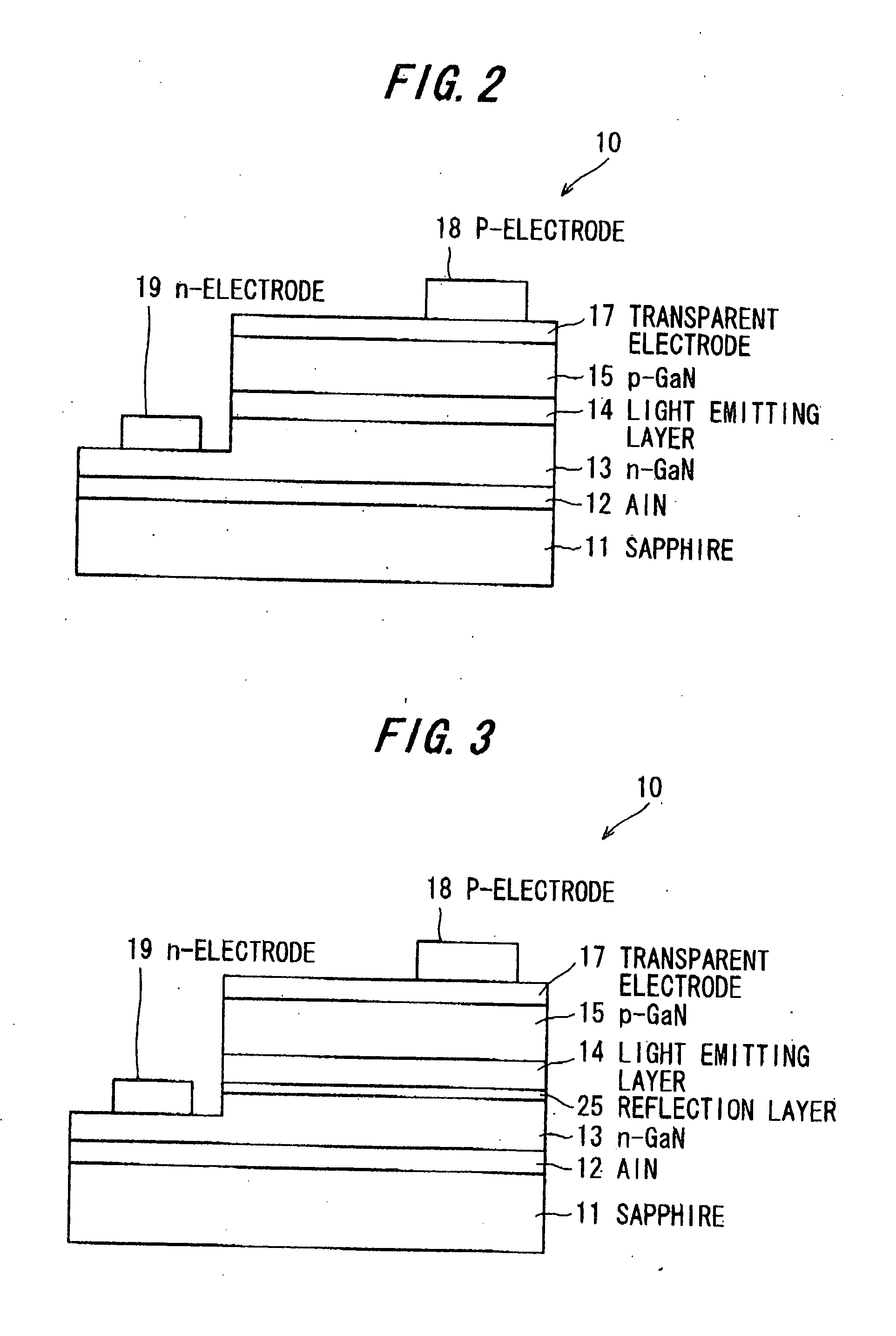

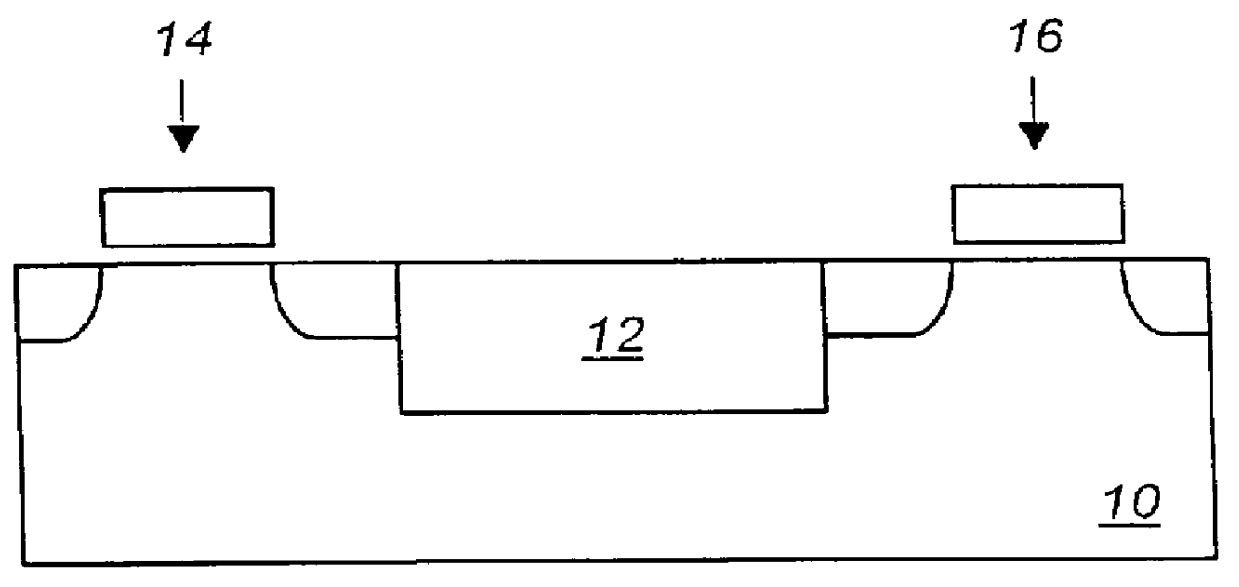

Light emitting apparatus and light emitting method

InactiveUS20050001225A1Improve propertiesIncrease brightnessSolid-state devicesBulk negative resistance effect devicesRare-earth elementSilicon nitride

A light emitting apparatus has a light emitting element with an emission wavelength in the range of 360 to 550 nm and a rare-earth element doped oxide nitride phosphor or cerium ion doped lanthanum silicon nitride phosphor. Part of light radiated from the light emitting element is wavelength-converted by the phosphor. The light emitting apparatus radiates white light generated by a mixture of the wavelength-converted light and the other part of light radiated from the light emitting element.

Owner:TOYODA GOSEI CO LTD +1

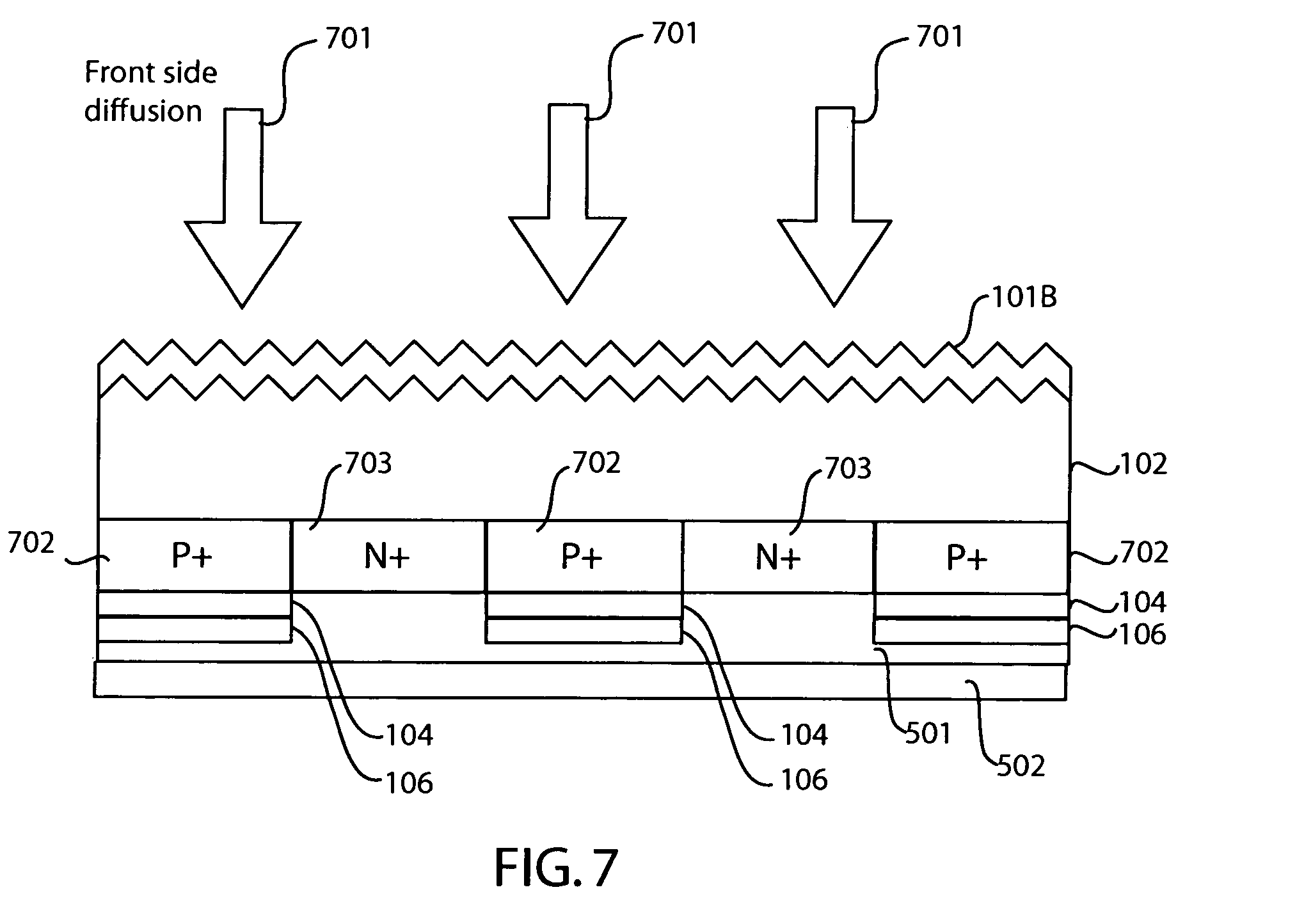

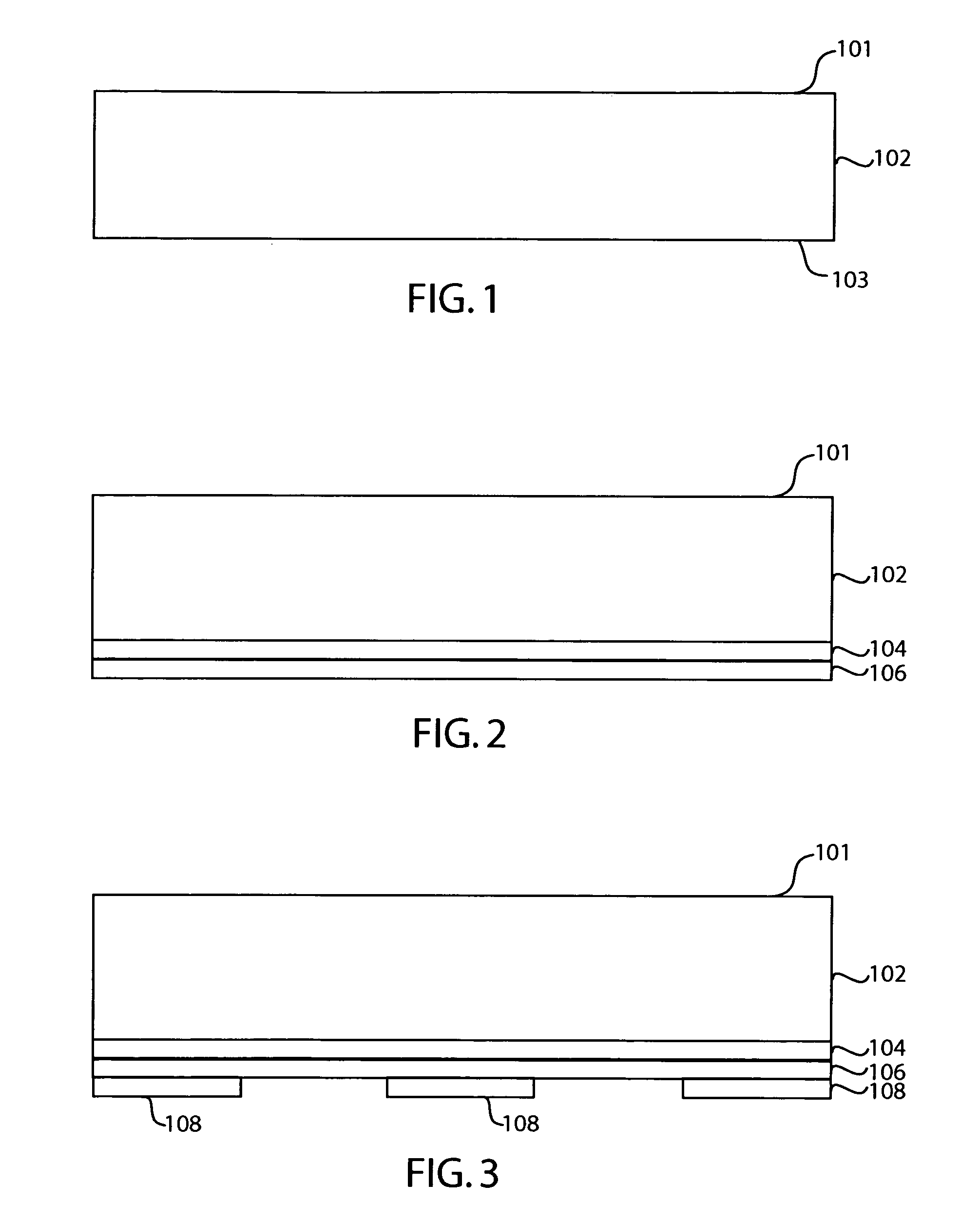

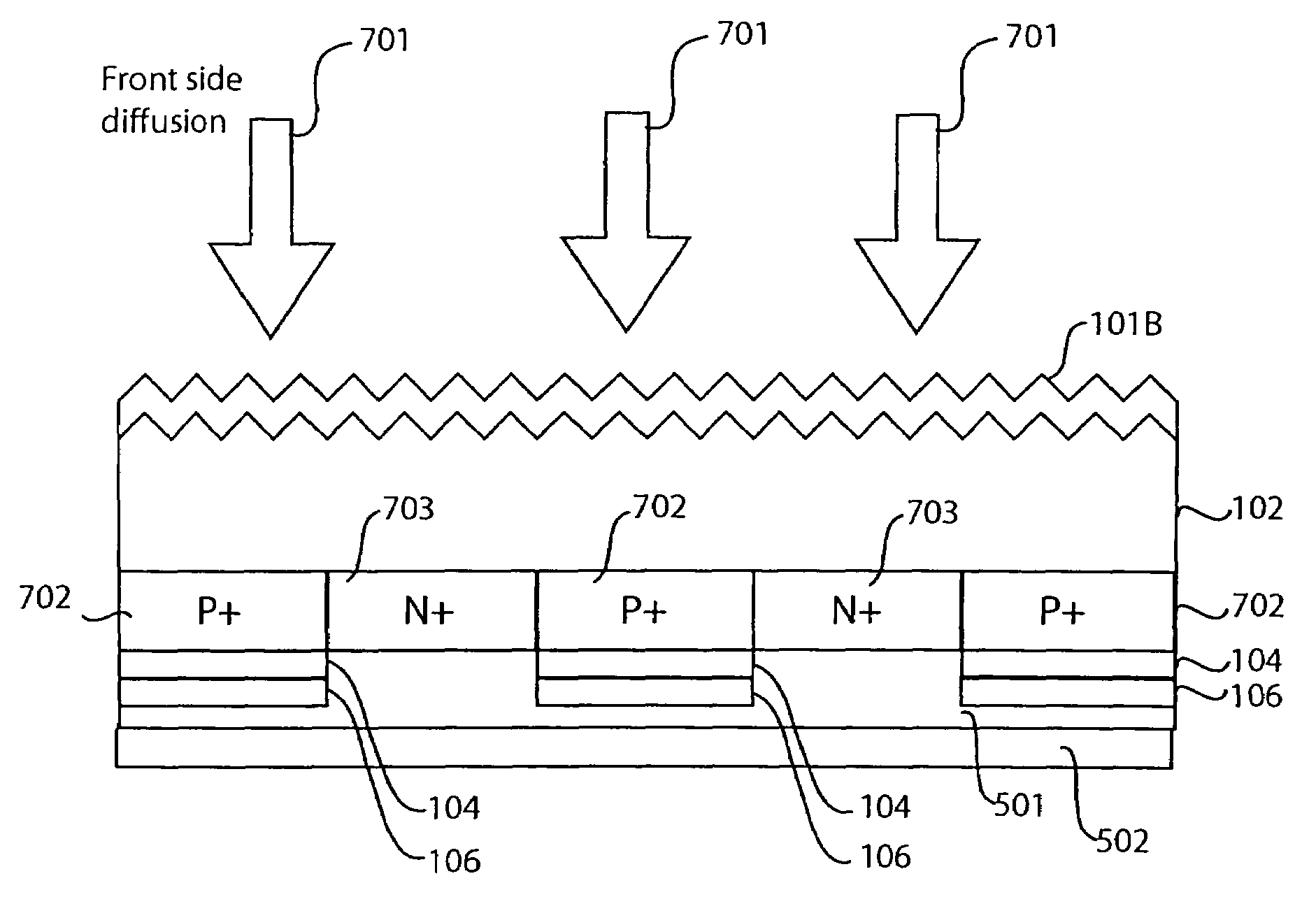

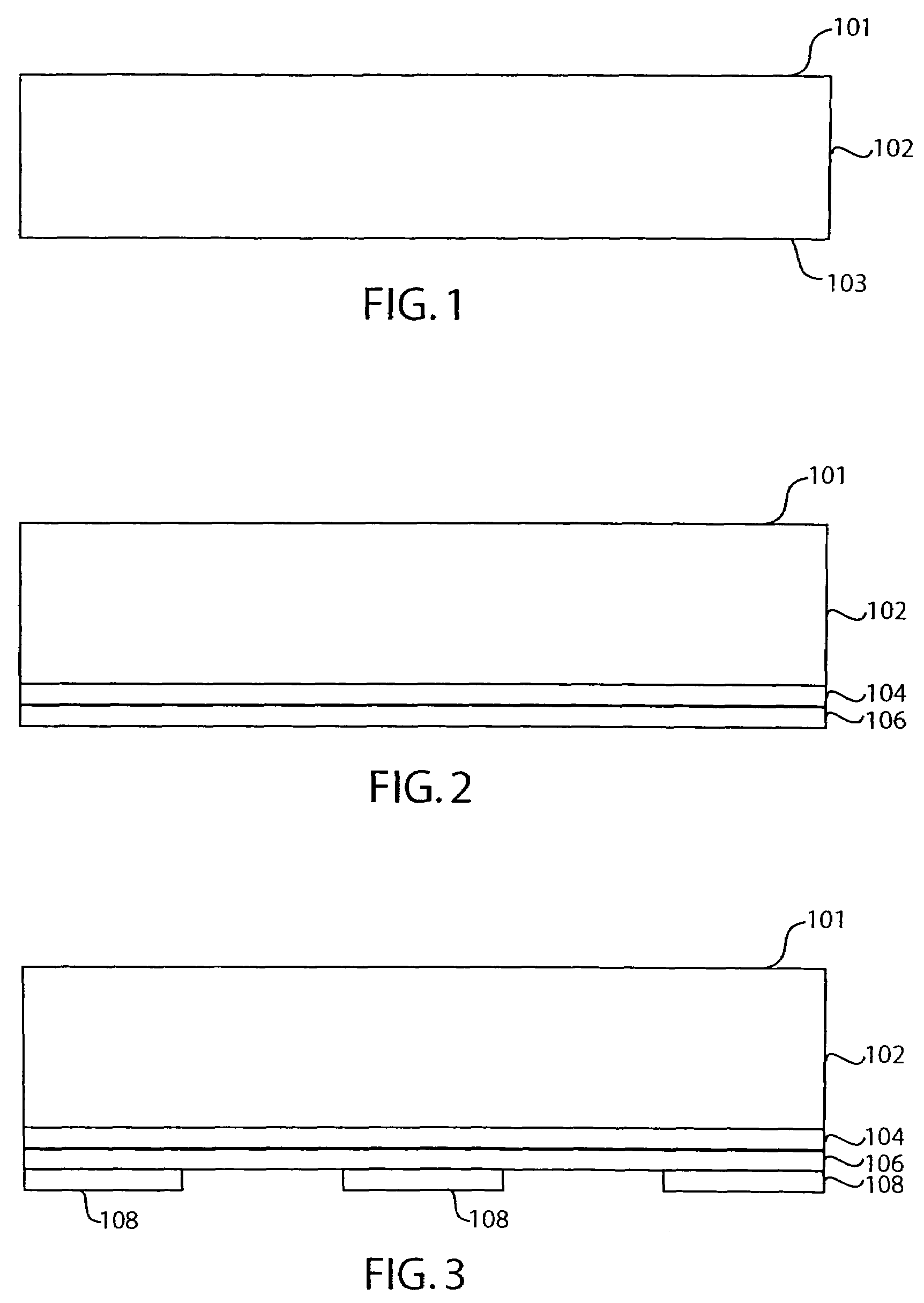

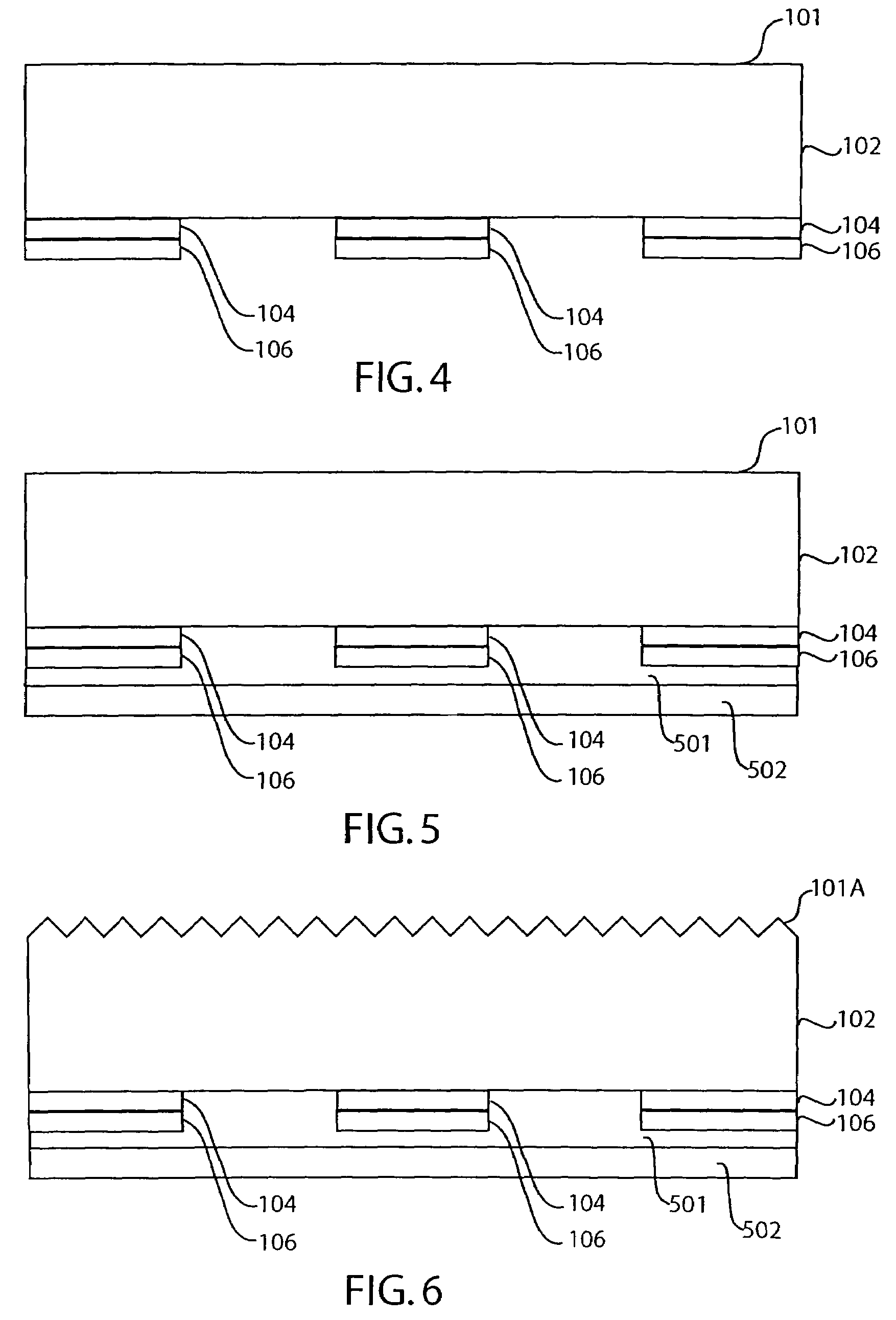

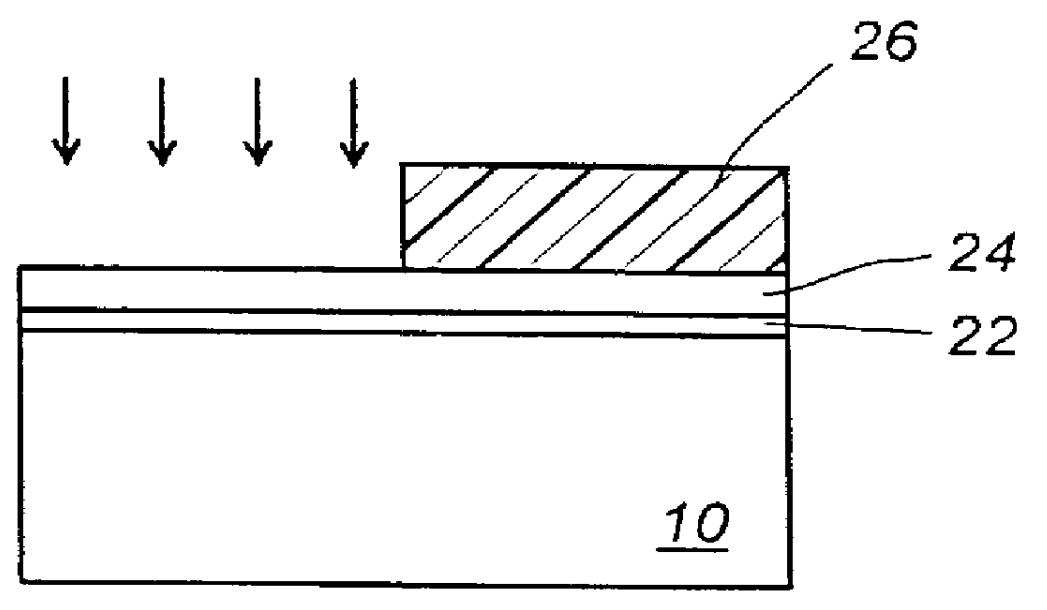

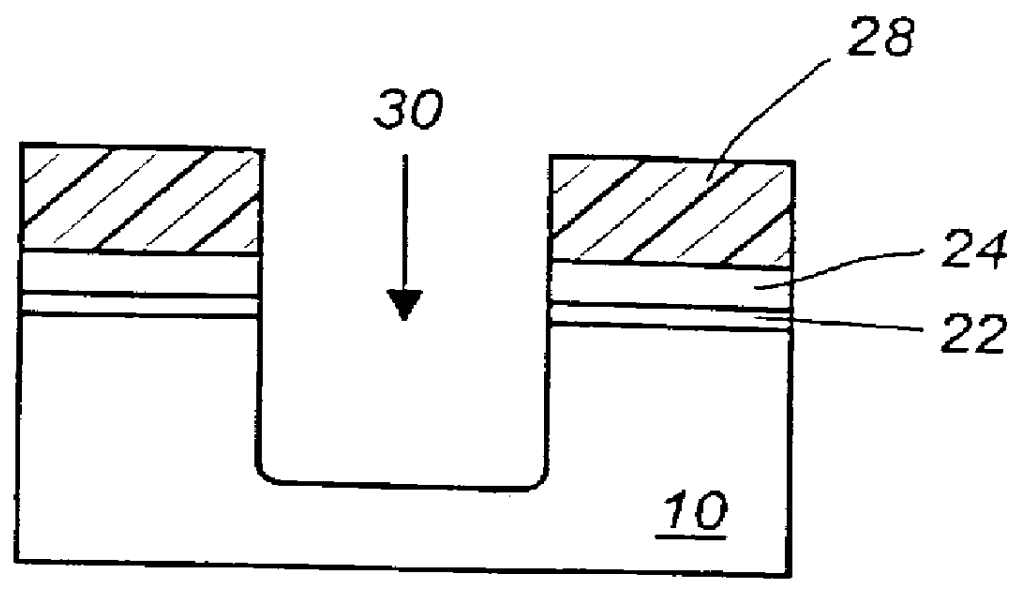

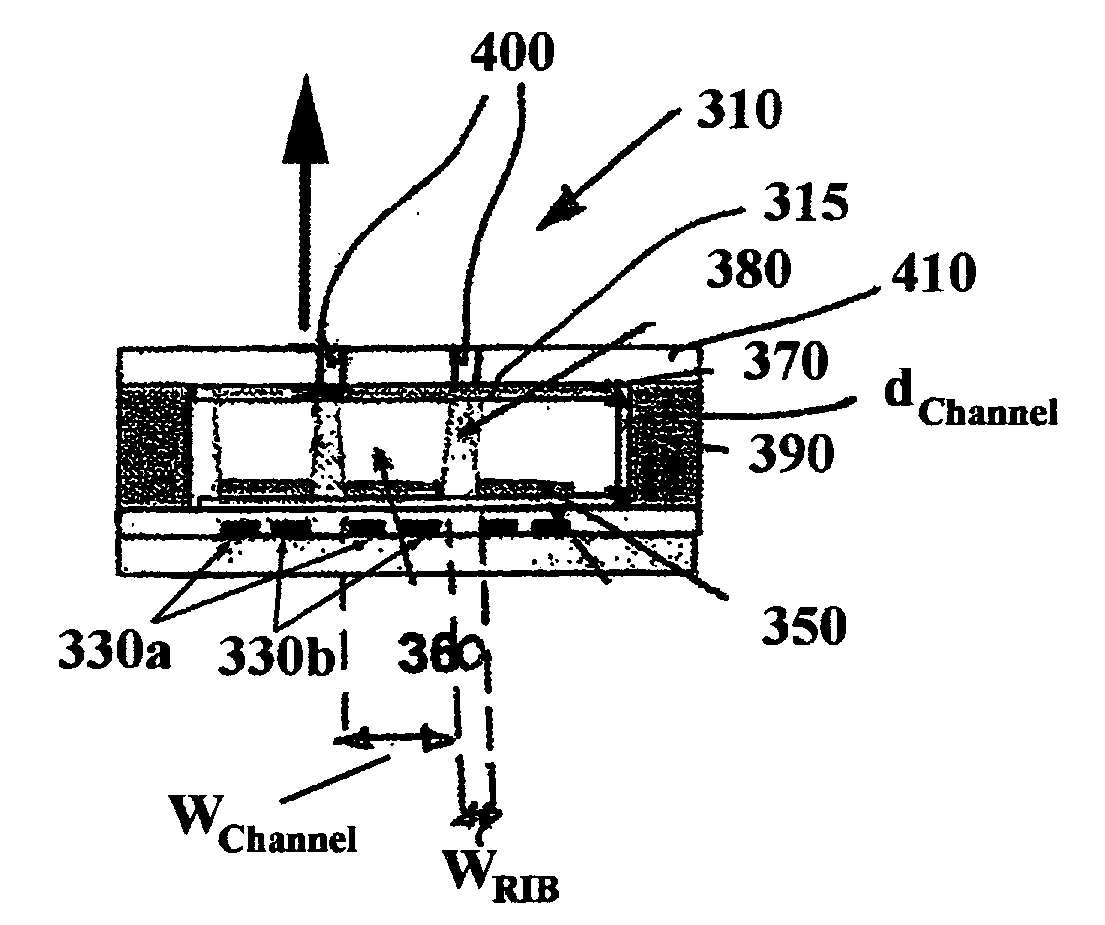

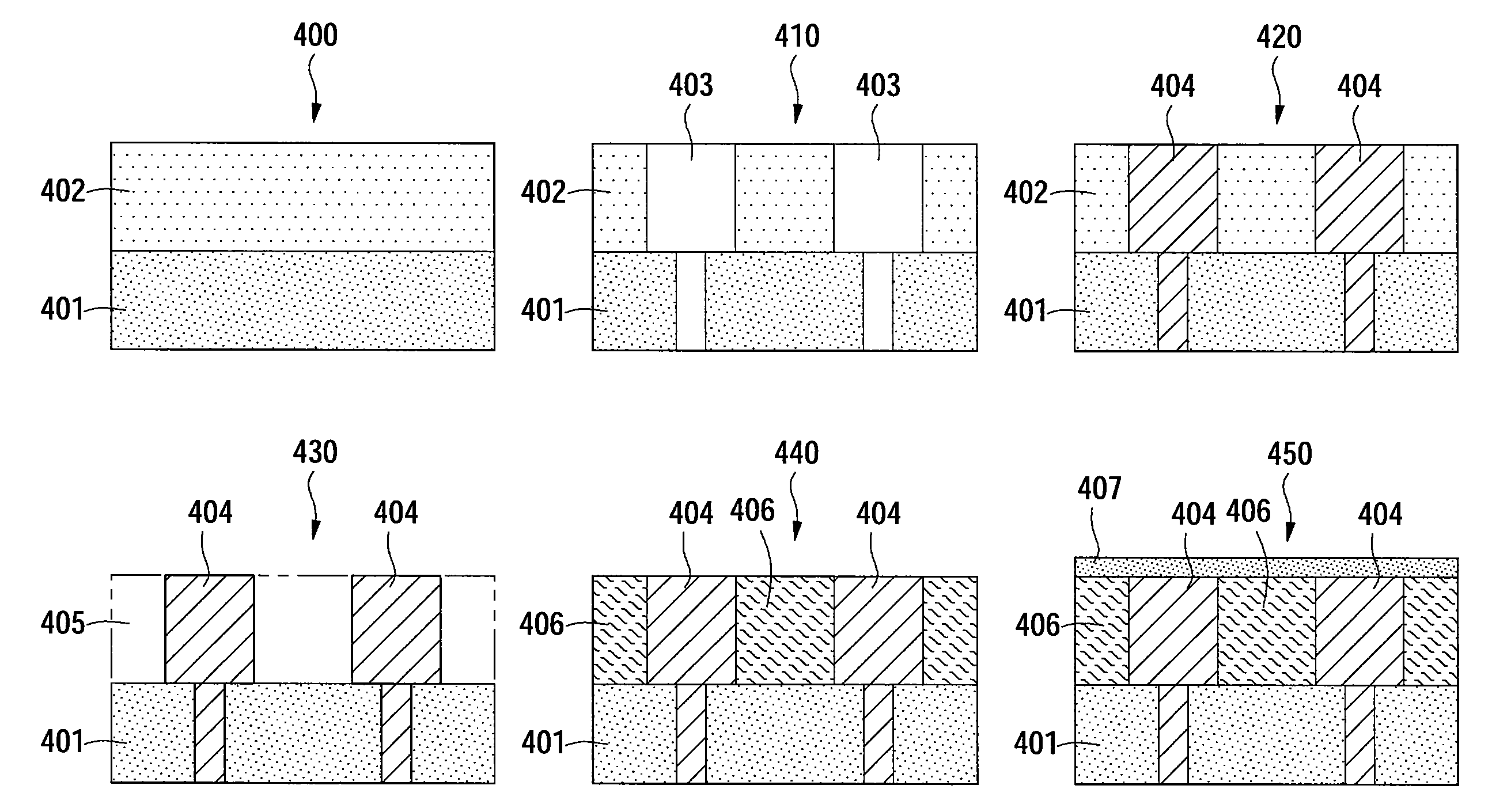

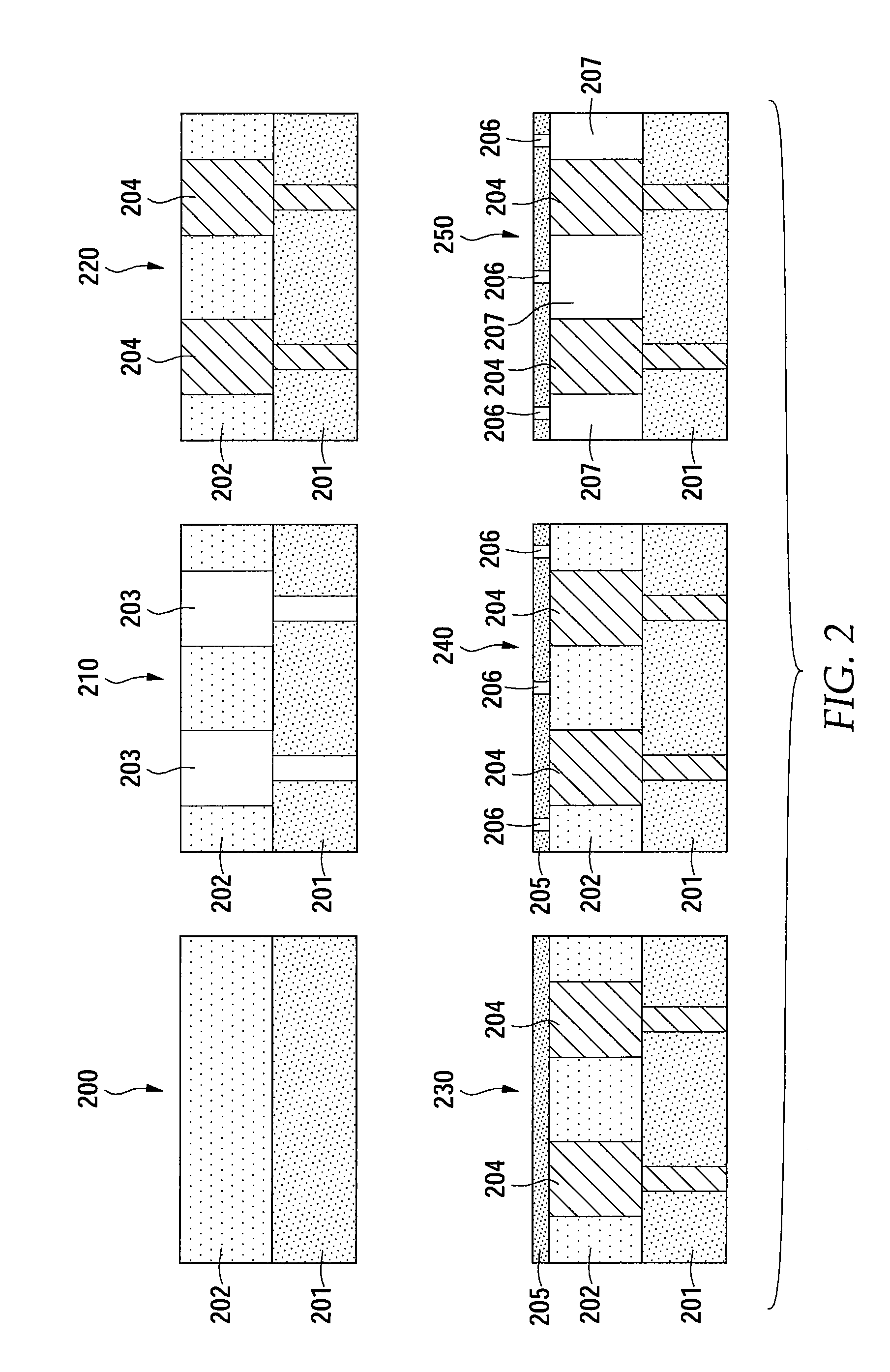

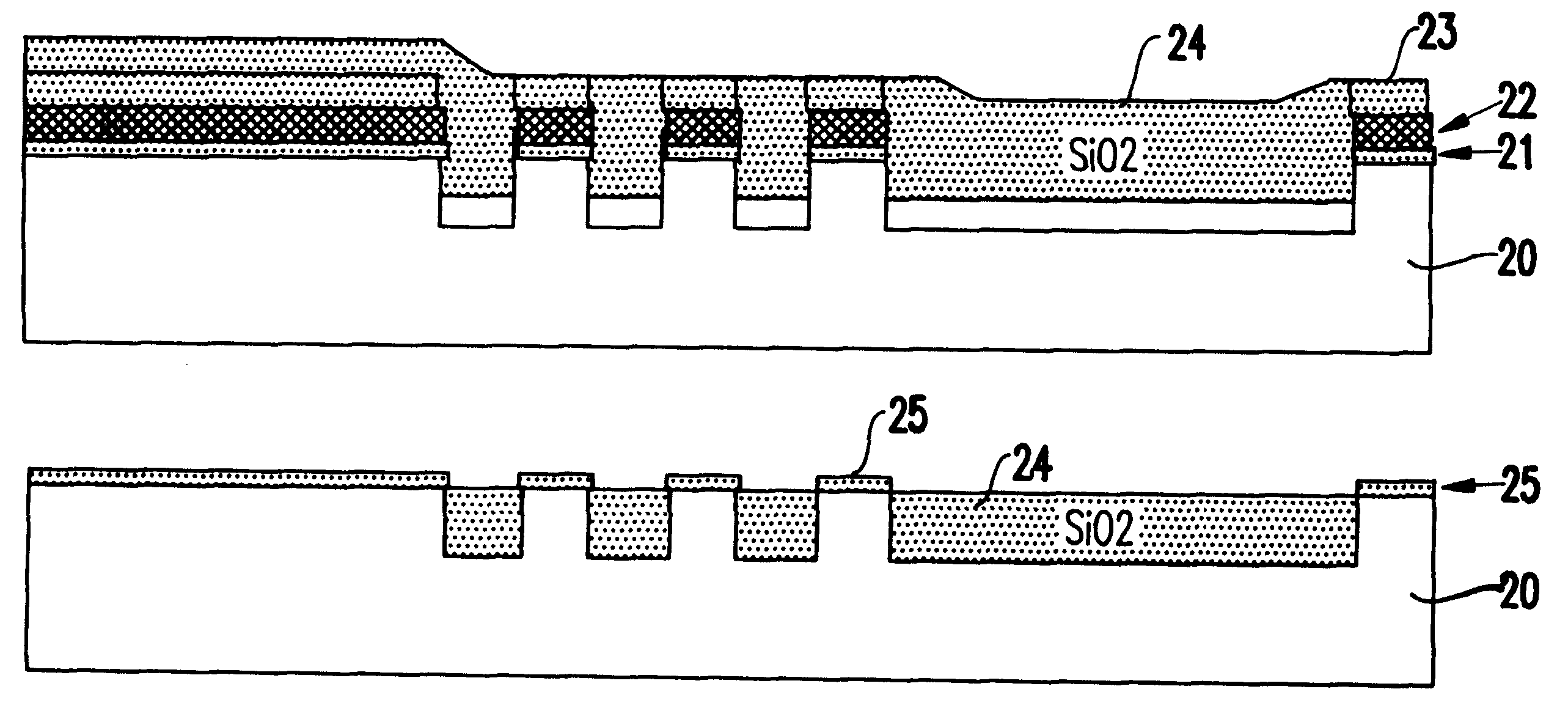

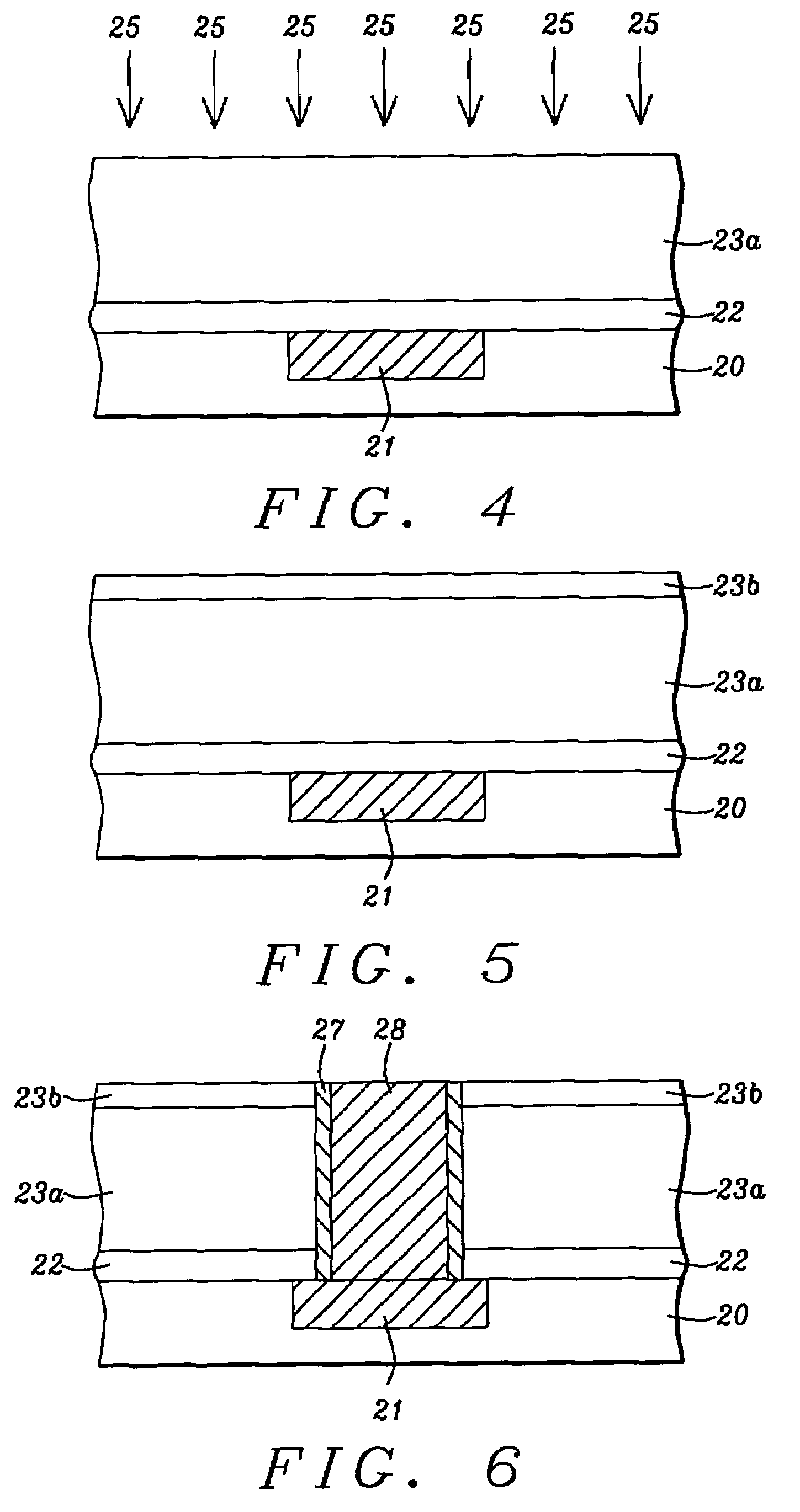

Use of doped silicon dioxide in the fabrication of solar cells

In one embodiment, a method of forming doped regions in a substrate of a back side contact solar cell includes the steps of depositing a first doped oxide layer on a back side of a substrate, depositing a first undoped oxide layer over the first doped oxide layer, diffusing a first dopant from the first doped oxide layer into the substrate to form a first doped region in the substrate, and diffusing a second dopant into the substrate by way of a front side of the substrate, wherein the diffusion of the first dopant and the second dopant into the substrate are performed in-situ. The method may further include the steps of patterning the first doped and undoped oxide layers to expose portions of the back side of the substrate and depositing a second doped and undoped oxide layers on the back side of the substrate.

Owner:MAXEON SOLAR PTE LTD +1

Use of doped silicon dioxide in the fabrication of solar cells

In one embodiment, a method of forming doped regions in a substrate of a back side contact solar cell includes the steps of depositing a first doped oxide layer on a back side of a substrate, depositing a first undoped oxide layer over the first doped oxide layer, diffusing a first dopant from the first doped oxide layer into the substrate to form a first doped region in the substrate, and diffusing a second dopant into the substrate by way of a front side of the substrate, wherein the diffusion of the first dopant and the second dopant into the substrate are performed in-situ. The method may further include the steps of patterning the first doped and undoped oxide layers to expose portions of the back side of the substrate and depositing a second doped and undoped oxide layers on the back side of the substrate.

Owner:MAXEON SOLAR PTE LTD

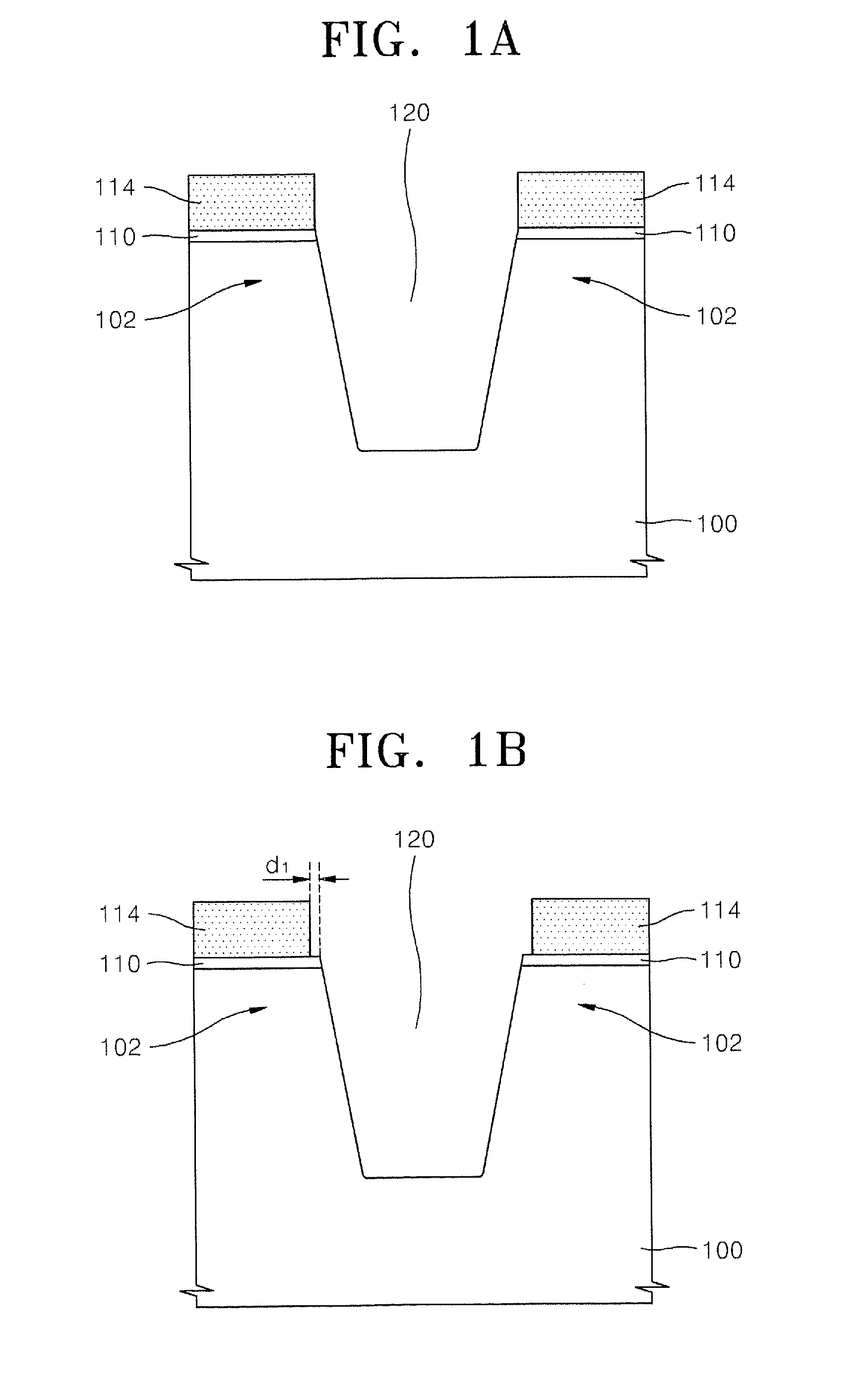

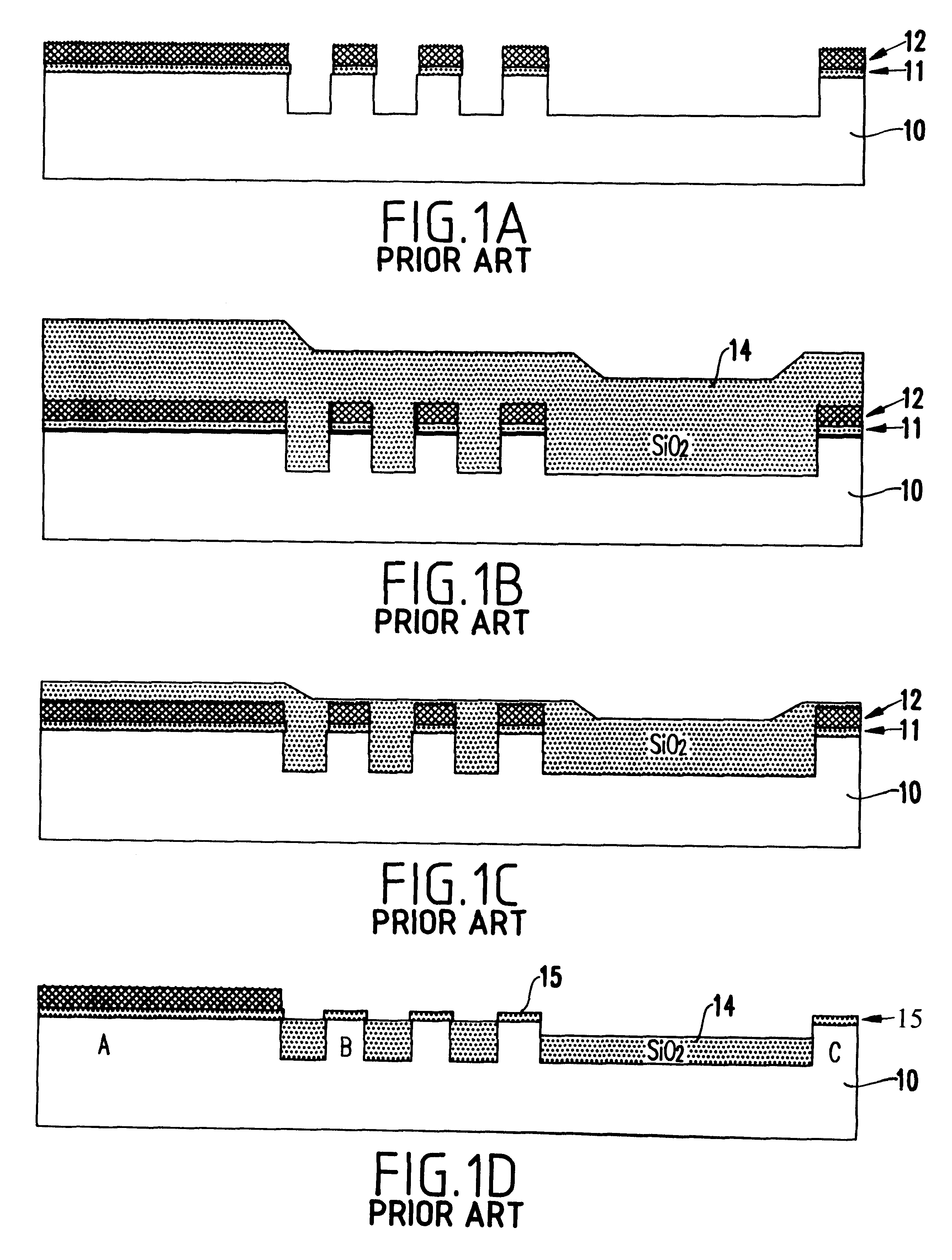

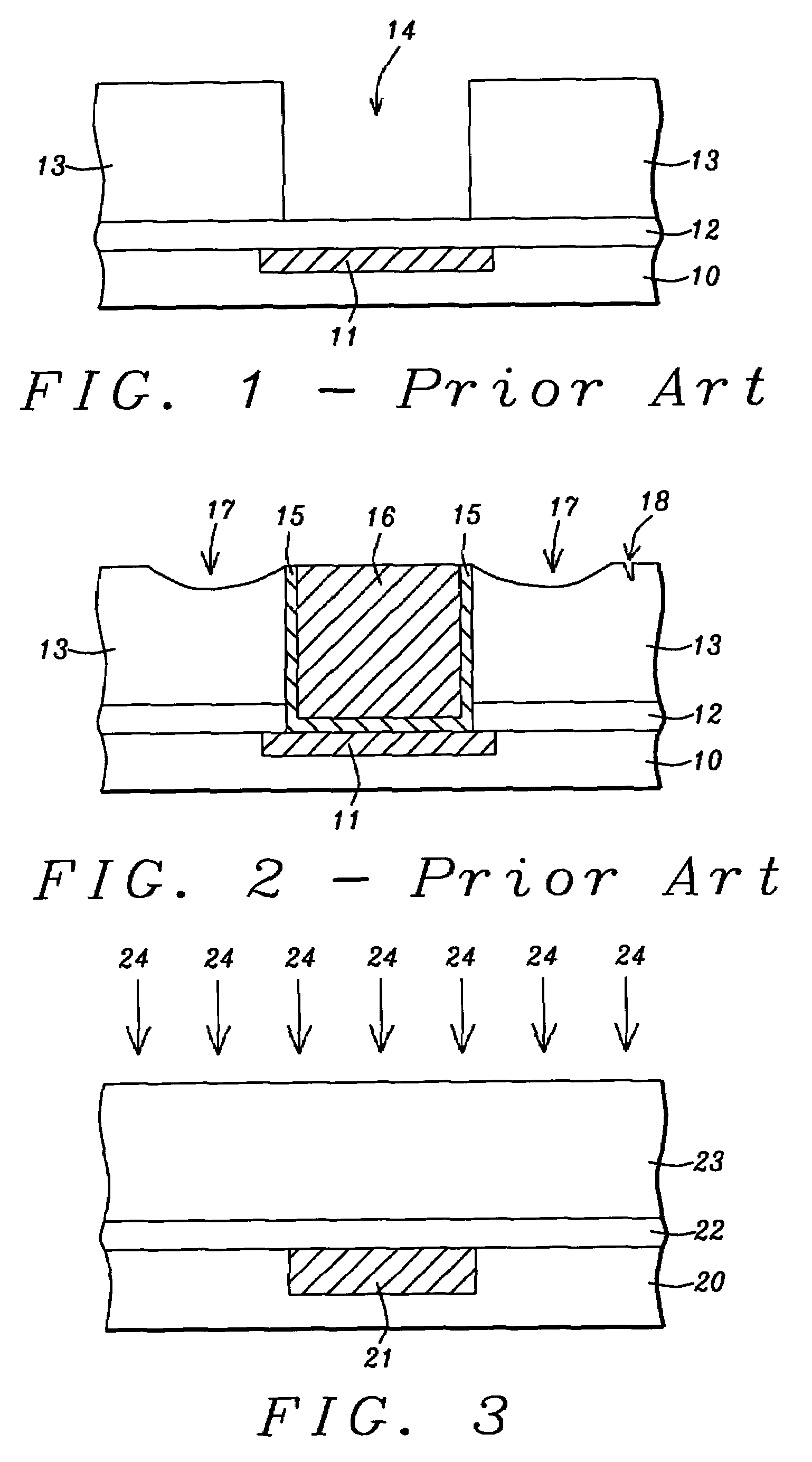

Method for forming self-aligned contact in semiconductor device

ActiveUS20050239282A1Prevent short-circuitingRule out the possibilitySemiconductor/solid-state device manufacturingDevice materialEngineering

A method for forming a self-aligned contact on a semiconductor substrate provided with a plurality of field-effect transistors. The method comprises the steps of forming a first insulating layer comprising a nitride along a profile of a gate structure and a junction region, forming a temporary layer comprising a doped oxide on the first insulating layer, removing a portion of the temporary layer by performing a selective etch of the oxide with a mask while leaving a plug portion of the temporary layer over the junction region, forming a second insulating layer comprising an undoped oxide in a region where the portion of the temporary layer is removed, removing the plug portion by performing a selective etch of the undoped oxide to form a contact hole, removing a portion of the first insulating layer at a bottom of the contact hole, and forming a conductive contact in the contact hole.

Owner:NAN YA TECH

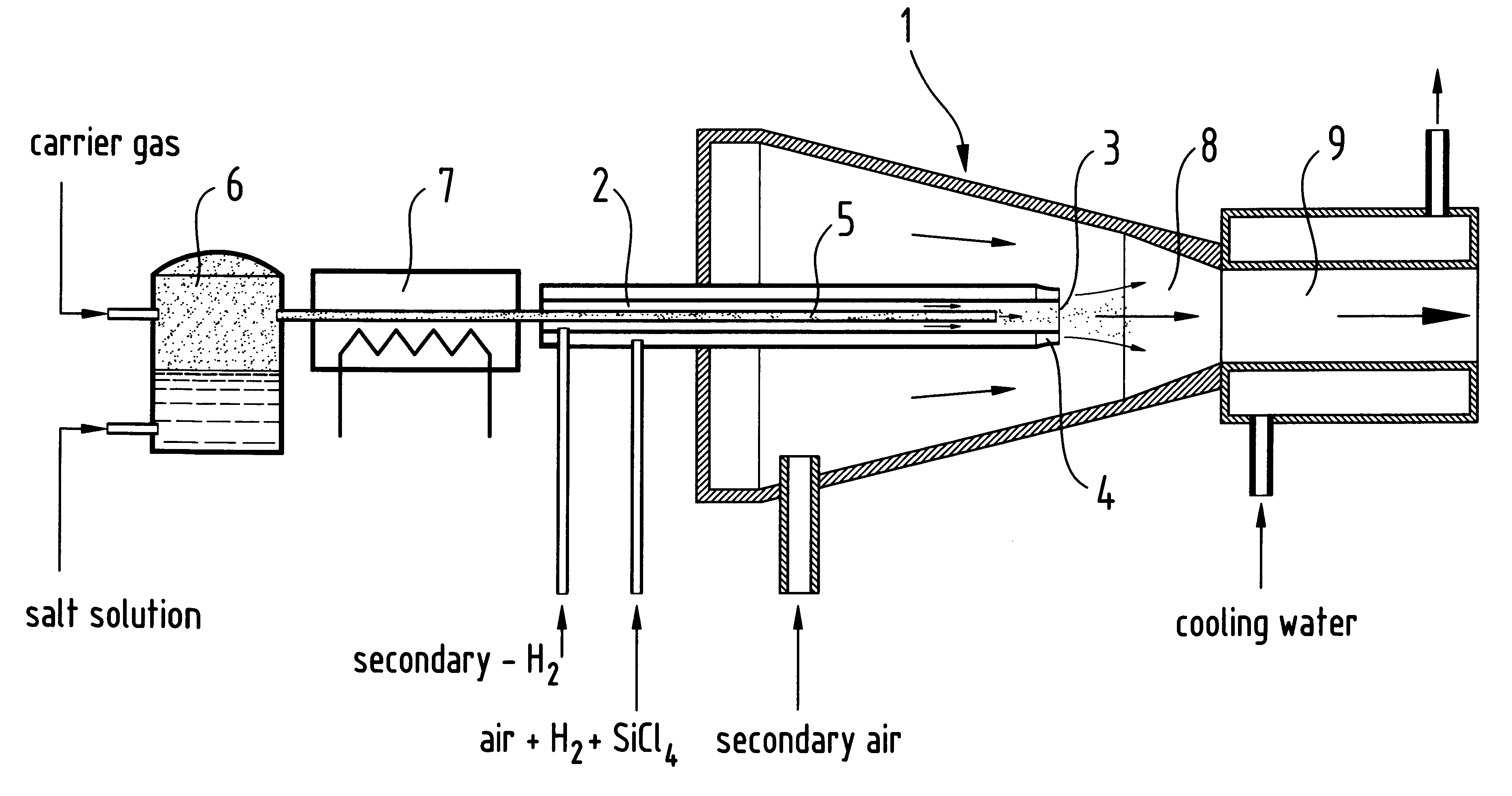

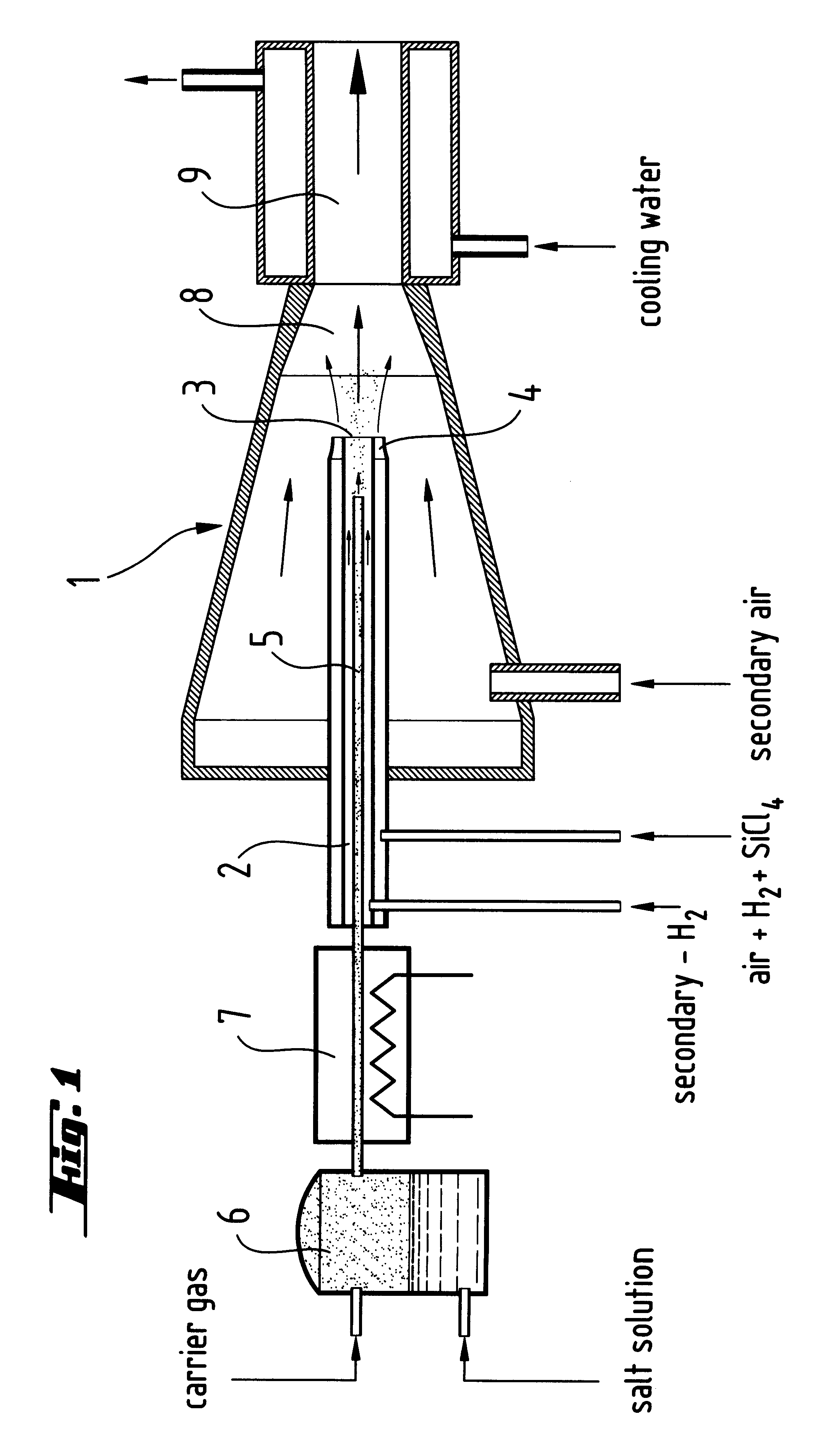

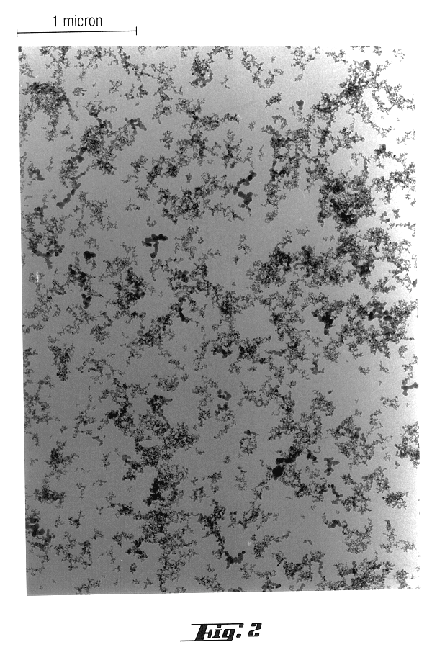

Doped, pyrogenically prepared oxides

InactiveUS6328944B1Germanium dioxidePipe protection by thermal insulationDoped oxideAqueous solution

Doped, pyrogenically prepared oxides of metals and / or non-metals which are doped with one or more doping components in an amount of 0.00001 to 20 wt. %. The doping component may be a metal and / or non-metal or an oxide and / or a salt of a metal and / or a non-metal. The BET surface area of the doped oxide may be between 5 and 600 m2 / g. The doped pyrogenically prepared oxides of metals and / or non-metals are prepared by adding an aerosol which contains an aqueous solution of a metal and / or non-metal to the gas mixture during the flame hydrolysis of vaporizable compounds of metals and / or non-metals.

Owner:EVONIK DEGUSSA GMBH

Two step post-deposition treatment of ILD layer for a lower dielectric constant and improved mechanical properties

InactiveUS20050064698A1Increase resistanceImprove the immunityDecorative surface effectsSemiconductor/solid-state device detailsMoistureMechanical property

A method of lowering the dielectric constant of an organosilicon low k dielectric layer while improving the hardness and thermal stability is provided. A deposited layer of carbon doped oxide, HSQ, or MSQ is cured and treated with a He plasma which improves hardness for a subsequent CMP step and lowers the dielectric constant. There is no loss of H2O or CH4 during the He treatment. The low k dielectric layer is then treated with a H2 plasma which converts some of the Si—O and Si—CH3 bonds near the surface to Si—H bonds, thereby further lowering the dielectric constant and increasing thermal stability that improves breakdown resistance. Moisture uptake is also reduced. The method is especially useful for interconnect schemes with deep sub-micron ground rules. Surprisingly, the k value obtained from two different plasma treatments is lower than when two He treatments or two H2 treatment are performed.

Owner:TAIWAN SEMICON MASNUFACTURING

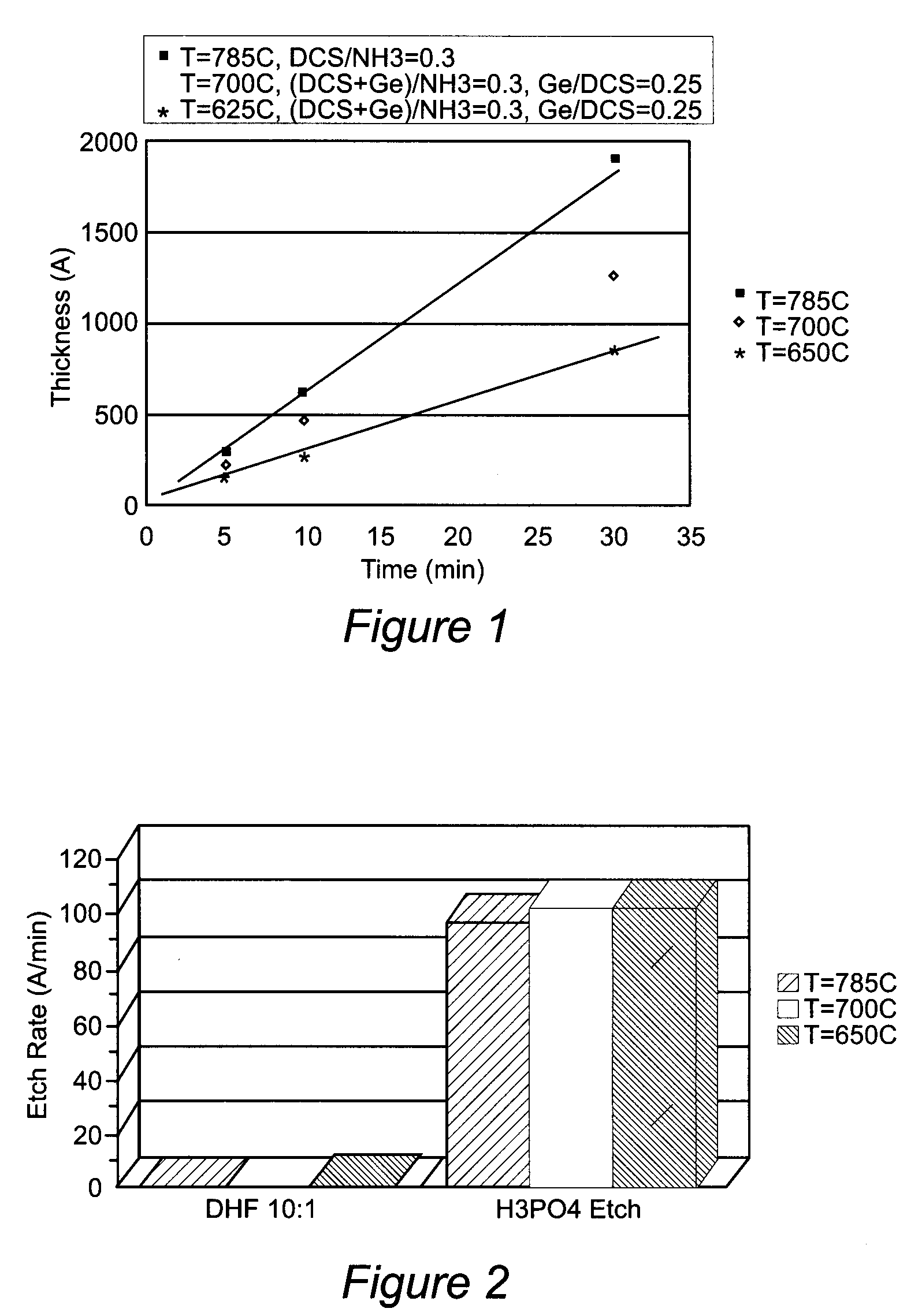

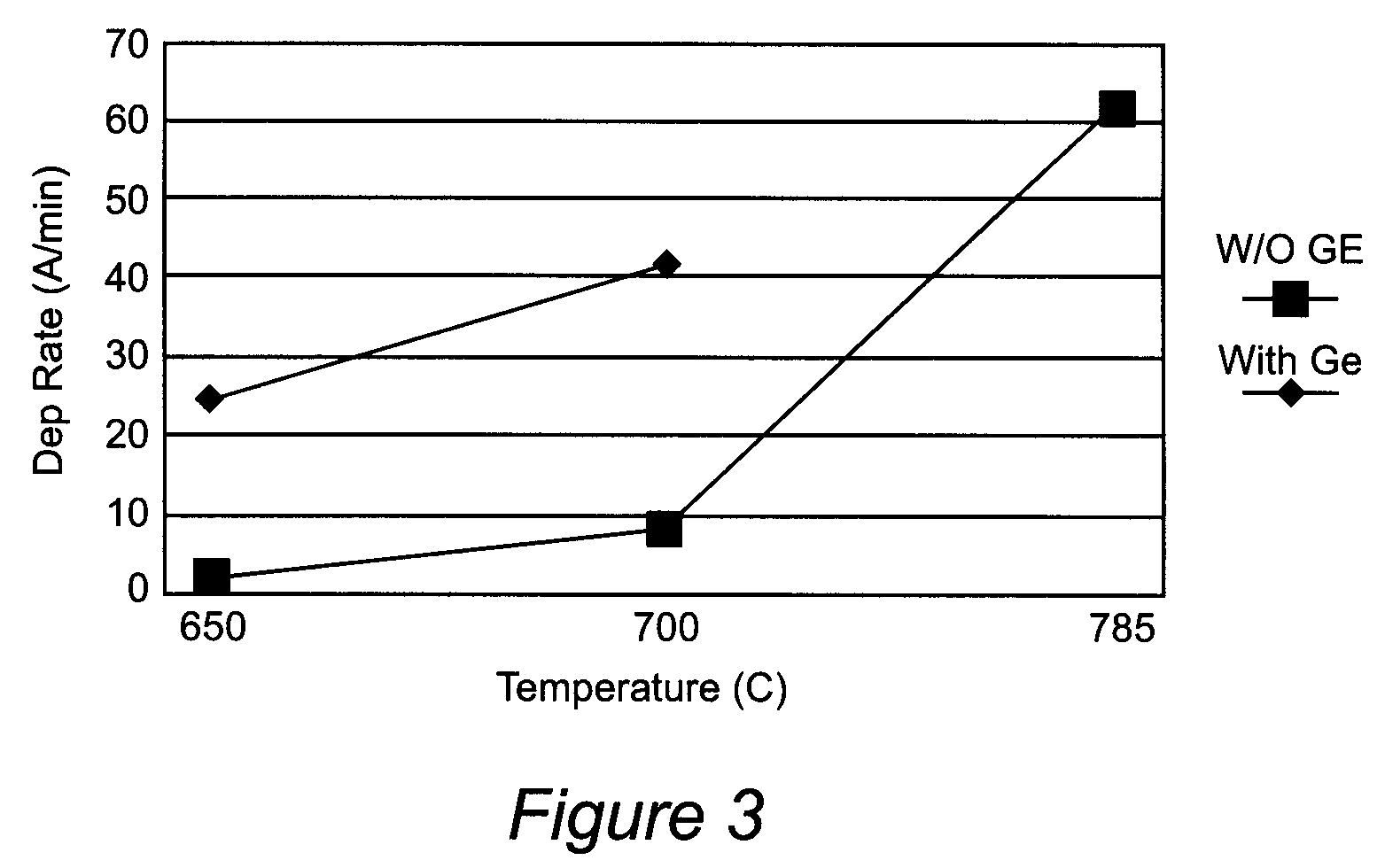

Doped nitride film, doped oxide film and other doped films

InactiveUS20050287747A1Increase deposition rateImprove device performanceTransistorSemiconductor/solid-state device manufacturingDopantSilicon oxide

Adding at least one non-silicon precursor (such as a germanium precursor, a carbon precursor, etc.) during formation of a silicon nitride, silicon oxide, silicon oxynitride or silicon carbide film improves the deposition rate and / or makes possible tuning of properties of the film, such as tuning of the stress of the film. Also, in a doped silicon oxide or doped silicon nitride or other doped structure, the presence of the dopant may be used for measuring a signal associated with the dopant, as an etch-stop or otherwise for achieving control during etching.

Owner:GLOBALFOUNDRIES INC

Formulations for cleaning memory device structures

InactiveUS20080125342A1Inorganic/elemental detergent compounding agentsOrganic detergent compounding agentsBorophosphosilicate glassSilicon oxide

A removal composition and process for removing silicon-containing layers from a microelectronic device having said layers thereon. The removal composition selectively removes layers including, but not limited to, silicon oxide, plasma enhanced tetraethyl orthosilicate (P-TEOS), borophosphosilicate glass (BPSG), plasma enhanced oxide (PEOX), high density plasma oxide (HDP), phosphosilicate glass (PSG), spin-on-dielectrics (SOD), thermal oxide, updoped silicate glass, sacrificial oxides, silicon-containing organic polymers, silicon-containing hybrid organic / inorganic materials, organosilicate glass (OSG), TEOS, fluorinated silicate glass (FSG), hemispherical grain (HSQ), carbon-doped oxide (CDO) glass, and combinations thereof, relative to lower electrode, device substrate, and / or etch stop layer materials.

Owner:ADVANCED TECH MATERIALS INC

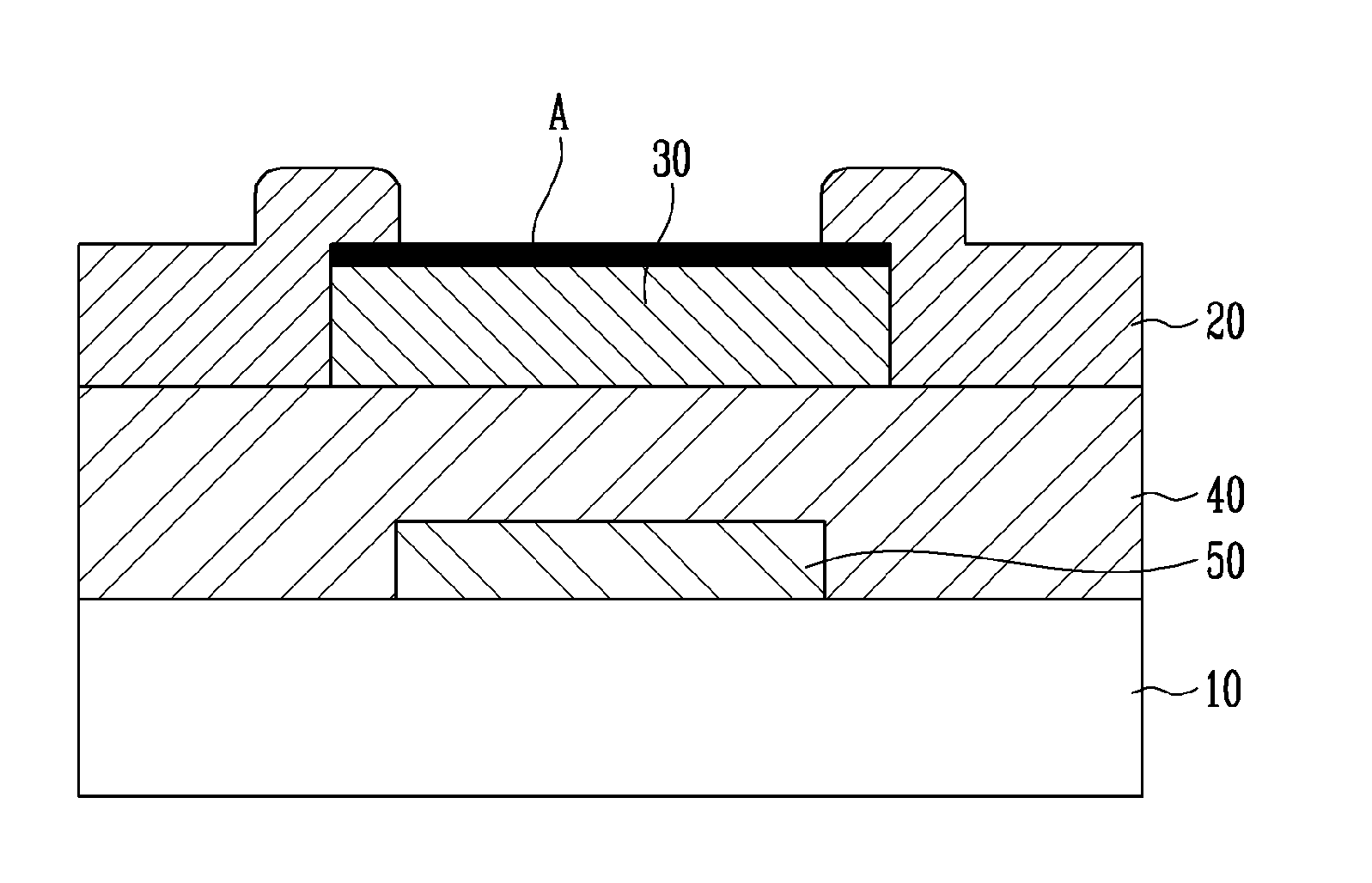

Thin film transistor using boron-doped oxide semiconductor thin film and method of fabricating the same

ActiveUS20100155716A1Guaranteed smooth progressTransistorSemiconductor/solid-state device manufacturingDoped oxideBoron

Provided are a thin film transistor, to which a boron-doped oxide semiconductor thin film is applied as a channel layer, and a method of fabricating the same. The thin film transistor includes source and drain electrodes, a channel layer, a gate insulating layer, and a gate electrode, which are formed on a substrate. The channel layer is an oxide semiconductor thin film doped with boron. Therefore, it is possible to remarkably improve electrical characteristics and high temperature stability of the thin film transistor.

Owner:ELECTRONICS & TELECOMM RES INST

Light emitting apparatus and light emitting method

ActiveUS20070164308A1Improve propertiesIncrease brightnessDischarge tube luminescnet screensLamp detailsFluorescenceDoped oxide

A light emitting apparatus has a light emitting element with an emission wavelength in the range of 360 to 550 nm and a rare-earth element doped oxide nitride phosphor or cerium ion doped lanthanum silicon nitride phosphor. Part of light radiated from the light emitting element is wavelength-converted by the phosphor. The light emitting apparatus radiates white light generated by a mixture of the wavelength-converted light and the other part of light radiated from the light emitting element.

Owner:TOYODA GOSEI CO LTD

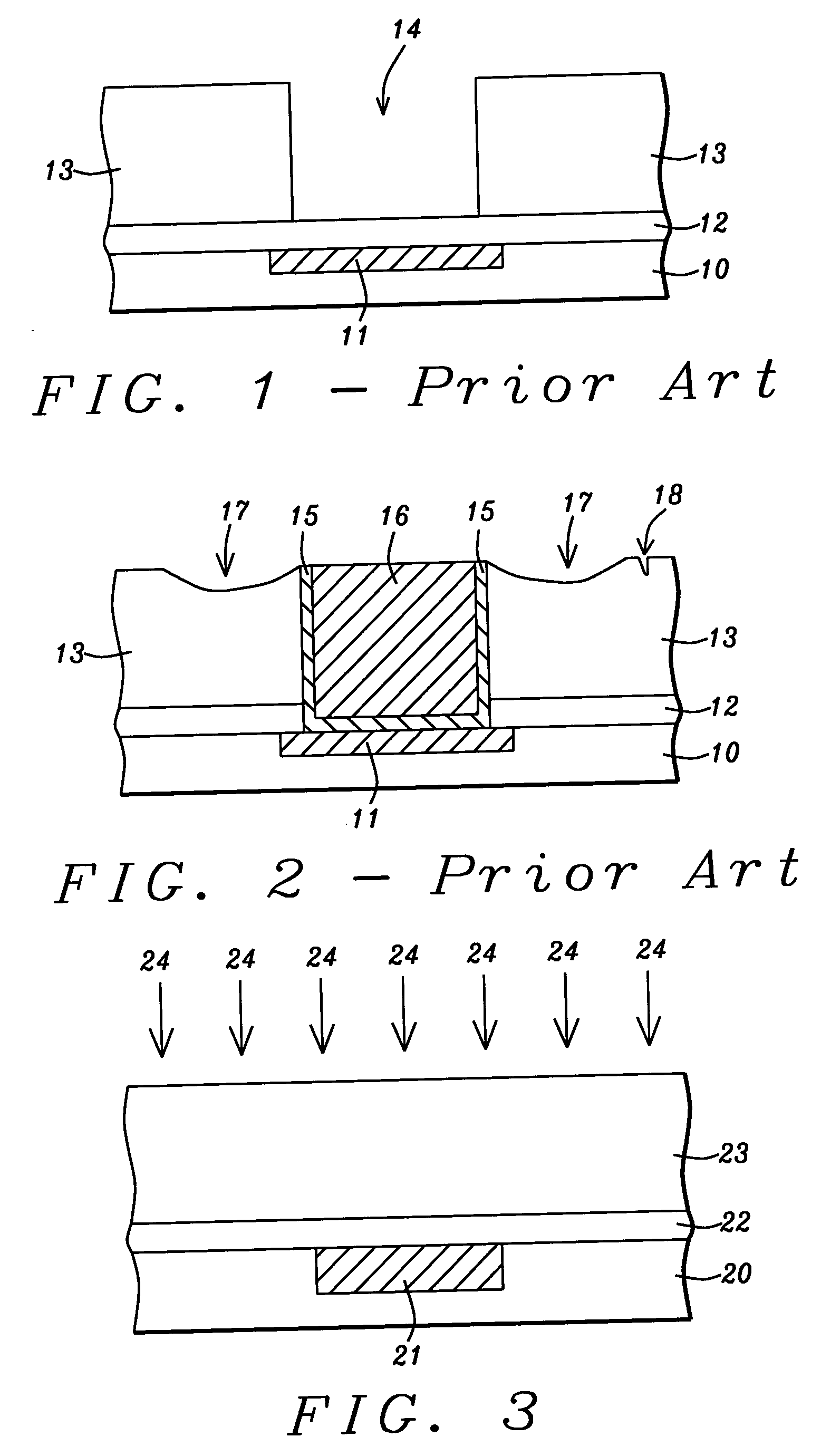

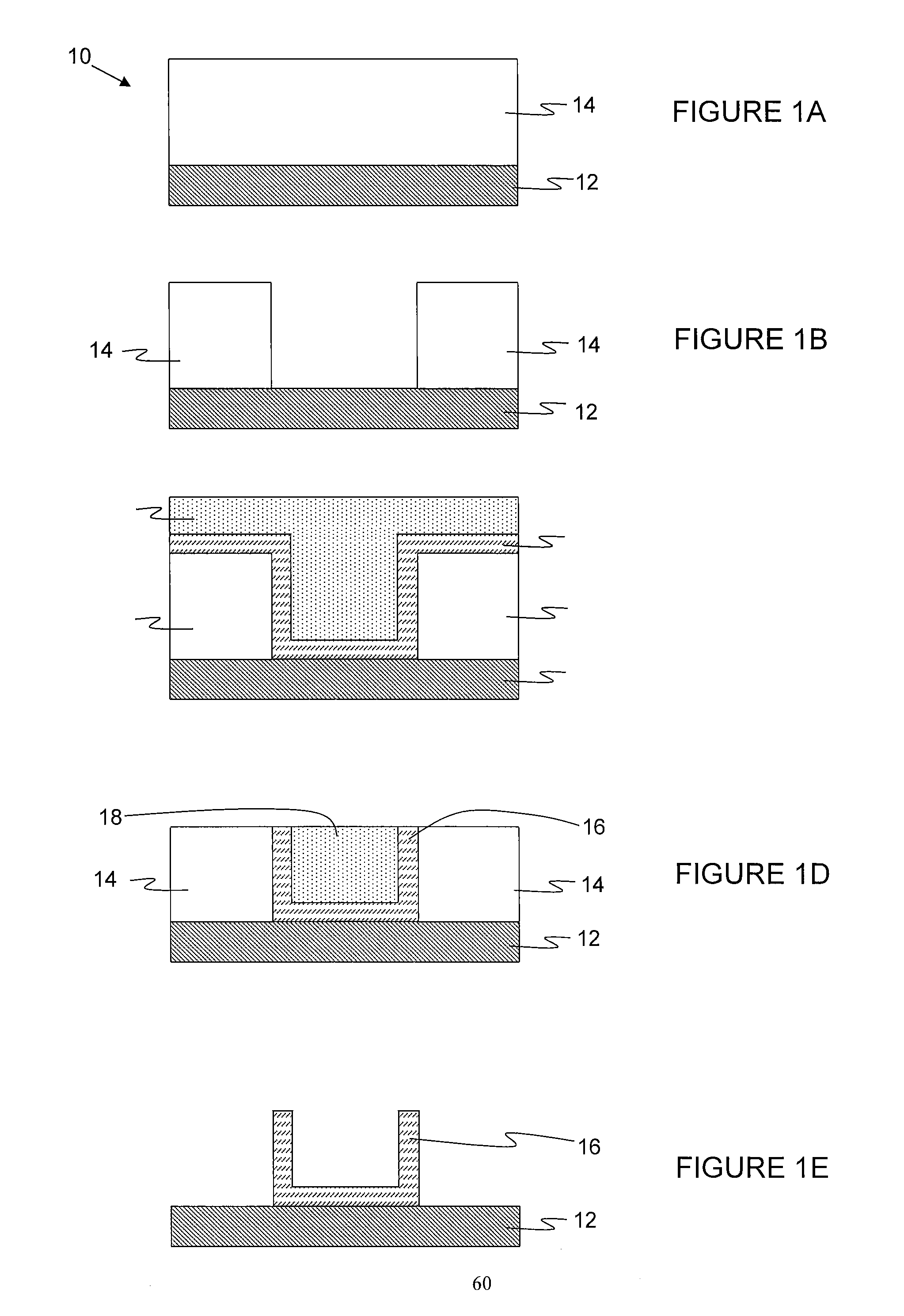

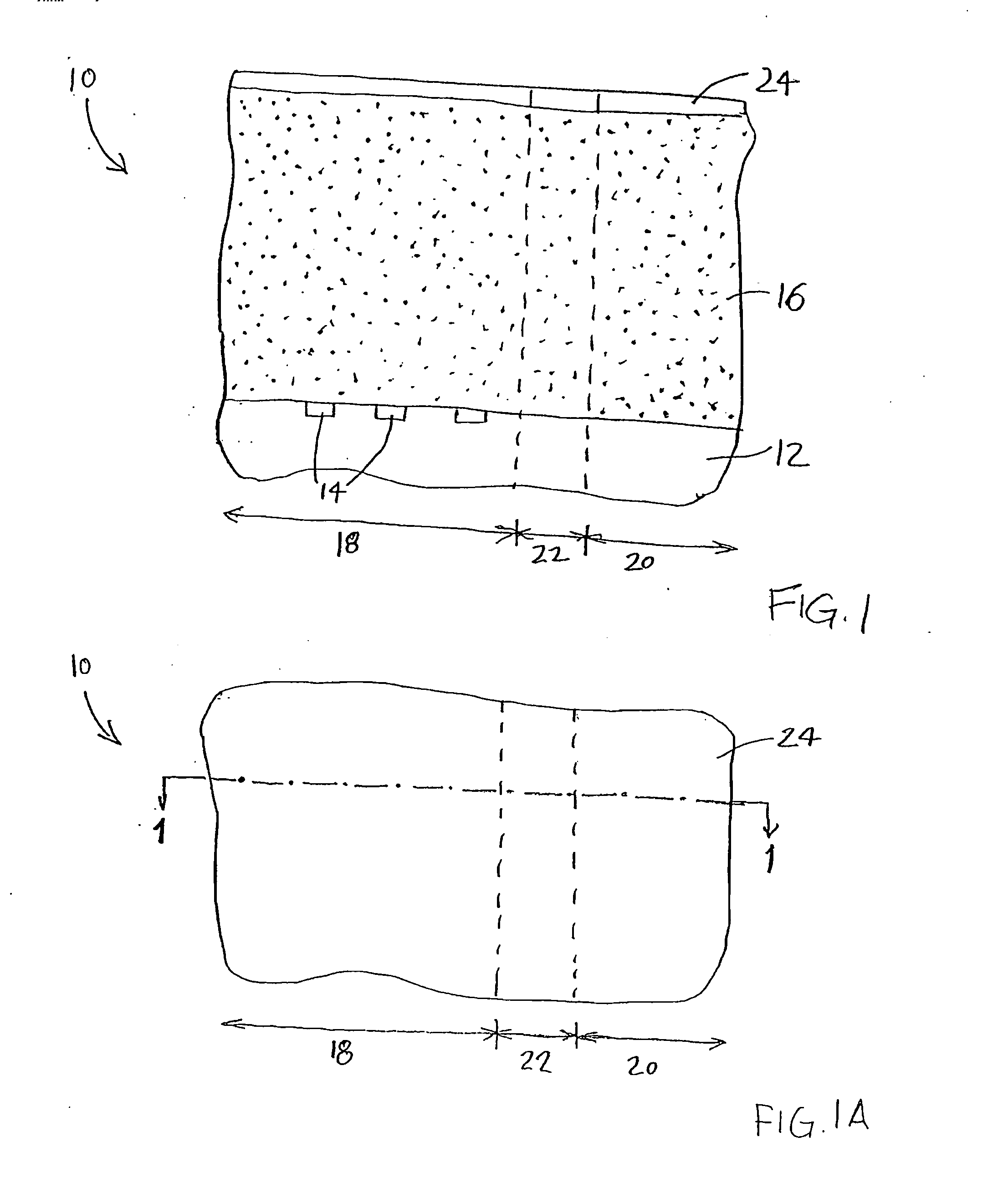

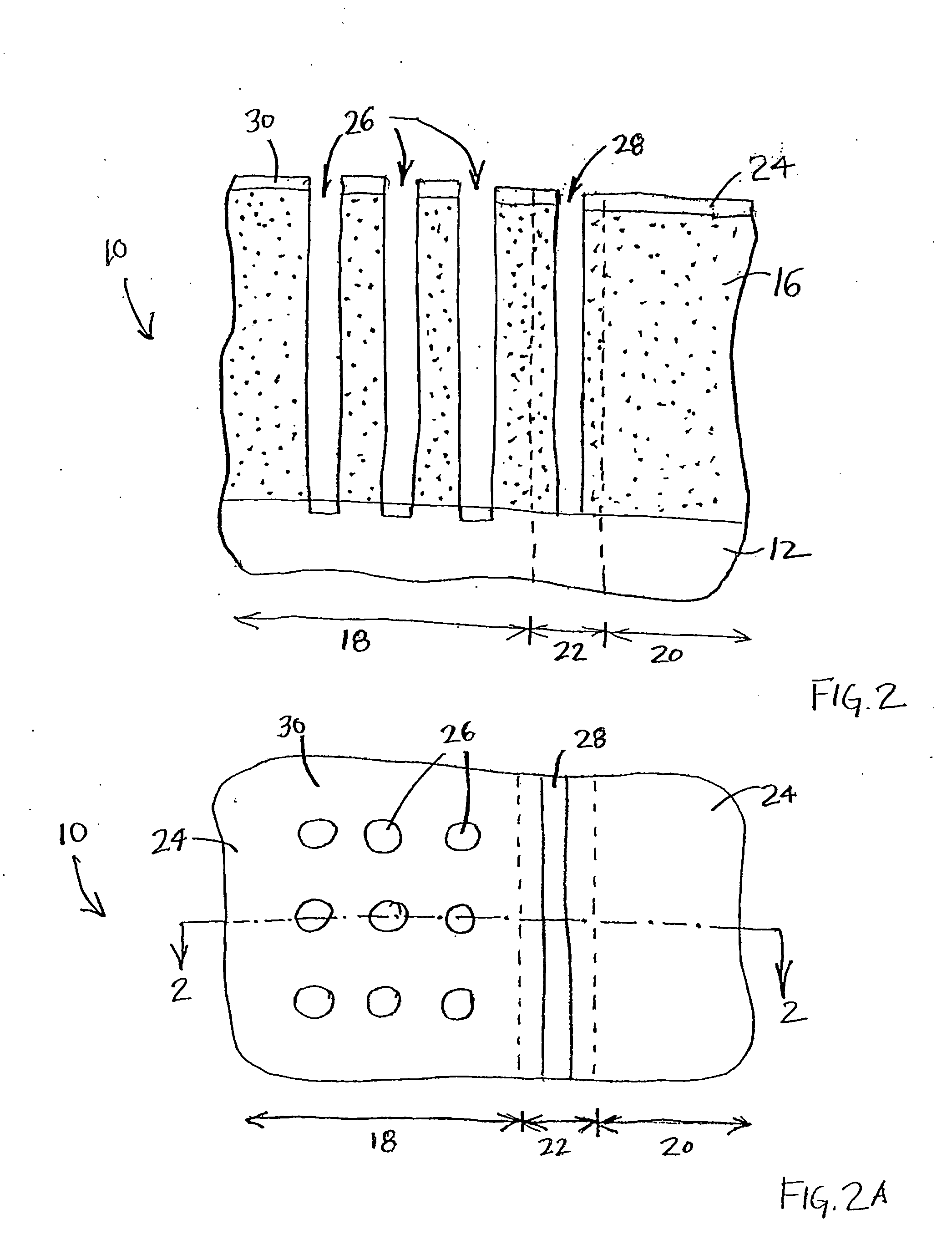

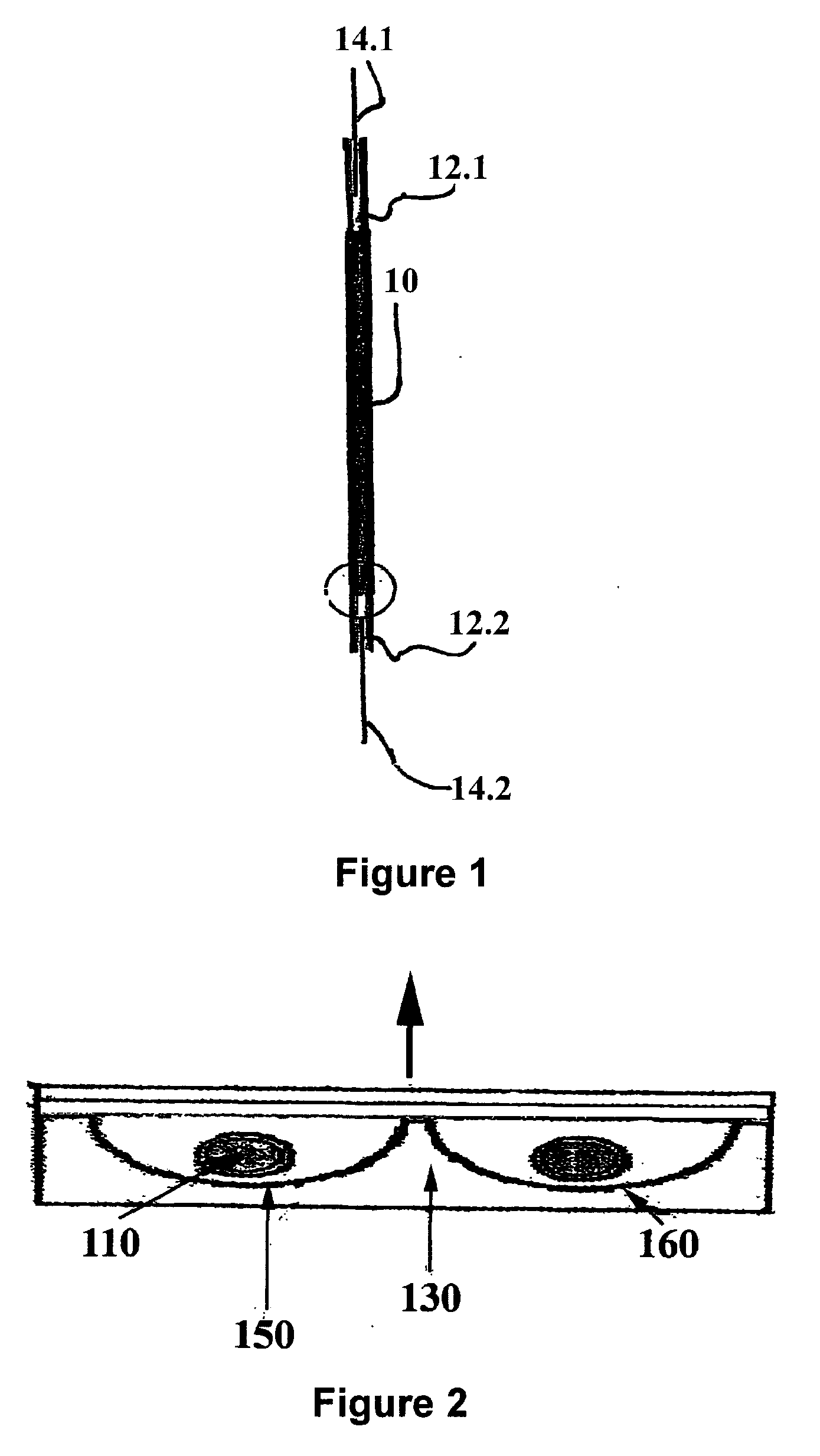

Shallow trench isolation for semiconductor devices

A shallow trench isolation structure is formed by providing a pad layer and a silicon nitride polish stop layer on a surface of a P-type silicon substrate. The silicon nitride polish stop layer and the pad oxide layer are patterned to define openings corresponding to portions of the substrate that will be etched to form trenches. Trenches are defined in the P-type silicon substrate by anisotropic etching. A boron doped oxide or glass is deposited along the walls and floor of the trench. An undoped TEOS oxide is provided over the doped oxide or glass to complete filling of the trench. The device is subjected to a high temperature reflow process, causing the dielectric materials to flow, partially planarizing the device and causing the boron of the first layer to diffuse into the walls and floor of the trench. Chemical mechanical polishing removes excess portions of the dielectric layers. The silicon nitride polish stop layer and the pad oxide layer are removed and conventional processing is performed to complete devices on the substrate. Diffusion of boron into the walls of the trench forms a self-aligned field doping region for the shallow trench isolation structure using relatively few processing steps.

Owner:UNITED MICROELECTRONICS CORP

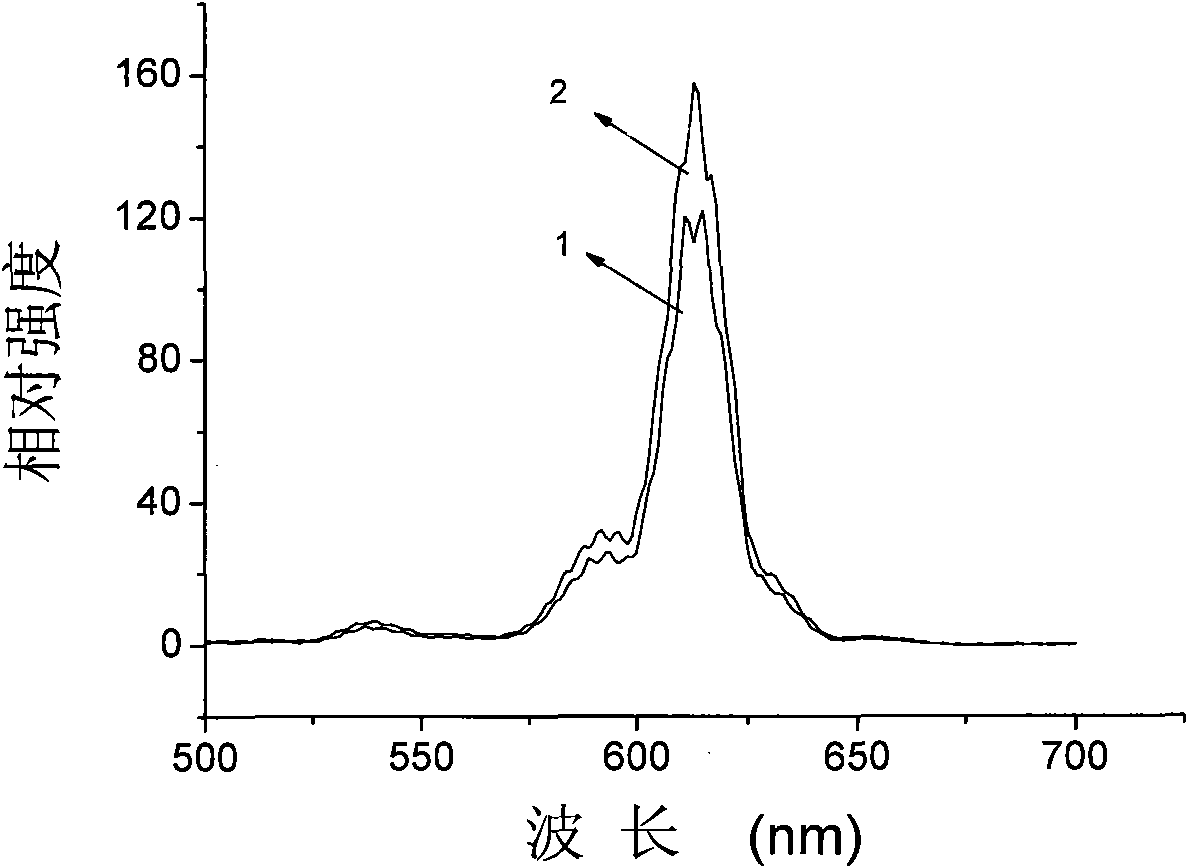

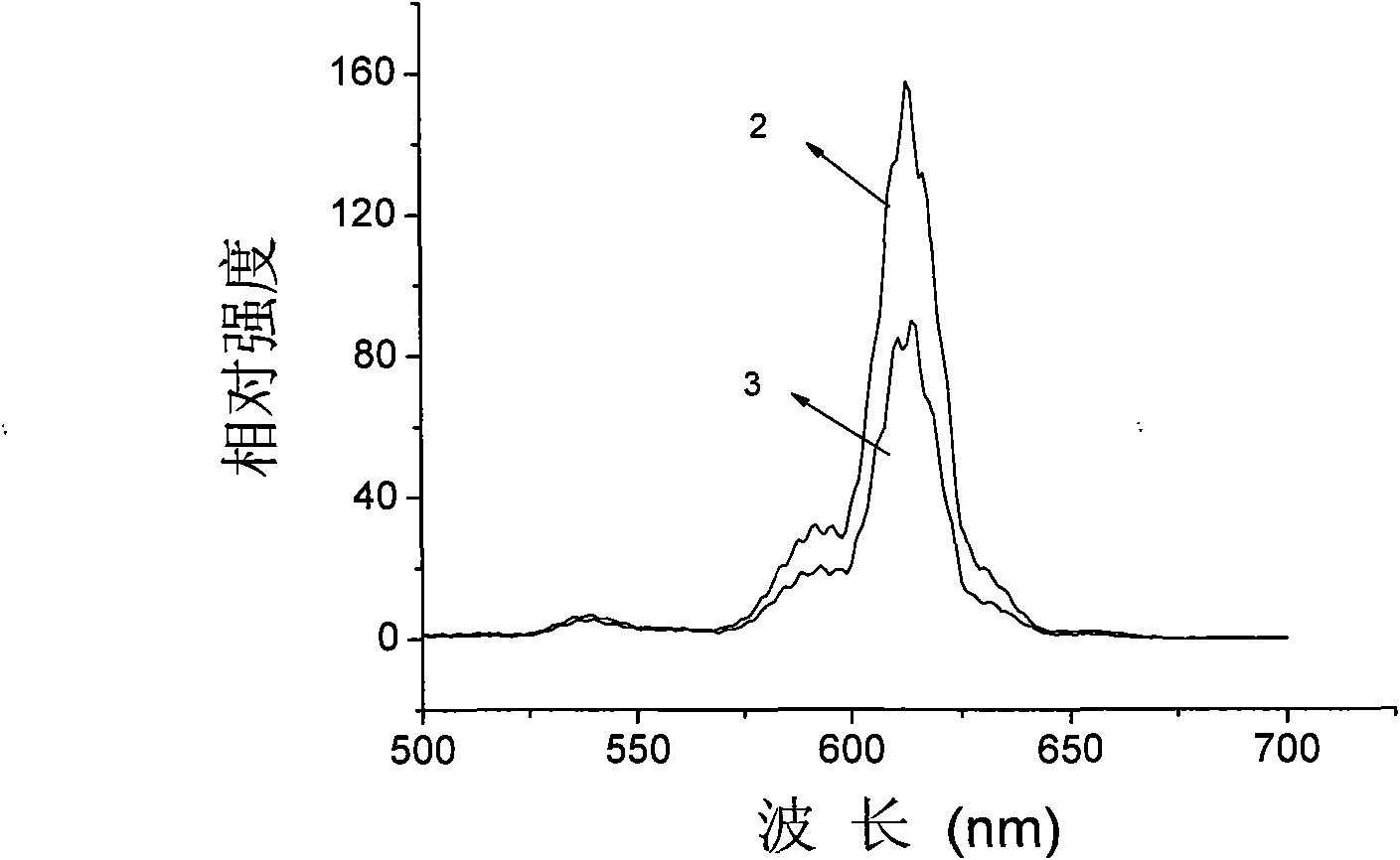

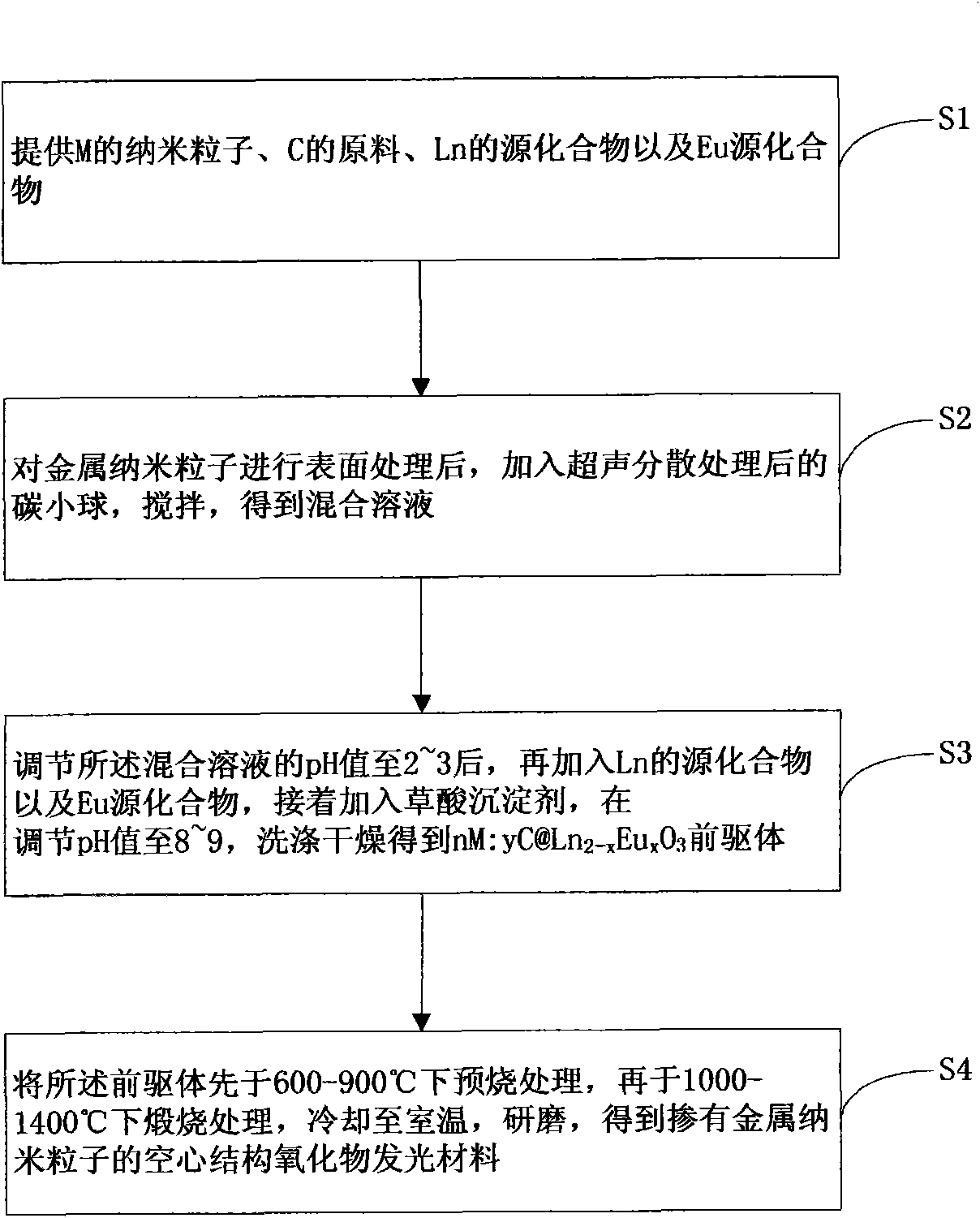

Metal-nanoparticle-doped oxide luminescent material with hollow structure and preparation method thereof

InactiveCN102337136AImprove luminosityEasy to operateLuminescent compositionsDoped oxideProcess conditions

The invention belongs to the field of a luminescent material and discloses a metal-nanoparticle-doped oxide luminescent material with a hollow structure and a preparation method thereof. The chemical formula of the oxide luminescent material is nM:yC@Ln2-xEuxO3; wherein M is one type of Ag, Au, Pt, Pd and Cu nano-particles, Ln is one of Gd, Y, La and Lu, C is a small carbon ball, x is greater than 0 but less than or equal to 1.5, n is the molar ratio of M nanoparticles to Ln2-xEuxO3 and is greater than 0 but less than or equal to 1*10-3, y is the molar ratio of C to Ln2-xEuxO3 and is greater than 0 but less than or equal to 1, @ means coating, Ln2-xEuxO3 is a shell, nM is a core, and nM:yC is of a hollow structure. The prepared oxide luminescent material has excellent luminescent performance. The preparation method has the advantages that the operation is simple, no pollution can be caused, the process conditions are simple and can be easily controlled, the preparation temperature is low and the like, energy can be saved, and industrial production can be facilitated.

Owner:OCEANS KING LIGHTING SCI&TECH CO LTD +1

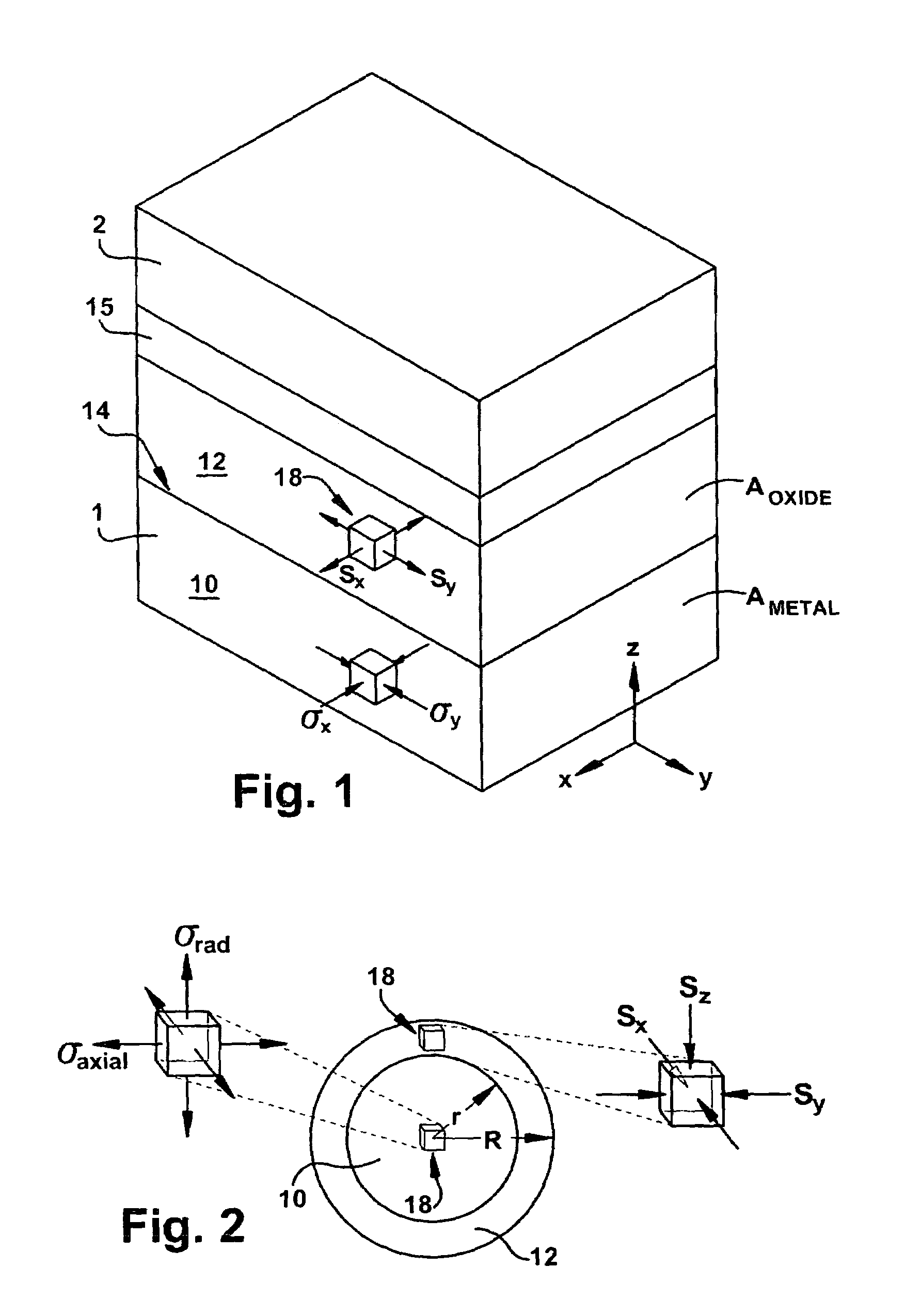

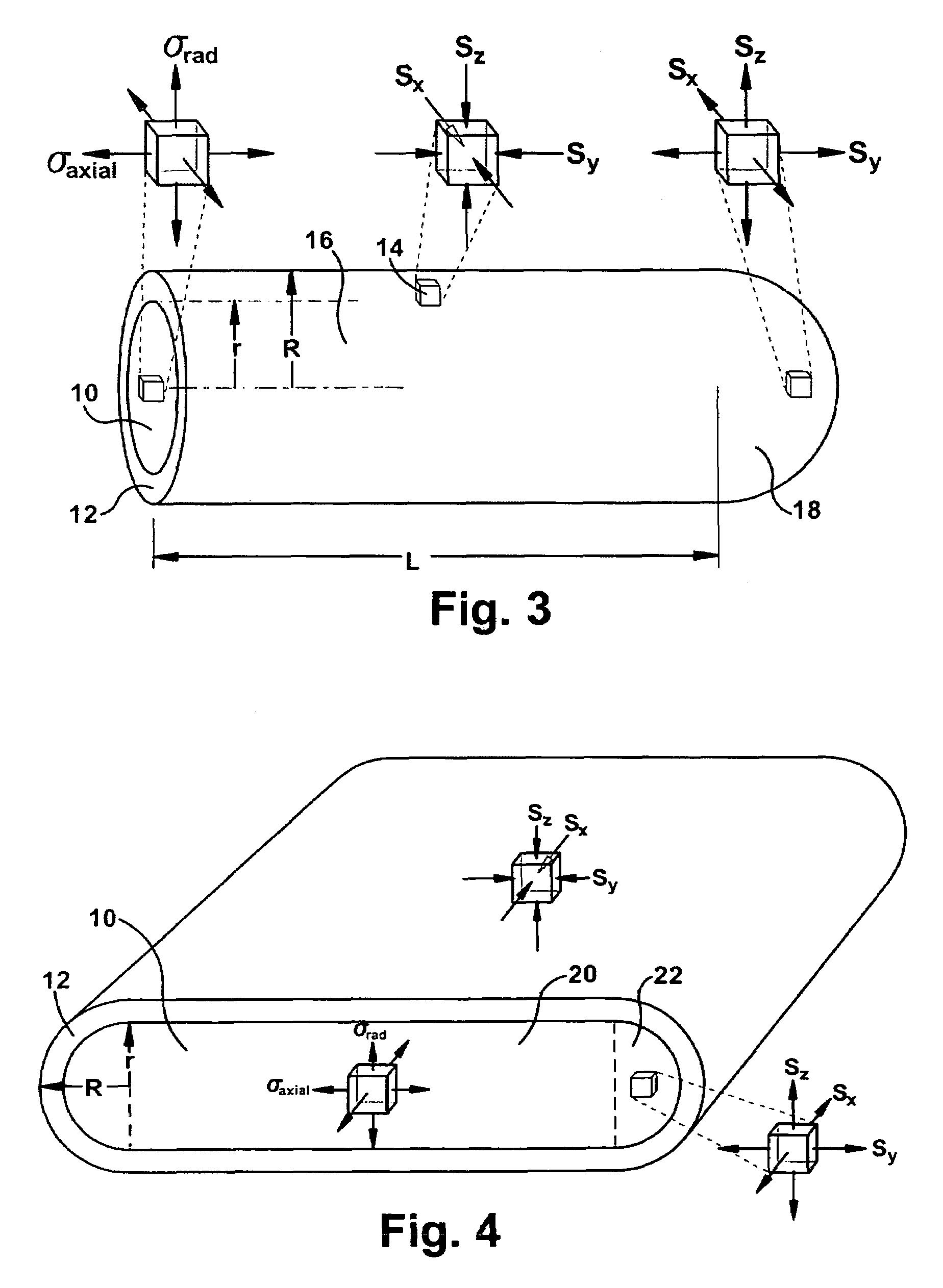

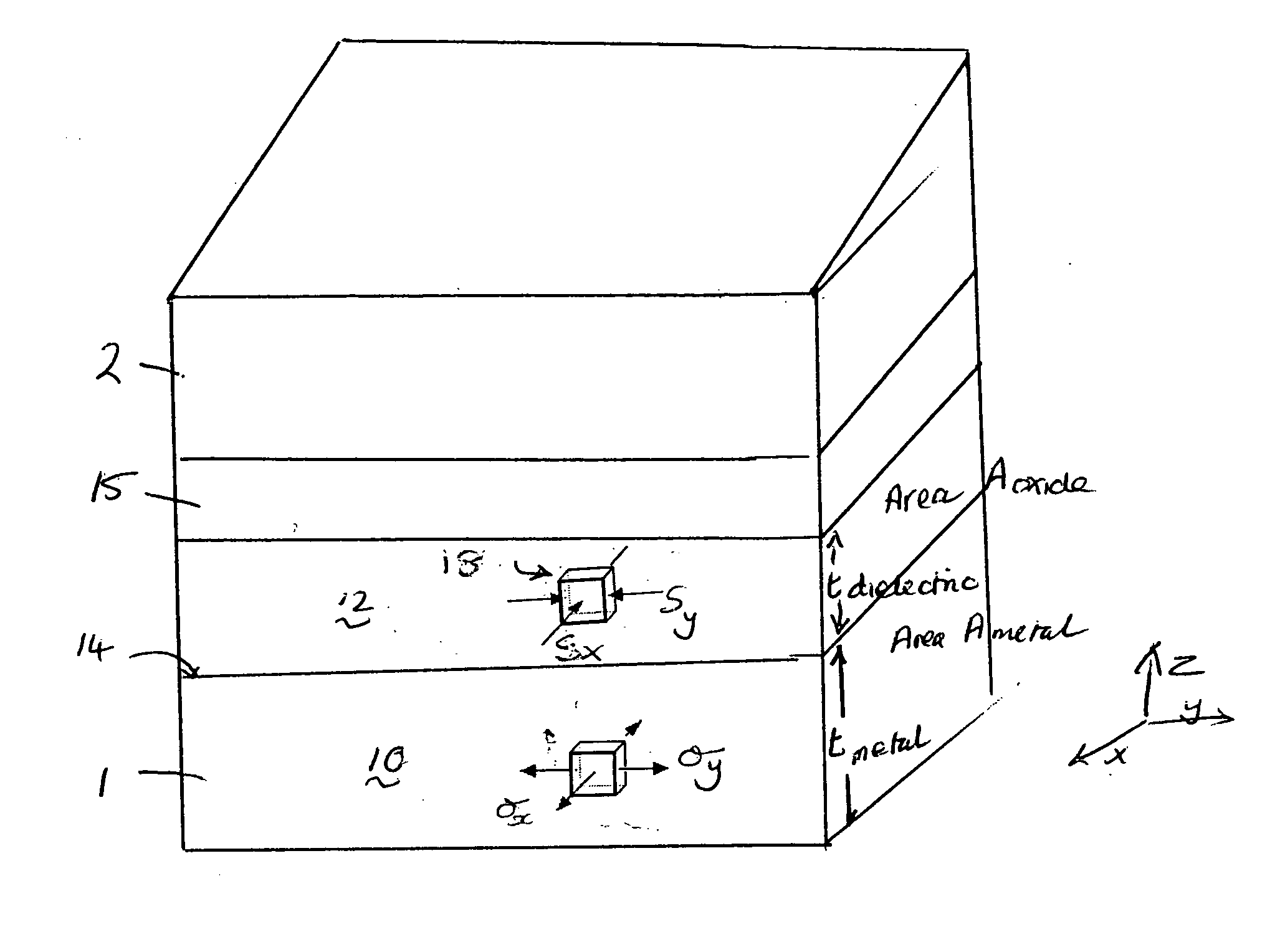

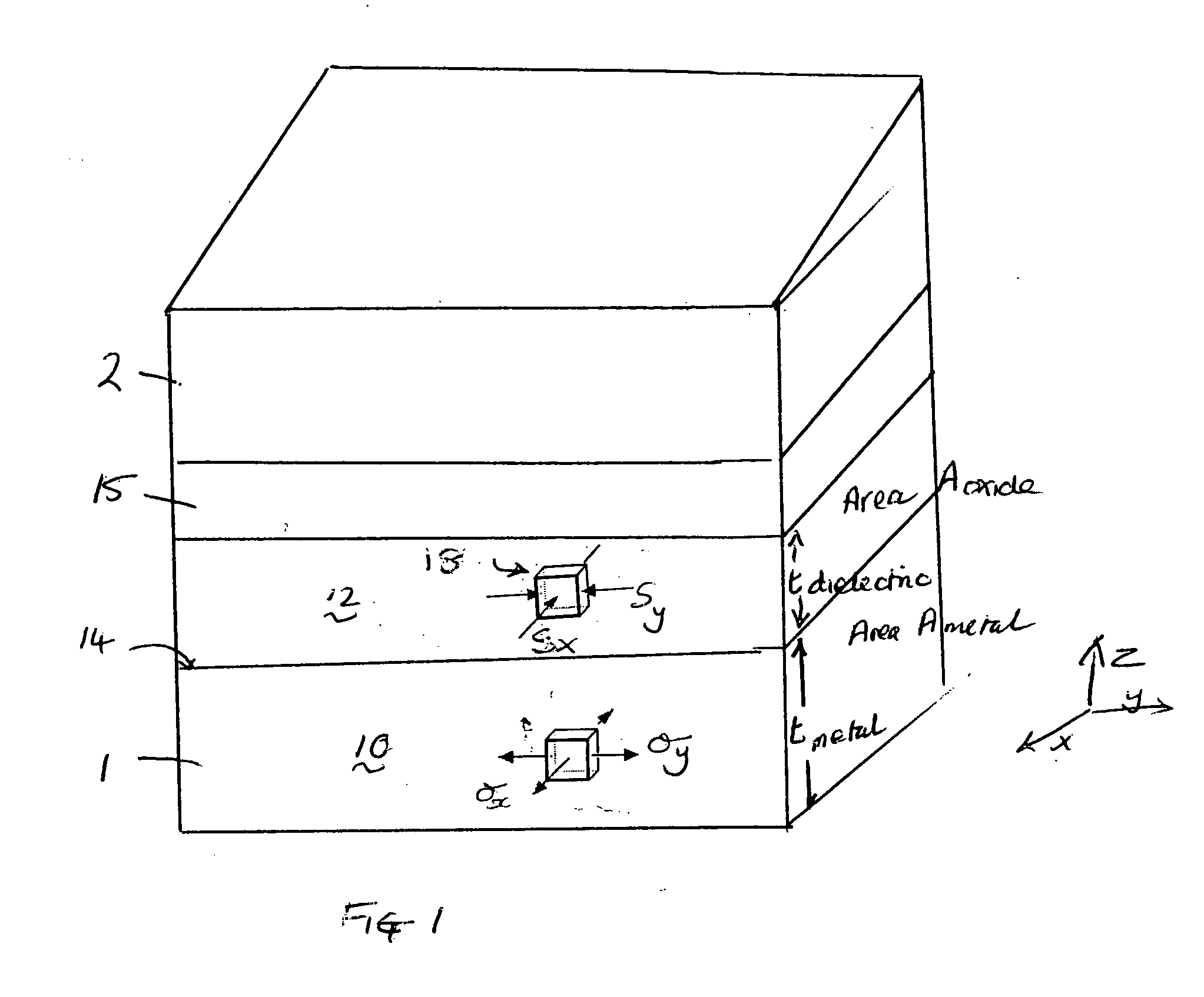

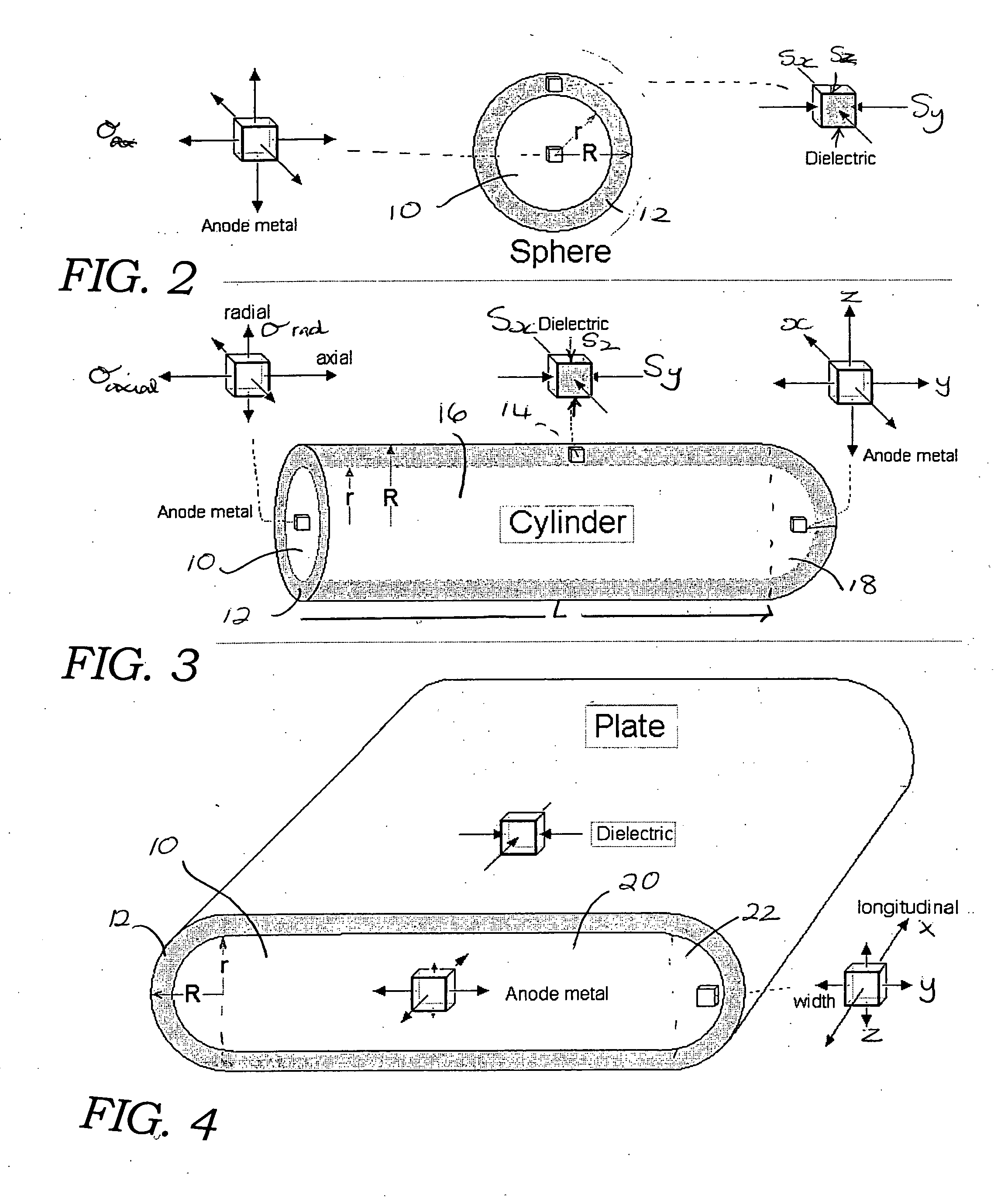

Strong substrate alloy and compressively stressed dielectric film for capacitor with high energy density

A capacitor anode (1) includes a substrate (10) which is formed from an alloy, metal, or metal compound which has a high tensile yield strength and high elastic modulus. The material has a composition which can be anodized, yielding an adherent and compressively stressed dielectric film (12) of pure, mixed, alloyed, or doped oxide that has a high usable dielectric strength (e.g., over 50 V / μm) and high dielectric constant (e.g., 20 to over 10,000). A capacitor formed from the anode has a high energy density.

Owner:CASE WESTERN RESERVE UNIV

Highly selective doped oxide etchant

InactiveUS20070207622A1High densityImprove etch selectivityDecorative surface effectsSemiconductor/solid-state device manufacturingHydrofluoric acidOrganic acid

Etch solutions for selectively etching doped oxide materials in the presence of silicon nitride, titanium nitride, and silicon materials, and methods utilizing the etch solutions, for example, in the construction of container capacitor constructions are provided. The etch solutions are formulated as a mixture of hydrofluoric acid and an organic acid having a dielectric constant less than water, optionally with an inorganic acid, and a pH of 1 or less.

Owner:MICRON TECH INC

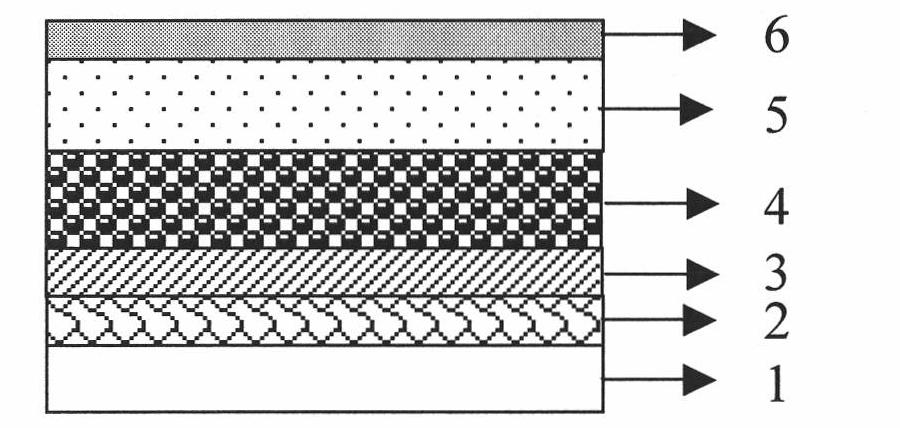

Non-vacuum solar spectrum selective absorption coating and preparation method thereof

ActiveCN102121757ASolve high temperature oxidationImprove absorption rateSolar heat devicesLayered productsIr reflectionLow emissivity

The invention relates to a non-vacuum solar spectrum selective absorption coating and a preparation method thereof. The preparation method comprises the following steps: (1) selecting copper or stainless steel with low infrared emissivity as a base material; (2) selecting oxide resistant to high-temperature oxidation, nitride and complex or doped oxide as a film material, wherein a metal or an alloy serves as a bonding force increased layer, metal nitride or pure metal serves as a high infrared reflecting layer, an absorption layer is composed of two conducting particle ceramic layers with different metal nitride conducting particle volume fractions, and aluminium nitride and aluminium oxide serve as an antireflection layer; (3) controlling the components and contents of different film materials by controlling gas flow and sputtering power; (4) cleaning the base material before the base material is placed into a vacuum chamber, and carrying out argon ion bombarding on the surface of the base material before sputtering is carried out; and (5) obtaining a multilayer coating, wherein the thickness of the coating is less than 500nm, and the coating has high absorption rate alpha (0.9-0.97) in the solar spectrum range (0.3-2.5microns) and has extremely low emissivity epsilon (0.02-0.18) in the infrared region (2.5-50microns).

Owner:GRIMAT ENG INST CO LTD

Backlight system with ir absorption properties

InactiveUS20090109654A1Stable against solarizationImprove stabilityIncadescent screens/filtersElectric discharge tubesDisplay deviceIr absorption

A backlight system for background illumination of displays or screens includes at least one light source with a glass envelope, whereby the glass composition of the glass envelope is doped with one or more doping oxides which absorb the IR-radiation, and / or whereby the glass envelope has an outside and / or inside coating which absorbs the IR-radiation, and / or whereby the backlight system has a coating on components other than the glass envelope, absorbing the IR-radiation.

Owner:SCHOTT AG

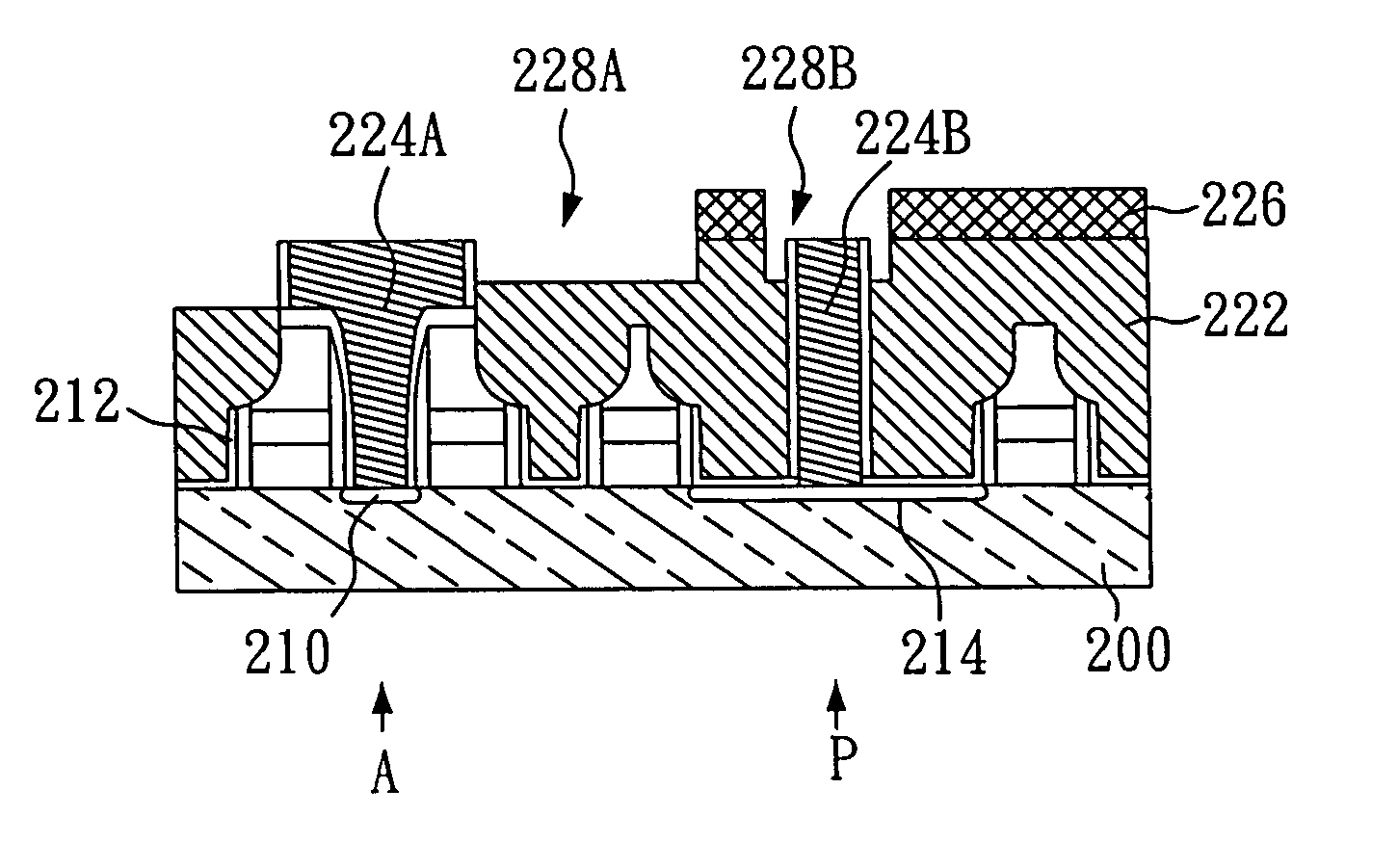

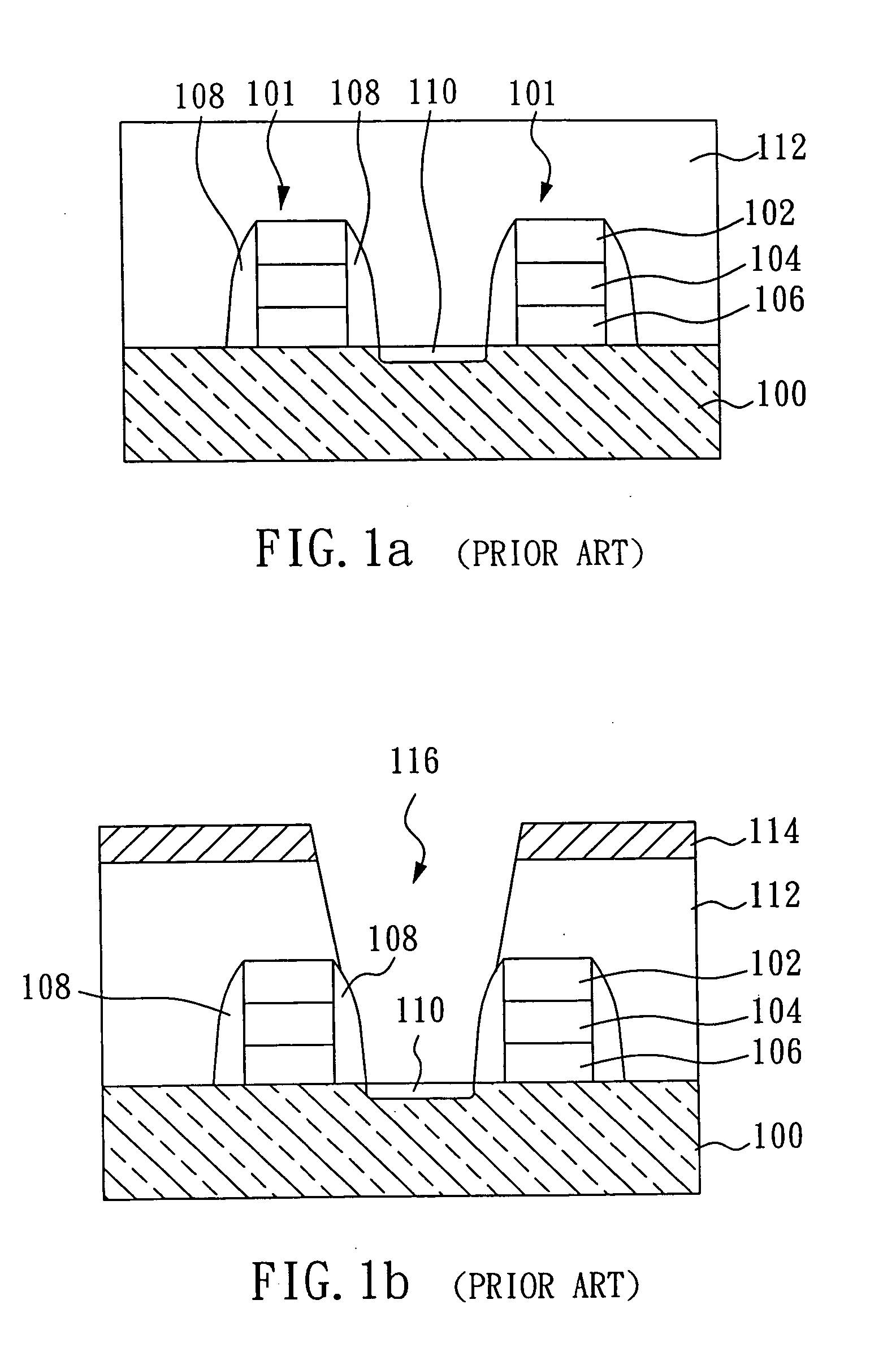

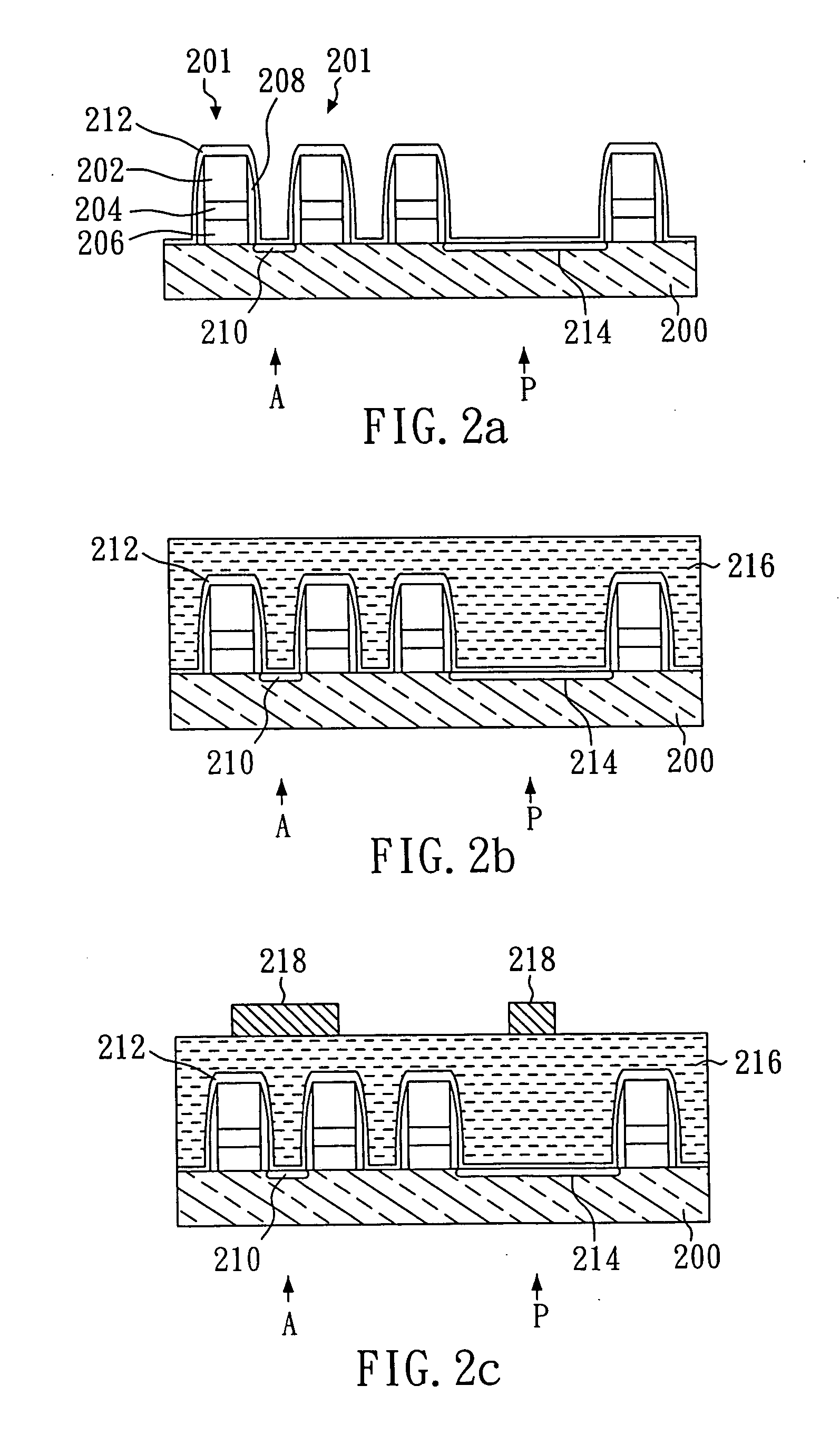

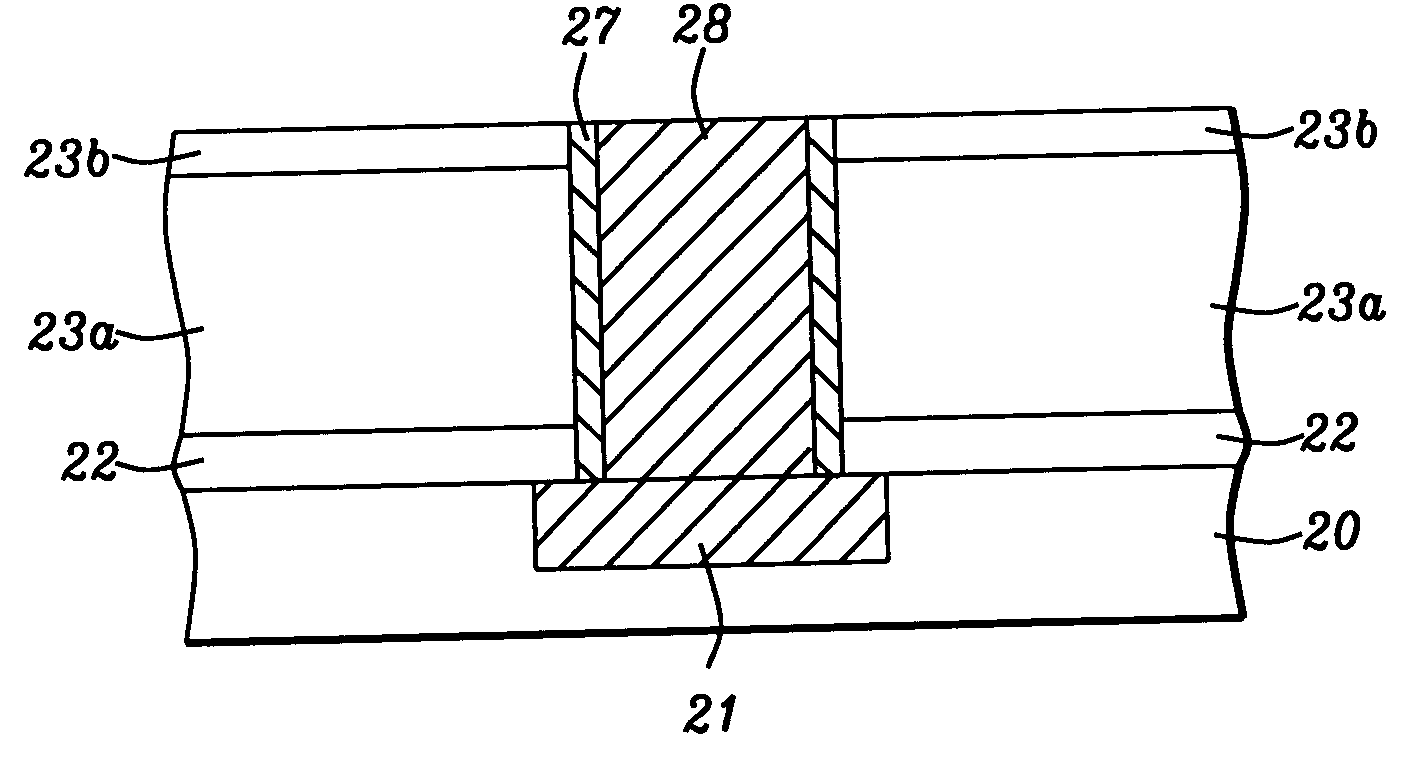

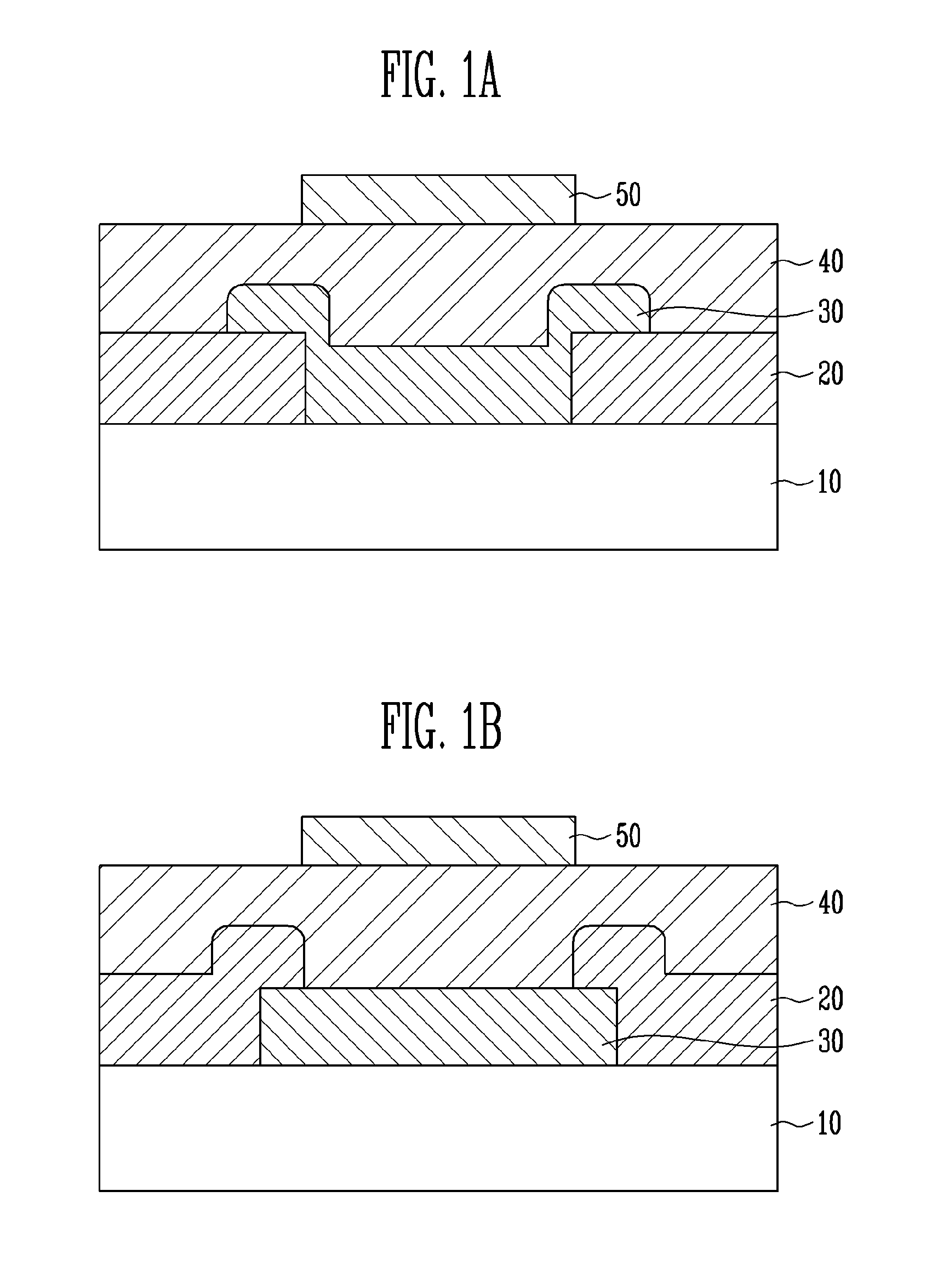

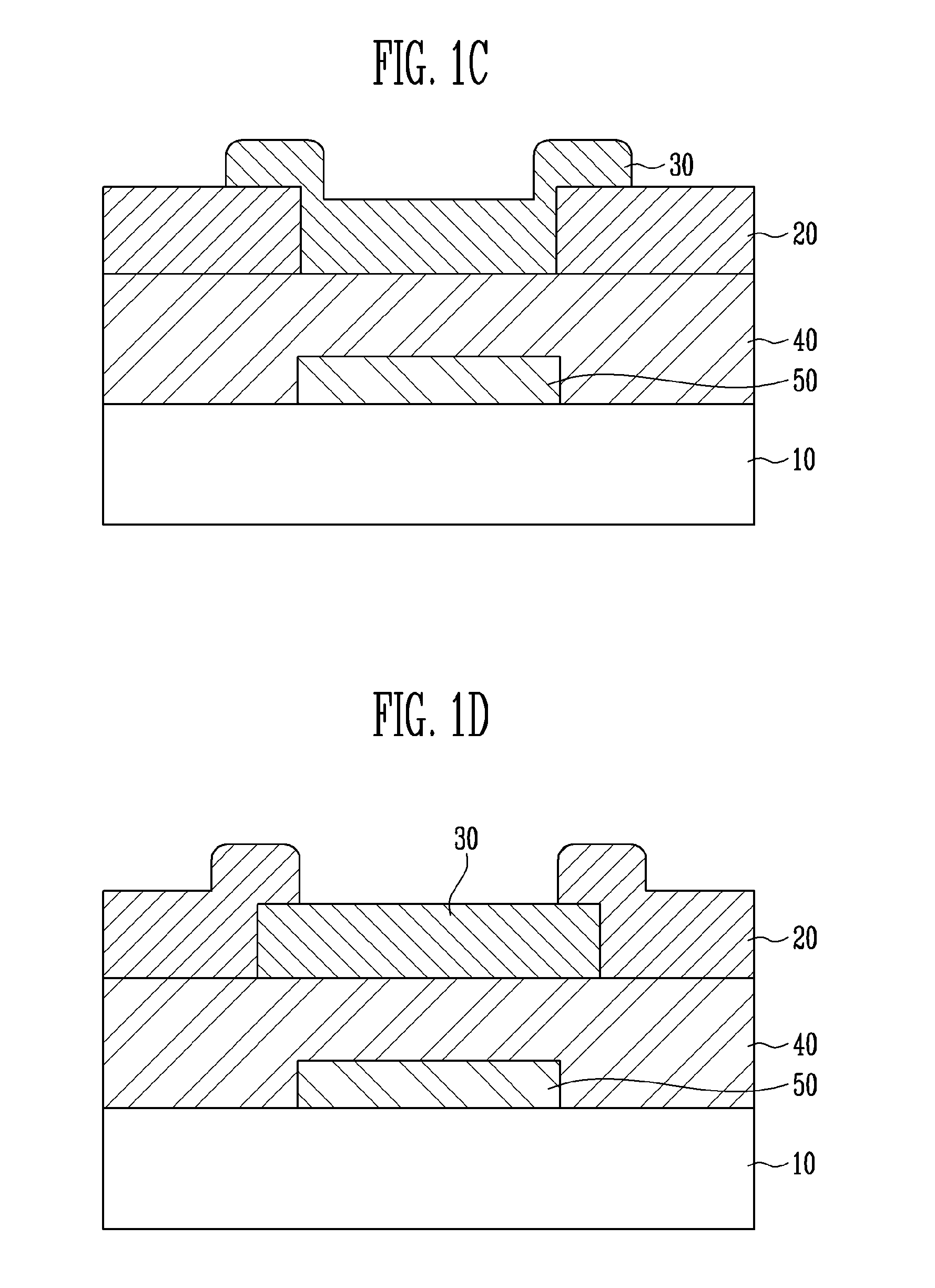

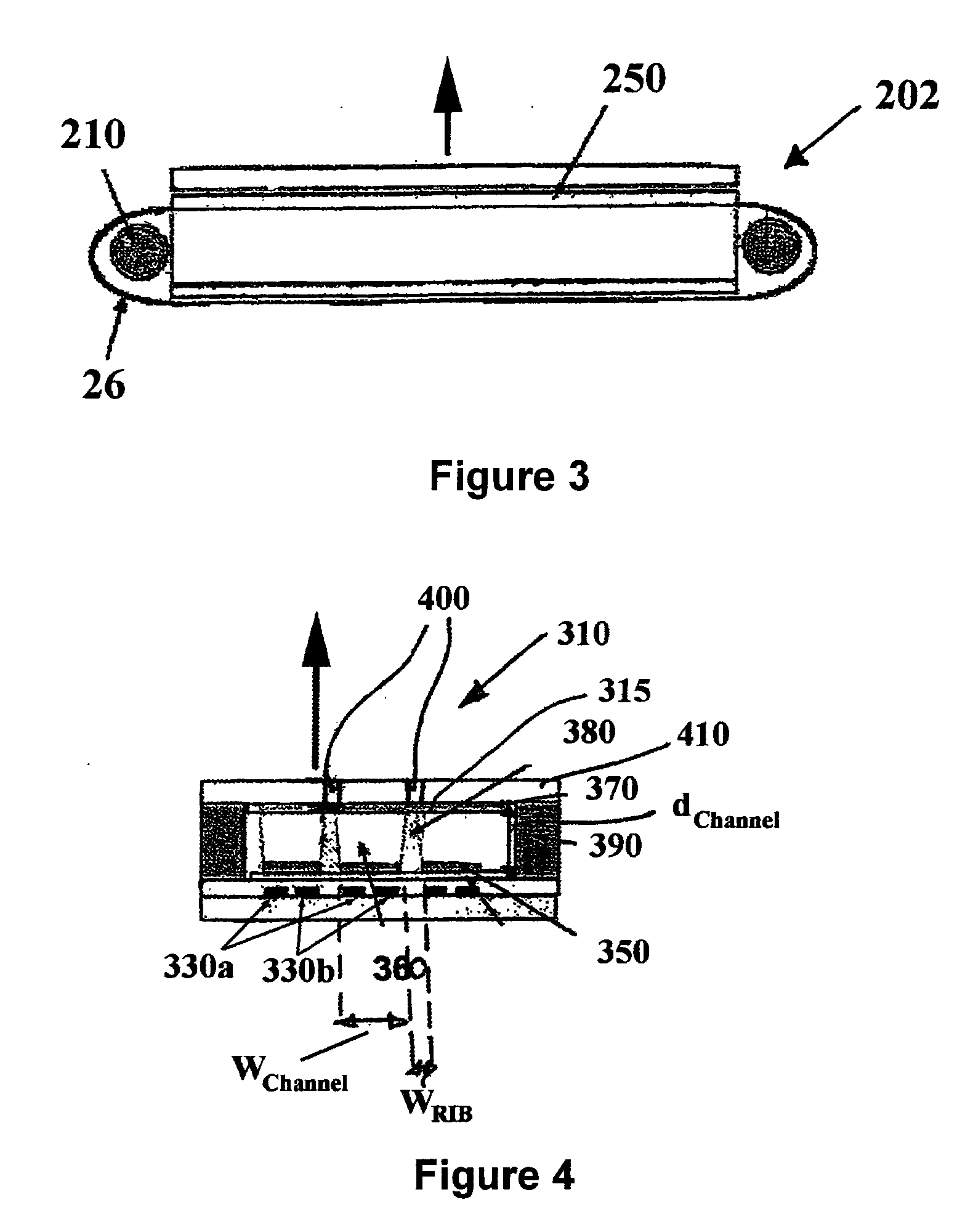

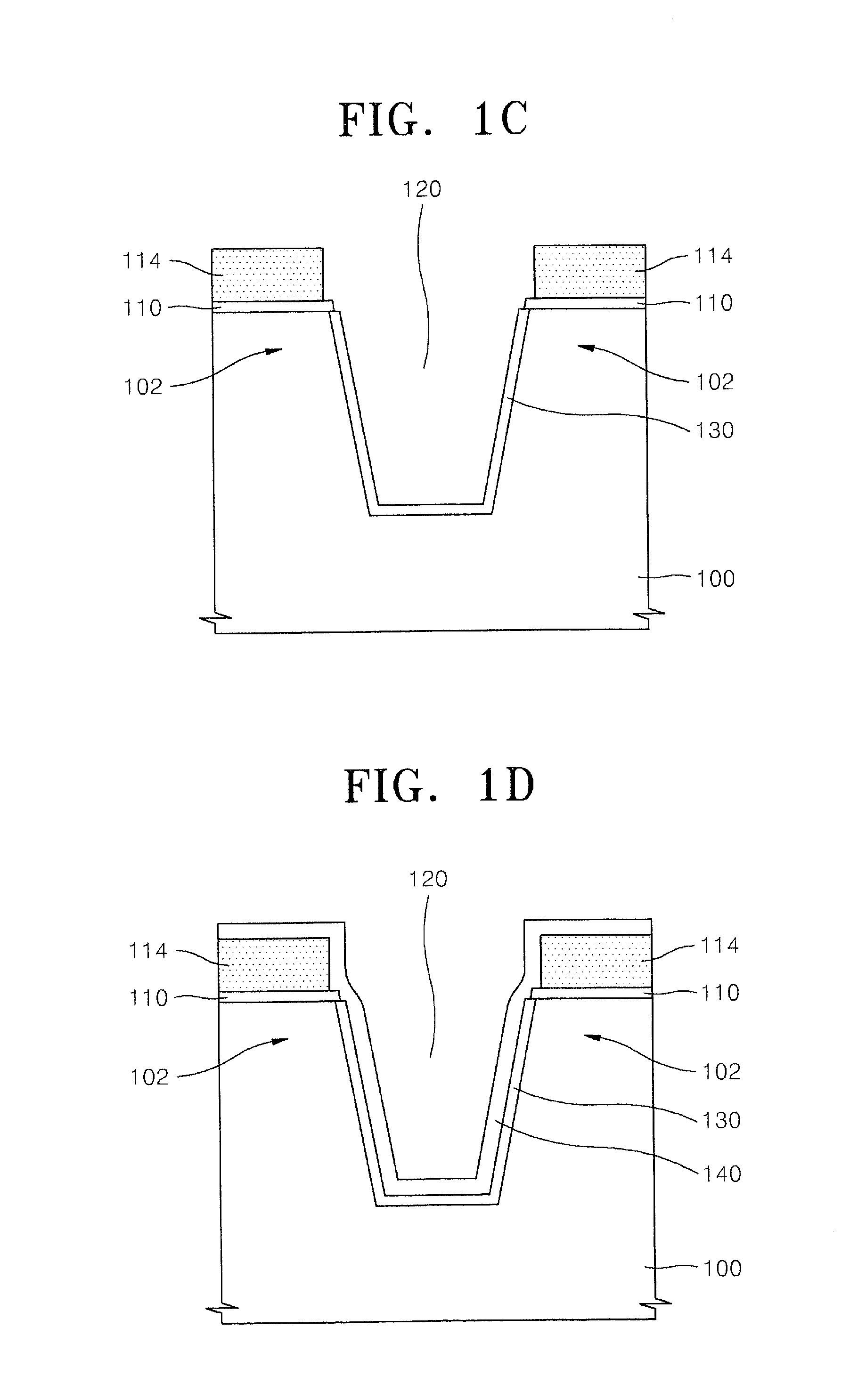

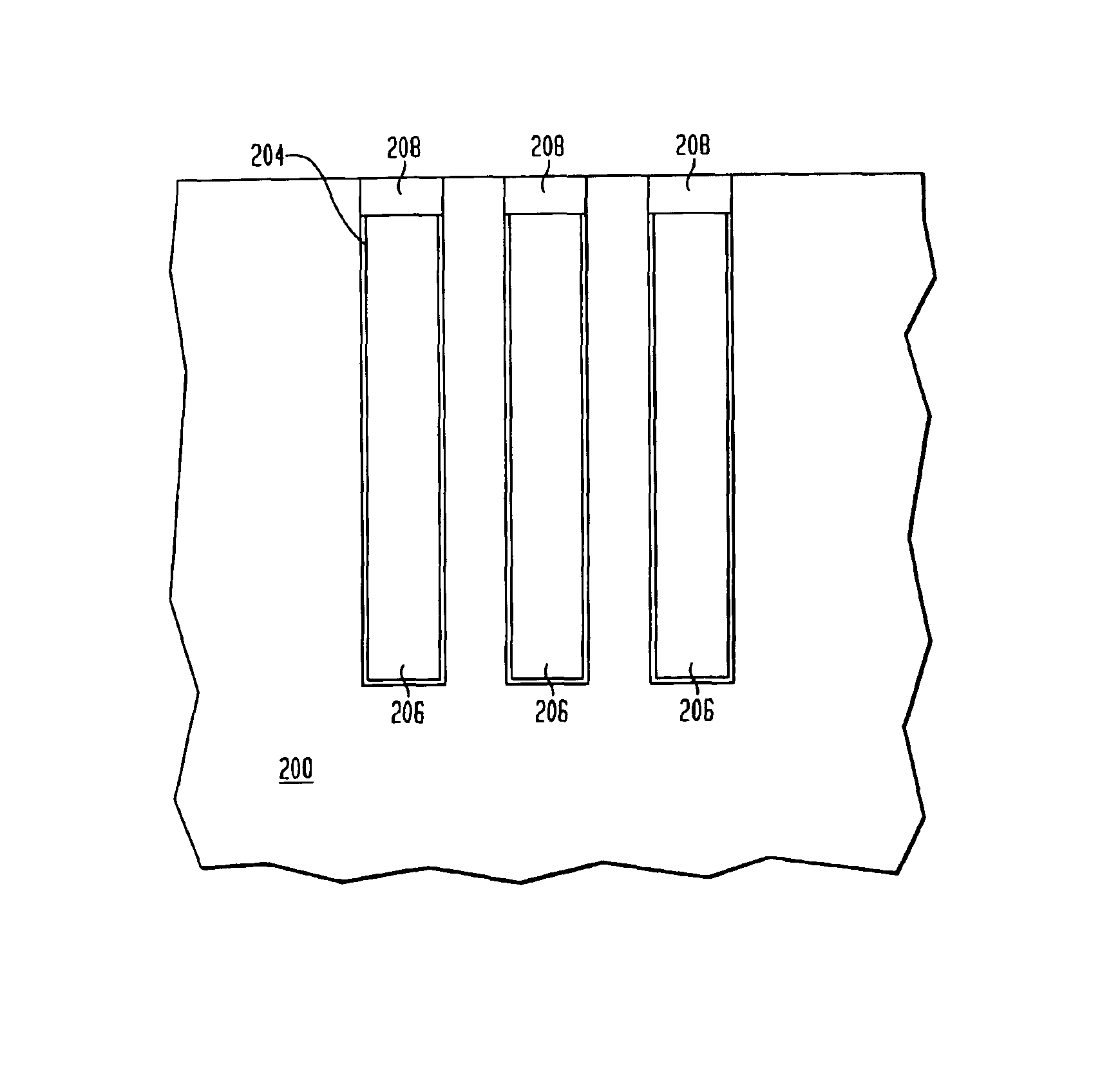

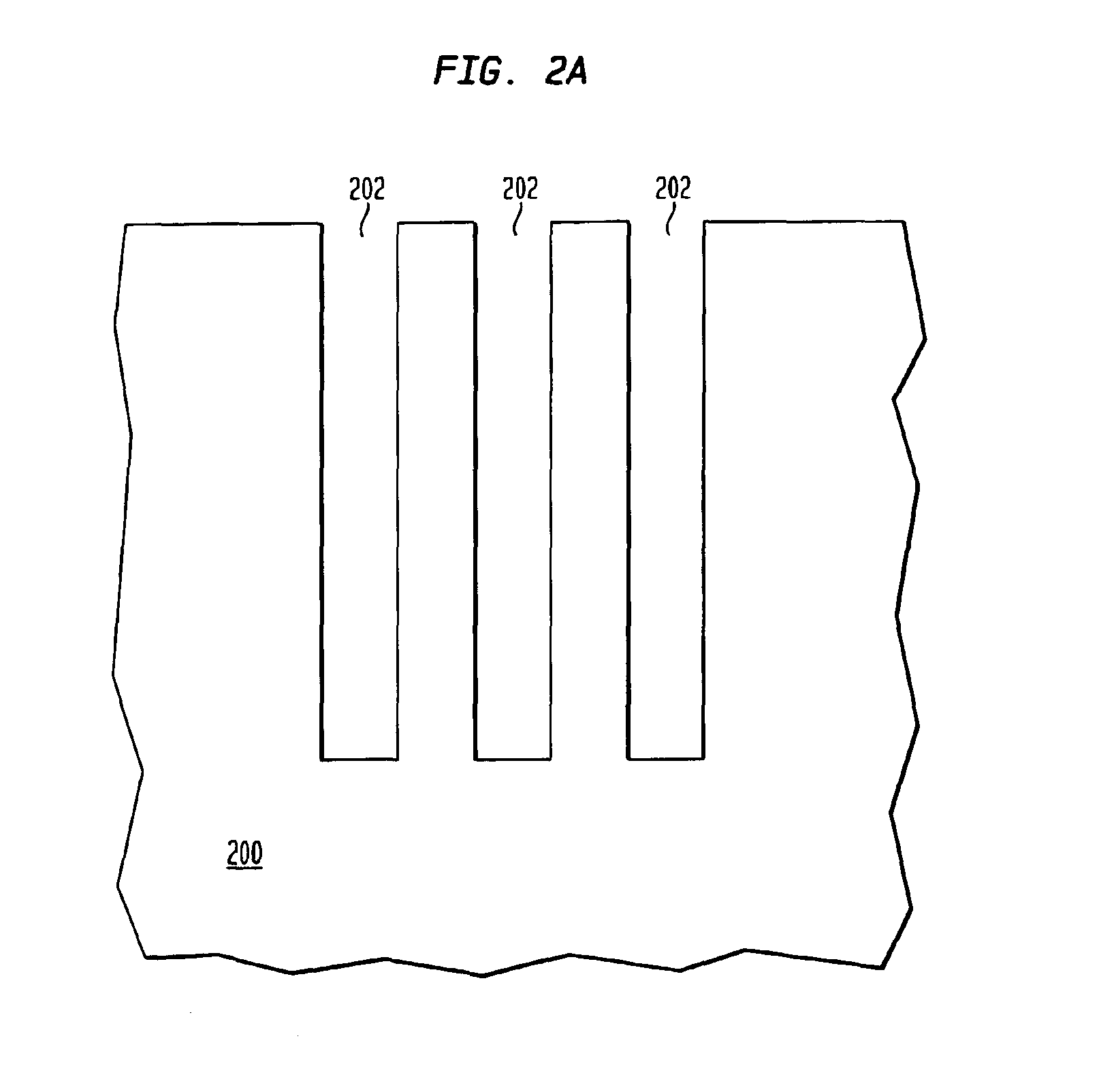

Shallow trench isolation structures for semiconductor devices including doped oxide film liners and methods of manufacturing the same

InactiveUS20090020845A1Improve corrosion resistanceSemiconductor/solid-state device detailsSolid-state devicesDopantEngineering

A semiconductor device includes a substrate having a trench, a sidewall liner that covers inner walls of the trench, a doped oxide film liner on the sidewall liner in the trench, and a gap-fill insulating film that buries the trench on the doped oxide film liner. In order to form the doped oxide film liner, an oxide film liner is doped with a dopant under a plasma atmosphere. Related methods are also disclosed.

Owner:SAMSUNG ELECTRONICS CO LTD

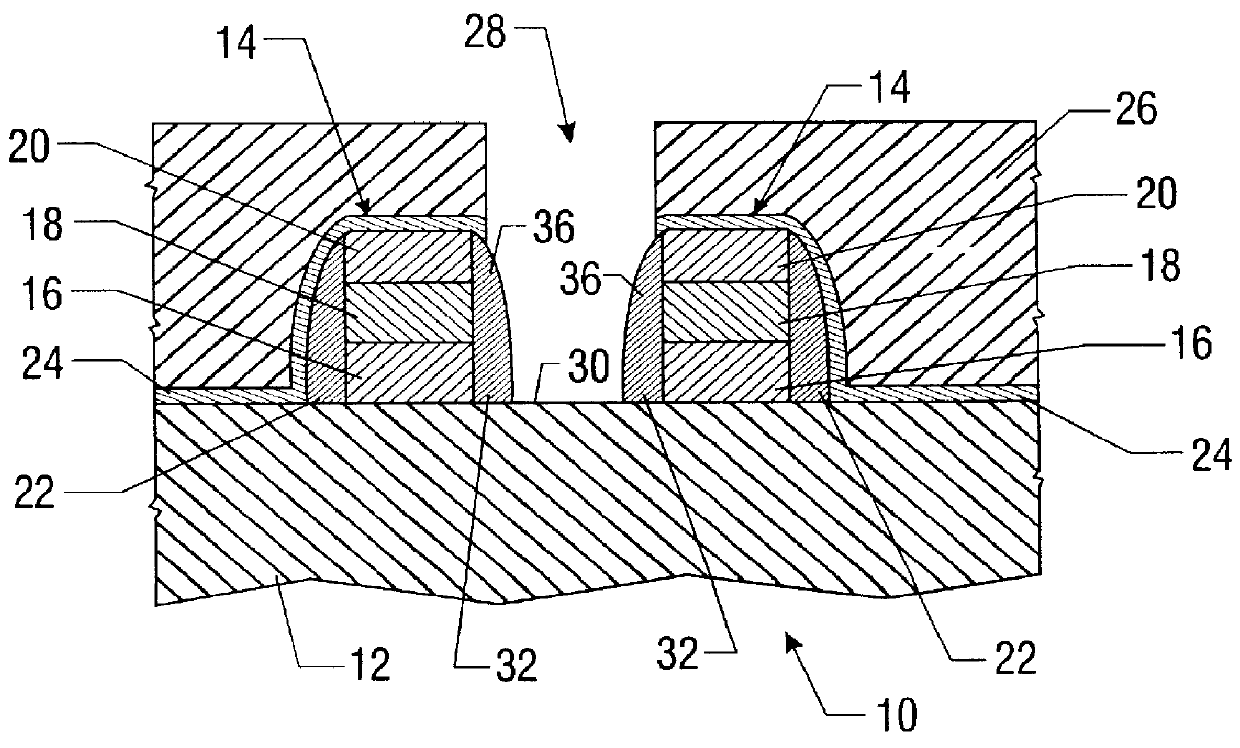

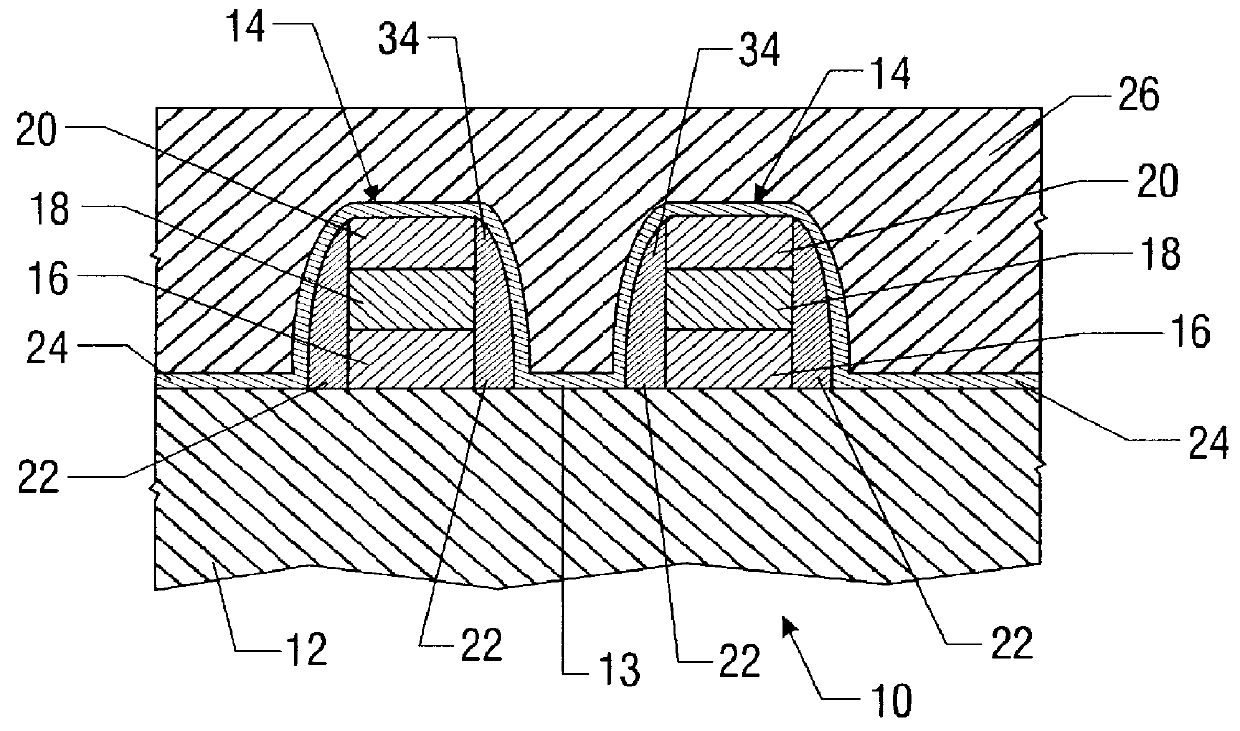

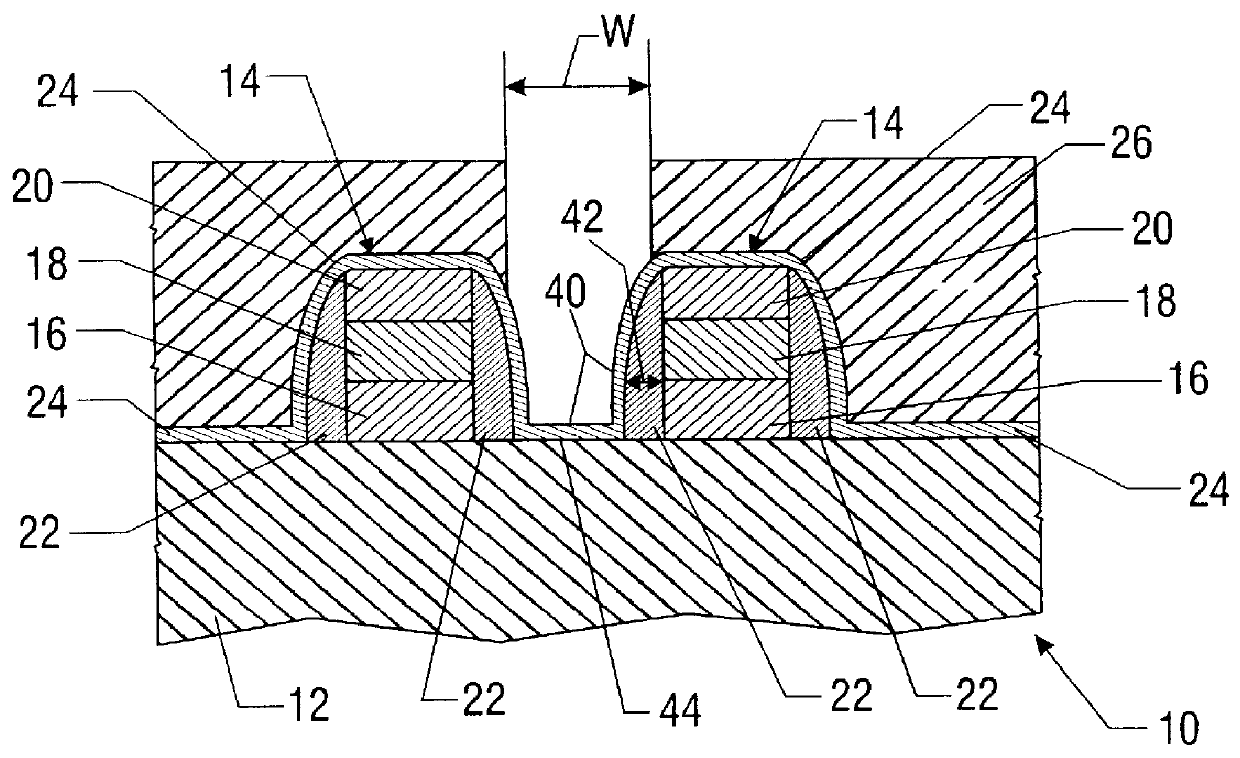

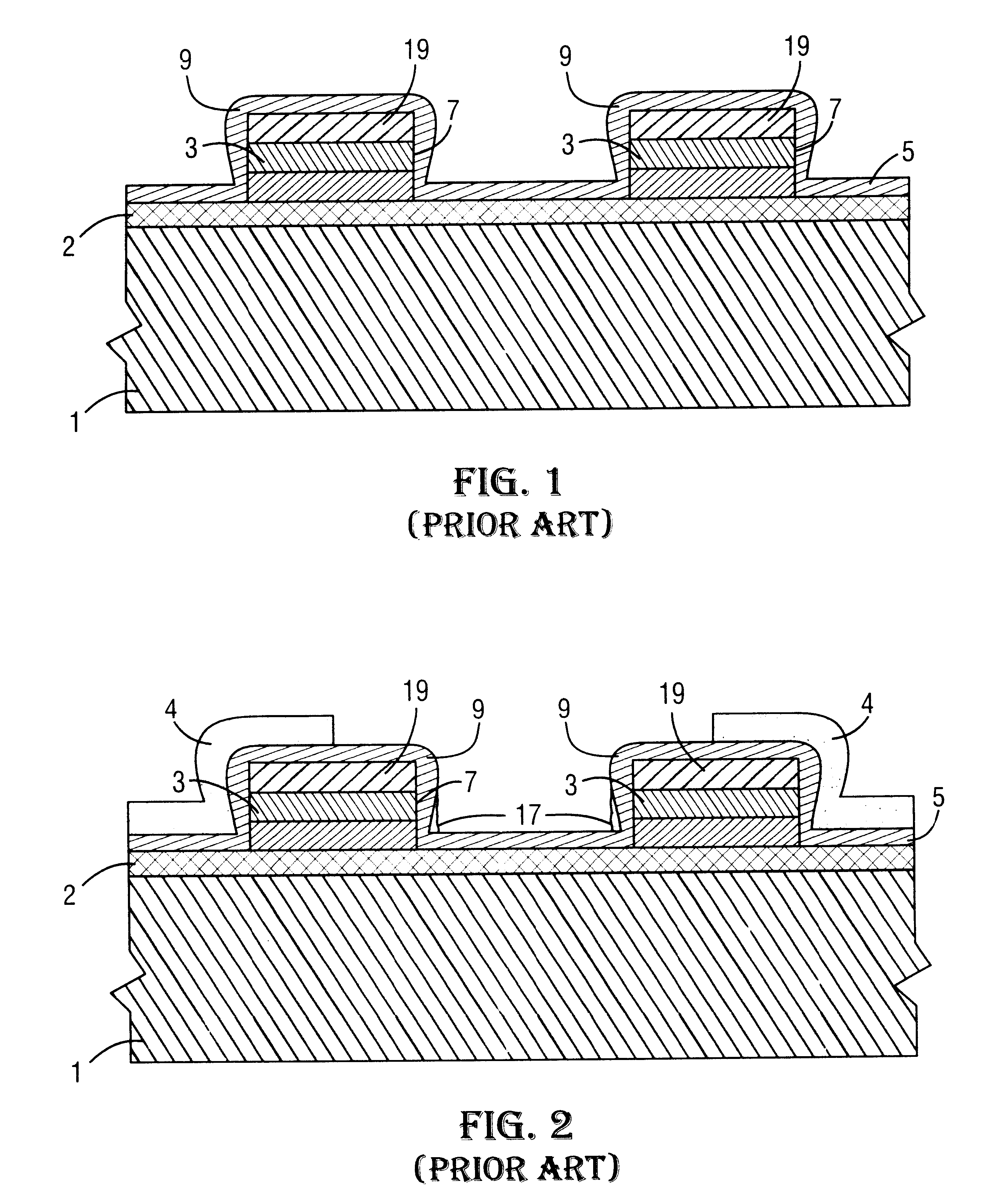

Semiconductor structure useful in a self-aligned contact having multiple insulation layers of non-uniform thickness

InactiveUS6018184ATransistorSemiconductor/solid-state device detailsInsulation layerSemiconductor structure

A semiconductor processing method is provided for making contact openings. It includes depositing several insulative layers and performing an anisotropic etch. One layer is a conformal oxide covering the contact area and adjacent structures. A second layer is a breadloafed oxide deposited over the contact area and adjacent structures. A third layer is a doped oxide deposited over the two lower layers. The anisotropic etch is performed through the oxide layers to the contact area located on a lower substrate. The etch is selectively more rapid in the third oxide than in the two other oxides. The breadloafed oxide provides additional protection and reduces the risk of etch-through to conductive structures adjacent the contact area. An alternate embodiment replaces the two lowest oxide layers by a breadloafed nitride layer. In this embodiment, the anisotropic etch is selectively more rapid in oxides than in nitrides.

Owner:MICRON TECH INC

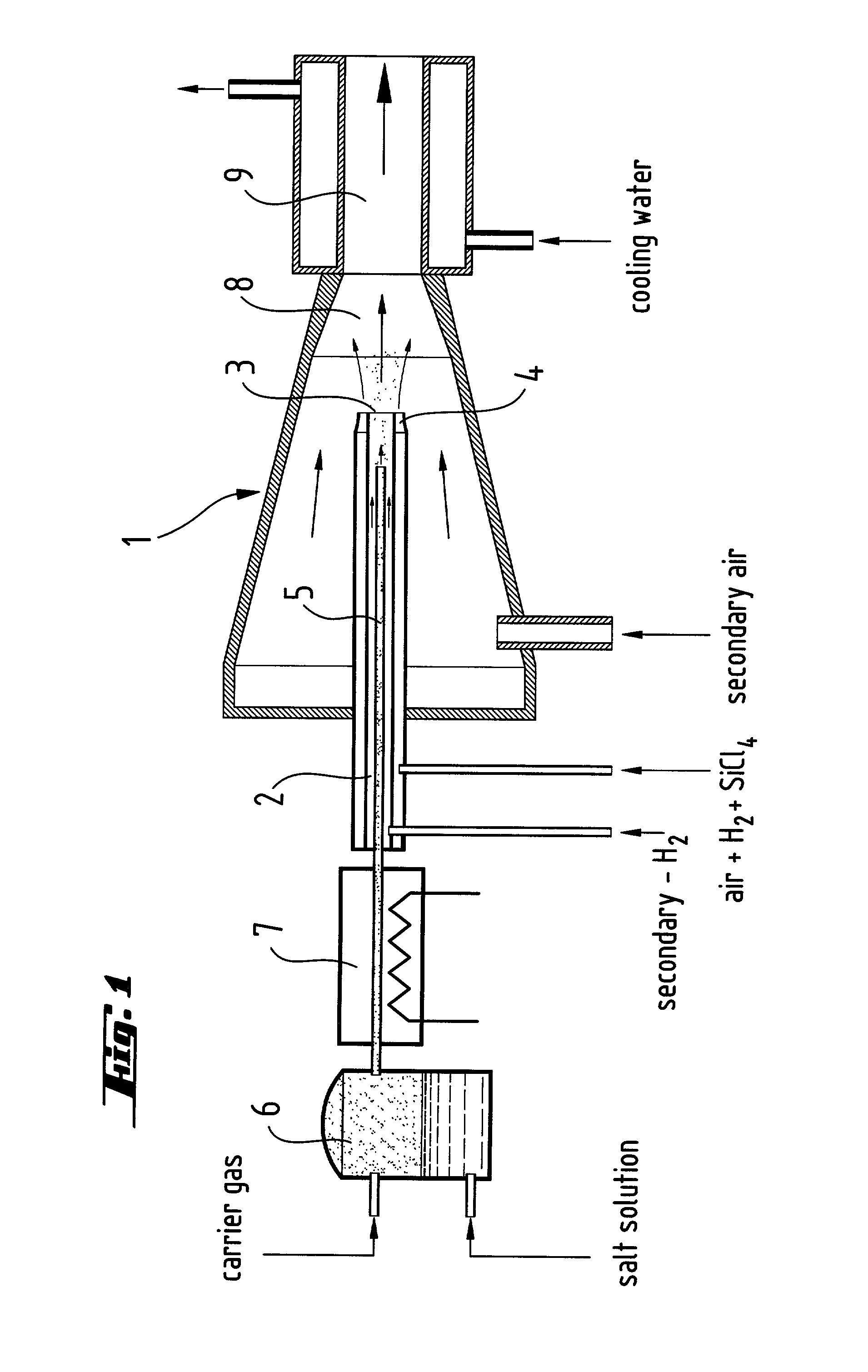

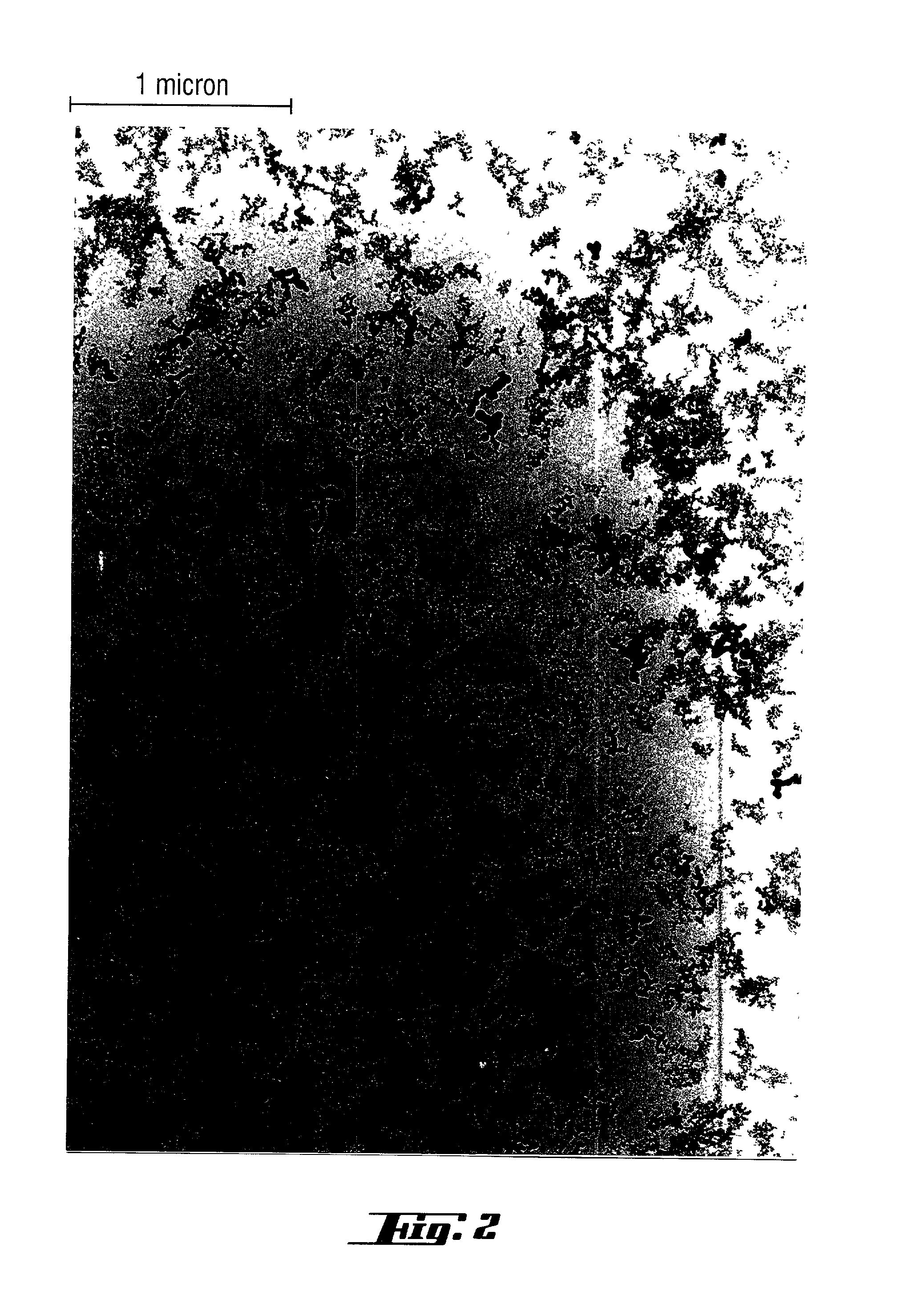

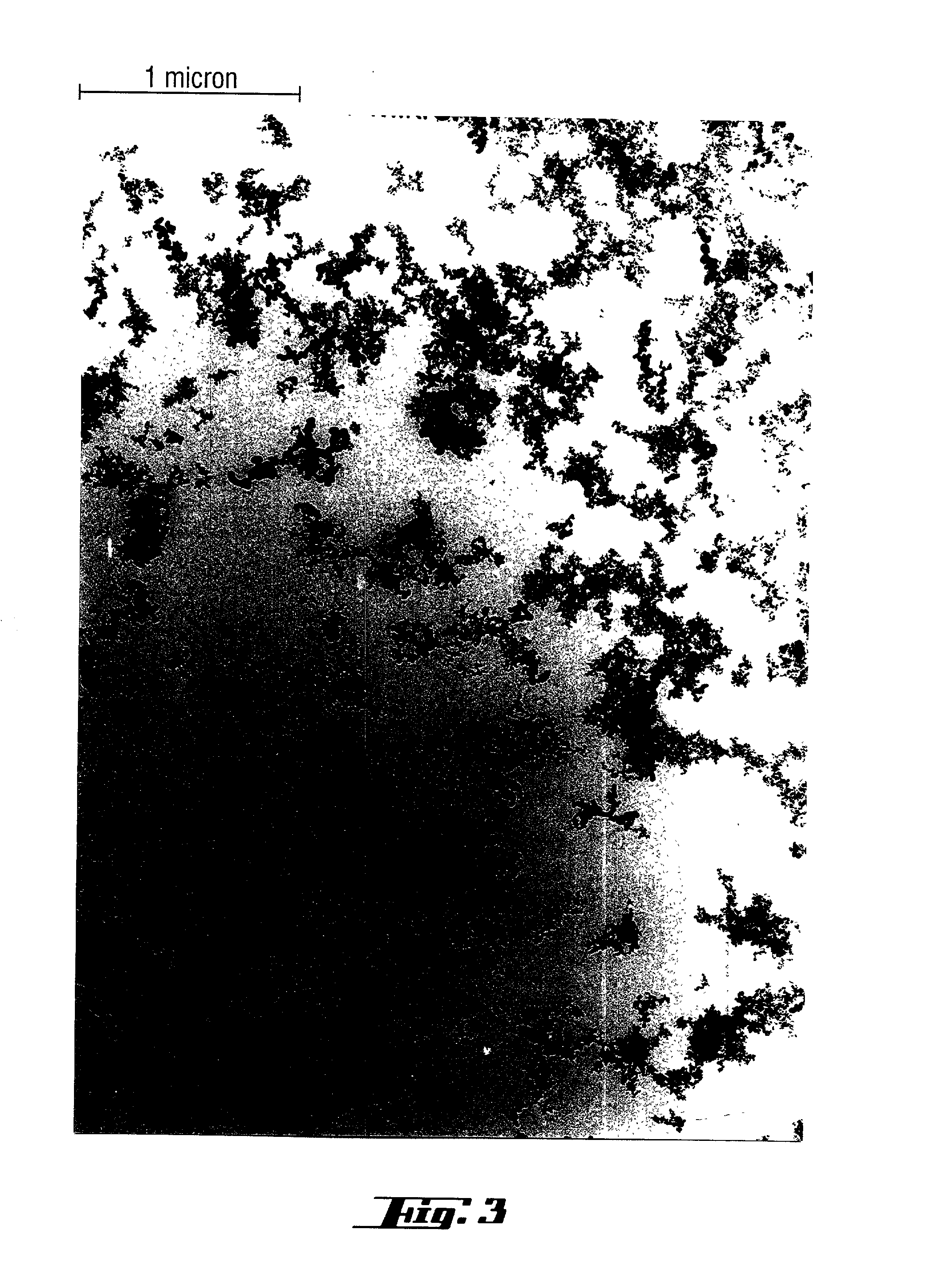

Doped, pyrogenically prepared oxides

Doped, pyrogenically prepared oxides of metals and / or non-metals which are doped with one or more doping components in an amount of 0.00001 to 20 wt. %. The doping component may be a metal and / or non-metal or an oxide and / or a salt of a metal and / or a non-metal. The BET surface area of the doped oxide may be between 5 and 600 m2 / g. The doped pyrogenically prepared oxides of metals and / or non-metals are prepared by adding an aerosol which contains an aqueous solution of a metal and / or non-metal to the gas mixture during the flame hydrolysis of vaporizable compounds of metals and / or non-metals.

Owner:EVONIK OPERATIONS GMBH

High potential gradient zinc oxide pressure-sensitive resistor material and preparation process thereof

InactiveCN102515742AExtended service lifeReduce energy consumptionVaristor coresHigh energyElectric power system

The invention relates to a high potential gradient zinc oxide pressure-sensitive resistor material and a preparation process thereof. The high potential gradient zinc oxide pressure-sensitive resistor material with uniform particle sizes is obtained by weighing a main material ZnO, a doping oxide, and a product rare earth oxide obtained by carrying out thermal decomposition on a rare earth oxalate or / and carbonate or / and hydroxide according to proportions, carrying out high energy wet grinding, drying, presintering at 200-800DEG C, carrying out high energy dry grinding, and sintering at 800-1100DEG C. The preparation process of the invention has the advantages of simplicity, low cost, environmental protection and low energy consumption, and the prepared zinc oxide pressure-sensitive resistor material can be used for preparing high quality lightning arrester products for ultrahigh electric power systems.

Owner:INST OF PROCESS ENG CHINESE ACAD OF SCI

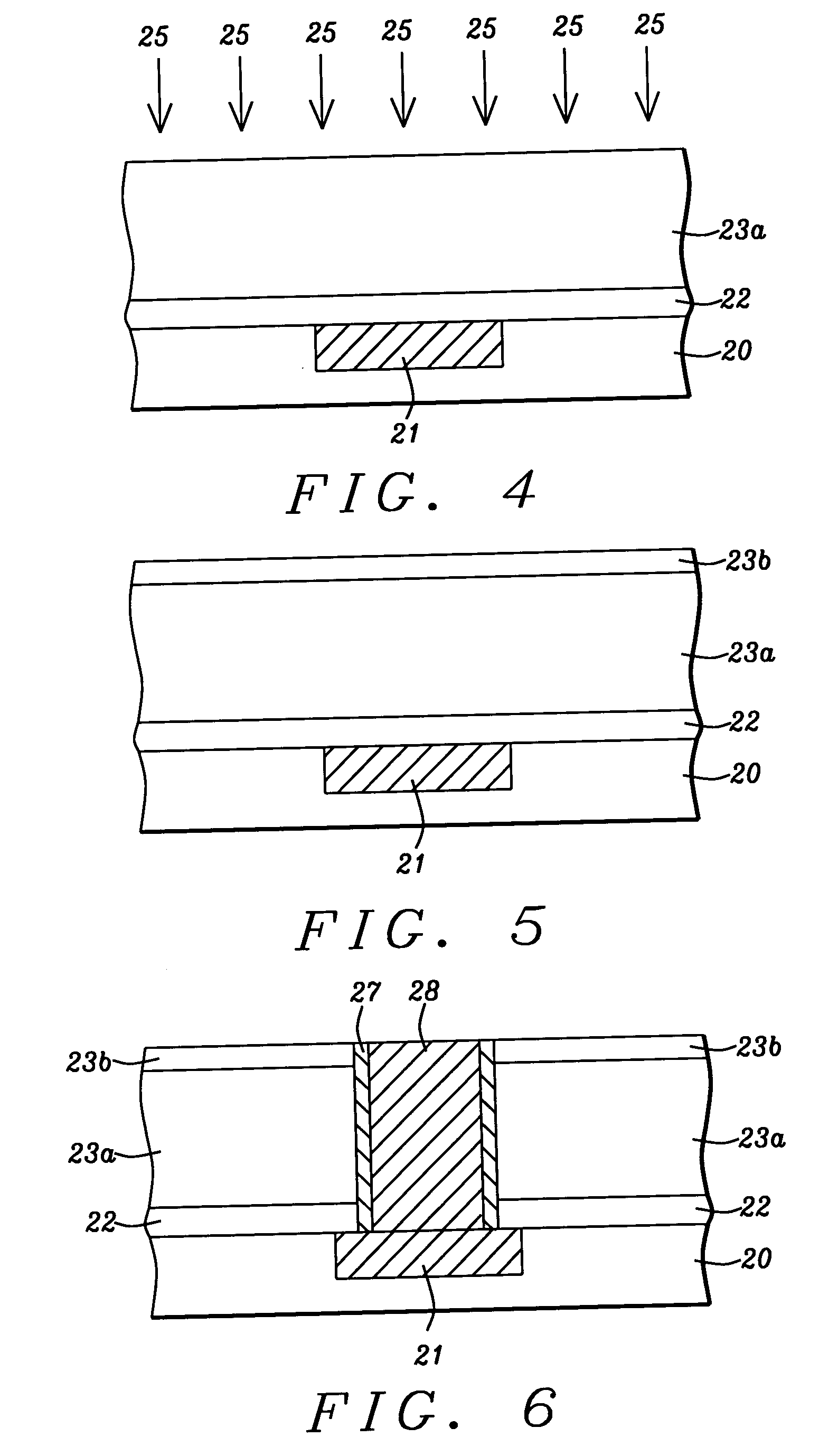

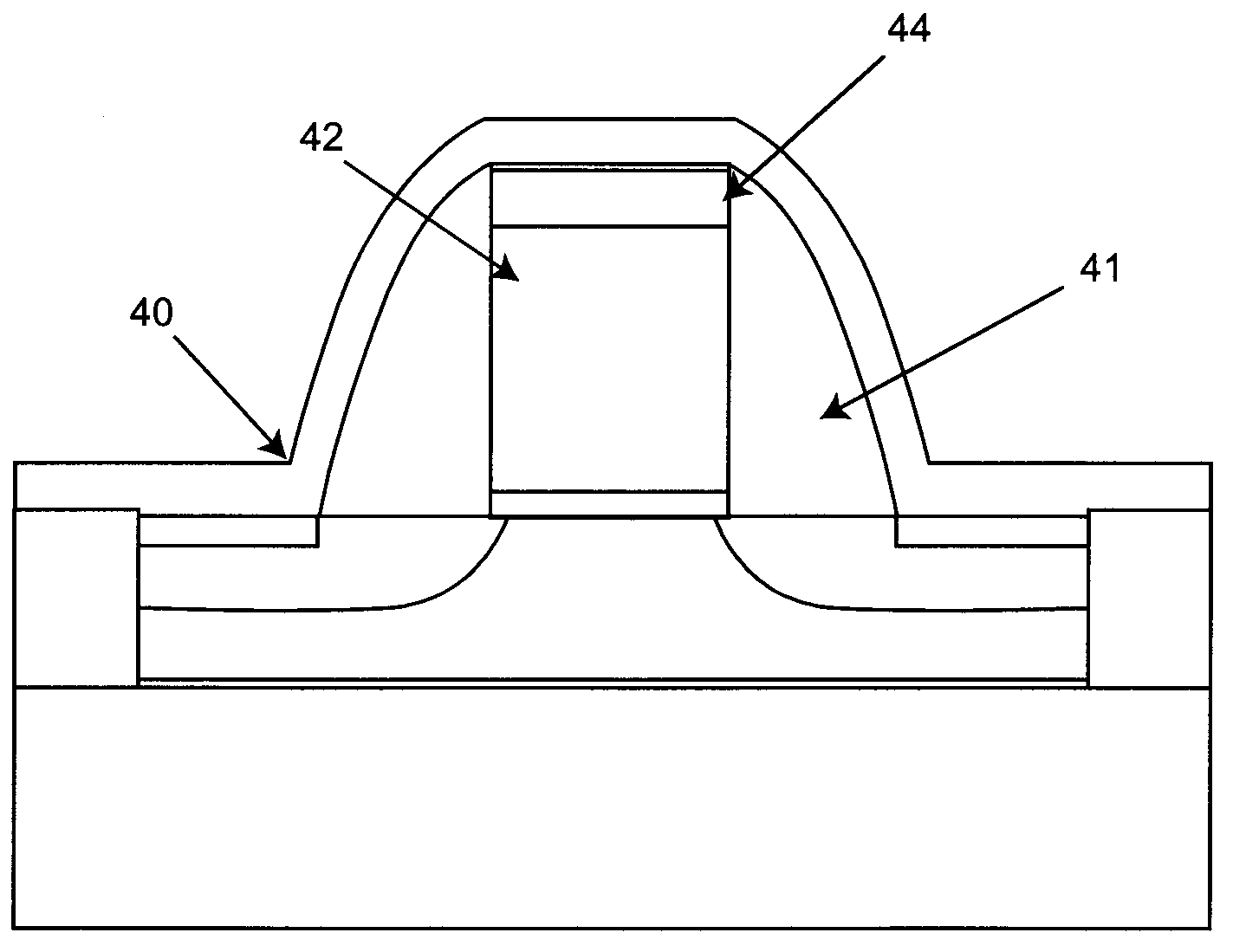

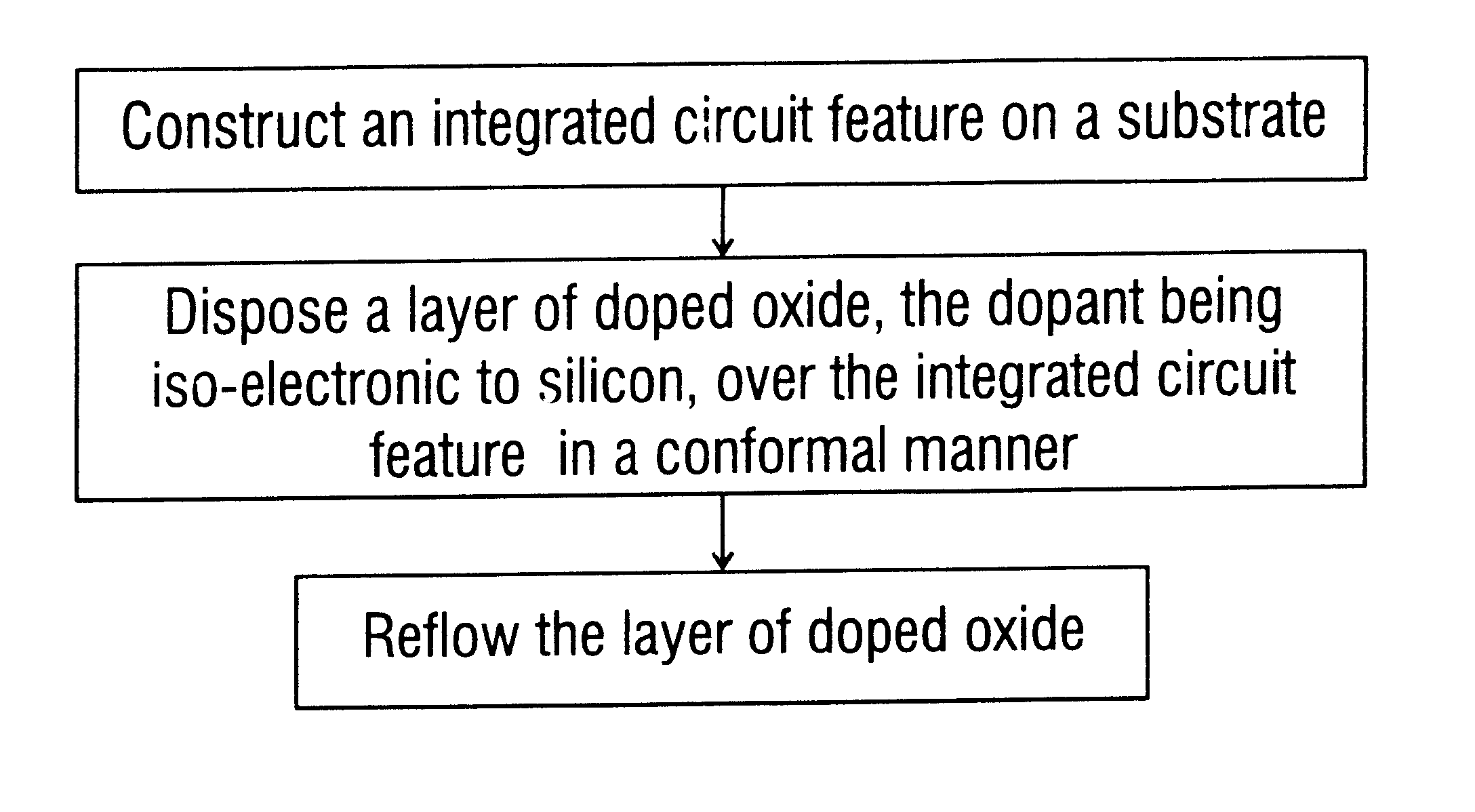

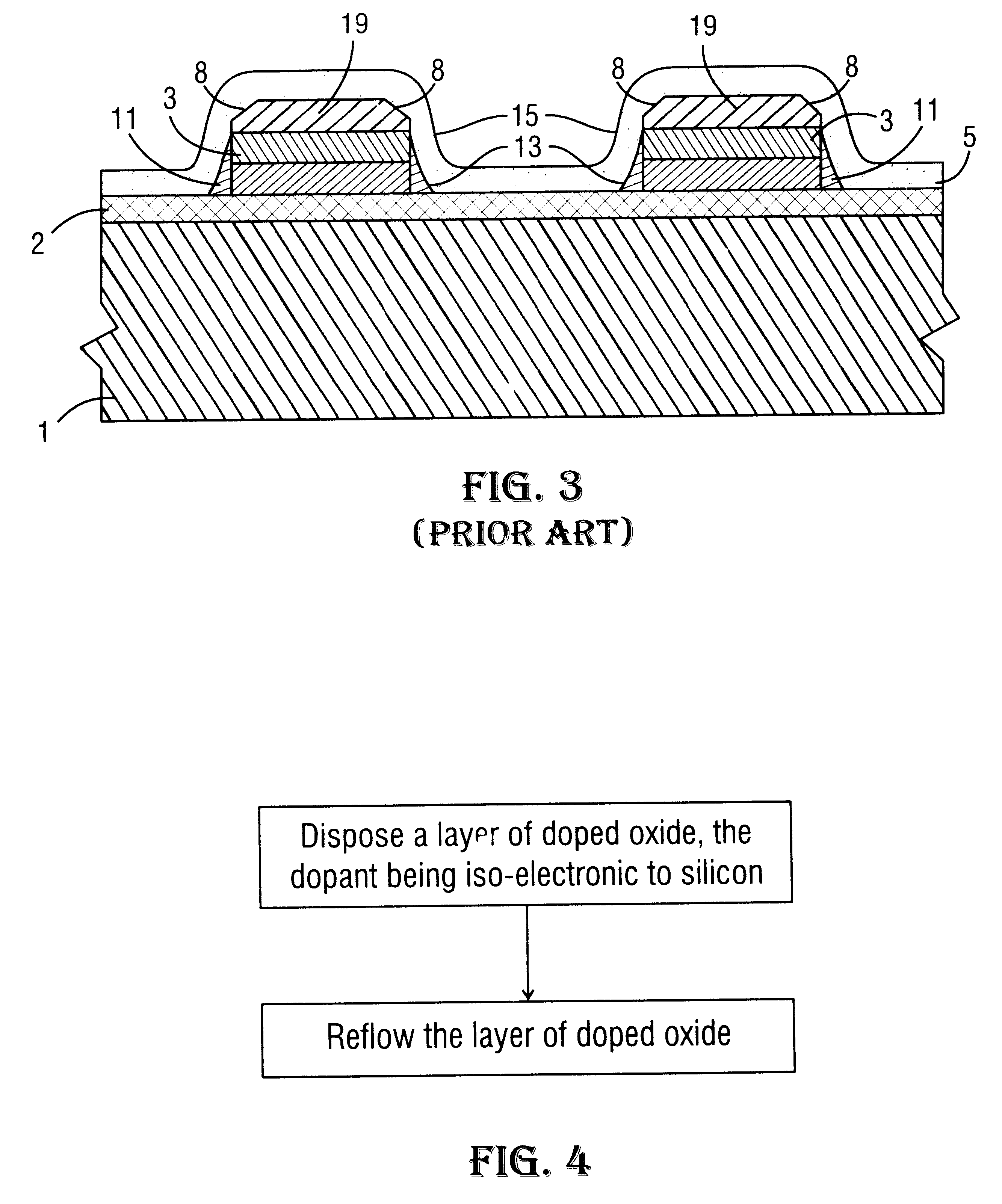

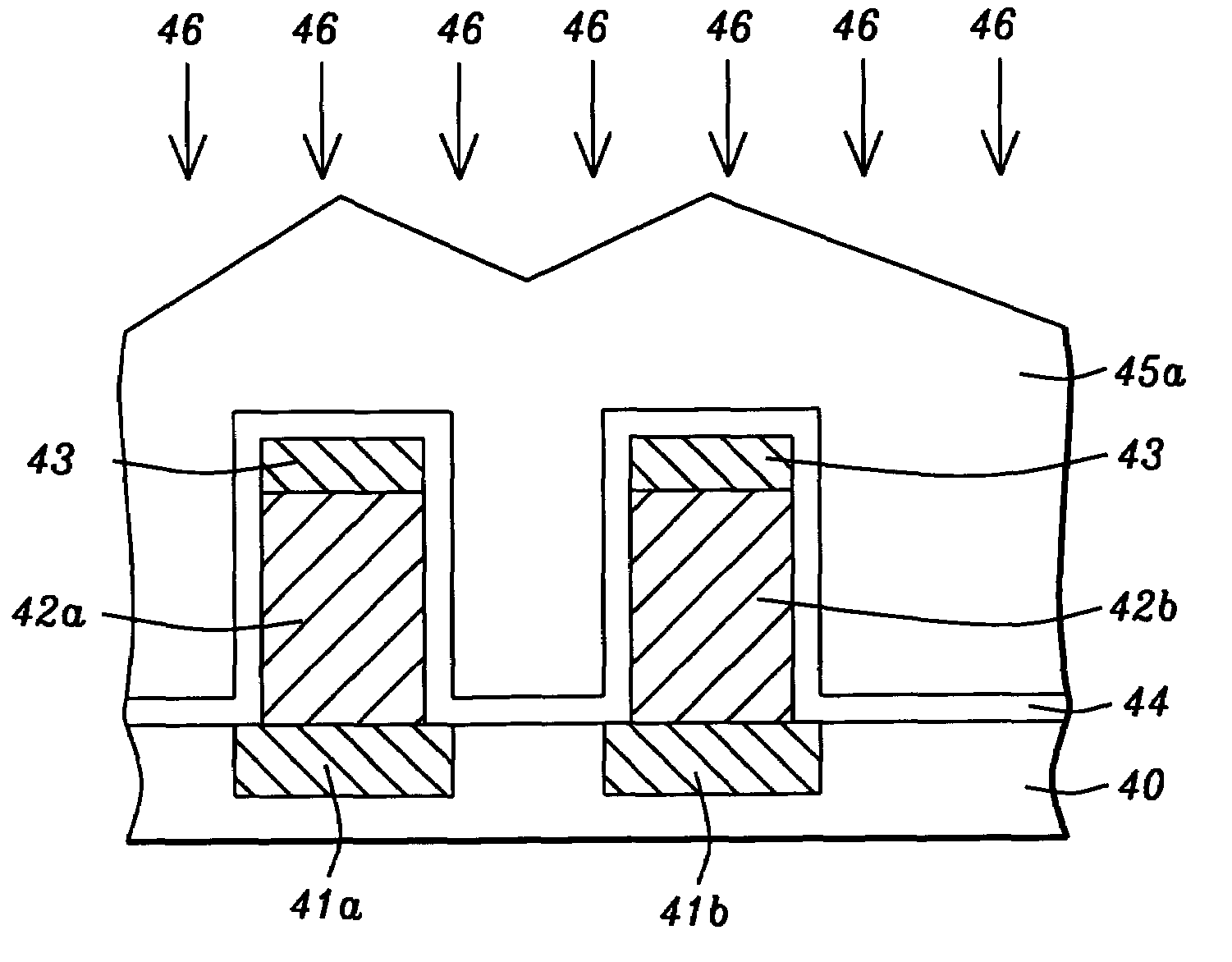

Flowable germanium doped silicate glass for use as a spacer oxide

InactiveUS6274479B1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantSilicate glass

The invention is a method for constructing an integrated circuit structure and an apparatus produced by the method. The method generally comprises constructing an integrated circuit structure by disposing a layer of doped oxide, the dopant being iso-electronic to silicon, and then reflowing the layer of doped oxide. Thus, the apparatus of the invention is an integrated circuit structure comprising a reflowed layer of doped oxide wherein the dopant is iso-electronic to silicon. In one particular embodiment, the method generally comprises constructing an integrated circuit feature on a substrate; disposing a layer of doped oxide, the dopant being iso-electronic to silicon, over the integrated circuit feature and the substrate in a substantially conformal manner; reflowing the layer of doped oxide; and etching the insulating layer and the oxide. Thus, in this particular embodiment, the apparatus comprises an integrated circuit feature constructed on a substrate and a reflowed layer of doped oxide, the dopant being iso-electronic to silicon, disposed over the integrated circuit feature and the substrate.

Owner:MICRON TECH INC

UV curing of pecvd-deposited sacrificial polymer films for air-gap ild

InactiveUS20080182403A1Solid-state devicesSemiconductor/solid-state device manufacturingUV curingPorous carbon

Embodiments of the invention generally provide a method of forming an air gap between conductive elements of a semiconductor device, wherein the air gap has a dielectric constant of approximately 1. The air gap may generally be formed by depositing a sacrificial material between the respective conductive elements, depositing a porous layer over the conductive elements and the sacrificial material, and then stripping the sacrificial material out of the space between the respective conductive elements through the porous layer, which leaves an air gap between the respective conductive elements. The sacrificial material may be, for example, a polymerized alpha terpinene layer, the porous layer may be, for example, a porous carbon doped oxide layer, and the stripping process may utilize a UV based curing process, for example.

Owner:APPLIED MATERIALS INC

Strong substrate alloy and compressively stressed dielectric film for capacitor with high energy density

InactiveUS20050168919A1Increase energy densityHigh operating requirementsLiquid electrolytic capacitorsCapacitor electrodesHigh energyAlloy

A capacitor anode (1) includes a substrate (10) which is formed from an alloy, metal, or metal compound which has a high tensile yield strength and high elastic modulus. The material has a composition which can be anodized, yielding an adherent and compressively stressed dielectric film (12) of pure, mixed, alloyed, or doped oxide that has a high usable dielectric strength (e.g., over 50 V / μm) and high dielectric constant (e.g., 20 to over 10,000). A capacitor formed from the anode has a high energy density.

Owner:CASE WESTERN RESERVE UNIV

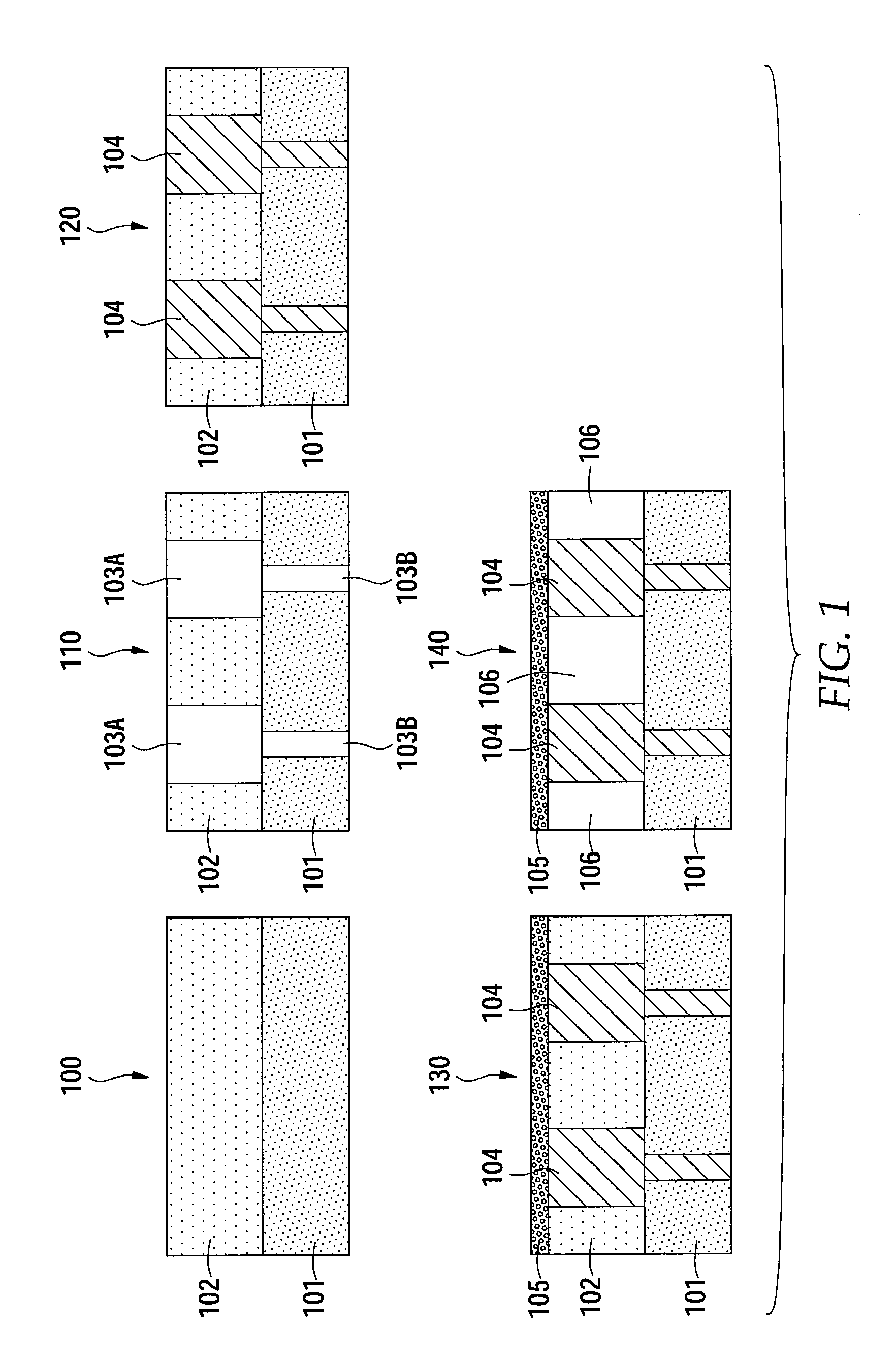

Trench isolation employing a doped oxide trench fill

InactiveUS6890833B2Acceptable interface qualityEffective diffusion barrierSemiconductor/solid-state device manufacturingOptoelectronicsDoped oxide

A trench isolation structure is formed in a substrate. One or more openings are formed in a surface of the substrate, and a liner layer is deposited at least along a bottom and sidewalls of the openings. A layer of doped oxide material is deposited at least in the openings, and the substrate is annealed to reflow the layer of doped oxide material. Only a portion near the surface of the substrate is removed from the layer of doped oxide material in the opening. A cap layer is deposited atop a remaining portion of the layer of doped oxide material in the opening.

Owner:IBM CORP +1

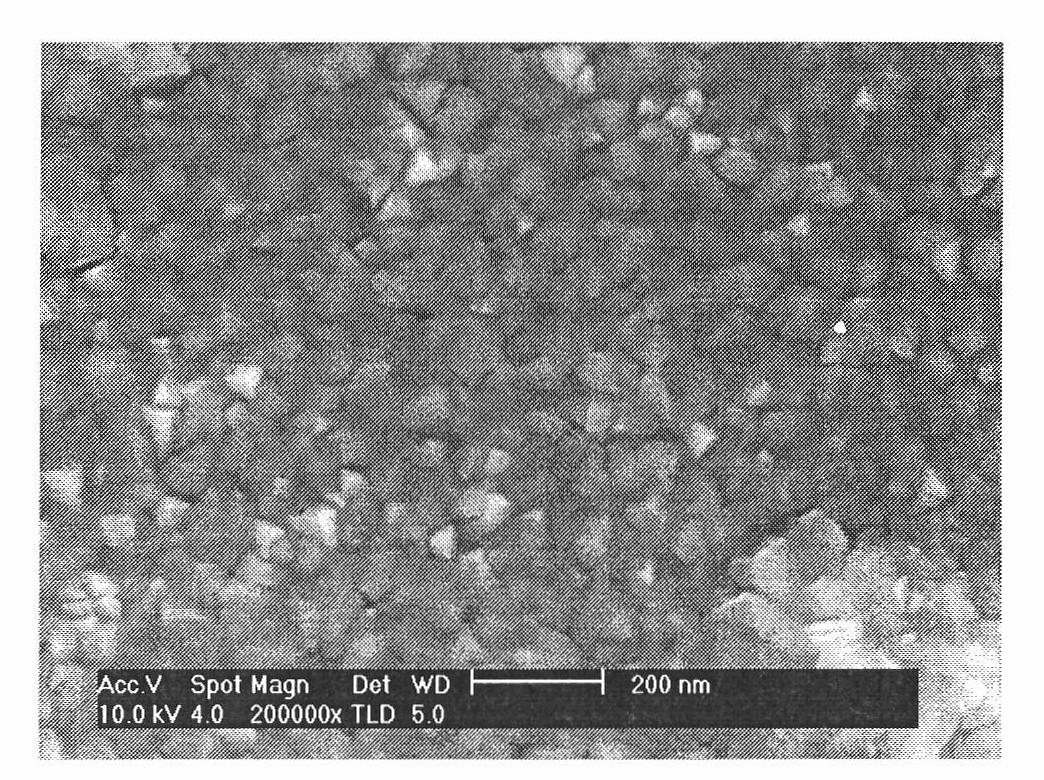

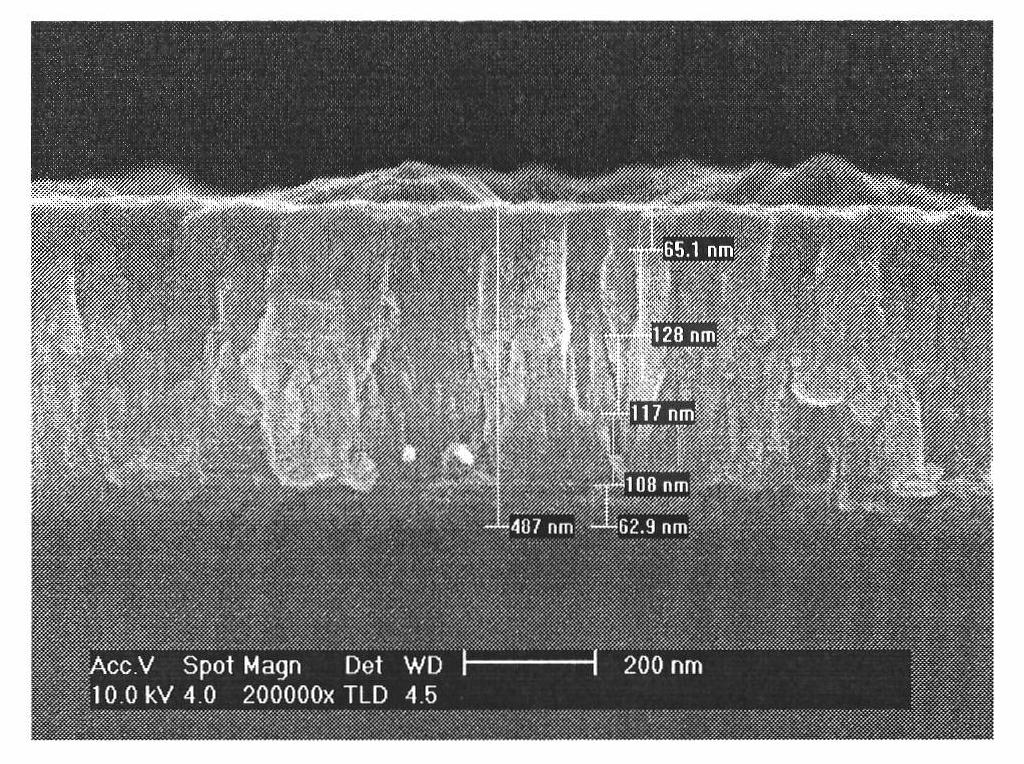

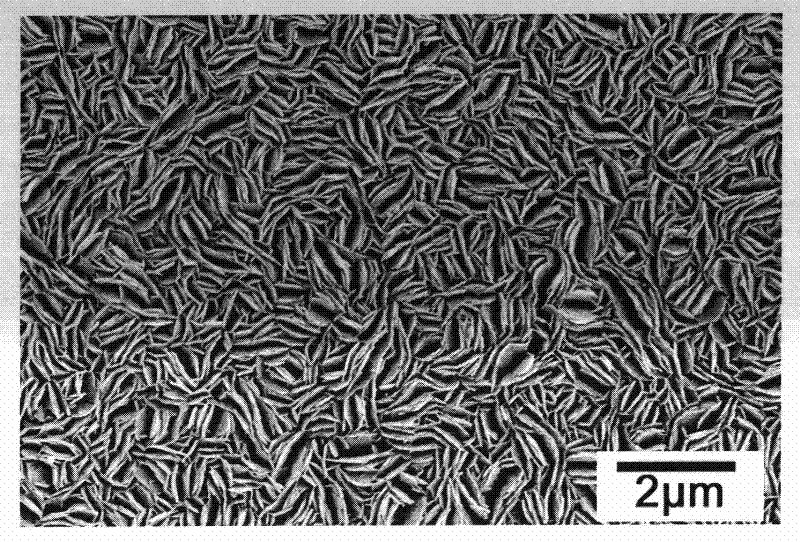

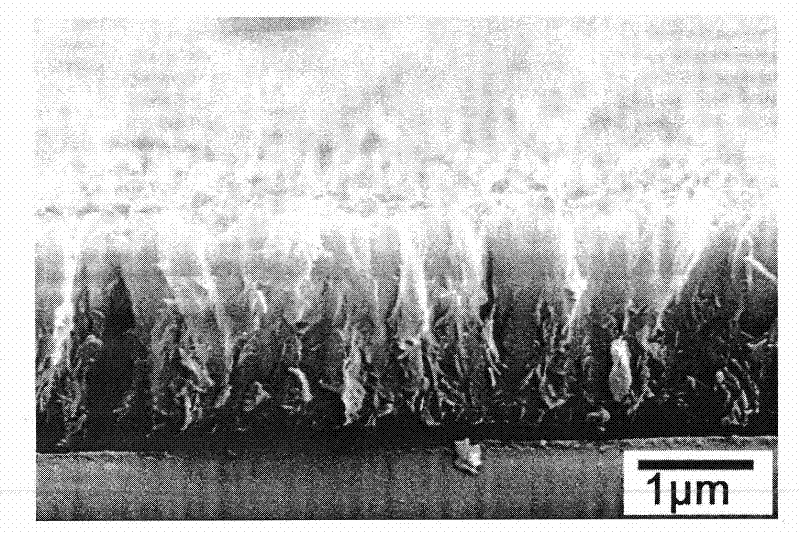

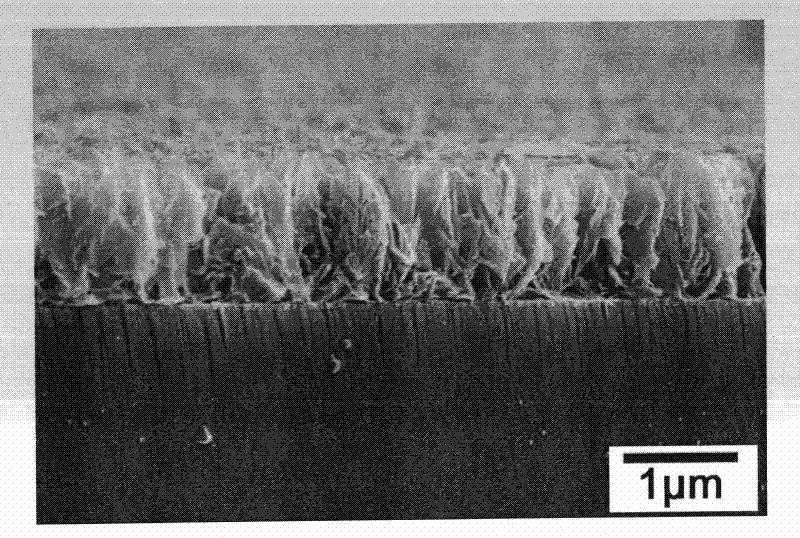

Silver doped titanium dioxide thin film and preparation method thereof

The invention belongs to the field of a precious metal doped oxide semiconductor thin film material and in particular relates to an Ag / TiO2 thin film material and a preparation method thereof. The invention is mainly characterized in that a sol-gel method and a solvent thermal synthesis method are combined, a TiO2 seed layer is prepared on the surface of a substrate by adopting the sol-gel method, and then a Ag / TiO2 nano slice is grown on the surface of the substrate of the TiO2 seed layer by adopting the solvent thermal synthesis method, thus the Ag / TiO2 thin film material which is composed of the Ag / TiO2 nano slice and is vertically grown on the substrate is obtained. The Ag / TiO2 thin film material provided by the invention has the advantages of titanium dioxide semiconductor material and silver and plays an important role in the fields such as antibacterial materials, solar cells, photocatalysis, deodorization, self cleaning and the like.

Owner:TECHNICAL INST OF PHYSICS & CHEMISTRY - CHINESE ACAD OF SCI

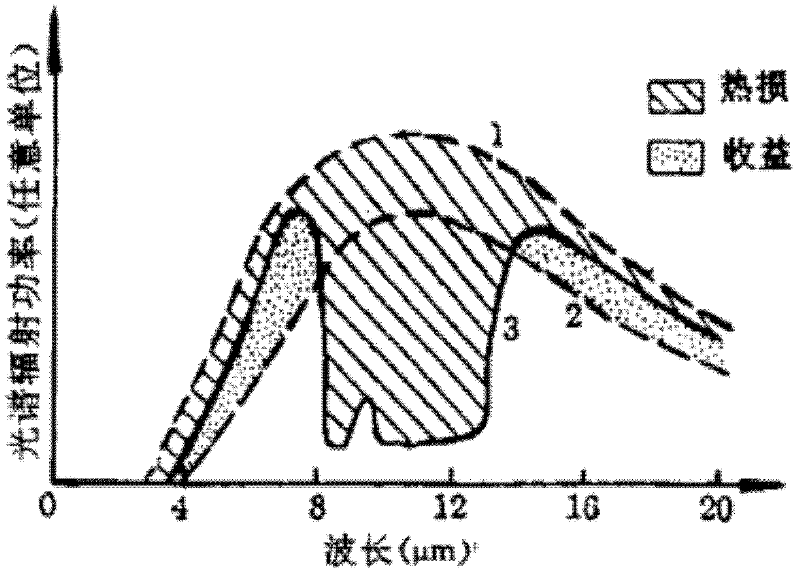

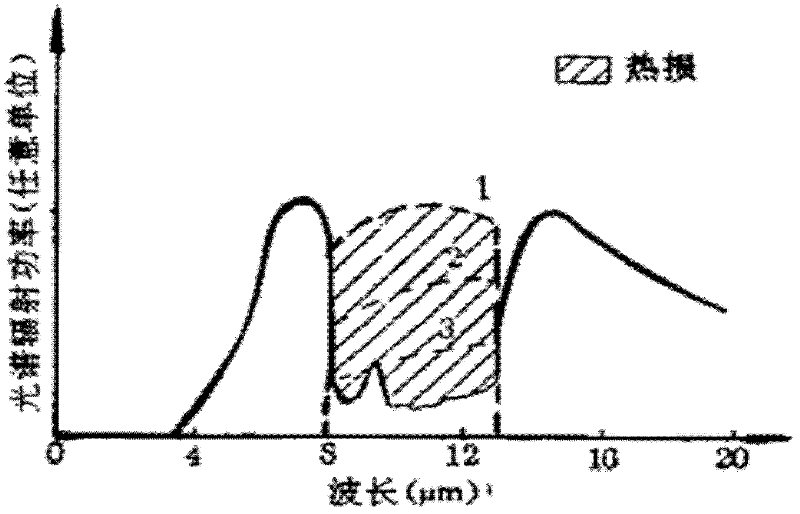

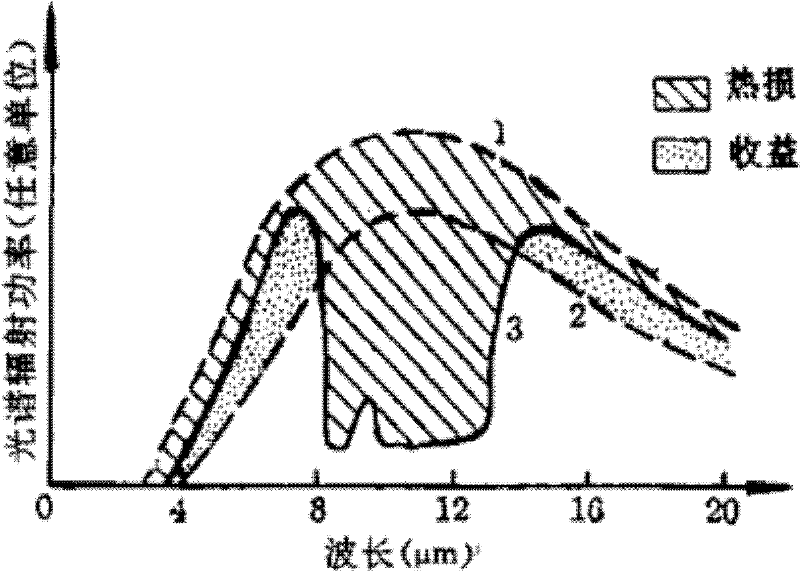

High-emission transparent heat-insulating paint in atmospheric window regions and preparation method thereof

InactiveCN102408806AHigh emissivityEffective coolingReflecting/signal paintsEmissivityDistilled water

The invention discloses a high-emission transparent heat-insulating paint in atmospheric window regions. The main material of the transparent heat-insulating paint is prepared from the following components in parts by weight: 30-70 parts of polymer emulsion, 10-30 parts of nano doped oxide powder, 2-30 parts of high-emission nano powder in atmospheric window regions, 1-10 parts of anionic dispersant, 2-20 parts of nonionic dispersant, 0.5-2 parts of defoaming agent, 0-5 parts of thickening agent, 1-2 parts of film forming assistant, 1-2 parts of antifreezing agent, 1-2 parts of leveling agentand 5-20 parts of distilled water. The invention also discloses a preparation method of the transparent heat-insulating paint, which comprises the following steps: after evenly mixing the components,regulating the pH value to 8.5-9.5 with a multifunctional assistant AMP-95 to obtain the high-emission-rate transparent heat-insulating paint in atmospheric window regions. The paint has high emission rate in atmospheric window regions, and can implement effective heat dissipation.

Owner:ZHEJIANG UNIV

Process for improving local uniformity of chemical mechanical polishing using a self-aligned polish rate enhancement layer

A method for making a semiconductor device, includes forming an oxide layer on a silicon substrate, forming a nitride layer over the oxide layer; depositing one of a doped oxide layer and an undoped porous oxide layer on the nitride layer, etching trenches through the one of the doped layer and the undoped porous oxide layer, the nitride layer, and the oxide layer, depositing an undoped oxide layer to fill the trenches, and patterning the undoped oxide by chemical mechanical polishing (CMP).

Owner:IBM CORP

Two step post-deposition treatment of ILD layer for a lower dielectric constant and improved mechanical properties

InactiveUS7250370B2Increase resistanceImprove the immunityDecorative surface effectsSemiconductor/solid-state device detailsMechanical propertyMoisture

A method of lowering the dielectric constant of an organosilicon low k dielectric layer while improving the hardness and thermal stability is provided. A deposited layer of carbon doped oxide, HSQ, or MSQ is cured and treated with a He plasma which improves hardness for a subsequent CMP step and lowers the dielectric constant. There is no loss of H2O or CH4 during the He treatment. The low k dielectric layer is then treated with a H2 plasma which converts some of the Si—O and Si—CH3 bonds near the surface to Si—H bonds, thereby further lowering the dielectric constant and increasing thermal stability that improves breakdown resistance. Moisture uptake is also reduced. The method is especially useful for interconnect schemes with deep sub-micron ground rules. Surprisingly, the k value obtained from two different plasma treatments is lower than when two He treatments or two H2 treatment are performed.

Owner:TAIWAN SEMICON MASNUFACTURING

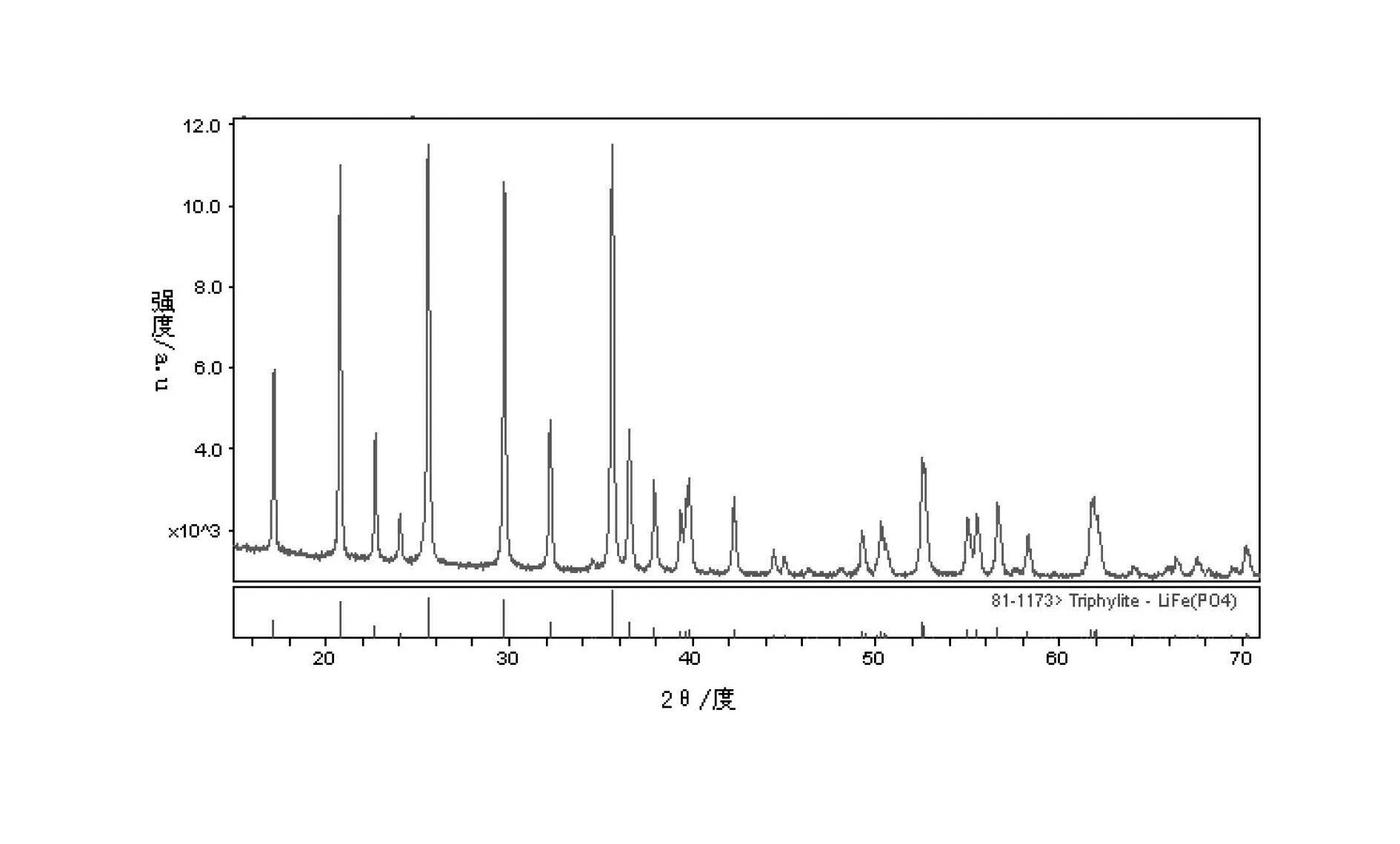

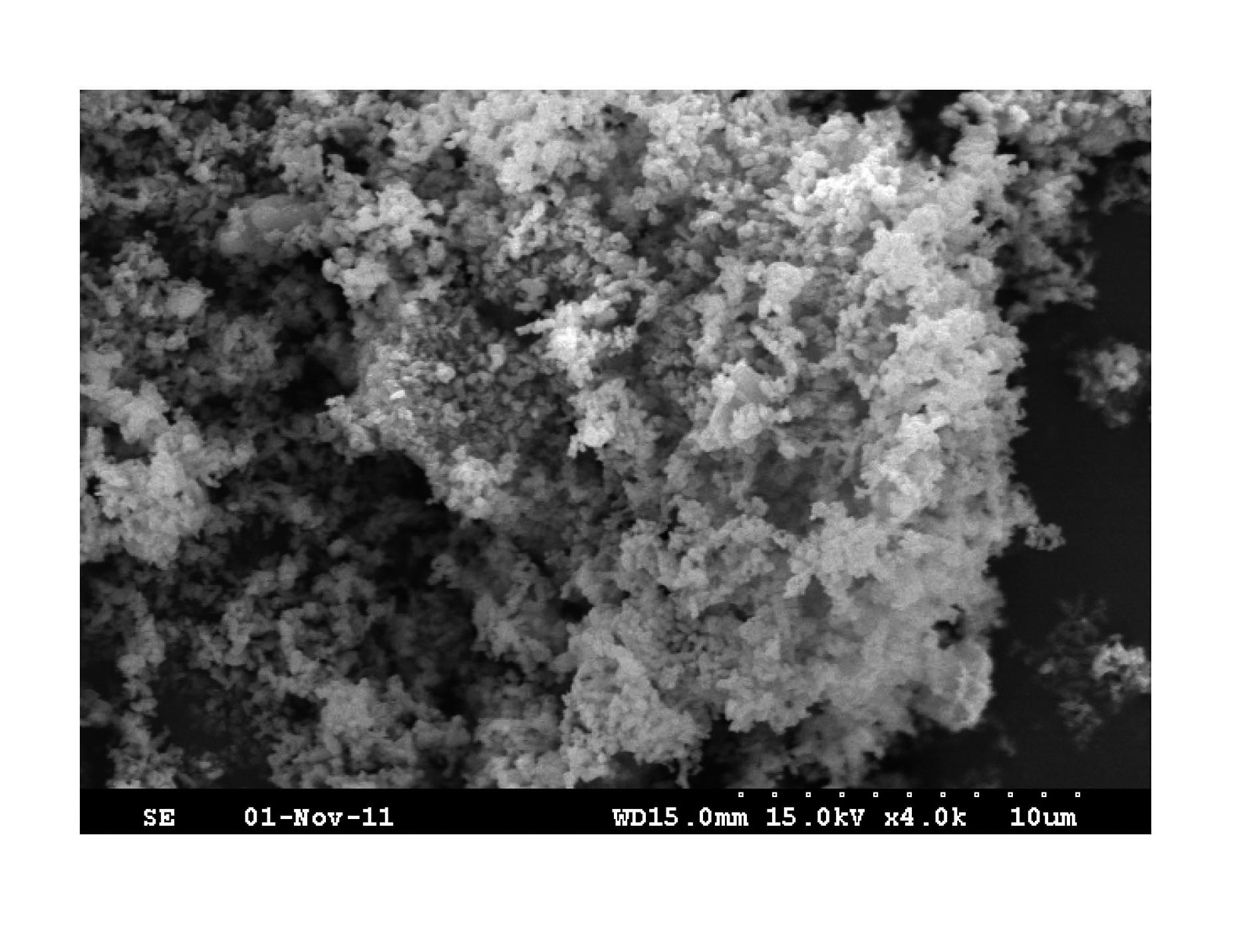

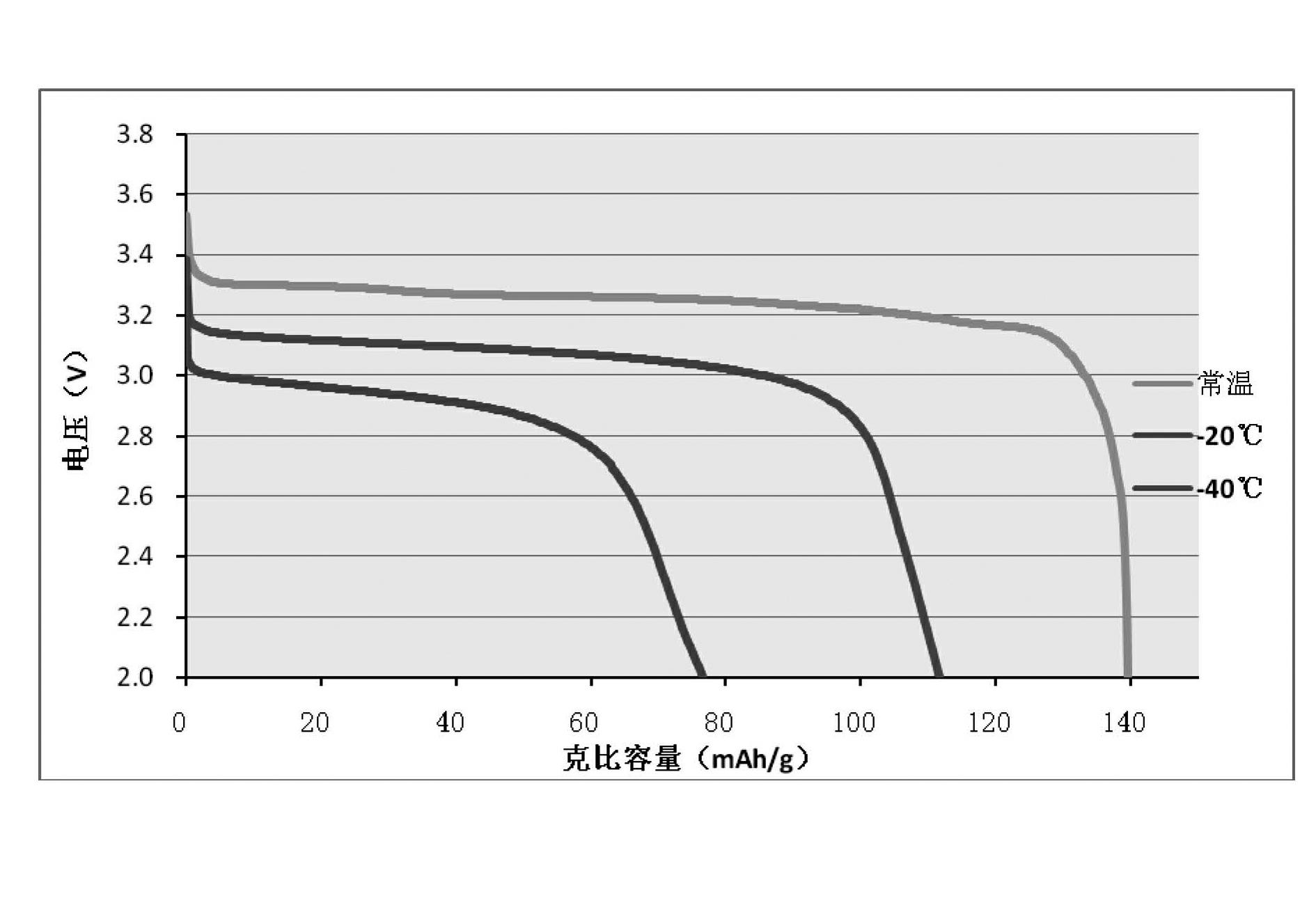

Preparation method for low-temperature nanometer lithium iron phosphate cathode material

The invention discloses a preparation method for a low-temperature nanometer lithium iron phosphate cathode material. The preparation method comprises the following steps of: adding a lithium source compound, a ferric source compound, a phosphorous source compound and water according to a proportion for mixing, adding metal ion doped oxide and a primary carbon source for mixing, performing primary high-energy superfine pulverization for 2 to 3 hours, performing spray-drying to obtain powder, and performing sieving; pre-treating the powder in an inert atmosphere at the temperature of 300 to 500 DEG C for 2 to 10 hours, performing cooling, adding a secondary carbon source and water, stirring the mixture, performing secondary high-energy superfine pulverization to obtain spherical powder, and performing sieving; and performing jet milling on the spherical powder, performing treatment in the inert atmosphere at 500 to 600 DEG C for 6 to 30 hours, performing thermal treatment at the high temperature of 600 to 900 DEG C for 10 to 30 hours, and performing cooling to obtain the low-temperature nanometer lithium iron phosphate cathode material with the granularity of 60 to 70 nanometers. When the low-temperature nanometer lithium iron phosphate cathode material is used for manufacturing the anode of a lithium ion battery, the battery has high low-temperature discharge performance.

Owner:XTC NEW ENERGY MATERIALS(XIAMEN) LTD

Doped Oxide powders in laser markings and methods of use

InactiveUS20130188003A1Increase contrastRecording apparatusDuplicating/marking methodsCopper oxideDoped oxide

Laser marking additives of at least one the core particle selected from the group consisting of copper oxide, chromium oxide, ceramic yellow, cobalt oxide, tungsten oxide, vanadium oxide, titanium oxide, ceramic red, molybdenum oxide, zinc sulfide and any combination thereof, and a coating covering at least part of the core particle comprising at least one oxide of a metal selected from the group consisting of Si, Ti, Ce, Zr, Zn, Al, Ba, Sr, La, Mg, Ca, V, Ta and mixtures thereof. This powder is used with 1064 nm wavelength laser (semiconductor lasers, fiber lasers) to change color in a plastic or polymer substrate to give contrast in laser marking plastics.

Owner:THAKER JAGDIP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com