Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1046 results about "Anisotropic etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

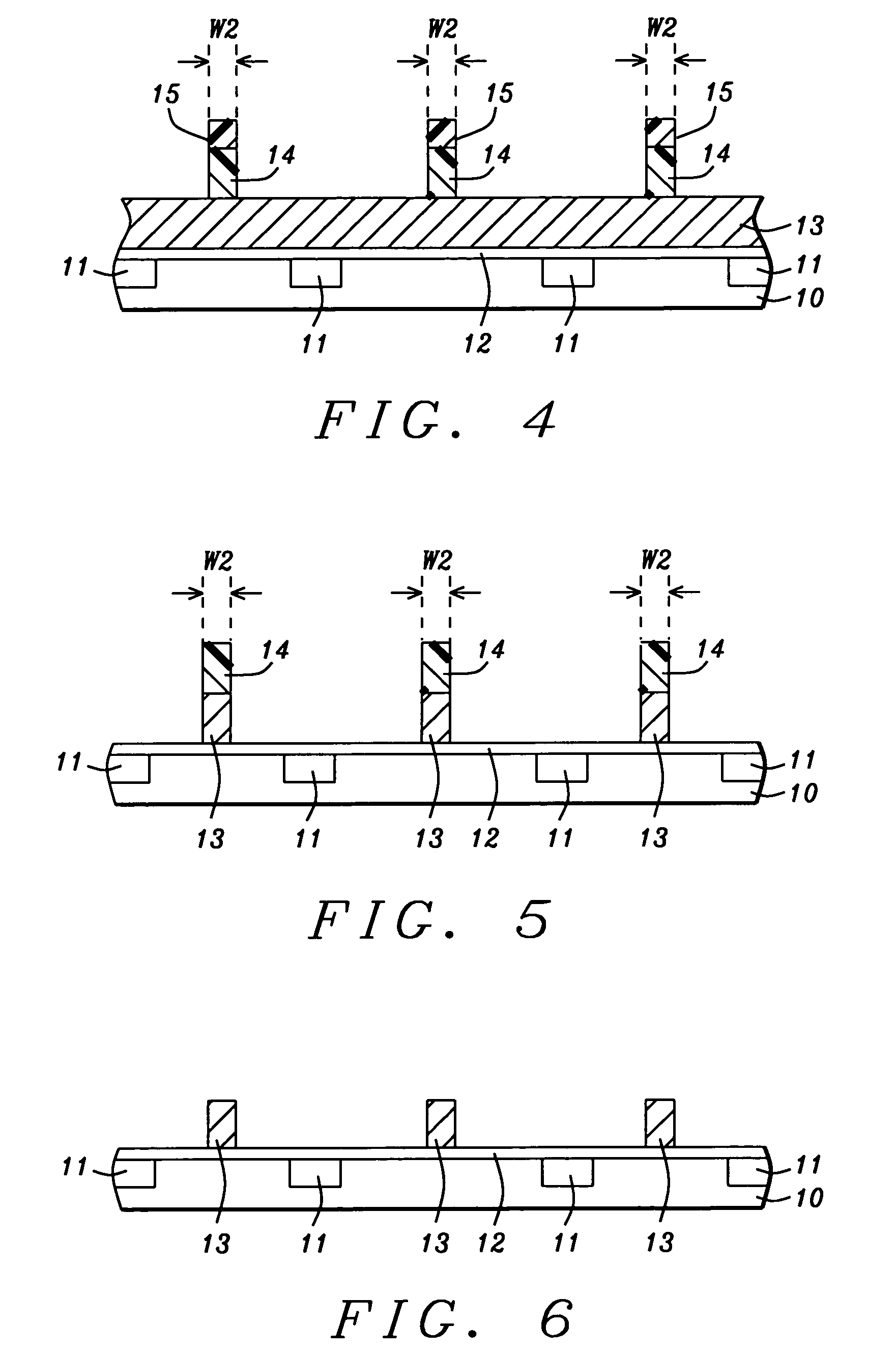

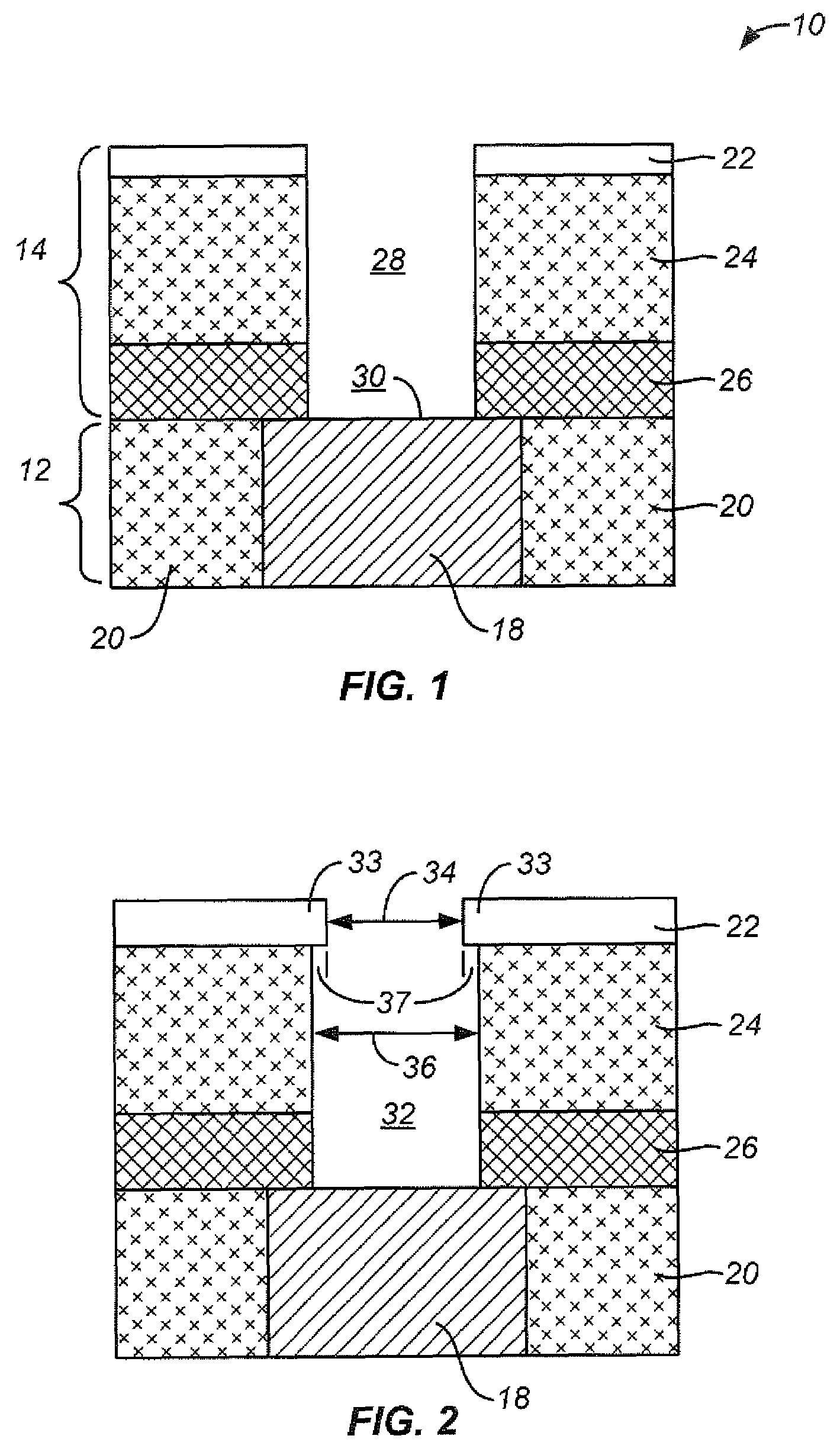

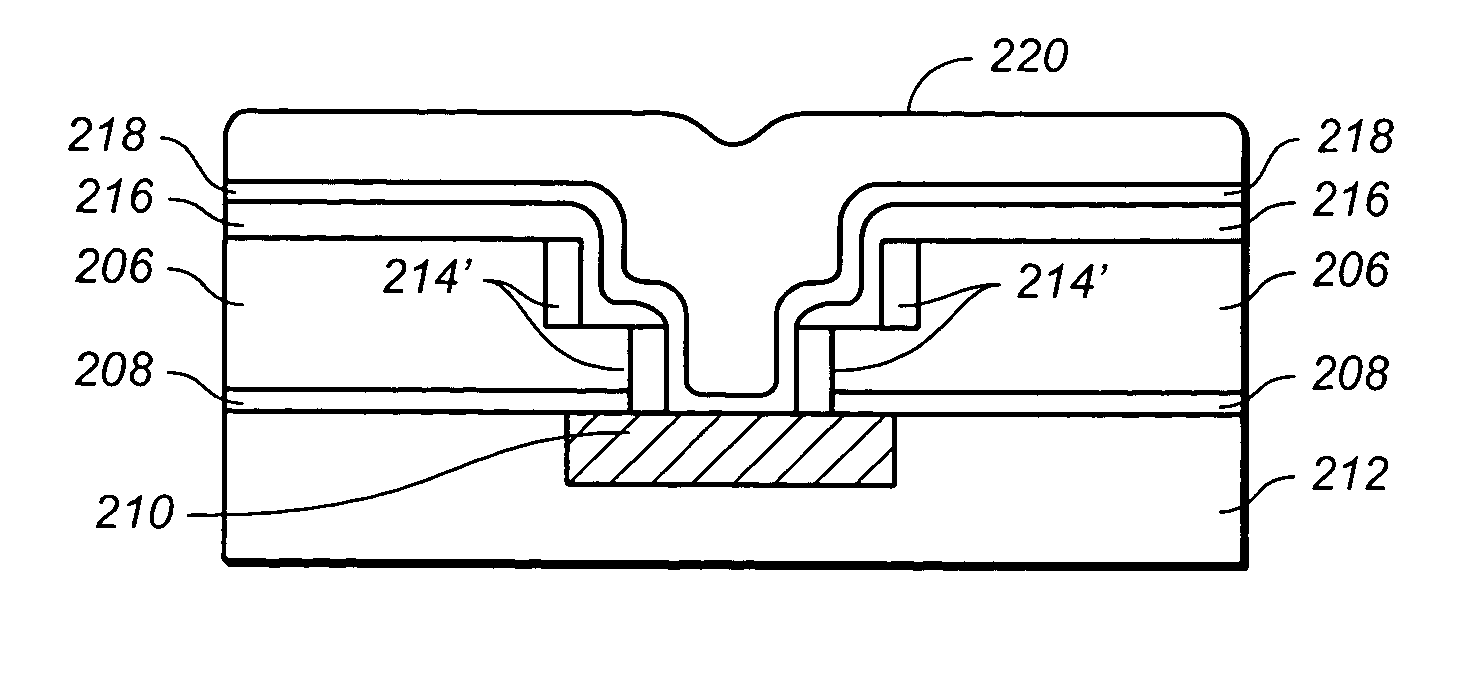

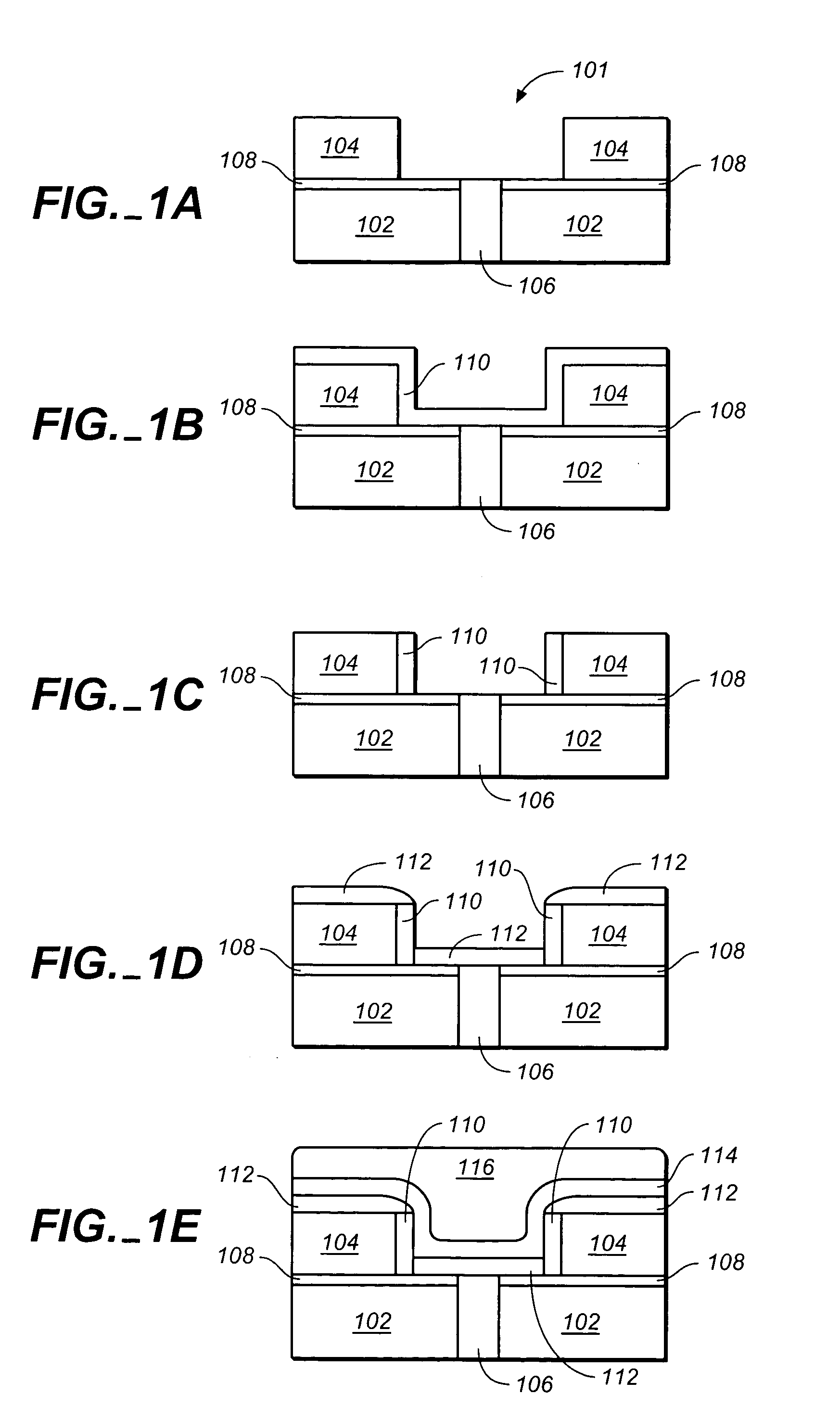

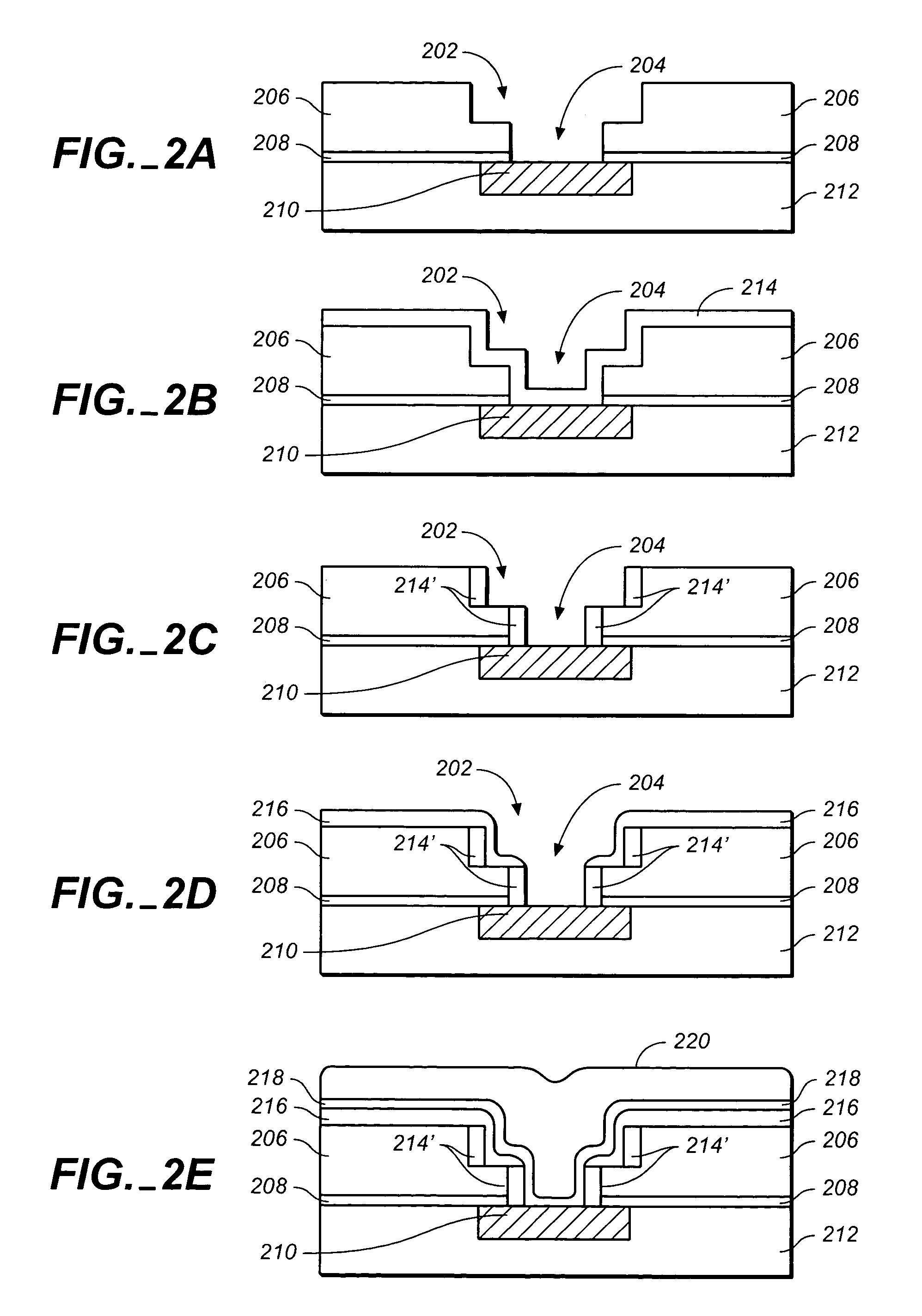

Method for critical dimension shrink using conformal pecvd films

InactiveUS20090286402A1Critical dimension reductionGood step coverageSemiconductor/solid-state device manufacturingLithographic artistAnisotropic etching

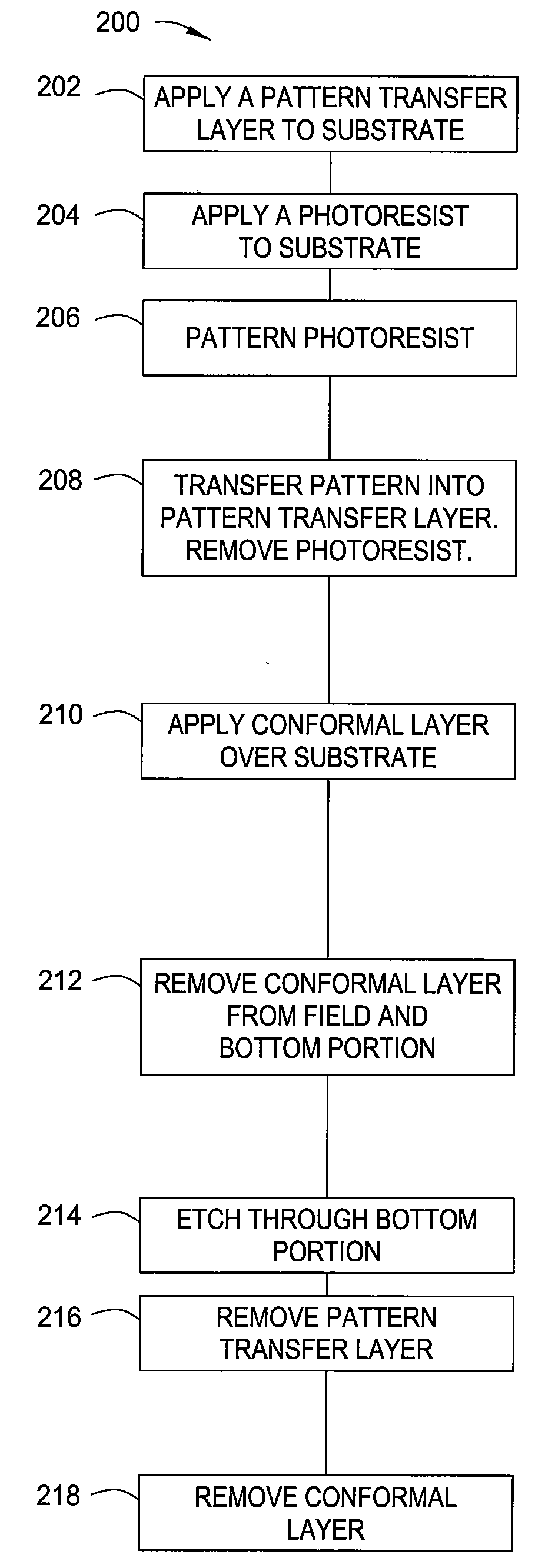

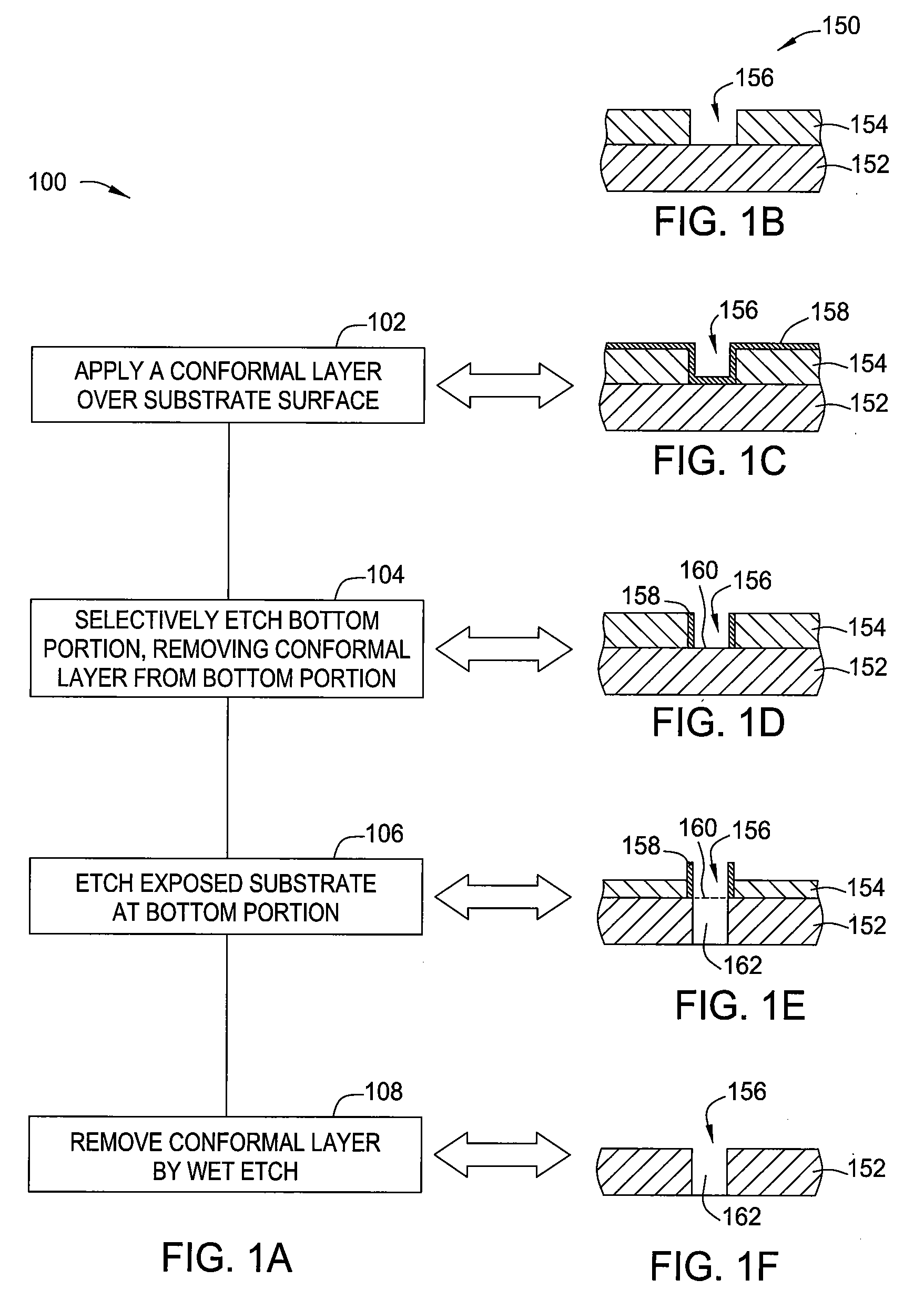

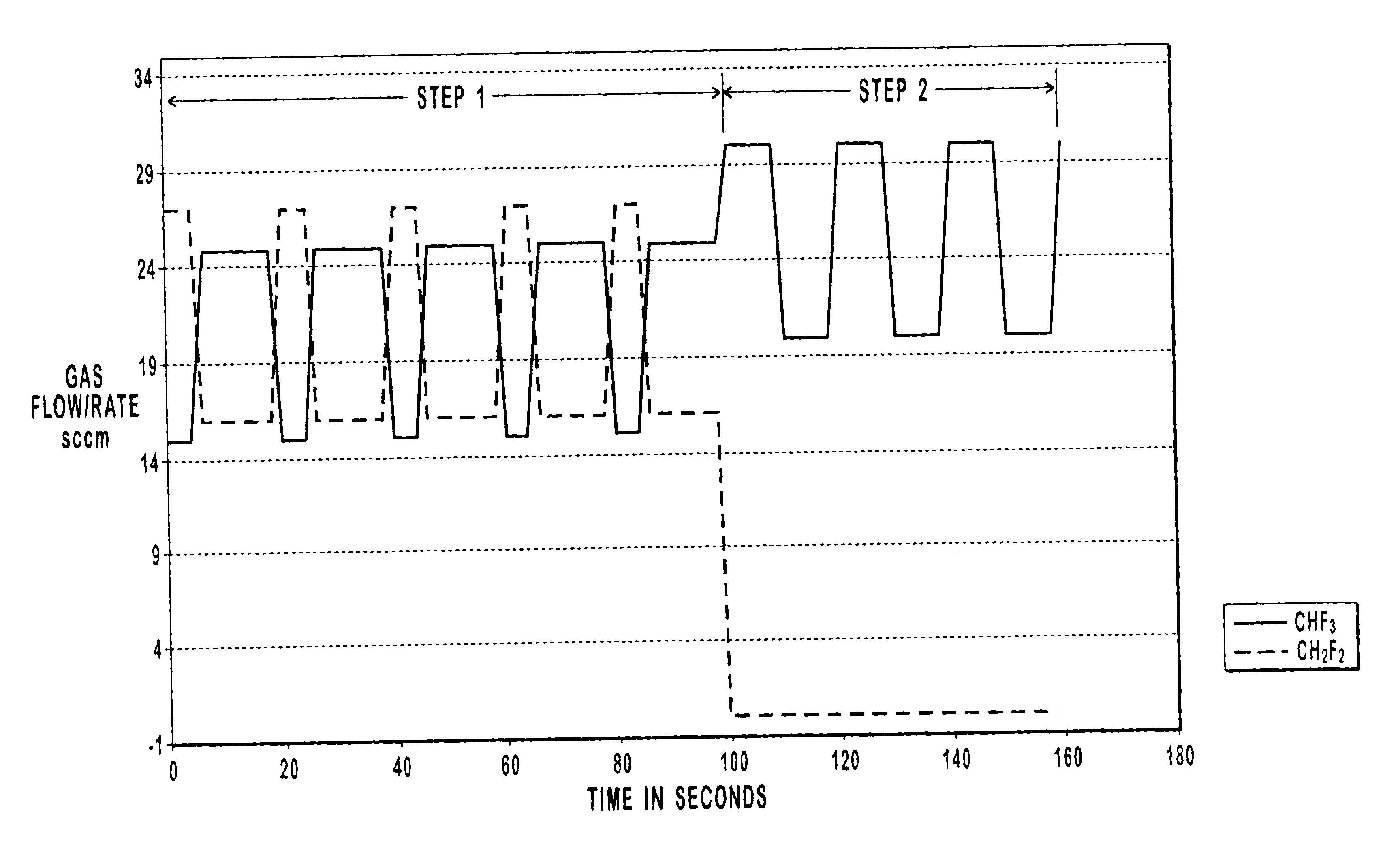

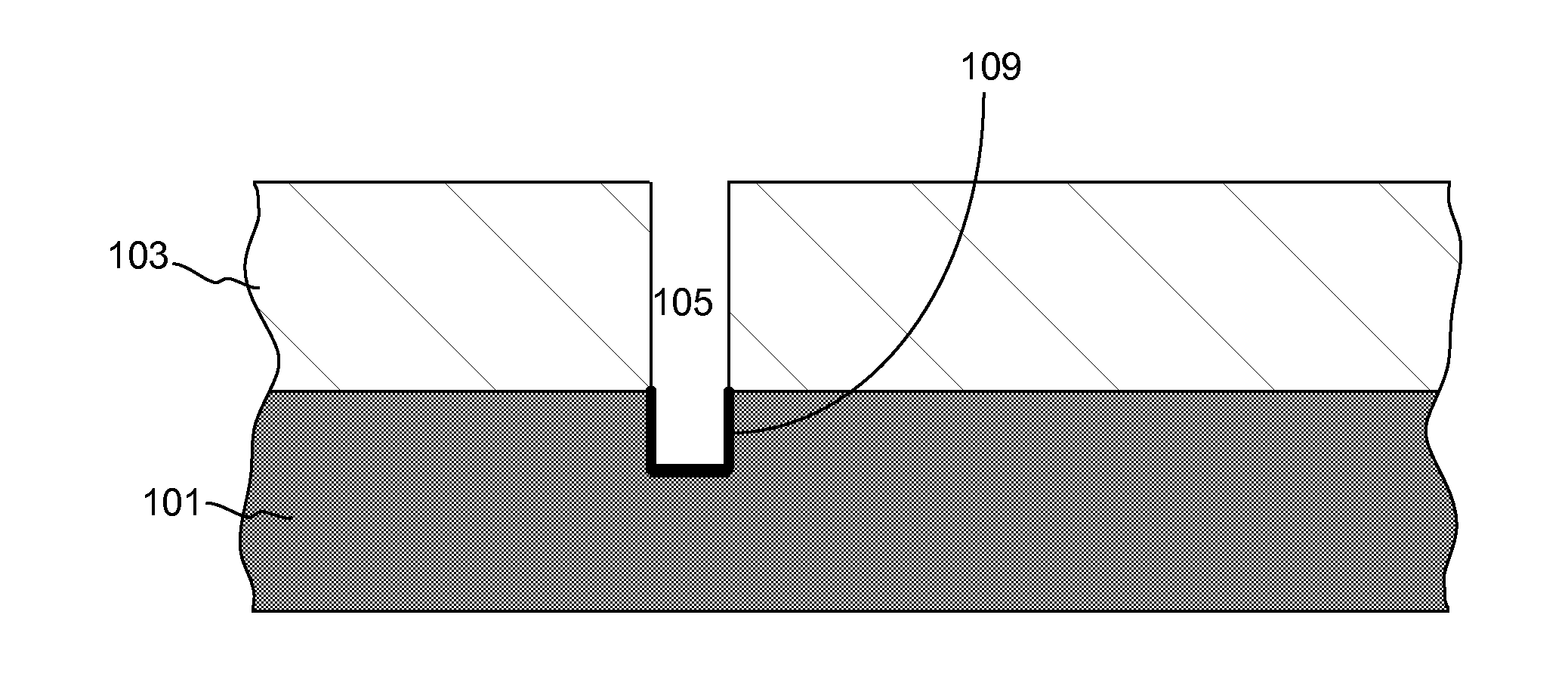

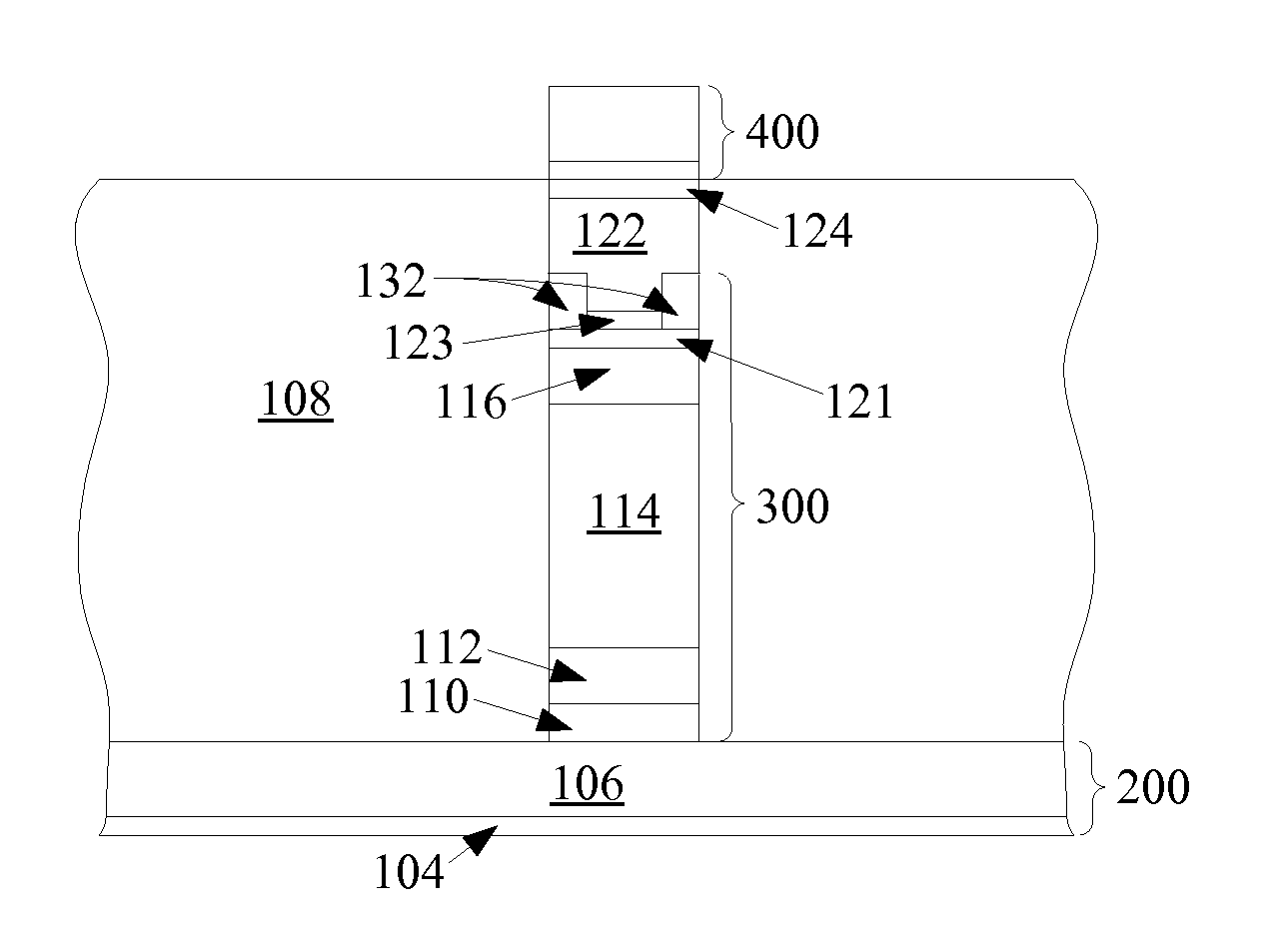

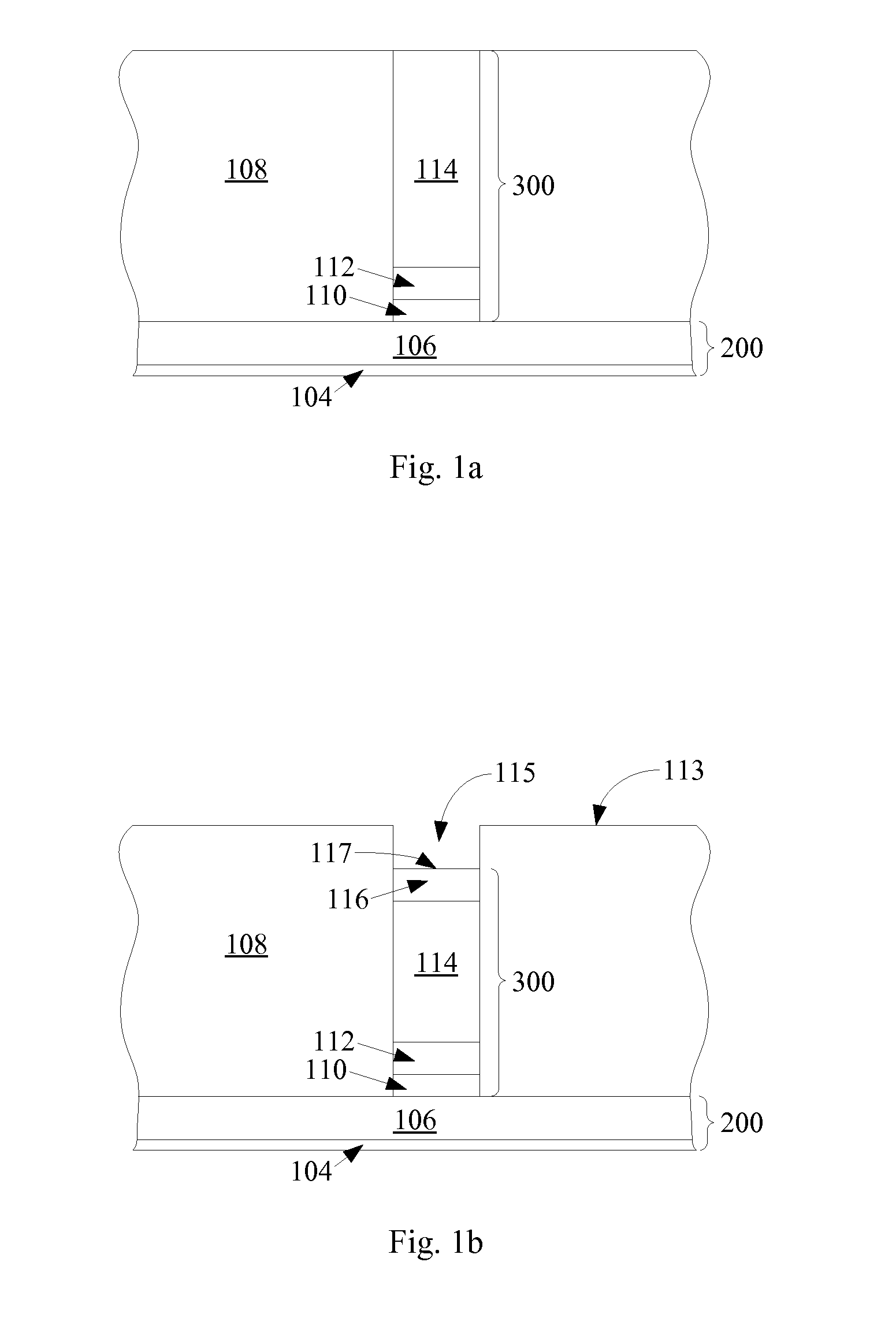

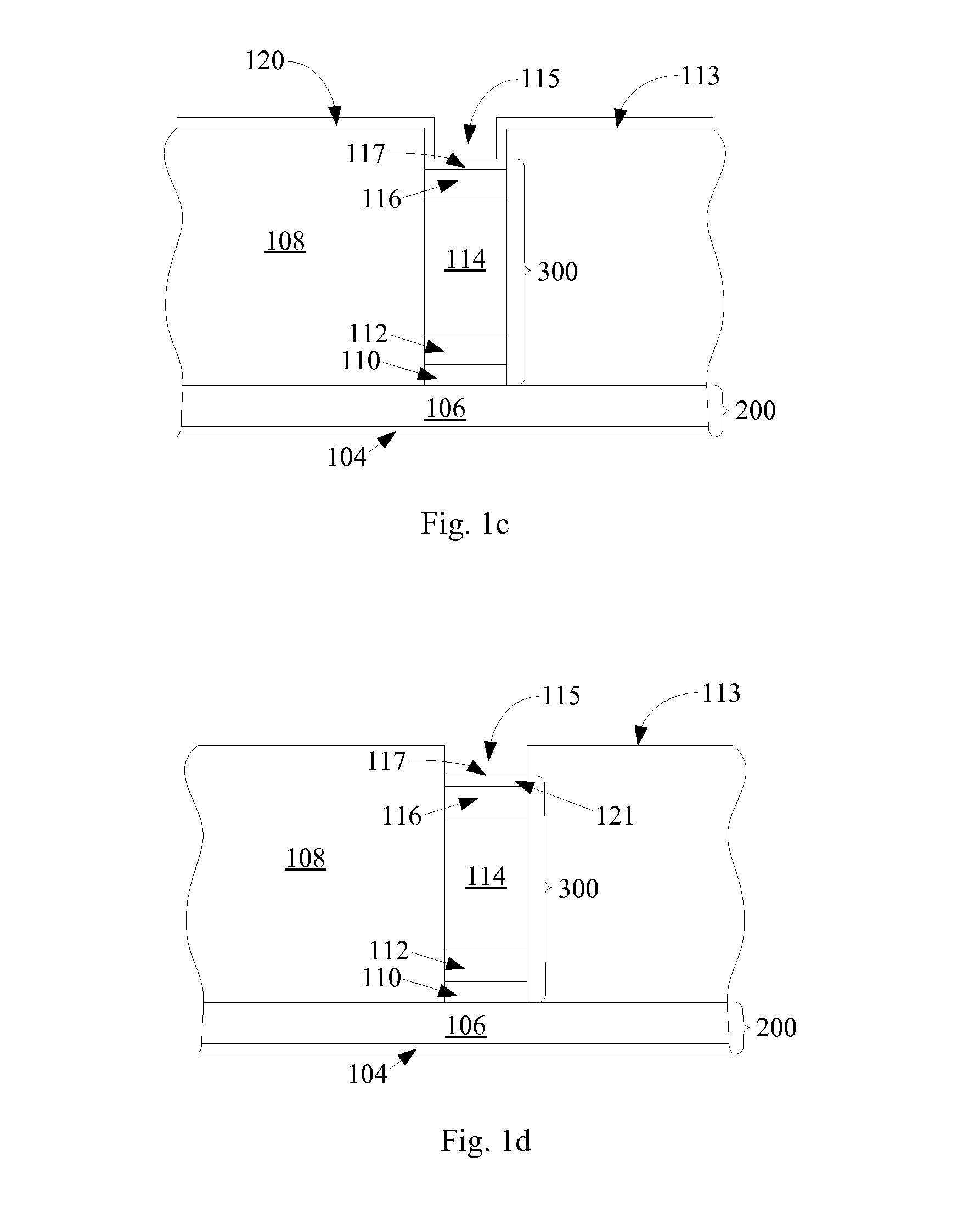

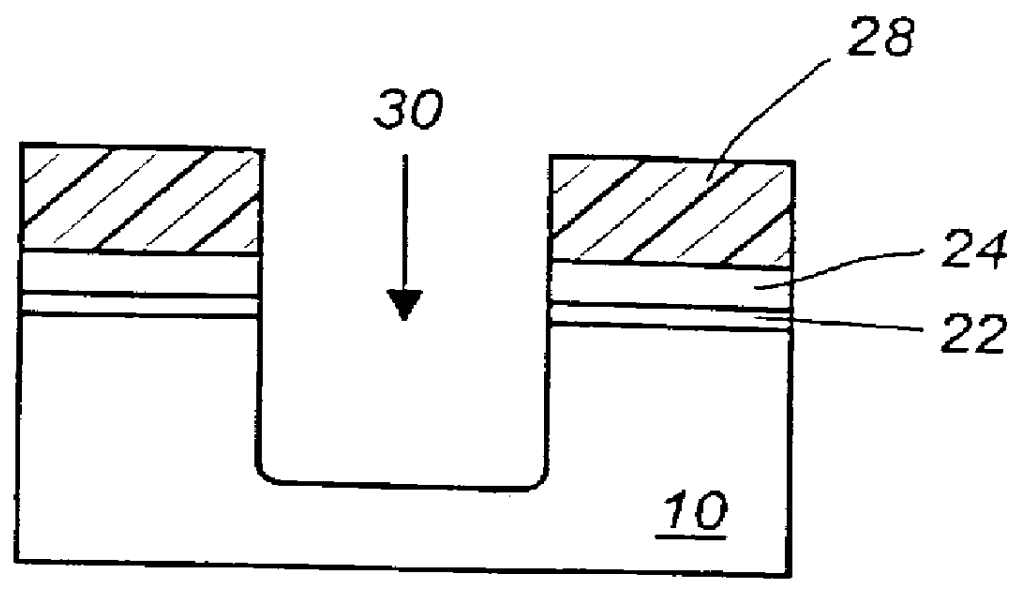

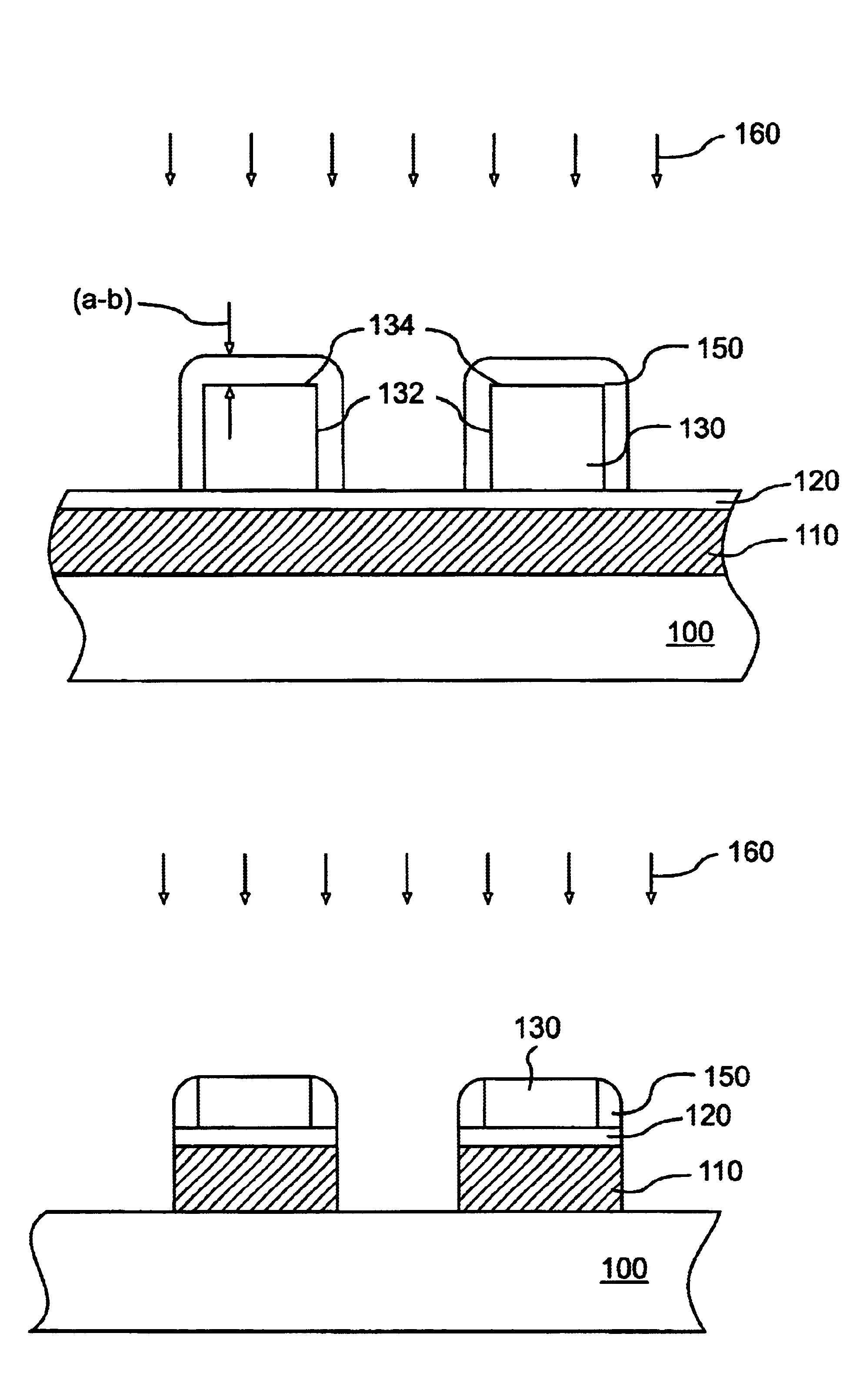

A method and apparatus for forming narrow vias in a substrate is provided. A pattern recess is etched into a substrate by conventional lithography. A thin conformal layer is formed over the surface of the substrate, including the sidewalls and bottom of the pattern recess. The thickness of the conformal layer reduces the effective width of the pattern recess. The conformal layer is removed from the bottom of the pattern recess by anisotropic etching to expose the substrate beneath. The substrate is then etched using the conformal layer covering the sidewalls of the pattern recess as a mask. The conformal layer is then removed using a wet etchant.

Owner:APPLIED MATERIALS INC

Gas pulsing for etch profile control

InactiveUS6784108B1Increase flow rateReduce flow rateElectric discharge tubesDecorative surface effectsEngineeringAnisotropic etching

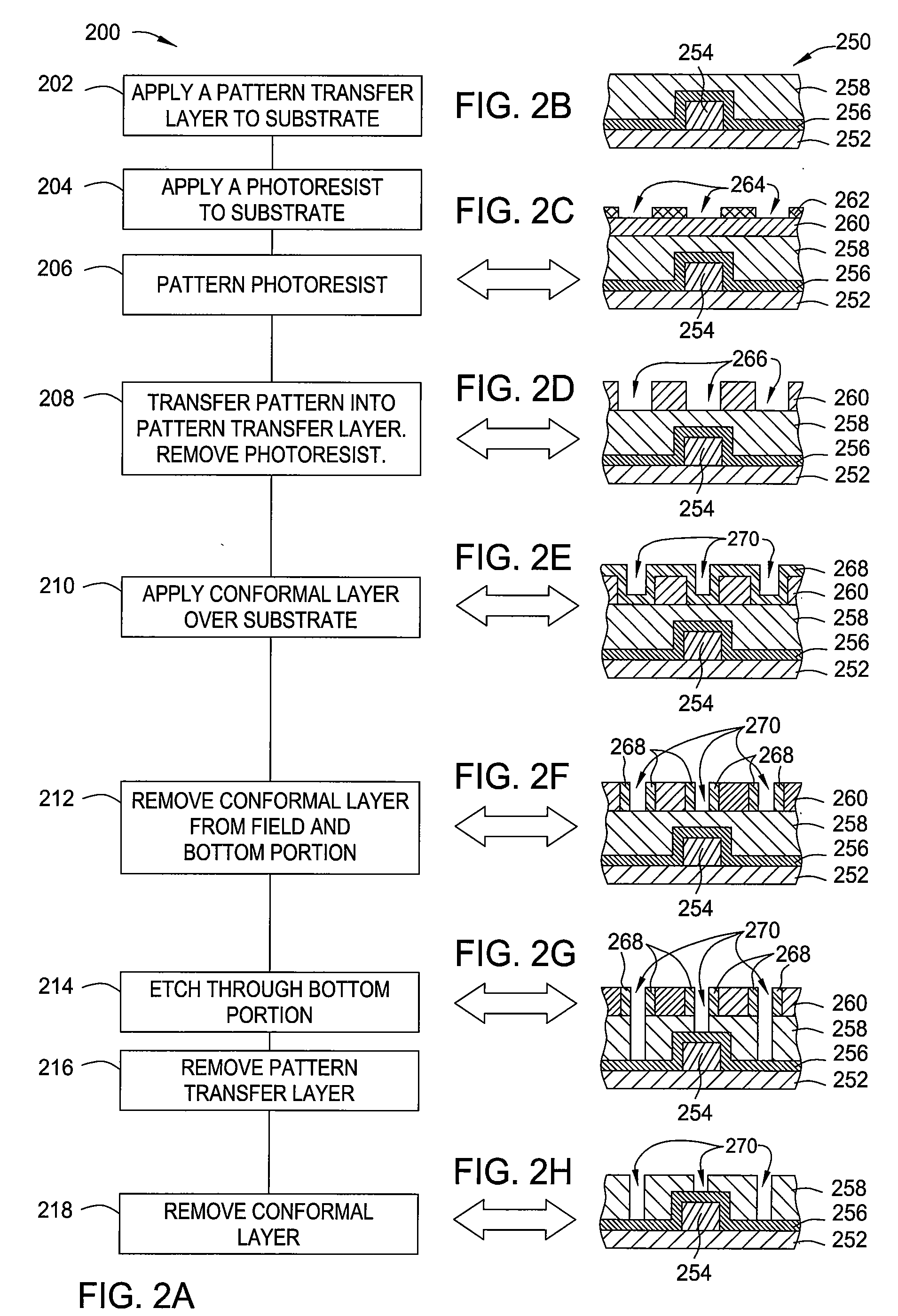

Etch profile control with pulsed gas flow and its applications to etching such as anisotropic etching of high aspect ratio features and etching of self-aligned contact structures in various processes. Pulsing can be applied according to this invention to the flow rate of a gas such as an etchant gas, a gas that leads to the deposition of a protective layer, a gas that modifies the deposition of a protective layer, and a gas that modifies etching.

Owner:MICRON TECH INC

Method of trimming technology

ActiveUS7354847B2Easy to controlAvoid insufficient thicknessSolid-state devicesSemiconductor/solid-state device manufacturingResistMOSFET

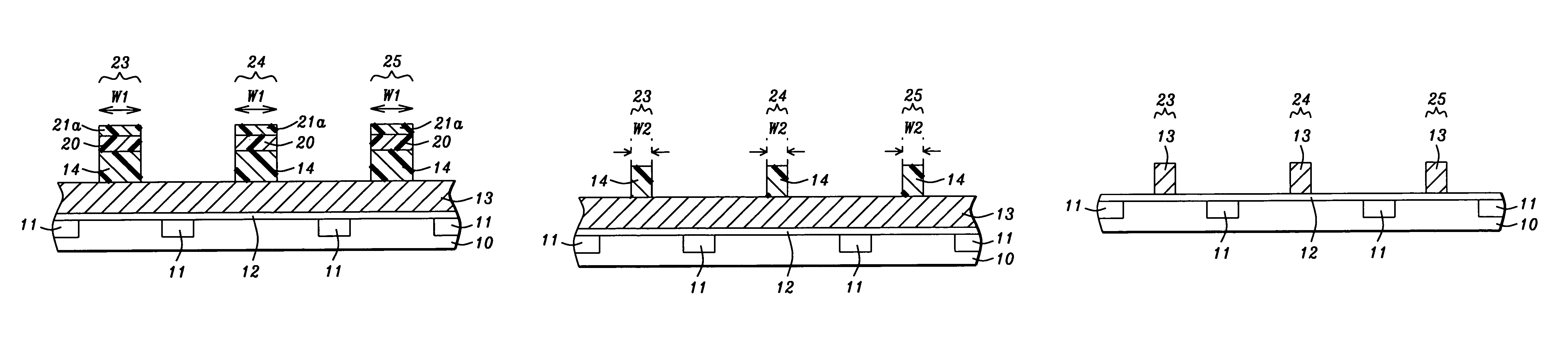

A process for trimming a photoresist layer during the fabrication of a gate electrode in a MOSFET is described. A bilayer stack with a top photoresist layer on a thicker organic underlayer is patternwise exposed with 193 nm or 157 nm radiation to form a feature having a width w1 in the top layer. A pattern transfer through the underlayer is performed with an anisotropic etch based on H2 / N2 and SO2 chemistry. The feature formed in the bilayer stack is trimmed by 10 nm or more to a width w2 by a HBr / O2 / Cl2 plasma etch. The pattern transfer through an underlying gate layer is performed with a third etch based on HBr / O2 / Cl2 chemistry. The underlayer is stripped by an O2 ashing with no damage to the gate electrode. Excellent profile control of the gate electrode is achieved and a larger (w1−w2) is possible than in prior art methods.

Owner:TAIWAN SEMICON MFG CO LTD

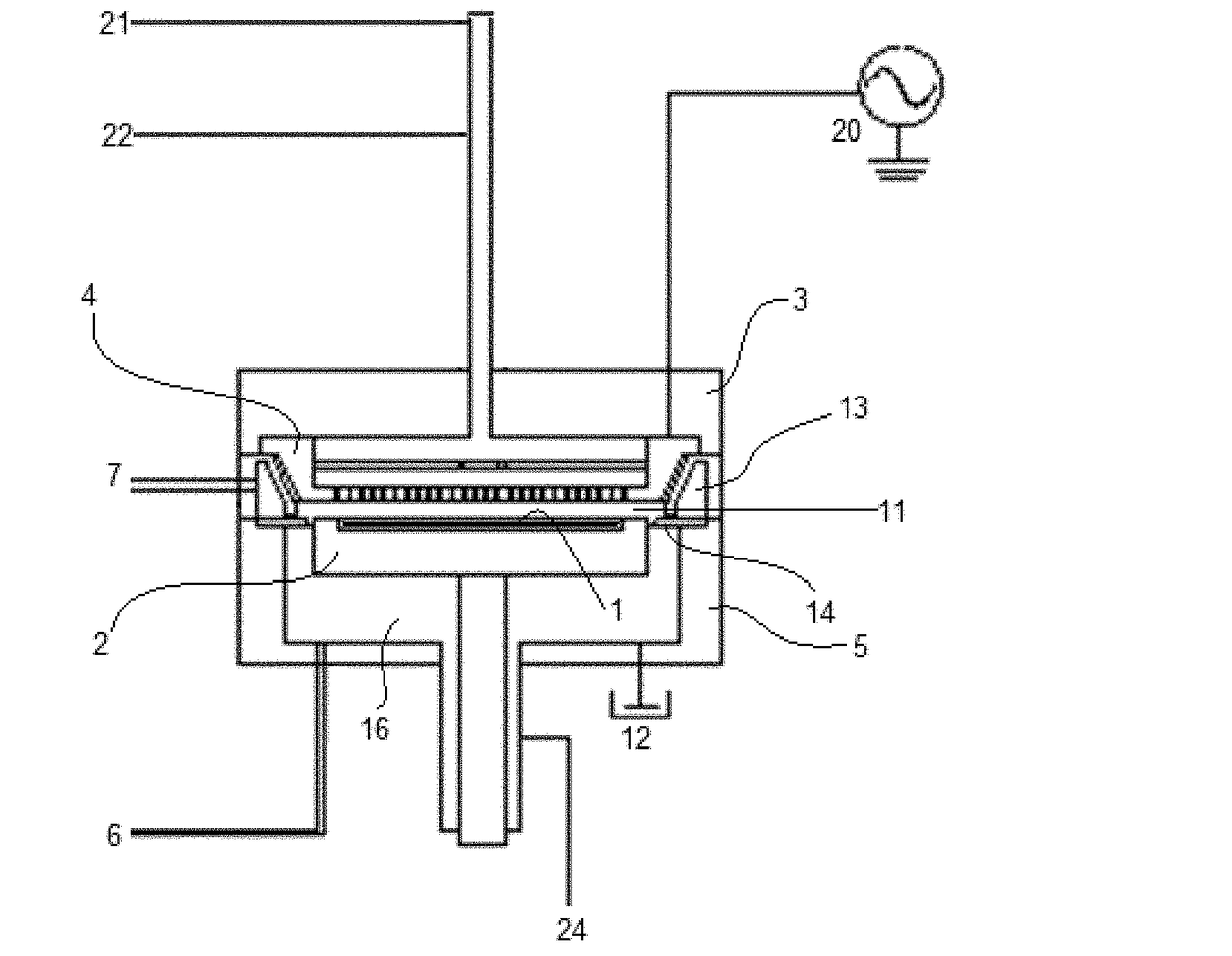

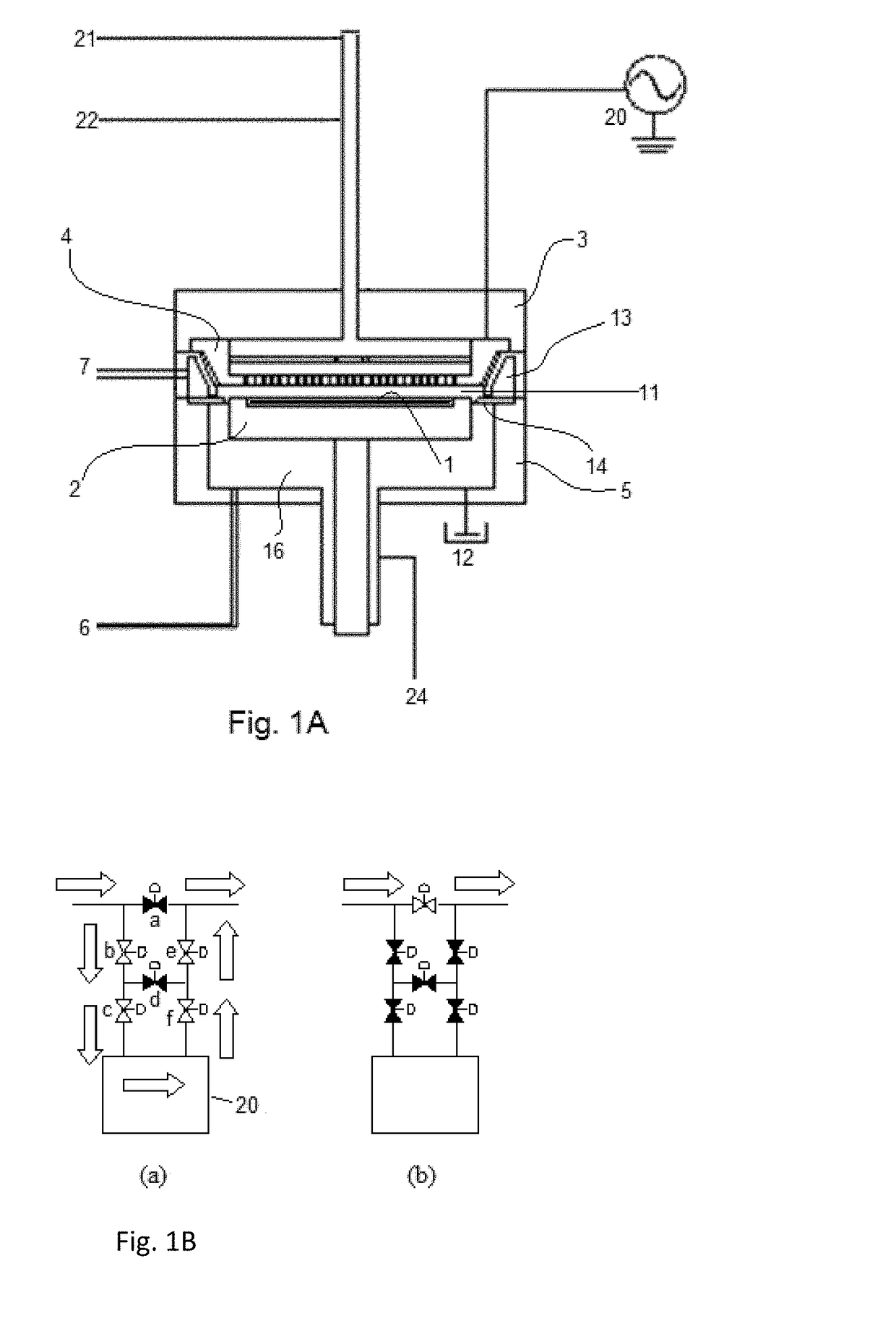

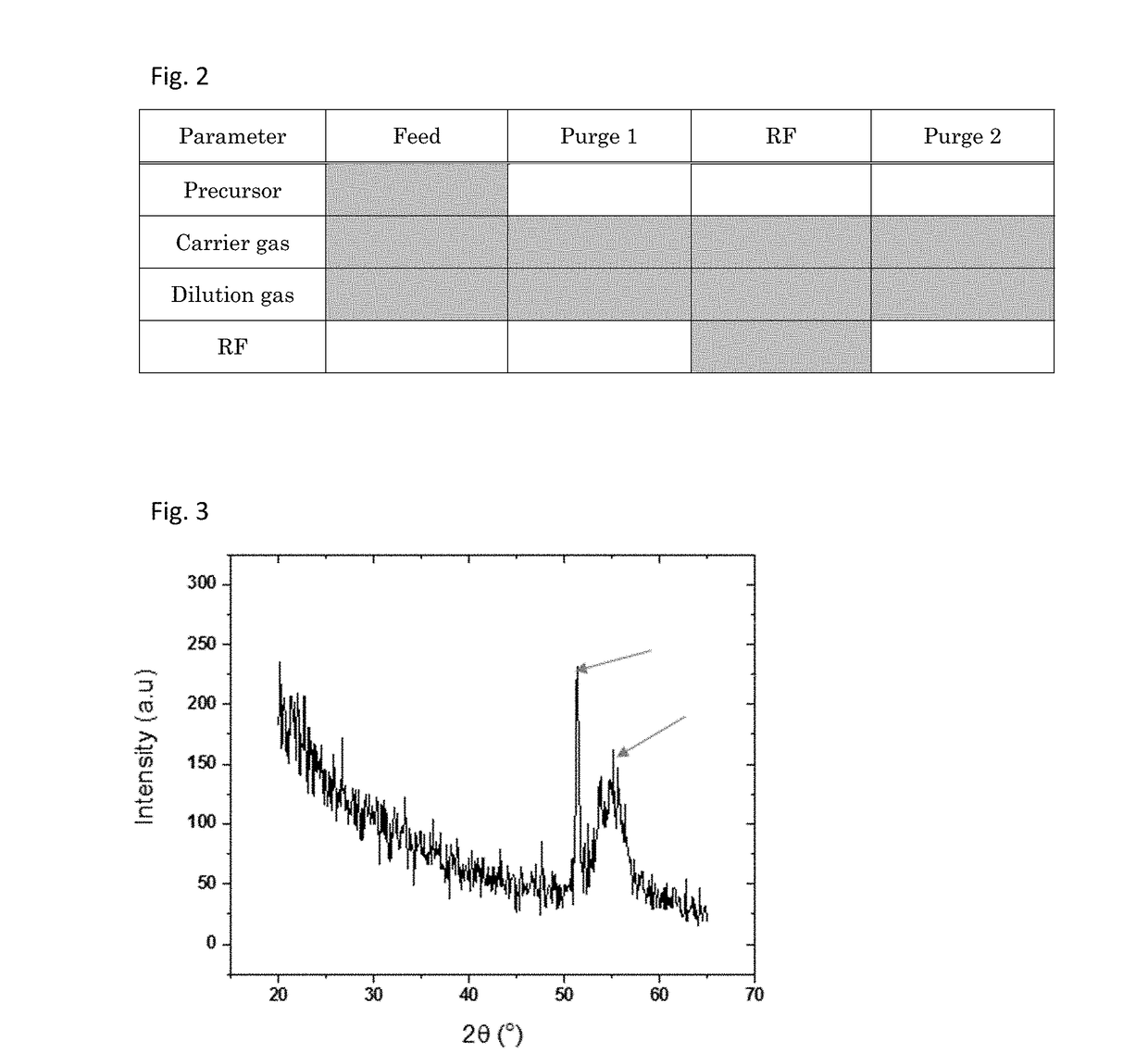

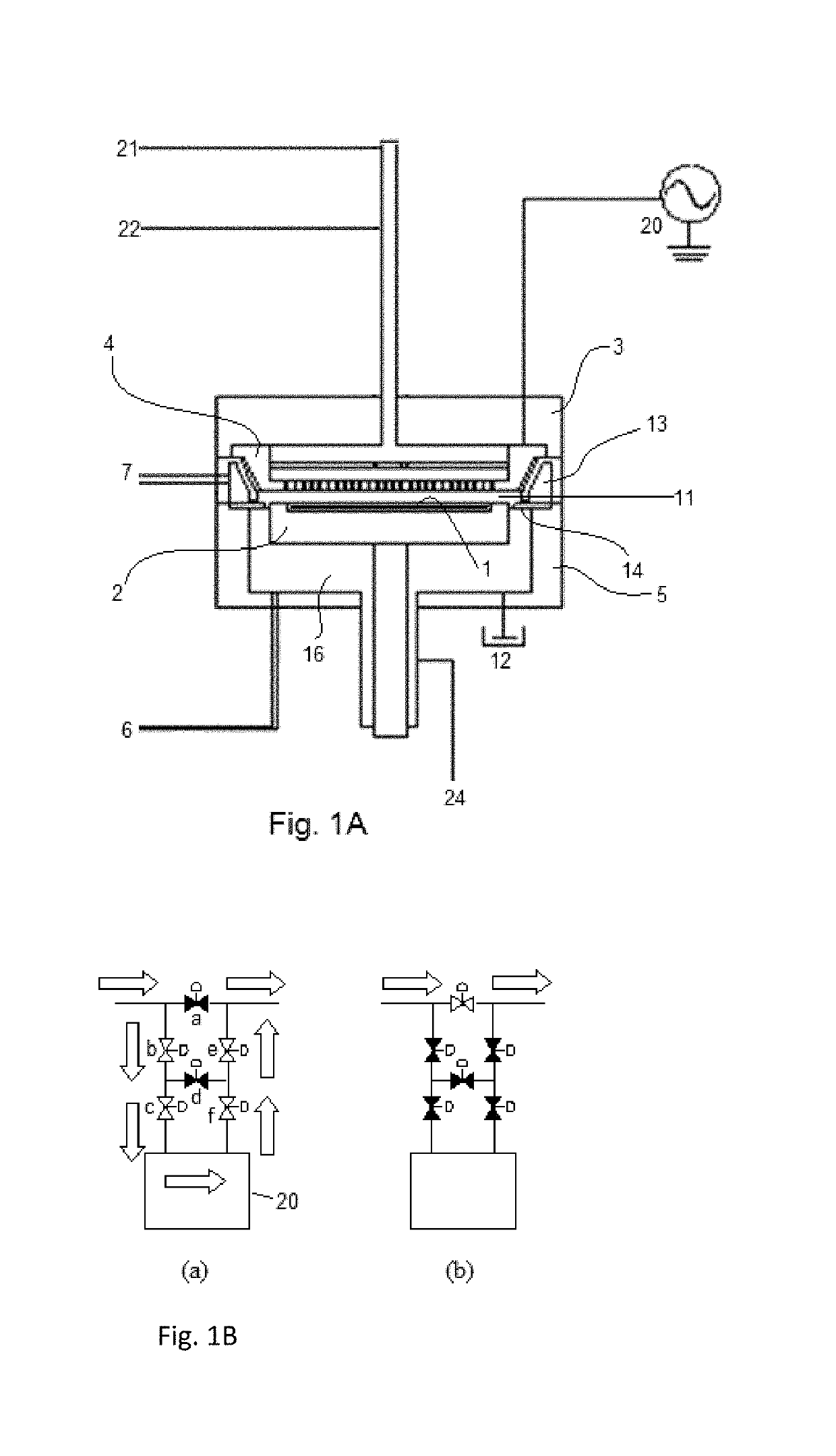

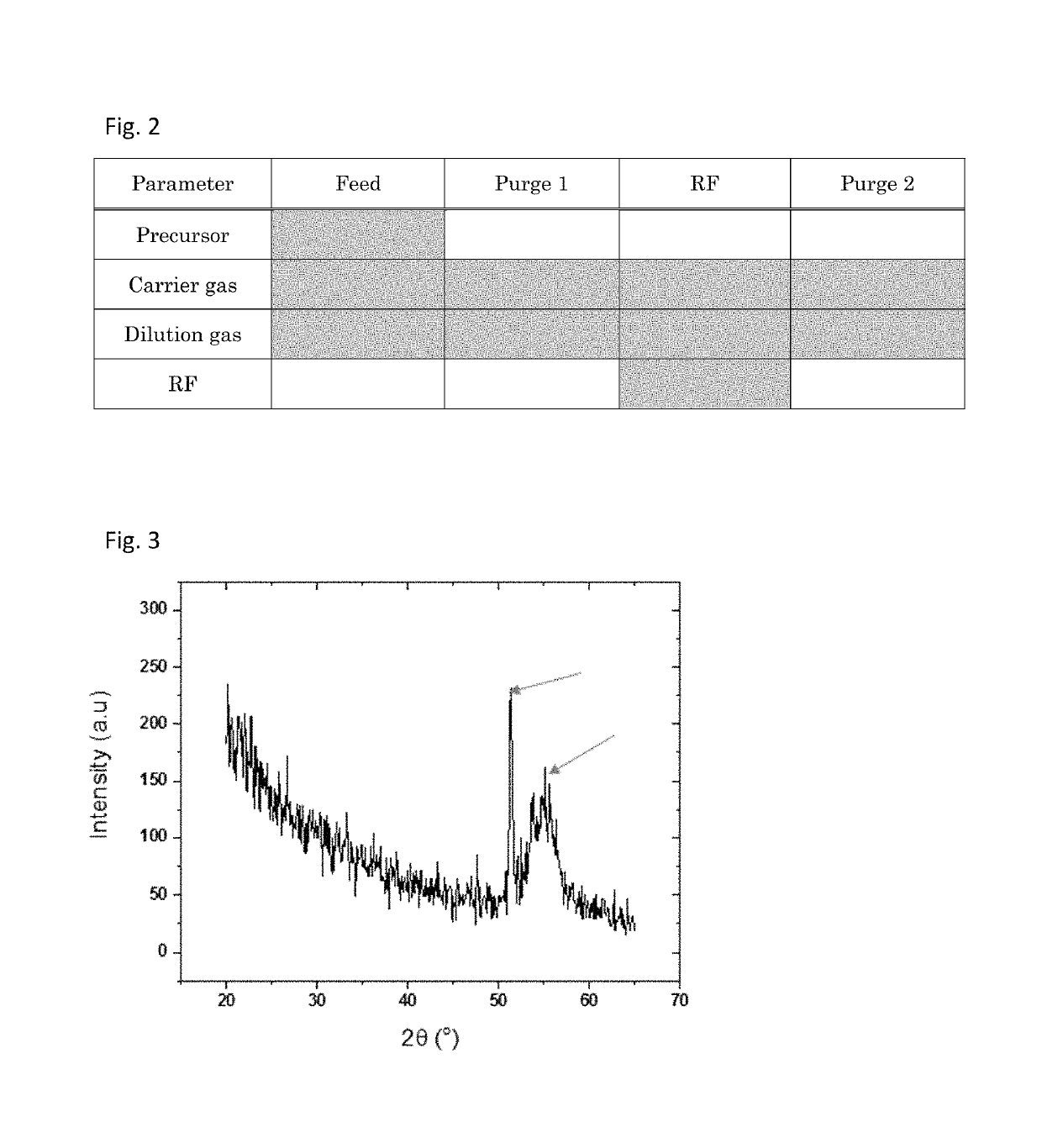

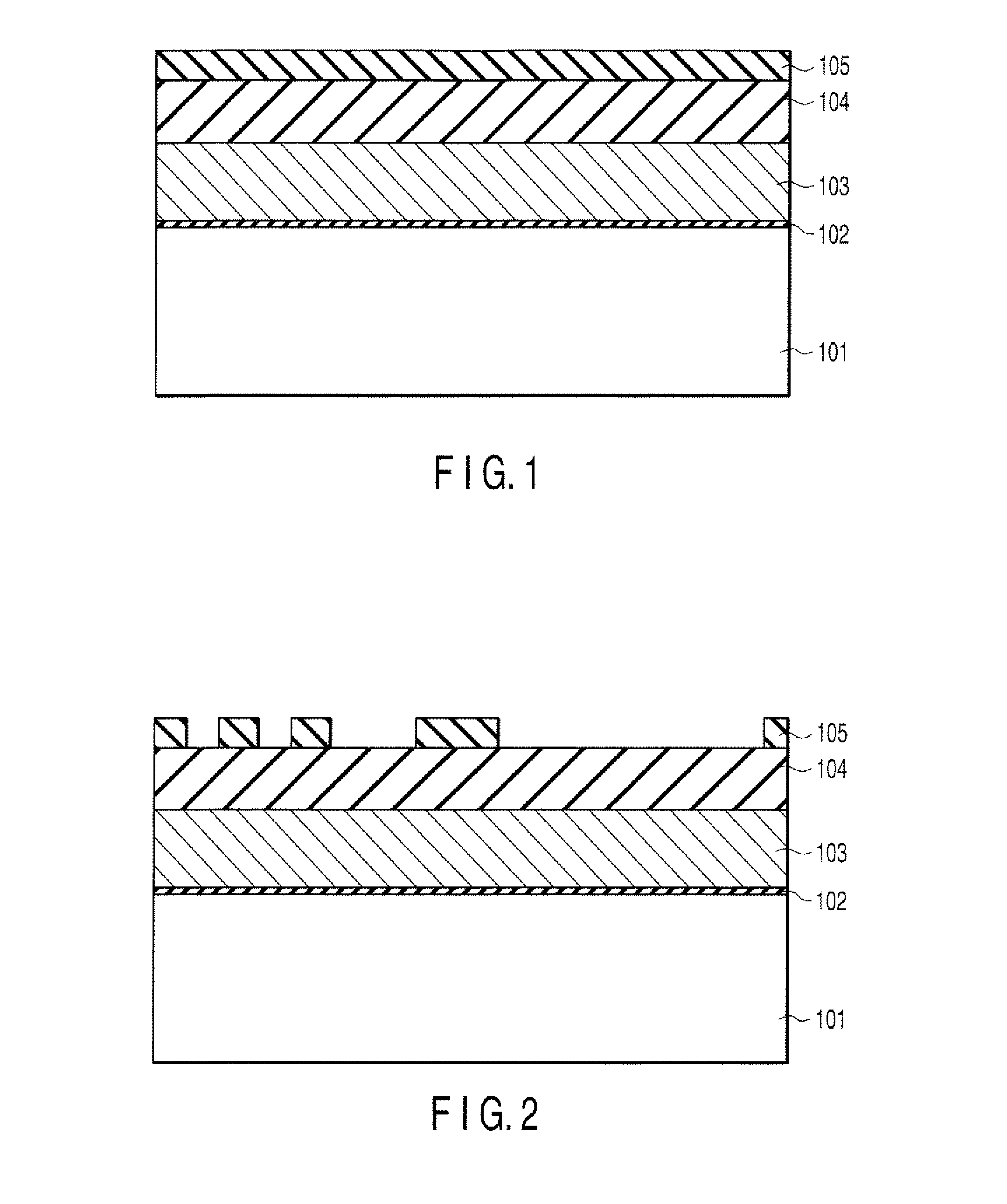

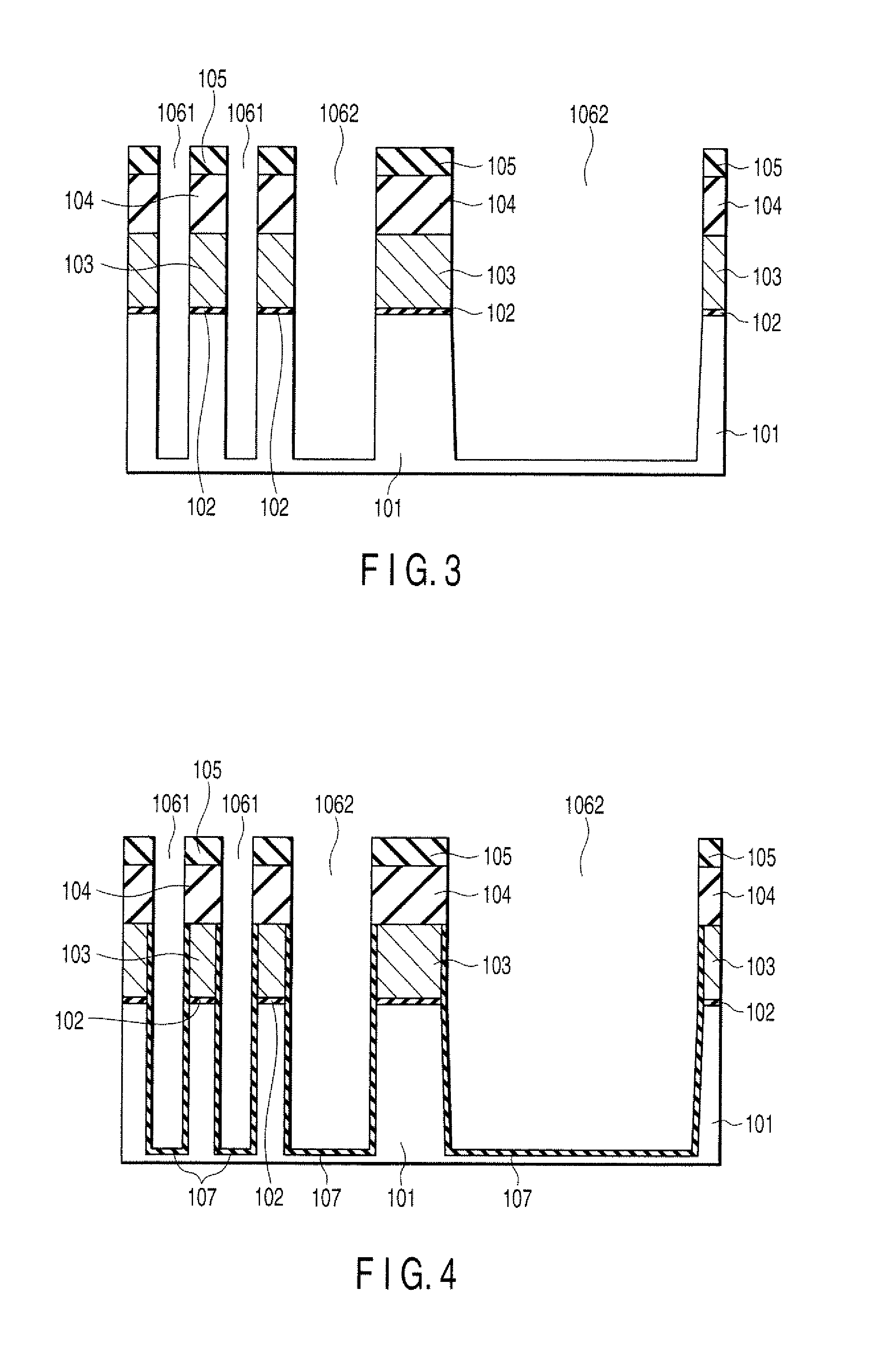

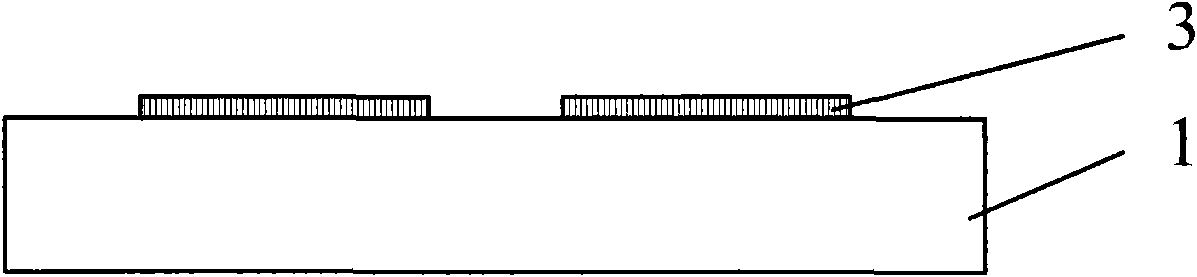

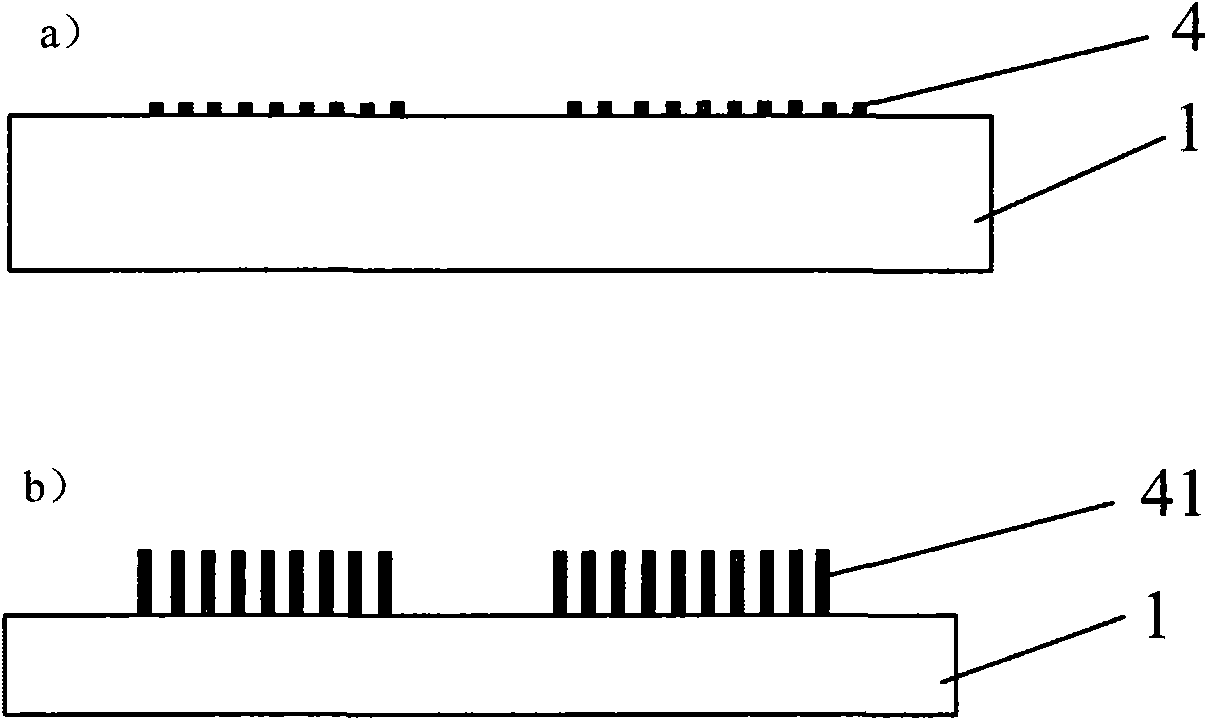

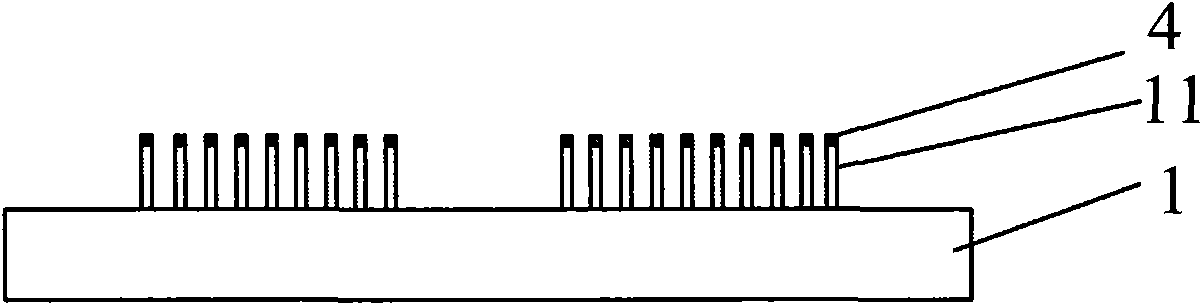

Method of topologically restricted plasma-enhanced cyclic deposition

ActiveUS20180151346A1Electric discharge tubesNitrogen-metal/silicon/boron binary compoundsEngineeringAnisotropic etching

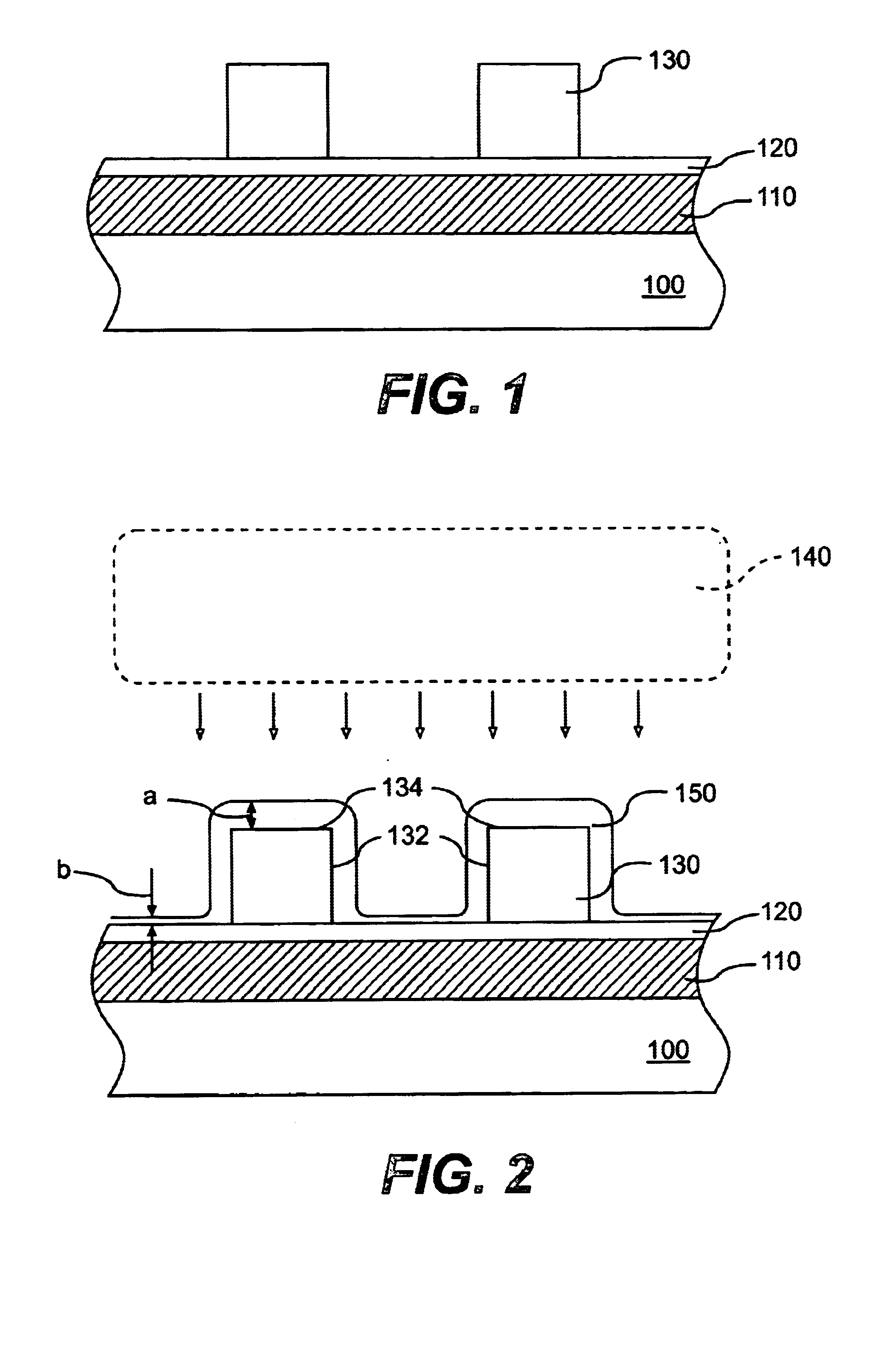

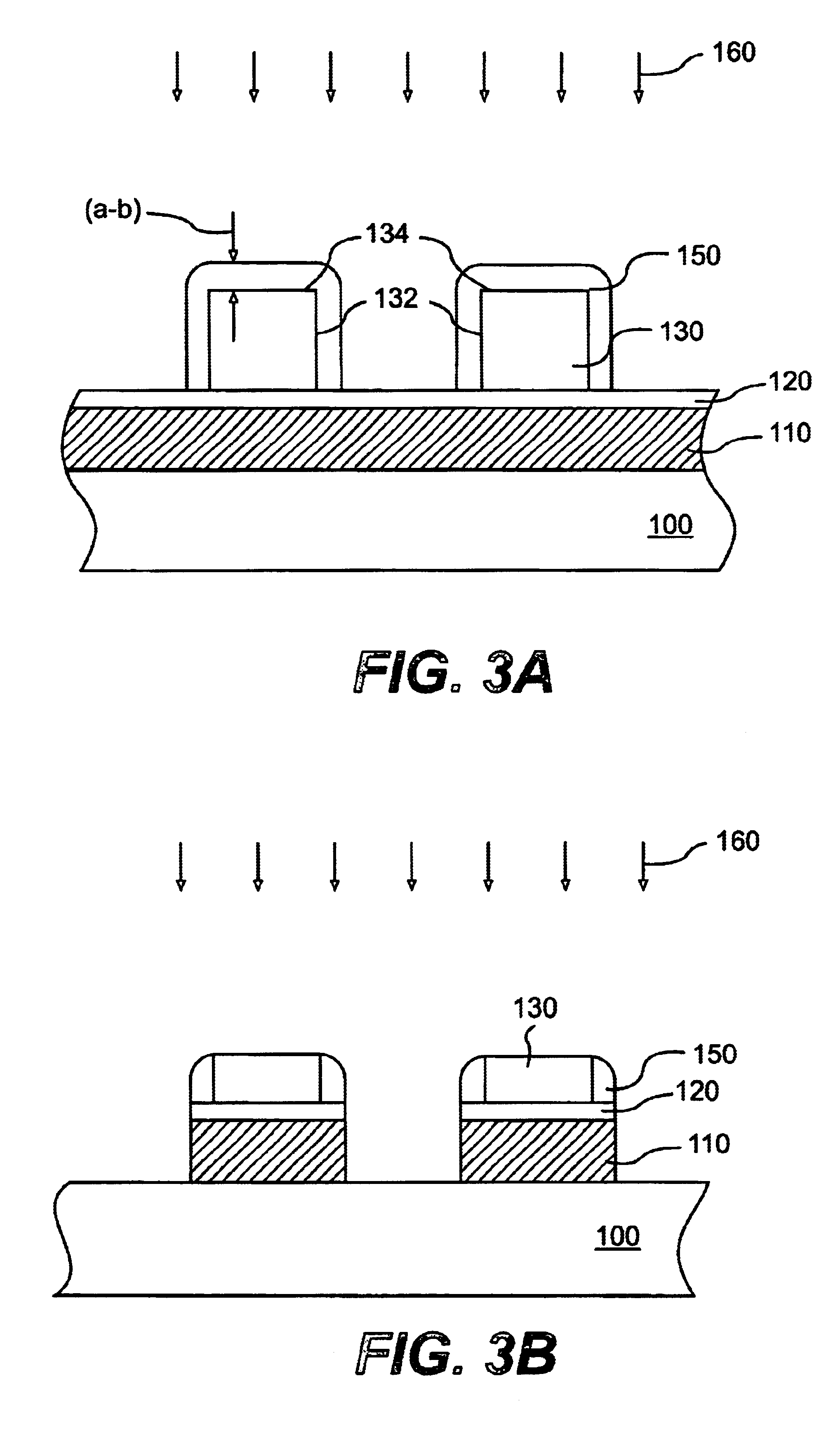

In an embodiment, a method for transferring a pattern constituted by vertical spacers arranged on a template with intervals to the template, includes depositing by plasma-enhanced cyclic deposition a layer as a spacer umbrella layer substantially only on a top surface of each vertical spacer made of silicon or metal oxide, wherein substantially no layer is deposited on sidewalls of the vertical spacers and on an exposed surface of the template, followed by transferring the pattern constituted by the vertical spacers to the template by anisotropic etching using the vertical spacers with the spacer umbrella layers.

Owner:ASM IP HLDG BV

Method of topologically restricted plasma-enhanced cyclic deposition of silicon or metal nitride

ActiveUS10340135B2Electric discharge tubesNitrogen-metal/silicon/boron binary compoundsAnisotropic etchingNitride

In an embodiment, a method for transferring a pattern constituted by vertical spacers arranged on a template with intervals to the template, includes depositing by plasma-enhanced cyclic deposition a layer as a spacer umbrella layer substantially only on a top surface of each vertical spacer made of silicon or metal oxide, wherein substantially no layer is deposited on sidewalls of the vertical spacers and on an exposed surface of the template, followed by transferring the pattern constituted by the vertical spacers to the template by anisotropic etching using the vertical spacers with the spacer umbrella layers.

Owner:ASM IP HLDG BV

Manufacturing method of semiconductor device using sti technique

InactiveUS20080182381A1Large widthSemiconductor/solid-state device manufacturingHigh densityAnisotropic etching

A first trench and a second trench having width wider than the first trench are simultaneously formed in a main surface area of a semiconductor substrate. The width of an opening portion of the first trench is made narrower by forming a first insulating film on the main surface of the semiconductor substrate and in the first and second trenches. A second insulating film is formed on the first insulating film by use of a high-density plasma-CVD method to form a void in the first trench while covering the opening portion of the first trench, and the second trench is filled with the second insulating film. Then, part of the second insulating film which covers the opening portion is removed by anisotropic etching and the void is filled with an insulating film having fluidity at the film formation time.

Owner:KK TOSHIBA

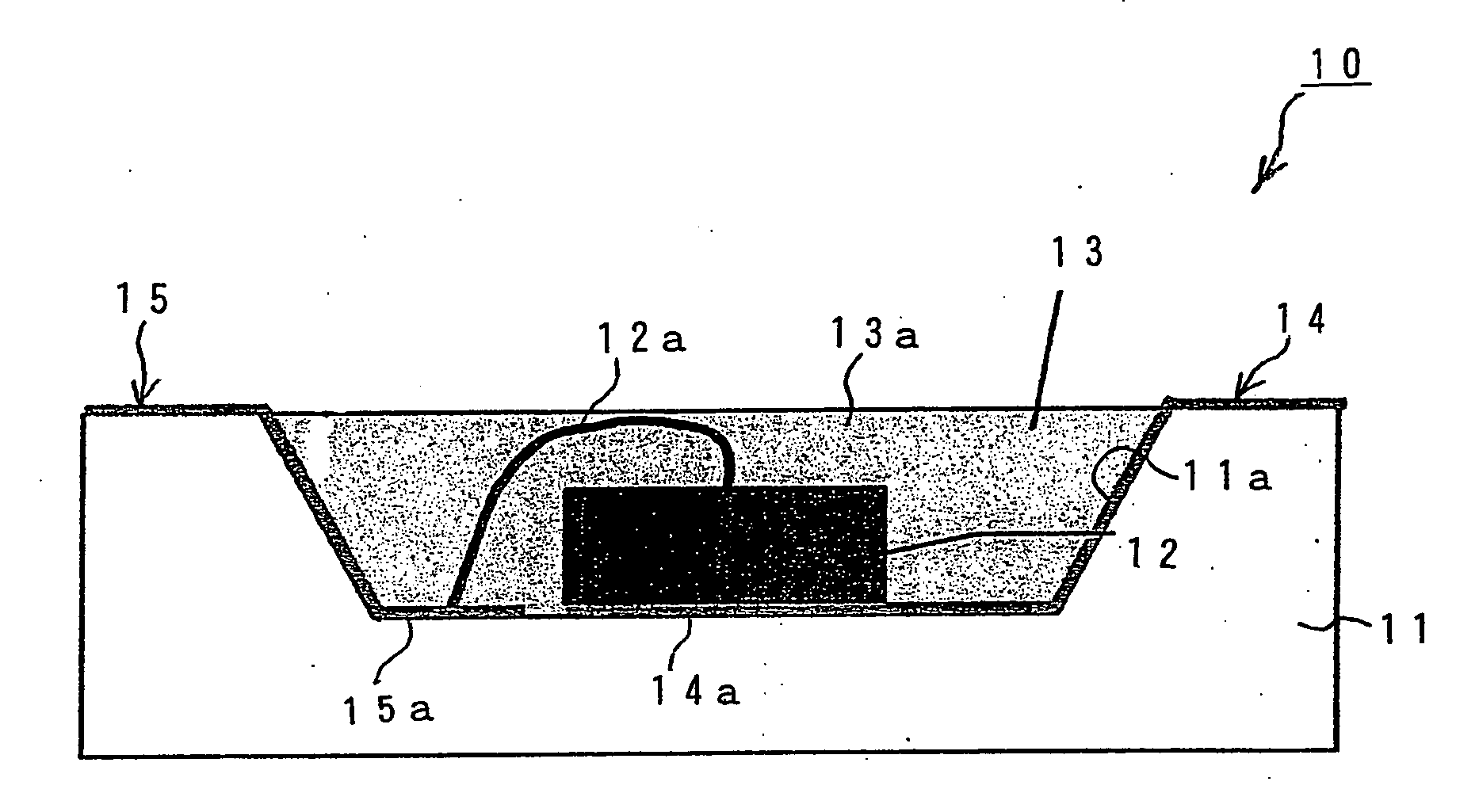

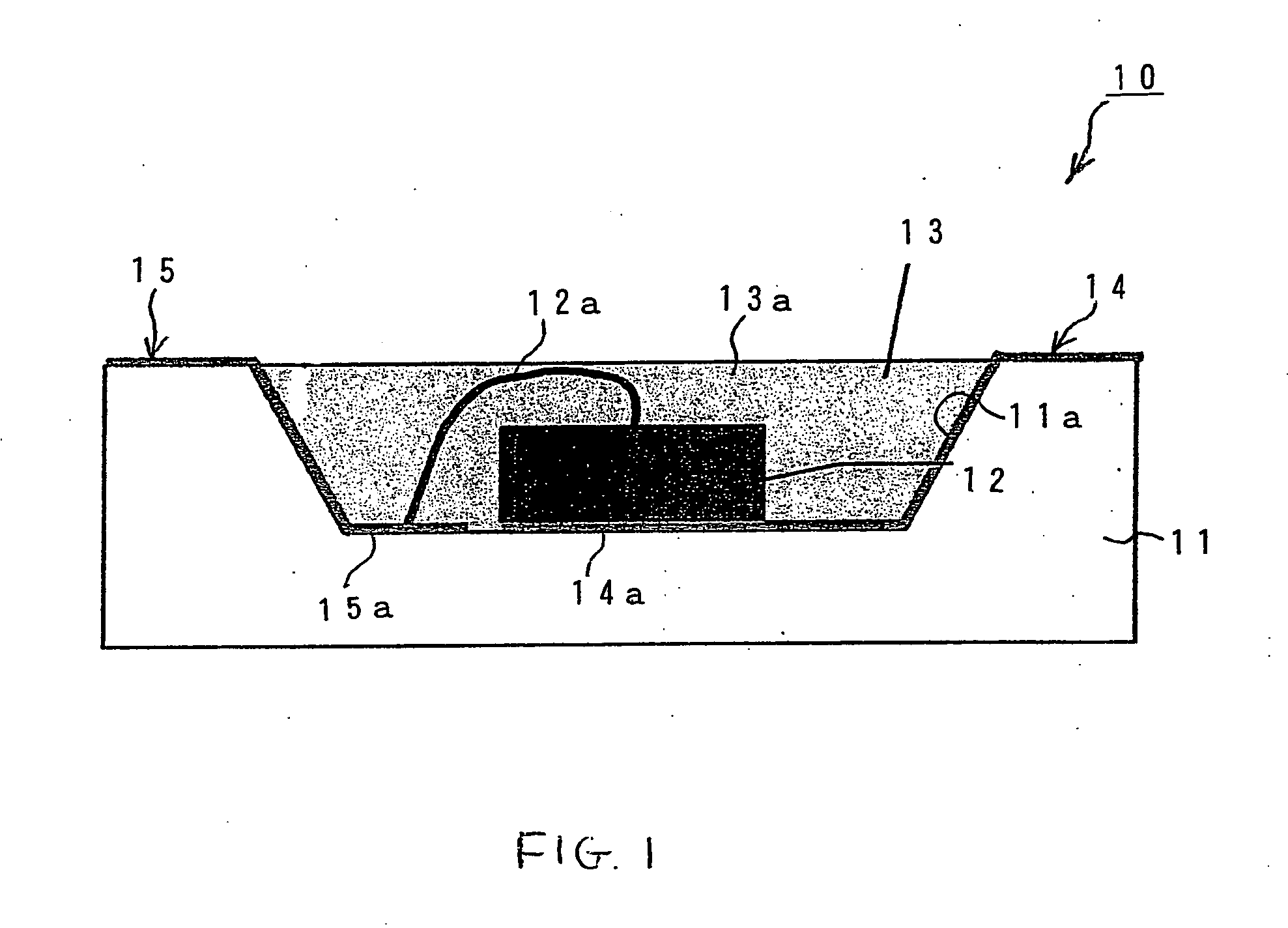

Led and fabrication method of same

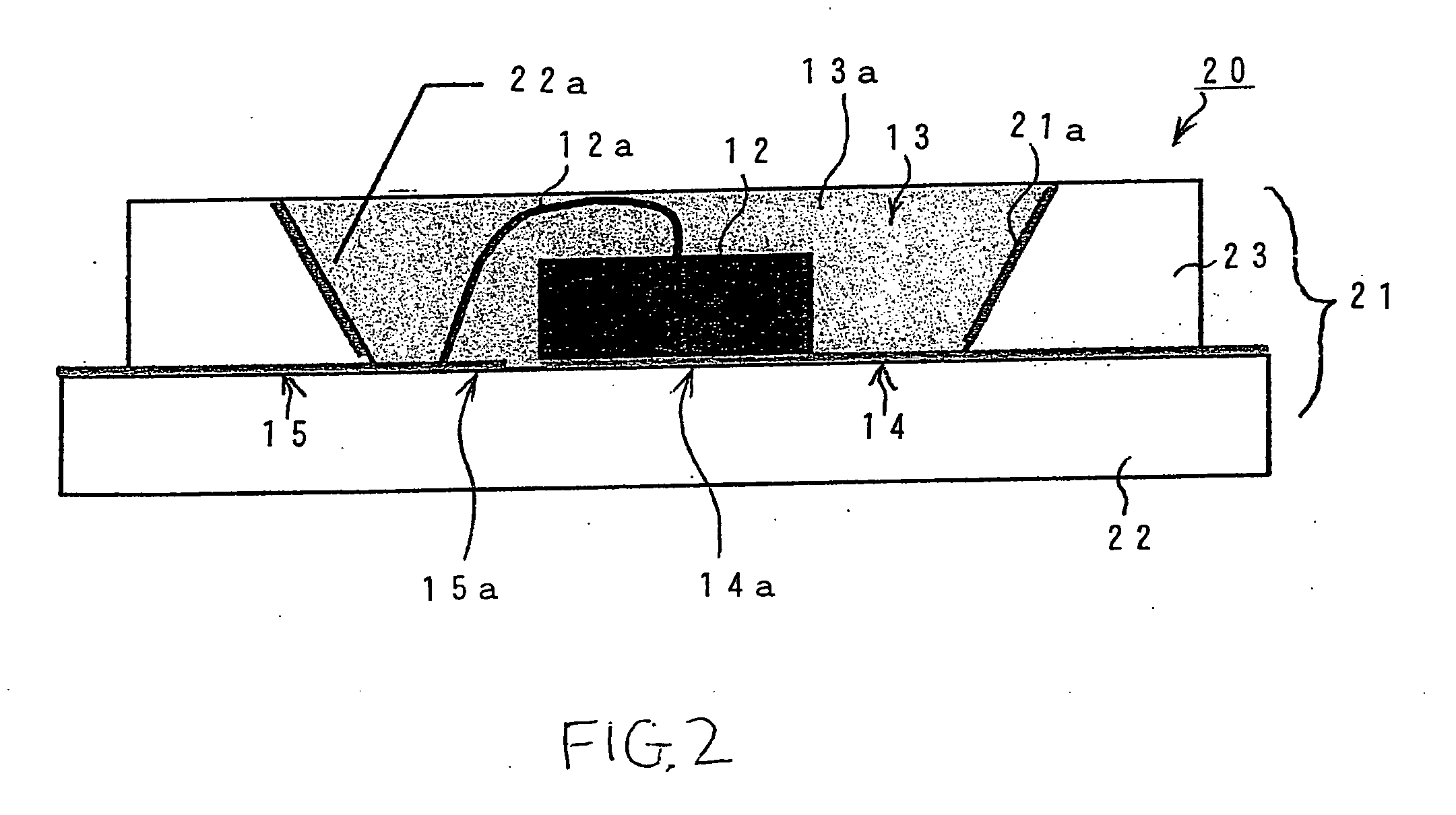

InactiveUS20060001055A1Easily and compactly configuredEasy to installTransistorSolid-state devicesEngineeringAnisotropic etching

An LED can include a silicon substrate and a pair of electrodes formed inside a horn that is formed on the silicon substrate by anisotropic etching. The LED can include an LED chip mounted inside the horn, the LED chip being electrically connected to the pair of electrodes. A resin mold made of a resin material can be filled in the horn.

Owner:STANLEY ELECTRIC CO LTD

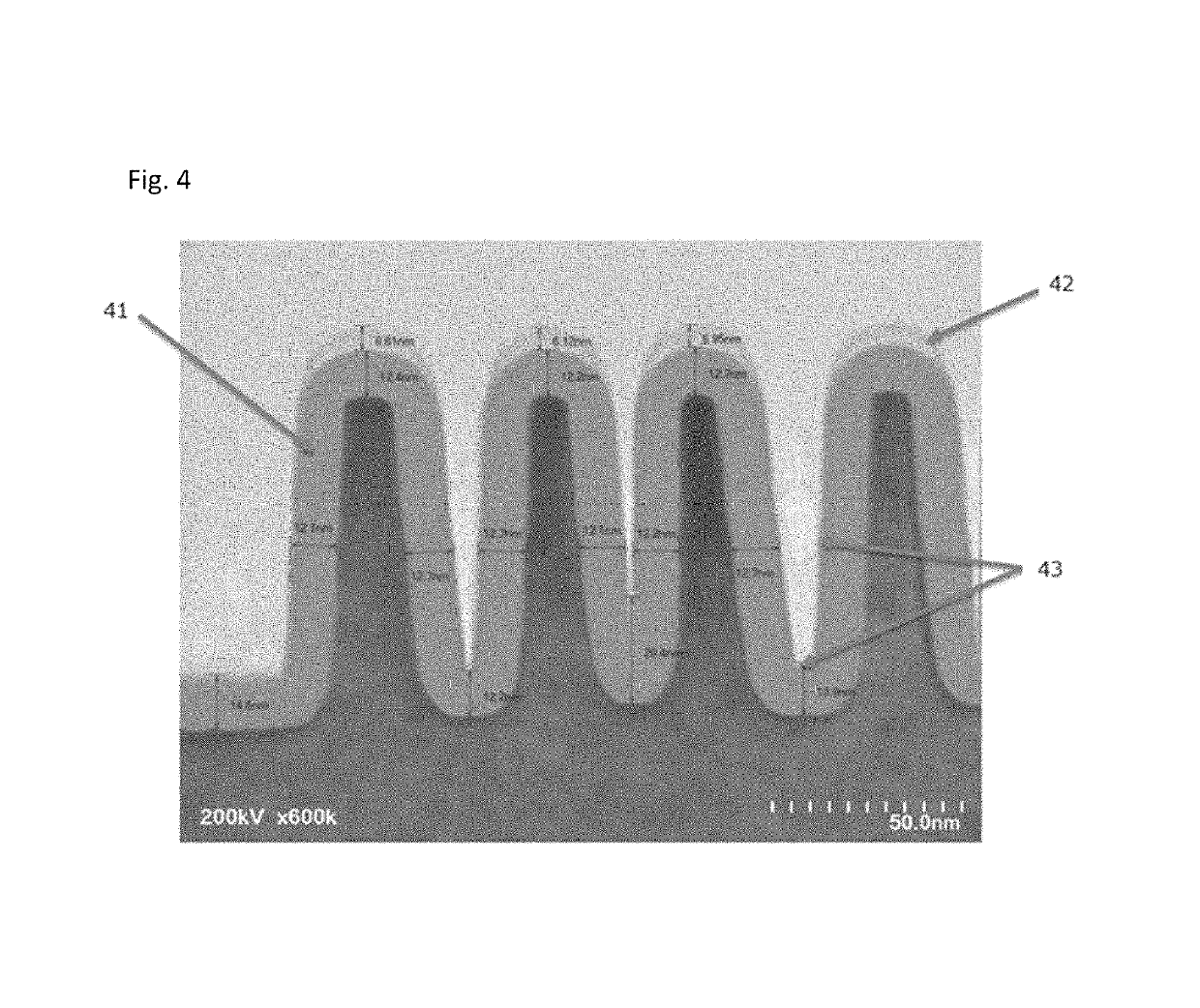

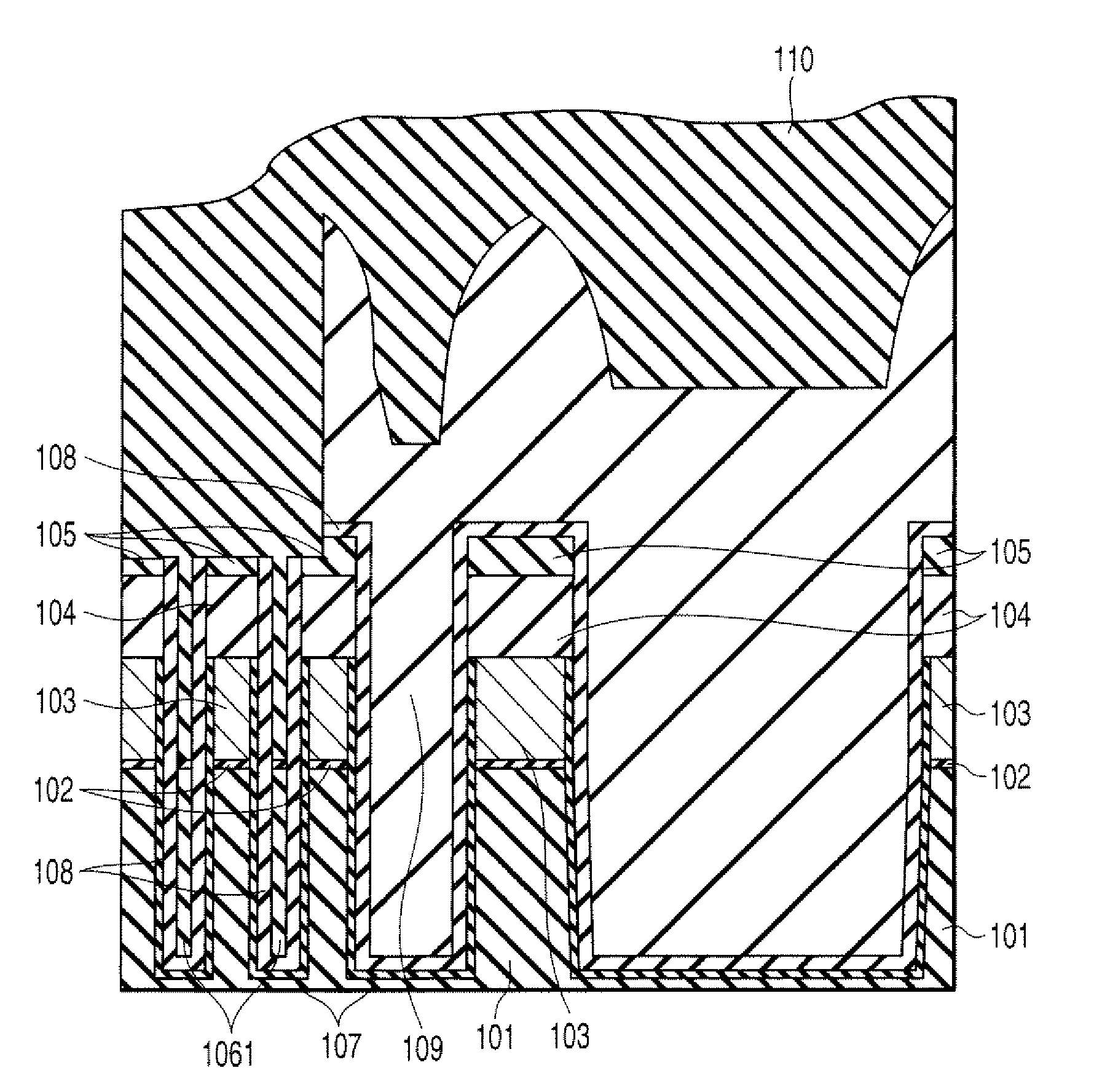

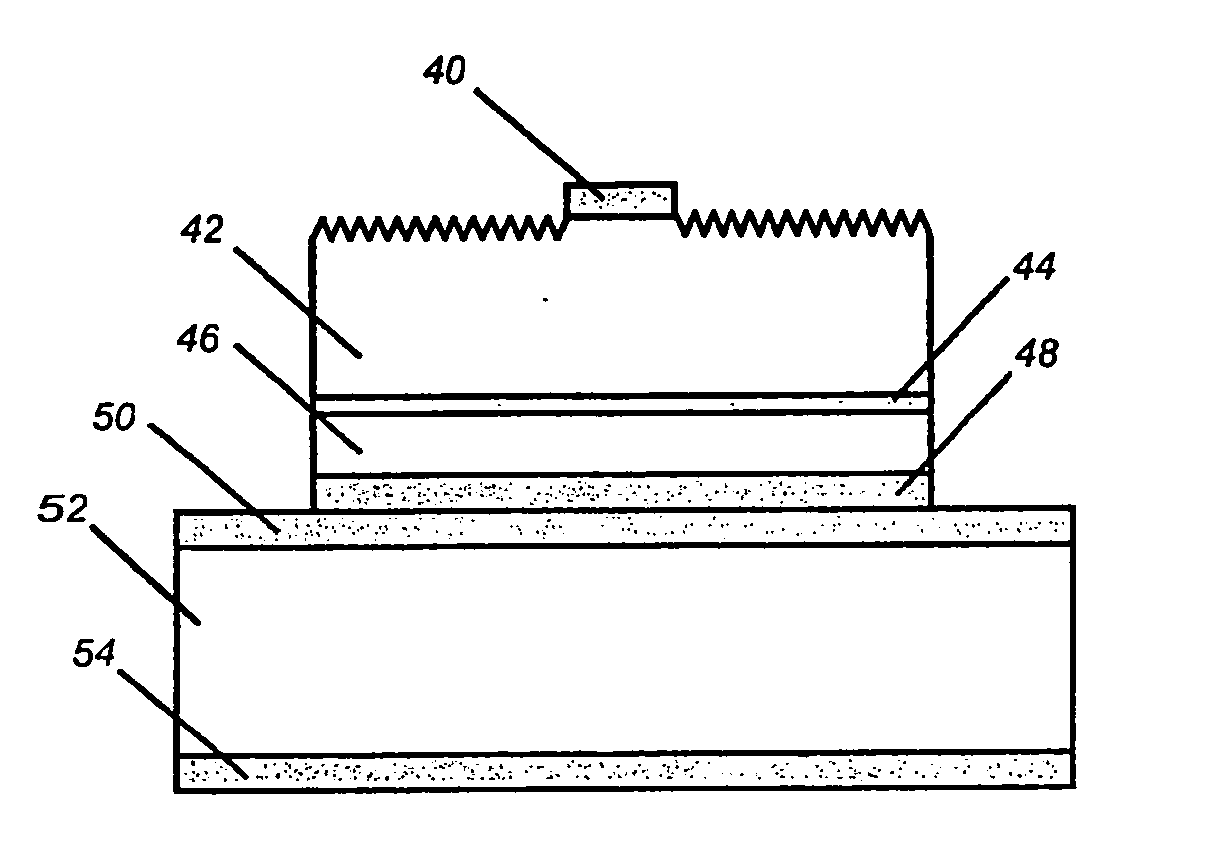

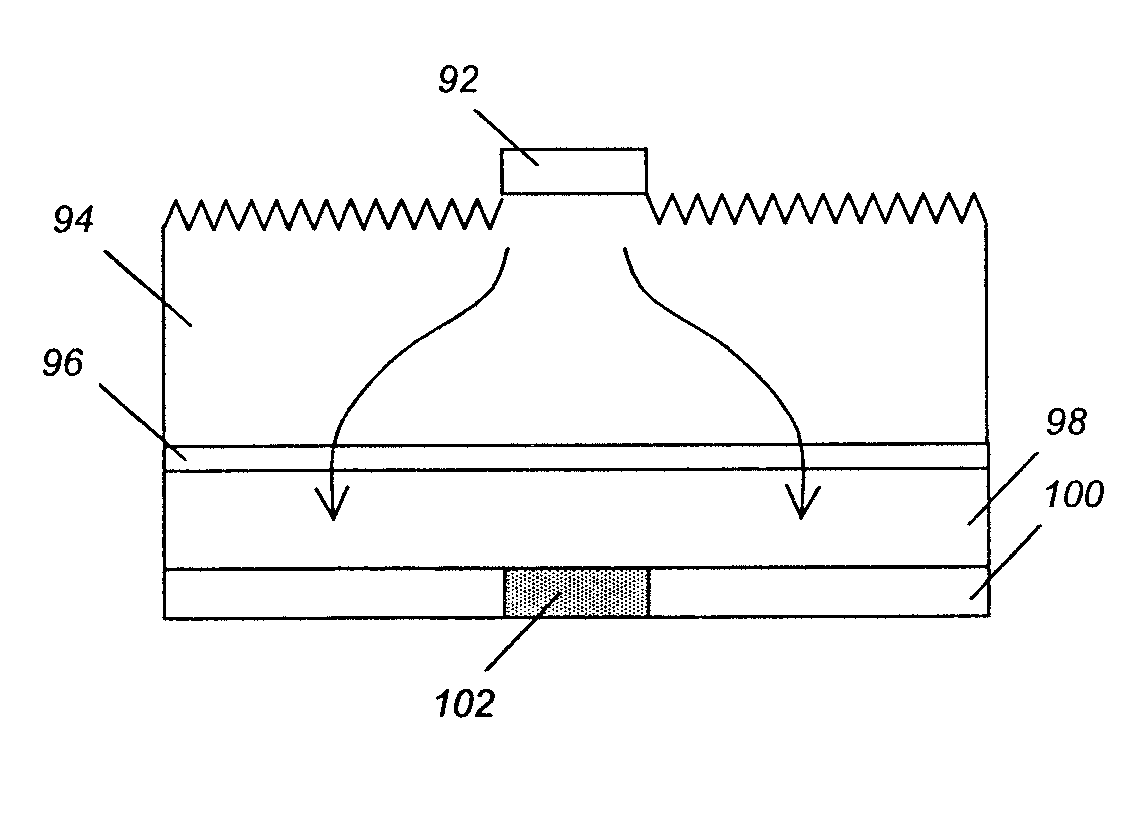

Highly efficient gallium nitride based light emitting diodes via surface roughening

ActiveUS20070121690A1Solid-state devicesSemiconductor/solid-state device manufacturingNitrogenLight reflection

A gallium nitride (GaN) based light emitting diode (LED), wherein light is extracted through a nitrogen face (N-face) (42) of the LED and a surface of the N-face (42) is roughened into one or more hexagonal shaped cones. The roughened surface reduces light reflections occurring repeatedly inside the LED, and thus extracts more light out of the LED. The surface of the N-face (42) is roughened by an anisotropic etching, which may comprise a dry etching or a photo-enhanced chemical (PEC) etching.

Owner:JAPAN SCI & TECH CORP

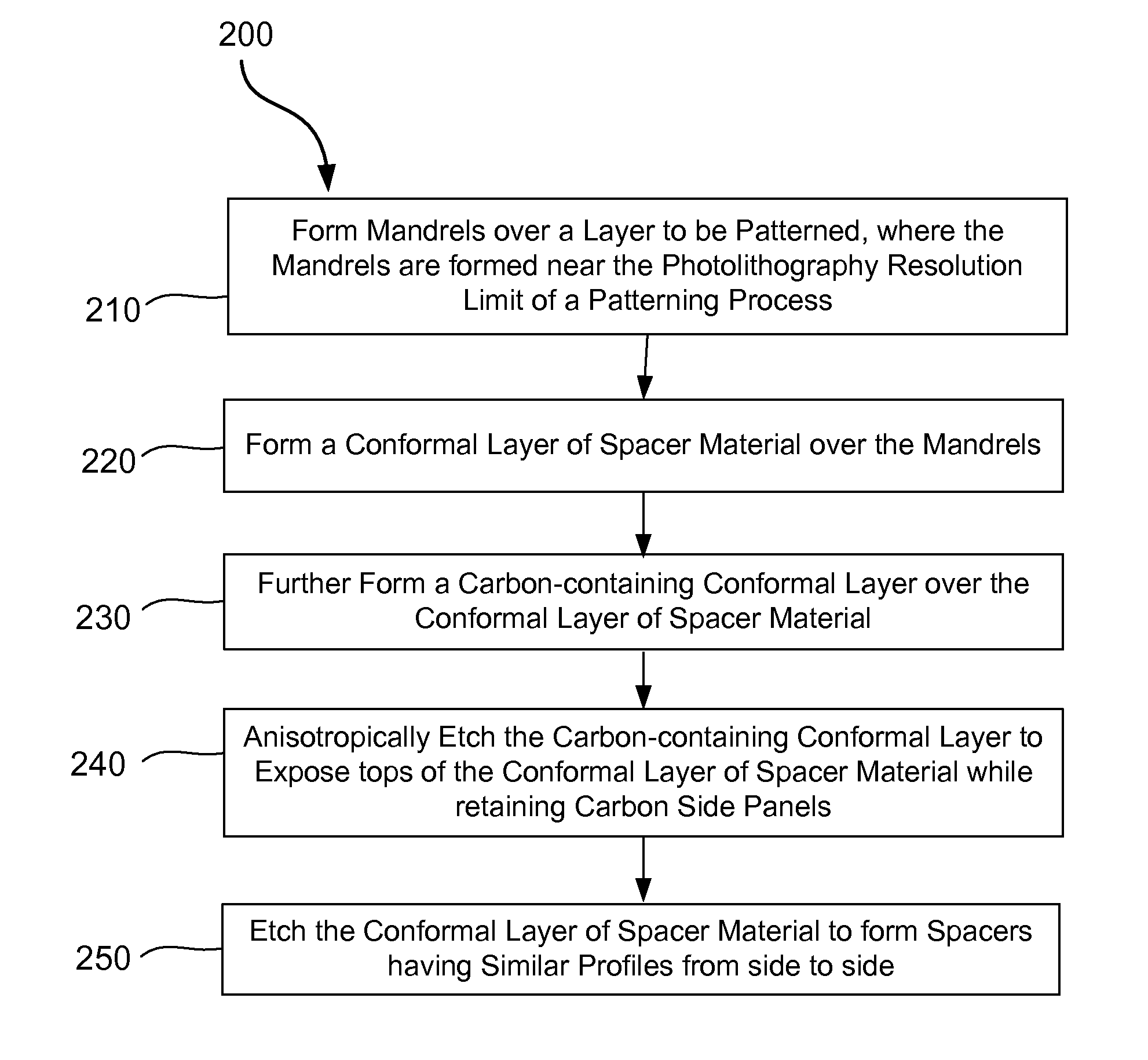

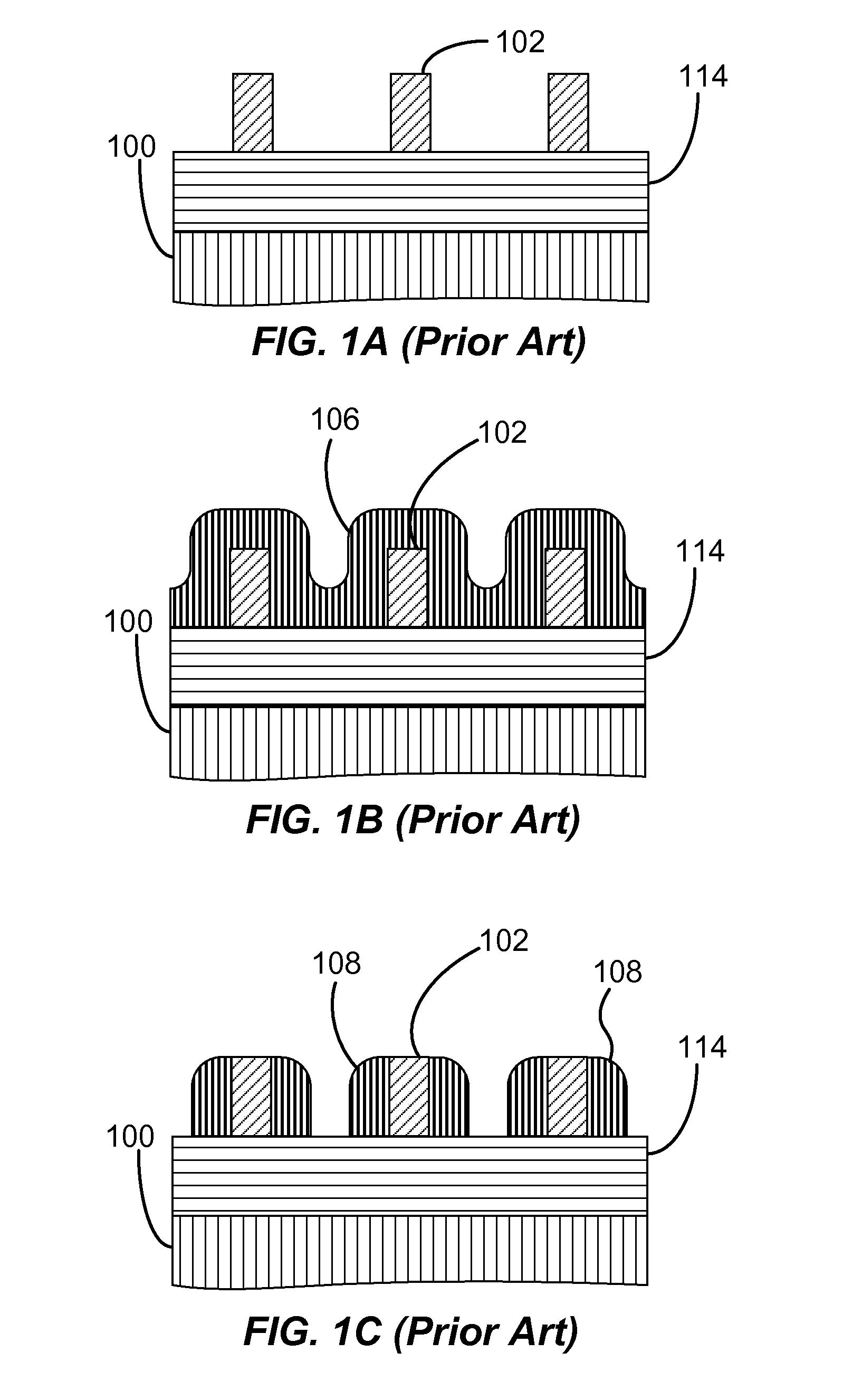

Spacer formation

Embodiments of the present invention pertain to methods of forming more symmetric spacers which may be used for self-aligned multi-patterning processes. A conformal spacer layer of spacer material is formed over mandrels patterned near the optical resolution of a photolithography system using a high-resolution photomask. A carbon-containing layer is further formed over the conformal spacer layer. The carbon-containing layer is anisotropically etched to expose the high points of the conformal spacer layer while retaining carbon side panels. The conformal spacer layer may then be etched to form spacers without the traditional skewing of the profile towards one side or the other.

Owner:APPLIED MATERIALS INC

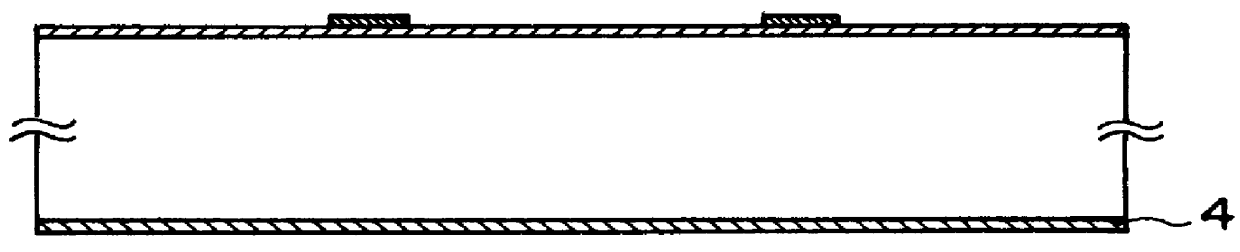

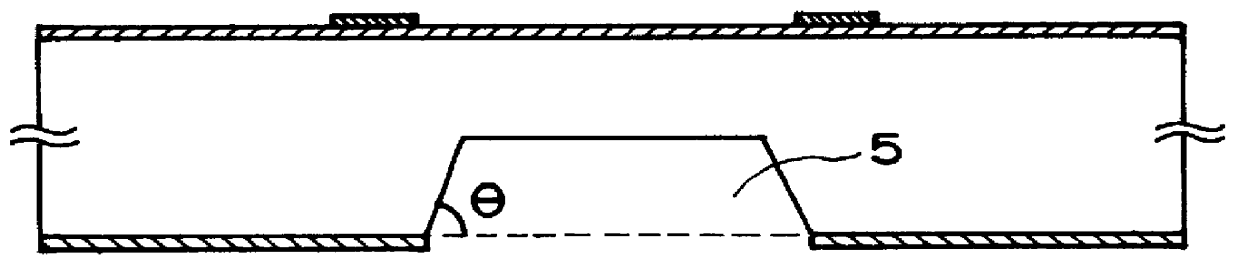

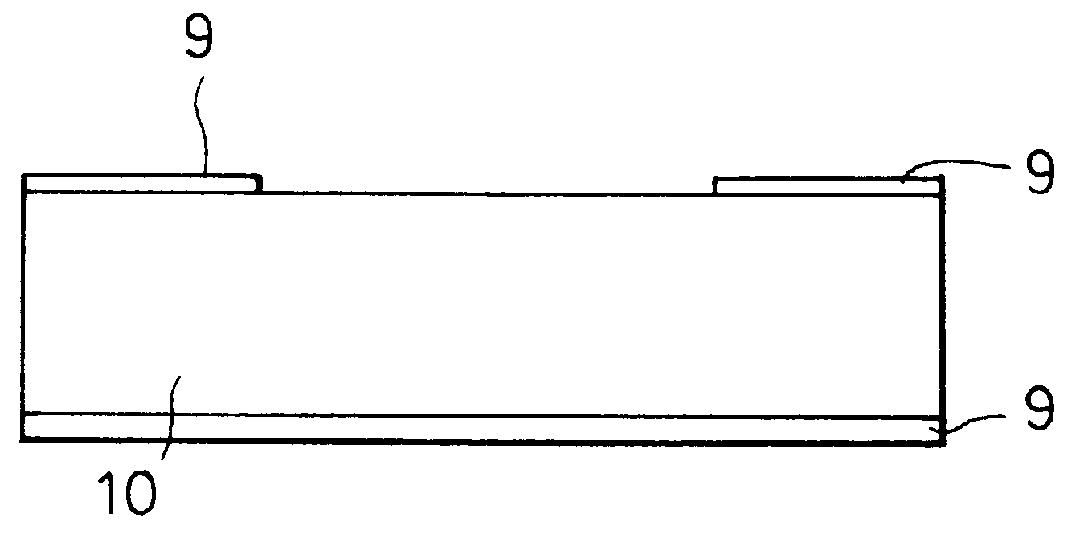

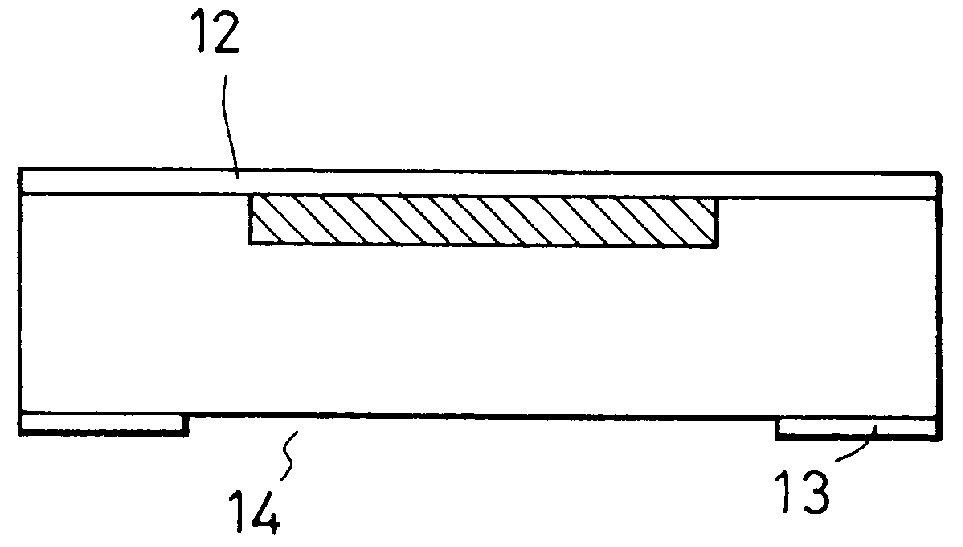

Manufacturing method of ink jet head

InactiveUS6139761ADistanceSimple processRecording apparatusSemiconductor/solid-state device manufacturingPressure generationSilicon oxide

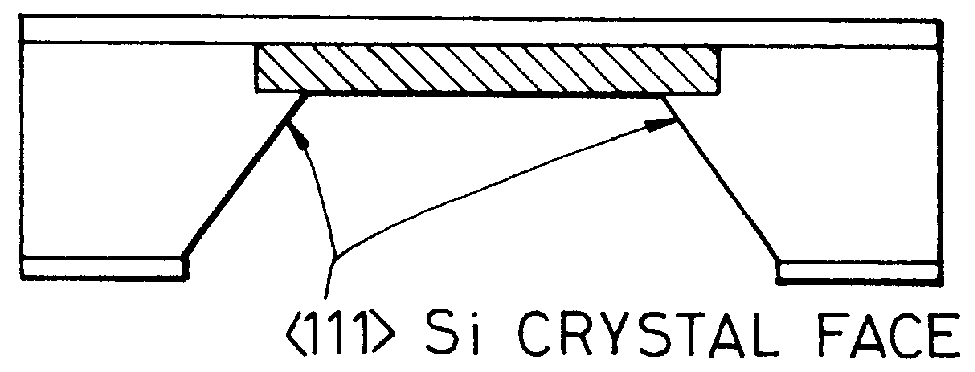

A manufacturing method for an ink jet head having an ink ejection pressure generation element for generating energy for ejecting ink, and an ink supply port for supplying the ink to an ink jet head, including the steps of preparing a silicon substrate; forming, on a surface of the silicon substrate, the ink ejection pressure generation element and silicon oxide film or silicon nitride film; forming anti-etching mask for forming an ink supply port on a back side of the silicon substrate; removing silicon on the back side of the silicon substrate at a position corresponding to the ink supply port portion through anisotropic etching; forming an ink ejection portion on a surface of the silicon substrate; and removing the silicon oxide film or silicon nitride film from the surface of the silicon substrate of the ink supply port portion.

Owner:CANON KK

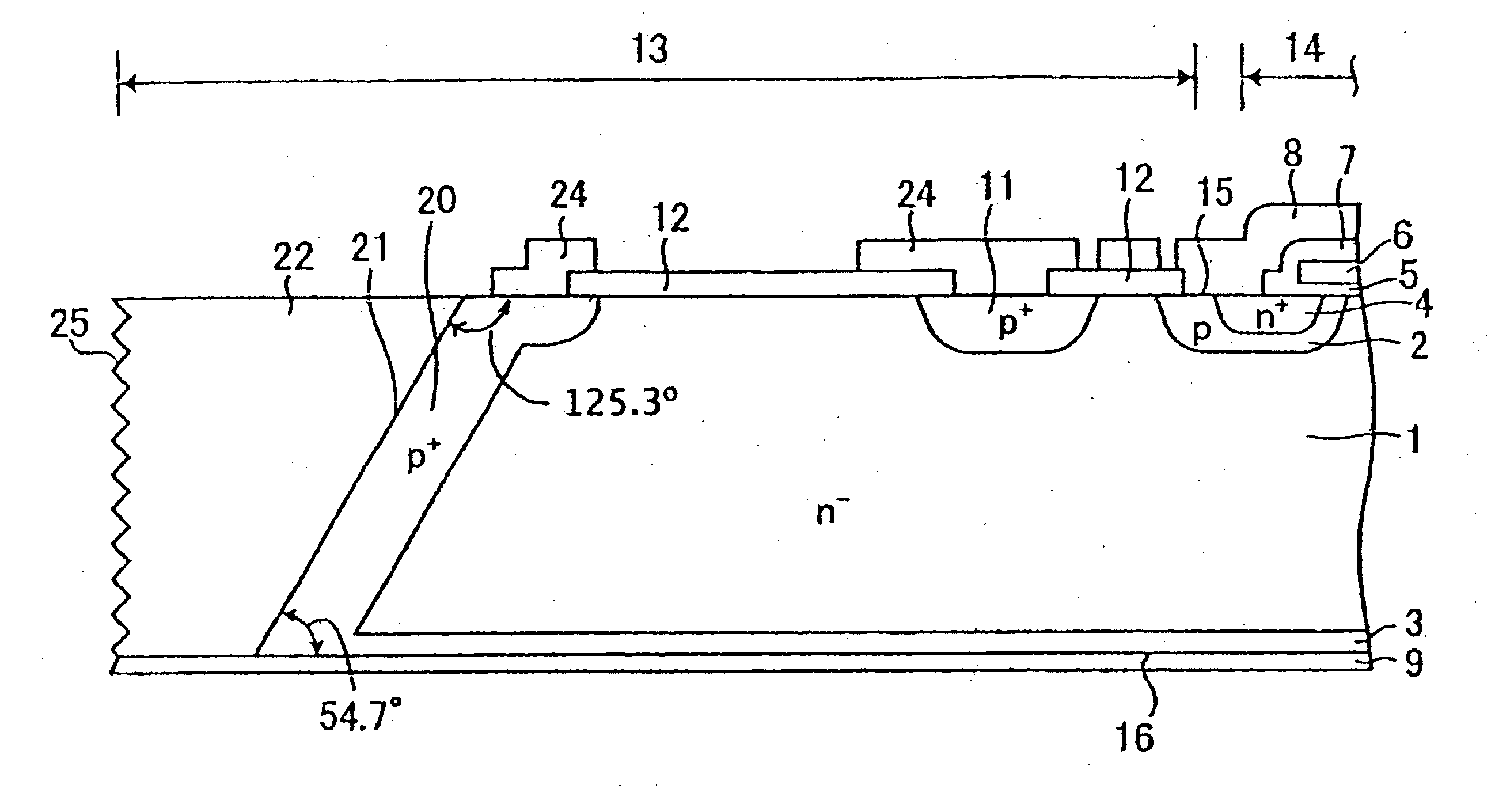

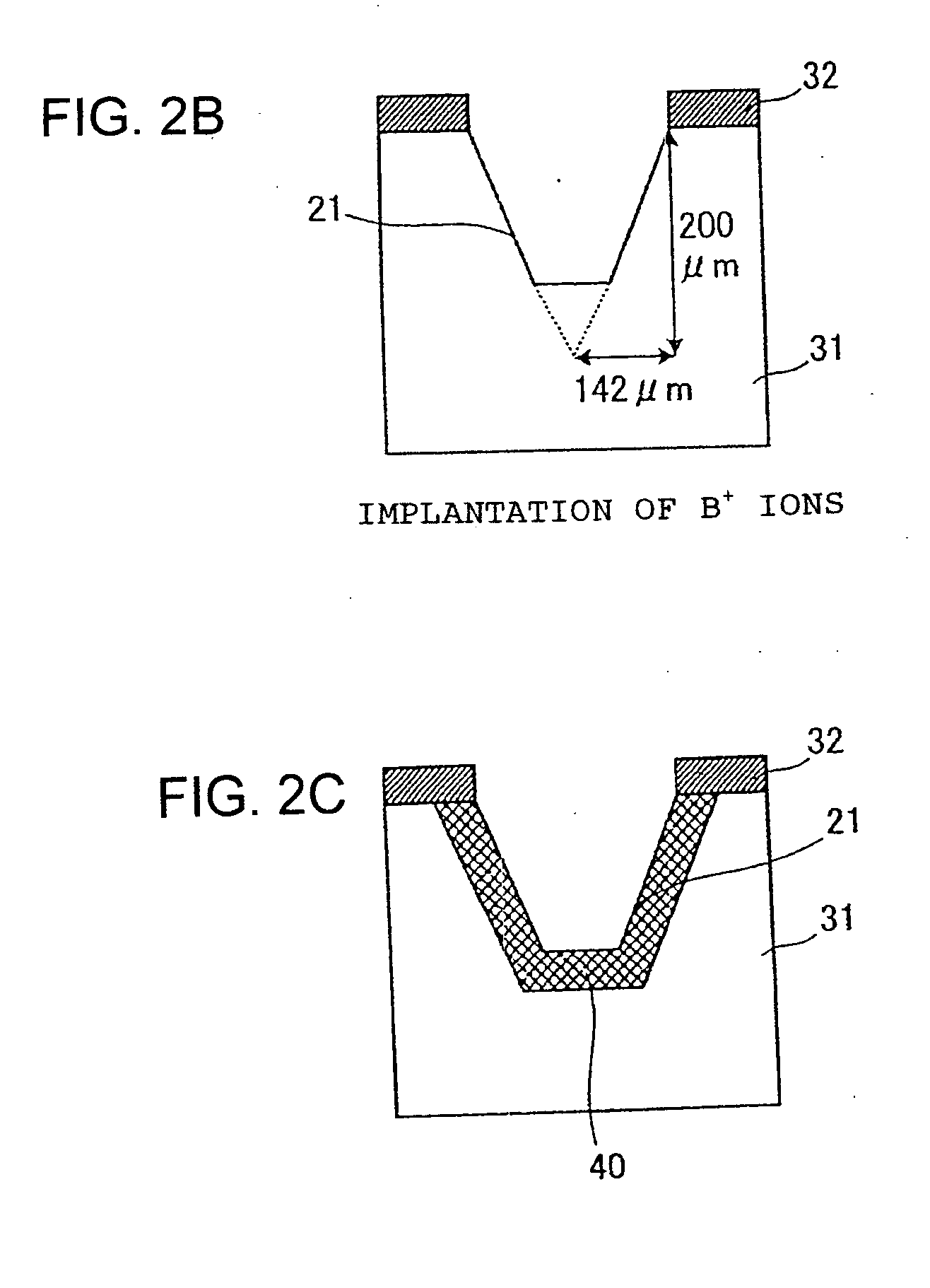

Method of producing a through-hole, silicon substrate having a through-hole, device using such a substrate, method of producing an ink-jet print head, and ink-jet print head

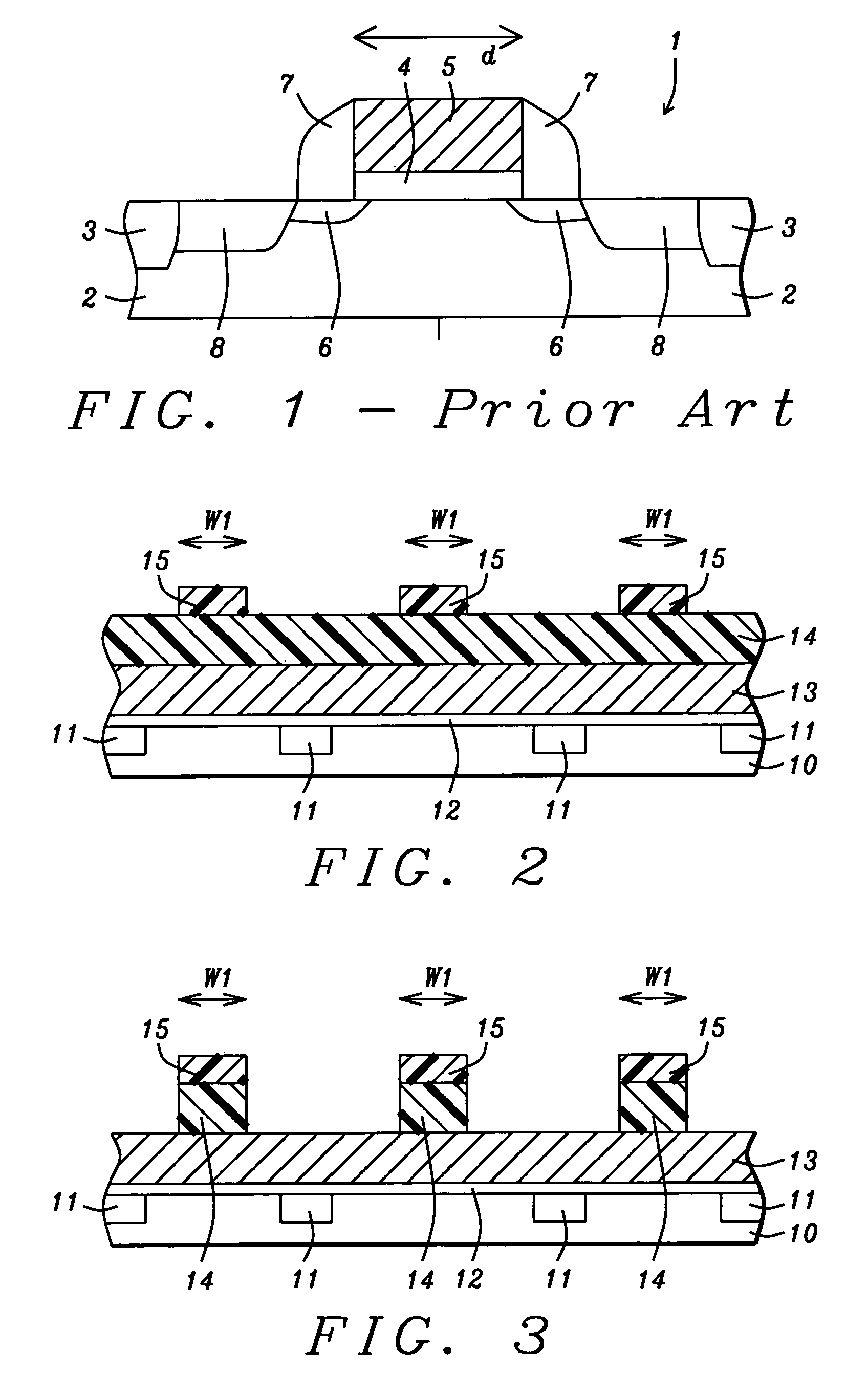

The invention provides a method of producing a through-hole, a substrate used to produce a through-hole, a substrate having a through-hole, and a device using such a through-hole or a substrate having such a through-hole, which are characterized in that: a through-hole can be produced only by etching a silicon substrate from its back side; the opening length d can be precisely controlled to a desired value regardless of the variations in the silicon wafer thickness, and the orientation flat angle, and also regardless of the type of a silicon crystal orientation-dependent anisotropic etchant employed; high productivity, high production reproducibility, and ease of production can be achieved; a high-liberality can be achieved in the shape of the opening end even if temperature treatment is performed at a high temperature for a long time; and a high-precision through-hole can be produced regardless of the shape of a device formed on the surface of a substrate.

Owner:CANON KK

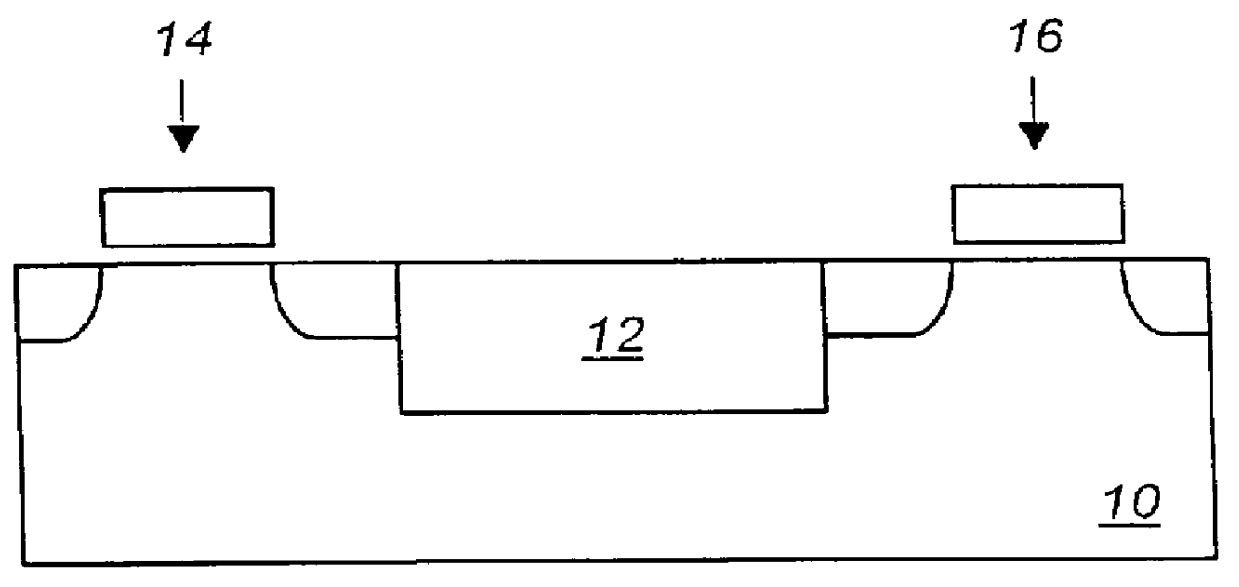

Amorphous etch stop for the anisotropic etching of substrates

ActiveUS7045407B2Semiconductor/solid-state device manufacturingSemiconductor devicesAnisotropic etchingCantilever

Methods of forming an amorphous etch stop layer by implanting a substrate with an element that is electrically neutral within the substrate are described. The use of elements that are electrically neutral within the substrate prevents electrical interference by the elements if they diffuse to other areas within the substrate. The amorphous etch stop layer may be used as a hard mask in the fabrication of transistors or other devices such as a cantilever.

Owner:INTEL CORP

Method for Making a Self-Converged Memory Material Element for Memory Cell

ActiveUS20080138929A1Semiconductor/solid-state device manufacturingAnisotropic etchingMaterial element

A self-converged memory material element is created during the manufacture of a memory Cell comprising a base layer, with a bottom electrode, and an upper layer having a third, planarization stop layer over the base layer, a second layer over the third layer, and the first layer over the second layer. A keyhole opening is formed through the upper layer to expose the bottom electrode. The first layer has an overhanging portion extending into the opening. A dielectric material is deposited into the keyhole opening so to create a self-converged void within the keyhole opening. An anisotropic etch forms a sidewall of the dielectric material in the keyhole opening with an electrode hole aligned with the void and exposing the bottom electrode. A memory material is deposited into the electrode hole in contact with the bottom electrode and is planarized down to the third layer to create the memory material element.

Owner:MACRONIX INT CO LTD

Shaping a cover glass

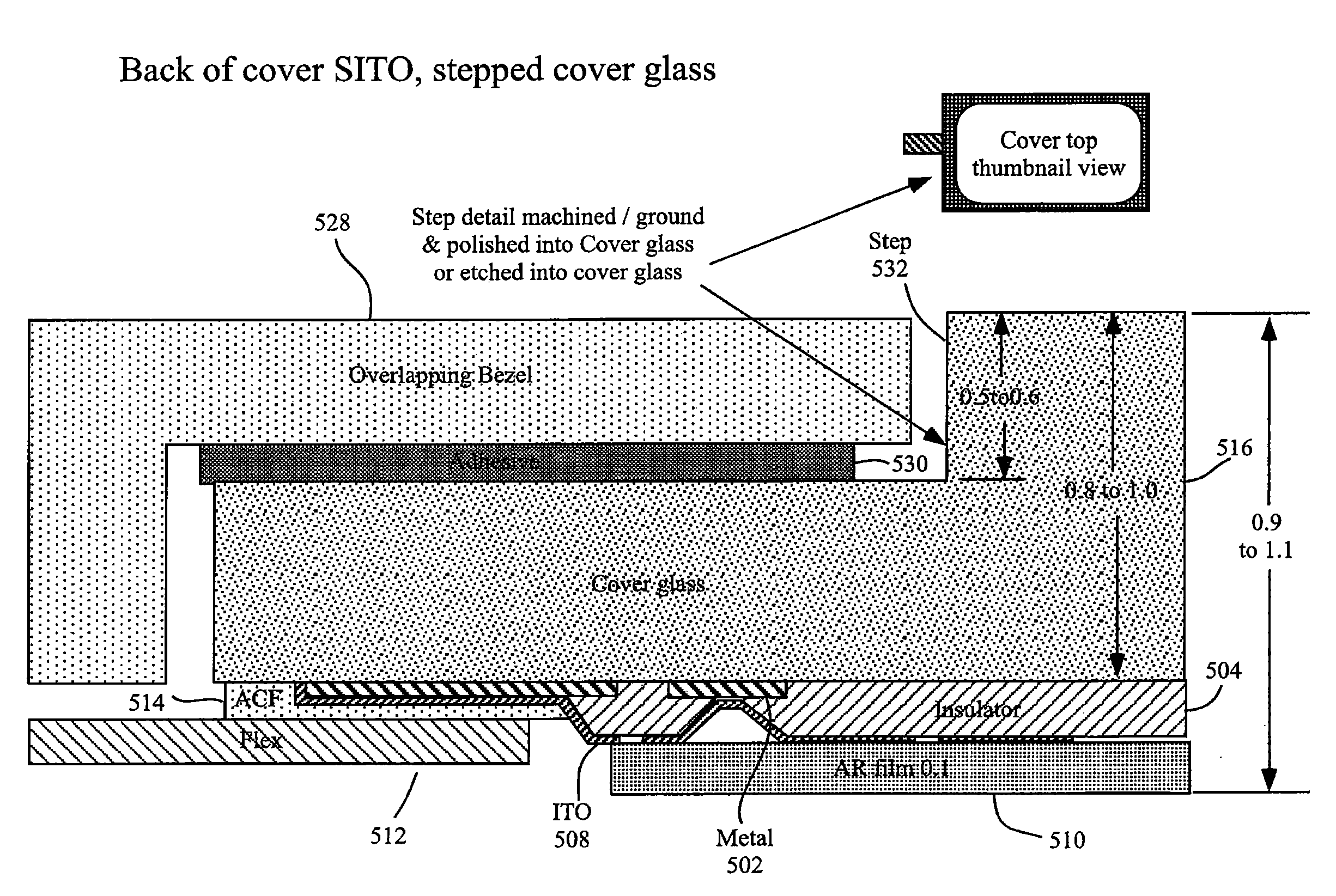

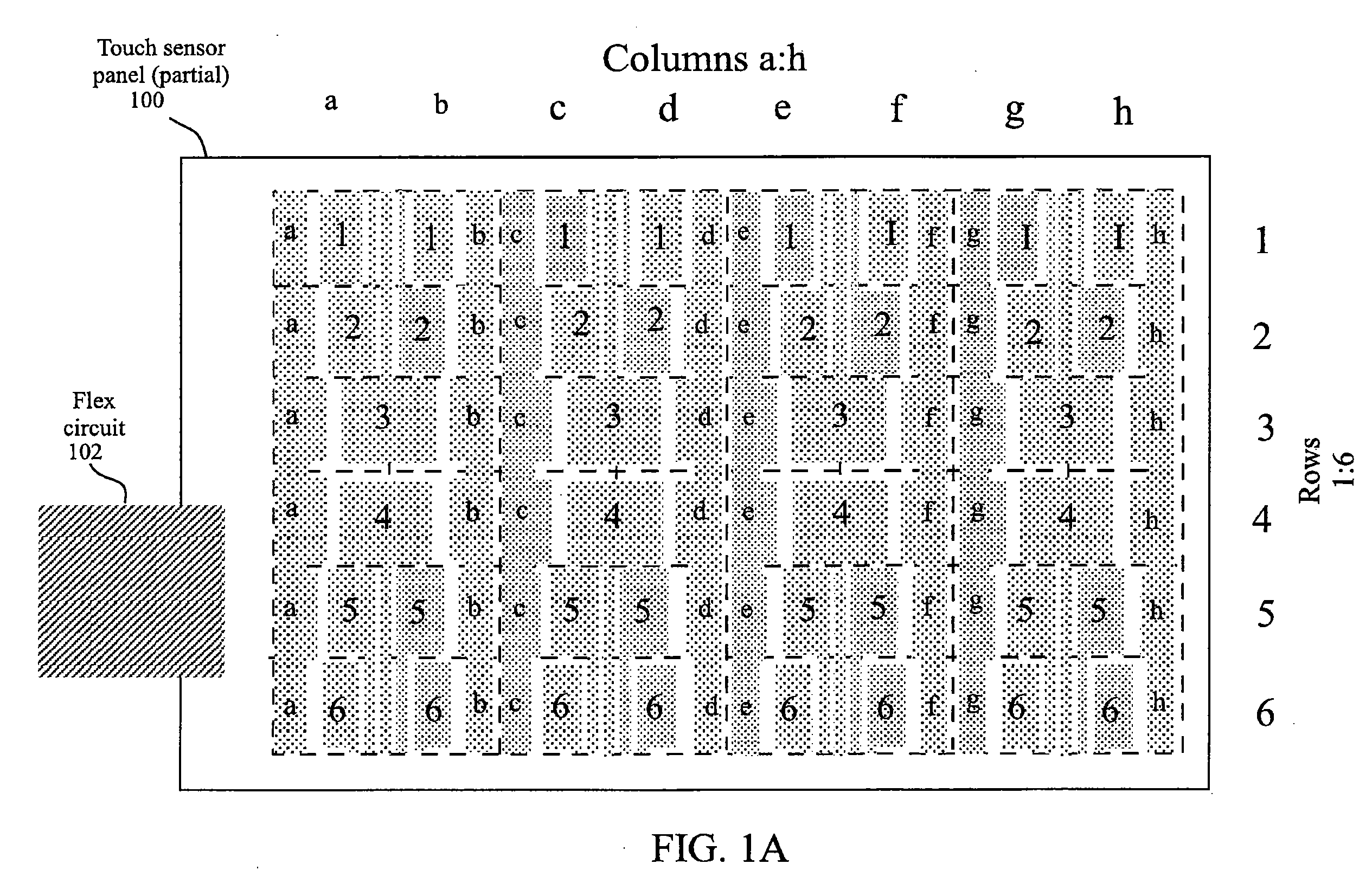

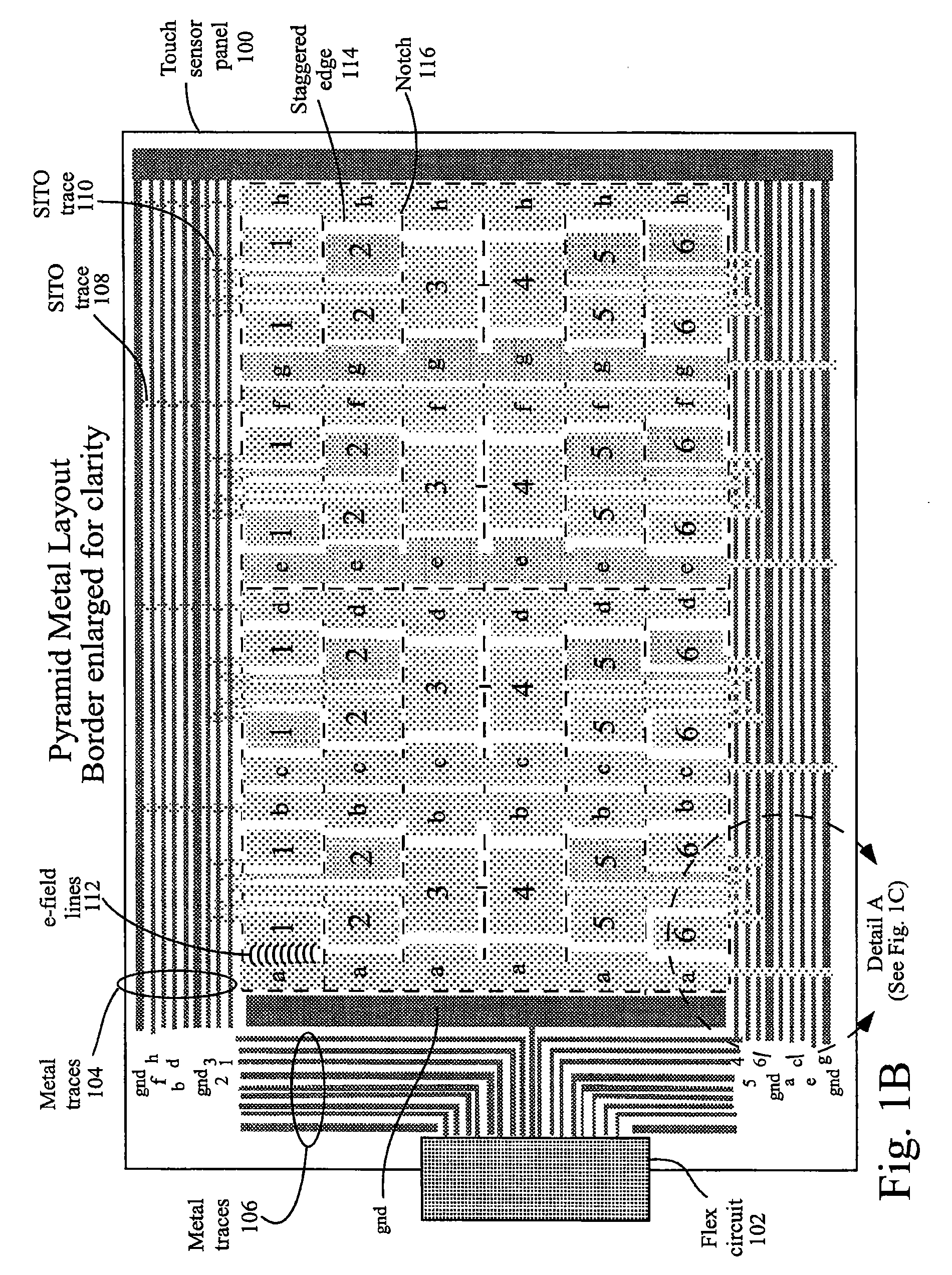

ActiveUS20090090694A1Pleasing shapeTransmission systemsDecorative surface effectsEngineeringAnisotropic etching

The fabrication of a touch sensor panel having co-planar single-layer touch sensors fabricated on the back side of a cover glass is disclosed. It can be desirable from a manufacturing perspective to perform all thin-film processing steps on a motherglass before separating it into separate parts. To perform thin-film processing on a motherglass before separation, a removable sacrificial layer such as a photoresist can be applied over the thin-film layers. Next, the motherglass can be scribed and separated, and grinding and polishing steps can be performed prior to removing the sacrificial layer. In alternative embodiments, after the protective sacrificial layer is applied, the bulk of the coverglass can be dry-etched using a very aggressive anisotropic etching that etches primarily in the z-direction. In this embodiment, the etching can be patterned using photolithography to create rounded corners or any other shape. The photoresist can then be removed.

Owner:APPLE INC

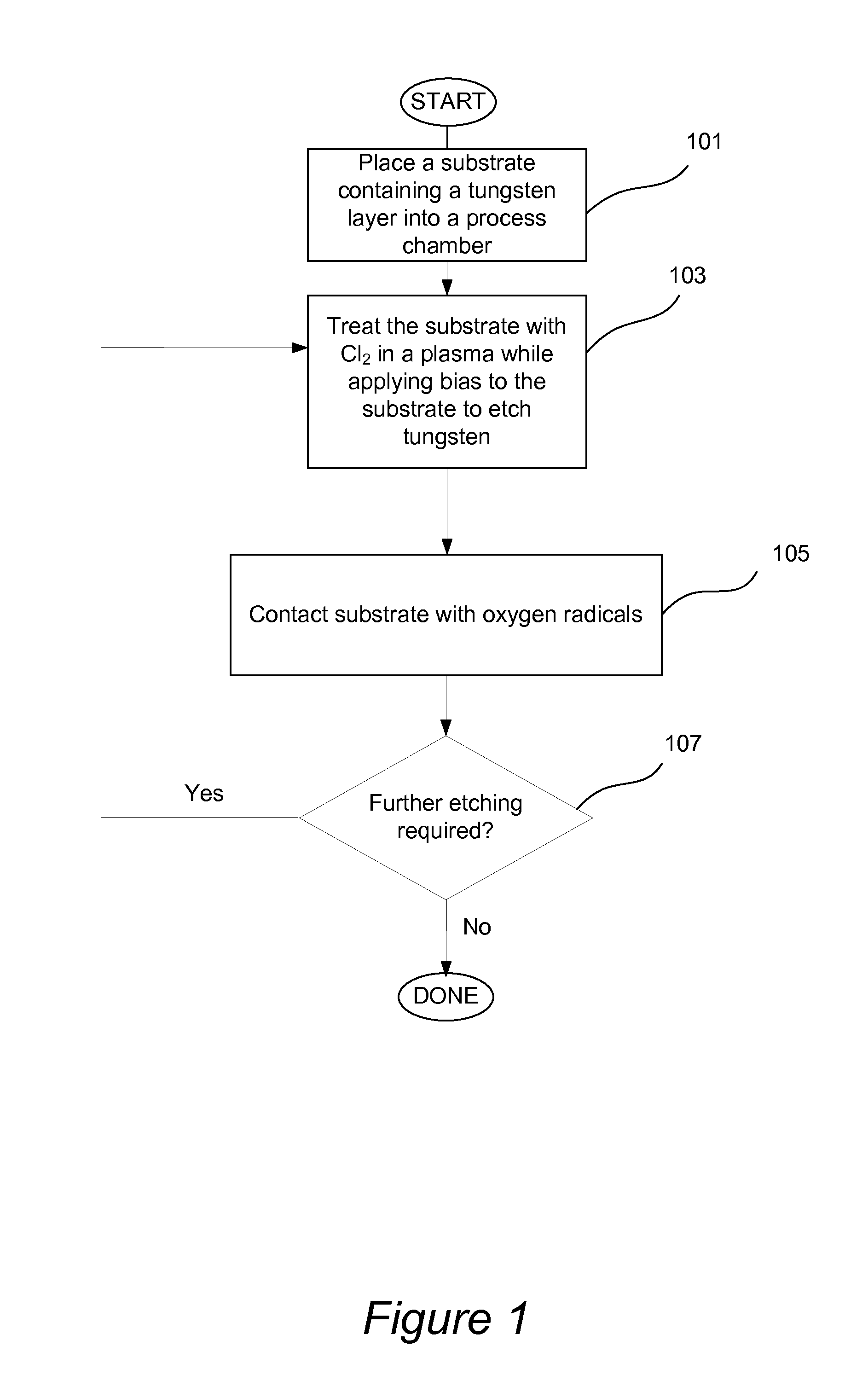

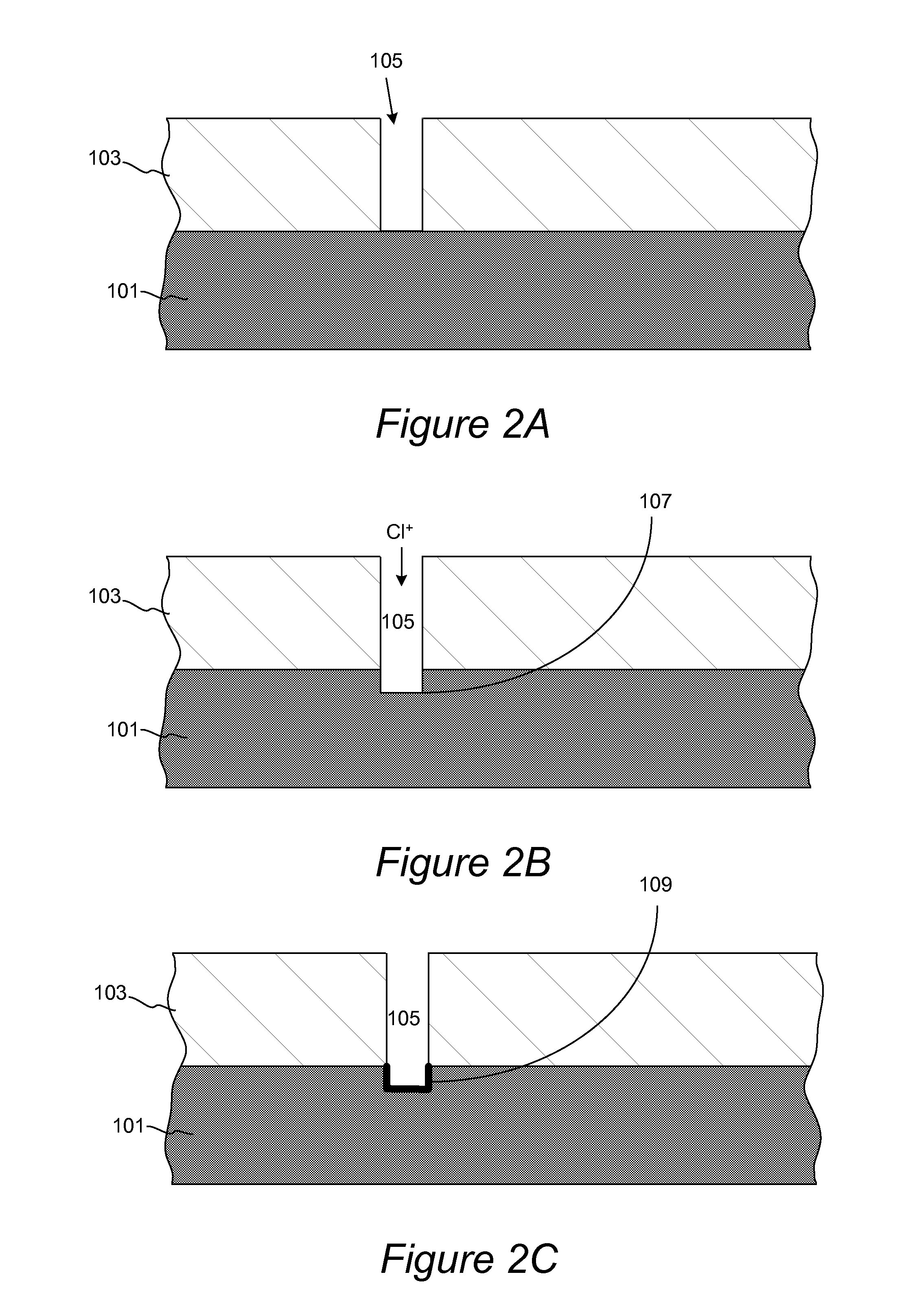

Method and apparatus for anisotropic tungsten etching

ActiveUS20160196985A1Electric discharge tubesSemiconductor/solid-state device manufacturingSilicon oxideOxygen

Methods for anisotropically etching a tungsten-containing material (such as doped or undoped tungsten metal) include cyclic treatment of tungsten surface with Cl2 plasma and with oxygen-containing radicals. Treatment with chlorine plasma is performed while the substrate is electrically biased resulting in predominant etching of horizontal surfaces on the substrate. Treatment with oxygen-containing radicals passivates the surface of the substrate to etching, and protects the vertical surfaces of the substrate, such as sidewalls of recessed features, from etching. Treatment with Cl2 plasma and with oxygen-containing radicals can be repeated in order to remove a desired amount of material. Anisotropic etching can be performed selectively in a presence of dielectric materials such as silicon oxide, silicon nitride, and silicon oxynitride.

Owner:LAM RES CORP

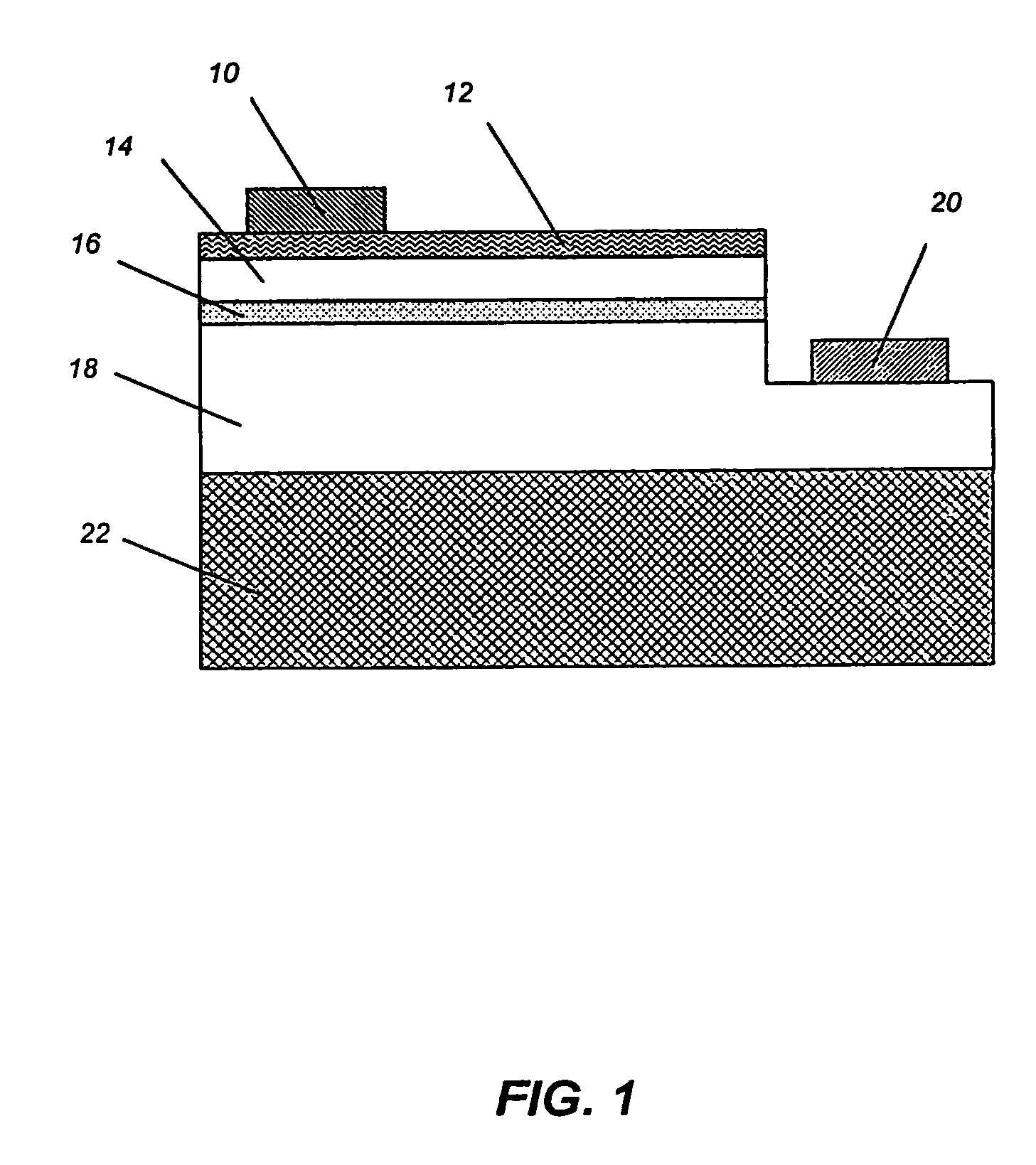

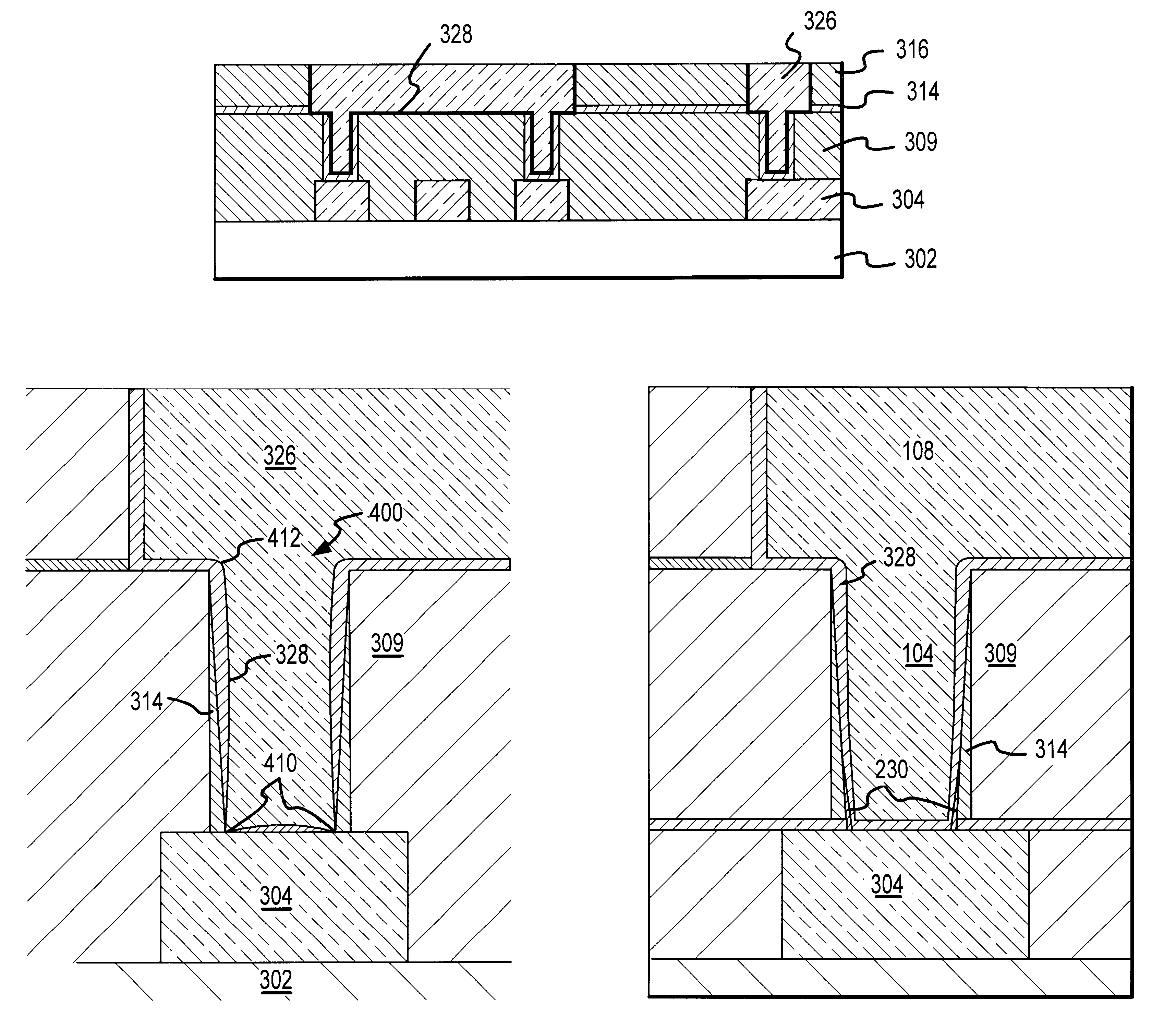

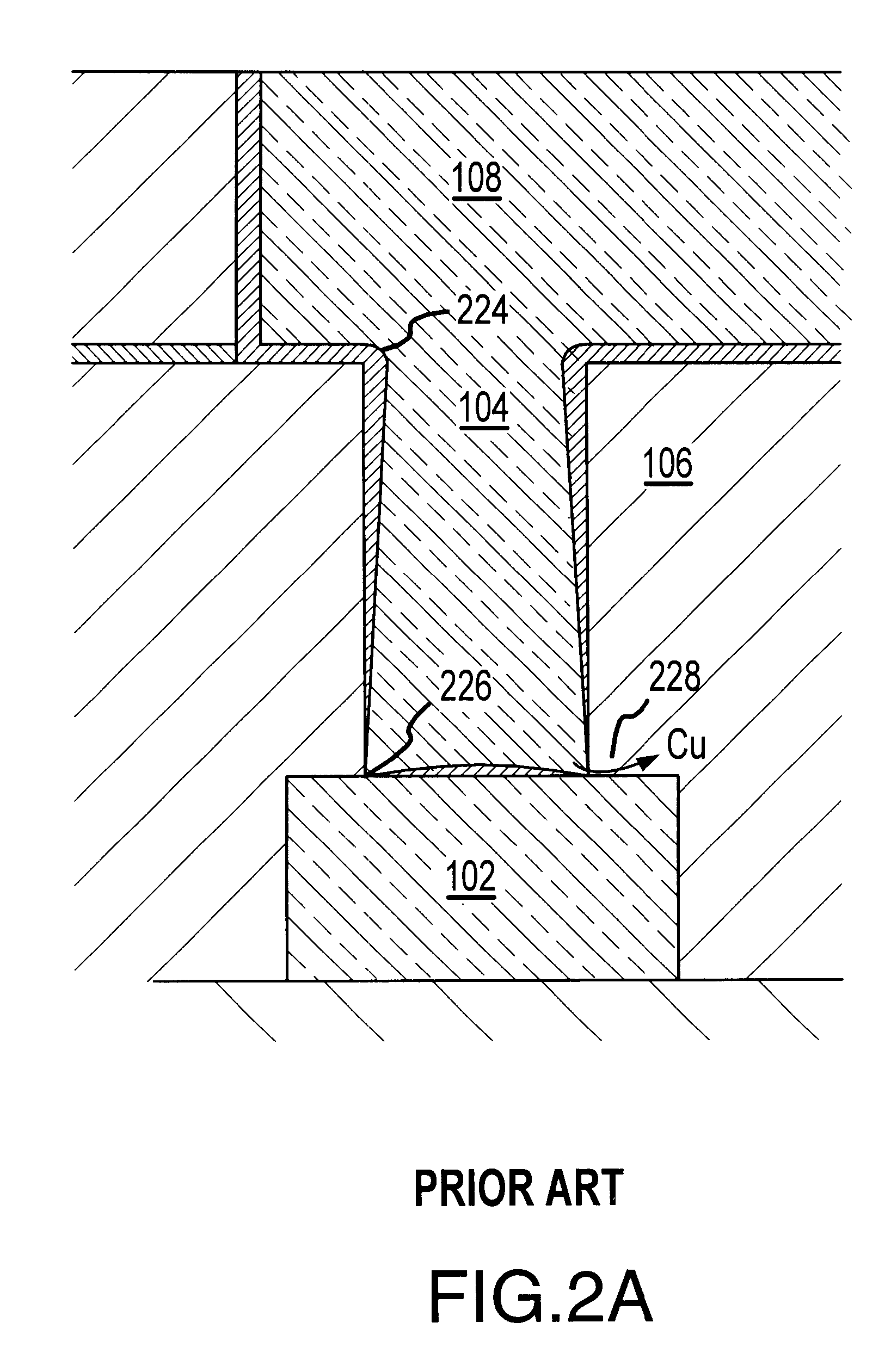

Dual-damascene interconnect structures and methods of fabricating same

InactiveUS6417094B1Solid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDielectric

An interconnect fabrication process and structure provides barrier enhancement at the via sidewalls and improved capability to fabricate high aspect ratio dual damascene interconnects. A via structure is patterned into the via dielectric first, then a dielectric barrier (for example, anisotropically etched silicon nitride) is formed only along the via sidewalls in the dual damascene structure prior to deposition of a metal barrier (for example, Ta / TaN). In this way, the effective barrier thickness along the bottom of the via is increased, eliminating the structure's susceptibility to metal migration. The absence of dielectric barrier along the interconnect trench sidewalls leads to low interconnect resistance and low interconnect capacitance. The present invention also provides an improved fabrication method for obtaining high aspect ratio dual damascene interconnect structures.

Owner:NEWPORT FAB

Nonvolatile phase change memory cell having a reduced contact area

InactiveUS7728318B2Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryDielectric surface

Owner:SANDISK CORP

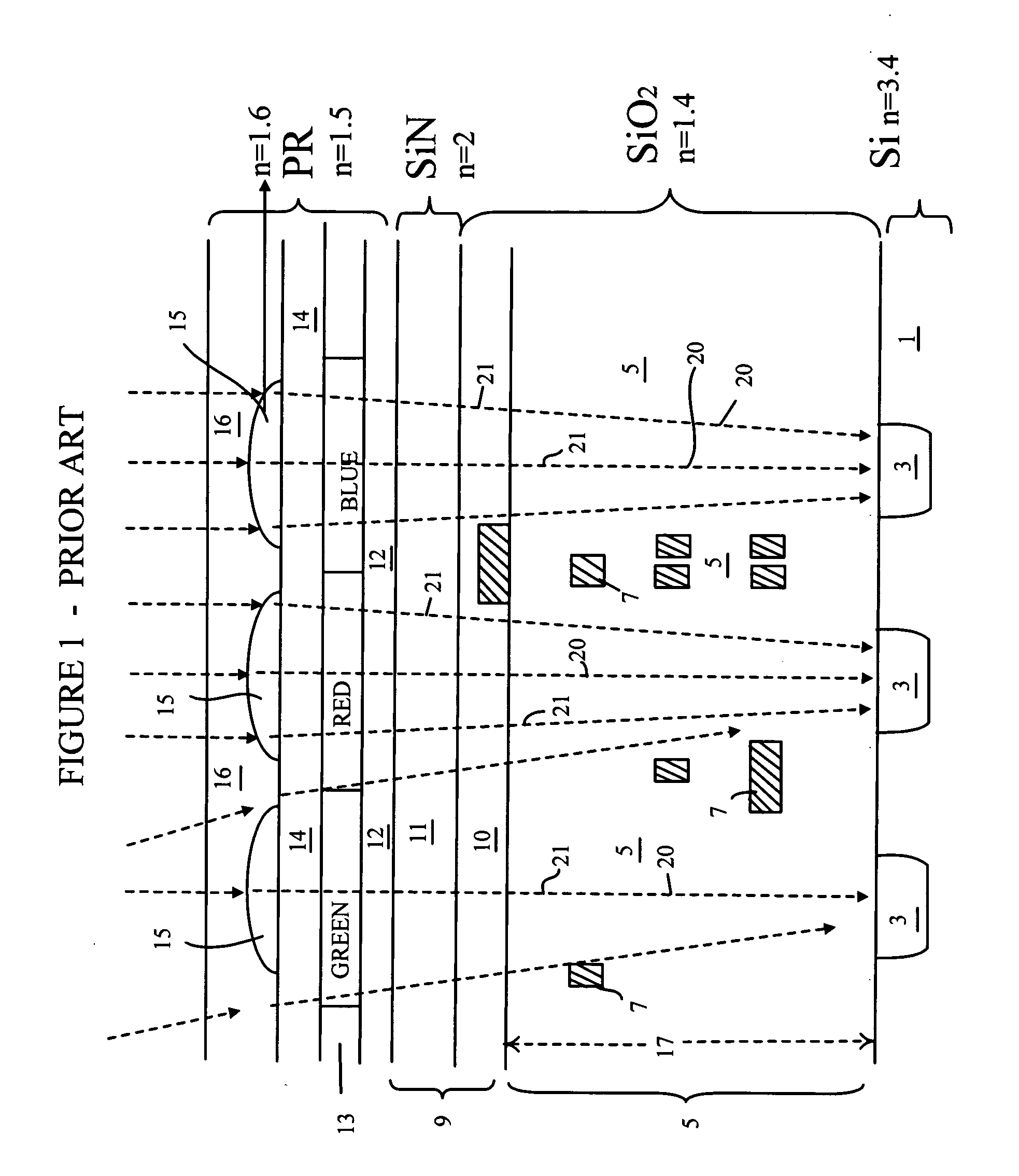

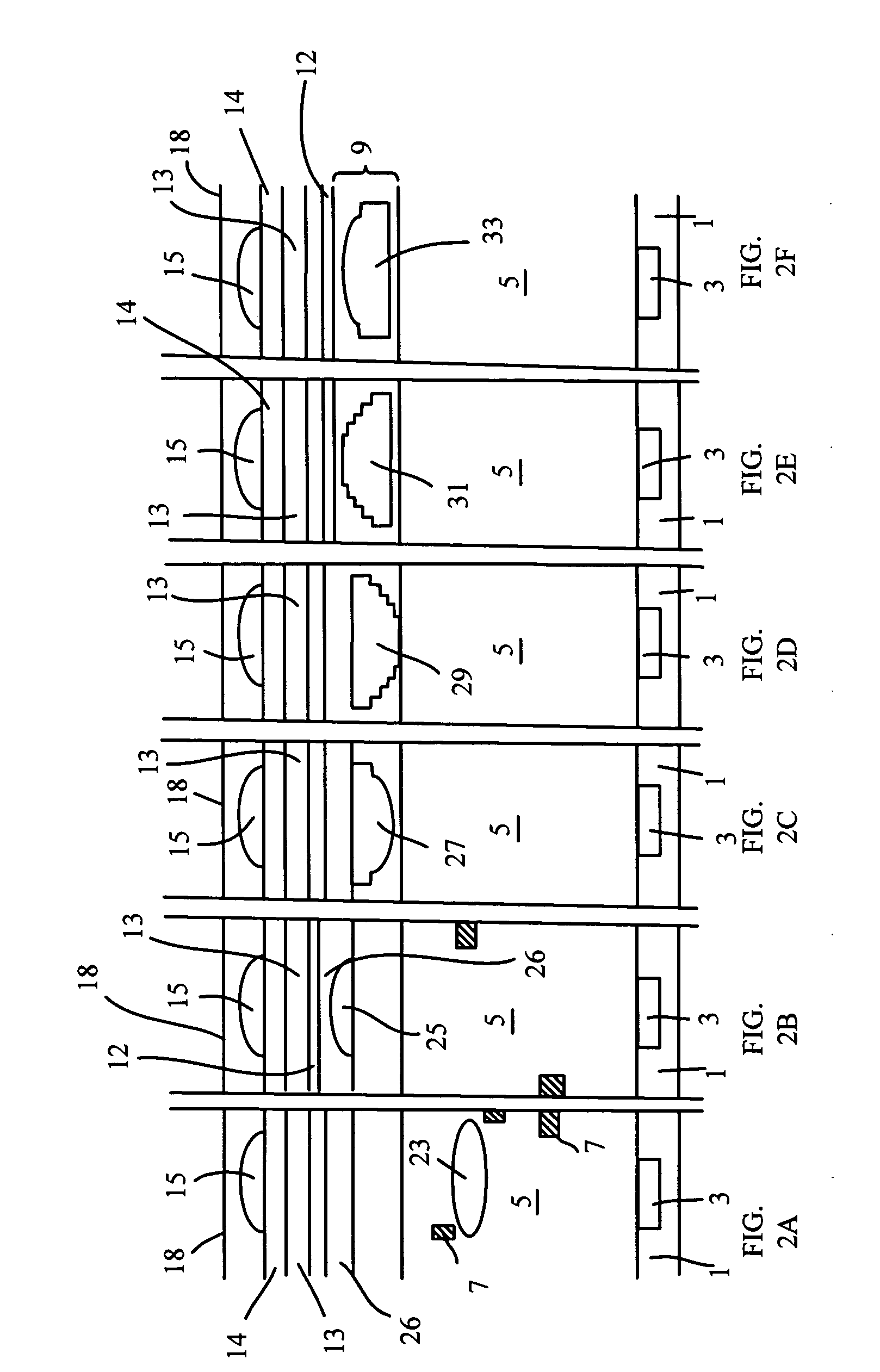

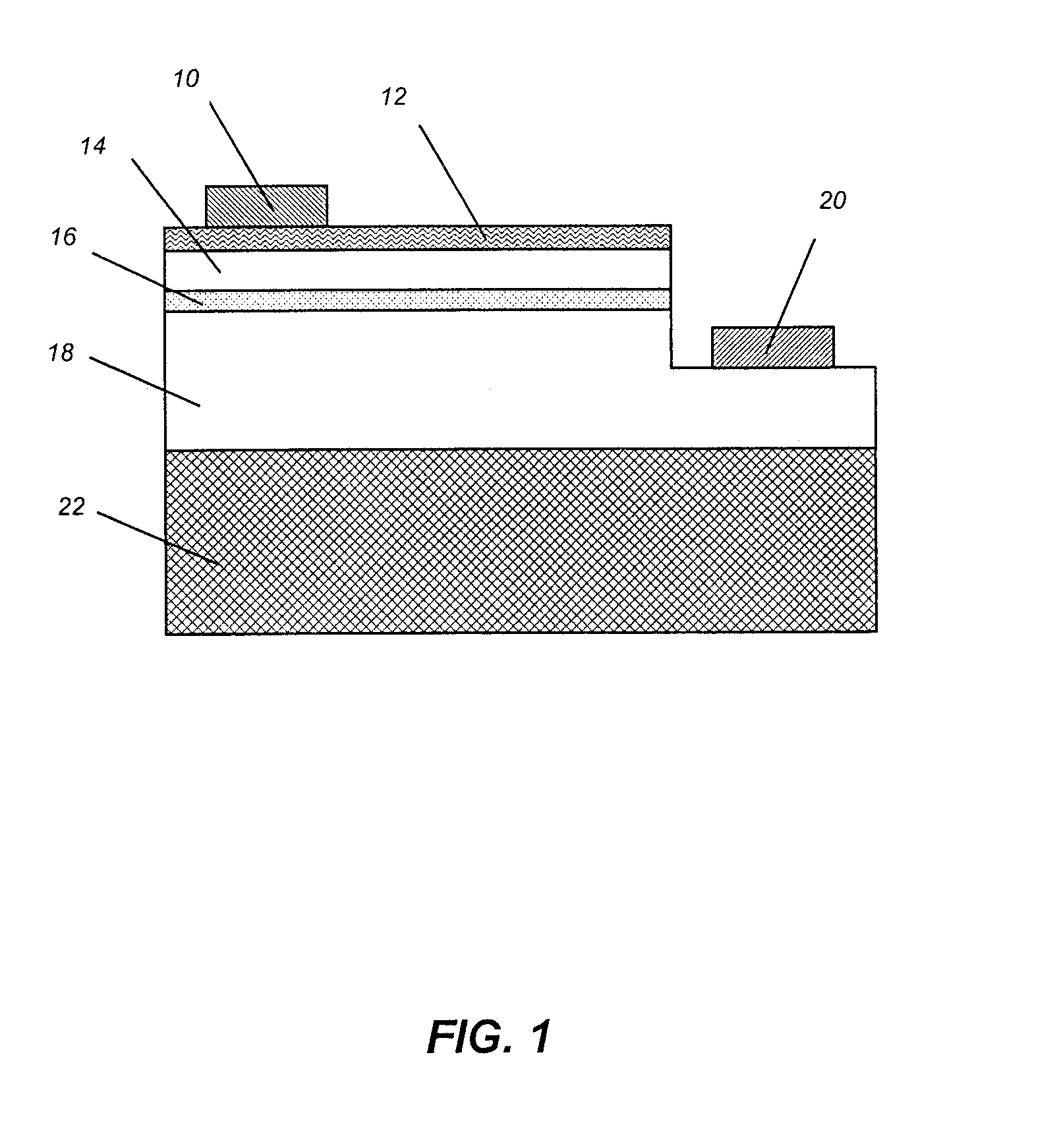

Lens structures suitable for use in image sensors and method for making the same

InactiveUS20050274968A1Solid-state devicesSemiconductor/solid-state device manufacturingResistPhotosensitive polymer

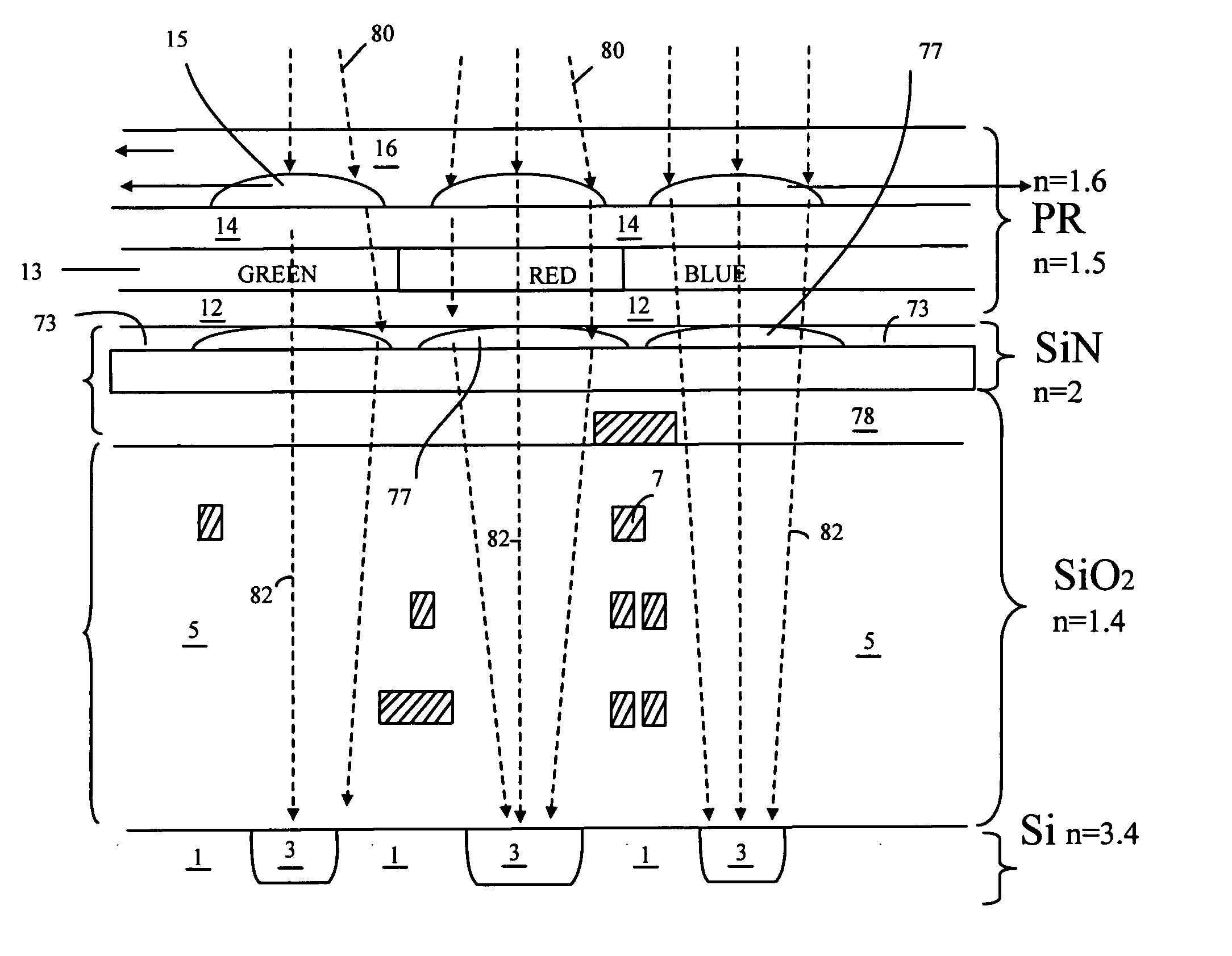

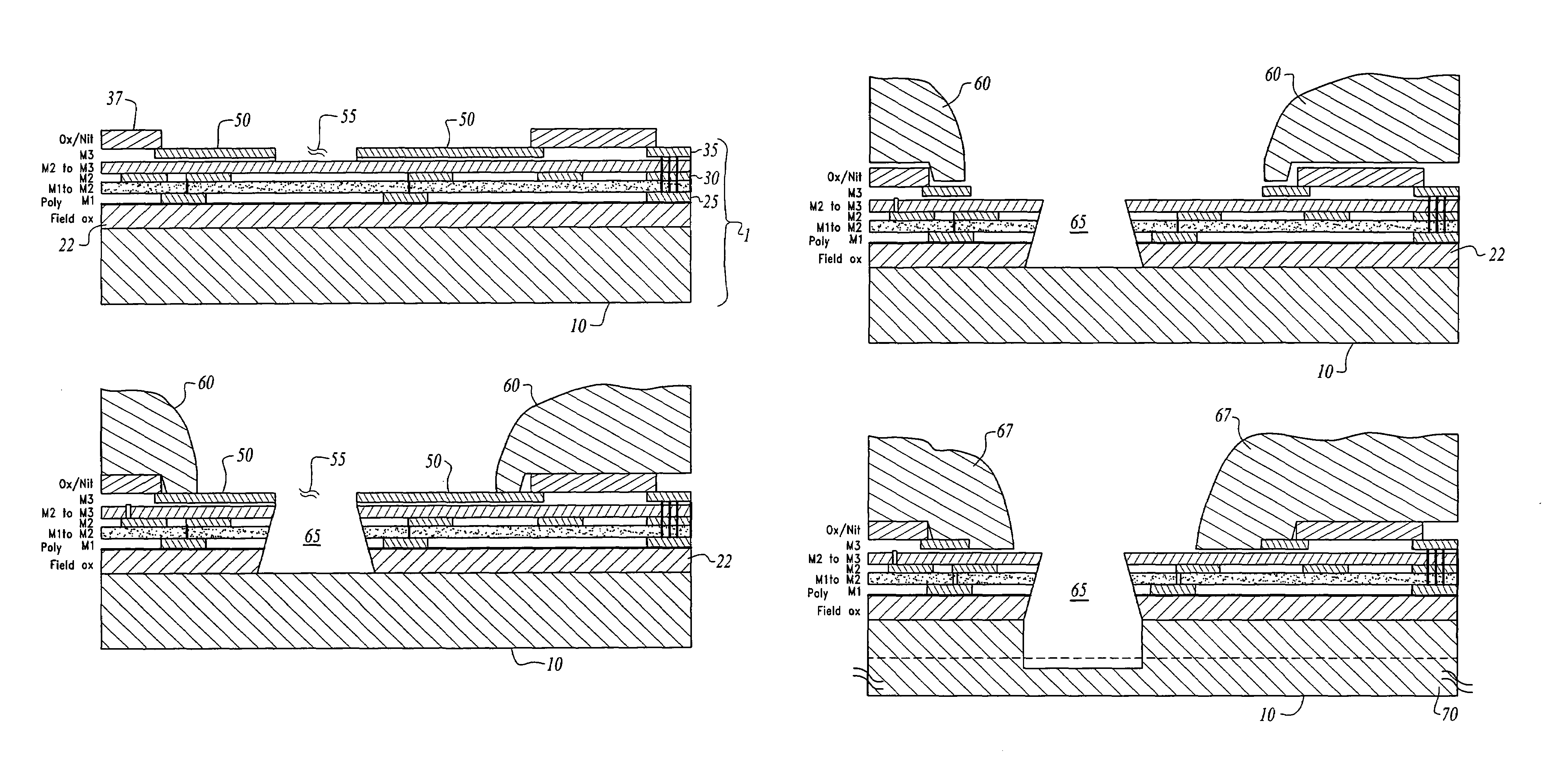

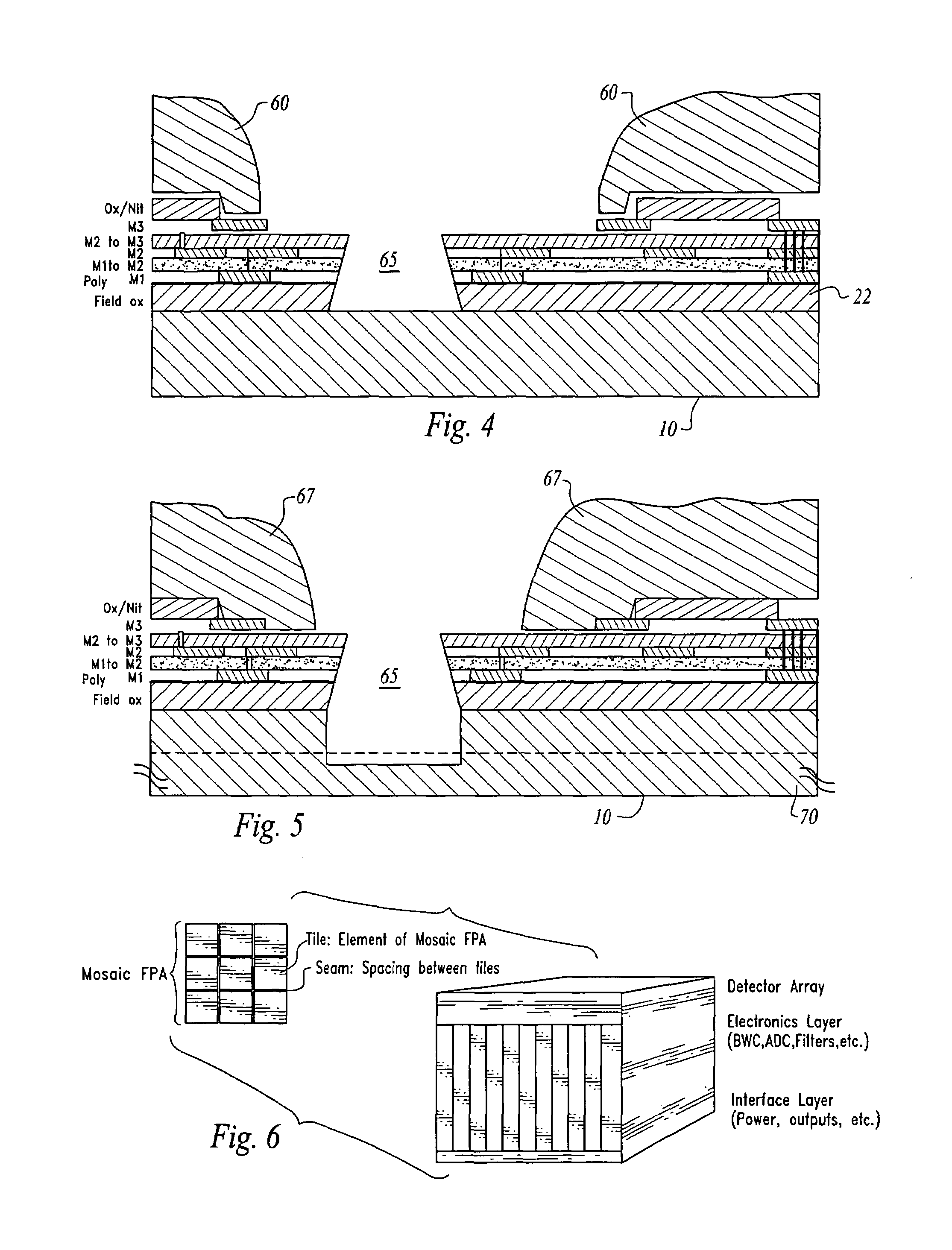

An image sensor includes a double-microlens structure with an outer microlens aligned over an inner microlens, both microlenses aligned over a corresponding photosensor. The inner or outer microlens may be formed by a silylation process in which a reactive portion of a photoresist material reacts with a silicon-containing agent. The inner or outer microlens may be formed by step etching of a dielectric material, the step etching process including a series of alternating etch steps including an anisotropic etching step and an etching step that causes patterned photoresist to laterally recede. Subsequent isotropic etching processes may be used to smooth the etched step structure and form a smooth lens. A thermally stable and photosensitive polymeric / organic material may also be used to form permanent inner or outer lenses. The photosensitive material is coated then patterned using photolithography, reflowed, then cured to form a permanent lens structure.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS20060038206A1Improve reliabilityLow costTransistorSolid-state devicesDevice materialSemiconductor chip

A thin semiconductor wafer, on which a top surface structure and a bottom surface structure that form a semiconductor chip are formed, is affixed to a supporting substrate by a double-sided adhesive tape. Then, on the thin semiconductor wafer, a trench to become a scribing line is formed by wet anisotropic etching with a crystal face exposed so as to form a side wall of the trench. On the side wall of the trench with the crystal face thus exposed, an isolation layer for holding a reverse breakdown voltage is formed by ion implantation and low temperature annealing or laser annealing so as to be extended to the top surface side while being in contact with a p collector region as a bottom surface diffused layer. Then, laser dicing is carried out to neatly dice a collector electrode, formed on the p collector region, together with the p collector region, without presenting any excessive portions and any insufficient portions under the isolation layer. Thereafter, the double-sided adhesive tape is removed from the collector electrode to produce semiconductor chips. A highly reliable reverse-blocking semiconductor device can thus be formed at a low cost.

Owner:FUJI ELECTRIC HLDG CO LTD

Micro fluid control detection device based on surface-enhanced Raman scattering active substrate

ActiveCN101792112AIncrease productivityHighly integratedNanostructure manufactureDecorative surface effectsFiberFluid control

The invention discloses a micro fluid control detection device based on surface-enhanced Raman scattering active substrate. The micro fluid control detection device is obtained by the method including the following steps: photoresist is coated on substrate in spinning way, prebaking, exposure, developing and fixing are sequentially carried out on the photoresist, so as to form photoresist graph in micro fluid shape; plasma dry etching is carried out on the photoresist, thus forming nano granular structure or nano fiber upright structure in vertical distribution on the substrate; the nano granular structure is a mask, anisotropic etching is carried out on the substrate, thus forming nano column on the substrate; metal nano granular layer is sputtered on the silicon nano column or nano fiber upright structure, so as to obtain surface-enhanced Raman scattering active substrate; and a silicon-PDMS double-layer structure SERS micro fluid control detection device which has no impurity interference and can be monitored in real time is formed by combining micro fluid device and processing technology thereof. The micro fluid control device not only can be used for detection of liquid analyte to be analyzed but also can be used for detection of colloid and gas analyte to be analyzed.

Owner:PEKING UNIV

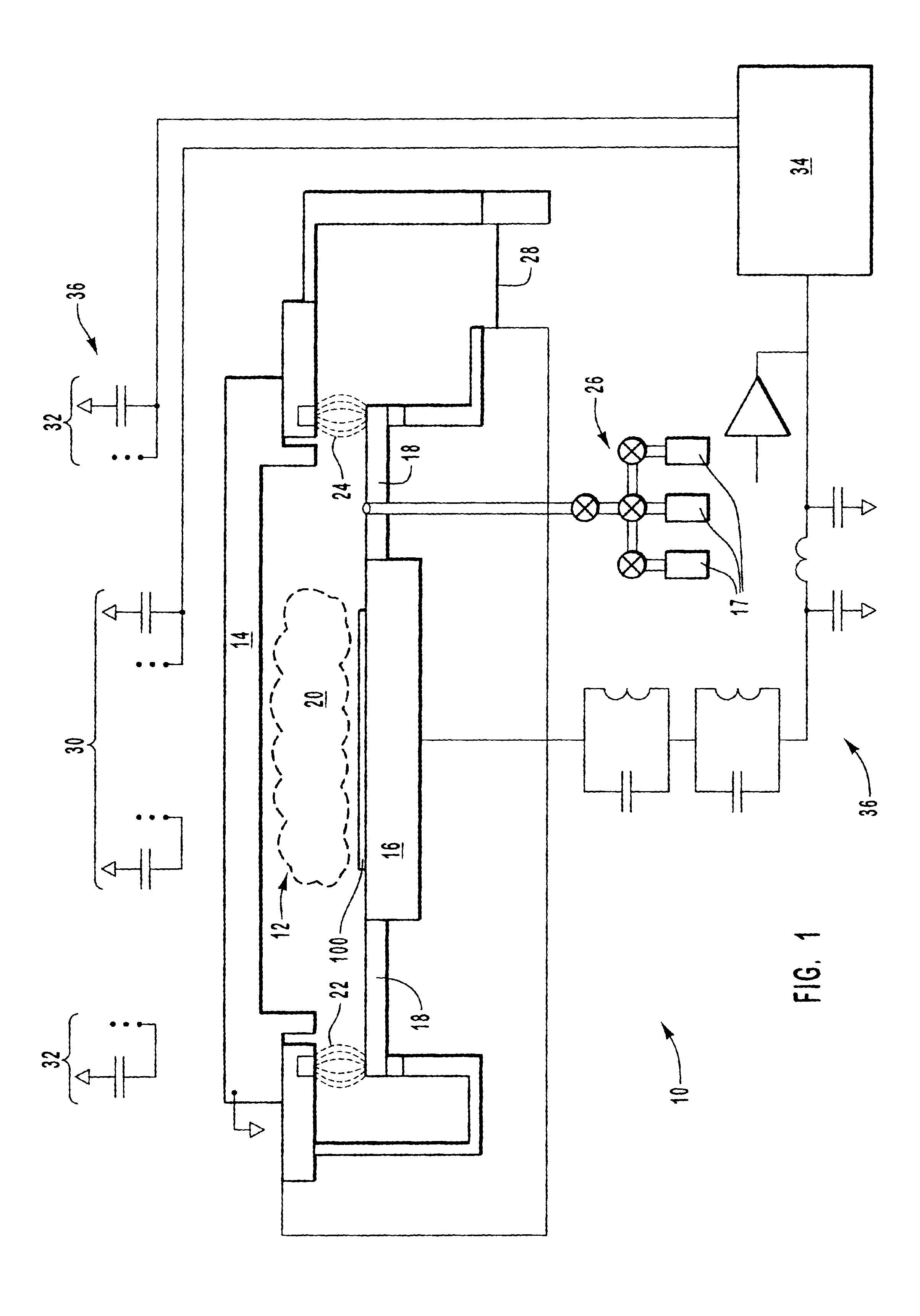

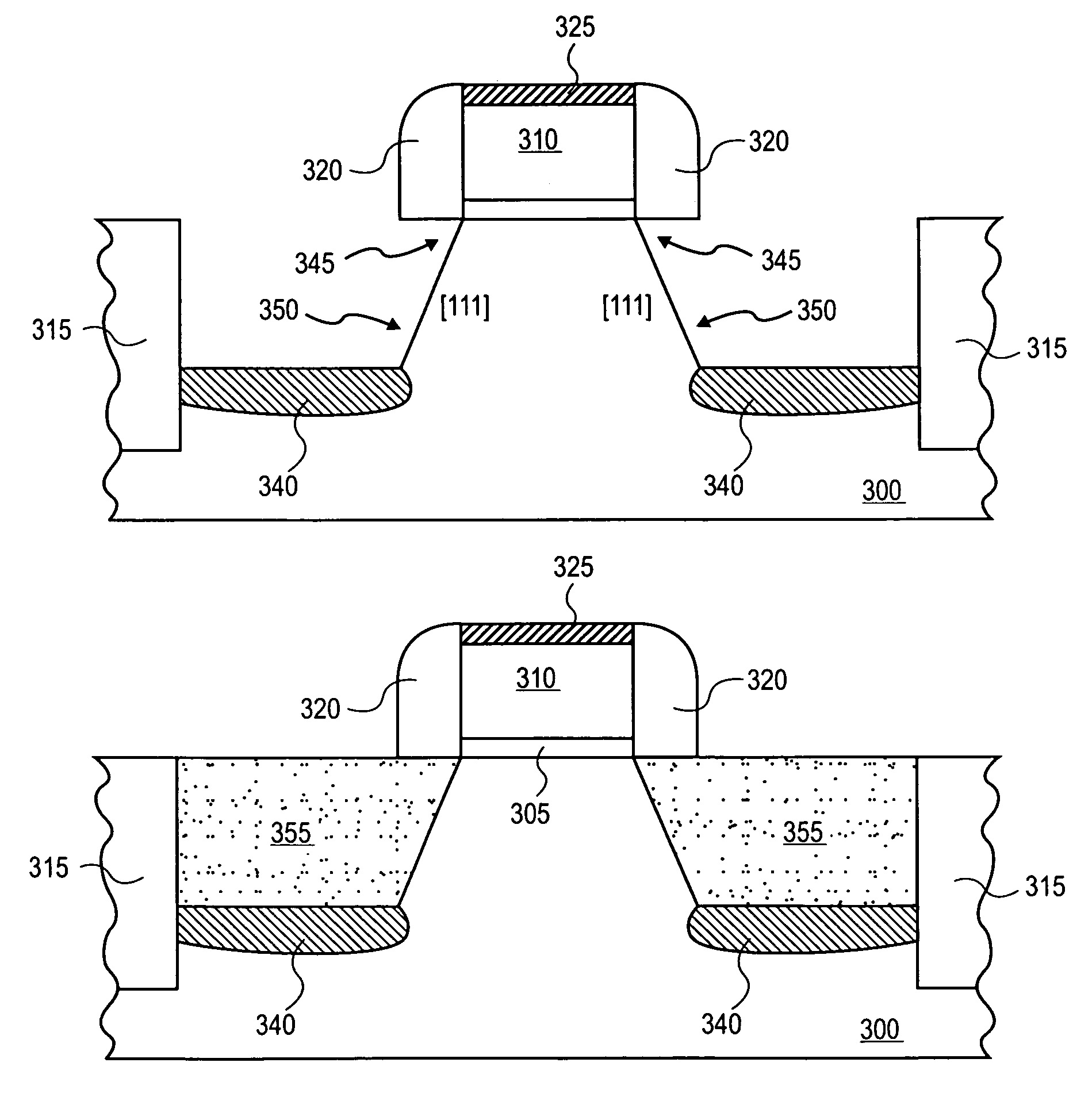

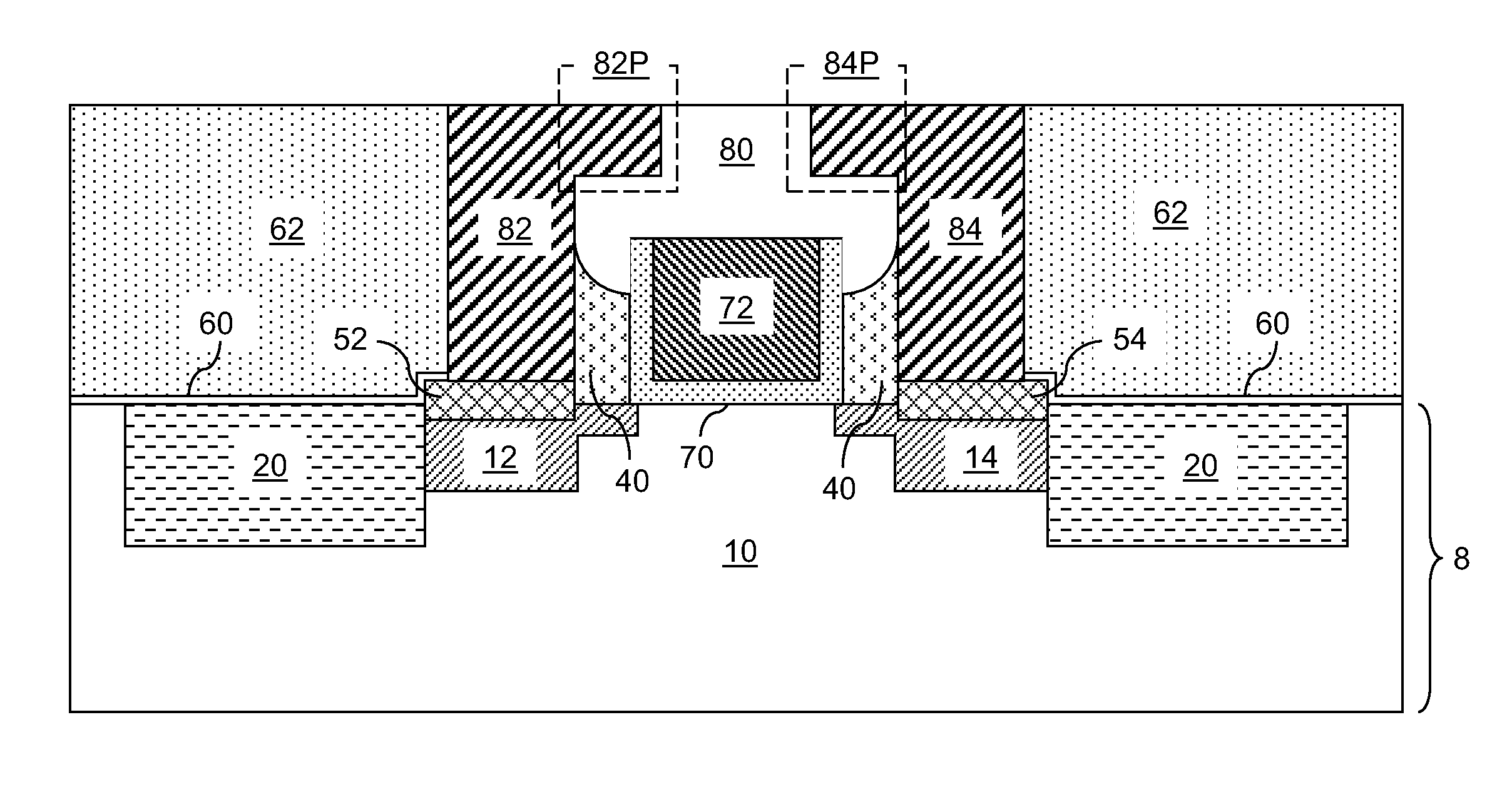

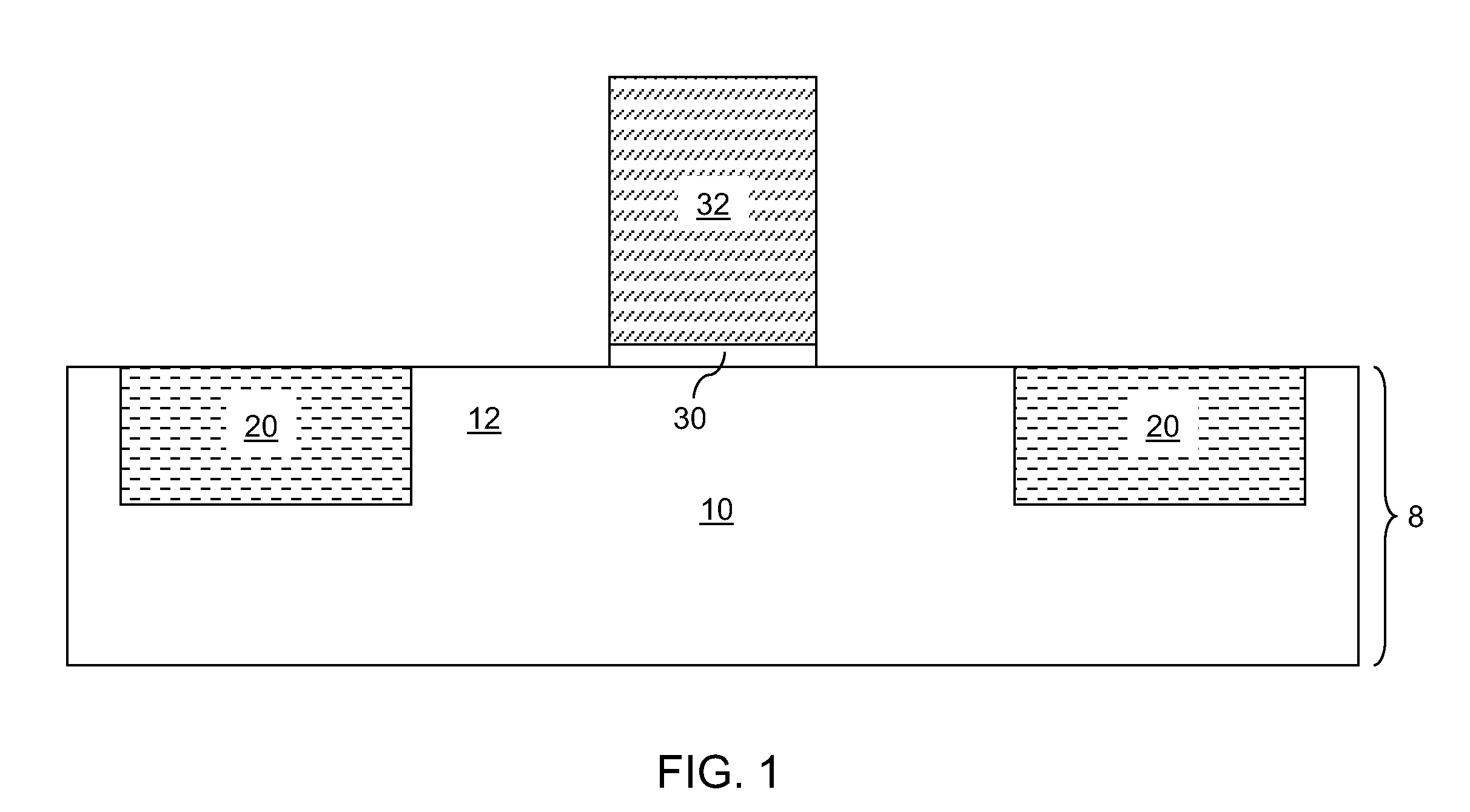

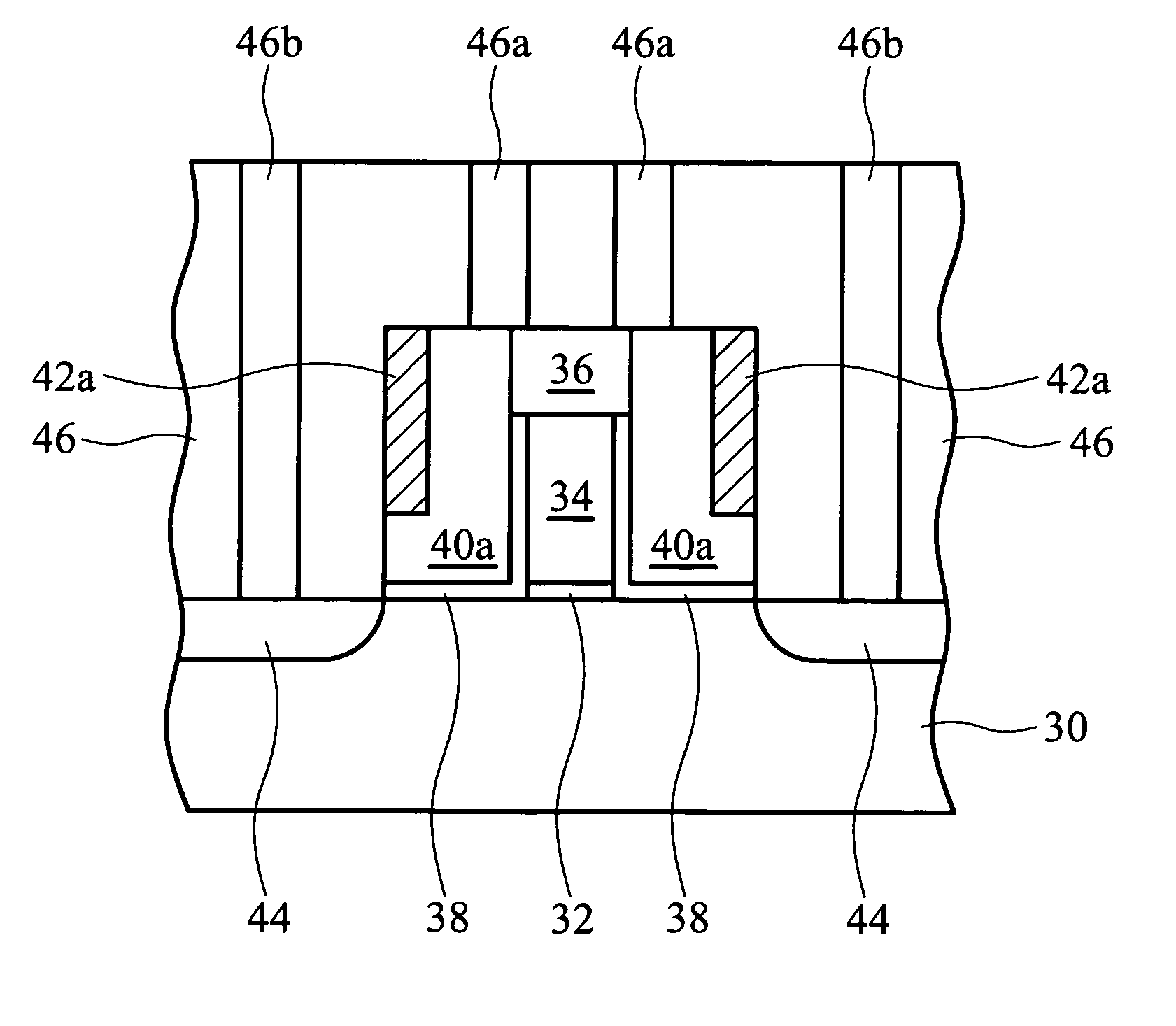

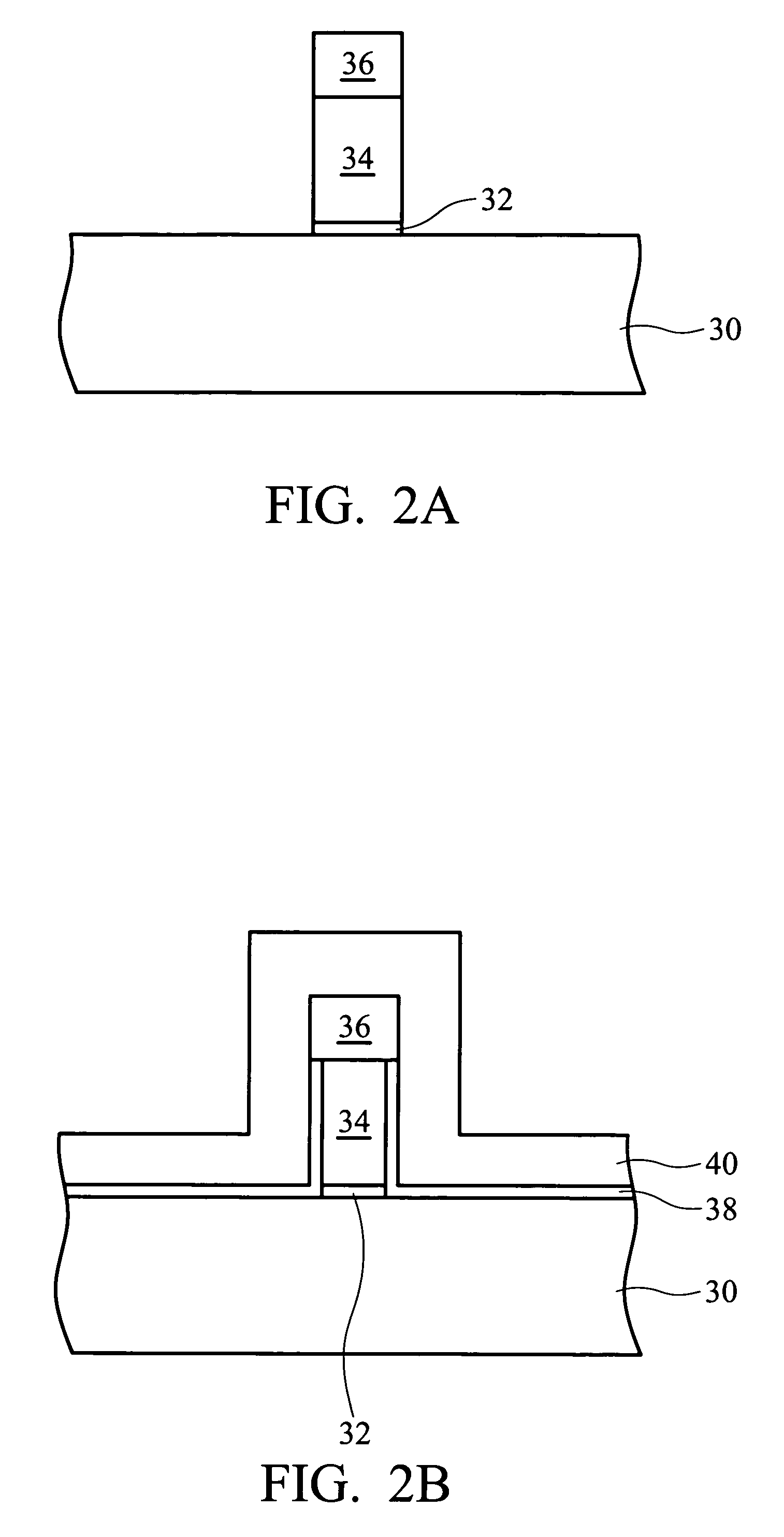

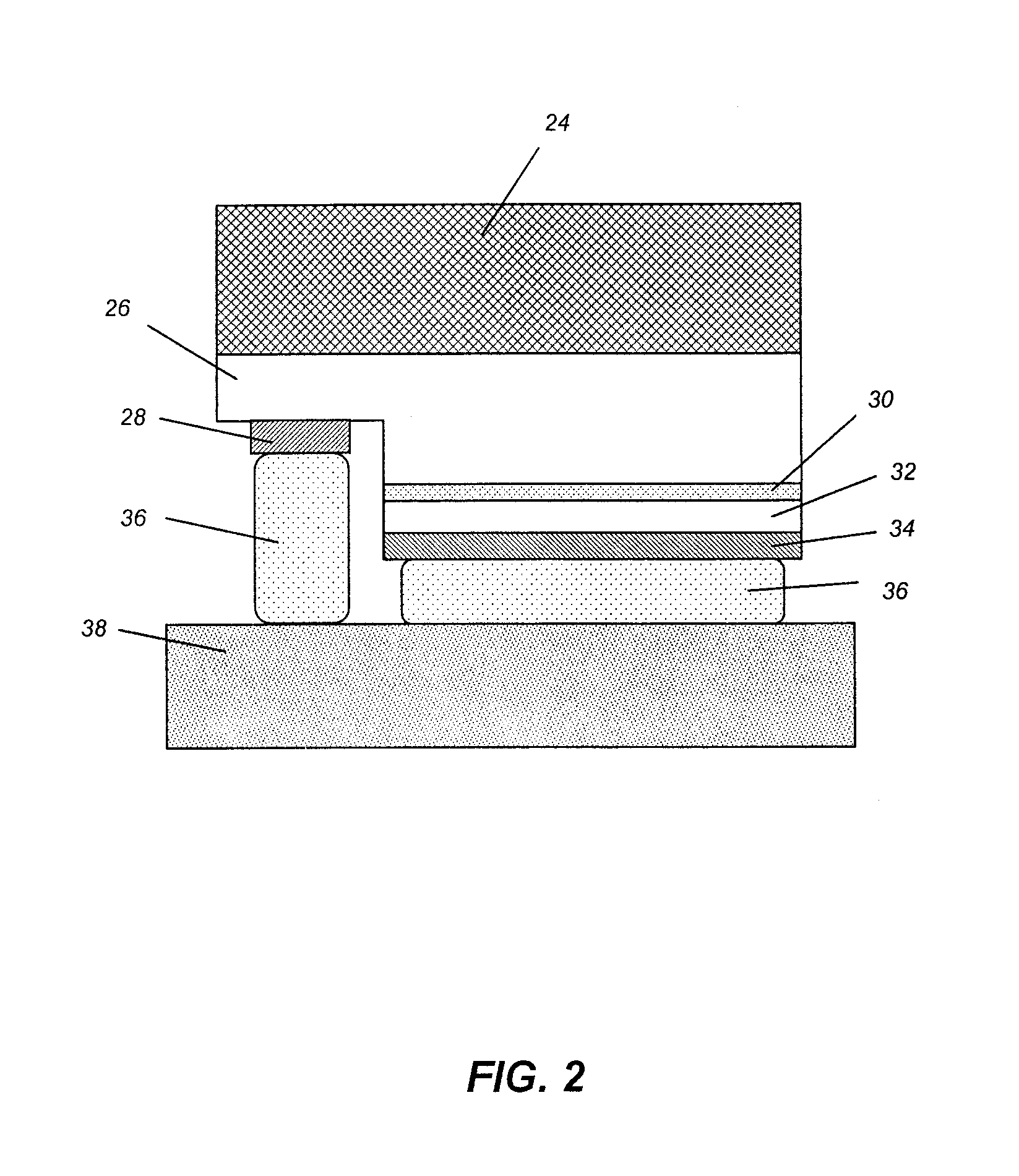

Replacement gate mosfet with self-aligned diffusion contact

A replacement gate field effect transistor includes at least one self-aligned contact that overlies a portion of a dielectric gate cap. A replacement gate stack is formed in a cavity formed by removal of a disposable gate stack. The replacement gate stack is subsequently recessed, and a dielectric gate cap having sidewalls that are vertically coincident with outer sidewalls of the gate spacer is formed by filling the recess over the replacement gate stack. An anisotropic etch removes the dielectric material of the planarization layer selective to the material of the dielectric gate cap, thereby forming at least one via cavity having sidewalls that coincide with a portion of the sidewalls of the gate spacer. A portion of each diffusion contact formed by filling the at least one via cavity overlies a portion of the gate spacer and protrudes into the dielectric gate cap.

Owner:GLOBALFOUNDRIES US INC

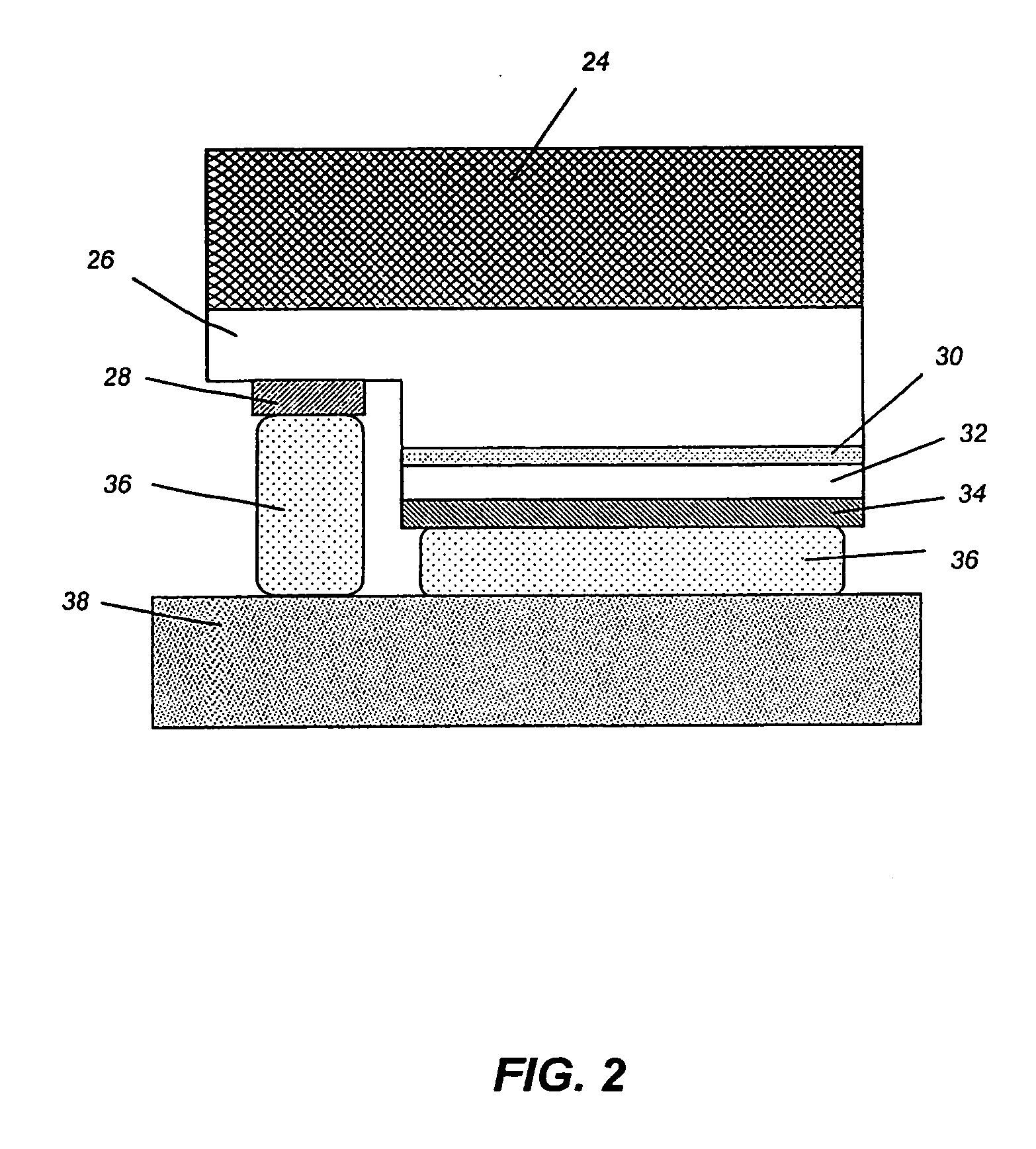

Method and structure for creating ultra low resistance damascene copper wiring

InactiveUS6987059B1Lower resistanceSimple and available process techniqueSemiconductor/solid-state device manufacturingDielectricCopper-wiring

A low resistance copper damascene interconnect structure is formed by providing a thin dielectric film such as SiC or SiOC formed on the sidewalls of the via and trench structures to function as a copper diffusion barrier layer. The dielectric copper diffusion barrier formed on the bottom of the trench structure is removed by anisotropic etching to expose patterned metal areas. The residual dielectric thus forms a dielectric diffusion barrier film on the sidewalls of the structure, and coupled with the metal diffusion barrier subsequently formed in the trench, creates a copper diffusion barrier to protect the bulk dielectric from copper leakage.

Owner:BELL SEMICON LLC

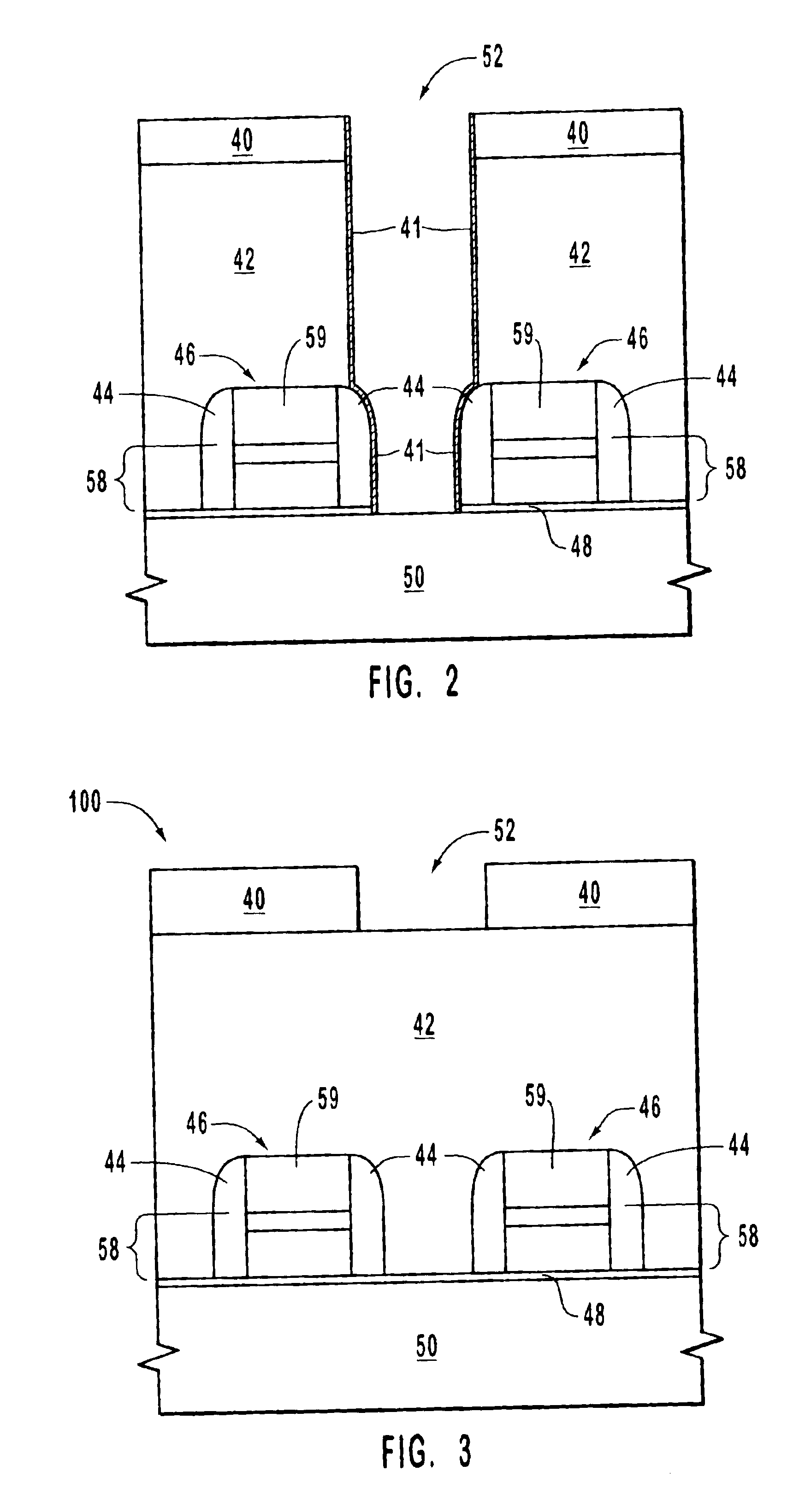

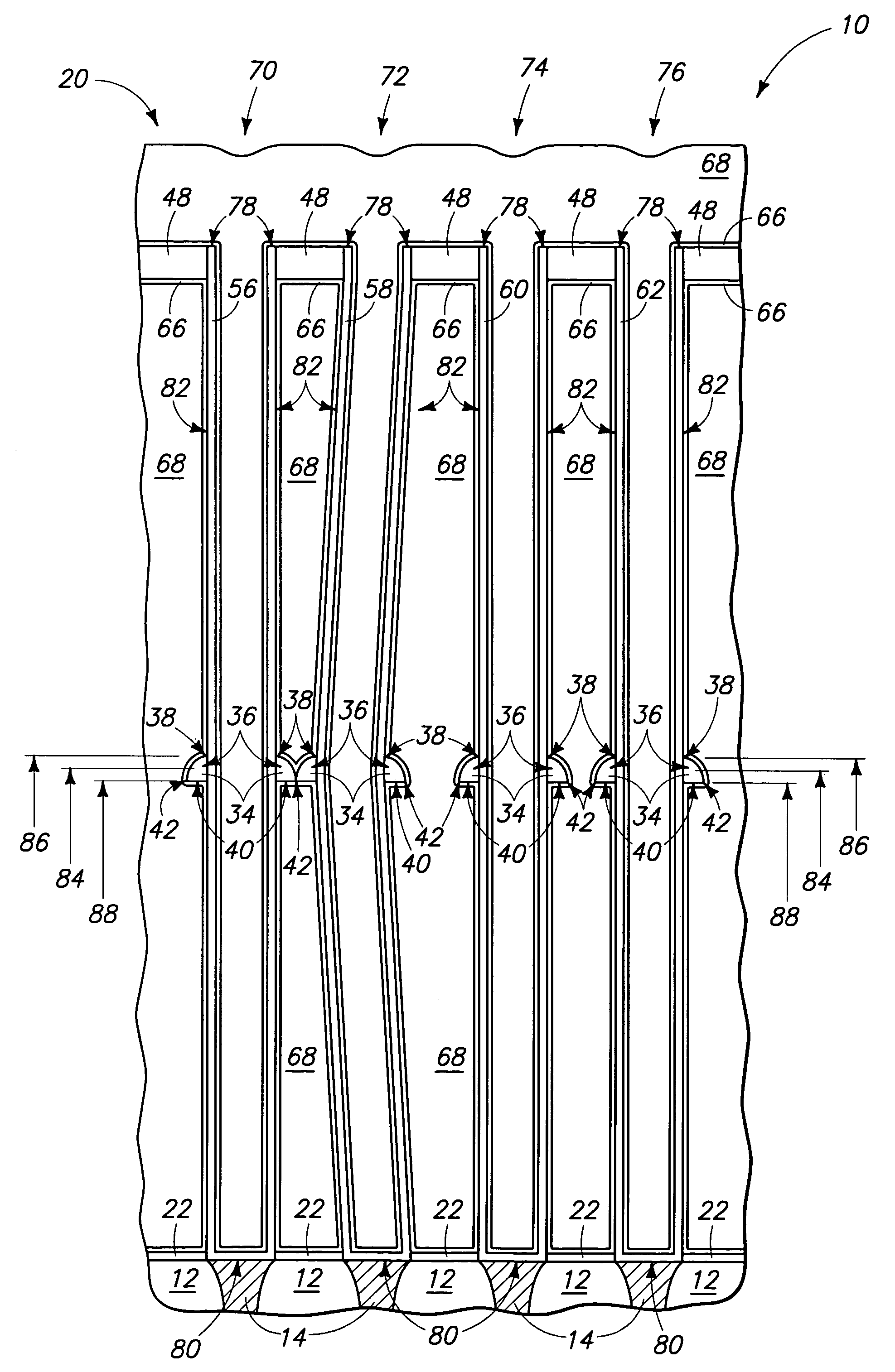

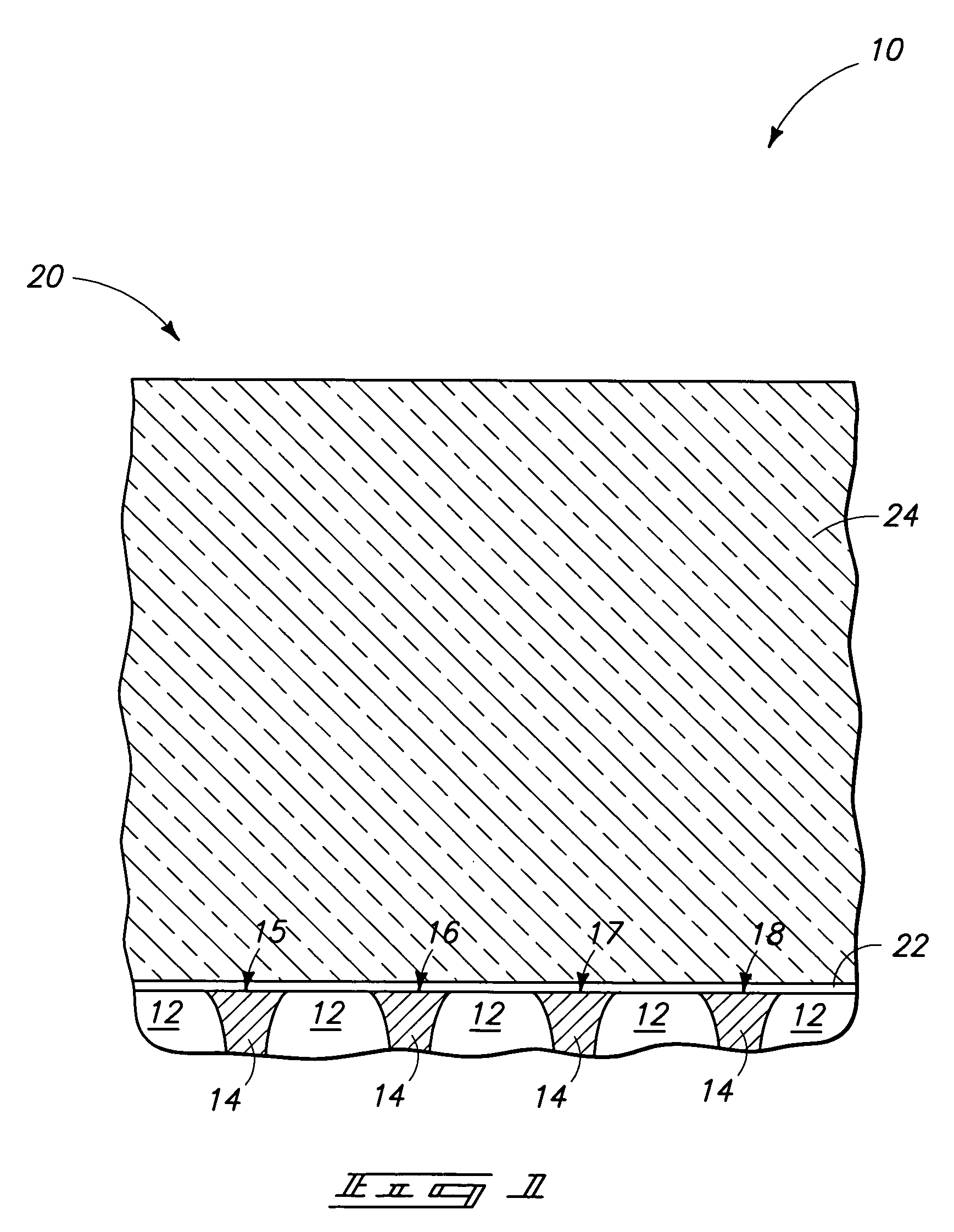

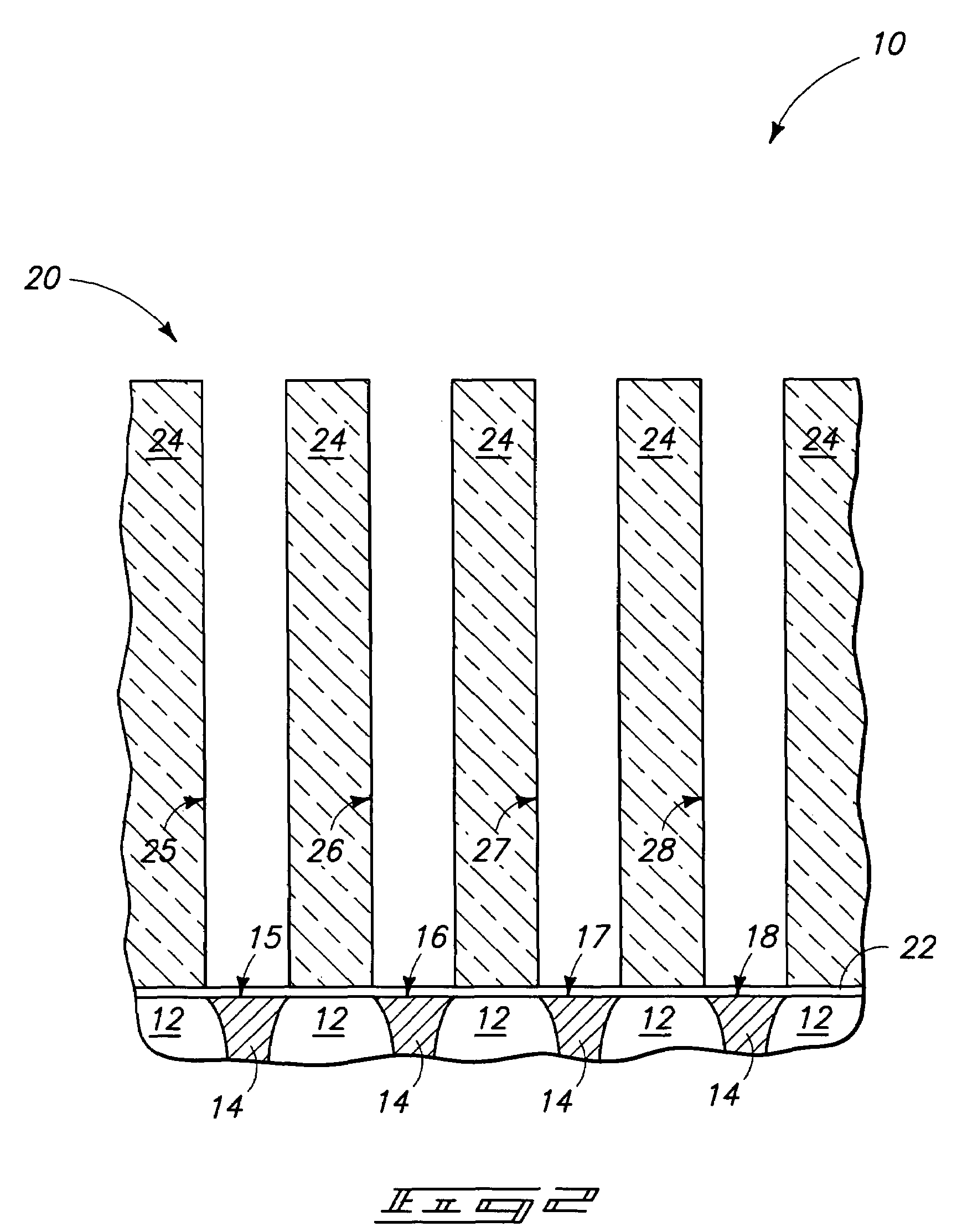

Methods of forming a plurality of capacitors

ActiveUS7544563B2Solid-state devicesSemiconductor/solid-state device manufacturingElectrical connectionAnisotropic etching

The invention includes methods and integrated circuitry. Pillars project outwardly from openings in a first material over individual capacitor storage node locations. Insulative material is deposited over the first material laterally about sidewalls of the projecting pillars, and is anisotropically etched effective to expose underlying first material and leave electrically insulative material received laterally about the sidewalls of the projecting pillars. Openings are formed within a second material to the pillars. The pillars are etched from the substrate through the openings in the second material, and individual capacitor electrodes are formed within the openings in electrical connection with the storage node locations. The individual capacitor electrodes have the anisotropically etched insulative material received laterally about their outer sidewalls. The individual capacitor electrodes are incorporated into a plurality of capacitors. Other implementations and aspects are contemplated.

Owner:MICRON TECH INC

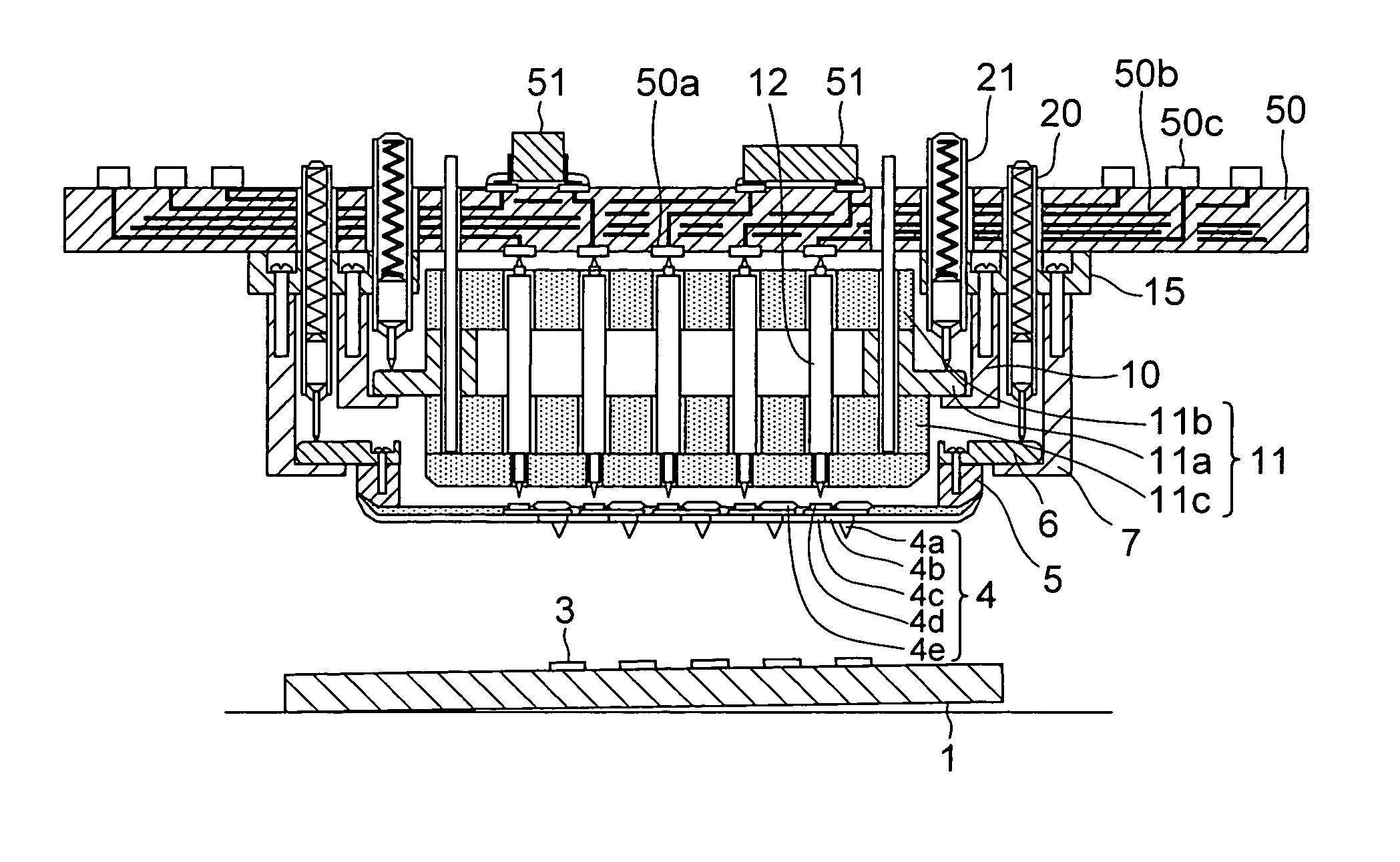

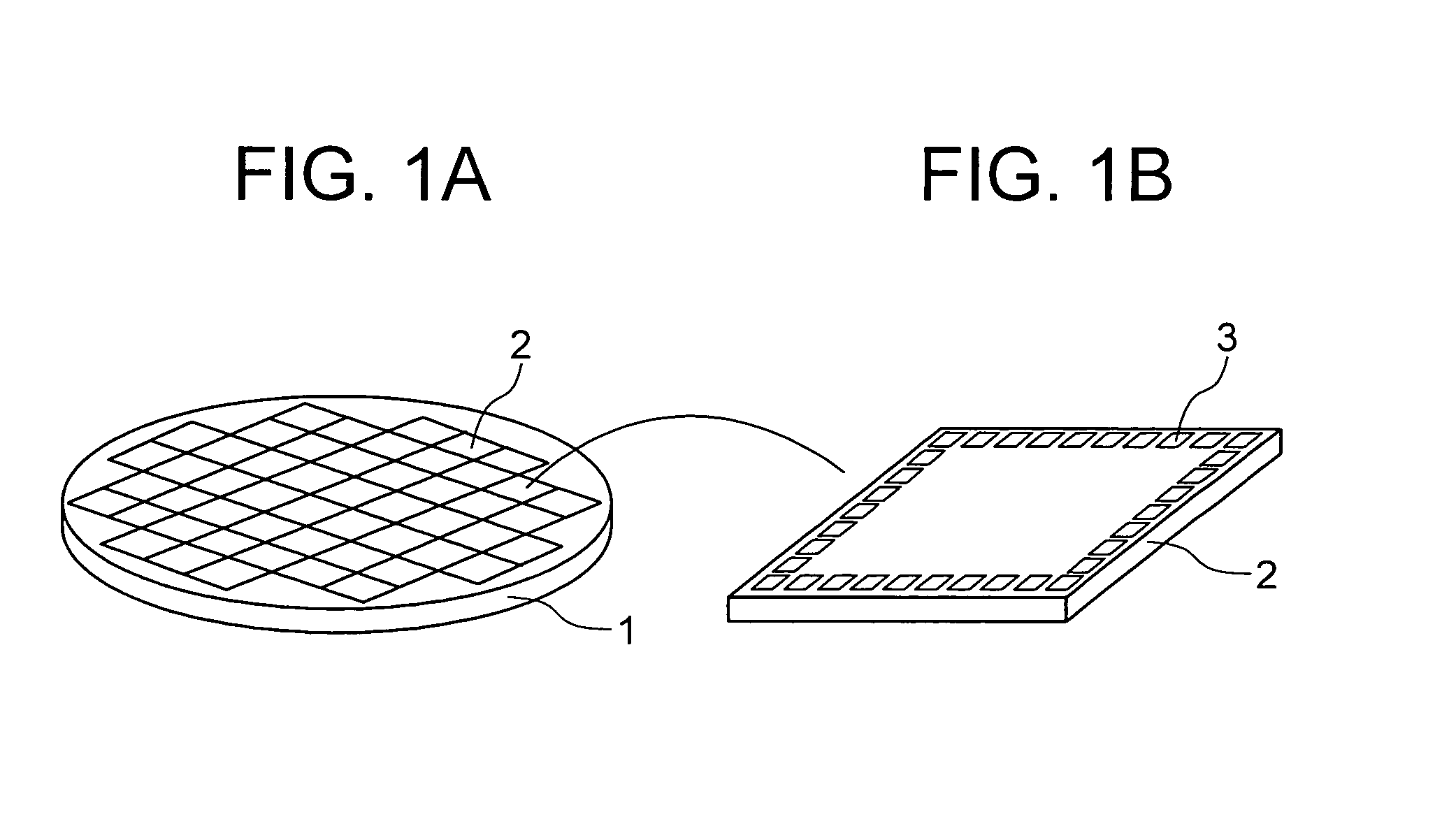

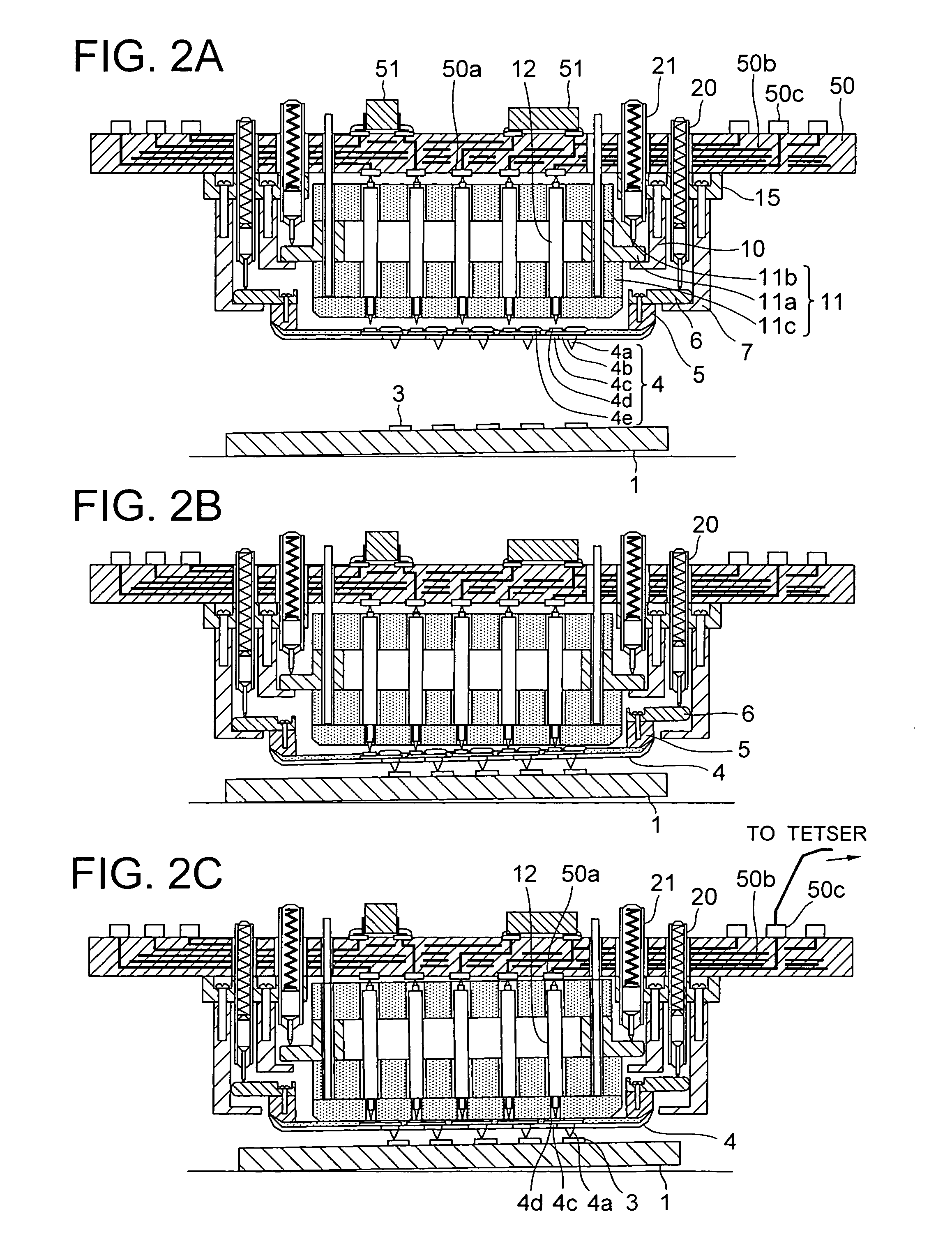

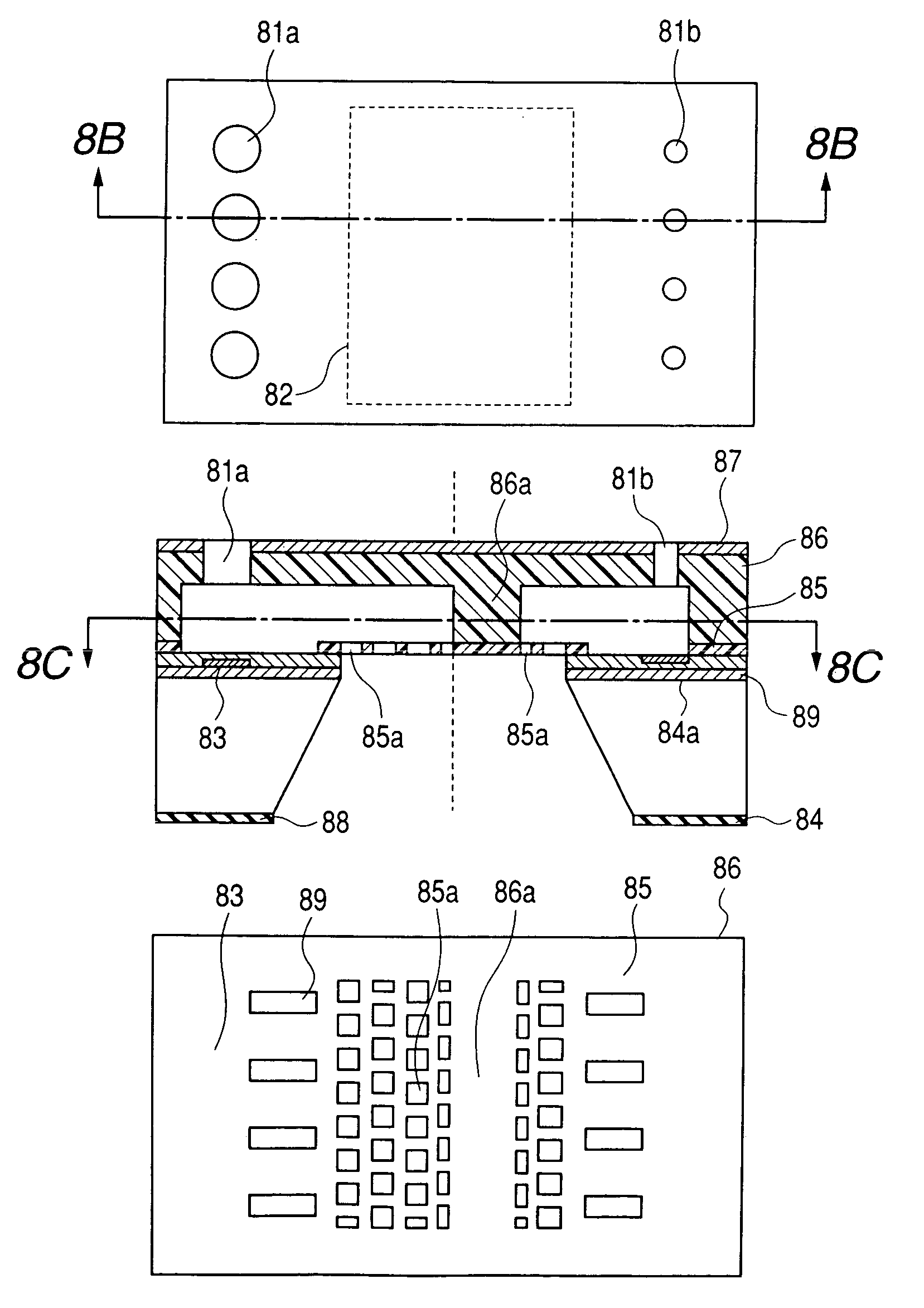

Probe sheet, probe card, semiconductor test equipment and semiconductor device fabrication method

InactiveUS7049837B2Reduce manufacturing costLow costSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityProbe card

Owner:RENESAS ELECTRONICS CORP

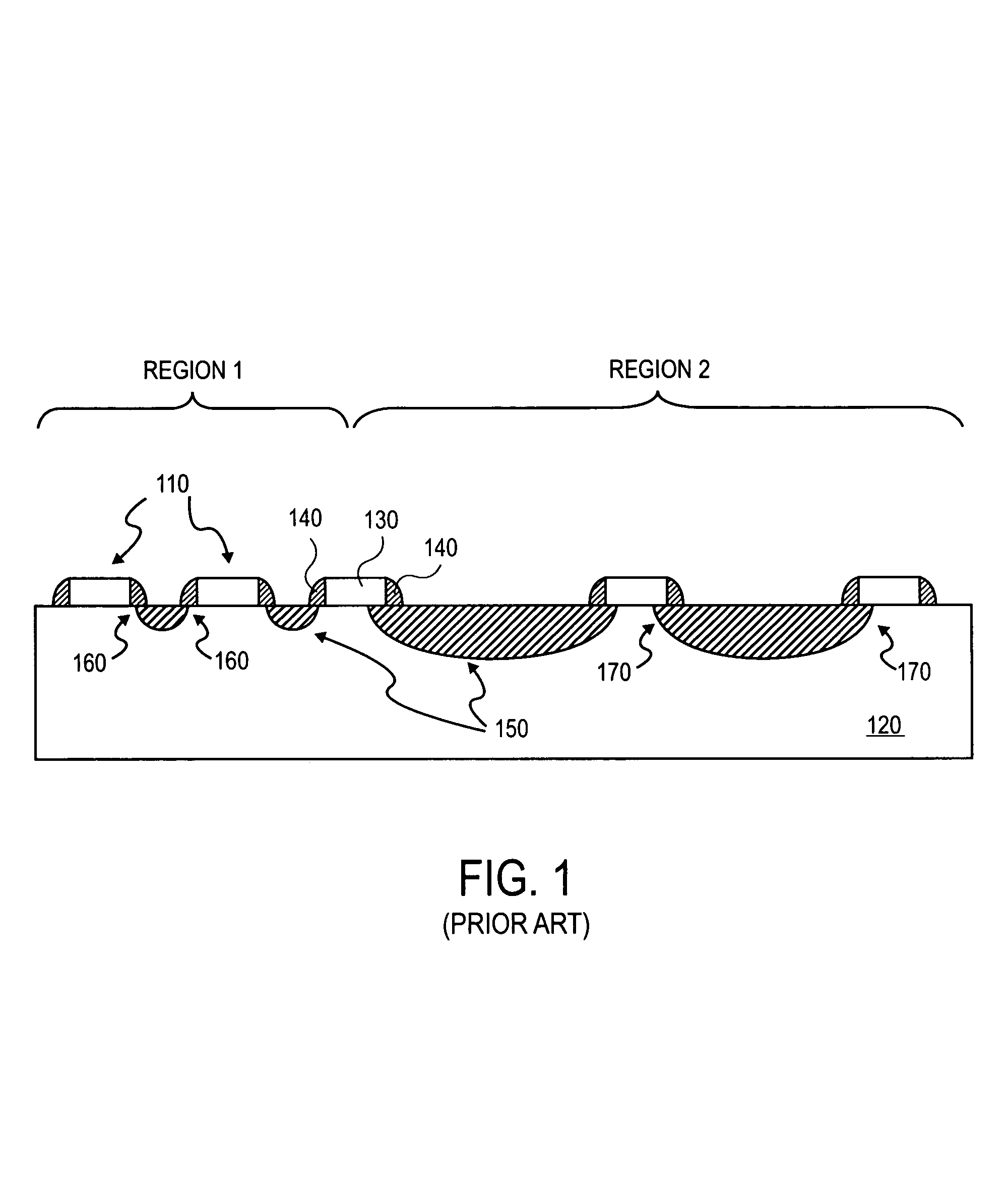

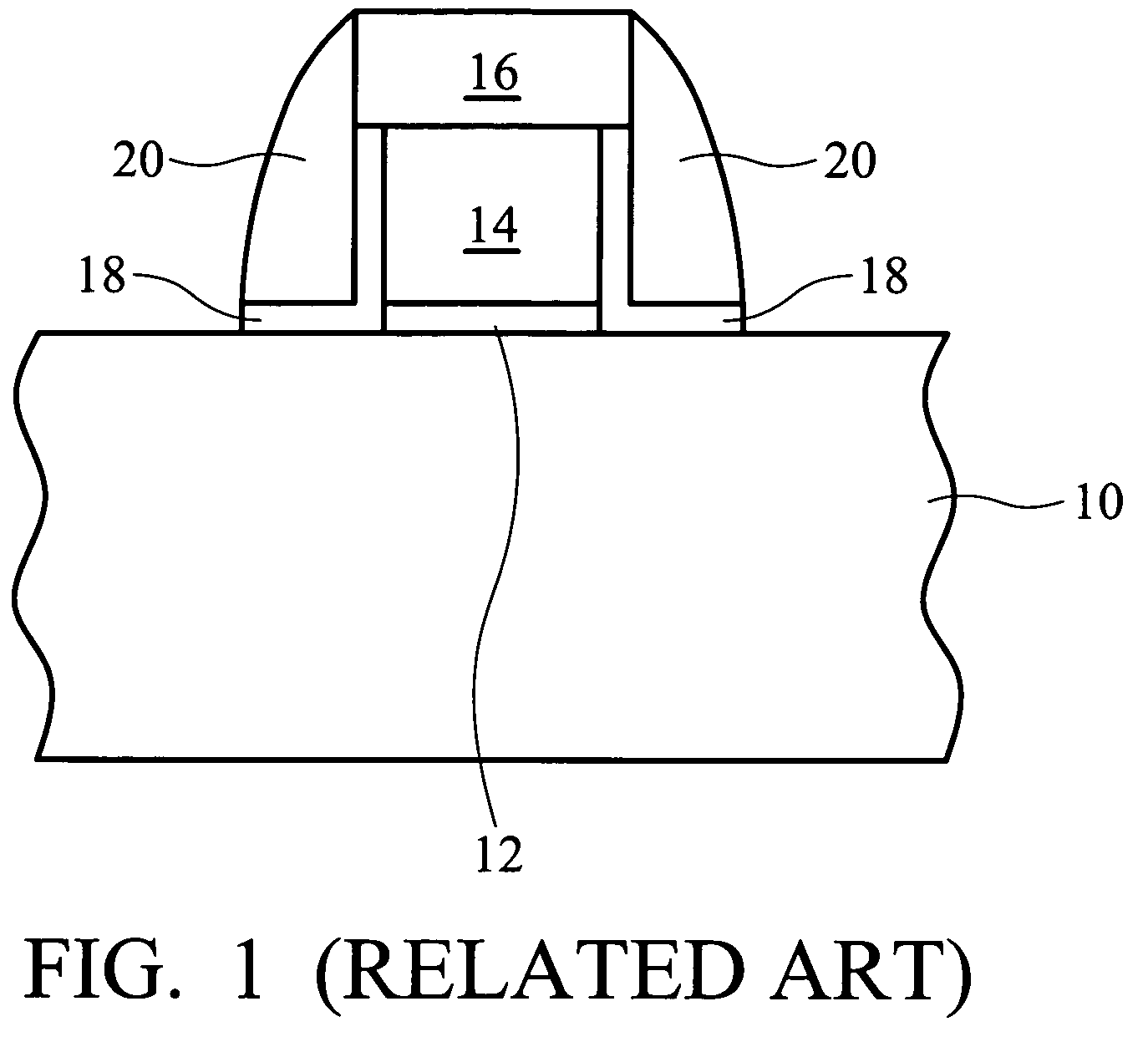

Shallow trench isolation for semiconductor devices

A shallow trench isolation structure is formed by providing a pad layer and a silicon nitride polish stop layer on a surface of a P-type silicon substrate. The silicon nitride polish stop layer and the pad oxide layer are patterned to define openings corresponding to portions of the substrate that will be etched to form trenches. Trenches are defined in the P-type silicon substrate by anisotropic etching. A boron doped oxide or glass is deposited along the walls and floor of the trench. An undoped TEOS oxide is provided over the doped oxide or glass to complete filling of the trench. The device is subjected to a high temperature reflow process, causing the dielectric materials to flow, partially planarizing the device and causing the boron of the first layer to diffuse into the walls and floor of the trench. Chemical mechanical polishing removes excess portions of the dielectric layers. The silicon nitride polish stop layer and the pad oxide layer are removed and conventional processing is performed to complete devices on the substrate. Diffusion of boron into the walls of the trench forms a self-aligned field doping region for the shallow trench isolation structure using relatively few processing steps.

Owner:UNITED MICROELECTRONICS CORP

Method for precision integrated circuit die singulation using differential etch rates

A preprocessed semiconductor substrate such as a wafer is provided with a metal etch mask which defines singulation channels on the substrate surface. An isotropic etch process is used to define a singulation channel with a first depth extending into the semiconductor substrate material. A second anisotropic etch process is used to increase the depth of the singulation channel while providing substantially vertical singulation channel sidewalls. The singulation channel can be extended through the depth of the substrate or, in an alternative embodiment, a predetermined portion of the inactive surface of the substrate removed to expose the singulation channels. In this manner, semiconductor die can be precisely singulated from a wafer while maintaining vertical die sidewalls.

Owner:NYTELL SOFTWARE LLC

Self-aligned conductive spacer process for sidewall control gate of high-speed random access memory

InactiveUS7176084B2Semiconductor/solid-state device manufacturingSemiconductor devicesStatic random-access memoryRandom access memory

A self-aligned conductive spacer process for fabricating sidewall control gates on both sides of a floating gate for high-speed RAM applications, which can well define dimensions and profiles of the sidewall control gates. A conductive layer is formed on the dielectric layer to cover a floating gate patterned on a semiconductor substrate. Oxide spacer are formed on the conductive layer adjacent to the sidewalls of the floating gate. Performing an anisotropic etch process on the conductive layer and using the oxide spacers as a hard mask, a conductive spacers are self-aligned fabricated at both sides of the floating gate, serving as sidewall control gates.

Owner:TAIWAN SEMICON MFG CO LTD

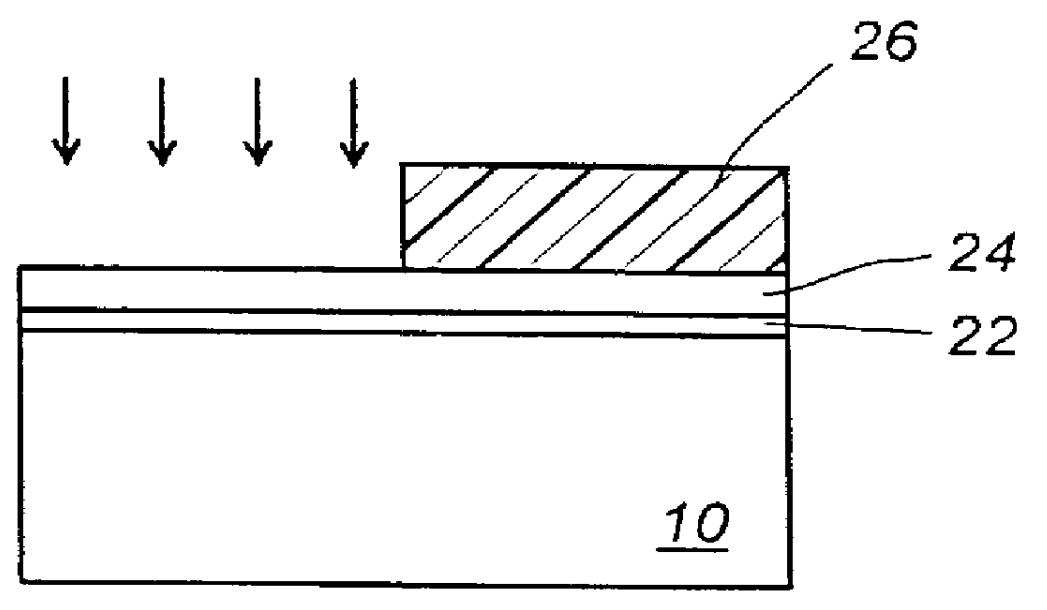

Highly efficient gallium nitride based light emitting diodes via surface roughening

ActiveUS20100025717A1Solid-state devicesSemiconductor/solid-state device manufacturingLight reflectionNitrogen

A gallium nitride (GaN) based light emitting diode (LED), wherein light is extracted through a nitrogen face (N-face) of the LED and a surface of the N-face is roughened into one or more hexagonal shaped cones. The roughened surface reduces light reflections occurring repeatedly inside the LED, and thus extracts more light out of the LED. The surface of the N-face is roughened by an anisotropic etching, which may comprise a dry etching or a photo-enhanced chemical (PEC) etching.

Owner:RGT UNIV OF CALIFORNIA

Method for reducing dimensions between patterns on a photoresist

InactiveUS6750150B2Reducing distance separating patternImprove the immunitySemiconductor/solid-state device manufacturingPhotosensitive material processingSemiconductor materialsInorganic materials

A semiconductor manufacturing method that includes defining a substrate, depositing a polysilicon layer over the substrate, depositing a layer of photoresist over the polysilicon layer, patterning and defining the photoresist layer, depositing a layer of inorganic material over the patterned and defined photoresist layer, wherein the layer of inorganic material is conformal and photo-insensitive, and anisotropic etching the layer of inorganic material and the layer of semiconductor material.

Owner:MACRONIX INT CO LTD

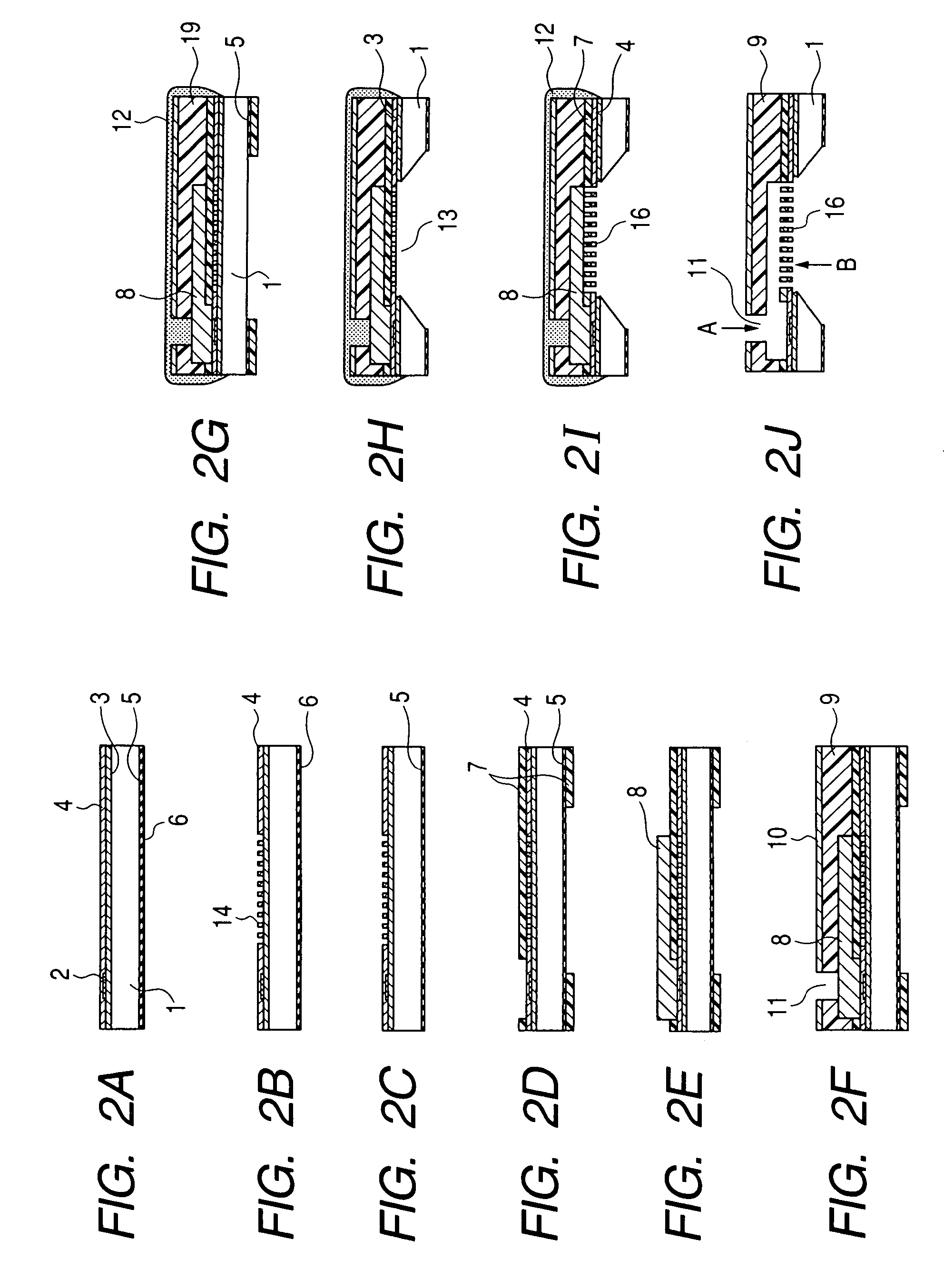

Method of manufacturing ink jet recording head, ink jet recording head, and ink jet cartridge

A method of manufacturing an ink jet head which discharges ink, comprising: a step of preparing a silicon substrate; a step of forming a membrane having a layer in which a plurality of holes are disposed to constitute a filter mask, and a layer with which a first surface is coated in such a manner that the first surface is not exposed from the plurality of holes on the first surface of the substrate; a step of forming a close contact enhancing layer on the membrane formed on the substrate; a step of forming a channel constituting member on the close contact enhancing layer to constitute a plurality of discharge ports and a plurality of ink channels communicating with the plurality of discharge ports; a step of forming an ink supply port communicating with the plurality of ink channels in the silicon substrate by anisotropic etching from a second surface facing the first surface of the substrate; and a step of forming a filter in a portion of the close contact enhancing layer positioned in an opening of the ink supply port using the layer of the membrane in which a plurality of holes are disposed as the mask.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com