Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5056 results about "Hard mask" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

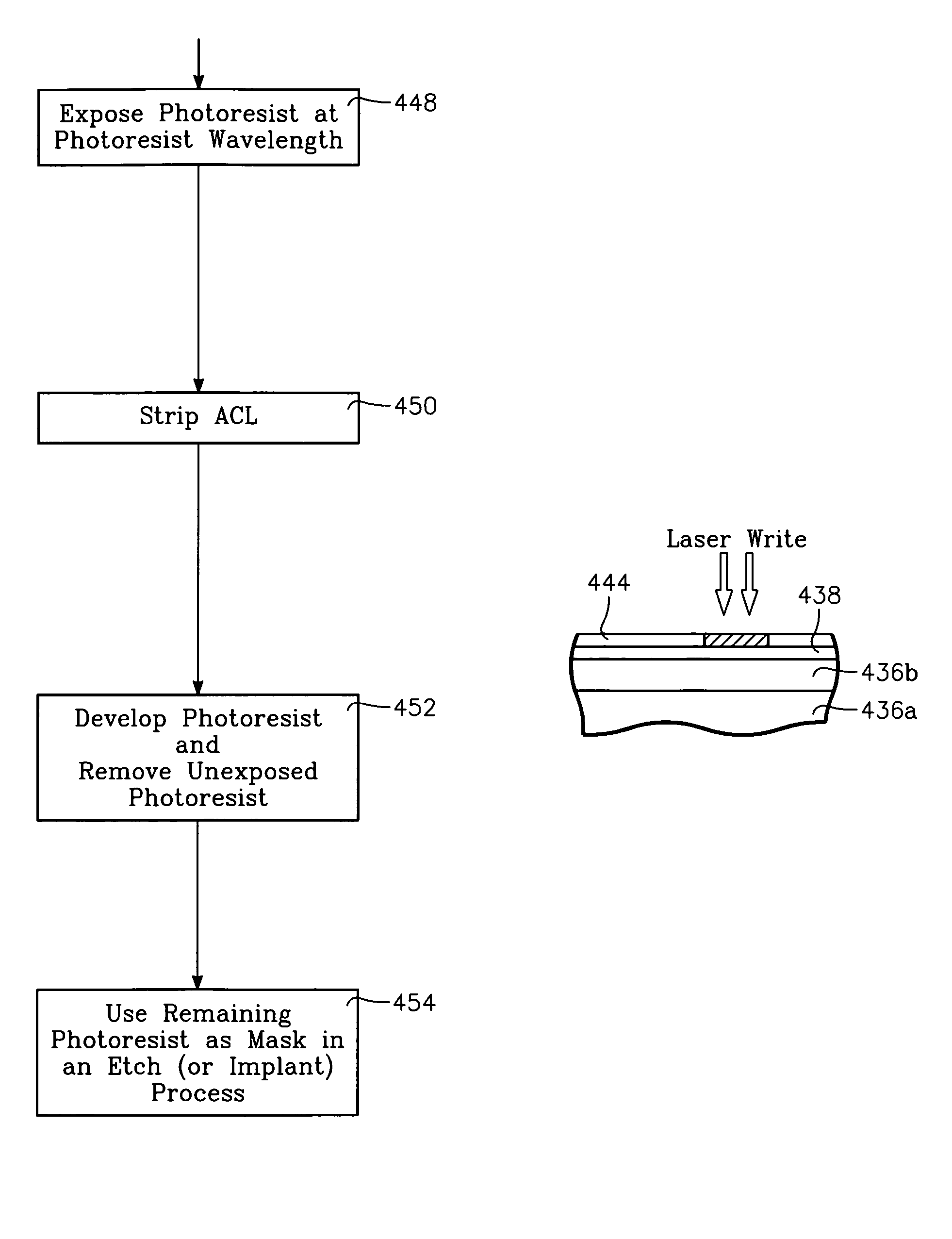

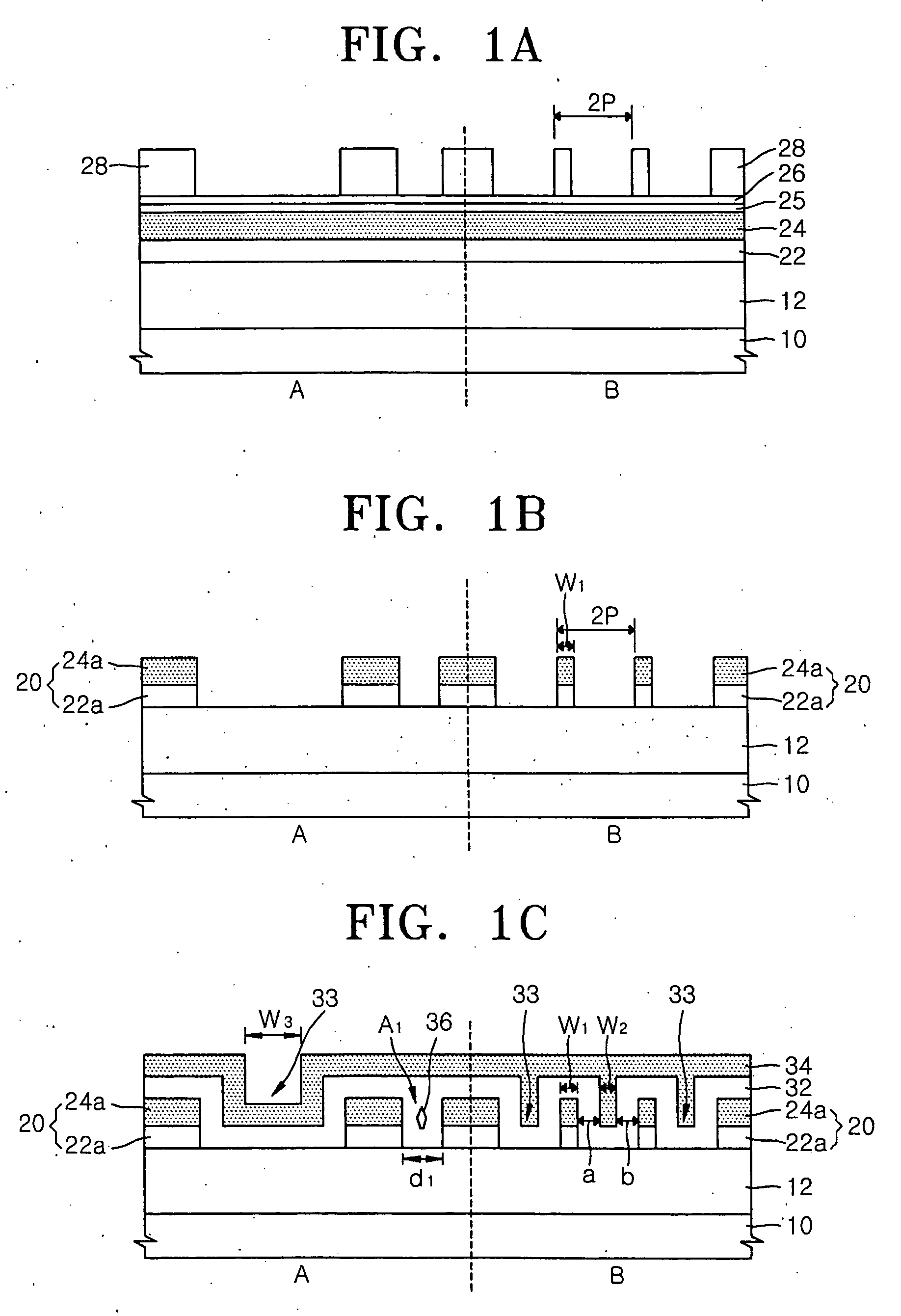

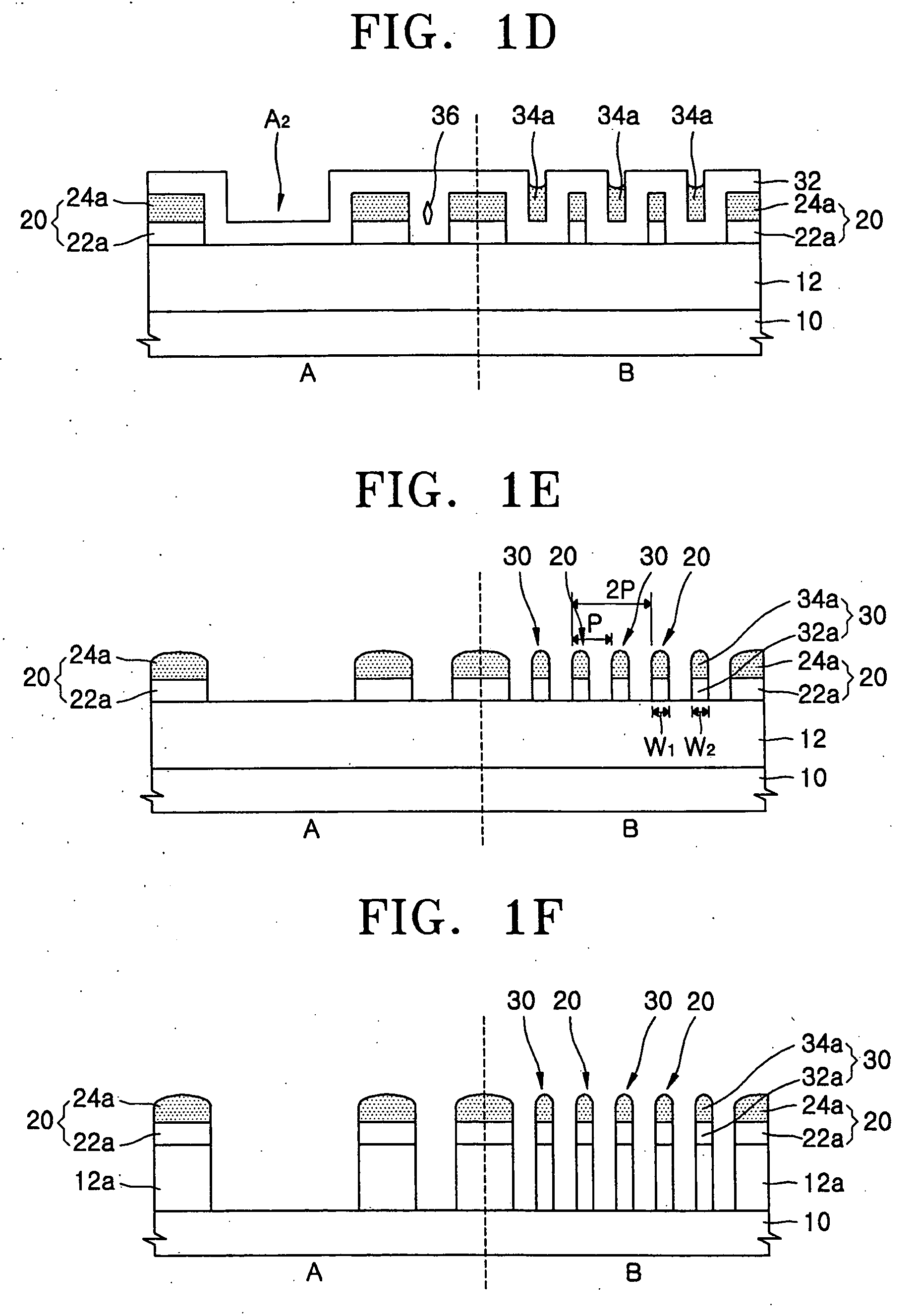

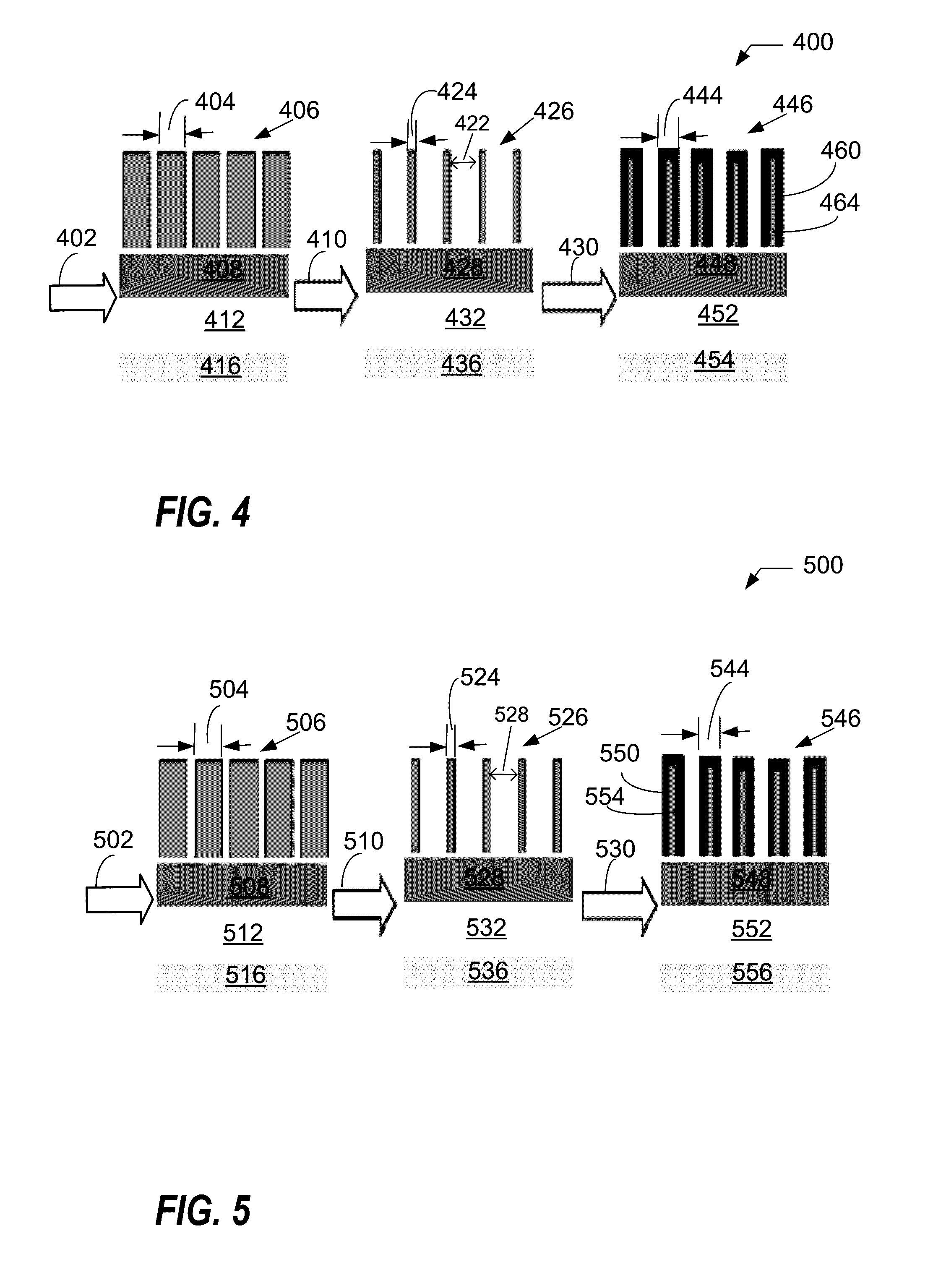

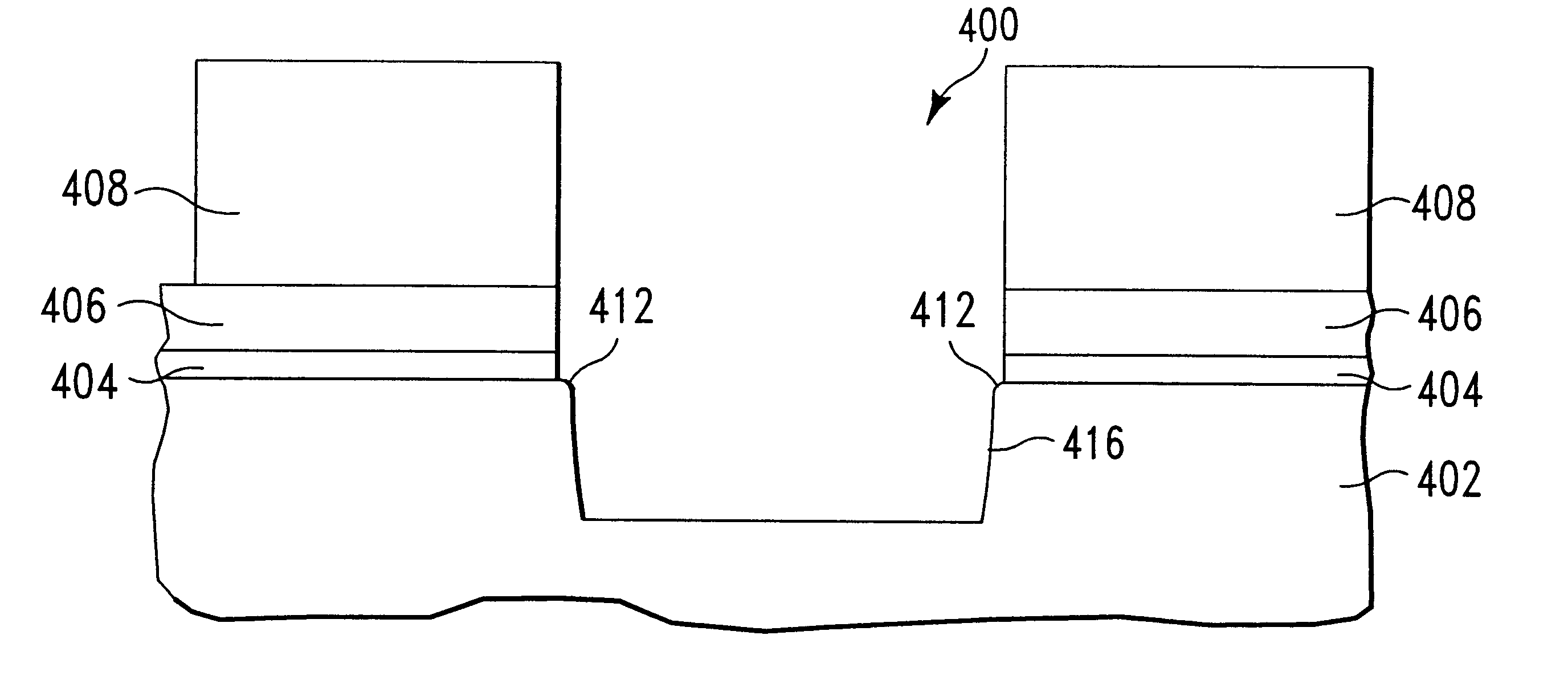

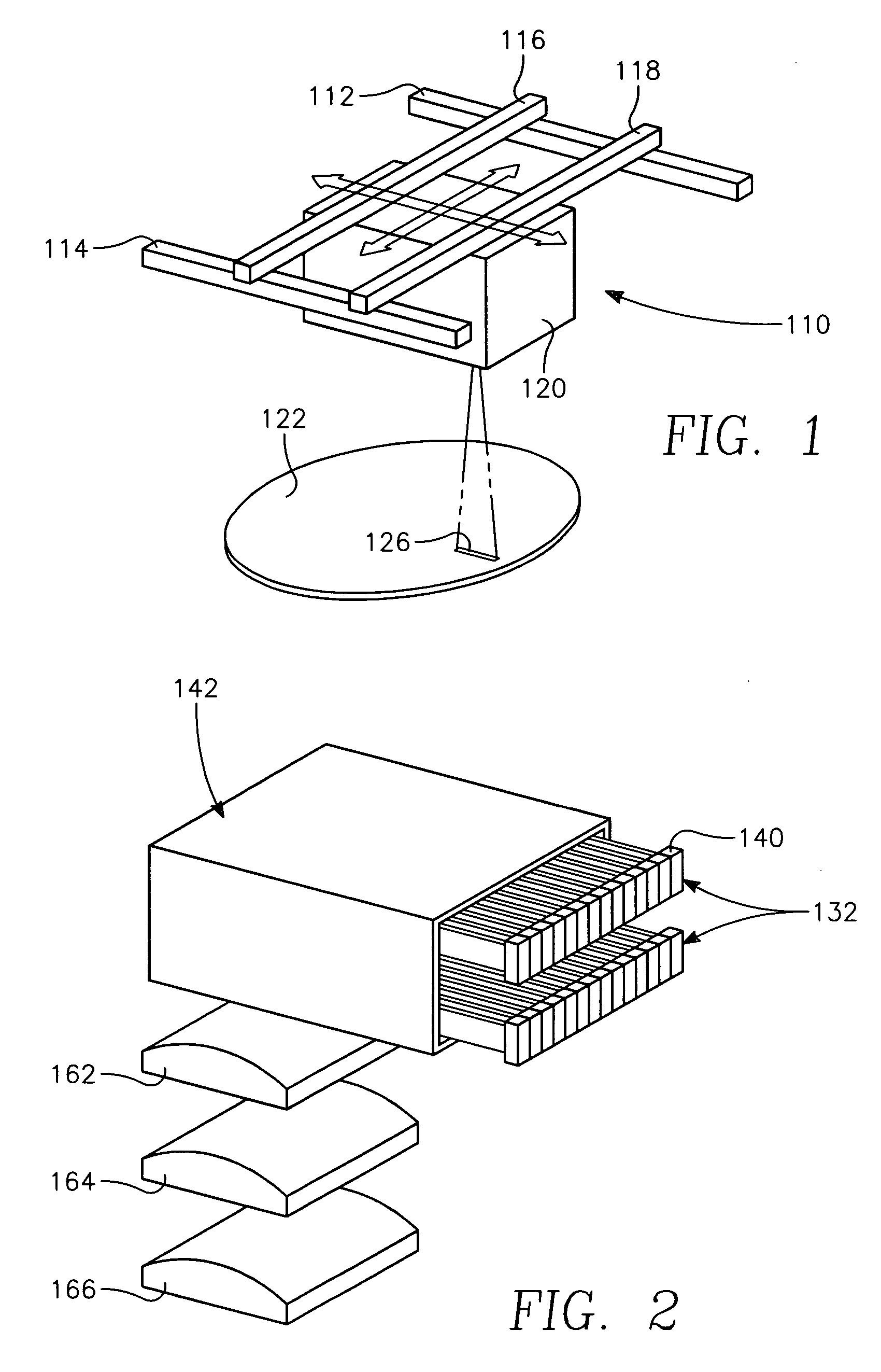

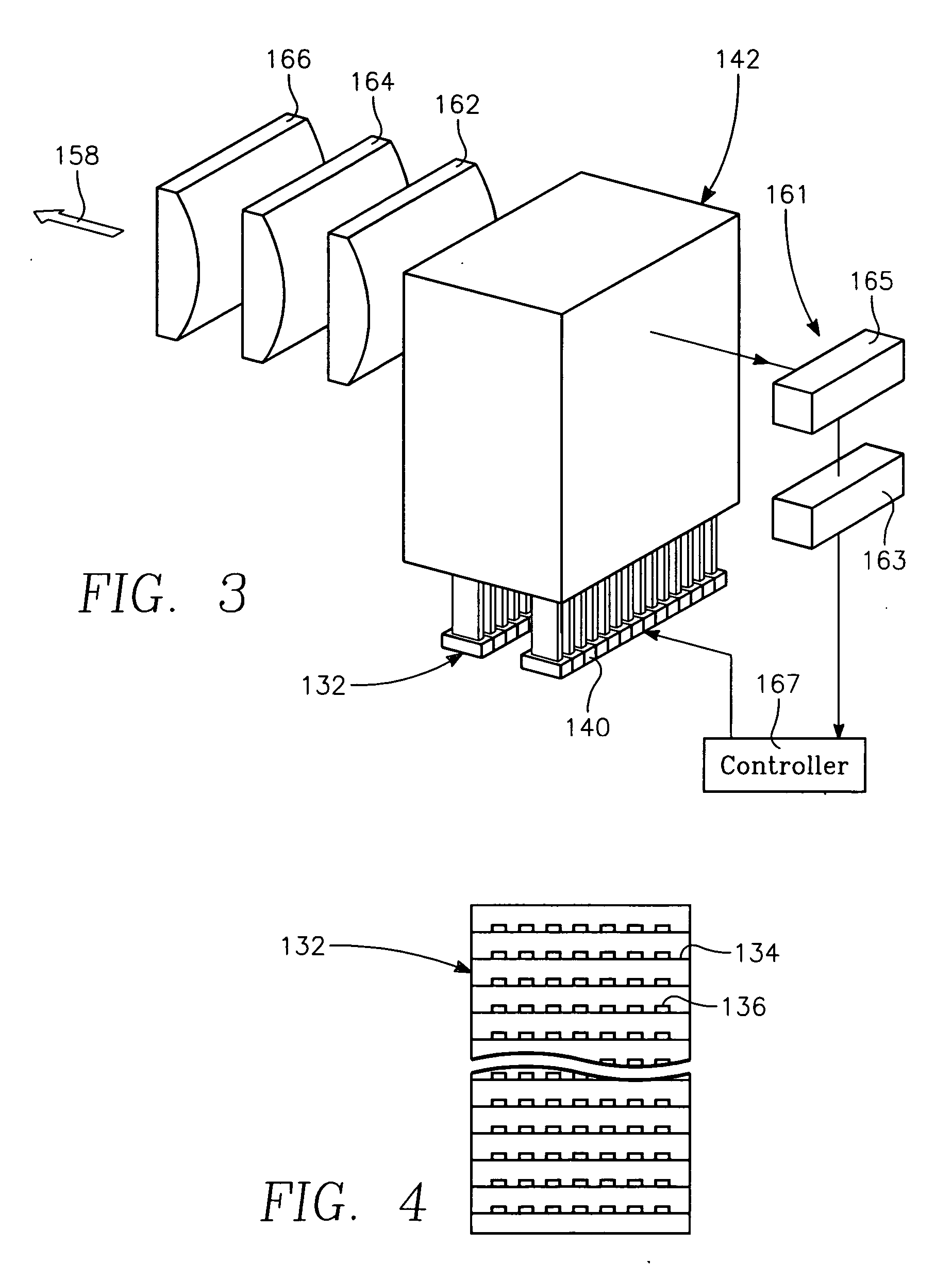

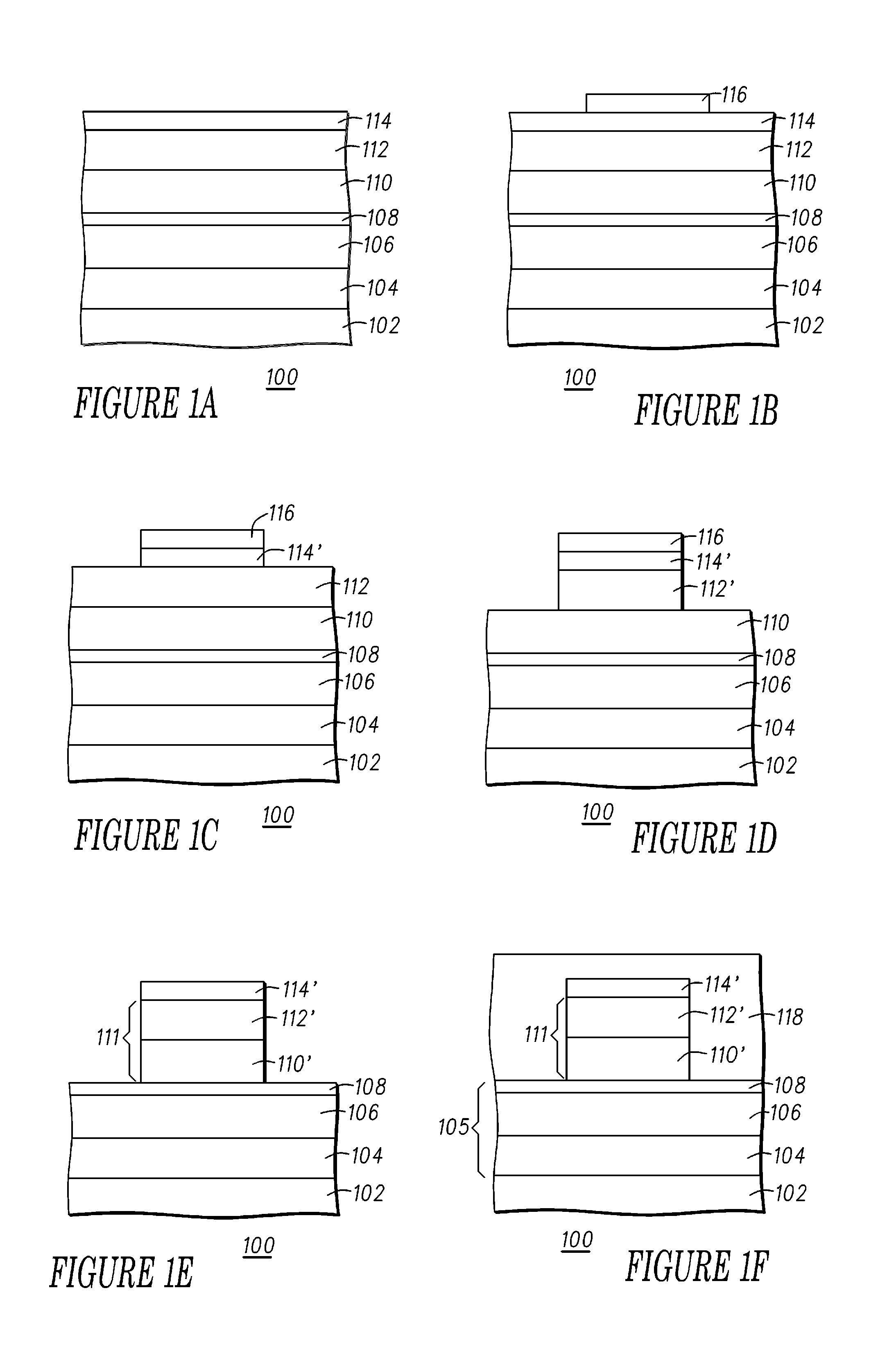

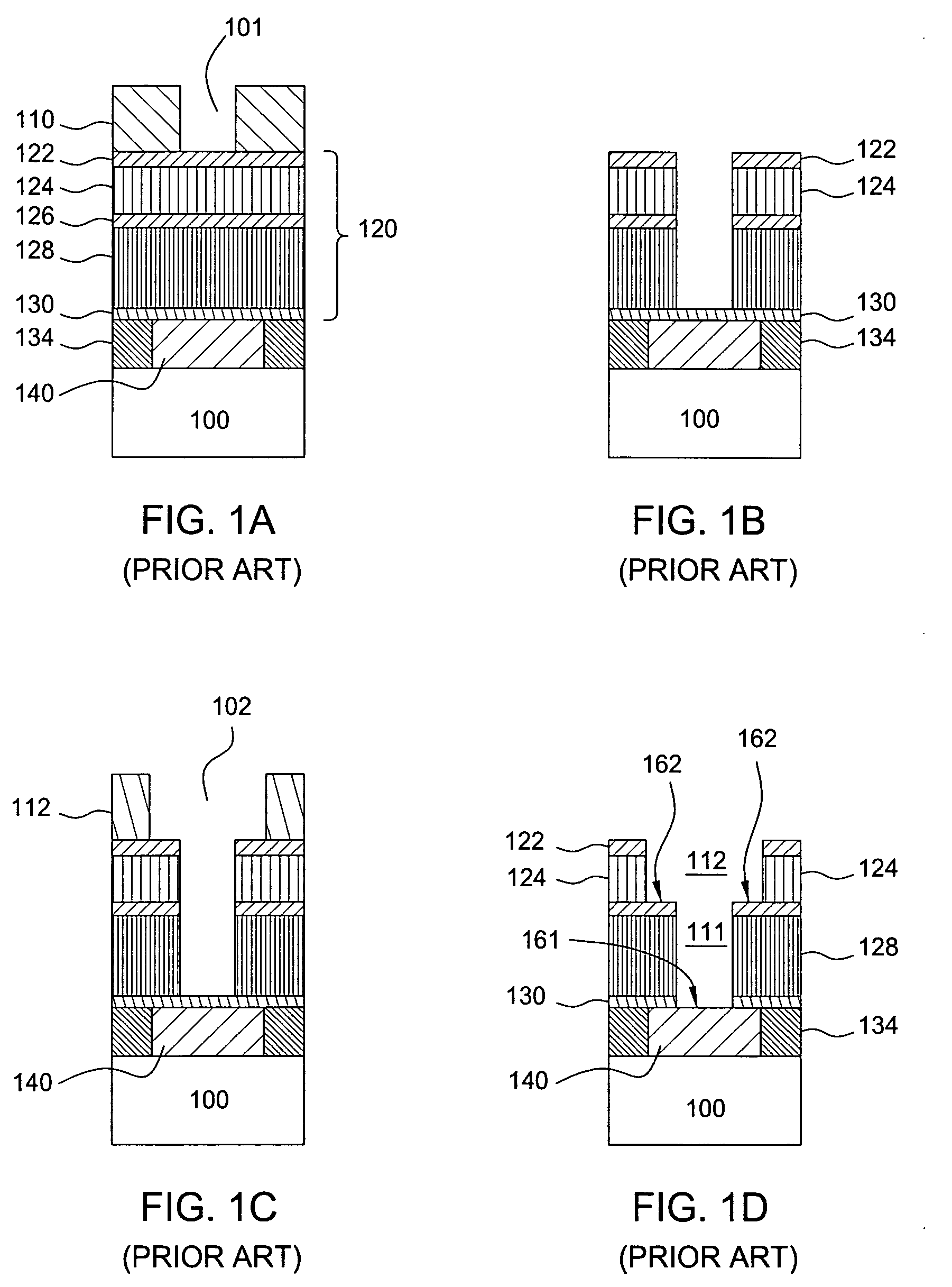

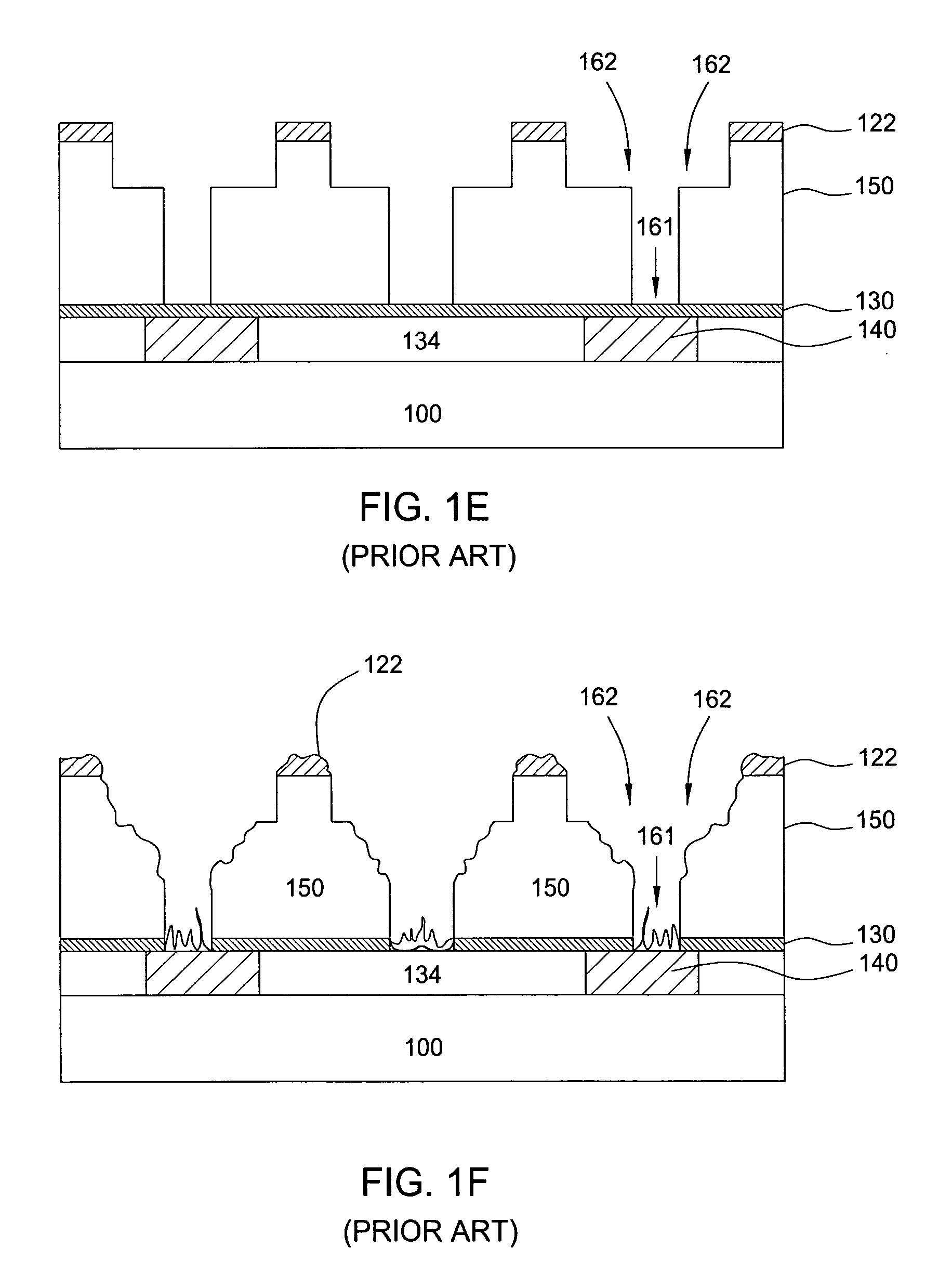

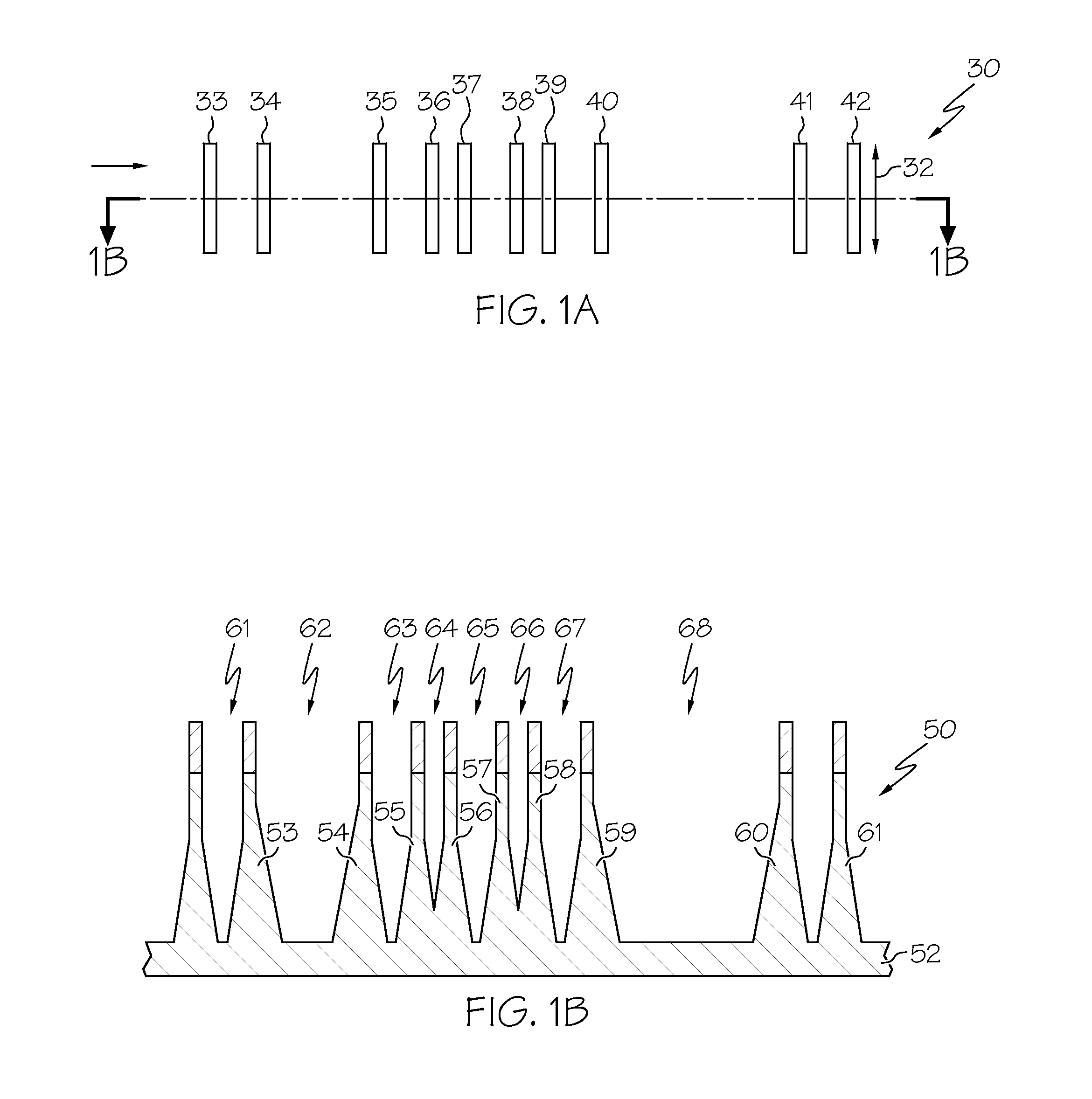

Method for integrated circuit fabrication using pitch multiplication

InactiveUS7115525B2Electric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

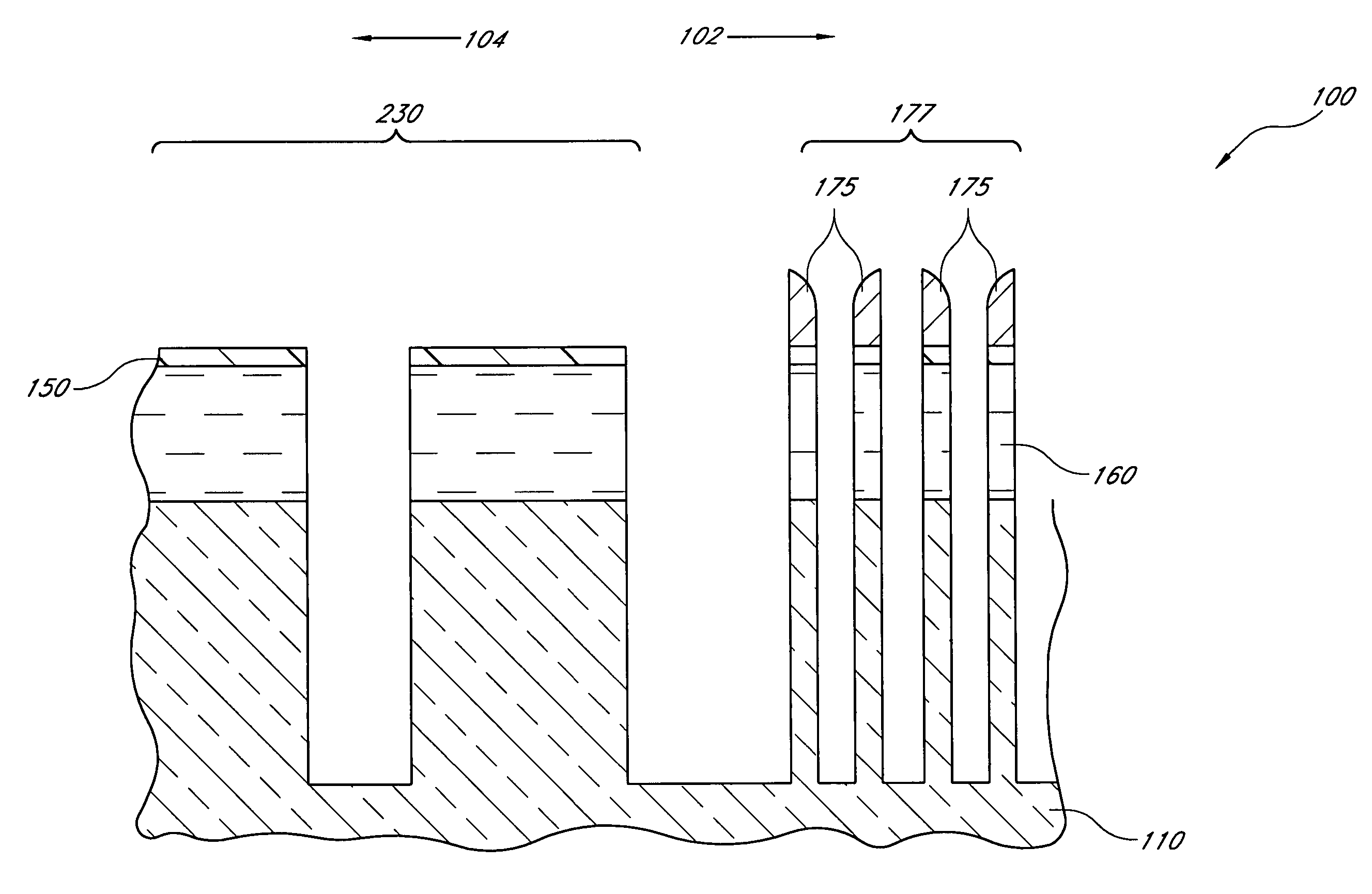

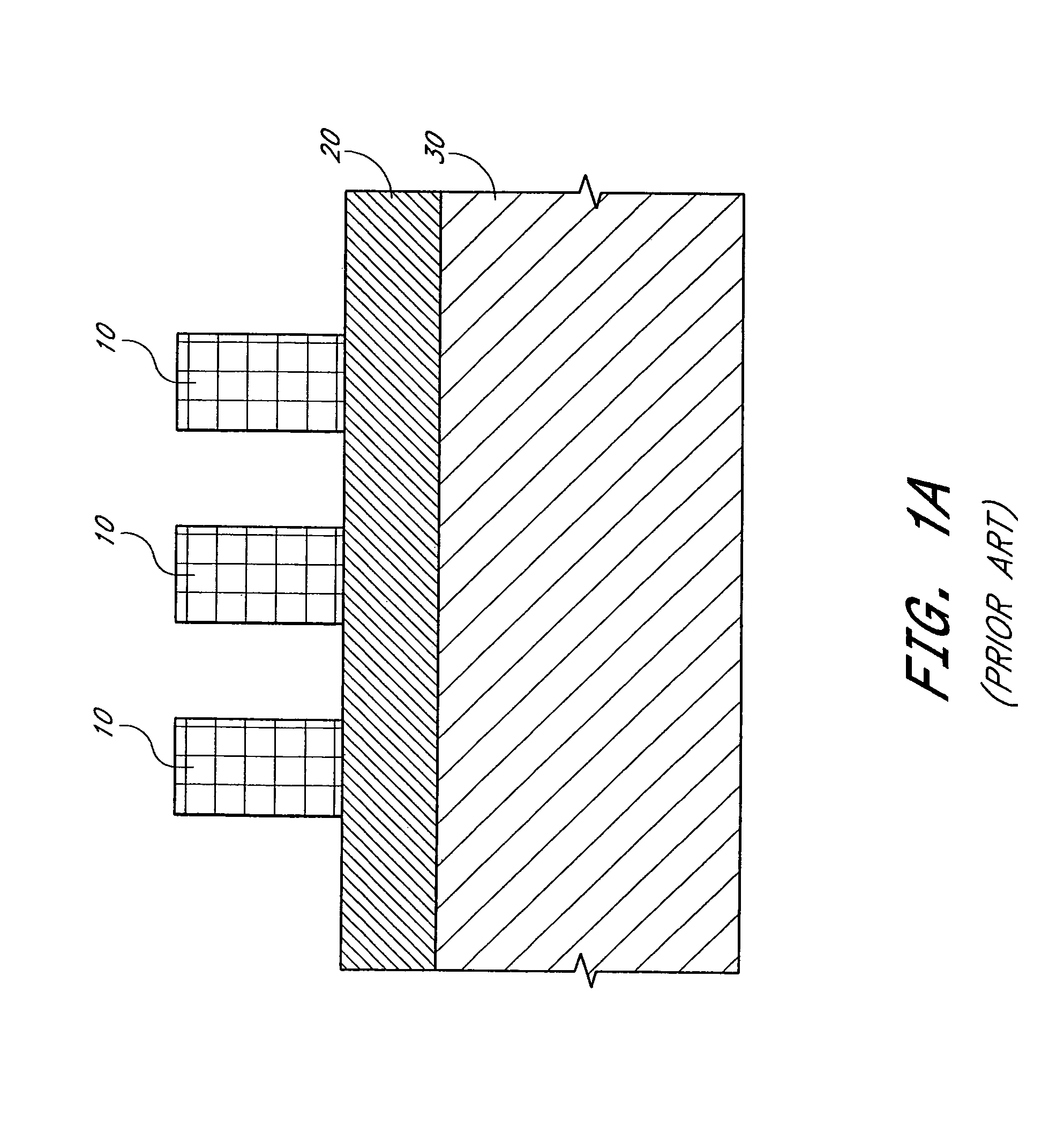

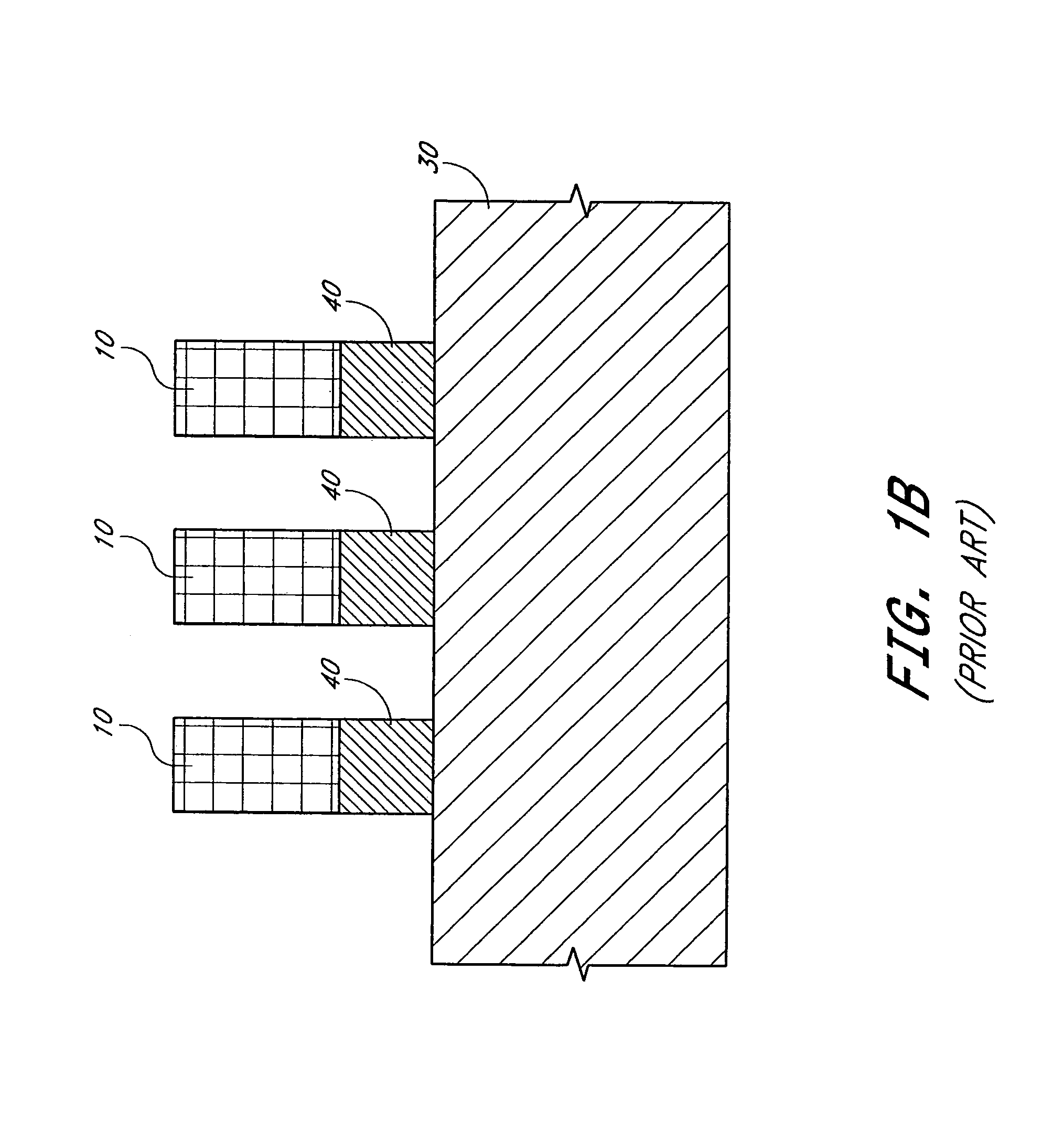

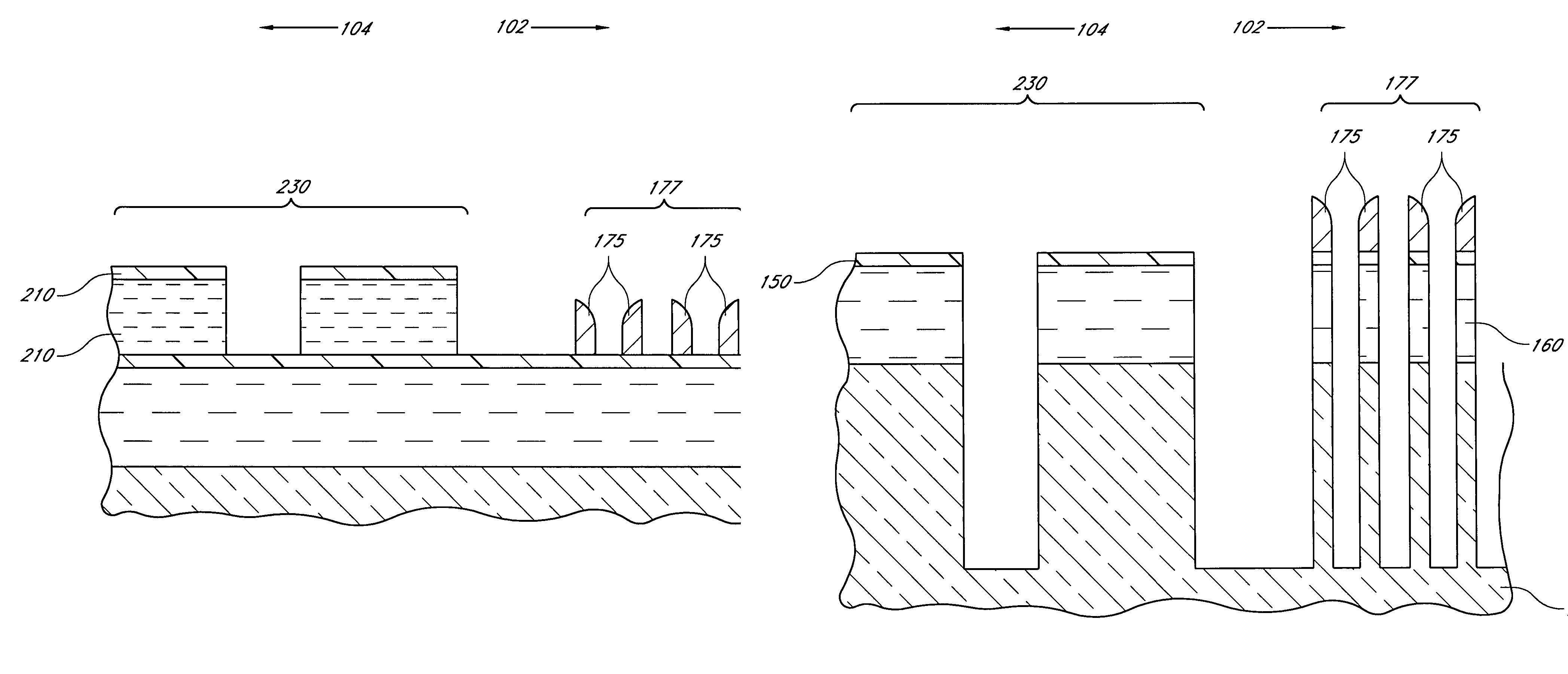

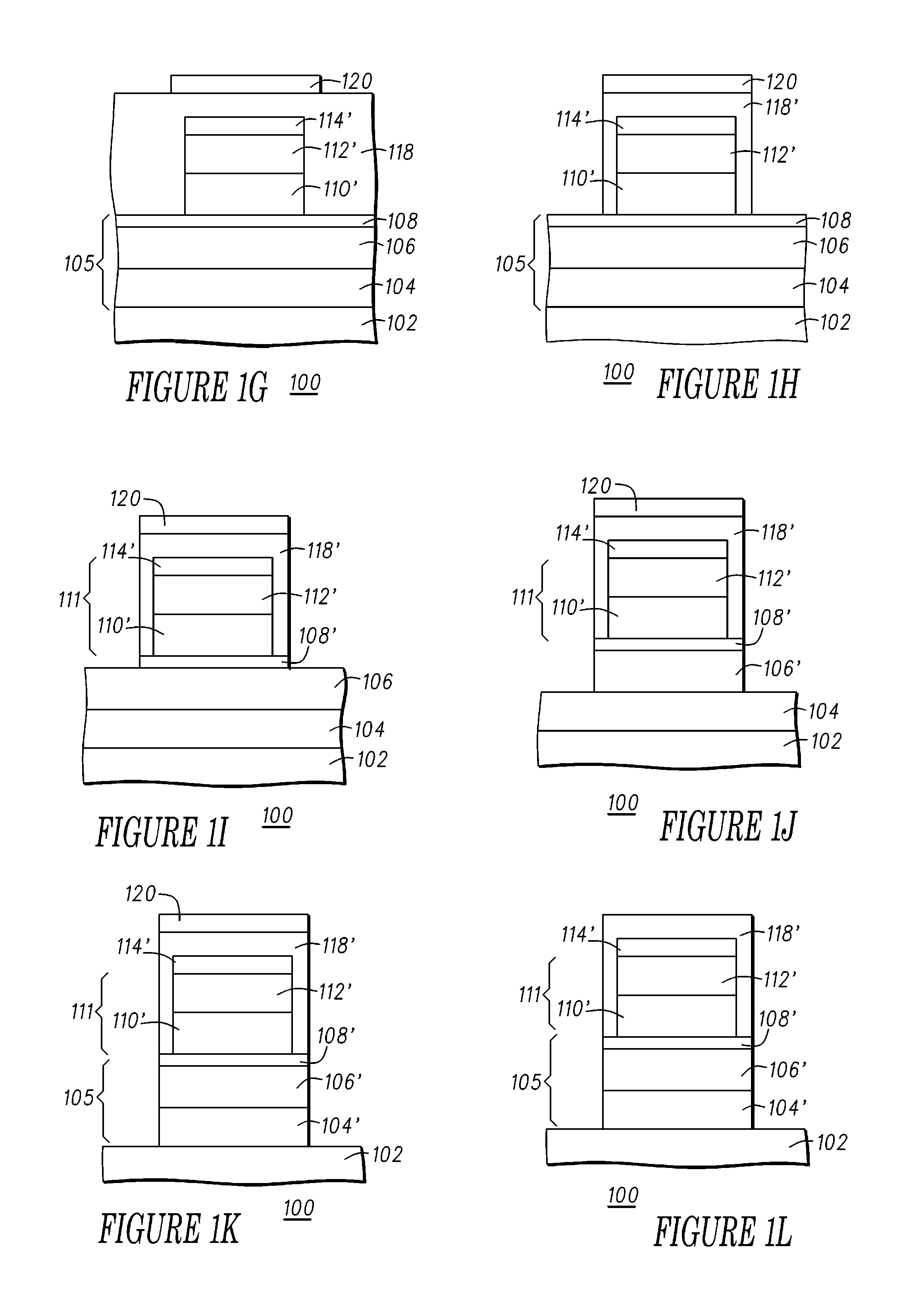

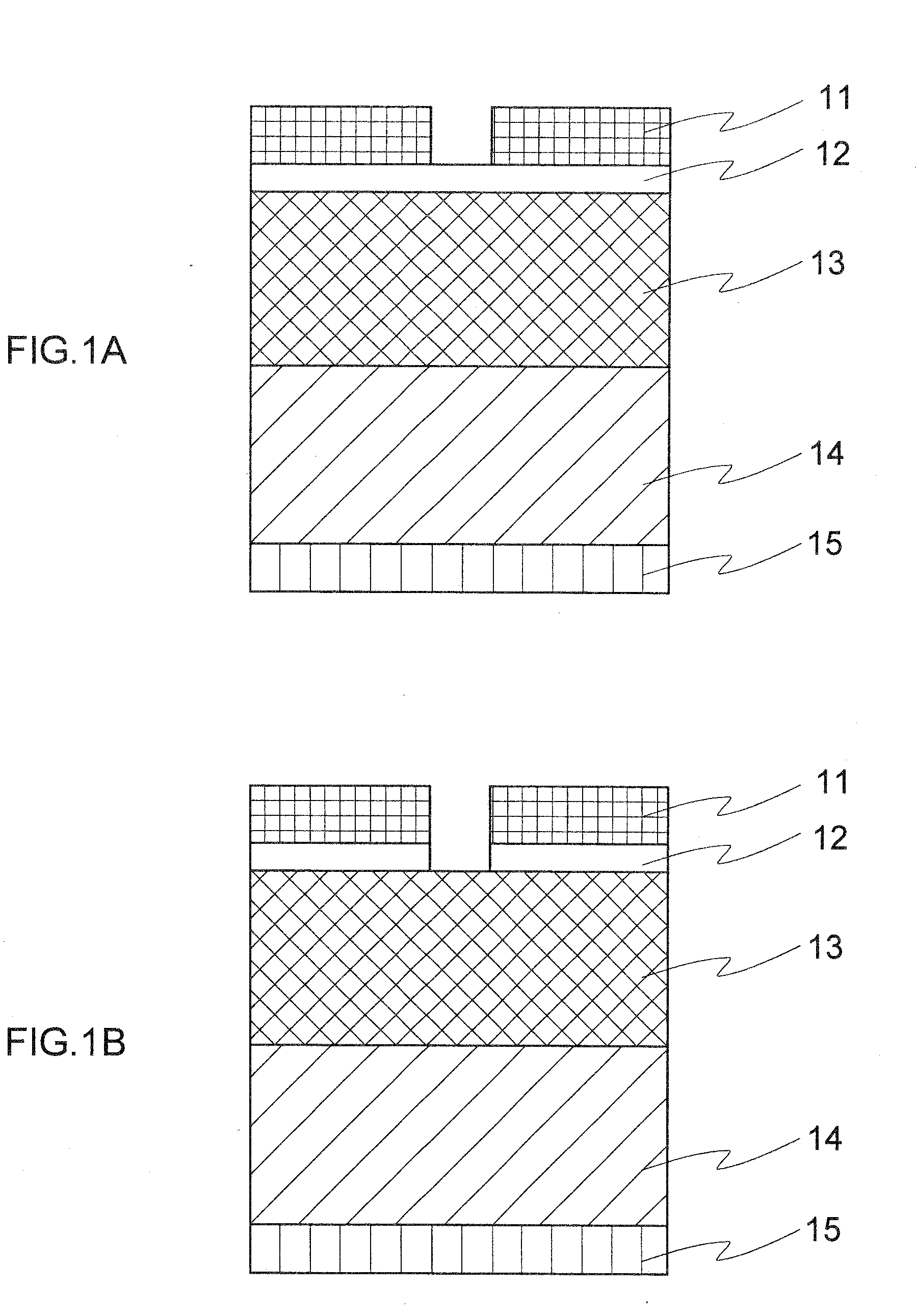

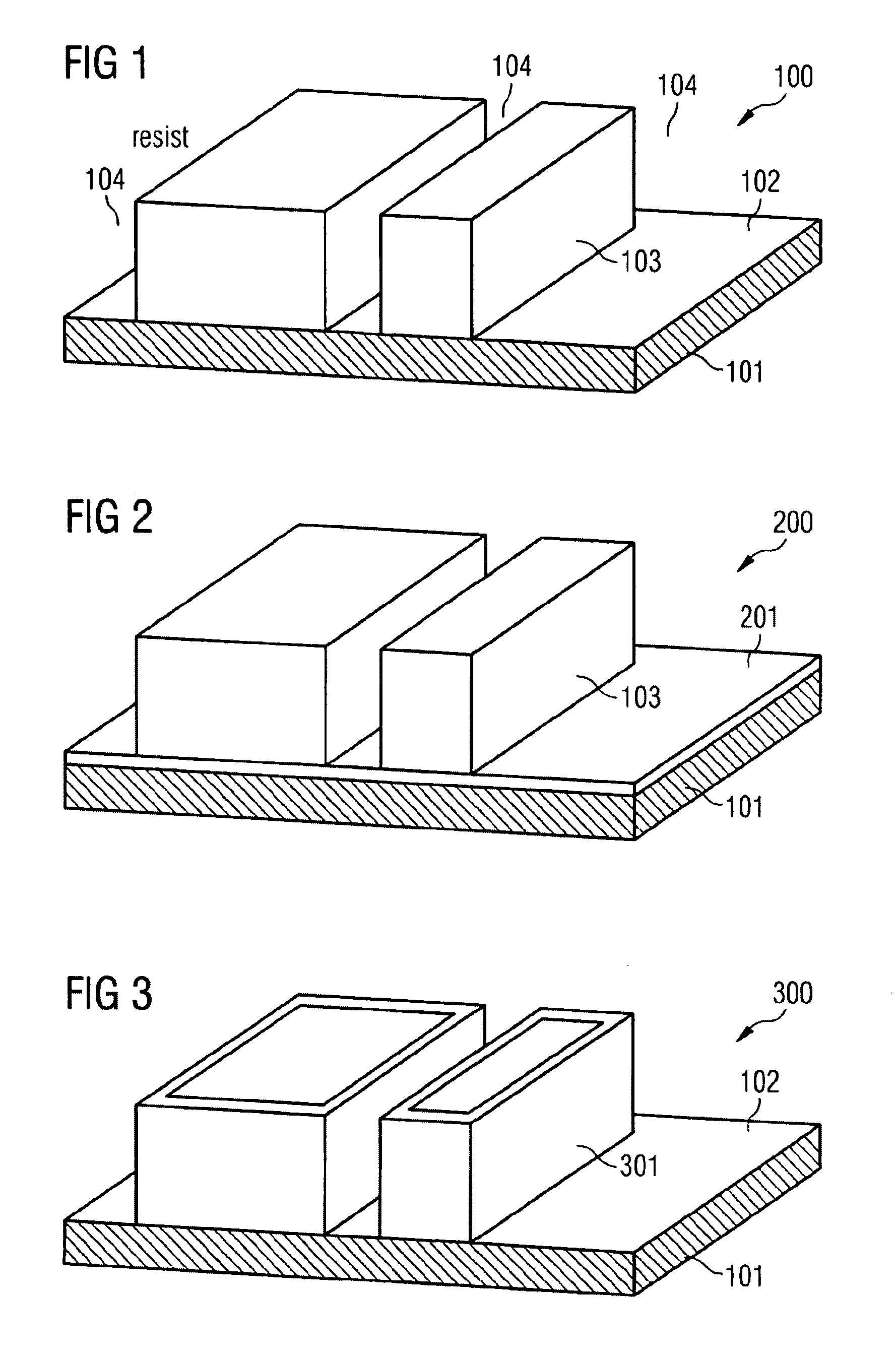

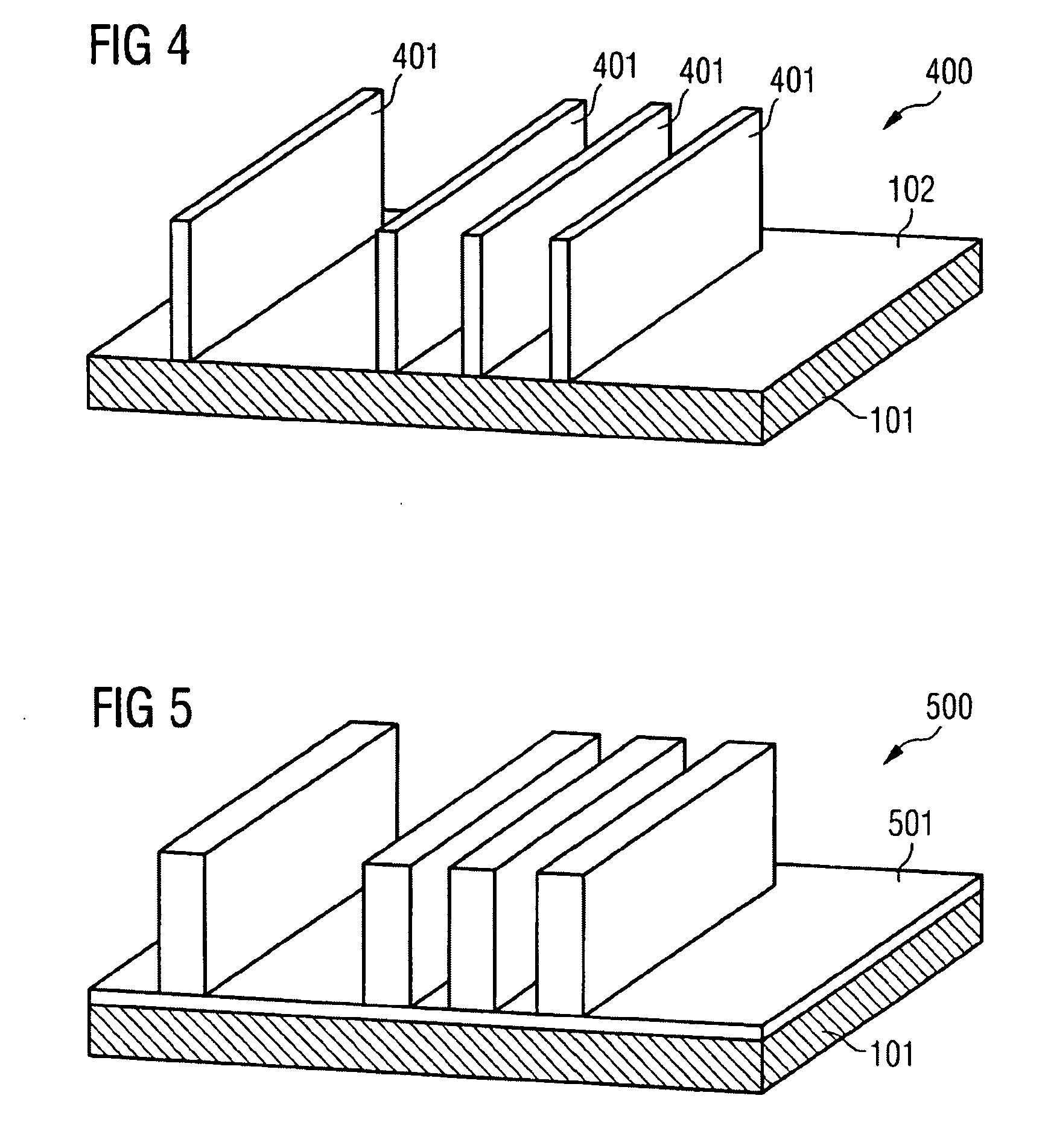

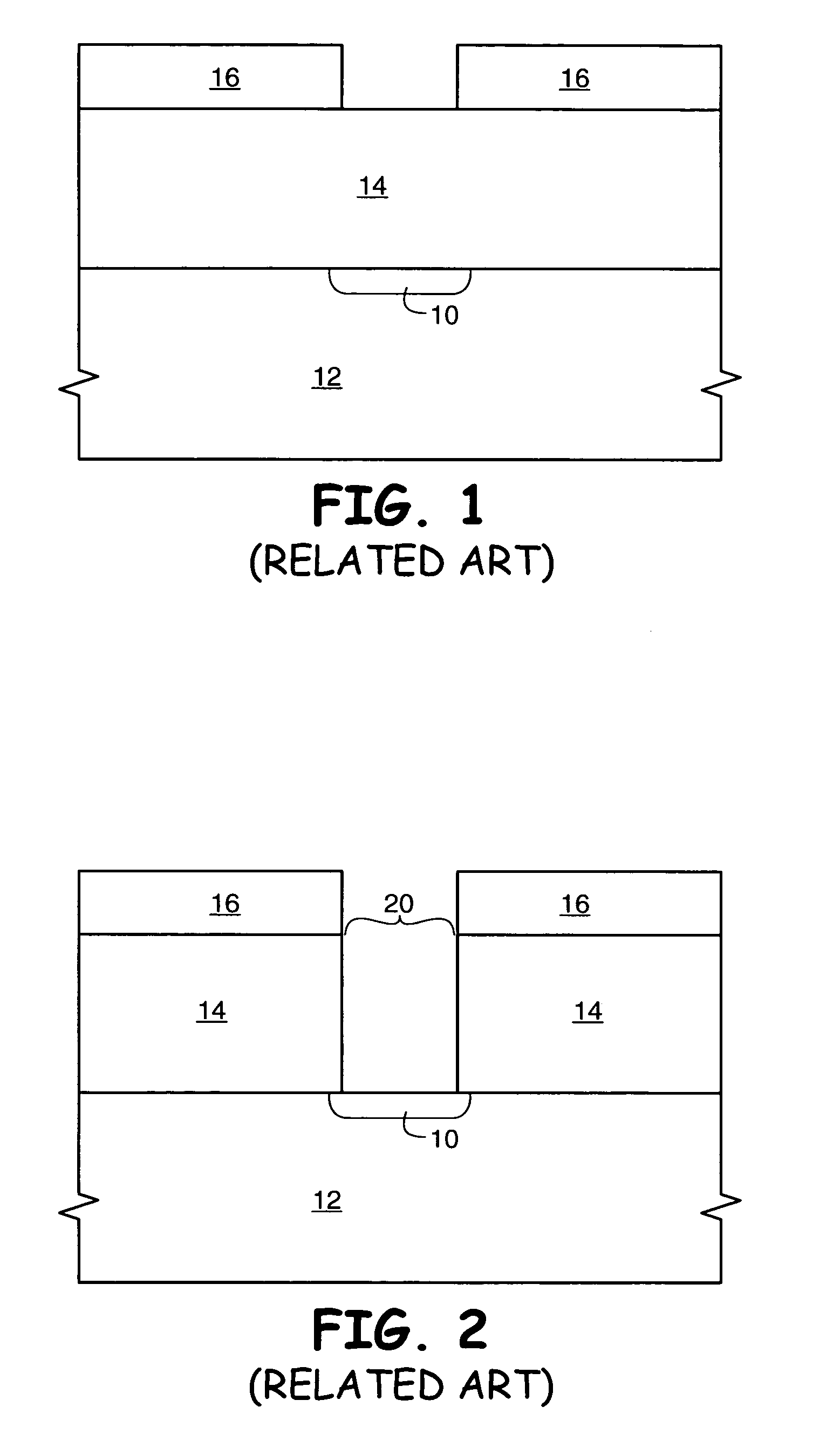

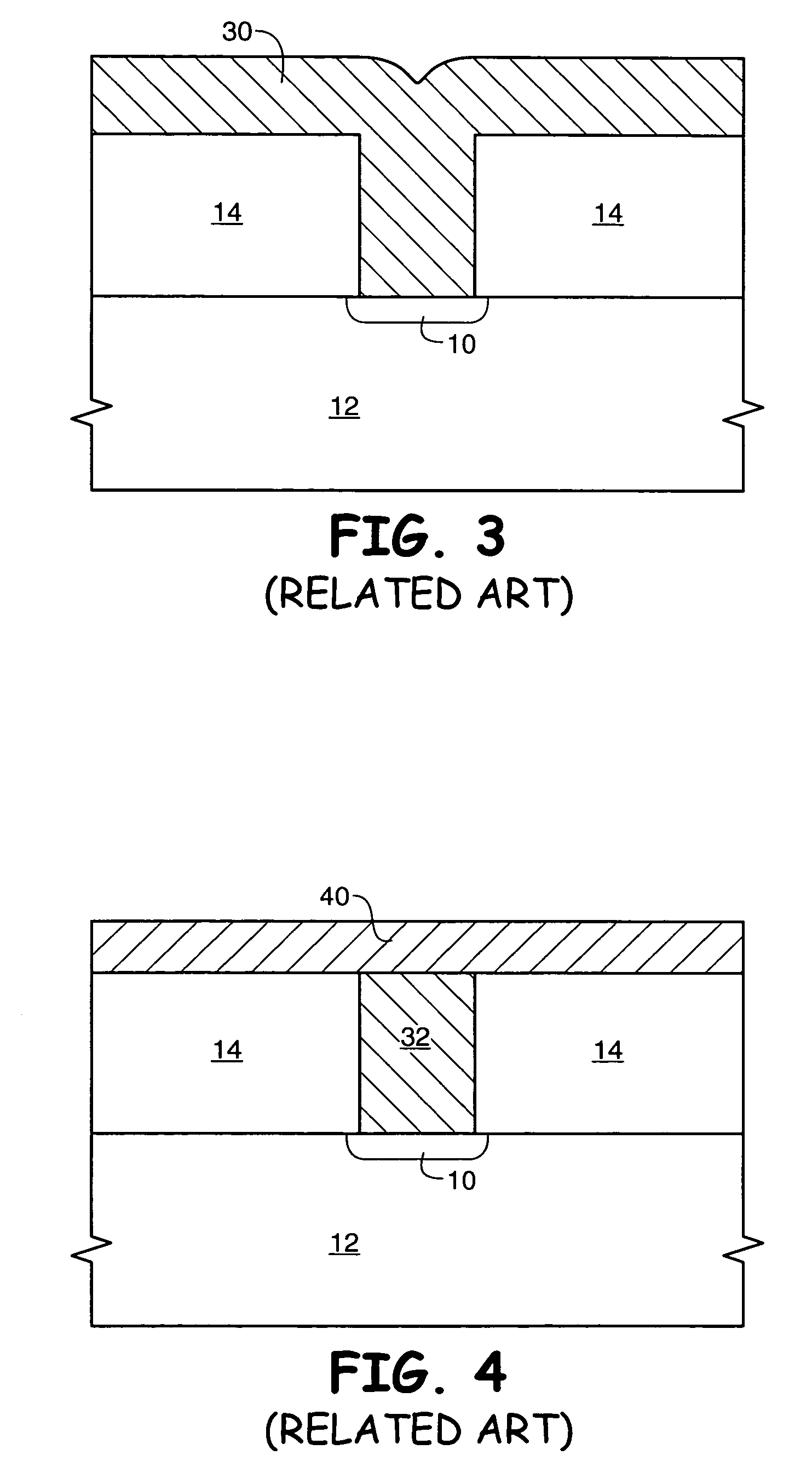

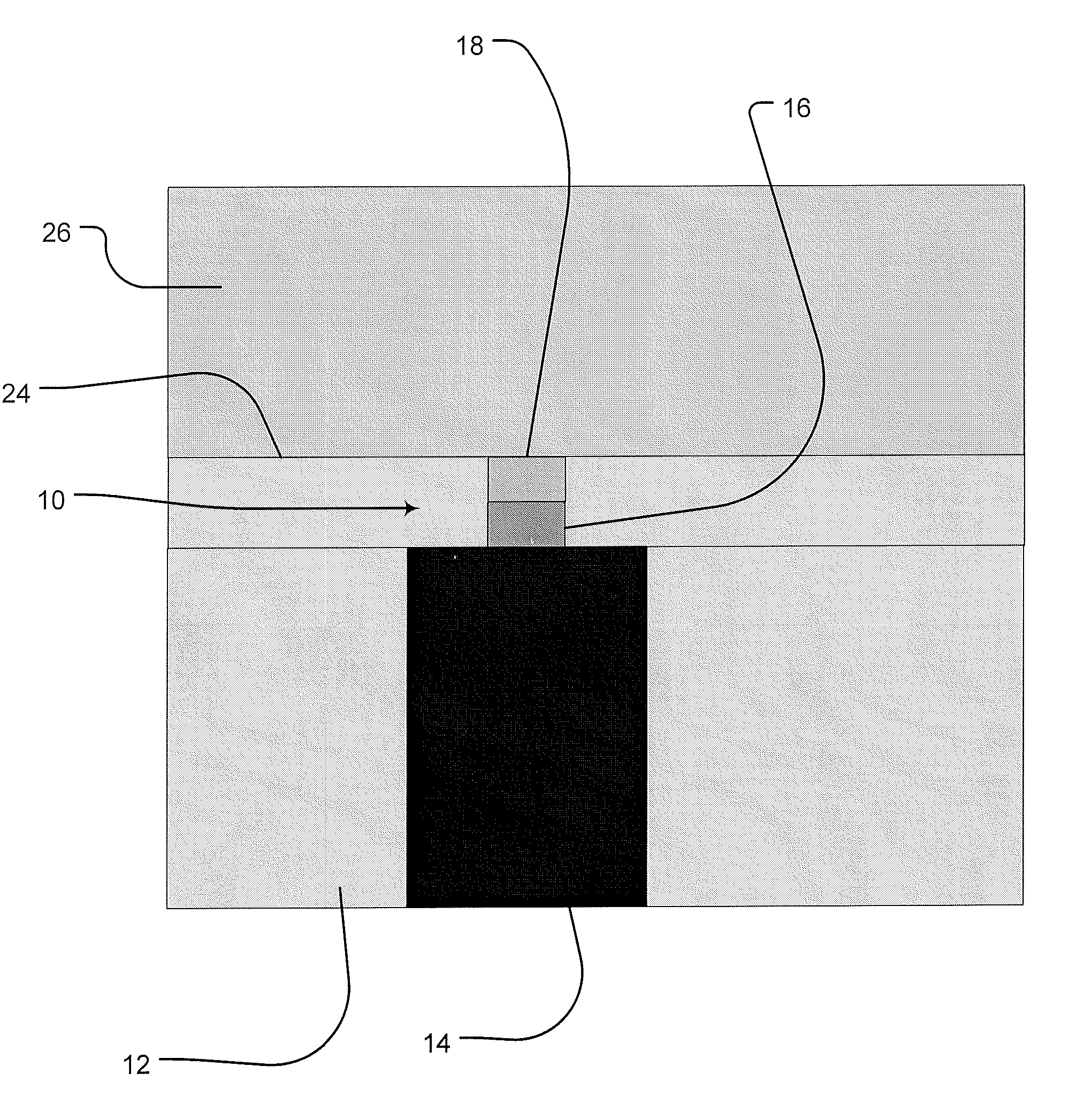

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

Method for integrated circuit fabrication using pitch multiplication

InactiveUS20060046484A1Electric discharge tubesSemiconductor/solid-state device manufacturingImage resolutionDifferences size

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

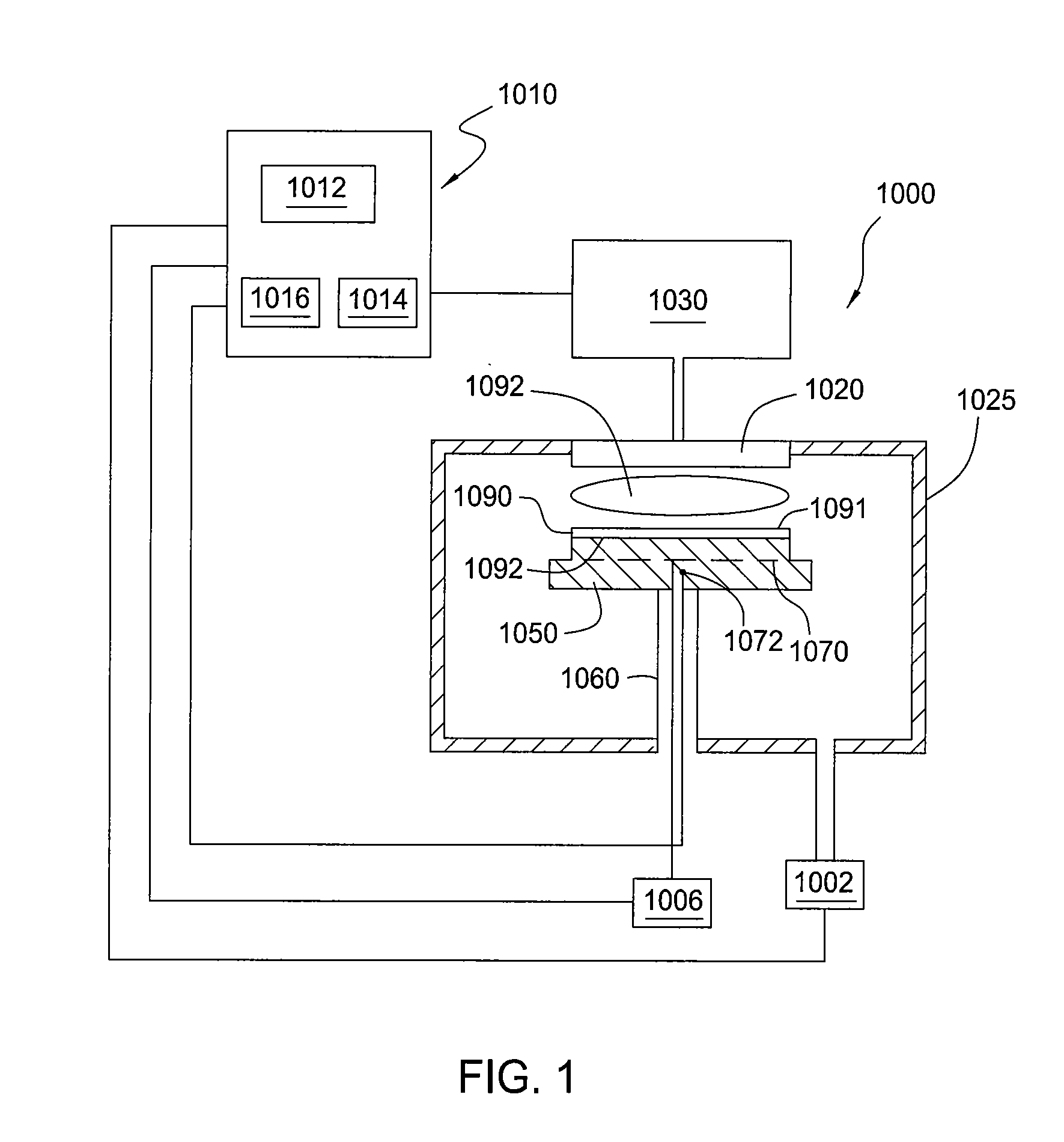

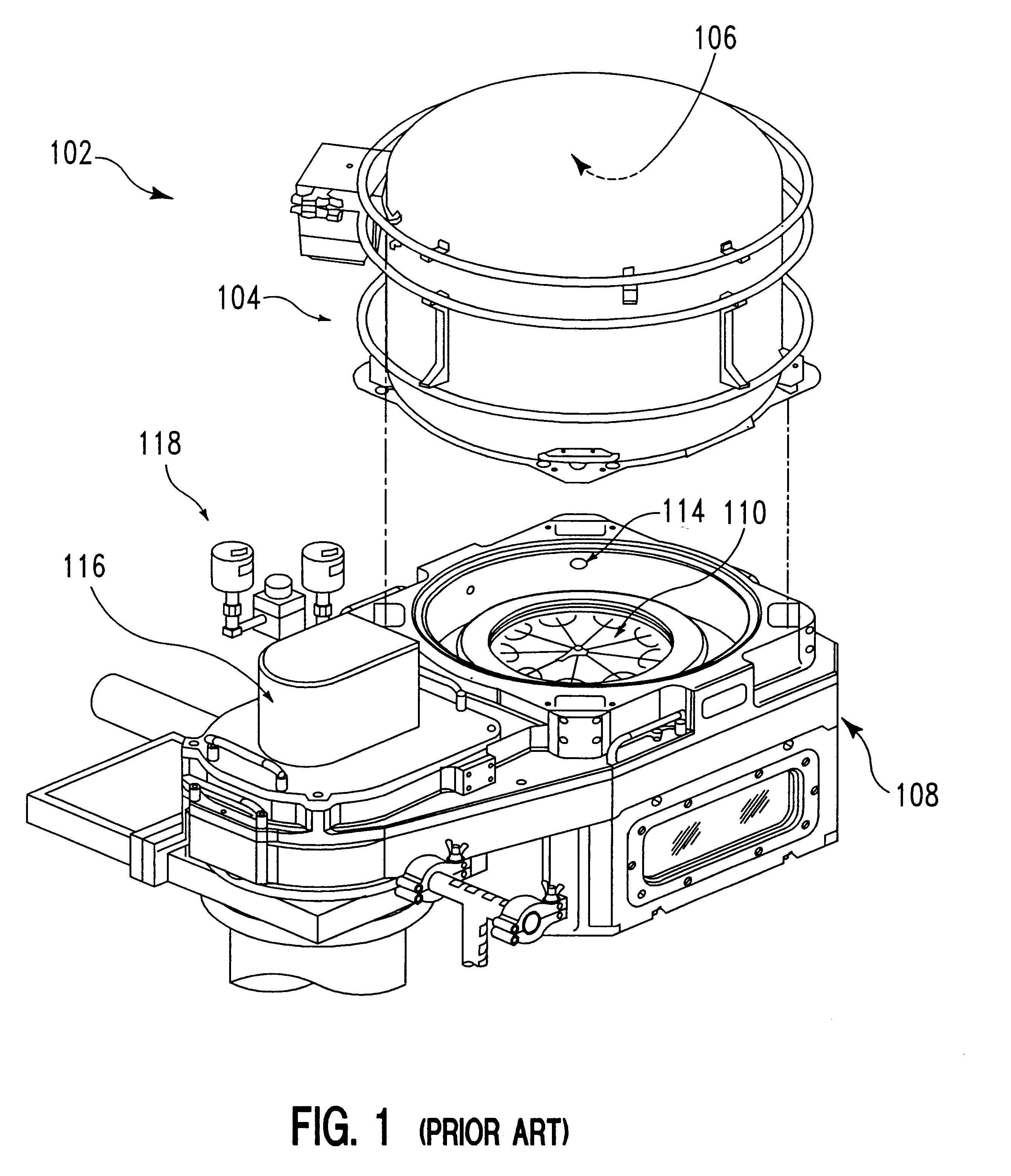

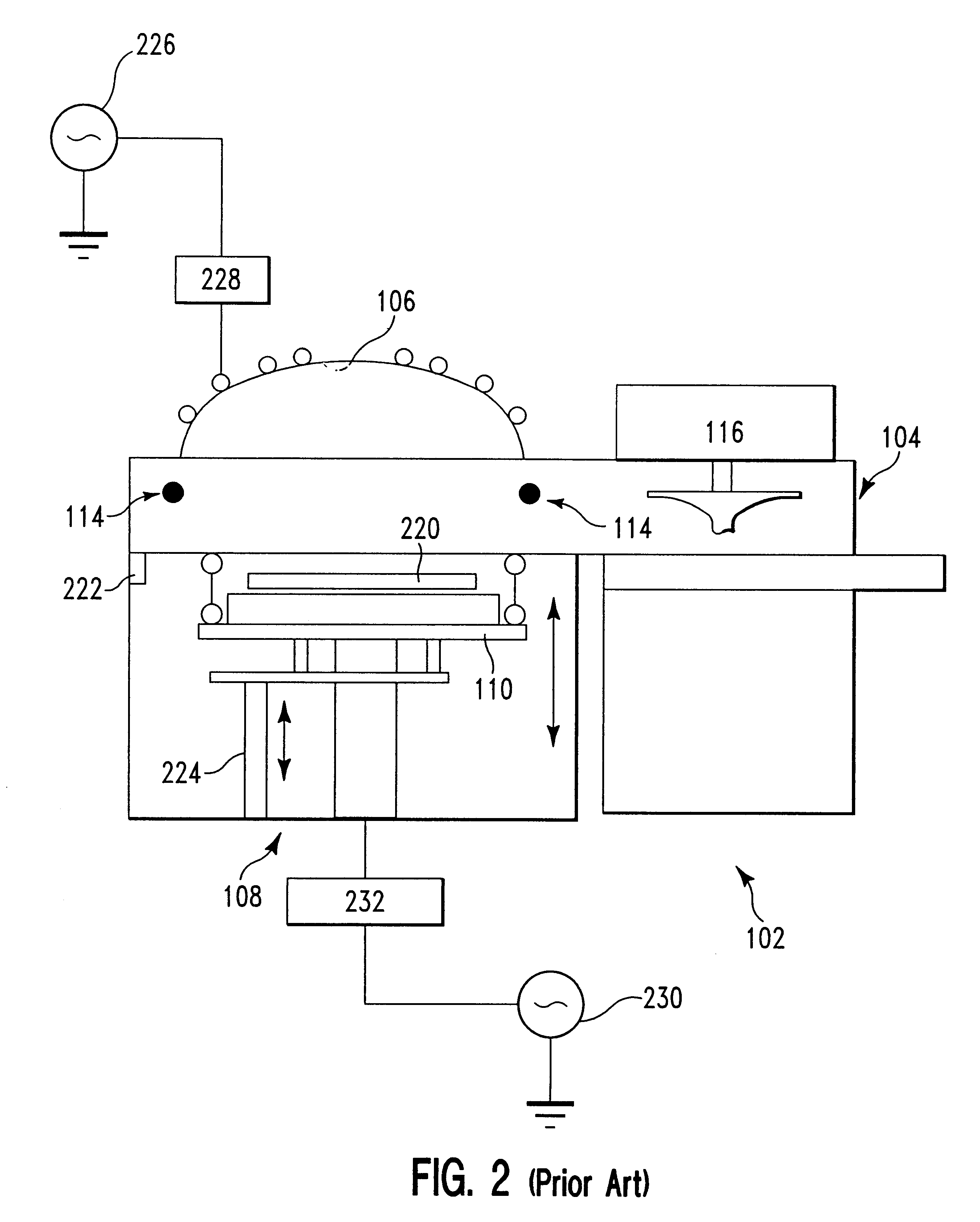

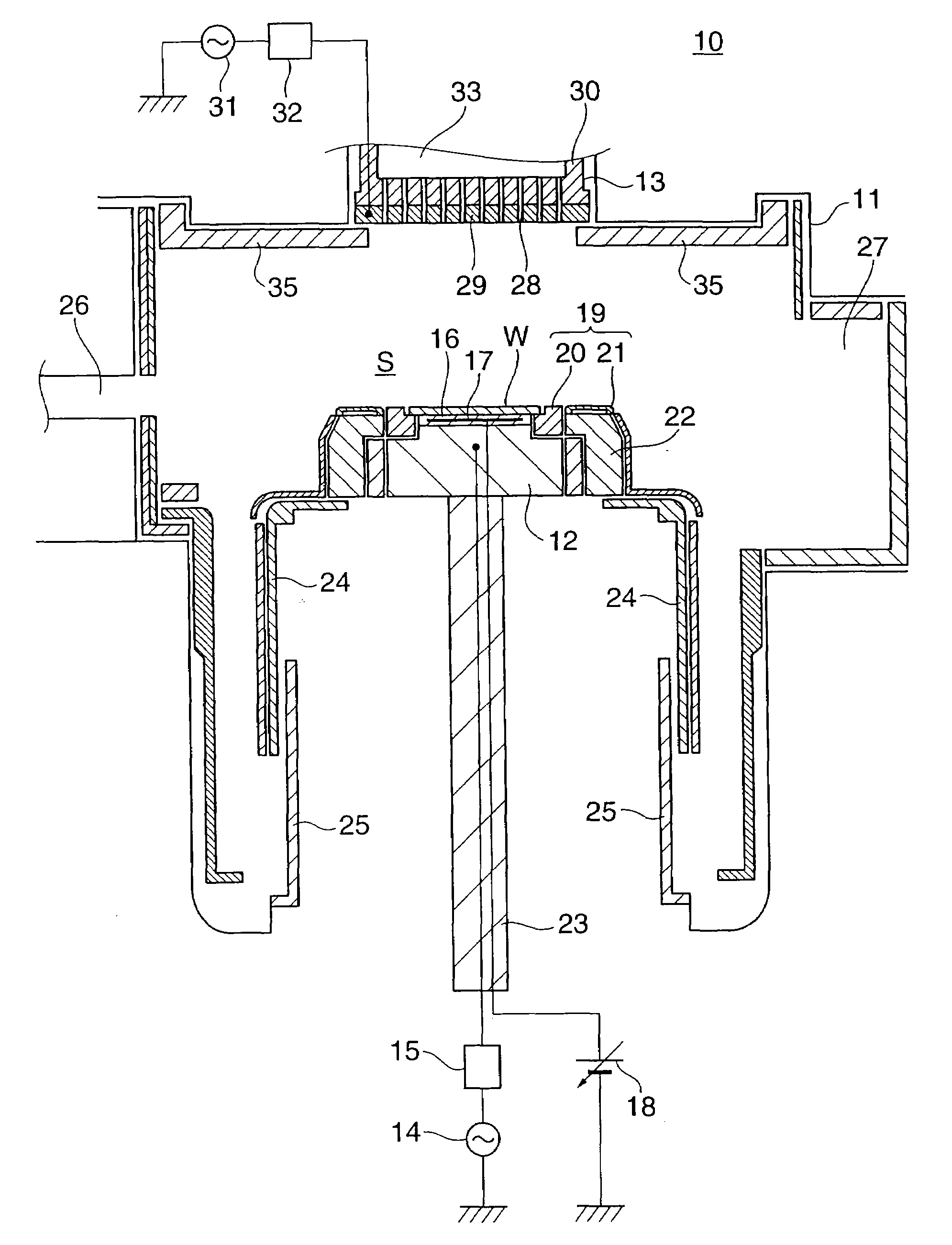

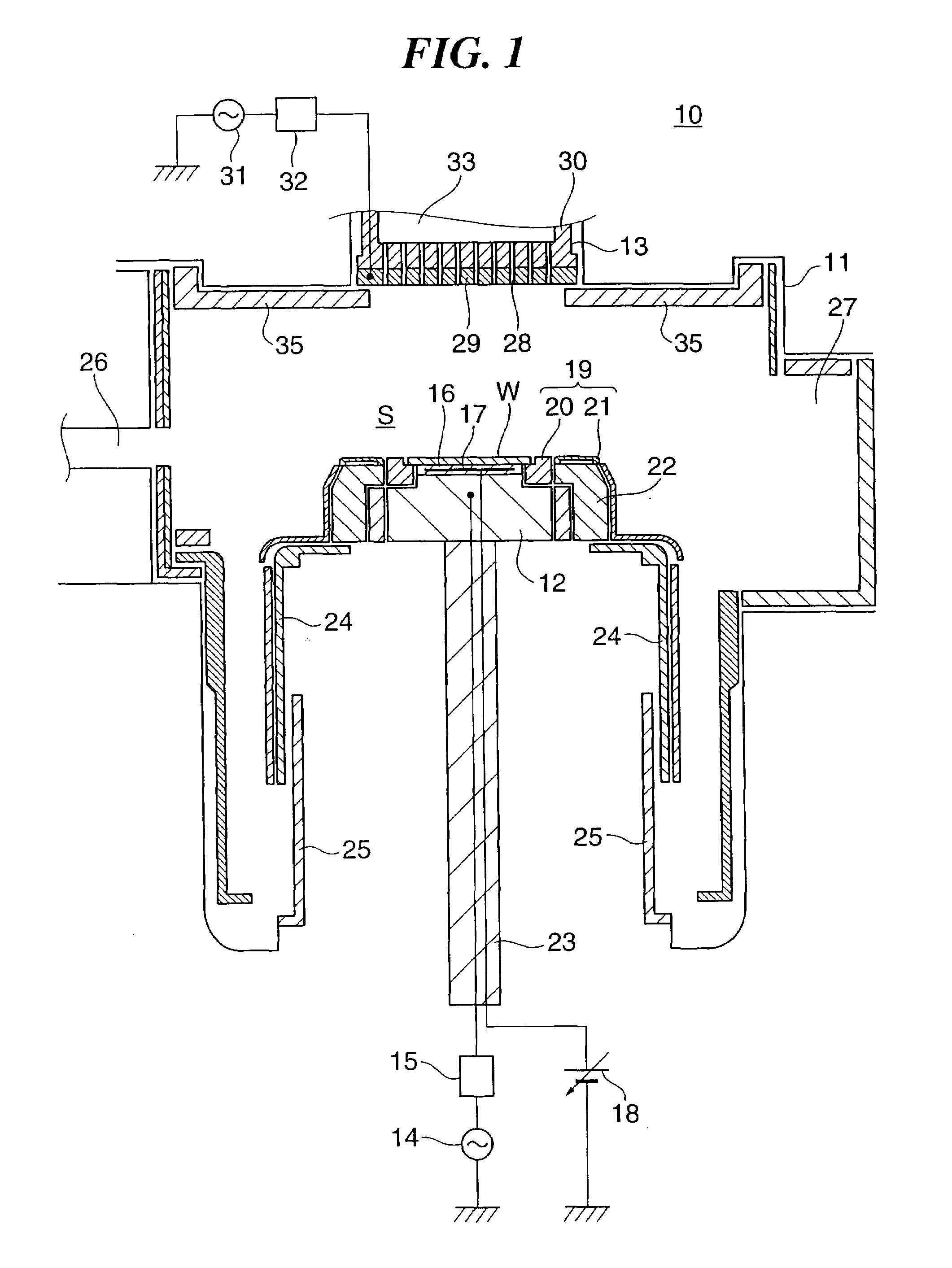

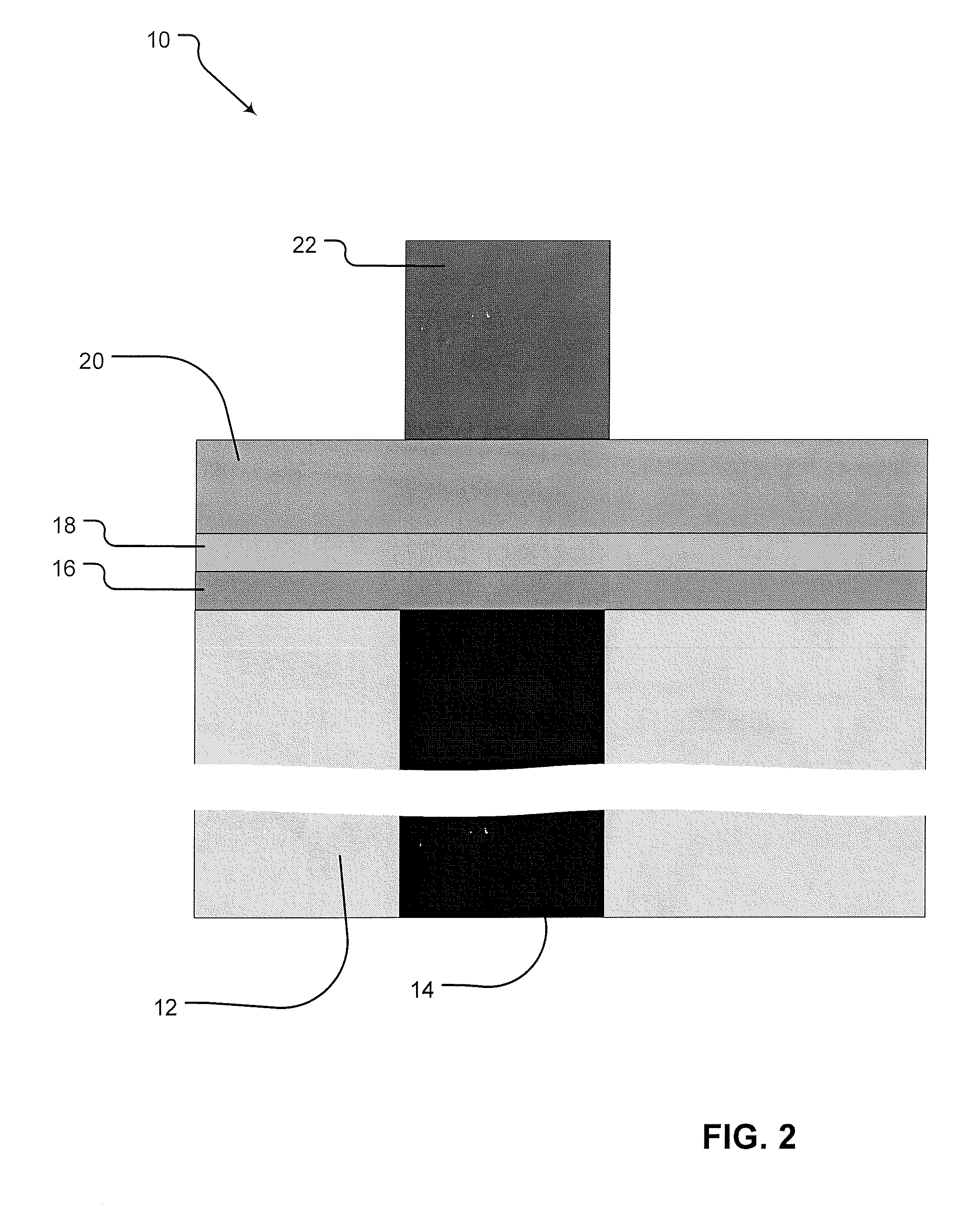

Semiconductor substrate process using a low temperature deposited carbon-containing hard mask

InactiveUS7323401B2Electric discharge tubesRadiation applicationsLow temperature depositionPlasma current

A method of processing a thin film structure on a semiconductor substrate using an optically writable mask includes placing the substrate in a reactor chamber, the substrate having on its surface a target layer to be etched in accordance with a predetermined pattern, and depositing a carbon-containing hard mask layer on the substrate by (a) introducing a carbon-containing process gas into the chamber, (b) generating a reentrant toroidal RF plasma current in a reentrant path that includes a process zone overlying the workpiece by coupling plasma RF source power to an external portion of the reentrant path, and (c) coupling RF plasma bias power or bias voltage to the workpiece. The method further includes photolithographically defining the predetermined pattern in the carbon-containing hard mask layer, and etching the target layer in the presence of the hard mask layer.

Owner:APPLIED MATERIALS INC

Method of forming pattern using fine pitch hard mask

A method of forming a first hard mask pattern including a plurality of first line patterns formed on the etch target layer in a first direction and having a first pitch. A third layer is formed on sidewalls and an upper surface of the first hard mask pattern, such that the third layer includes a top surface having a recess formed between two adjacent first line patterns. A second hard mask pattern including a plurality of second line patterns each extending in the first direction within the recess is formed. Then, the third layer is anisotropically etched to selectively expose an etch target layer between the first line patterns and the second line patterns. Then, the etch target layer is anisotropically etched using the first hard mask pattern and the second hard mask pattern as an etch mask.

Owner:SAMSUNG ELECTRONICS CO LTD

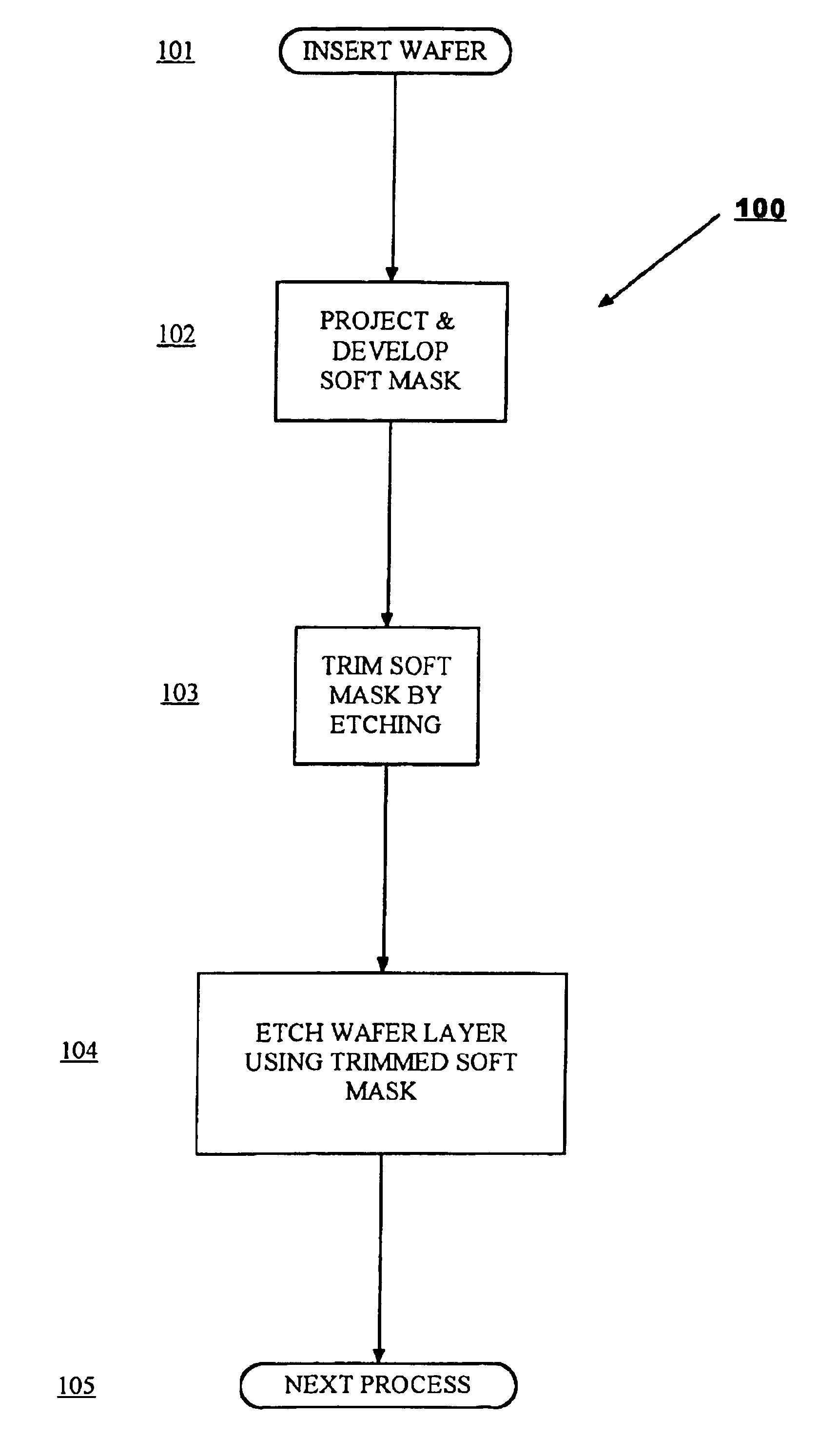

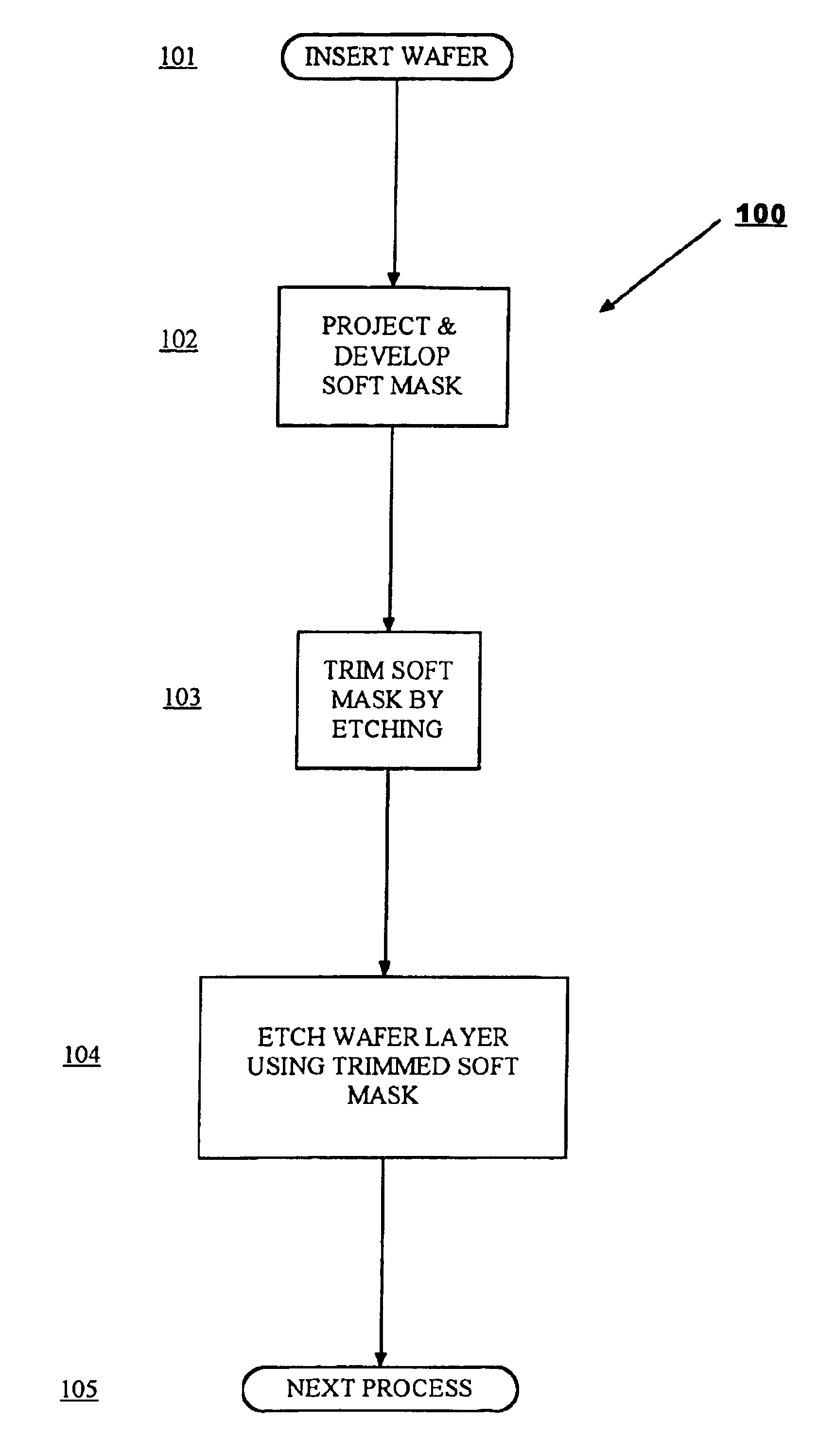

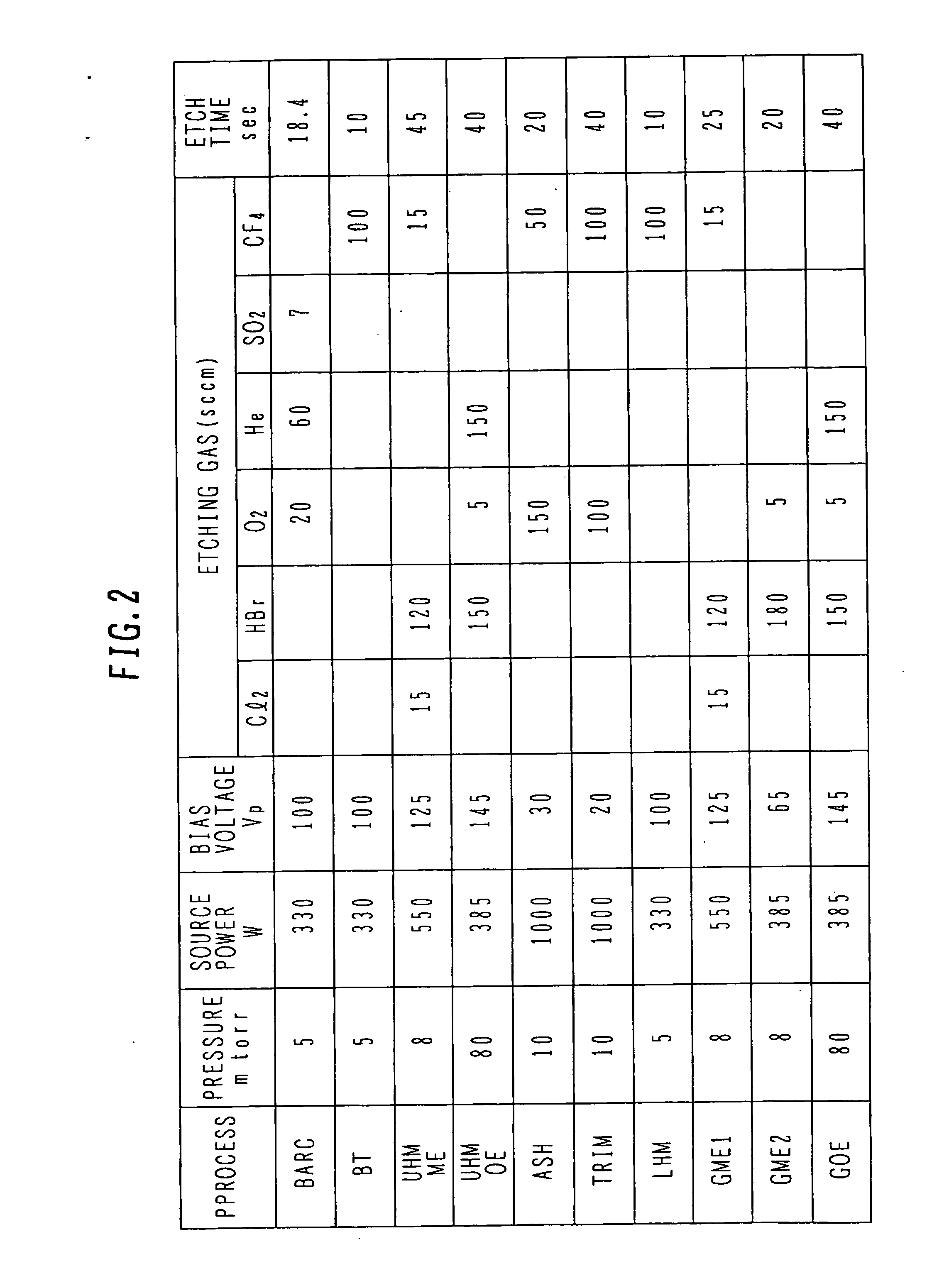

Gate linewidth tailoring and critical dimension control for sub-100 nm devices using plasma etching

InactiveUS6864041B2Tight tolerance variationMinimal variationVacuum gauge using ionisation effectsDecorative surface effectsImage resolutionLine width

A method of fabricating an electronic chip on a wafer in which a first mask at a predetermined lower resolution is developed on the wafer and then etched under a first set of conditions for a predetermined period to achieve a mask that is below the resolution limit of current lithography. The etched mask is then used as a hard mask for etching material on a lower layer.

Owner:INT BUSINESS MASCH CORP

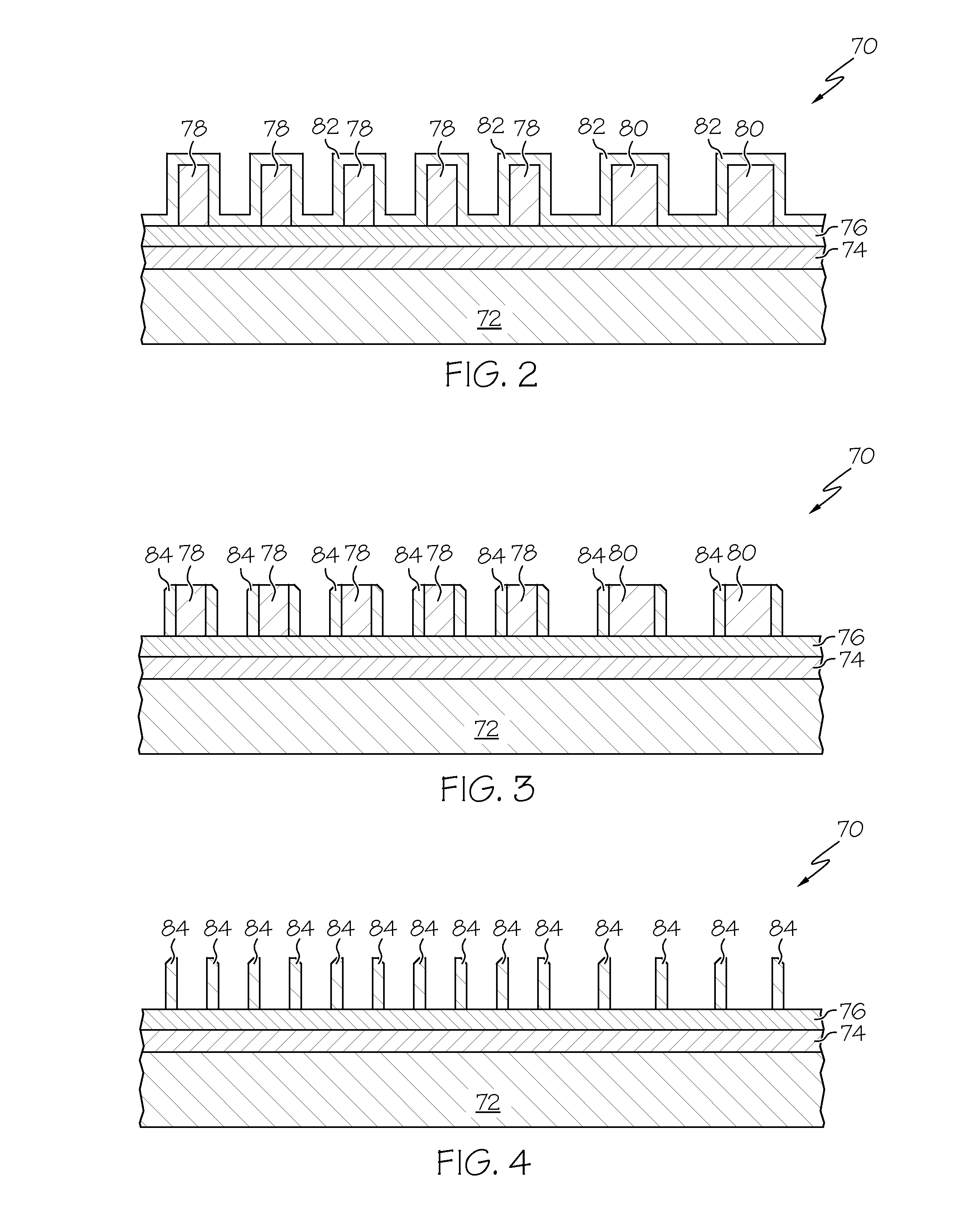

Planarizing etch hardmask to increase pattern density and aspect ratio

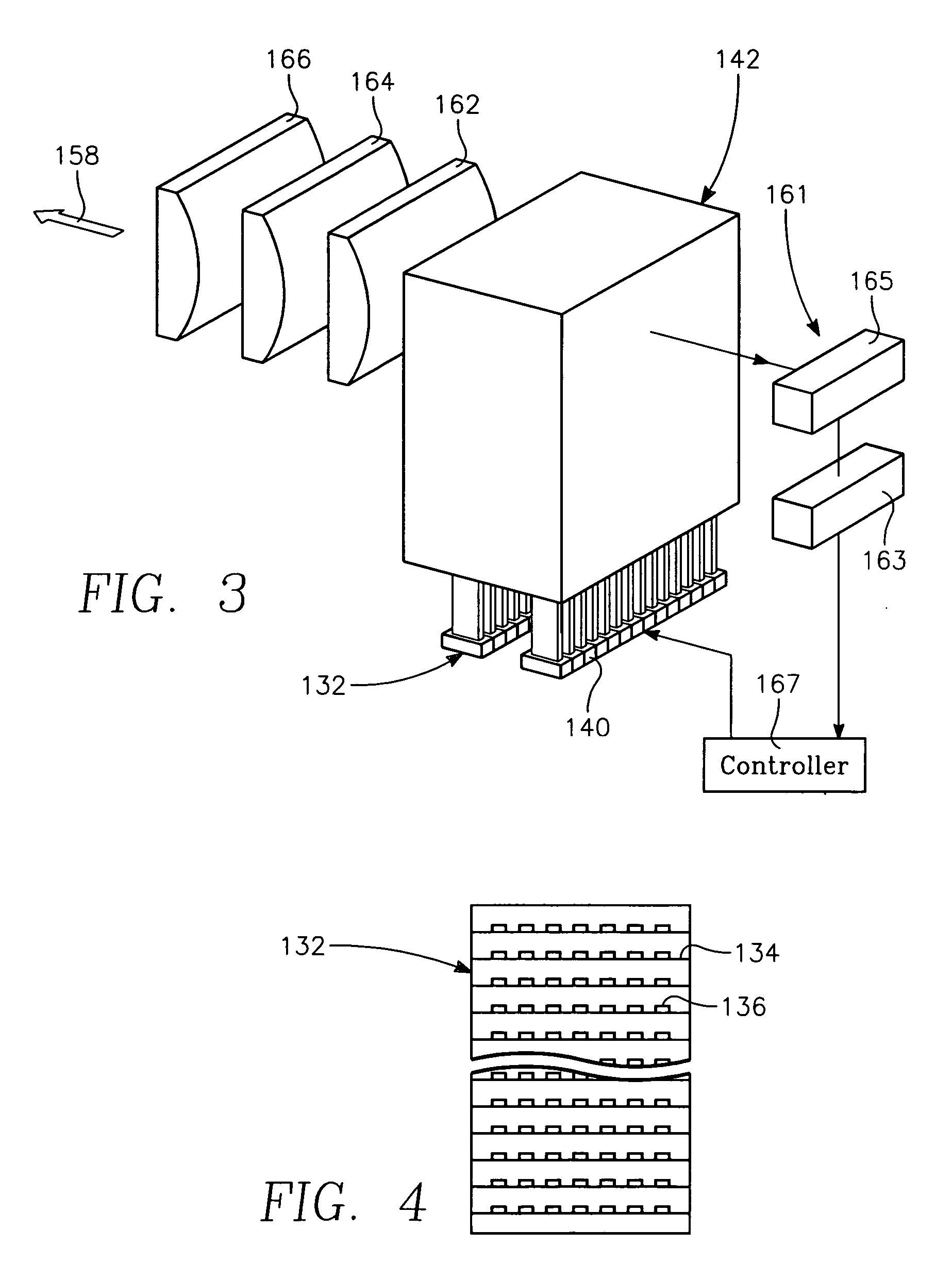

InactiveUS20110291243A1Easy to disassembleAdd depthSemiconductor/solid-state device detailsSolid-state devicesAnti-reflective coatingEngineering

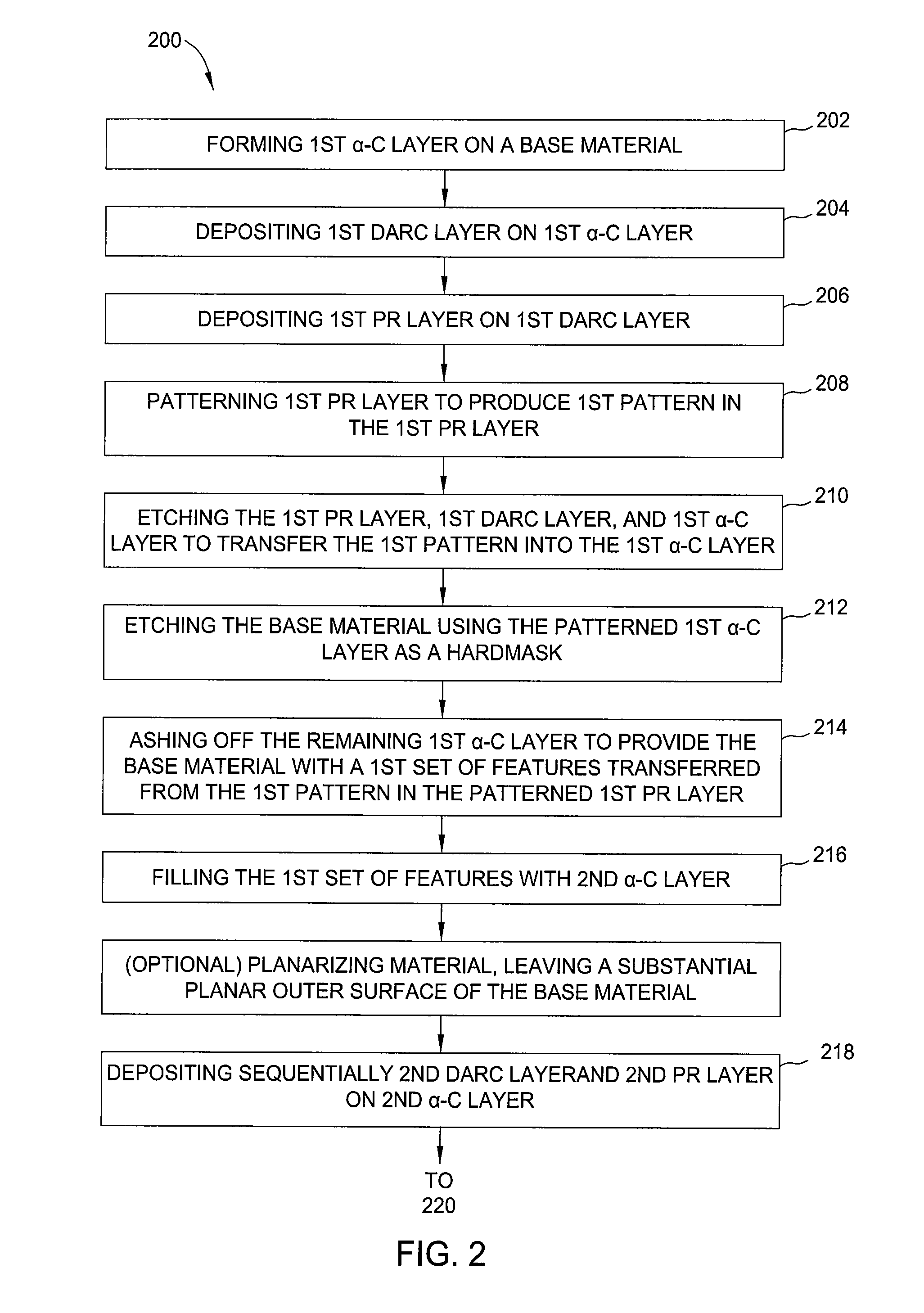

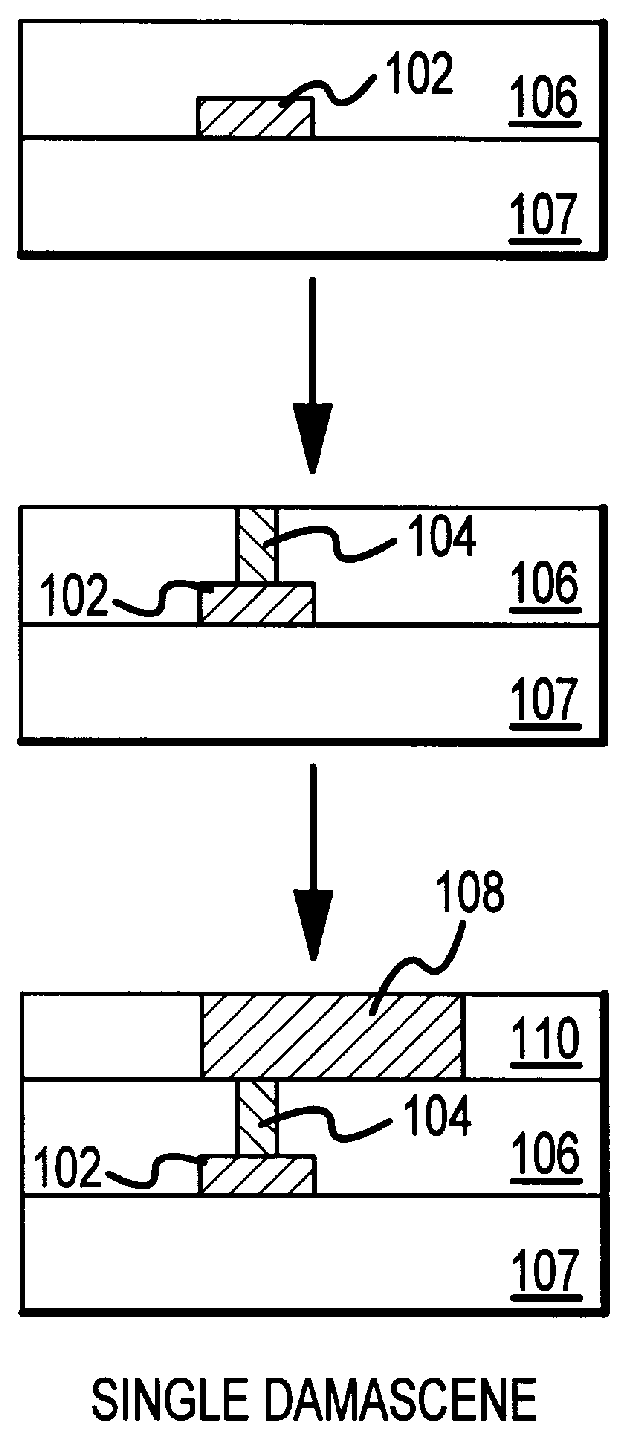

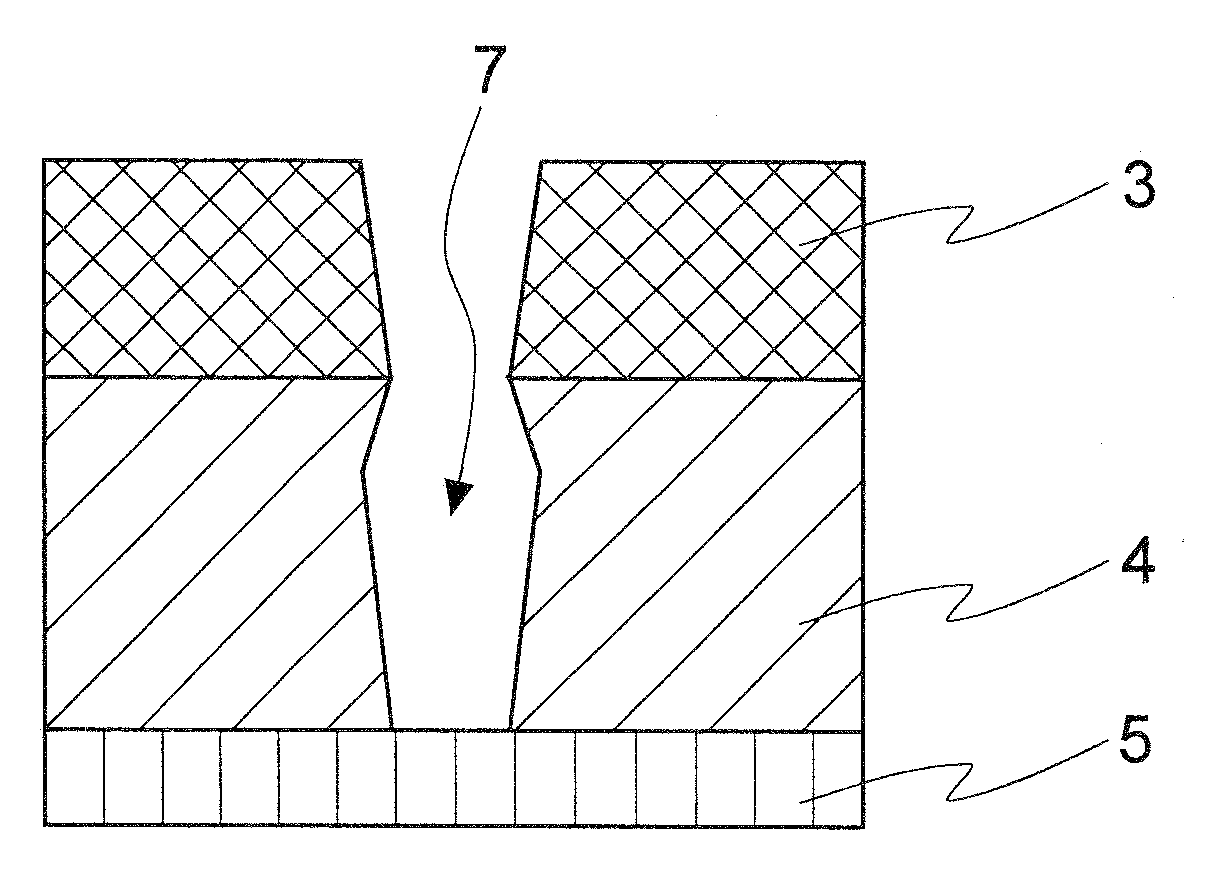

Methods for manufacturing a semiconductor device in a processing chamber are provided. In one embodiment, a method includes depositing over a substrate a first base material having a first set of interconnect features, filling an upper portion of the first set of interconnect features with an ashable material to an extent capable of protecting the first set of interconnect features from subsequent processes while being easily removable when desired, planarizing an upper surface of the first base material such that an upper surface of the ashable material filled in the first set of interconnect features is at the same level with the upper surface of the first base material, providing a substantial planar outer surface of the first base material, depositing a first film stack comprising a second base material on the substantial planar outer surface of the first base material, forming a second set of interconnect features in the second base material, wherein the second set of interconnect features are aligned with the first set of interconnect features, and removing the ashable material from the first base material, thereby extending a feature depth of the semiconductor device by connecting the second set of interconnect features to the first set of interconnect features. In another embodiment, a method includes providing a base material having a first film stack deposited thereon, wherein the base material is formed over the substrate and having a first set of interconnect features filled with an amorphous carbon material, the first film stack comprising a first amorphous carbon layer deposited on a surface of the base material, a first anti-reflective coating layer deposited on the first amorphous carbon layer, and a first photoresist layer deposited on the first anti-reflective coating layer, and patterning a portion of the first photoresist layer by shifting laterally a projection of a mask on the first photoresist layer relative to the substrate a desired distance, thereby introducing into the first photoresist layer a first feature pattern to be transferred to the underlying base material, wherein the first feature pattern is not aligned with the first set of interconnect features.

Owner:APPLIED MATERIALS INC

UV treatment of etch stop and hard mask films for selectivity and hermeticity enhancement

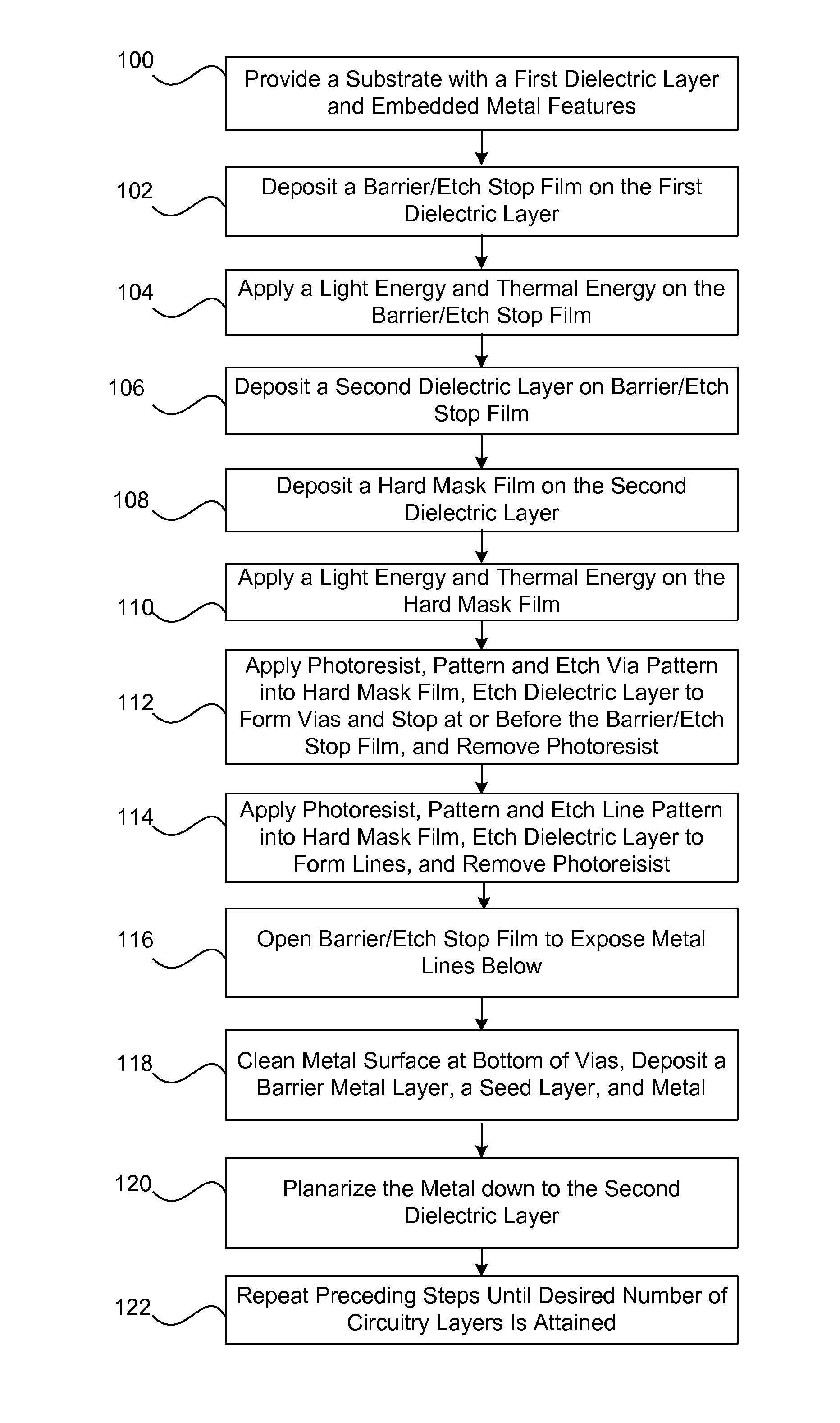

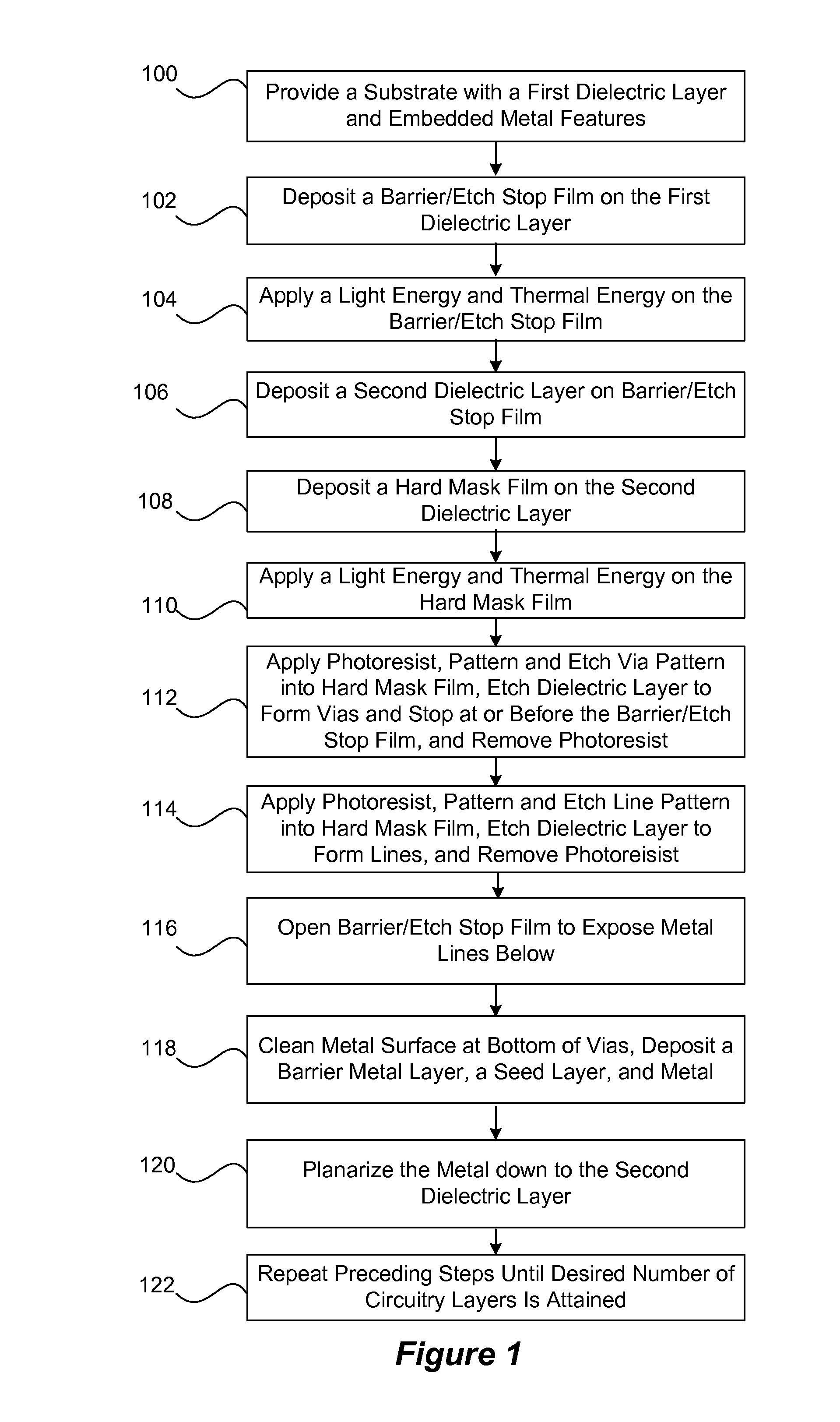

ActiveUS8242028B1Increase hermeticityHigh selectivitySemiconductor/solid-state device manufacturingThermal energyHydrogen

A method for the ultraviolet (UV) treatment of etch stop and hard mask film increases etch selectivity and hermeticity by removing hydrogen, cross-linking, and increasing density. The method is particularly applicable in the context of damascene processing. A method provides for forming a semiconductor device by depositing an etch stop film or a hard mask film on a substrate and exposing the film to UV radiation and optionally thermal energy. The UV exposure may be direct or through another dielectric layer.

Owner:NOVELLUS SYSTEMS

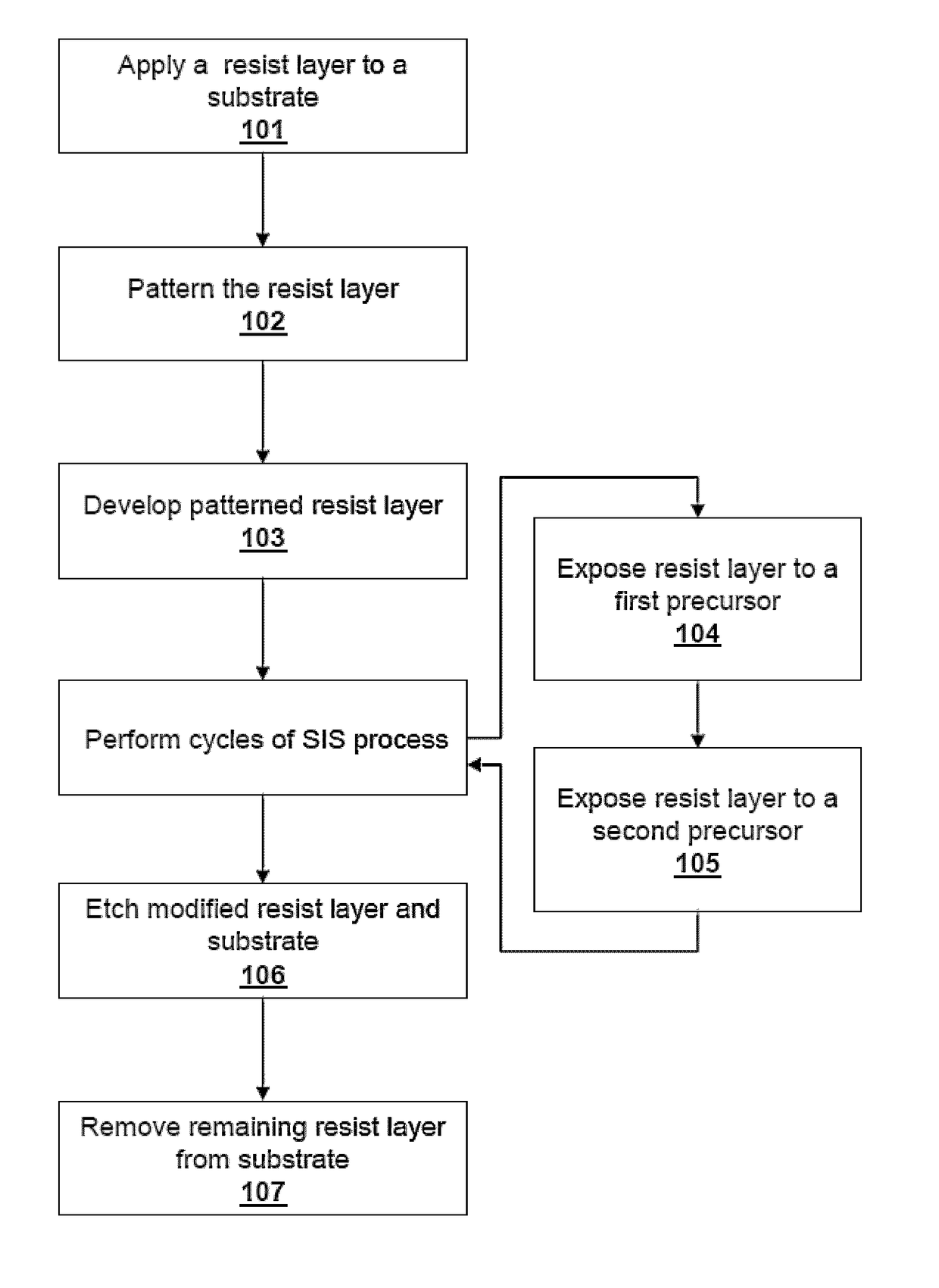

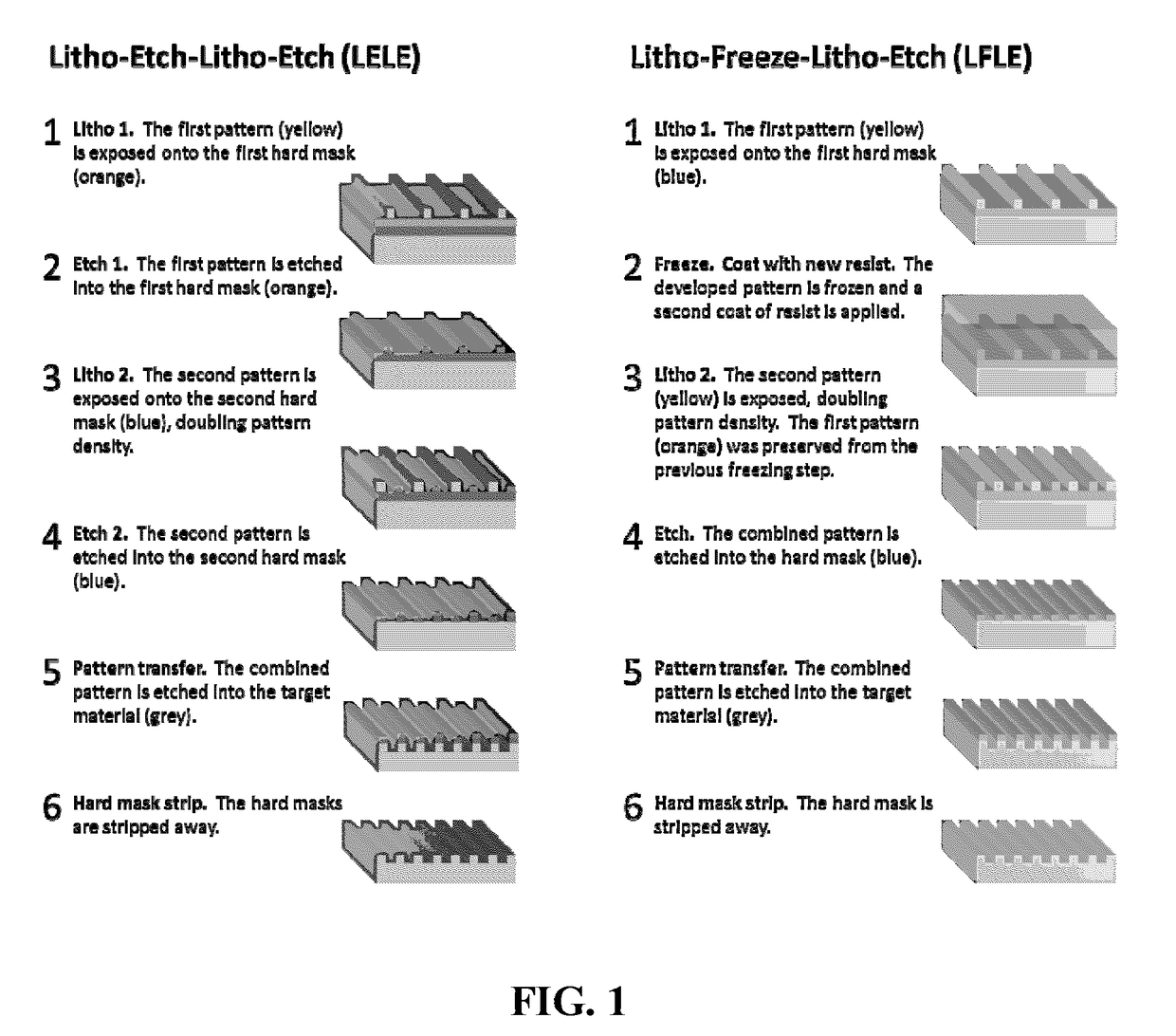

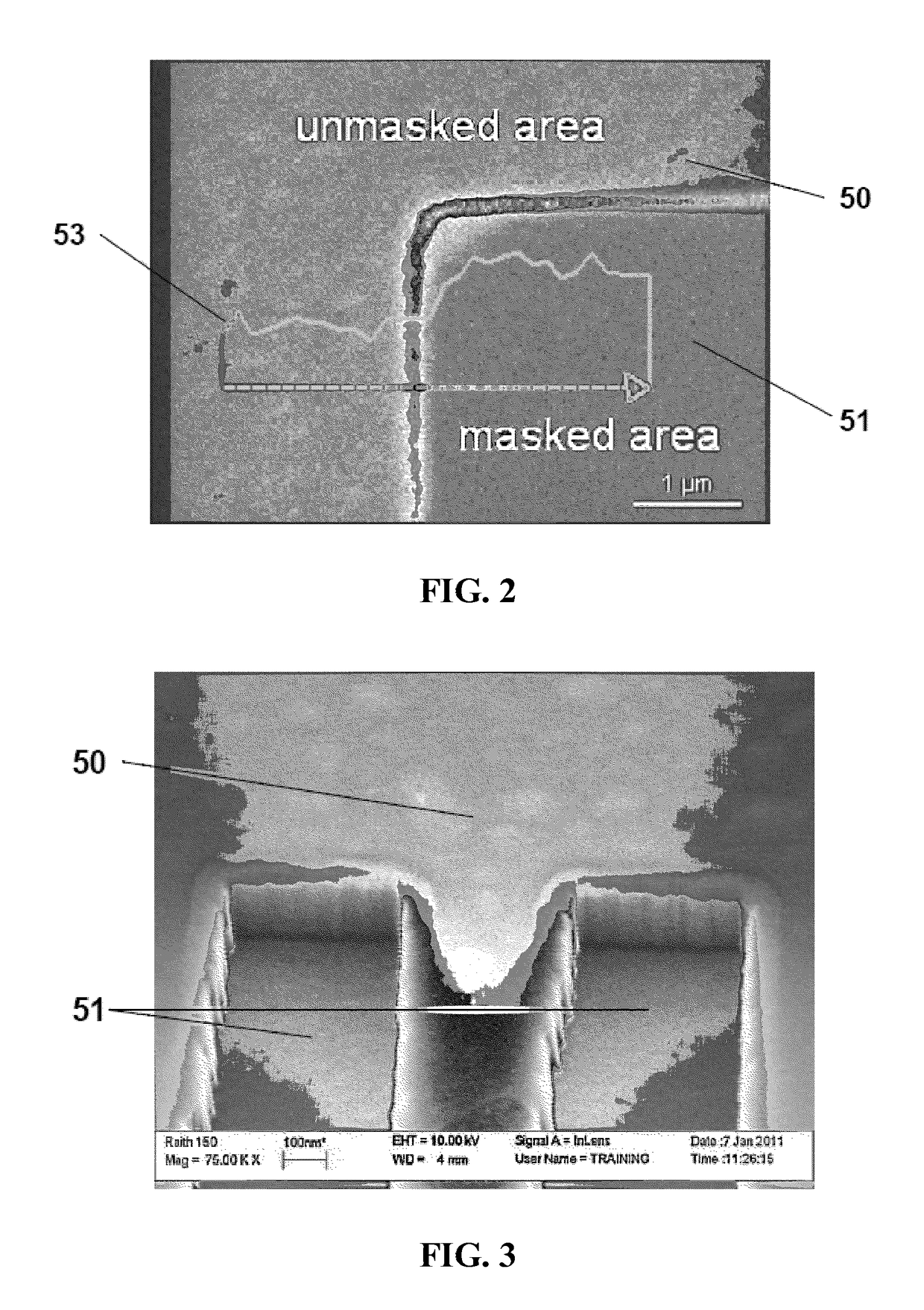

Sequential Infiltration Synthesis for Enhancing Multiple-Patterning Lithography

ActiveUS20130256265A1Reduce in quantityImprove throughputDecorative surface effectsPhotomechanical apparatusPhotoresistMultiple patterning lithography

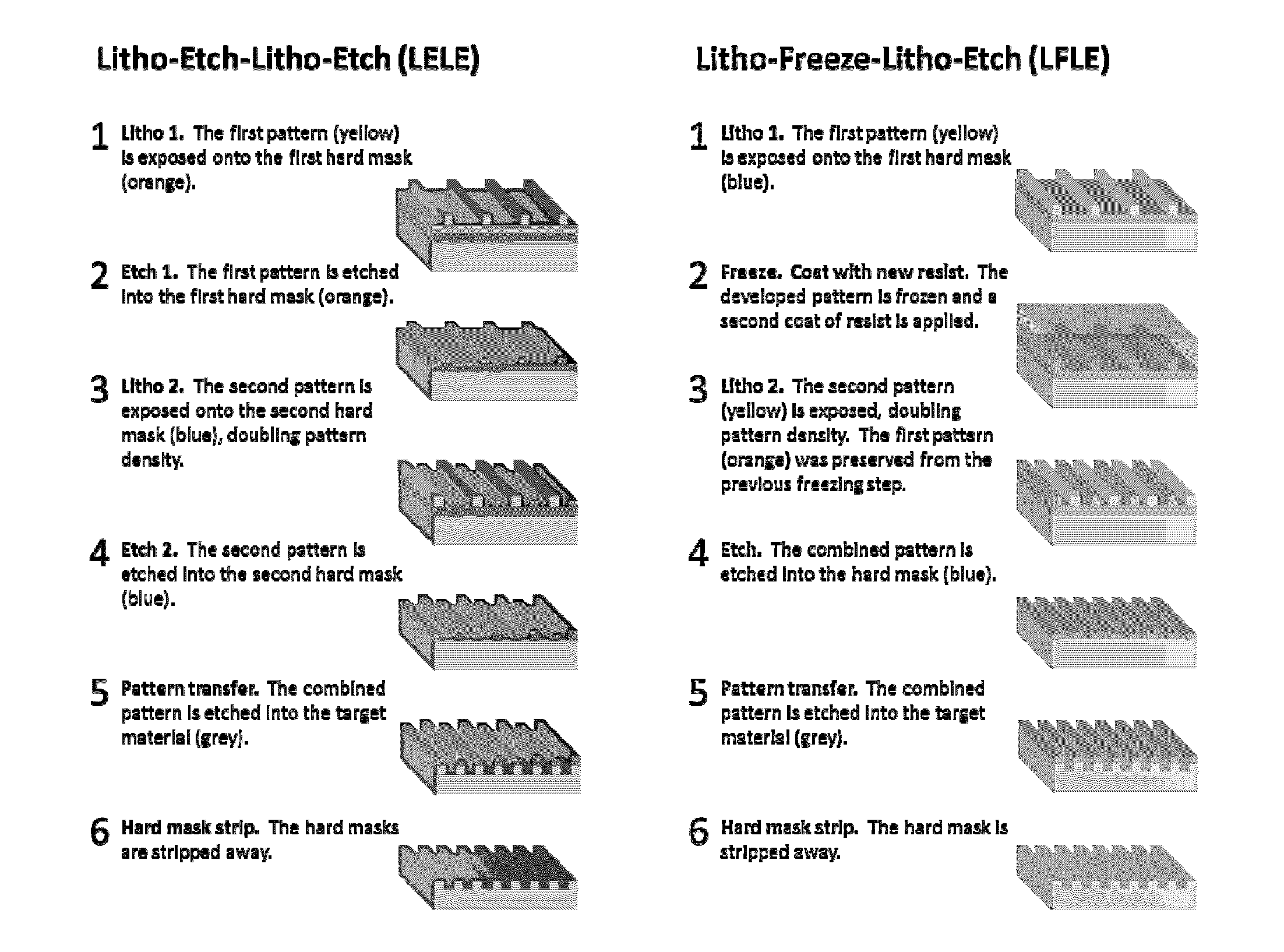

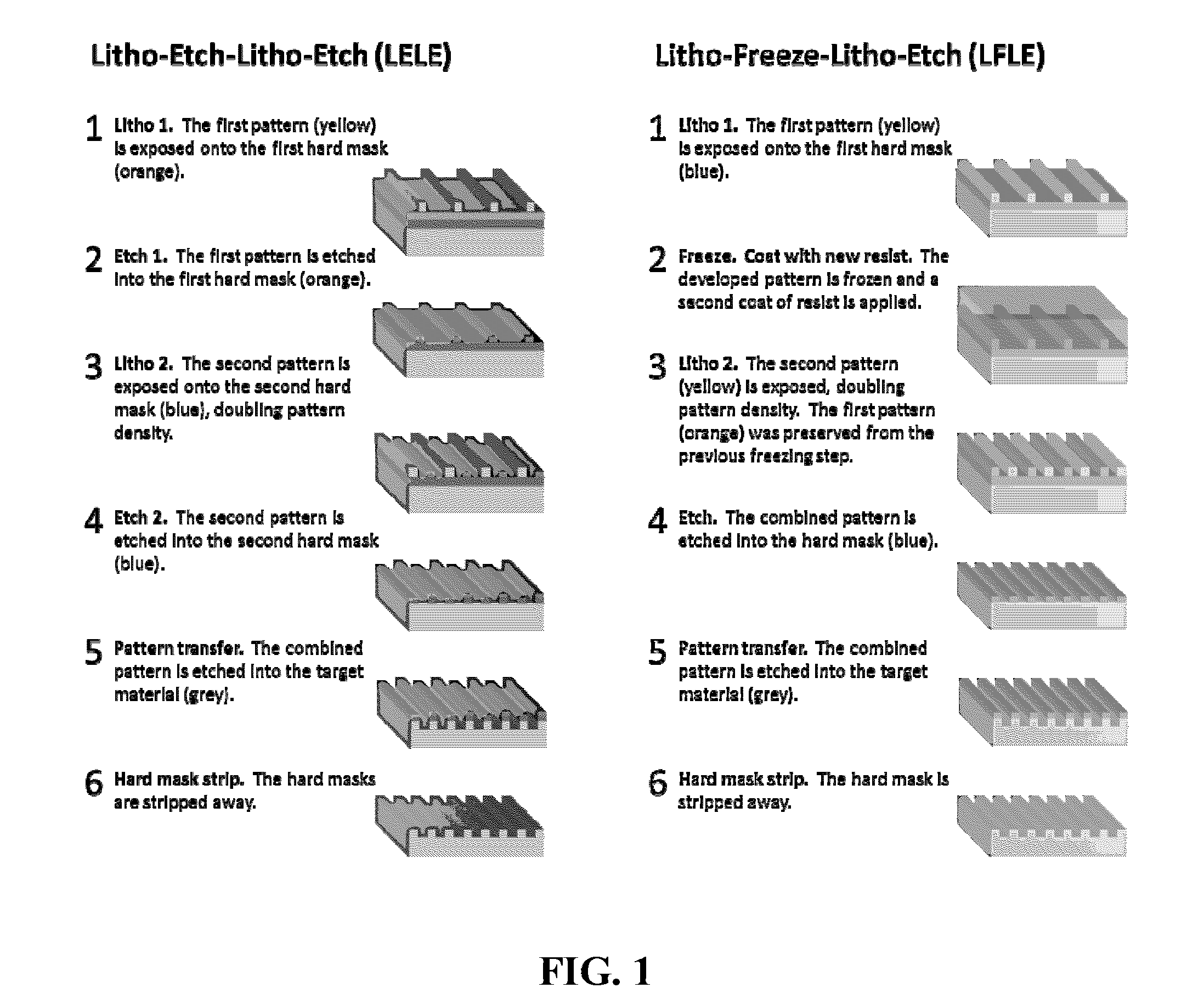

Simplified methods of multiple-patterning photolithography using sequential infiltration synthesis to modify the photoresist such that it withstands plasma etching better than unmodified resist and replaces one or more hard masks and / or a freezing step in MPL processes including litho-etch-litho-etch photolithography or litho-freeze-litho-etch photolithography.

Owner:UCHICAGO ARGONNE LLC

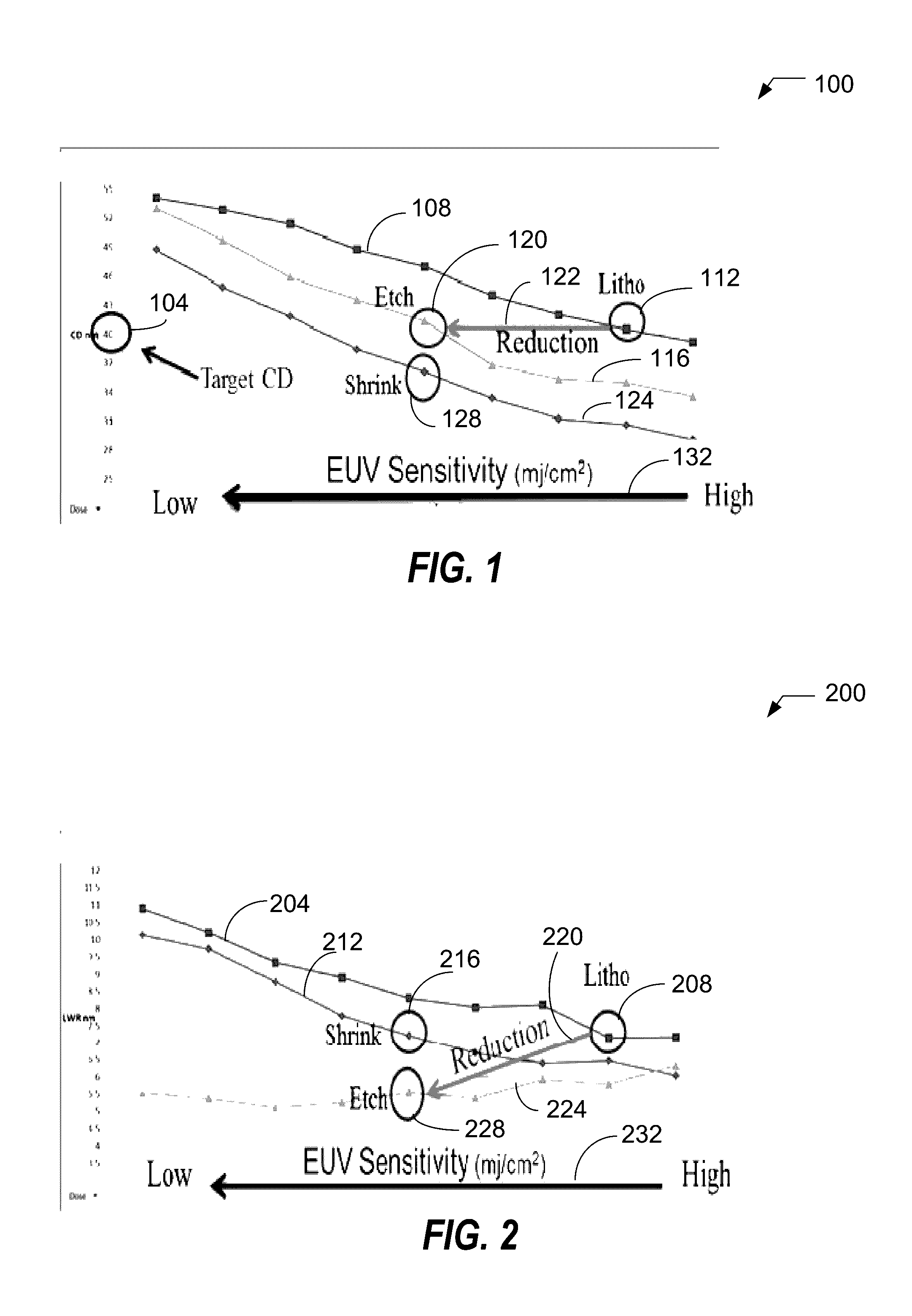

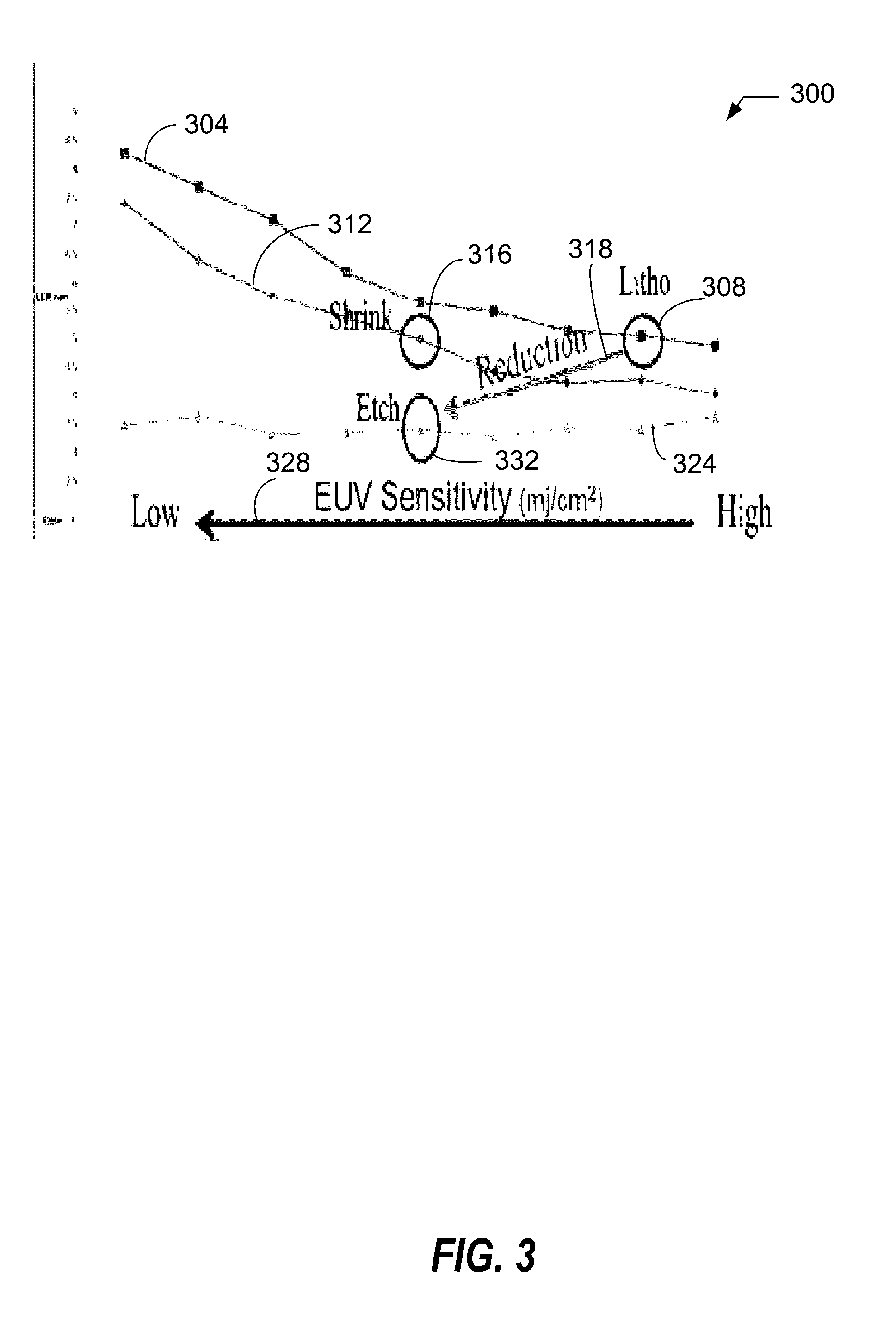

Extreme ultra-violet sensitivity reduction using shrink and growth method

ActiveUS20160334709A1Substrate throughput can be increasedImprove throughputPhotomechanical exposure apparatusPhotosensitive material processingCooking & bakingLine width

Provided is a method for patterning a substrate, comprising: forming a layer of radiation-sensitive material on a substrate; preparing a pattern in the layer of radiation-sensitive material using a lithographic process, the pattern being characterized by a critical dimension (CD) and a roughness; following the preparing the pattern, performing a CD shrink process to reduce the CD to a reduced CD; and performing a growth process to grow the reduced CD to a target CD. Roughness includes a line edge roughness (LER), a line width roughness (LWR), or both LER and LWR. Performing the CD shrink process comprises: coating the pattern with a hard mask, the coating generating a hard mask coated resist; baking the hard mask coated resist in a temperature range for a time period, the baking generating a baked coated resist; and developing the baked coated resist in deionized water.

Owner:TOKYO ELECTRON LTD

Method for etching a trench having rounded top and bottom corners in a silicon substrate

The present invention provides straight forward methods for plasma etching a trench having rounded top corners, or rounded bottom corners, or both in a silicon substrate. A first method for creating a rounded top corner on the etched silicon trench comprises etching both an overlying silicon oxide layer and an upper portion of the silicon substrate during a "break-through" step which immediately precedes the step in which the silicon trench is etched. The plasma feed gas for the break-through step comprises carbon and fluorine. In this method, the photoresist layer used to pattern the etch stack is preferably not removed prior to the break-through etching step. Subsequent to the break-through step, a trench is etched to a desired depth in the silicon substrate using a different plasma feed gas composition. A second method for creating a rounded top corner on the etched silicon trench comprises formation of a built-up extension on the sidewall of an overlying patterned silicon nitride hard mask during etch (break-through) of a silicon oxide adhesion layer which lies between the hard mask and a silicone substrate. The built-up extension upon the silicon nitride sidewall acts as a sacrificial masking material during etch of the silicon trench, delaying etching of the silicon at the outer edges of the top of the trench. This permits completion of trench etching with delayed etching of the top corner of the trench and provides a more gentle rounding (increased radius) at the top corners of the trench. During the etching of the silicon trench to its final dimensions, it is desirable to round the bottom corners of the finished silicon trench. We have discovered that a more rounded bottom trench corner is obtained using a two-step silicon etch process where the second step of the process is carried out at a higher process chamber pressure than the first step.

Owner:APPLIED MATERIALS INC

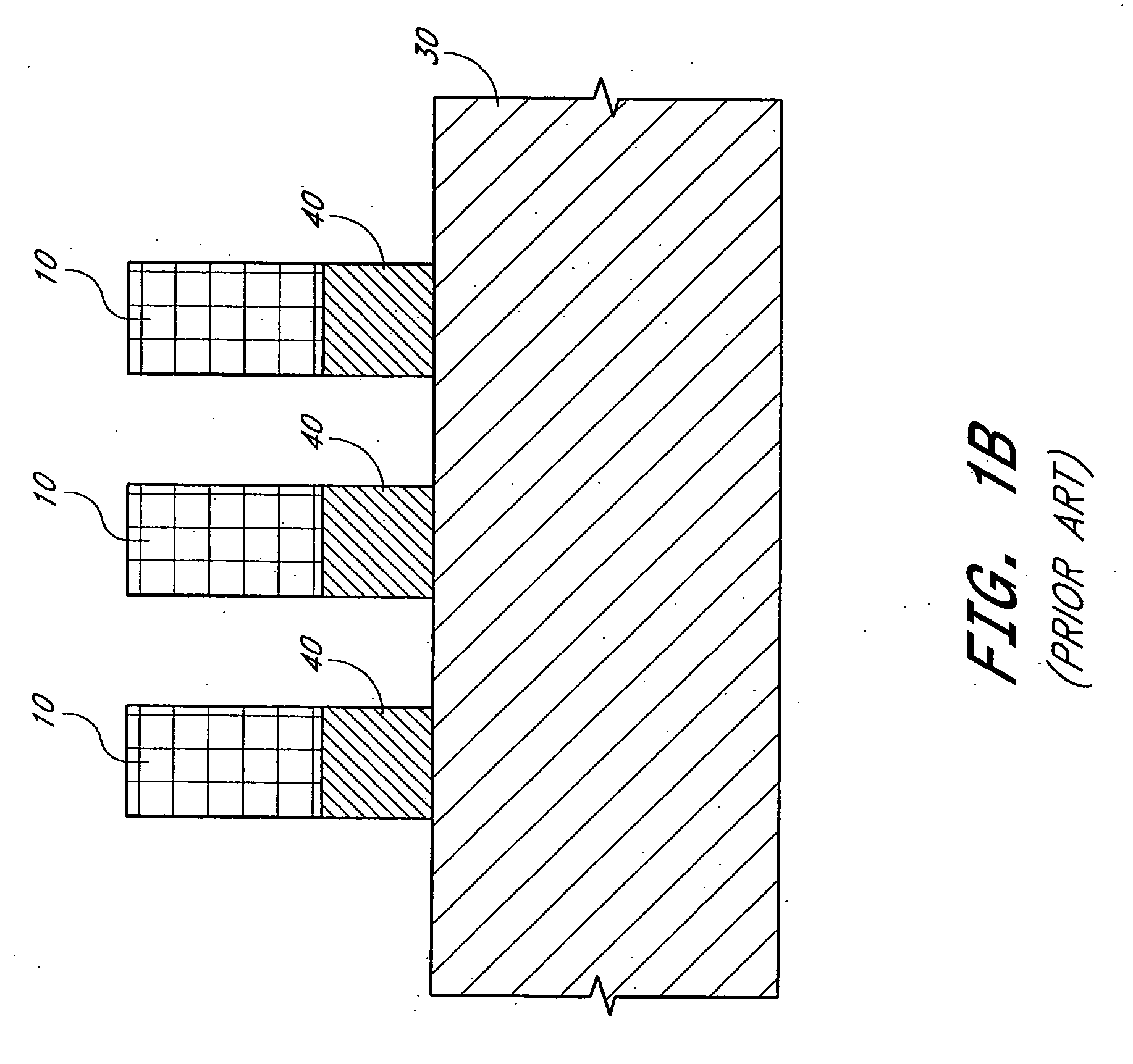

Semiconductor substrate process using a low temperature deposited carbon-containing hard mask

InactiveUS20070032054A1Electric discharge tubesRadiation applicationsLow temperature depositionPlasma current

A method of processing a thin film structure on a semiconductor substrate using an optically writable mask includes placing the substrate in a reactor chamber, the substrate having on its surface a target layer to be etched in accordance with a predetermined pattern, and depositing a carbon-containing hard mask layer on the substrate by (a) introducing a carbon-containing process gas into the chamber, (b) generating a reentrant toroidal RF plasma current in a reentrant path that includes a process zone overlying the workpiece by coupling plasma RF source power to an external portion of the reentrant path, and (c) coupling RF plasma bias power or bias voltage to the workpiece. The method further includes photolithographically defining the predetermined pattern in the carbon-containing hard mask layer, and etching the target layer in the presence of the hard mask layer.

Owner:APPLIED MATERIALS INC

Hardmask of amorphous carbon-hydrogen (a-C:H) layers with tunable etch resistivity

InactiveUS20040000534A1Decorative surface effectsSemiconductor/solid-state device manufacturingForming gasAmorphous carbon

A process of using a-C:H layer as a hardmask material with tunable etch resistivity in a RIE process that alleviates the addition of a layer forming gas to the etchant when making a semiconductor device, comprising: a) providing a semiconductor substrate; b) forming a hardmask of amorphous carbon-hydrogen (a-C:H) layer by plasma enhancement over the semiconductor substrate; c) forming an opening in the hardmask layer to form an exposed surface portion of the hardmask layer; and d) etching the exposed surface portion of the hardmask layer without the addition of a layer forming gas using RIE to form a trench feature with sufficient masking and side wall protection.

Owner:POLARIS INNOVATIONS

Sequential infiltration synthesis for enhancing multiple-patterning lithography

ActiveUS9684234B2Reduce in quantityImprove throughputDecorative surface effectsSemiconductor/solid-state device manufacturingPhotoresistMultiple patterning lithography

Simplified methods of multiple-patterning photolithography using sequential infiltration synthesis to modify the photoresist such that it withstands plasma etching better than unmodified resist and replaces one or more hard masks and / or a freezing step in MPL processes including litho-etch-litho-etch photolithography or litho-freeze-litho-etch photolithography.

Owner:UCHICAGO ARGONNE LLC

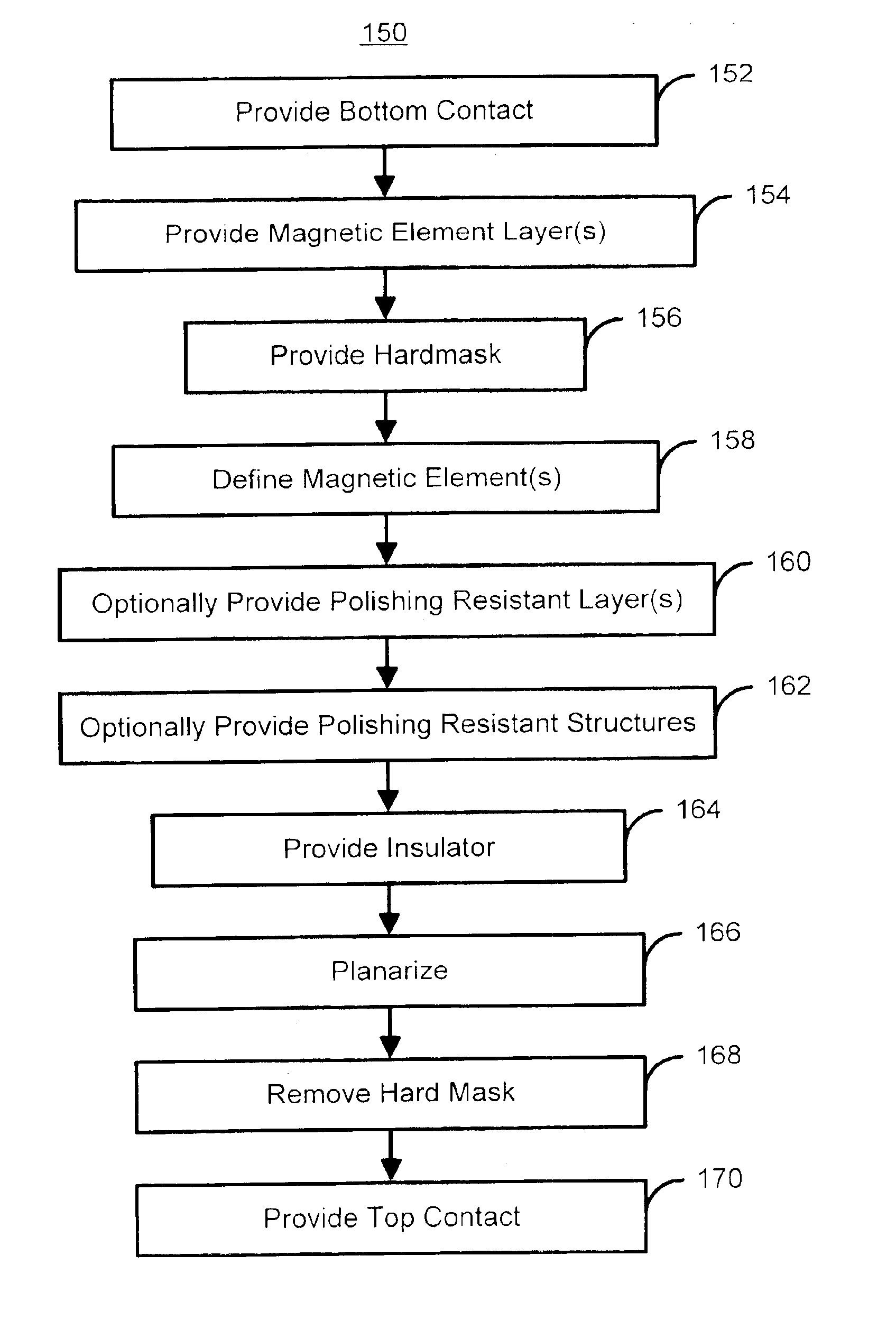

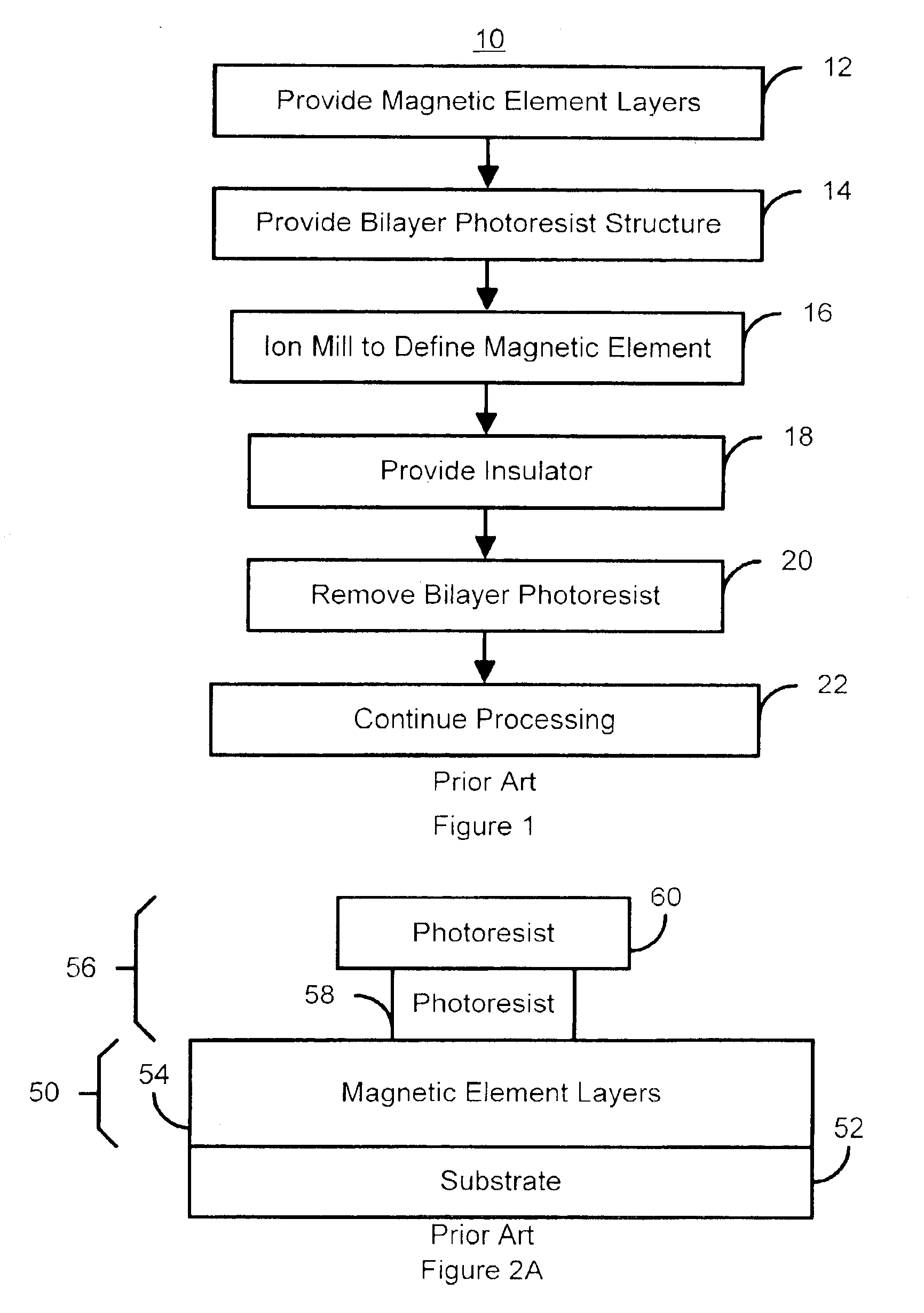

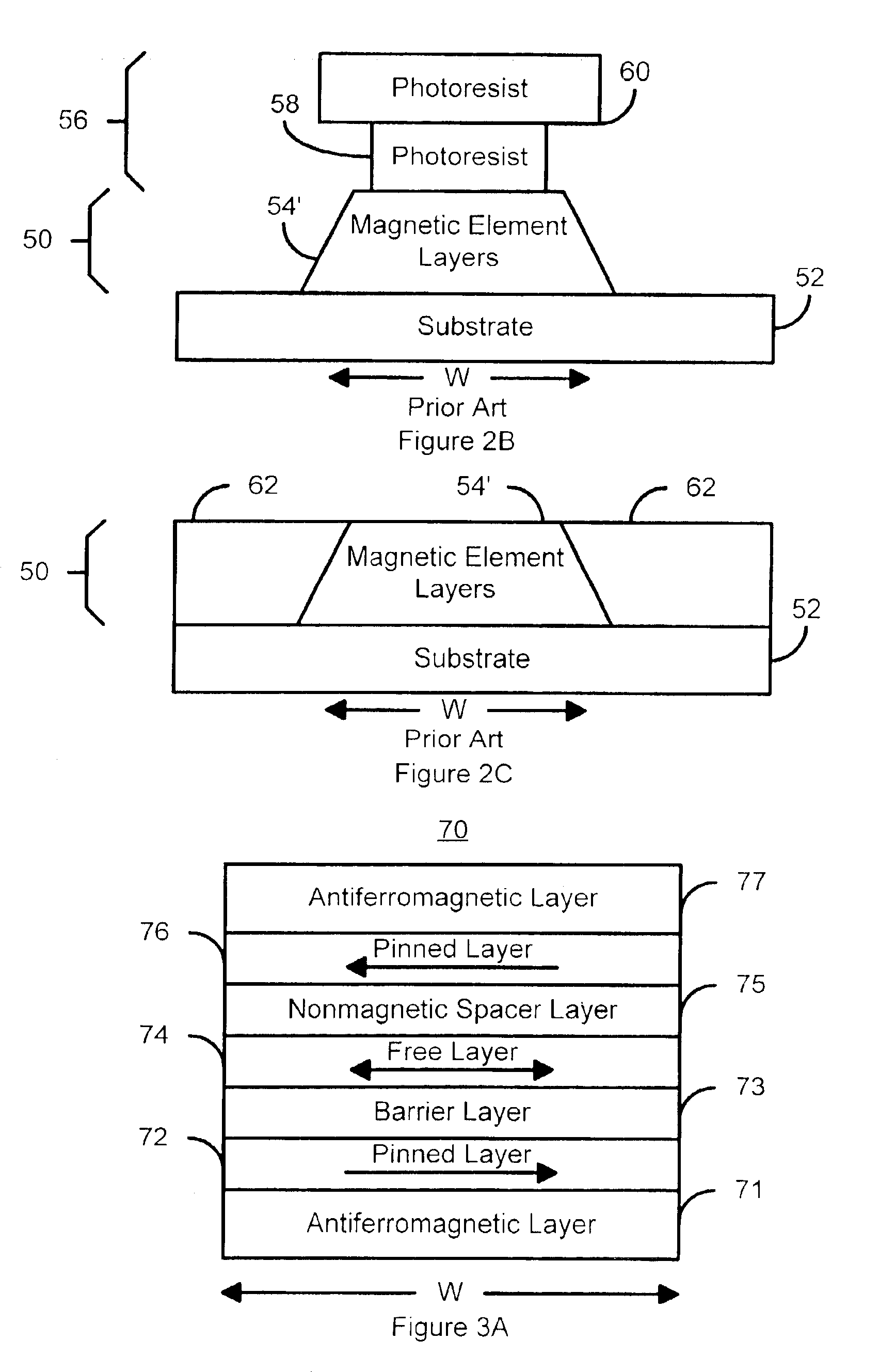

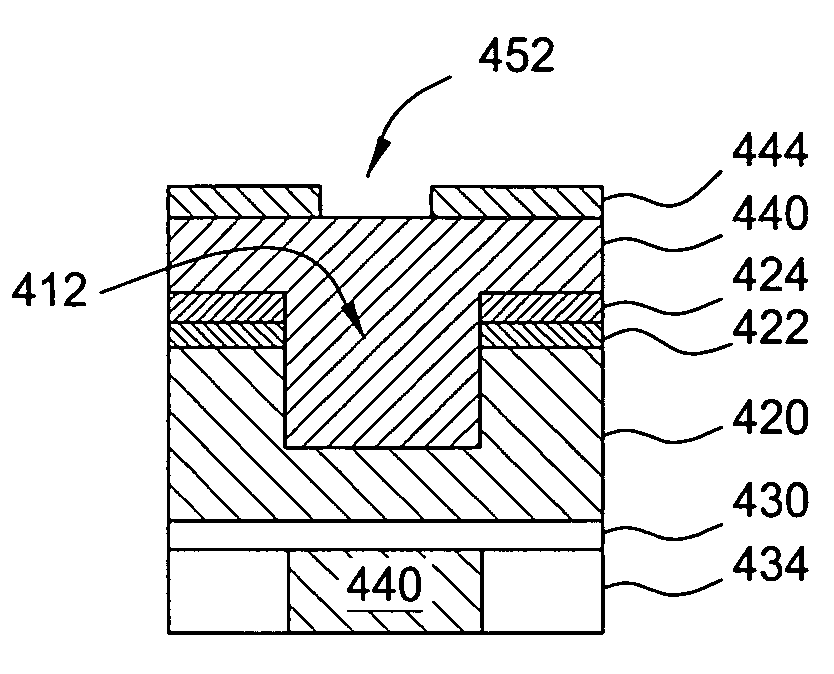

Methods for providing a sub .15 micron magnetic memory structure

ActiveUS6933155B2Small sizeSemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentMagnetic memoryEngineering

A method for providing a magnetic element is disclosed. The method includes providing at least one magnetic element layer and providing a hard mask structure for masking a portion of the at least one magnetic element layer. The hard mask structure is made from hard mask material(s) that are etchable for defining the hard mask structure. The hard mask structure also acts as a mask during definition of a width of the magnetic element. The method also includes defining the width of the magnetic element by removing a portion of the at least one magnetic element layer using the hard mask structure as a mask. The hard mask structure preferably acts as a polishing stop for a planarization step, such as a chemical mechanical polish, polishing resistant structures might be provided to improve planarization of a magnetic memory incorporating the magnetic element.

Owner:SAMSUNG SEMICON

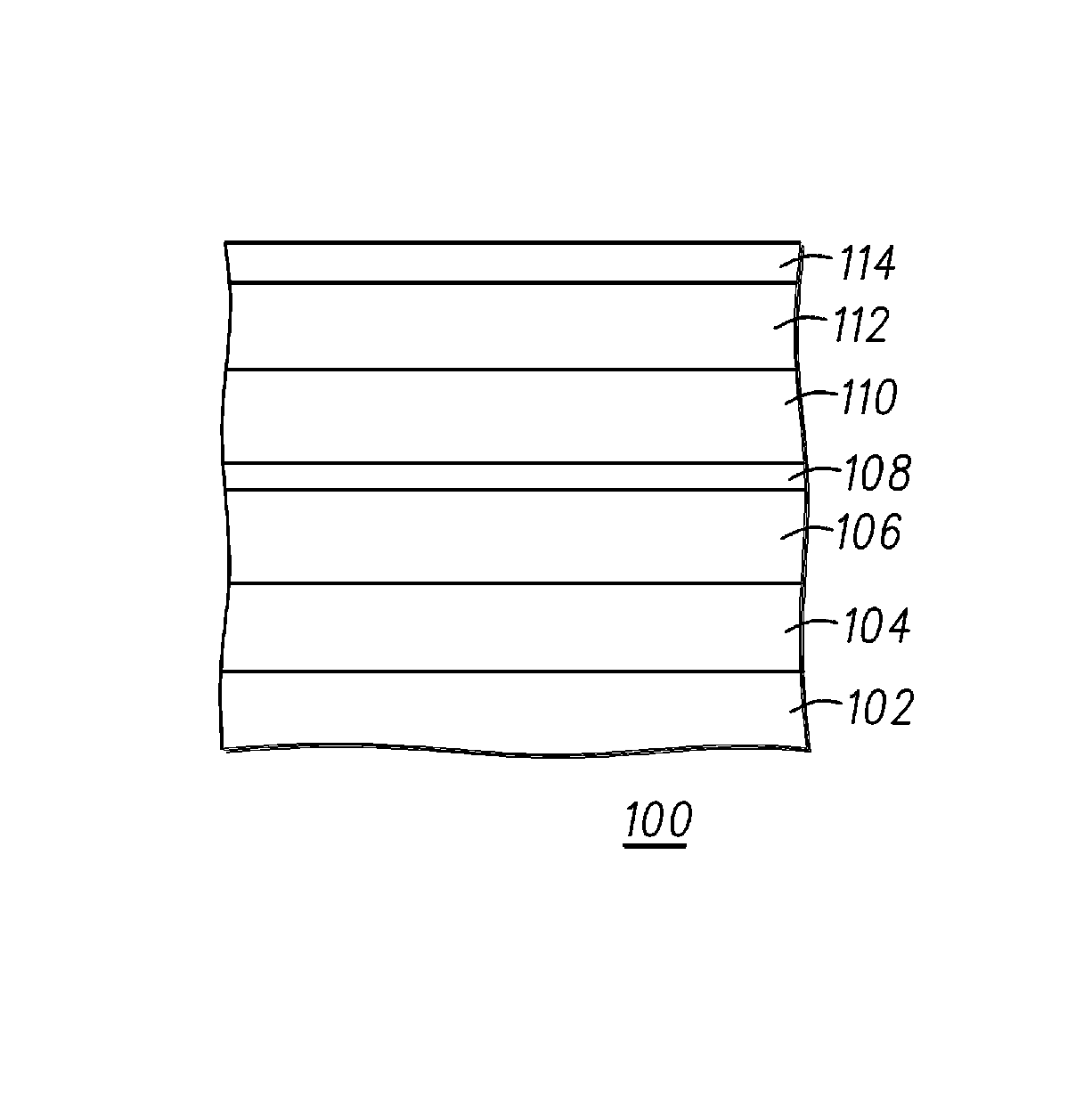

Method of manufacturing a magnetoresistive-based device

ActiveUS8747680B1Decorative surface effectsSemiconductor/solid-state device manufacturingMagnetic reluctanceHard mask

A method of manufacturing a magnetoresistive-based device having magnetic material layers formed between a first electrically conductive layer and a second electrically conductive layer, the magnetic materials layers including a tunnel barrier layer formed between a first magnetic materials layer and a second magnetic materials layer, including removing the first electrically conductive layer and the first magnetic materials layer unprotected by a first hard mask, to form a first electrode and a first magnetic materials, respectively; and removing the tunnel barrier layer, second magnetic materials layer, and second electrically conductive layer unprotected by the second hard mask to form a tunnel barrier, second magnetic materials, and a second electrode.

Owner:EVERSPIN TECHNOLOGIES

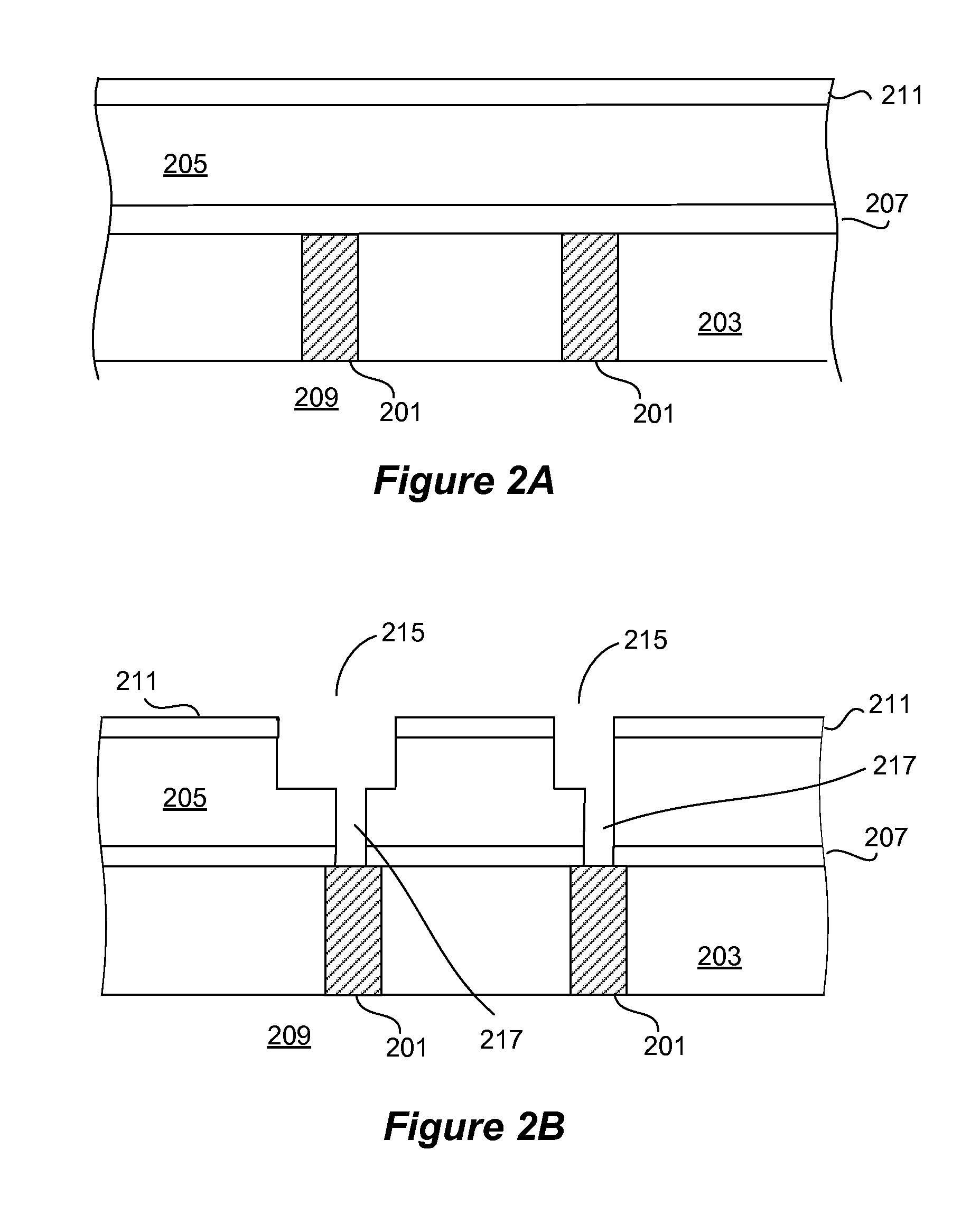

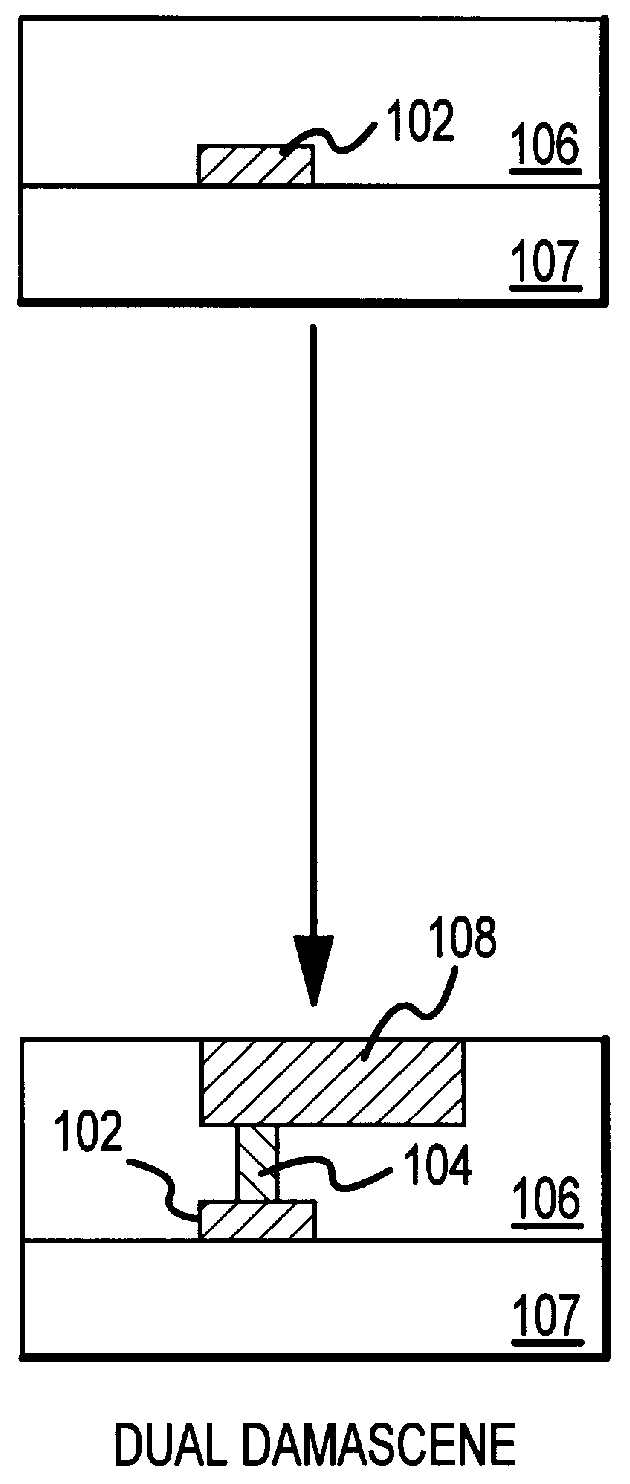

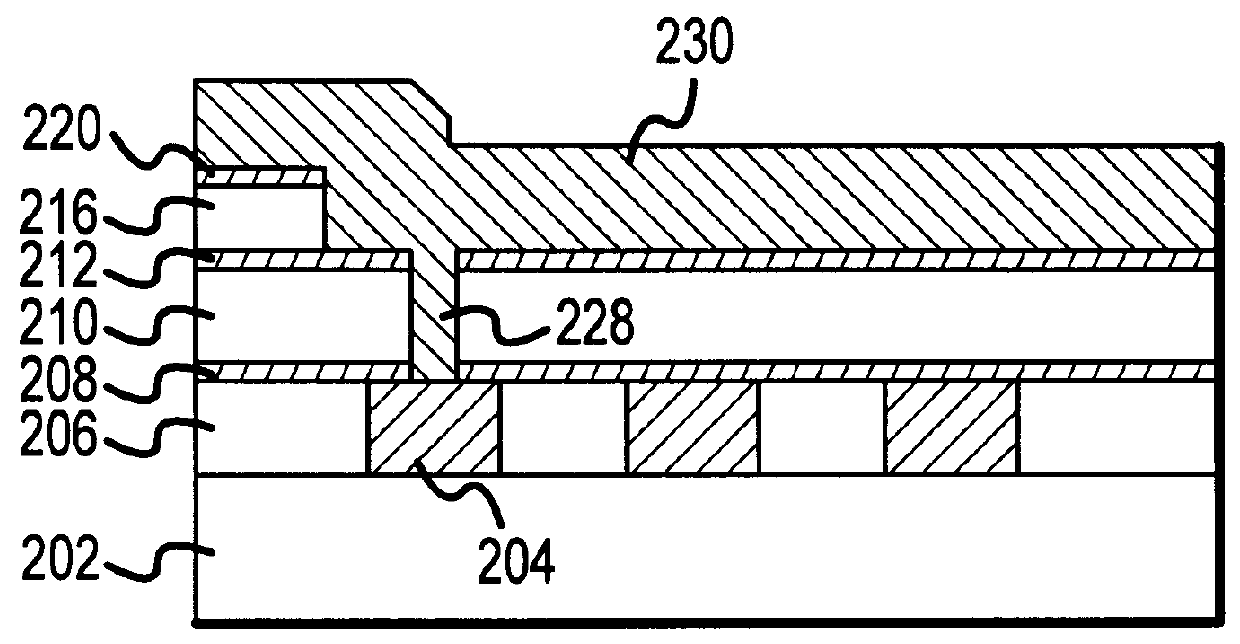

Methods for forming high-performing dual-damascene interconnect structures

Dual damascene methods and structures are provided for IC interconnects which use a dual-damascene process incorporating a low-k dielectric material, high conductivity metal, and an improved hard mask scheme. A pair of hard masks are employed: a silicon dioxide layer and a silicon nitride layer, wherein the silicon dioxide layer acts to protect the silicon nitride layer during dual damascene etch processing, but is subsequently sacrificed during CMP, allowing the silicon nitride layer to act as a the CMP hard mask. In this way, delamination of the low-k material is prevented, and any copper-contaminated silicon dioxide material is removed.

Owner:NEWPORT FAB

Method for manufacturing semiconductor device

InactiveUS20090081879A1Increased anisotropySemiconductor/solid-state device manufacturingSilicon oxideSemiconductor

There is provided a method for manufacturing a semiconductor device including processing a substrate to be processed by using an amorphous carbon hard mask that includes processing an amorphous carbon film formed on the substrate to be processed to provide a hard mask, and forming a protective film comprising a silicon oxide film on a sidewall of the amorphous carbon film exposed during or after processing the amorphous carbon film; and the protective film preferably formed by sputtering an intermediate mask comprising at least a silicon oxide on the amorphous carbon film.

Owner:ELPIDA MEMORY INC

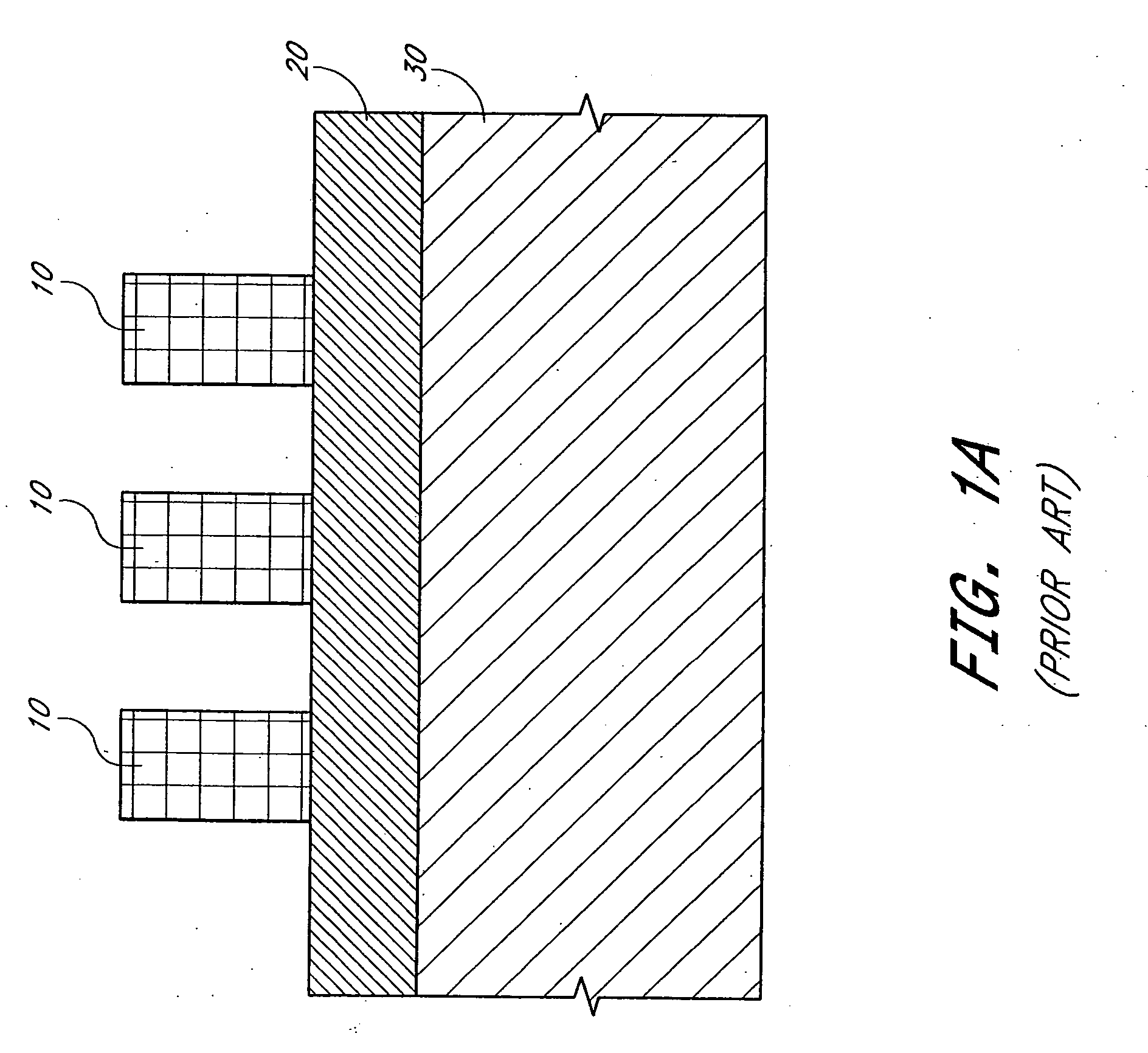

Hard mask arrangement

InactiveUS20060234138A1Reduce spacingIncrease processing costSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentCarrying capacityLateral region

An interconnect connection structure having first and second interconnects and multiple connection elements that electrically connect the first interconnect to the second interconnect is described. The multiple connection elements are formed laterally in a lateral region of the first and second interconnects relative to an overlay orientation of the interconnects. A central region may be free of connection elements so that electro-migration properties of the connection structure are improved and the current-carrying capacity is increased.

Owner:FEHLHABER RODGER +1

Resistive random access memory and method for manufacturing the same

ActiveUS20100112810A1Improve the immunityReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesStatic random-access memoryRandom access memory

A resistive random access memory including, an insulating layer, a hard mask layer, a bottom electrode, a memory cell and a top electrode is provided. The insulating layer is disposed on the bottom electrode. The insulating layer has a contact hole having a first width. The hard mask layer has an opening. A portion of the memory cell is exposed from the opening and has a second width smaller than the first width. The top electrode is disposed on the insulating layer and is coupled with the memory cell.

Owner:MACRONIX INT CO LTD

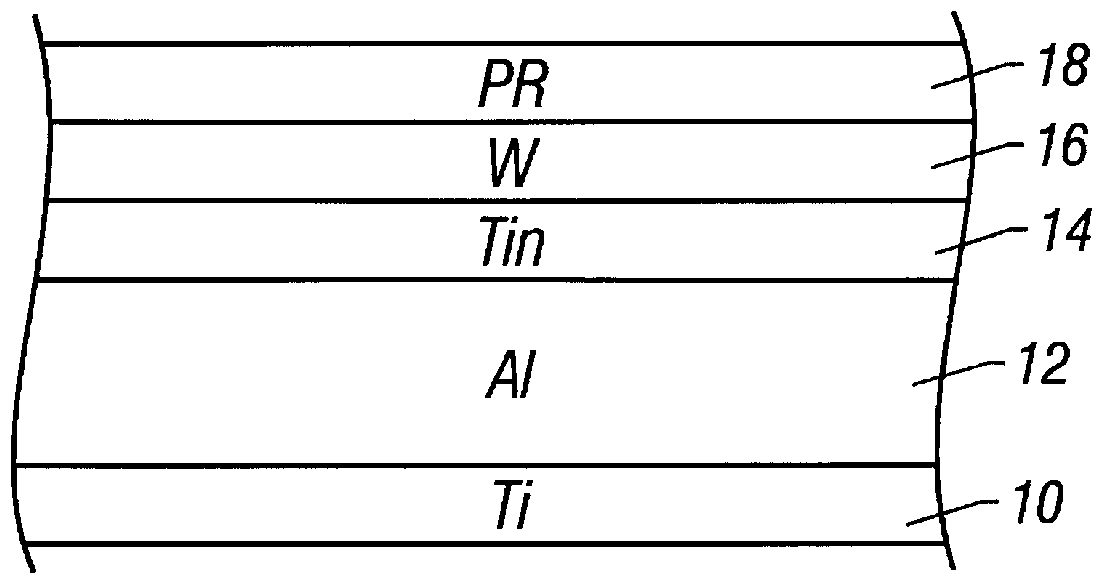

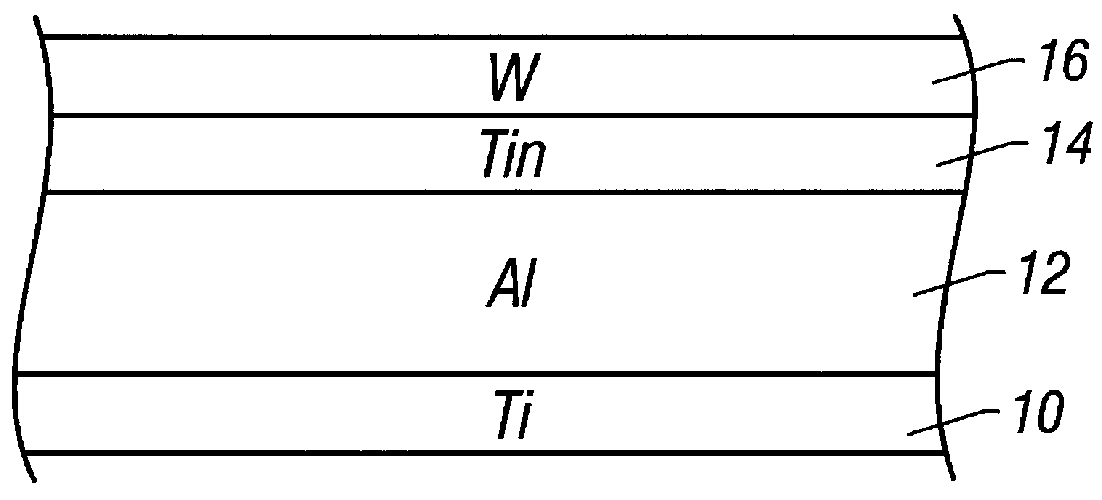

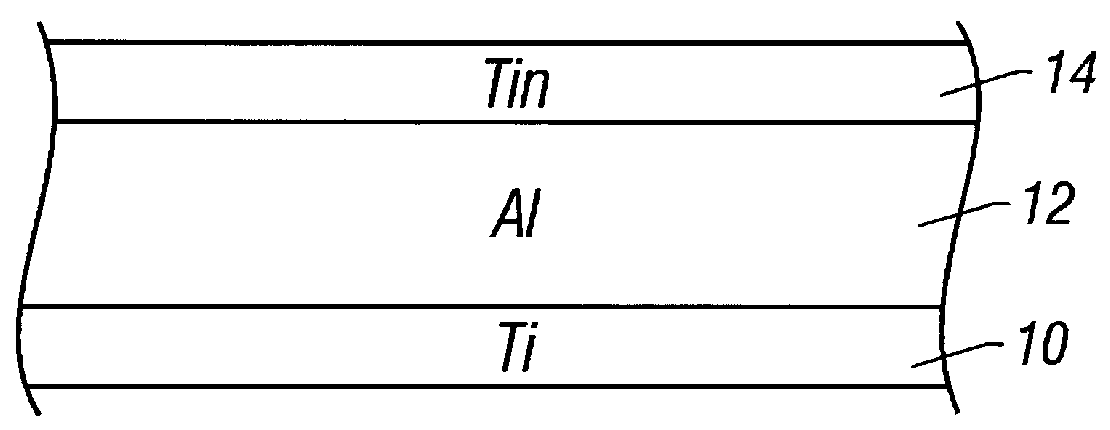

Method of making an interconnect using a tungsten hard mask

InactiveUS6087269AReduce thicknessImproved metal pitchSemiconductor/solid-state device manufacturingPhotoresistTungsten

An interconnect layer is fabricated using a tungsten hard mask by forming a tungsten based layer over an aluminum based layer. A photoresist layer is deposited over the tungsten based layer and patterned. The tungsten based layer is patterned by applying a fluorine-based etchant using the photoresist layer as an etch mask. Then the aluminum based layer is patterned by applying a chlorine based etchant using the tungsten based layer as an etch mask.

Owner:ADVANCED MICRO DEVICES INC

Dual damascene fabrication with low k materials

The invention provides methods and apparatuses for fabricating a dual damascene structure on a substrate. First, trench lithography and trench patterning are performed on the surface of a substrate to etch a low-k dielectric material layer to a desired etch depth to form a trench prior to forming of a via. The trenches can be filled with an organic fill material and a dielectric hard mask layer can be deposited. Then, via lithography and via resist pattering are performed. Thereafter, the dielectric hard mask and the organic fill material are sequentially etched to form vias on the surface of the substrate, where the trenches are protected by the organic fill material from being etched. A bottom etch stop layer on the bottom of the vias is then etched and the organic fill material is striped. As a result, the invention provides good patterned profiles of the via and trench openings of a dual damascene structure.

Owner:APPLIED MATERIALS INC

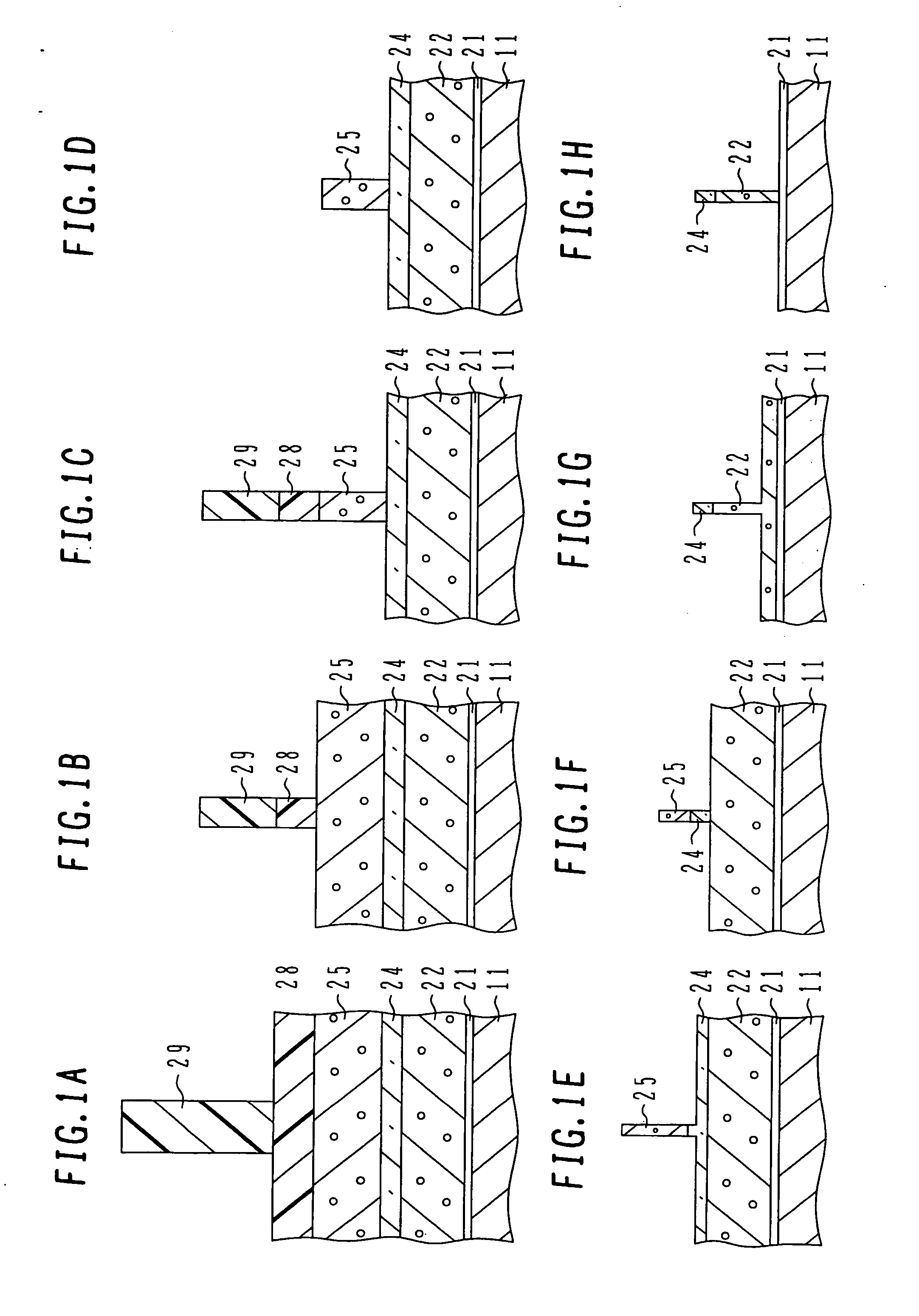

Manufacture method for micro structure

InactiveUS20070037101A1Easy to etchImprove controllabilitySemiconductor/solid-state device manufacturingPhotosensitive material processingResistMicro structure

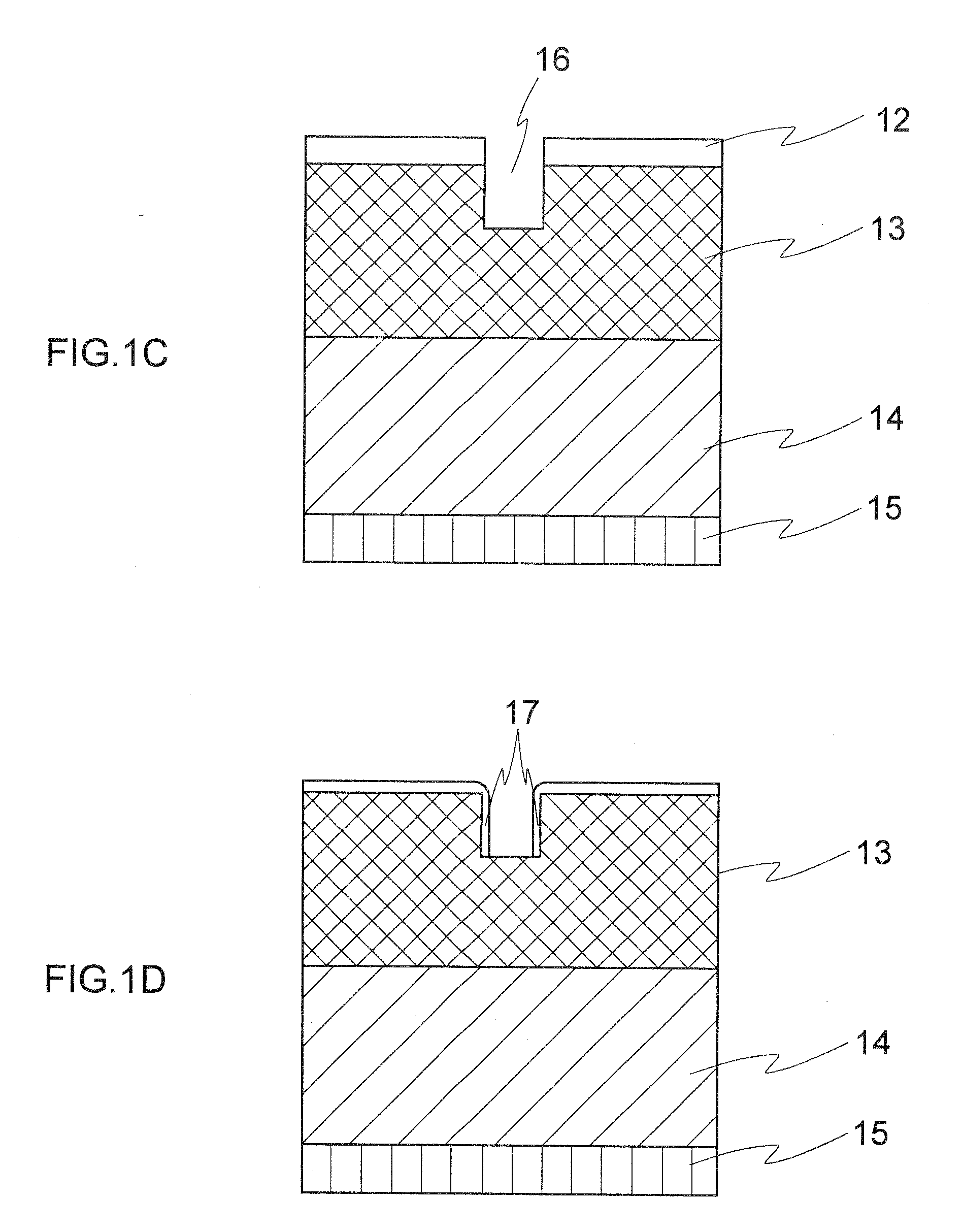

A micro structure manufacture method includes the steps of: (a) preparing an etching object having an etching target film, provided with a lower hard mask layer and an upper hard mask layer stacked on the etching target film; (b) forming a resist pattern above the etching object; (c) etching the upper hard mask film by using the resist pattern as an etching mask to form an upper hard mask; (d) after the step (c), removing the resist pattern; (e) after the step (d), thinning the upper hard mask by etching; (f) etching the lower hard mask film by using the thinned upper hard mask as an etching mask to form a lower hard mask; and (g) etching the etching target film by using the upper hard mask and the lower hard mask as an etching mask, wherein the upper hard mask film is capable of being more easily etched, using the resist pattern as a mask, than the lower hard mask film. The micro structure manufacture method can etch a fine pattern with good yield.

Owner:FUJITSU LTD

Method of making semiconductor device

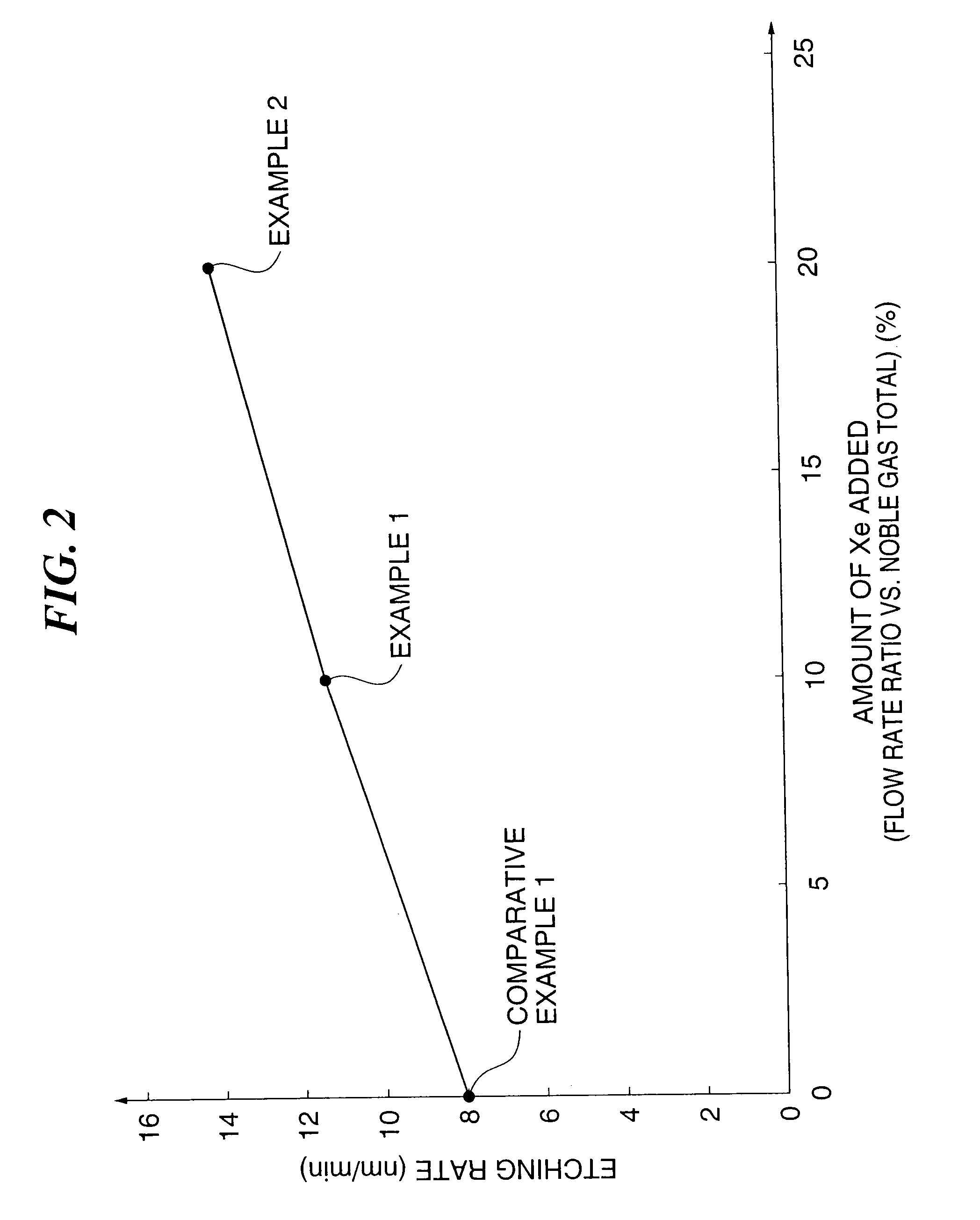

InactiveUS20080261404A1Improve controllabilityGood etchingElectric discharge tubesSemiconductor/solid-state device manufacturingNoble gasControllability

A plasma processing method, which enables the etching controllability for a high-dielectric-constant insulating film to be improved. A substrate having a high-dielectric-constant gate insulating film and a hard mask formed thereon is subjected to etching processing using a plasma of a processing gas containing a noble gas and a reducing gas.

Owner:TOKYO ELECTRON LTD

Method for forming sublithographic features during the manufacture of a semiconductor device and a resulting in-process apparatus

A method for forming a semiconductor device comprises forming a layer to be etched, then forming a hard mask layer over the layer to be etched. The hard mask is etched to form an opening defined by first and second cross-sectional sidewalls in the hard mask layer. In one embodiment, the opening in the hard mask layer is formed at the minimum limits allowable by optical lithography. A conformal spacer layer is formed over the hard mask layer and on the sidewalls of the hard mask, then spacer etched to form first and second cross-sectional spacers along the first and second sidewalls in the patterned hard mask layer. The hard mask and spacers are preferably formed from amorphous carbon. The layer to be etched is etched using the hard mask layer and the spacers as a pattern, then the hard mask layer and spacers are removed.

Owner:ROUND ROCK RES LLC

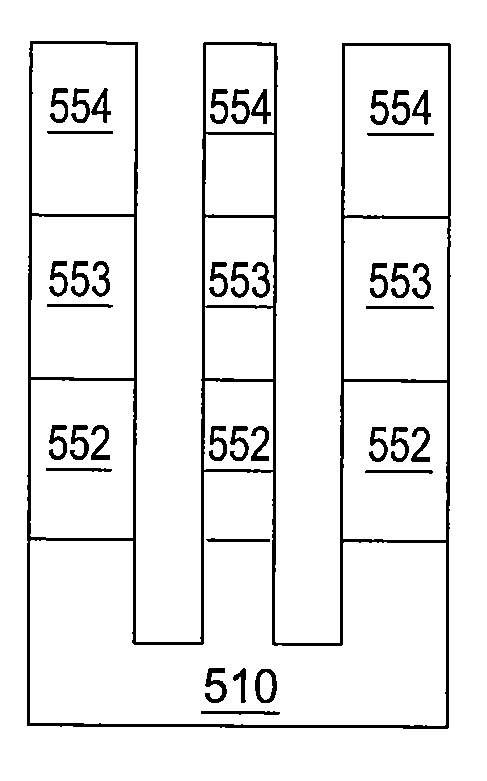

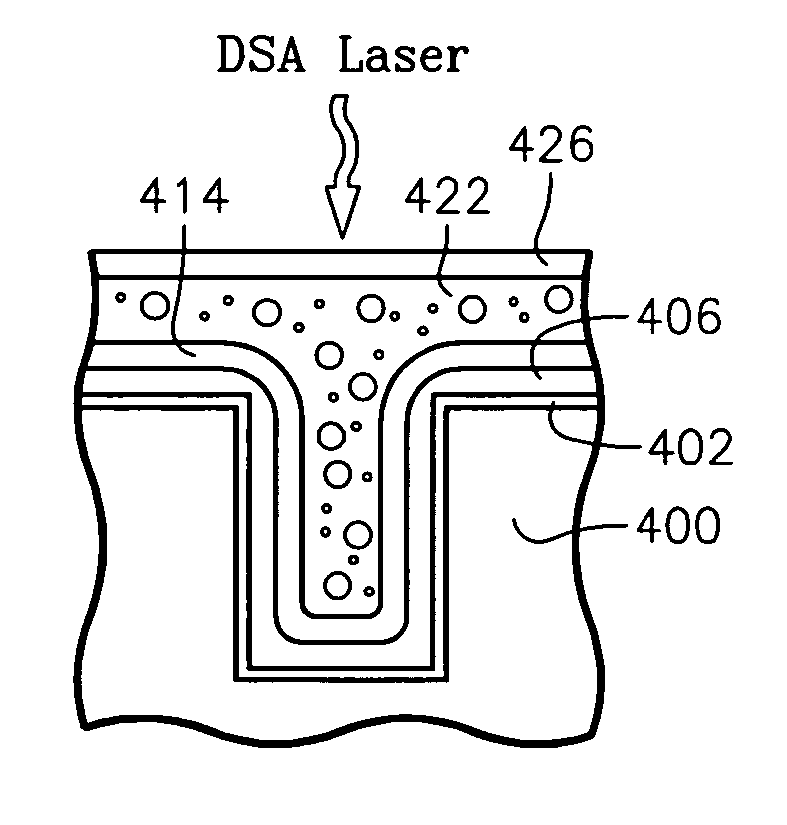

Method for Fabricating a Pillar-Shaped Phase Change Memory Element

InactiveUS20070158632A1Photomechanical apparatusSemiconductor/solid-state device manufacturingPhase-change memoryPhase-change material

A method of fabricating a sub-feature size pillar structure on an integrated circuit. The process first provides a substrate having formed thereon a phase change layer, an electrode layer and a hard-mask layer. Then there is formed a feature-size hard-mask, by lithographically patterning, etching and stripping a photoresist layer, followed by trimming the hard-mask to a selected sub-feature size, wherein the trimming step is highly selective between the electrode and phase change material layers and the hard-mask. The final steps are trimming the electrode and phase change layers to the size of the hard-mask and removing the hard-mask.

Owner:MACRONIX INT CO LTD

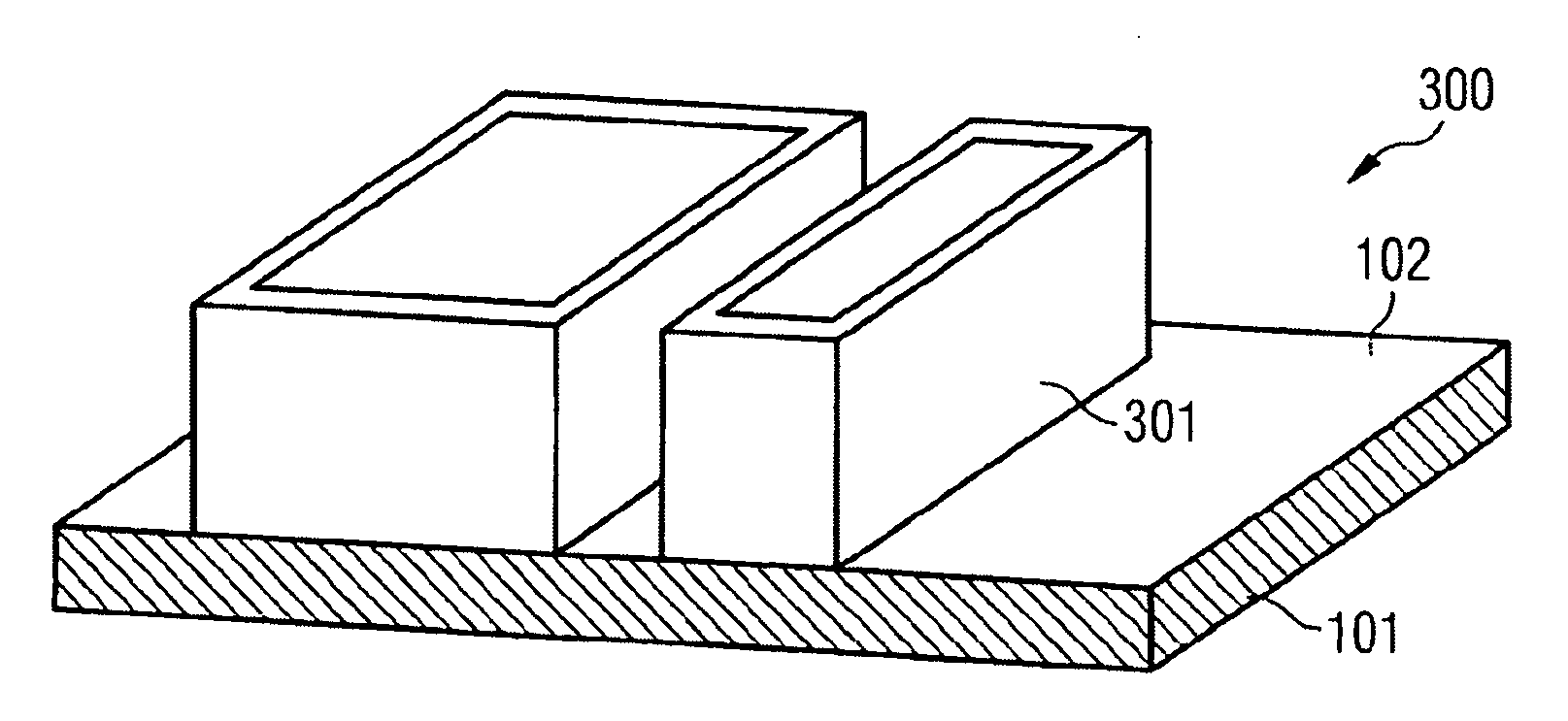

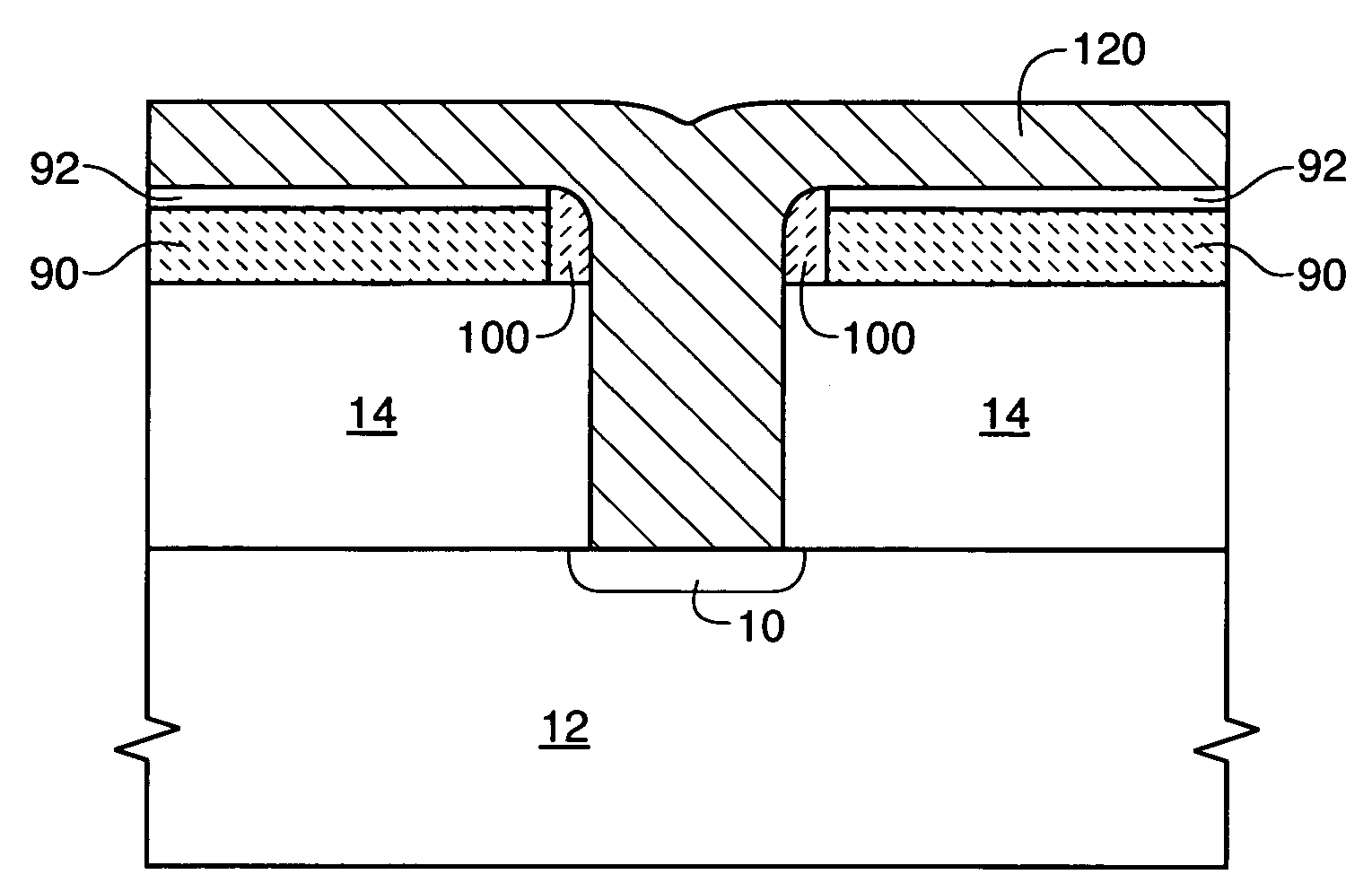

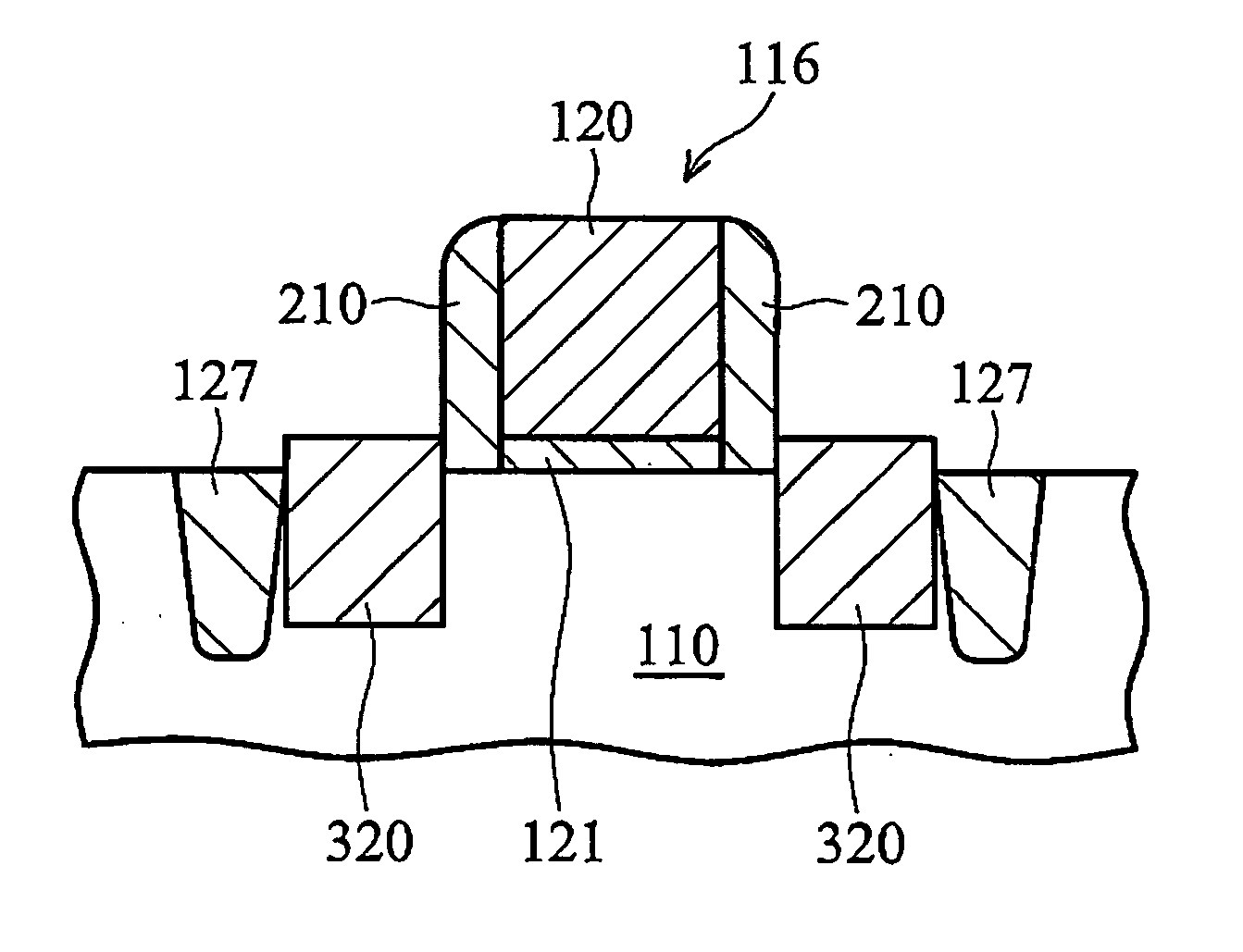

Methods for fabricating finfet integrated circuits on bulk semiconductor substrates

ActiveUS20130309838A1Reduce the overall heightSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Methods are provided for fabricating FinFET integrated circuits on bulk semiconductor substrates. In accordance with one embodiment a patterned hard mask that defines locations of a regular array of a plurality of fins is formed overlying a semiconductor substrate. Portions of the patterned hard mask are removed using a cut mask to form a modified hard mask. The substrate is etched using the modified hard mask as an etch mask to form a plurality of fins extending upwardly from the substrate and separated by trenches. Selected ones of the plurality of fins are at least partially removed to form isolation regions and an insulating material is deposited to fill the trenches and to cover the at least partially removed selected ones of the plurality of fins.

Owner:GLOBALFOUNDRIES US INC

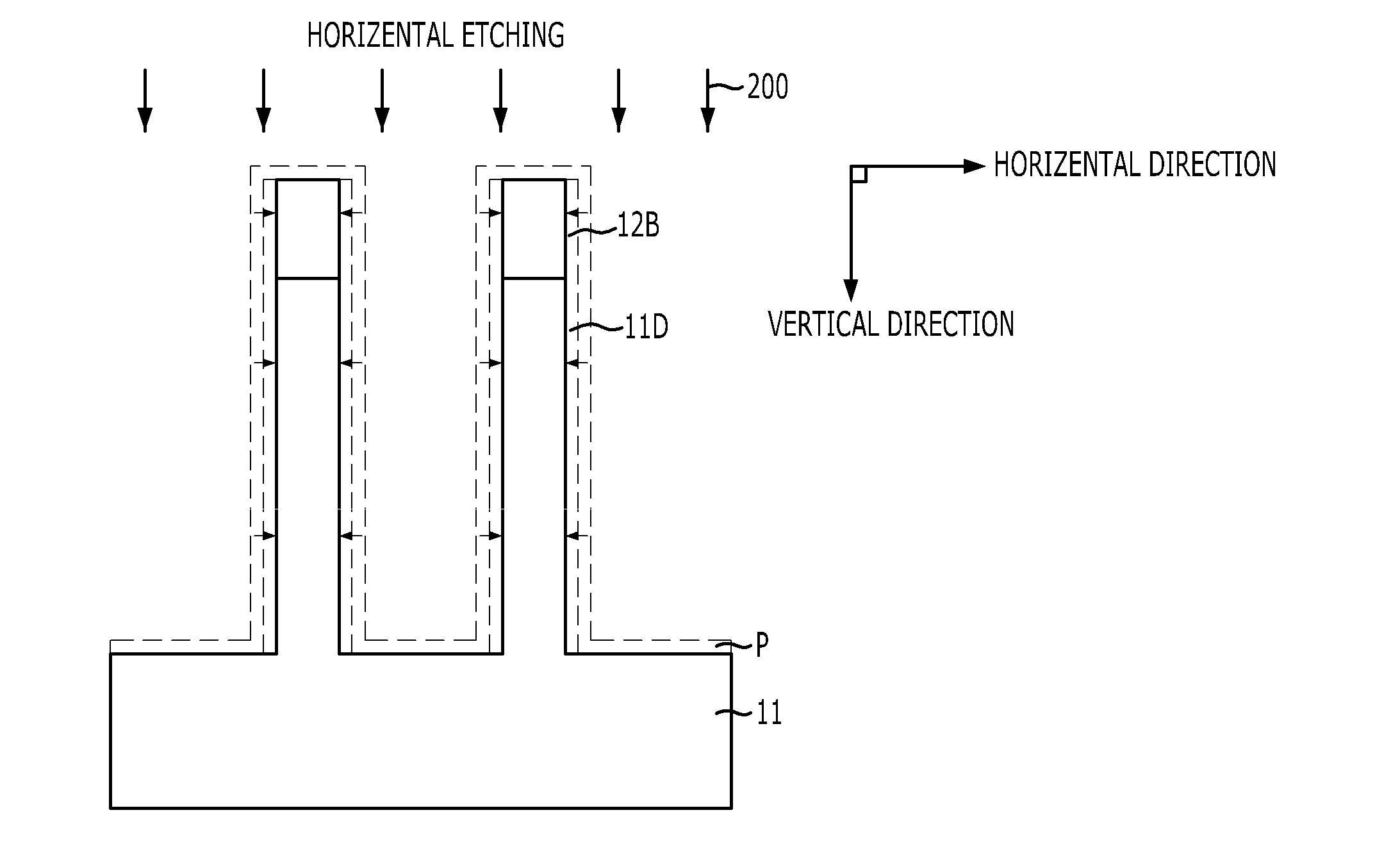

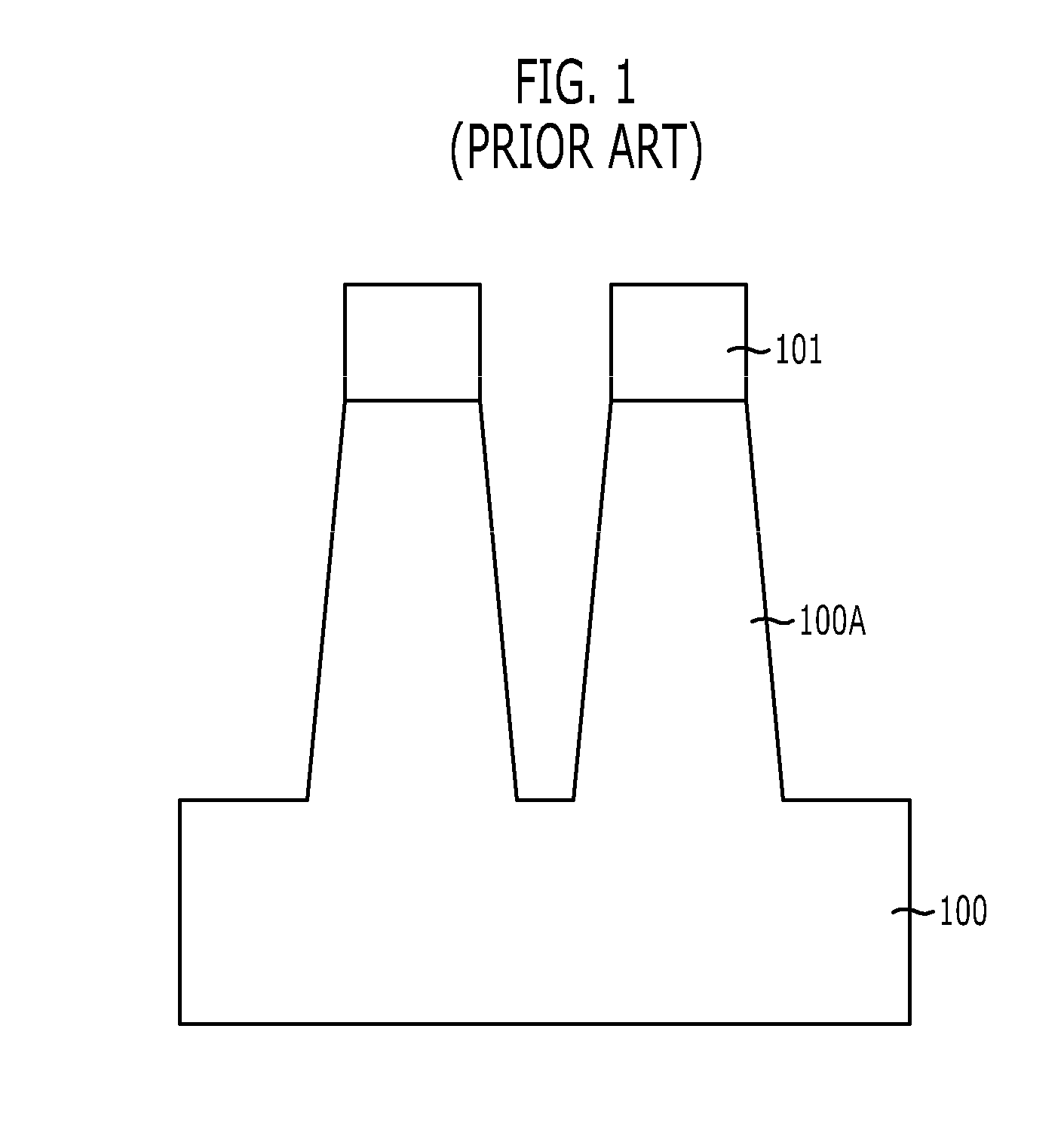

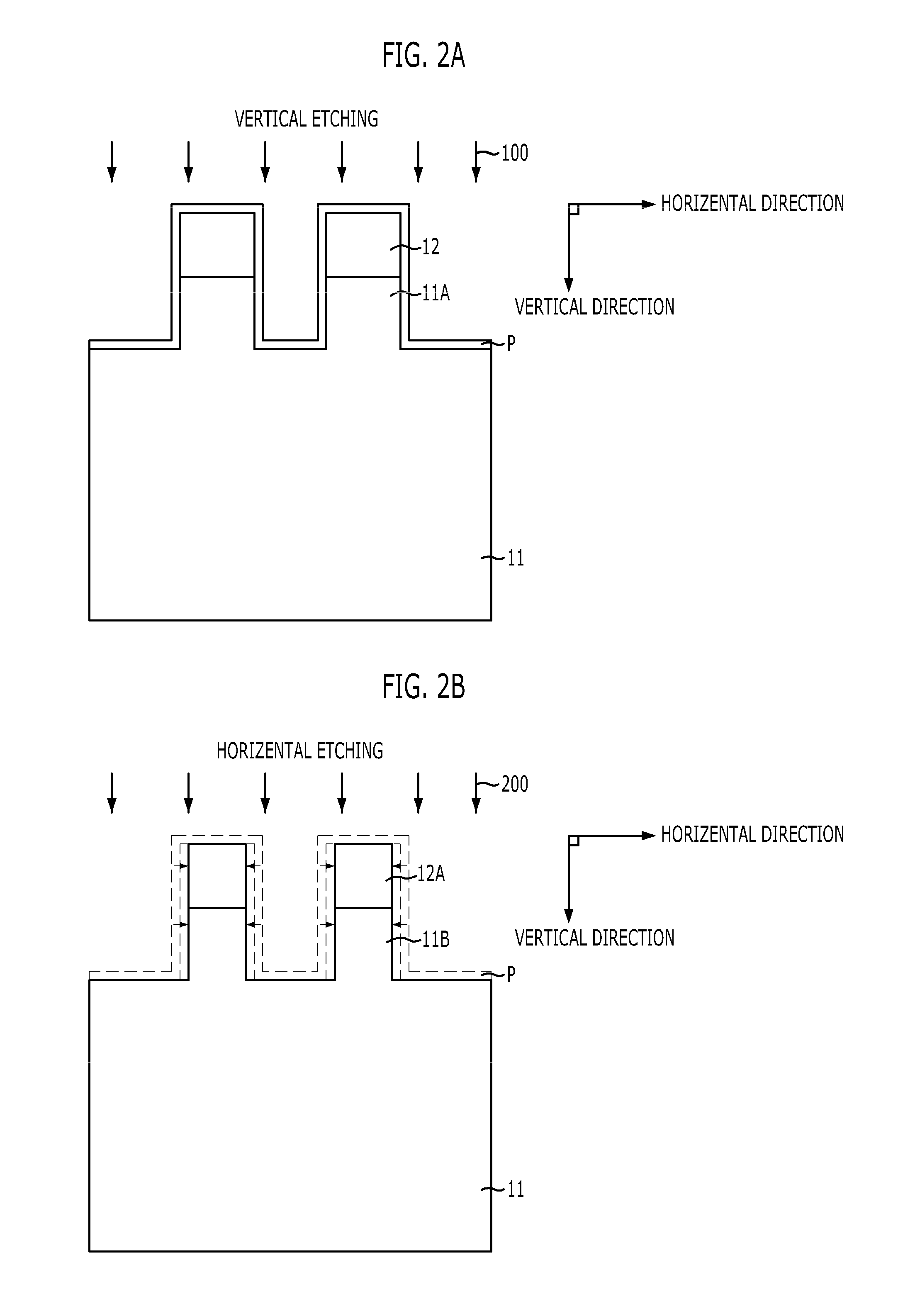

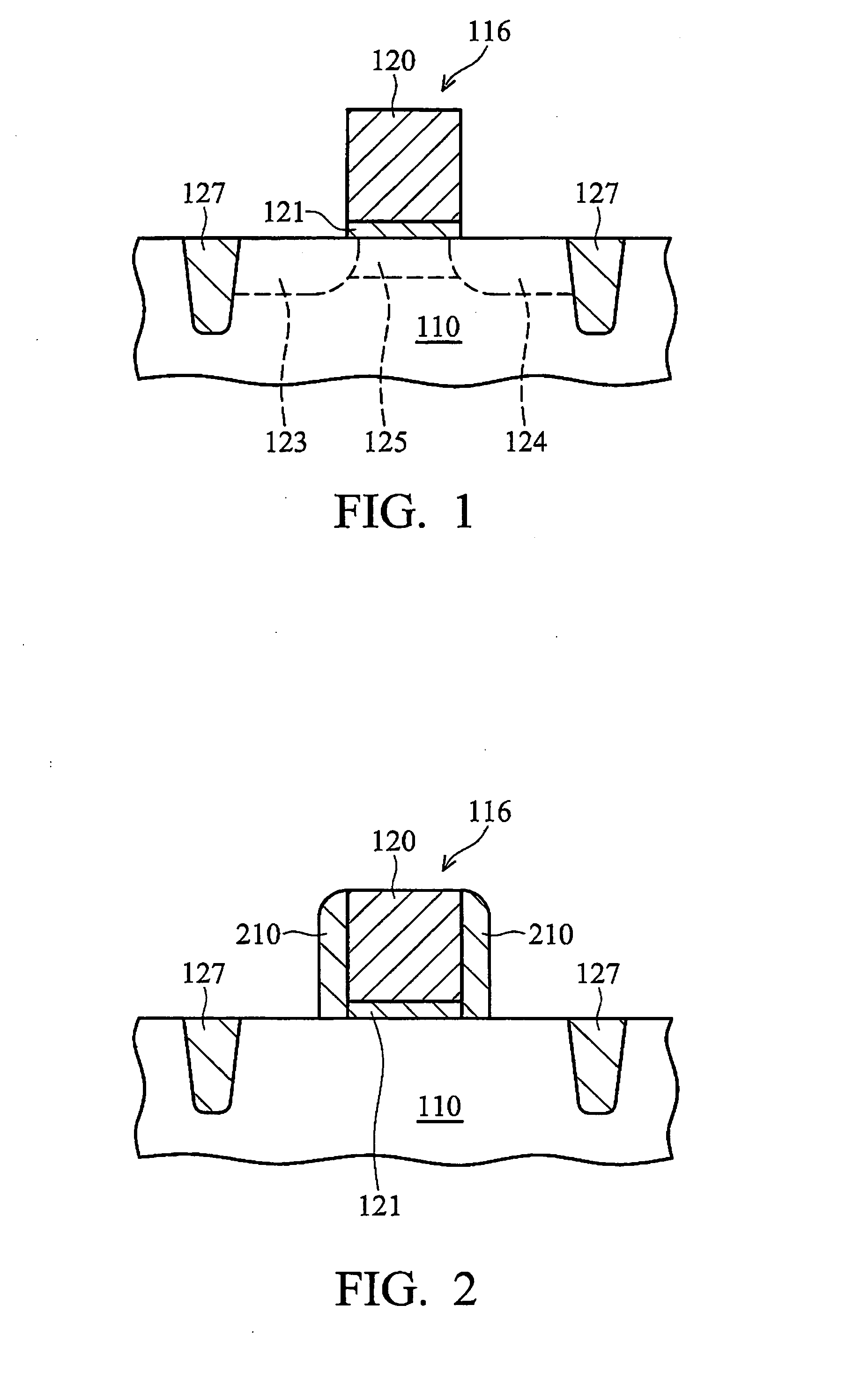

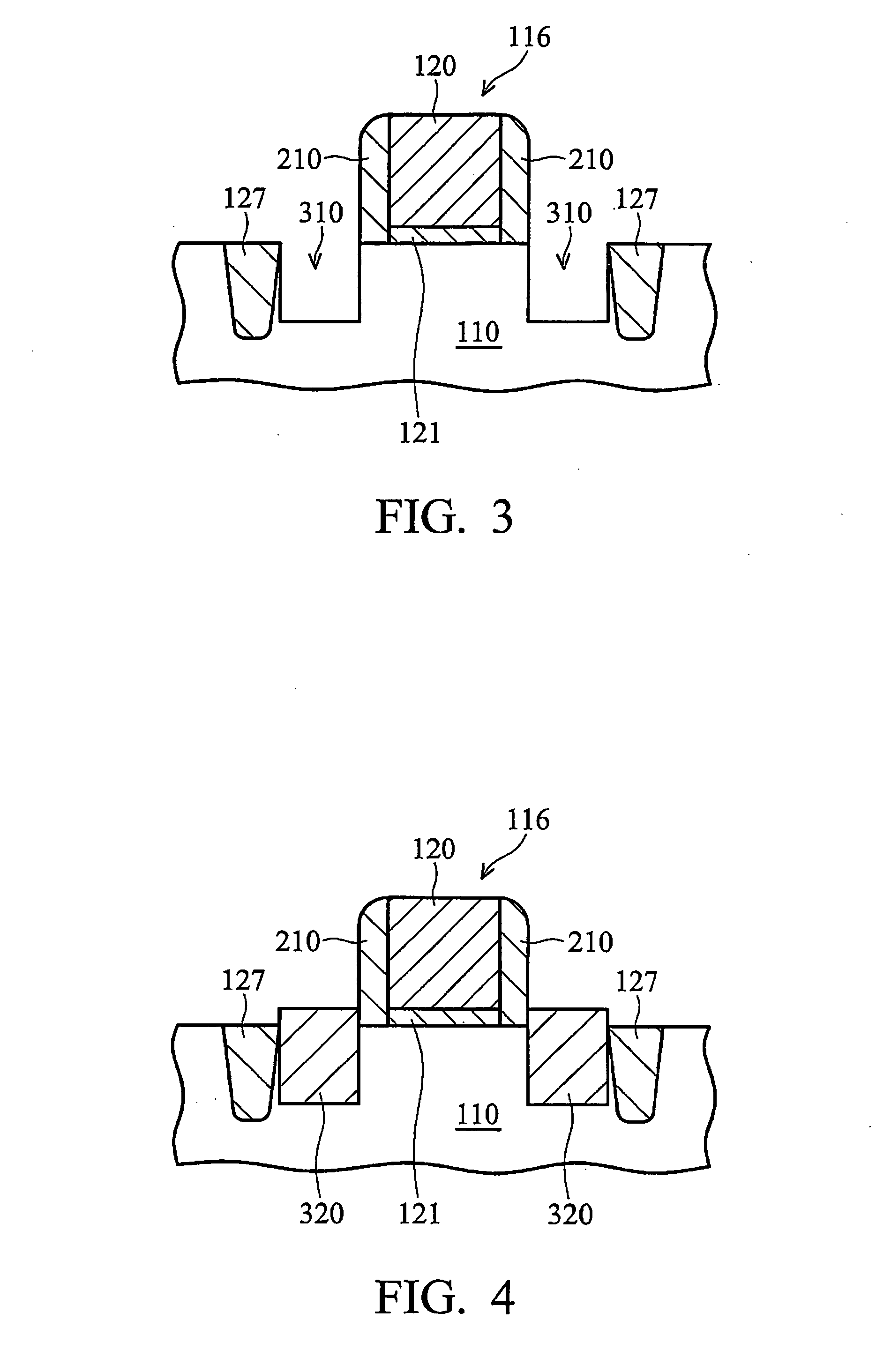

Method for forming active pillar of vertical channel transistor

ActiveUS20100055917A1Reduce horizontal widthOvercome limitationsSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLine width

A method for forming an active pillar of a vertical channel transistor includes forming a hard mask pattern on a substrate, etching vertically the substrate using the hard mask pattern as an etch barrier to form an active pillar, and etching horizontally to remove by-product remaining on the exposed substrate, the hard mask pattern and the active pillar and at the same time to reduce line width of the hard mask pattern and the active pillar, wherein a unit cycle in which the vertical etching and the horizontal etching are each performed subsequently once, respectively, is performed repeatedly at least two times or more. According to the present invention, an active pillar having vertical profiles on its sidewalls and having height and line width (or diameter) required in a highly integrated vertical channel transistor can be provided.

Owner:SK HYNIX INC

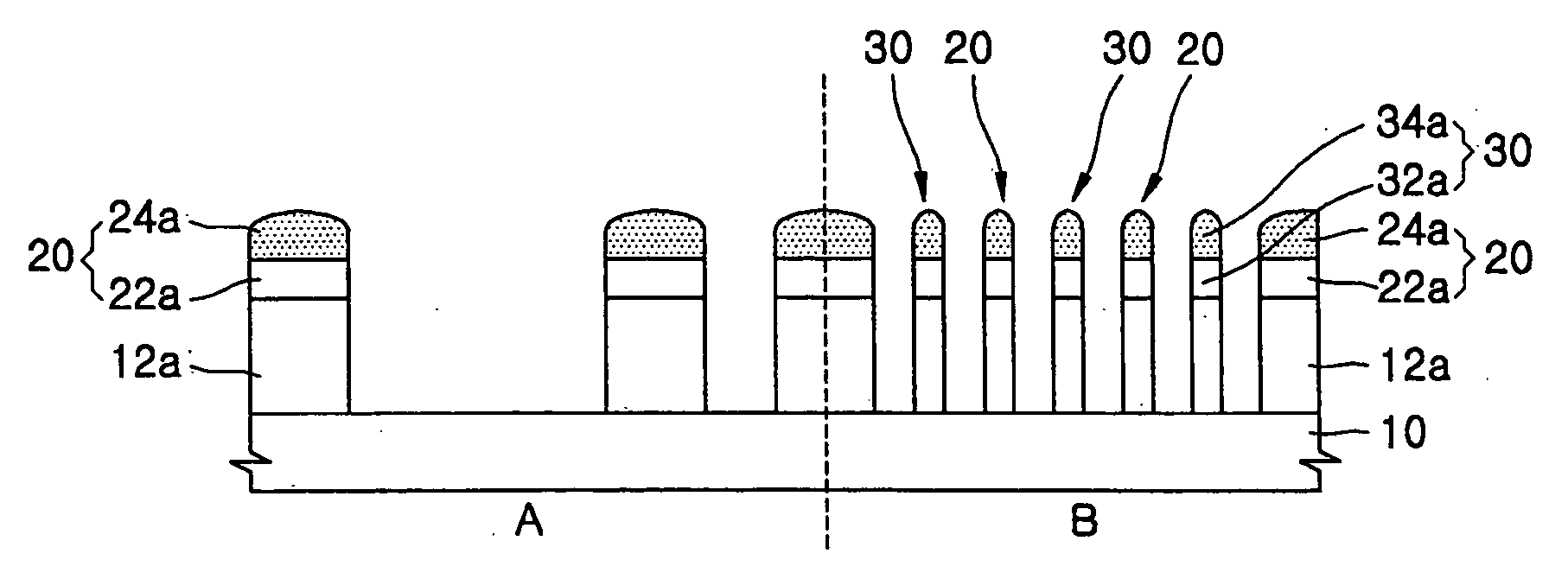

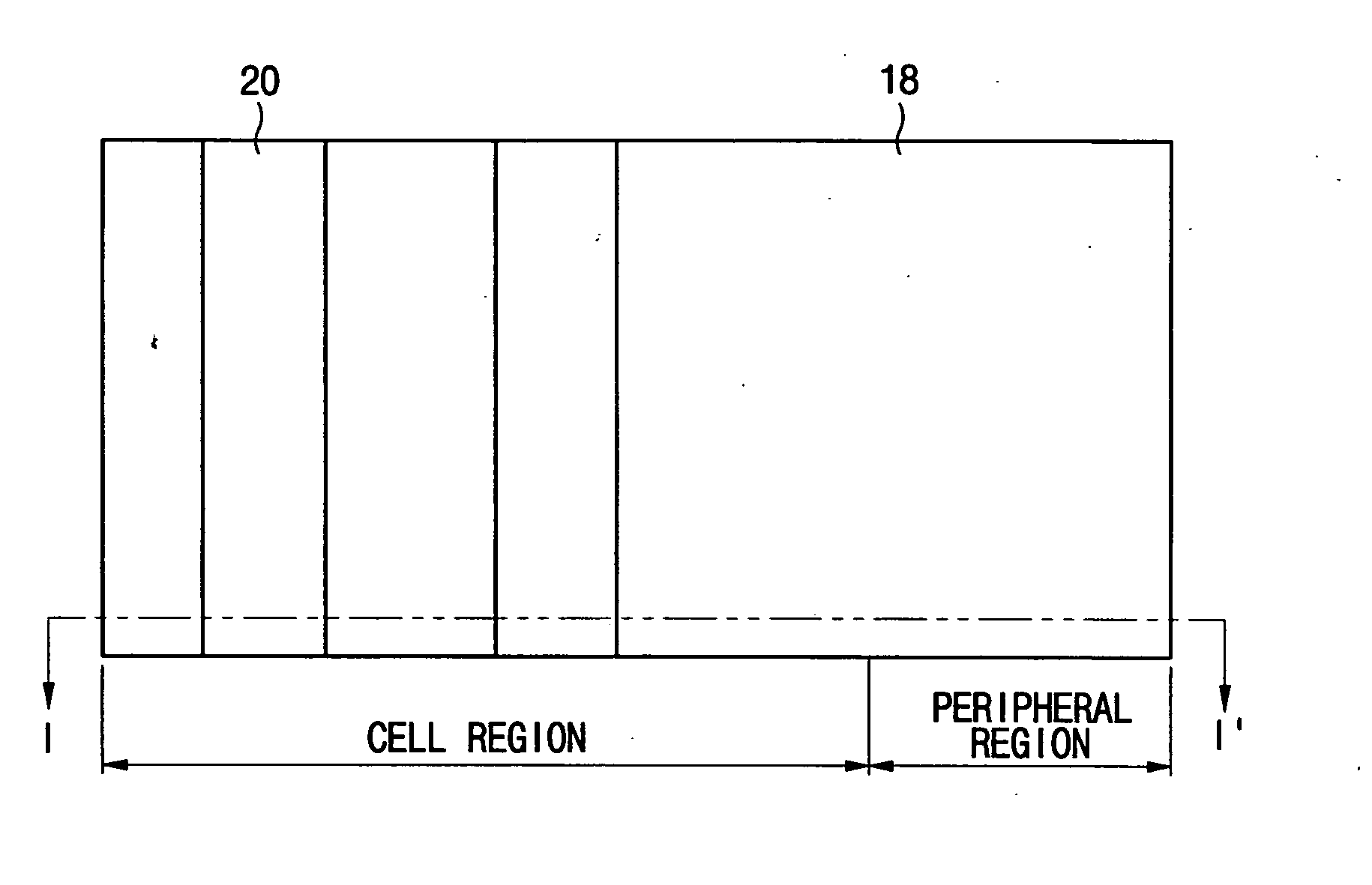

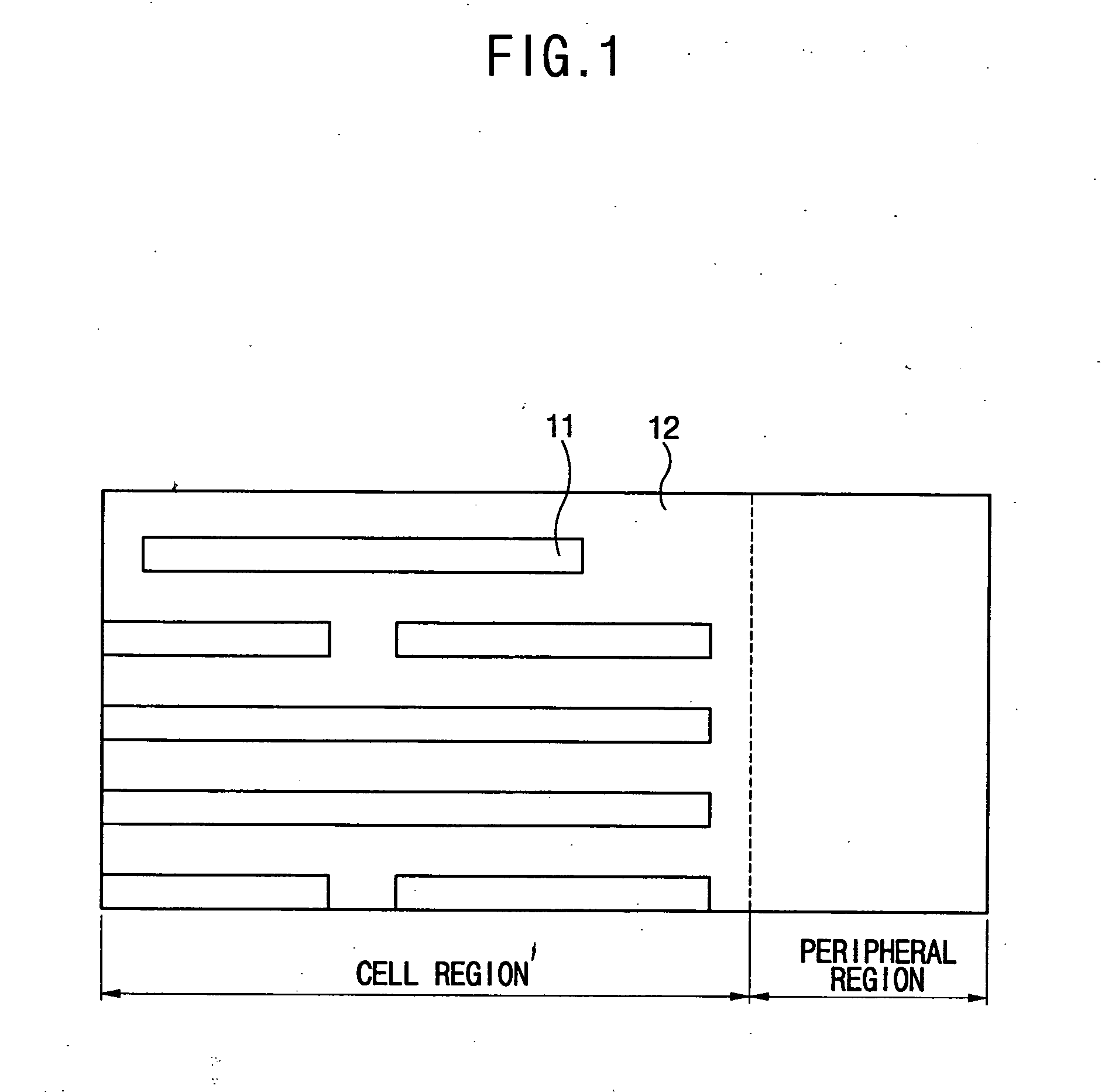

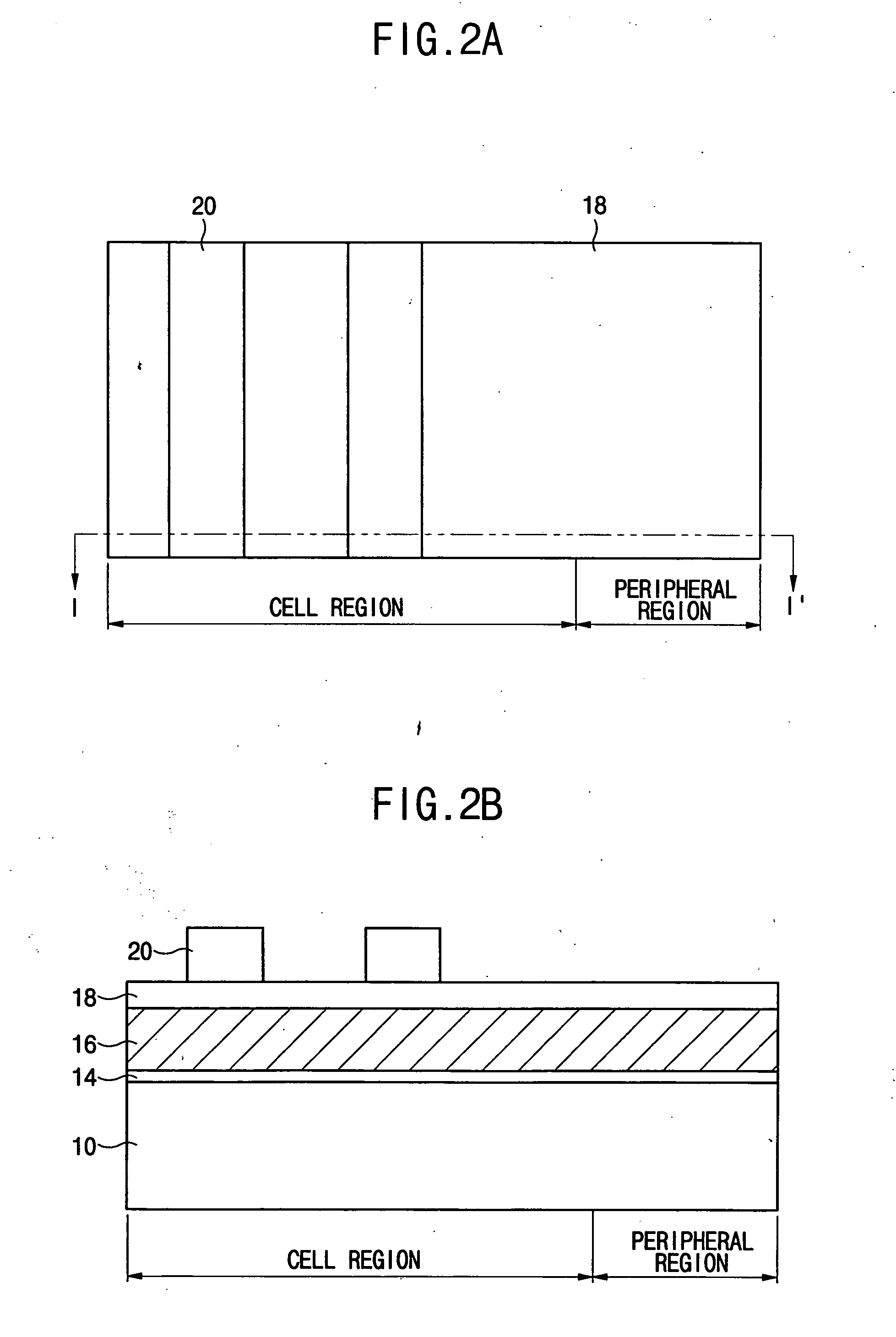

Method of forming a pattern in a semiconductor device and method of forming a gate using the same

InactiveUS20050142497A1Small line widthLine width variationPhotomechanical apparatusSemiconductor/solid-state device manufacturingDevice materialCell region

A method of forming a pattern in a semiconductor device is described. A substrate divided into cell and peripheral regions is provided, and an object layer is formed on a substrate. A buffer pattern is formed on the object layer in the cell region along a first direction. A spacer is formed along a sidewall of the buffer pattern in the cell region, and a hard mask layer remains on the object layer in the peripheral region. The buffer layer is removed, and the spacer is separated along a second direction different from the first direction, thereby forming a cell hard mask pattern. A peripheral hard mask pattern is formed in the peripheral region. A minute pattern is formed using the cell and peripheral hard mask patterns in the substrate. Therefore, a line width variation or an edge line roughness due to the photolithography process is minimized.

Owner:SAMSUNG ELECTRONICS CO LTD

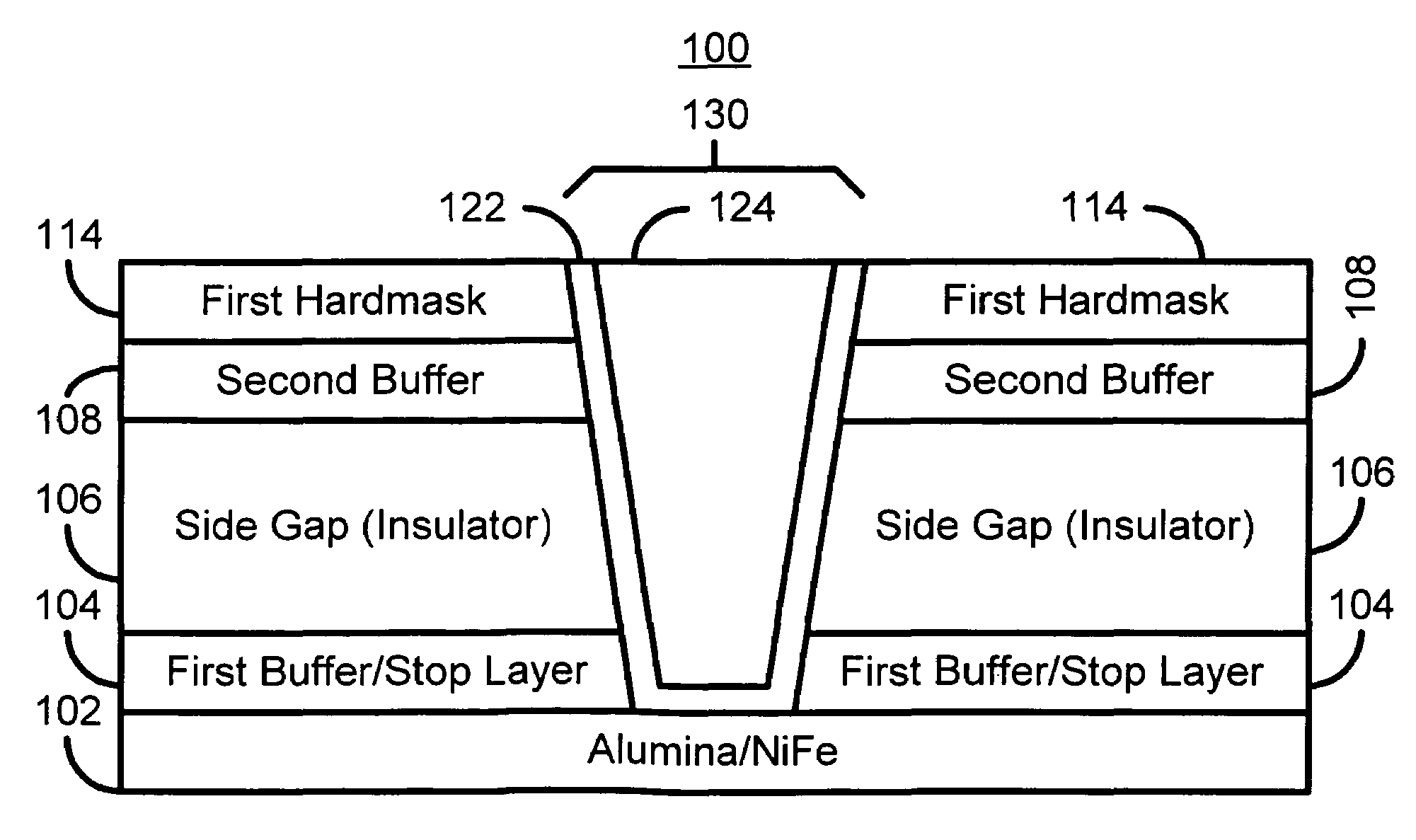

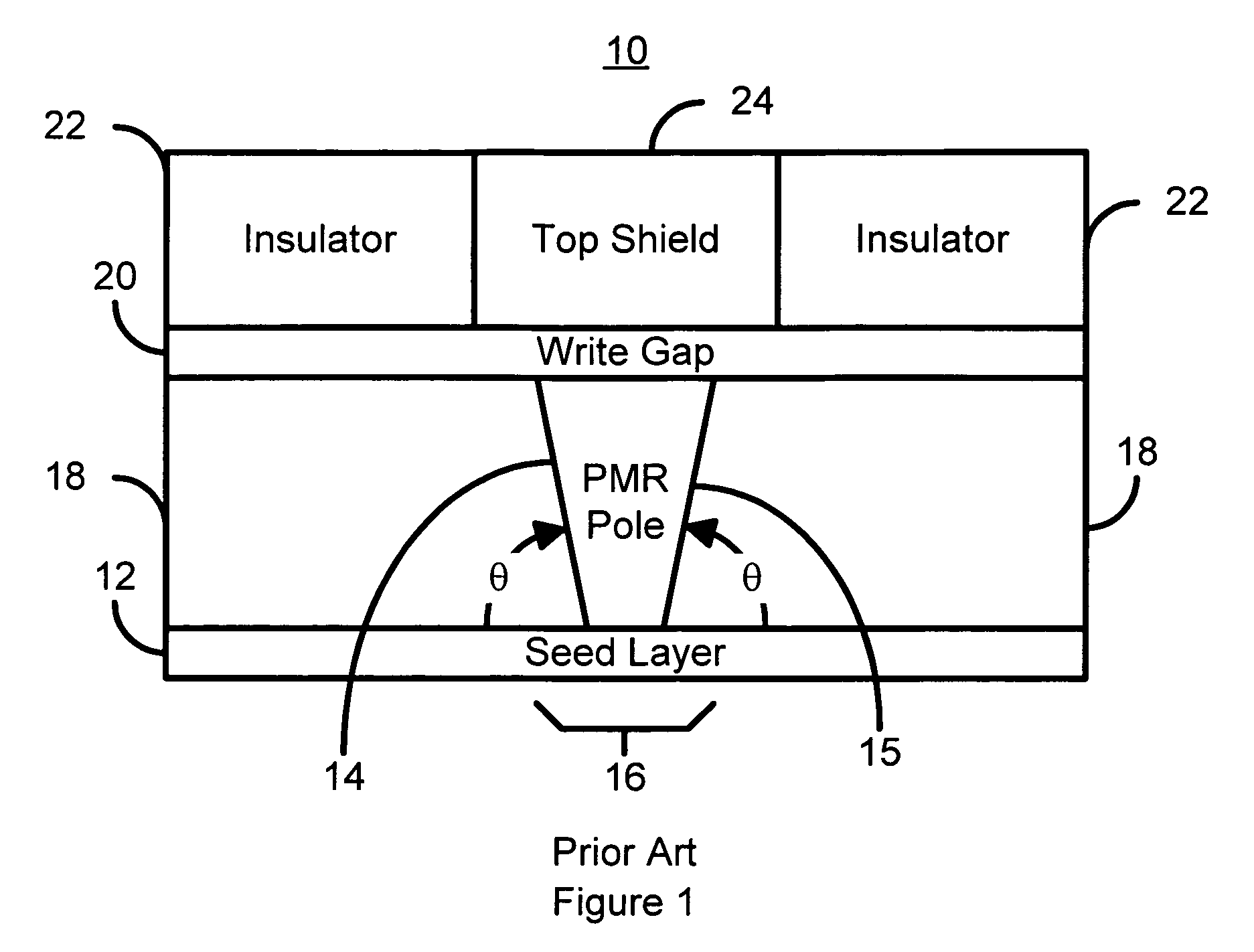

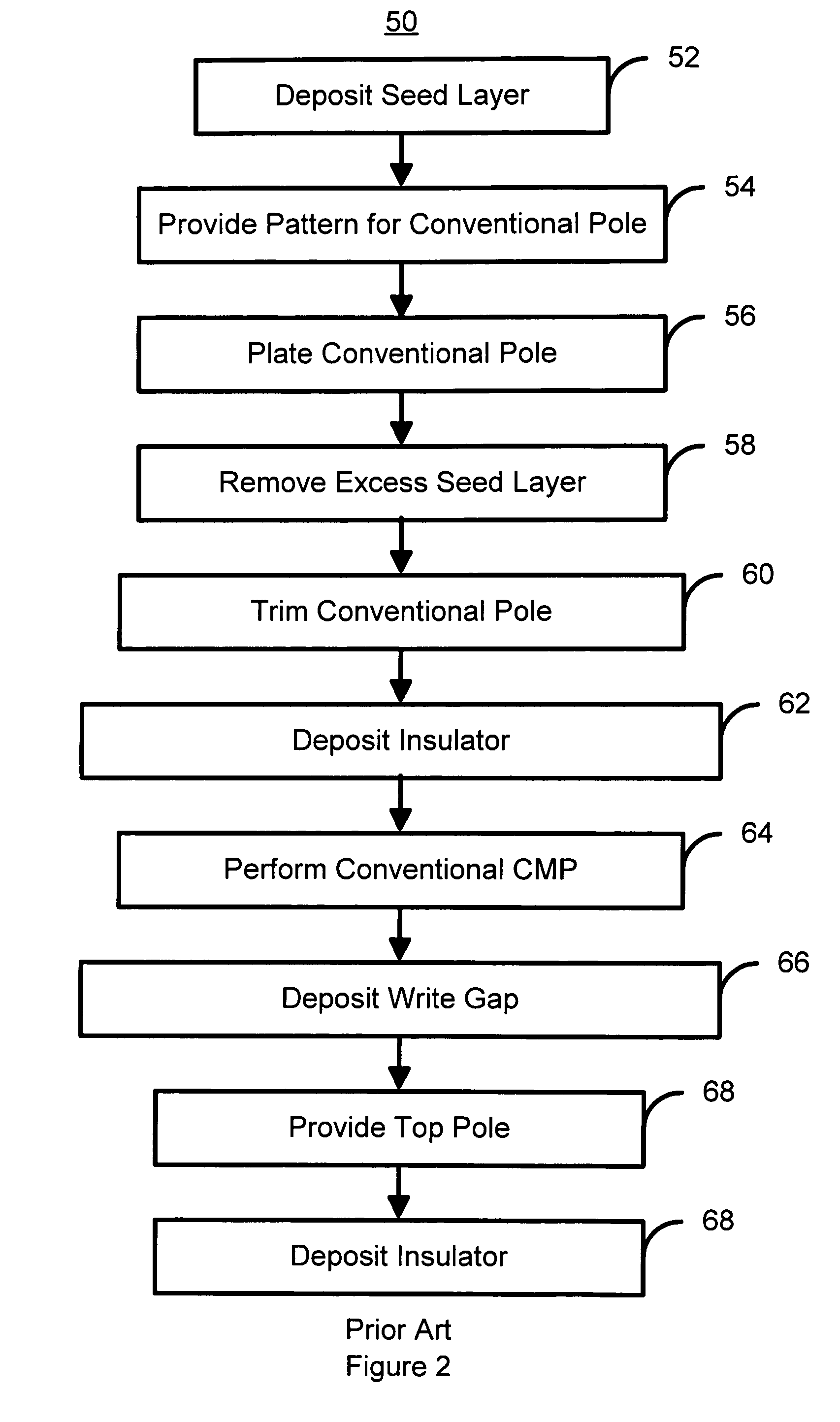

Damascene process for fabricating poles in recording heads

A method and system for manufacturing a pole for a magnetic recording head. The method and system include providing an insulator and fabricating at least one hard mask on the insulator. The at least one hard mask has an aperture therein. The method and system also include removing a portion of the insulator to form a trench within the insulator. The trench is formed under the aperture. The method and system further include depositing at least one ferromagnetic material. The pole includes a portion of the ferromagnetic material within the trench.

Owner:WESTERN DIGITAL TECH INC

SiGe selective growth without a hard mask

InactiveUS20080083948A1Semiconductor/solid-state device manufacturingSemiconductor devicesTensile strainCharge carrier mobility

MOS transistors having localized stressors for improving carrier mobility are provided. Embodiments of the invention comprise a gate electrode formed over a substrate, a carrier channel region in the substrate under the gate electrode, and source / drain regions on either side of the carrier channel region. The source / drain regions include an embedded stressor having a lattice spacing different from the substrate. In a preferred embodiment, the substrate is silicon and the embedded stressor is SiGe or SiC. An epitaxy process that includes using HCl gas selectively forms a stressor layer within the crystalline source / drain regions and not on polycrystalline regions of the structure. A preferred epitaxy process dispenses with the source / drain hard mask required of conventional methods. The embedded SiGe stressor applies a compressive strain to a transistor channel region. In another embodiment, the embedded stressor comprises SiC, and it applies a tensile strain to the transistor channel region.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com