Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

229 results about "Stressor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A stressor is a chemical or biological agent, environmental condition, external stimulus or an event that causes stress to an organism. Psychologically speaking, a stressor can be events or environments that an individual would consider demanding, challenging, and or threaten the individual's safety.

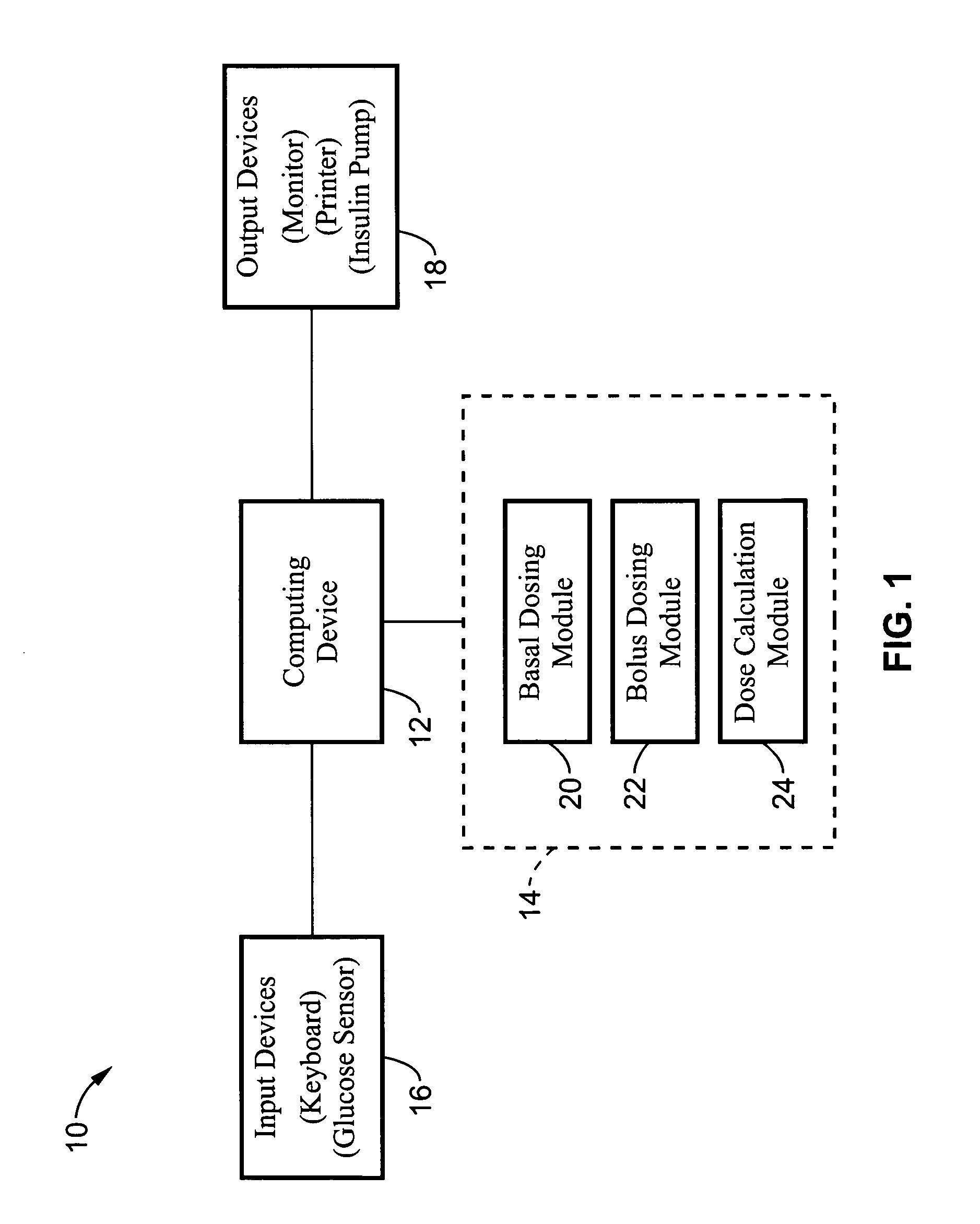

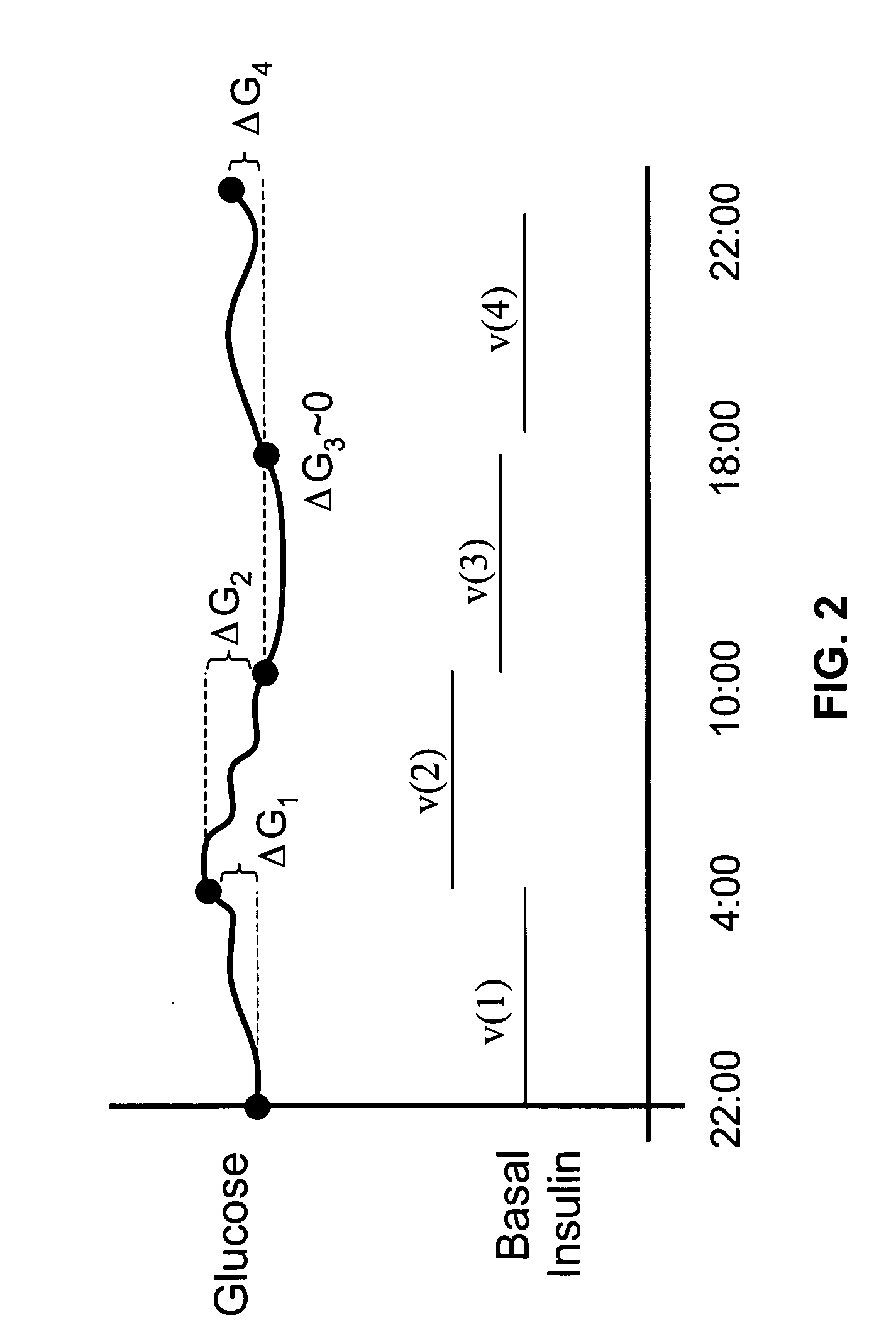

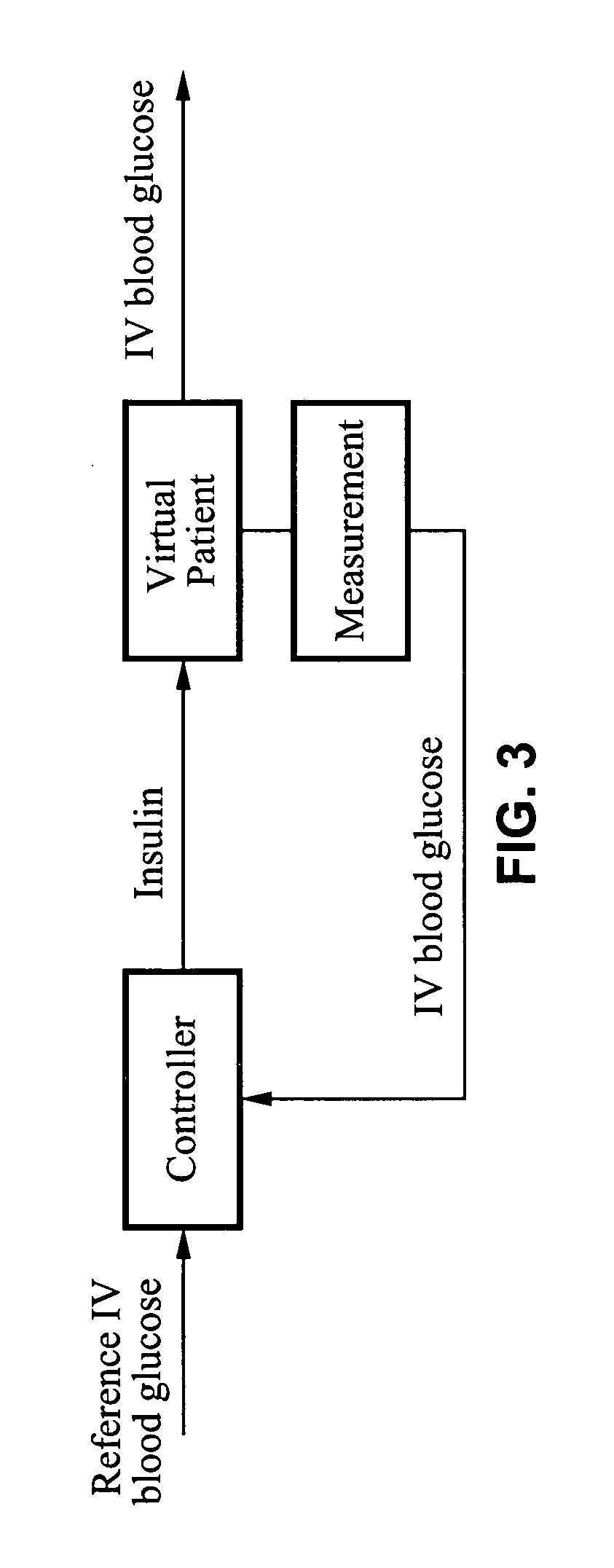

Method and apparatus for glucose control and insulin dosing for diabetics

ActiveUS7651845B2Accurately predicting insulin bolus dosagesProcess controlPeptide/protein ingredientsDrug and medicationsMonitors blood glucoseGlycemic

Owner:RGT UNIV OF CALIFORNIA

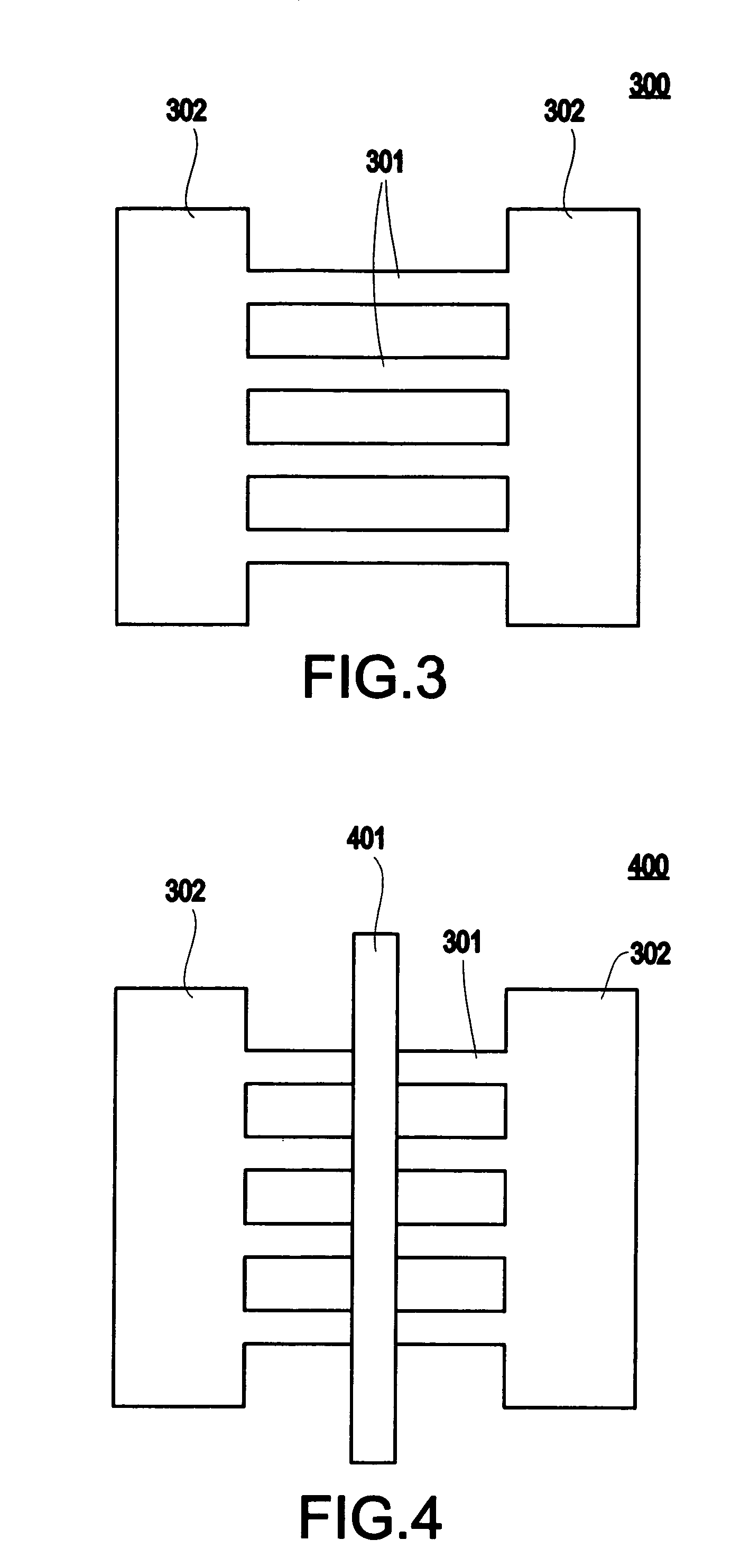

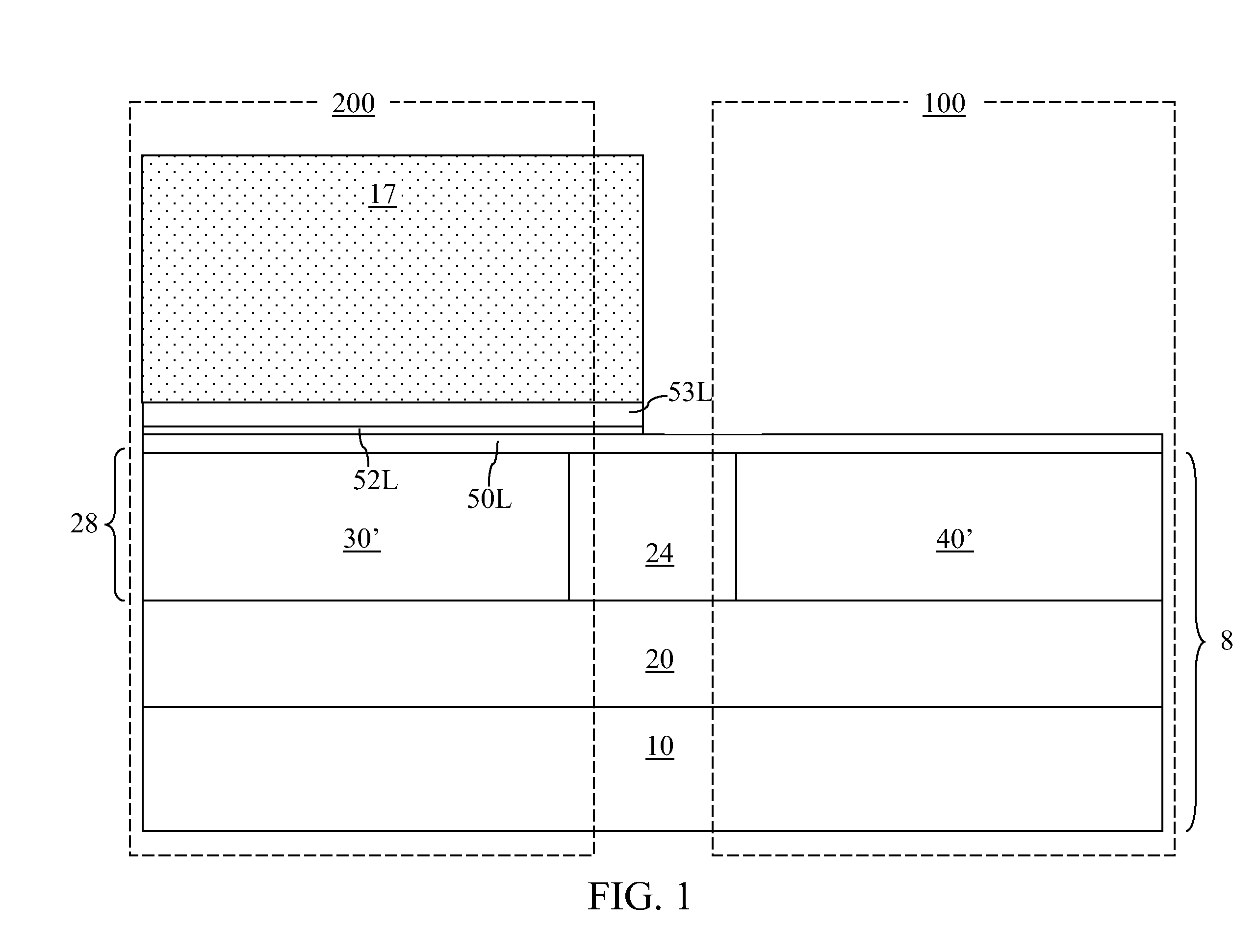

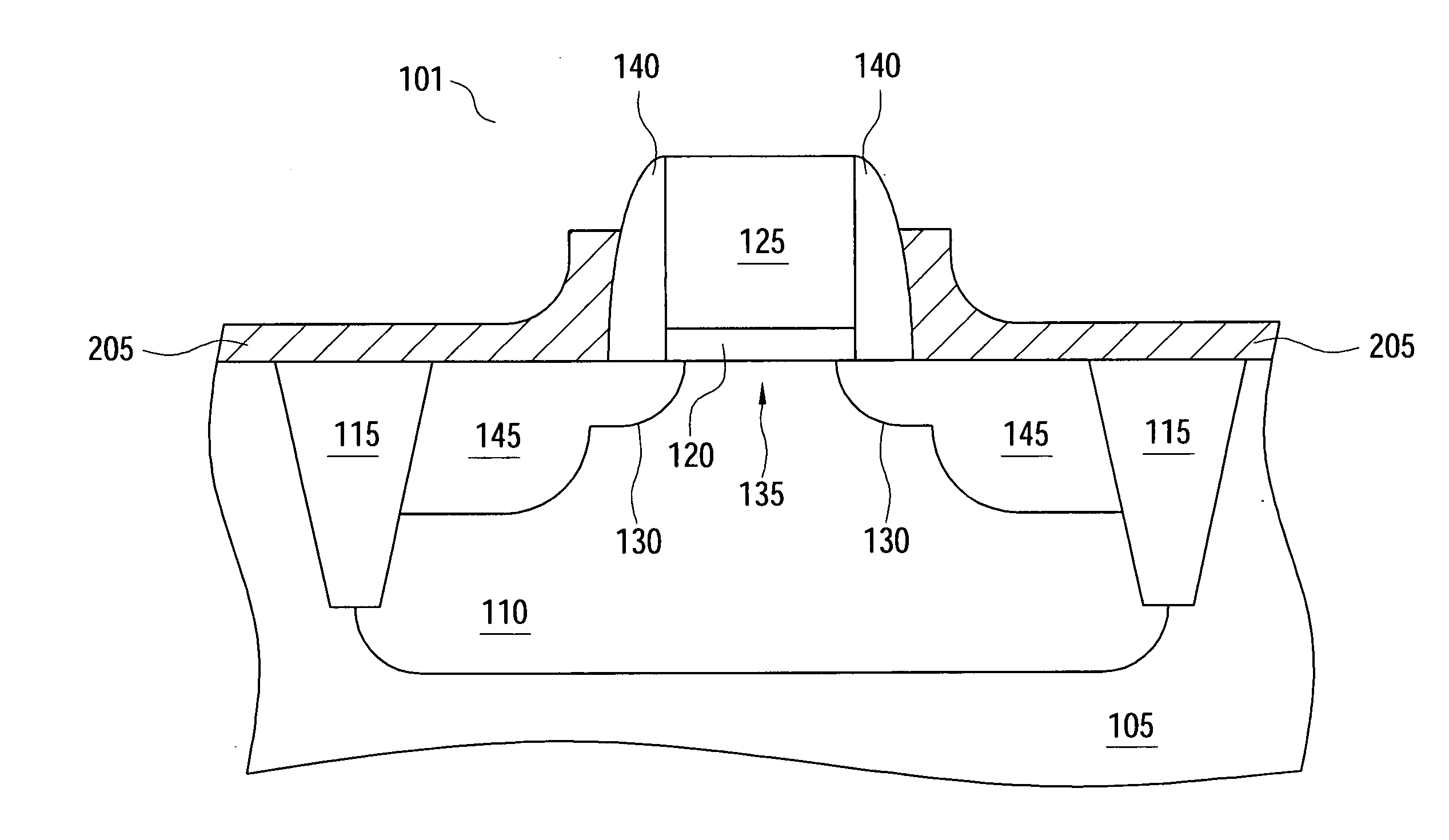

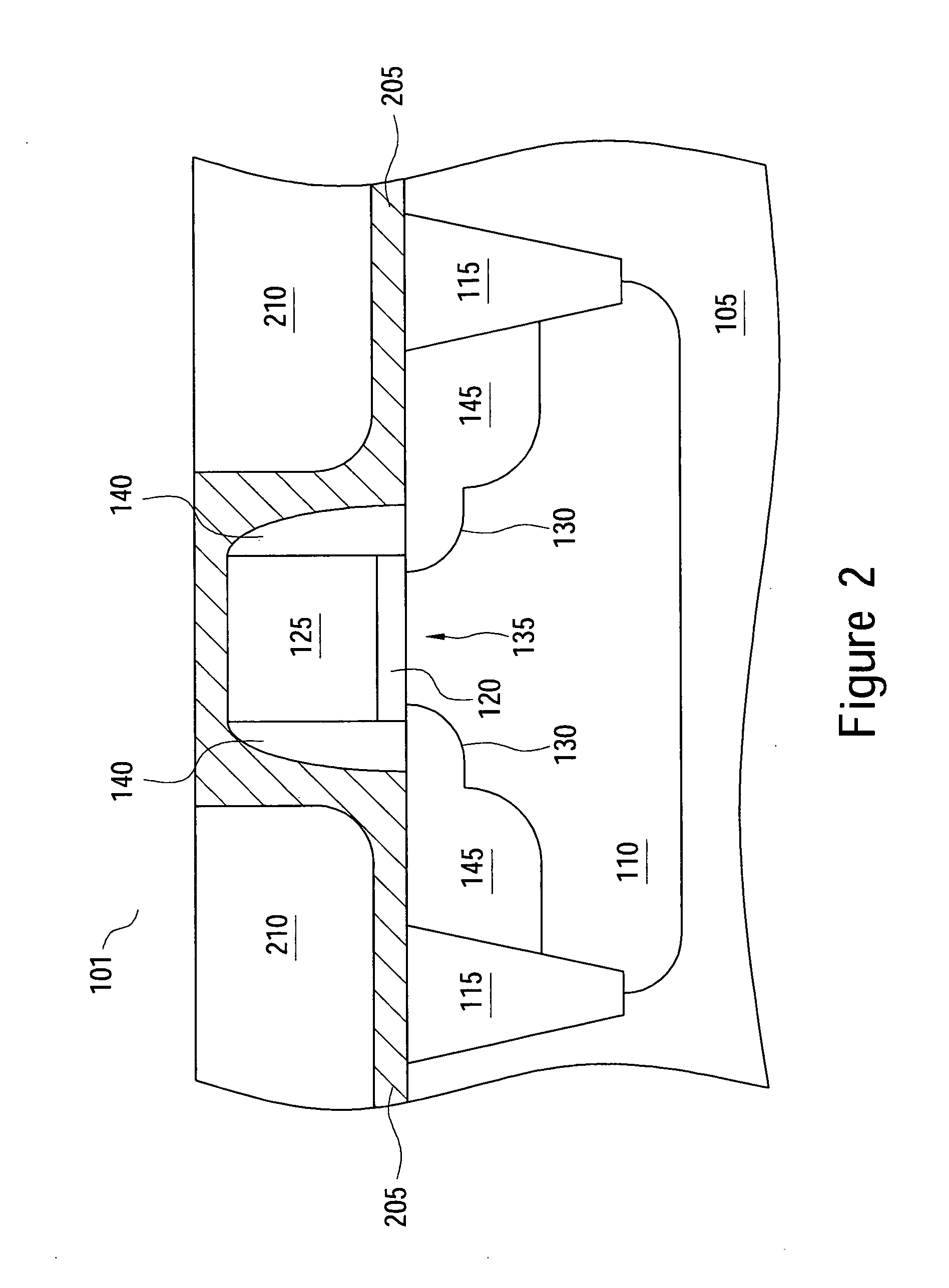

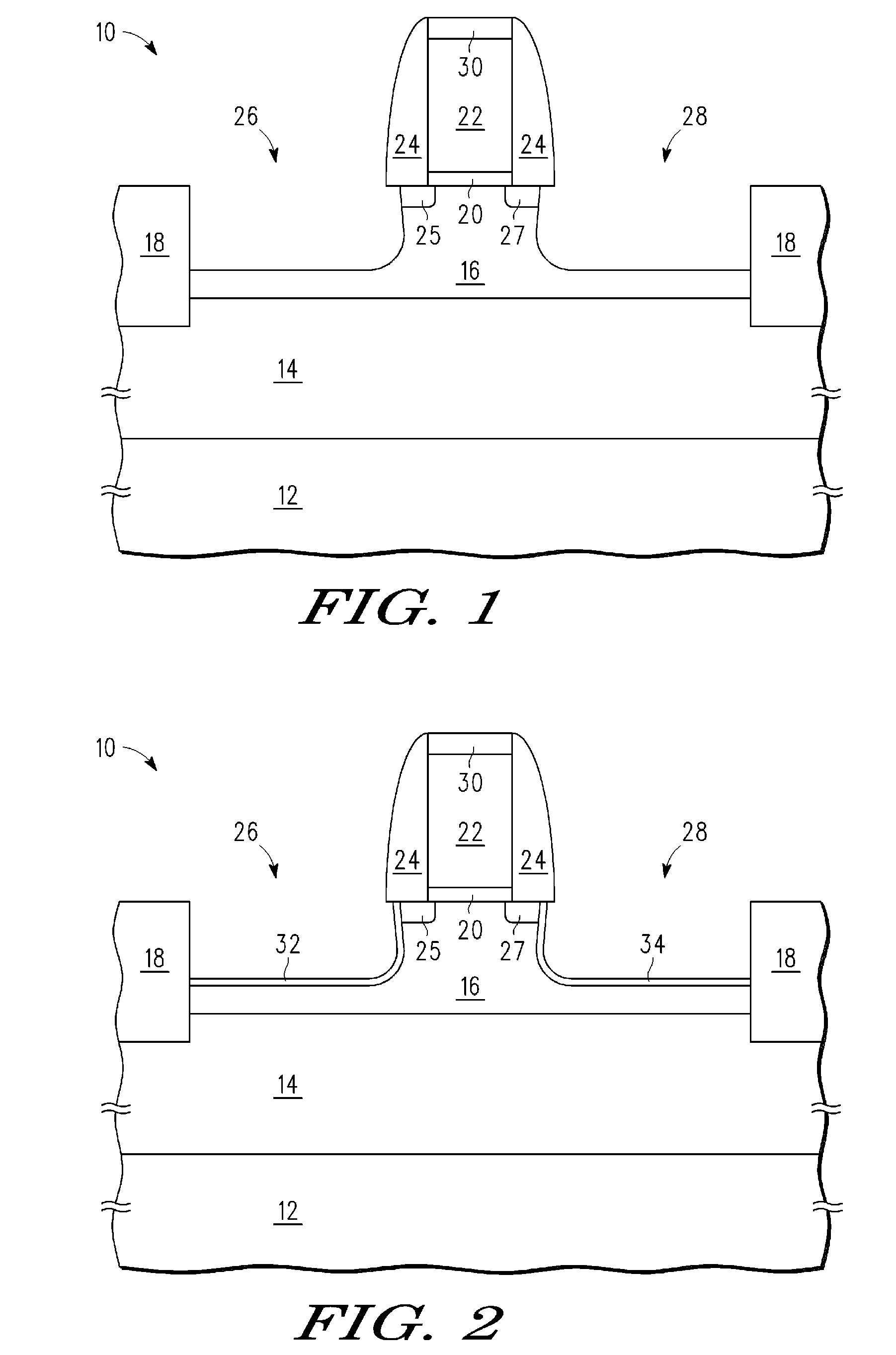

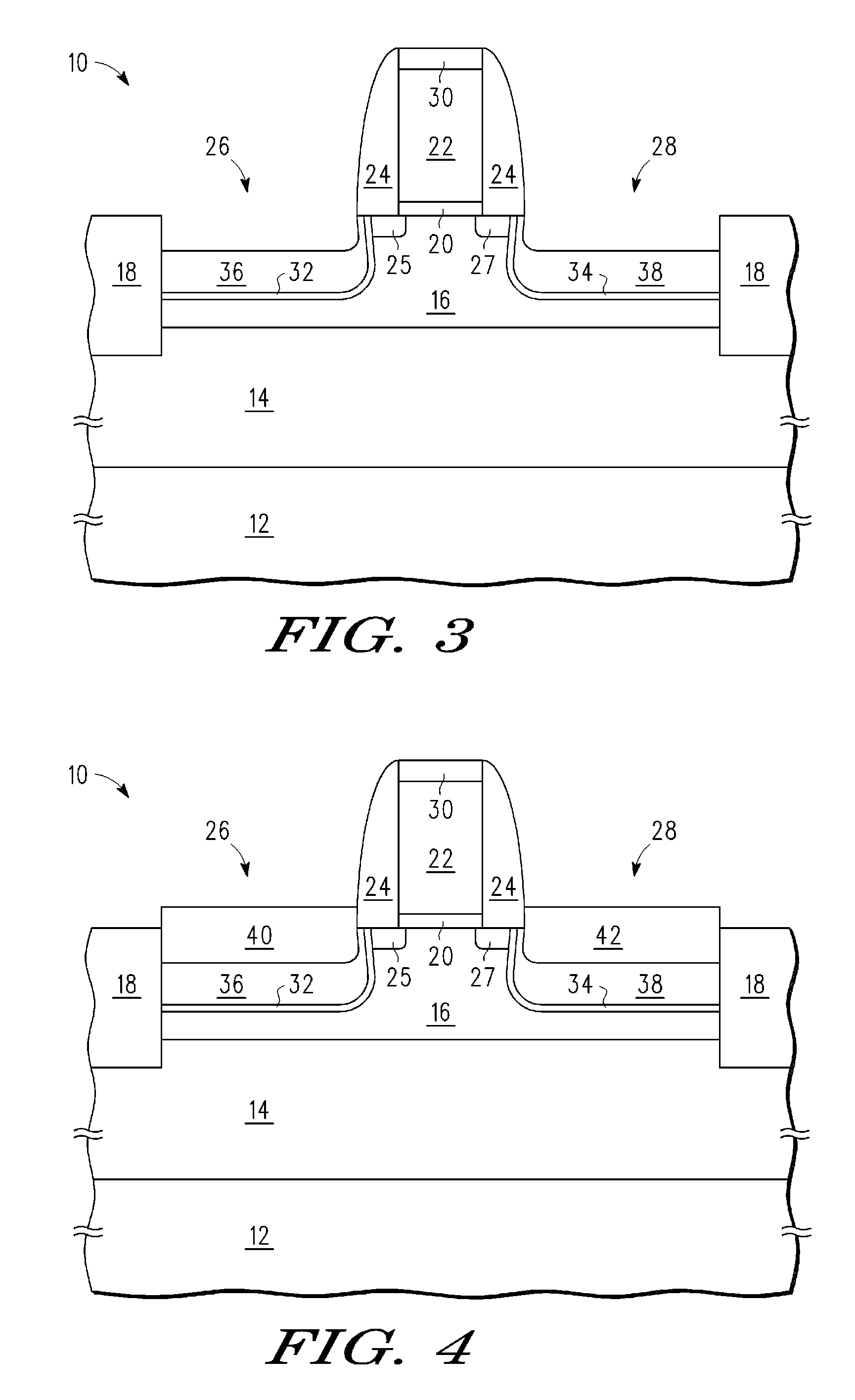

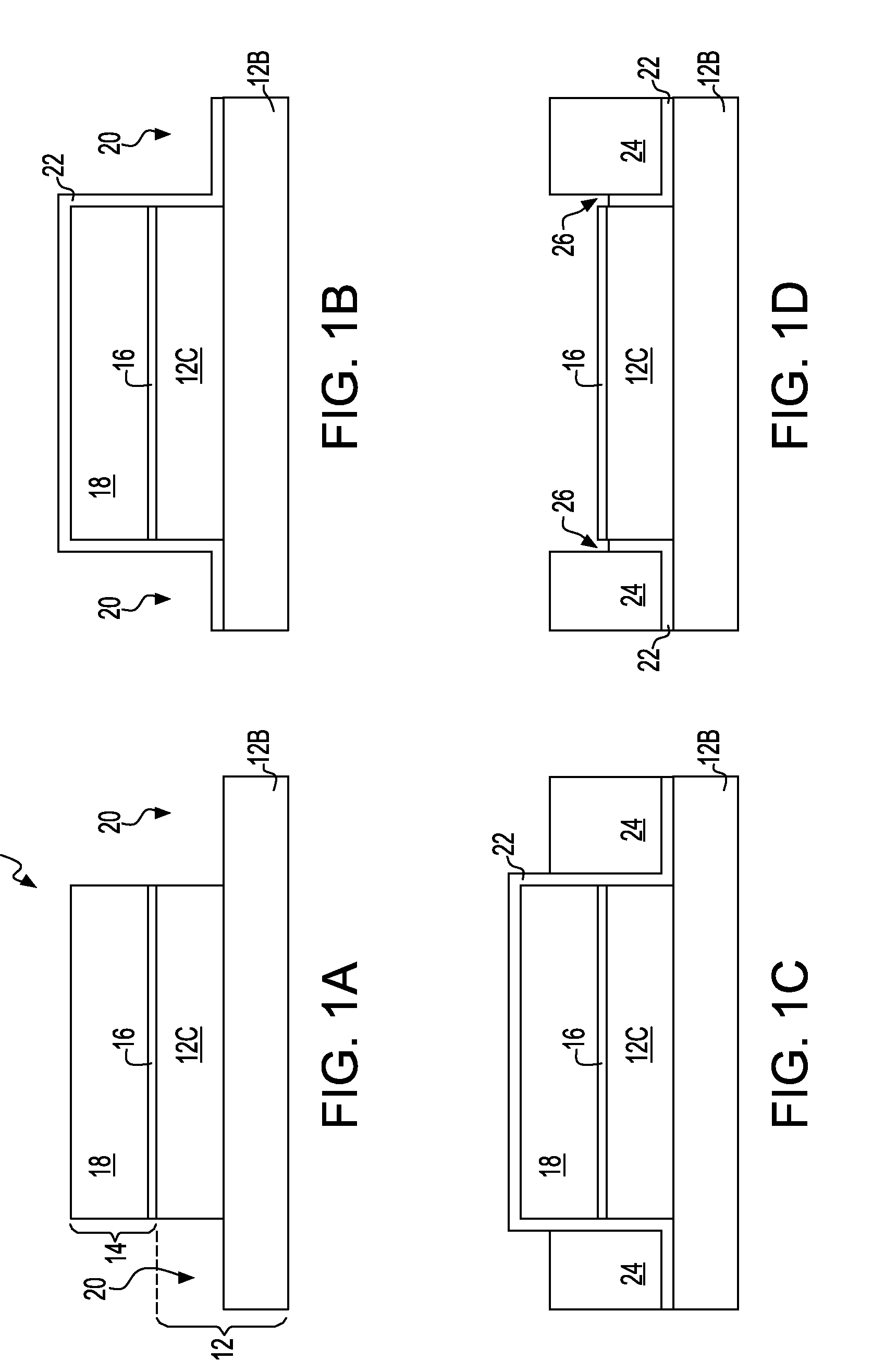

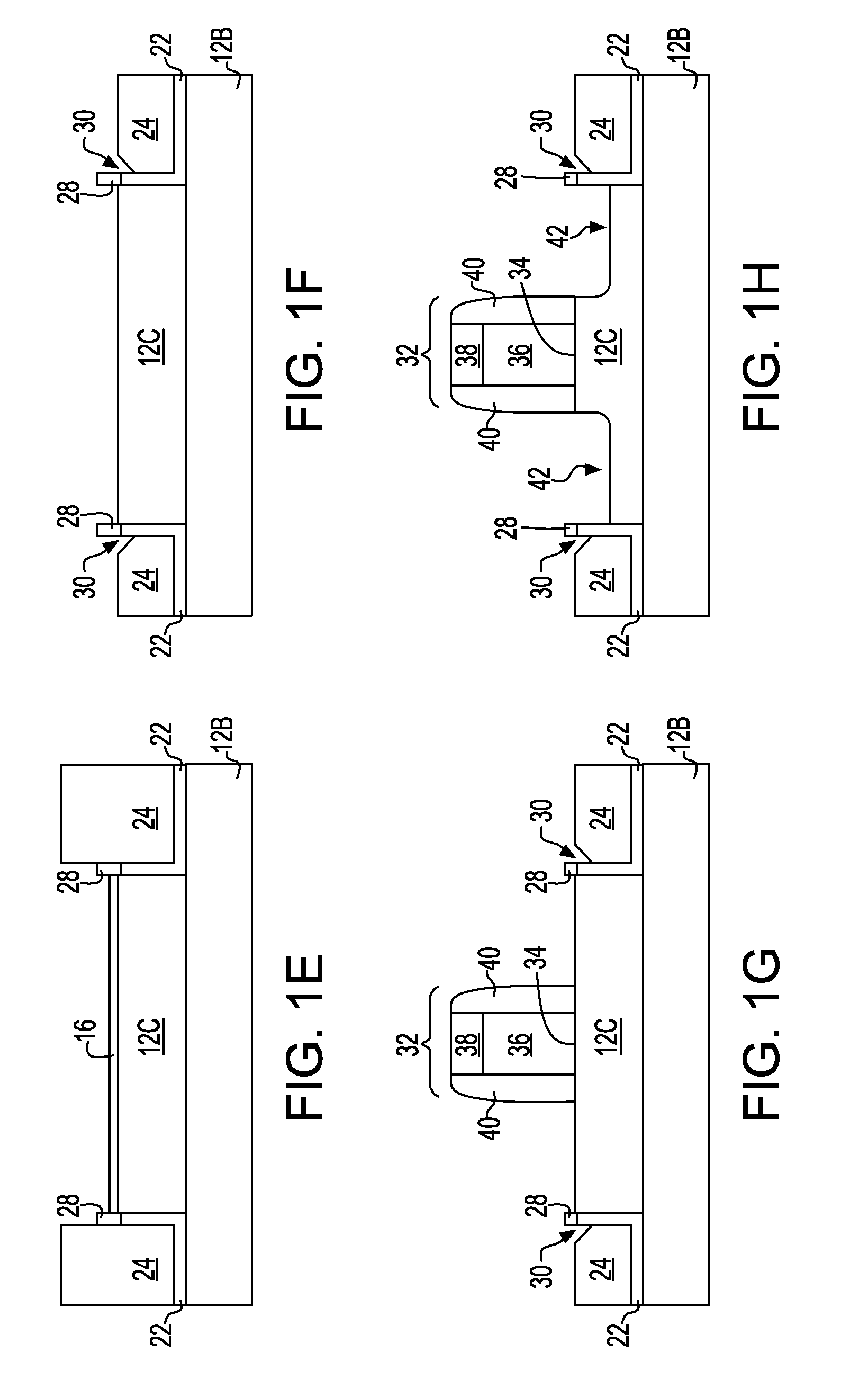

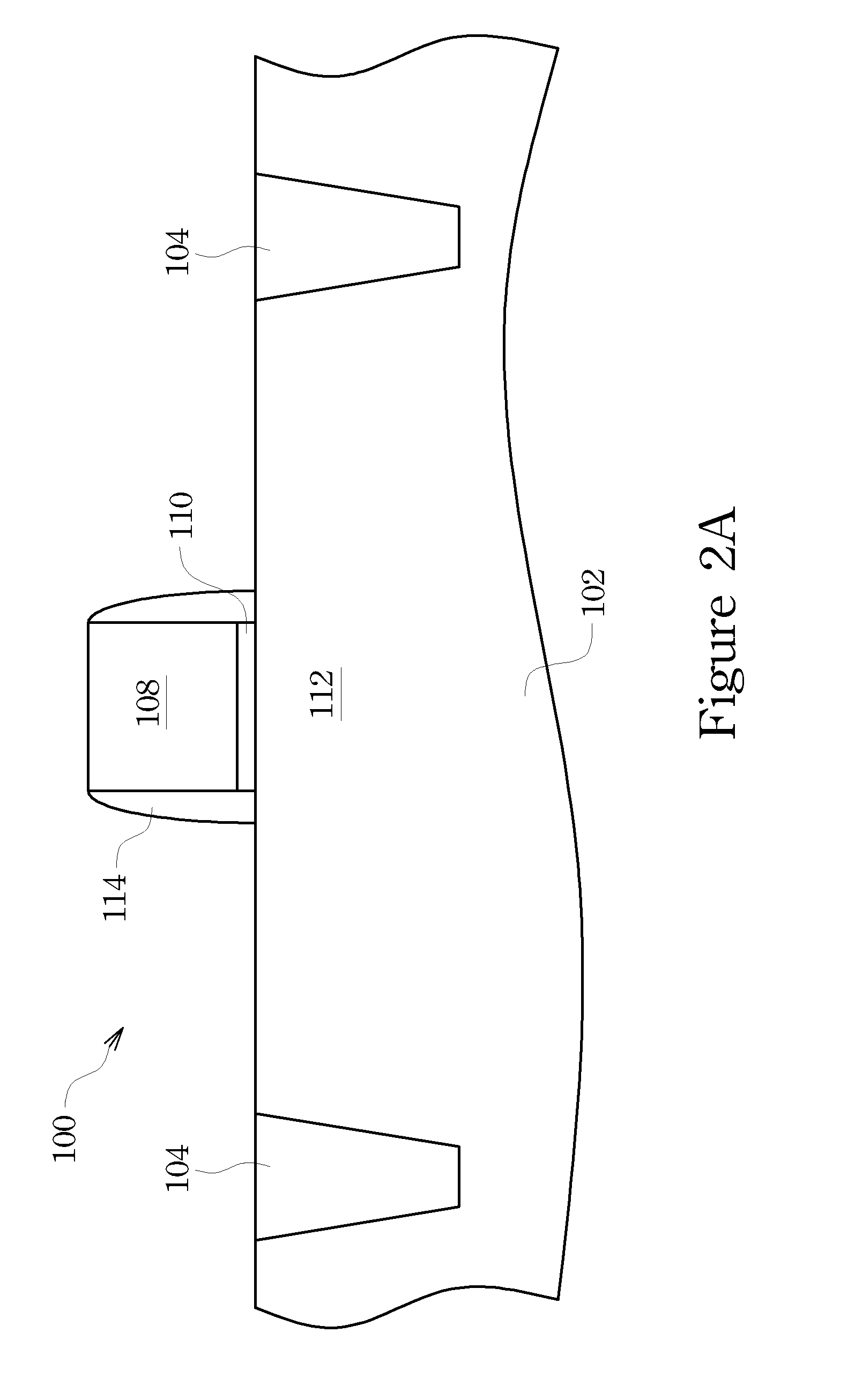

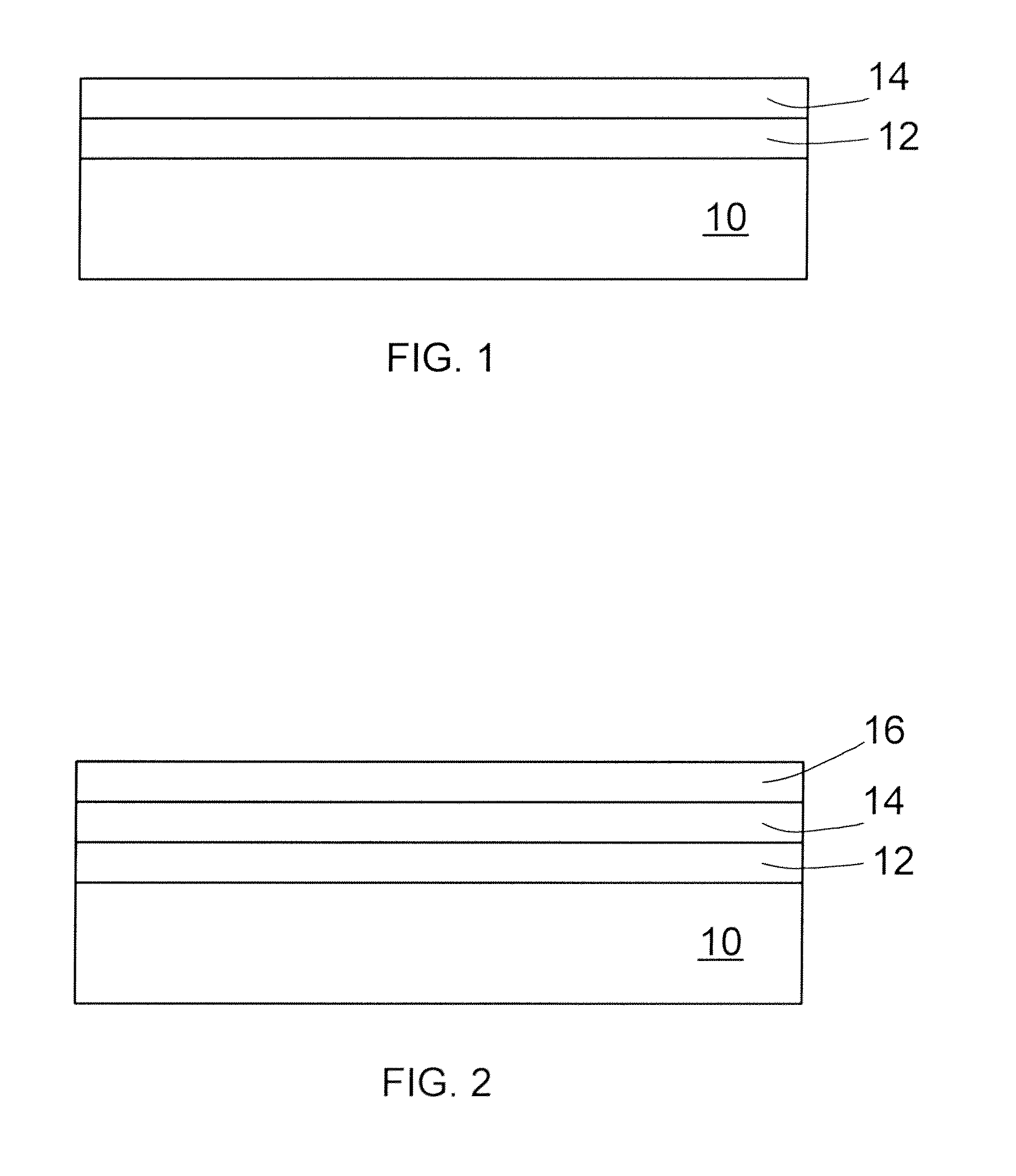

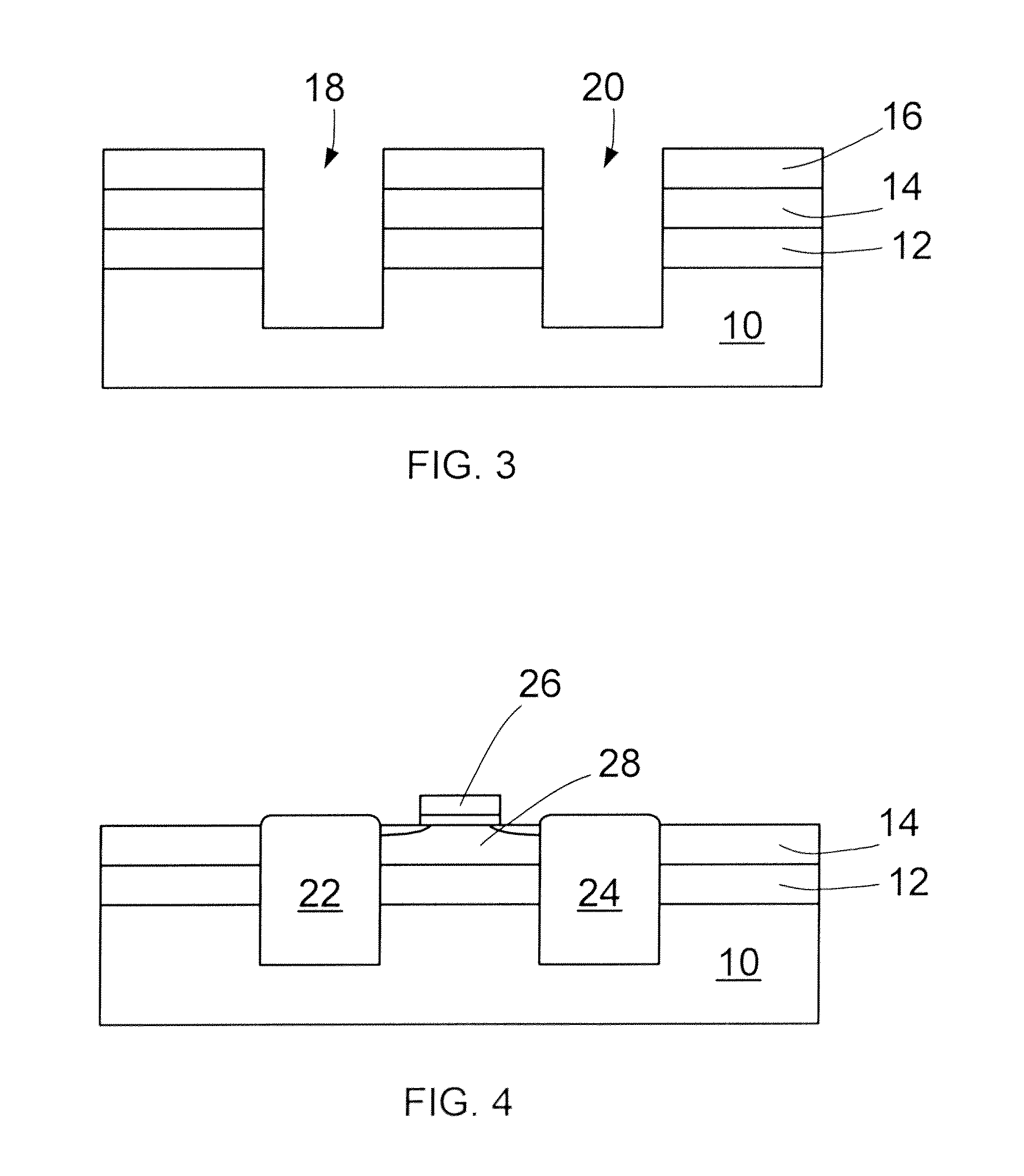

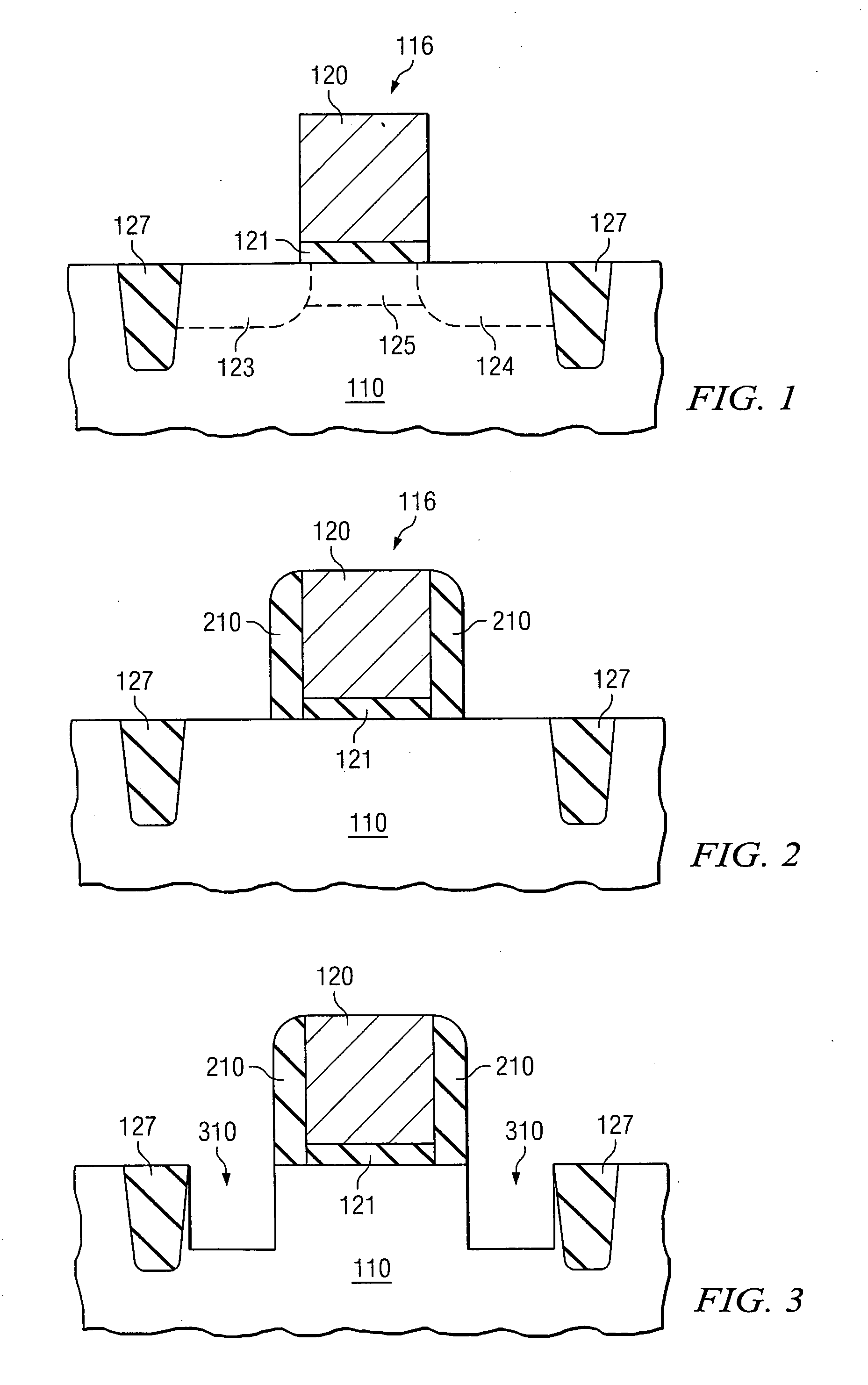

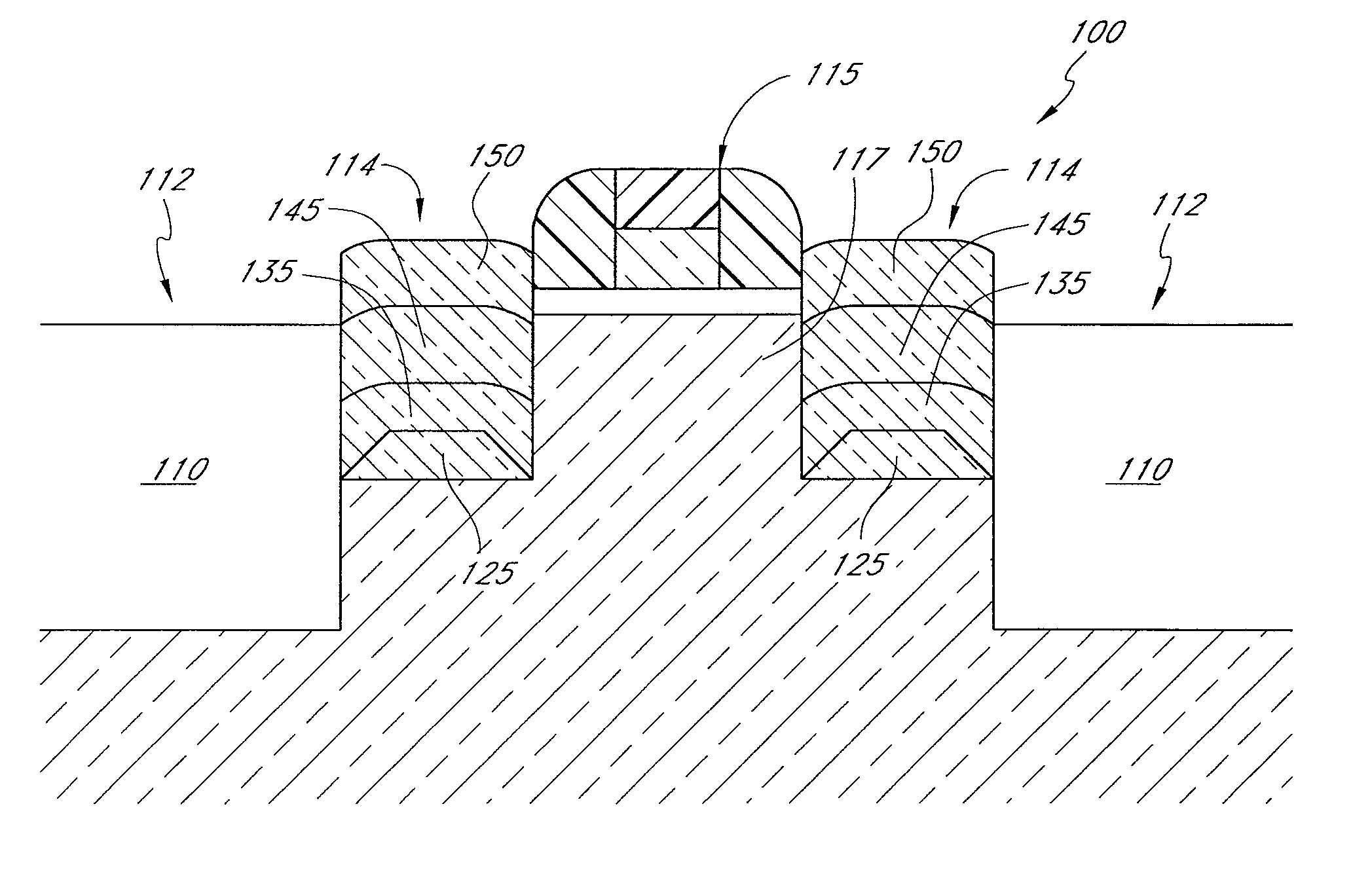

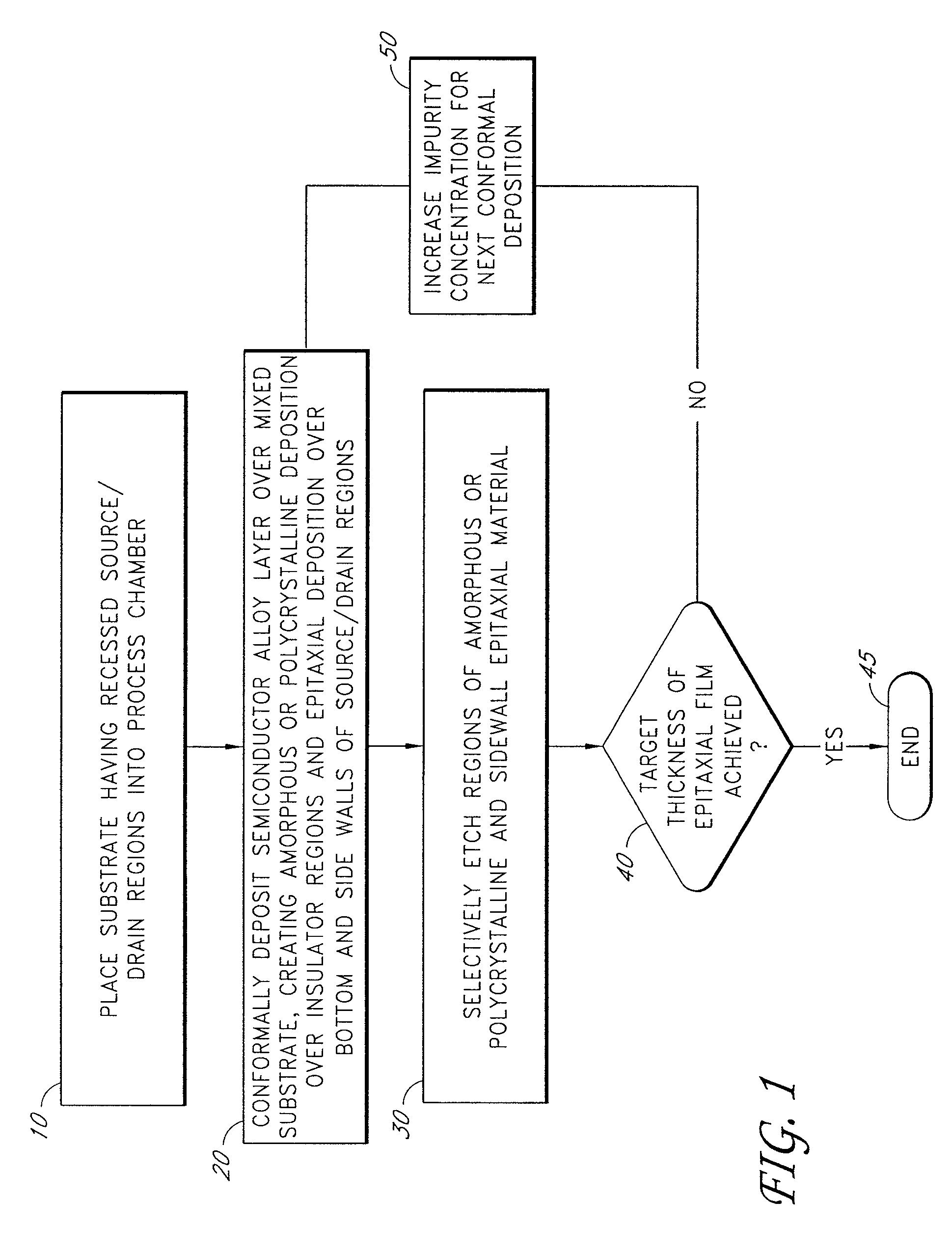

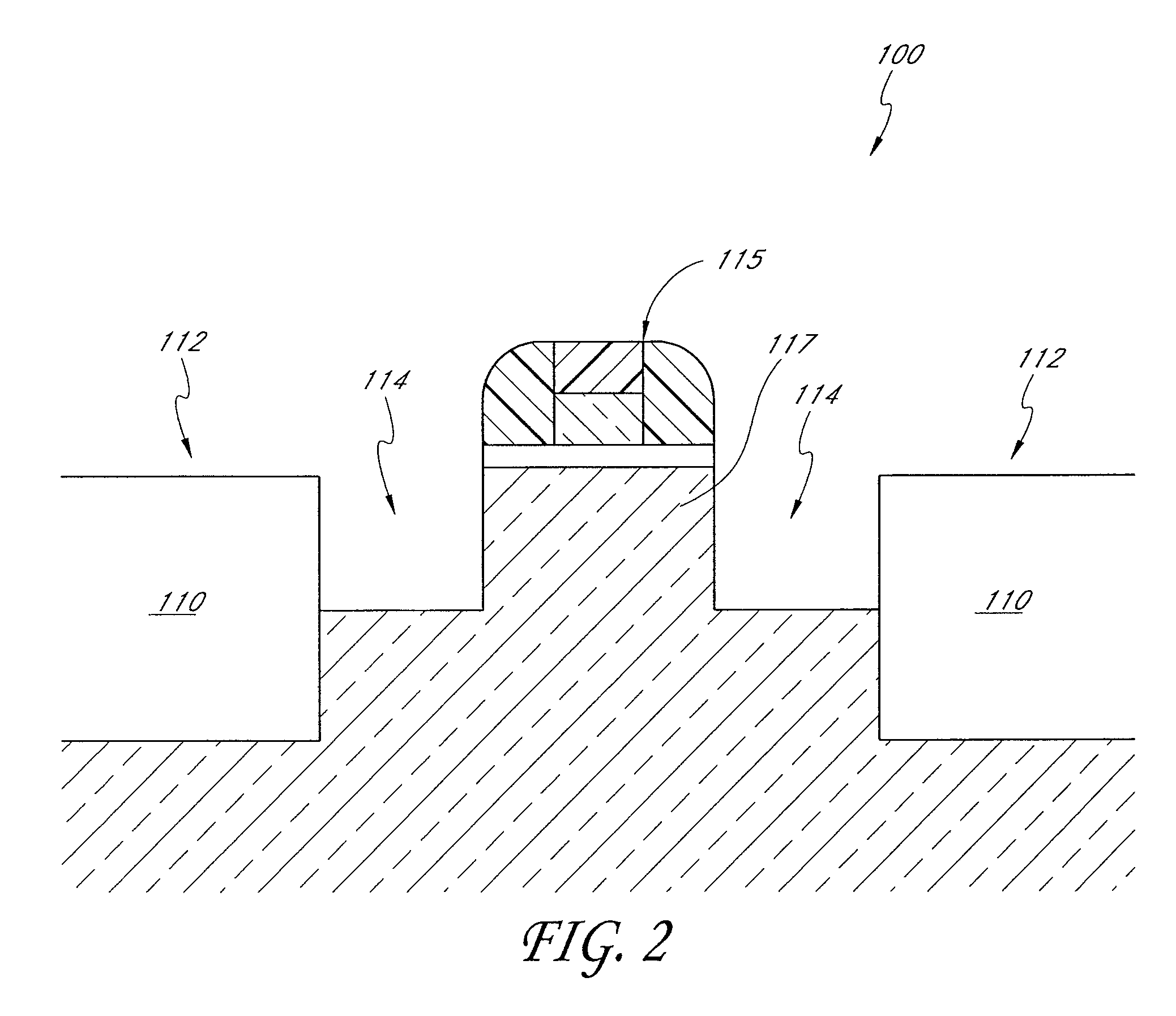

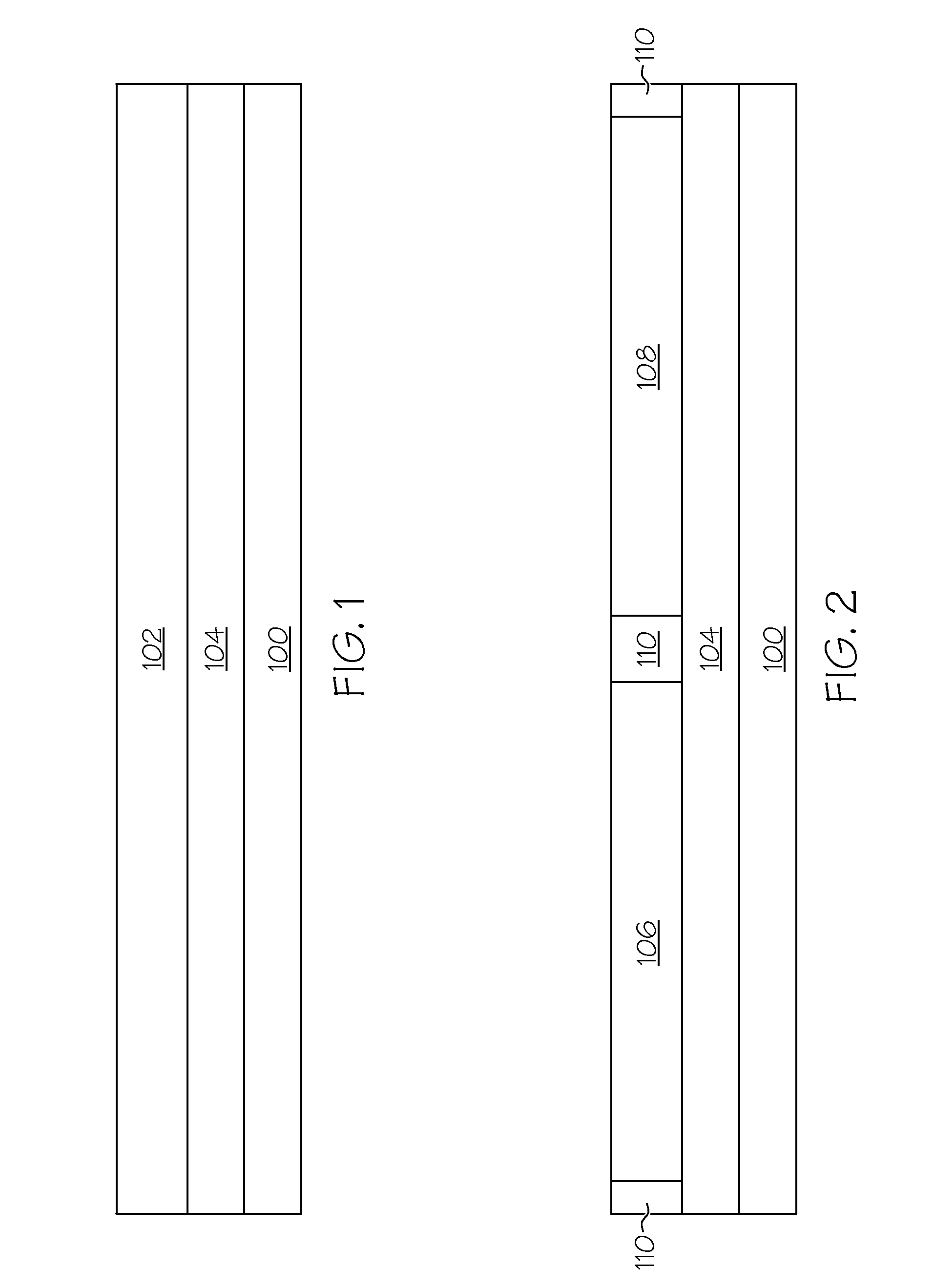

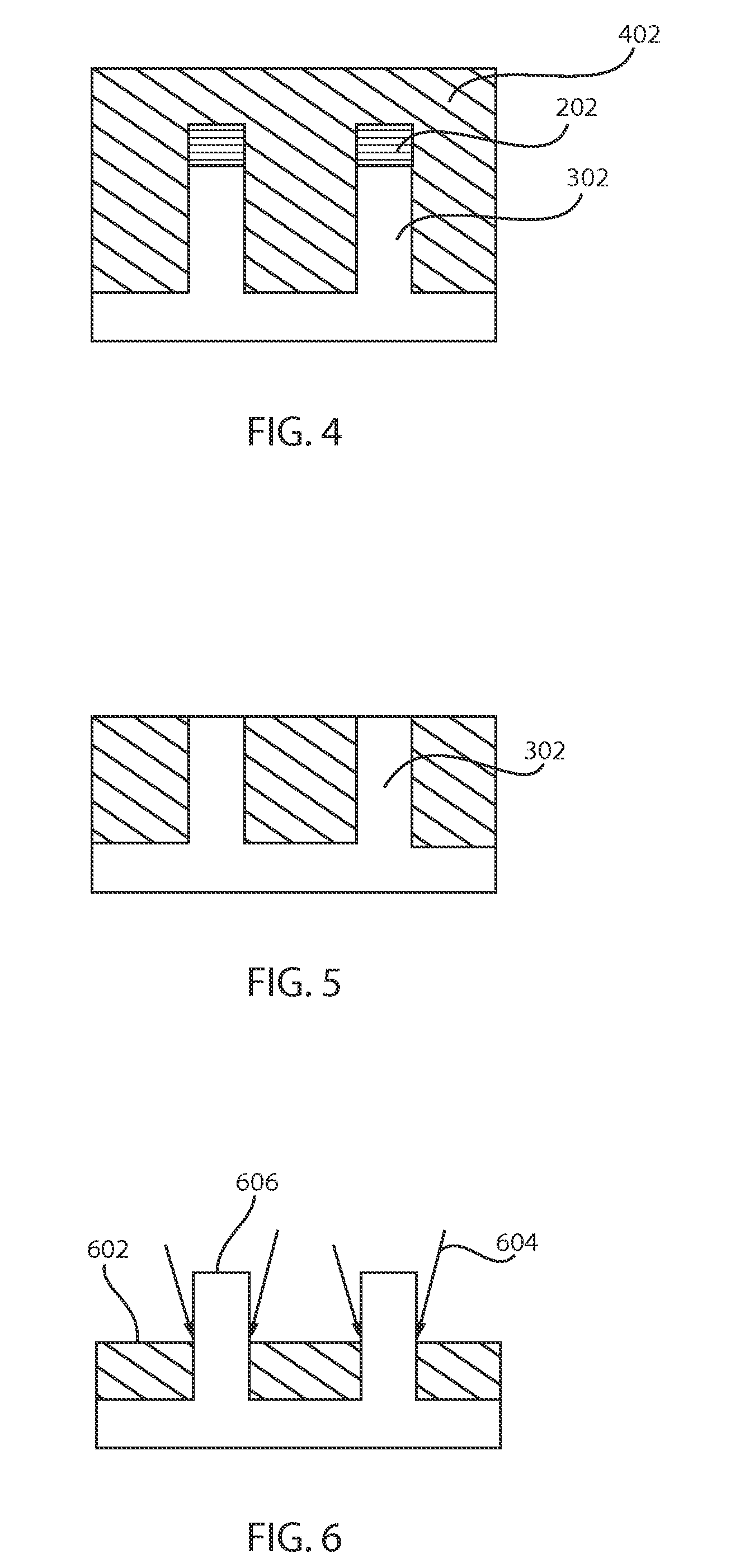

Method to control source/drain stressor profiles for stress engineering

ActiveUS20070235802A1Reduce duplicationSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedGate dielectric

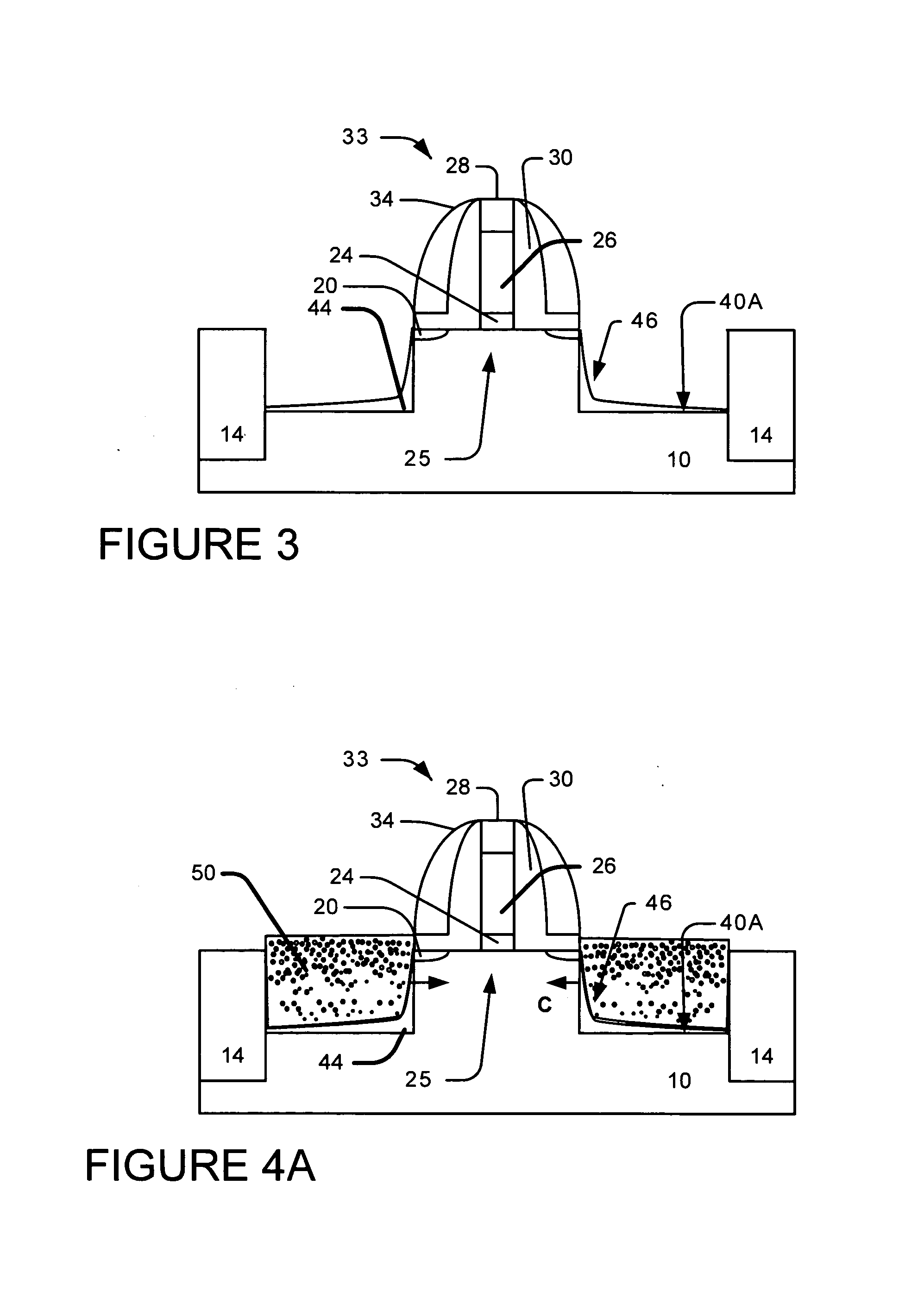

An example embodiment of a strained channel transistor structure comprises the following: a strained channel region comprising a first semiconductor material with a first natural lattice constant; a gate dielectric layer overlying the strained channel region; a gate electrode overlying the gate dielectric layer; and a source region and drain region oppositely adjacent to the strained channel region, one or both of the source region and drain region are comprised of a stressor region comprised of a second semiconductor material with a second natural lattice constant different from the first natural lattice constant; the stressor region has a graded concentration of a dopant impurity and / or of a stress inducing molecule. Another example embodiment is a process to form the graded impurity or stress inducing molecule stressor embedded S / D region, whereby the location / profile of the S / D stressor is not defined by the recess depth / profile.

Owner:IBM CORP +2

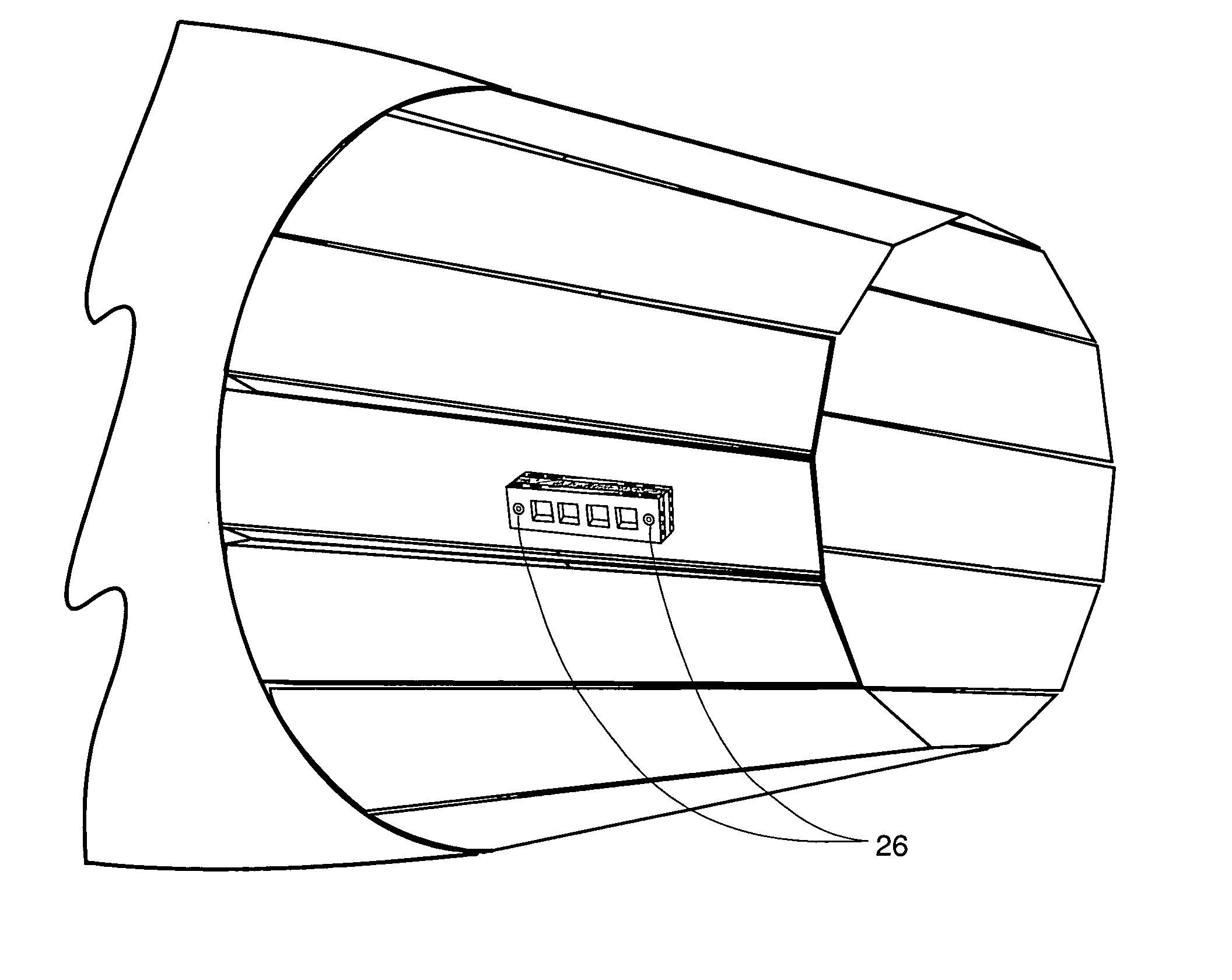

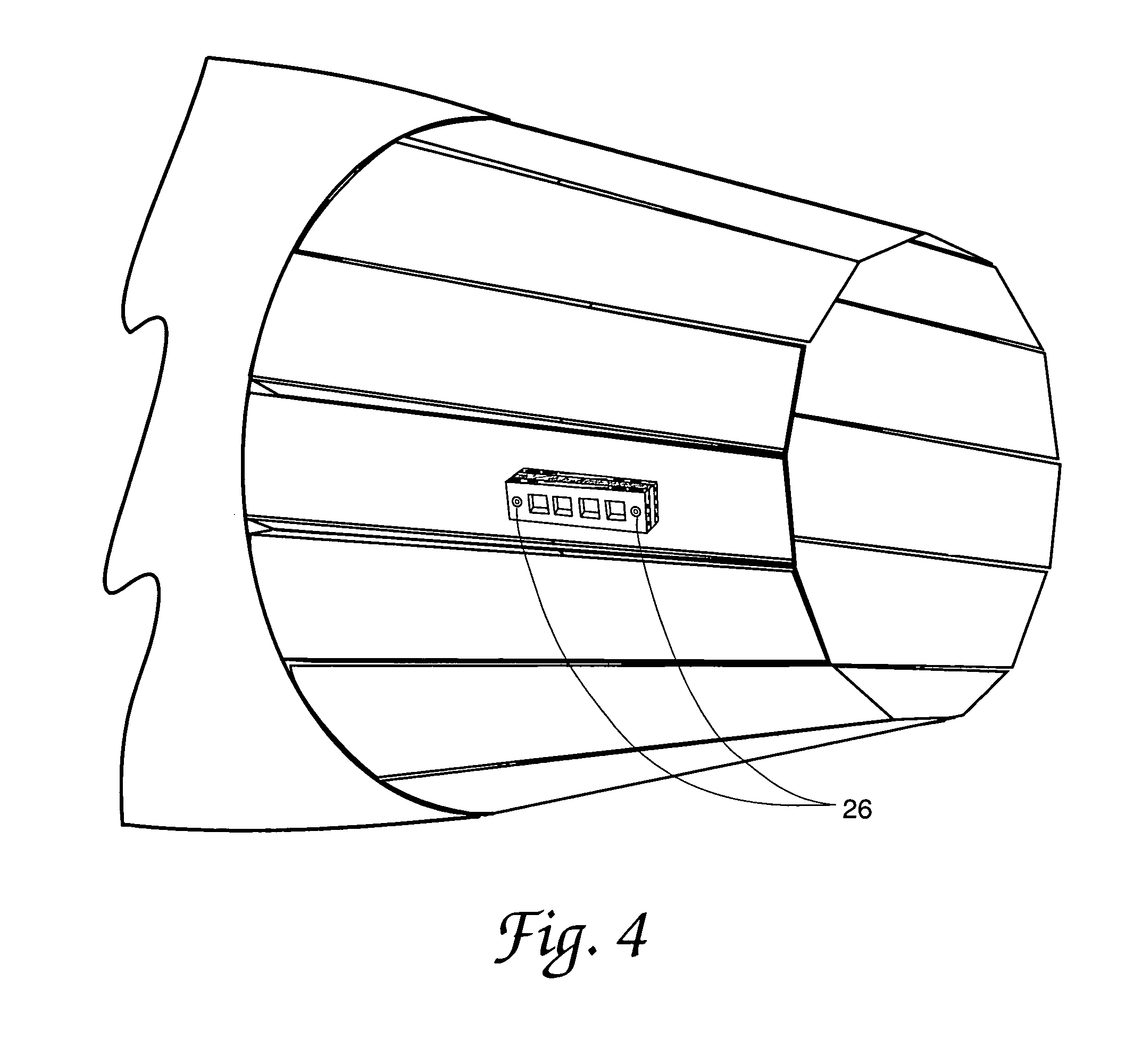

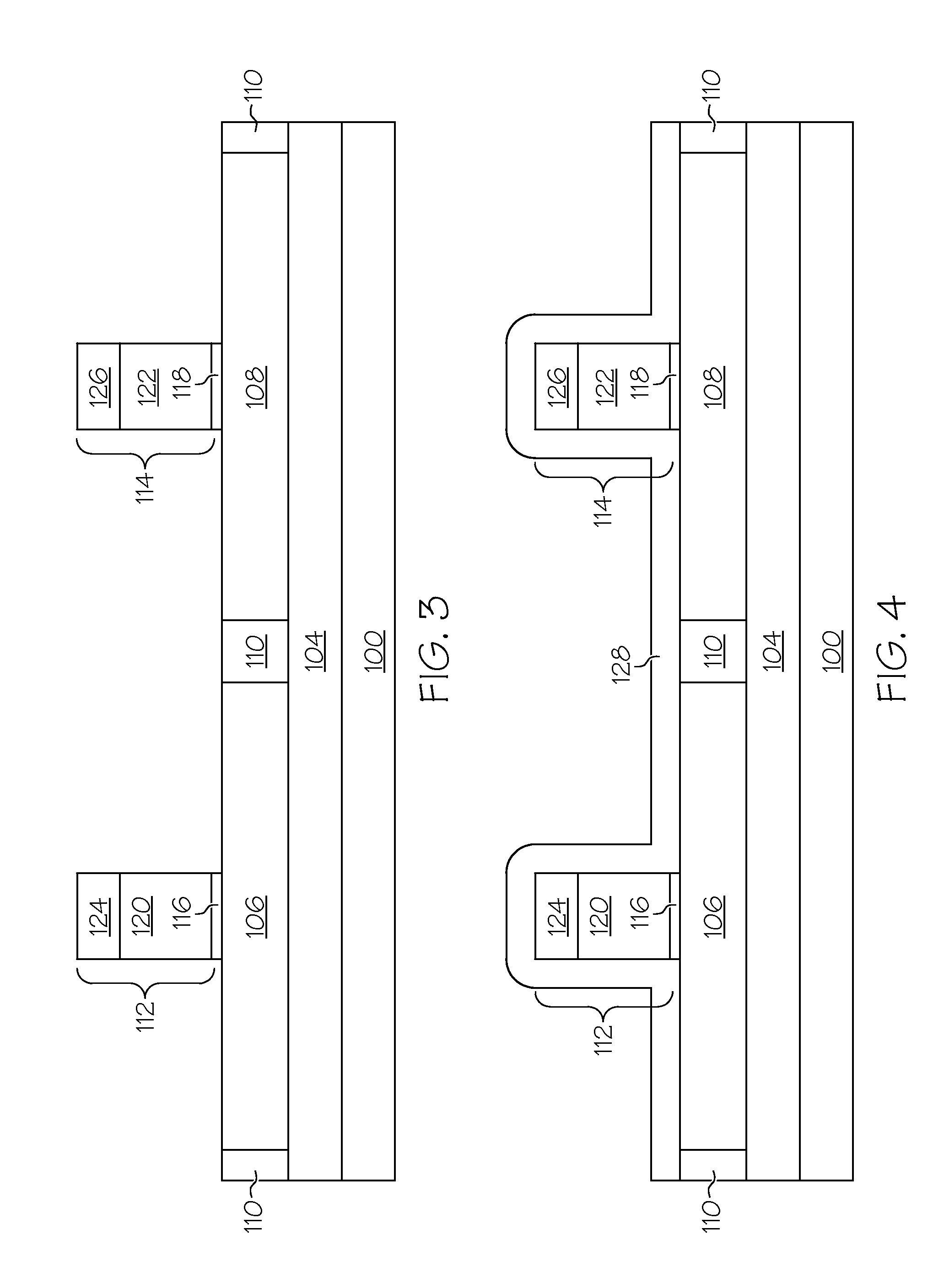

Method and structure for strained finfet devices

ActiveUS20060014338A1High carrier mobilityImprove mobilityTransistorSemiconductor/solid-state device manufacturingEngineeringStressor

A method (and structure) of forming an electronic device includes forming at least one localized stressor region within the device.

Owner:GLOBALFOUNDRIES US INC

Dual-SiGe epitaxy for MOS devices

ActiveUS20080128746A1Increase pressureReduce impurity diffusionSemiconductor/solid-state device manufacturingSemiconductor devicesGate stackStressor

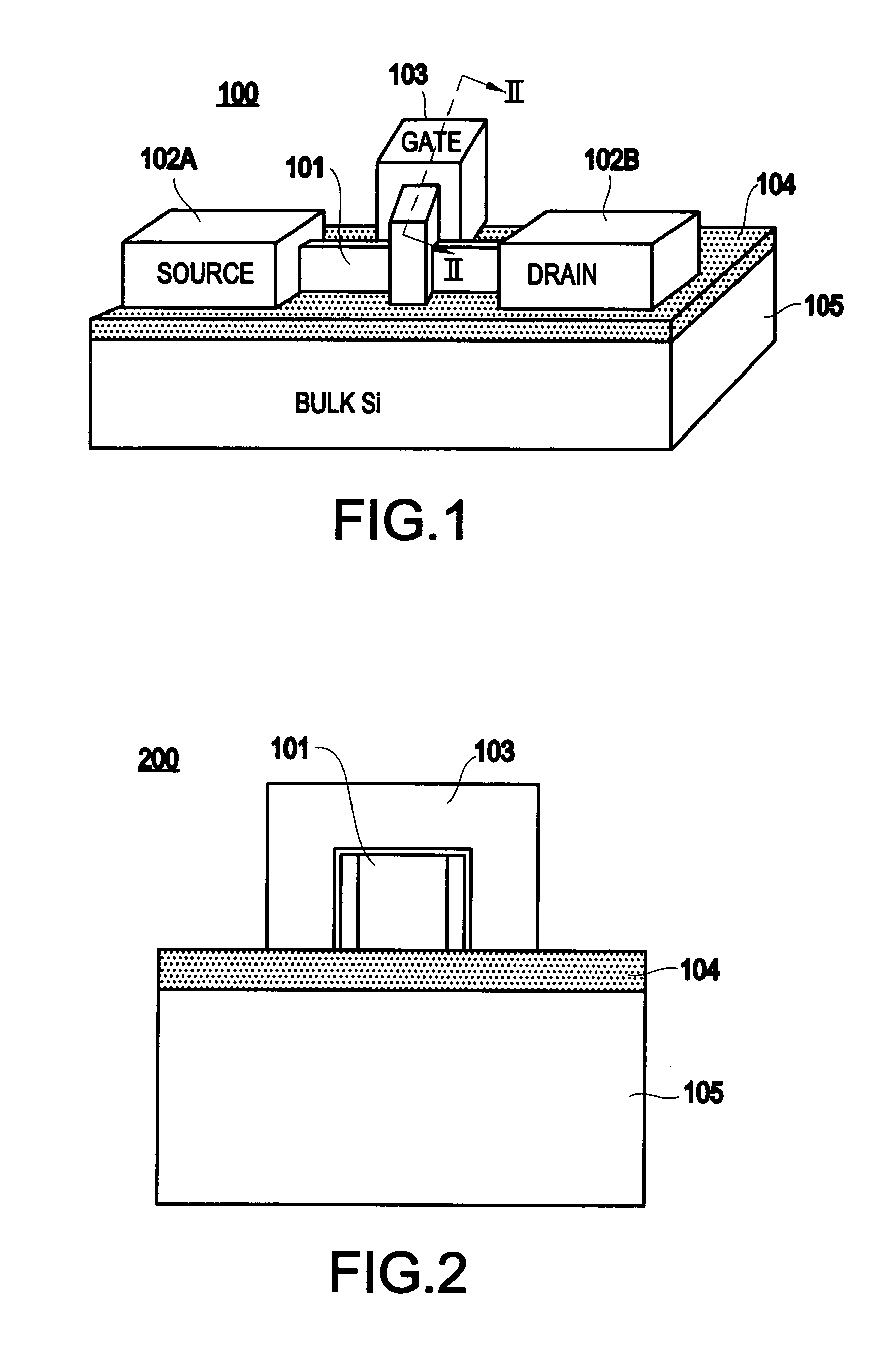

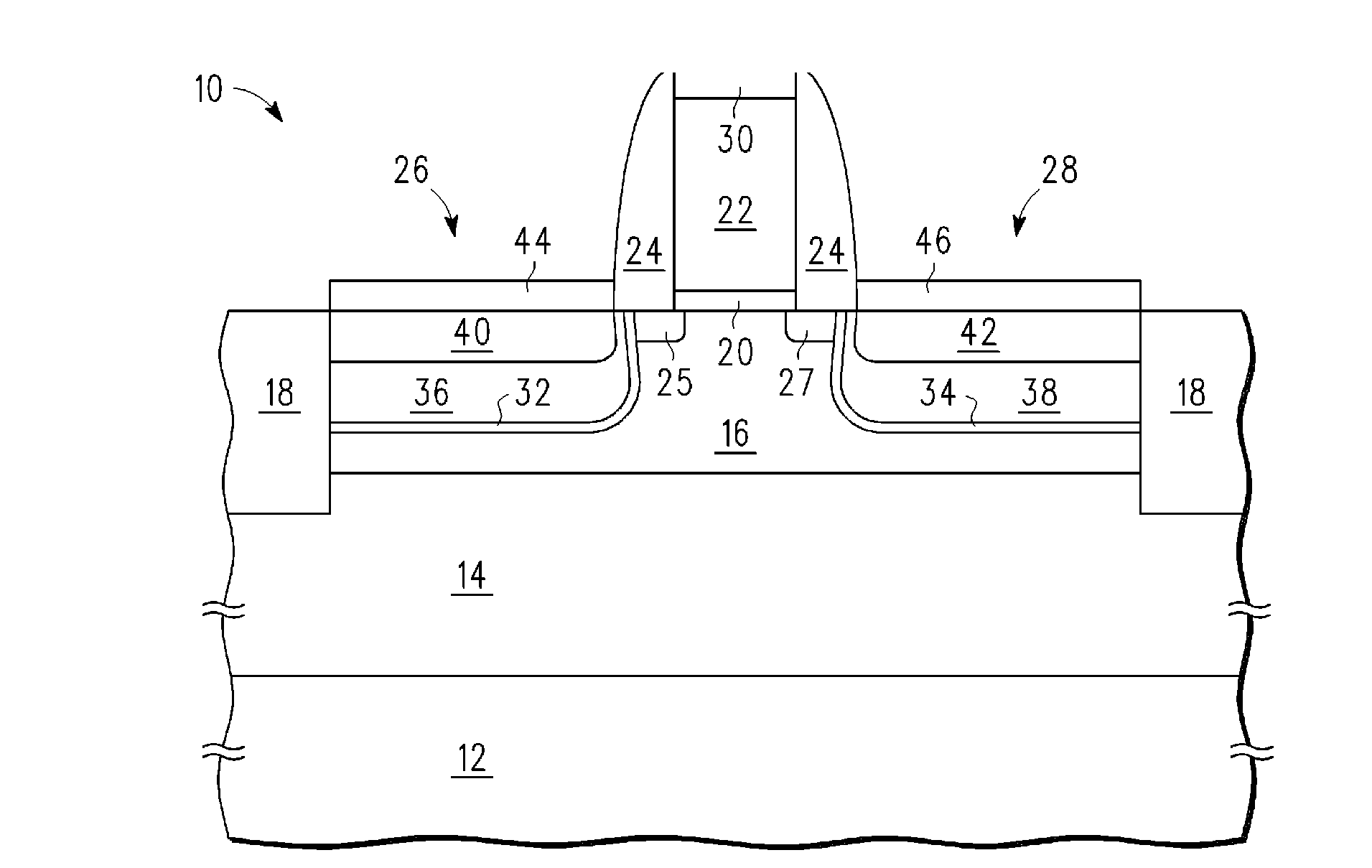

A semiconductor includes a semiconductor substrate, a gate stack on the semiconductor substrate, and a stressor having at least a portion in the semiconductor substrate and adjacent to the gate stack. The stressor includes a first stressor region and a second stressor region on the first stressor region, wherein the second stressor region extends laterally closer to a channel region underlying the gate stack than the first stressor region.

Owner:TAIWAN SEMICON MFG CO LTD

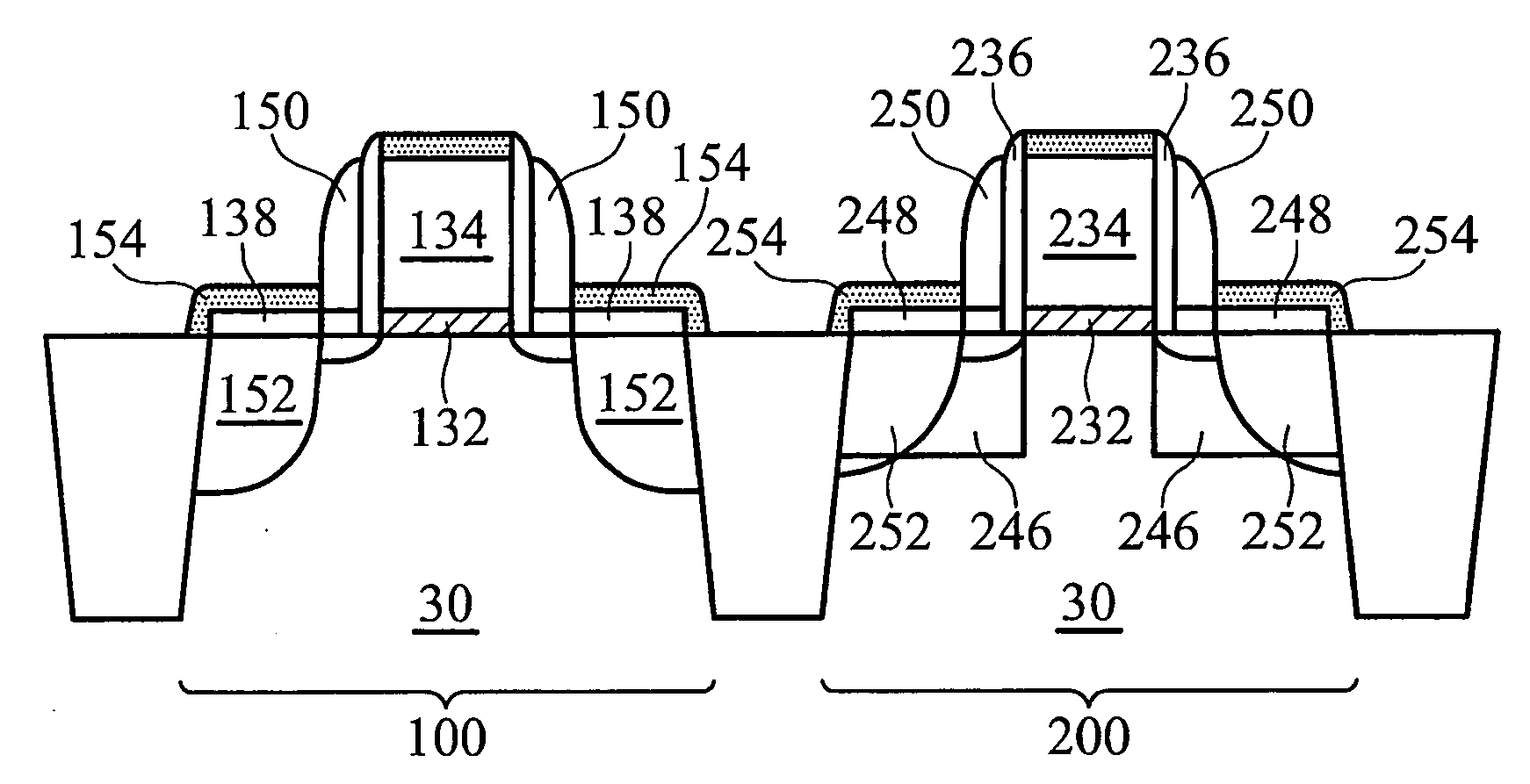

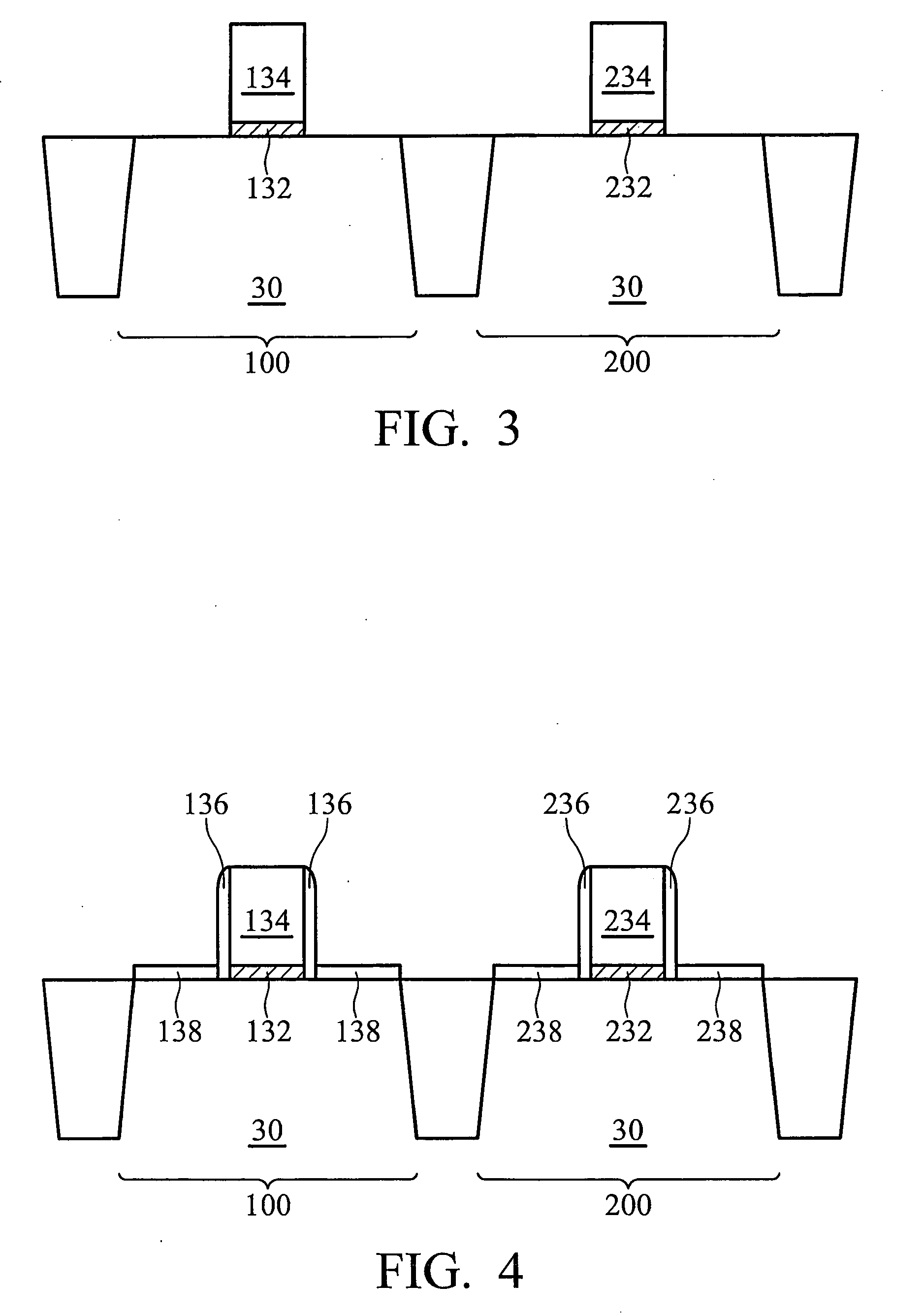

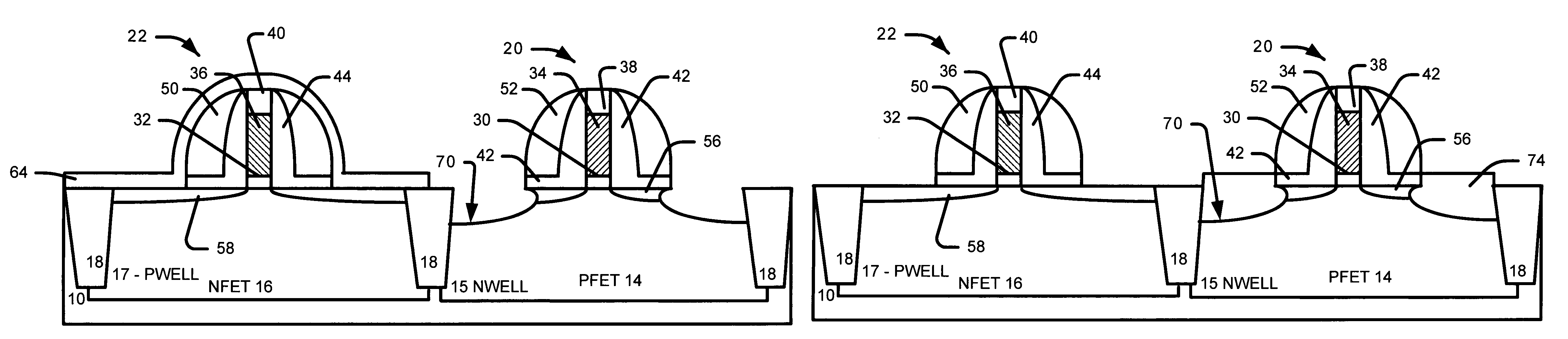

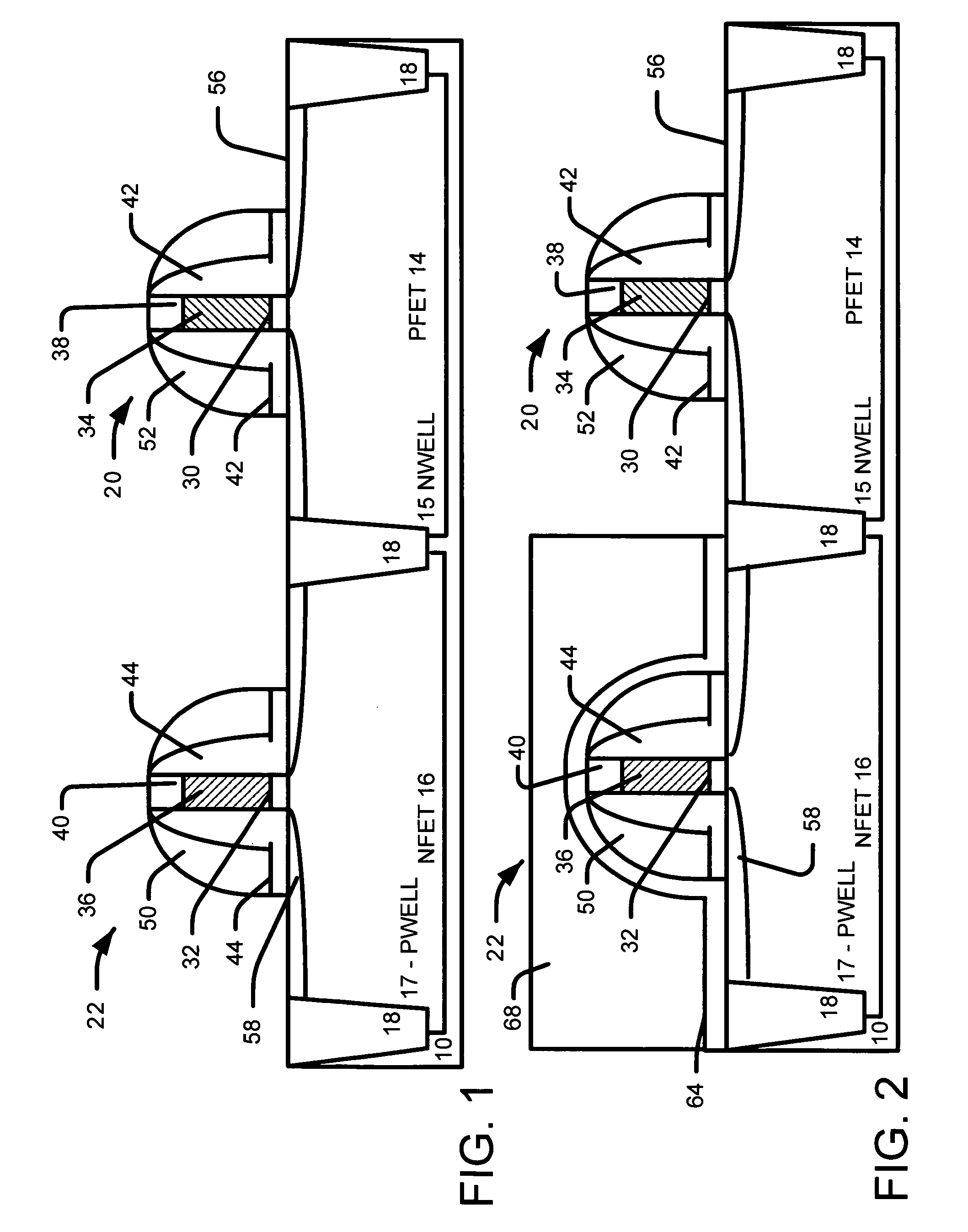

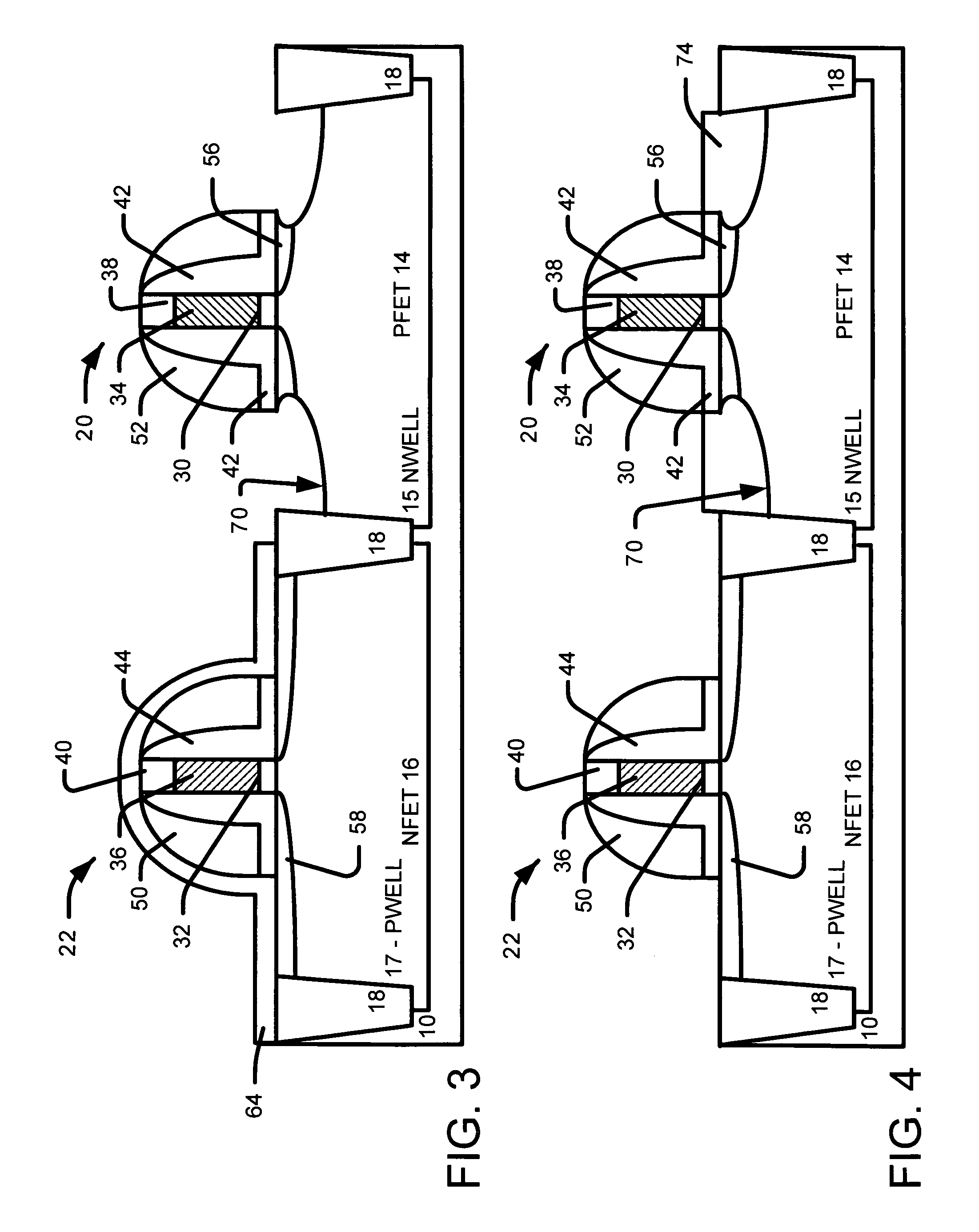

Formation of raised source/drain structures in NFET with embedded SiGe in PFET

A structure and method for forming raised source / drain structures in a NFET device and embedded SiGe source / drains in a PFET device. We provide a NFET gate structure over a NFET region in a substrate and PFET gate structure over a PFET region. We provide NFET SDE regions adjacent to the NFET gate and provide PFET SDE regions adjacent to the PFET gate. We form recesses in the PFET region in the substrate adjacent to the PFET second spacers. We form a PFET embedded source / drain stressor in the recesses. We form a NFET S / D epitaxial Si layer over the NFET SDE regions and a PFET S / D epitaxial Si layer over PFET embedded source / drain stressor. The epitaxial Si layer over PFET embedded source / drain stressor is consumed in a subsequent salicide step to form a stable and low resistivity silicide over the PFET embedded source / drain stressor. We perform a NFET S / D implant by implanting N-type ions into NFET region adjacent to the NFET gate structure and into the NFET S / D stressor Si layer to form the raised NFET source / drains.

Owner:TAIWAN SEMICON MFG CO LTD +1

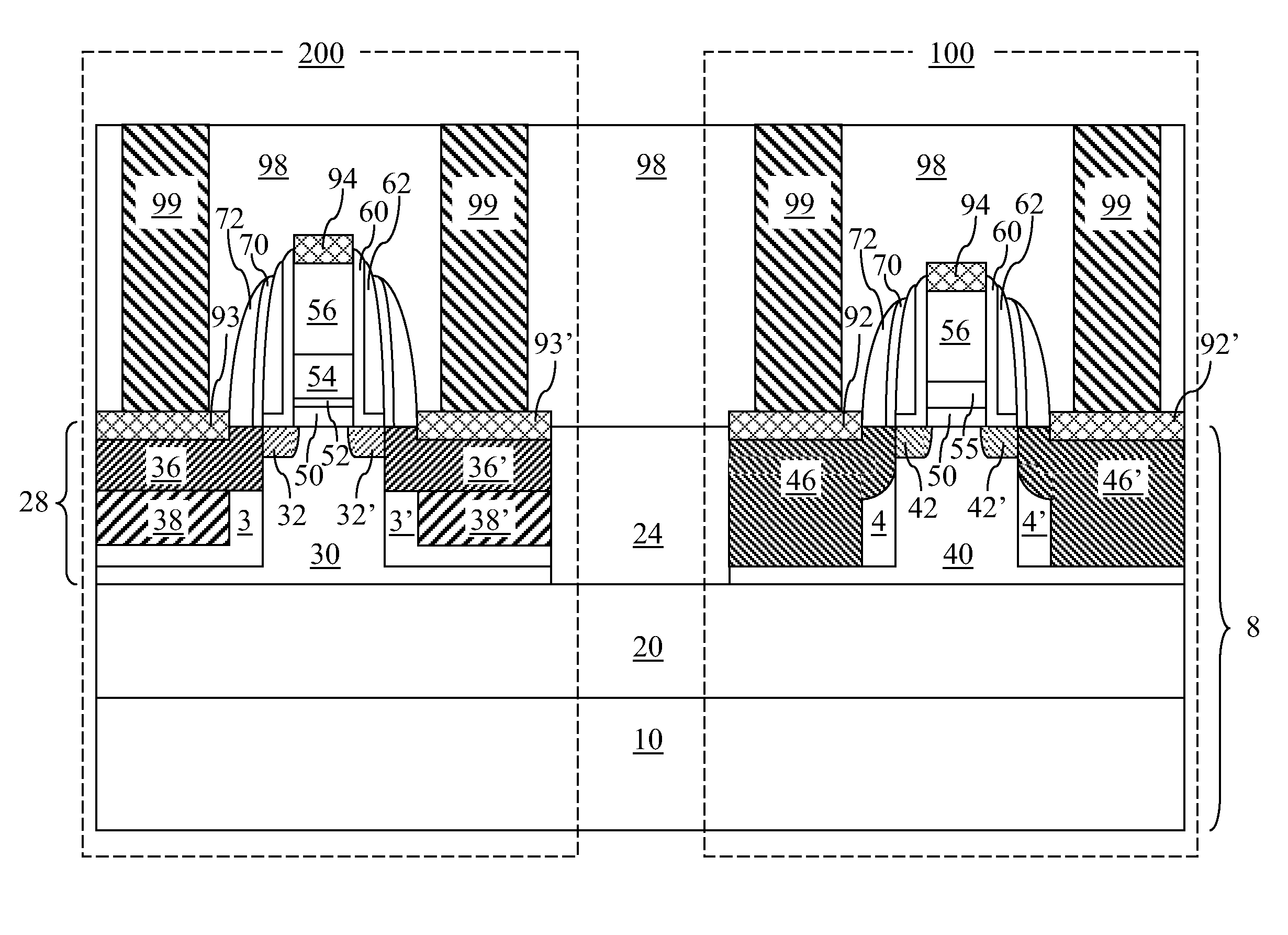

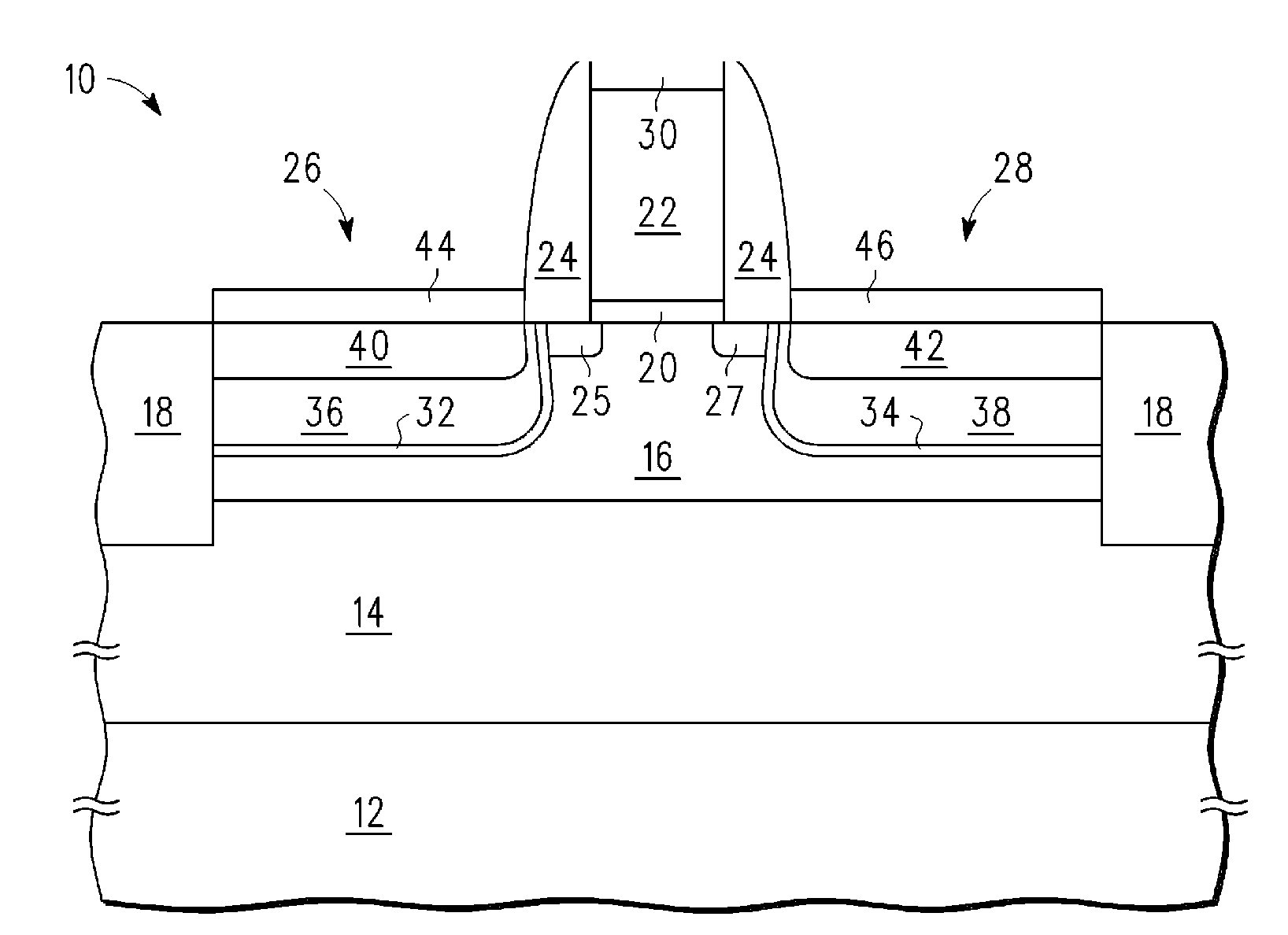

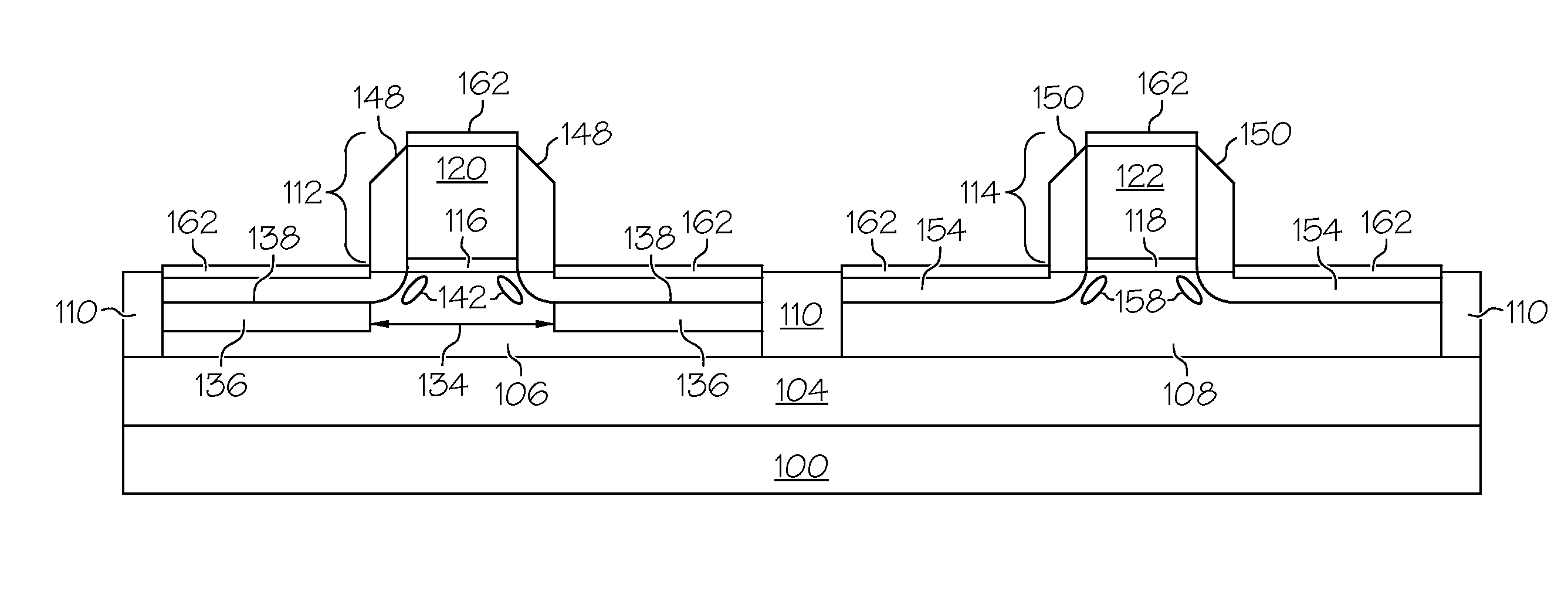

CMOS Transistors With Silicon Germanium Channel and Dual Embedded Stressors

ActiveUS20100224938A1High hole mobilityHigh electron mobilityTransistorSolid-state devicesHigh concentrationMOSFET

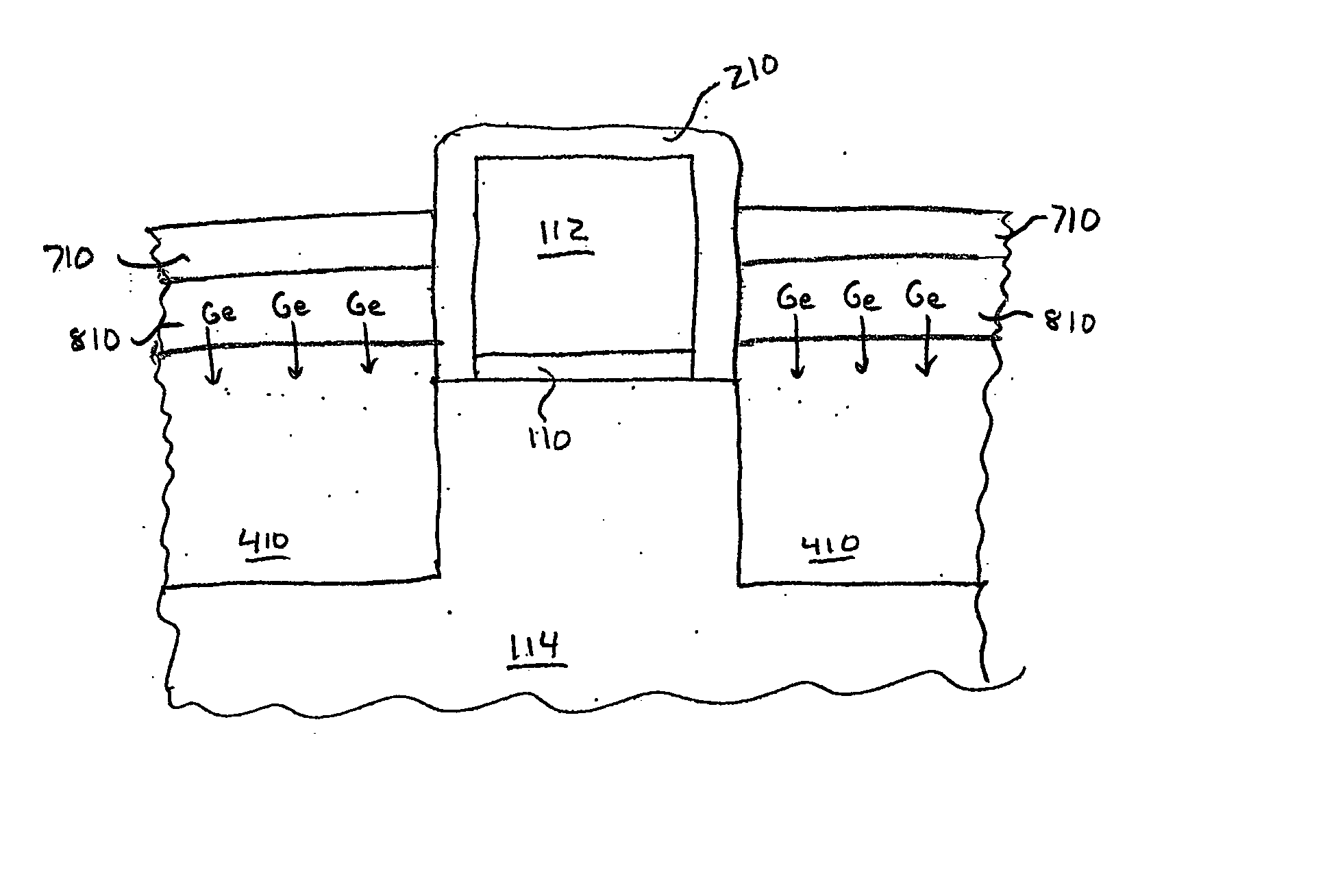

A p-type MOSFET of a CMOS structure has a silicon-germanium alloy channel to which a longitudinal compressive stress is applied by embedded epitaxial silicon-germanium alloy source and drain regions comprising a silicon-germanium alloy having a higher concentration of germanium than the channel of the p-type MOSFET. An n-type MOSFET of the CMOS structure has a silicon-germanium alloy channel to which a longitudinal tensile stress is applied by embedded epitaxial silicon source and drain regions comprising silicon. The silicon-germanium alloy channel in the p-type MOSFET provides enhanced hole mobility, while the silicon-germanium alloy channel in the n-type MOSFET provides enhanced electron mobility, thereby providing performance improvement to both the p-type MOSFET and the n-type MOSFET.

Owner:GLOBALFOUNDRIES US INC

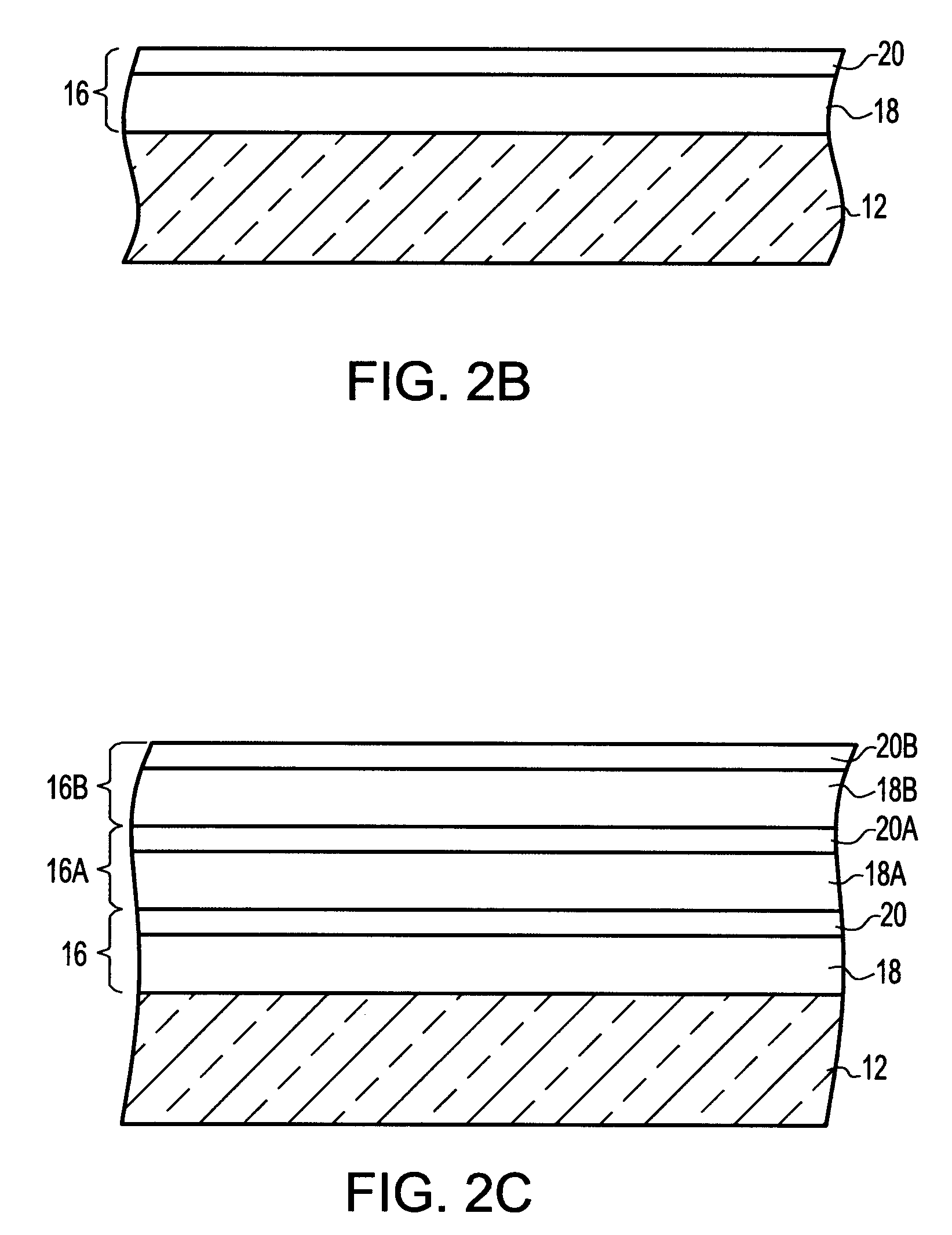

Method of producing highly strained pecvd silicon nitride thin films at low temperature

InactiveUS20060223290A1Increase pressureImprove stress conditionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingStressorMaterials science

A method for increasing the level of stress for amorphous thin film stressors by means of modifying the internal structure of such stressors is provided. The method includes first forming a first portion of an amorphous film stressor material on at least a surface of a substrate, said first portion having a first state of mechanical strain defining a first stress value. After the forming step, the first portion of the amorphous film stressor material is densified such that the first state of mechanical strain is not substantially altered, while increasing the first stress value. In some embodiments, the steps of forming and densifying are repeated any number of times to obtain a preselected and desired thickness for the stressor.

Owner:GLOBALFOUNDRIES INC

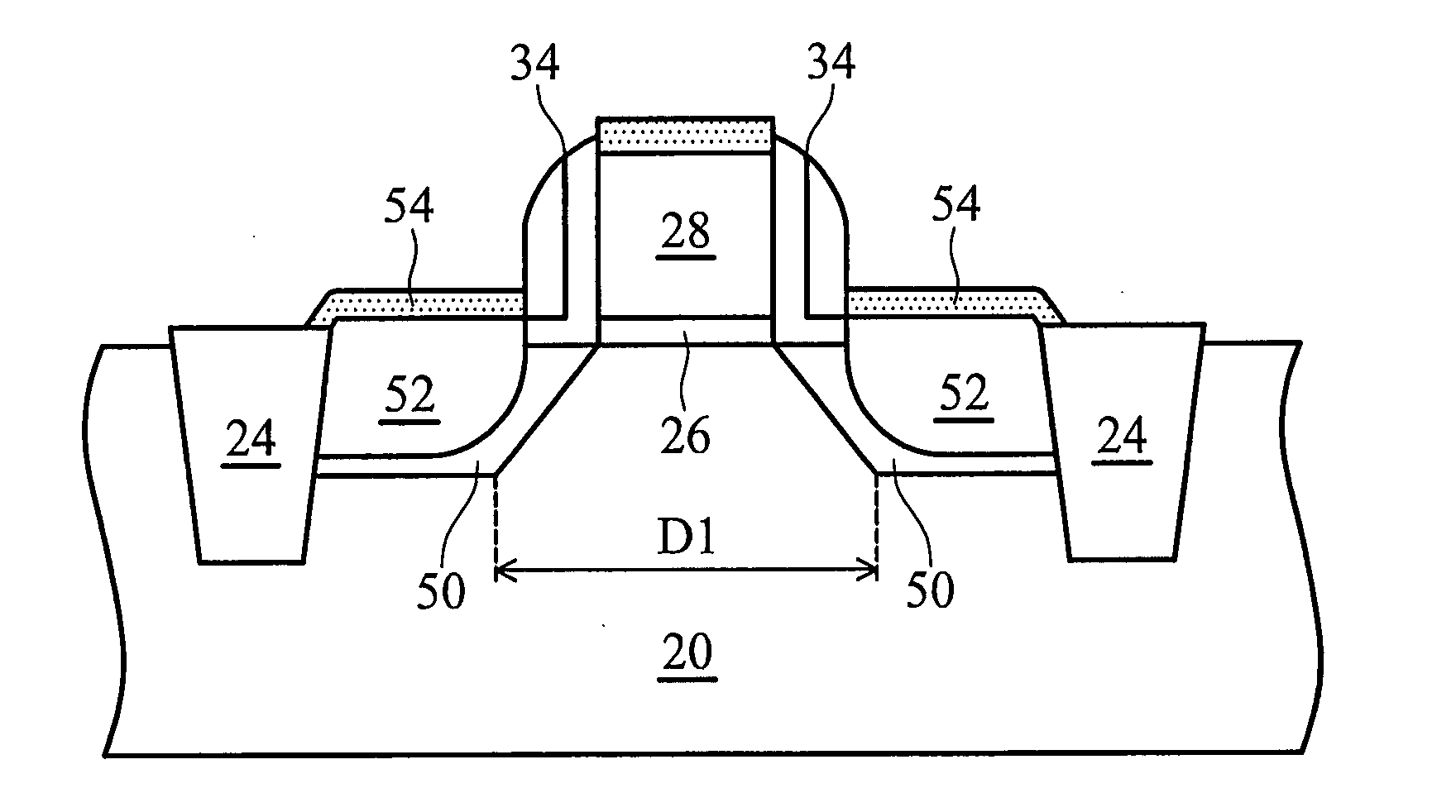

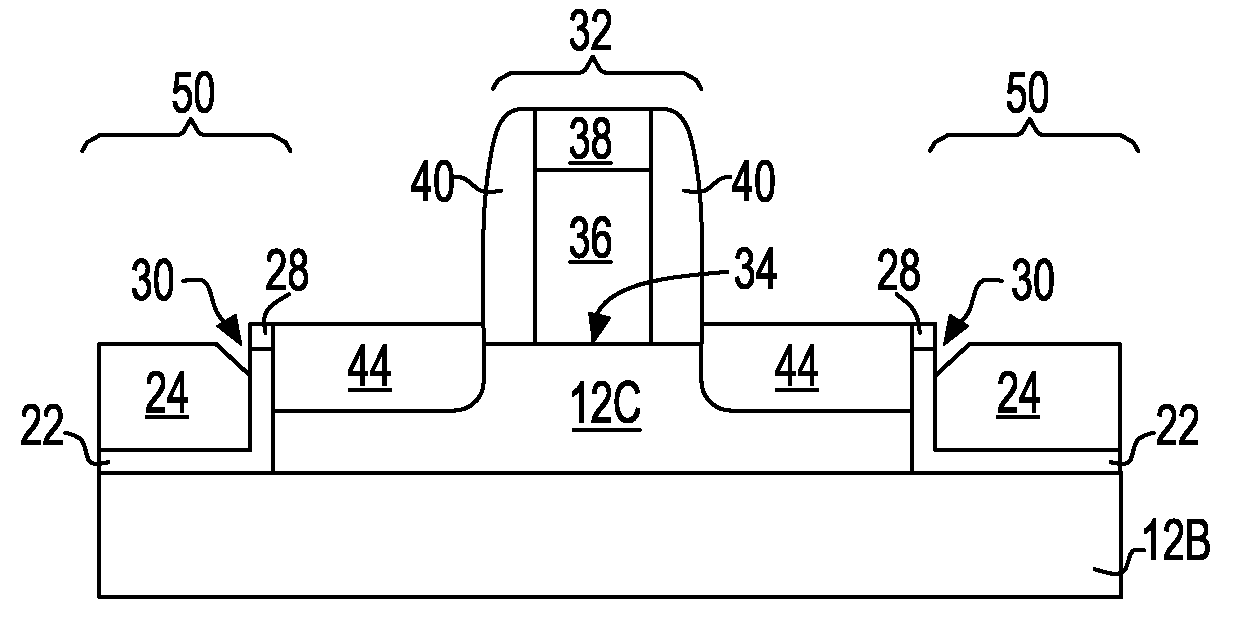

MOS devices with partial stressor channel

ActiveUS20080067557A1Reduce probabilityIncrease pressureTransistorSemiconductor/solid-state device detailsGate dielectricSemiconductor structure

A semiconductor structure includes a semiconductor substrate having a first lattice constant; a gate dielectric on the semiconductor substrate; a gate electrode on the semiconductor substrate; and a stressor having at least a portion in the semiconductor substrate and adjacent the gate electrode. The stressor has a tilted sidewall on a side adjacent the gate electrode. The stressor includes a first stressor layer having a second lattice constant substantially different from the first lattice constant; and a second stressor layer on the first stressor layer, wherein the second stressor has a third lattice constant substantially different from the first and the second lattice constants.

Owner:TAIWAN SEMICON MFG CO LTD

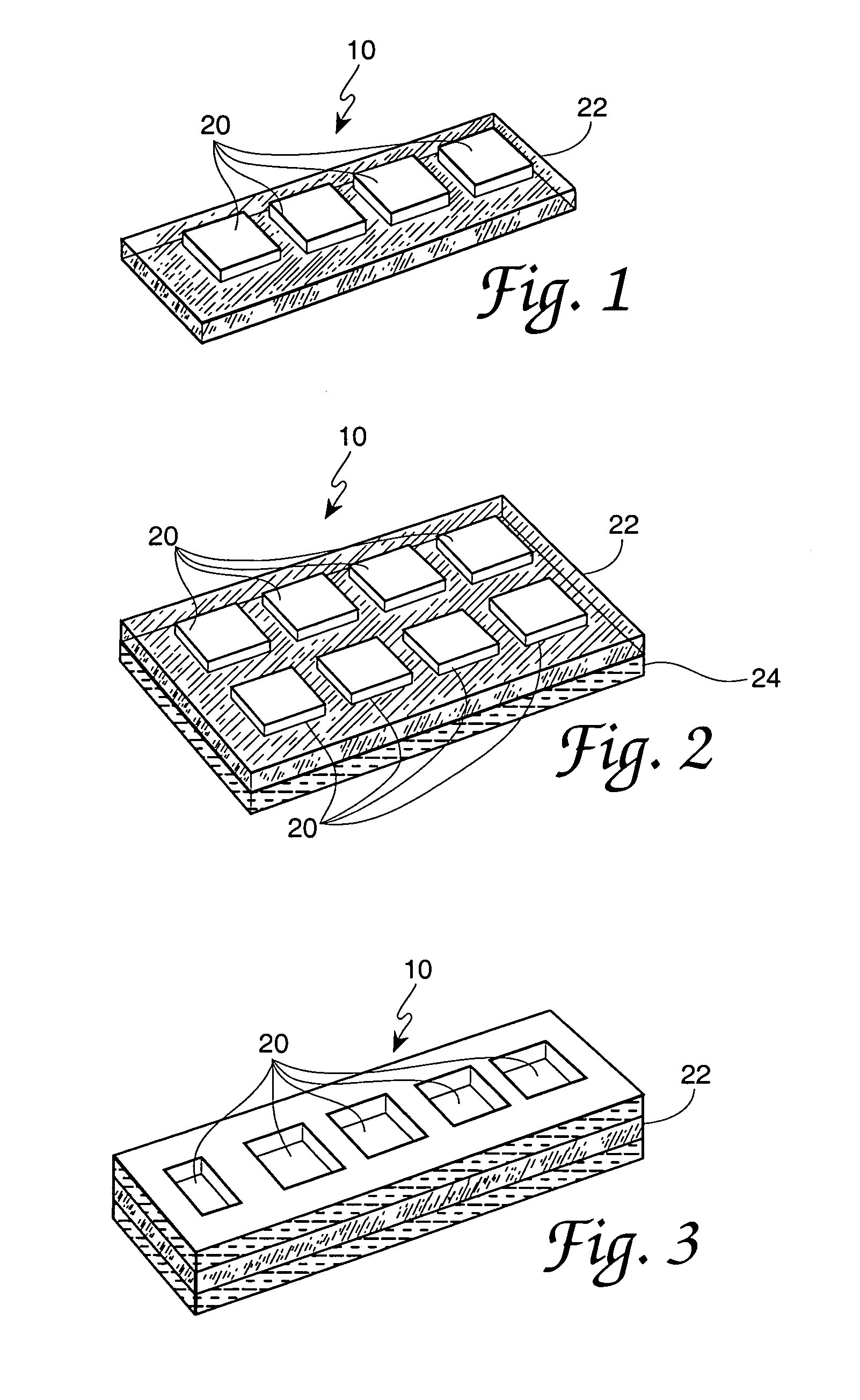

Multi-layer source/drain stressor

InactiveUS20080197412A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsStressor

A method for forming a semiconductor device includes forming a recess in a source region and a recess in a drain region of the semiconductor device. The method further includes forming a first semiconductor material layer in the recess in the source region and a second semiconductor material layer in the recess in the drain region, wherein each of the first semiconductor material layer and the second semiconductor material layer are formed using a stressor material having a first ratio of an atomic concentration of a first element and an atomic concentration of a second element, wherein the first element is silicon and a first level of concentration of a doping material. The method further includes forming additional semiconductor material layers overlying the first semiconductor material layer and the second semiconductor material layer that have a different ratio of the atomic concentration of the first element and the second element.

Owner:NORTH STAR INNOVATIONS

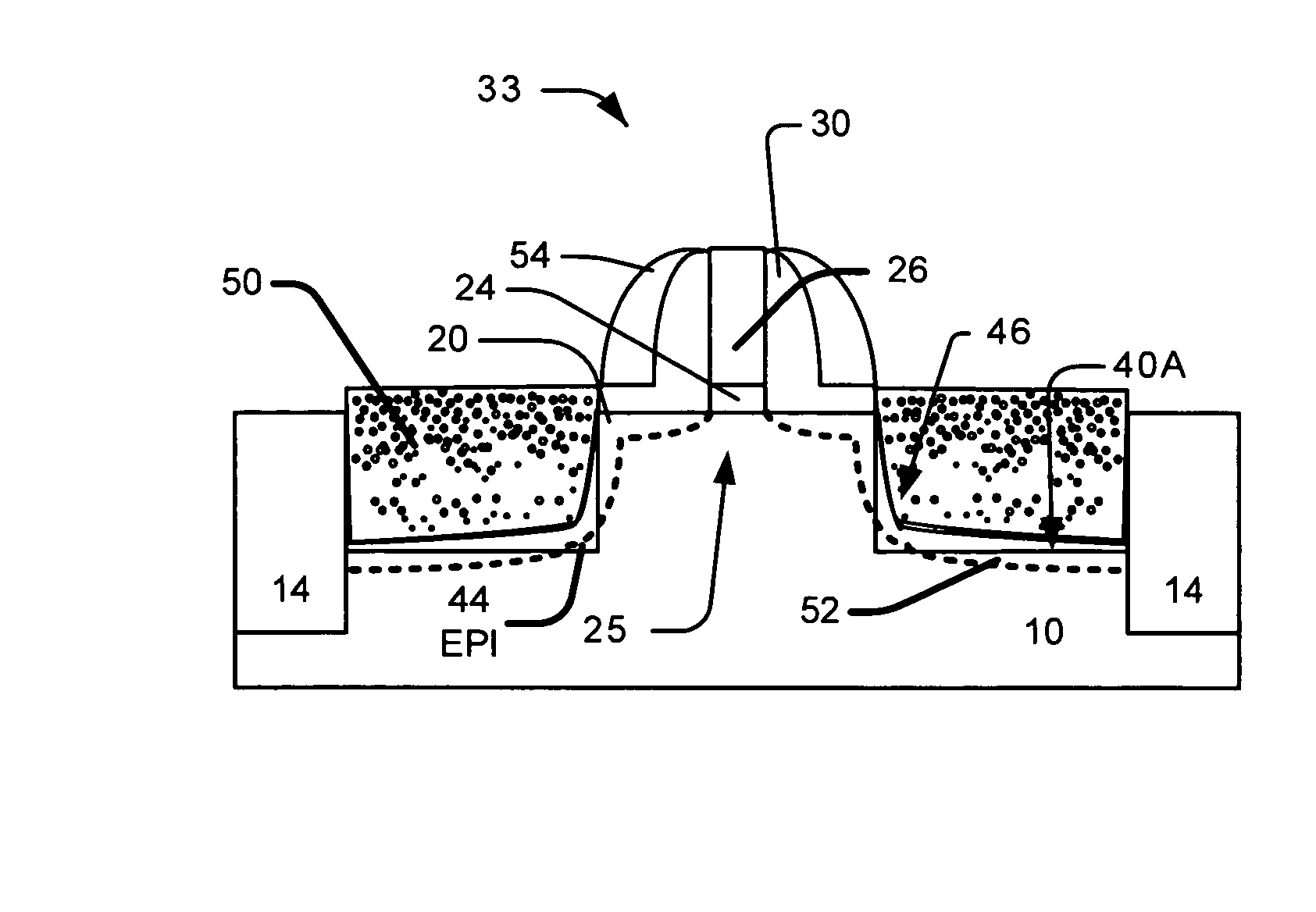

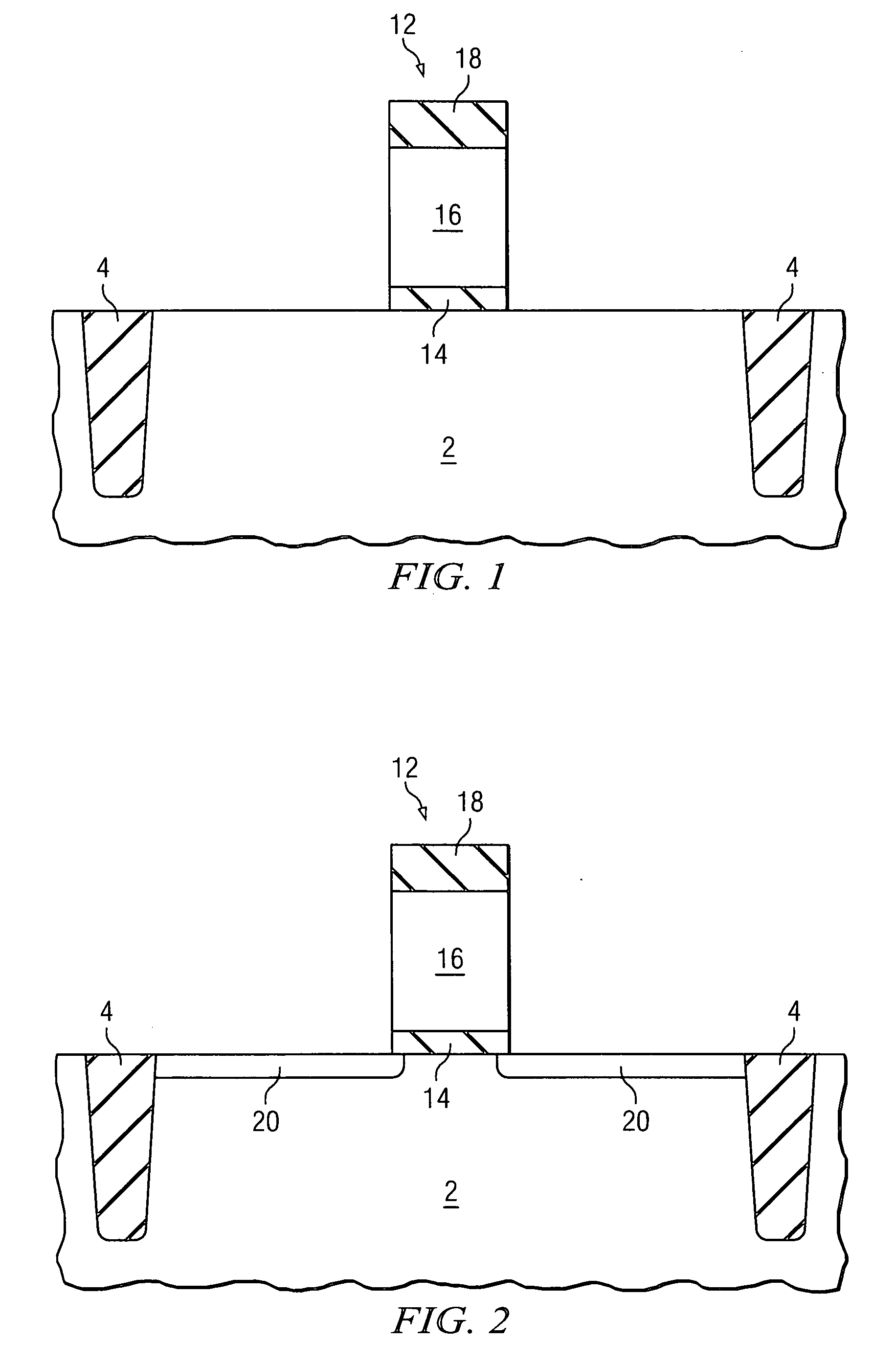

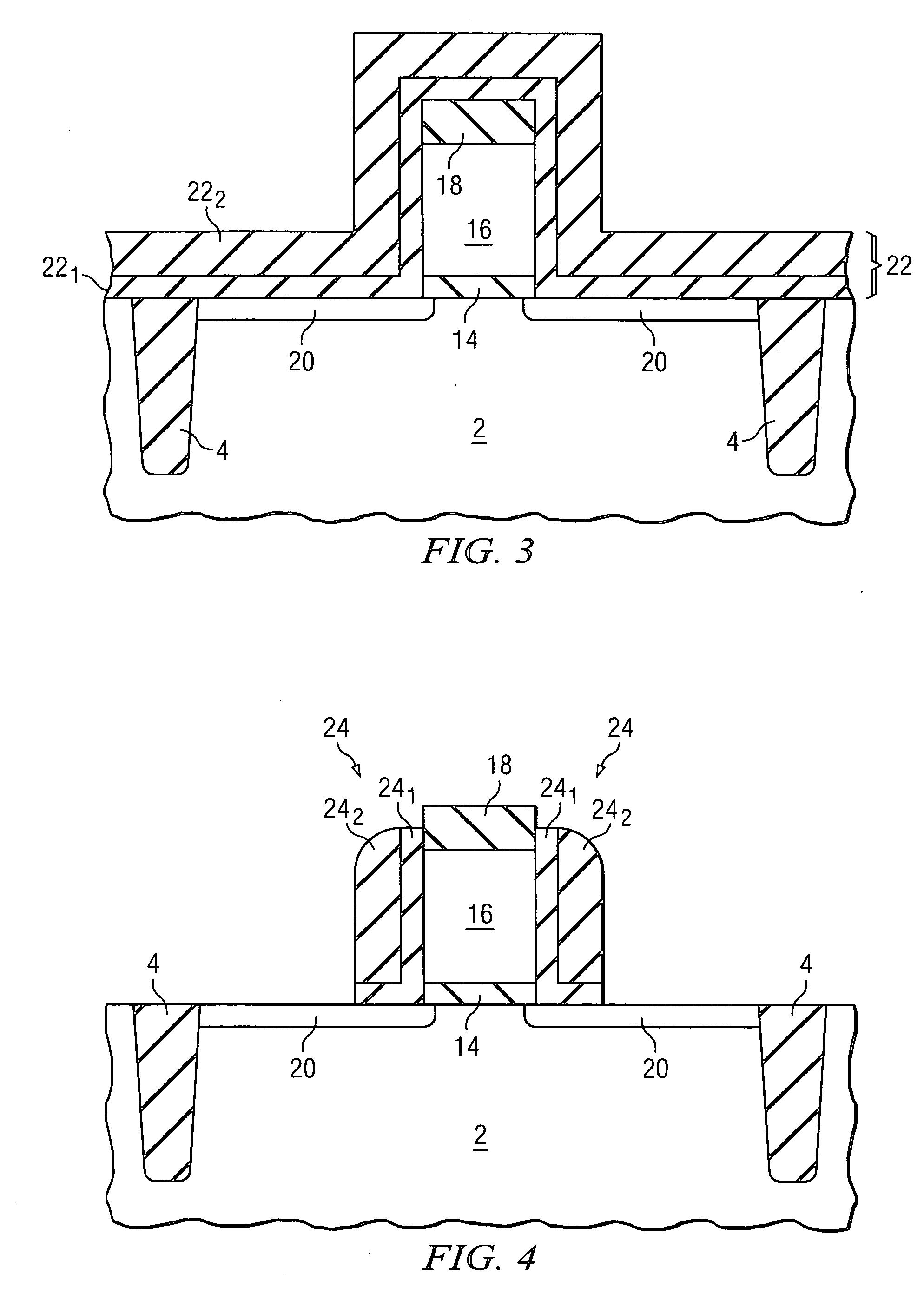

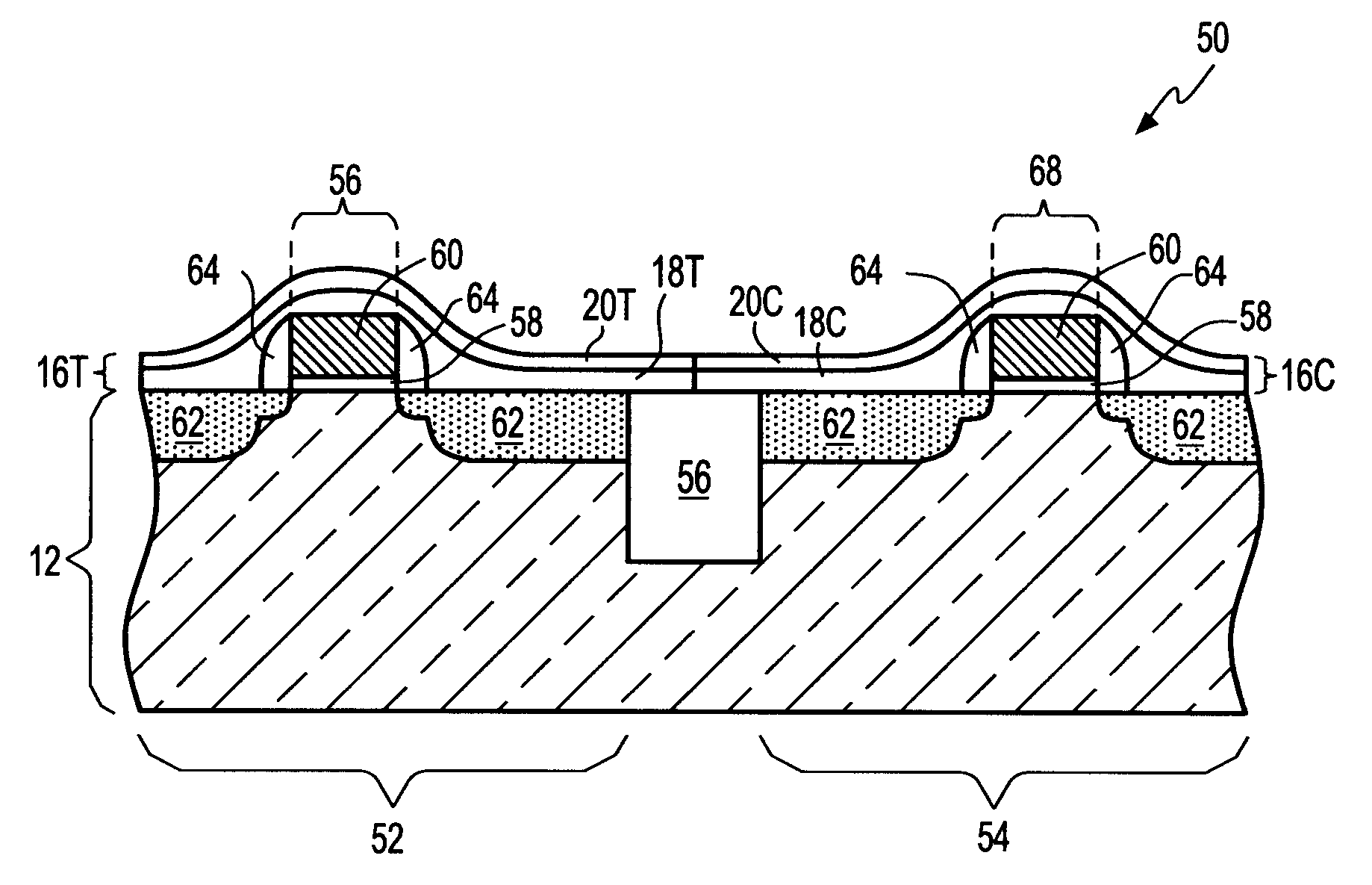

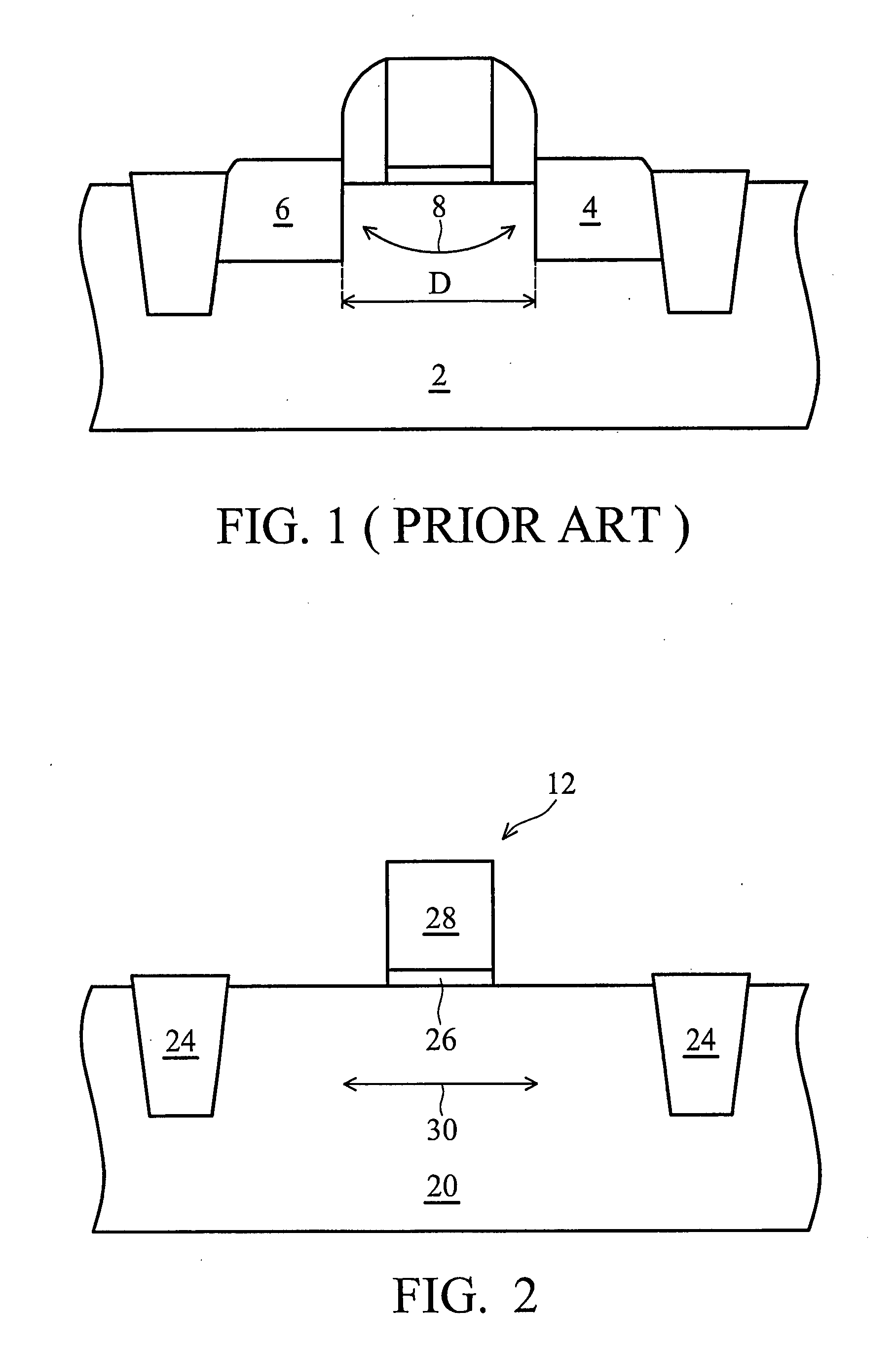

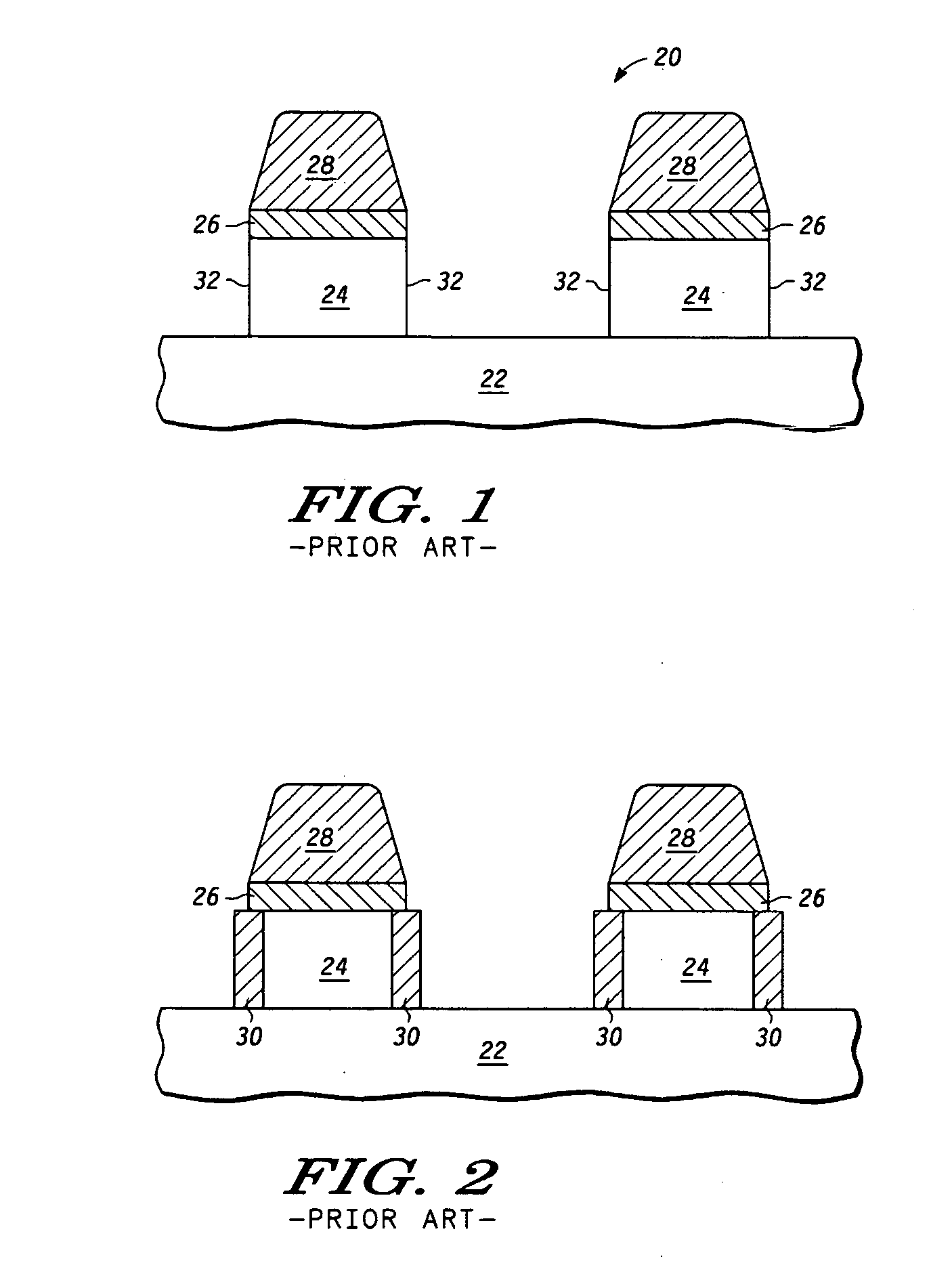

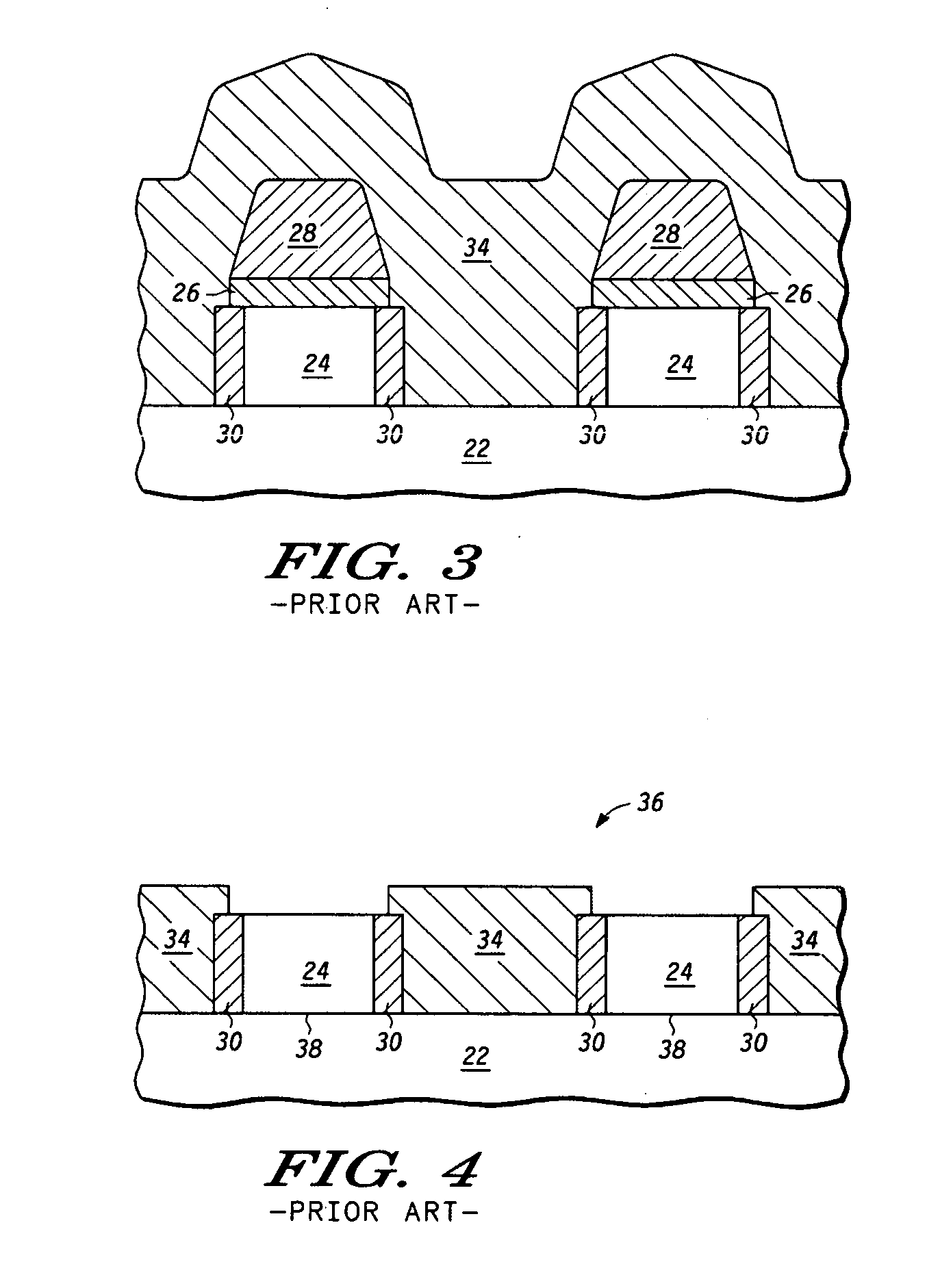

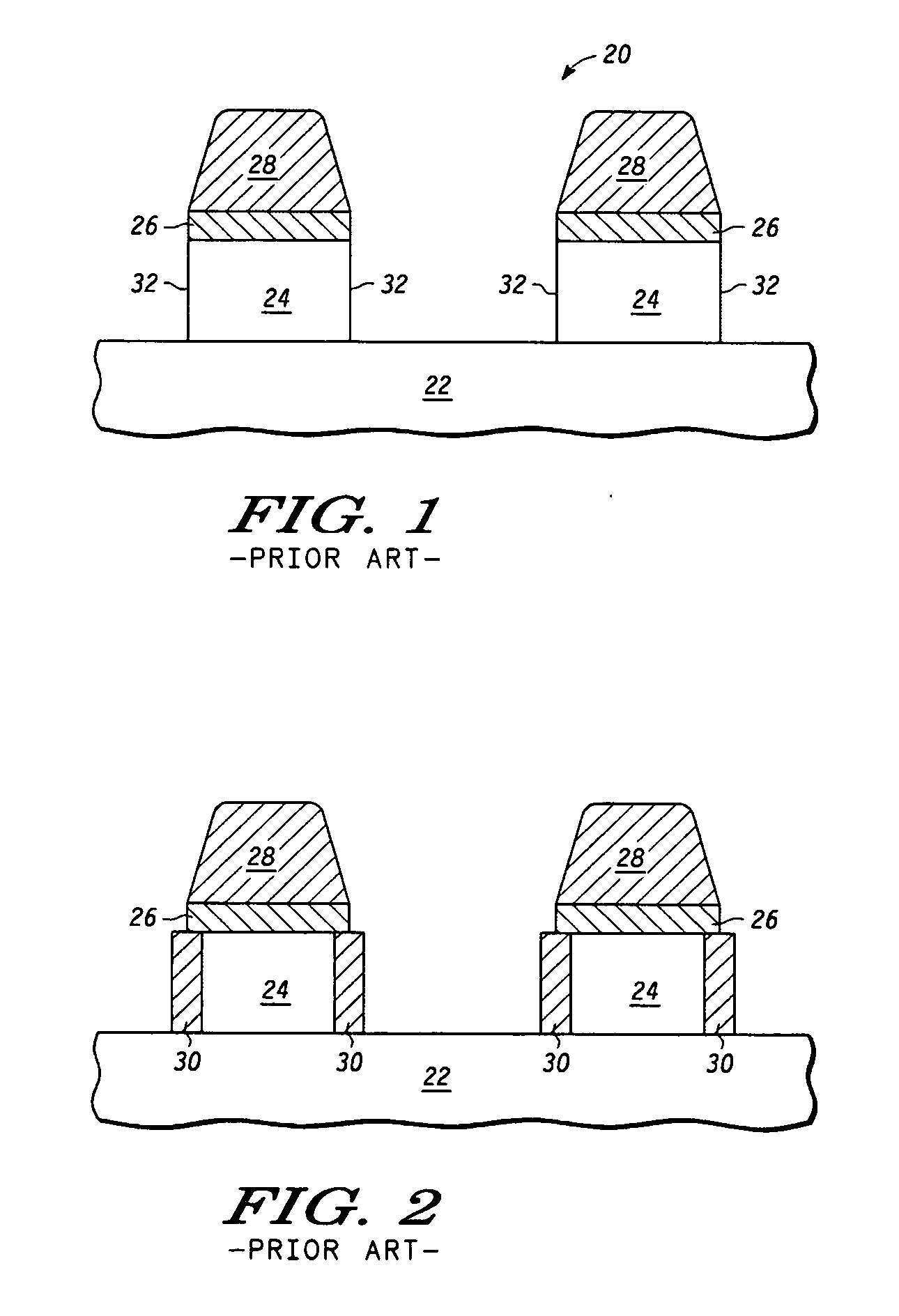

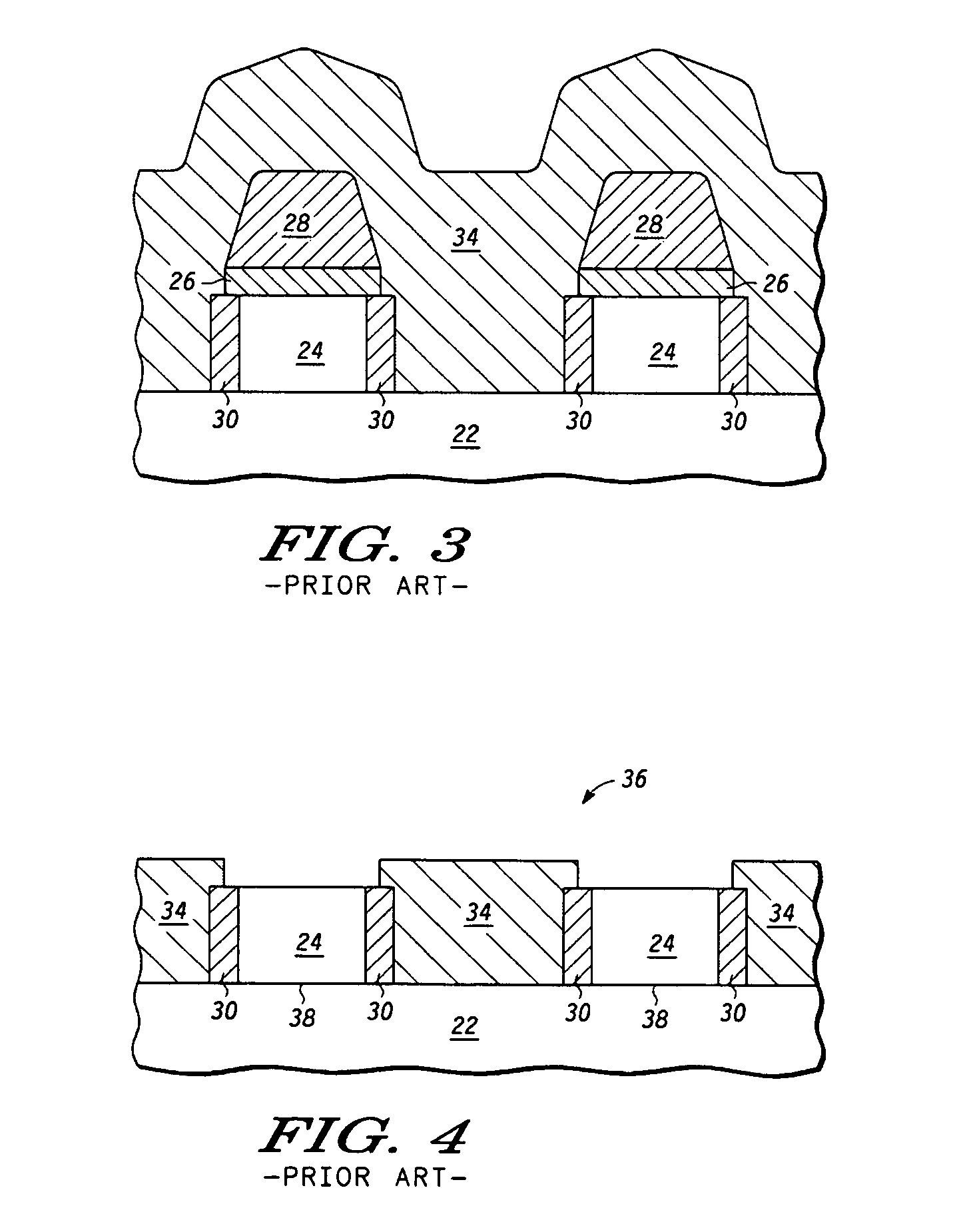

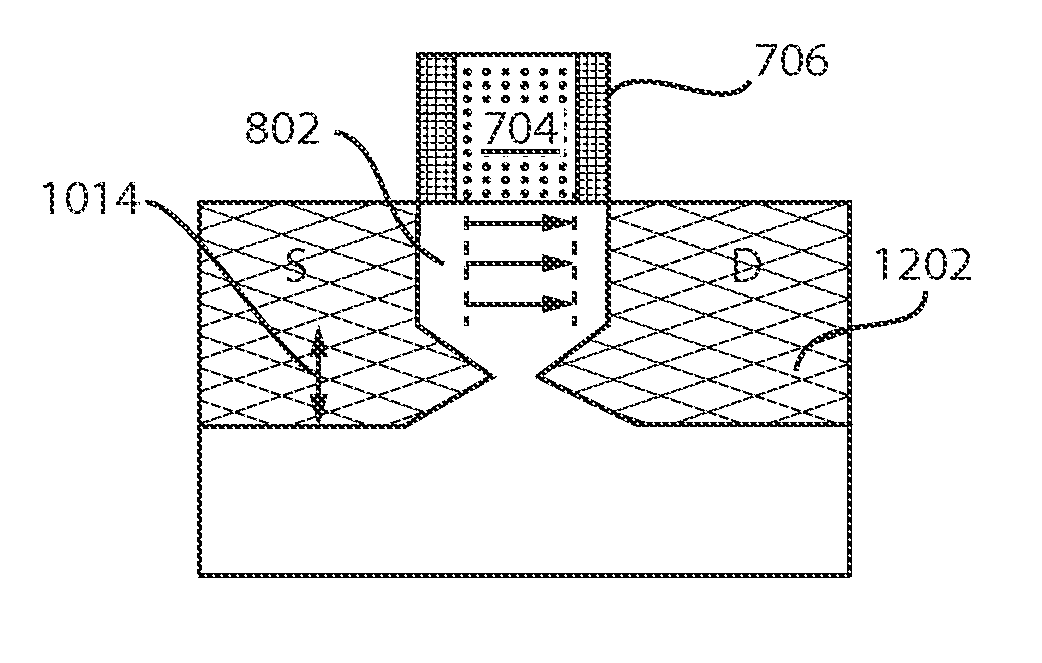

MOSFET device with localized stressor

InactiveUS20060151808A1Easy to operateSemiconductor/solid-state device manufacturingDigital video signal modificationMOSFETReaction layer

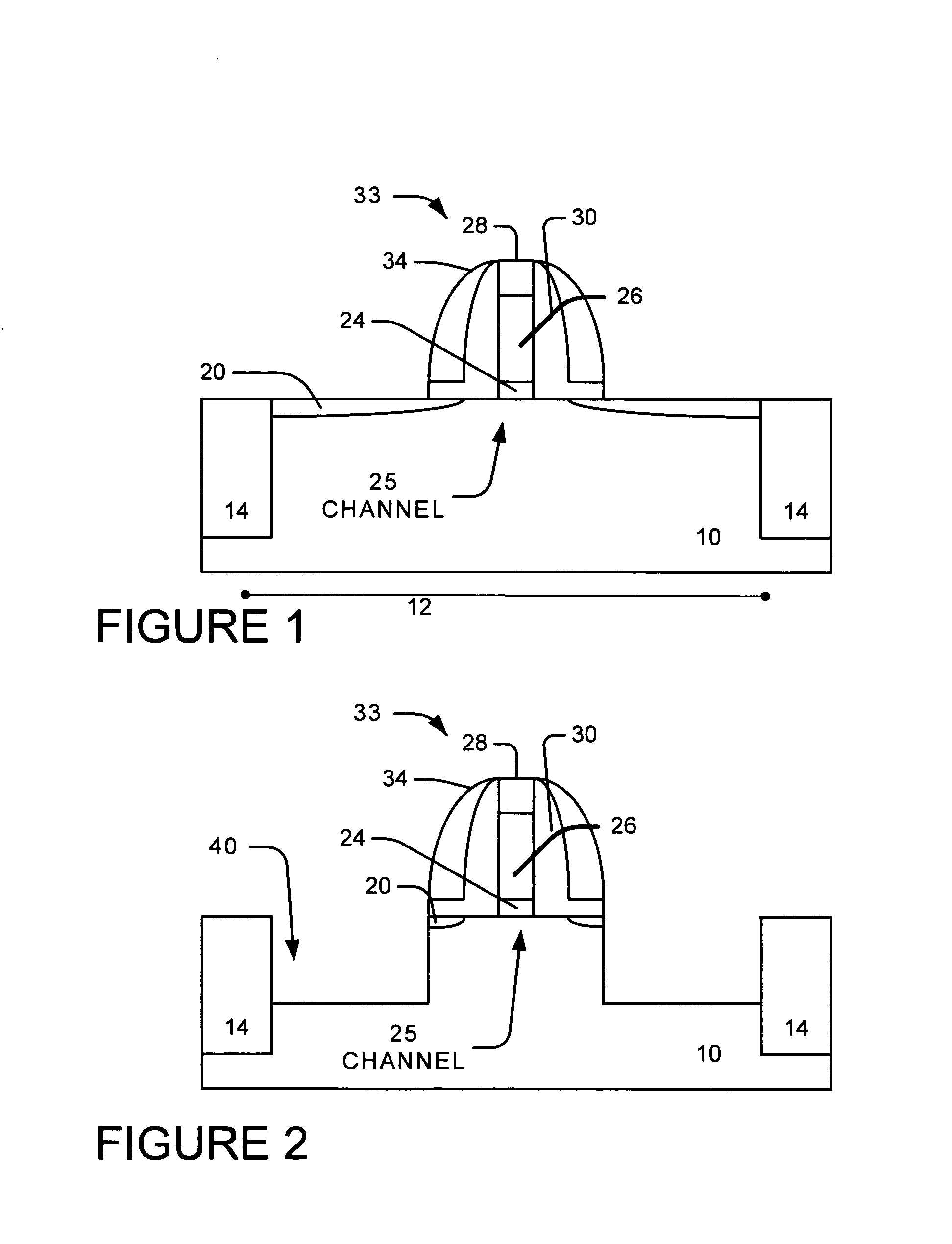

MOSFETs having localized stressors are provided. The MOSFET has a stress-inducing layer formed in the source / drain regions, wherein the stress-inducing layer comprises a first semiconductor material and a second semiconductor material. A treatment is performed on the stress-inducing layer such that a reaction is caused with the first semiconductor material and the second semiconductor material is forced lower into the stress-inducing layer. The stress-inducing layer may be either a recessed region or non-recessed region. A first method involves forming a stress-inducing layer, such as SiGe, in the source / drain regions and performing a nitridation or oxidation process. A nitride or oxide film is formed in the top portion of the stress-inducing layer, forcing the Ge lower into the stress-inducing layer. Another method embodiment involves forming a reaction layer over the stress-inducing layer and performing a treatment process to cause the reaction layer to react with the stress-inducing layer.

Owner:TAIWAN SEMICON MFG CO LTD

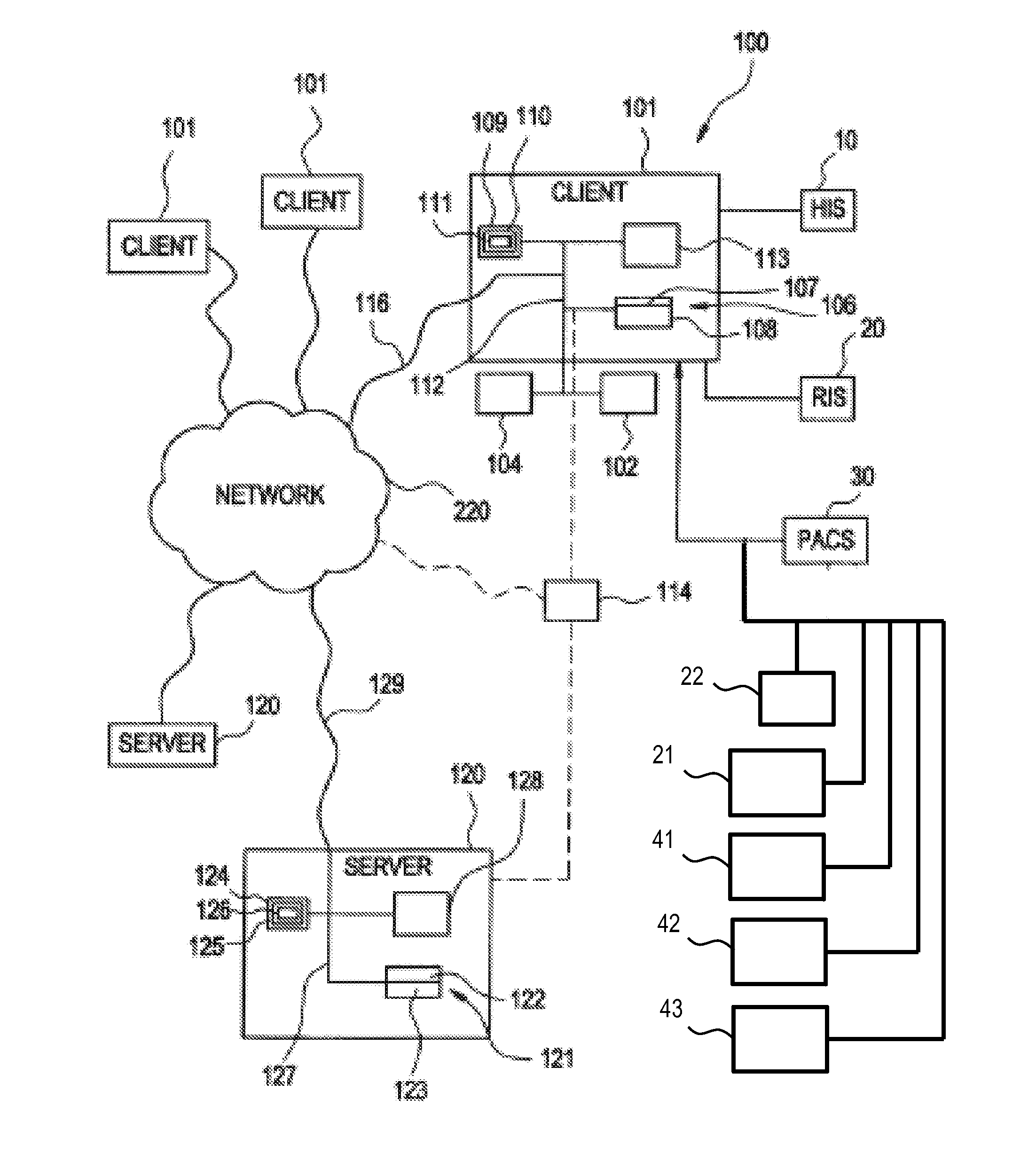

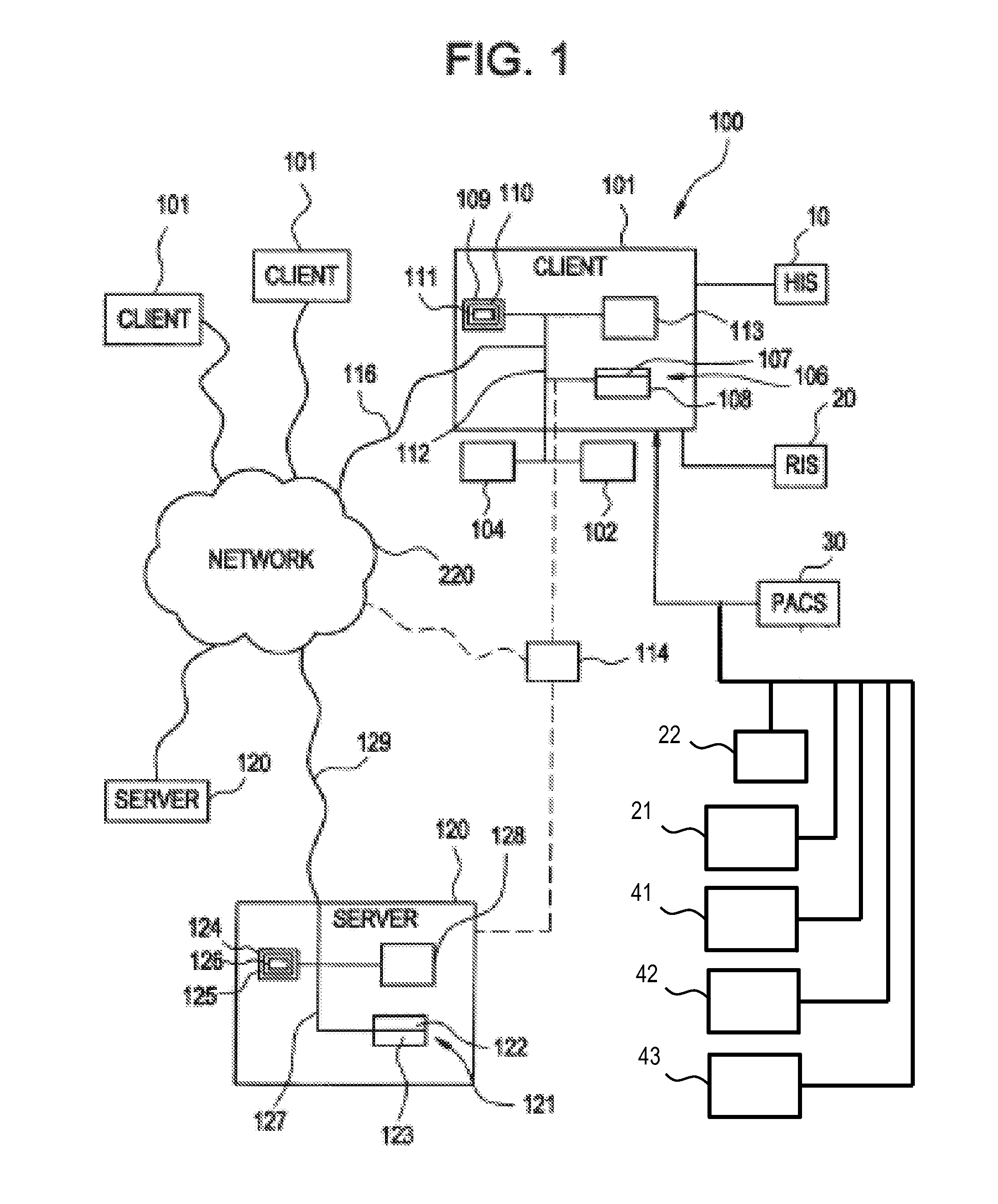

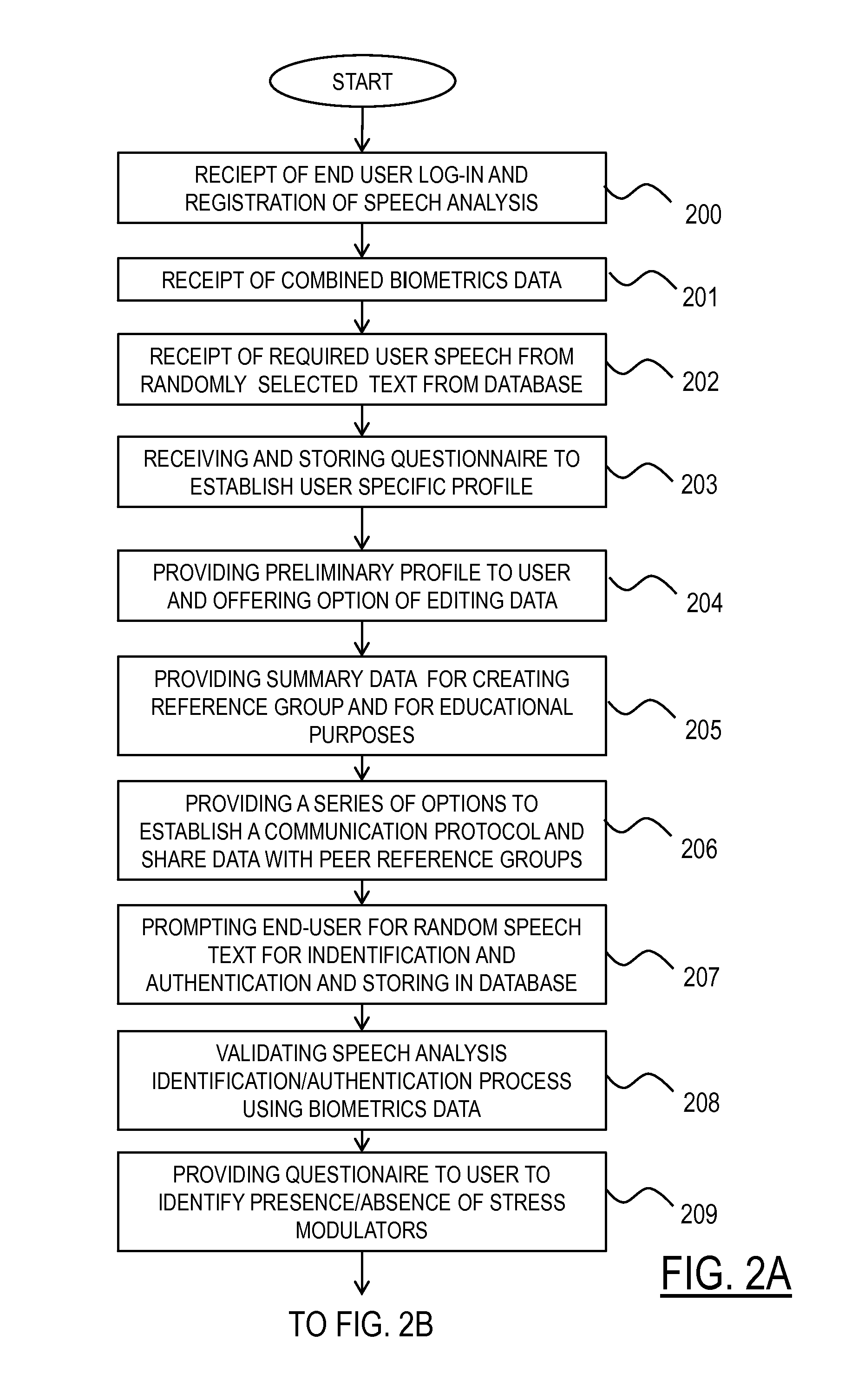

Method and apparatus of speech analysis for real-time measurement of stress, fatigue, and uncertainty

ActiveUS20130311190A1Measurement uncertaintyImprove the level ofSpeech analysisMedical equipmentQuality assuranceStressor

The present invention utilizes speech analysis to provide real-time measurement of end-user stress, fatigue, and uncertainty in decision-making. The present invention monitors “technology-induced” stressors by increasing the inherent functionality of individual monitoring technologies, so as to perform multiple applications in a single setting. In addition to the continued use of speech recognition technology for computerized report transcription, the present invention simultaneously measures and analyzes occupational stress and fatigue in real-time, specific to the unique profile of each individual end-user and context of the task being performed. The derived user-specific stress / fatigue analytics may be used in the creation of a number of workflow and quality enhancing deliverables, including customizable intervention strategies for stress / fatigue reduction, creation of automated workflow templates, and targeted quality assurance and peer review.

Owner:REINER BRUCE

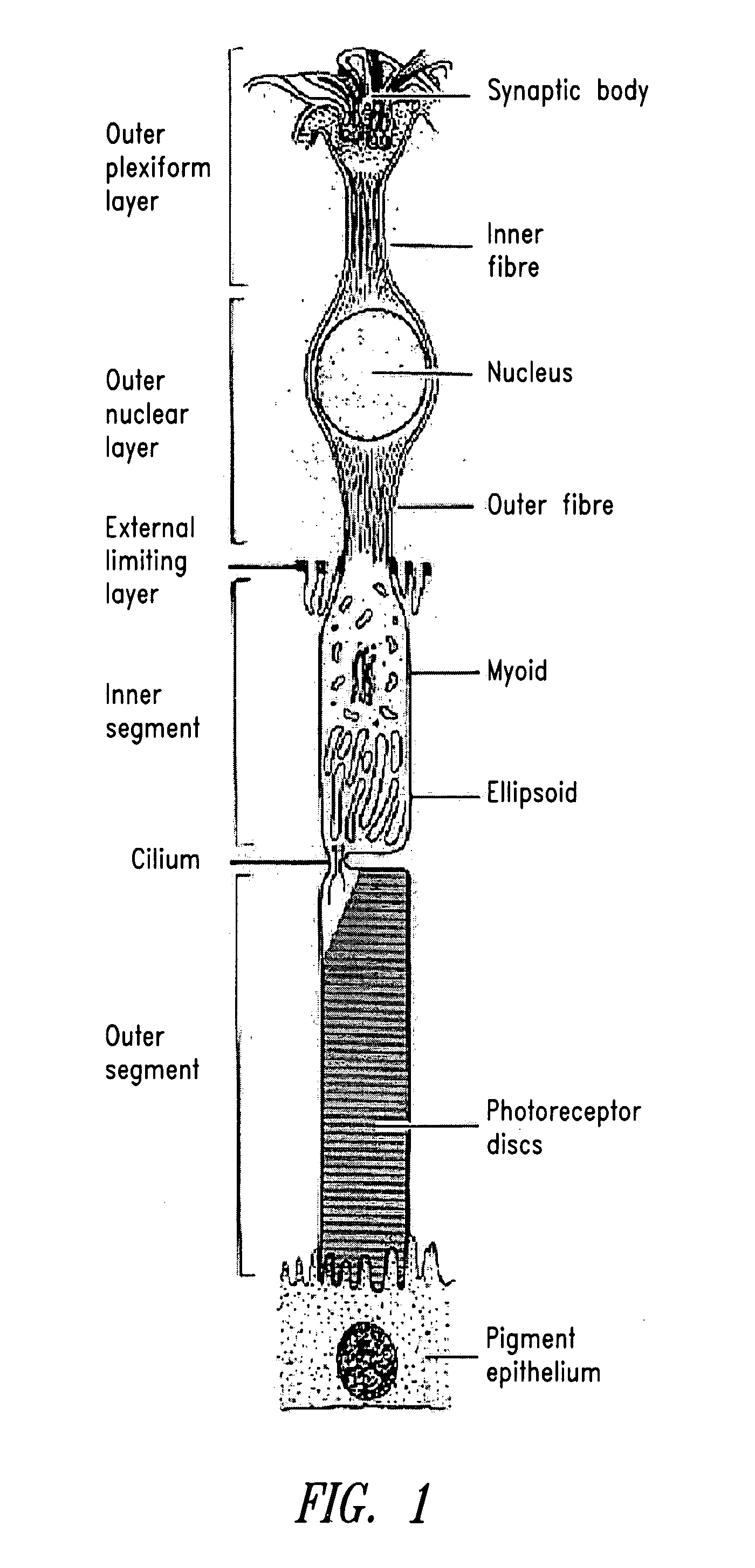

Extended primary retinal cell culture and stress models, and methods of use

A cell culture system related to extended in vitro culture of mature retinal cells and methods for preparing the cell culture system are provided. Also provided is a retinal cell culture stress model related to extended in vitro culture of mature retinal cells in the presence of a stressor and methods for using the cell culture stress model. The invention provides a cell culture system comprising a long-term culture of mature retinal cells, without requiring addition of other types of non-retinal cells such as purified glia, or cells isolated from ciliary bodies within the eye, and the addition of a stressor such as light, A2E, cigarette smoke condensate, glutamate, or hydrostatic pressure. Methods for identifying bioactive agents that alter viability, neurodegeneration, or survival of retinal cells using the retinal cell culture stress system are also provided.

Owner:ACUACELA INC

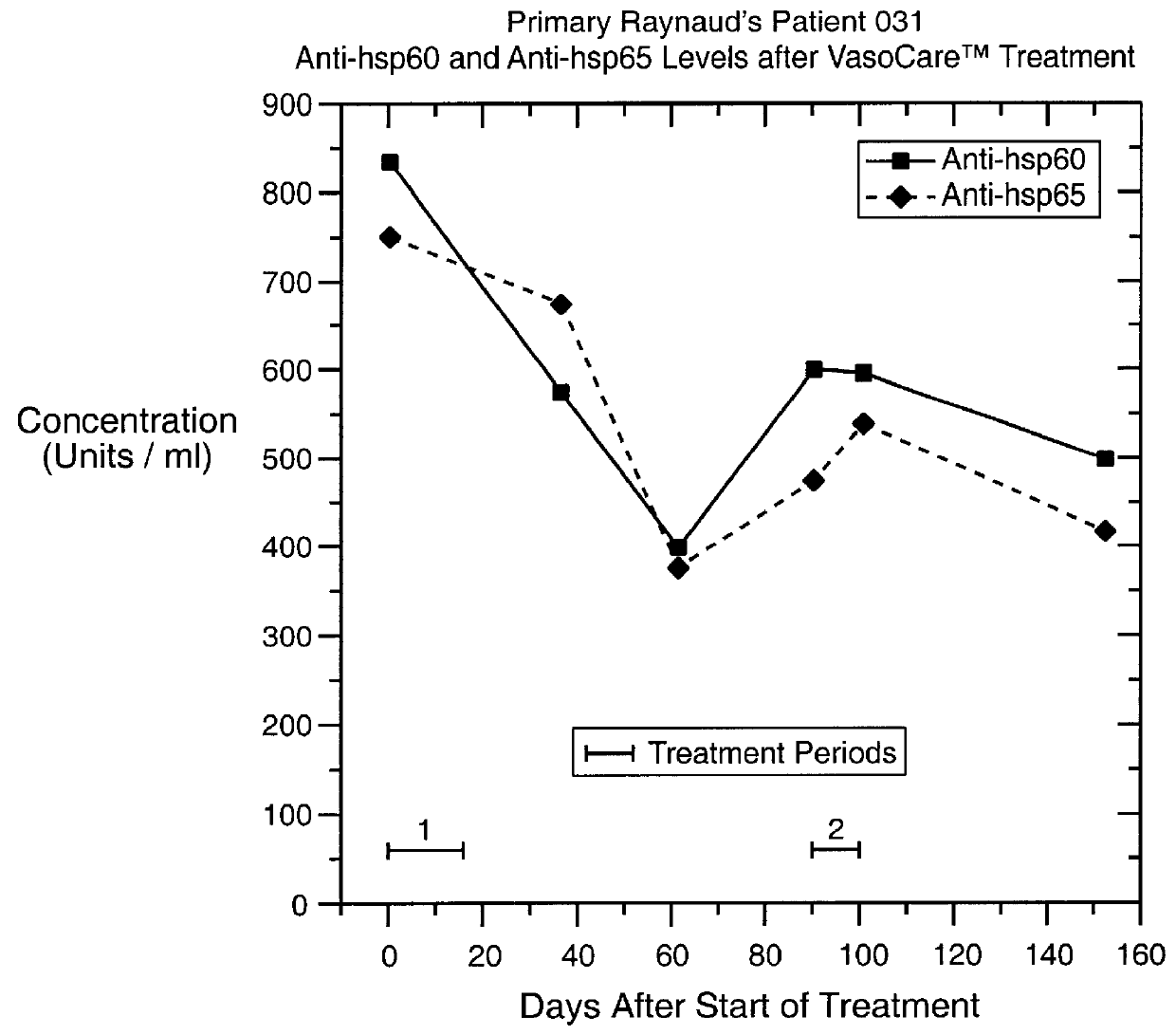

Method of treating atherosclerosis

InactiveUS6669965B2Reduce the number of cellsReadily phagocytosedBiocideEnergy modified materialsAtheromaStressor

A method of treating or preventing atherosclerosis in a mammalian subject comprises: (a) extracting the aliquot of blood from the subject; (b) treating the aliquot of blood ex vivo with at least one stressor selected from the group consisting of an oxidizing agent, ultraviolet radiation and elevated temperature; and (c) administering the aliquot of blood treated in step (b) to the subject. Preferably, the aliquot has a volume of from about 0.01 ml to about 400 ml and is treated simultaneously by ozone gas and ultraviolet radiation at a temperature of from 37-55° C.

Owner:VASOGEN IRELAND LTD

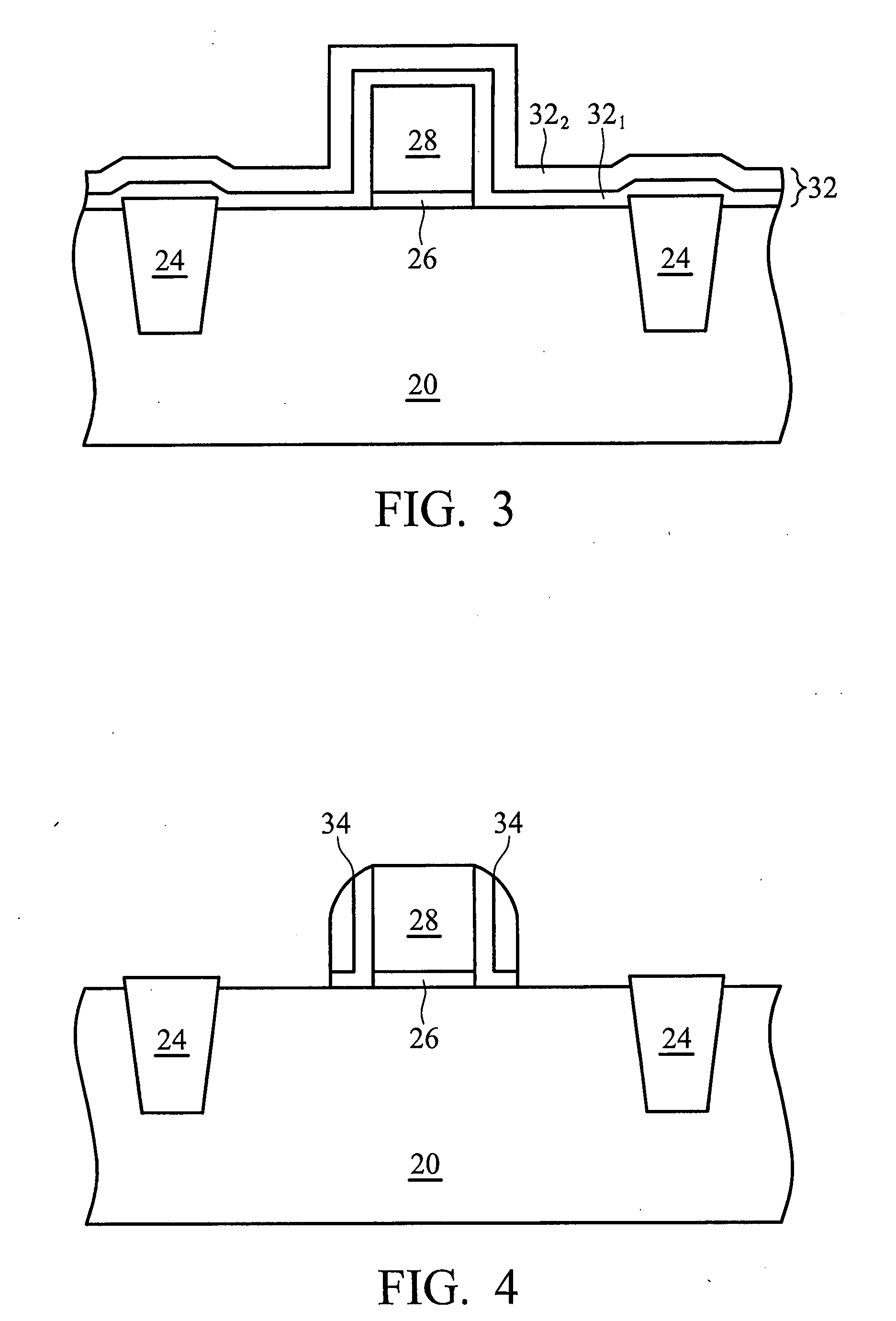

Advanced forming method and structure of local mechanical strained transistor

InactiveUS20070287240A1High carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEngineering

Embodiments of the invention provide a semiconductor fabrication method and a structure for strained transistors. A method comprises forming a stressor layer over a MOS transistor. The stressor layer is selectively etched over the gate electrode, thereby affecting strain conditions within the MOSFET channel region. An NMOS transistor may have a tensile stressor layer, and a PMOS transistor may have compressive stressor layer.

Owner:TAIWAN SEMICON MFG CO LTD

Multi-layer source/drain stressor

InactiveUS7544997B2Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsStressor

Owner:NORTH STAR INNOVATIONS

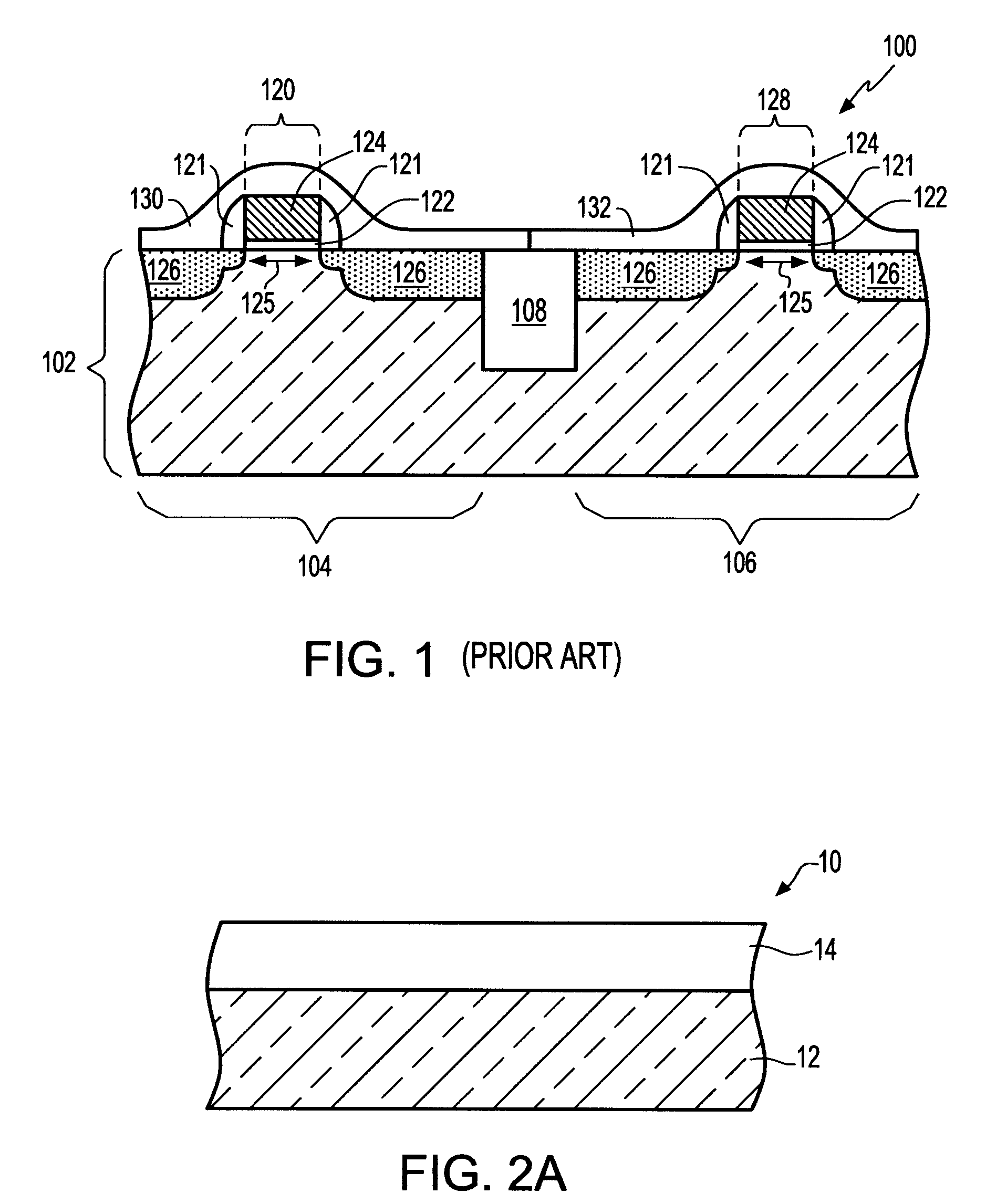

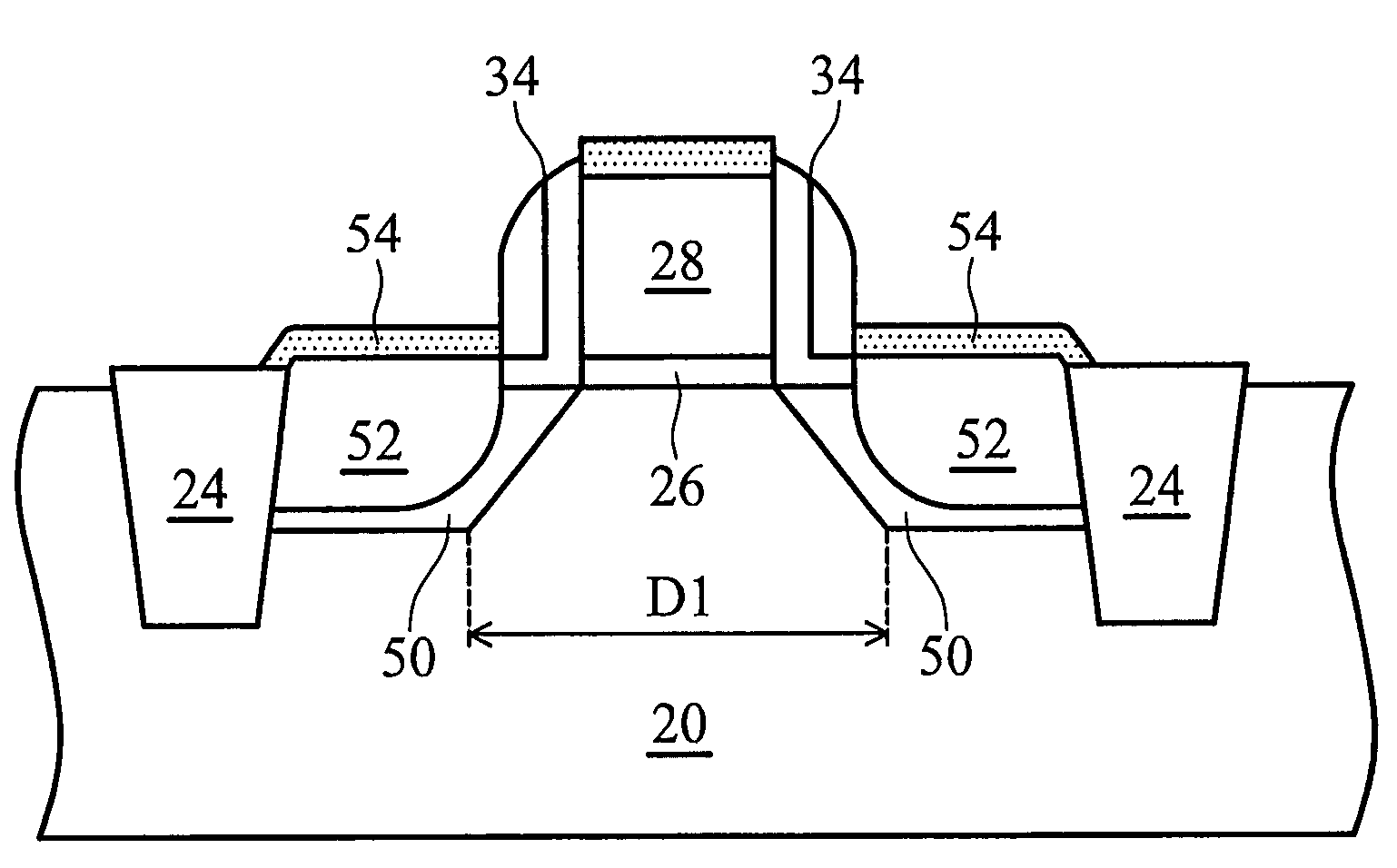

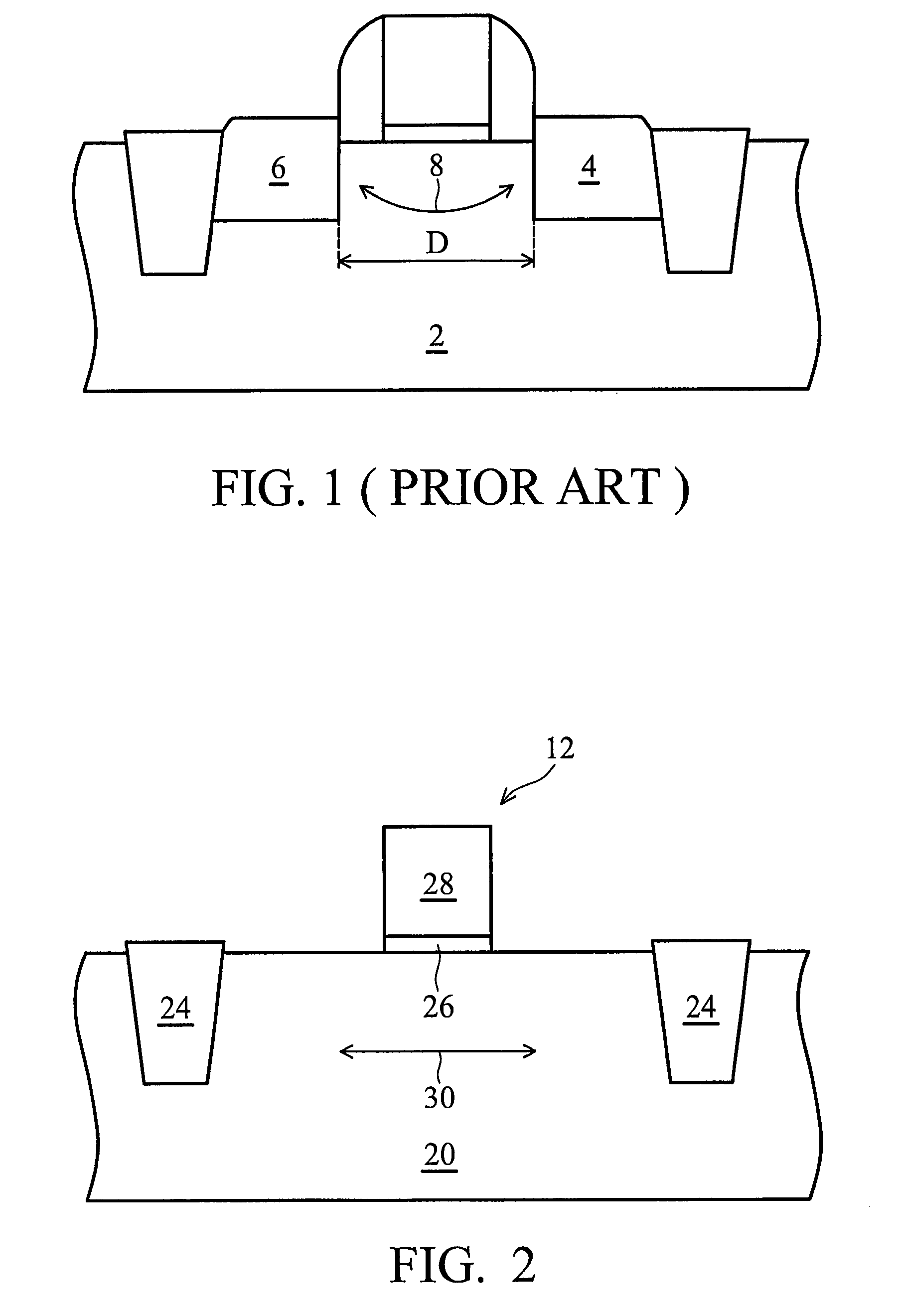

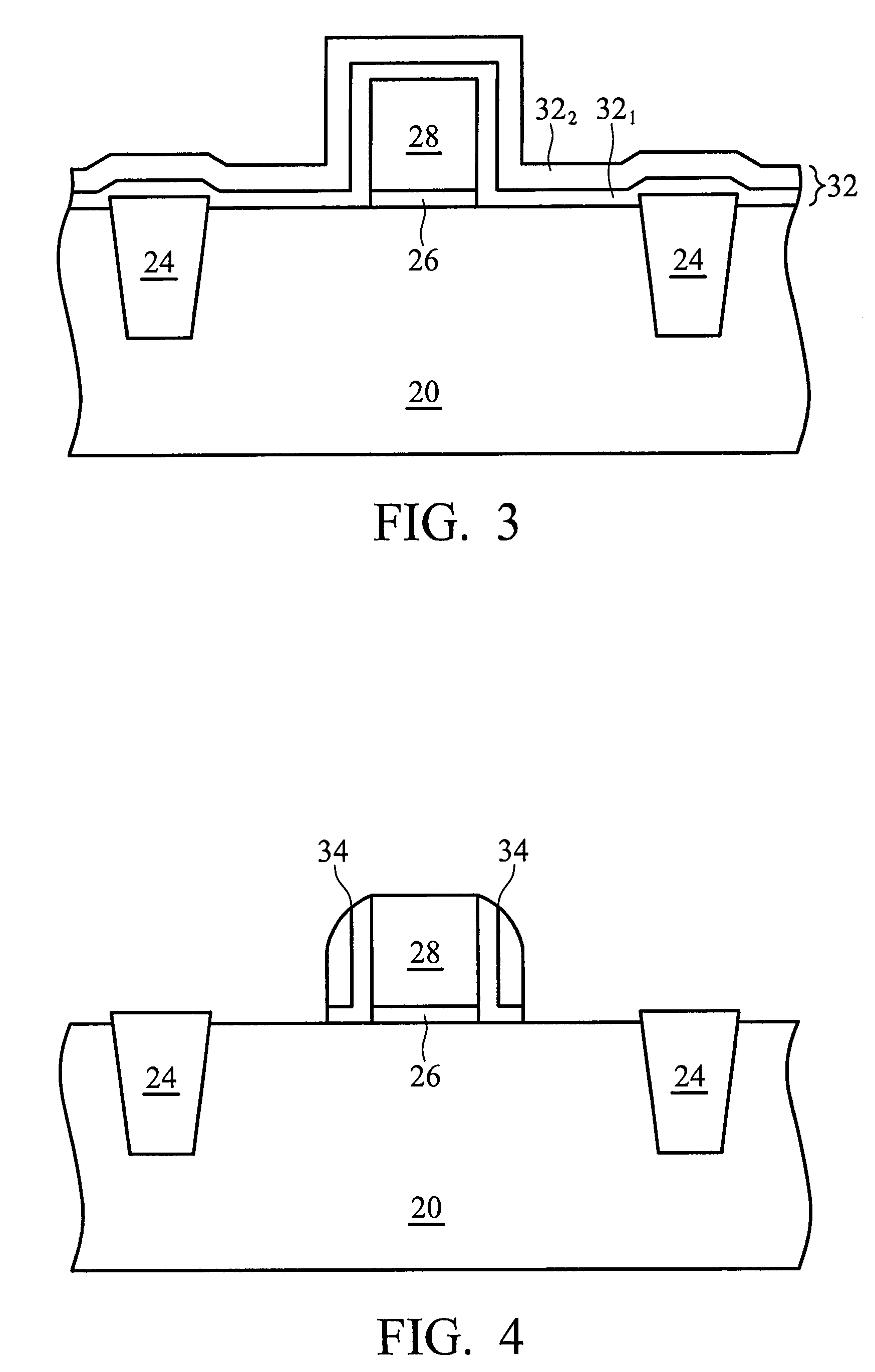

Stress liner surrounded facetless embedded stressor mosfet

The present invention provides an STI bounded transistor structure having enhanced performance which is not diminished due to embedded stressor facets that can be present at the edge of the source / drain regions that contacts an embedded stressor material. Considering that the facet in the prior art is due to an STI divot formed during several necessary wet etching processes, the MOSFET source / drain edge of the inventive structure is surrounded by a liner to prevent facet growth during the epitaxial growth of the stressor material. As such, a part of the semiconductor substrate edge is preserved. The liner employed in the present invention is a stress engineering material such as, for example, silicon nitride.

Owner:GLOBALFOUNDRIES INC

Source/Drain Carbon Implant and RTA Anneal, Pre-SiGe Deposition

ActiveUS20090273034A1Avoid damageImprove short channel effectSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesDopantDevice material

A semiconductor device system, structure, and method of manufacture of a source / drain to retard dopant out-diffusion from a stressor are disclosed. An illustrative embodiment comprises a semiconductor substrate, device, and method to retard sidewall dopant out-diffusion in source / drain regions. A semiconductor substrate is provided with a gate structure, and a source and drain on opposing sides of the gate structure. Recessed regions are etched in a portion of the source and drain. Doped stressors are embedded into the recessed regions. A barrier dopant is incorporated into a remaining portion of the source and drain.

Owner:TAIWAN SEMICON MFG CO LTD

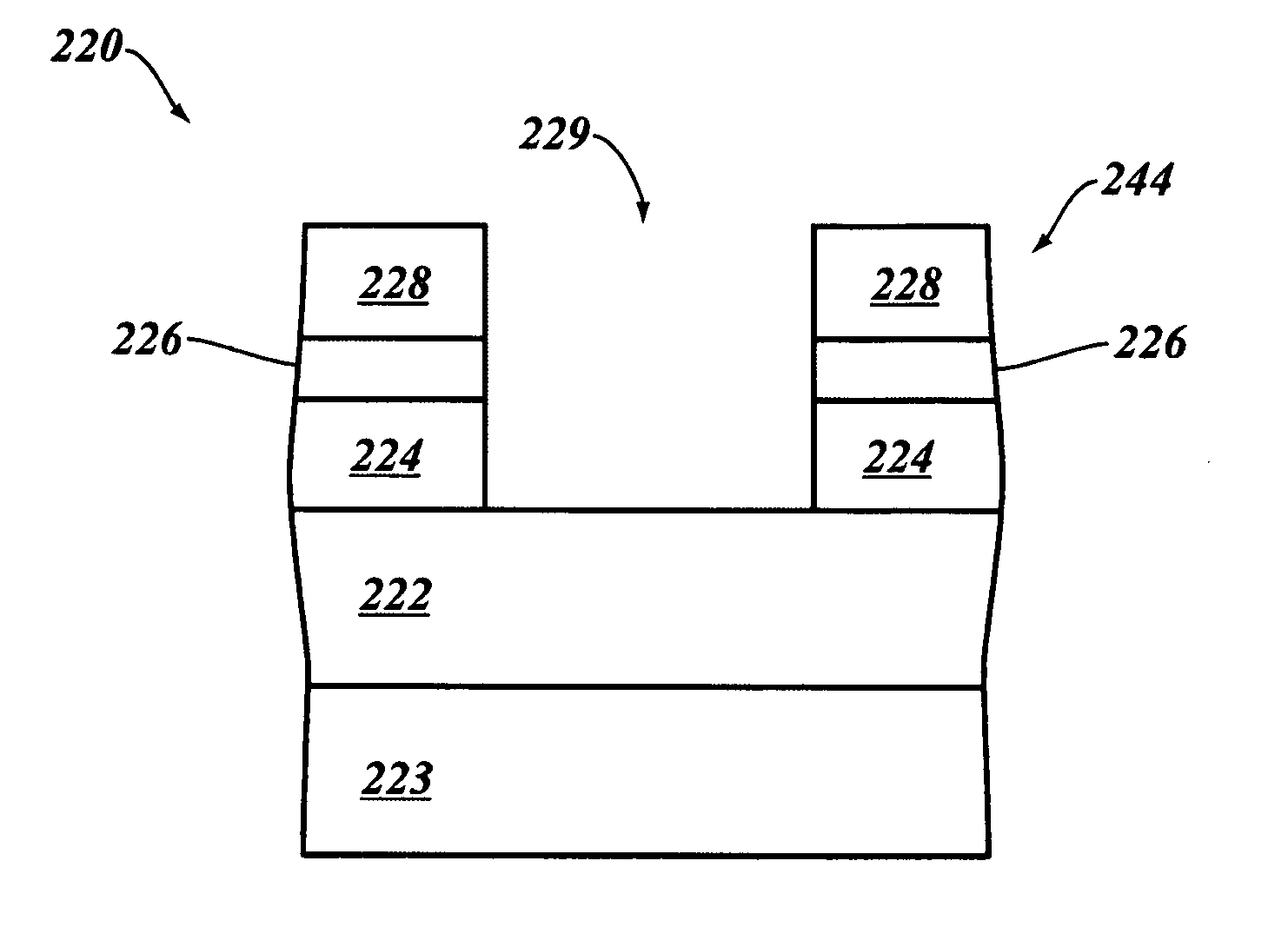

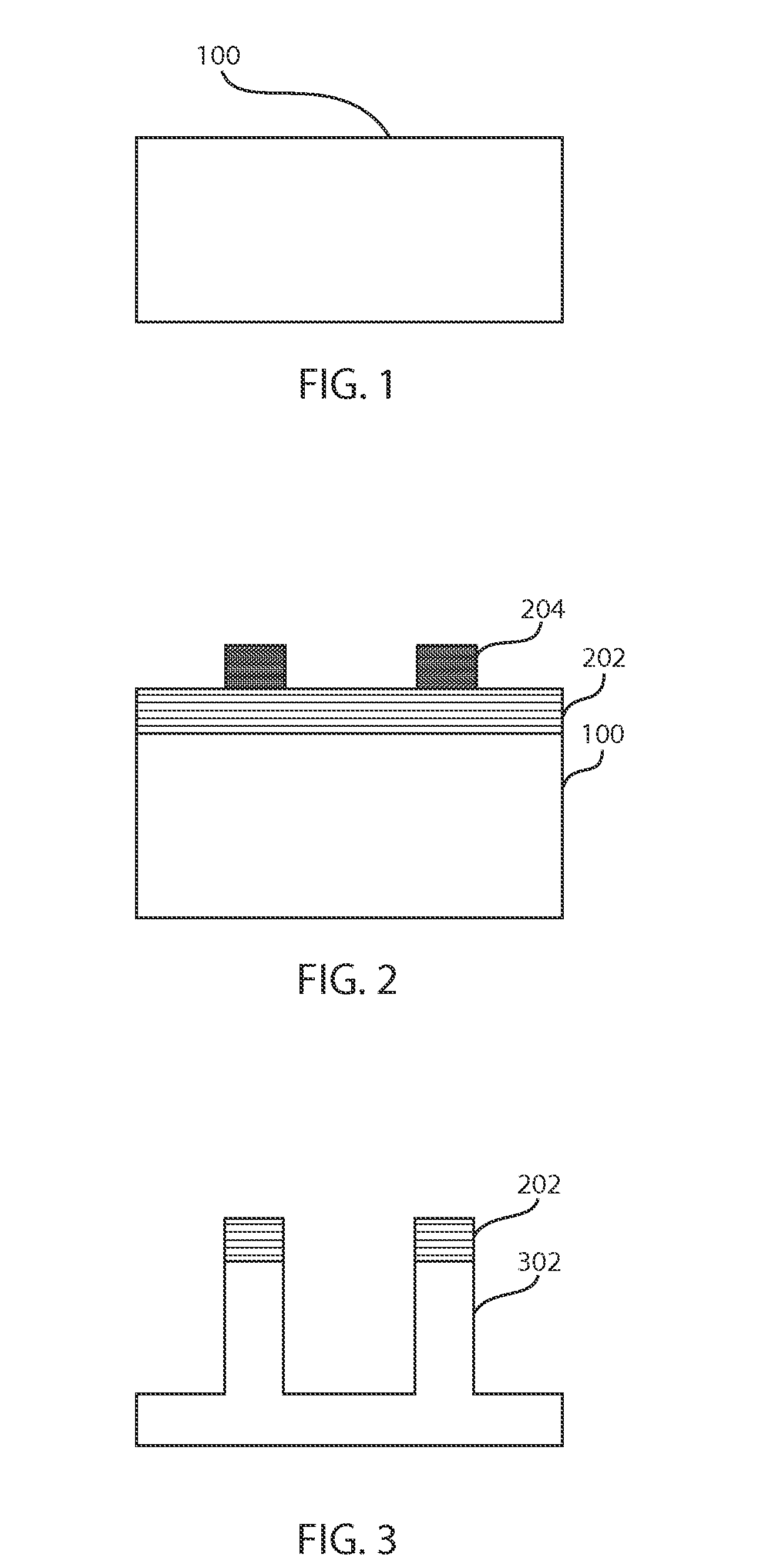

Method for forming a stressor structure

InactiveUS20070224772A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor structure

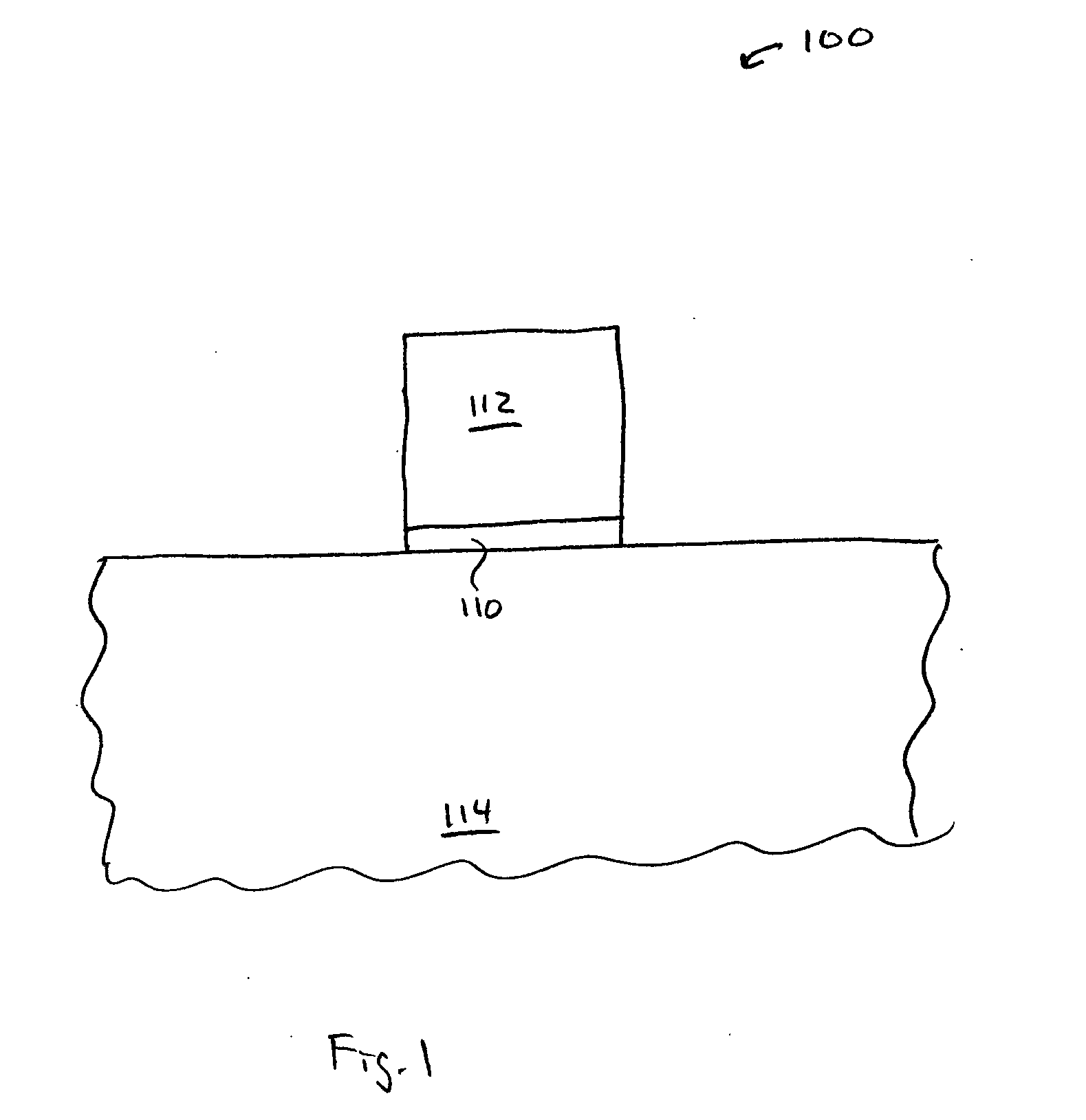

A method for making a semiconductor device is provided herein. In accordance with the method, a semiconductor structure is provided which comprises an active semiconductor layer (224) disposed on a buried dielectric layer (222). A trench (229) is created in the semiconductor structure which exposes a portion of the buried dielectric layer. An oxide layer (250) is formed over the surfaces of the trench, and at least one stressor structure (255) is formed over the oxide layer.

Owner:FREESCALE SEMICON INC

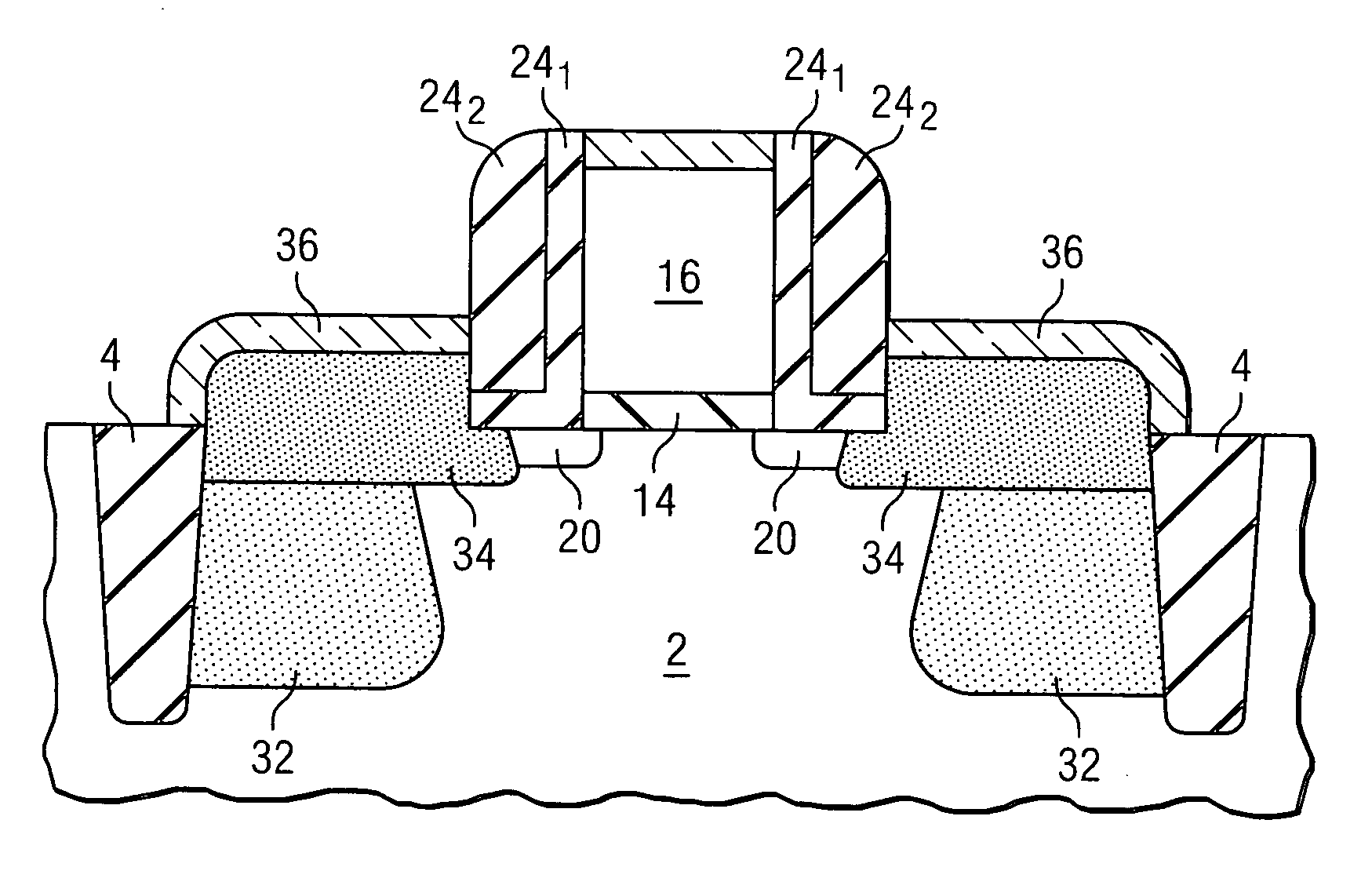

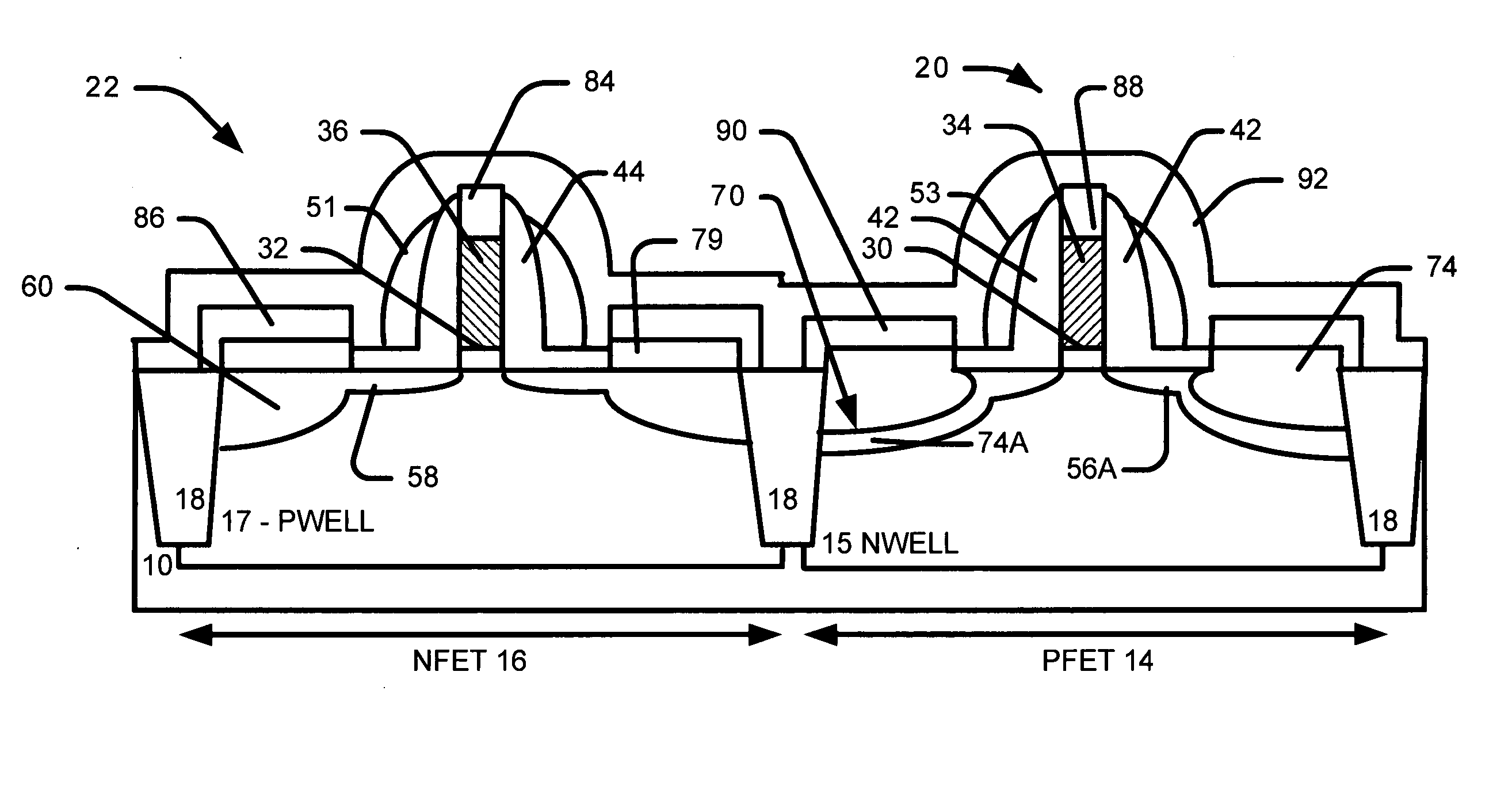

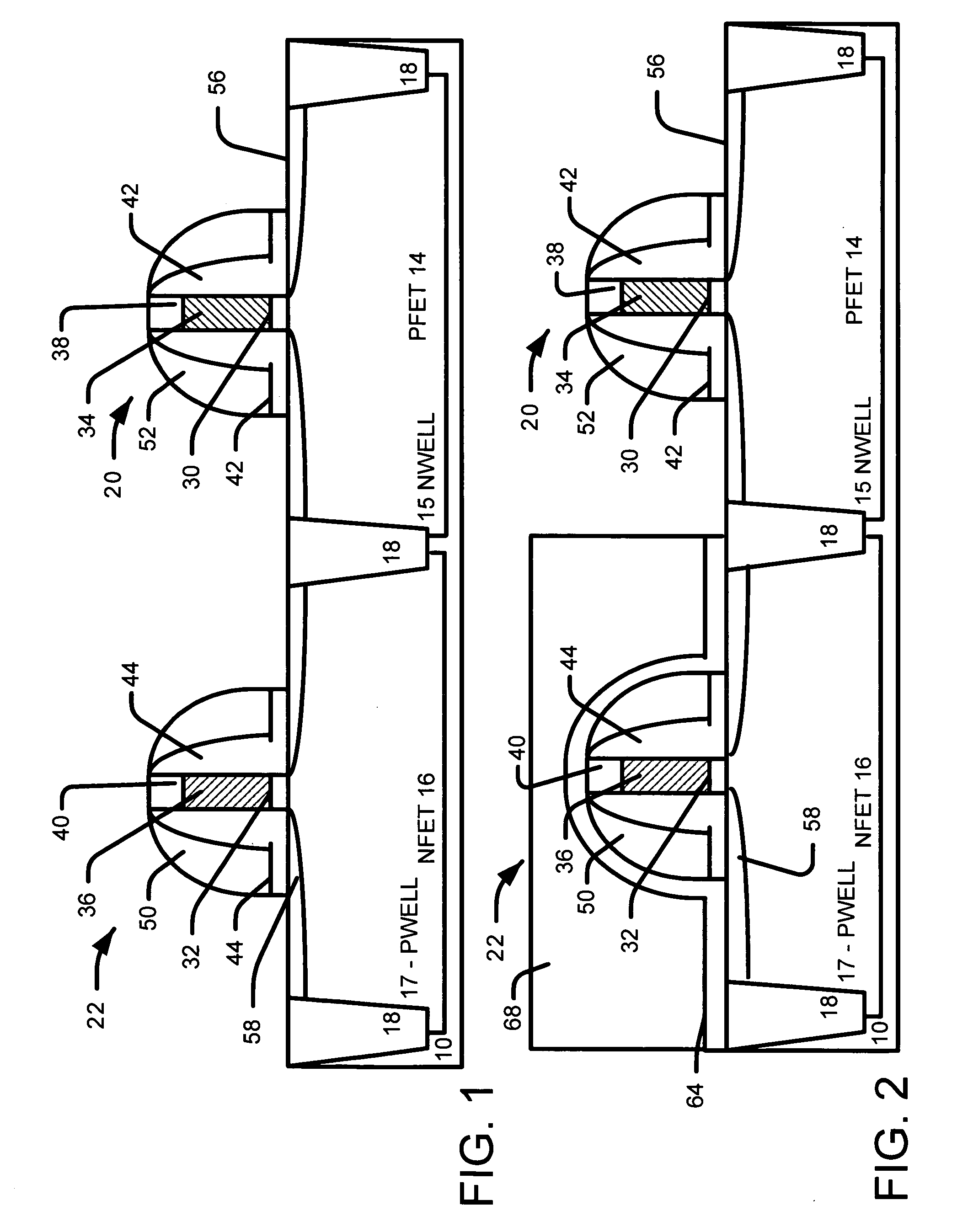

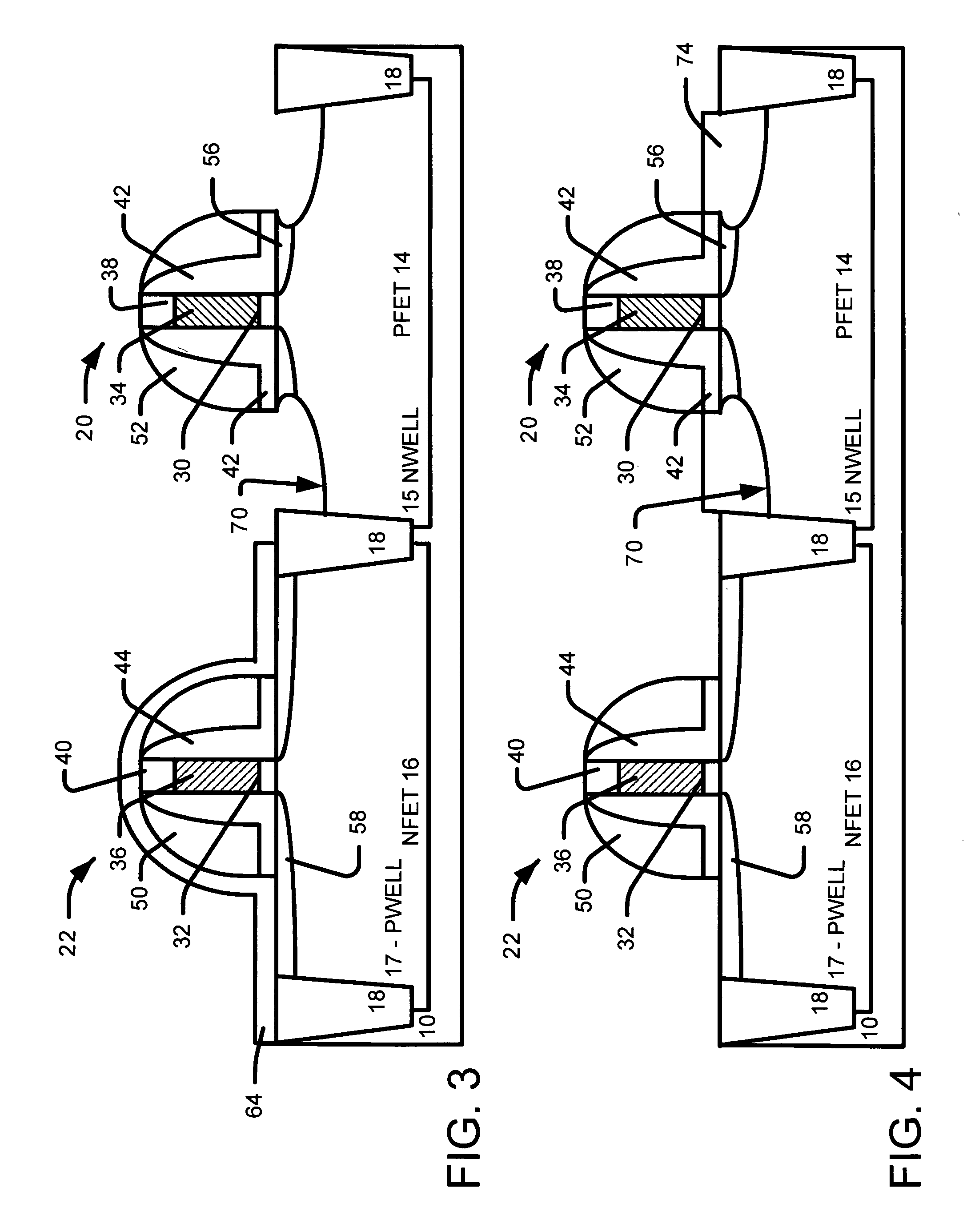

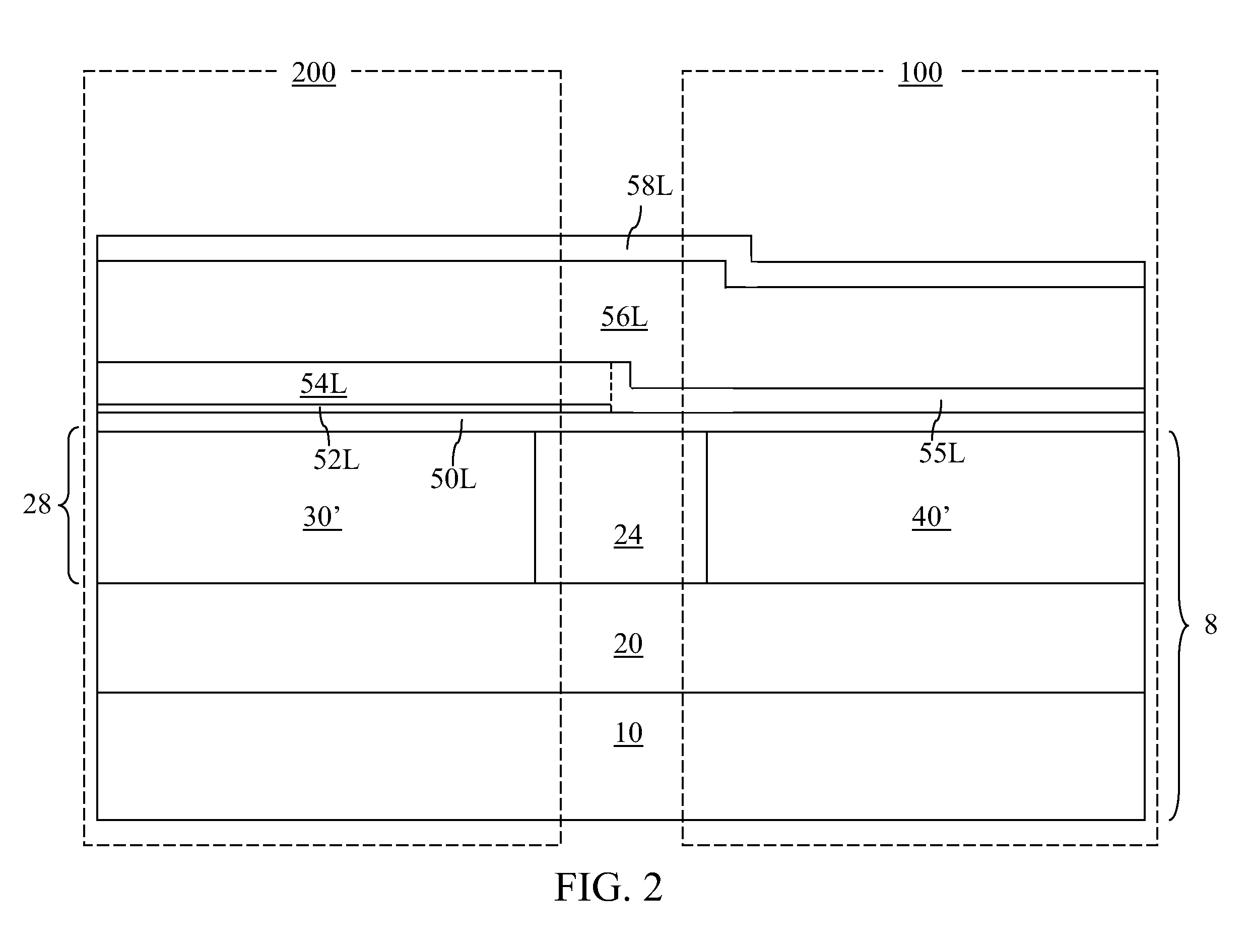

CMOS device with raised source and drain regions

ActiveUS20080102573A1Short channel performanceReduce the probability of activationTransistorSemiconductor/solid-state device manufacturingCMOSSemiconductor structure

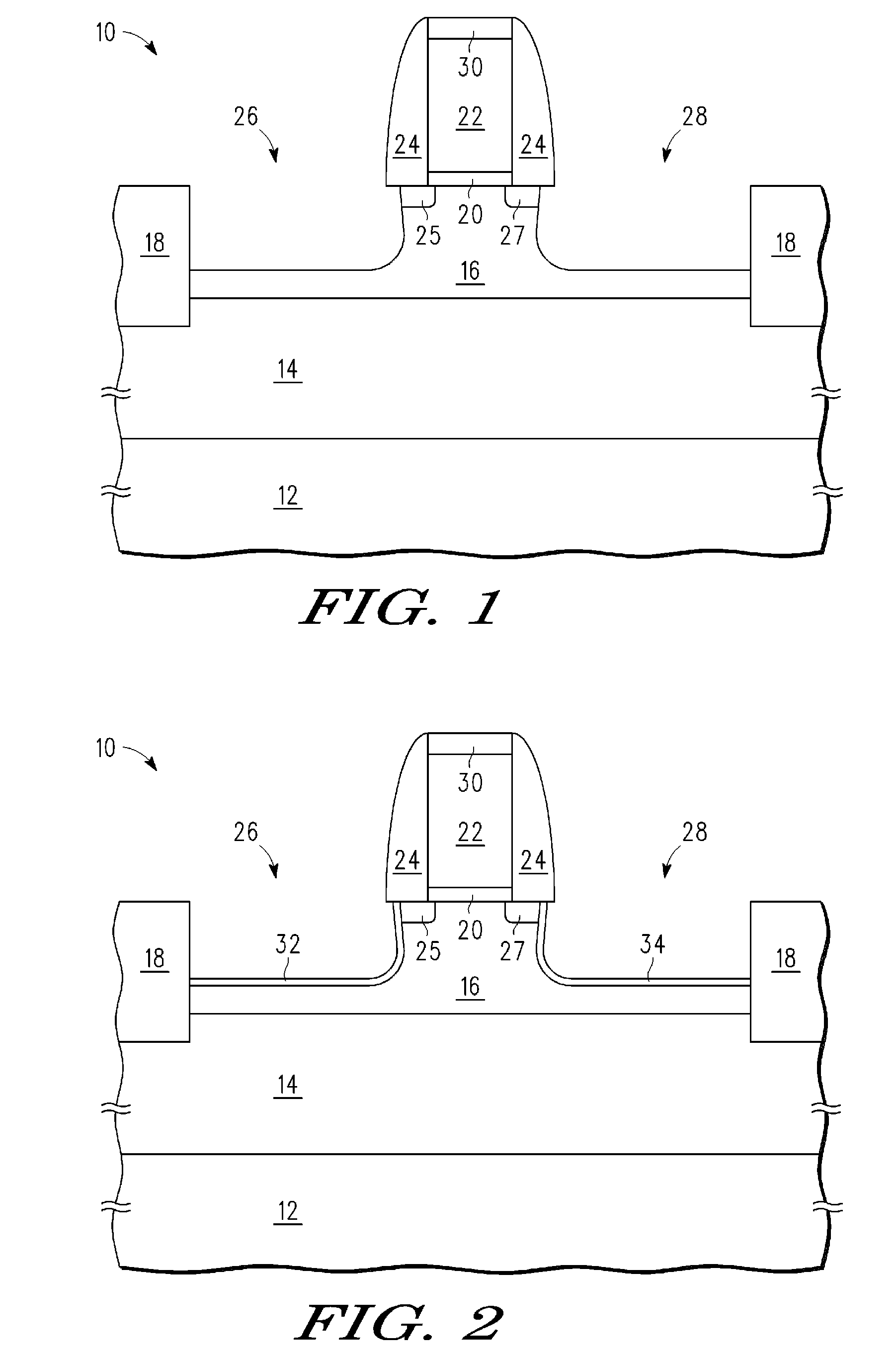

A method of forming a semiconductor structure includes forming a PMOS device and an NMOS device. The step of forming the PMOS device includes forming a first gate stack on a semiconductor substrate; forming a first offset spacer on a sidewall of the first gate stack; forming a stressor in the semiconductor substrate using the first offset spacer as a mask; and epitaxially growing a first raised source / drain extension (LDD) region on the stressor. The step of forming the NMOS device includes forming a second gate stack on the semiconductor substrate; forming a second offset spacer on a sidewall of the second gate stack; epitaxially growing a second raised LDD region on the semiconductor substrate using the second offset spacer as a mask; and forming a deep source / drain region adjoining the second raised LDD region.

Owner:TAIWAN SEMICON MFG CO LTD

Strained Semiconductor Using Elastic Edge Relaxation, a Buried Stressor Layer and a Sacrificial Stressor Layer

ActiveUS20110092047A1Semiconductor/solid-state device manufacturingSemiconductor devicesStressorActive layer

The present invention relates to creating an active layer of strained semiconductor using a combination of buried and sacrificial stressors. That is, a process can strain an active semiconductor layer by transferring strain from a stressor layer buried below the active semiconductor layer and by transferring strain from a sacrificial stressor layer formed above the active semiconductor layer. As an example, the substrate may be silicon, the buried stressor layer may be silicon germanium, the active semiconductor layer may be silicon and the sacrificial stressor layer may be silicon germanium. Elastic edge relaxation is preferably used to efficiently transfer strain to the active layer.

Owner:ACORN TECH INC

Formation of raised source/drain structures in NFET with embedded SiGe in PFET

A structure and method for forming raised source / drain structures in a NFET device and embedded SiGe source / drains in a PFET device. We provide a NFET gate structure over a NFET region in a substrate and PFET gate structure over a PFET region. We provide NFET SDE regions adjacent to the NFET gate and provide PFET SDE regions adjacent to the PFET gate. We form recesses in the PFET region in the substrate adjacent to the PFET second spacers. We form a PFET embedded source / drain stressor in the recesses. We form a NFET S / D epitaxial Si layer over the NFET SDE regions and a PFET S / D epitaxial Si layer over PFET embedded source / drain stressor. The epitaxial Si layer over PFET embedded source / drain stressor is consumed in a subsequent salicide step to form a stable and low resistivity silicide over the PFET embedded source / drain stressor. We perform a NFET S / D implant by implanting N-type ions into NFET region adjacent to the NFET gate structure and into the NFET S / D stressor Si layer to form the raised NFET source / drains.

Owner:TAIWAN SEMICON MFG CO LTD +1

Thermal history sensor

InactiveUS6974249B1Accurate informationHigh opacityThermometers using mean/integrated valuesThermometers using physical/chemical changesBaseline dataMetallurgy

An improved thermal history sensor having multiple glass ceramic substrates with unique compositions is disclosed. By positioning the sensor adjacent to a component subject to thermal stressors, each of the glass ceramic substrates react with a different rate of nucleation and crystal growth and thus yield a specific measure of opacity. By comparing these values representing the opacity for each glass ceramic substrate, or thermal history fingerprint, to baseline data, information about the expected remaining useful lifetime of the component may be obtained.

Owner:AIR FORCE US SEC THE THE

MOS devices with partial stressor channel

ActiveUS7554110B2Reduce probabilityIncrease pressureTransistorSemiconductor/solid-state device detailsGate dielectricSemiconductor structure

Owner:TAIWAN SEMICON MFG CO LTD

Anti-stress fermentation protein feed and producing method thereof

The invention provides an anti-stress fermentation protein feed which is produced by composite bacterium inoculation and high-temperature and moderate-temperature fermentation of a plant derived protein raw material, a terrestrial animal derived protein raw material and a marine animal derived protein raw material. Macromolecular substances in the protein feed are digested and decomposed into micromolecular substances, stressors in nutritional ingredients are decreased, anti-stress active factors such as genistein, glutathione and glucosamine are increased, the immunity of fed animals is improved, and the protein feed shows a good anti-stress capability. The invention further provides a producing method of the anti-stress fermentation protein feed. The feed product with high functionality, good anti-stress effect and high economical efficiency is obtained with the adoption of the multiple derived protein raw materials, a specific formula and an appropriate matching ratio and by mixed fermentation through a special secondary fermentation process.

Owner:BEIJING GOLDENWAY BIO TECH

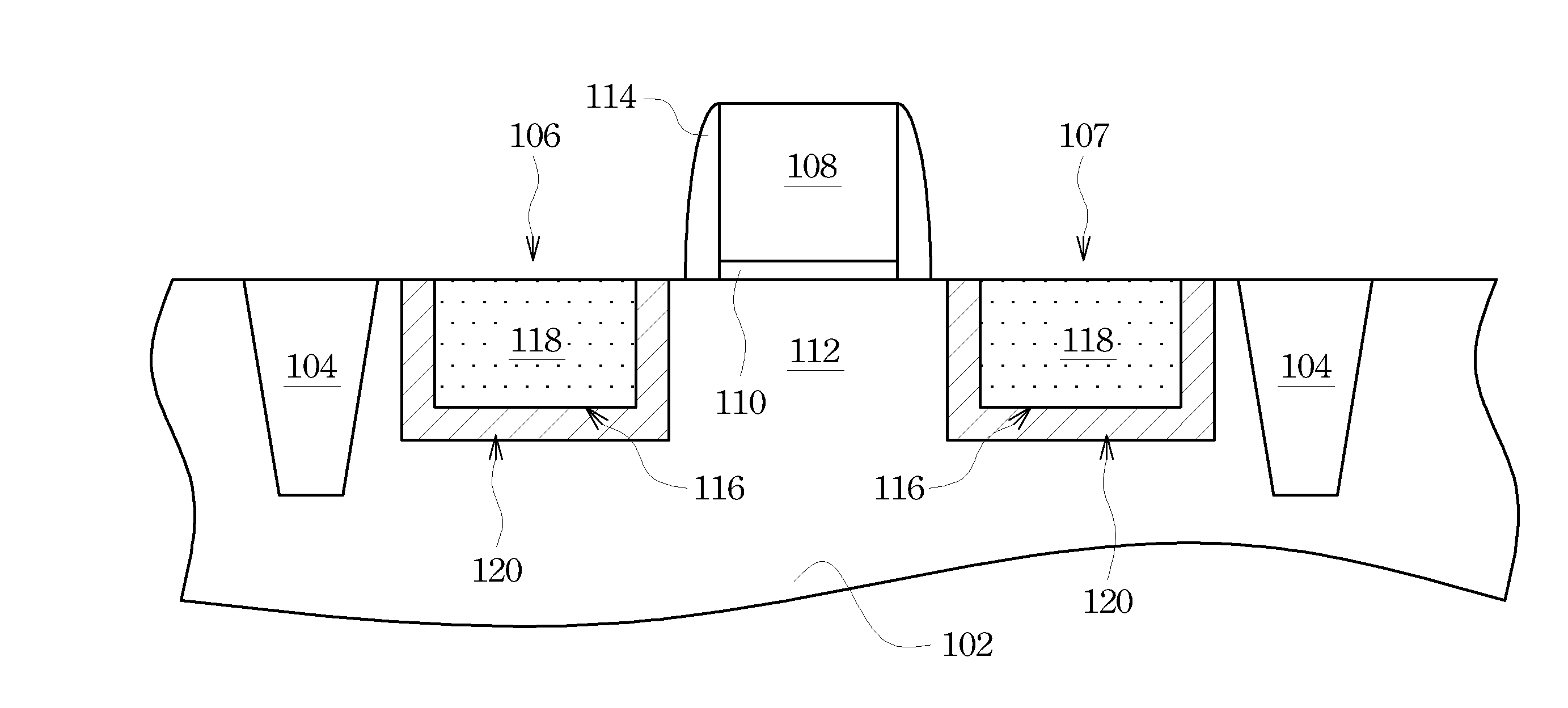

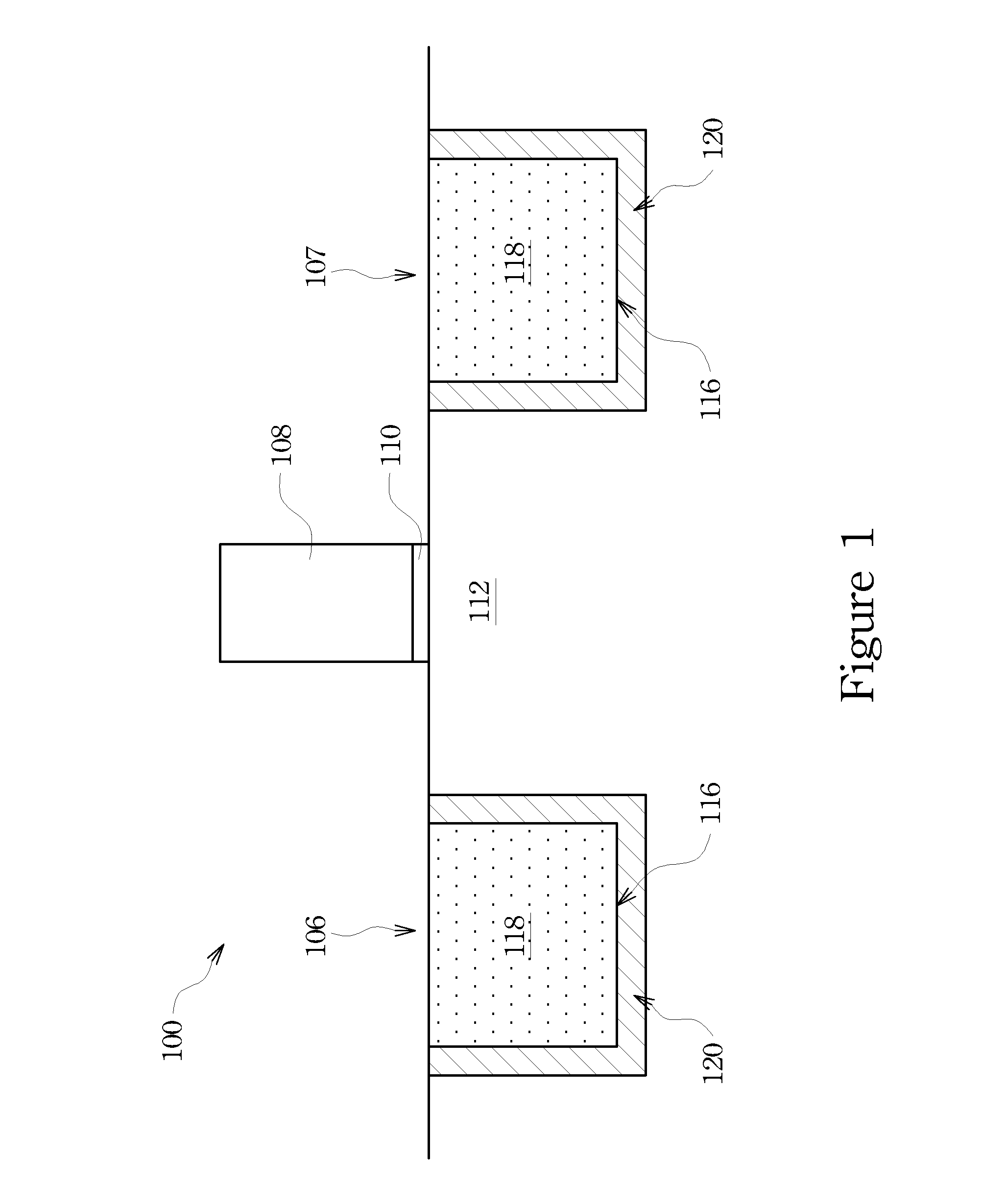

Embedded SiGe stressor with tensile strain for NMOS current enhancement

ActiveUS20070057287A1Improve device performanceSame materialSemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainEngineering

MOS devices having localized stressors are provided. Embodiments of the invention comprise a gate electrode formed over a substrate and source / drain regions formed on either side of the gate electrode. The source / drain regions include an embedded stressor and a capping layer on the embedded stressor. Preferably, the embedded stressor has a lattice spacing greater than the substrate lattice spacing. In a preferred embodiment, the substrate is silicon and the embedded stressor is silicon germanium. A method of manufacturing is also provided, wherein strained PMOS and NMOS transistors may be formed simultaneously.

Owner:TAIWAN SEMICON MFG CO LTD

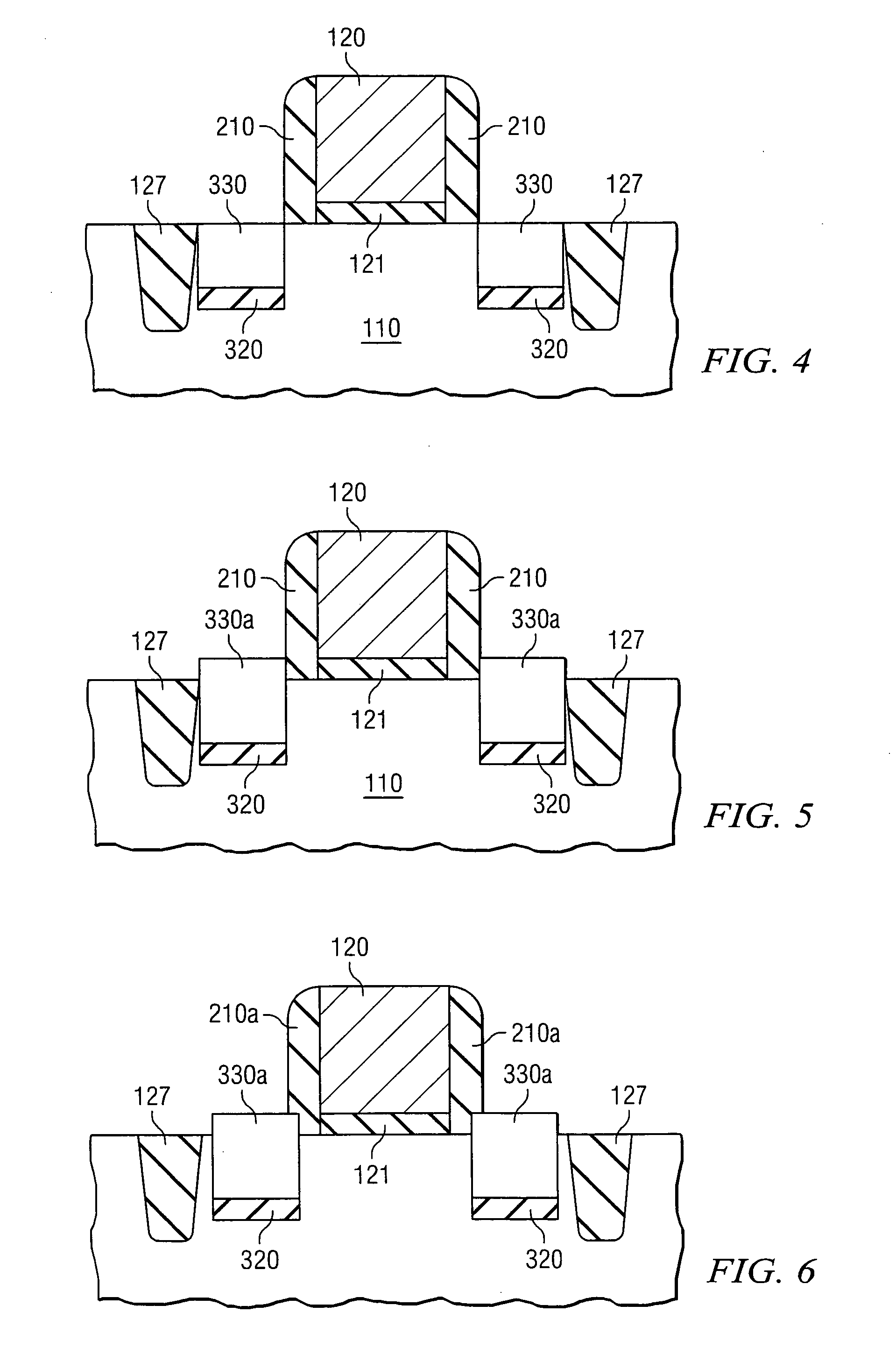

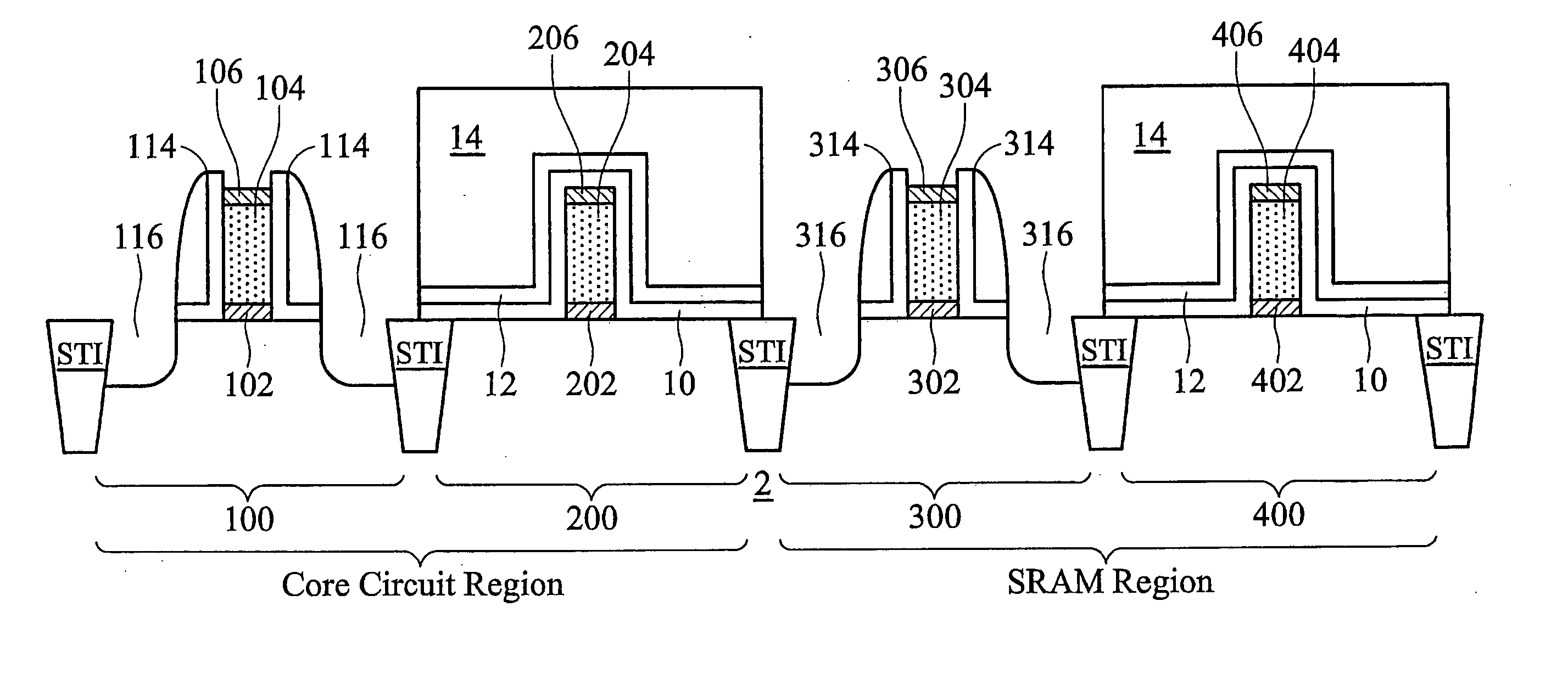

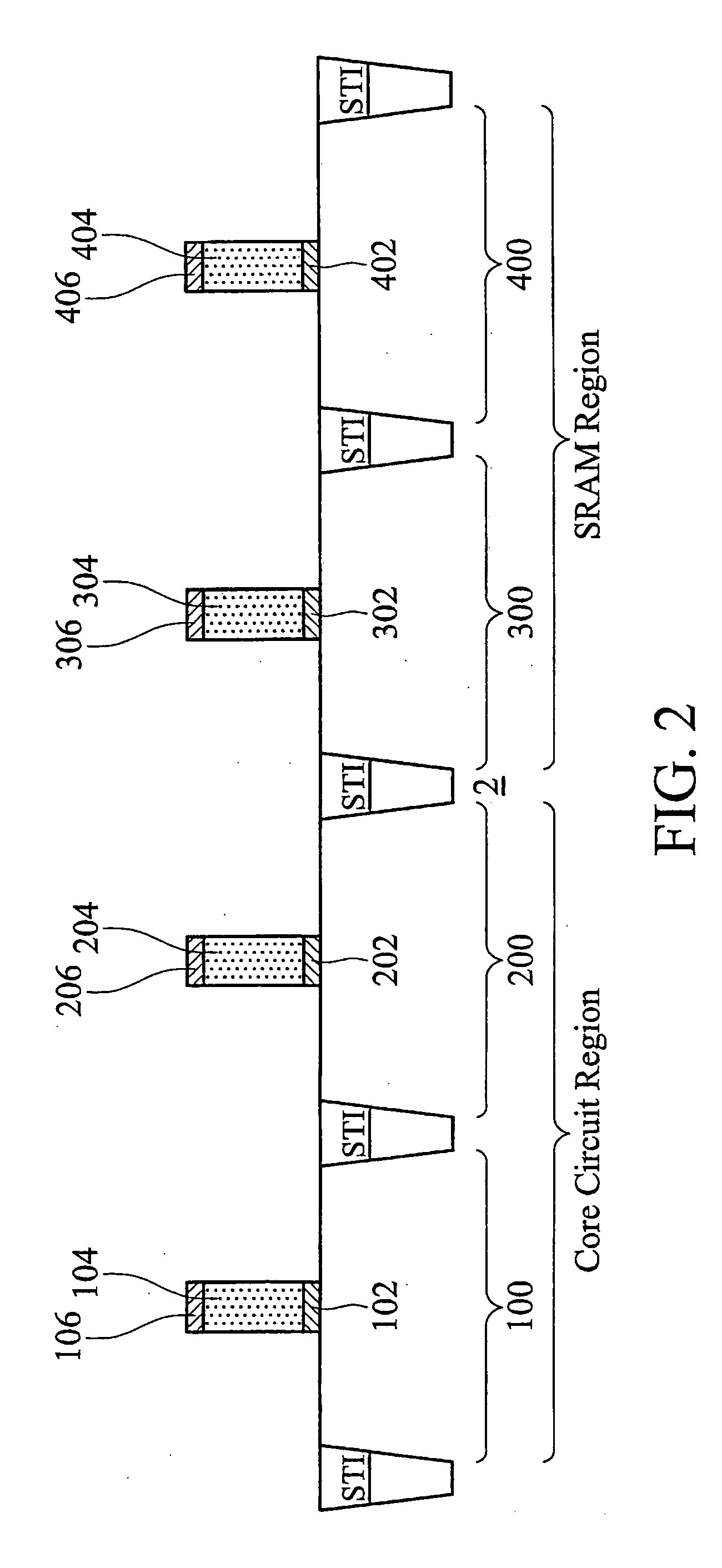

Write margin improvement for SRAM cells with SiGe stressors

ActiveUS20070235817A1Total current dropWrite margins of SRAM cells are improvedTransistorSolid-state devicesWrite marginSemiconductor structure

A semiconductor structure including SRAM cells with improved write margins and a method for forming the same are provided. The semiconductor structure comprises a substrate including a core circuit and an SRAM cell. The SRAM cell includes a pull-up PMOS device that comprises a first source / drain region in the substrate, a first SiGe stressor having a portion overlapping at least a portion of the first source / drain region, and a first current-tuning region having a portion overlapping at least a portion of the first source / drain region. The core circuit comprises a core PMOS device that comprises a second source / drain region in the substrate, and a second SiGe stressor having a portion overlapping at least a portion of the second source / drain region. The core PMOS device is free of current-tuning regions.

Owner:TAIWAN SEMICON MFG CO LTD

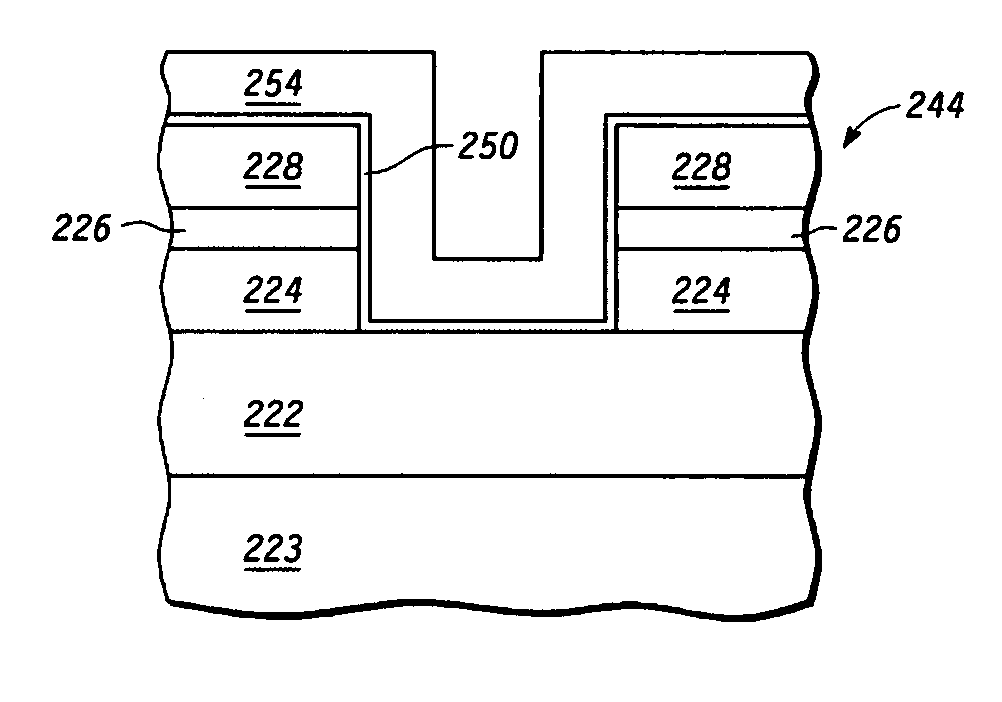

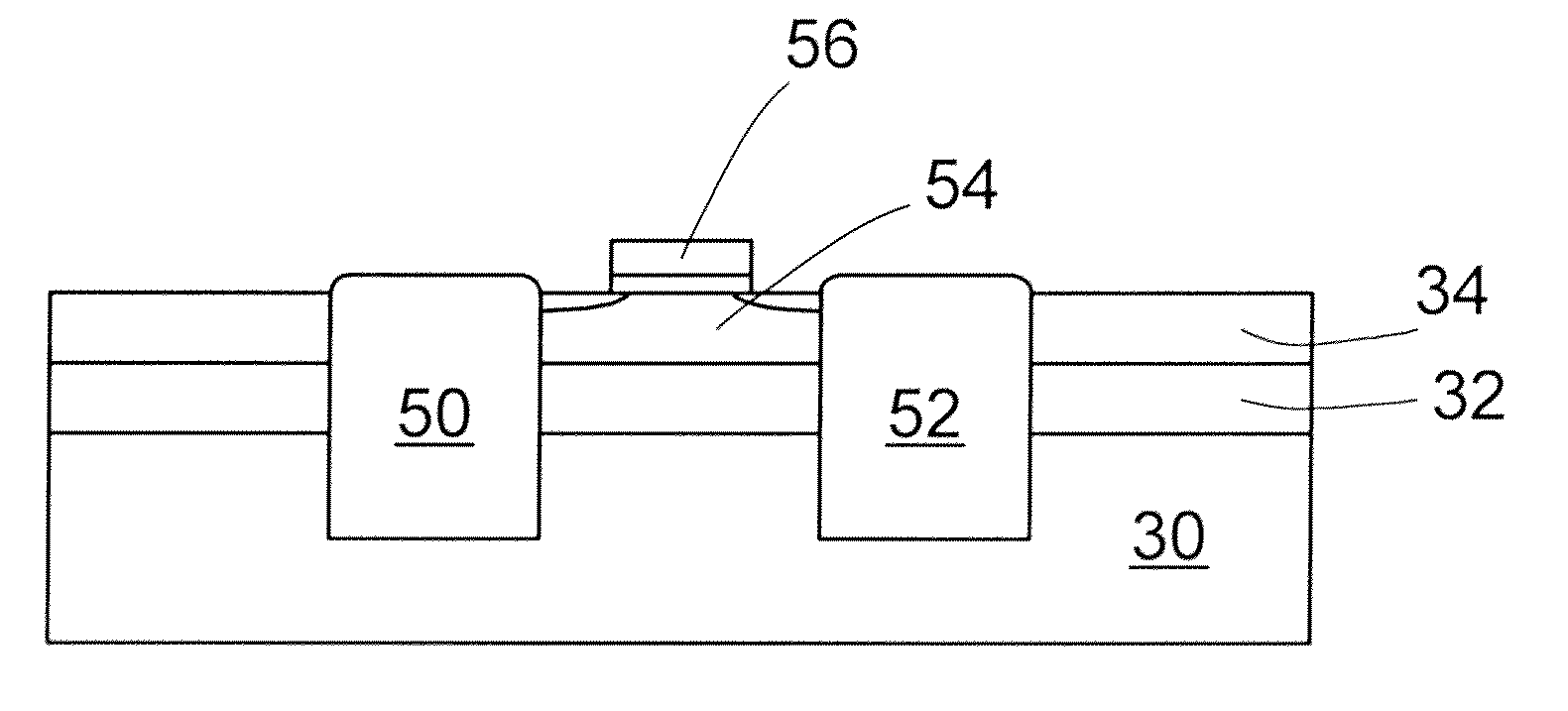

STI stressor integration for minimal phosphoric exposure and divot-free topography

InactiveUS20070249129A1Semiconductor/solid-state device manufacturingDevice materialSemiconductor structure

A method for making a semiconductor device is provided herein. In accordance with the method, a semiconductor structure is provided which comprises an active semiconductor layer (224) disposed on a buried dielectric layer (222). A trench (229) is created in the semiconductor structure which exposes a portion of the buried dielectric layer. An oxide layer (250) is formed over the surfaces of the trench, and at least one stressor structure (254) is formed over the oxide layer.

Owner:FREESCALE SEMICON INC

Stressor for engineered strain on channel

A semiconductor substrate having recesses filled with heteroepitaxial silicon-containing material with different portions having different impurity concentrations. Strained layers can fill recessed source / drain regions in a graded, bottom-up fashion. Layers can also line recess sidewalls with one concentration of strain-inducing impurity and fill the remainder to the recess with a lower concentration of the impurity. In the latter case, the sidewall liner can be tapered.

Owner:ASM IP HLDG BV

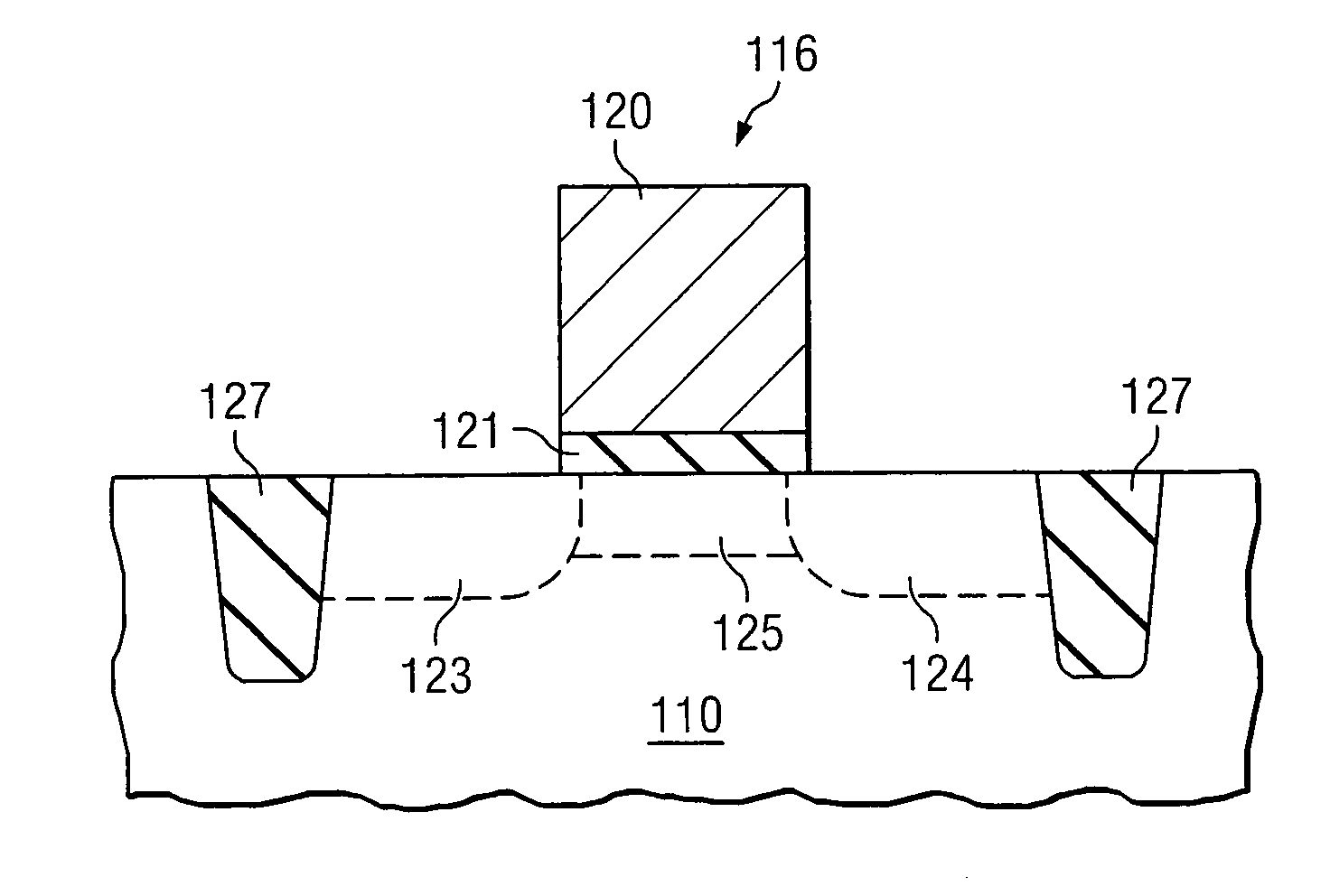

Method for fabricating a semiconductor device with self-aligned stressor and extension regions

InactiveUS20100047985A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedSemiconductor materials

Methods are provided for fabricating a MOS transistor having self-aligned stressor and extension regions. A method comprises forming a gate stack overlying a layer of semiconductor material and forming a spacer about sidewalls of the gate stack. The method further comprises forming cavities in the layer of semiconductor material, wherein the cavities are substantially aligned with the spacer. The method further comprises forming a stress-inducing semiconductor material in the cavities, and implanting ions of a conductivity-determining impurity type into the stress-inducing semiconductor material using the gate stack and the spacer as an implantation mask.

Owner:GLOBALFOUNDRIES INC

Embedded stressors for multigate transistor devices

ActiveUS20130154029A1High carrier mobilityImprove mobilitySemiconductor devicesCharge carrier mobilityEngineering

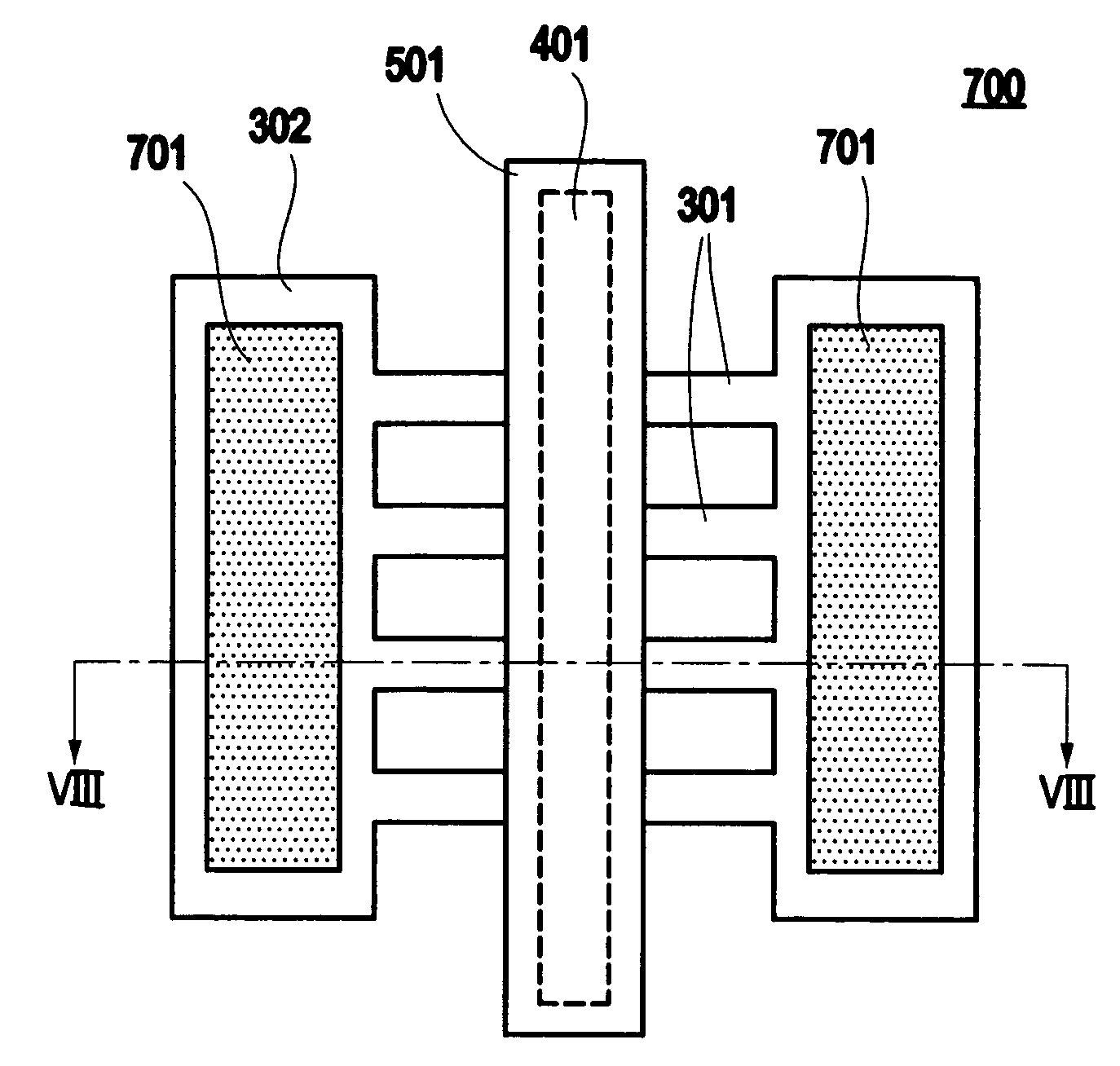

Multigate transistor devices and methods of their fabrication are disclosed. In accordance with one method, a fin and a gate structure that is disposed on a plurality of surfaces of the fin are formed. In addition, at least a portion of an extension of the fin is removed to form a recessed portion that is below the gate structure, is below a channel region of the fin, and includes at least one angled indentation. Further, a terminal extension is grown in the at least one angled indentation below the channel region and along a surface of the channel region such that the terminal extension provides a stress on the channel region to enhance charge carrier mobility in the channel region.

Owner:TOAGOSEI CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com