Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

606 results about "Epitaxial silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Substrate susceptors for receiving semiconductor substrates to be deposited upon and methods of depositing materials over semiconductor substrates

In one implementation, a substrate susceptor for receiving a semiconductor substrate for selective epitaxial silicon-comprising depositing thereon, where the depositing comprises measuring emissivity of the susceptor from at least one susceptor location in a non-contacting manner, includes a body having a front substrate receiving side, a back side, and a peripheral edge. At least one susceptor location from which emissivity is to be measured is received on at least one of the front substrate receiving side, the back side, and the edge. Such at least one susceptor location comprises an outermost surface comprising a material upon which selective epitaxial silicon will not deposit upon during selective epitaxial silicon depositing on a semiconductor substrate received by the susceptor for at least an initial thickness of epitaxial silicon depositing on said substrate. Other aspects and implementations are contemplated.

Owner:MICRON TECH INC

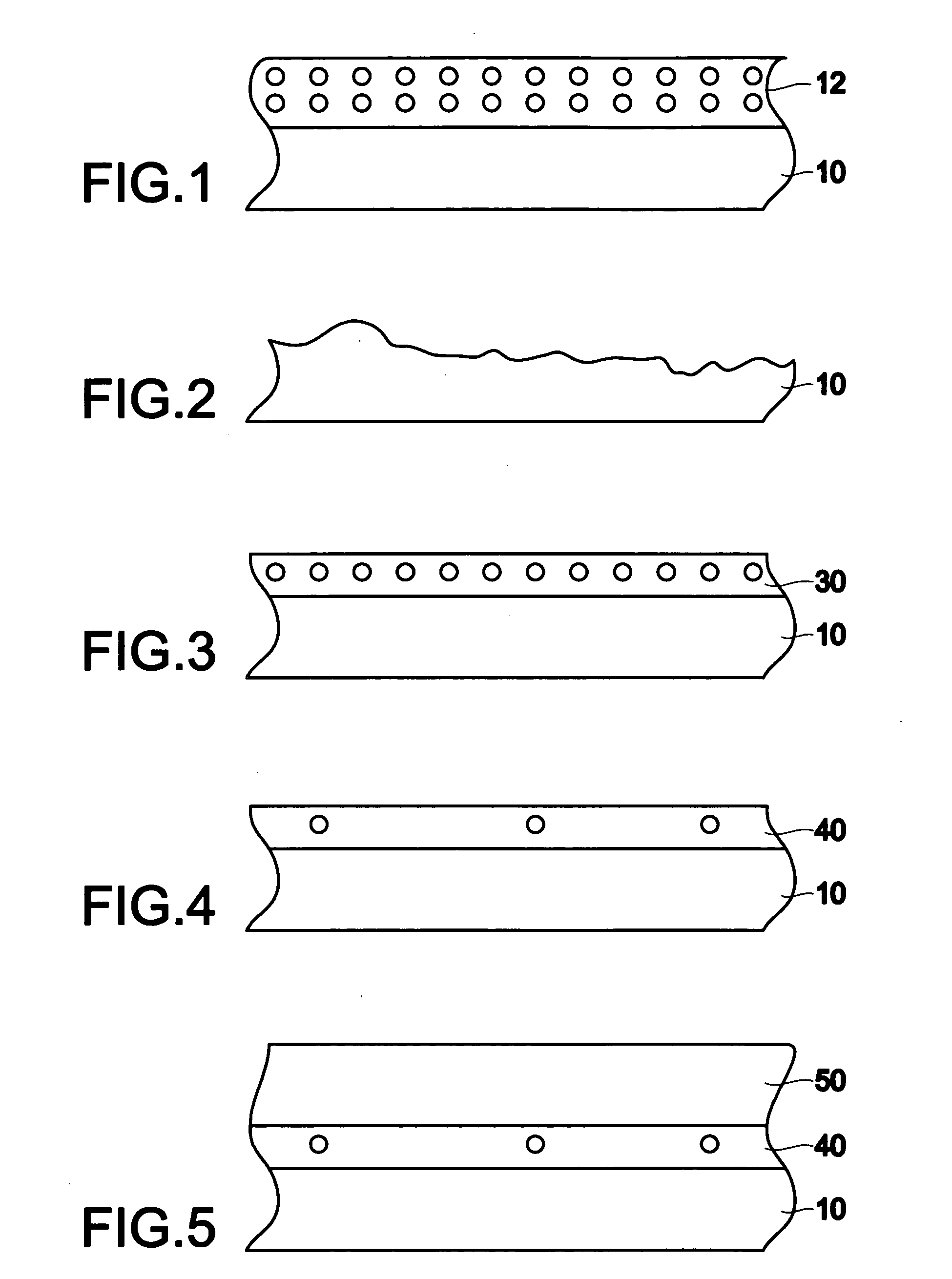

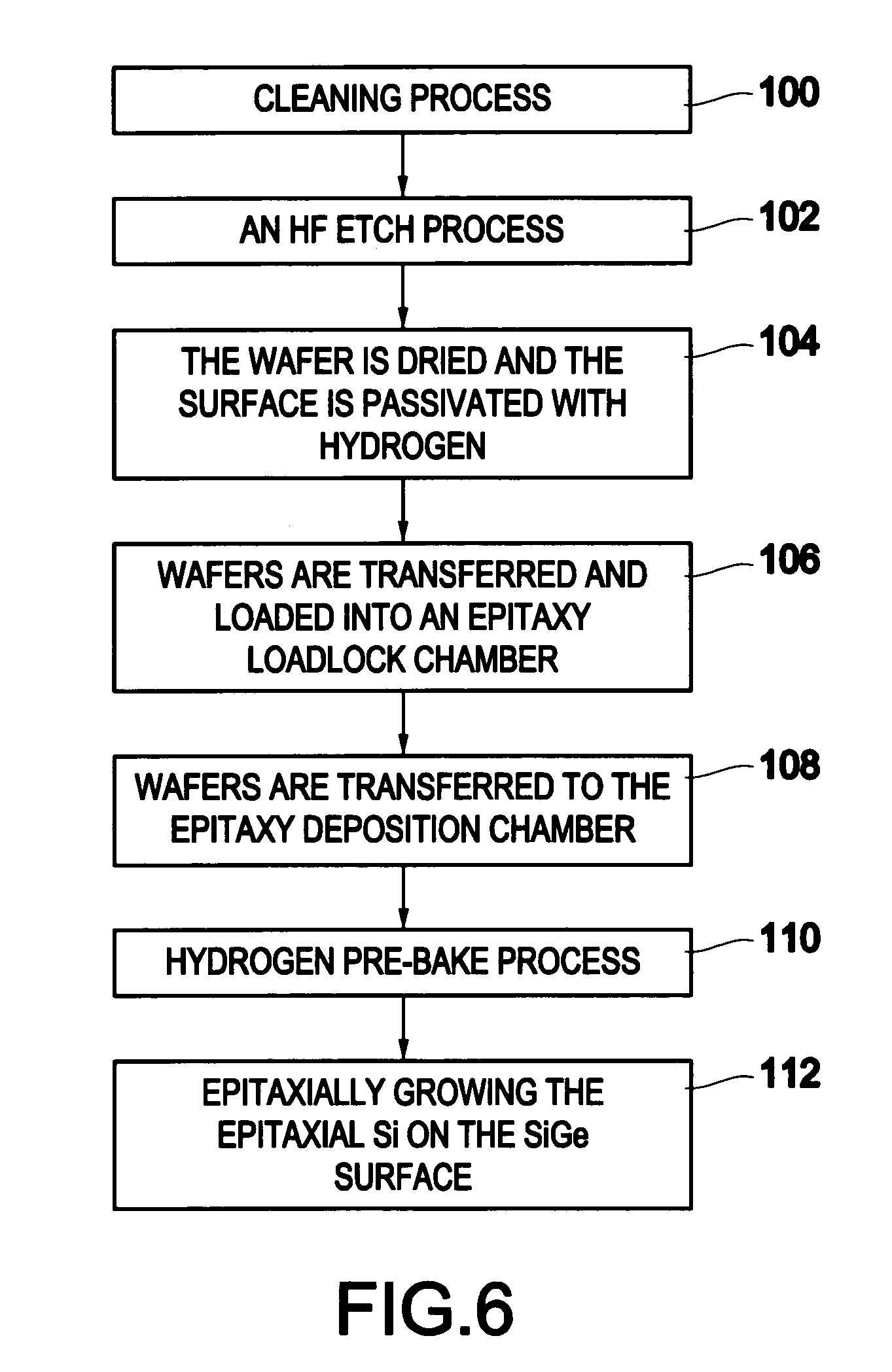

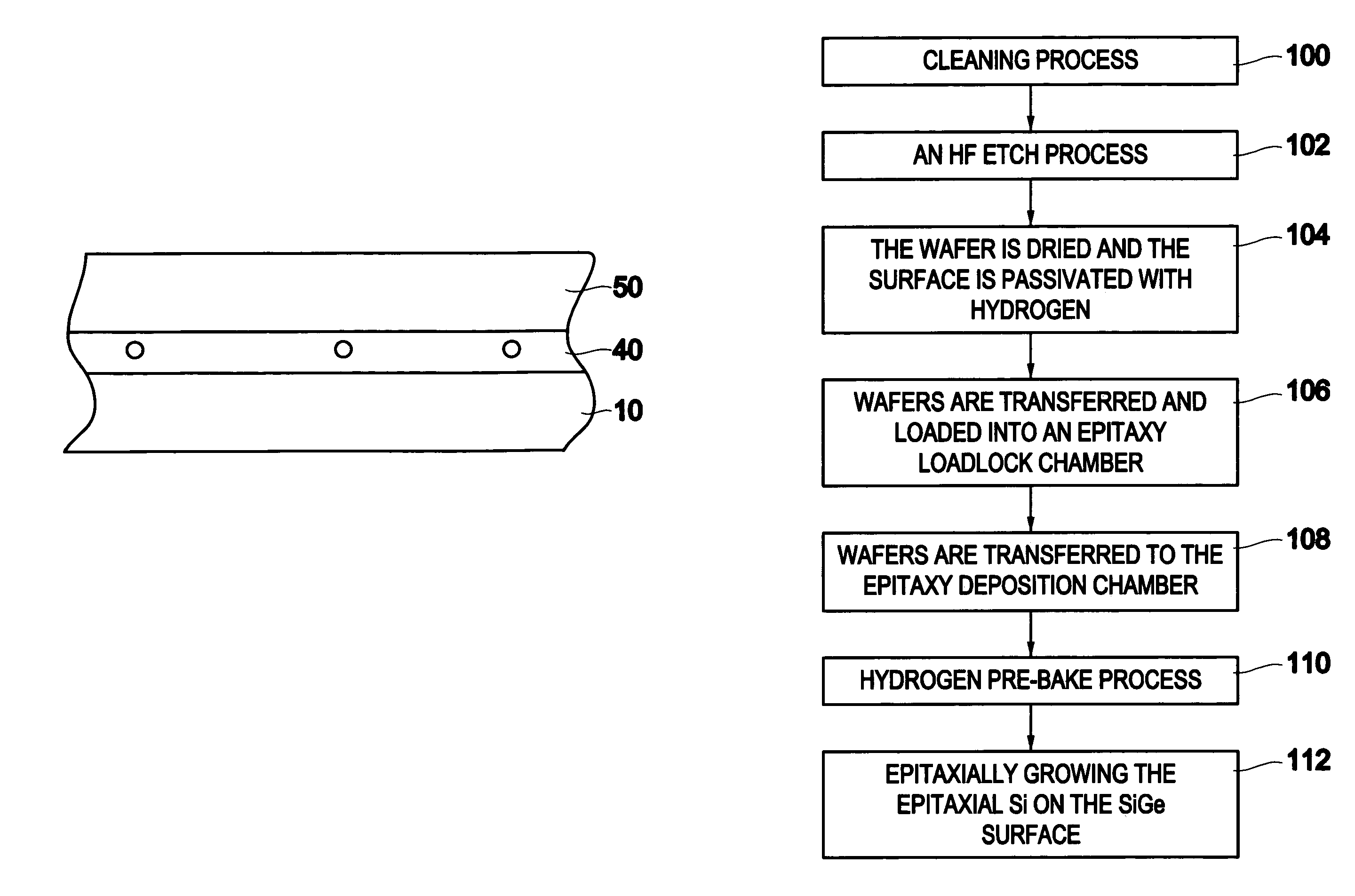

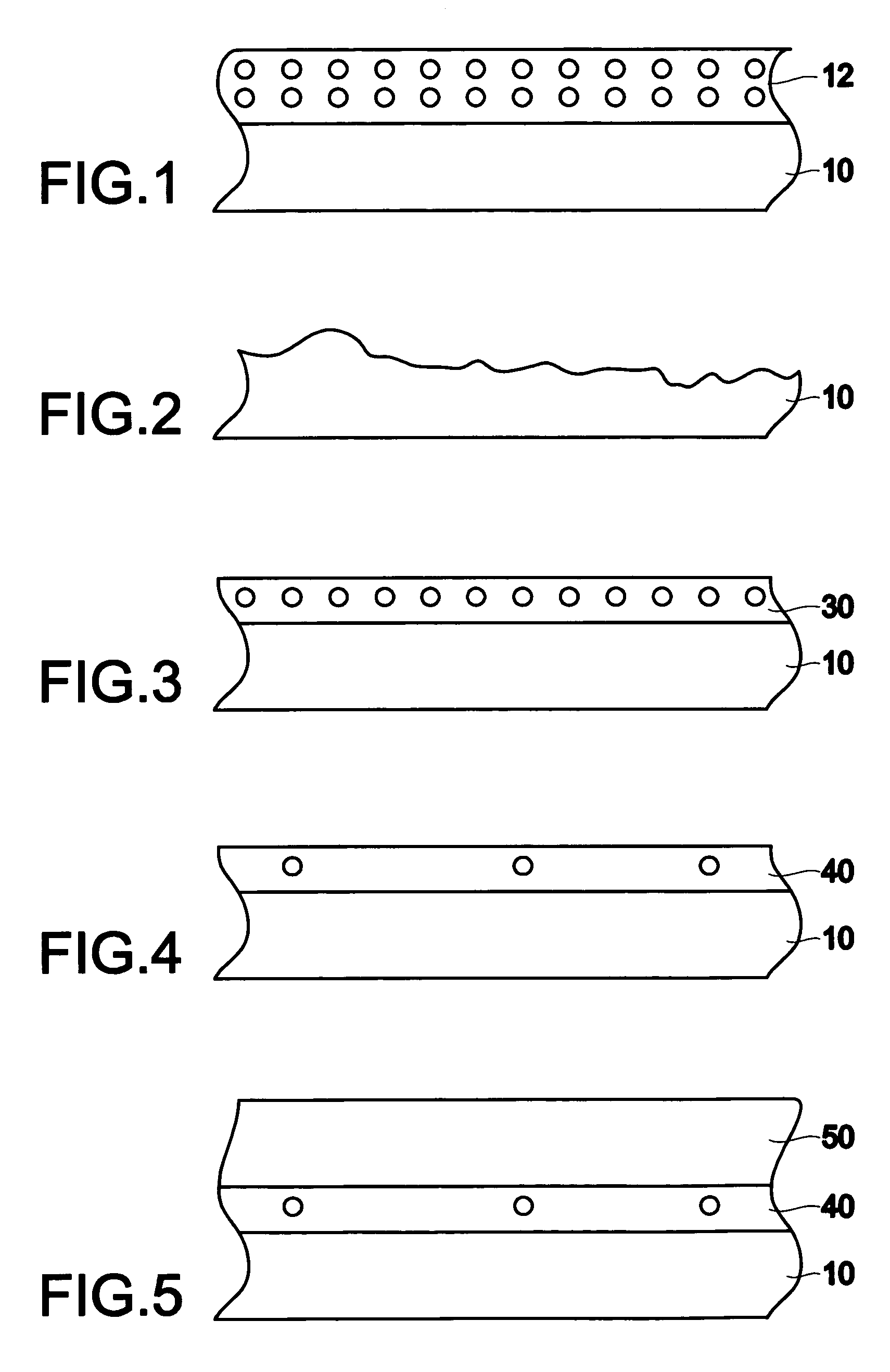

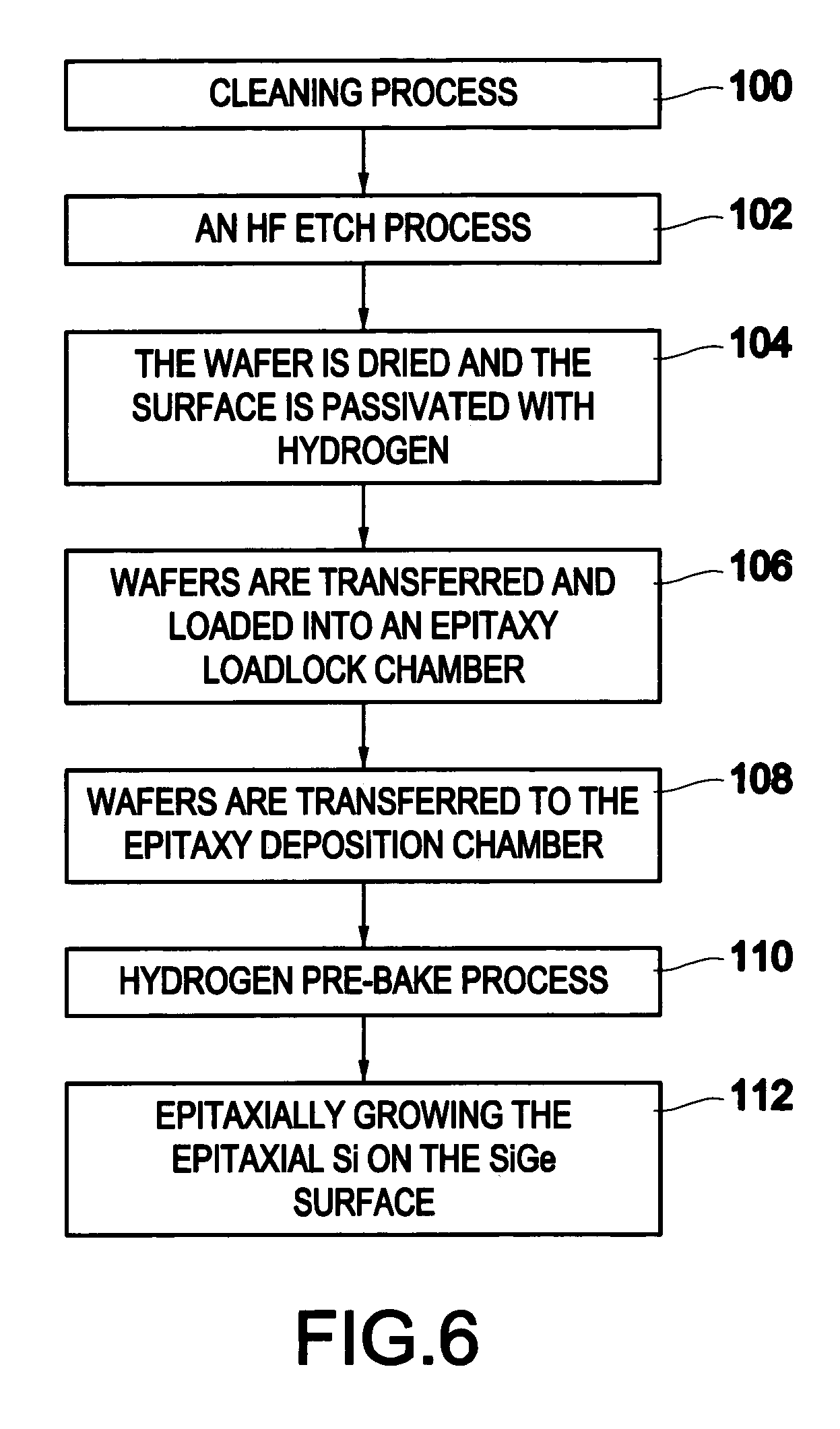

Method of preventing surface roughening during hydrogen pre-bake of SiGe substrates using chlorine containing gases

InactiveUS20050148162A1Prevent surfaceAvoid creatingPolycrystalline material growthSemiconductor/solid-state device manufacturingPartial oxidationSilicon on insulator

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves only a sub-monolayer of oxygen (typically 1×1013-1×1015 / cm2 of oxygen) at the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process in a chlorine containing environment which heats the silicon germanium, strained silicon, or thin silicon-on-insulator surface sufficiently to remove the remaining oxygen from the surface. By introducing a small amount of chlorine containing gases, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:IBM CORP

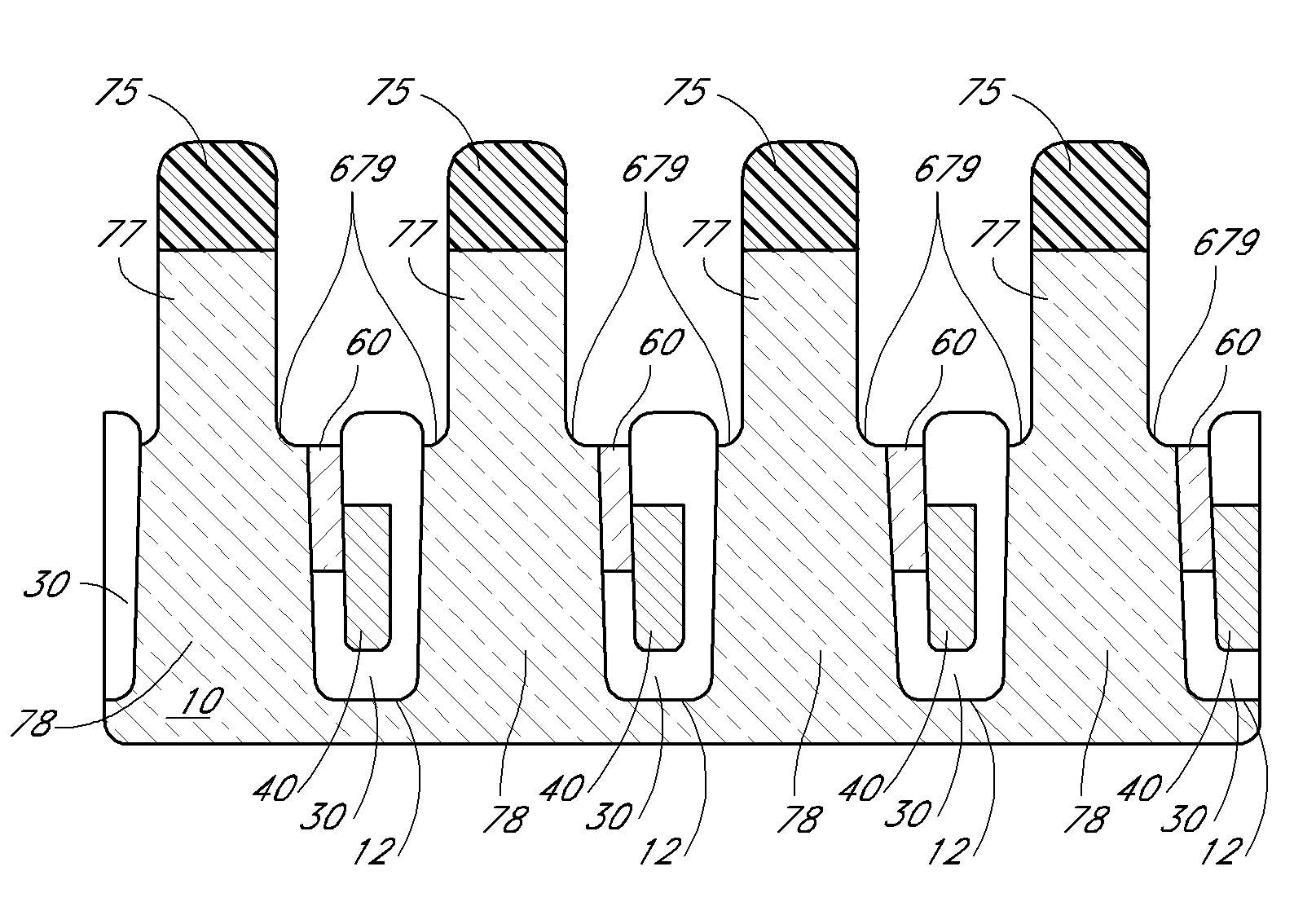

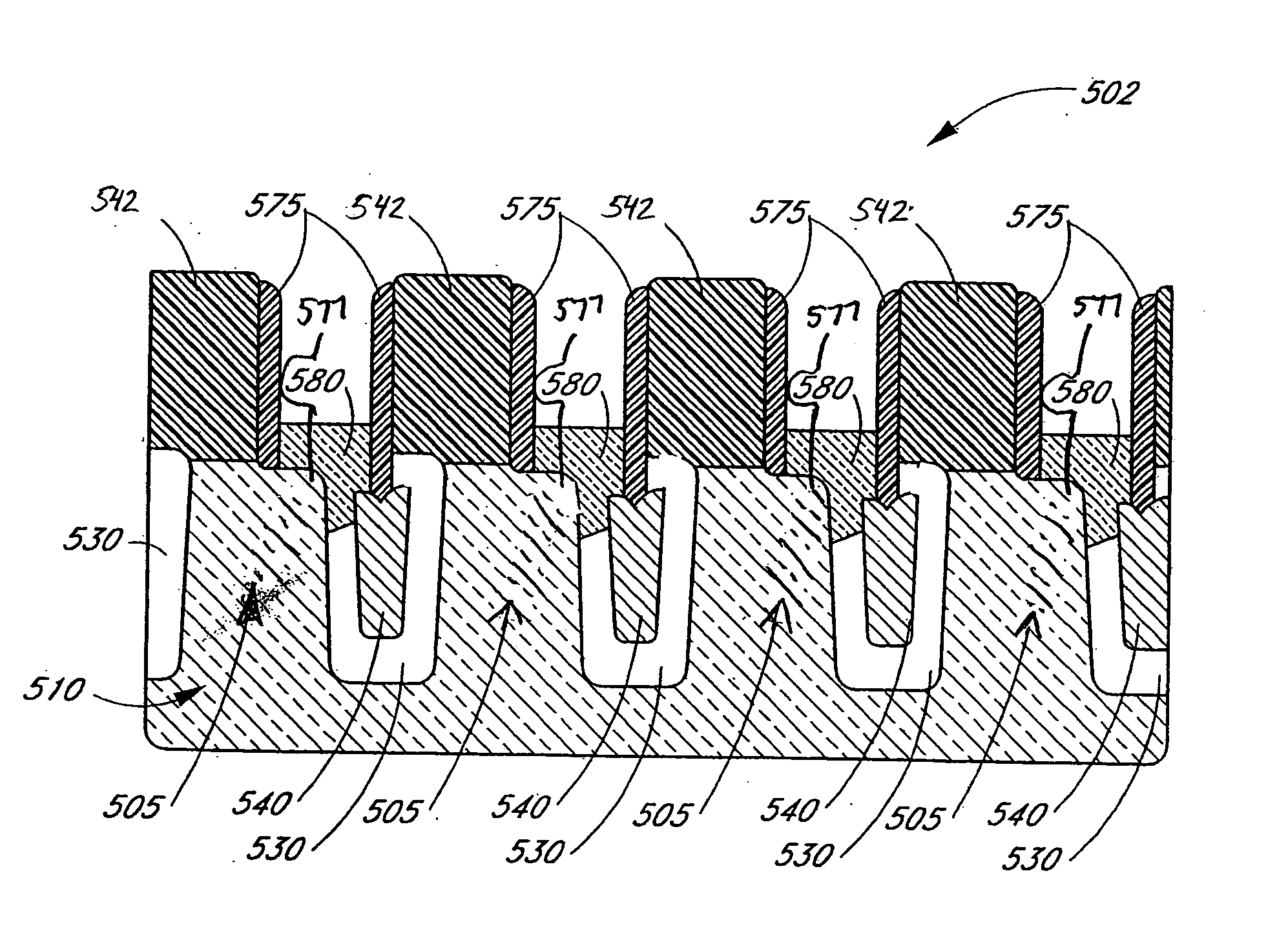

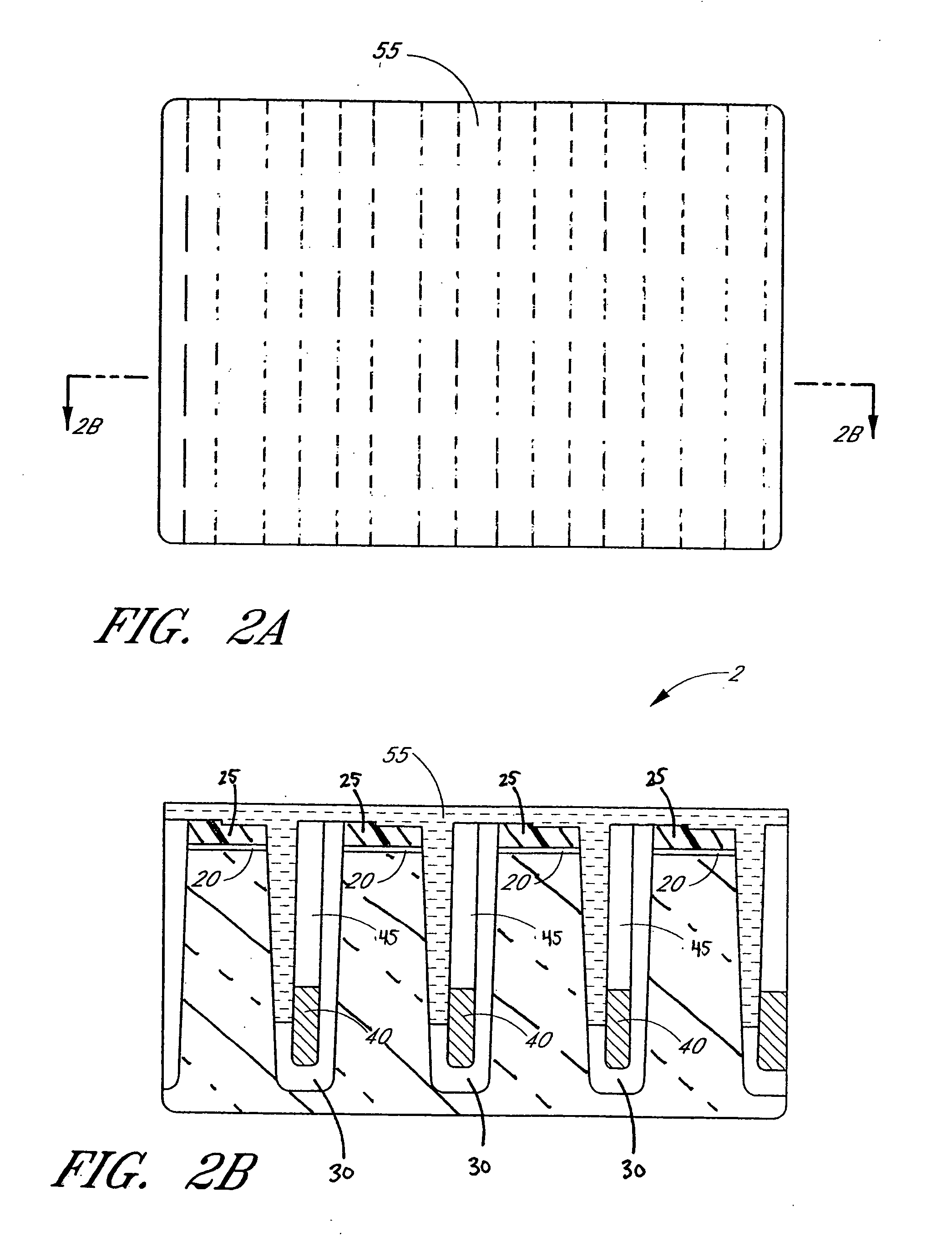

Vertical transistors

Vertical transistors for memory cells, such as 4F2 memory cells, are disclosed. The memory cells use digit line connections formed within the isolation trench to connect the digit line with the lower active area. Vertical transistor pillars can be formed from epitaxial silicon or etched from bulk silicon. Memory cells can be formed by creating a cell capacitor electrically connected to each transistor pillar.

Owner:MICRON TECH INC

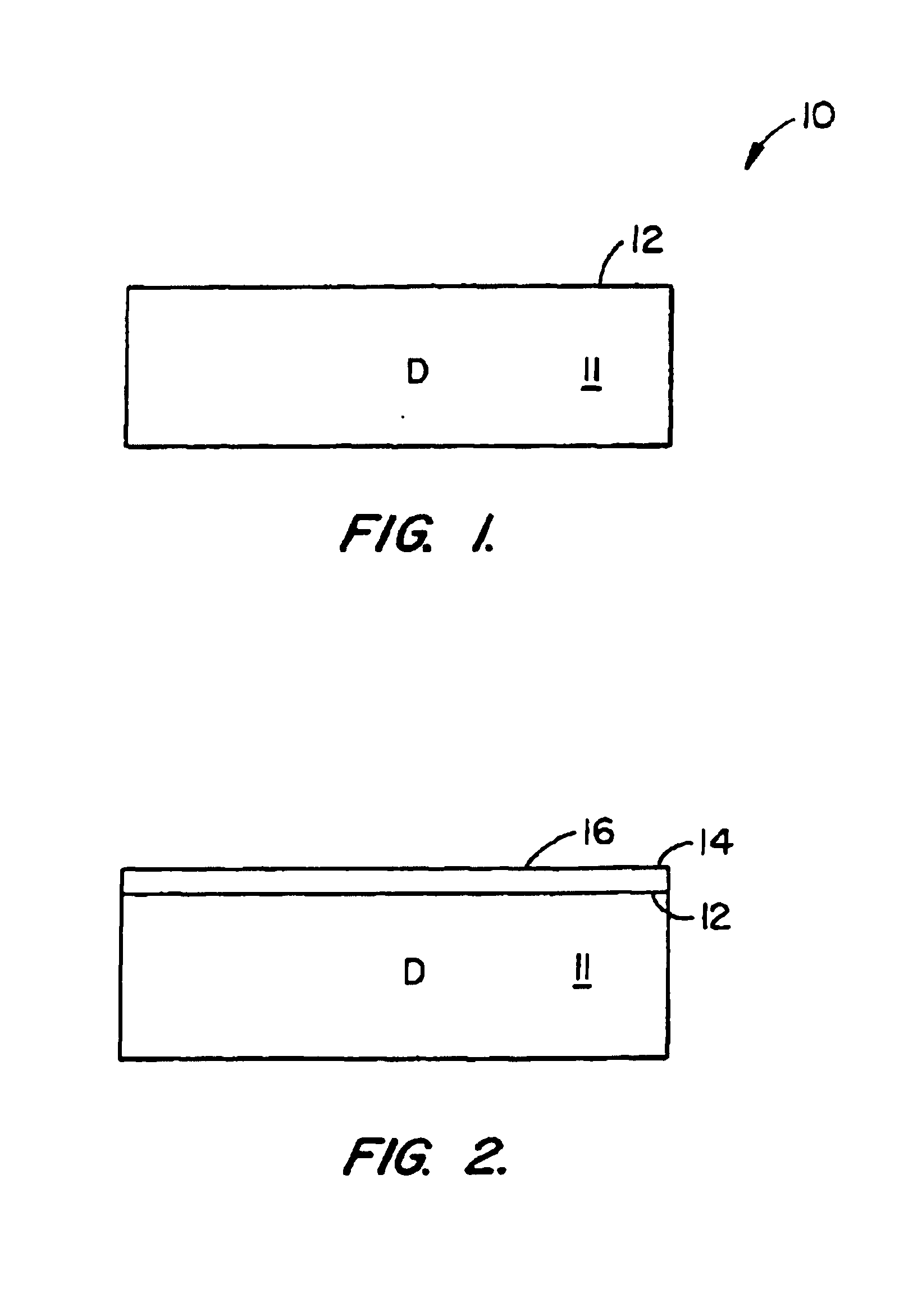

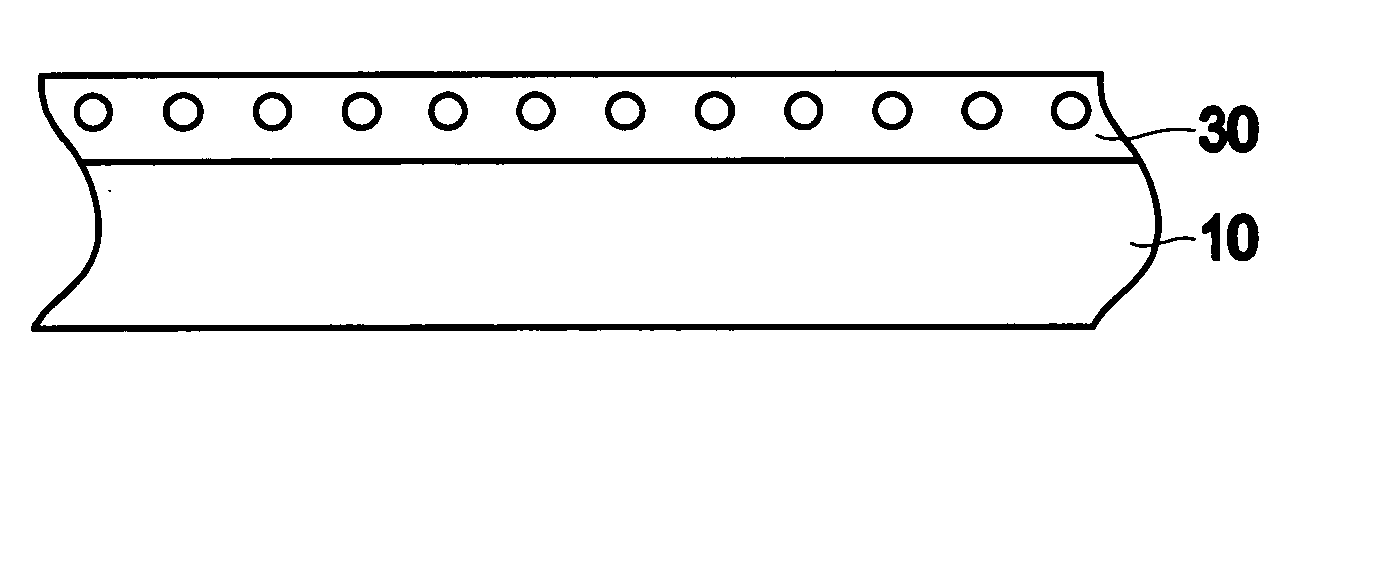

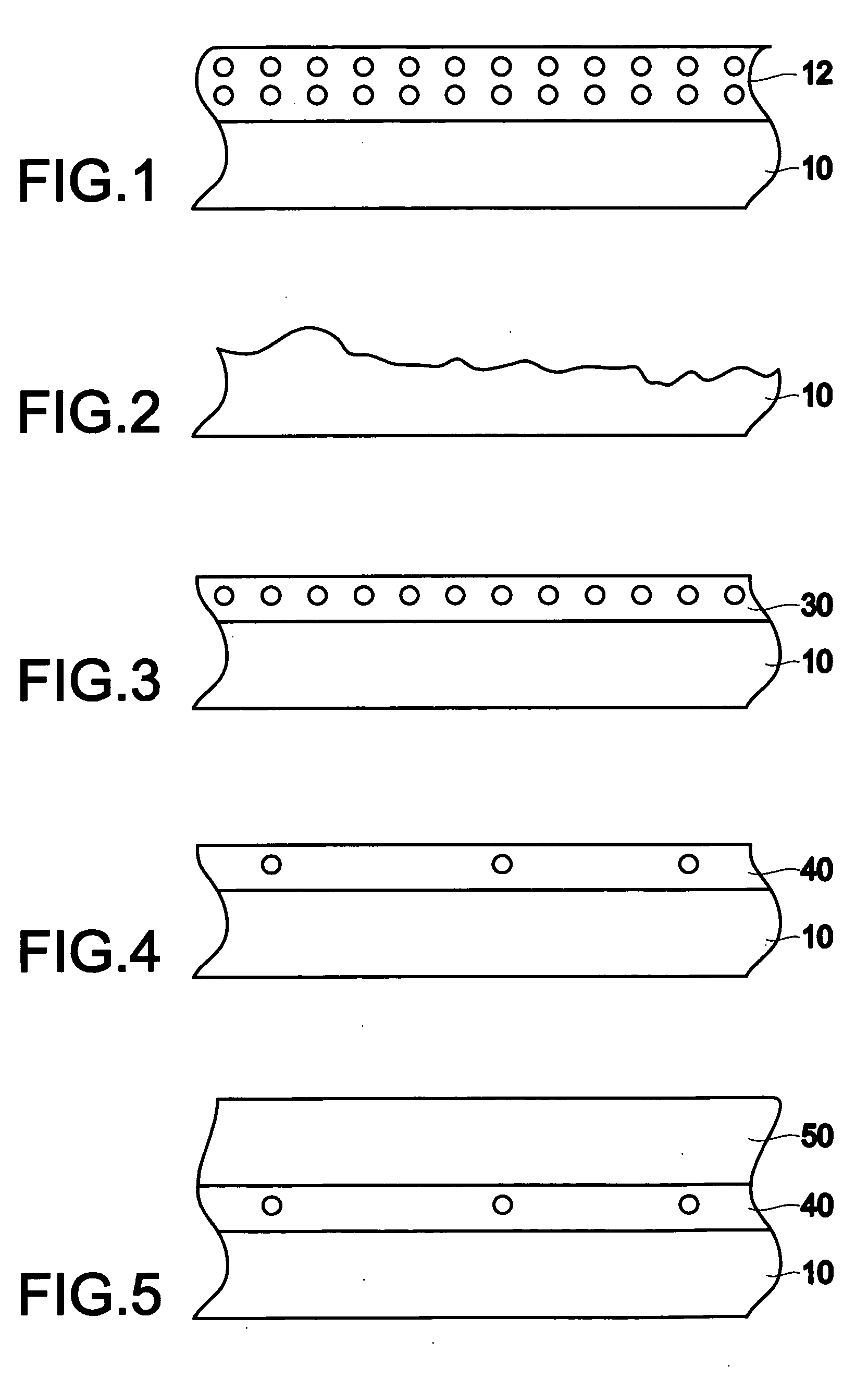

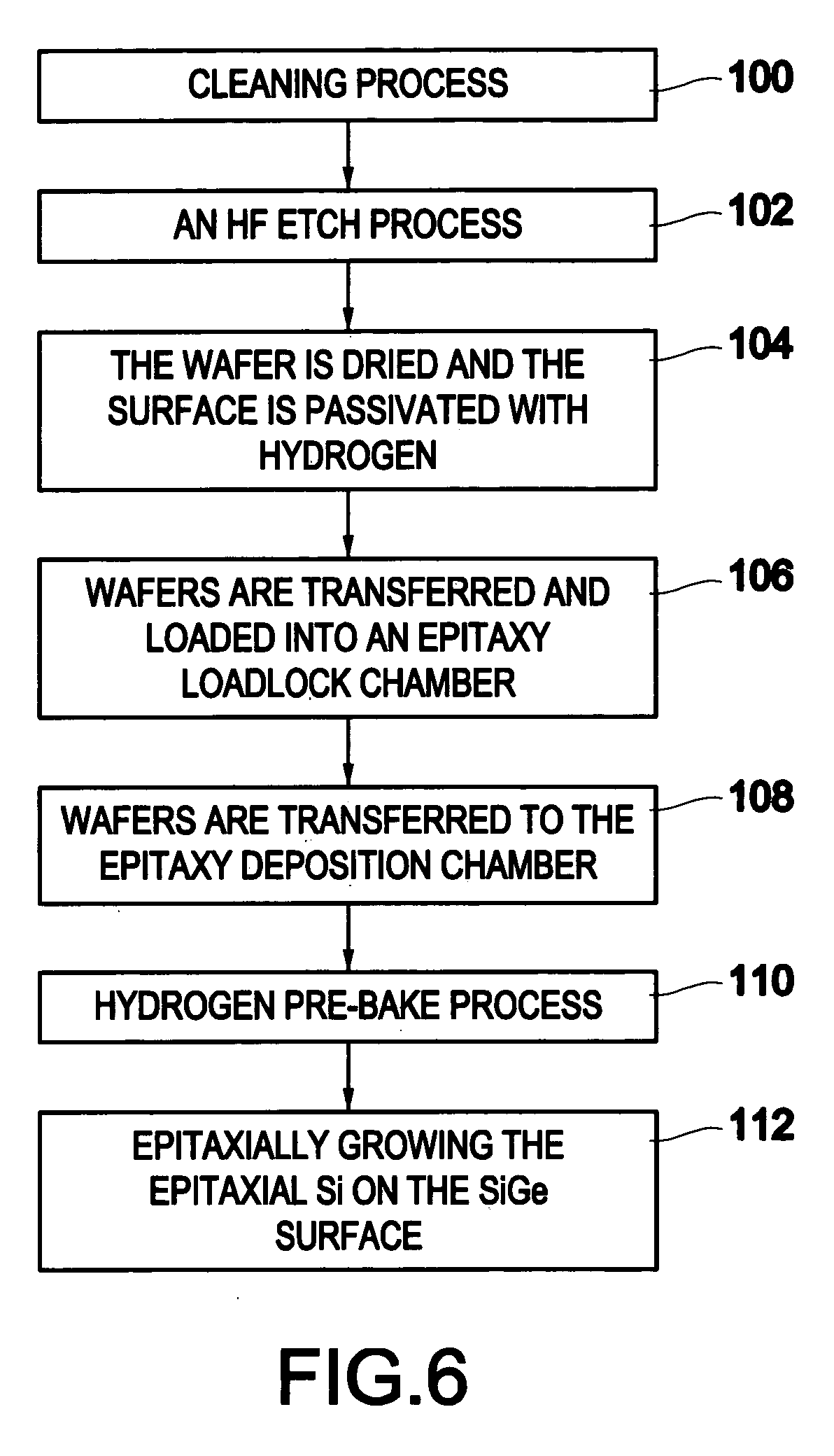

Method of preventing surface roughening during hydrogen prebake of SiGe substrates

InactiveUS6958286B2Polycrystalline material growthSemiconductor/solid-state device manufacturingRough surfaceHydrofluoric acid

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves a first amount of oxygen (typically 1×1013−1×1015 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process which heats the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface sufficiently to remove additional oxygen from the surface and leave a second amount of oxygen, less than the first amount, on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The heating process leaves an amount of at least 5×1012 / cm2 of oxygen (typically, between approximately 1×1013 / cm2 and approximately 5×1013 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. By leaving a small amount of oxygen on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:INT BUSINESS MASCH CORP

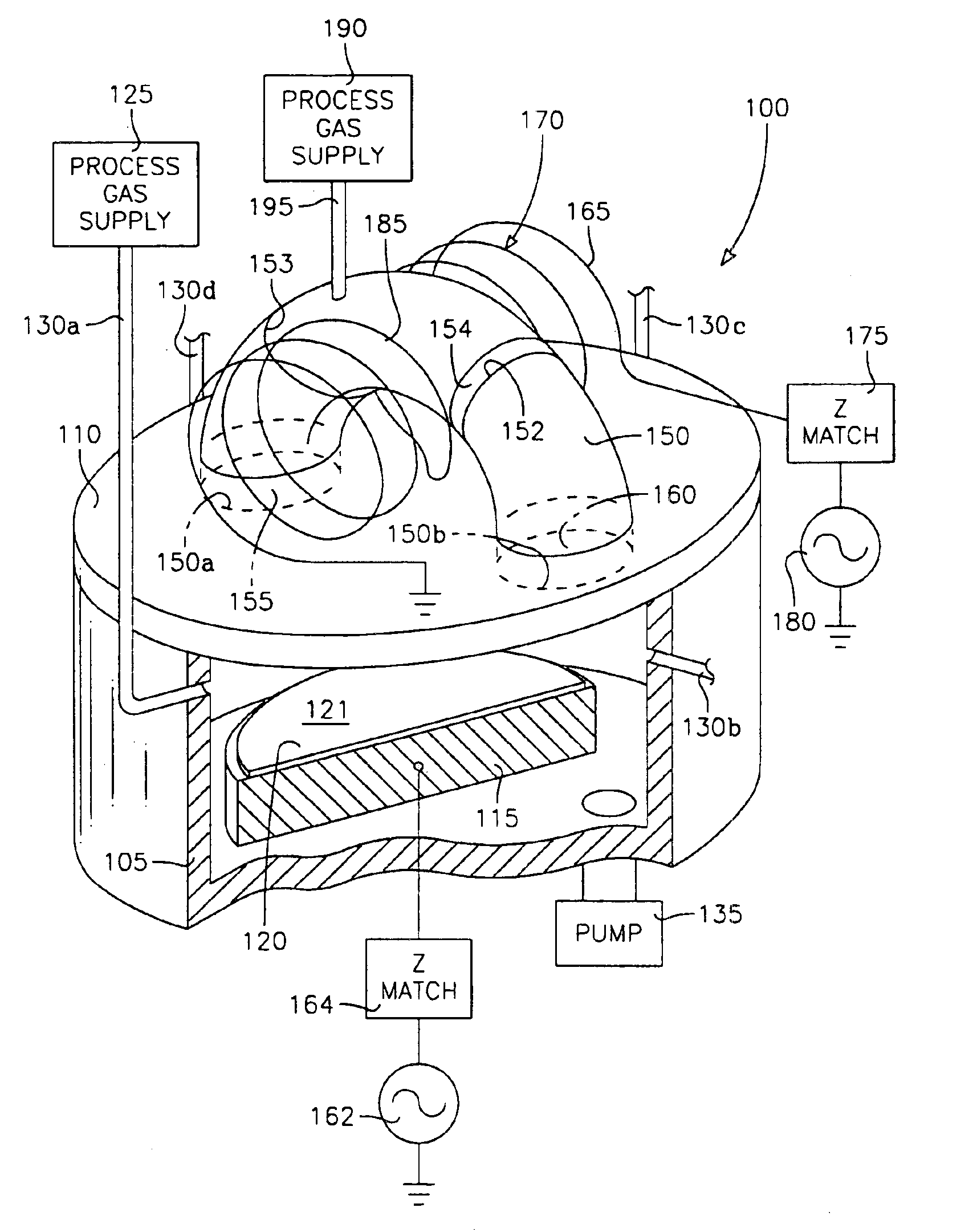

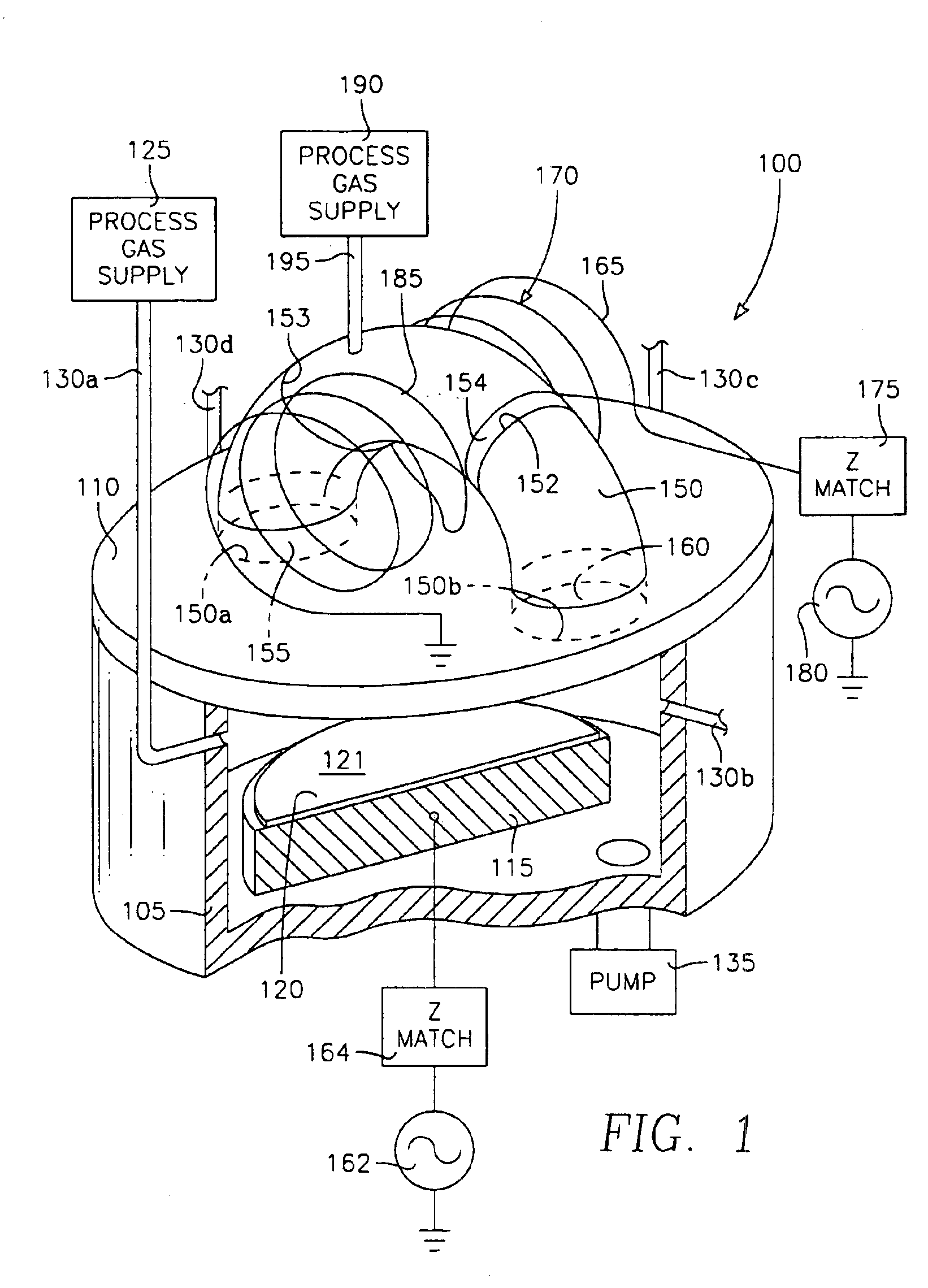

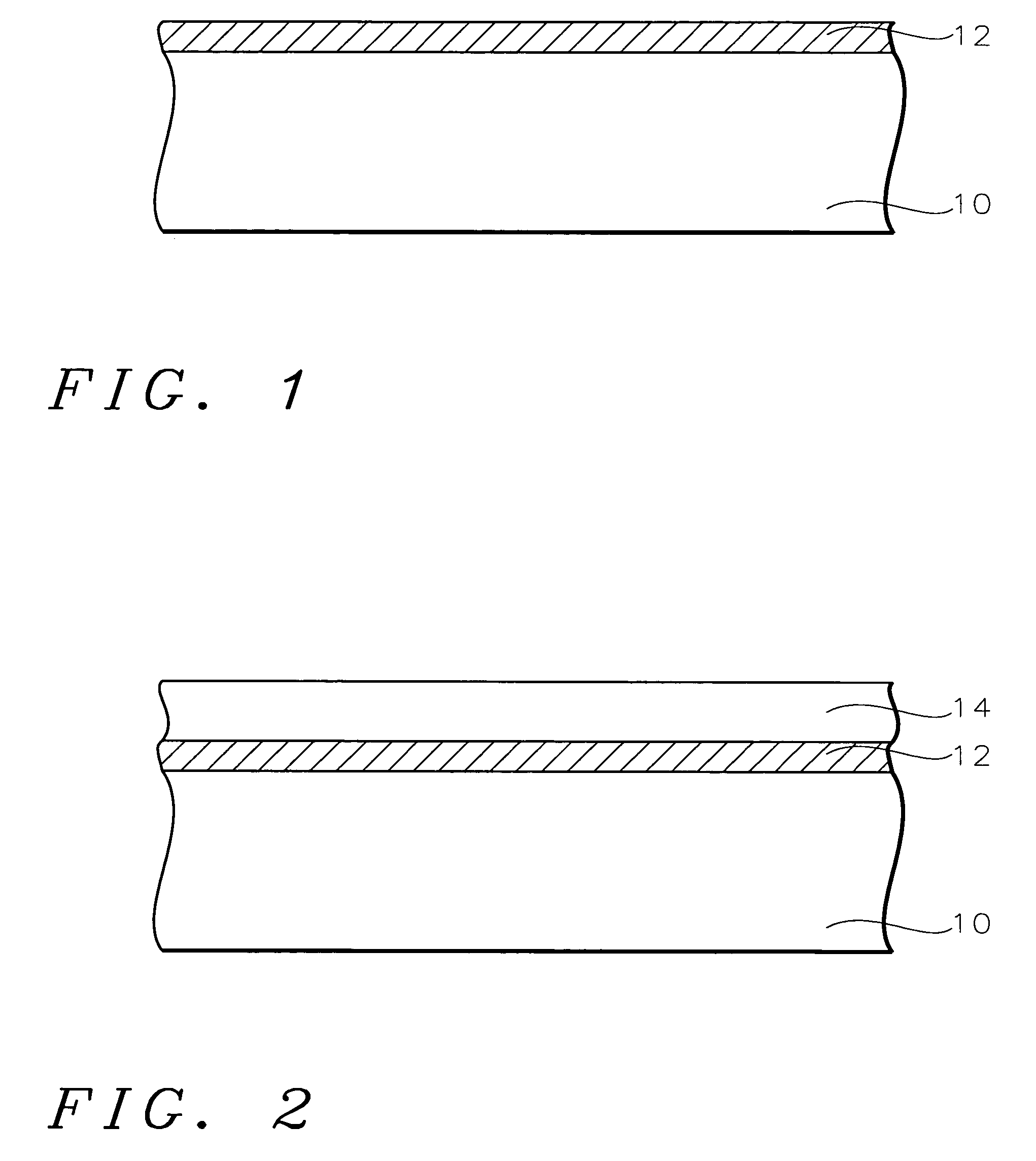

Fabrication of silicon-on-insulator structure using plasma immersion ion implantation

InactiveUS6893907B2Reduce oxygen concentrationElectric discharge tubesSemiconductor/solid-state device manufacturingSurface layerPlasma-immersion ion implantation

A method of fabricating a silicon-on-insulator structure having a silicon surface layer in a semiconductor workpiece, is carried out by maintaining the workpiece at an elevated temperature and producing an oxygen-containing plasma in the chamber while applying a bias to the workpiece and setting the bias to a level corresponding to an implant depth in the workpiece below the silicon surface layer to which oxygen atoms are to be implanted, whereby to form an oxygen-implanted layer in the workpiece having an oxygen concentration distribution generally centered at the implant depth and having a finite oxygen concentration in the silicon surface layer. The oxygen concentration in the silicon surface layer is then reduced to permit epitaxial silicon deposition.

Owner:APPLIED MATERIALS INC

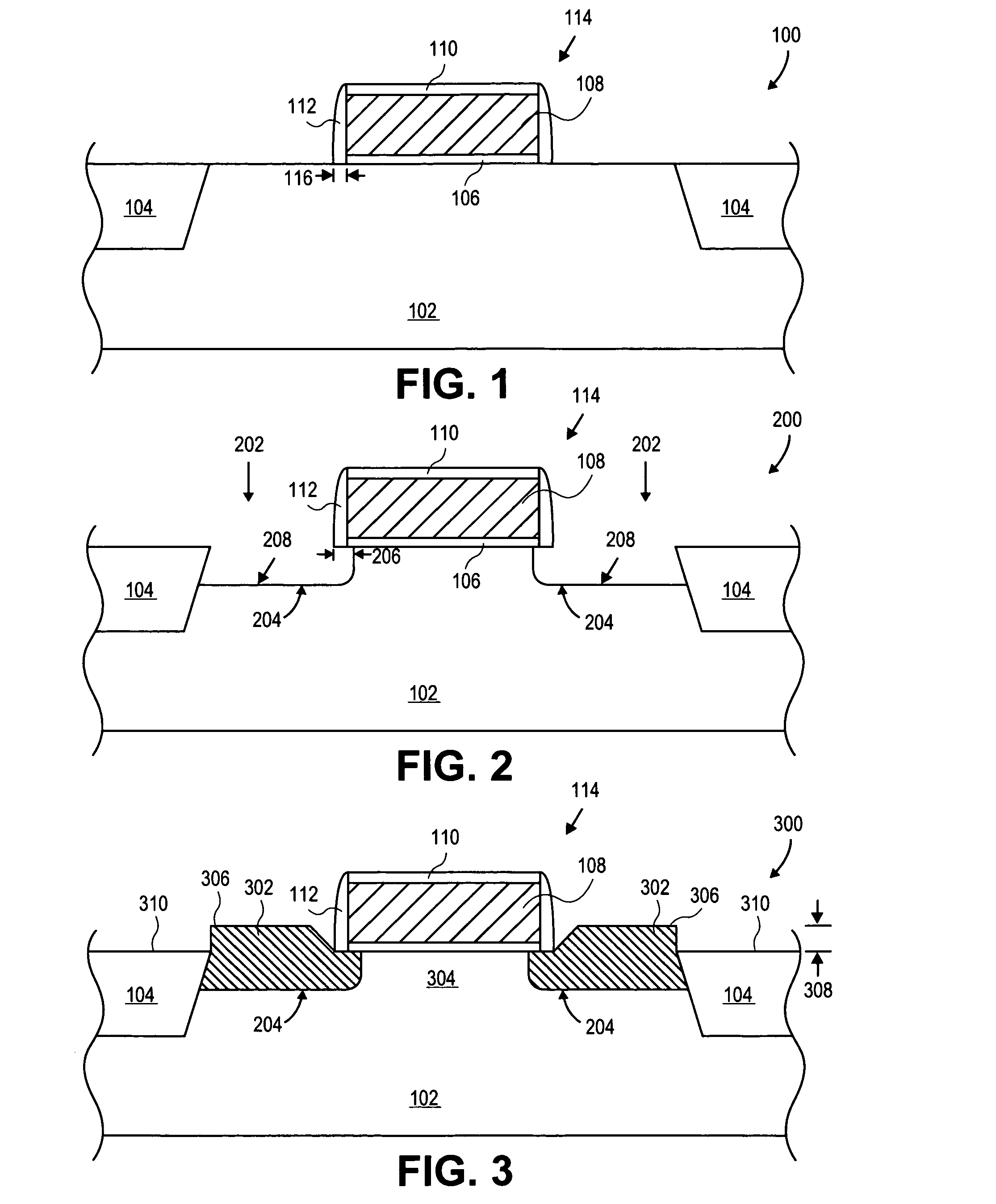

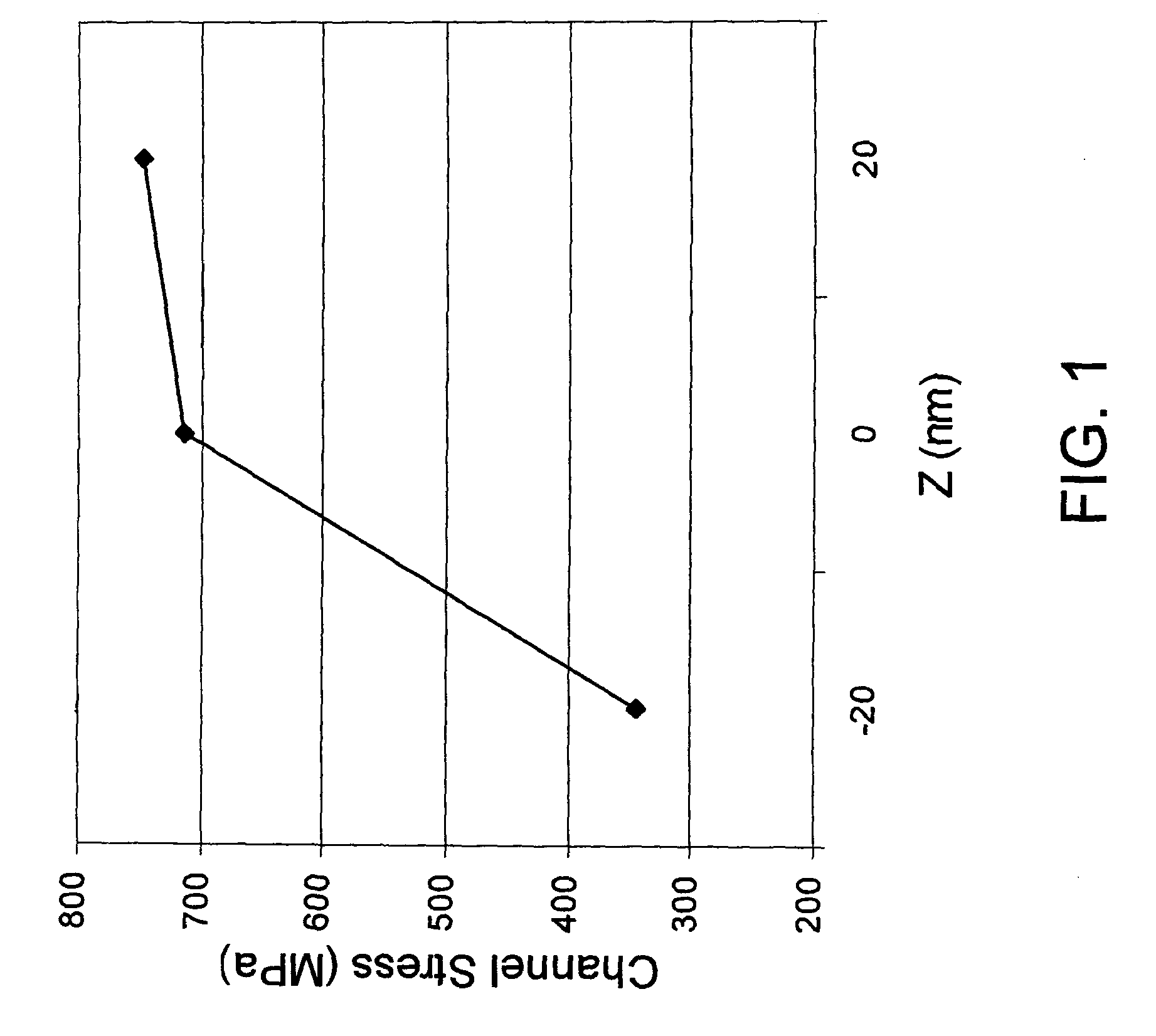

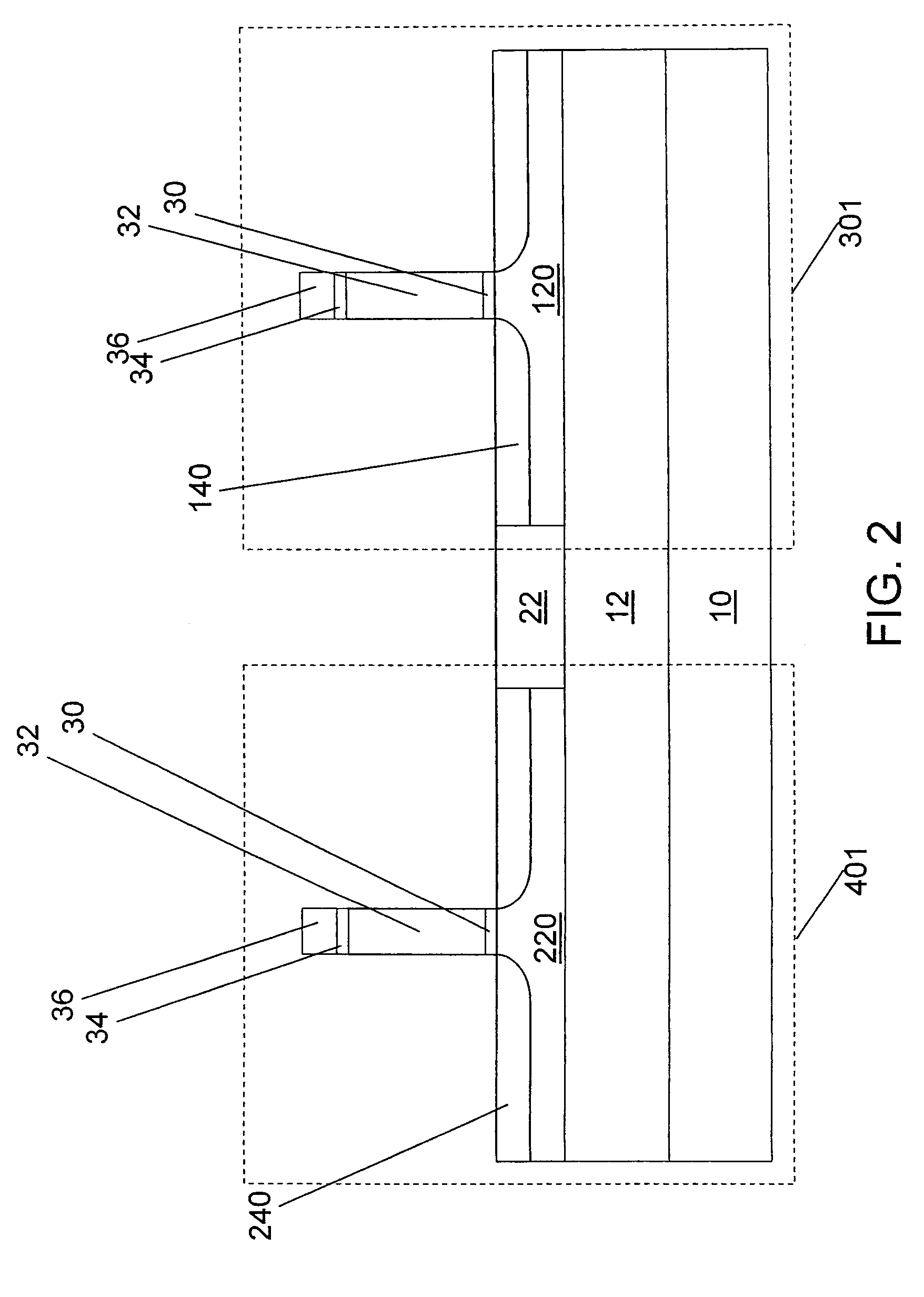

Method for forming an integrated circuit

ActiveUS7402872B2Semiconductor/solid-state device manufacturingSemiconductor devicesContact resistanceEpitaxial silicon

A method is described for manufacturing an n-MOS semiconductor transistor. Recesses are formed in a semiconductor substrate adjacent a gate electrode structure. Silicon is embedded in the recesses via a selective epitaxial growth process. The epitaxial silicon is in-situ alloyed with substitutional carbon and in-situ doped with phosphorus. The silicon-carbon alloy generates a uniaxial tensile strain in the channel region between the source and drain, thereby increasing electron channel mobility and the transistor's drive current. The silicon-carbon alloy decreases external resistances by reducing contact resistance between source / drain and silicide regions and by reducing phosphorous diffusivity, thereby permitting closer placement of the transistor's source / drain and channel regions.

Owner:TAHOE RES LTD

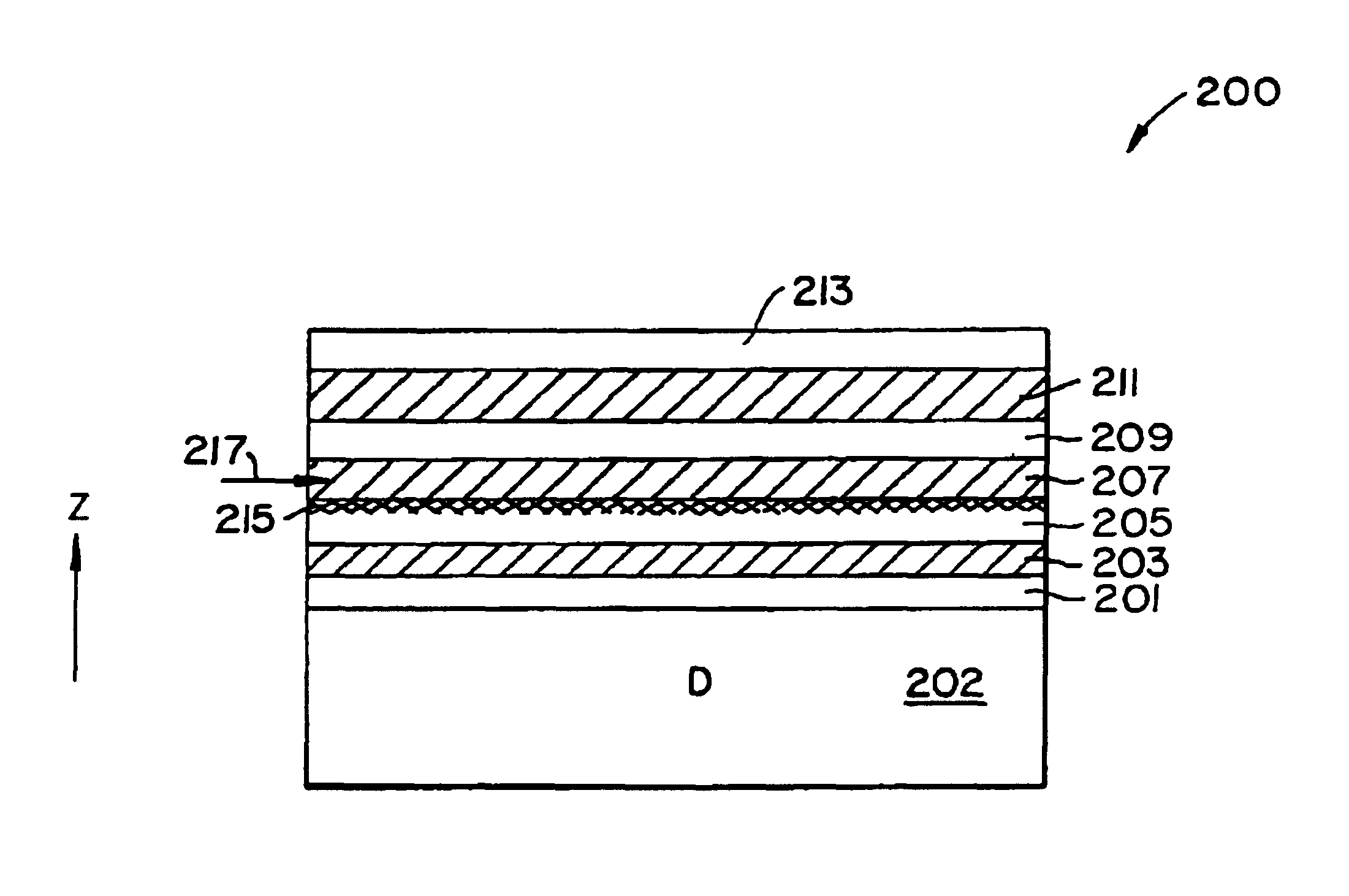

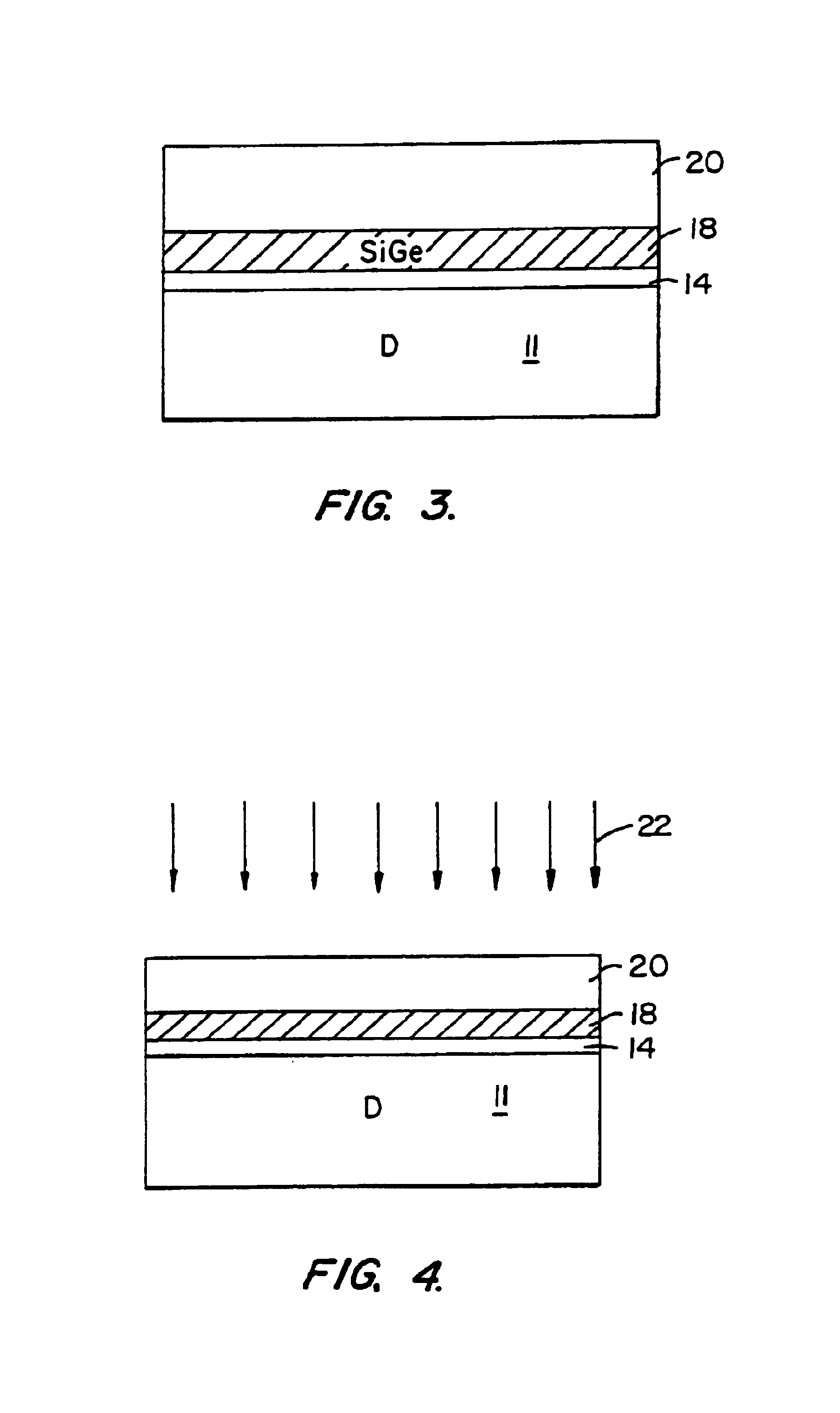

Cleaving process to fabricate multilayered substrates using low implantation doses

InactiveUS7056808B2Improve efficiencyQuality improvementSolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationControl manner

A method of forming substrates, e.g., silicon on insulator, silicon on silicon. The method includes providing a donor substrate, e.g., silicon wafer. The method also includes forming a cleave layer on the donor substrate that contains the cleave plane, the plane of eventual separation. In a specific embodiment, the cleave layer comprising silicon germanium. The method also includes forming a device layer (e.g., epitaxial silicon) on the cleave layer. The method also includes introducing particles into the cleave layer to add stress in the cleave layer. The particles within the cleave layer are then redistributed to form a high concentration region of the particles in the vicinity of the cleave plane, where the redistribution of the particles is carried out in a manner substantially free from microbubble or microcavity formation of the particles in the cleave plane. That is, the particles are generally at a low dose, which is defined herein as a lack of microbubble or microcavity formation in the cleave plane. The method also includes providing selected energy to the donor substrate to cleave the device layer from the cleave layer at the cleave plane, whereupon the selected energy is applied to create a controlled cleaving action to remove the device layer from a portion of the cleave layer in a controlled manner.

Owner:SILICON GENERAL CORPORATION

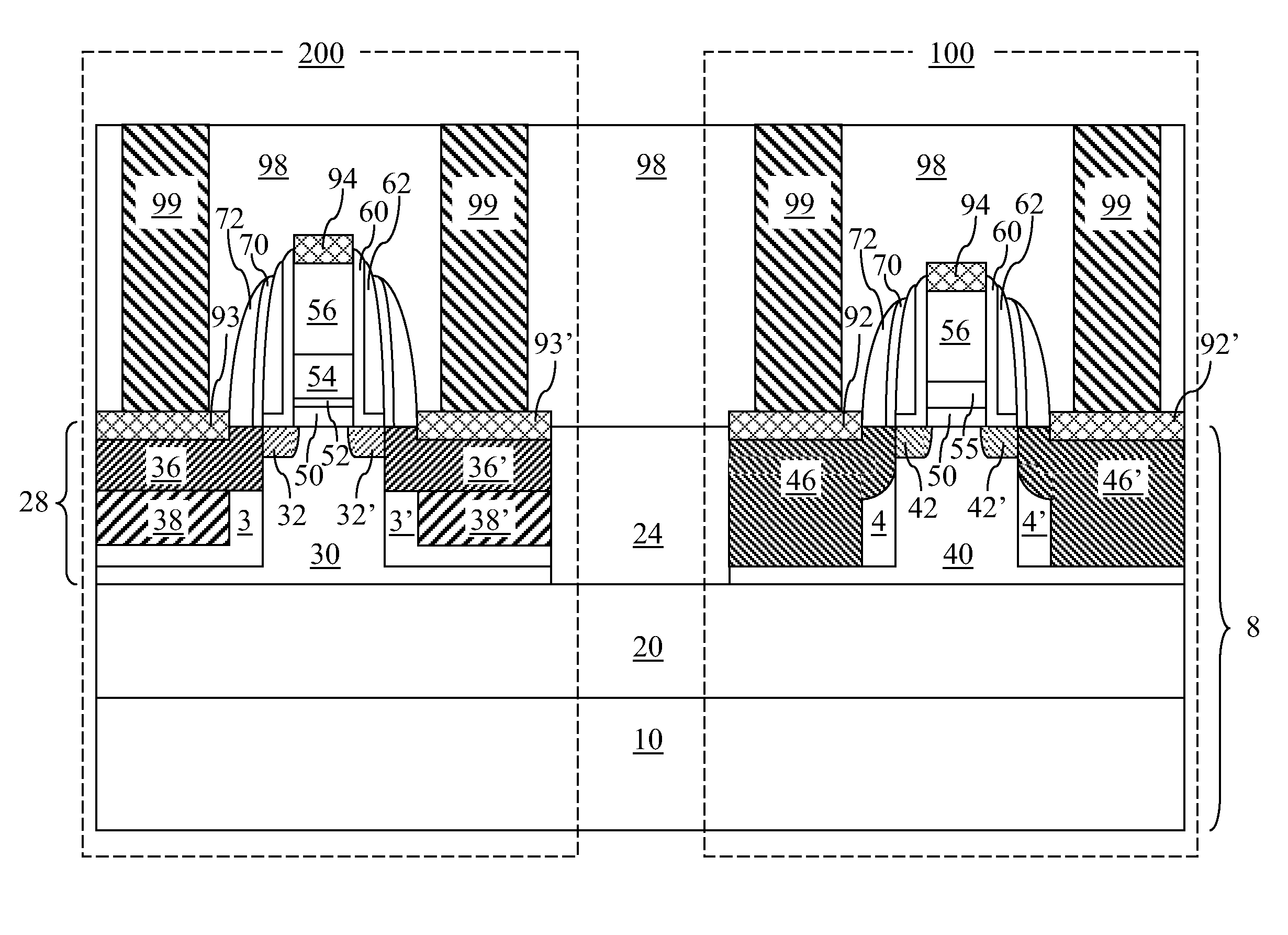

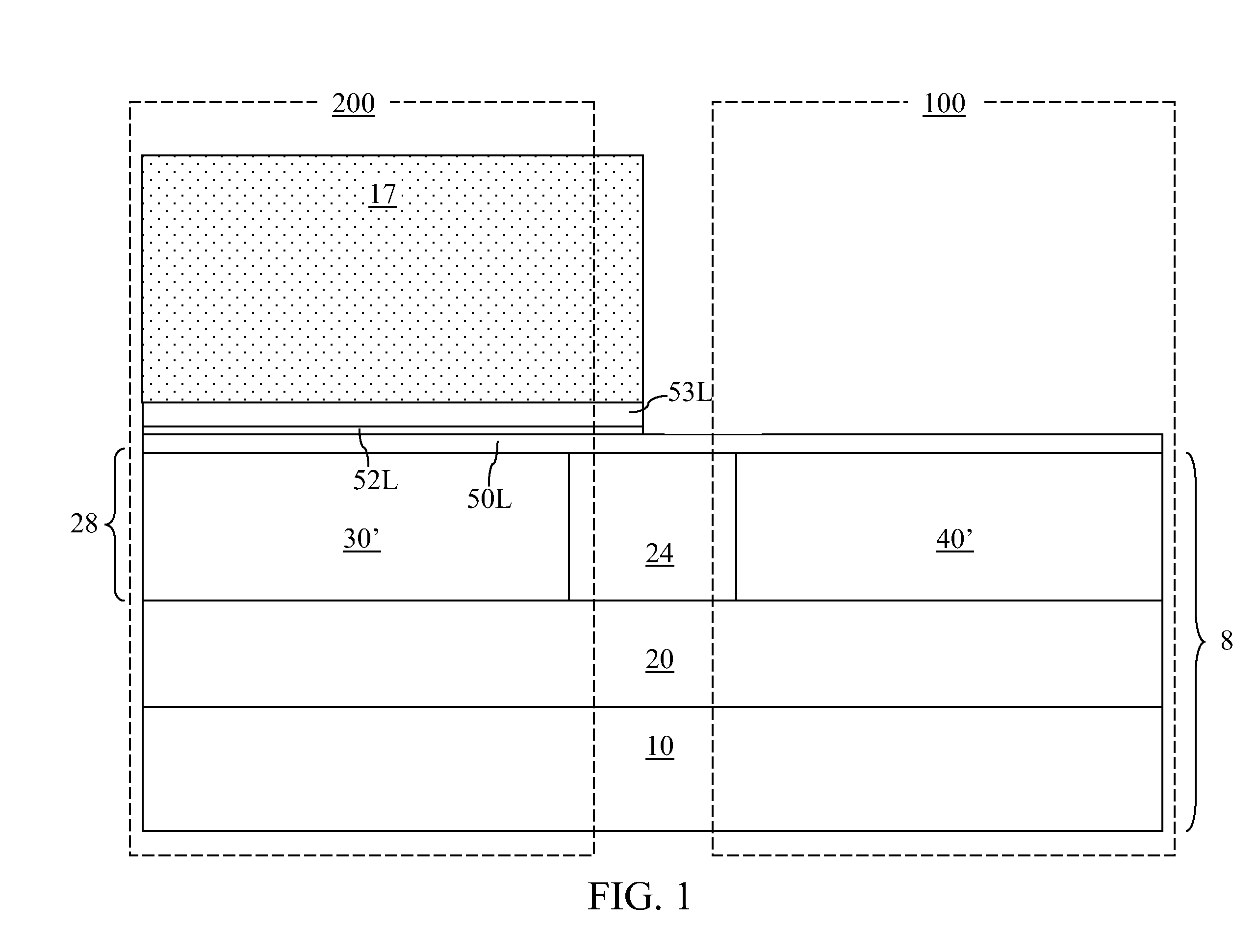

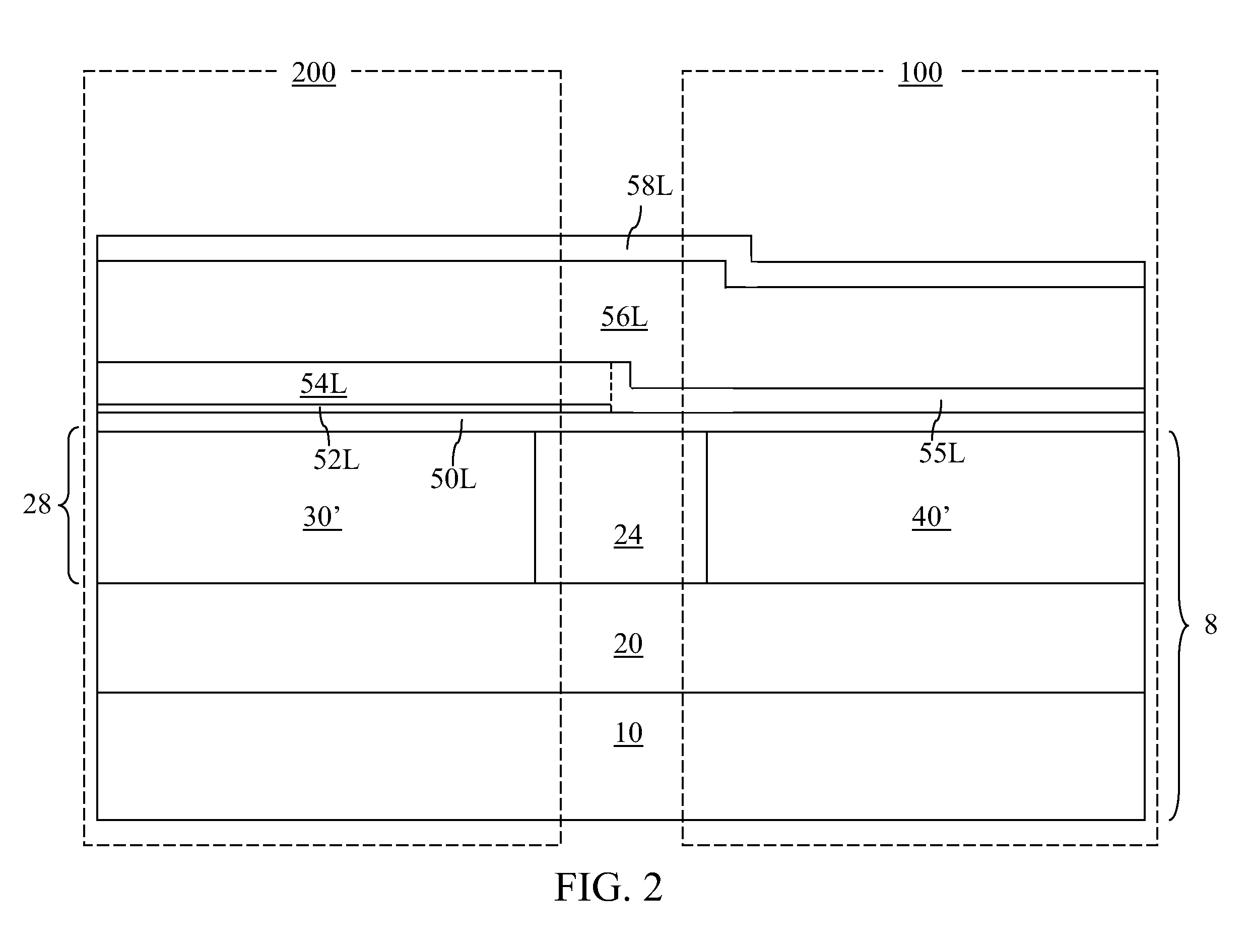

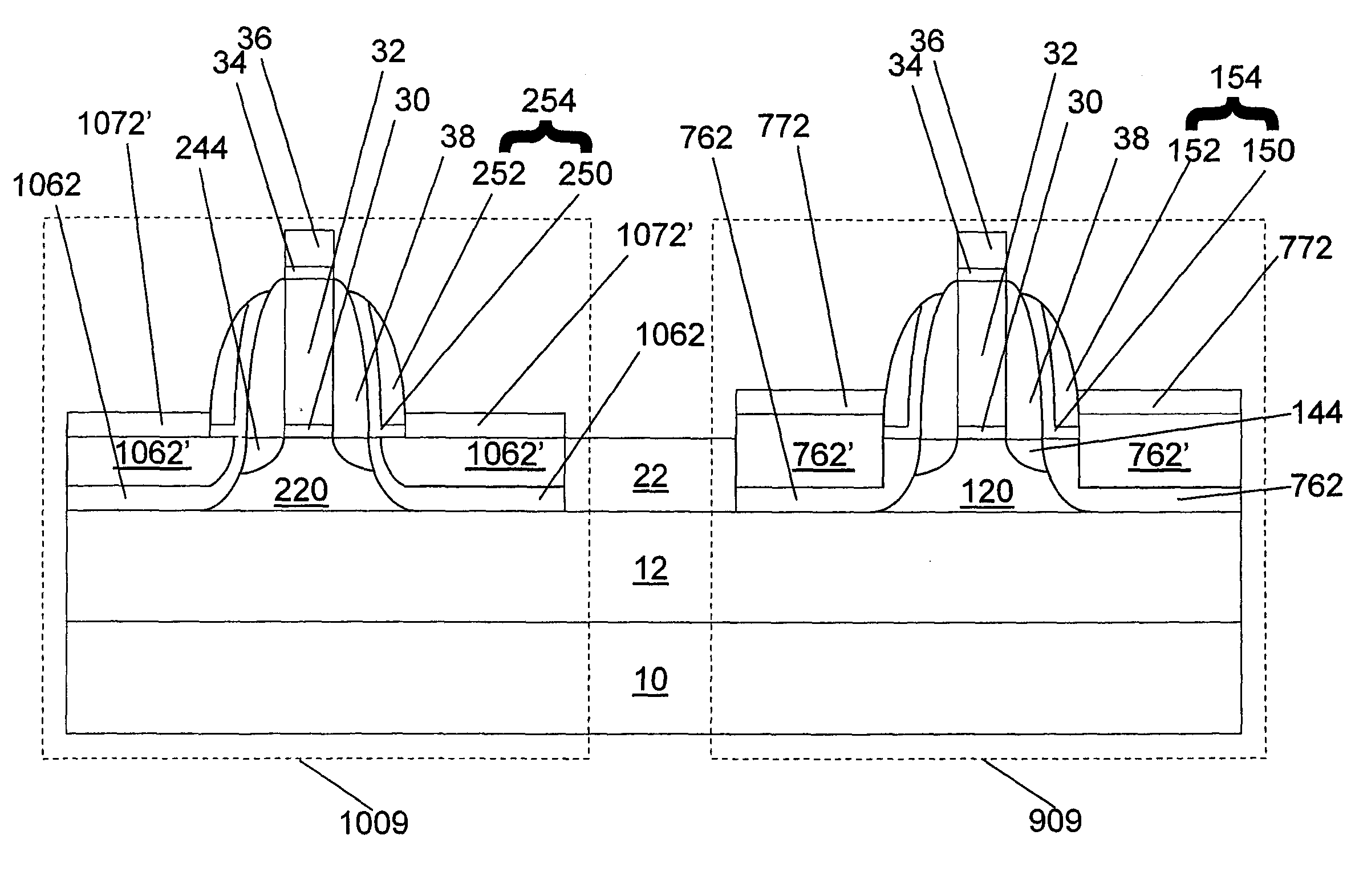

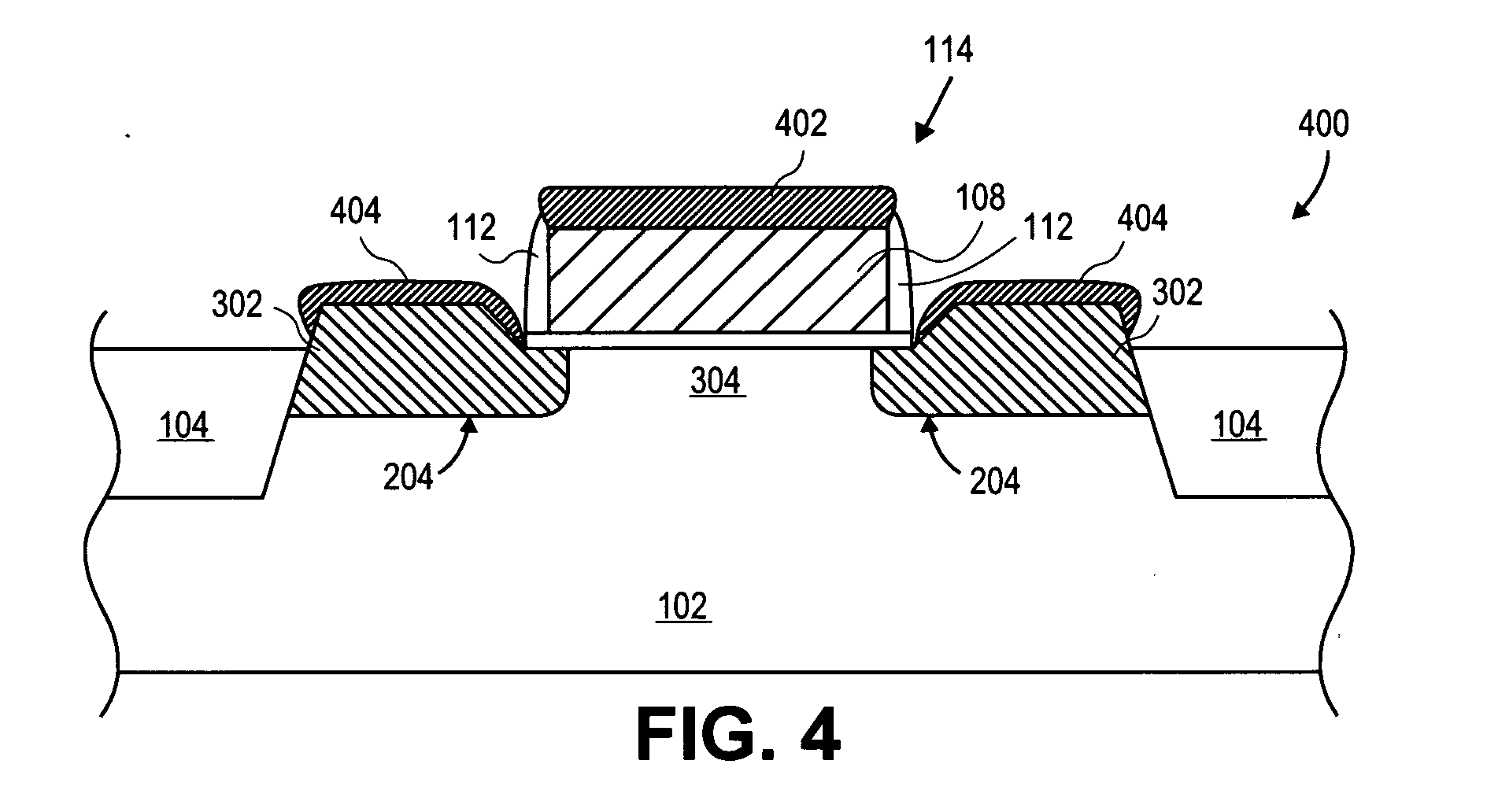

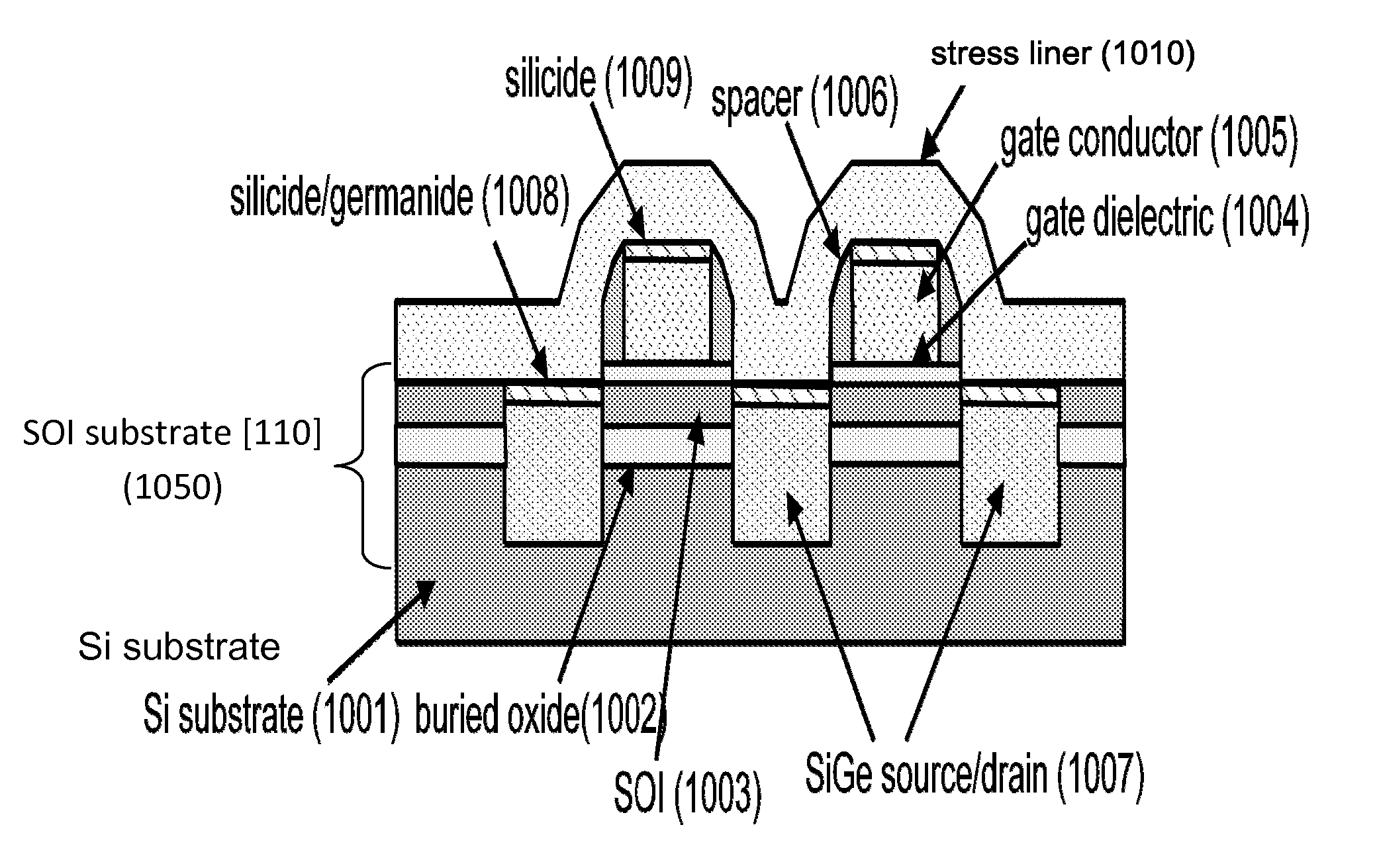

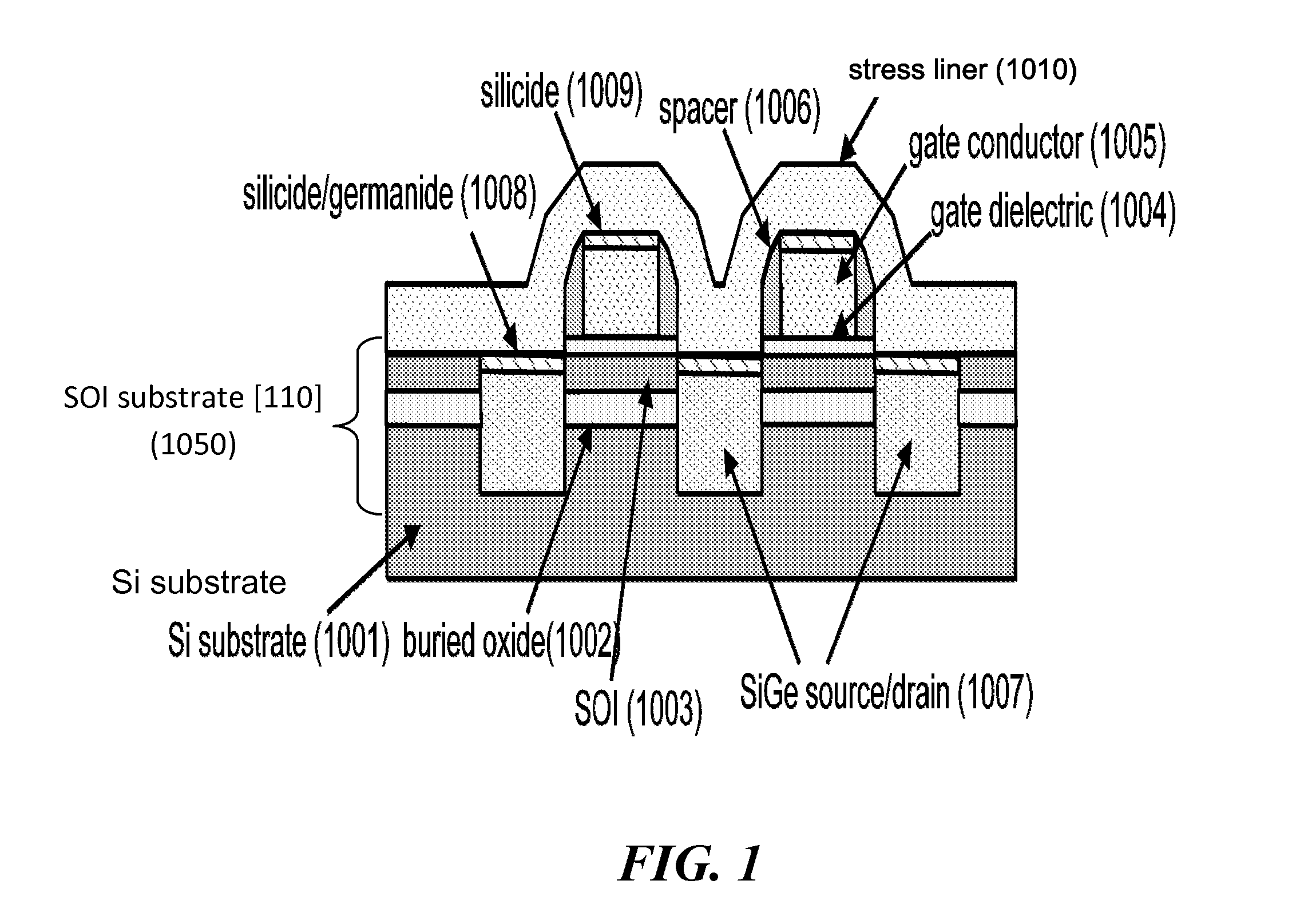

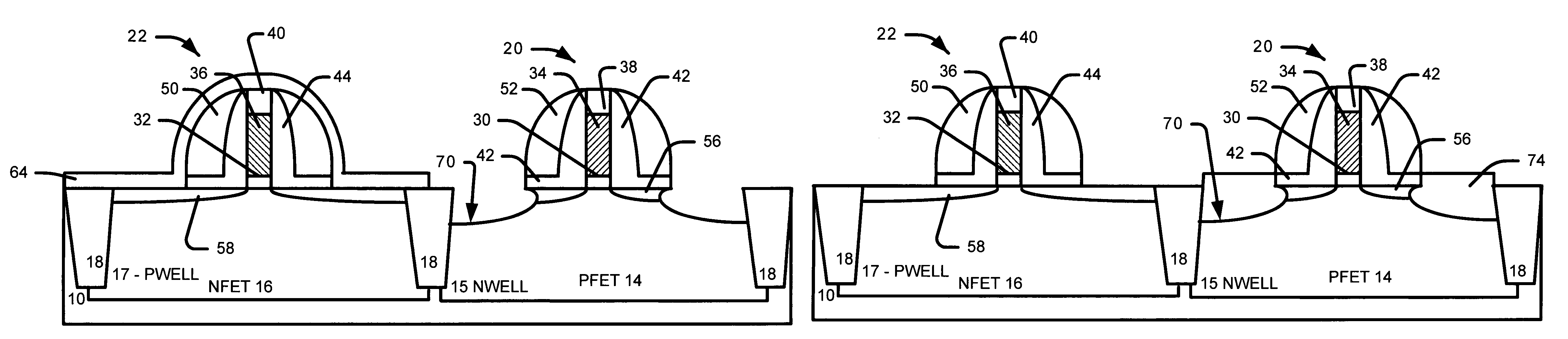

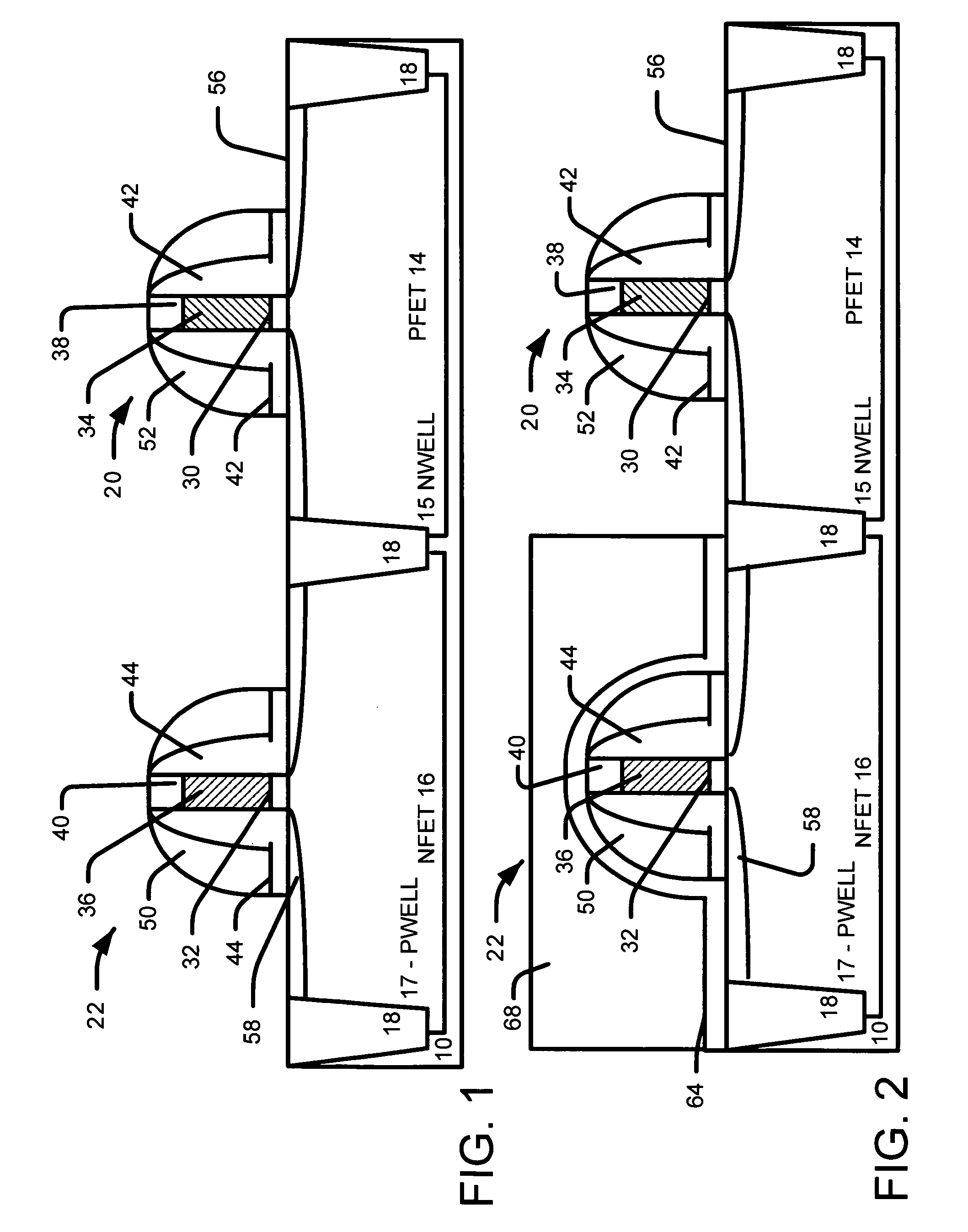

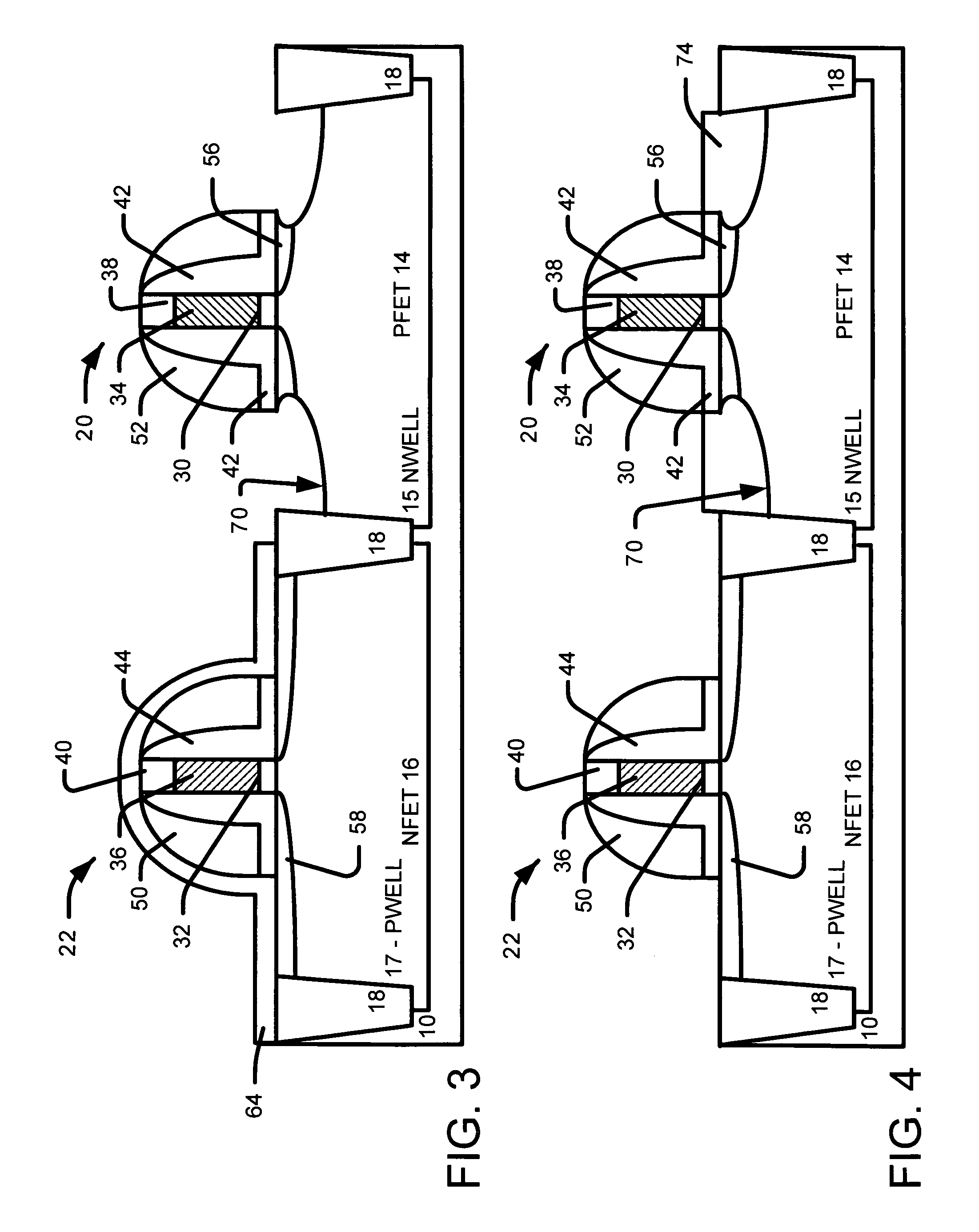

CMOS Transistors With Silicon Germanium Channel and Dual Embedded Stressors

ActiveUS20100224938A1High hole mobilityHigh electron mobilityTransistorSolid-state devicesHigh concentrationMOSFET

A p-type MOSFET of a CMOS structure has a silicon-germanium alloy channel to which a longitudinal compressive stress is applied by embedded epitaxial silicon-germanium alloy source and drain regions comprising a silicon-germanium alloy having a higher concentration of germanium than the channel of the p-type MOSFET. An n-type MOSFET of the CMOS structure has a silicon-germanium alloy channel to which a longitudinal tensile stress is applied by embedded epitaxial silicon source and drain regions comprising silicon. The silicon-germanium alloy channel in the p-type MOSFET provides enhanced hole mobility, while the silicon-germanium alloy channel in the n-type MOSFET provides enhanced electron mobility, thereby providing performance improvement to both the p-type MOSFET and the n-type MOSFET.

Owner:GLOBALFOUNDRIES US INC

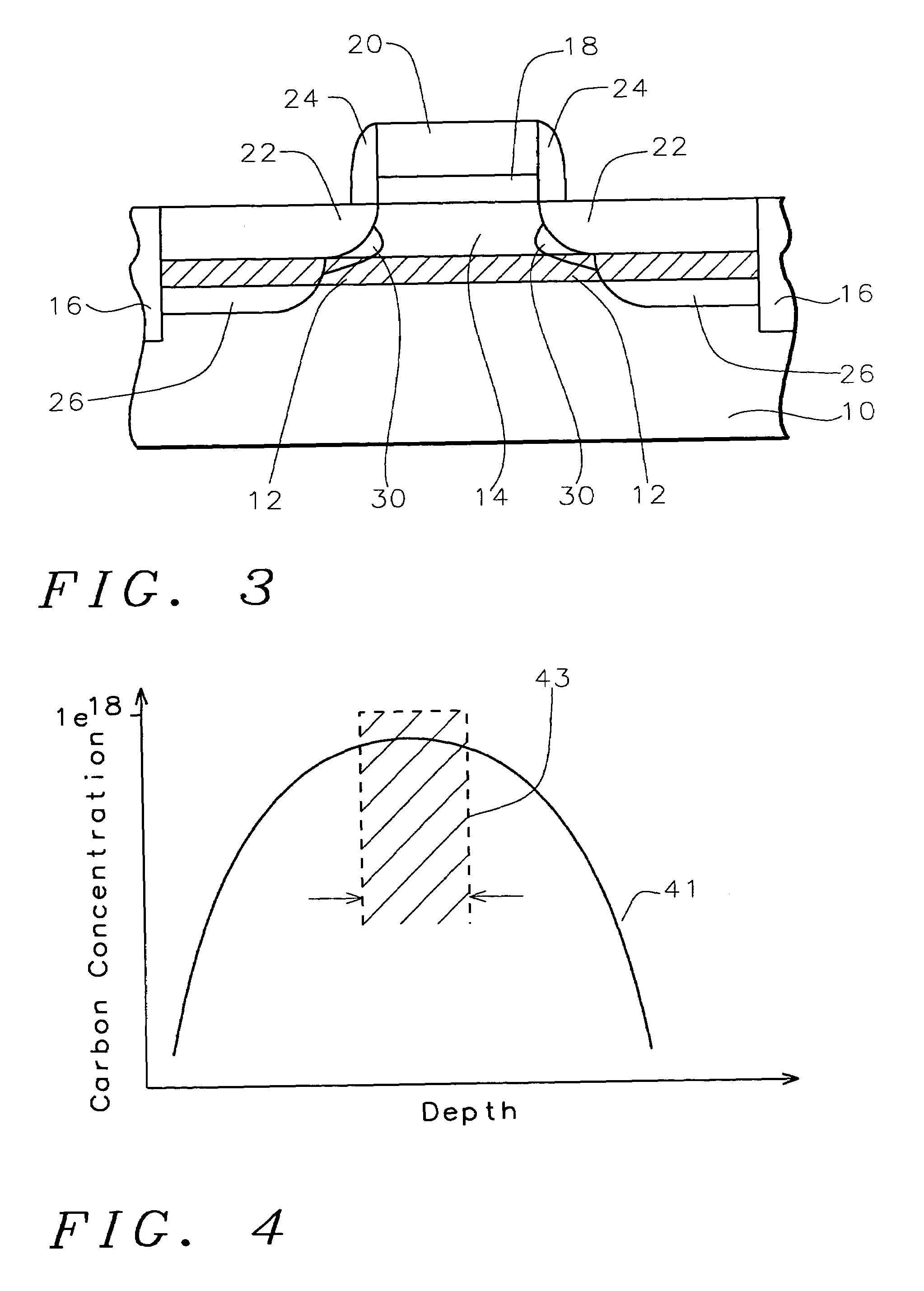

End of range (EOR) secondary defect engineering using substitutional carbon doping

A method for incorporating carbon into a wafer at the interstitial a-c silicon interface of the halo doping profile is achieved. A bulk silicon substrate is provided. A carbon-doped silicon layer is deposited on the bulk silicon substrate. An epitaxial silicon layer is grown overlying the carbon-doped silicon layer to provide a starting wafer for the integrated circuit device fabrication. An integrated circuit device is fabricated on the starting wafer by the following steps. A gate electrode is formed on the starting wafer. LDD and source and drain regions are implanted in the starting wafer adjacent to the gate electrode. Indium is implanted to form halo implants adjacent to the LDD regions and underlying the gate electrode wherein the halo implants extend to an interface between the epitaxial silicon layer and the carbon-doped silicon layer wherein carbon ions in the carbon-doped silicon layer act as a silicon interstitial sink for silicon interstitials formed by the halo implants to prevent end of range secondary defect formation.

Owner:TAIWAN SEMICON MFG CO LTD

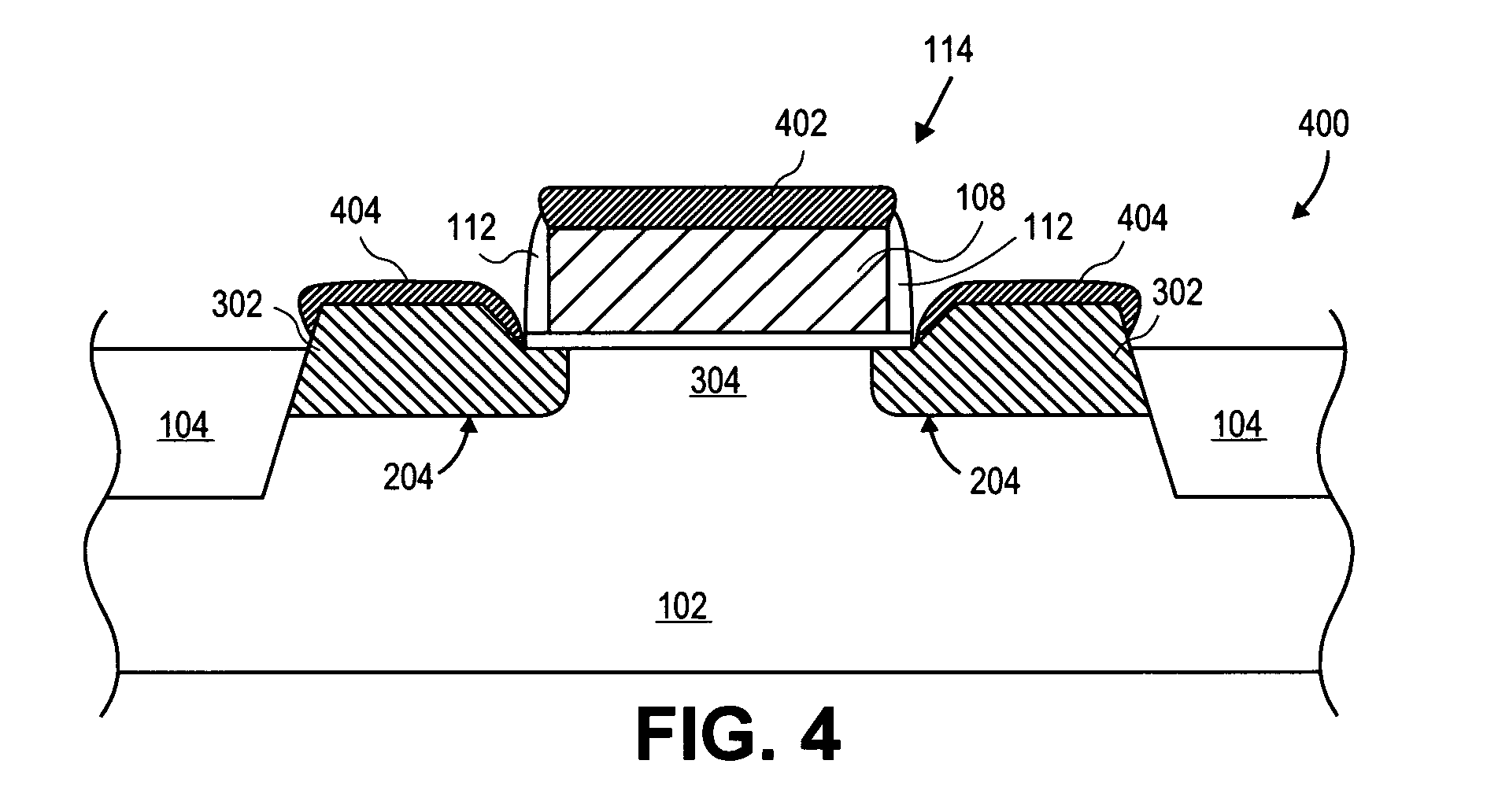

Structure and method for mobility enhanced MOSFETs with unalloyed silicide

ActiveUS8217423B2Stable and low contact resistanceReduce contact resistanceTransistorSolid-state devicesMOSFETSalicide

While embedded silicon germanium alloy and silicon carbon alloy provide many useful applications, especially for enhancing the mobility of MOSFETs through stress engineering, formation of alloyed silicide on these surfaces degrades device performance. The present invention provides structures and methods for providing unalloyed silicide on such silicon alloy surfaces placed on semiconductor substrates. This enables the formation of low resistance contacts for both mobility enhanced PFETs with embedded SiGe and mobility enhanced NFETs with embedded Si:C on the same semiconductor substrate. Furthermore, this invention provides methods for thick epitaxial silicon alloy, especially thick epitaxial Si:C alloy, above the level of the gate dielectric to increase the stress on the channel on the transistor devices.

Owner:AURIGA INNOVATIONS INC

finFETS and methods of making same

A method of fabricating and a structure of a merged multi-fin finFET. The method includes forming single-crystal silicon fins from the silicon layer of an SOI substrate having a very thin buried oxide layer and merging the end regions of the fins by growing vertical epitaxial silicon from the substrate and horizontal epitaxial silicon from ends of the fins such that vertical epitaxial silicon growth predominates.

Owner:AURIGA INNOVATIONS INC

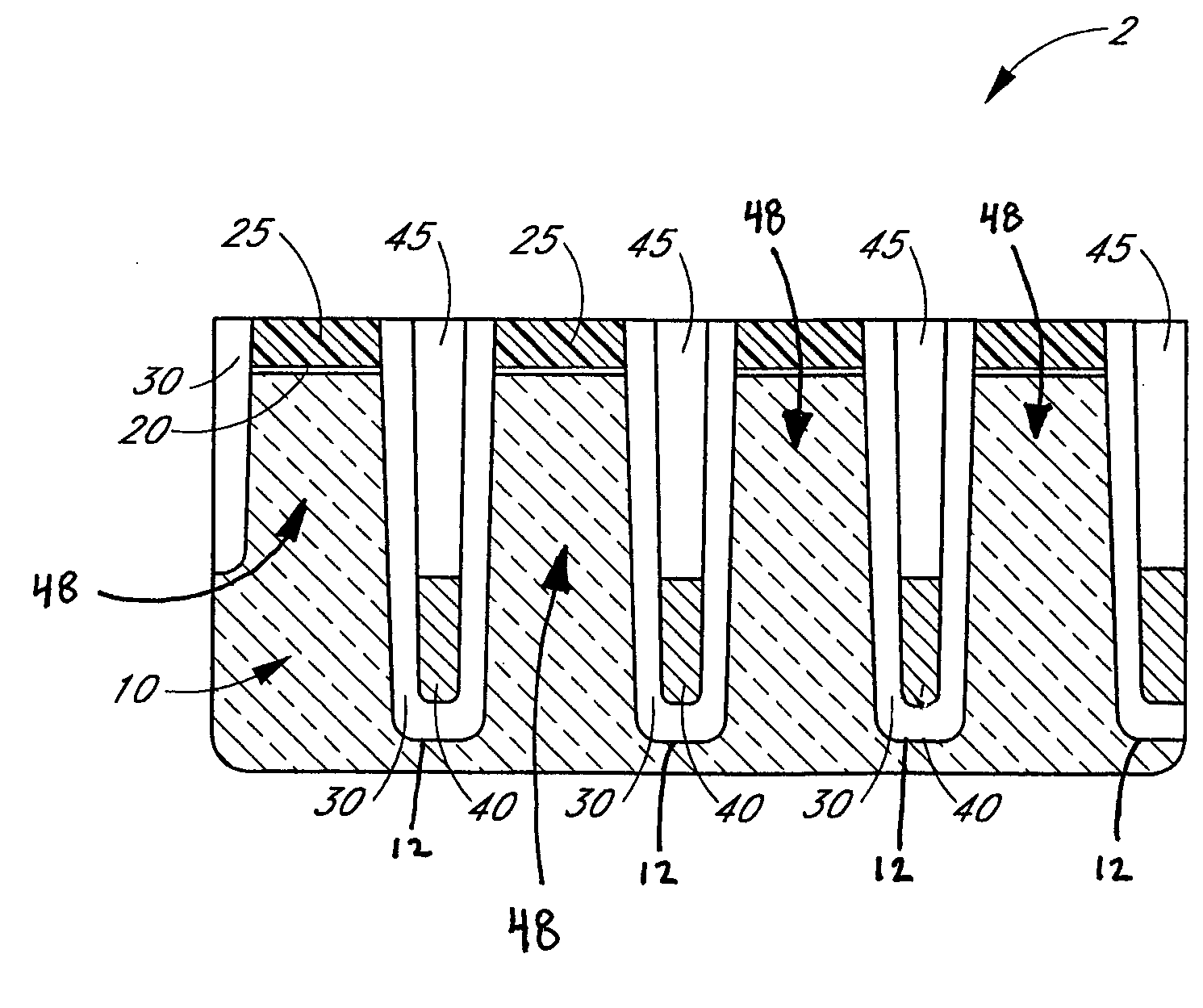

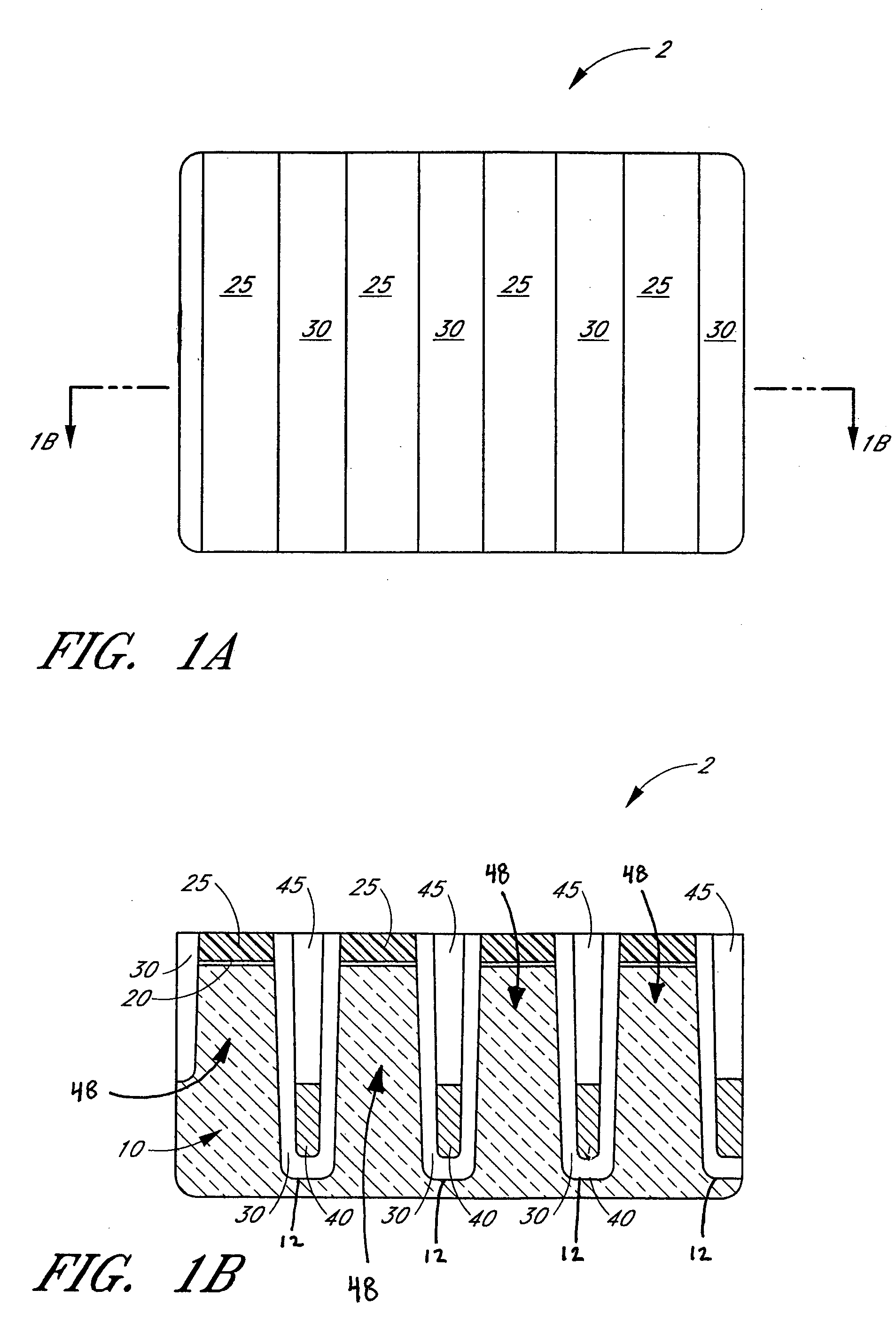

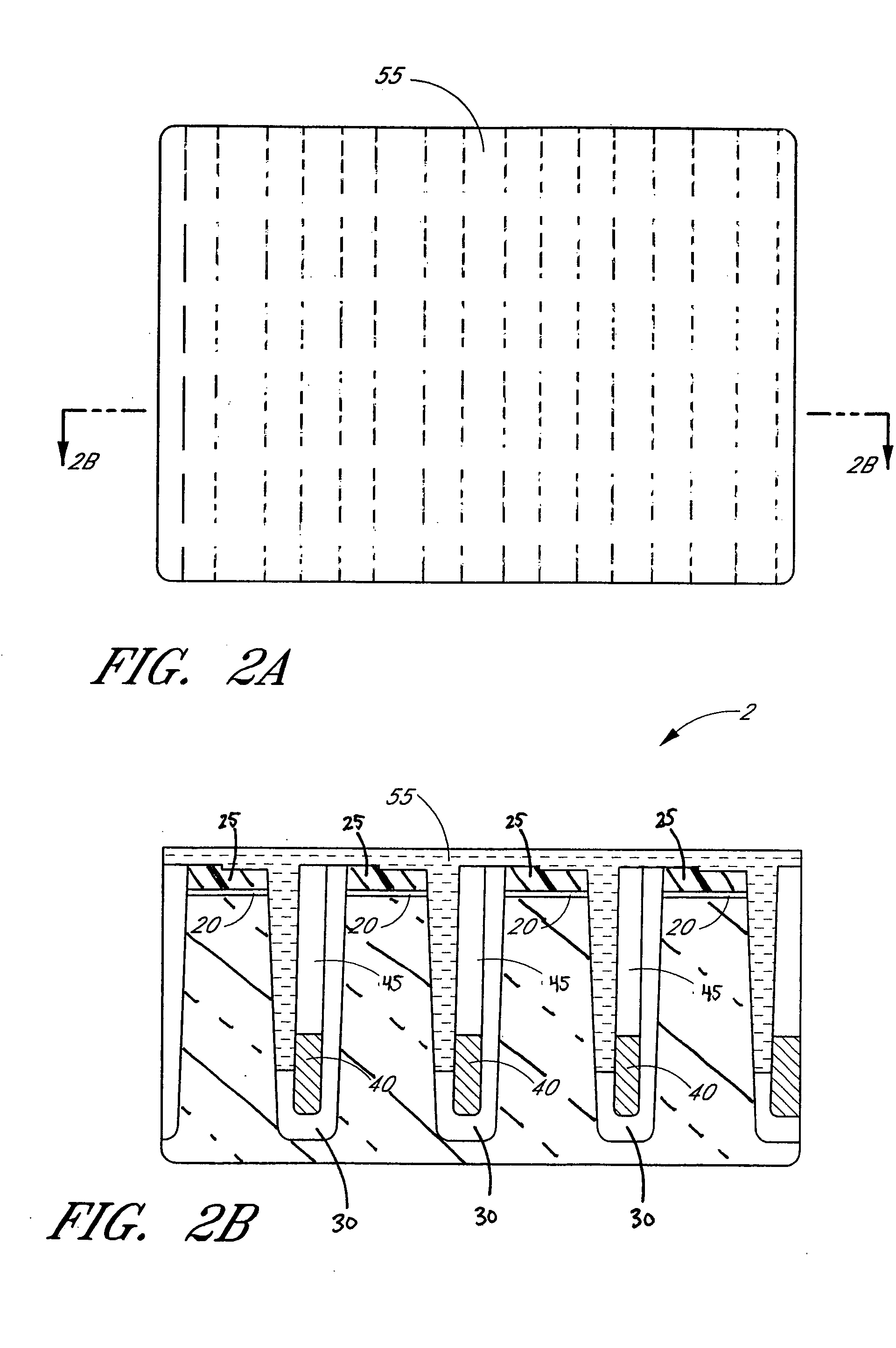

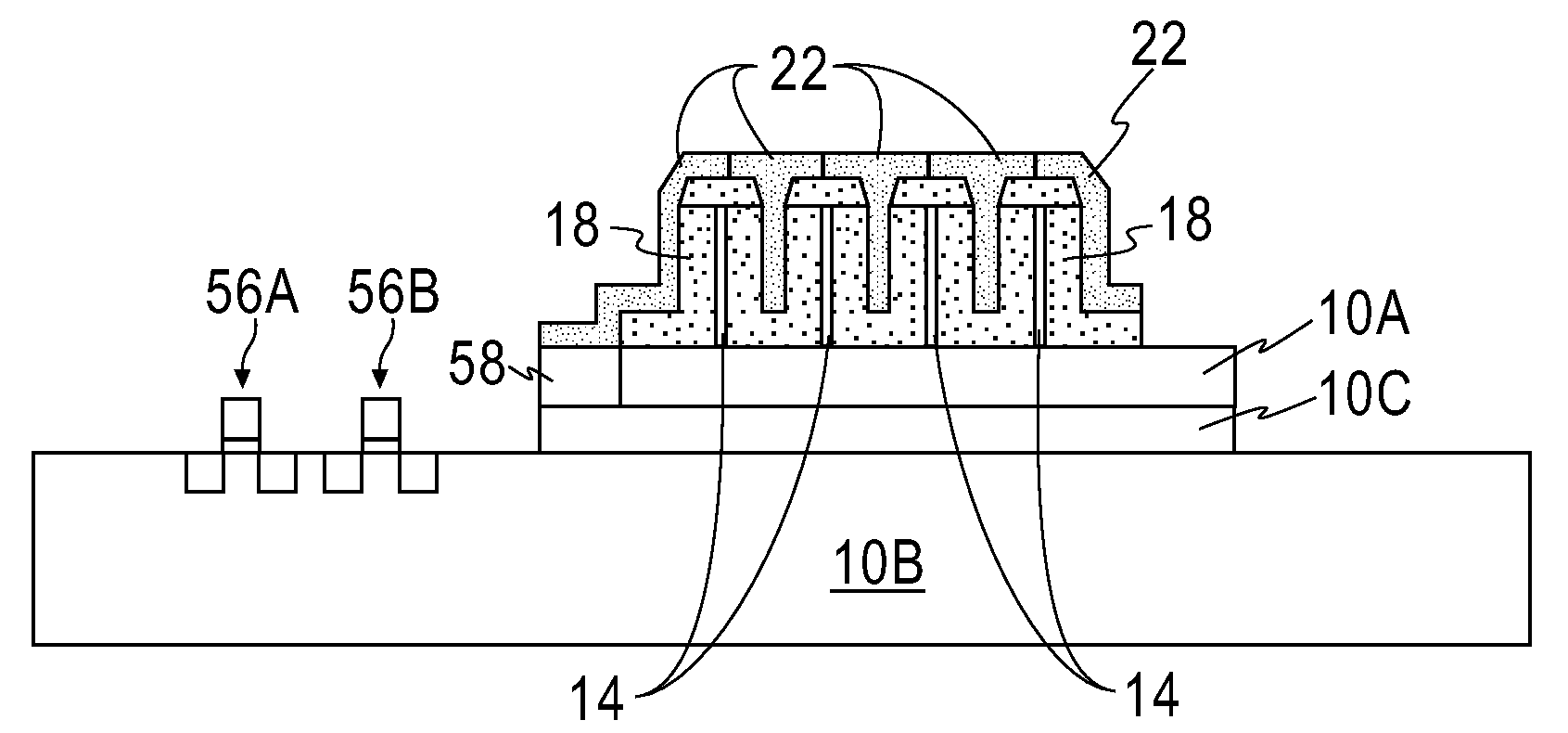

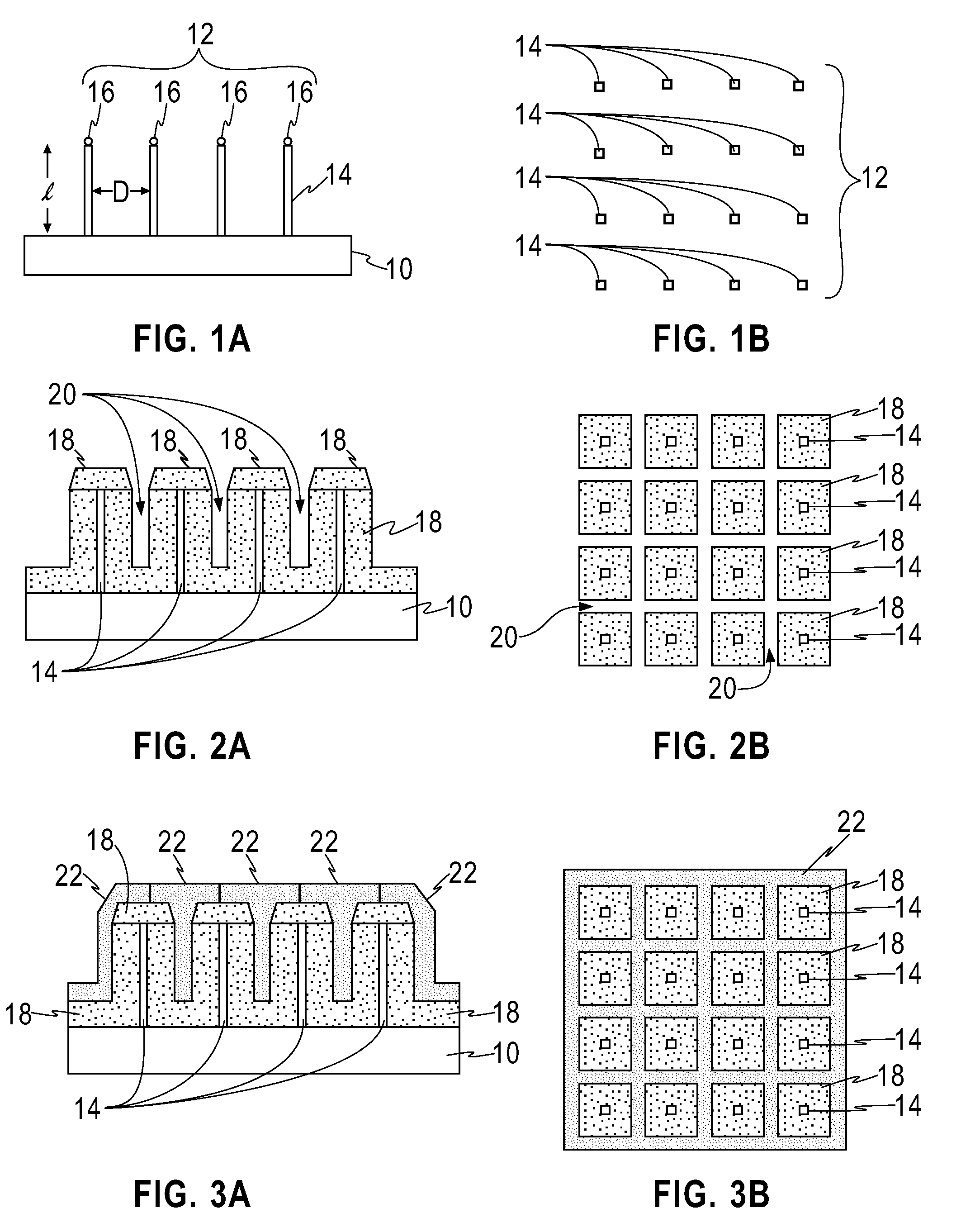

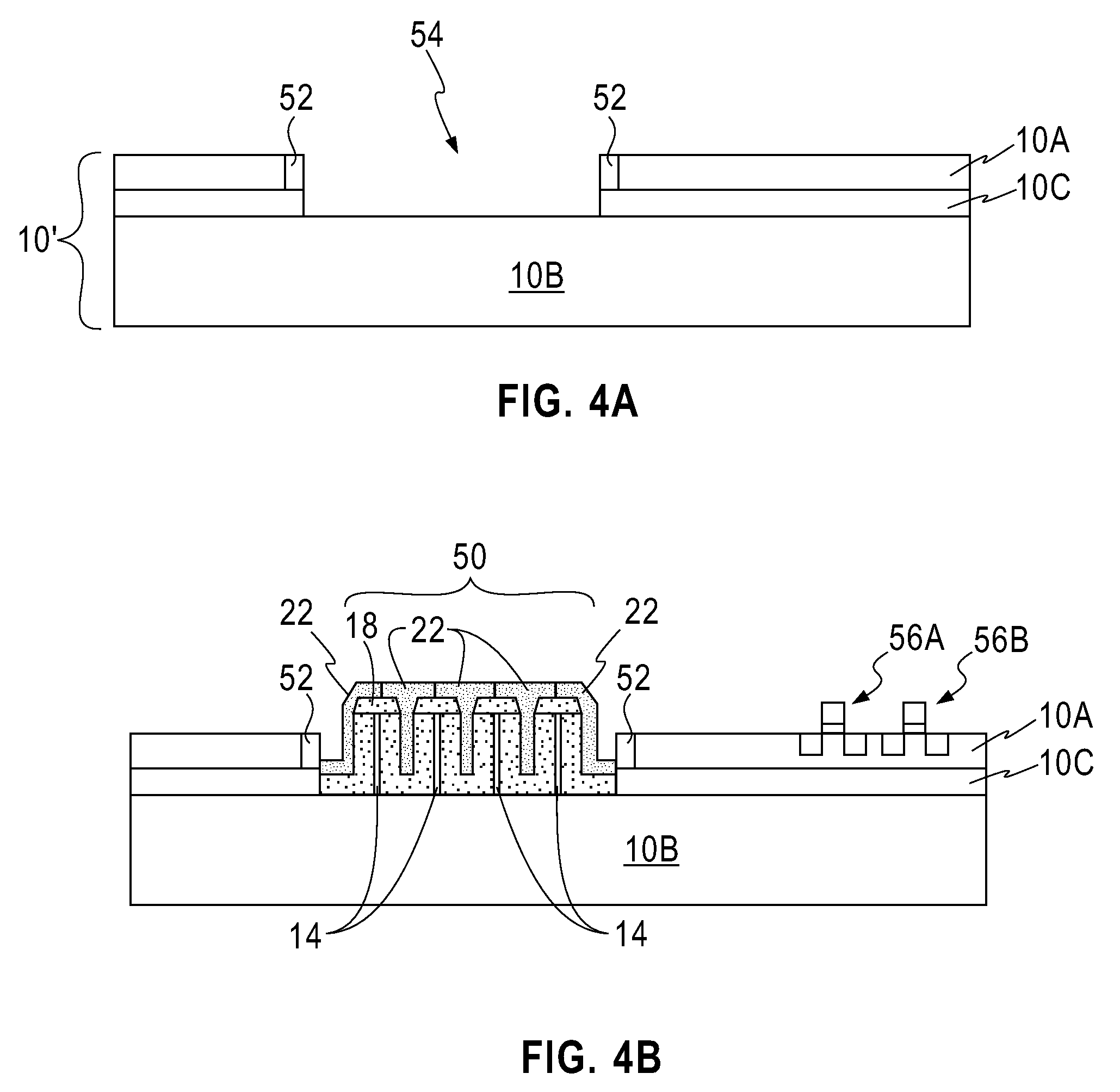

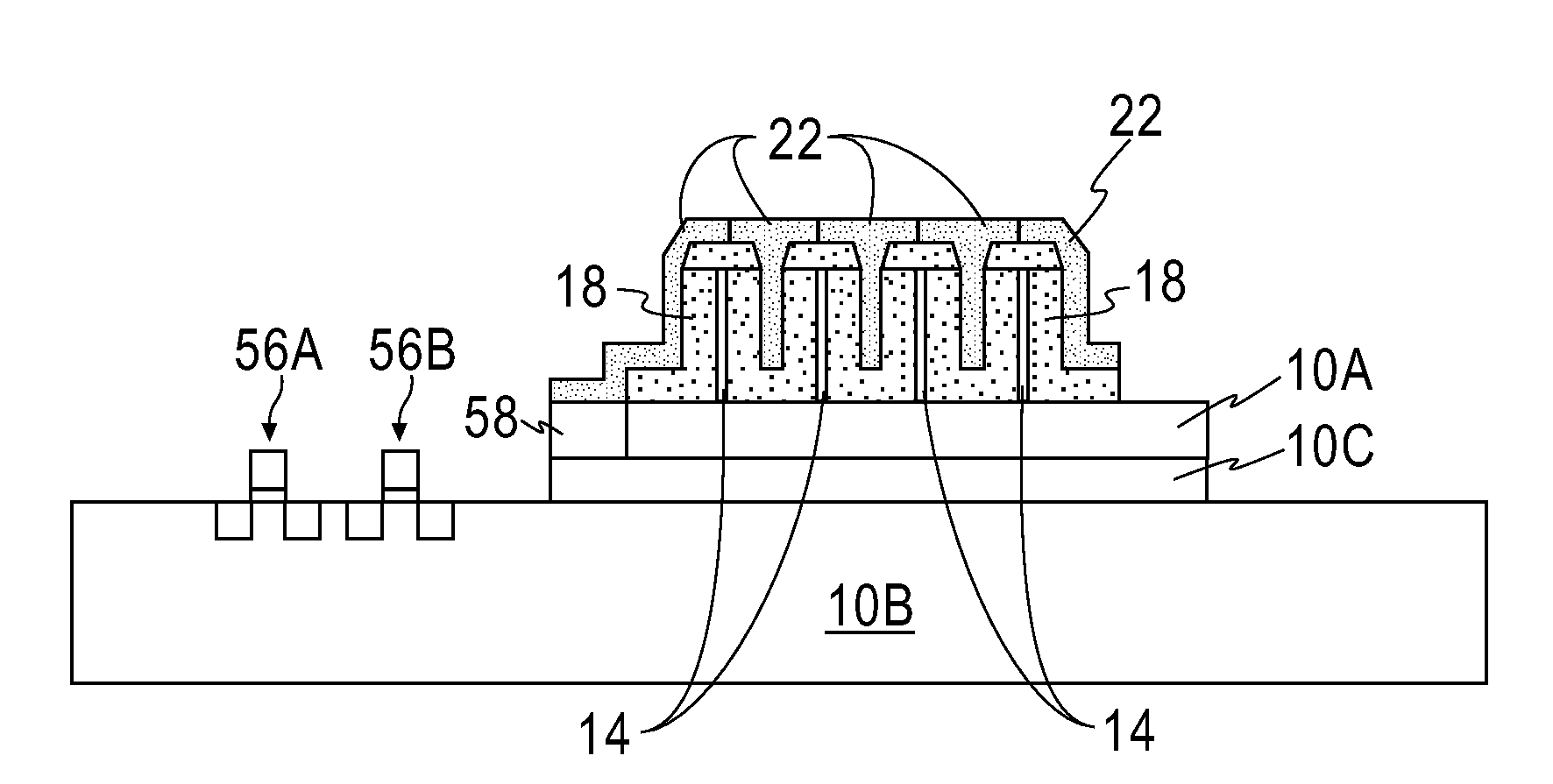

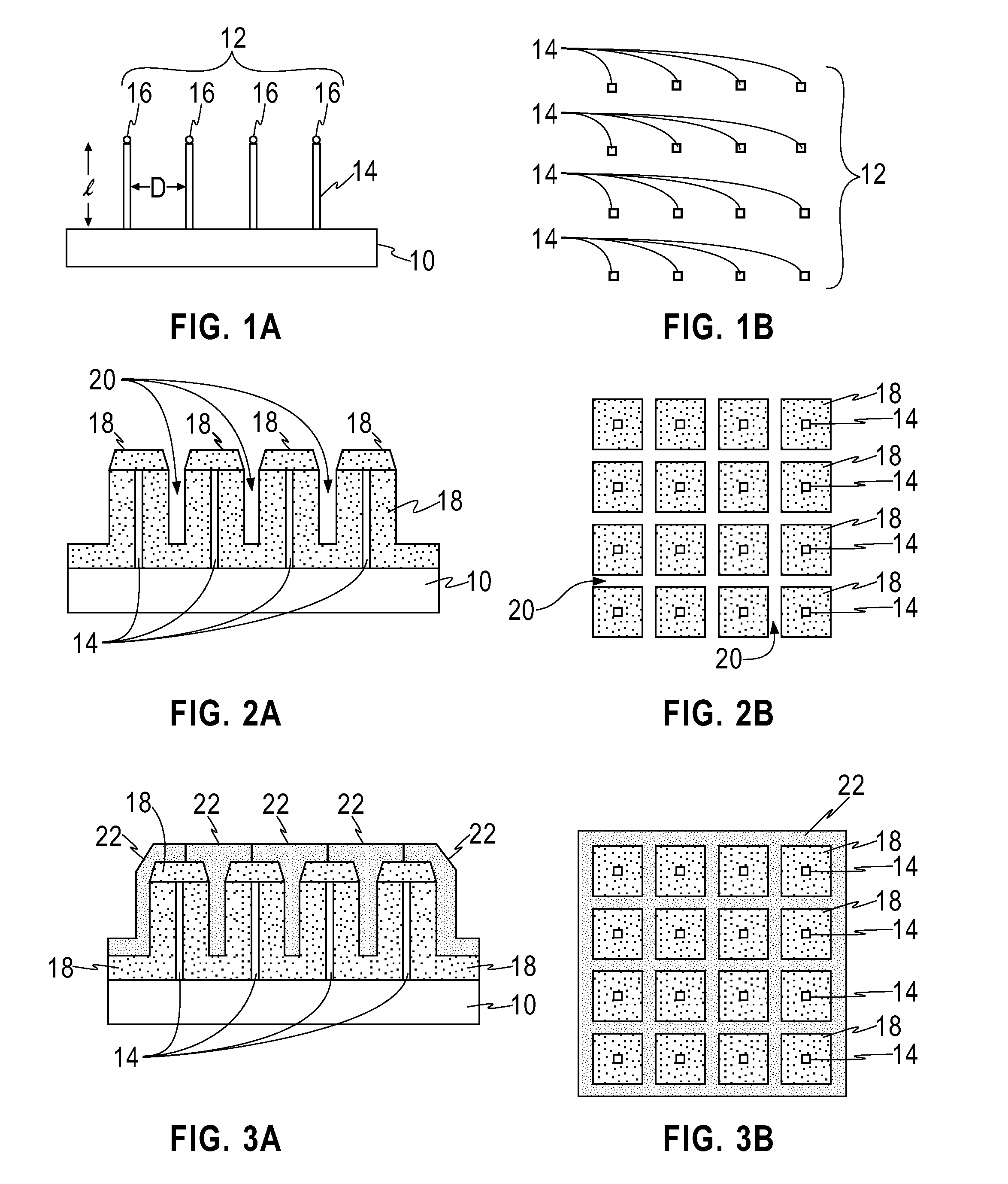

Capacitive micromachined ultrasound transducer fabricated with epitaxial silicon membrane

InactiveUS7037746B1Semiconductor/solid-state device manufacturingMechanical vibrations separationTransducerOptoelectronics

A capacitive micromachined ultrasound transducer (cMUT) cell is presented. The cMUT cell includes a lower electrode. Furthermore, the cMUT cell includes a diaphragm disposed adjacent to the lower electrode such that a gap having a first gap width is formed between the diaphragm and the lower electrode, wherein the diaphragm comprises one of a first epitaxial layer or a first polysilicon layer. In addition, a stress reducing material is disposed in the first epitaxial layer.

Owner:GENERAL ELECTRIC CO

Method for forming an integrated circuit

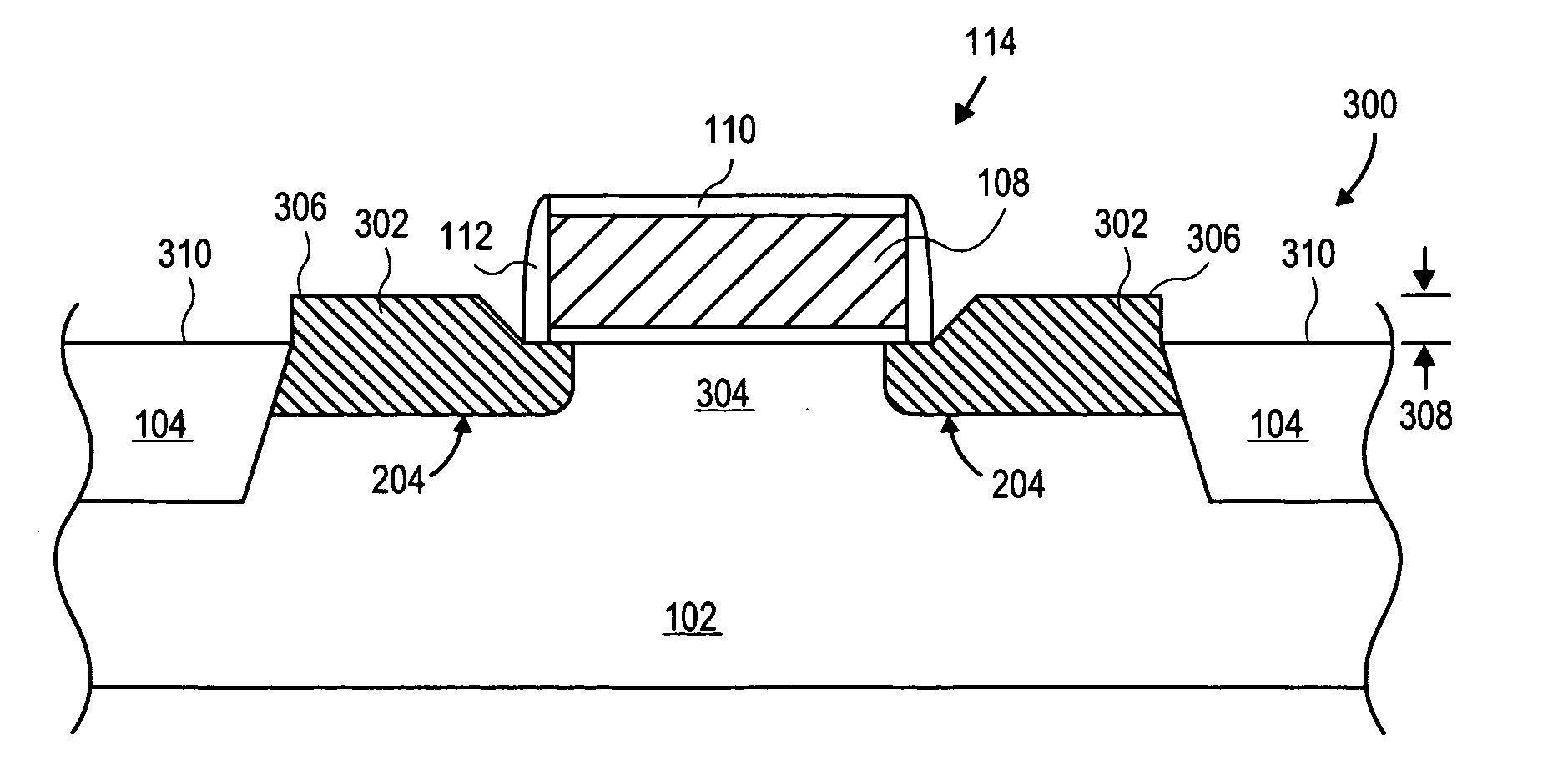

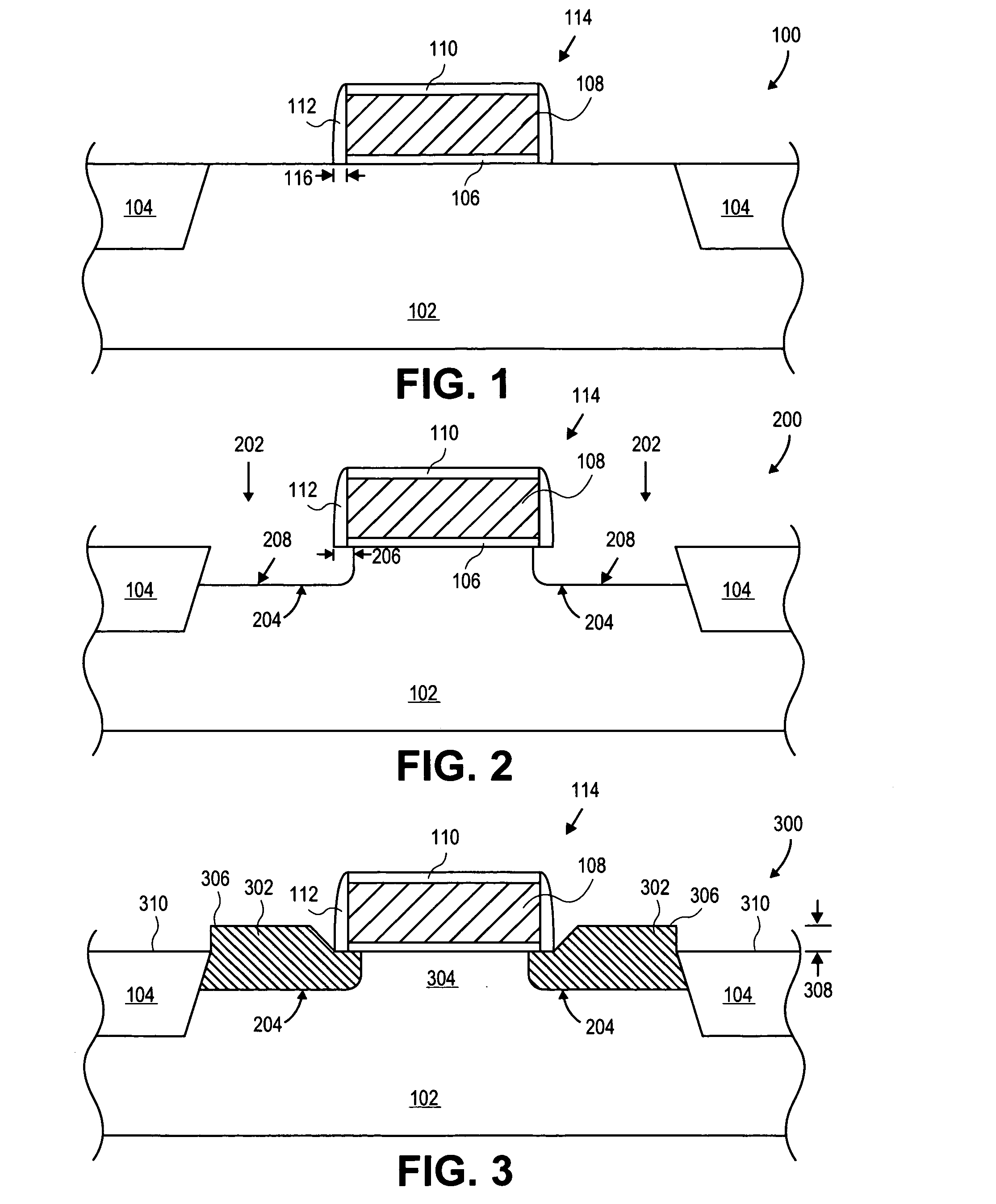

ActiveUS20060131665A1Semiconductor/solid-state device manufacturingSemiconductor devicesContact resistanceEpitaxial silicon

A method is described for manufacturing an n-MOS semiconductor transistor. Recesses are formed in a semiconductor substrate adjacent a gate electrode structure. Silicon is embedded in the recesses via a selective epitaxial growth process. The epitaxial silicon is in-situ alloyed with substitutional carbon and in-situ doped with phosphorus. The silicon-carbon alloy generates a uniaxial tensile strain in the channel region between the source and drain, thereby increasing electron channel mobility and the transistor's drive current. The silicon-carbon alloy decreases external resistances by reducing contact resistance between source / drain and silicide regions and by reducing phosphorous diffusivity, thereby permitting closer placement of the transistor's source / drain and channel regions.

Owner:TAHOE RES LTD

Method of preventing surface roughening during hydrogen prebake of SiGe substrates

InactiveUS20050148161A1Avoid creatingAvoid roughnessPolycrystalline material growthSemiconductor/solid-state device manufacturingHydrofluoric acidRough surface

The invention forms an epitaxial silicon-containing layer on a silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface and avoids creating a rough surface upon which the epitaxial silicon-containing layer is grown. In order to avoid creating the rough surface, the invention first performs a hydrofluoric acid etching process on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. This etching process removes most of oxide from the surface, and leaves a first amount of oxygen (typically 1×1013-1×1015 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The invention then performs a hydrogen pre-bake process which heats the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface sufficiently to remove additional oxygen from the surface and leave a second amount of oxygen, less than the first amount, on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. The heating process leaves an amount of at least 5×1012 / cm2 of oxygen (typically, between approximately 1×1013 / cm2 and approximately 5×1013 / cm2 of oxygen) on the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. By leaving a small amount of oxygen on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface, the heating processes avoid changing the roughness of the silicon germanium, patterned strained silicon, or patterned thin silicon-on-insulator surface. Then the process of epitaxially growing the epitaxial silicon-containing layer on the silicon germanium, patterned strained silicon, or patterned silicon-on-insulator surface is performed.

Owner:IBM CORP

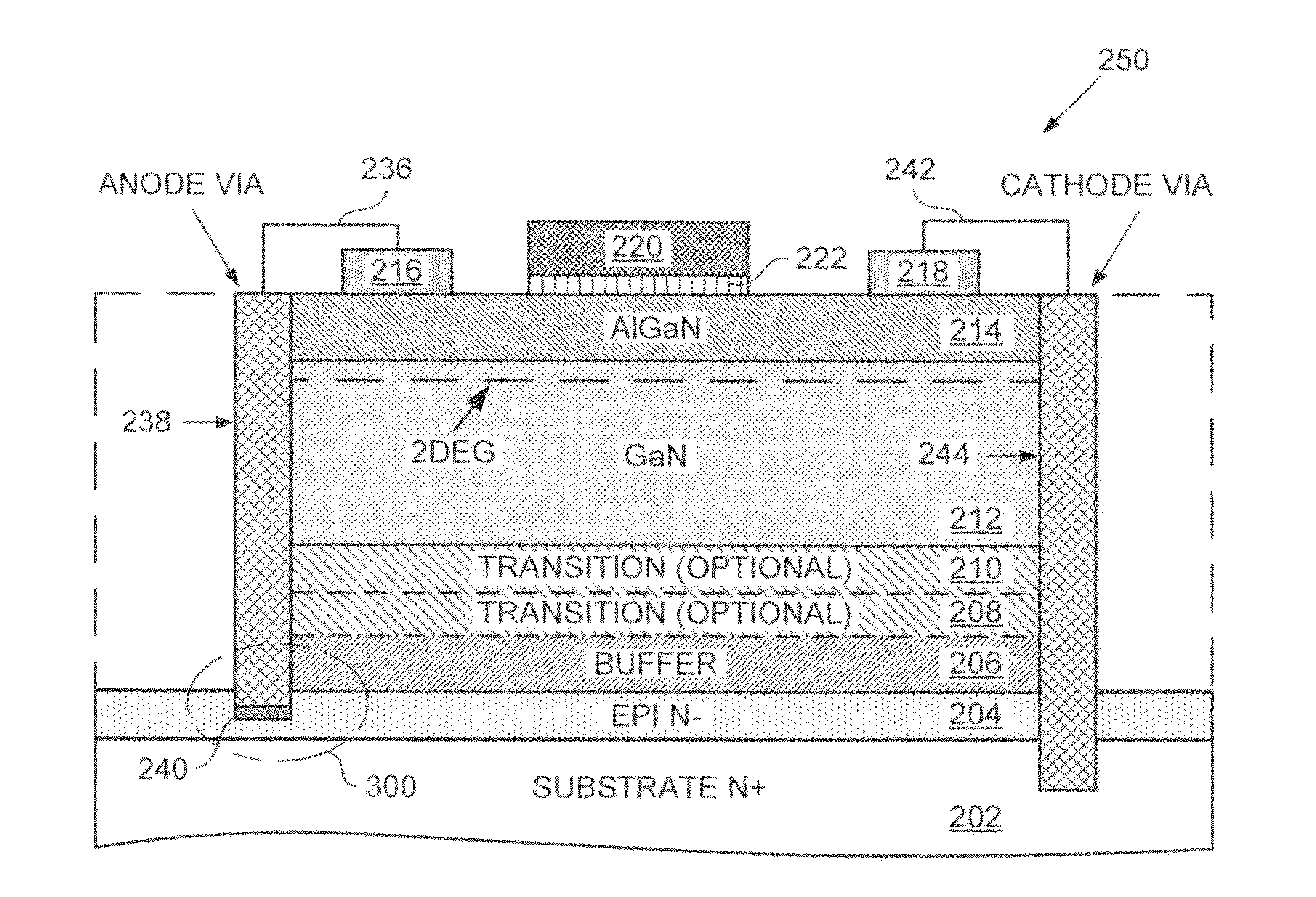

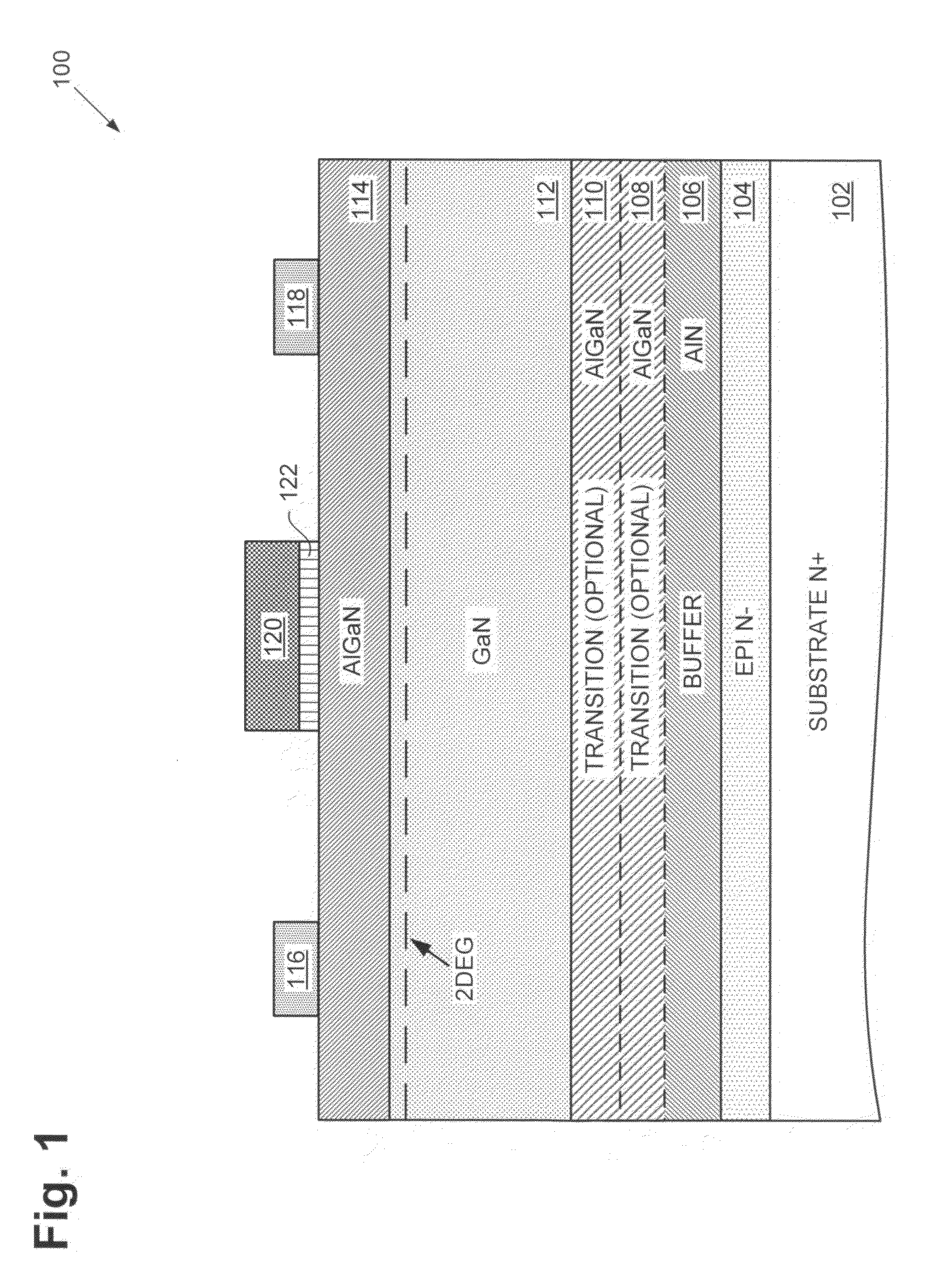

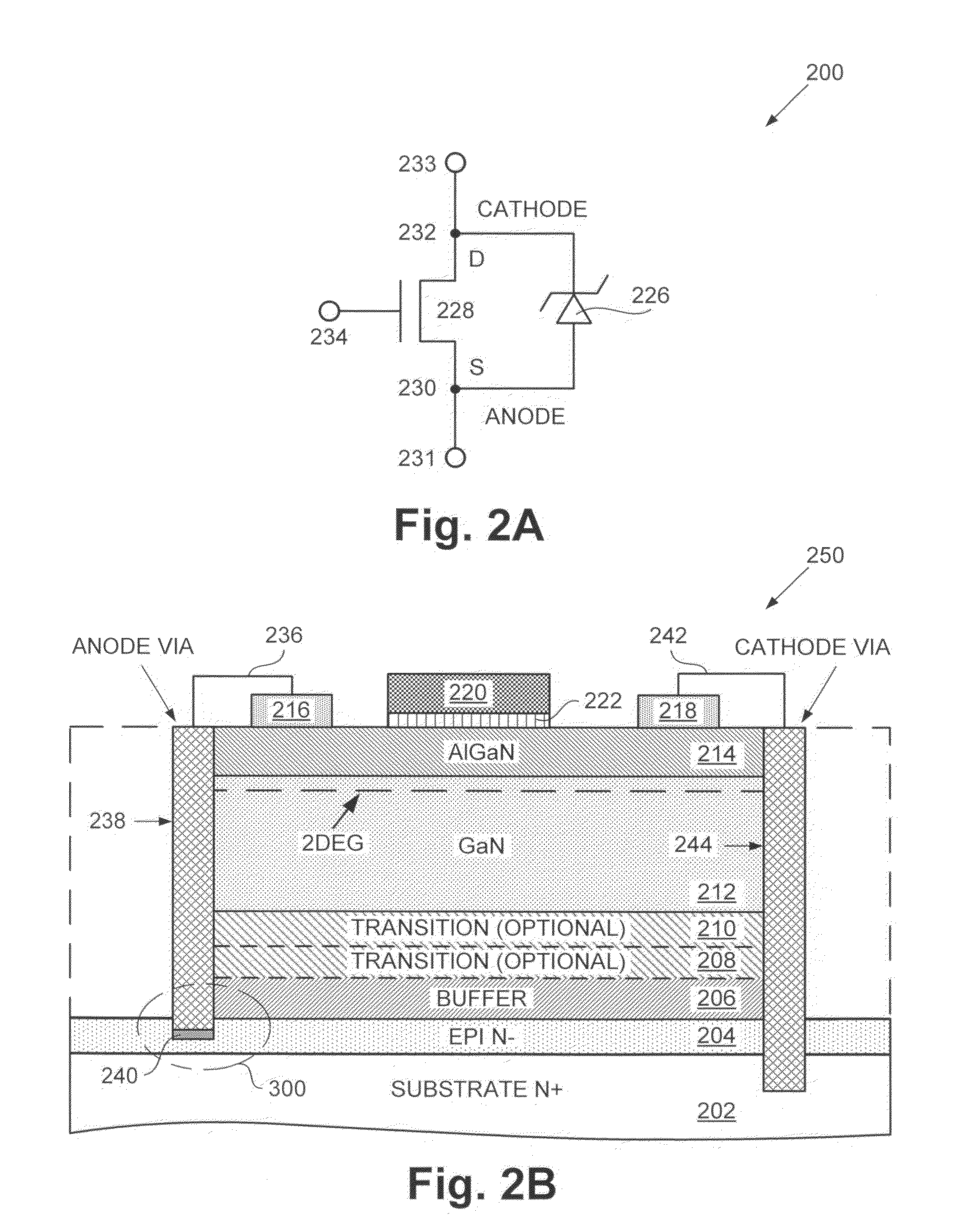

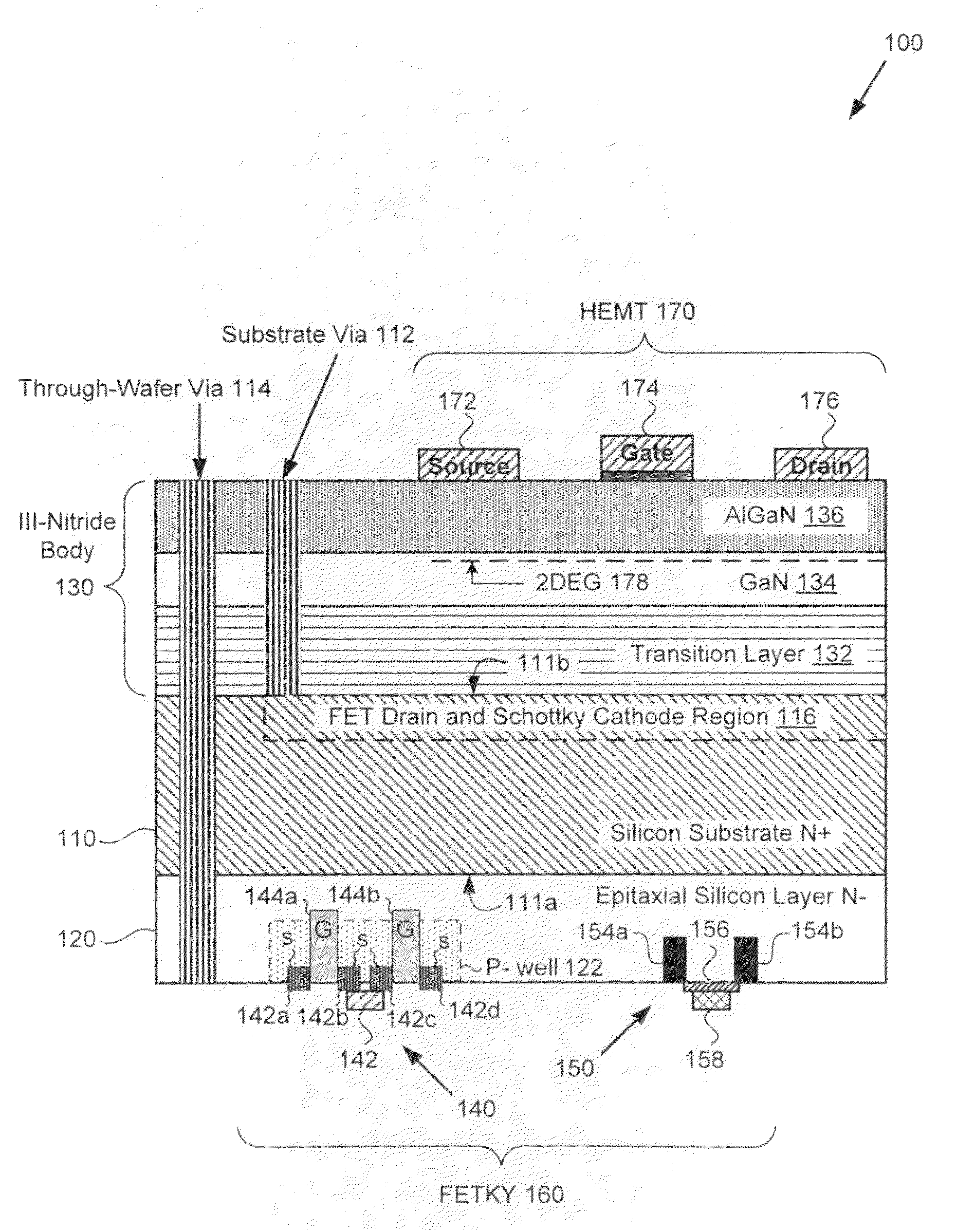

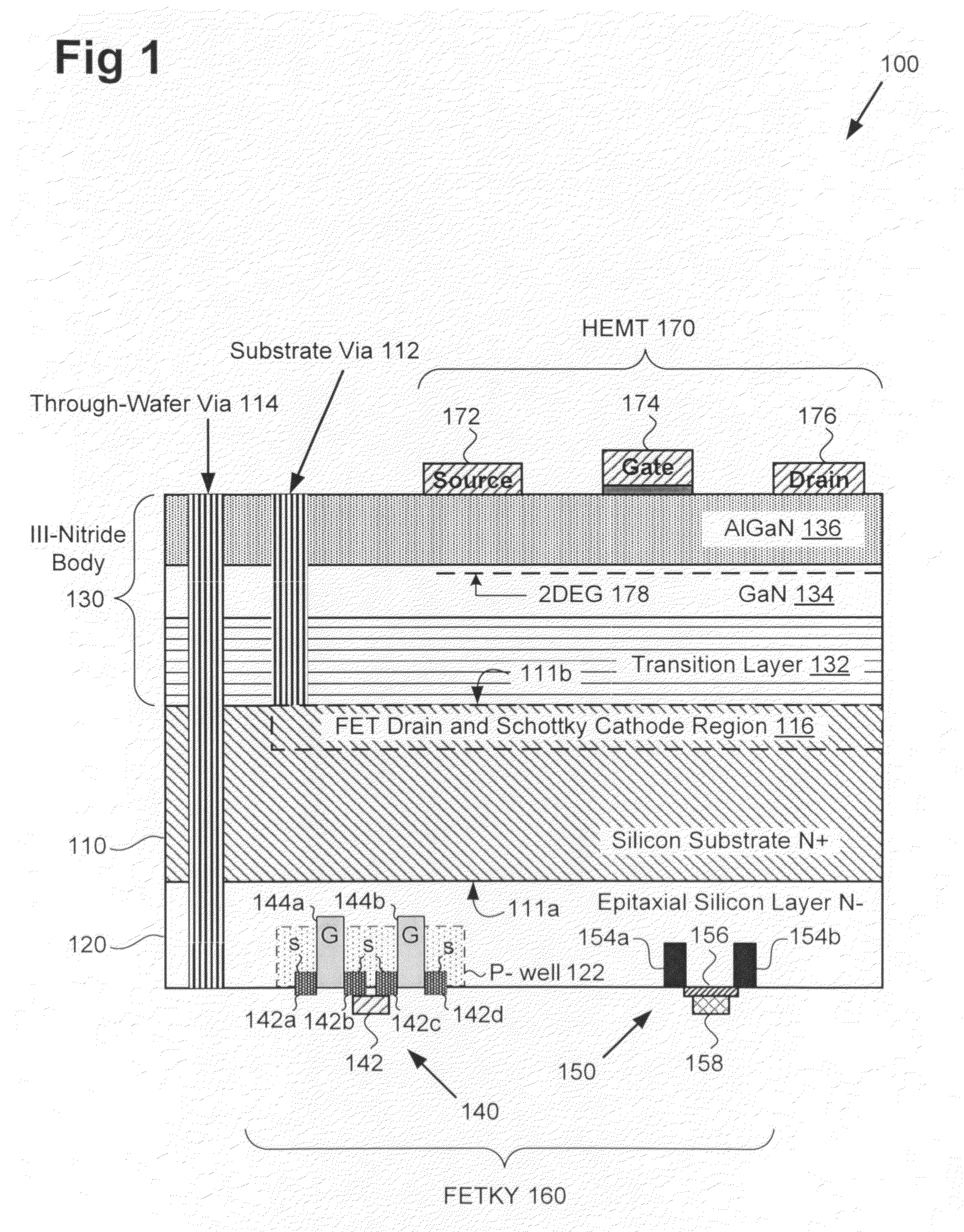

Monolithic integration of silicon and group III-V devices

Disclosed is a monolithically integrated silicon and group III-V device that includes a group III-V transistor formed in a III-V semiconductor body disposed over a silicon substrate. At least one via extends through the III-V semiconductor body to couple at least one terminal of the group III-V transistor to a silicon device formed in the silicon substrate. The silicon device can be a Schottky diode, and the group III-V transistor can be a GaN HEMT. In one embodiment an anode of the Schottky diode is formed in the silicon substrate. In another embodiment, the anode of the Schottky diode is formed in a lightly doped epitaxial silicon layer atop the silicon substrate. In one embodiment a parallel combination of the Schottky diode and the group III-V transistor is formed, while in another embodiment is series combination is formed.

Owner:INFINEON TECH AMERICAS CORP

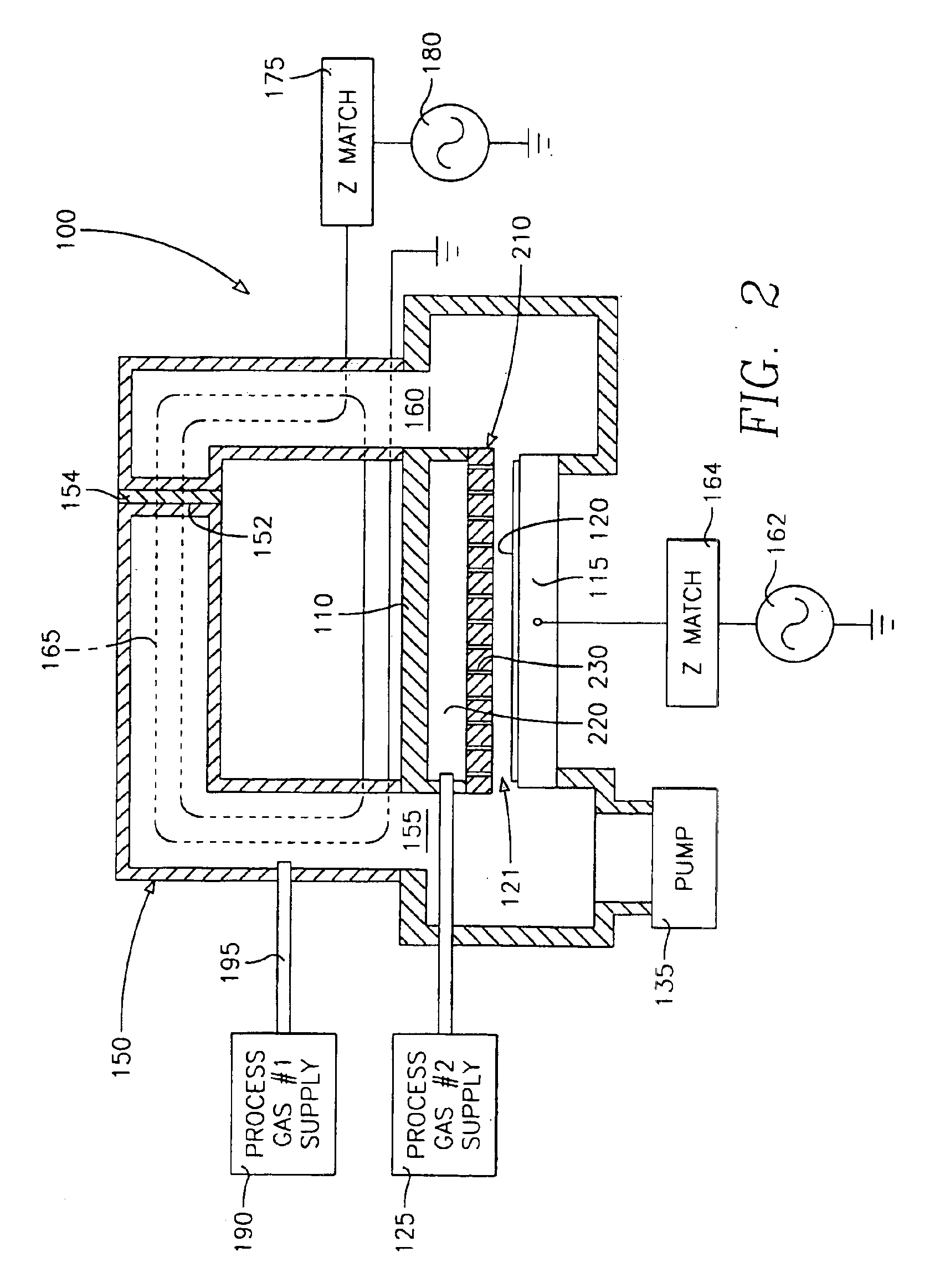

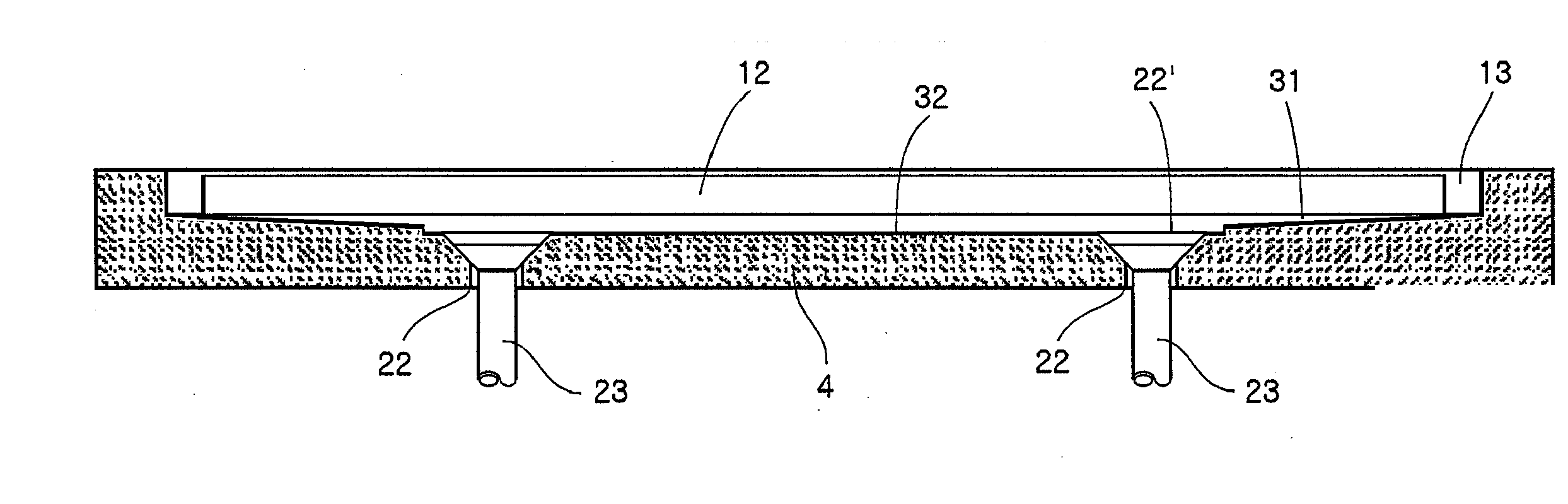

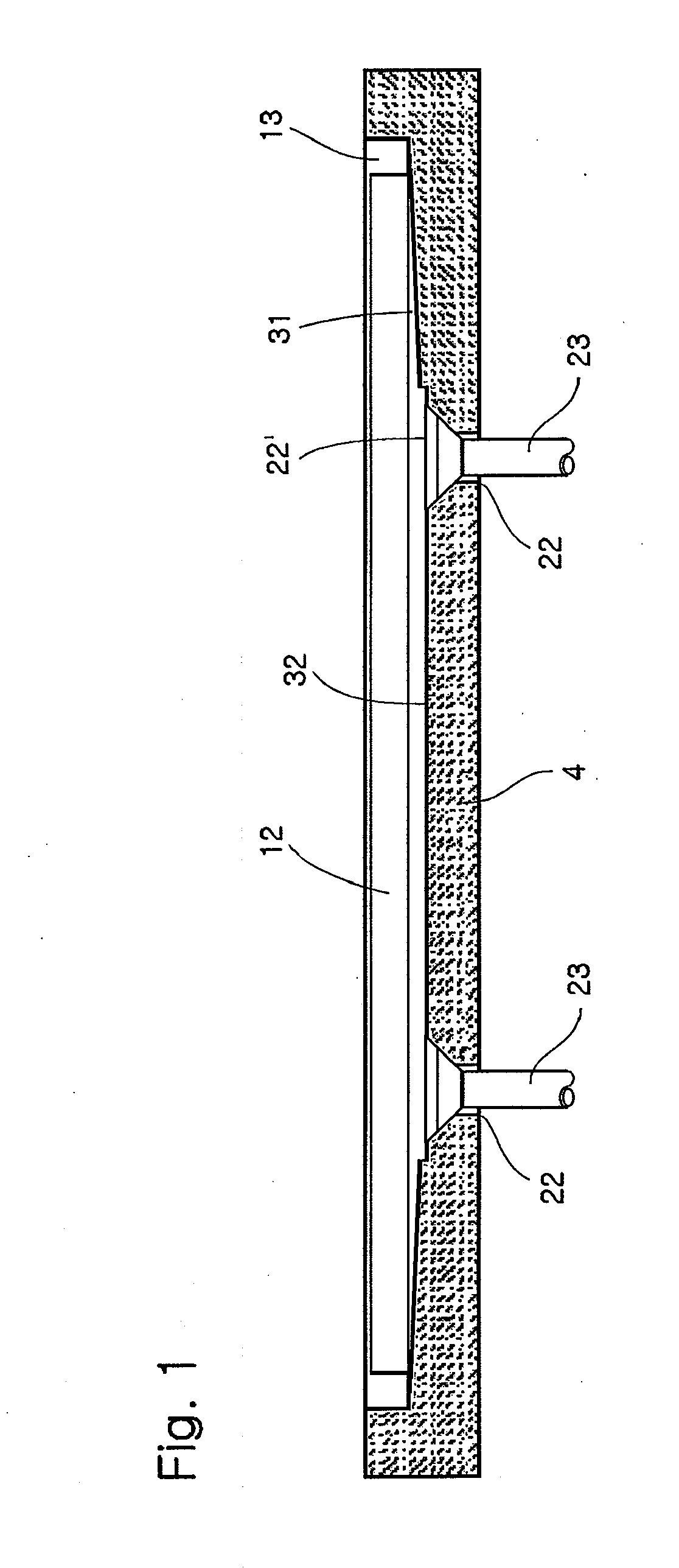

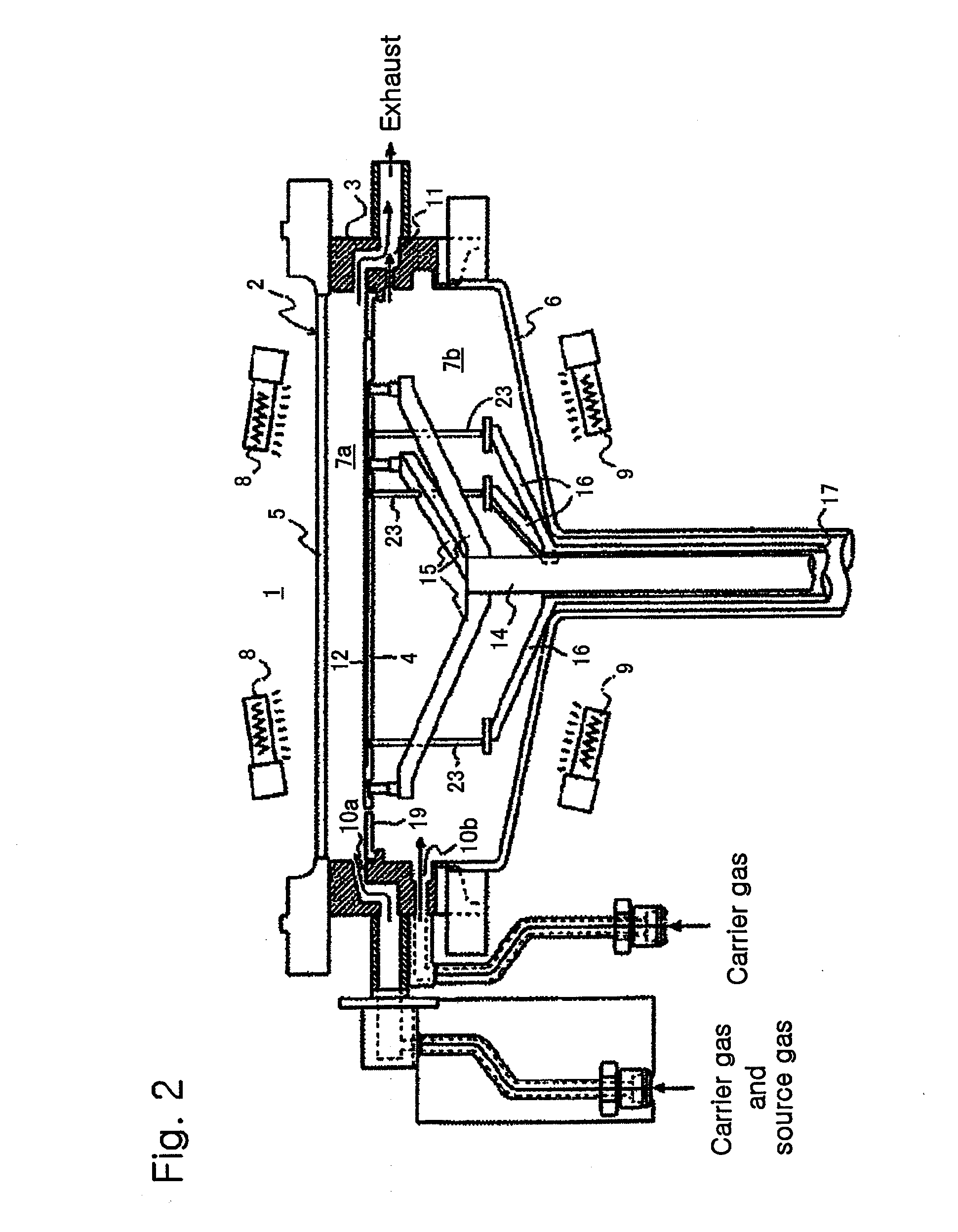

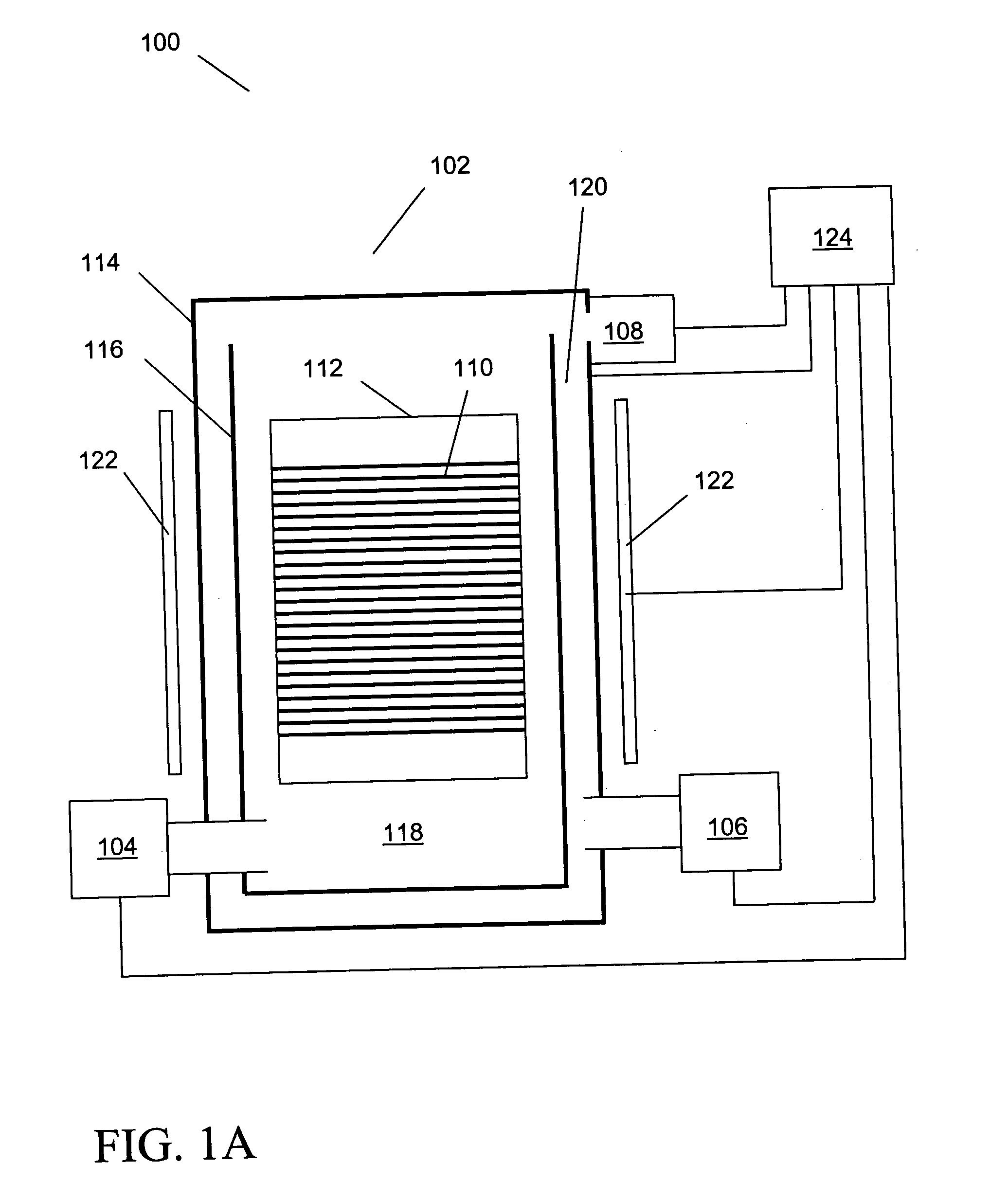

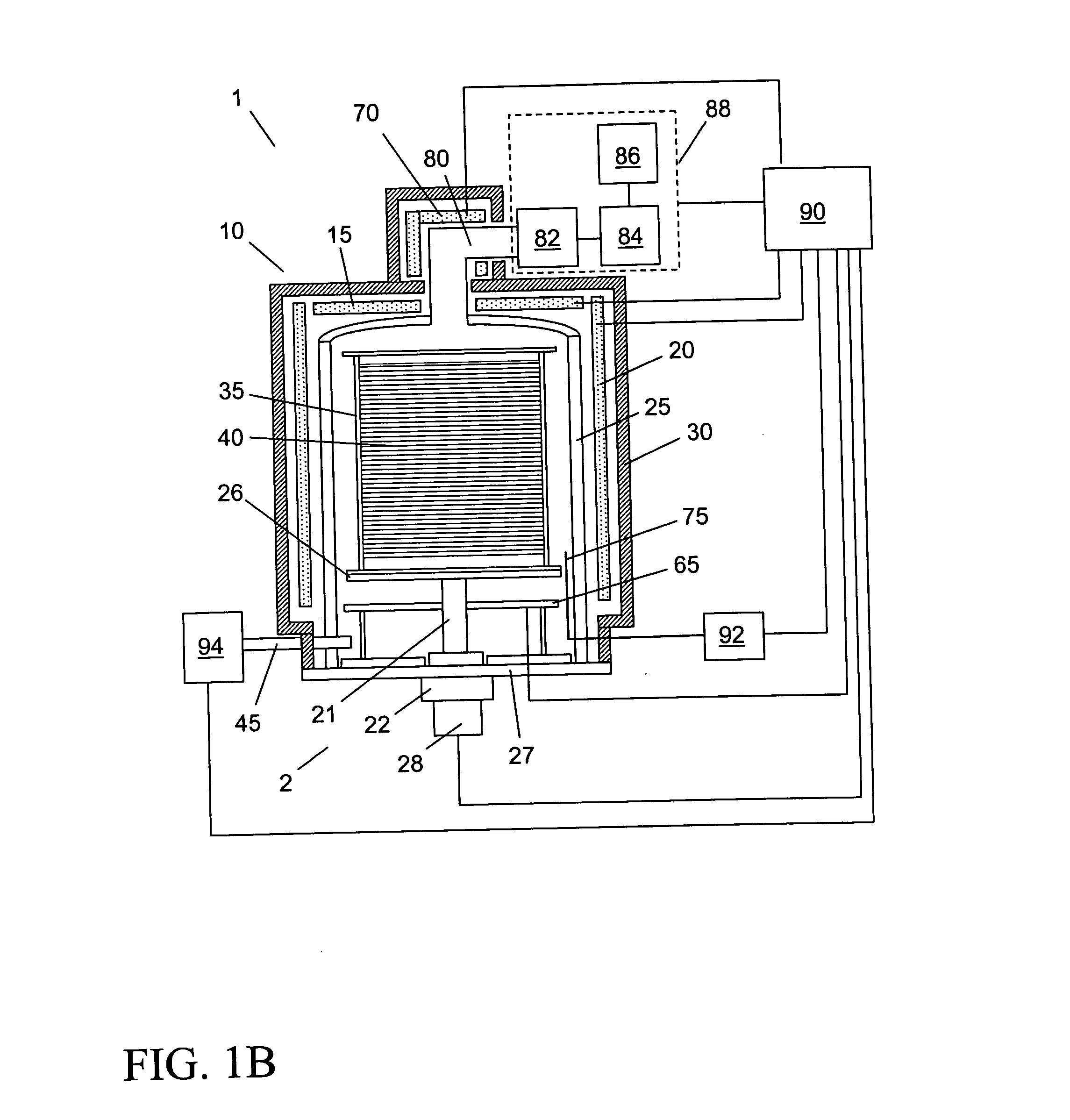

Method of manufacturing epitaxial silicon wafer and apparatus thereof

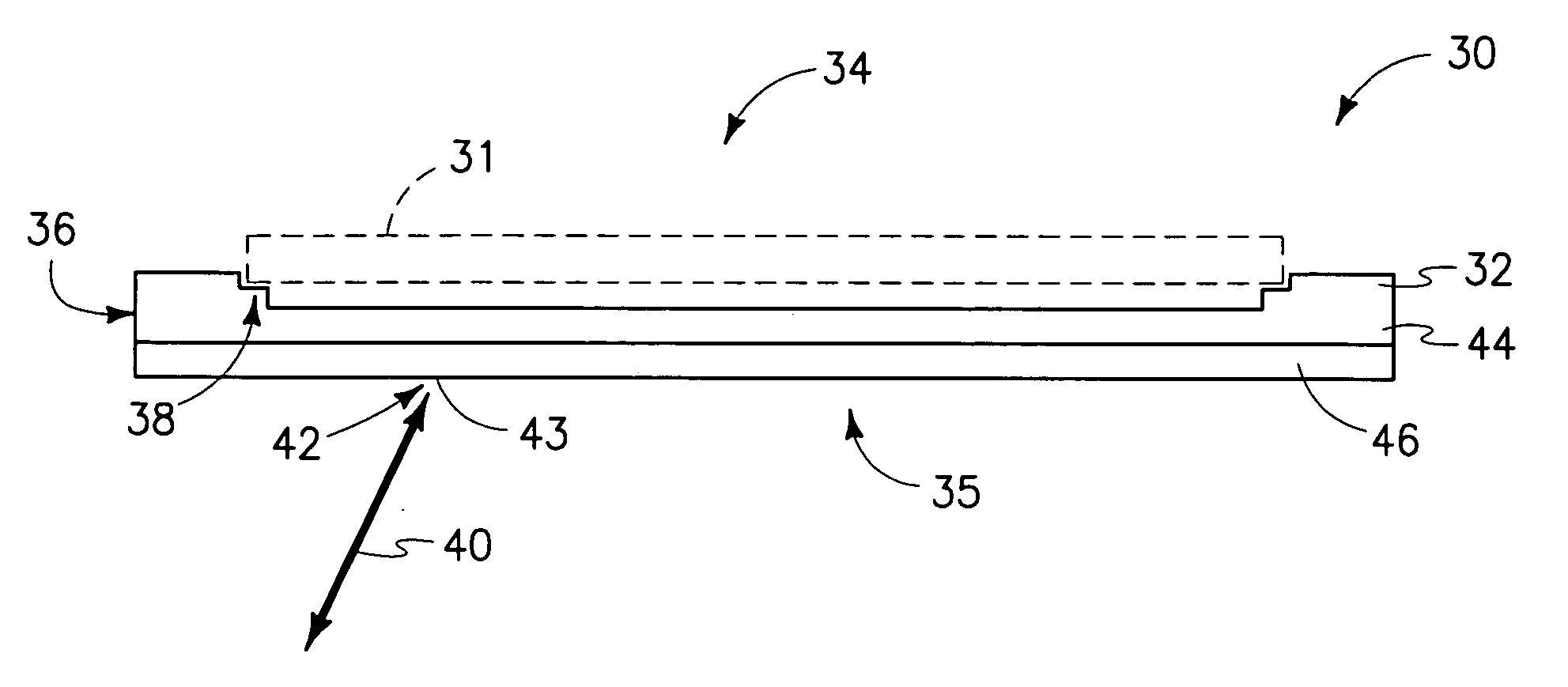

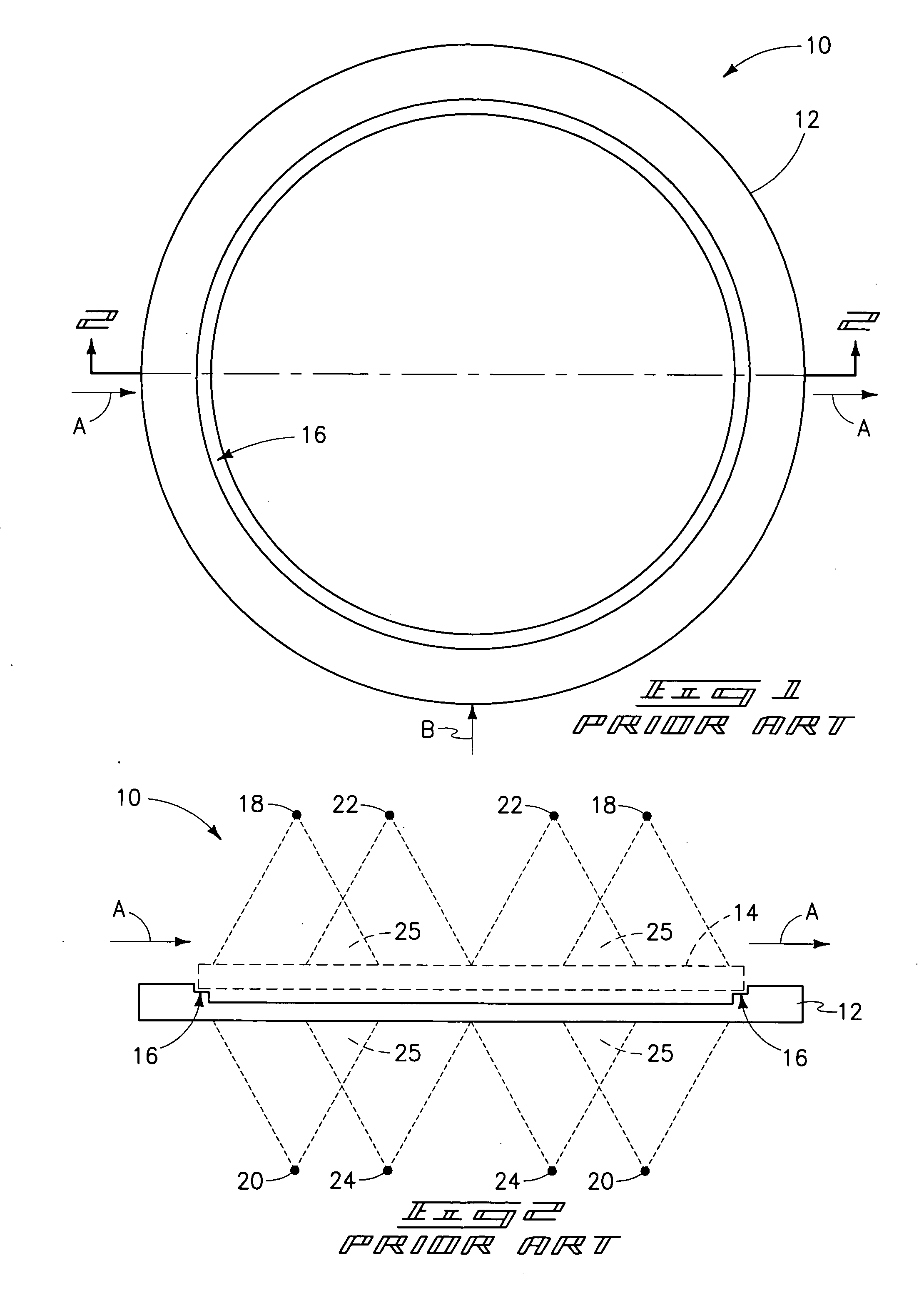

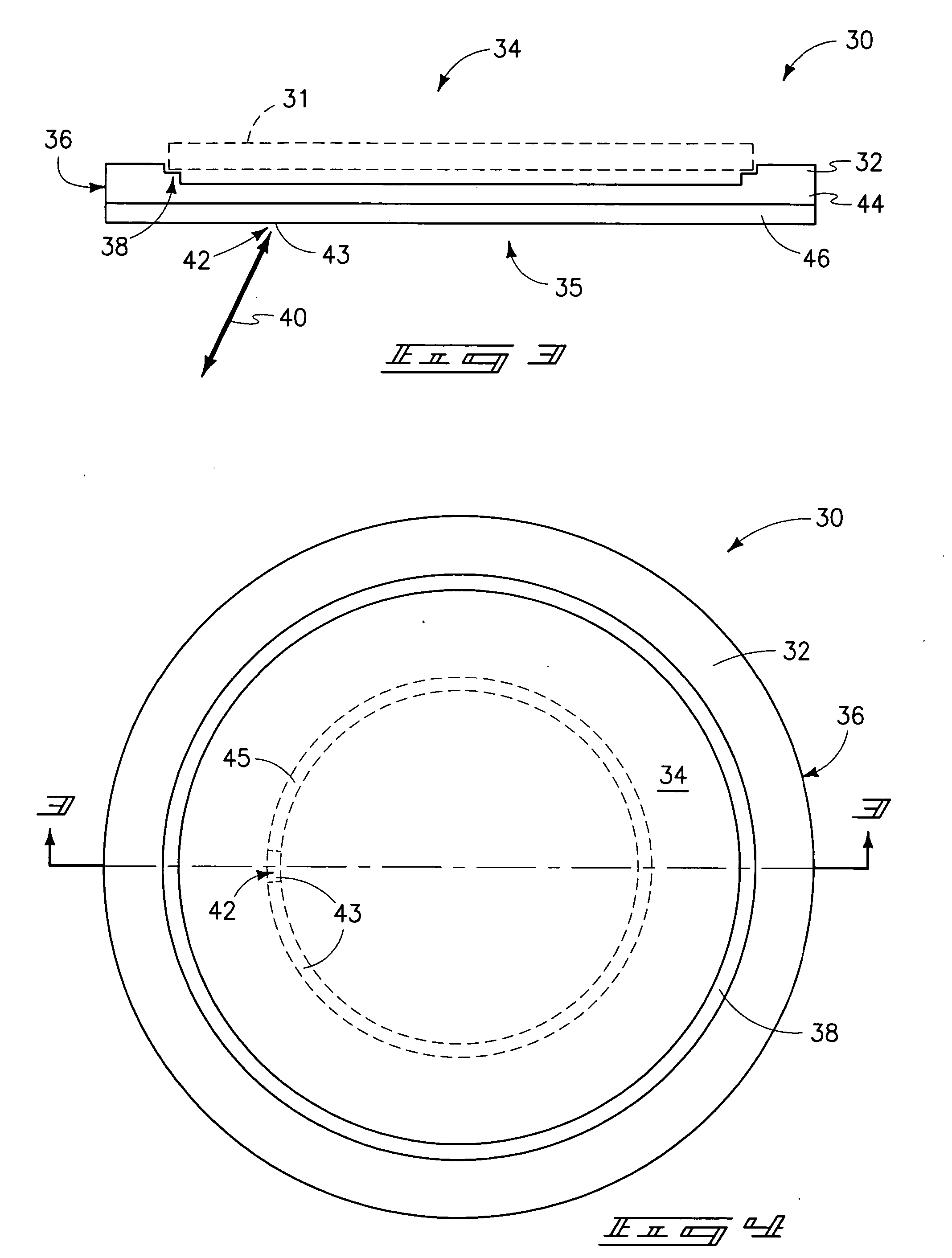

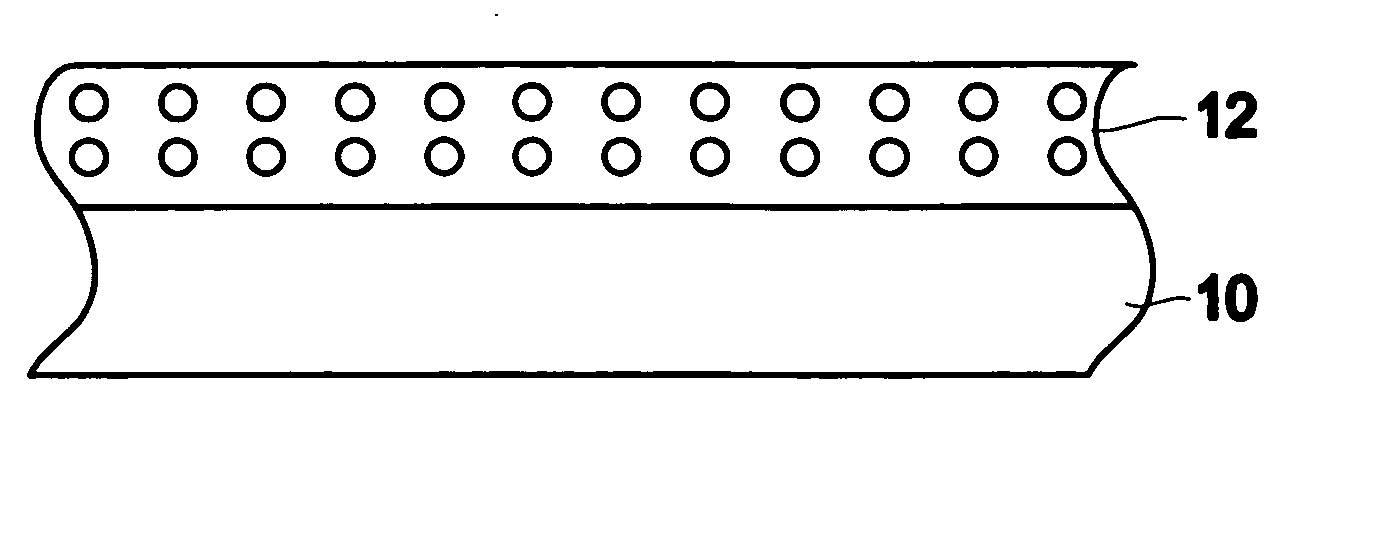

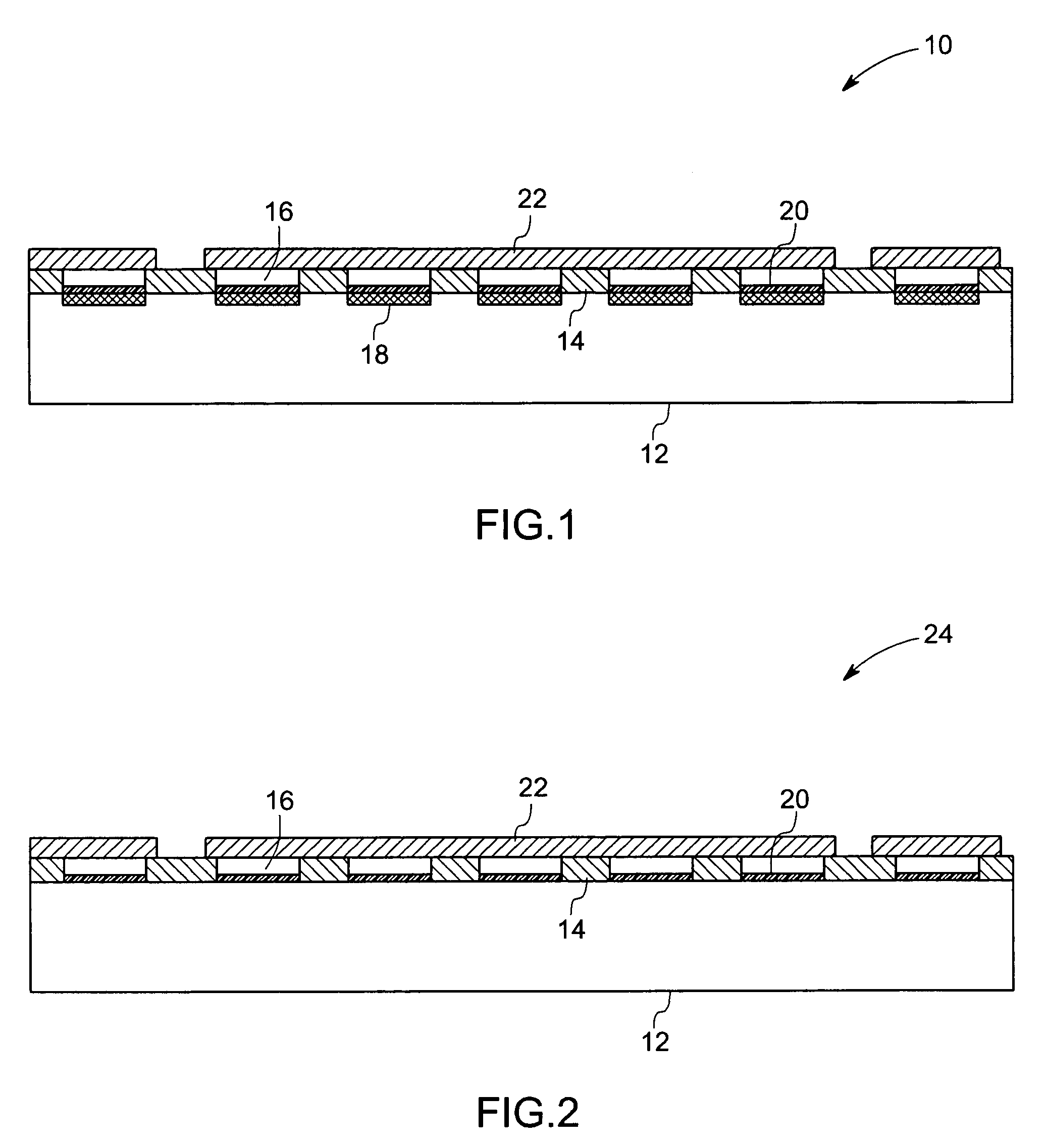

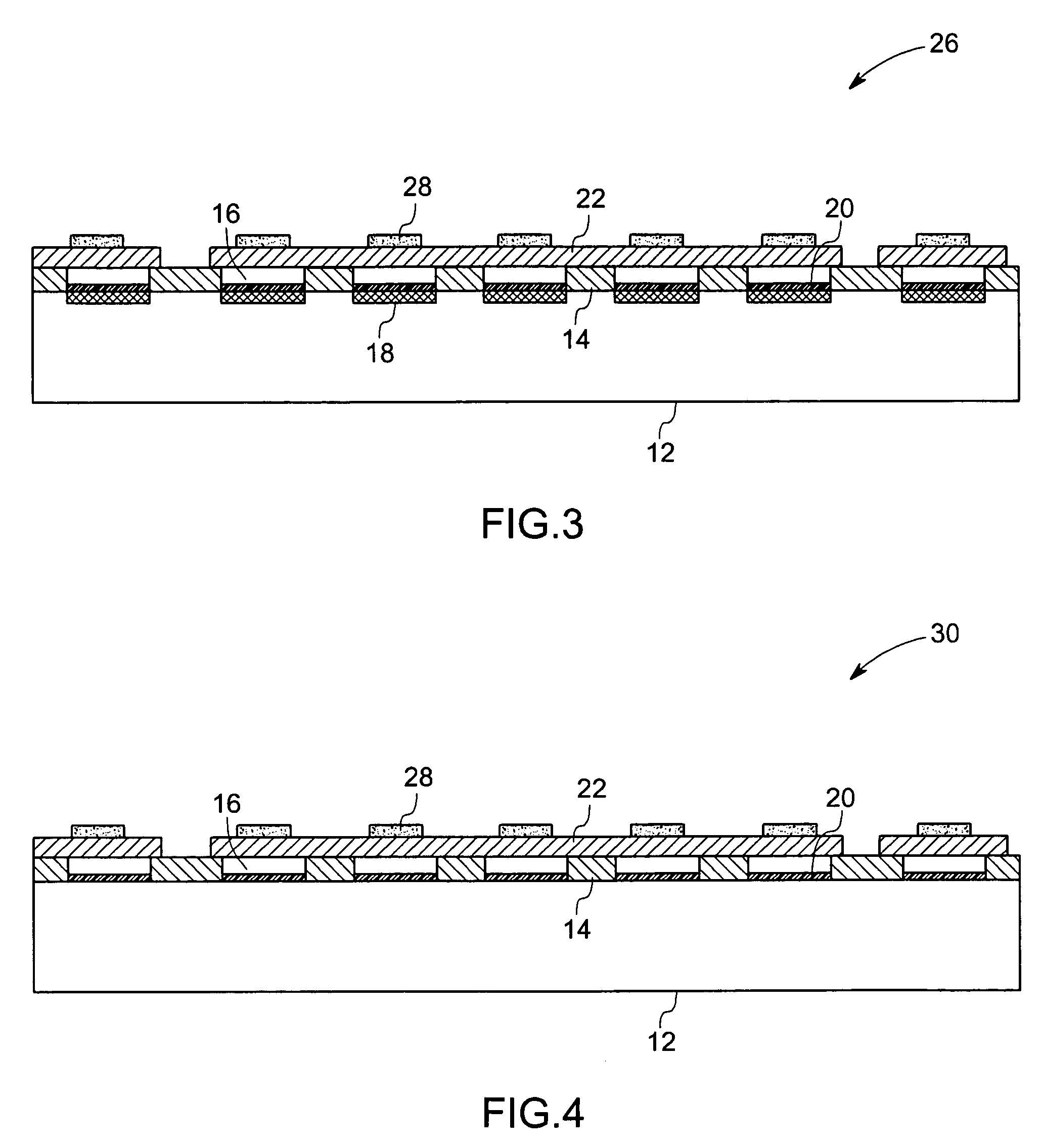

ActiveUS20070227441A1Improve uniformityPolycrystalline material growthSemiconductor/solid-state device manufacturingSusceptorWafering

A method of forming an epitaxial layer to increase flatness of an epitaxial silicon wafer is provided. In particular, a method of controlling the epitaxial layer thickness in a peripheral part of the wafer is provided. An apparatus for manufacturing an epitaxial wafer by growing an epitaxial layer with reaction of a semiconductor wafer and a source gas in a reaction furnace comprising: a pocket in which the semiconductor wafer is placed; a susceptor fixing the semiconductor; orientation-dependent control means dependent on a crystal orientation of the semiconductor wafer and / or orientation-independent control means independent from the crystal orientation of the semiconductor wafer, wherein the apparatus may improve flatness in a peripheral part of the epitaxial layer.

Owner:SUMCO TECHXIV

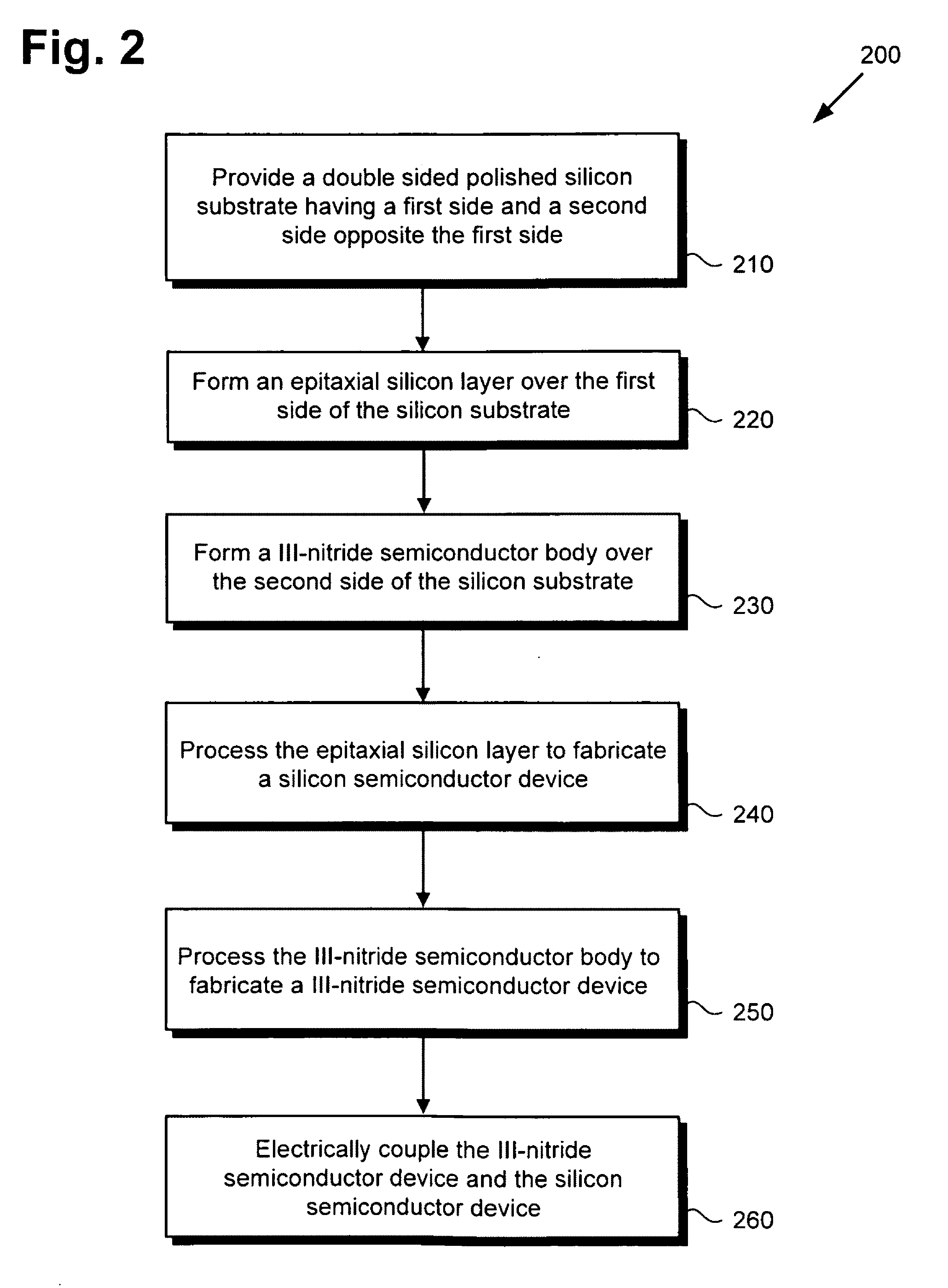

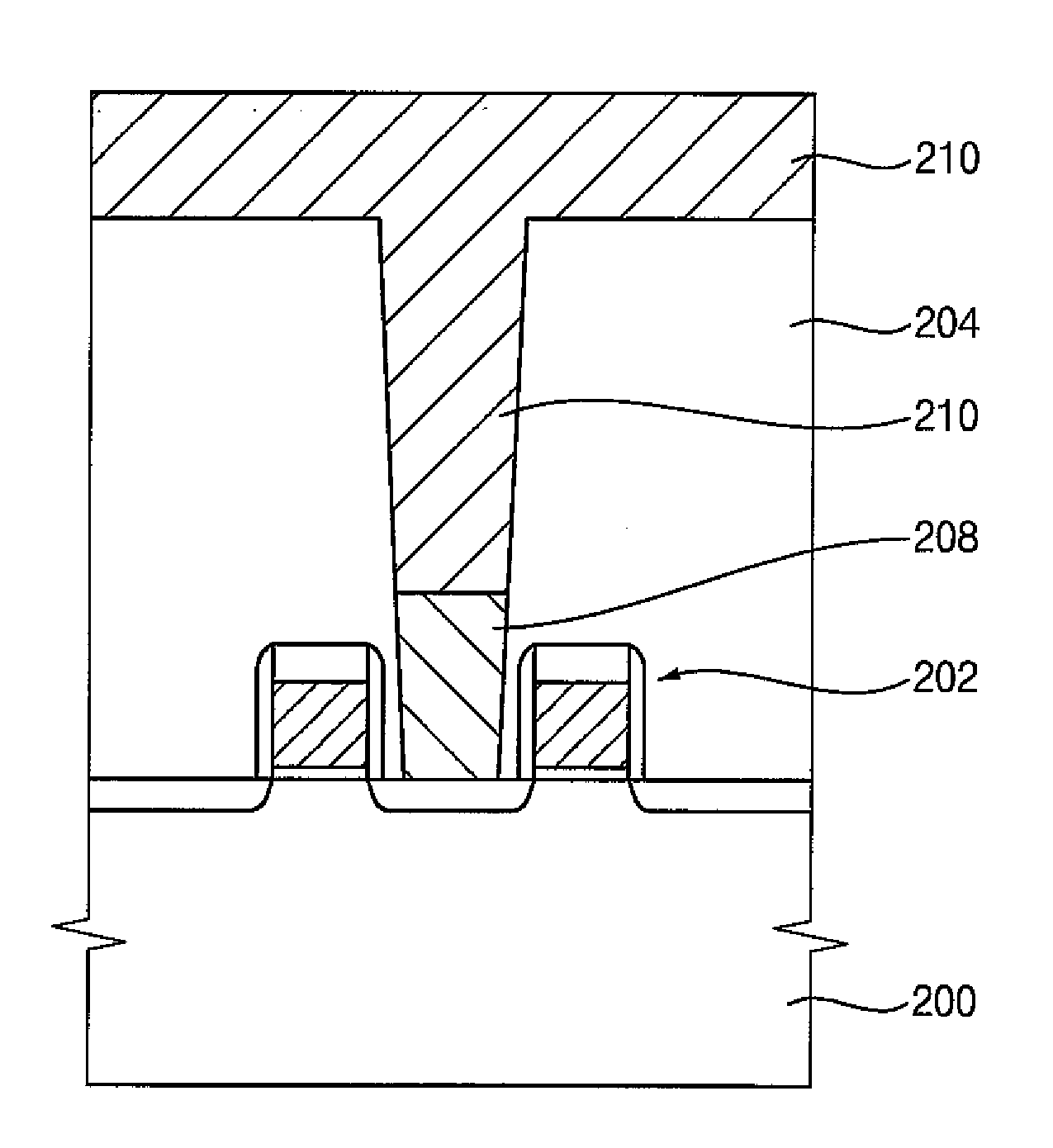

Monolithic vertically integrated composite group III-V and group IV semiconductor device and method for fabricating same

InactiveUS7915645B2TransistorSemiconductor/solid-state device detailsPower semiconductor deviceEngineering

According to one disclosed embodiment, a monolithic vertically integrated composite device comprises a double sided semiconductor substrate having first and second sides, a group IV semiconductor layer formed over the first side and comprising at least one group IV semiconductor device, and a group III-V semiconductor body formed over the second side and comprising at least one group III-V semiconductor device electrically coupled to the at least one group IV semiconductor device. The composite device may further comprise a substrate via and / or a through-wafer via providing electric coupling. In one embodiment, the group IV semiconductor layer may comprise an epitaxial silicon layer, and the at least one group IV semiconductor device may be a combined FET and Schottky diode (FETKY) fabricated on the epitaxial silicon layer. In one embodiment, the at least one group III-V semiconductor device may be a III-nitride high electron mobility transistor (HEMT).

Owner:INFINEON TECH AMERICAS CORP

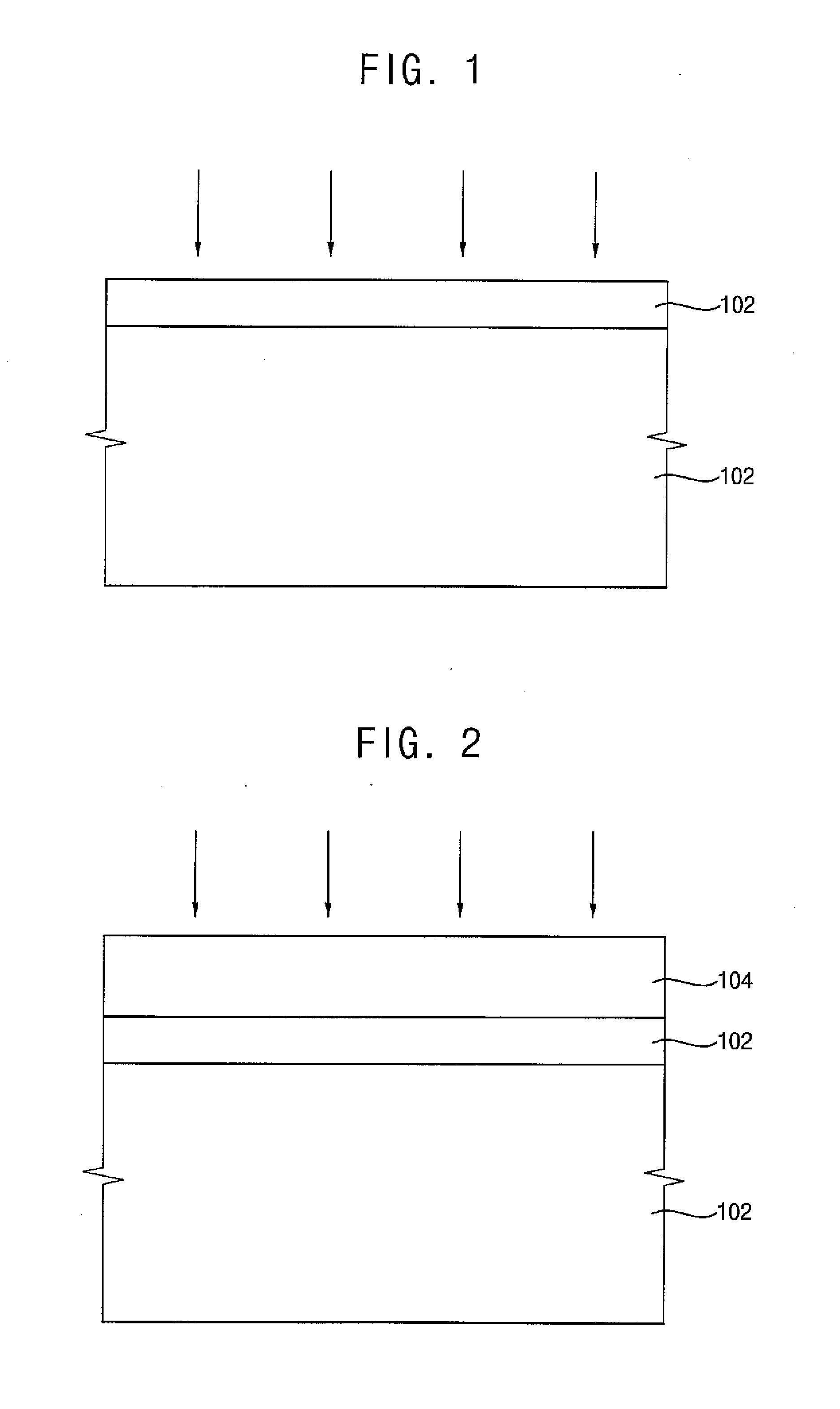

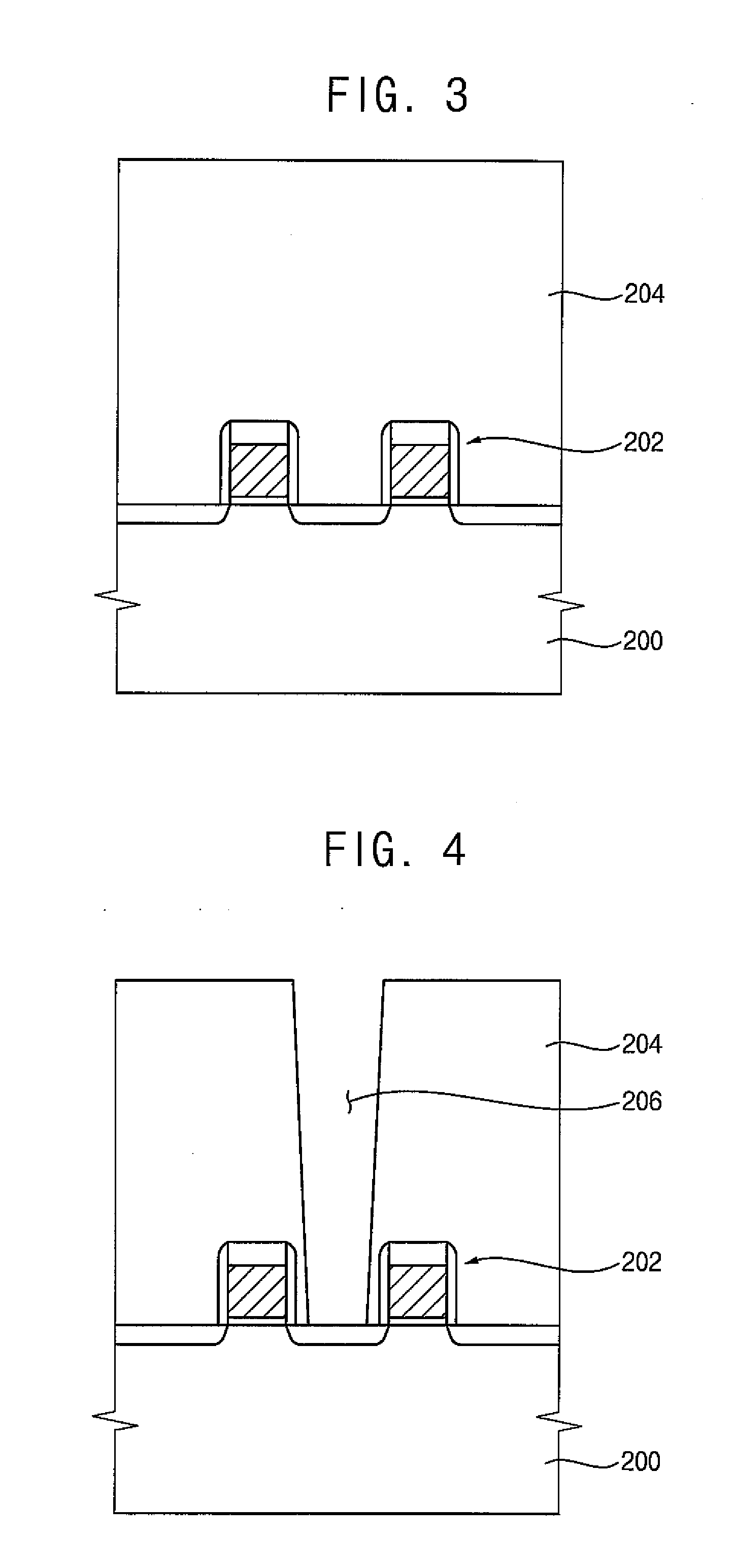

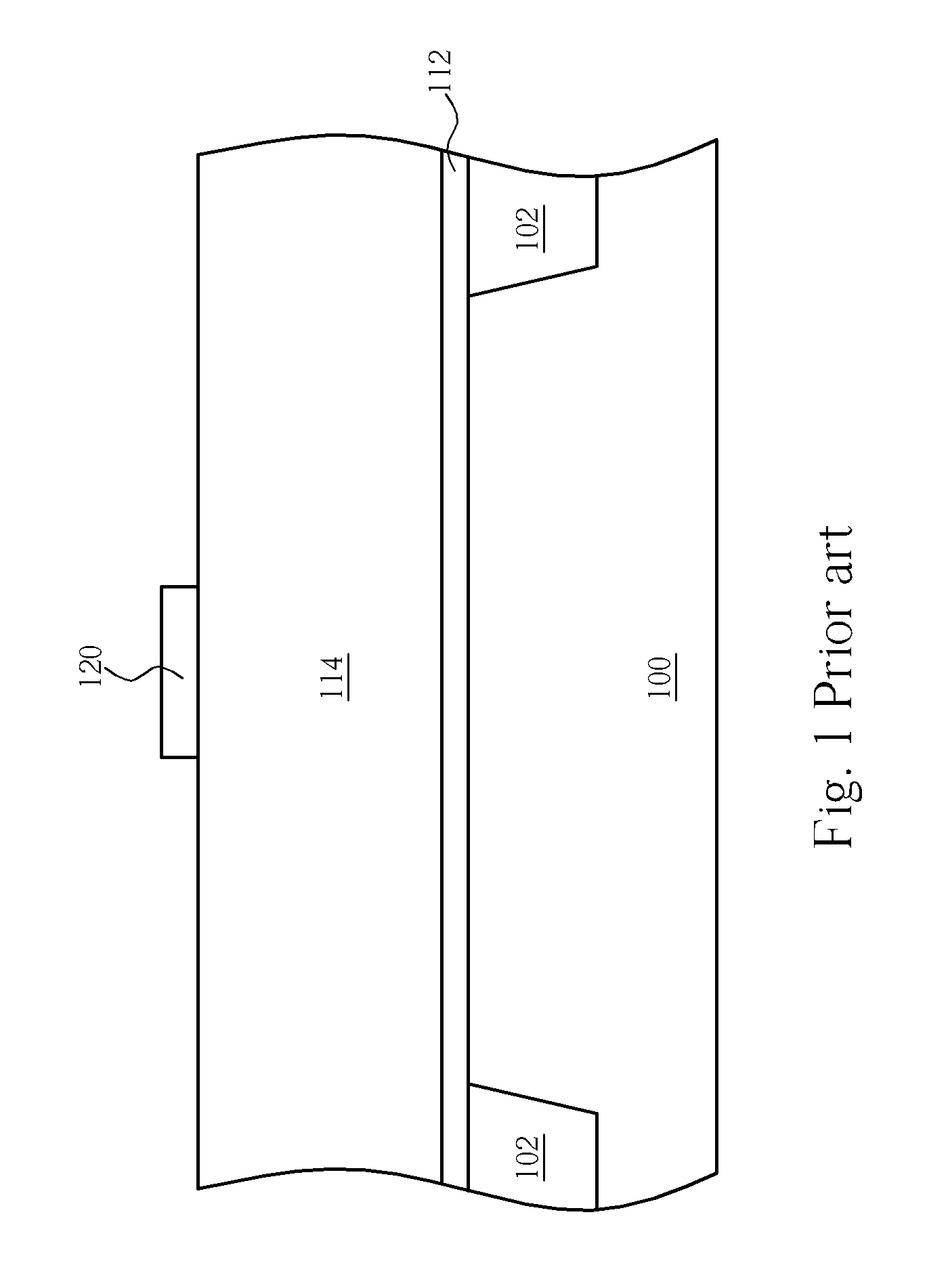

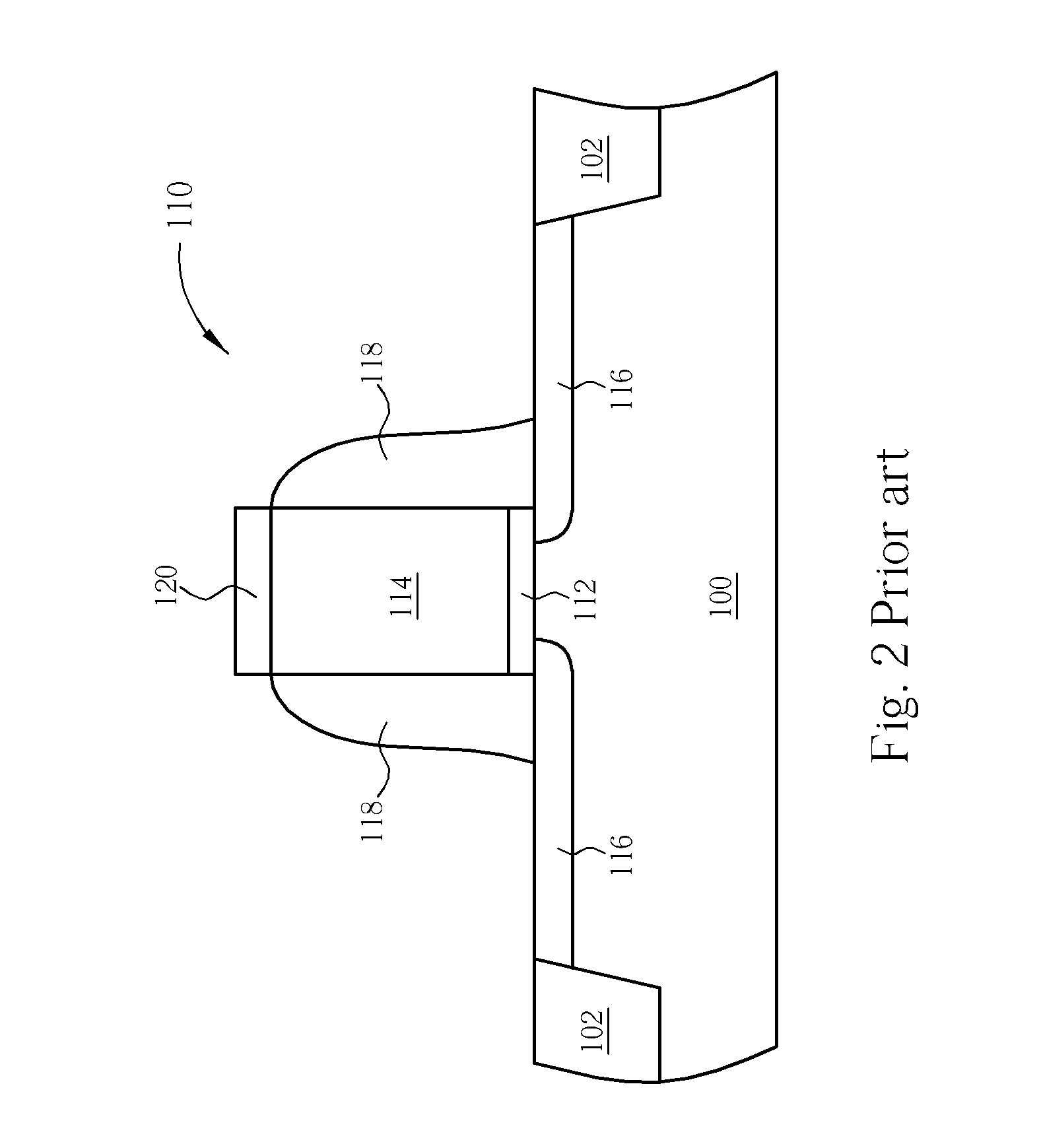

Method forming epitaxial silicon structure

InactiveUS20080286957A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingHydrogen chlorideSilicon

A method of forming an epitaxial silicon structure is disclosed. The method includes performing a first epitaxial growth process using a first source gas including silicon (Si) and hydrogen chloride (HCl) to form a first epitaxial silicon layer on a substrate, and performing a second epitaxial growth process using a second source gas including silicon (Si) and chlorine (Cl) to form a second epitaxial silicon layer on the first epitaxial silicon layer.

Owner:SAMSUNG ELECTRONICS CO LTD

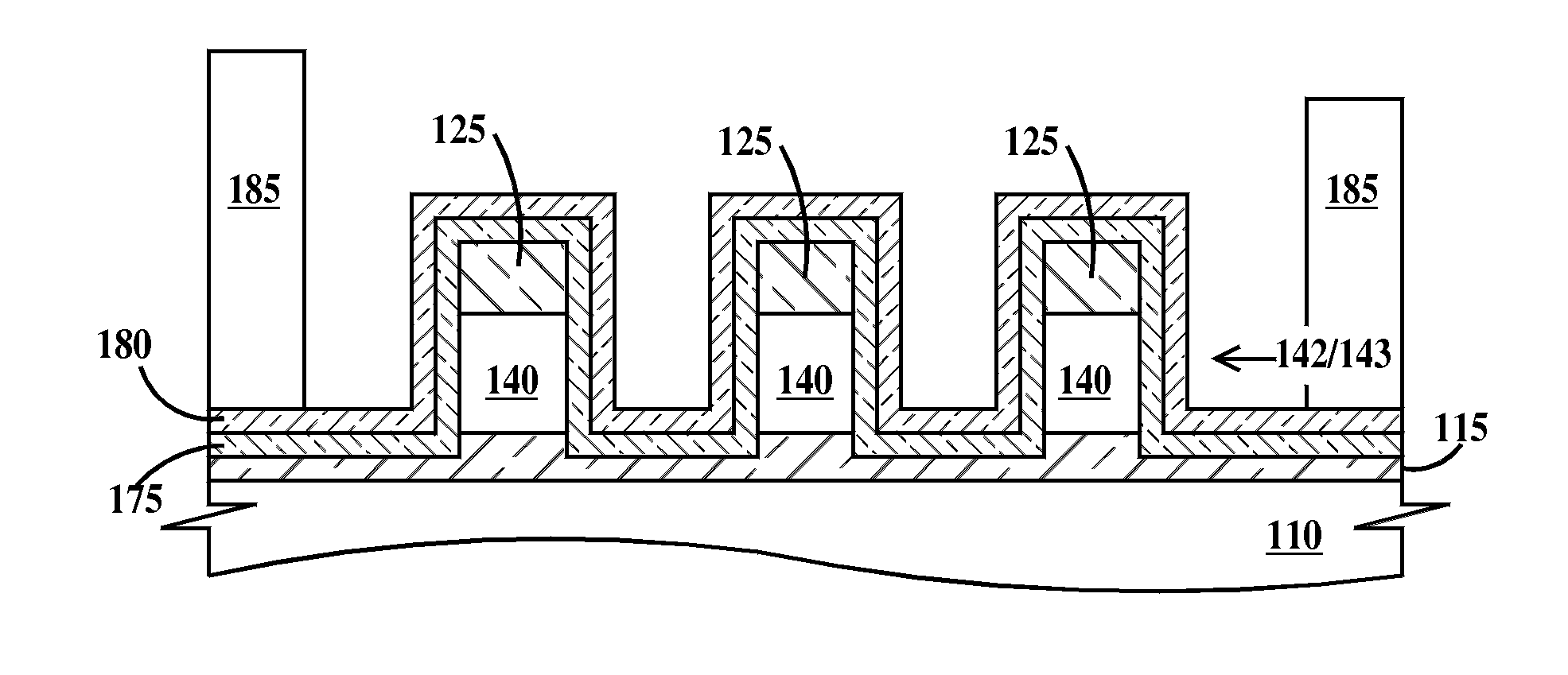

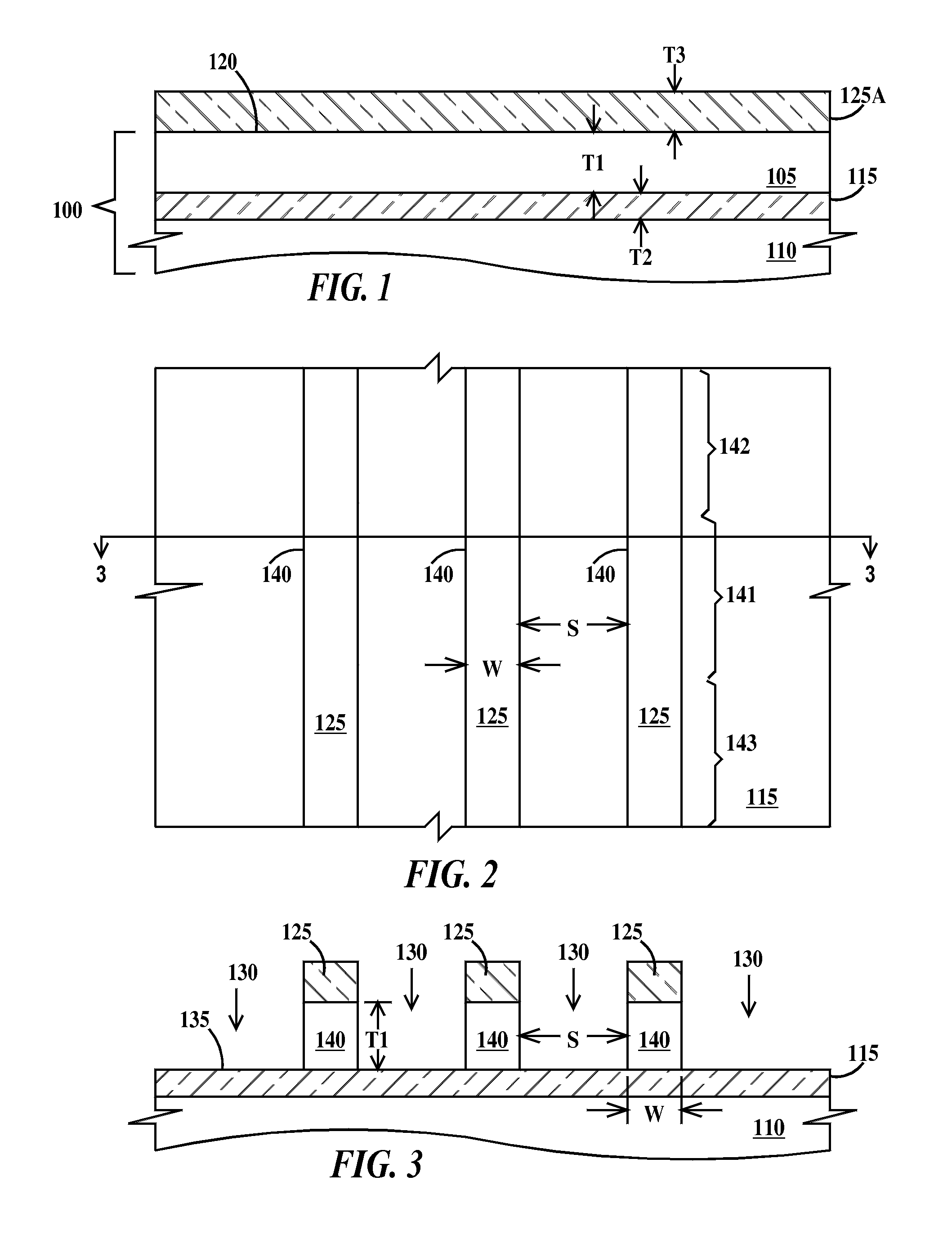

Vertical transistors

ActiveUS20060258084A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringCapacitor

Vertical transistors for memory cells, such as 4F2 memory cells, are disclosed. The memory cells use digit line connections formed within the isolation trench to connect the digit line with the lower active area. Vertical transistor pillars can be formed from epitaxial silicon or etched from bulk silicon. Memory cells can be formed by creating a cell capacitor electrically connected to each transistor pillar.

Owner:MICRON TECH INC

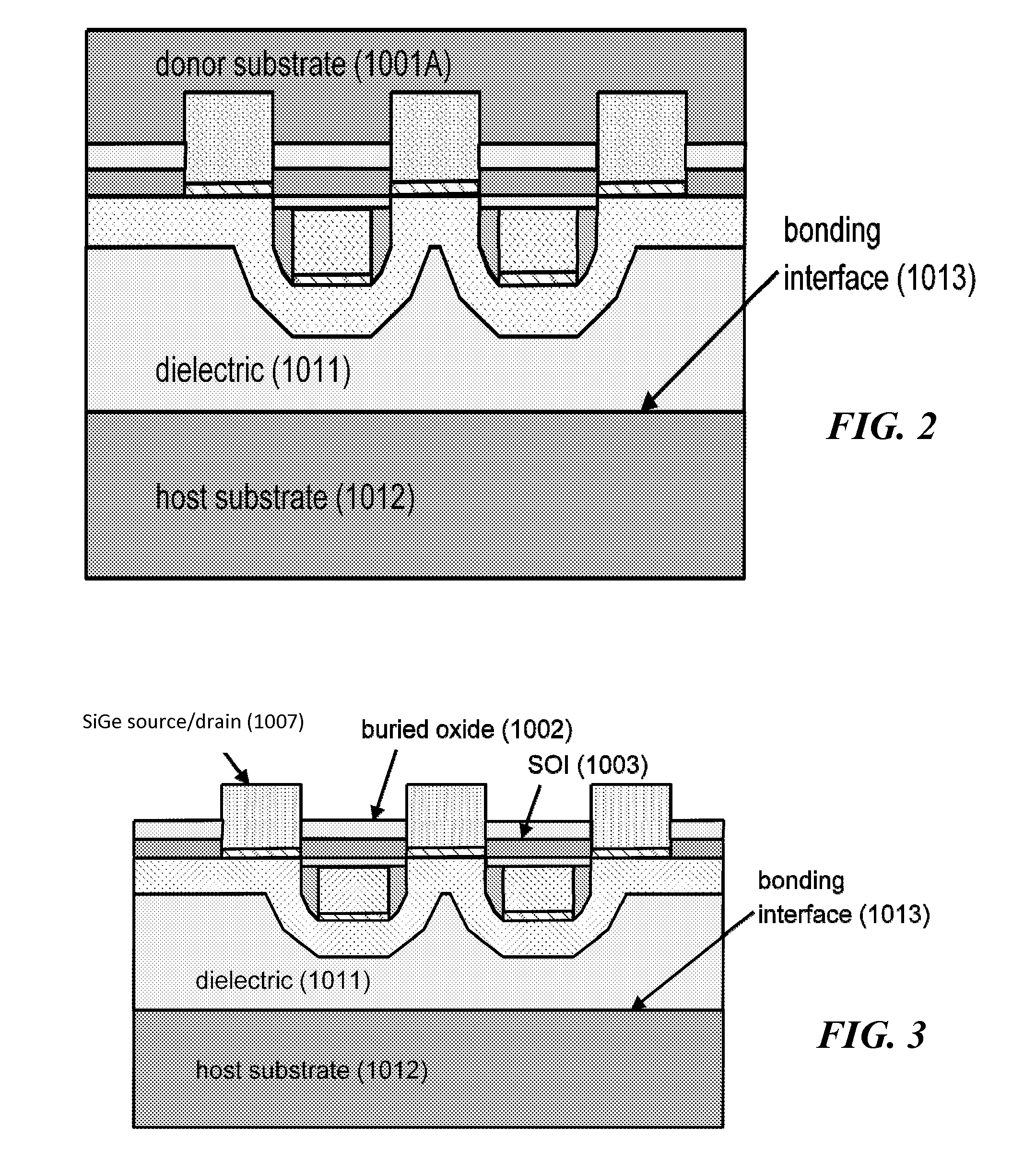

Structure for self-aligned silicide contacts to an upside-down fet by epitaxial source and drain

InactiveUS20110241073A1Induce strainTransistorSemiconductor/solid-state device detailsSalicideDielectric

A method for fabricating an upside-down p-FET includes: fully etching source and drain regions in a donor substrate by etching a silicon-on-insulator layer through buried oxide and partially etching the silicon substrate; refilling a bottom and sidewall surfaces of the etched source and drain regions with epitaxial silicide / germanide to form e-SiGe source and drain regions; capping the source and drain regions with self-aligning silicide / germanide; providing a silicide layer formed over the gate conductor line; providing a first stress liner over the gate and the e-SiGe source and drain regions; depositing a planarized dielectric over the self-aligning silicide / germanide; inverting the donor substrate; bonding the donor substrate to a host wafer; and selectively exposing the buried oxide and the e-SiGe source and drain regions by removing the donor wafer.

Owner:GLOBALFOUNDRIES US INC

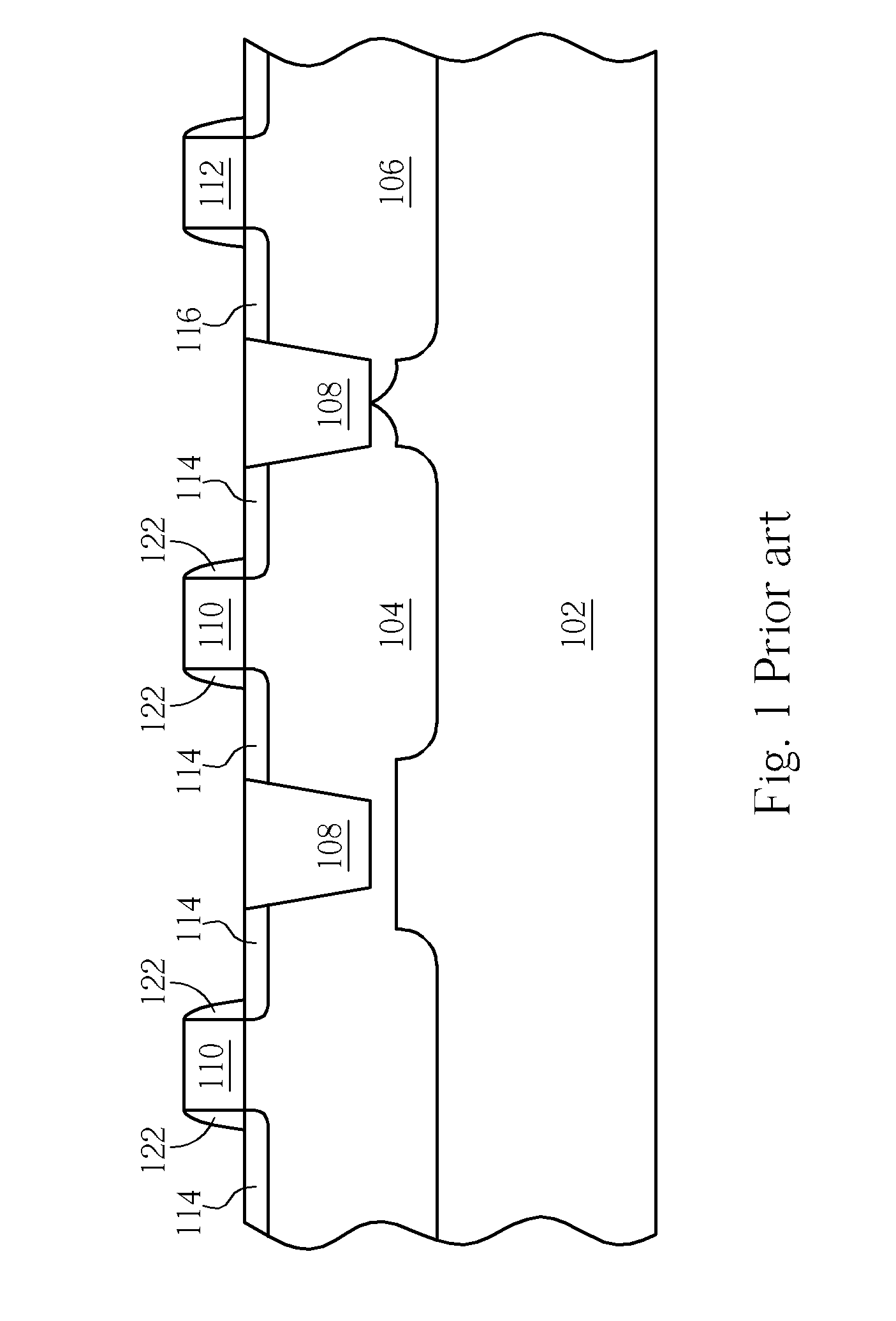

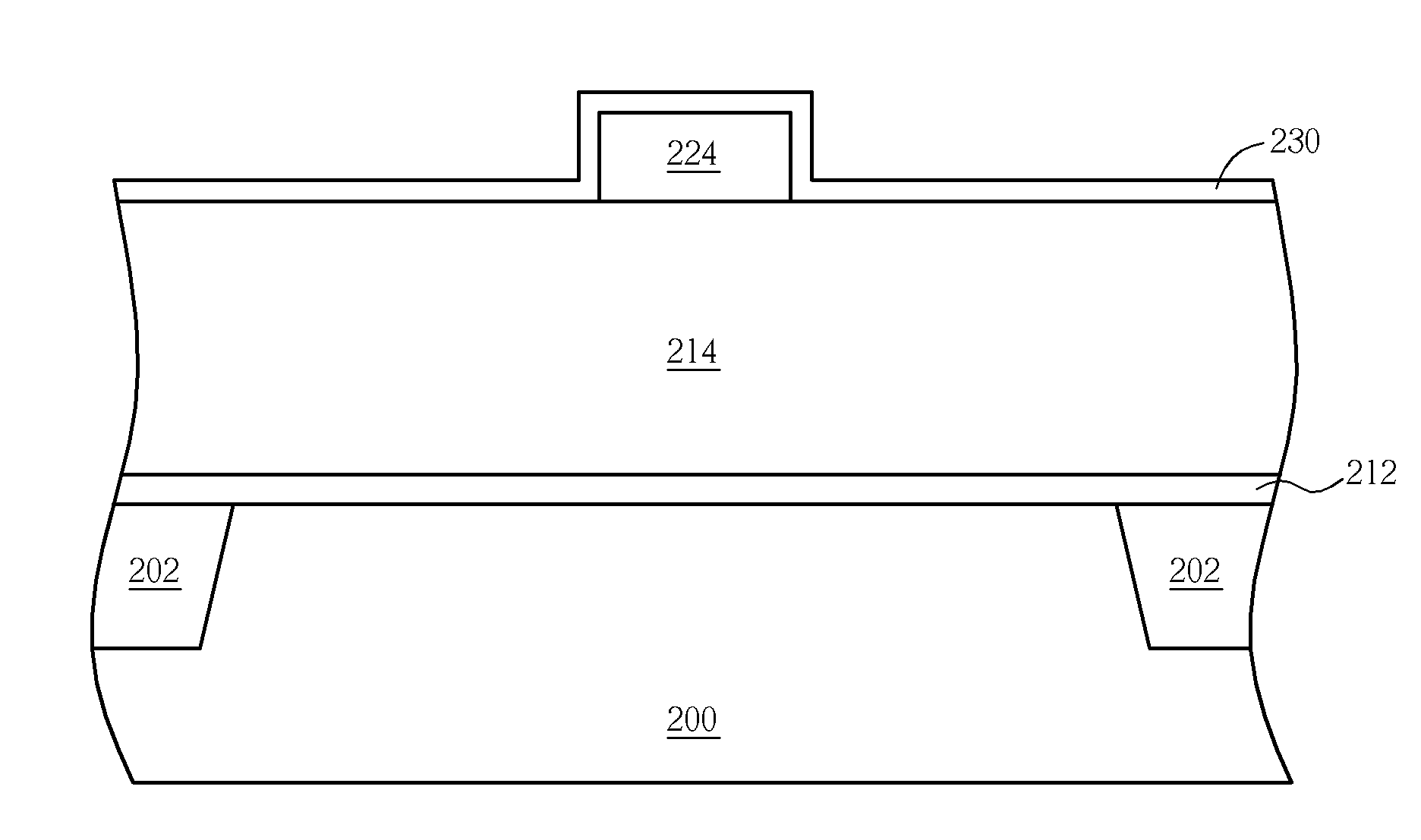

Method of manufacturing complementary metal oxide semiconductor transistor

ActiveUS20080085577A1Easy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesResistCMOS

A method of manufacturing a CMOS is disclosed. A substrate has a first gate and a second gate. A dielectric layer and a patterned photo-resist layer are formed sequentially on the substrate. After an etching process, the dielectric layer without the photo-resist layer forms a spacer around the first gate, and the dielectric layer with the photo-resist layer forms a block layer on the second gate. The recesses are formed in the substrate of two lateral sides of the first gate. The epitaxial silicon layers are formed in the recesses.

Owner:UNITED MICROELECTRONICS CORP

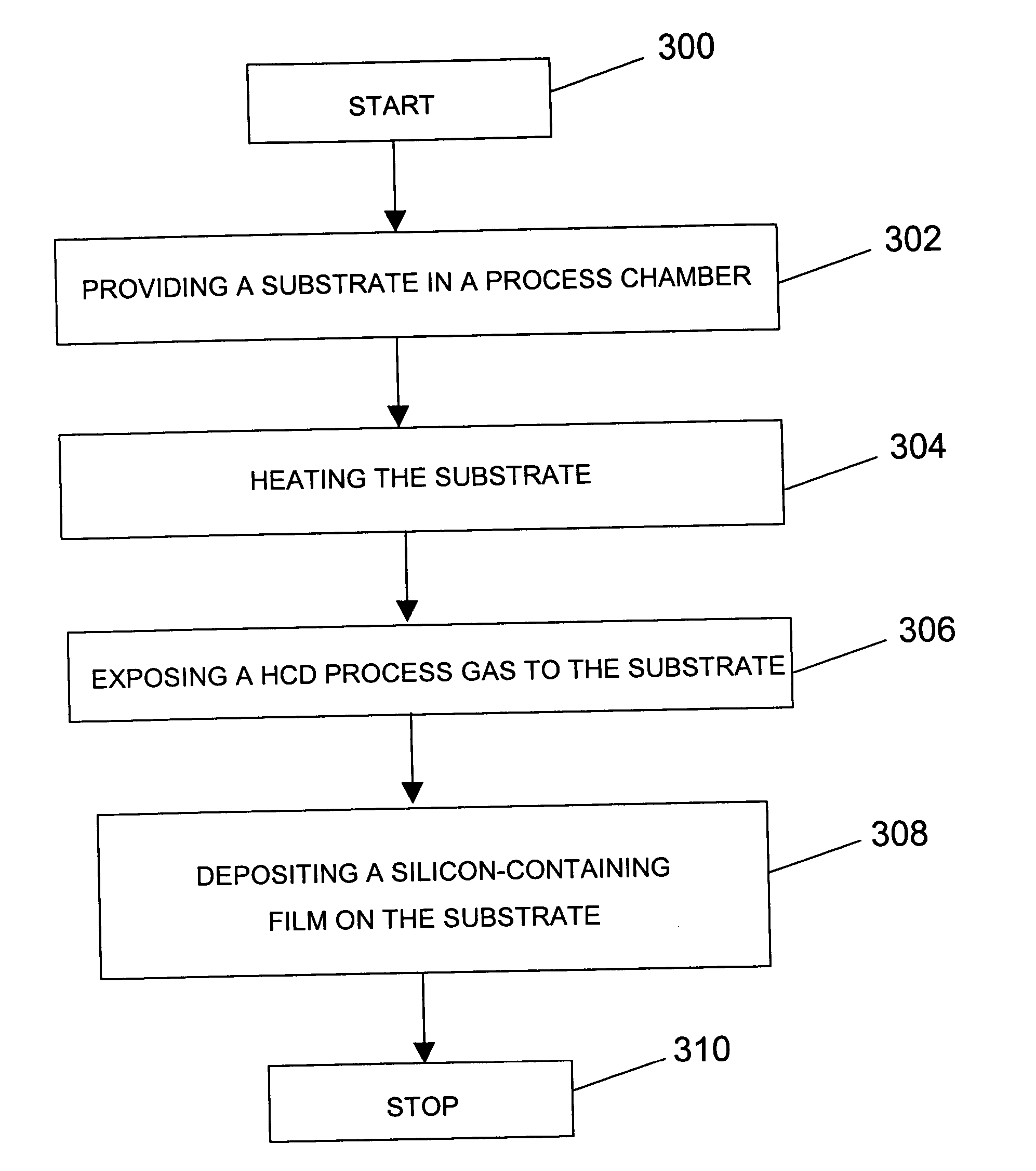

Deposition of silicon-containing films from hexachlorodisilane

InactiveUS20050066892A1Cost effectiveIntegrated cost-effectivelyPolycrystalline material growthFrom solid stateDeposition processHandling system

A method is provided for depositing a silicon-containing film on a substrate by a low pressure deposition process in a processing system. A silicon-containing film can be formed on a substrate by providing a substrate in a process chamber of a processing system, heating the substrate, and exposing a hexachlorodisilane (HCD) process gas to the substrate. The method can selectively deposit an epitaxial silicon-containing film on a silicon surface of a substrate or, alternately, non-selectively deposit a silicon-containing film on a substrate. A processing tool containing a processing system for forming a silicon-containing film on s substrate using a HCD process gas is provided.

Owner:TOKYO ELECTRON LTD

Vertical transistors

Vertical transistors for memory cells, such as 4F2 memory cells, are disclosed. The memory cells use digit line connections formed within the isolation trench to connect the digit line with the lower active area. Vertical transistor pillars can be formed from epitaxial silicon or etched from bulk silicon. Memory cells can be formed by creating a cell capacitor electrically connected to each transistor pillar.

Owner:MICRON TECH INC

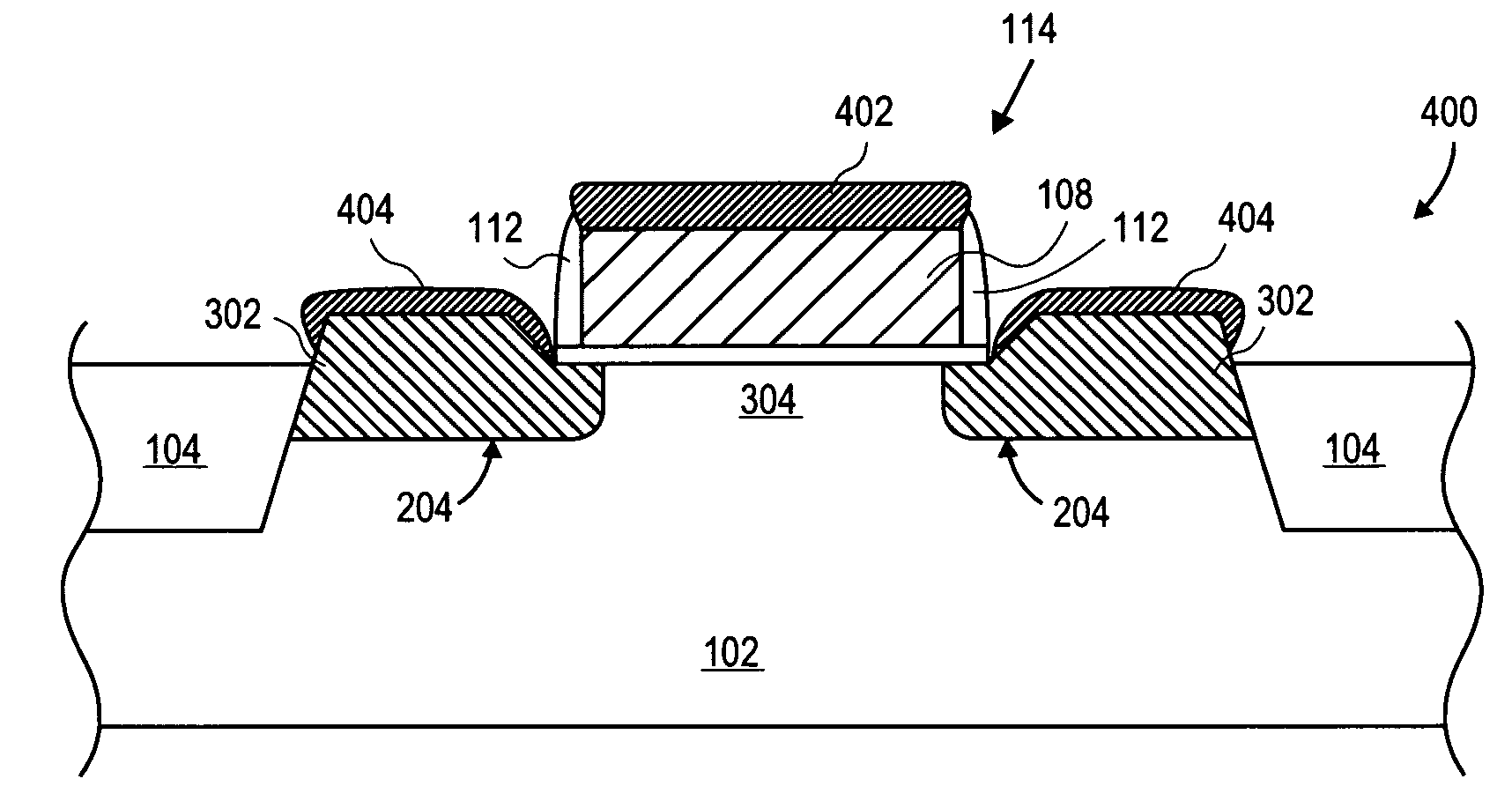

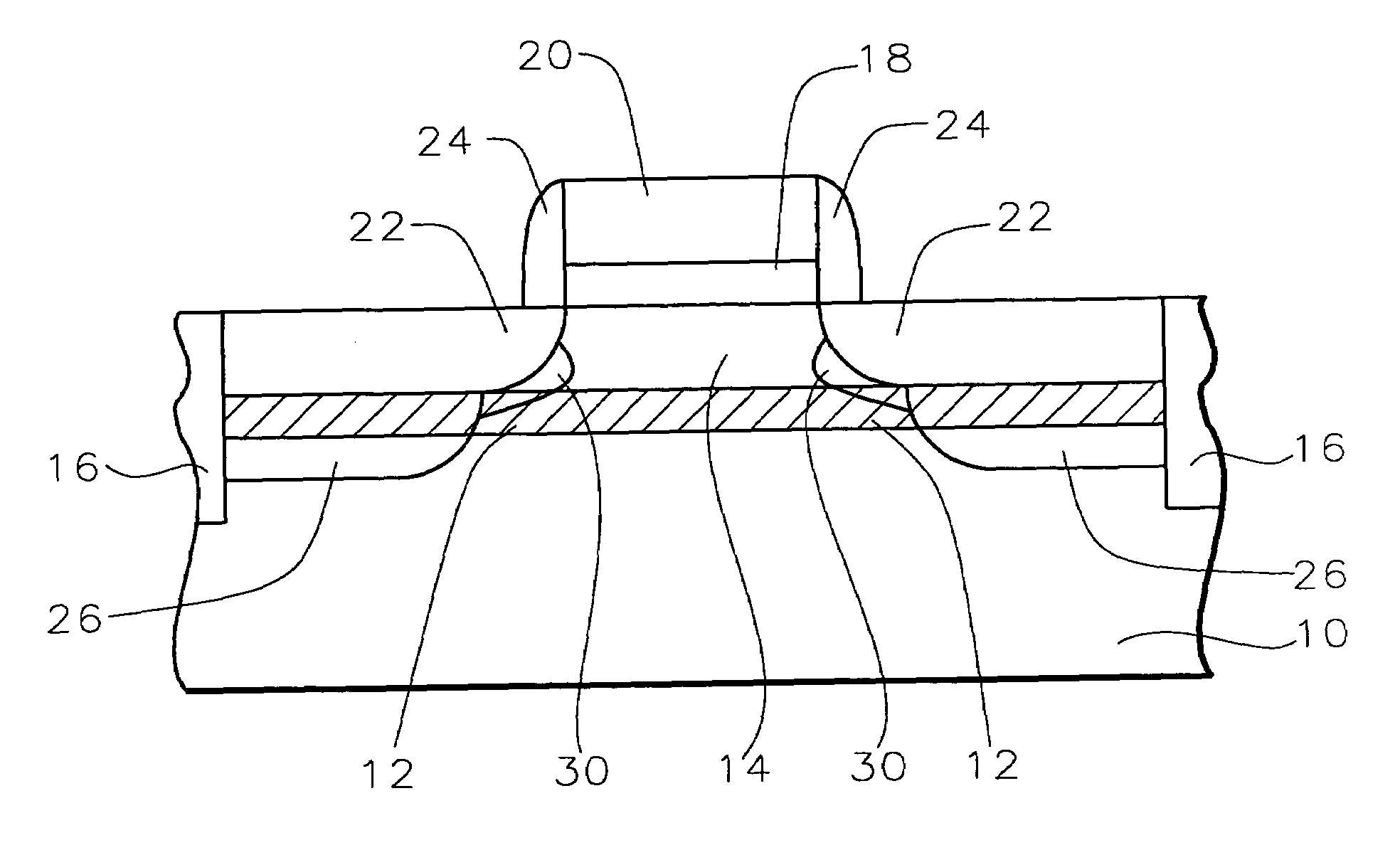

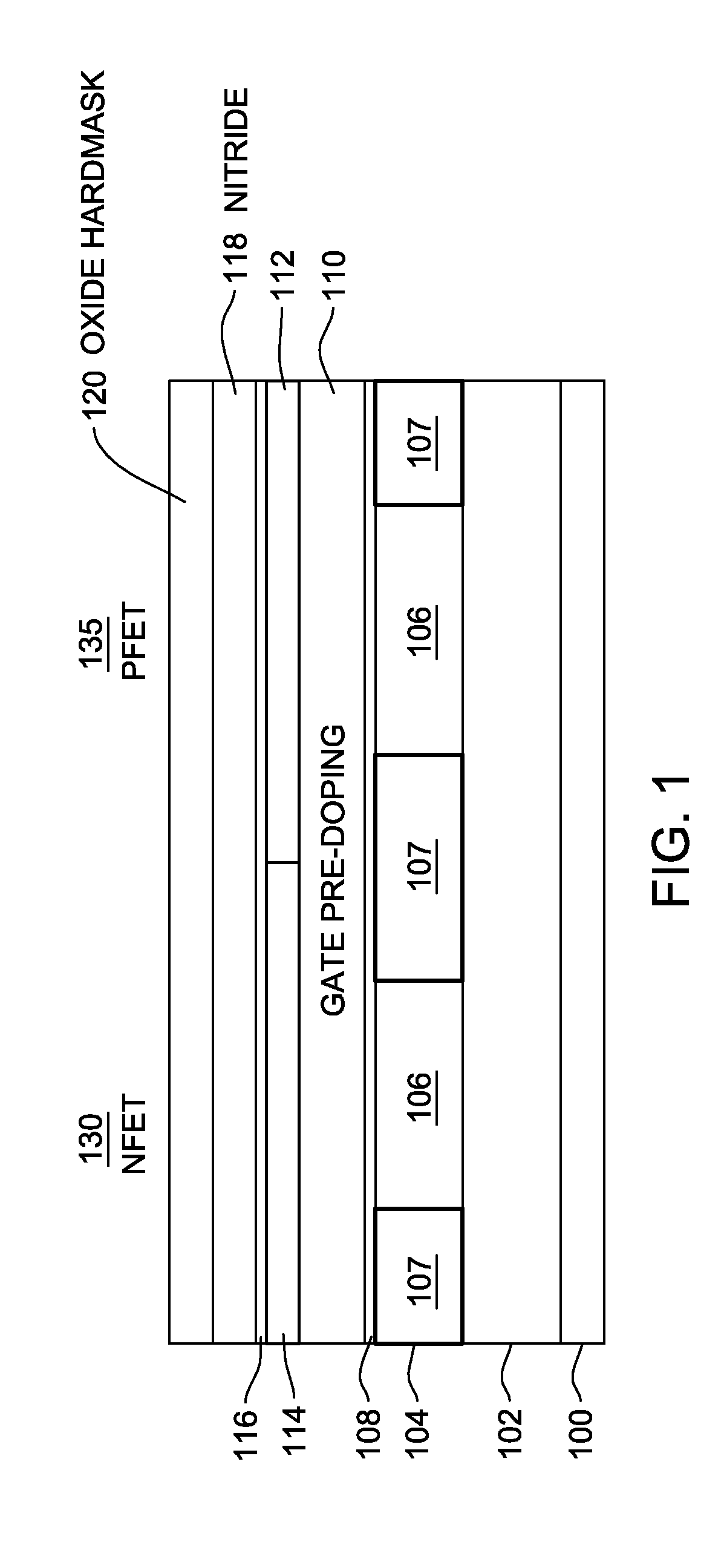

In situ doped embedded sige extension and source/drain for enhanced PFET performance

ActiveUS7176481B2Growth inhibitionSolid-state devicesSemiconductor/solid-state device manufacturingDopantIn situ doping

Disclosed is an integrated circuit structure and a method of making such a structure that has a substrate and P-type and N-type transistors on the substrate. The N-type transistor extension and source / drain regions comprise dopants implanted into the substrate. The P-type transistor extension and source / drain regions partially include a strained epitaxial silicon germanium, wherein the strained silicon germanium comprises of two layers, with a top layer that is closer to the gate stack than the bottom layer. The strained silicon germanium is in-situ doped and creates longitudinal stress on the channel region.

Owner:MICROSOFT TECH LICENSING LLC

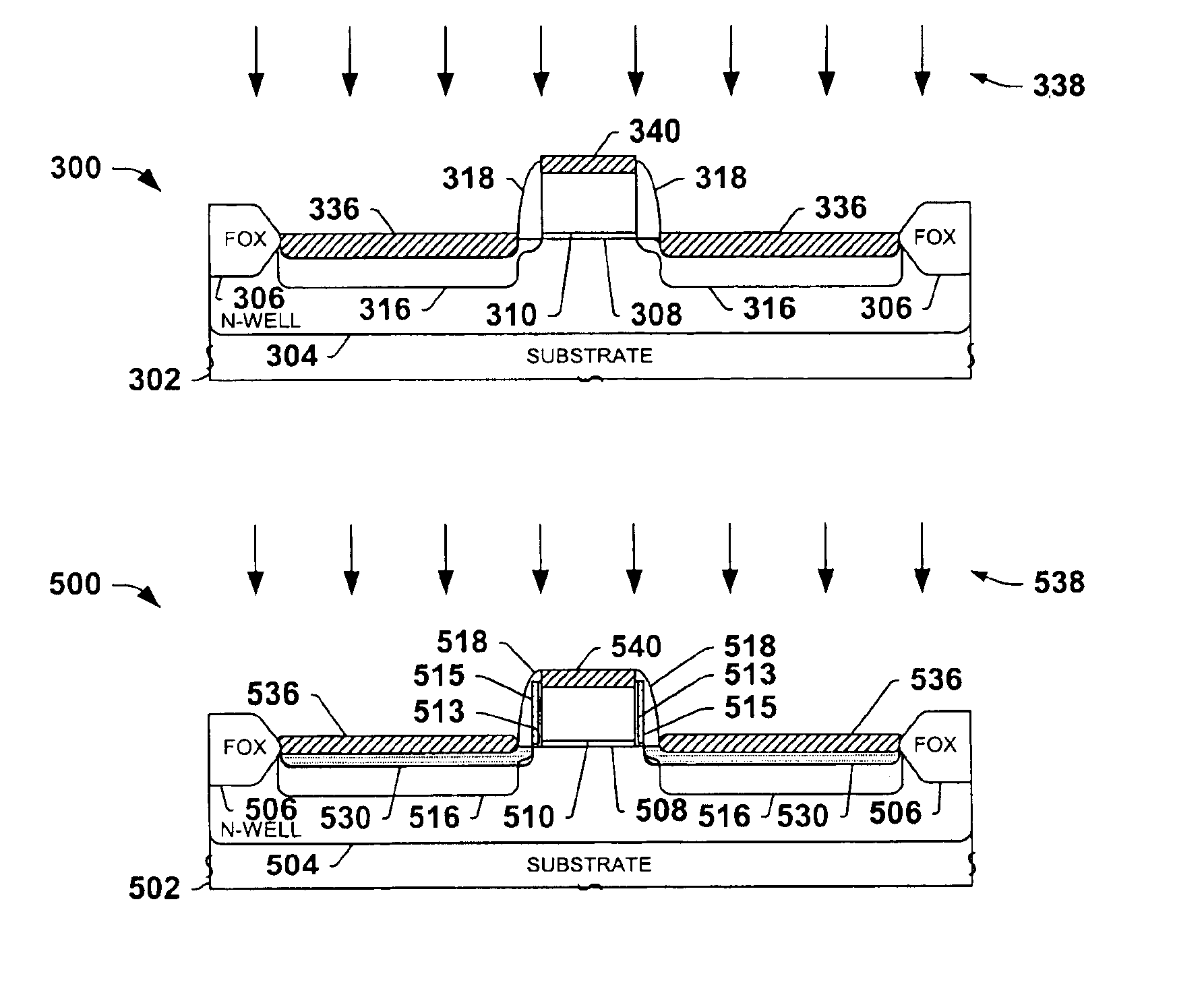

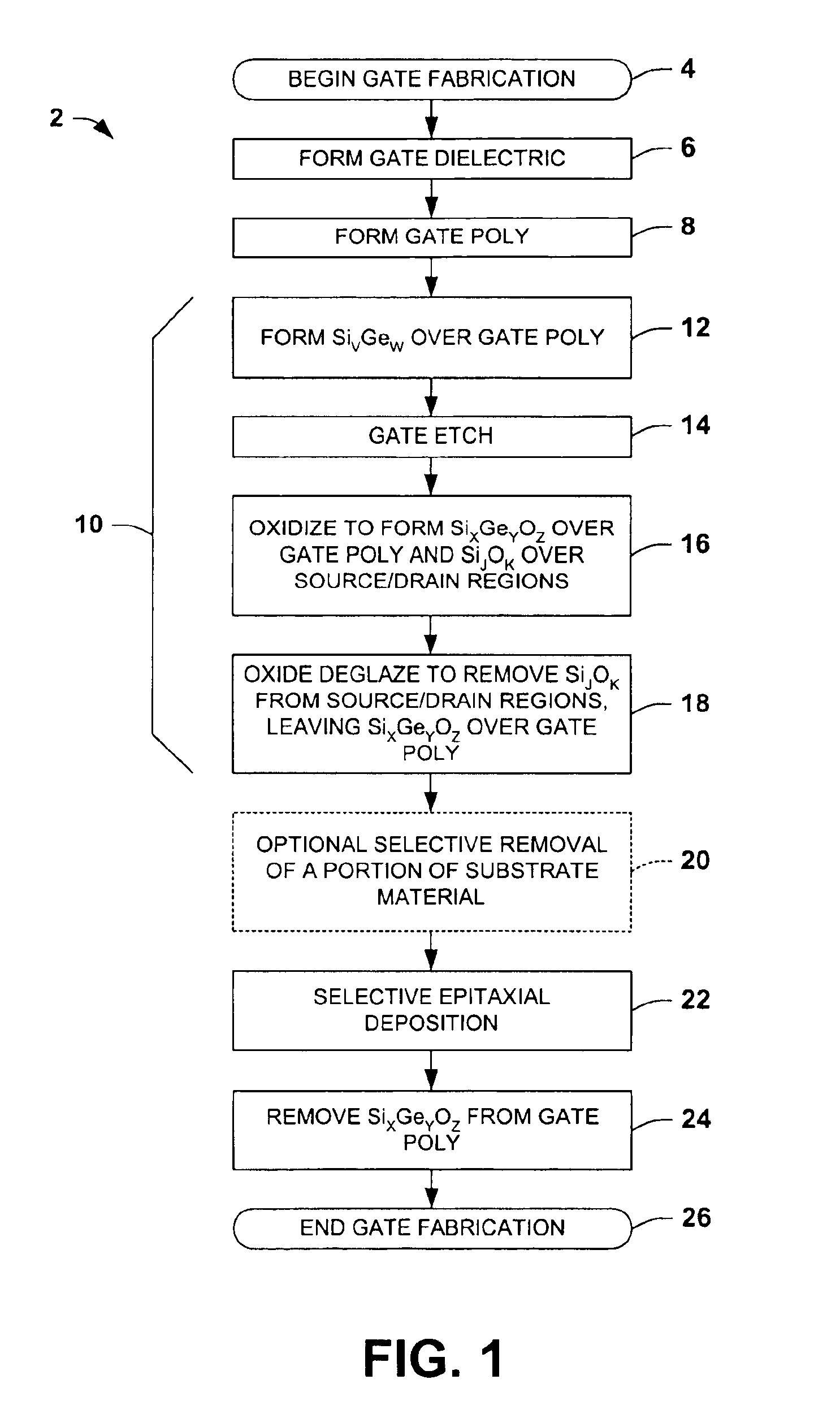

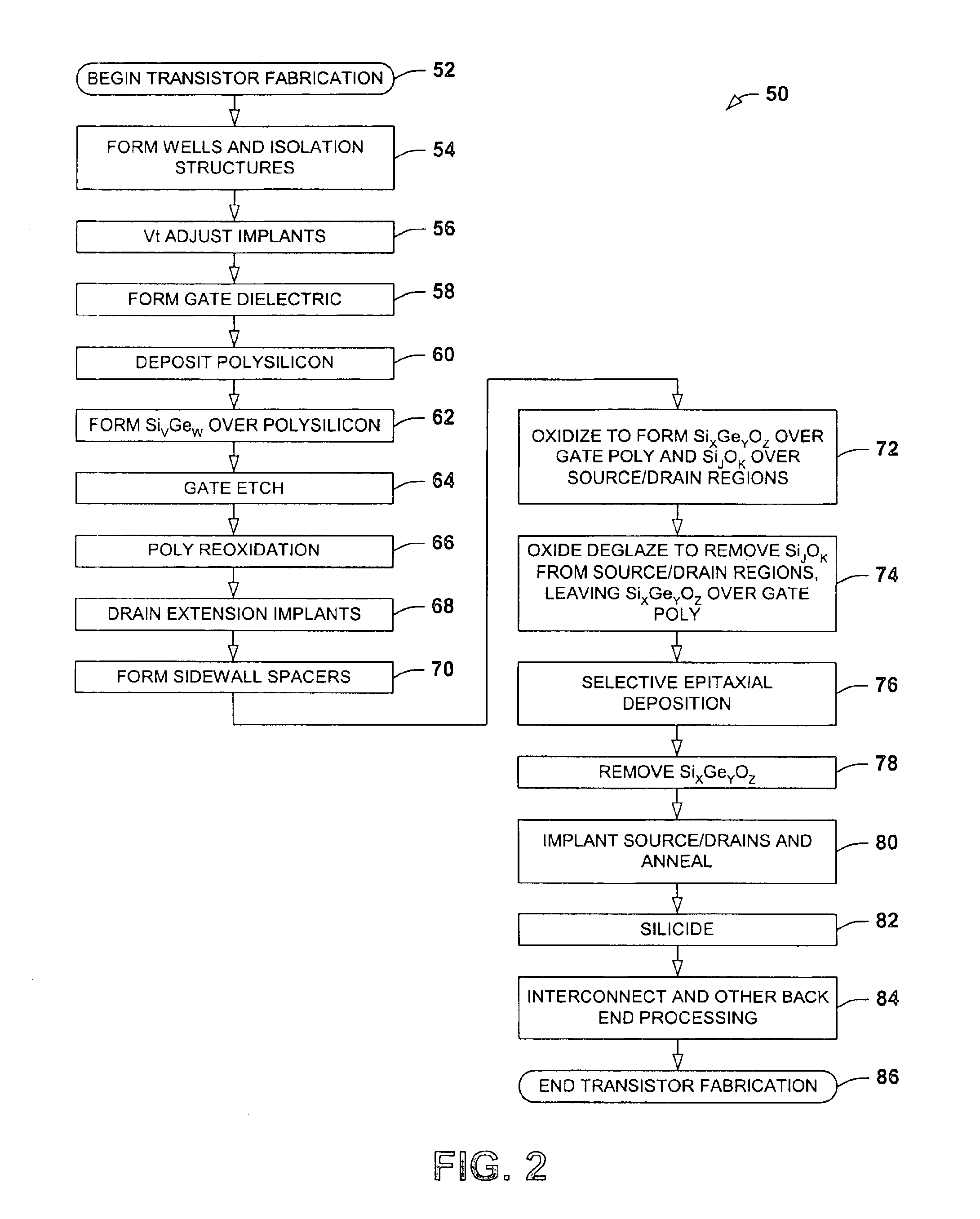

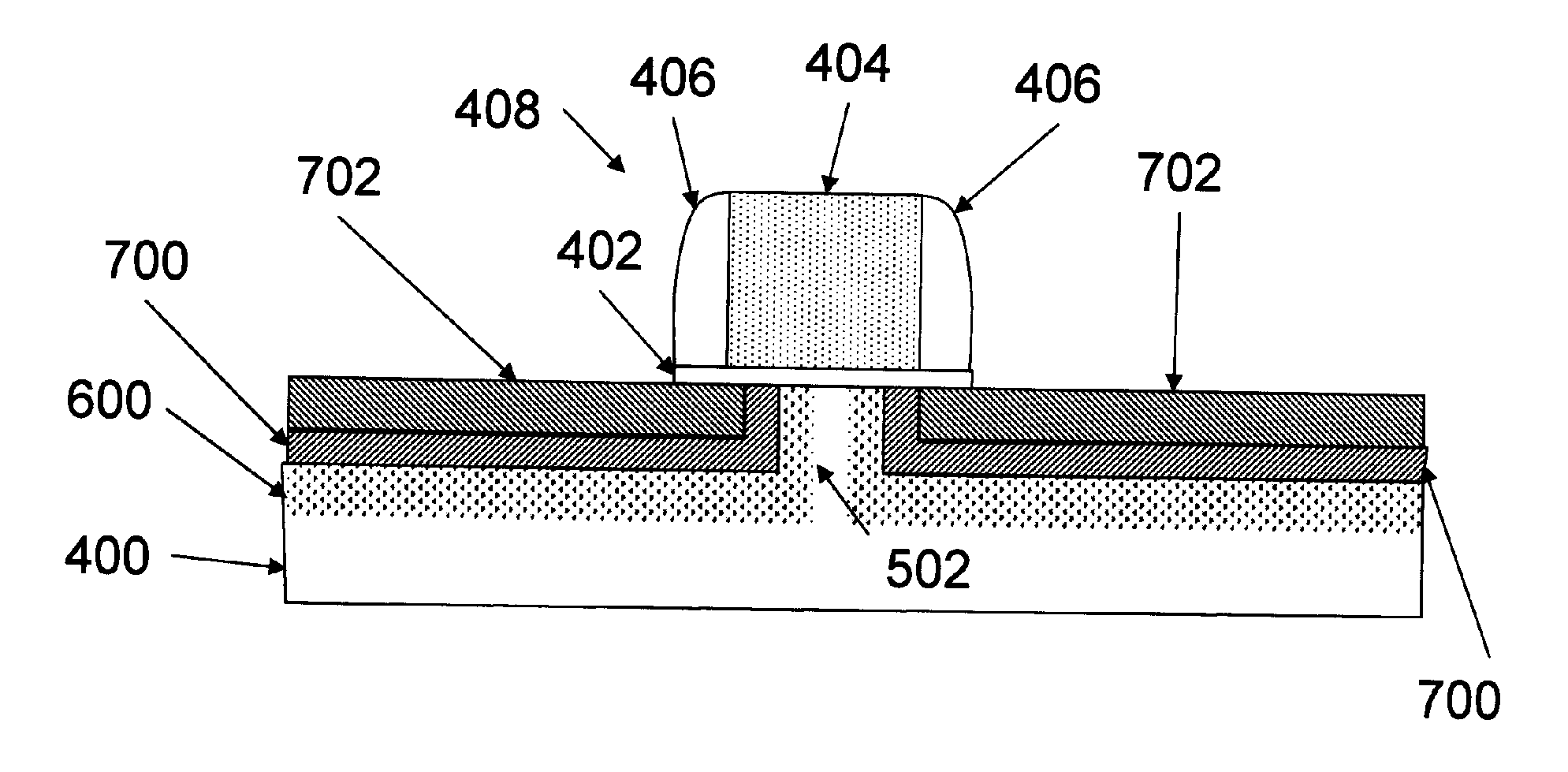

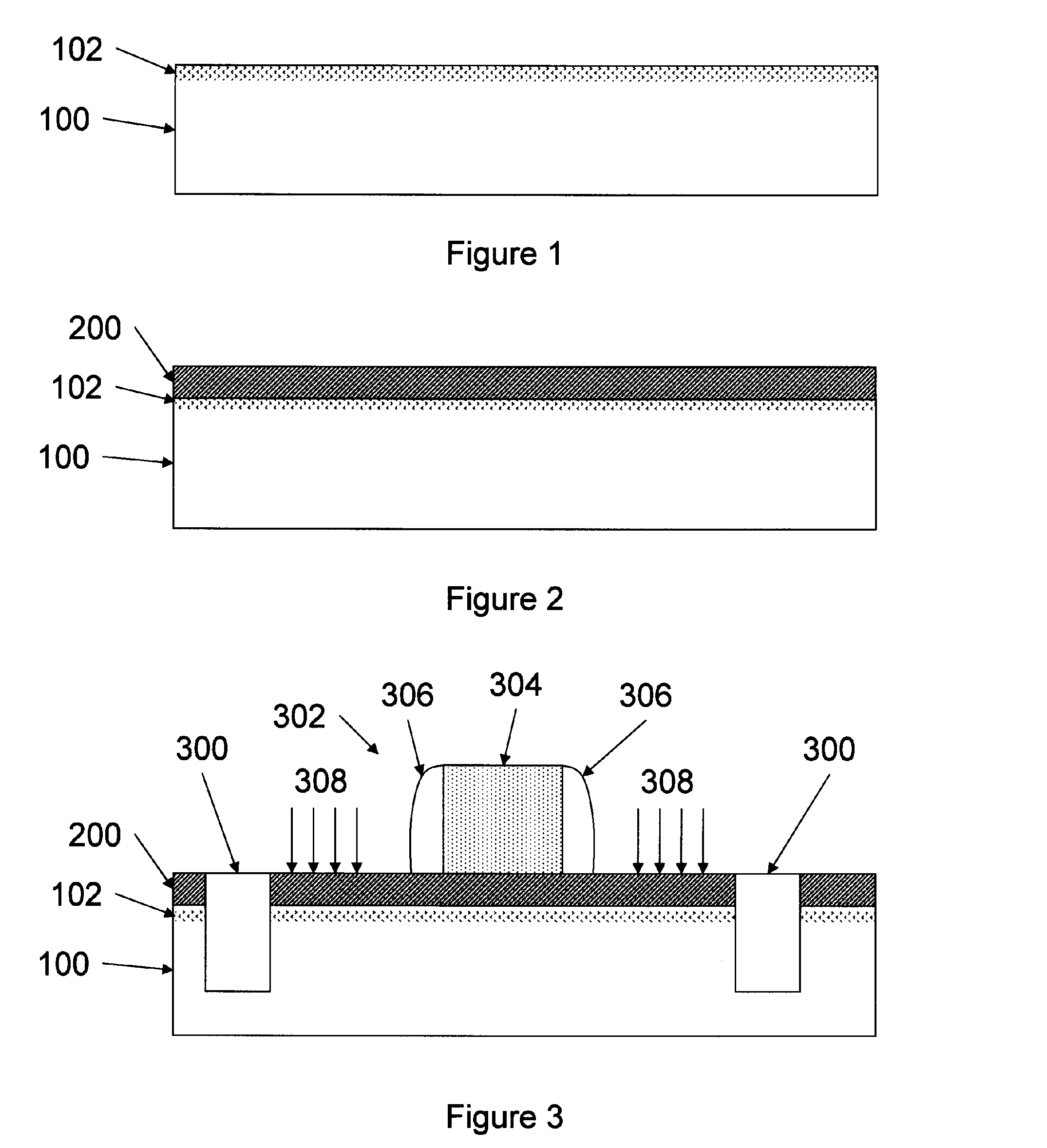

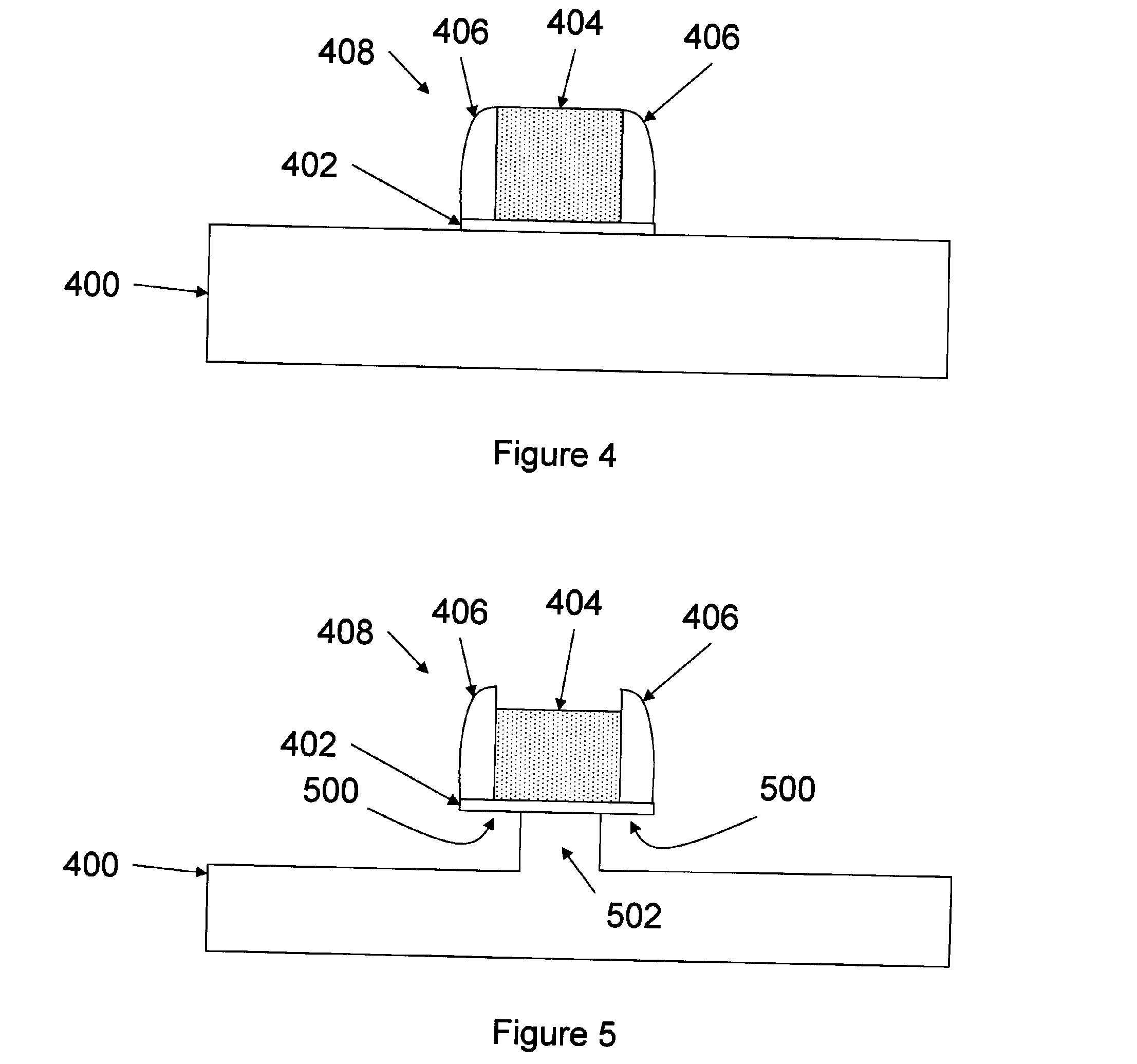

Method for preventing polysilicon mushrooming during selective epitaxial processing

ActiveUS6872610B1Well formedTransistorSemiconductor/solid-state device manufacturingProtection layerEpitaxial silicon

Methods are presented, in which an oxide protection layer is provided on a gate structure for protection against poly mushrooming during selective epitaxial silicon deposition in fabricating elevated or recessed source transistors. In one implementation, the protection layer is constructed by depositing silicon germanium over a gate polysilicon layer prior to gate patterning, and oxidizing the device to form a silicon germanium oxide over the gate polysilicon. The protection layer is then removed following selective epitaxial deposition.

Owner:TEXAS INSTR INC

Ultra shallow junction formation by epitaxial interface limited diffusion

ActiveUS20060076627A1Maximizing dopant activationIncrease oxygen contentSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorOxygen content

A method of forming a field effect transistor creates shallower and sharper junctions, while maximizing dopant activation in processes that are consistent with current manufacturing techniques. More specifically, the invention increases the oxygen content of the top surface of a silicon substrate. The top surface of the silicon substrate is preferably cleaned before increasing the oxygen content of the top surface of the silicon substrate. The oxygen content of the top surface of the silicon substrate is higher than other portions of the silicon substrate, but below an amount that would prevent epitaxial growth. This allows the invention to epitaxially grow a silicon layer on the top surface of the silicon substrate. Further, the increased oxygen content substantially limits dopants within the epitaxial silicon layer from moving into the silicon substrate.

Owner:GLOBALFOUNDRIES US INC

Method for manufacturing mos transistors utilizing a hybrid hard mask

ActiveUS20080233746A1Avoid damageResists consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

A method for manufacturing MOS transistor with hybrid hard mask includes providing a substrate having a dielectric layer and a polysilicon layer thereon, forming a hybrid hard mask having a middle hard mask and a spacer hard mask covering sidewalls of the middle hard mask on the polysilicon layer, performing a first etching process to etch the polysilicon layer and the dielectric layer through the hybrid hard mask to form a gate structure, performing a second etching process to form recesses in the substrate at two sides of the gate structure, and performing a SEG process to form epitaxial silicon layers in each recess.

Owner:UNITED MICROELECTRONICS CORP

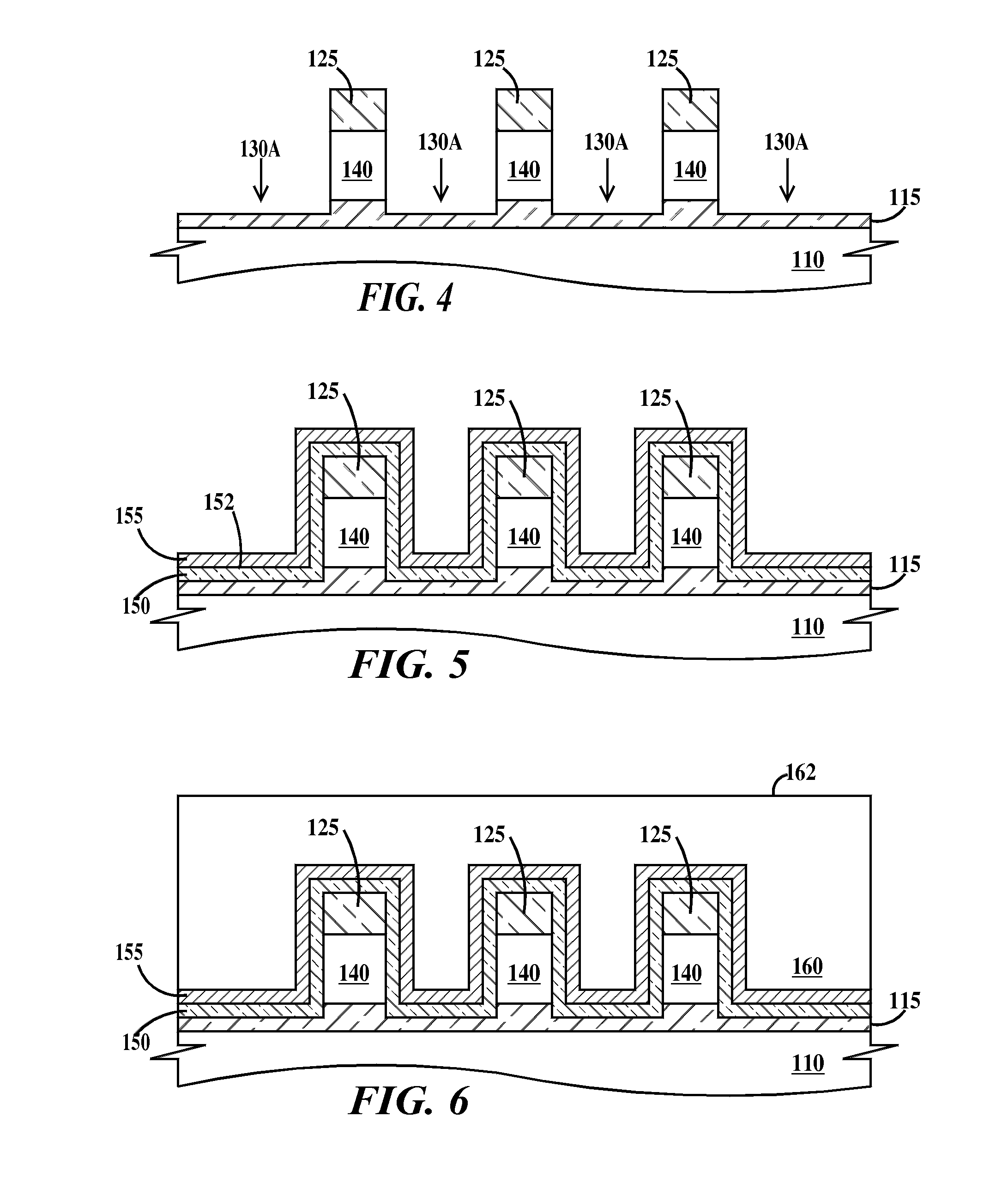

Fast p-i-n photodetector with high responsitivity

InactiveUS20090289320A1Eliminate the problemHigh recombination rateTransistorFinal product manufactureSemiconductor materialsPhotodetector

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:IBM CORP

Fast p-i-n photodetector with high responsitivity

ActiveUS20090305454A1Easy to integrateHigh rateFinal product manufactureNanoinformaticsSemiconductor materialsPhotodetector

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:IBM CORP

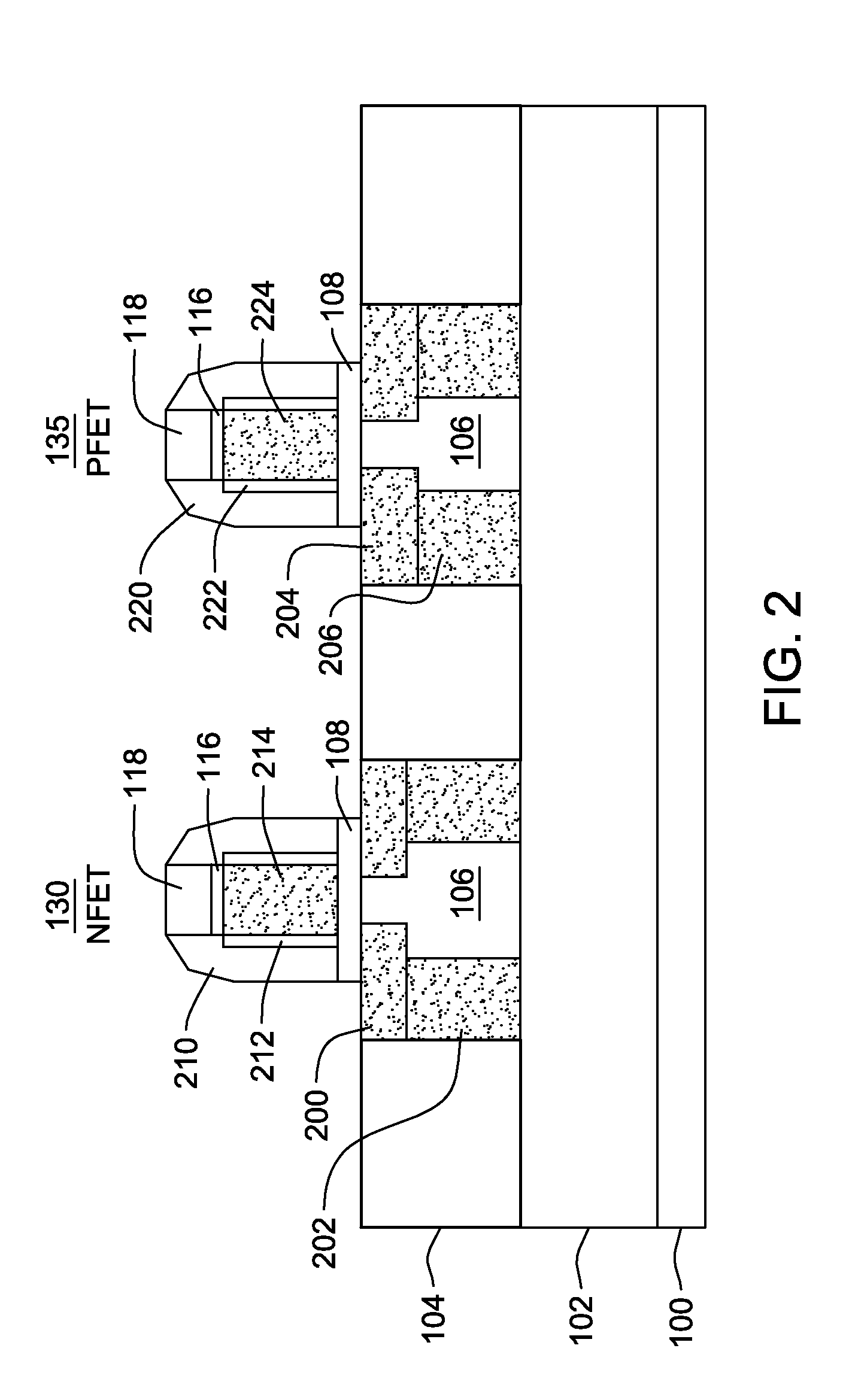

Formation of raised source/drain structures in NFET with embedded SiGe in PFET

A structure and method for forming raised source / drain structures in a NFET device and embedded SiGe source / drains in a PFET device. We provide a NFET gate structure over a NFET region in a substrate and PFET gate structure over a PFET region. We provide NFET SDE regions adjacent to the NFET gate and provide PFET SDE regions adjacent to the PFET gate. We form recesses in the PFET region in the substrate adjacent to the PFET second spacers. We form a PFET embedded source / drain stressor in the recesses. We form a NFET S / D epitaxial Si layer over the NFET SDE regions and a PFET S / D epitaxial Si layer over PFET embedded source / drain stressor. The epitaxial Si layer over PFET embedded source / drain stressor is consumed in a subsequent salicide step to form a stable and low resistivity silicide over the PFET embedded source / drain stressor. We perform a NFET S / D implant by implanting N-type ions into NFET region adjacent to the NFET gate structure and into the NFET S / D stressor Si layer to form the raised NFET source / drains.

Owner:TAIWAN SEMICON MFG CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com