Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4279 results about "Block layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Organic electroluminescent element, illuminator, display and compound

InactiveUS20050069729A1Improve emission efficiencySolution to short lifeMethine/polymethine dyesSolid-state devicesOrganic electroluminescenceBoron

An organic electroluminescent element comprising a light emission layer and a hole blocking layer adjacent to the light emission layer, wherein, (i) the light emission layer contains a compound having a specified partial structure and having a molecular weight of not more than 1700; and (ii) the hole blocking layer contains a derivative selected from the group consisting of a styryl derivative, a boron derivative and a carboline derivative.

Owner:KONICA MINOLTA INC

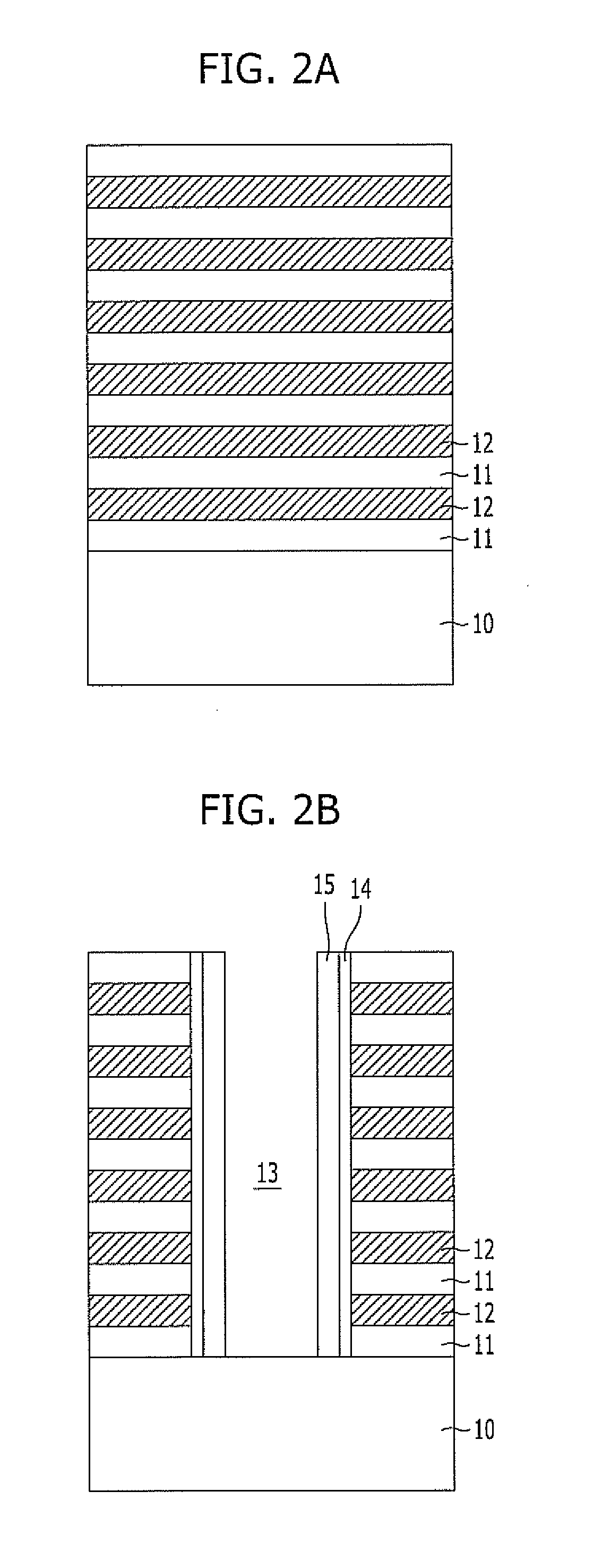

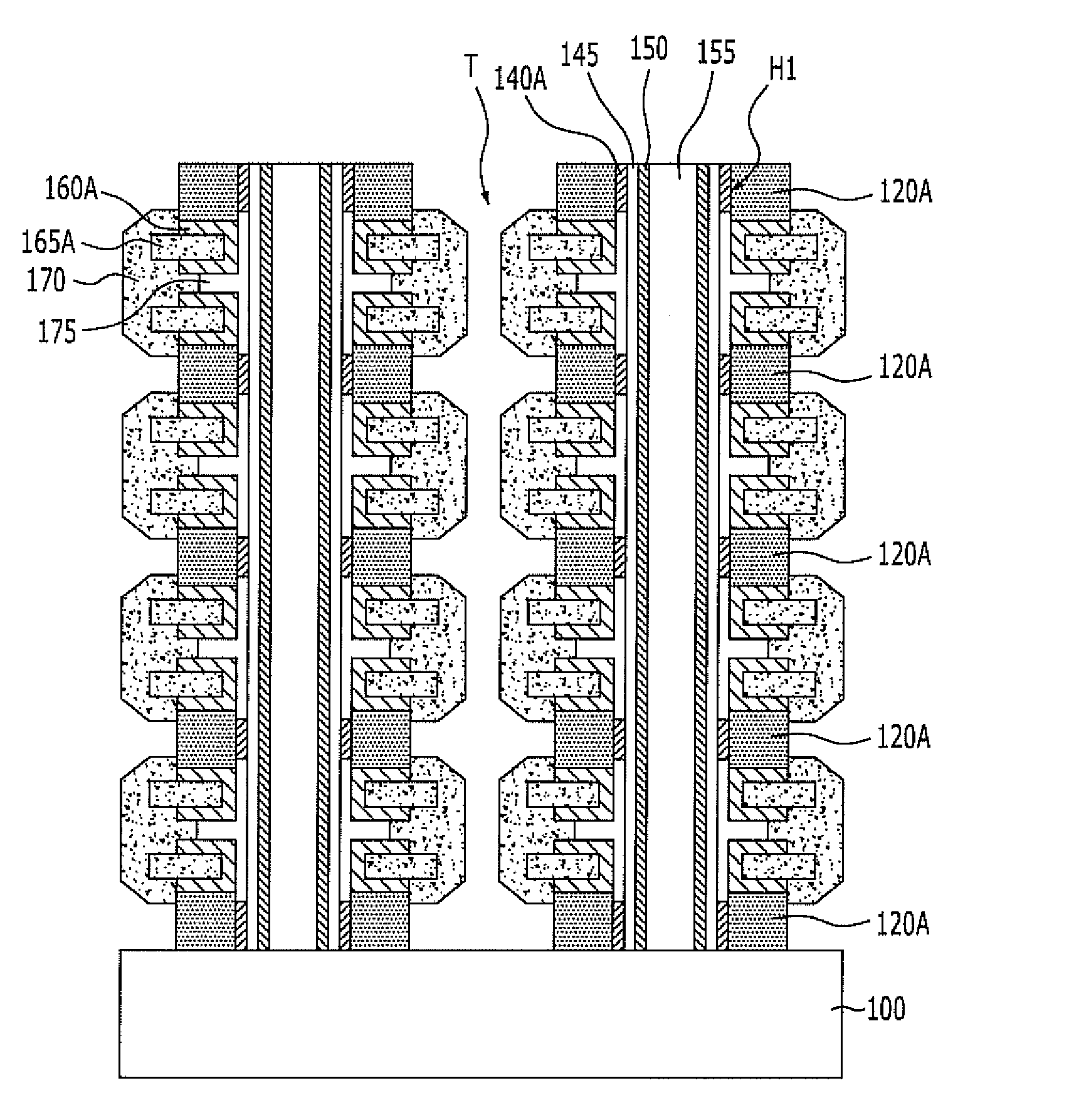

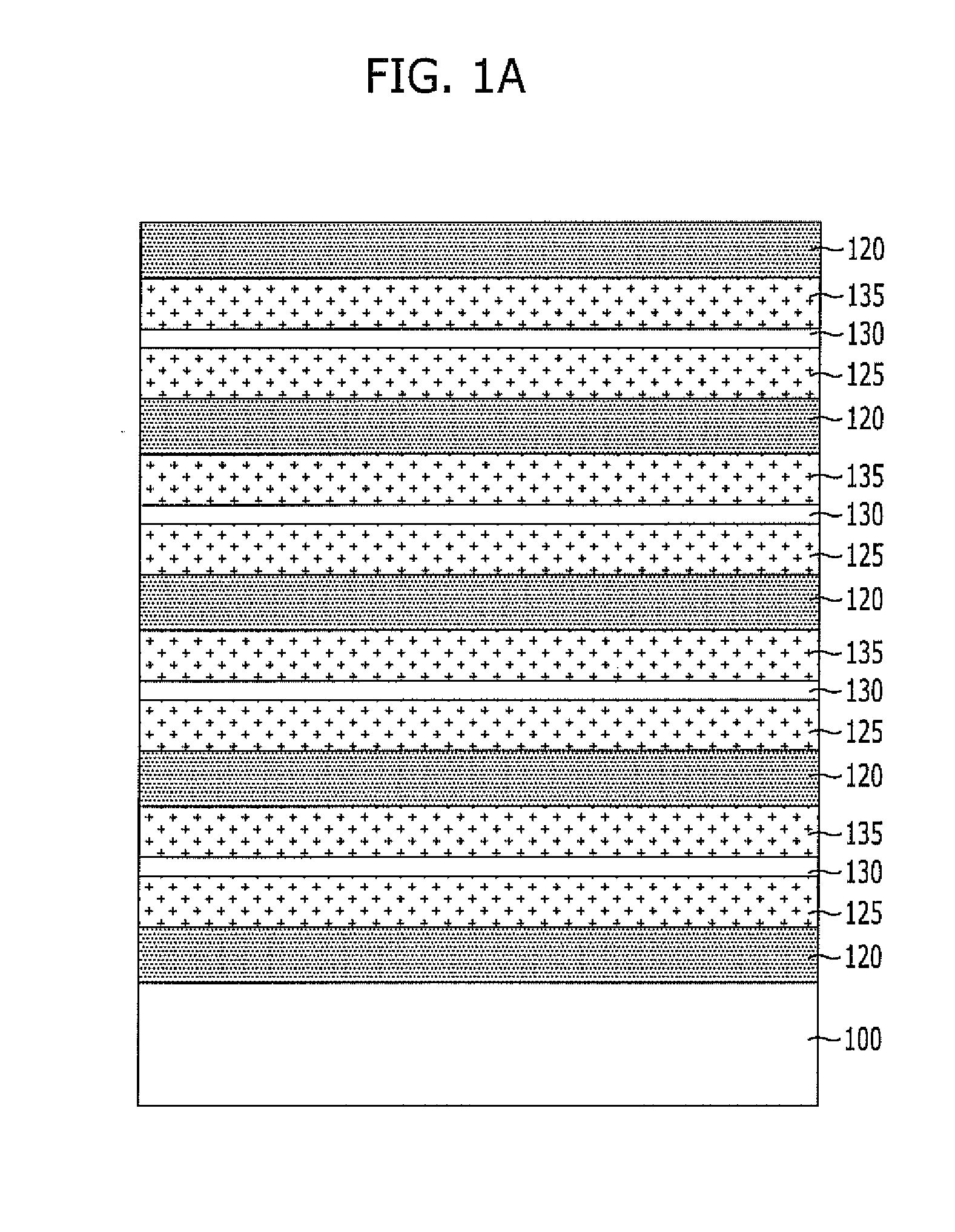

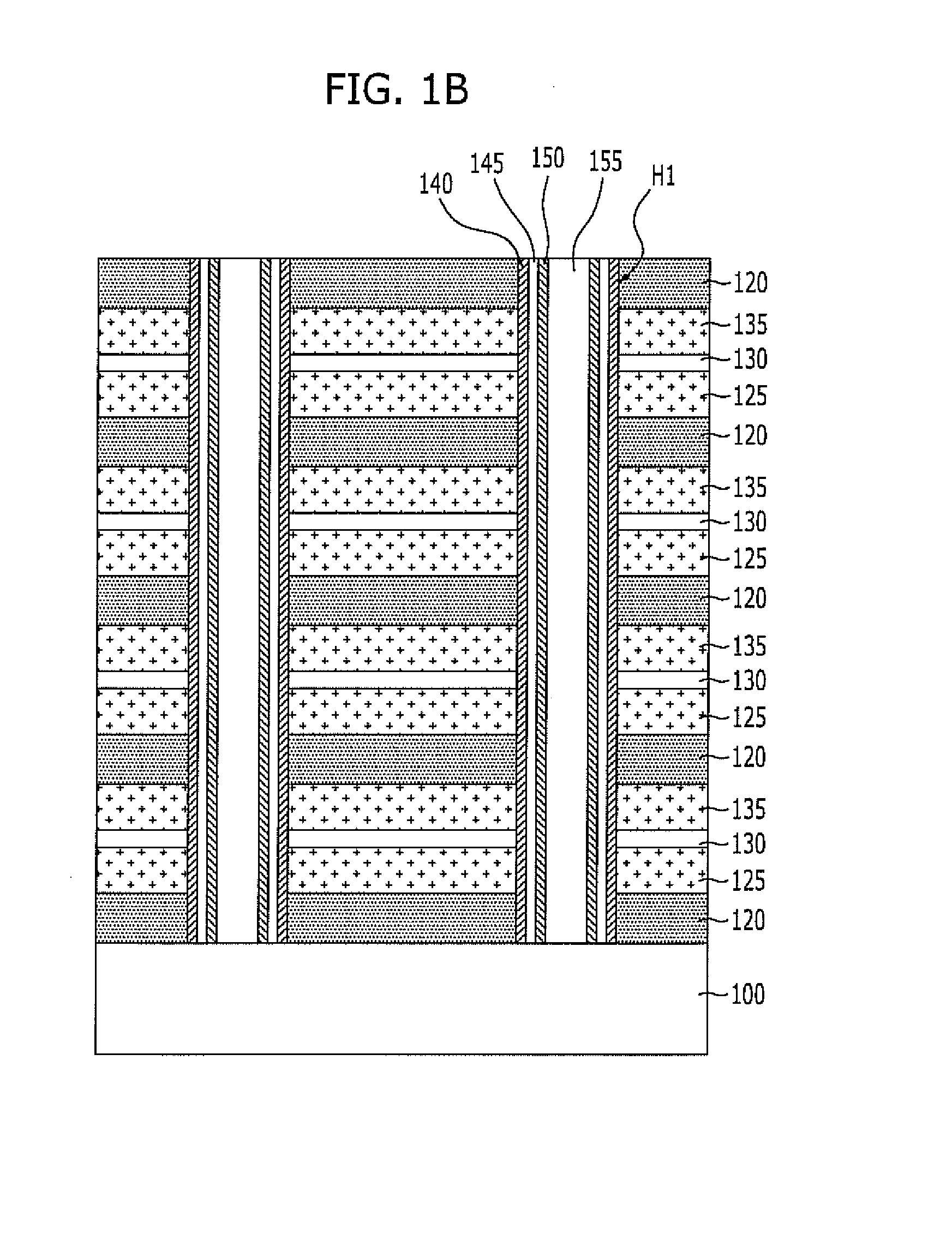

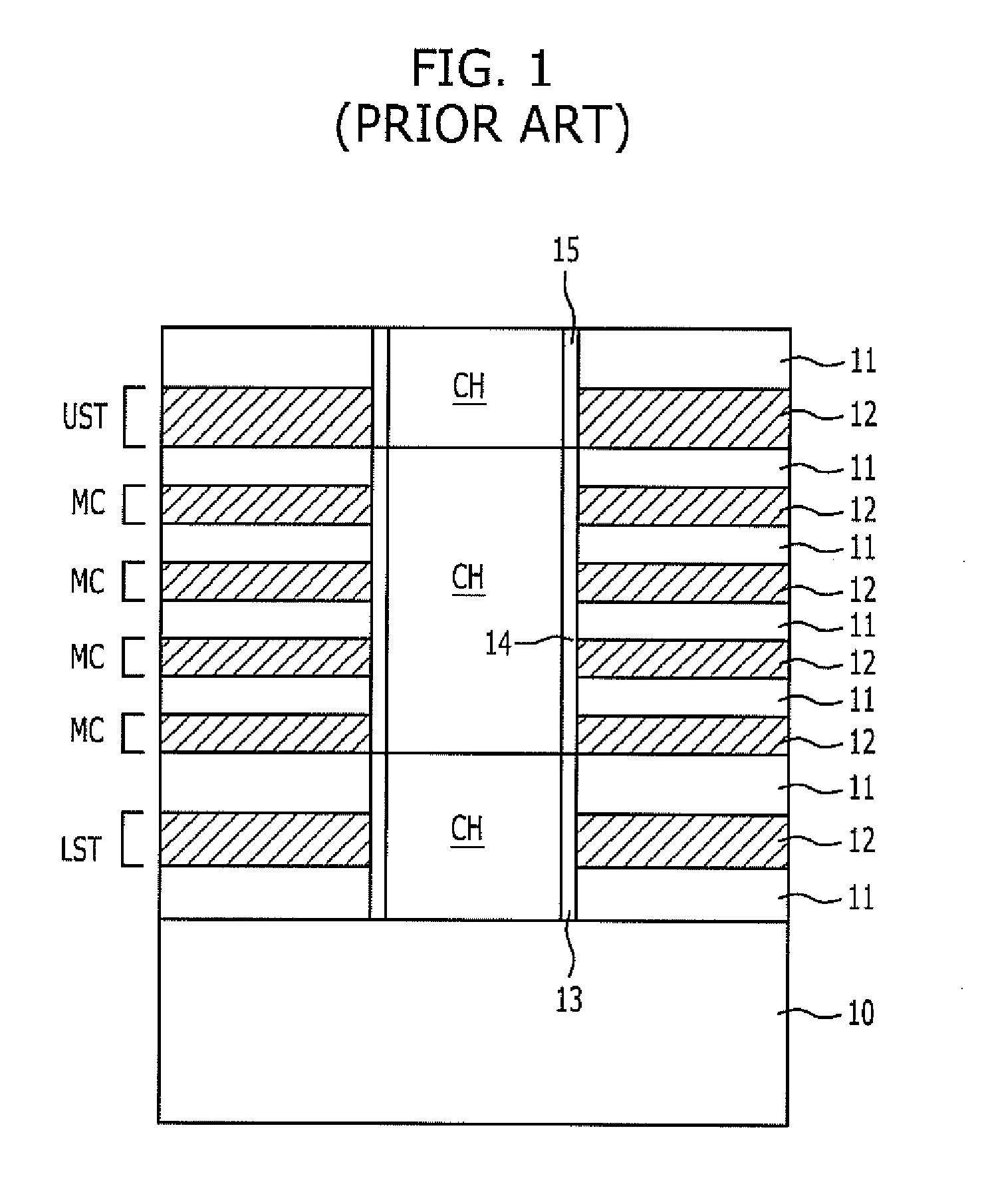

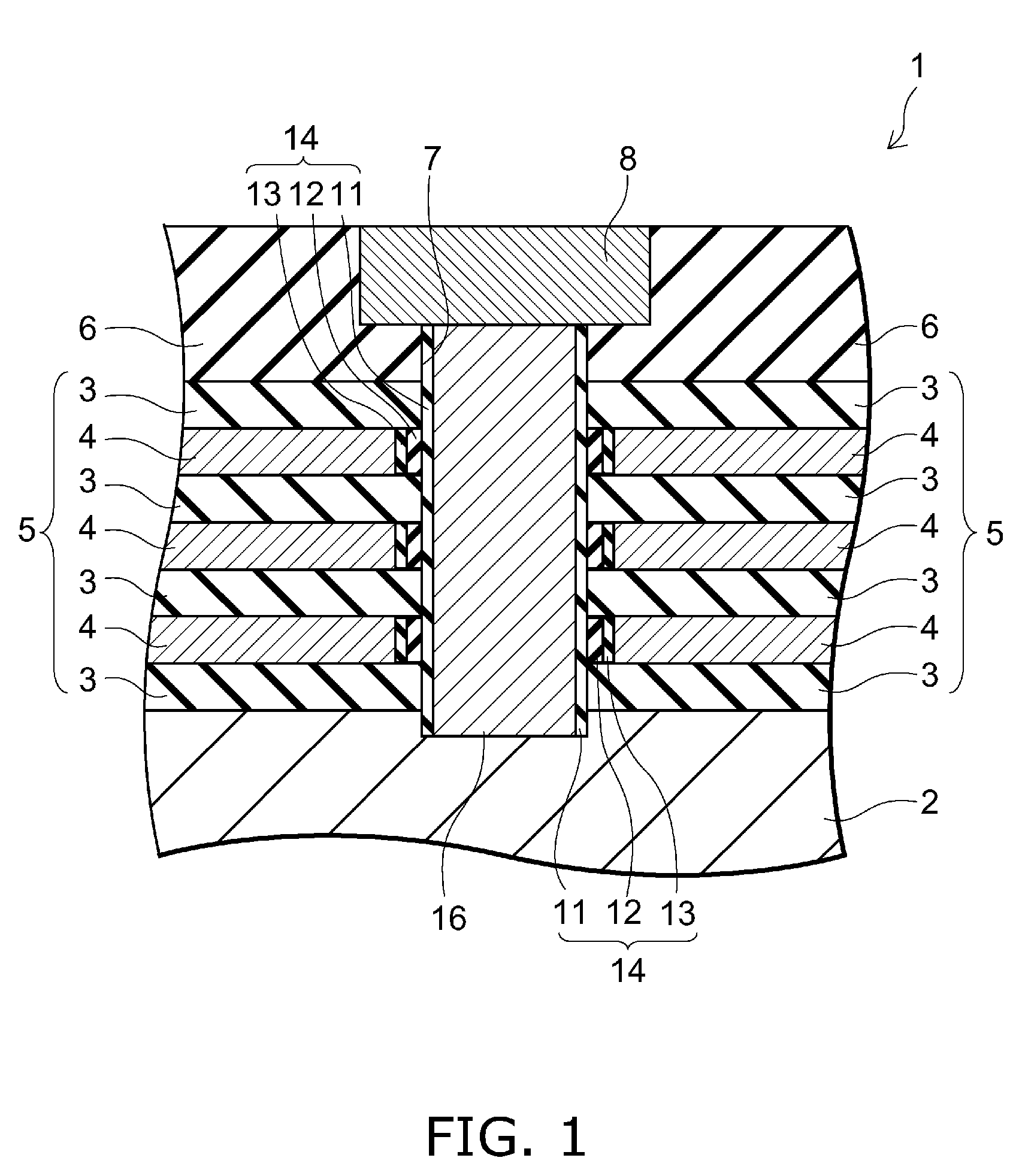

Vertical channel type nonvolatile memory device and method for fabricating the same

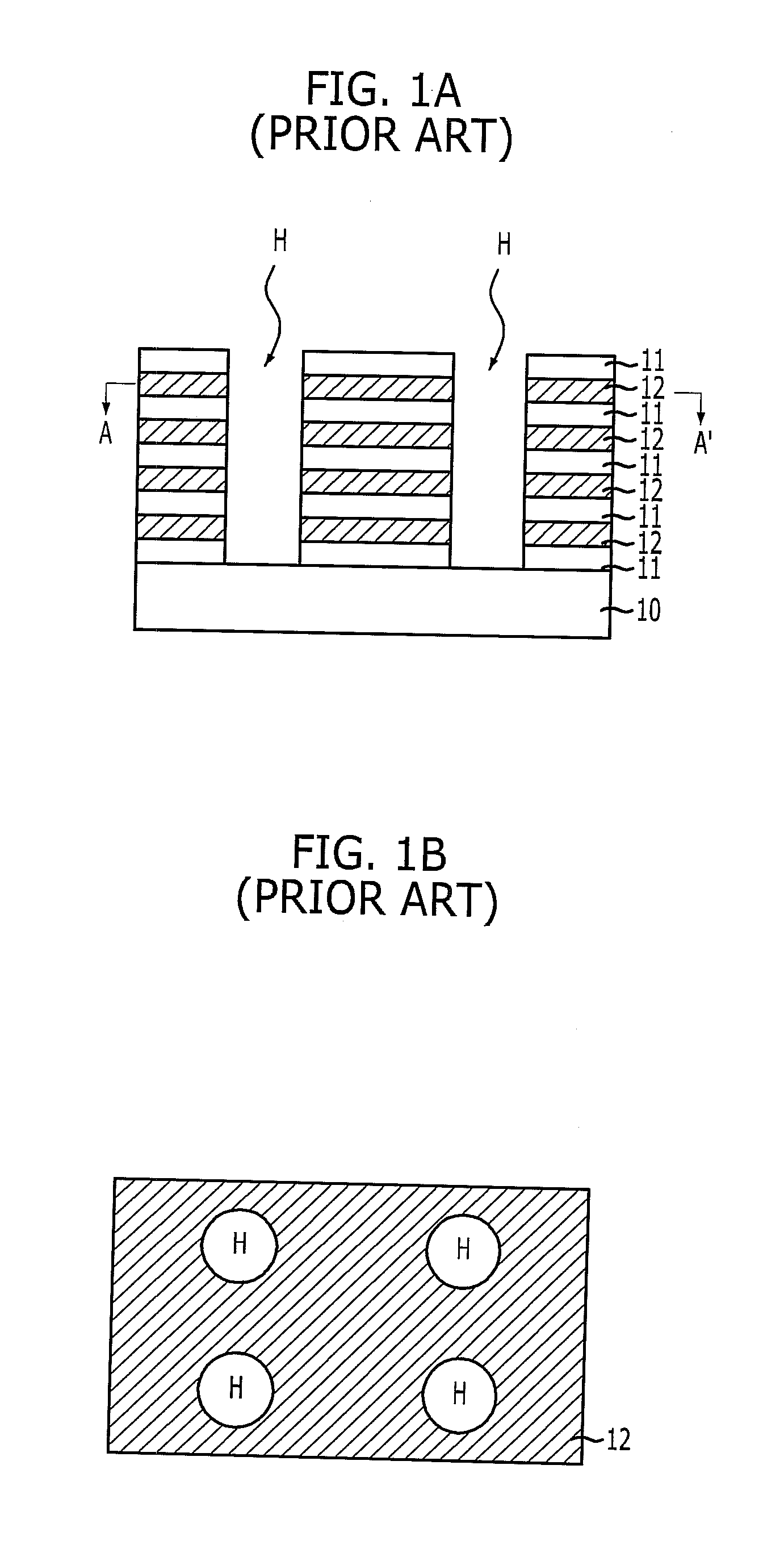

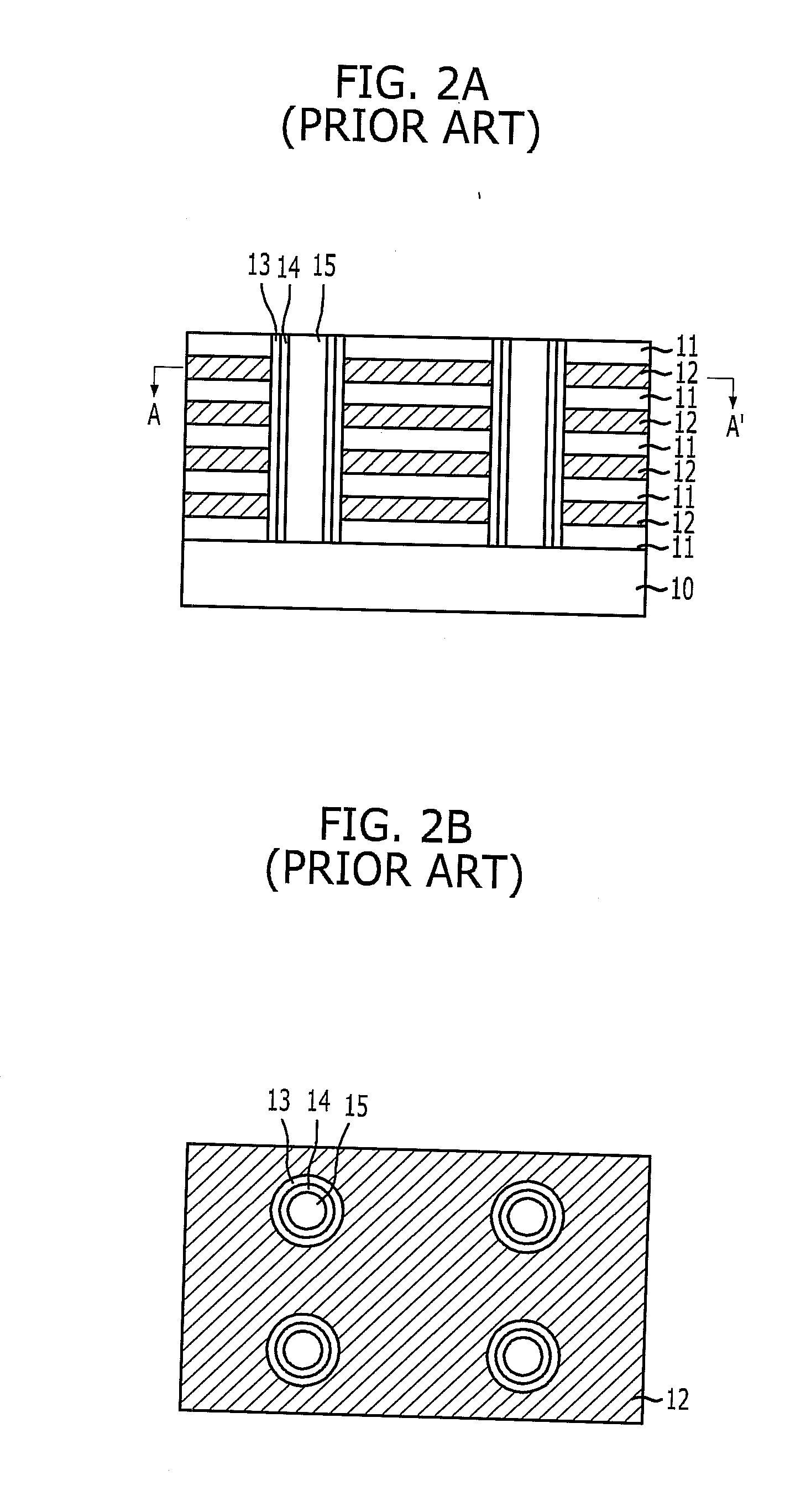

A method for fabricating, a vertical channel type nonvolatile memory device includes: alternately forming a plurality of sacrificial layers and a plurality of interlayer dielectric layers over a semiconductor substrate; etching the sacrificial layers and the interlayer dielectric layers to form a plurality of first openings for channel each of which exposes the substrate; filling the first openings to form a plurality of channels protruding from the semiconductor substrate; etching the sacrificial layers and the interlayer dielectric layers to form second openings for removal of the sacrificial layers between the channels; exposing sidewalls of the channels by removing the sacrificial layers exposed by the second openings; and forming a tunnel insulation layer, a charge trap layer, a charge blocking layer, and a conductive layer for gate electrode on the exposed sidewalls of the channels.

Owner:SK HYNIX INC

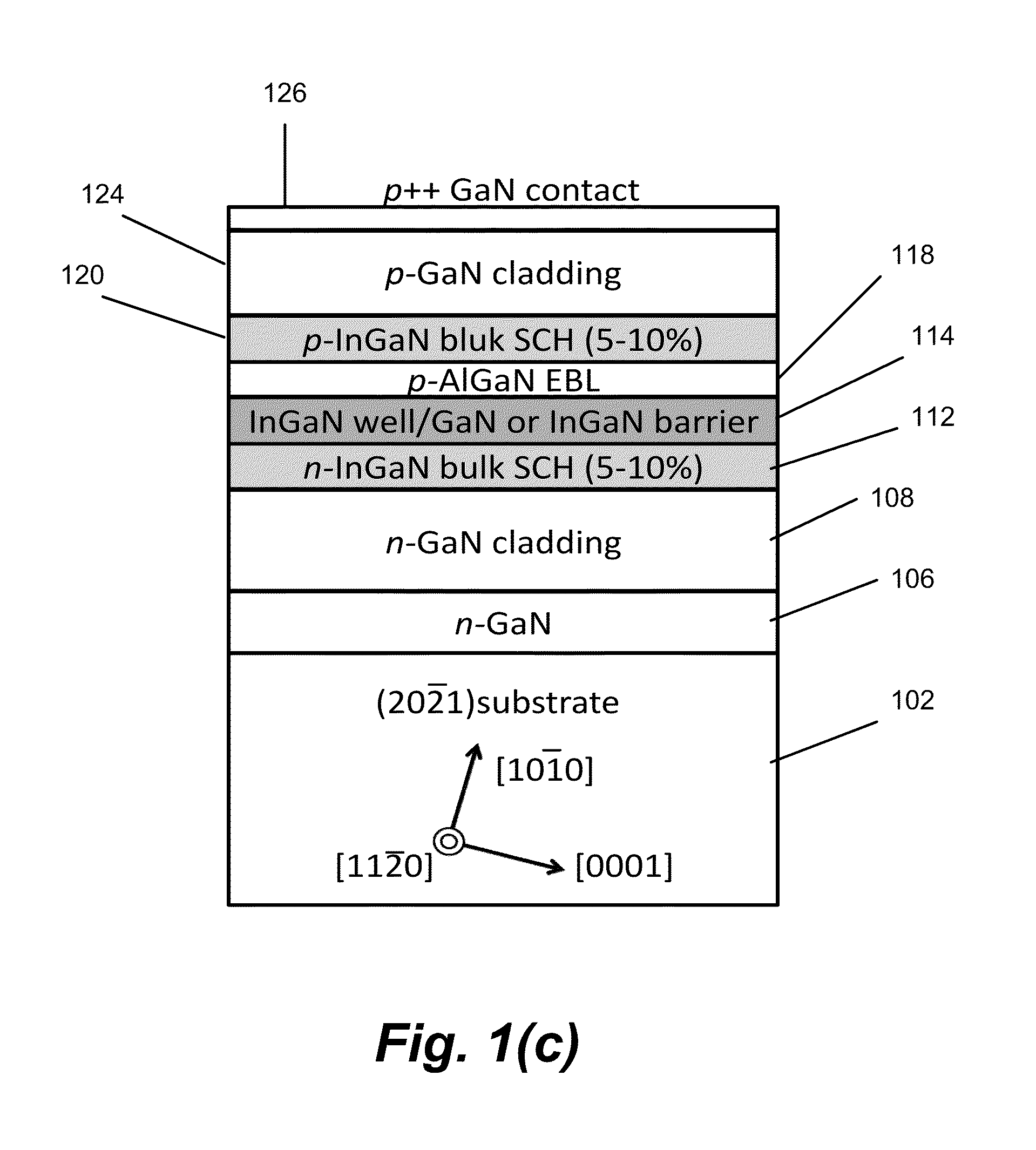

LONG WAVELENGTH NONPOLAR AND SEMIPOLAR (Al,Ga,In)N BASED LASER DIODES

InactiveUS20100309943A1Simple structureImprove electricityOptical wave guidanceLaser detailsContact layerStimulated emission

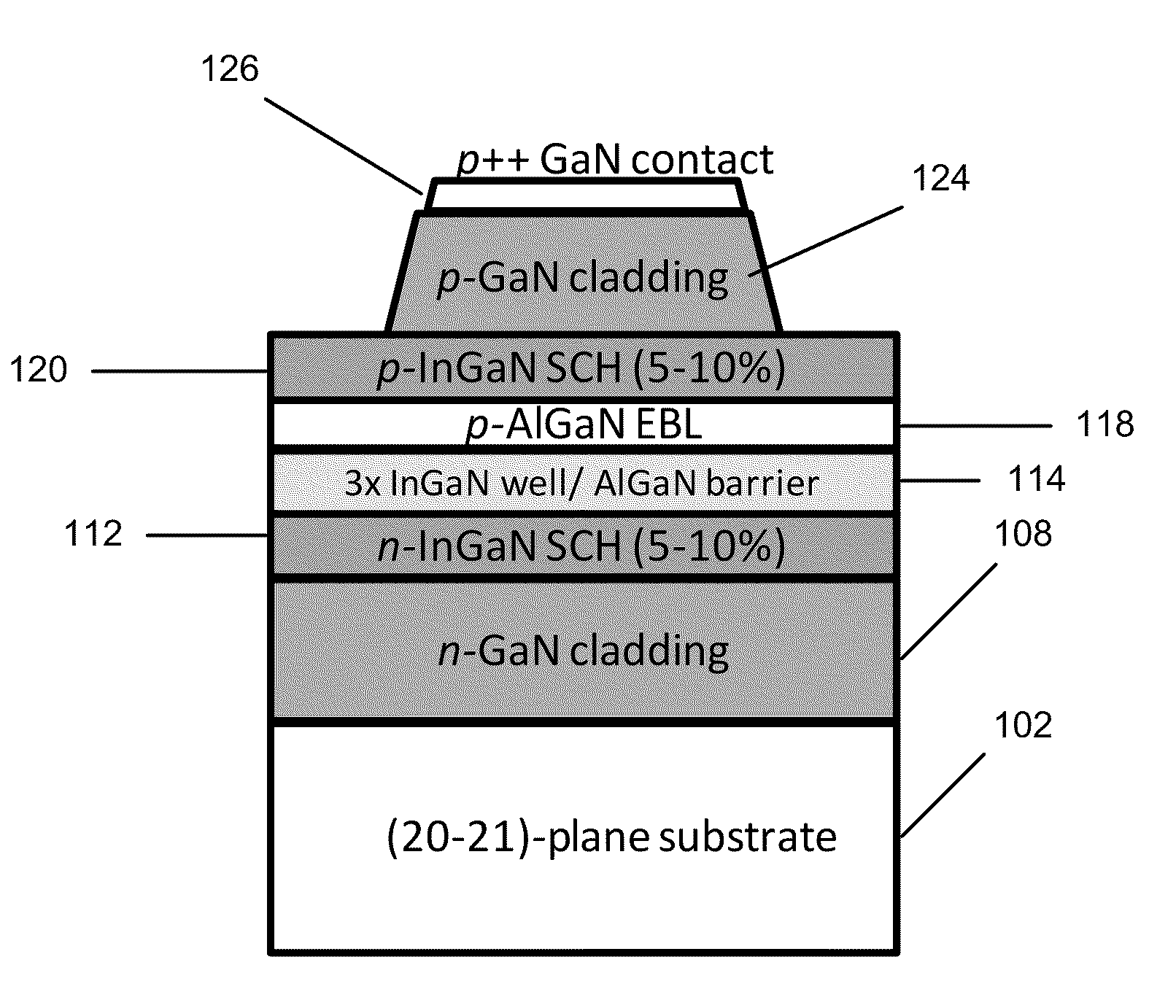

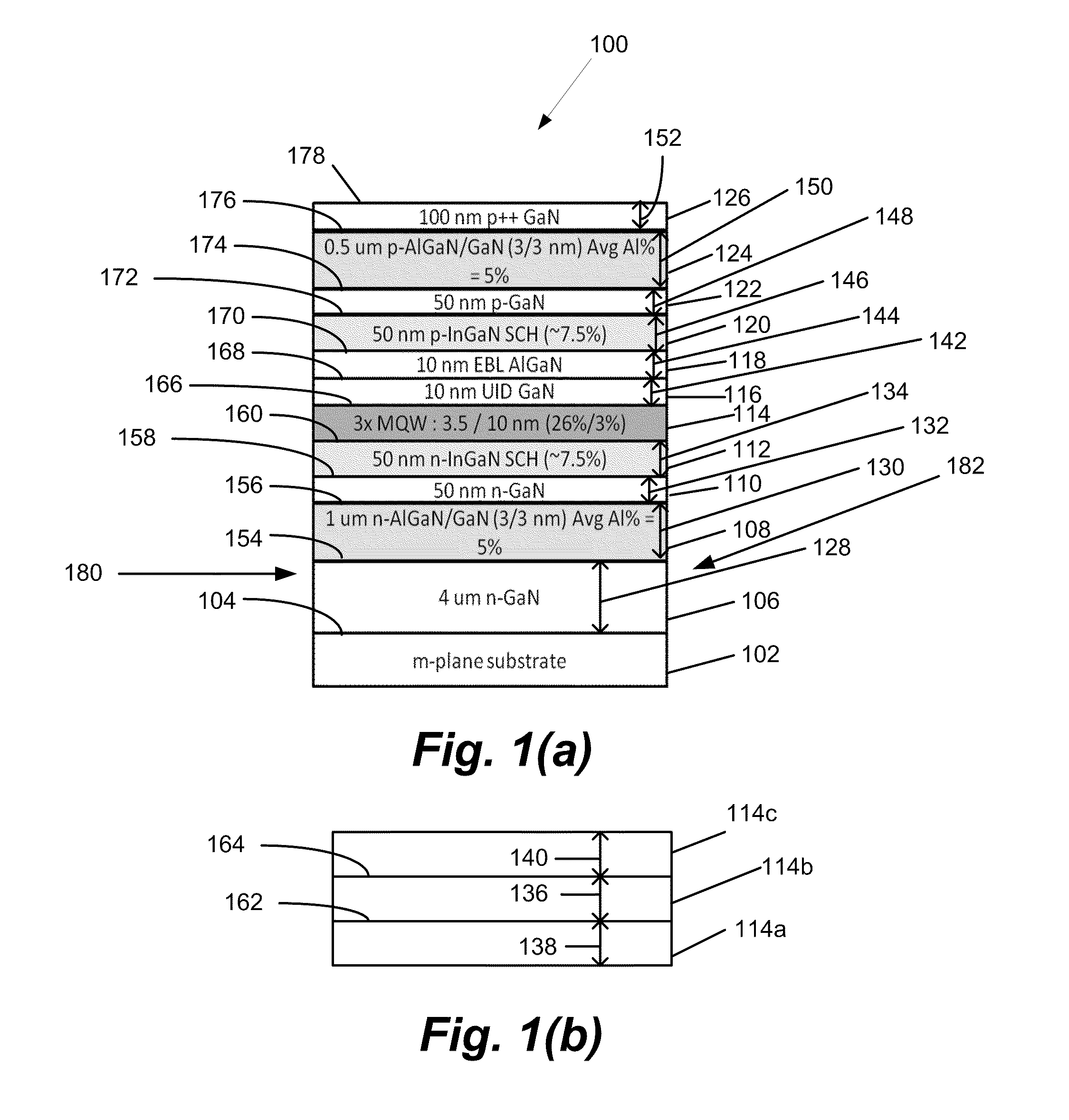

A laser diode, grown on a miscut nonpolar or semipolar substrate, with lower threshold current density and longer stimulated emission wavelength, compared to conventional laser diode structures, wherein the laser diode's (1) n-type layers are grown in a nitrogen carrier gas, (2) quantum well layers and barrier layers are grown at a slower growth rate as compared to other device layers (enabling growth of the p-type layers at higher temperature), (3) high Al content electron blocking layer enables growth of layers above the active region at a higher temperature, and (4) asymmetric AlGaN SPSLS allowed growth of high Al containing p-AlGaN layers. Various other techniques were used to improve the conductivity of the p-type layers and minimize the contact resistance of the contact layer.

Owner:RGT UNIV OF CALIFORNIA

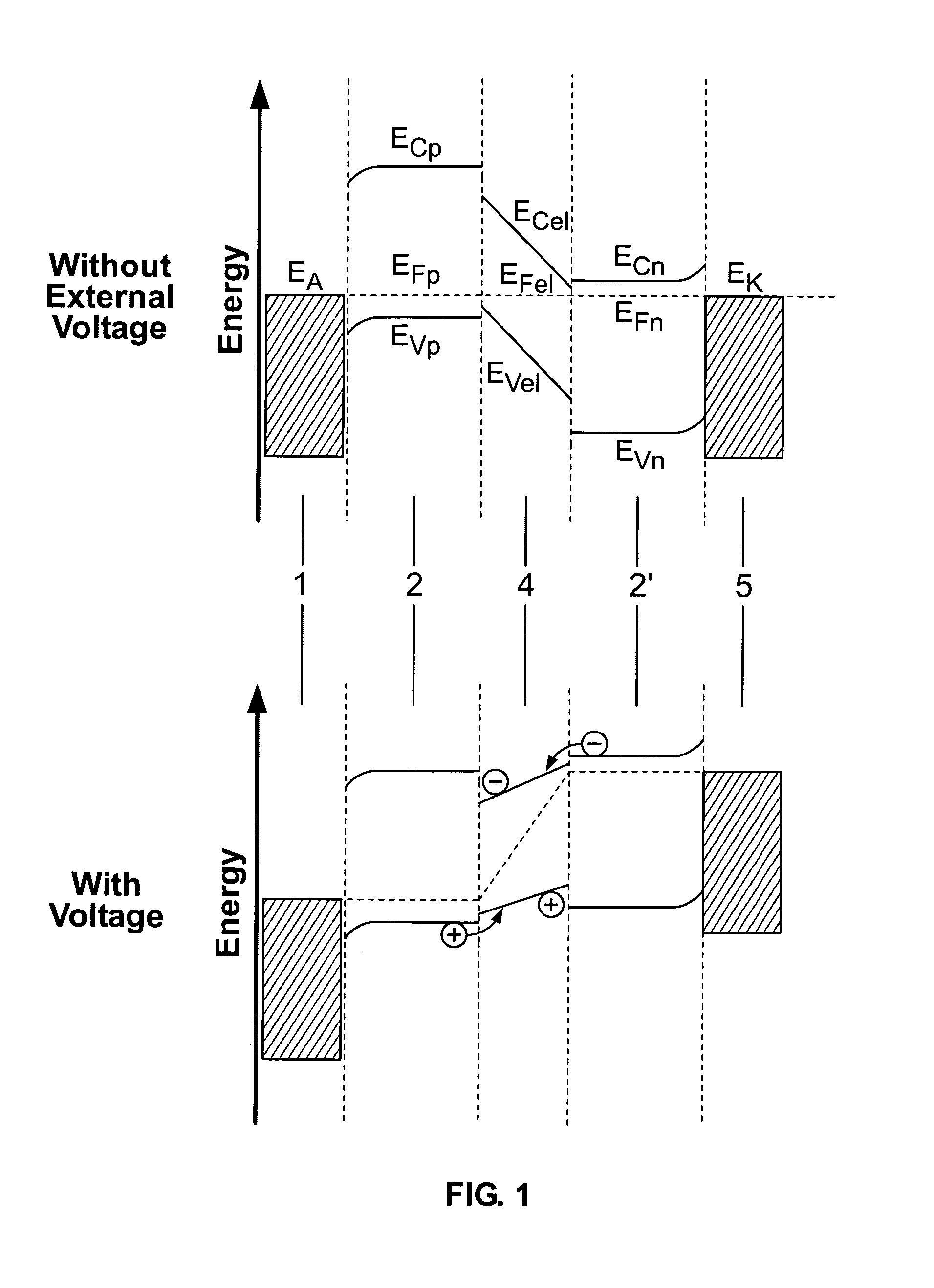

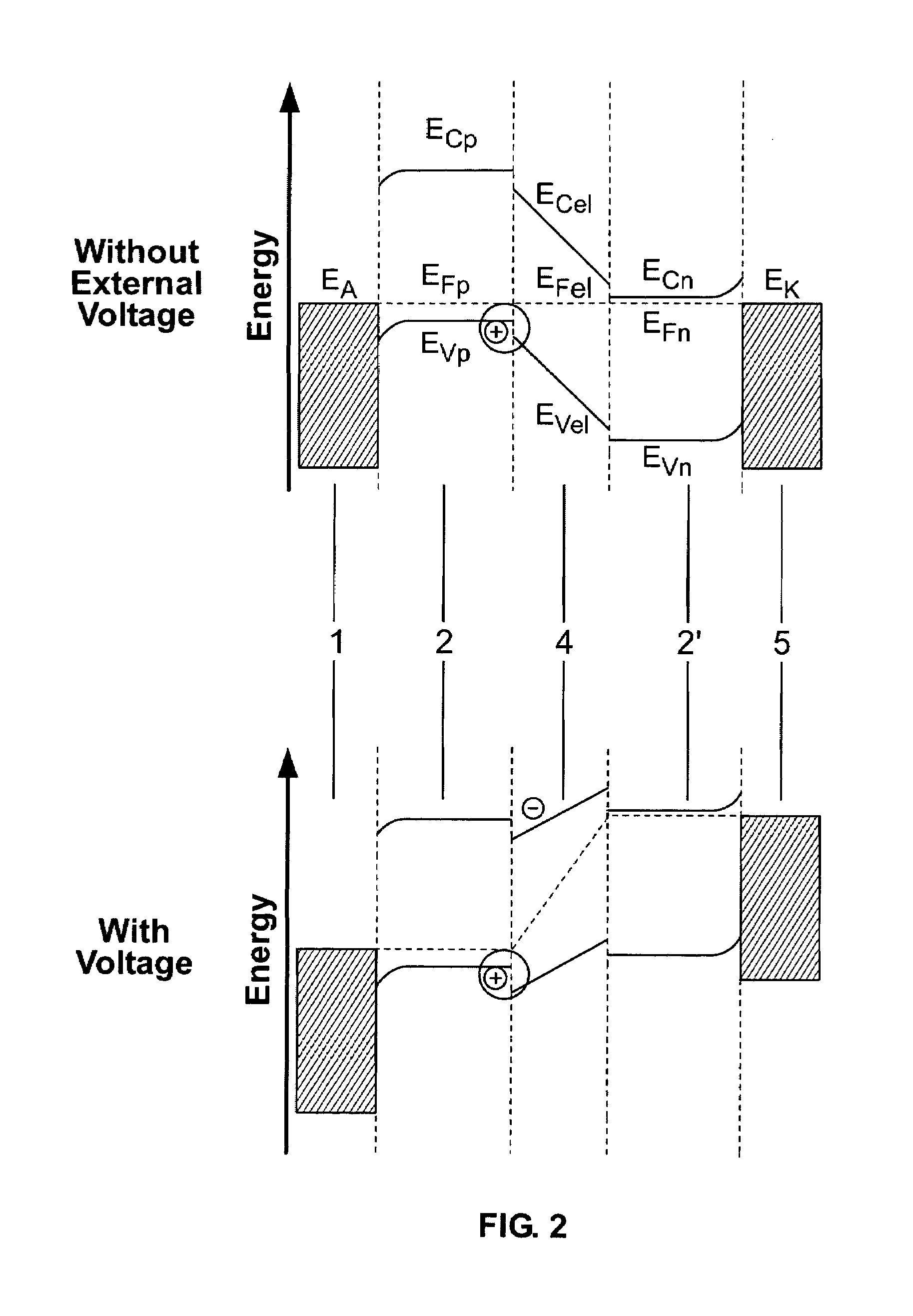

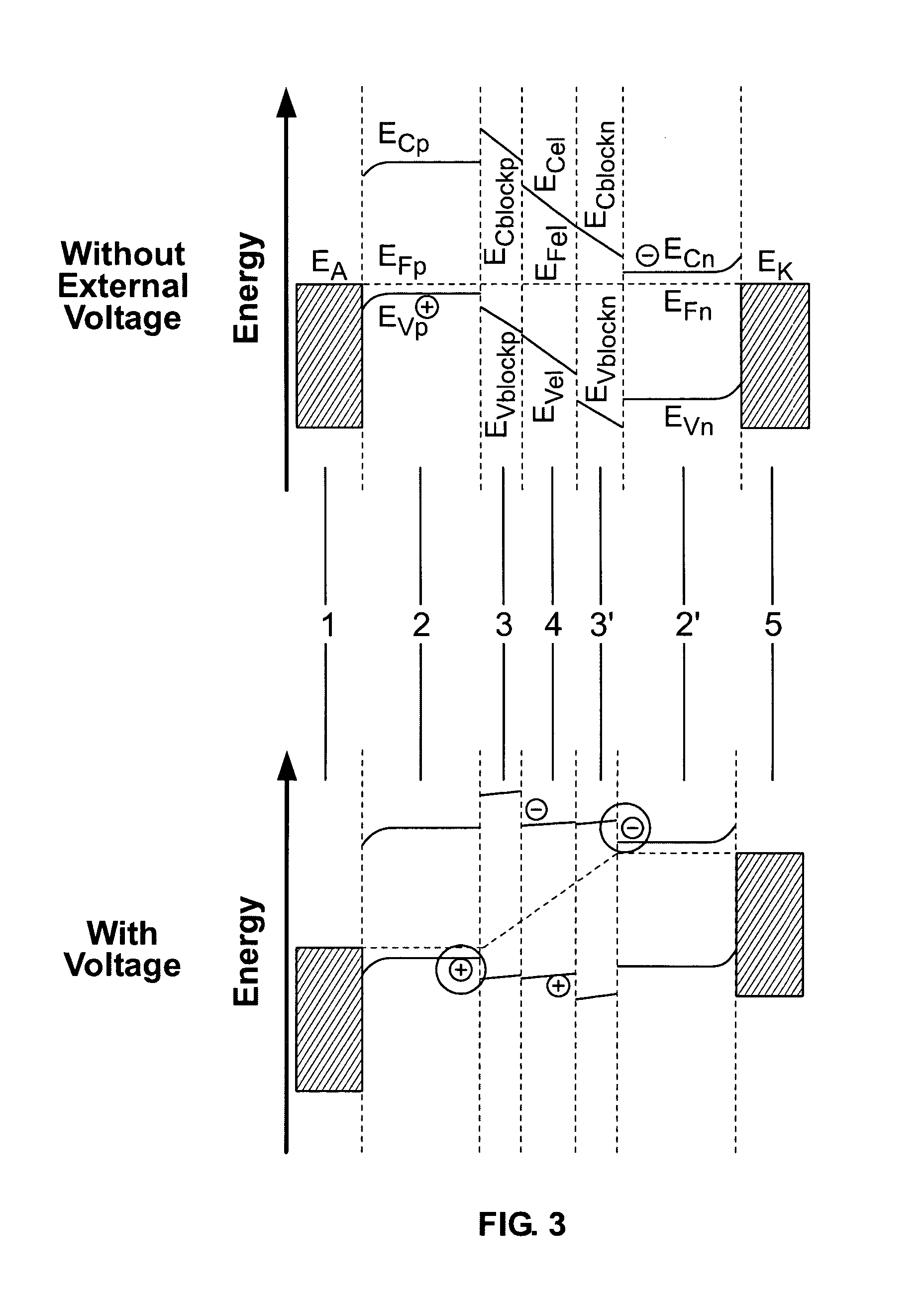

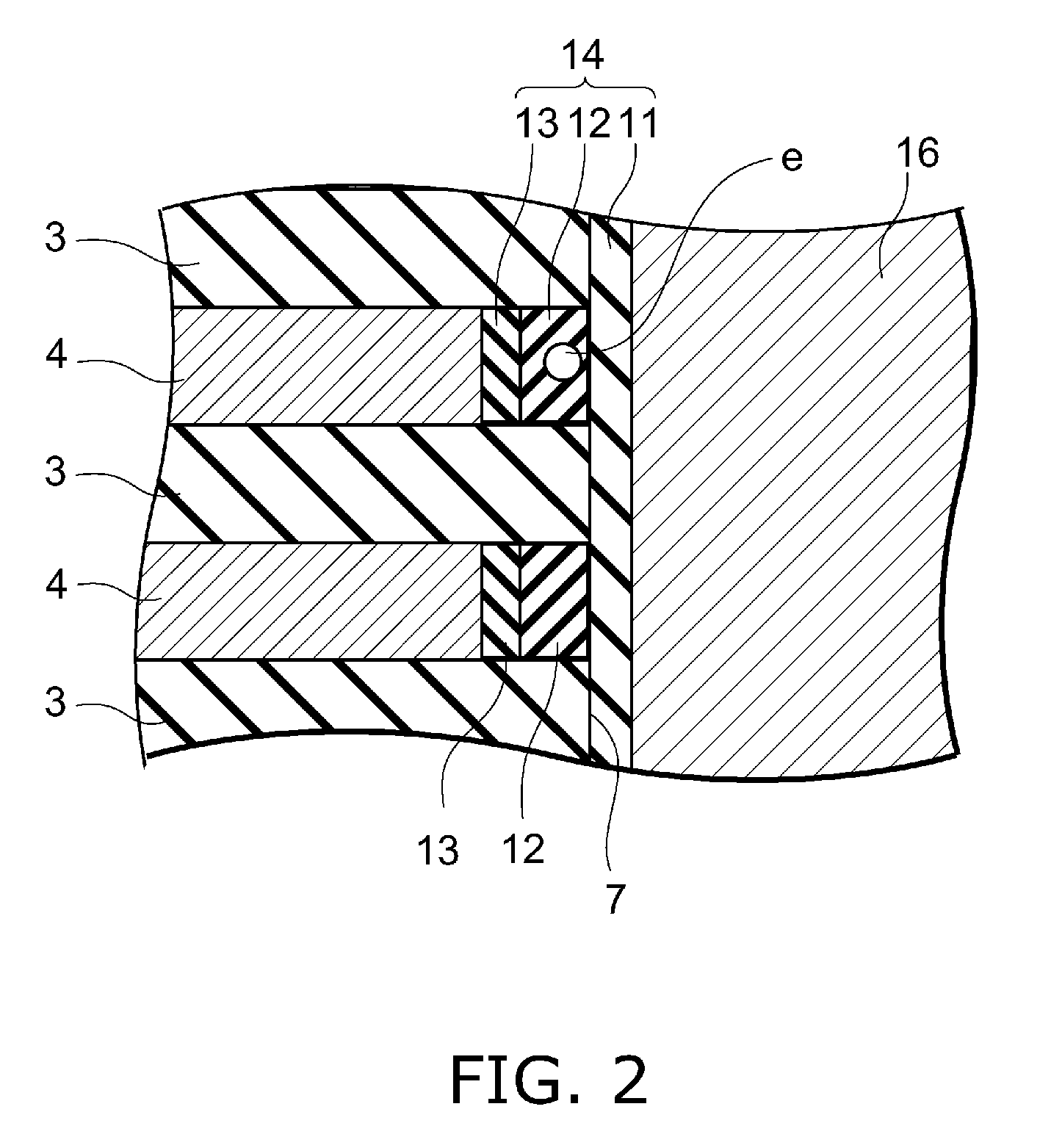

Light emitting component comprising organic layers

InactiveUS7074500B2Inhibit injectionDischarge tube luminescnet screensElectroluminescent light sourcesTransport layerCharge carrier

The invention relates to a light-emmiting component having organic layers, in particular to an organic light-emmiting diode. The component has at least one doped charge carrier transport layer (2), a light-emmiting layer (4) and contact layers (1, 5) and also has a blocking layer (3; 3′) wherein an organic material is provided between the charge carrier transport layer (2, 2′) and the light-emmiting layer (4). The energy levels of the charge carried transport layer are chosen in such a way that efficient doping is possible and the blocking layer nevertheless ensures that non-radiating recombination processes on the interface with the emitting layer are prevented.

Owner:NOVALED GMBH

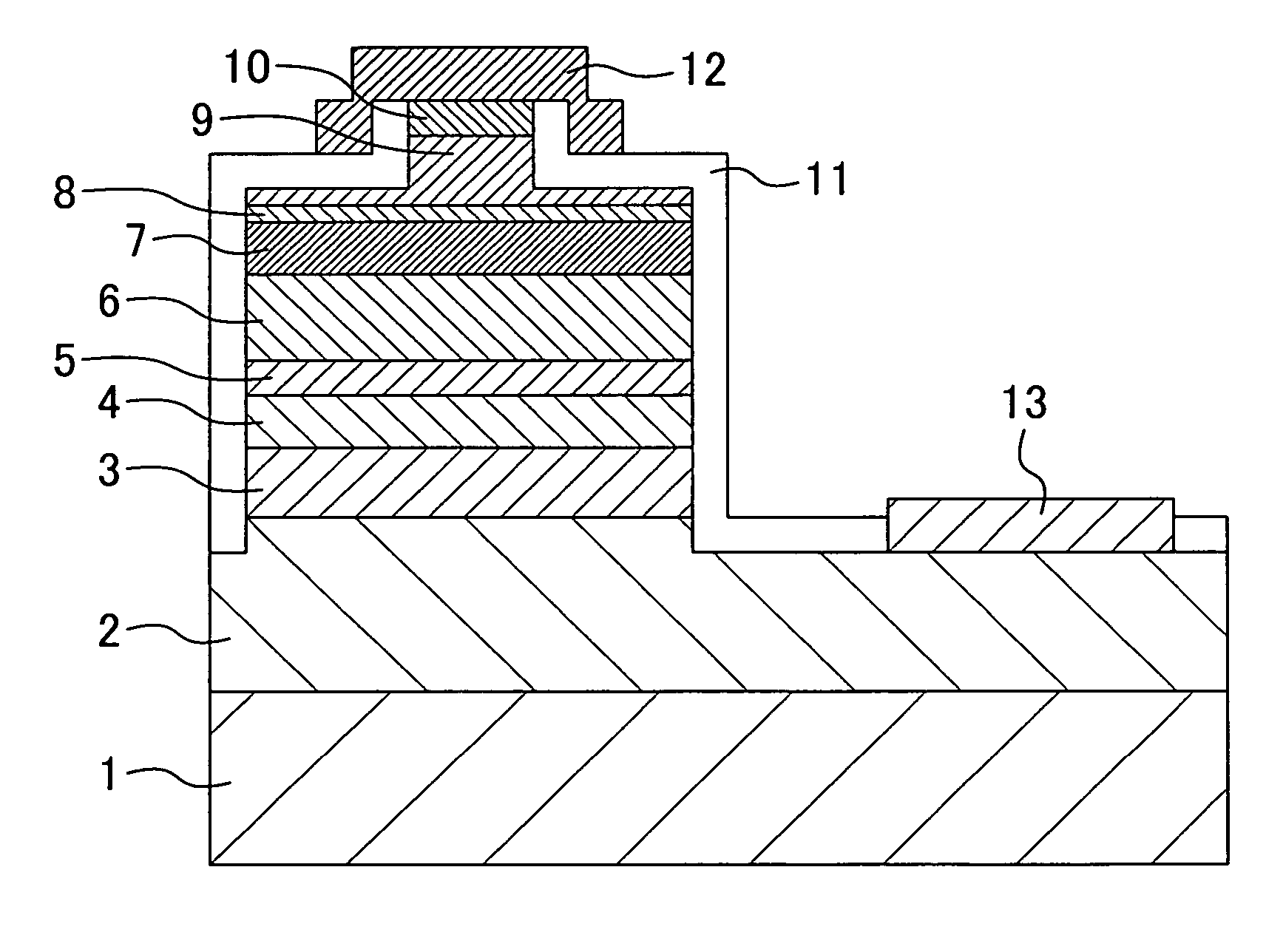

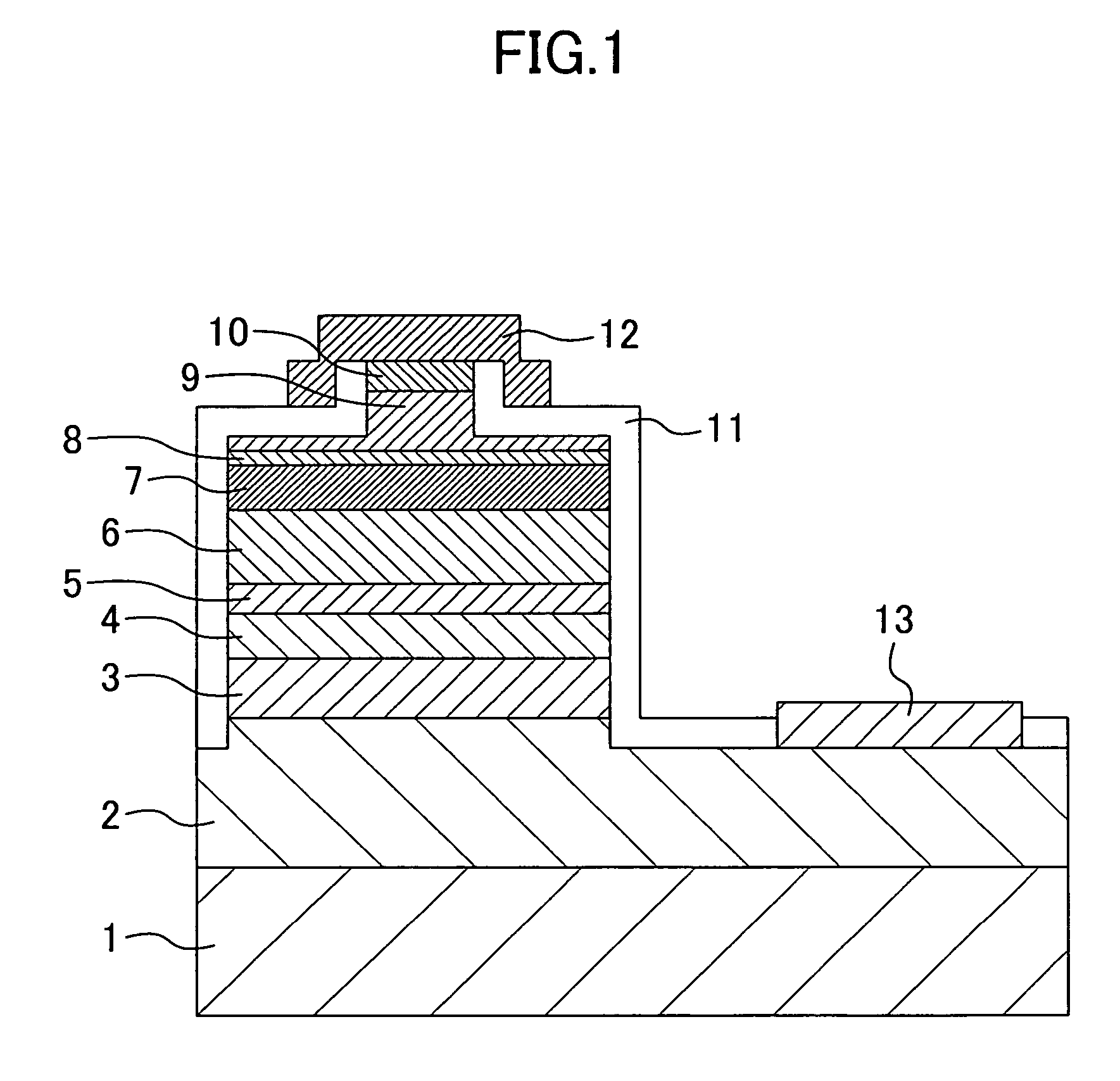

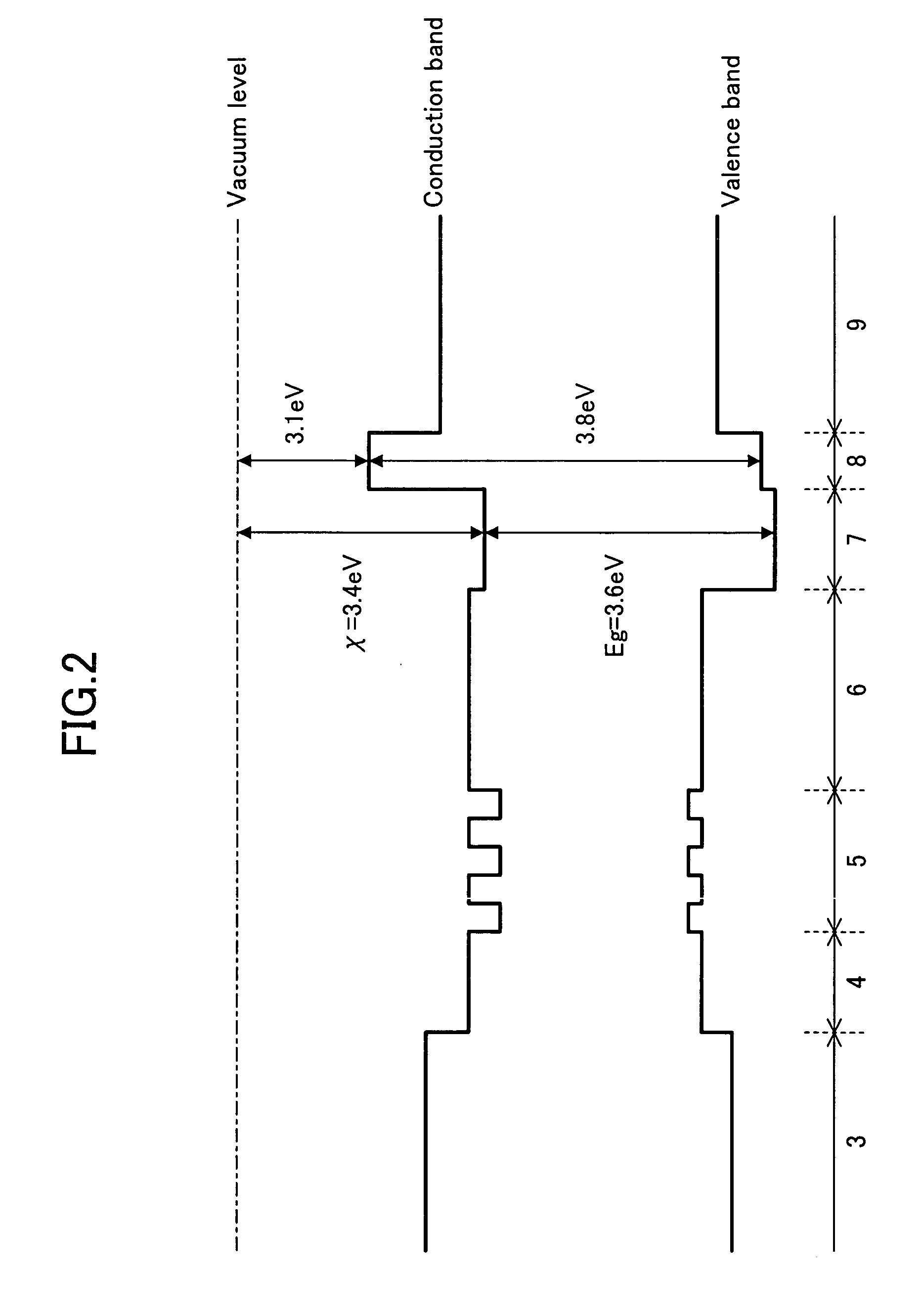

Group III nitride semiconductor light emitting device

InactiveUS20070110112A1Increase fixed chargeEasy to overflowOptical wave guidanceSolid-state devicesElectron blocking layerActive layer

A group III nitride semiconductor light emitting device according to the present invention includes an immediate layer formed of AlxGa1-x-yInyN (0<x<1, 0<y<1, x+y<1) between an active layer and a cladding layer and an electron blocking layer formed of p-type group III nitride semiconductor having a smaller electron affinity than that of the intermediate layer so as to be in contact with the intermediate layer. The semiconductor light emitting layer may be a laser diode or a LED.

Owner:PANASONIC CORP

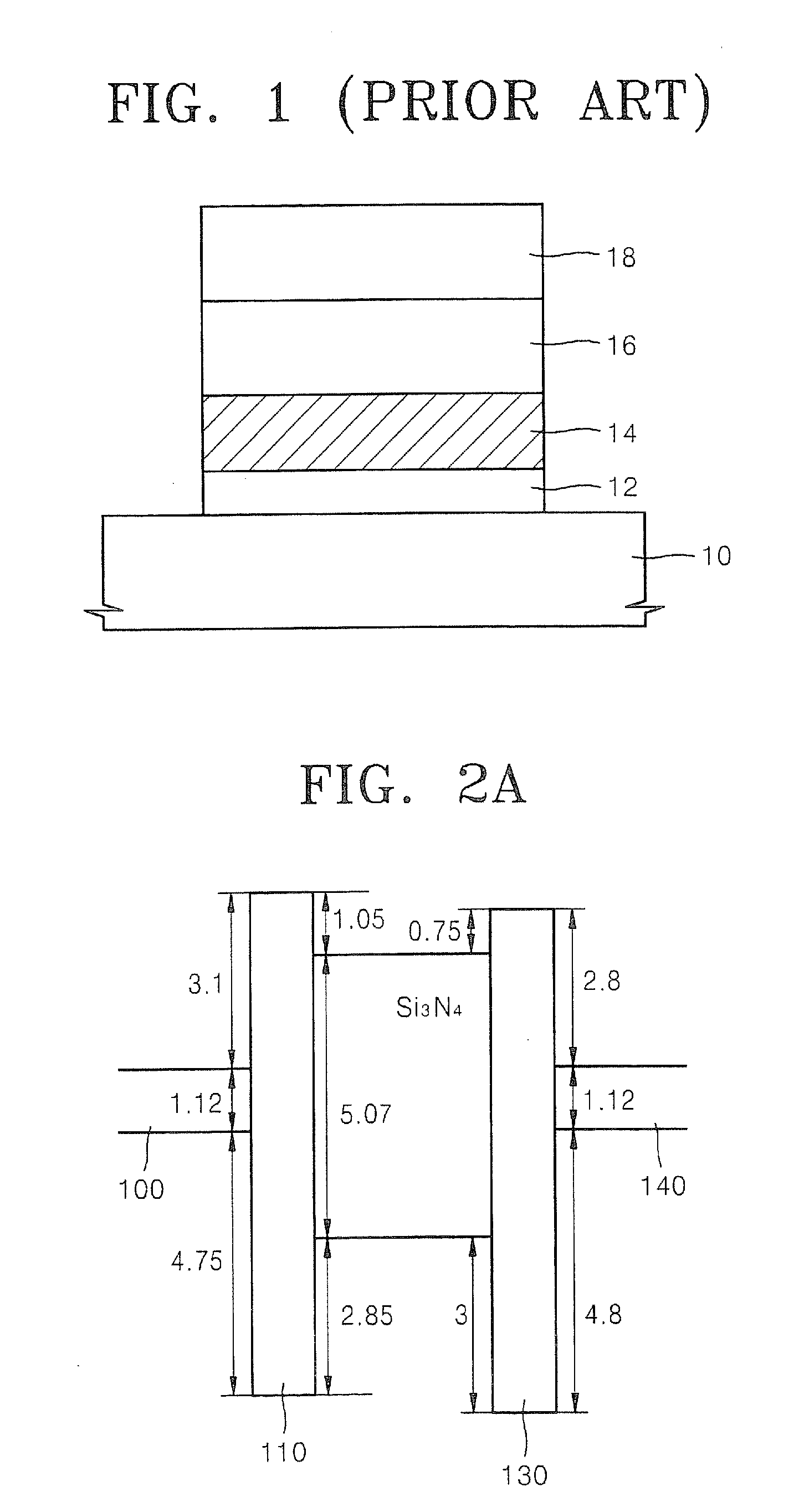

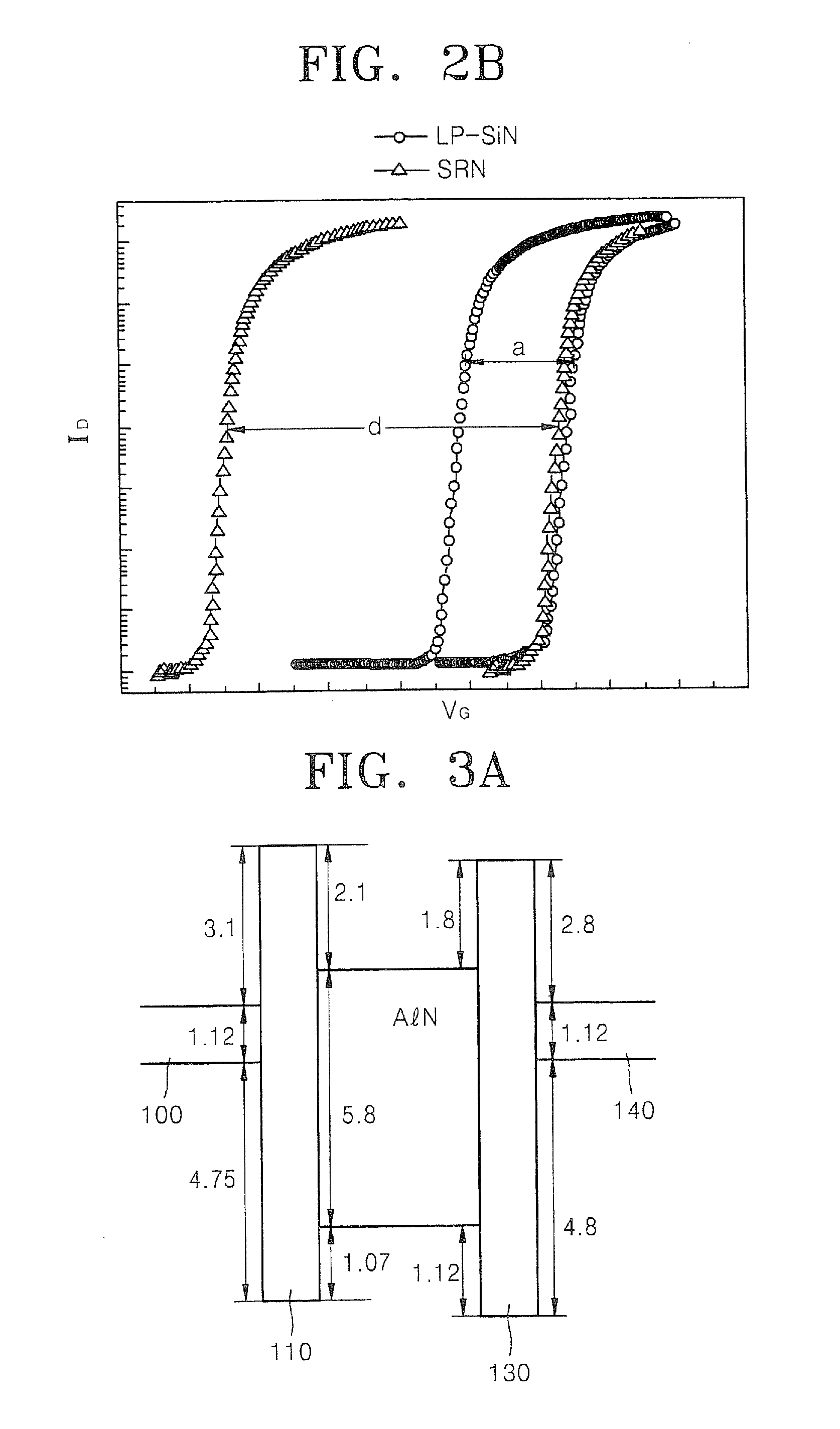

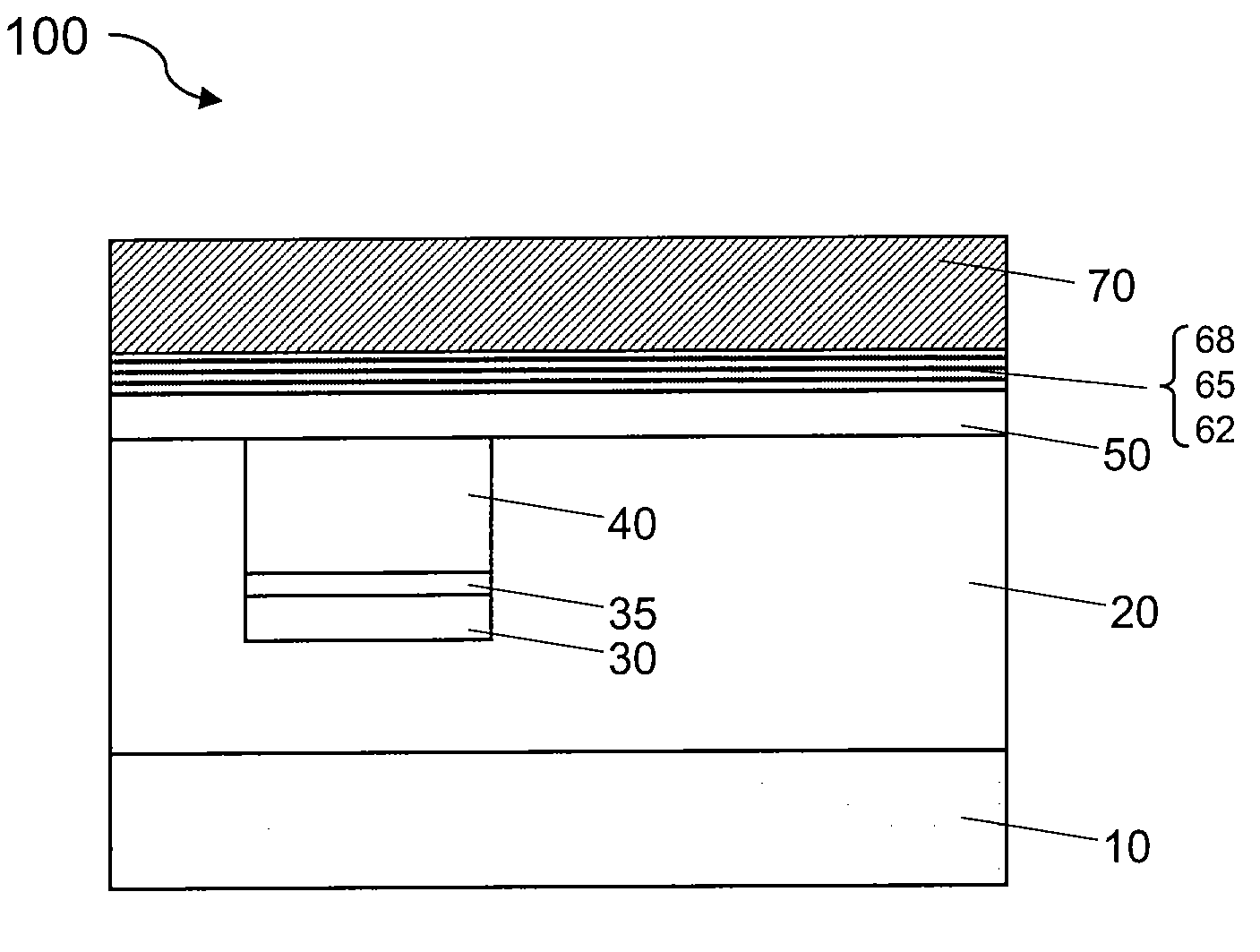

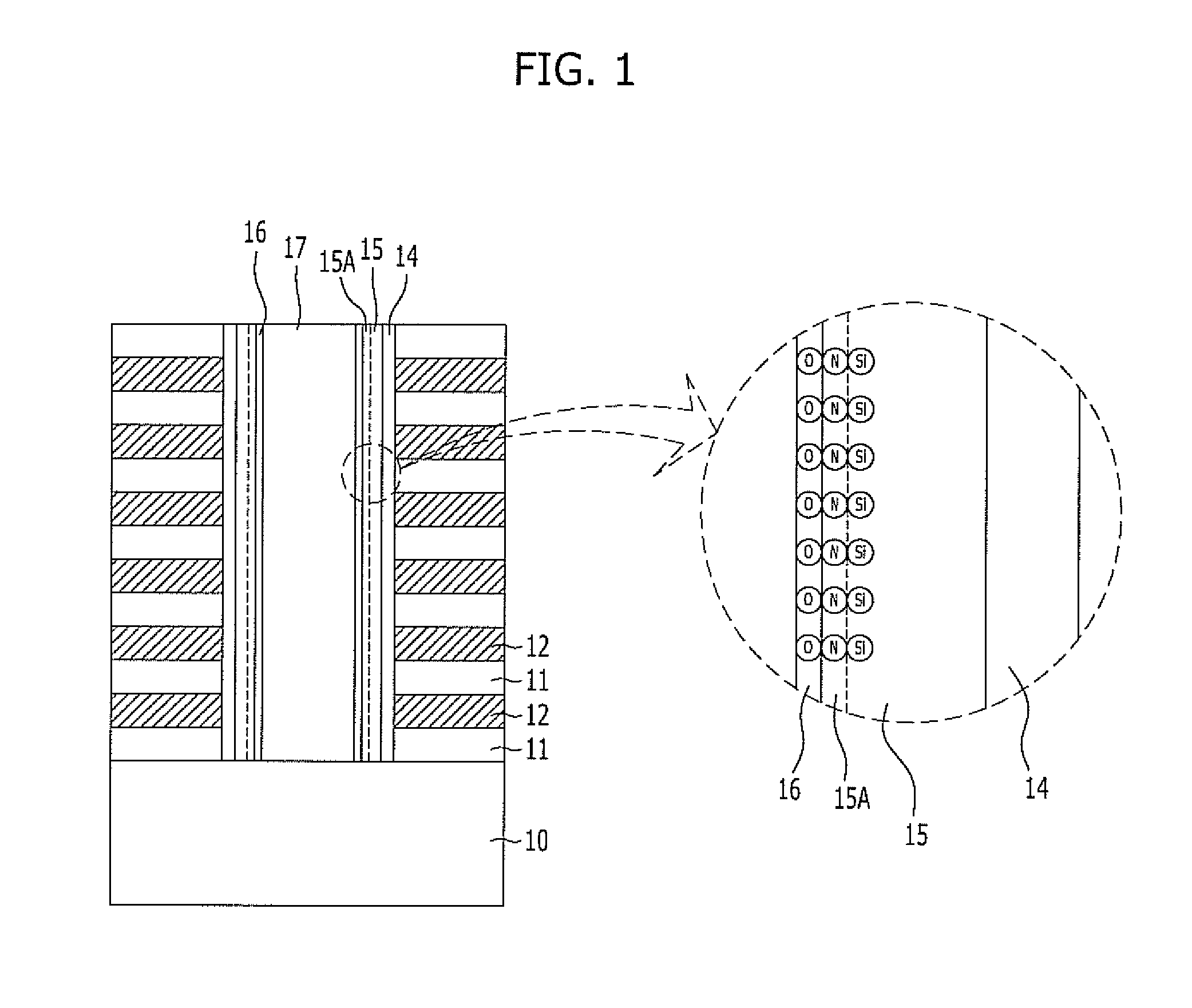

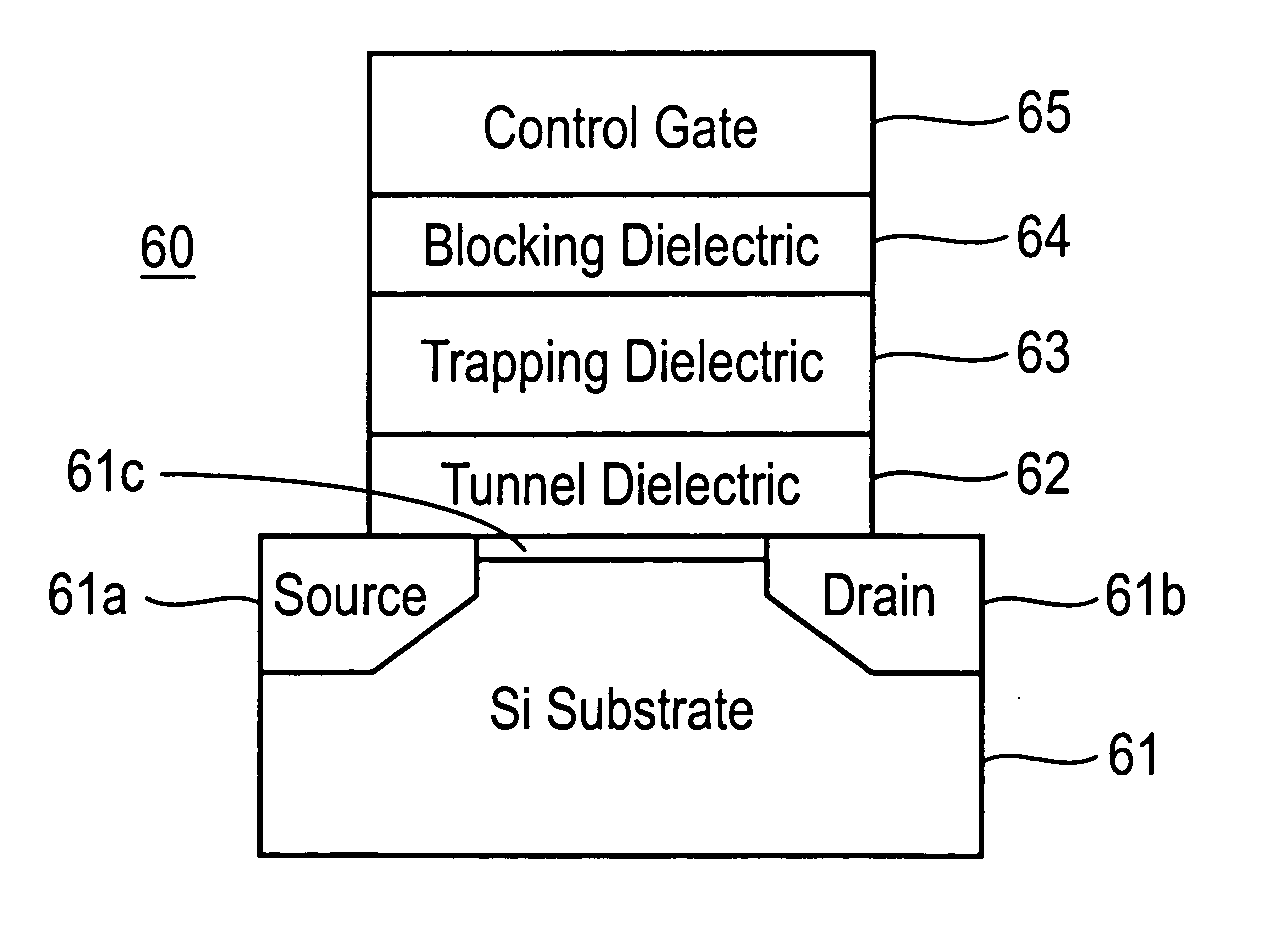

Semiconductor memory device including charge trap layer with stacked nitride layers

A semiconductor memory device includes a semiconductor substrate, a tunnel insulating layer, charge trap layer, and a blocking layer. The tunnel insulating layer is on the semiconductor substrate. The charge trap layer is on the tunnel insulating layer and includes at least one pair of a first nitride layer with a higher trap density of holes than electrons and a second nitride layer with a higher trap density of electrons than holes. The blocking layer is on the charge trap layer opposite to the tunnel insulating layer. The first nitride layer may include silicon rich nitride, which may have a ratio of silicon to nitride of greater than 1 and less than or equal to 2. The second nitride layer may include aluminum nitride which may have a hexagonal crystalline structure.

Owner:SAMSUNG ELECTRONICS CO LTD

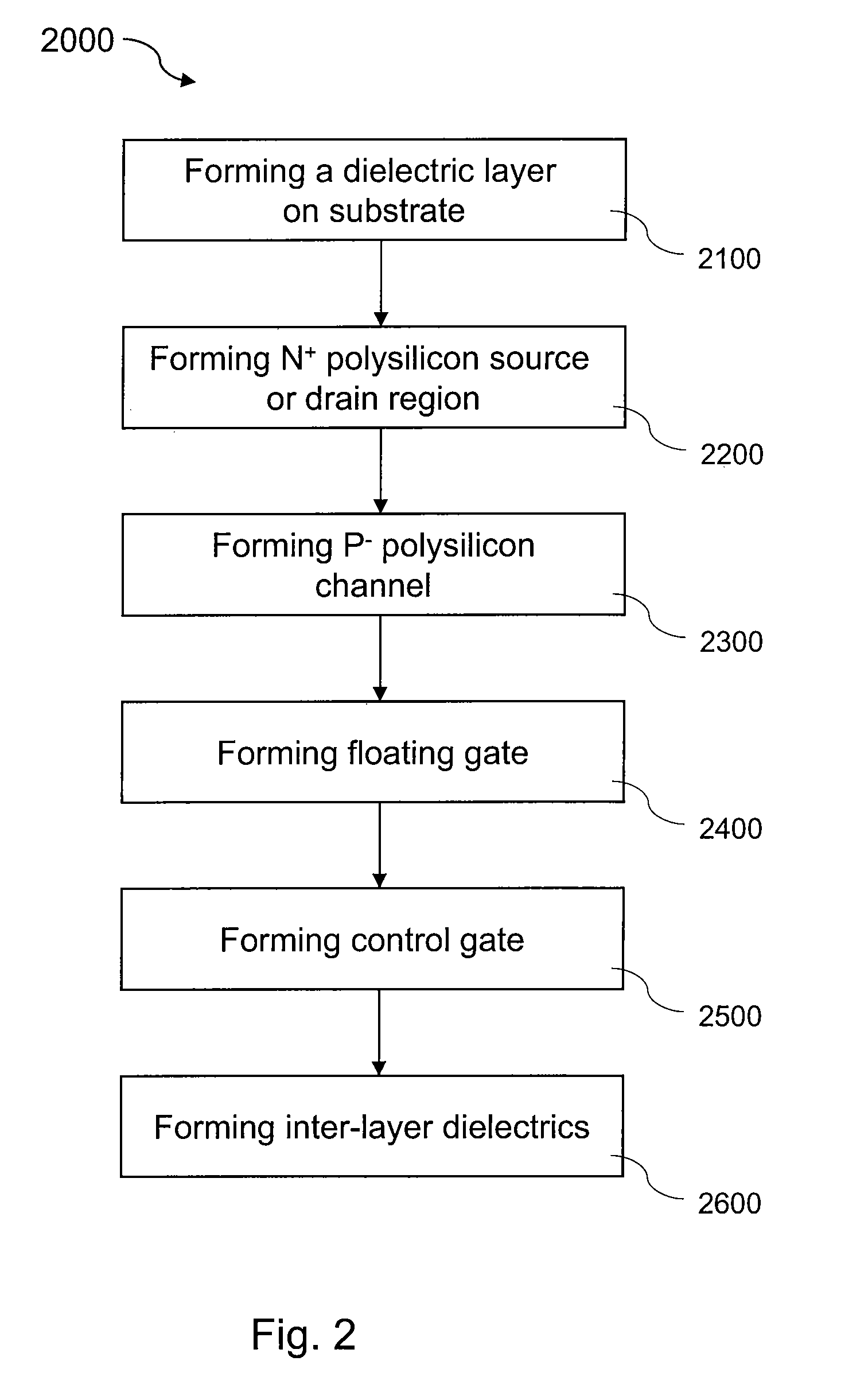

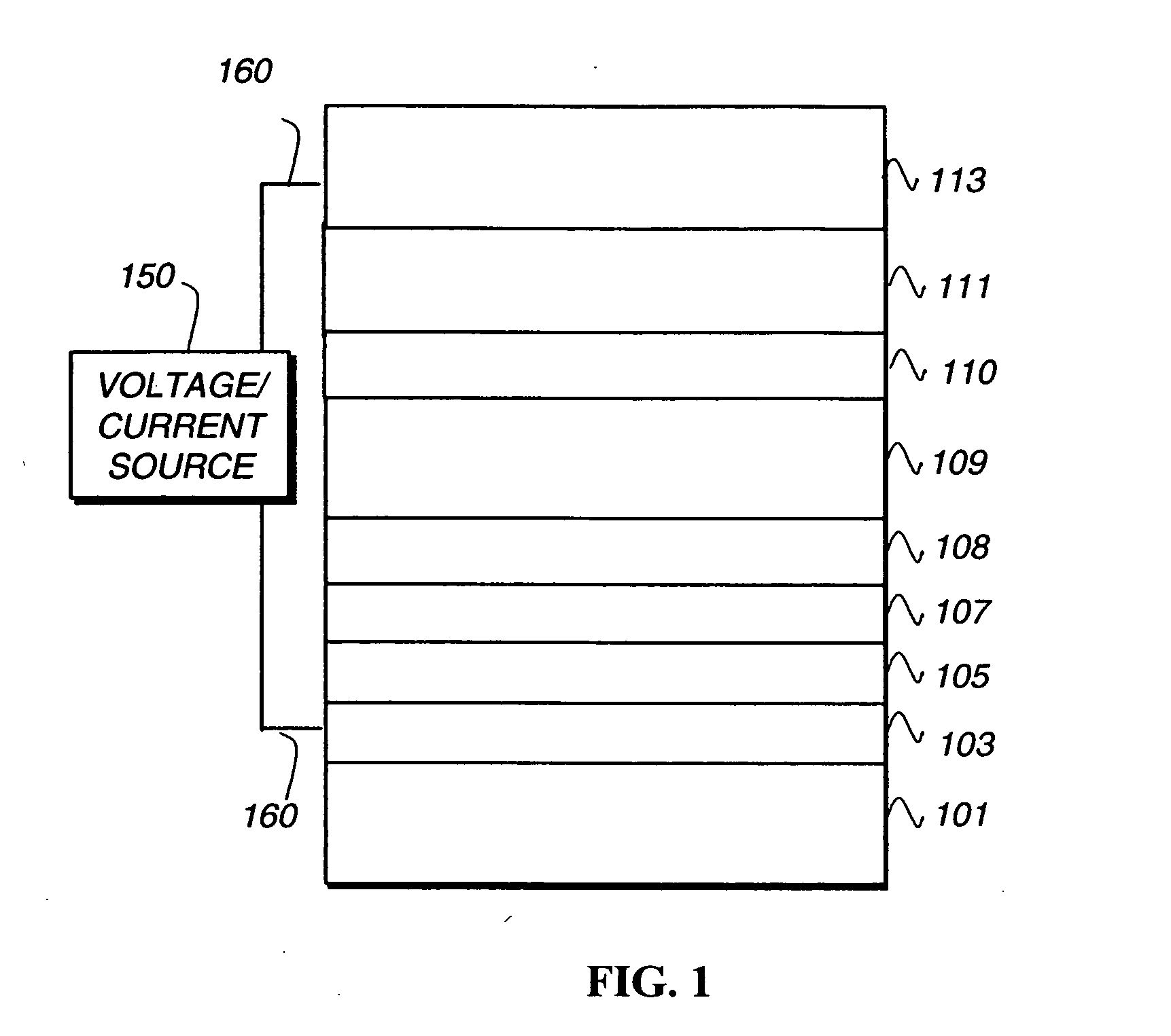

TFT floating gate memory cell structures

ActiveUS20100001282A1Improve reliabilitySmall geometric cell sizeTransistorSemiconductor/solid-state device manufacturingDiffusion barrierDielectric layer

A device having thin-film transistor (TFT) floating gate memory cell structures is provided. The device includes a substrate, a dielectric layer on the substrate, and one or more source or drain regions being embedded in the dielectric layer. the dielectric layer being associated with a first surface. Each of the one or more source or drain regions includes an N+ polysilicon layer on a diffusion barrier layer which is on a first conductive layer. The N+ polysilicon layer has a second surface substantially co-planar with the first surface. Additionally, the device includes a P− polysilicon layer overlying the co-planar surface and a floating gate on the P− polysilicon layer. The floating gate is a low-pressure CVD-deposited silicon layer sandwiched by a bottom oxide tunnel layer and an upper oxide block layer. Moreover, the device includes at least one control gate made of a P+ polysilicon layer overlying the upper oxide block layer. A method of making the same memory cell structure is provided and can be repeated to integrate the structure three-dimensionally.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

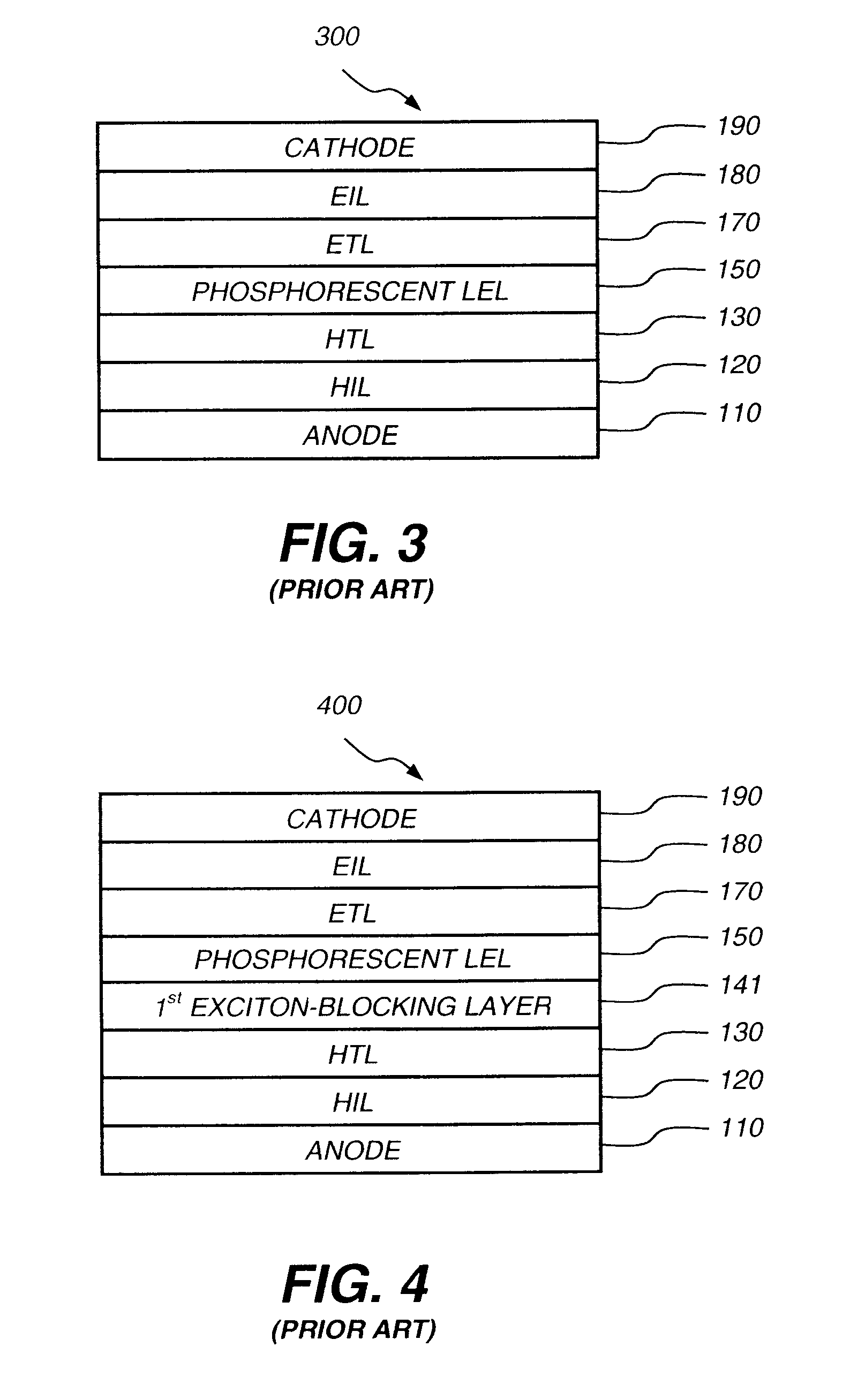

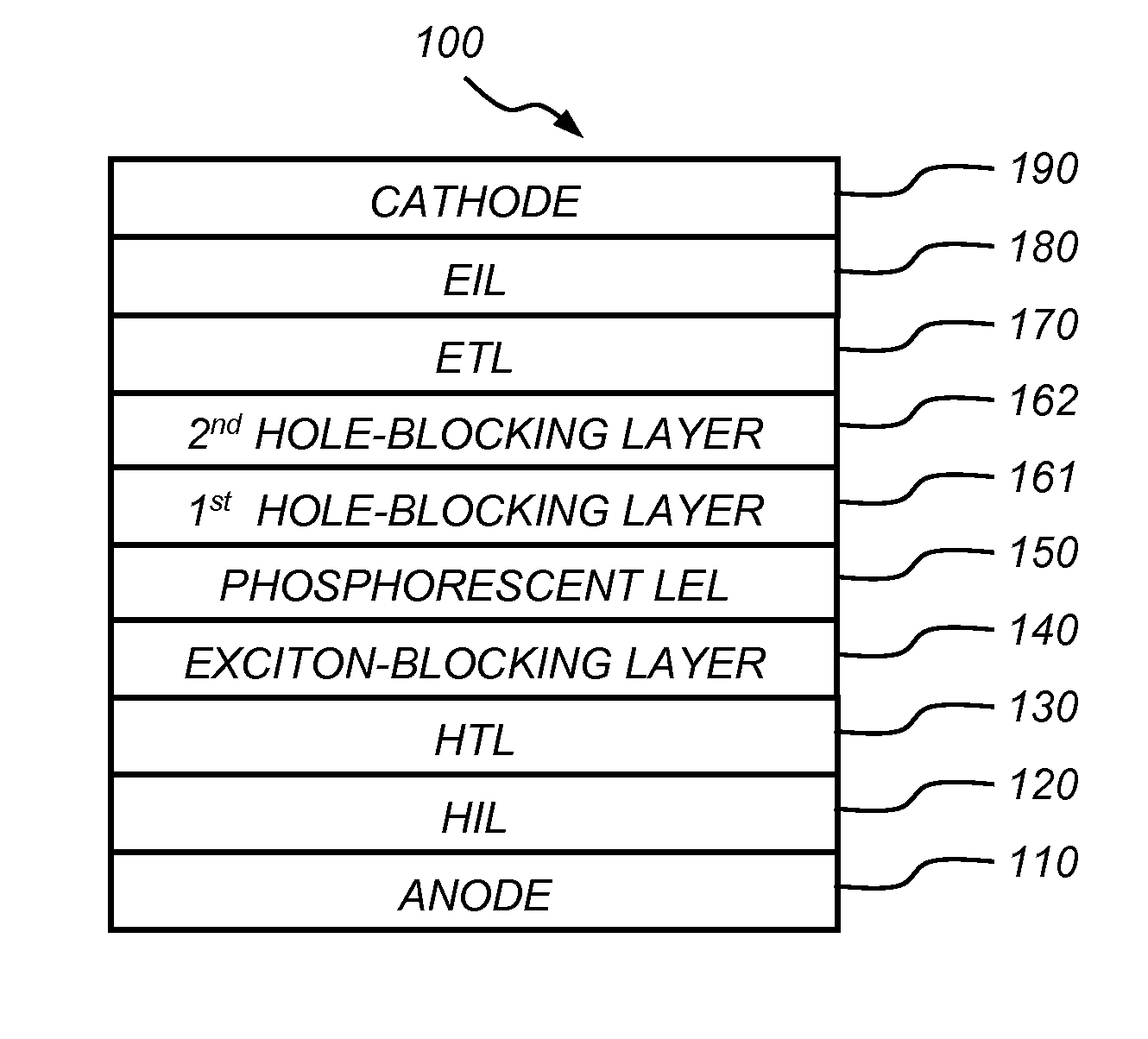

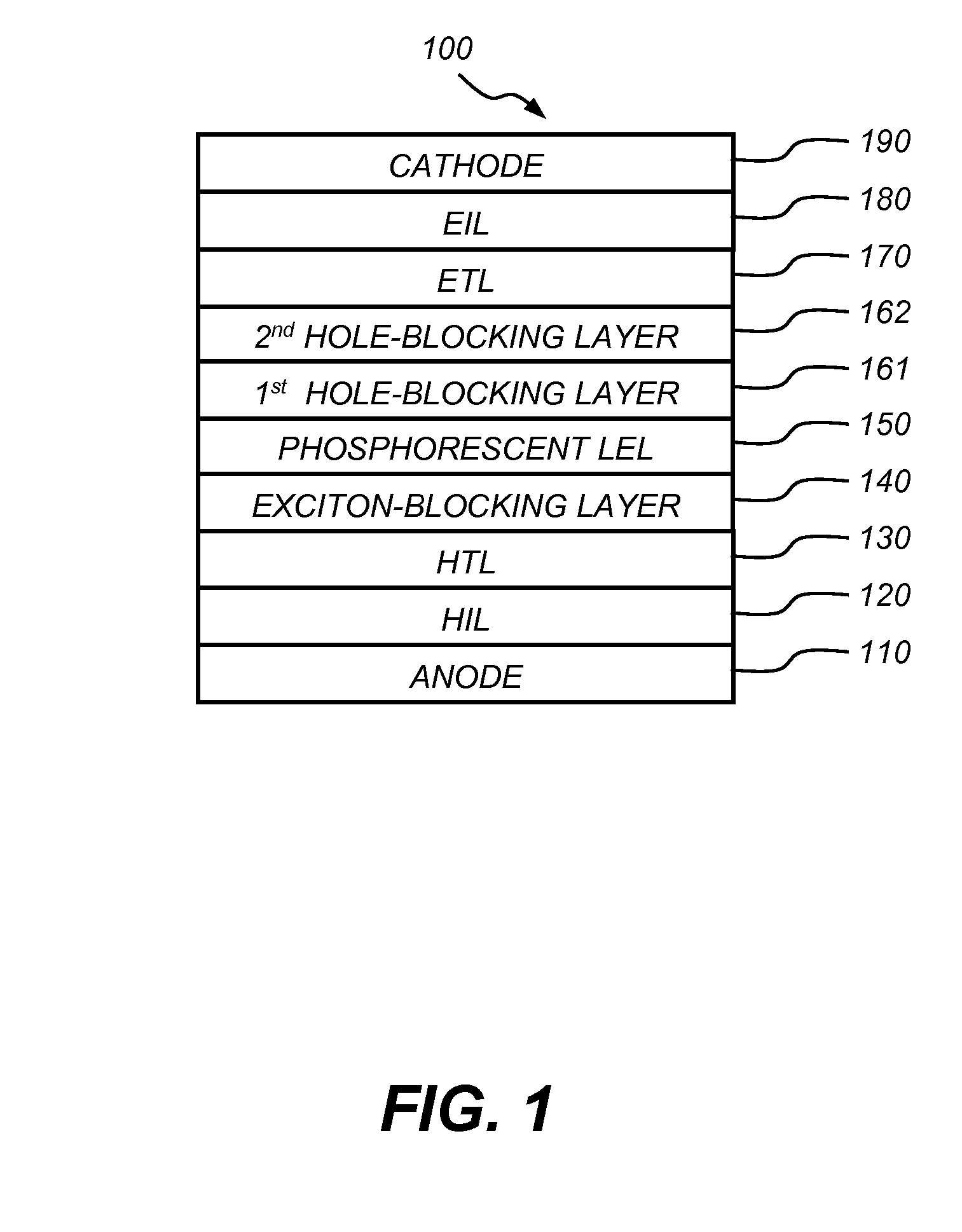

Phosphorescent oleds with exciton blocking layer

ActiveUS20060134460A1Improve efficiencyReduce the driving voltageDischarge tube luminescnet screensElectroluminescent light sourcesElectron holePhosphorescent oleds

An electroluminescent device comprises a cathode and an anode; and, located therebetween, a light-emitting layer (LEL) comprising at least one hole transporting co-host and at least one electron transporting co-host, together with at least one phosphorescent emitter, and wherein the triplet energy of each of the co-host materials is greater than the triplet energy of the phosphorescent emitter, and further containing an exciton blocking layer comprising a hole transporting material with triplet energy greater or equal to 2.5 eV adjacent the emitting layer on the anode side. The invention provides devices that emit light with high luminous efficiency at low voltage.

Owner:GLOBAL OLED TECH

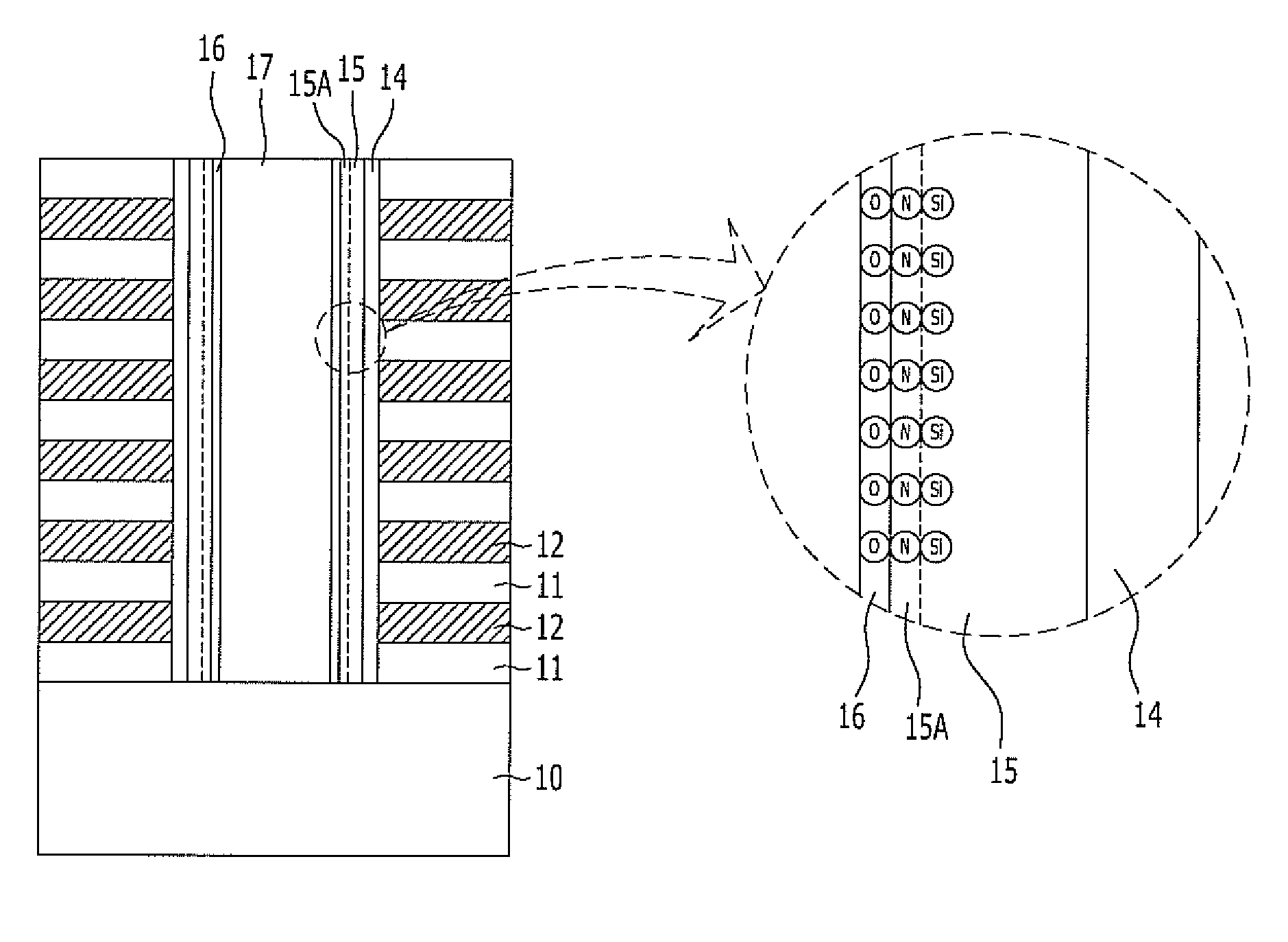

Nonvolatile memory device and method for fabricating the same

InactiveUS20110266611A1Excellent characteristicsIncrease speedSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerDielectric layer

A nonvolatile memory device includes a plurality of interlayer dielectric layers and conductive layers for gate electrodes alternately stacked over a substrate, a channel trench passing through the interlayer dielectric layers and the conductive layers and exposing the substrate, a charge blocking layer and a charge trap or charge storage layer formed on sidewalls of the trench, a coupling prevention layer formed at the surface of the charge trap or charge storage layer, and a tunnel insulation layer formed over the coupling prevention layer.

Owner:SK HYNIX INC

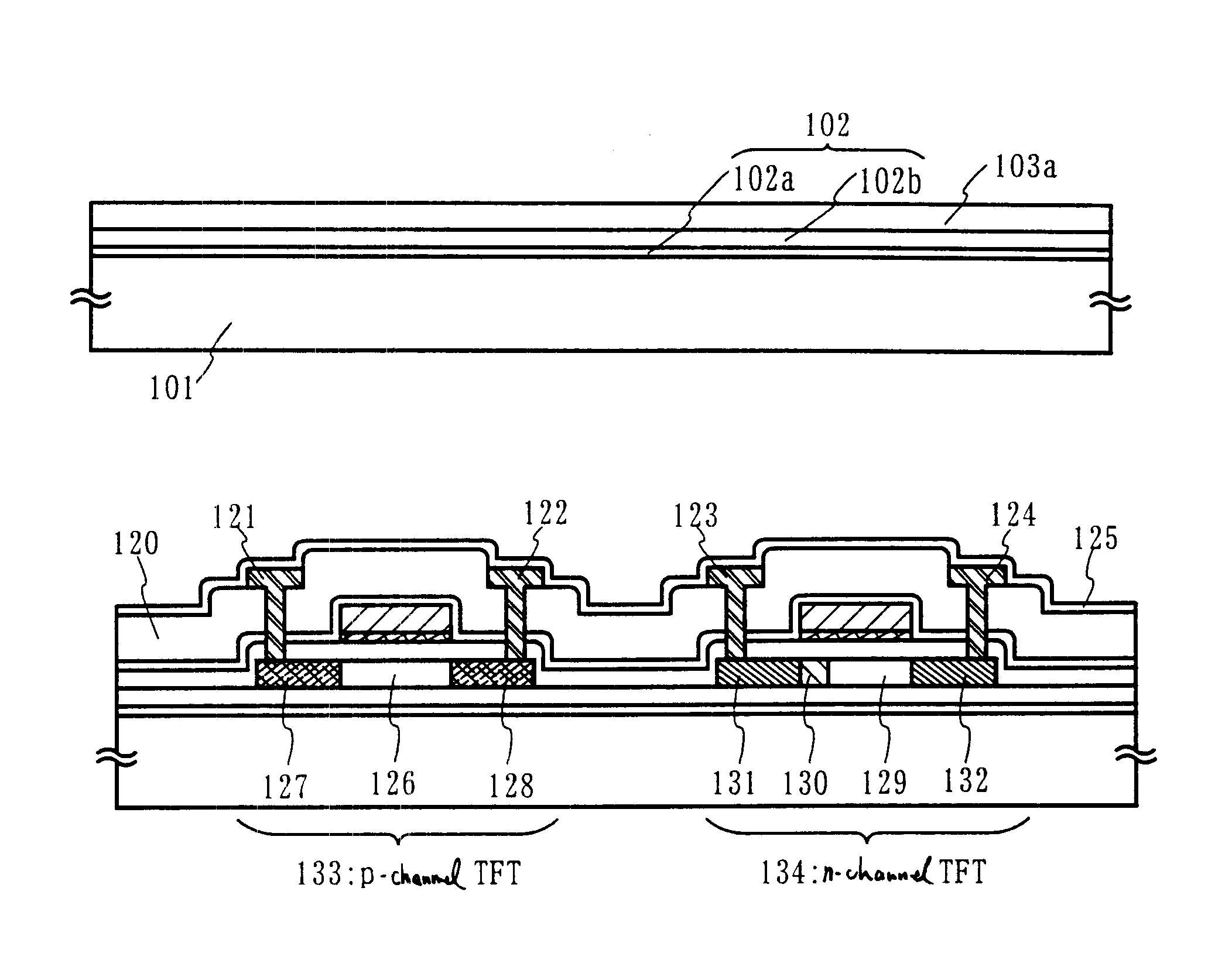

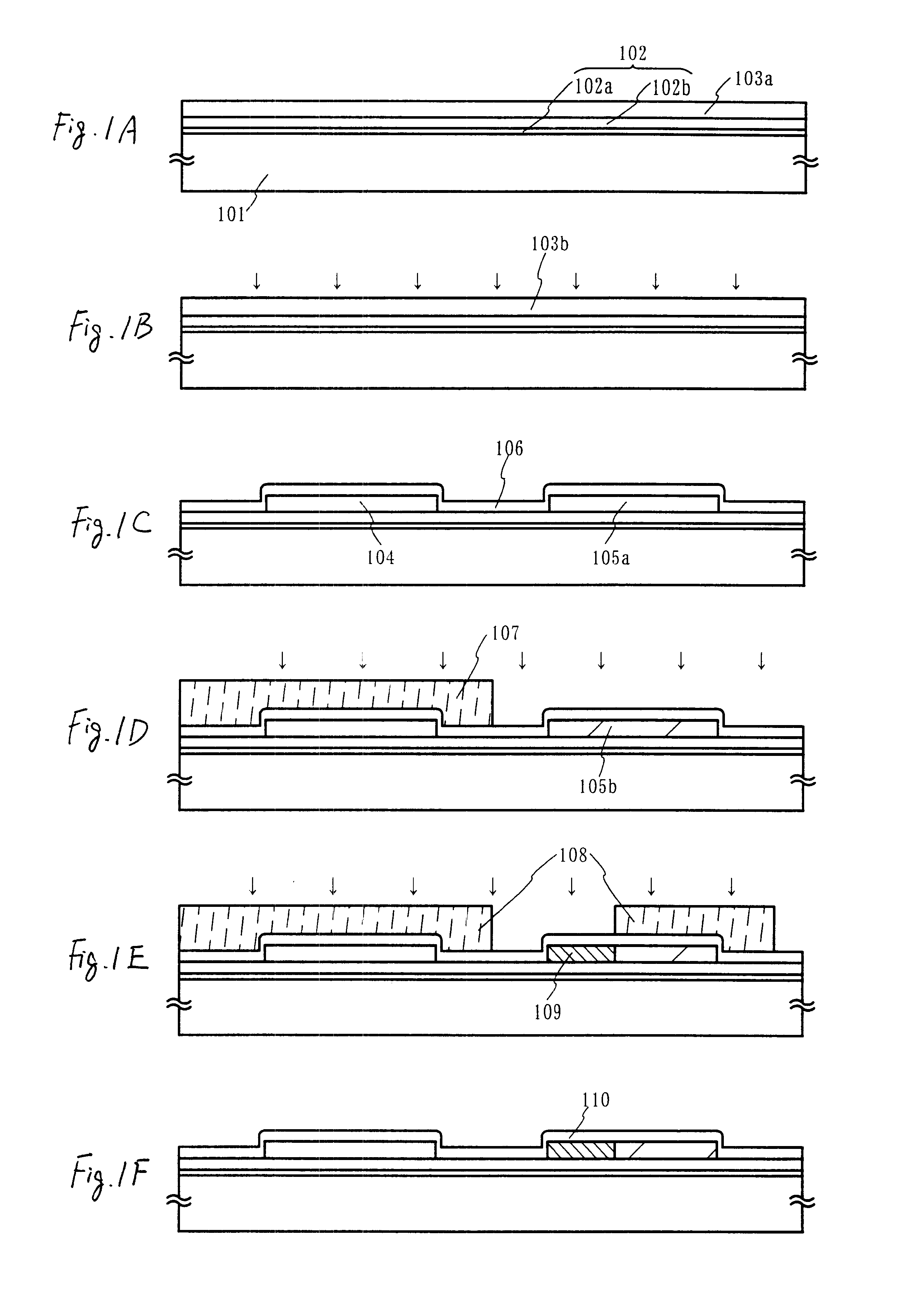

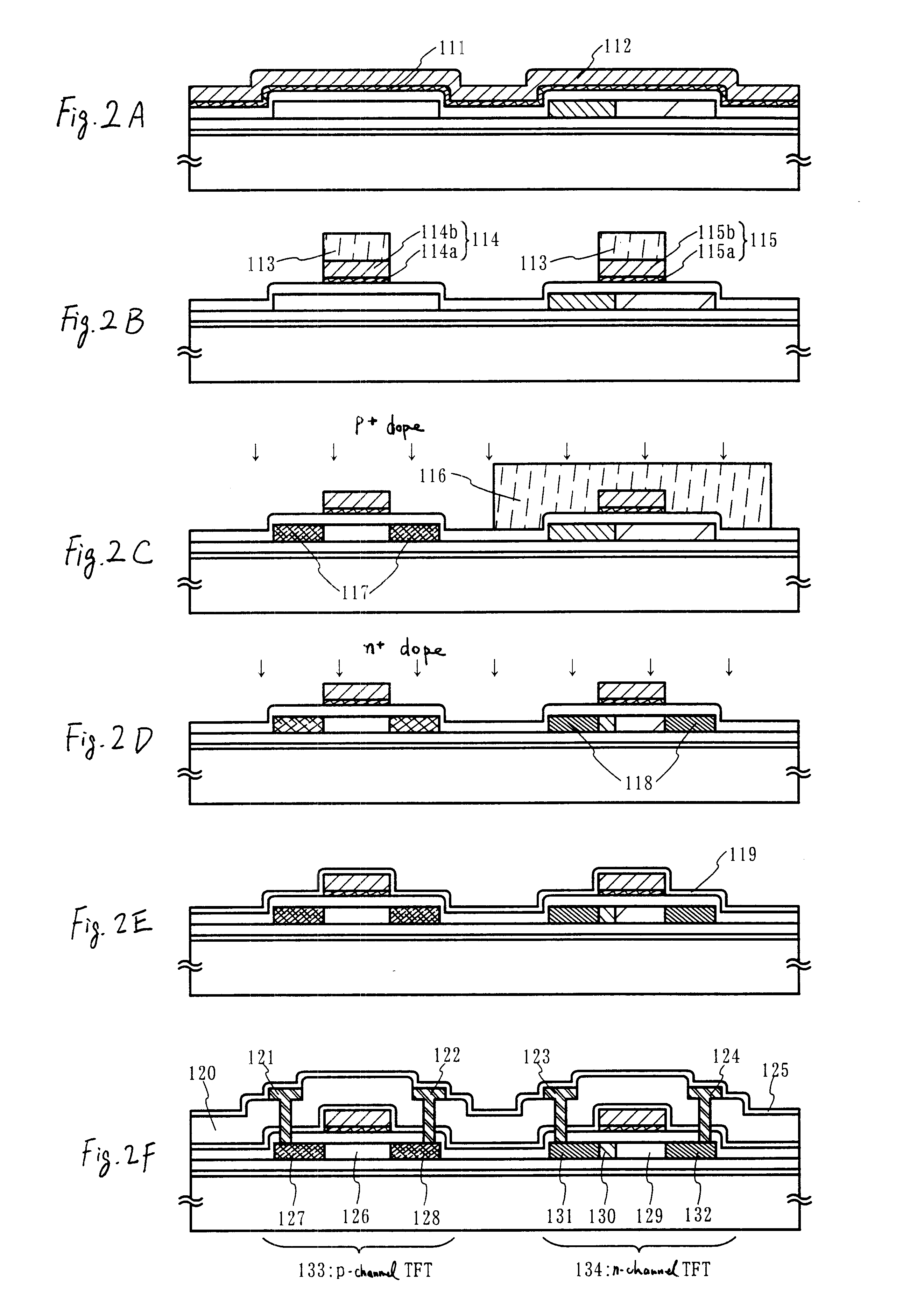

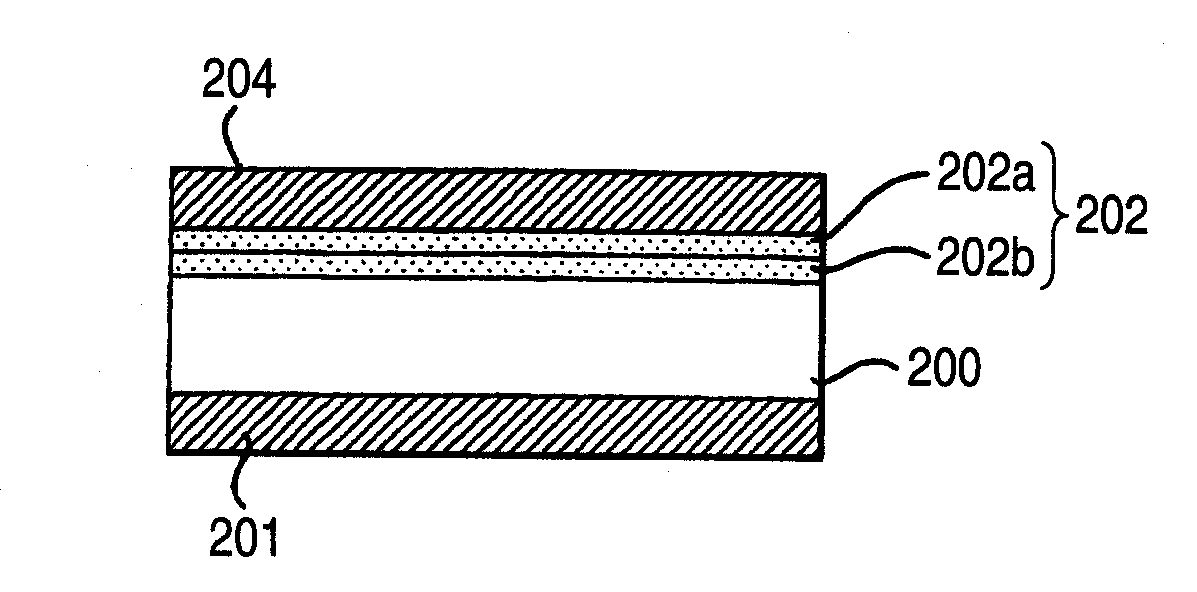

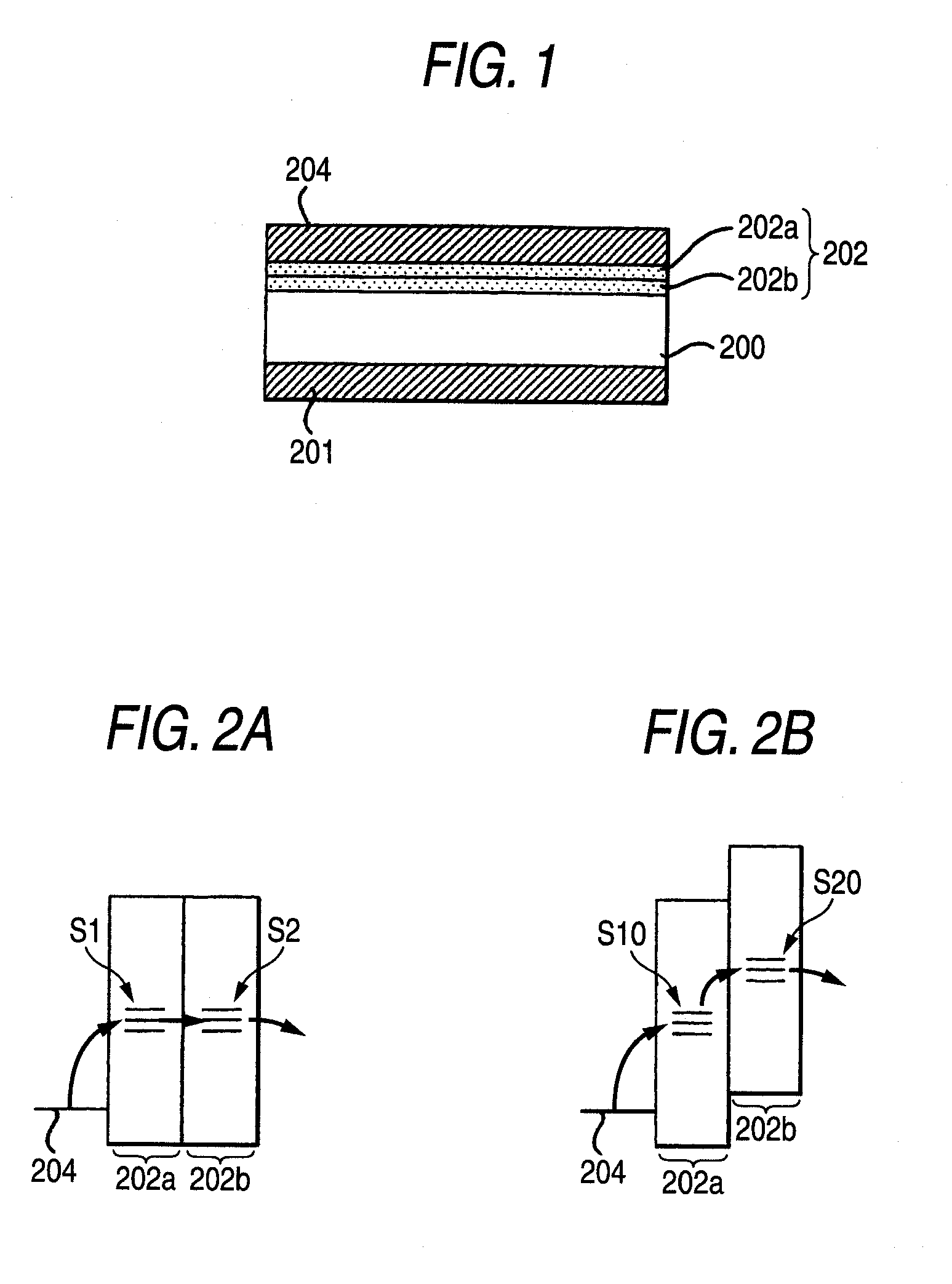

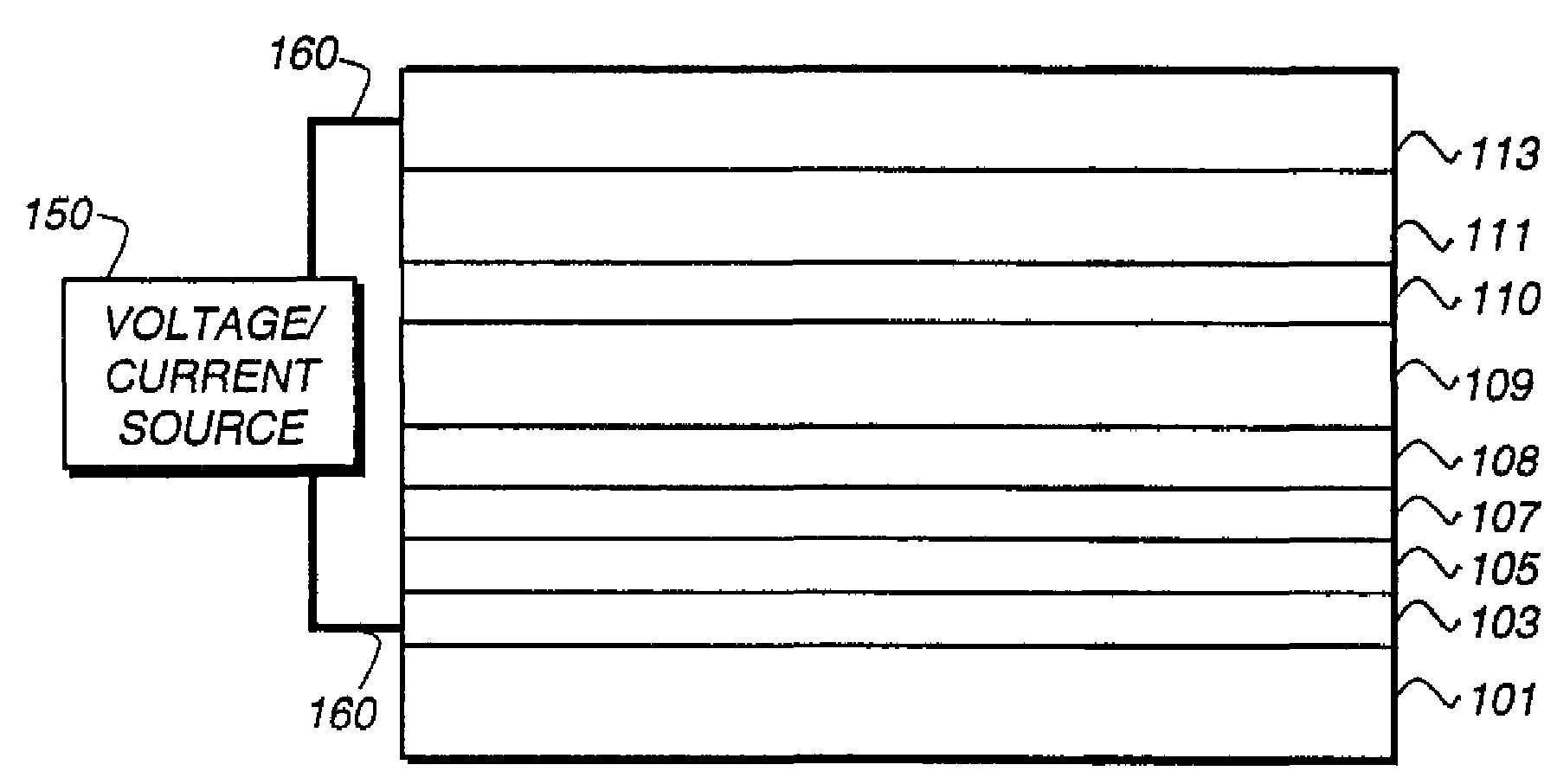

Oxynitride laminate "blocking layer" for thin film semiconductor devices

Channel doping is an effective method for controlling Vth, but if Vth shifts to the order of -4 to -3 V when forming circuits such as a CMOS circuit formed from both an n-channel TFT and a P-channel TFT on the same substrate, then it is difficult to control the Vth of both TFTs with one channel dope. In order to solve the above problem, the present invention forms a blocking layer on the back channel side, which is a laminate of a silicon oxynitride film (A) manufactured from SiH4, NH3, and N2O, and a silicon oxynitride film (B)manufactured from SiH4and N2O. By making this silicon oxynitride film laminate structure, contamination by alkaline metallic elements from the substrate can be prevented, and influence by stresses, caused by internal stress, imparted to the TFT can be relieved.

Owner:SEMICON ENERGY LAB CO LTD

Non-volatile memory device and method for fabricating the same

InactiveUS20130161726A1Improve erase operation characteristicImprove operating characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingInter layerDielectric layer

A non-volatile memory device includes a channel layer vertically extending from a substrate, a plurality of inter-layer dielectric layers and a plurality of gate electrodes that are alternately stacked along the channel layer, and an air gap interposed between the channel layer and each of the plurality of gate electrodes. The non-volatile memory device may improve erase operation characteristics by suppressing back tunneling of electrons by substituting a charge blocking layer interposed between a gate electrode and a charge storage layer with an air gap, and a method for fabricating the non-volatile memory device.

Owner:SK HYNIX INC

Atomic layer deposition of tungsten material

InactiveCN101308794ASemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseNucleation

An implementing mode of the invention provides an improved technology for depositing materials containing tungsten. The technology utilizes an infusion technology and a gaseous phase deposition technology, such as atomic layer deposition (ALD), to provide tungsten-containing materials with obviously improved surface evenness and yield. In one implementing mode, a method for forming tungsten-containing materials on a substrate is provided. The method comprises deposing a substrate, which contains a bottom coating deposited thereon, in a technological chamber; exposing the substrate orderly in a precursor of tungsten and reducing gases so as to deposit a tungsten nucleation layer on the bottom coating, during the ALD technology; and depositing a tungsten block layer on the tungsten nucleation layer. The invention is characterized in that the reducing gases comprise a hydrogen gas / hydride flow ratio of 40:1, 100:1, 500:1, 800: 1, 1000:1 or more, and comprise hydride such as diborane, silicane or silicoethane.

Owner:APPLIED MATERIALS INC

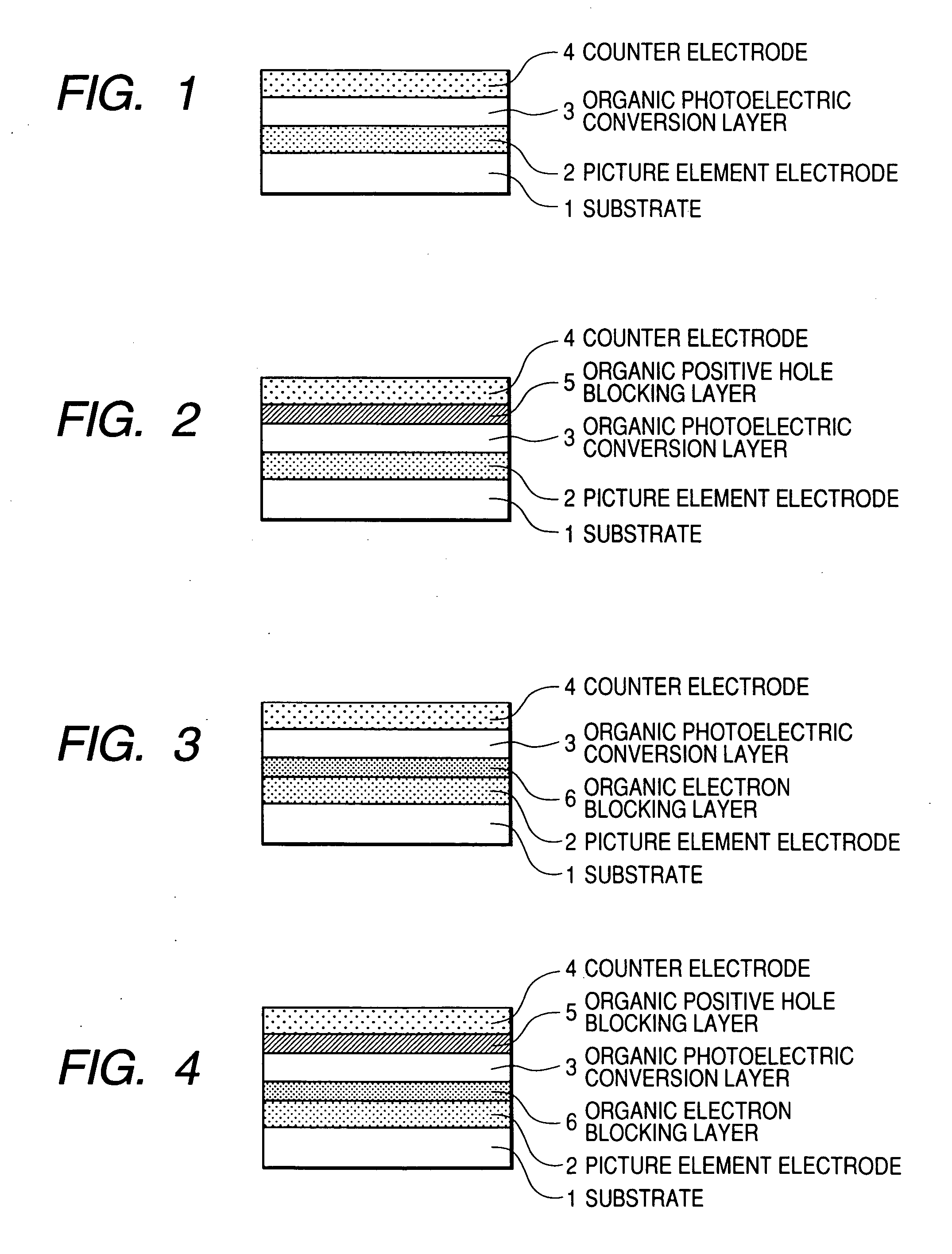

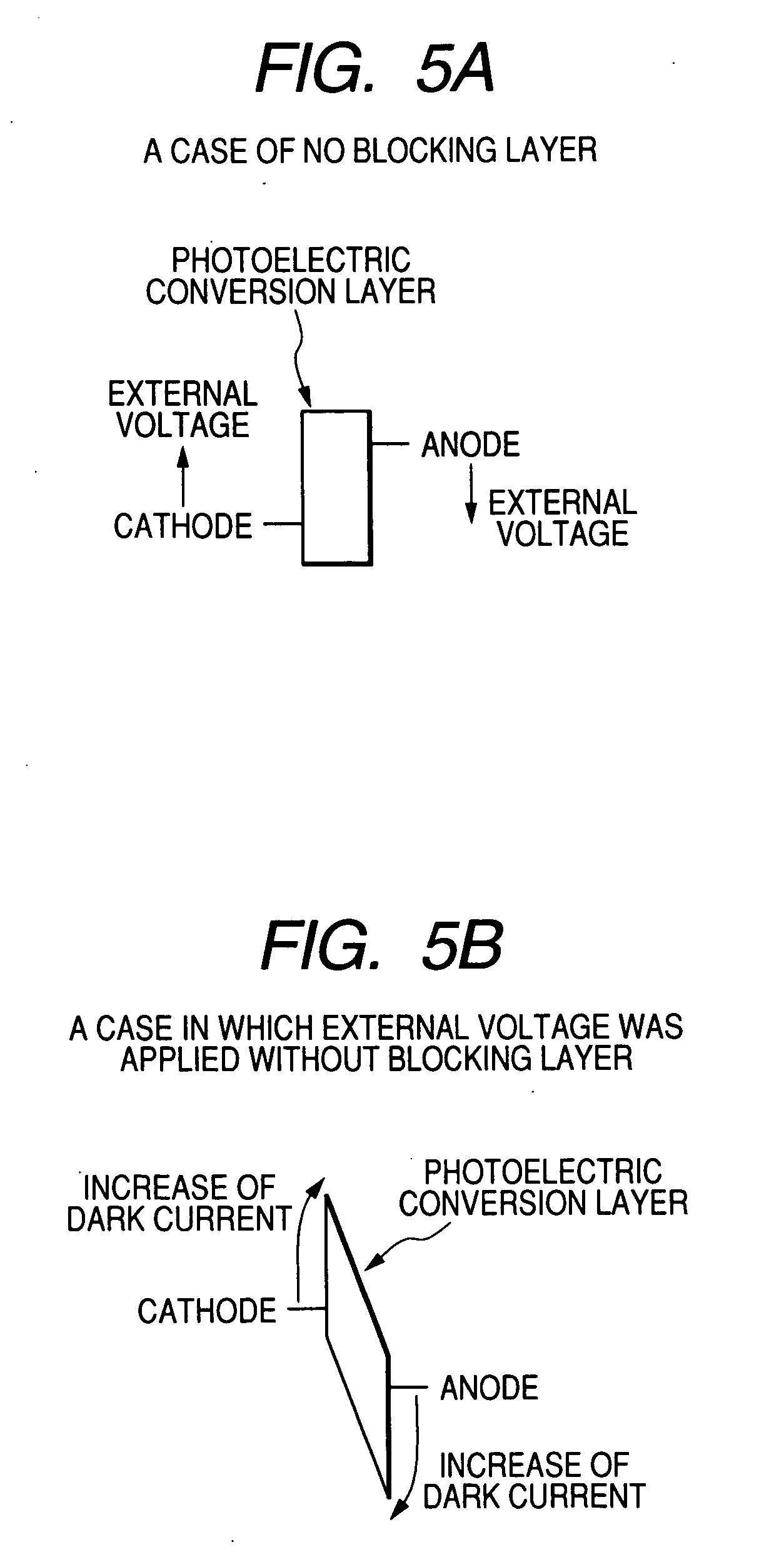

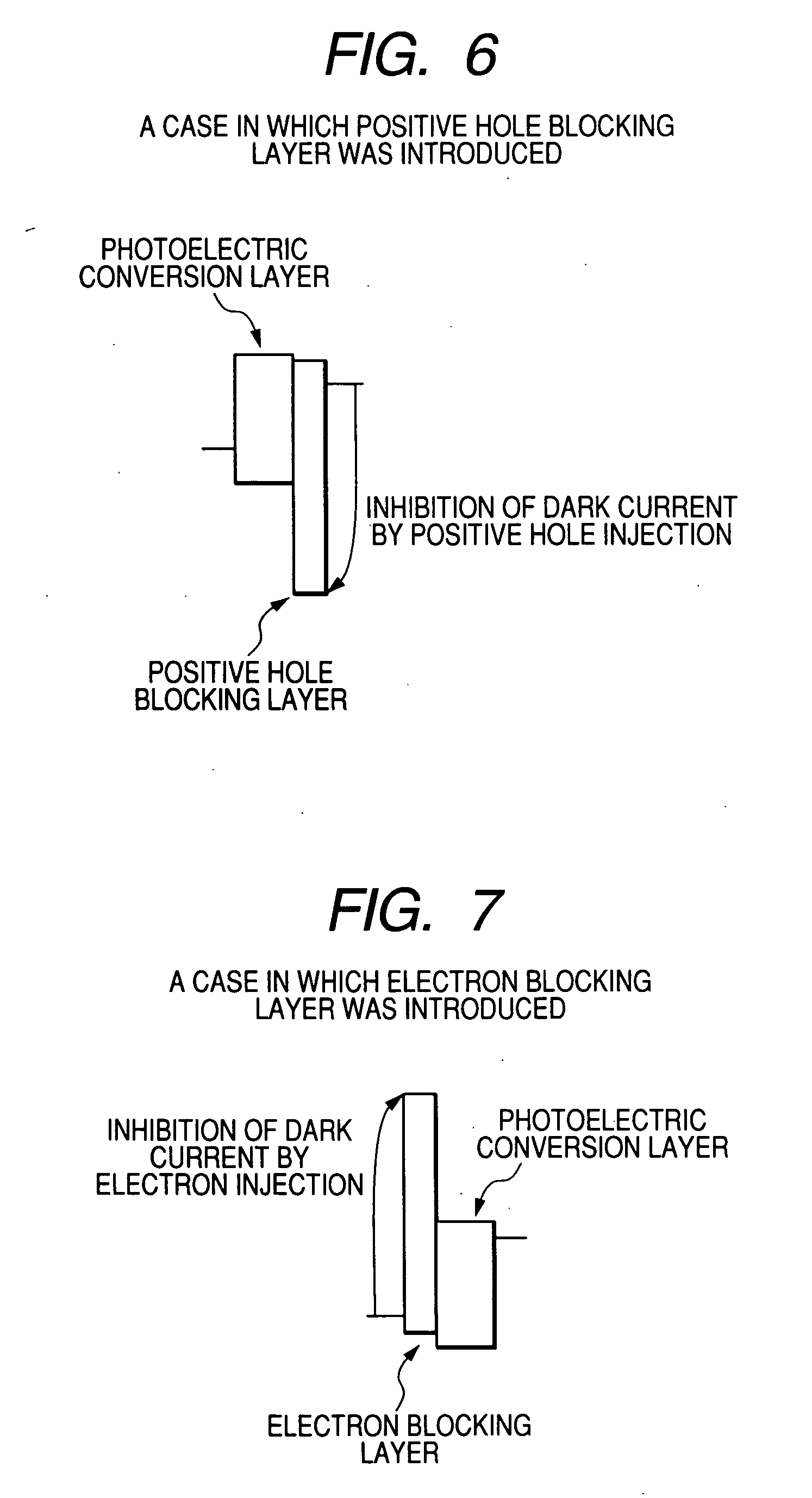

Photoelectric conversion element and solid-state image pickup device

InactiveUS20080035965A1Effective reduction in dark currentTotal current dropTelevision system detailsSolid-state devicesPhotoelectric conversionEngineering

A photoelectric conversion element comprises a photoelectric conversion section that includes: a pair of electrodes; and a photoelectric conversion layer disposed between the pair of electrodes, wherein the photoelectric conversion section further comprises between one of the pair of electrodes and the photoelectric conversion layer a first charge-blocking layer that restrains injection of charges from the one of the electrodes into the photoelectric conversion layer when a voltage is applied to the pair of electrodes, and the first charge-blocking layer comprises a plurality of layers.

Owner:FUJIFILM CORP

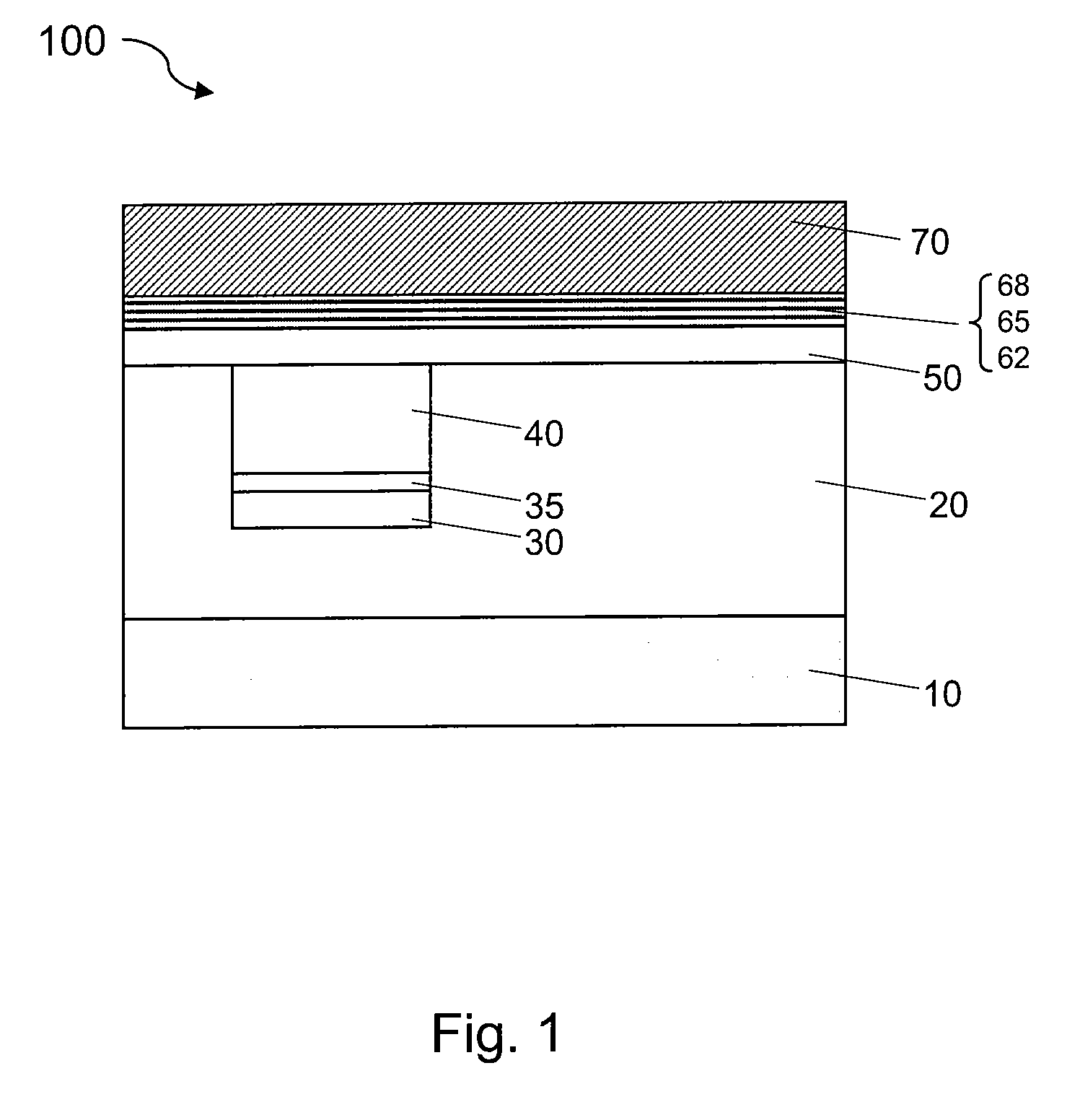

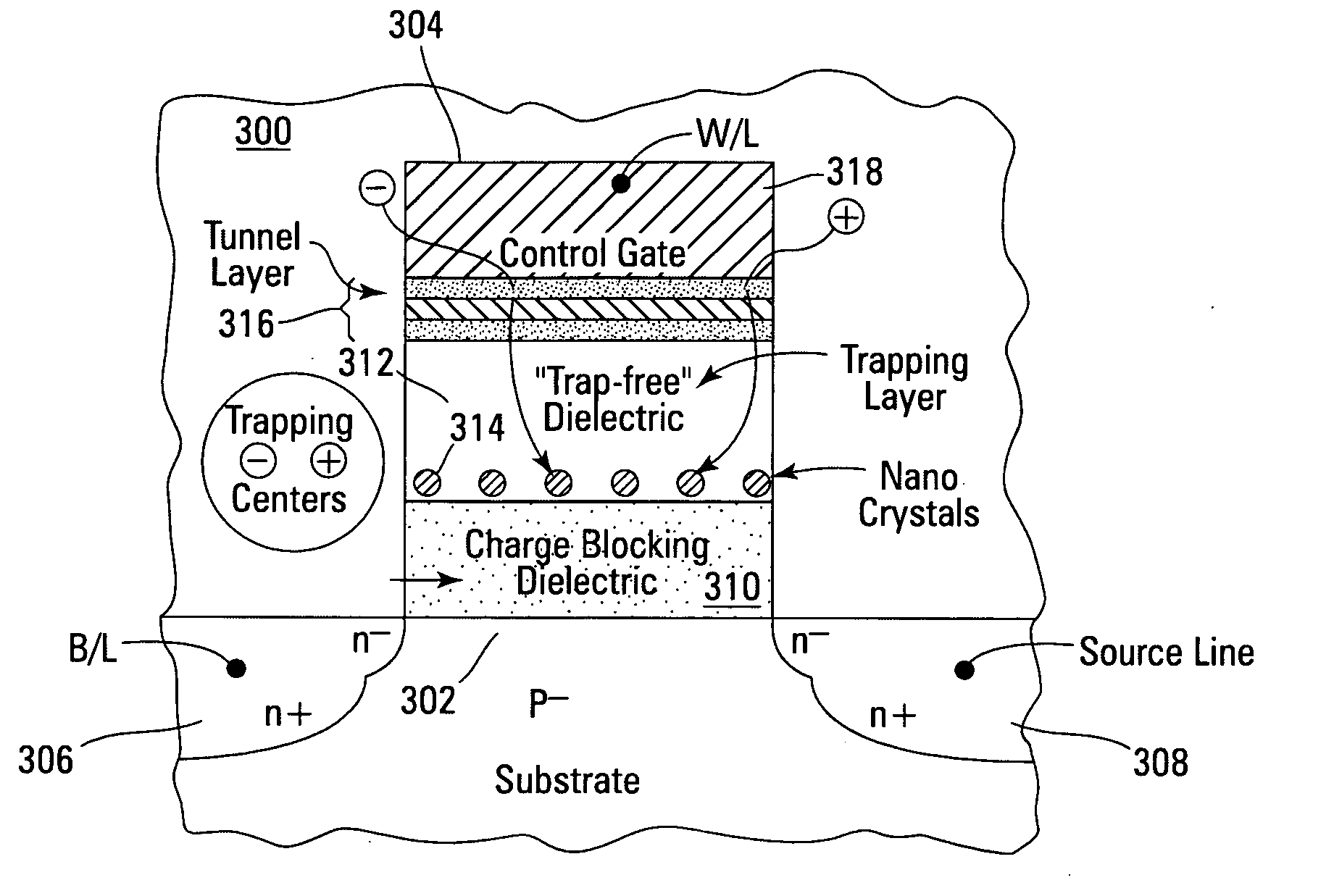

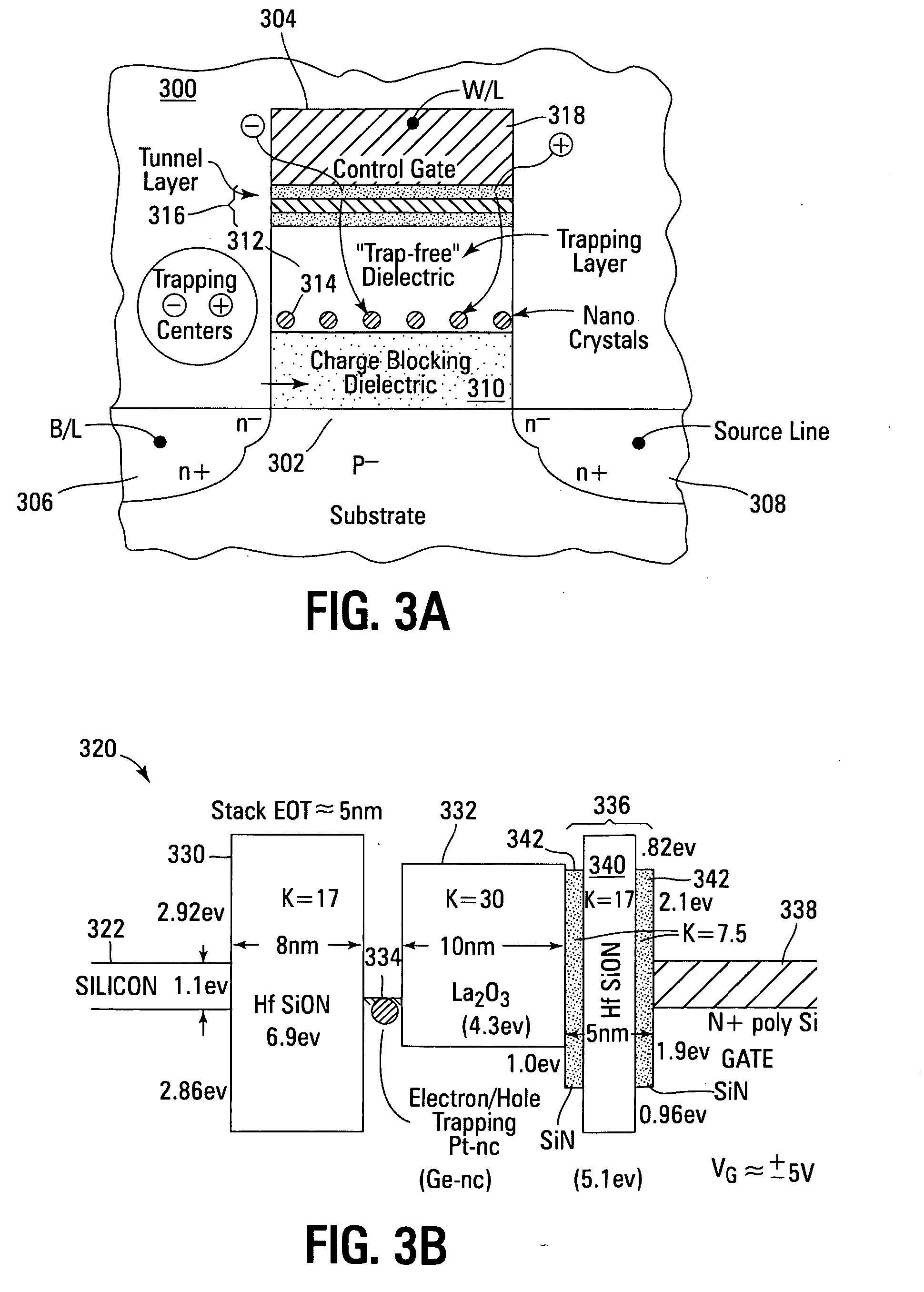

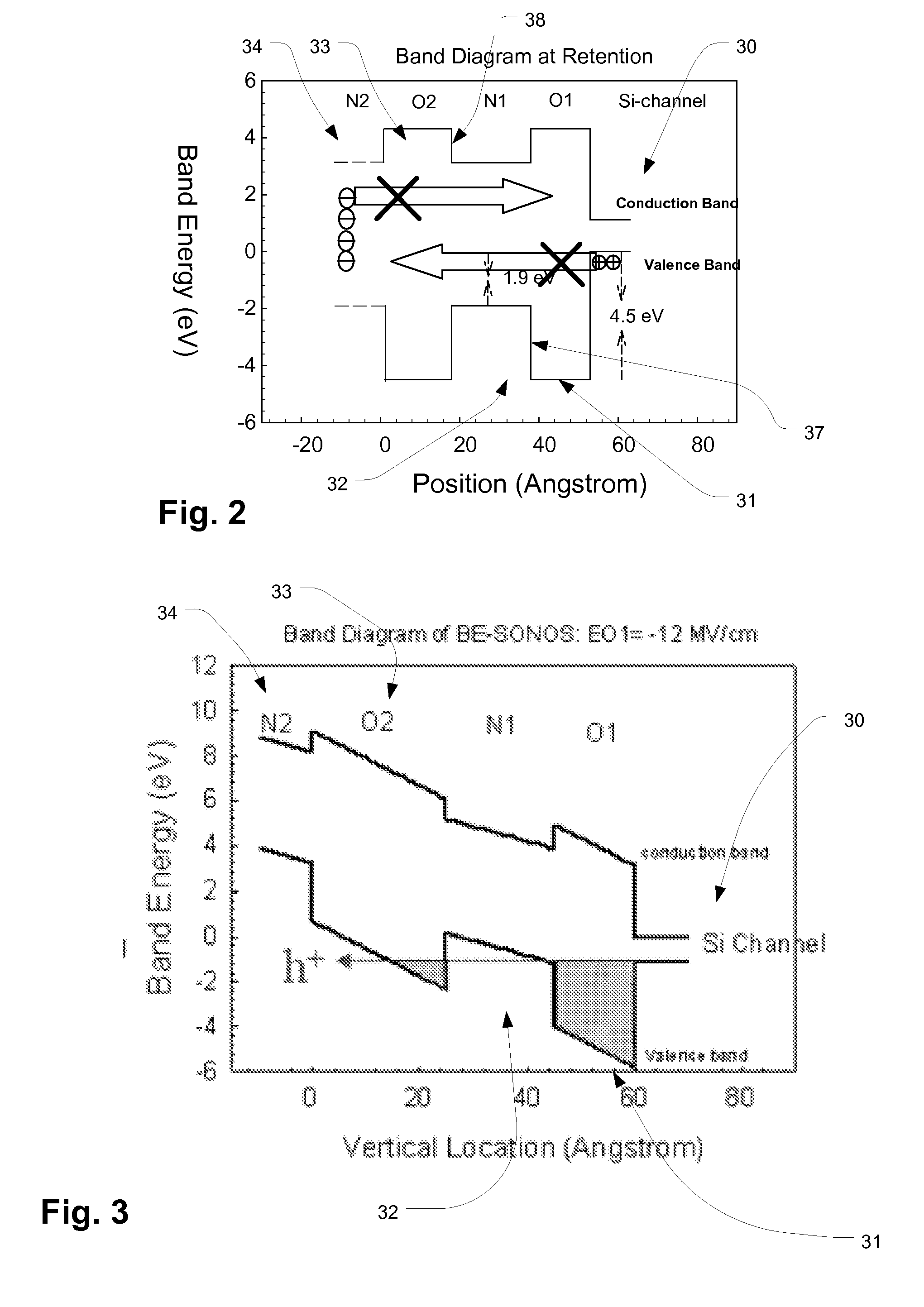

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

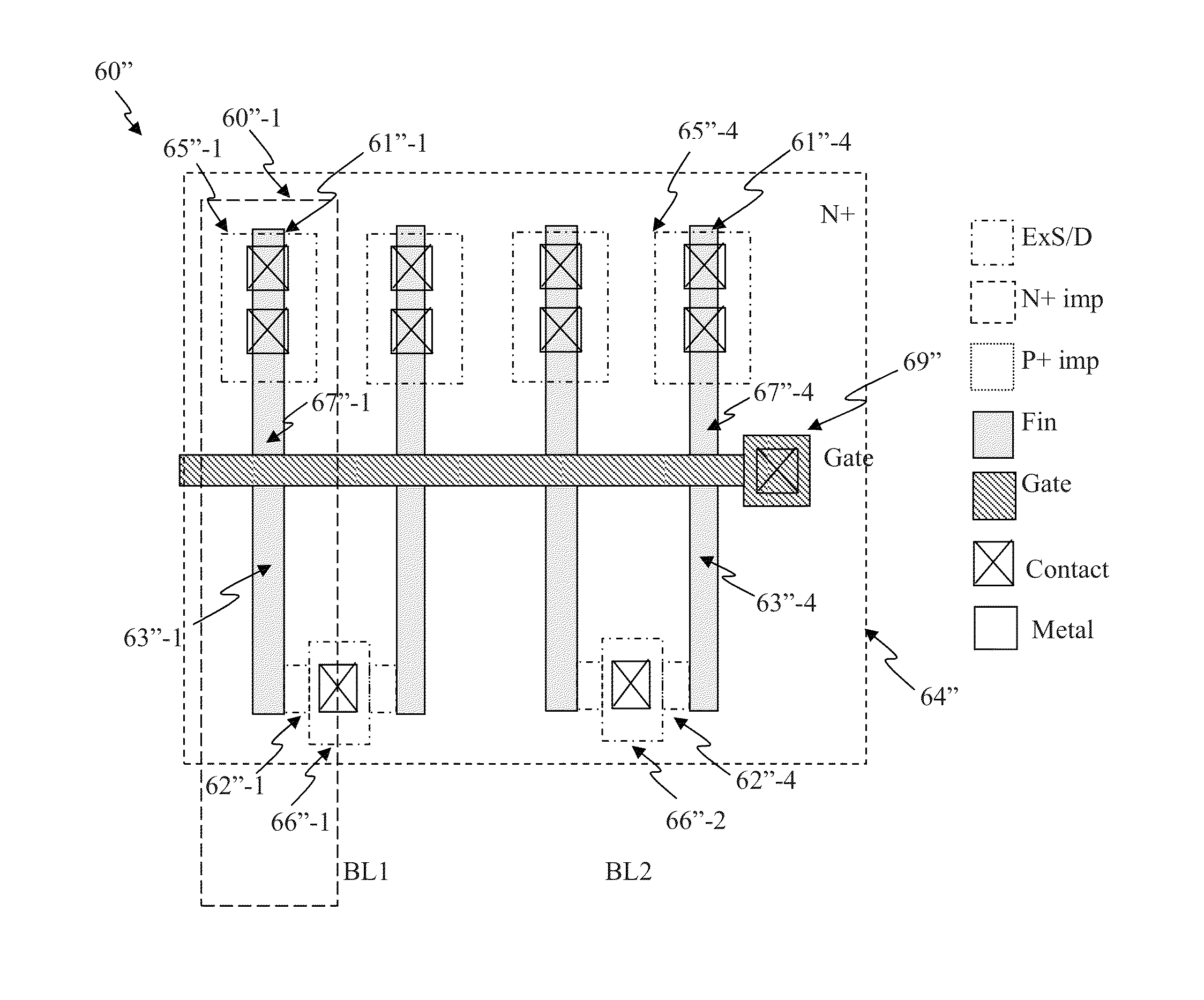

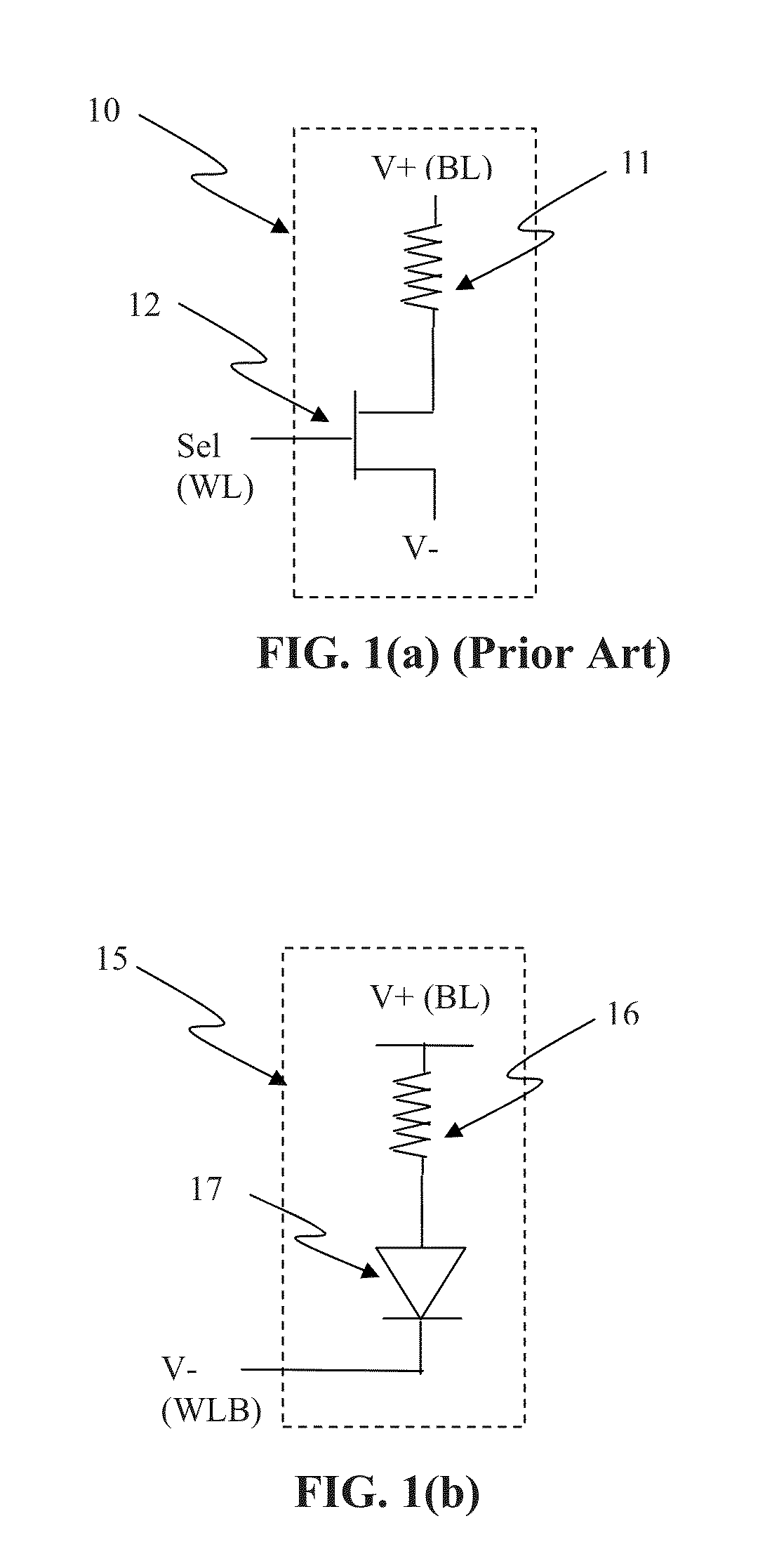

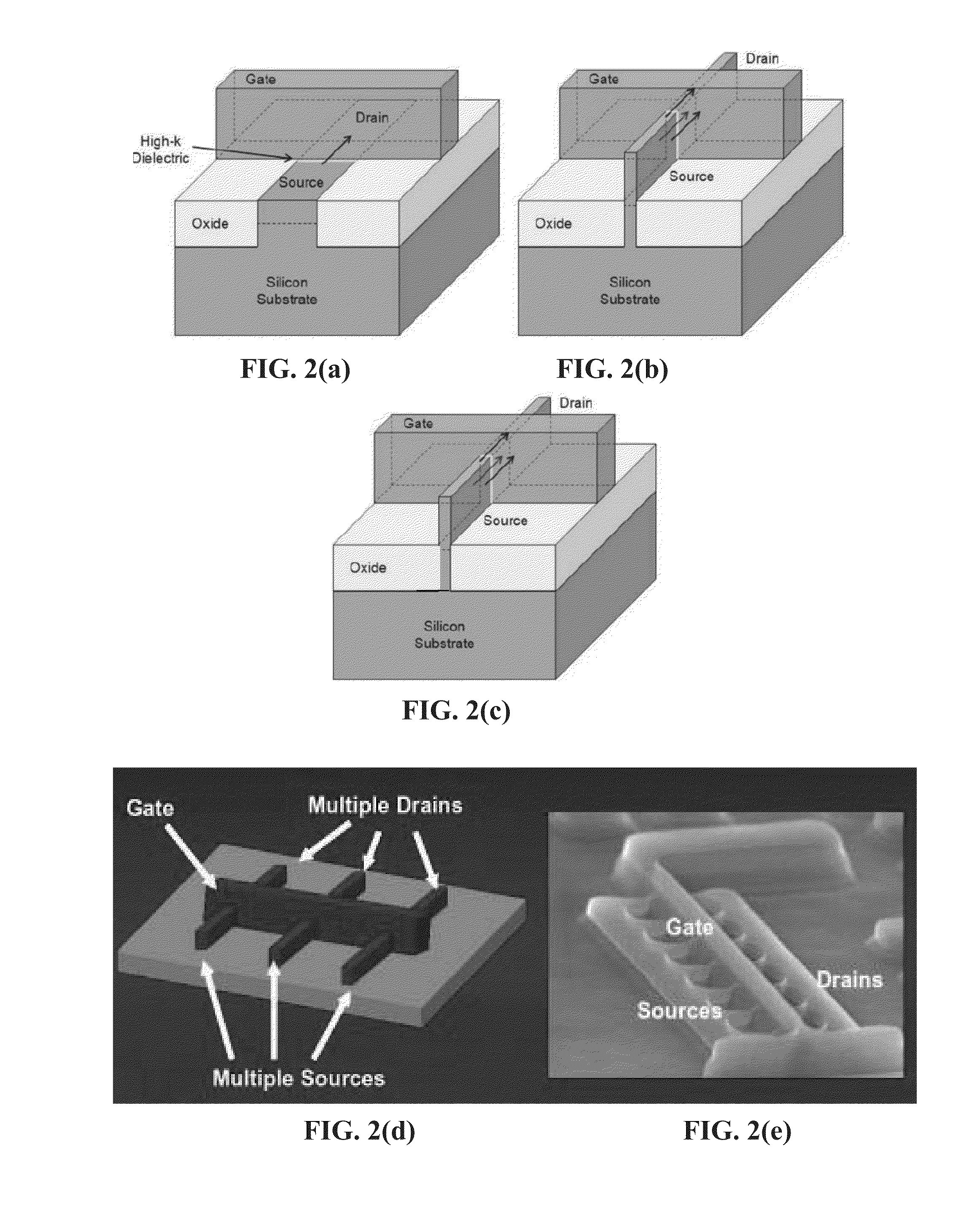

Circuit and system of using finfet for building programmable resistive devices

ActiveUS20130148409A1Small cell sizeLow costSolid-state devicesRead-only memoriesHemt circuitsEngineering

Junction diodes or MOS devices fabricated in standard FinFET technologies can be used as program selectors or One-Time Programmable (OTP) element in a programmable resistive device, such as interconnect fuse, contact / via fuse, anti-fuse, or emerging nonvolatile memory such as MRAM, PCRAM, CBRAM, or RRAM. The MOS or diode can be built on at least one fin structure or at least one active region that has at least one first active region and a second active region. The first and the second active regions can be isolated by a dummy MOS gate or silicide block layer (SBL) to construct a diode.

Owner:ATTOPSEMI TECH CO LTD

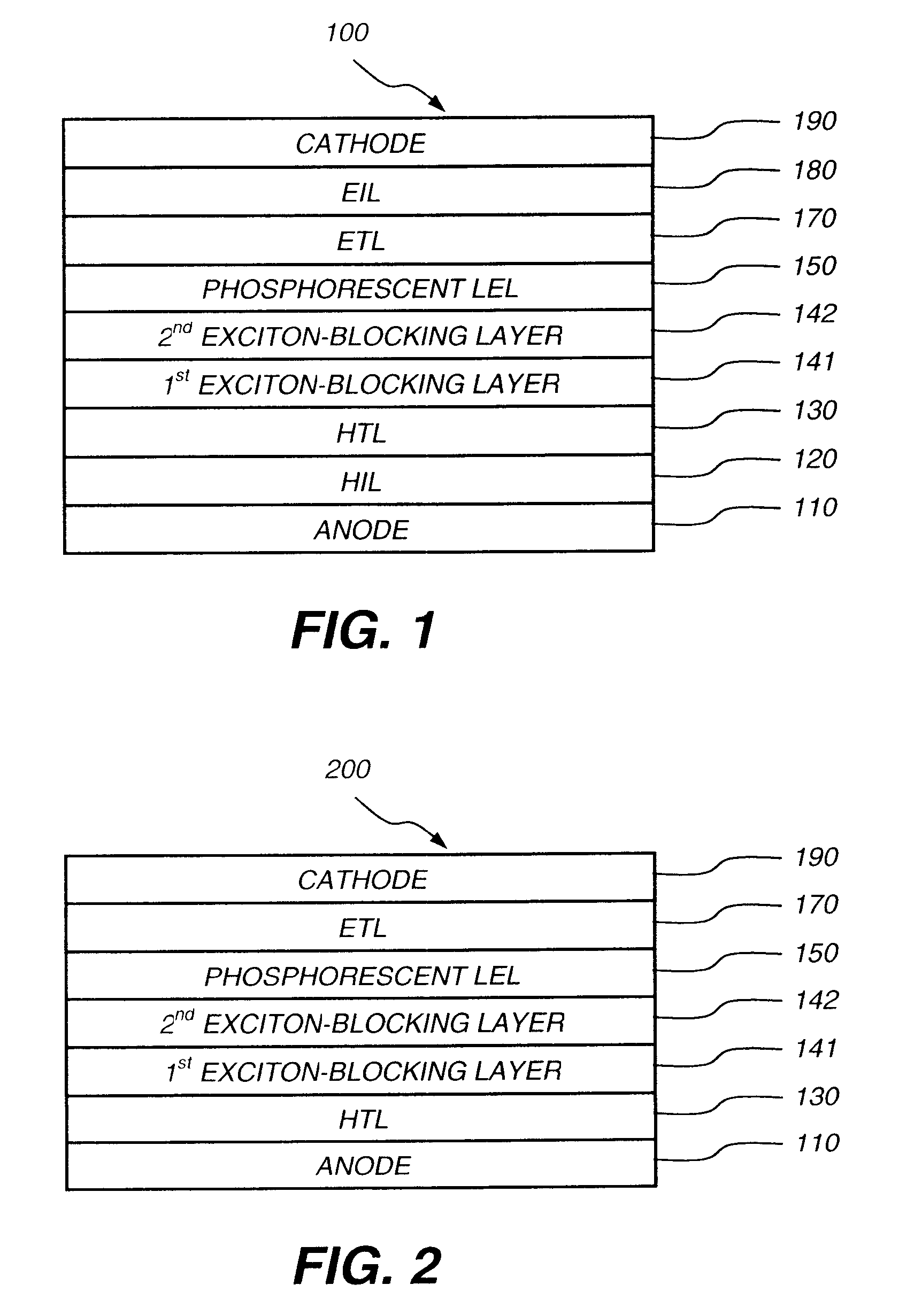

Phosphorescent OLEDs with exciton blocking layer

ActiveUS7597967B2Improve efficiencyReduce the driving voltageDischarge tube luminescnet screensLamp detailsPhosphorescent oledsLow voltage

An electroluminescent device comprises a cathode and an anode; and, located therebetween, a light-emitting layer (LEL) comprising at least one hole transporting co-host and at least one electron transporting co-host, together with at least one phosphorescent emitter, and wherein the triplet energy of each of the co-host materials is greater than the triplet energy of the phosphorescent emitter, and further containing an exciton blocking layer comprising a hole transporting material with triplet energy greater or equal to 2.5 eV adjacent the emitting layer on the anode side. The invention provides devices that emit light with high luminous efficiency at low voltage.

Owner:GLOBAL OLED TECH

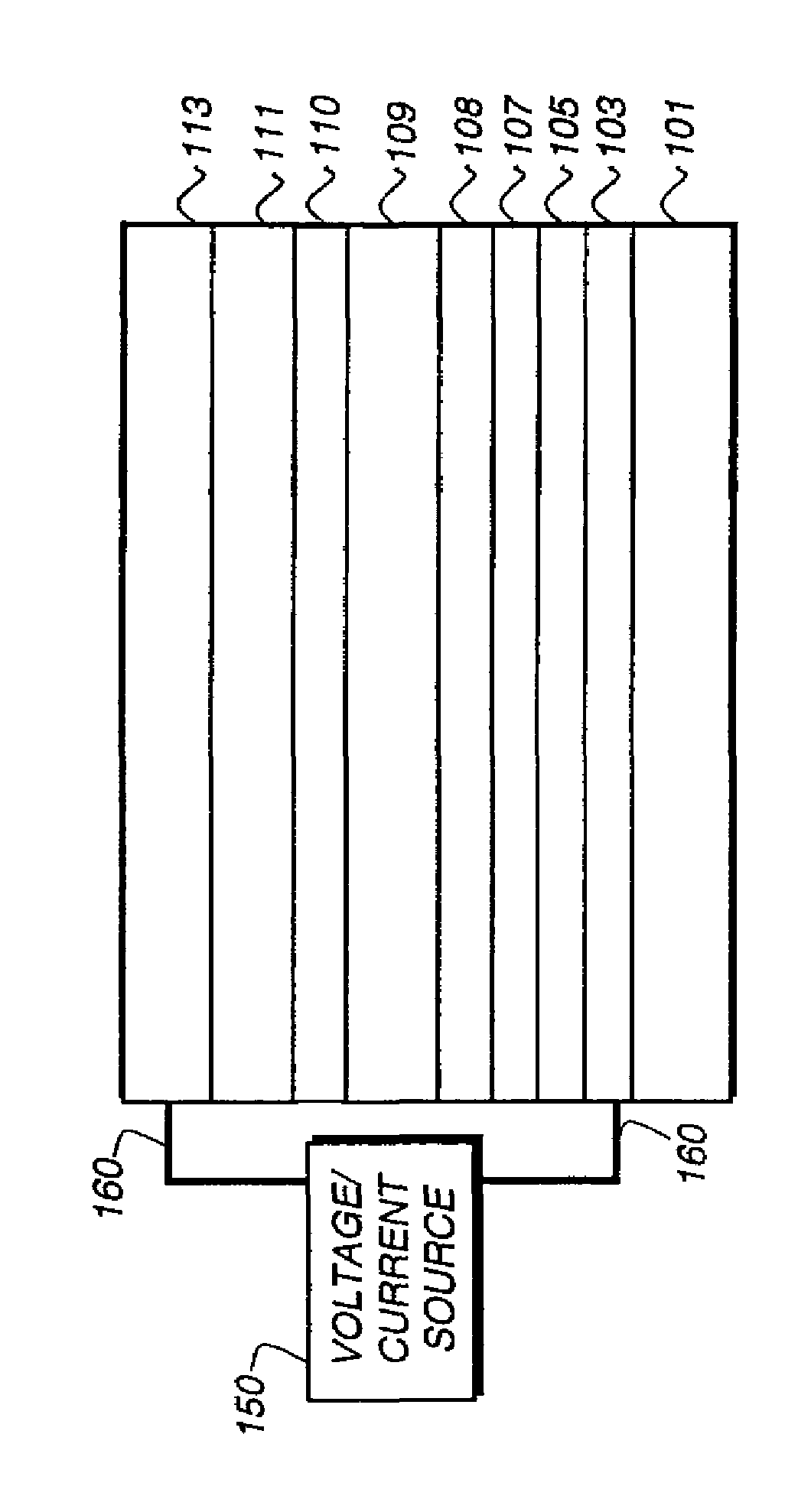

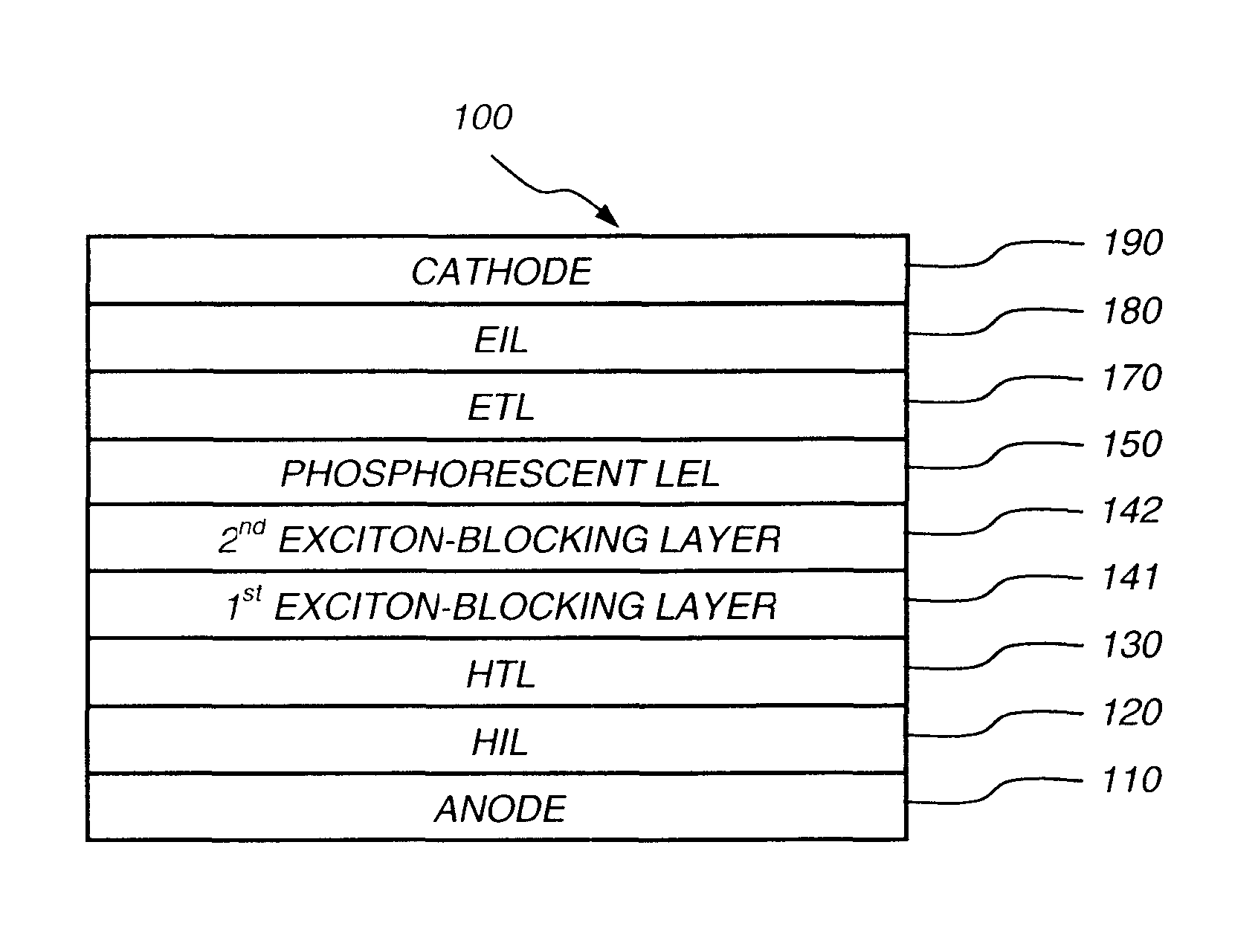

Phosphorescent oled having double exciton-blocking layers

ActiveUS8034465B2Good effectImprove efficiencyDischarge tube luminescnet screensElectroluminescent light sourcesDopantElectron hole

An organic light-emitting device comprising an anode; a cathode; a hole-transporting layer disposed between the anode and the cathode; a phosphorescent light-emitting layer disposed between the hole-transporting layer and the cathode, wherein the phosphorescent light-emitting layer includes at least one host and at least one phosphorescent dopant; a first exciton-blocking layer disposed between the hole-transporting layer and the phosphorescent light-emitting layer; wherein the first exciton-blocking layer has a triplet energy greater than the triplet energy of the host in the phosphorescent light-emitting layer; and a second exciton-blocking layer disposed between the first exciton-blocking layer and the phosphorescent light-emitting layer, wherein the second exciton-blocking layer is in contact with the phosphorescent light-emitting layer, and wherein the second exciton-blocking layer has a triplet energy less than the triplet energy of the first exciton-blocking layer.

Owner:GLOBAL OLED TECH

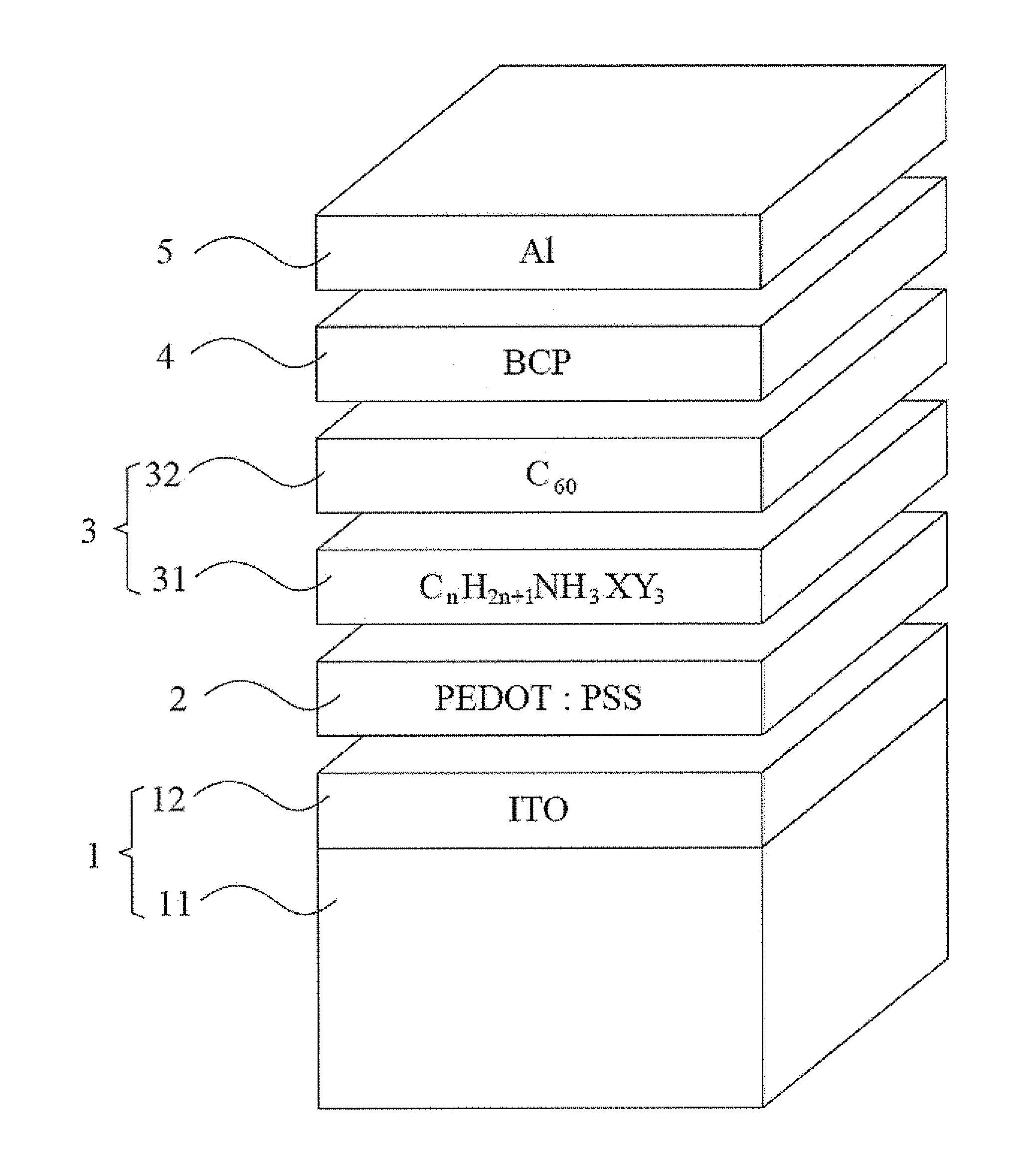

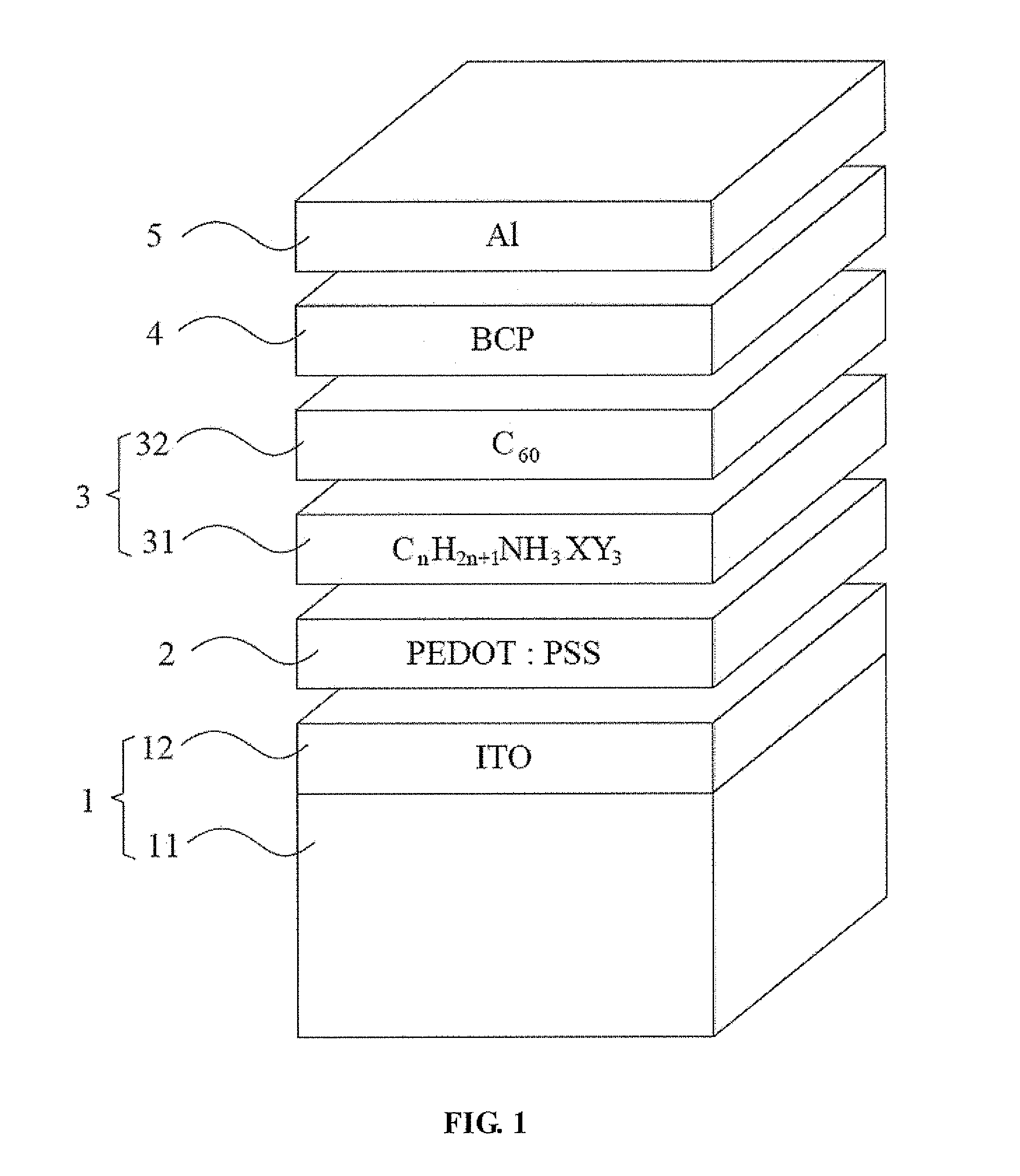

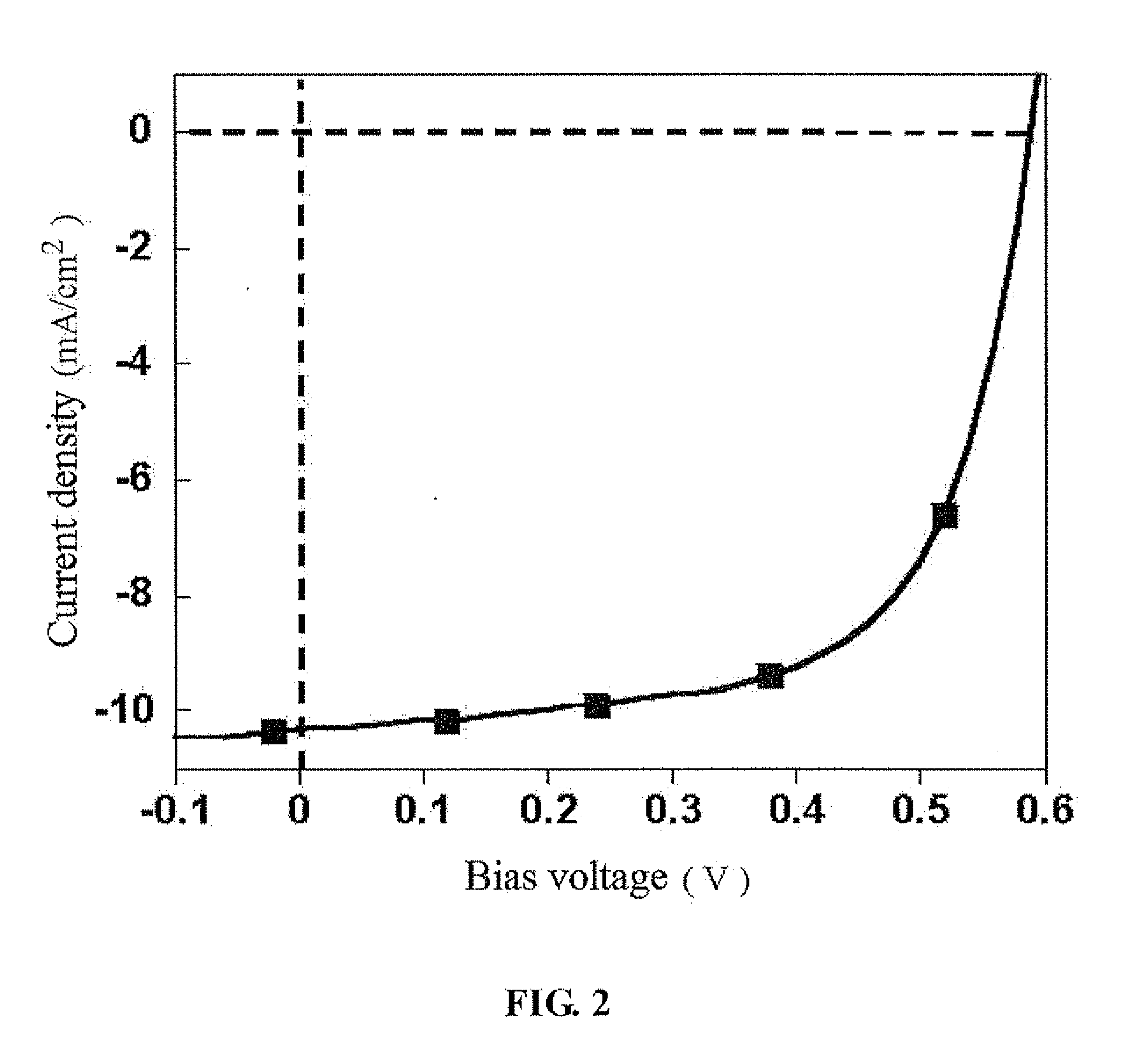

Hybrid organic solar cell with perovskite structure as absorption material and manufacturing method thereof

ActiveUS20140332078A1Low costSimple processFinal product manufactureSolid-state devicesHeterojunctionOrganic solar cell

A hybrid organic solar cell (HOSC) with perovskite structure as absorption material and a manufacturing method thereof are provided. The HOSC includes a conductive substrate, a hole transport layer, an active layer, a hole blocking layer and a negative electrode. The active layer has a light absorption layer (LAL) and an electron acceptor layer (EAL). The LAL is made of perovskite material represented by the following equation: CnH2n+1NH3XY3, n is positive integer form 1 to 9; X is Pb, Sn or Ge; and Y is at least one of I, Br or Cl. The EAL is made of at least one type of fullerene or derivatives thereof. A planar heterojunction (PHJ) is formed between the LAL and the EAL. The LAL has simple structure and fabricating process with relatively low cost, so that it is advantageous to carry out the mass production of HOSCs of flexible solid-state form.

Owner:NAT CHENG KUNG UNIV

Photoconductive imaging members

A photoconductive imaging member comprised of a supporting substrate, a hole blocking layer, an optional adhesive layer, a photogenerator layer, and a charge transport layer, and wherein said blocking layer is comprised of a polyhaloalkylstyrene.

Owner:XEROX CORP

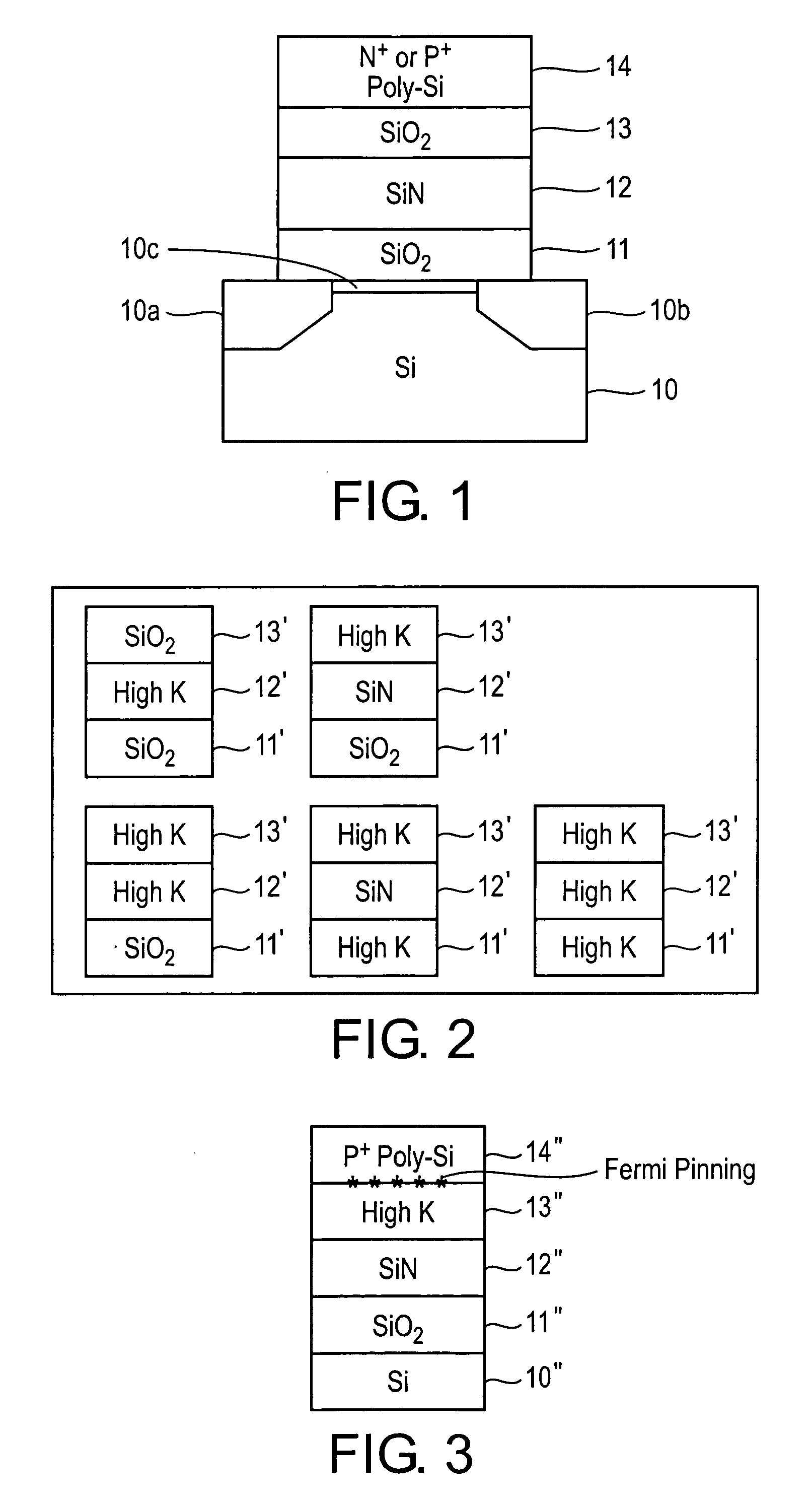

Non-volatile semiconductor memory device with alternative metal gate material

A non-volatile semiconductor memory device comprises a substrate including a source region, a drain region and a channel region provided between the source region and the drain region with a gate stack located above the channel region with a metal gate located above the gate stack. The metal gate is comprised of a metal having a specific metal work function relative to a composition of a layer of the gate stack that causes electrons to travel through the entire thickness of the blocking layer via direct tunneling. The gate stack preferably comprises a multiple layer stack selected from a group of multiple layer stacks consisting of: ONO, ONH, OHH, OHO, HHH, or HNH, where O is an oxide material, N is SiN, and H is a high κ material.

Owner:SAMSUNG ELECTRONICS CO LTD

Organic photoelectric conversion element and image element

InactiveUS20070063156A1Photoelectric conversion efficiency is not reducedImprove photoelectric conversion efficiencySolid-state devicesInvestigating moving sheetsElectron holeWork function

An organic photoelectric conversion element comprises: a pair of electrodes; an organic photoelectric conversion layer arranged between the pair of electrodes; and an positive hole blocking layer arranged between one of the pair of electrodes and the organic photoelectric conversion layer, wherein an ionization potential of the positive hole blocking layer is larger than a work function of the adjoining electrode by 1.3 eV or more, and wherein an electron affinity of the positive hole blocking layer is equal to or larger than that of the adjoining organic photoelectric conversion layer. An electron blocking layer may be arranged between the other one of the pair of electrodes and the organic photoelectric conversion layer, wherein its electron affinity is smaller than a work function of the adjoining electrode by 1.3 eV or more, and its ionization potential is equal to or smaller than that of the adjoining organic photoelectric conversion layer.

Owner:FUJIFILM CORP +1

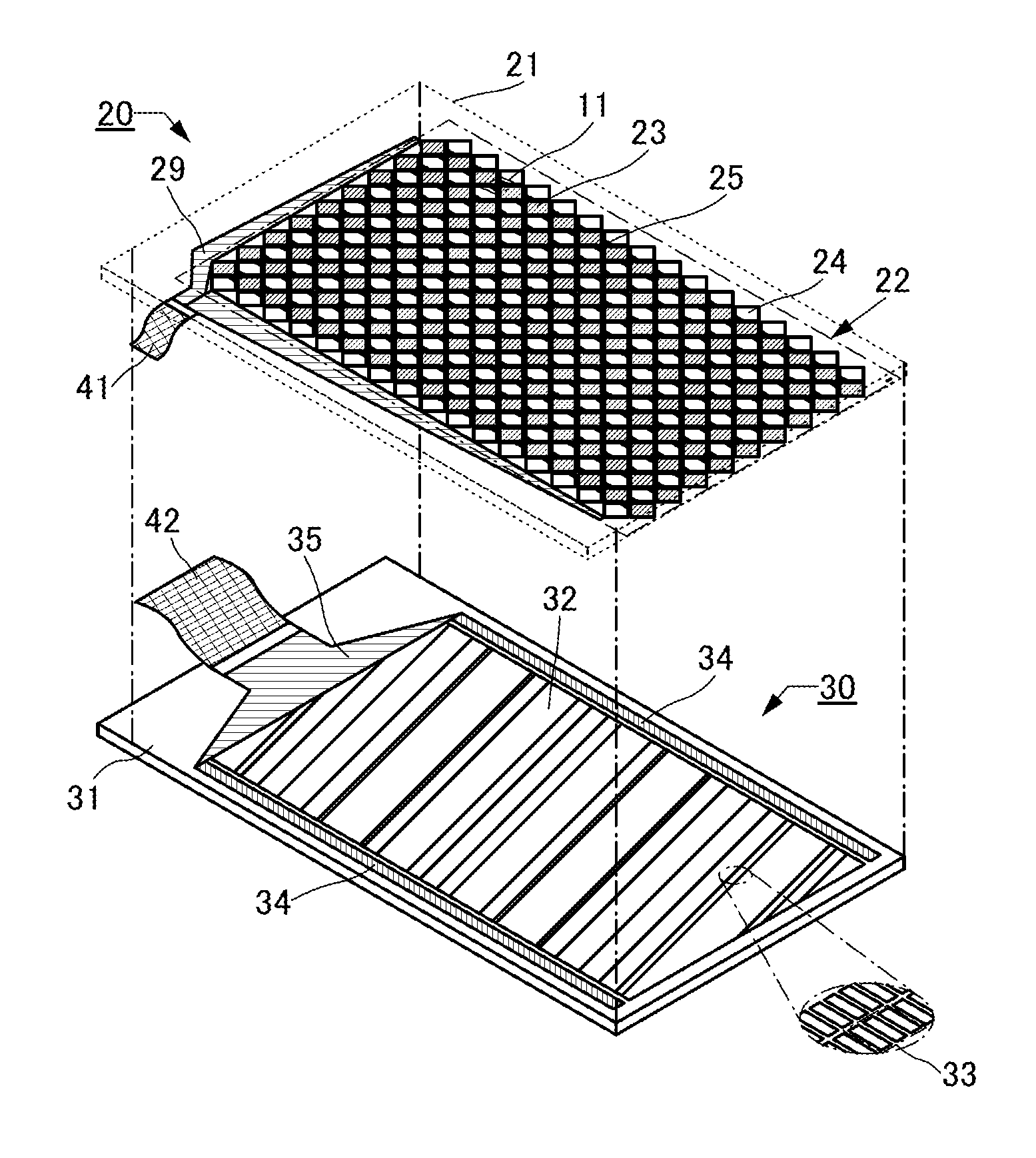

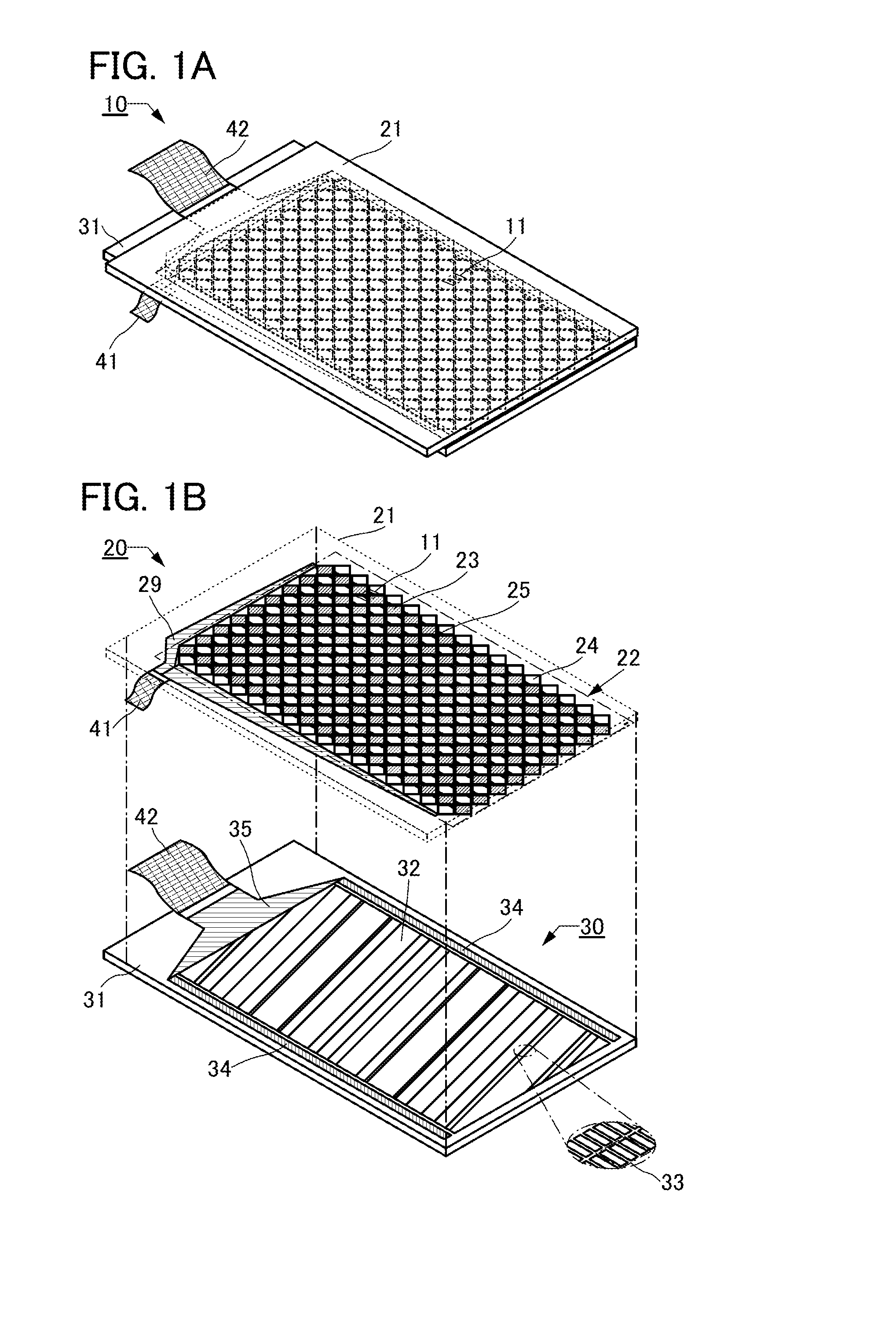

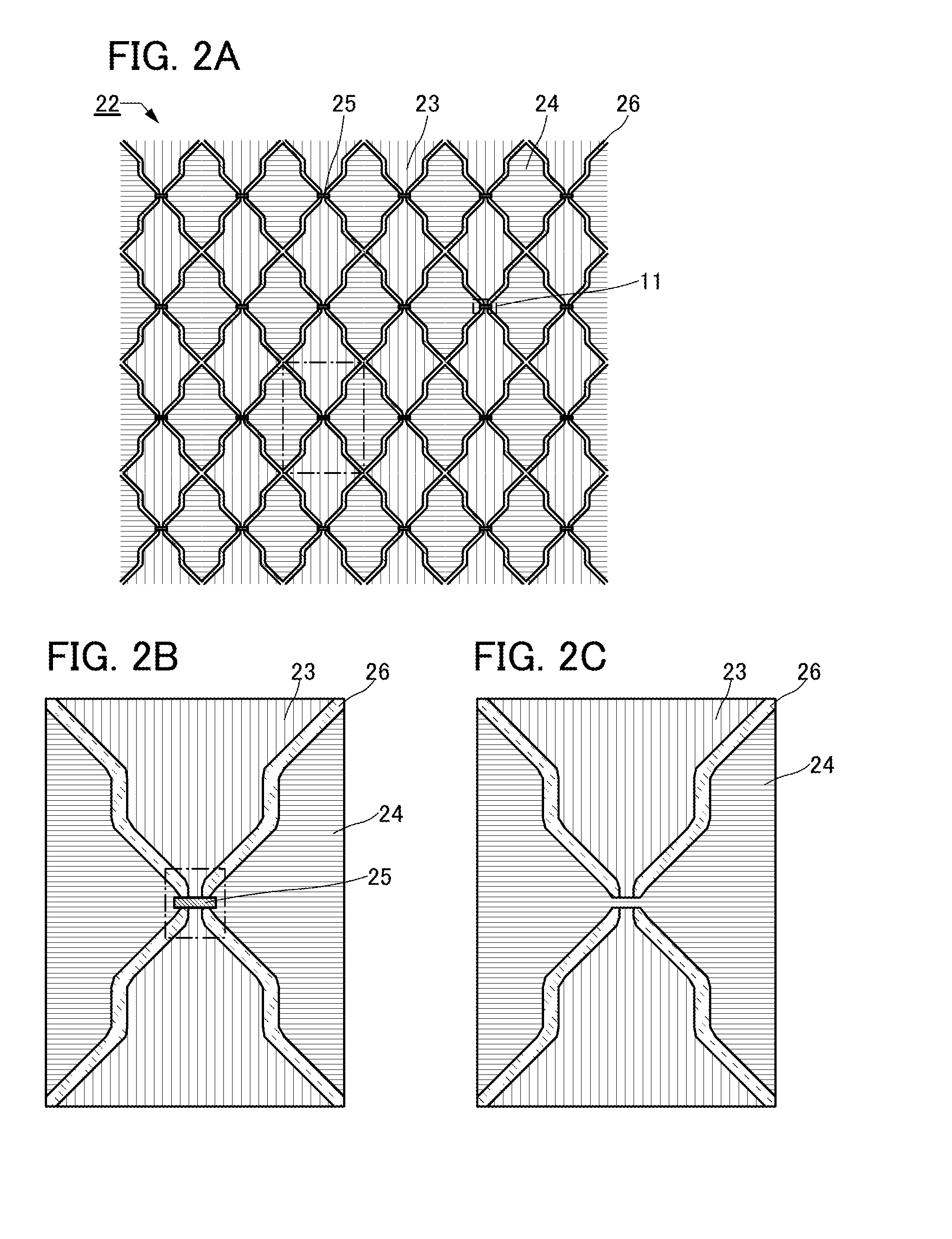

Touch panel

InactiveUS20150346866A1High detection sensitivityImprove reliabilityDigital computer detailsDetails for portable computersEngineeringBlocking layer

To increase the detection sensitivity of a touch panel, provide a thin touch panel, provide a foldable touch panel, or provide a lightweight touch panel. A display element and a capacitor forming a touch sensor are provided between a pair of substrates. Preferably, a pair of conductive layers forming the capacitor each have an opening. The opening and the display element are provided to overlap each other. A light-blocking layer is provided between a substrate on the display surface side and the pair of conductive layers forming the capacitor.

Owner:SEMICON ENERGY LAB CO LTD

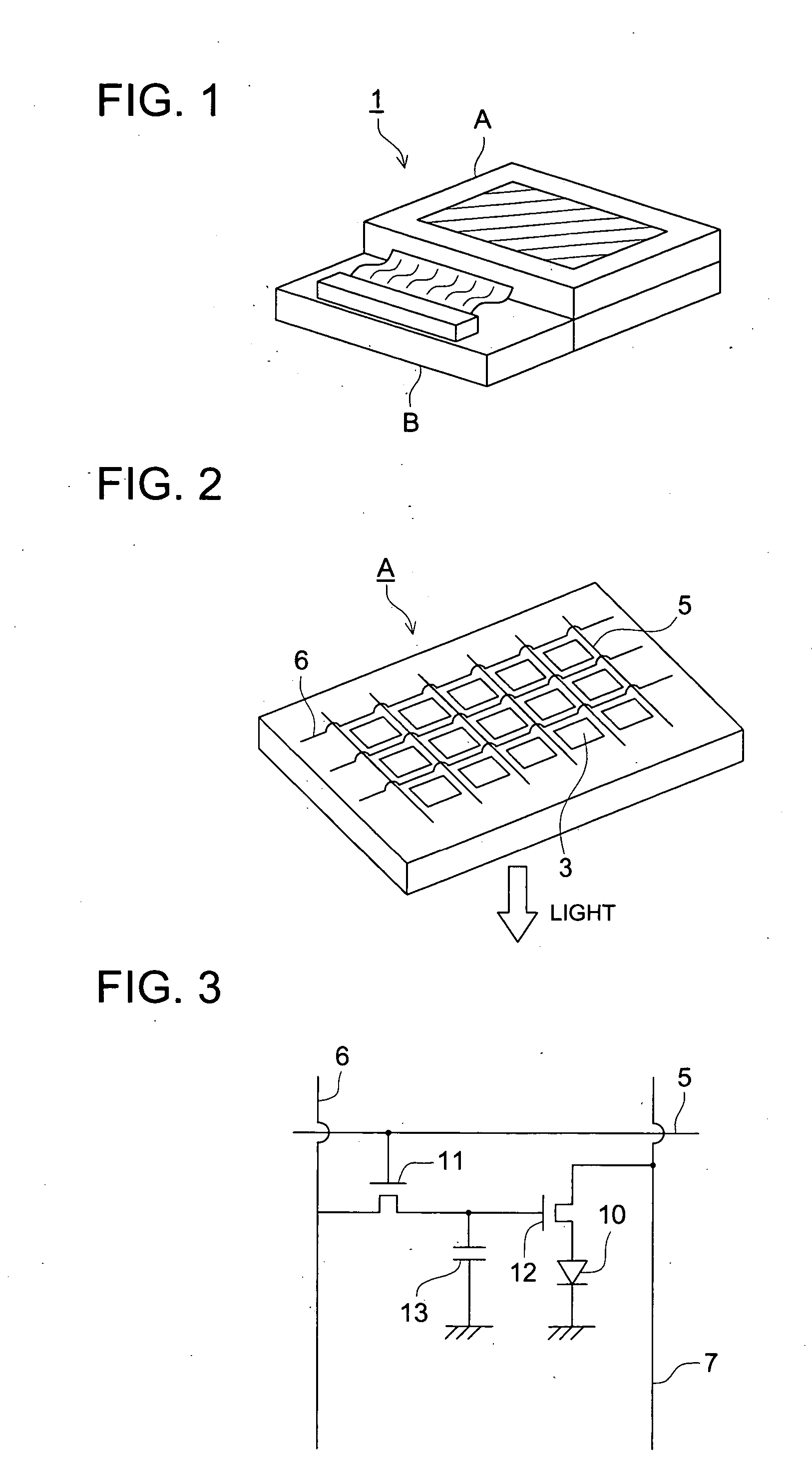

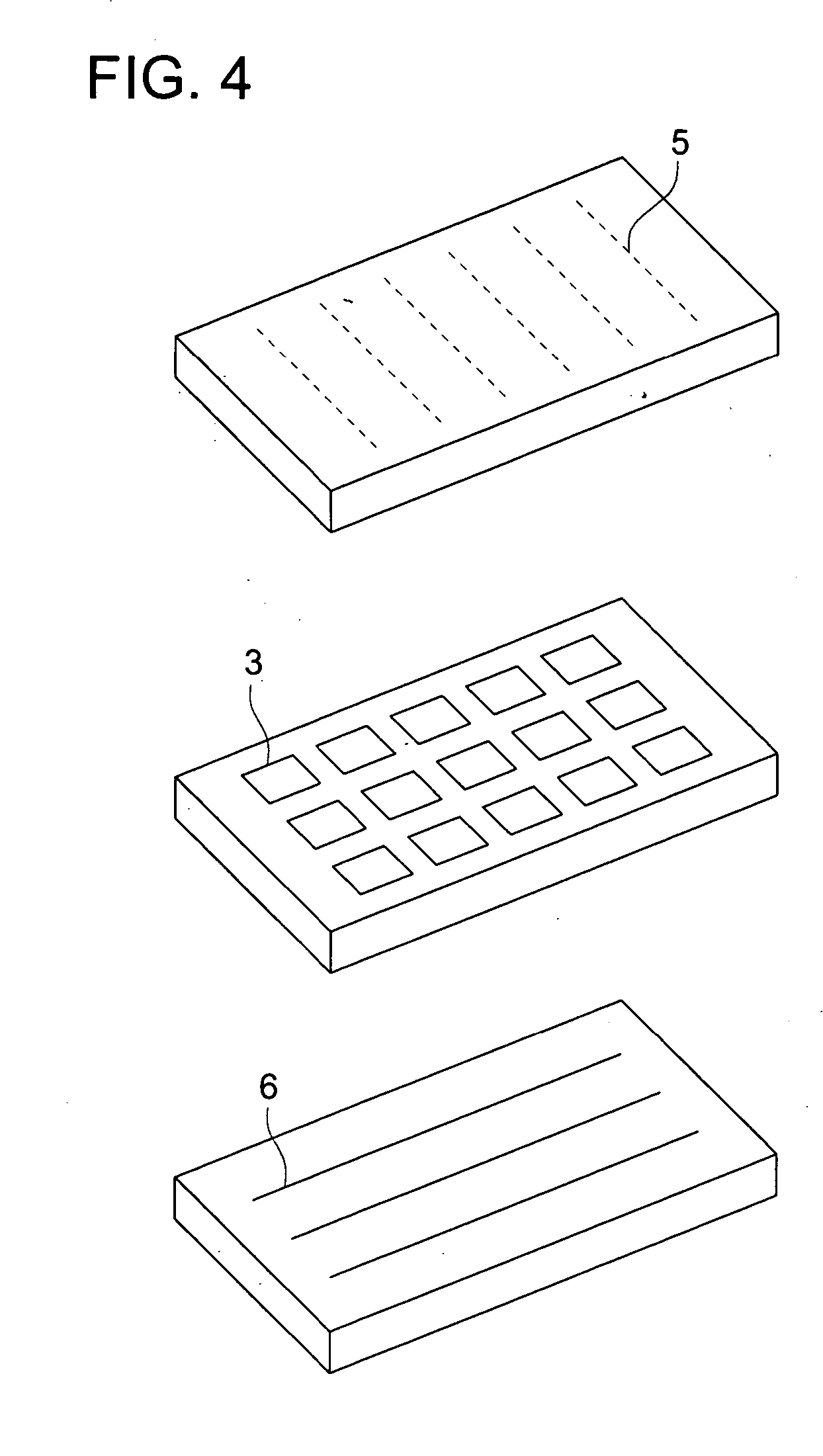

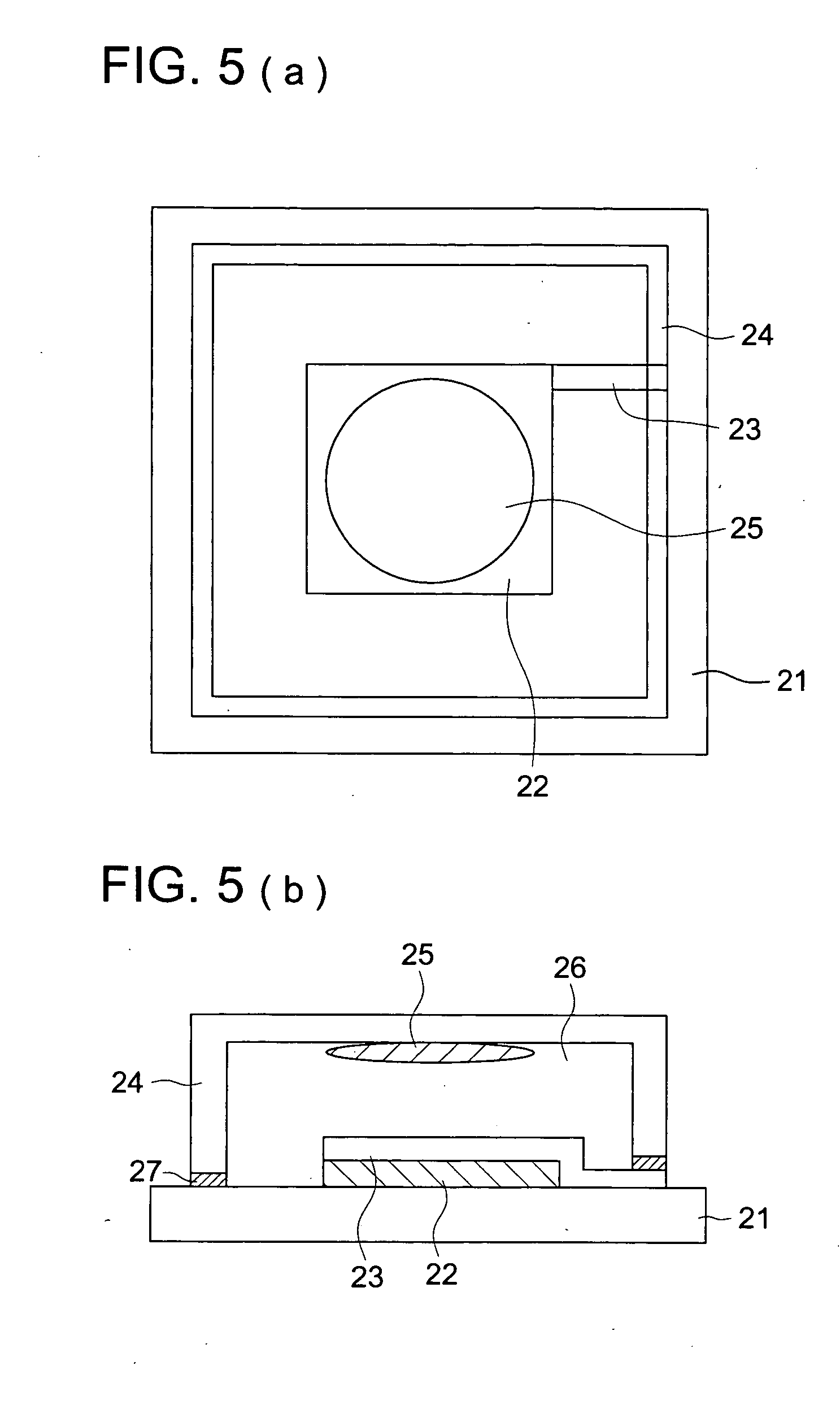

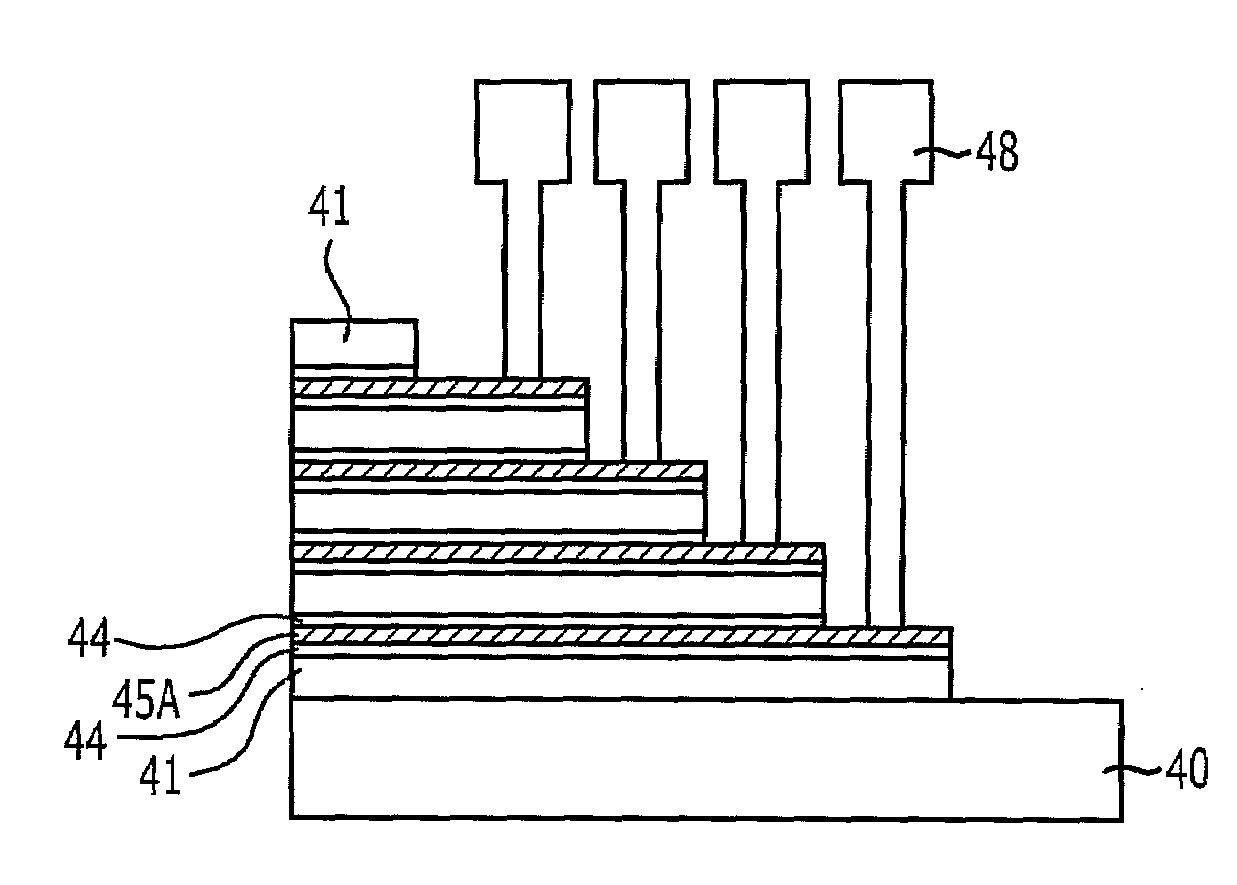

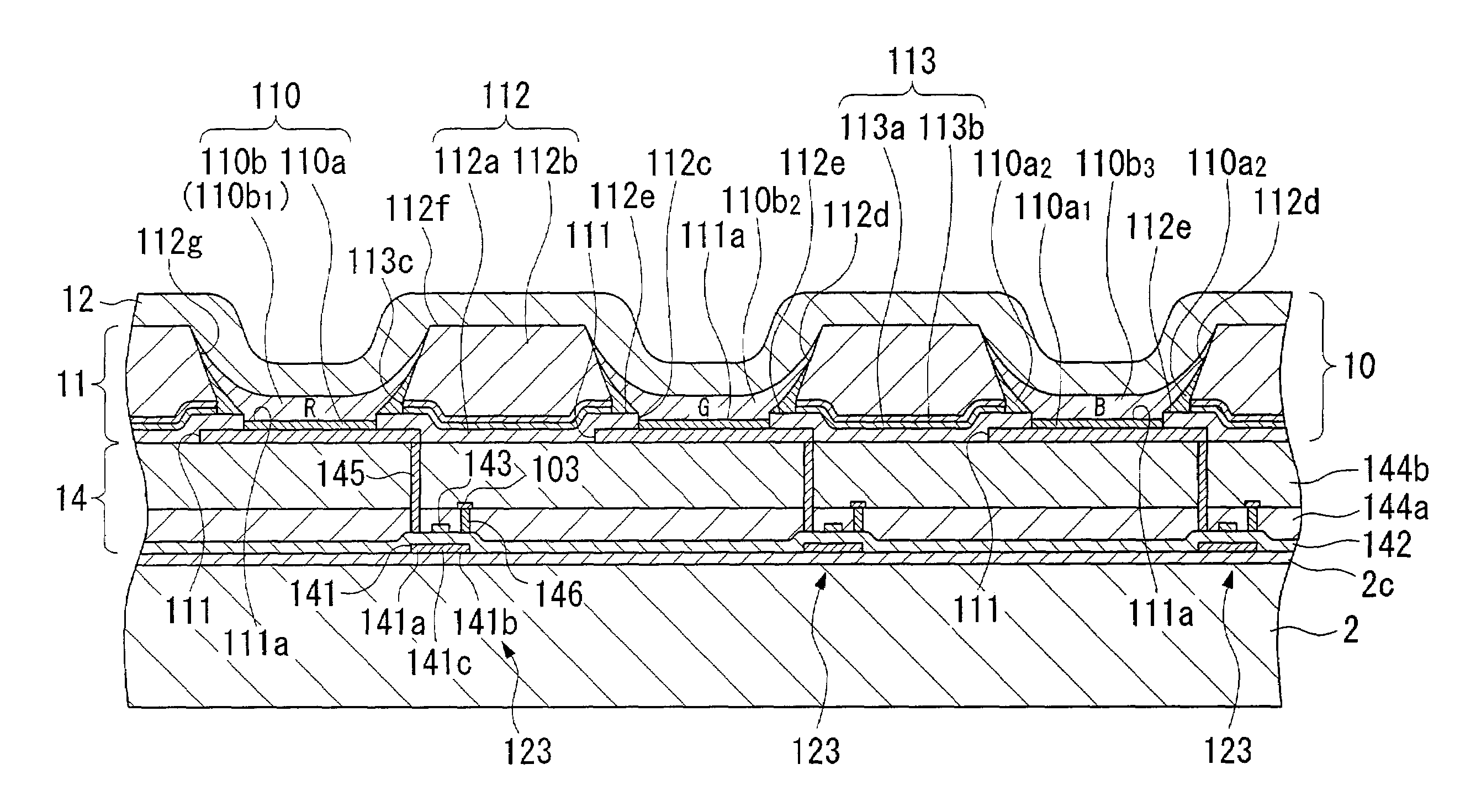

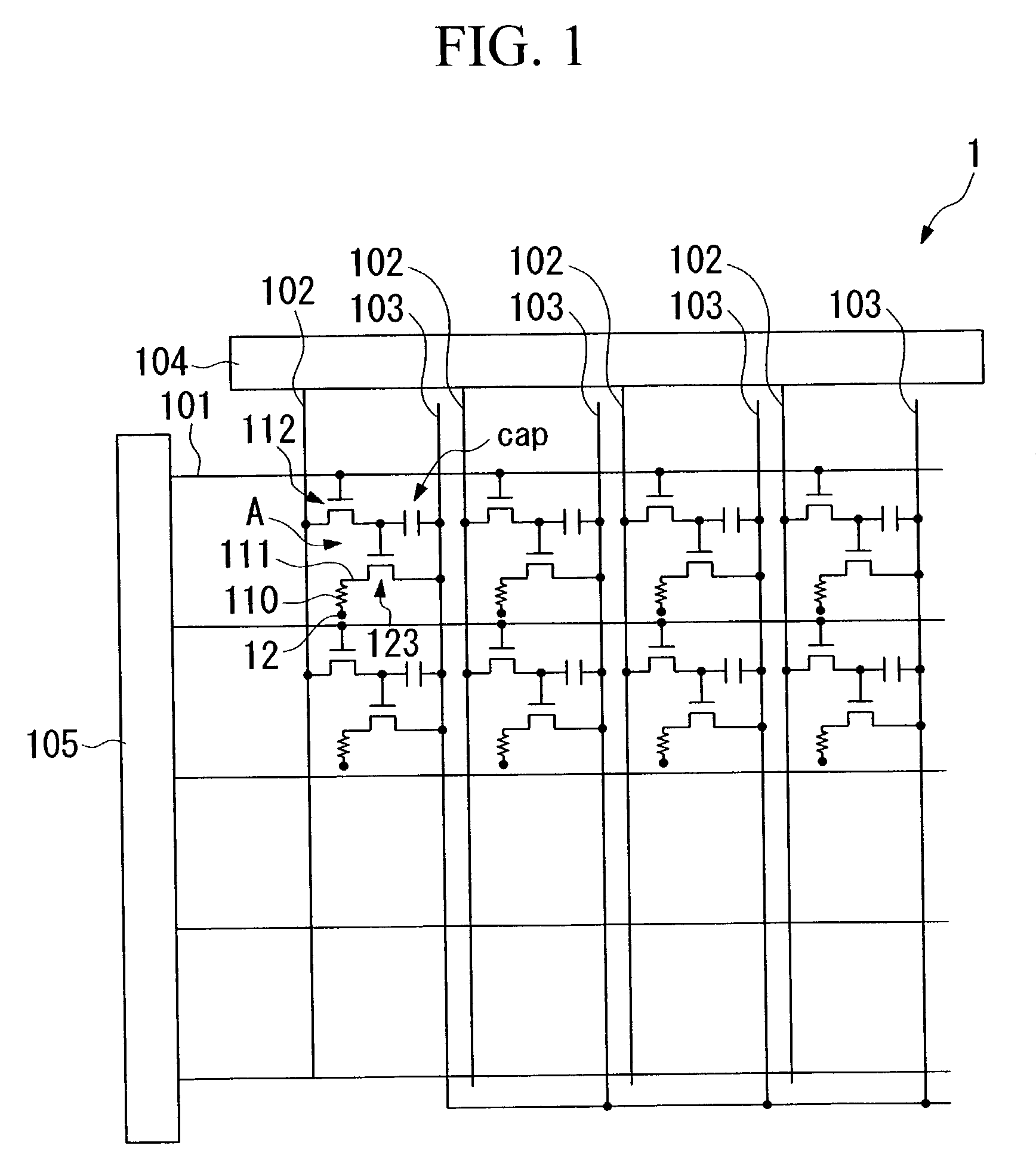

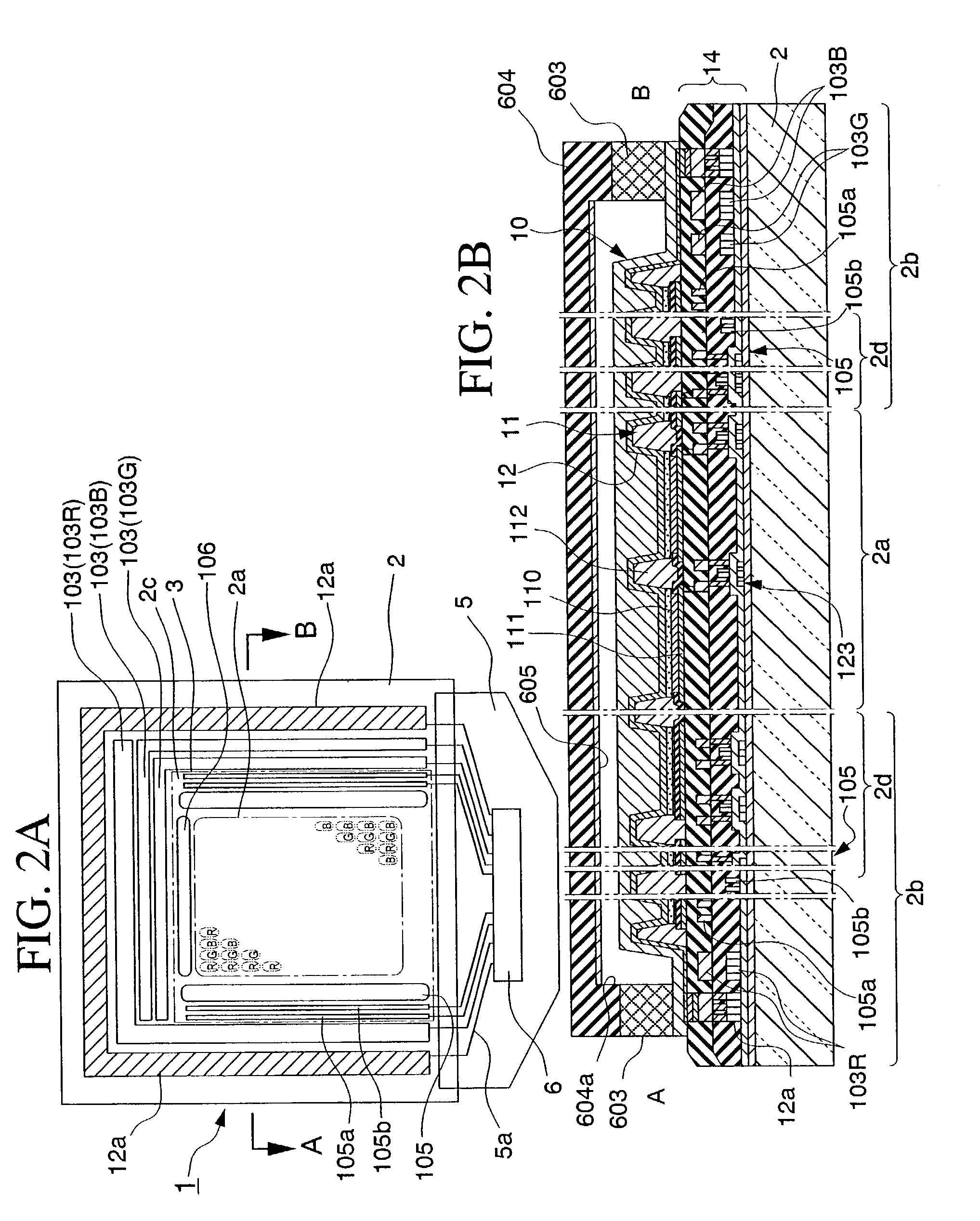

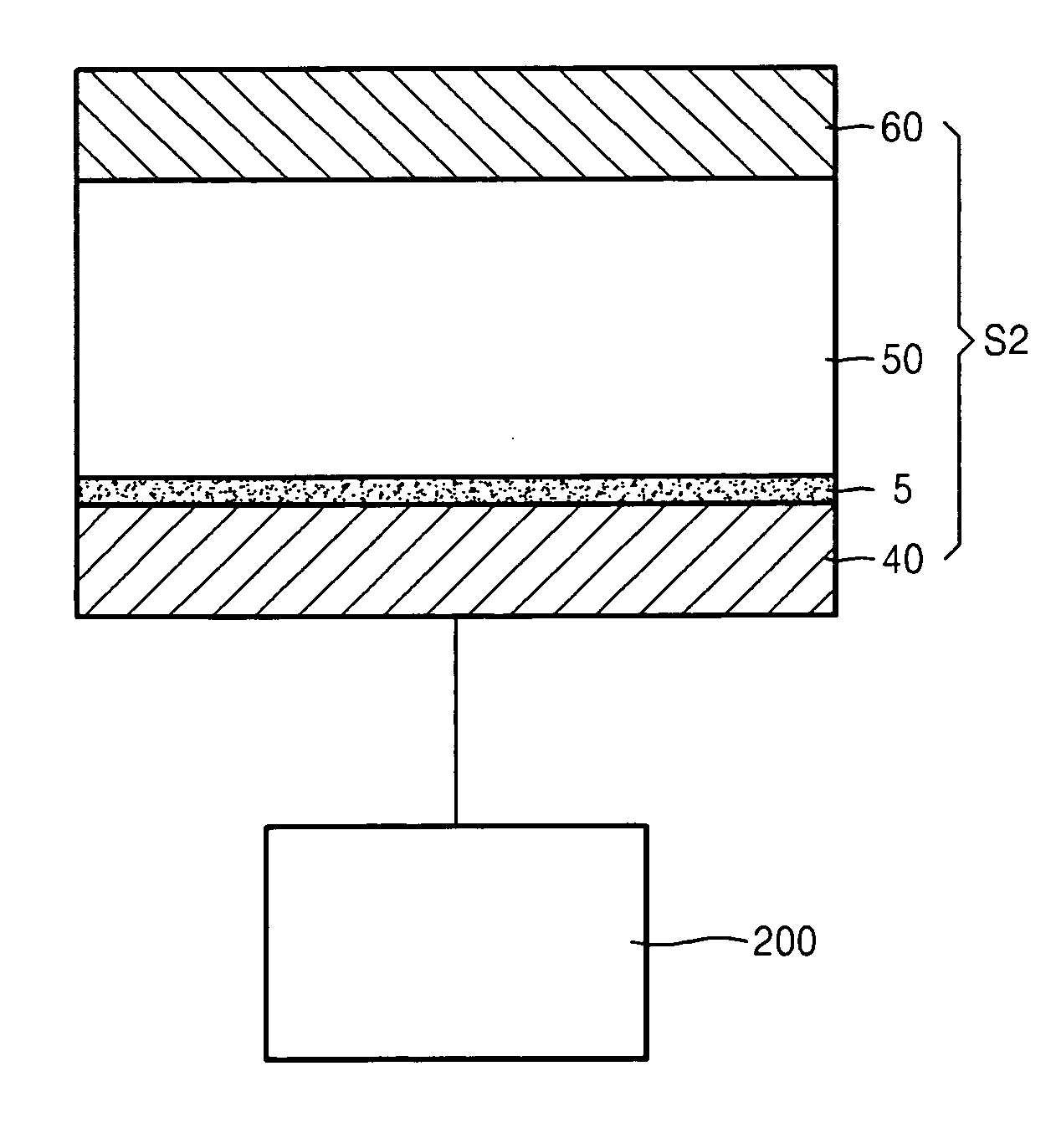

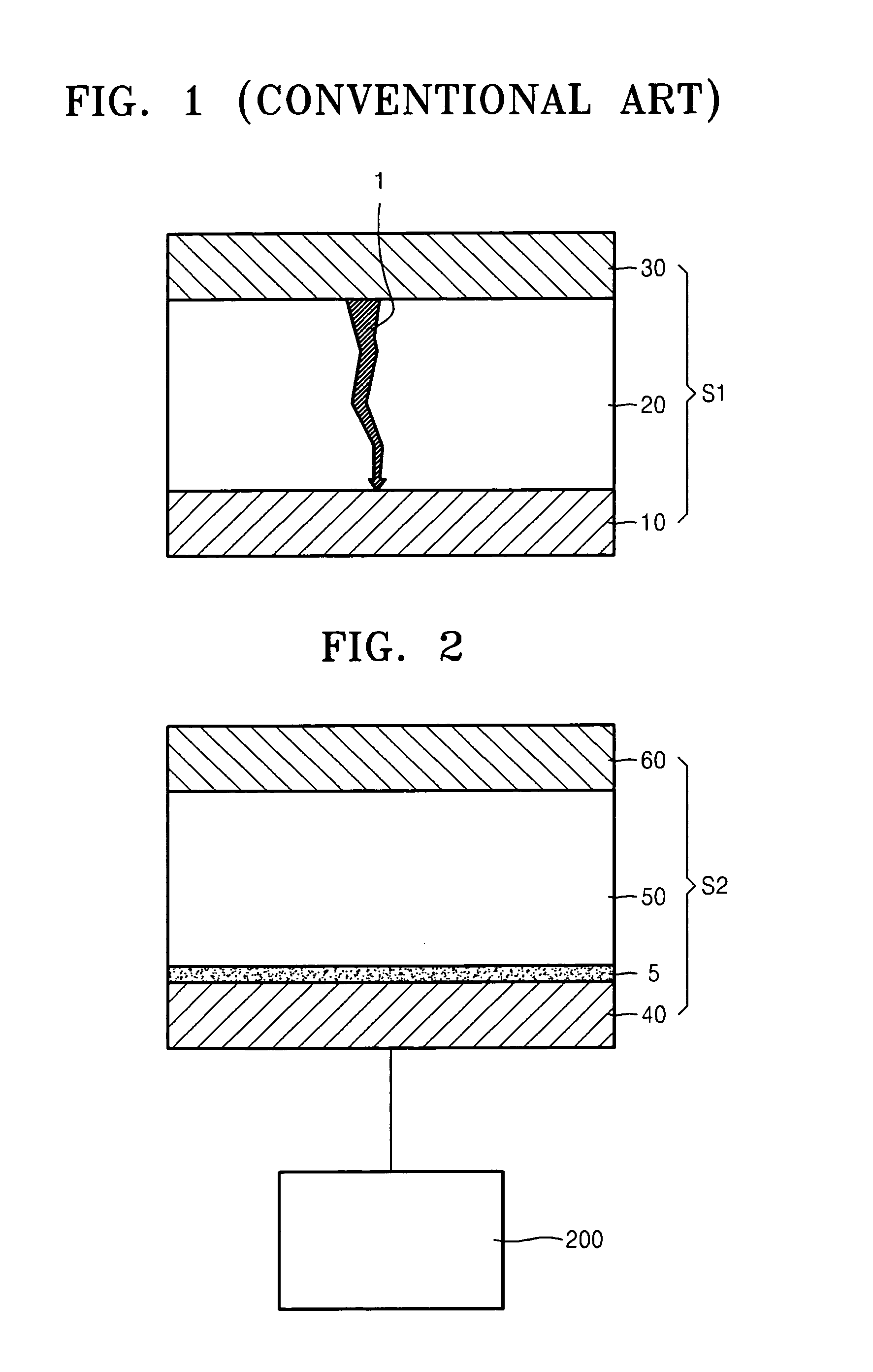

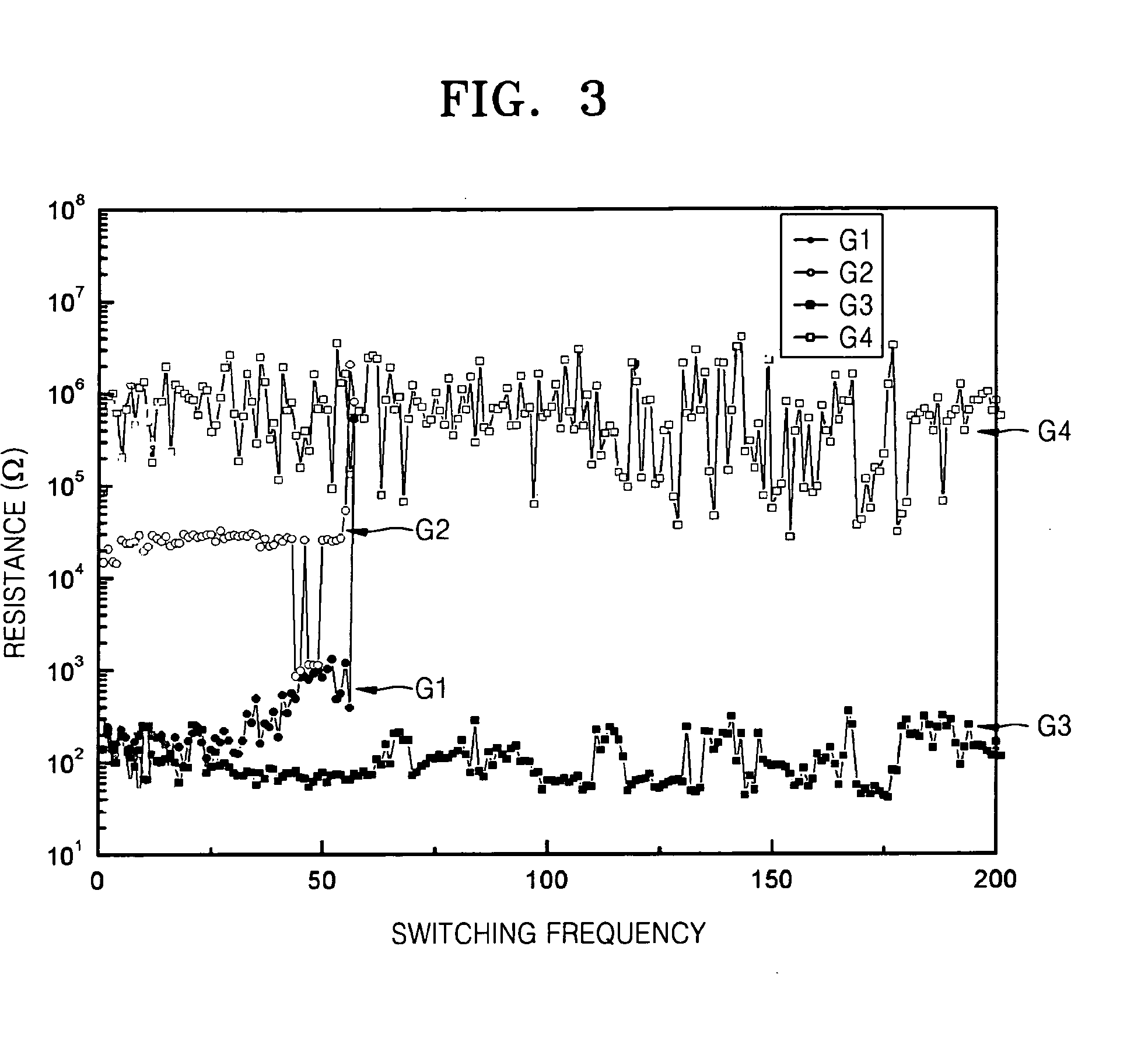

Display device having light blocking layer, and electric device

InactiveUS7012367B2AdhesionImprove adhesionDischarge tube luminescnet screensElectroluminescent light sourcesDisplay deviceEngineering

A display apparatus is provided that prevents shortening of the life of the luminescent elements and has a superior contrast ratio. The display apparatus is composed by forming a plurality of luminescent elements on a substrate and providing bank sections between each of the luminescent elements. The bank sections are formed from a first bank layer located on the side of the substrate and a second bank layer formed on the first bank layer. A light blocking layer is then provided between the first bank layer and the second bank layer.

Owner:SEIKO EPSON CORP

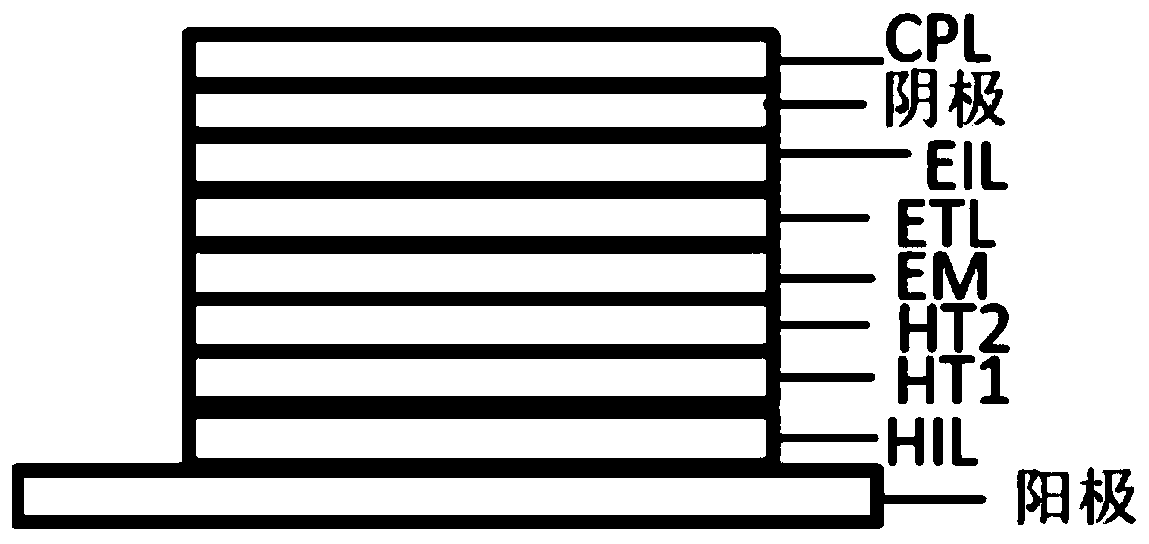

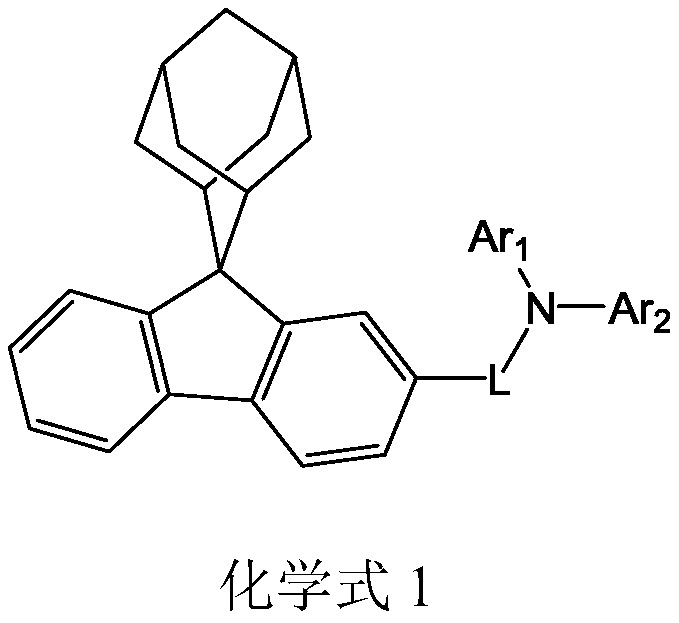

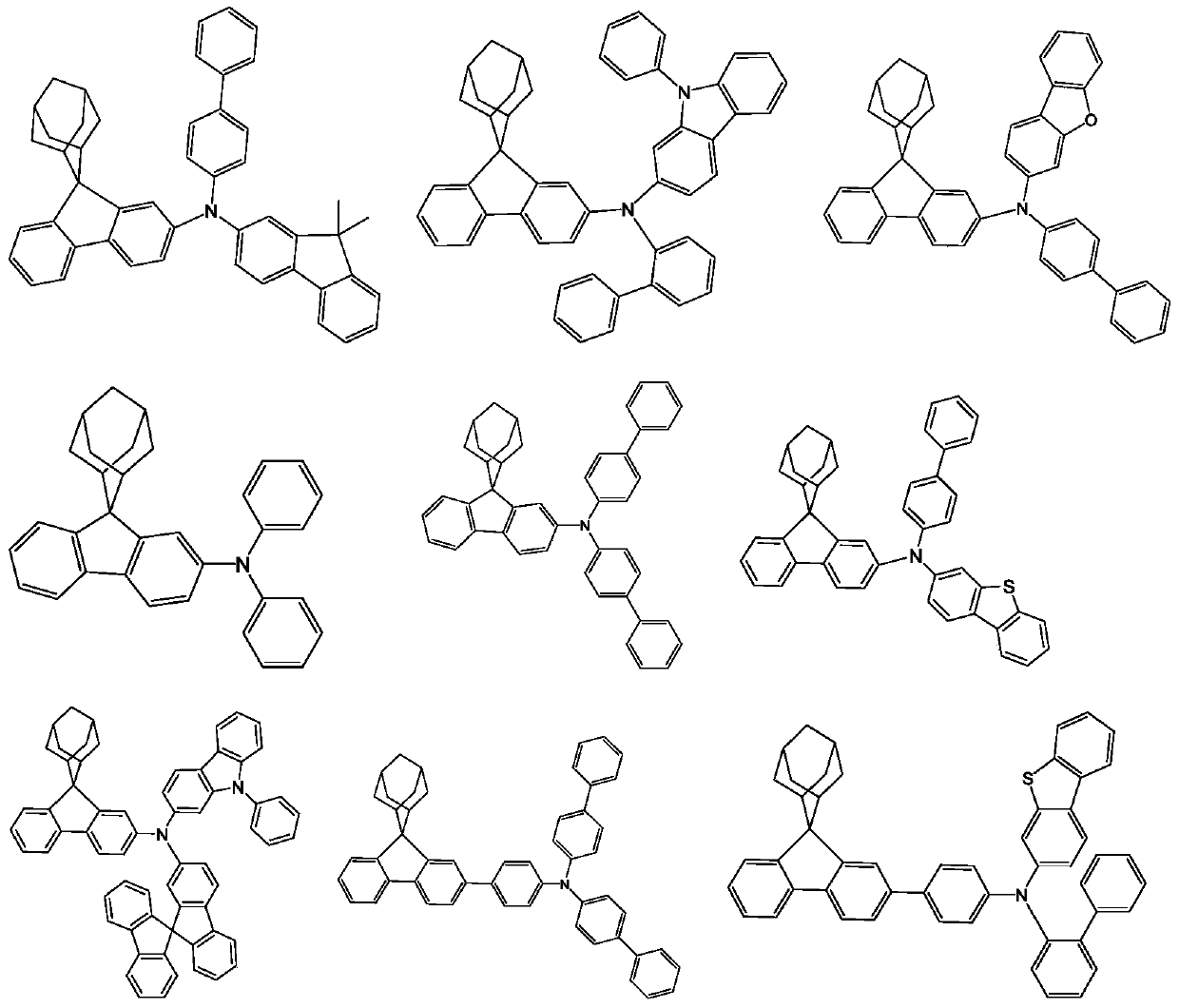

Organic electroluminescent material and organic electroluminescent device containing material

InactiveCN110128279AIncrease electron densityEnhanced hole conductivityOrganic chemistrySolid-state devicesOrganic electroluminescenceBlock layer

The invention provides an organic electroluminescent material and an organic electroluminescent device containing the material. The material has a structural formula shown in the description. The material provided by the invention is used as a hole transporting layer, a hole injecting layer or an electron blocking layer of the organic electroluminescent device, so that the organic electroluminescent device has a lower driving voltage, higher luminous efficiency, and a better service life.

Owner:SHAANXI LIGHTE OPTOELECTRONICS MATERIAL CO LTD

Resistive random access memory device

Provided is a resistive random access memory device that includes a storage node connected to a switching device. The resistive random access memory device includes a first electrode, a resistance variable layer, and a second electrode which are sequentially stacked, wherein a diffusion blocking layer is formed between the first electrode and the resistance variable layer or between the resistance variable layer or / and the second electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

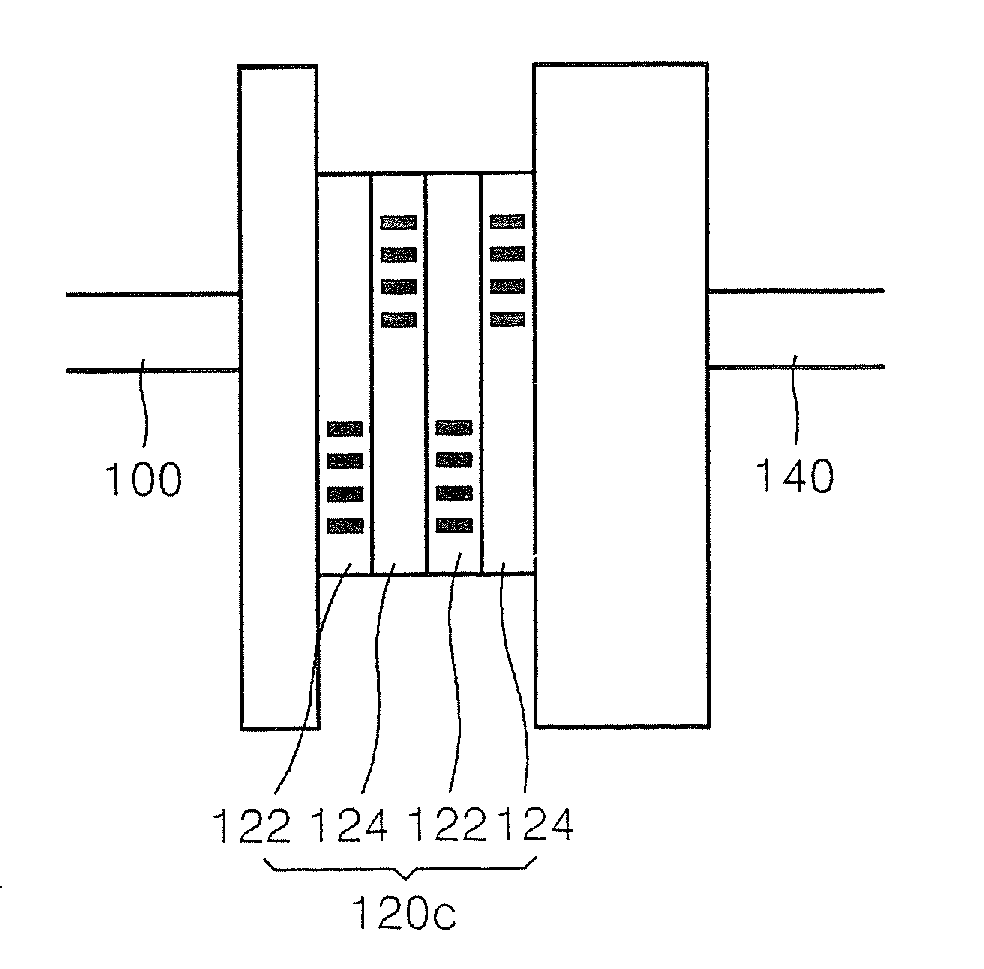

Vertical channel type nonvolatile memory device and method for fabricating the same

ActiveUS20110147823A1Solid-state devicesSemiconductor/solid-state device manufacturingInter layerEngineering

A method for fabricating a vertical channel type nonvolatile memory device includes forming alternately a plurality of interlayer dielectric layers and a plurality of conductive layers over a substrate, forming a trench having a plurality of recesses on a surface of the trench by etching the plurality of interlayer dielectric layers and a plurality of conductive layers, wherein the plurality of recesses are formed at a certain interval on the surface of the trench, forming a charge blocking layer over a plurality of surfaces of the plurality of recesses, forming a charge storage layer over the charge blocking layer for filling a plurality of the remaining recesses with a charge storage material, forming a tunnel dielectric layer to cover the charge storage layer, and forming a vertical channel layer by filling the remaining trench.

Owner:SK HYNIX INC

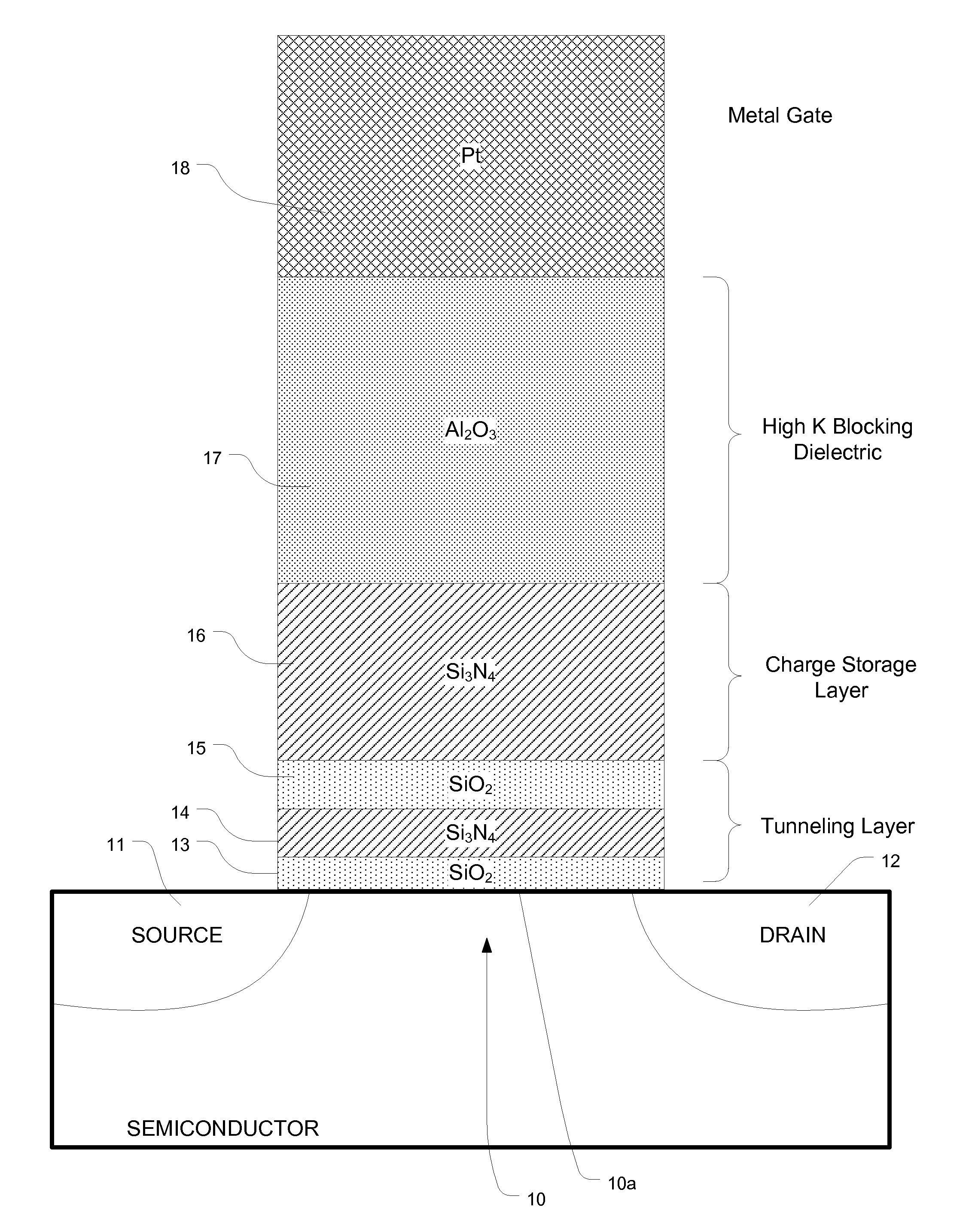

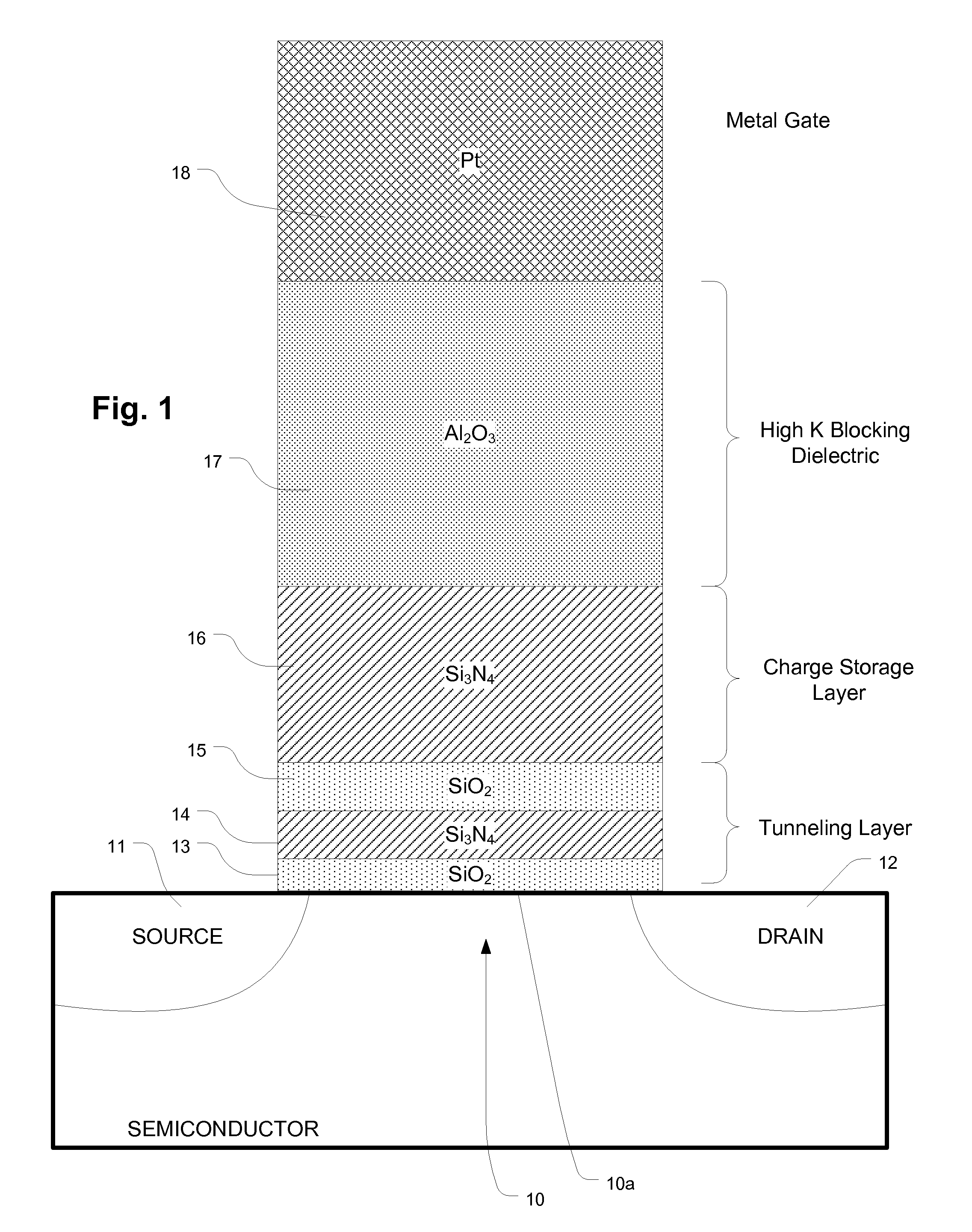

Charge trapping memory cell with high speed erase

InactiveUS20090039414A1Eliminates hole tunneling barrierEffectively preventing charge leakageSolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a metal or metal compound gate, such as a platinum gate, by a blocking layer of material having a high dielectric constant, such as aluminum oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric. Fast program and erase speeds with memory window as great as 7 V are achieved.

Owner:MACRONIX INT CO LTD

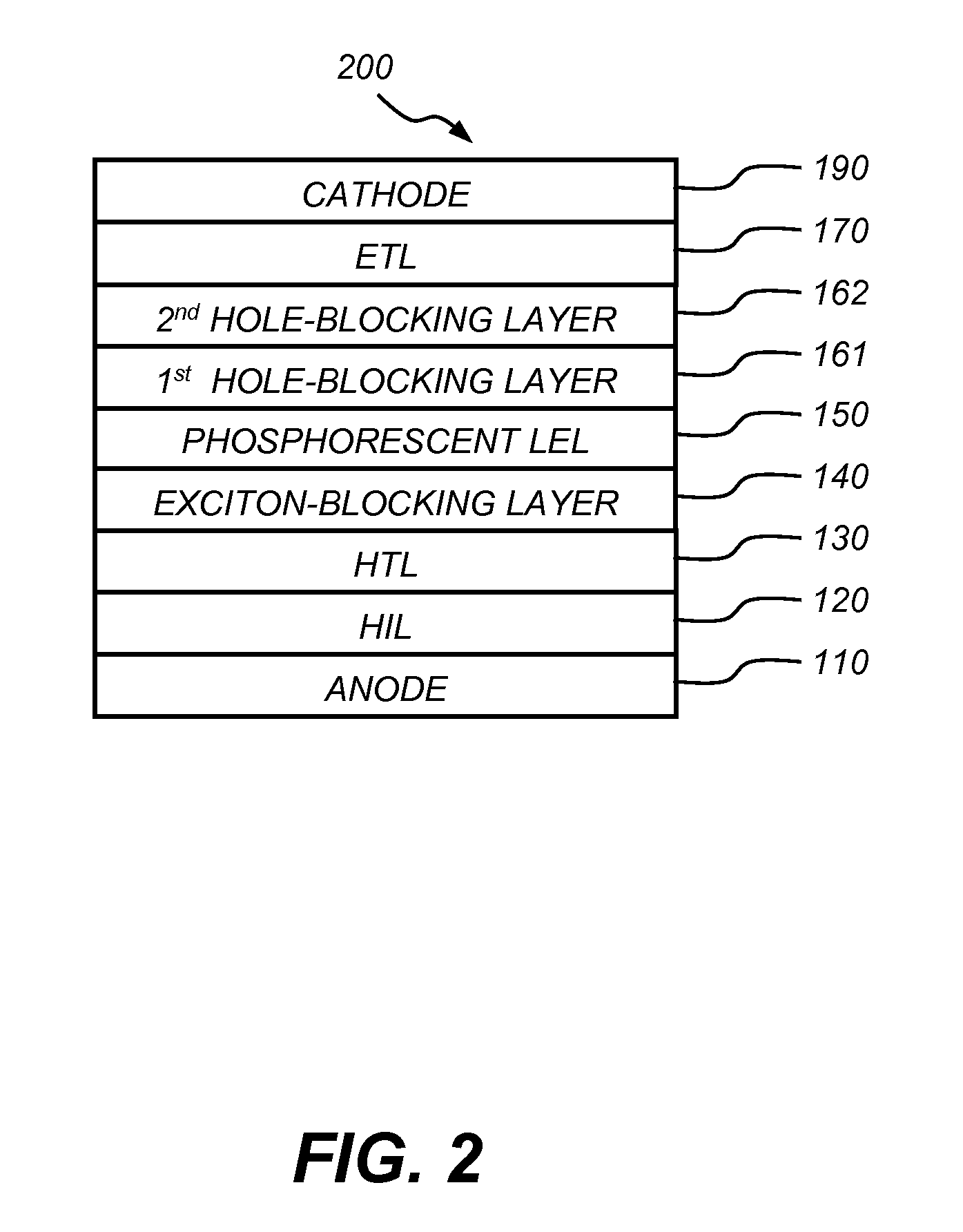

Phosphorescent OLED having double hole-blocking layers

InactiveUS20090191427A1Good effectFacilitates electron injectionSolid-state devicesNatural mineral layered productsDopantPhosphorescent oleds

An organic light-emitting device has a first hole-blocking layer in contact with a phosphorescent light-emitting layer and a second hole-blocking layer in contact with the first. The material in the first hole-blocking layer has a triplet energy greater than the host of the phosphorescent layer and the material in the second hole-blocking layer has a triplet energy higher than the dopant in the phosphorescent layer. Both hole-blocking materials have lower HOMO energies than the host of the phosphorescent light-emitting layer

Owner:GLOBAL OLED TECH

Semiconductor memory device and method for manufacturing same

A laminated body is formed by alternately laminating a plurality of dielectric films and electrode films on a silicon substrate. Next, a through hole extending in the lamination direction is formed in the laminated body. Next, a selective nitridation process is performed to selectively form a charge layer made of silicon nitride in a region of an inner surface of the through hole corresponding to the electrode film. Next, a high-pressure oxidation process is performed to form a block layer made of silicon oxide between the charge layer and the electrode film. Next, a tunnel layer made of silicon oxide is formed on an inner side surface of the through hole. Thus, a flash memory can be manufactured in which the charge layer is split for each electrode film.

Owner:KIOXIA CORP

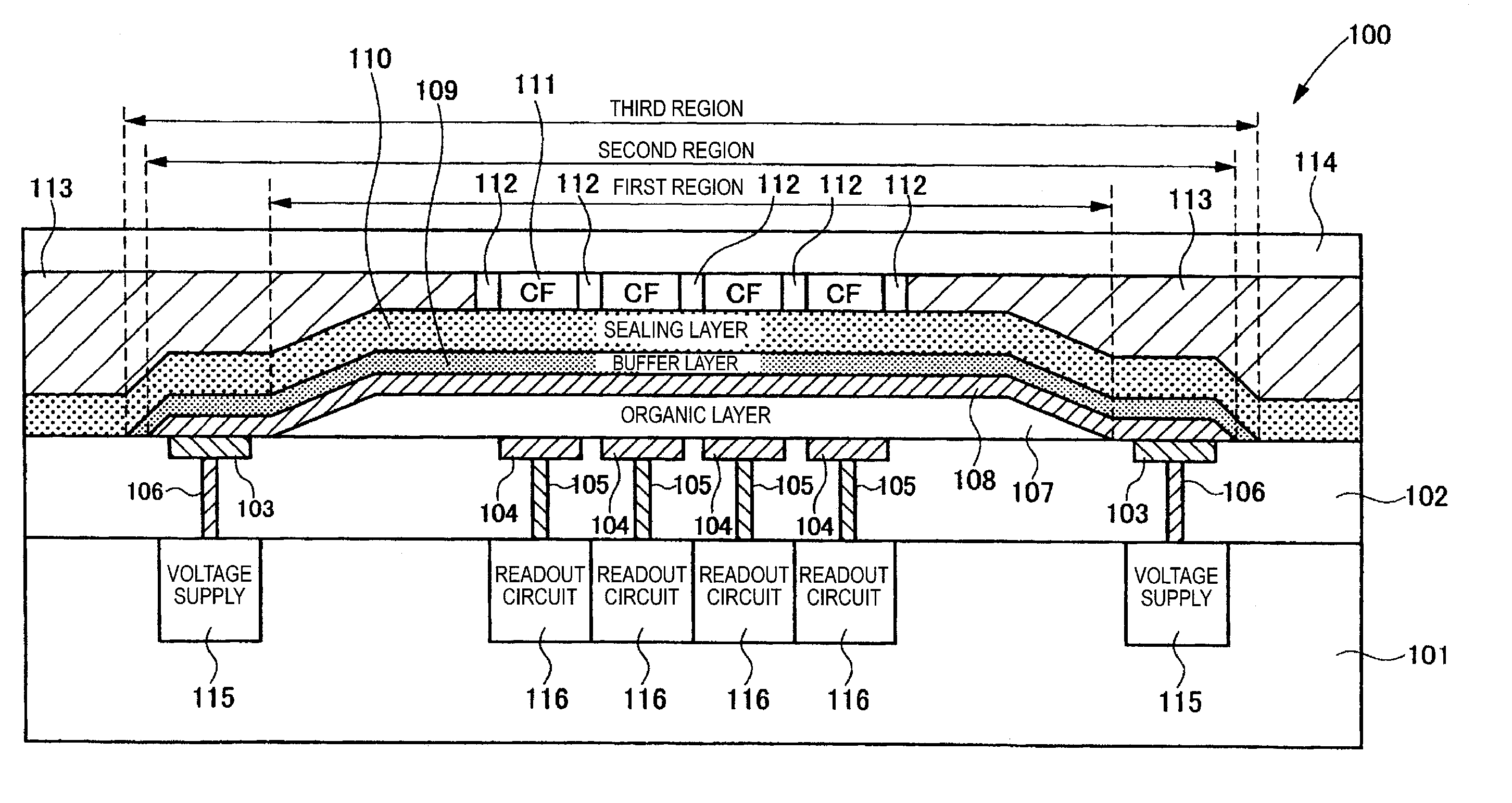

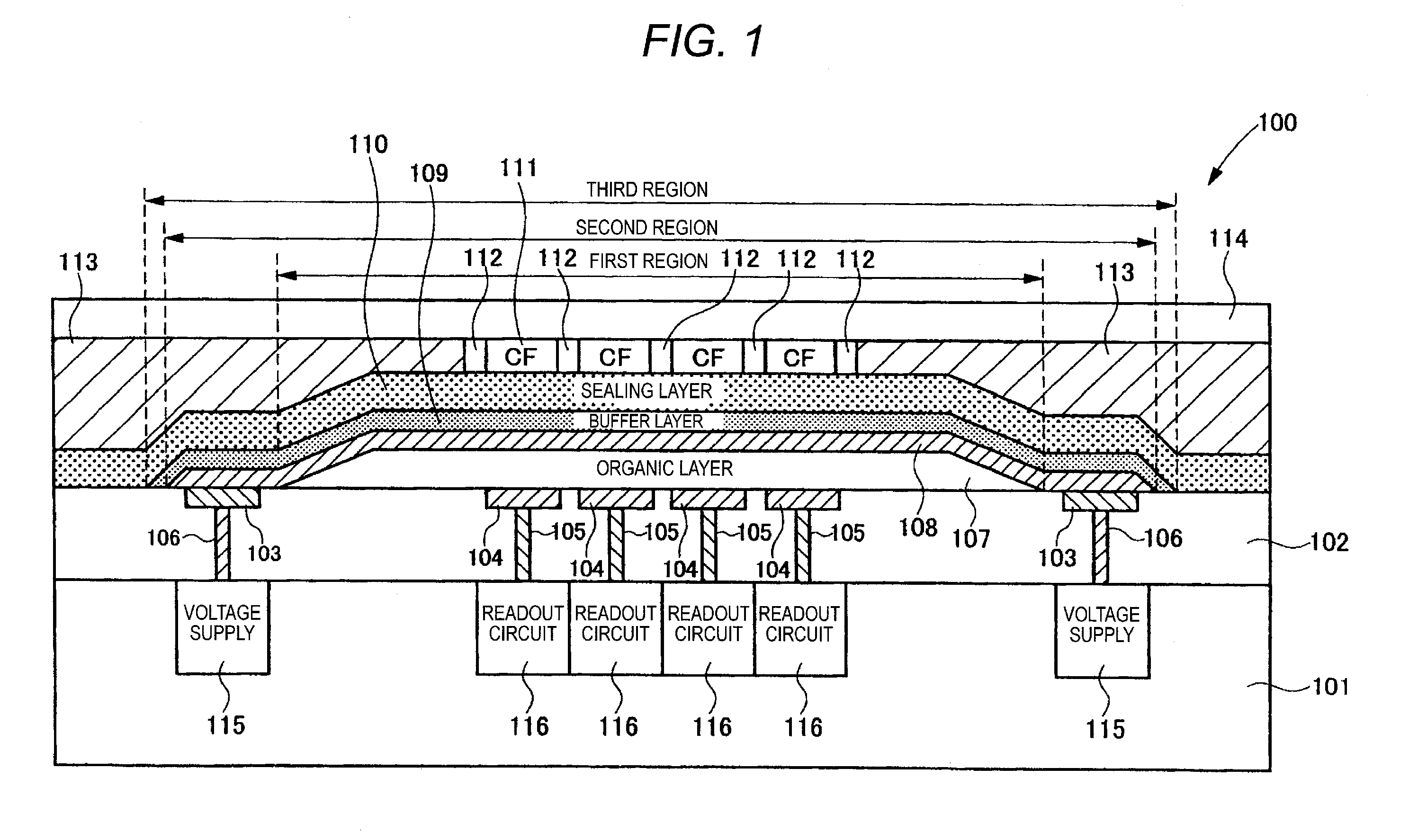

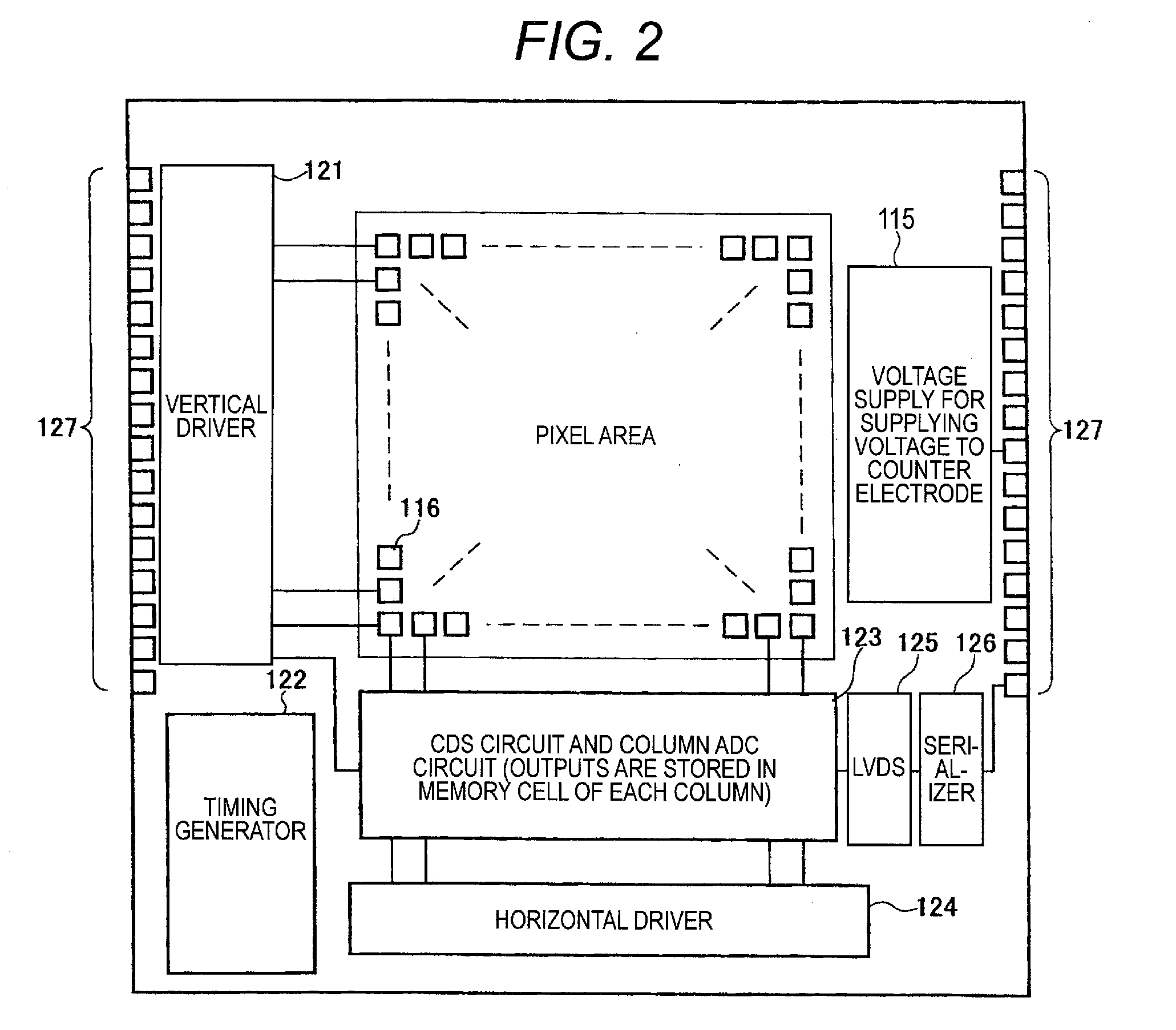

Solid-state imaging device, process of making solid state imaging device, digital still camera, digital video camera, mobile phone, and endoscope

ActiveUS20110049591A1Reduce dark currentImprove signal-to-noise ratioTelevision system detailsSolid-state devicesIonizationBlock layer

A solid-state imaging device includes an array of pixels, each pixel includes: a pixel electrode; an organic layer; a counter electrode; a sealing layer; a color filter; a readout circuit; and a light-collecting unit as defined herein, the photoelectric layer contains an organic p type semiconductor and an organic n type semiconductor, the organic layer further includes a charge blocking layer as defined herein, an ionization potential of the charge blocking layer and an electron affinity of the organic n type semiconductor in the photoelectric layer has a difference of at least 1 eV, and the sealing layer includes a first sealing sublayer formed by atomic layer deposition and a second sealing sublayer formed by physical vapor deposition and containing one of a metal oxide, a metal nitride, and a metal oxynitride.

Owner:FUJIFILM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com