Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

137 results about "Trap density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

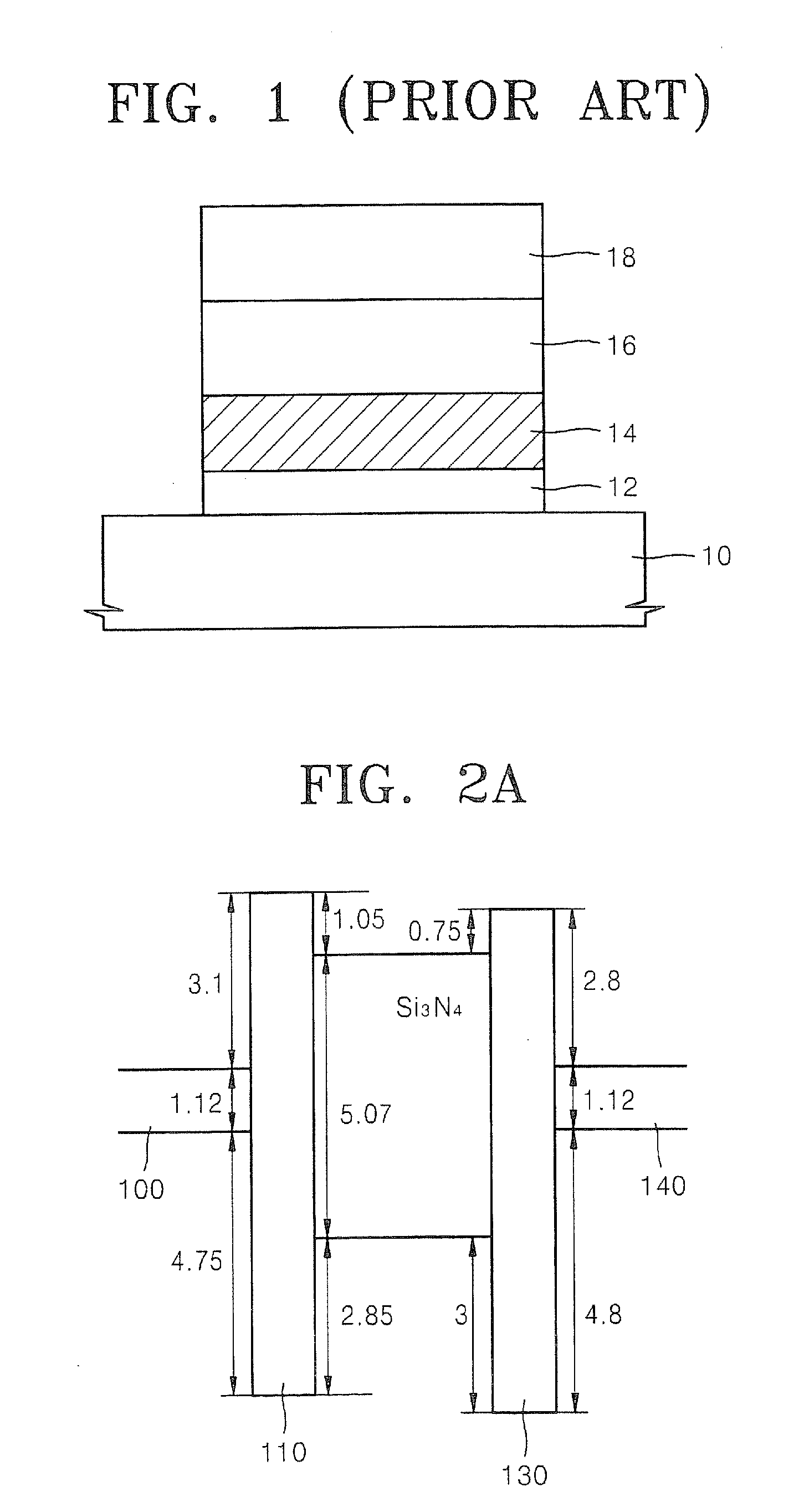

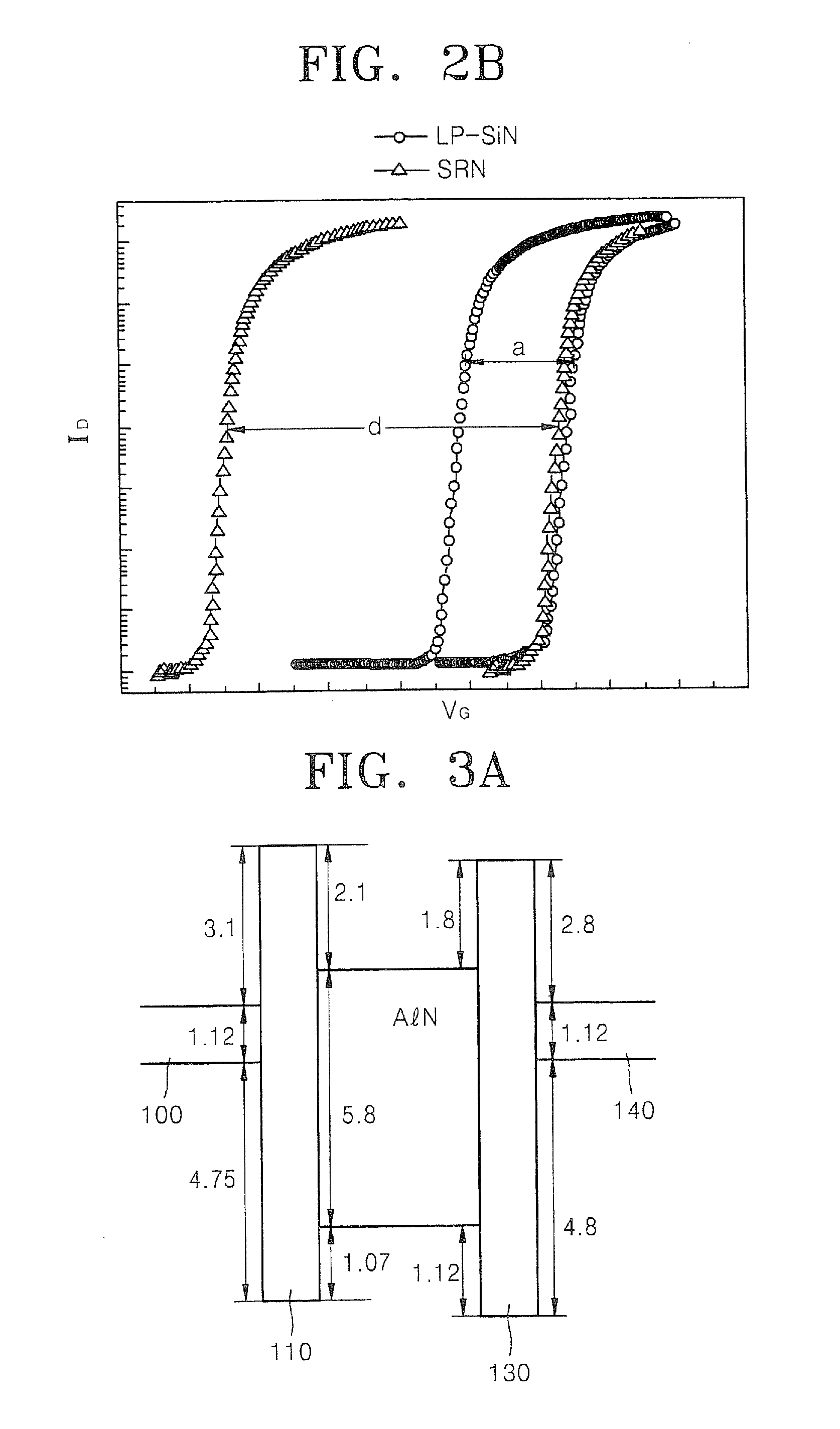

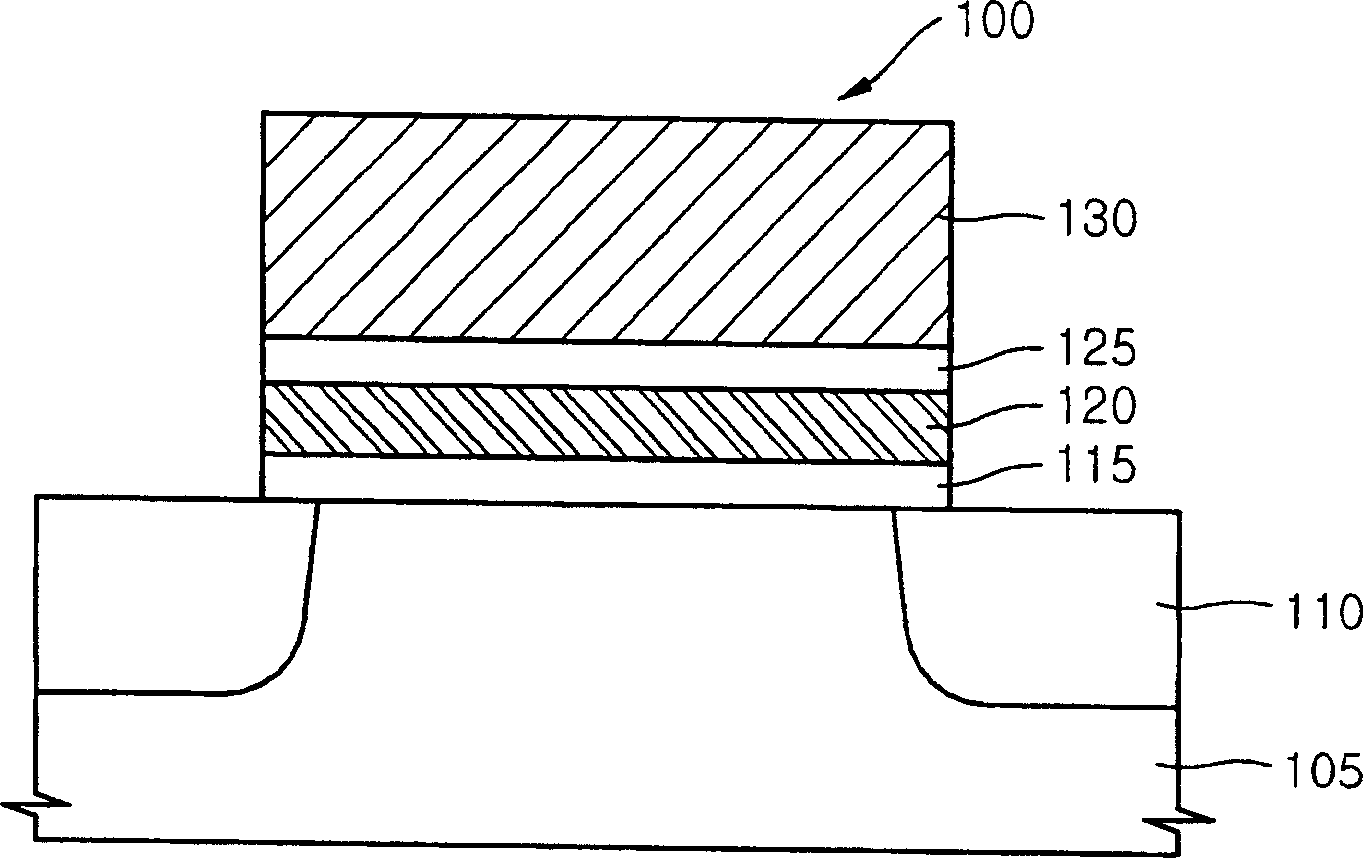

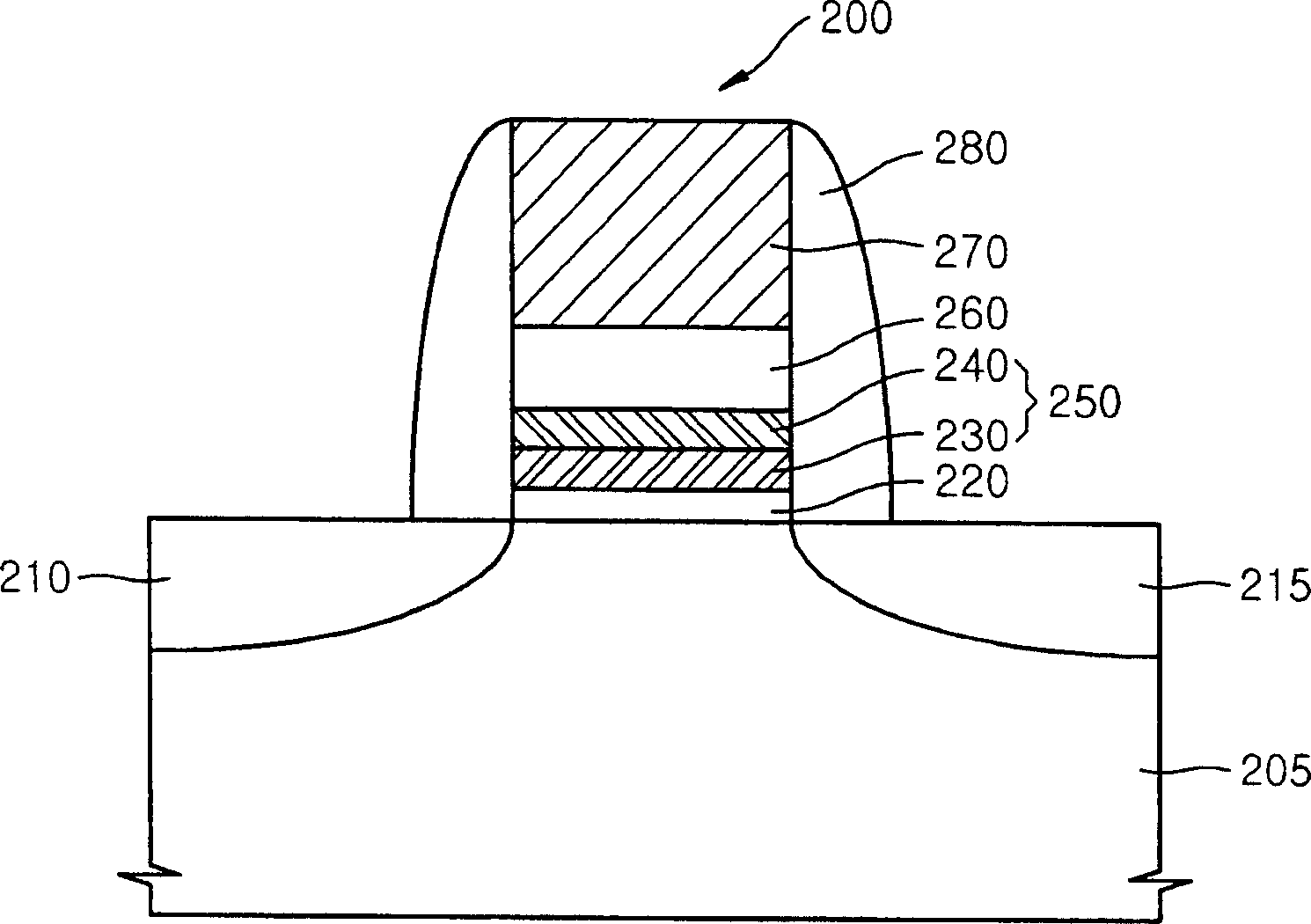

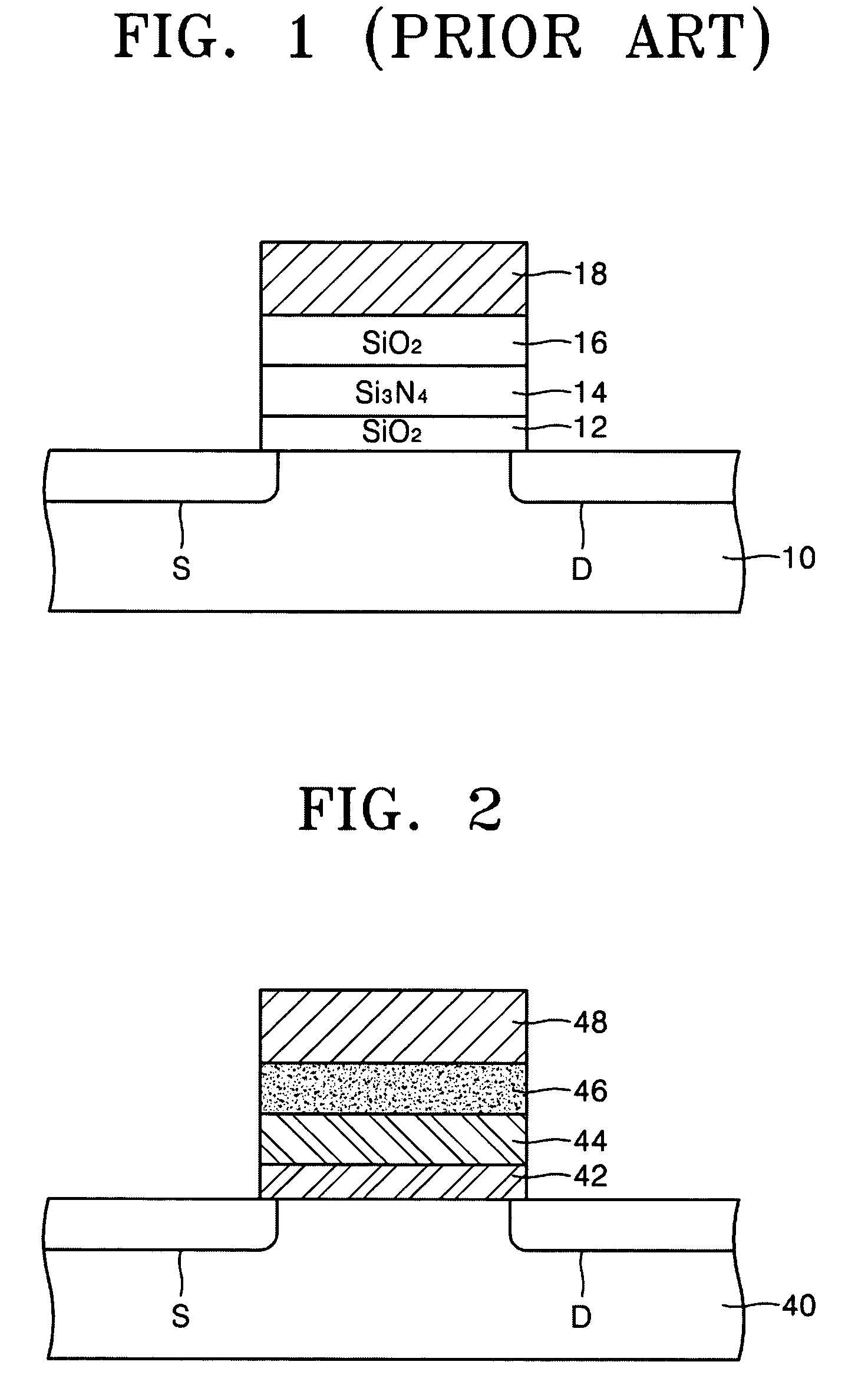

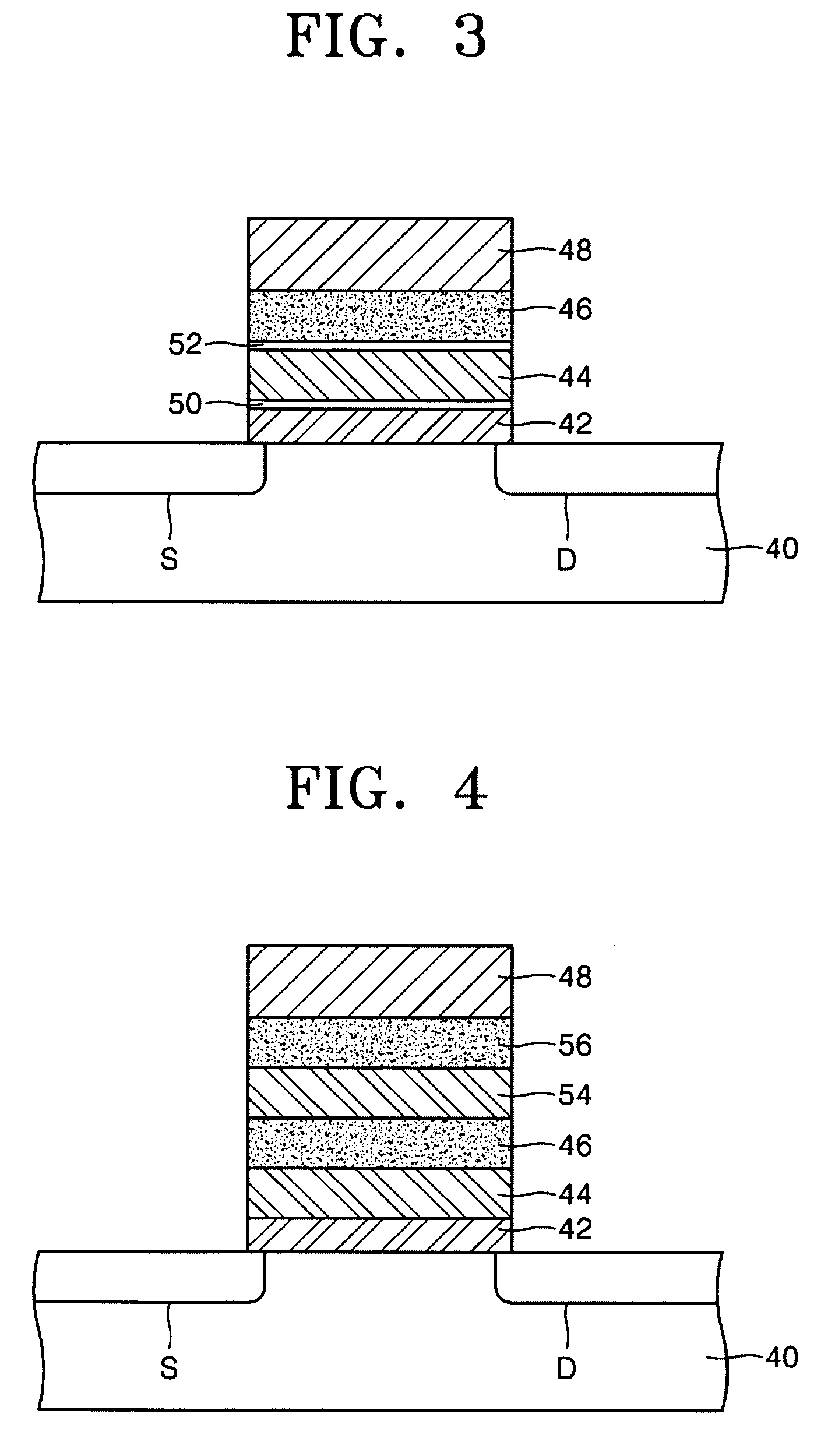

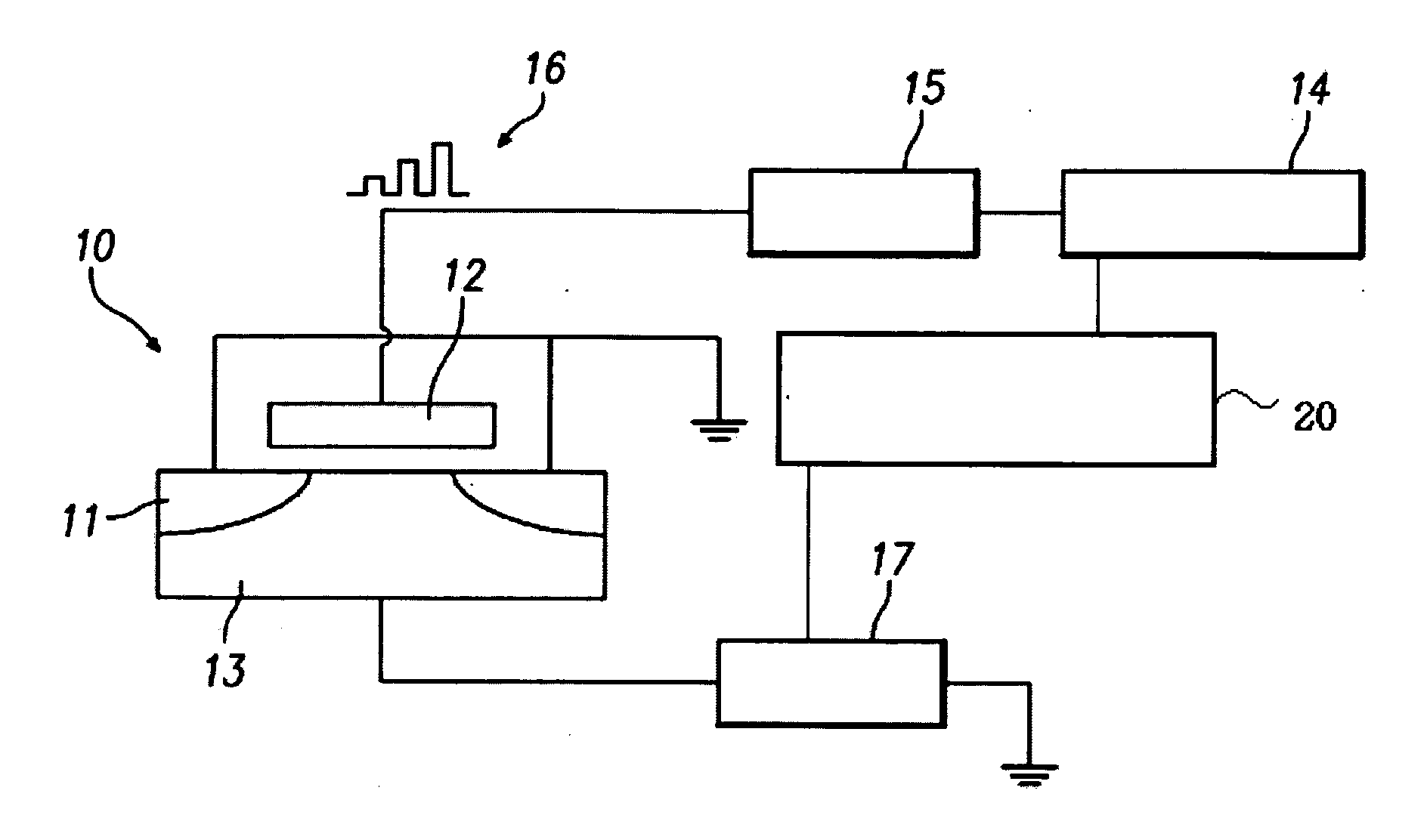

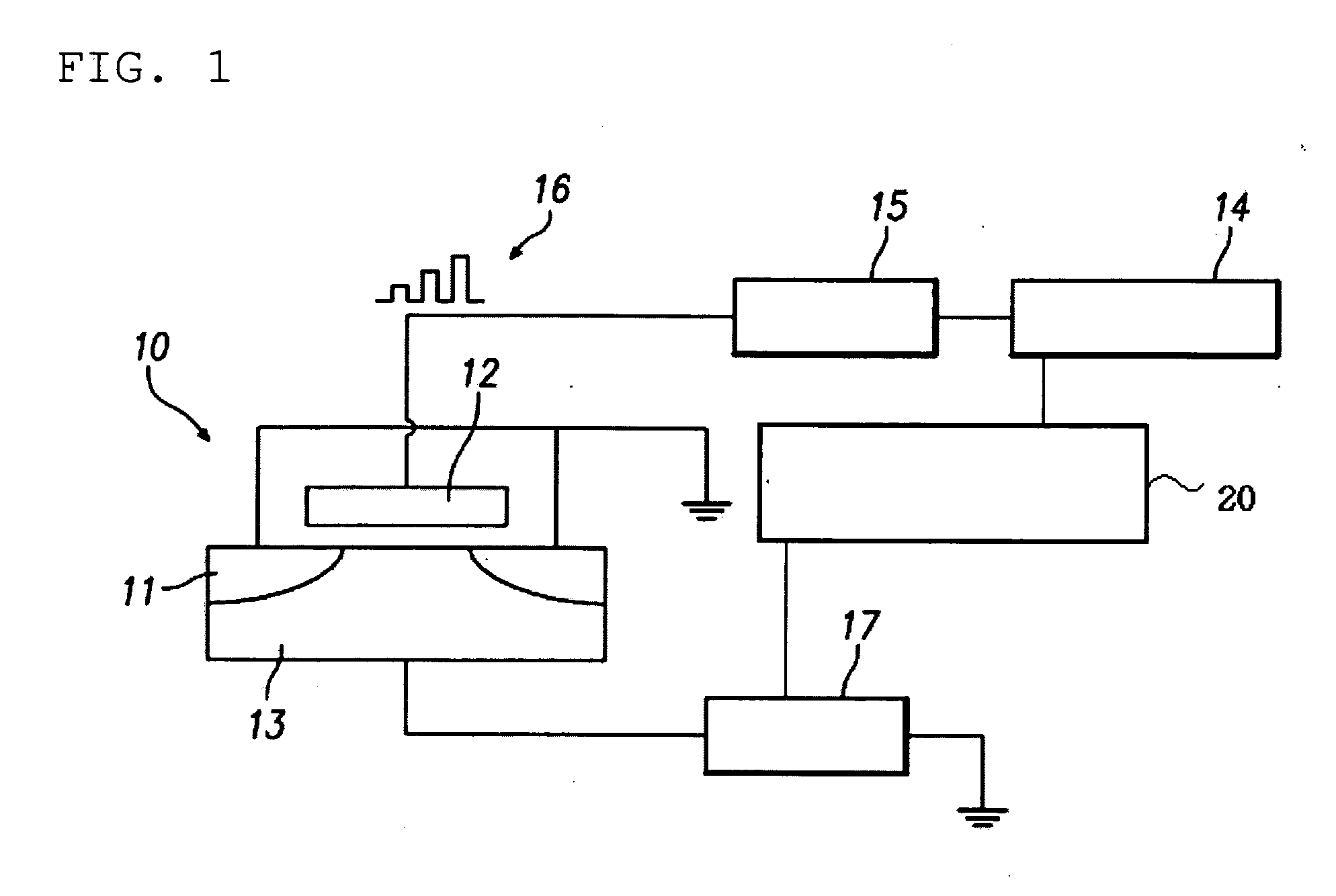

Semiconductor memory device including charge trap layer with stacked nitride layers

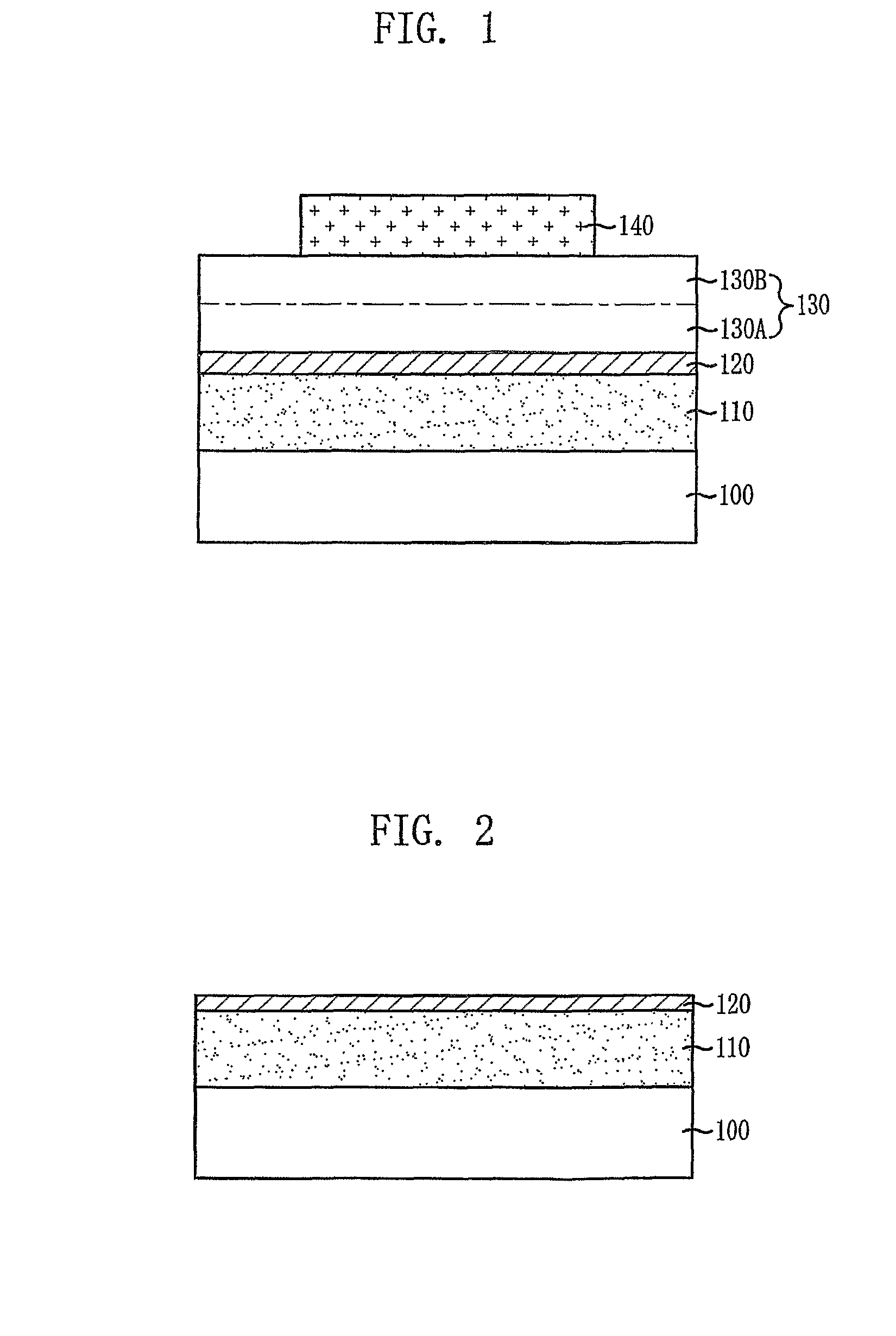

A semiconductor memory device includes a semiconductor substrate, a tunnel insulating layer, charge trap layer, and a blocking layer. The tunnel insulating layer is on the semiconductor substrate. The charge trap layer is on the tunnel insulating layer and includes at least one pair of a first nitride layer with a higher trap density of holes than electrons and a second nitride layer with a higher trap density of electrons than holes. The blocking layer is on the charge trap layer opposite to the tunnel insulating layer. The first nitride layer may include silicon rich nitride, which may have a ratio of silicon to nitride of greater than 1 and less than or equal to 2. The second nitride layer may include aluminum nitride which may have a hexagonal crystalline structure.

Owner:SAMSUNG ELECTRONICS CO LTD

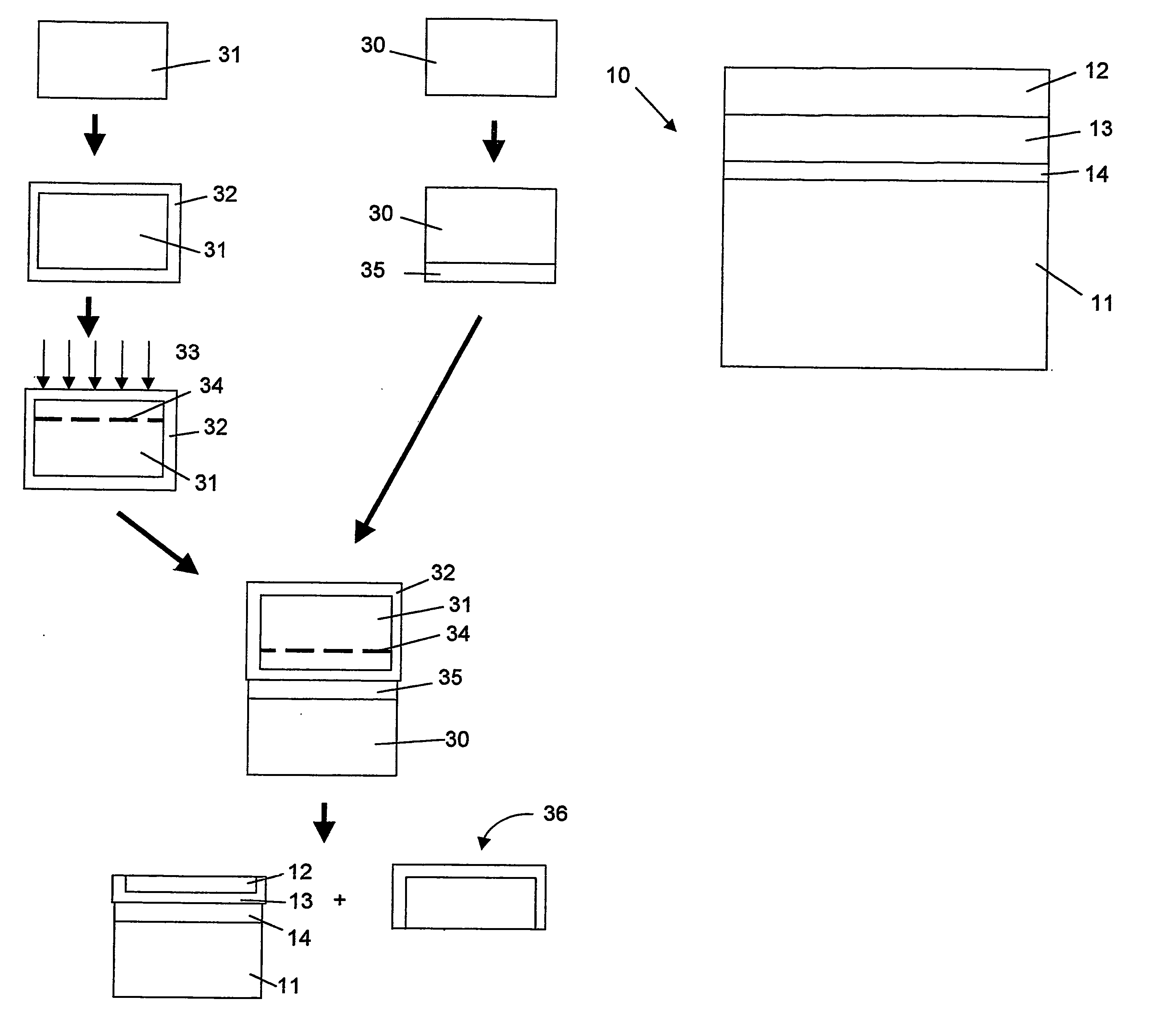

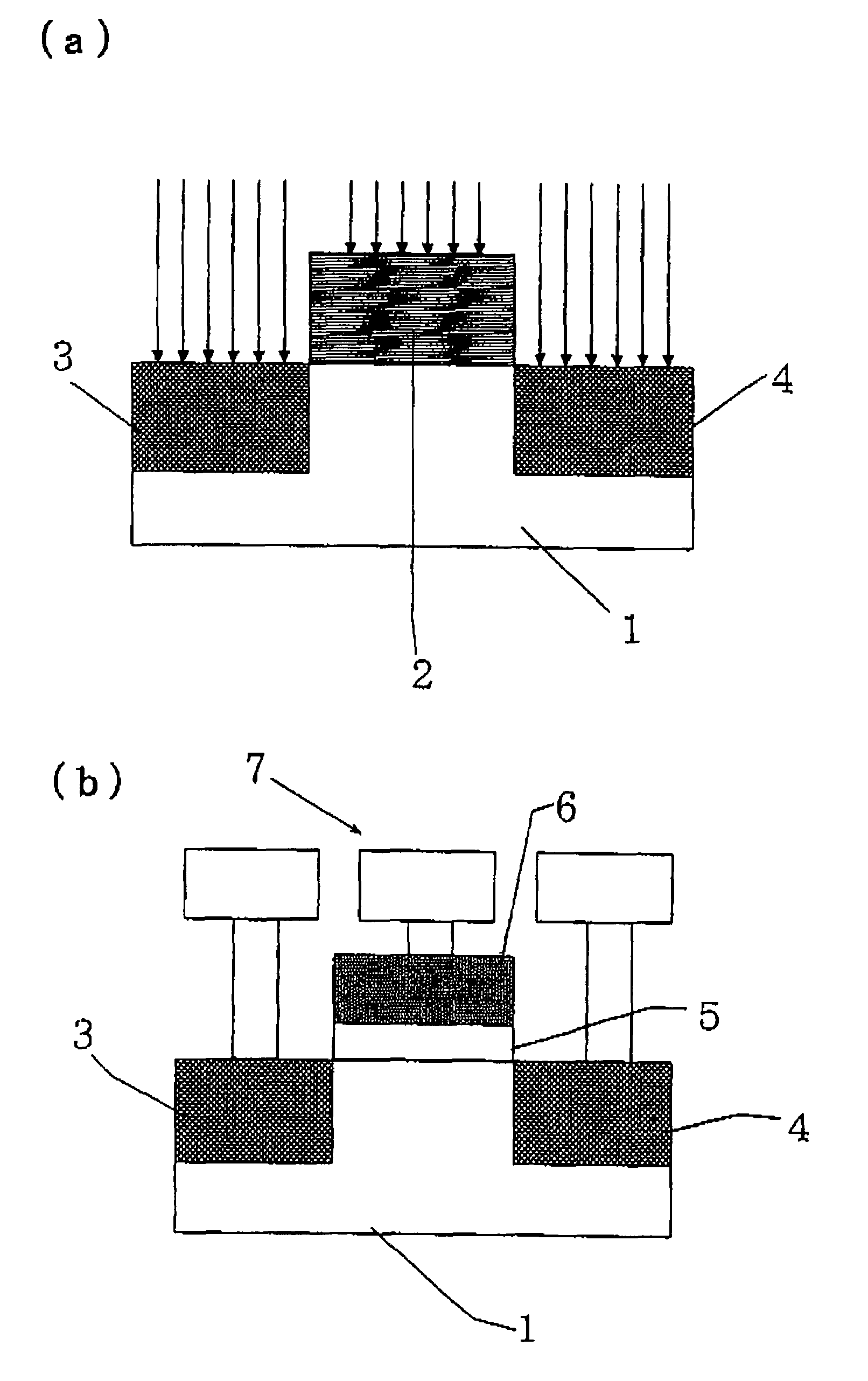

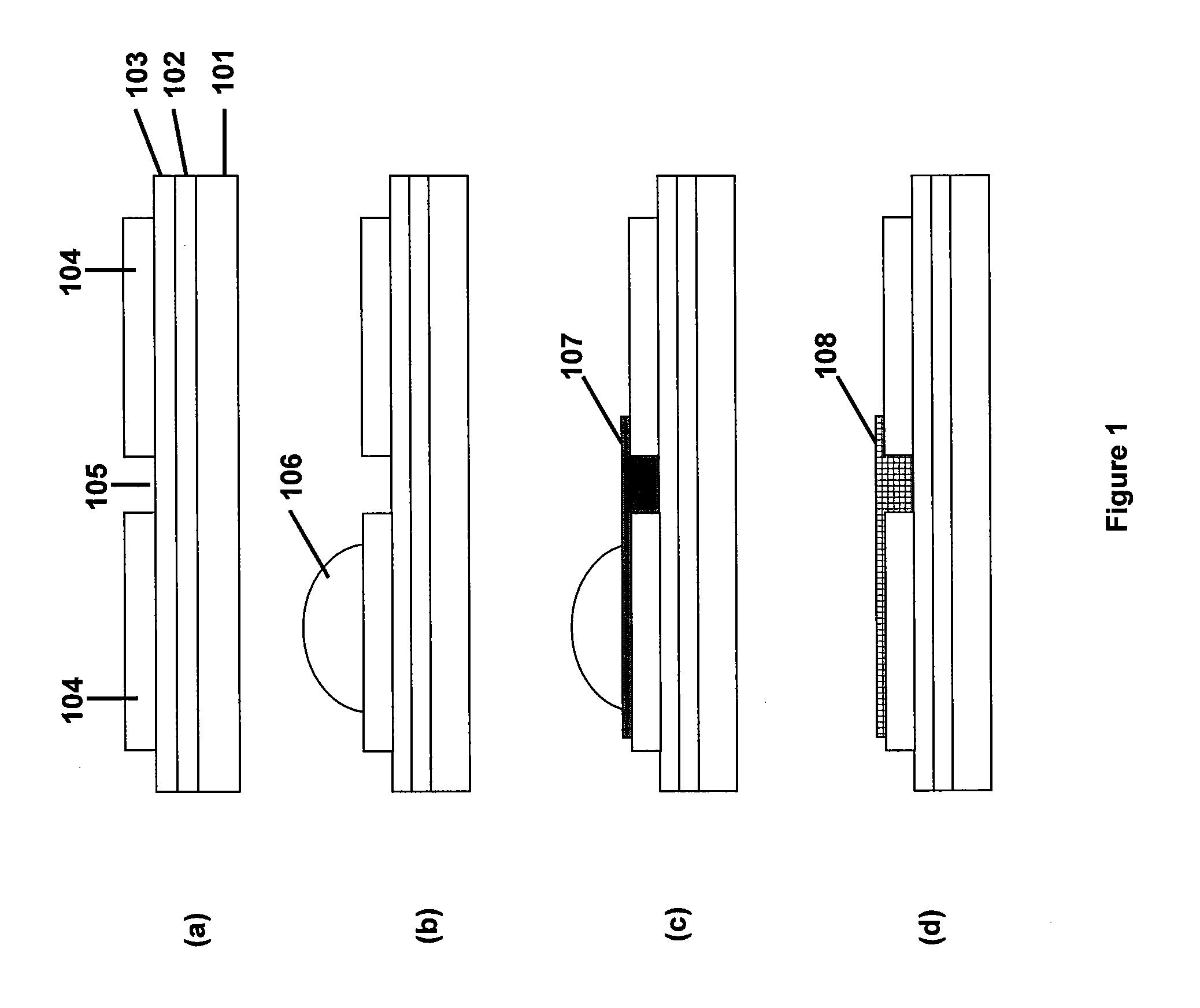

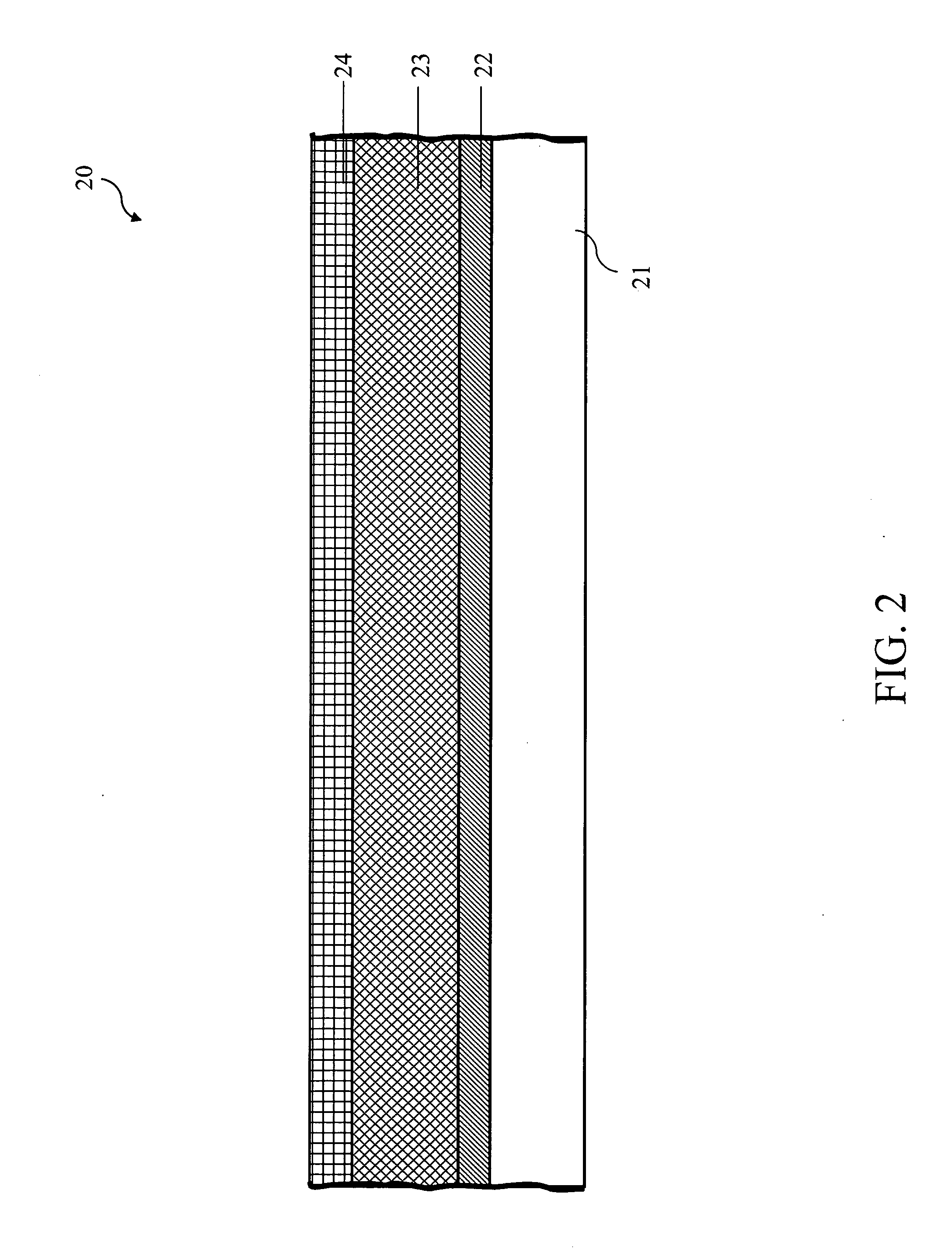

Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses

InactiveUS20070032040A1Reduce and minimiseElectrical losses are reducedSolid-state devicesSemiconductor/solid-state device manufacturingInter layerSemiconductor structure

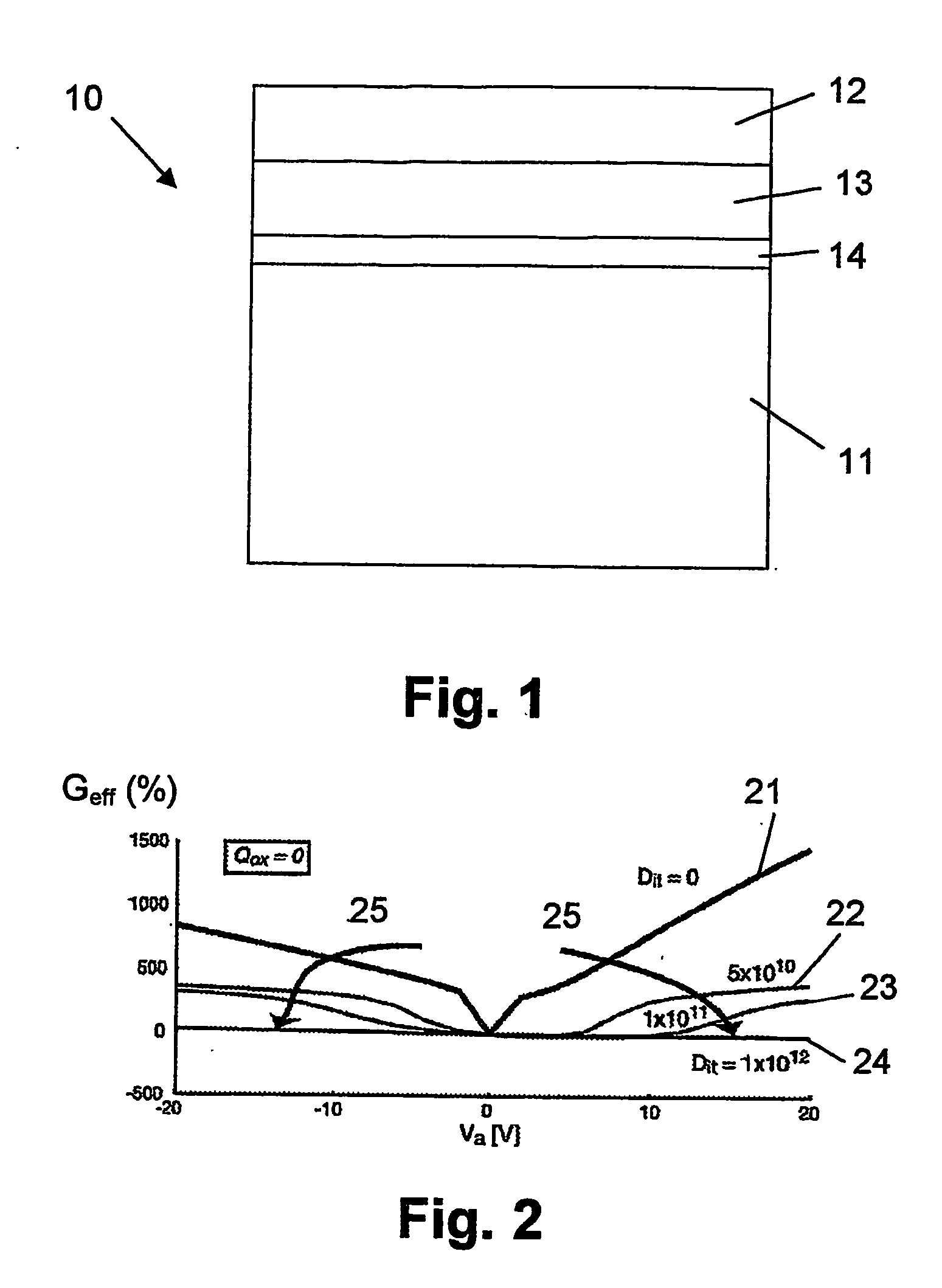

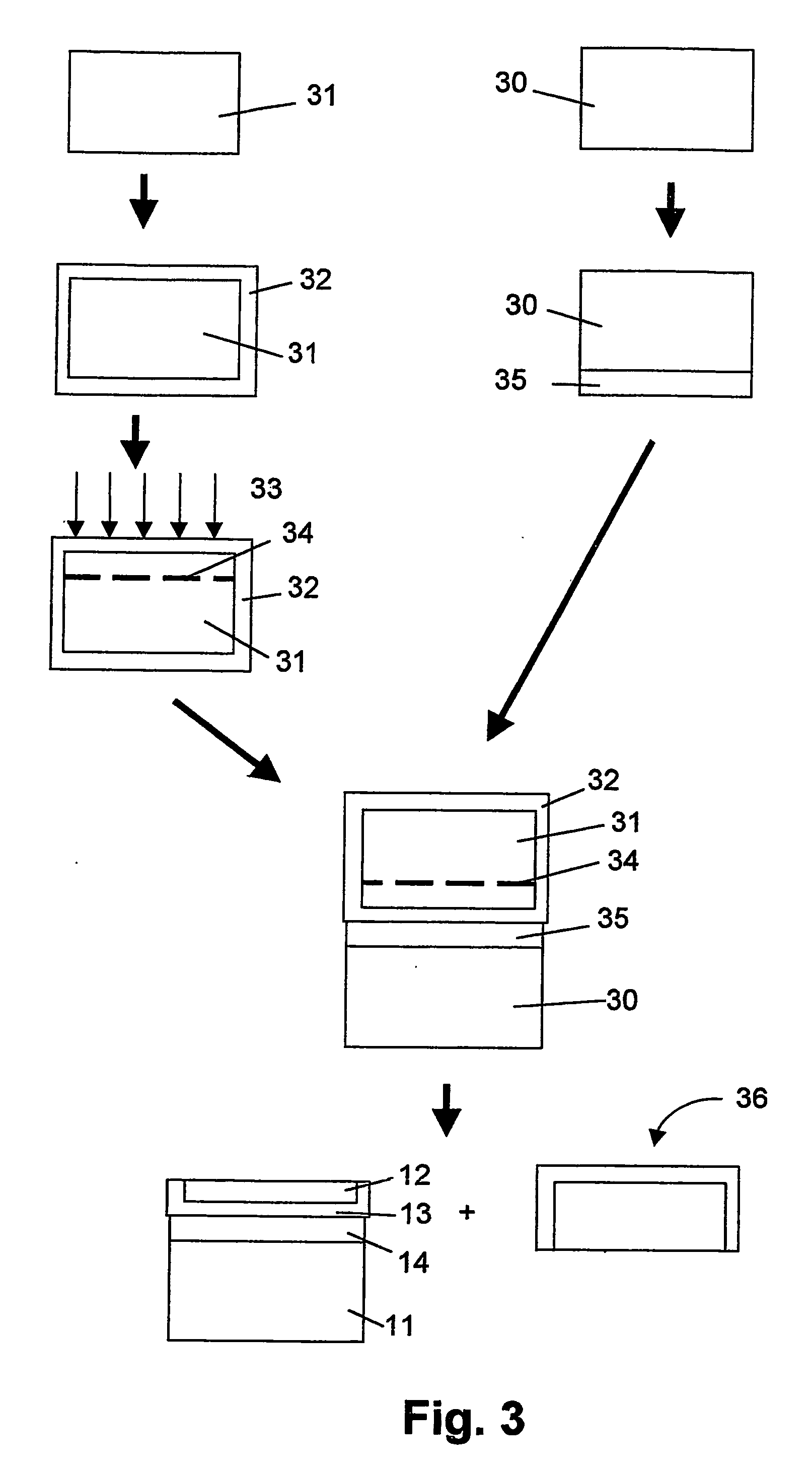

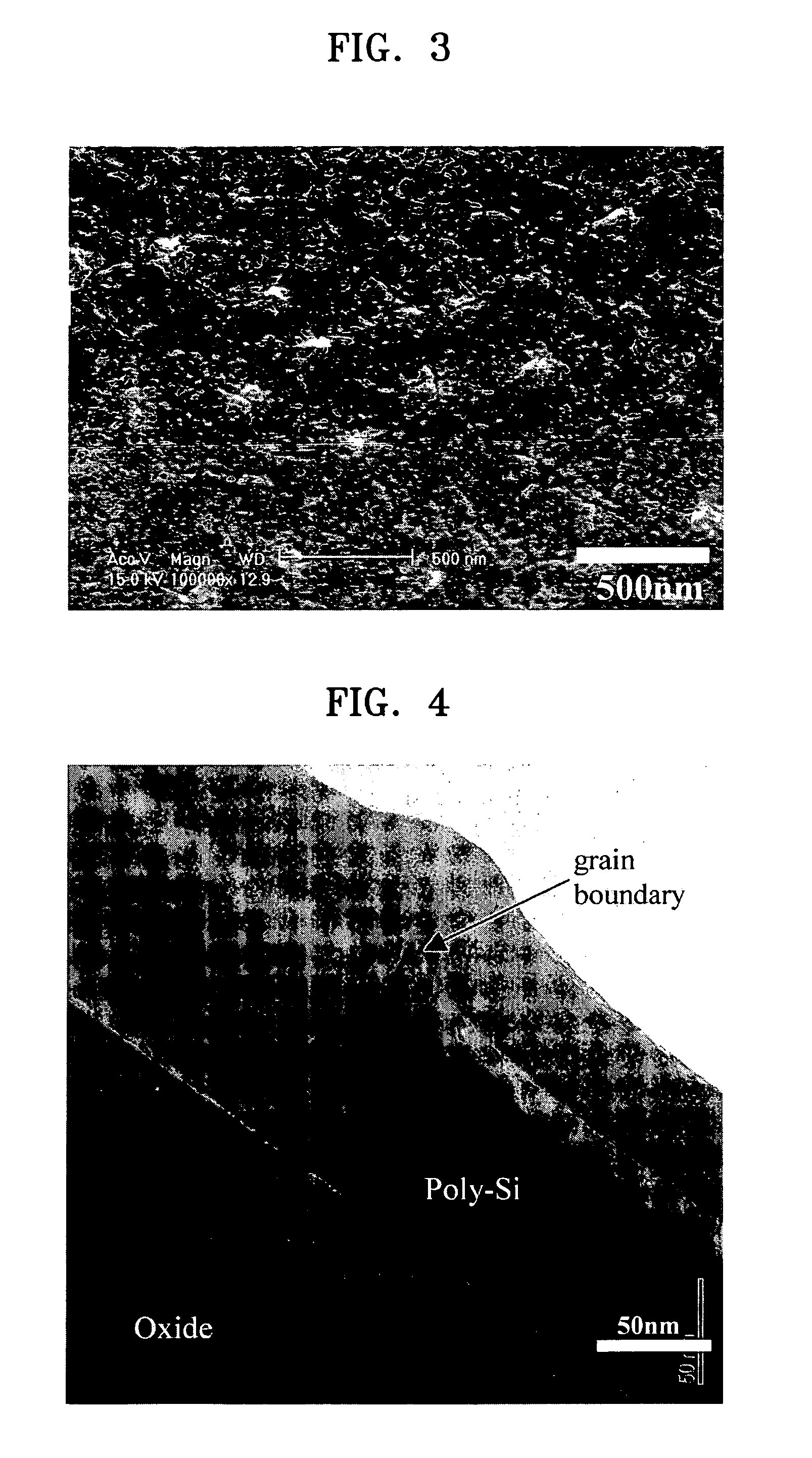

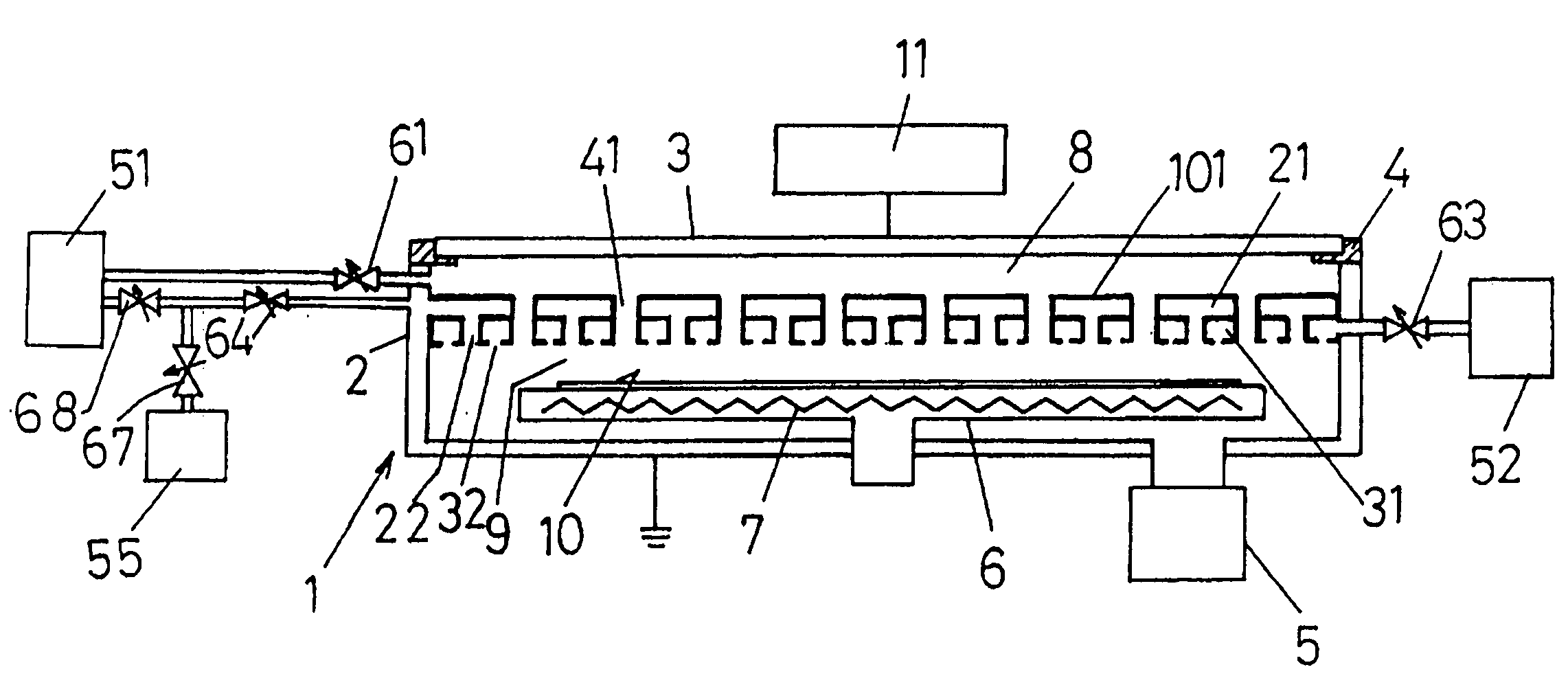

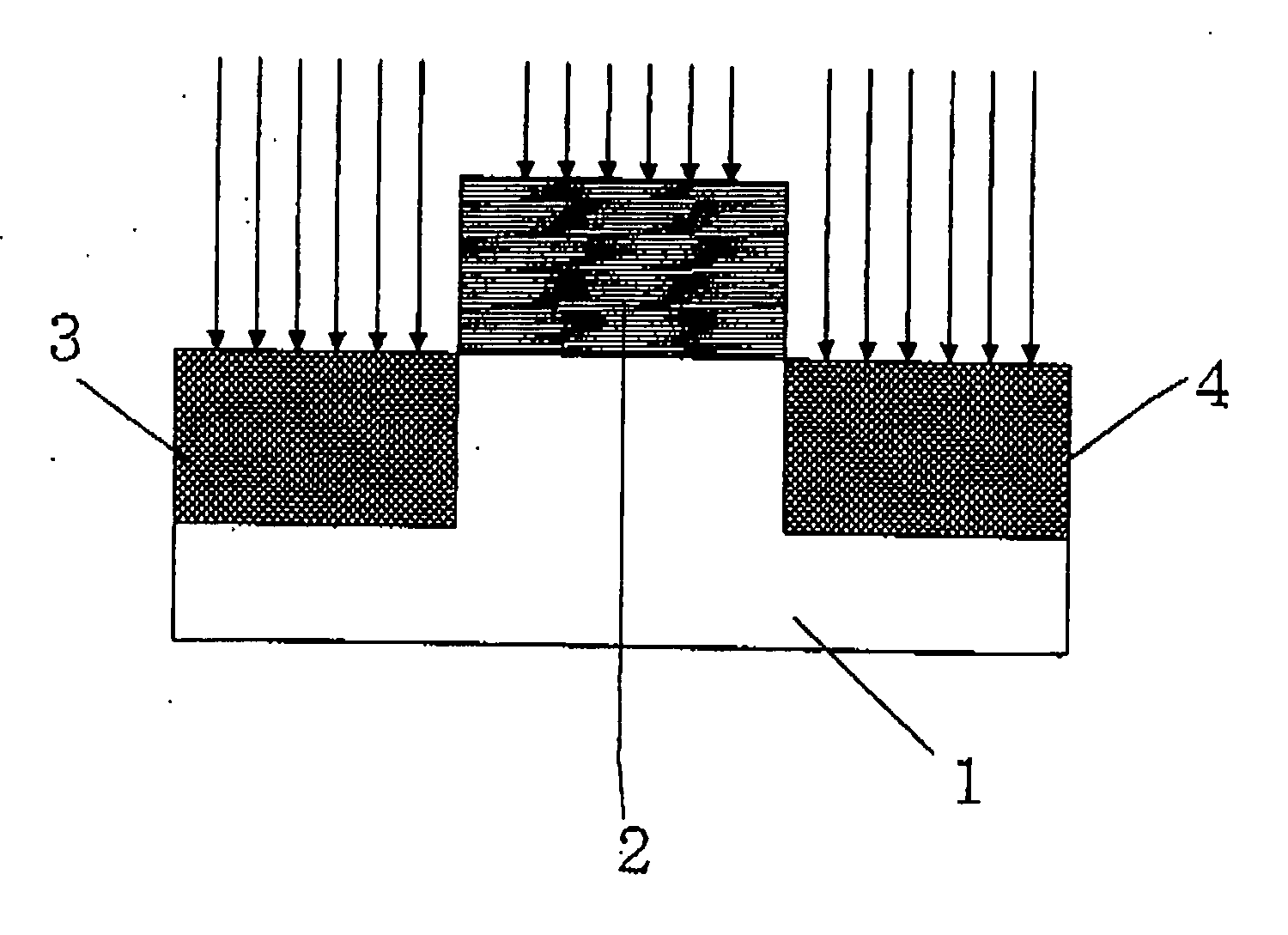

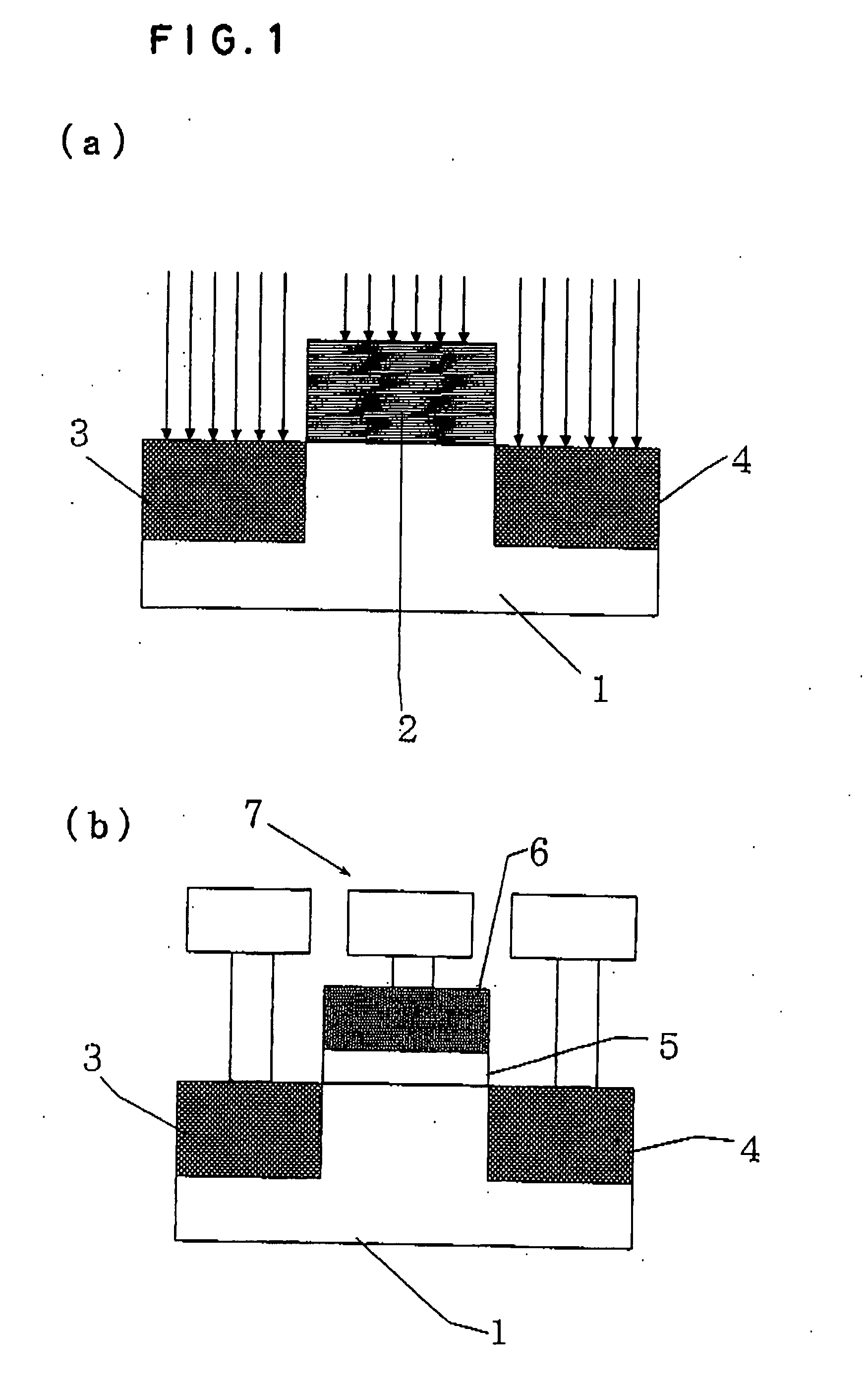

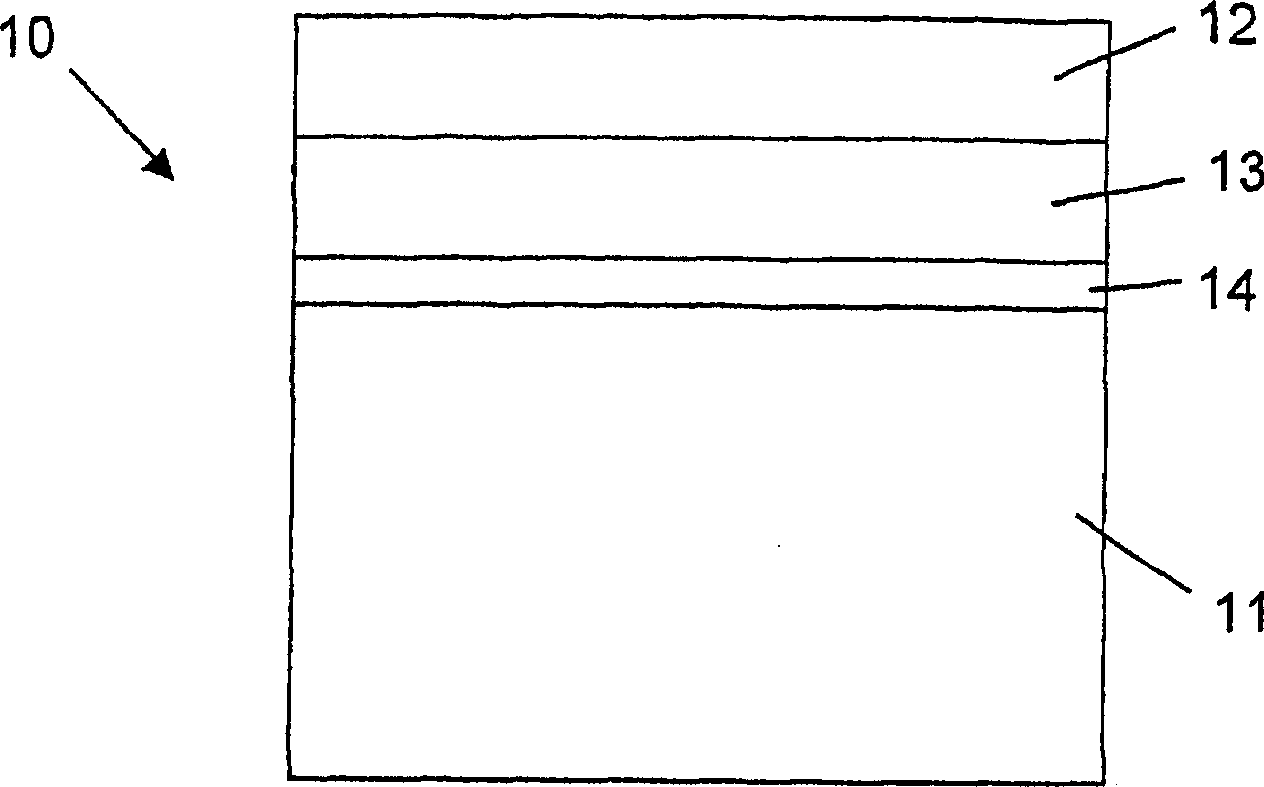

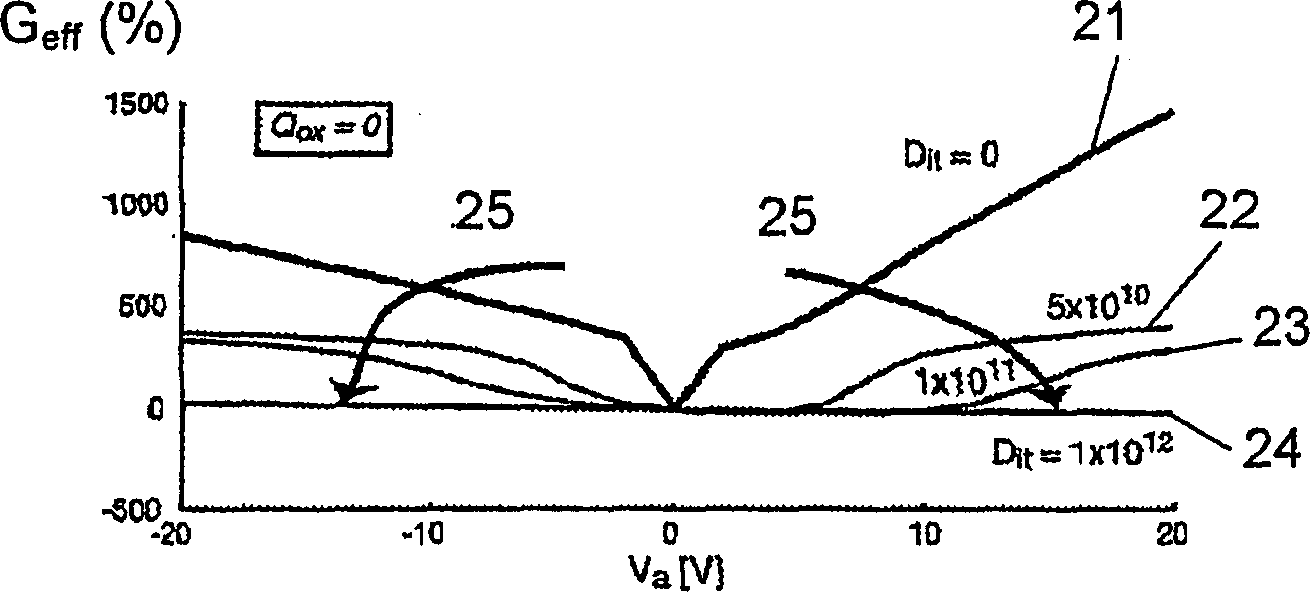

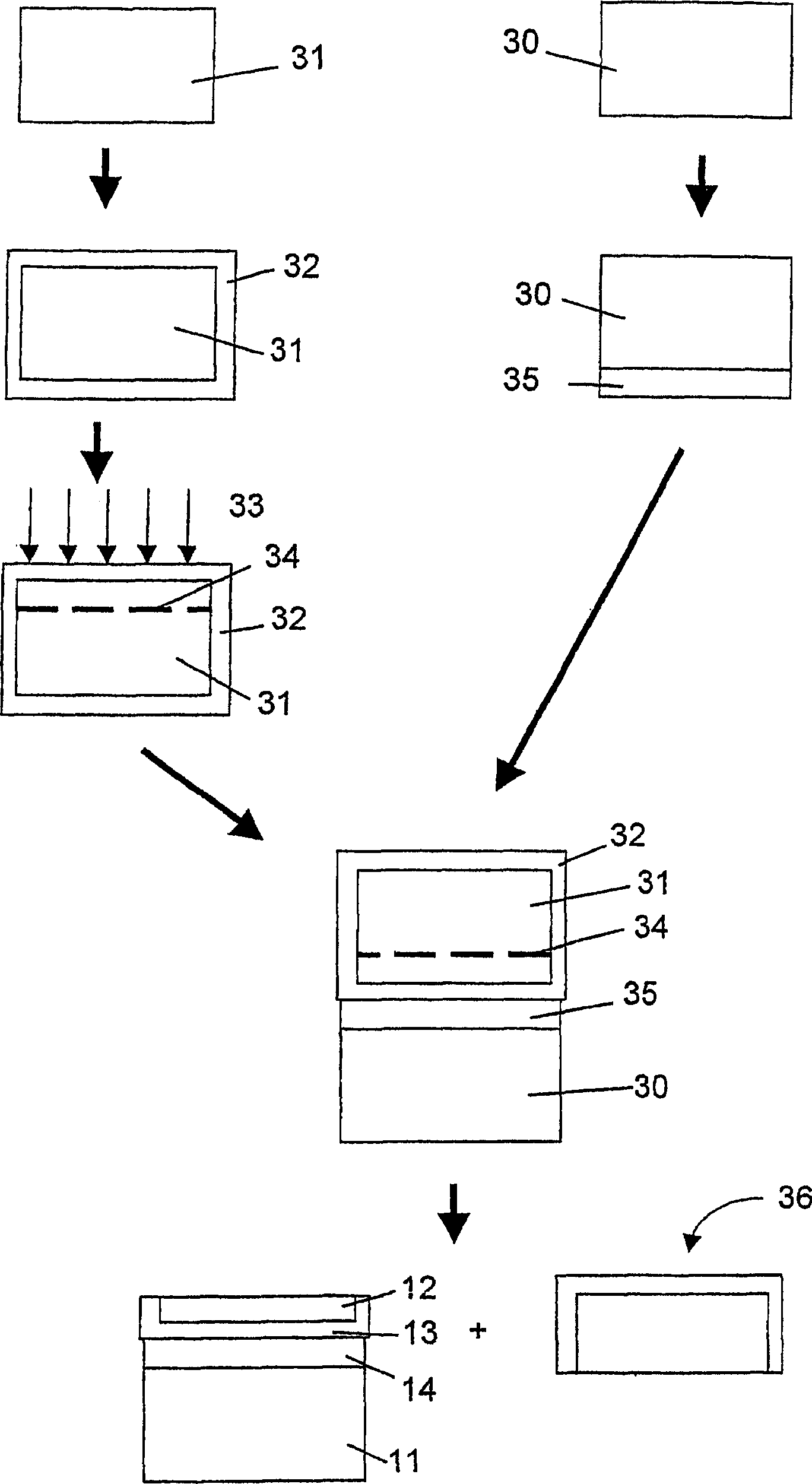

The present invention provides a method of manufacturing a multilayer semiconductor structure featuring reduced ohmic losses with respect to standard multilayer semiconductor structures. The semiconductor structure comprises a high resistivity silicon substrate with resistivity higher than 3 KΩ.cm, an active semiconductor layer and an insulating layer in between the silicon substrate and the active semiconductor layer. The method comprises suppressing ohmic losses inside the high resistivity silicon substrate by increasing, with regard to prior art devices, charge trap density between the insulating layer and the silicon substrate. In particular this may be obtained by applying an intermediate layer in between the silicon substrate and the insulating layer, the intermediate layer comprising grains having a size, wherein the mean size of the grains of the intermediate layer is smaller than 150 nm, preferably smaller than 50 nm.

Owner:UNIV CATHOLIQUE DE LOVAIN

Method of fabricating poly-crystalline silicon thin film and method of fabricating transistor using the same

InactiveUS7563659B2Refined grain sizeHigh energyTransistorSemiconductor/solid-state device manufacturingInductively coupled plasmaSilicon thin film

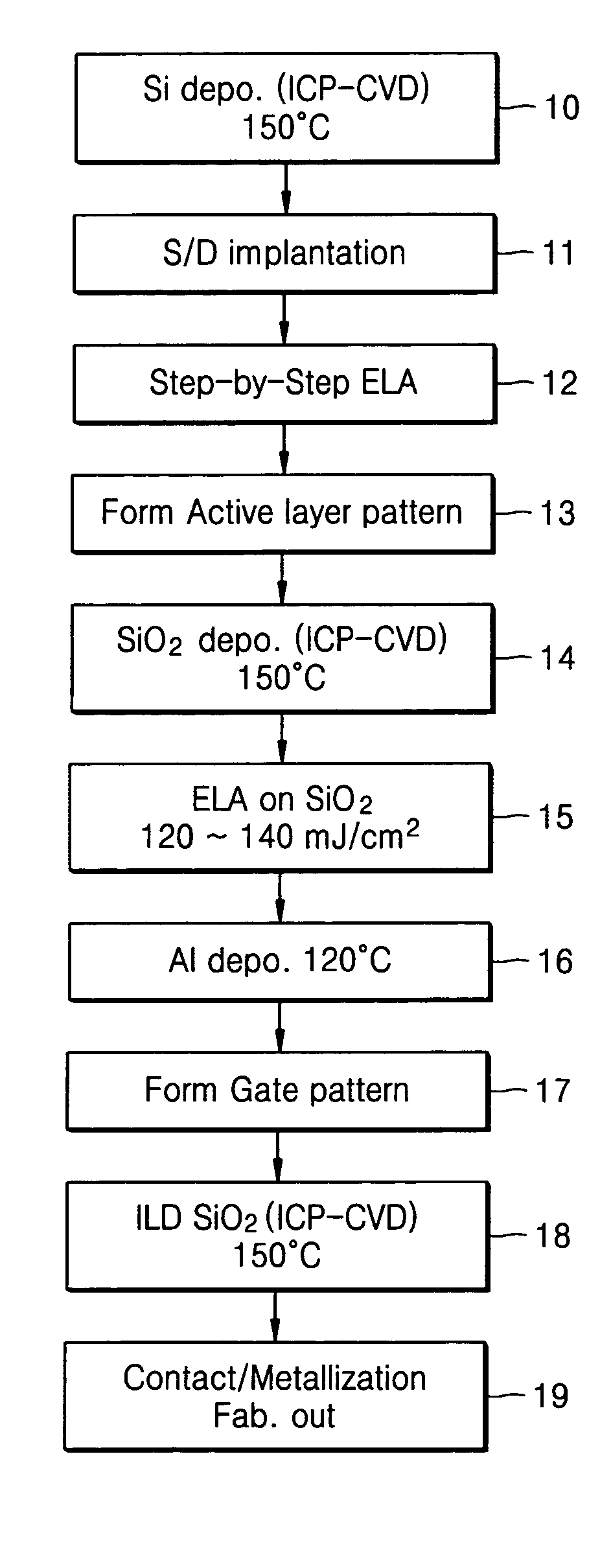

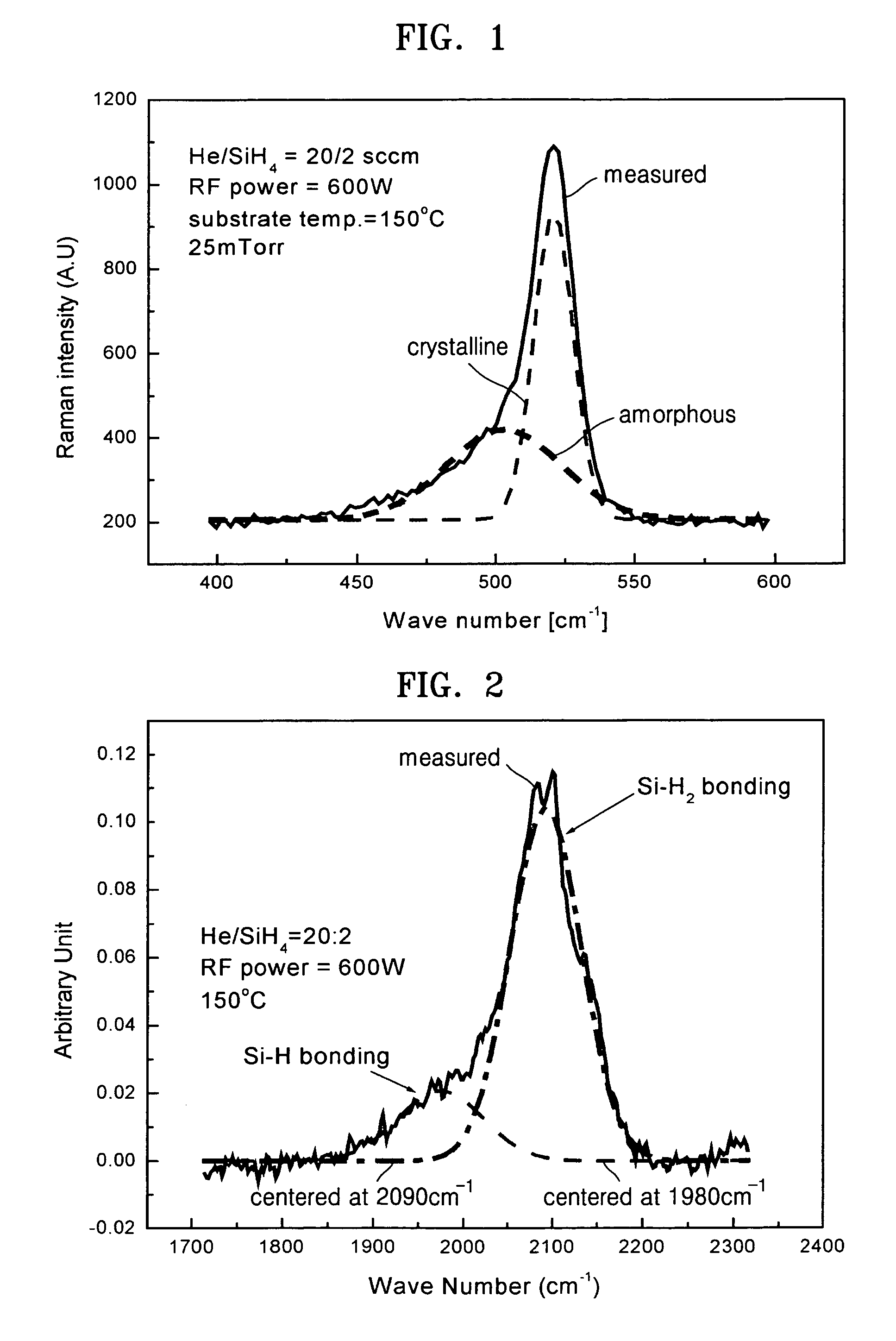

A method of fabricating a poly-Si thin film and a method of fabricating a poly-Si TFT using the same are provided. The poly-Si thin film is formed at a low temperature using inductively coupled plasma chemical vapor deposition (ICP-CVD). After the ICP-CVD, excimer laser annealing (ELA) is performed while increasing energy by predetermined steps. A poly-Si active layer and a SiO2 gate insulating layer are deposited at a temperature of about 150° C. using ICP-CVD. The poly-Si has a large grain size of about 3000 Å or more. An interface trap density of the SiO2 can be as high as 1011 / cm2. A transistor having good electrical characteristics can be fabricated at a low temperature and thus can be formed on a heat tolerant plastic substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

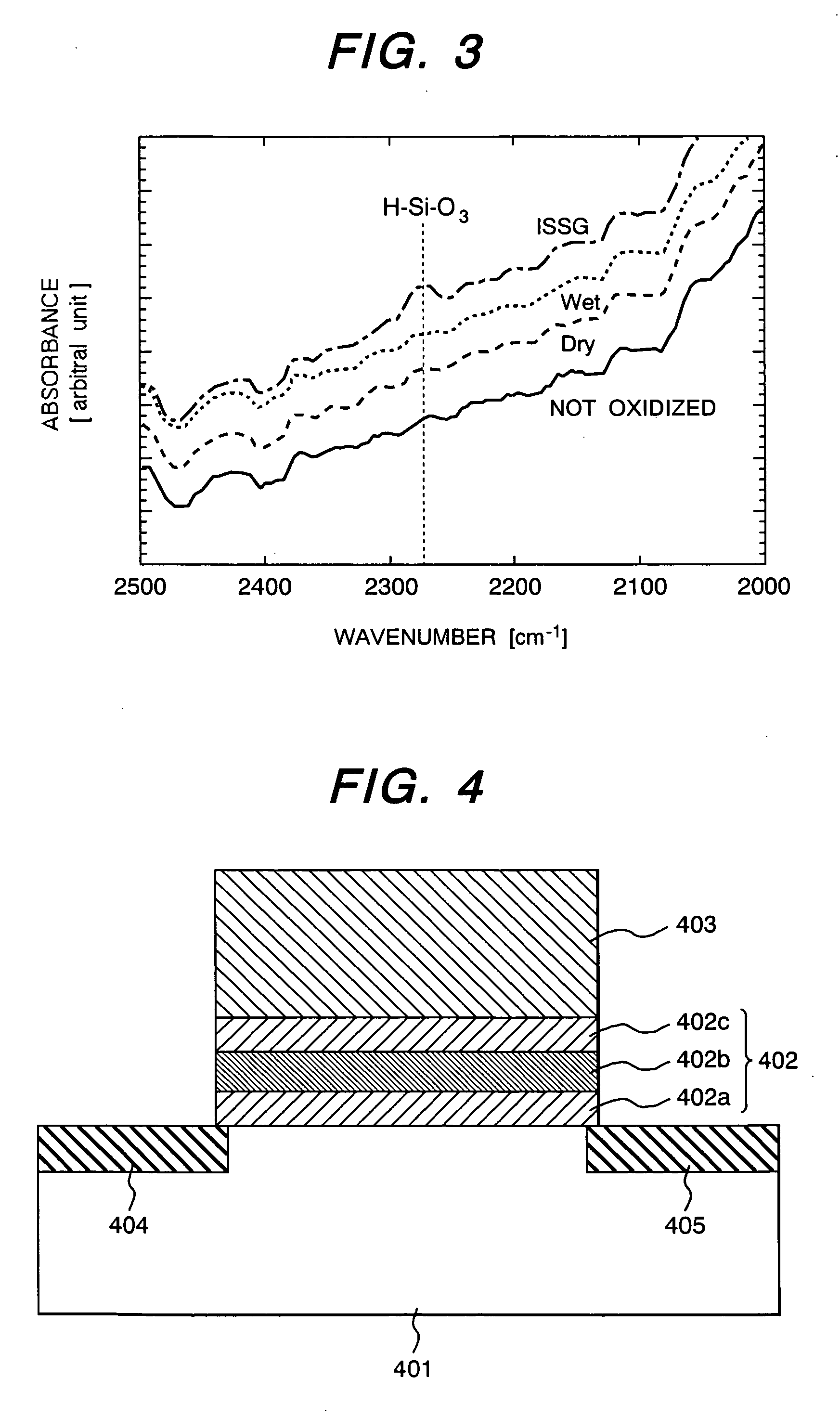

Method for Thin Film Formation

InactiveUS20090202721A1Improve interface propertiesLow densitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingNitrogenSilicon oxide

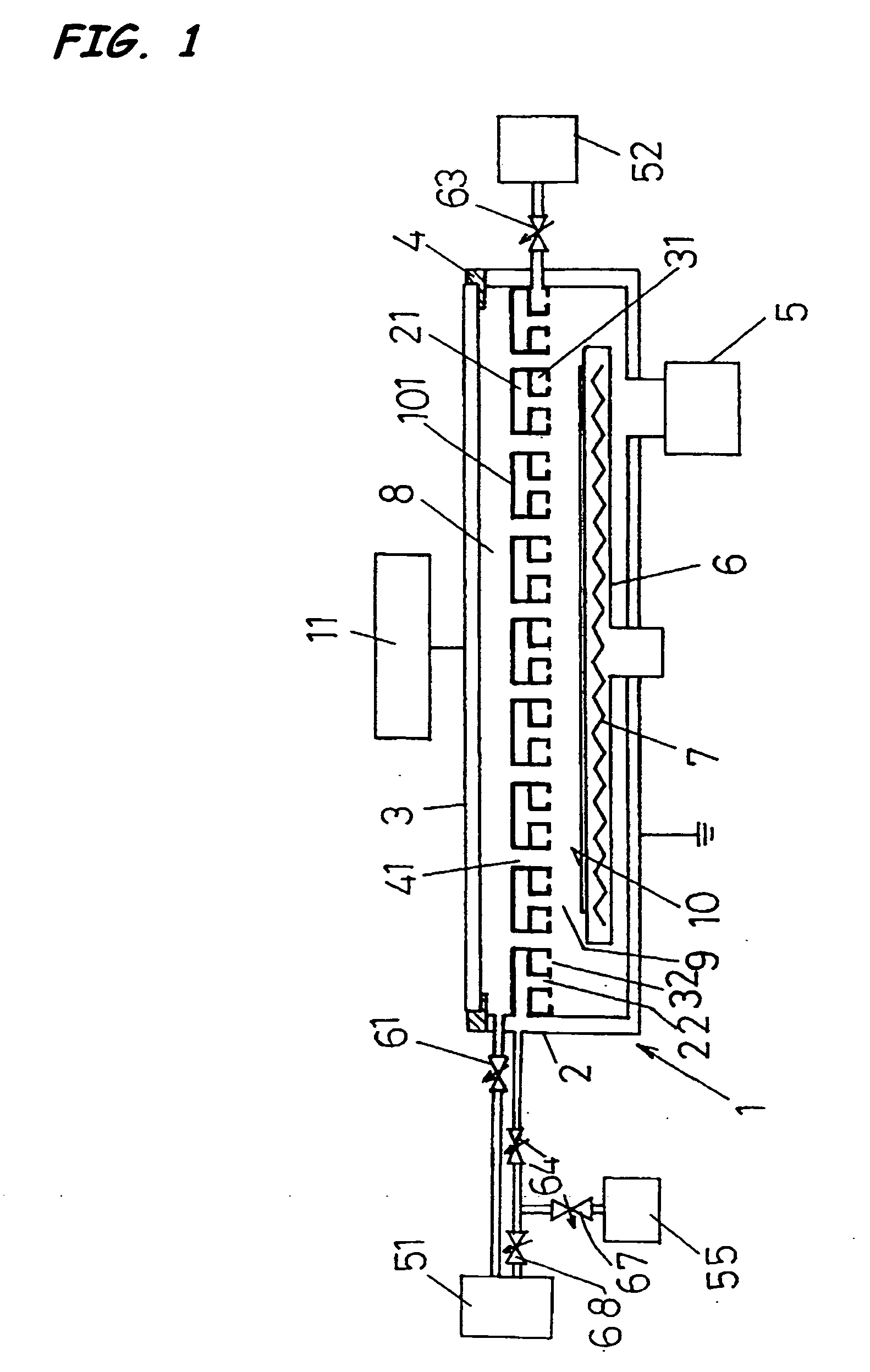

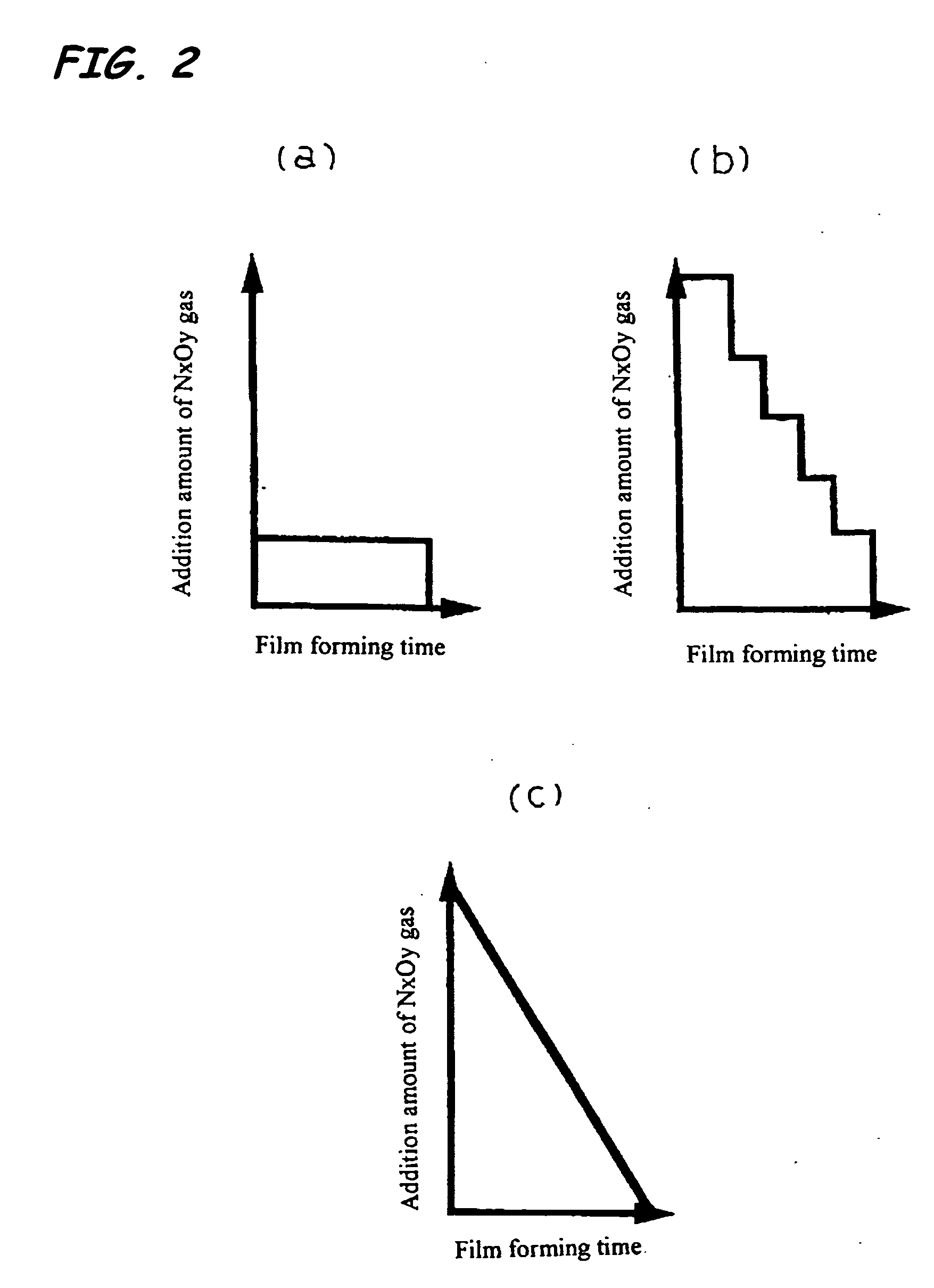

A method for thin film formation that can form, at a low temperature, a good thin film having a good interfacial property between a silicon substrate and a silicon oxide film and having a low interfacial trap density is provided.The method for thin film formation comprises generating plasma within a vacuum vessel to generate an active species (radical) and forming a silicon oxide film on a silicon substrate using this active species and a material gas, wherein, in addition to the material gas, a nitrogen atom-containing gas is introduced into the vacuum vessel in its film forming space where the active species (radical) and the material gas come into contact with each other for the first time and are reacted with each other to form a silicon film on the silicon substrate, and wherein the flow rate of the nitrogen atom-containing gas during the formation of the silicon oxide film on the silicon substrate is regulated so as to be the maximum value at least at the time of the start of formation of the silicon film on the silicon substrate.

Owner:NEC CORP

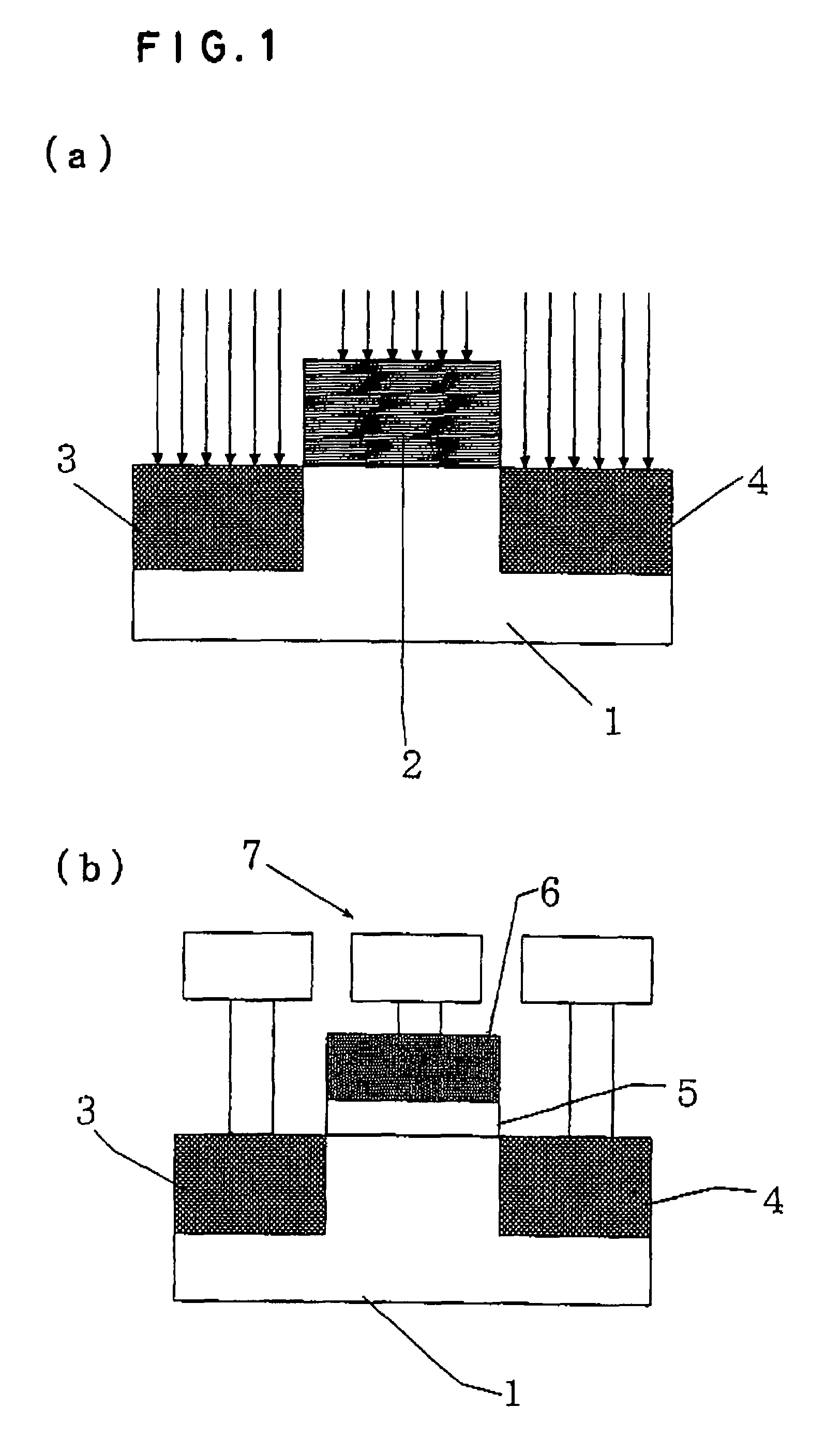

Semiconductor device and its manufacturing method

ActiveUS20050245034A1Increase temperatureLow densityTransistorSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

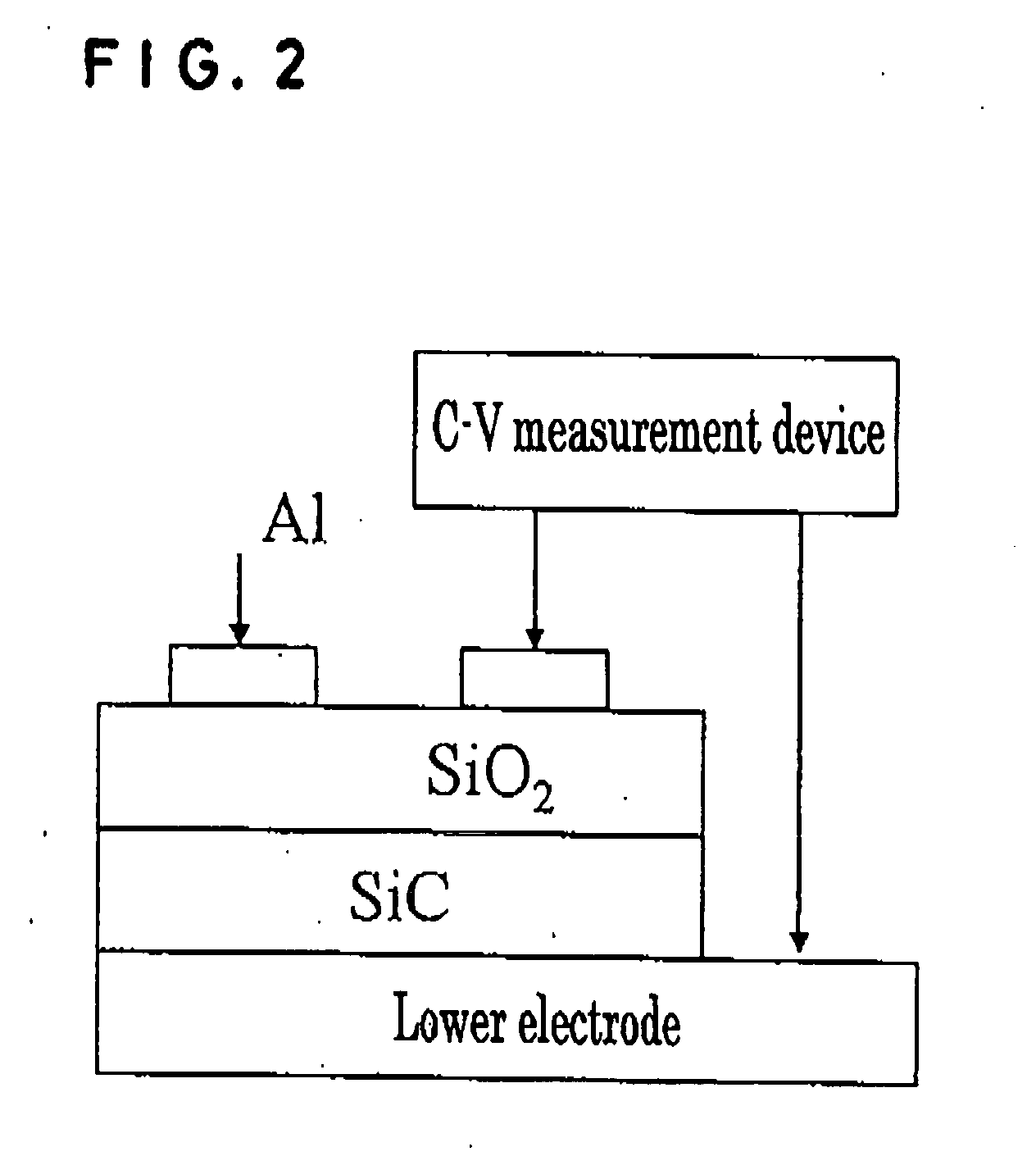

A semiconductor device and a method of manufacturing the device using a (000-1)-faced silicon carbide substrate are provided. A SiC semiconductor device having a high voltage resistancehigh blocking voltage and high channel mobility is manufactured by opting the heat treatment method used following the gate oxidation. The method of manufacturing a semiconductor device includes the steps of forming a gate insulation layer on a semiconductor region formed of silicon carbide having a (000-1) face orientation, forming a gate electrode on the gate insulation layer, forming an electrode on the semiconductor region, cleaning the semiconductor region surface. The gate insulation layer is formed in an atmosphere containing 1% or more H2O (water) vapor at a temperature of from 800° C. to 1150° C. to reduce the interface trap density of the interface between the gate insulation layer and the semiconductor region.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Method of forming bottom oxide for nitride flash memory

ActiveUS20070069283A1Read-only memoriesSemiconductor/solid-state device manufacturingHydrogen concentrationTrapping

A non-volatile memory device on a semiconductor substrate may include a bottom oxide layer over the substrate, a middle layer of silicon nitride over the bottom oxide layer, and a top oxide layer over the middle layer. The bottom oxide layer may have a hydrogen concentration of up to 5E19 cm−3 and an interface trap density of up to 5E11 cm−2 eV−1. The three-layer structure may be a charge-trapping structure for the memory device, and the memory device may further include a gate over the structure and source and drain regions in the substrate.

Owner:MACRONIX INT CO LTD

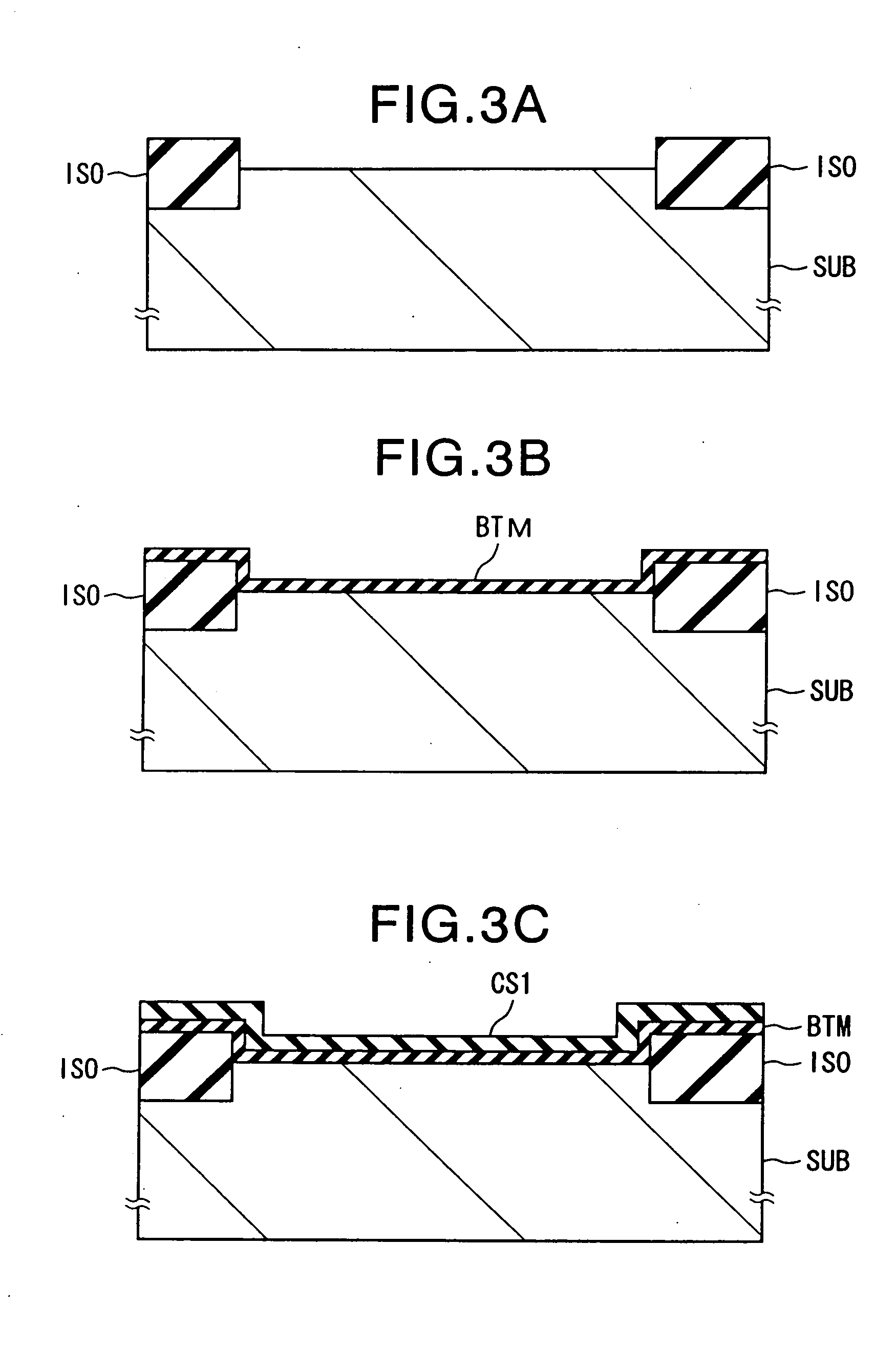

Non-volatile semiconductor memory device and method for producing same

InactiveUS20050230766A1Reduce voltageIncrease speedTransistorSolid-state devicesVolumetric Mass DensityChemical vapor deposition

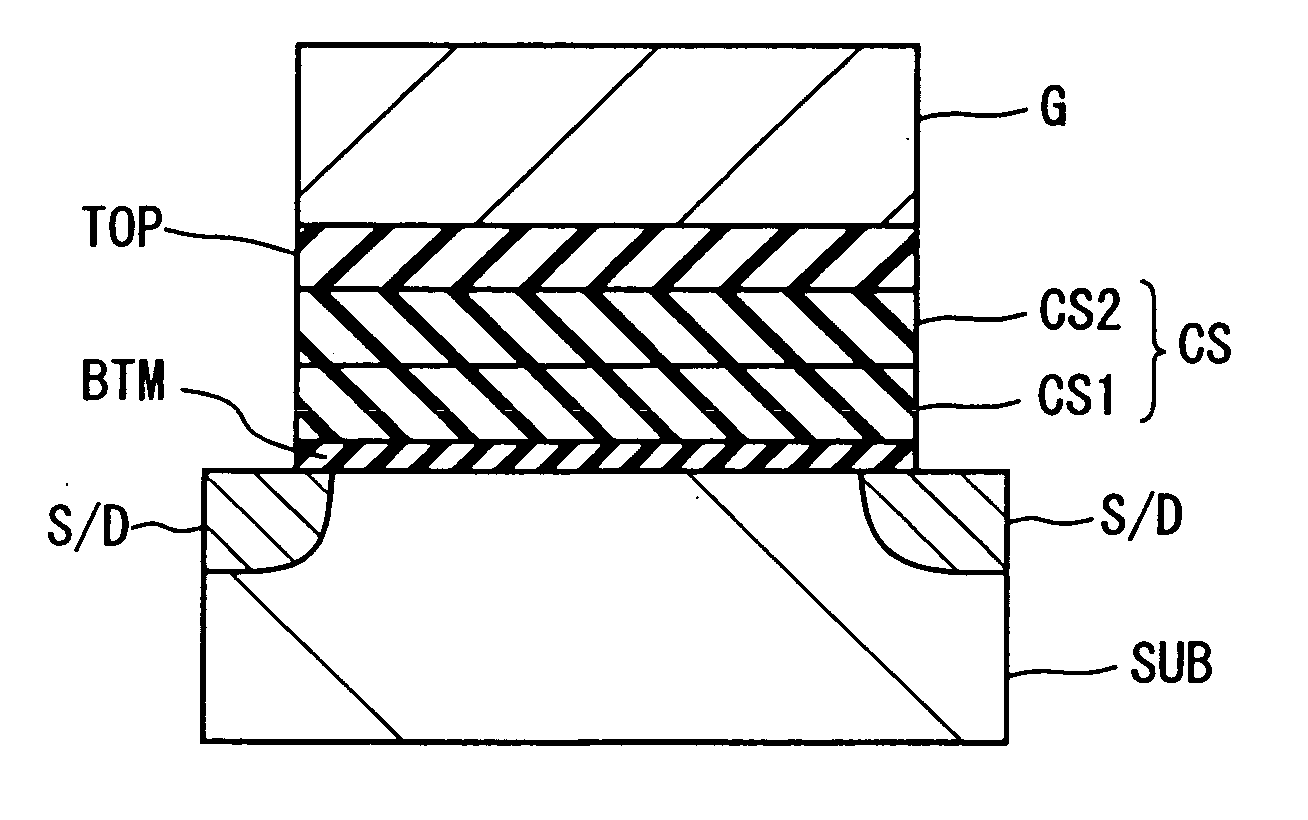

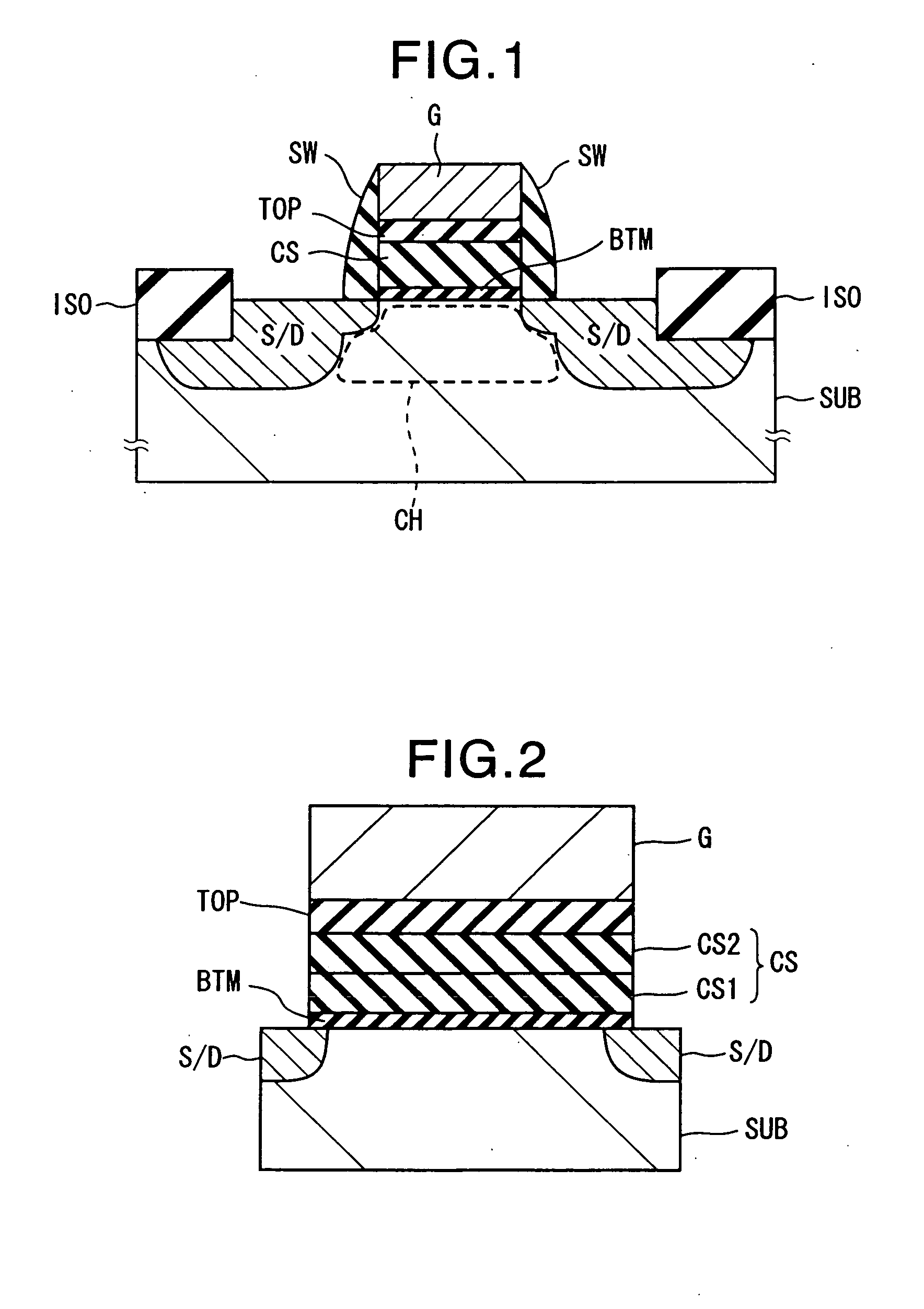

The memory device has a plurality of dielectric films including charge storage layers CS having a charge holding capability therein and stacked on an active region of a semiconductor SUB and electrodes G on the plurality of dielectric films. Each charge storage layer CS includes a first nitride film CS1 made of silicon nitride or silicon oxynitride and a second nitride film CS2 made of silicon nitride or silicon oxynitride and having a higher charge trap density than the first nitride film CS1. The first nitride film CS1 is formed by chemical vapor deposition using a first gas which contains a first silicon-containing gas containing chlorine with a predetermined percent composition and a nitrogen-containing gas as starting materials. The second nitride film CS2 is formed by chemical vapor deposition using a second gas which contains a second silicon-containing gas having a lower chlorine percent composition than the above predetermined percent composition and a nitrogen-containing gas as starting materials.

Owner:SONY CORP

Memory device and manufacturing method thereof

InactiveUS20100065803A1Effective controlInhibit migrationSemiconductor/solid-state device manufacturingDigital storageEngineeringVolumetric Mass Density

Provided is a resistance variable non-volatile memory device using a trap-controlled Space Charge Limited Current (SCLC), and a manufacturing method thereof. The memory device includes a bottom electrode; an inter-electrode dielectric thin film diffusion prevention film formed on the bottom electrode; a dielectric thin film formed on the inter-electrode dielectric thin film diffusion prevention film and having a plurality of layers with different charge trap densities; and a top electrode formed on the dielectric thin film.

Owner:ELECTRONICS & TELECOMM RES INST

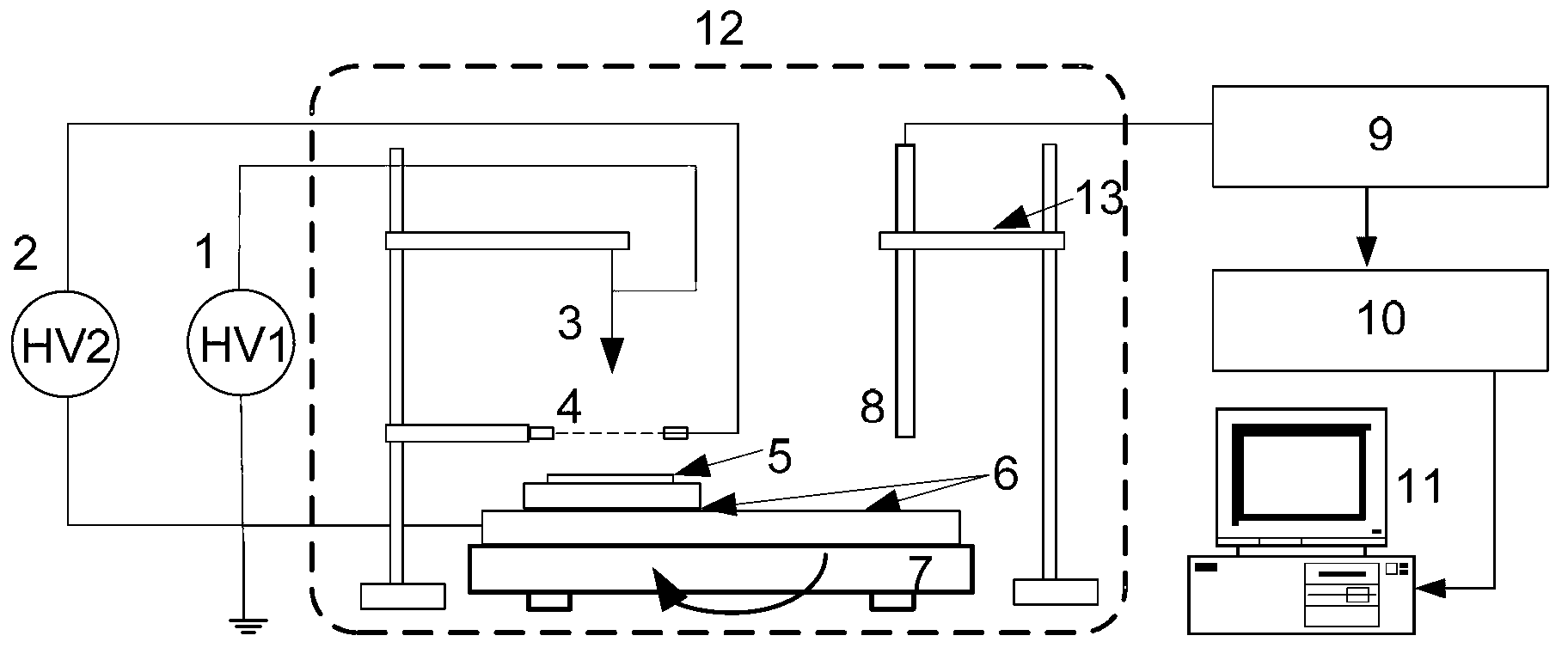

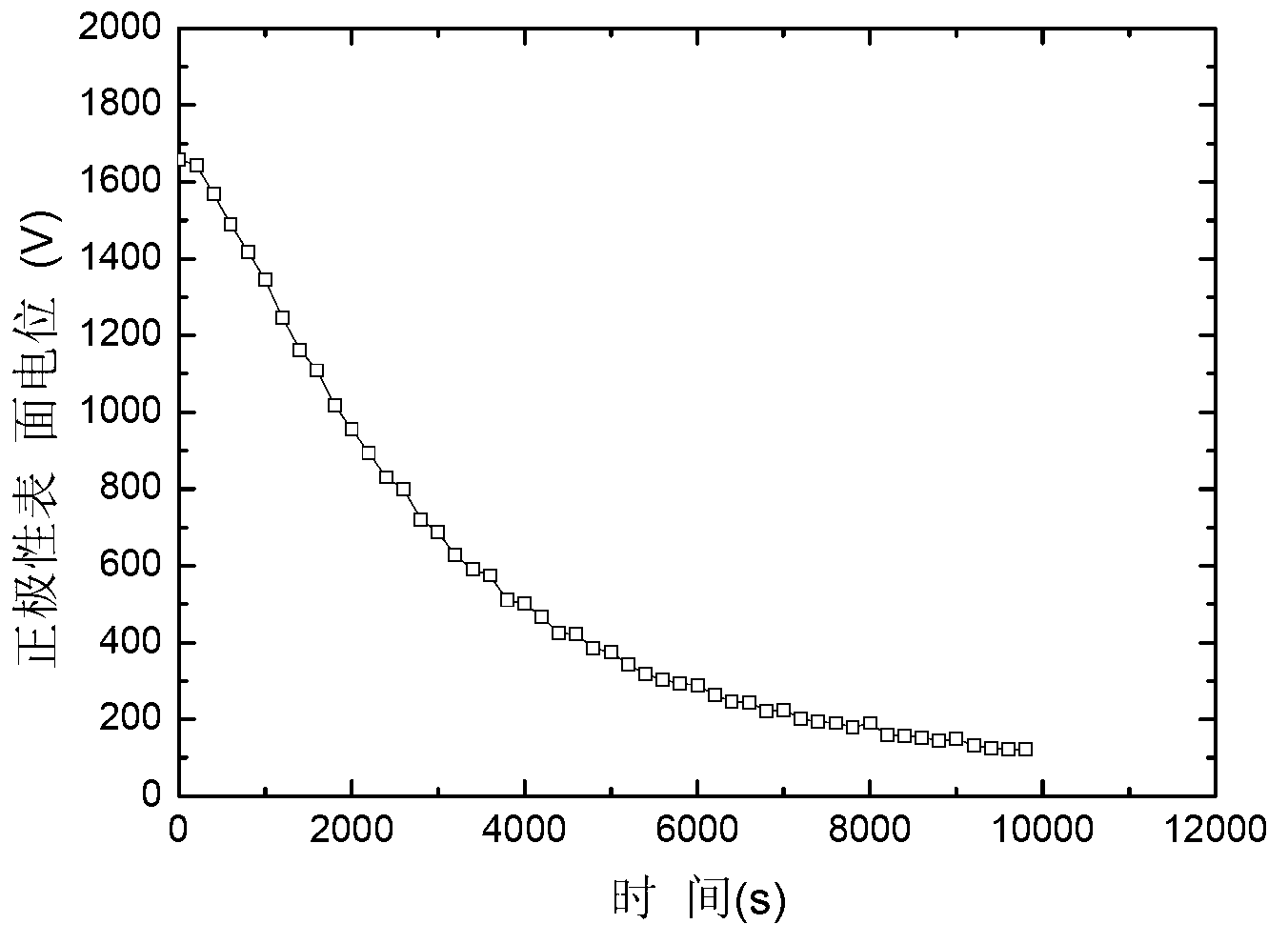

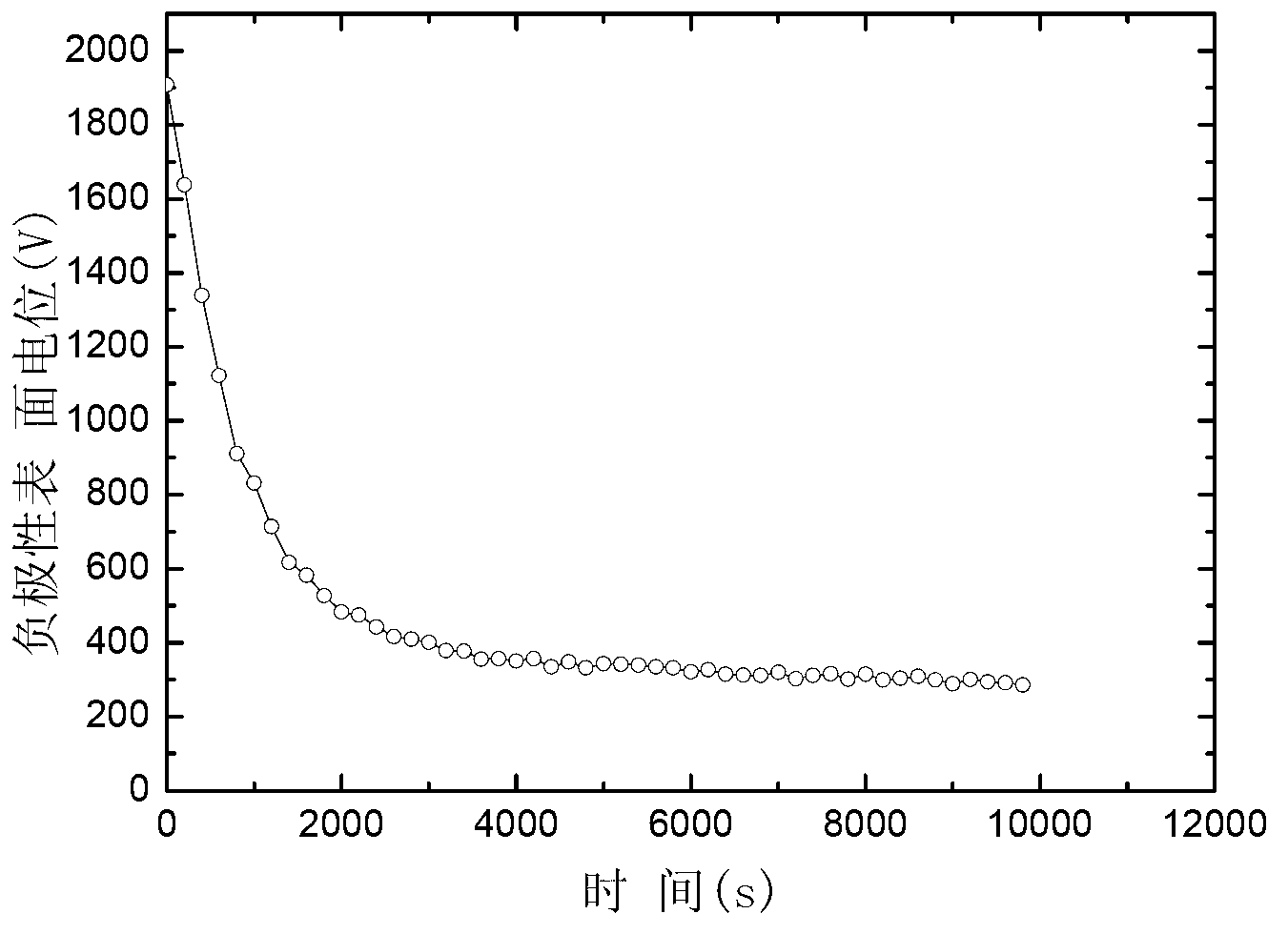

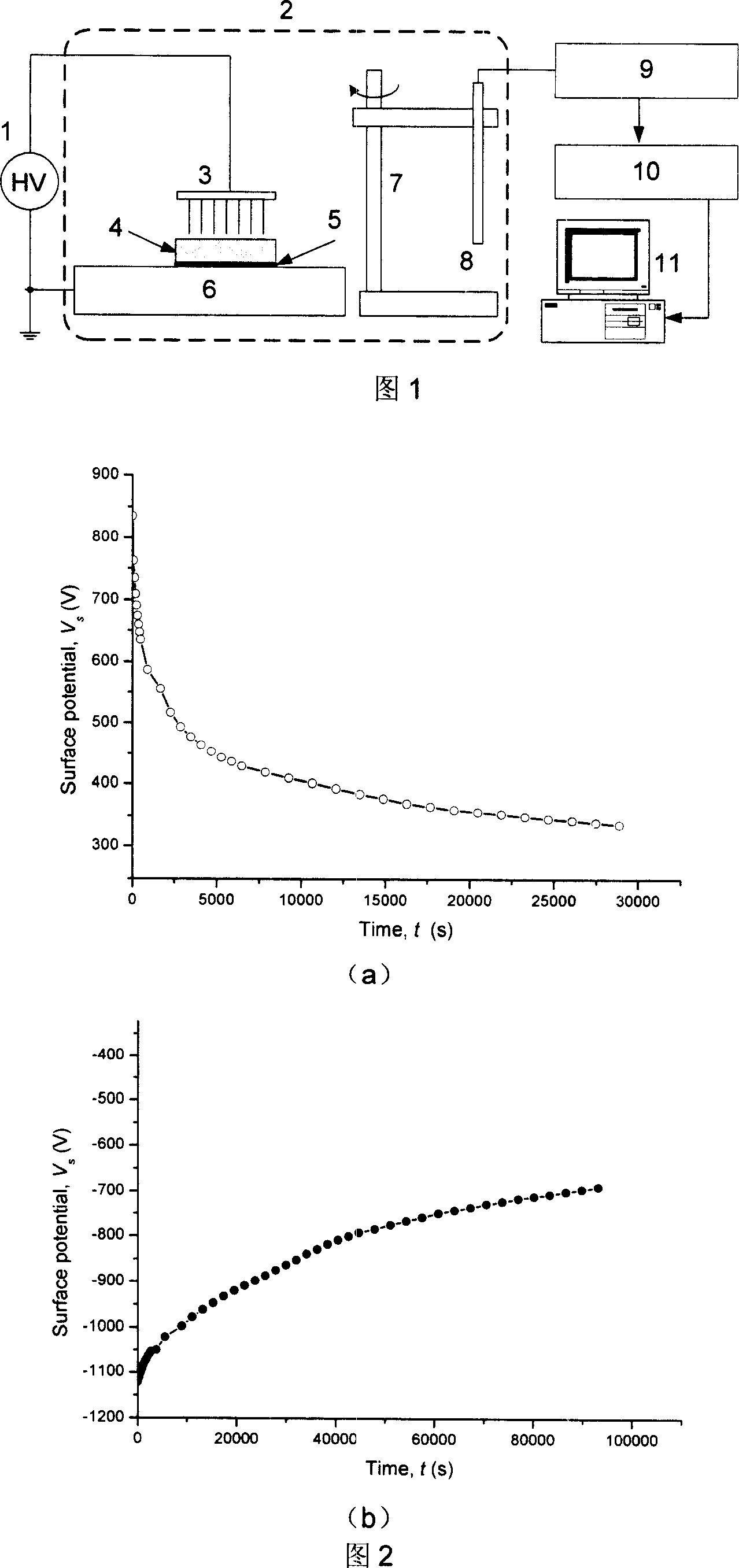

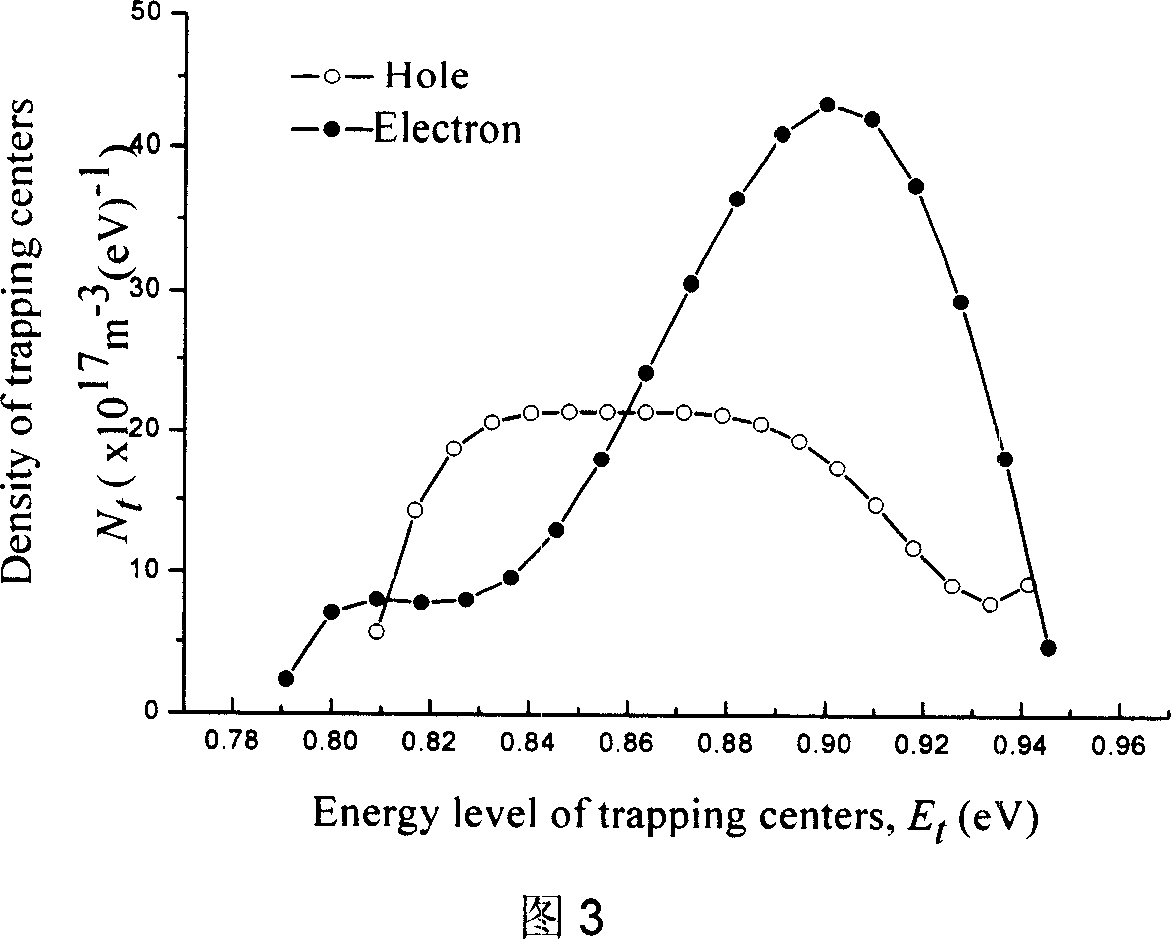

Measuring device and measuring method for trap parameter of solid dielectric material

InactiveCN102841123AFully injectedUniform electric field distributionMaterial analysis by electric/magnetic meansPolymer insulationCorona discharge

The invention discloses a measuring device and method for a trap parameter of solid dielectric. The solid dielectric material is charged by using a three-electrode corona discharge system; a material sample to be tested is placed below a single-needle electrode and a metal mesh electrode; the sample is adhered to a metal disc electrode through conductive silicone grease and is charged by the three-electrode system; after charging is ended, an external voltage is removed, and short circuit discharge is performed to remove surface free loads; surface potential of the measured sample is attenuated; and the trap energy level and the trap density parameter of the material can be calculated through a signal conditioning circuit and a data acquisition system. The measuring device comprises a constant temperature box, the three-electrode coronate charging system, a surface potential measuring system, a sample preheating system, a rotary electrode and a temperature and humidity control system. The invention provides an effective analysis means for research in representation of an aging condition of a polymer insulating material and an aging rule of polymer by the trap parameter and research in aspects such as a solid dielectric surface electrification phenomenon and surface flashover performance influence.

Owner:XI AN JIAOTONG UNIV

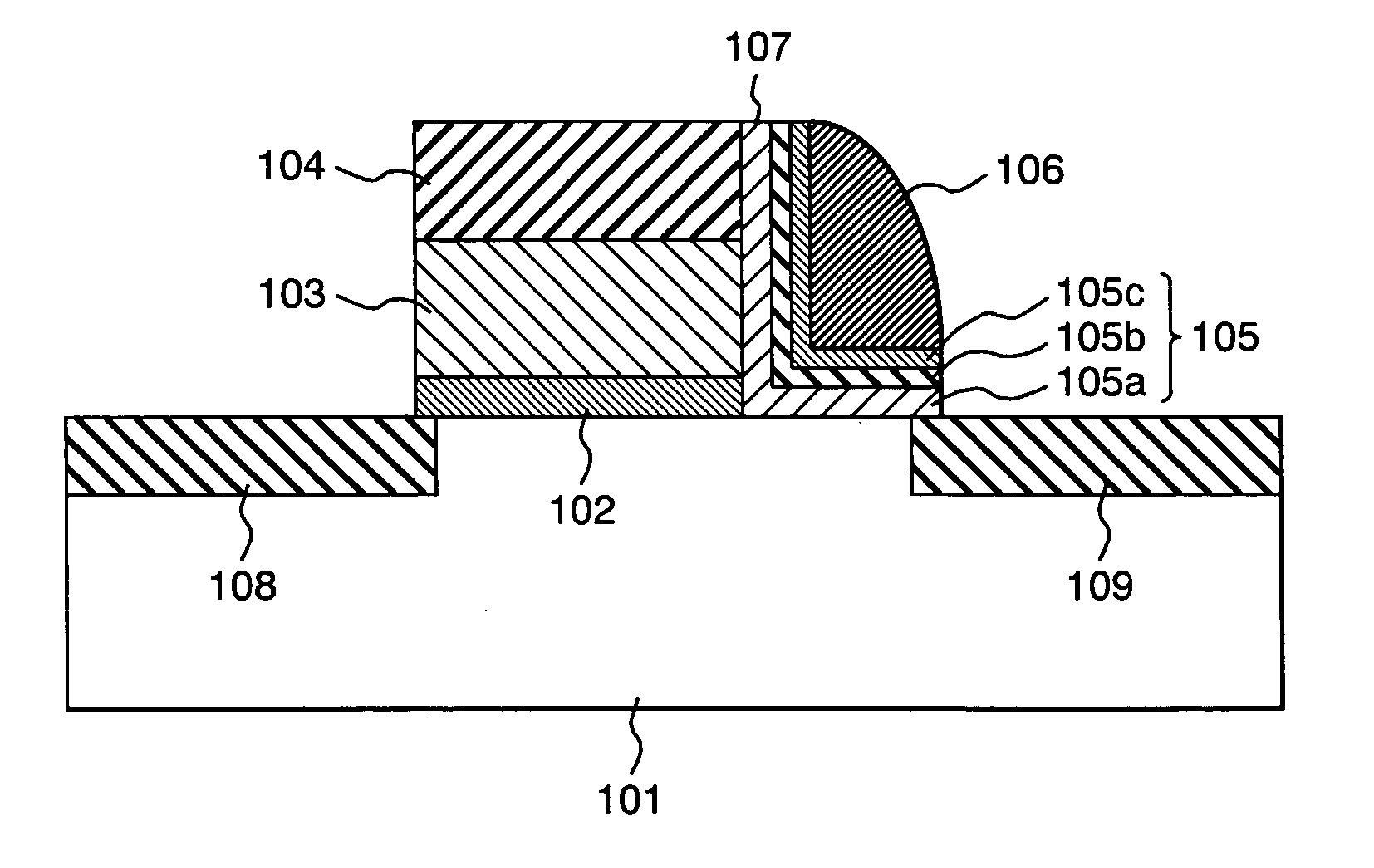

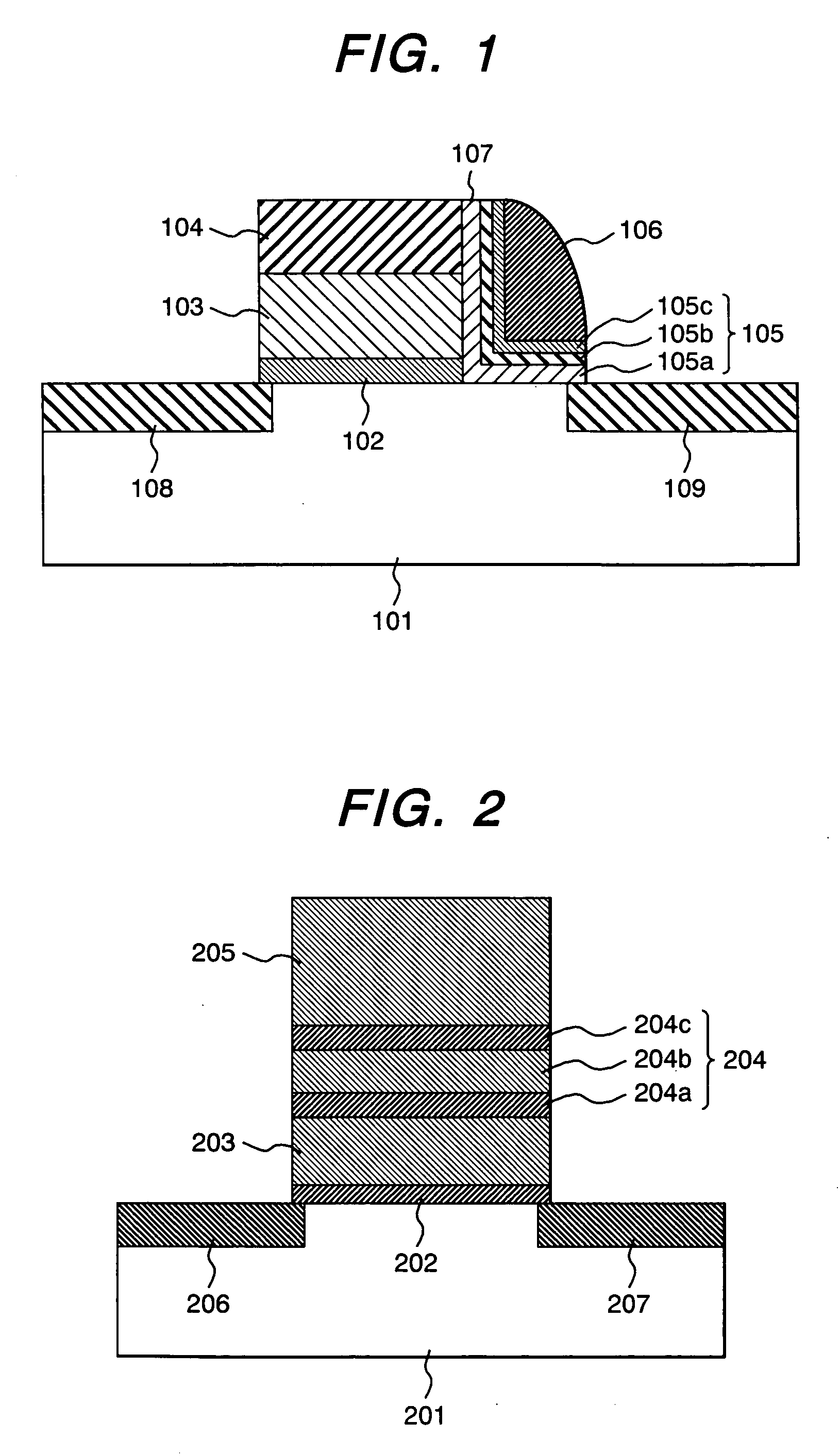

Method of manufacturing nonvolatile semiconductor memory device

ActiveUS20050272198A1Reduce in quantityImprove attributesTransistorSolid-state devicesHigh concentrationTrapping

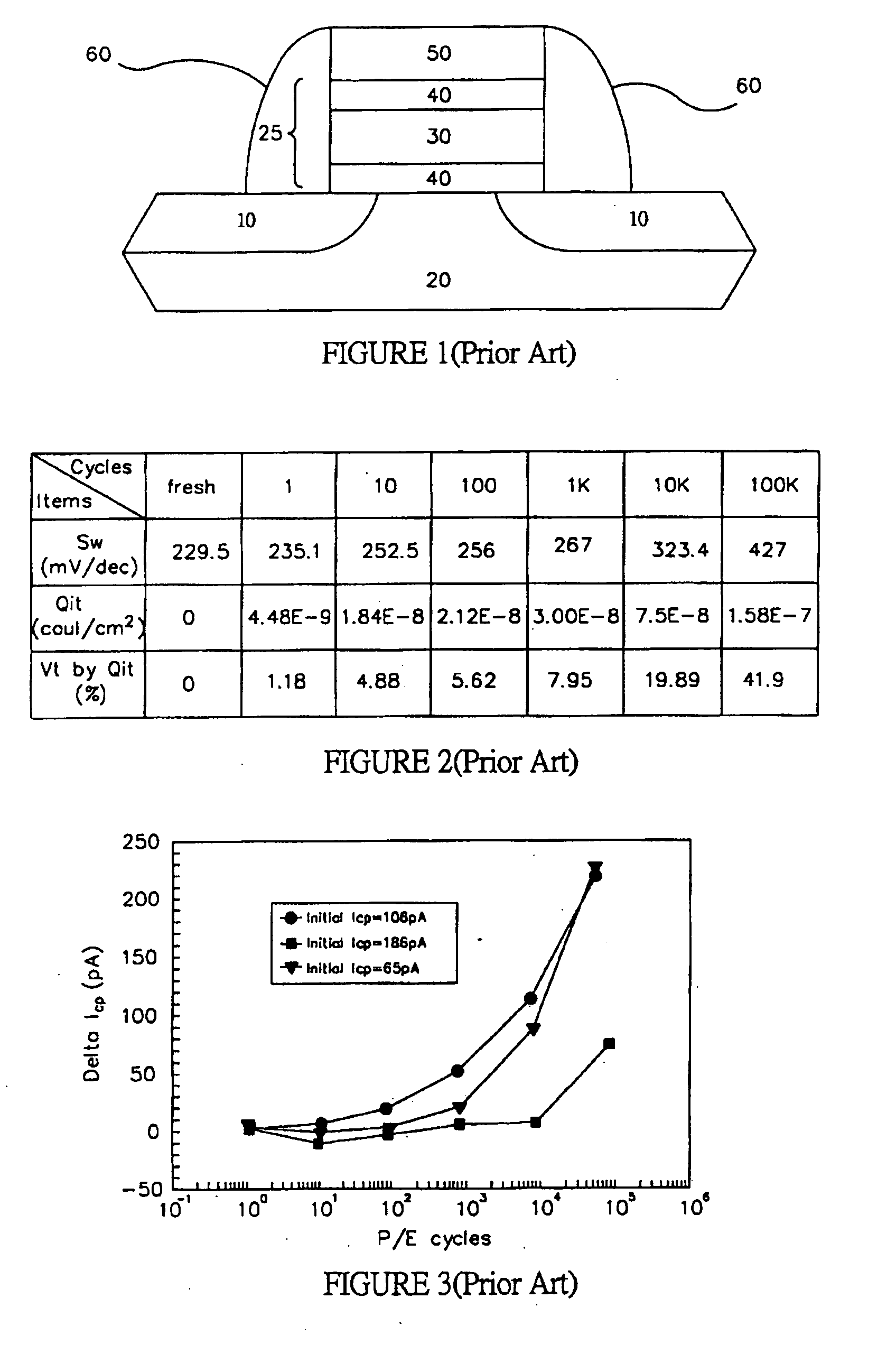

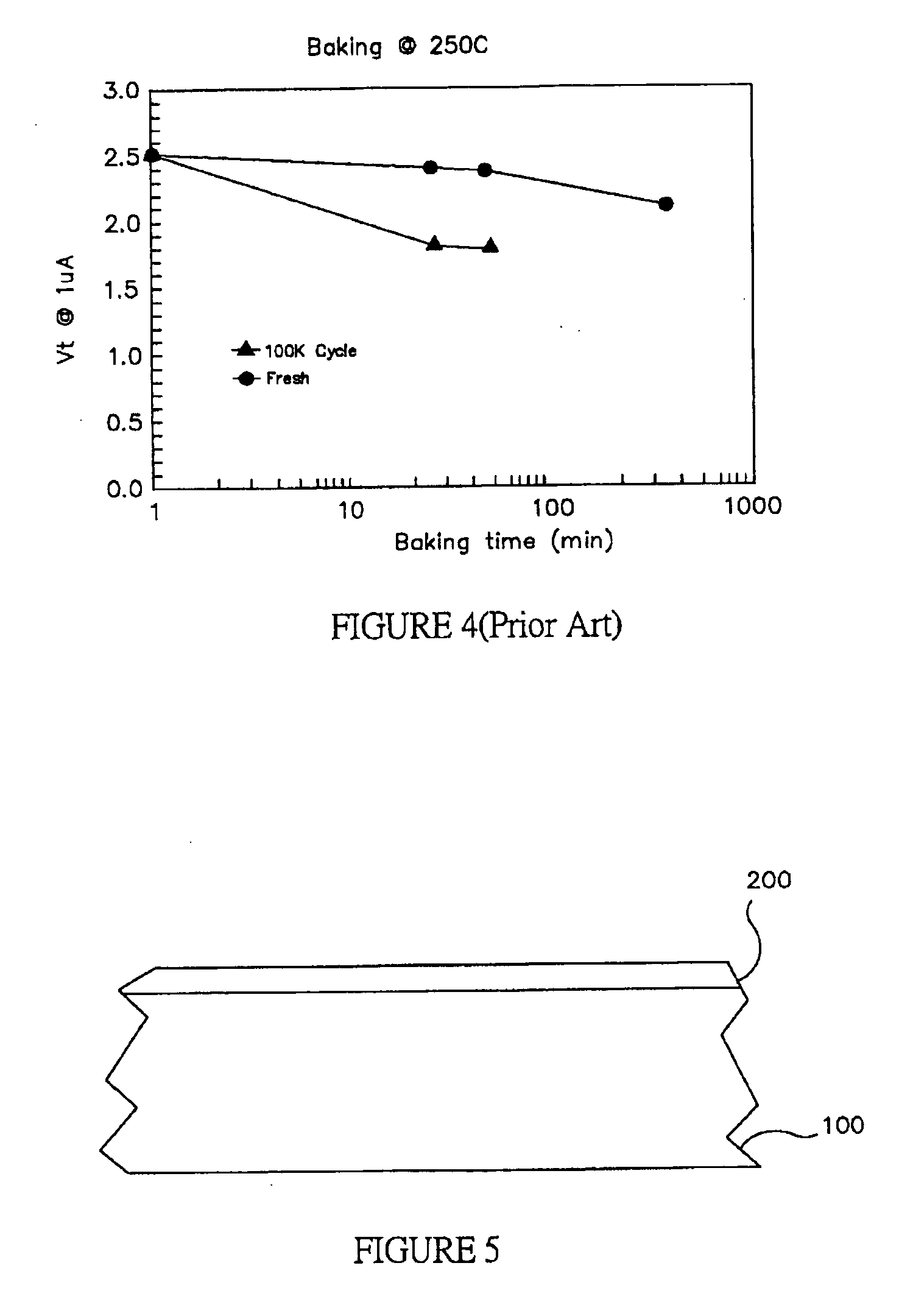

Conventionally, a MONOS type nonvolatile memory is fabricated by subjecting a silicon nitride film to ISSG oxidation to form a top silicon oxide film of ONO structure. If the ISSG oxidation conditions are severe, repeats of programming / erase operation cause increase of interface state density (Dit) and electron trap density. This does not provide a sufficient value of the on current, posing a problem in that the deterioration of charge trapping properties cannot be suppressed. For the solution to the problem, the silicon nitride film is oxidized by means of a high concentration ozone gas to form the top silicon oxide film.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and its manufacturing method

ActiveUS7338869B2Low densityImprove channel mobilityTransistorSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

Owner:NAT INST OF ADVANCED IND SCI & TECH

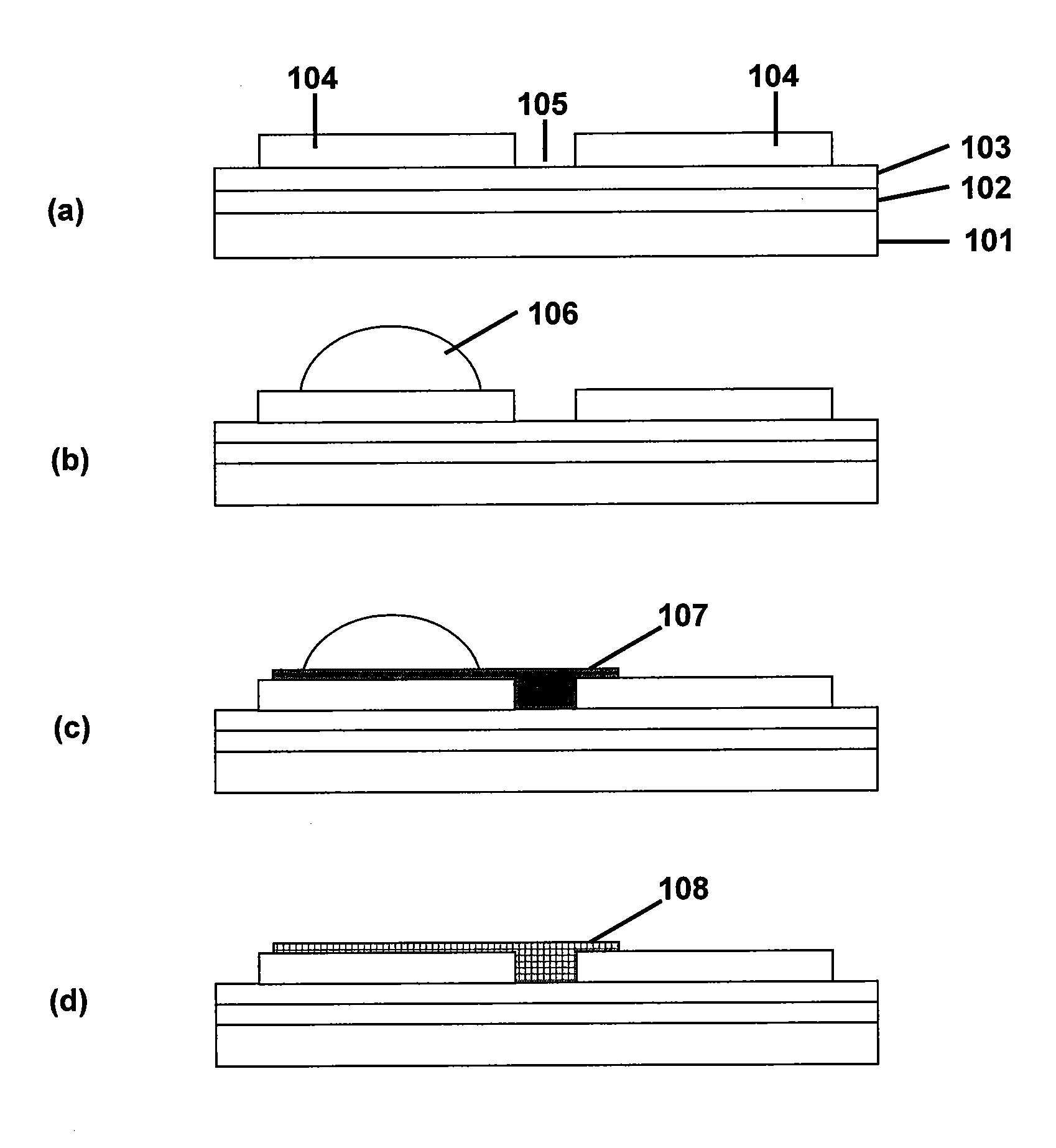

Forming active channel regions using enhanced drop-cast printing

ActiveUS20100155710A1Improve solubilityImprove electrical performanceMaterial nanotechnologyElectroluminescent light sourcesOrganic field-effect transistorDisplay device

An active region or channel for printed, organic or plastic electronics or polymer semiconductors, such as organic field-effect transistors (OFETs), is obtained by using an enhanced inkjet drop-cast printing technique. A two-liquid system is employed to achieve the direct growth of well-oriented organic crystals at the active region of channel. High-performance electrical properties exhibiting high carrier mobility and low threshold voltage are obtained due to the proper orientation of molecules in the grown crystal in a highest mobility direction, due to the absence of grain boundaries, and due to low trap densities. The hydrophobic-hydrophilic interactions between the liquids utilized, which results in the fabrication of low-cost and mass-producible printable electronic devices for applications in flexible displays, electronic signages, photovoltaic panels, membrane keyboards, radio frequency identification tags (RFIDs), electronic sensors, and integrated electronic circuits.

Owner:SEOUL NAT UNIV R&DB FOUND

Inclusion of nitrogen at the silicon dioxide-silicon carbide interace for passivation of interface defects

InactiveUS6939756B1Reduced interface trap densityLow densitySemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenSilicon dioxide

A method for manufacturing a silicon carbide semiconductor device. In one embodiment, the method includes the following steps: a layer of silicon dioxide is formed on a silicon carbide substrate to create a silicon dioxide / silicon carbide interface and then nitrogen is incorporated at the silicon dioxide / silicon carbide interface for reduction in an interface trap density. The silicon carbide substrate, in one embodiment, includes a n-type 4H-silicon carbide.

Owner:VANDERBILT UNIV

Oxynitride bilayer formed using a precursor inducing a high charge trap density in a top layer of the bilayer

ActiveUS8067284B1Increase the number ofSemiconductor/solid-state device manufacturingSemiconductor devicesTrappingNitrogen oxide

A semiconductor device including a bilayer charge storing layer and methods of forming the same are provided. Generally, the method includes: (i) forming a first layer of the bilayer charge storing layer; and (ii) forming a second layer formed on a surface of the first layer, the second layer including an oxynitride charge trapping layer. Preferably, the first layer includes a substantially trap free oxynitride layer. More preferably, the oxynitride charge trapping layer includes a significantly higher stoichiometric composition of silicon than that of the first layer. In certain embodiments, the oxynitride charge trapping layer has a concentration of carbon selected to increase the number of traps therein. Other embodiments are also disclosed.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

Method and system for measuring trap parameter of insulating material of polymer

InactiveCN101004433AImprove stabilityImprove anti-electromagnetic interference performanceTesting dielectric strengthResistance/reactance/impedenceCircular discPolymer insulation

A method for measuring defect parameter of polymer insulation material includes setting a multi-needle electrode in insulated box, sticking test sample of said material grounding metal disc electrode in said box, placing multi-needle electrode above test sample to charge said test sample by utilizing high voltage DC power, moving test sample onto another grounding disc electrode to use short-circuit to discharge said test sample, utilizing capacity electrostatic probe to measure out surface potential of said test sample and obtaining defect energy level and defect density of insulation material through calculation.

Owner:XI AN JIAOTONG UNIV

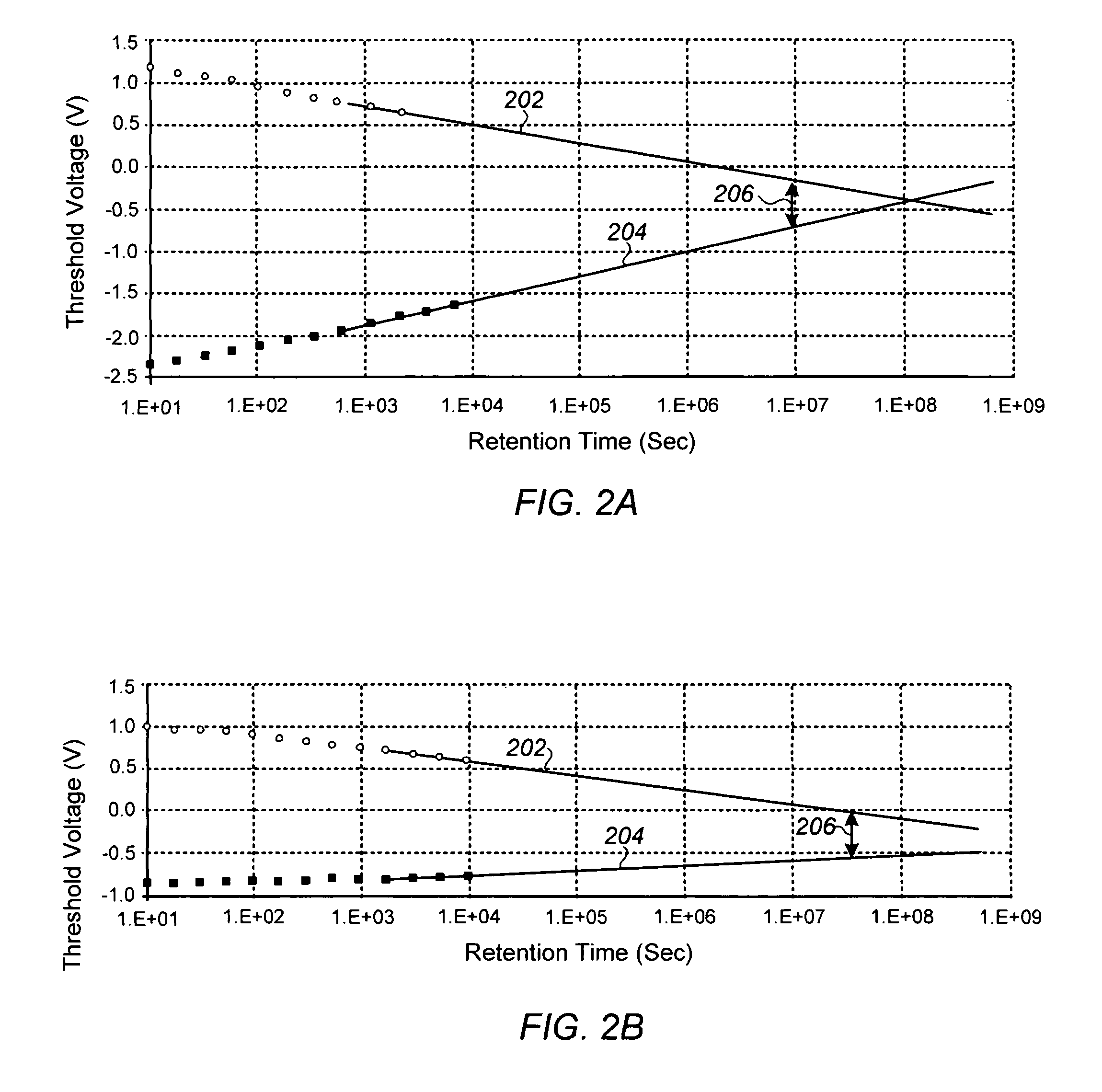

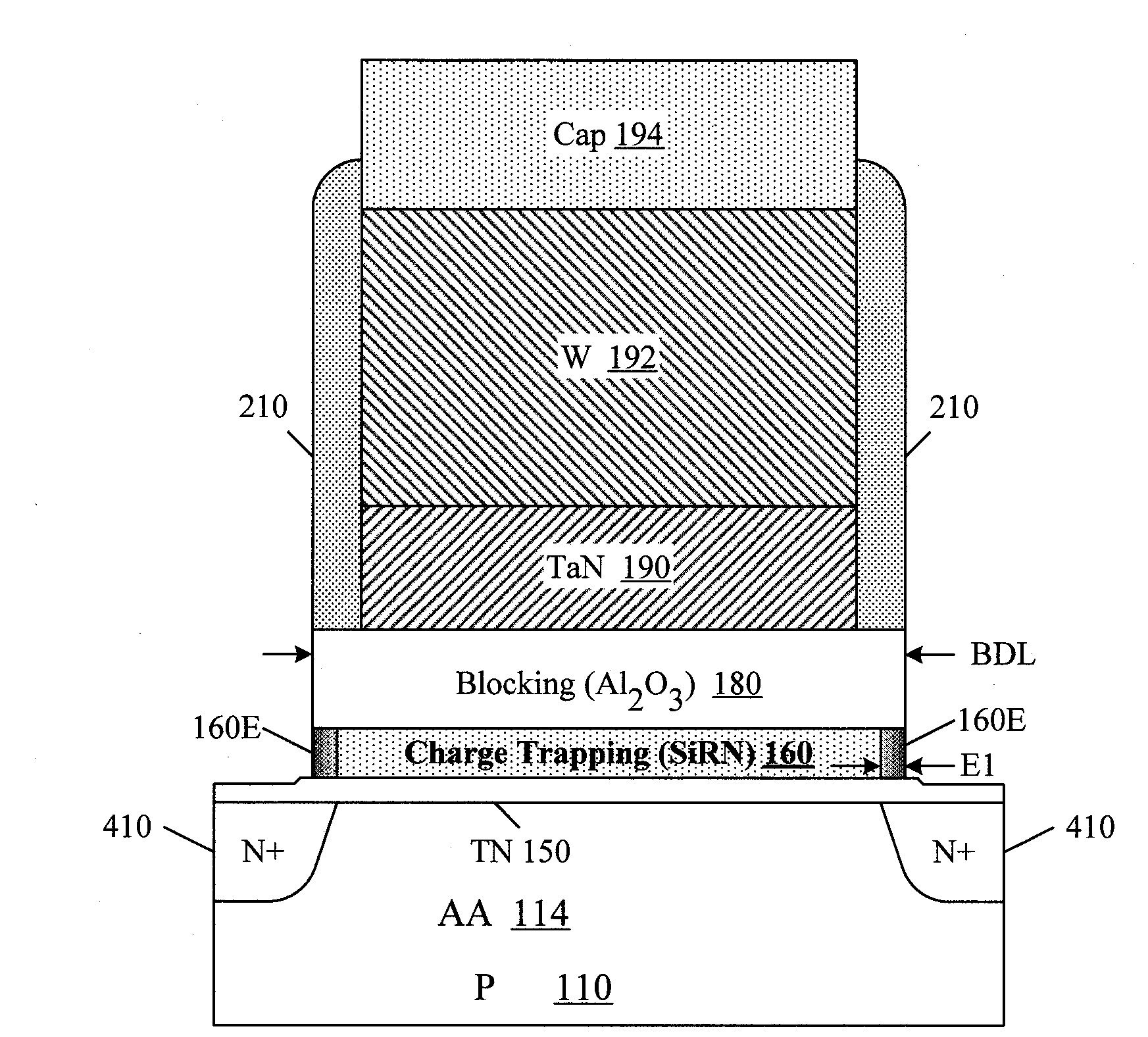

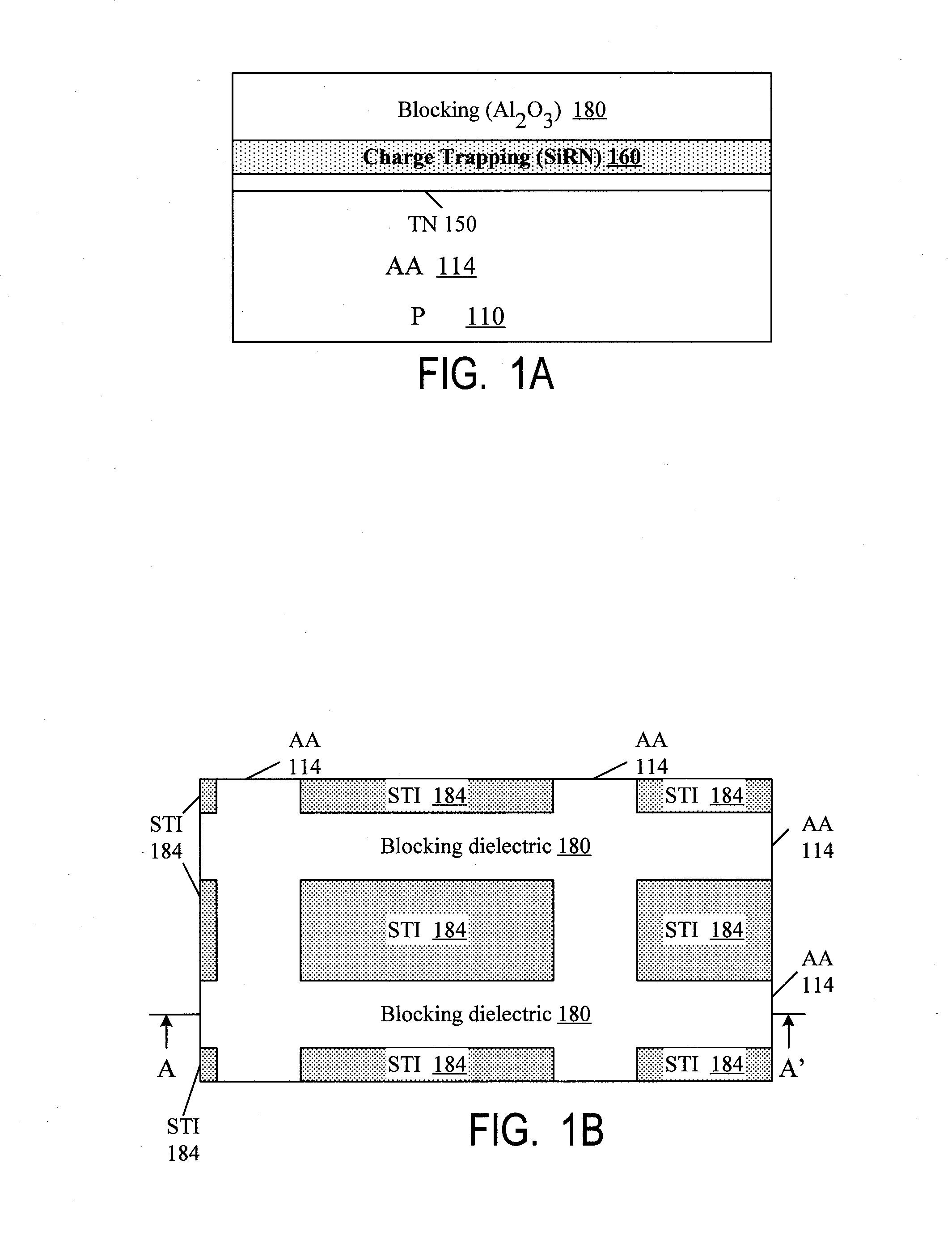

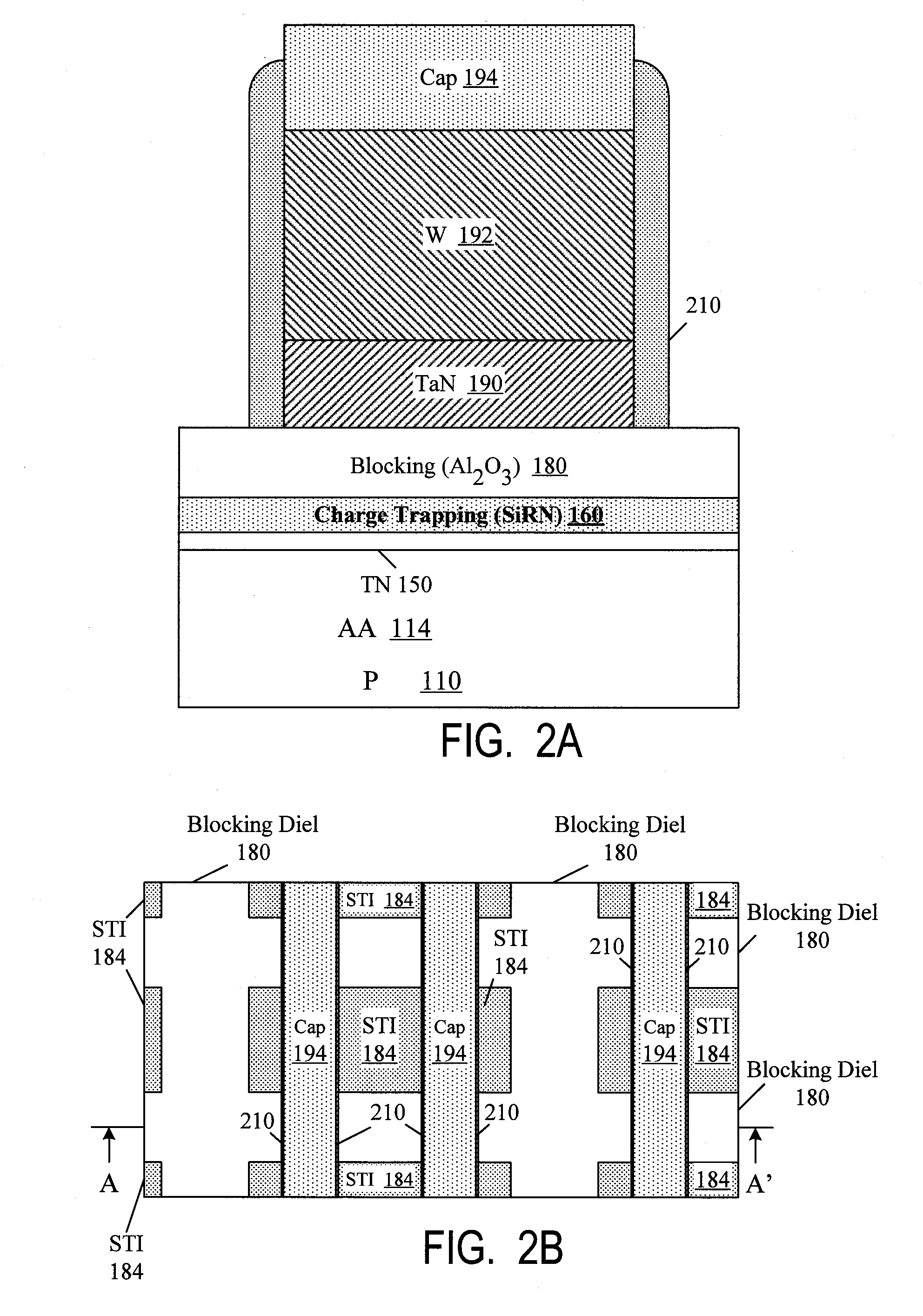

Nonvolatile memories with charge trapping dielectric modified at the edges

InactiveUS20100059808A1Reduce charge densityTotal current dropTransistorSolid-state devicesDielectricTrapping

A nonvolatile memory cell has charge trapping dielectric (160) which has been modified (i.e. oxidized) adjacent to edges of blocking dielectric (180). The modification reduces the charge-trapping density adjacent to the edges of the blocking dielectric, and hence reduces the leakage current at the edges. Other features are also provided.

Owner:PROMOS TECH PTE LTD

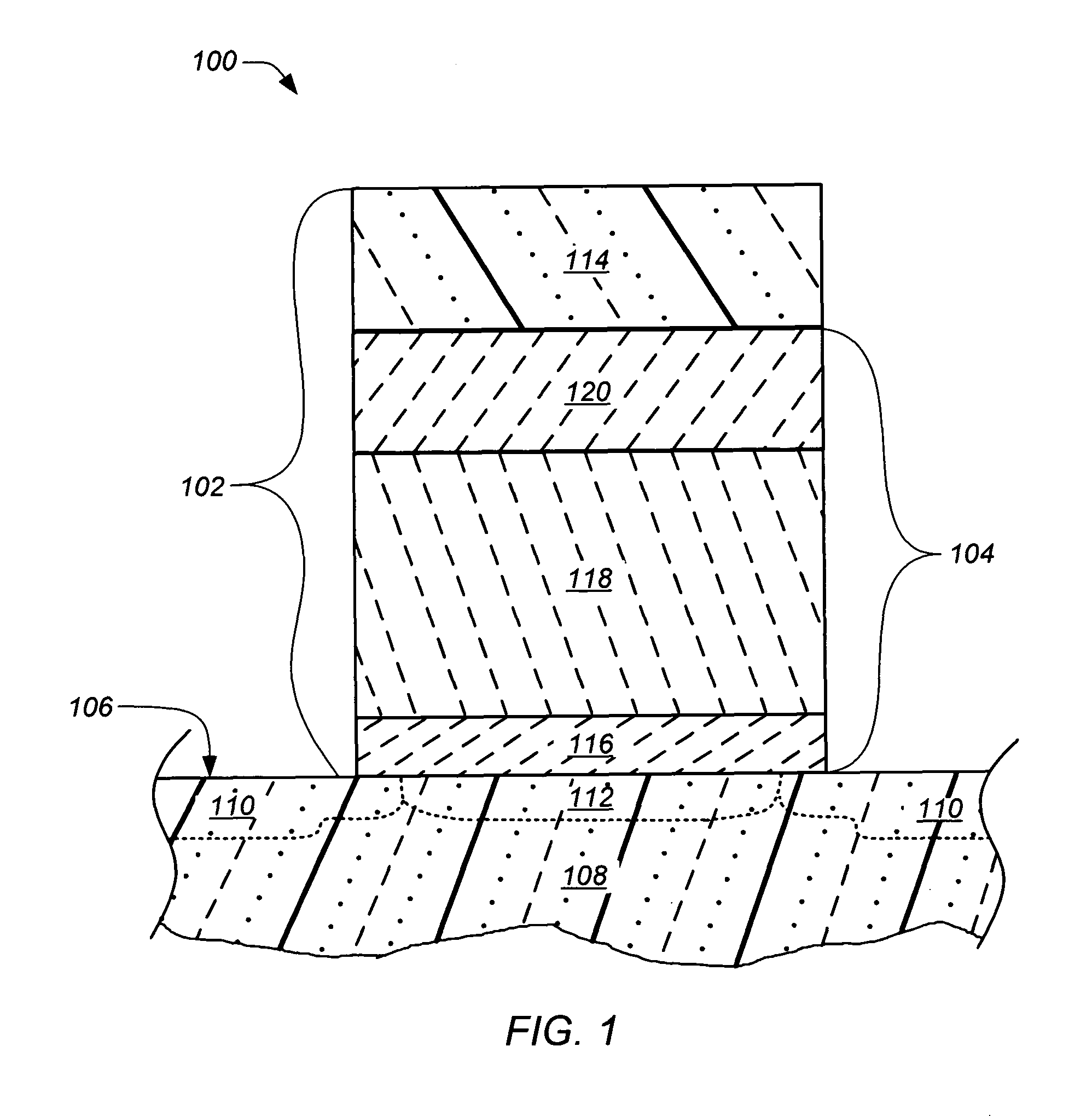

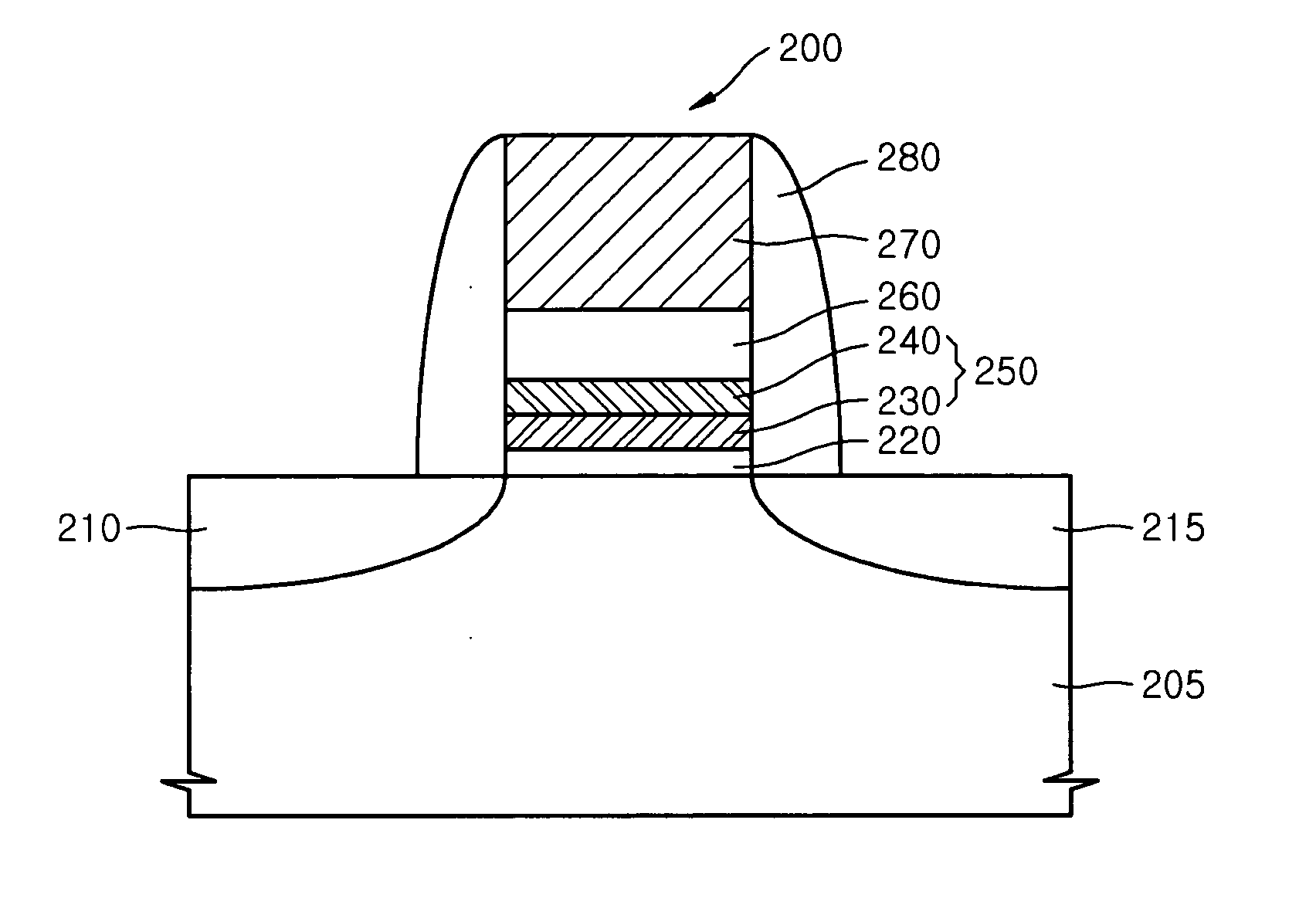

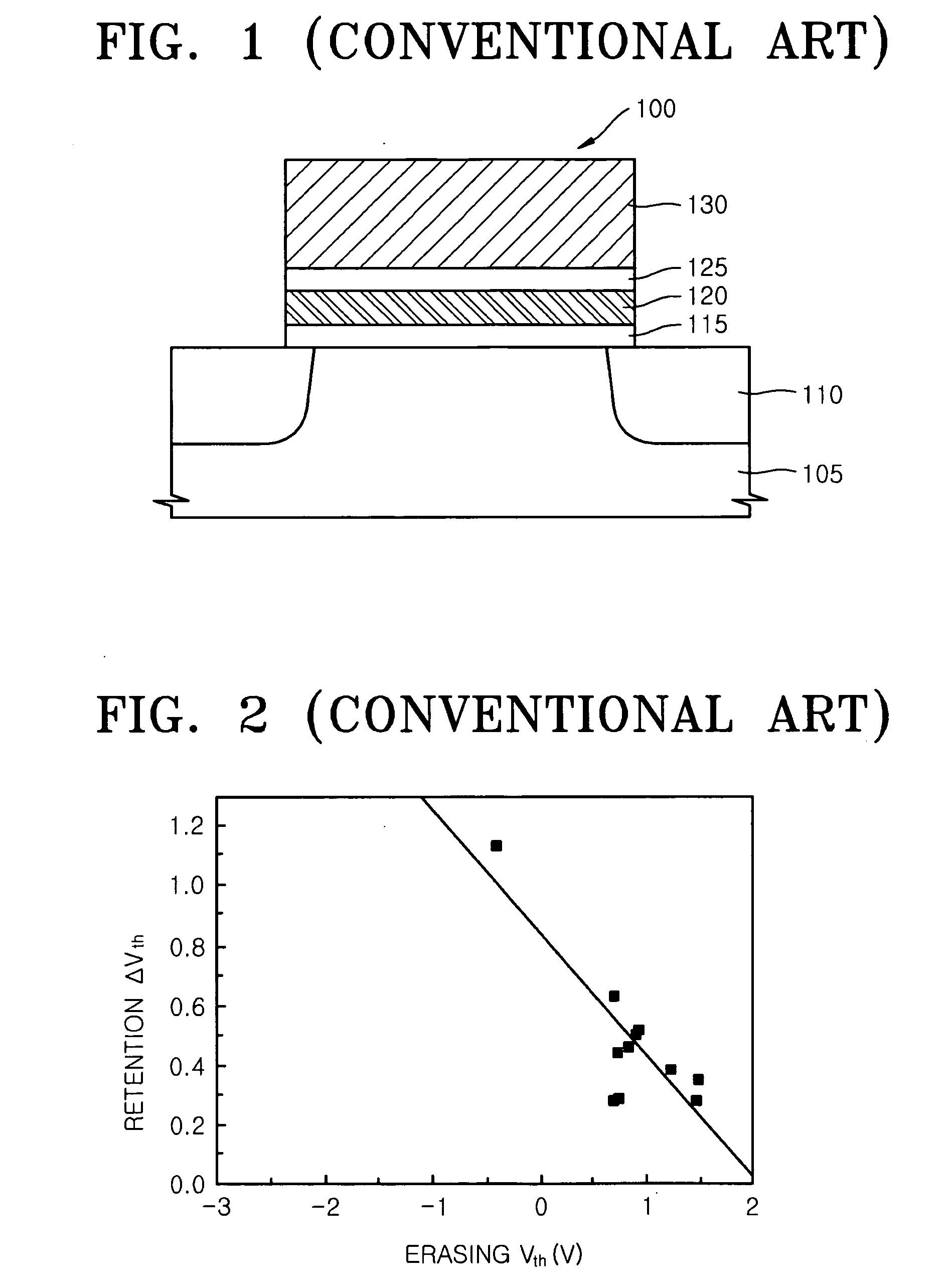

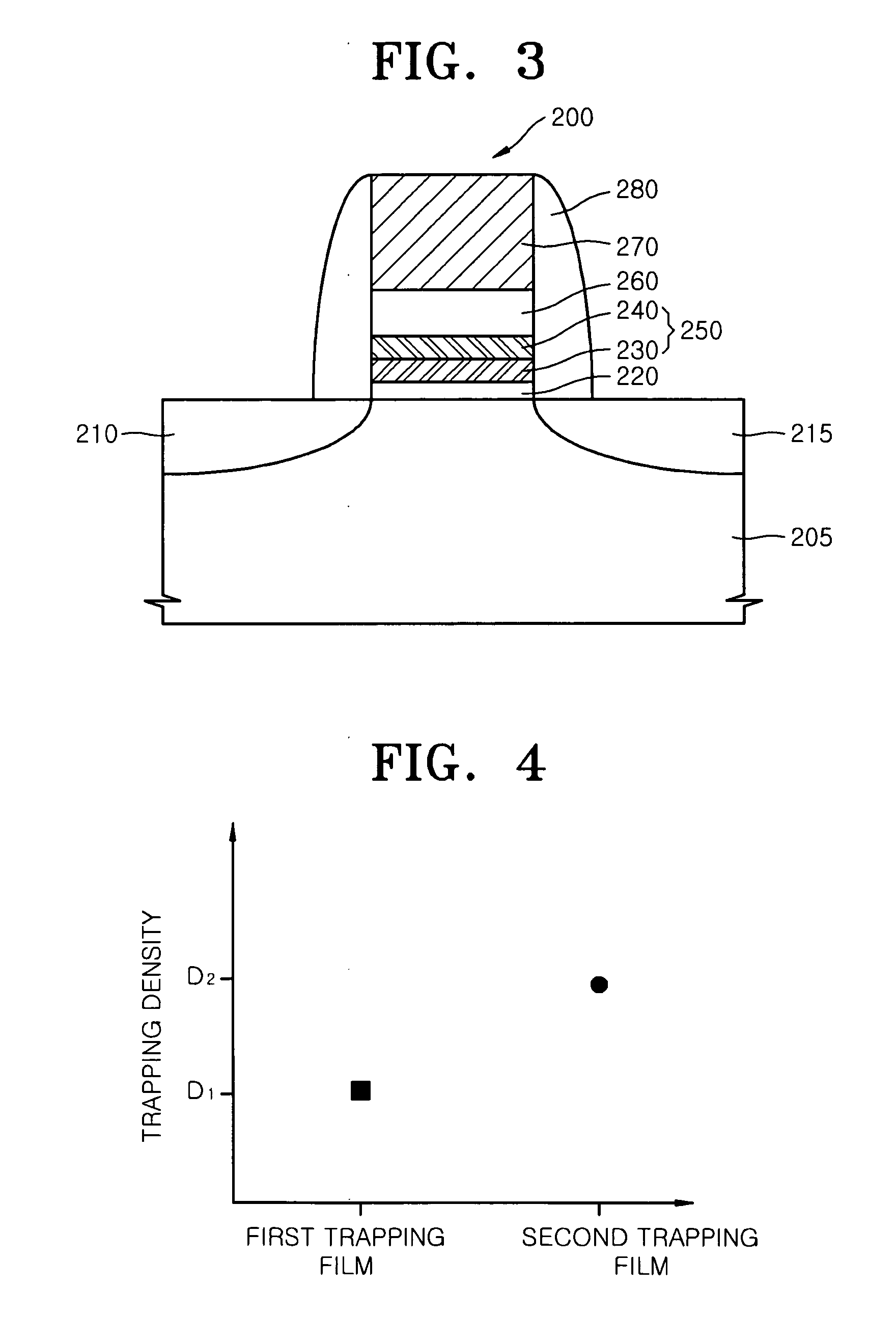

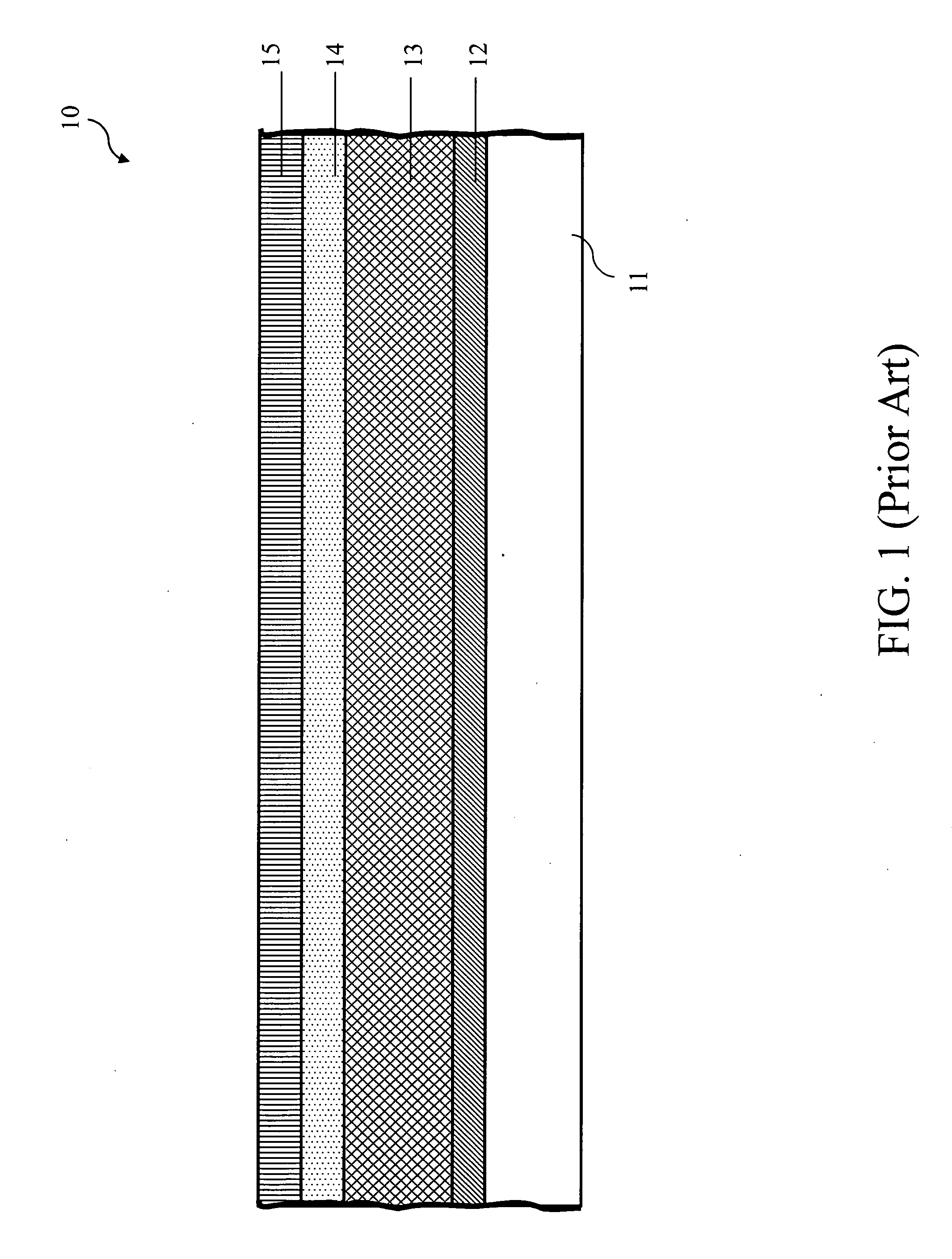

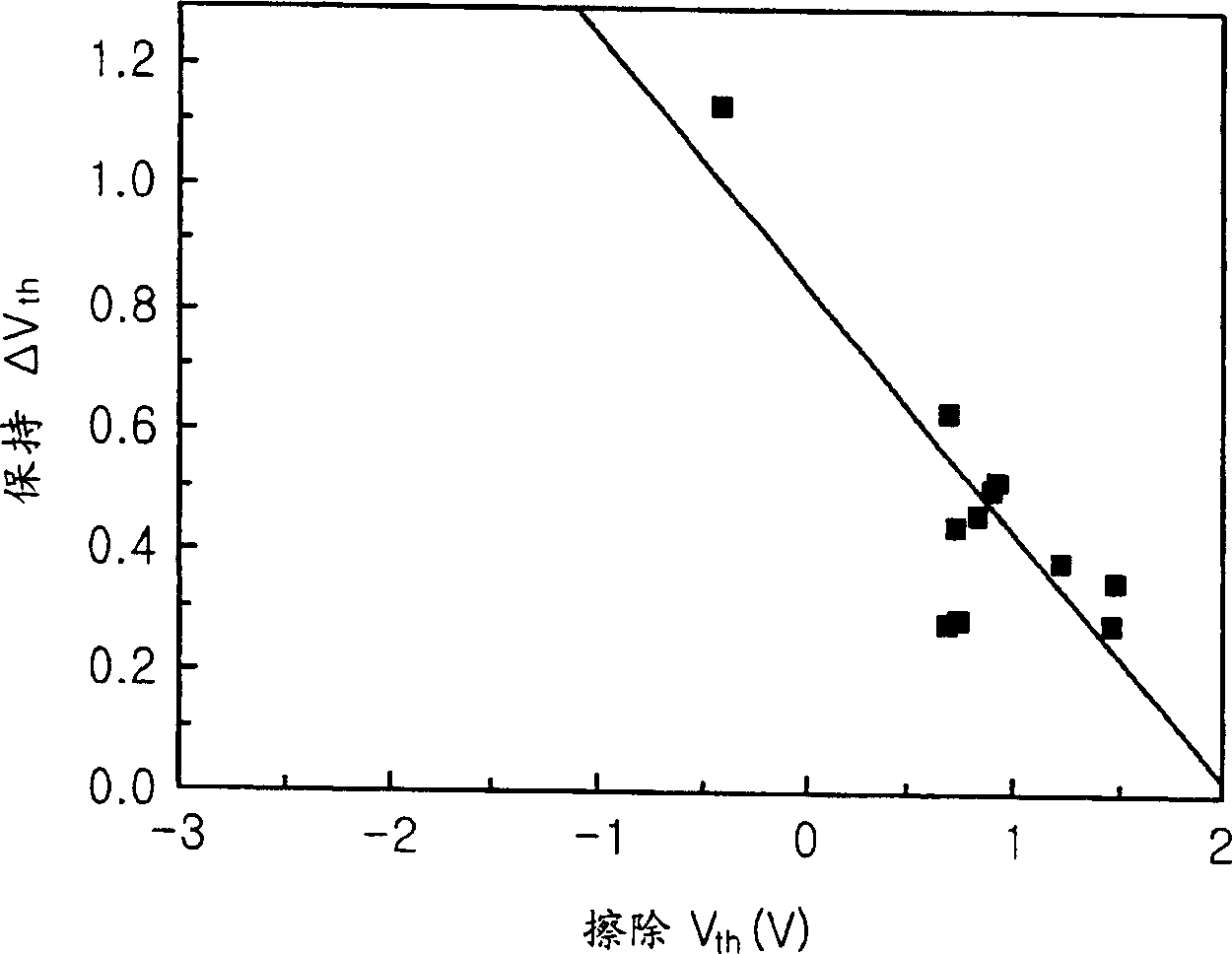

Nonvolatile memory device having a plurality of trapping films

InactiveUS20060255399A1Improved and comparable retention characteristicImprove programming efficiencySemiconductor devicesTrappingSilicon oxide

Provided is a nonvolatile memory device which includes a tunneling insulating film formed on a semiconductor substrate, a storage node formed on the tunneling insulating film, a blocking insulating film formed on the storage node, and a control gate electrode formed on the blocking insulating film. The storage node includes at least two trapping films having different trap densities, and the blocking insulating film has a dielectric constant greater than that of the silicon oxide film.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film solar cell structure and fabricating method thereof

InactiveUS20120024366A1Reduced interface trap densityImprove power conversion efficiencyFinal product manufactureVacuum evaporation coatingEngineeringElectric field

A thin film solar cell structure and the fabricating method thereof are disclosed. A passivation layer is embedded into the thin film solar cell structure to be in contact with an absorbing layer. The interface trap density of the absorbing layer is reduced by the surface electric field of the passivation layer. The invention helps improve the power conversion efficiency and protect the absorbing layer.

Owner:NAT TAIWAN UNIV

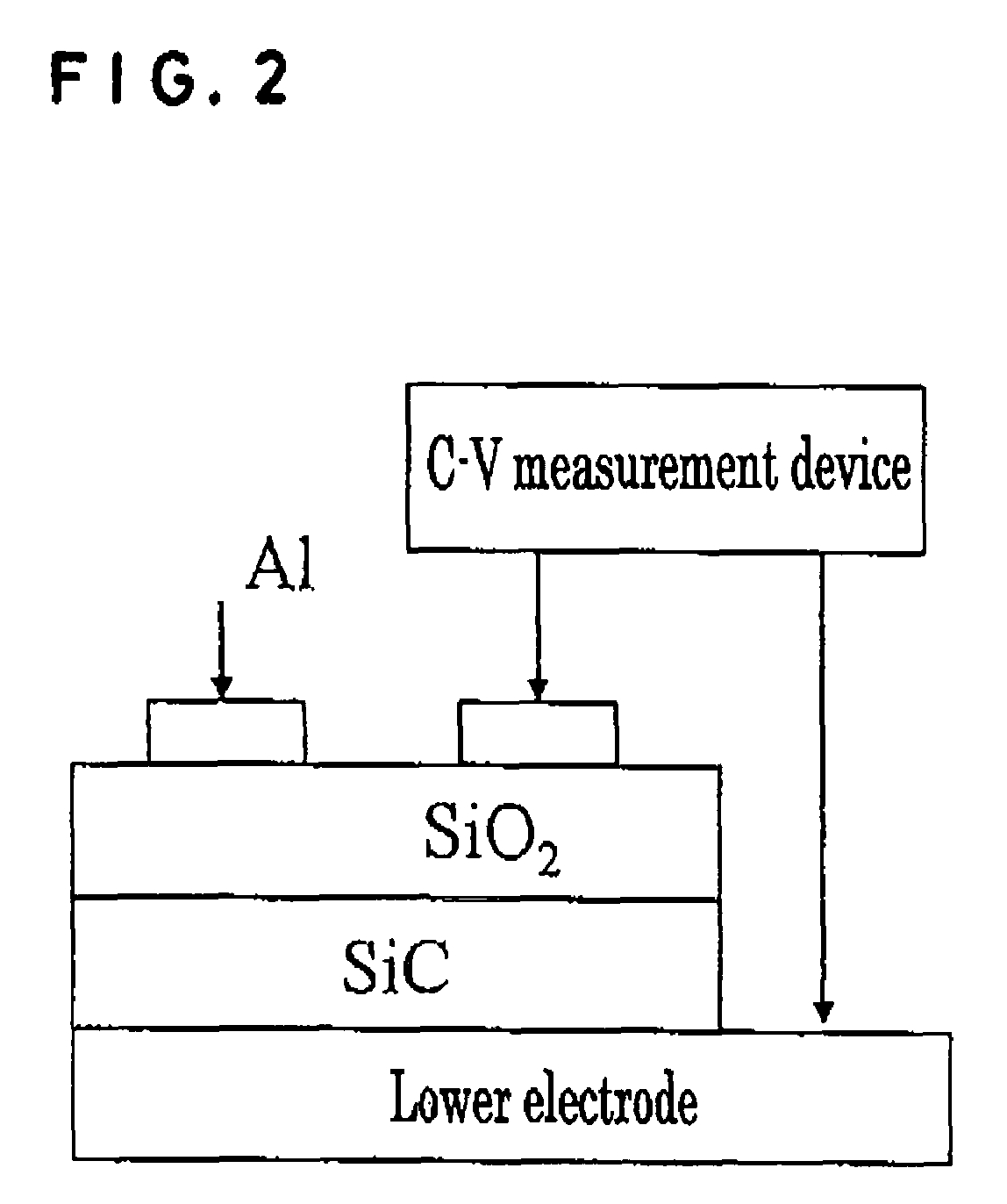

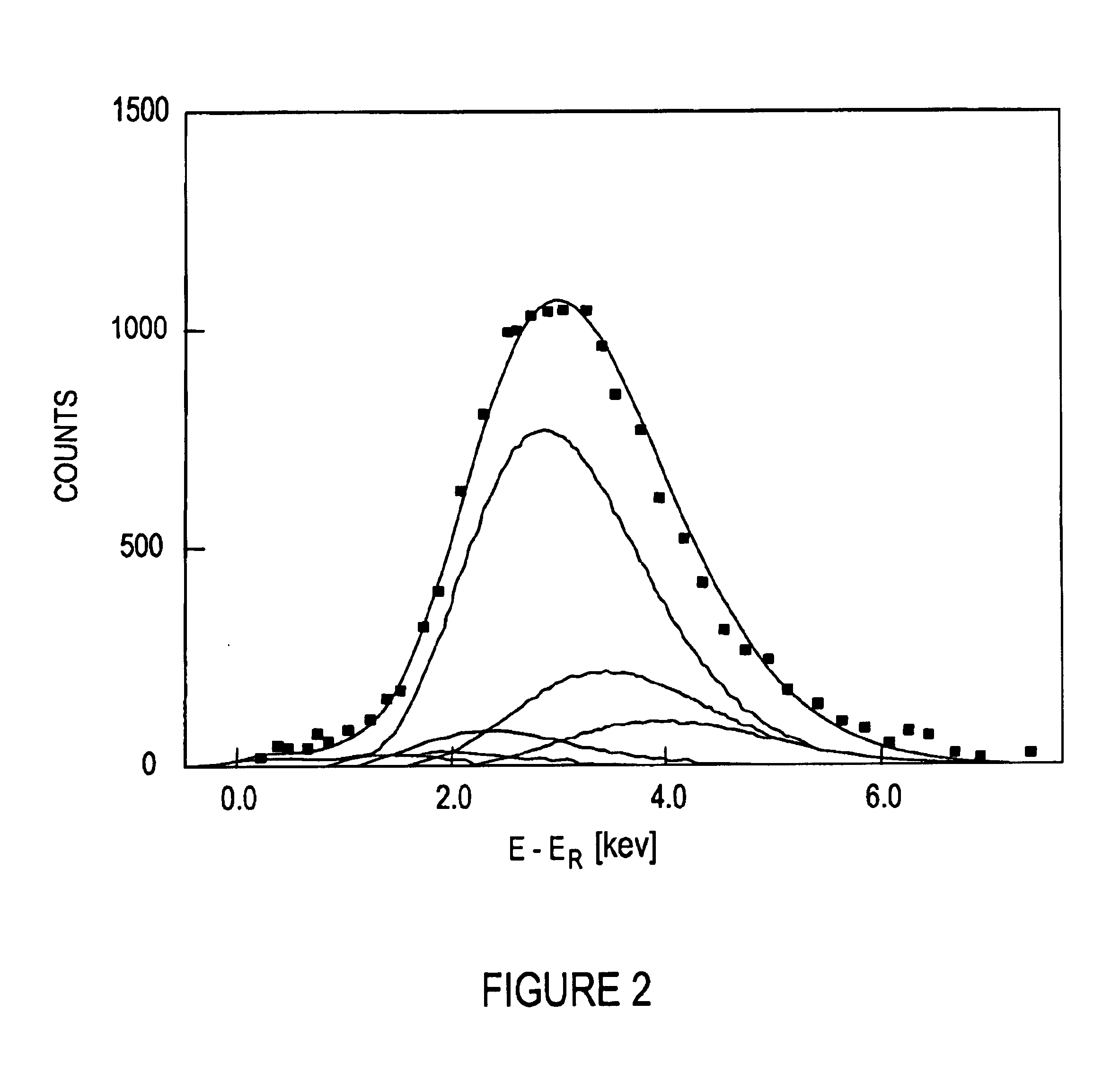

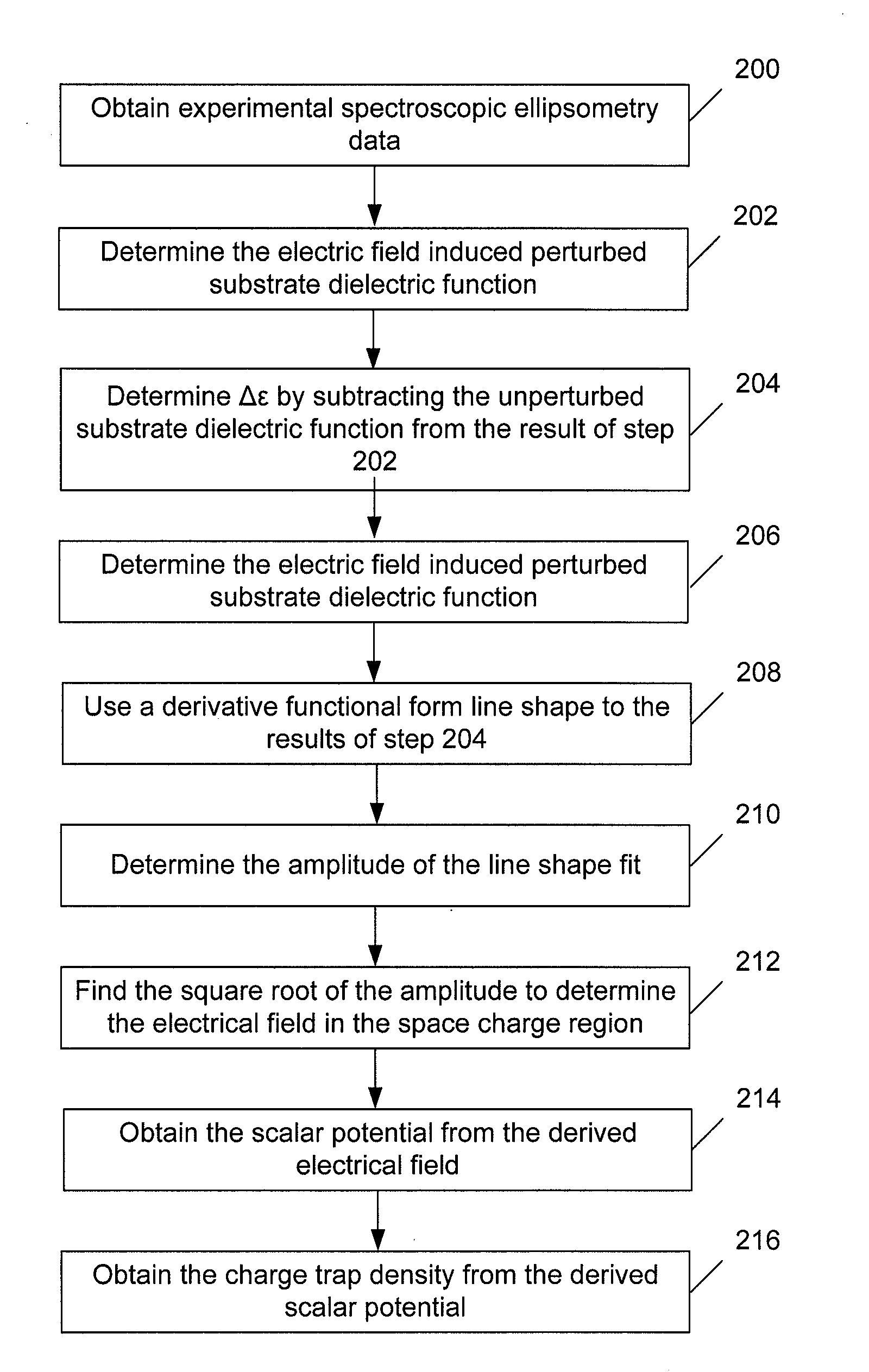

Methods and Systems for Determining Trapped Charge Density in Films

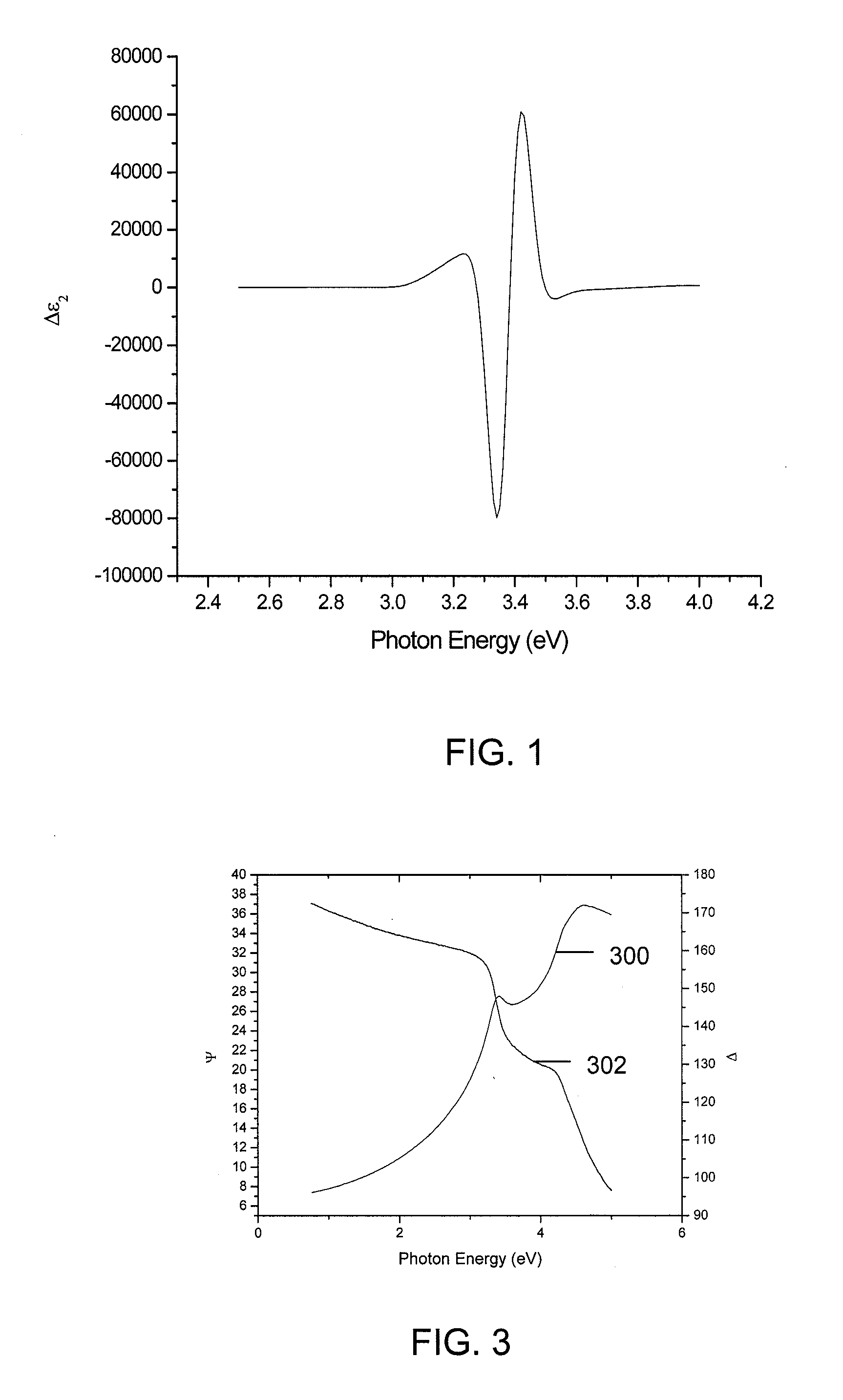

InactiveUS20070213954A1Improve accuracySemiconductor/solid-state device testing/measurementSolid-state devicesScalar potentialSemiconductor materials

Methods and systems for determining a charge trap density between a semiconductor material and a dielectric material are disclosed. In one respect, spectroscopic data of the semiconductor material may be determined and used to determine a change in dielectric function. A line shape fit of the change in the dielectric function may be applied using derivative function form. The amplitude of the line shape fit may be determined and used to determine an electric field of a space charge region of the semiconductor material. By applying Poisson's equations, the scalar potential due to the electric field in the space charge region may be determined. Subsequently, using the scalar potential the charge trap density may be determined.

Owner:SEMATECH

Mos transistors having high-k offset spacers that reduce external resistance and methods for fabricating the same

InactiveUS20080258225A1TransistorSemiconductor/solid-state device manufacturingGate stackEngineering

MOS transistors having high-k spacers and methods for fabricating such transistors are provided. One exemplary method comprises forming a gate stack overlying a semiconductor substrate and forming an offset spacer about sidewalls of the gate stack. The offset spacer is formed of a high-k dielectric material that results in a low interface trap density between the offset spacer and the semiconductor substrate. First ions of a conductivity-determining impurity type are implanted into the semiconductor substrate using the gate stack and the offset spacer as an implantation mask to form spaced-apart impurity-doped extensions.

Owner:ADVANCED MICRO DEVICES INC

Non-volatile memory possessing a plurality of capture film

The present invention provides one kind of non-volatile memory, which includes tunnel insulating film formed on the semiconductor substrate, memory nodes formed on the tunnel insulating film, barrier insulating film formed on the memory nodes, and control grid formed on the barrier insulating film. The memory node includes at least two layers of capture film of different trap density, and the barrier insulating film possesses dielectric constant greater than that of silicon oxide film.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method of manufacturing same

ActiveUS20080203400A1Enhance layeringReduce defectsTransistorSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

A semiconductor device and a method of manufacturing the device using a (000-1)-faced silicon carbide substrate are provided. A SiC semiconductor device having a high blocking voltage and high channel mobility is manufactured by optimizing the heat-treatment method used following the gate oxidation. The method of manufacturing a semiconductor device includes the steps of forming a gate insulation layer on a semiconductor region formed of silicon carbide having a (000-1) face orientation, forming a gate electrode on the gate insulation layer, forming an electrode on the semiconductor region, cleaning the semiconductor region surface. The gate insulation layer is formed in an atmosphere containing 1% or more H2O (water) vapor at a temperature of from 800° C. to 1150° C. to reduce the interface trap density of the interface between the gate insulation layer and the semiconductor region.

Owner:NAT INST OF ADVANCED IND SCI & TECH

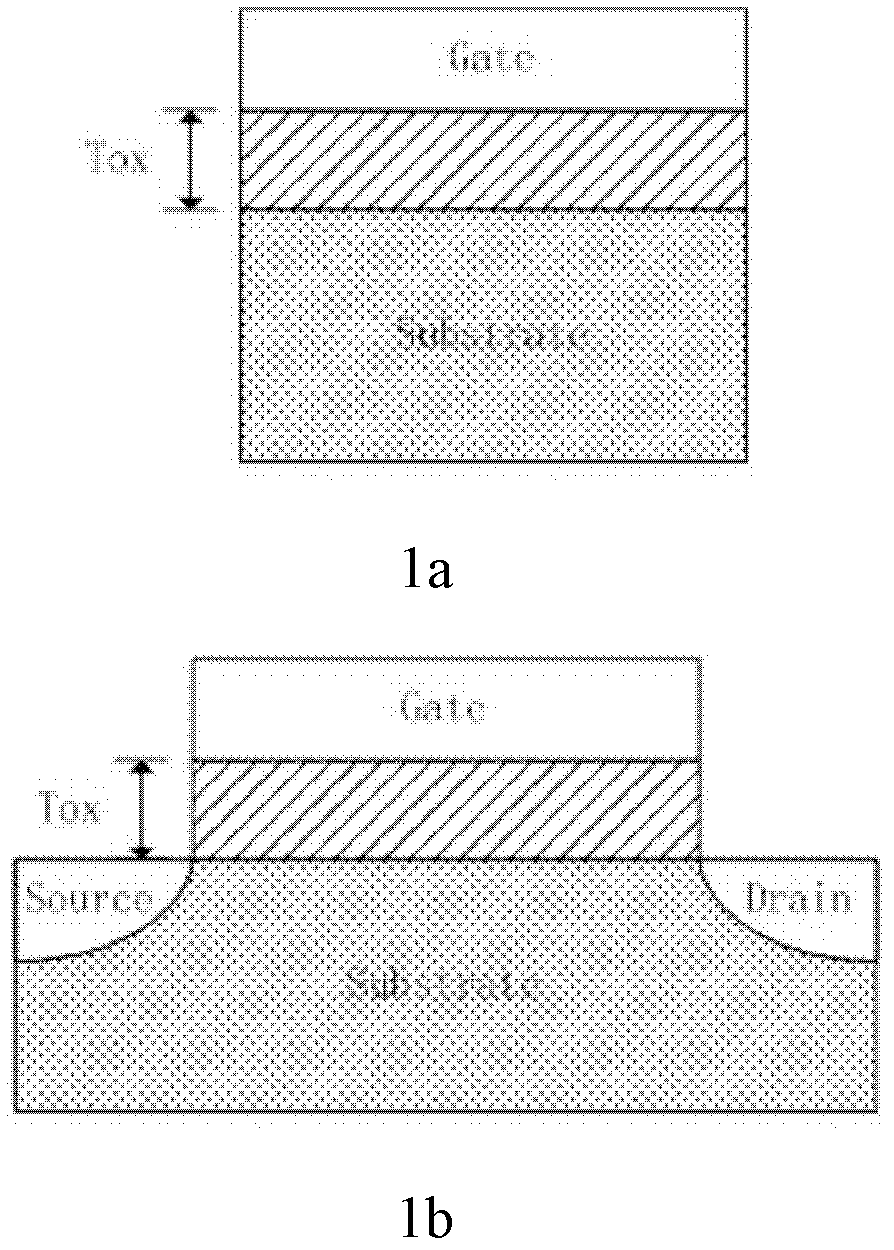

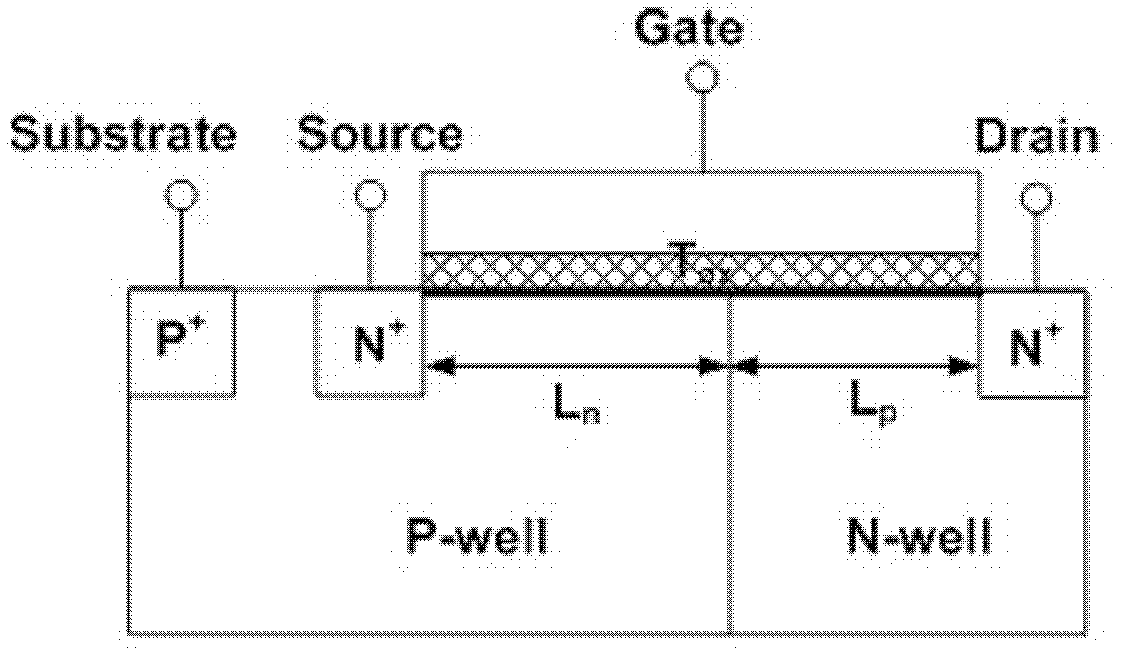

Gate-oxidizing-layer interface-trap density-testing structure and testing method

ActiveCN102522386AReduce areaReduce layout areaSemiconductor/solid-state device detailsSolid-state devicesMOSFETCapacitance

The invention discloses a gate-oxidizing-layer interface-trap density-testing structure and testing method, which relates to the technical field of the quality and reliability testing for MOS (Metal Oxide Semiconductor) devices. The testing structure comprises an n-type MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) and a corresponding p-type gate-oxidizing-layer capacitor or a p-type MOSFET and a corresponding n-type gate-oxidizing-layer capacitor; and the n-type MOSFET and the corresponding p-type gate-oxidizing-layer capacitor or the p-type MOSFET and the corresponding n-type gate-oxidizing-layer capacitor are shared with a grid electrode. The testing for the gate-oxidizing-layer interface-trap density of n-type and p-type MOS devices can be finished by adopting the same testing structure according to the invention, so that the measuring time is shortened, the testing efficiency is improved, and the testing cost is lowered.

Owner:PEKING UNIV

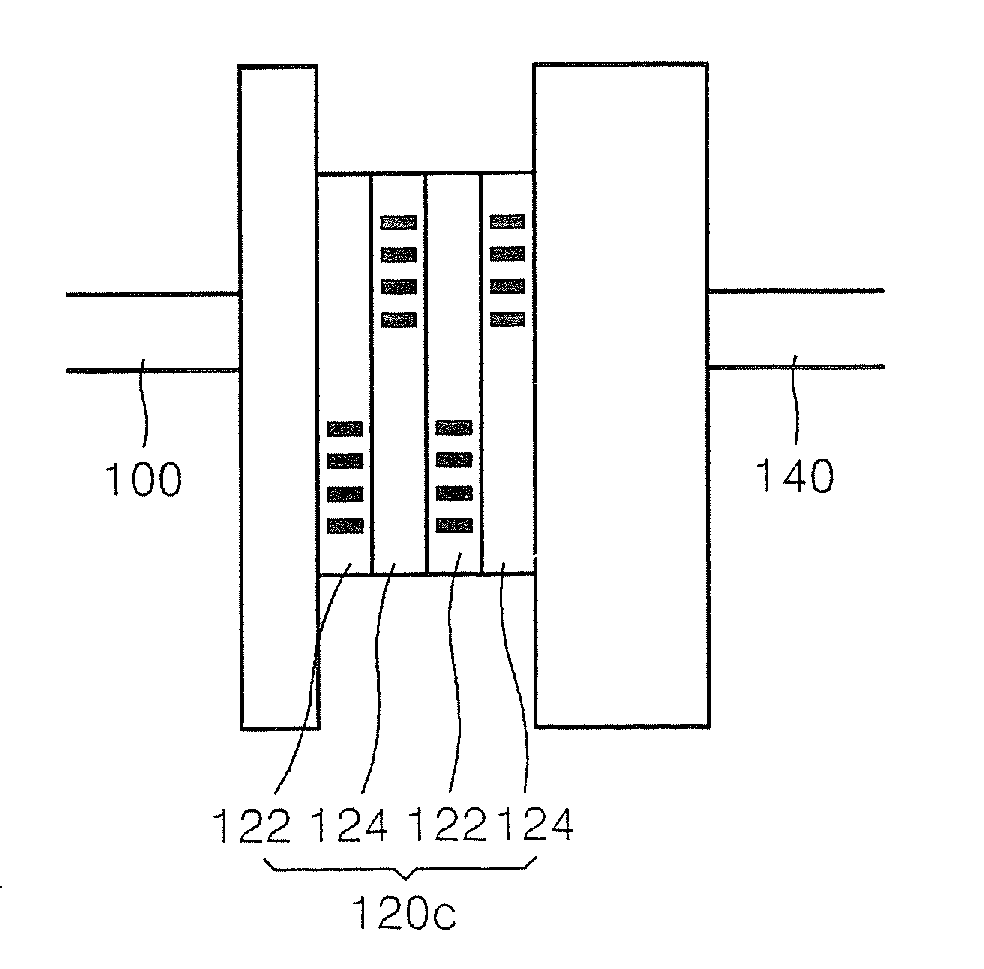

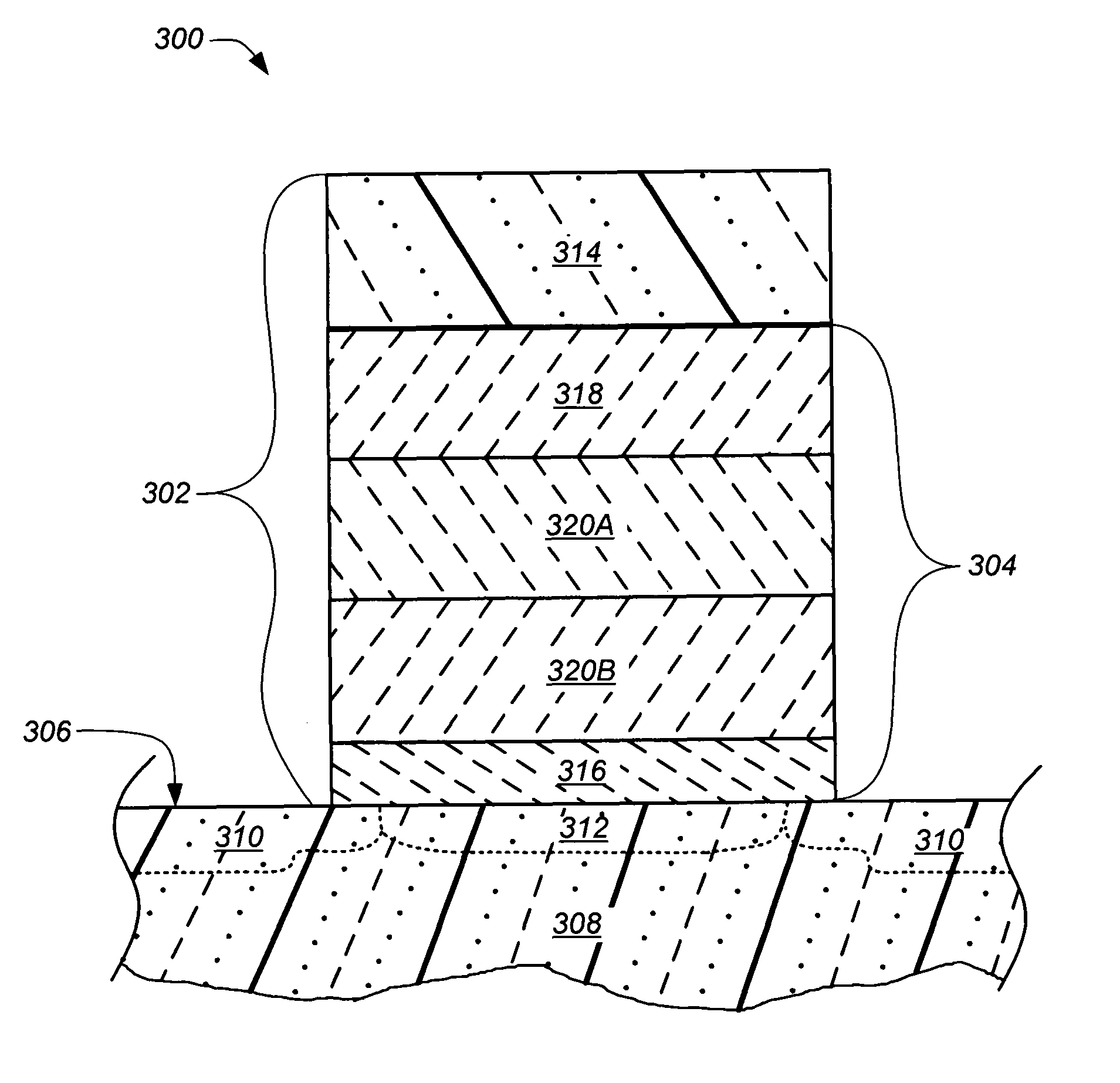

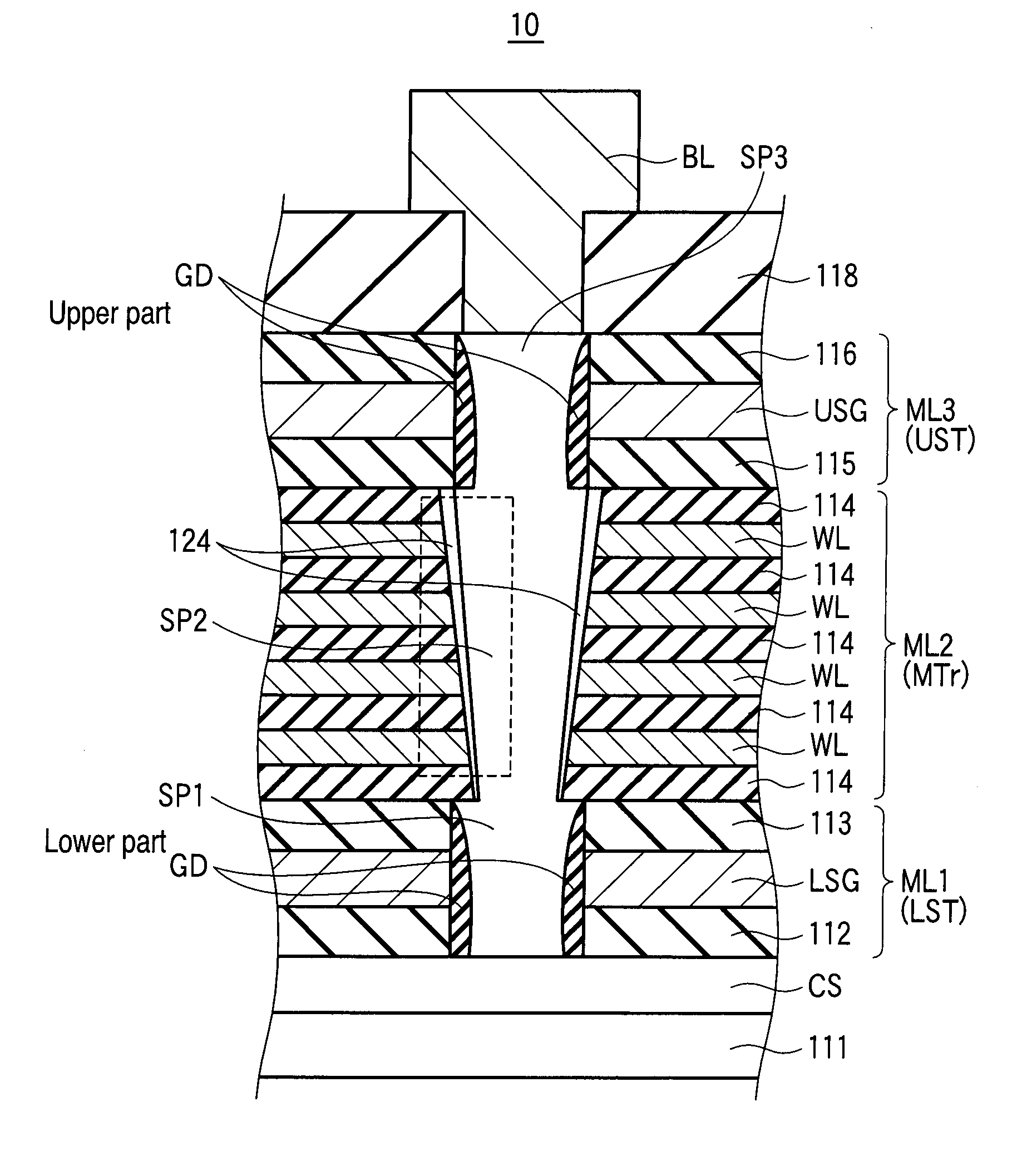

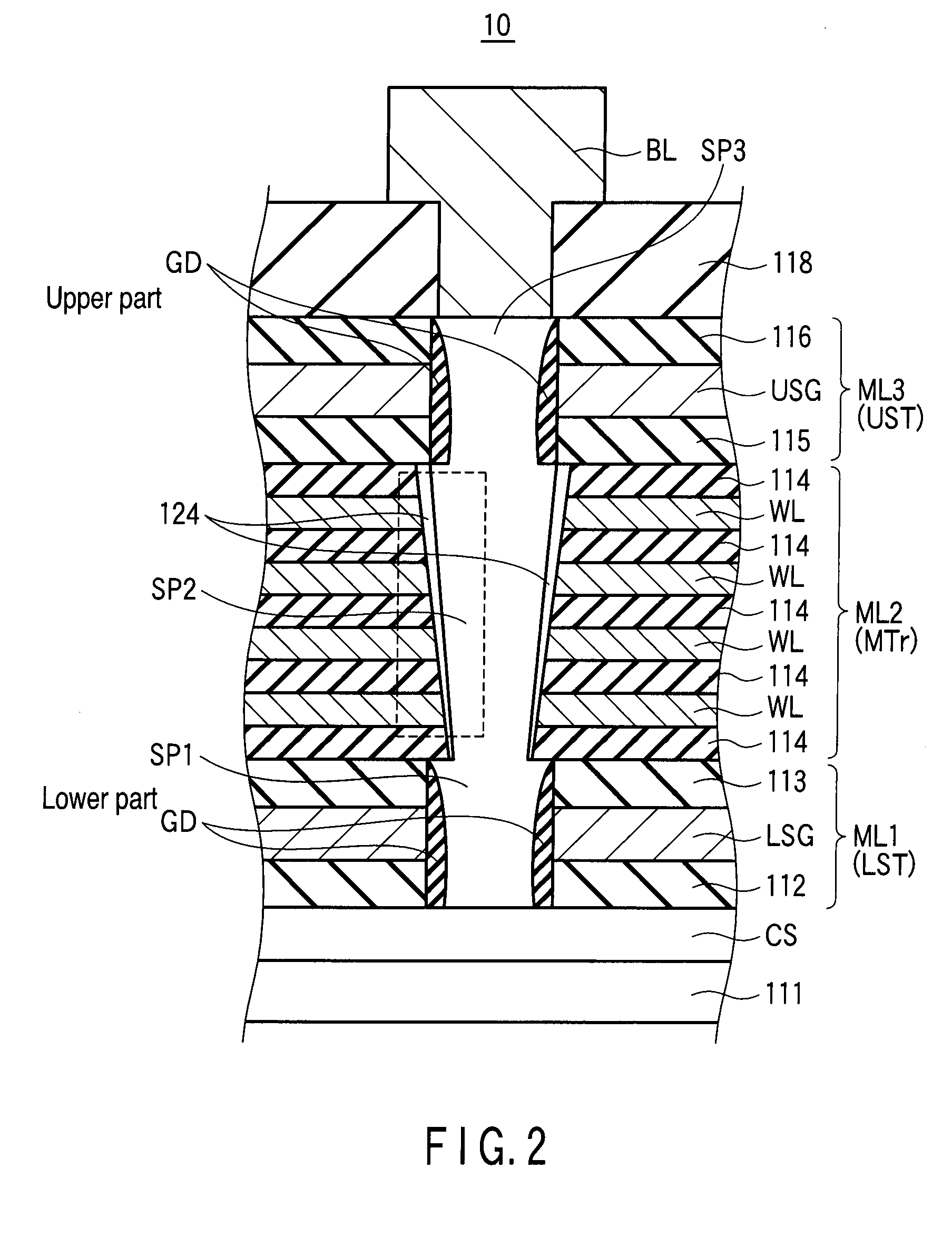

Semiconductor memory device having three-dimensionally arranged memory cells, and manufacturing method thereof

A first select transistor is formed on a semiconductor substrate. Memory cell transistors are stacked on the first select transistor and connected in series. A second select transistor is formed on the memory cell transistors. The memory cell transistors include a tapered semiconductor pillar which increases in diameter from the first select transistor toward the second select transistor, a tunnel dielectric film formed on the side surface of the semiconductor pillar, a charge storage layer which is formed on the side surface of the tunnel dielectric film and which increases in charge trap density from the first select transistor side toward the second select transistor side, a block dielectric film formed on the side surface of the charge storage layer, and conductor films which are formed on the side surface of the block dielectric film and which serve as gate electrodes.

Owner:KIOXIA CORP

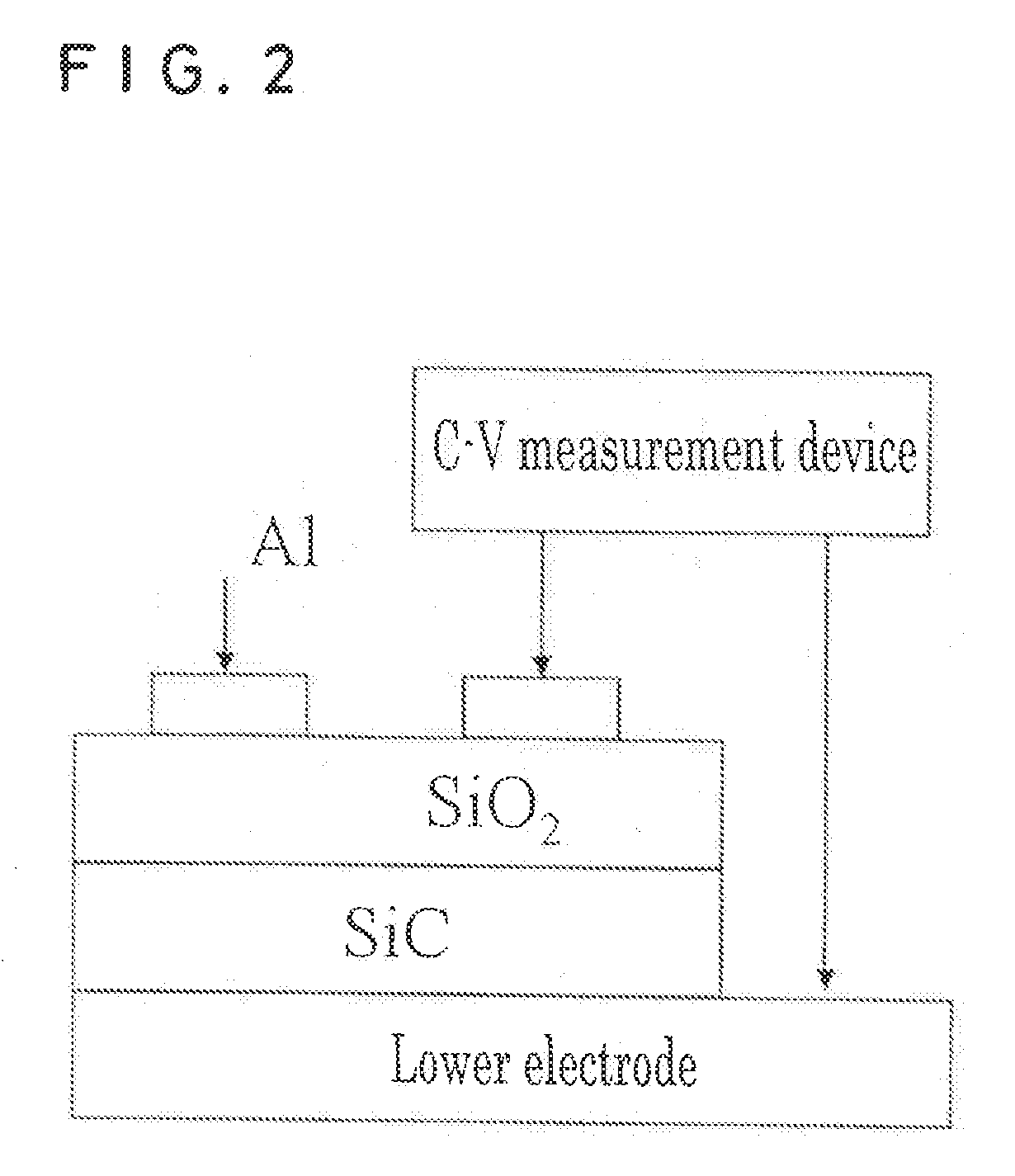

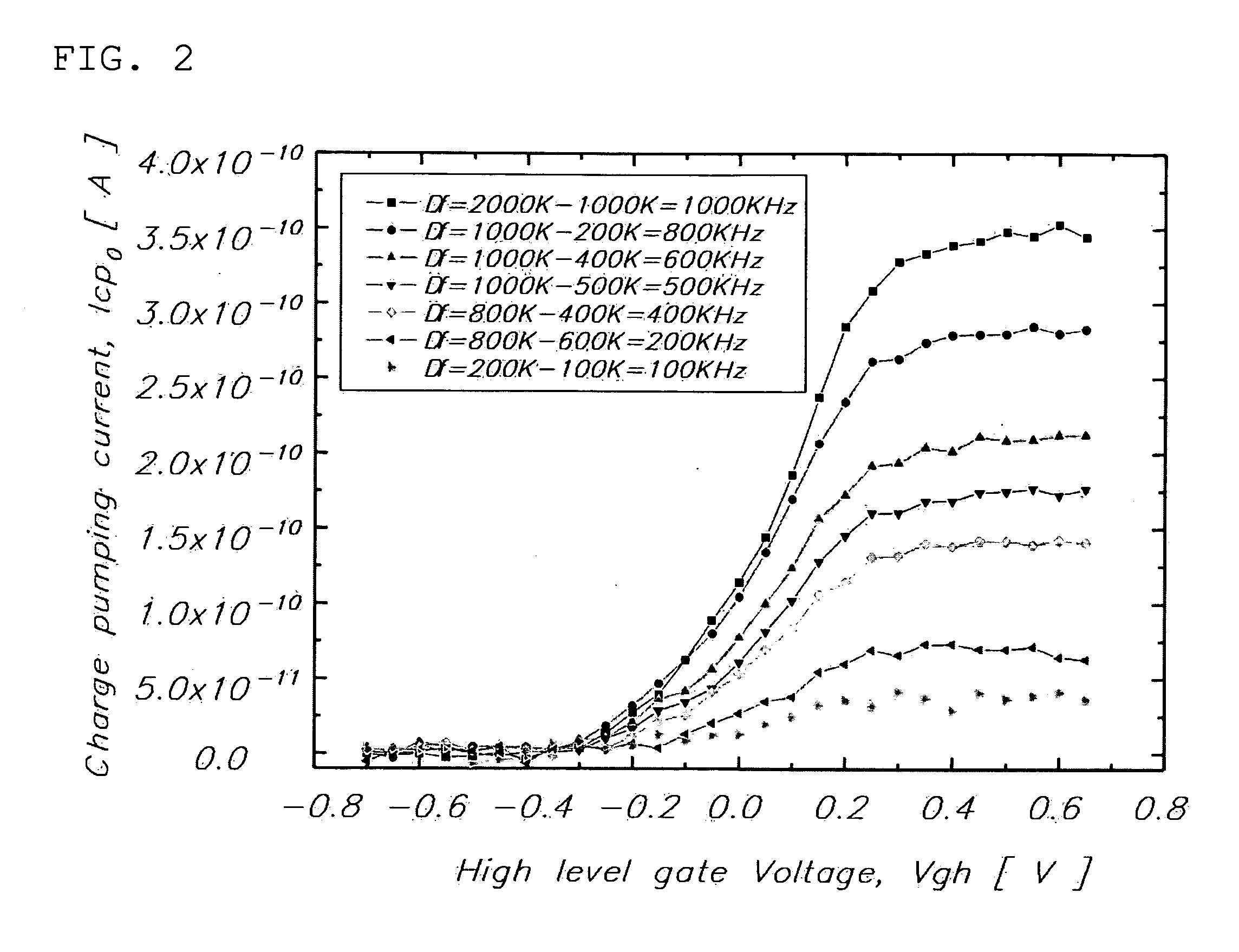

Method and device of measuring interface trap density in semiconductor device

InactiveUS7592828B2Accurately measure and calculateSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceSemiconductorElectrical current

A method is provided for measuring interface trap density in a semiconductor device. In the method, measurement parameters are input to a host computer. A pulse condition is set at a pulse generator using the measurement parameters. A pulse of a predetermined frequency generated by the pulse generator is applied to a gate of a transistor, and a charge pumping current is measured from a bulk of the transistor. A charge pumping current measurement may be repeated for a plurality of frequencies while changing the frequency until a set frequency is reached. A pure charge pumping current is calculated for each frequency where a gate tunneling leakage current is removed from the charge pumping current measured for each frequency. Interface trap density is calculated from the calculated pure charge pumping current for each frequency.

Owner:DONGBU ELECTRONICS CO LTD

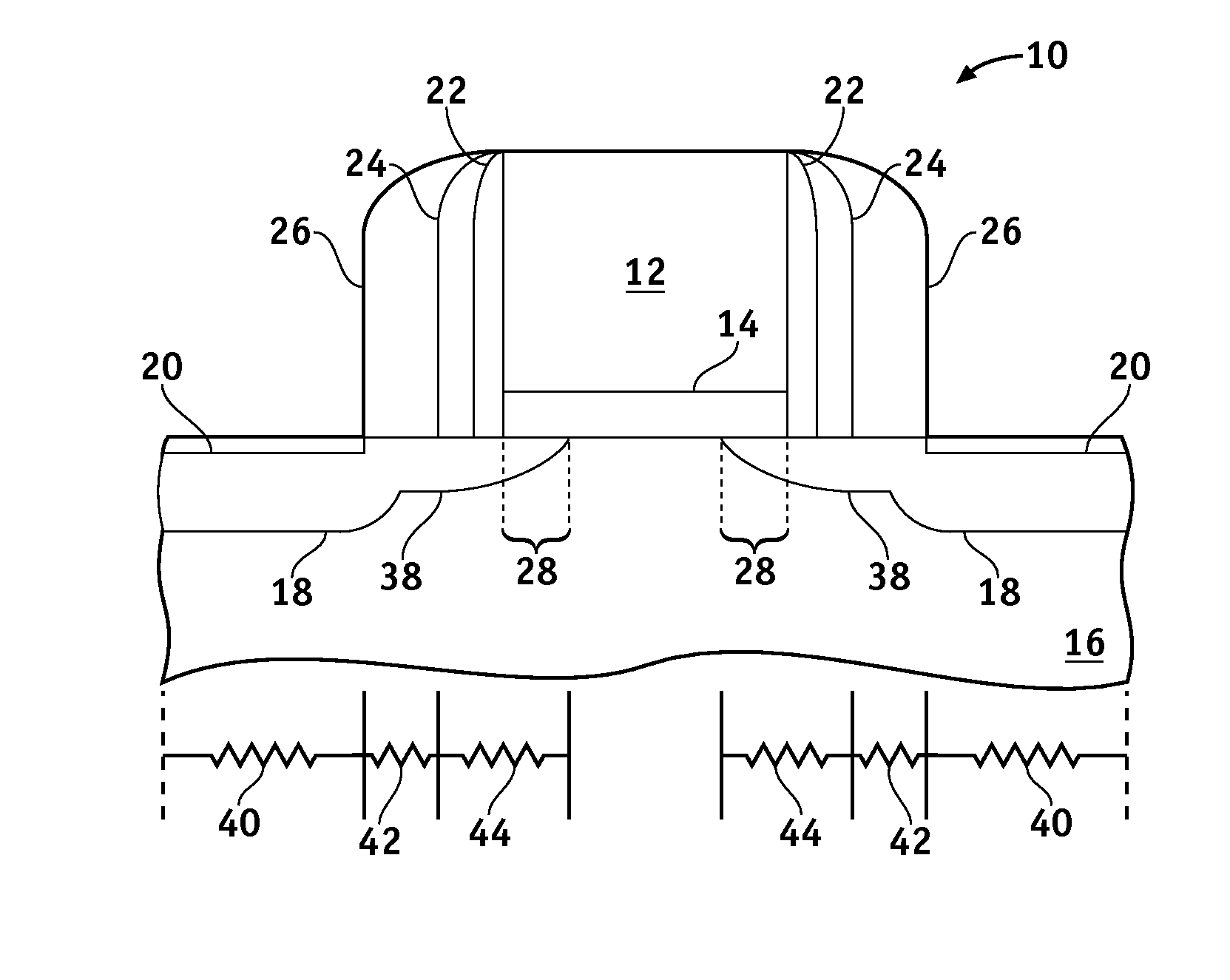

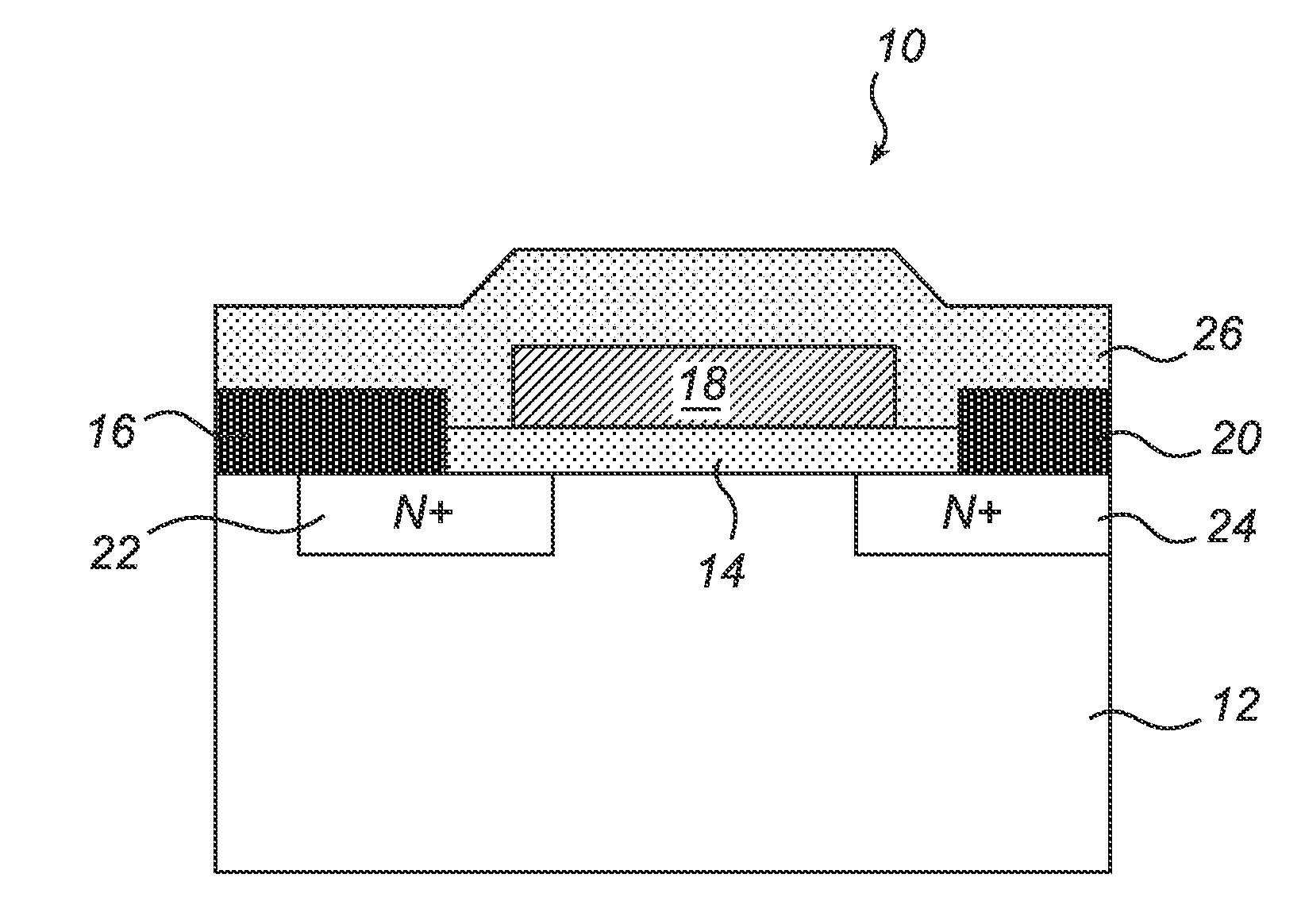

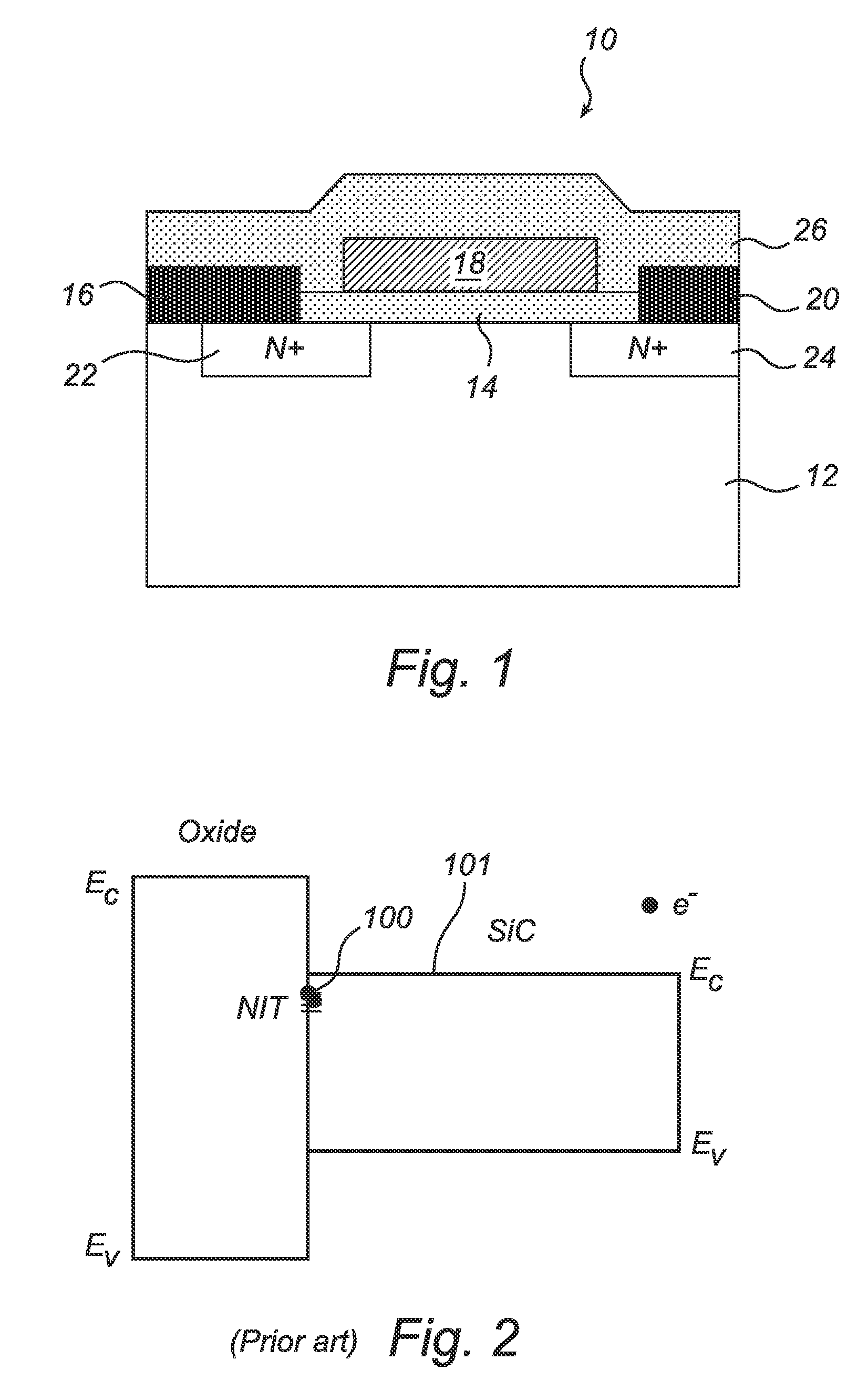

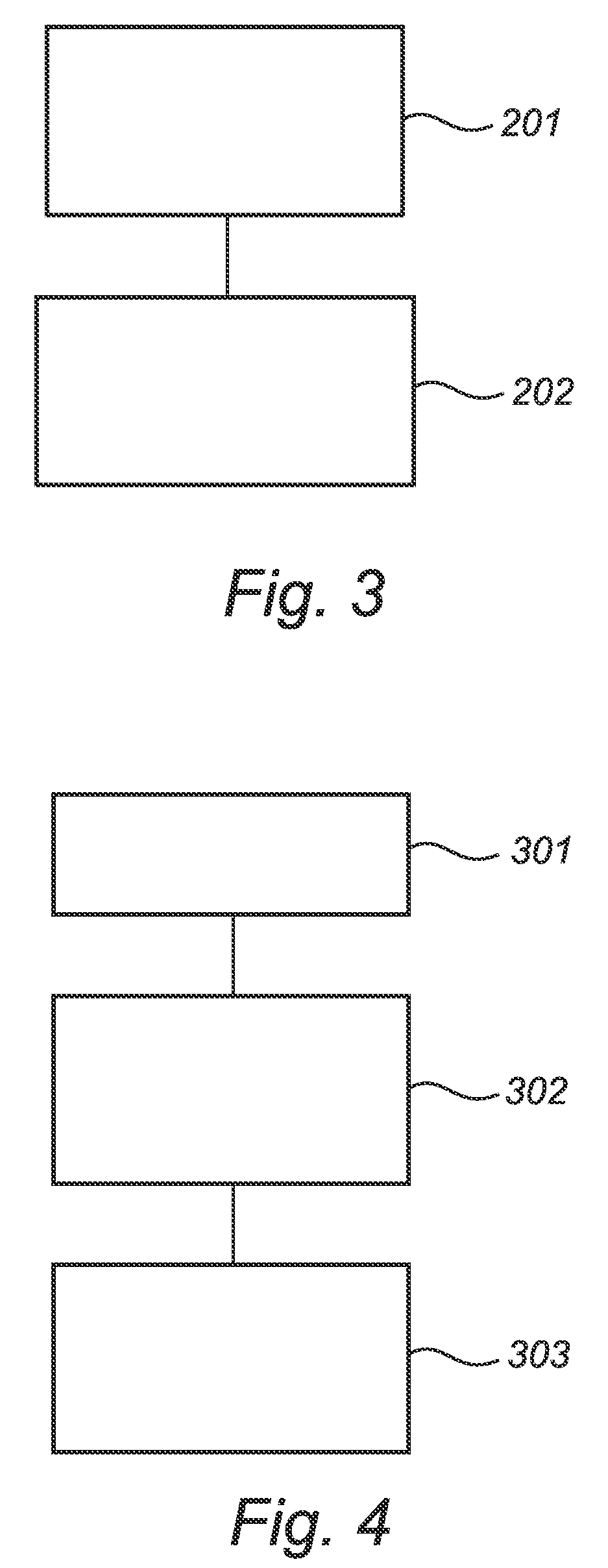

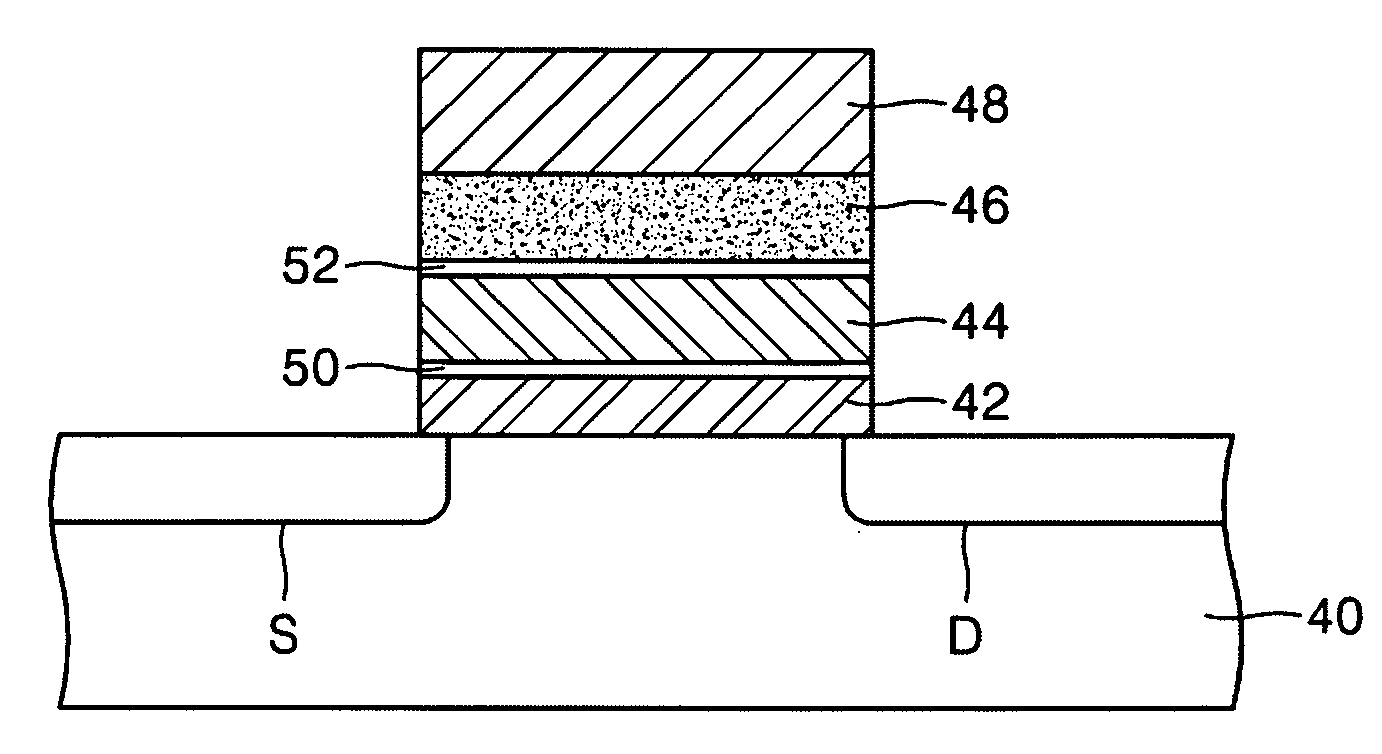

Method for improving inversion layer mobility in a silicon carbide mosfet

ActiveUS20100006860A1Improved inversion channel mobilityLower threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHydrogen annealing

A method of manufacturing a semiconductor device based on a SiC substrate (12), comprising the steps of forming (201) an oxide layer (14) on a Si-terminated face of the SiC substrate (12) at an oxidation rate sufficiently high to achieve a near interface trap density below 5×1011 cm−2; and annealing (202) the oxidized SiC substrate in a hydrogen-containing environment, in order to passivate deep traps formed in the oxide-forming step, thereby enabling manufacturing of a SiC-based MOSFET (10) having improved inversion layer mobility and reduced threshold voltage. It has been found by the present inventors that the density of DTs increases while the density of NITs decreases when the Si-face of the SiC substrate is subject to rapid oxidation. According to the present invention, the deep traps formed during the rapid oxidation can be passivated by hydrogen annealing, thus leading to a significantly decreased threshold voltage for a semiconductor device formed on the oxide.

Owner:UNITED MICROELECTRONICS CORP

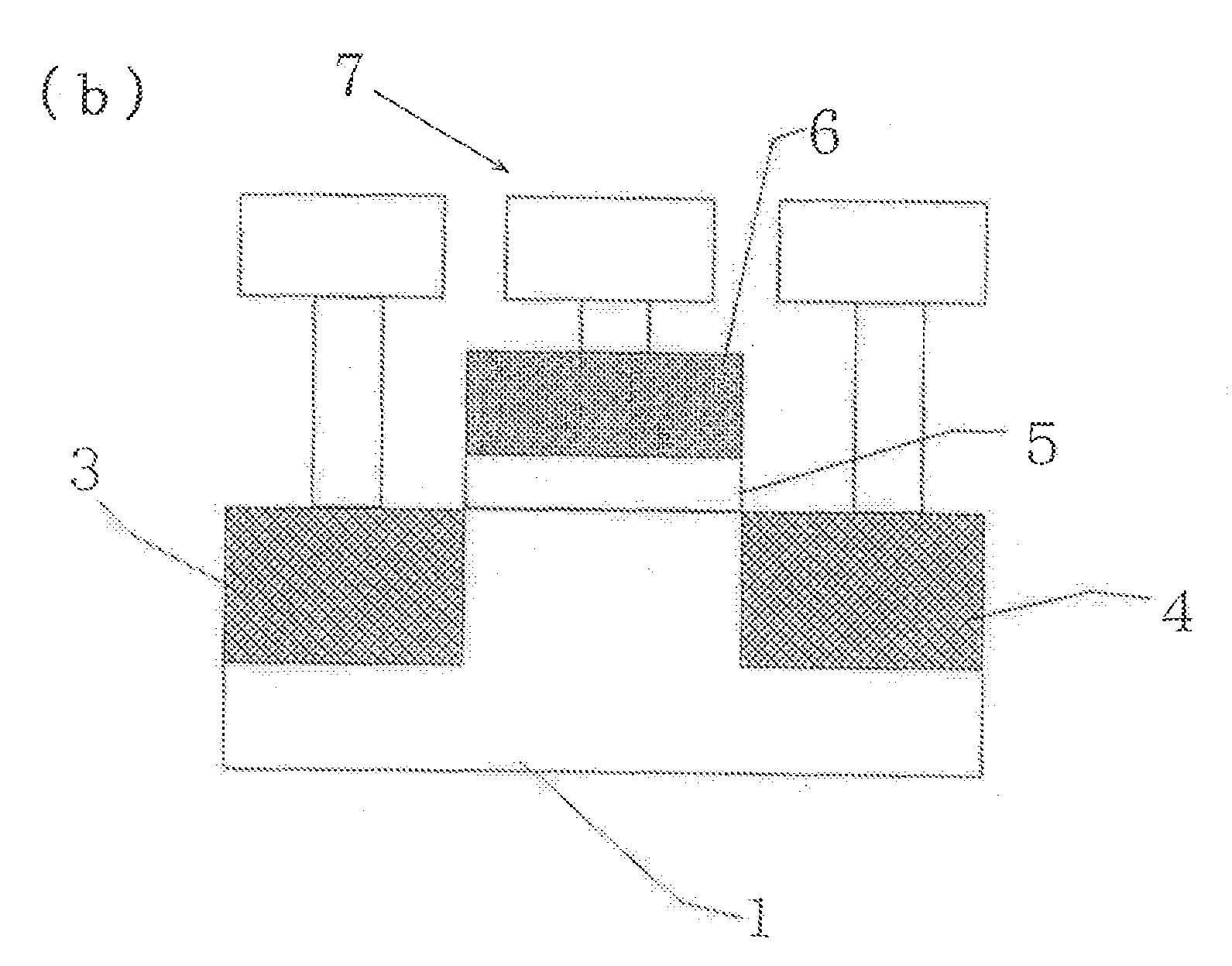

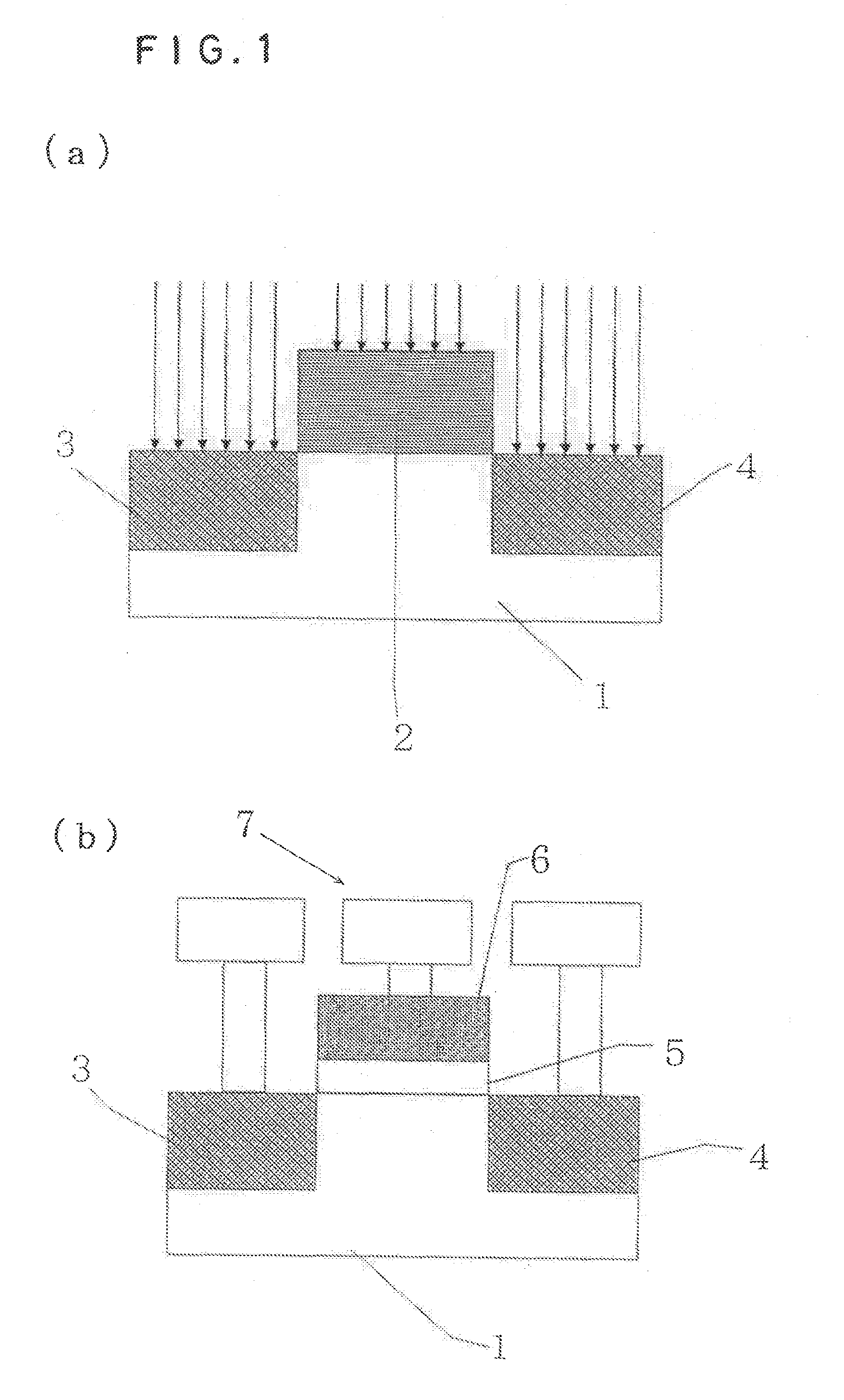

Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses

InactiveCN1856873ASolid-state devicesSemiconductor/solid-state device manufacturingInter layerSemiconductor structure

The present invention provides a method of manufacturing a multilayer semiconductor structure featuring reduced ohmic losses with respect to standard multilayer semiconductor structures. The semiconductor structure comprises a high resistivity silicon substrate with resistivity higher than 3 Kohm.cm, an active semiconductor layer and an insulating layer in between the silicon substrate and the active semiconductor layer. The method comprises suppressing ohmic losses inside the high resistivity silicon substrate by increasing, with regard to prior art devices, charge trap density between the insulating layer and the silicon substrate. In particular this may be obtained by applying an intermediate layer in between the silicon substrate and the insulating layer, the intermediate layer comprising grains having a size, wherein the mean size of the grains of the intermediate layer is smaller than 150 nm, preferably smaller than 50 nm.

Owner:ЮНІВЕРСИТЕ КАТОЛІК ДЕ ЛУВЕН

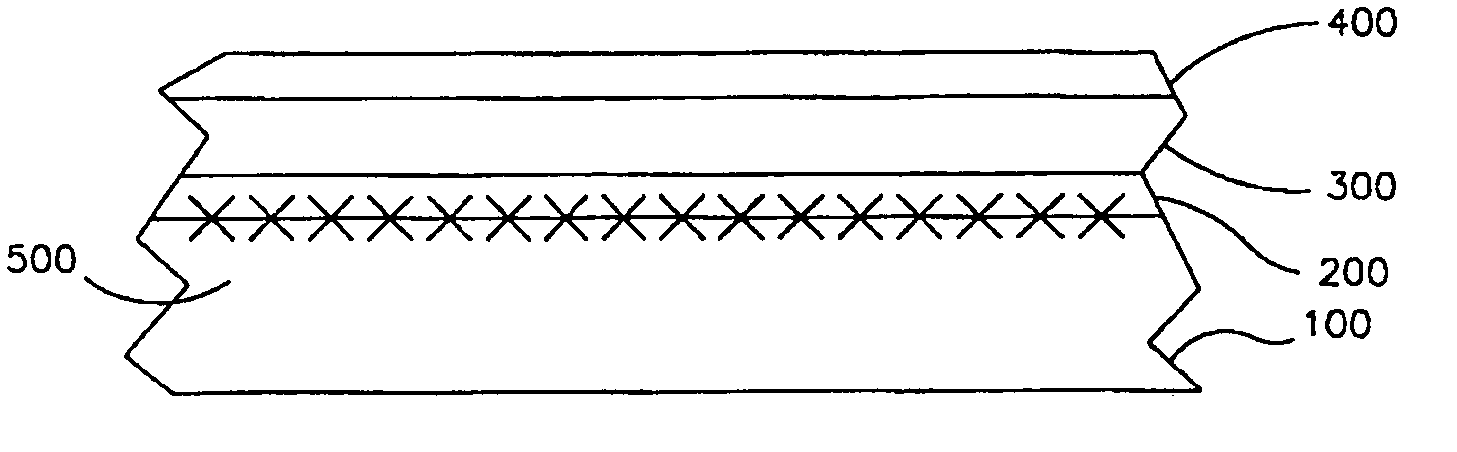

Semiconductor-on-insulator substrate with a diffusion barrier

InactiveUS20090102026A1Inhibited DiffusionSemiconductor/solid-state device detailsSolid-state devicesDopantGate dielectric

A diffusion barrier layer is incorporated between a top semiconductor layer and buried oxide layer. The diffusion barrier layer blocks diffusion of dopants into or out of buried oxide layer. The diffusion barrier layer may comprise a dielectric material such as silicon oxynitride or a high-k gate dielectric material. Alternately, the diffusion barrier layer may comprise a semiconductor material such as SiC. Such materials provide less charge trapping than a silicon nitride layer, which causes a high level of interface trap density and charge in the buried oxide layer. Thus, diffusion of dopants from and into semiconductor devices through the buried oxide layer is suppressed by the diffusion barrier layer without inducing a high interface trap density or charge in the buried oxide layer.

Owner:TAIWAN SEMICON MFG CO LTD

Nonvolatile semiconductor memory device having a gate stack and method of manufacturing the same

ActiveUS7420256B2High speedReduce trap densityTransistorSolid-state devicesGate stackVolumetric Mass Density

A nonvolatile semiconductor memory device includes a semiconductor substrate having a source region and a drain region, and a gate stack formed on the semiconductor substrate between and in contact with the source and drain regions. The gate stack includes, in sequential order from the substrate: a tunneling film; a first trapping material film doped with a first predetermined impurity, the first trapping material film having a higher dielectric constant than the nitride film (Si3N4); a first insulating film having a higher dielectric constant than a nitride film; and a gate electrode. Such a nonvolatile semiconductor memory device can effectively control the trap density according to the doping concentration, thereby increasing the write / erase speed of data at a low operating voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and device of measuring interface trap density in semiconductor device

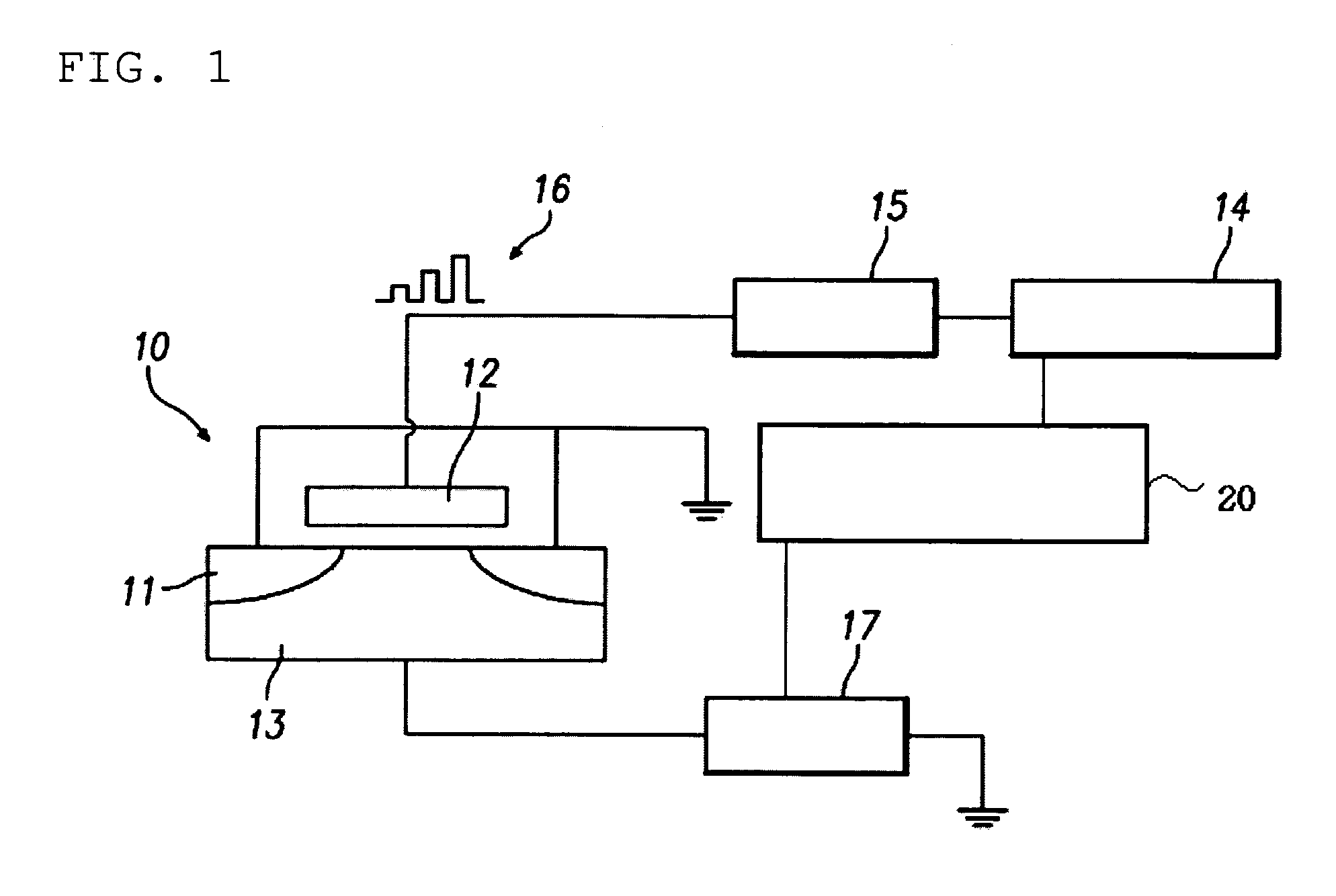

InactiveUS20070152673A1Accurate measurementAccurate calculationSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceDevice materialDrain current

A method is provided for measuring interface trap density in a semiconductor device. In the method, measurement parameters are input to a host computer. A pulse condition is set at a pulse generator using the measurement parameters. A pulse of a predetermined frequency generated by the pulse generator is applied to a gate of a transistor, and a charge pumping current is measured from a bulk of the transistor. A charge pumping current measurement may be repeated for a plurality of frequencies while changing the frequency until a set frequency is reached. A pure charge pumping current is calculated for each frequency where a gate tunneling leakage current is removed from the charge pumping current measured for each frequency. Interface trap density is calculated from the calculated pure charge pumping current for each frequency.

Owner:DONGBU ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com