Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1189 results about "Silicon thin film" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

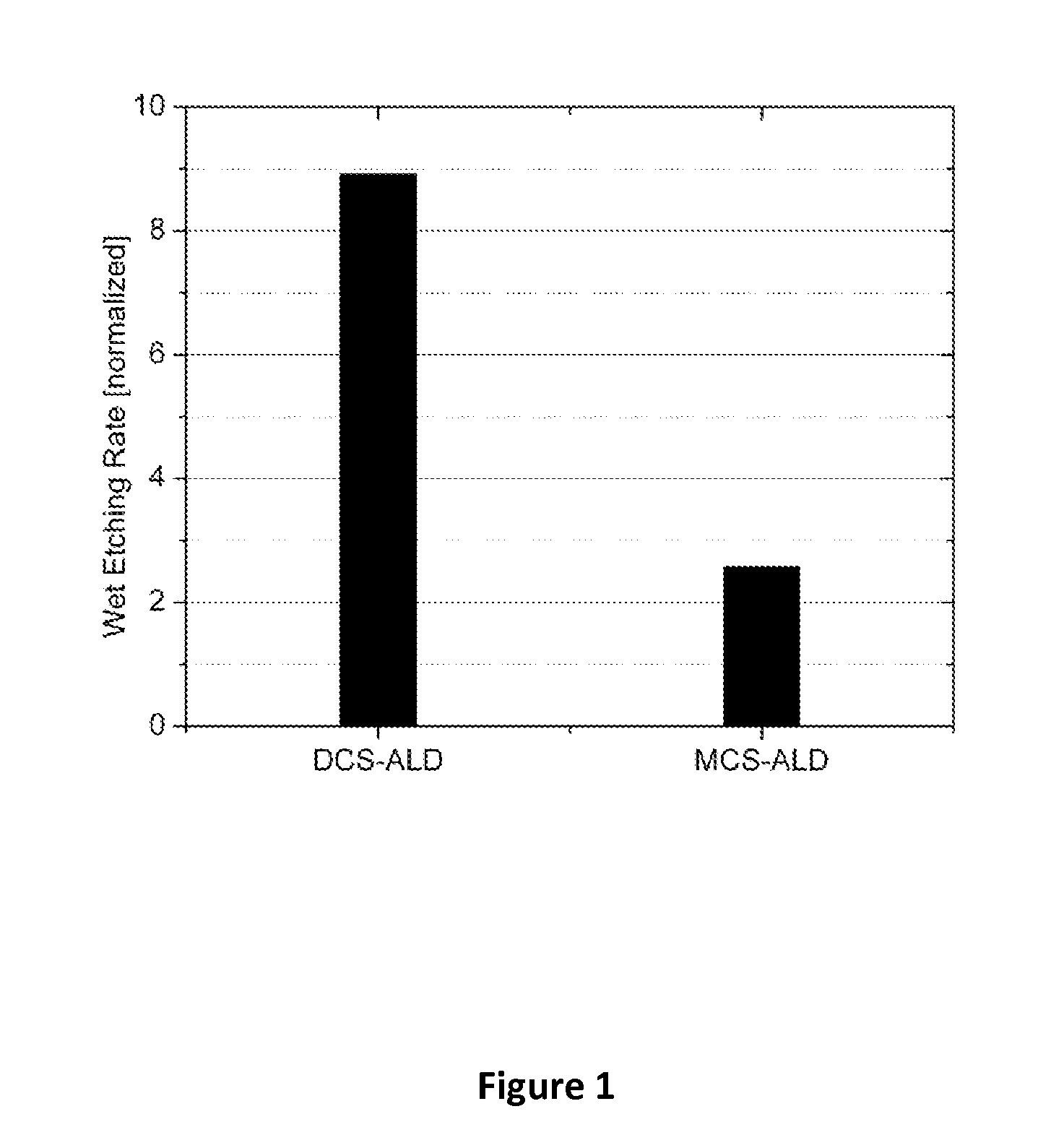

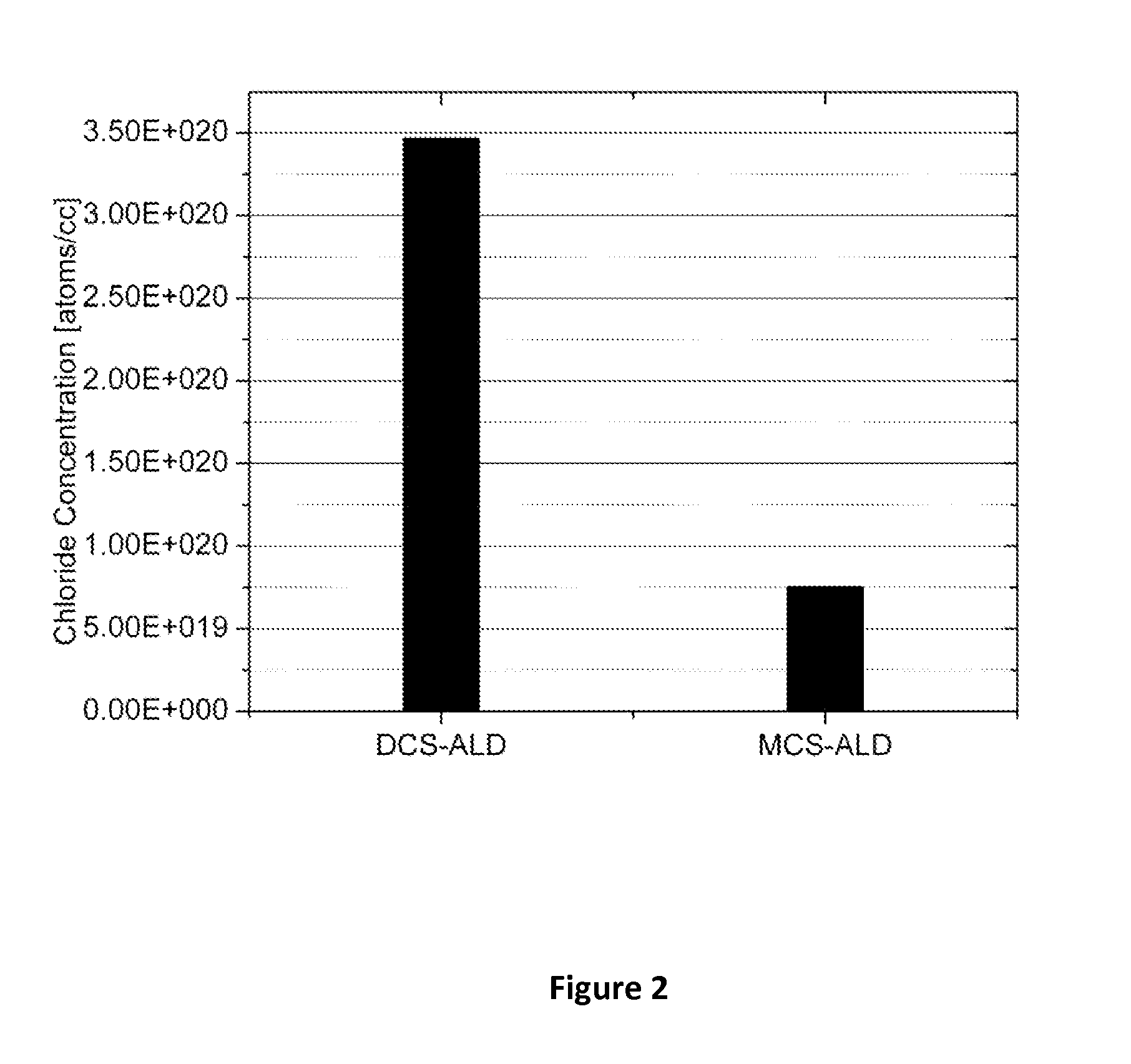

Low Temperature Deposition of Silicon-Containing Films

ActiveUS20100304047A1Low deposition temperatureSemiconductor/solid-state device manufacturingSpecial surfacesLow temperature depositionDeposition temperature

This invention discloses the method of forming silicon nitride, silicon oxynitride, silicon oxide, carbon-doped silicon nitride, carbon-doped silicon oxide and carbon-doped oxynitride films at low deposition temperatures. The silicon containing precursors used for the deposition are monochlorosilane (MCS) and monochloroalkylsilanes. The method is preferably carried out by using plasma enhanced atomic layer deposition, plasma enhanced chemical vapor deposition, and plasma enhanced cyclic chemical vapor deposition.

Owner:TOKYO ELECTRON LTD +1

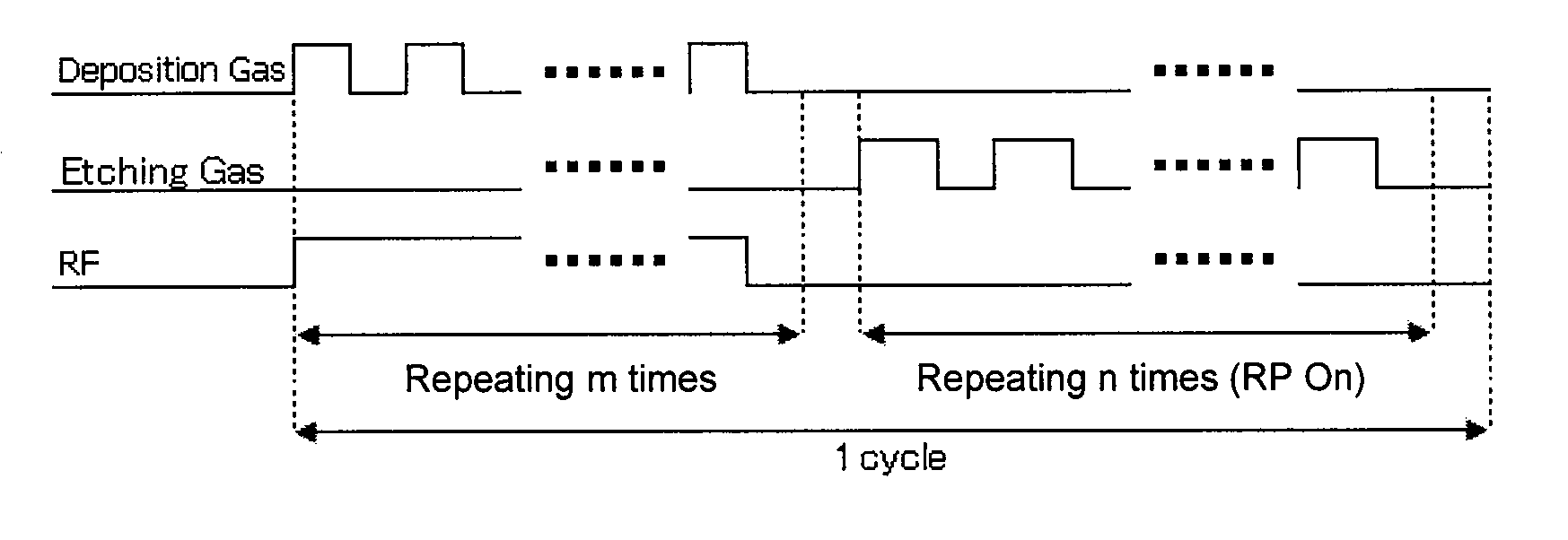

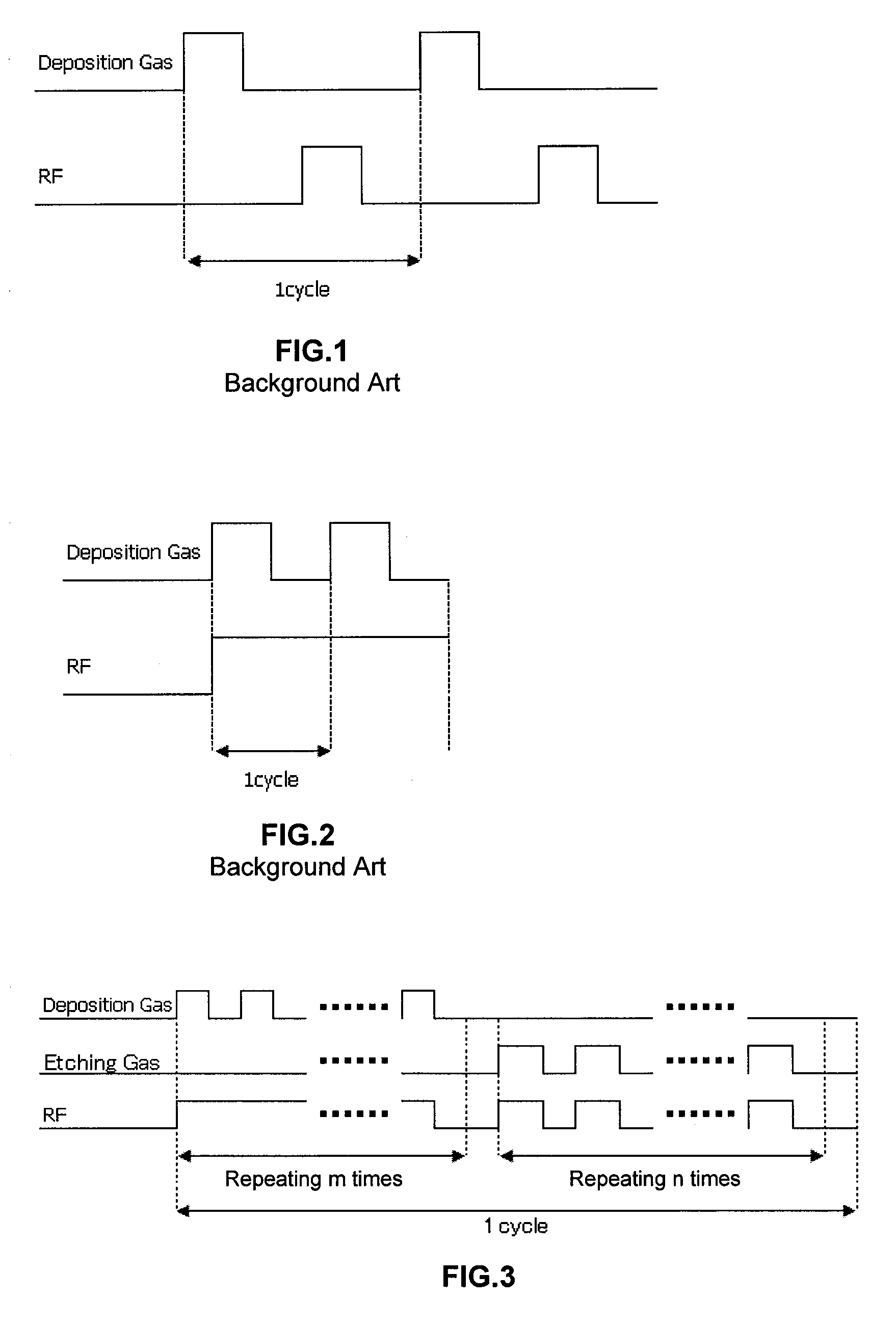

Method of tailoring conformality of Si-containing film

ActiveUS8669185B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingThin membraneEngineering

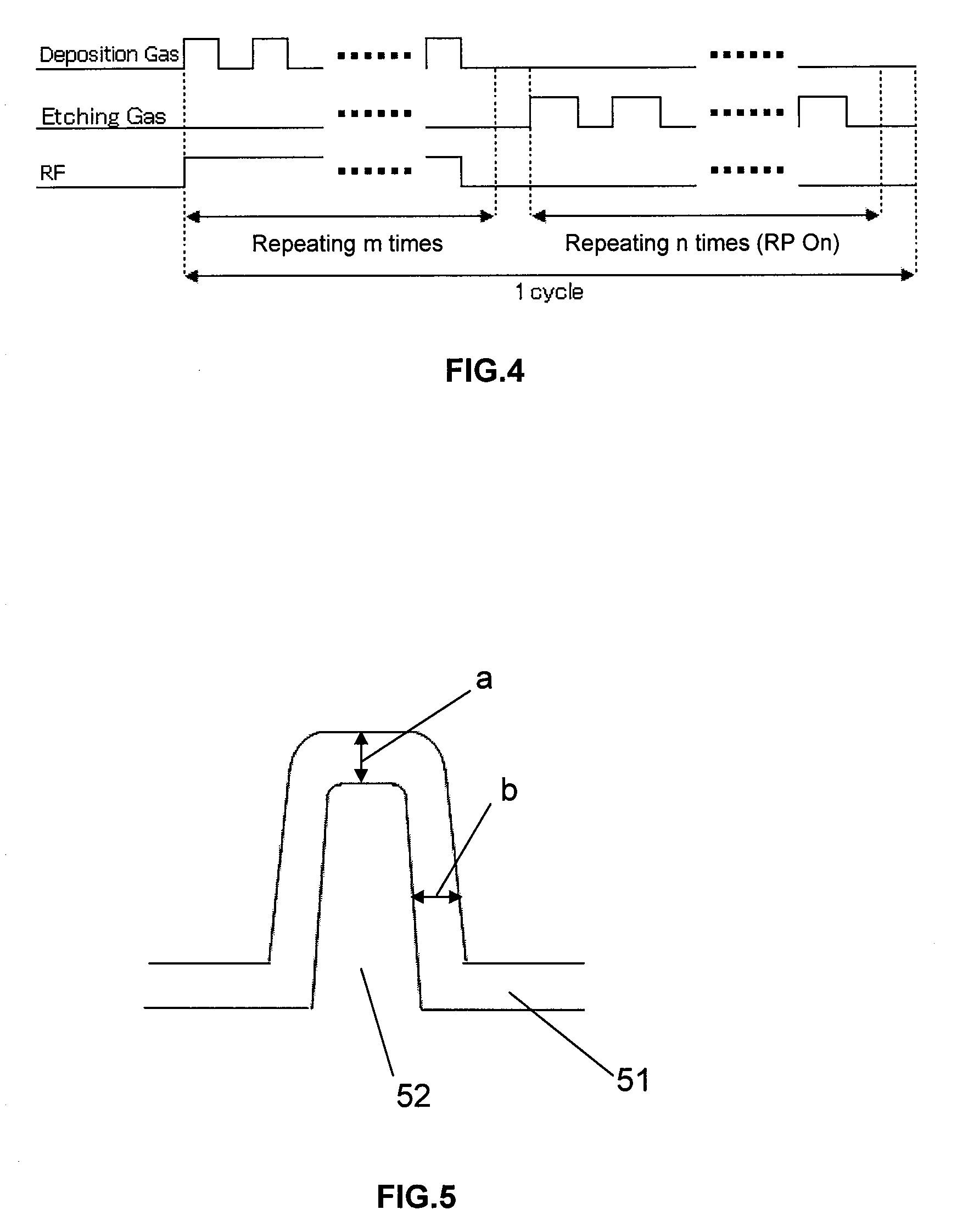

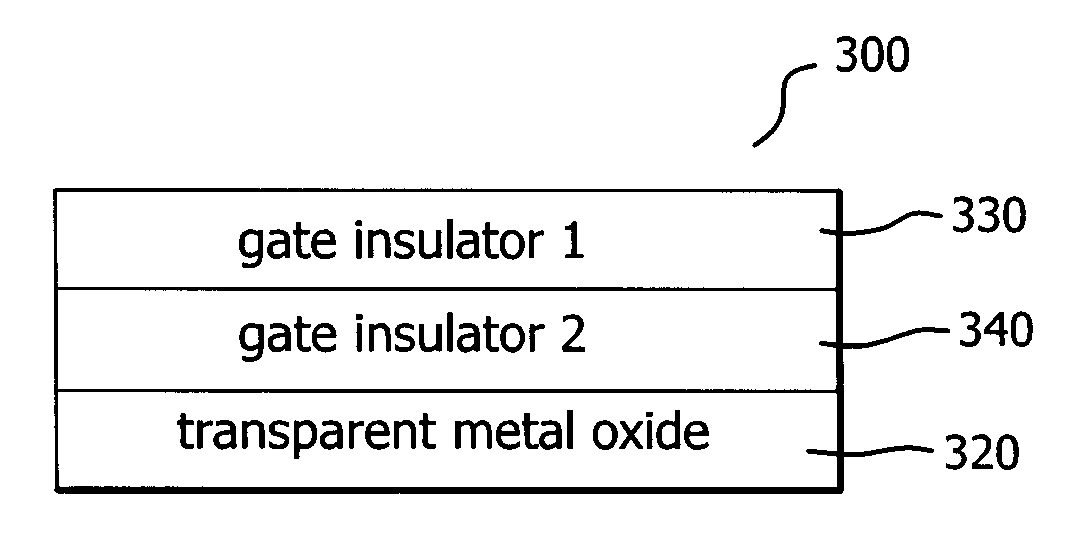

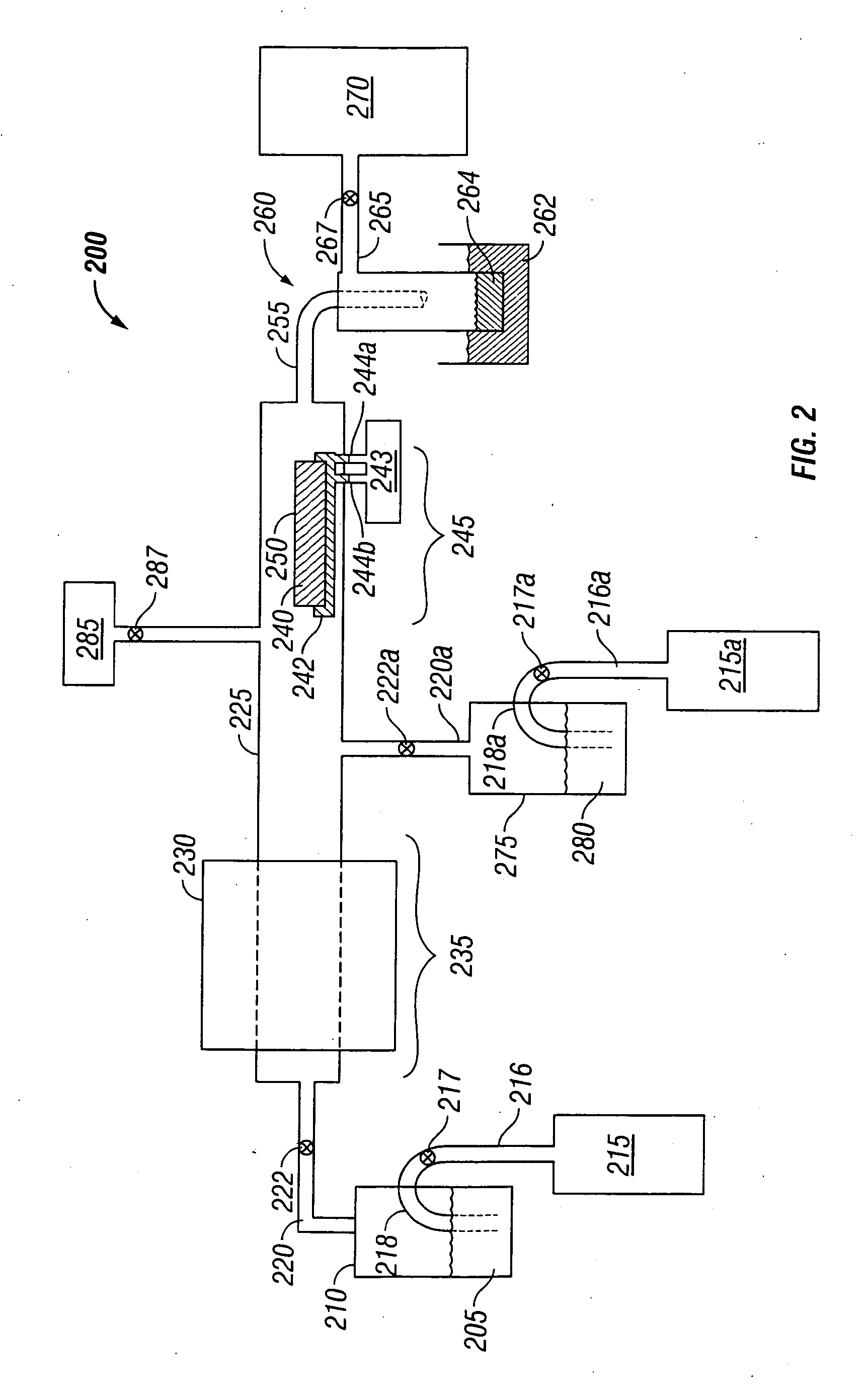

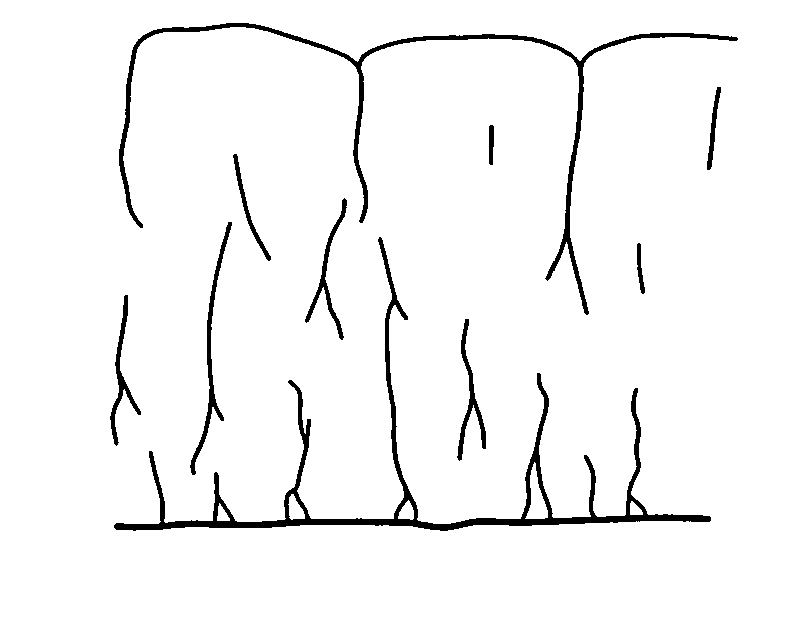

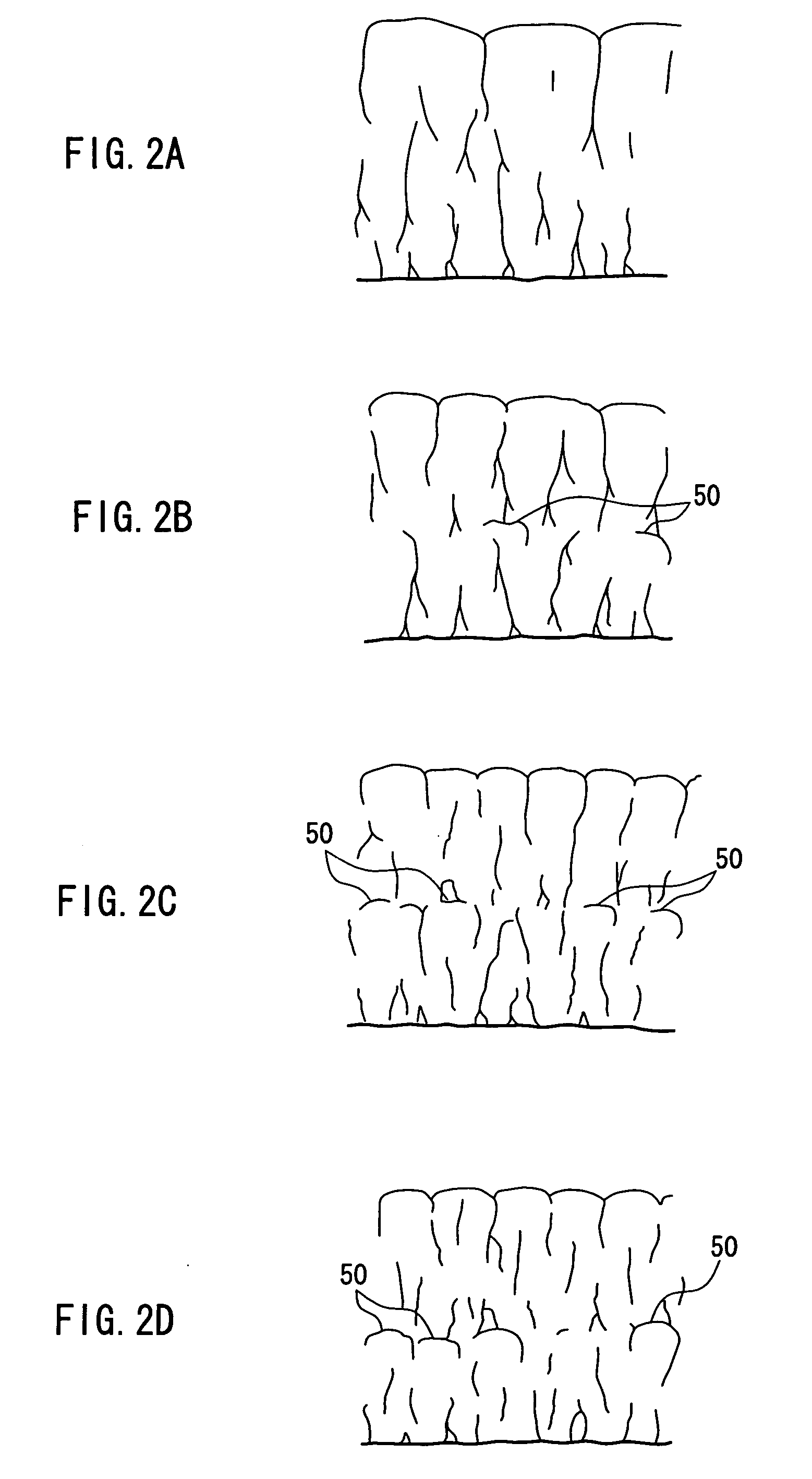

A method of tailoring conformality of a film deposited on a patterned surface includes: (I) depositing a film by PEALD or pulsed PECVD on the patterned surface; (II) etching the film, wherein the etching is conducted in a pulse or pulses, wherein a ratio of an etching rate of the film on a top surface and that of the film on side walls of the patterns is controlled as a function of the etching pulse duration and the number of etching pulses to increase a conformality of the film; and (III) repeating (I) and (II) to satisfy a target film thickness.

Owner:ASM JAPAN

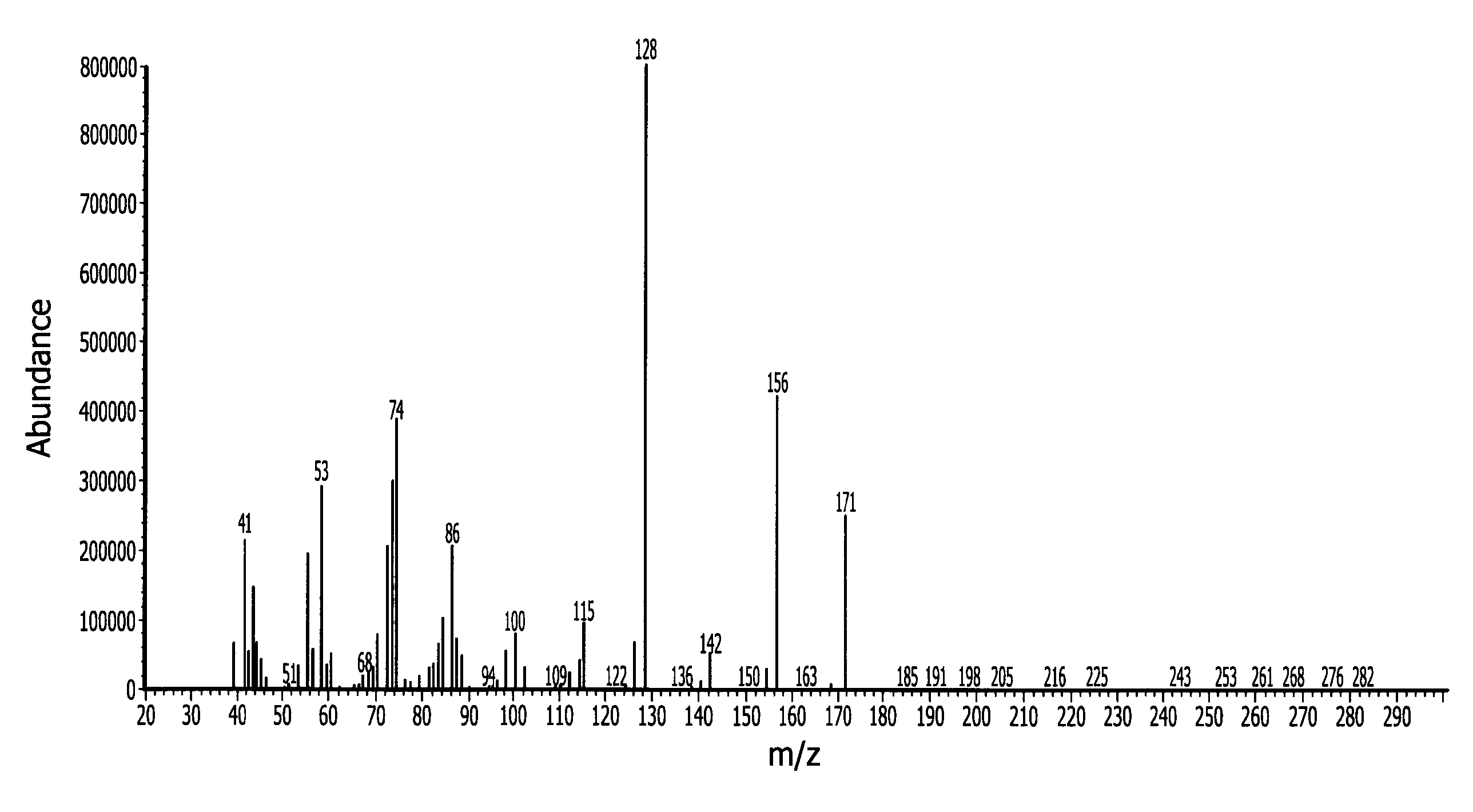

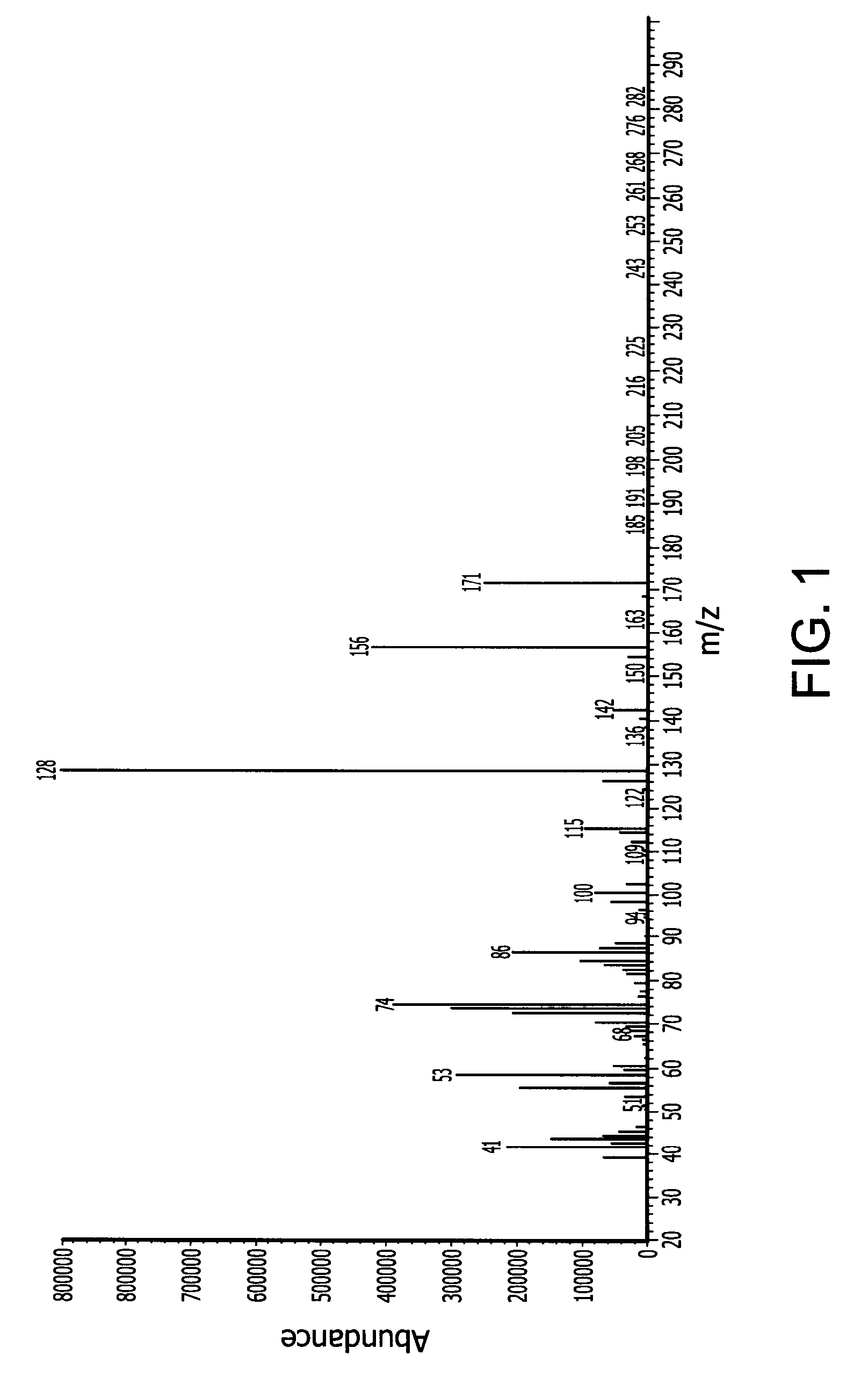

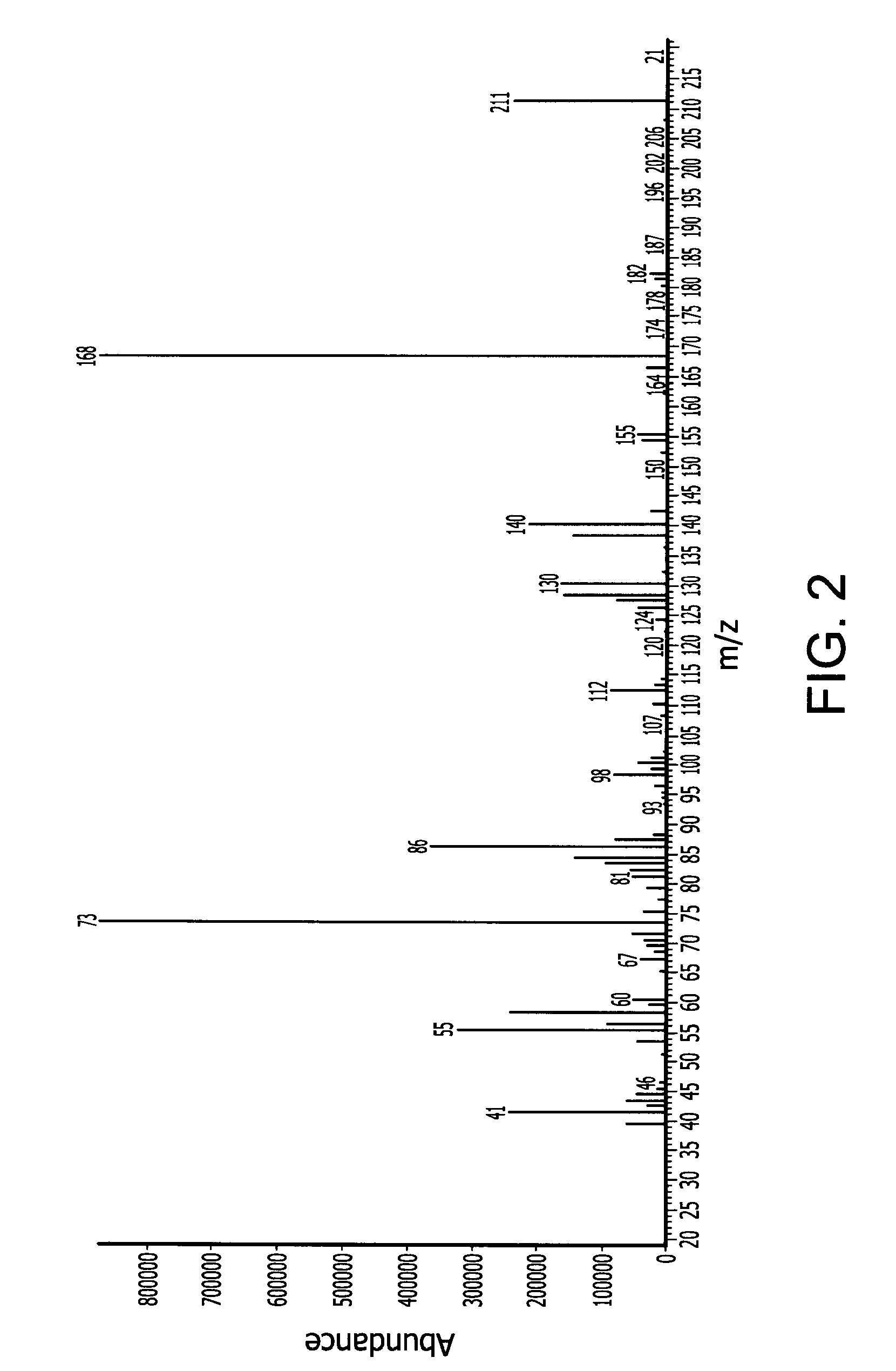

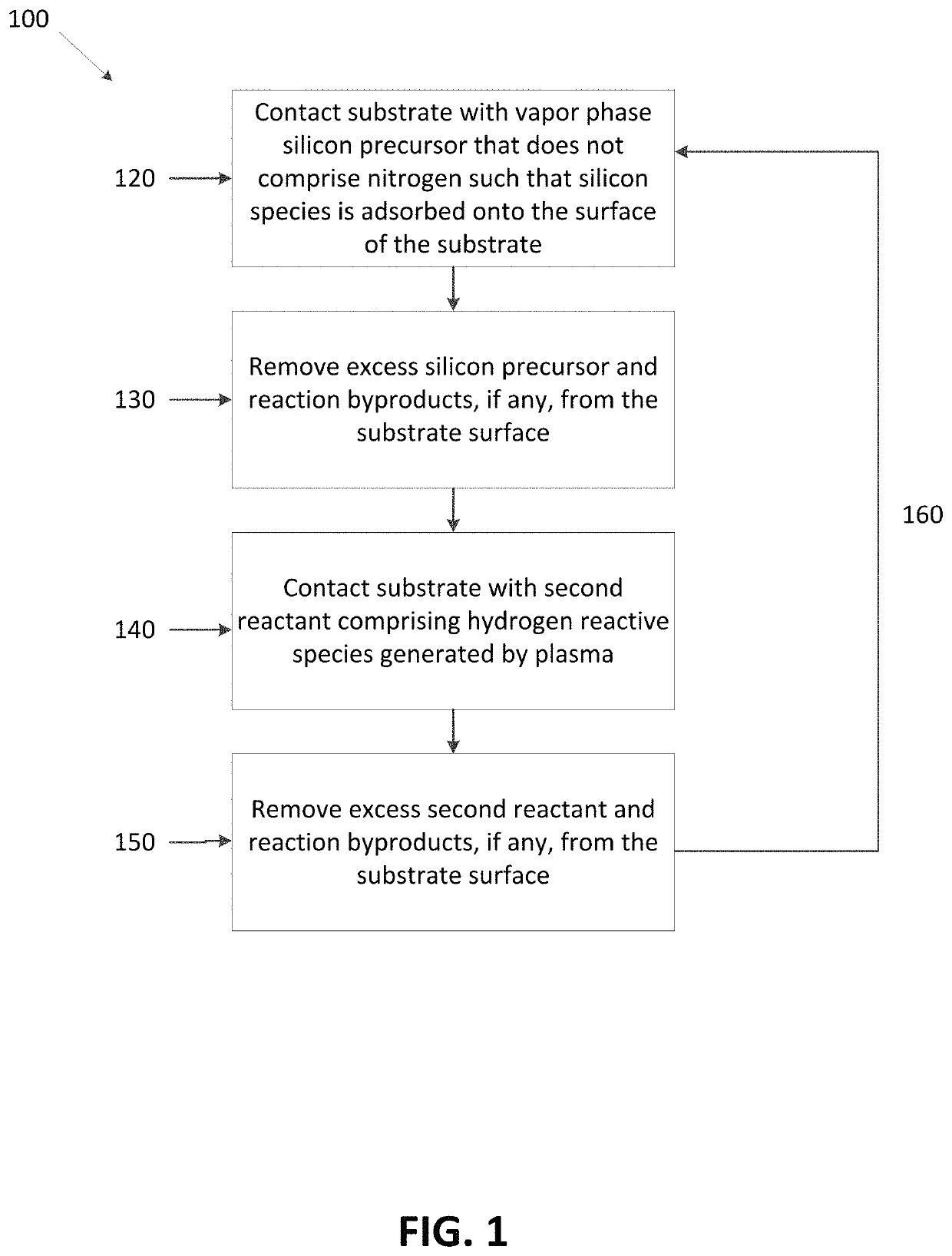

Compositions and methods for making silicon containing films

ActiveUS20150014823A1Semiconductor/solid-state device detailsSolid-state devicesTriethylsilaneDeposition process

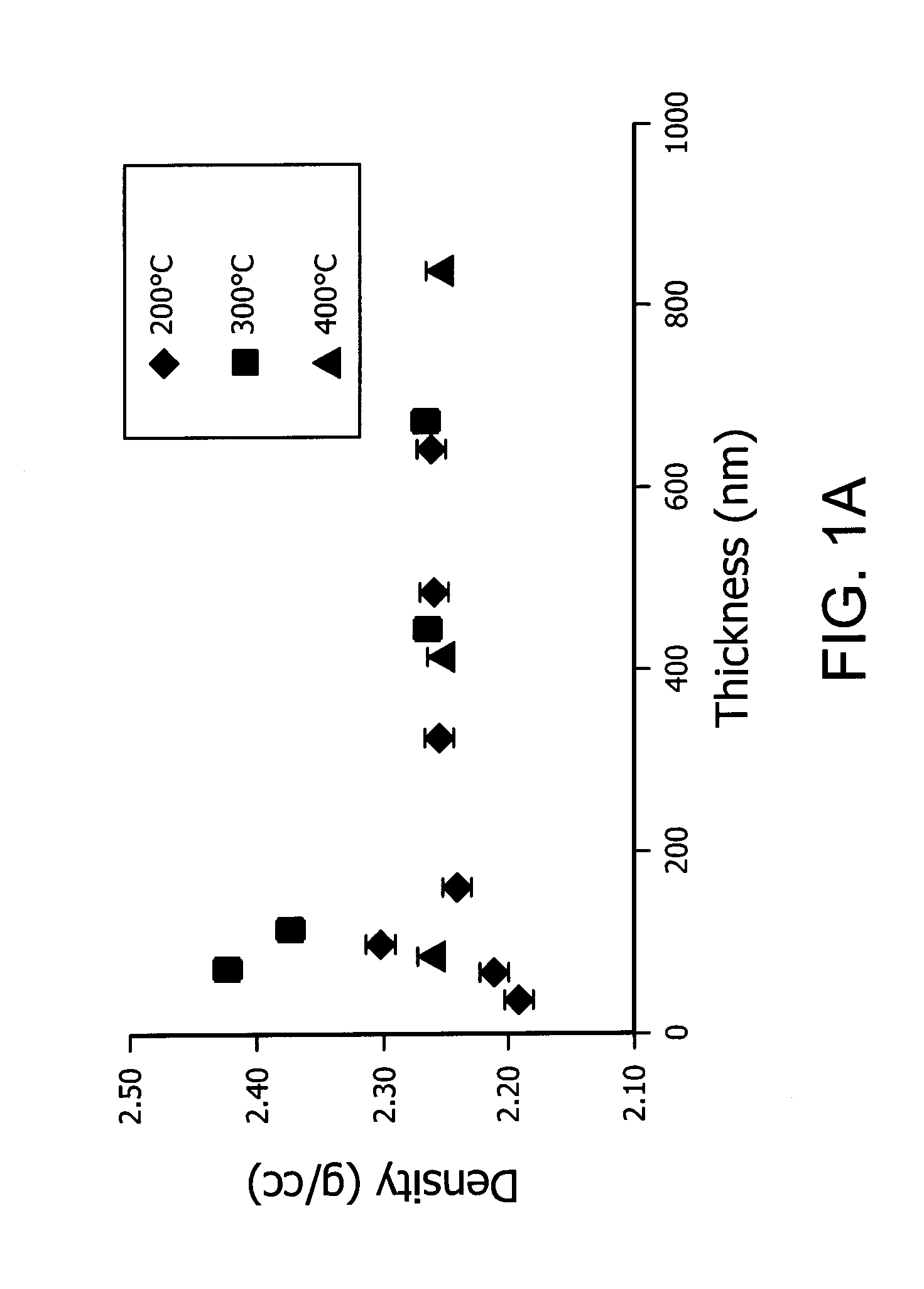

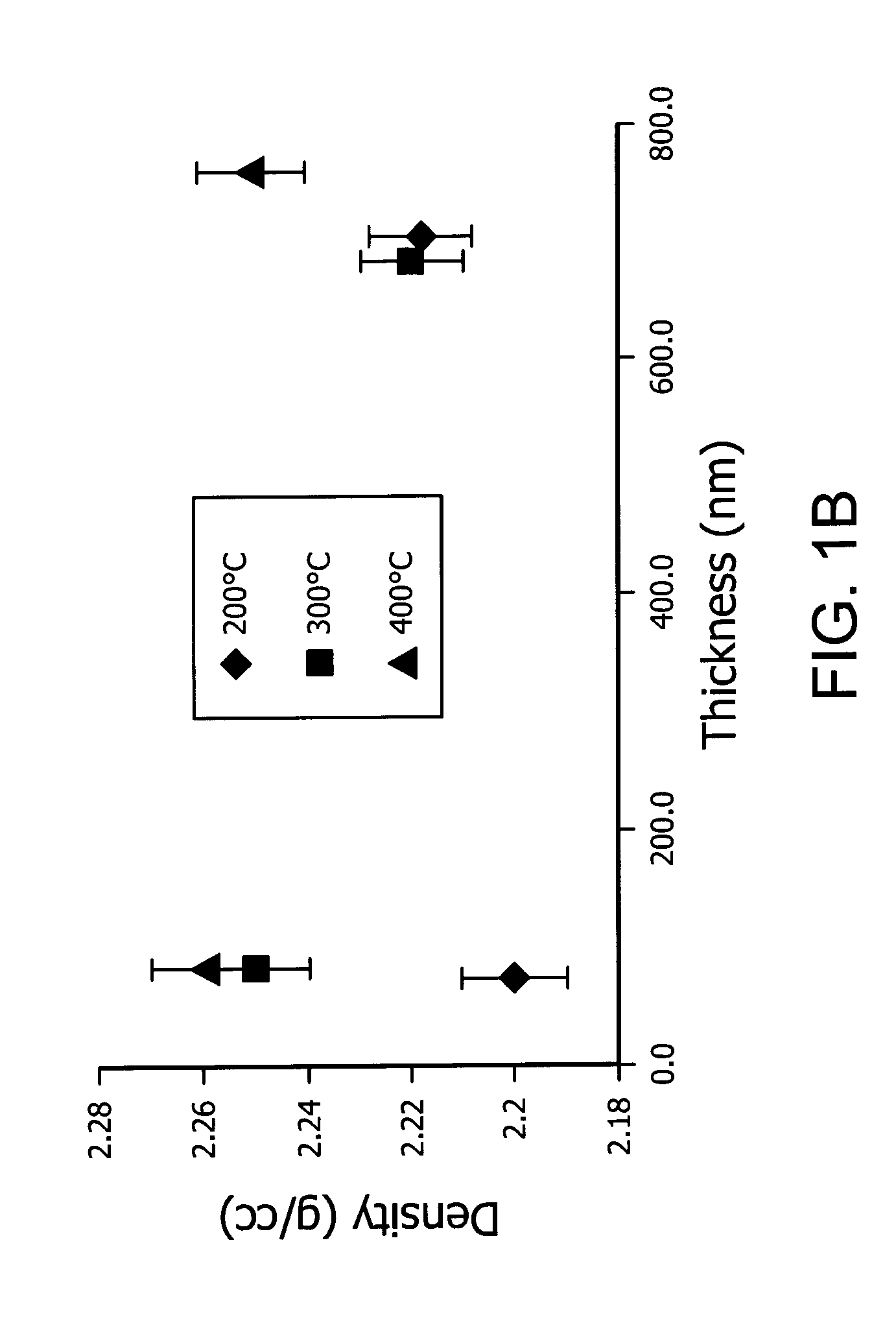

Described herein are low temperature processed high quality silicon containing films. Also disclosed are methods of forming silicon containing films at low temperatures. In one aspect, there are provided silicon-containing film having a thickness of about 2 nm to about 200 nm and a density of about 2.2 g / cm3 or greater wherein the silicon-containing thin film is deposited by a deposition process selected from a group consisting of chemical vapor deposition (CVD), plasma enhanced chemical vapor deposition (PECVD), cyclic chemical vapor deposition (CCVD), plasma enhanced cyclic chemical vapor deposition (PECCVD, atomic layer deposition (ALD), and plasma enhanced atomic layer deposition (PEALD), and the vapor deposition is conducted at one or more temperatures ranging from about 25° C. to about 400° C. using an alkylsilane precursor selected from the group consisting of diethylsilane, triethylsilane, and combinations thereof.

Owner:VERSUM MATERIALS US LLC

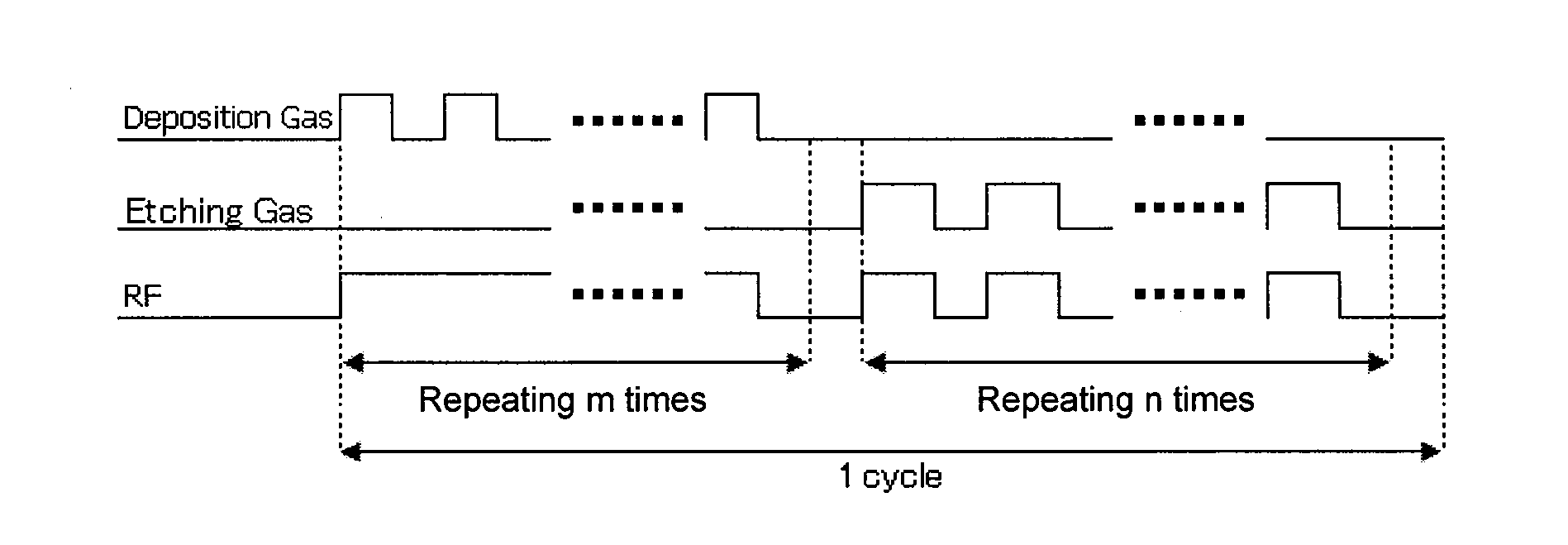

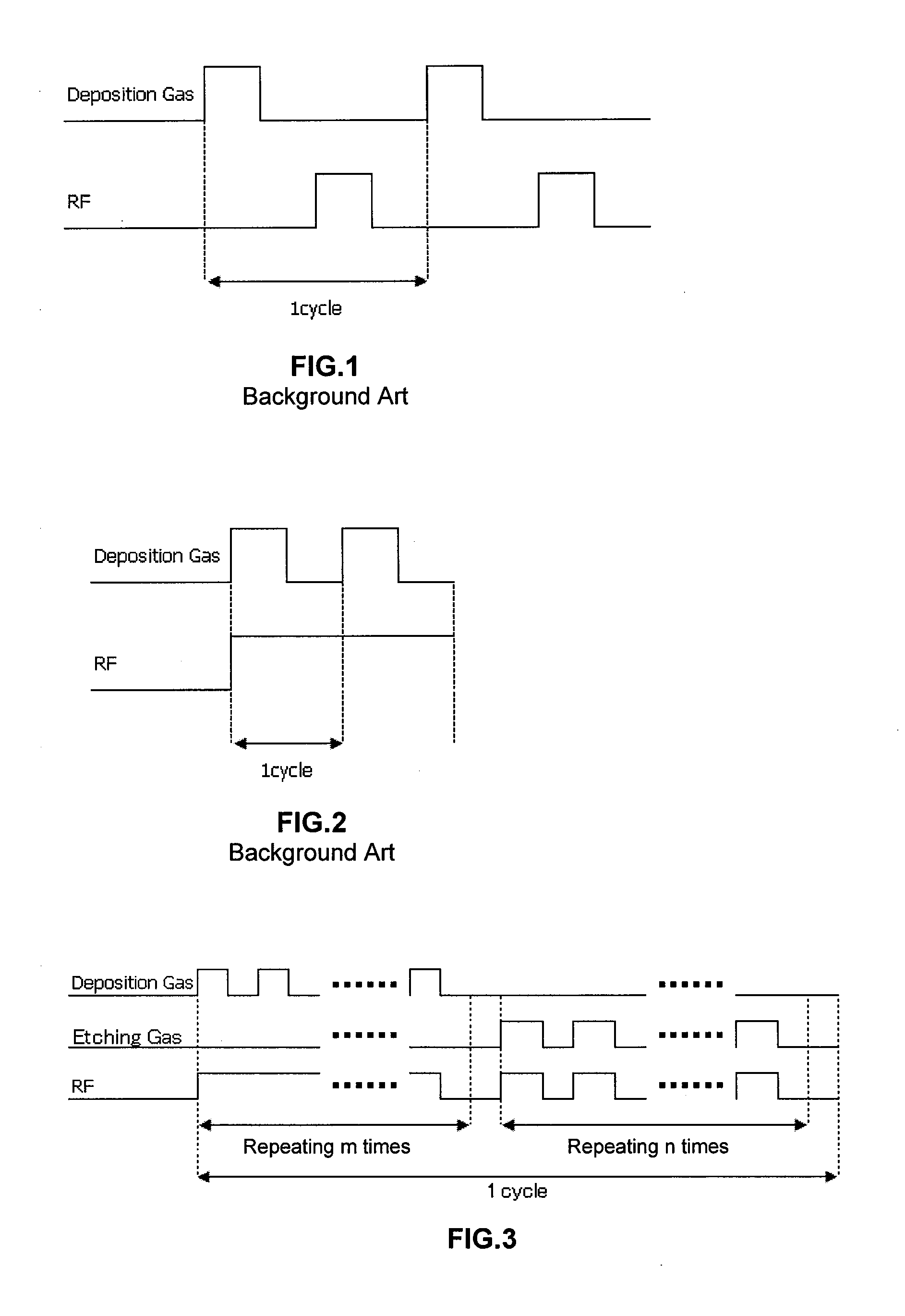

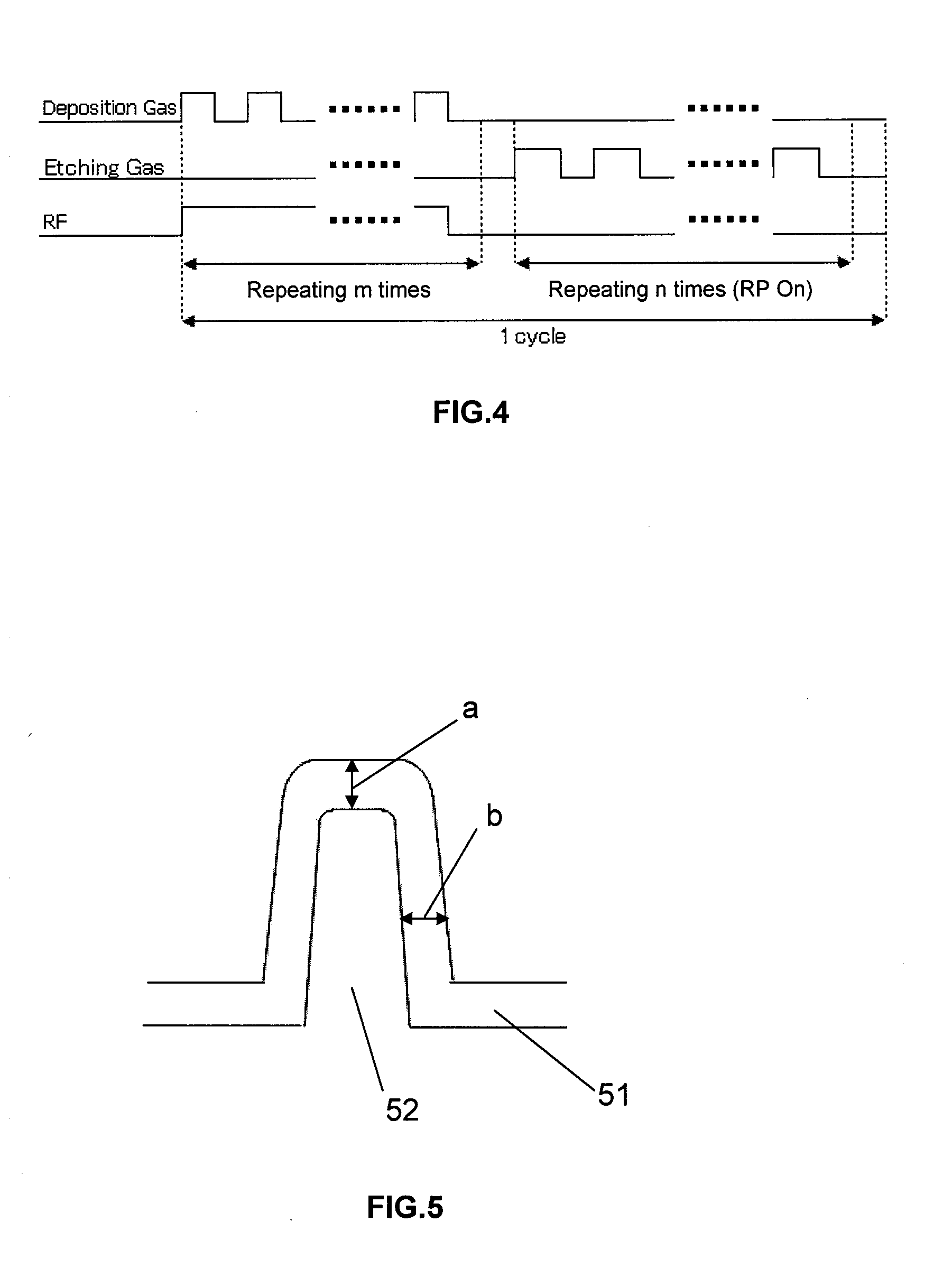

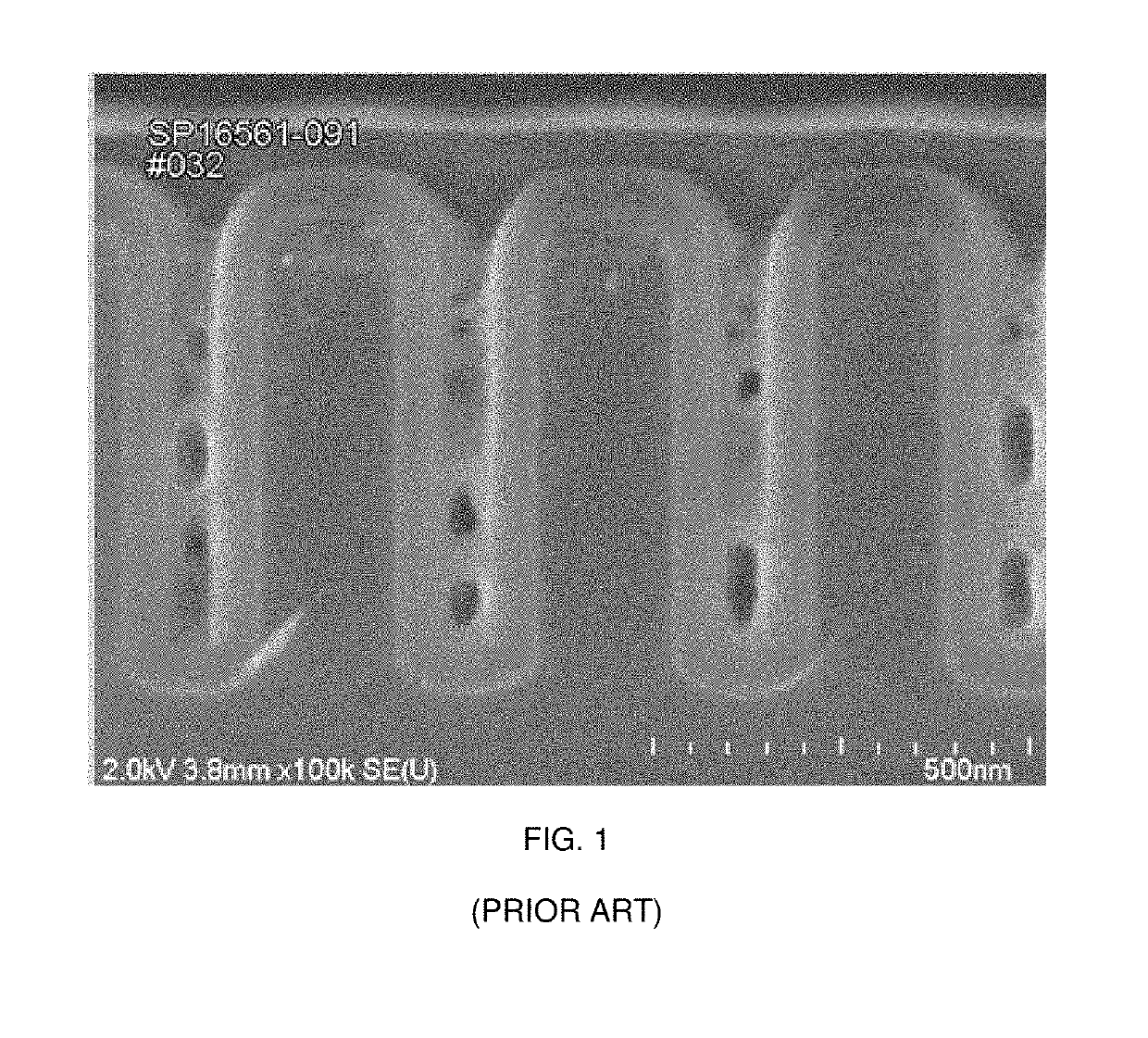

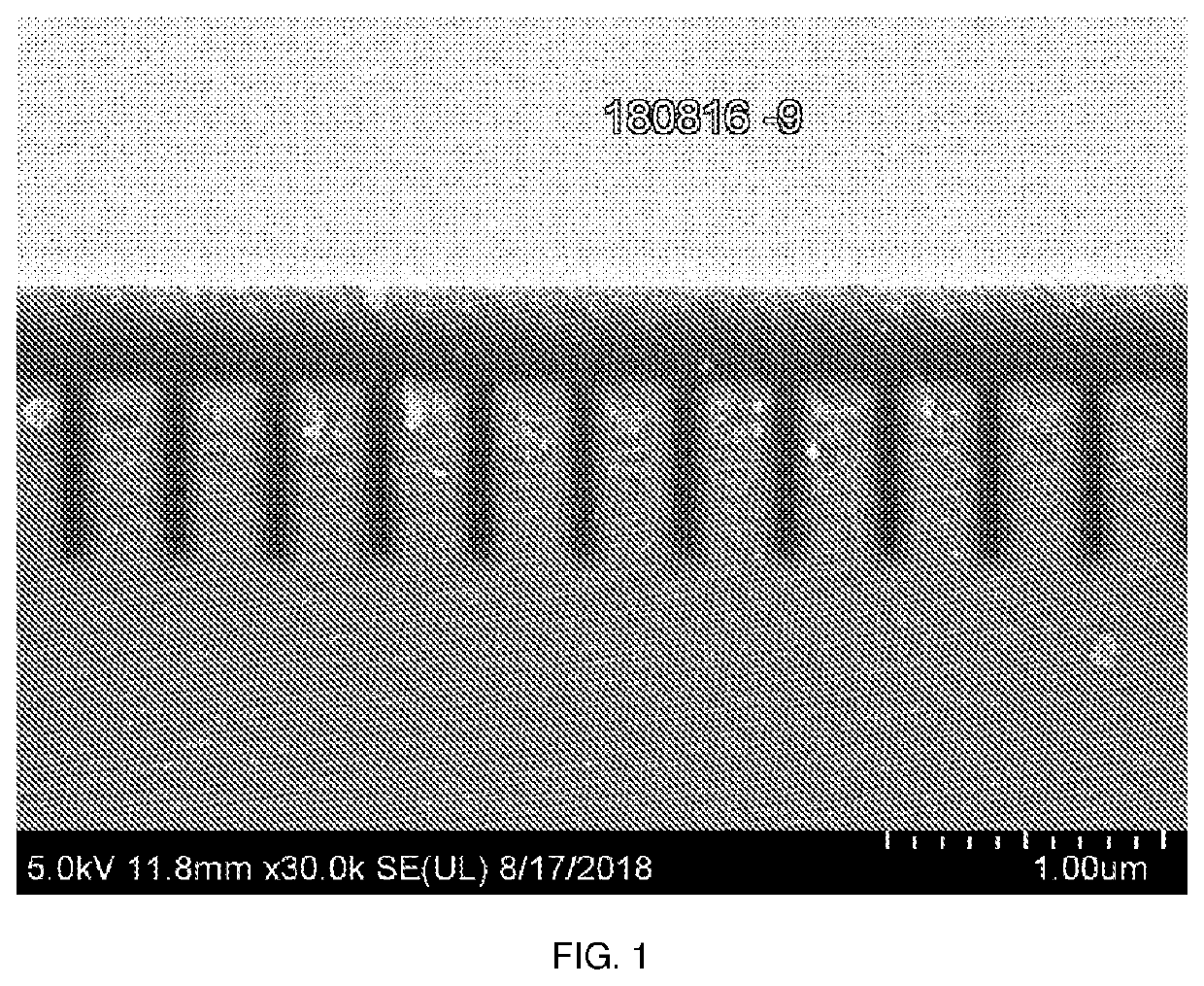

METHOD OF TAILORING CONFORMALITY OF Si-CONTAINING FILM

ActiveUS20120028469A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingThin membraneSilicon thin film

A method of tailoring conformality of a film deposited on a patterned surface includes: (I) depositing a film by PEALD or pulsed PECVD on the patterned surface; (II) etching the film, wherein the etching is conducted in a pulse or pulses, wherein a ratio of an etching rate of the film on a top surface and that of the film on side walls of the patterns is controlled as a function of the etching pulse duration and the number of etching pulses to increase a conformality of the film; and (III) repeating (I) and (II) to satisfy a target film thickness.

Owner:ASM JAPAN

Apparatus, precursors and deposition methods for silicon-containing materials

A method for making a Si-containing material comprises transporting a pyrolyzed Si-precursor to a substrate and polymerizing the pyrolyzed Si-precursor on the substrate to form a Si-containing film. Polymerization of the pyrolyzed Si-precursor may be carried out in the presence of a porogen to thereby form a porogen-containing Si-containing film. The porogen may be removed from the porogen-containing Si-containing film to thereby form a porous Si-containing film. Preferred porous Si-containing films have low dielectric constants and thus are suitable for various low-k applications such as in microelectronics and microelectromechanical systems.

Owner:ASM JAPAN

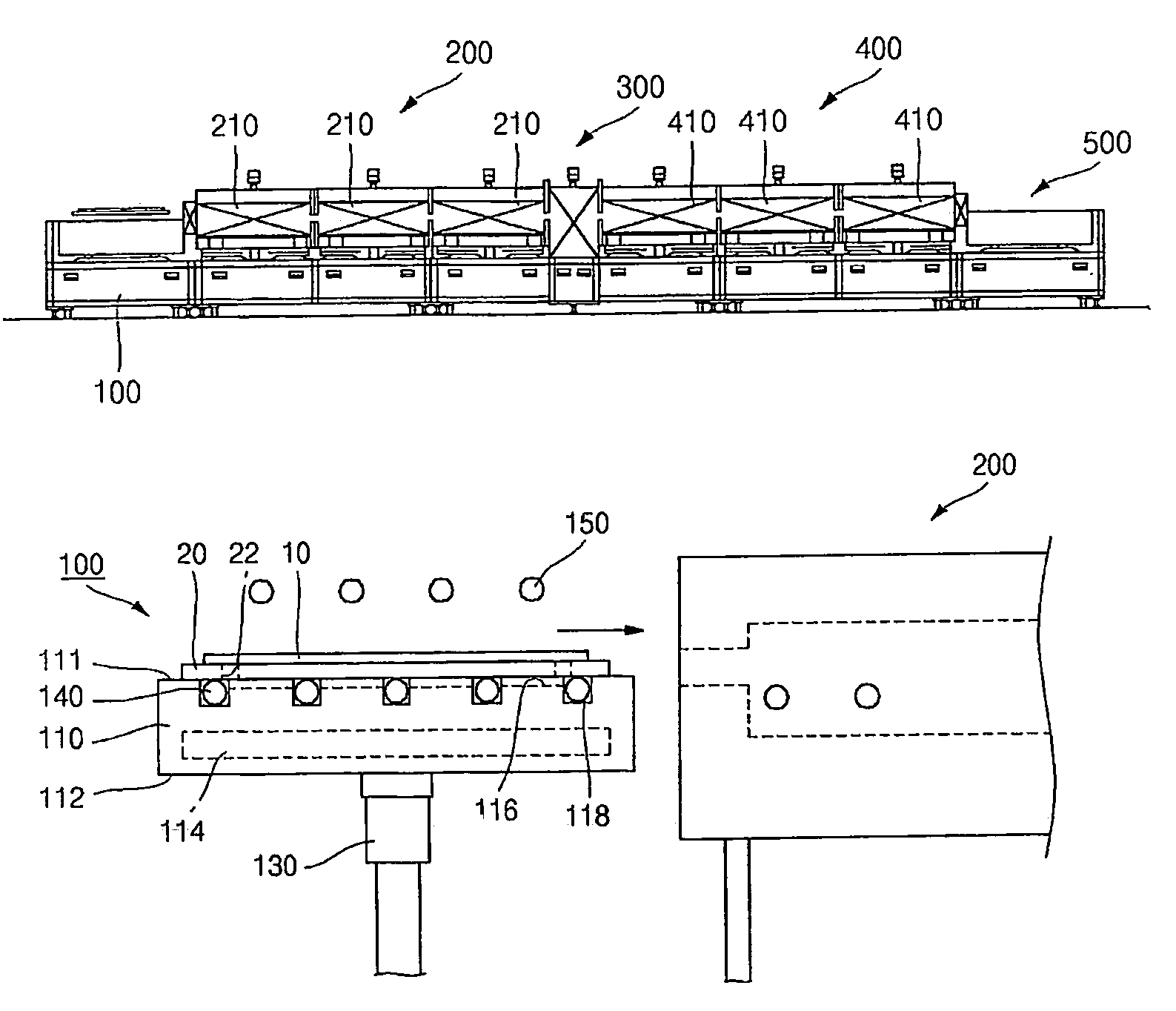

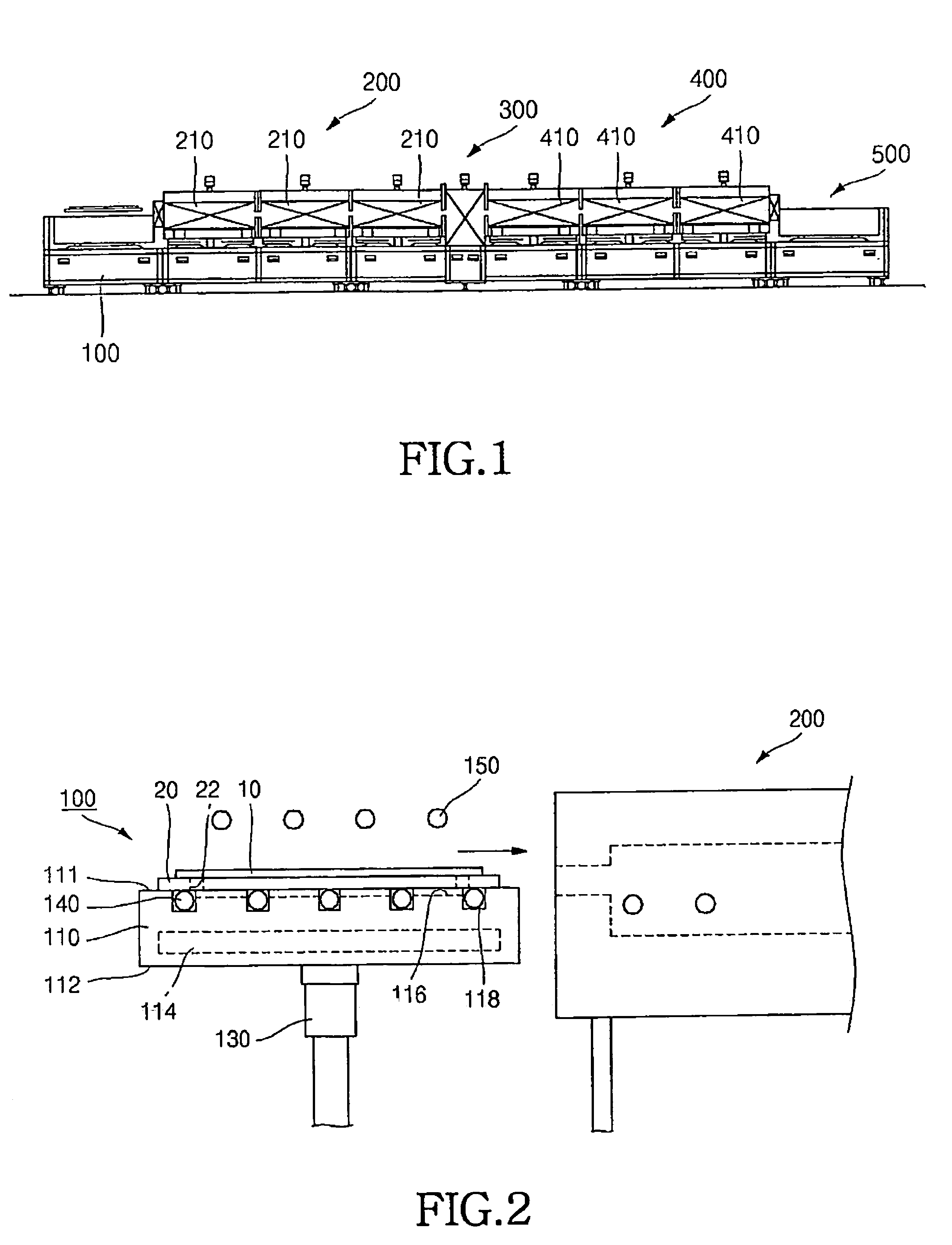

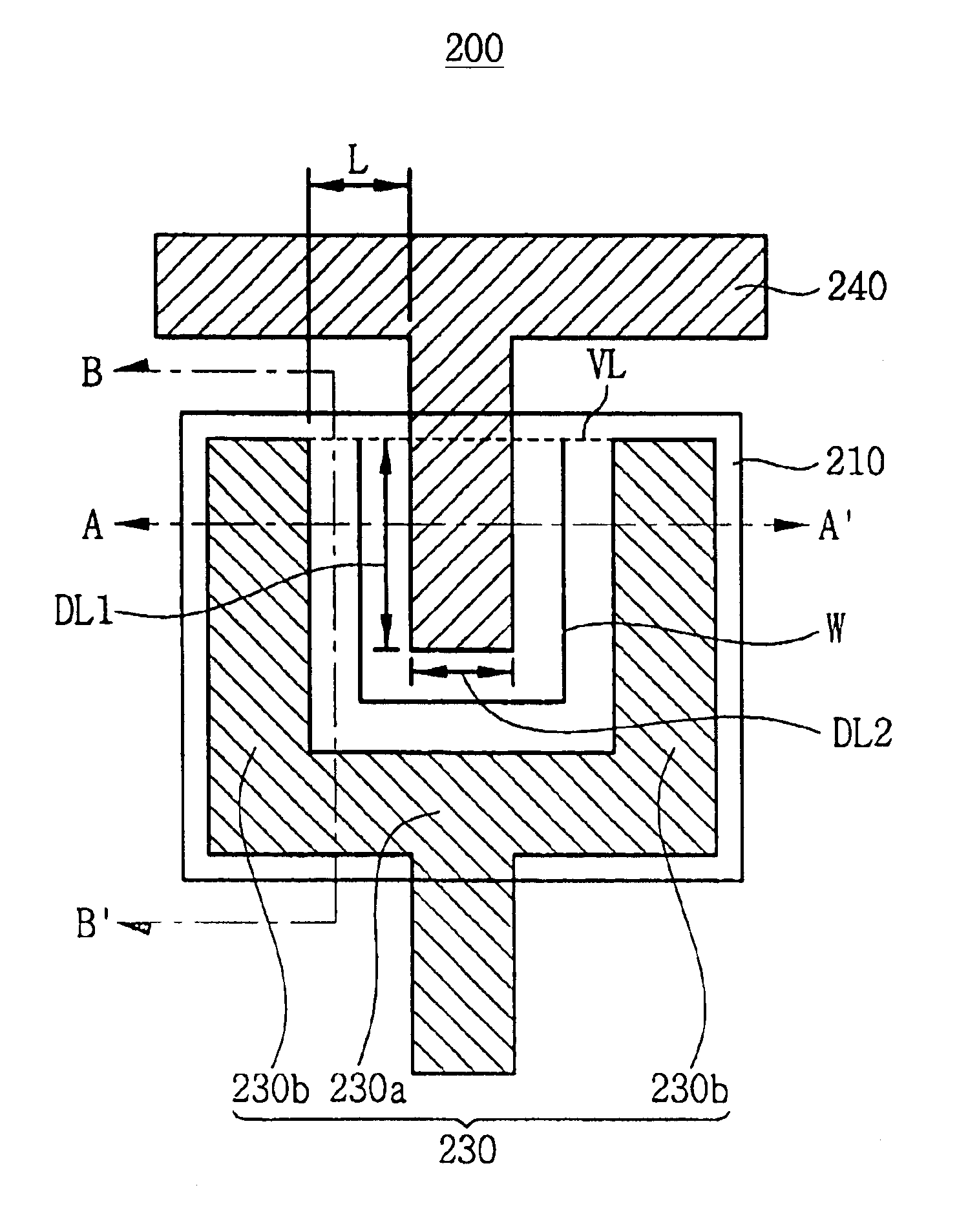

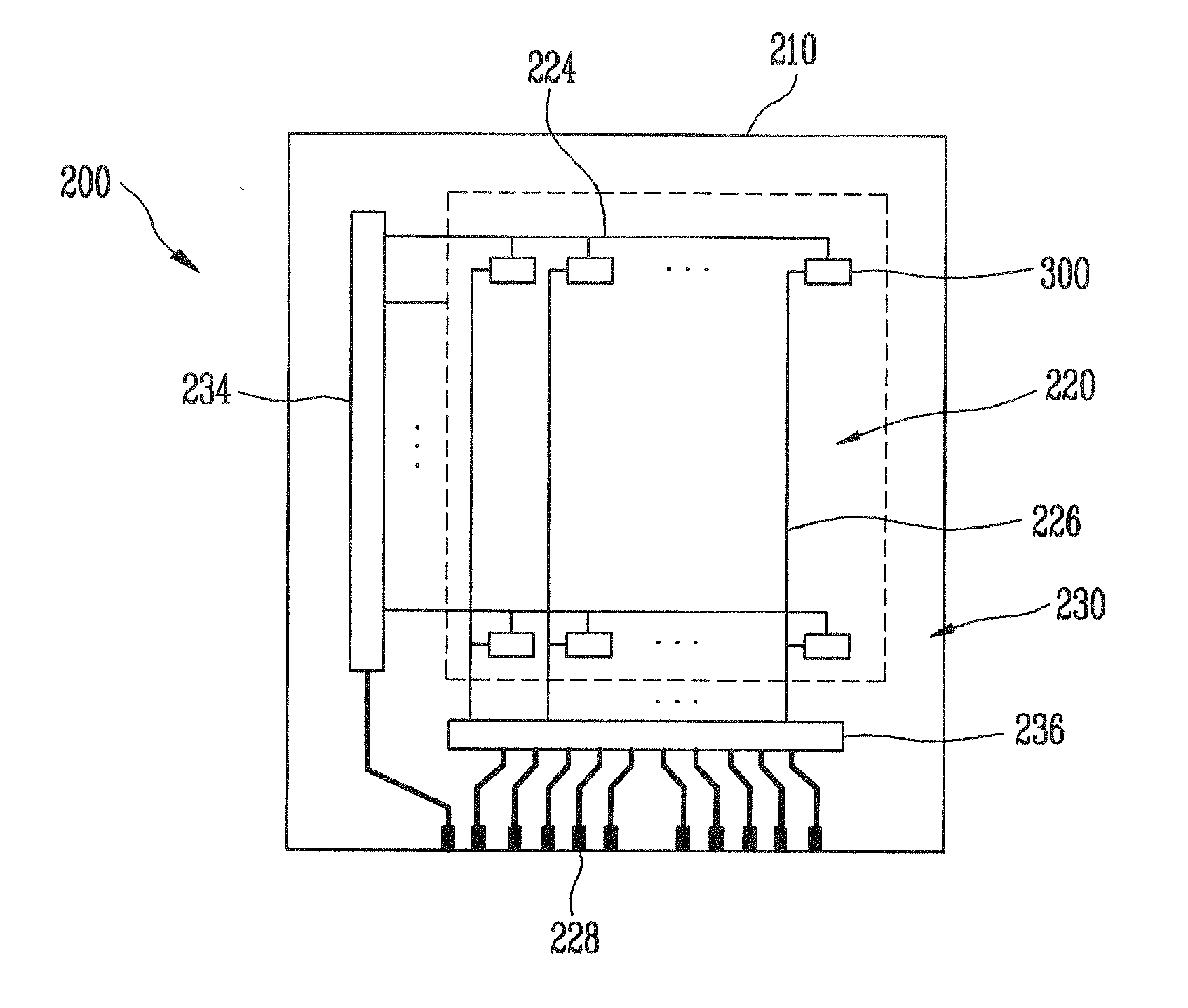

System for heat treatment of semiconductor device

InactiveUS7989736B2Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingElectromotive forceSilicon thin film

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

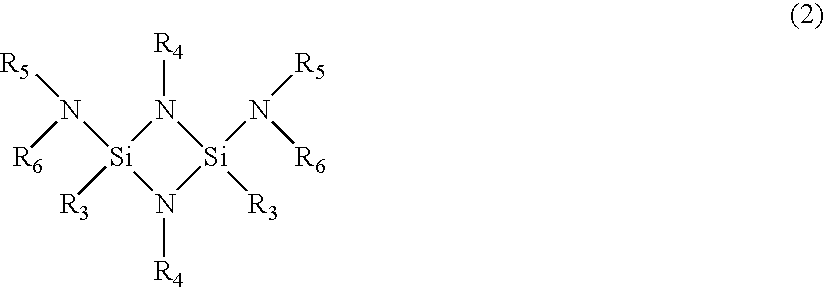

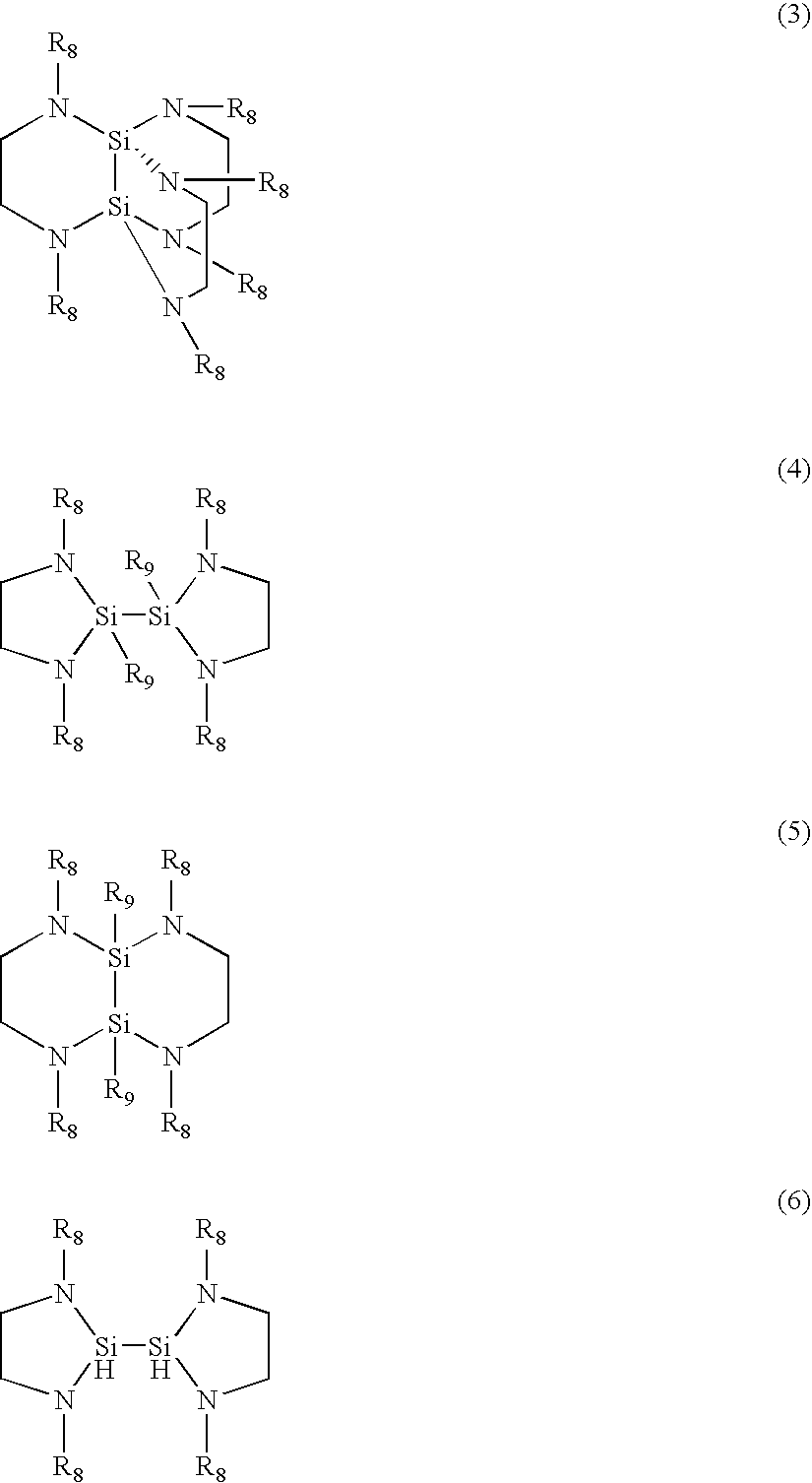

Organoaminosilane precursors and methods for making and using same

Described herein are organoaminosilane precursors which can be used to deposit silicon containing films which contain silicon and methods for making these precursors. Also disclosed herein are deposition methods for making silicon-containing films or silicon containing films using the organoaminosilane precursors described herein. Also disclosed herein are the vessels that comprise the organoaminosilane precursors or a composition thereof that can be used, for example, to deliver the precursor to a reactor in order to deposit a silicon-containing film.

Owner:VERSUM MATERIALS US LLC

Precursors and flowable CVD methods for making low-K films to fill surface features

A method for depositing a silicon-containing film, the method comprising: placing a substrate comprising at least one surface feature into a flowable CVD reactor which is at a temperature of from about −20° C. to about 400° C.; introducing into the reactor at least one silicon-containing compound having at least one acetoxy group to at least partially react the at least one silicon-containing compound to form a flowable liquid oligomer wherein the flowable liquid oligomer forms a silicon oxide coating on the substrate and at least partially fills at least a portion of the at least one surface feature. Once cured, the silicon oxide coating has a low k and excellent mechanical properties.

Owner:VERSUM MATERIALS US LLC

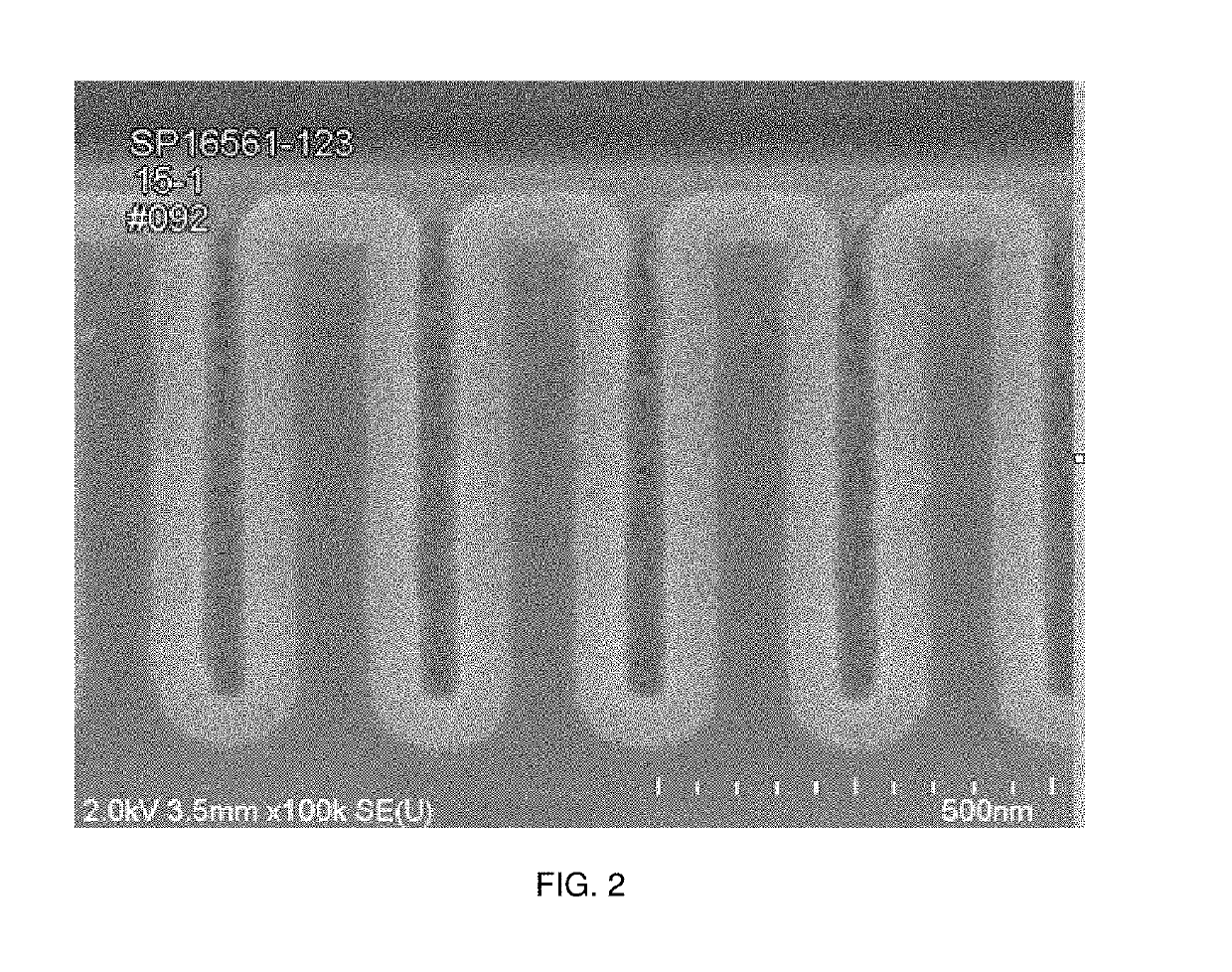

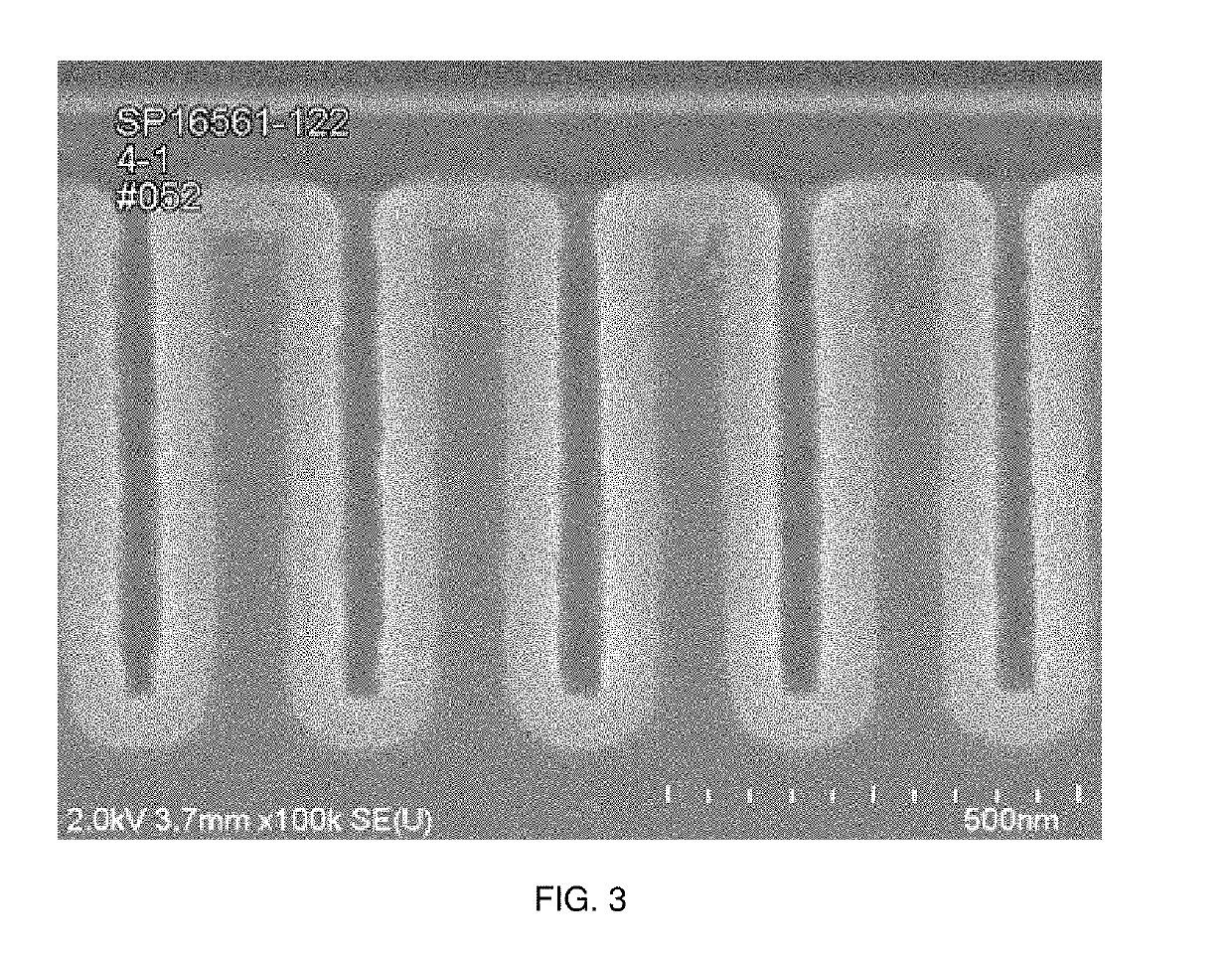

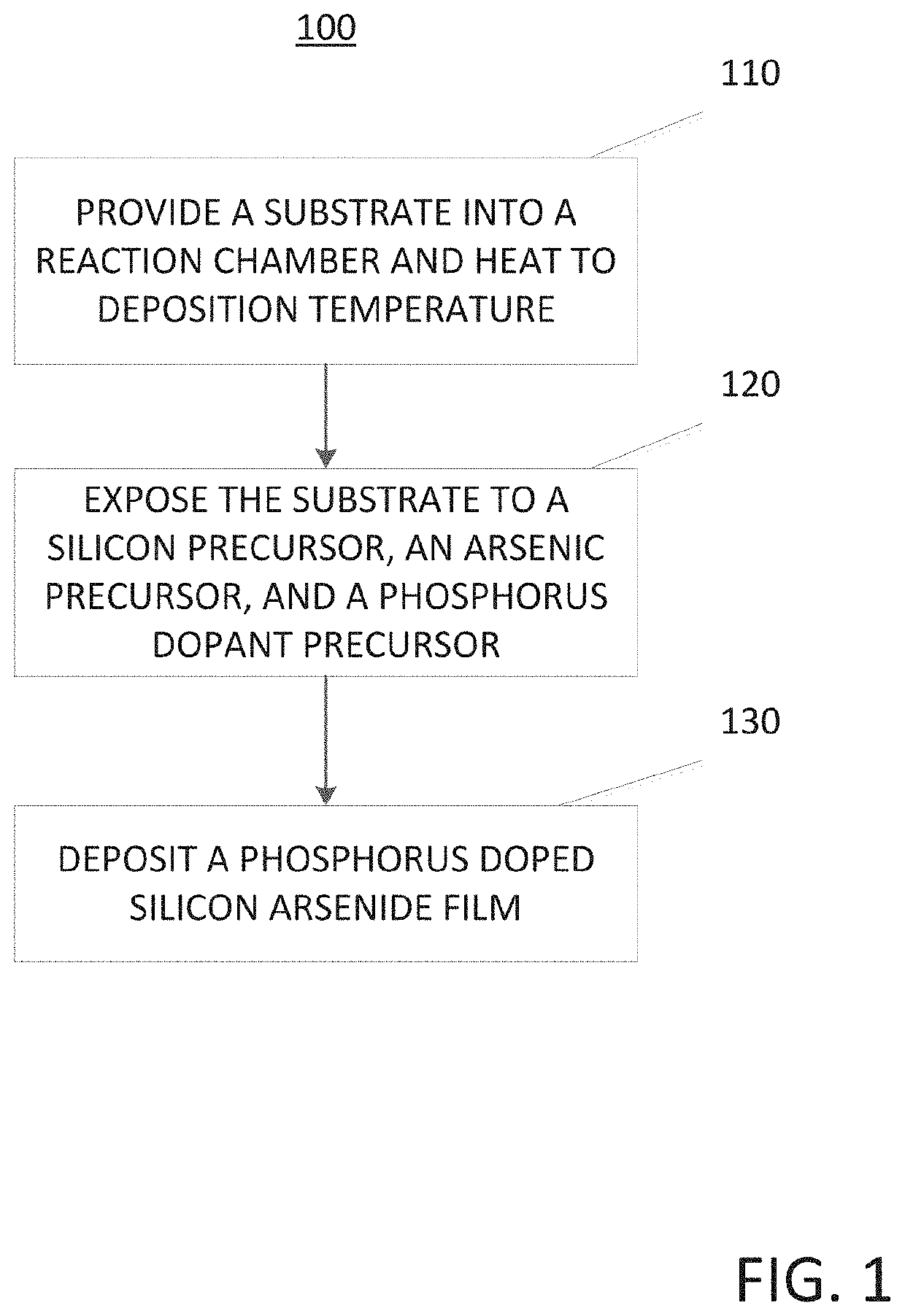

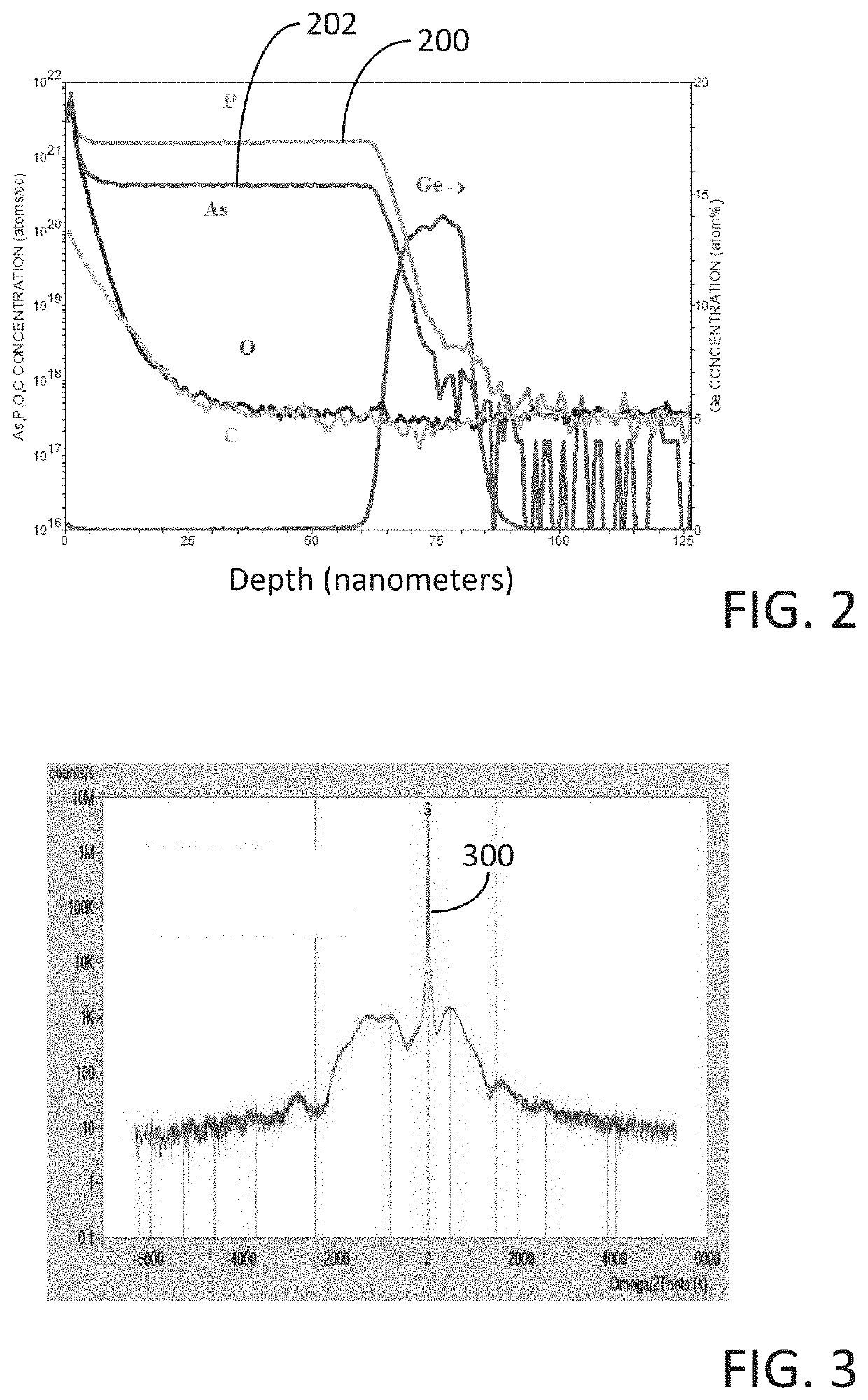

Method for depositing a phosphorus doped silicon arsenide film and related semiconductor device structures

ActiveUS20200395444A1Inhibited DiffusionTransistorPolycrystalline material growthDevice materialSilicon thin film

A method for depositing a phosphorus doped silicon arsenide film is disclosed. The method may include, providing a substrate within a reaction chamber, heating the substrate to a deposition temperature, exposing the substrate to a silicon precursor, an arsenic precursor, and a phosphorus dopant precursor, and depositing the phosphorus doped silicon arsenide film over a surface of the substrate. Semiconductor device structures including a phosphorus doped silicon arsenide film deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

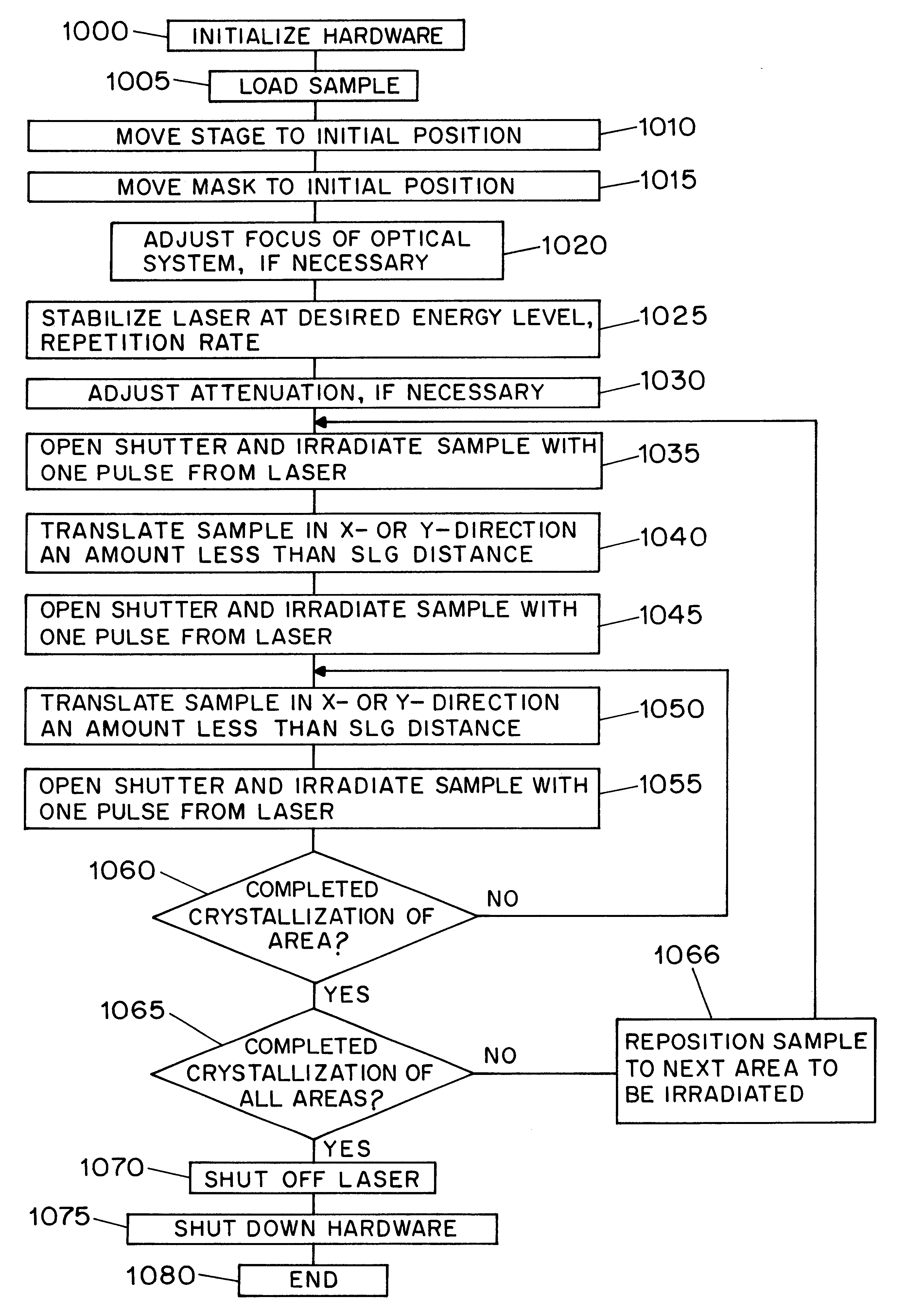

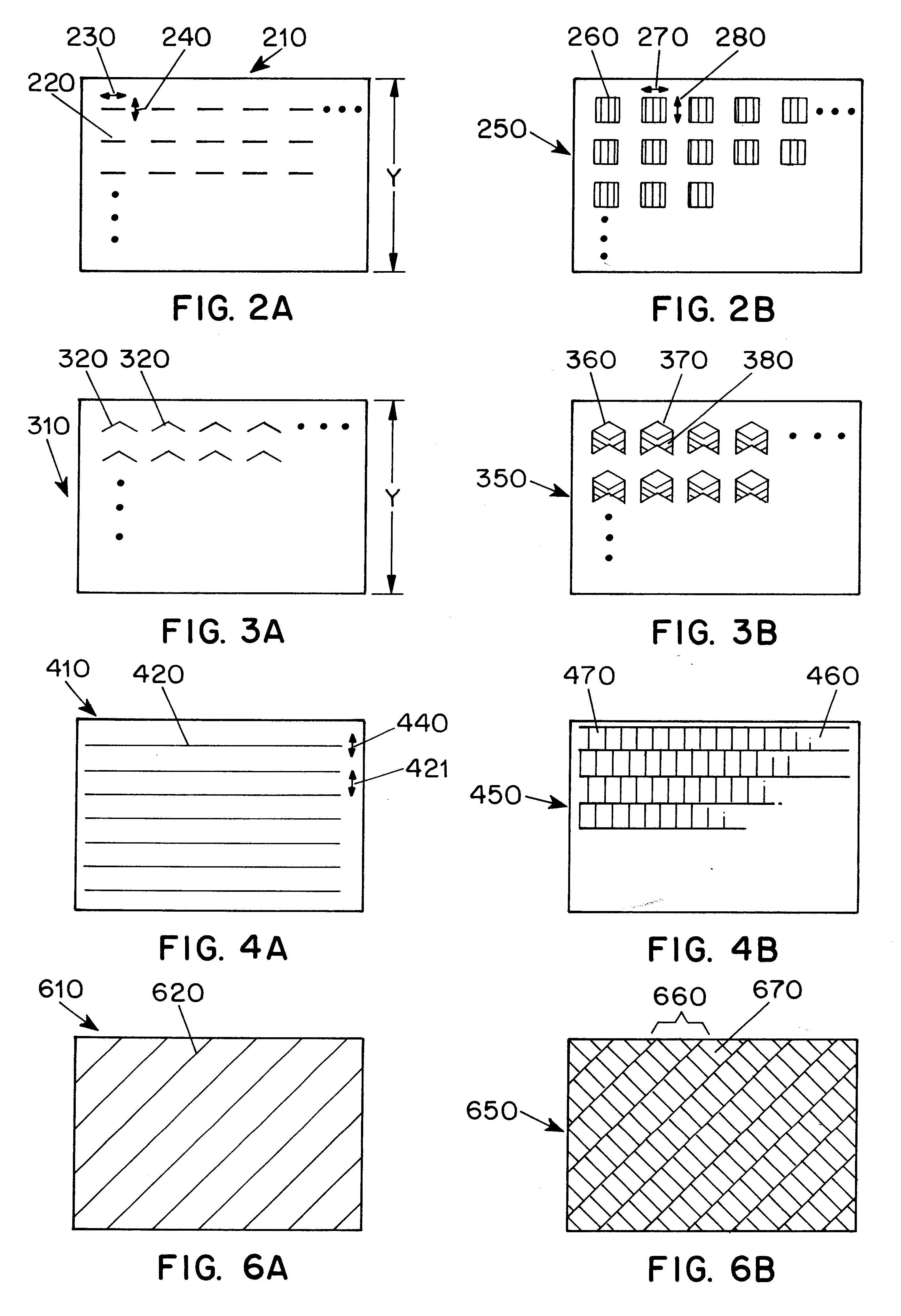

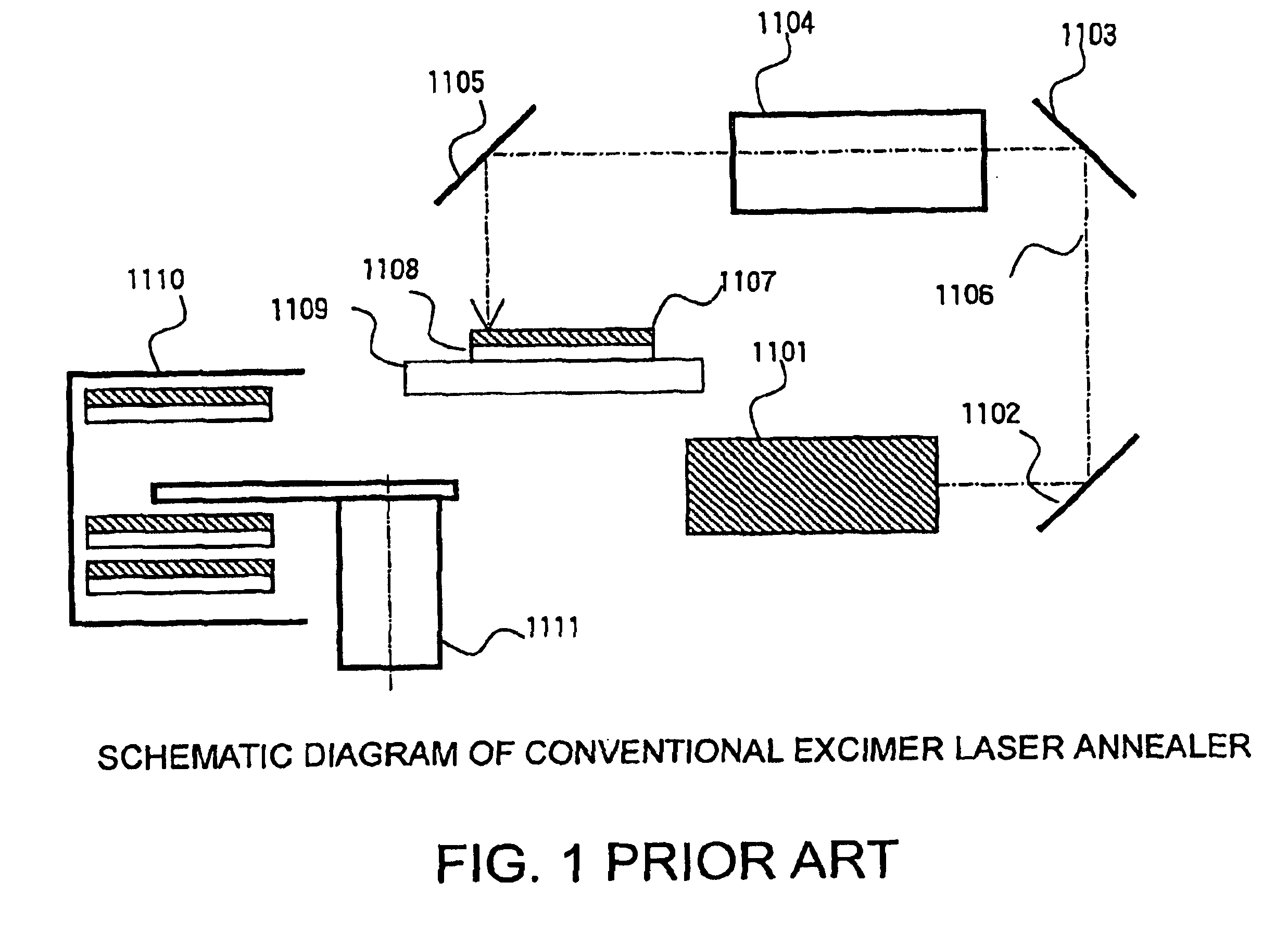

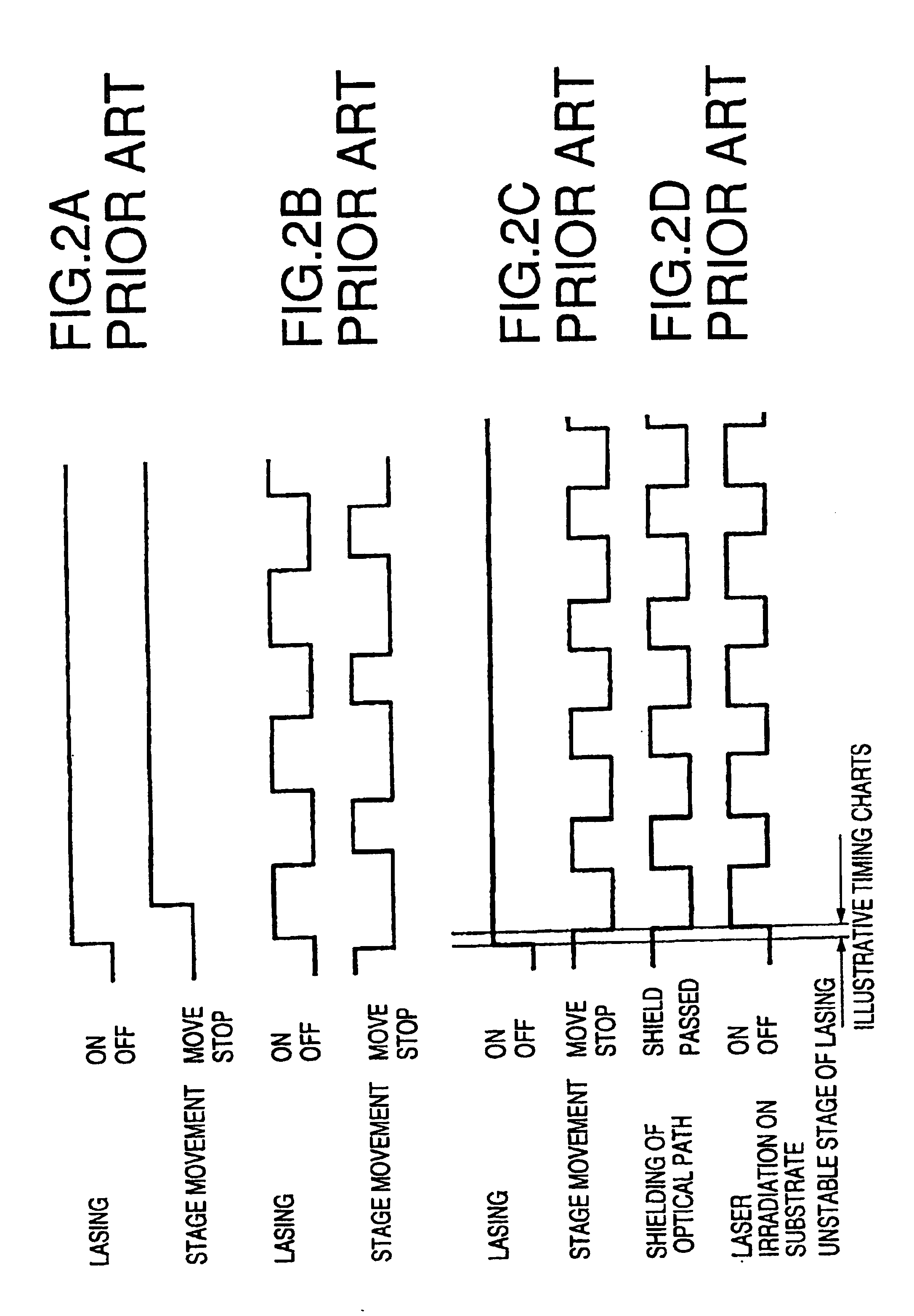

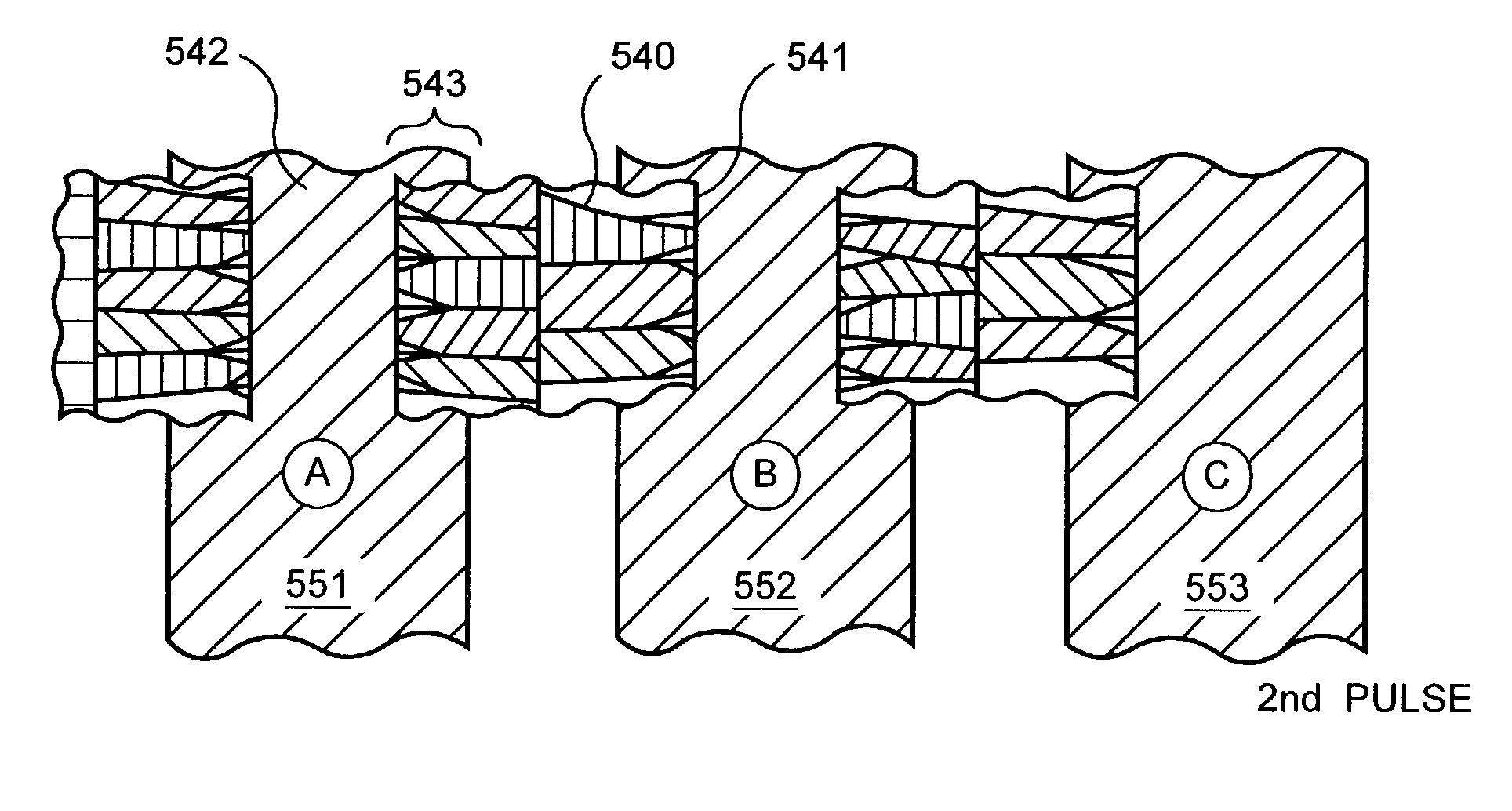

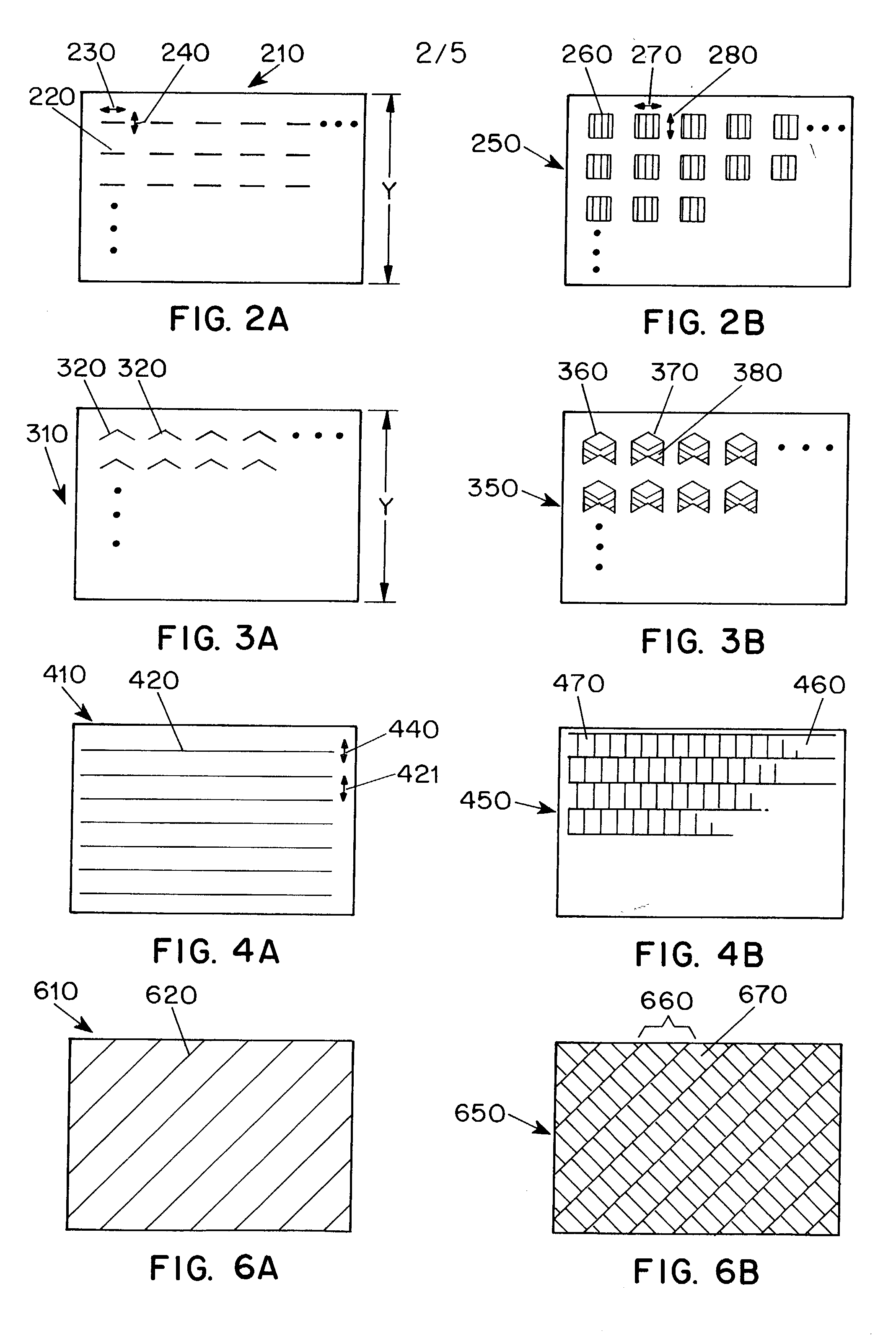

Methods for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Methods for processing an amorphous silicon thin film sample into a polycrystalline silicon thin film are disclosed. In one preferred arrangement, a method includes the steps of generating a sequence of excimer laser pulses, controllably modulating each excimer laser pulse in the sequence to a predetermined fluence, homoginizing each modulated laser pulse in the sequence in a predetermined plane, masking portions of each homogenized fluence controlled laser pulse in the sequence with a two dimensional pattern of slits to generate a sequence of fluence controlled pulses of line patterned beamlets, each slit in the pattern of slits being sufficiently narrow to prevent inducement of significant nucleation in region of a silicon thin film sample irradiated by a beam let corresponding to the slit, irradiating an amorphous silicon thin film sample with the sequence of fluence controlled slit patterned beamlets to effect melting of portions thereof corresponding to each fluence controlled patterned beamlet pulse in the sequence of pulses of patterned beamlets, and controllably sequentially translating a relative position of the sample with respect to each of the fluence controlled pulse of slit patterned beamlets to thereby process the amorphous silicon thin film sample into a single or polycrystalline silicon thin film.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

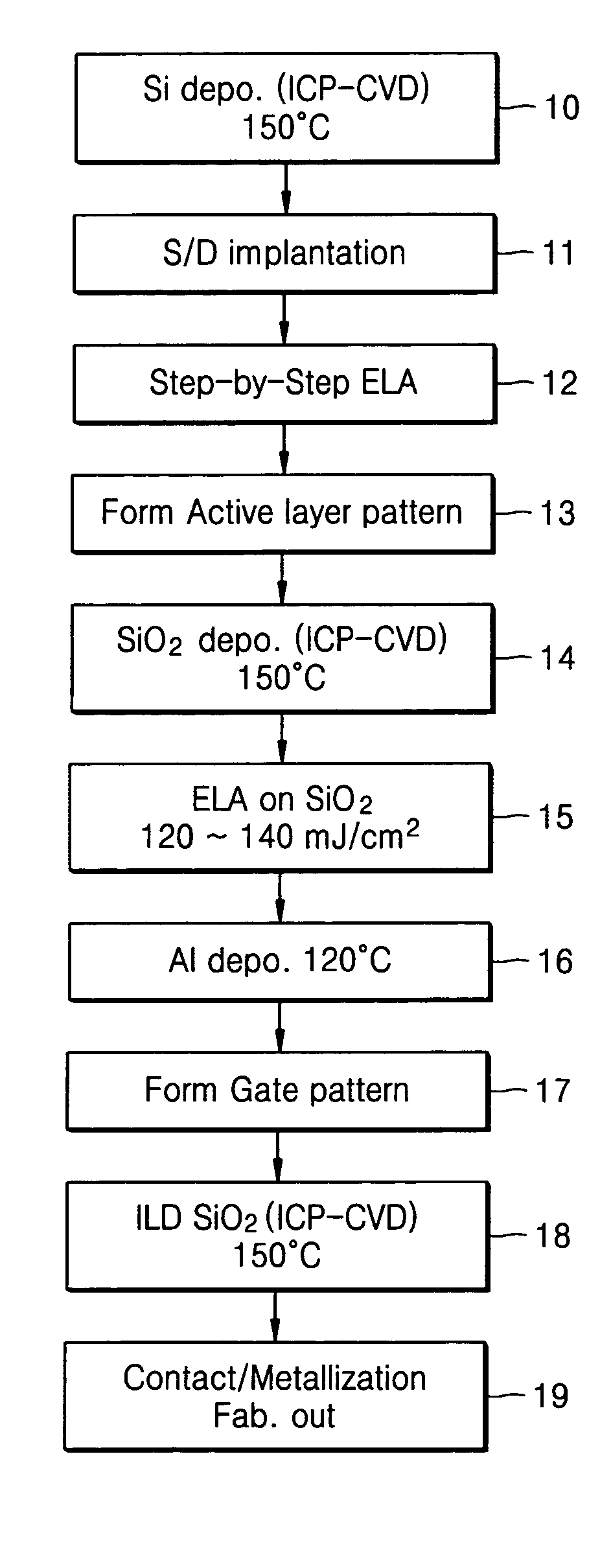

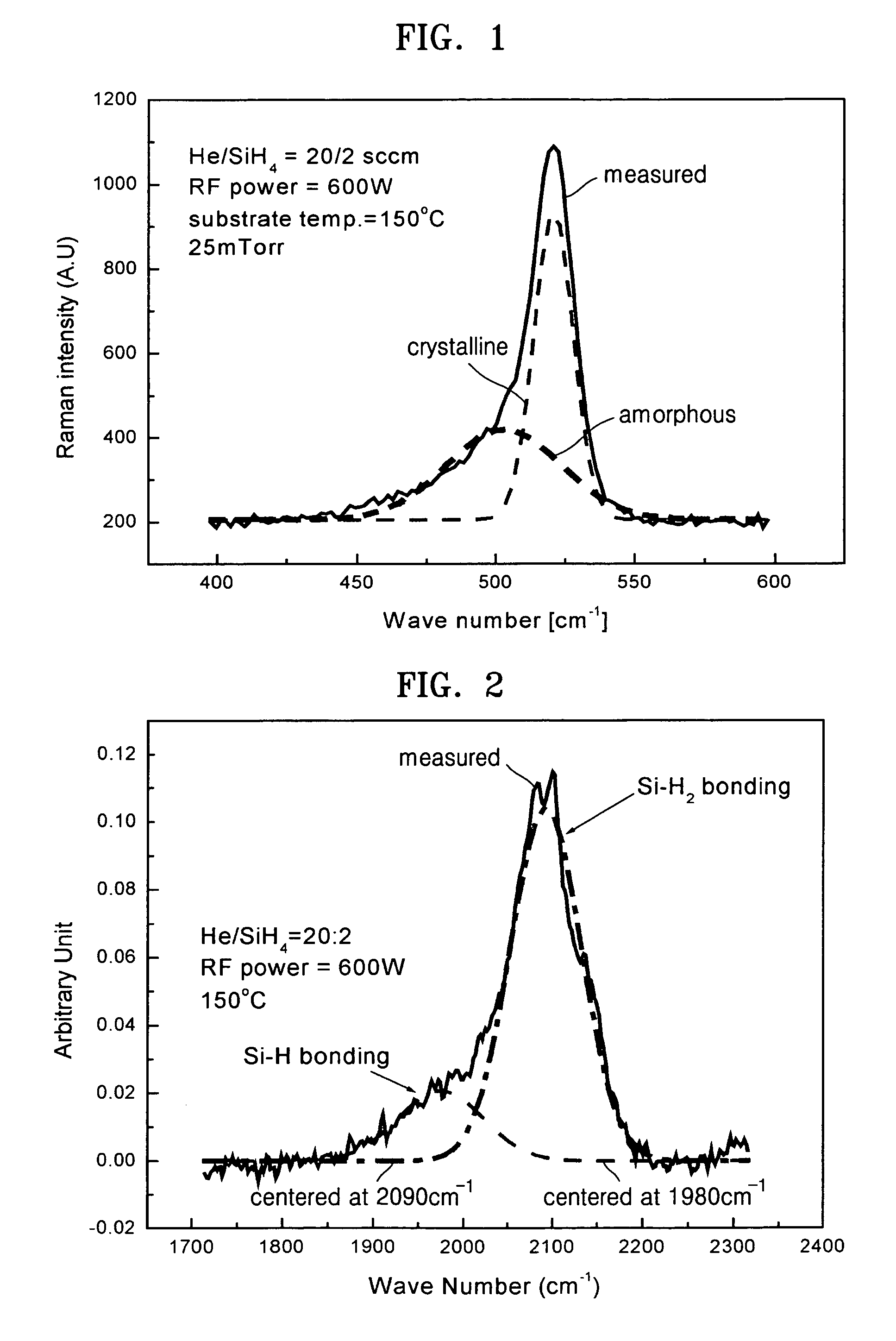

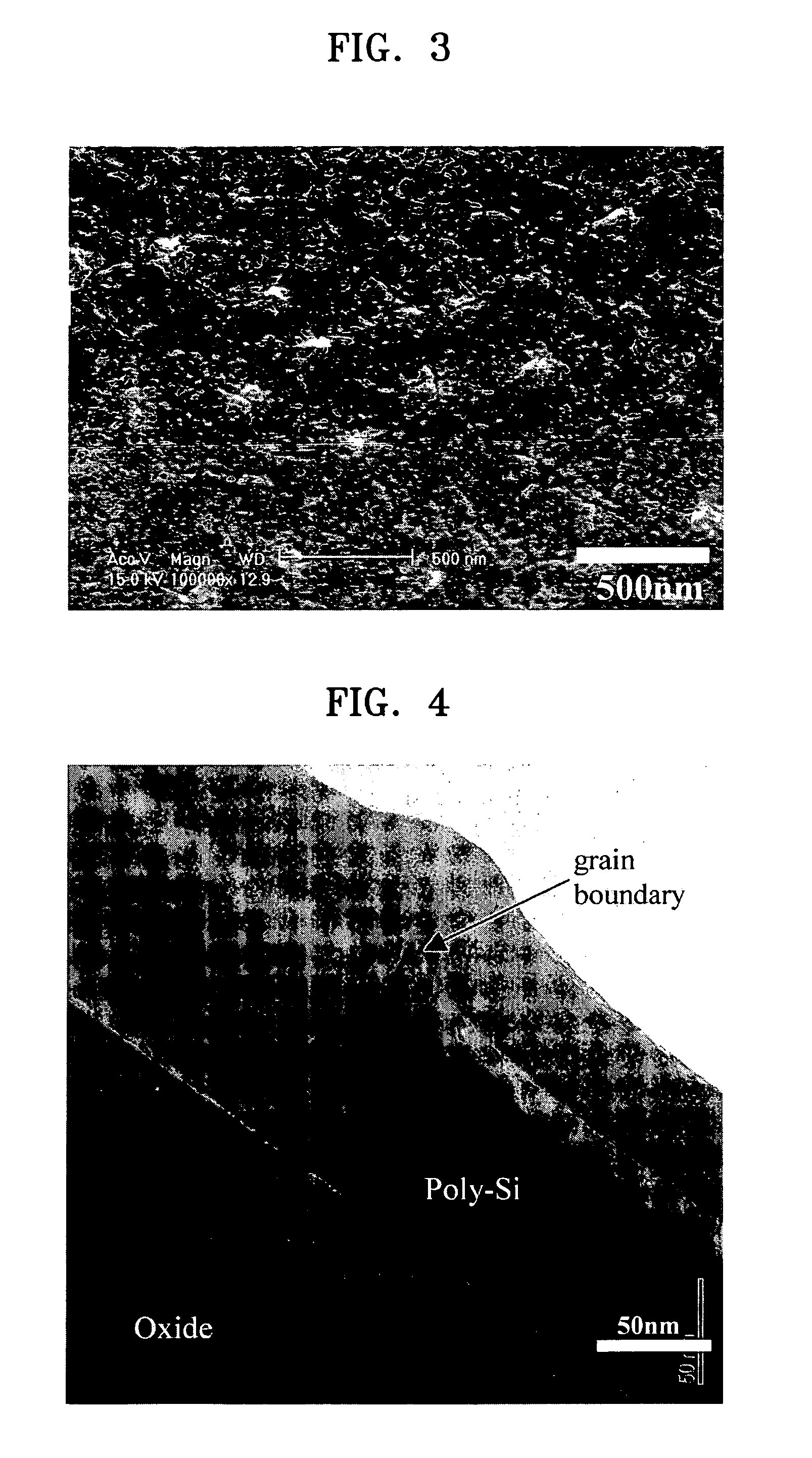

Method of fabricating poly-crystalline silicon thin film and method of fabricating transistor using the same

InactiveUS7563659B2Refined grain sizeHigh energyTransistorSemiconductor/solid-state device manufacturingInductively coupled plasmaSilicon thin film

A method of fabricating a poly-Si thin film and a method of fabricating a poly-Si TFT using the same are provided. The poly-Si thin film is formed at a low temperature using inductively coupled plasma chemical vapor deposition (ICP-CVD). After the ICP-CVD, excimer laser annealing (ELA) is performed while increasing energy by predetermined steps. A poly-Si active layer and a SiO2 gate insulating layer are deposited at a temperature of about 150° C. using ICP-CVD. The poly-Si has a large grain size of about 3000 Å or more. An interface trap density of the SiO2 can be as high as 1011 / cm2. A transistor having good electrical characteristics can be fabricated at a low temperature and thus can be formed on a heat tolerant plastic substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

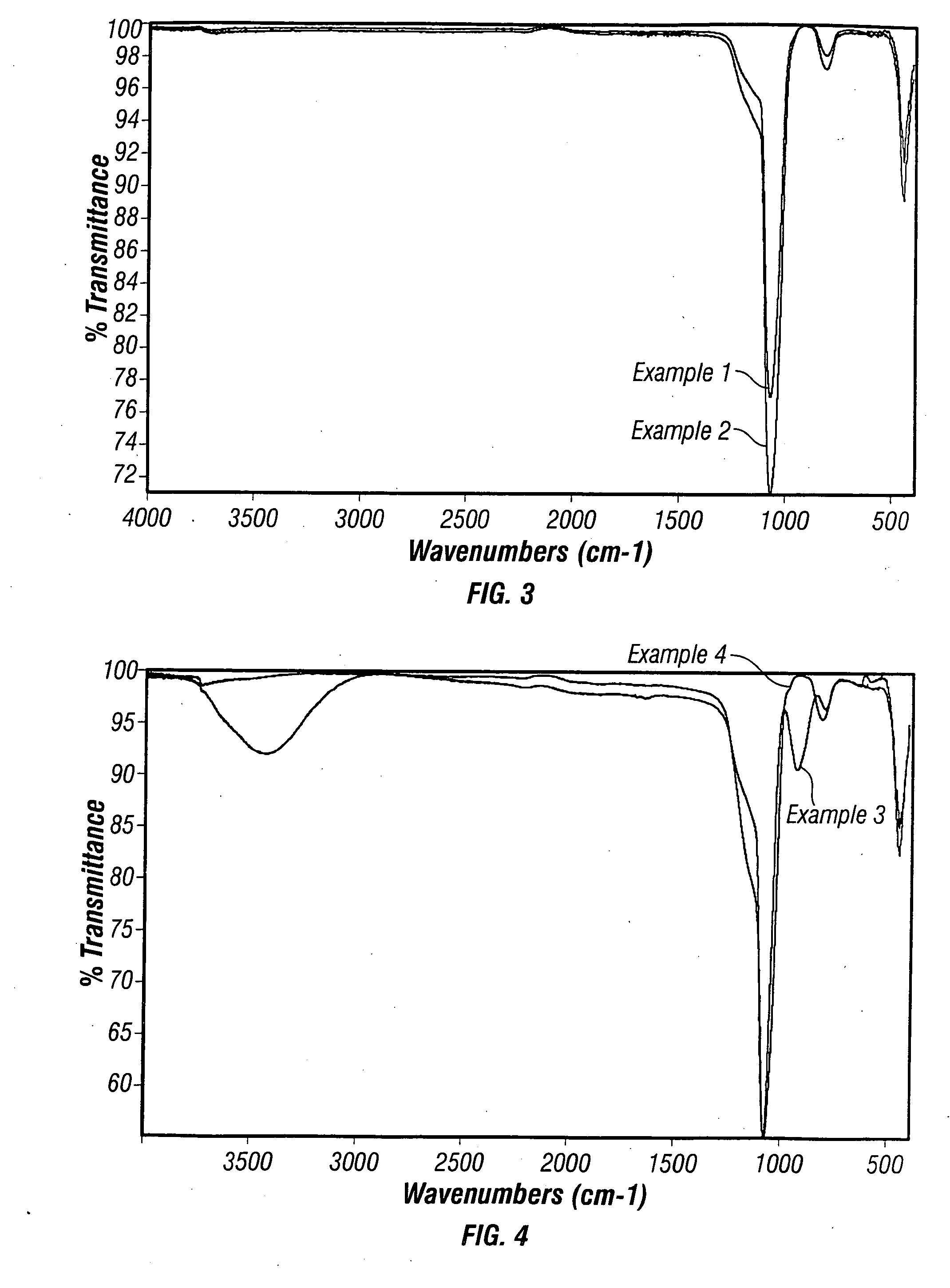

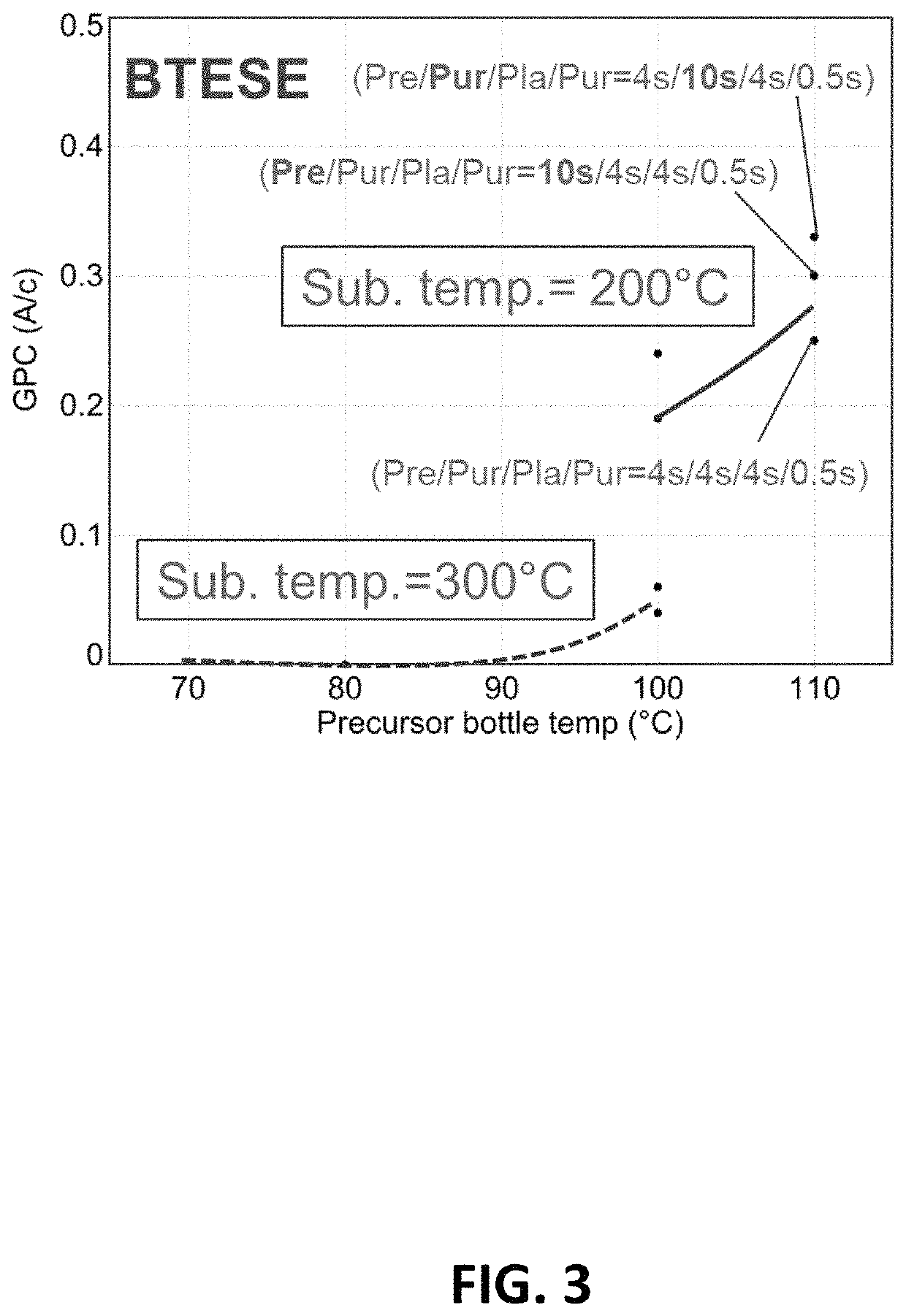

Formation of SiOC thin films

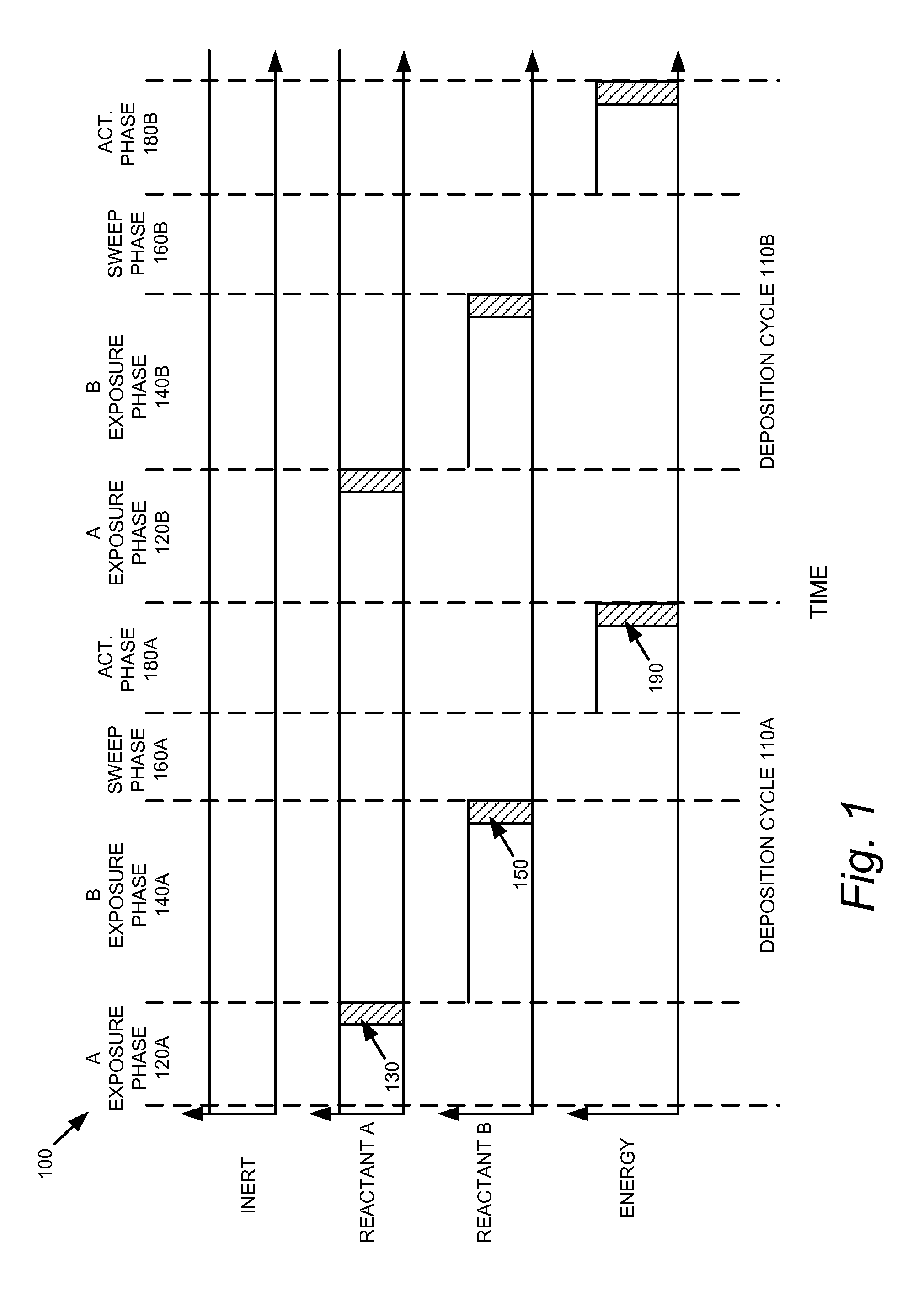

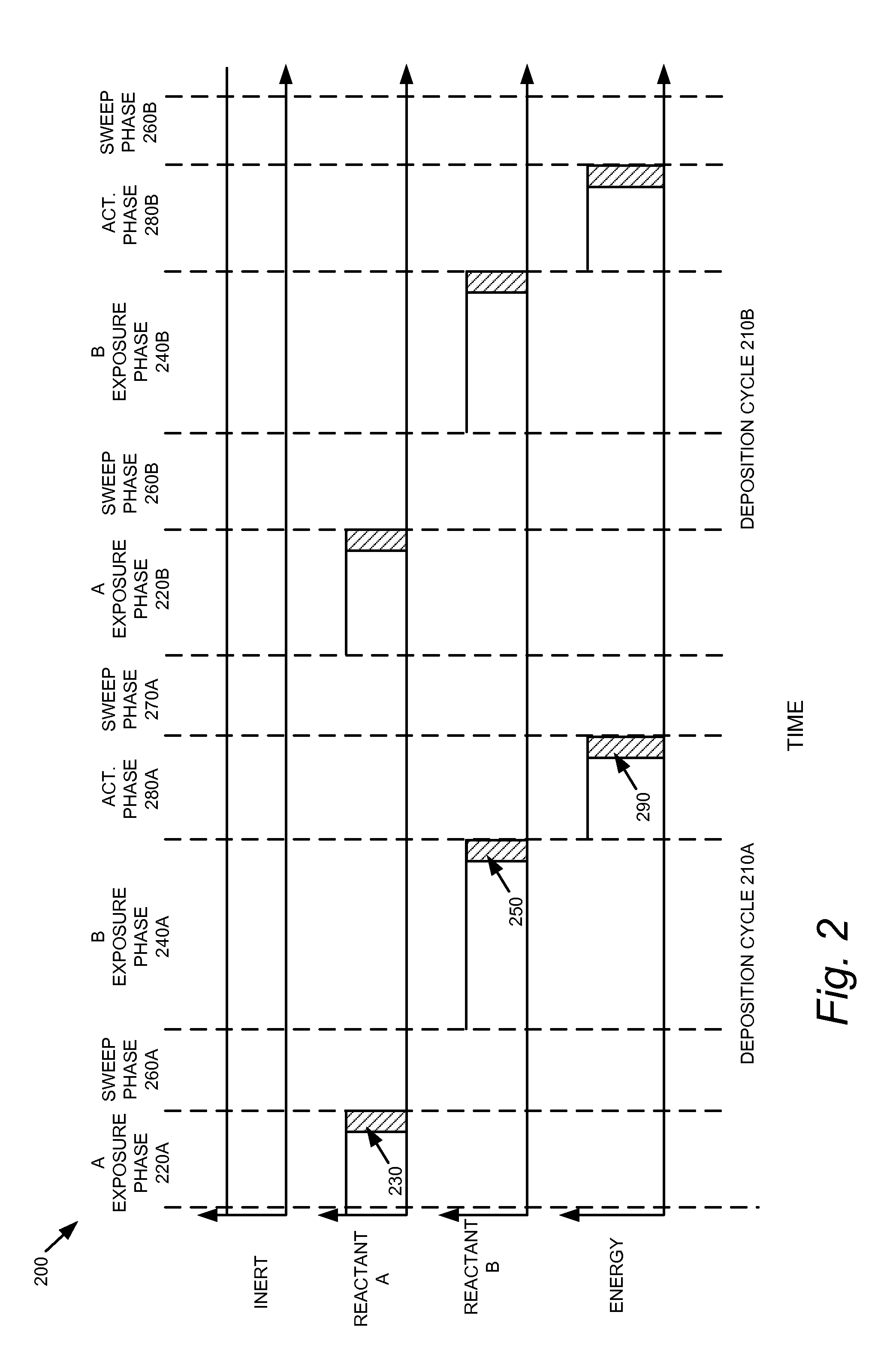

ActiveUS10600637B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicon oxideSilicon thin film

Methods for depositing silicon oxycarbide (SiOC) thin films on a substrate in a reaction space are provided. The methods can include at least one plasma enhanced atomic layer deposition (PEALD) cycle including alternately and sequentially contacting the substrate with a silicon precursor that does not comprise nitrogen and a second reactant that does not include oxygen. In some embodiments the methods allow for the deposition of SiOC films having improved acid-based wet etch resistance.

Owner:ASM IP HLDG BV

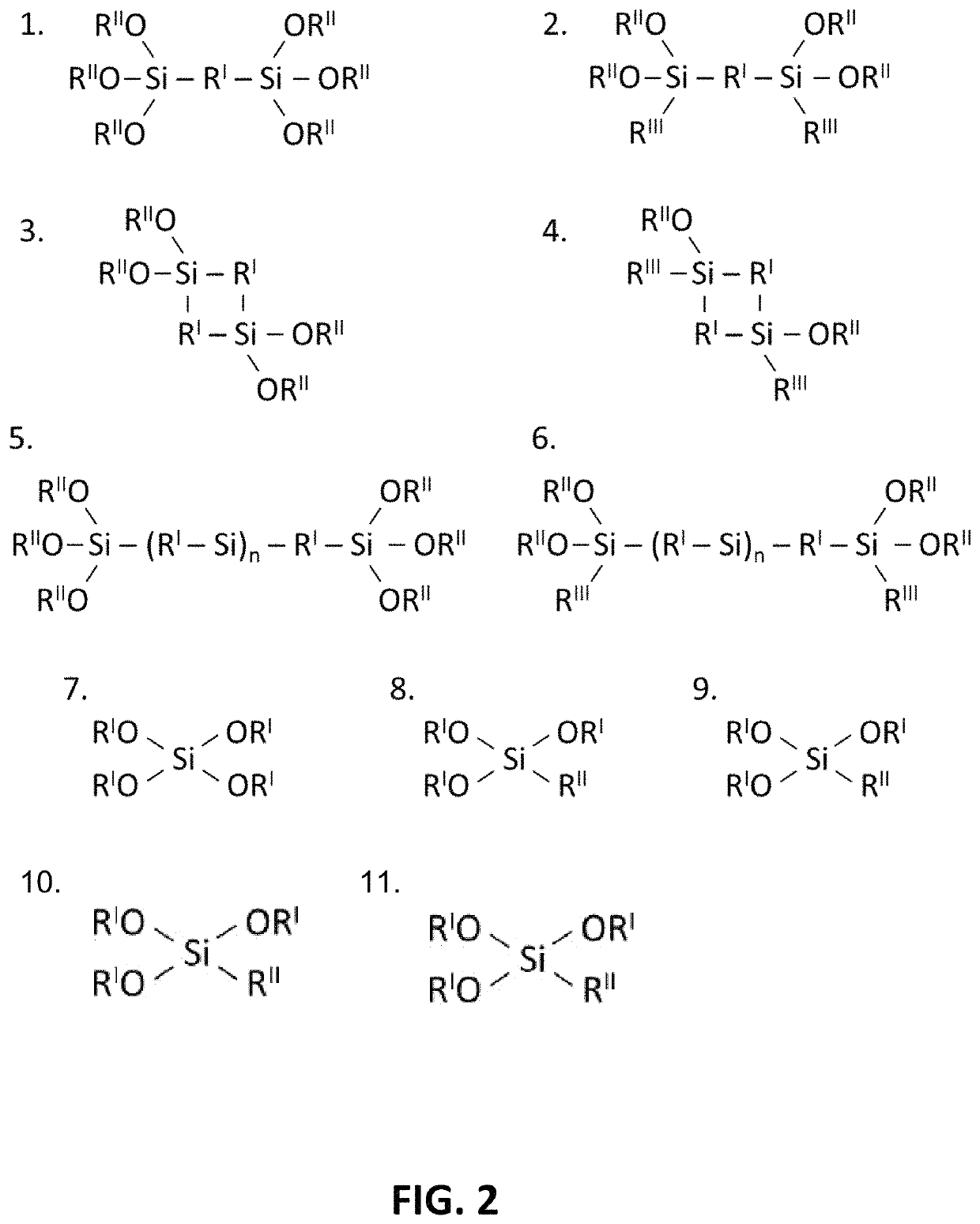

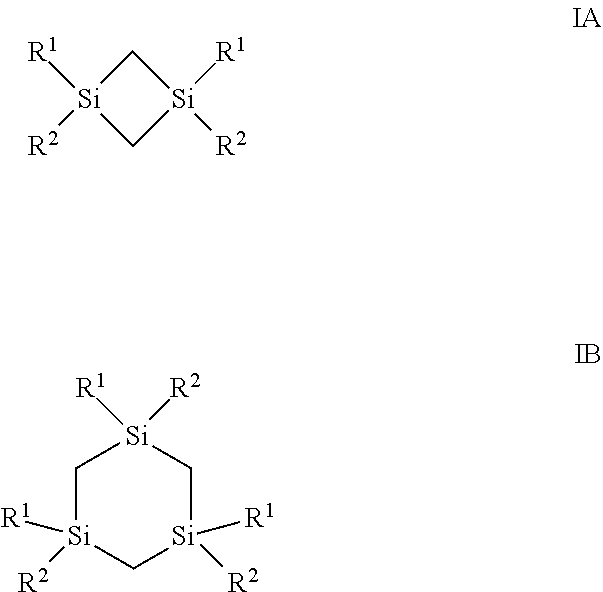

Compositions and methods for depositing silicon-containing films

PendingUS20200270749A1Group 4/14 element organic compoundsSemiconductor/solid-state device manufacturingDielectric membranePhysical chemistry

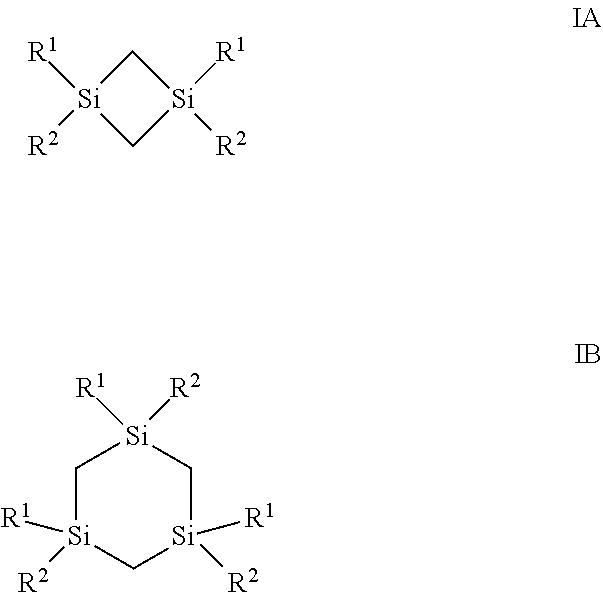

Described herein are compositions and methods of forming a dielectric film comprising silicon and carbon onto at least a surface of a substrate, the method comprising introducing into a reactor at least one silacycloalkane precursor selected from the group consisting of compounds represented by the structure of Formula IA and compounds represented by the structure of Formula IB: as defined herein.

Owner:VERSUM MATERIALS US LLC

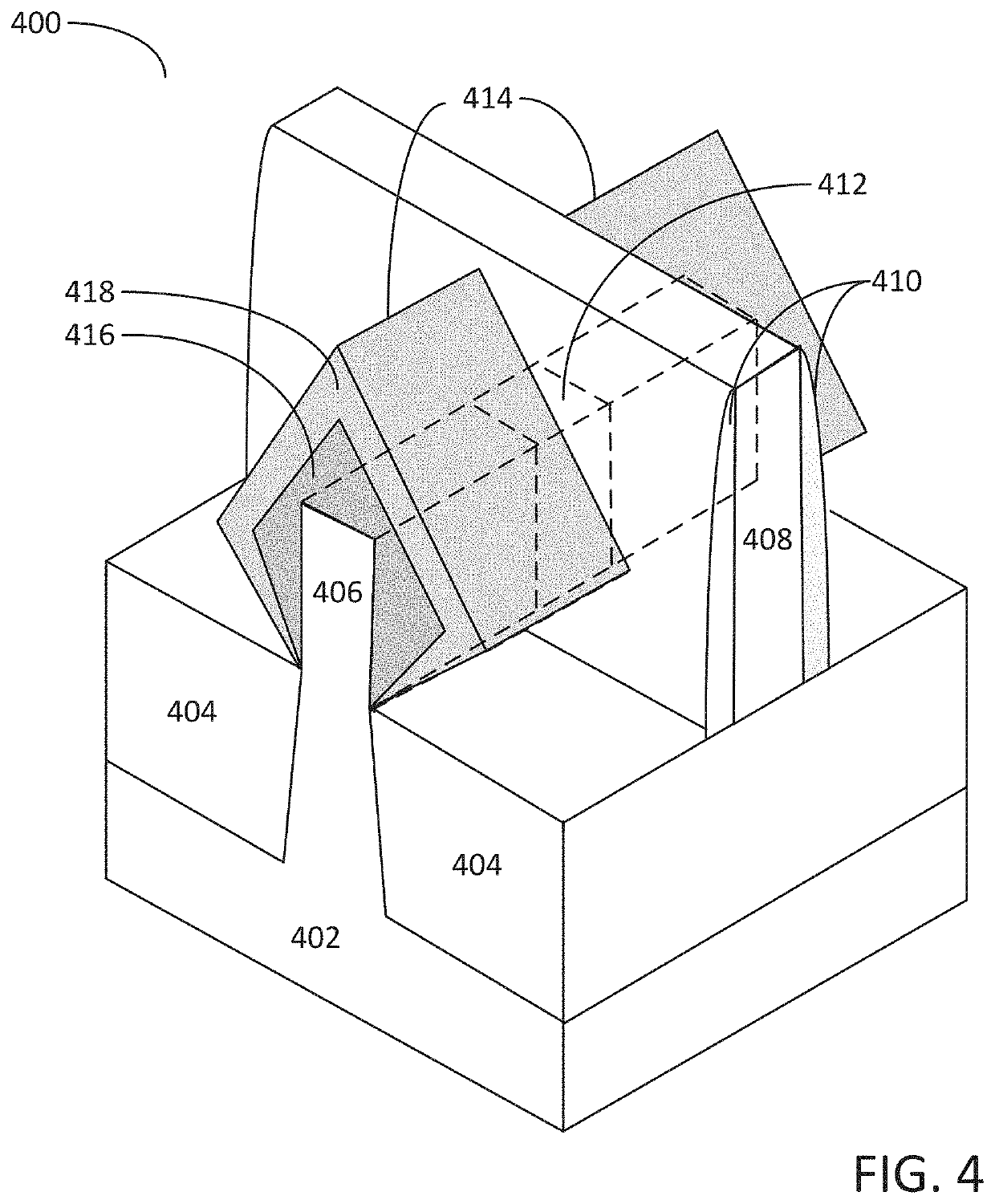

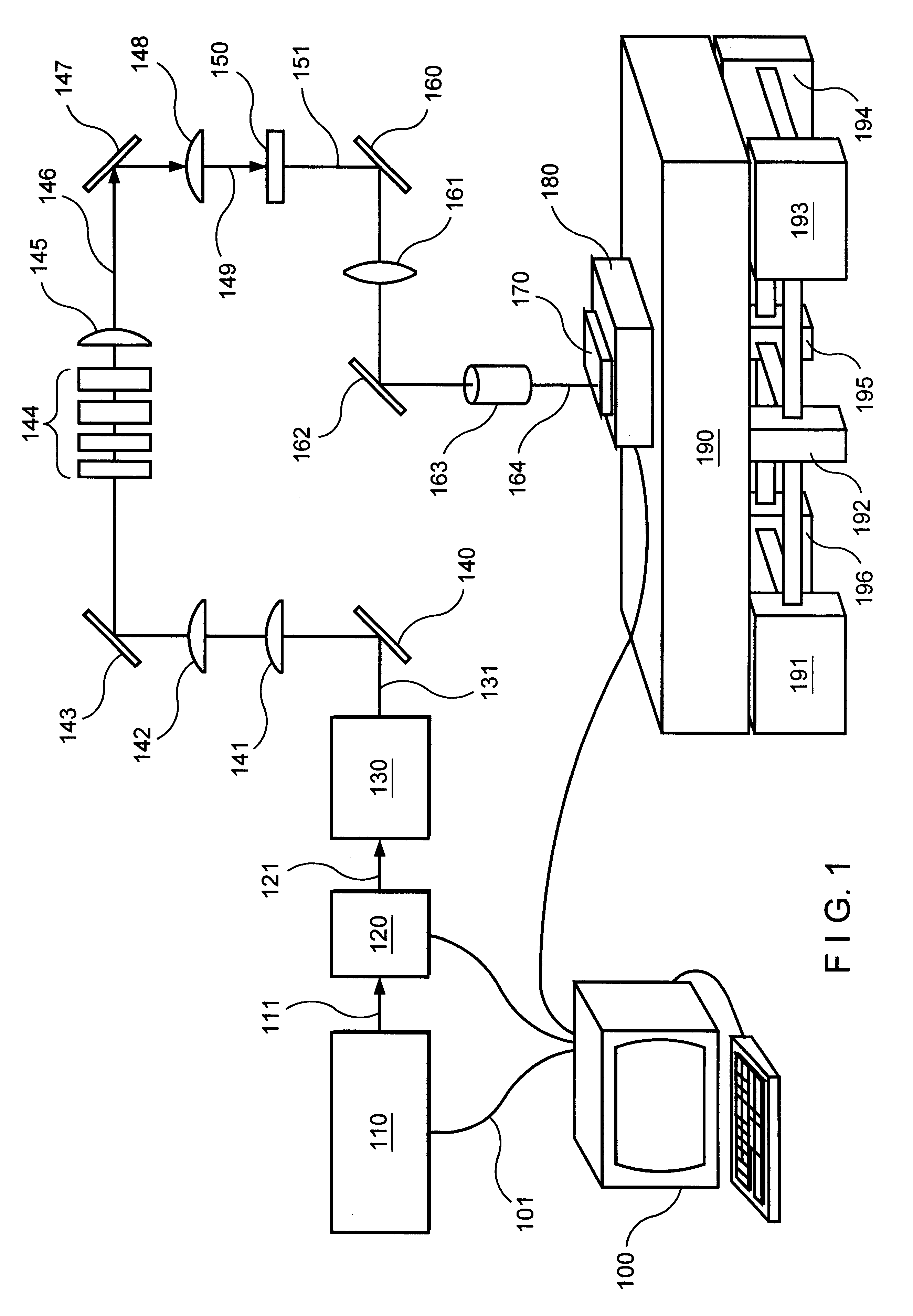

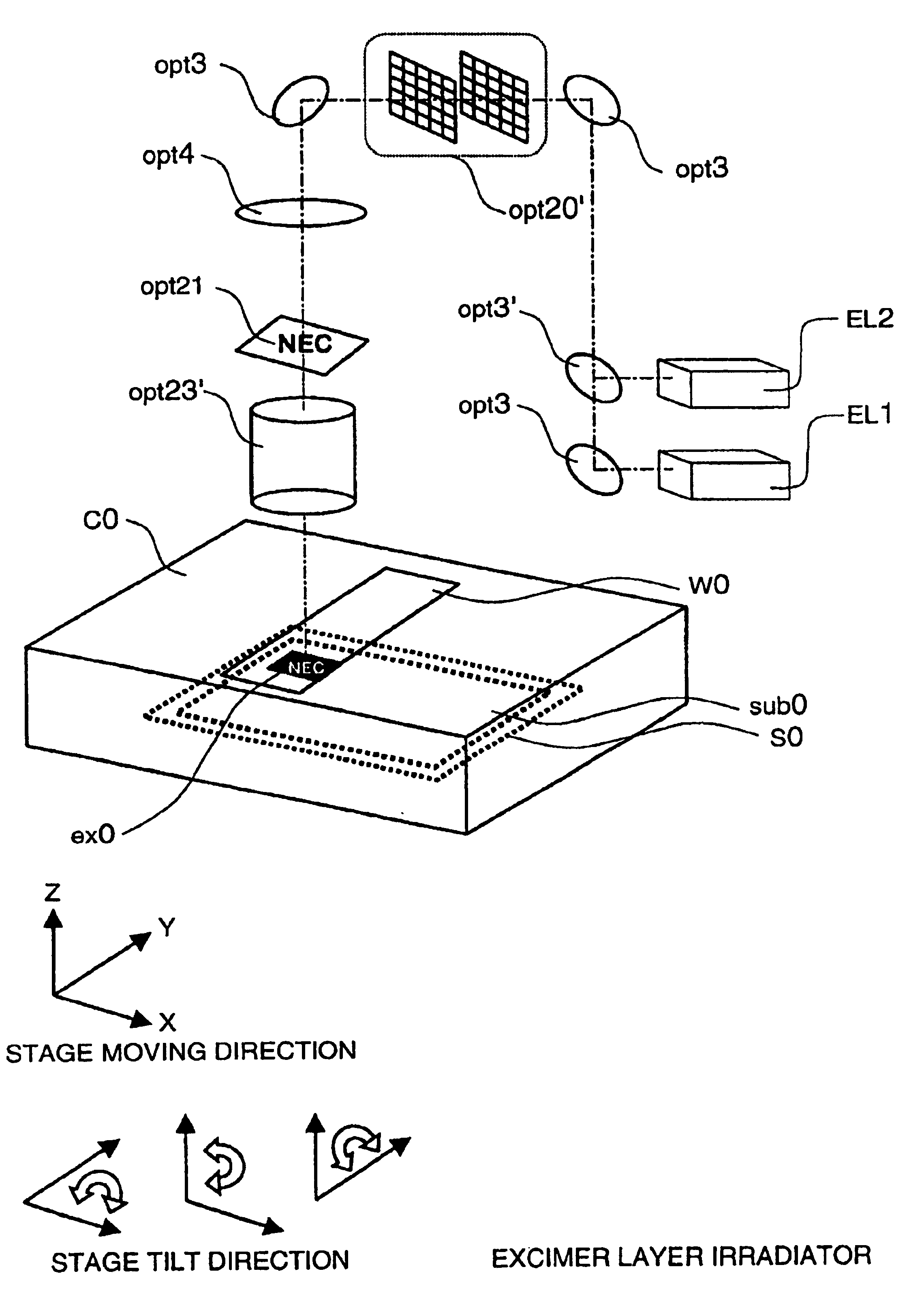

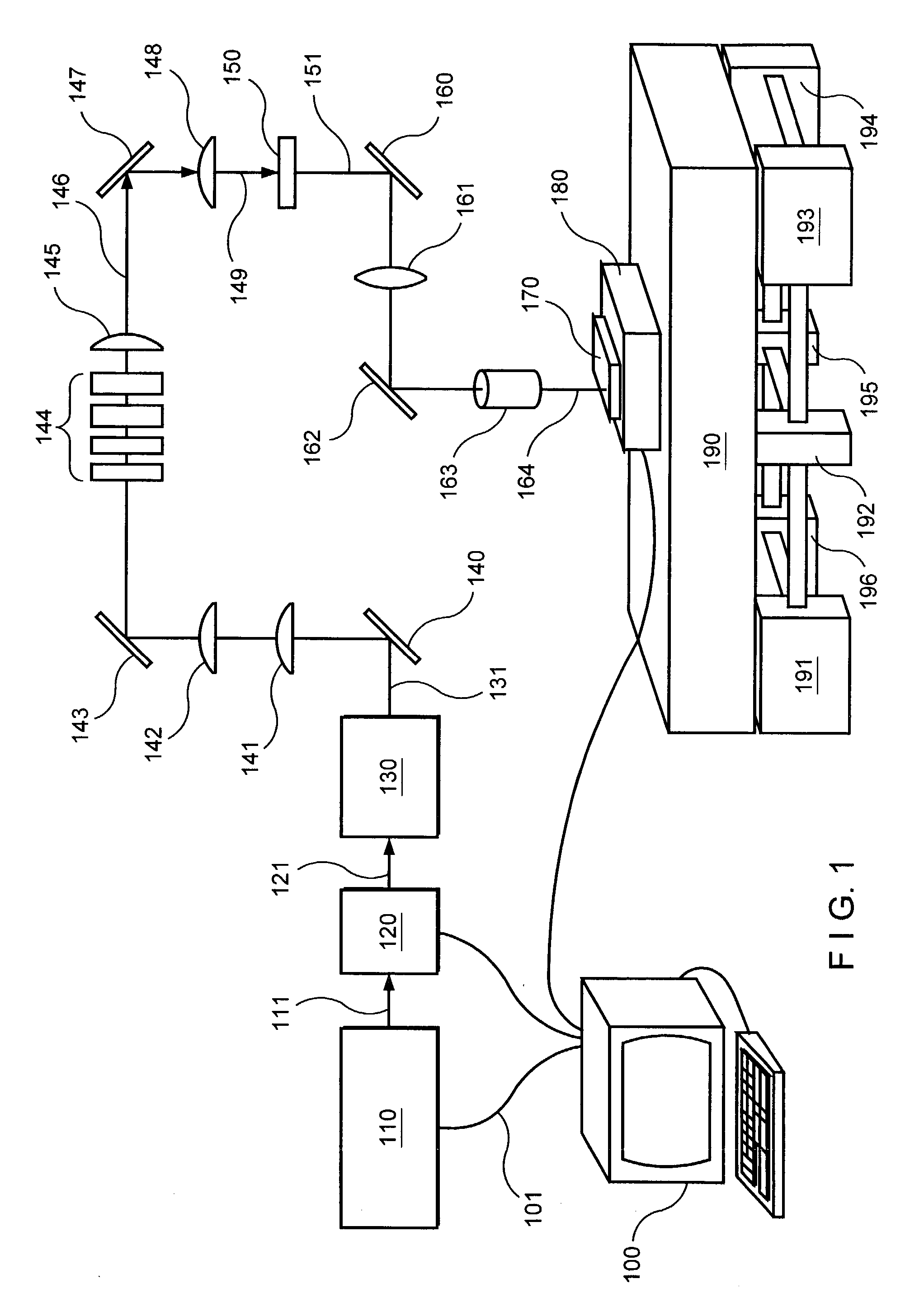

Systems and methods using sequential lateral solidification for producing single or polycrystalline silicon thin films at low temperatures

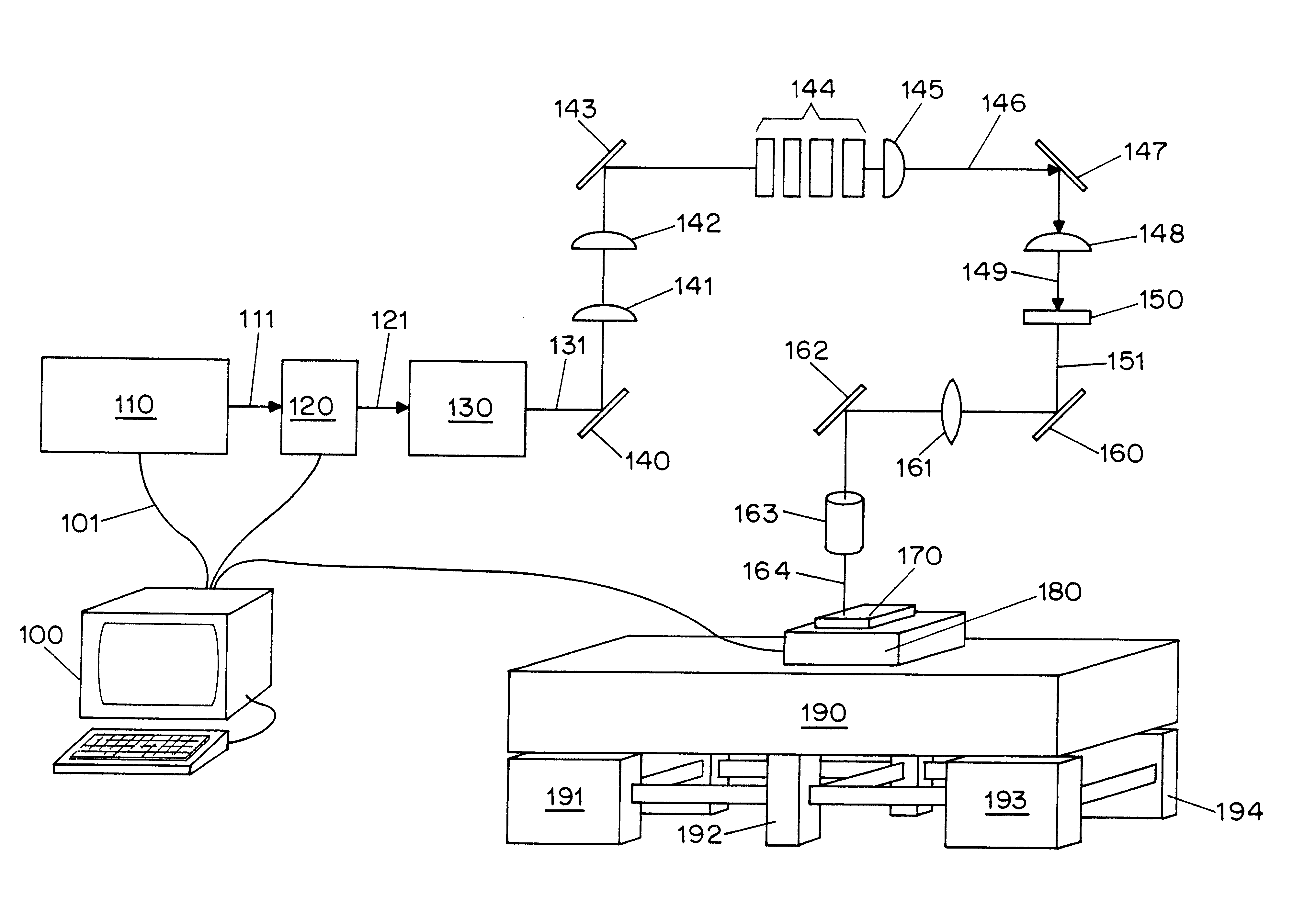

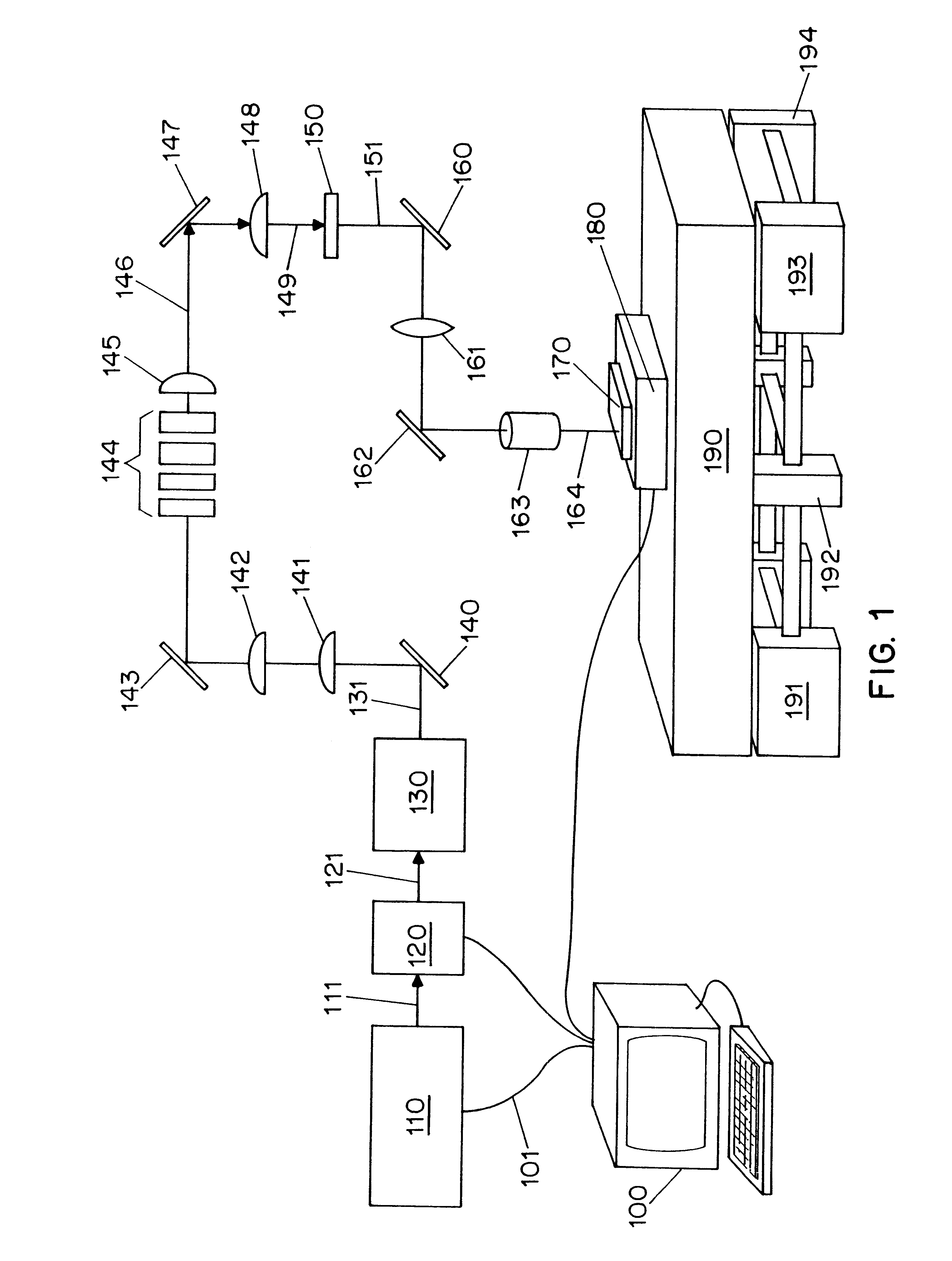

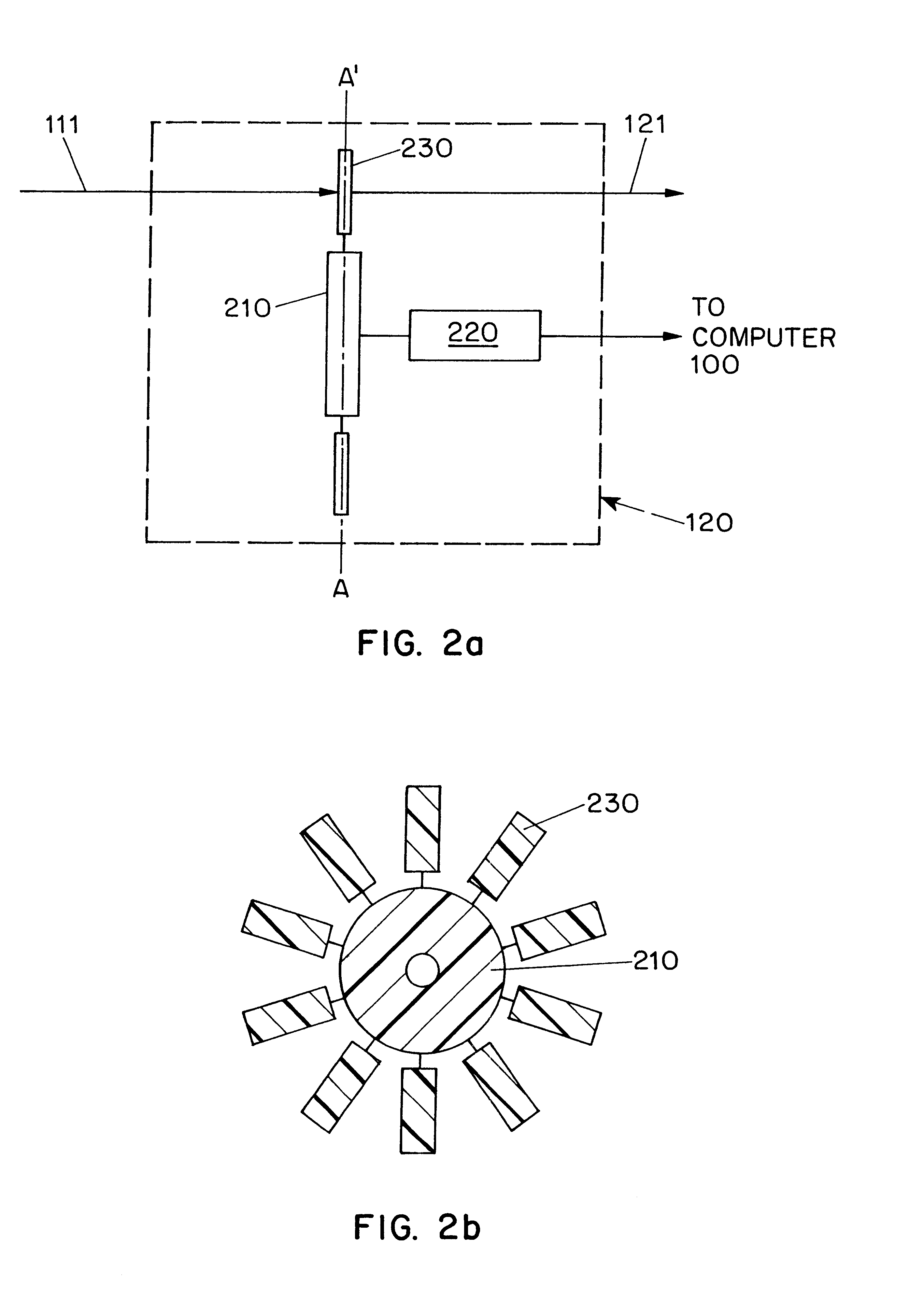

System and methods for processing an amorphous silicon thin film sample into a single or polycrystalline silicon thin film are disclosed. The system includes an excimer laser for generating a plurality of excimer laser pulses of a predetermined fluence, an energy density modulator for controllably modulating fluence of the excimer laser pulses, a beam homoginizer for homoginizing modulated laser pulses in a predetermined plane, a mask for masking portions of the homoginized modulated laser pulses into patterned beamlets, a sample stage for receivingthe patterned beamlets to effect melting of portions of any amorphous silicon thin film sample placed thereon corresponding to the beamlets, translating means for controllably translating a relative position of the sample stage with respect to a position of the mask and a computer for controlling the controllable fluence modulation of the excimer laser pulses and the controllable relative positions of the sample stage and mask, and for coordinating excimer pulse generation and fluence modulation with the relative positions of the sample stage and mask, to thereby process amorphous silicon thin film sample into a single or polycrystalline silicon thin film by sequential translation of the sample stage relative to the mask and irradiation of the sample by patterned beamlets of varying fluence at corresponding sequential locations thereon.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Method for preparing electrode material for lithium battery

InactiveUS6887511B1Improve adhesionReduce expansionElectrode carriers/collectorsVacuum evaporation coatingAmorphous siliconOptoelectronics

Owner:SANYO ELECTRIC CO LTD

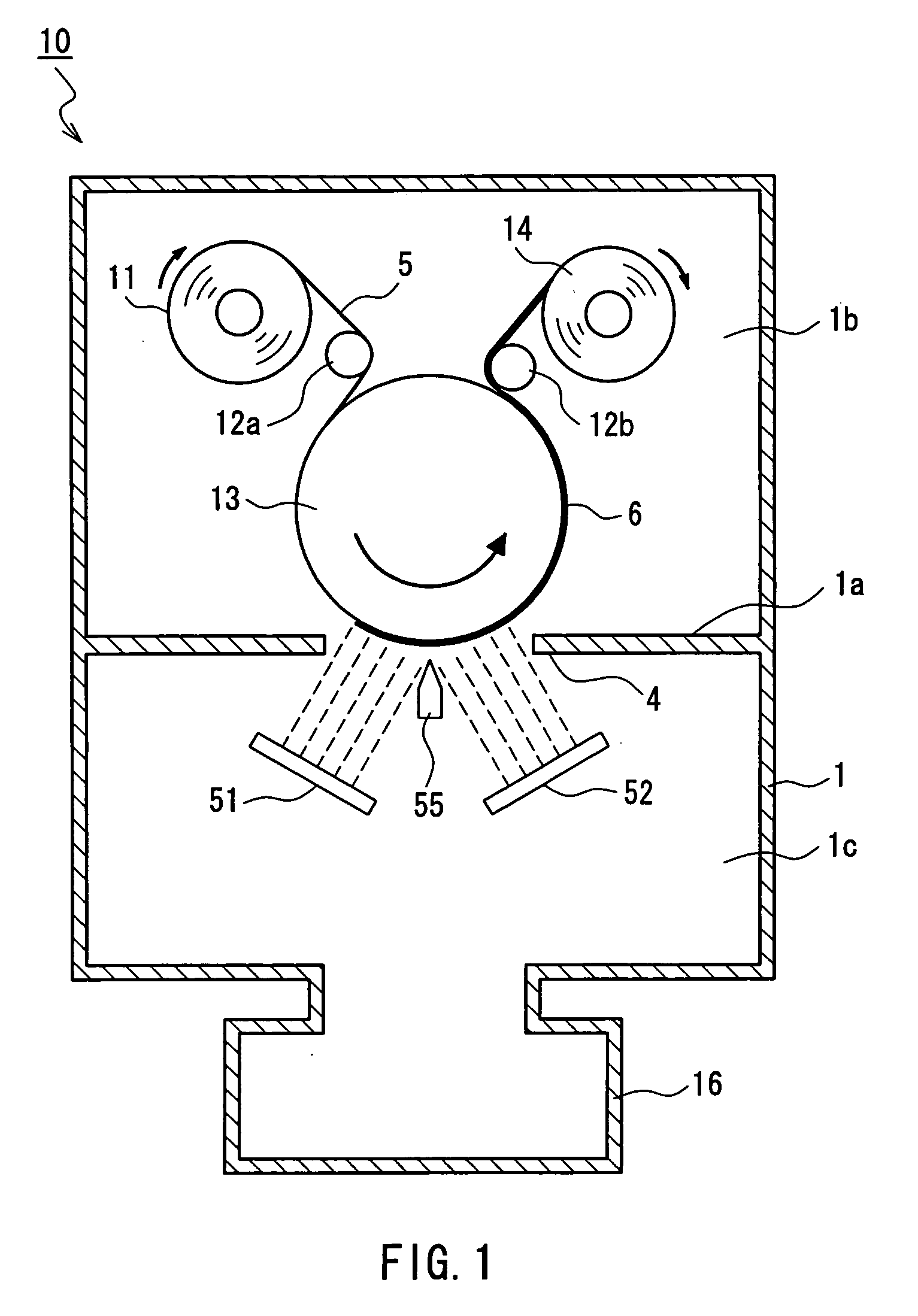

System for the formation of a silicon thin film and a semiconductor-insulating film interface

InactiveUS6861614B1Reduced trap state densityGood reproducibilityTransistorLaser detailsSilicon thin filmState density

In a semiconductor thin film forming system for modifying a predetermined region of a semiconductor thin film by exposing the semiconductor thin film to a projected light patterned through a pattern formed on a photo mask, the system includes a mechanism (opt20′) for uniformizing the light for exposure in a predetermined area on the photo mask. This system can provide a crystallized silicon film having a trap state density less than 1012 cm−2 and can provide a silicon-insulating film interface exhibiting a low interface state density.

Owner:NEC CORP +1

Composition and method for low temperature deposition of silicon-containing films such as films including silicon nitride, silicon dioxide and/or silicon-oxynitride

ActiveUS20040096582A1Silicon organic compoundsPolycrystalline material growthLow temperature depositionGas phase

Silicon precursors for forming silicon-containing films in the manufacture of semiconductor devices, such as low dielectric constant (k) thin films, high k gate silicates, low temperature silicon epitaxial films, and films containing silicon nitride (Si3N4), siliconoxynitride (SiOxNy) and / or silicon dioxide (SiO2). The precursors of the invention are amenable to use in low temperature (e.g., <500° C.) chemical vapor deposition processes, for fabrication of ULSI devices and device structures.

Owner:ENTEGRIS INC

Methods for producing uniform large-grained and grain boundary location manipulated polycrystalline thin film semiconductors using sequential lateral solidification

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

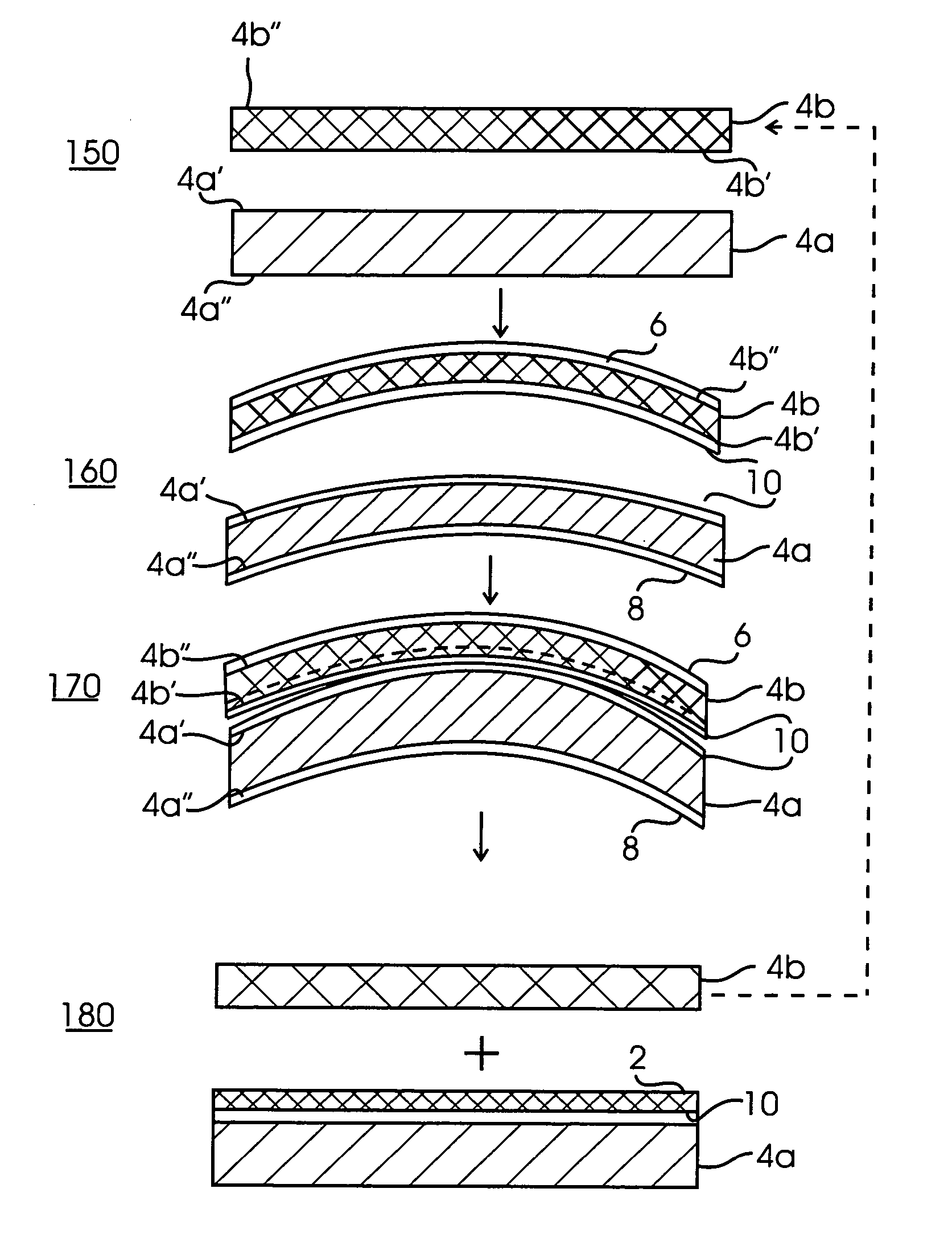

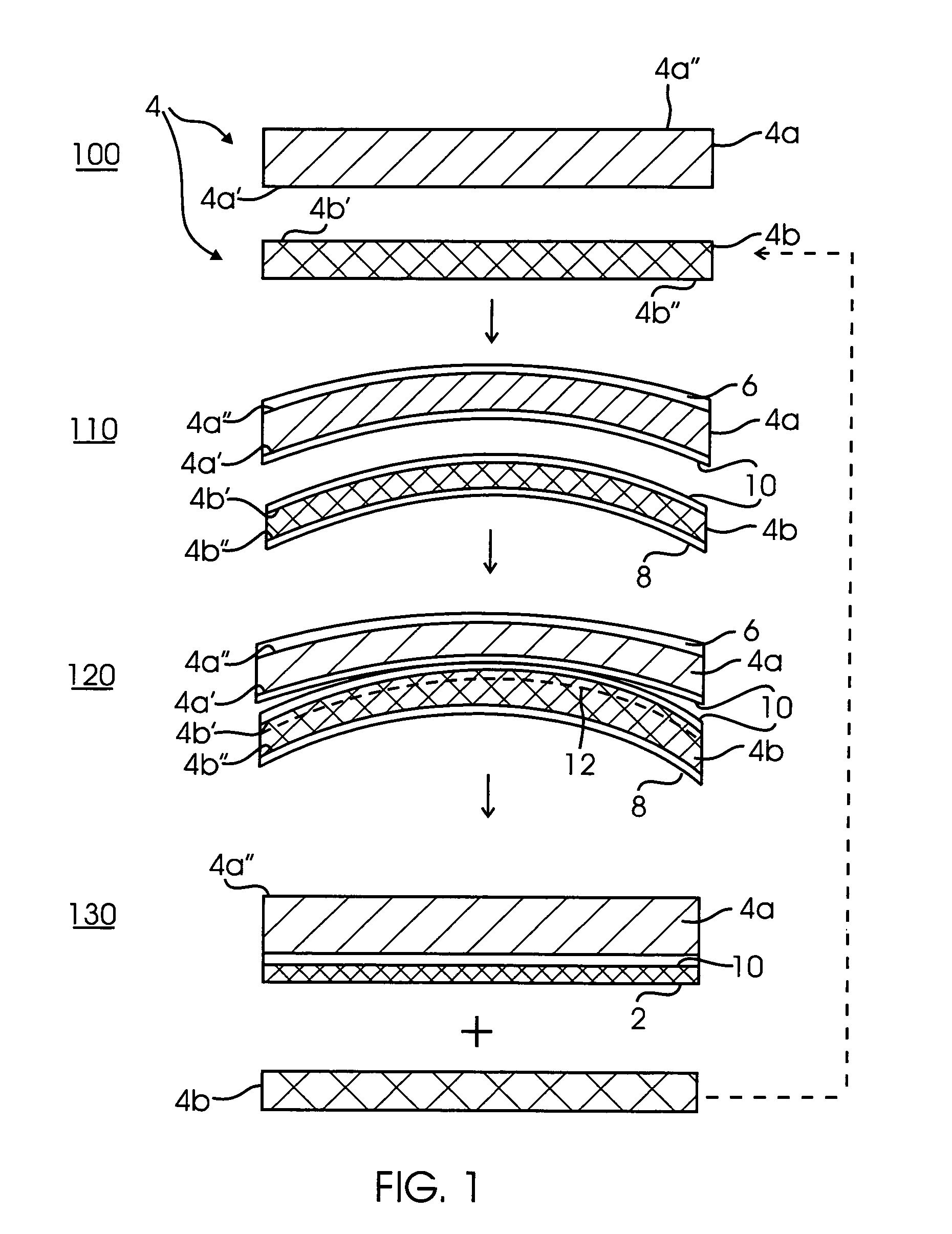

Method for producing dislocation-free strained crystalline films

ActiveUS20060292822A1Small thicknessSemiconductor/solid-state device manufacturingHydrogenOptoelectronics

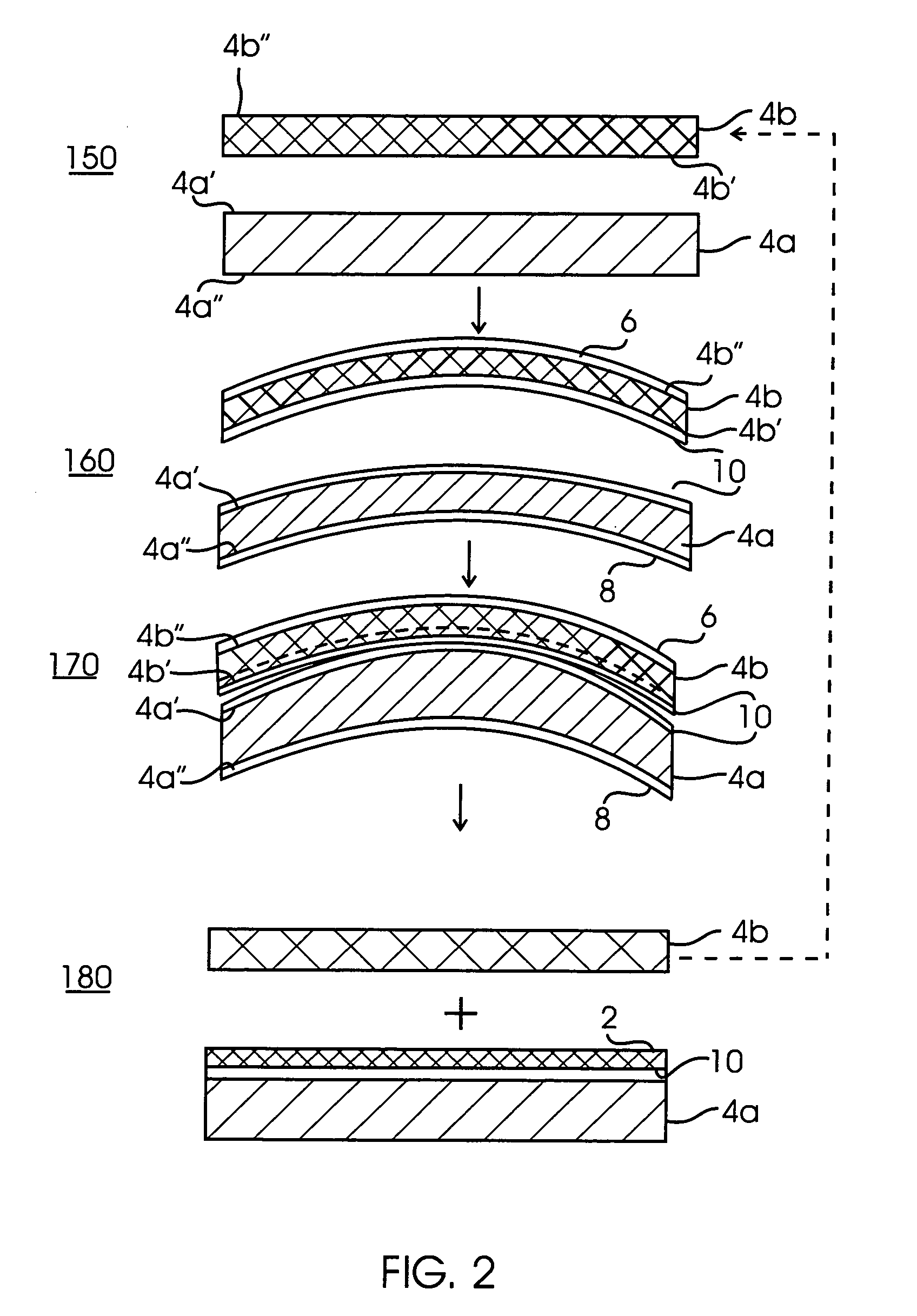

A method for forming dislocation-free strained silicon thin film includes the step of providing two curved silicon substrates. One substrate is curved by the presence of silicon dioxide on a back surface. The other substrate is curved by the presence of a silicon nitride layer. One of the substrates is subject to hydrogen implantation and the two substrates are bonded to one another in an annealing process. The two substrates are separated, thereby leaving a layer of strained silicon on a front side of one of the substrates. A back side layer of silicon dioxide or silicon nitride is then removed to restore the substrate to a substantially planar state. The method may be employed to form dislocation-free strained silicon thin films. The films may be under tensile or compressive strain.

Owner:RGT UNIV OF CALIFORNIA

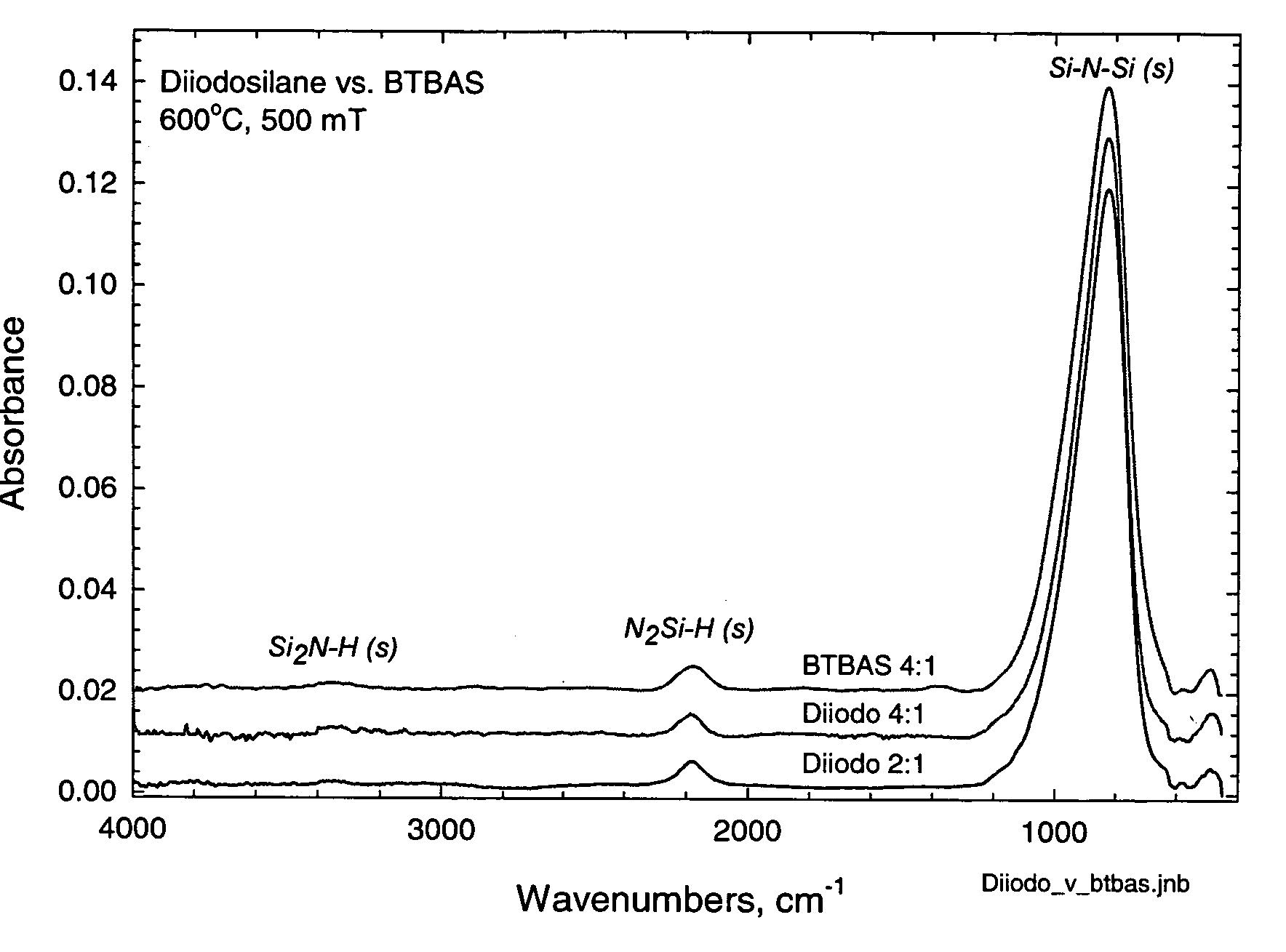

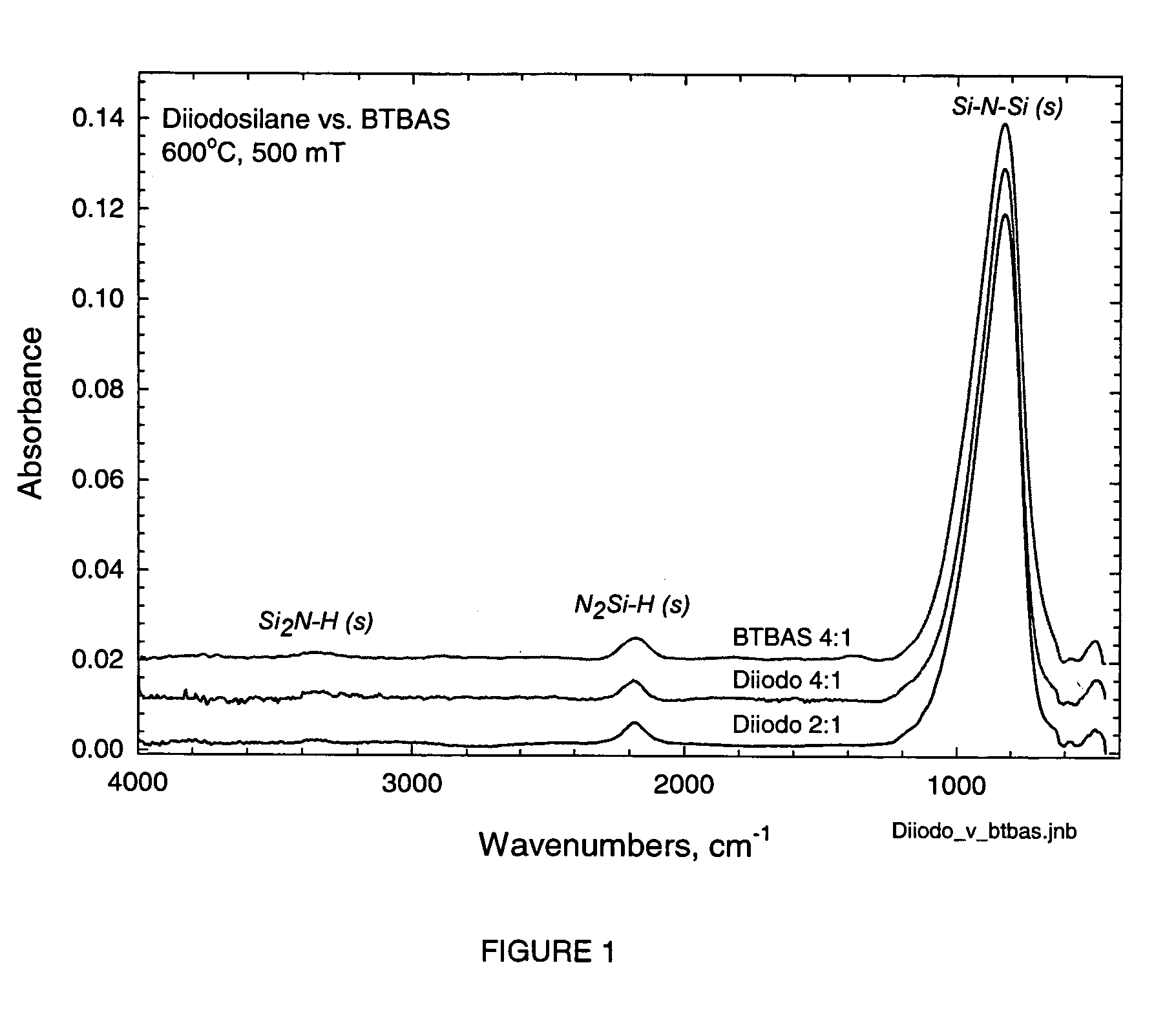

Precursors for depositing silicon-containing films and processes thereof

InactiveUS20050181633A1Satisfies needSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenReactive gas

Inorganic precursors, namely iodosilane precursors, for the low temperature, low pressure deposition of silicon-containing films is provided therein. In one aspect, there is provided a process for forming a silicon-containing film process comprising: introducing a substrate and gaseous reagents comprising an iodosilane precursor having three or less iodine atoms bound to the silicon atom and at least one reagent selected from an oxygen-containing reactive gas, a nitrogen-containing reactive gas, a hydrogen-containing reactive gas and mixtures thereof into a reaction chamber; heating the reaction chamber to one or more temperatures ranging from 200° C. to 900° C. to form the silicon containing film on the substrate, provided that if the iodosilane precursor has three iodine atoms bound to the silicon atom then the heating step is conducted at one or more pressures less than 600 Torr.

Owner:VERSUM MATERIALS US LLC

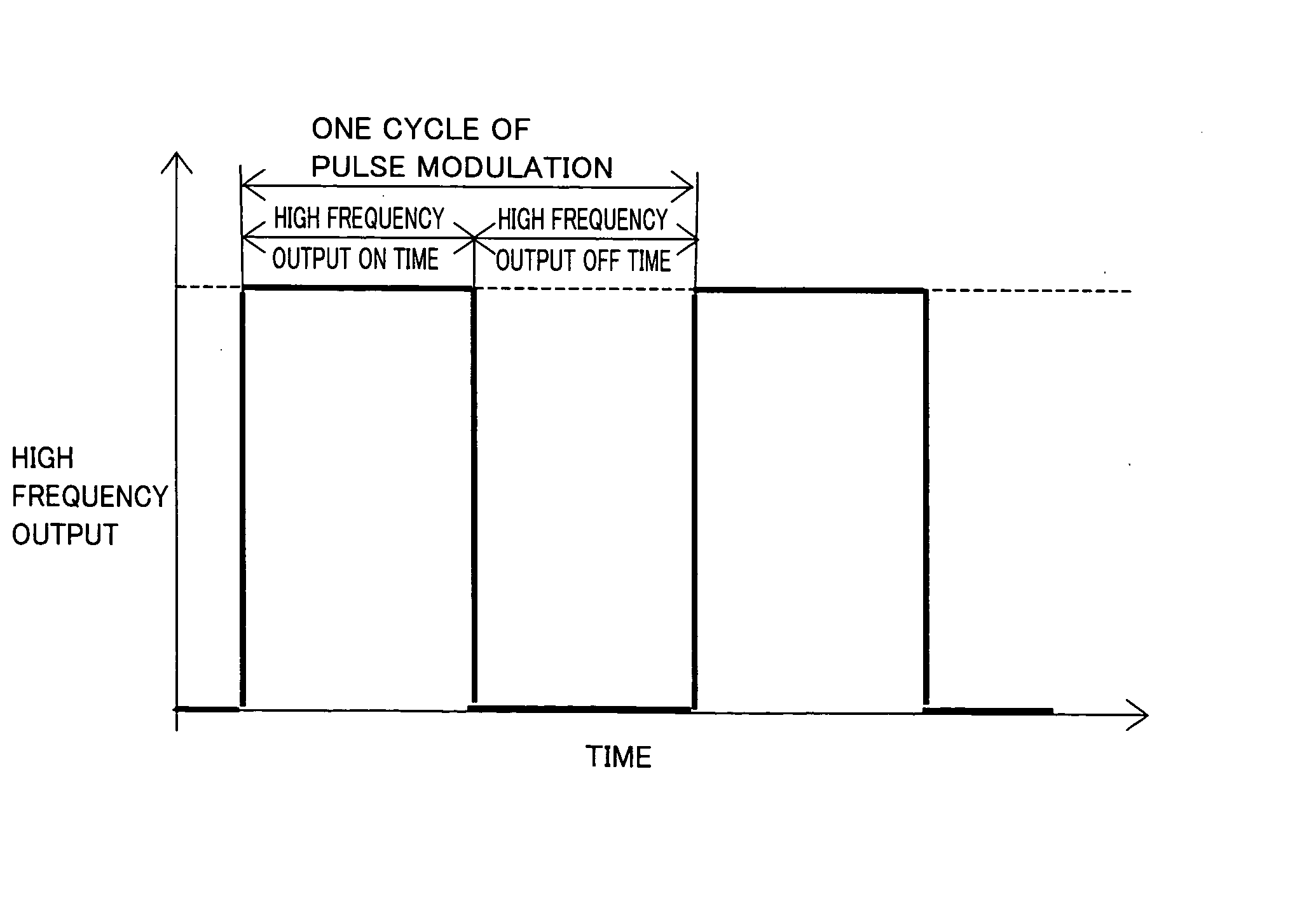

Manufacturing method of silicon thin film solar cell

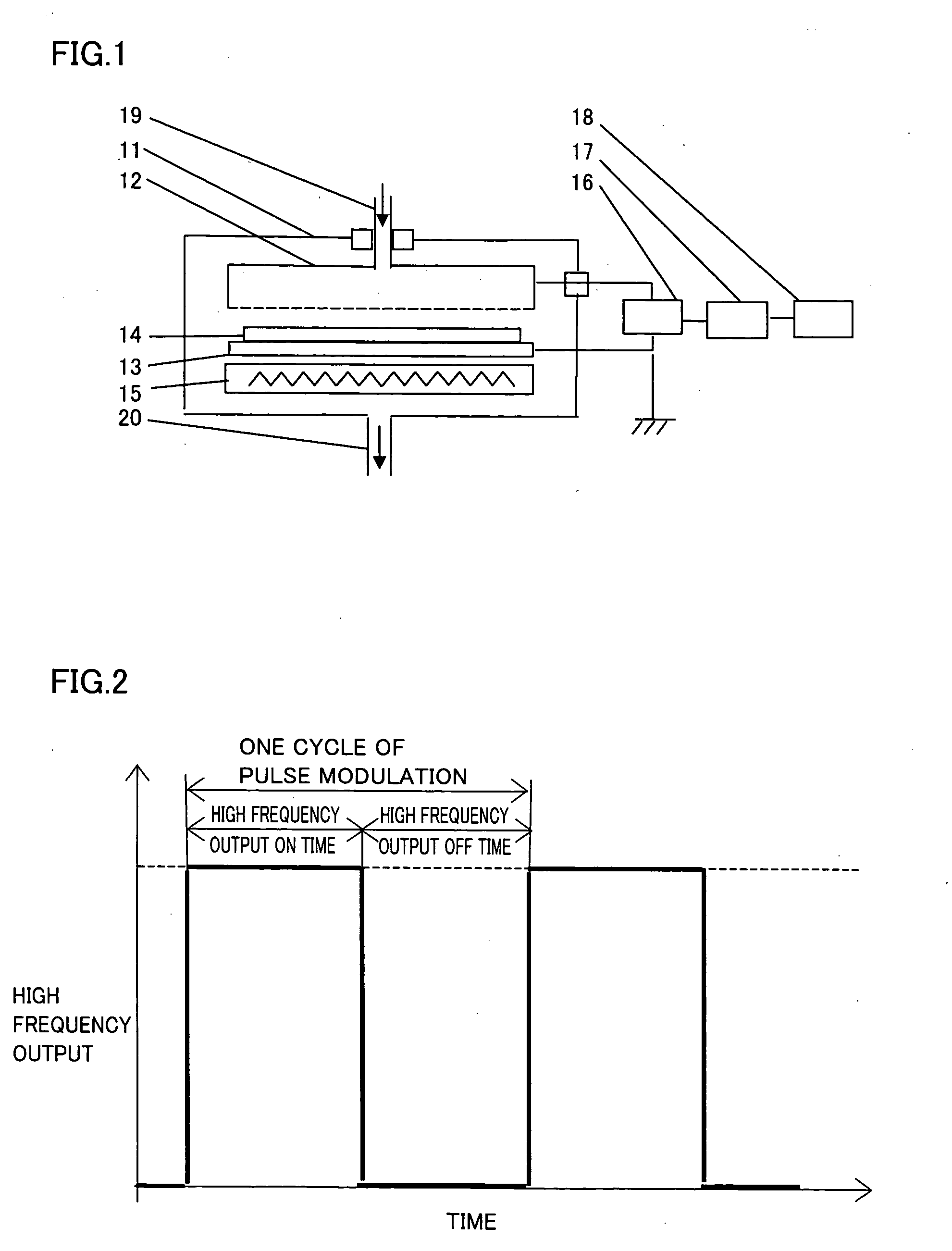

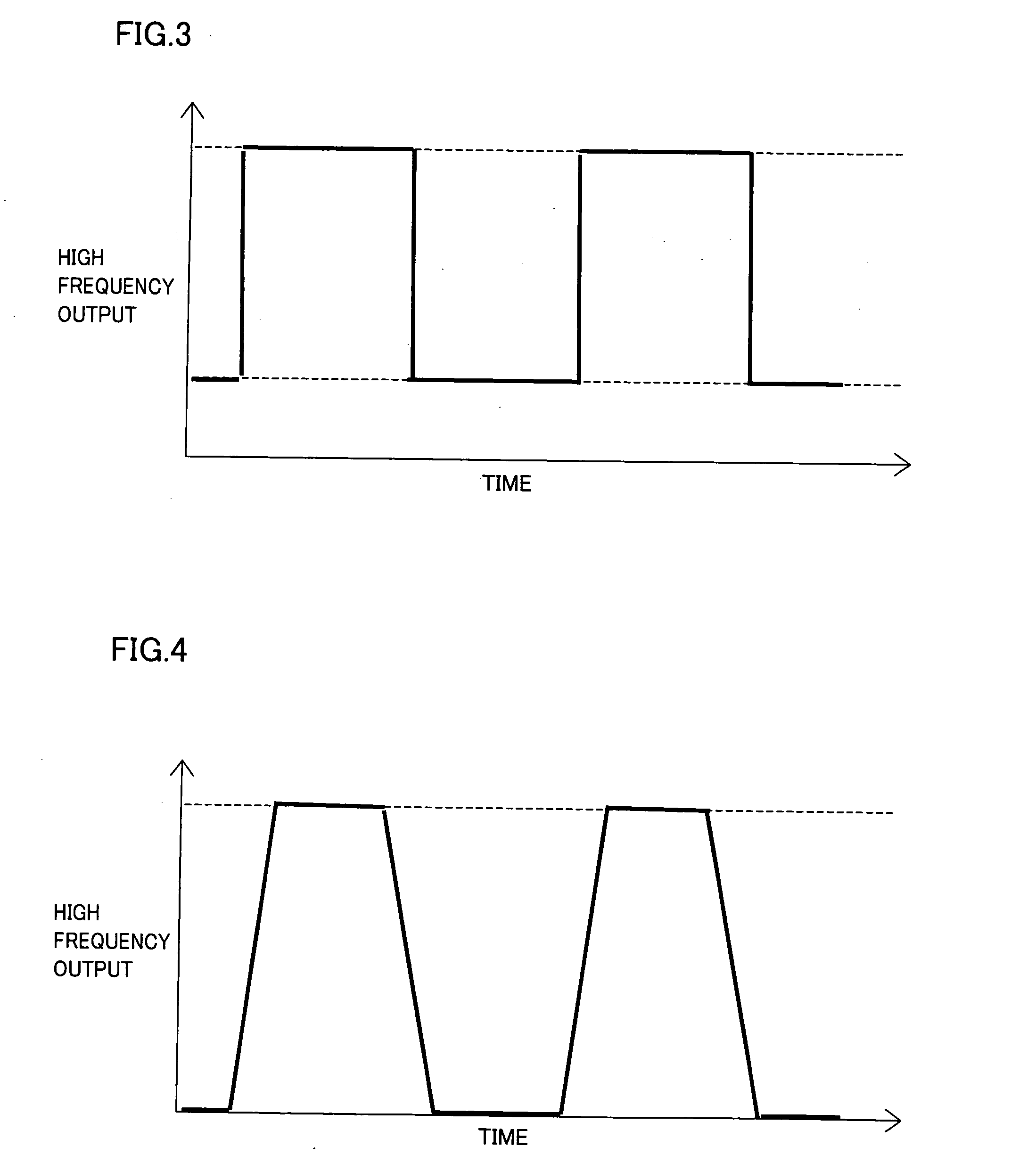

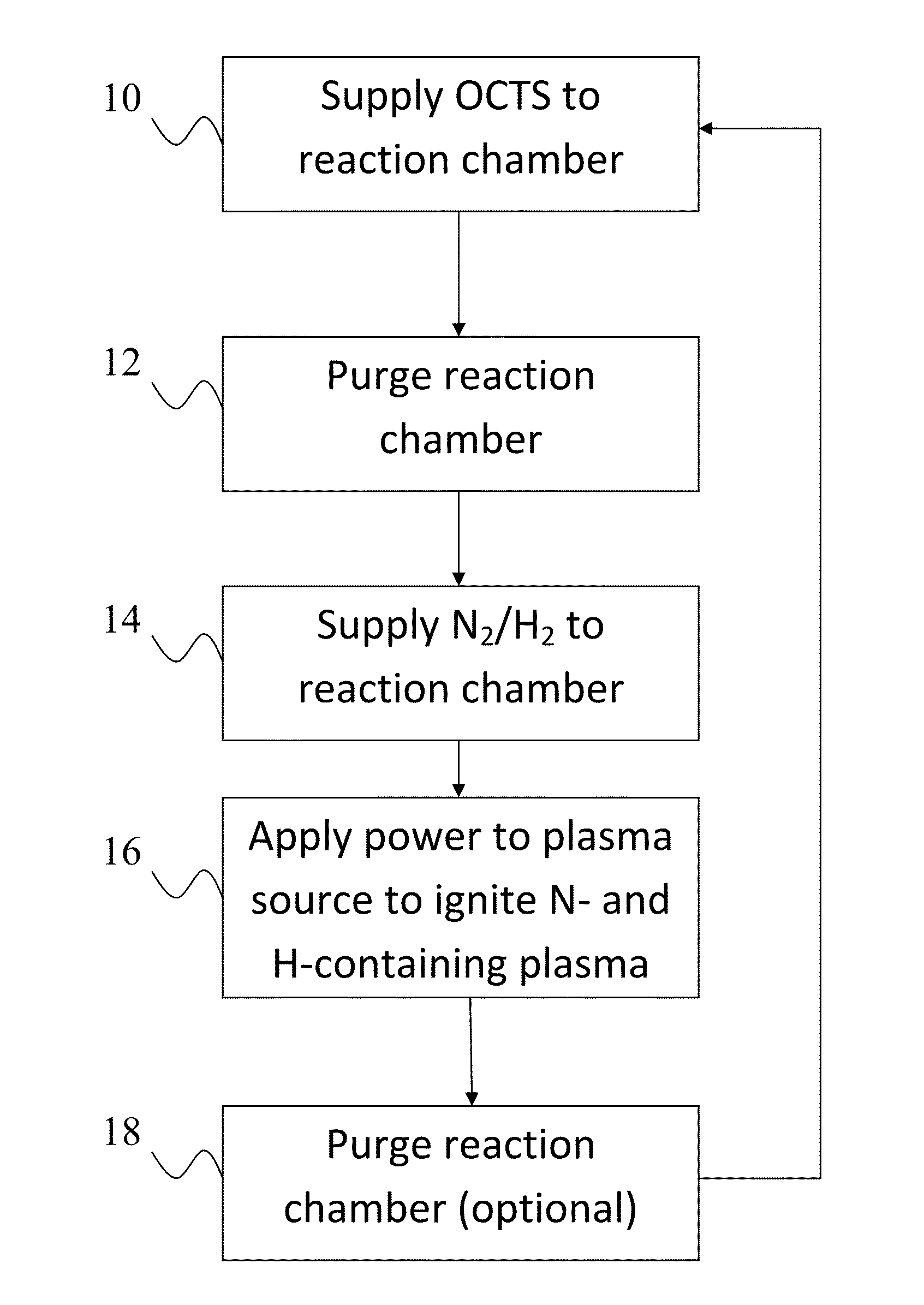

InactiveUS20050022864A1Lower performance requirementsIncrease currentFinal product manufactureSemiconductor/solid-state device manufacturingHigh frequency powerSilicon thin film

To uniformly form a silicon thin film for a solar cell, having an i layer formed with crystalline silicon, on a substrate of a large area to provide a high power solar cell, in a manufacturing method of a silicon thin film solar cell, a silicon thin film, having a structure such that an i layer is sandwiched between a p layer and an n layer, is formed on a substrate with a high frequency plasma CVD method, wherein i layer is formed with crystalline silicon using plasma with pulse-modulated high frequency power, one cycle of pulse modulation includes an ON state for outputting high frequency power and an OFF state for not outputting, an output waveform is modulated to be rectangular, a time of the ON state is 1-100 microseconds, and a time of the OFF state is 5 microseconds or longer.

Owner:SHARP KK

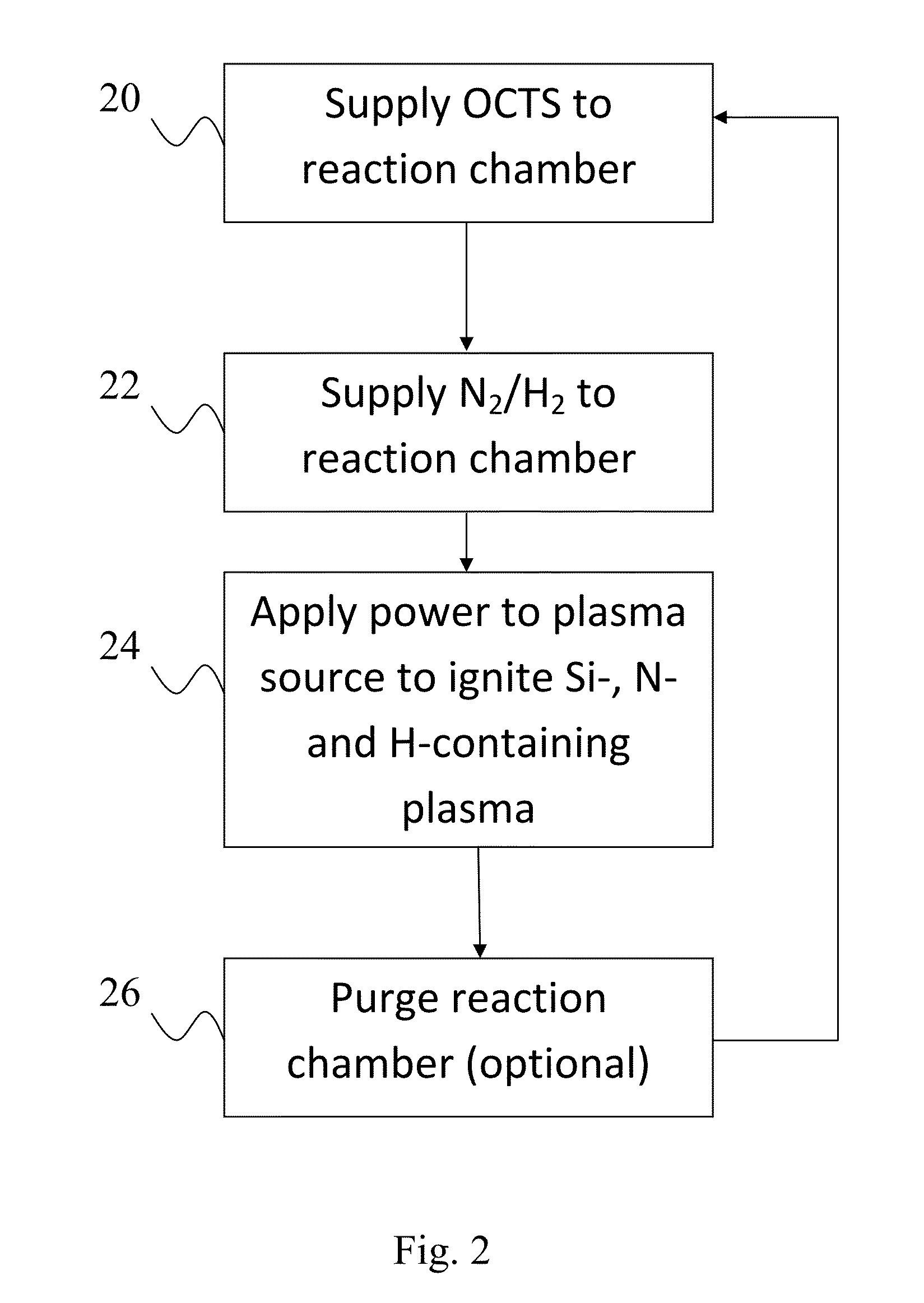

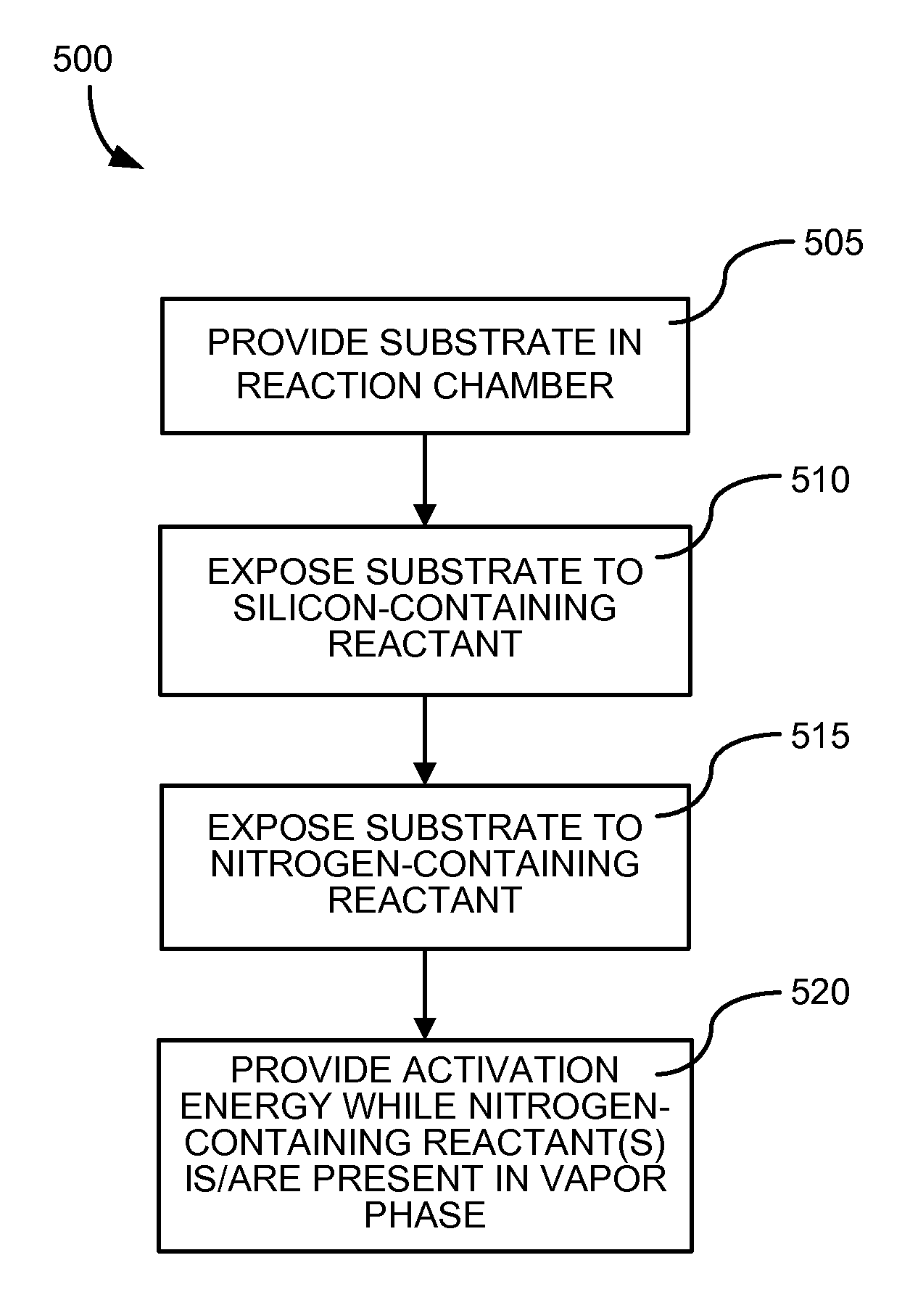

Methods for forming silicon nitride thin films

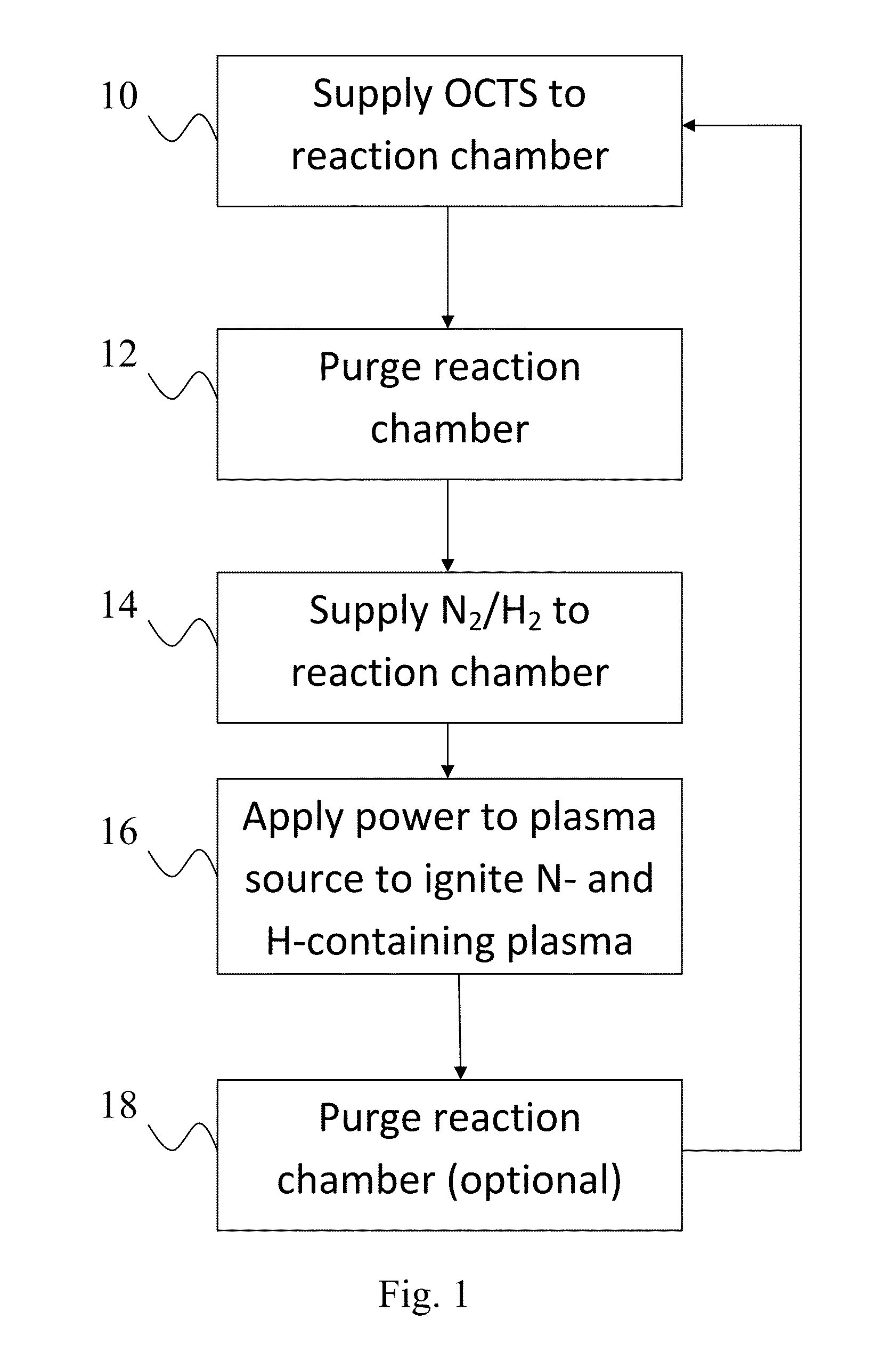

ActiveUS20140273527A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicon nitrideReaction chamber

The present invention relates to methods of forming silicon nitride thin films on a substrate in a reaction chamber by plasma enhanced atomic layer deposition (PEALD). Exemplary methods include the steps of (i) introducing an octahalotrisilane Si3X8 silicon precursor, such as octachlorotrisilane (OCTS) Si3Cl8, into a reaction space containing a substrate, (ii) introducing a nitrogen containing plasma into the reaction space, and wherein steps (i), (ii) and any steps in between constitute one cycle, and repeating said cycles a plurality of times until an atomic layer nitride film having a desired thickness is obtained.

Owner:ASM IP HLDG BV

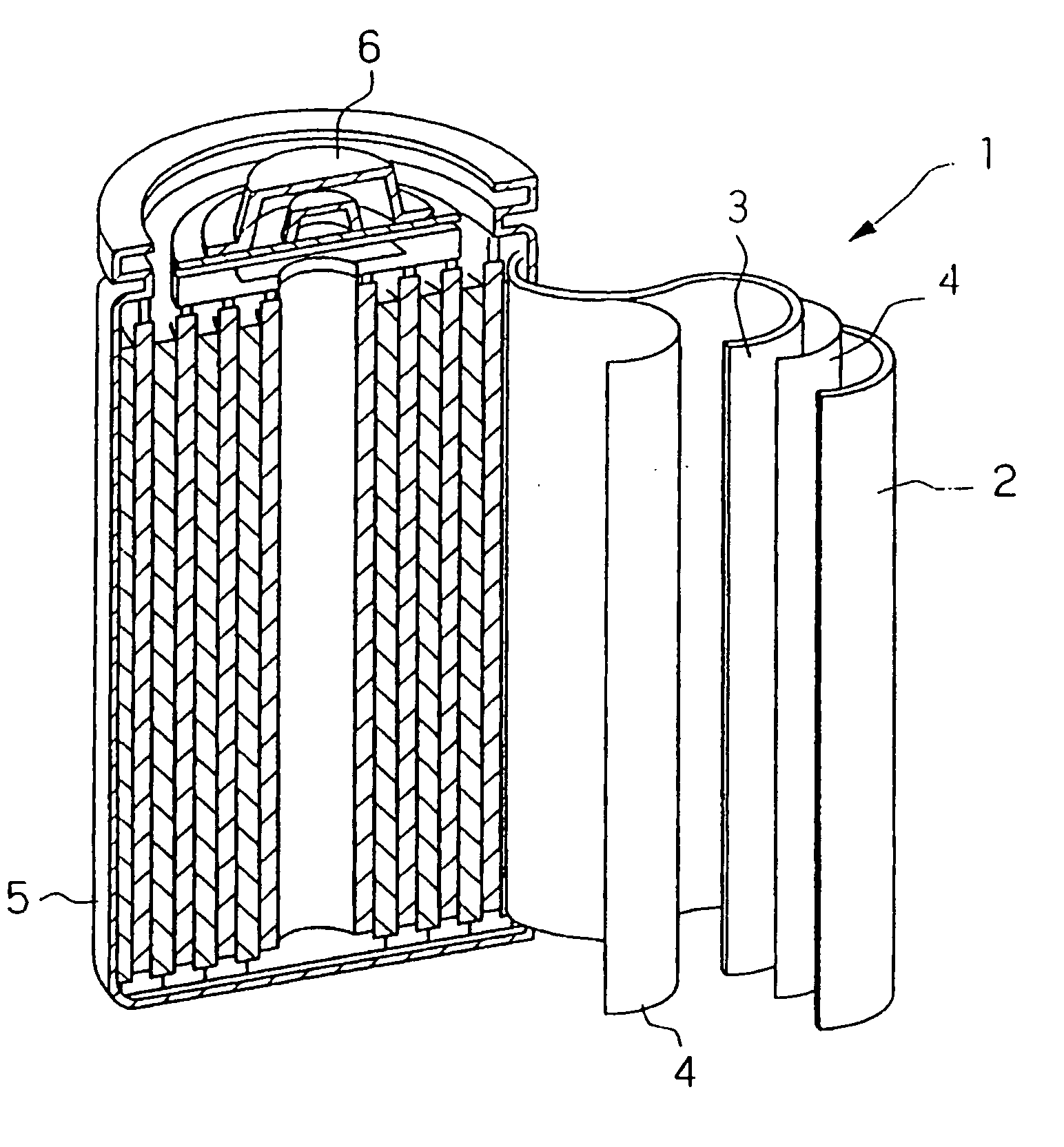

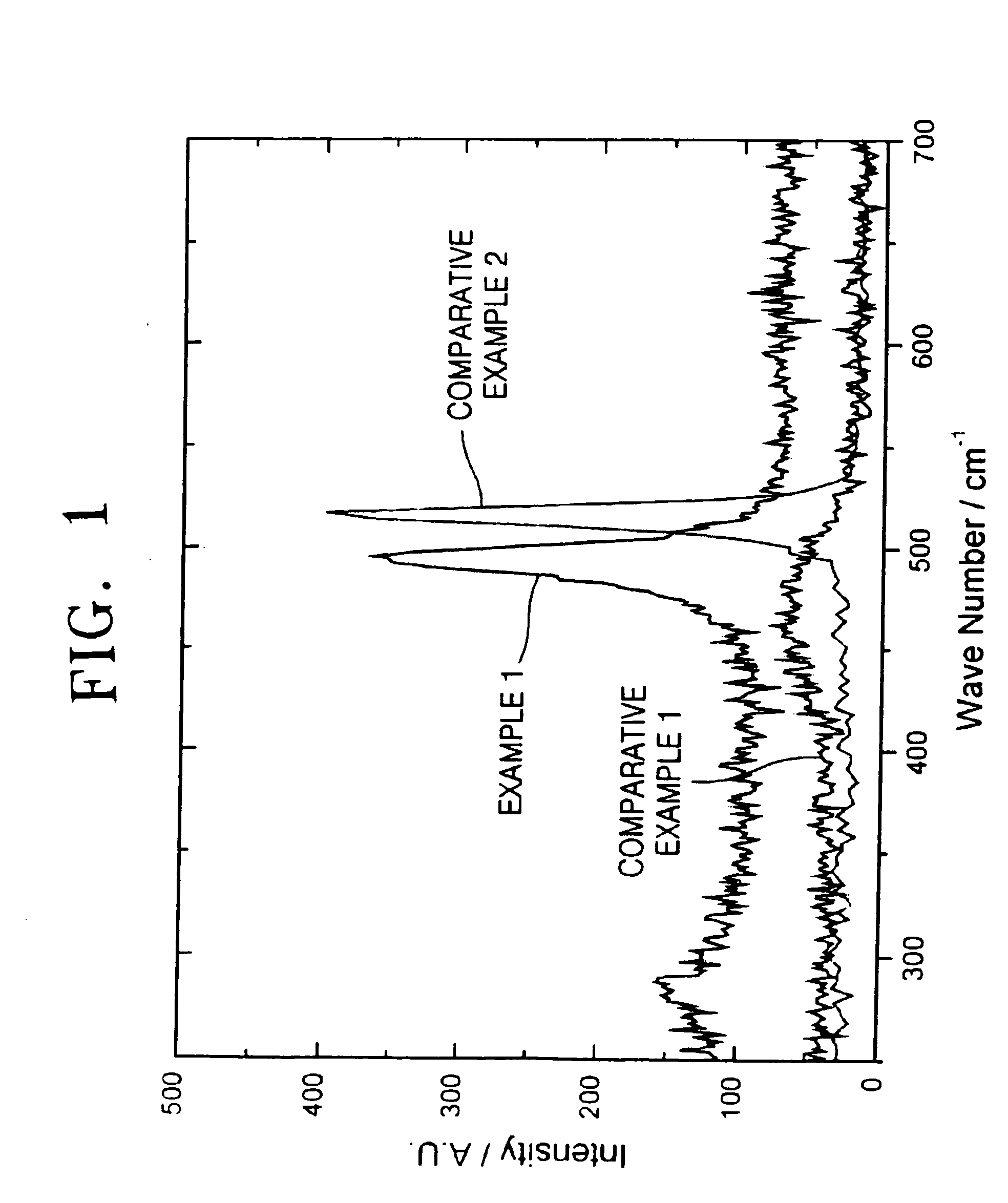

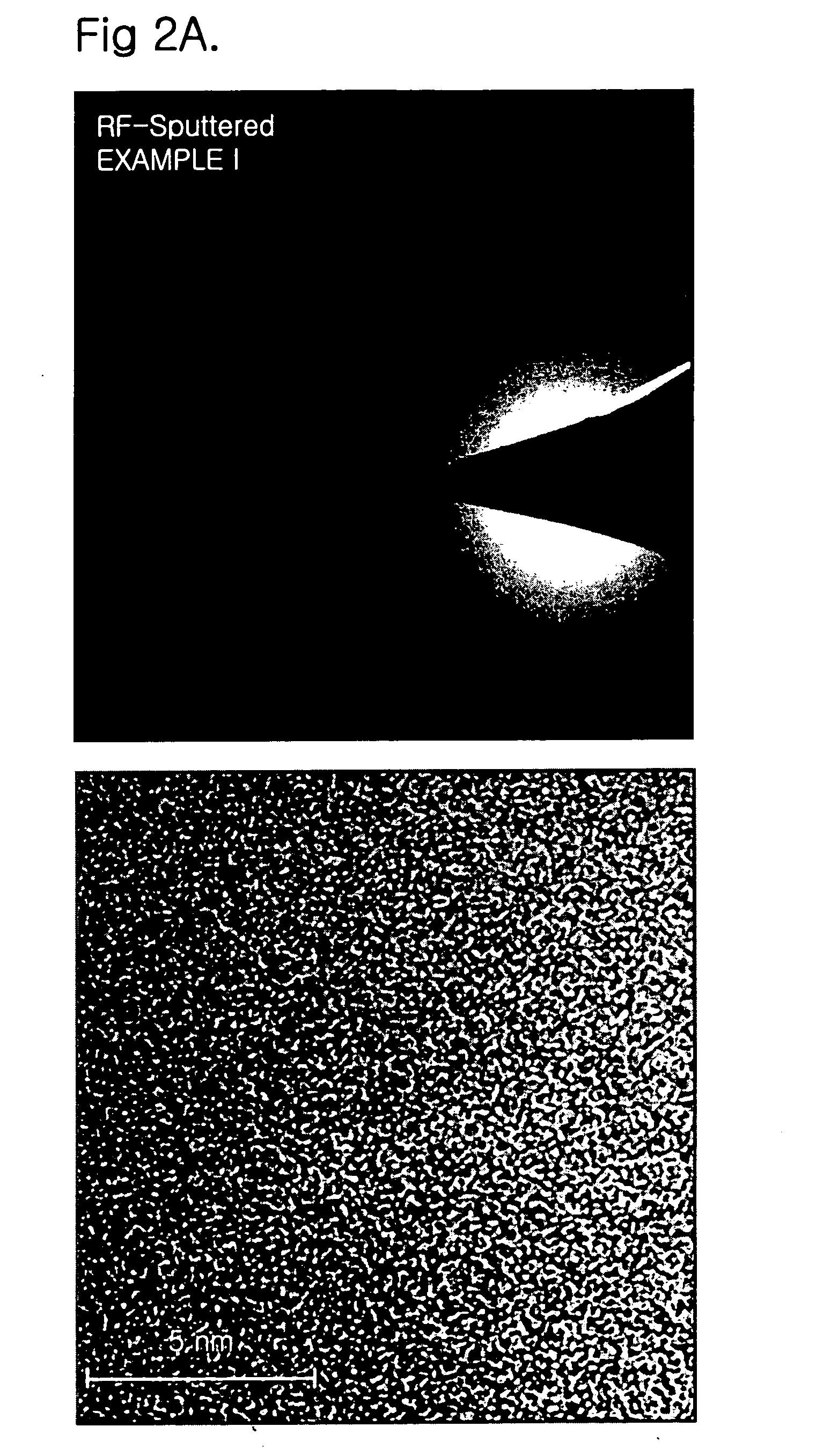

Anode active material, method of preparing the same, and anode and lithium battery containing the anode active material

An anode active material is provided. The anode active material includes a silicon thin film containing crystalline silicon having a Raman shift in a Raman spectrum ranging from about 490 to about 500 cm−1 and a full width at half maximum (FWHM) ranging from about 10 to about 30 cm−1. The volume of the anode active material does not change significantly during charging and discharging. Thus, a lithium battery employing the anode active material has an excellent capacity retention rate and a longer cycle lifetime.

Owner:SAMSUNG SDI CO LTD

Silicon thin film anode for lithium secondary battery and preparation method thereof

ActiveUS20090061319A1Increase capacityExcellent characteristicsElectrode carriers/collectorsVacuum evaporation coatingCarbon coatingReducing atmosphere

Disclosed are a silicon thin film anode for a lithium secondary battery having enhanced cycle characteristics and capacity and a preparation method thereof. A preparation method for a silicon thin film anode for a lithium secondary battery, comprises: preparing a collector including a metal; forming an anode active material layer including a silicon on the collector; forming one or more interface stabilizing layer, by annealing the collector and the anode active material layer under one of an inert atmosphere, a reduced atmosphere, and a vacuum atmosphere to react a metallic component of at least one of the collector and the anode active material layer with a silicon component of the anode active material layer at an interface therebetween; and forming a carbon coating layer on the anode active material layer by performing an annealing process in a hydrocarbon atmosphere.

Owner:KOREA INST OF SCI & TECH

Methods for uv-assisted conformal film deposition

InactiveUS20130196516A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingBiological activationElectromagnetic radiation

Described are methods of making silicon nitride (SiN) materials and other silicon-containing films, including carbon-containing and / or oxygen-containing films such as SiCN (also referred to as SiNC), SiON and SiONC films, on substrates. According to various embodiments, the methods involve electromagnetic radiation-assisted activation of one or more reactants. In certain embodiments, for example, the methods involve ultraviolet (UV) activation of vapor phase amine coreactants. The methods can be used to deposit silicon-containing films, including SiN and SiCN films, at temperatures below about 400° C.

Owner:NOVELLUS SYSTEMS

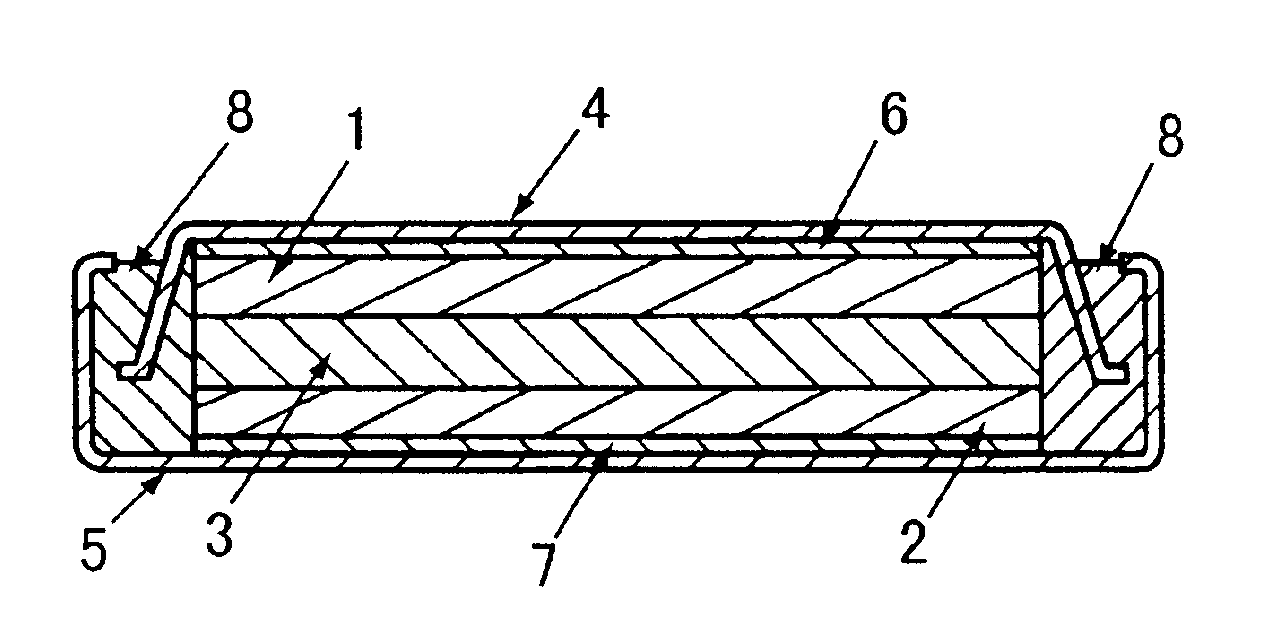

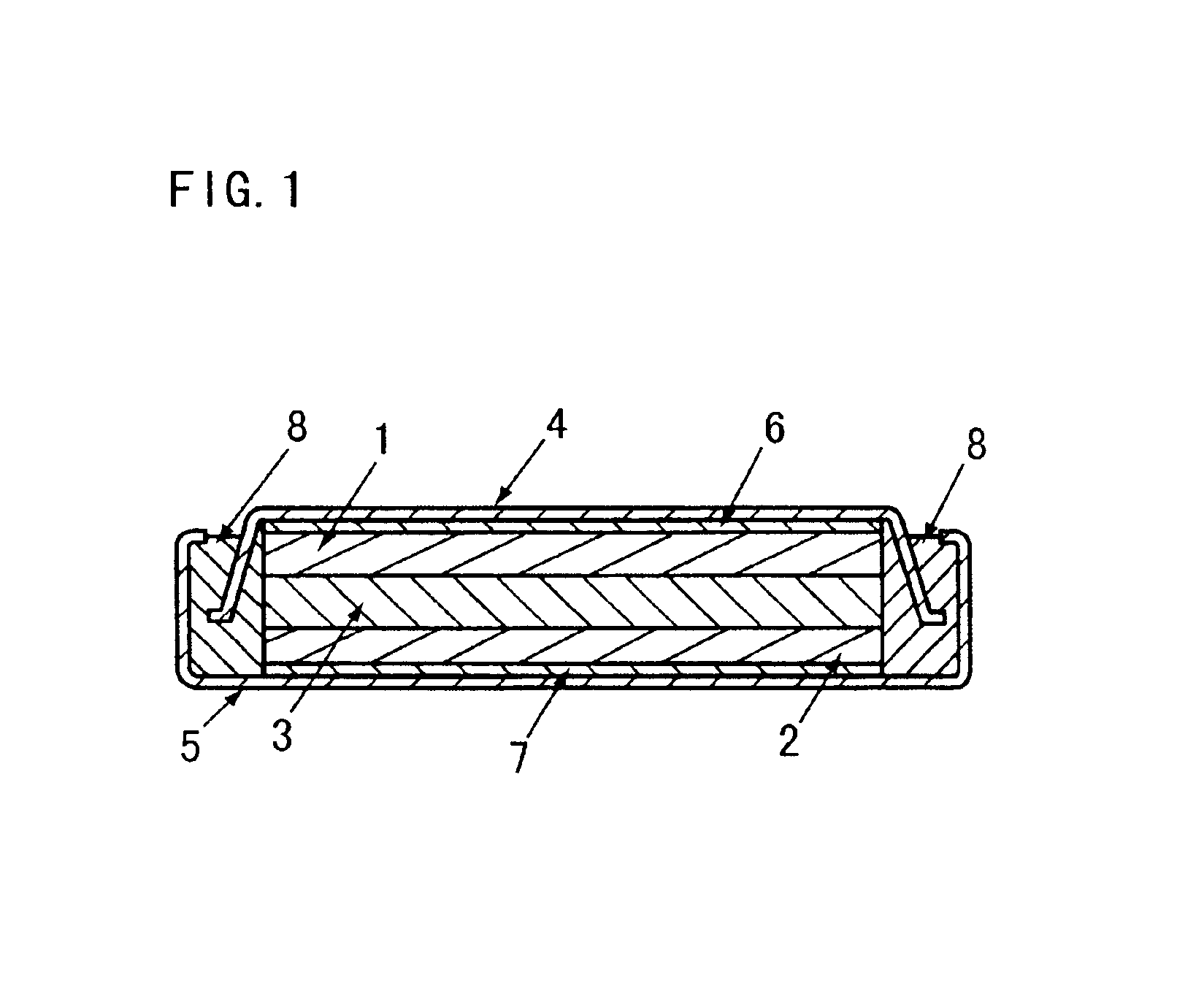

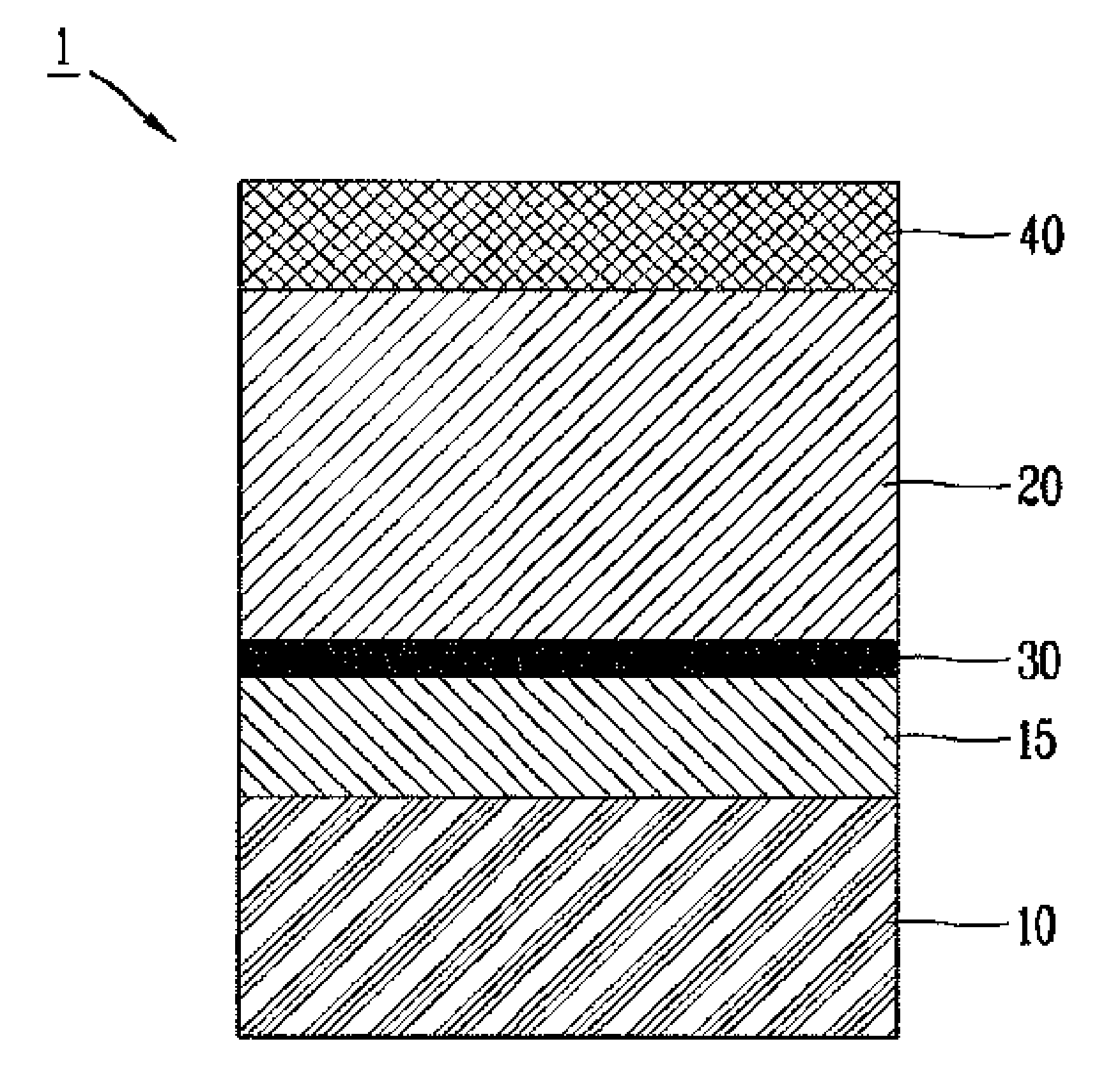

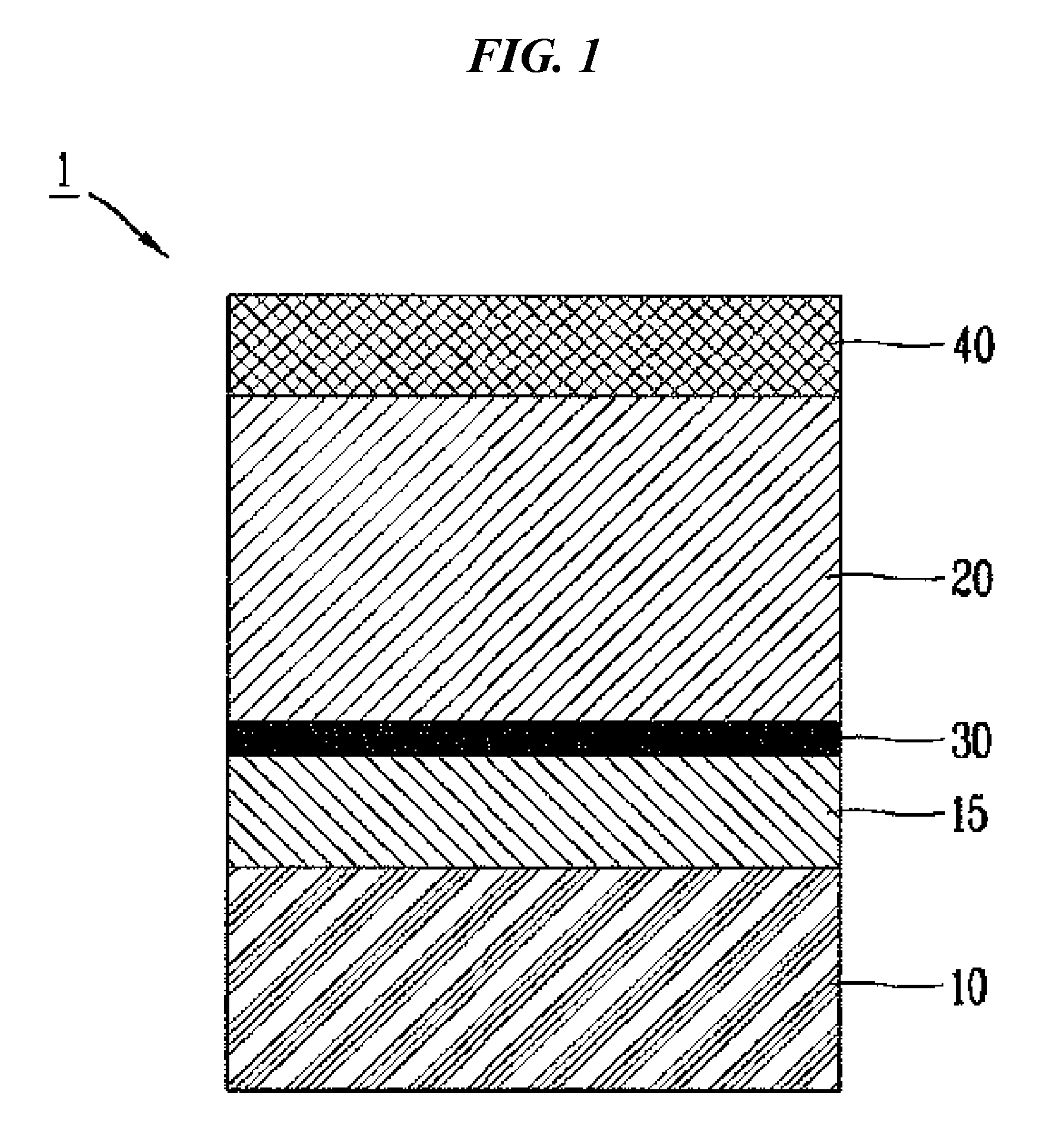

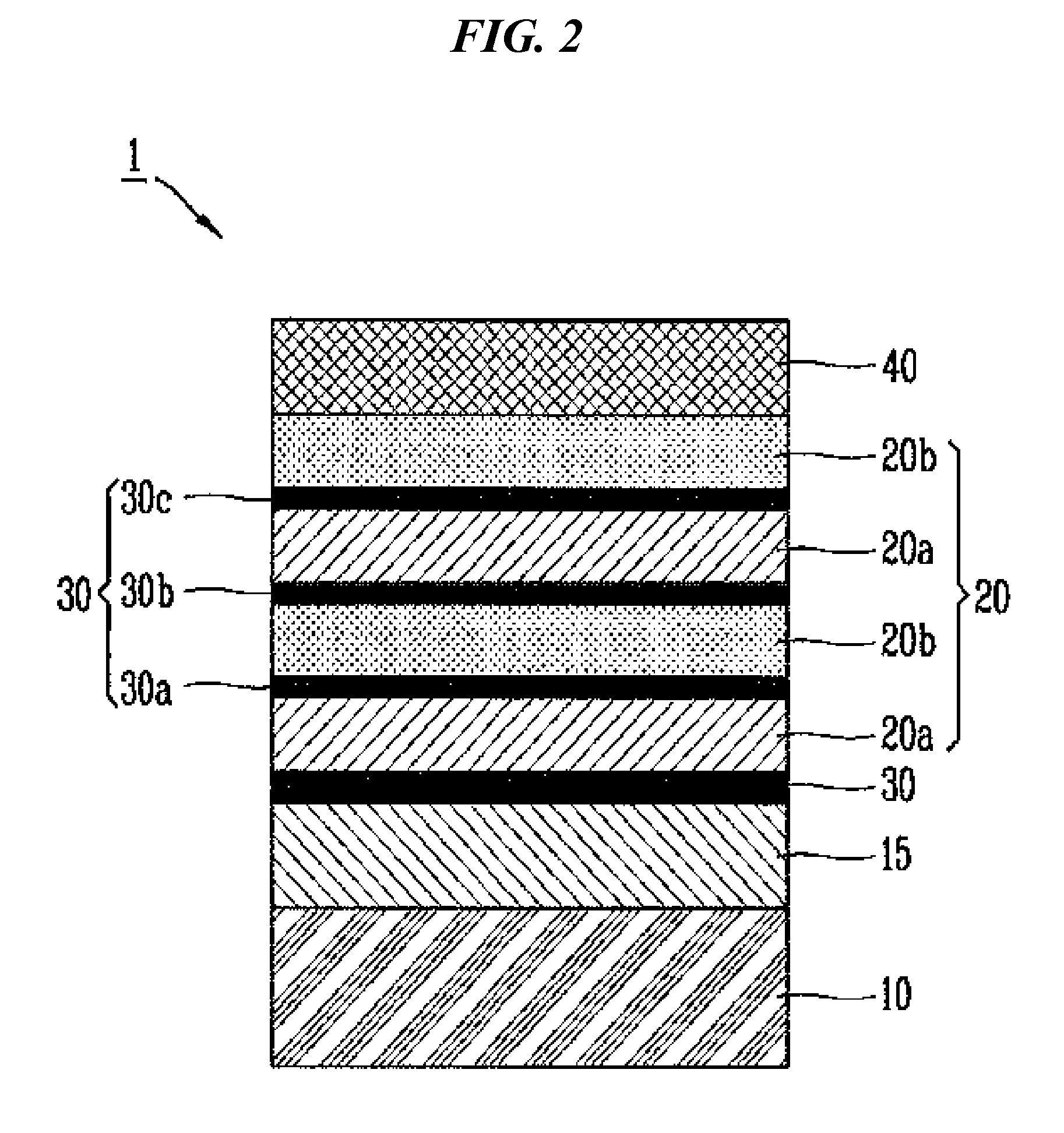

Energy device and method for producing the same

ActiveUS20050118503A1Large capacity and cycle characteristicFinal product manufacturePrimary cellsSilicon thin filmSilicon particle

A negative active material thin film provided on a collector layer directly or via an underlying layer has a multi-layered configuration including at least two silicon thin films containing silicon as a main component. Because of this, even when the thickness of the negative active material thin film is increased, the increase in thickness of one silicon thin film can be prevented by increasing the number of silicon thin films. Thus, the diameter of silicon particles substantially in an inverse truncated cone shape is not enlarged in the silicon thin film. Accordingly, in an energy device having a thin film mainly containing silicon as a negative active material, even when the thickness of the negative active material layer is increased to obtain a larger capacity, cycle characteristics are not degraded.

Owner:PANASONIC CORP

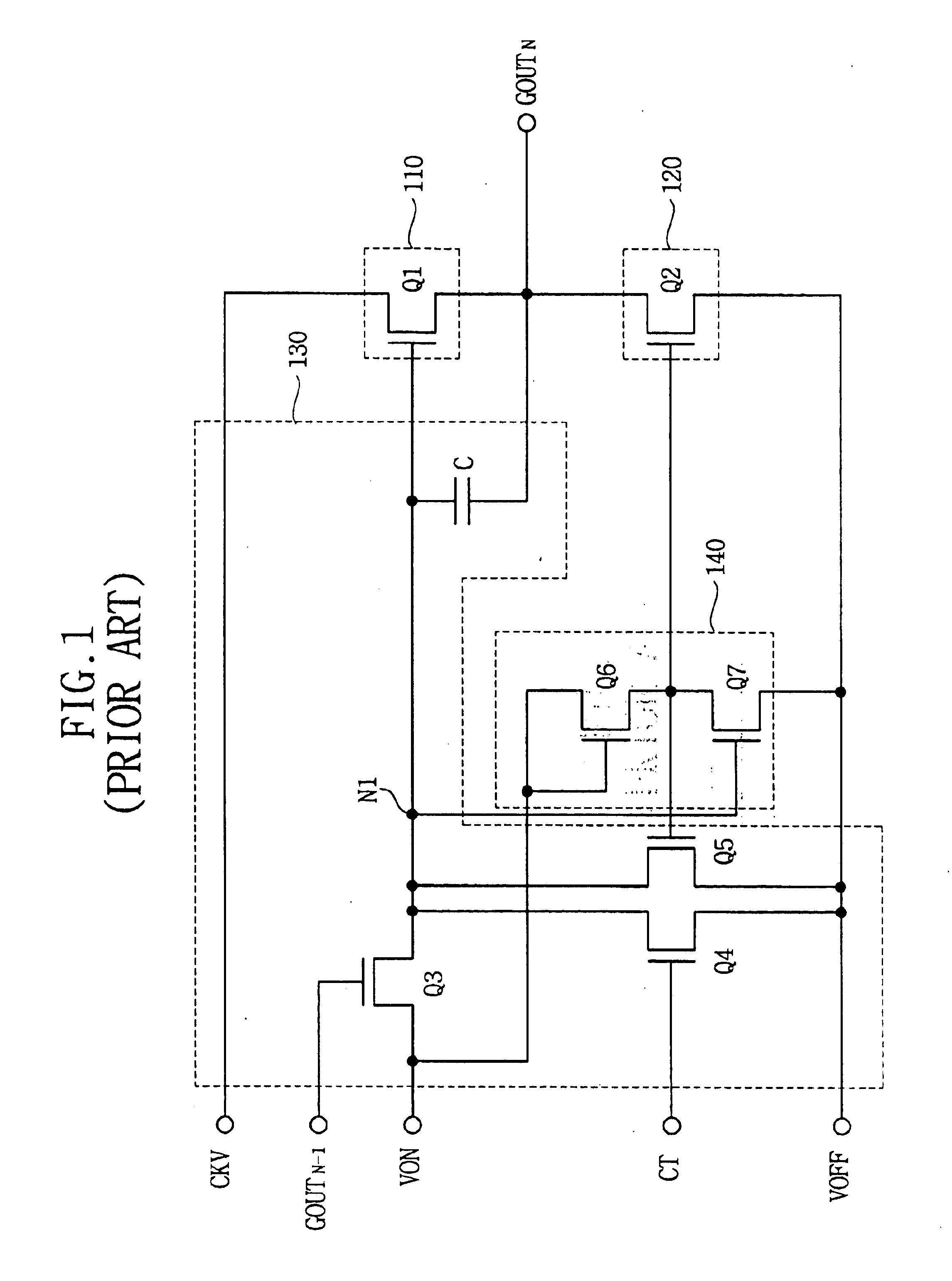

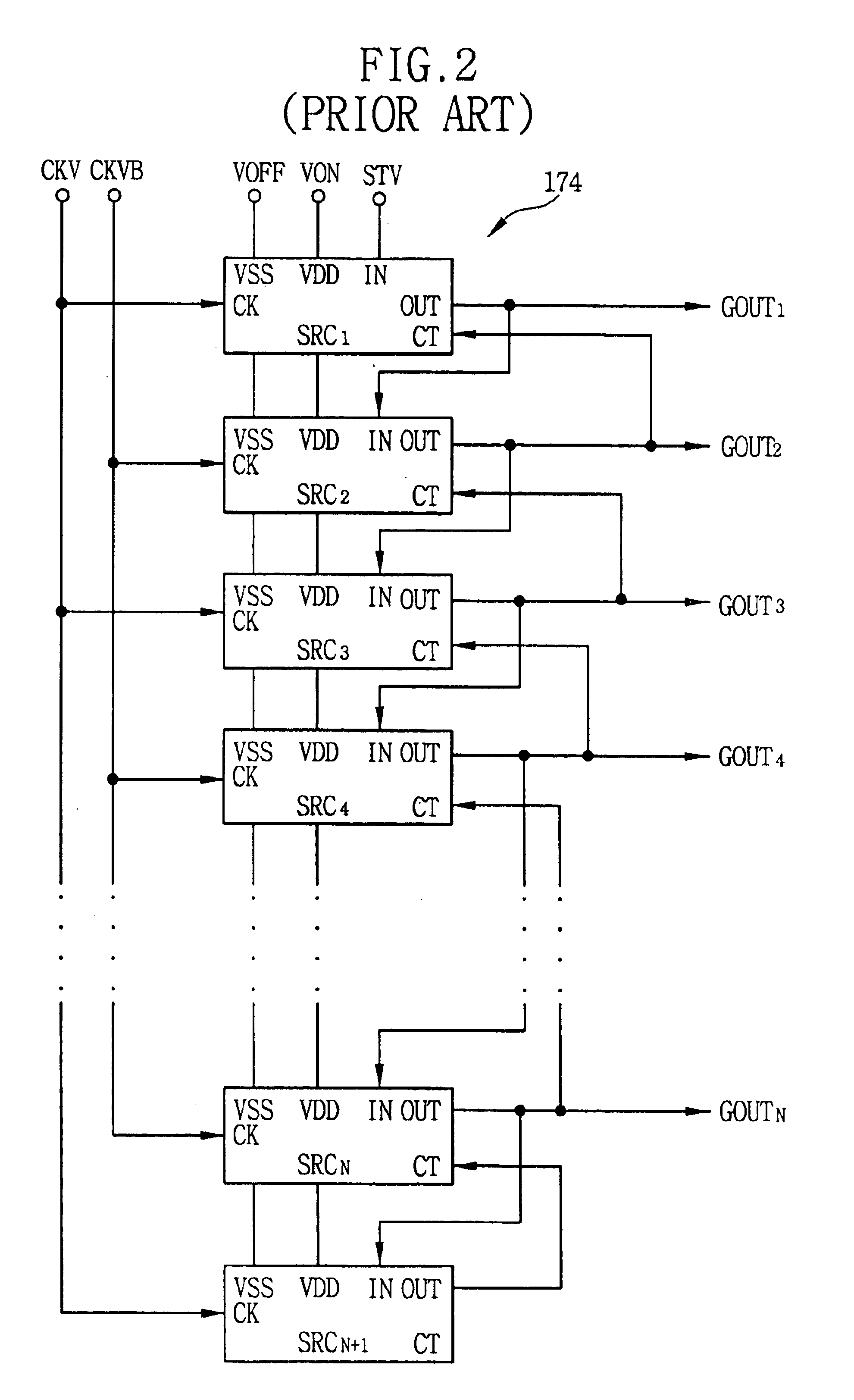

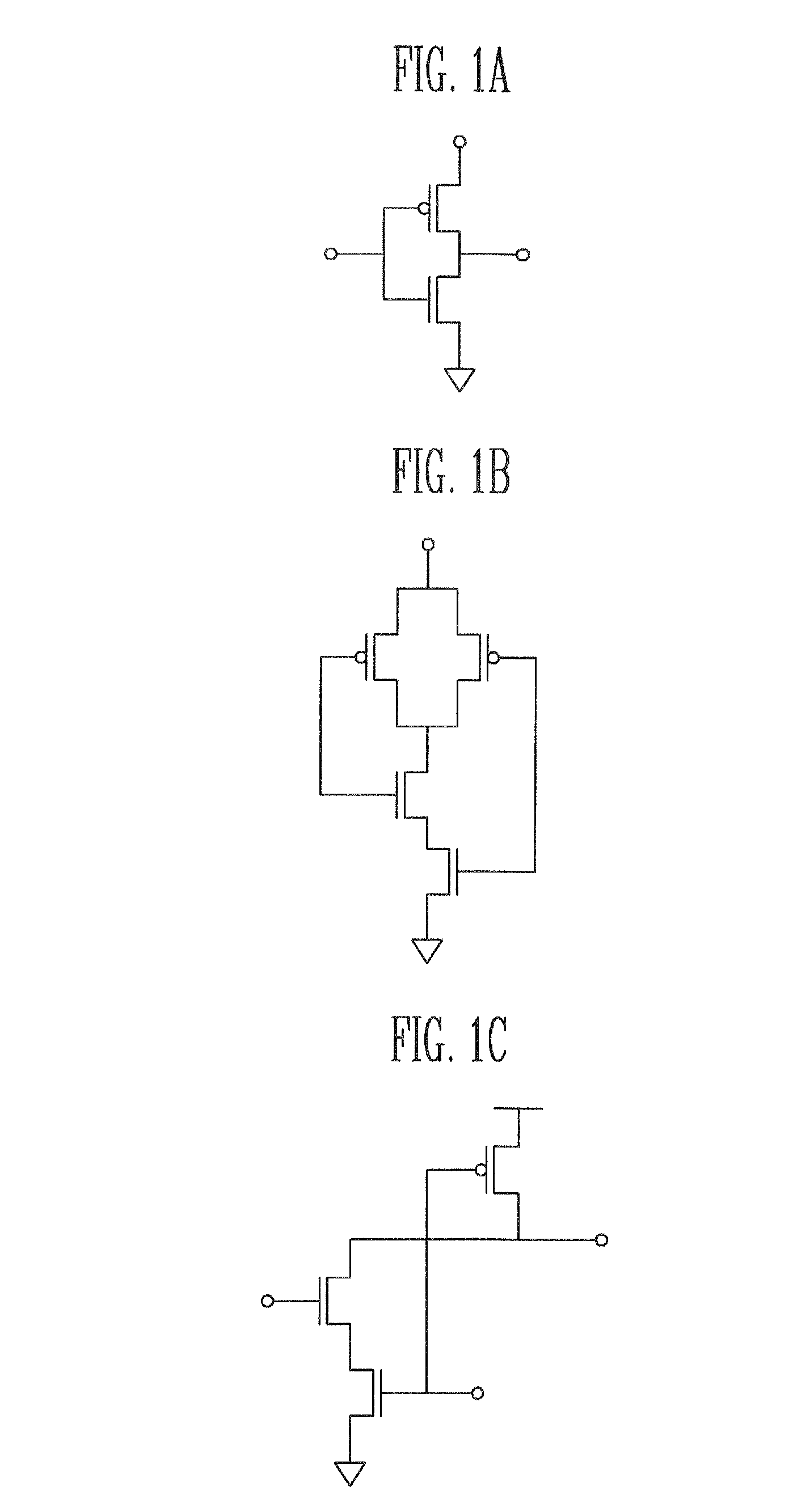

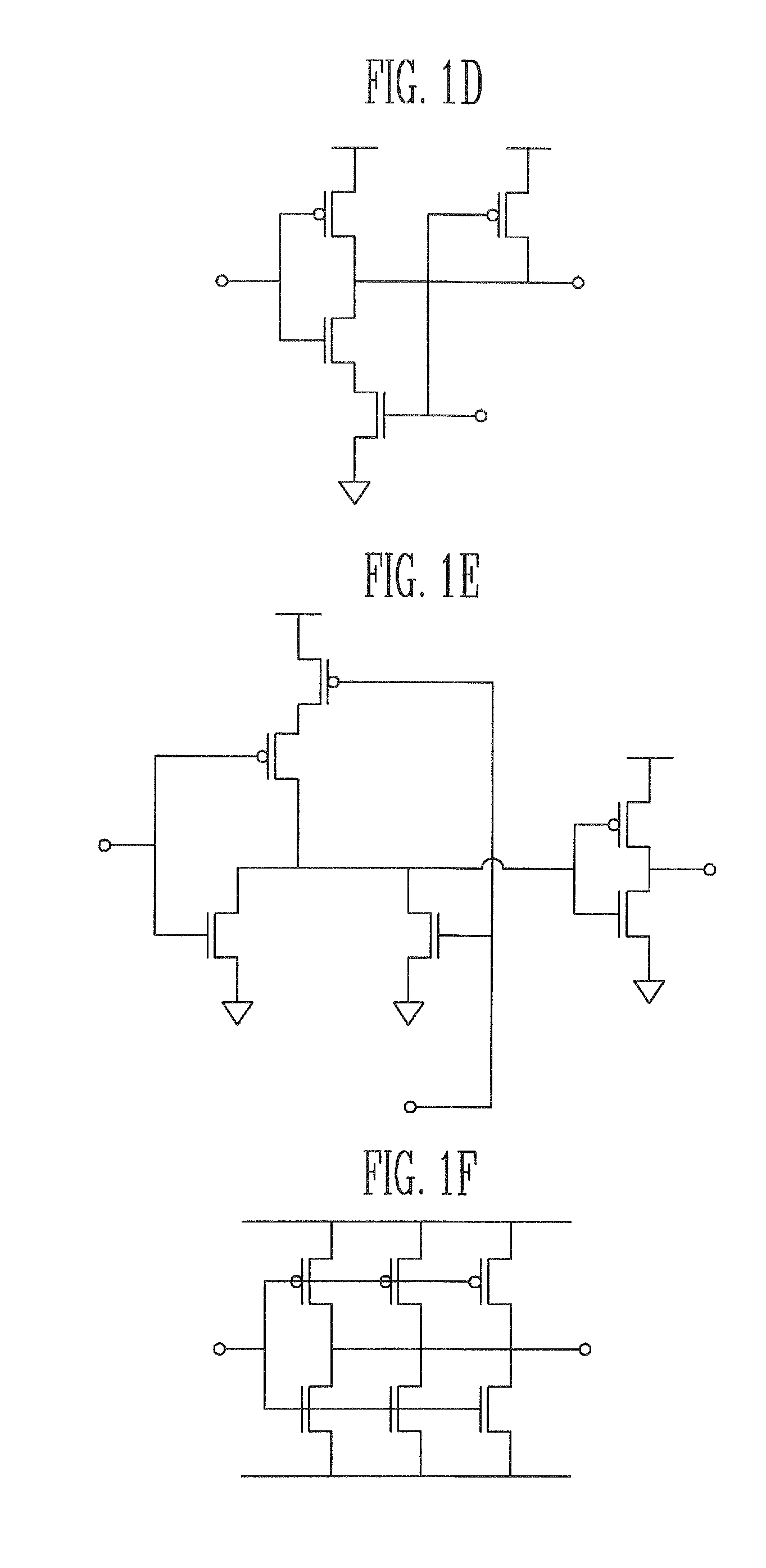

Amorphous-silicon thin film transistor and shift resister having the same

An amorphous-silicon thin film transistor and a shift resister shift resister having the amorphous-silicon TFT include a first conductive region, a second conductive region and a third conductive region. The first conductive region is formed on a first plane spaced apart from a substrate by a first distance. The second conductive region is formed on a second plane spaced apart from the substrate by a second distance. The second conductive region includes a body conductive region and two hand conductive regions elongated from both ends of the body conductive region to form an U-shape. The third conductive region is formed on the second plane. The third conductive region includes an elongated portion. The elongated portion is disposed between the two hand conductive regions of the second conductive region. The amorphous-silicon TFT and the shift resister having the amorphous TFT reduce a parasitic capacitance between the gate electrode and drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

Method for preparing silicon thin film heterojunction solar cell

InactiveCN1588649AAvoid damageReduce hydrogen contentFinal product manufacturePhotovoltaic energy generationHeterojunctionSilicon thin film

A prepn. method of silicon thin film heterojunction solar cell includes following steps: cleaning substrate, semiconductor cleaning technology is used to do primary cleaing to substrate surface, then do ultrasonic cleaning in deionized water several times; nitrogen blow drying; prepare nitrinsic amorphous silicon layer by heater chemical vapour phase depositing technology, tungsten filament temp. is measured by pyrometer, temp of heater and sample are determined separately by two electric thermo-couples, temp. is controlled by electric temp. controller; to react and grow thin film on substrate surface; to redeposit a transmitting layer on intrinsic amorphous silicon thin film; front and back electrodes forming, sputtering technology is used to form front and back electrodes; finally to proceed vacuum heat annealing process. The thin film produced by the invention has illumination stability, the photoconduction gain can reach to 10 to the power 6 on Am1.5 100mW / cm2 standard illumination.

Owner:SHANGHAI JIAO TONG UNIV

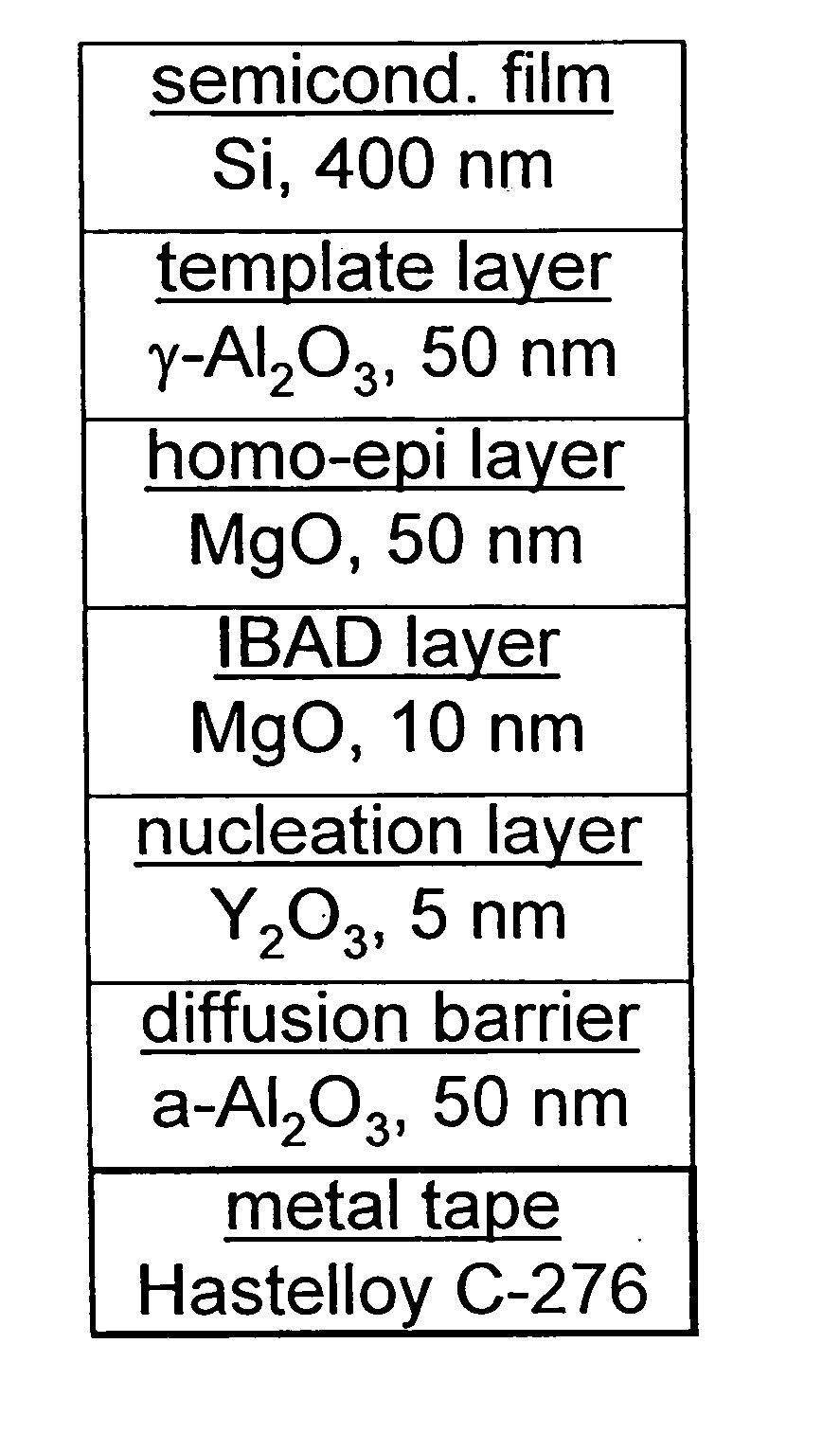

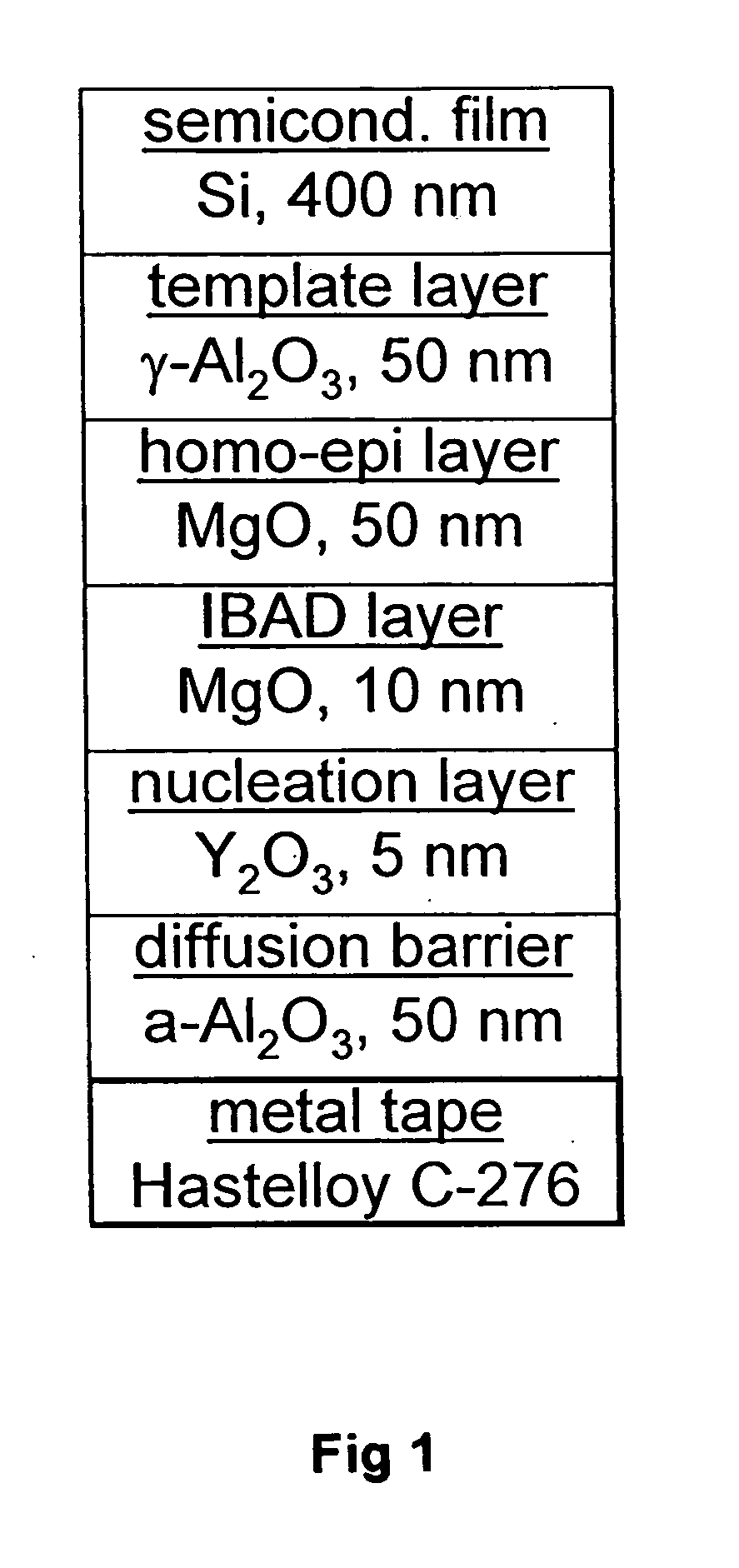

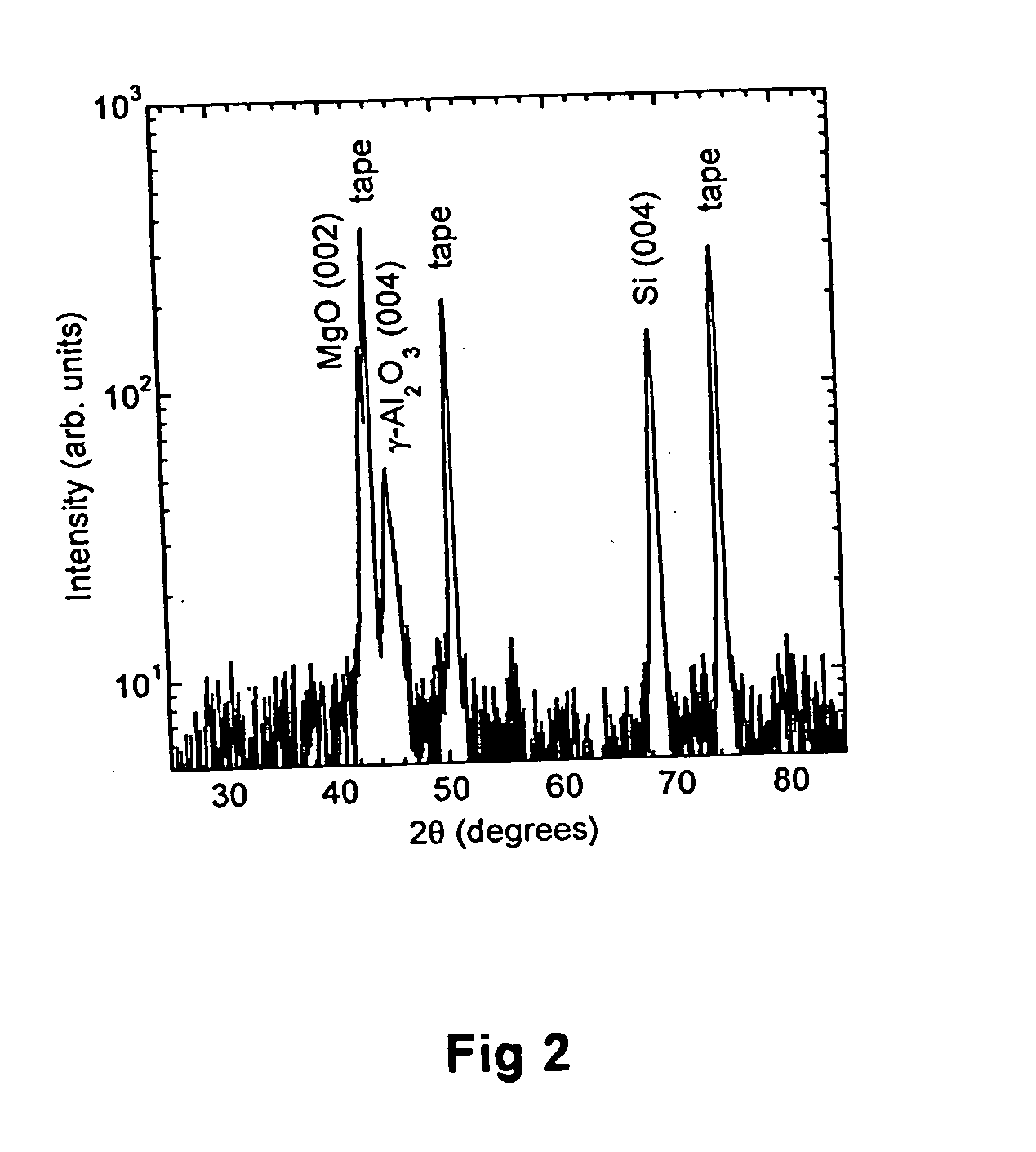

Near single-crystalline, high-carrier-mobility silicon thin film on a polycrystalline/amorphous substrate

InactiveUS20060115964A1Low chemical reactivityPolycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor materialsCharge carrier mobility

A template article including a base substrate including: (i) a base material selected from the group consisting of polycrystalline substrates and amorphous substrates, and (ii) at least one layer of a differing material upon the surface of the base material; and, a buffer material layer upon the base substrate, the buffer material layer characterized by: (a) low chemical reactivity with the base substrate, (b) stability at temperatures up to at least about 800° C. under low vacuum conditions, and (c) a lattice crystal structure adapted for subsequent deposition of a semiconductor material; is provided, together with a semiconductor article including a base substrate including: (i) a base material selected from the group consisting of polycrystalline substrates and amorphous substrates, and (ii) at least one layer of a differing material upon the surface of the base material; and, a buffer material layer upon the base substrate, the buffer material layer characterized by: (a) low chemical reactivity with the base substrate, (b) stability at temperatures up to at least about 800° C. under low vacuum conditions, and (c) a lattice crystal structure adapted for subsequent deposition of a semiconductor material, and, a top-layer of semiconductor material upon the buffer material layer.

Owner:LOS ALAMOS NATIONAL SECURITY

CMOS thin film transistor, method of fabricating the same and organic light emitting display device having the same

ActiveUS20100176395A1Simple manufacturing processMaintain electrical performanceTransistorSolid-state devicesCMOSOxide thin-film transistor

Owner:SAMSUNG DISPLAY CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com