Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

201 results about "Arsenide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In chemistry, an arsenide is a compound of arsenic with a less electronegative element or elements. Many metals form binary compounds containing arsenic, and these are called arsenides. They exist with many stoichiometries, and in this respect arsenides are similar to phosphides.

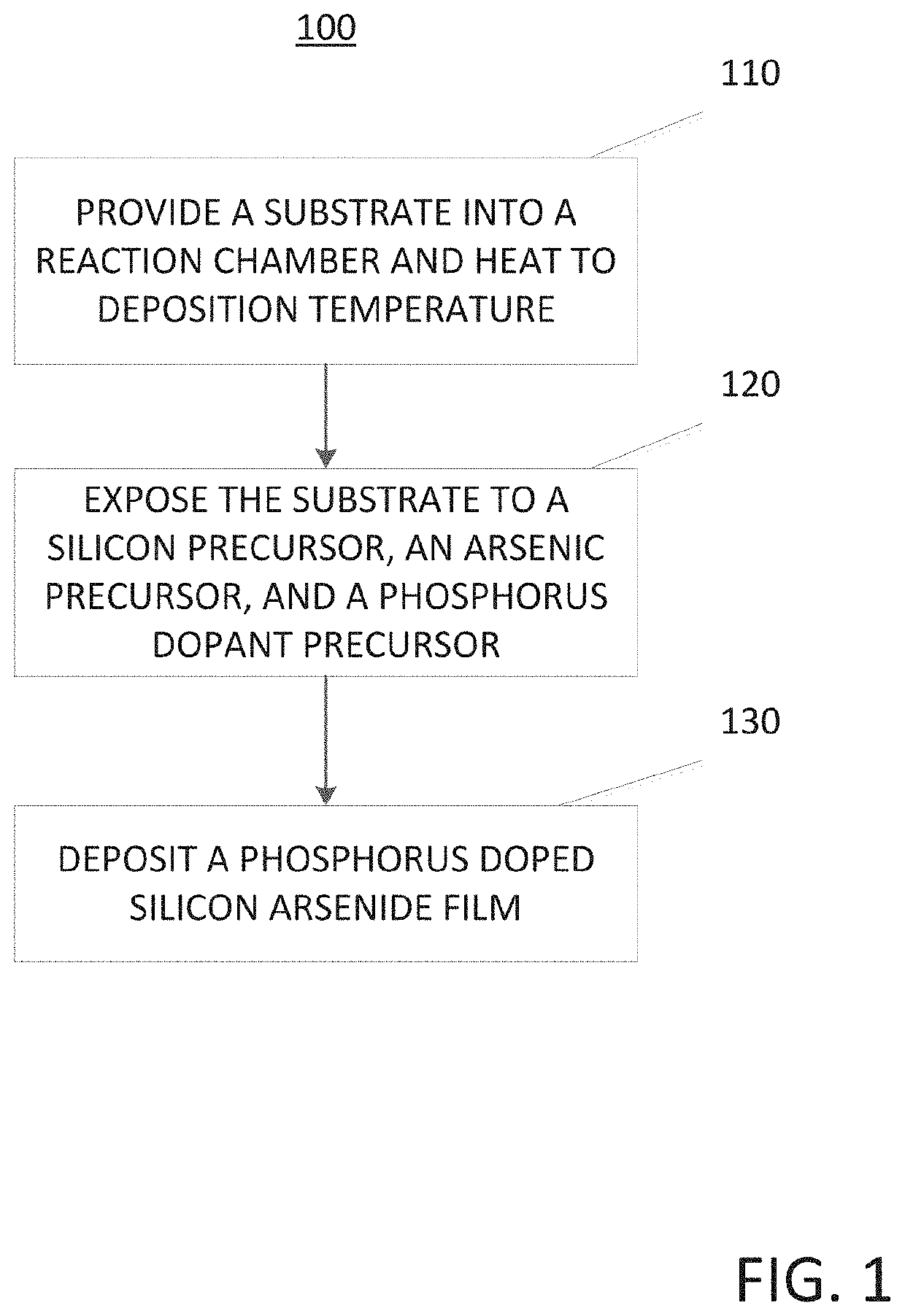

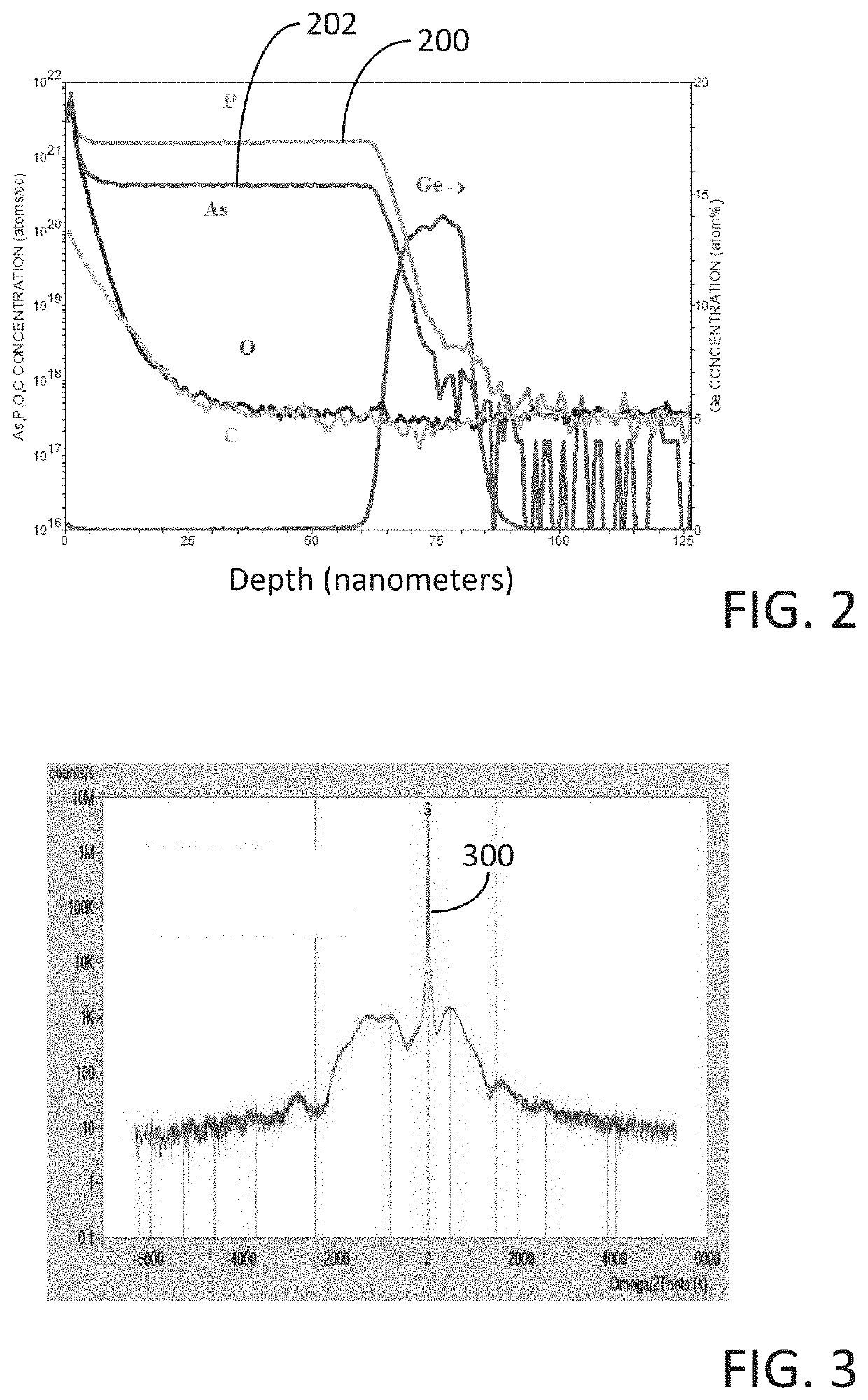

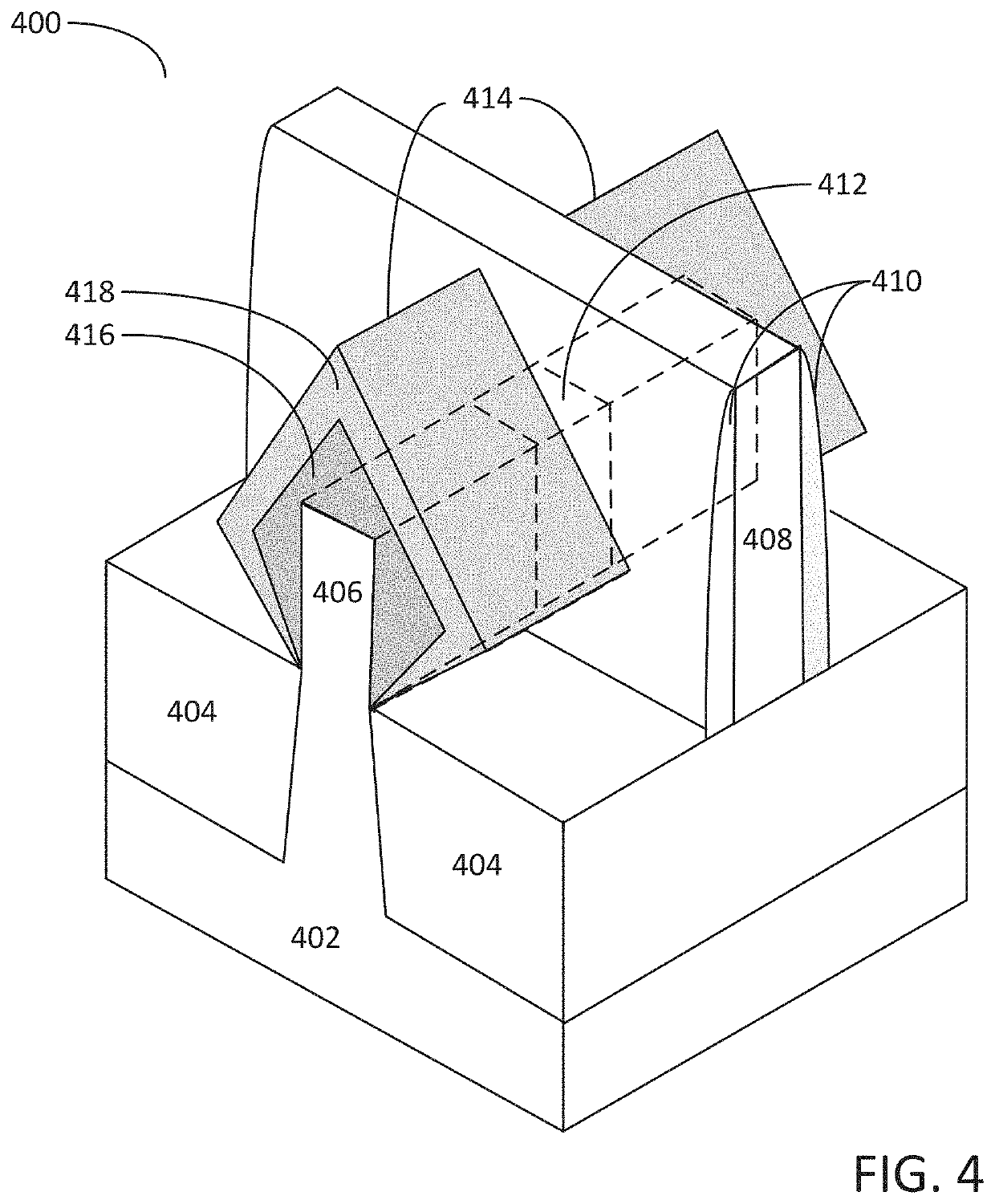

Method for depositing a phosphorus doped silicon arsenide film and related semiconductor device structures

ActiveUS20200395444A1Inhibited DiffusionTransistorPolycrystalline material growthDevice materialSilicon thin film

A method for depositing a phosphorus doped silicon arsenide film is disclosed. The method may include, providing a substrate within a reaction chamber, heating the substrate to a deposition temperature, exposing the substrate to a silicon precursor, an arsenic precursor, and a phosphorus dopant precursor, and depositing the phosphorus doped silicon arsenide film over a surface of the substrate. Semiconductor device structures including a phosphorus doped silicon arsenide film deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

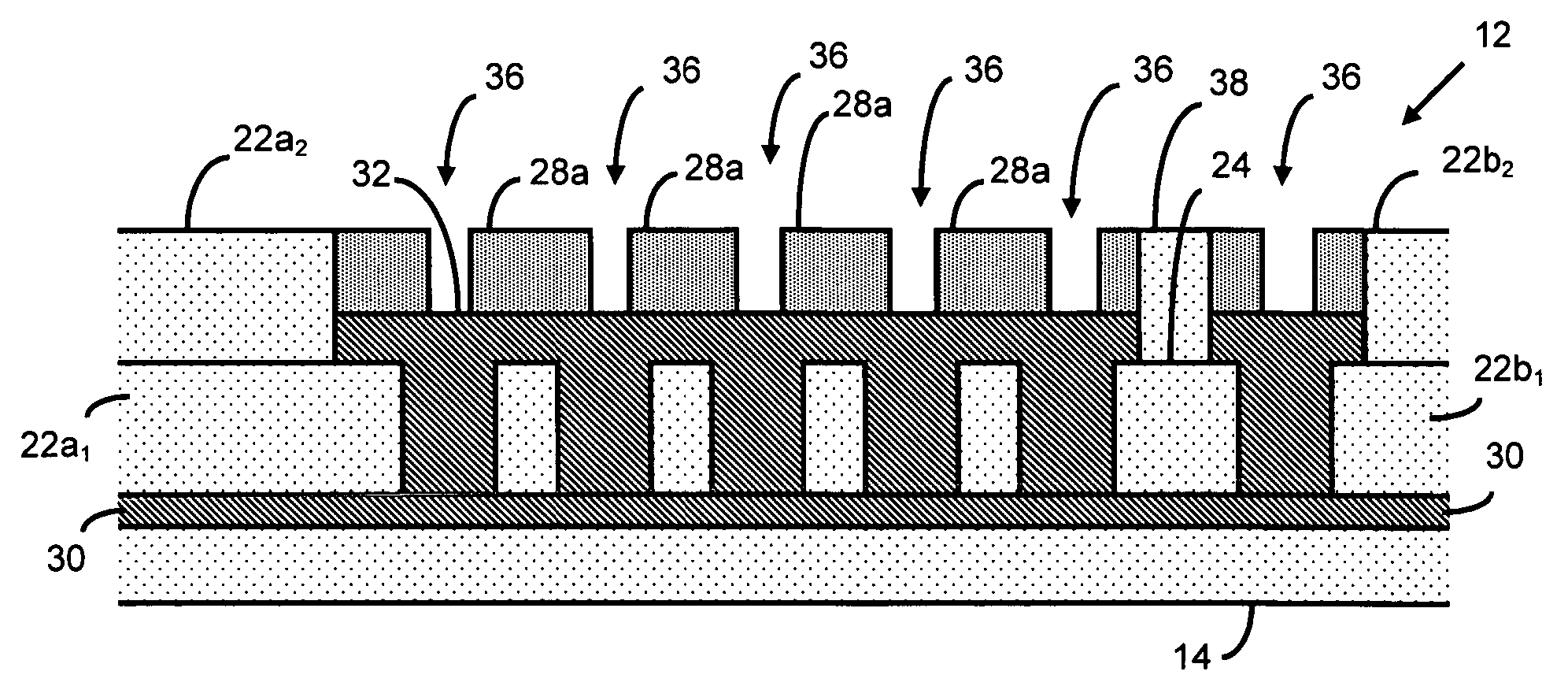

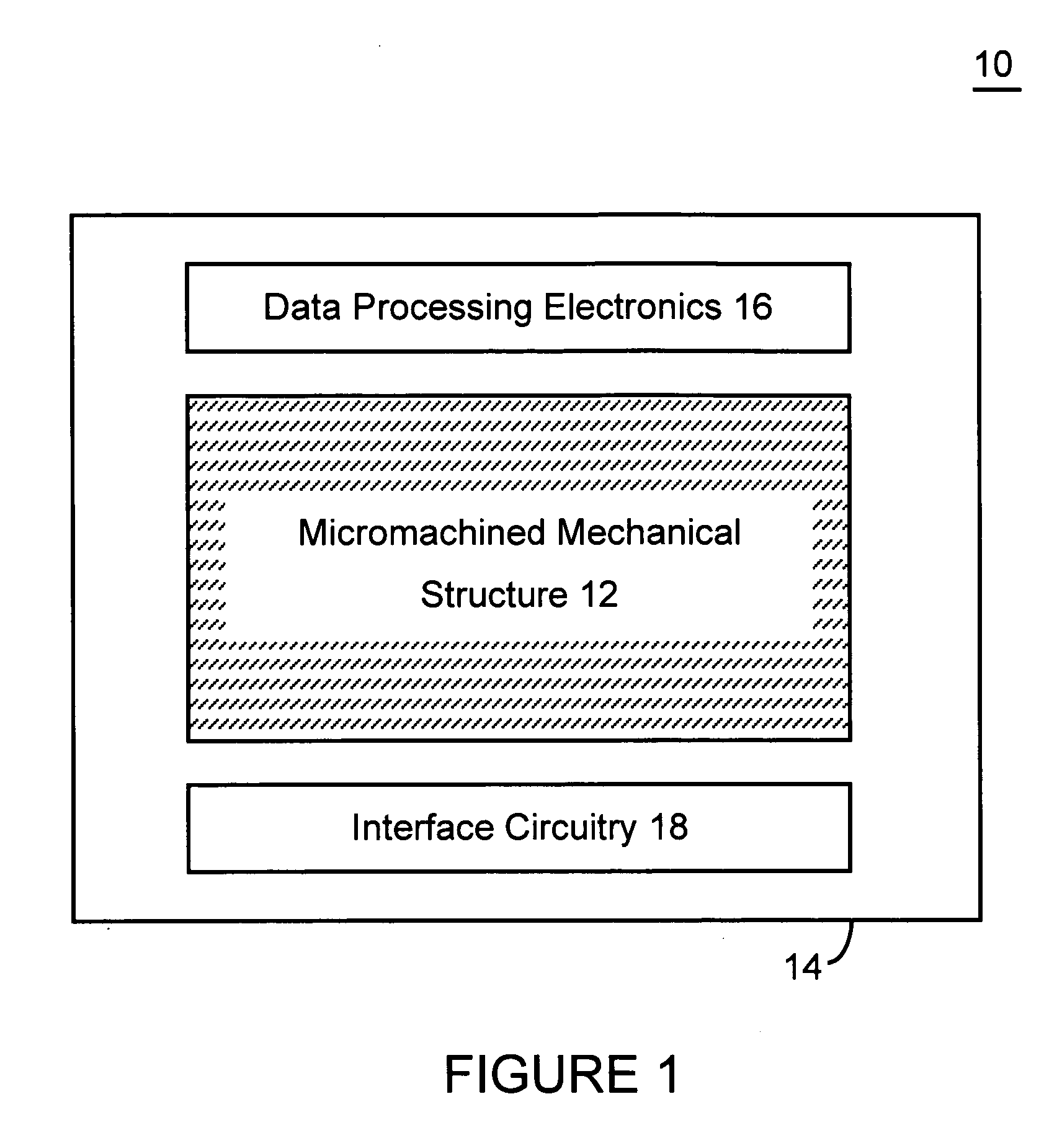

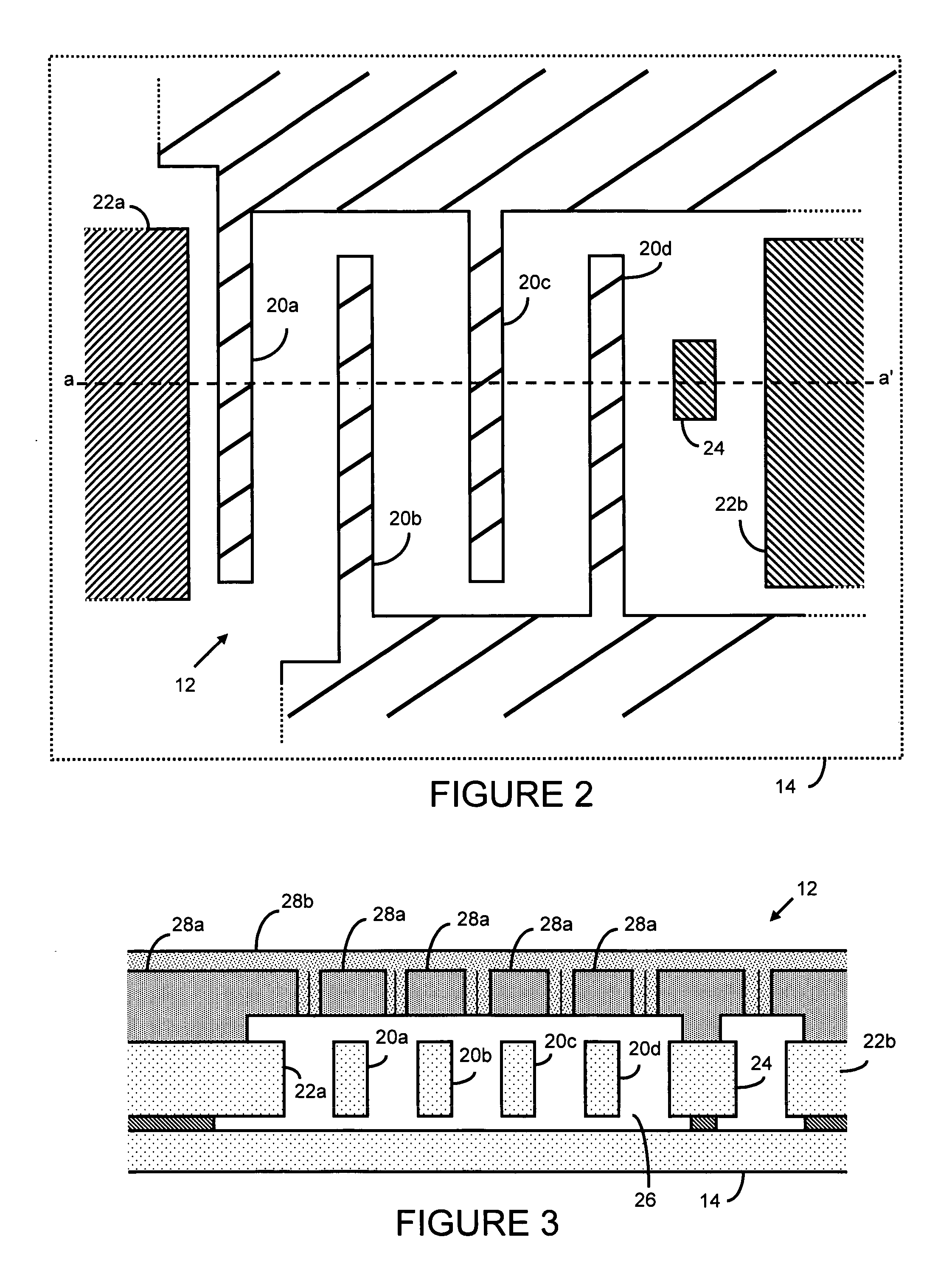

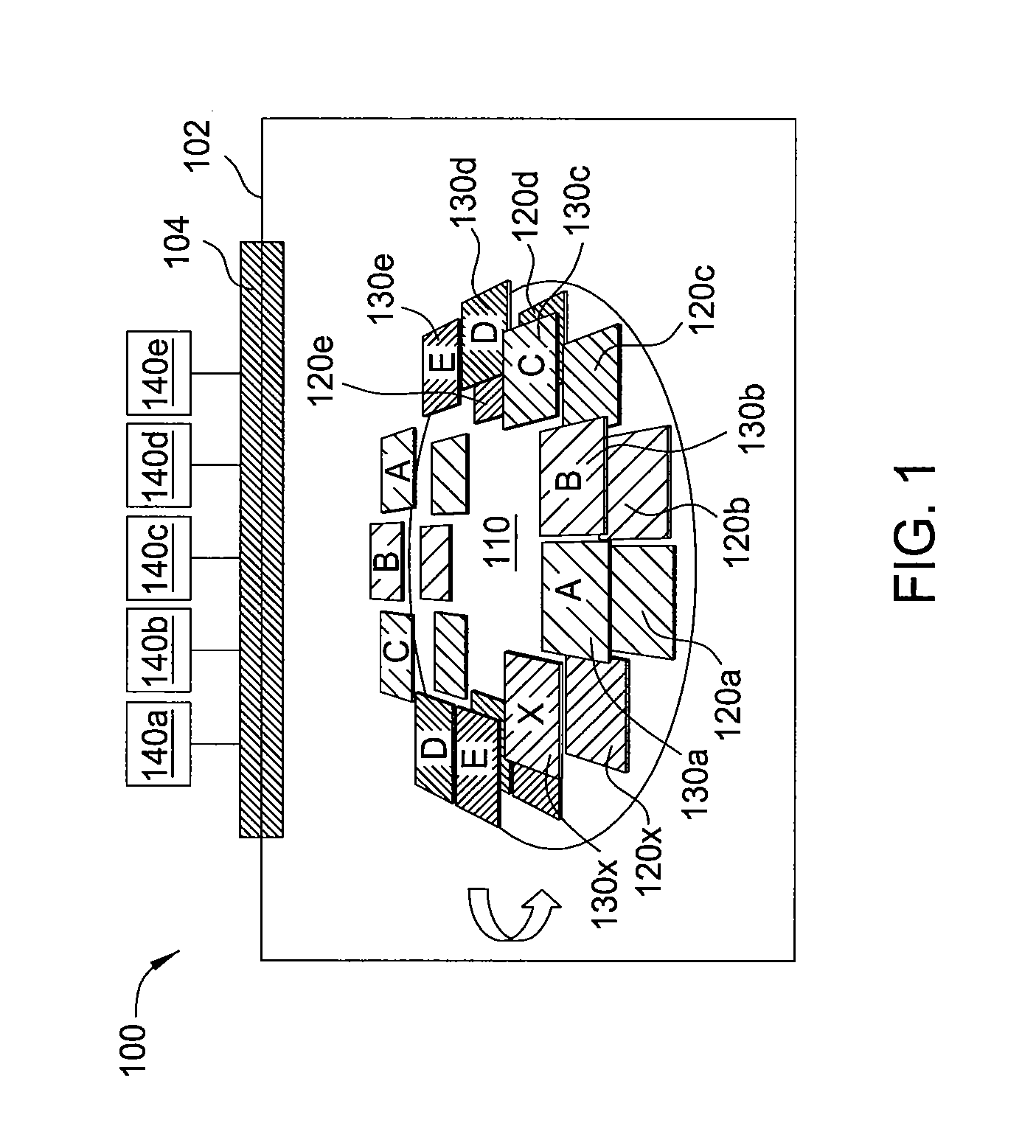

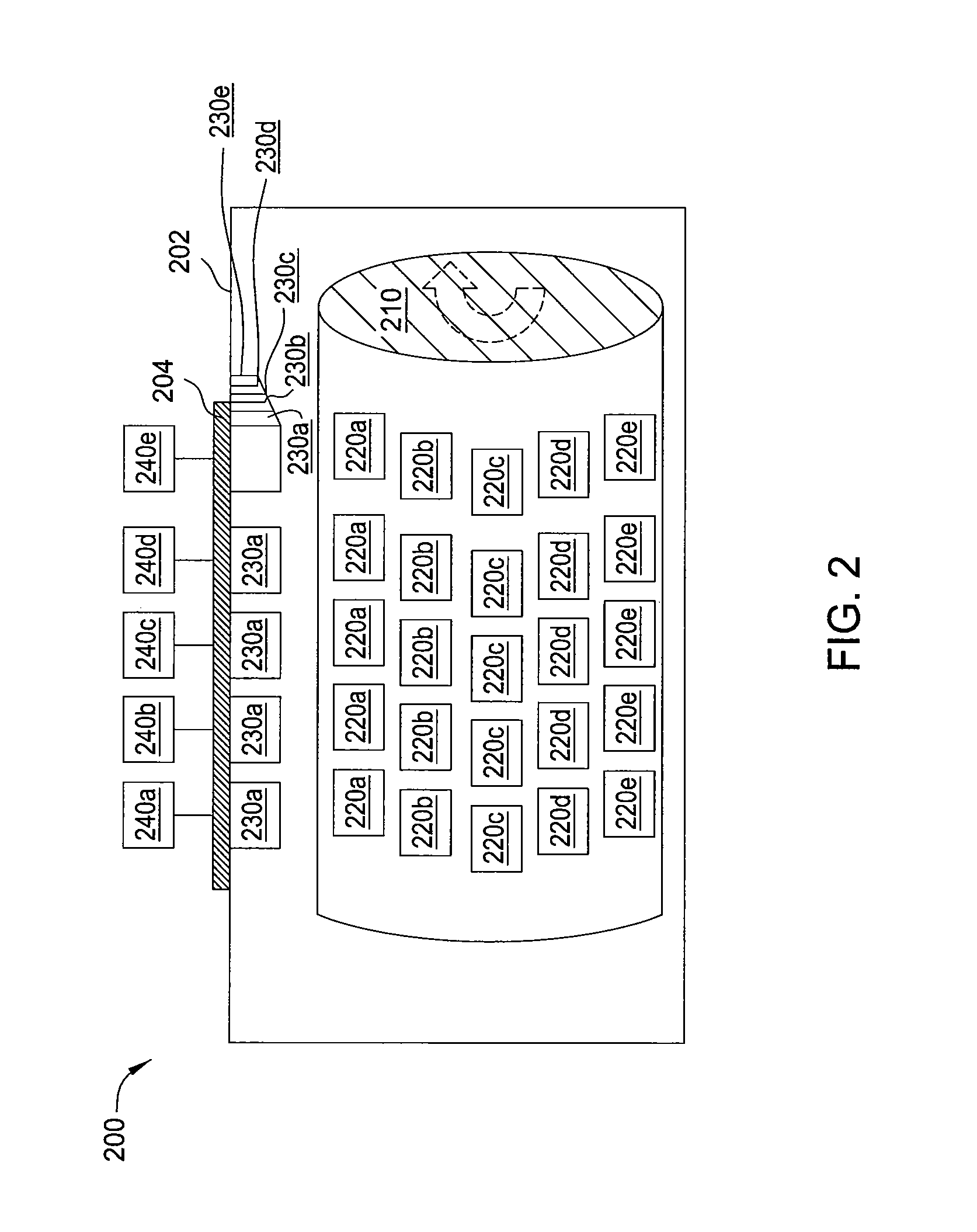

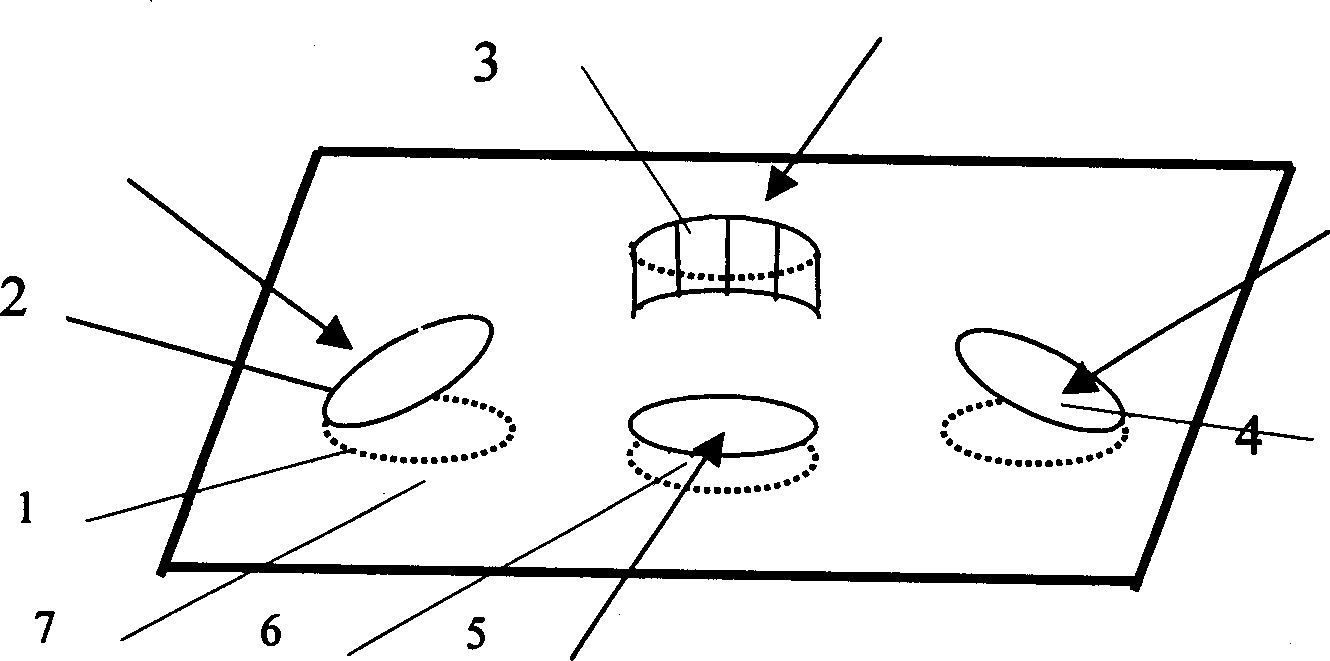

Microelectromechanical systems, and methods for encapsulating and fabricating same

ActiveUS20060108652A1Acceleration measurement using interia forcesSemiconductor/solid-state device detailsIntegrated circuitEngineering

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a MEMS device, and technique of fabricating or manufacturing a MEMS device, having mechanical structures encapsulated in a chamber prior to final packaging. The material that encapsulates the mechanical structures, when deposited, includes one or more of the following attributes: low tensile stress, good step coverage, maintains its integrity when subjected to subsequent processing, does not significantly and / or adversely impact the performance characteristics of the mechanical structures in the chamber (if coated with the material during deposition), and / or facilitates integration with high-performance integrated circuits. In one embodiment, the material that encapsulates the mechanical structures is, for example, silicon (polycrystalline, amorphous or porous, whether doped or undoped), silicon carbide, silicon-germanium, germanium, or gallium-arsenide.

Owner:ROBERT BOSCH GMBH

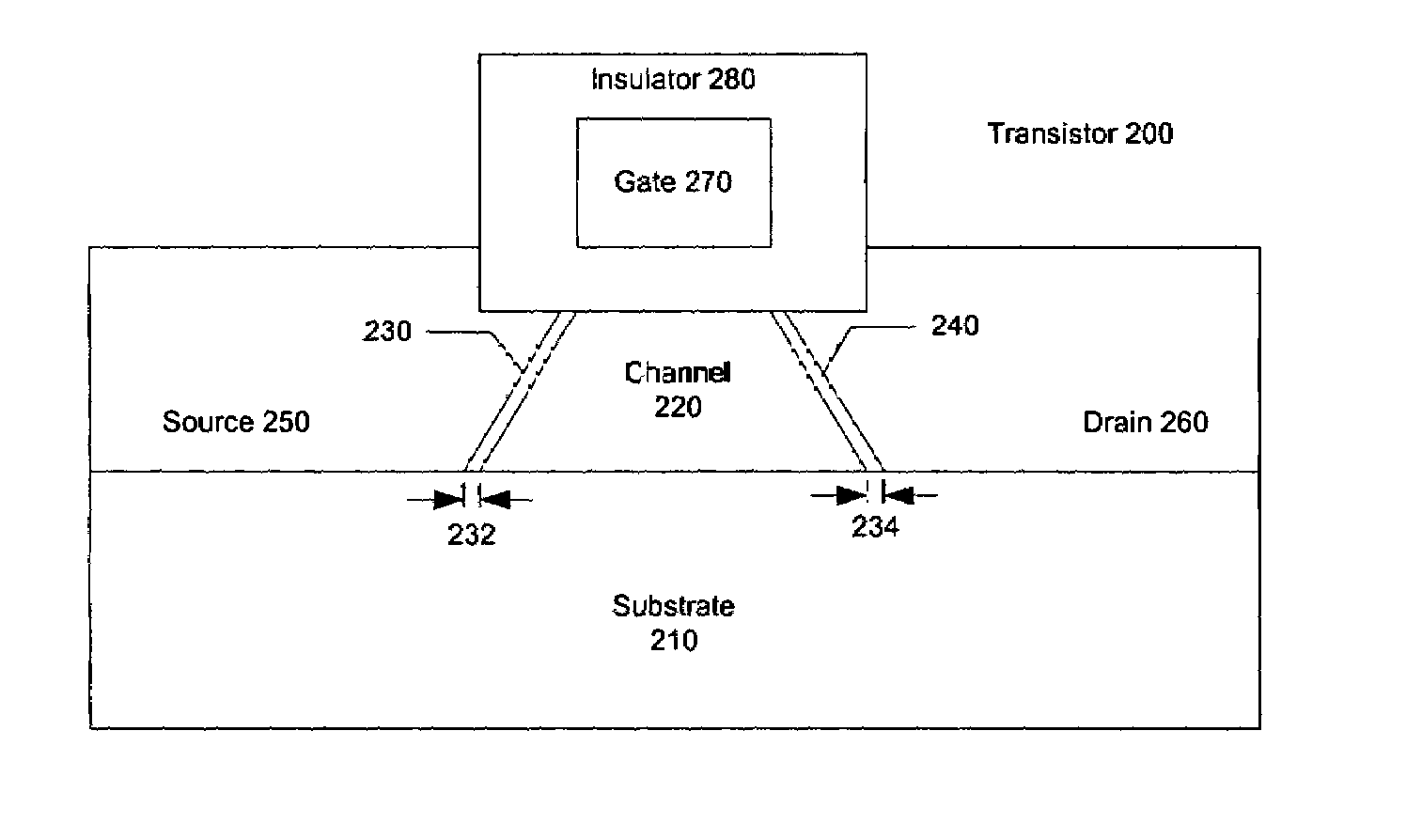

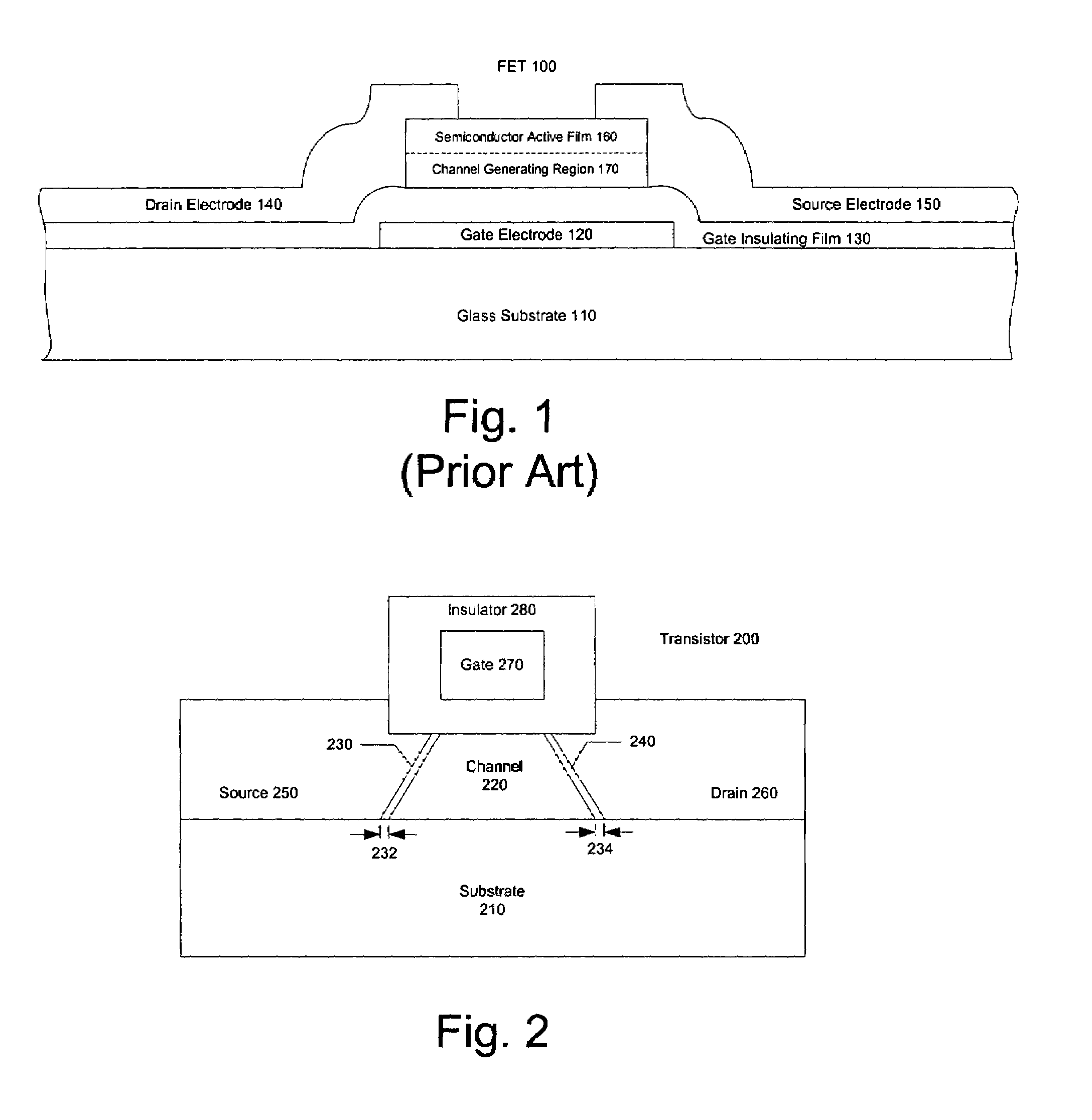

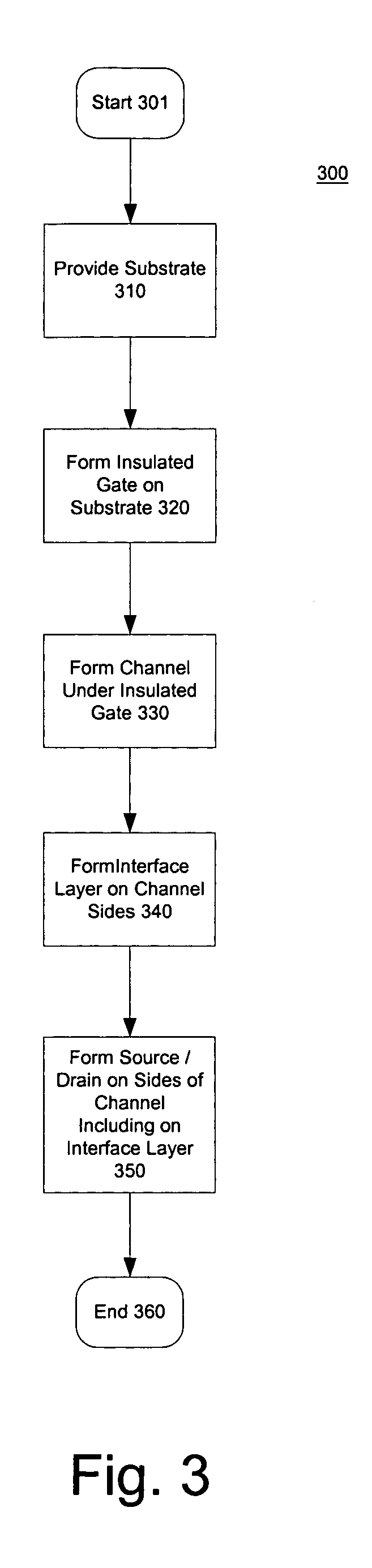

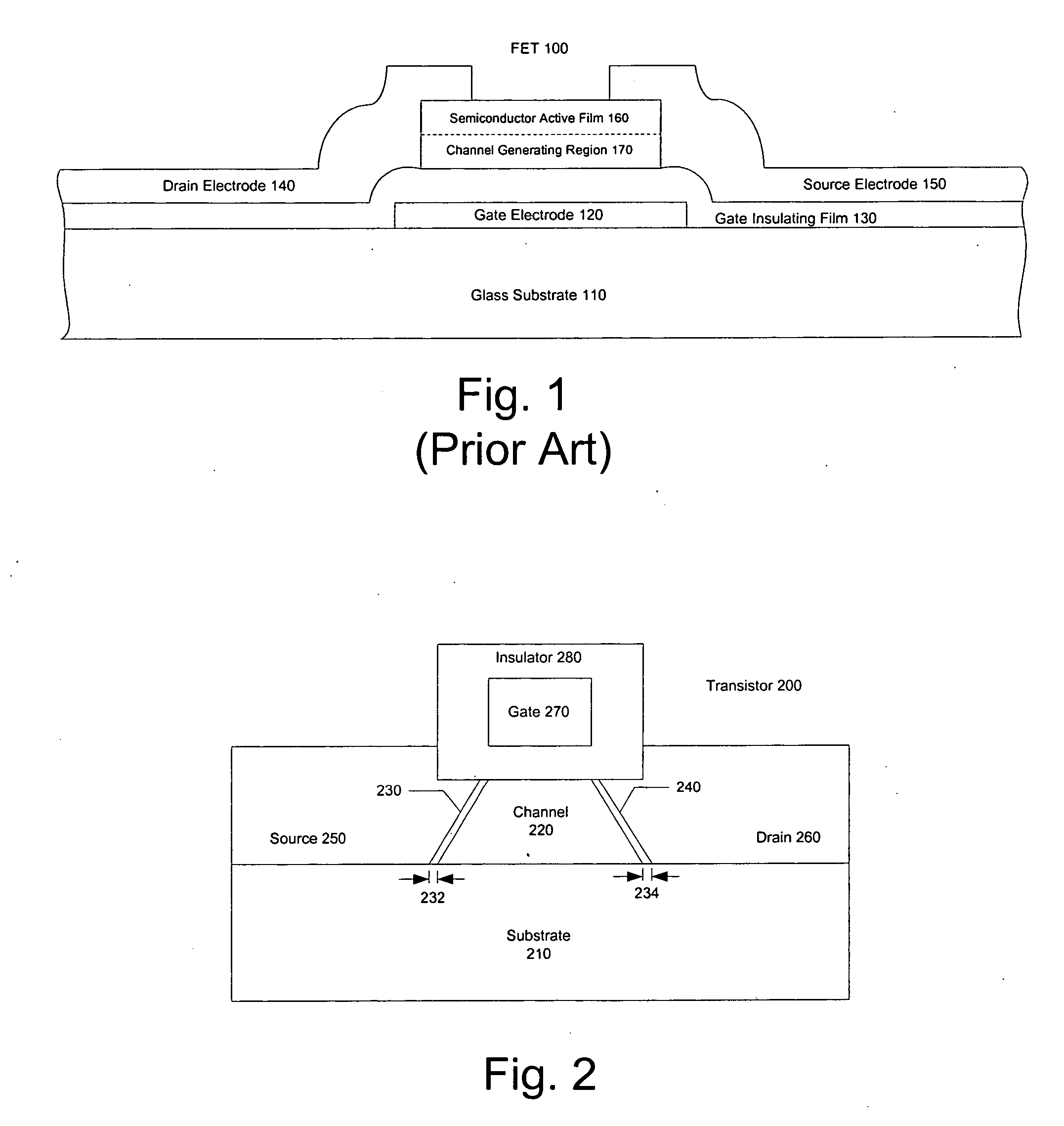

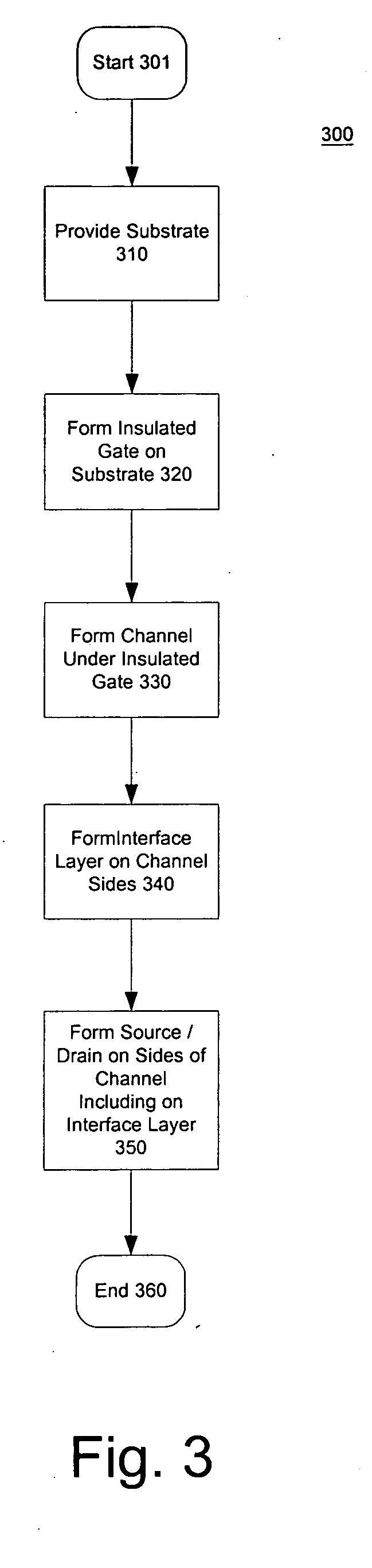

Insulated gate field effect transistor having passivated Schottky barriers to the channel

InactiveUS7112478B2Reduce the impactReduce impactTransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

A transistor includes a semiconductor channel disposed nearby a gate and in an electrical path between a source and a drain, wherein the channel and at least one of the source or the drain are separated by an interface layer so as to form a channel-interface layer-source / drain junction in which a Fermi level of the semiconductor channel is depinned in a region near the junction and the junction has a specific contact resistance of less than approximately 1000 Ω-μm2. The interface layer may include a passivating material such as a nitride, a fluoride, an oxide, an oxynitride, a hydride and / or an arsenide of the semiconductor of the channel. In some cases, the interface layer consists essentially of a monolayer configured to depin the Fermi level of the semiconductor of the channel, or an amount of passivation material sufficient to terminate all or a sufficient number of dangling bonds of the semiconductor channel to achieve chemical stability of the surface. Also, the interface layer may include a separation layer of a material different than the passivating material. Where used, the separation layer has a thickness sufficient to reduce effects of metal-induced gap states in the semiconductor channel.

Owner:ACORN SEMI LLC

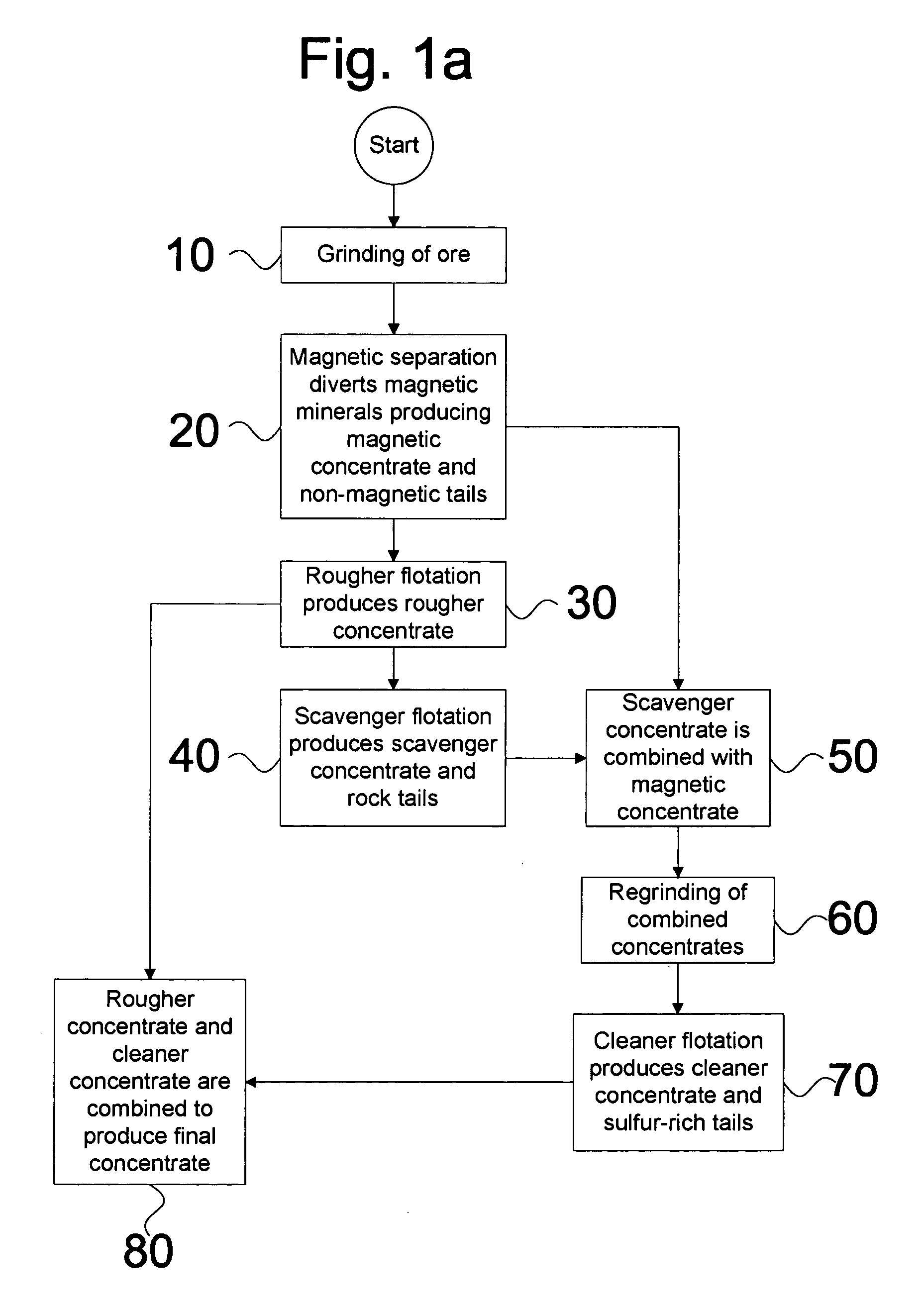

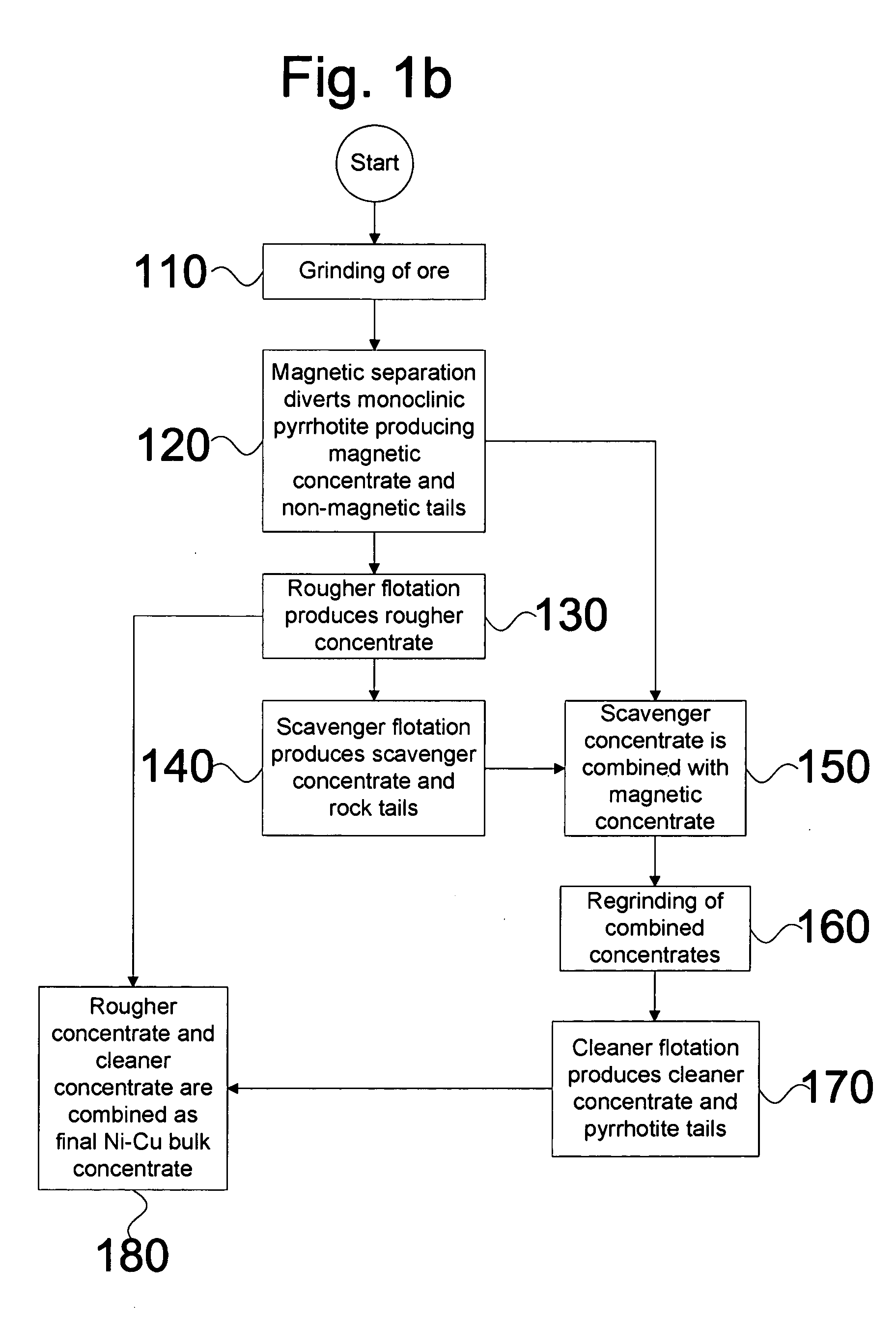

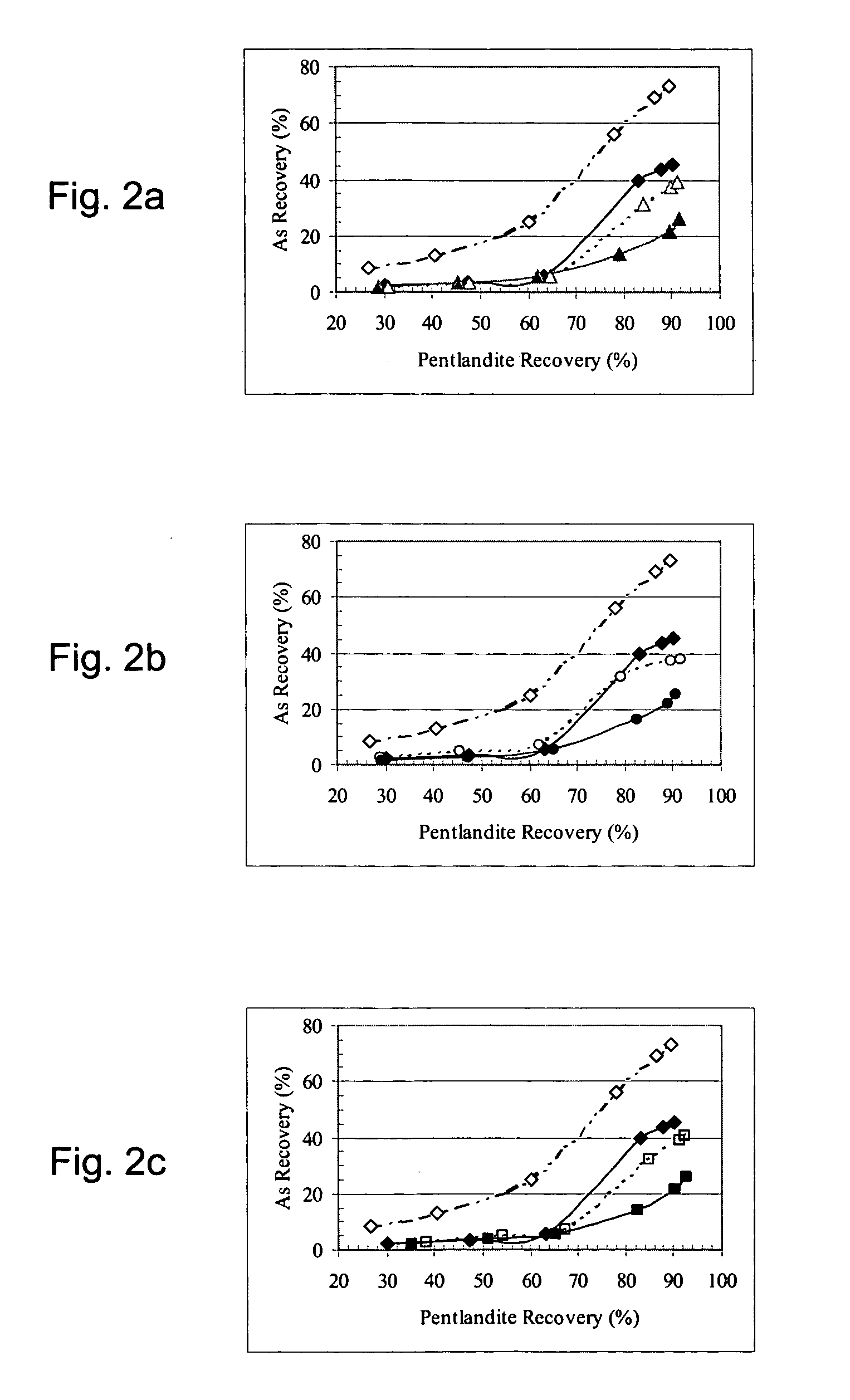

Arsenide depression in flotation of multi-sulfide minerals

A mineral separation process includes wet-grinding the ore to liberation of minerals, oxidizing the slurry using air, hydrogen peroxide or other oxidants and floating the valuable minerals at a pH between about 9.0 and 10.0 with a xanthate as collector, and a combination of a polyamine and a sulfur containing species as depressants for arsenide minerals. This depressant suite effectively depresses the flotation of arsenide minerals with no effect on the flotation of the valuable minerals.

Owner:INCO

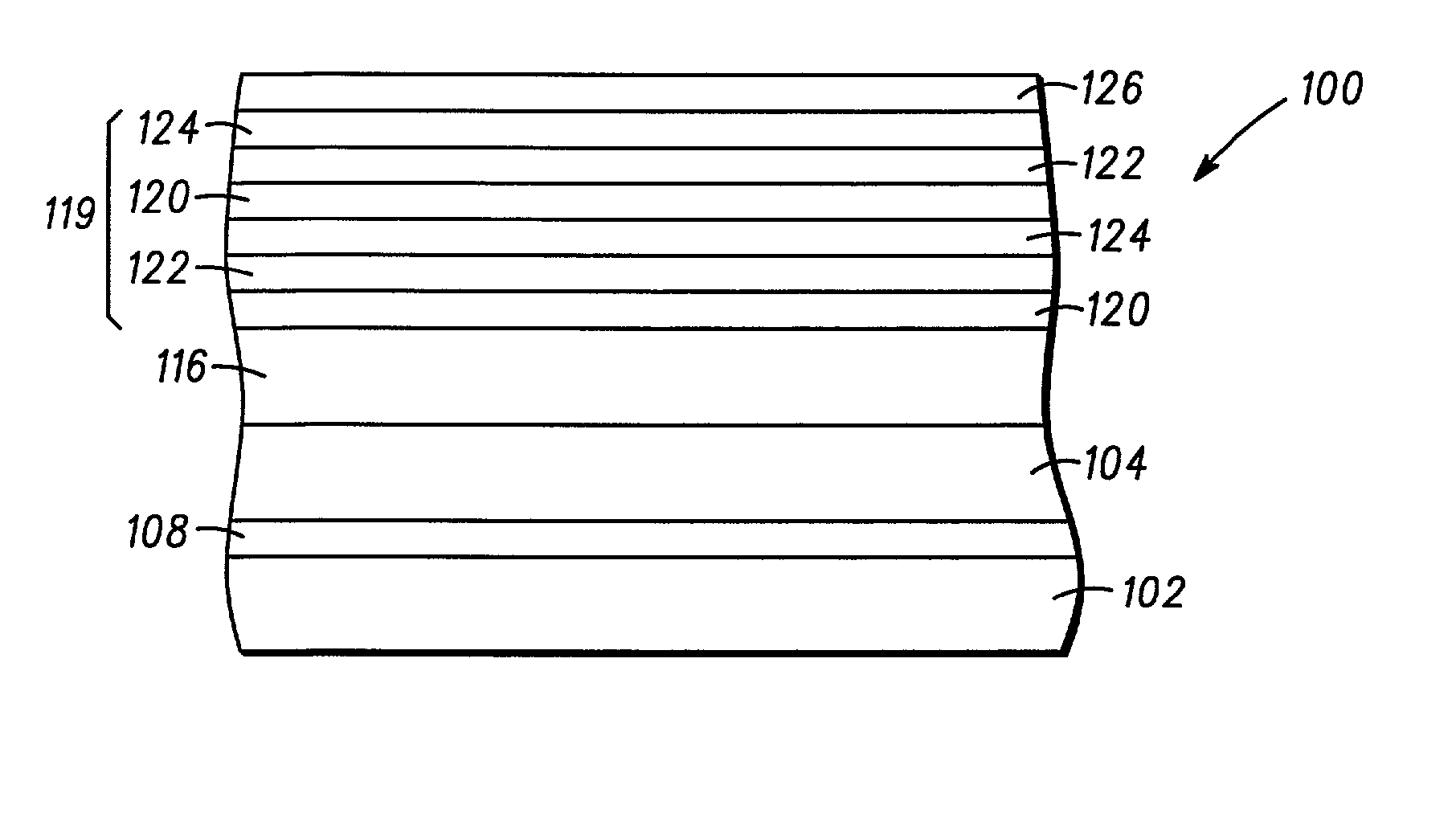

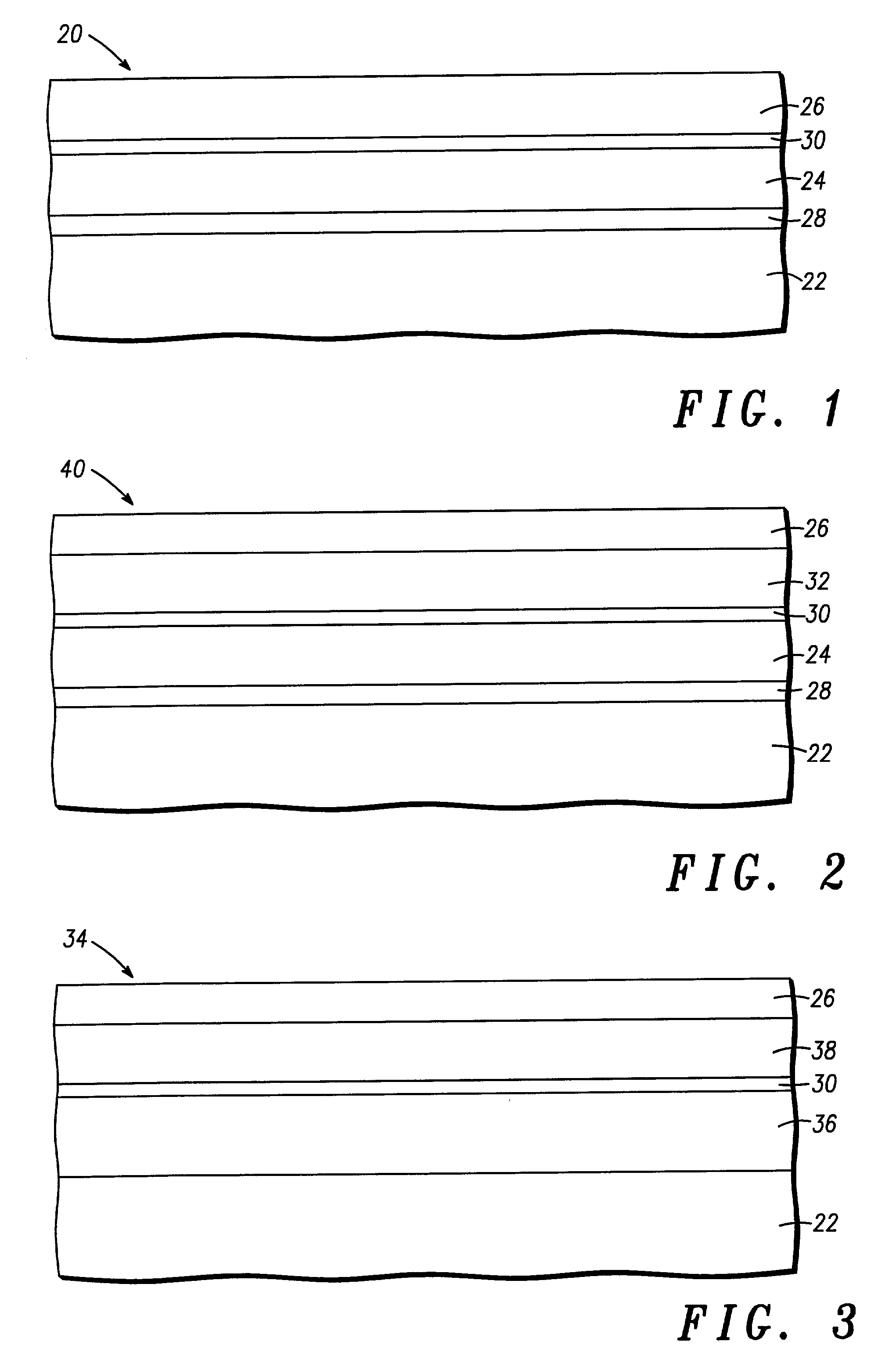

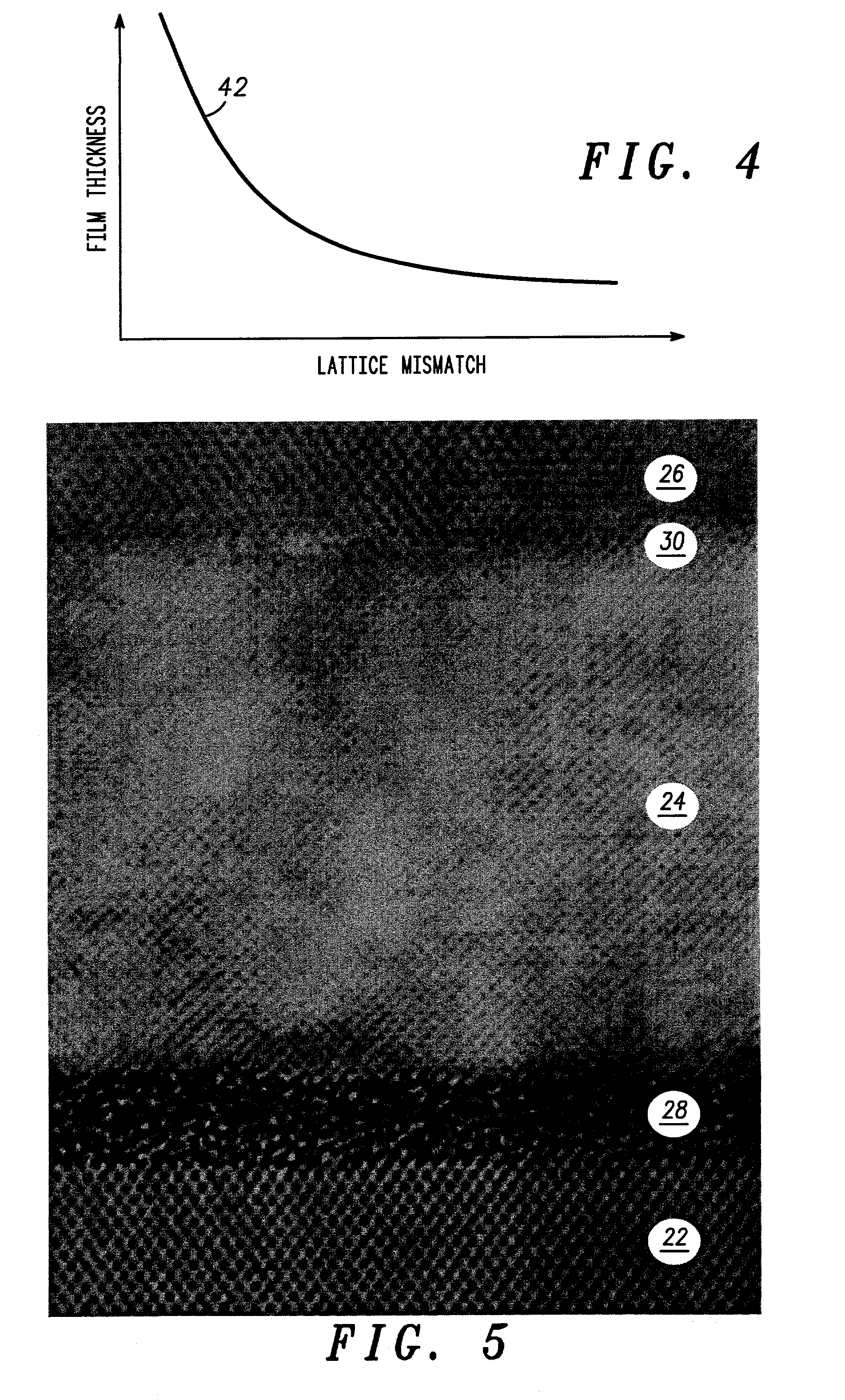

Structure and method for fabricating semiconductor structures and devices utilizing the formation of a compliant III-V arsenide nitride substrate used to form the same

InactiveUS20030013223A1Laser detailsSemiconductor laser structural detailsStrontium titanium oxideLattice mismatch

High quality epitaxial layers of monocrystalline III-V arsenide nitride materials can be grown overlying monocrystalline substrates such as large silicon wafers by forming a compliant substrate for growing the monocrystalline layers. One way to achieve the formation of a compliant substrate includes first growing an accommodating buffer layer on a silicon wafer. The accommodating buffer layer is a layer of monocrystalline oxide spaced apart from the silicon wafer by an amorphous interface layer of silicon oxide. The amorphous interface layer dissipates strain and permits the growth of a high quality monocrystalline oxide accommodating buffer layer. The accommodating buffer layer is lattice matched to both the underlying silicon wafer and the overlying monocrystalline III-V arsenide nitride material layer. Any lattice mismatch between the accommodating buffer layer and the underlying silicon substrate is taken care of by the amorphous interface layer. In addition, an accommodating buffer layer comprising a barium strontium titanium oxide and a monocrystalline III-V arsenide nitride layer, such as GaAsN, having a nitrogen concentration ranging from 1-5% function to further reduce any lattice mismatch between layers.

Owner:MOTOROLA INC

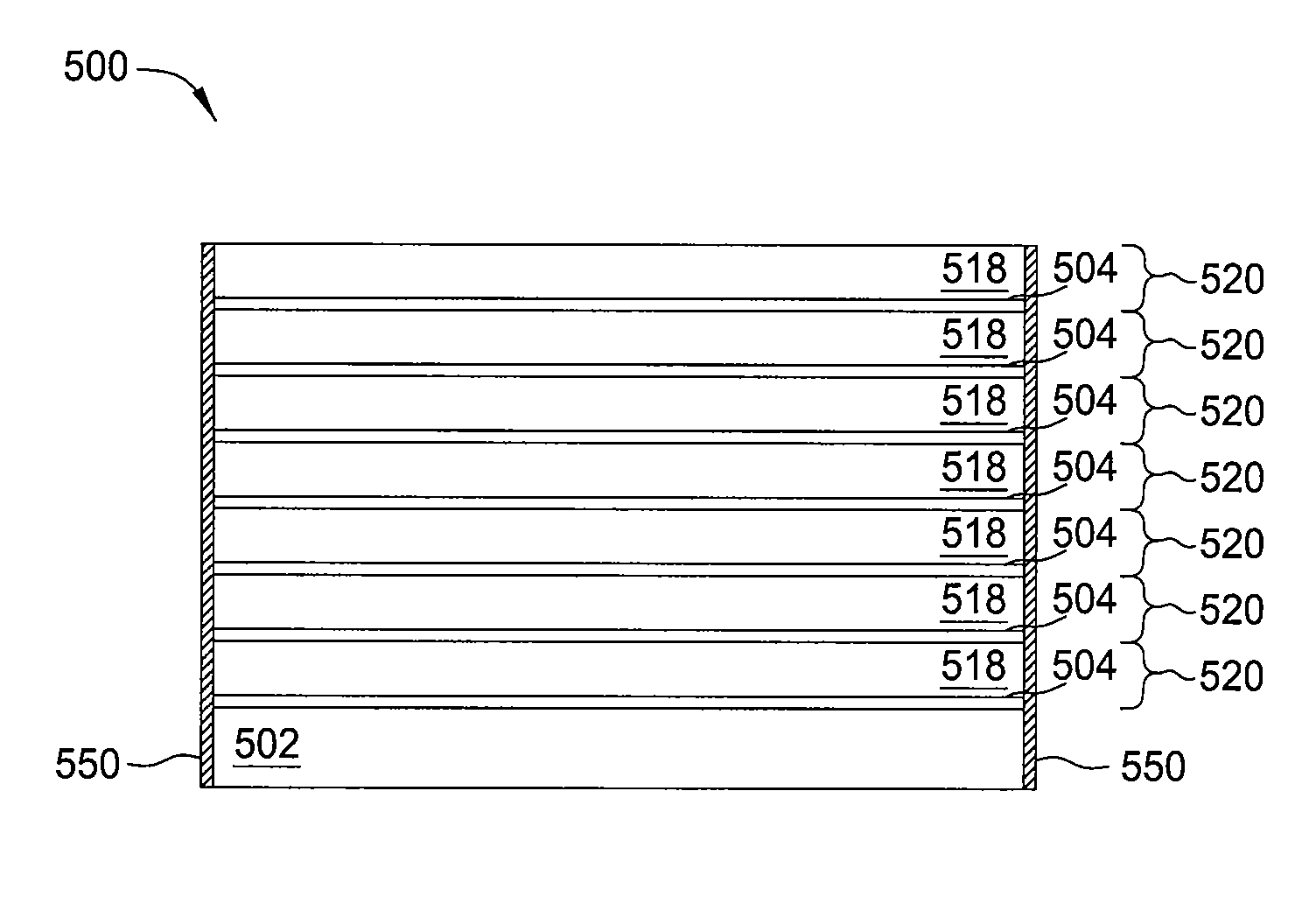

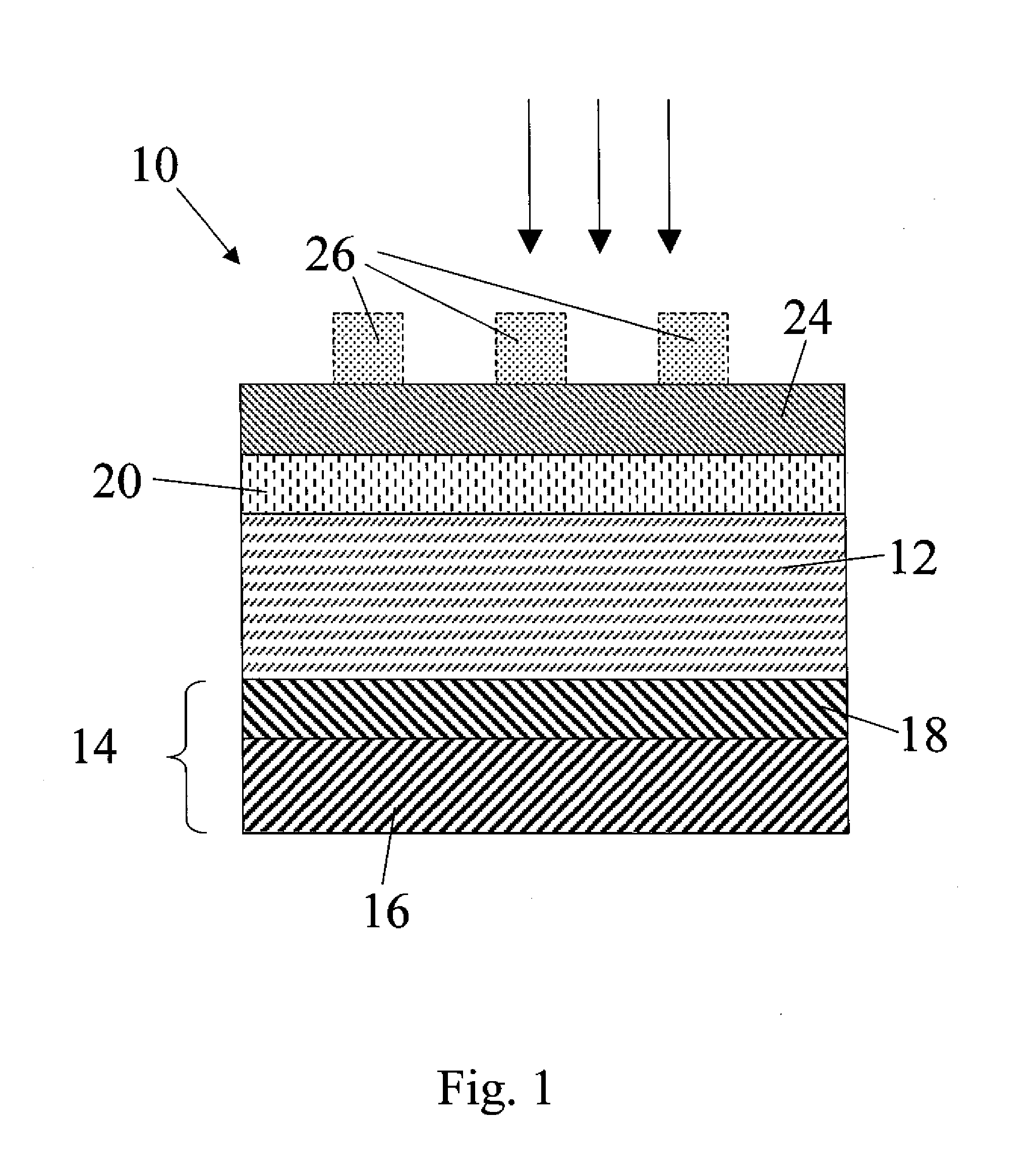

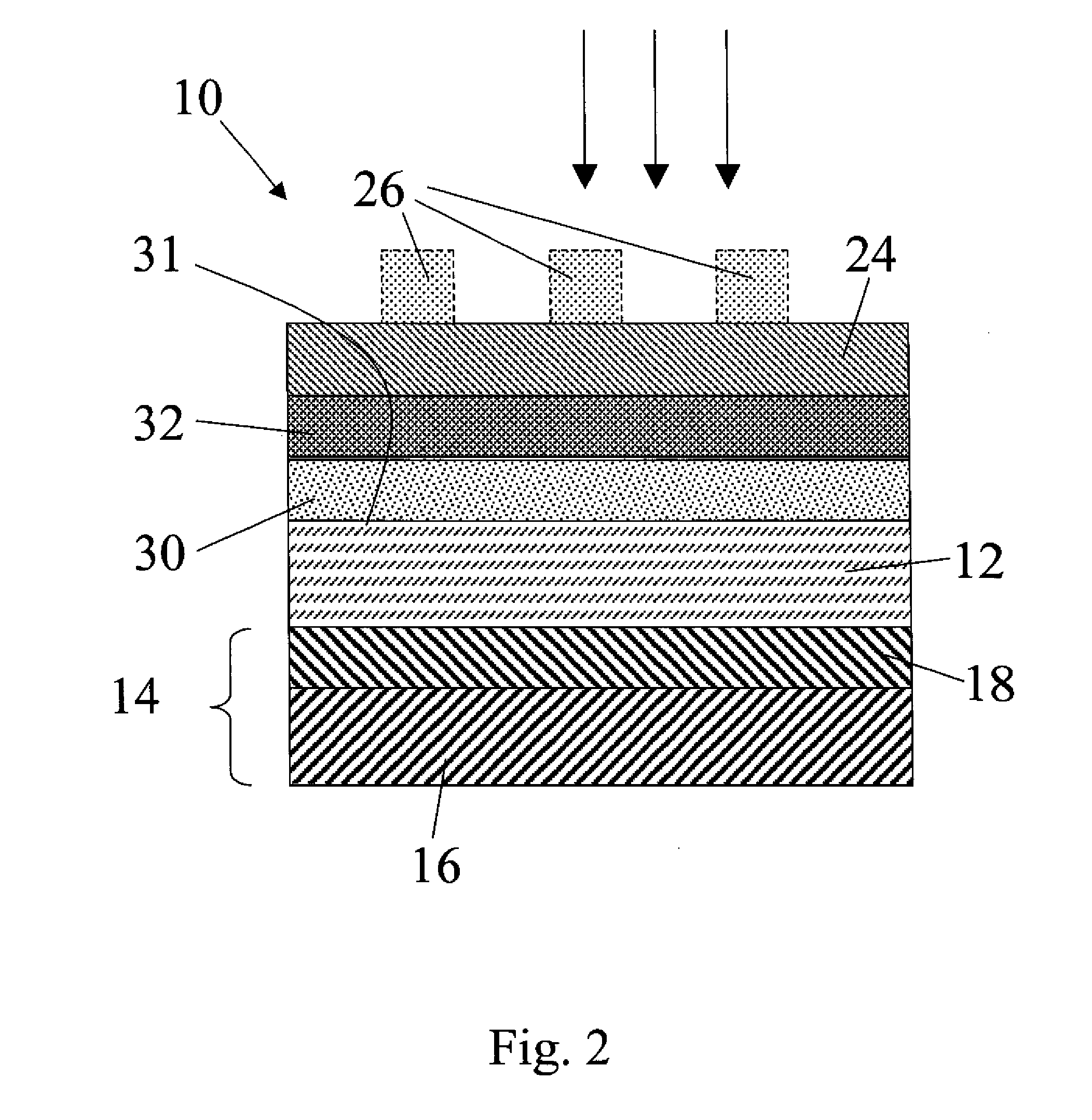

Multiple stack deposition for epitaxial lift off

Embodiments of the invention are provided for a thin film stack containing a plurality of epitaxial stacks disposed on a substrate and a method for forming such a thin film stack. In one embodiment, the epitaxial stack contains a first sacrificial layer disposed over the substrate, a first epitaxial film disposed over the first sacrificial layer, a second sacrificial layer disposed over the first epitaxial film, and a second epitaxial film disposed over the second sacrificial layer. The thin film stack may further contain additional epitaxial films disposed over sacrificial layers. Generally, the epitaxial films contain gallium arsenide alloys and the sacrificial layers contain aluminum arsenide alloys. Methods provide the removal of the epitaxial films from the substrate by etching away the sacrificial layers during an epitaxial lift off (ELO) process. The epitaxial films are useful as photovoltaic cells, laser diodes, or other devices or materials.

Owner:ALTA DEVICES INC

Insulated gate field effect transistor having passivated schottky barriers to the channel

InactiveUS20070026591A1Reduce impactTransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

A transistor includes a semiconductor channel disposed nearby a gate and in an electrical path between a source and a drain, wherein the channel and at least one of the source or the drain are separated by an interface layer so as to form a channel-interface layer-source / drain junction in which a Fermi level of the semiconductor channel is depinned in a region near the junction and the junction has a specific contact resistance of less than approximately 1000 Ω-μm2. The interface layer may include a passivating material such as a nitride, a fluoride, an oxide, an oxynitride, a hydride and / or an arsenide of the semiconductor of the channel. In some cases, the interface layer consists essentially of a monolayer configured to depin the Fermi level of the semiconductor of the channel, or an amount of passivation material sufficient to terminate all or a sufficient number of dangling bonds of the semiconductor channel to achieve chemical stability of the surface. Also, the interface layer may include a separation layer of a material different than the passivating material. Where used, the separation layer has a thickness sufficient to reduce effects of metal-induced gap states in the semiconductor channel.

Owner:ACORN SEMI LLC

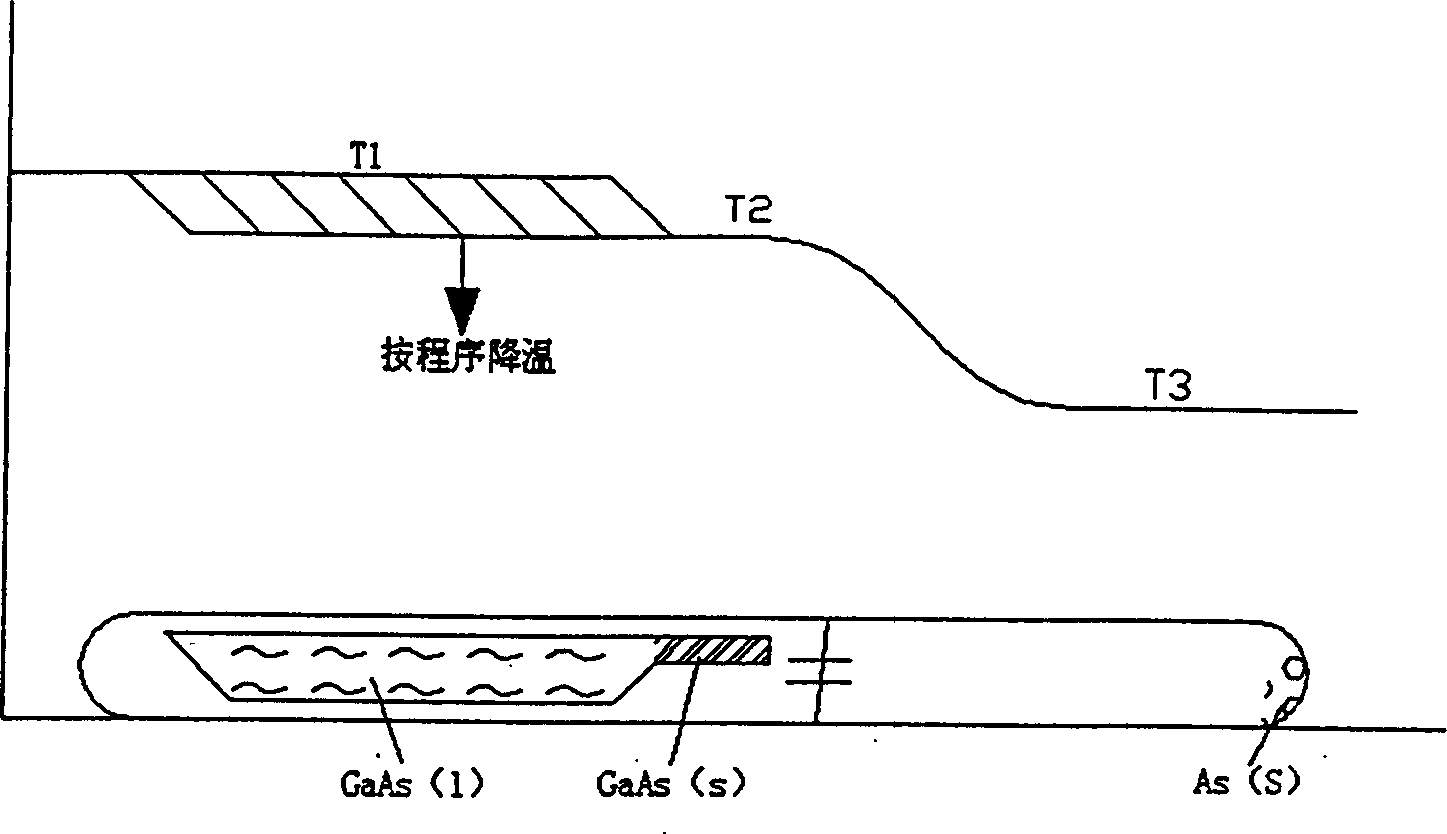

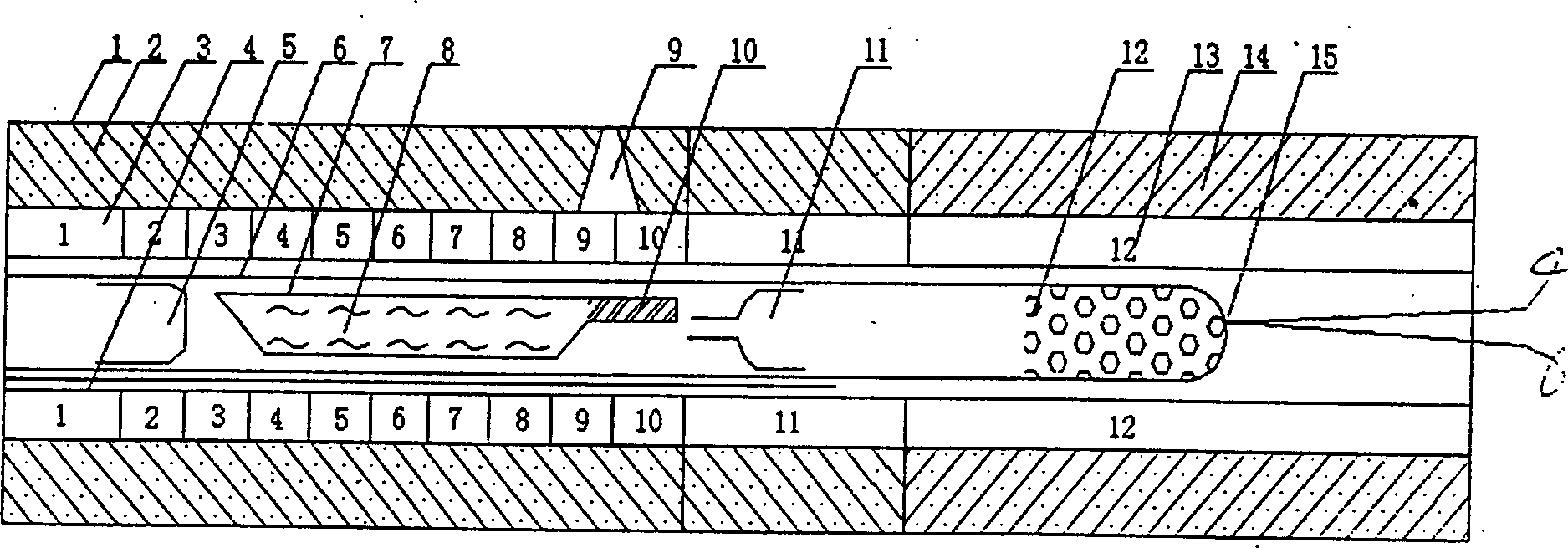

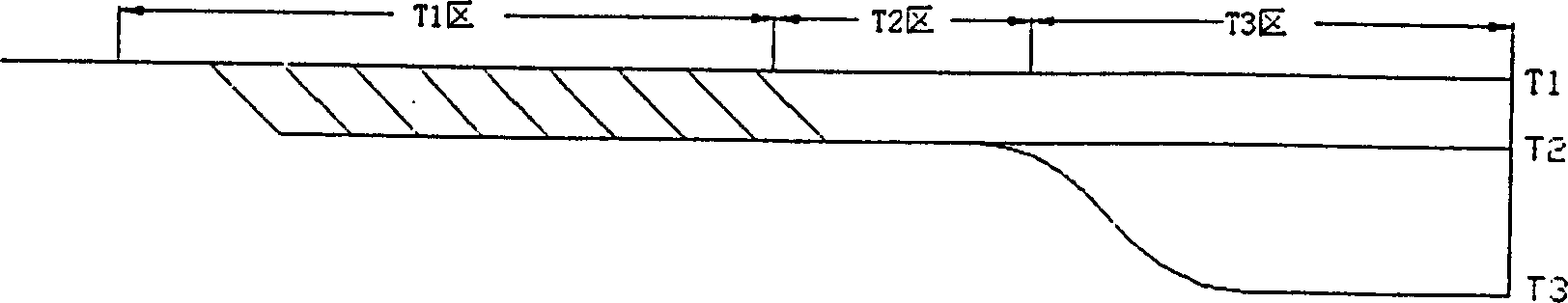

Method for growth of gallium arsenide monocrystal by gradient freeze method in horizontal three-temperature-zone furnace

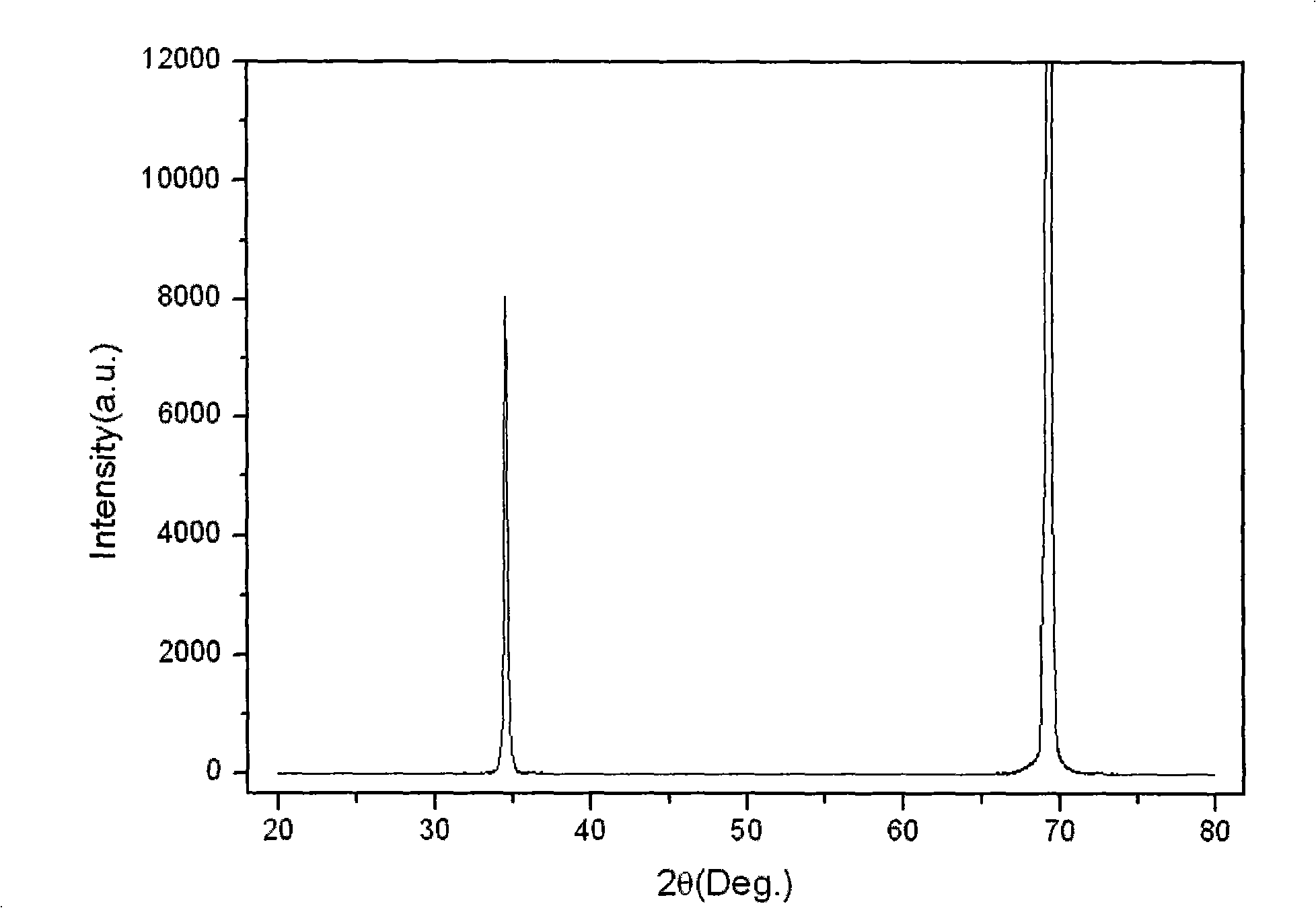

InactiveCN1844487AHigh degree of automationReduce manufacturing costPolycrystalline material growthFrom frozen solutionsSingle crystalConcretion

This invention relates to the arsenide gallium single-crystal growth with level three temperature areas gradient concretion method, the character as follows: the furnace where the single-crystal grows is not moved; the temperature of high temperature T1 decreases gradually according to the single-crystal shaping point temperature, and the decreasing rate inosculates to the single-crystal growth rate.

Owner:尹庆民 +1

Group iib/va semiconductors suitable for use in photovoltaic devices

InactiveUS20110309477A1Good semiconductor performanceImprove electronic performanceSemiconductor/solid-state device manufacturingPhotovoltaic energy generationDopantSemiconductor materials

The present invention relates to devices, particularly photovoltaic devices, incorporating Group IIB / VA semiconductors such phosphides, arsenides, and / or antimonides of one or more of Zn and / or Cd. In particular, the present invention relates to methodologies, resultant products, and precursors thereof in which electronic performance of the semiconductor material is improved by causing the Group IIB / VA semiconductor material to react with at least one metal-containing species (hereinafter co-reactive species) that is sufficiently co-reactive with at least one Group VA species incorporated into the Group IIB / VA semiconductor as a lattice substituent (recognizing that the same and / or another Group VA species also optionally may be incorporated into the Group IIB / VA semiconductor in other ways, e.g., as a dopant or the like).

Owner:CALIFORNIA INST OF TECH +1

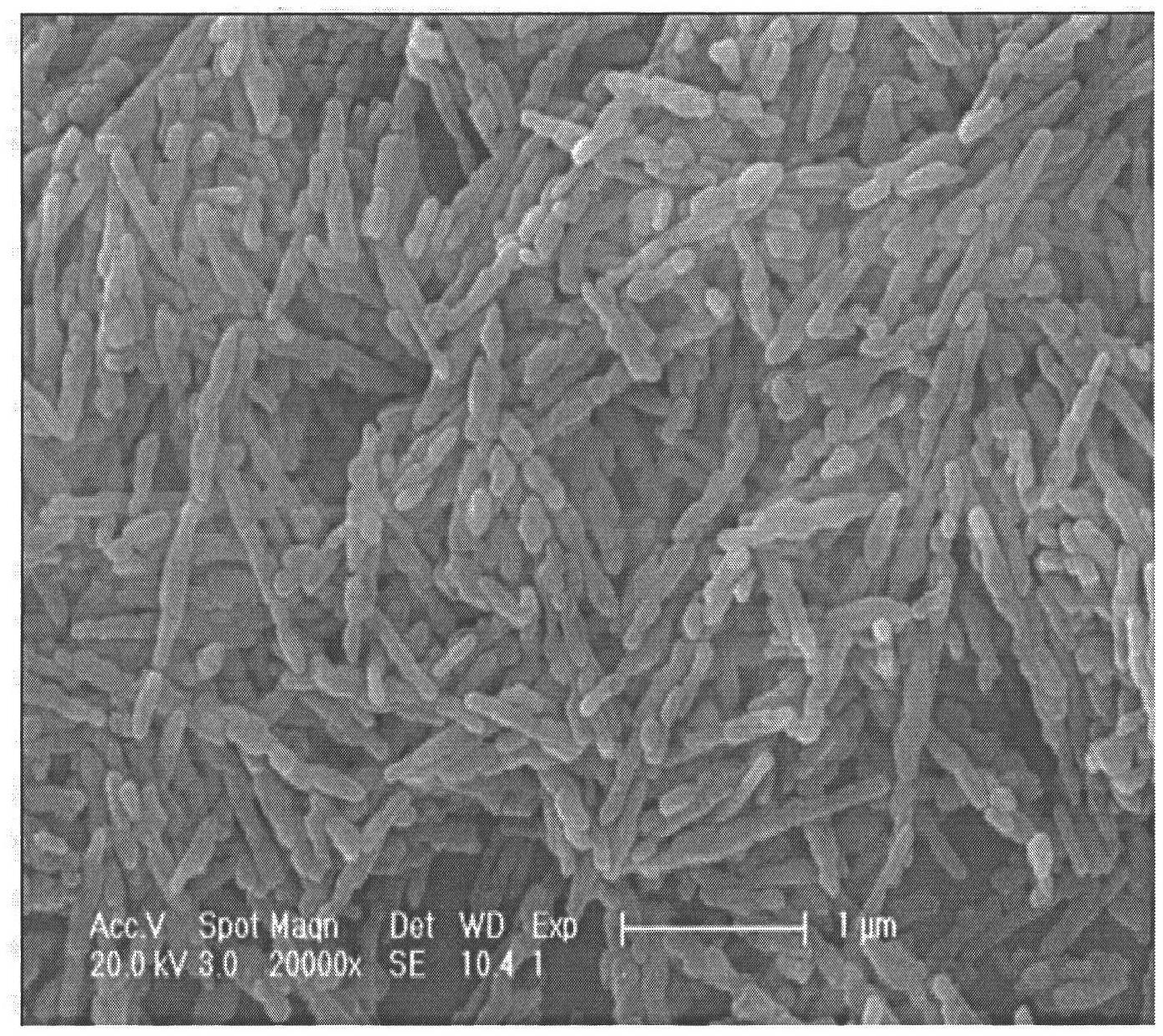

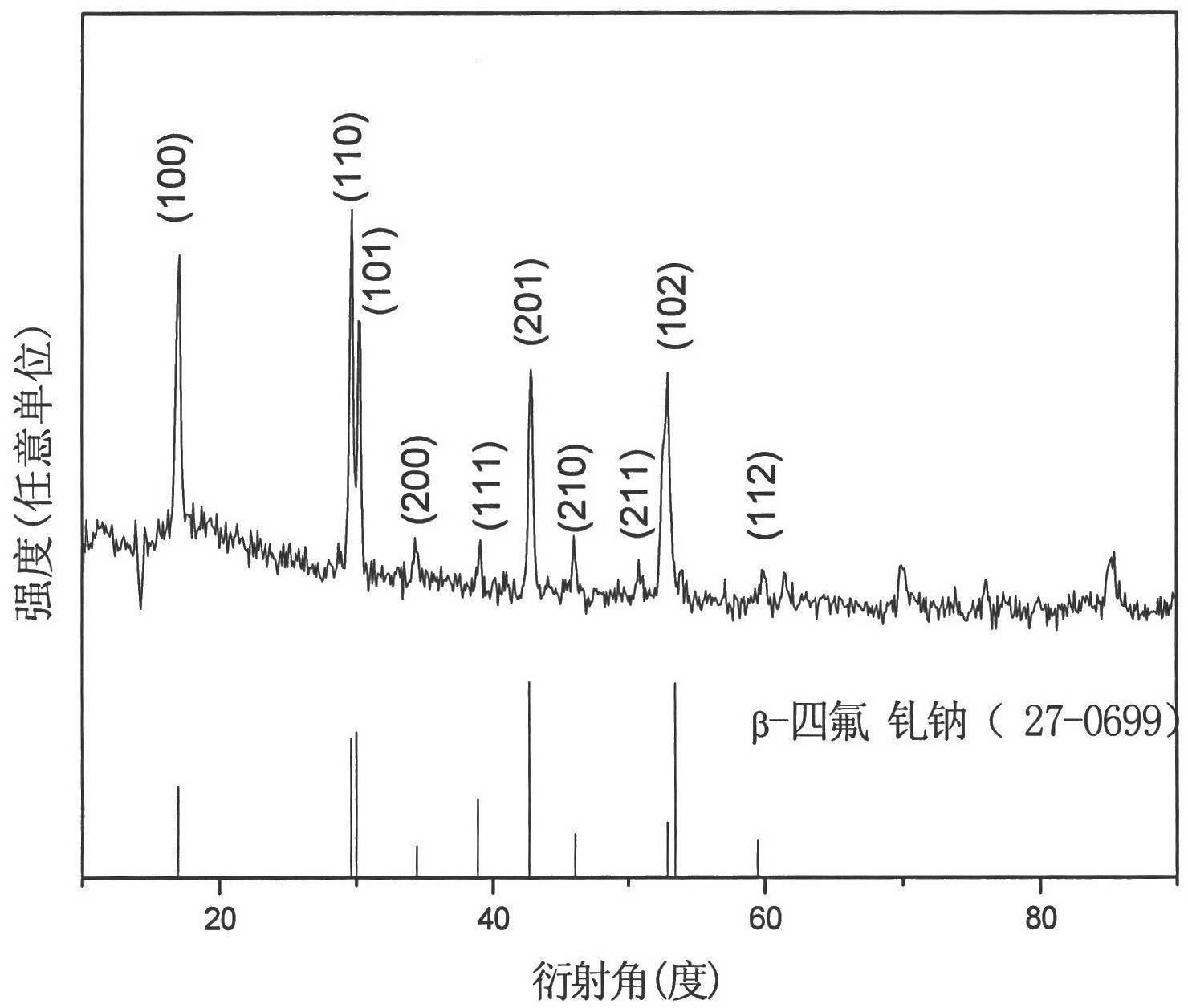

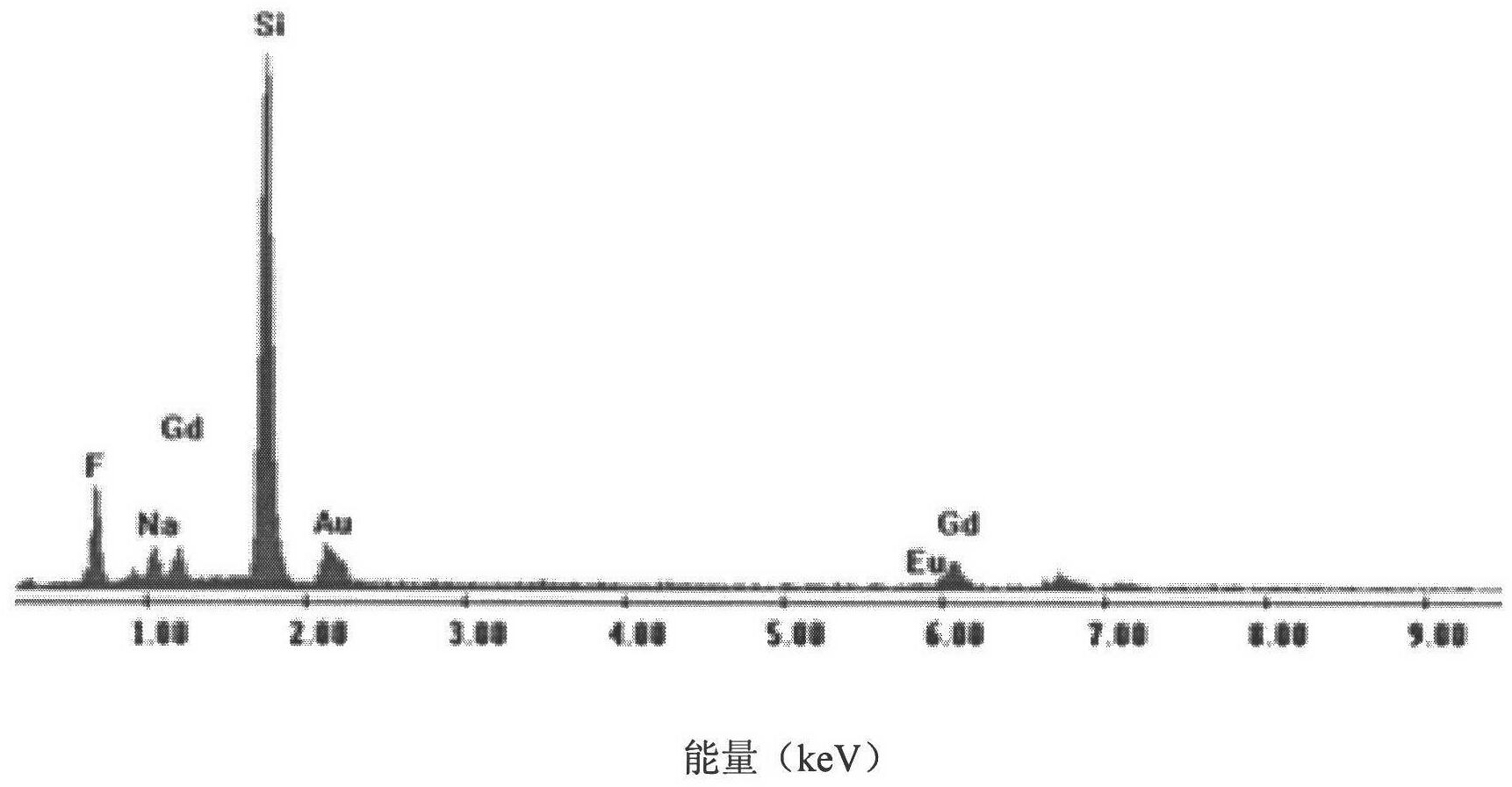

Europium ion-doped sodium gadolinium tetrafluoride luminescent nanorod and preparation method thereof

The invention provides a method for preparing rare earth ion europium-doped sodium gadolinium tetrafluoride (NaGdF4:Eu3+) luminescent nanorods and a method thereof, belonging to the technical field of preparation of rare earth doped luminescent materials. The present invention comprises the following steps: (1) mixing compound rare earth ions and sodium lauryl sulfate in proportion, and then adding fluoride to form a mixed solution; (2) carrying out hydrothermal reaction on the mixed solution at a certain temperature and time, Obtain the NaGdF4:Eu3+luminescent nanorods. The method has a simple synthesis process and is easy to produce in batches, and the prepared NaGdF4:Eu3+ nanorods have good red luminescent properties. The invention uses rare earth metal oxides as raw materials and sodium lauryl sulfate as a surfactant, and the whole reaction is carried out in an aqueous solution without any organic solvent, which is economical and environmentally friendly, has strong practicability, and has wide application prospects.

Owner:CHANGCHUN UNIV OF SCI & TECH

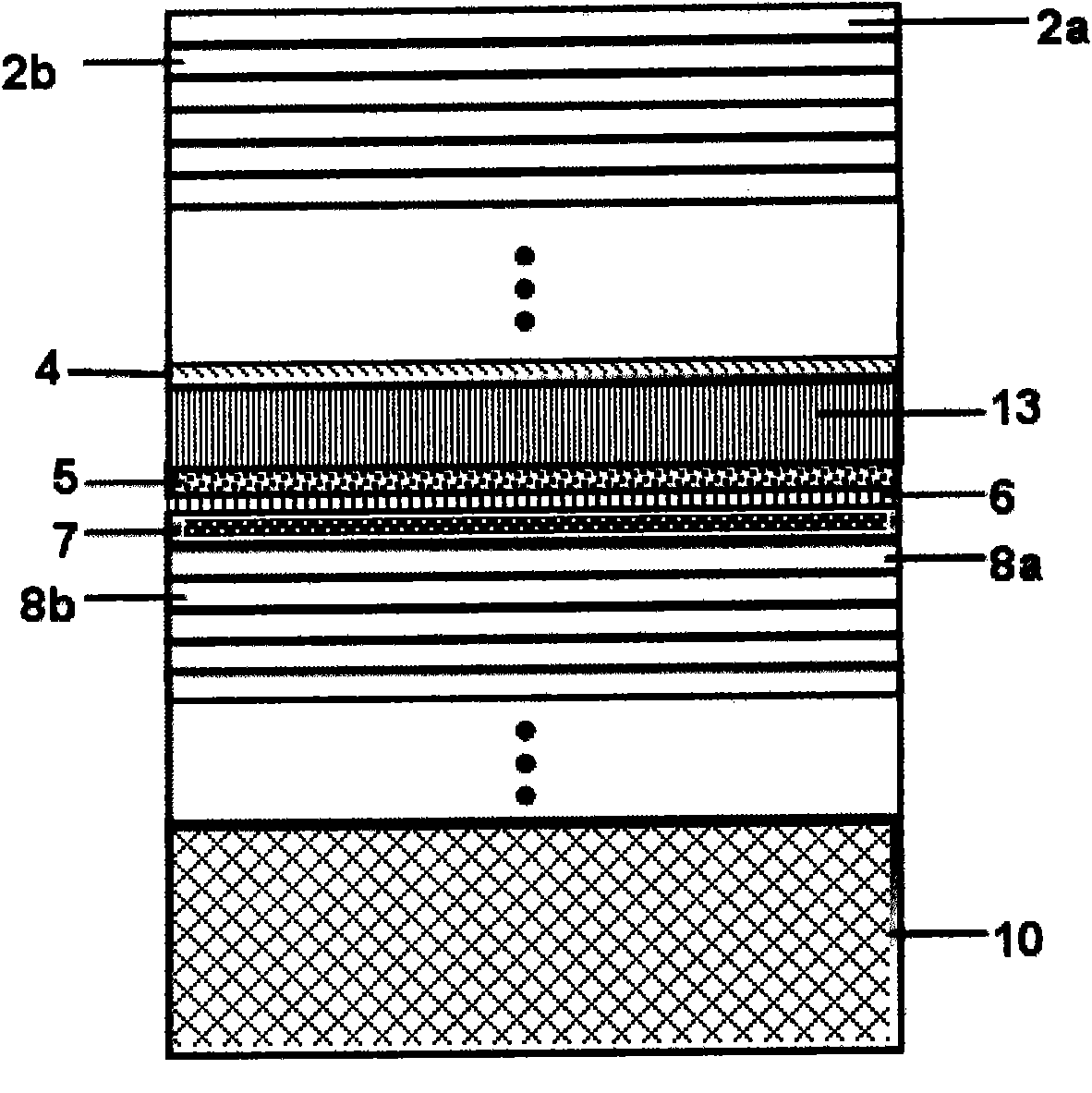

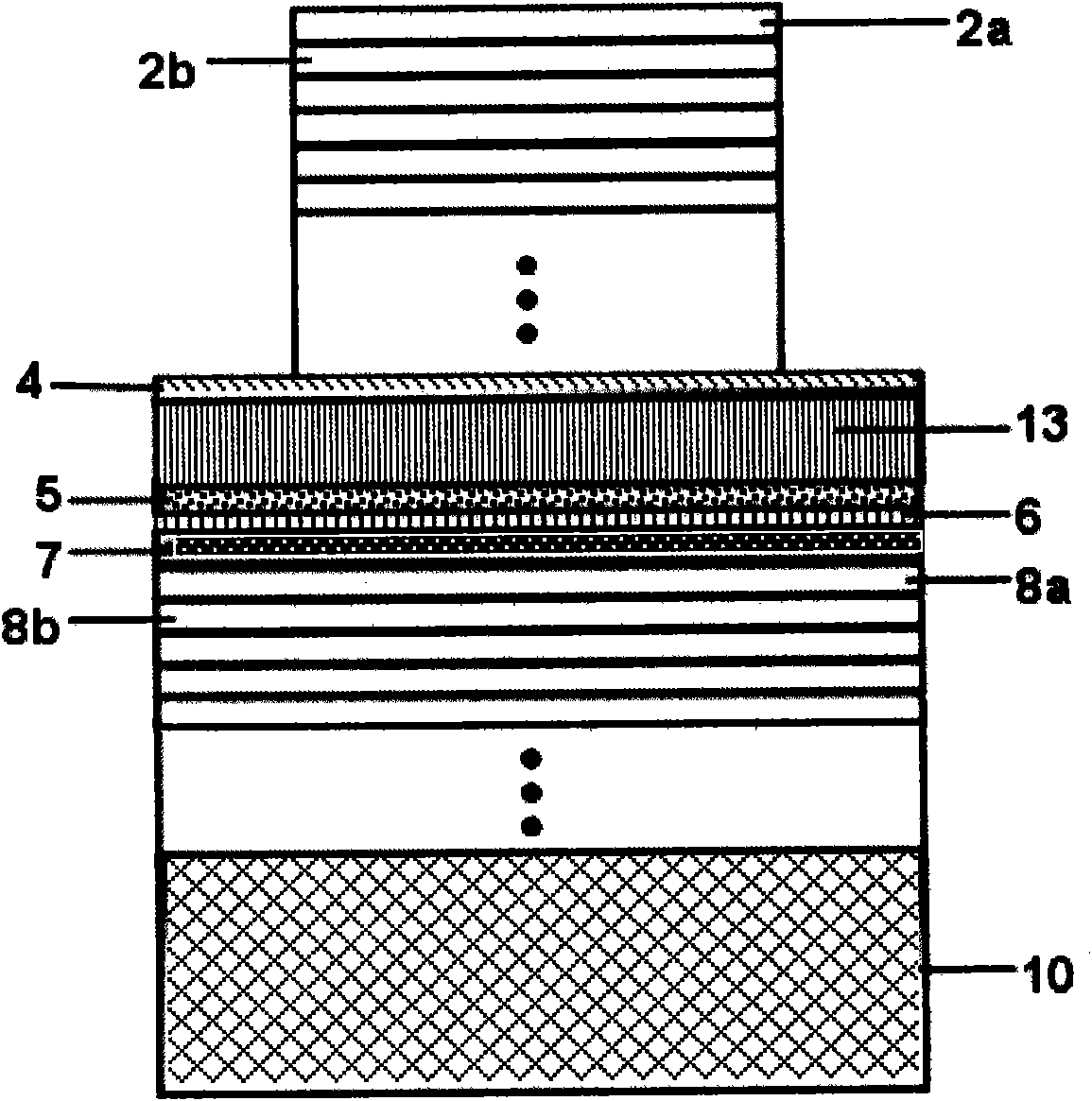

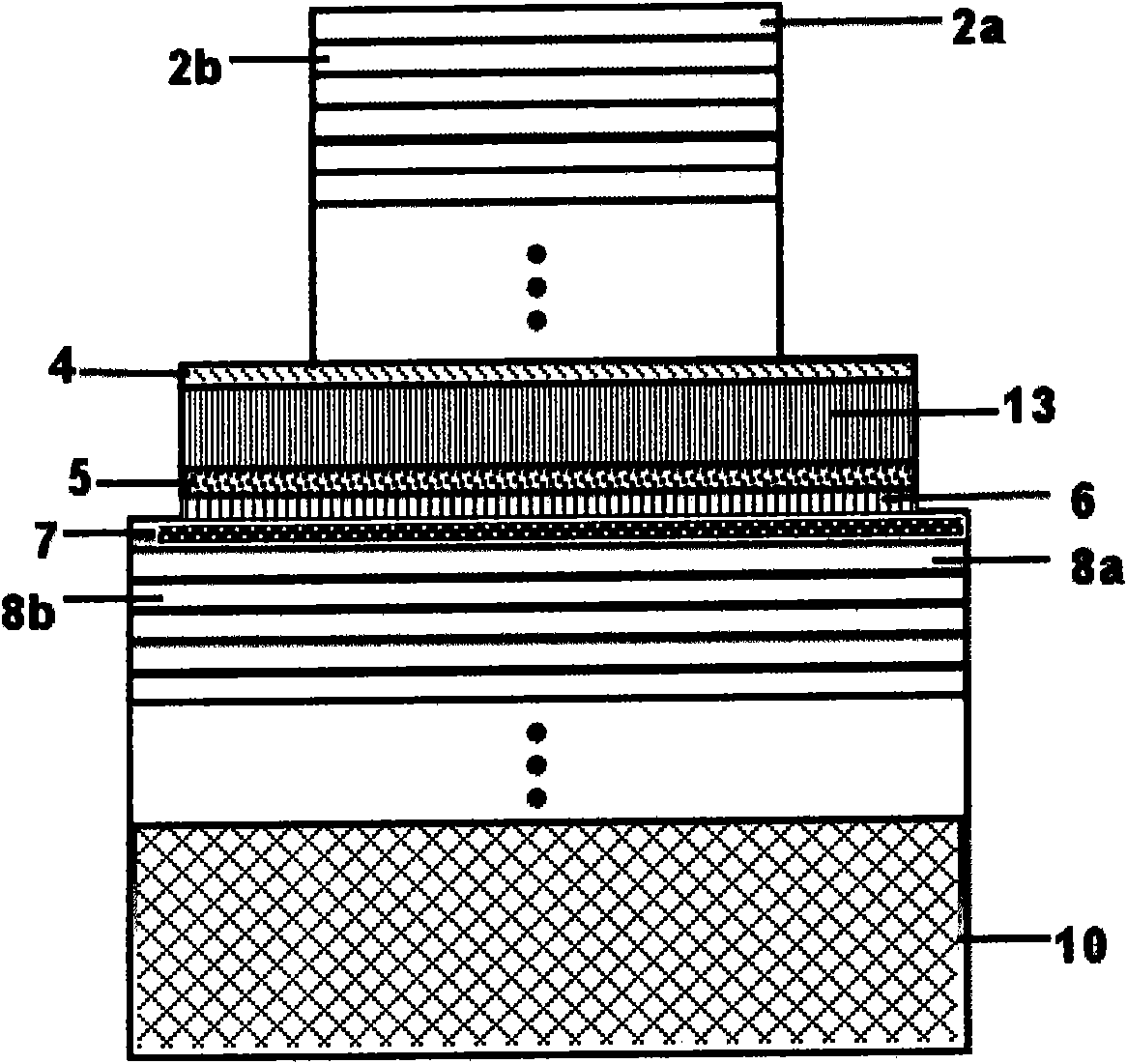

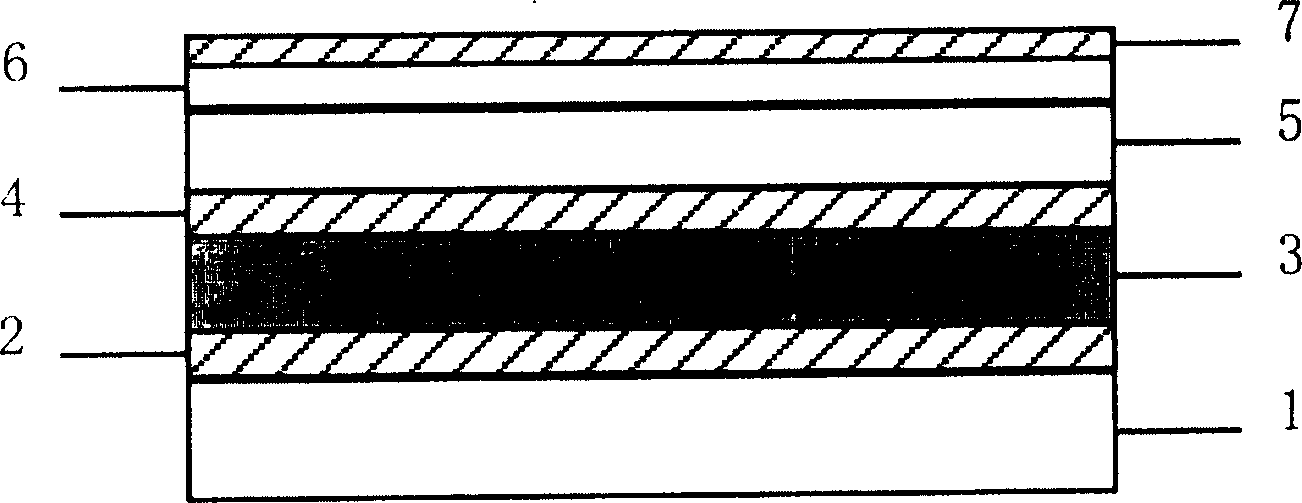

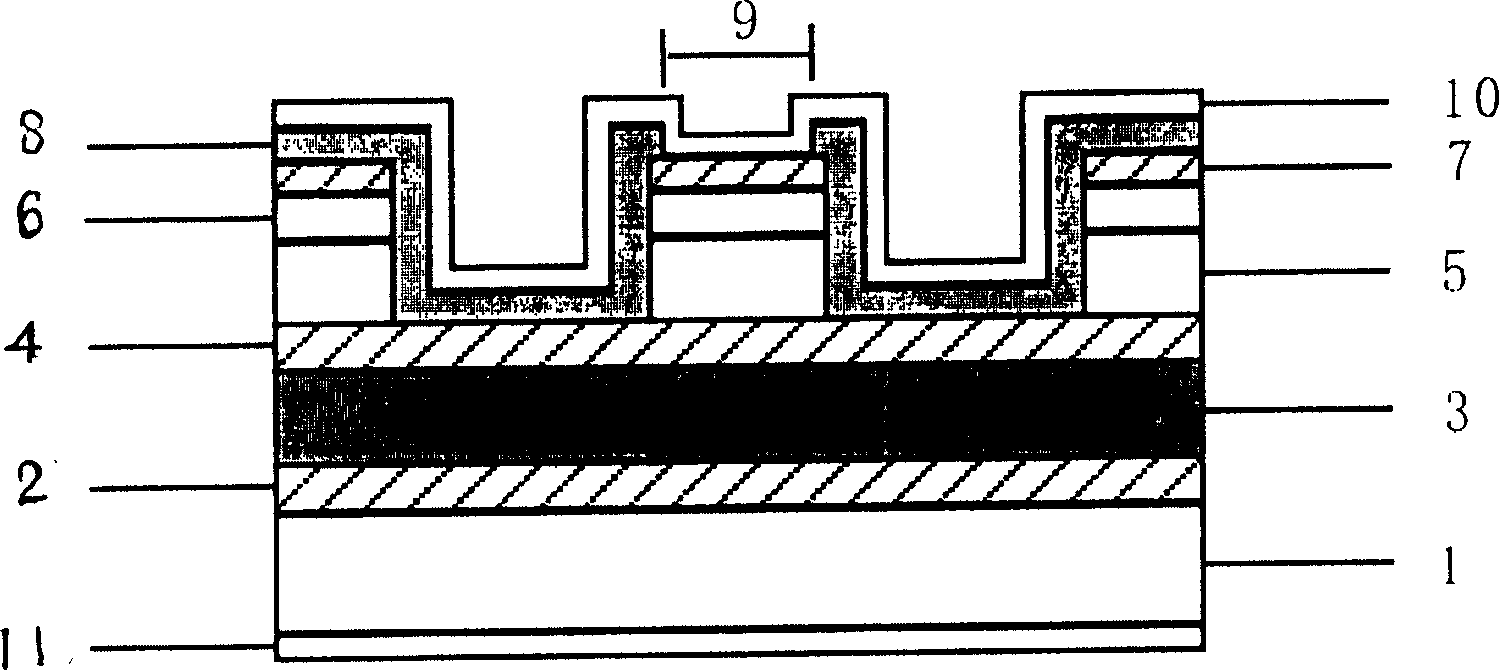

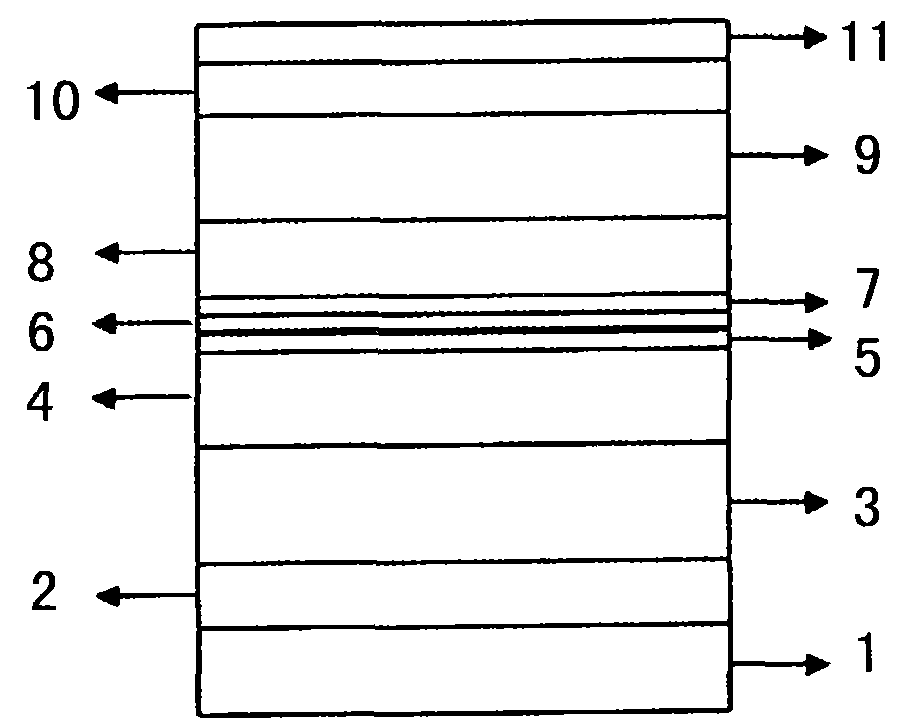

Bridge type nano grating tunable vertical cavity surface emitting laser and preparation method thereof

InactiveCN102013633AEnhanced inhibitory effectFunction increaseLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserElectron

The invention relates to a surface nano grating-based wavelength tunable vertical cavity surface emitting laser and a preparation method, which belong to the field of semiconductor photoelectronic devices. The laser has an inner cavity contact laminated structure; a positive electrode layer (1) is arranged on a P-type ohmic contact layer (5); an air-gap layer (12), a gallium arsenide layer (2a), and a gallium aluminum arsenide layer (2b) are arranged above the ohmic contact layer (5) in turn; a gallium aluminum arsenide oxidation current limitation layer (6), an active region (7), an n-type gallium aluminum arsenide layer (8a), an n-type gallium arsenide (8b), an n-type gallium arsenide substrate (10), and a substrate electrode layer (11) are formed below the ohmic contact layer (5) in turn; and a nano grating (15) is positioned on the surface of the gallium arsenide layer (2a). The thickness of the air-gas layer can be subjected to mechanical adjustment of an electrostatic force and the like, so that photon phase change can be transmitted in the resonant cavity of a laser and an outputted light beam passes through the nano grating (15) immediately; therefore, a wavelength and polarization can be simultaneously controlled.

Owner:BEIJING UNIV OF TECH

Synergistic leaching-copper arsenate removing method for leaching residues in high-iron zinc calcine and high-iron zinc sulfide concentrate

InactiveCN103789544AHigh recovery rateEfficient reductionProcess efficiency improvementHydrometallurgyCopper sulfate

The invention belongs to the field of wet metallurgy of zinc, and particularly relates to a synergistic leaching-copper arsenate removing method for leaching residues in high-iron zinc calcine and high-iron zinc sulfide concentrate. The method comprises the following steps: mixing the leaching residues in the high-iron zinc calcine with the high-iron zinc sulfide concentrate; mixing zinc electrowinning waste liquor and a part of sulfuric acid-containing solution prepared from concentrated sulfuric acid and synergistically leaching; adding a reaction dosage of industrial iron powder into a synergistically-leached copper arsenate-removing primary solution; replenishing a proper amount of copper sulfate as required; reacting; performing liquid-solid separation on reaction ore pulp to obtain cuprous arsenide precipitate serving as a copper-leaching raw material and a copper arsenate-removing secondary solution; returning the copper arsenate-removing secondary solution to a zinc hydrometallurgy process to further recover valuable metals therein. The method is clean and efficient, efficient leaching of copper and efficient reduction of Fe<3+> can be realized, the solution treatment amount is small, the comprehensive recovery rate of valuable metals in a zinc hydrometallurgy process is increased comprehensively, and the smelting flow is simplified.

Owner:KUNMING UNIV OF SCI & TECH TECH IND SALES MANAGEMENT +1

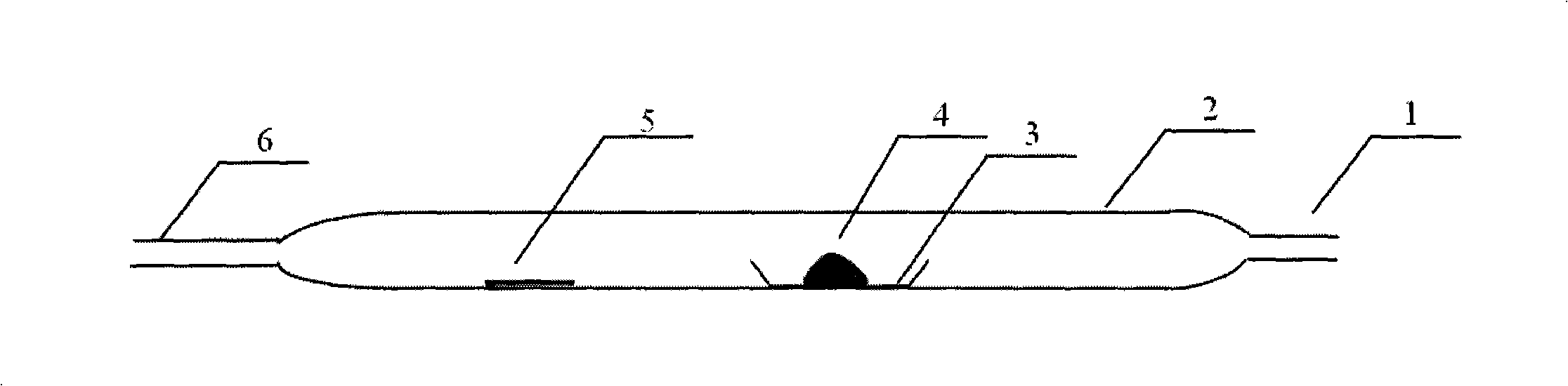

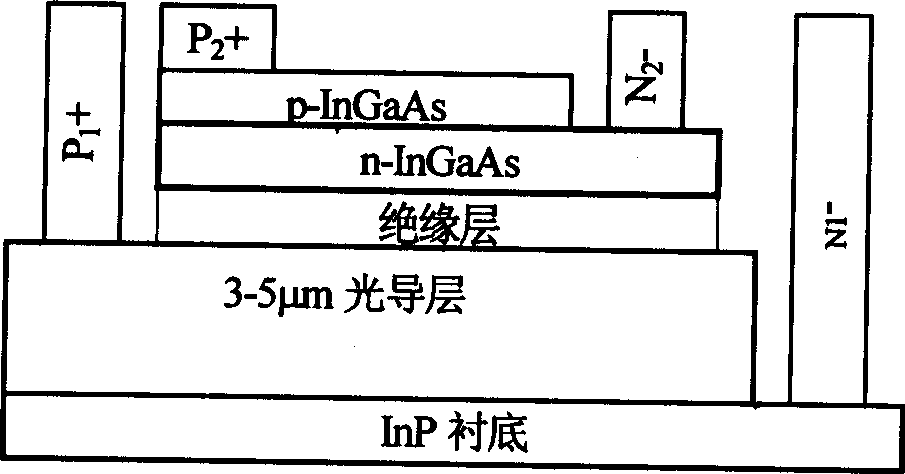

Indium phosphide-base quantum cascade semiconductor laser and producing method

InactiveCN1741329AImprove cooling effectIncrease peak output powerLaser detailsSemiconductor lasersInsulation layerIndium

A semiconductor laser cascaded by indium phosphide based quantum consists of a N type of indium phosphide substrate , a N type of indium gallium arsenide bottom wave guide layer ,an active region of indium gallium arsenide / indium aluminum arsenide alternitation in 35 cycles , a N type of indium gallium arsenide top wave guide layer , a N type of indium phosphide top clad layer , a N type of indium phosphide contact layer , a N type of indium gallium arsenide ohm contact layer , insulation layer on double channel mesa , a front N type of electrode and a back N type of electrode .

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

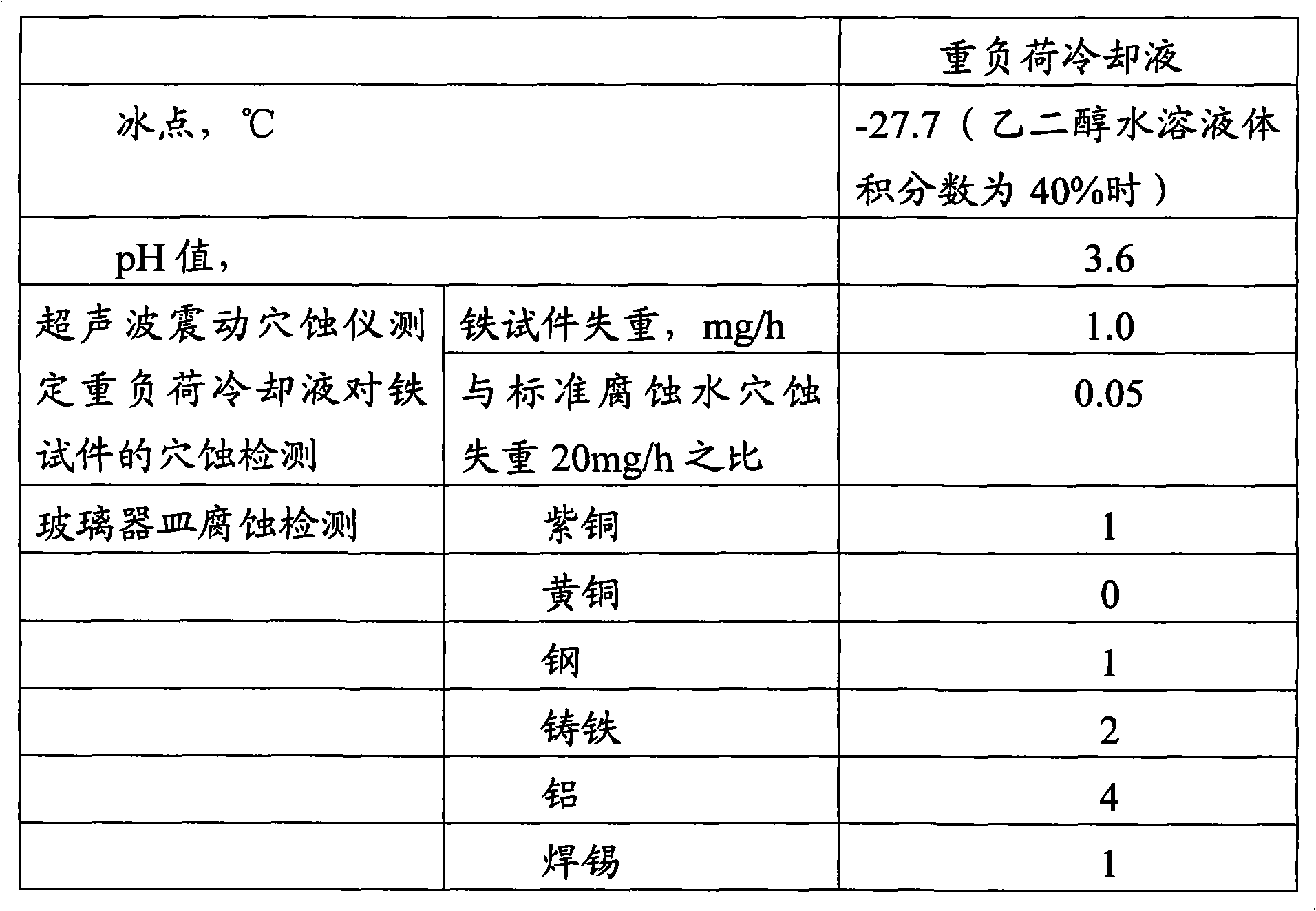

Cavitation corrosion resisting coolant used for heavy-duty engine and preparing method thereof

InactiveCN101550332AAvoid corrosionFormulation ScienceHeat-exchange elementsEngineeringSodium nitrite

The present invention relates to a cavitation corrosion resisting coolant used for heavy-duty engine, wherein the cavitation corrosion resisting coolant comprises the following components by weight: 10-90 parts of soft water, 10-90 parts of glycol, 0.1-1.4 parts of sodium borate, 0.3-2 parts of sodium benzoate, 0.2-2.5 parts of sebacic acid, 0.08-1 part of iodine arsenide, 0.2-3 parts of benzotriazole, 0.03-0.4 part of sodium molybdate, 0.04-0.4 part of sodium nitrite, 0.05-0.5 part of sodium hydroxide, 0.05-0.5 part of corrosion resisting stabilizing agent, 0.005-0.05 part of antifoaming agent and 0.001-0.01 part of colorant. The method of the invention comprises the following steps: (1) adopting a reaction still with mixing function in normal temperature, placing the soft water into the reaction still according to the ratio; (2) adding glycol according to the amount, mixing until the time when the glycol is totally dissolved; (3) weighting the sodium borate, sodium benzoate, sebacic acid, iodine arsenide, benzotriazole, JN-4 corrosion resisting stabilizing agent, sodium molybdate, sodium nitrite, sodium hydroxide, antifoaming agent and colorant, mixing for preparing a complexing agent; (4) adding the complexing agent into the reaction still and mixing to uniform; and (5) checking the freezing point, boiling point, pH value and color of coolant routinely, and then filtering and filling. The cavitation corrosion resisting coolant of the invention has the advantages of simple preparing and remarkable effect.

Owner:TIANJIN PORT (GROUP) COMPANY

Growth method of gallium arsenide monocrystal or germanium arsenide monocrystal

ActiveCN101724886AReduce contentLow costPolycrystalline material growthFrom frozen solutionsMetallurgySingle crystal

The invention relates to a growth method of gallium arsenide monocrystal or germanium arsenide monocrystal, which belongs to the field of crystal growth. Firstly, PBN is flattened with sand paper No. 1200 till PBN has no obvious steps, then PBN is put in mixed washing liquid of de-ionized water, ammonia and oxyful in the volume ratio of 2:1:1 to be immersed for 30 minutes, and then PBN is cleaned with de-ionized water; PBN is baked for about 30 minutes in a baking furnace at 180 to 220 DEG C in vacuum state, and then is baked for more than 30 minutes in the baking furnace at 900 to 1050 DEG C in vacuum state; 1atm high purity oxygen is filled into PBN, to ensure that PBN is baked for more than 30 minutes in the baking furnace at 900 to 1050 DEG C; after PBN is cooled down to 50 DEG C, clear polycrystalline material is directly loaded, the loading is accomplished within 2 minutes, the loading environment temperature is controlled to be between 20 to 25 DEG C, and the humidity is controlled to be below 40 percent; and after the loading, the crystal growth is accomplished according to traditional VGF process. The growth method of gallium arsenide monocrystal or germanium arsenide monocrystal not only ensures that the content of impurity B in the grown monocrystal is reduced, but also ensures that the quality of a substrate is not affected.

Owner:山西中科晶电信息材料有限公司

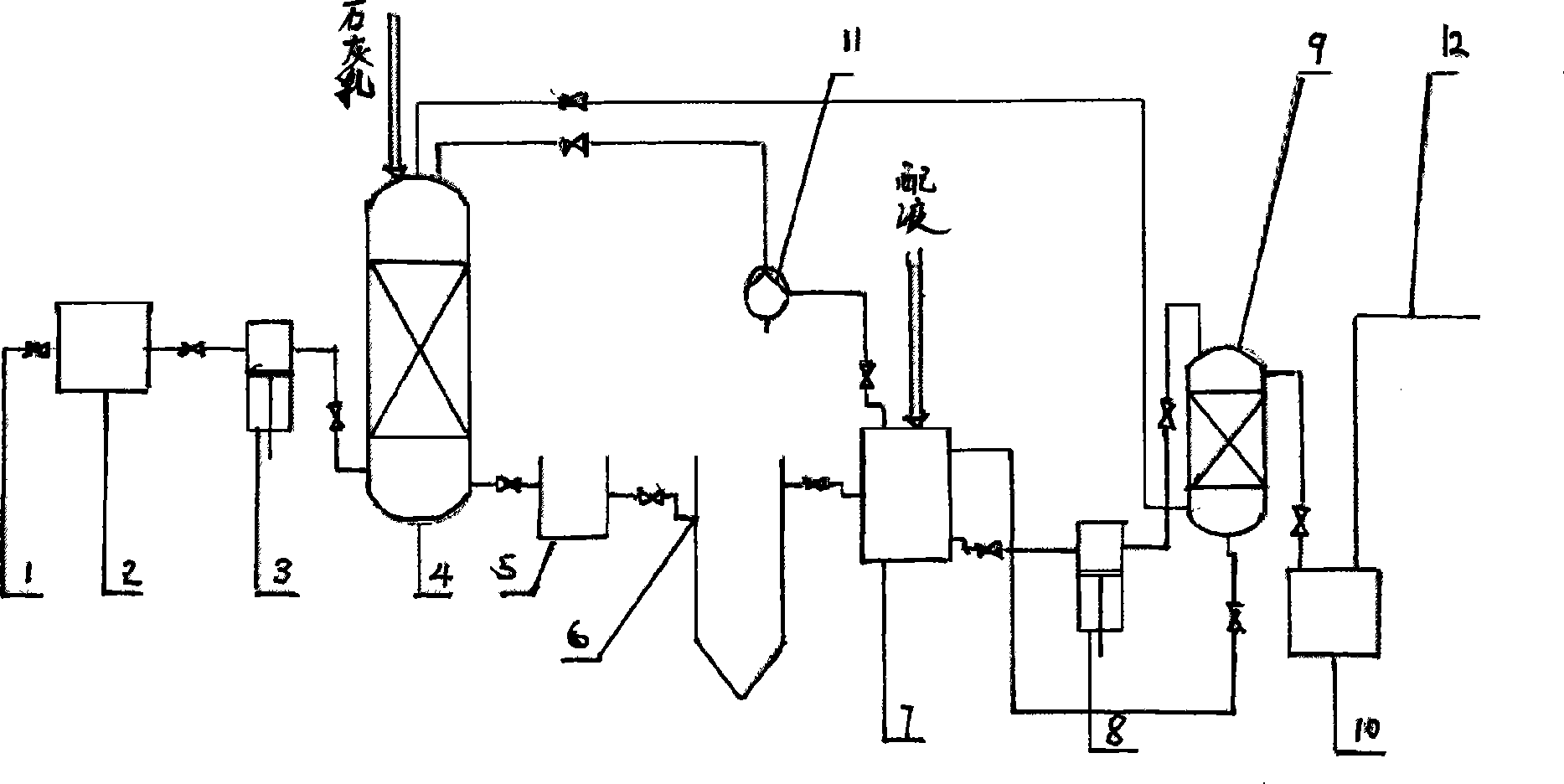

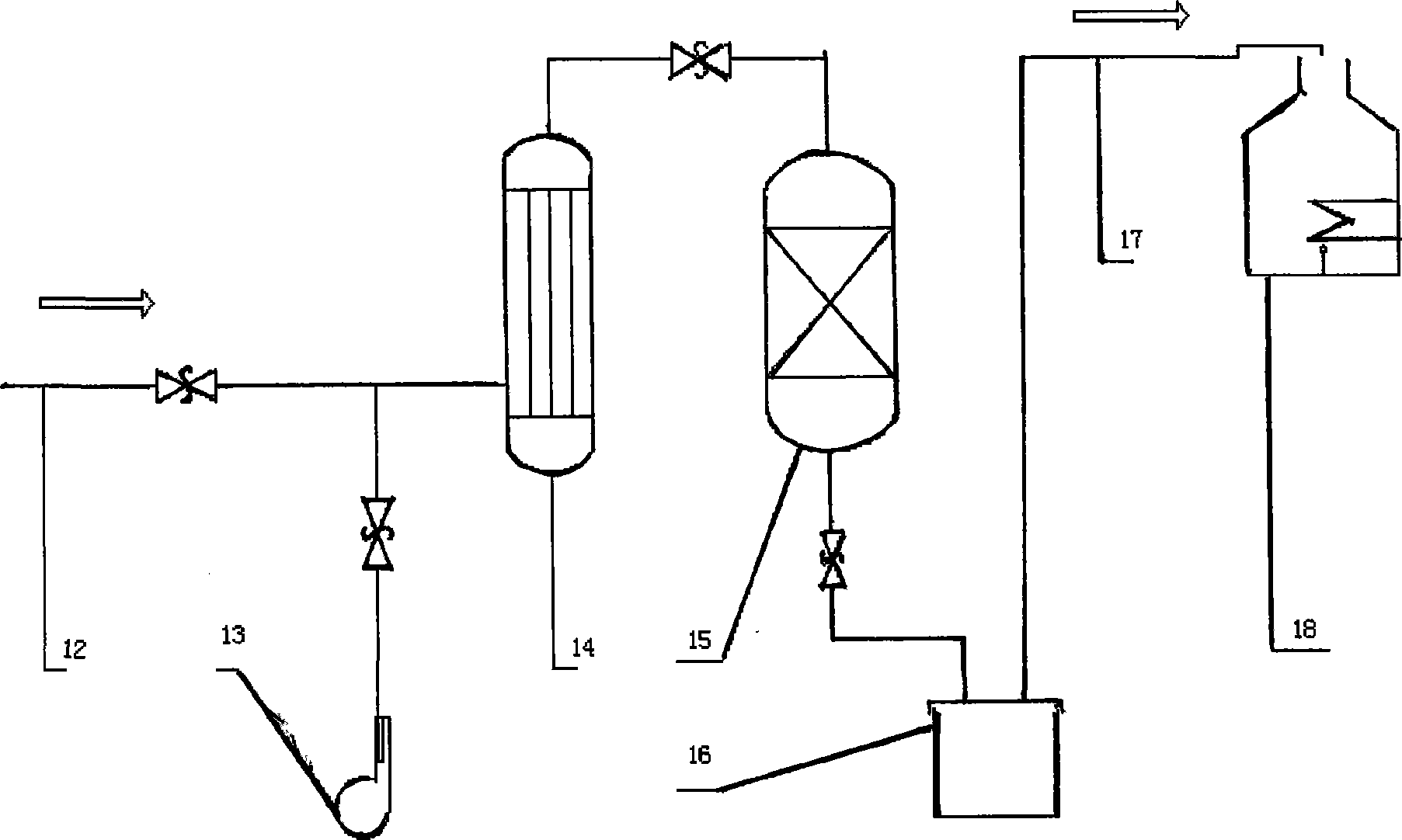

Purification method for yellow phosphorus exhaust gas and device thereof

The invention discloses a yellow phosphoric tail gas purification method and a device thereof. Aiming at the characteristics of tail gas containing multi-form impurities such as phosphide, sulphide, arsenide, fluorid and the like, the pretreatment of yellow phosphoric tail gas utilization is effectively carried out. The yellow phosphoric tail gas fuel gas purification device comprises a yellow phosphoric tail gas fuel gas pretreatment device (I) and a yellow phosphoric tail gas fuel gas follow-up purifying device (II). A special dephosphorization desulphurization dearsenization unit triplet catalytic oxidation catalyst is used for absorbing H2S and PH3 and residual AsH3 in a tower. The invention comprises a turbulence little lime washing dust-removal system, a washer lime cream washing, and adesorption fluroid, part arsenide and phosphorus, oxysulphide system. The invention realizes that the yellow phosphoric tail gas with the thermal value as high as 10048-11723KJ / Nm is effectively utilized, solves the key difficult problem that yellow phosphorus manufactures can not effectively use yellow phosphoric tail gas as fuel gas. The purified yellow phosphoric tail gas can meet the fuel gas requirements of a gas fired boiler and a fuel gas electric generating set and can be circularly and comprehensively used by the yellow phosphoric manufactures, thus laying the foundation for the sustainable development of the yellow phosphorus industry.

Owner:KUNMING UNIV OF SCI & TECH

Nanocomposite material for the production of index of refraction gradient films

The invention relates to solid or gel-type nanocomposite material which can be polymerised, containing a) 4.9 95.9 wt. % of a soluble polymer; b) 4-95 wt. % of a partially or totally condensed silane selected from the group of epoxyalkoxysilanes, alkoxysilanes and alkylalkoxysilanes, the silane having an inorganic condensation degree of between 33-100% and an organic conversion degree of between 0-95%; c) 0-60 wt. % of an acrylate; d) 0.1-50 wt. % of surface modified nanometric particles selected from the group of oxides, sulphides, selenides, tellurides, halogenides, carbides, arsenides, antimonides, nitrides, phosphides, carbonates, carboxylates, phosphates, sulphates, silicates, titanates, zirconates, aluminates, stannates, plumbates and a mixed oxides; e) 0-50 wt.-% of a plasticiser, f) 0-5 wt. % of a thermal or photochemical cross-linking initiator, sensitizer, auxiliary wetting agent, adhesive agent, antioxidant, stabiliser, colouring agent, photochrome material and thermochrome material in relation to the total weight (dry weight) of the nanocomposite material.

Owner:TOMOEGAWA PAPER CO LTD

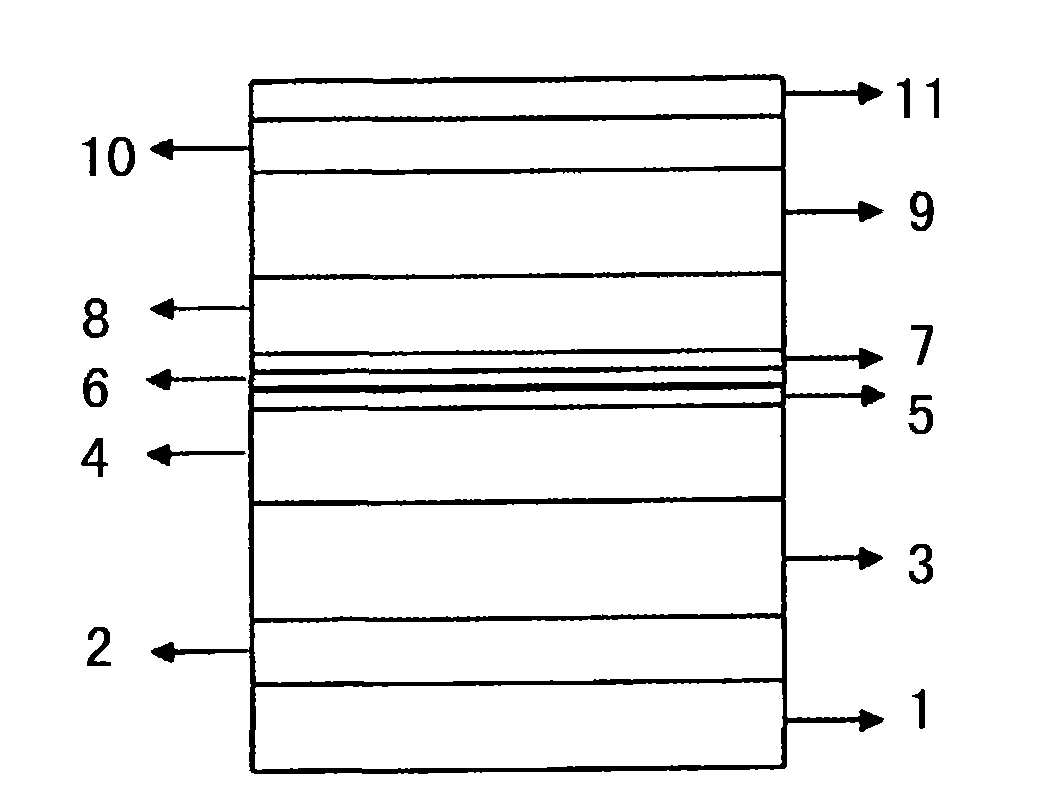

Asymmetrical 980nm semiconductor laser structure with high power and wide waveguide

InactiveCN101820136AImprove electro-optical conversion efficiencyIncrease output powerOptical wave guidanceLaser detailsQuantum wellLower upper

The invention relates to an asymmetrical 980nm semiconductor laser structure with high power and wide waveguide, comprising a substrate, a buffer layer, an N-type lower limiting layer, a lower upper waveguide layer, a lower barrier layer, a quantum well layer, an upper barrier layer, an upper waveguide layer, a P-type upper limiting layer, a transitional layer and an electrode contact layer. The substrate is an N-type gallium arsenide material of a surface (100) and is used for the epitaxial growth of each layer material of a laser thereon; the buffer layer is made of an N-type gallium arsenide material and manufactured on the substrate; the N-type lower limiting layer is made of an N-type gallium aluminum arsenide material and manufactured on the buffer layer; the lower waveguide layer is made of an N-type gallium aluminum arsenide material and manufactured on the lower limiting layer; the lower barrier layer is made of gallium phosphorus arsenide material and manufactured on the lower waveguide layer; the quantum well layer is manufactured on the lower barrier layer; the upper barrier layer is manufactured on the quantum well layer; the upper waveguide layer is manufactured on the upper barrier layer; the P-type upper limiting layer is made of a P-type gallium aluminum arsenide material and manufactured on the upper waveguide layer; the transitional layer is made of a gallium arsenide material and manufactured on the P-type upper limiting layer; and the electrode contact layer is made of a gallium arsenide material and manufactured on the transitional layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method of preparing type p ZnO nano-wire

InactiveCN101319369AOvercome preparation difficultiesPolycrystalline material growthZinc oxides/hydroxidesDopantGas phase

The invention relates to a method for preparing a p-type ZnO nano-wire, belonging to the semiconductor doping technical field. The invention relates to a doping technology for the p-type ZnO nano-wire, in particular to a doping technology by adoption of the chemical vapor deposition technology and utilization of arsenide as a p-type dopant of ZnO. The doping technology is characterized in that: the doping technology adopts the arsenide as a doping source of the p-type ZnO and utilizes the chemical vapor deposition technology to prepare the arsenic doped p-type ZnO nano-wire. Under the condition that the heating temperature is between 400 and 700 DEG C, the proportion of arsenic doped into the ZnO is controlled by adjusting the mol ratio of the arsenide and zinc, so as to perform growth of the p-type ZnO. The doping technology has the advantages that: the doping technology provides a simple and effective growth technology for preparing the p-tyype ZnO nano-wire with high quality and strong controllability, overcomes the defect of difficult doping of the p-type ZnO nano-wire, and further realizes a p-n junction photoelectric device of the ZnO nano-wire.

Owner:LIAONING NORMAL UNIVERSITY

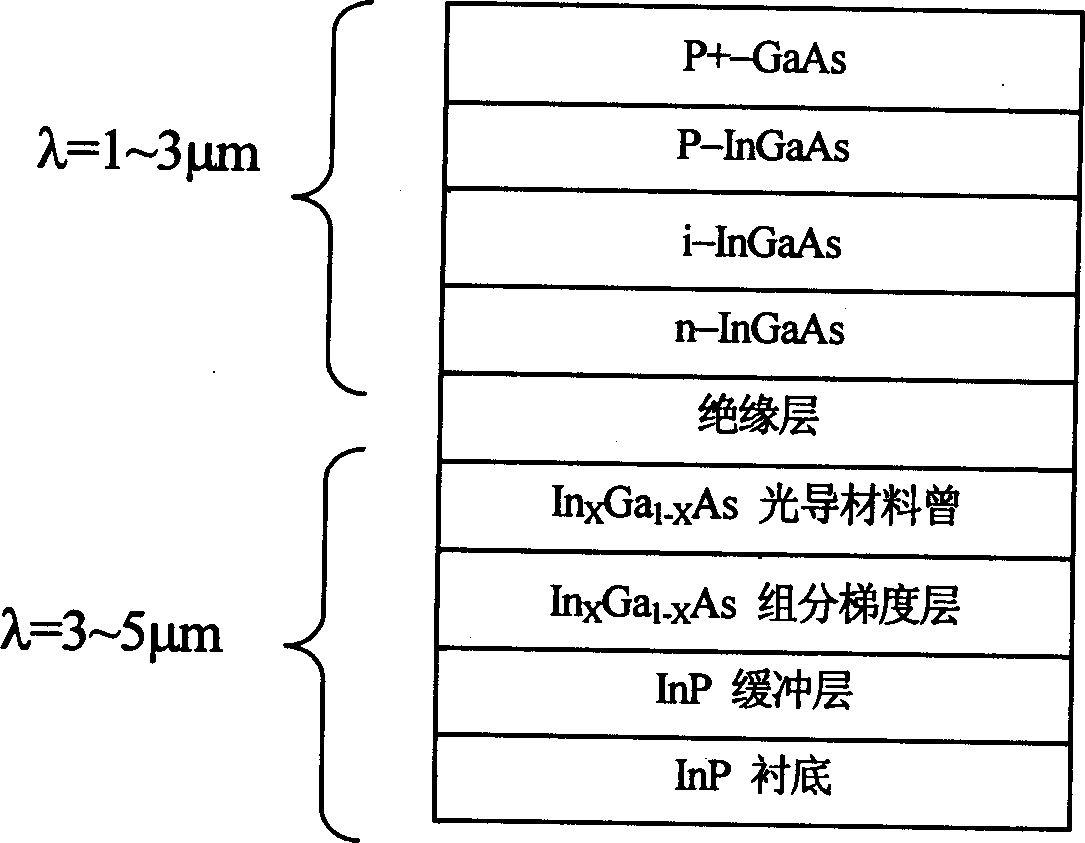

Double-colour indium-gallium-arsenide infrared detector and producing method and application thereof

InactiveCN1848460AReduce volumeReduce weightFinal product manufactureSemiconductor devicesWave bandIndium

The present invention relates to a two-color InGaAs infrared detector. It is characterized by that on the InP substrate are successively grown a photoconductive layer which has InxGa1-x As material and is suitable for detecting 3-5 micrometer infrared wave, an insulating layer and an InGaAs material layer which has PIN structure and is suitable for detecting 1-3 micrometer infrared wave. Said invention also provides the concrete steps of its preparation method, and said infrared detector can be used for preparing the device for multiway measuring infrared signal.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Method for purifying copper electrolyte by using chemical reduction method

InactiveCN101717960ASimple processLow costPhotography auxillary processesProcess efficiency improvementElectrolysisHydrogen

The invention provides a method for purifying a copper electrolyte by using a chemical reduction method. The method comprises the following steps of adding reducing agents comprising hydrazine hydrate, sulfur dioxide and the like, and a compound which contains Cl-irons, Br-irons and I-irons and is used as additives in the copper electrolyte, filtering after the reduction reaction, or evaporating and crystallizing copper sulfate and filtering to obtain the purified electrolyte, and adding the purified electrolyte in an electrolytic bath to return to an electrolyzing system. Adopting the chemical reduction method to purify the electrolyte, the invention eliminates black copper powder and arsenide hydrogen generated in an electro-deposition method and greatly reduces the energy consumption during purifying the copper electrolyte.

Owner:郑雅杰

Method for processing low concentration arsenide in water

InactiveCN105130048AGood removal effectGood flocculation and sedimentation effectMultistage water/sewage treatmentHigh concentrationSolubility

The invention discloses a method for processing low concentration arsenide in water. The water is suitable for processing low concentration arsenide in water, or carrying out deep treatment on high concentration arsenic-containing wastewater. The method organically combines a traditional flocculation coprecipitation technology with a hydroxyl free radical oxidation system, iron ions and hydrogen peroxide form hydroxyl free radicals with extremely strong oxidizability, a Fe-(.OH) reaction system composed of the iron ions and hydroxyl groups can efficiently complete conversion of trivalent arsenic, an iron ion complex generated in the .OH generation process continuously participates in a reaction to generate FeAsO4 with very small solubility, and the arsenide is removed in a precipitate form. The method enhances the adsorption and coacervation effects of fine particles difficult to settle, and the processed arsenide concentration can meet III type water quality requirements in Underground Water Quality Standard (GB / T14848-93).

Owner:CHANGCHUN GOLD RES INST

Capacitors Including Inner and Outer Electrodes

InactiveUS20150187865A1Reduce leakageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

Provided are capacitor stacks for use in integrated circuits and methods of fabricating these stacks. A capacitor stack includes a dielectric layer and one or two inner electrode layers, such as a positive inner electrode layer and a negative inner electrode layer. The inner electrode layers directly interface the dielectric layer. The stack may also include outer electrode layers. The inner electrode layers are either chemically stable or weakly chemically unstable, while in contact with the dielectric layer based on the respective phase diagrams. Furthermore, the electron affinity of the positive inner electrode layer may be less than the electron affinity of the dielectric layer. The sum of the electron affinity and bandgap of the negative inner electrode layer may be less than that of the dielectric layer. In some embodiments, inner electrode layers are formed from heavily doped semiconducting materials, such as gallium arsenide or gallium aluminum arsenide.

Owner:INTERMOLECULAR

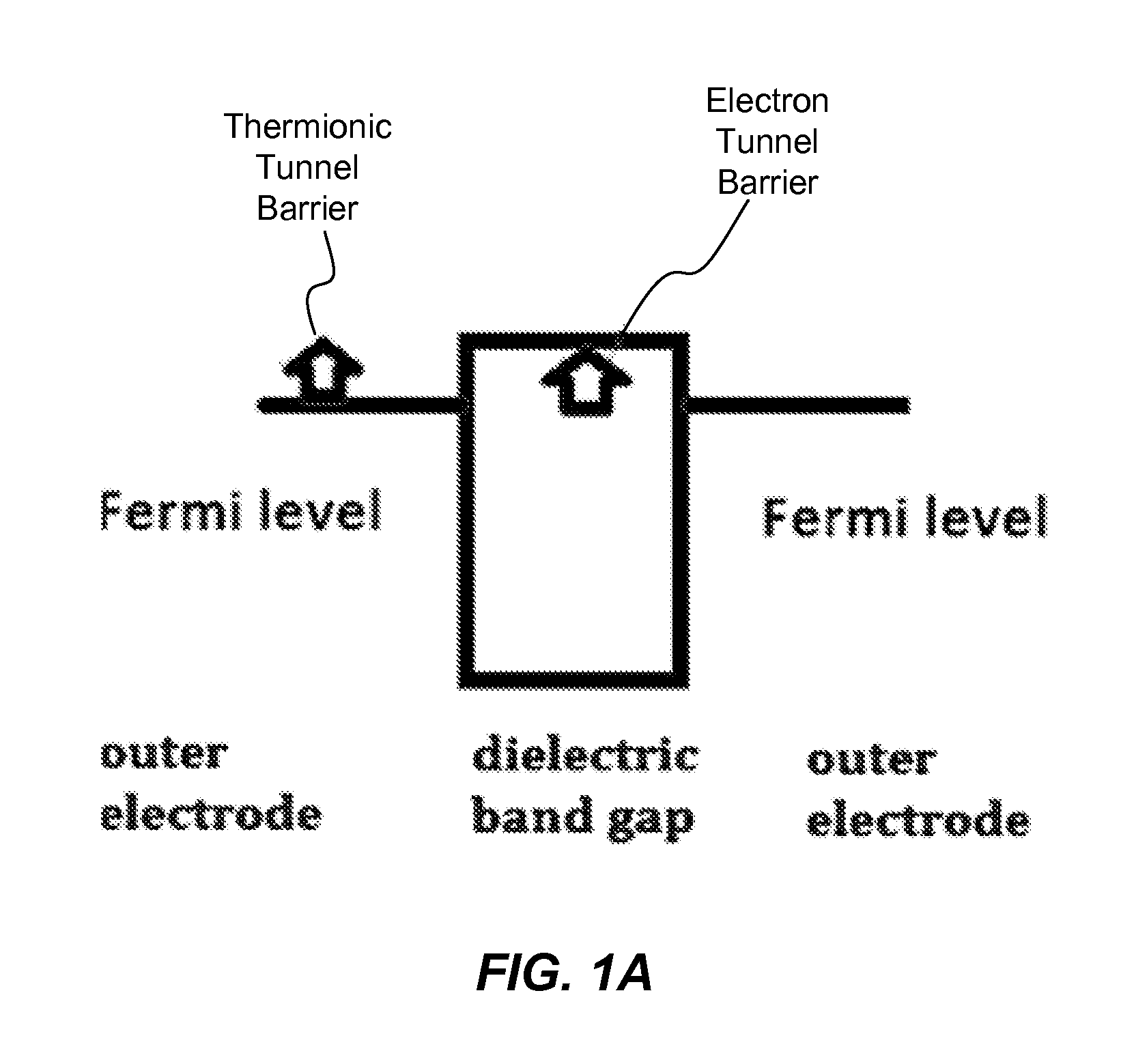

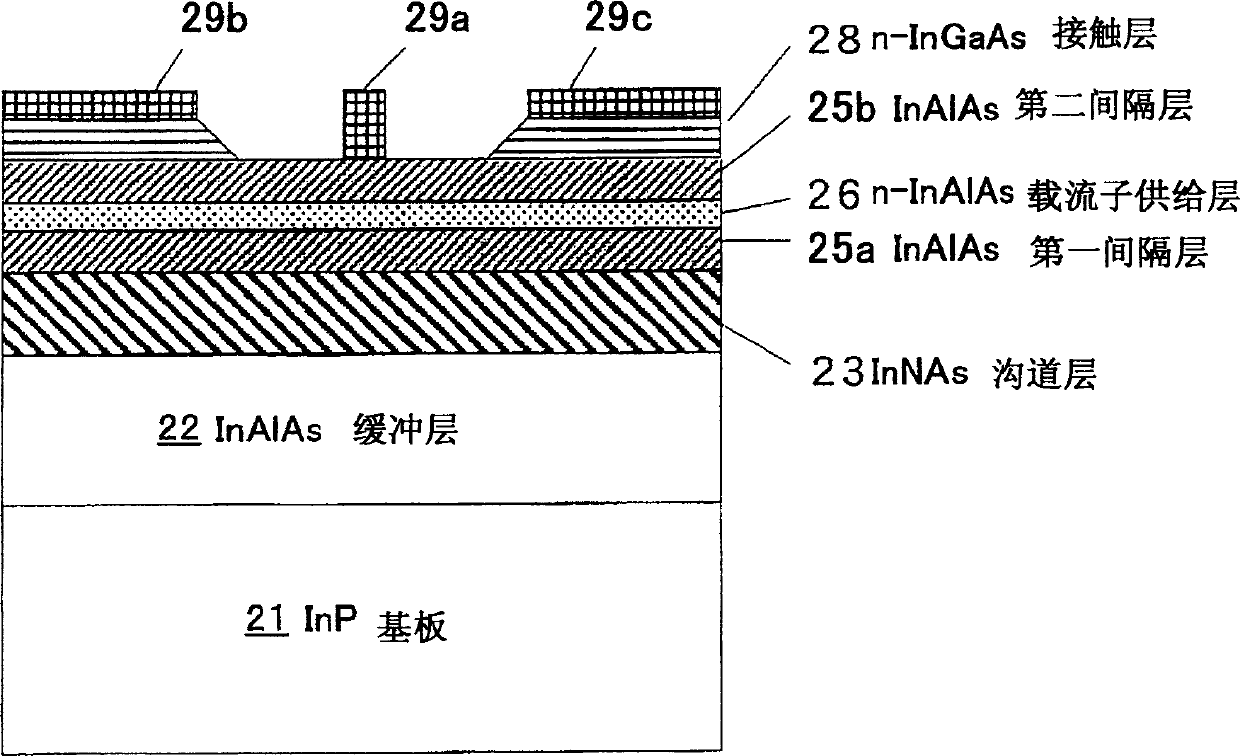

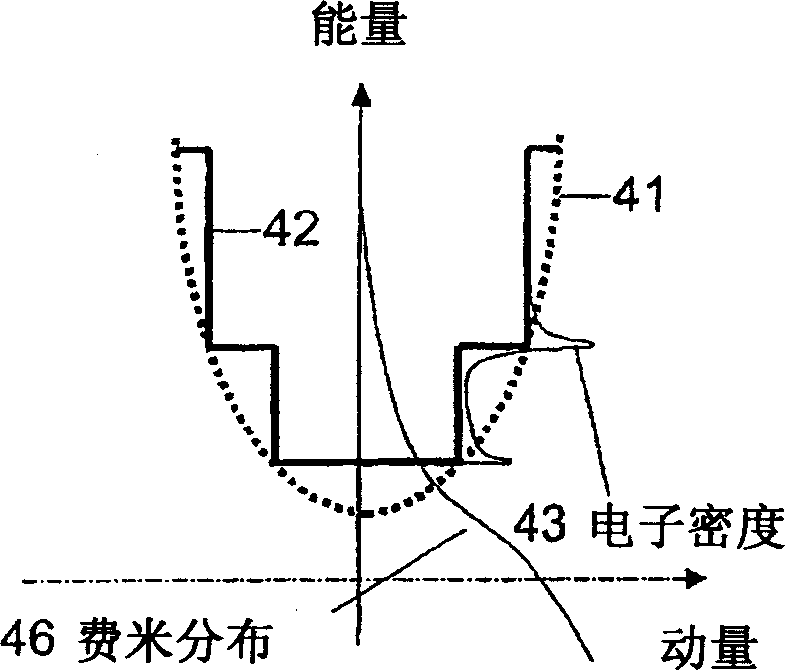

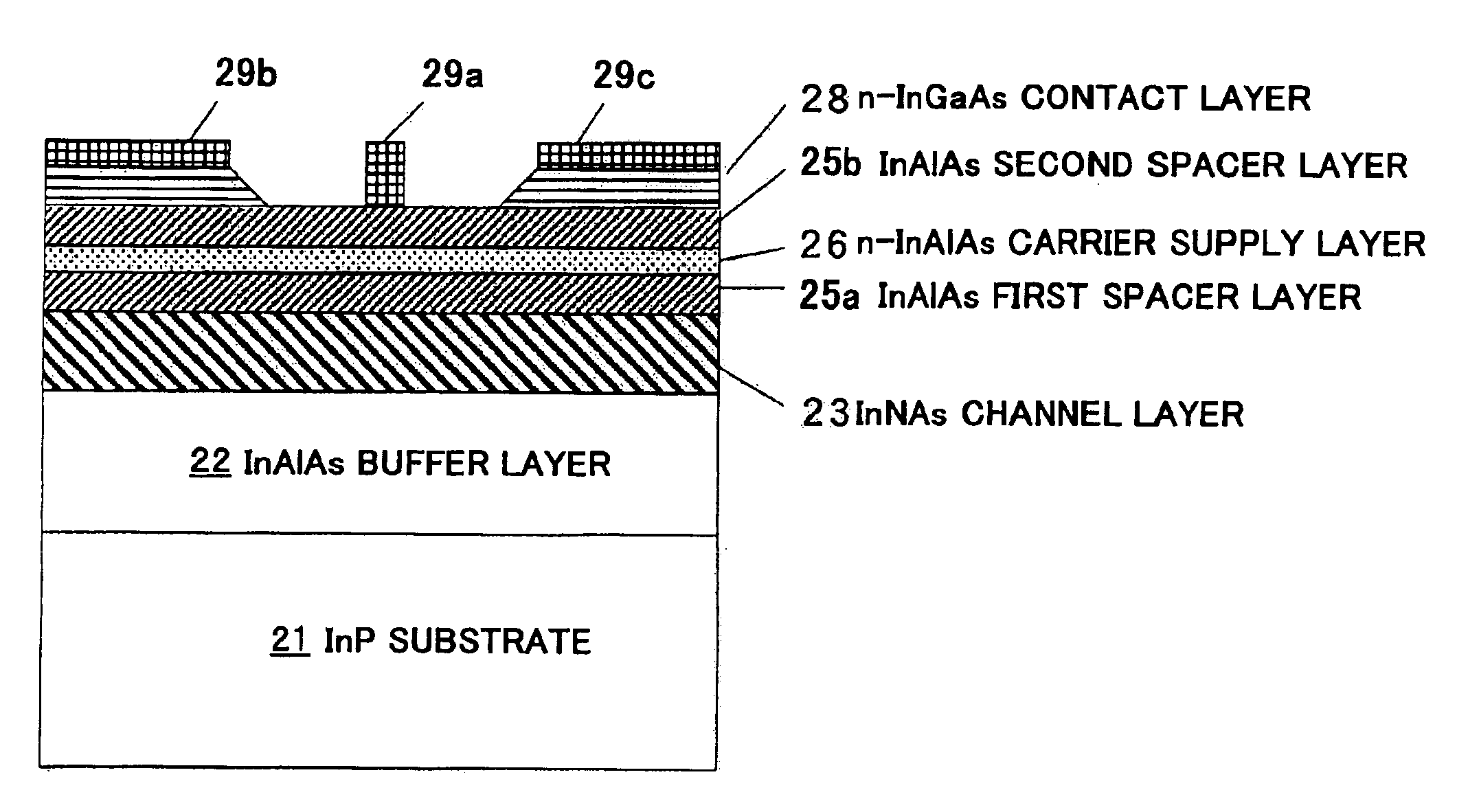

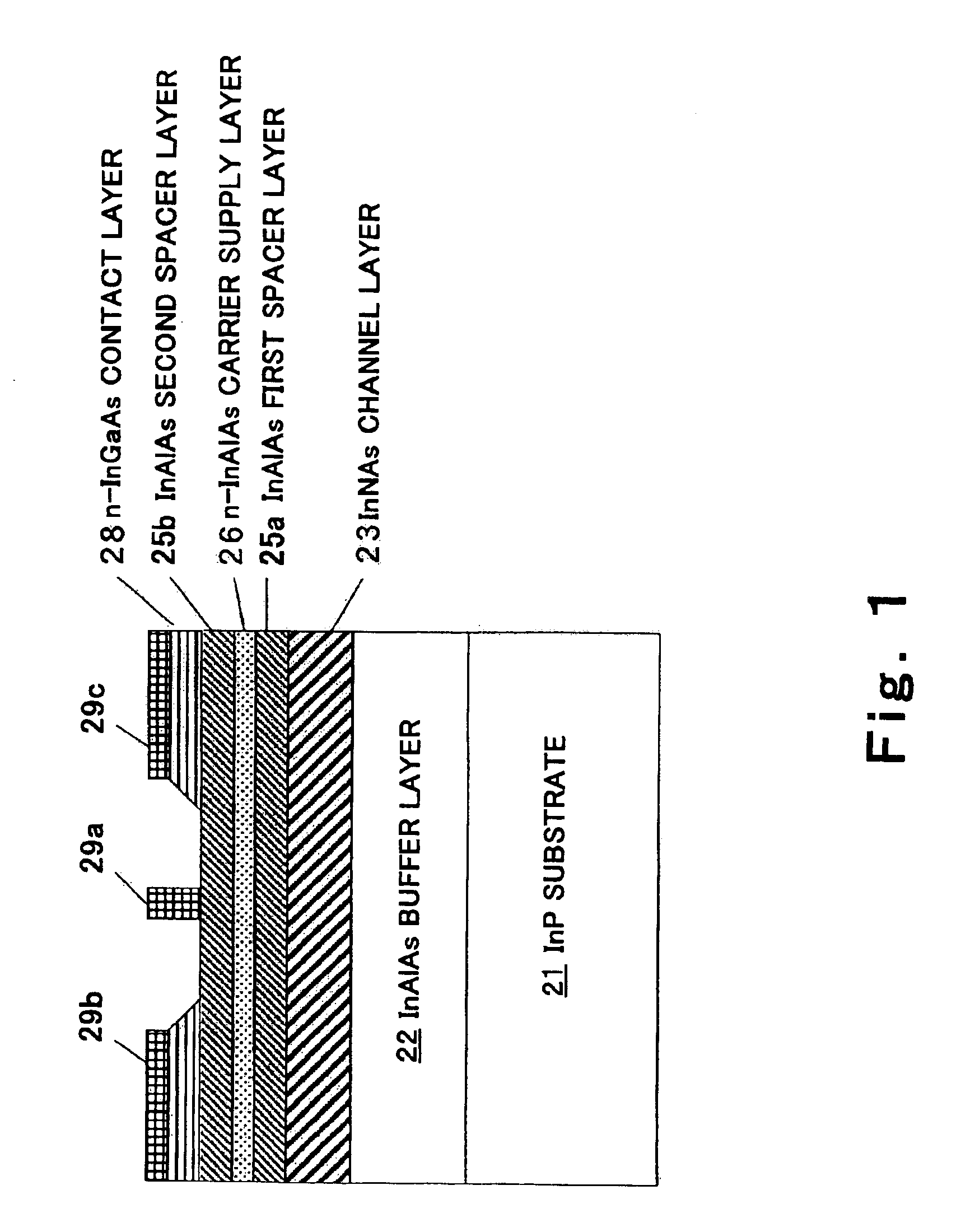

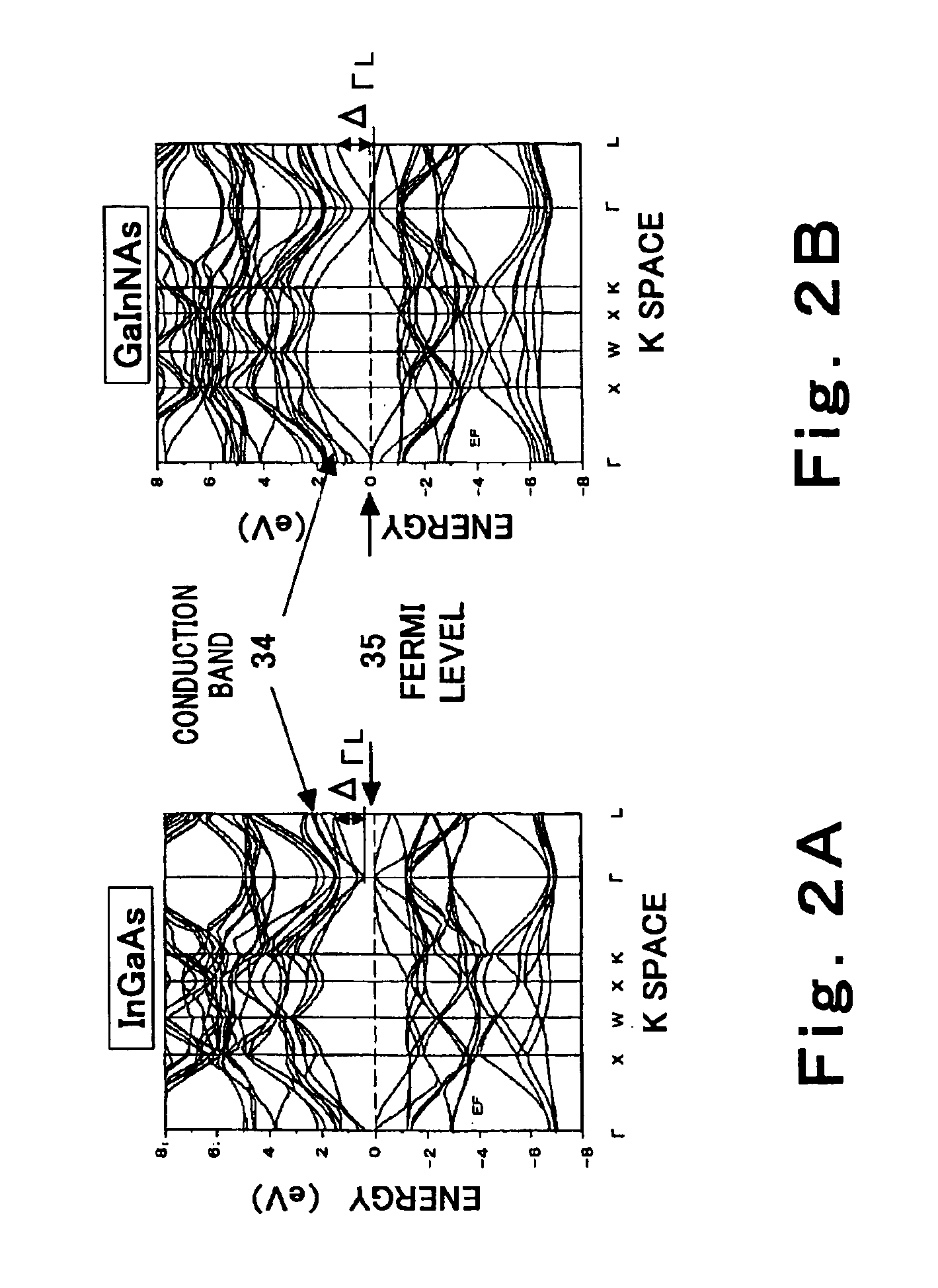

Gallium-indium-nitride-arsenide based epitaxial wafer and hetero-field effect transistor using the same, and its manufacturing method

InactiveCN1692483ASemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionCharge carrier

A hetero-field-effect transistor comprises an InP substrate (21), a channel layer (23) formed on a buffer layer (22) on the InP substrate, a spacer layer (25a) made of a semiconductor having a bandgap larger than that of the channel layer and having a heterojunction with the channel layer, and a carrier supply layer (26) adjacent to the spacer layer. The channel layer includes a predetermined semiconductor layer made of a compound semiconductor the composition of which is expressed by chemical formula GaxIn1-xNyA1-y, where A is As or Sb, the number x is 0<=x<=0.2, the number y is 0.03<=y<=0.10.

Owner:PANASONIC CORP

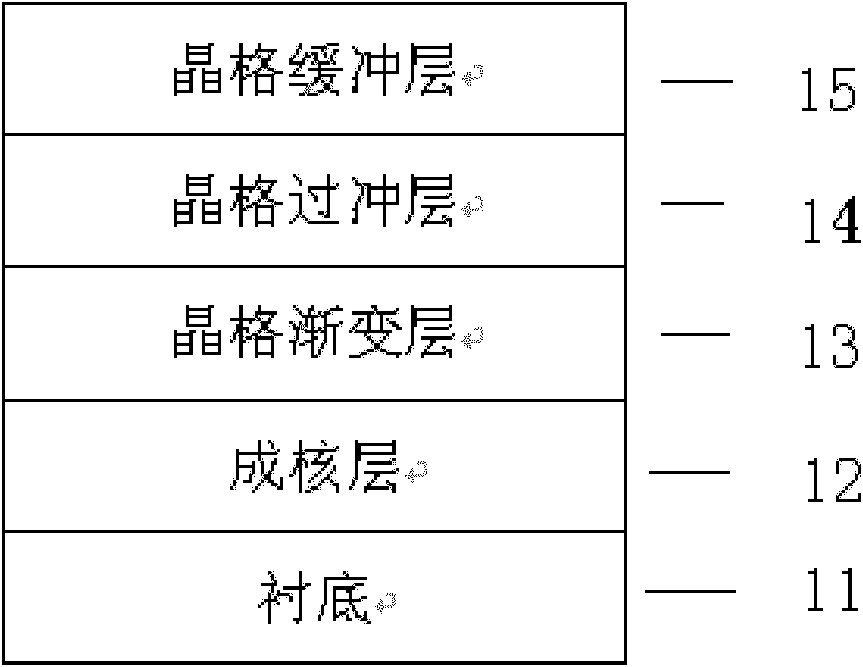

Method for manufacturing lattice graded buffer layer

ActiveCN102011182AControllable threading dislocation densityReduce dependenceFrom chemically reactive gasesThreading dislocationsEpitaxial material

The invention relates to a method for manufacturing a lattice graded buffer layer, which comprises the following steps of: (1) using a commercial germanium single crystal, arsenide gallium single crystal or indium phosphide single crystal as a substrate; (2) epitaxially forming a layer of material in lattice matching with the substrate material as a nucleation layer by utilizing epitaxial technology; (3) epitaxially growing a lattice graded layer on the nucleation layer until the lattice of the material of a top layer has an ideal lattice constant or a lattice constant slightly lower than theideal lattice constant, wherein the lattice graded layer consists of a plurality of indium gallium arsenide materials with gradually increased components; (4) epitaxially forming a layer of indium gallium arsenide material with the lattice constant more than the ideal lattice constant on the lattice graded layer as a lattice overshoot layer; and (5) epitaxially forming a layer of material which has the lattice constant equal to the ideal lattice constant and is the same as that grown on an adjacent upper layer thereof as the lattice buffer layer. The method solves the problem of influence of device appearance degradation caused by lattice mismatching between a conventional epitaxial material and the substrate, and can effectively control threading dislocation density on the surface of a device.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST +1

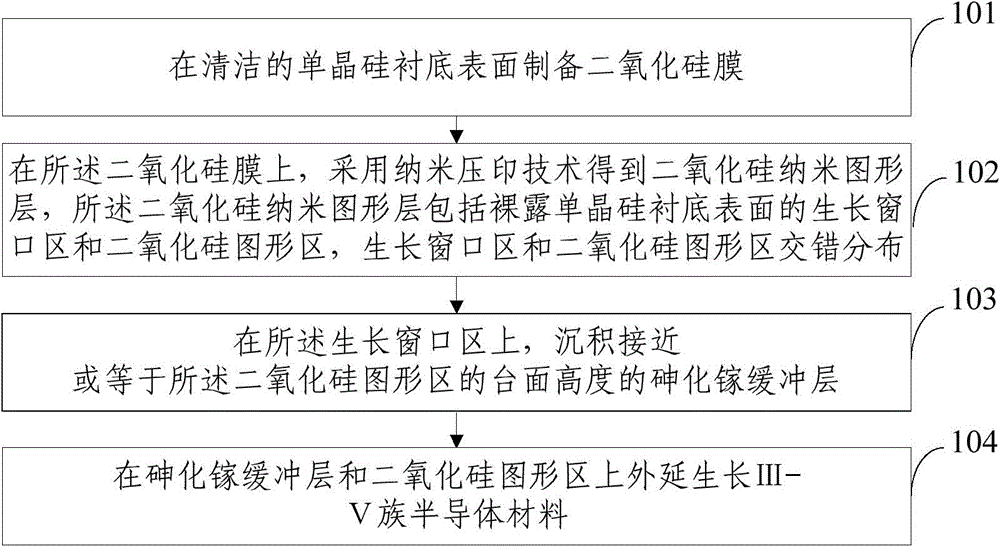

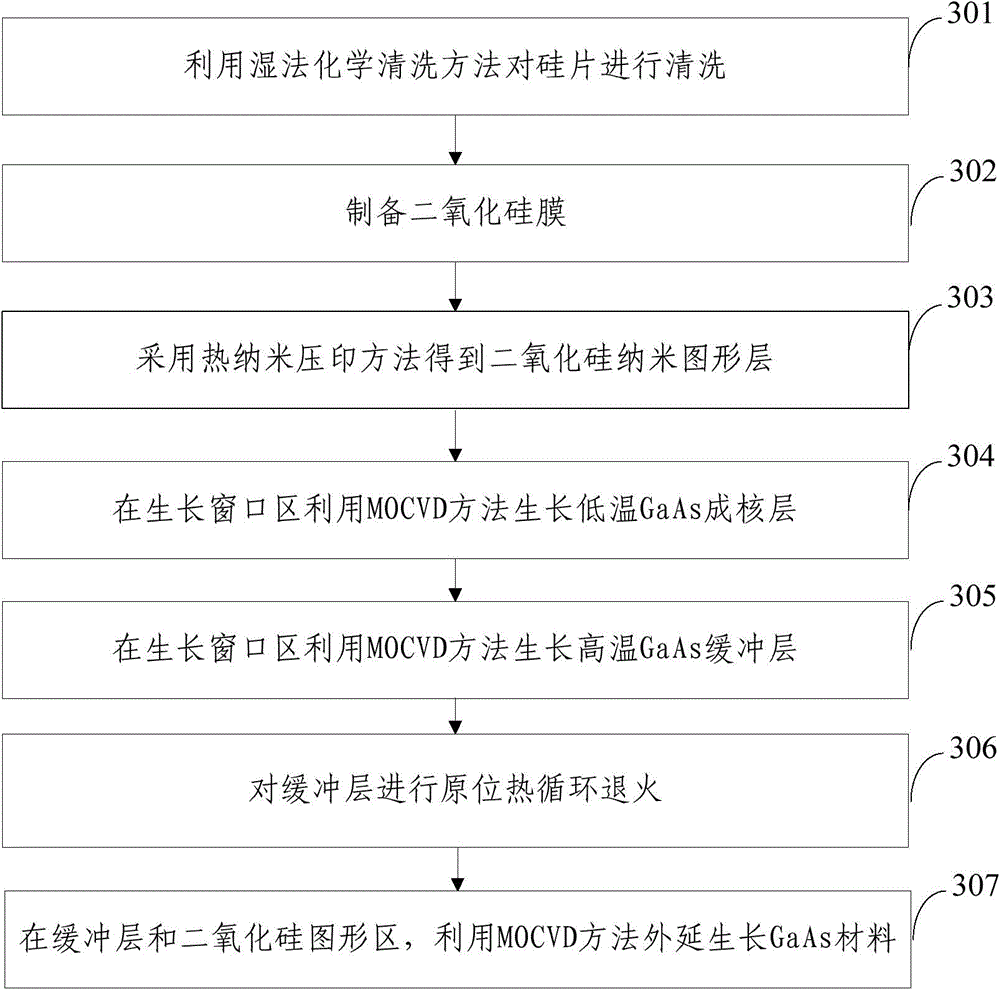

Method and system for preparing silicon-based III-V gallium arsenide semiconductor material

ActiveCN104576326ABreaking the Size Limit ProblemGood for growth preparationSemiconductor/solid-state device manufacturingSemiconductor materialsSilicon dioxide

The invention provides a method and a system for preparing a silicon-based III-V gallium arsenide semiconductor material. The method comprises the following steps: preparing a silicon dioxide film on a clean single crystal silicon substrate surface; obtaining a silicon dioxide nanometer pattern layer on the silicon dioxide film by adopting the nanometer imprinting technology, wherein the silicon dioxide nanometer pattern layer comprises a growth window area exposed on the single crystal silicon substrate surface and a silicon dioxide pattern area, and the growth window area and the silicon dioxide pattern area are arranged in a staggered manner; depositing a galium arsenide buffer layer on the growth window area, wherein the height of the galium arsenide buffer layer is close to or equal to that of a table surface of the silicon dioxide pattern area; growing the III-V semiconductor material on the galium arsenide buffer layer and the silicon dioxide pattern area in an extension manner. According to the method, the silicon dioxide nanometer pattern layer is prepared by adopting the nanometer imprinting technology to be used as a pattern substrate for growth of the semiconductor material, and the problem of limitation of material sizes is solved, so that the growth and the preparation of industrial materials are facilitated, the material production cost is effectively lowered, and the method has a broad application prospect.

Owner:BEIJING UNIV OF POSTS & TELECOMM

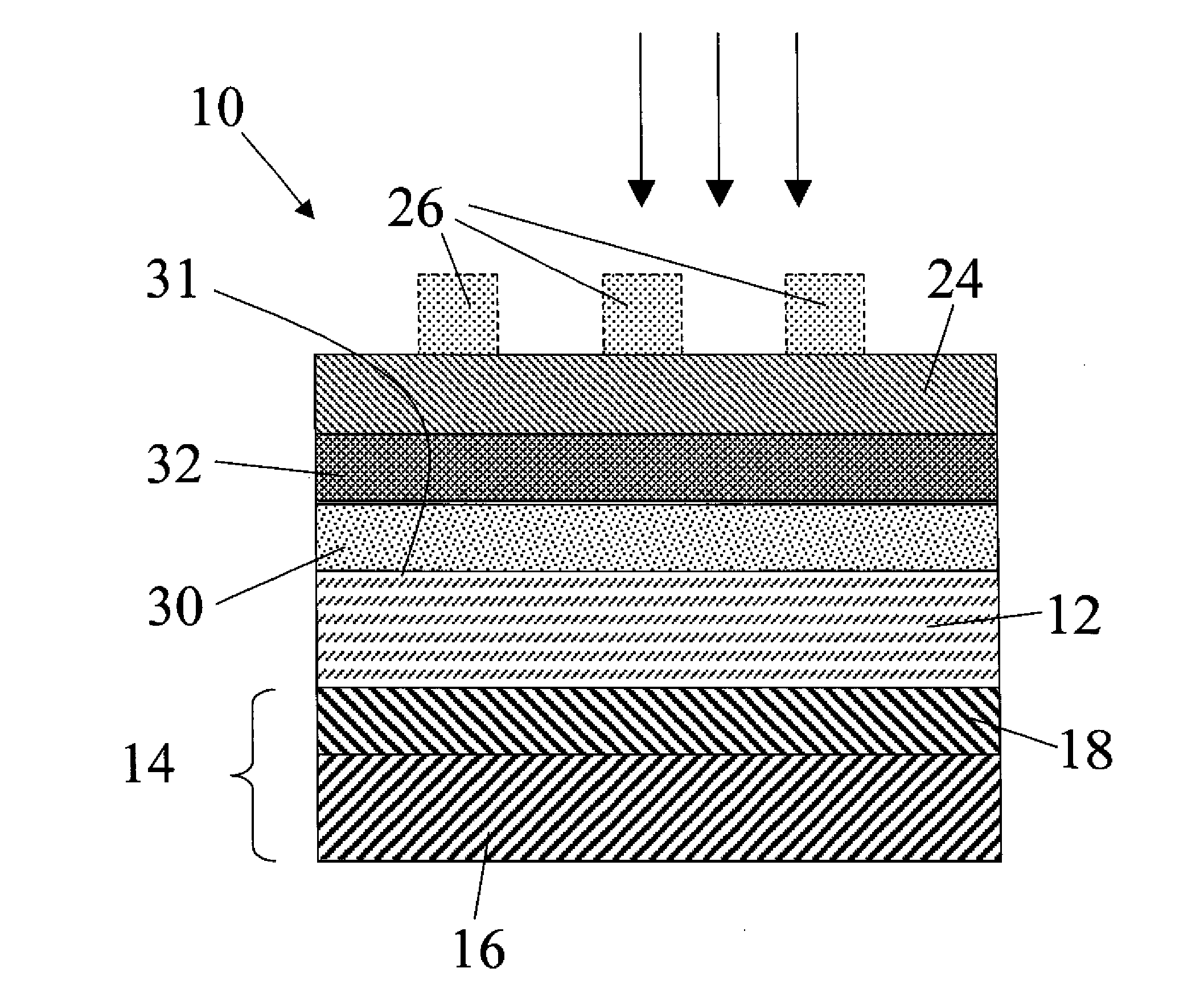

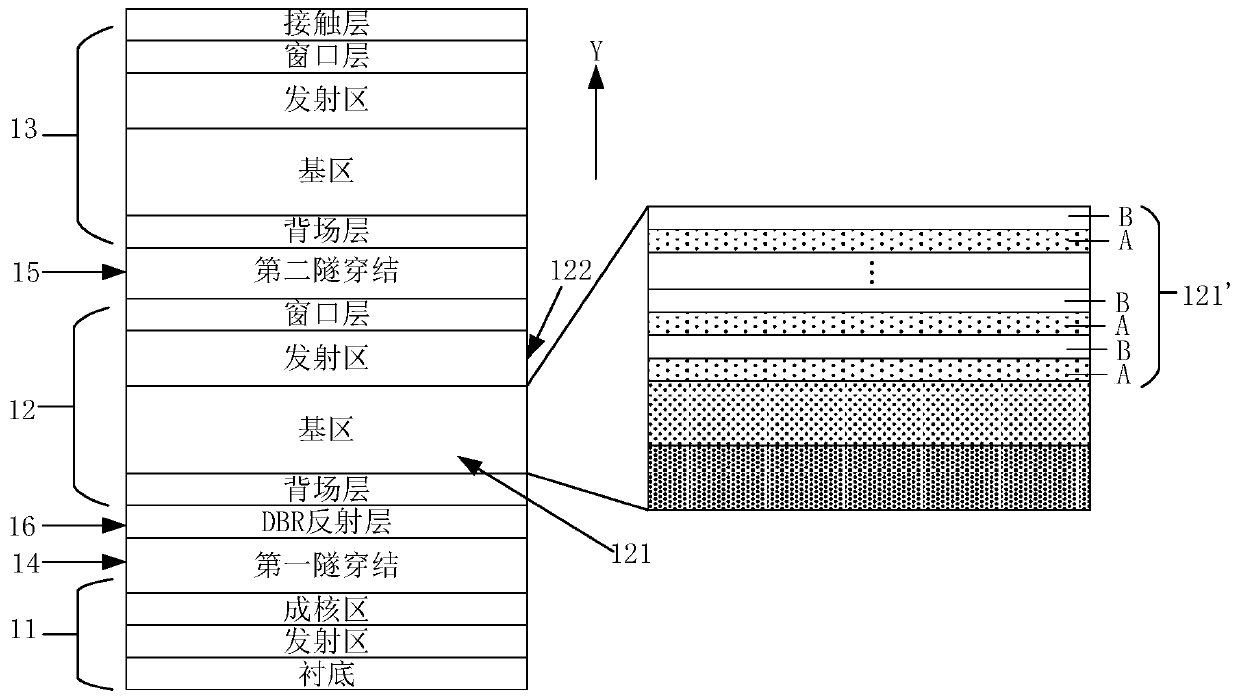

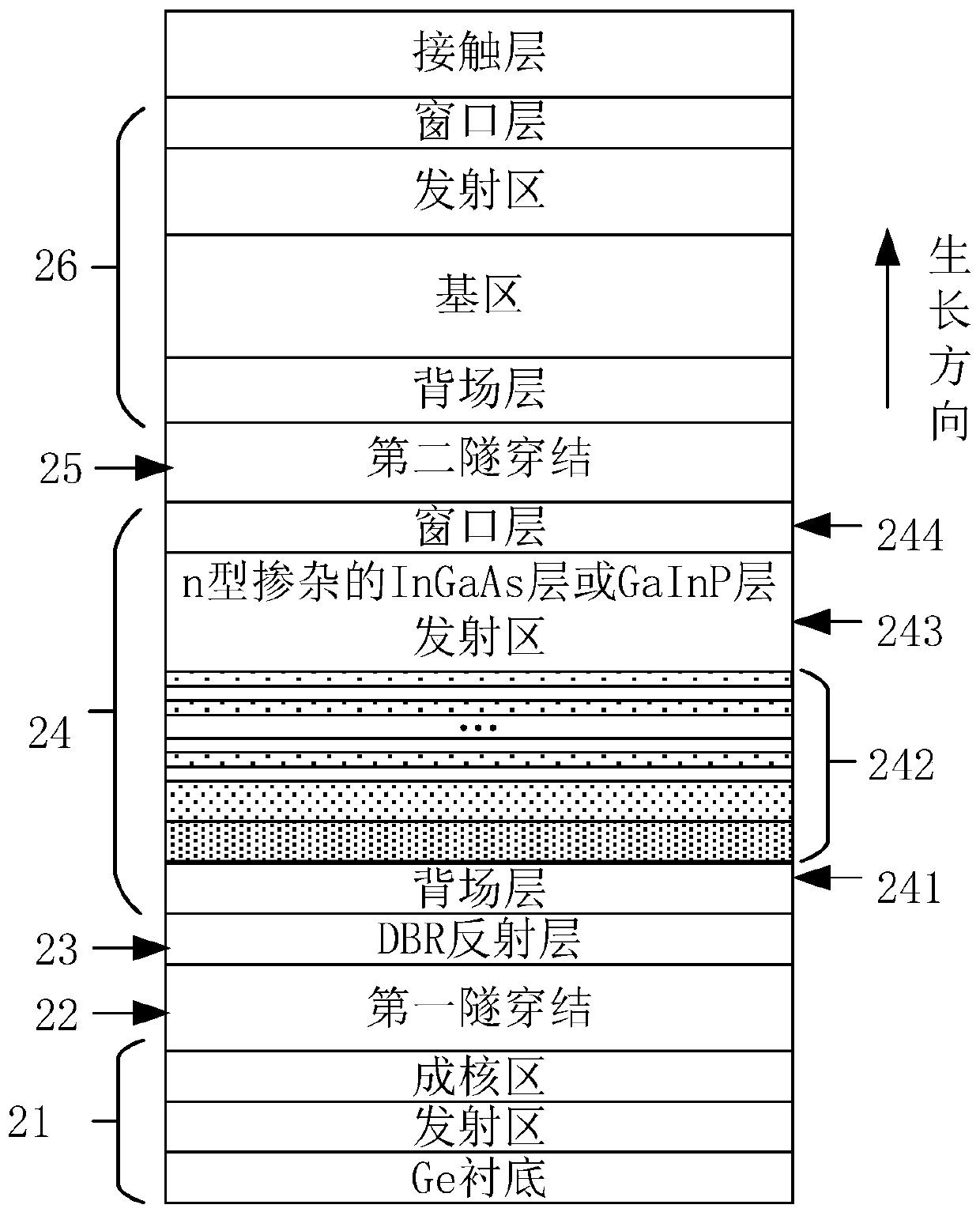

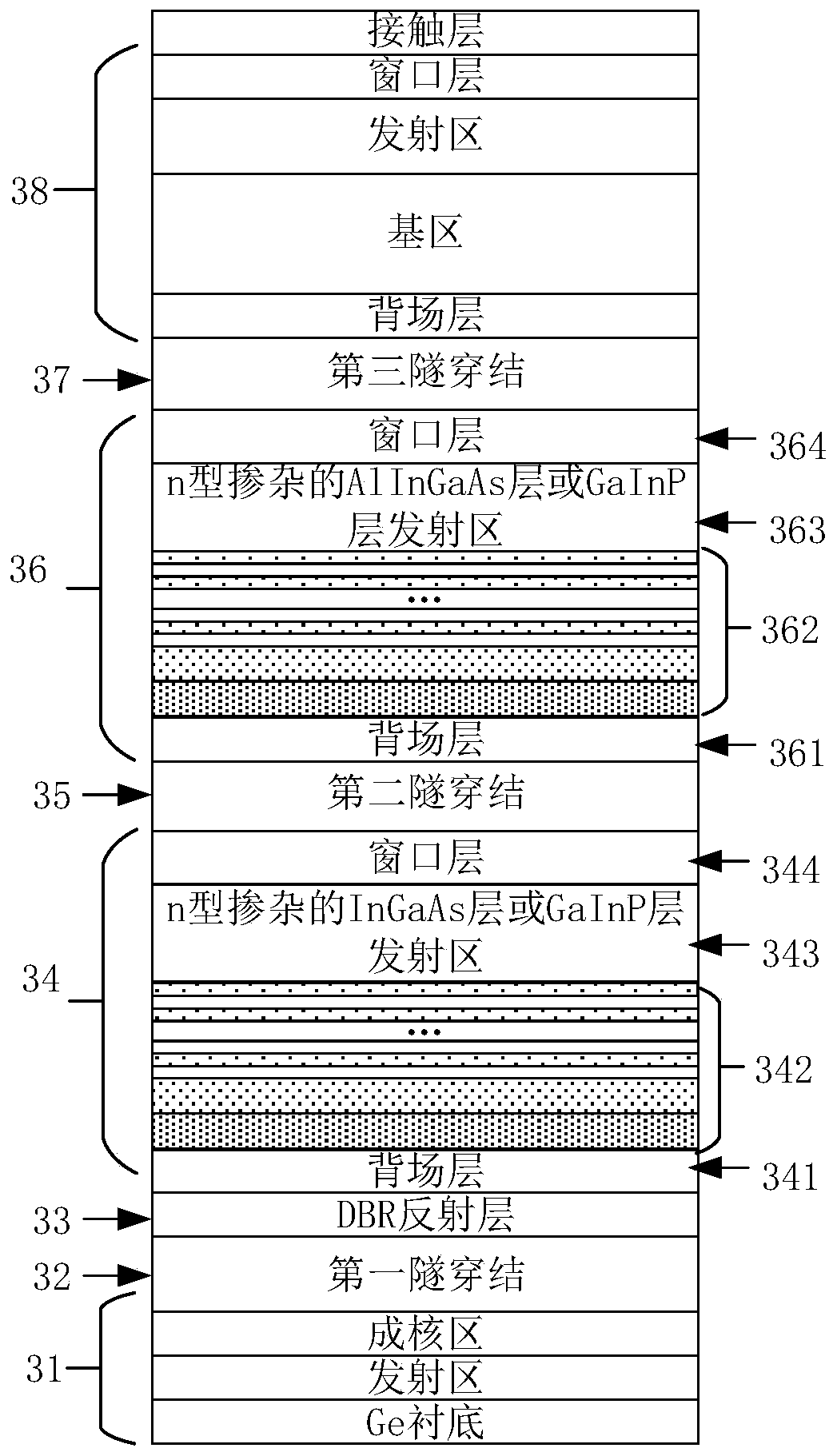

Arsenide multi-junction solar cell and manufacturing method thereof

ActiveCN109860325AImprove performanceImprove radiation resistanceFinal product manufacturePhotovoltaic energy generationCharge carrierNon doped

The present invention provides an arsenide multi-junction solar cell and a manufacturing method thereof. The arsenide multi-junction solar cell comprises at least three-junction sub cells, wherein thebase region of at least one-junction sub cell is an arsenide base region which is formed in a doping gradation mode, in a region with a low dosage concentration, doping layers and non-doping layers are alternately grown to reduce the average carrier concentration, close to a PN-junction region, of the base region, and an inverse proportion relationship of a width and an average carrier concentration in an exhaust region is obtained. Therefore, the technical scheme provided by the invention can increase the thickness of the exhaust region and can improve the collection effect of carriers so asto improve the cell performances, and the base region in the mode increases the migration rate of few of carries through adoption of a mode of alternate growth of the doping layers and the non-dopinglayers so as to increase the diffusion length of few of carriers, finally lives of the carriers and improve the anti-irradiation properties of the cells.

Owner:YANGZHOU CHANGELIGHT

Gallium indium nitride arsenide based epitaxial wafer, a hetero field effect transistor using the wafer, and a method of fabricating the hetero field effect transistor

InactiveUS6861679B2High electron mobilityIncrease speedSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierField-effect transistor

A hetero field effect transistor according to the present invention comprises an InP substrate, a channel layer provided on the InP substrate with a buffer layer disposed between the InP substrate and the channel layer, a spacer layer constituted by a semiconductor having a band gap larger than that of the channel layer formed to hetero-join to the channel layer, and a carrier supply layer formed to be adjacent to the spacer layer, wherein the channel layer comprises a predetermined semiconductor layer constituted by a compound semiconductor represented by a formula GaxIn1−xNyA1−y in which A is As or Sb, composition x satisfies 0≦x≦0.2, and composition y satisfies 0.03≦y≦0.10.

Owner:PANASONIC CORP

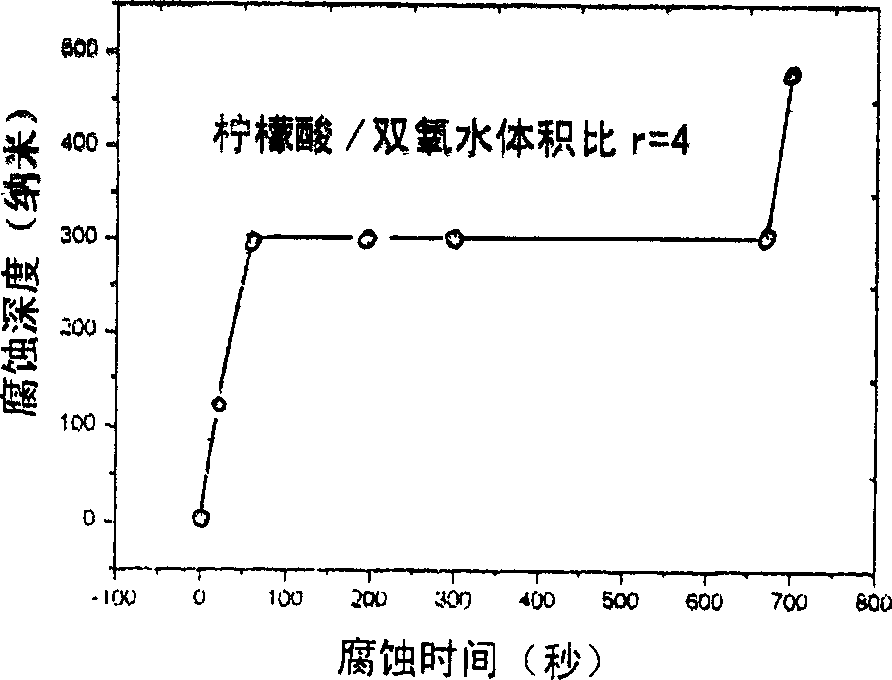

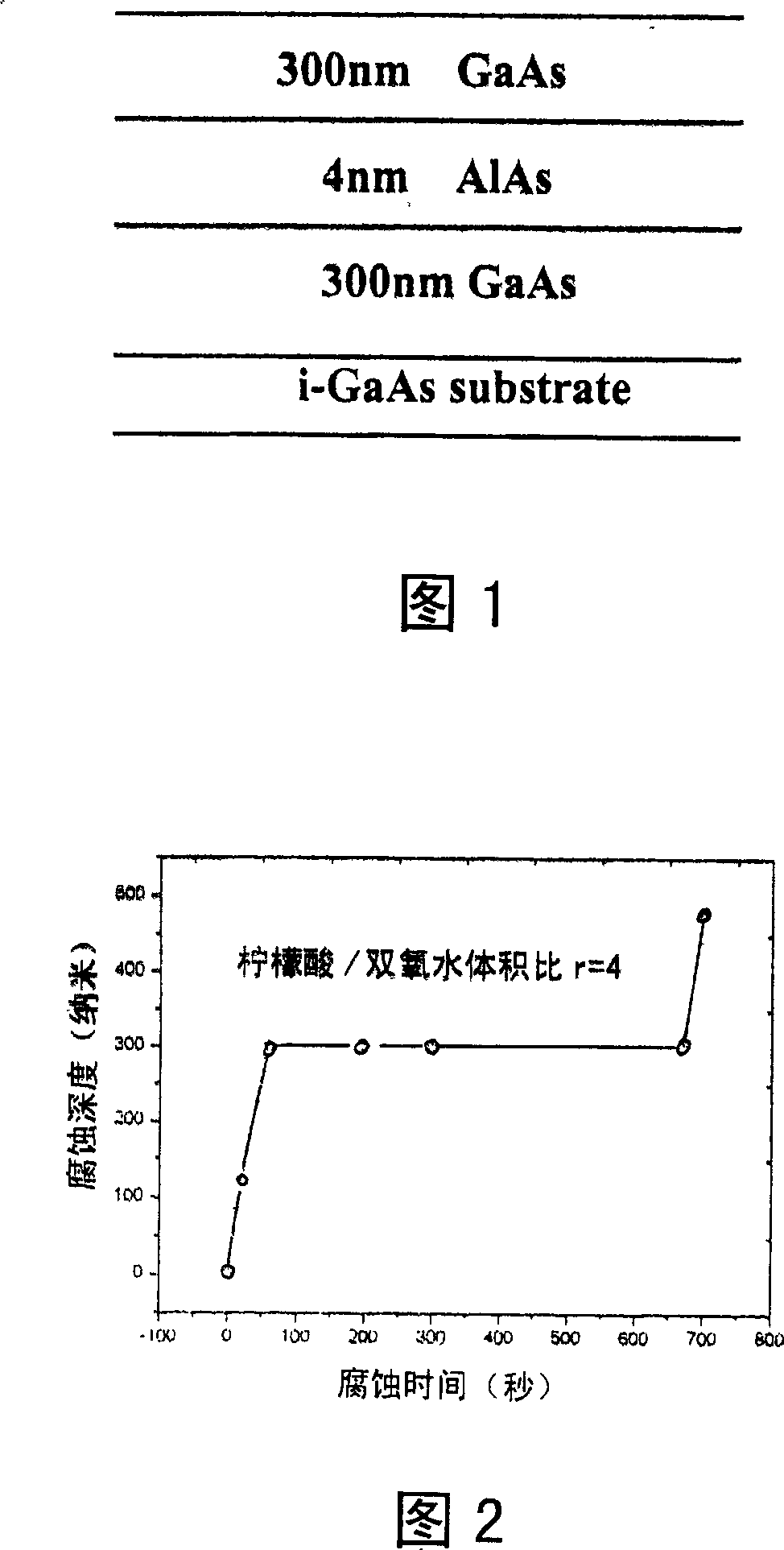

Chemical corrosion liquid in high selection ratio of gallium arsenide in aluminum arsenide / gallium arsenide

This invention relates to a chemical corrosive with high selectivity towards gallium arsenide among gallium arsenide / aluminium arsenide mixture. It uniquely contains citric acid solution and oxydol with a volume ratio of 4:1 and is compatible with gallium arsenide integration technique. Besides, it also has the advantages of nontoxic solution and simple technique.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

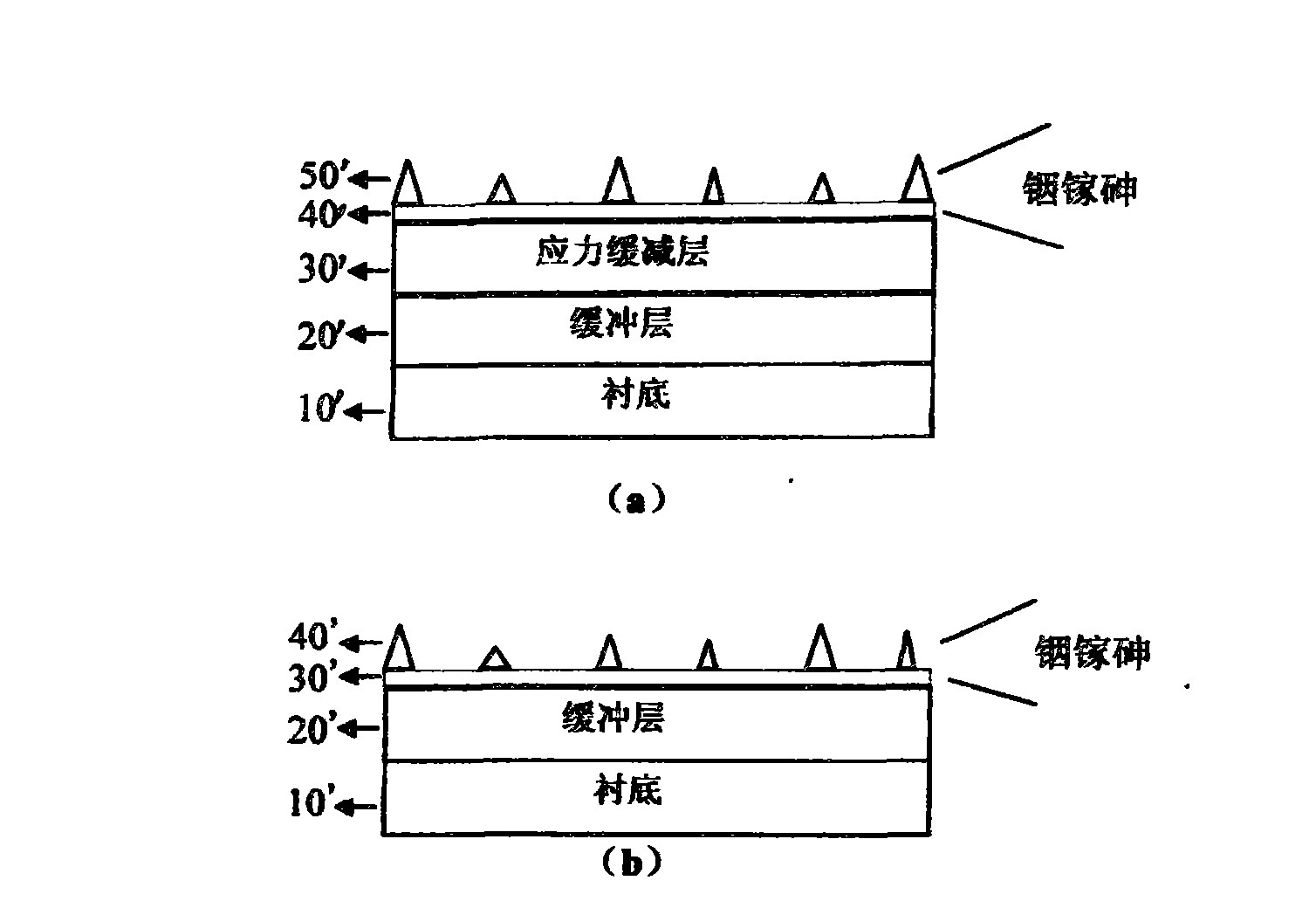

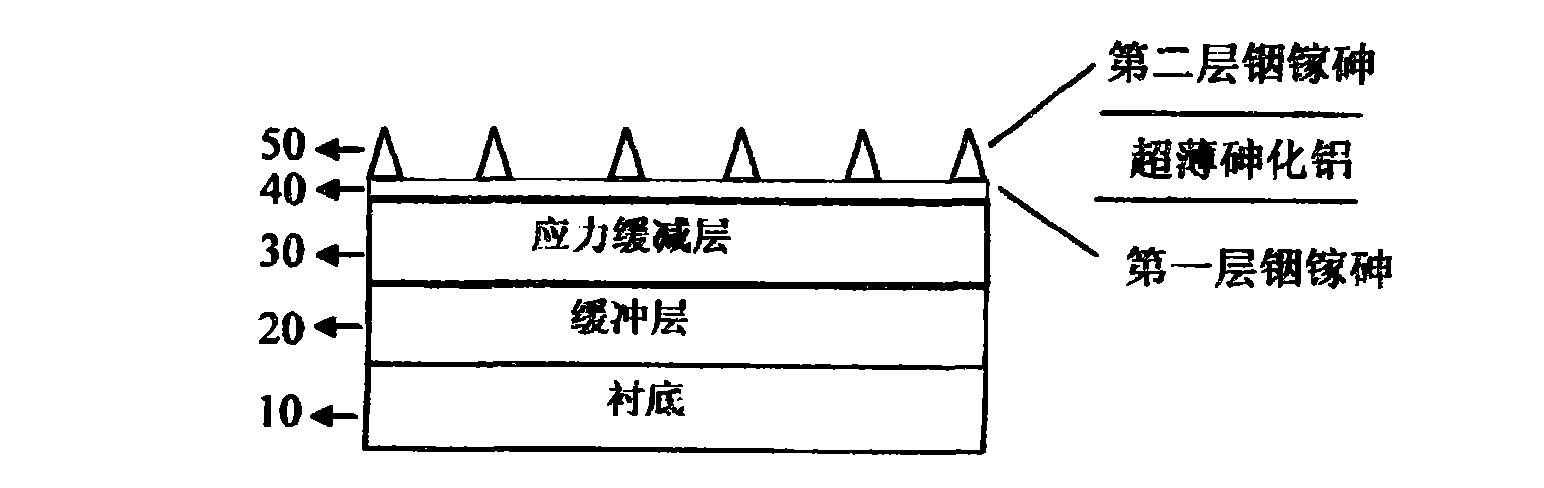

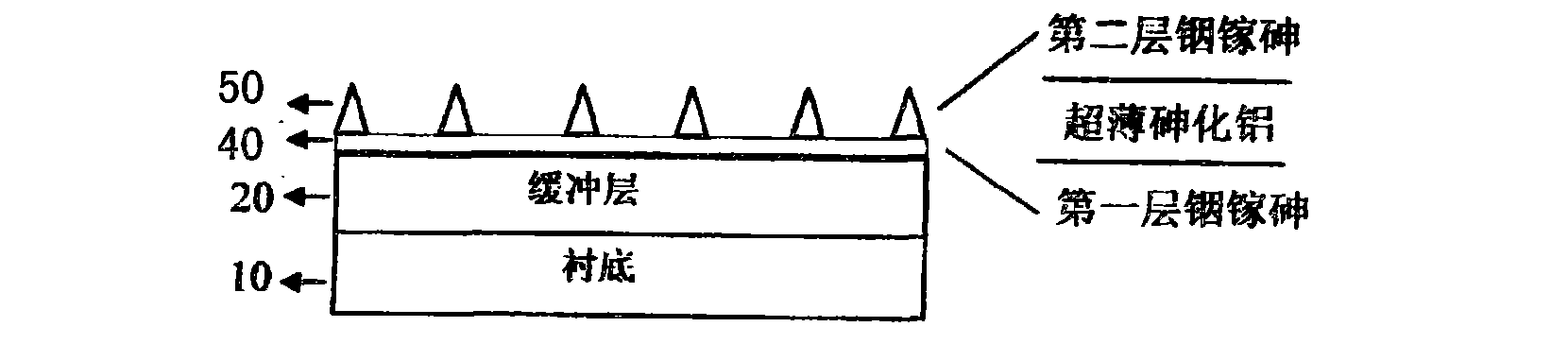

Growth method for controlling nucleation of self-organization In-Ga-As quantum dots

InactiveCN101540357AImprove uniformityExpand the range of optionsSemiconductor devicesGas phaseDislocation

The invention provides a growth method for controlling the nucleation of self-organization In-Ga-As quantum dots, which is characterized by comprising the following: step 1, choosing a substrate; step 2, depositing a buffer layer on the substrate by adopting a molecular beam epitaxy method or a metal-organic chemical vapor deposition method so as to isolate impurities and dislocation in the substrate and allow a growth surface to be leveler; step 3, depositing a stress buffering-reducing layer on the buffer layer so as to buffer and reduce strain between the buffer layer and In-Ga-As material; and step 4, sequentially depositing a first In-Ga-As layer, ultra-thin aluminum arsenide and a second In-Ga-As layer on the stress buffering-reducing layer, forming an In-Ga-As soakage layer and an In-Ga-As quantum-dot layer and finishing growth preparation.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com